Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

88results about How to "Improve defect density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

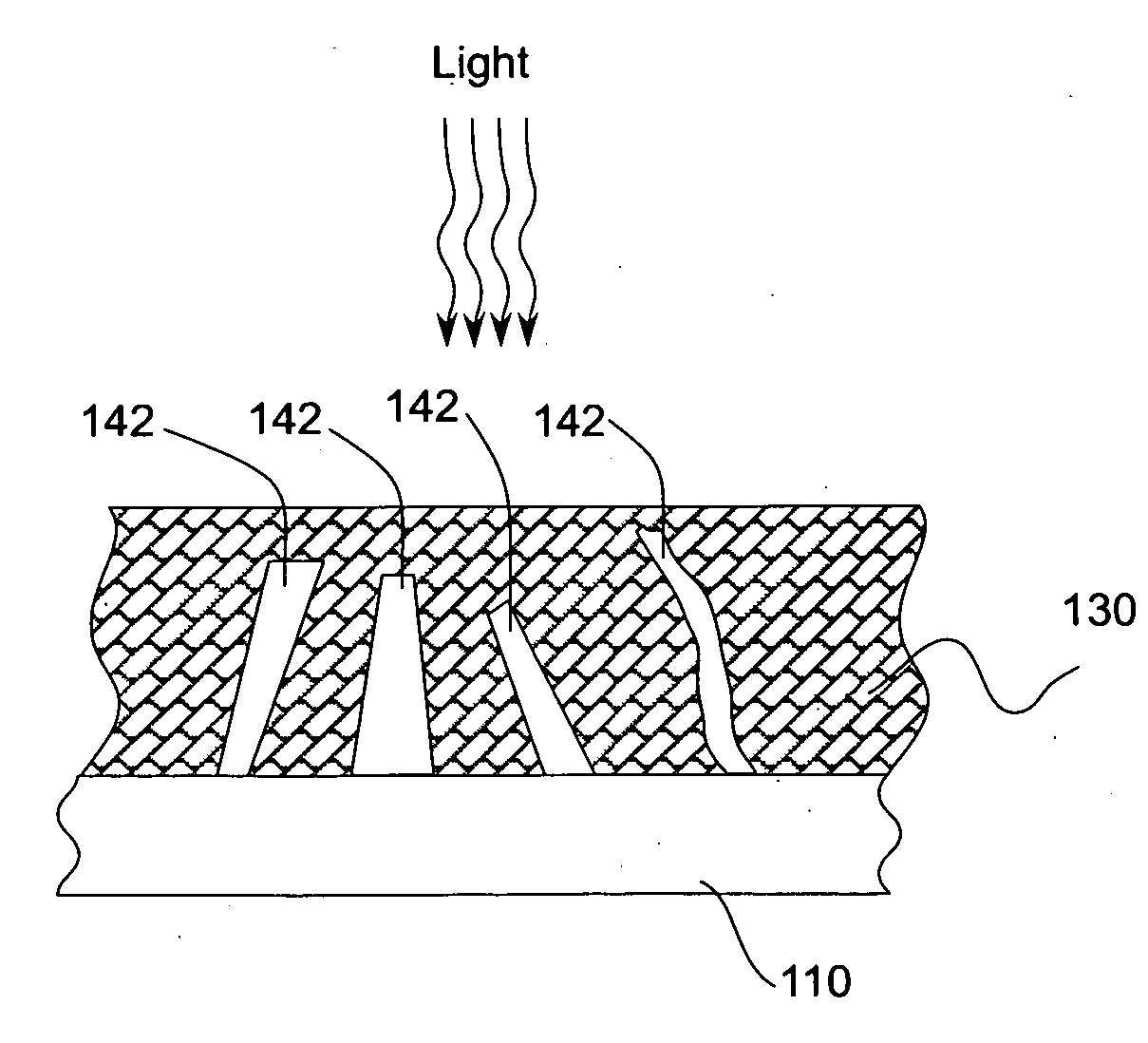

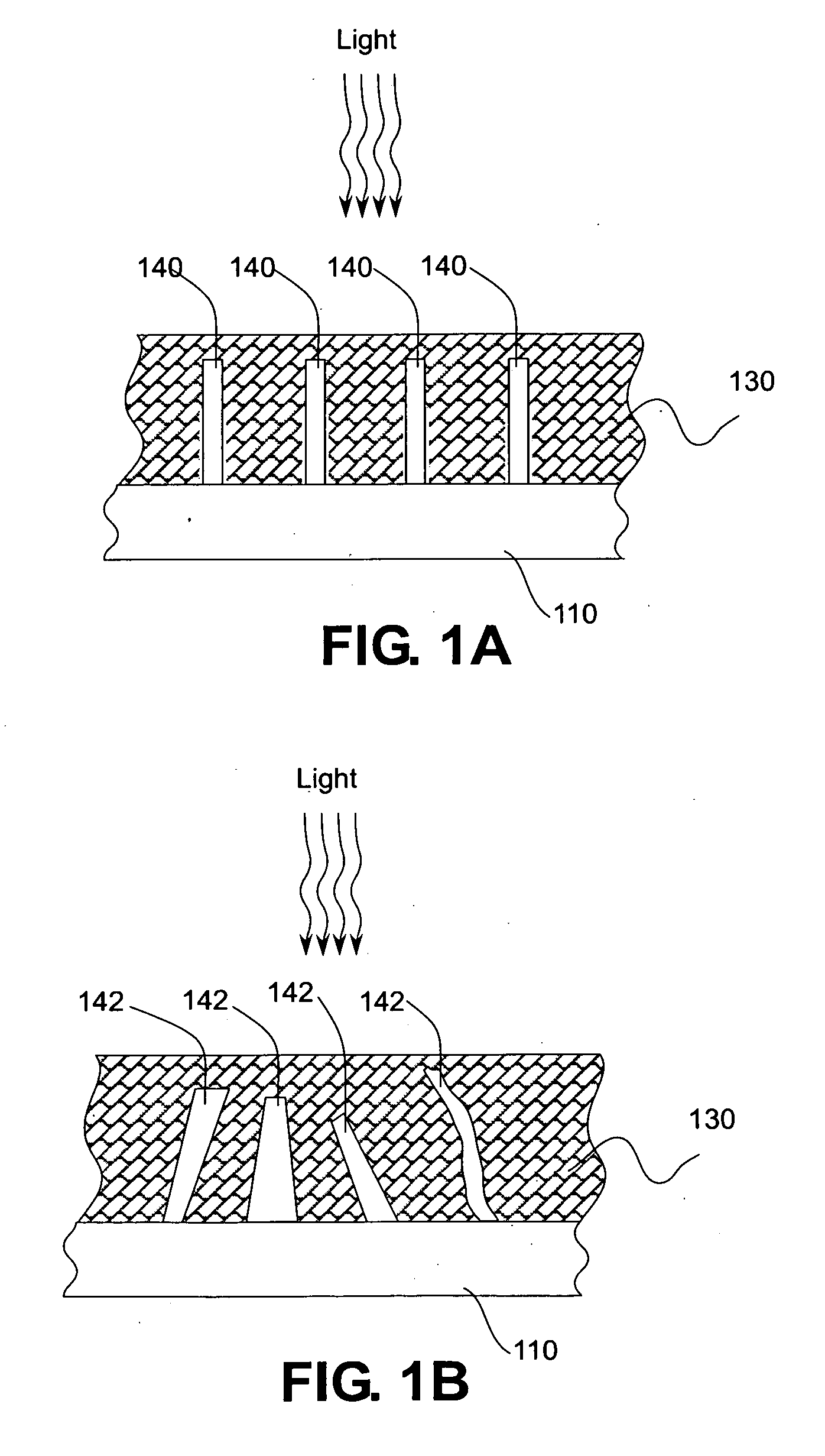

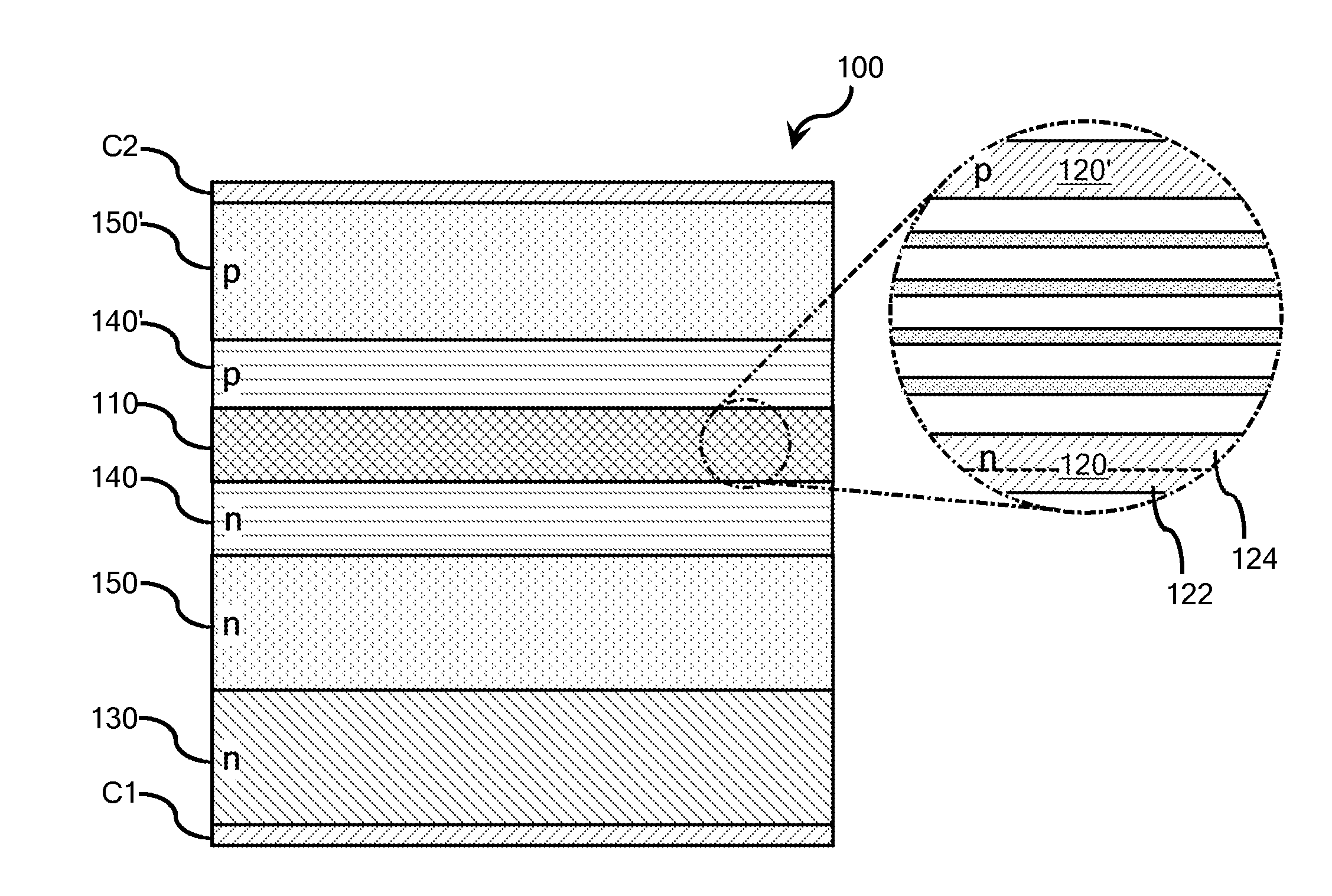

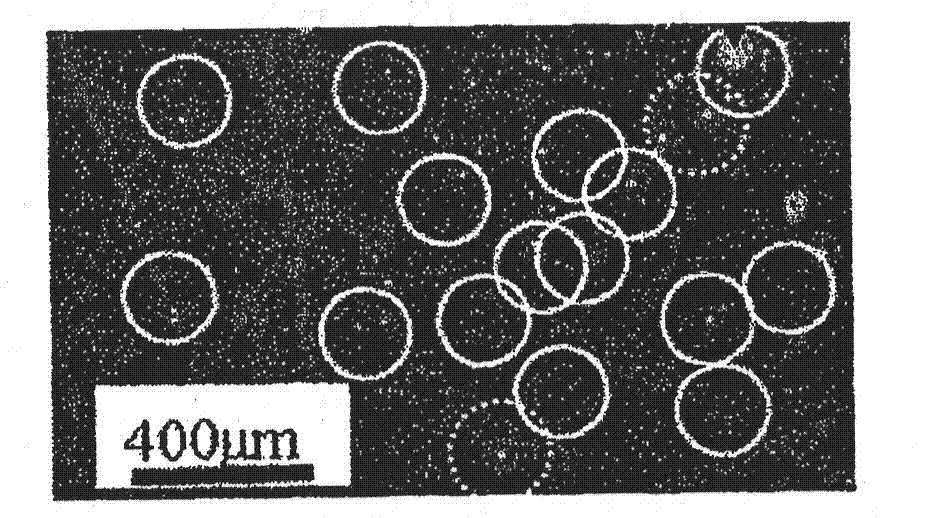

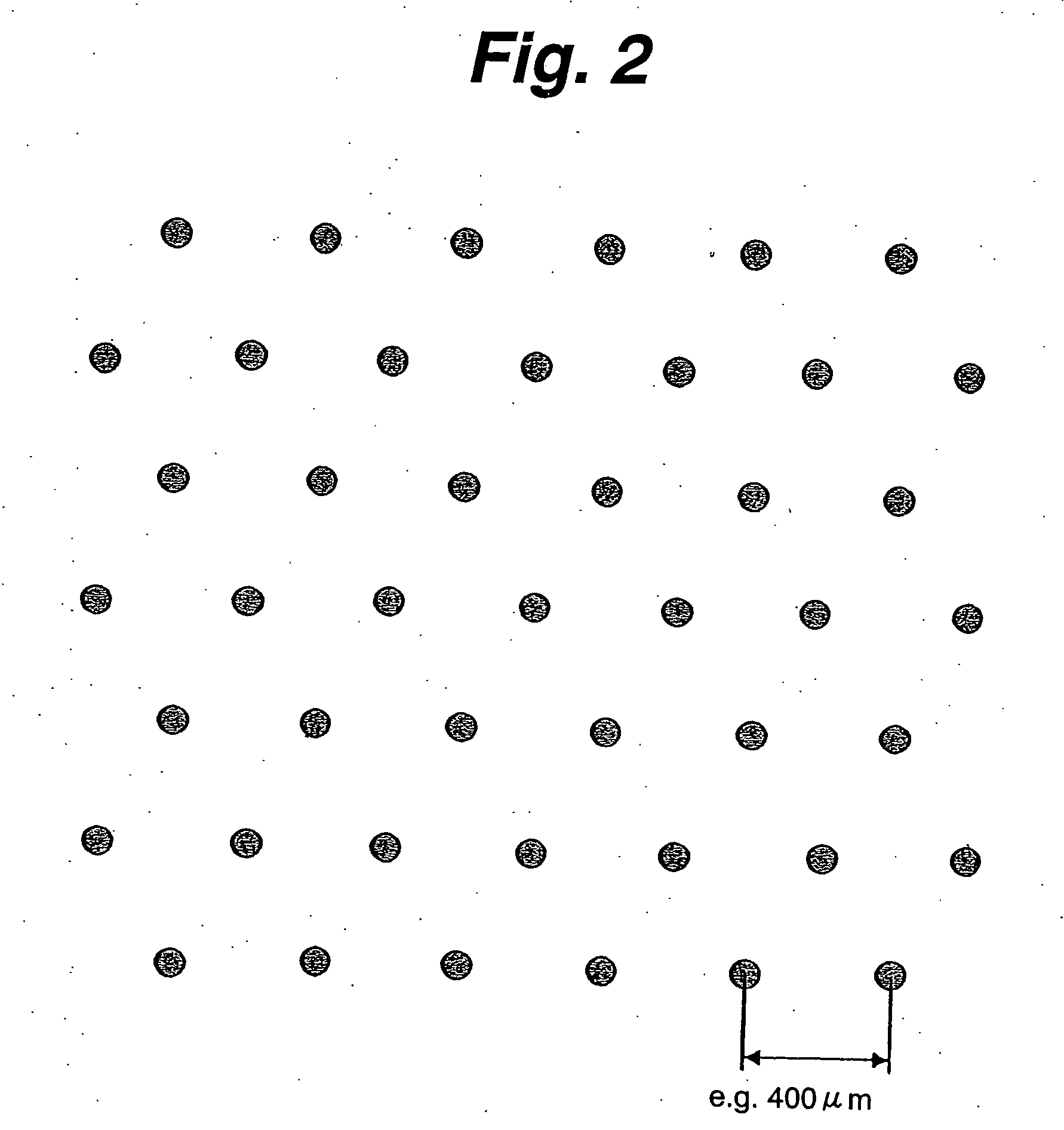

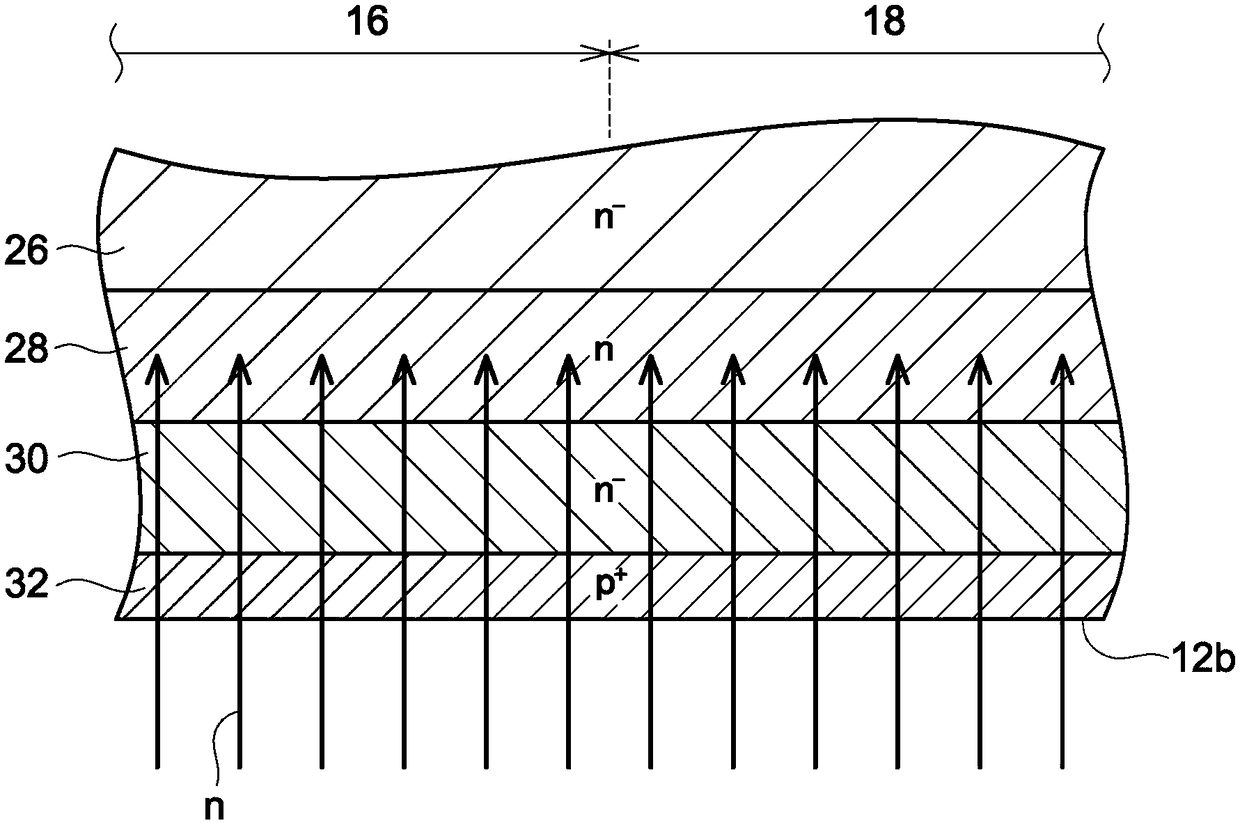

Structures of ordered arrays of semiconductors

InactiveUS20090020150A1Low minority-carrier diffusion lengthImprove equipment efficiencyElectrolytic capacitorsPV power plantsSemiconductor structureCharge carrier

A device having arrays of semiconductor structures with dimensions, ordering and orientations to provide for light absorption and charge carrier separation. The semiconductor structures are formed with relatively high aspect ratios, that is, the structures are long in the direction of received light, but have relatively small radii to facilitate efficient radial collection of carriers.

Owner:CALIFORNIA INST OF TECH

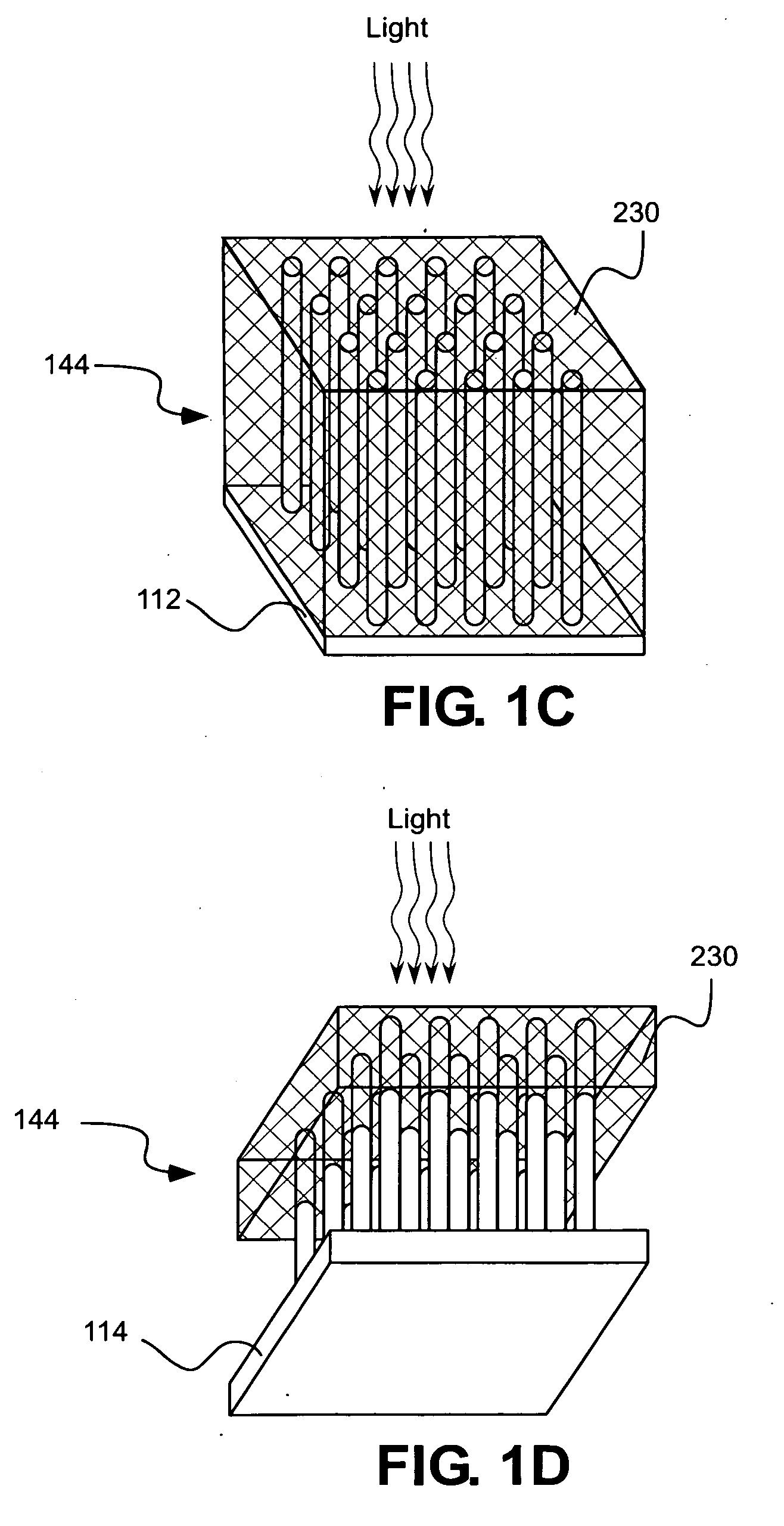

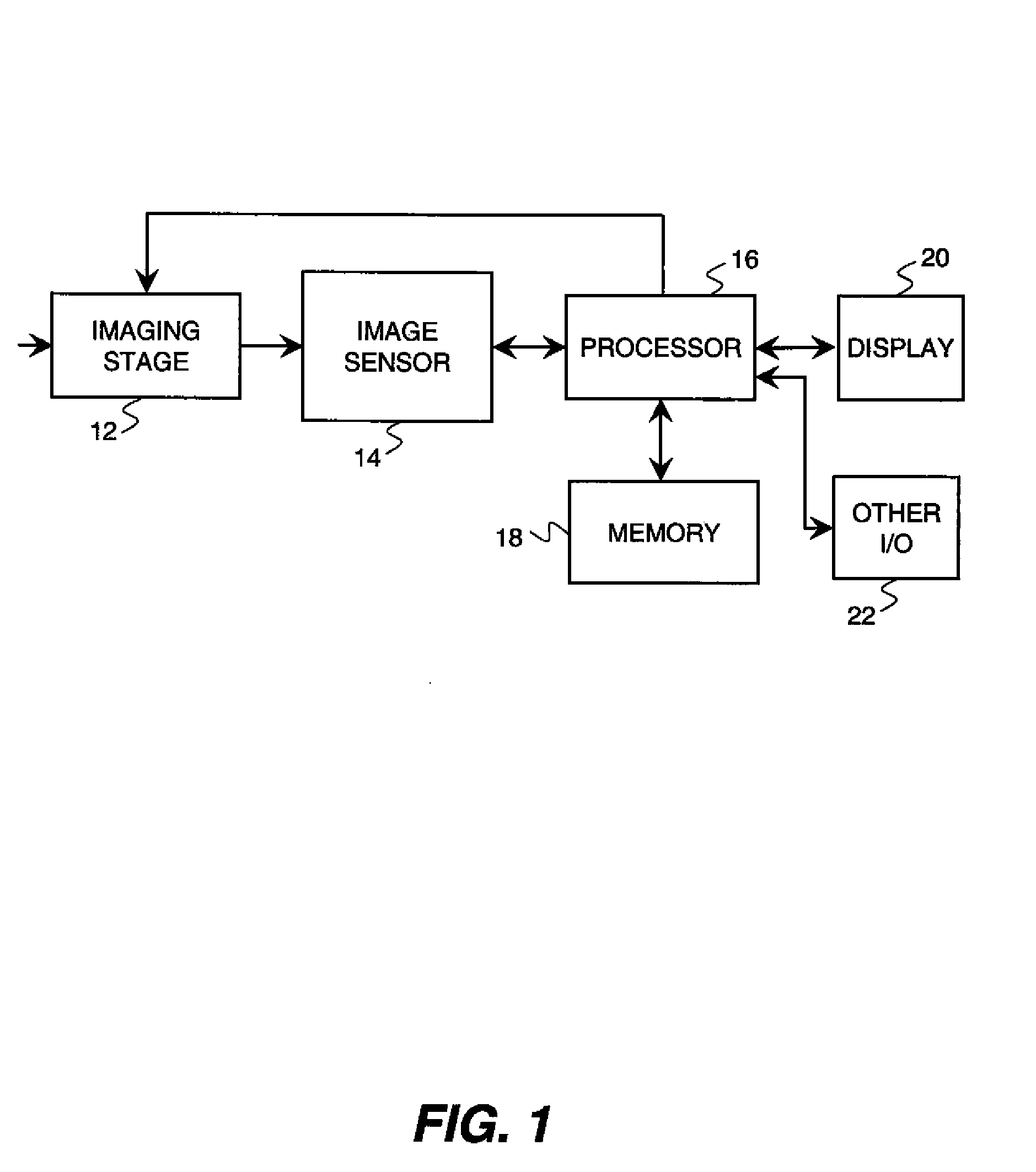

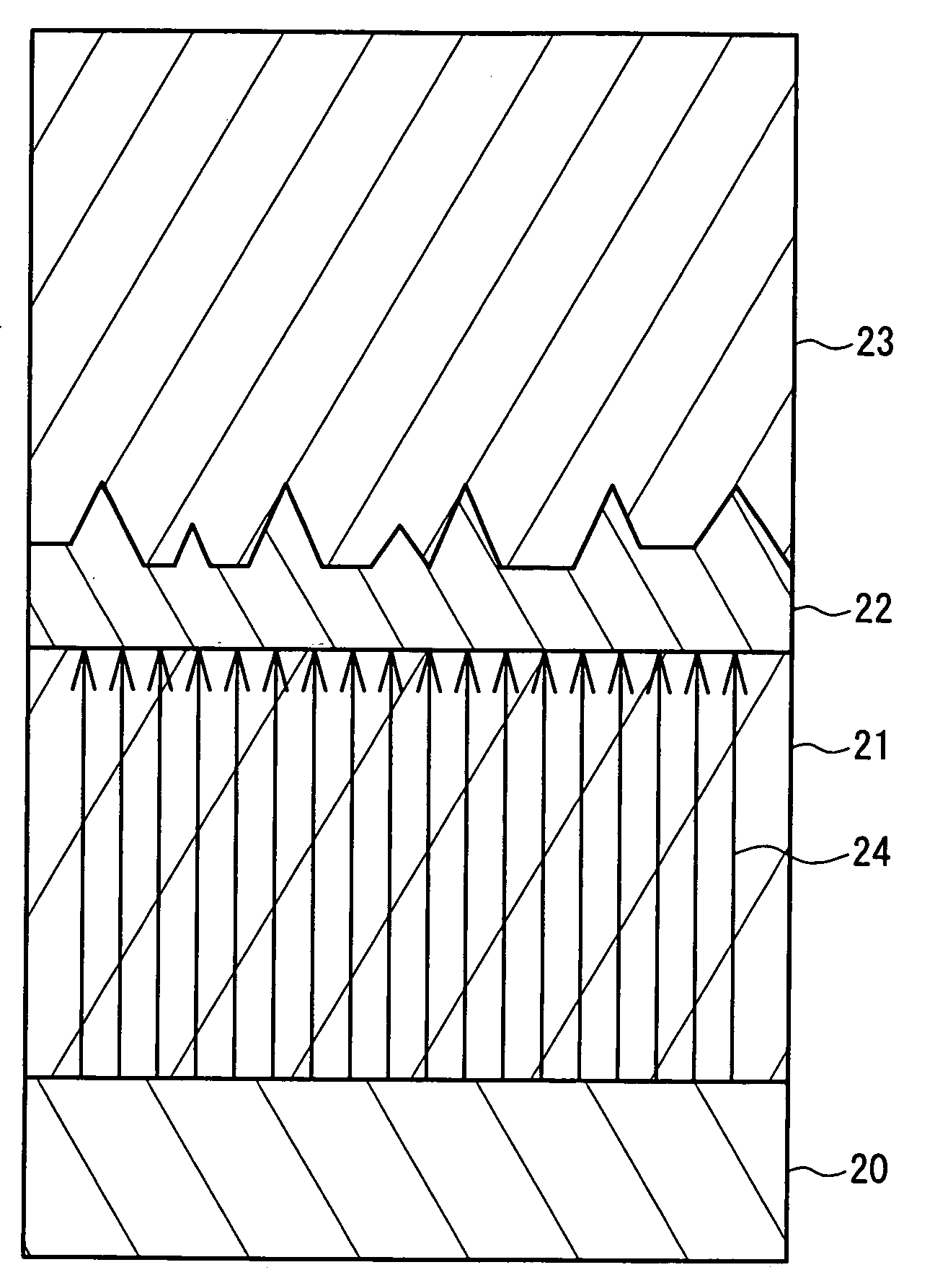

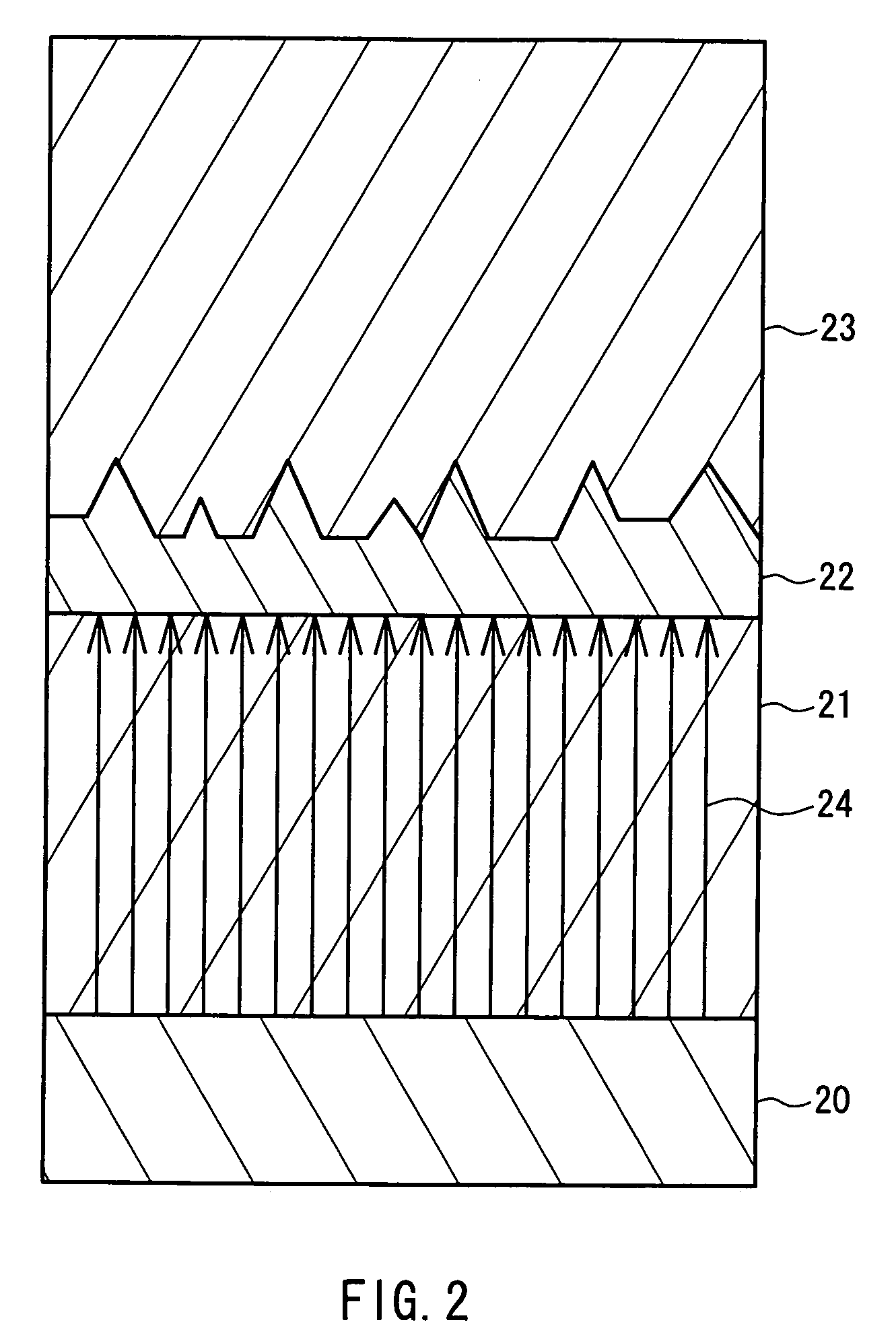

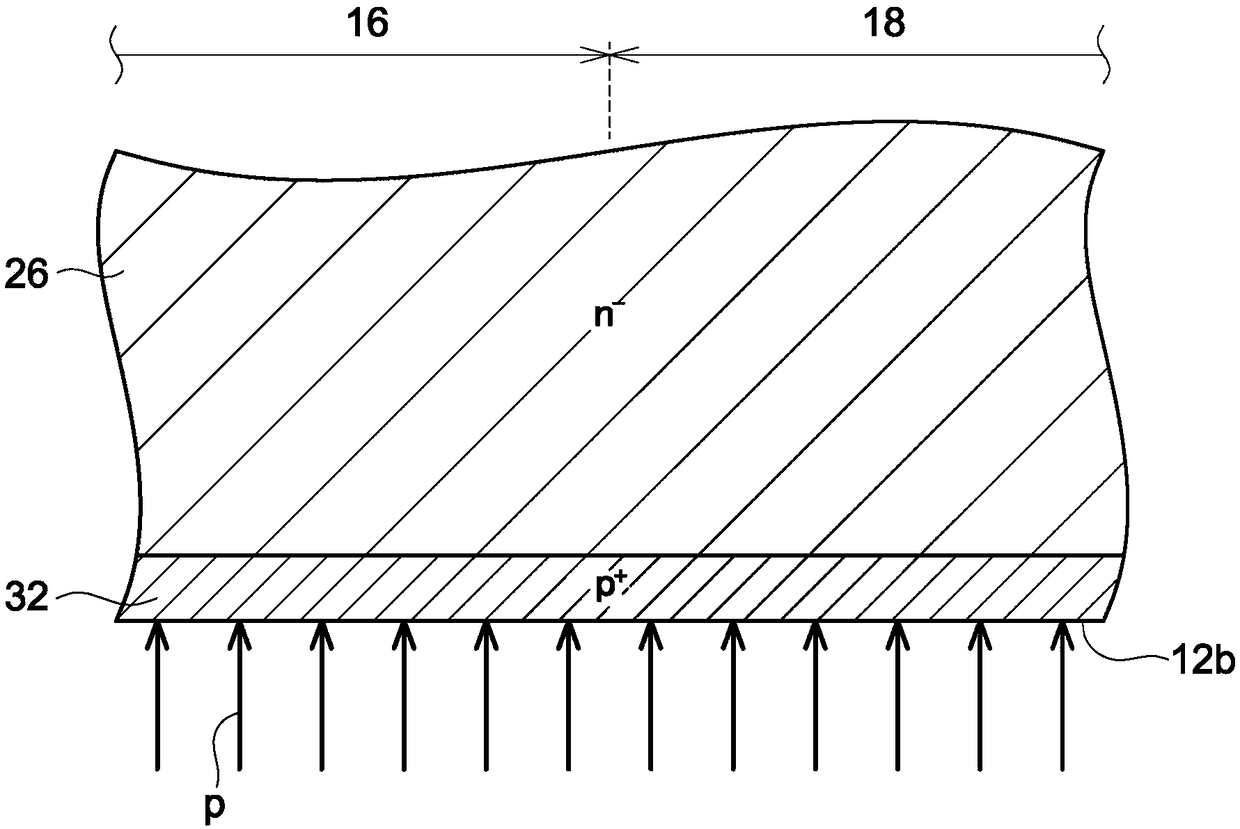

Image sensor with reduced red light crosstalk

InactiveUS20100026824A1Improve performanceReduce red light crosstalkTelevision system detailsSolid-state devicesPixel arrayRed light

An image sensor having a pixel array includes a sensor layer comprising a plurality of photosensitive elements of the pixel array, a circuit layer comprising circuitry associated with the pixel array, and a crosstalk reduction layer arranged between the sensor layer and the circuit layer and configured to reduce crosstalk between adjacent ones of the photosensitive elements. The crosstalk reduction layer may comprise, for example, an amorphous silicon germanium (a-SiGe) layer specifically configured to reduce red light crosstalk in the image sensor. The image sensor may be implemented in a digital camera or other type of digital imaging device.

Owner:EASTMAN KODAK CO

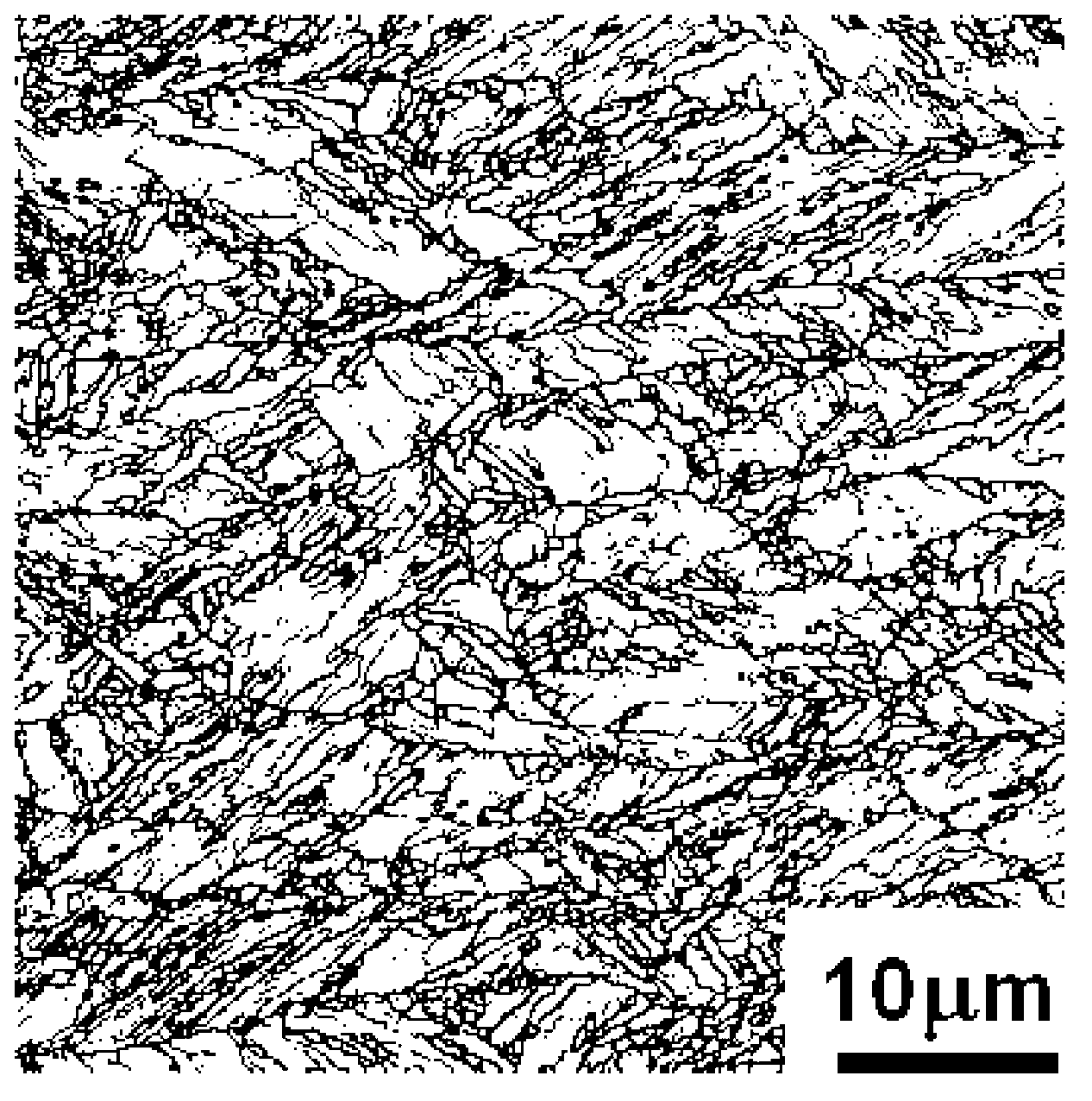

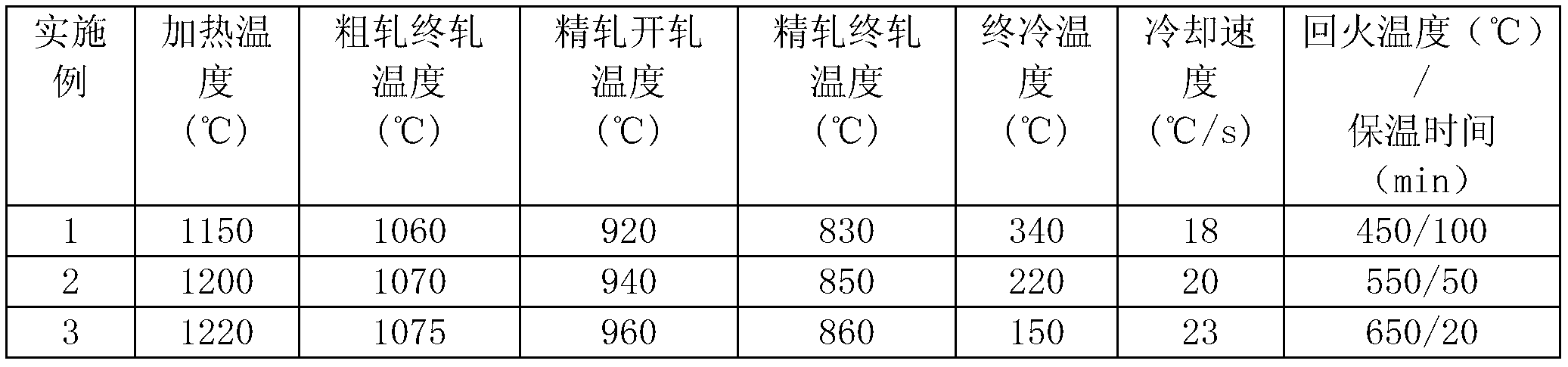

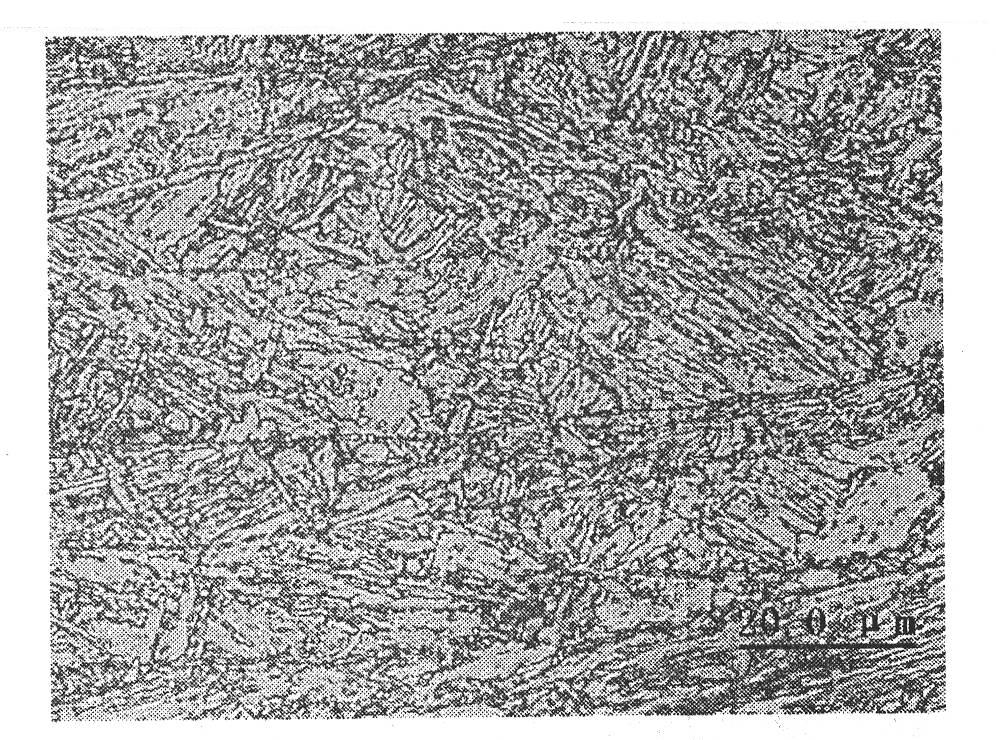

Ultrahigh-strength steel plate steel plate with yield strength of 960MPa-level, and manufacturing method thereof

The invention relates to an ultrahigh-strength steel plate steel plate with yield strength of 960MPa-level, and a manufacturing method thereof. The steel plate comprises the chemical components of: 0.06-0.11% of C, 0.10-0.50% of Si, 1.20-1.60% of Mn, less than 0.015% of P, less than 0.005% of S, 0.20-0.50% of Cr, 0.10-0.30% of Ni, 0.10-0.30% of Mo, 0.02-0.05% of Nb, 0.02-0 .06% of V, 0.008-0.03% of Ti, 0.0005-0.003% of B, 0.02-0.05% of Al, and balance of Fe. According to the invention, through two-stage controlled rolling, and direct quenching and tempering, a refined tempered martensite or lower bainite structure is obtained. Defects such as long process, high energy consumption, large alloy addition amount, and the like of traditional quenching and tempering process are overcome. The obtained steel plate has good toughness and cold bending performance.

Owner:NANJING IRON & STEEL CO LTD +1

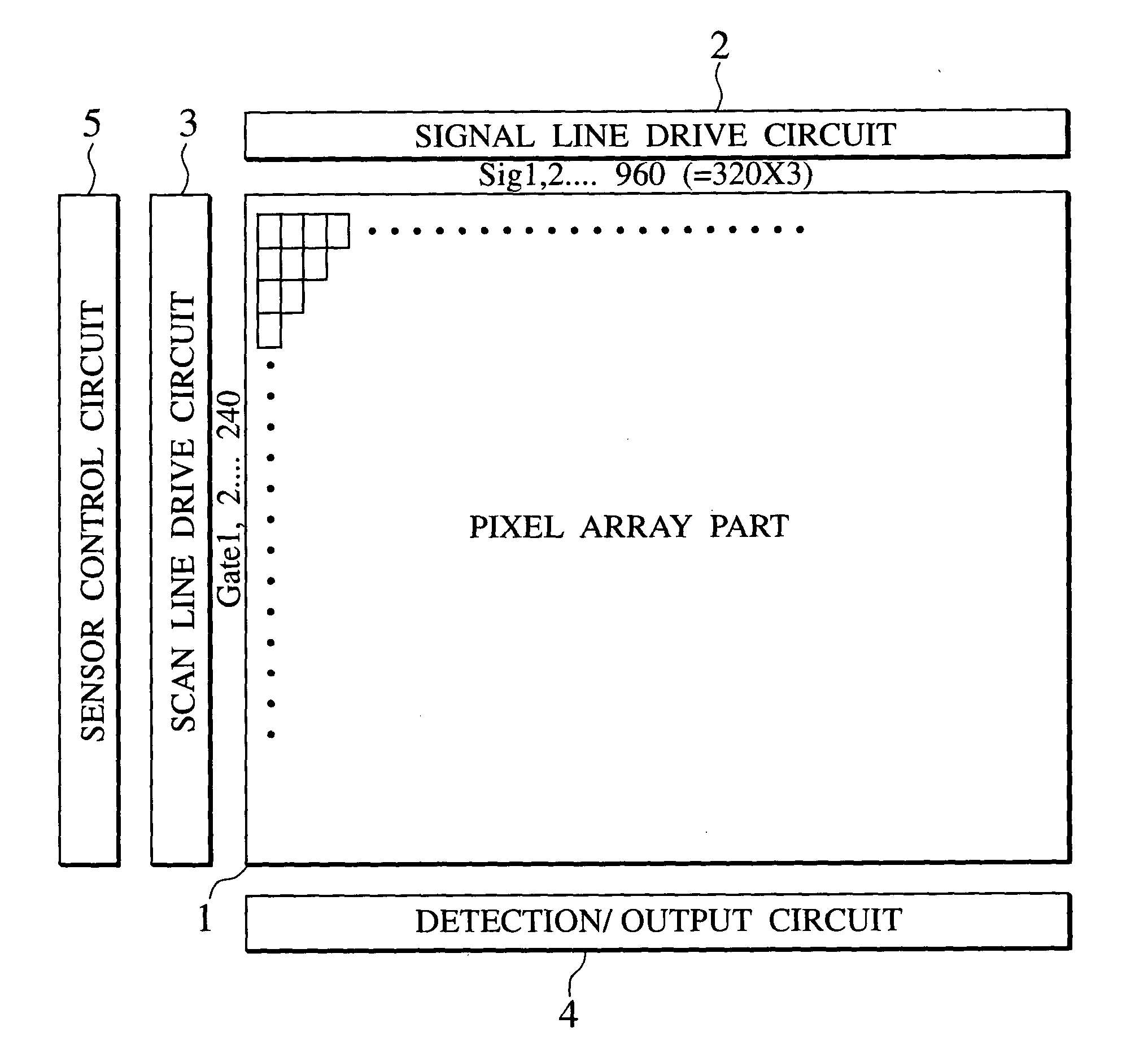

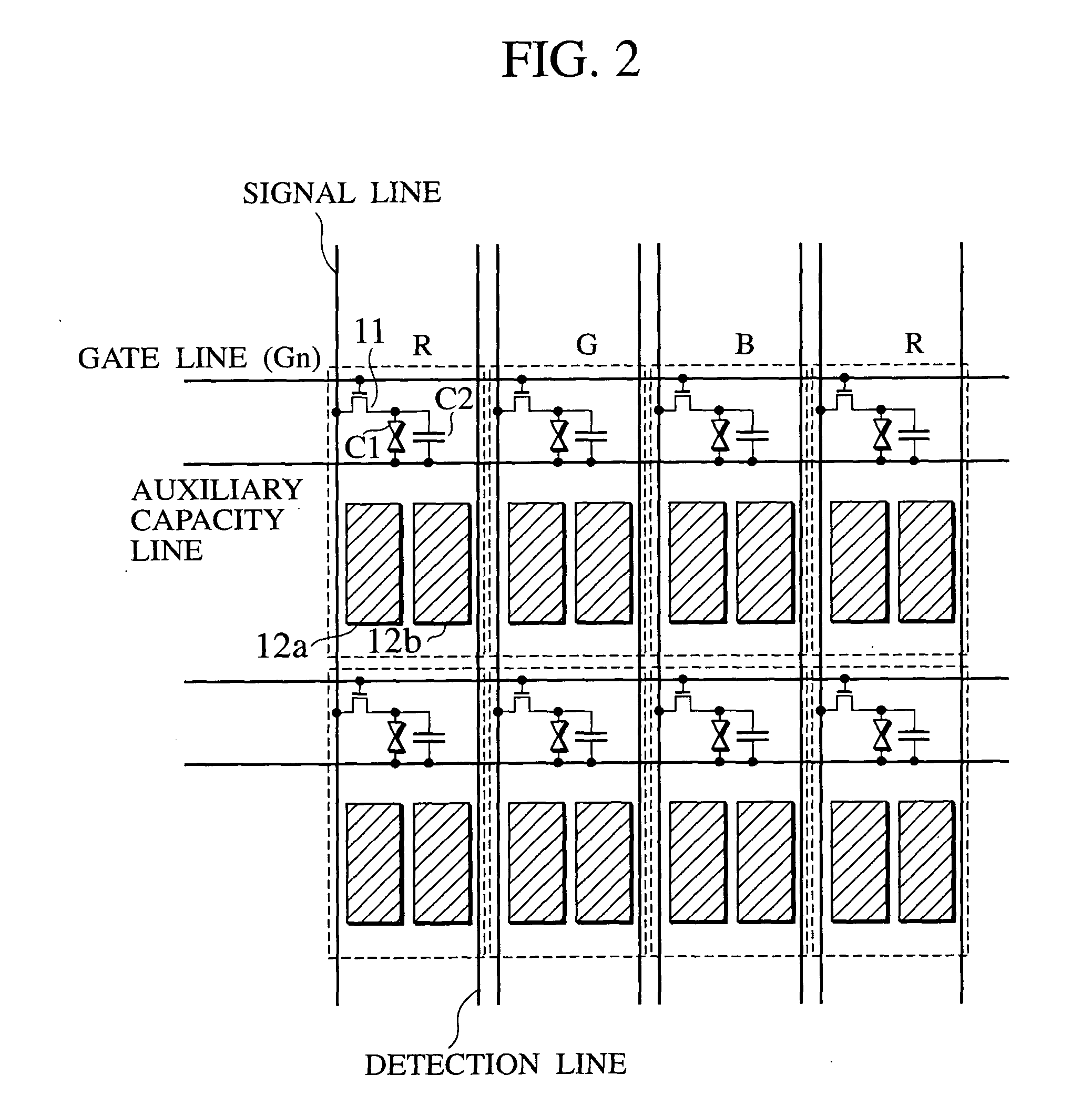

Suppression of leakage current in image acquisition

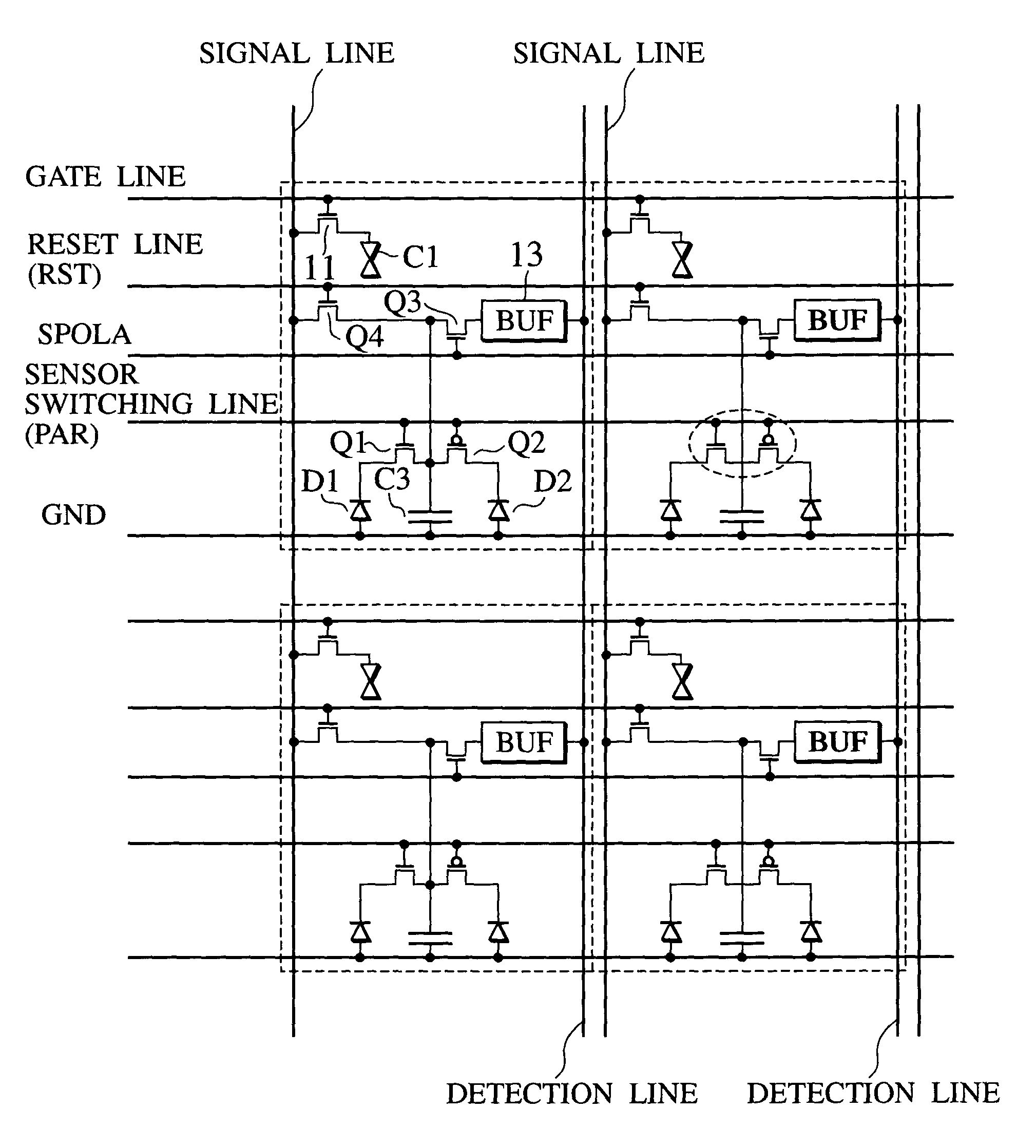

ActiveUS20040043676A1Current can be suppressedHigh sensitivityTransistorElectrically conductive connectionsDisplay deviceDangling bond

In a manufacturing process of a display device, hydrogenation in an I layer of photodiodes D1 and D2 is progressed less than that in a channel portion of a pixel TFT, and a defect density due to dangling bonds not terminated in the I layer of the photodiodes D1 and D2 is made higher than a defect density in the channel portion of the pixel TFT. Thus, while suppressing a leakage current of the pixel TFT, the sensitivity of the photodiodes D1 and D2 to light is improved. Moreover, a gate electrode is provided above an i region of a pin-type optical sensor diode with an insulating film interposed therebetween. Thus, a gate voltage can control a threshold of a bias voltage when a current starts to flow into the optical sensor diode and a leakage current is prevented from flowing into the optical sensor diode.

Owner:JAPAN DISPLAY CENT INC

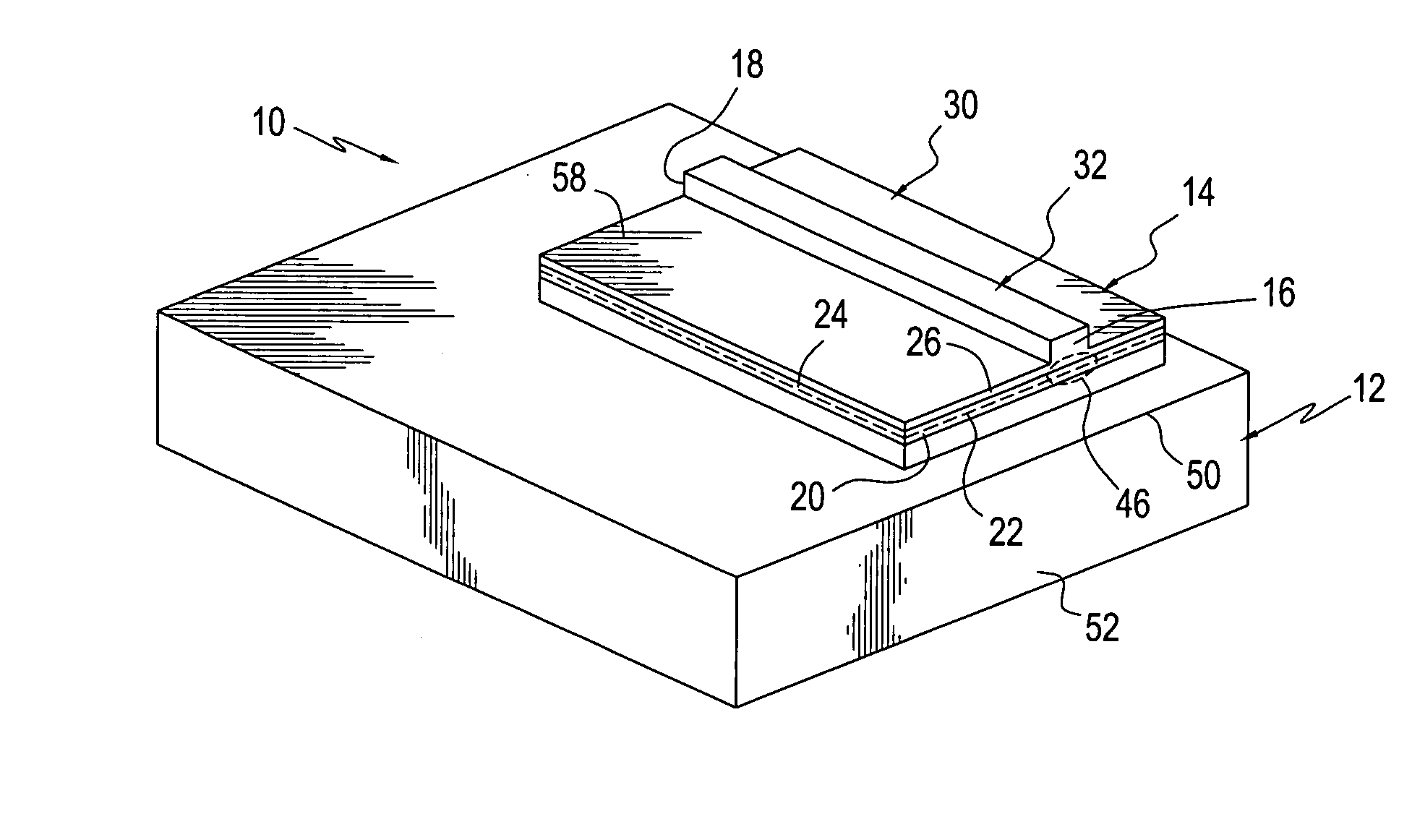

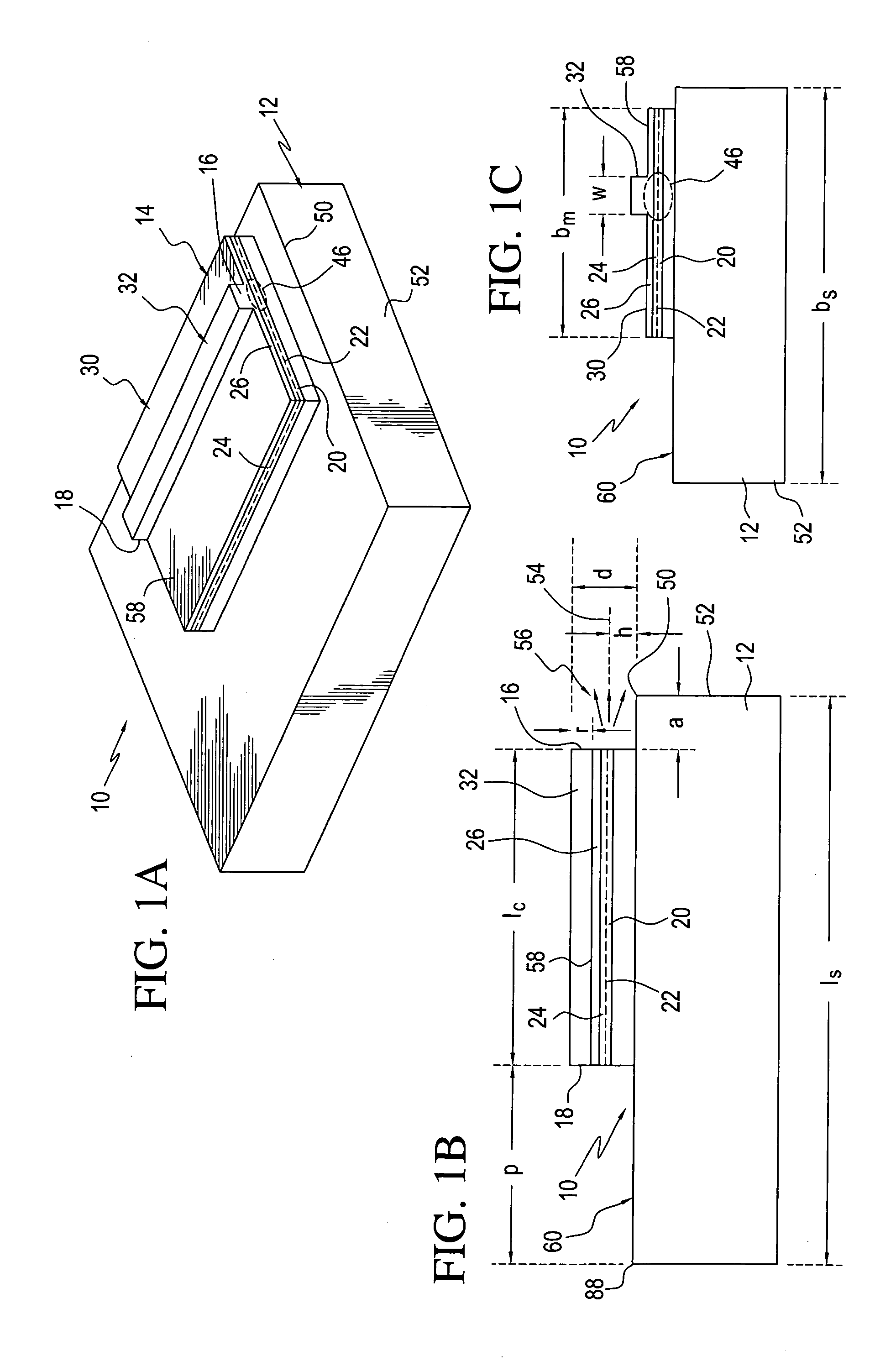

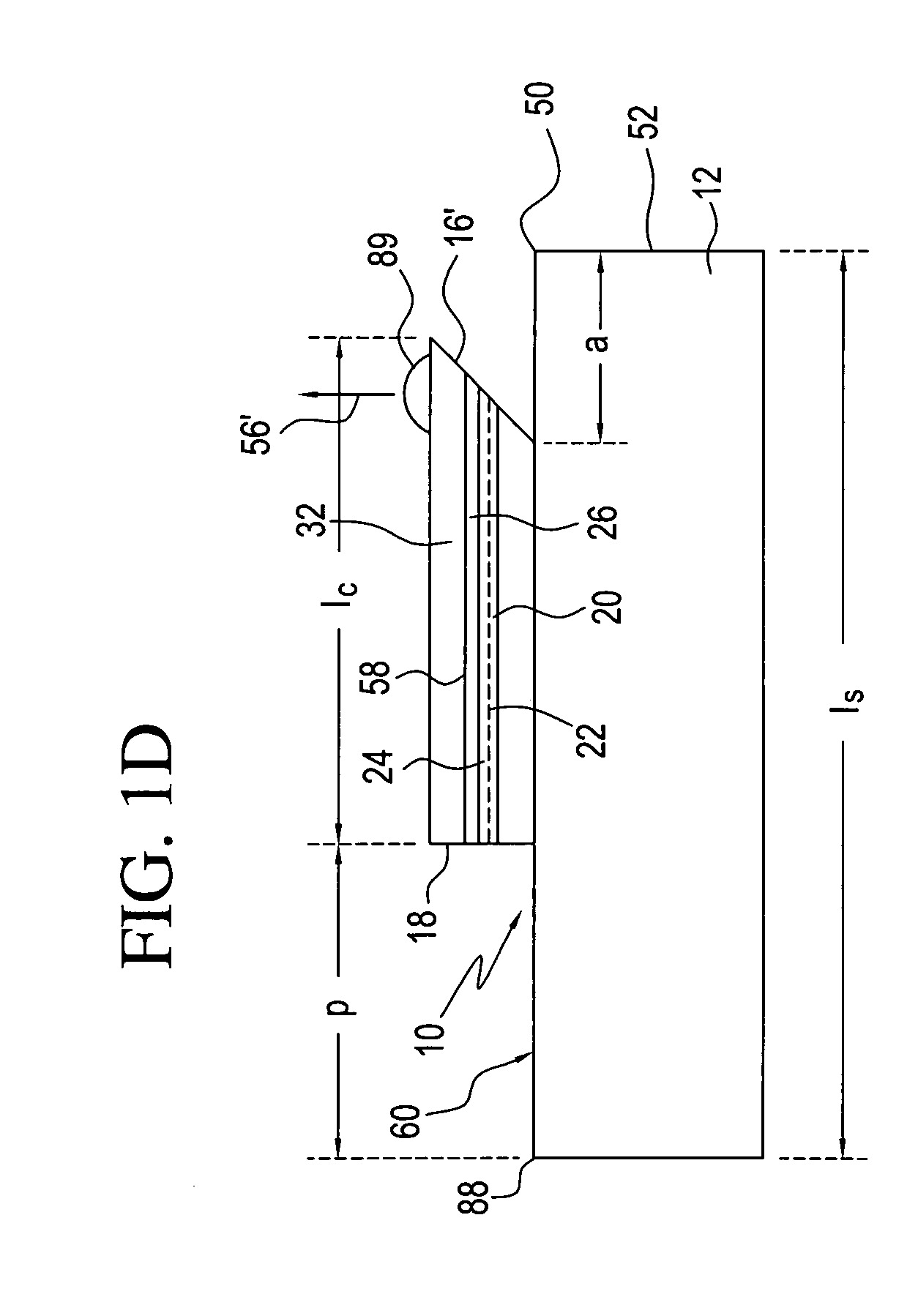

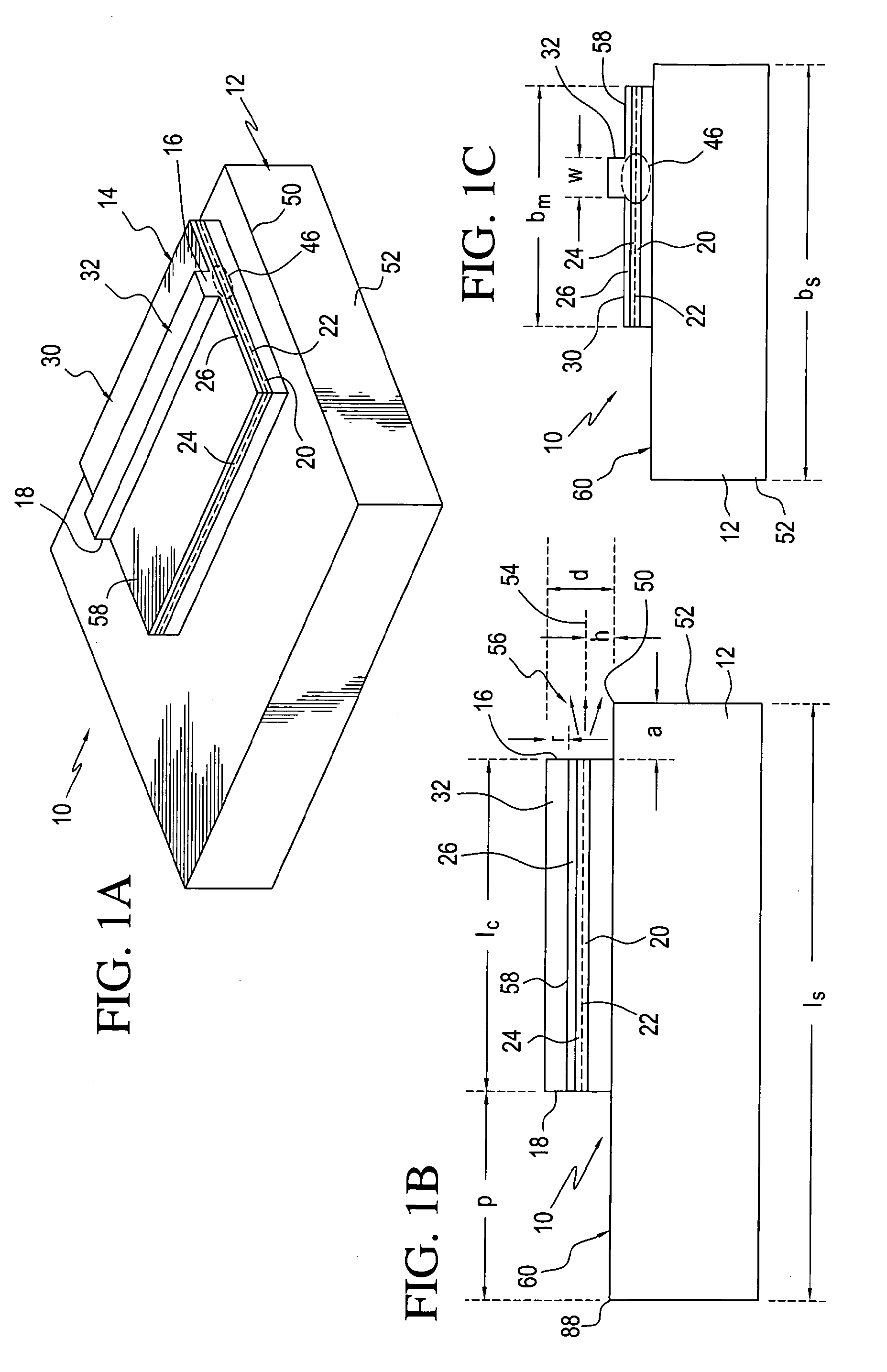

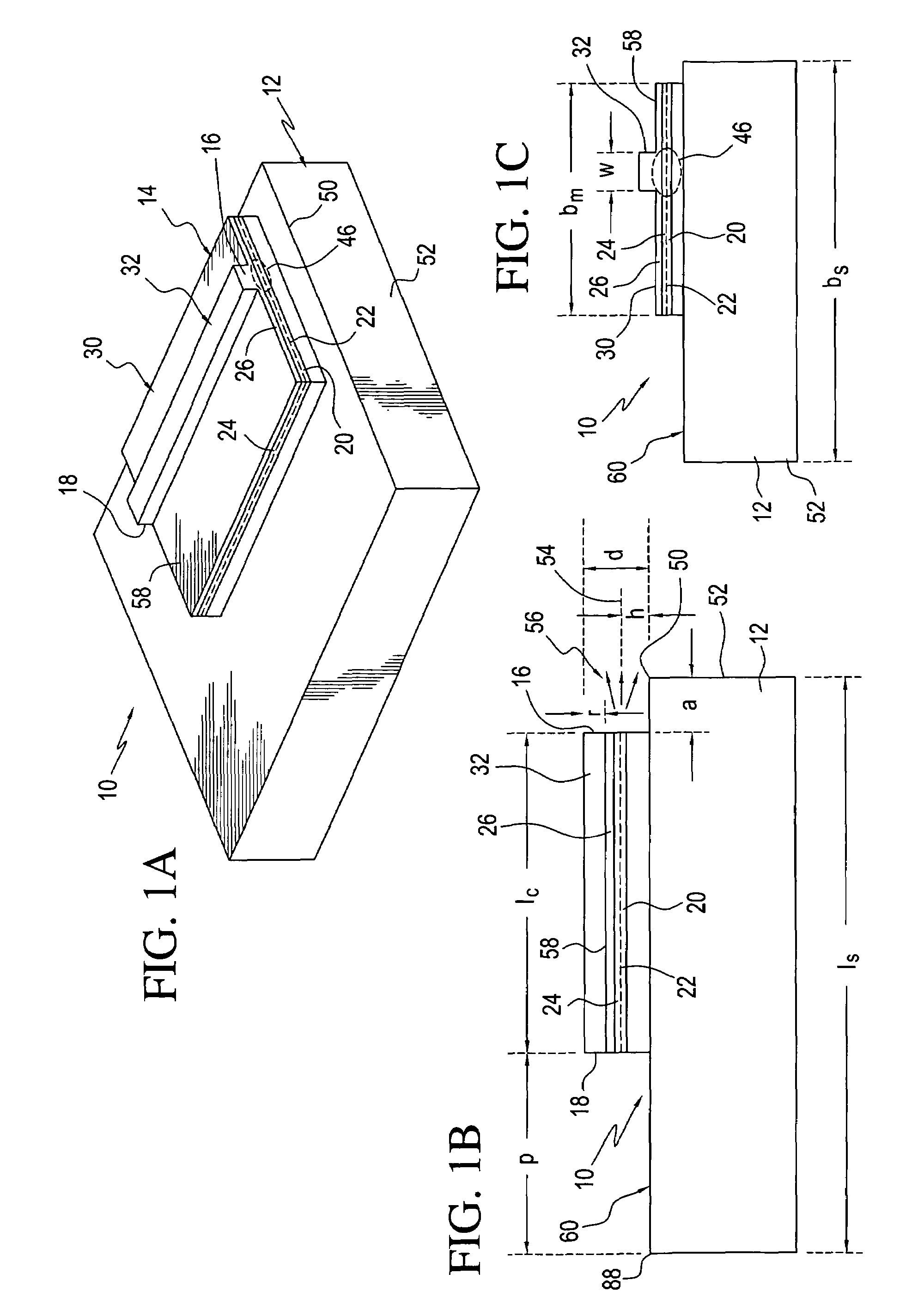

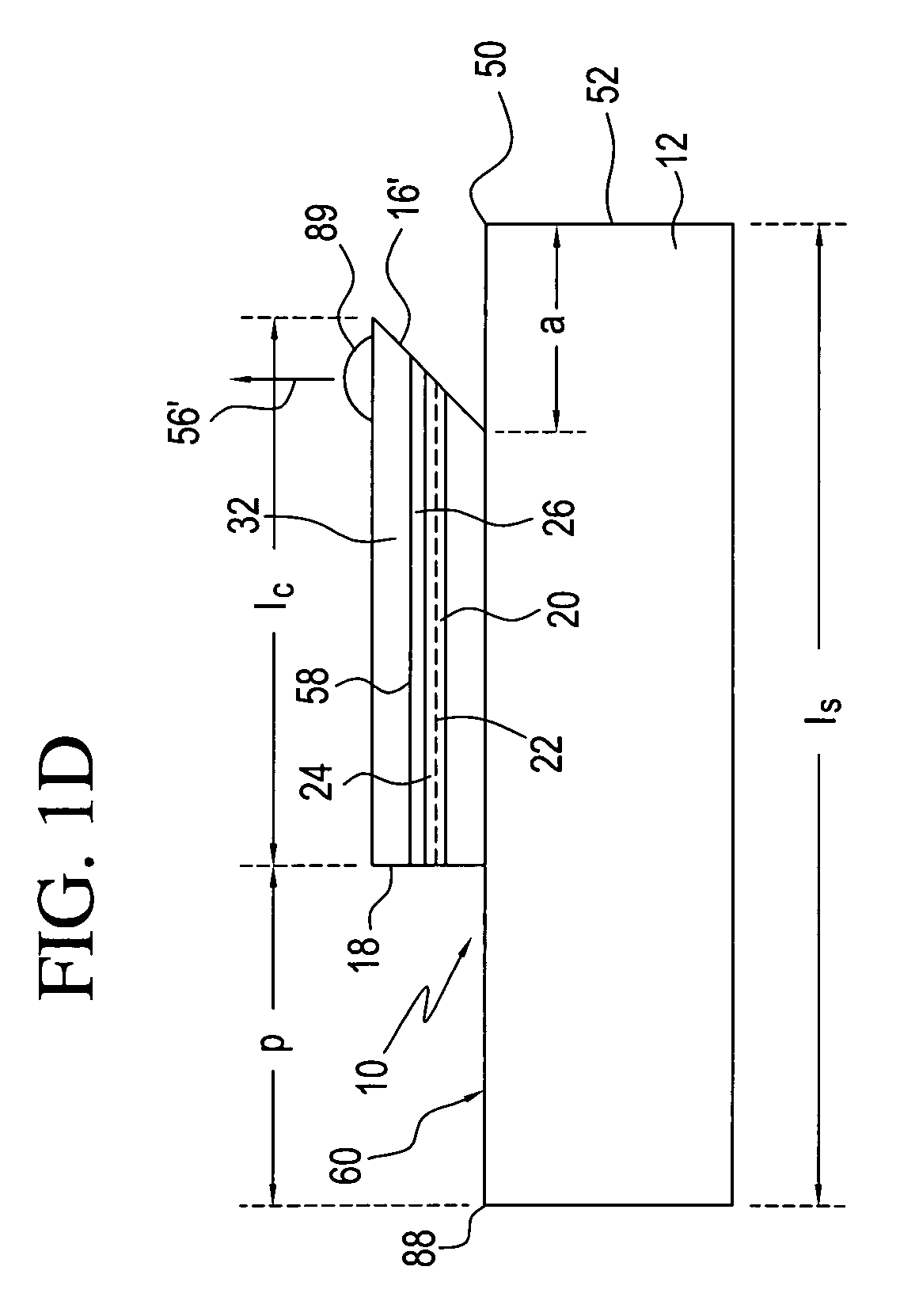

Low cost InGaAIN based lasers

ActiveUS20070045637A1Reduce obstaclesHigh strengthOptical wave guidanceLaser detailsSemiconductor chipContact layer

A method and structure for producing lasers having good optical wavefront characteristics, such as are needed for optical storage includes providing a laser wherein an output beam emerging from the laser front facet is essentially unobstructed by the edges of the semiconductor chip in order to prevent detrimental beam distortions. The semiconductor laser structure is epitaxially grown on a substrate with at least a lower cladding layer, an active layer, an upper cladding layer, and a contact layer. Dry etching through a lithographically defined mask produces a laser mesa of length lc and width bm. Another sequence of lithography and etching is used to form a ridge structure with width w on top of the mesa. The etching step also forming mirrors, or facets, on the ends of the laser waveguide structures. The length ls and width bs of the chip can be selected as convenient values equal to or longer than the waveguide length lc and mesa width bm, respectively. The waveguide length and width are selected so that for a given defect density D, the yield YD is larger than 50%.

Owner:MACOM TECH SOLUTIONS HLDG INC

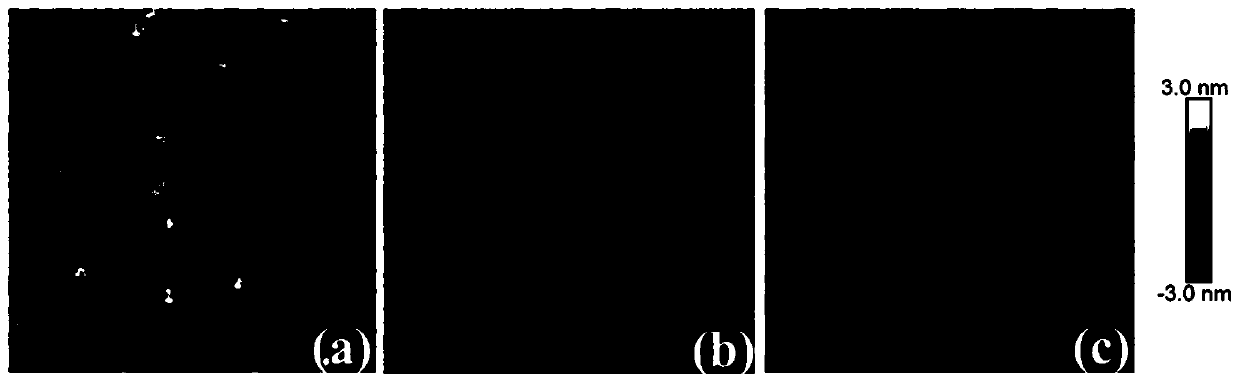

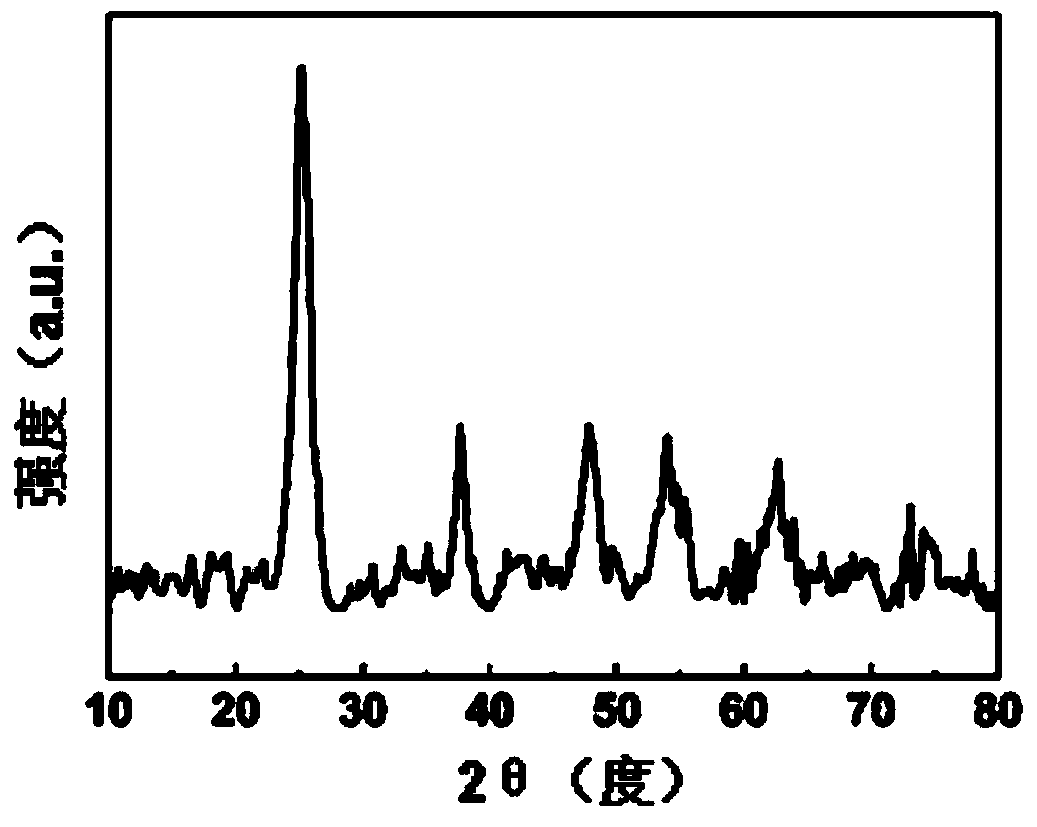

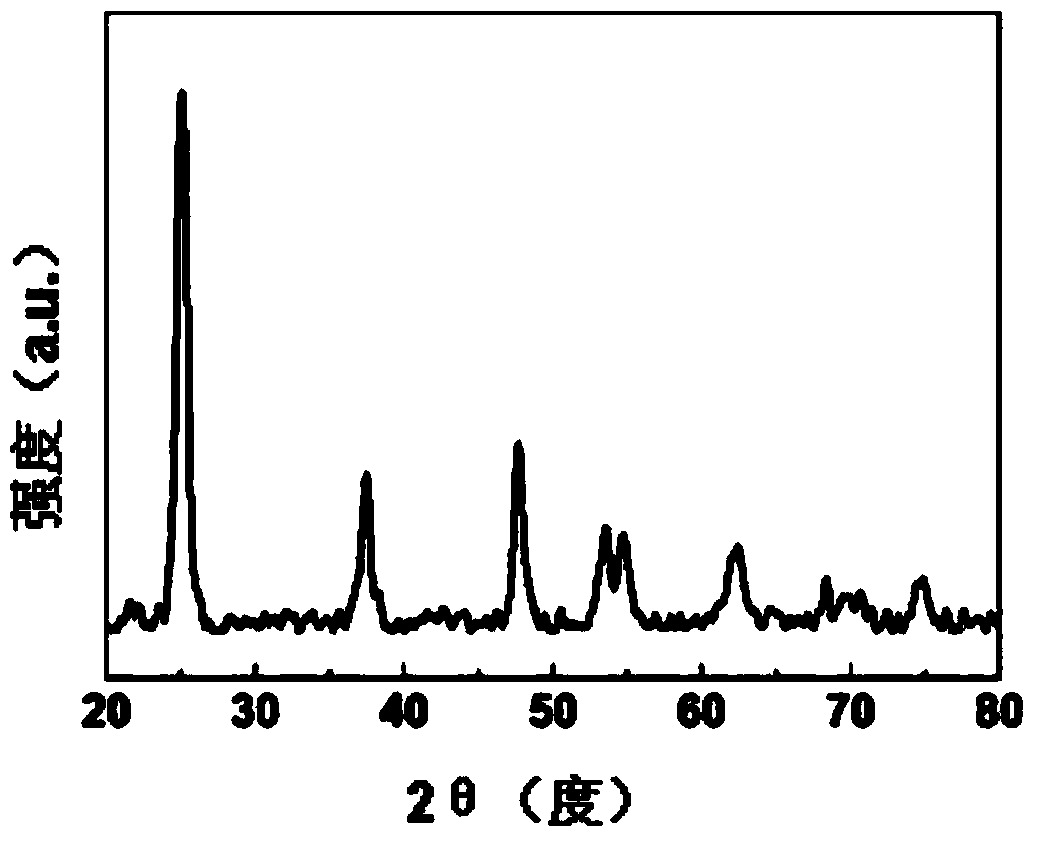

Growth of GaAs epitaixial layers on Si substrate by using a novel GeSi buffer layer

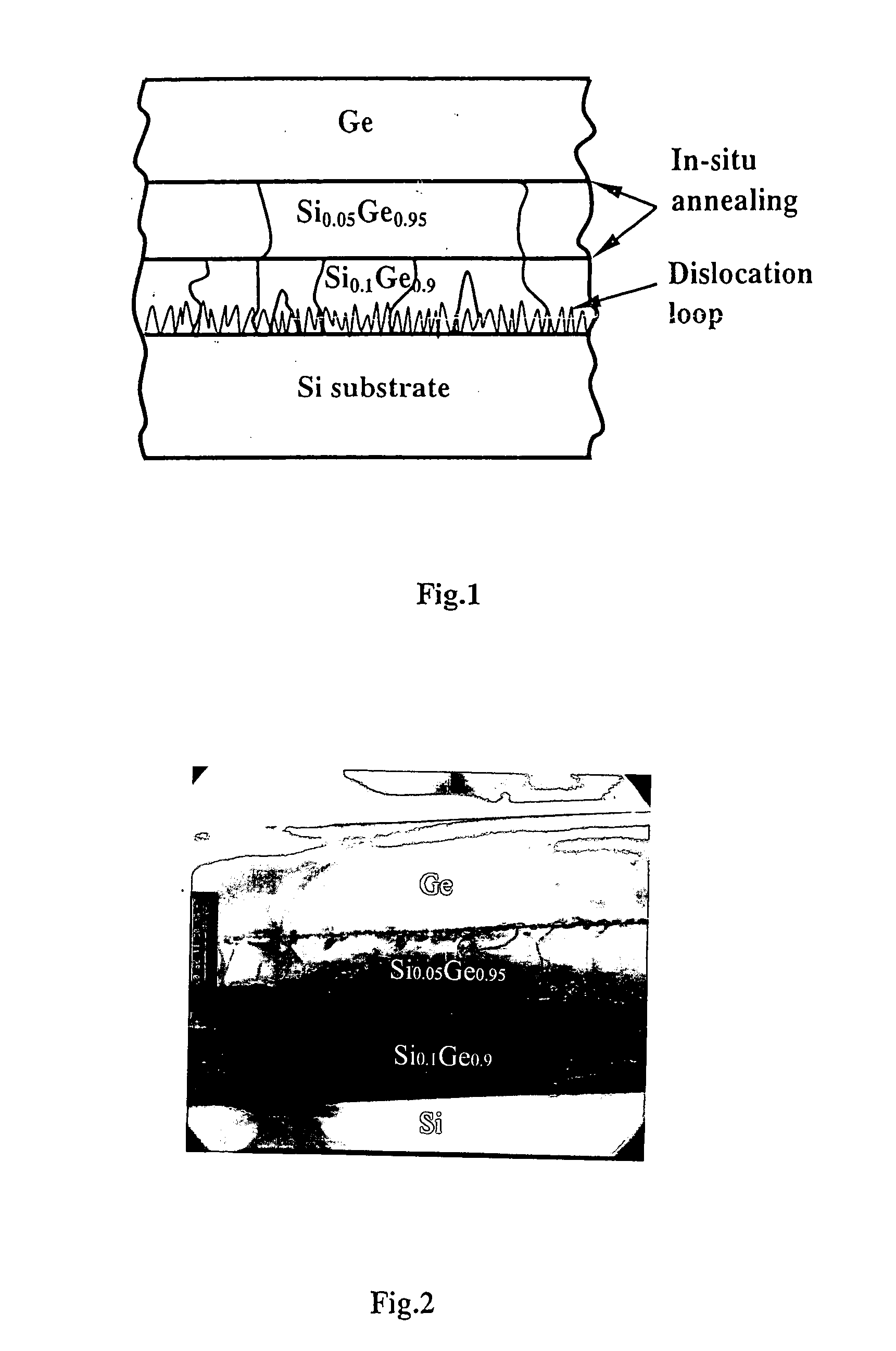

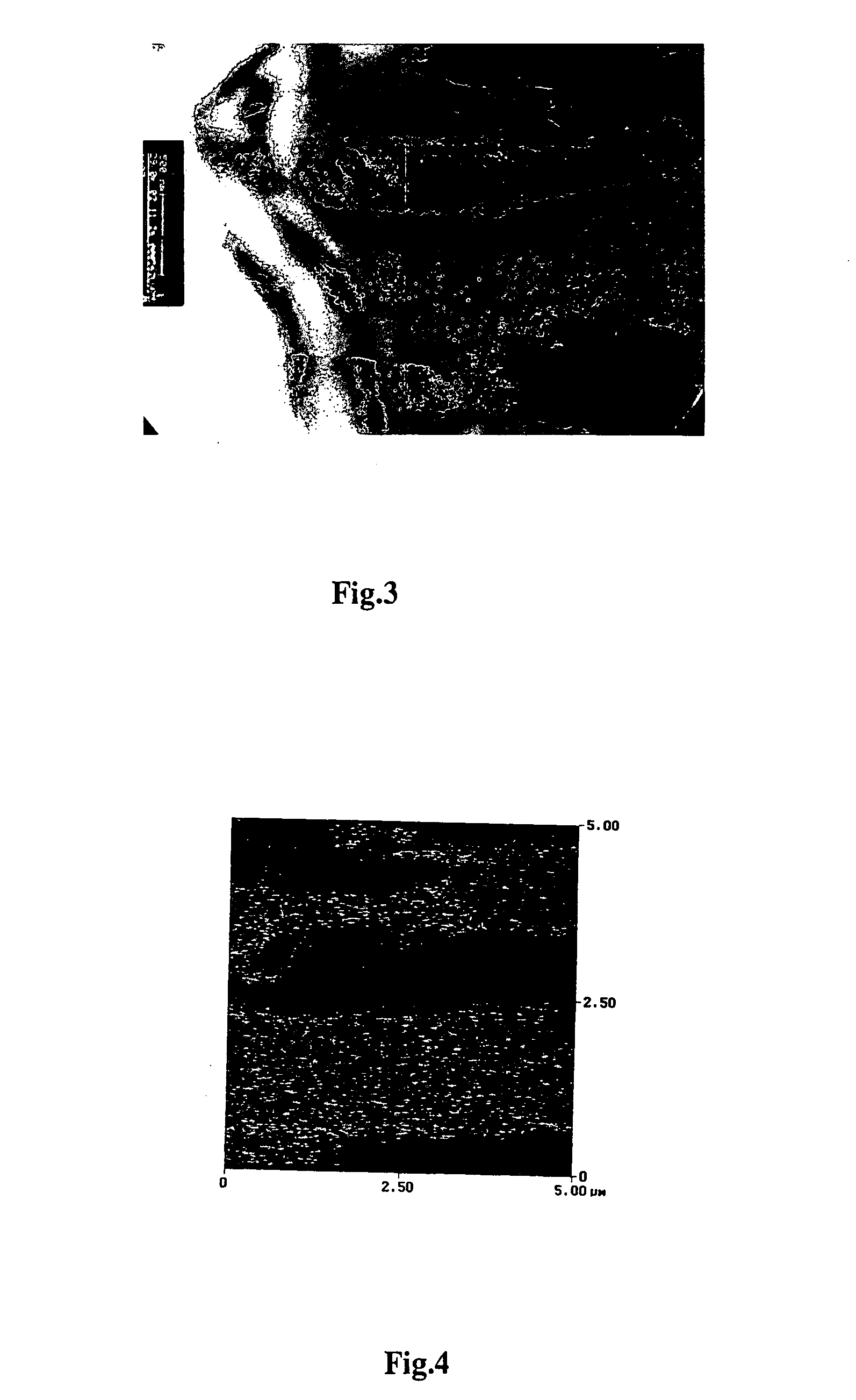

InactiveUS20050023552A1Reduce thicknessFlatten surface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesUltra-high vacuumGas phase

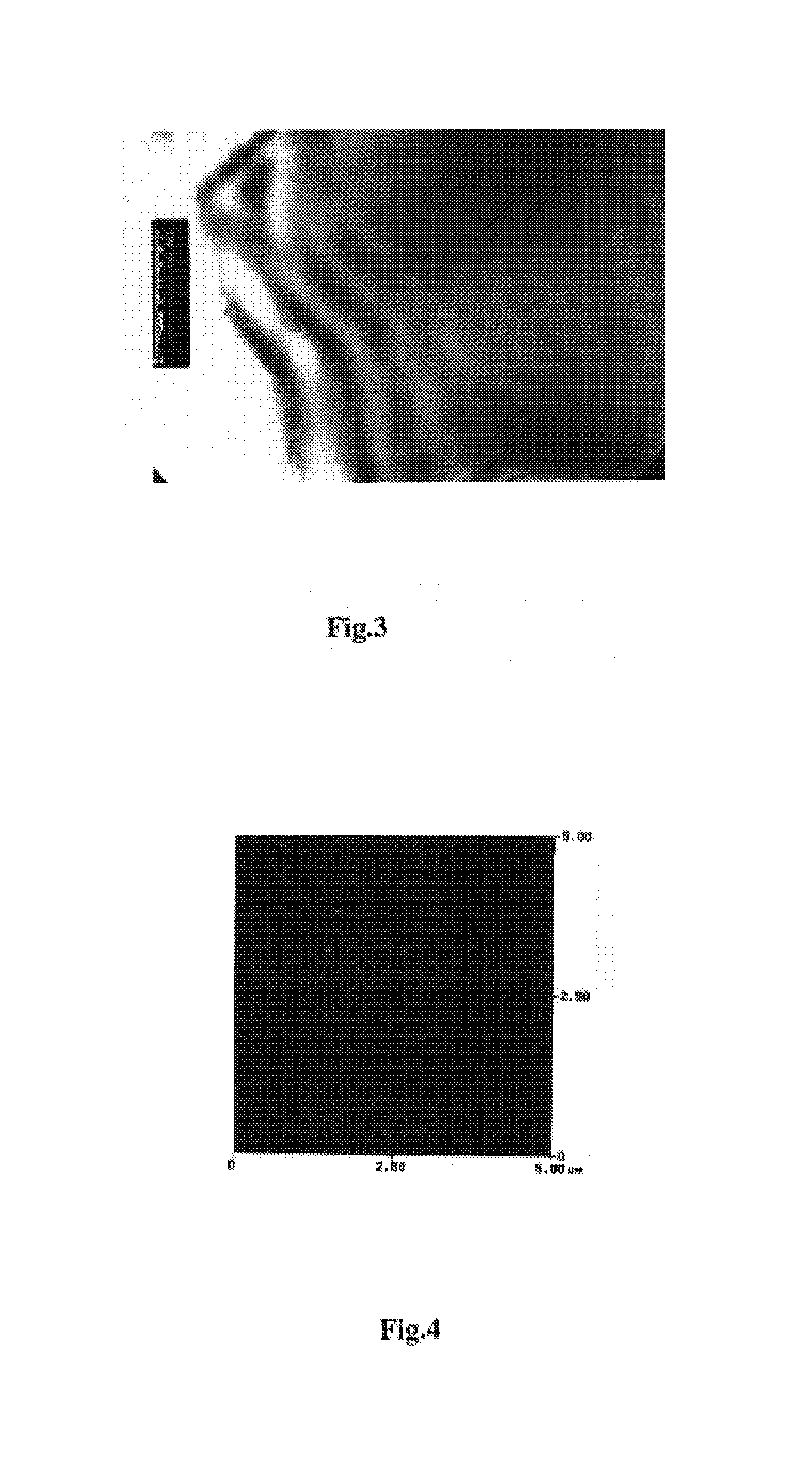

This invention provides a process for growing Ge epitaixial layers on Si substrate by using ultra-high vacuum chemical vapor deposition (UHVCVD), and subsequently growing a GaAs layer on Ge film of the surface of said Ge epitaixial layers by using metal organic chemical vapor deposition (MOCVD). The process comprises steps of, firstly, pre-cleaning a silicon wafer in a standard cleaning procedure, dipping it with HF solution and prebaking to remove its native oxide layer. Then, growing a high Ge-composition epitaixial layer, such as Si0.1Ge0.9 in a thickness of 0.8 μm on said Si substrate by using ultra-high vacuum chemical vapor deposition under certain conditions. Thus, many dislocations are generated and located near the interface and in the low of part of Si0.1Ge0.9 due to the large mismatch between this layer and Si substrate. Furthermore, a subsequent 0.8 μm Si0.05Ge0.95 layer, and / or optionally a further 0.8 μm Si0.02Ge0.98 layer, are grown. They form strained interfaces of said layers can bend and terminate the propagated upward dislocation very effectively. Therefore, a film of pure Ge is grown on the surface of said epitaixial layers. Finally, a GaAs epitaixial layer is grown on said Ge film by using MOCVD.

Owner:NAT CHIAO TUNG UNIV

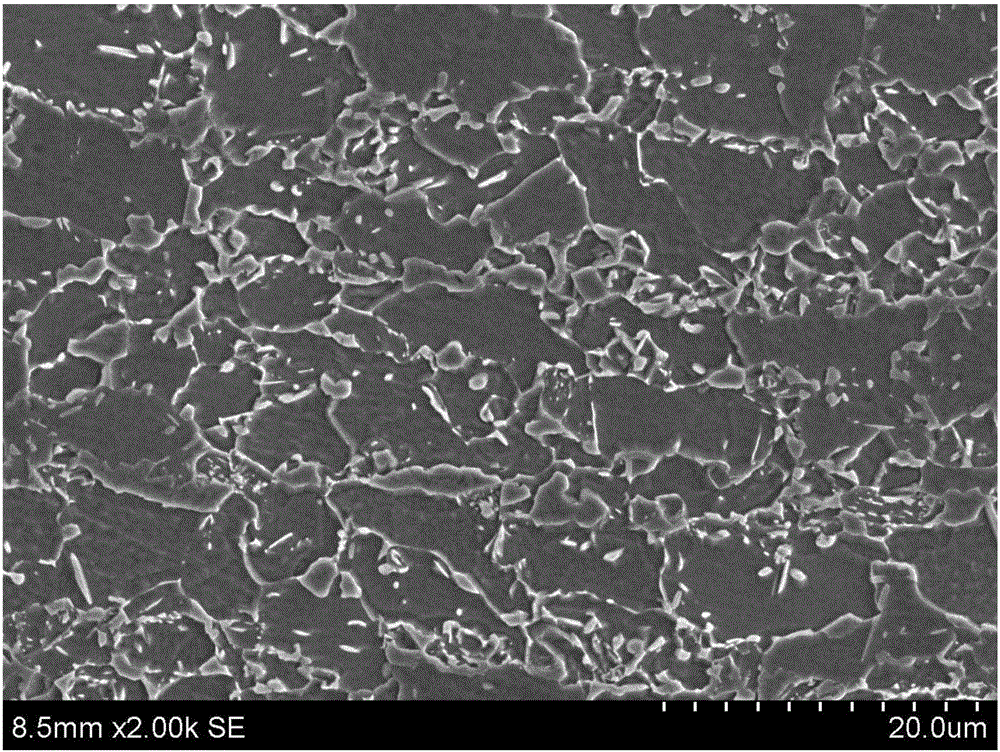

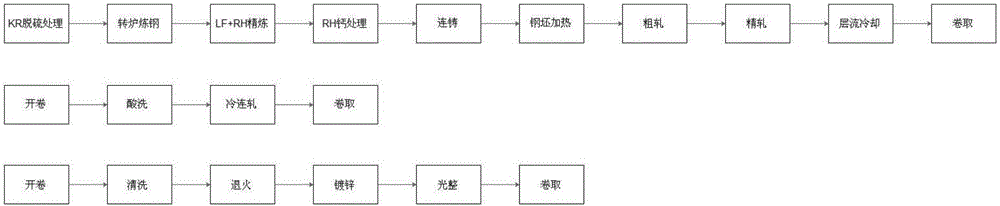

Zinc-plated double-phase steel and production method thereof

The invention belongs to the technical field of cold rolled steel and discloses zinc-plated double-phase steel and a production method of the zinc-plated double-phase steel. The zinc-plated double-phase steel comprises, by weight percentage, 0.085%-0.115% of C, 0.15%-0.24% of Si, 1.45%-1.55% of Mn, not larger than 0.015% of P, not larger than 0.005% of S, 0.025%-0.065% of Alt, 0.14%-0.24% of Cr, 0.24%-0.29% of Mo, not larger than 0.006% of N and the balance Fe and other inevitable impurities. The production method includes the steps of KR desulfuration, converter steelmaking, LF+RH refining treatment, RH calcium treatment, continuous steel casing, billet heating, rough rolling, finish rolling, laminar cooling and winding; unwinding, acid pickling, cold continuous rolling and winding; and unwinding, cleaning, annealing, zinc plating, finishing and winding. Through composition design and process control, the zinc-plated double-phase steel is suitable for annealing production lines having the rapid cooling segment or not.

Owner:SHOUGANG CORPORATION

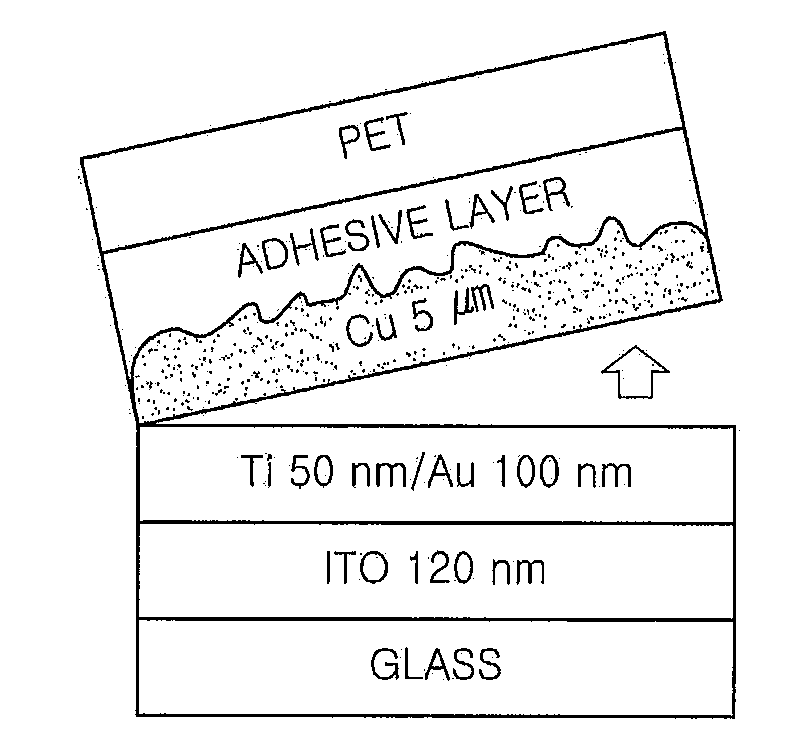

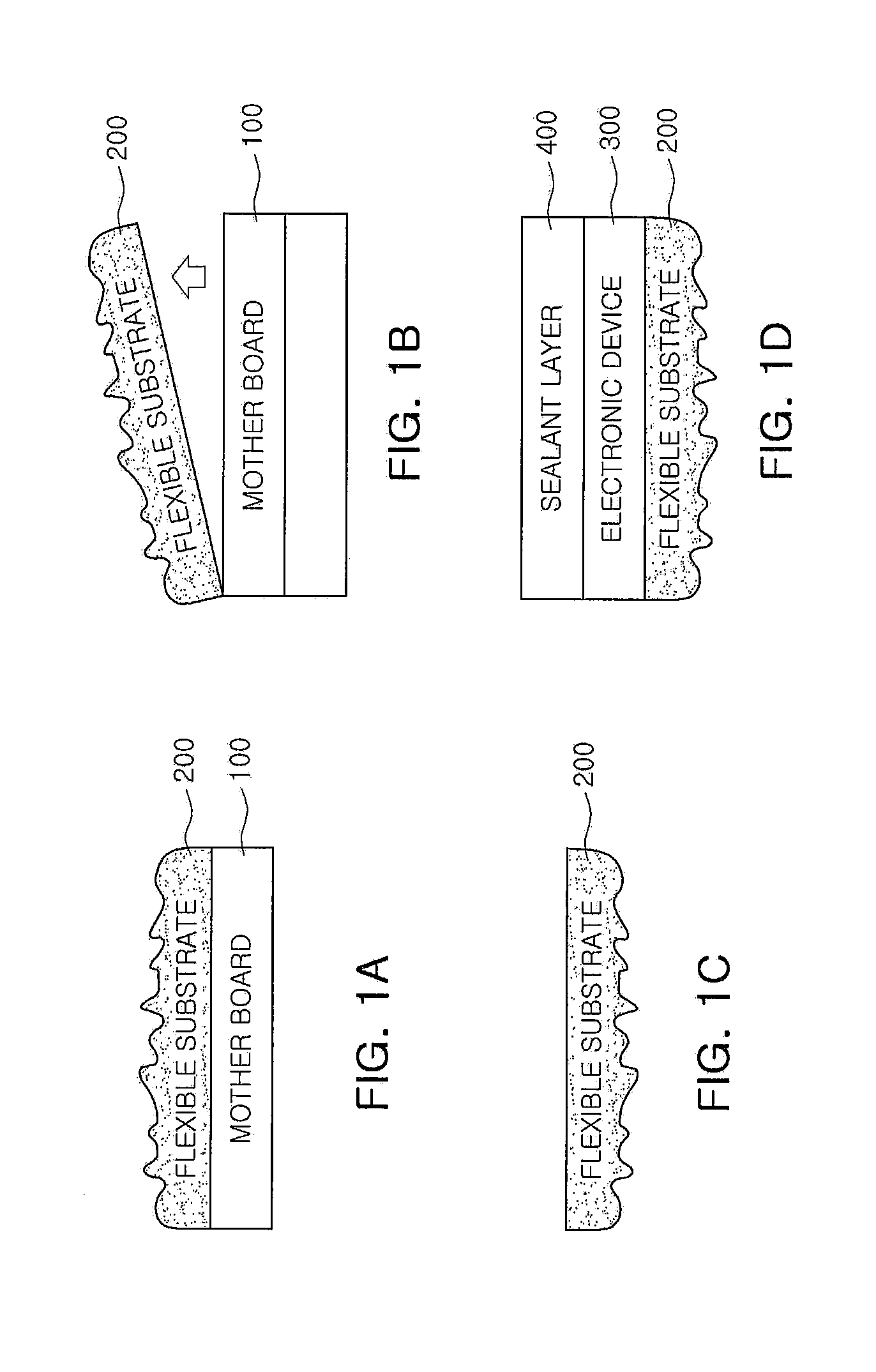

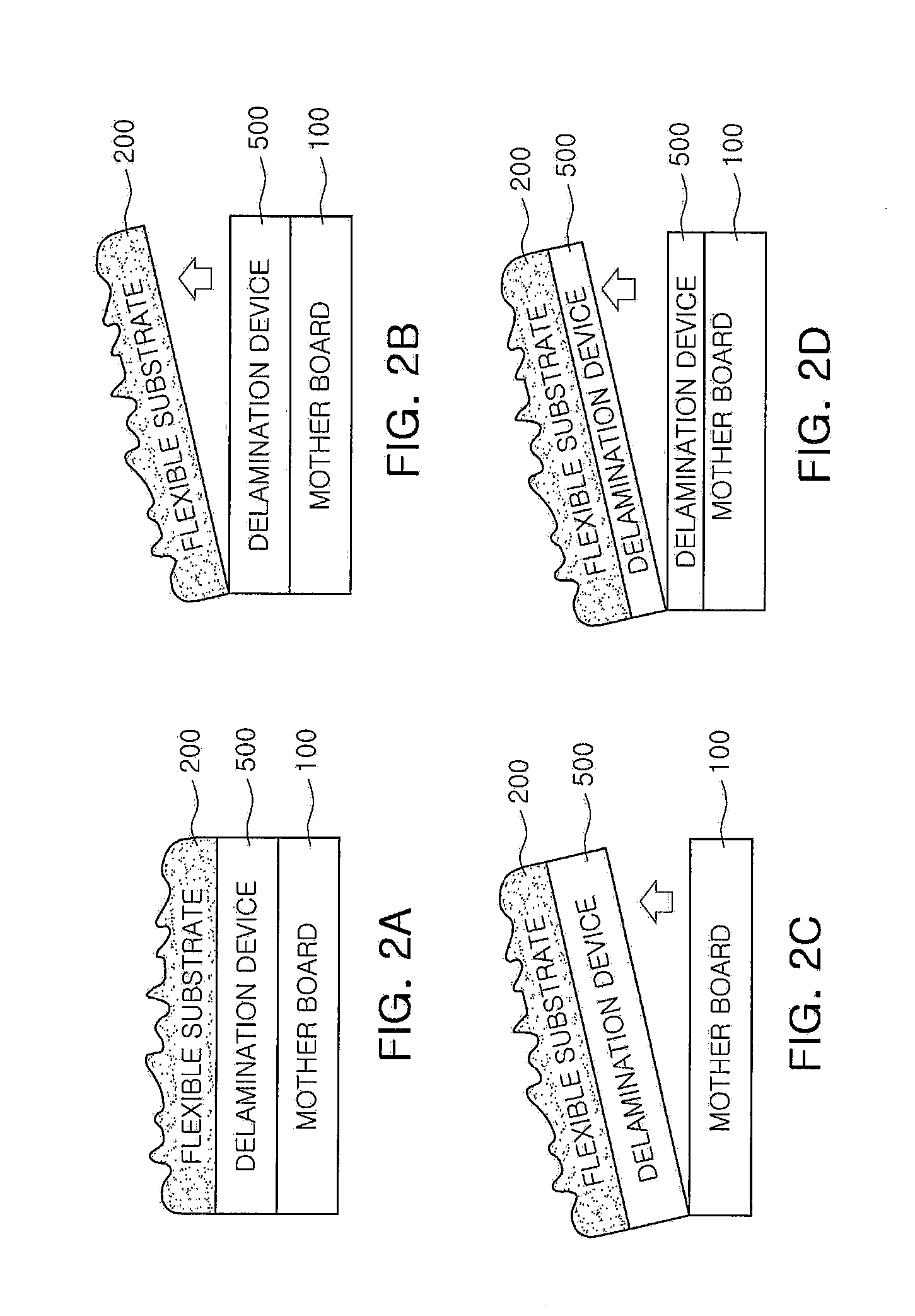

Flexible electronic device, method for manufacturing same, and a flexible substrate

InactiveUS20130105203A1Improve performanceLow costPrinted circuit assemblingCircuit bendability/stretchabilitySurface roughnessThermal expansion

The present invention relates to resolving issues concerning deterioration in the performance and yield of a flexible electronic device, caused by low manufacturing temperatures, high degrees of surface roughness, a high thermal expansion coefficients, and bad handling characteristics of typical flexible substrates. The method for manufacturing a flexible electronic device according to the present invention includes: forming a flexible substrate on a motherboard while physically separating the interface therebetween so that the interfacial bonding therebetween has a yield strength less than that of the flexible substrate; and forming an electronic device on the separated surface of the flexible substrate which had previously been in contact with the motherboard.

Owner:POHANG IRON & STEEL CO LTD

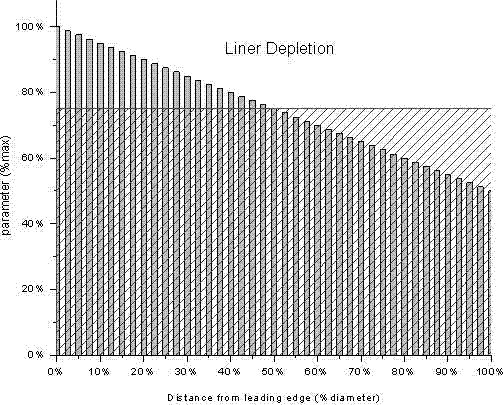

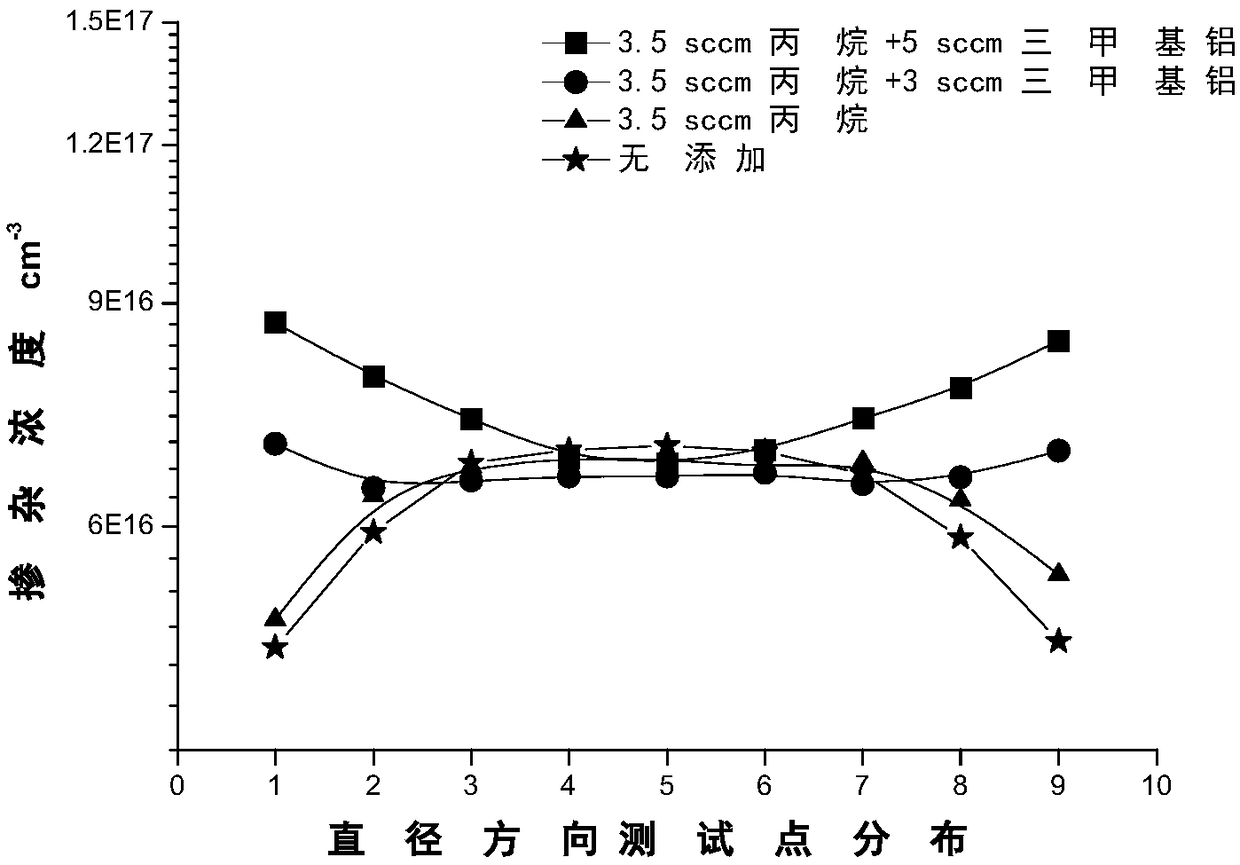

Method for increasing uniformity of on-chip n-type doping concentration of silicon carbide epitaxial wafer

ActiveCN103614779ADoping Concentration Uniformity OptimizationEnlarge selection windowPolycrystalline material growthAfter-treatment detailsSilanesGas phase

The invention relates to a method for increasing the uniformity of on-chip n-type doping concentration of a silicon carbide epitaxial wafer. According to the method, a chemical vapor deposition growth technology serves as basis; a silicon surface silicon carbide substrate with the deviation (11-20) direction of 4 degrees or 8 degrees is adopted; silane and propane serve as growth sources; hydrogen chloride serves as an auxiliary gas for inhibiting gas phase nucleation of a silicon component; hydrogen serves as a carrier gas and a diluent gas; nitrogen serves as an n-type doping agent. A small amount of process gas silane or propane is added into a base air floatation gas and is pushed by the air floatation gas serving as a carrier gas to the edge of the substrate to finely adjust the carbon silicon ratio of the edge of the substrate, so that the doping efficiency of the n-type doping source on the edge of the substrate is changed, the doping concentration deviation of the edge point and the central point of the epitaxial wafer caused by non-linear exhausting is effectively reduced, and the uniformity of the on-chip doping concentration of the epitaxial wafer is effectively optimized on the premise of not changing key process parameters. The selection window of the key process parameters is enlarged and technical support is provided for the growth of a high-quality silicon carbide epitaxial material.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

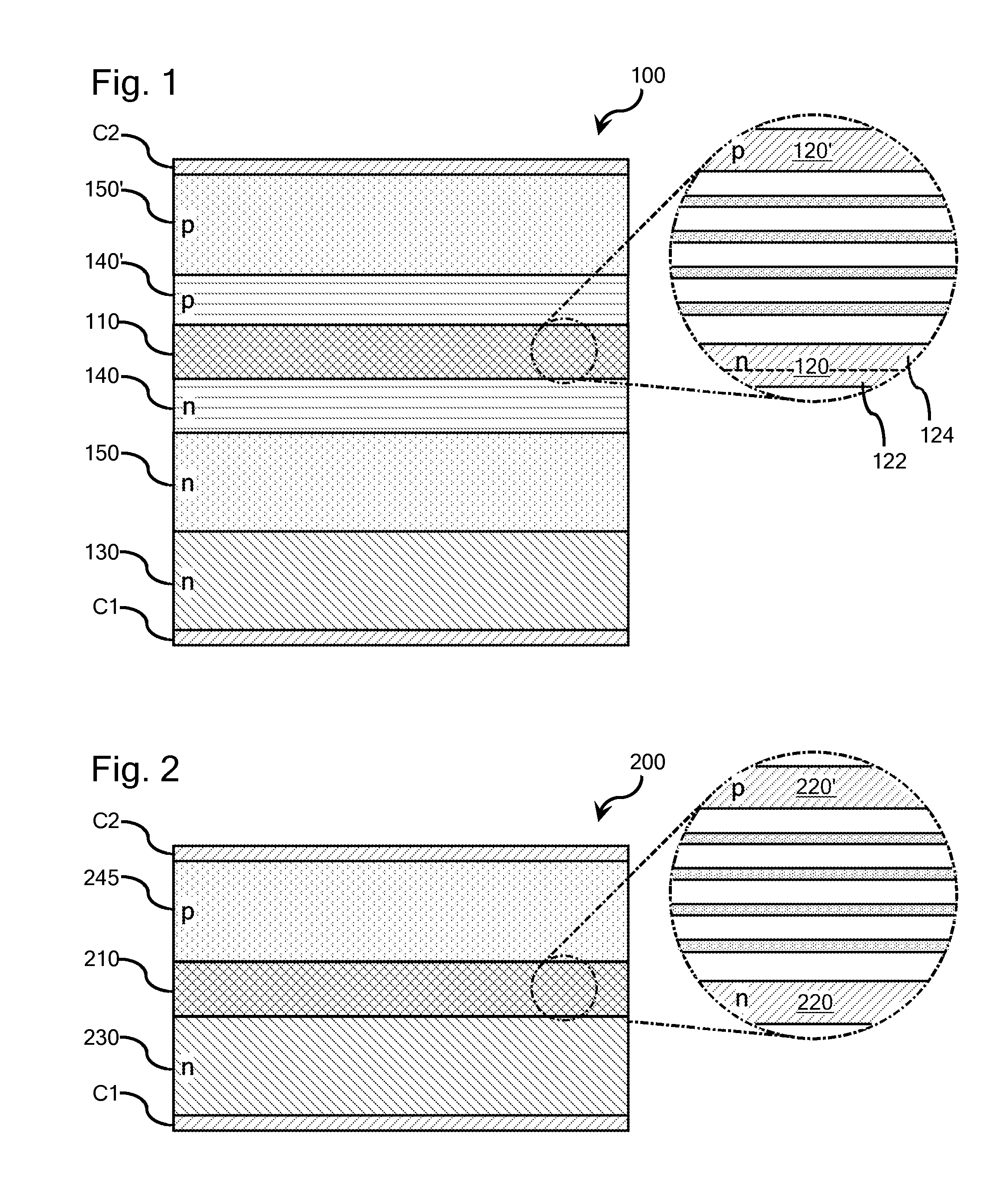

Hole blocking layers in non-polar and semi-polar green light emitting devices

InactiveUS8379684B1Prevent penetrationWide bandgapSolid-state devicesNanoopticsElectricitySemiconductor materials

Light emitting devices are provided comprising an active region interposed between n-type and p-type sides of the device and a hole blocking layer interposed between the active region and the n-type side of the device. The active region comprises an active MQW structure and is configured for electrically-pumped stimulated emission of photons in the green portion of the optical spectrum. The n-type side of the light emitting device comprises an n-doped semiconductor region. The p-type side of the light emitting device comprises a p-doped semiconductor region. The n-doped semiconductor region comprises an n-doped non-polar or n-doped semi-polar substrate. Hole blocking layers according to the present disclosure comprise an n-doped semiconductor material and are interposed between the non-polar or semi-polar substrate and the active region of the light emitting device. The hole blocking layer (HBL) composition is characterized by a wider bandgap than that of the quantum well barrier layers of the active region.

Owner:THORLABS QUANTUM ELECTRONICS

Low Cost InGaAlN Based Lasers

ActiveUS20080298413A1High optical wavefront qualityReduce yieldOptical wave guidanceLaser detailsSemiconductor chipContact layer

A method and structure for producing lasers having good optical wavefront characteristics, such as are needed for optical storage includes providing a laser wherein an output beam emerging from the laser front facet is essentially unobstructed by the edges of the semiconductor chip in order to prevent detrimental beam distortions. The semiconductor laser structure is epitaxially grown on a substrate with at least a lower cladding layer, an active layer, an upper cladding layer, and a contact layer. Dry etching through a lithographically defined mask produces a laser mesa of length lc and width bm. Another sequence of lithography and etching is used to form a ridge structure with width won top of the mesa. The etching step also forming mirrors, or facets, on the ends of the laser waveguide structures. The length ls and width bs of the chip can be selected as convenient values equal to or longer than the waveguide length lc and mesa width bm, respectively. The waveguide length and width are selected so that for a given defect density D, the yield YD is larger than 50%.

Owner:MACOM TECH SOLUTIONS HLDG INC

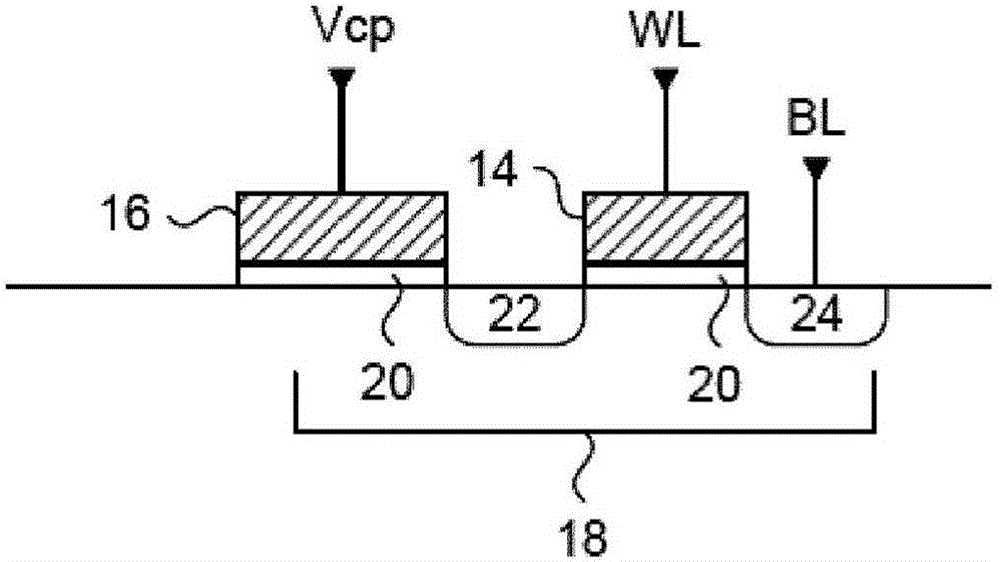

Anti-fuse memory cell

ActiveCN105849861AImprove breakdown performanceUniform thicknessSemiconductor/solid-state device detailsSolid-state devicesThin oxideGate oxide

An anti-fuse memory cell having a variable thickness gate oxide. The variable thickness gate oxide is formed by depositing a first oxide over a channel region of the anti-fuse memory cell, removing the first oxide in a thin oxide area of the channel region, and then thermally growing a second oxide in the thin oxide area. The remaining first oxide defines a thick oxide area of the channel region. The second oxide growth occurs under the remaining first oxide, but at a rate less than thermal oxide growth in the thin oxide area. This results in a combined thickness of the first oxide and the second oxide in the thick oxide area being greater than second oxide in the thin oxide area.

Owner:SYNOPSYS INC

Method for improving uniformity of p-type doping concentration in silicon carbide epitaxial wafer

ActiveCN108796616ADoping Concentration Uniformity OptimizationExcellent background concentrationDiffusion/dopingGraphite substrateChemical vapor deposition

The invention discloses a method for improving the uniformity of p-type doping concentration in a silicon carbide epitaxial wafer. Based on a chemical vapor deposition growth technique, a small amountof silicon source, carbon source, hydrogen chloride, trimethylaluminum and the like are added into a substrate air-floating gas, and then a small amount of process gas is pushed to an edge of a graphite substrate by taking the air-floating gas as a carrier gas, so that the p-type doping efficiency of the edge of the substrate is finely adjusted. By adopting the method, the deviation of the dopingconcentration of an edge point and a center point caused by nonlinear depletion of the epitaxial wafer is effectively reduced, and the uniformity of the intra-wafer doping concentration of the epitaxial wafer is effectively optimized without changing key process parameters. The process is compatible with conventional SiC epitaxial processes, and has a relatively high promotion value.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Epitaxial growth method for reducing interface thermal resistance of gallium nitride high-electron-mobility field-effect transistor

ActiveCN110211865AImprove defect densityGrowth interface protectionSemiconductor/solid-state device manufacturingSemiconductor devicesGas phaseNitrogen gas

The invention relates to an epitaxial growth method for reducing interface thermal resistance of a gallium nitride high-electron-mobility field-effect transistor. An epitaxial material is grown through a vapor phase epitaxial growth method of metal organic matter chemical vapor deposition and the like. A gallium nitride epitaxial wafer comprises a substrate, a lower aluminium nitride nucleating layer, an upper aluminium nitride nucleating layer, a gallium nitride transition layer, a gallium nitride buffer layer, a barrier layer and a cap layer from the bottom up in sequence. The carrier gasesused in the growing process of the lower aluminium nitride nucleating layer and the upper aluminium nitride nucleating layer are hydrogen and nitrogen respectively. The carrier gas used in the growingprocess of the gallium nitride transition layer is nitrogen. The carrier gas used in the growing process of the gallium nitride buffer layer is hydrogen or a mixture of hydrogen and nitrogen. Throughthe carrier gas conversion process, the method reduces defect density in the aluminum nitride nucleating layer and the gallium nitride layer, improves interface quality of the aluminum nitride nucleating layer and the gallium nitride layer, and effectively reduces the interface thermal resistance of the gallium nitride high-electron-mobility field-effect transistor.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Preparation method of tin-doped titanium dioxide

InactiveCN103523826AIncrease the degree of distortionIncrease lattice defect densityTitanium dioxideMetal/metal-oxides/metal-hydroxide catalystsIonPolytetrafluoroethylene

The invention discloses a preparation method of tin-doped titanium dioxide, and relates to a preparation method of titanium dioxide. The preparation method disclosed by the invention is used for solving the technical problem that the product obtained by existing methods for preparing Sn4<+> ion-doped TiO2 is poor in dispersibility. The preparation method comprises the following steps: adding dibutyl phthalate and crystalloid tin tetrachloride into absolute ethyl alcohol; adding ethylene glycol; then, sequentially adding concentrated hydrochloric acid and deionized water; adding polyvinylpyrrolidone; stirring to obtain a stable and transparent yellow sol; transferring the yellow sol to a stainless steel reaction kettle for reaction with a polytetrafluoroethylene liner; naturally cooling to room temperature; washing with absolute ethyl alcohol and distilled water; filtering; collecting a white precipitate; drying the white precipitate, grinding and packaging to obtain the tin-doped titanium dioxide. The tin-doped titanium dioxide prepared by the method provided by the invention is better in dispersibility, and the grain size is about 10 nanometers. The invention belongs to the field of preparation of titanium dioxide.

Owner:HEILONGJIANG UNIV

Silicon carbide epitaxial wafer and process for production thereof, silicon carbide bulk substrate for epitaxial growth purposes and process for production thereof, and heat treatment apparatus

ActiveCN102859654AEasy to manufactureShorten production timePolycrystalline material growthSemiconductor/solid-state device manufacturingWaferingProduct gas

Disclosed is a process for producing a silicon carbide epitaxial wafer which has extremely superior surface flatness and has extremely low densities of carrot defects and triangular defects that usually appear after the occurrence of epitaxial growth. The silicon carbide epitaxial wafer can be produced through: a first step of annealing a silicon carbide bulk substrate that has a tilt angle against the face <0001> of smaller than 5 degrees in a reduction gas atmosphere at a first temperature (T1) for a treatment time (t); a second step of decreasing the temperature of the substrate in a reduction gas atmosphere; and a third step of supplying at least a gas containing silicon atoms and a gas containing carbon atoms at a second temperature (T2) that is lower than the annealing temperature (T1) employed in the first step to cause epitaxial growth.

Owner:MITSUBISHI ELECTRIC CORP

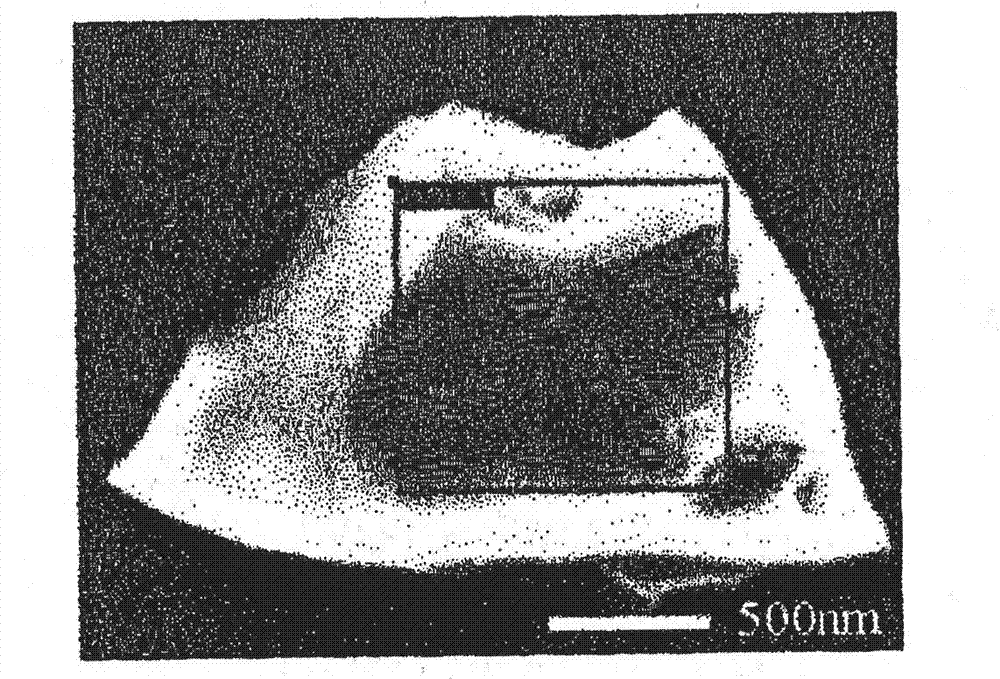

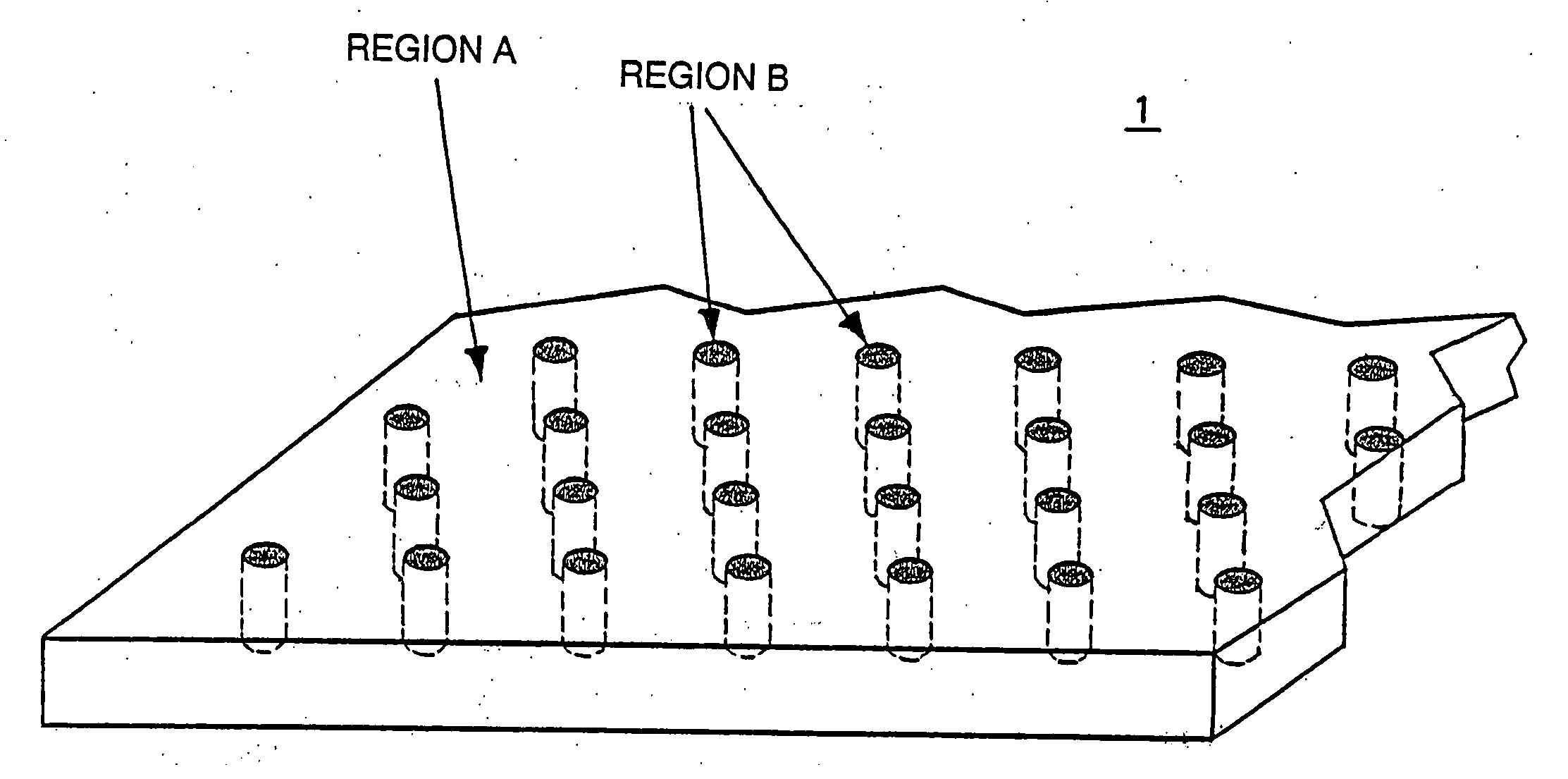

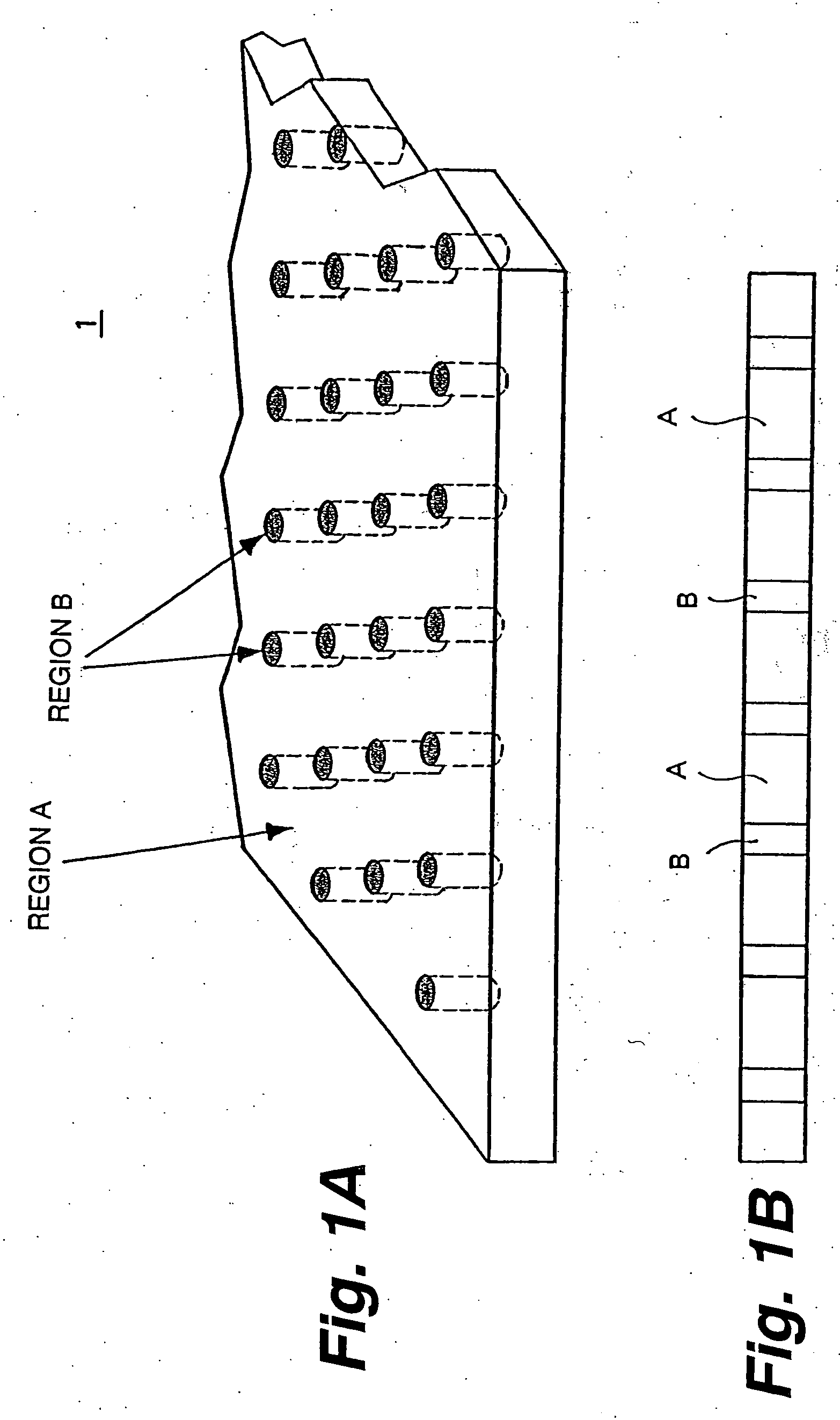

Method of manufacturing a semiconductor light emitting device, semiconductor light emitting device, method of manufacturing a semiconductor device, semiconductor device, method of manufacturing a device, and device

InactiveUS20050227392A1Improve propertiesControlling positionOptical wave guidancePolycrystalline material growthDevice materialVolumetric Mass Density

When a semiconductor light emitting device or a semiconductor device is manufactured by growing nitride III-V compound semiconductor layers, which will form a light emitting device structure or a device structure, on a nitride III-V compound semiconductor substrate composed of a first region in form of a crystal having a first average dislocation density and a plurality of second regions having a second average dislocation density higher than the first average dislocation density and periodically aligned in the first region, device regions are defined on the nitride III-V compound semiconductor substrate such that the device regions do not substantially include second regions, emission regions or active regions of devices finally obtained do not include second regions.

Owner:SONY CORP +1

Seawater corrosion resistant ultra-low carbon bainite steel and preparation method thereof

ActiveCN101880835AIncrease nucleation rateImprove defect densityTemperature control deviceRoom temperatureWater cooling

The invention discloses seawater corrosion resistant ultra-low carbon bainite steel and a preparation method thereof. The bainite steel comprises the following components in percentage by weight: 0.02 to 0.05 percent of C, 1.0 to 1.5 percent of Mn, less than 0.006 percent of S, 0.24 to 0.40 percent of Si, 0.04 to 0.09 percent of P, 0.05 to 0.2 percent of Ni, 0.3 to 0.5 percent of Cu, 0.03 to 0.04 percent of Nb, 0.2 to 0.4 percent of Mo, 0.002 to 0.005 percent of B, less than 0.08 percent of Al, less than or equal to 0.06 percent of Cr and the balance of Fe; and the tissue is granular bainite. The preparation method comprises the following steps of: smelting molten steel with vacuum and casting the molten steel to form ingots, roughly rolling the ingots in an austenite recrystallization area after soaking treatment, then finely rolling the ingots in an austenite non-recrystallization area, cooling the rolled ingots to between 450 and 500 DEG C with water after rolling, and cooling the rolled ingots in the air to room temperature. The seawater corrosion resistant ultra-low carbon bainite steel has good comprehensive mechanical property, low raw material cost, simple production process and good seawater corrosion resistance based on excellent mechanical property and welding property.

Owner:NORTHEASTERN UNIV +1

Group III nitride crystals usable as group III nitride substrate, method of manufacturing the same, and semiconductor device including the same

InactiveUS7309534B2Quality improvementEfficient preparationPolycrystalline material growthSemiconductor/solid-state device manufacturingIndiumNitrogen

The present invention provides a method of manufacturing Group III nitride crystals that are of high quality, are manufactured highly efficiently, and are useful and usable as a substrate that is used in semiconductor manufacturing processes. The method of manufacturing Group III nitride crystals includes: forming a first layer made of a semiconductor that is expressed by a composition formula of AlsGatIn1-s-tN (where 0≦s≦1, 0≦t≦1, and s+t≦1); forming a second layer by bringing the surface of the first layer into contact with a melt in an atmosphere including nitrogen, wherein the second layer includes greater defects in a crystal structure, such as a dislocation density for example, than those of the first layer, and the melt includes alkali metal and at least one Group III element selected from the group consisting of gallium, aluminum, and indium; and forming a third layer through crystal growth in the melt in an atmosphere including nitrogen, wherein the third layer is made of a semiconductor that is expressed by a composition formula of AluGavIn1-u-vN (where 0≦u≦1, 0≦v≦1, and u+v≦1), and the third layer has less defects in a crystal structure, such as a dislocation density for example, than those of the second layer.

Owner:PANASONIC CORP +1

Growth of GaAs epitaxial layers on Si substrate by using a novel GeSi buffer layer

InactiveUS7259084B2Reduce thicknessSurface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesUltra-high vacuumGas phase

This invention provides a process for growing Ge epitaxial layers on Si substrate by using ultra-high vacuum chemical vapor deposition (UHVCVD), and subsequently growing a GaAs layer on Ge film of the surface of said Ge epitaxial layers by using metal organic chemical vapor deposition (MOCVD).The process comprises steps of, firstly, pre-cleaning a silicon wafer in a standard cleaning procedure, dipping it with HF solution and prebaking to remove its native oxide layer. Then, growing a high Ge-composition epitaxial layer, such as Si0.1Ge0.9 in a thickness of 0.8 μm on said Si substrate by using ultra-high vacuum chemical vapor deposition under certain conditions. Thus, many dislocations are generated and located near the interface and in the low of part of Si01.Ge0.9 due to the large mismatch between this layer and Si substrate.Furthermore, a subsequent 0.8 μm Si0.05Ge0.95 layer, and / or optionally a further 0.8 μm Si0.02Ge0.98 layer, are grown. They form strained interfaces of said layers can bend and terminate the propagated upward dislocation very effectively. Therefore, a film of pure Ge is grown on the surface of said epitaxial layers.Finally, a GaAs epitaxial layer is grown on said Ge film by using MOCVD.

Owner:NAT CHIAO TUNG UNIV

Growth of GaAs expitaxial layers on Si substrate by using a novel GeSi buffer layer

InactiveUS20070134901A1Reduce thicknessSurface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesGas phaseUltra-high vacuum

This invention provides a process for growing Ge epitaixial layers on Si substrate by using ultra-high vacuum chemical vapor deposition (UHVCVD), and subsequently growing a GaAs layer on Ge film of the surface of said Ge epitaixial layers by using metal organic chemical vapor deposition (MOCVD). The process comprises steps of, firstly, pre-cleaning a silicon wafer in a standard cleaning procedure, dipping it with HF solution and prebaking to remove its native oxide layer. Then, growing a high Ge-composition epitaixial layer, such as Si0.1Ge0.9 in a thickness of 0.8 μm on said Si substrate by using ultra-high vacuum chemical vapor deposition under certain conditions. Thus, many dislocations are generated and located near the interface and in the low of part of Si0.1Ge0.9 due to the large mismatch between this layer and Si substrate. Furthermore, a subsequent 0.8 μm Si0.05Ge0.95 layer, and / or optionally a further 0.8 μm Si0.02Ge0.98 layer, are grown. They form strained interfaces of said layers can bend and terminate the propagated upward dislocation very effectively. Therefore, a film of pure Ge is grown on the surface of said epitaixial layers. Finally, a GaAs epitaixial layer is grown on said Ge film by using MOCVD.

Owner:NAT CHIAO TUNG UNIV

Annealing method to reduce defects of epitaxial films and epitaxial films formed therewith

InactiveCN102969241AReduced annealing methodReduce lattice stressSemiconductor/solid-state device manufacturingFrom chemically reactive gasesGas phaseOptoelectronics

An annealing method to reduce defects of epitaxial films and epitaxial films formed therewith. The annealing method includes features as follows: apply a pressure ranged from 10 MPa to 6,000 MPa to an epitaxial film grown on a substrate through a vapor phase deposition process and heat the epitaxial film at a temperature lower than the melting temperature of the epitaxial film. Through applying pressure to the epitaxial film, the lattice strain of the epitaxial film is alleviated, and therefore the defect density of the epitaxial film also decreases.

Owner:RITEDIA CORPORATION

Sos substrate having low defect density in the vicinity of interface

InactiveUS20120126362A1Reduce defect densityImprove defect densitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorVisible light irradiation

A bonded SOS substrate having a semiconductor film on or above a surface of a sapphire substrate is obtained by a method with the steps of implanting ions from a surface of a semiconductor substrate to form an ion-implanted layer; activating at least a surface from which the ions have been implanted; bonding the surface of the semiconductor substrate and the surface of the sapphire substrate at a temperature of 50° C. to 350° C.; heating the bonded substrates at a maximum temperature from 200° C. to 350° C. to form a bonded body; and irradiating visible light from a sapphire substrate side or a semiconductor substrate side to the ion-implanted layer of the semiconductor substrate for embrittling an interface of the ion-implanted layer, while keeping the bonded body at a temperature higher than the temperature at which the surfaces of the semiconductor substrate and the sapphire substrate were bonded.

Owner:SHIN ETSU CHEM IND CO LTD

Suppression of leakage current in image acquisition

ActiveUS7265740B2Inhibit currentHigh sensitivityTransistorElectrically conductive connectionsDisplay deviceDangling bond

In a manufacturing process of a display device, hydrogenation in an I layer of photodiodes D1 and D2 is progressed less than that in a channel portion of a pixel TFT, and a defect density due to dangling bonds not terminated in the I layer of the photodiodes D1 and D2 is made higher than a defect density in the channel portion of the pixel TFT. Thus, while suppressing a leakage current of the pixel TFT, the sensitivity of the photodiodes D1 and D2 to light is improved. Moreover, a gate electrode is provided above an i region of a pin-type optical sensor diode with an insulating film interposed therebetween. Thus, a gate voltage can control a threshold of a bias voltage when a current starts to flow into the optical sensor diode and a leakage current is prevented from flowing into the optical sensor diode.

Owner:JAPAN DISPLAY CENTRAL CO LTD

Method of manufacturing semiconductor device

ActiveCN108074810AReduce defect densityImprove defect densityTransistorSolid-state devicesCrystallographic defectIrradiation

The present invention provides a method of manufacturing a semiconductor device that allows suppressing the relative positional misalignment between a cathode region and a crystal defect region. The method of manufacturing a semiconductor device having a diode includes: implanting charged particles into a first range and a second range in a semiconductor substrate from at least one of a first surface of the semiconductor substrate and a second surface of the semiconductor substrate located on an opposite side of the first surface so as to increase crystal defect densities in the first range and the second range; implanting n-type impurities into the first range from the first surface so as to make a region amorphous, the region being in the first range and disposed at the first surface; irradiating the first surface with first laser after the implantation of the charged particles and the implantation of the n-type impurities so as to heat the first range and the second range; and crystallizing the region which has been made amorphous in or after the irradiation of the first laser.

Owner:DENSO CORP

Crystal growth furnace for preparing single crystal by PVT method and application thereof

ActiveCN111058088AMany piecesIncreasing the thicknessPolycrystalline material growthFrom condensed vaporsCarbide siliconSemiconductor materials

The invention discloses a crystal growth furnace for preparing single crystals through a PVT method and an application of the crystal growth furnace, which belong to the field of semiconductor material preparation. The crystal growth furnace for preparing the single crystals by the PVT method comprises a crucible, a heat preservation structure, a furnace body and a heating coil which are arrangedfrom inside to outside, and further comprises a seed crystal column arranged in the crucible. The side wall of the crucible comprises an interlayer, the interlayer comprises an inner side wall and anouter side wall, the porosity of the inner side wall is higher than that of the outer side wall, and the interlayer forms a raw material cavity; the extension directions of the seed crystal column andthe central axis of the crucible are approximately the same, and a crystal growth cavity is formed between the seed crystal column and the inner surface of the inner side wall; the heating coil induces and heats the side wall of the crucible, so that the raw materials in the raw material cavity penetrate through the inner side wall after sublimation, and are conveyed to the surface of the seed crystal column in the crystal growth cavity along the radial gas phase for crystal growth. The crystal growth furnace can be used for efficiently and quickly preparing the silicon carbide single crystalwith extremely low defect density and the substrate of the silicon carbide single crystal, so that a technical foundation is laid for large-scale commercialization of high-quality and low-cost silicon carbide substrates.

Owner:SICC CO LTD

Low cost InGaAIN based lasers

ActiveUS7408183B2High optical wavefront qualityReduce yieldOptical wave guidanceLaser detailsSemiconductor chipContact layer

Owner:MACOM TECH SOLUTIONS HLDG INC

Preparation method of SOI (Silicon-On-Insulator) substrate material and SOI material

InactiveCN107785302ASuppresses surface parasitic conductanceImprove defect densitySolid-state devicesSemiconductor/solid-state device manufacturingHigh resistanceCapacitance

The invention discloses a preparation method of an SOI substrate material and an SOI material and belongs to the SOI wafer preparation technical field. An intrinsic polycrystalline or amorphous silicon layer is grown on the back surface of an SOI substrate wafer provided with a doped polycrystalline layer or doped amorphous silicon layer, so that the substrate material can be formed; the SOI material is made of the SOI substrate material; the doped polycrystalline layer or doped amorphous silicon layer is combined with silicon oxide, so that higher defect density can be realized, and therefore, capacitance variation can be limited, and the power of generated harmonics can be reduced; and since the intrinsic polycrystalline or amorphous silicon layer is grown on the back surface, so that impurities introduced during a doping process can be decreased, and therefore, the RF substrate loss of the high-resistance SOI substrate can be reduced, the linear characteristics of the substrate canbe increased, direct-current voltage bias can be decreased, the high-resistance SOI substrate can be compatible with a CMOS, and the loss of radio frequency can be decreased.

Owner:SHENYANG SILICON TECH

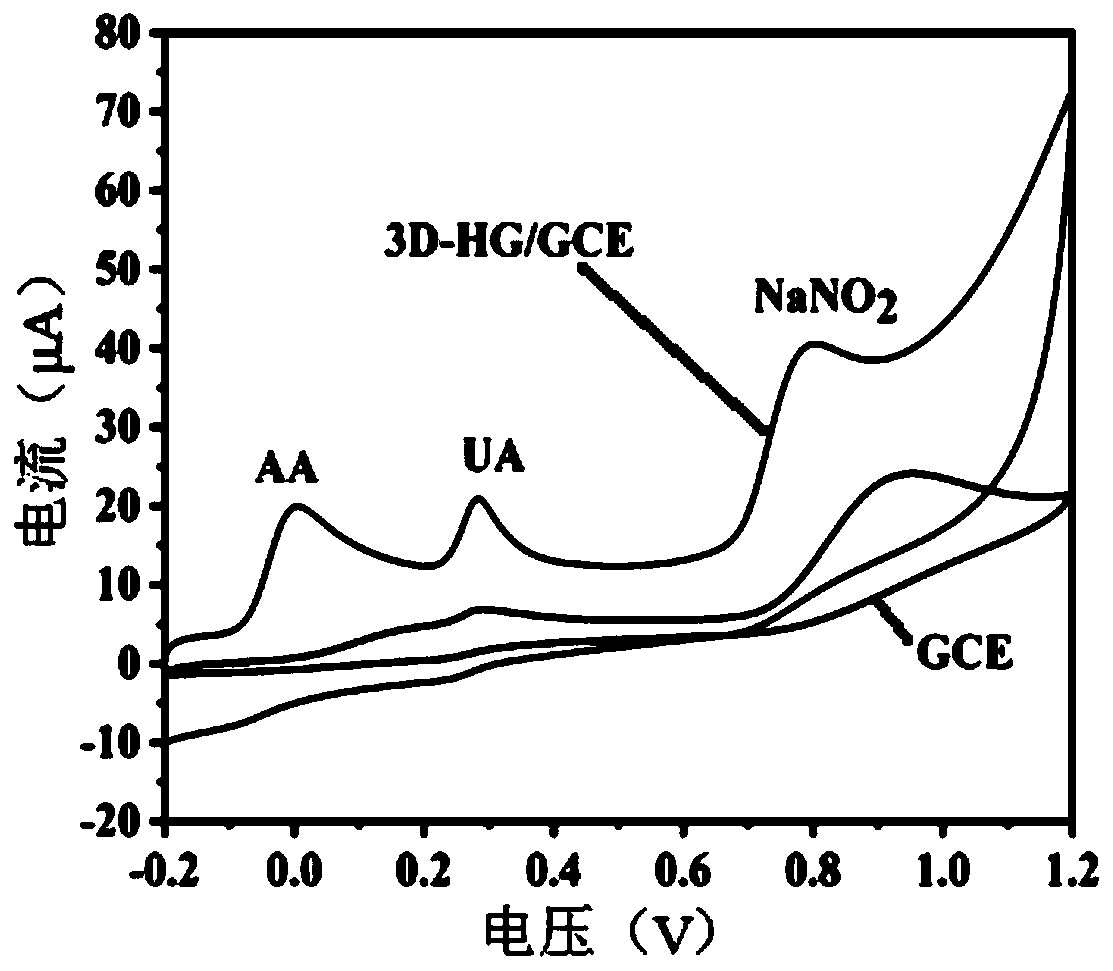

Three-dimensional porous graphene-based electrochemical electrode material, preparation and application thereof

ActiveCN110194445AImprove conductivityImprove defect densityMaterial nanotechnologyGrapheneVacuum pumpingIn plane

The invention relates to a three-dimensional porous graphene-based electrochemical electrode material, a preparation and application thereof. Three-dimensional porous graphene is prepared by hydrothermal method, and has abundant three-dimensional micron-pores and two-dimensional in-plane nanopores, the three-dimensional porous graphene-based electrochemical electrode material is obtained by: adding a suspension of the above graphene dropwise to the center of a substrate, and conducting vacuum pumping and drying at room temperature. The three-dimensional porous graphene-based electrochemical electrode material provided by the invention can be applied to electrochemical sensors to detect the content of ascorbic acid, uric acid or nitrite, and has the advantages of high sensitivity, short response time, strong anti-interference ability, good repeatability, good long-term stability and high recovery rate.

Owner:SHANGHAI UNIV OF ENG SCI

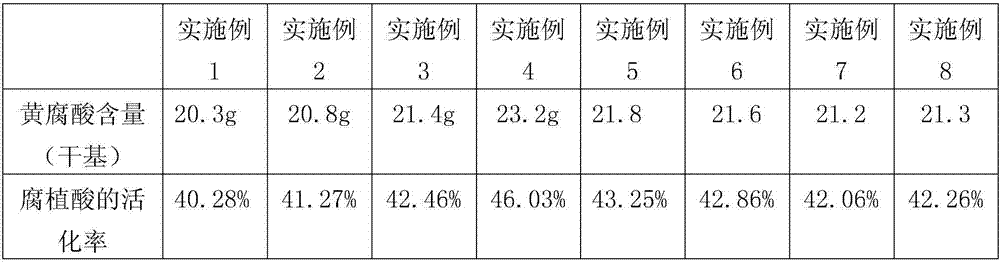

Method for extracting fulvic acid salt from photocatalyst activated lignite

ActiveCN107987283AImprove defect densityIncrease concentrationBiological activationUltraviolet irradiation

The invention provides a method for extracting fulvic acid salt from photocatalyst activated lignite. The method comprises the following steps: uniformly mixing lignite powder and water, adding alkalito regulate the pH value to be 10-11, stirring for 2-3 hours at a temperature of 50-80 DEG C, and performing solid-liquid separation to obtain a humate solution; and adding an oxidizing agent and a photocatalyst, and stirring under ultraviolet irradiation for 3-5 hours, thereby obtaining the fulvic acid salt product. The method disclosed by the invention is simple in production process, low in cost, high in humic acid activation rate in lignite, high in fulvic acid salt extraction rate and suitable for popularization and application in agricultural production.

Owner:QUJING NORMAL UNIV +3

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com