Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

22406results about "Printed circuit assembling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

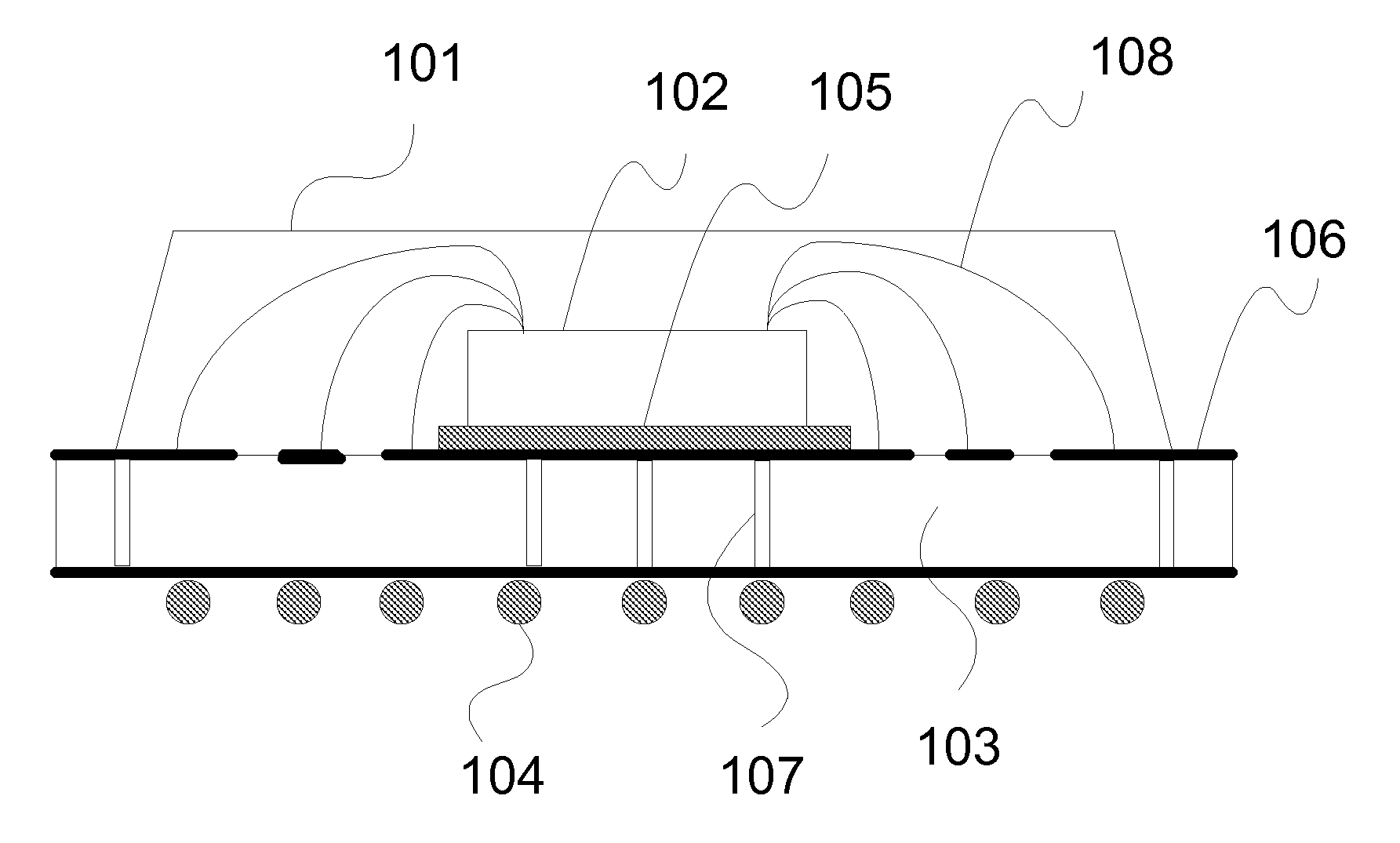

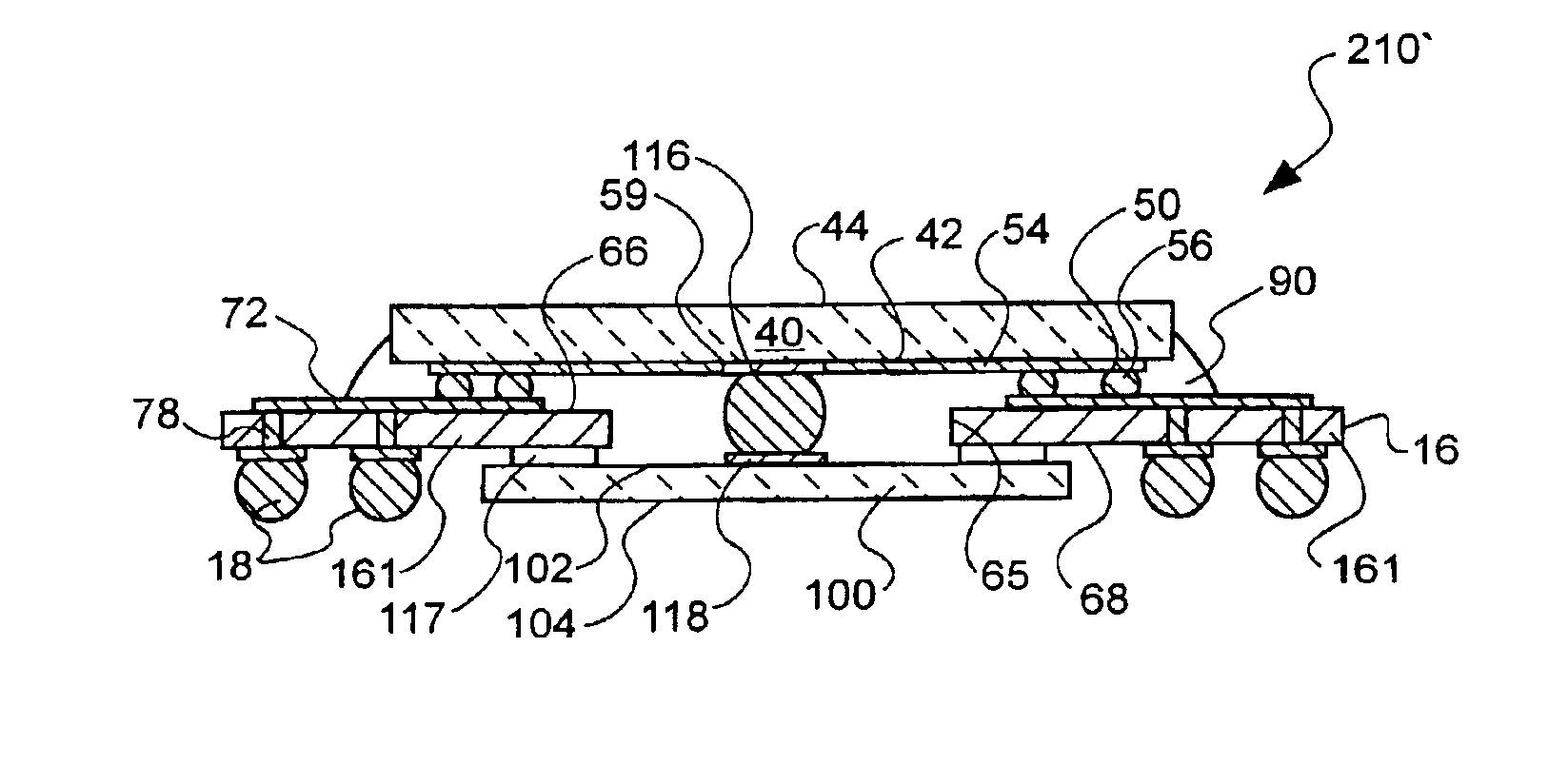

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS7619901B2Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

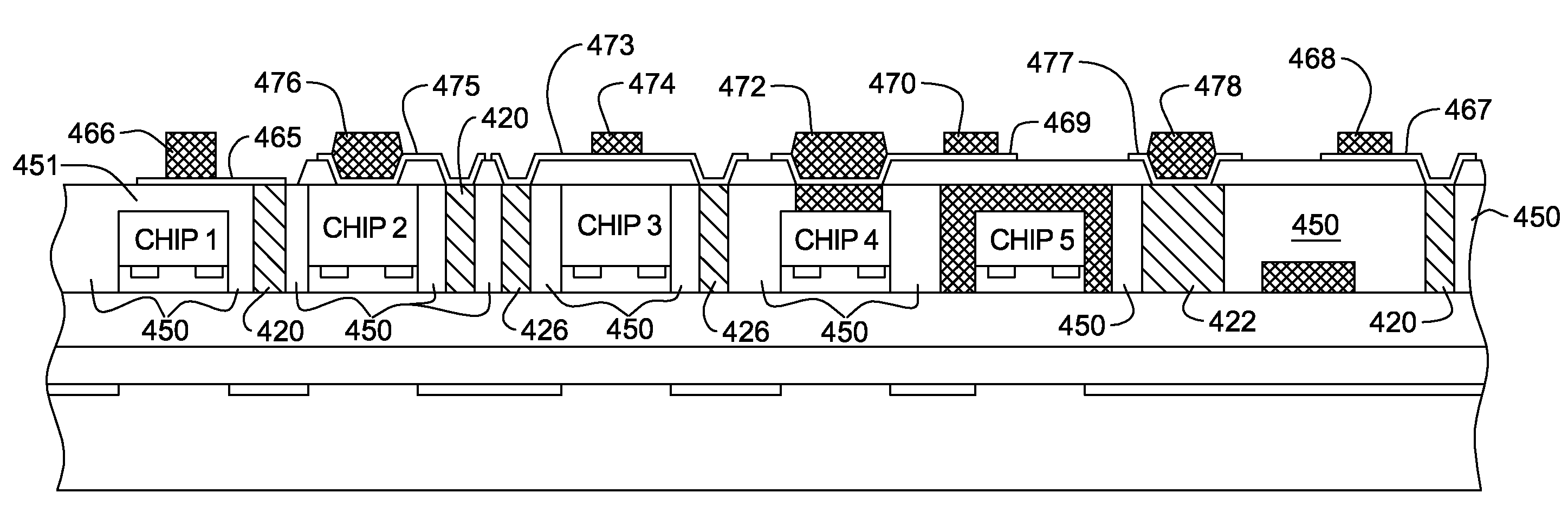

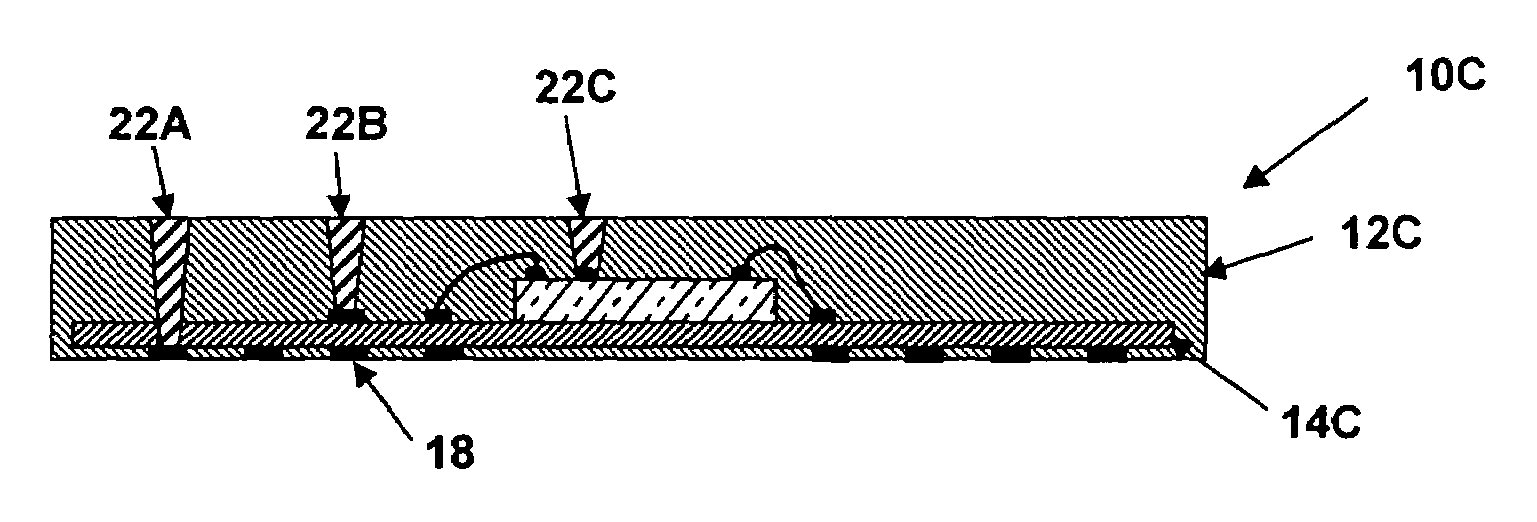

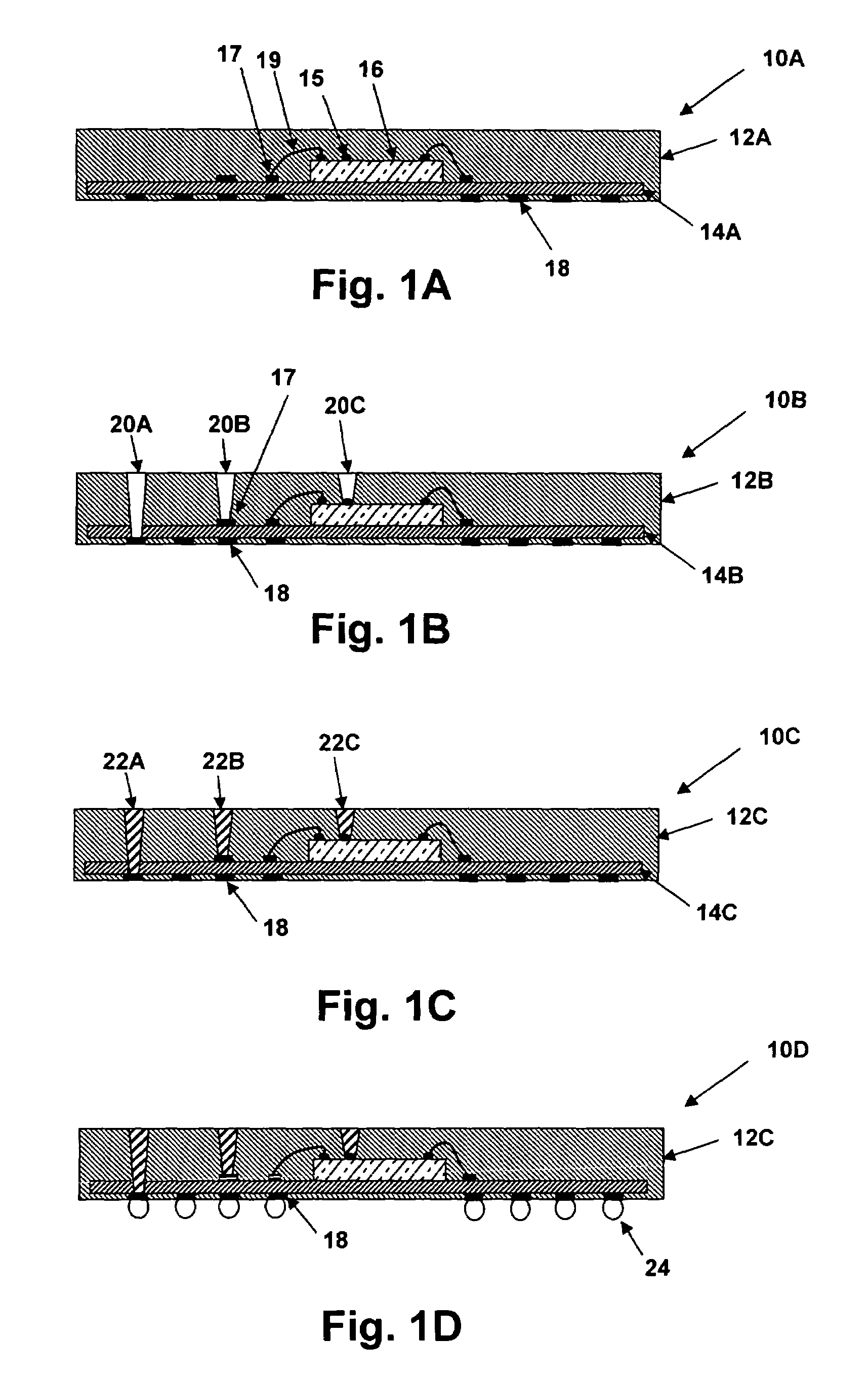

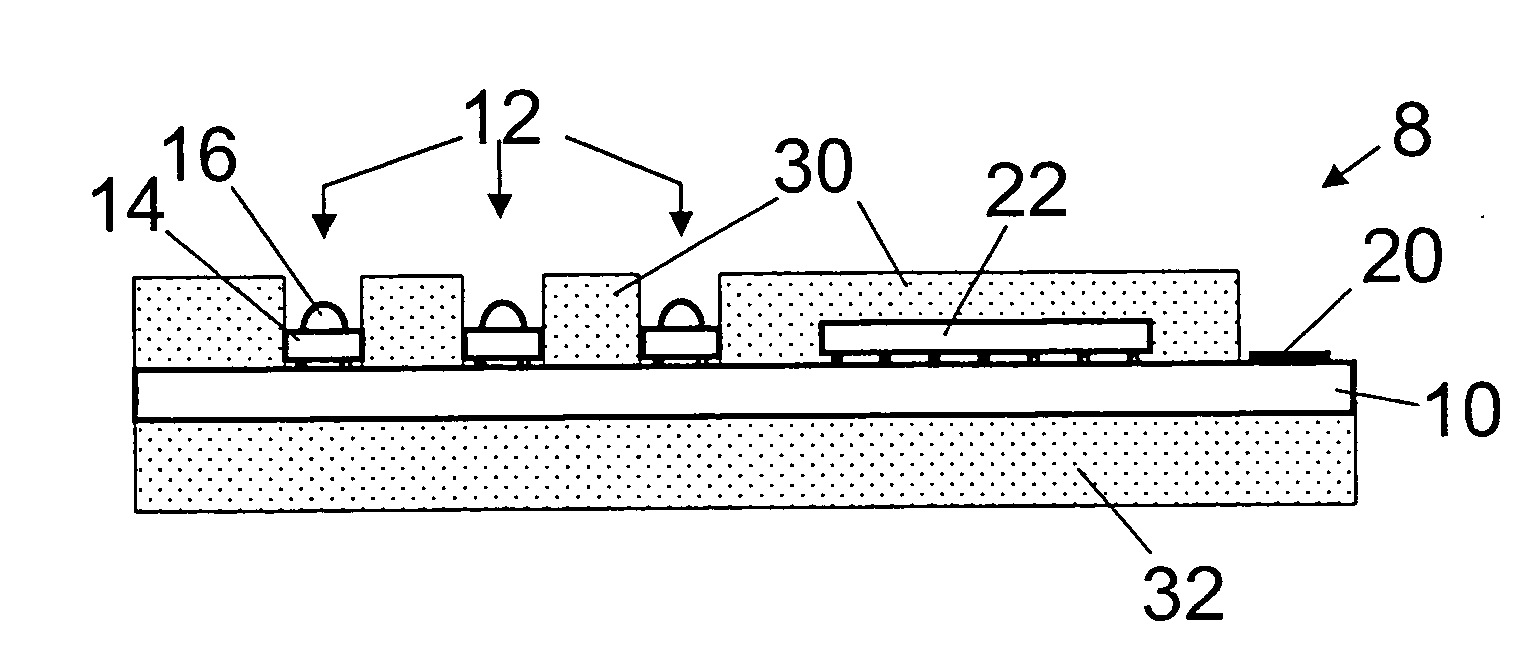

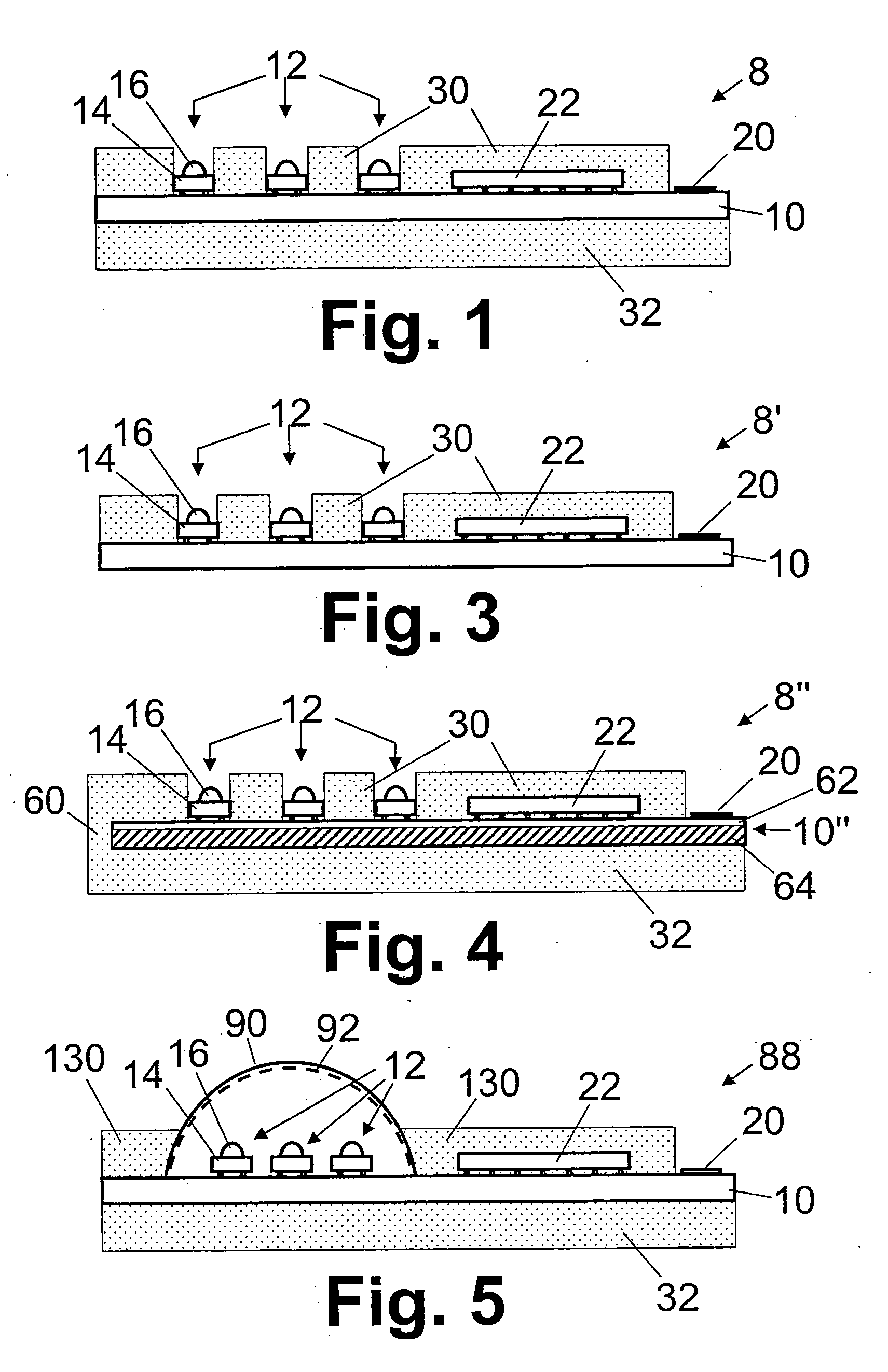

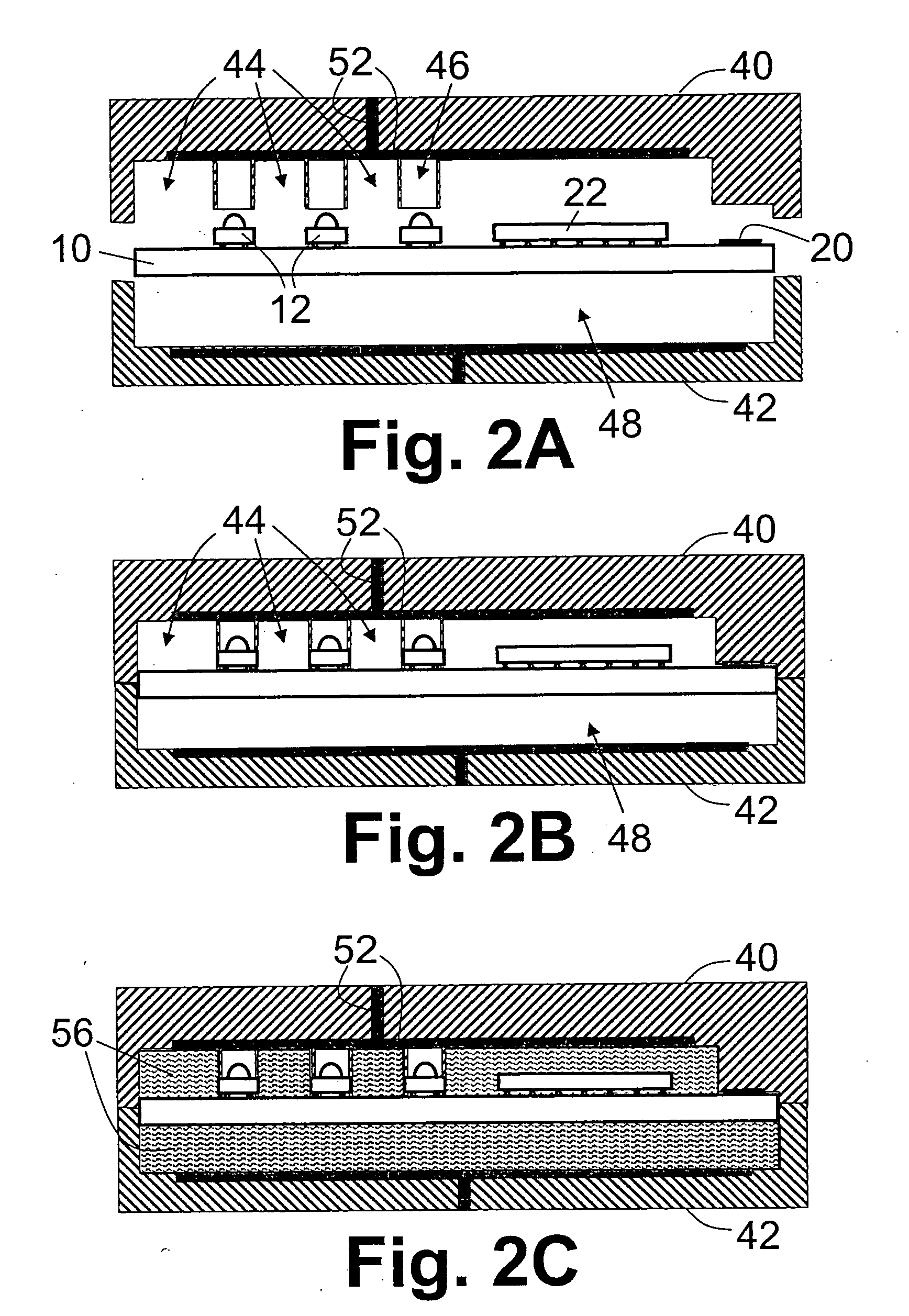

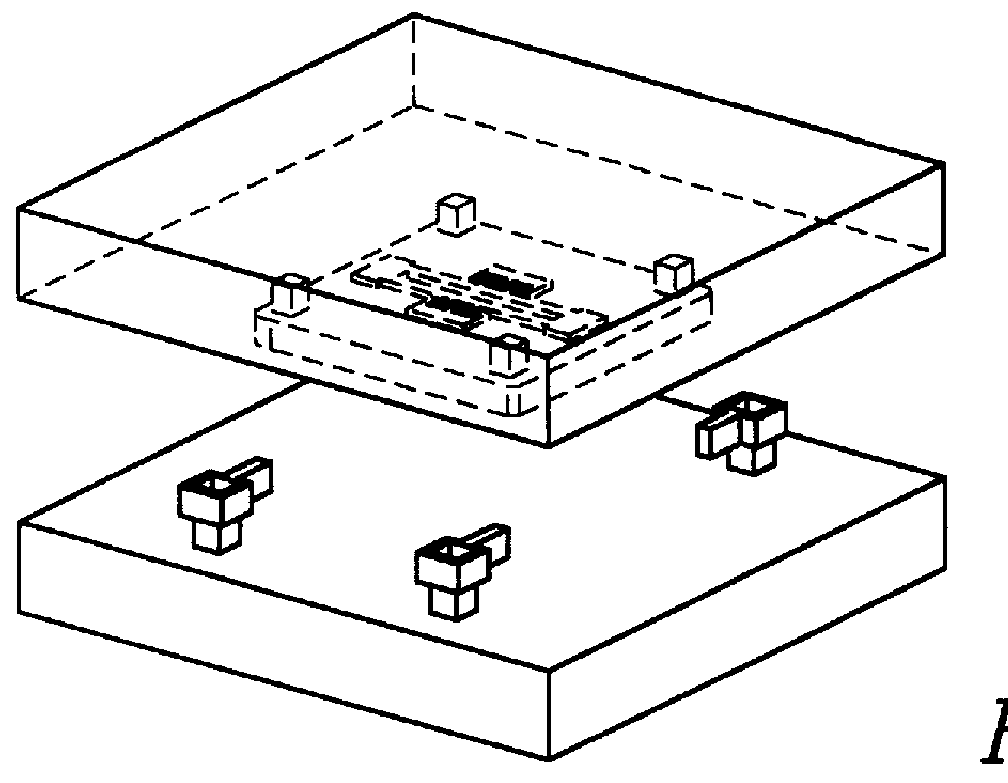

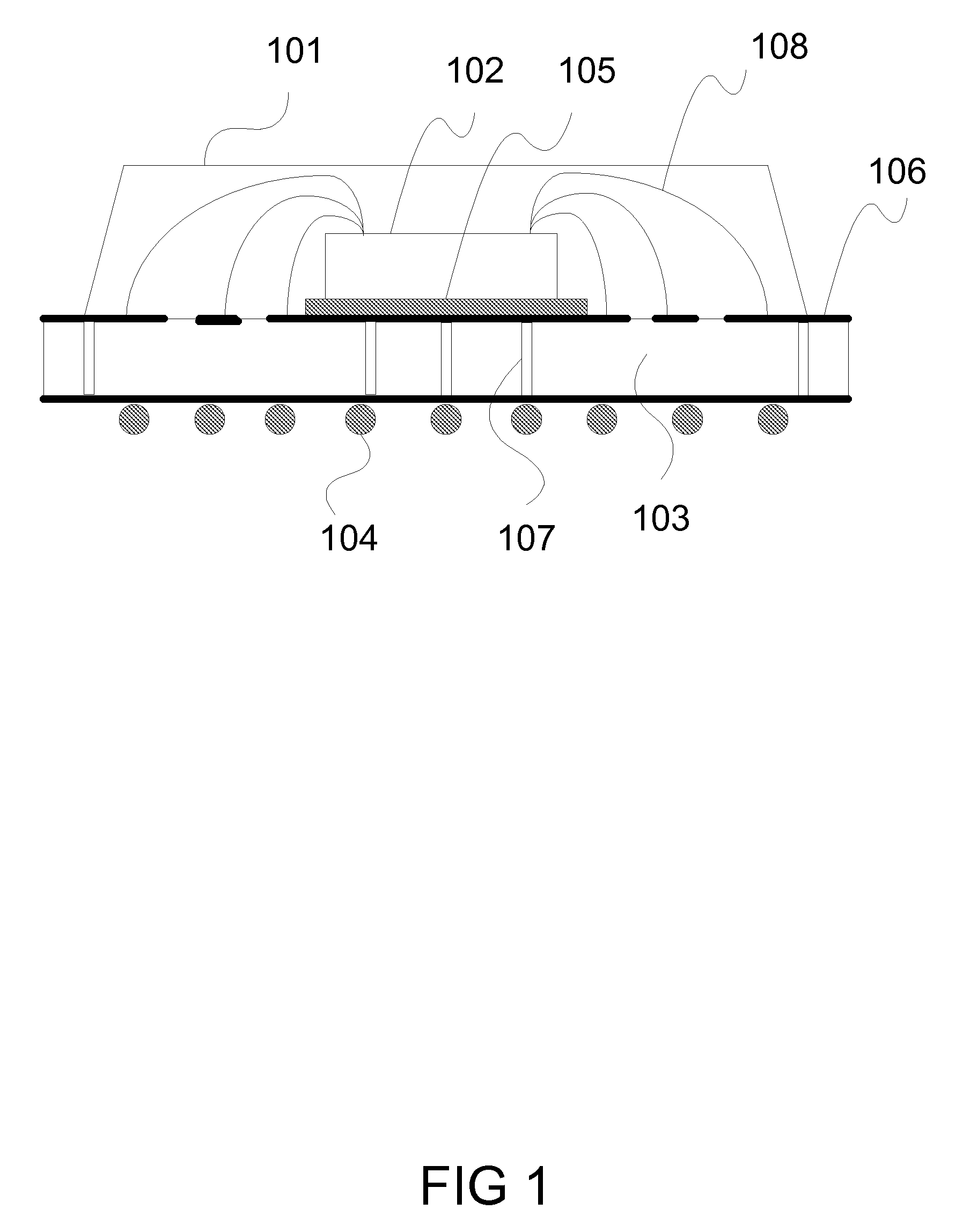

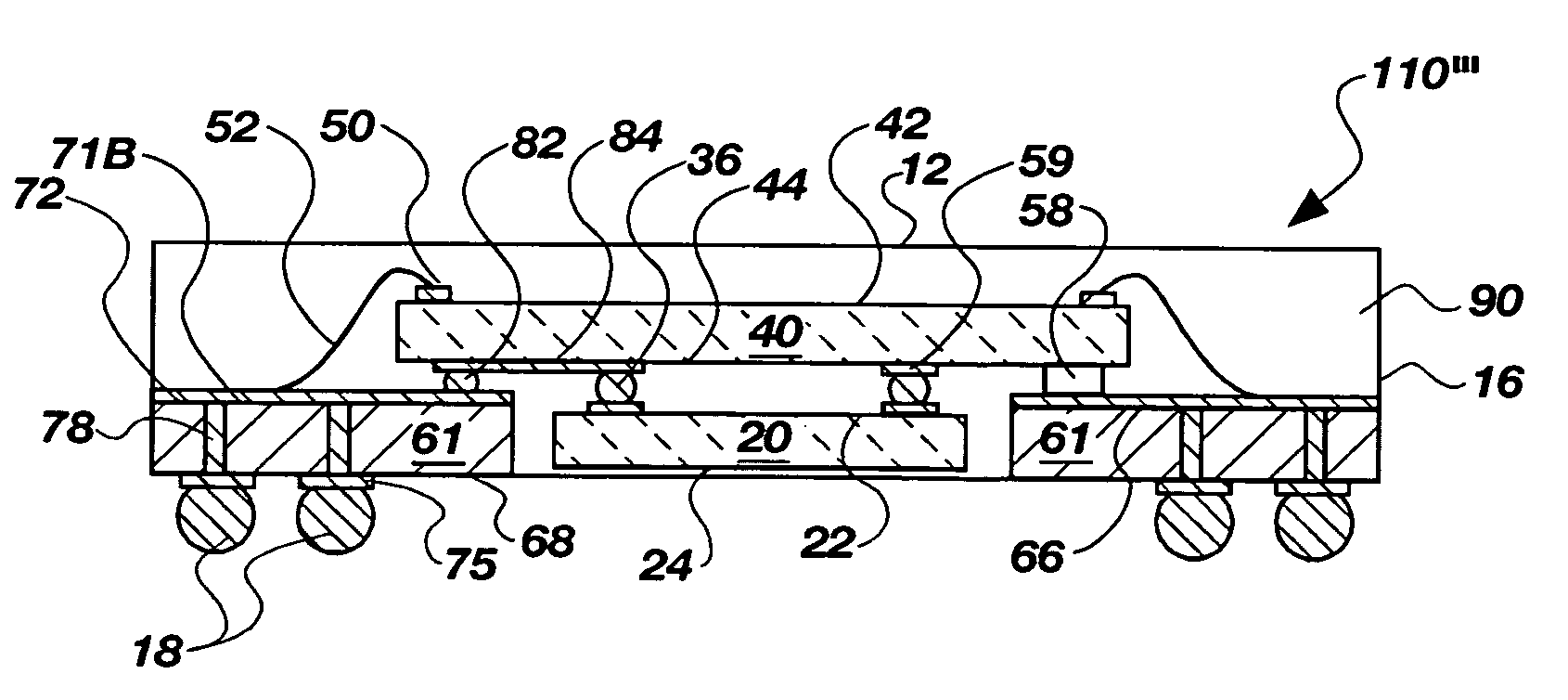

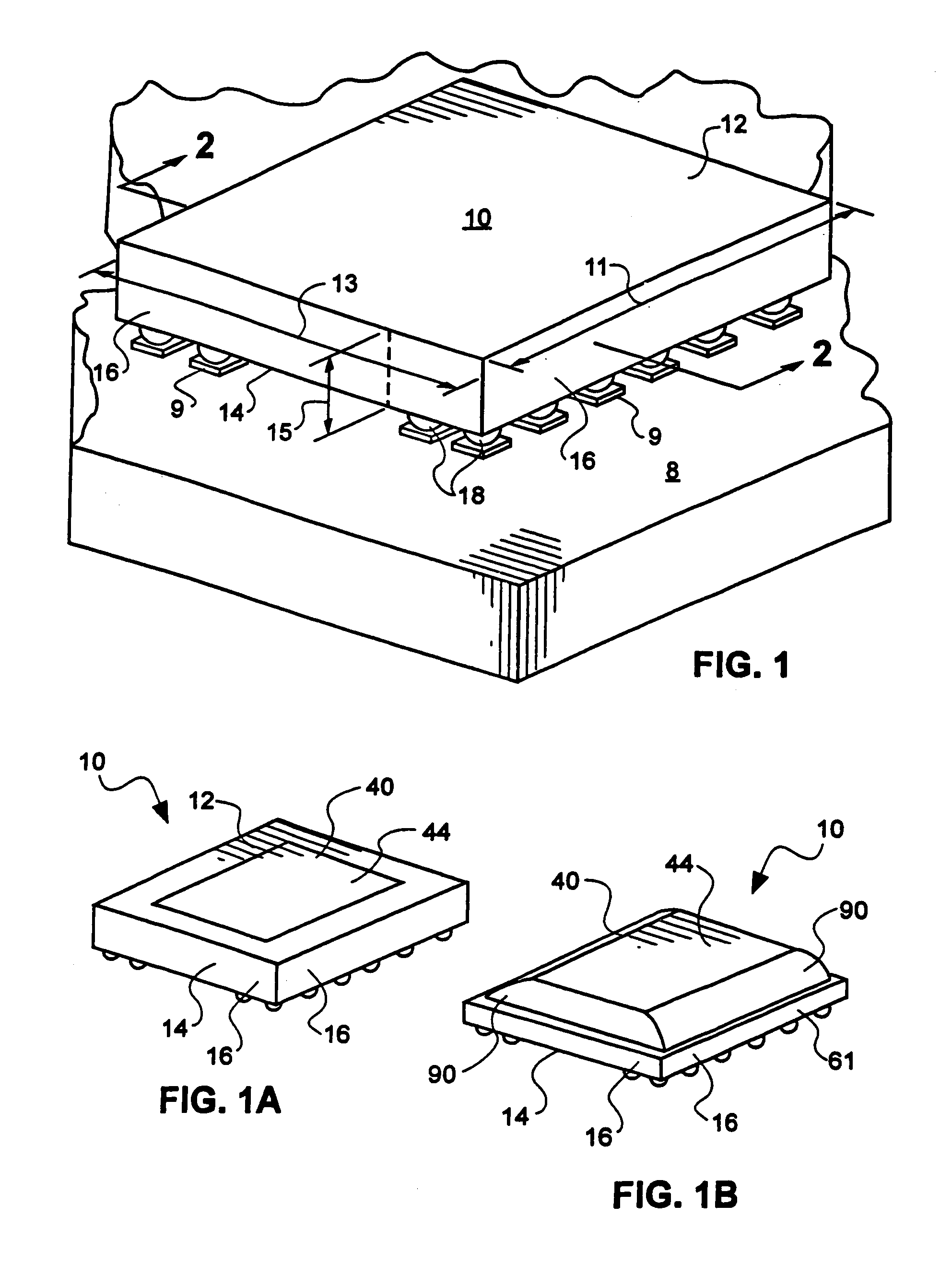

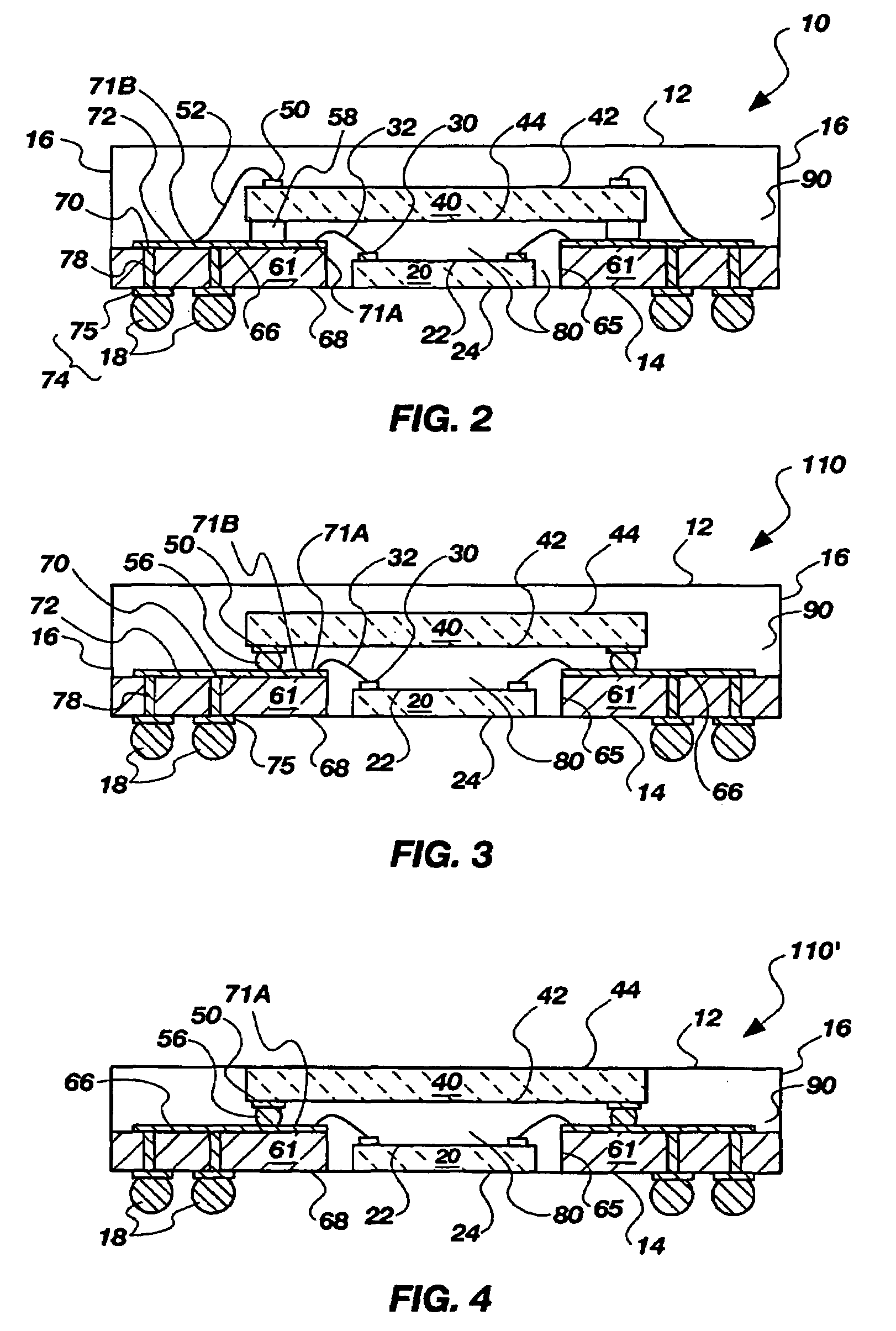

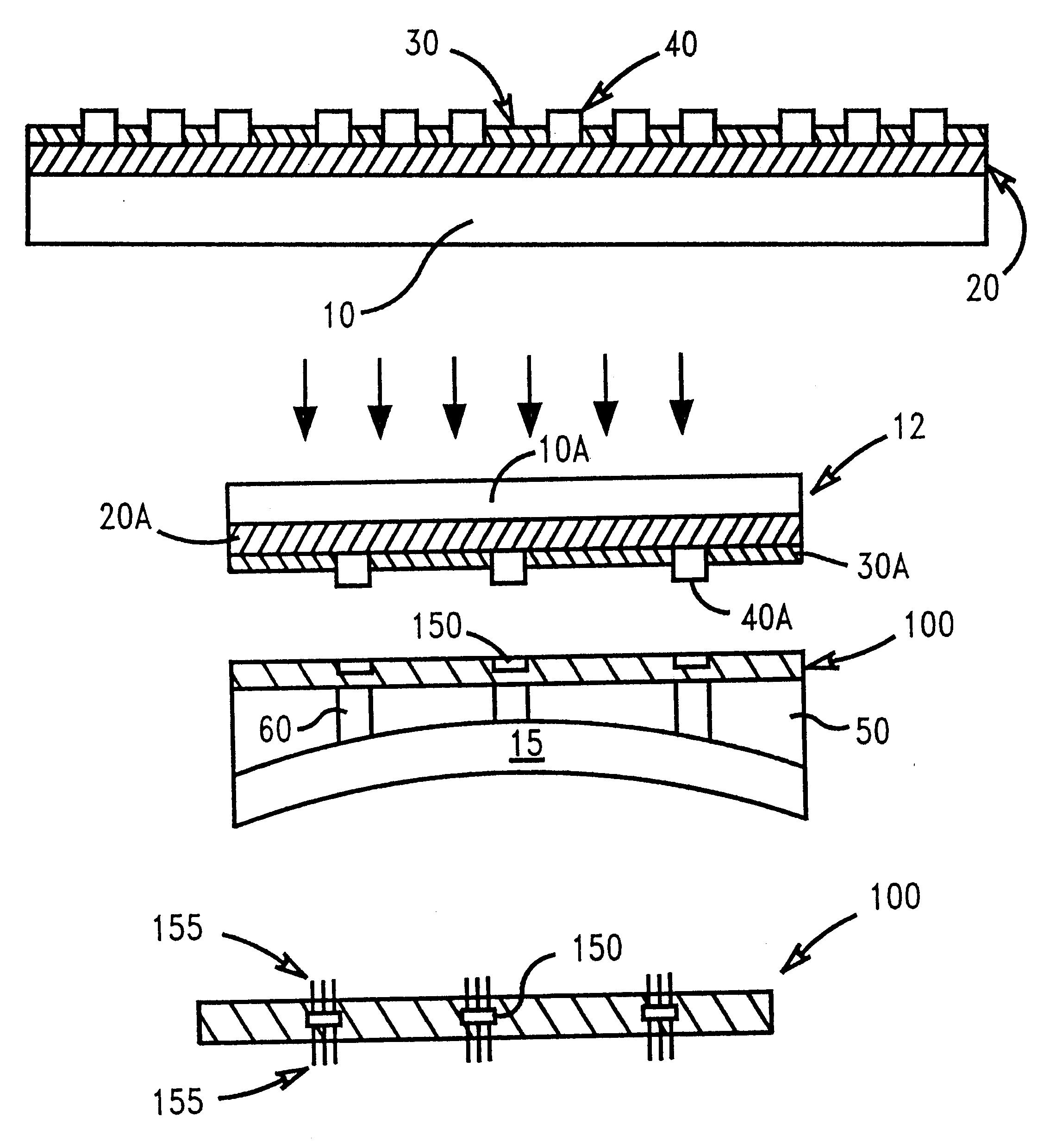

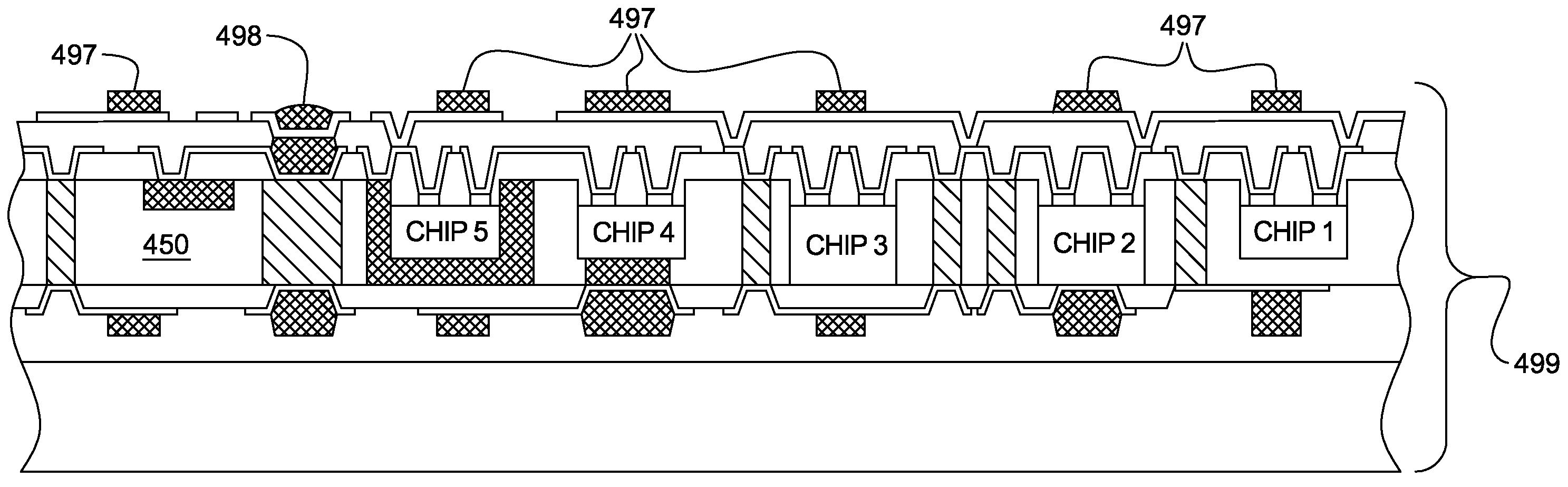

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

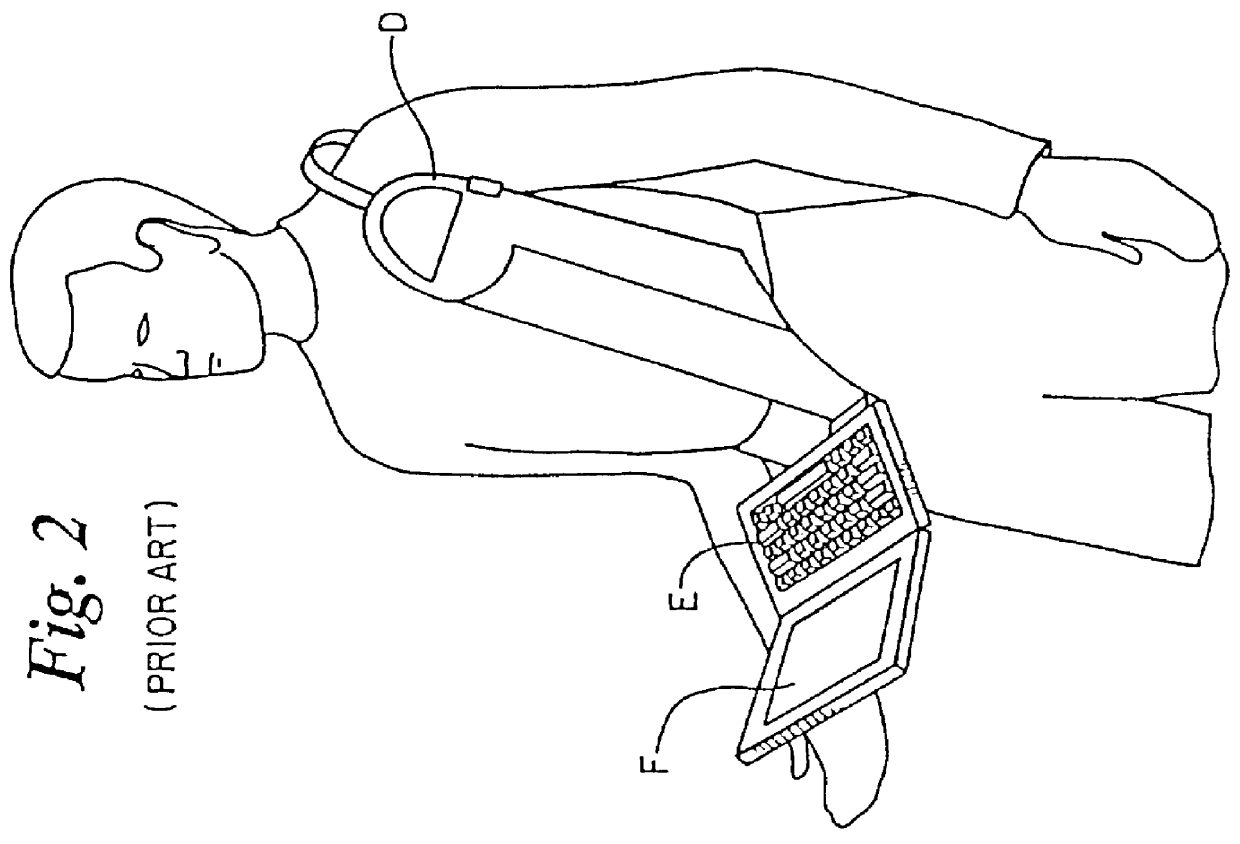

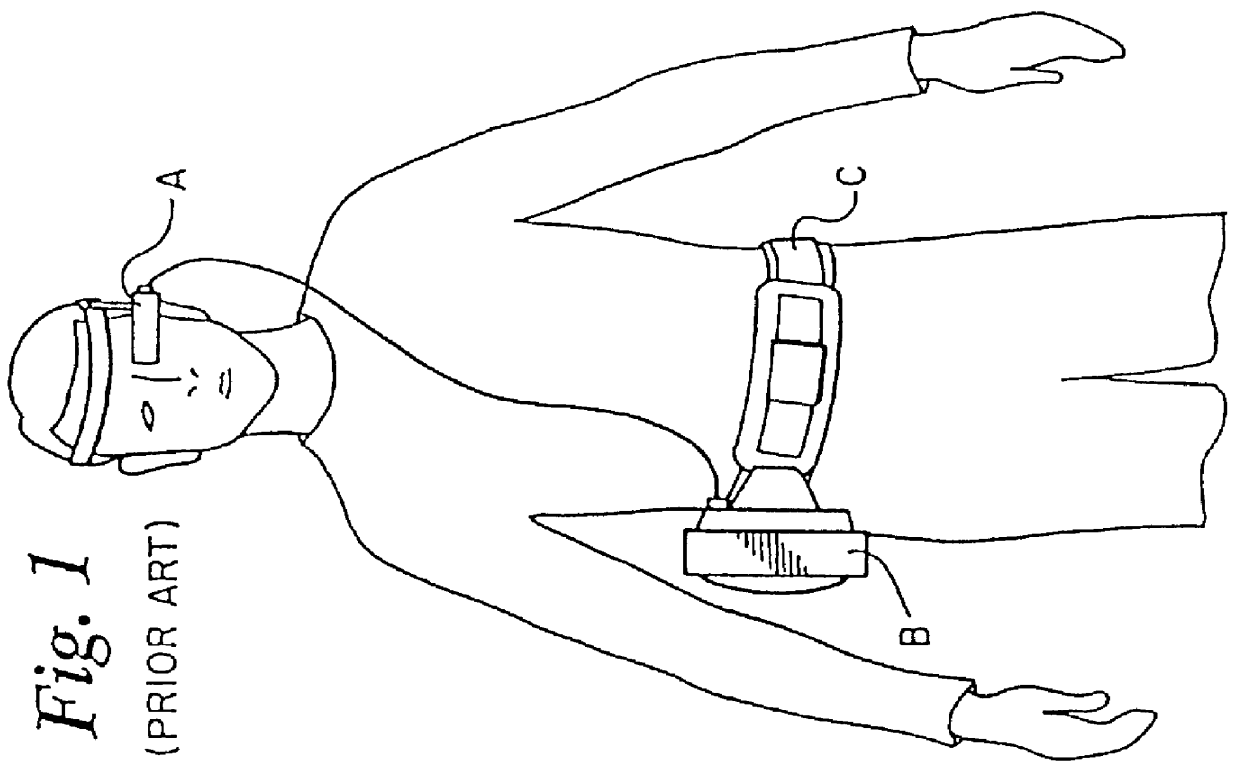

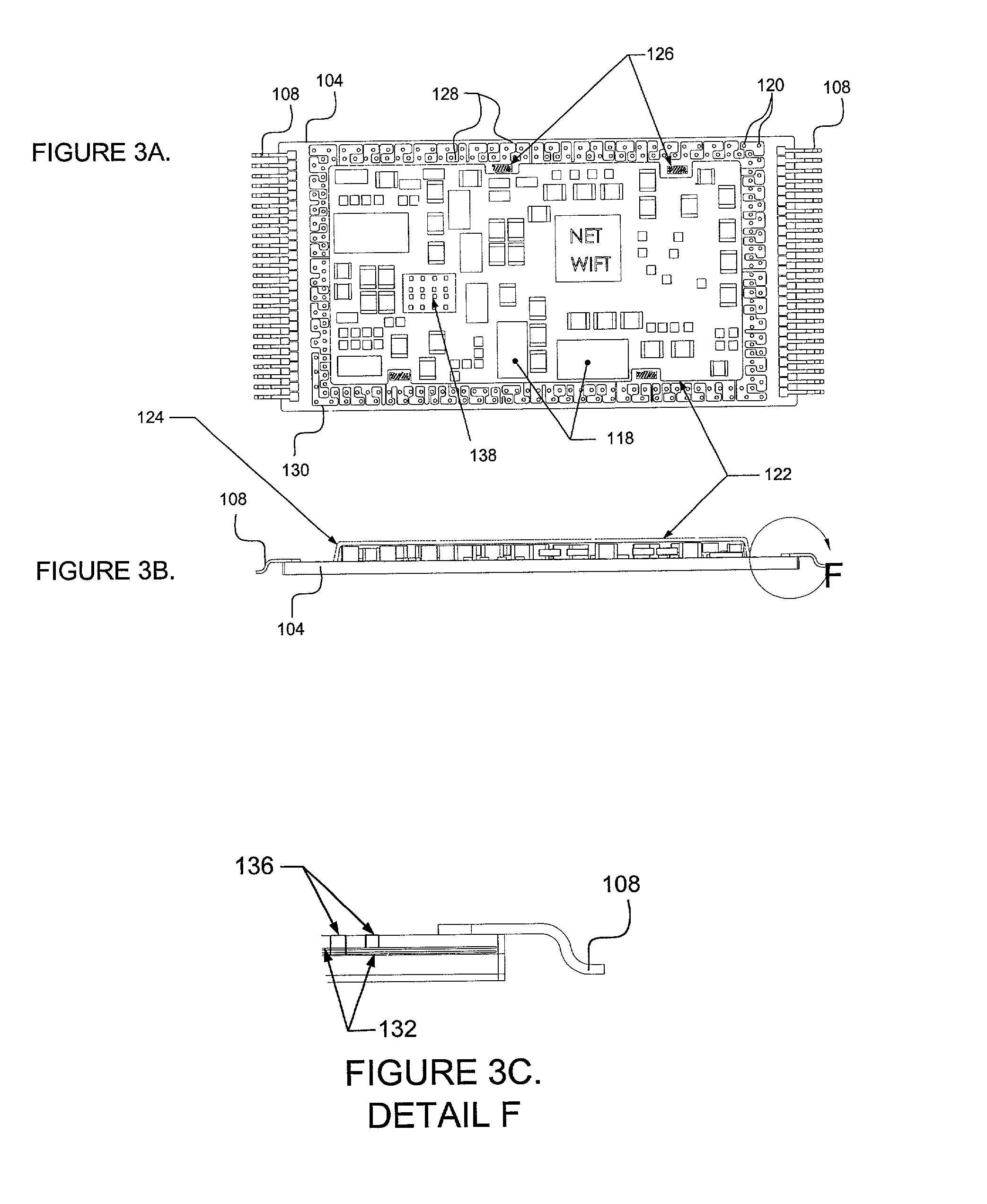

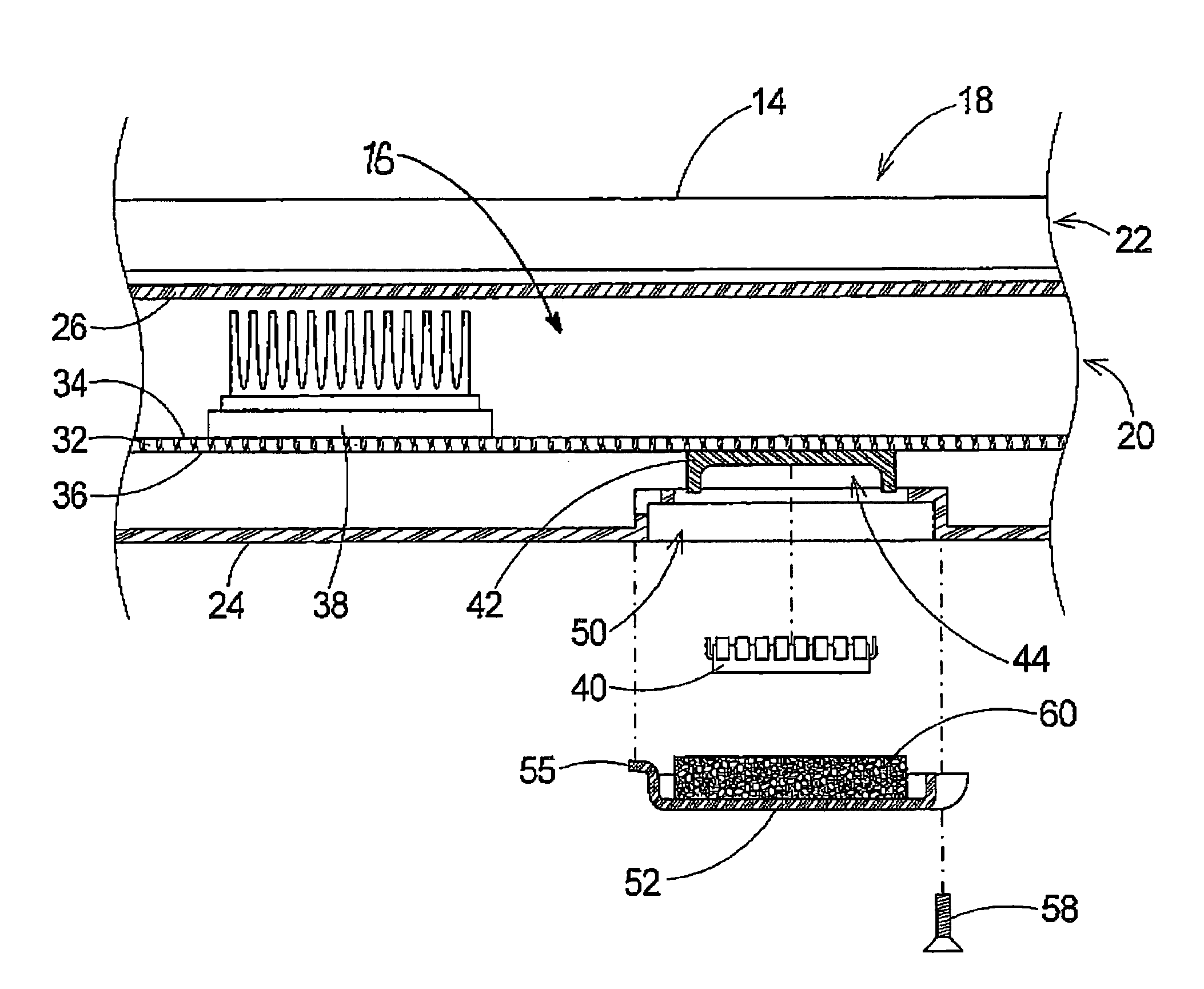

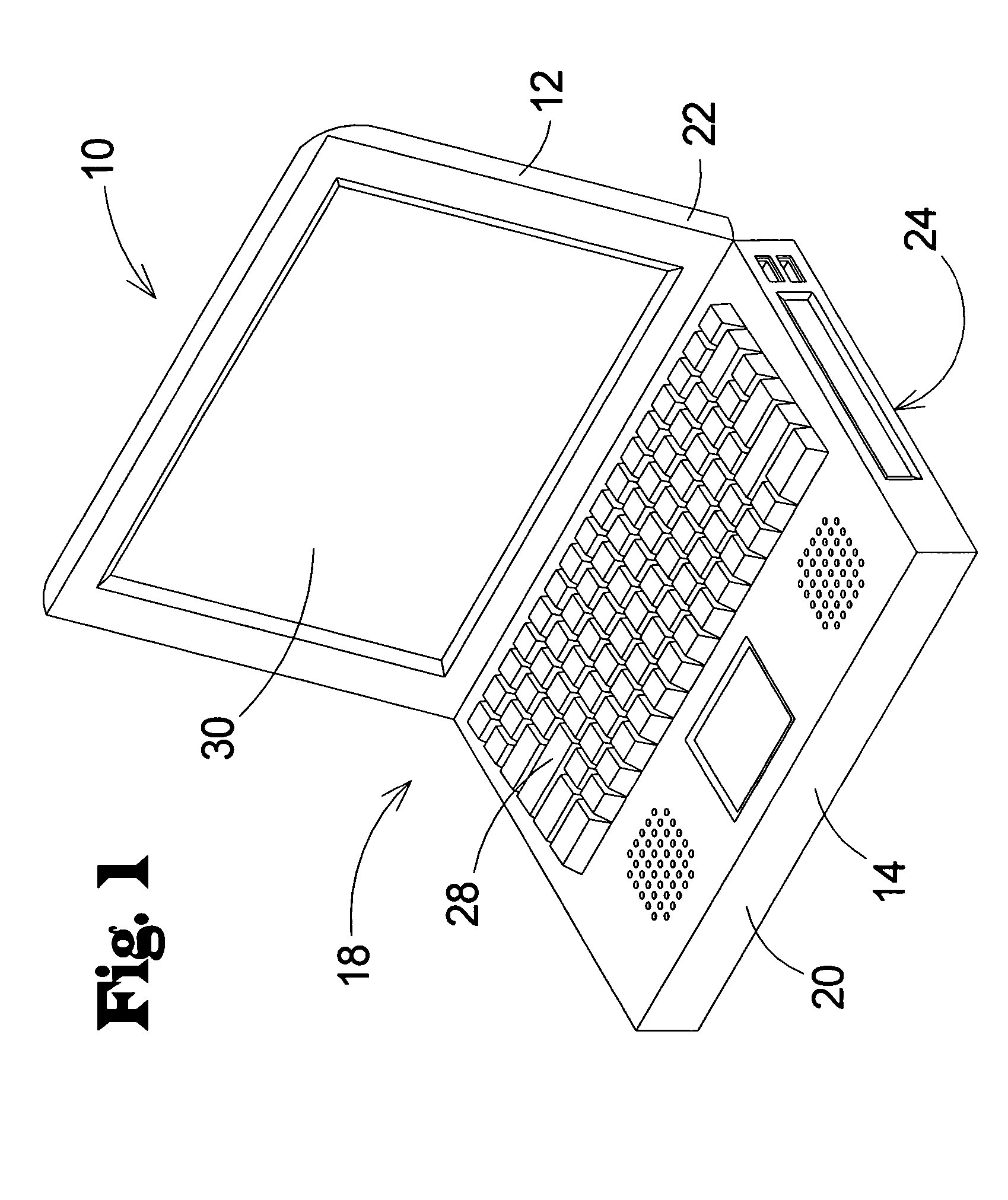

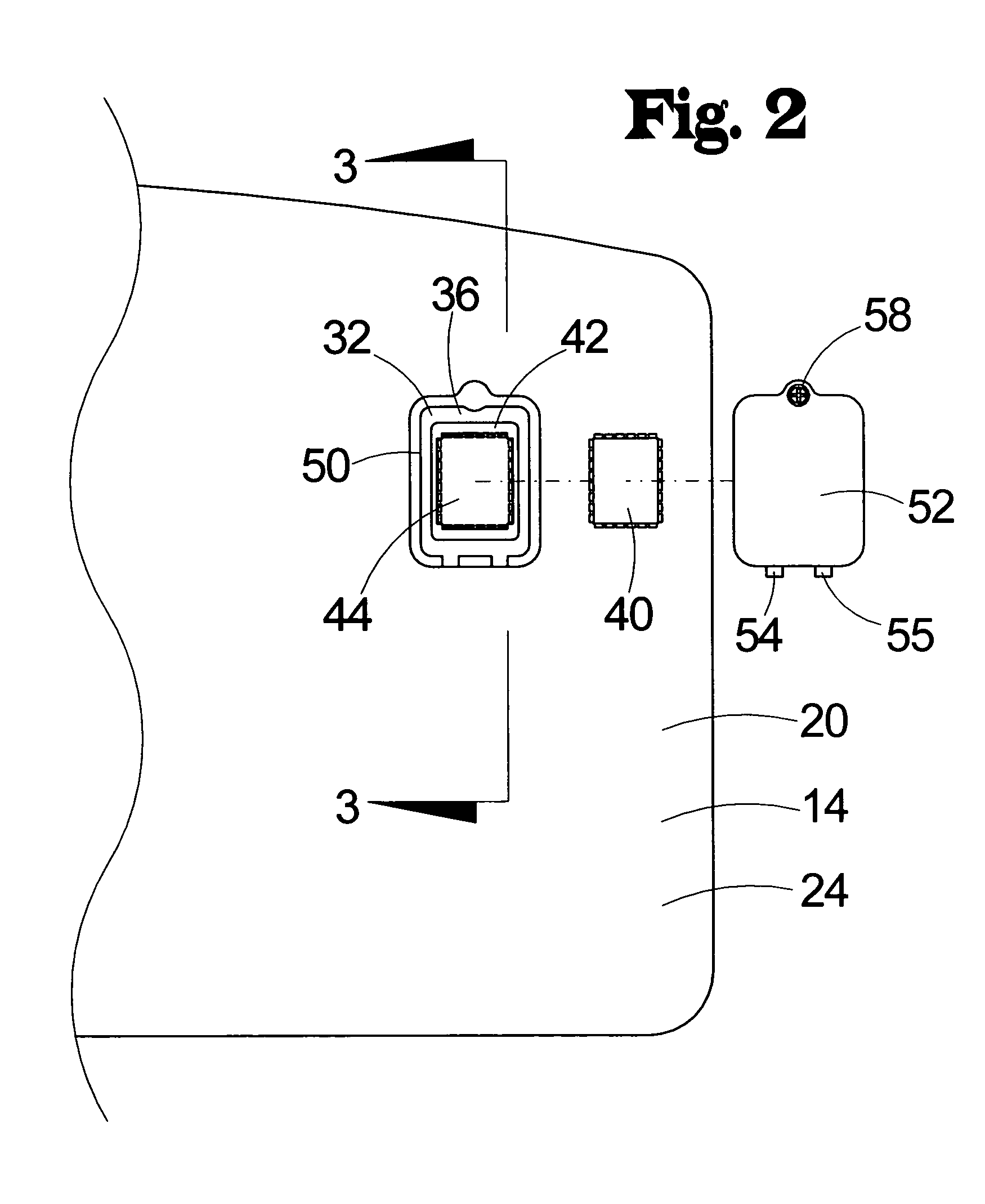

Flexible wearable computer

InactiveUS6108197AEasily and comfortably be expandedIncreased durabilityInput/output for user-computer interactionPrinted circuit assemblingComputer moduleRadio frequency

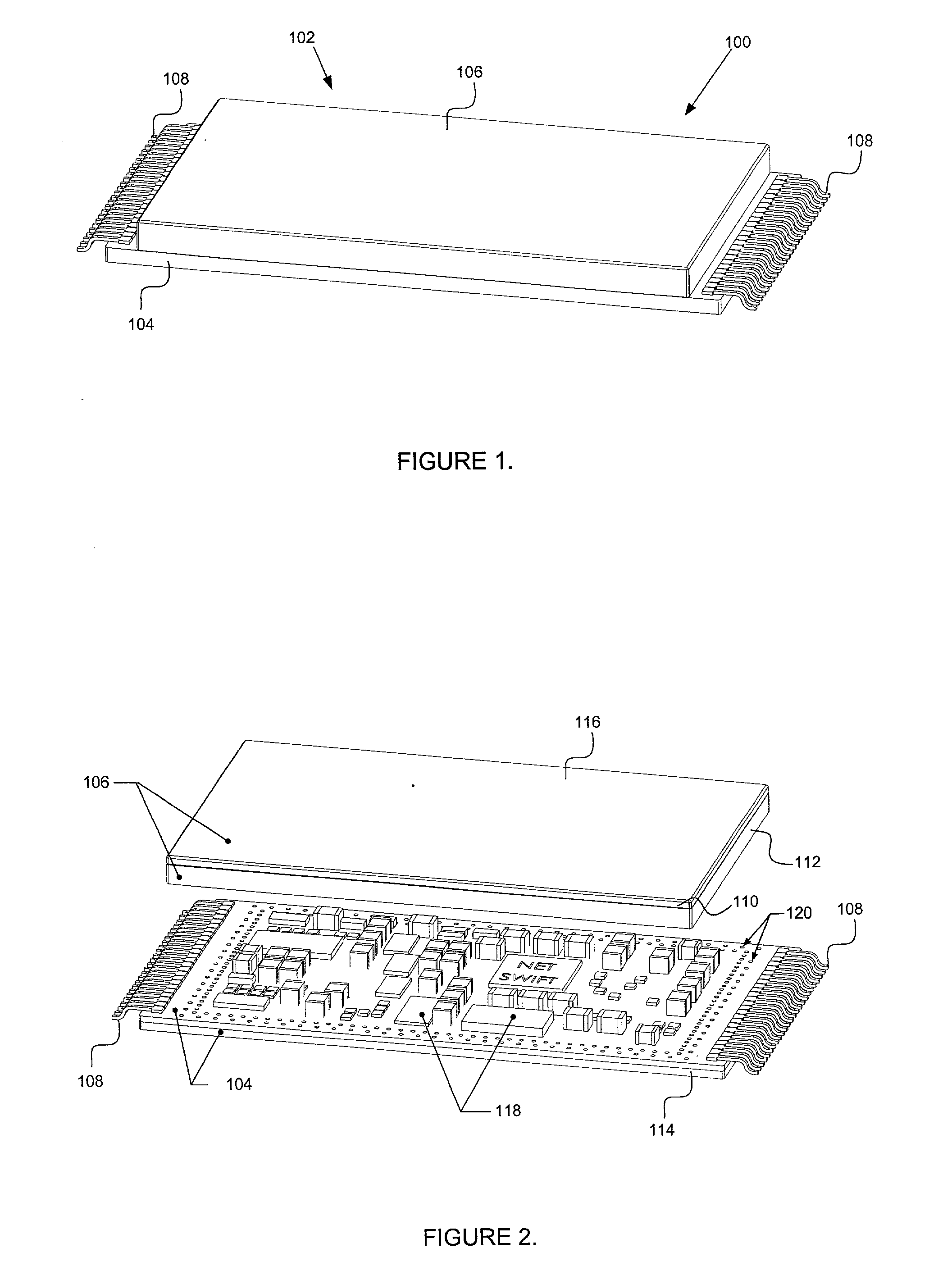

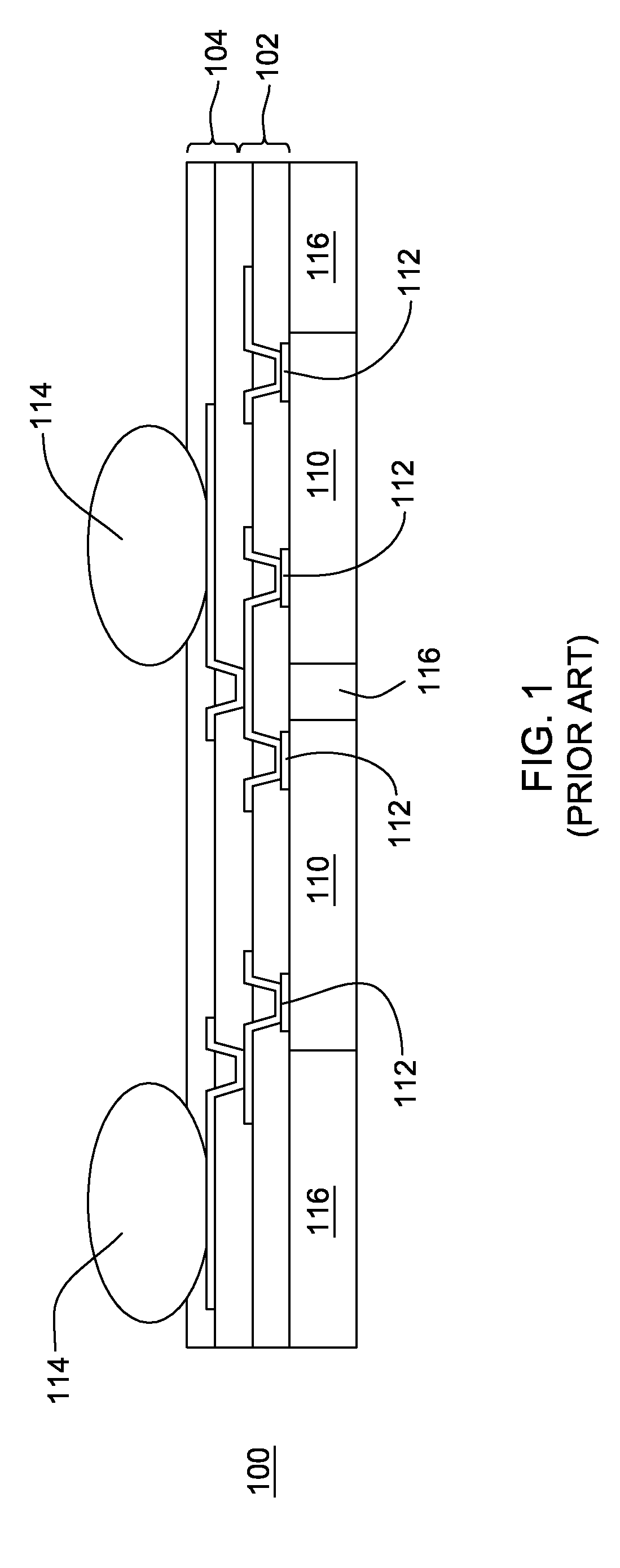

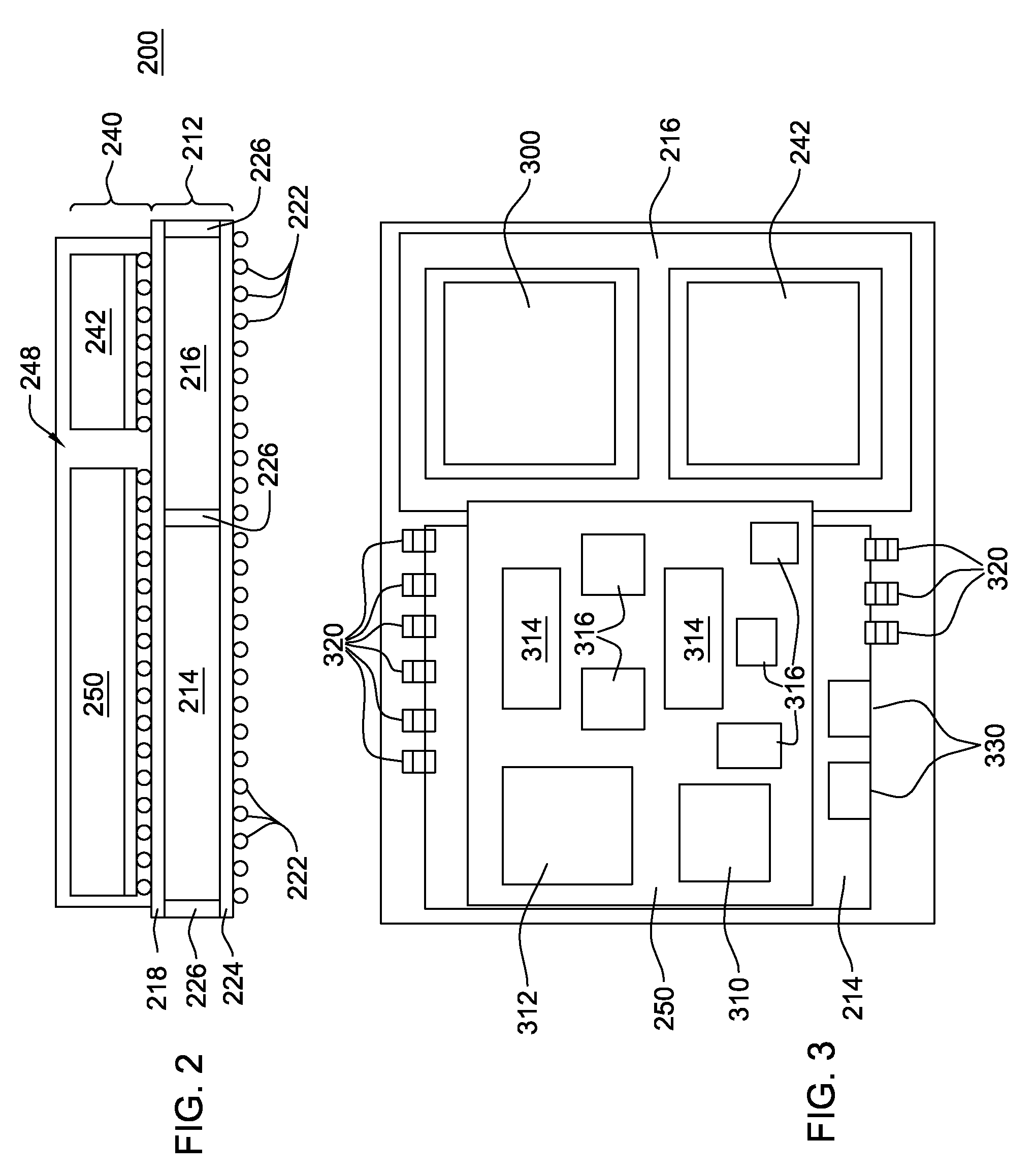

A wearable computing device includes computing-device component modules and flexible circuitry passing into the modules. The modules can include a top module portion and a bottom module portion, the flexible circuitry passing between the top and bottom portions. Wireless communication, e.g. by radio frequency, with a peripheral and / or a local area network is also contemplated.

Owner:EMBEDDED TECH +1

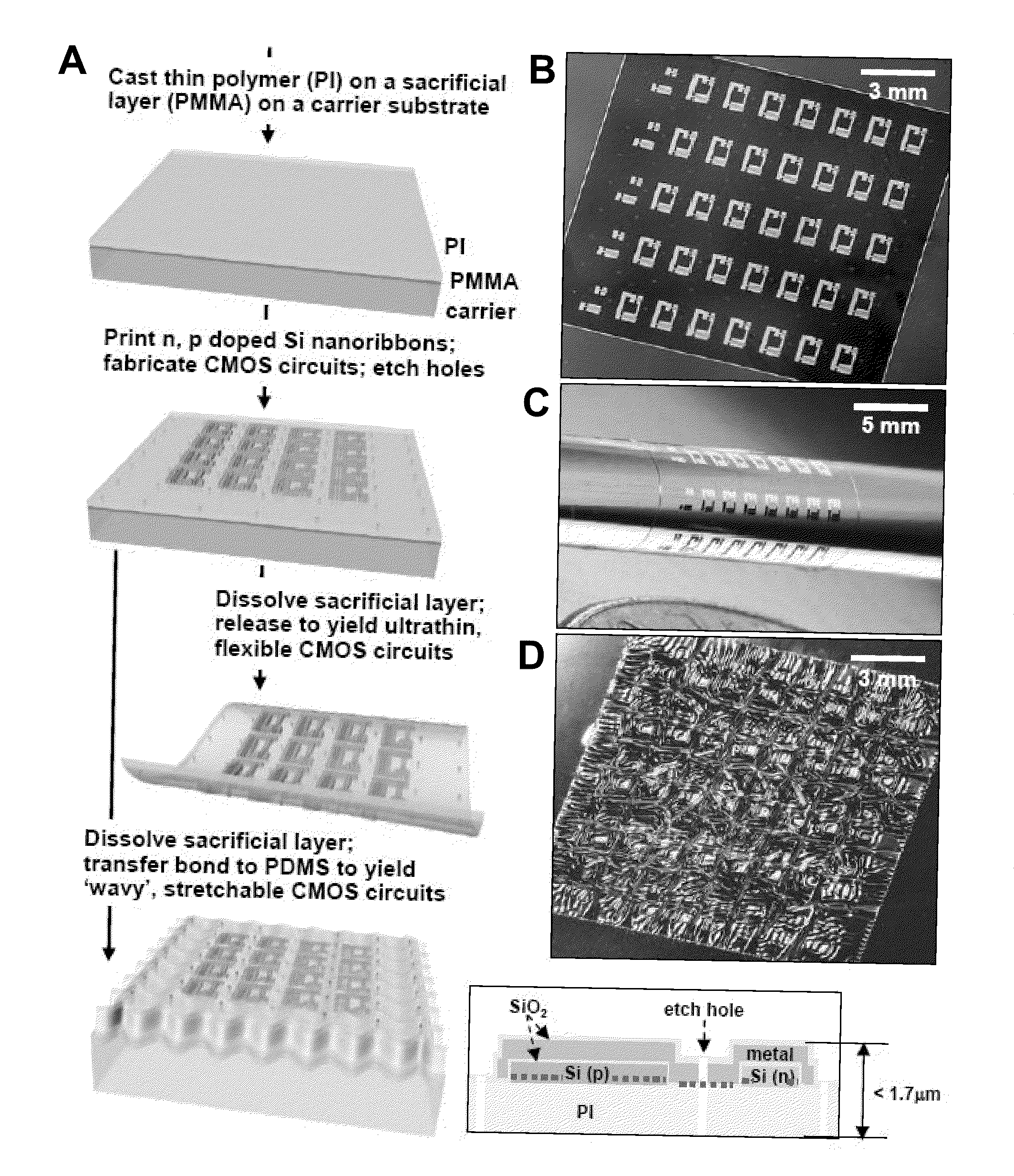

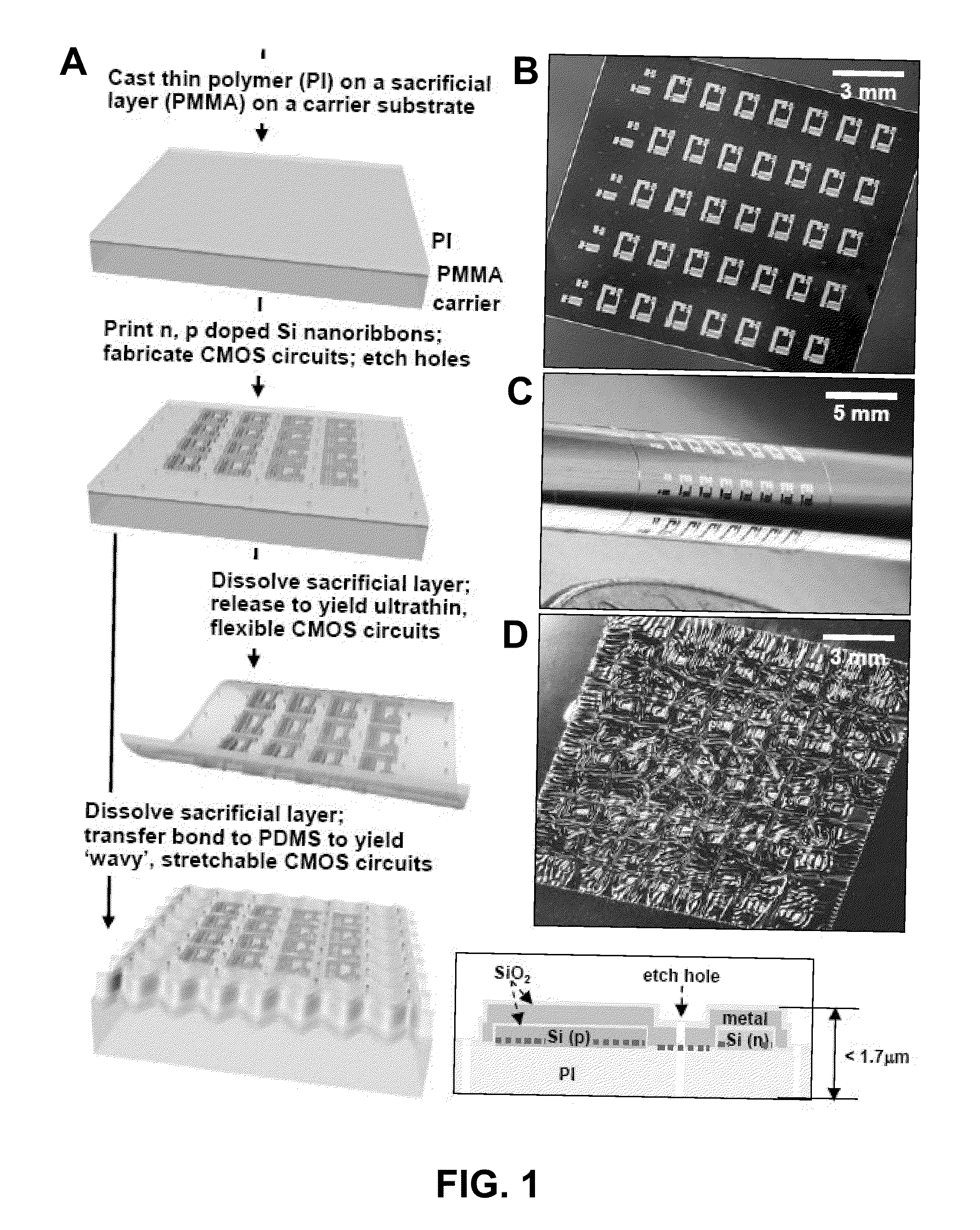

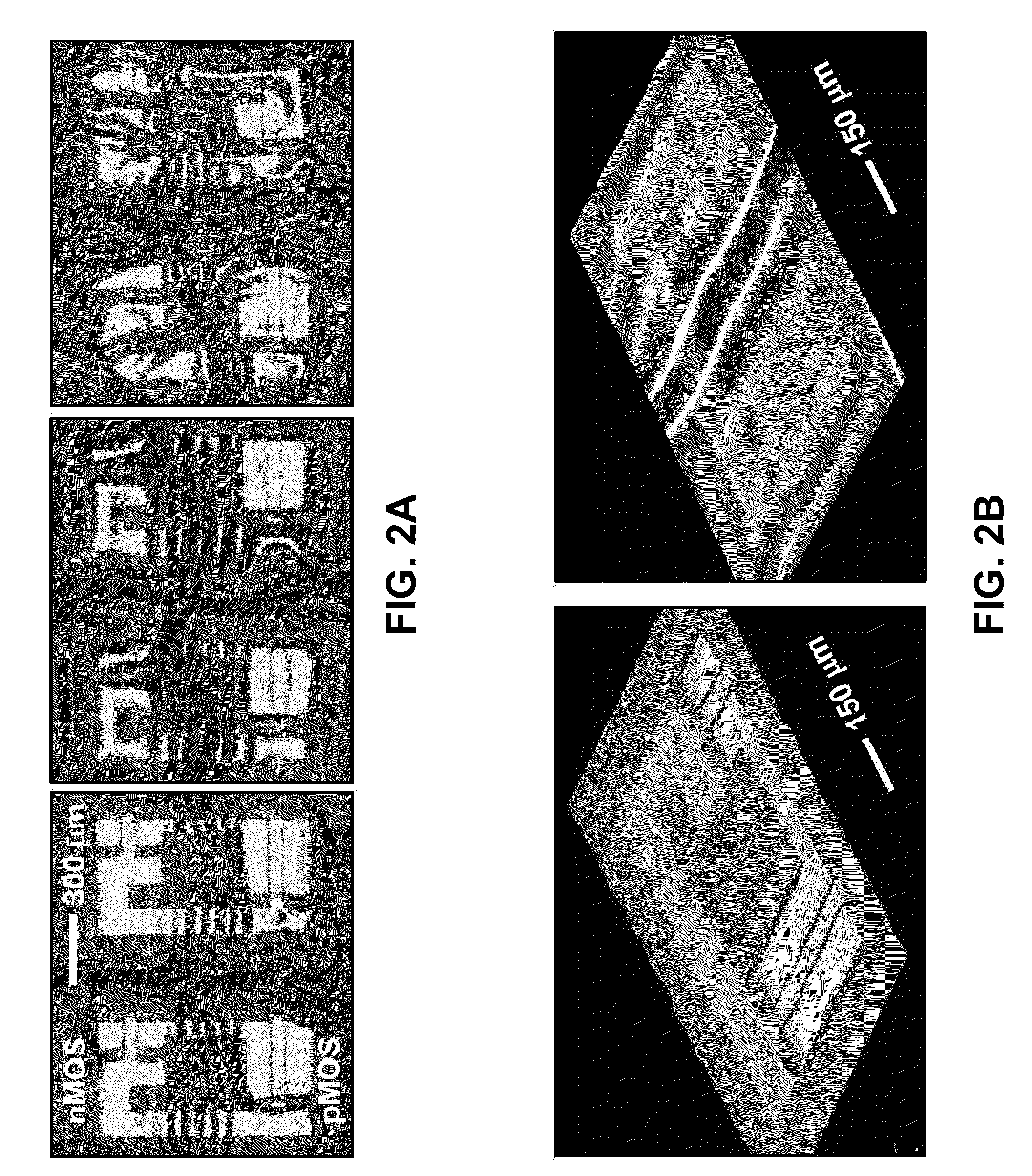

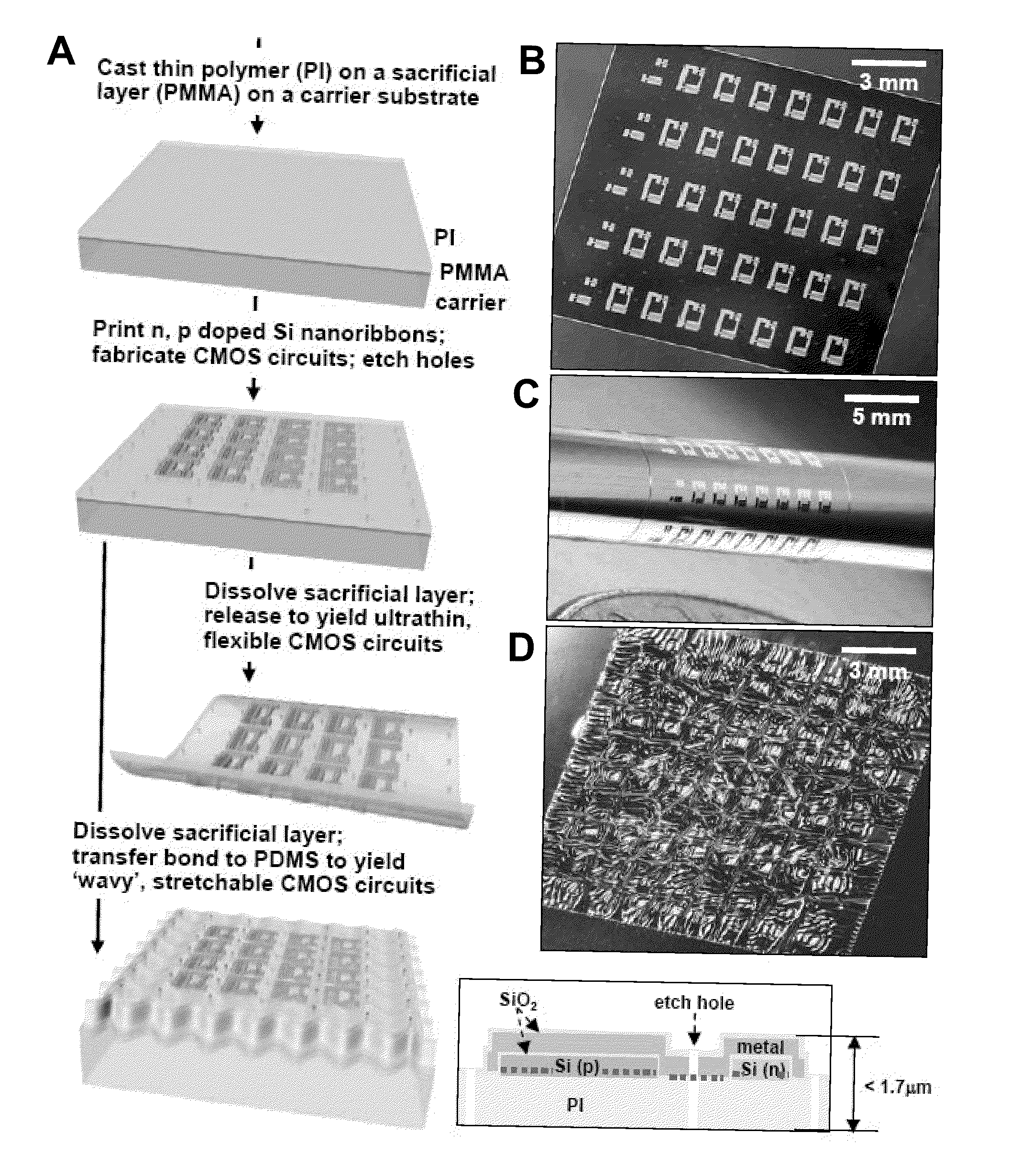

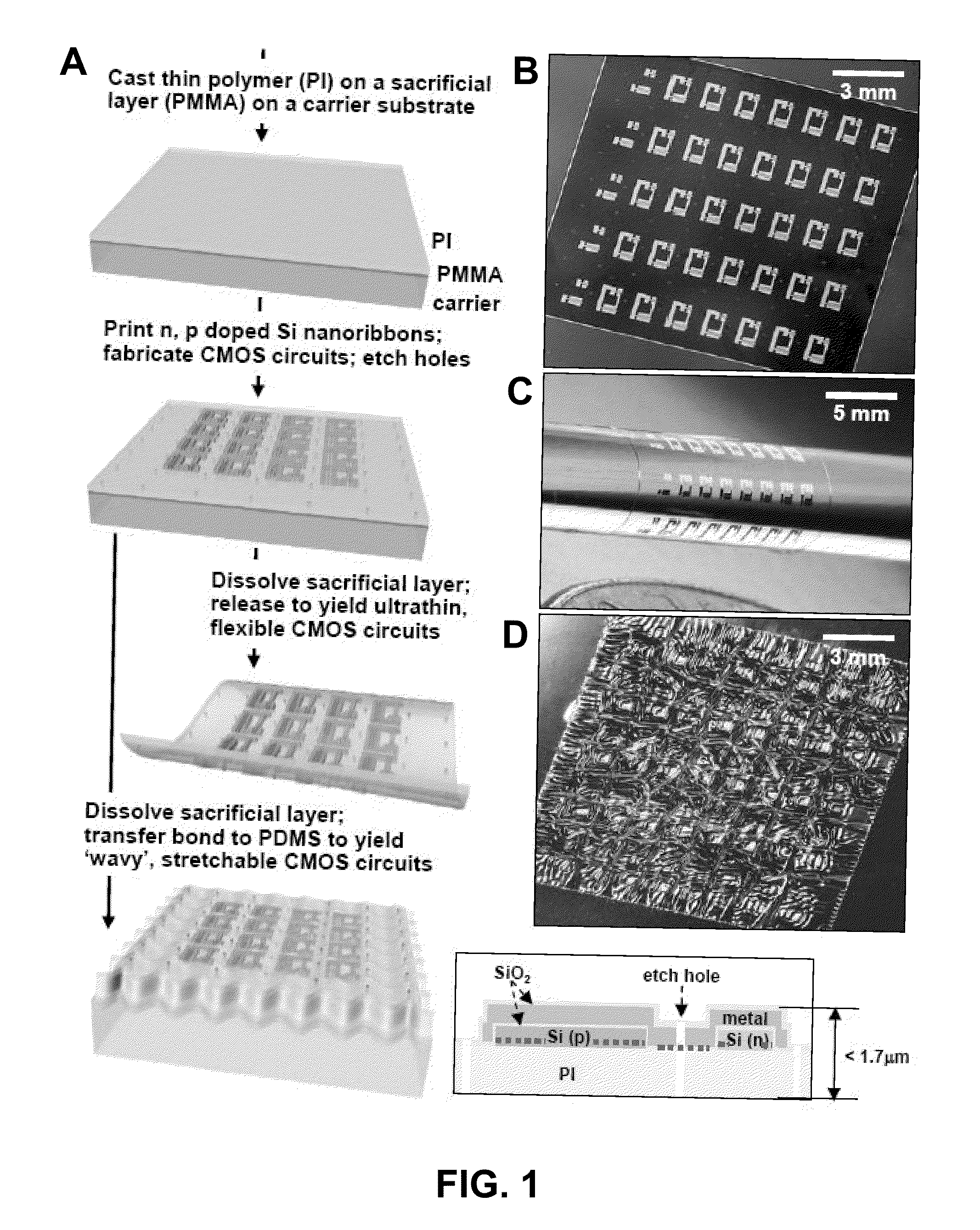

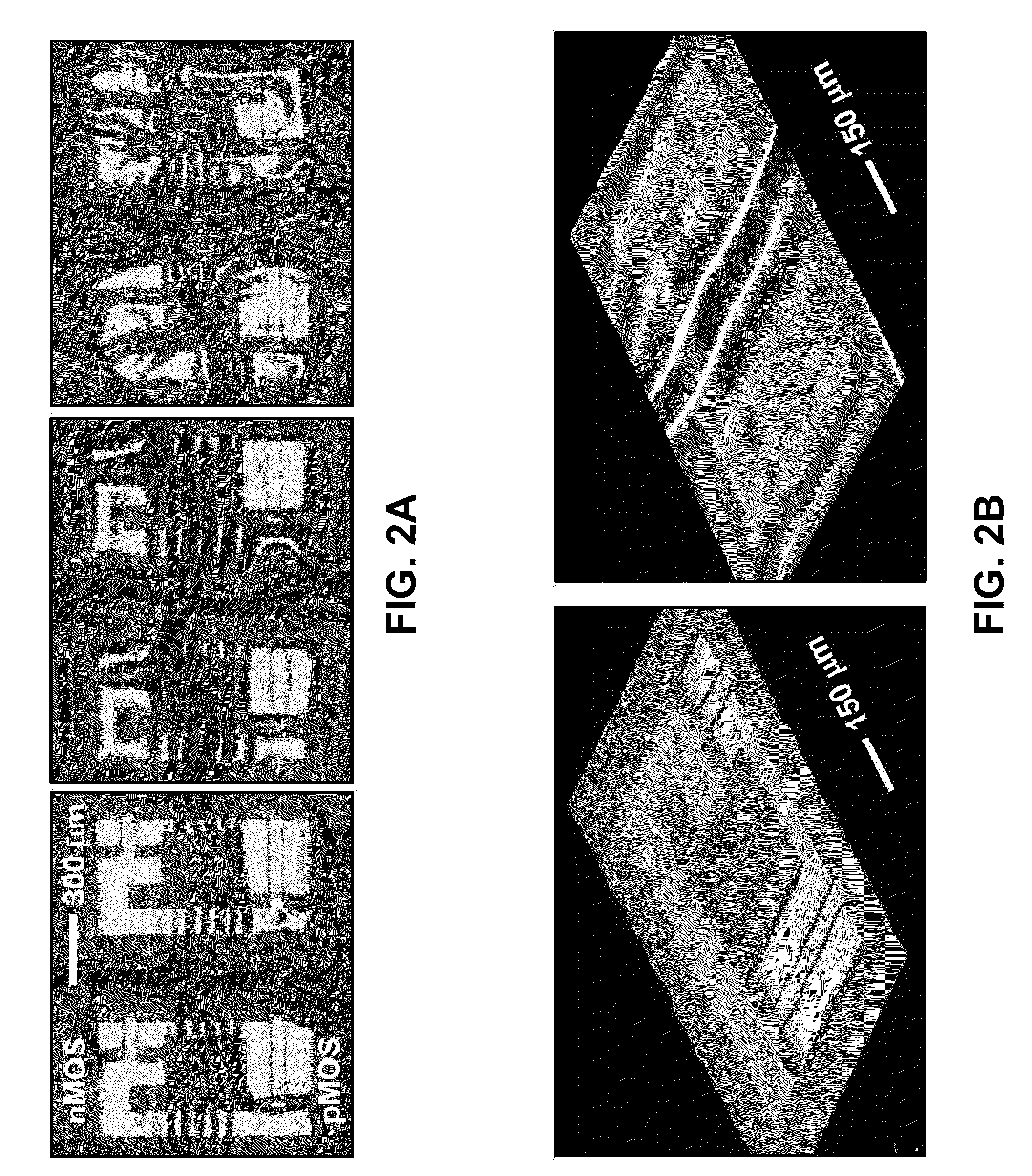

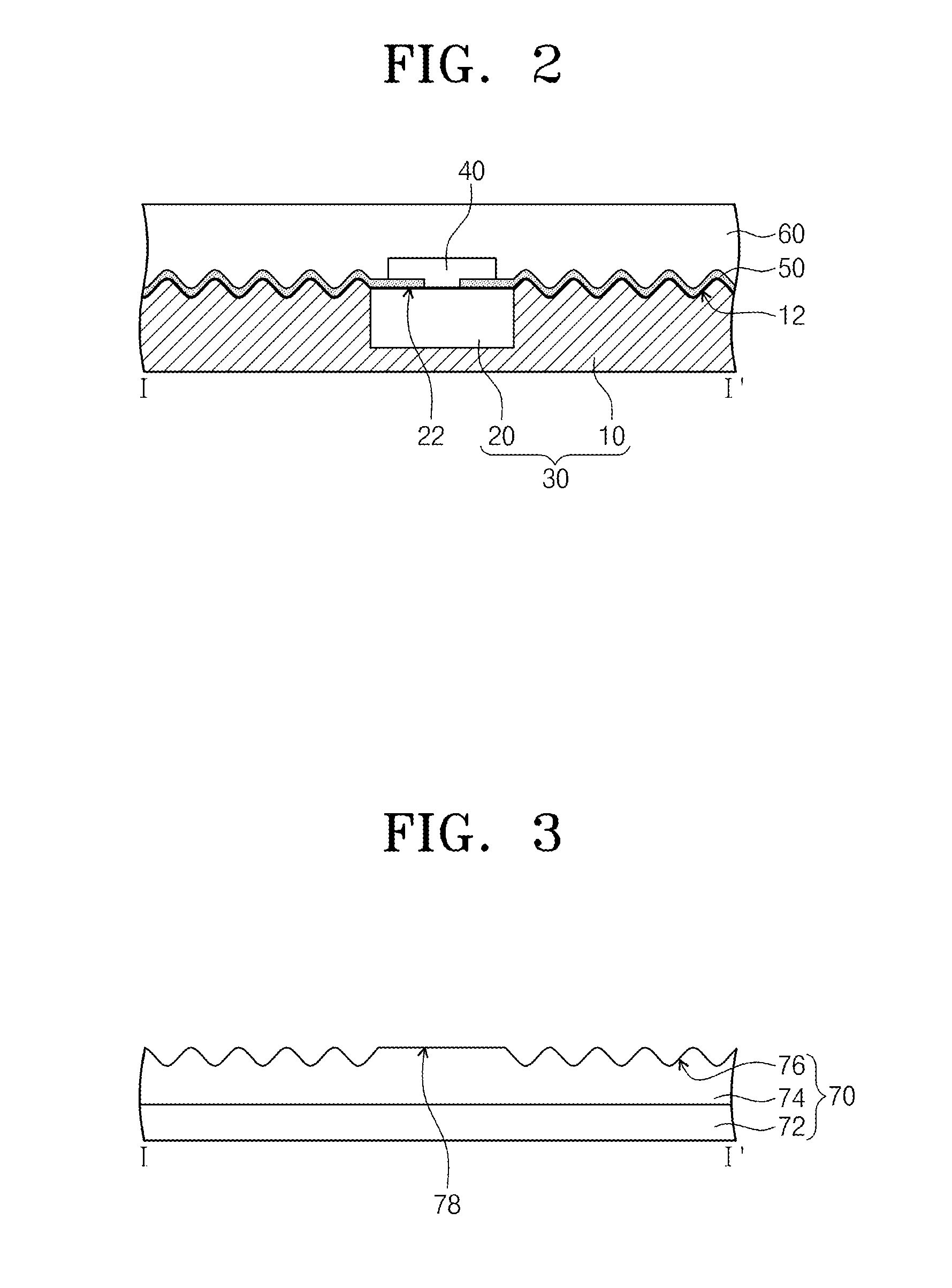

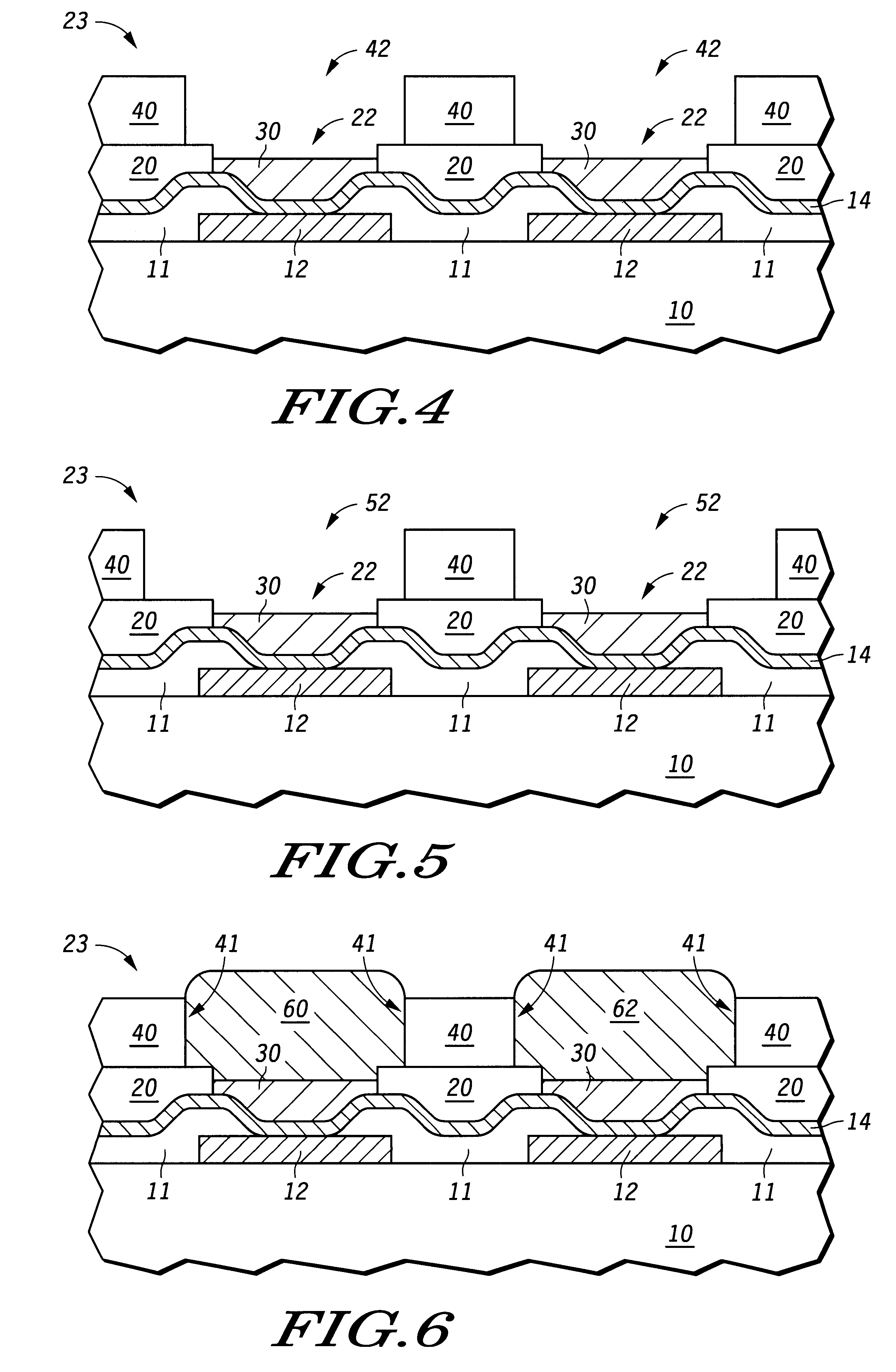

Stretchable and Foldable Electronic Devices

ActiveUS20100002402A1Easy to useQuality improvementWave amplification devicesSemiconductor/solid-state device detailsIsolation layerEngineering

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Method of manufacturing a semiconductor package

InactiveUS7185426B1Printed circuit assemblingSemiconductor/solid-state device detailsElectrical conductorSemiconductor package

A semiconductor package including top-surface terminals for mounting another semiconductor package provides a three-dimensional circuit configuration that can provide removable connection of existing grid-array packages having a standard design. A semiconductor die is mounted on an electrically connected to a circuit substrate having terminals disposed on a bottom side for connection to an external system. The die and substrate are encapsulated and vias are laser-ablated or otherwise formed through the encapsulation to terminals on the top surface of the substrate that provide a grid array mounting lands to which another grid array semiconductor package may be mounted. The bottom side of the vias may terminate and electrically connect to terminals on the substrate, terminals on the bottom of the semiconductor package (through terminals) or terminals on the top of the semiconductor die. The vias may be plated, paste-filled, filled with a low melting point alloy and may have a conical profile for improved plating performance.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

LED lighting assemblies with thermal overmolding

ActiveUS20070121326A1Thermal conductivityPoint-like light sourceElectric circuit arrangementsEffect lightEngineering

One or more light emitting diode diodes (LEDs) are attached to a printed circuit board. The attached LEDs are connectable with a power source via circuitry of the printed circuit board. An overmolding material is insert molded an over at least portions of the printed circuit board proximate to the LEDs to form a free standing high thermal conductivity material overmolding that covers at least portions of the printed circuit board proximate to the LEDs. The free standing high thermal conductivity material has a melting temperature greater than about 100° C. and has a thermal conductivity greater than or about 1 W / m·K. In some embodiments, the free standing high thermal conductivity material is a thermoplastic material.

Owner:GE LIGHTING SOLUTIONS LLC

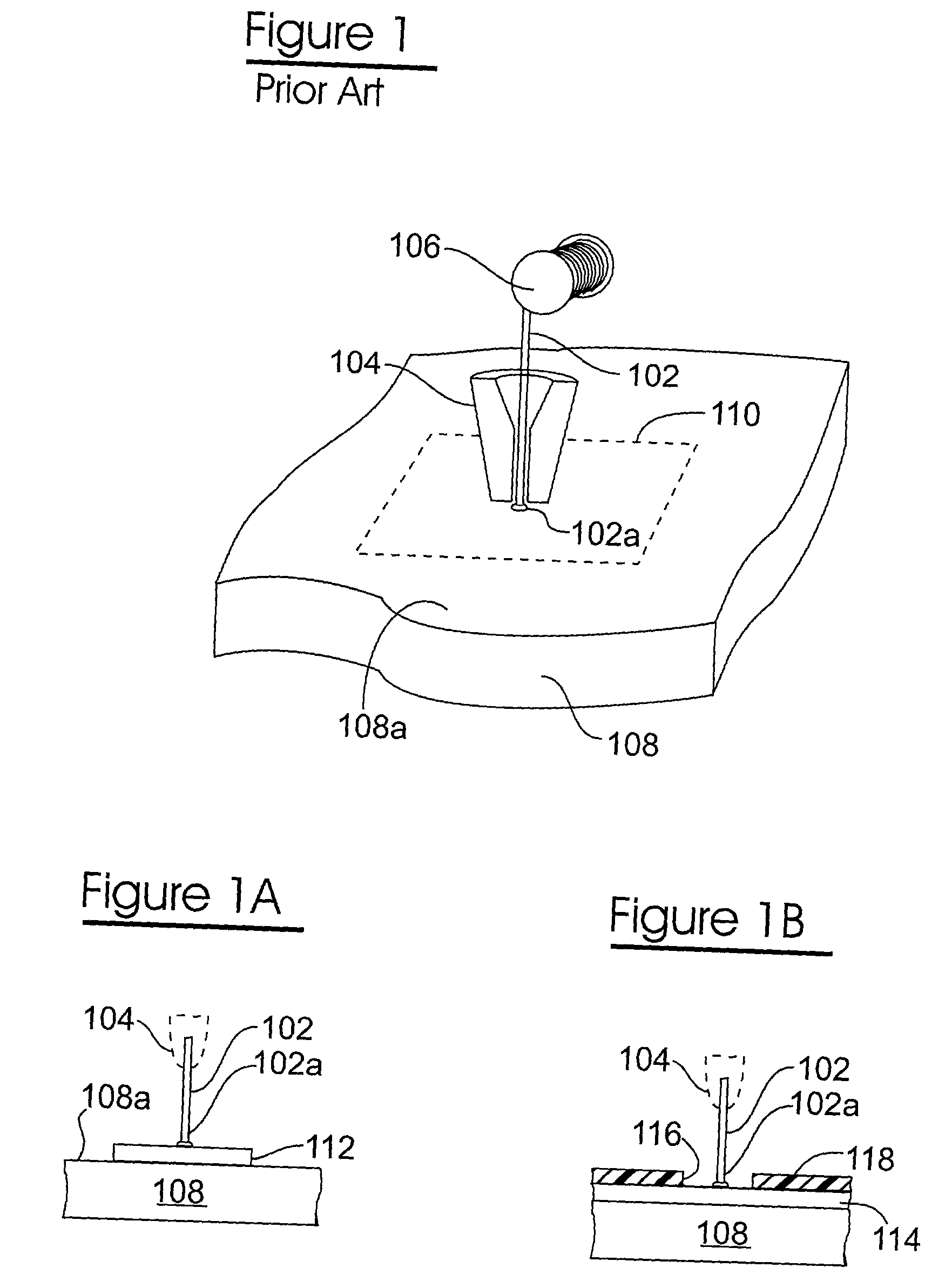

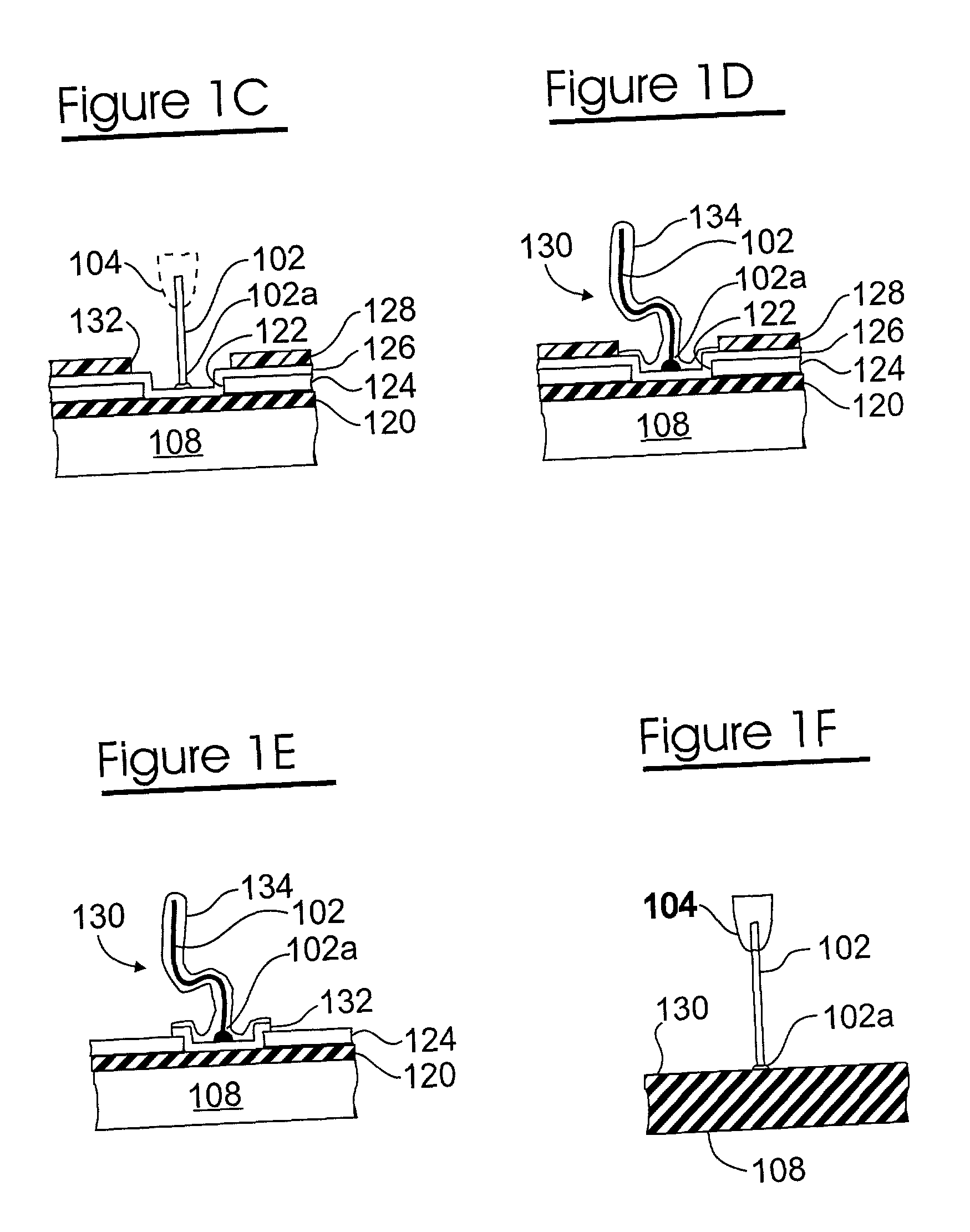

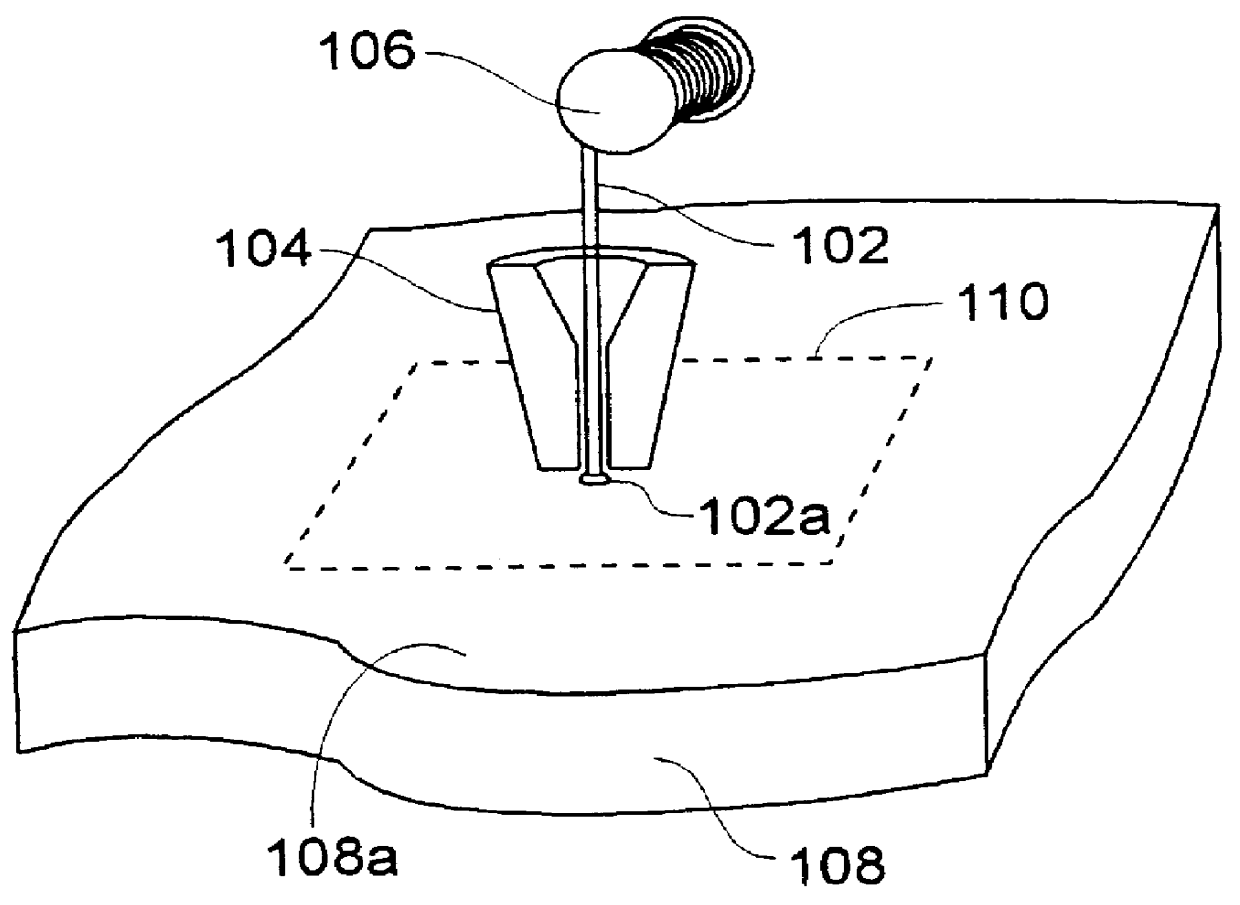

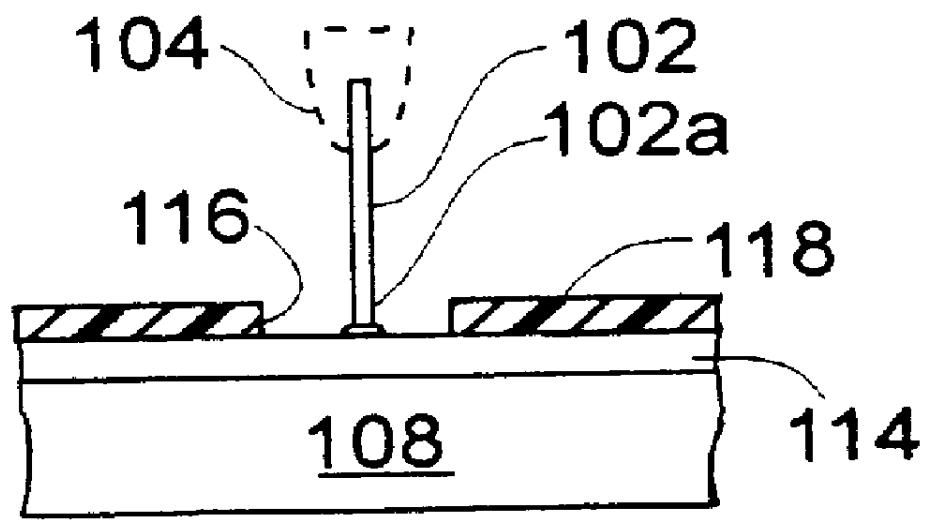

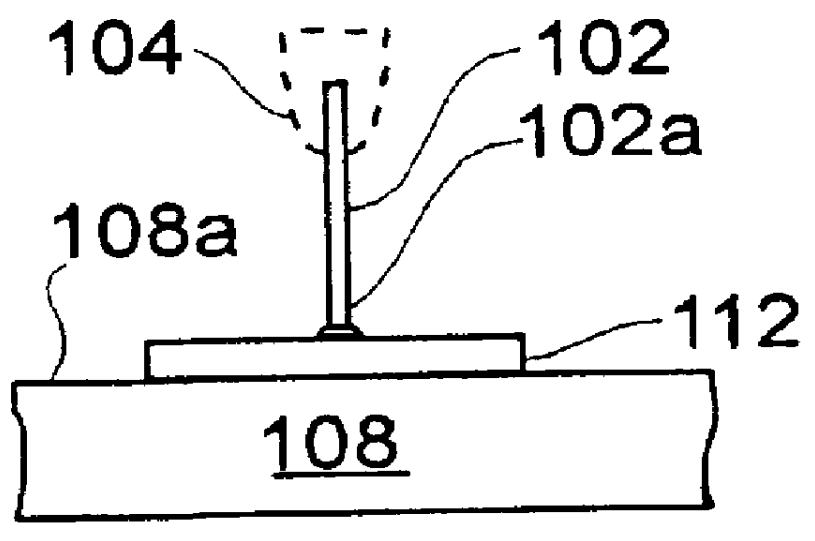

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

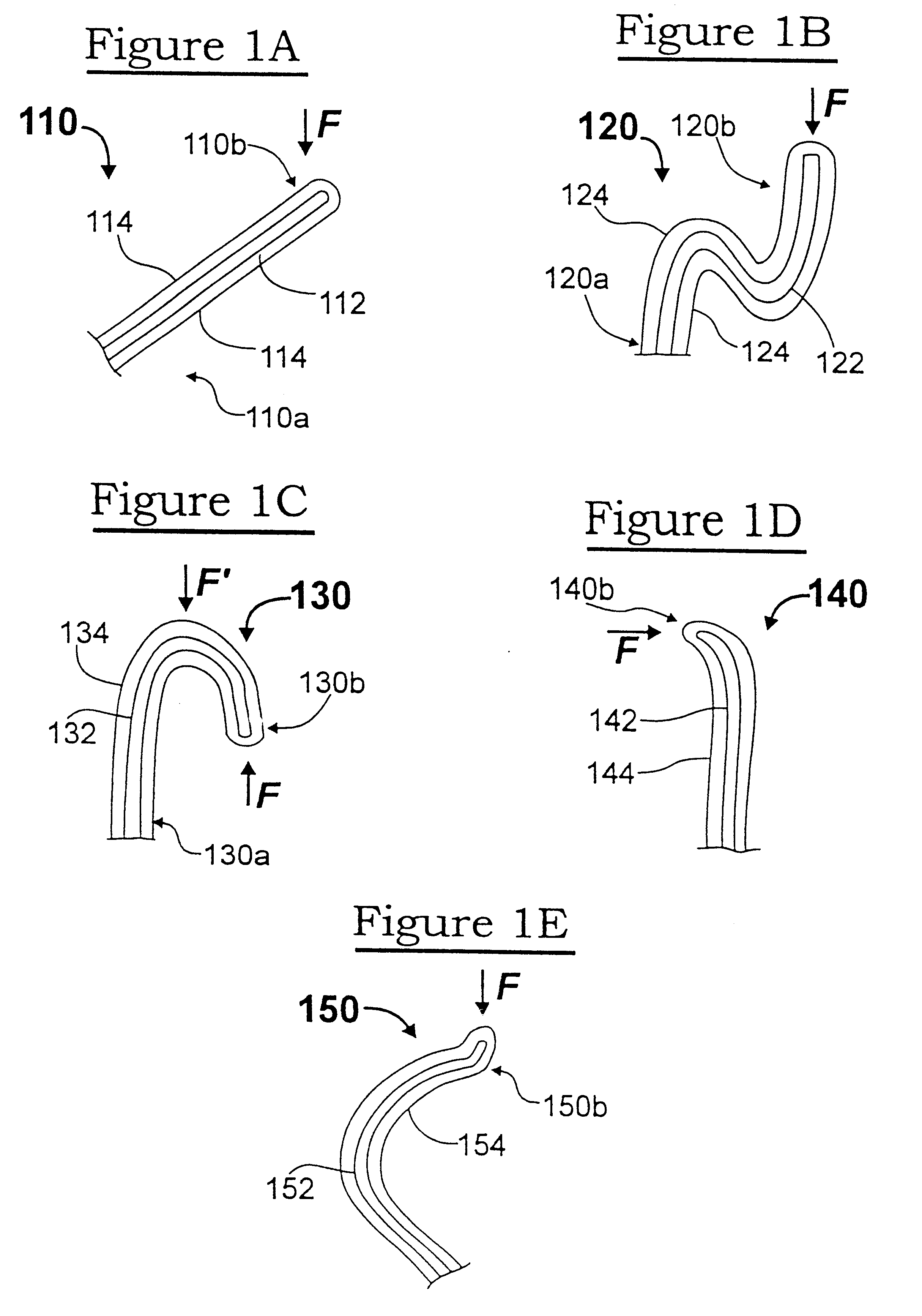

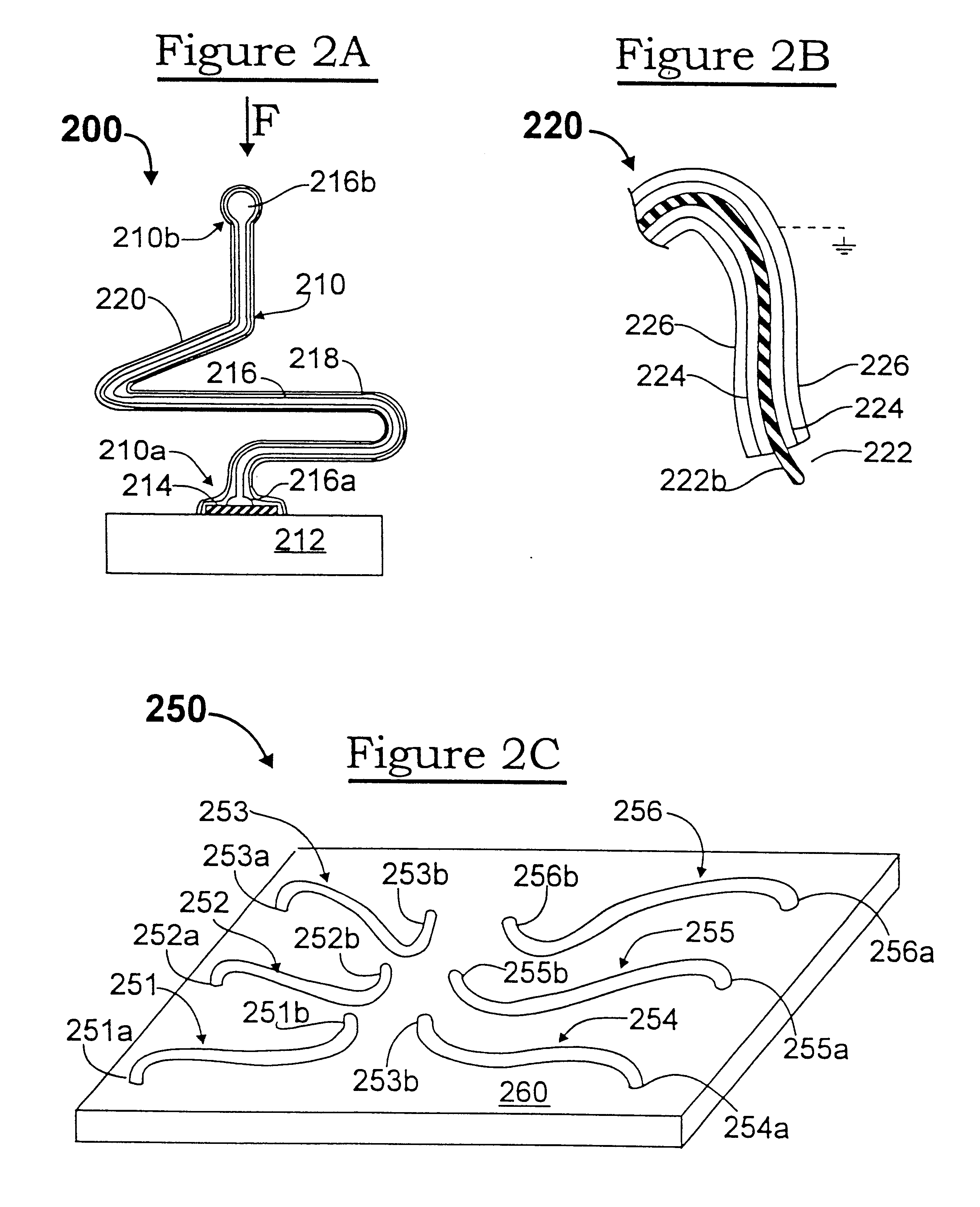

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

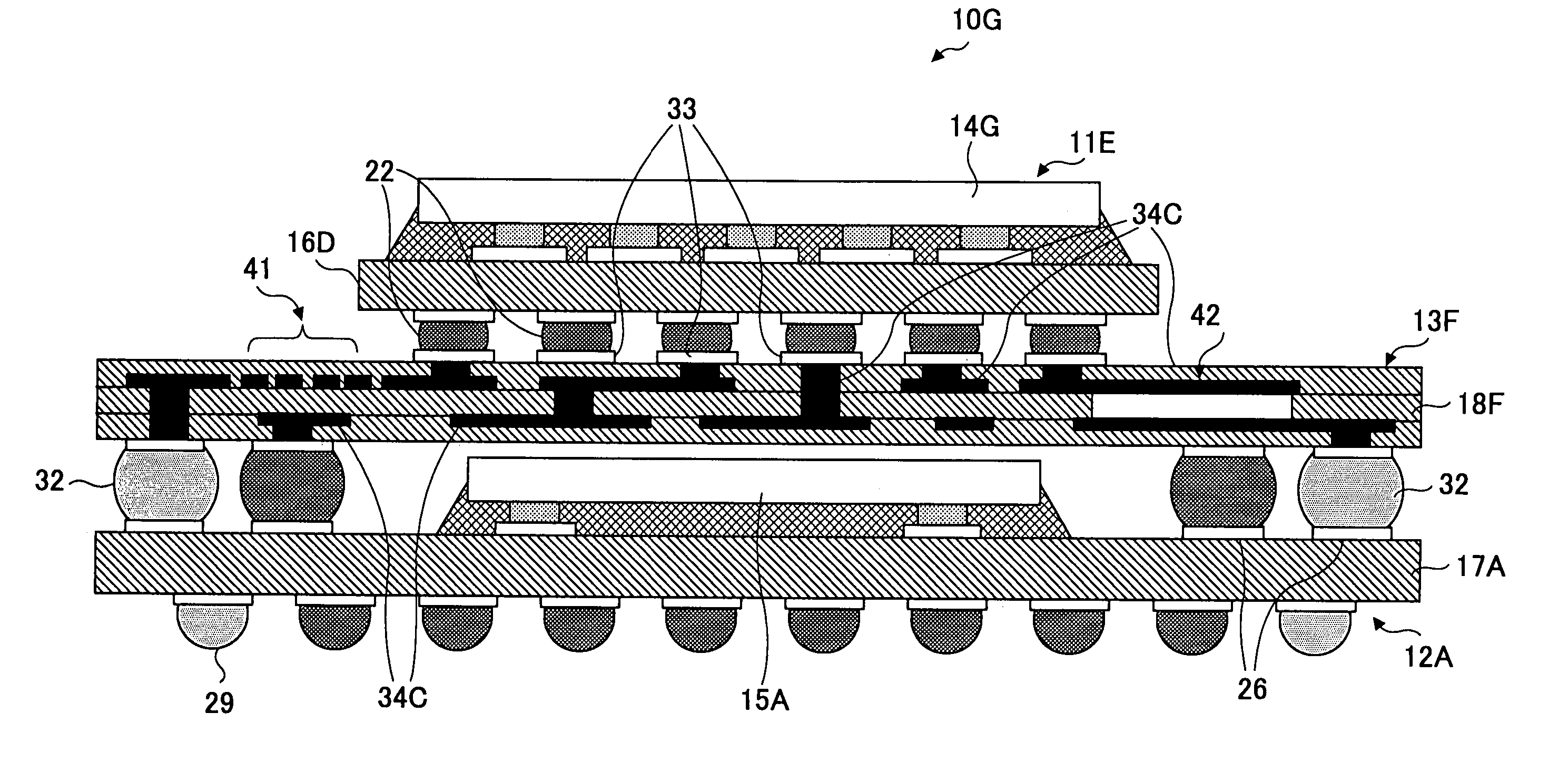

Stacked semiconductor device

ActiveUS7049692B2Eliminate the problemPrinted circuit assemblingSemiconductor/solid-state device detailsGeneral purposeEngineering

A stacked semiconductor device is disclosed that has a three-dimensional structure using general-purpose semiconductor device units (semiconductor devices) that are stacked with an interposer substrate being provided between an upper device unit and a lower device unit. The upper device unit includes a semiconductor device, a first wiring substrate, and an external connection terminal. The lower device unit includes a semiconductor device, a second wiring substrate, and a connection electrode that is prepared on the upper surface of the second wiring substrate. The interposer substrate includes a circuit board, a first conductive material connecting to the connection electrode, a second conductive material formed in a form position of the external connection terminal that is electrically connected to the second conductive material, and a third conductive material for electrically connecting the first conductive material and the second conductive material.

Owner:SOCIONEXT INC

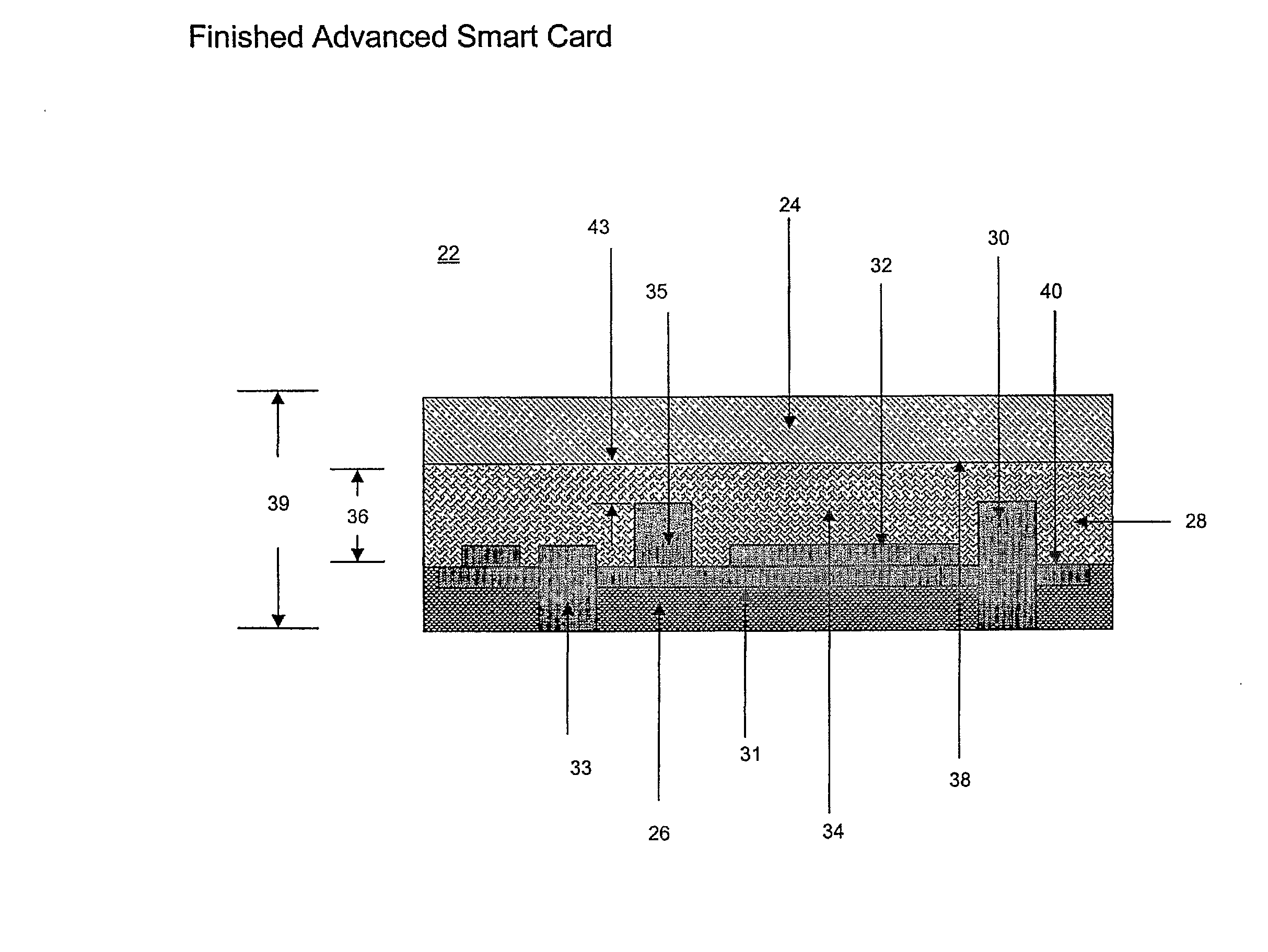

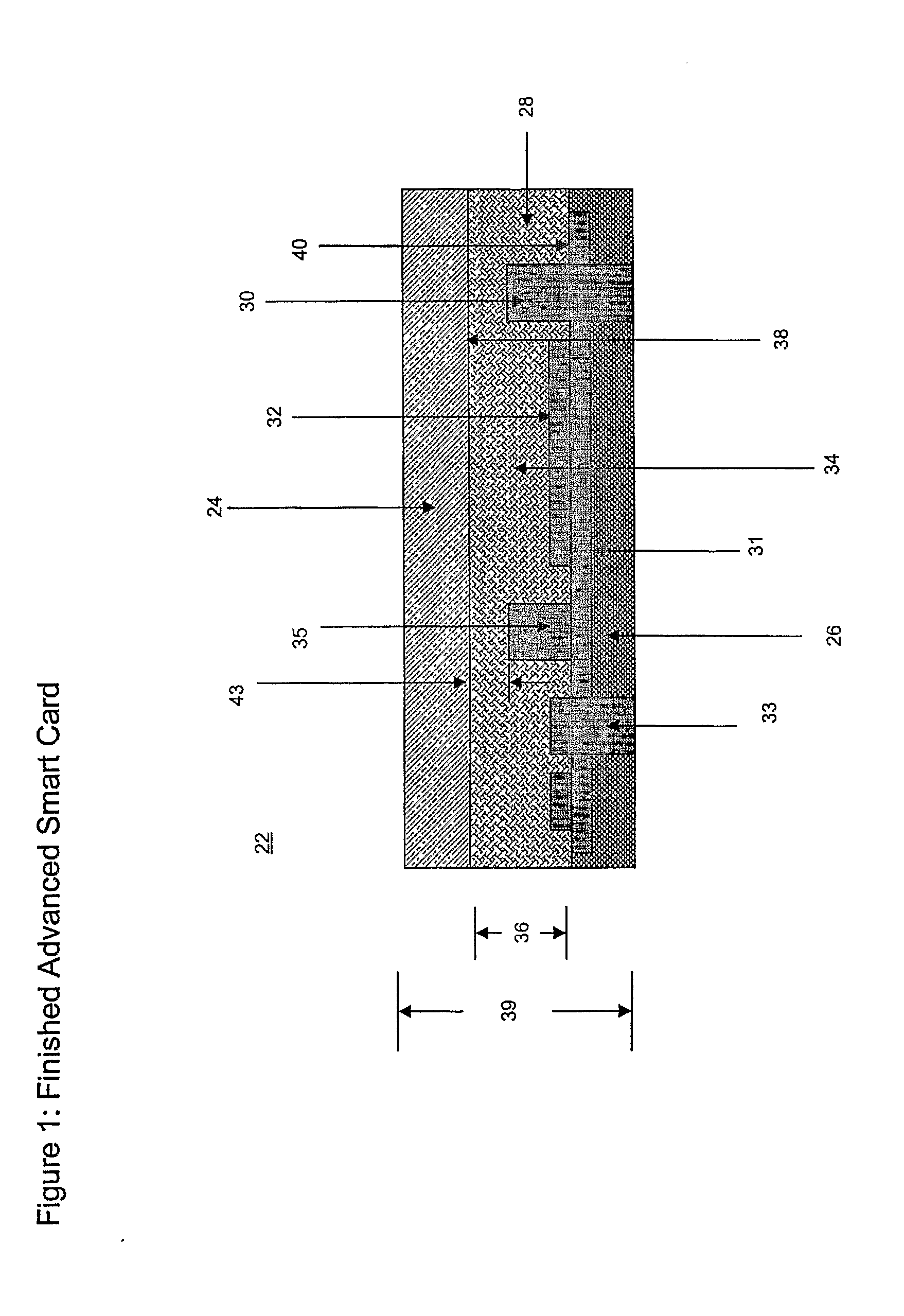

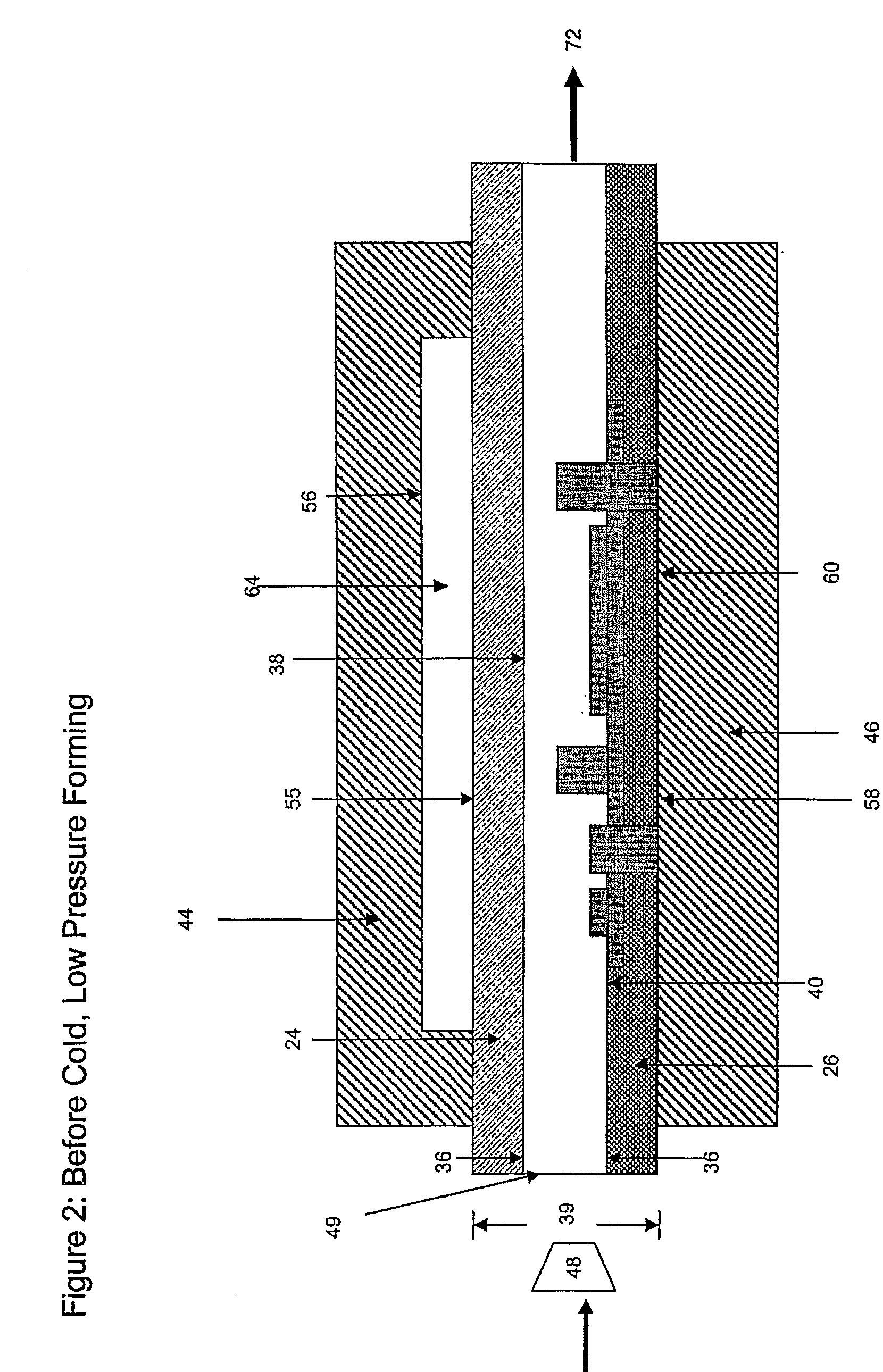

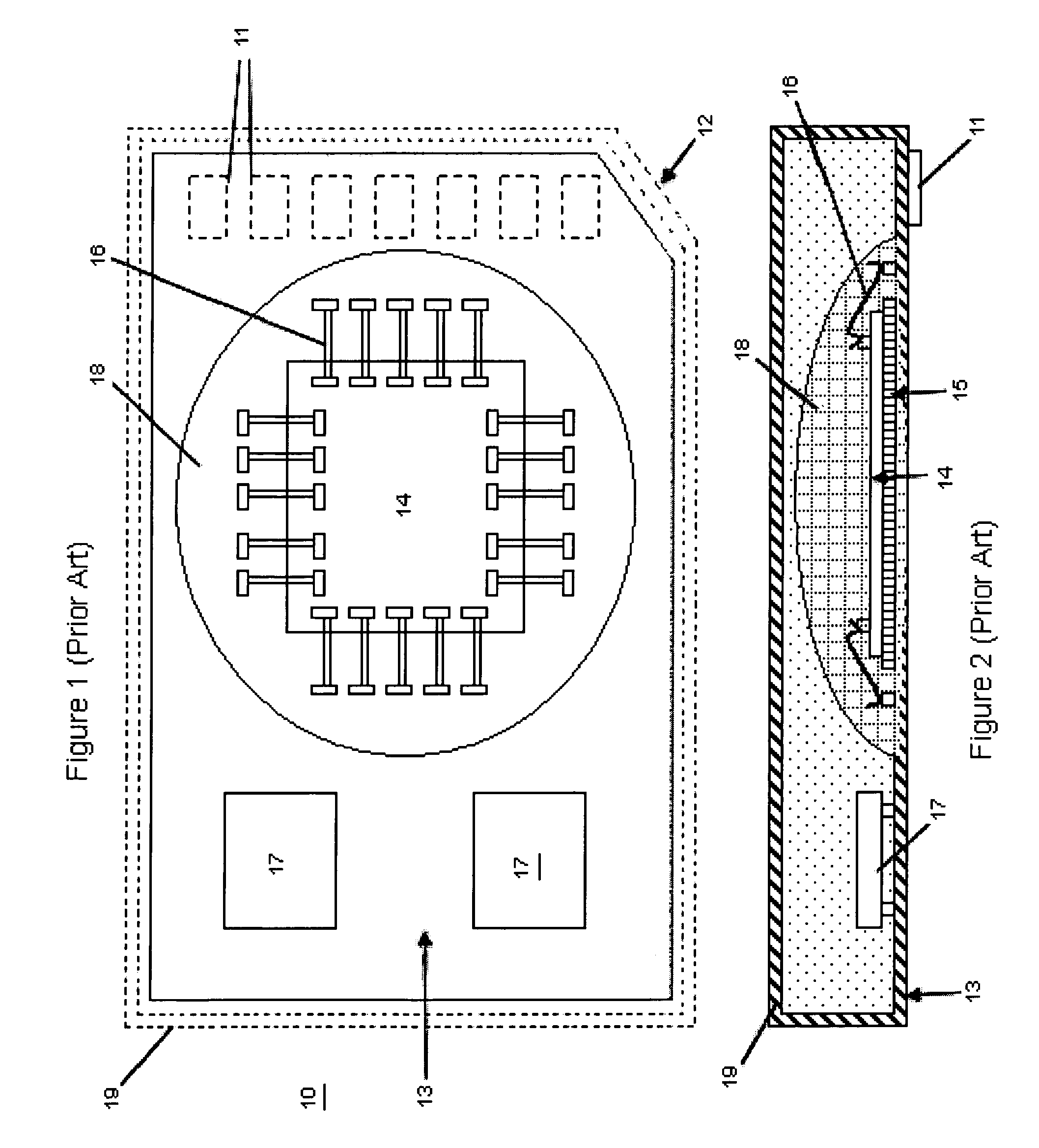

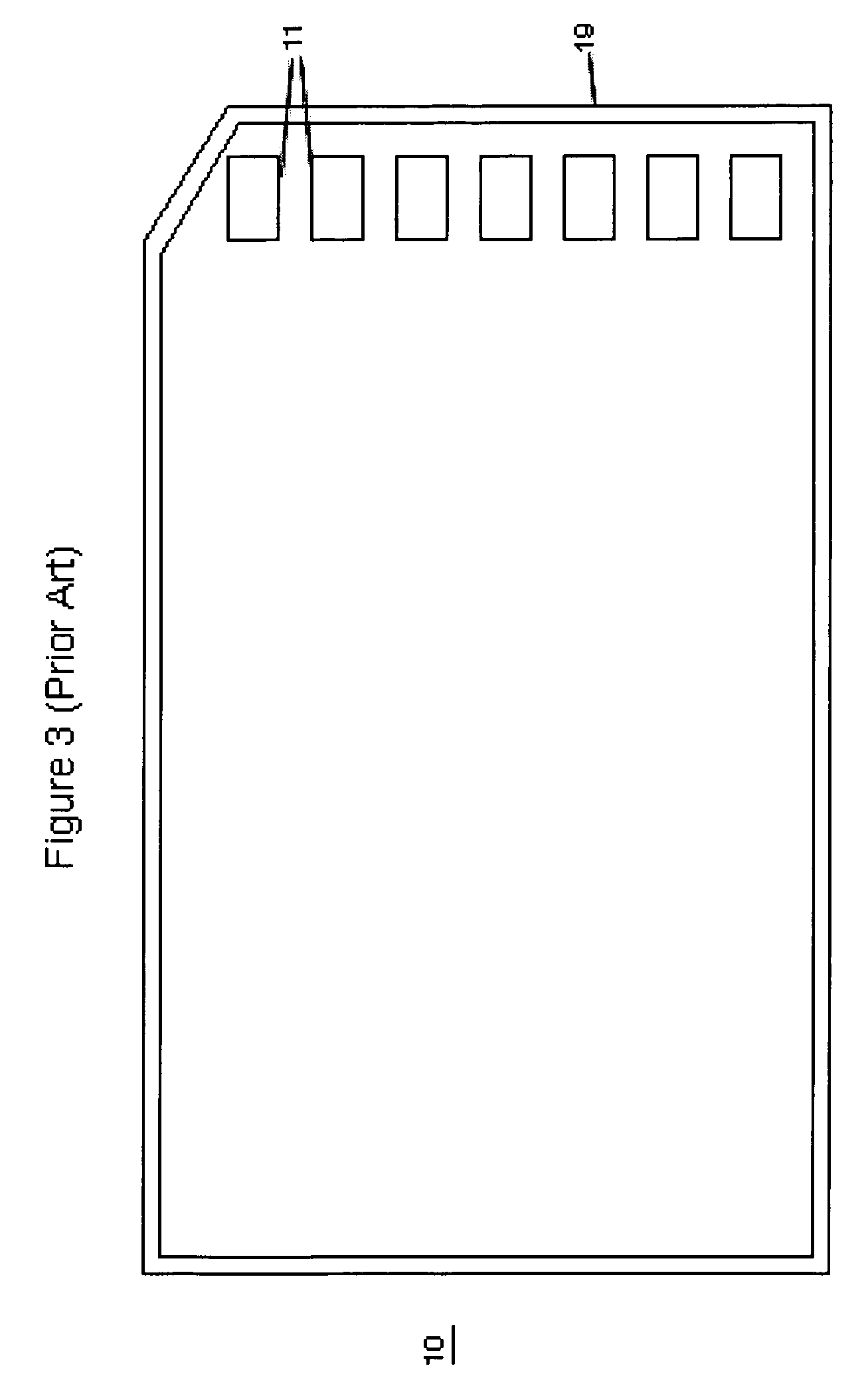

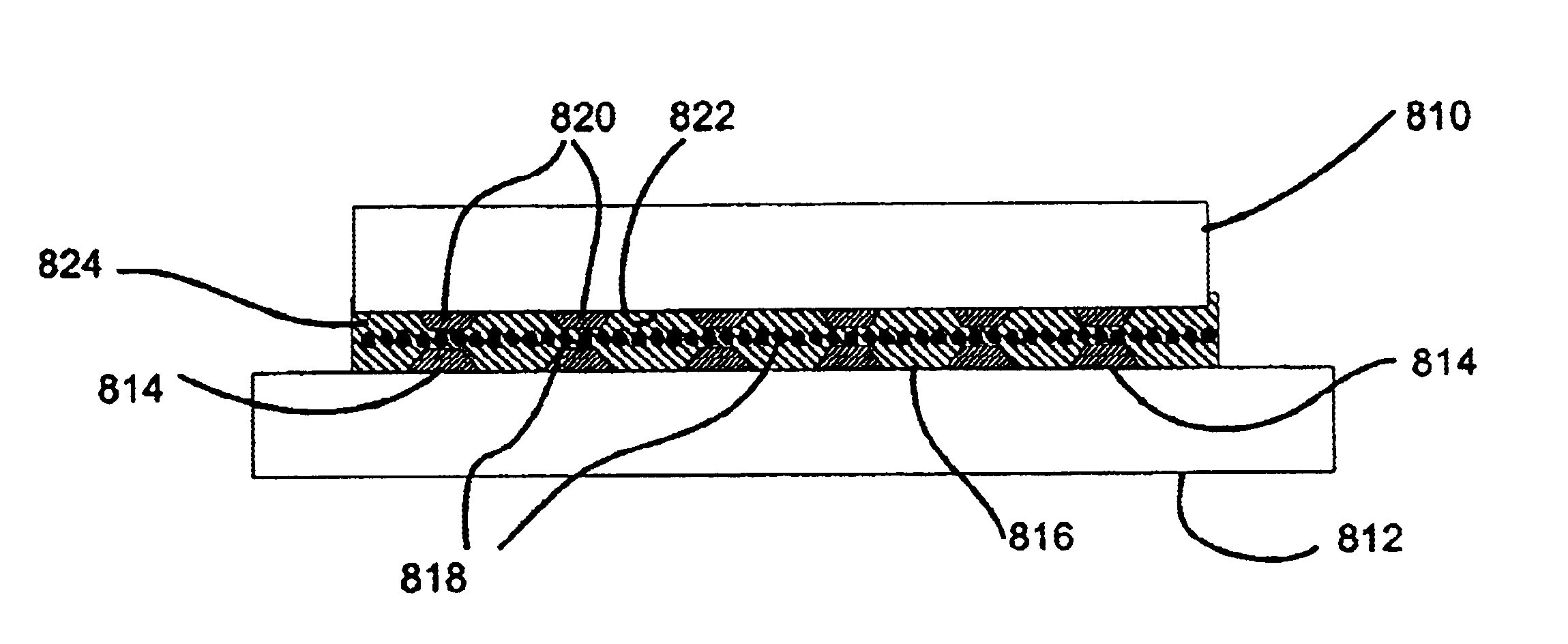

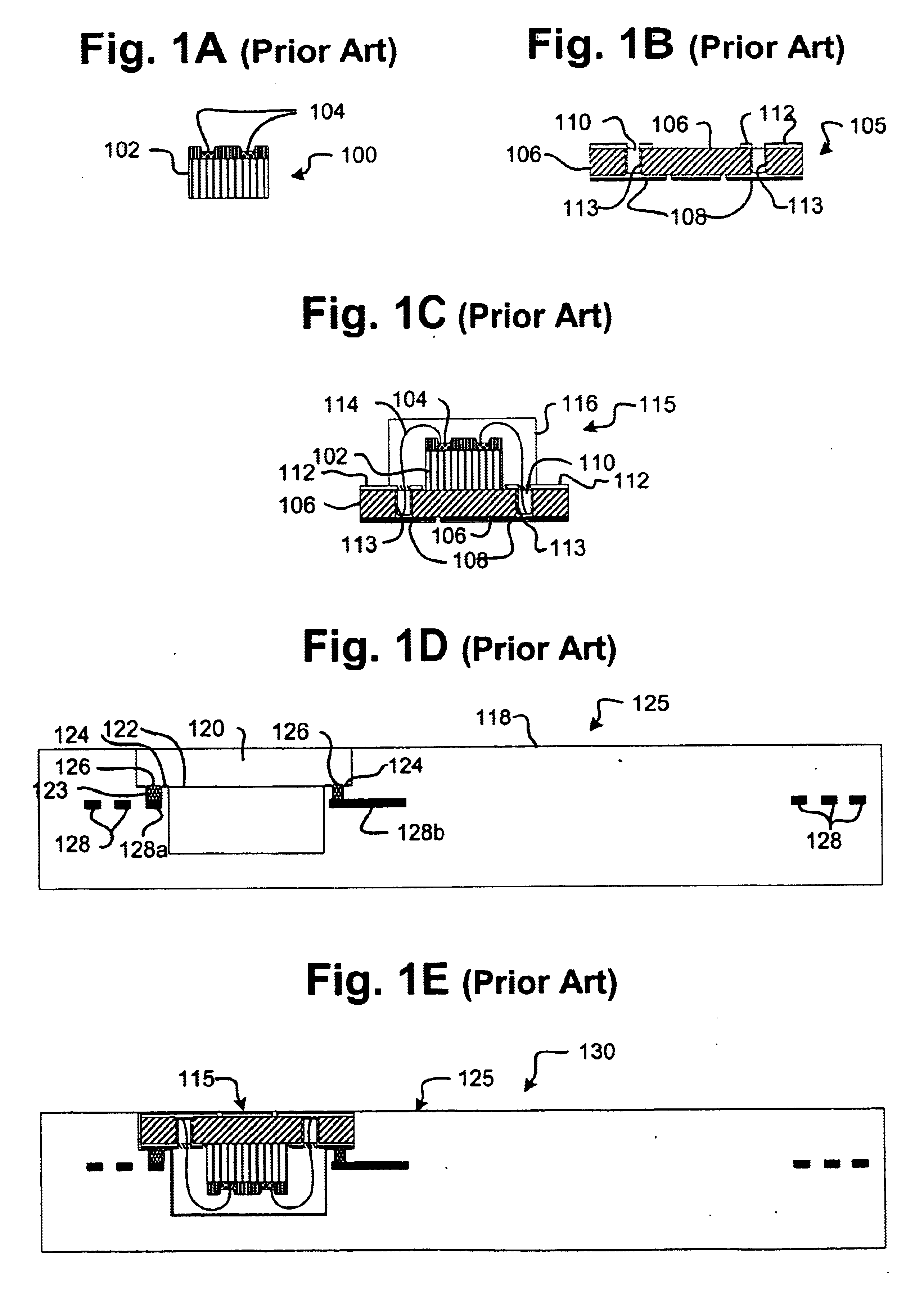

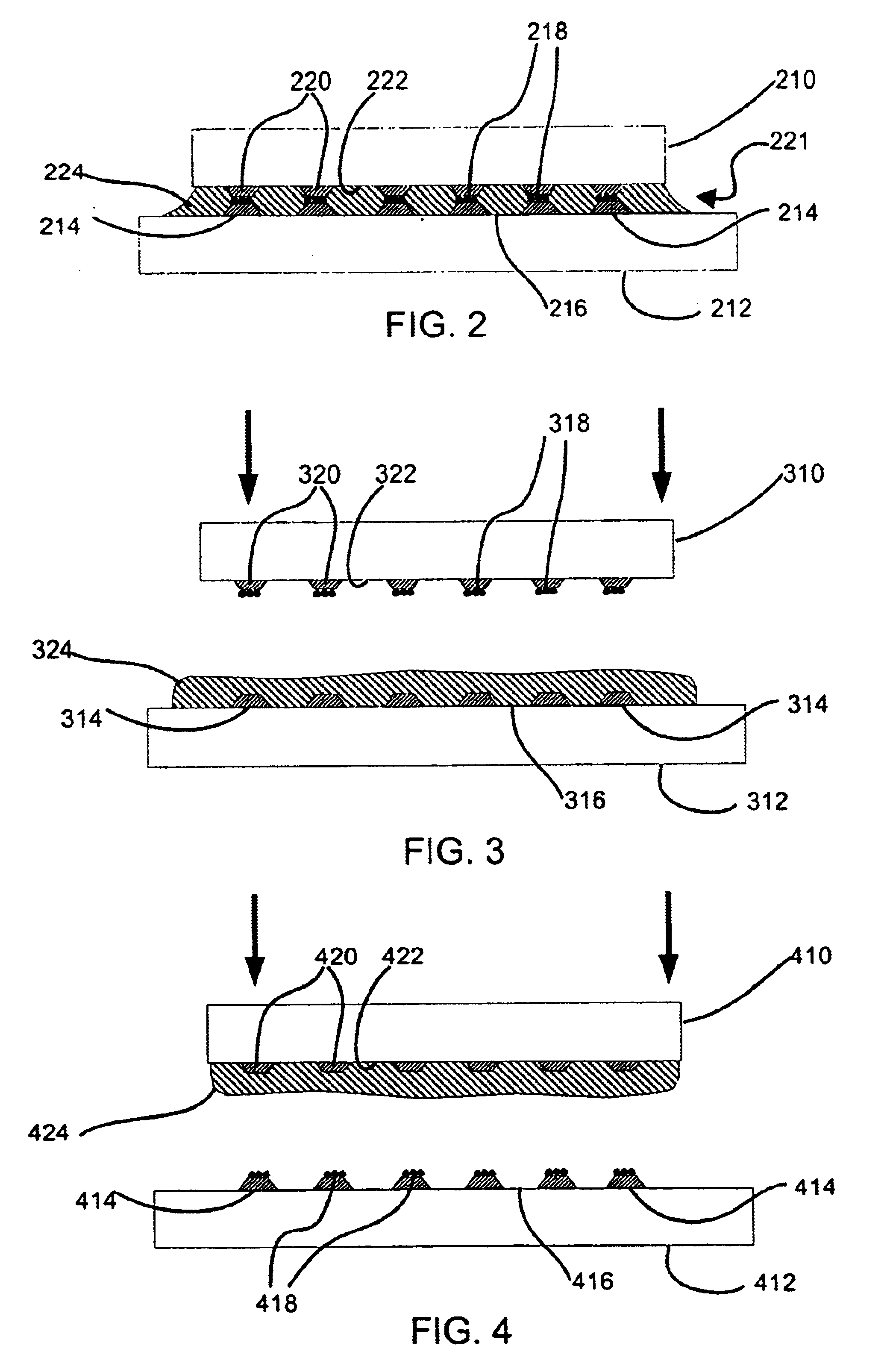

Method for Making Advanced Smart Cards With Integrated Electronics Using Isotropic Thermoset Adhesive Materials With High Quality Exterior Surfaces

InactiveUS20080096326A1Speed up the flowPrinted circuit assemblingLine/current collector detailsIntegrated electronicsSmart card

Advanced Smart Cards and similar form factors (e.g. documents, tags) having high quality external surfaces of Polyvinylchloride (PVC), Polycarbonate (PC), synthetic paper or other suitable material can be made with highly sophisticated electronic components (e.g. Integrated Circuit chips, batteries, microprocessors, Light Emitting Diodes, Liquid Crystal Displays, polymer dome switches, and antennae), integrated in the bottom layer of the card structure, through use of injection molded thermosetting or thermoplastic material that becomes the core layer of said Advanced Smart Cards. A lamination finishing process can provide a high quality lower surface, and the encapsulation of the electronic components in the thermosetting or thermoplastic material provides protection from the lamination heat and pressure.

Owner:CARDXX

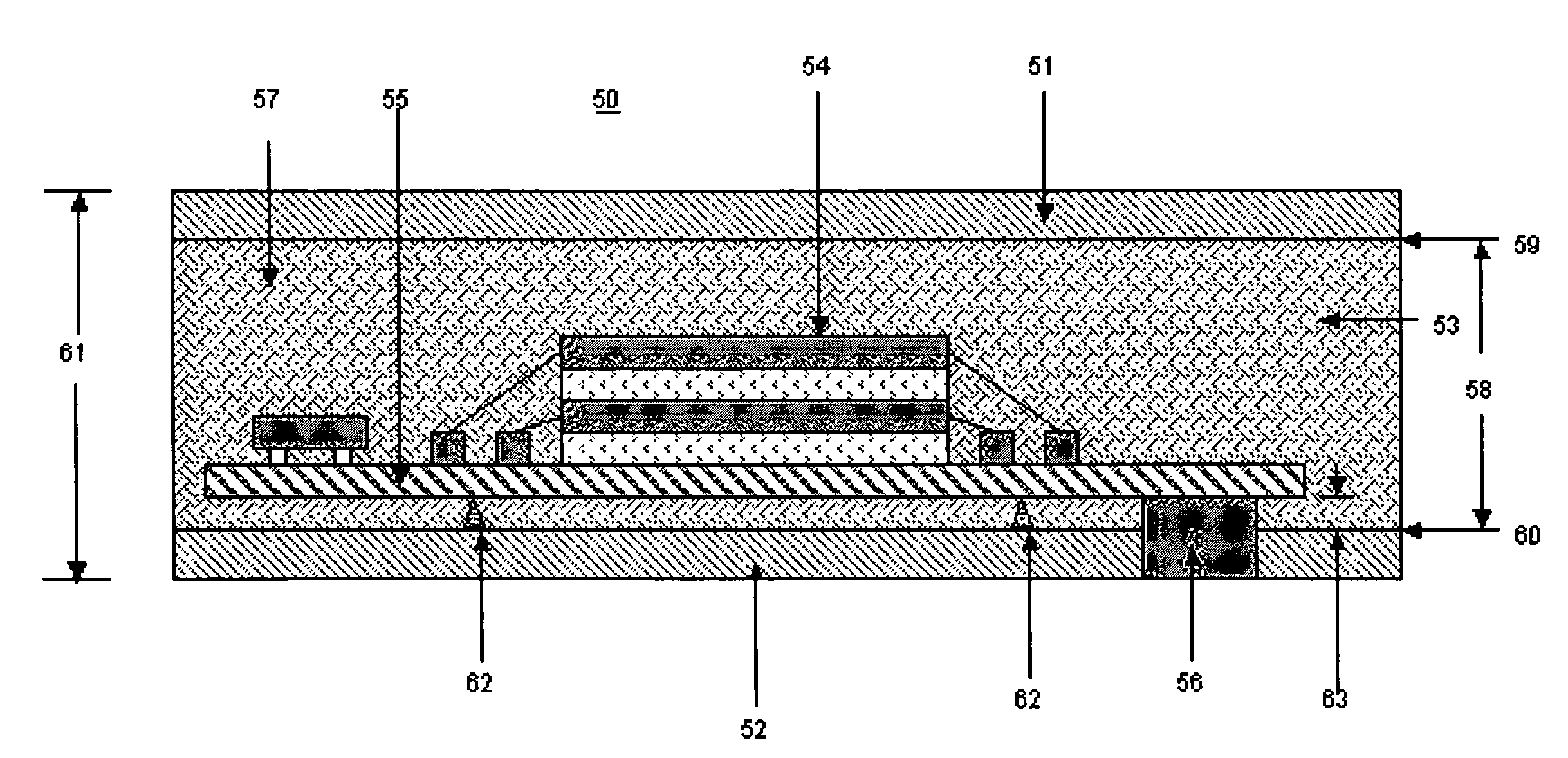

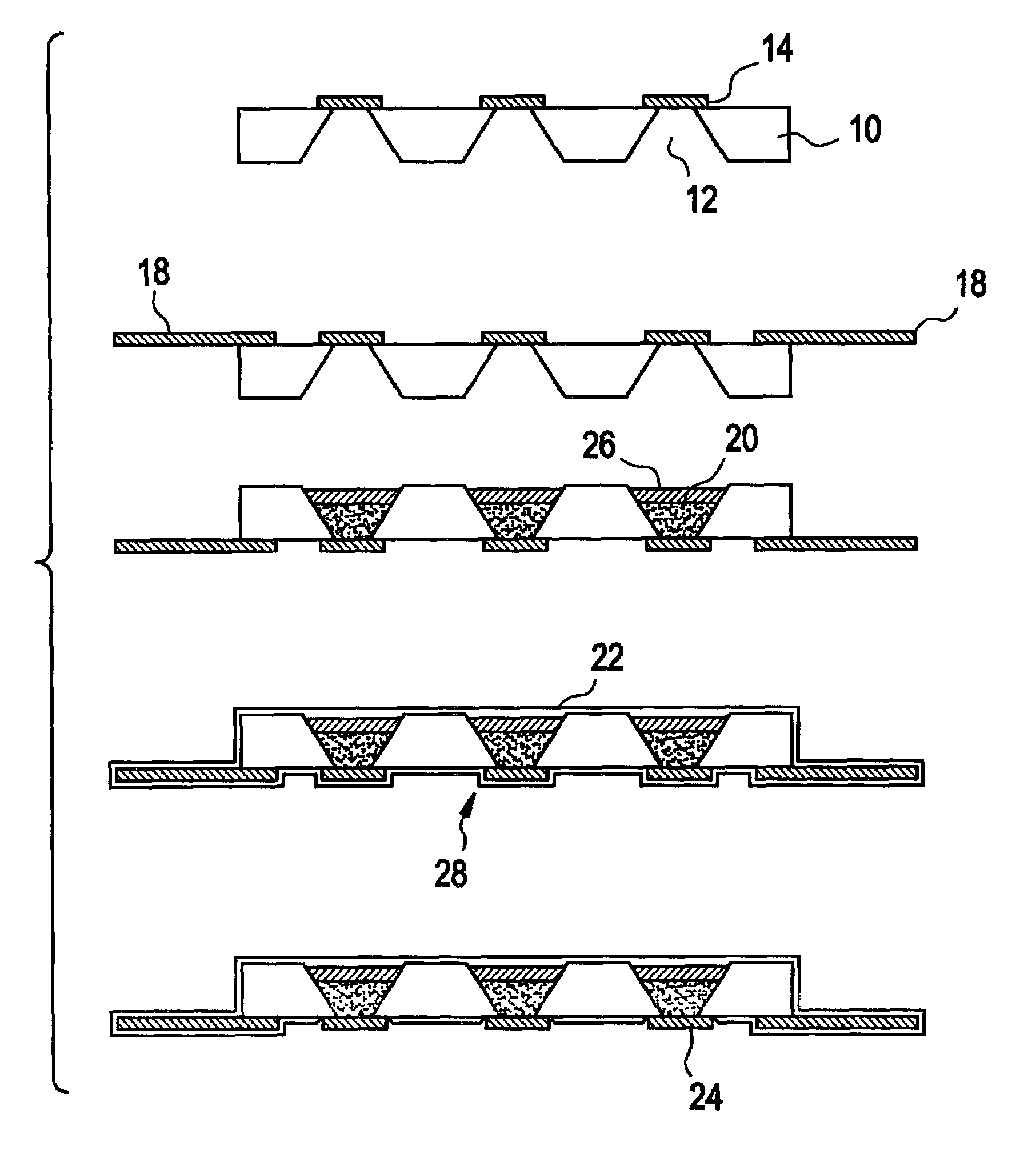

Method for making memory cards and similar devices using isotropic thermoset materials with high quality exterior surfaces

InactiveUS7225537B2Shorten the timeQuality improvementPrinted circuit assemblingLine/current collector detailsEngineeringInjection moulding

Memory Cards containing Integrated Circuits and other electronic components (e.g. resistors) in a variety of form factors having high quality external surfaces of polycarbonate, synthetic paper (e.g. Teslin), or other suitable material (e.g. PVC) can be made through use of injection molded thermoplastic material or thermosetting material that becomes the core layer of said Memory Cards and similar devices. The object of the invention is to provide the following properties to Memory Cards: rapid production cycle, high volume manufacturing throughput, security, electronics protection, better tamper resistance, durability, and highly reliable complex electronics encapsulation, achieved through a process utilizing low temperature and low pressure.

Owner:CARDXX

Wafer-to-wafer transfer of microstructures using break-away tethers

InactiveUS6142358AReduce tensionSemiconductor/solid-state device detailsWelding/cutting auxillary devicesOptoelectronicsMicrostructure

Break-away tethers to secure electronic, mechanical, optical, or other microstructures, during release from one substrate and transfer to another. Microstructures are fabricated with integrated tethers attaching them to a first substrate. The structures are undercut by etching and contacted and bonded to a second substrate. First and second substrates are separated, breaking the tethers.

Owner:RGT UNIV OF CALIFORNIA

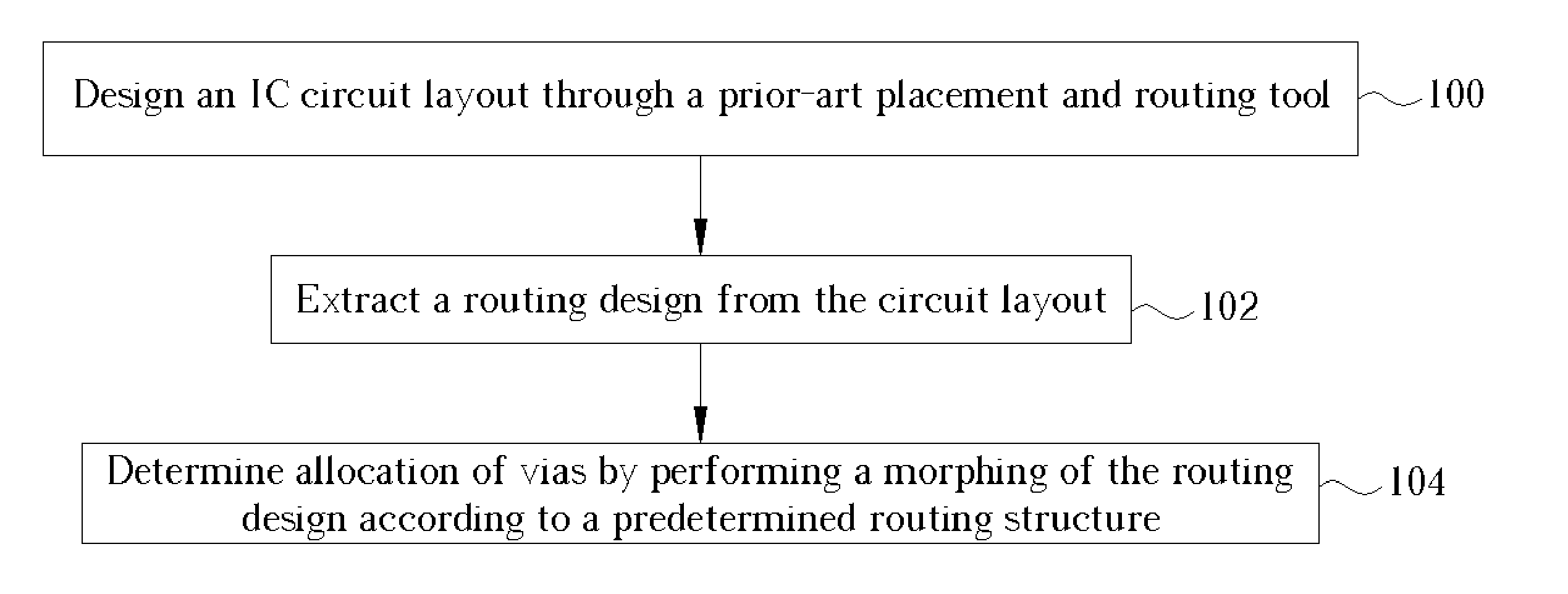

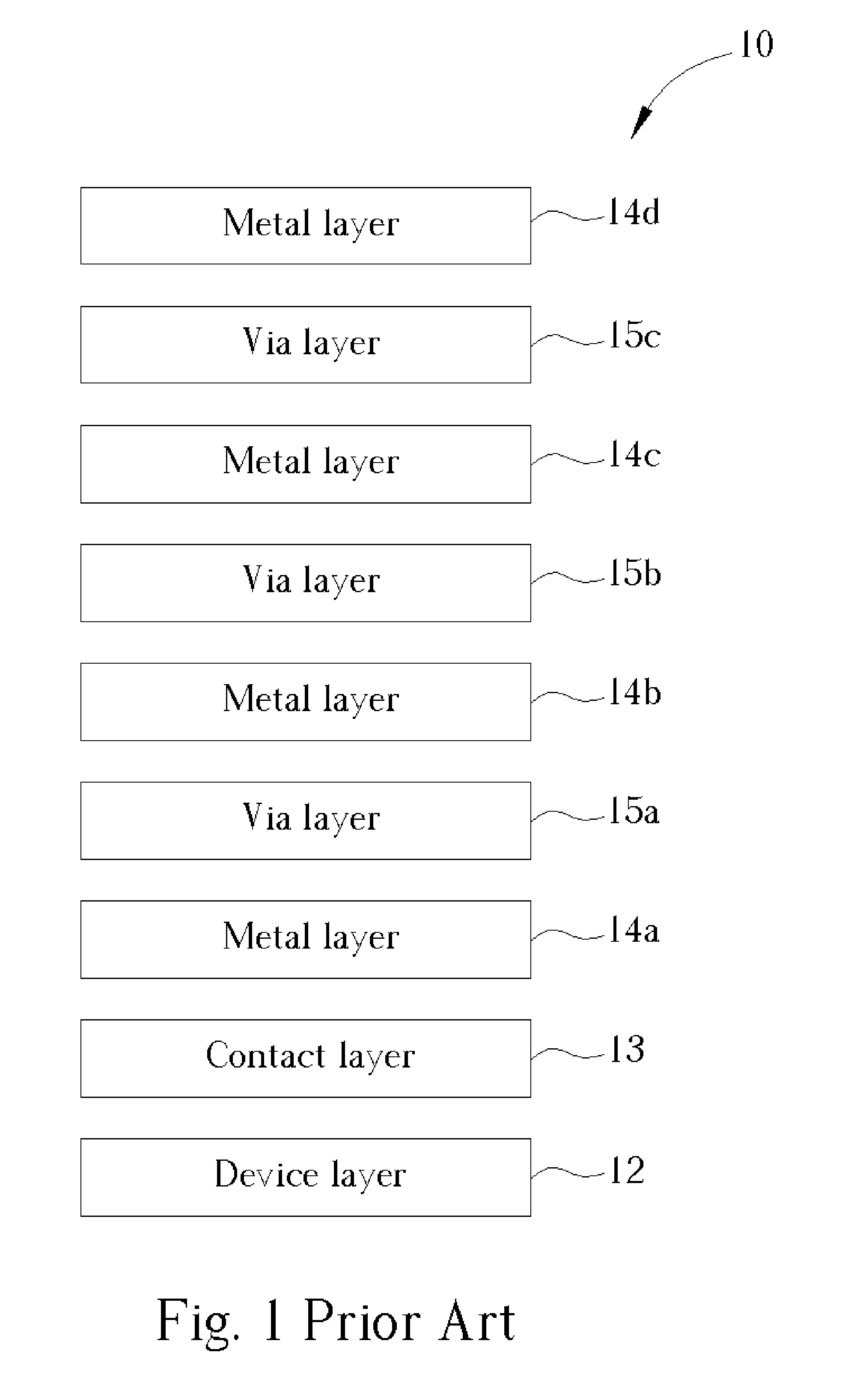

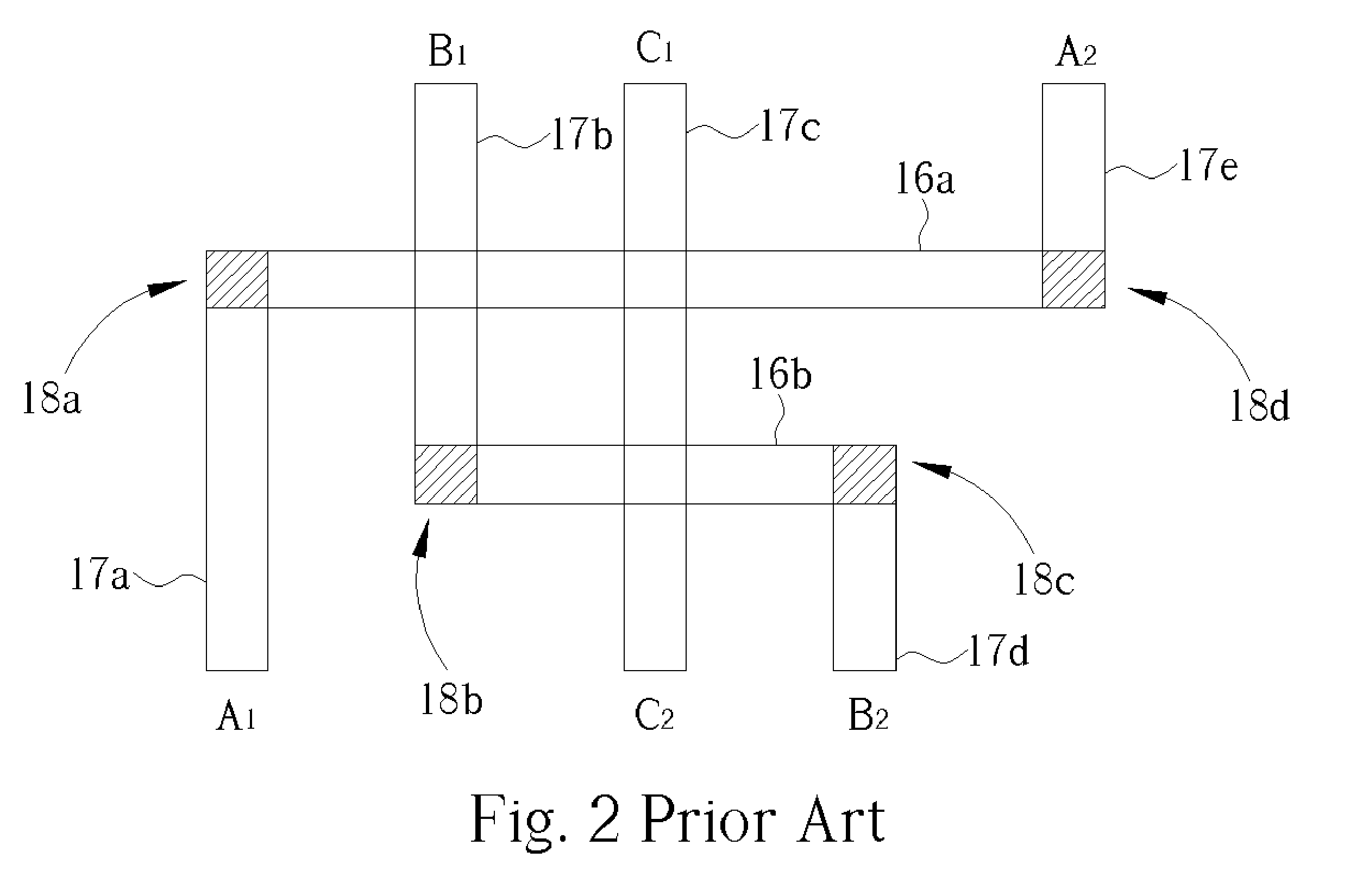

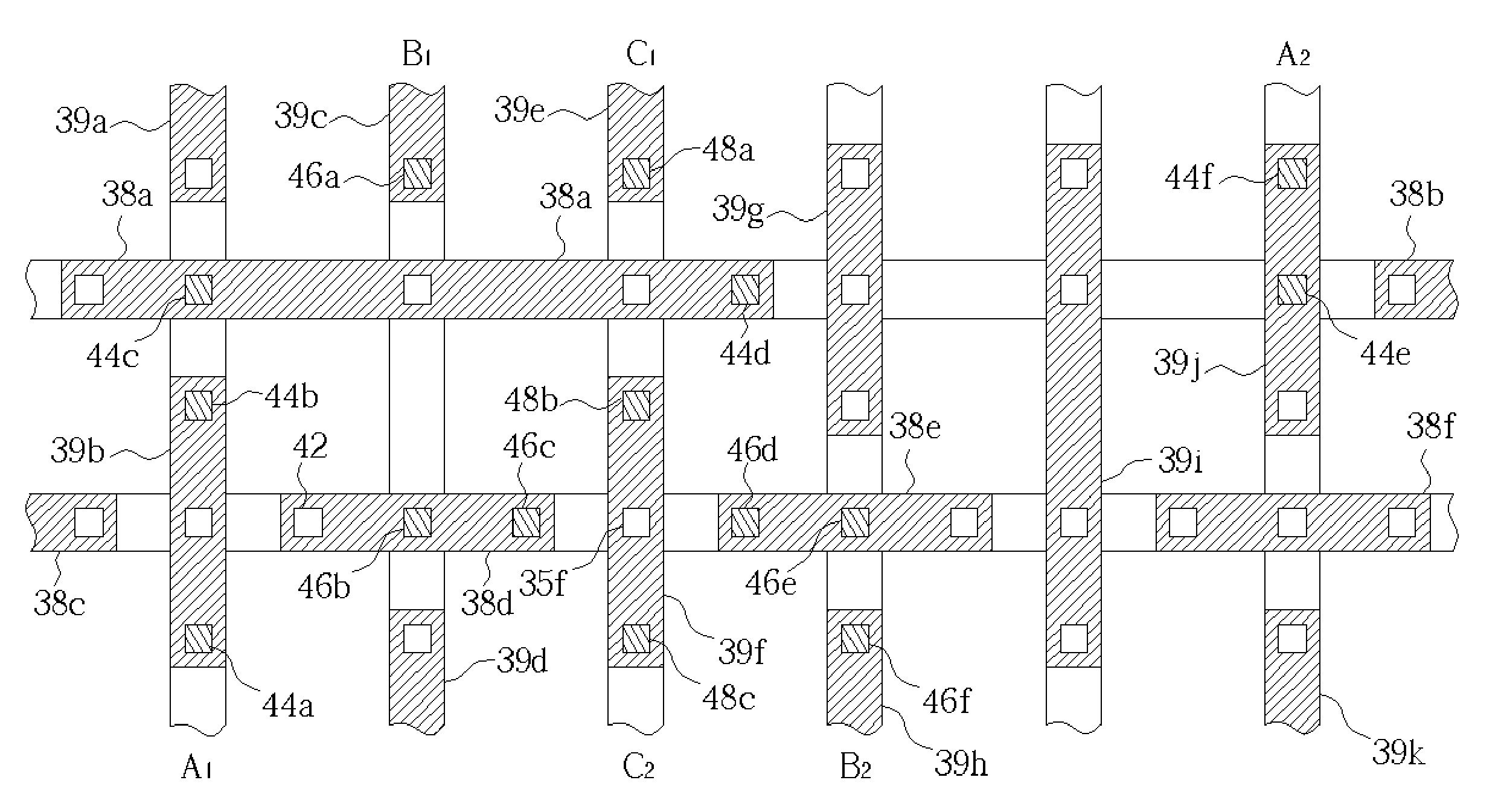

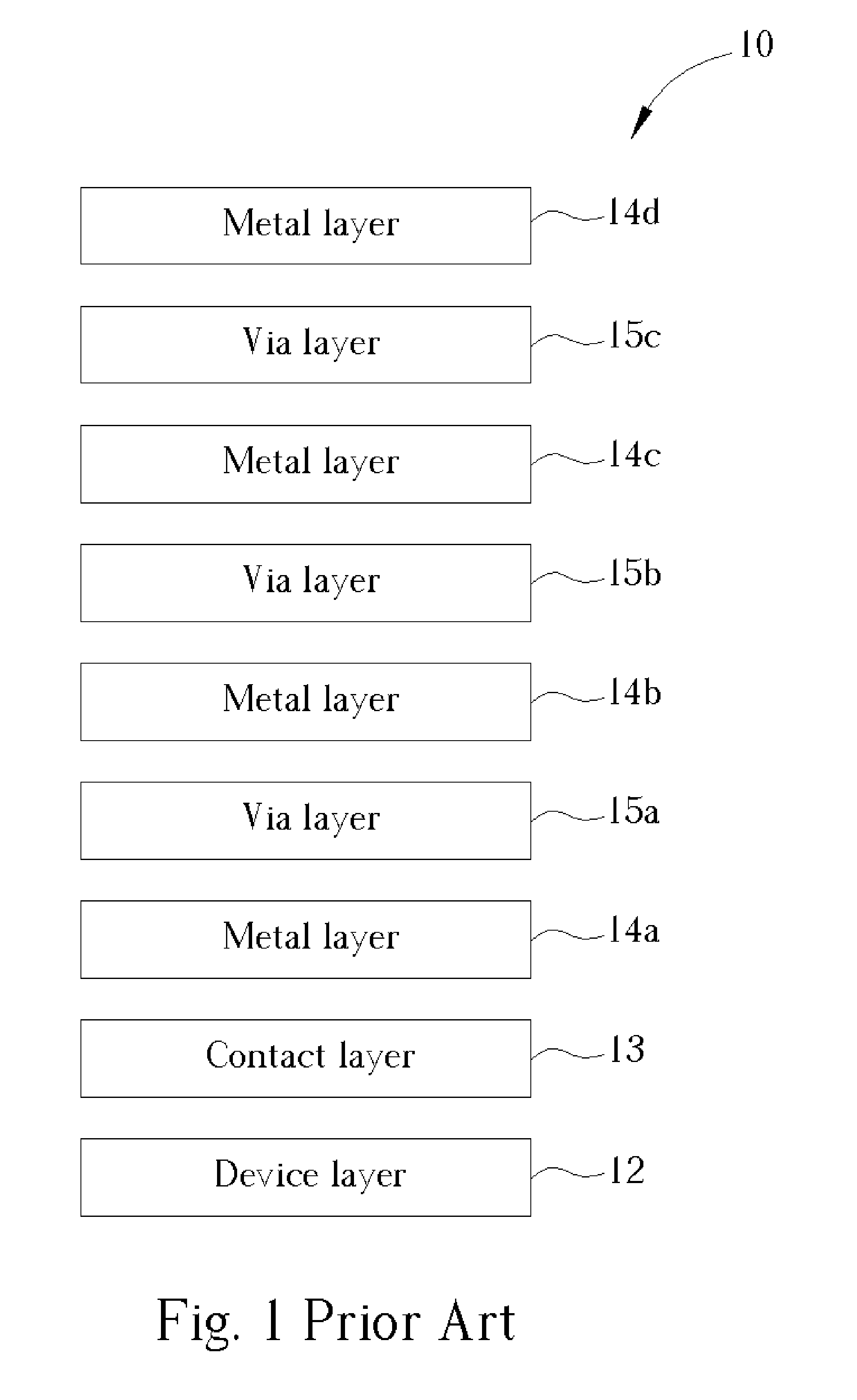

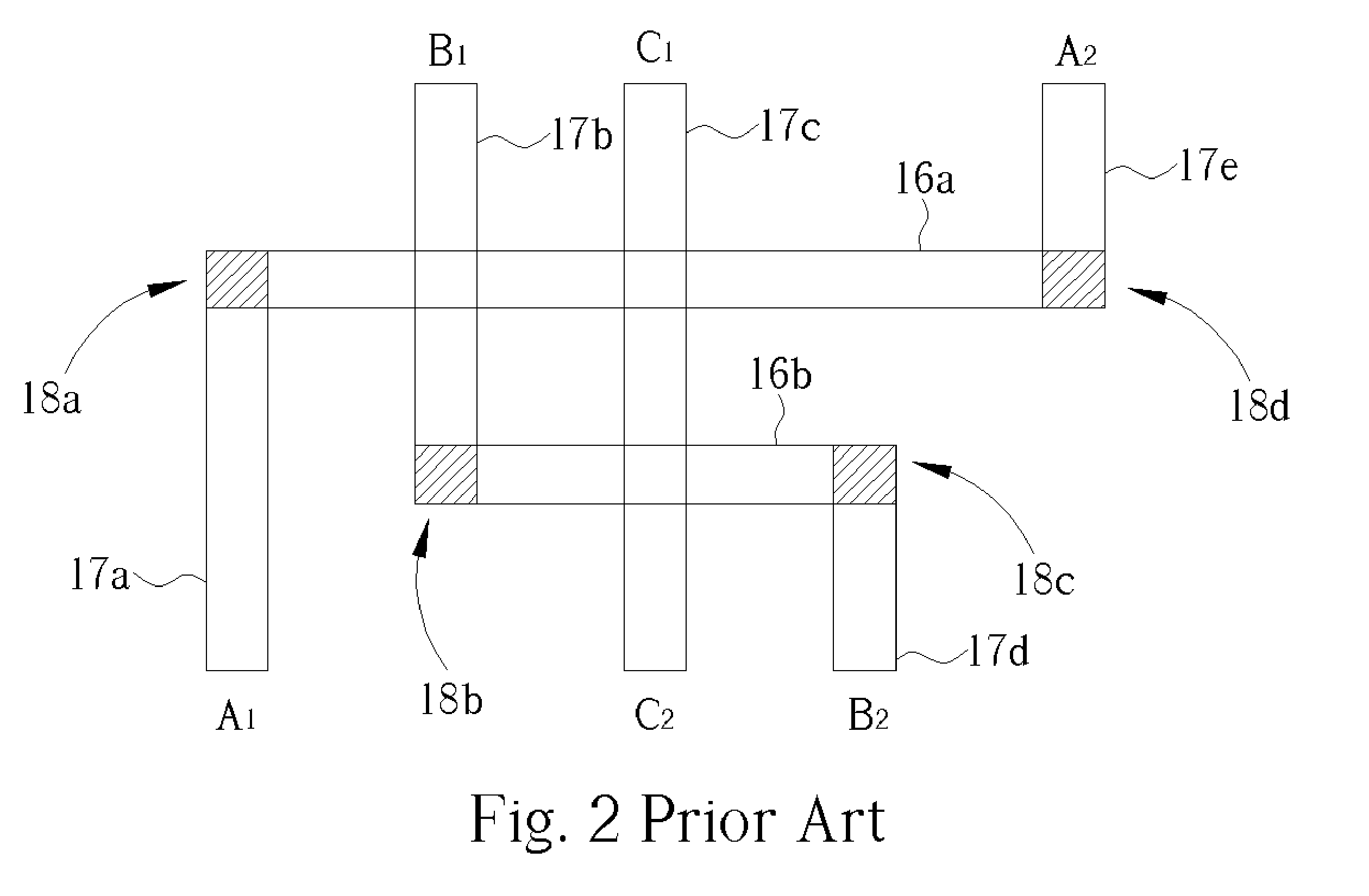

Method for programming a routing layout design through one via layer

ActiveUS20050055828A1Avoid feesPrinted circuit assemblingLine/current collector detailsComputer science

A method for programming a routing layout design through one via layer includes forming a plurality of metal traces on a first routing layer and a second routing layer, and positioning a plurality of vias within a via layer disposed between the first and second routing layers for connecting the metal traces on the first and second routing layers according to a first current route defined by a predetermined circuit layout design to connect a first node and a second node so as to establish a second current route equivalent to the first current route.

Owner:FARADAY TECH CORP

Component and antennae assembly in radio frequency identification devices

InactiveUS6853087B2Easy to produceAdditional componentPrinted circuit assemblingSemiconductor/solid-state device detailsAdhesiveSmart card

Permanent physical and electrical attachment of electrically conductive contacts of a first component in a RFID device, such as a smart card or smart inlay, is made to the electrically conductive contacts of a second component of the device, for example, a conductive area, such as an antenna. Attachment is achieved by co-depositing metal and electrically conductive hard particles upon the conductive contacts of either the first or second components and then using a non-conductive adhesive to provide permanent bond between the components and their conductive contacts.

Owner:NANOPIERCE TECH

Stacking Integrated Circuits containing Serializer and Deserializer Blocks using Through Silicon Via

ActiveUS20100058580A1Reduce and eliminate inductanceReduce and eliminate and capacitancePrinted circuit assemblingSemiconductor/solid-state device detailsThrough-silicon viaIntegrated circuit

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

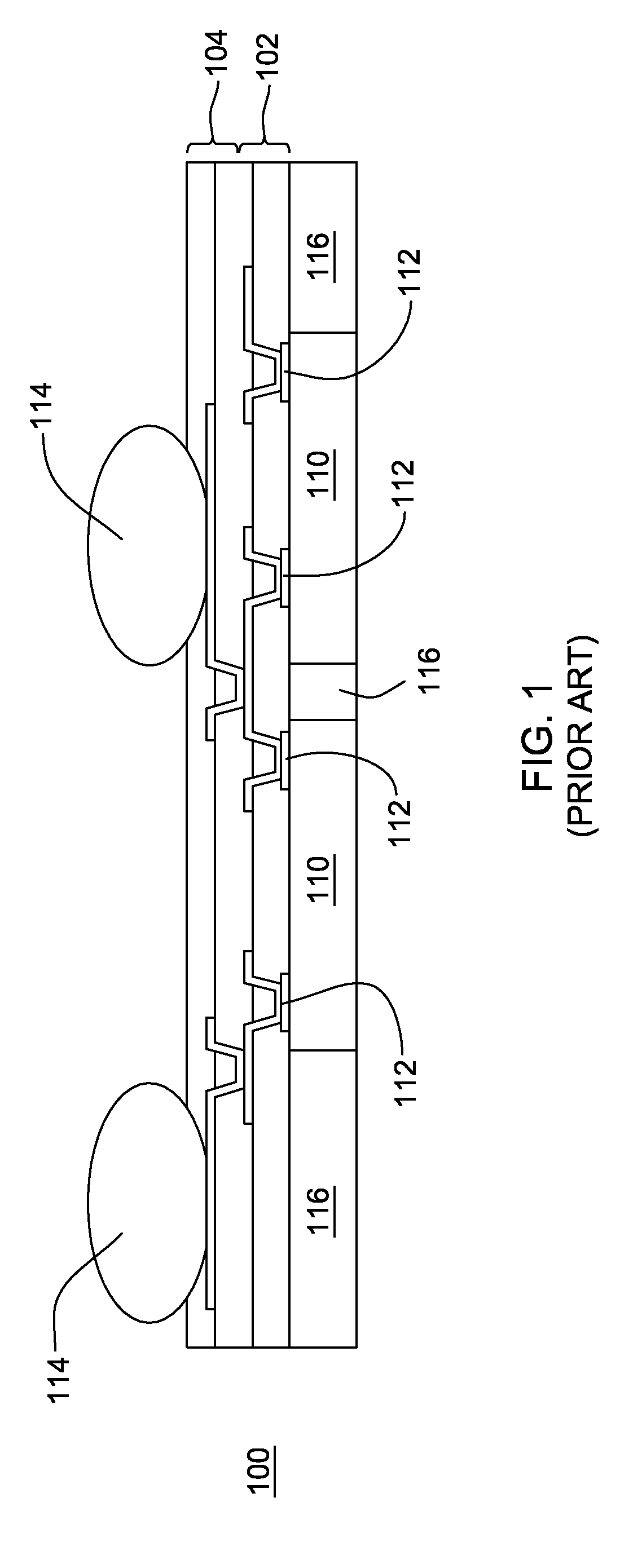

Security module system, apparatus and process

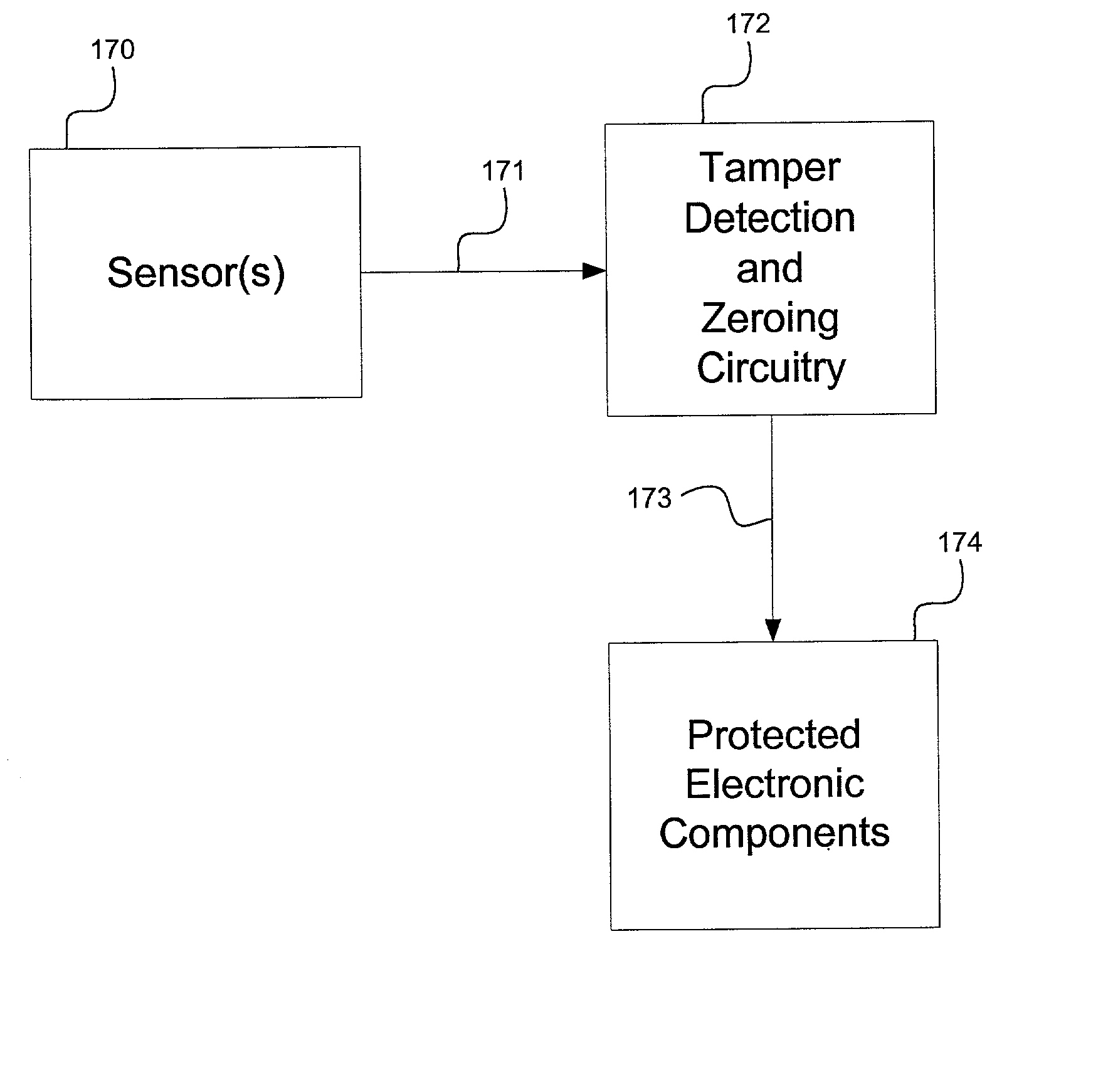

InactiveUS20020002683A1Easy to changeImprove protectionPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringShort circuit

A system, method and apparatus for protecting circuit components from unauthorized access. The circuit components to be protected are disposed on a first layer of a substrate with a plurality of layers. A cover member composed of a plurality of layers is abutted to the substrate, defining an enclosure space for enclosing the circuit components to be protected. A three-dimensional resistive network sensor surrounds the protected circuit components. The sensor comprises at least one conduction path in at least one of the layers below the first layer of the substrate and at least one conduction path in at least one of the layers of the cover member and also comprises a plurality of vias transverse to and electrically connecting the conduction paths. A short or open in the sensor will be detected by a tamper detection circuit that is disposed on the first layer of a substrate.

Owner:SAFENET

Stretchable and foldable electronic devices

ActiveUS8552299B2Easy to useQuality improvementWave amplification devicesSemiconductor/solid-state device detailsIsolation layerSemiconductor

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

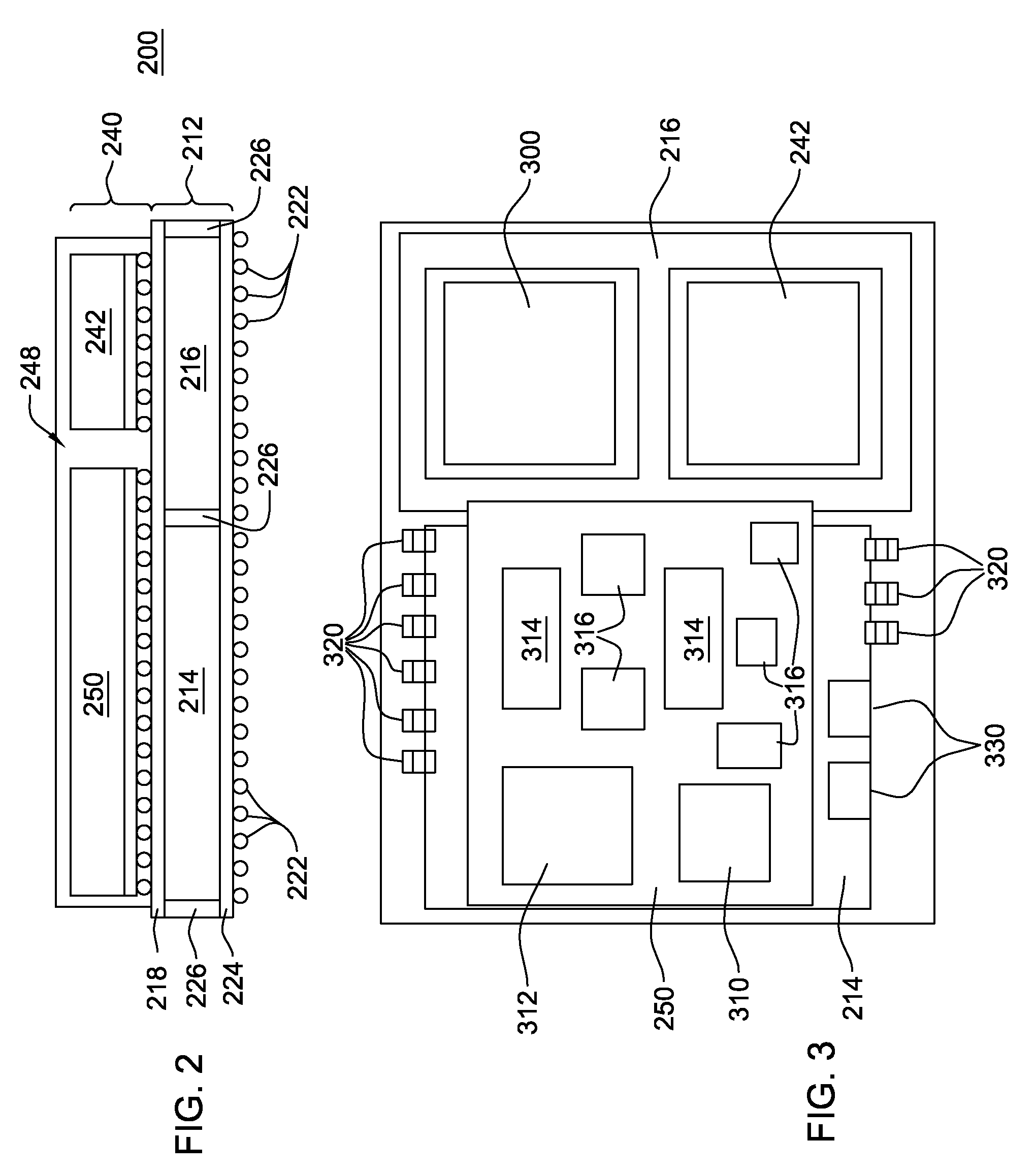

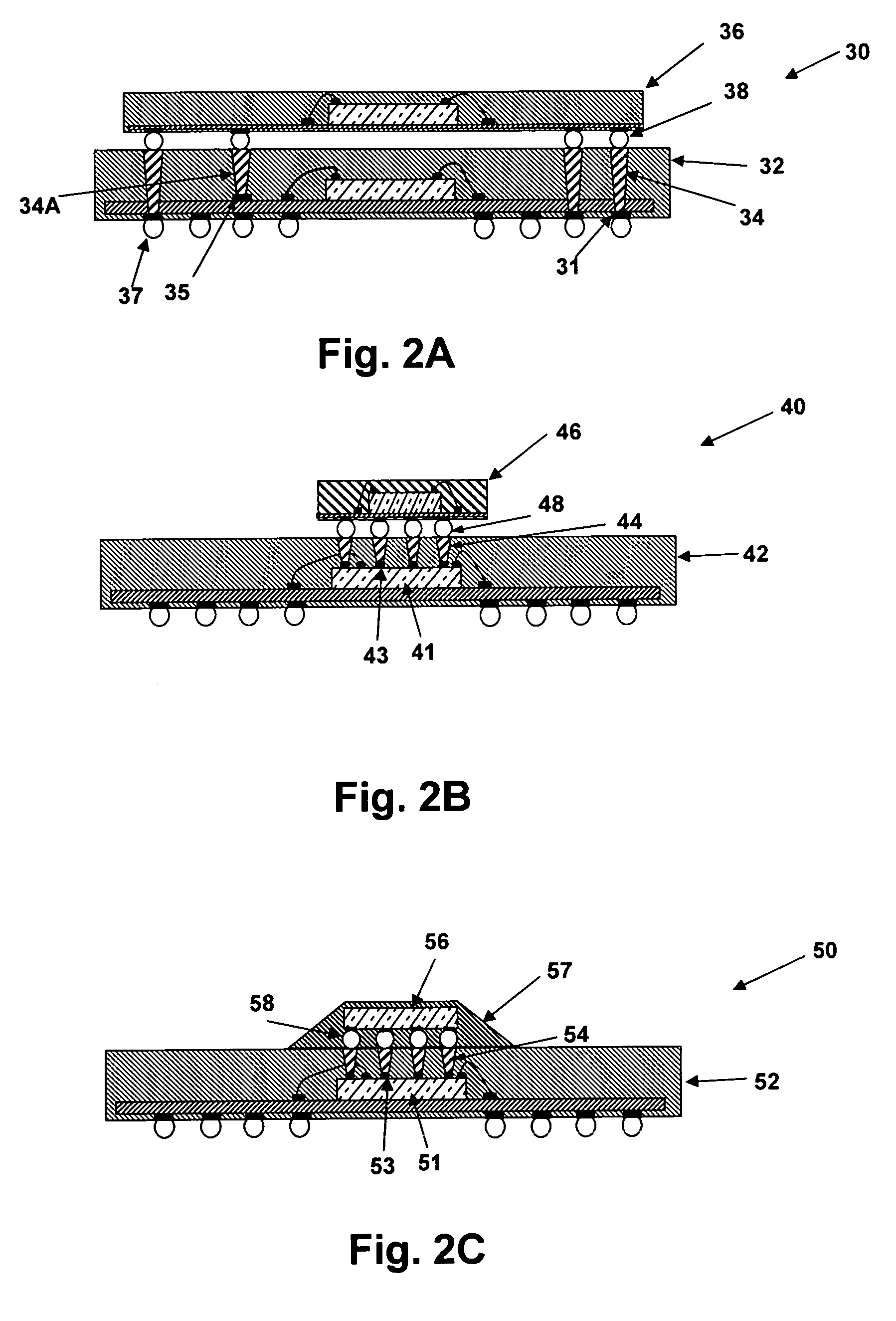

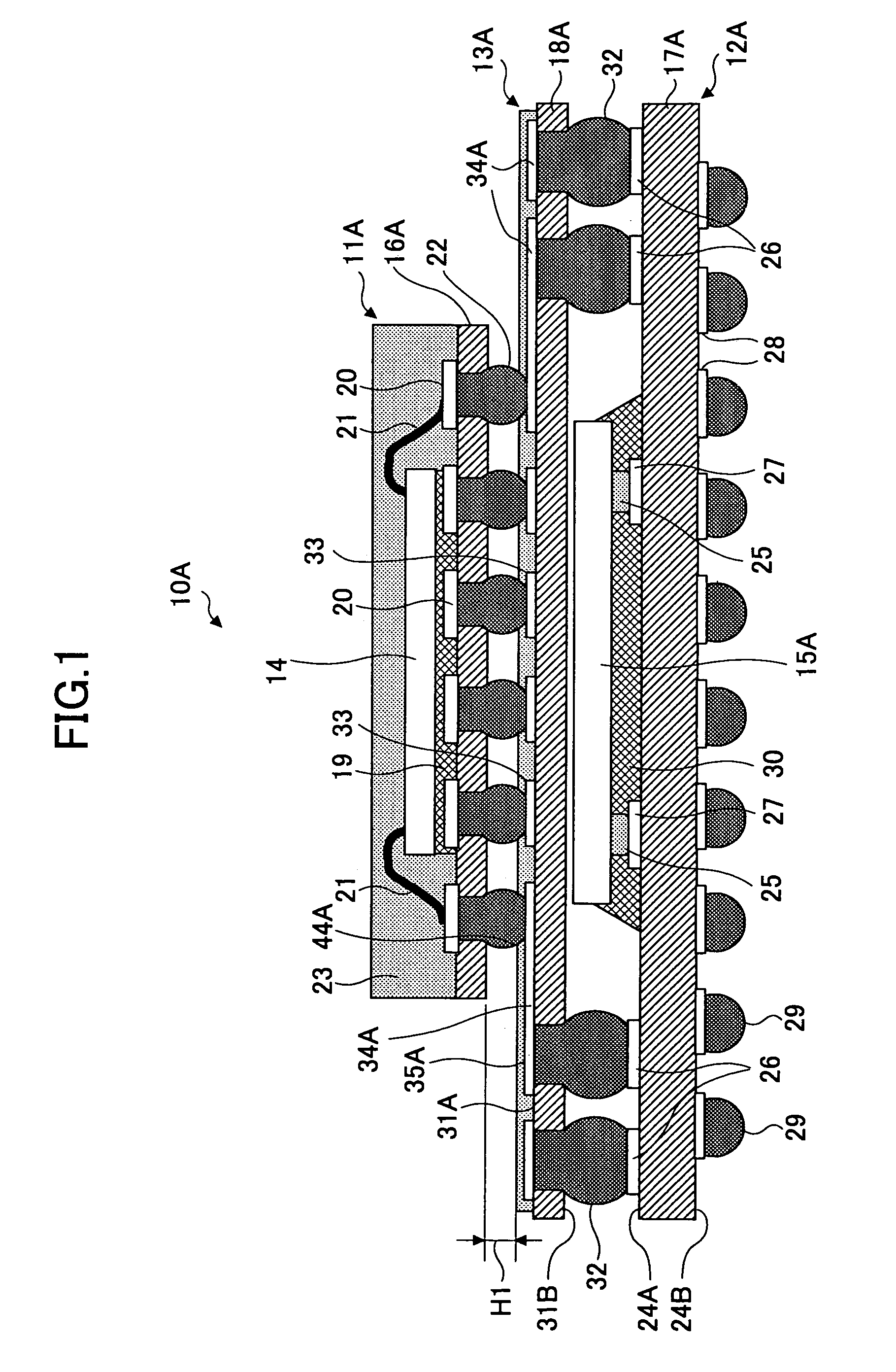

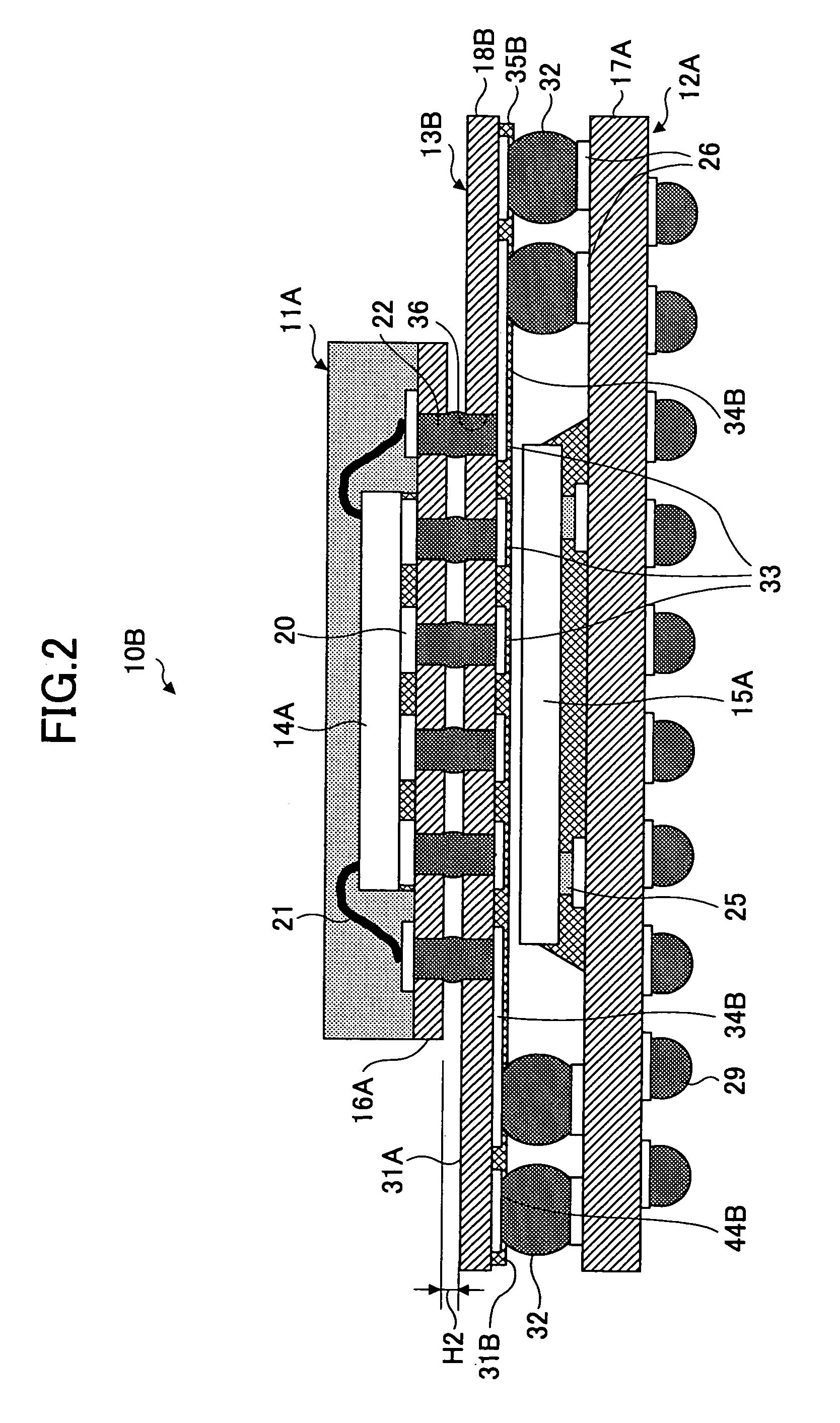

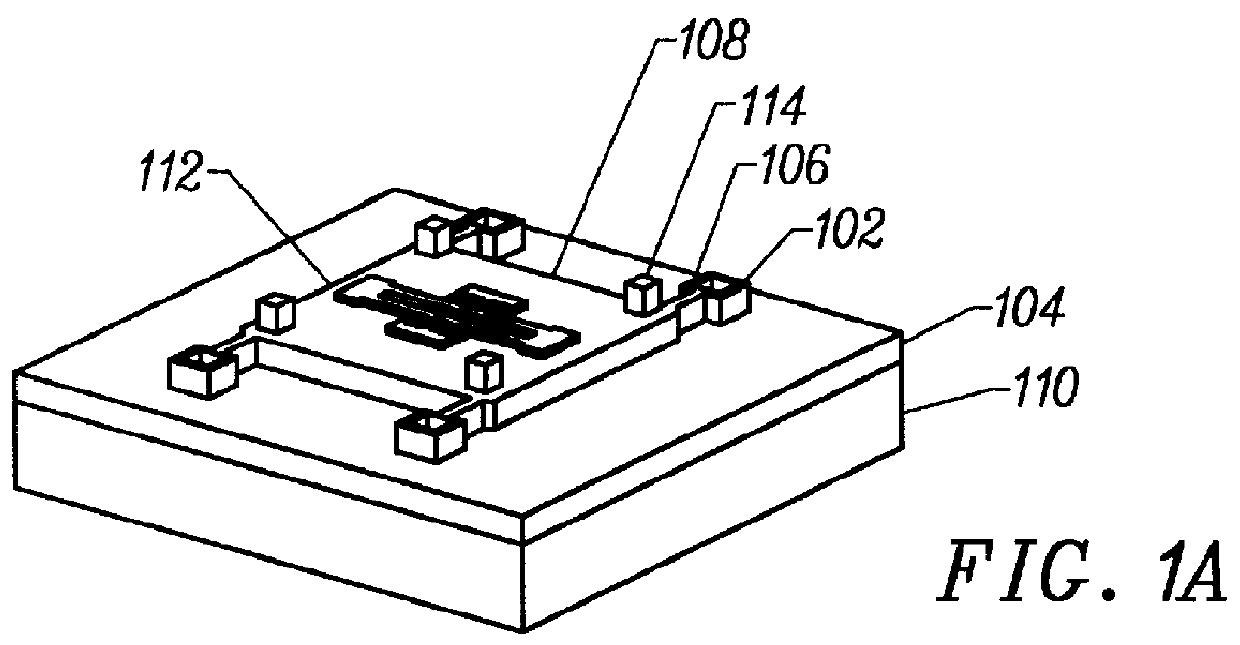

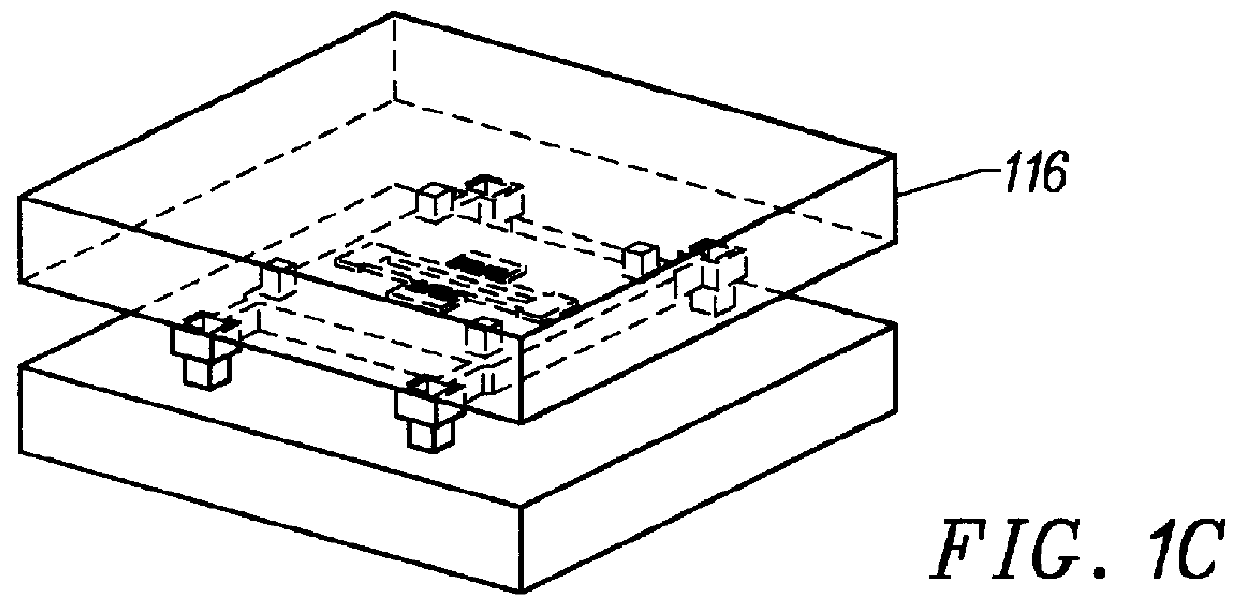

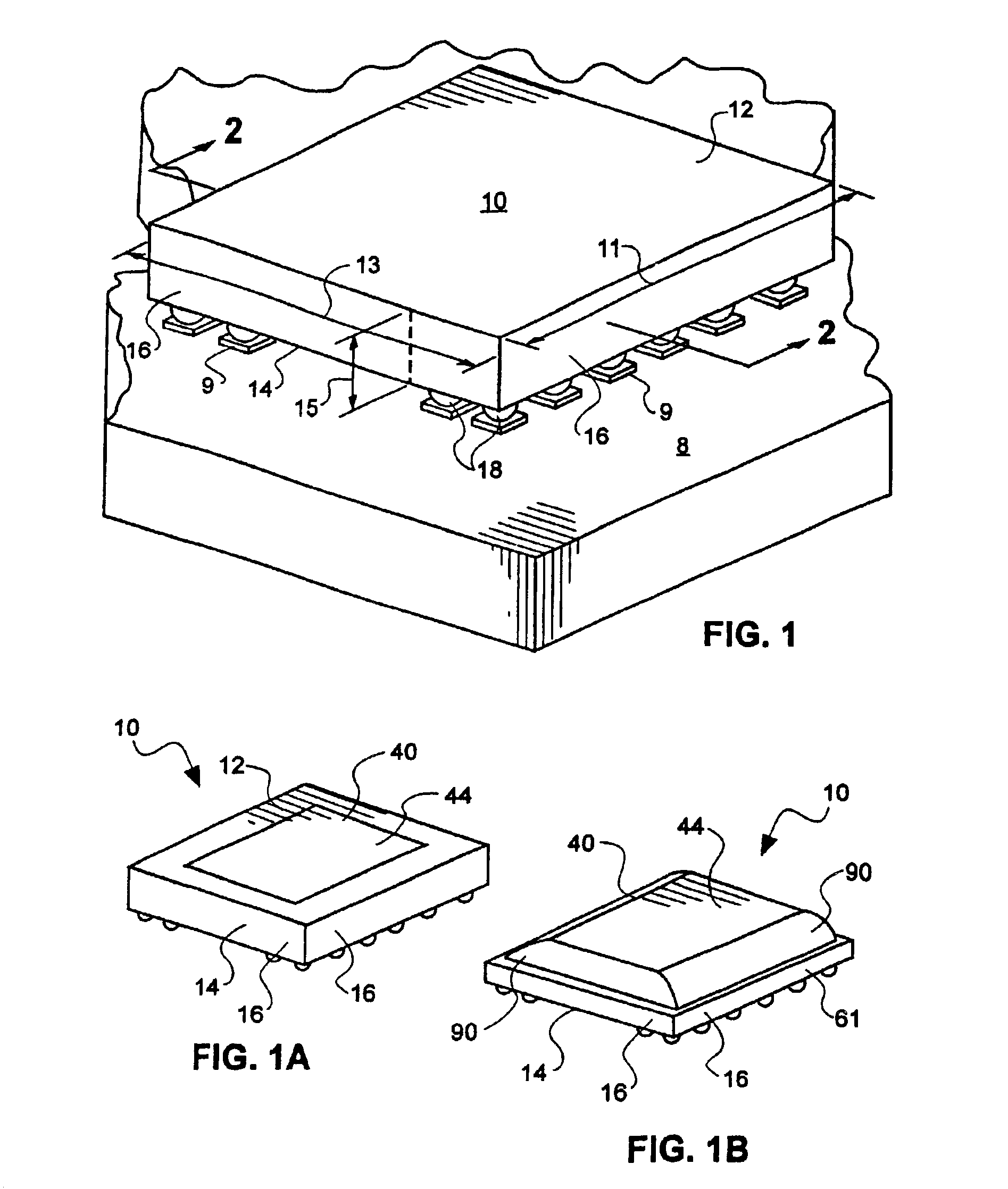

Methods for assembling multiple semiconductor devices

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

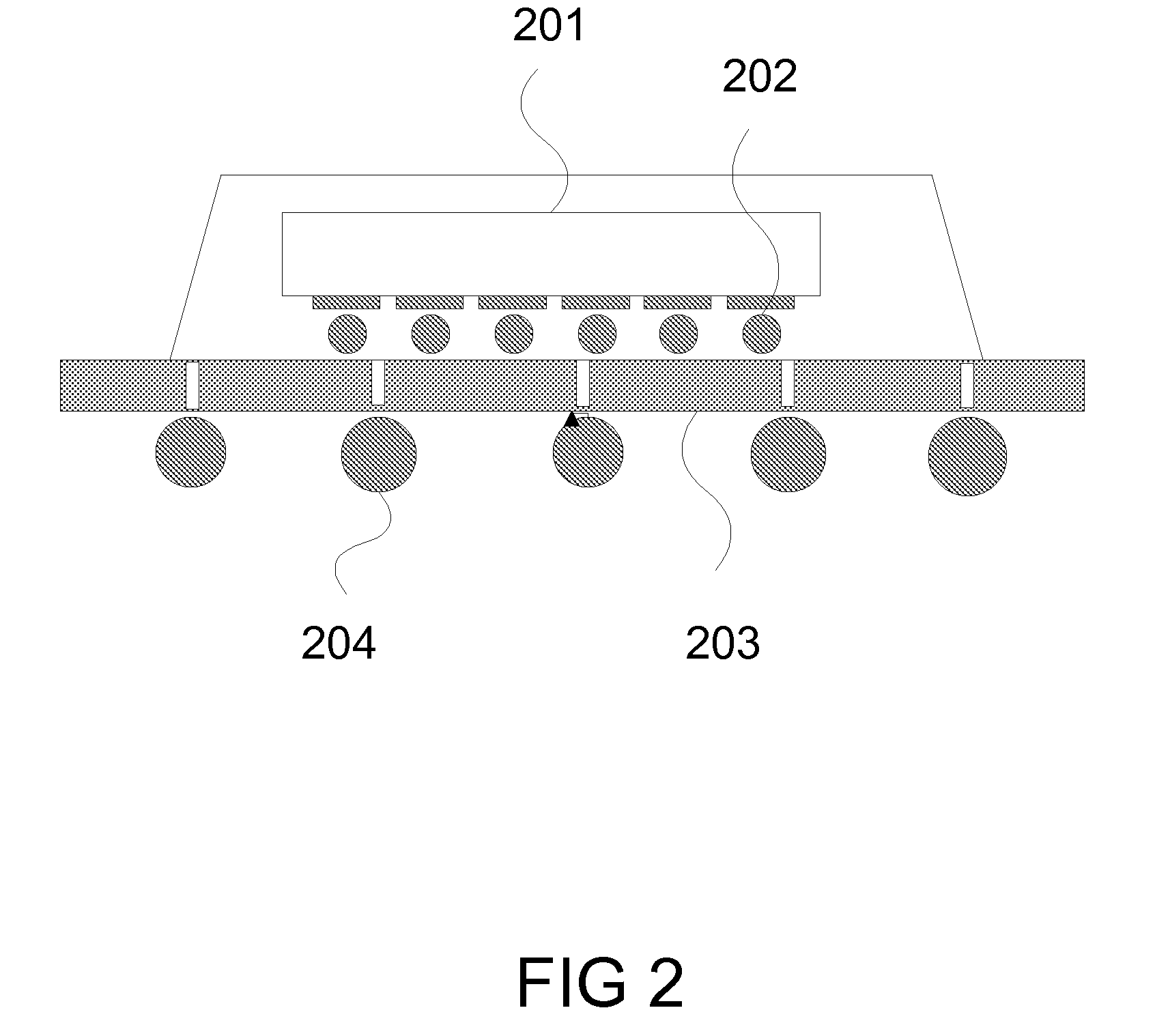

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

Method of interconnecting electronic components using a plurality of conductive studs

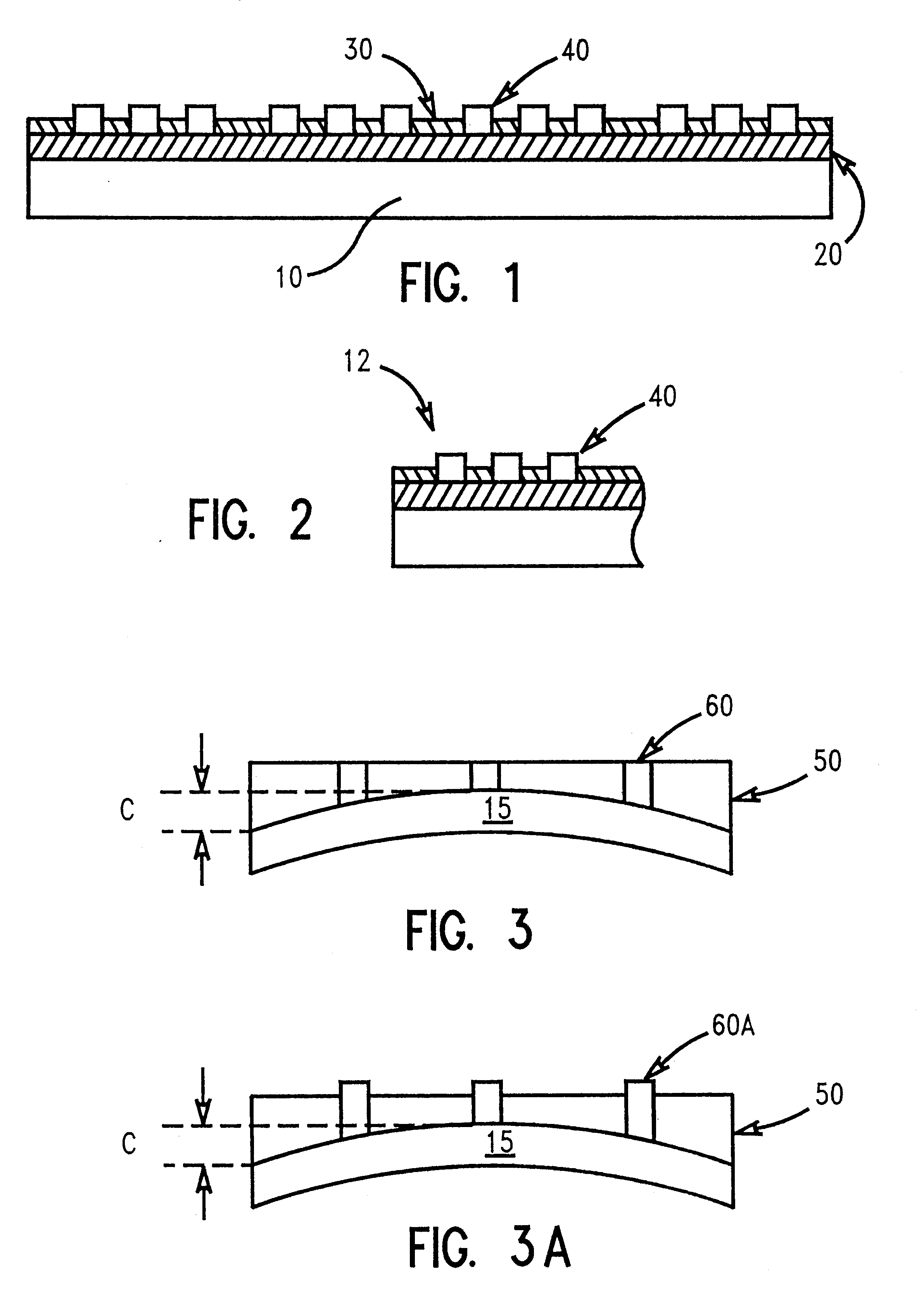

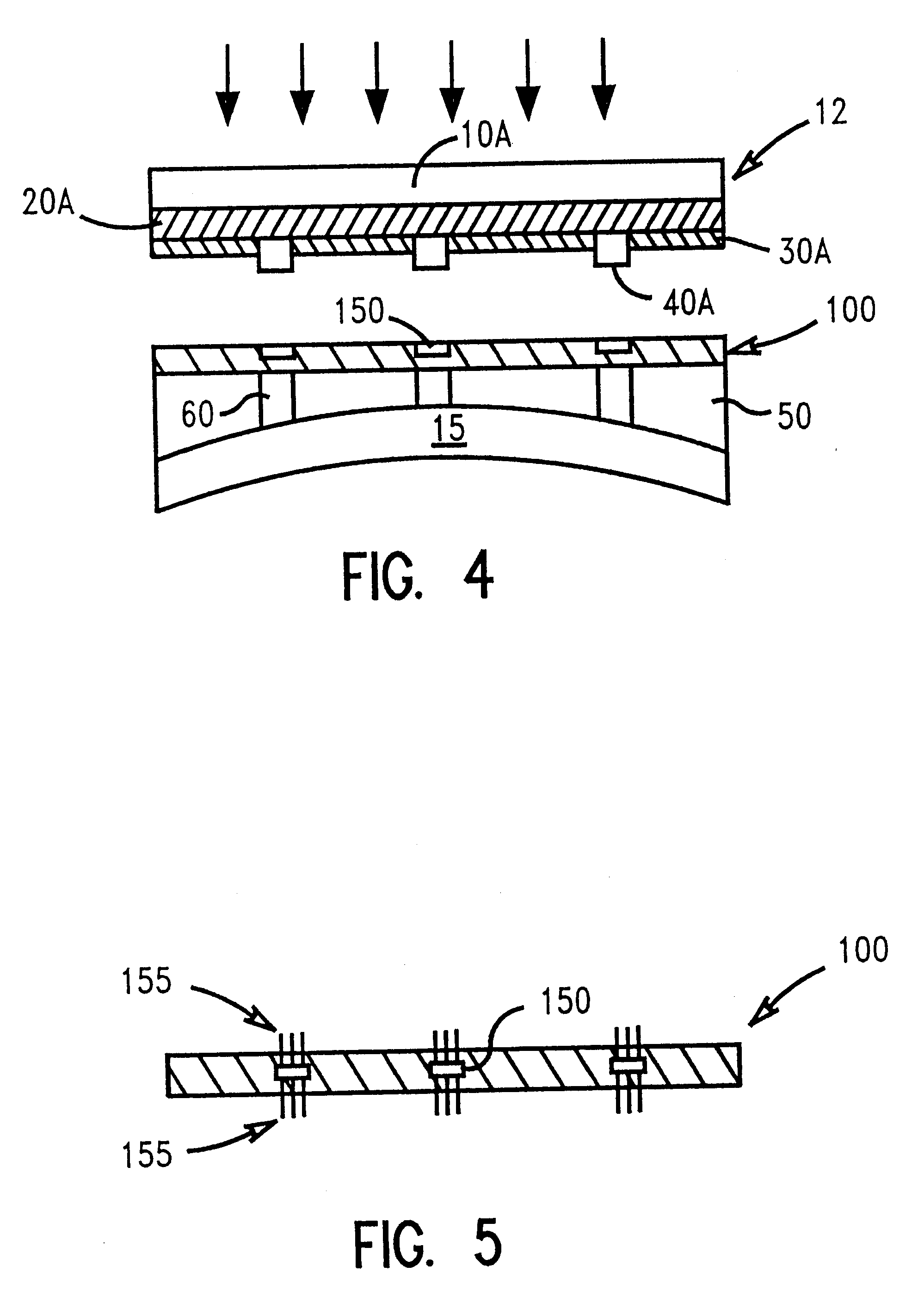

InactiveUS6258625B1Printed circuit assemblingSemiconductor/solid-state device detailsDielectricContact pad

A method of interconnecting electronic components by using a plurality of conductive studs on a surface of a first electronic component and a plurality of corresponding conductive vias on the surface of a second electronic component. Camber on the surface of electronic components may be overcome by coating the surface with a dielectric, planarizing the dielectric, and forming conductive vias corresponding to the contact pads thereon. The conductive studs are substantially lead-free and preferably comprise of copper.

Owner:IBM CORP

Stretchable electric device and manufacturing method thereof

InactiveUS20140299362A1Well formedImproving operation reliability and life-cyclePrinted circuit assemblingCircuit bendability/stretchabilityEngineering

Owner:ELECTRONICS & TELECOMM RES INST

Semiconductor device assemblies and packages including multiple semiconductor devices and methods

InactiveUS6906415B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

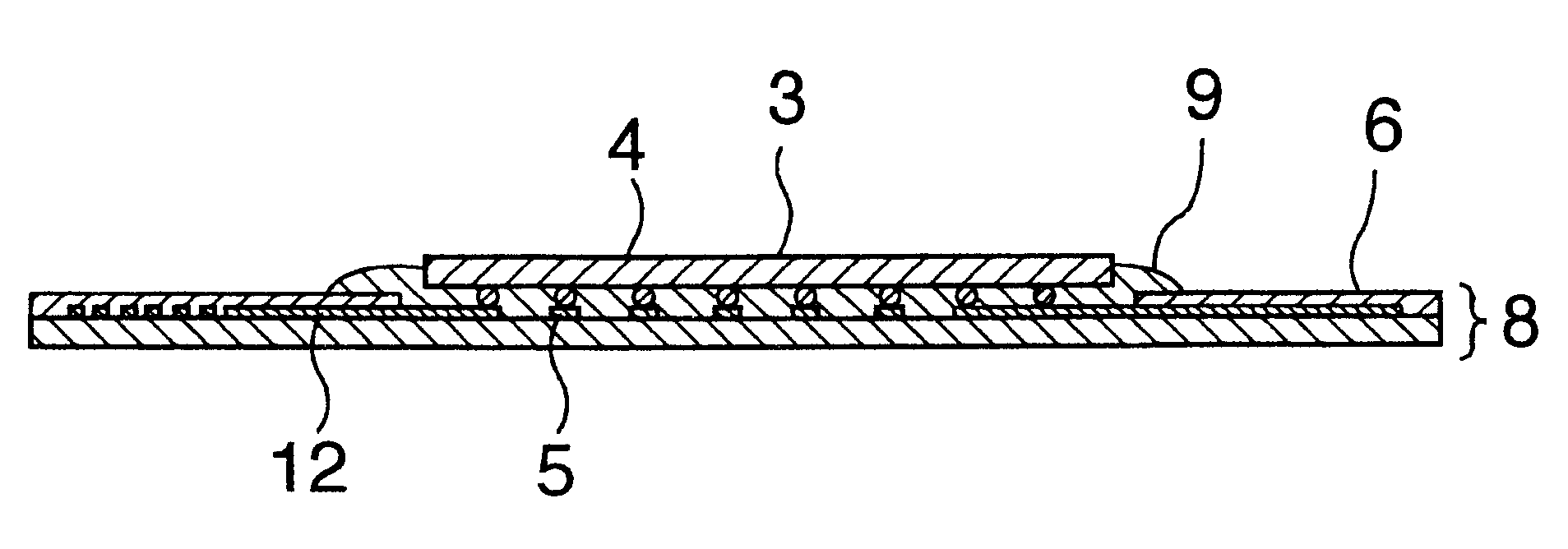

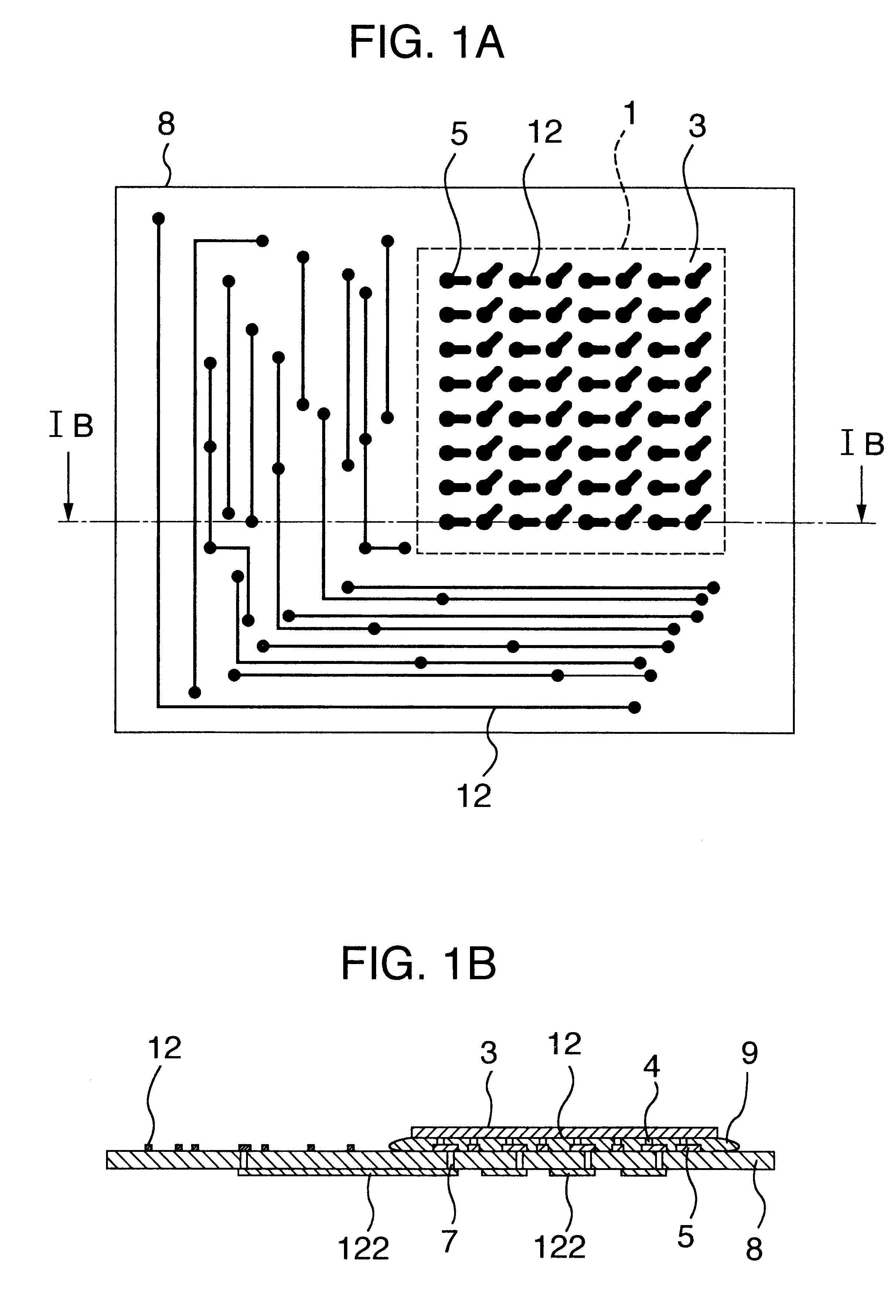

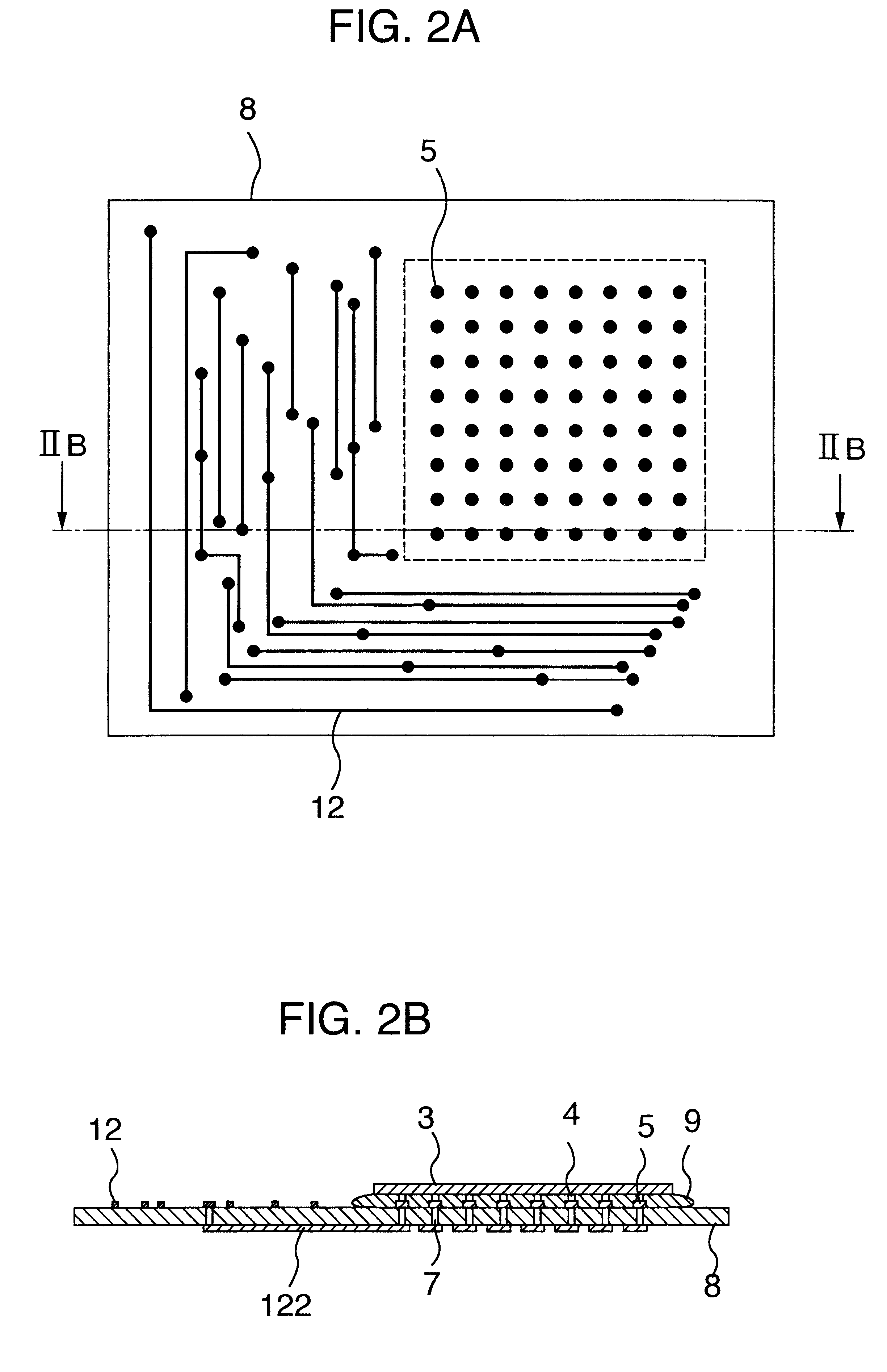

Substrate for mounting semiconductor chips

InactiveUS6281450B1Improve connection reliabilityImprove batch productivitySemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical conductor

A substrate for mounting a semiconductor chip having bumps using an adhesive thereon, said substrate being, for instance, provided with an insulating coating having an opening in the semiconductor chip mounting area so that the wiring conductors will not be exposed to the substrate surface near the boundary of the semiconductor chip mounting area, is improved in connection reliability and has high mass productivity.

Owner:HITACHI CHEM CO LTD

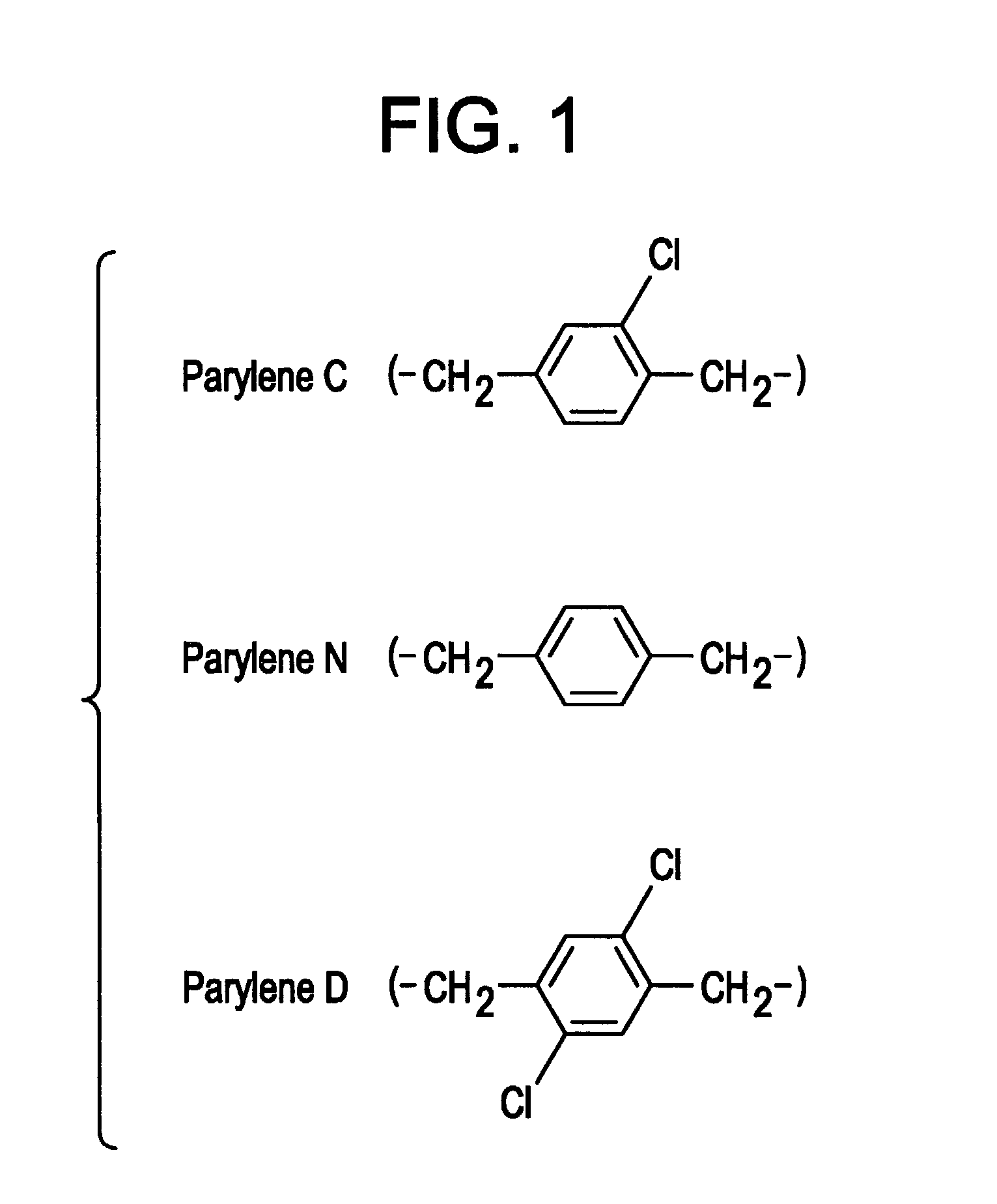

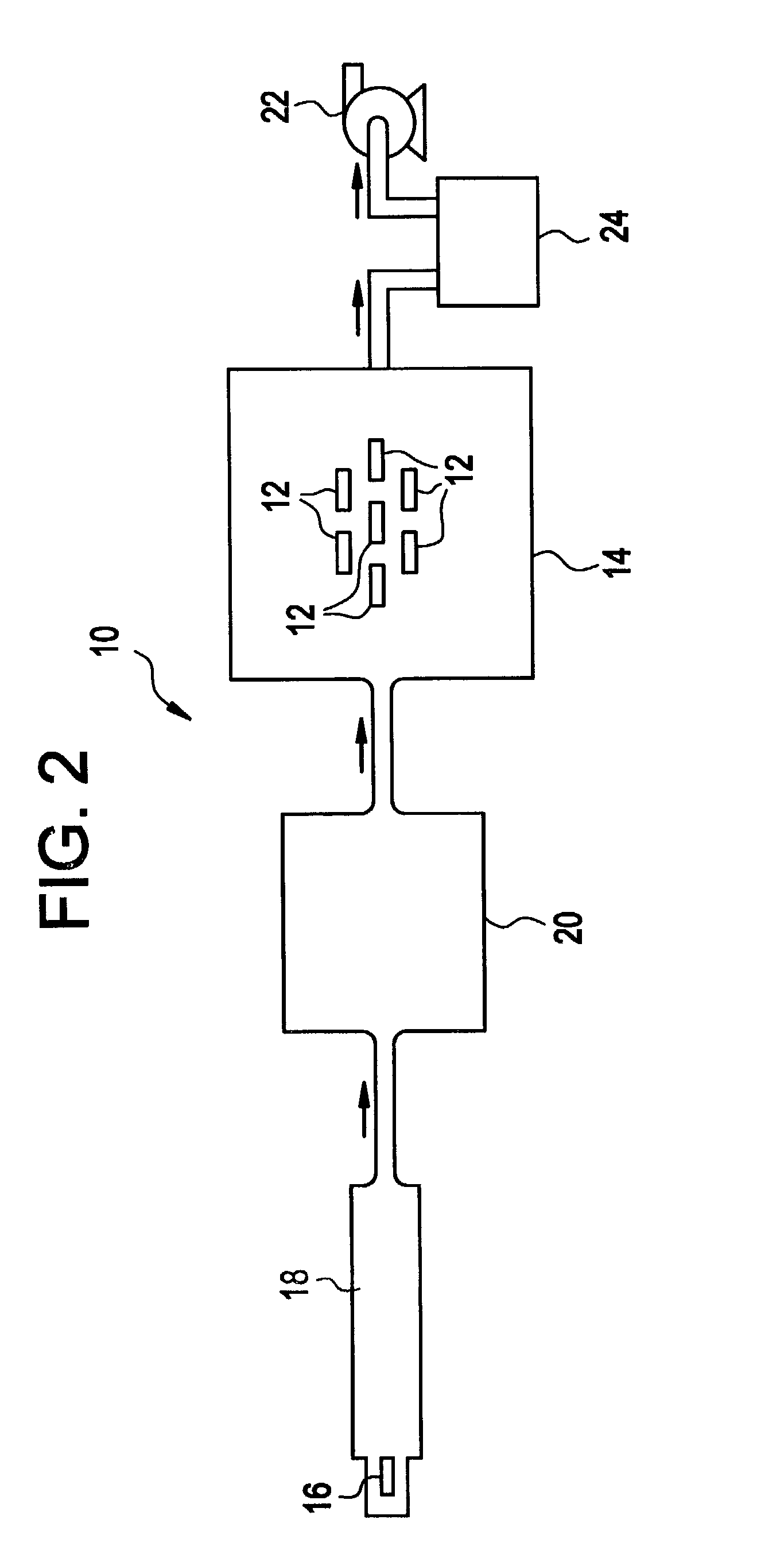

Methods for conformal coating and sealing microchip reservoir devices

InactiveUS6973718B2Reduce adverse reactionsPrinted circuit assemblingLiquid surface applicatorsParyleneGas phase

Methods are provided for conformally coating microchip devices and for sealing reservoirs containing molecules or devices in a microchip device. One method comprises (i) providing a substrate having a plurality of reservoirs having reservoir openings in need of sealing; (ii) loading reservoir contents comprising molecules, a secondary device, or both, into the reservoirs; and (iii) applying a conformal coating barrier layer, such as a vapor depositable polymeric material, e.g., parylene, onto the reservoir contents over at least the reservoir openings to seal the reservoir openings. Another method comprises vapor depositing a conformal coating material onto a microchip device having at least two reservoirs and reservoir caps positioned over molecules or devices stored in the reservoirs, and providing that the conformal coating does not coat or is removed from the reservoir caps.

Owner:MICROCHIPS INC

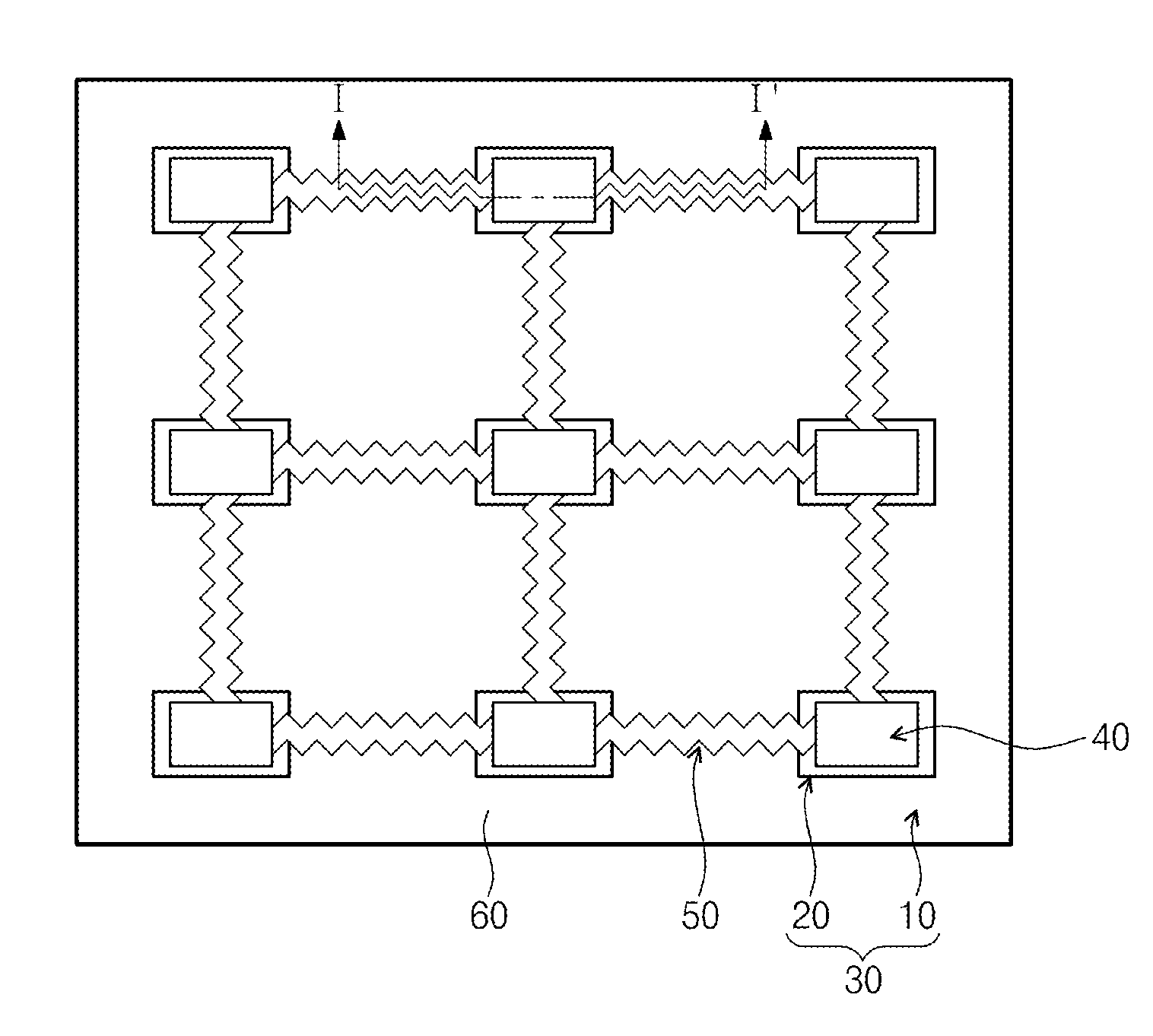

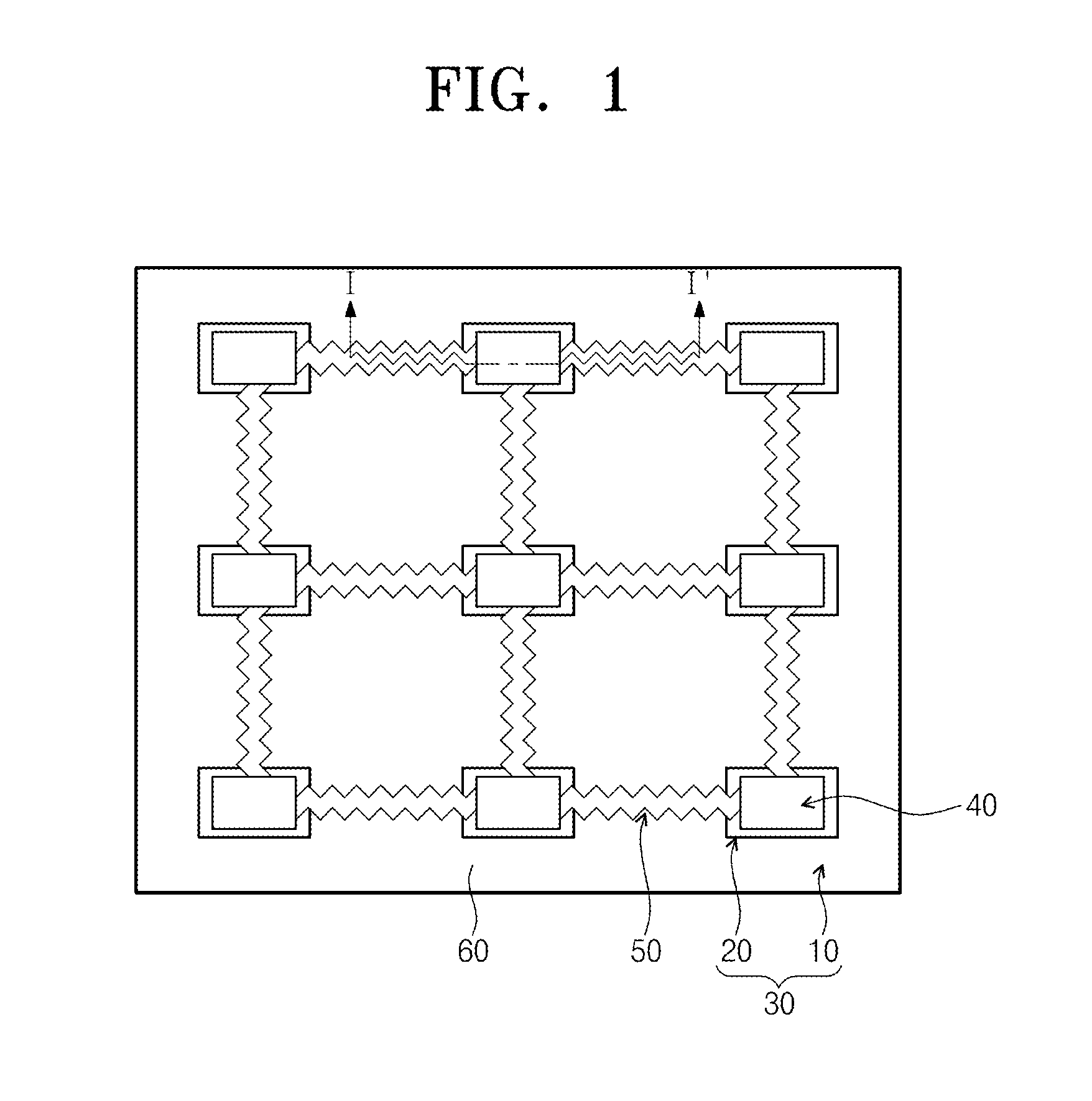

Method for programming a routing layout design through one via layer

A method for programming a routing layout design through one via layer includes forming a plurality of metal traces on a first routing layer and a second routing layer, and positioning a plurality of vias within a via layer disposed between the first and second routing layers for connecting the metal traces on the first and second routing layers according to a first current route defined by a predetermined circuit layout design to connect a first node and a second node so as to establish a second current route equivalent to the first current route.

Owner:FARADAY TECH CORP

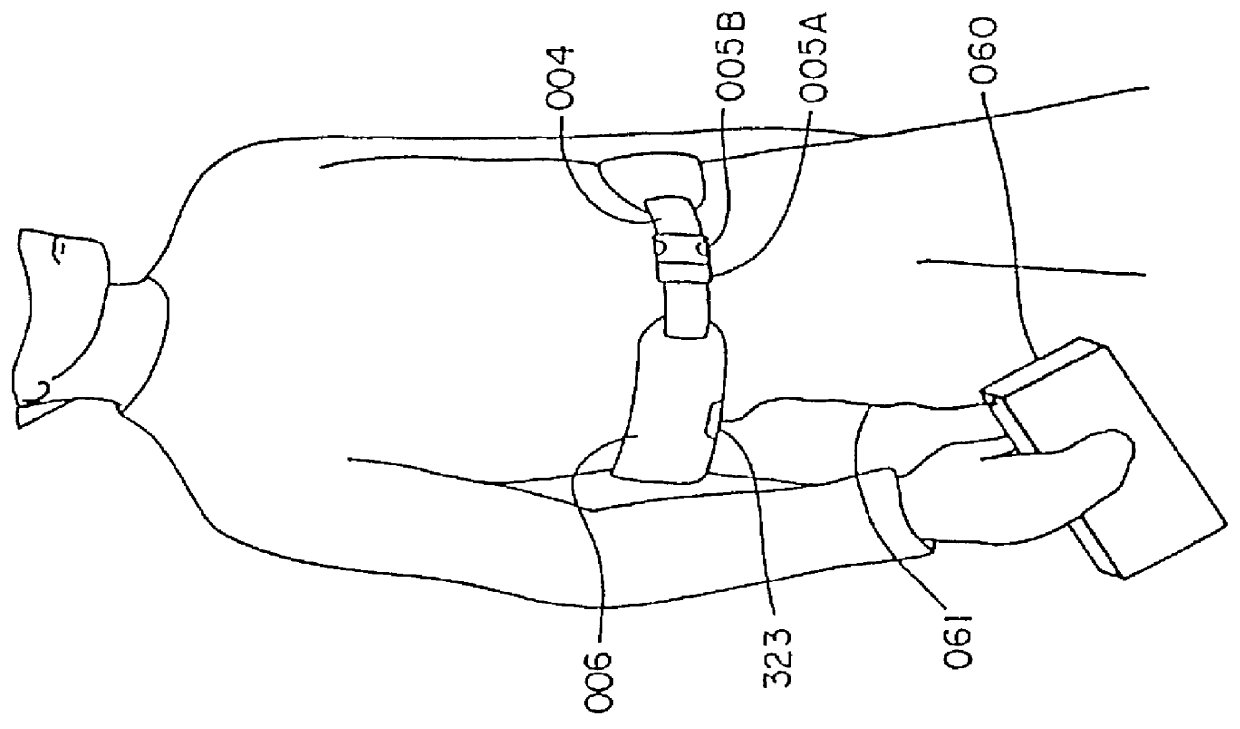

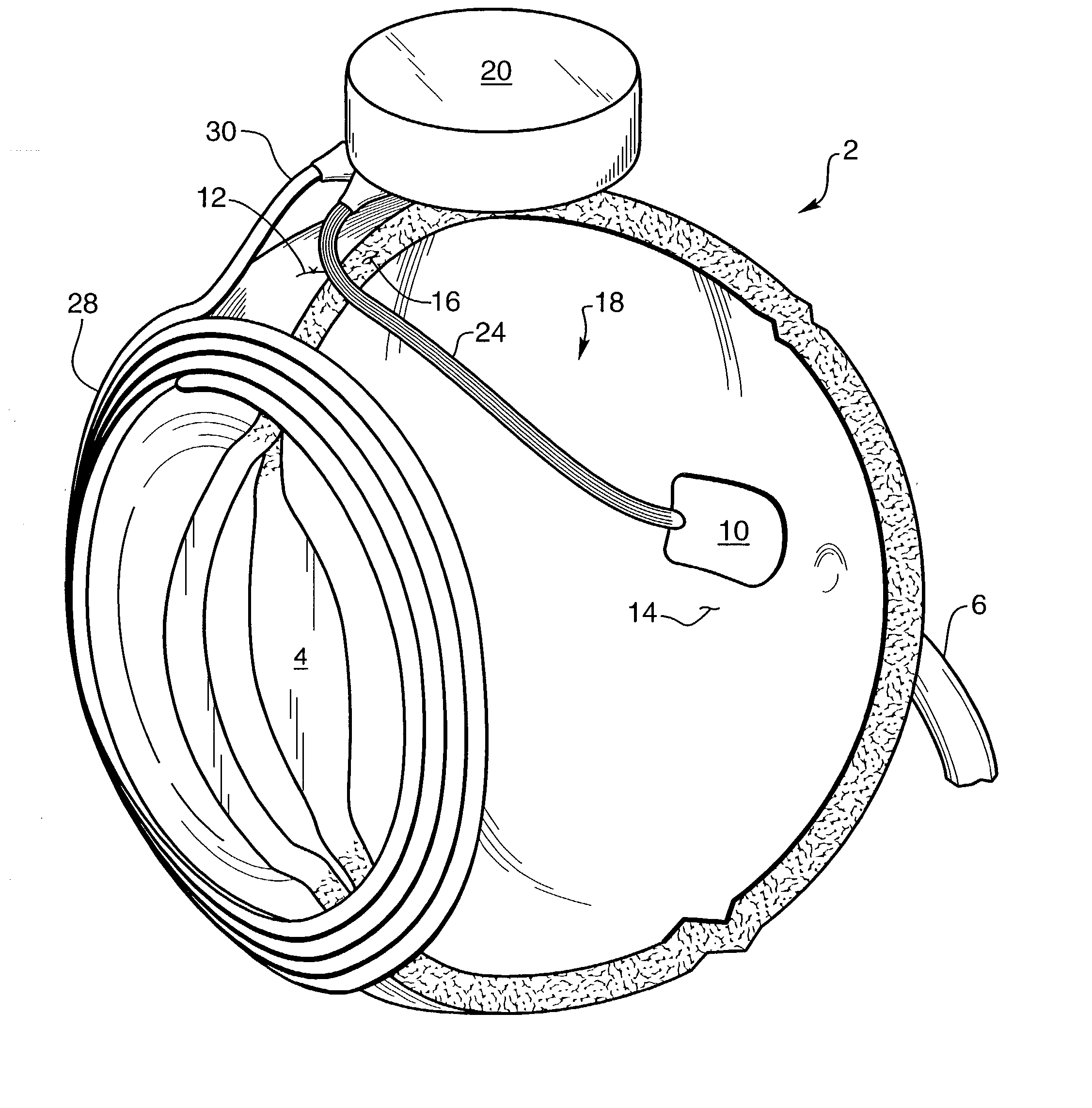

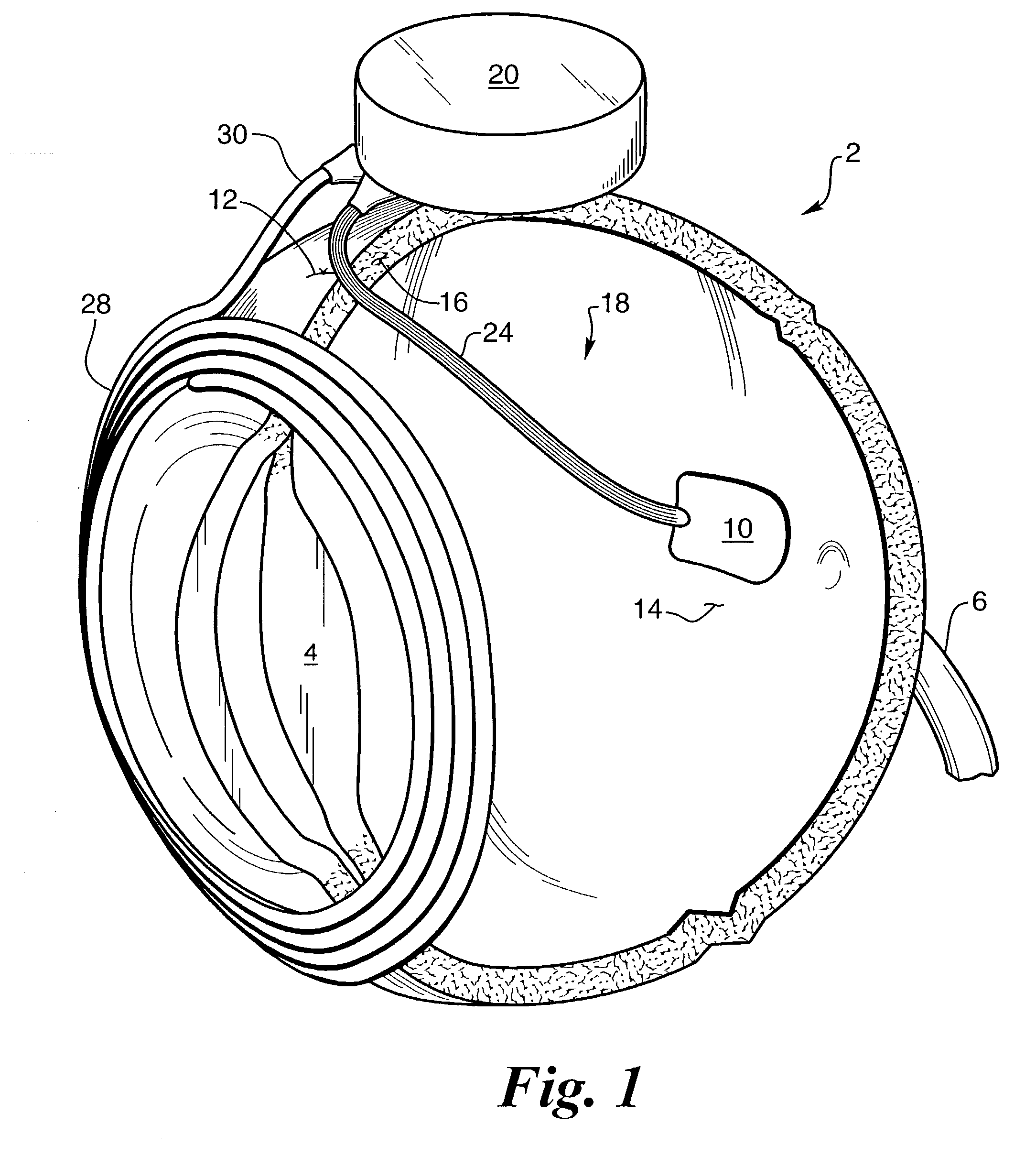

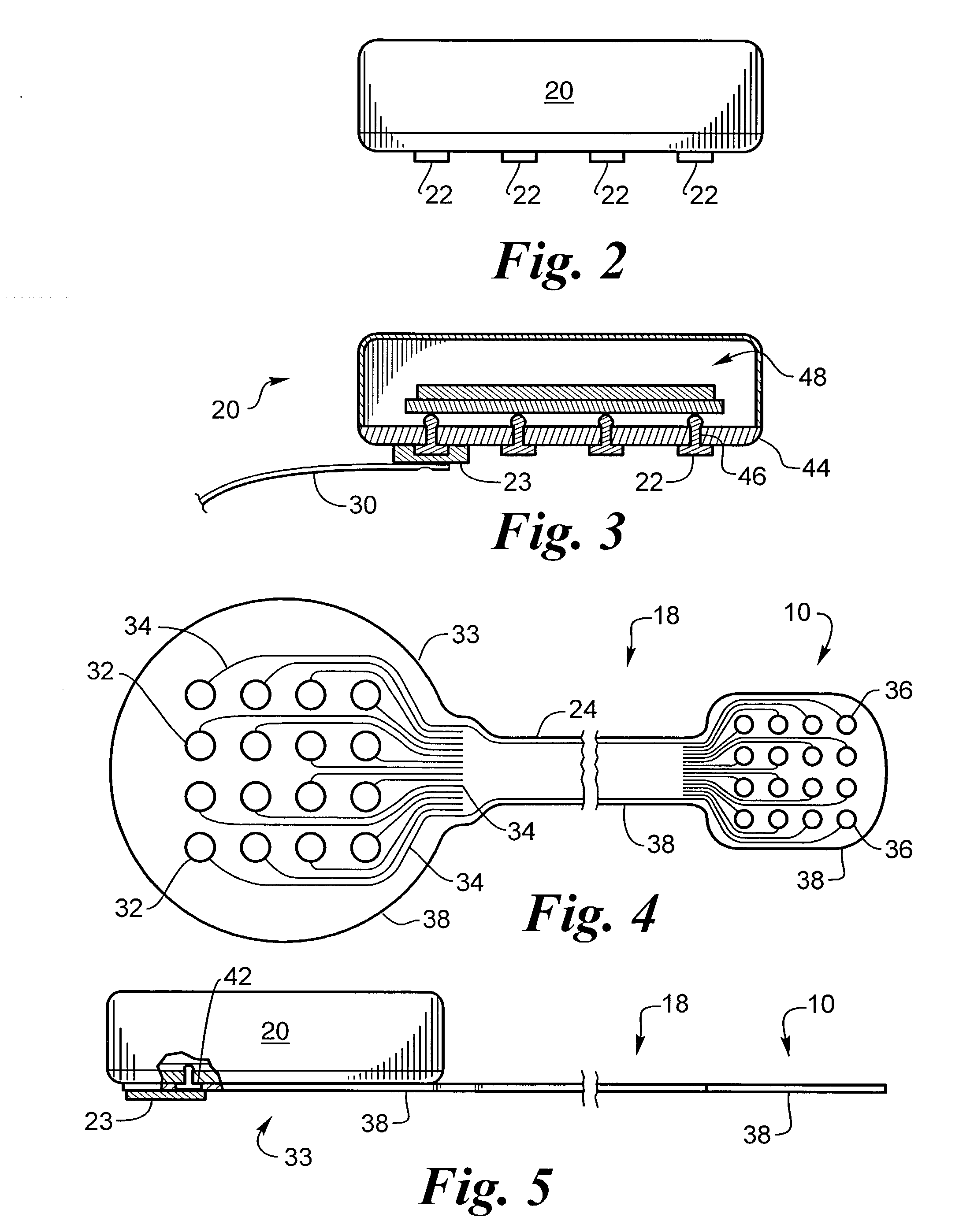

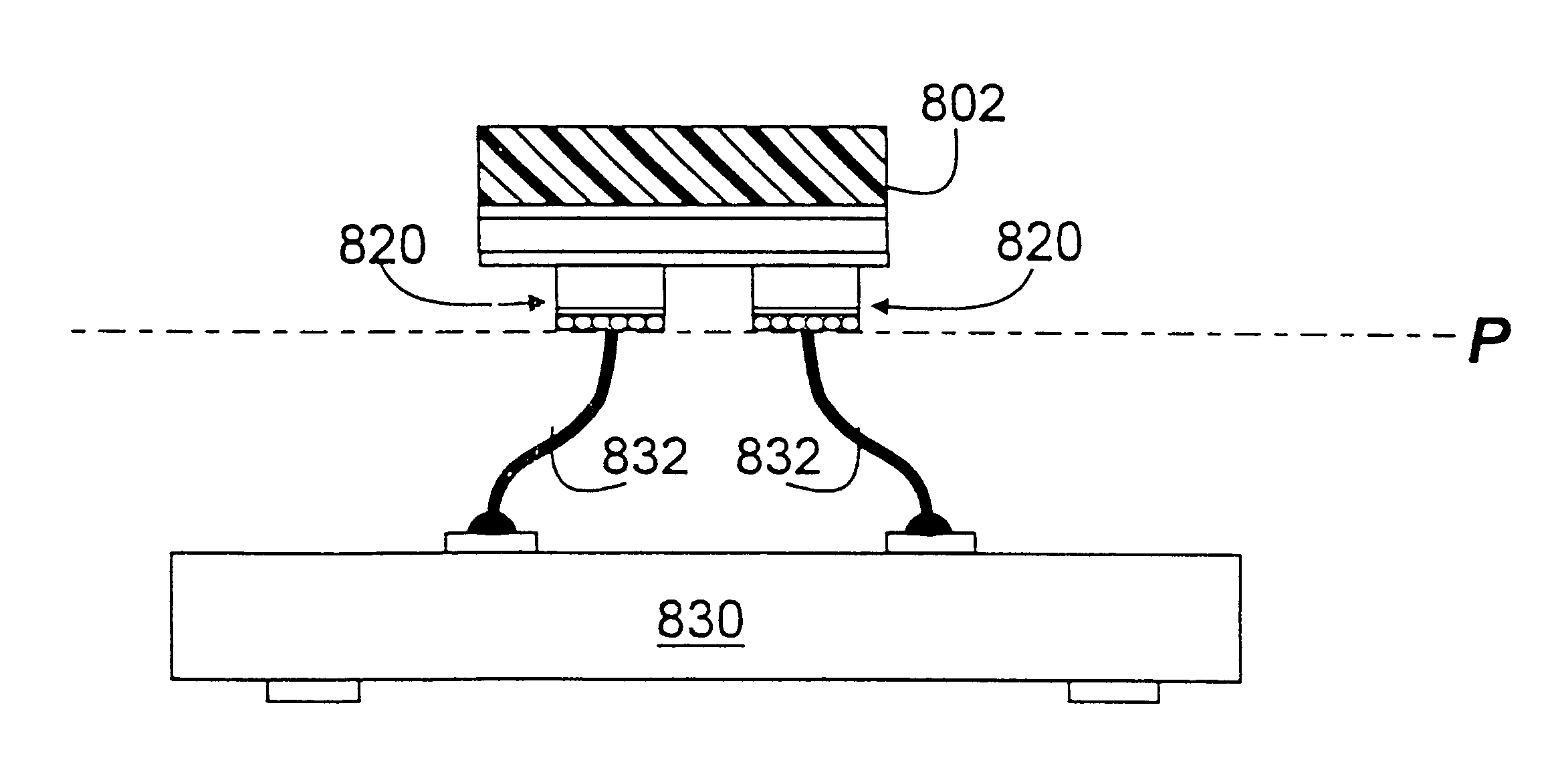

Biocompatible bonding method and electronics package suitable for implantation

ActiveUS20030233134A1Uniform propertySemiconductor/solid-state device detailsSolid-state devicesFlexible circuitsHermetic seal

The invention is directed to a method of bonding a hermetically sealed electronics package to an electrode or a flexible circuit and the resulting electronics package, that is suitable for implantation in living tissue, such as for a retinal or cortical electrode array to enable restoration of sight to certain non-sighted individuals. The hermetically sealed electronics package is directly bonded to the flex circuit or electrode by electroplating a biocompatible material, such as platinum or gold, effectively forming a plated rivet-shaped connection, which bonds the flex circuit to the electronics package. The resulting electronic device is biocompatible and is suitable for long-term implantation in living tissue.

Owner:CORTIGENT INC +1

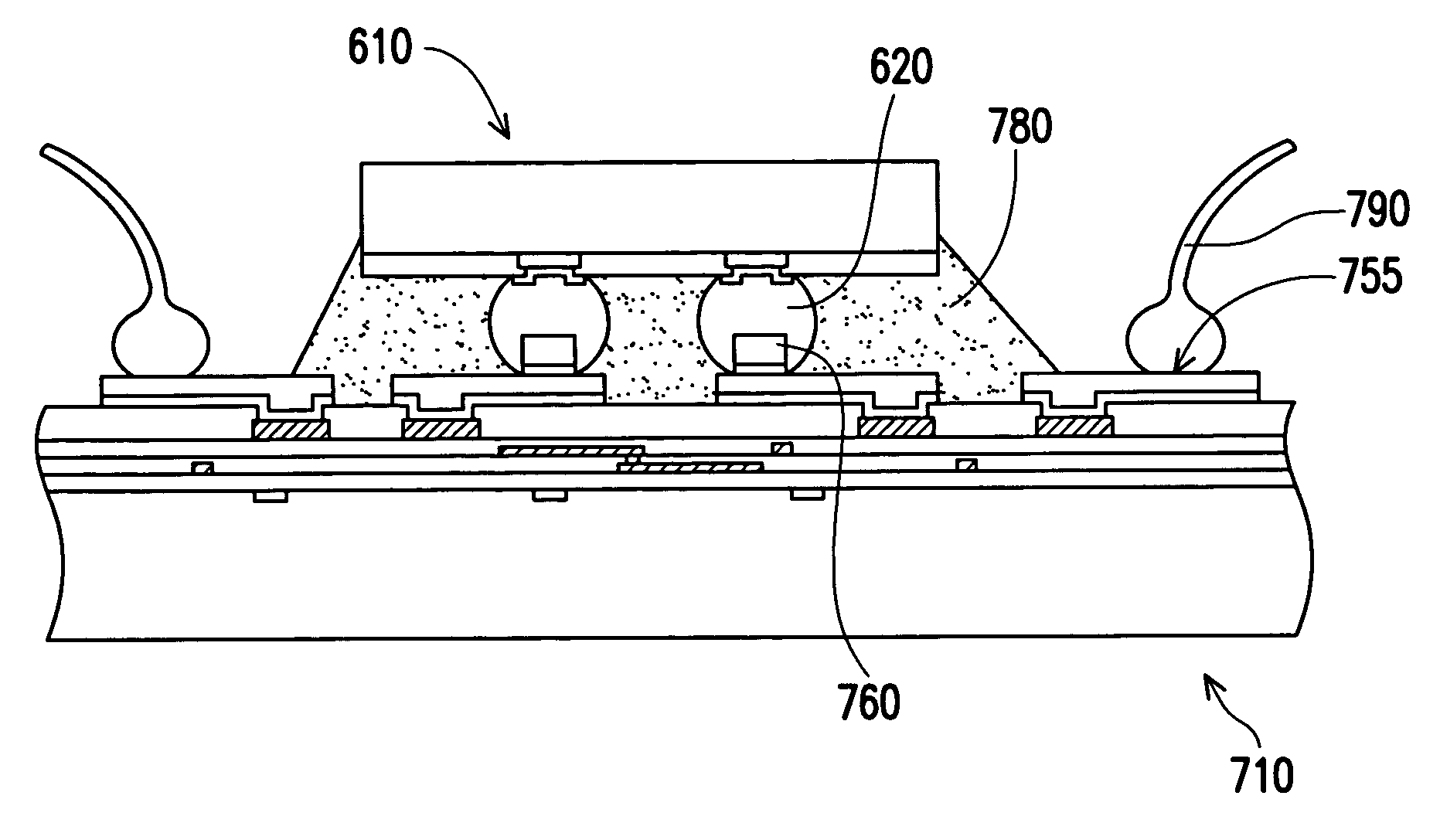

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS20080316714A1Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

Probe card assembly and kit, and methods of using same

InactiveUS6246247B1Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

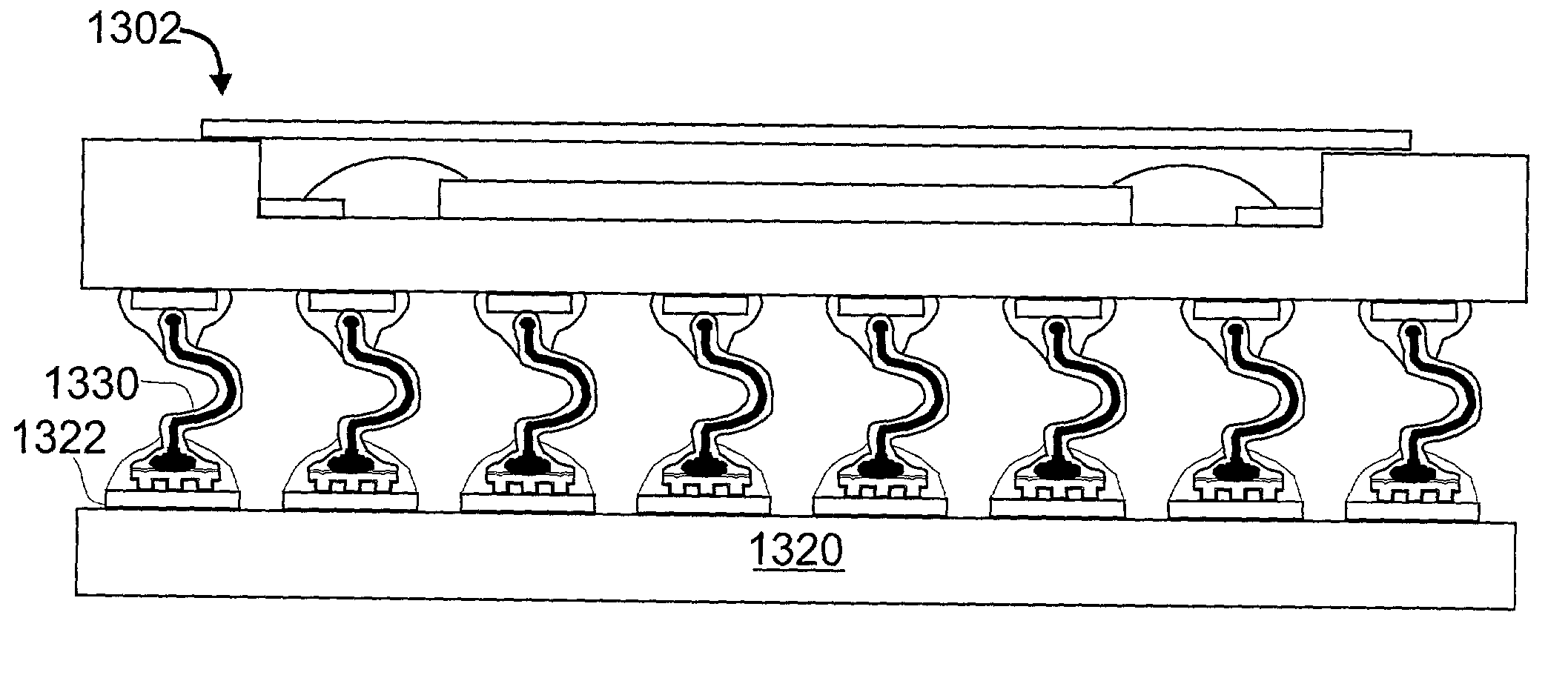

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly thereto (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are "stacked up" so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

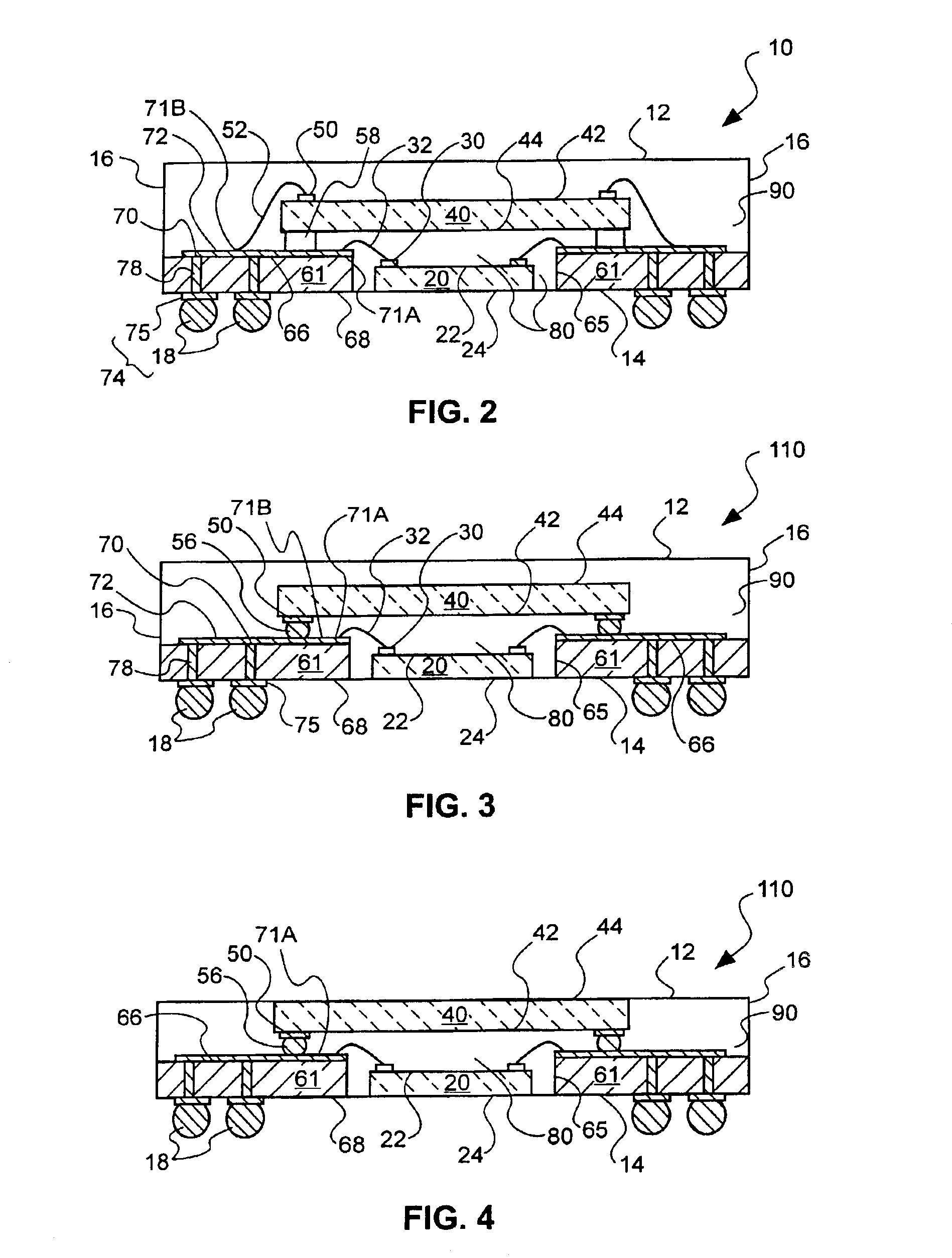

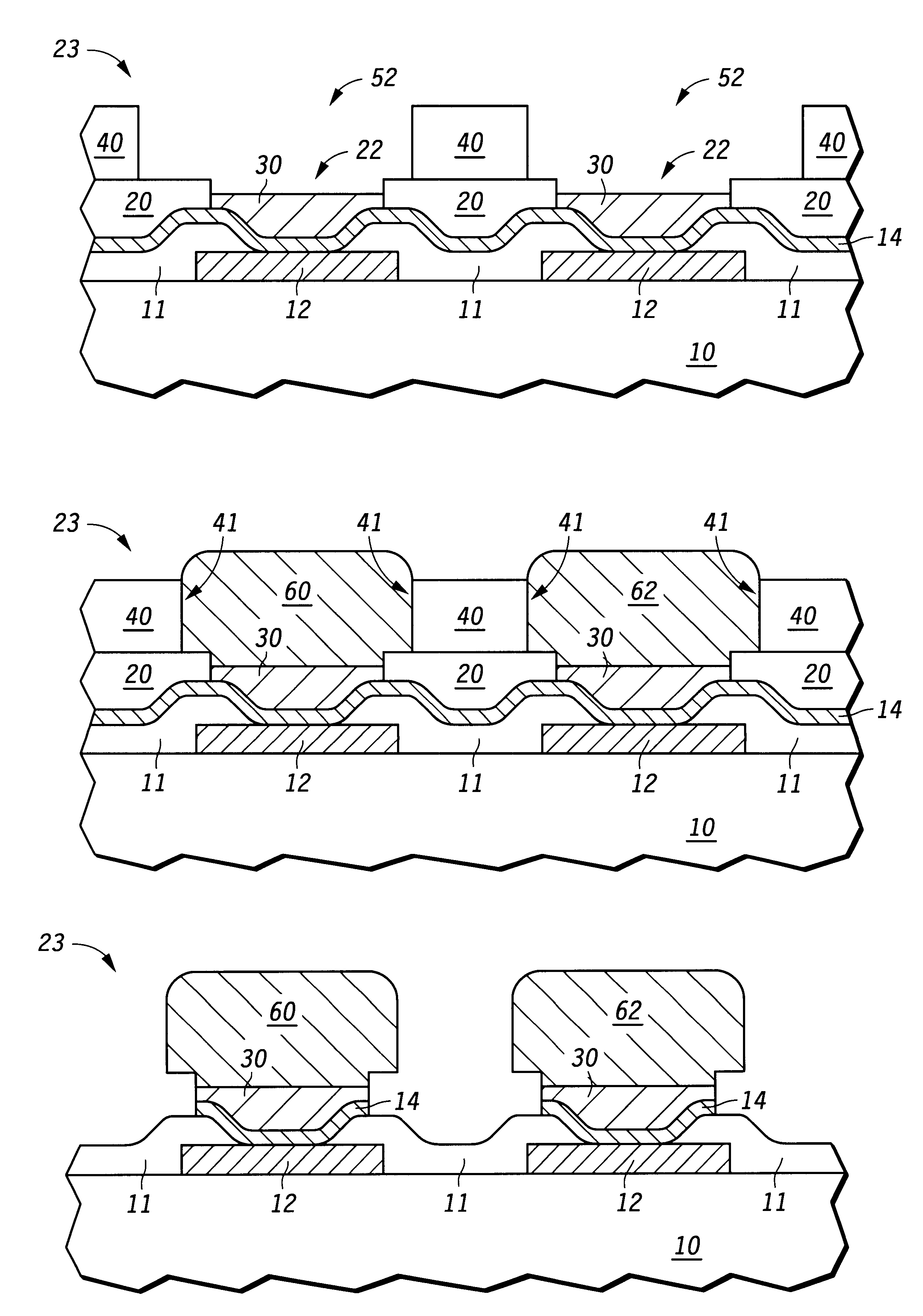

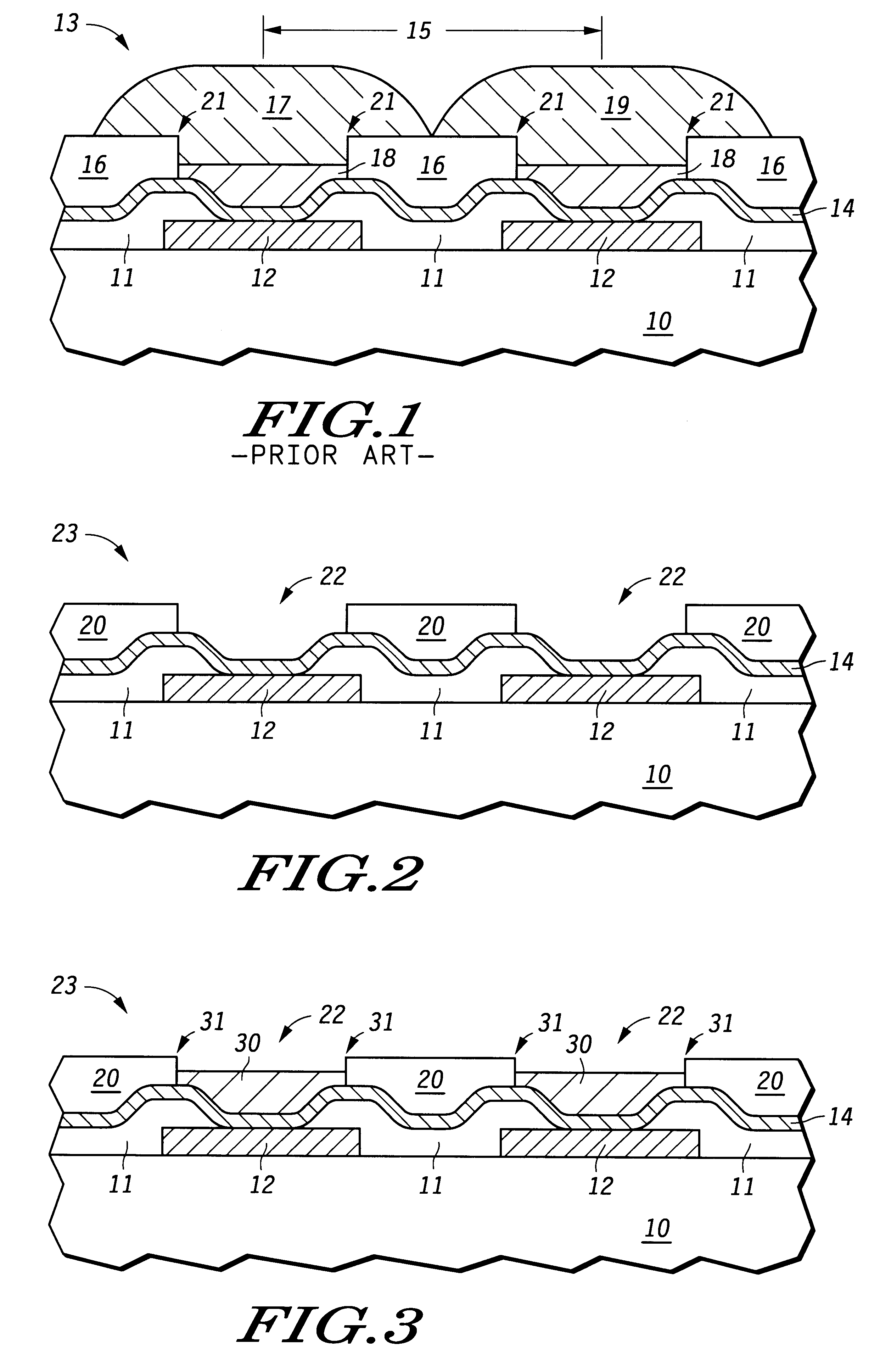

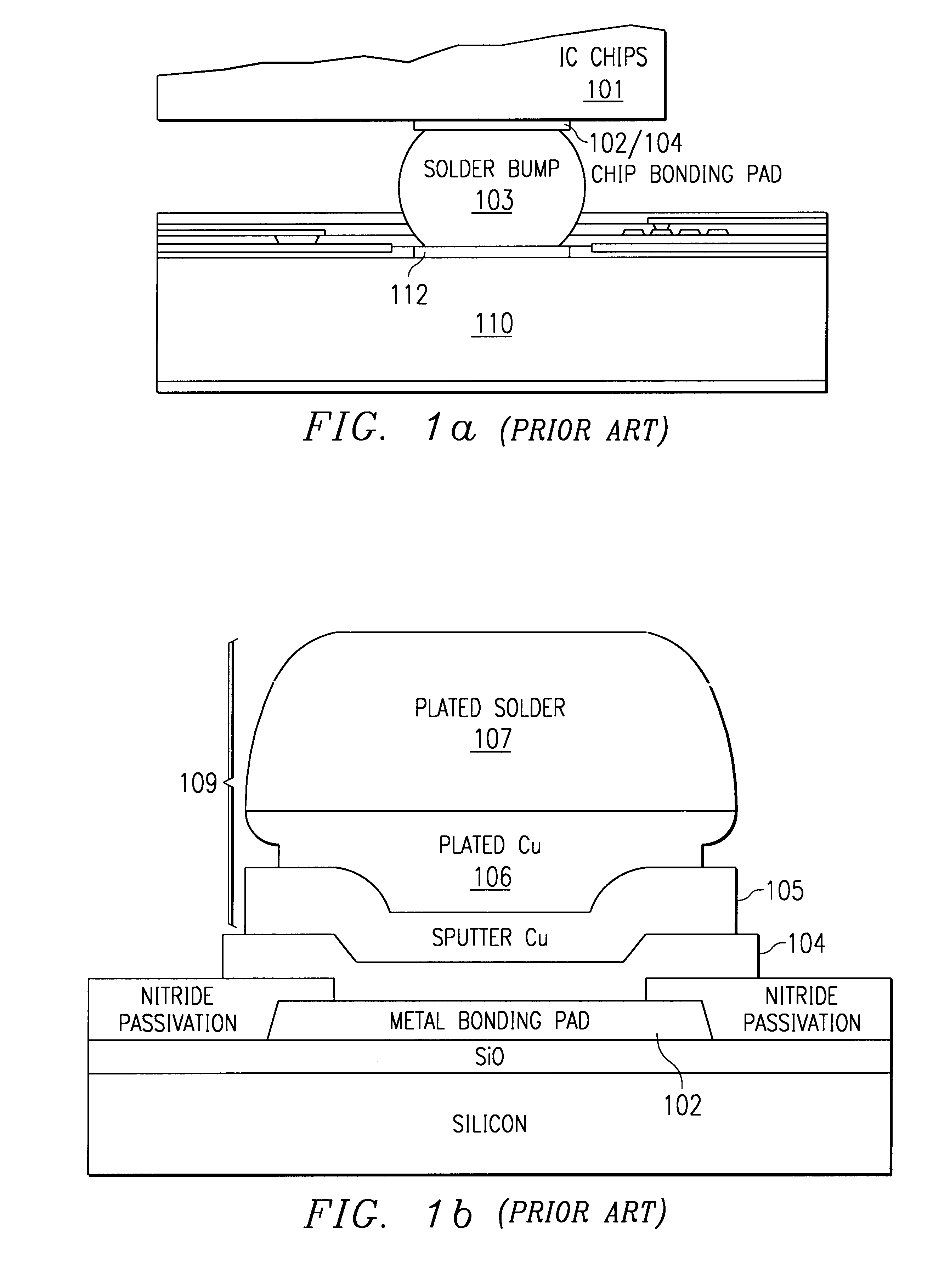

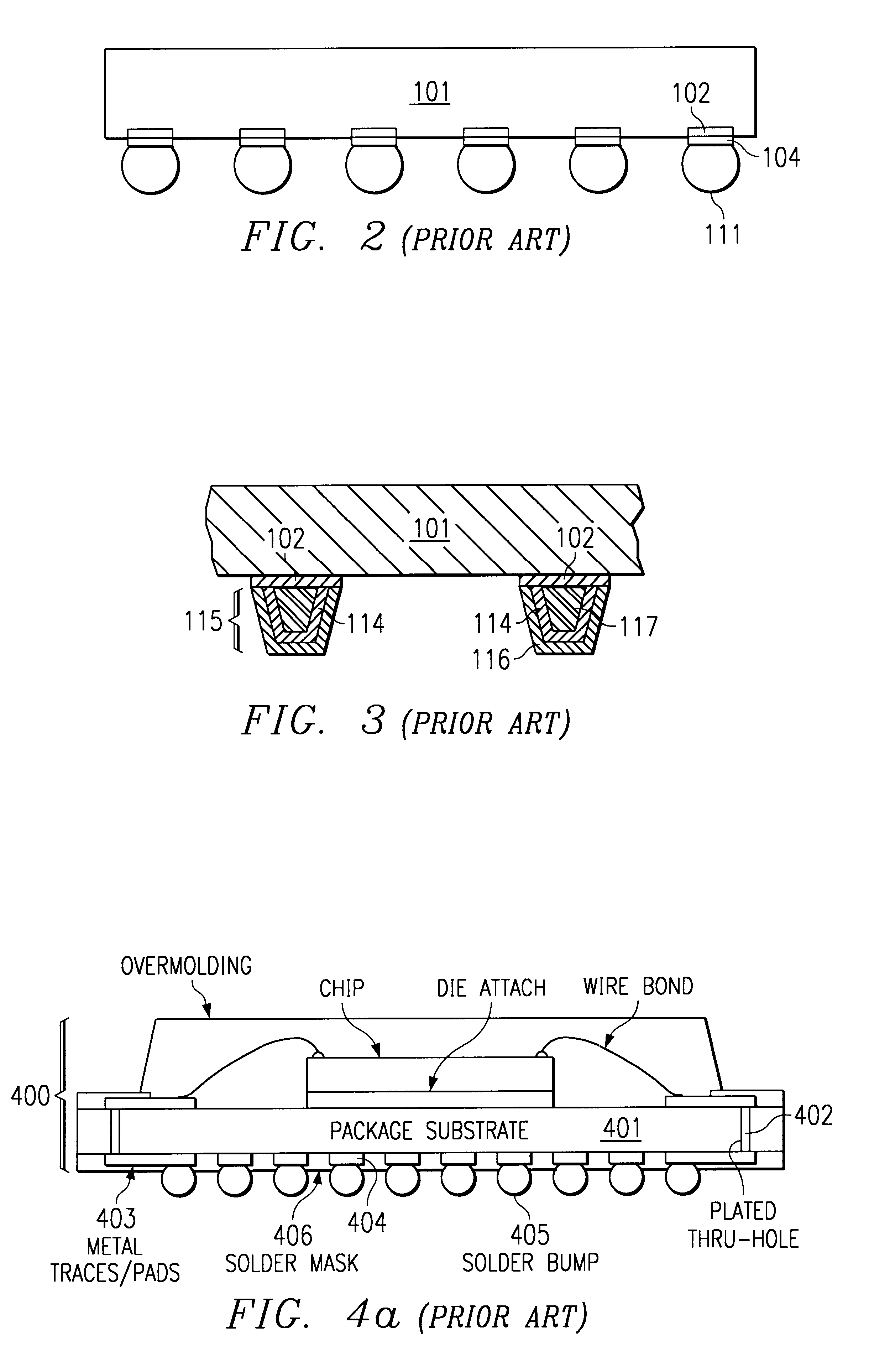

Fine pitch bumping with improved device standoff and bump volume

Embodiments of the present invention relate generally to solder bump formation and semiconductor device assemblies. One embodiment related to a method for forming a bump structure includes providing a semiconductor device (10) having a bond pad (12), and forming a first masking layer (20) overlying the bond pad (12). The first masking layer (20) is patterned to form a first opening (22) overlying at least a portion of the bond pad (12). A second masking layer (40) is formed overlying the first masking layer (20), and the second masking layer (40) is patterned to form a second opening (42) overlying at least a portion of the first opening (22). The method further includes forming a stud (30) at least within the first opening (22) and a solder bump (60) at least within the second opening (42).

Owner:NORTH STAR INNOVATIONS

System for assembling computers to provide a favorable import classification

ActiveUS7420815B2Easy to installLower levelPrinted circuit assemblingCasings/cabinets/drawers detailsBIOSElectrical and Electronics engineering

Owner:GATEWAY

Chip package with multiple chips connected by bumps

InactiveUS7242099B2Improve assembly reliabilityPrecise alignmentPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringChip-scale package

A method of assembling chips. A first chip and a second chip are provided. At least one conductive pillar is formed on the first chip, and a conductive connecting material is formed on the conductive pillar. The second chip also comprises at least one conductive pillar. The first chip is connected to the second chip via the conductive pillars and the conductive connecting material.

Owner:QUALCOMM INC

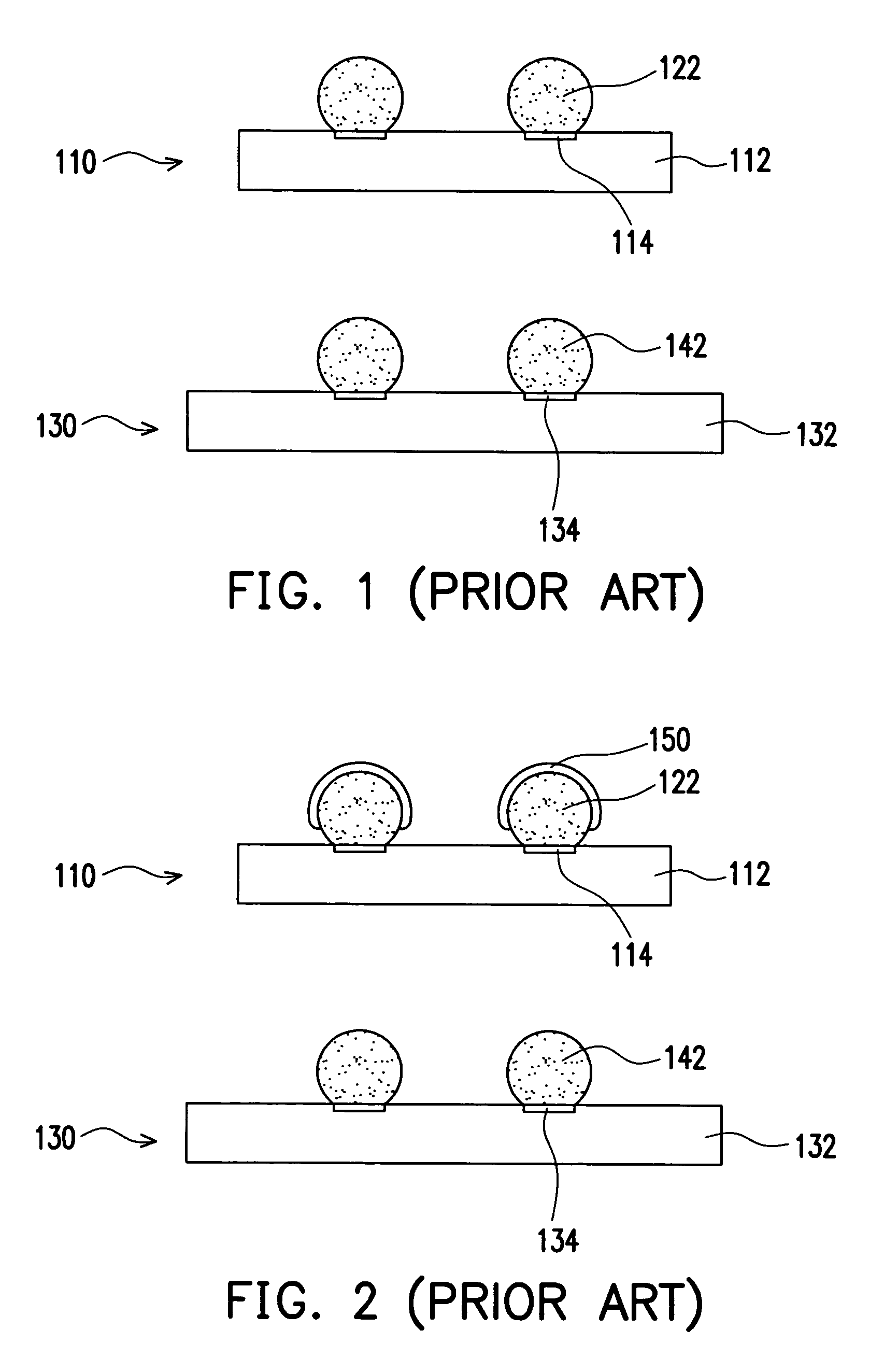

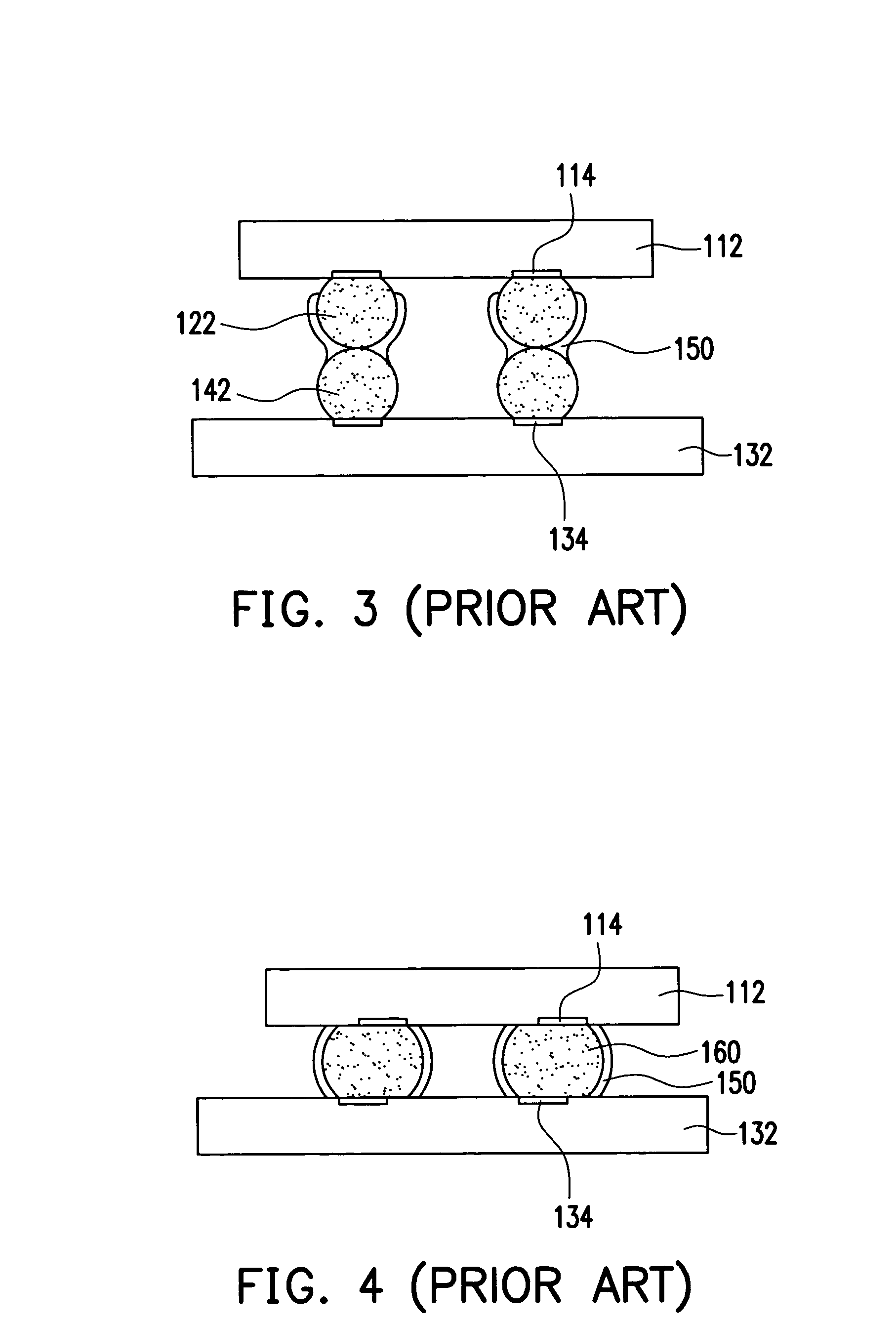

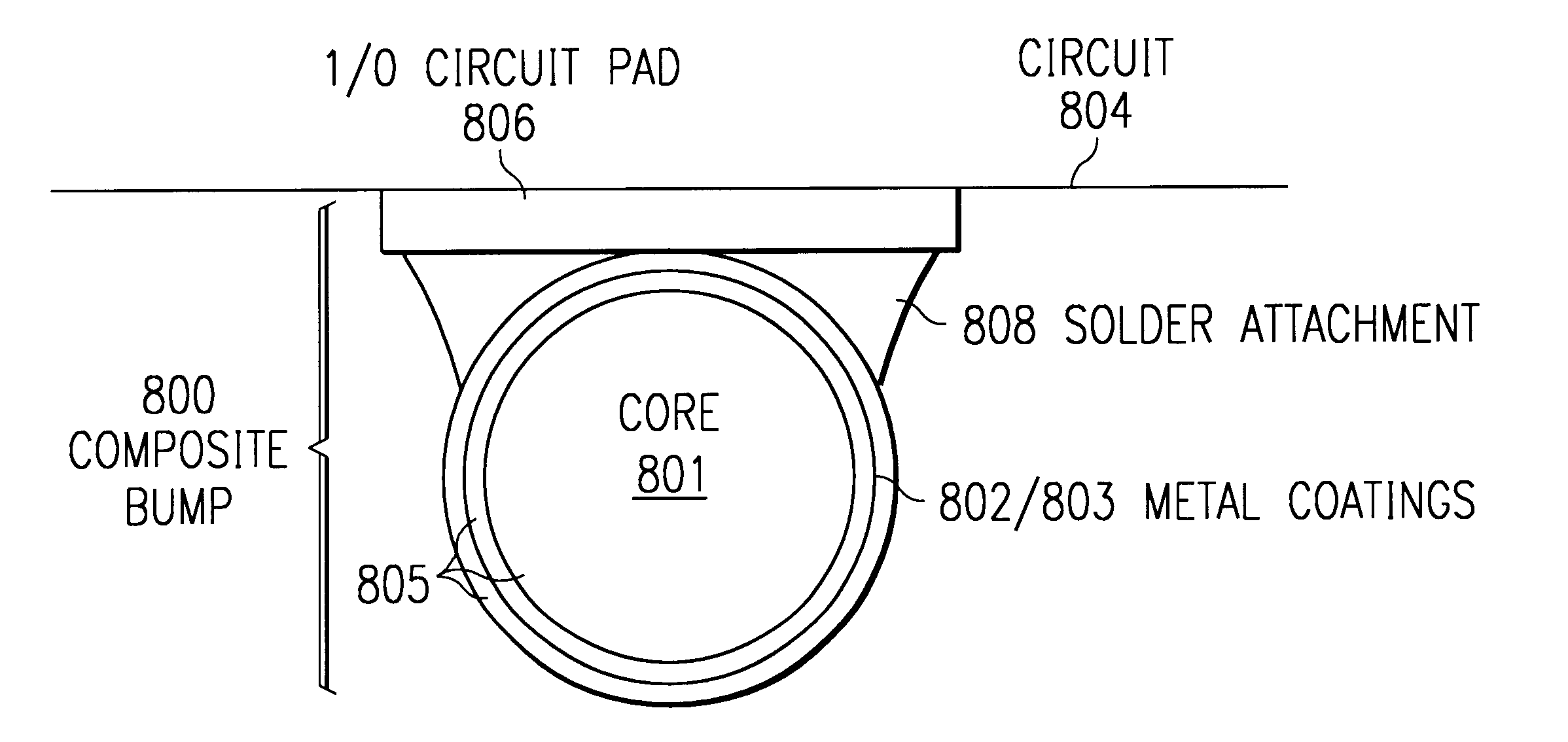

Composite connection structure and method of manufacturing

InactiveUS6337445B1Improve reliability and performanceImprove thermal conductivityPrinted circuit assemblingFinal product manufactureContact padSolder paste

A bump connection structure and a method of attachment to integrated circuits or packages is provided which comprises a prefabricated core structure coated with solderable metal layers to form a composite bump. Said composite bump is aligned to contact pads of the chip or package which have been coated with solder paste, and the assembly heated to form a metallurgical bond. The prefabricated core structures are comprised of metal, plastic or ceramic of the size and dictated by package standards. The connection structure is preferably lead free.

Owner:TEXAS INSTR INC

Popular searches

Semiconductor/solid-state device manufacturing Electrical connection printed elements Electrical apparatus contructional details Printed circuits structural associations Semiconductor devices Printed electric component incorporation Cross-talk/noise/interference reduction Printed circuit aspects Printed circuit non-printed electric components association Circuit thermal arrangements

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com