Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3263results about How to "Improve connection reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

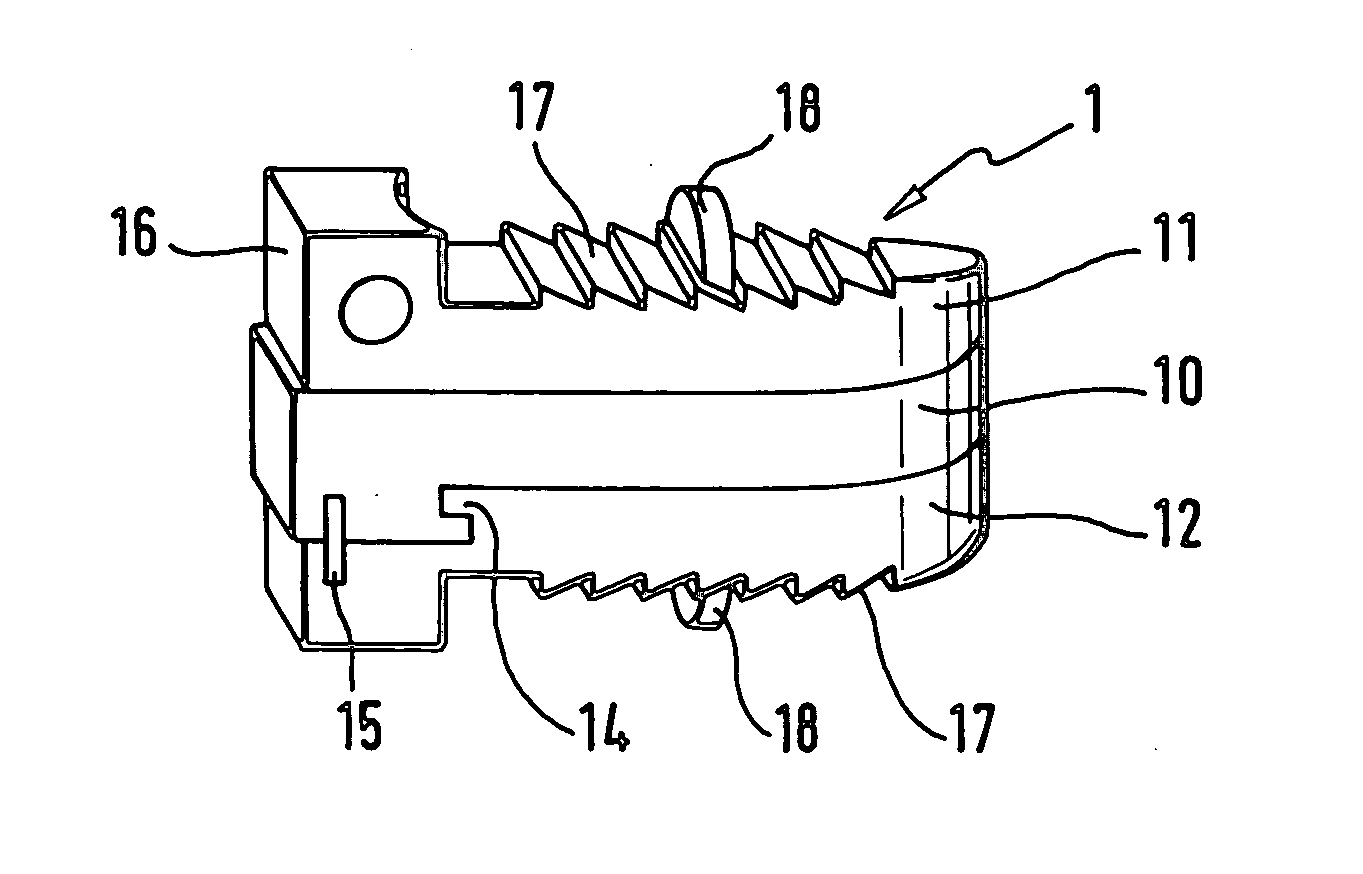

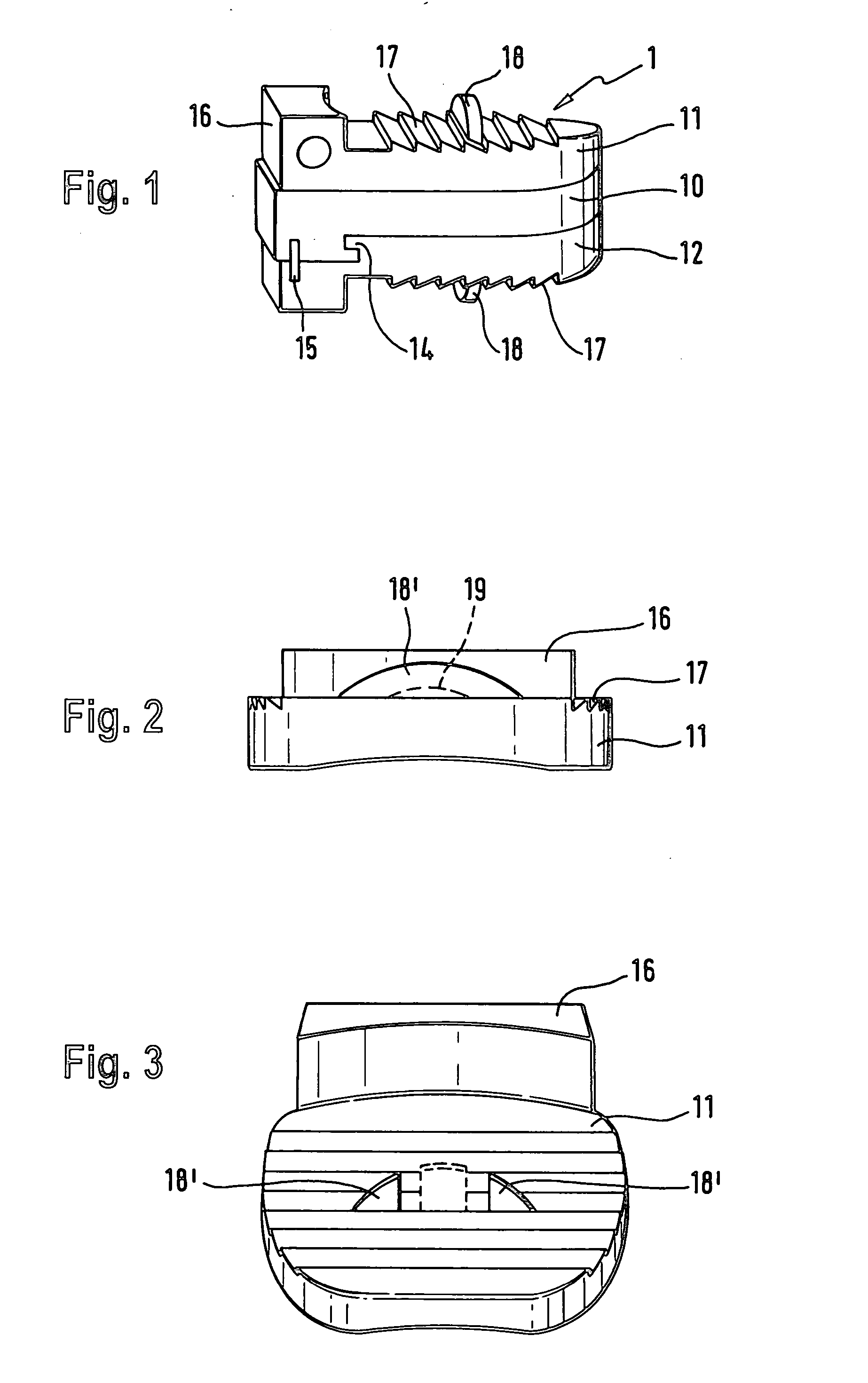

Cervical Intervertebral Disc Prosthesis Comprising An Anti-Dislocation Device And Instruments

InactiveUS20080027550A1Easily advancedImprove connection reliabilityInternal osteosythesisJoint implantsUnintended MovementSpinal column

A cervical intervertebral prosthesis includes lower and upper anchoring plates with a prosthesis core arranged between them to create an articulated connection. The anchoring plates are designed to bear with their anchoring plate surfaces on adjacent vertebral bodies. At least one anchoring plate surface has a rib-like projection thereon which can be used to engage in the vertebral body with a form fit. In order to produce a corresponding recess in the vertebral body, an instrument having a handle, a stem, a head part and an excavating element that can be retracted into the head part may be used. This permits considerably improved securing of the cervical intervertebral prosthesis against unintended movement. The medullary canal running along the posterior margin of the vertebral column is in this way protected from damage.

Owner:CERVITECH INC

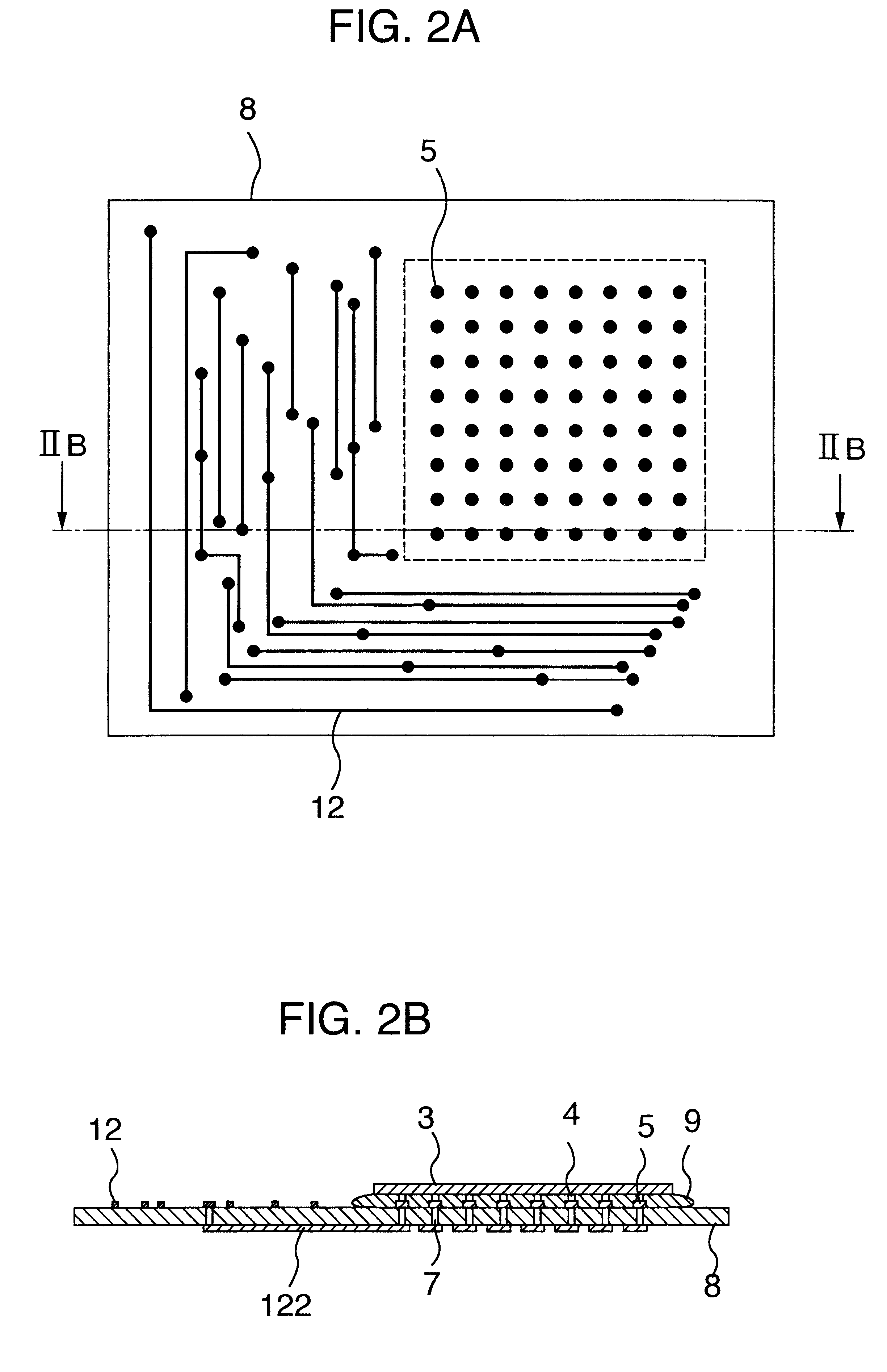

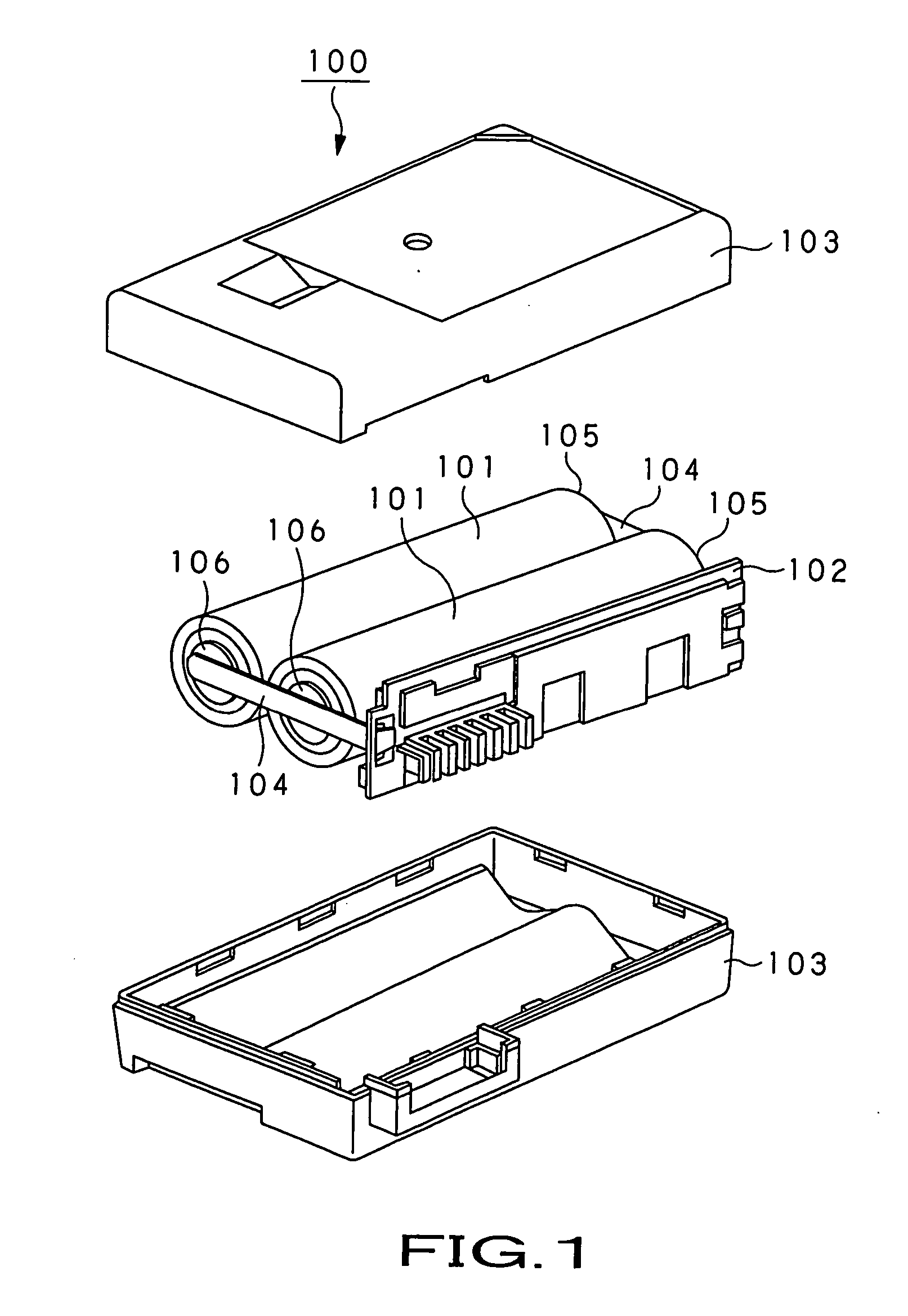

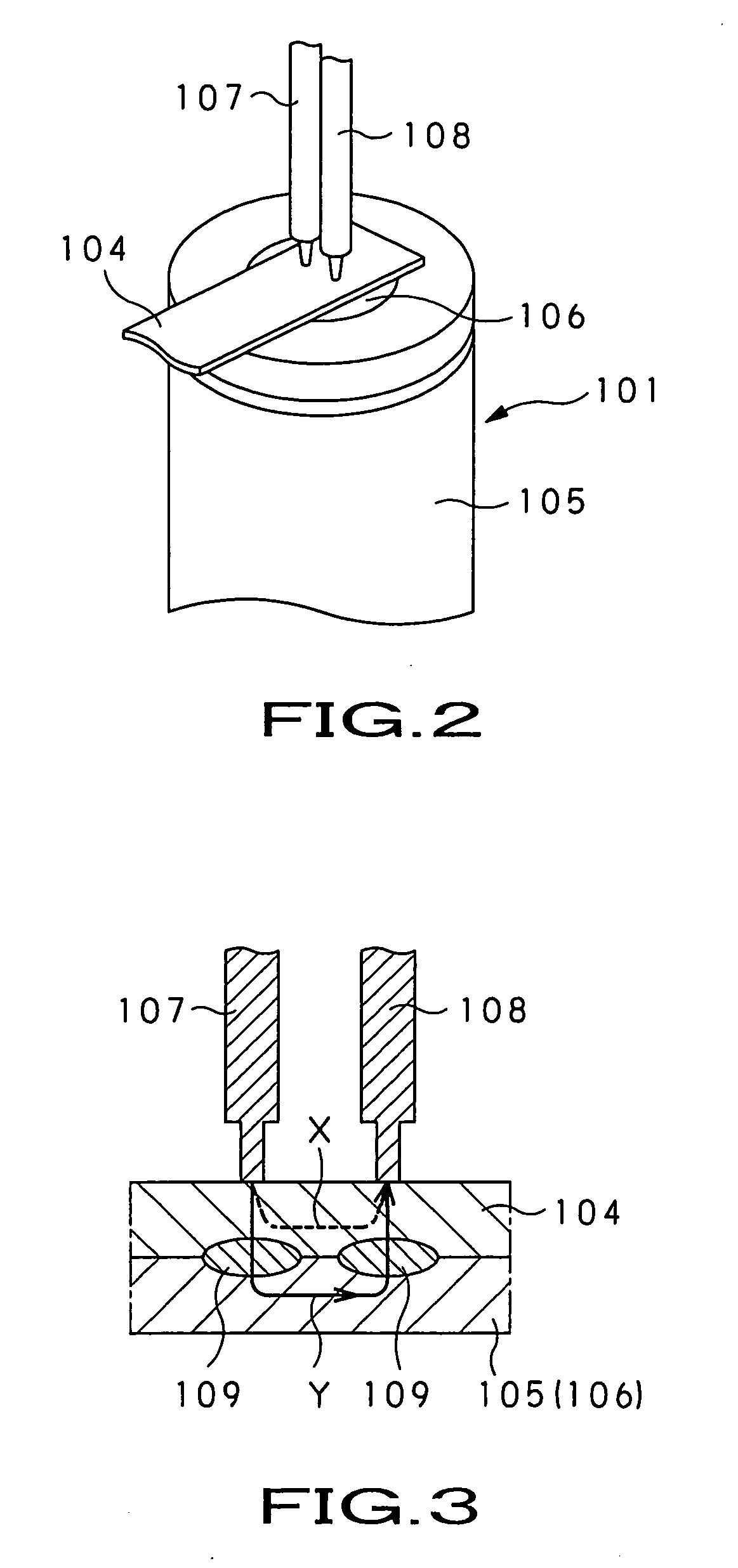

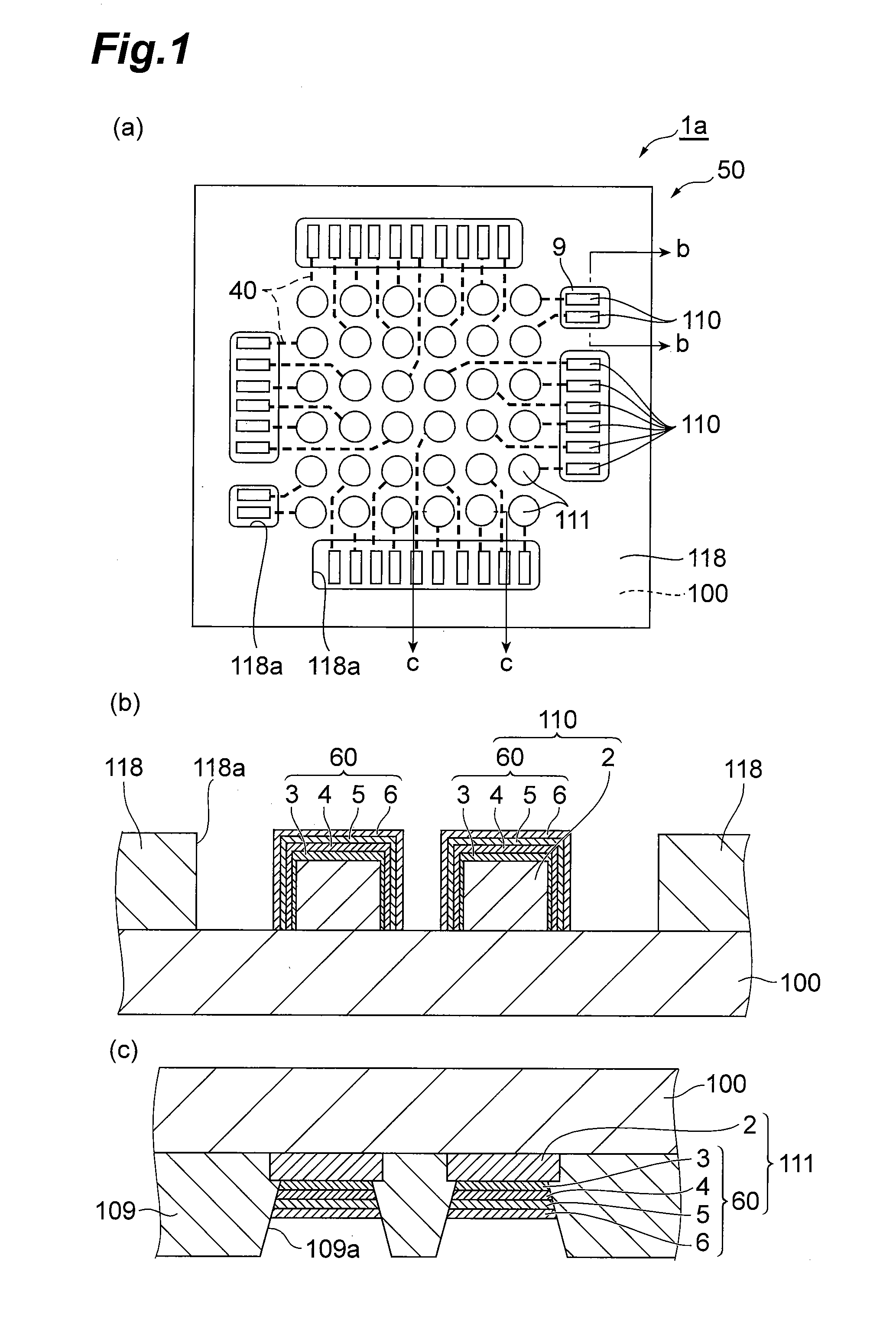

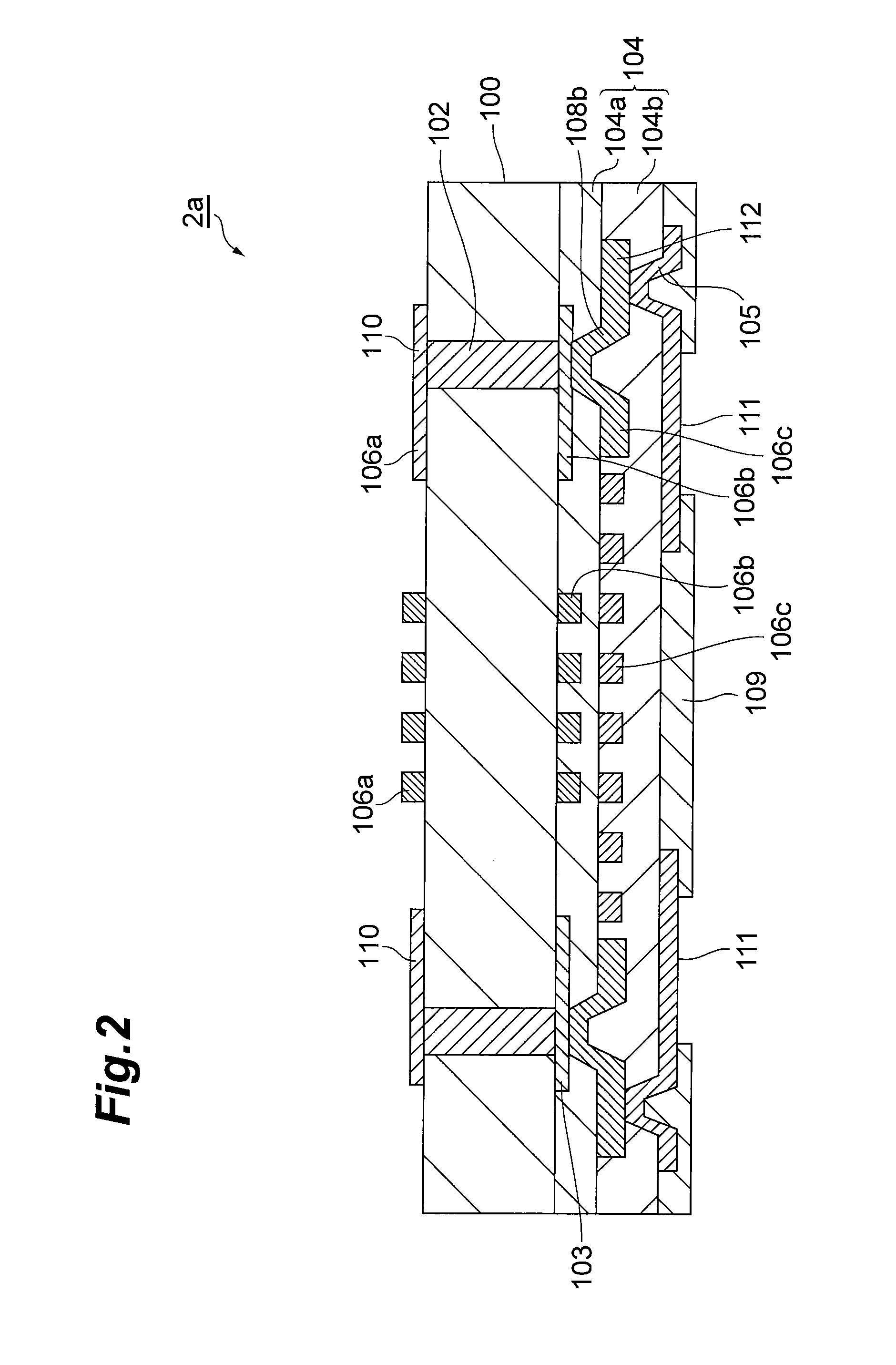

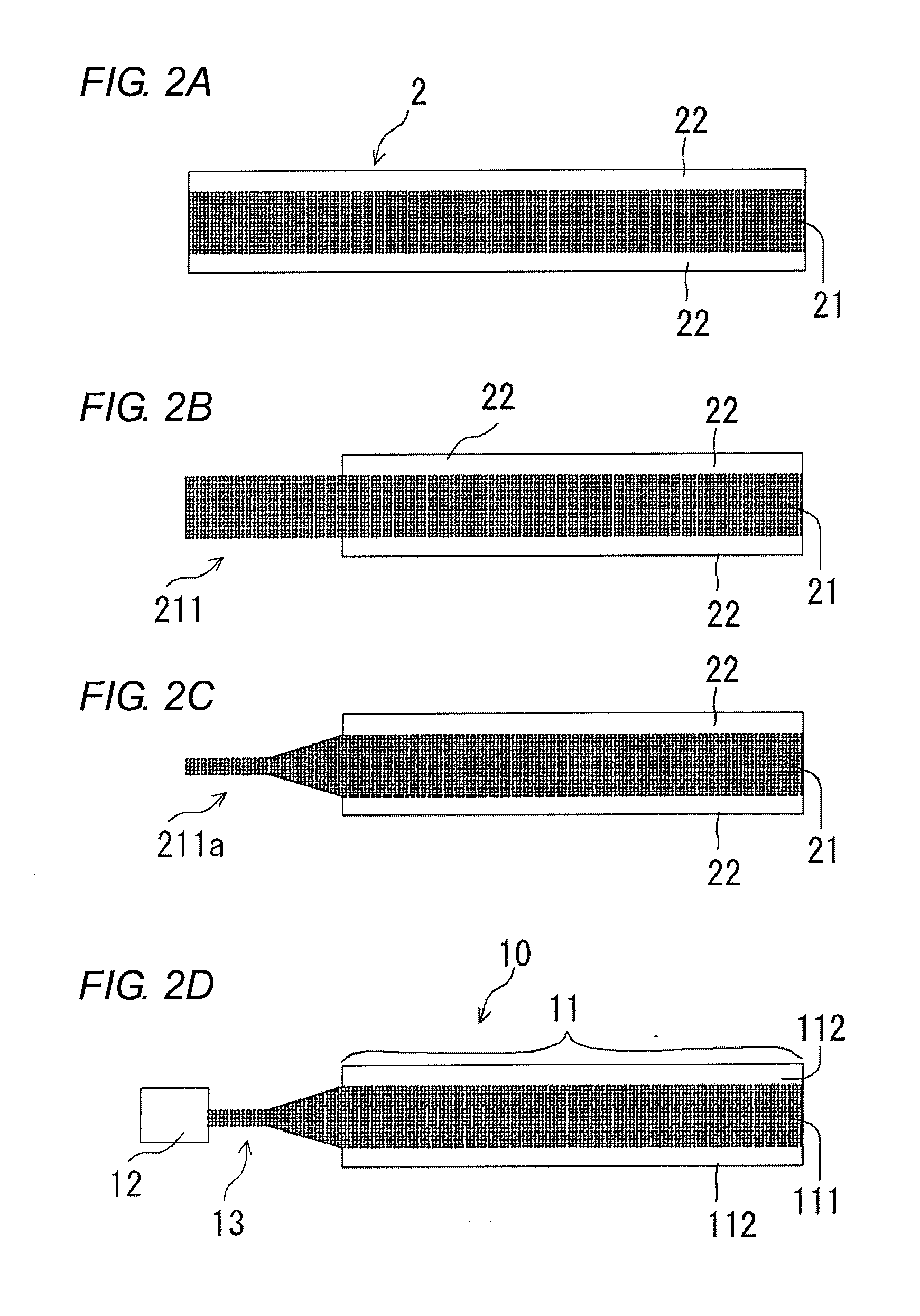

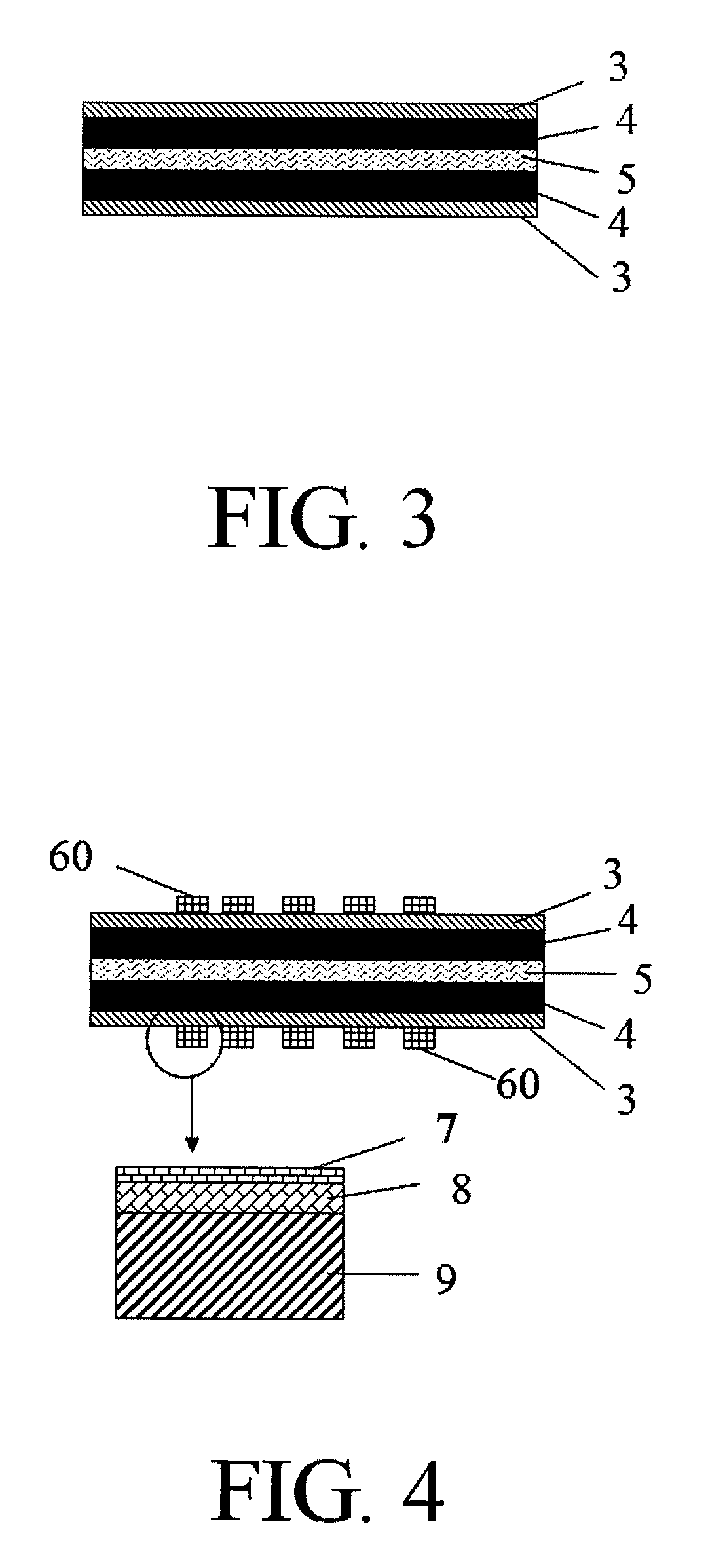

Ic chip mounting substrate, ic chip mounting substrate manufacturing method, optical communication device, and optical communication device manufacturing method

InactiveUS20060012967A1Improve connection reliabilitySmall sizeCircuit optical detailsSolid-state devicesResistElectrical conductor

An object of the present invention is to provide a substrate for mounting an IC chip which is a component for optical communication having an IC chip and an optical component integrally provided thereon, which can ensure a short distance between the IC chip and the optical component, which is excellent in electric signal transmission reliability and which can transmit optical signal through an optical path for transmitting optical signal. The substrate for mounting an IC chip of the present invention is a substrate for mounting an IC chip comprising: a substrate and, as serially built up on both faces thereof, a conductor circuit and an interlaminar insulating layer in an alternate fashion and in repetition; a solder resist layer formed as an outermost layer; and an optical element mounted thereto, wherein an optical path for transmitting optical signal, which penetrates the substrate for mounting an IC chip, is disposed.

Owner:IBIDEN CO LTD

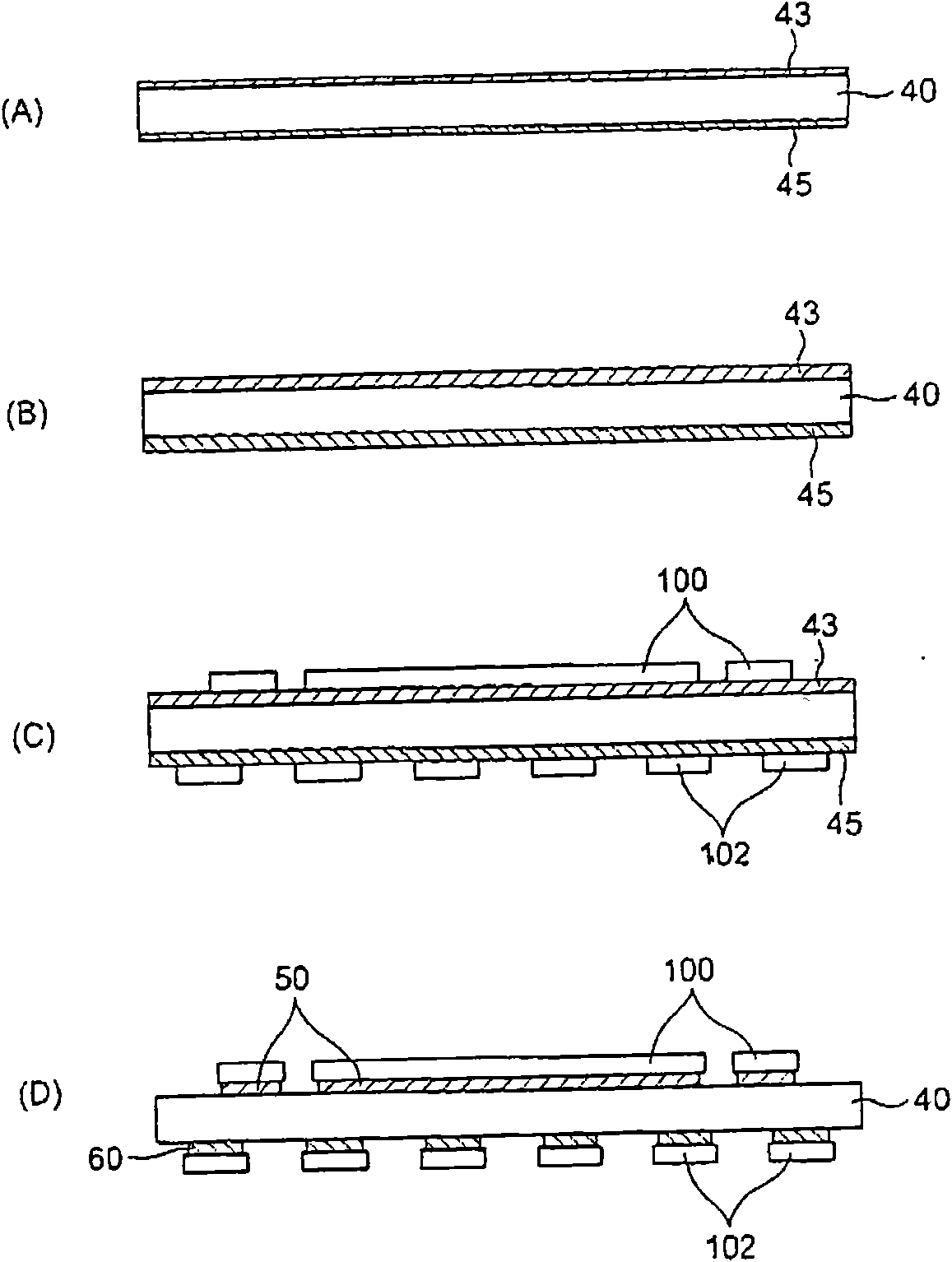

Substrate for mounting semiconductor chips

InactiveUS6281450B1Improve connection reliabilityImprove batch productivitySemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical conductor

A substrate for mounting a semiconductor chip having bumps using an adhesive thereon, said substrate being, for instance, provided with an insulating coating having an opening in the semiconductor chip mounting area so that the wiring conductors will not be exposed to the substrate surface near the boundary of the semiconductor chip mounting area, is improved in connection reliability and has high mass productivity.

Owner:HITACHI CHEM CO LTD

Optical-interference type display panel and method for making the same

InactiveUS7172915B2Improve antioxidant capacityConnecting qualitySemiconductor/solid-state device manufacturingVessels or leading-in conductors manufactureIndium tin oxideTransparent conducting film

Owner:SNAPTRACK

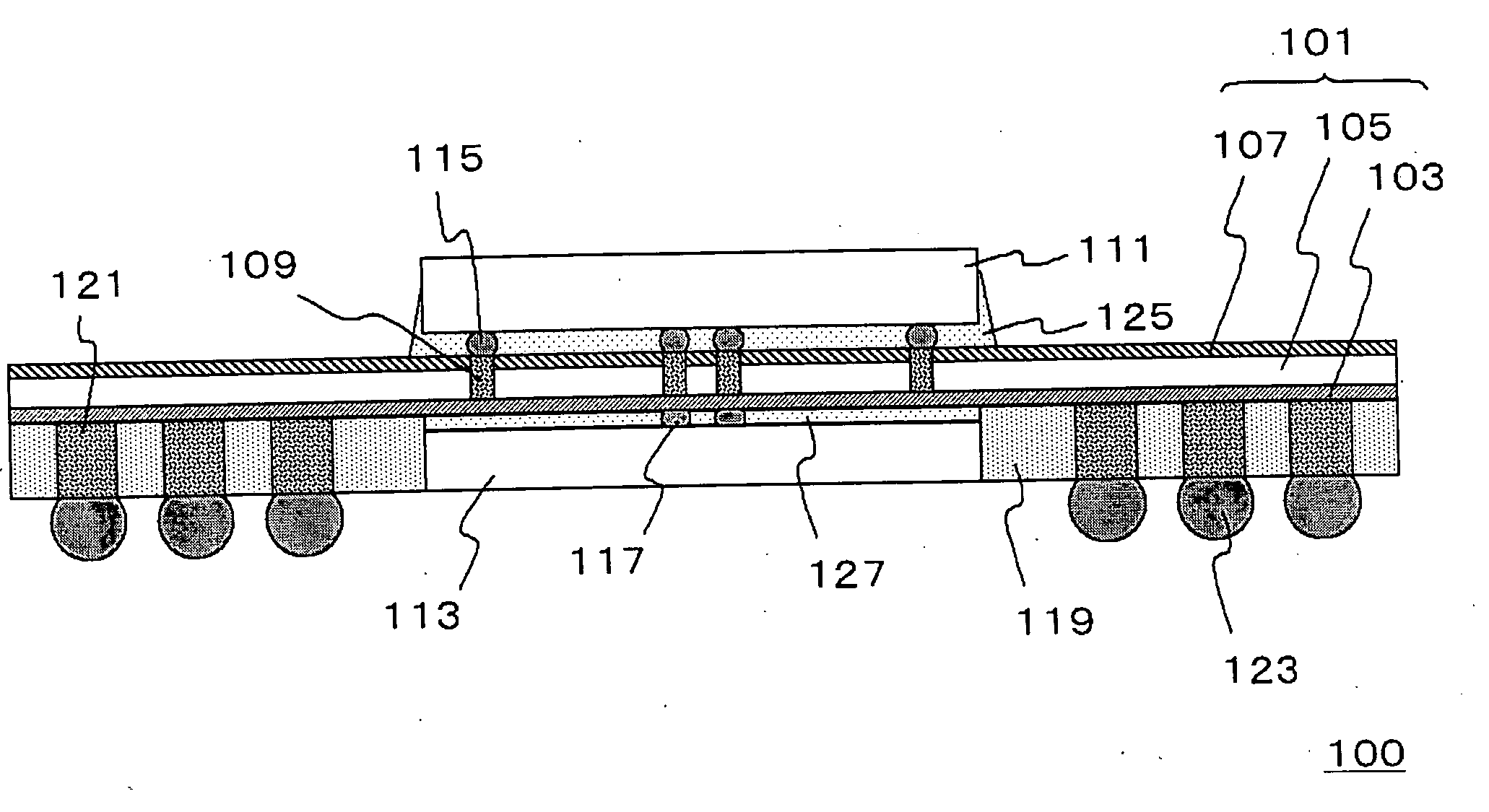

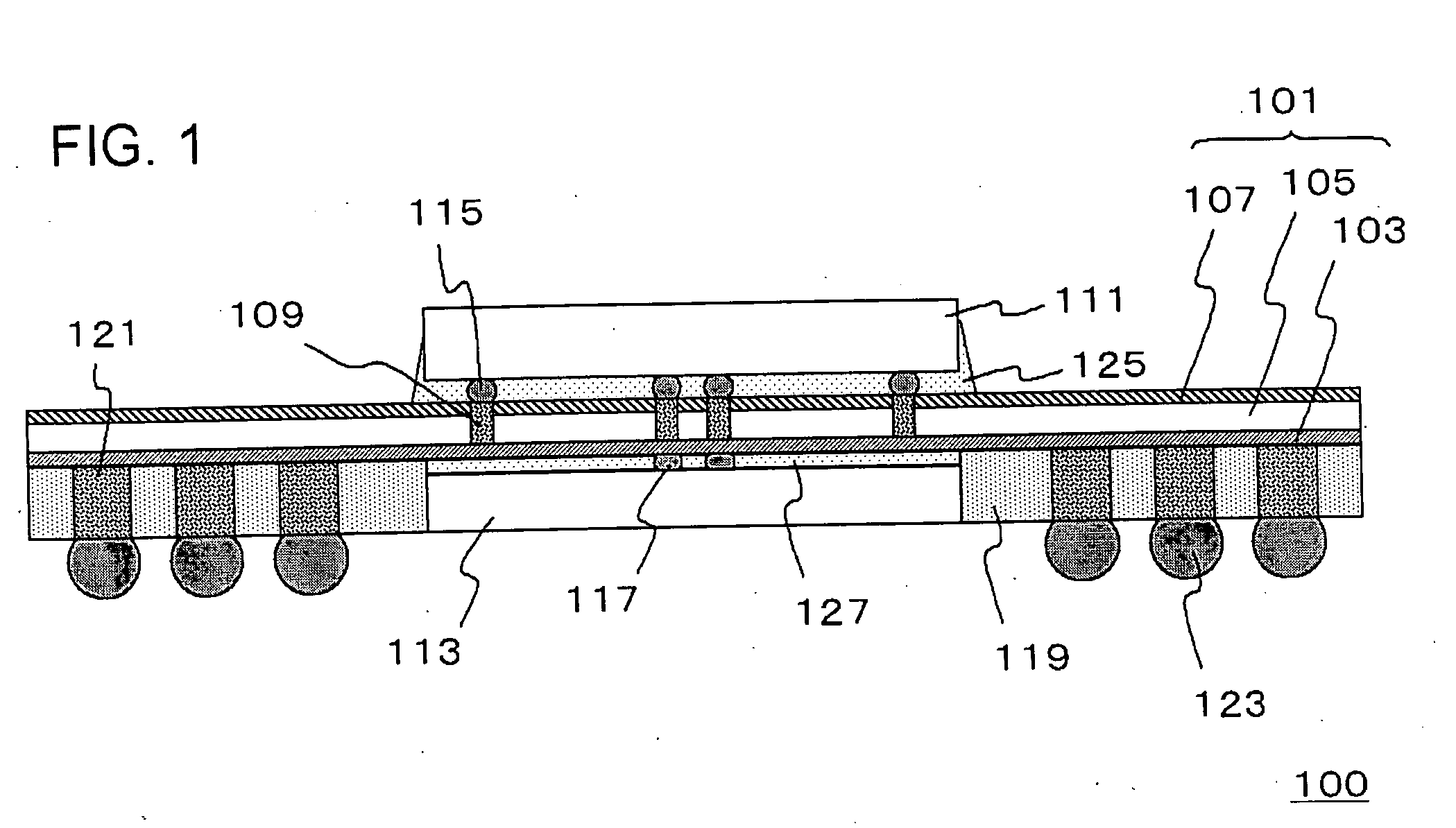

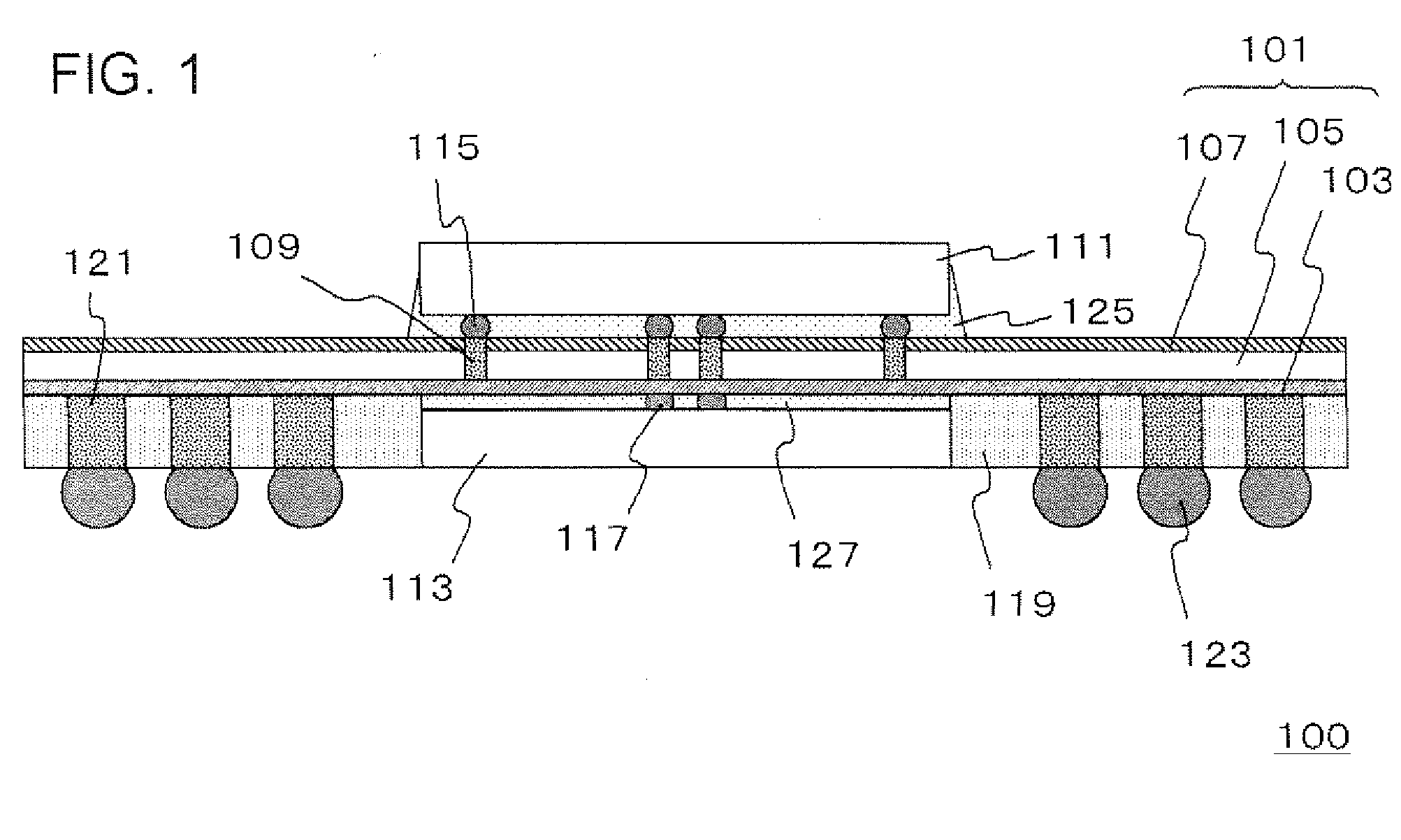

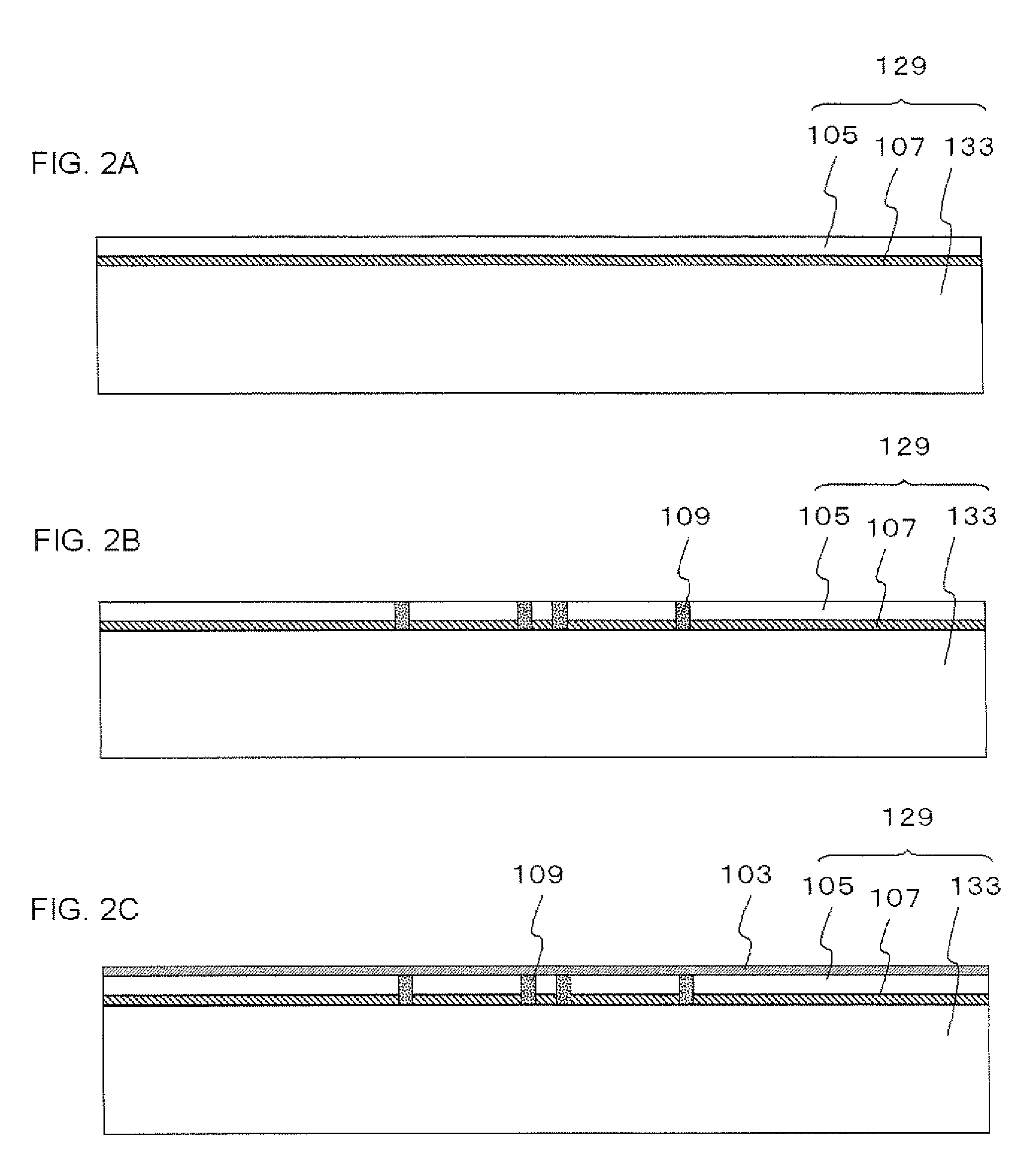

Semiconductor device and method for manufacturing the same

ActiveUS20060063312A1Excellent manufacturing stabilityWarpage suppressionSemiconductor/solid-state device detailsSolid-state devicesDevice materialSilicon

The semiconductor device 100 comprises a first semiconductor element 113 provided on a face on one side of a flat plate shaped interconnect component 101, an insulating resin 119 covering a face of a side where the first semiconductor element 113 of the interconnect component 101 is provided and a side face of the first semiconductor element 113, and a second semiconductor element 111 provided on a face on the other side of the interconnect component 101. The interconnect component 101 has a constitution where an interconnect layer 103, a silicon layer 105 and an insulating film 107 are sequentially formed. The interconnect layer 103 has a constitution where the interconnect layer 103 has a flat plate shaped insulating component and a conductive component extending through the insulating component. The first semiconductor element 113 is electrically connected with the second semiconductor element 111 through the conductive component.

Owner:RENESAS ELECTRONICS CORP

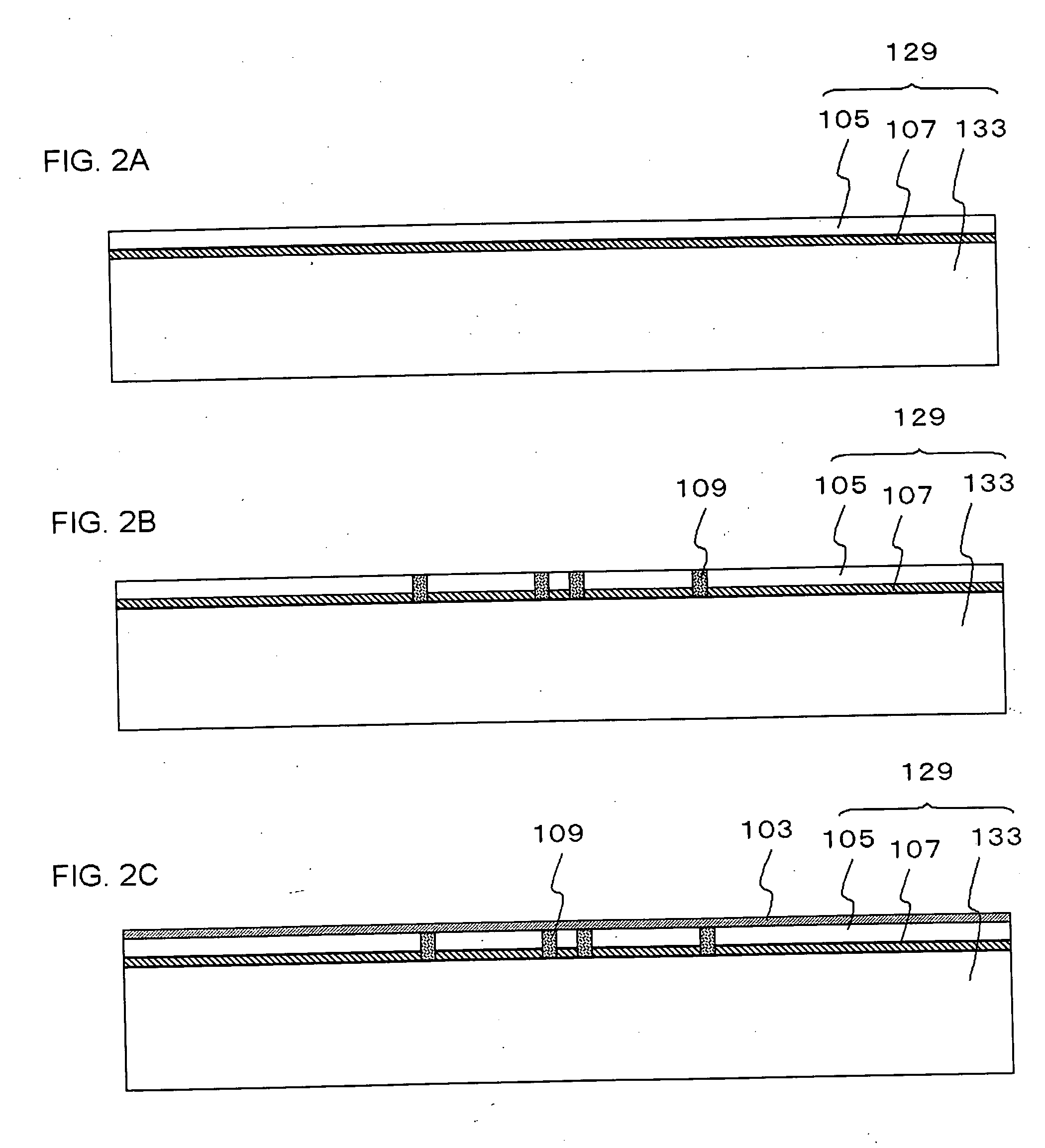

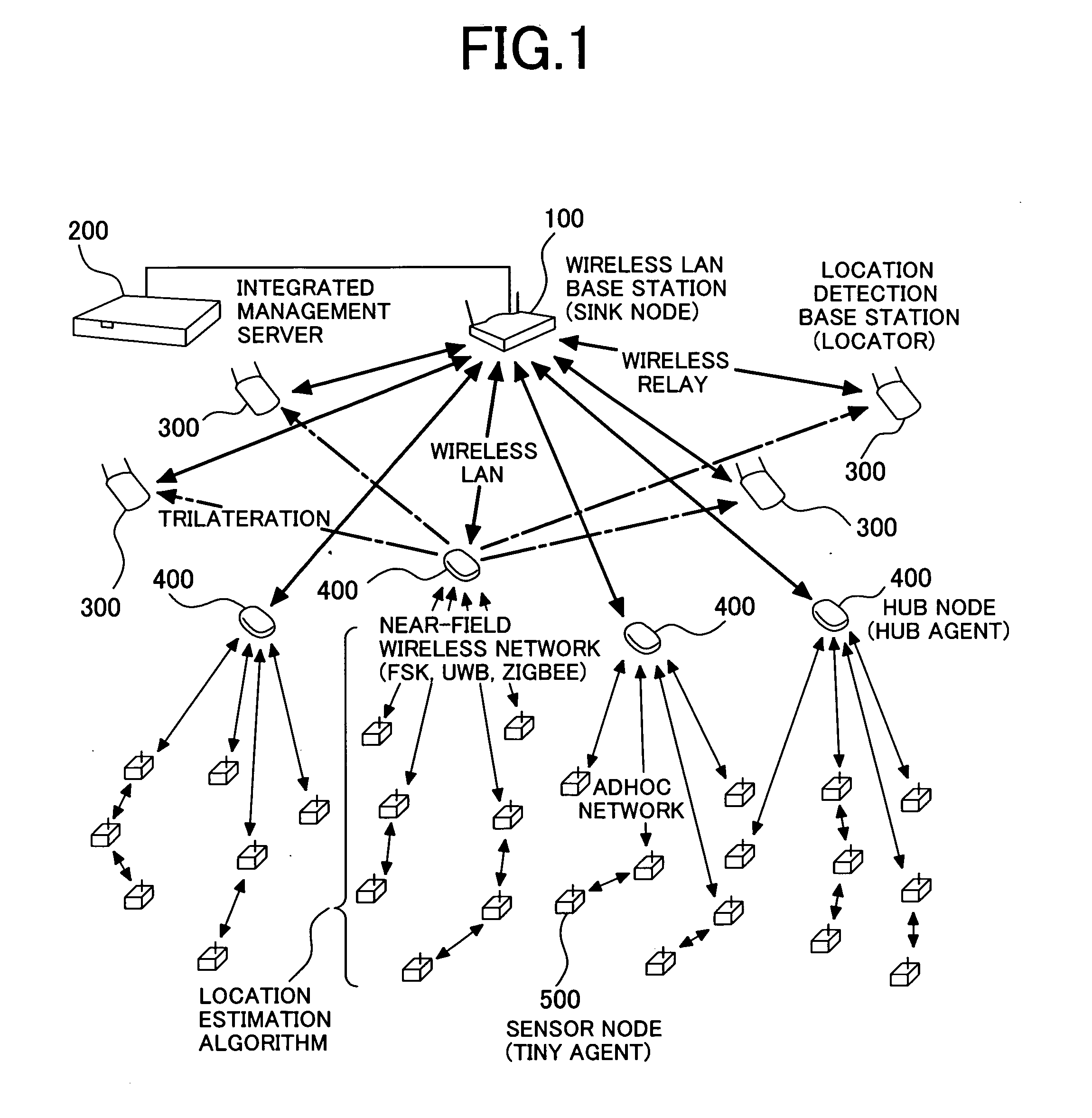

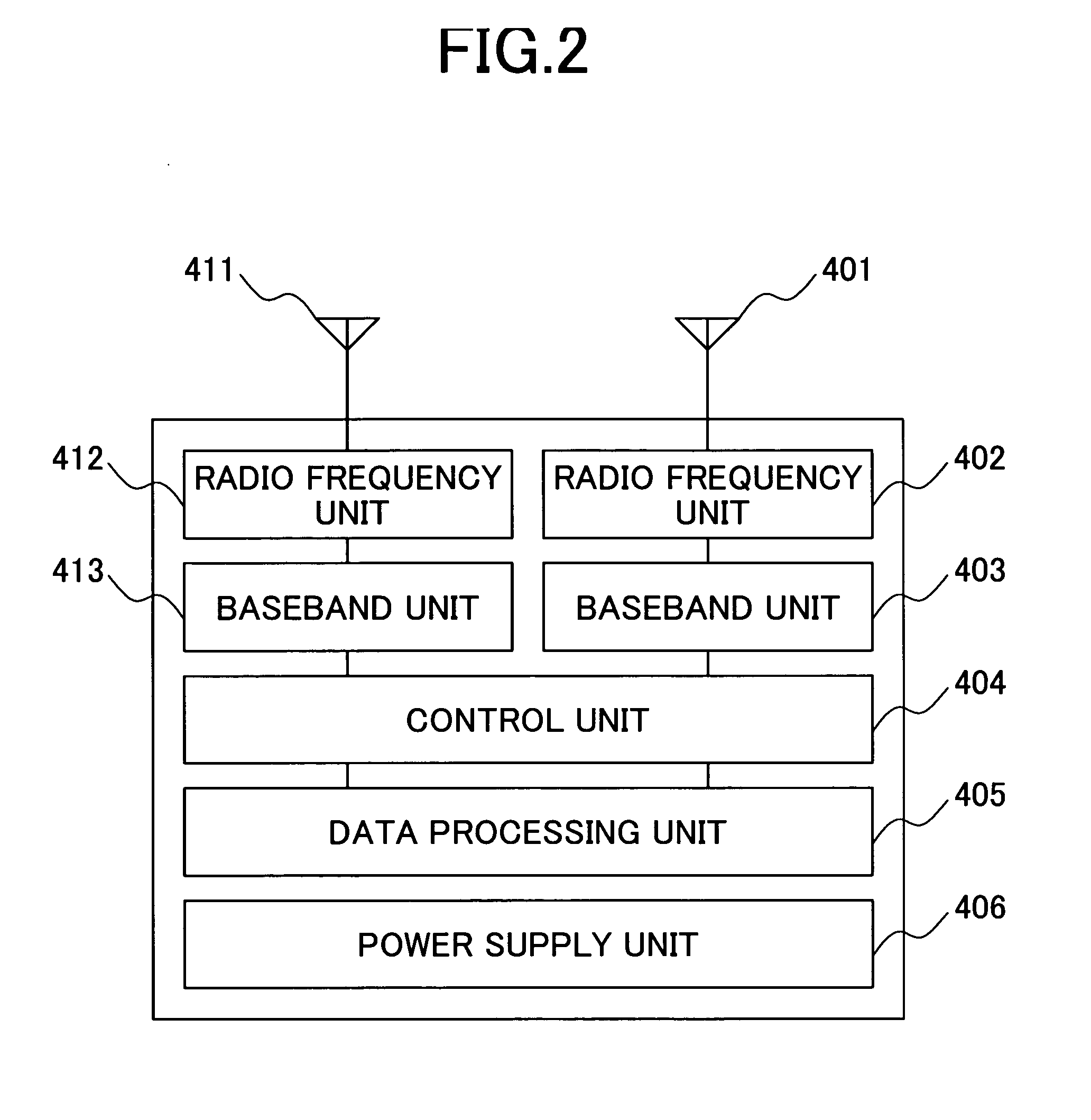

Wireless communication system for detecting location of the node

InactiveUS20050141465A1Improve connection reliabilityImprove data accuracyAssess restrictionNetwork topologiesCommunications systemSensor node

Provided is a wireless communication system easily establishing a connection path in a sensor network collecting data from a number of sensor nodes. The wireless communication system comprises a base station communicating by a first wireless communication system, plural first nodes communicating by the first wireless communication system and a second wireless communication system, and plural second nodes communicating by the second wireless communication system. The first node transmits the number of hops in the first wireless communication system to the second node. The second node obtains a reception condition of at least one of a signal transmitted by the first node and a signal transmitted by the second node, and selects a upper stage node to connect based on the number of hops in the first wireless communication system, the number of hops in the second wireless communication system, and the obtained reception condition information.

Owner:HITACHI LTD

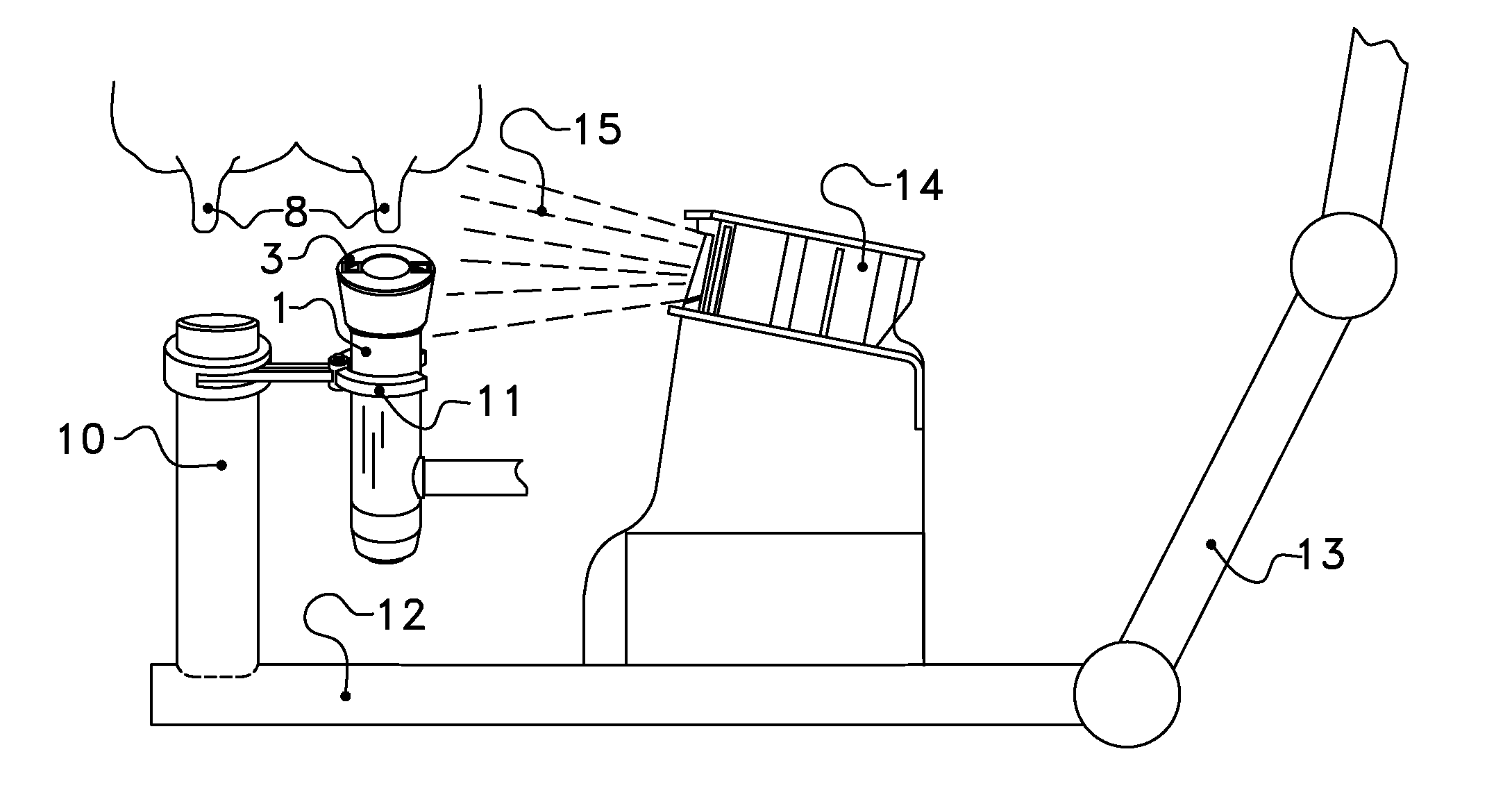

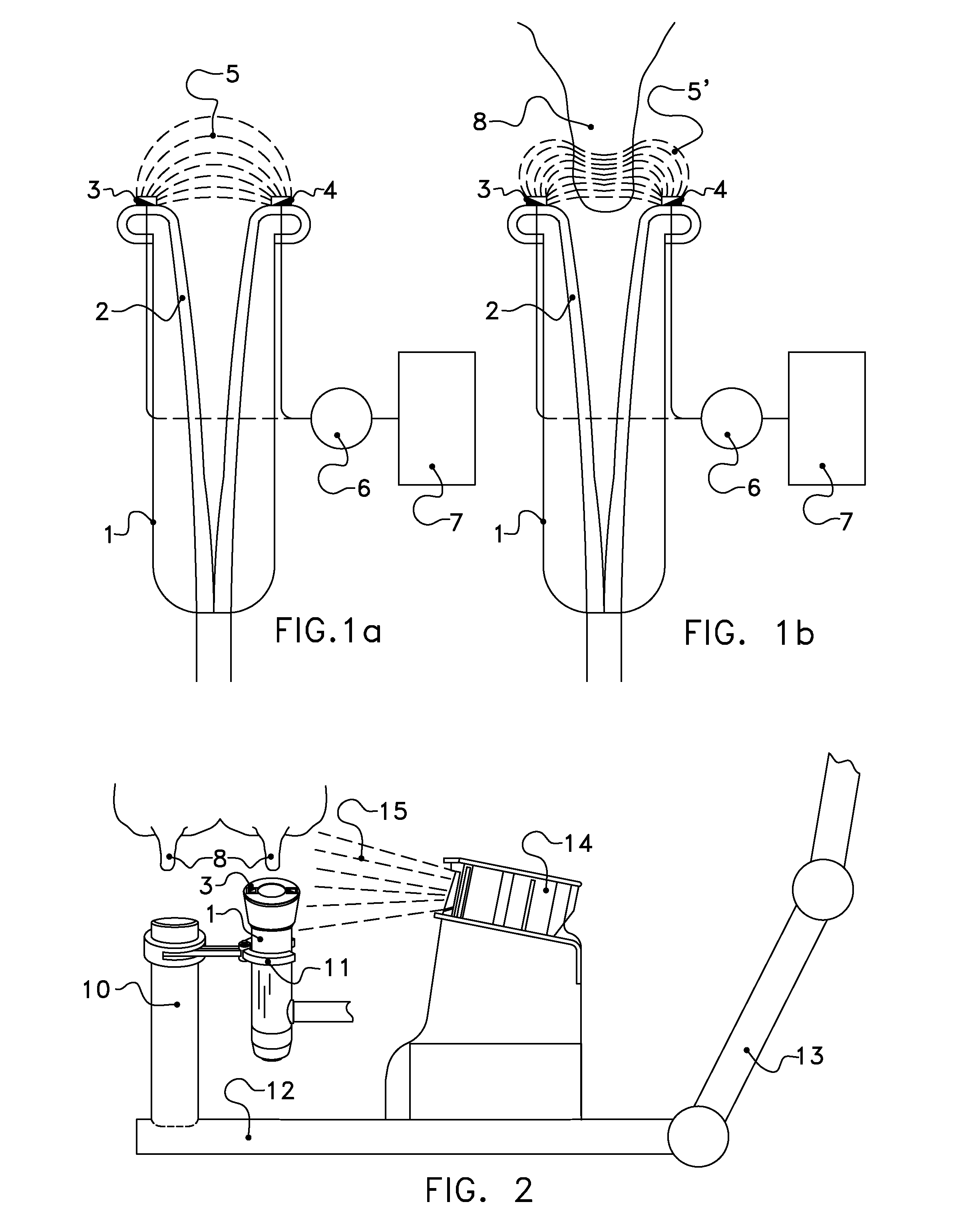

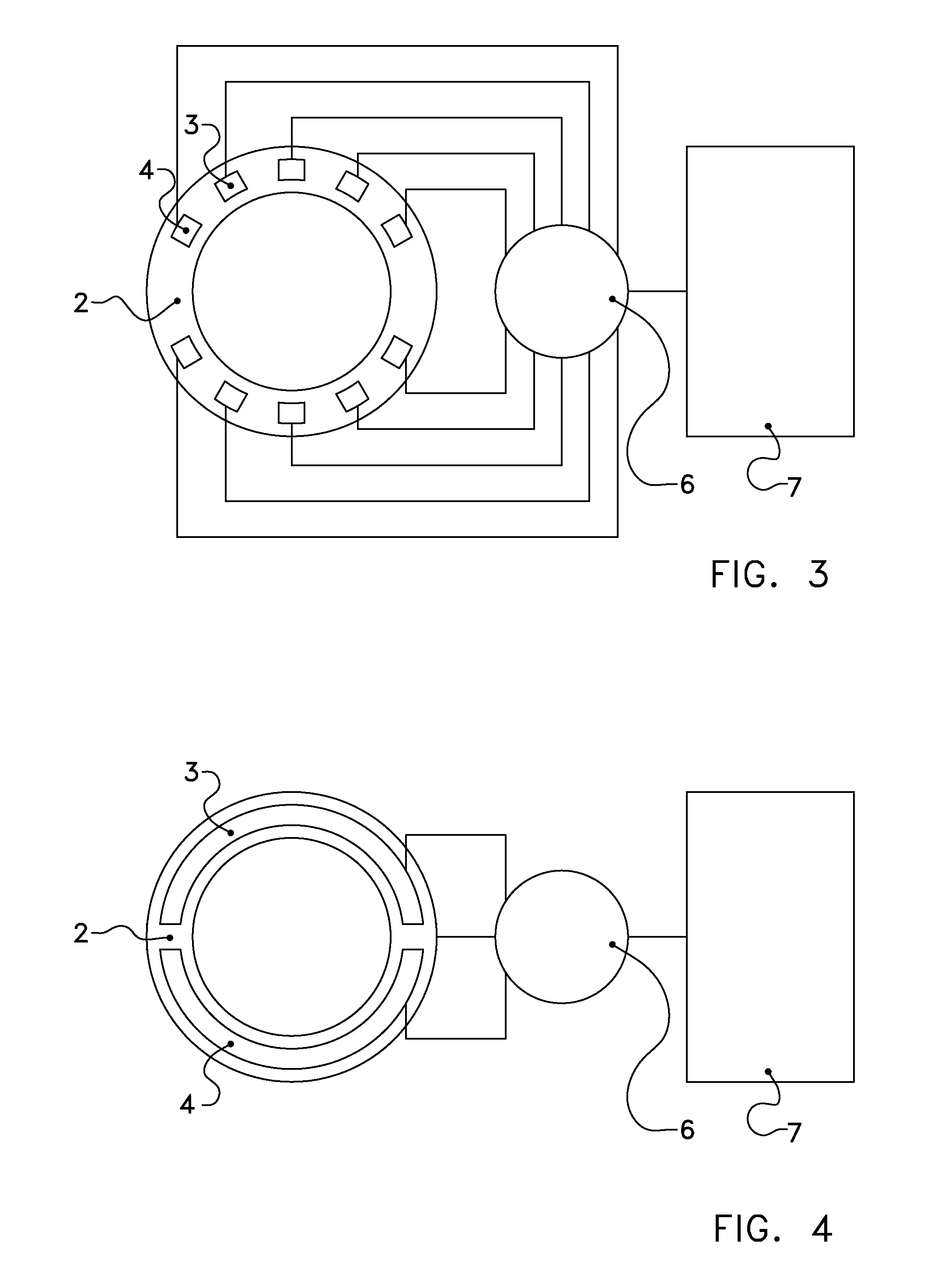

System for connecting a teat cup to a teat

The invention provides a system for connecting a teat cup to a teat, including a teat cup with an opening for receiving a teat, a robot arm for moving the teat cup, a teat cup positioning system with a 3D-sensor and a sensor device for measuring a control quantity, and for connecting the teat cup under the control of the 3D-camera and the control quantity. The sensor device includes at least two electrodes around the opening and a capacitive sensor configured to measure a quantity connected with the capacitance between the electrodes, in particular the capacitance between two electrodes. This system provides a reliable positioning with respect to a teat by, for example, maximization of the measured capacitance. The positioning system supports an optical 3D-sensor for the first, global positioning.

Owner:LELY PATENT

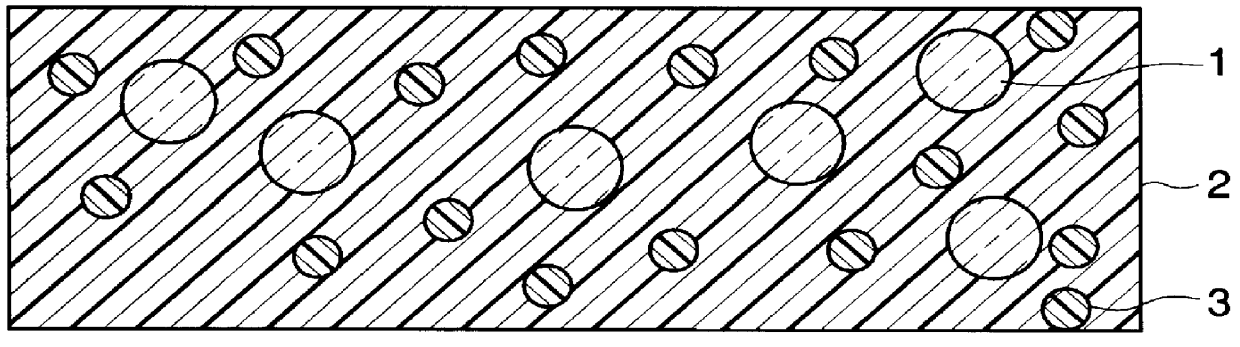

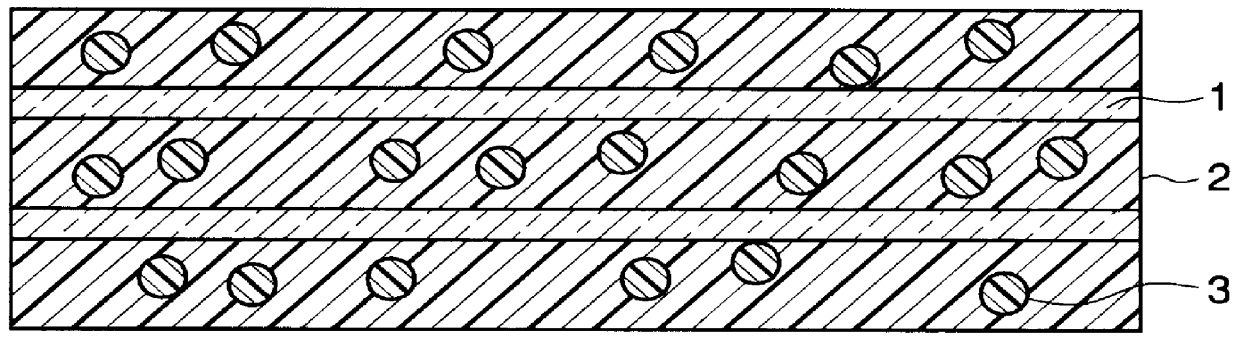

Laminate and multilayer printed circuit board

InactiveUS6114005AImprove connection reliabilityImprove featuresDielectric materialsSemiconductor/solid-state device detailsThermal expansionEngineering

A laminate capable of mounting semiconductor elements thereon; comprising an insulating layer which is constituted by a resin portion of sea-island structure and a woven reinforcement. The resin portion of sea-island structure is, for example, such that a resin as islands are dispersed in a resin as a matrix. Thus, the insulating layer exhibits a coefficient of thermal expansion of 3.0 DIFFERENCE 10 (ppm / K) in a planar direction thereof and a glass transition temperature of 150 DIFFERENCE 300 ( DEG C.). Owing to these physical properties, thermal stresses which the laminate undergoes in packaging the semiconductor elements thereon can be reduced, so that the connections of the laminate with the semiconductor elements can be made highly reliable.

Owner:HITACHI LTD

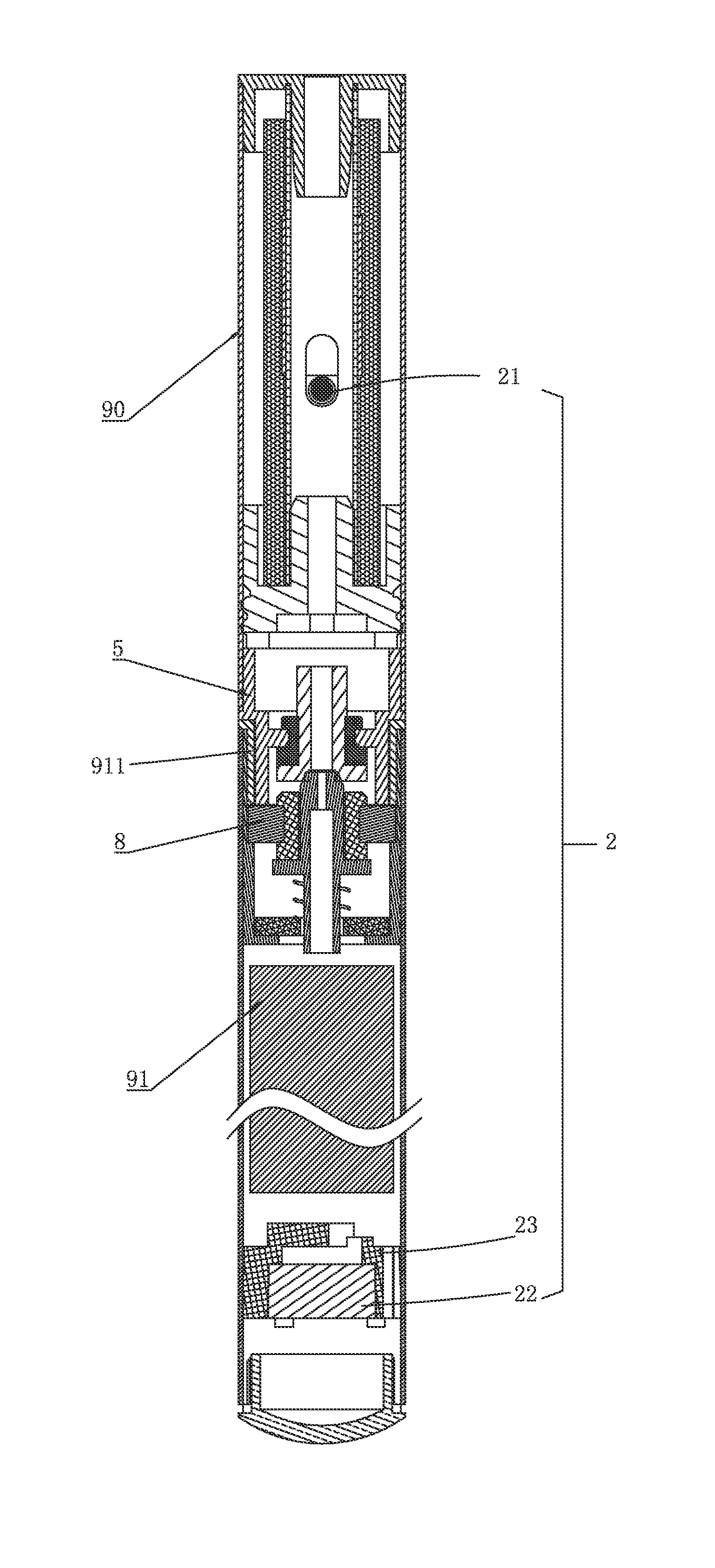

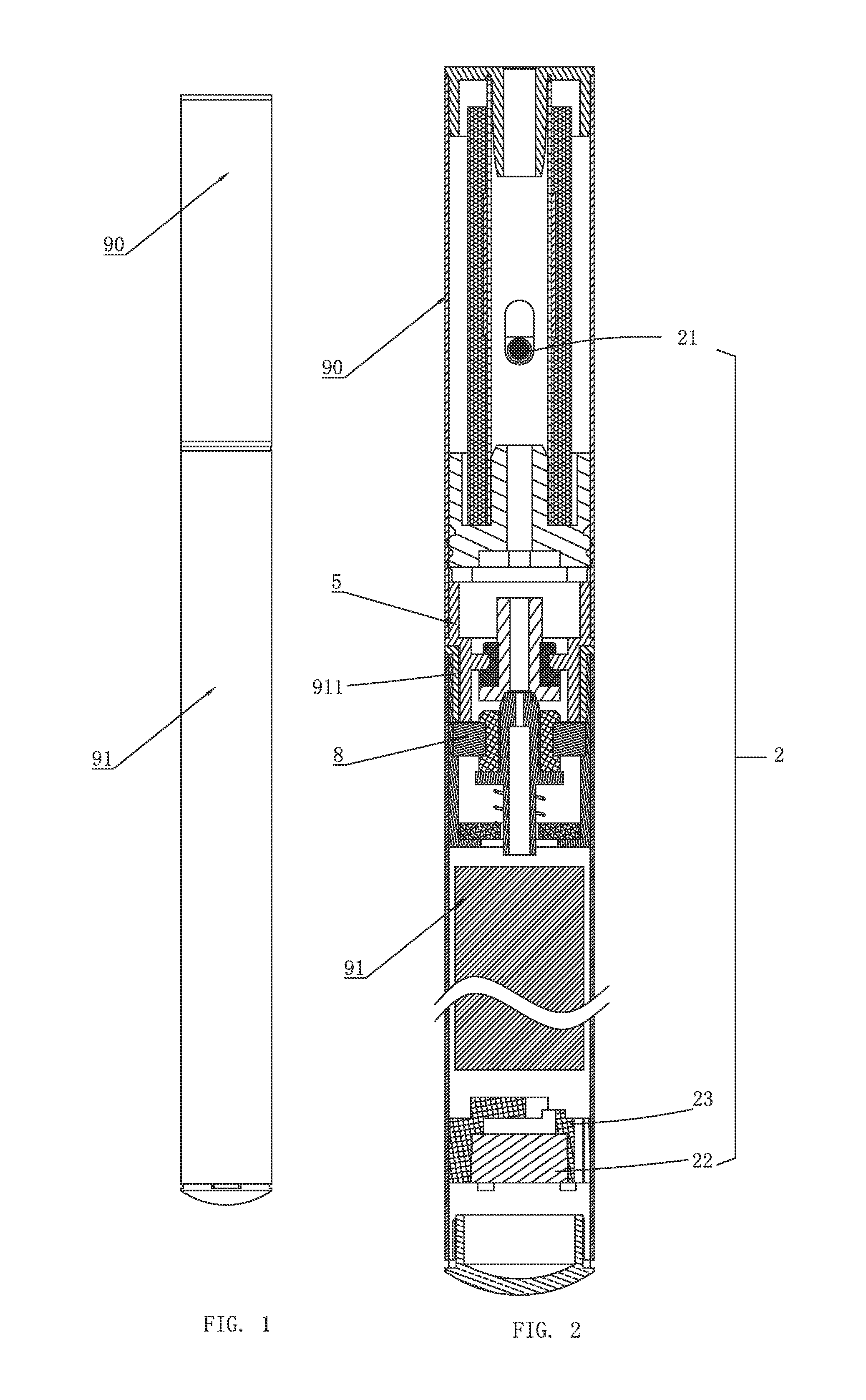

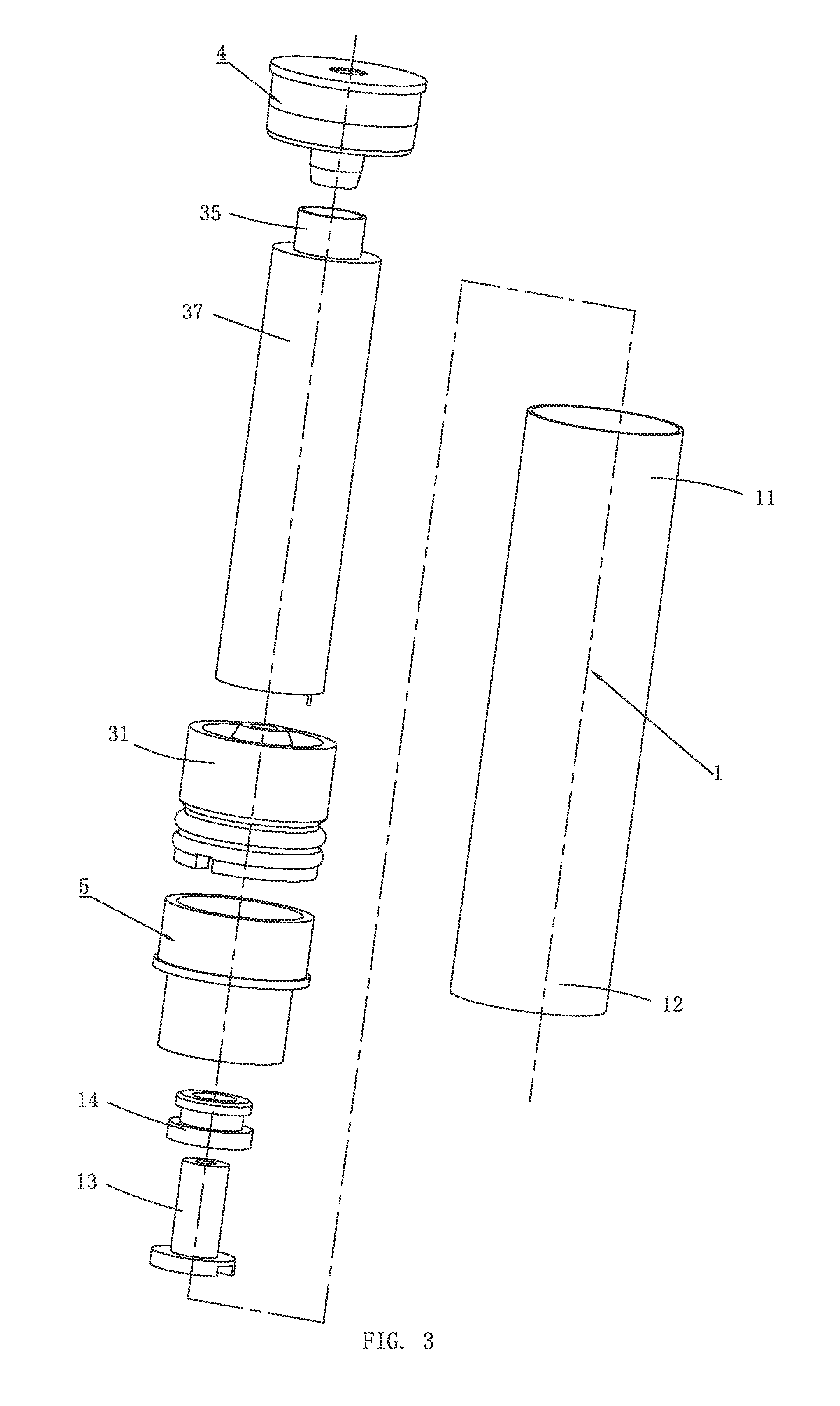

Electronic Cigarette

InactiveUS20140060528A1Easy to disassembleEasy constructionTobacco treatmentMedical devicesElectricityElectronic cigarette

Owner:HUIZHOU KIMREE TECH

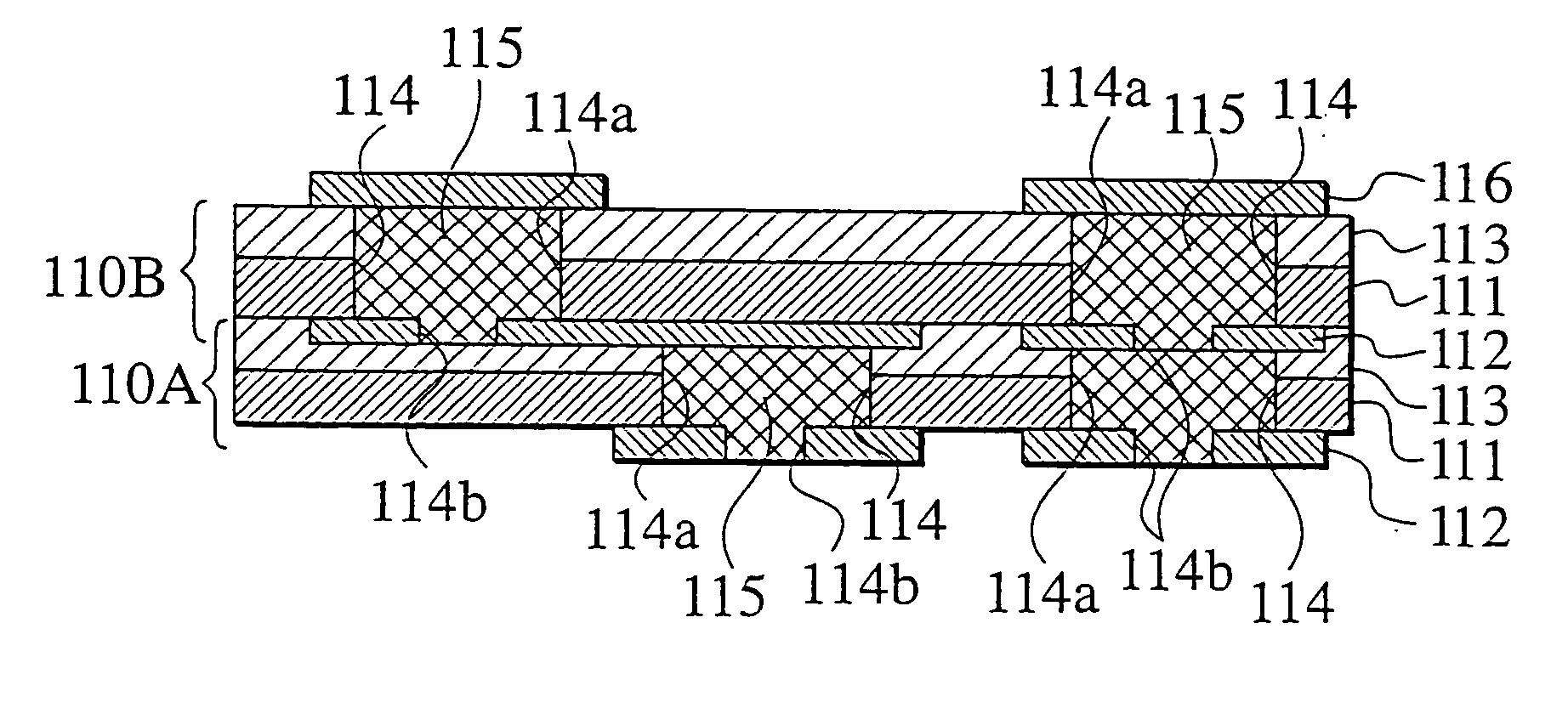

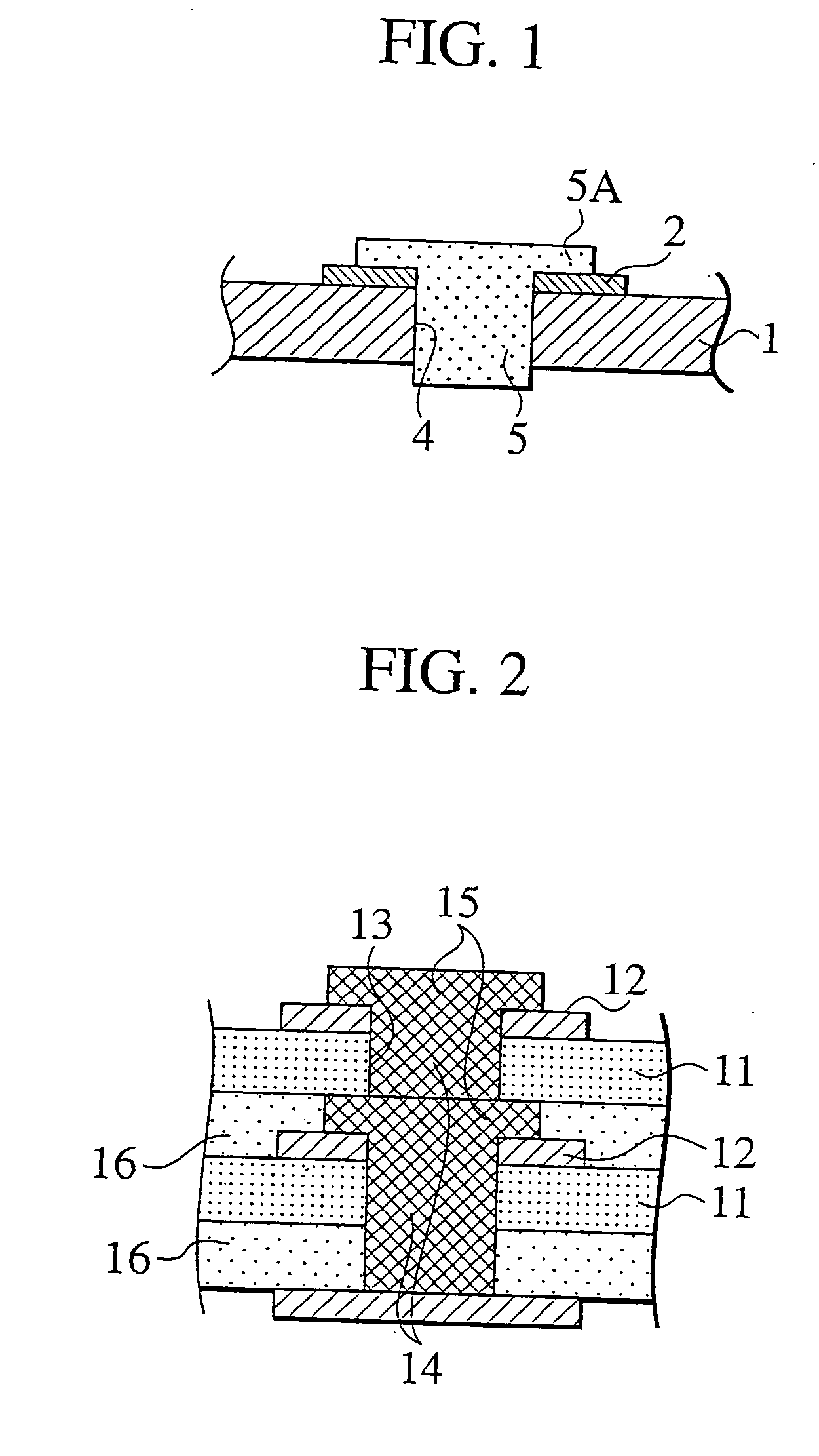

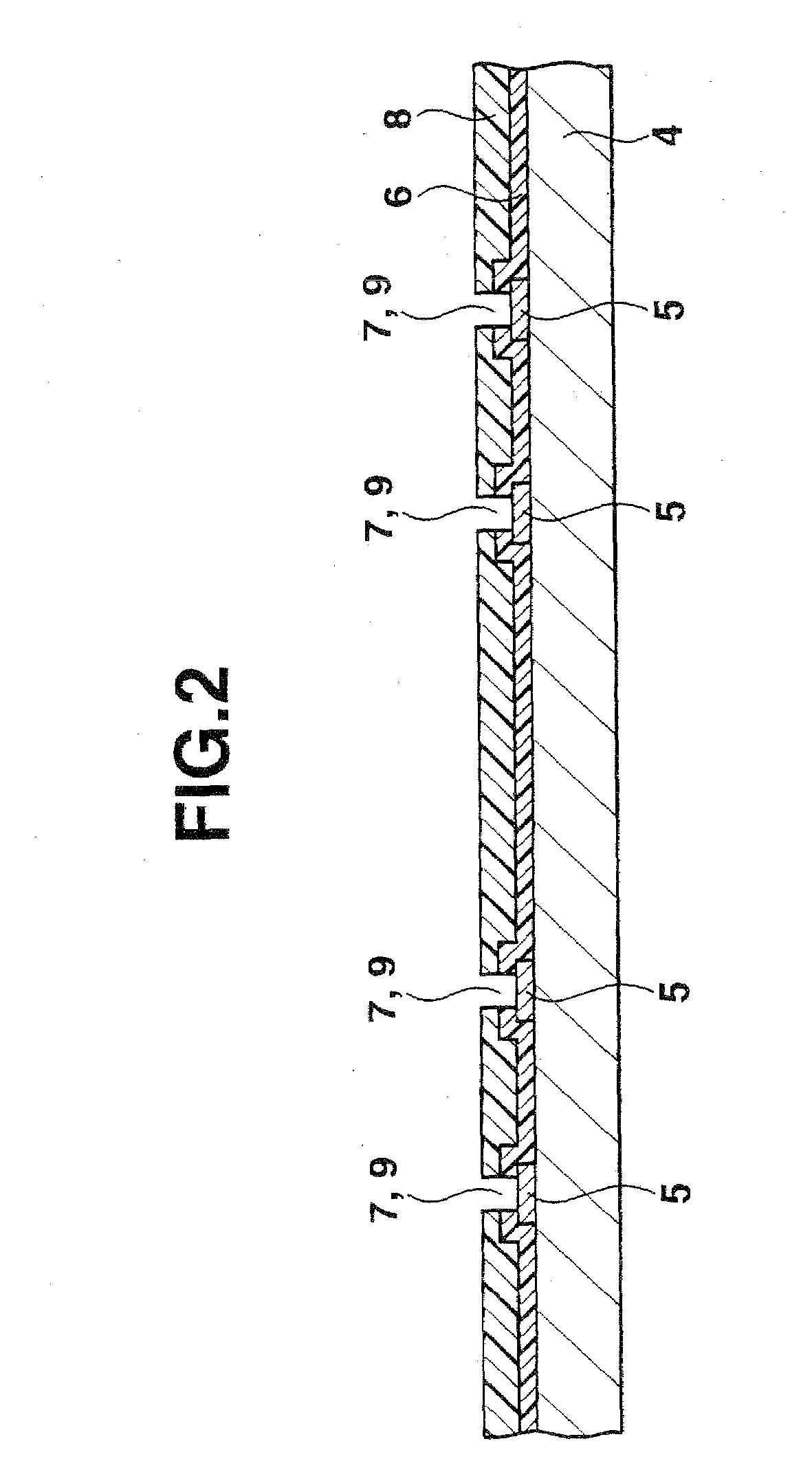

Multilayer wiring board, base for multilayer wiring board, printed wiring board and its manufacturing method

InactiveUS20050155792A1Solve the real problemIncrease contact areaSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionInterconnection

A multilayer wiring board assembly component comprises: an insulating substrate component (the insulating resin layer 111); a conductive layer 112 formed on one surface of said insulating substrate component 111 in the form of an electrode pattern; an adhesive layer 113 formed on the other surface of said insulating substrate component 111; and a conductive resin composition 115 with which is filled a through hole passing through said insulating substrate component 111, said adhesive layer and said conductive layer in order to make interlayer interconnection. The bore diameter of the conductive layer portion 114b of the through hole 114 is smaller than the bore diameter of the insulating resin layer portion and the adhesive layer portion 114a to establish electrical connection between the conductive resin composition 115 and the conductive layer 112 by the rare surface 112a of the conductive layer 112.

Owner:THE FUJIKURA CABLE WORKS LTD

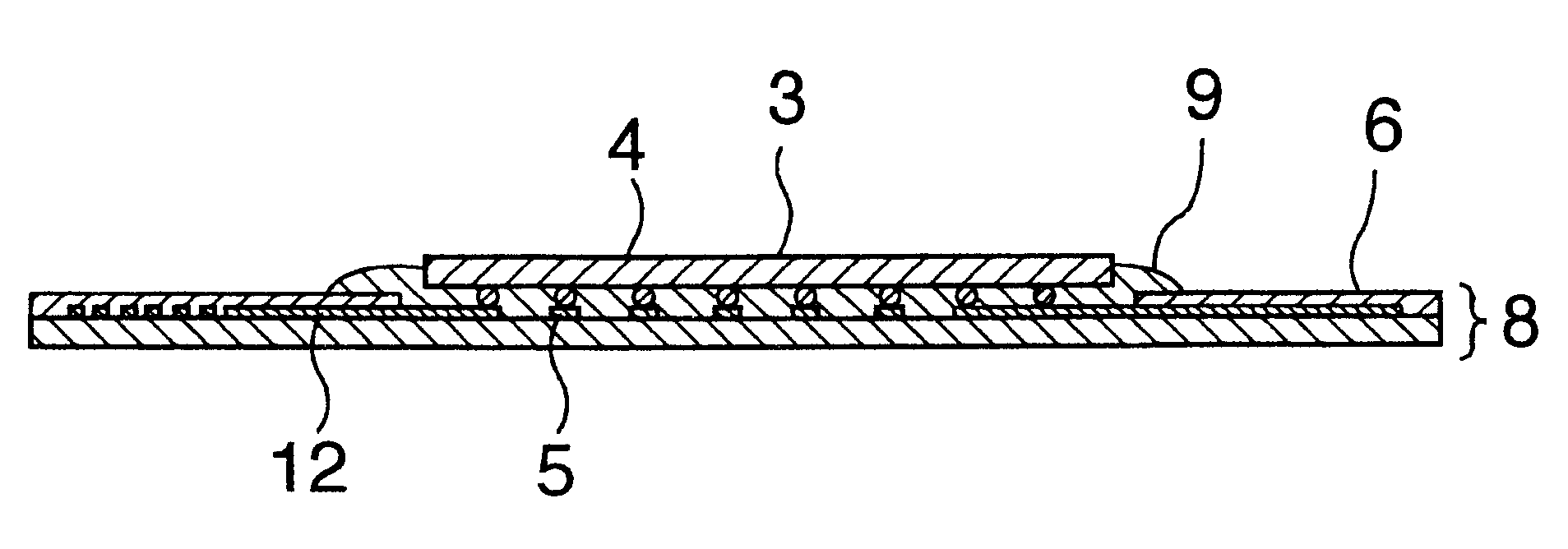

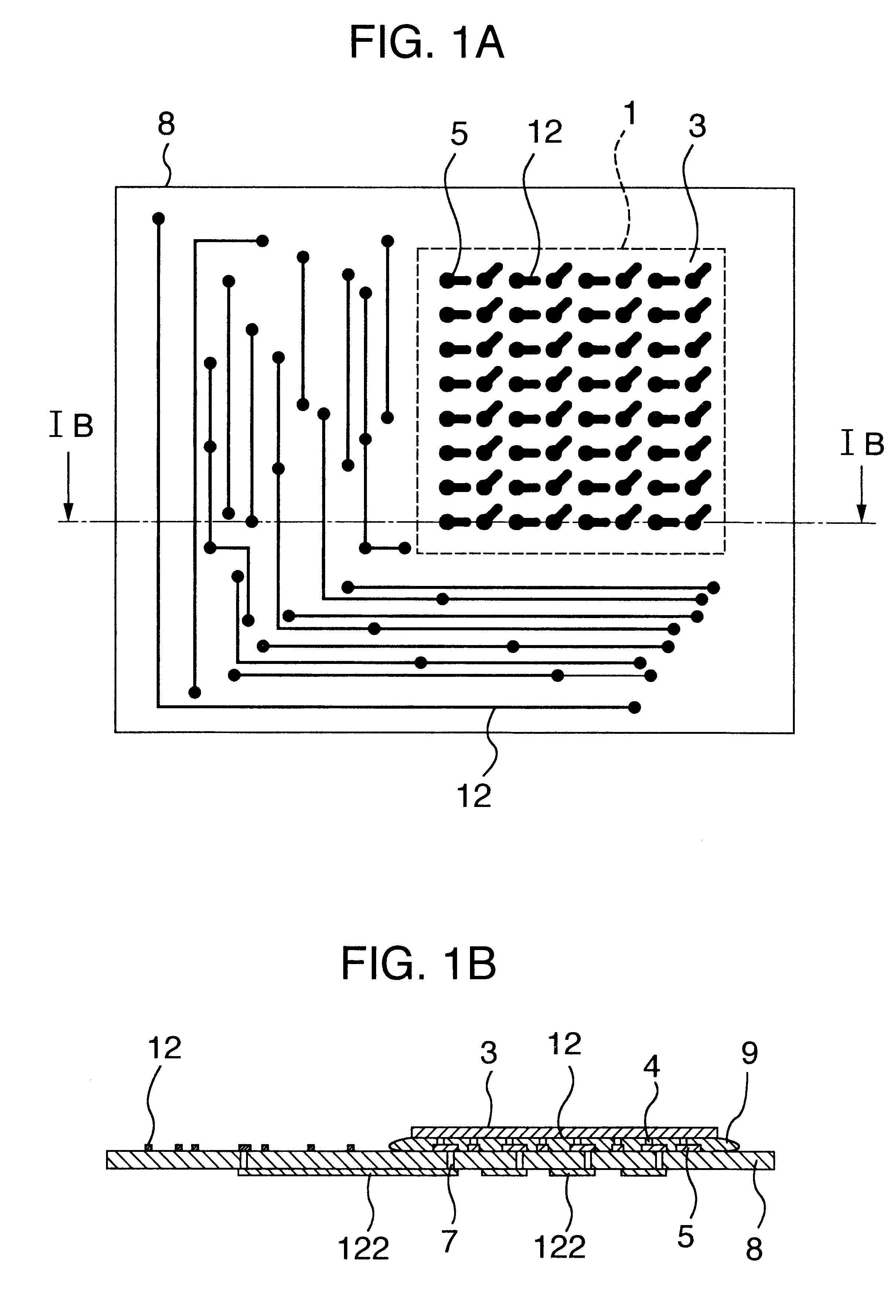

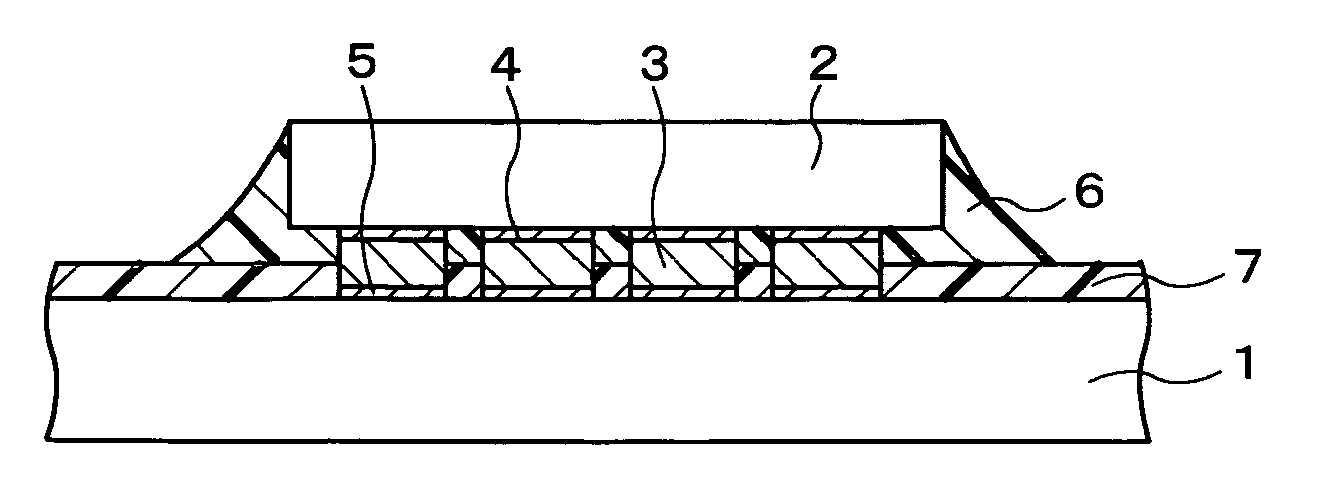

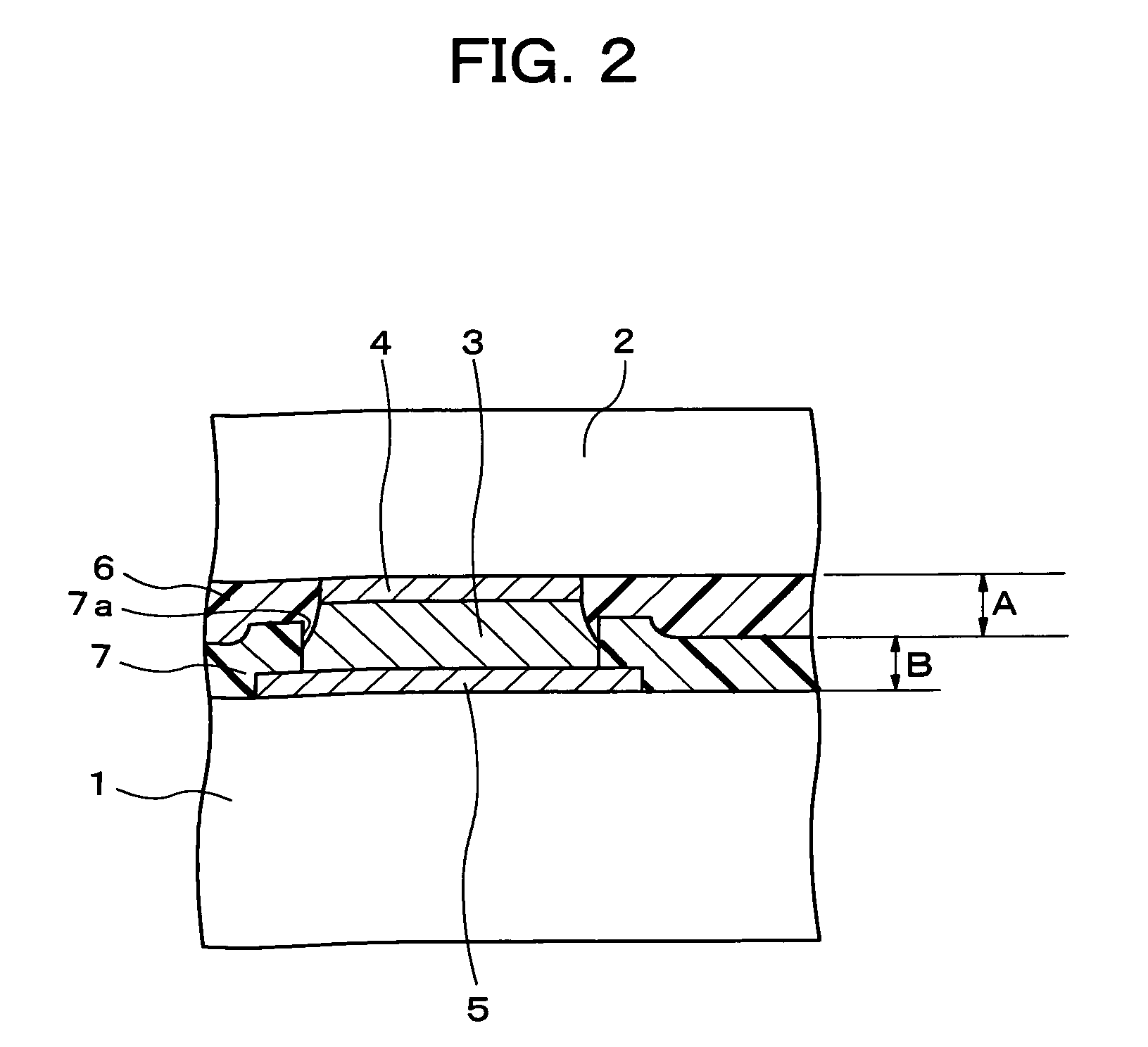

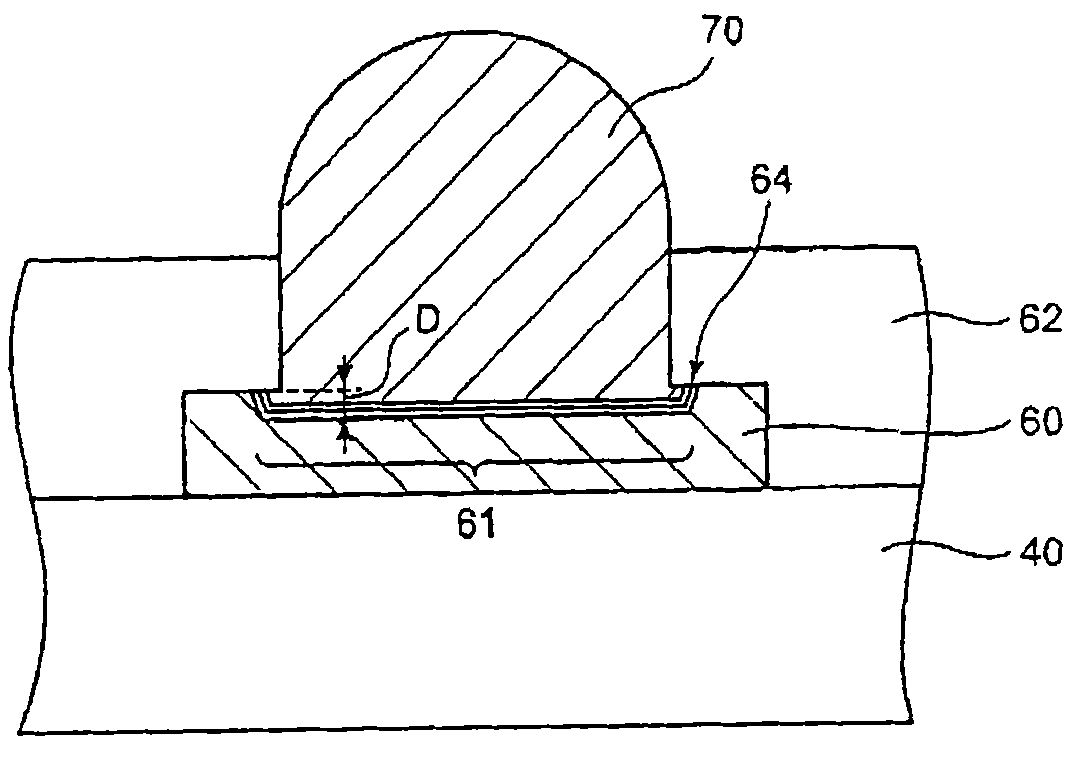

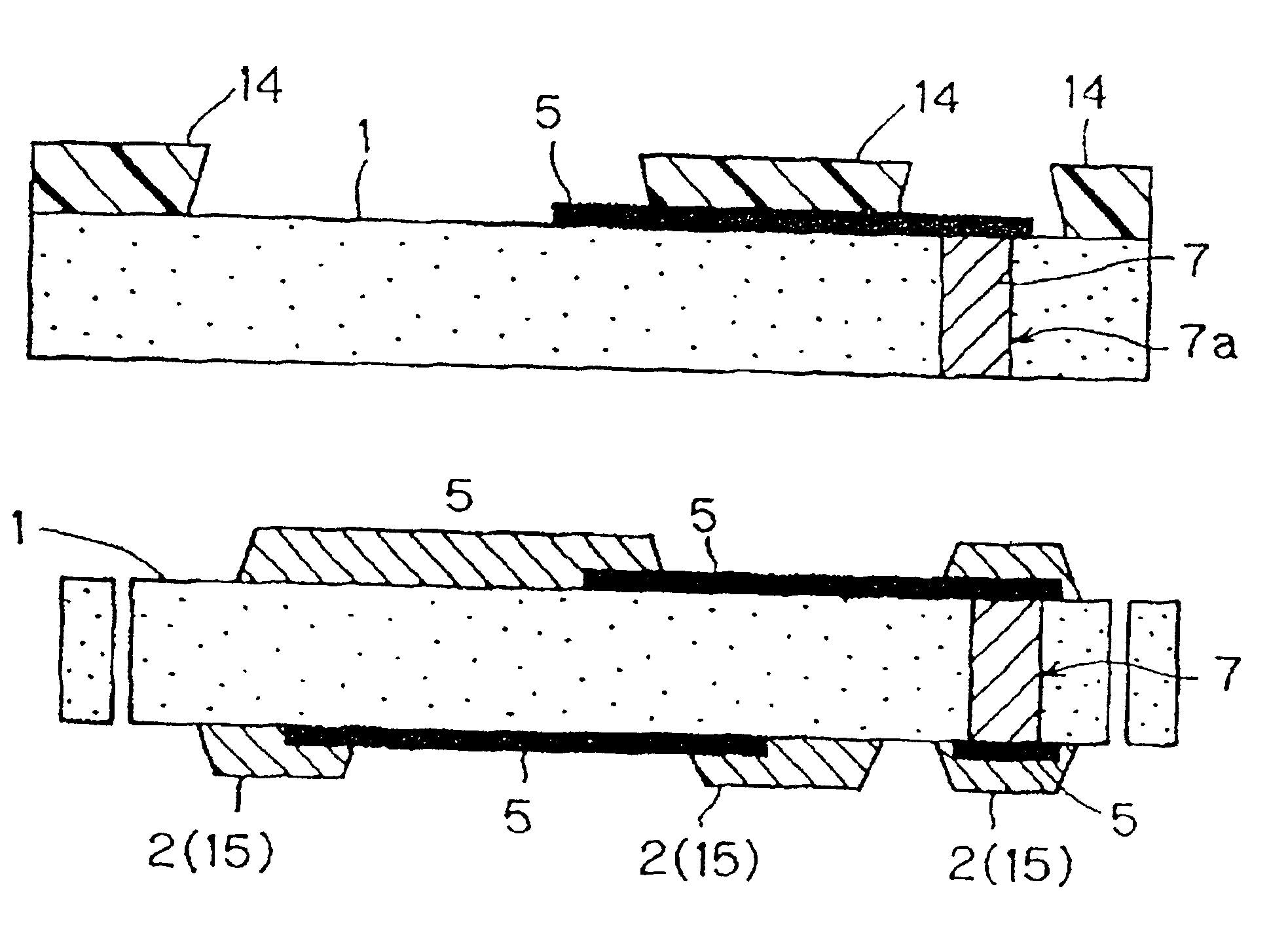

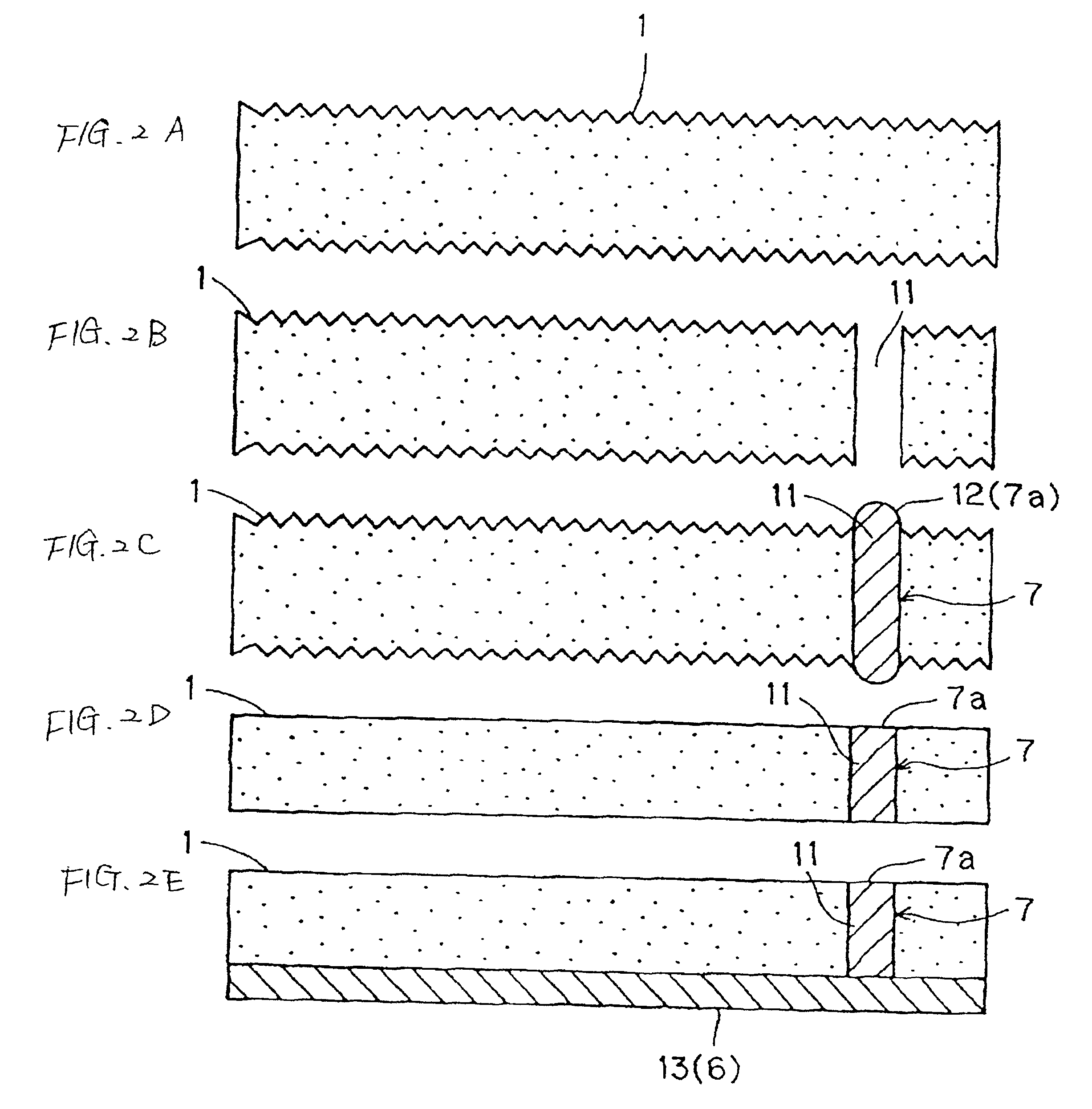

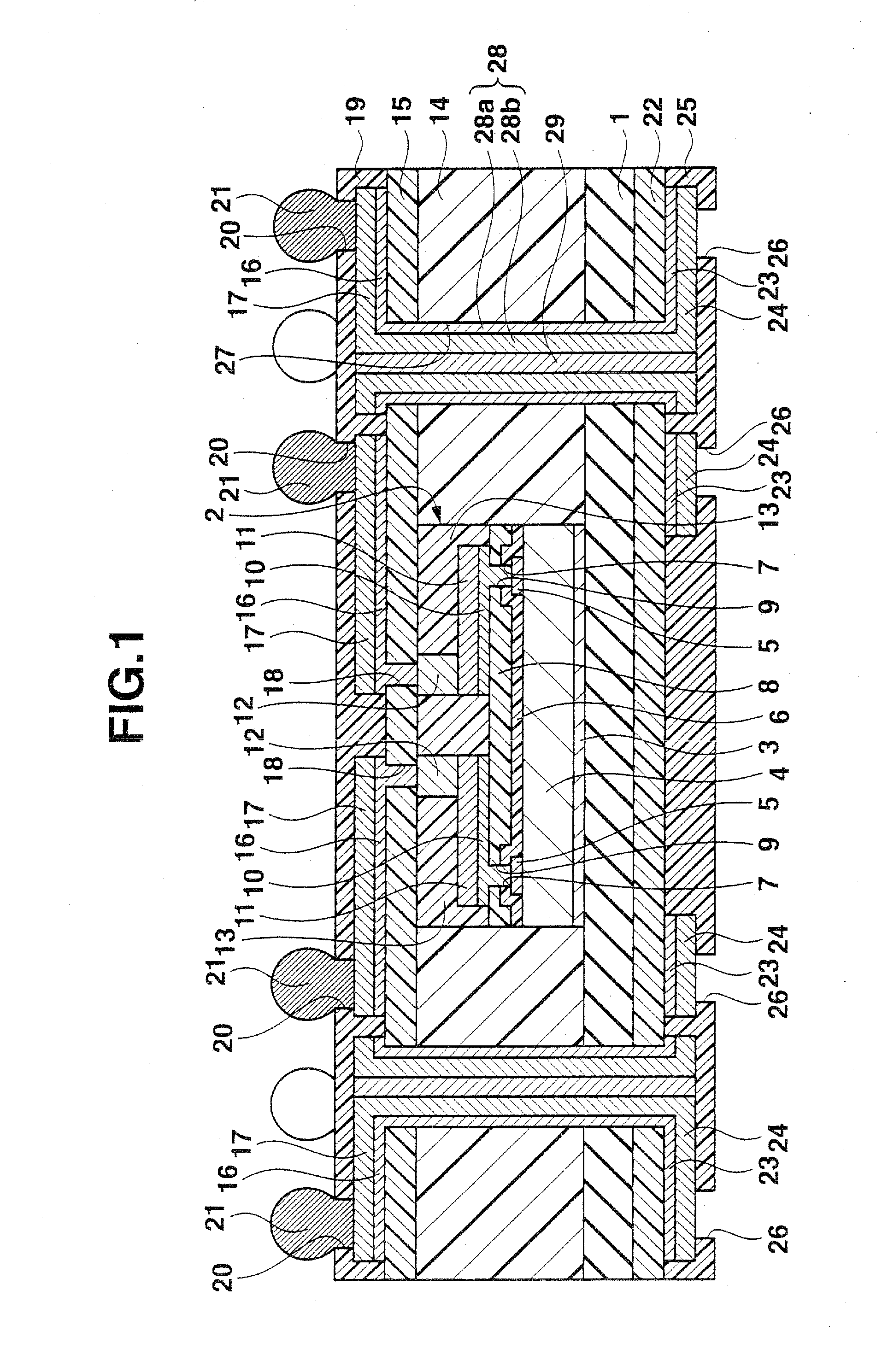

Semiconductor device and manufacturing method thereof

ActiveUS7902678B2Improve connection reliabilityOccurrence of short-circuiting between bumps can be preventedPrinted circuit assemblingFinal product manufactureResistEngineering

Electrode pads (5) and a solder resist (7) are disposed on the upper surface of a wiring board (1), and apertures (7a) are formed in the solder resist (7) so as to expose the electrode pads (5). Electrodes (4) are disposed on the lower surface of a semiconductor element (2). Electrodes (4) are connected to the electrode pads (5) by way of bumps (3). An underfill resin (6) is disposed in the area that excludes the solder resist (7) and the bumps (3) in the space between the wiring board (1) and the semiconductor element (2). Between the wiring board (1) and the semiconductor element (2), the thickness (B) of the solder resist (7) is equal to or greater than the thickness (A) of the underfill resin (6) on the solder resist (7). The volume (Vb) of the bumps (3) is less than the volume (Vs) of the apertures (7a).

Owner:GK BRIDGE 1

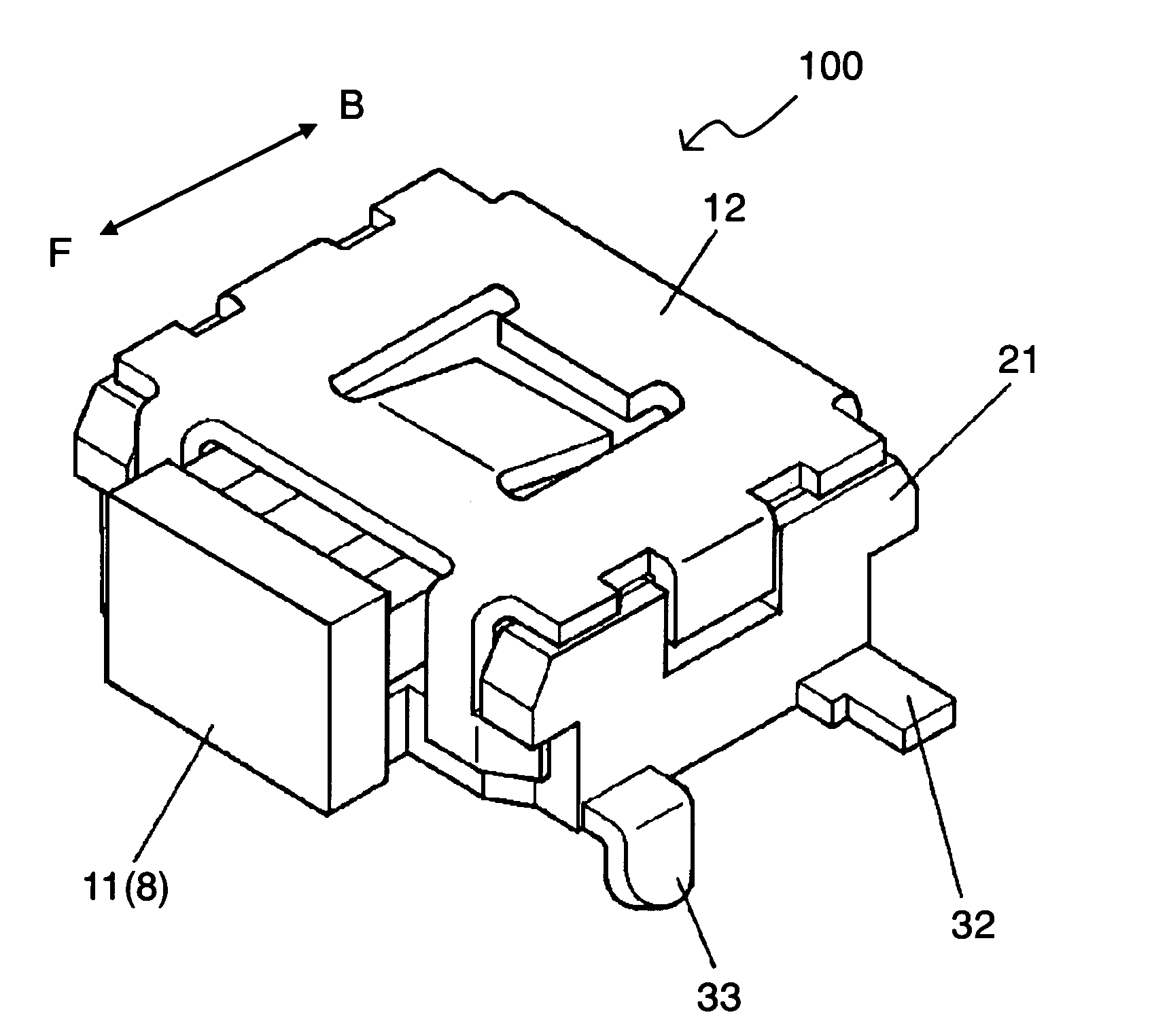

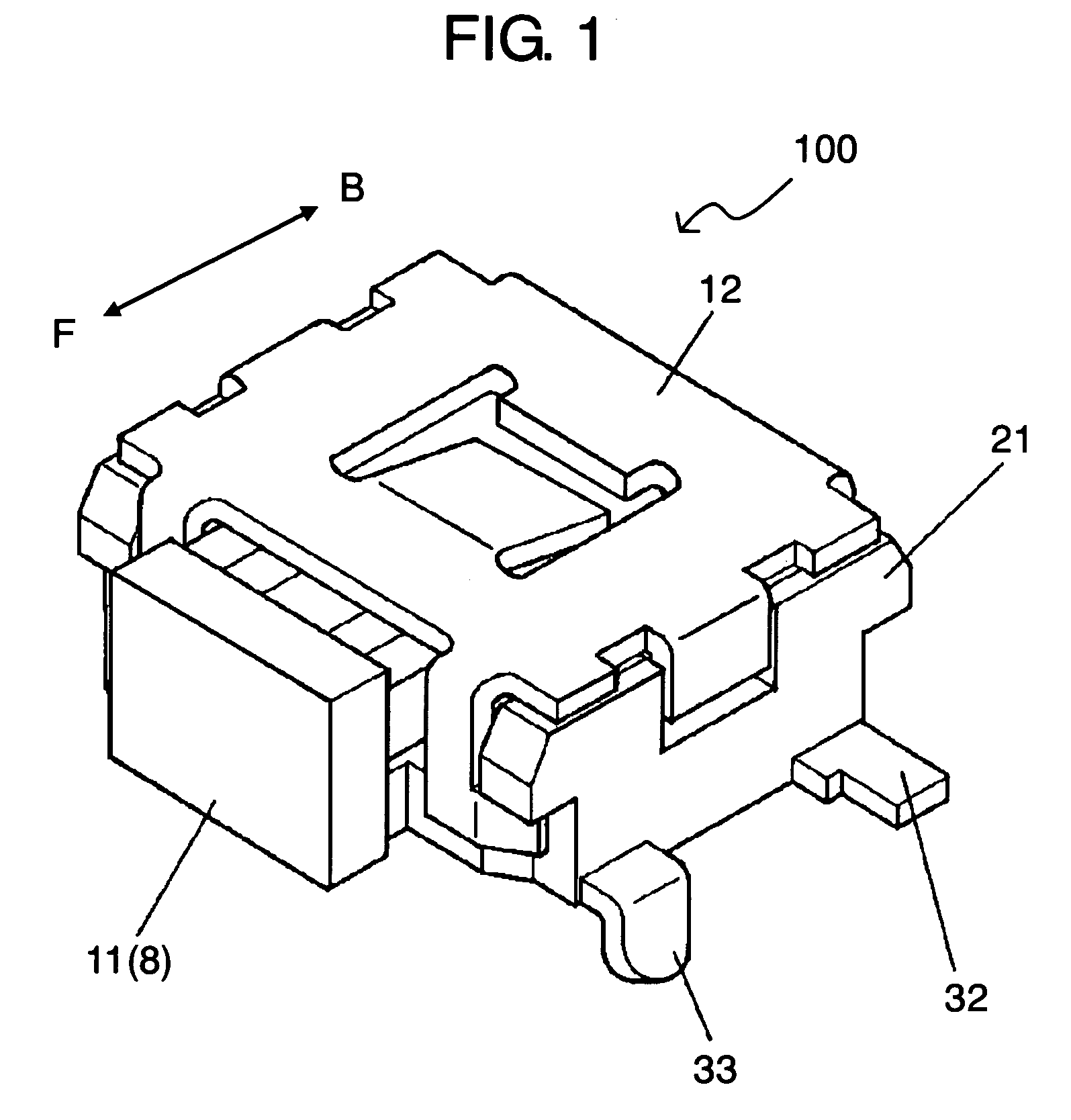

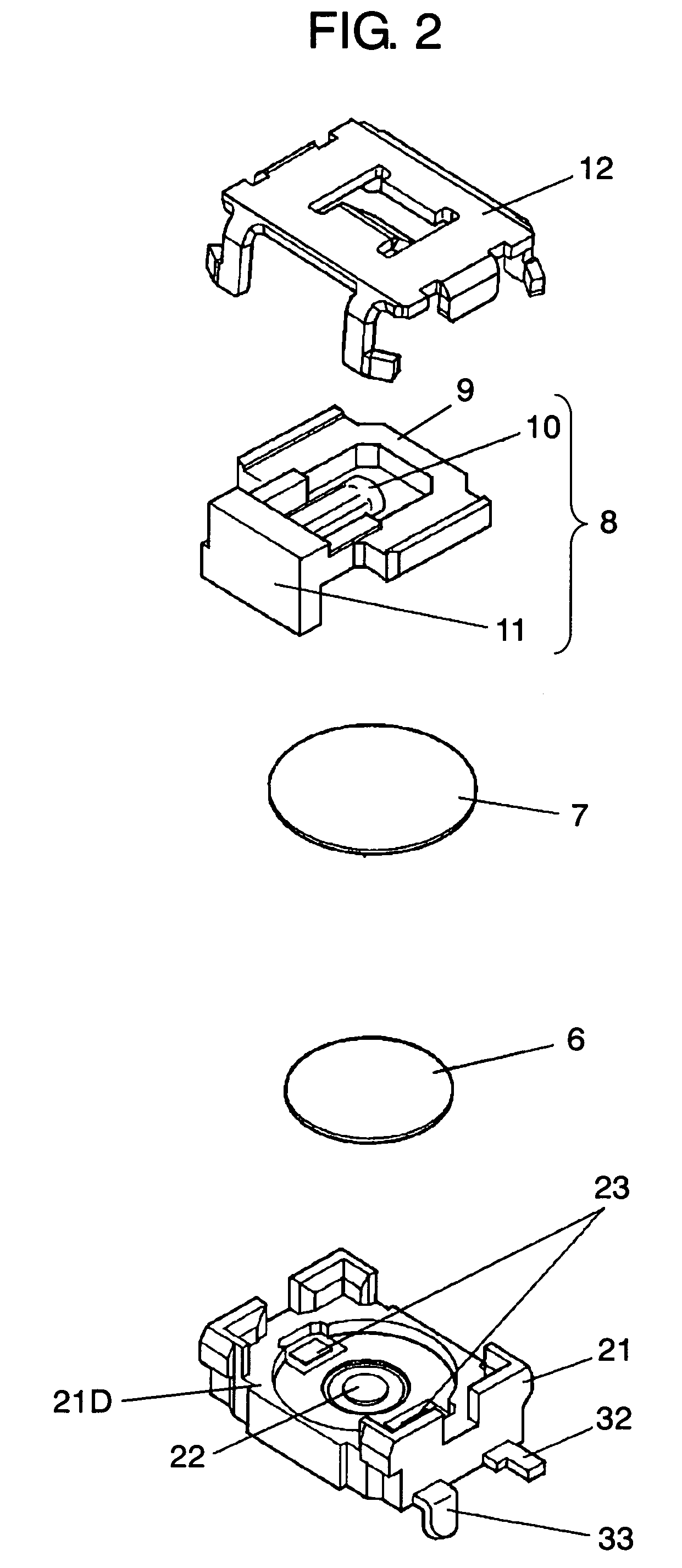

Push-on switch

ActiveUS7022928B2Improve connection reliabilityImprove quality controlContact driving mechanismsSnap-action arrangementsSurface mountingPush switch

Owner:PANASONIC CORP

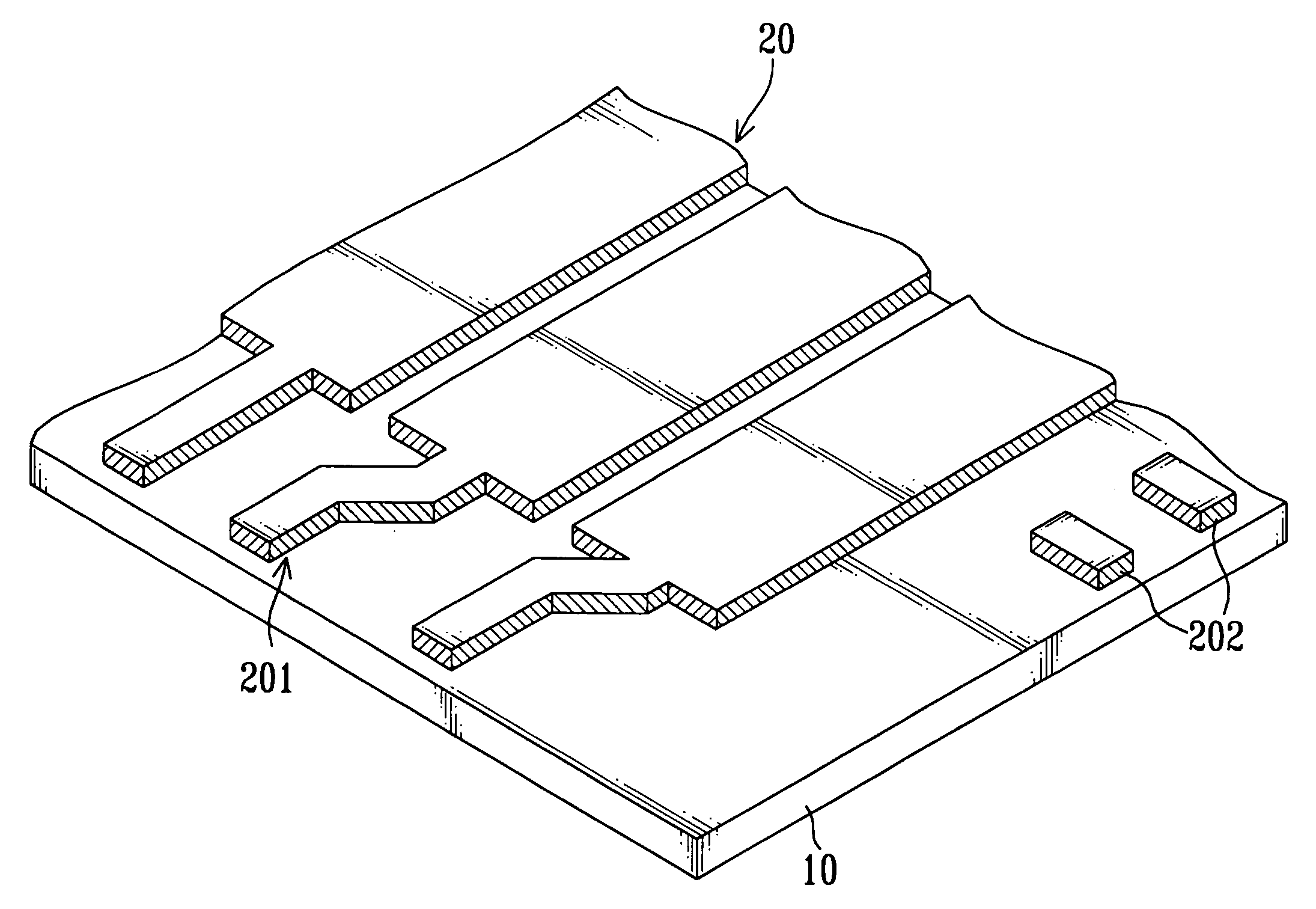

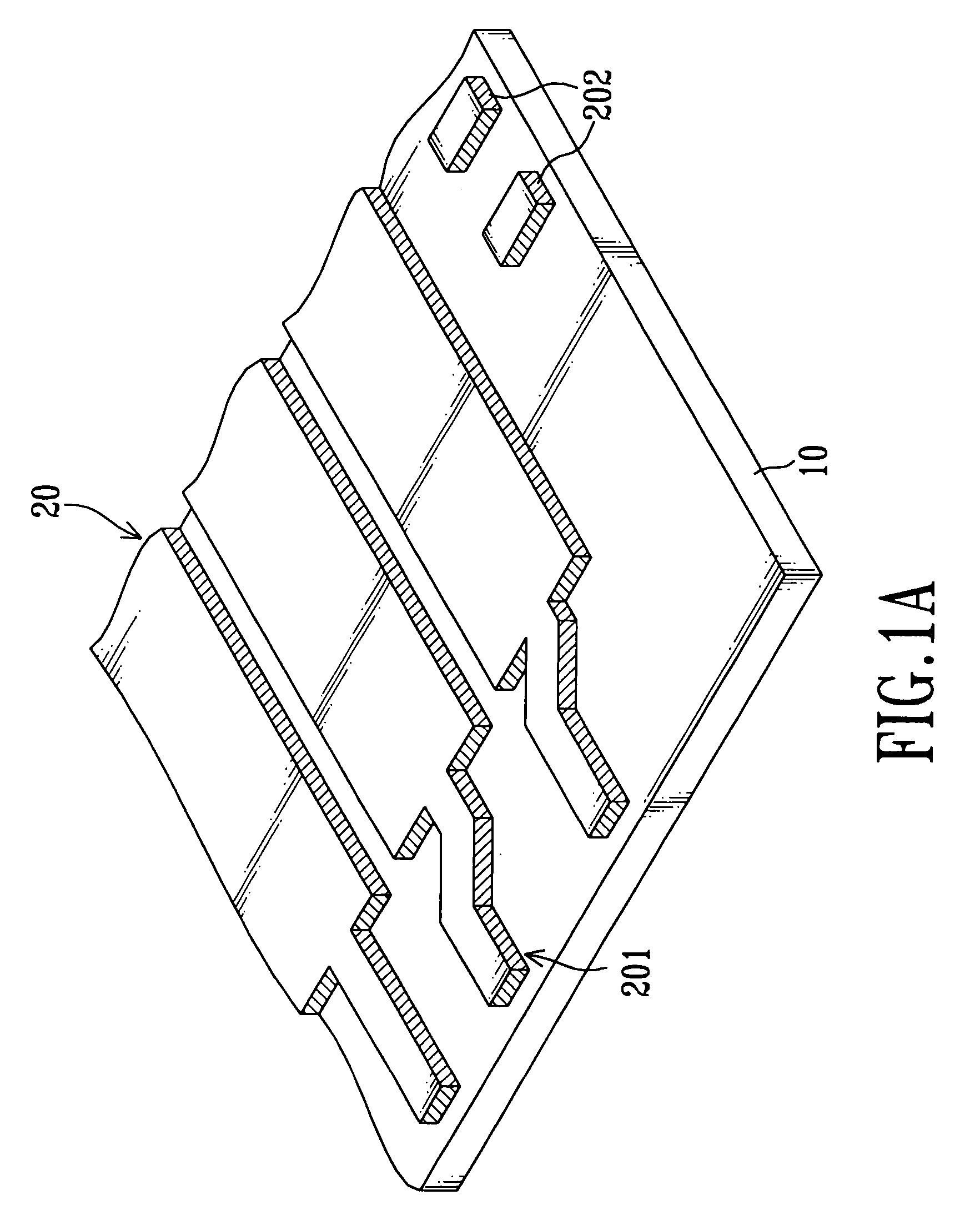

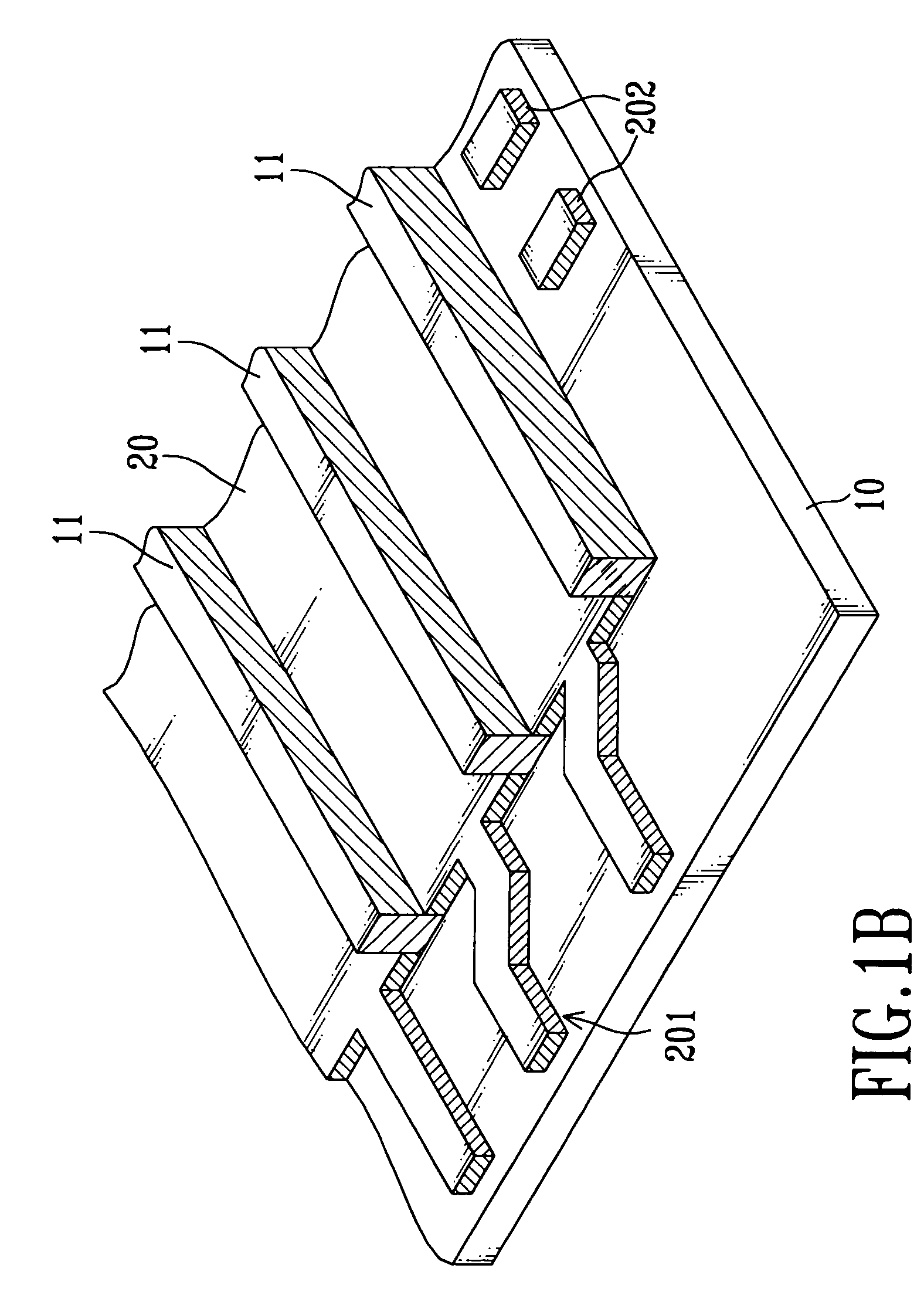

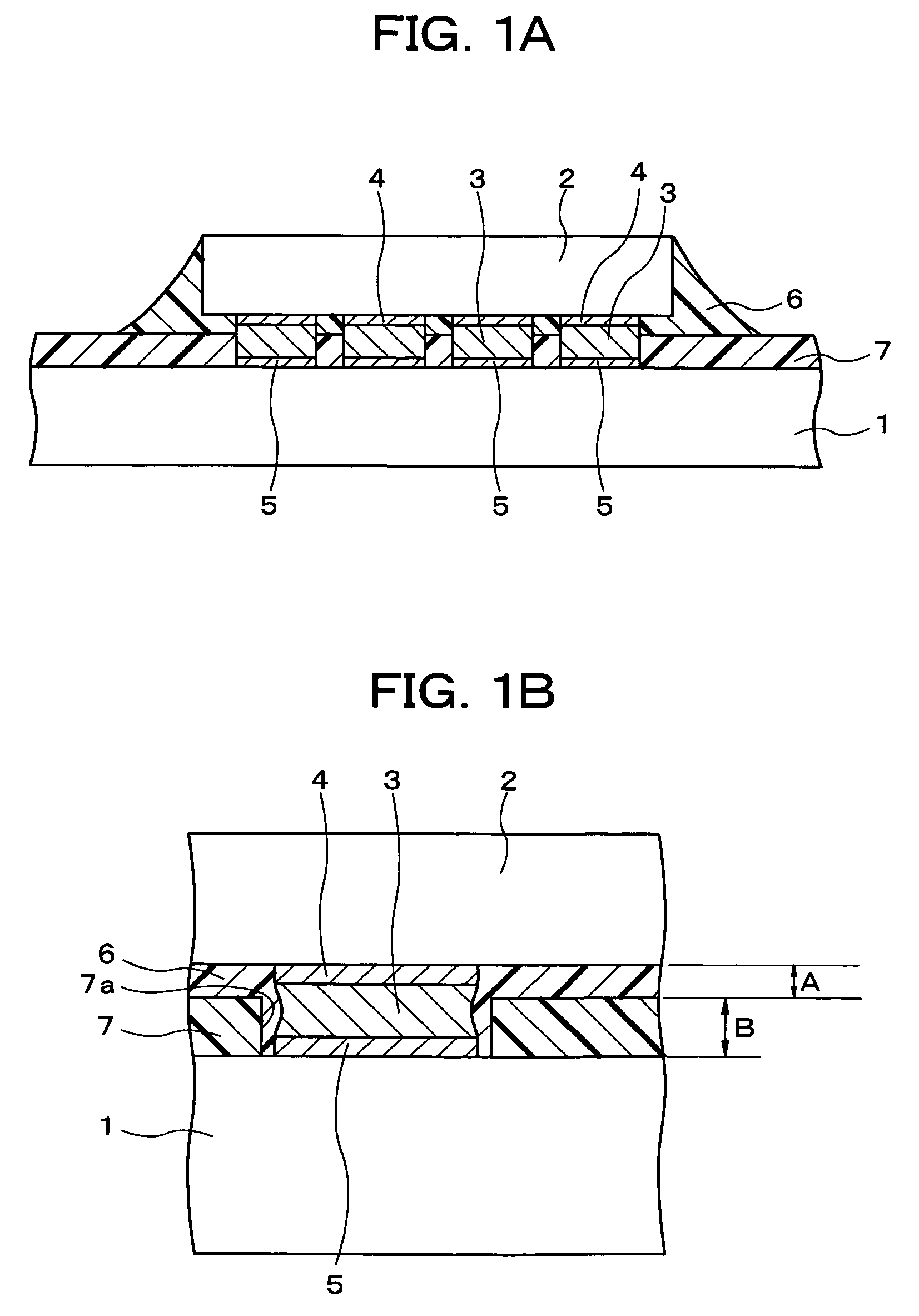

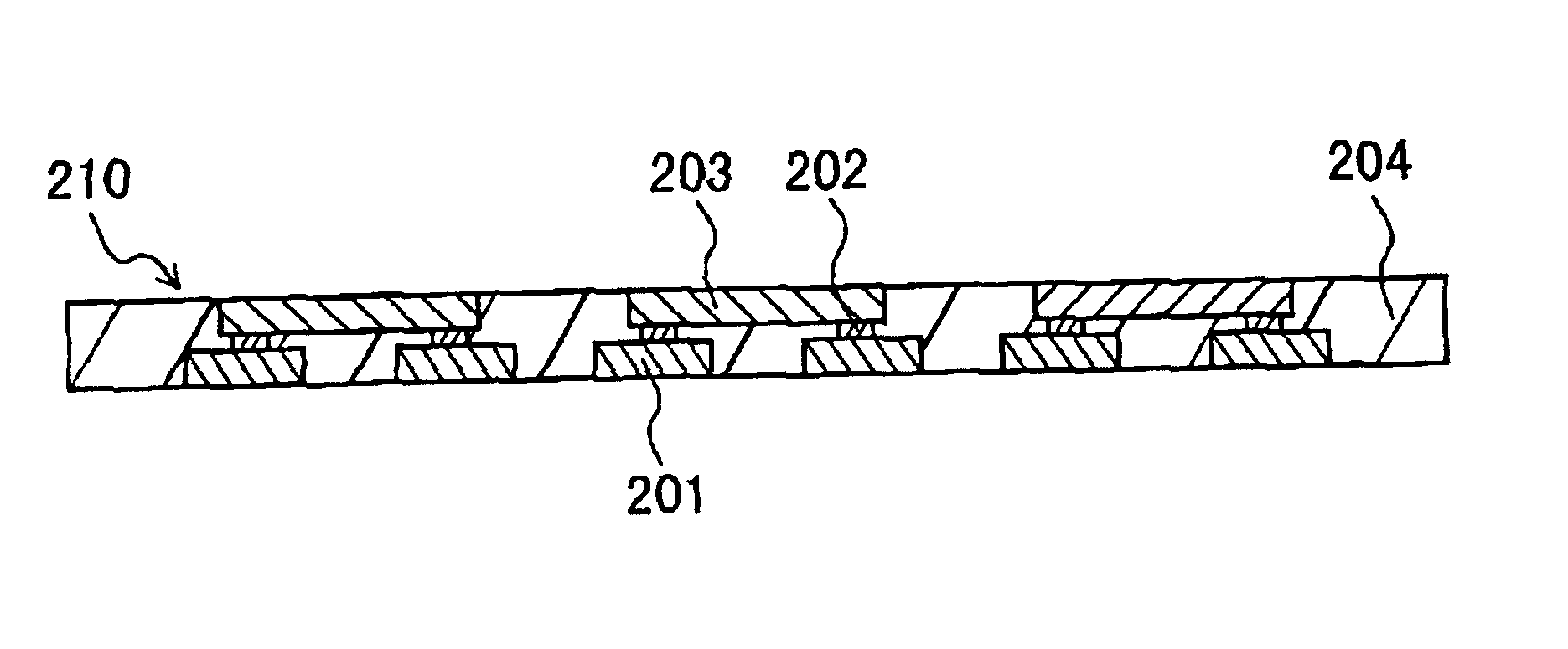

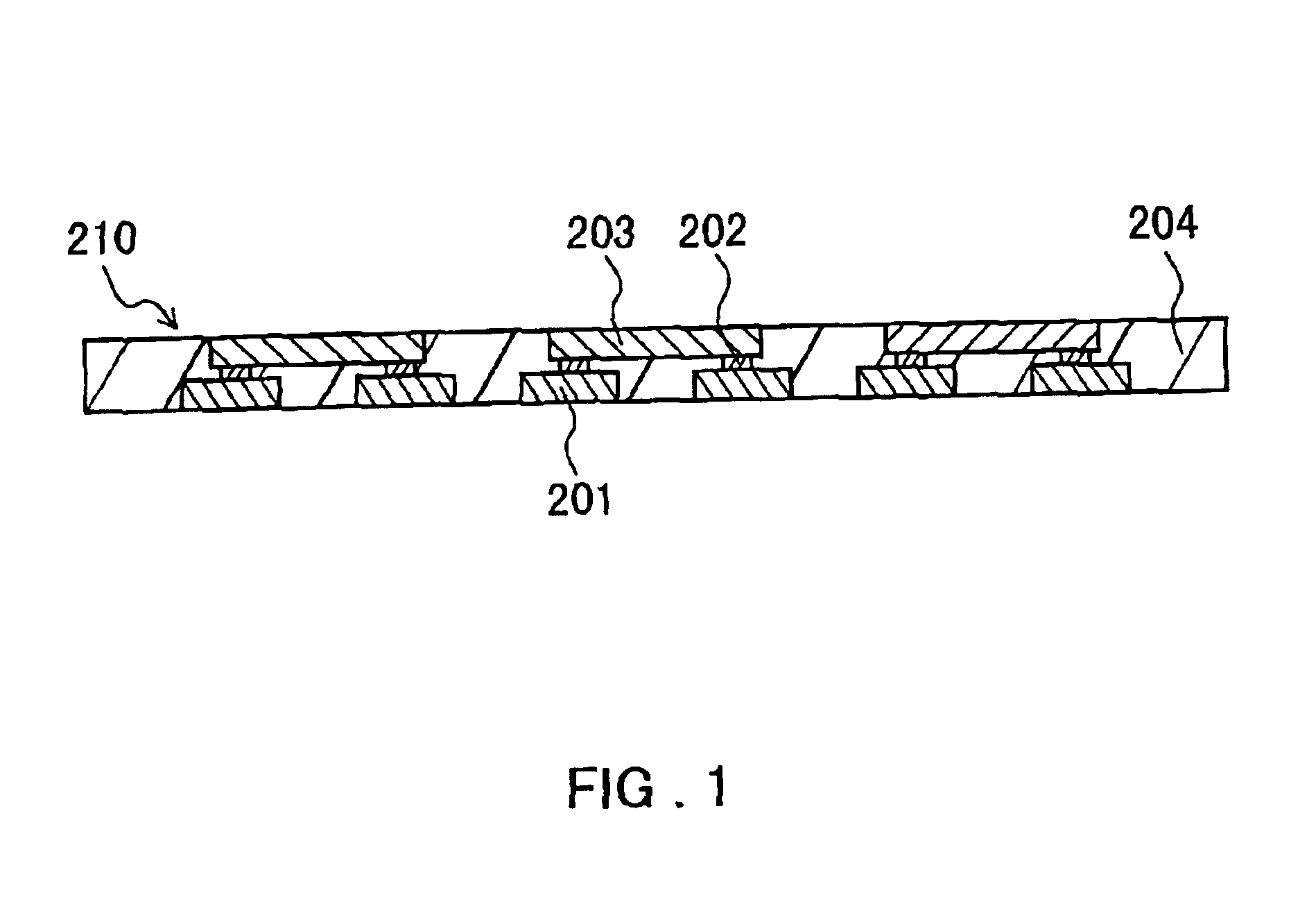

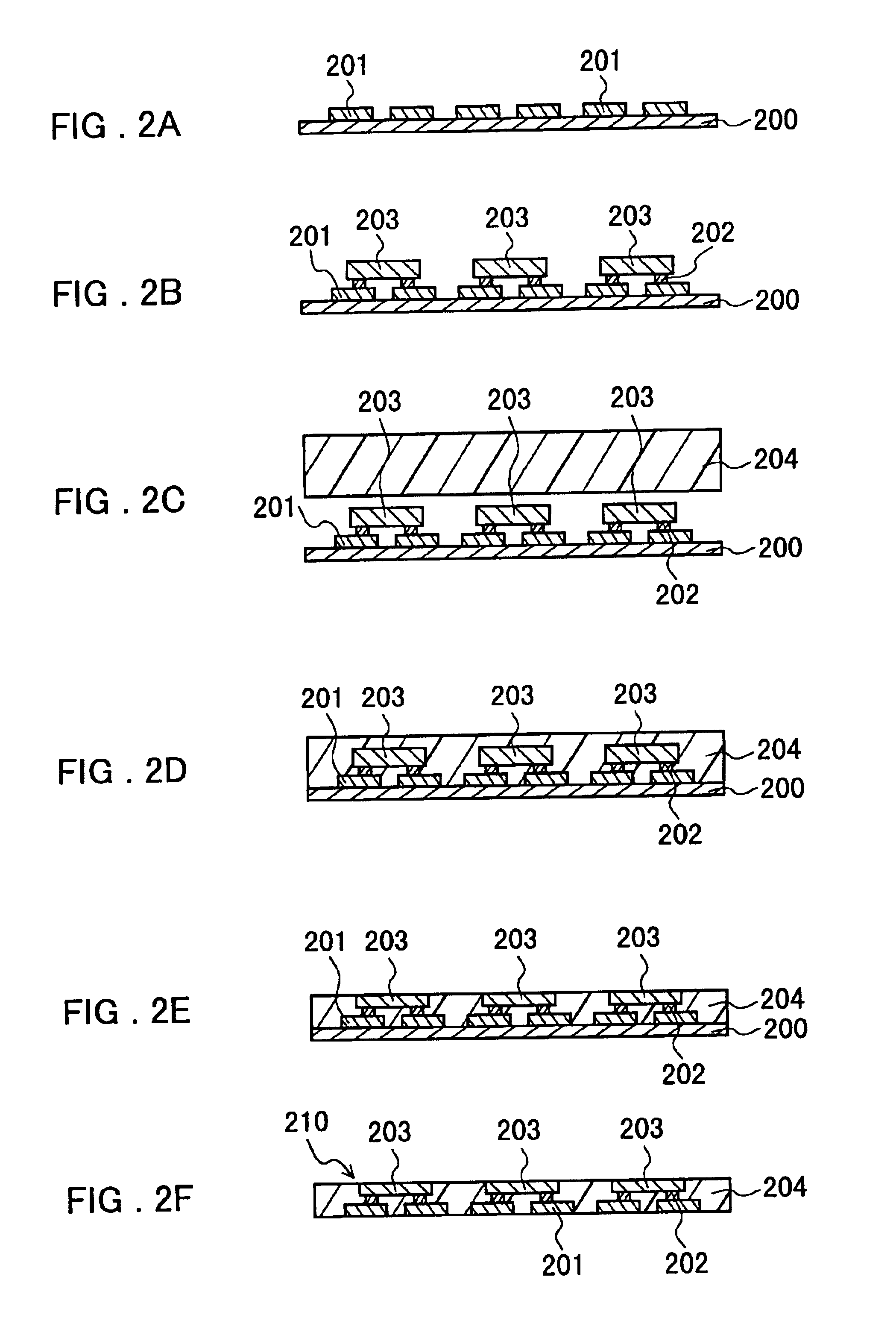

Module with built-in electronic elements and method of manufacture thereof

InactiveUS6798121B2Efficient preparationImprove connection reliabilityPiezoelectric/electrostriction/magnetostriction machinesSemiconductor/solid-state device detailsSemiconductor chipEngineering

At least two electric elements (203) such as semiconductor chips or surface acoustic wave devices are mounted on wiring patterns (201), and the electric elements (203) are sealed with a thermosetting resin composition (204). An upper surface of the at least two electric elements (203) and an upper surface of the thermosetting resin composition (204) are abraded at the same time, thereby forming surfaces substantially flush with each other. Since they are abraded while being sealed with the thermosetting resin composition (204), it is possible to reduce the thickness without damaging the electric elements (203). Also, the electric elements (203) and the wiring patterns (201) can be prevented from being contaminated by an abrasive liquid. In this manner, it is possible to obtain an electric element built-in module whose thickness can be reduced while maintaining its mechanical strength.

Owner:PANASONIC CORP

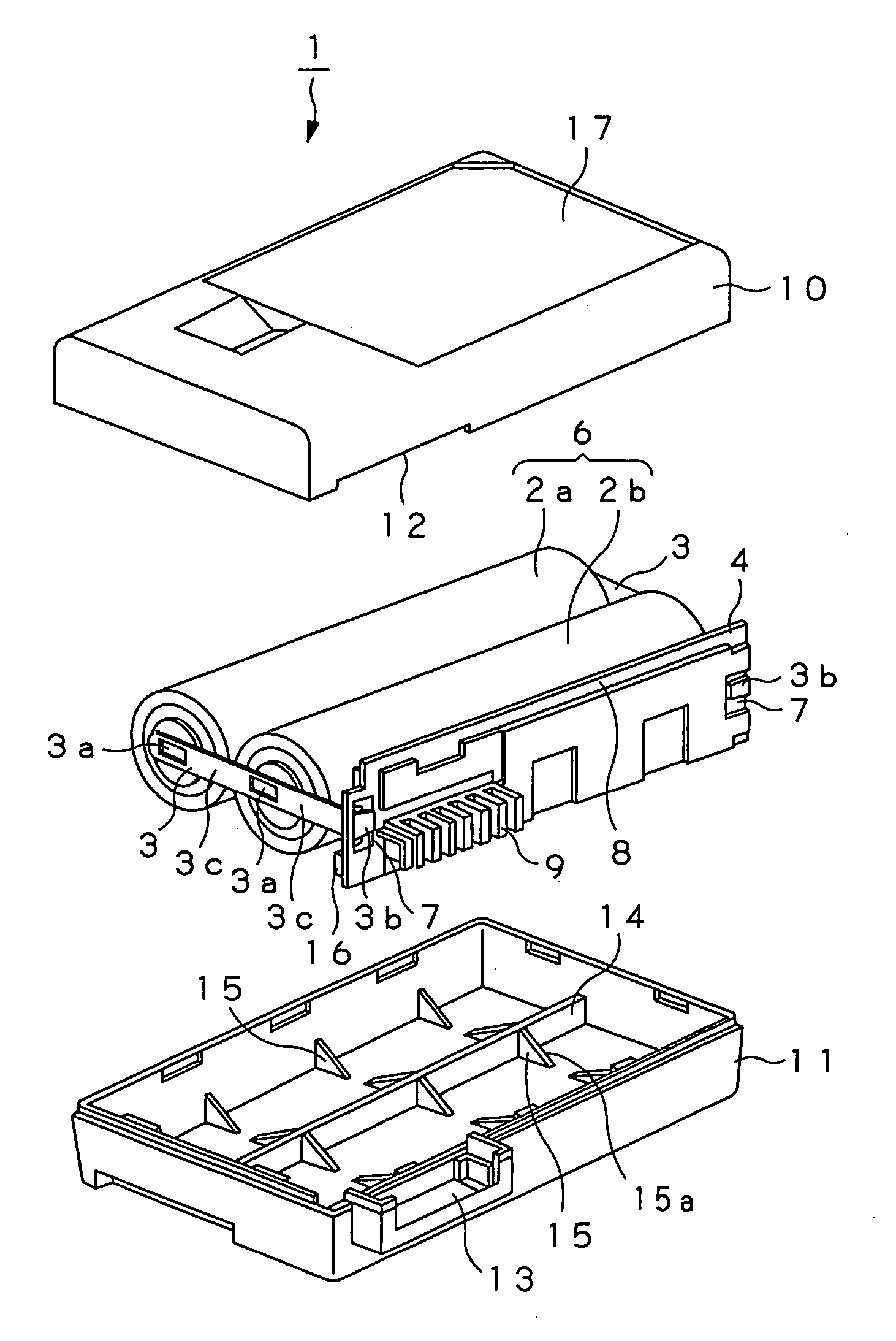

Lead terminal and power supply device

InactiveUS20060032667A1Improve welding strengthImprove electrical resistancePrinted electric component incorporationSoldered/welded conductive connectionsElectricityElectrical resistance and conductance

The present invention is directed to a power supply apparatus in which a battery and a circuit wiring board or boards are electrically connected by using lead terminals. The lead terminal (3) is adapted so that thickness of a welding portion (3a) is caused to be thinner than the thickness of a conductive portion (3b). Thus, current for welding flows to much degree in a thickness direction so that electric resistance of the welding portion becomes large, and heat based on the electric resistance also becomes large. From this fact, welding nugget (63) can be enlarged. As the result of the fact that large welding nugget is formed, the lead terminals are welded to terminal portions (37a) of the battery (2) with high reliability.

Owner:SONY CORP

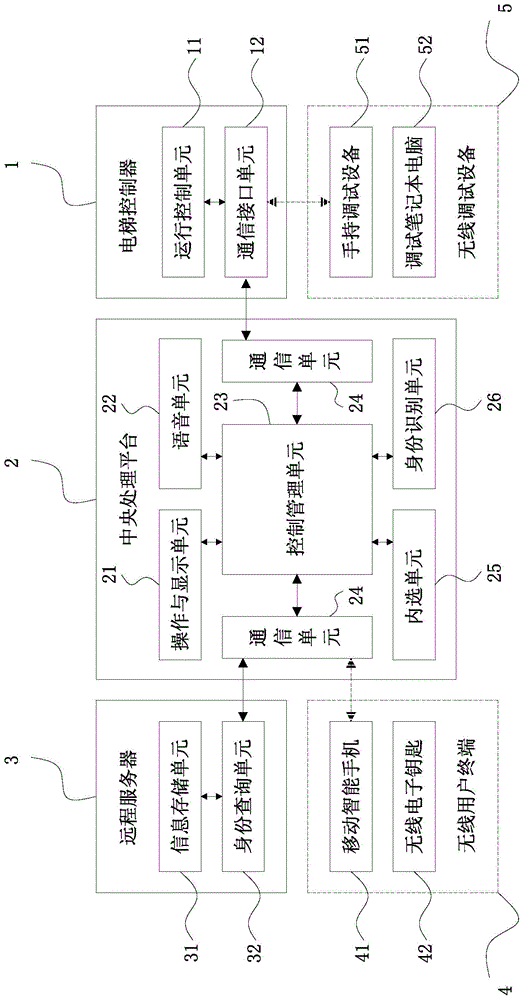

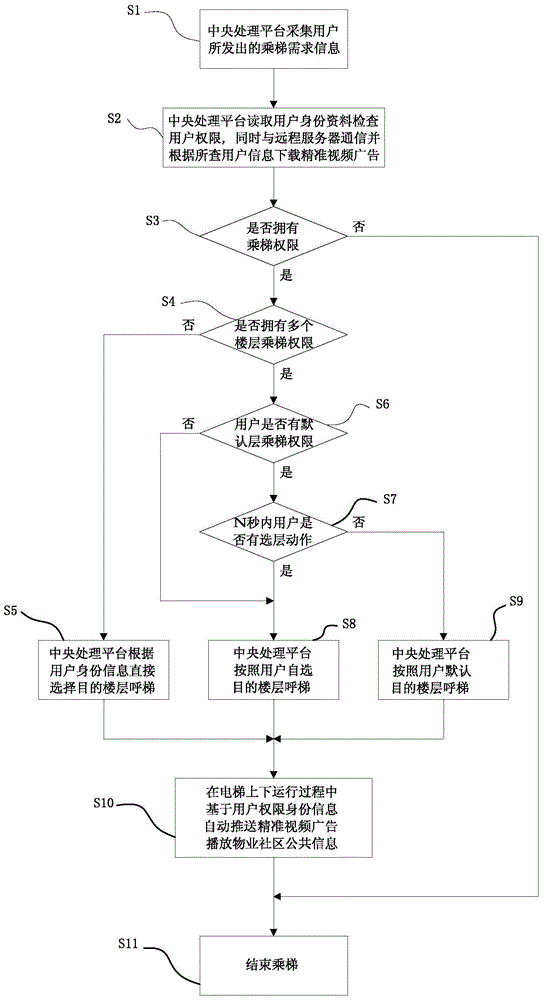

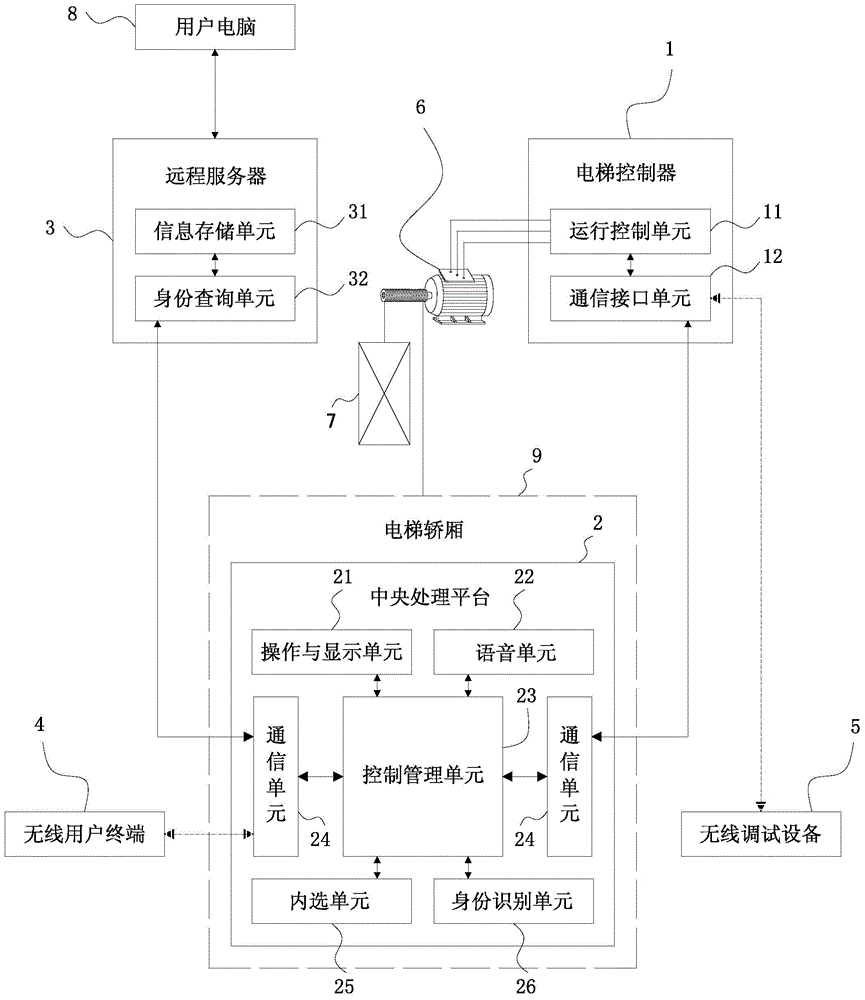

Intelligent elevator control system and method

ActiveCN104609270ARealize managementEasy access to elevatorsElevatorsIdentity recognitionControl system

An intelligent elevator control system comprises an elevator controller, a central processing platform and a remote server. The central processing platform is installed in an elevator cage and connected with the elevator controller and the remote server. The central processing platform is used for providing an operation interface for an elevator riding user or directly recognizing the elevator riding authority of the elevator riding user. The central processing platform judges whether the user has the elevator riding authority according to the operation of the user or the automatic recognition result and through the combination of the identity information, stored in the remote server, of the elevator riding user and controls the elevator controller correspondingly. The elevator controller controls the elevator cage to run. The elevator riding authority of the user is managed, and the user can conveniently ride an elevator through wireless identity recognition measures; for the cloud service network information of the user, precise video advertisements can be automatically pushed to the user and property community public information can be automatically broadcasted to the user; the requirements for vision and information are met when the user rides the elevator.

Owner:BEIJING SWORD ELECTRIC IND

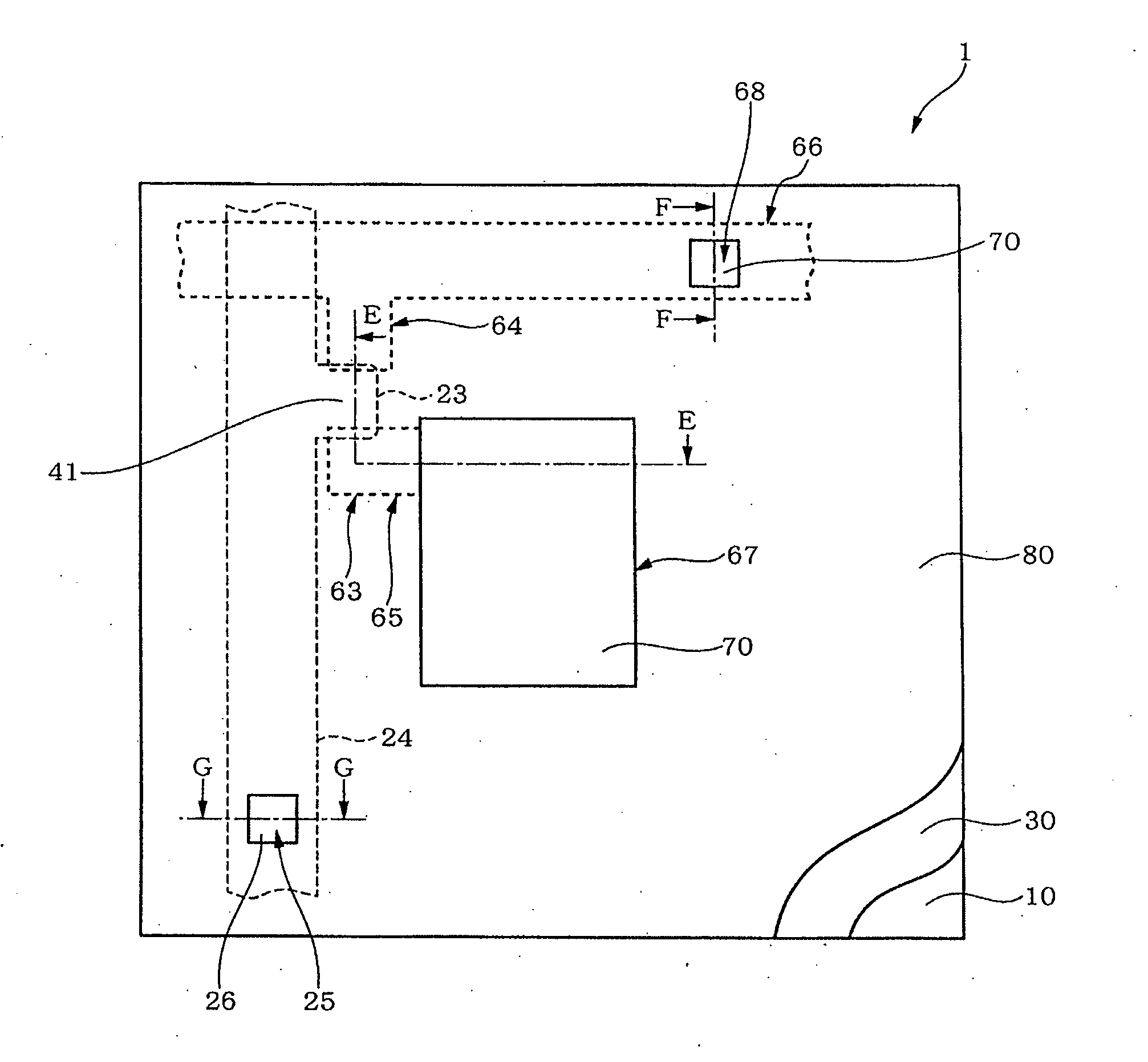

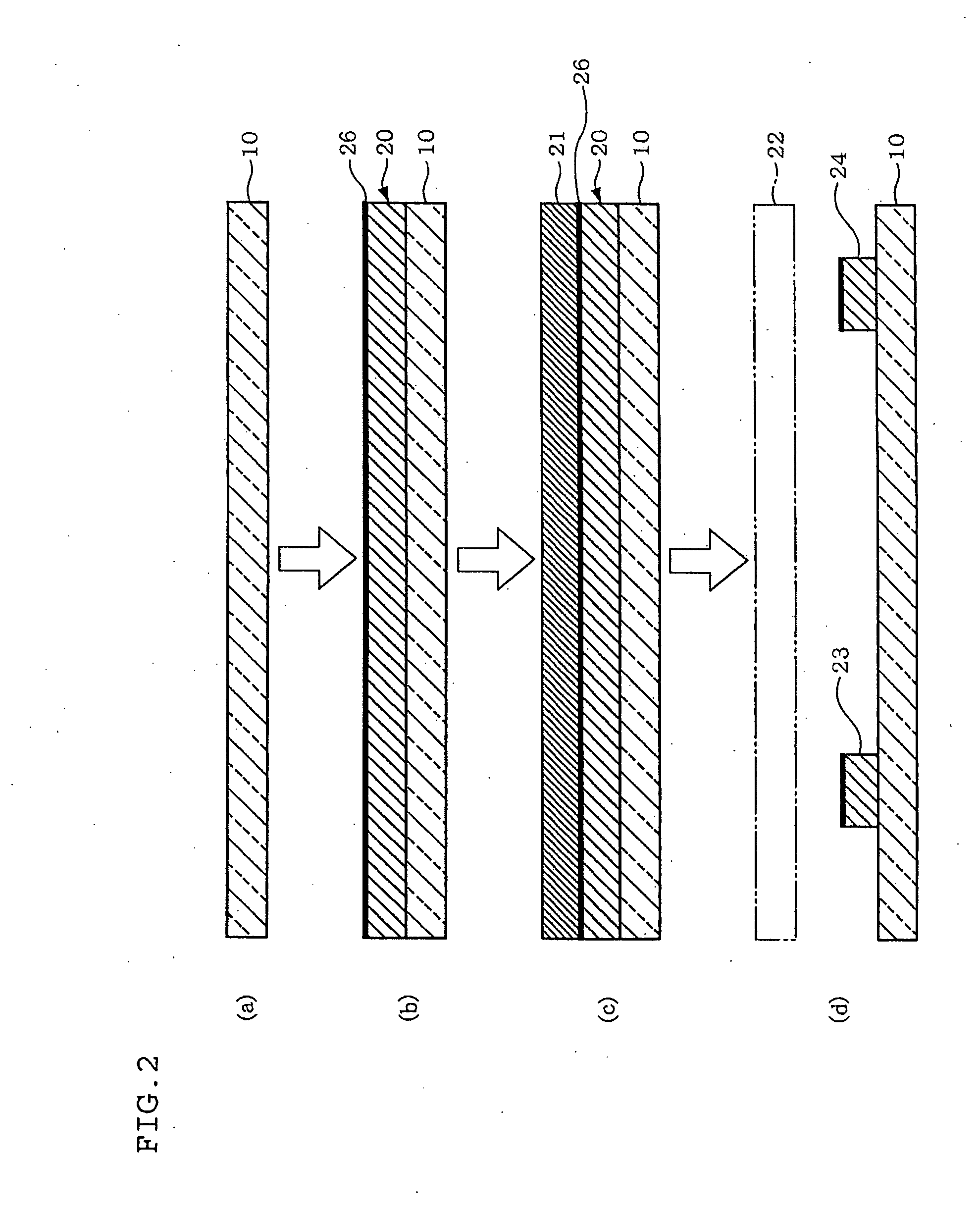

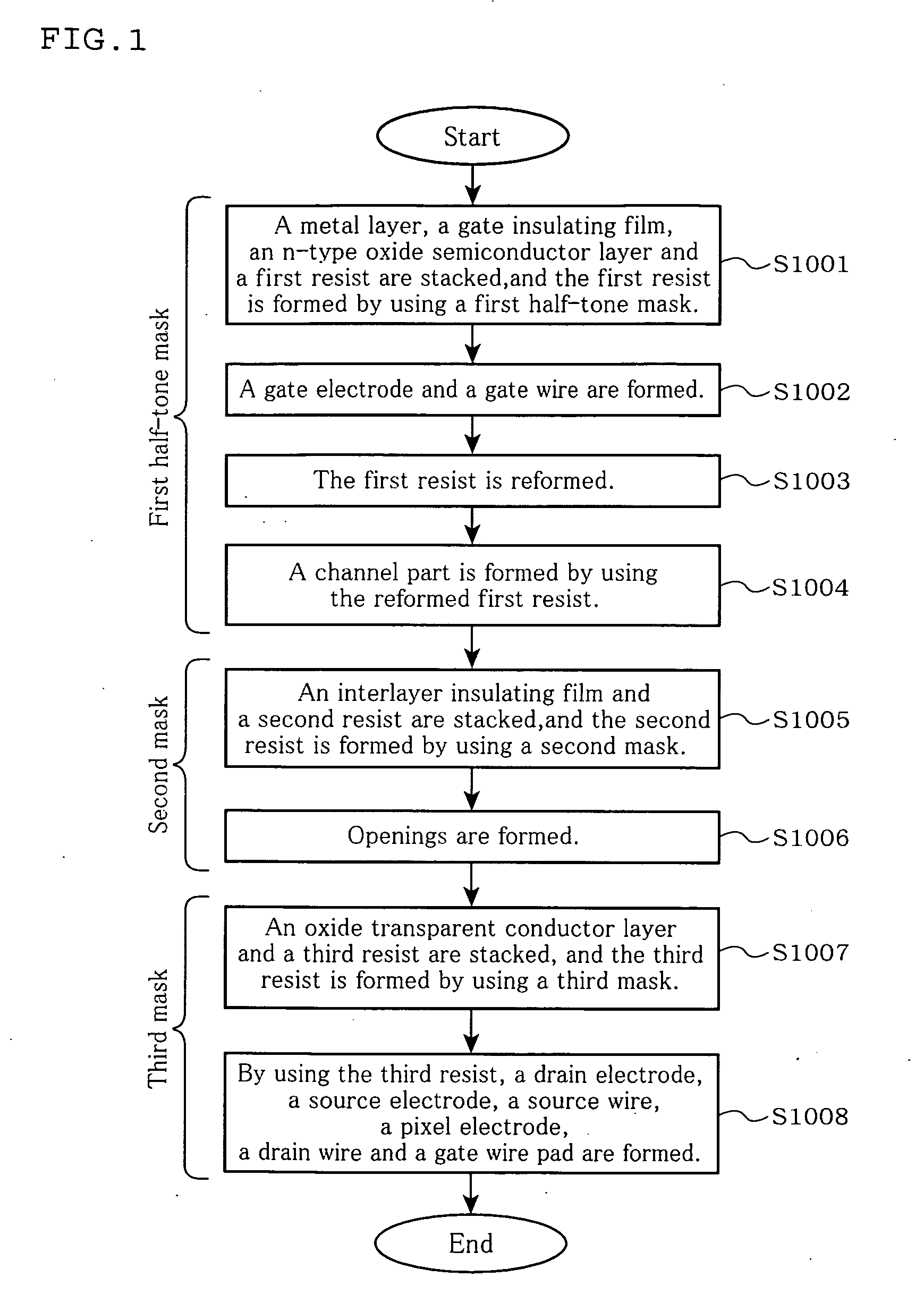

Reflective TFT substrate and method for manufacturing reflective TFT substrate

InactiveUS20100163876A1Improve connection reliabilityAvoid exposureTransistorSolid-state devicesManufacturing cost reductionEngineering

A reflective TFT substrate which can be operated for a prolonged period of time due to the presence of a protective insulating film, is free from occurrence of crosstalk, and is capable of significantly reducing manufacturing cost by decreasing the production steps in the production process. A reflective TFT substrate 1 comprises a substrate 10; a gate electrode 23 and a gate wire 24; a gate insulating film 30; an n-type oxide semiconductor layer 40; a metal layer 60 formed with a channel part 41 interposed therebetween; and a protective insulating film 80 which covers the upper part of the glass substrate 10 on which a pixel electrode 67, a drain wire pad 68 and a gate wire pad 25 are exposed, wherein the metal layer 60 functions at least as a source wire 65, a drain wire 66, a source electrode 63, a drain electrode 64 and the pixel electrode 67.

Owner:INOUE KAZUYOSHI +3

Semiconductor module and portable device

InactiveCN101819959AImprove connection reliabilityIncrease contact areaSemiconductor/solid-state device detailsSolid-state devicesSolder ballEngineering

The invention provides a semiconductor module and a portable device. A wiring layer including external connection regions is provided on a main surface of an insulating resin layer on a side opposite to that of a semiconductor device mounting face. The wiring layer is coated with a protection layer. An opening is provided to the protection layer such that each external connection region is exposed. Each external connection region has a curved surface recessed toward the insulating resin layer side. The entire area of each opening is filled with a solder ball for mounting a substrate, and the recess of each external connection region is filled with the solder ball, thereby connecting each solder ball to the intermediate layer.

Owner:SANYO ELECTRIC CO LTD

Connecting terminal, semiconductor package using connecting terminal and method for manufacturing semiconductor package

InactiveUS20100071940A1Improve connection reliabilityIncrease bonding strengthNon-insulated conductorsPrinted electric component incorporationElectrically conductiveElectroless plating

The connection reliability of connecting terminals with displacement gold plating films is improved by connecting terminals comprising a conductive layer, an electroless nickel plating film, a first palladium plating film which is a displacement or electroless palladium plating film with a purity of 99% by mass or greater, a second palladium plating film which is an electroless palladium plating film with a purity of at least 90% by mass and less than 99% by mass, and a displacement gold plating film, wherein the electroless nickel plating film, the first palladium plating film, the second palladium plating film and the displacement gold plating film are laminated in that order on one side of the conductive layer, and the displacement gold plating film is situated on the uppermost surface layer on the opposite side from the conductive layer.

Owner:HITACHI CHEM CO LTD

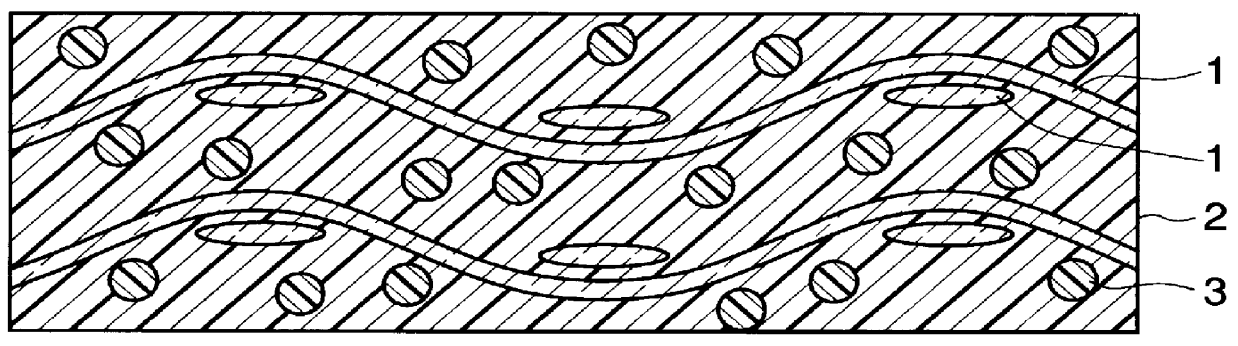

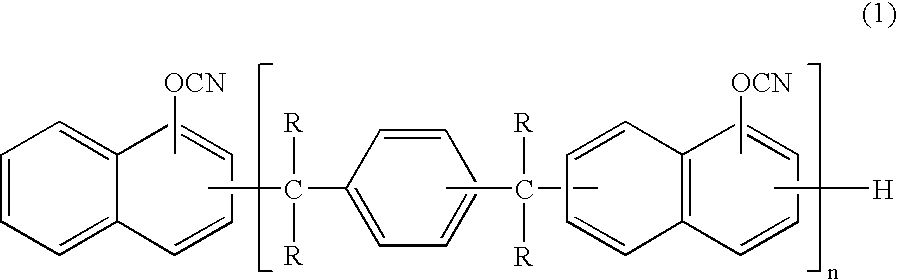

Prepreg and laminate

ActiveUS20090017316A1Improve flame retardant performanceImprove heat resistanceSpecial tyresElectrical equipmentThermal dilatationPolymer science

A prepreg for a printed wiring board, comprising a cyanate ester resin having a specific structure, a non-halogen epoxy resin, a silicone rubber powder as a rubber elasticity powder, an inorganic filler and a base material, which prepreg retains heat resistance owing to a stiff resin skeleton structure, has high-degree flame retardancy without the use of a halogen compound or a phosphorus compound as a flame retardant, and has a small thermal expansion coefficient in plane direction without using a large amount of inorganic filler, and a laminate comprising the above prepreg.

Owner:MITSUBISHI GAS CHEM CO INC

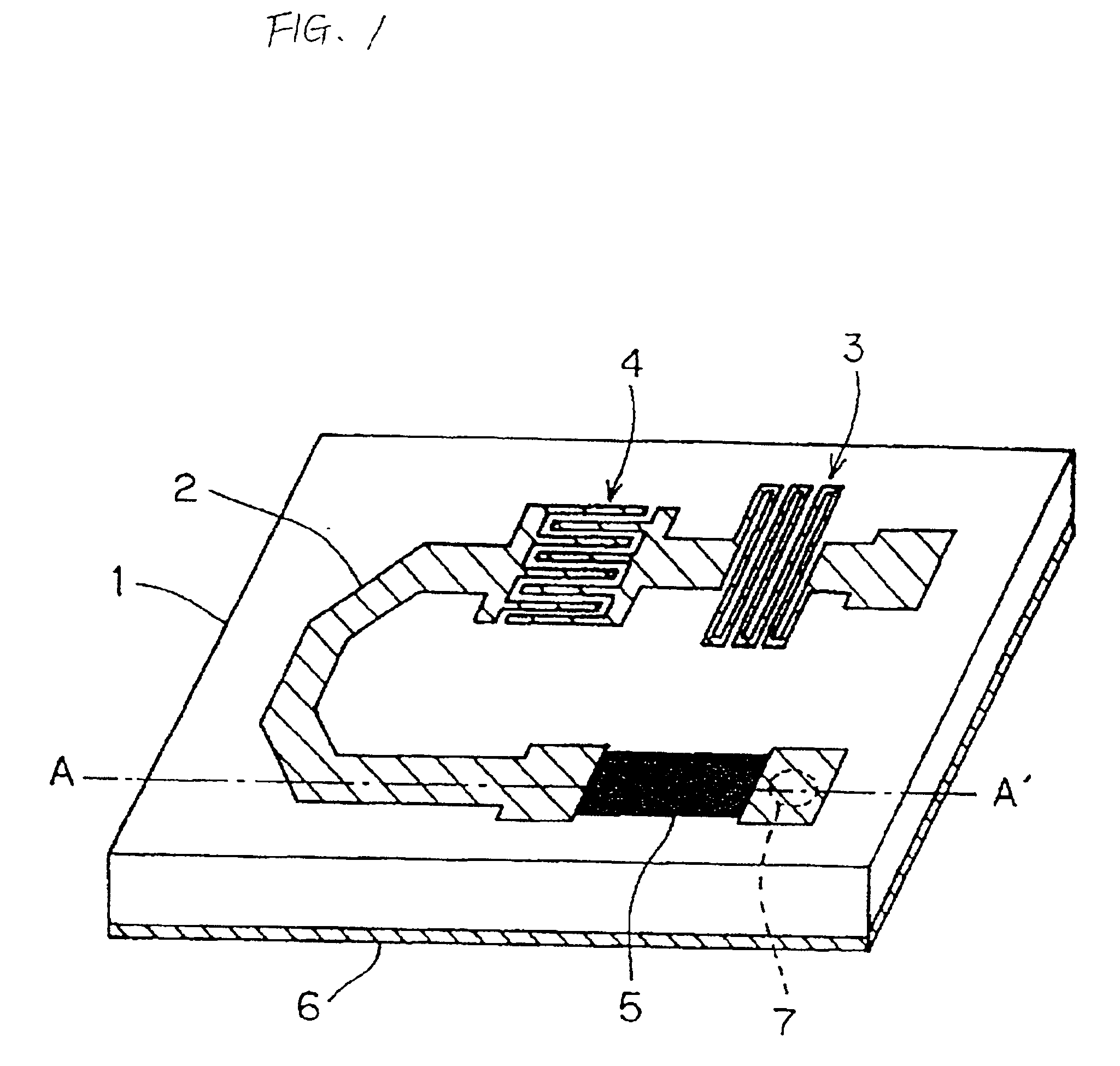

High frequency circuit chip and method of producing the same

InactiveUS6838377B2Small sizeEfficient productionSemiconductor/solid-state device detailsPrinted circuit aspectsMaterial PerforationElectrical and Electronics engineering

In the production of a high frequency circuit chip in which a wiring pattern is disposed on a substrate having a through-hole, a connecting electrode of the through-hole is formed by filling electrically conductive paste into a perforation and firing it, and the wiring pattern is formed by a lift-off method. Moreover, at least the surface of the substrate for the wiring pattern to be formed thereon is mirror-polished, and thereafter, the wiring pattern is formed on the mirror-polished surface by the lift-off method.

Owner:MURATA MFG CO LTD

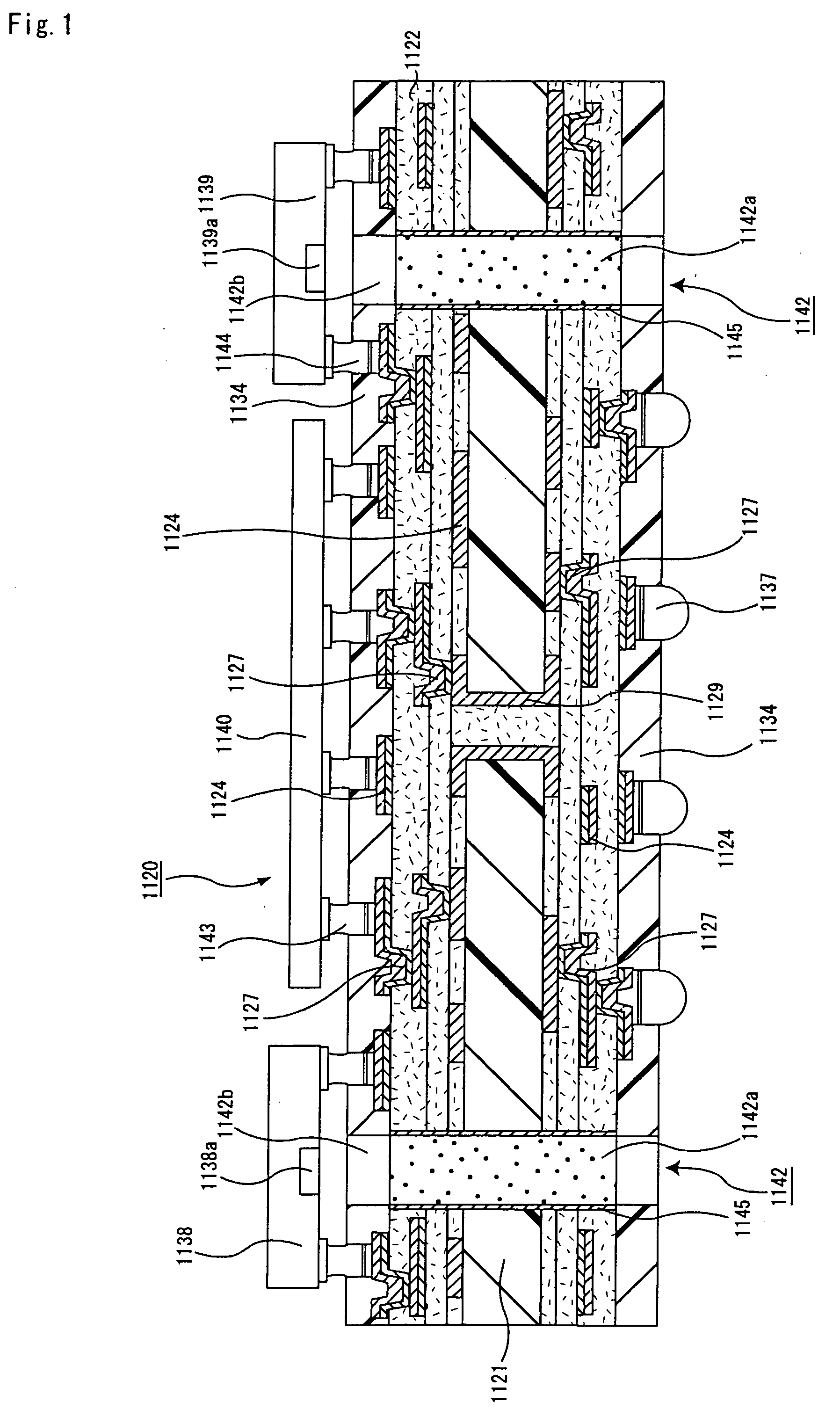

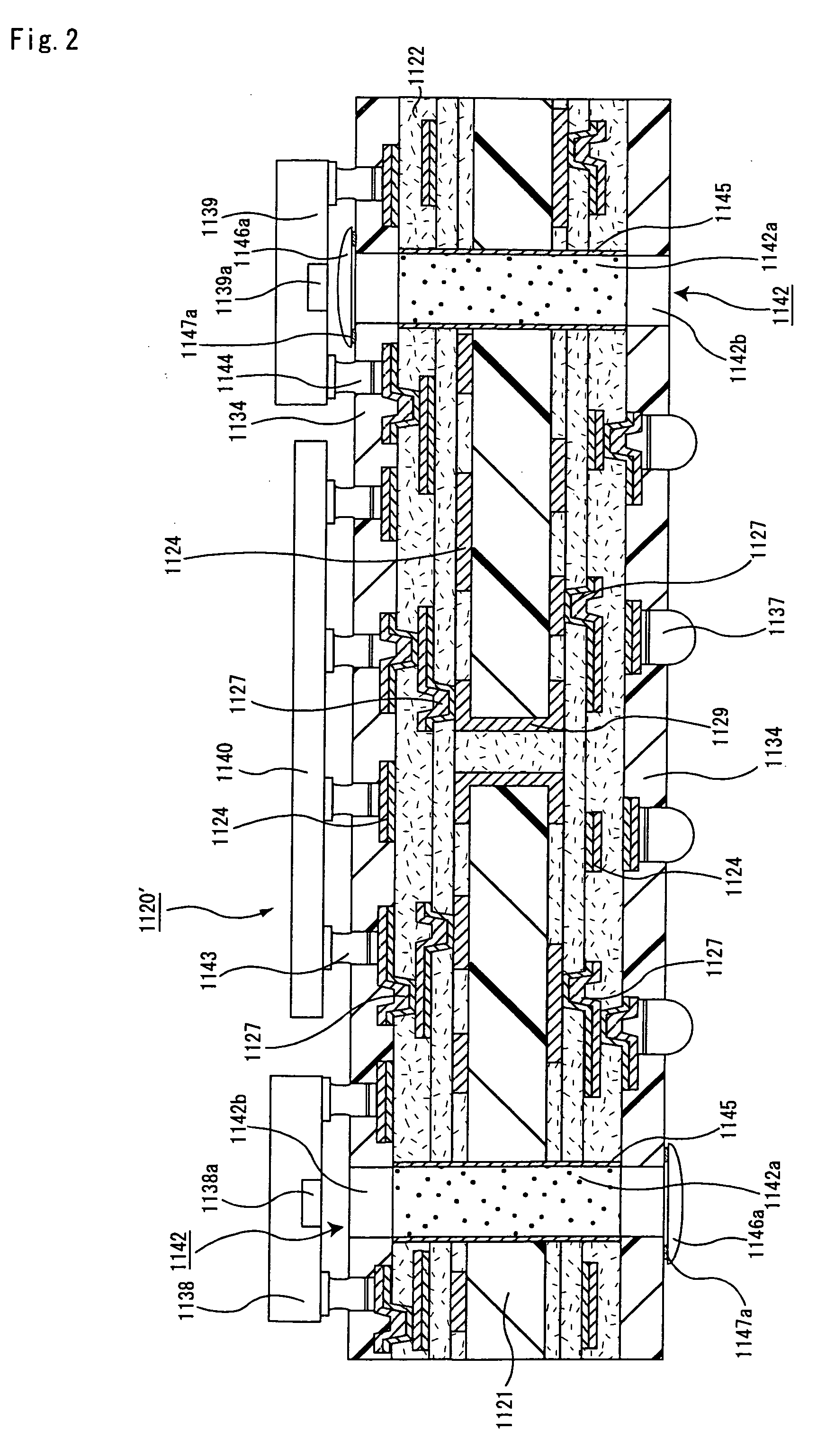

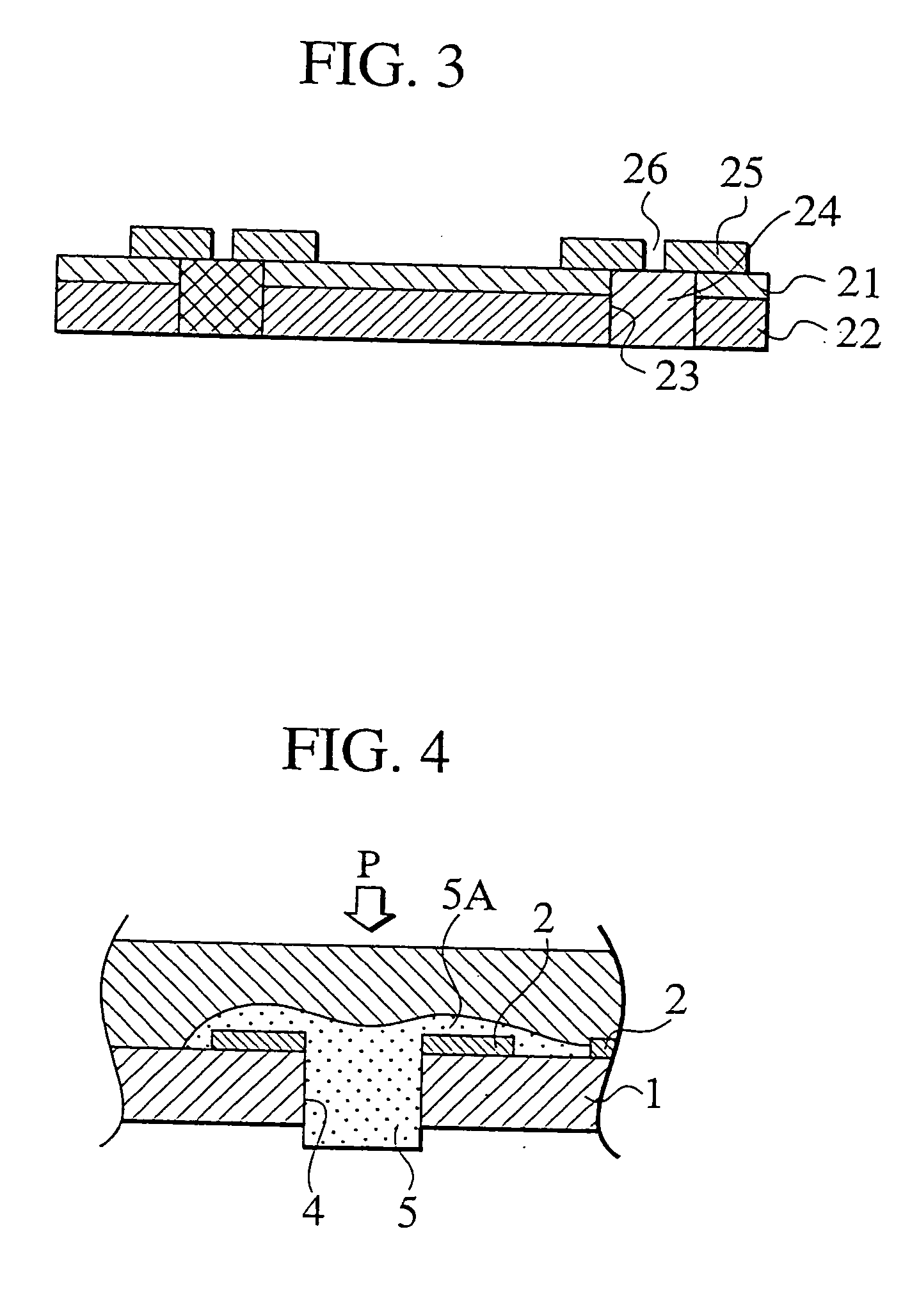

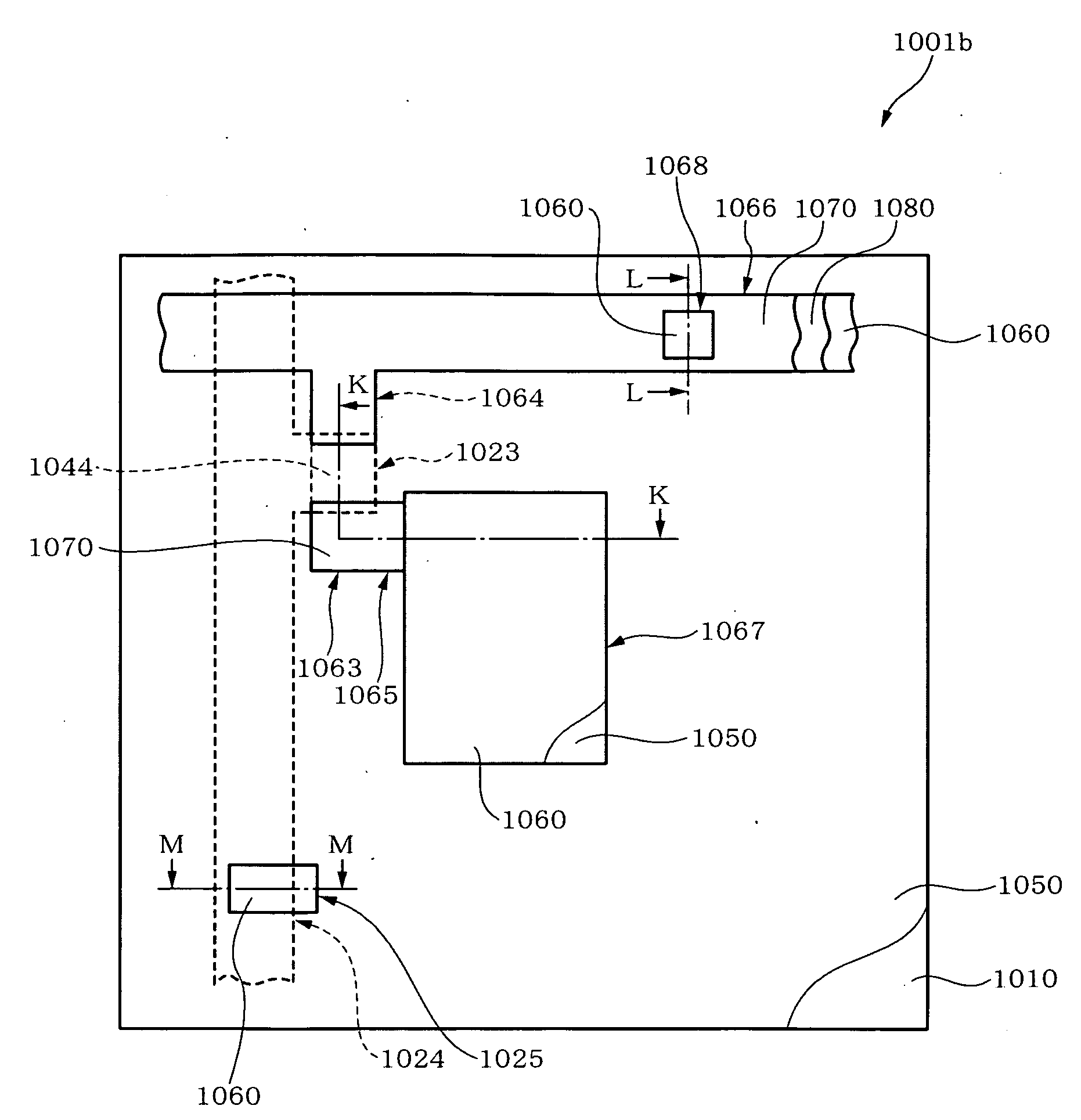

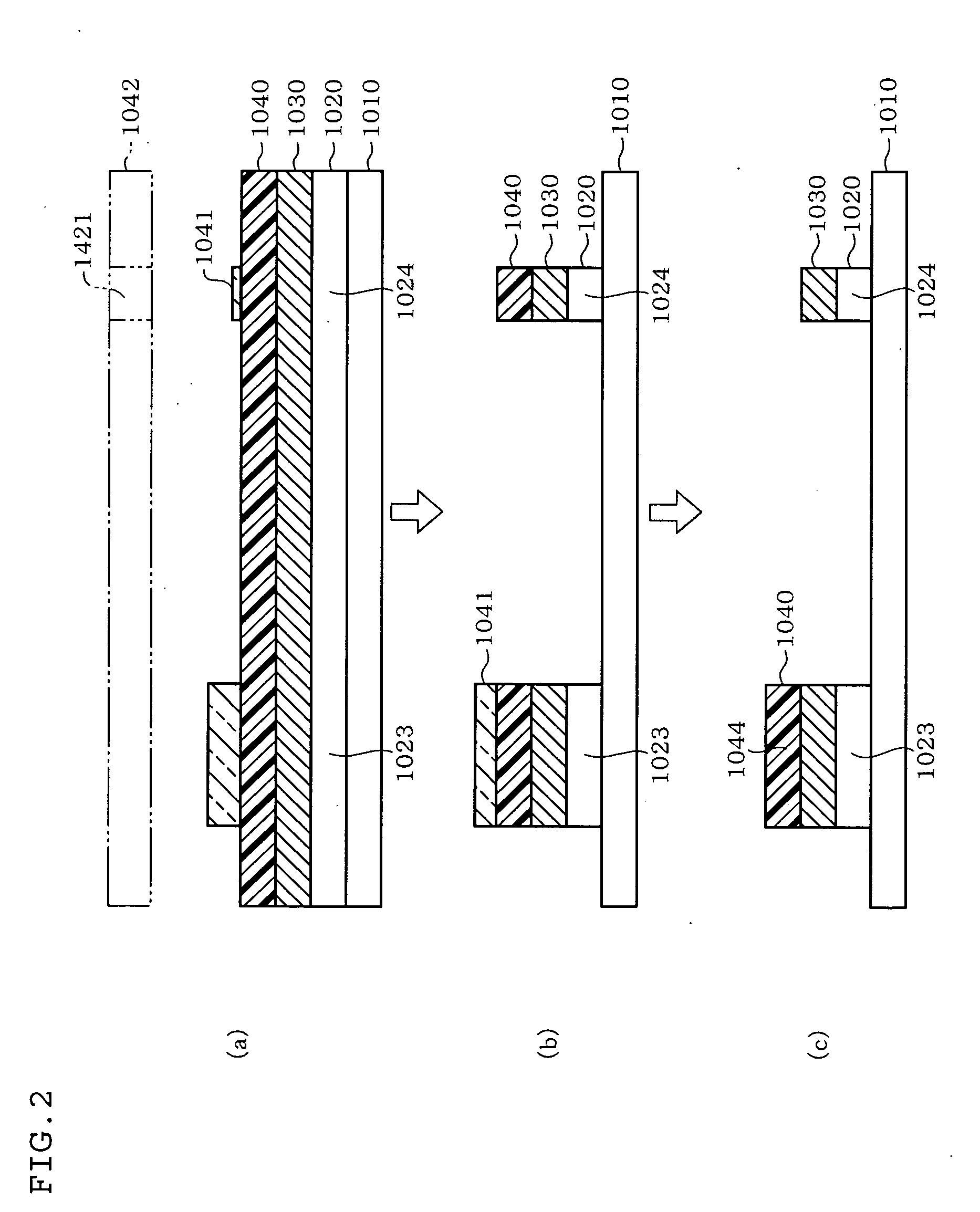

Tft Substrate, Reflective Tft Substrate and Method for Manufacturing These Substrates

InactiveUS20090001374A1Reduce production stepsReduce the number of masksTransistorSolid-state devicesManufacturing cost reductionElectrical conductor

An object of the invention is to propose a TFT substrate and a reflective TFT substrate which can be operated stably for a prolonged period of time, can be prevented from being suffering from crosstalk, and is capable of significantly reducing manufacturing cost by decreasing the number of production steps, as well as to propose the method for producing these substrates.A TFT substrate 1001 comprises: a glass substrate 1010; a gate electrode 1023 and a gate wire 1024 insulated by having their top surfaces covered with a gate insulating film 1030 and by having their side surfaces covered with an interlayer insulating film 1050; an n-type oxide semiconductor layer 1040 formed on the gate insulating film 1030 above the gate electrode 1023; an oxide transparent conductor layer 1060 formed on the n-type oxide semiconductor layer 1040 with a channel part 1044 interposed therebetween; and a channel guard 1500 for protecting the channel part 1044.

Owner:IDEMITSU KOSAN CO LTD

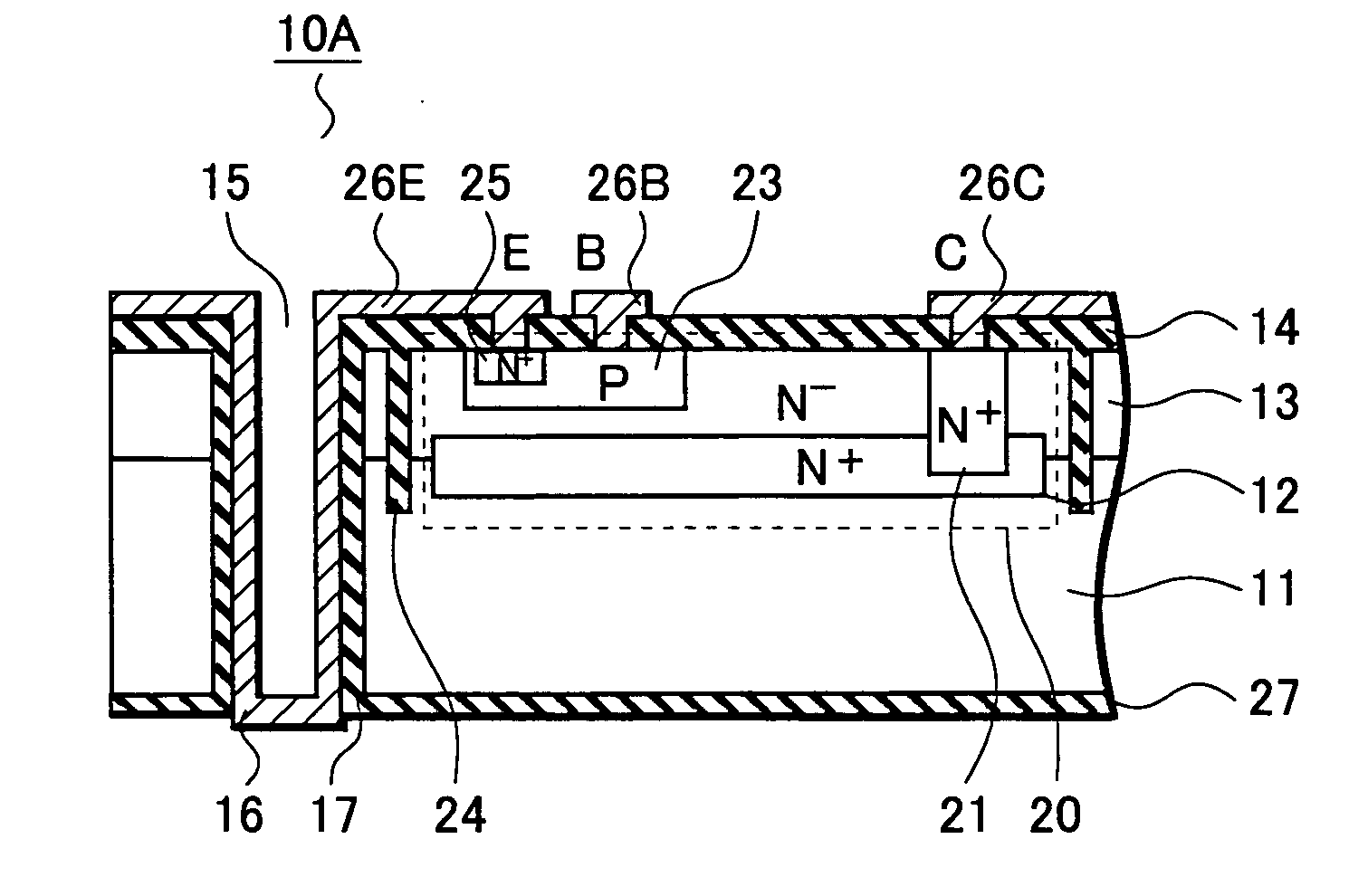

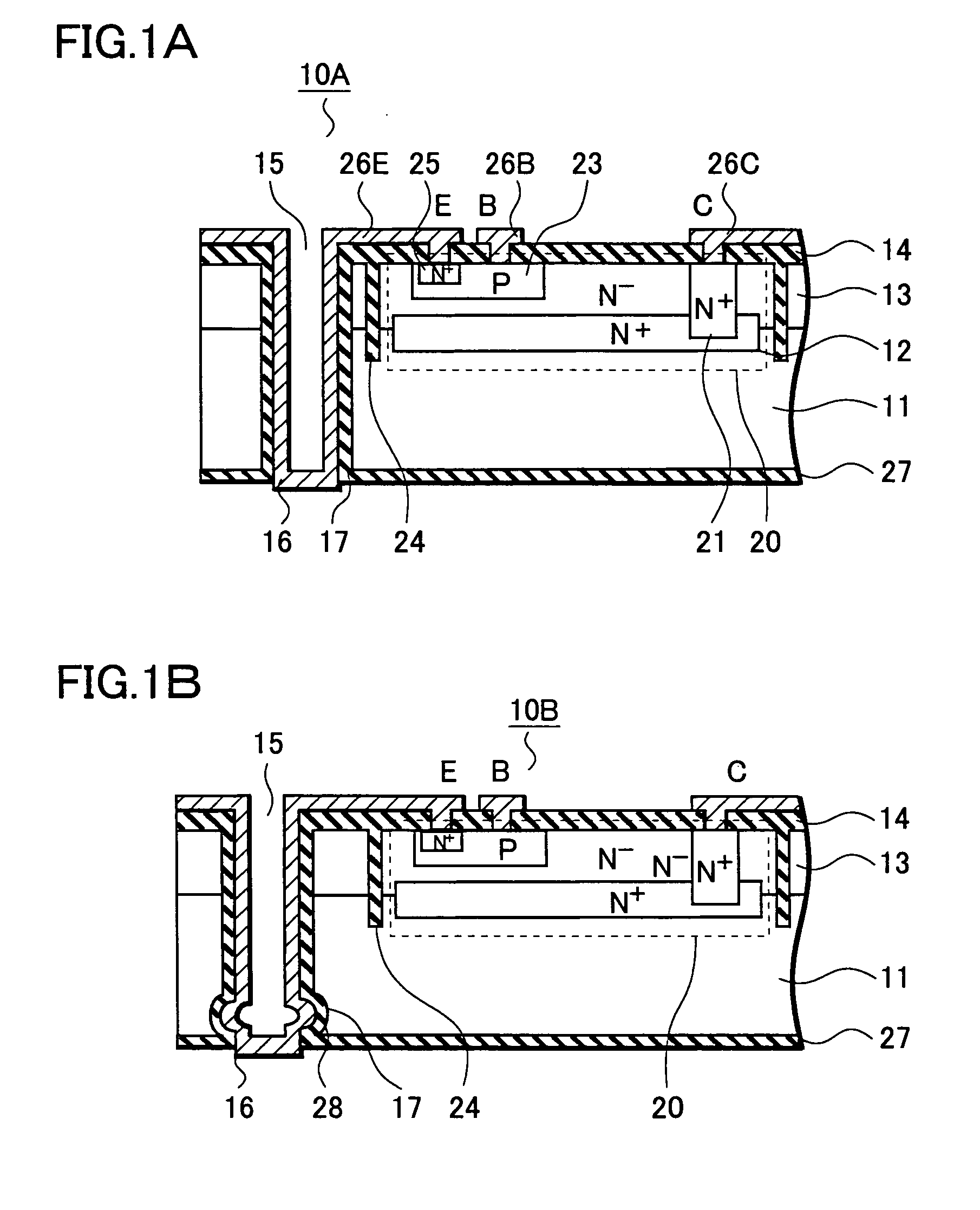

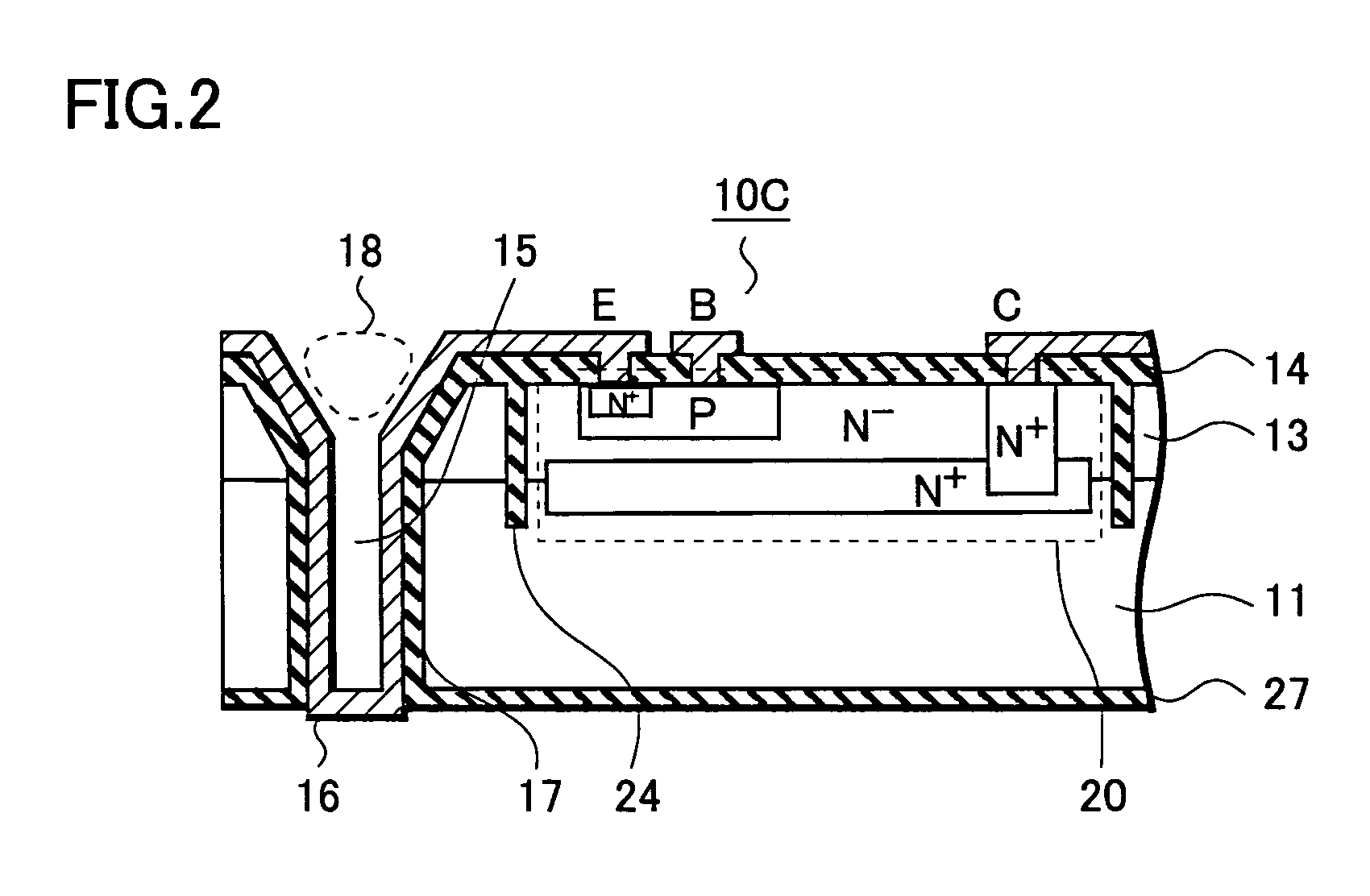

Semiconductor device, method of manufacturing the same, circuit board, and method of manufacturing the same

ActiveUS20070052067A1Improve connection reliabilityTransistorSemiconductor/solid-state device detailsEngineeringOxide

In the semiconductor device of the present invention, an active region is formed in an upper surface of a semiconductor substrate, and is surrounded by a trench filled with an oxide. A through-hole electrode electrically connected to the active region extends from the upper surface of the semiconductor substrate to a lower surface thereof. A bottom end of the through-hole electrode juts out of an insulating film covering the lower surface of the semiconductor substrate. Accordingly, a jutting portion of the through-hole electrode is embedded in the bonding material when the semiconductor device is mounted on a mounting board, and thus the connection reliability therebetween is improved.

Owner:SEMICON COMPONENTS IND LLC

Connection member, method of manufacturing the same and connection structure

InactiveUS20120156926A1Easy to implementReduce in quantityLine/current collector detailsCarpetsBand shapeElectrical and Electronics engineering

Owner:TOYOTA BOSHOKU KK

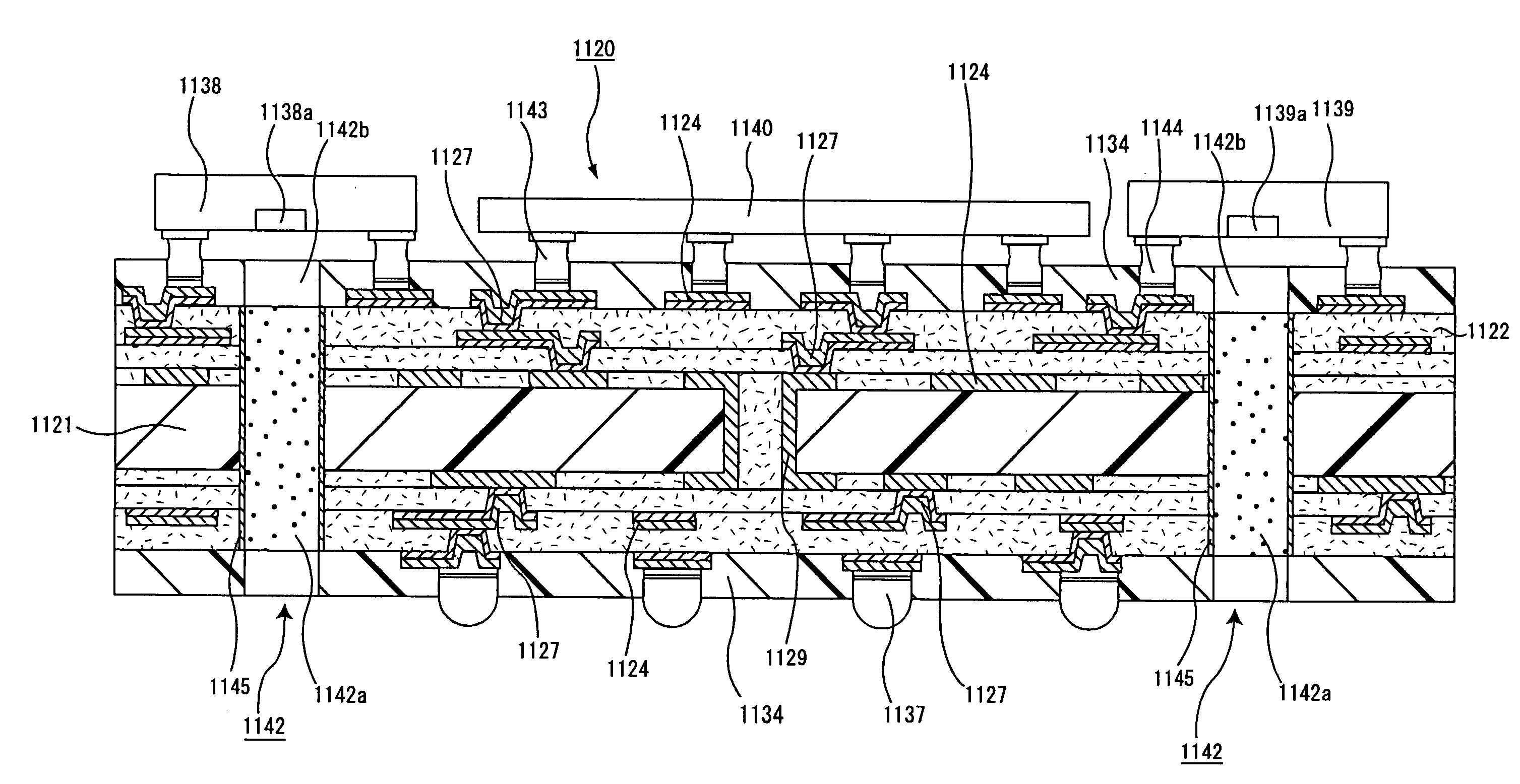

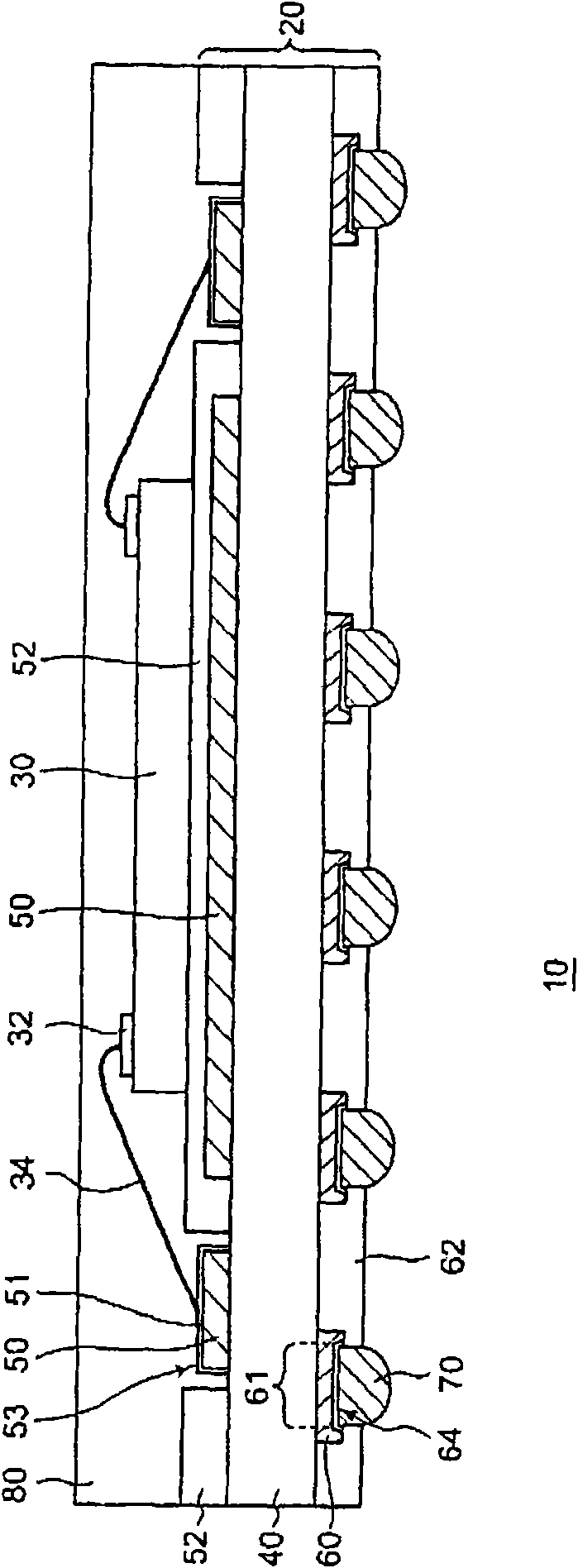

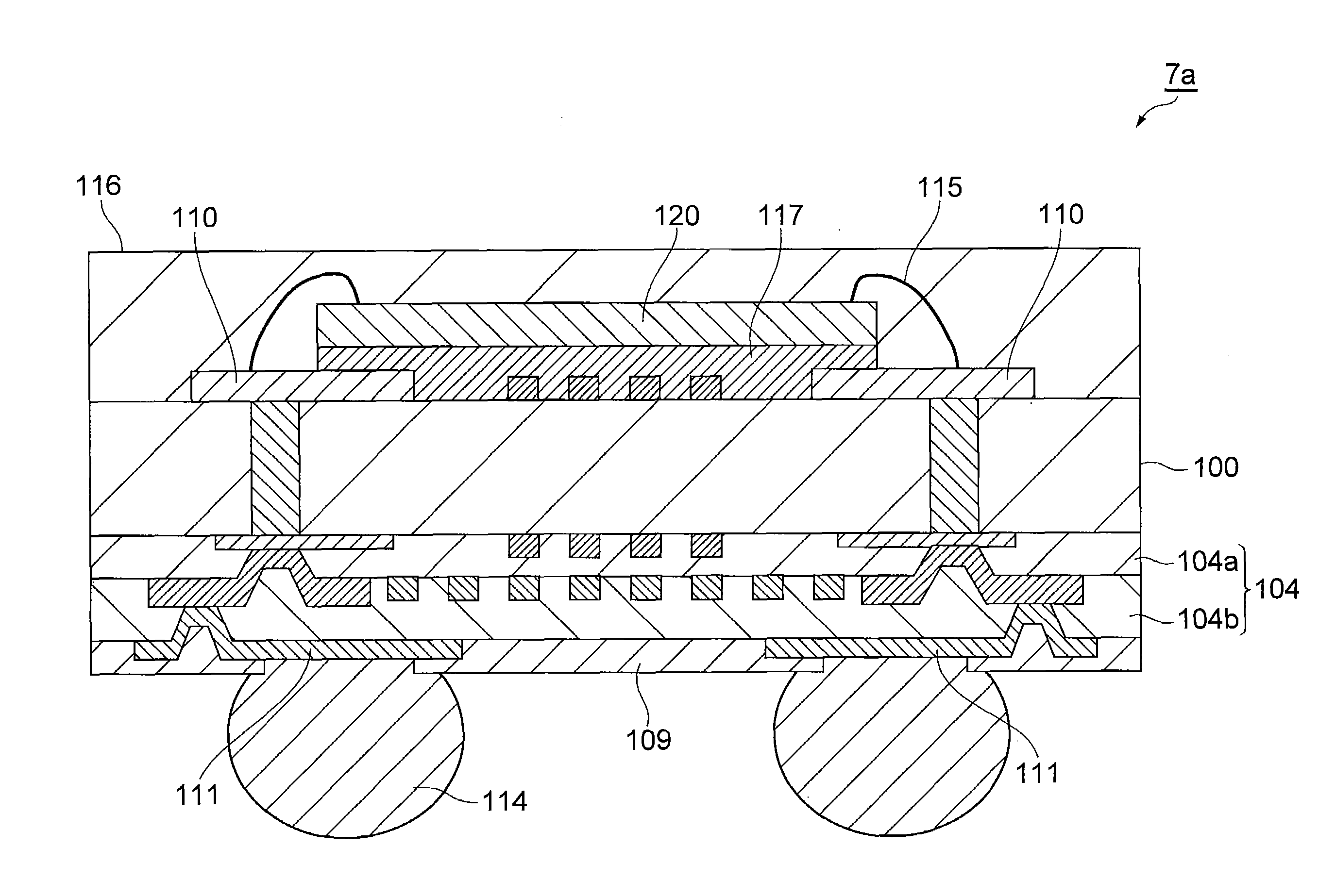

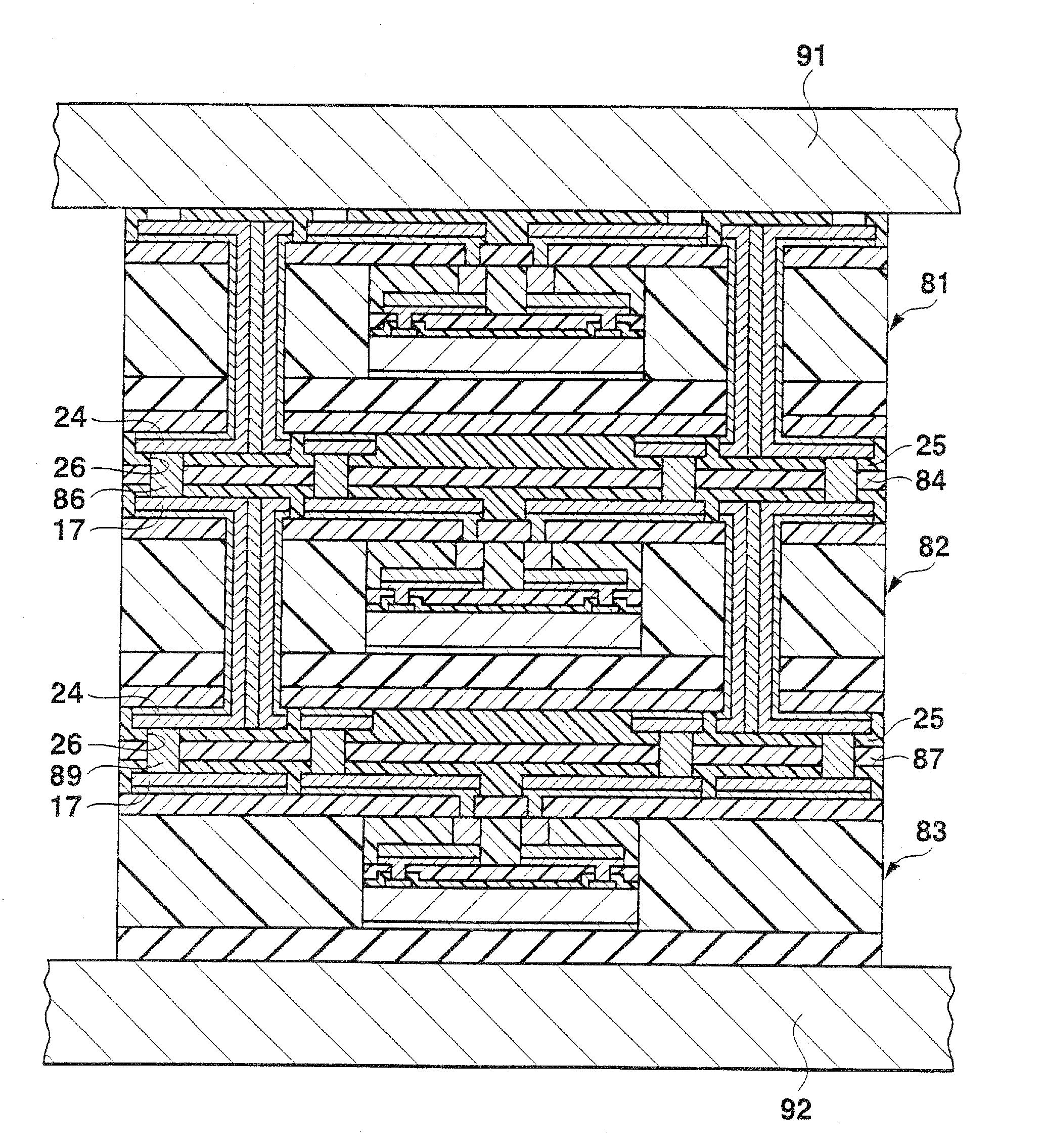

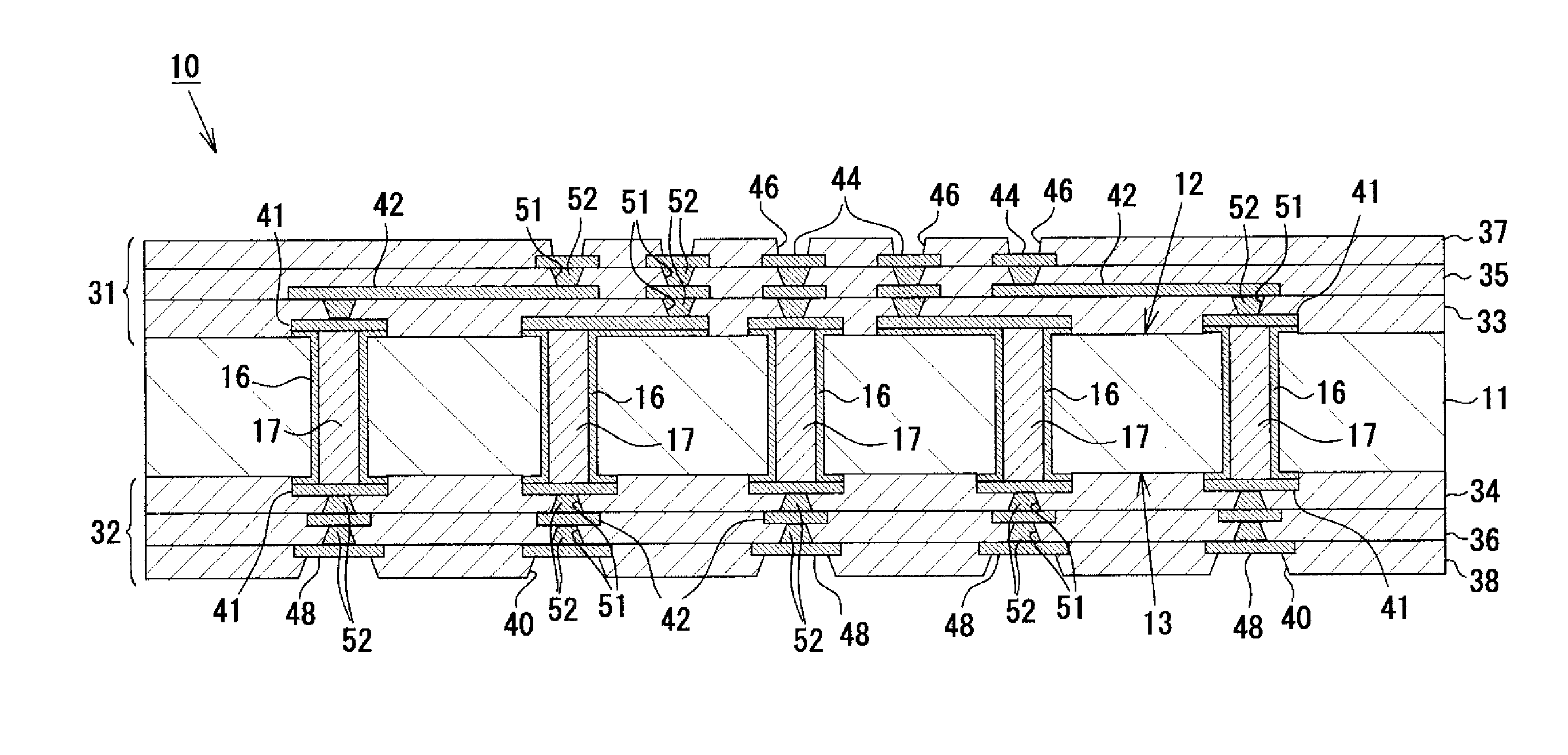

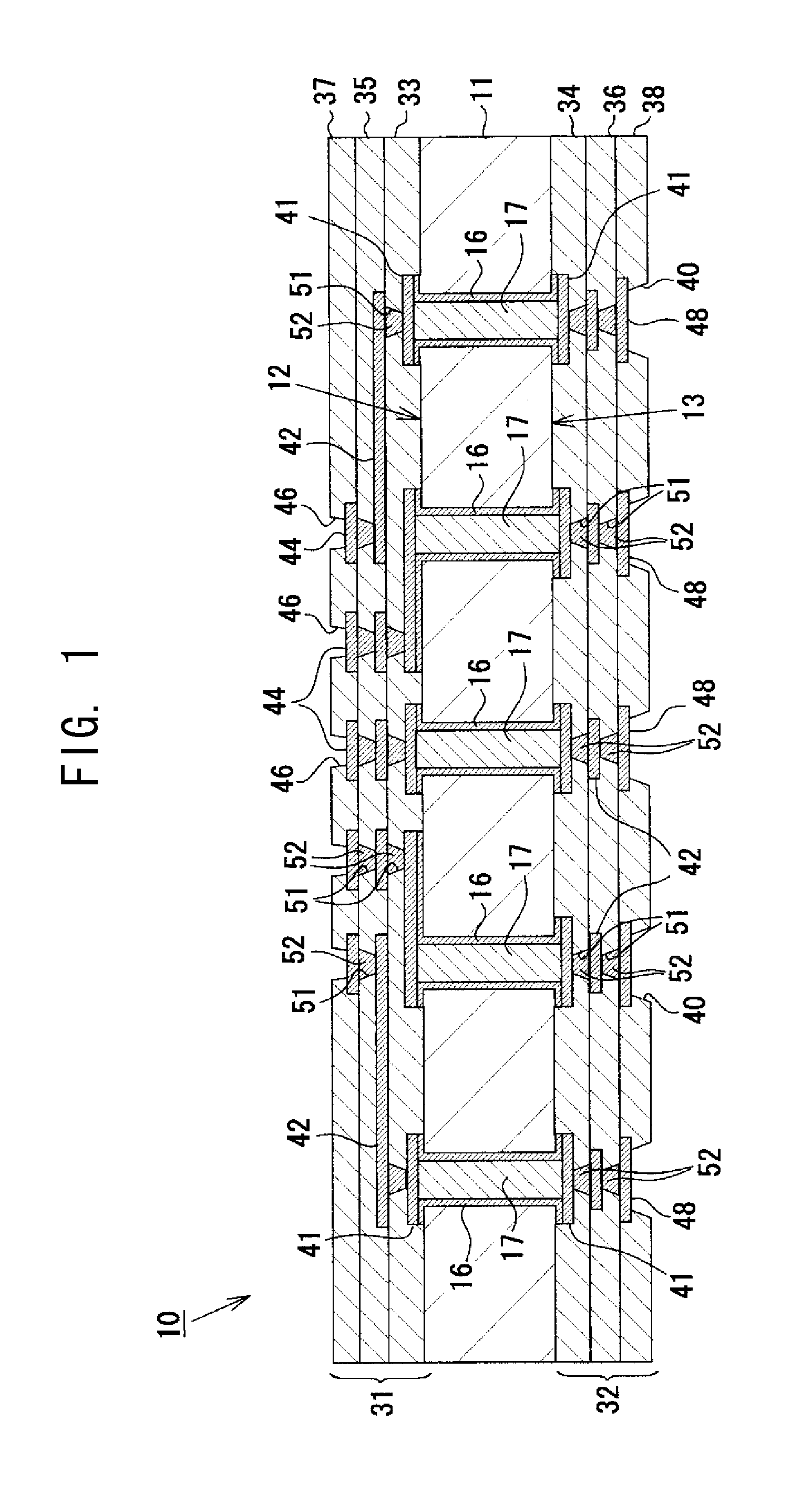

Semiconductor package including connected upper and lower interconnections, and manufacturing method thereof

InactiveUS20080166836A1Improve connection reliabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package includes a base plate, at least one semiconductor constructing body which is formed on one surface of the base plate and has a plurality of external connection electrodes formed on a semiconductor substrate, an insulating layer which is formed on one surface of the base plate around the semiconductor constructing body, upper interconnections which are formed on the insulating layer and each includes at least one interconnection layer, at least some of the upper interconnections are connected to the external connection electrodes of the semiconductor constructing body, lower interconnections which are formed on the other surface of the base plate and each includes at least one interconnection layer, and at least some of the lower interconnections which are electrically connected to the upper interconnections.

Owner:CMK +1

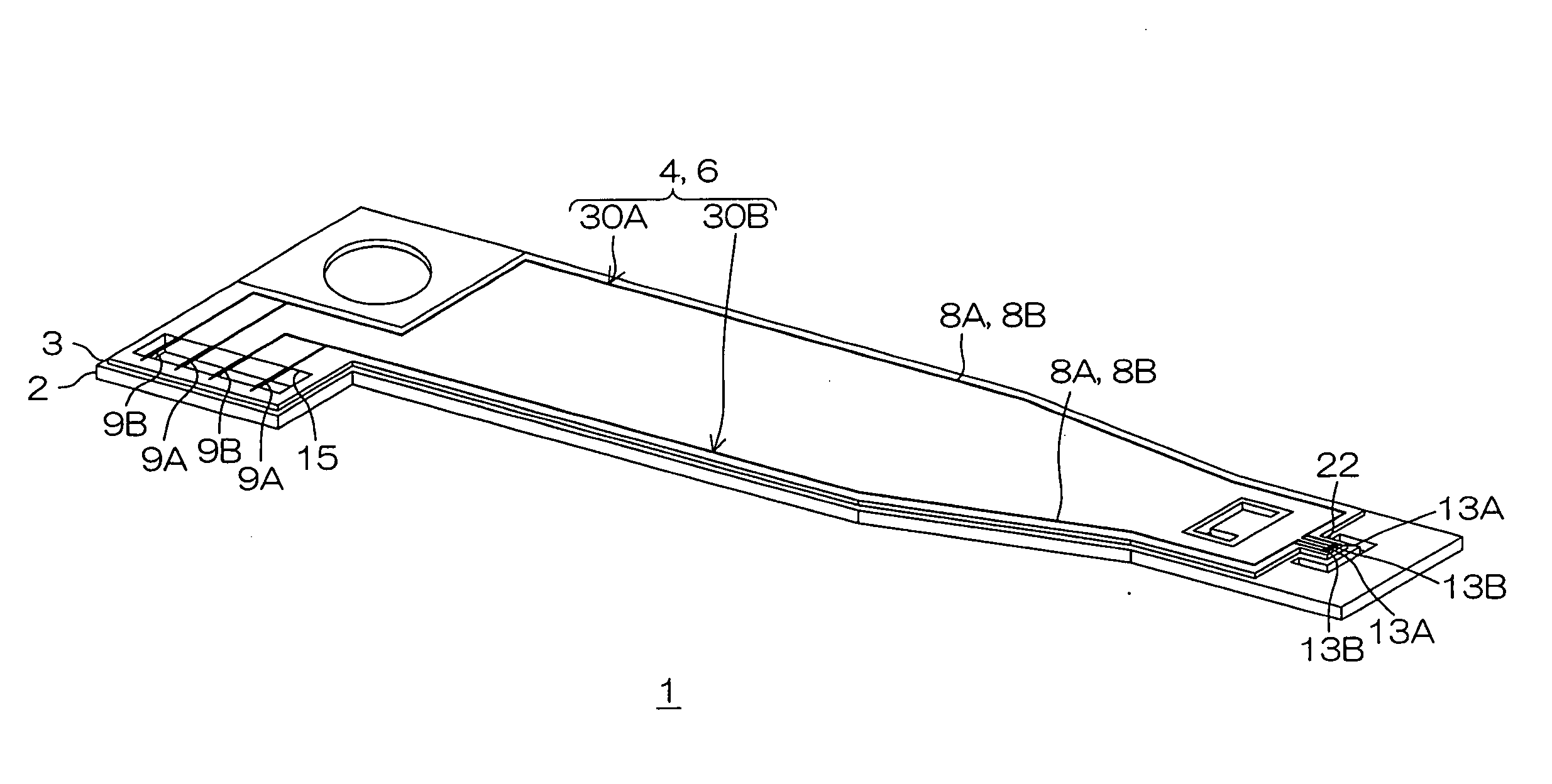

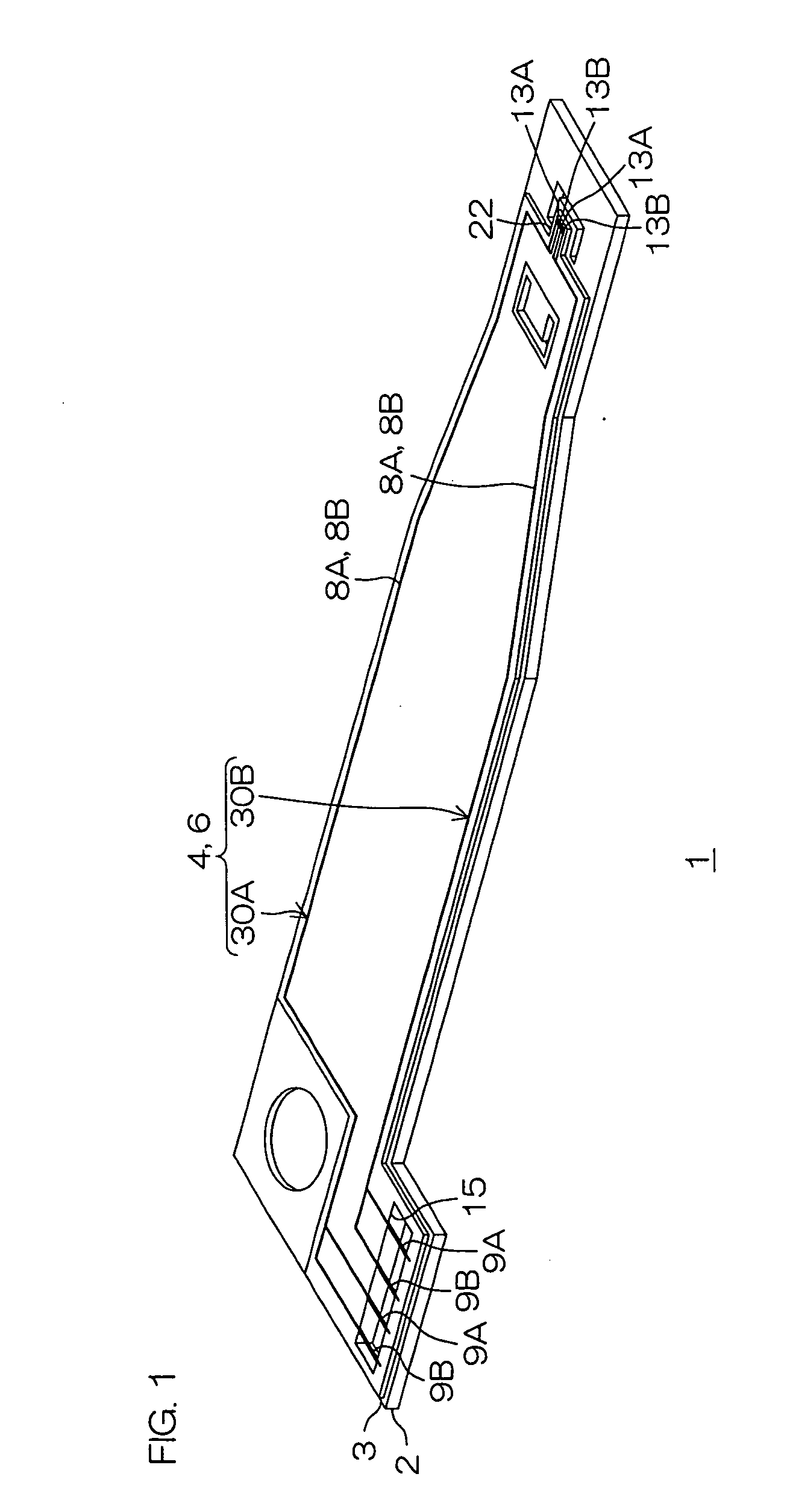

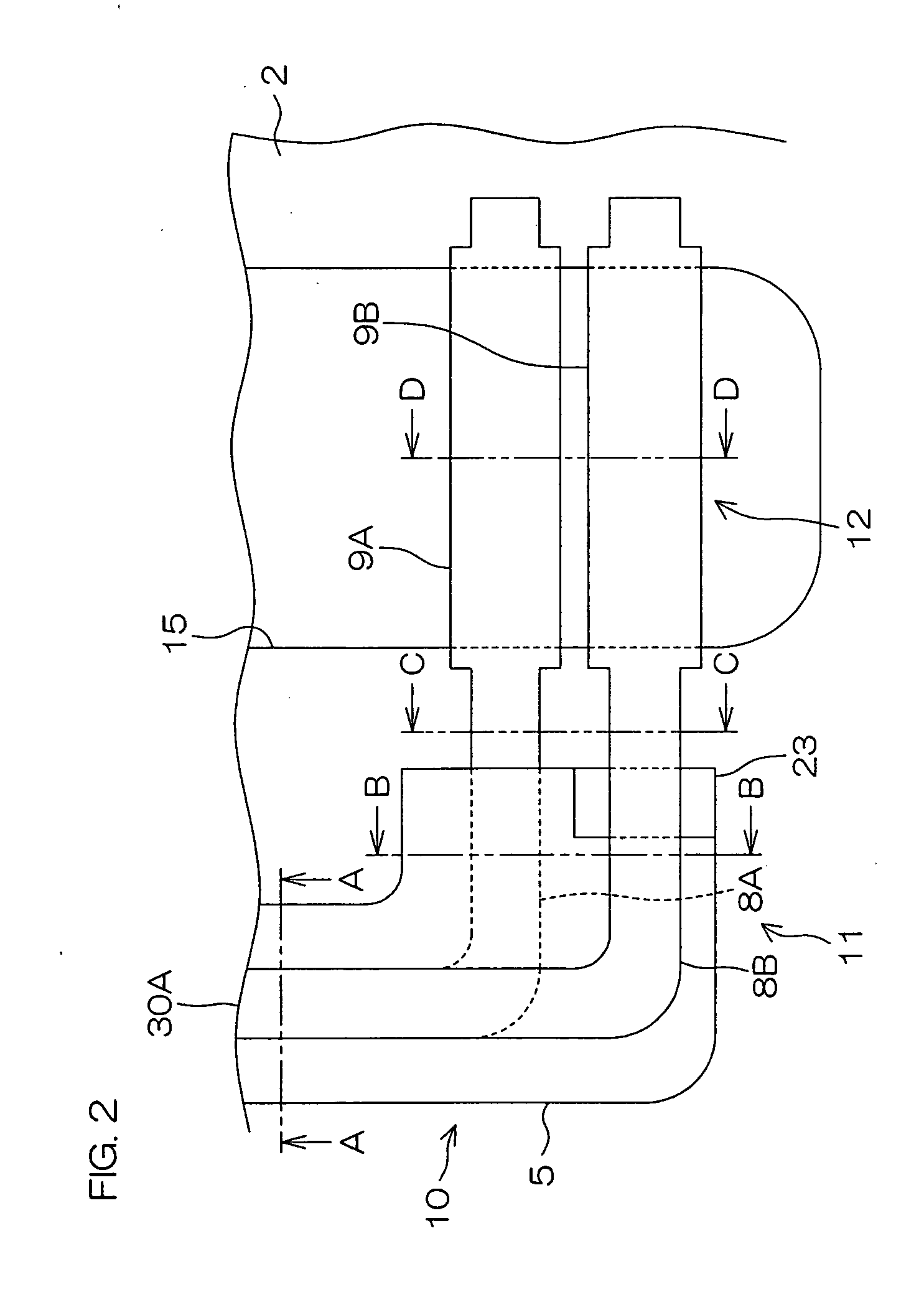

Wired circuit board

InactiveUS20090151994A1Firmly connectedImpedance stabilityElectrically conductive connectionsPrinted circuit aspectsPrinted circuit board

A wired circuit board includes a wiring formation portion, a terminal formation portion, and a middle portion formed therebetween. The wiring formation portion includes a first conductive layer formed on a first insulating layer, and a second conductive layer formed on a second insulating layer so as to overlap the first conductive layer in a thickness direction. The terminal formation portion includes the first and second conductive layers formed in parallel in the same plane. The middle portion includes the first conductive layer formed on the first insulating layer, and the second conductive layer formed on a portion of the second insulating layer extending from the wiring formation portion to a mid-point between the wiring formation portion and the terminal formation portion, and formed on a portion of the first insulating layer extending from the mid-point to the terminal formation portion.

Owner:NITTO DENKO CORP

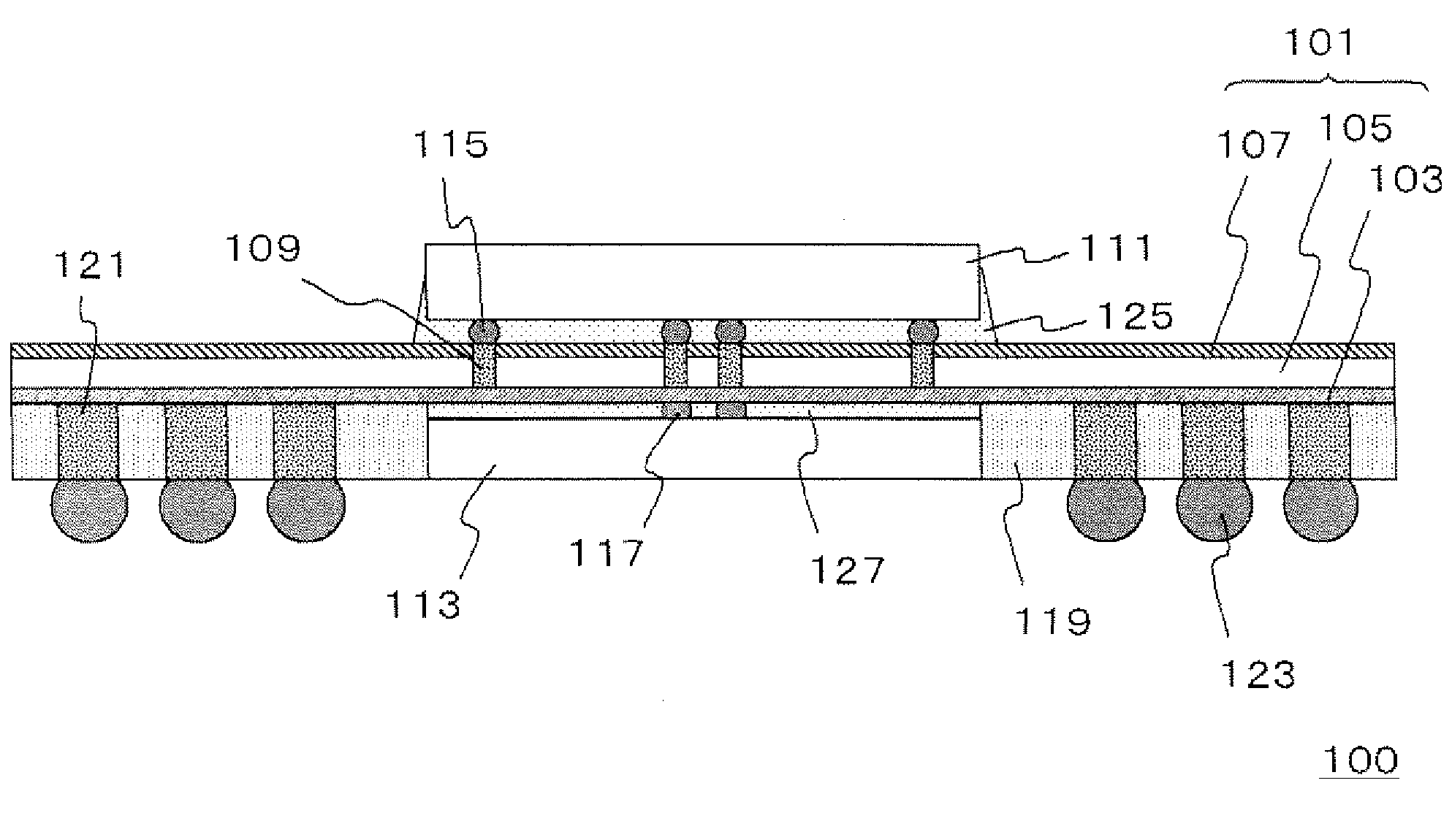

Semiconductor device having a sealing resin and method of manufacturing the same

InactiveUS20080265434A1Improve connection reliabilityHigh densitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSilicon

The semiconductor device 100 comprises a first semiconductor element 113 provided on a face on one side of a flat plate shaped interconnect component 101, an insulating resin 119 covering a face of a side where the first semiconductor element 113 of the interconnect component 101 is provided and a side face of the first semiconductor element 113, and a second semiconductor element 111 provided on a face on the other side of the interconnect component 101. The interconnect component 101 has a constitution where an interconnect layer 103, a silicon layer 105 and an insulating film 107 are sequentially formed. The interconnect layer 103 has a constitution where the interconnect layer 103 has a flat plate shaped insulating component and a conductive component extending through the insulating component. The first semiconductor element 113 is electrically connected with the second semiconductor element 111 through the conductive component.

Owner:RENESAS ELECTRONICS CORP

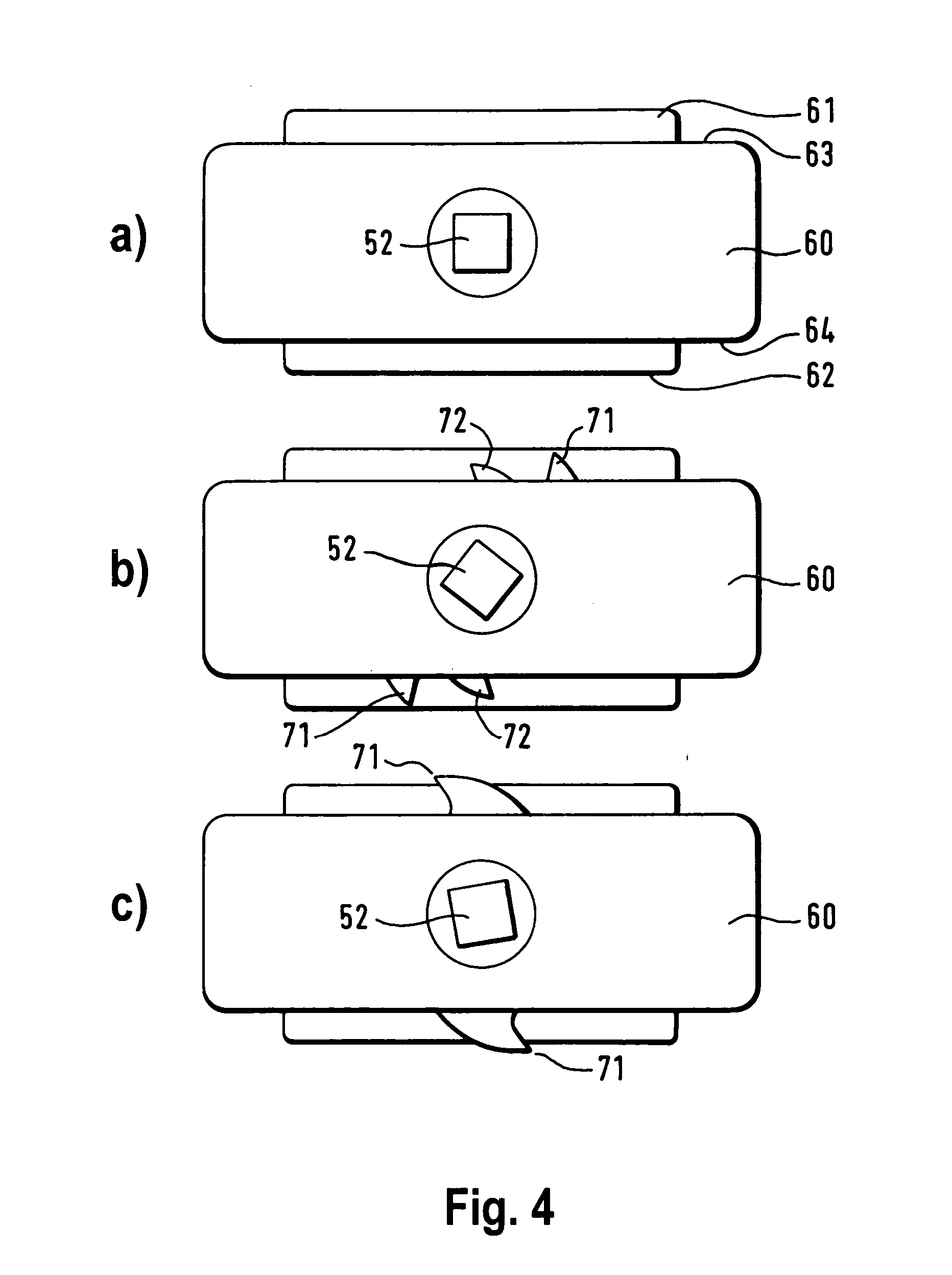

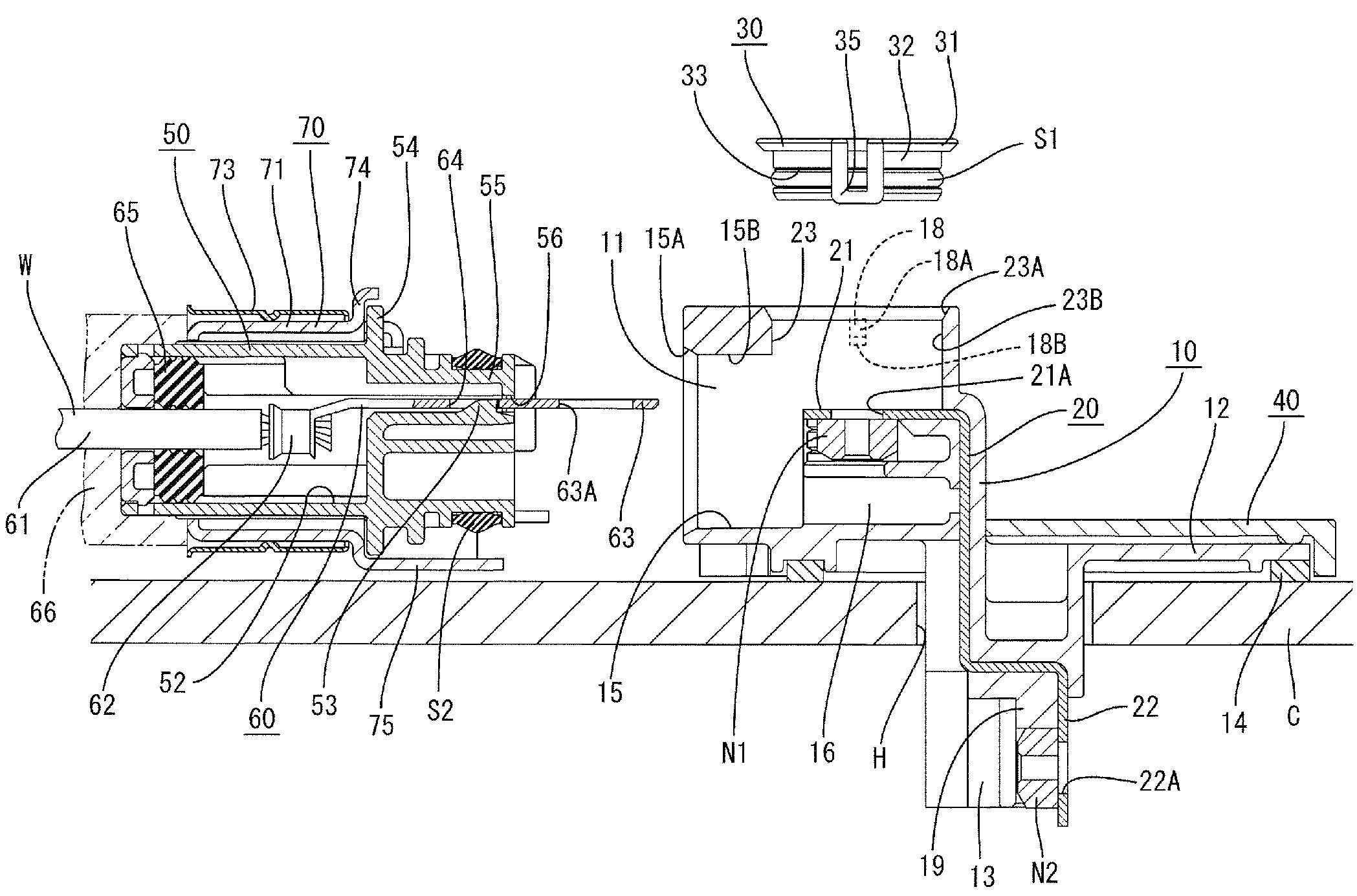

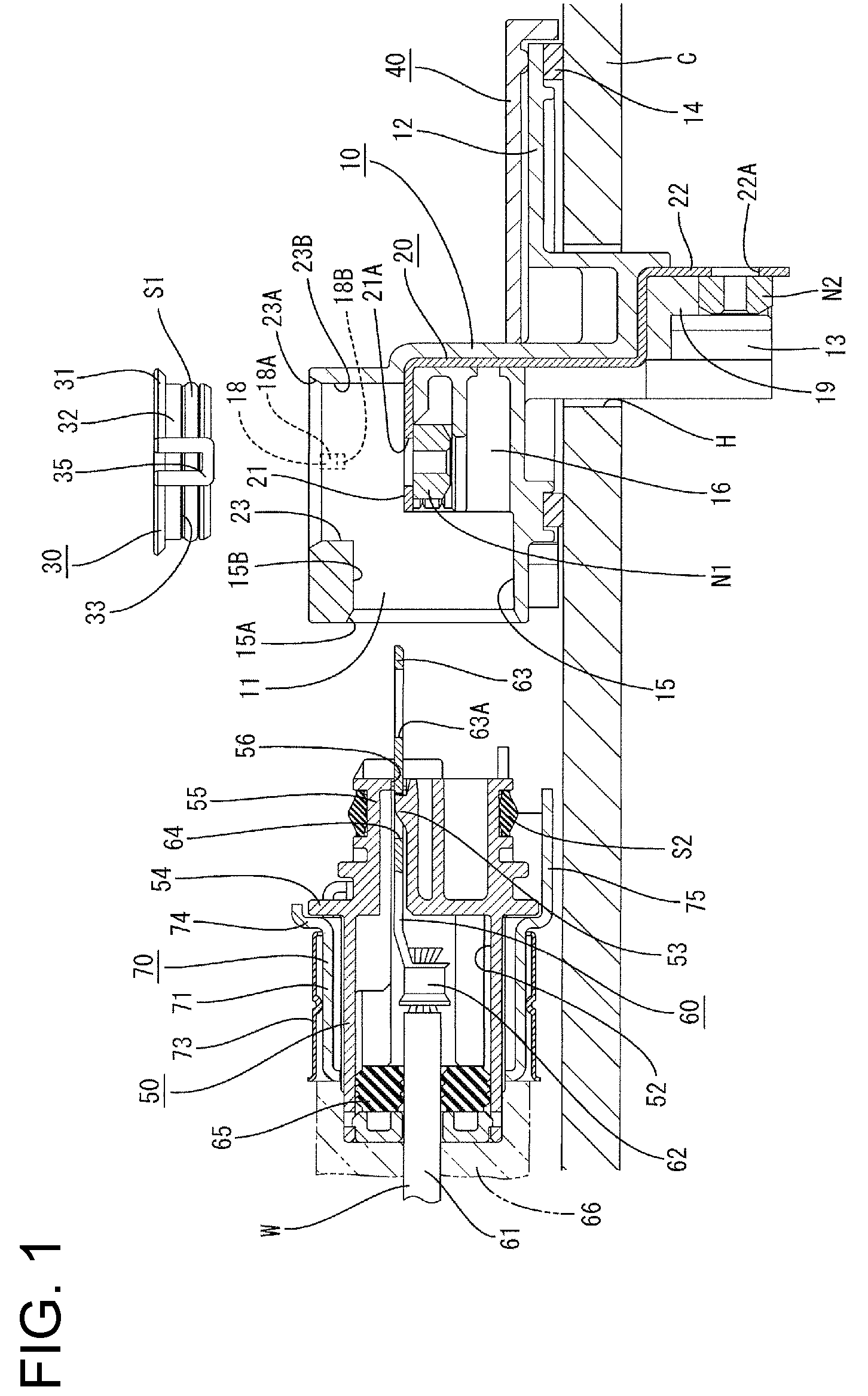

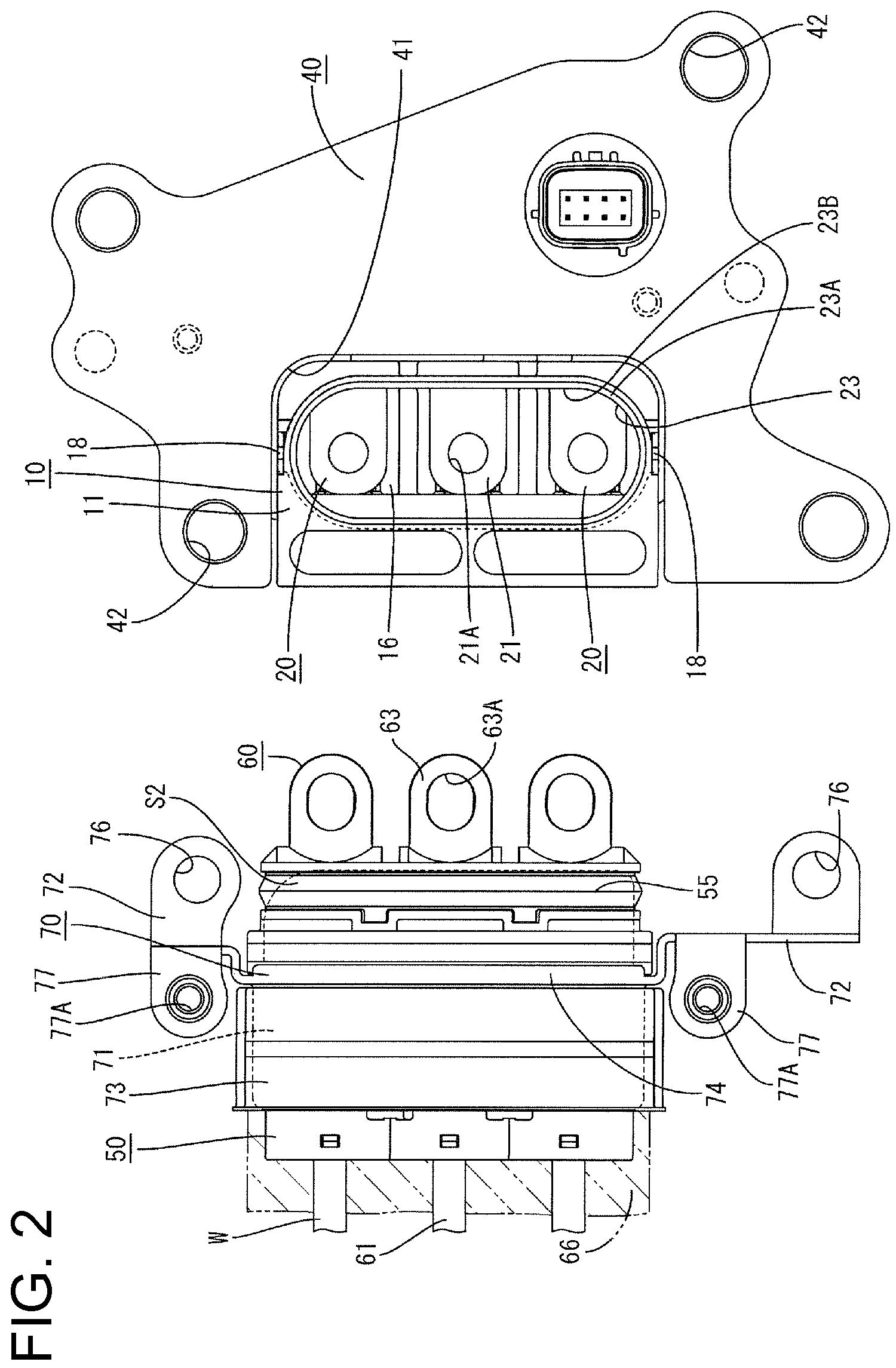

Device connector with mating terminals bolted together

ActiveUS7572150B2Improve connection reliabilityAvoid displacementVehicle connectorsCouplings bases/casesMatingEngineering

A device connector to be connected with device-side terminals accommodated in a metal case (C) is provided with a first housing (10) for holding first terminals (20) connectable with the device-side terminals by bolt tightening and a second housing (50) connectable with the first housing (10) and adapted to hold second terminals (60) fixed to ends of wires (61). Connecting portions (21, 63) of the first and second terminals (20, 60) are arranged one over the other in a fitting (11) to the second housing (50) and are respectively formed with bolt insertion holes (21A, 63A). The fitting (11) is formed with an operation hole (23) used for bolt tightening operations for the connecting portions (21, 63).

Owner:SUMITOMO WIRING SYST LTD

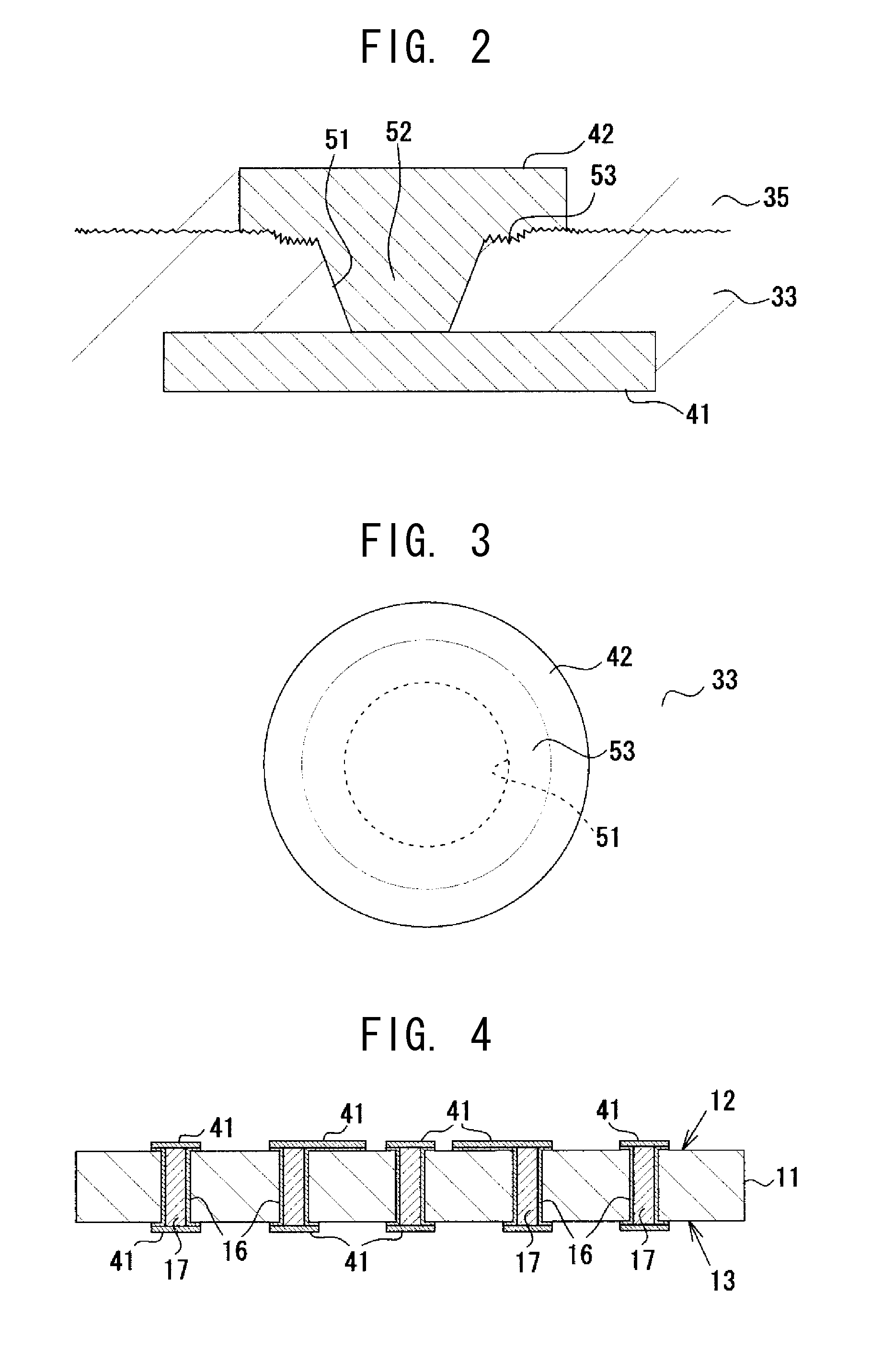

Multilayer wiring substrate and method of manufacturing the same

InactiveUS20120153463A1Avoid layeringDistribute pressureSemiconductor/solid-state device detailsPrinted circuit aspectsRough surfaceInsulation layer

To provide a multilayer wiring substrate in which the connection reliability of via conductors is enhanced, via holes are formed in a resin interlayer insulation layer which isolates a lower conductor layer from an upper conductor layer, and via conductors are formed in the via holes for connecting the lower conductor layer and the upper conductor layer. The surface of the resin interlayer insulation layer is a rough surface, and the via holes open at the rough surface of the resin interlayer insulation layer. Stepped portions are formed in opening verge regions around the via holes such that the stepped portions are recessed from peripheral regions around the opening verge regions. The stepped portions are higher in surface roughness than the peripheral regions.

Owner:NGK SPARK PLUG CO LTD

Multilayered circuit board and semiconductor device

InactiveUS8227703B2Avoid deformationImprove connection reliabilityPrinted electric component incorporationSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multilayered circuit board of the present invention has a single-side laminated structure and does not include a core substrate having via-holes formed therethrough and vias for providing electrical connection through the via-holes. The multilayered circuit board includes a plurality of pairs of layers, each pair including a conductor circuit layer and an insulator layer, wherein a glass transition temperature of each insulator layer is 170° C. or higher, a coefficient of thermal expansion at the glass transition temperature or lower of each insulator layer is 35 ppm or less, and a modulus of elasticity of each insulator layer is 5 GPa or more.

Owner:SUMITOMO BAKELITE CO LTD

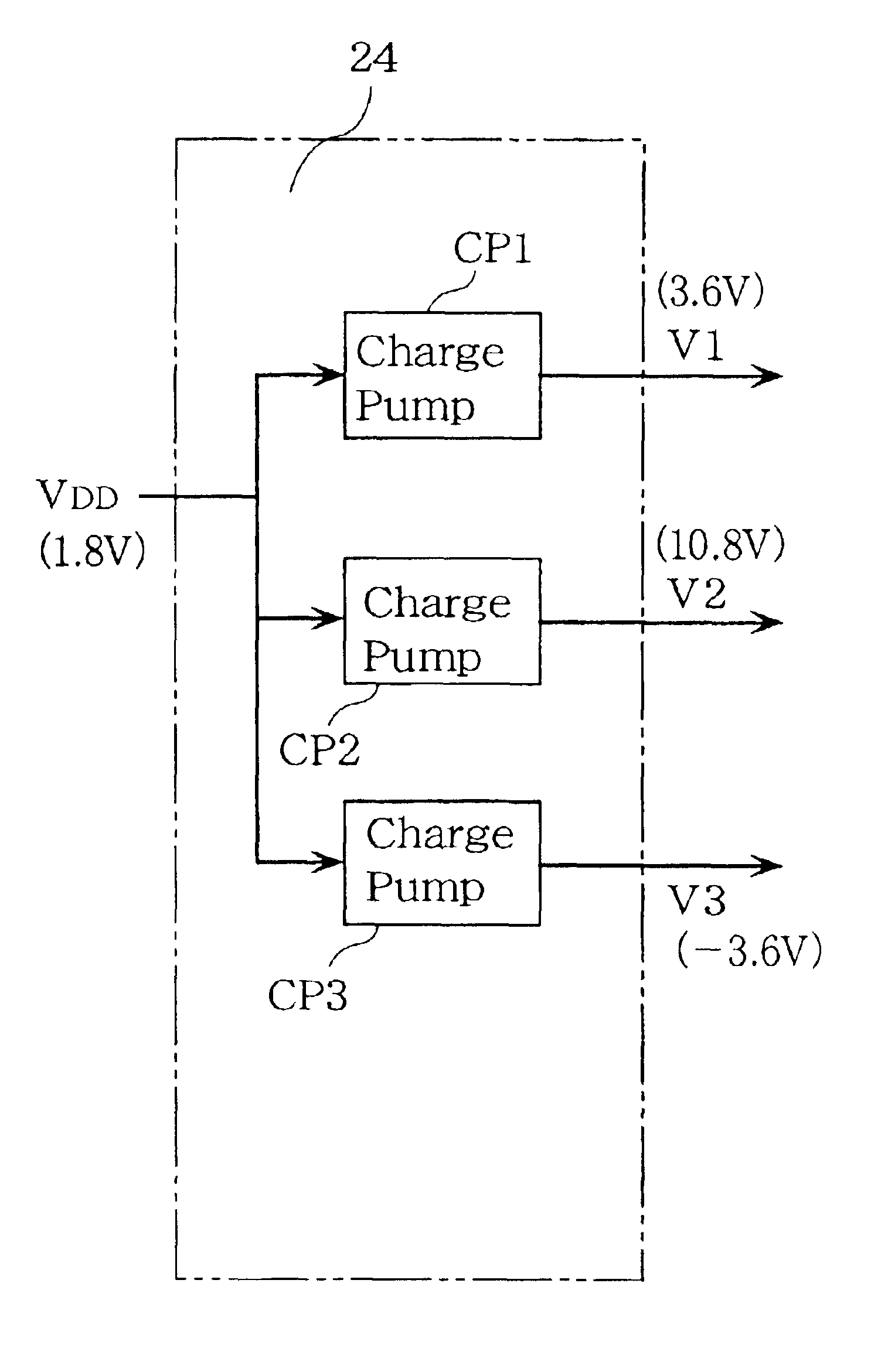

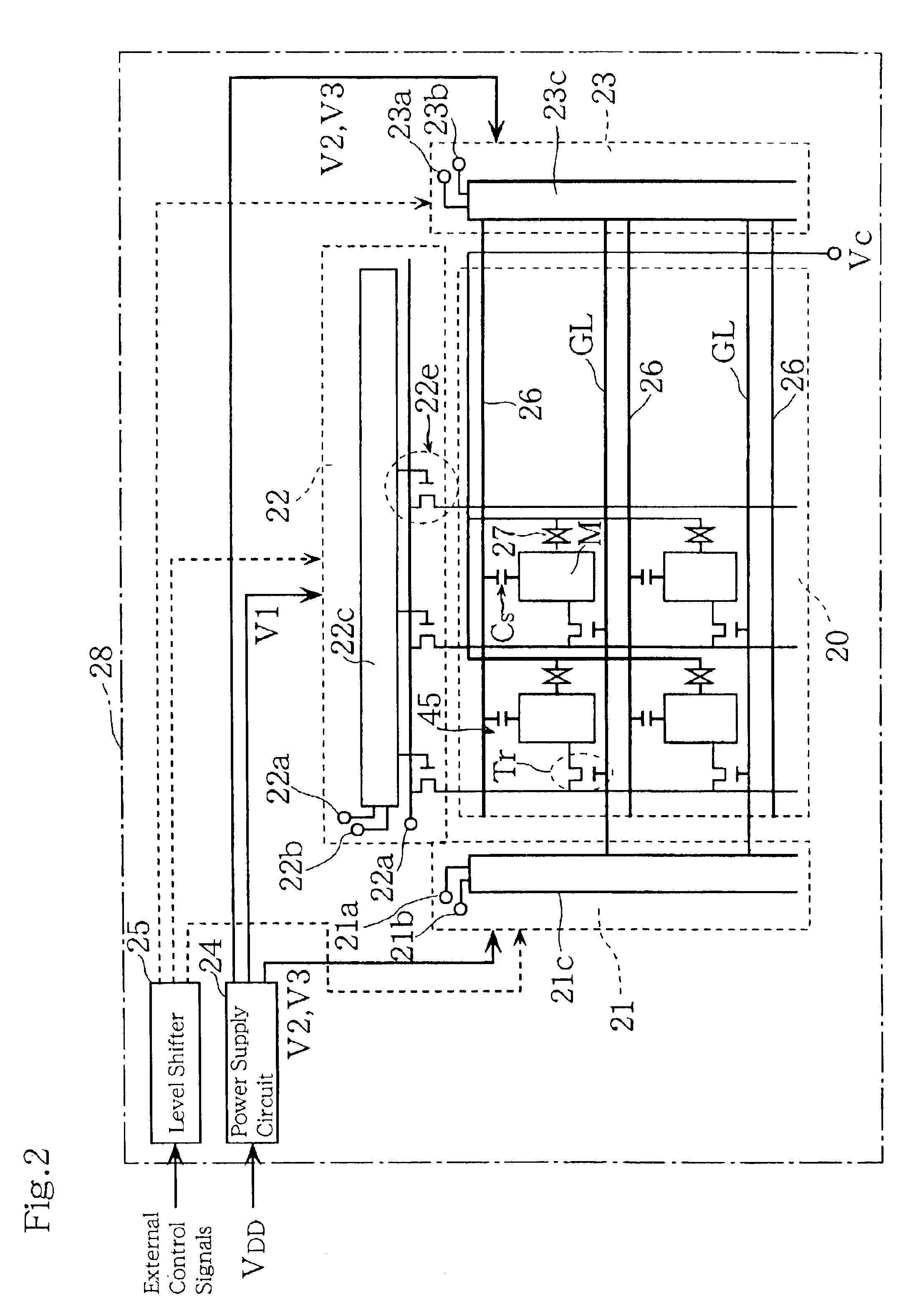

Display device

InactiveUS6909413B2Reduce weightReduce thicknessPower managementCurrent supply arrangementsDriver circuitLiquid-crystal display

The present invention provides a liquid crystal display device having a liquid crystal display portion, a gate driver circuit, a source driver circuit, and a power supply circuit, where the liquid crystal display portion includes unit pixels with pixel switching elements and pixel electrodes arranged in a matrix. The pixel switching elements are thin film transistors that are made of polycrystalline silicon semiconductor formed on an insulating substrate. The power supply circuit is a charge pump-type power supply circuit, is made of a polycrystalline silicon semiconductor, and is a built-in circuit integrally formed on an insulating substrate. With such a configuration, a liquid crystal display device that greatly reduces power consumption is realized.

Owner:JAPAN DISPLAY CENT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com