Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

17227 results about "Semiconductor chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor chip: A semiconductor device that can achieve certain functions by etching and wiring on a semiconductor chip. Not only silicon chips, but also common semiconductor materials such as gallium arsenide (gallium arsenide is poisonous, and some inferior circuit boards should not be curiously decomposed) and germanium.

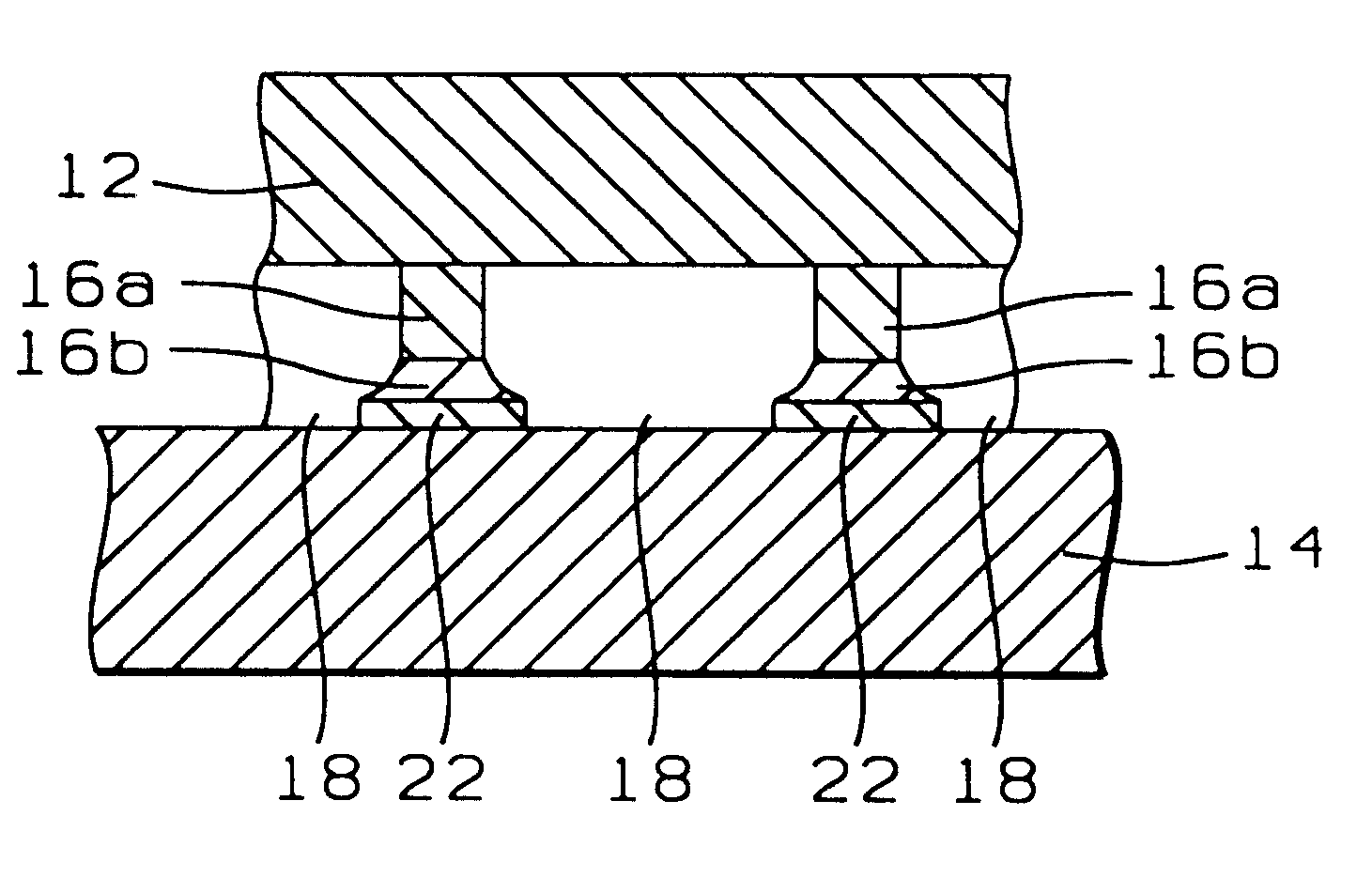

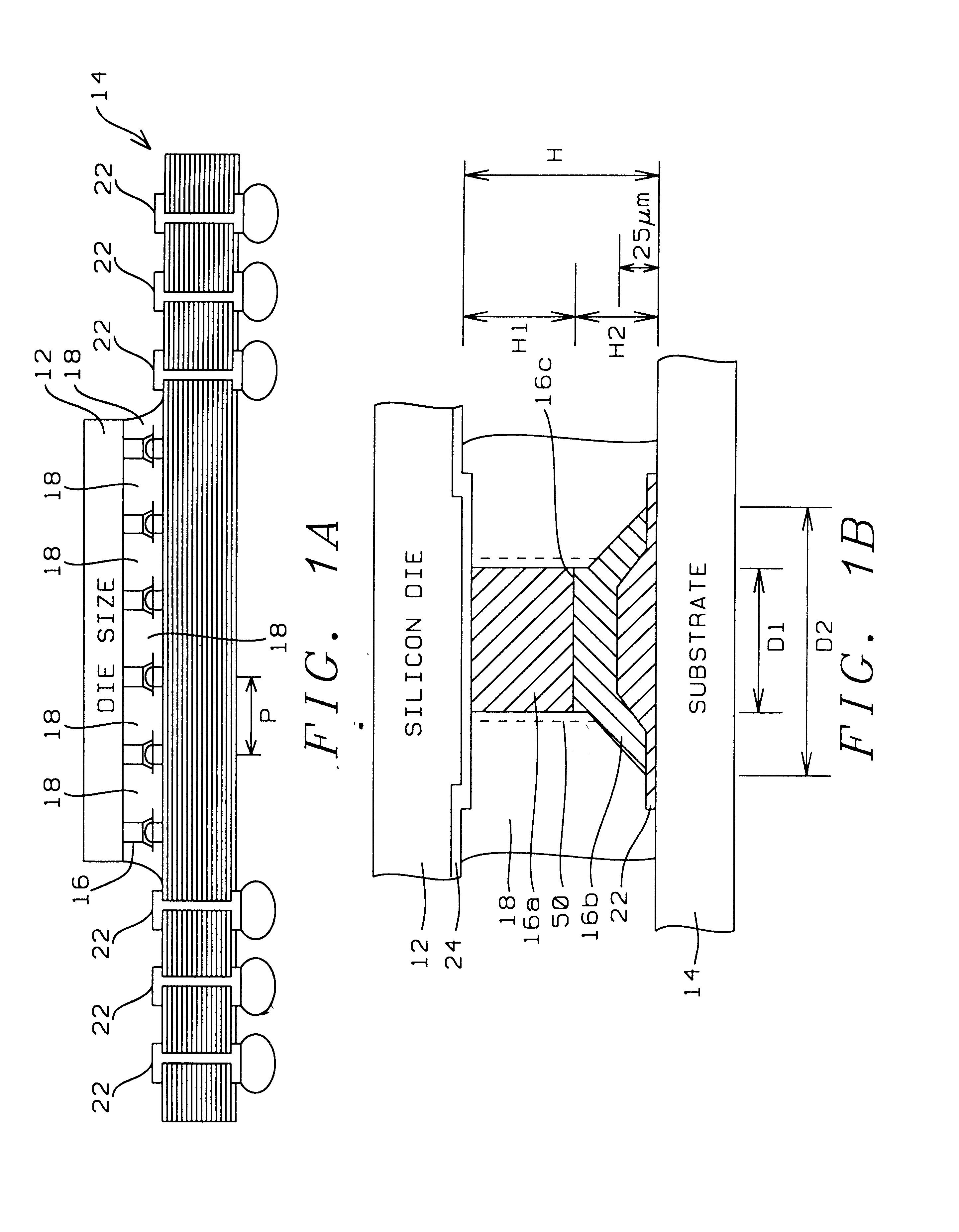

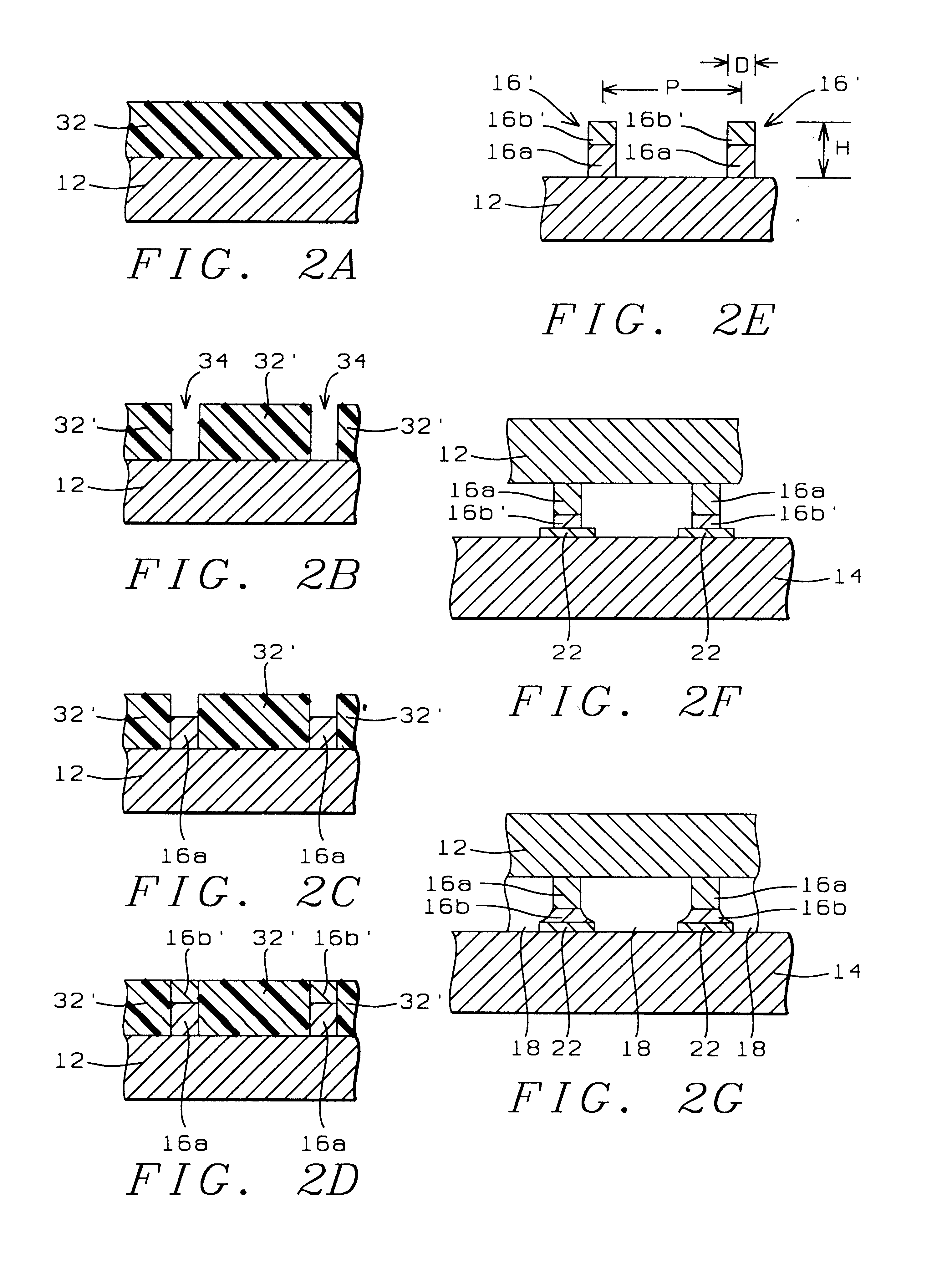

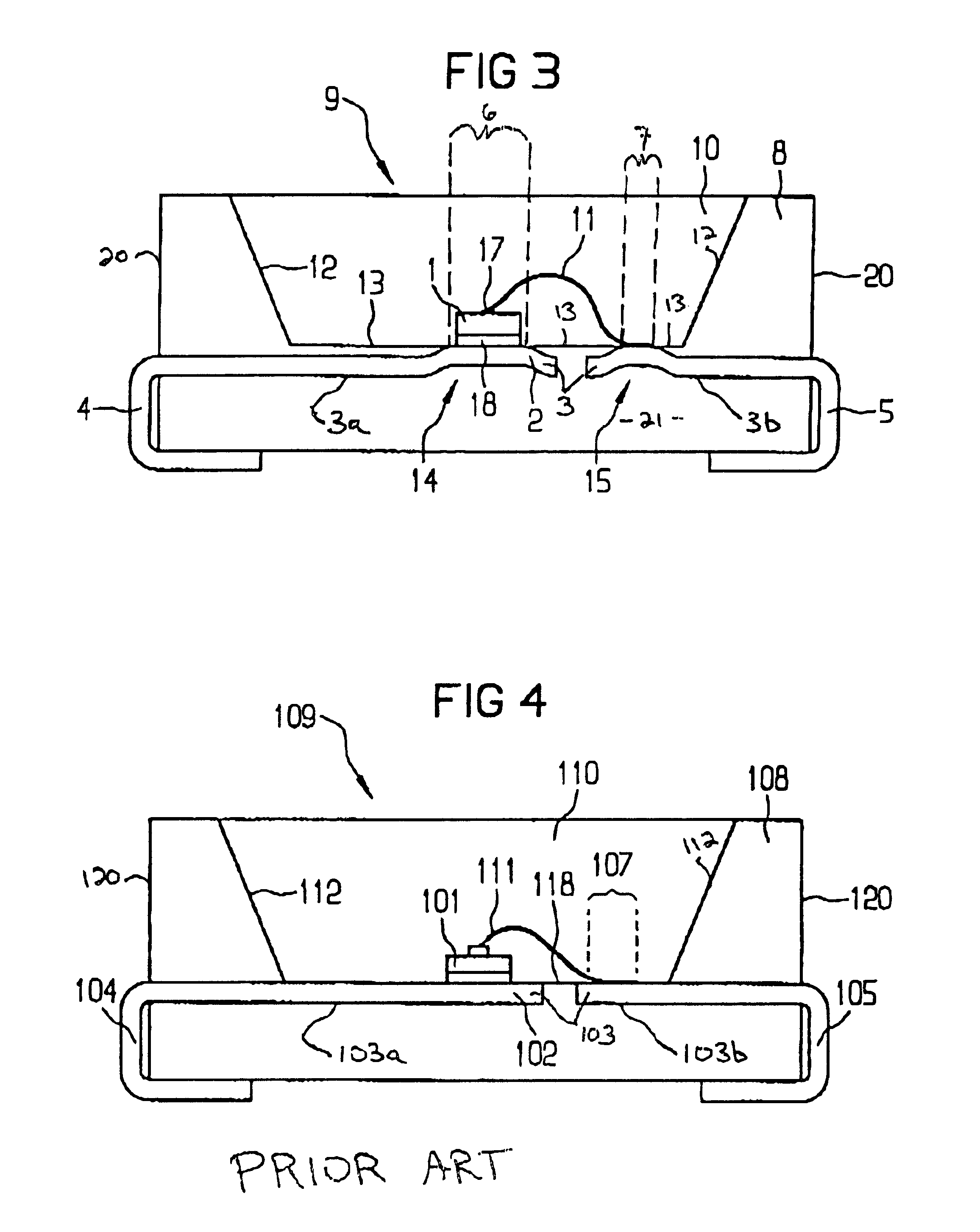

Pillar connections for semiconductor chips and method of manufacture

InactiveUS6578754B1Reduce chanceInduced in connectionSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor chip

A flip chip interconnect system comprises and elongated pillar comprising two elongated portions, one portion including copper and another portion including solder. The portion including copper is in contact with the semiconductor chip and has a length preferably of more than 55 microns to reduce the effect of .alpha. particles from the solder from affecting electronic devices on the chip. The total length of the pillar is preferably in the range of 80 to 120 microns.

Owner:ADVANPAK SOLUTIONS PTE

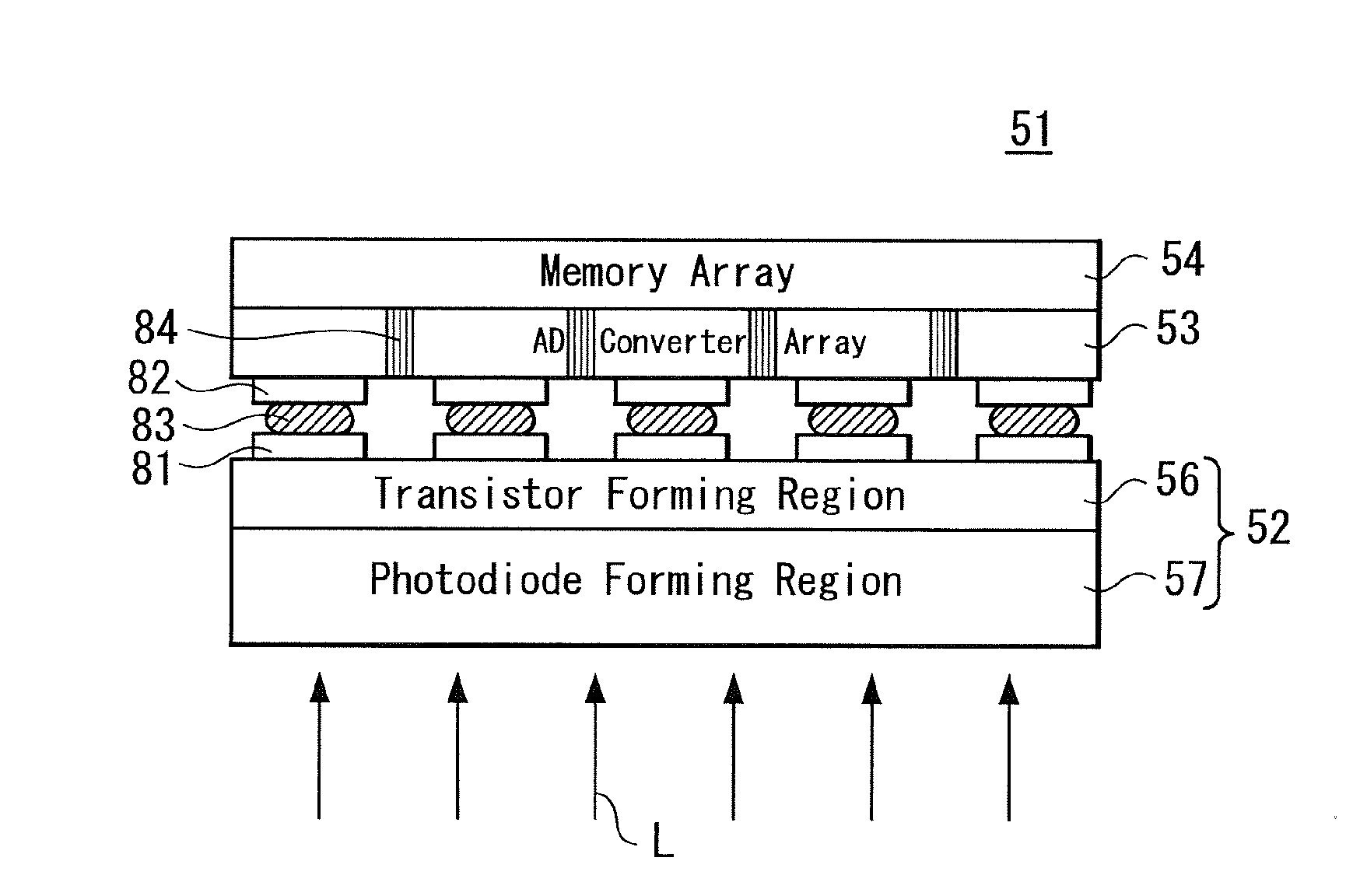

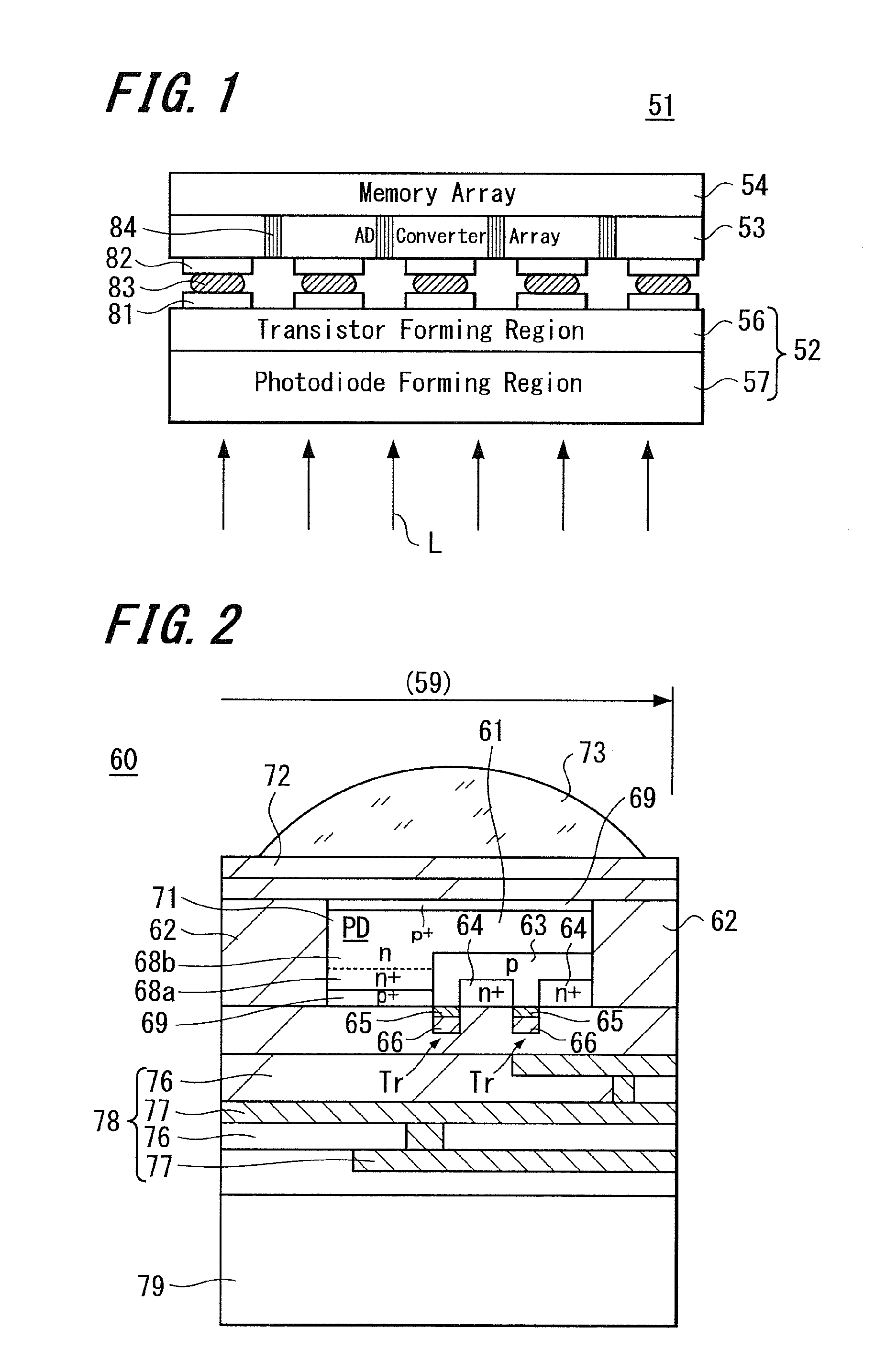

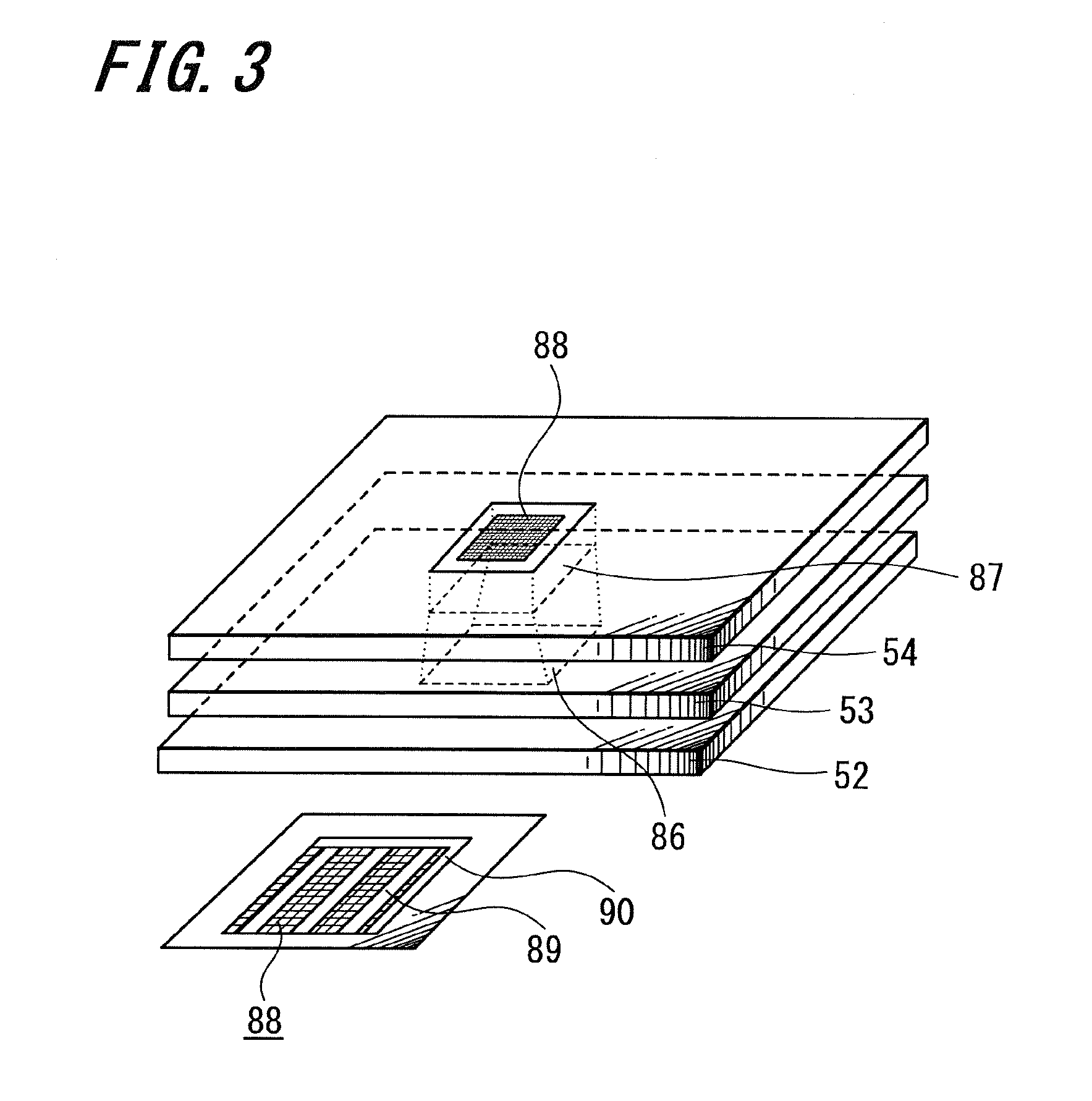

Semiconductor image sensor module and method of manufacturing the same

ActiveUS20100276572A1Increase the aperture ratioIncrease profitTransistorTelevision system detailsCMOSSemiconductor chip

A CMOS type semiconductor image sensor module wherein a pixel aperture ratio is improved, chip use efficiency is improved and furthermore, simultaneous shutter operation by all the pixels is made possible, and a method for manufacturing such semiconductor image sensor module are provided. The semiconductor image sensor module is provided by stacking a first semiconductor chip, which has an image sensor wherein a plurality of pixels composed of a photoelectric conversion element and a transistor are arranged, and a second semiconductor chip, which has an A / D converter array. Preferably, the semiconductor image sensor module is provided by stacking a third semiconductor chip having a memory element array. Furthermore, the semiconductor image sensor module is provided by stacking the first semiconductor chip having the image sensor and a fourth semiconductor chip having an analog nonvolatile memory array.

Owner:SONY CORP

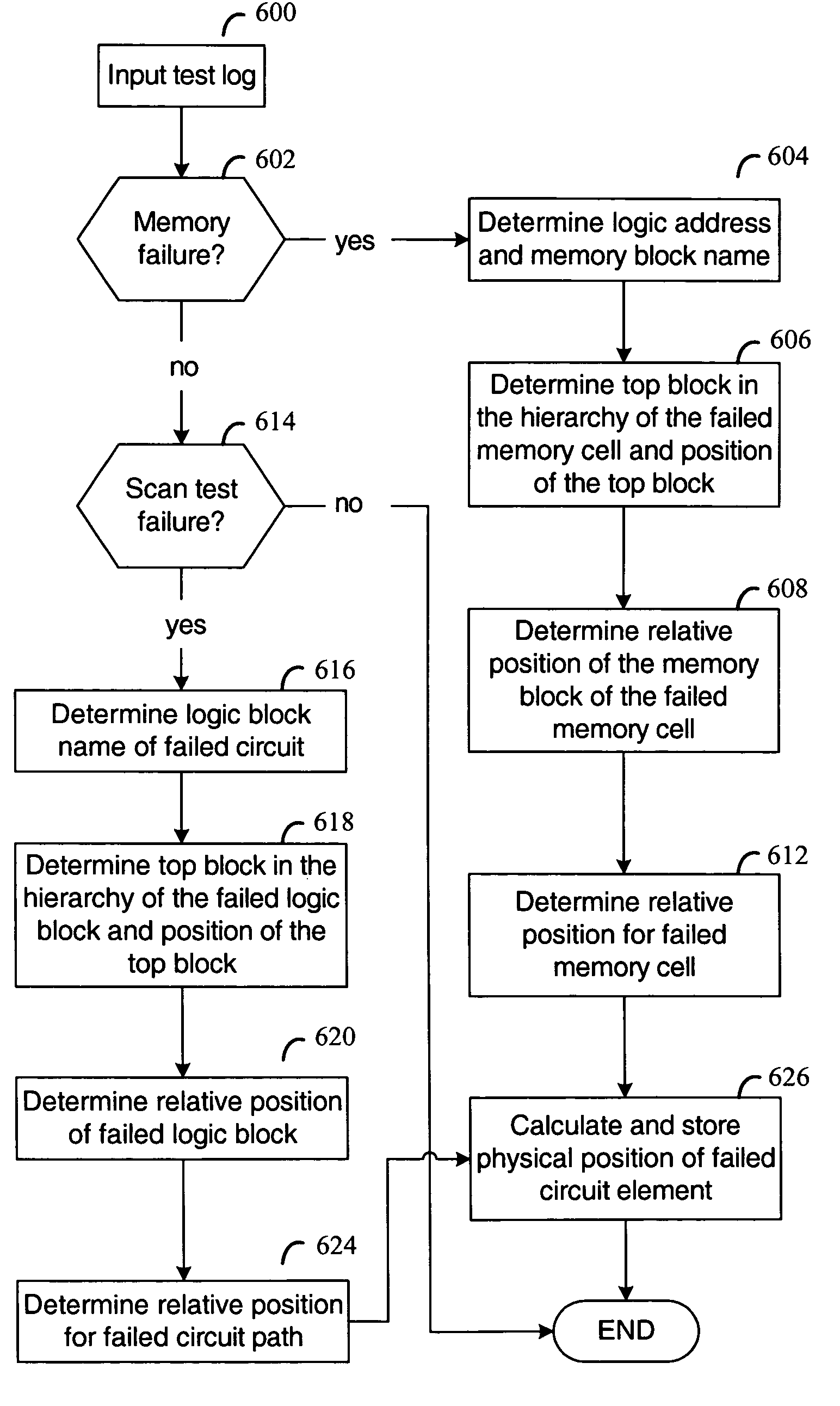

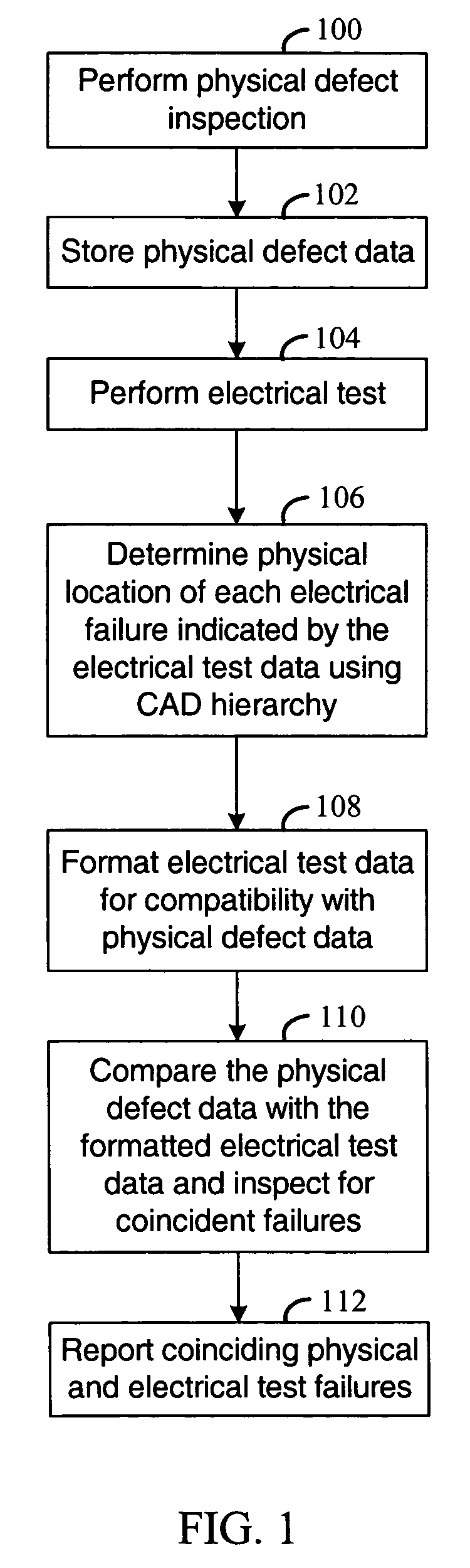

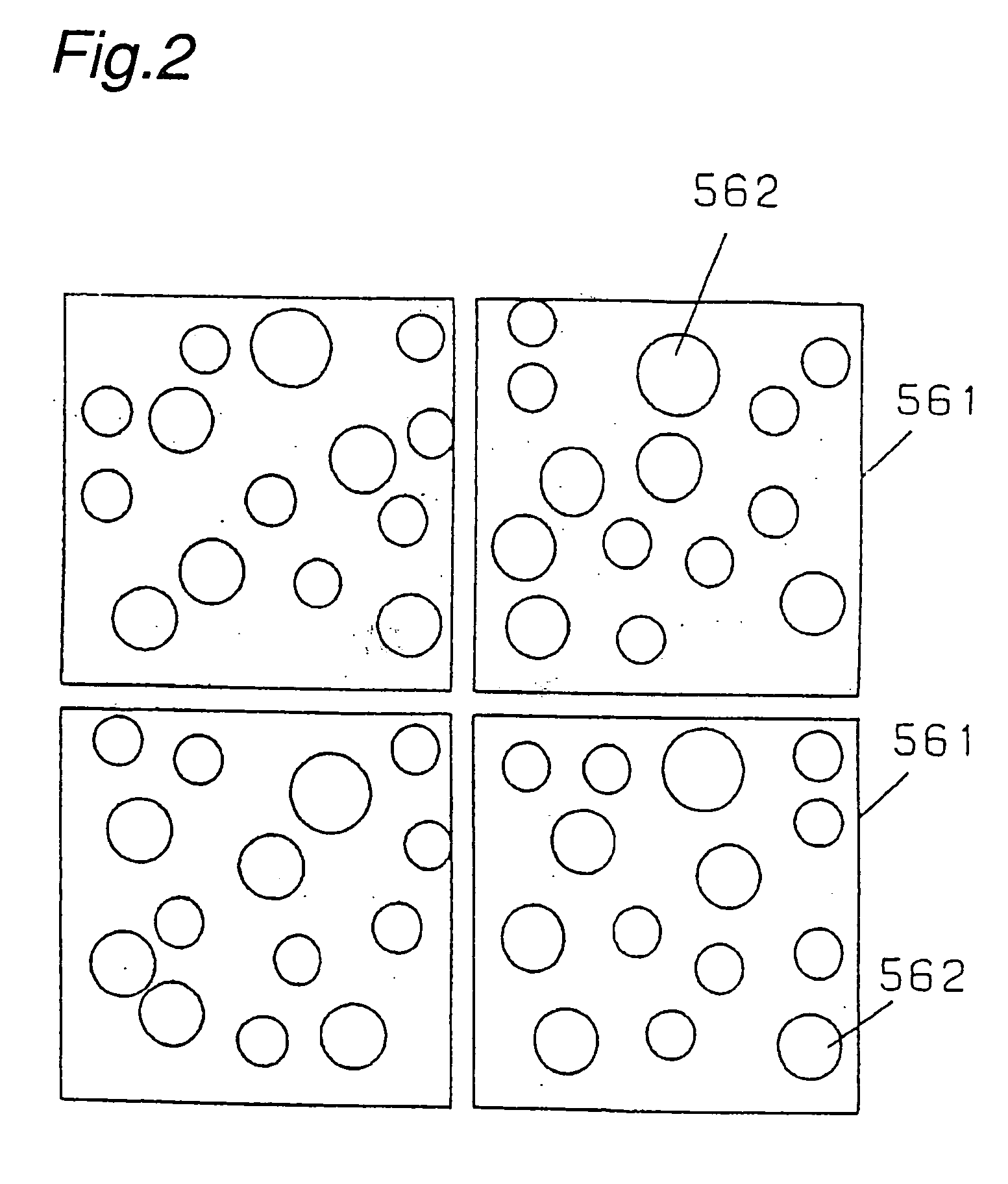

Correlation of electrical test data with physical defect data

ActiveUS6950771B1Improve yield analysisEasy to analyzeResistance/reactance/impedenceElectronic circuit testingData setDesign testing

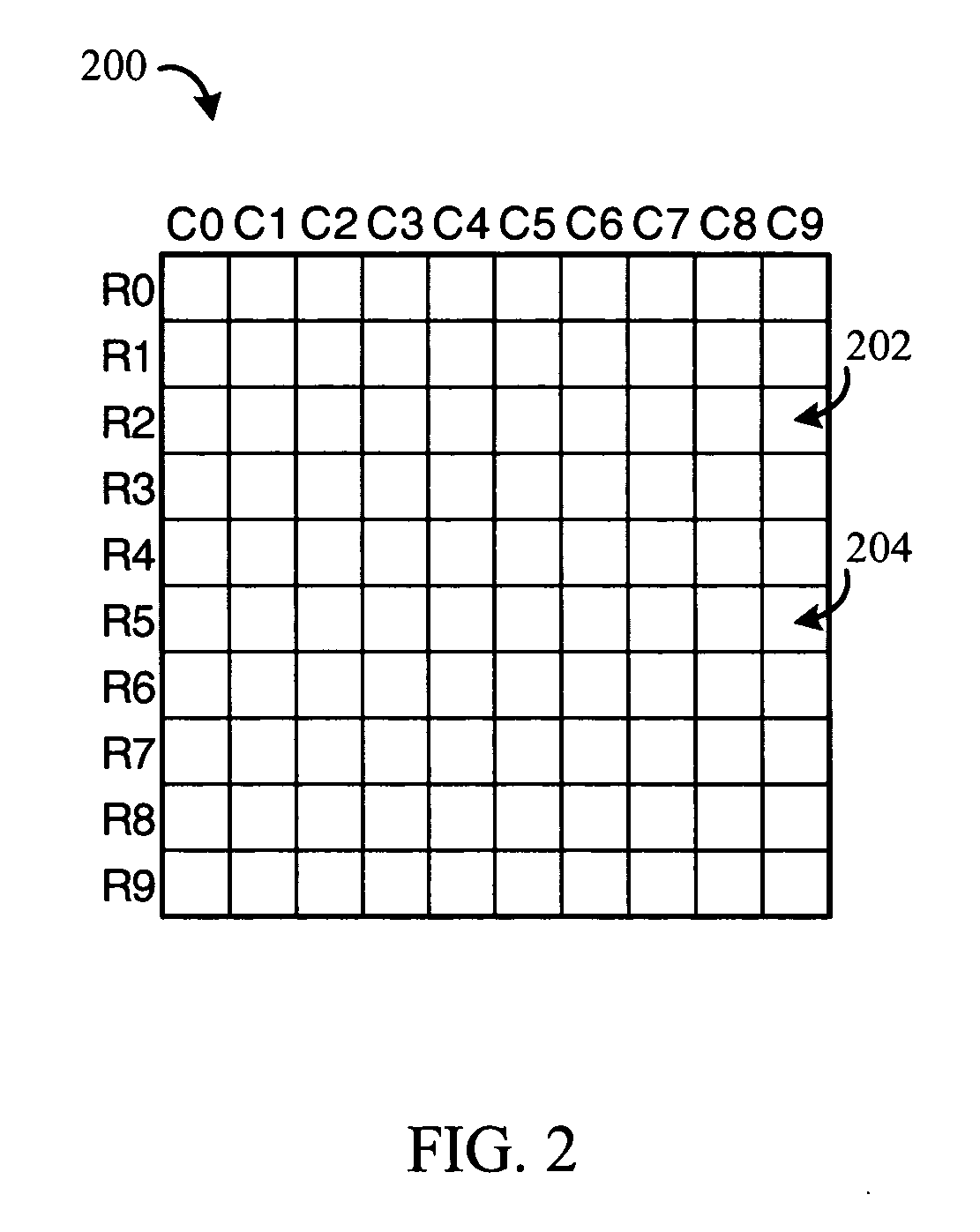

Method and apparatus are disclosed for analyzing defect data produced in testing a semiconductor chip from a logic design. In various embodiments, input for processing is a first inspection data set that identifies a first set of physical locations that are associated with defects detected during fabrication of the chip. Also input is a second test data set that includes one or more identifiers associated with failing circuitry in the chip. A second set of physical locations is determined from the one or more identifiers of failing circuitry, hierarchical relationships between blocks of the design, and placement information associated with the blocks. Each of the one or more identifiers is associated with at least one of the blocks. Correspondences are identified between physical locations in the first inspection data set and the second set of physical locations.

Owner:XILINX INC

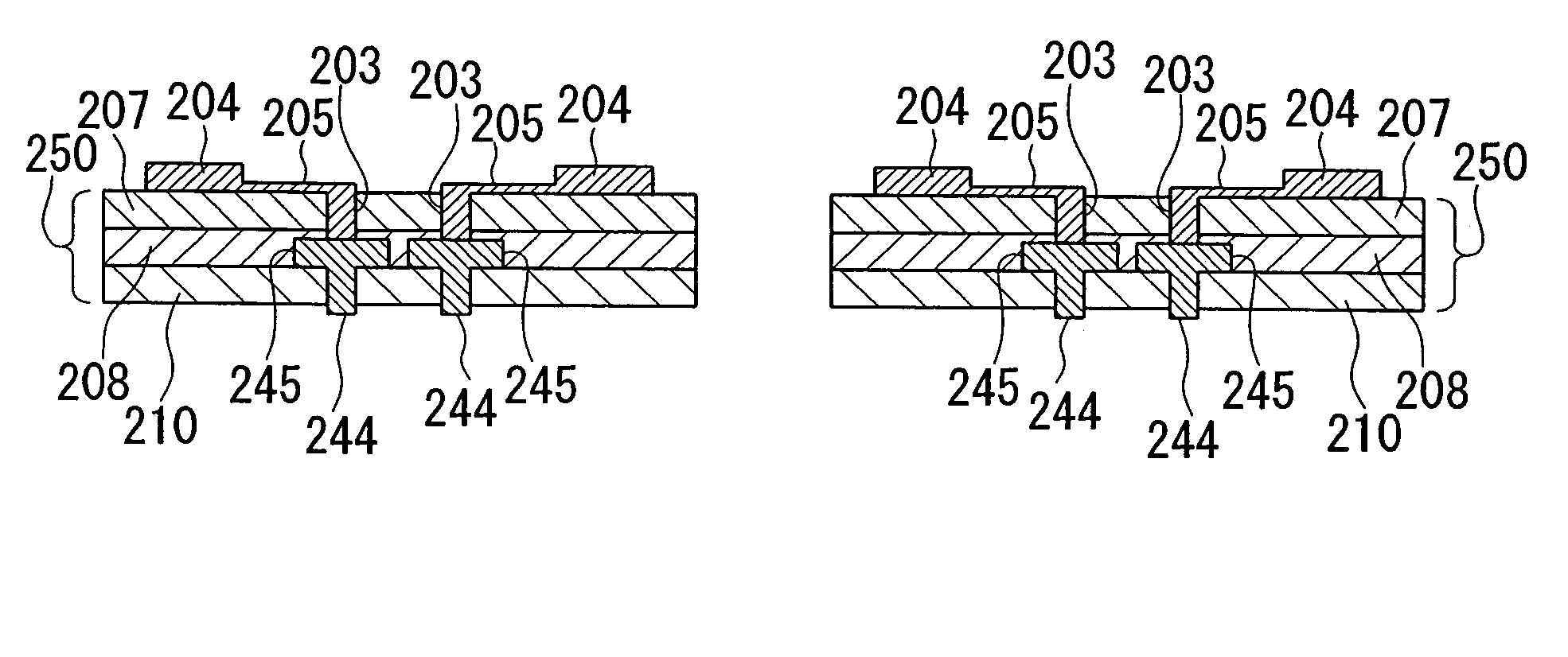

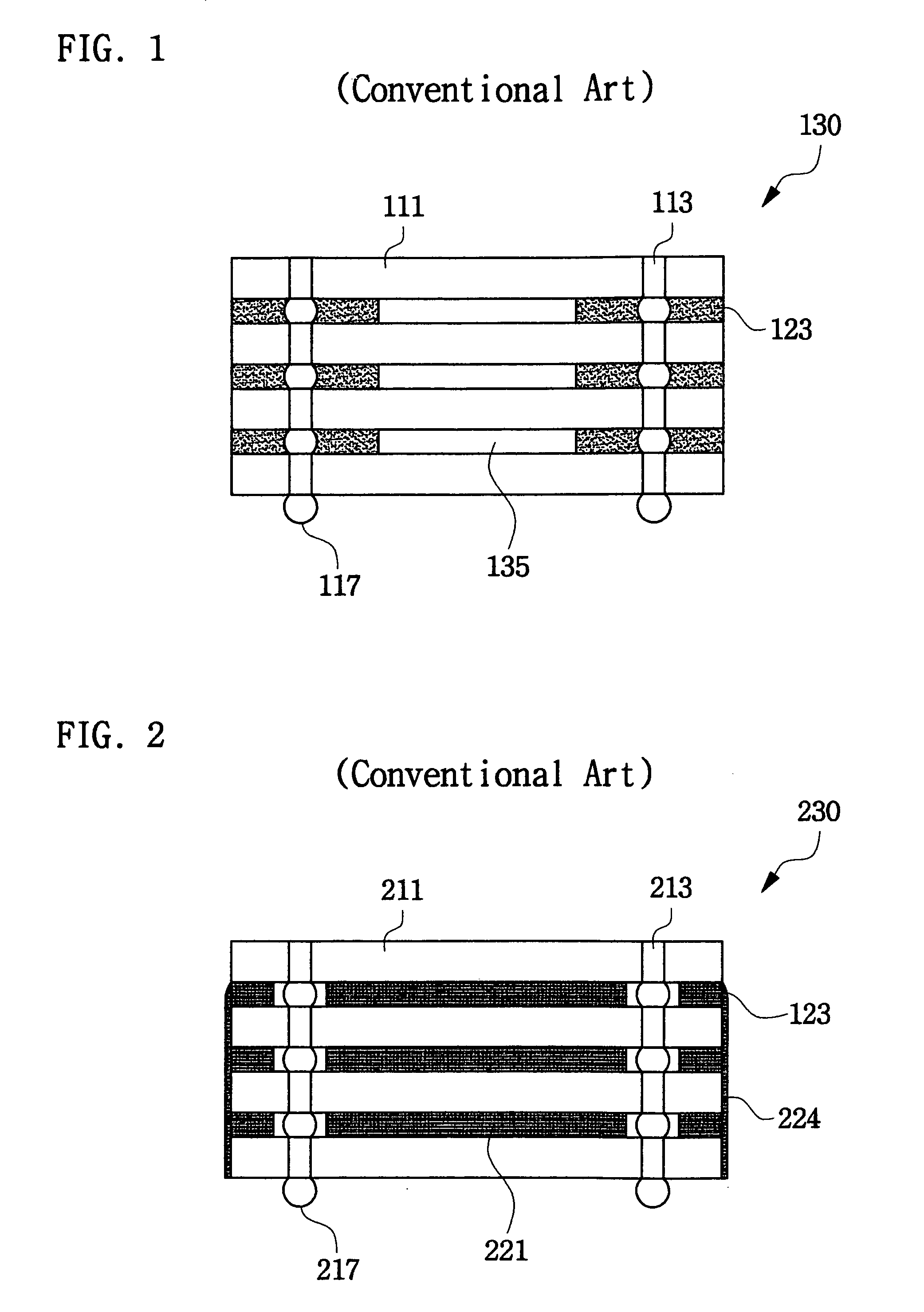

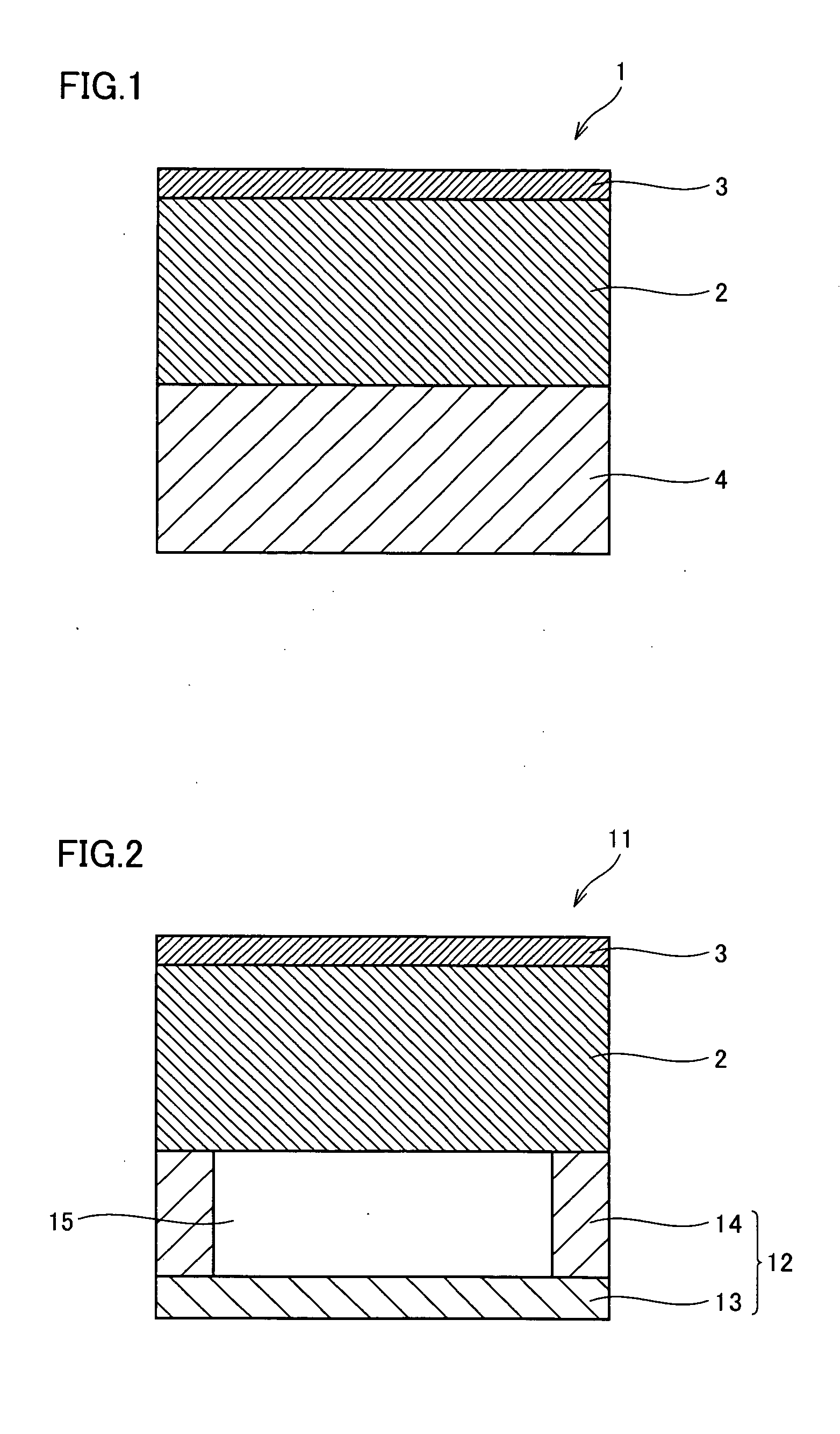

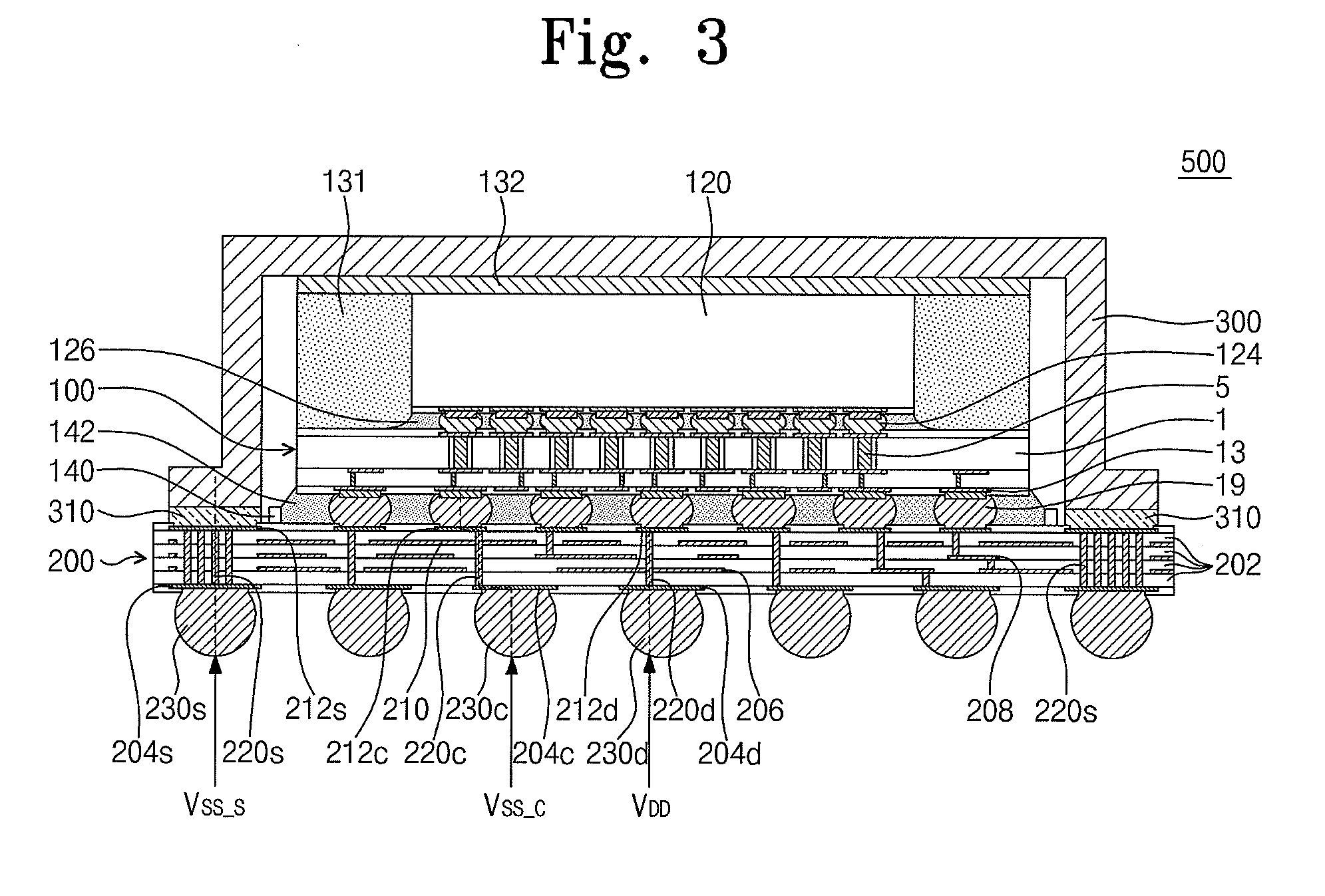

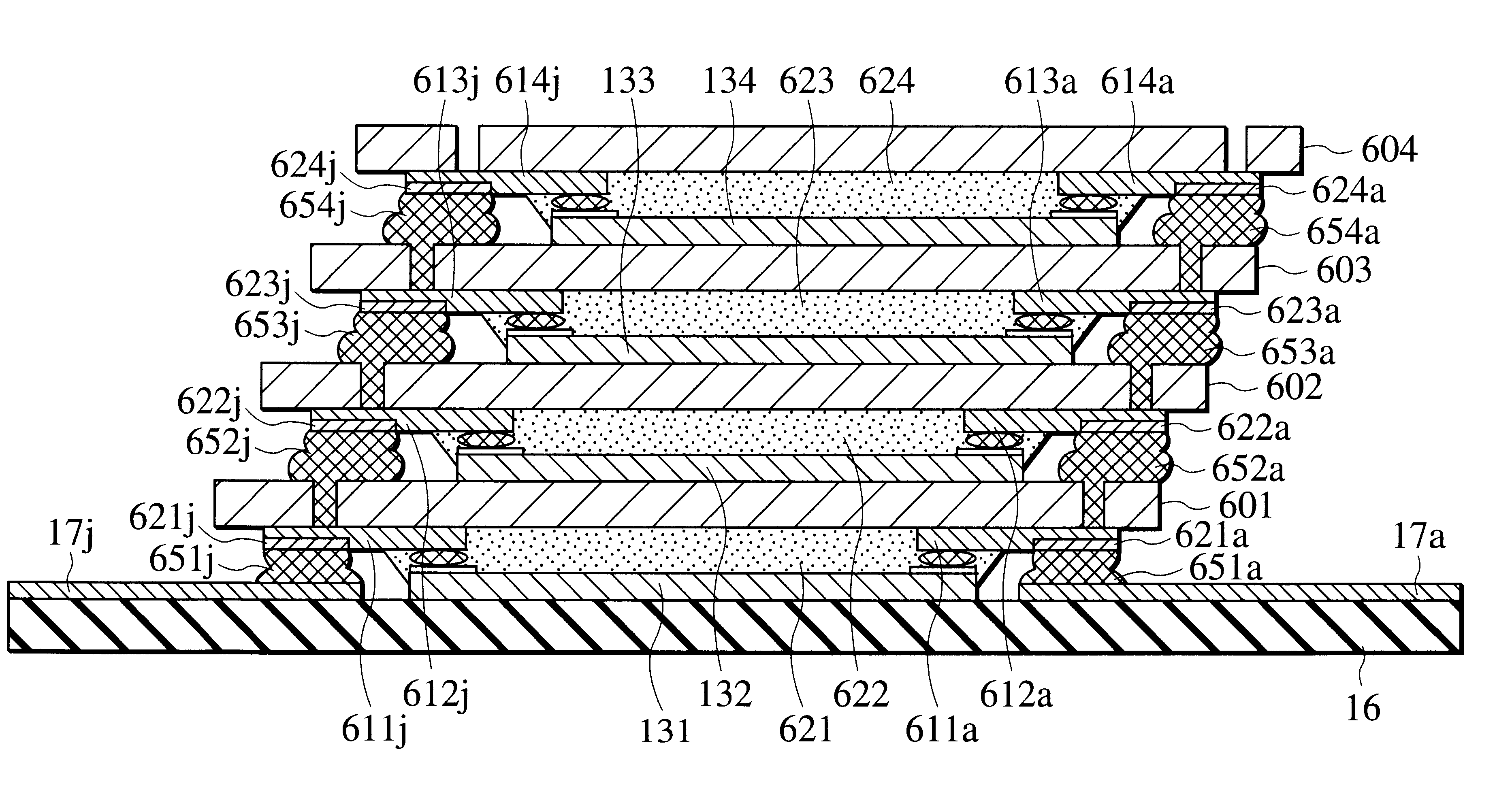

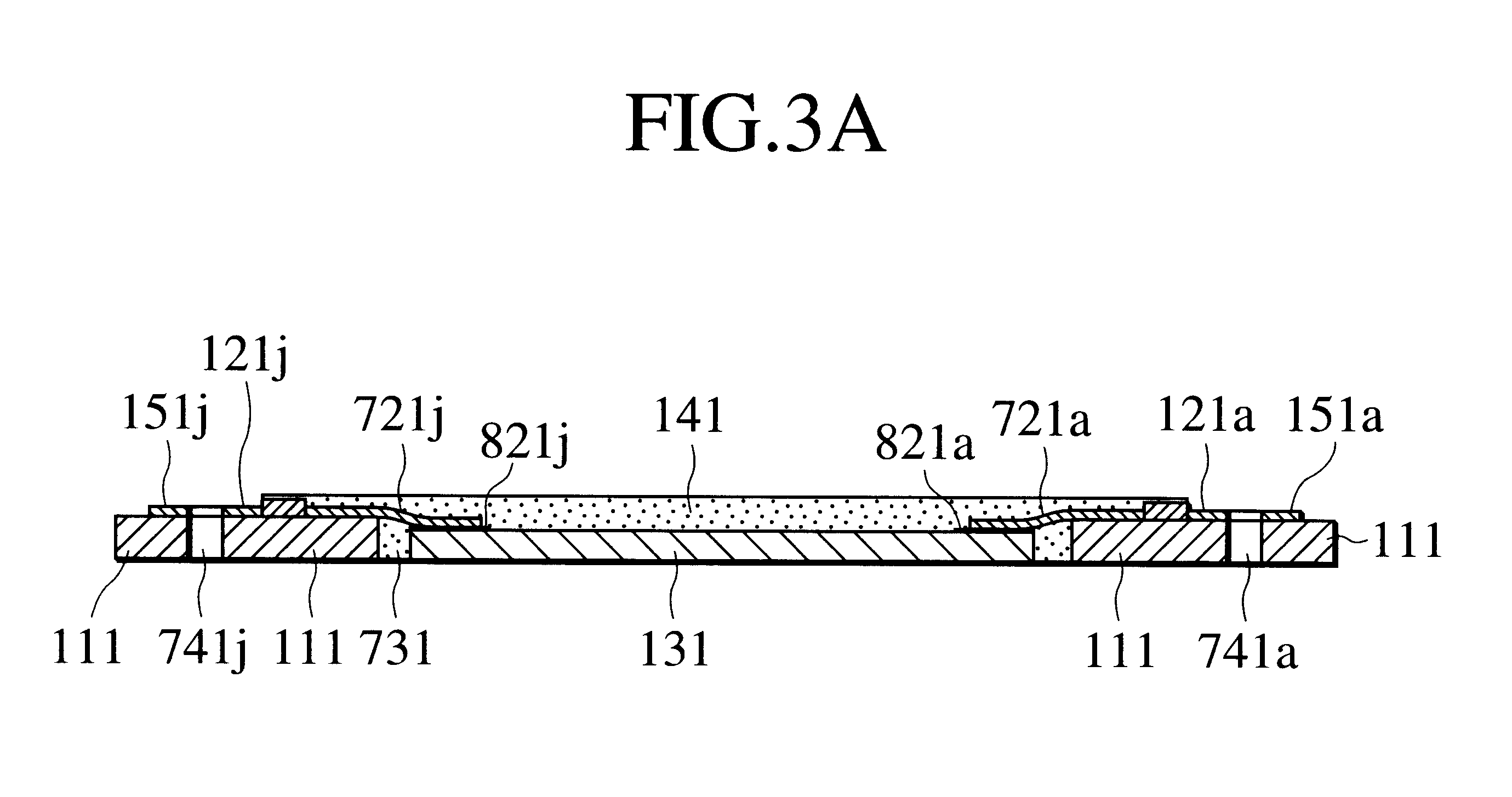

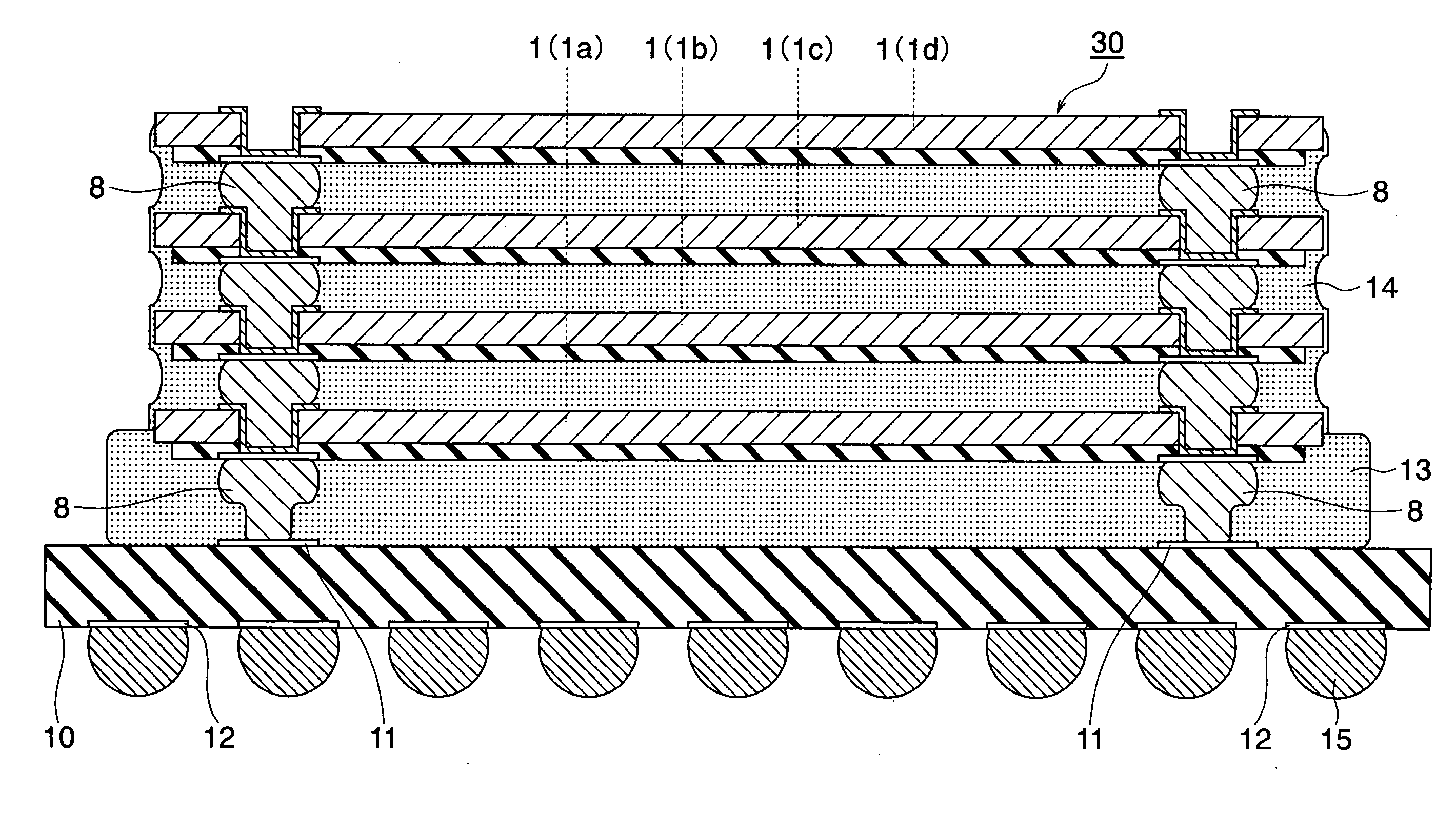

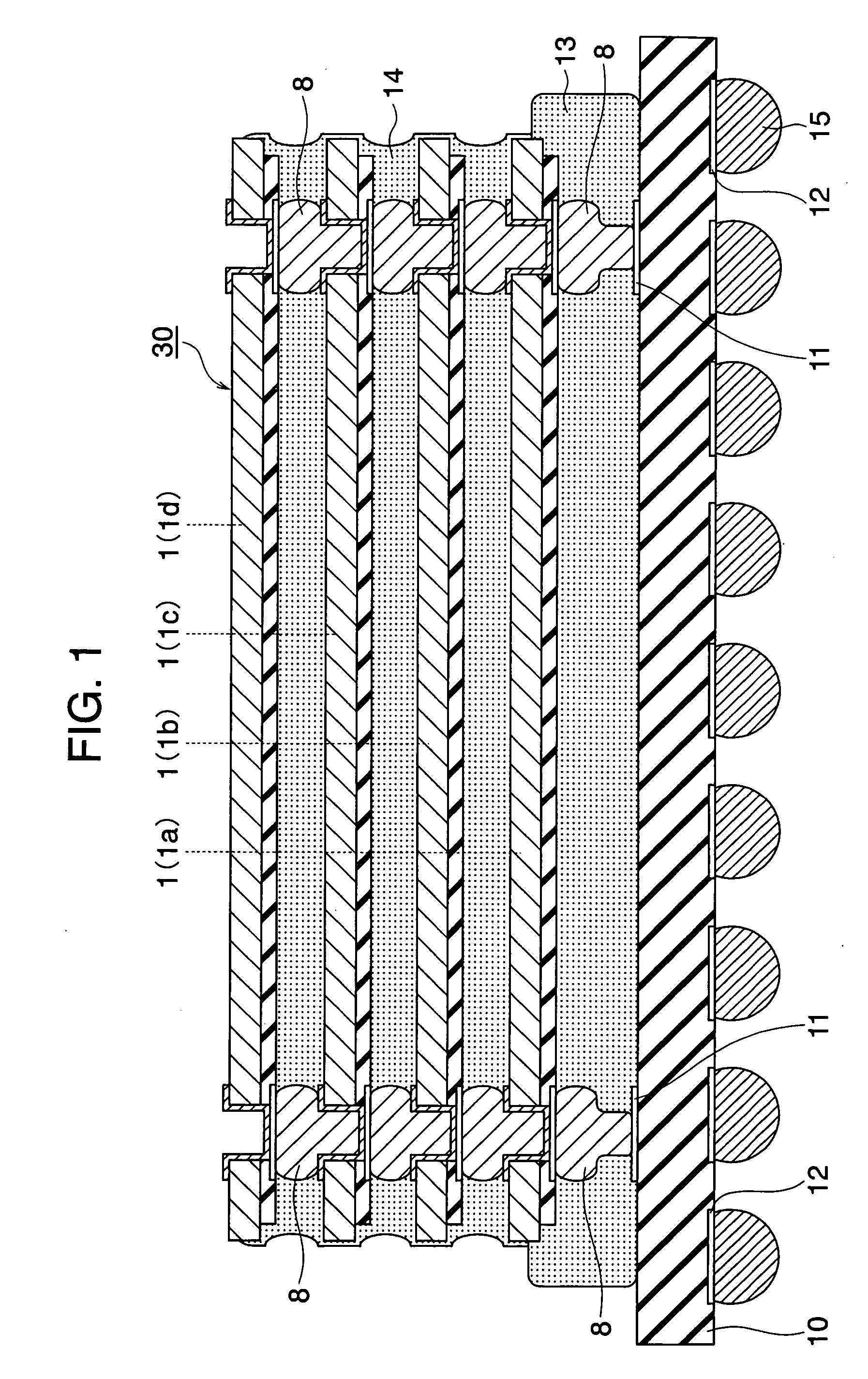

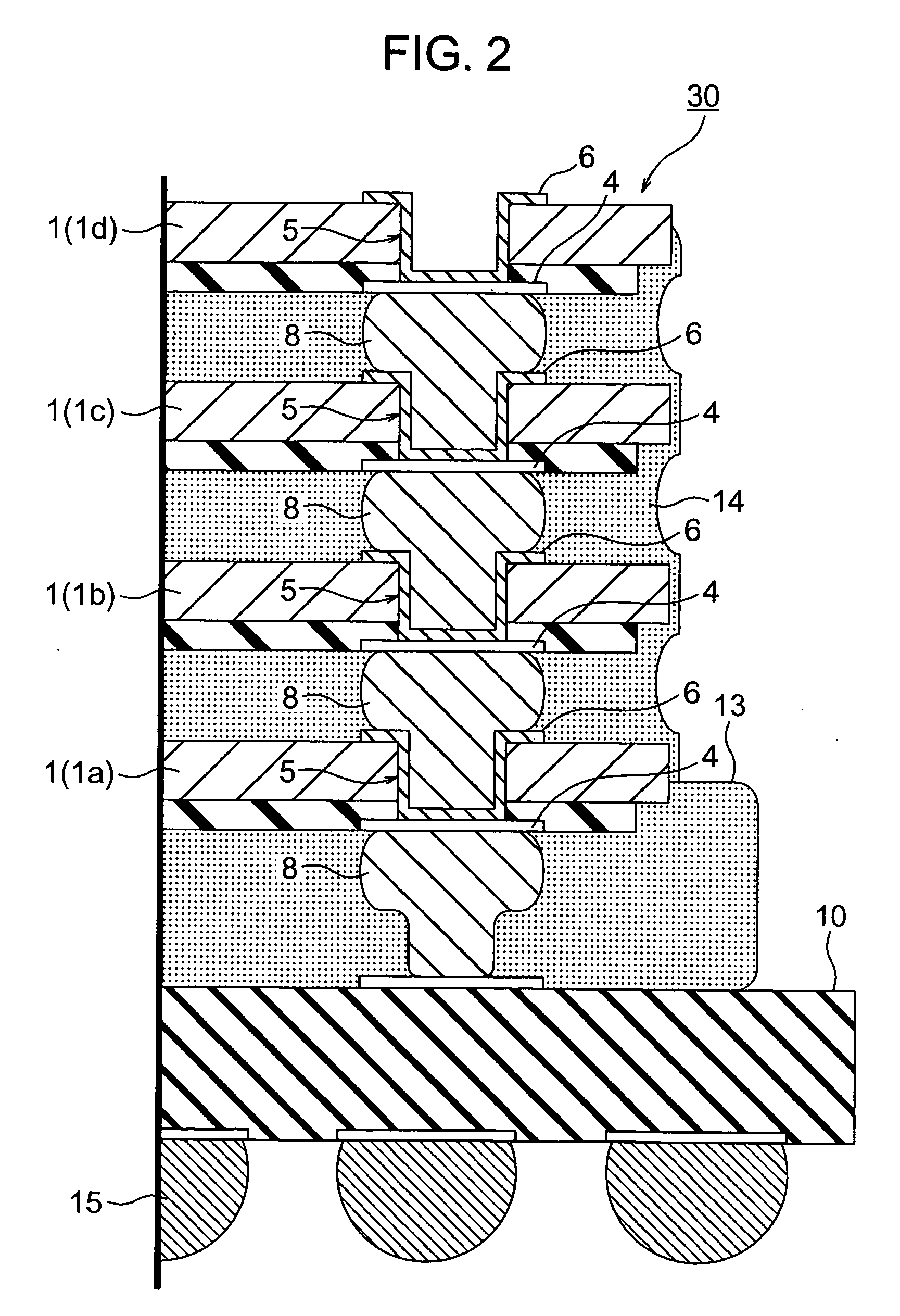

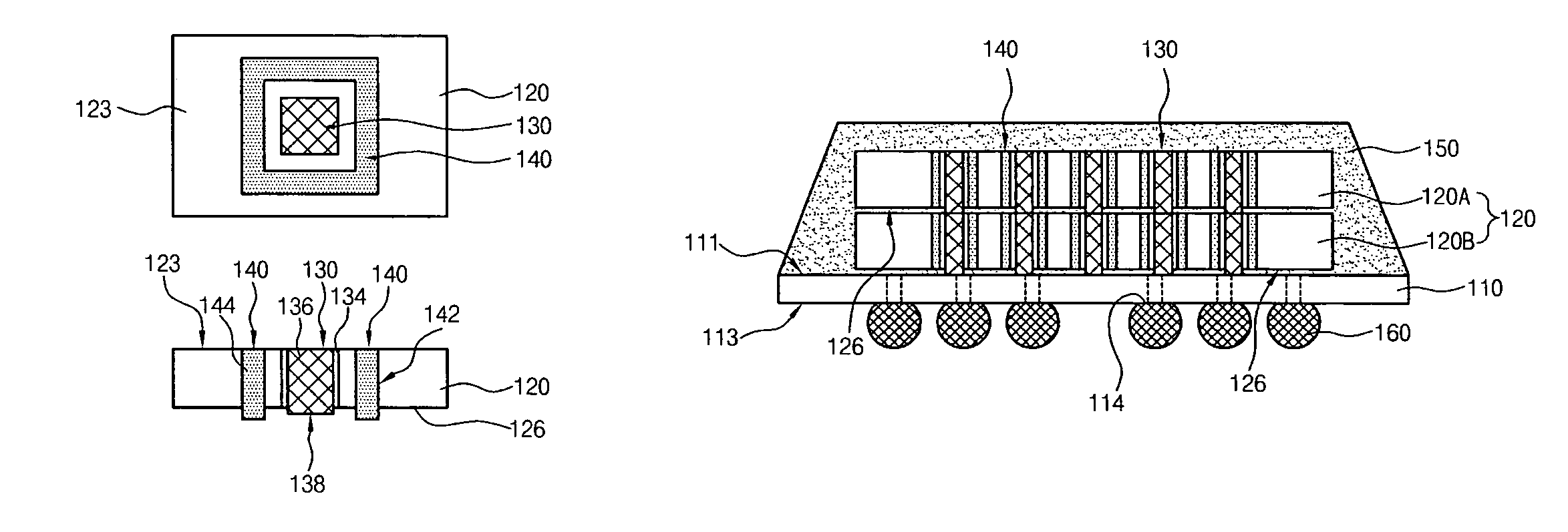

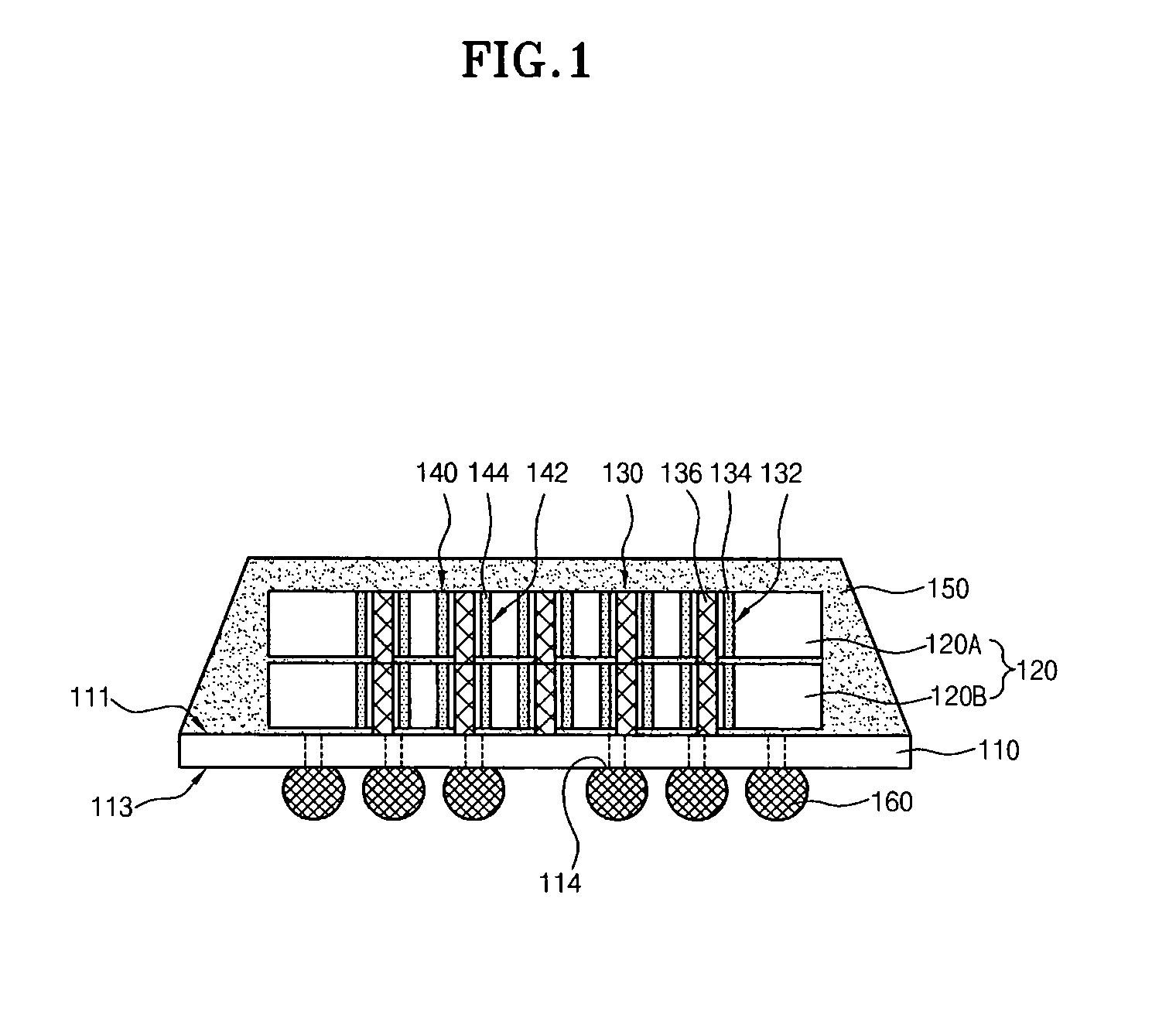

Intermediate chip module, semiconductor device, circuit board, and electronic device

ActiveUS7193308B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

An intermediate chip for electrically connecting semiconductor chips includes: a substrate having a first side and a second side; a trans-substrate conductive plug which projects to the first side of the substrate; a post electrode which is displaced from the trans-substrate conductive plug in plan view on the second side of the substrate; and wiring which is disposed in or on the substrate for coupling the trans-substrate conductive plug and the post electrode.

Owner:ADVANCED INTERCONNECT SYST LTD

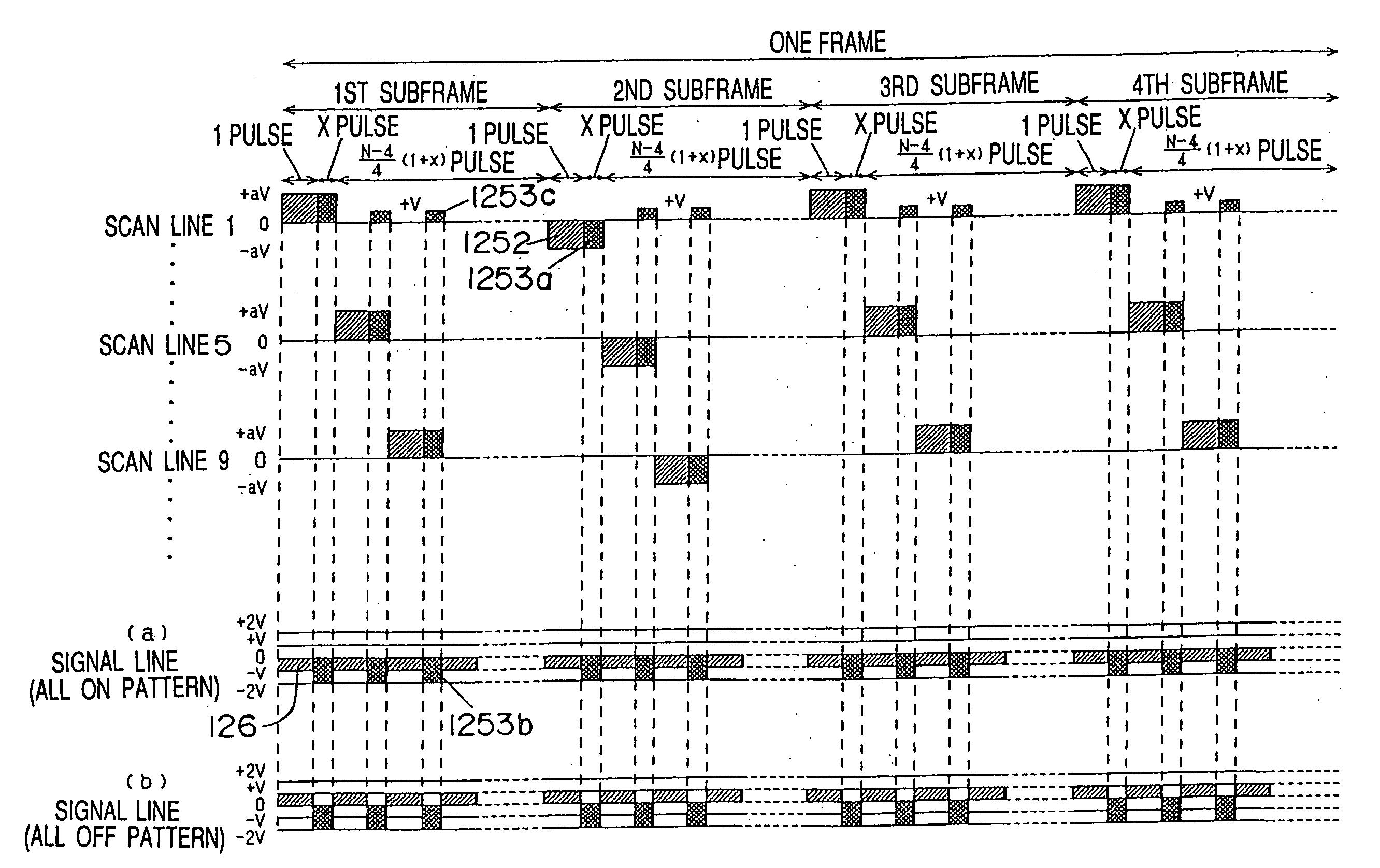

Display unit and drive system thereof and an information display unit

ActiveUS20040066363A1Easy to displayIncrease contrastCathode-ray tube indicatorsDigital output to display deviceSemiconductor chipData signal

In a display panel, a dummy pulse of a predetermined voltage signal is superimposed on a data signal and the dummy pulse has an amplitude much larger than the amplitude of the data signal, and thus a signal waveform applied to a light modulation layer such as LC layer is changed to a high frequency wave. The applying position of the dummy pulse is varied according to each color of R, G and B, or varied according to frame or field. By performing a MLS drive with the dummy pulse superimposed on the data signal, the amplitude difference between the selection signal and the data signal can be reduced. Thus, a common driver IC and a segment driver IC can be formed as one semiconductor chip to be placed on one side, constructing a three side free type.

Owner:JAPAN DISPLAY CENT INC

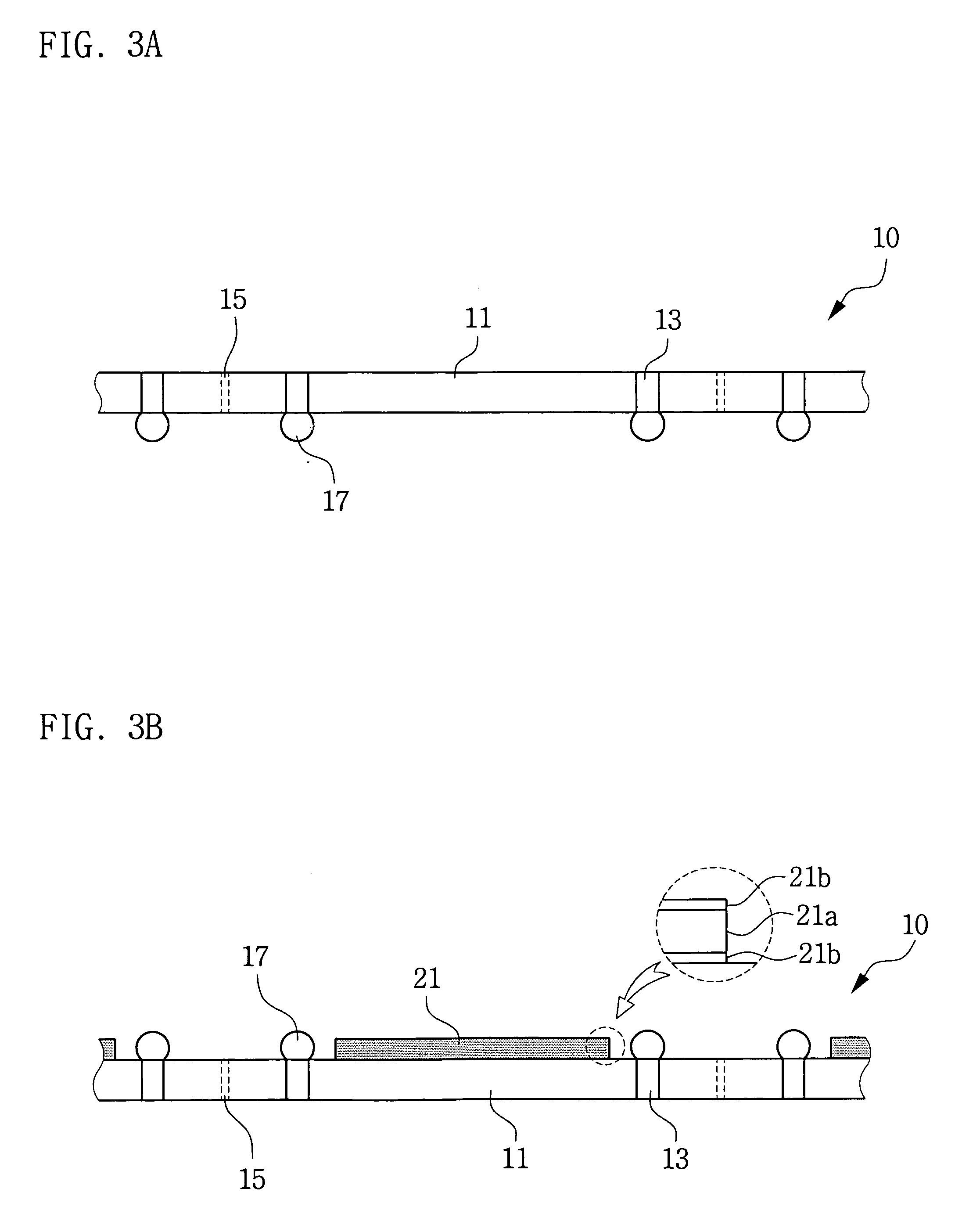

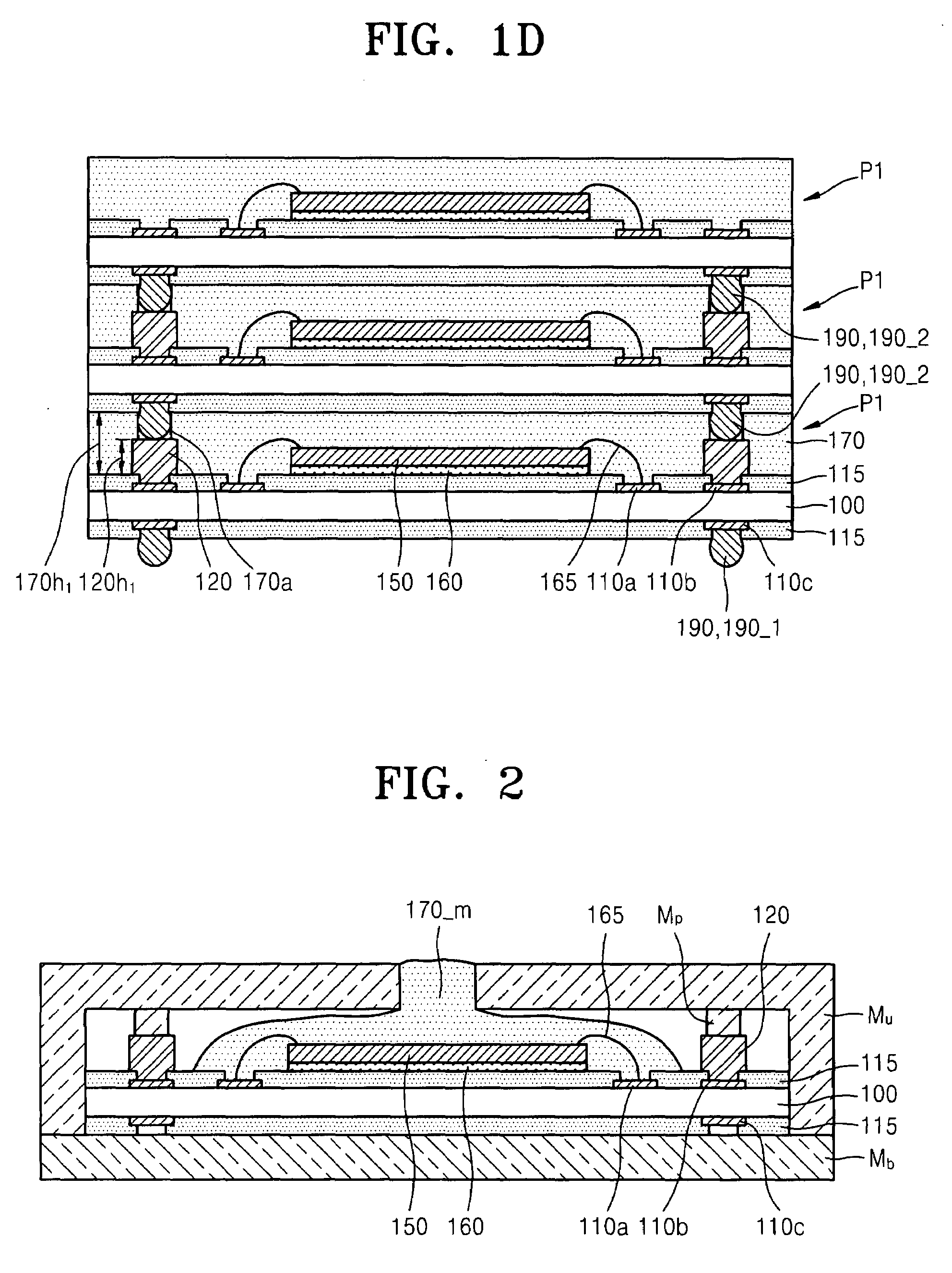

Method for manufacturing wafer level chip stack package

ActiveUS7151009B2Improve reliabilityHigh strengthSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

Provided is a method for manufacturing WLCSP devices that includes preparing at least two wafers, each wafer having a plurality of corresponding semiconductor chips, each semiconductor chip having through electrodes formed in the peripheral surface region, forming or applying a solid adhesive region to a central surface region, stacking a plurality of wafers and attaching corresponding chips provided on adjacent wafers with the solid adhesive region and connecting corresponding through electrodes of adjacent semiconductor chips, dividing the stacked wafers into individual chip stack packages, and injecting a liquid adhesive into a space remaining between adjacent semiconductor chips incorporated in the resulting chip stack package. By reducing the likelihood of void regions between adjacent semiconductor chips, it is expected that a method according to the exemplary embodiments of the present invention exhibit improved mechanical stability and reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

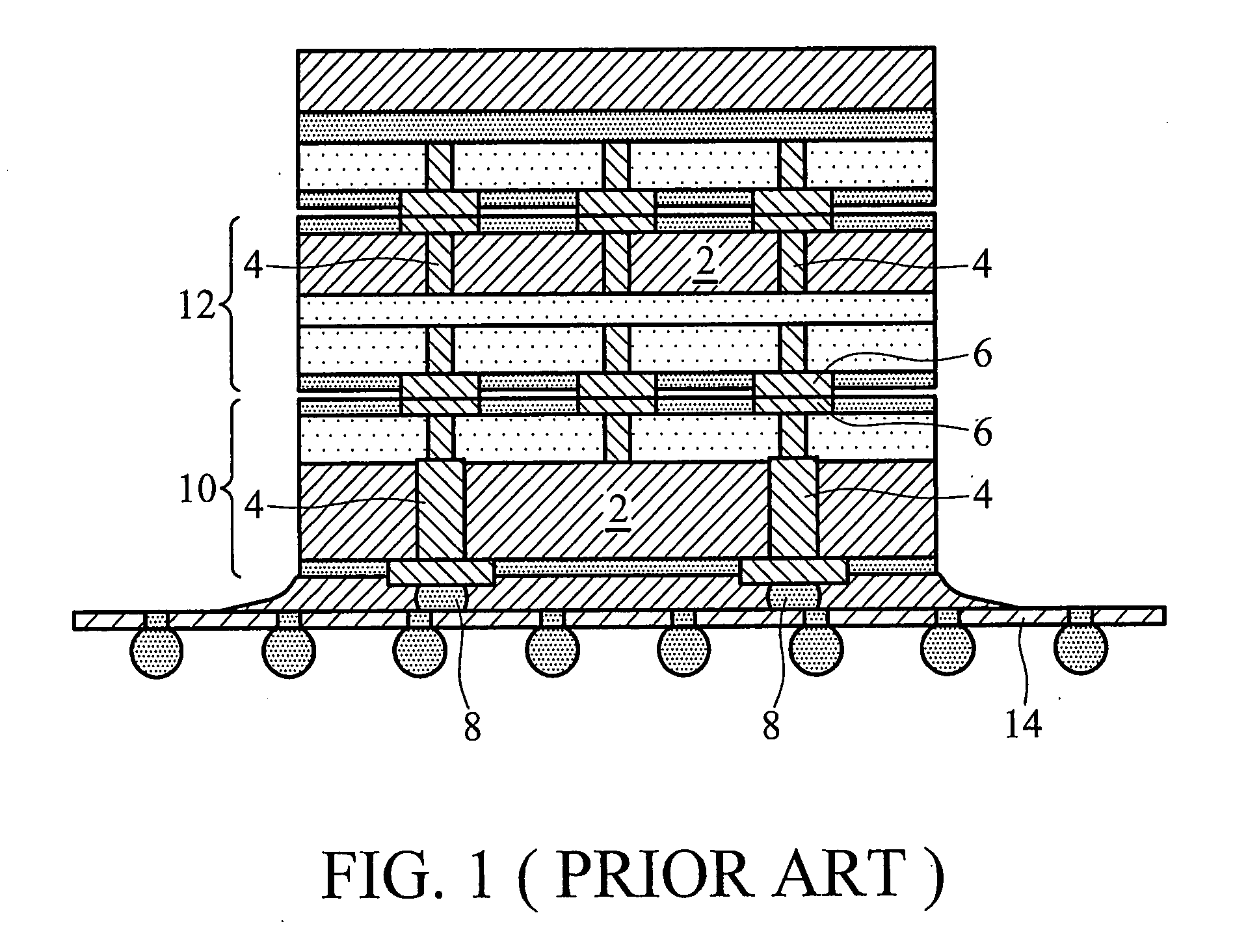

Multi-chip package (MCP) with a conductive bar and method for manufacturing the same

InactiveUS6908785B2Prevents adhesive strength failureIncreasing the thicknessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A multi-chip package (MCP) is provided. The MCP comprises a plurality of stacked semiconductor chips, each including a chip pad and a first insulating layer overlying the chip pad with an opening to expose a portion of the chip pad. Each chip additionally includes a pad redistribution line formed on the first insulating layer and a second insulating layer covering the pad redistribution line. A via hole is formed through the chip, the first insulating layer, a pad redistribution line and the second insulating layer. The MCP further includes a protective layer formed on the bottom of the lowest semiconductor chip. The protective layer includes a conductive pad formed opposite the bottom of the lowest semiconductor chip. A conductive bar extends through the via holes of the stacked semiconductor chips, from the conductive pad, and is electrically connected to the pad redistribution line of the stacked semiconductor chips.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor package and method for fabricating the same

InactiveUS6395578B1Improve cooling effectUniform encapsulationSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

Semiconductor packages having a thin structure capable of easily discharging heat from a semiconductor chip included therein, and methods for fabricating such semiconductor packages, are disclosed. An embodiment of a semiconductor package includes a semiconductor chip having a first major surface and a second major surface, the semiconductor chip being provided at the second major surface with a plurality of input / output pads; a circuit board including a resin substrate having a first major surface and a second major surface, a first circuit pattern formed at the first major surface and provided with a plurality of ball lands, a second circuit pattern formed at the second major surface and provided with a plurality of bond fingers connected with he ball lands by conductive via holes through the resin substrate, cover coats respectively coating the first and second circuit patterns while allowing the bond fingers and the ball lands to be exposed therethrough, and a central through hole adapted to receive the semiconductor chip therein; electrical conductors that electrically connect the input / output pads of the semiconductor chip with the bond fingers of the circuit board, respectively; a resin encapsulate that covers the semiconductor chip, the electrical conductors, and at least part of the circuit board; and, a plurality of conductive balls fused on the ball lands of the circuit board, respectively.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Wafer holder, heater unit used for wafer prober and having wafer holder, and wafer prober

InactiveUS20080211526A1Avoid contact failureAvoid temperature riseSleeve/socket jointsTurning machine accessoriesContact failureSemiconductor chip

By wafer holder including a chuck top for mounting a wafer and a supporter supporting the chuck top and having flatness of at most 0.1 mm, a heater unit for a wafer prober and the wafer prober using the wafer holder, a wafer holder and a wafer prober apparatus hardly deformable even under high load and capable of effectively preventing contact failure, and capable of preventing temperature increase in a driving system when a semiconductor wafer having semiconductor chips with minute circuitry that requires high accuracy is heated can be provided. In the wafer holder of the present invention, the flatness of the supporter is preferably at most 0.05 mm, and more preferably at most 0.01 mm.

Owner:SUMITOMO ELECTRIC IND LTD

Semiconductor package and method of forming the same

InactiveUS20120119346A1Semiconductor/solid-state device detailsSolid-state devicesElectromagnetic wave transmissionSemiconductor chip

Disclosed are a semiconductor package and a method of manufacturing the same. The semiconductor package comprises a package cap which is capable of radiating high temperatures and performs a shield function preventing transmission of electromagnetic waves into and / or out of the semiconductor package. The semiconductor package including the package cap prevents chip malfunctions and improves device reliability. The package cap is positioned to cover first and second semiconductor chips of a semiconductor package.

Owner:SAMSUNG ELECTRONICS CO LTD

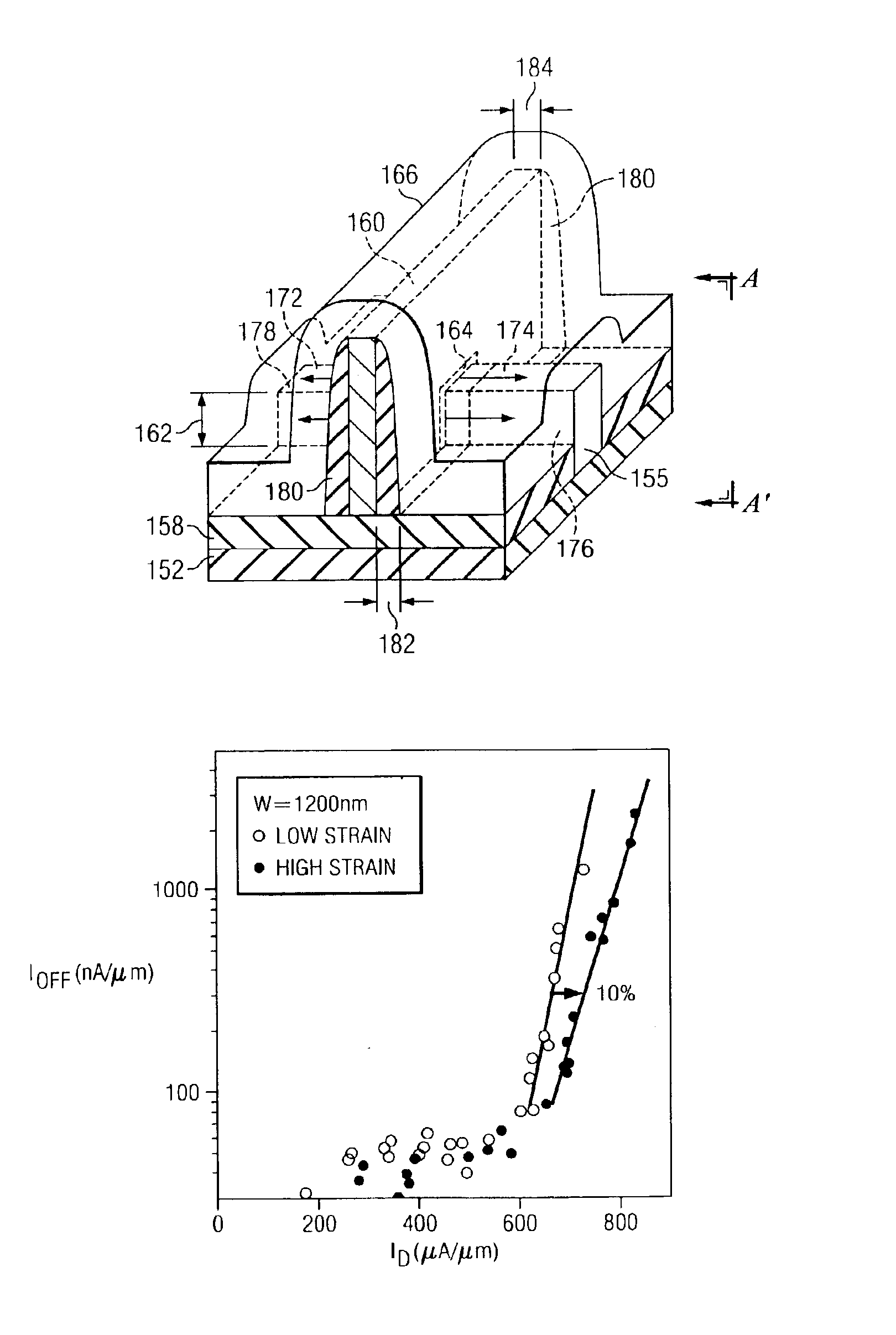

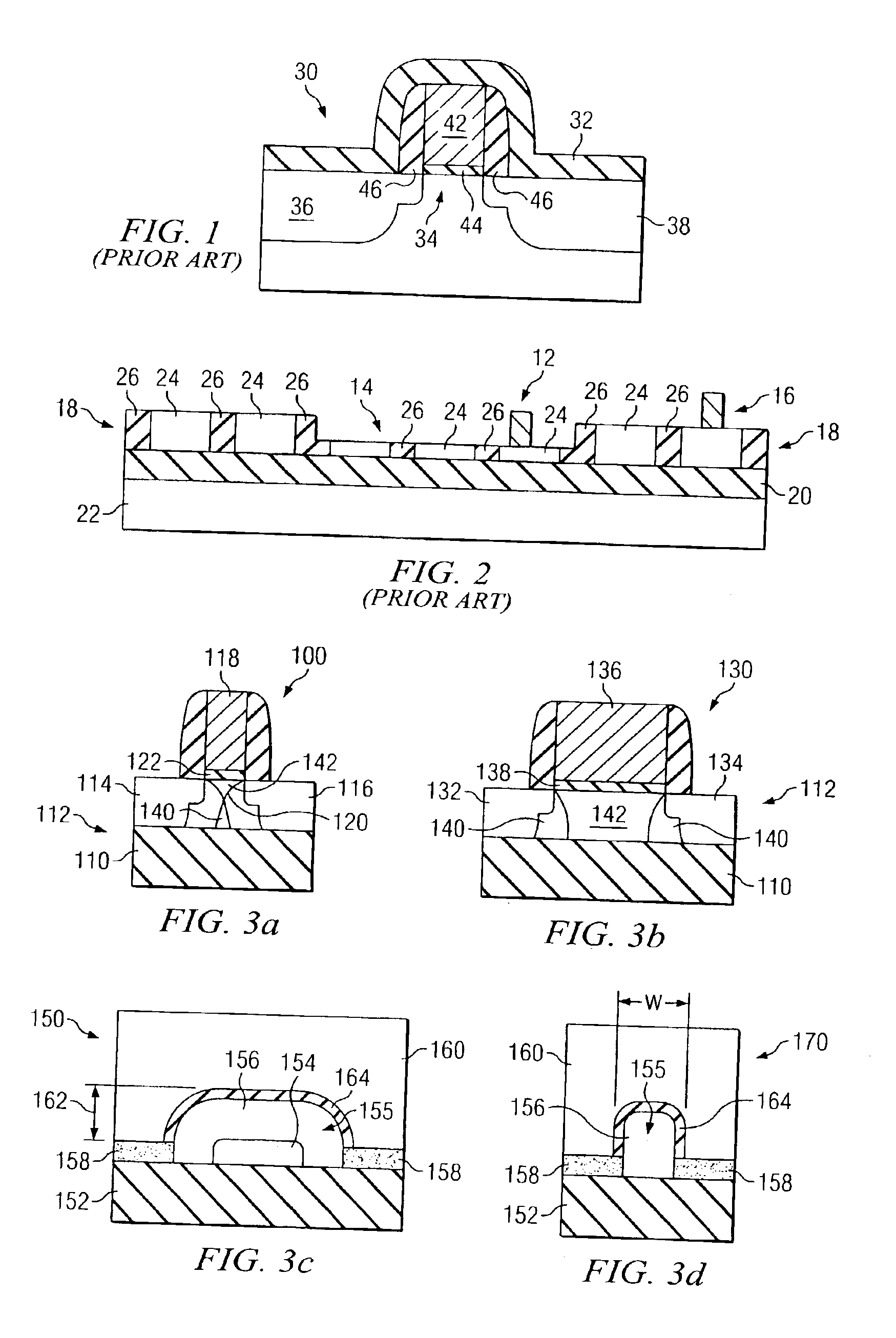

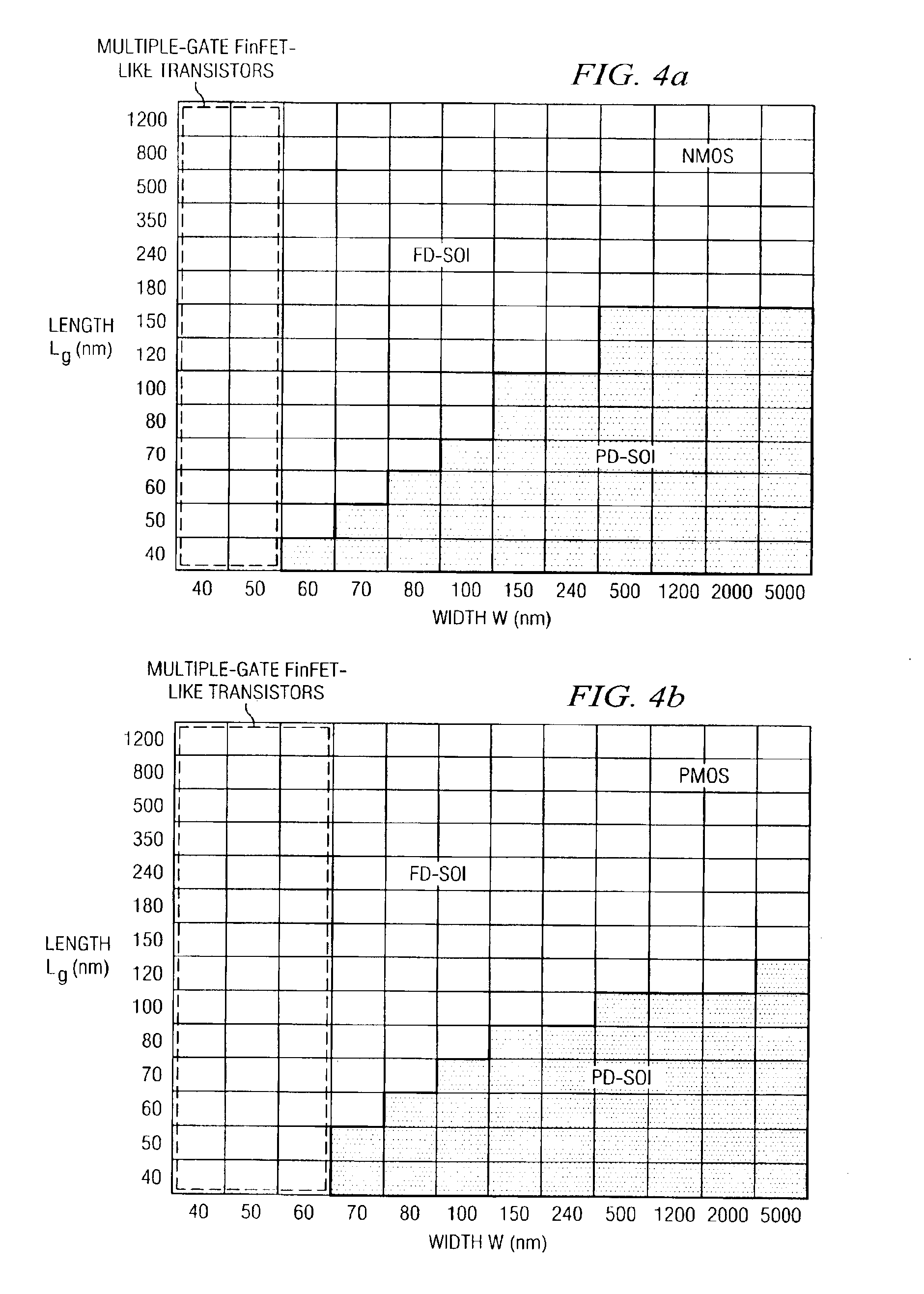

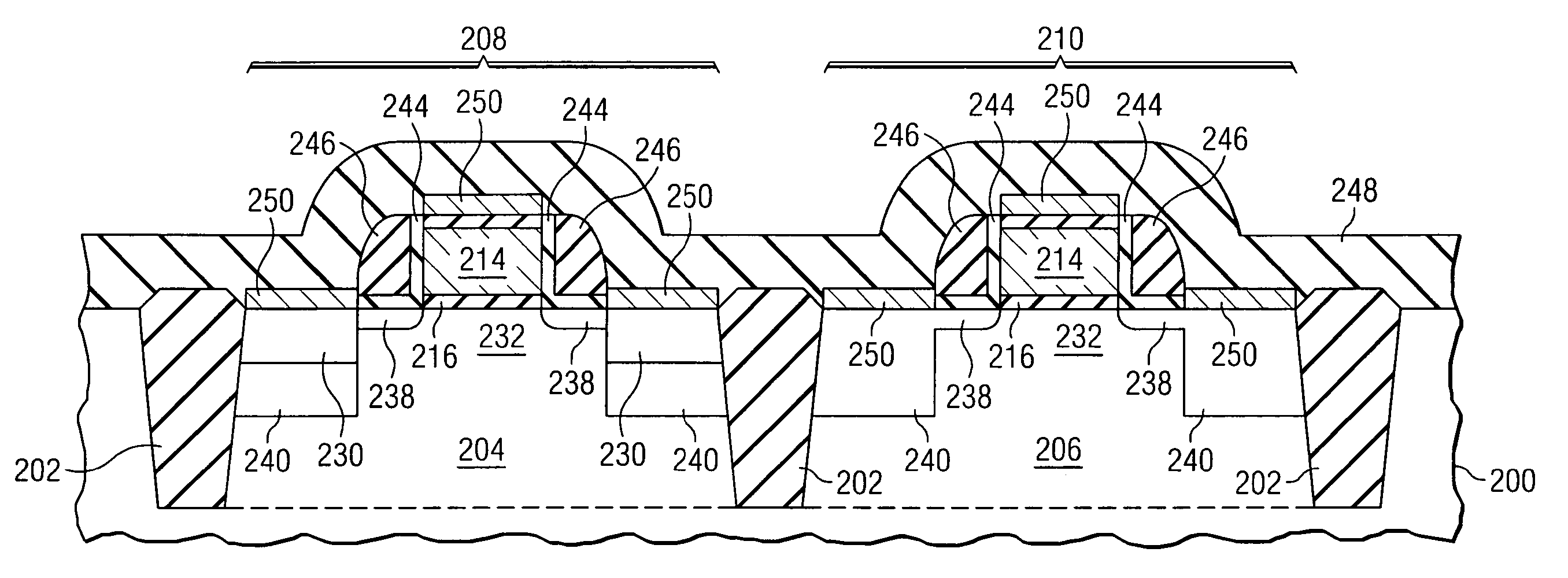

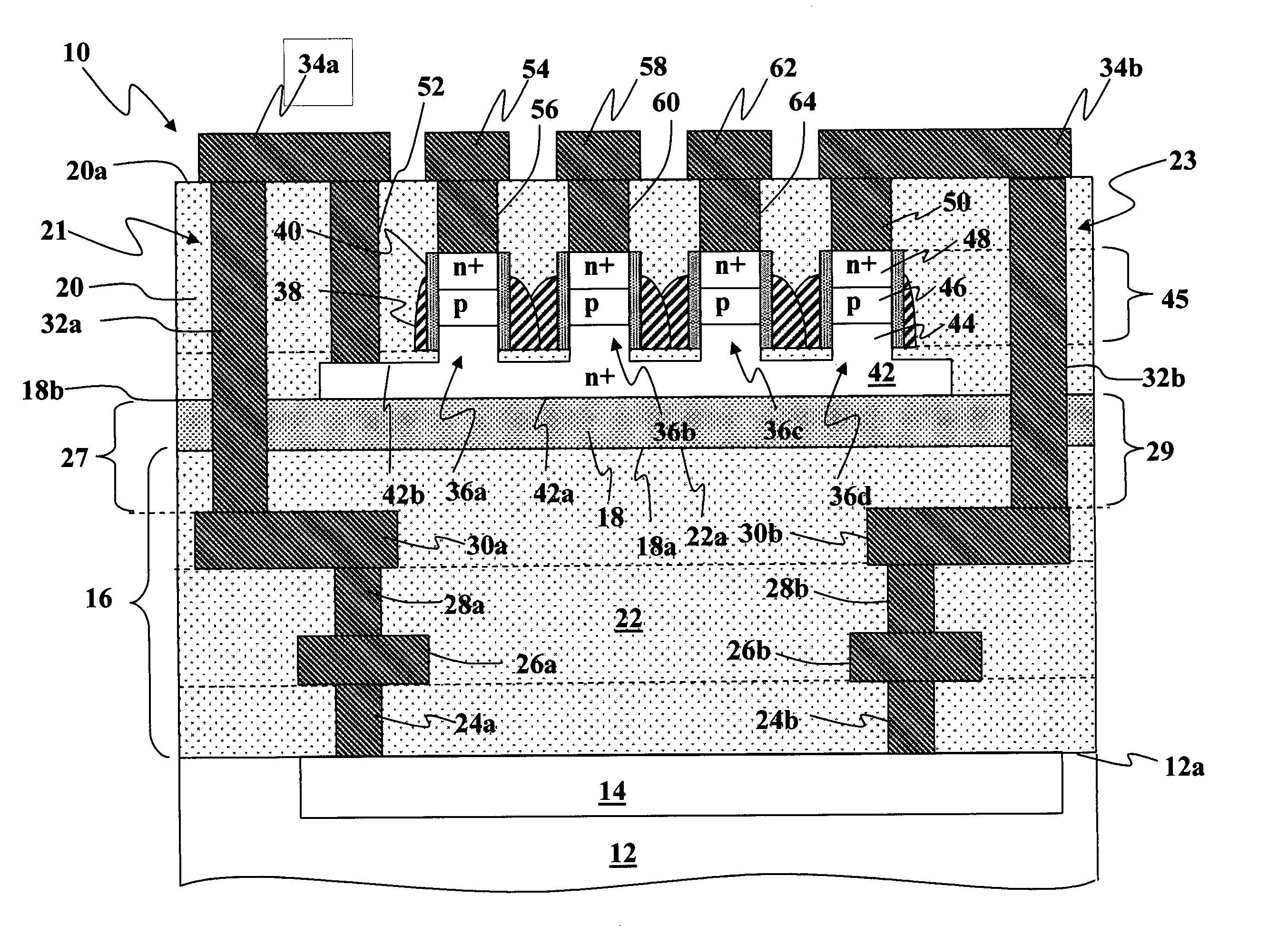

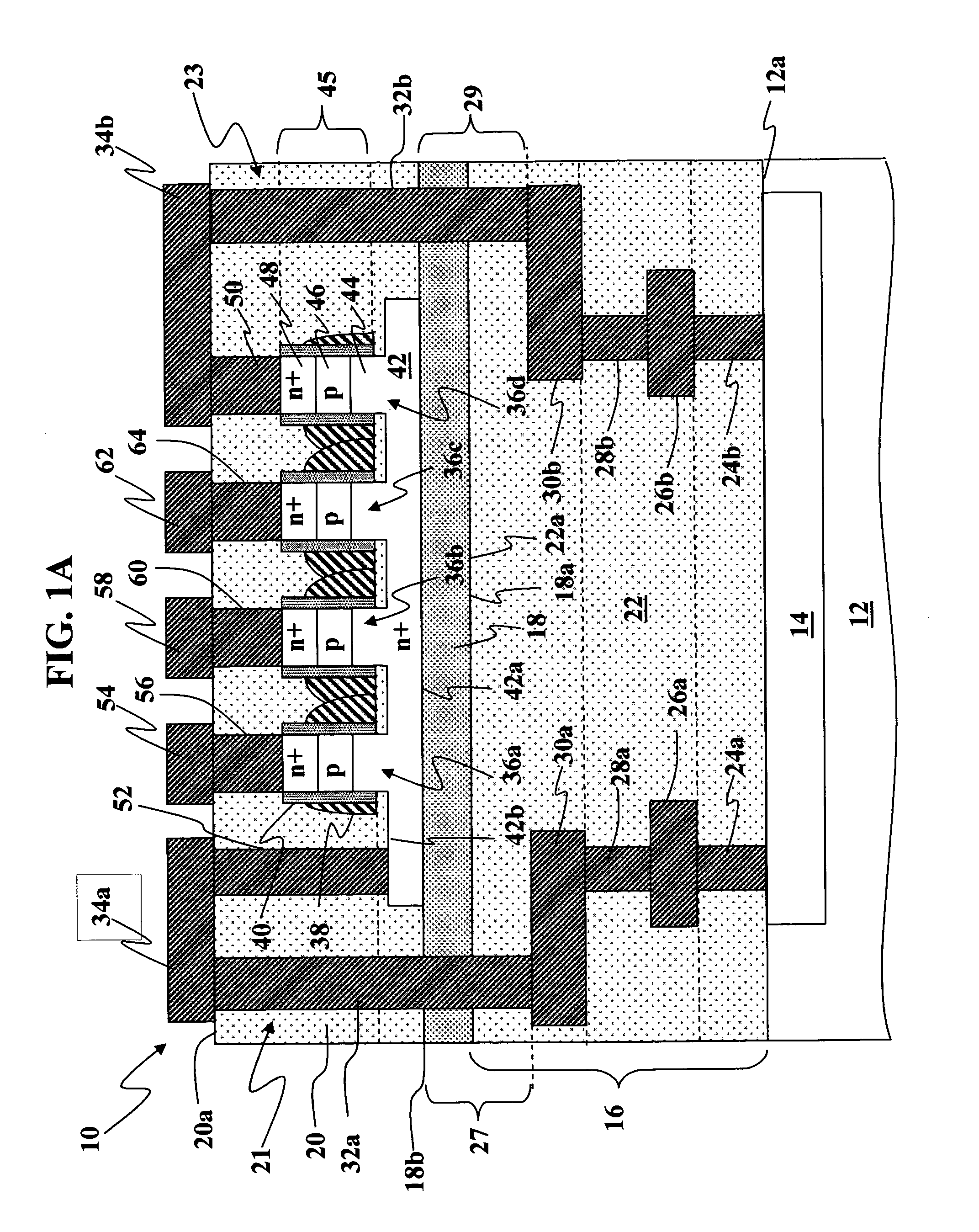

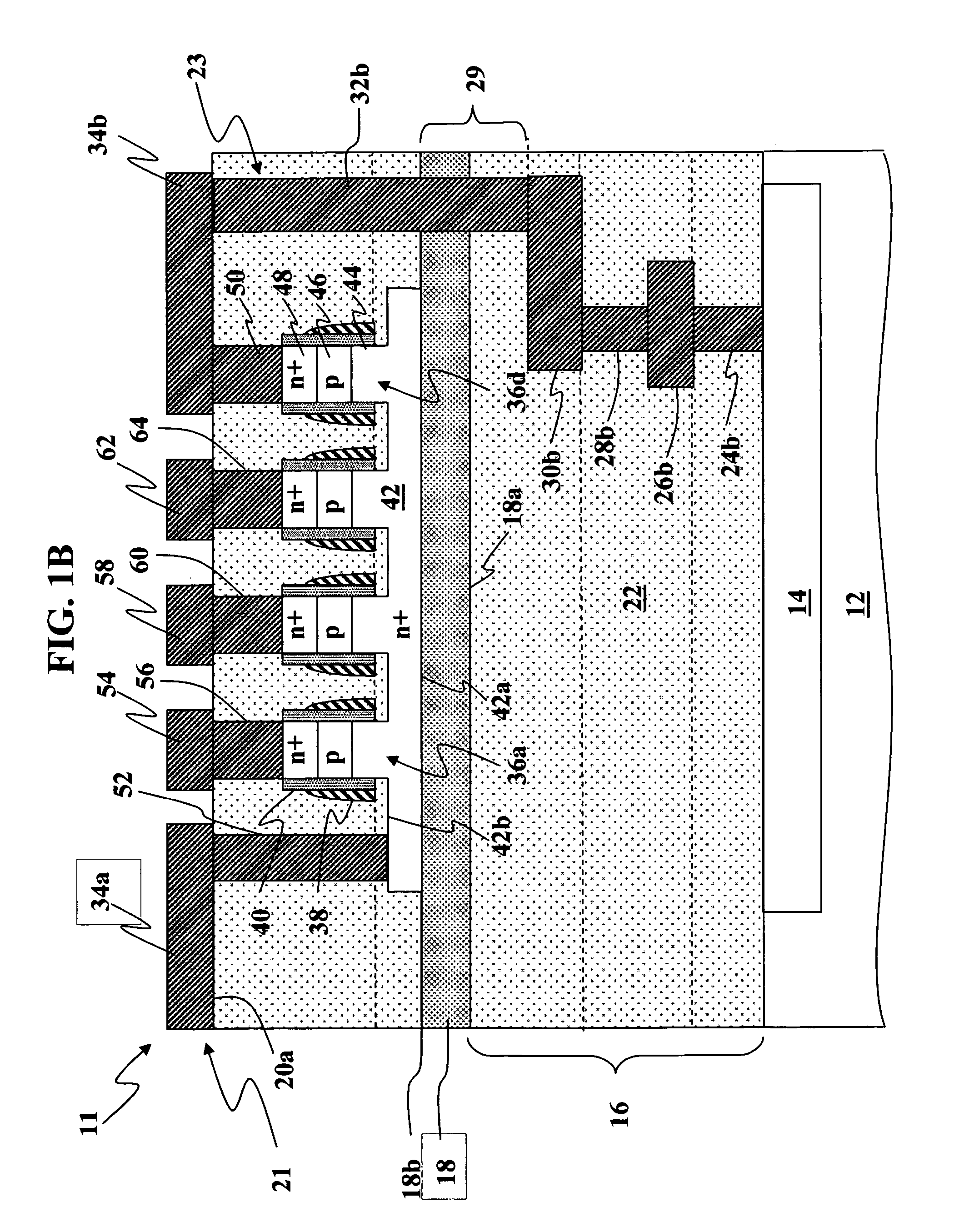

Semiconductor-on-insulator chip incorporating strained-channel partially-depleted, fully-depleted, and multiple-gate transistors

InactiveUS6867433B2Good effectSuppression of floating body effectTransistorSolid-state devicesMOSFETSemiconductor chip

In accordance with a preferred embodiment of the present invention, a silicon-on-insulator (SOI) chip includes a silicon layer of a predetermined thickness overlying an insulator layer. A multiple-gate fully-depleted SOI MOSFET including a strained channel region is formed on a first portion of the silicon layer. A planar SOI MOSFET including a strained channel region formed on another portion of the silicon layer. For example, the planar SOI MOSFET can be a planar fully-depleted SOI (FD-SOI) MOSFET or the planar SOI MOSFET can be a planar partially-depleted SOI (PD-SOI) MOSFET.

Owner:TAIWAN SEMICON MFG CO LTD

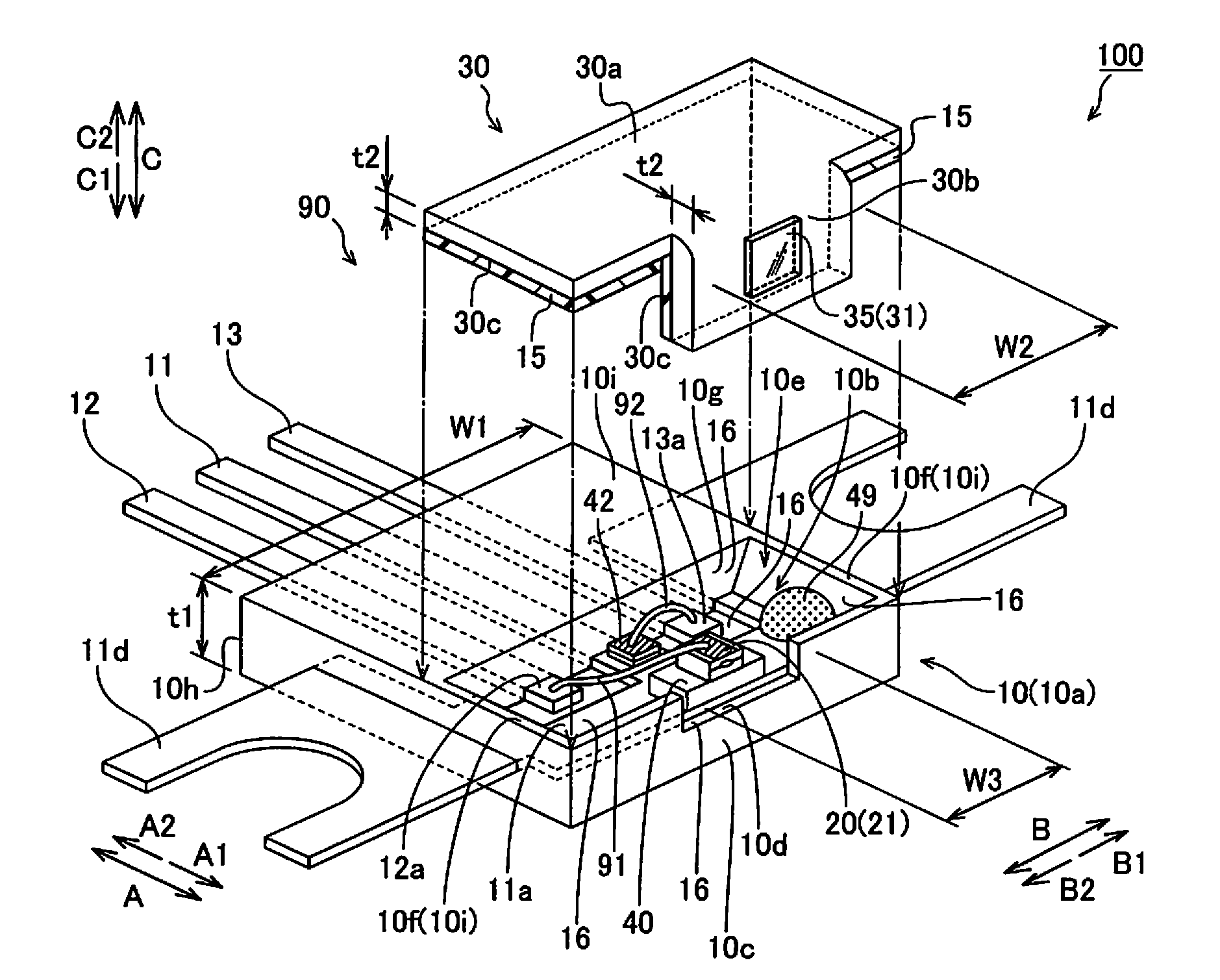

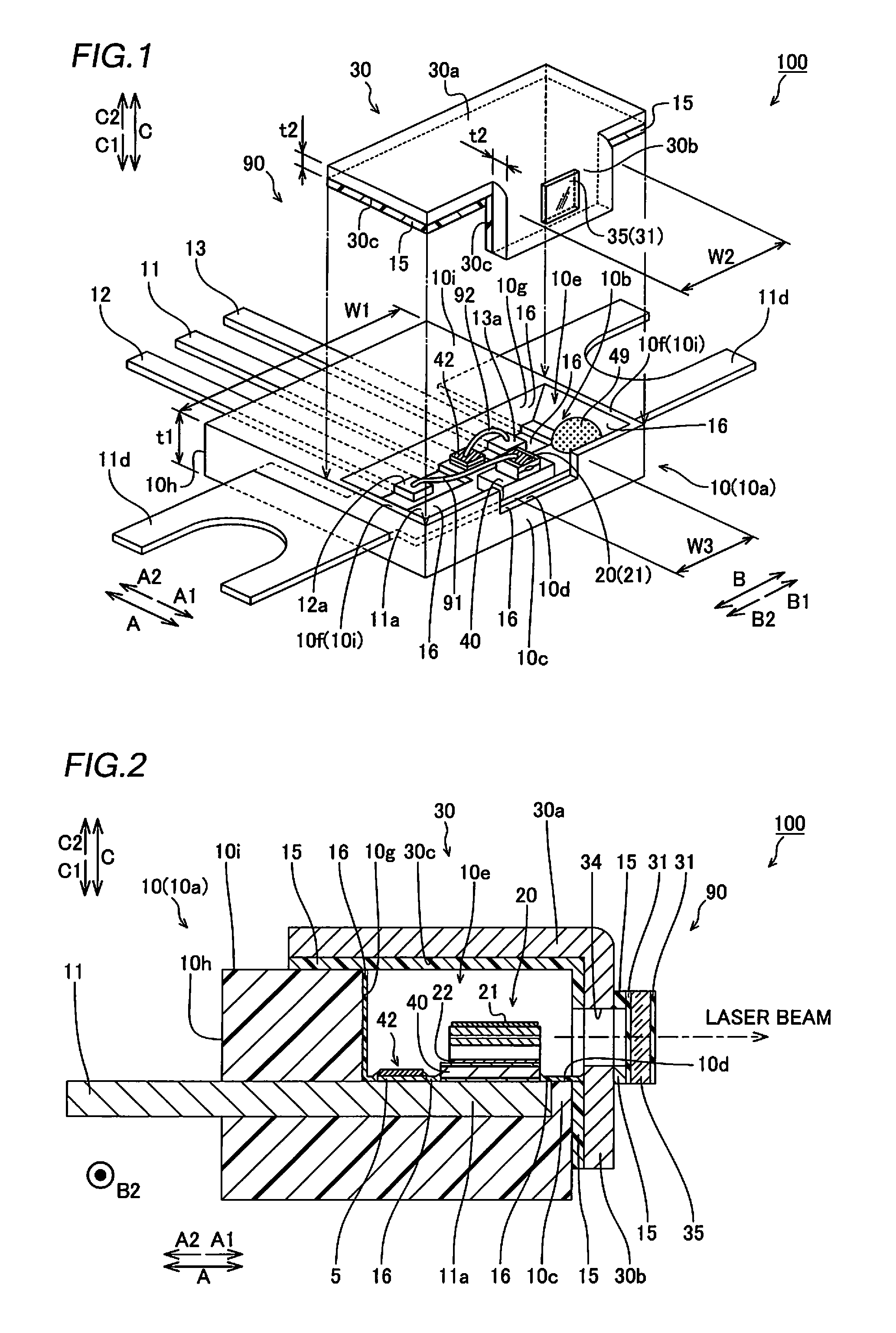

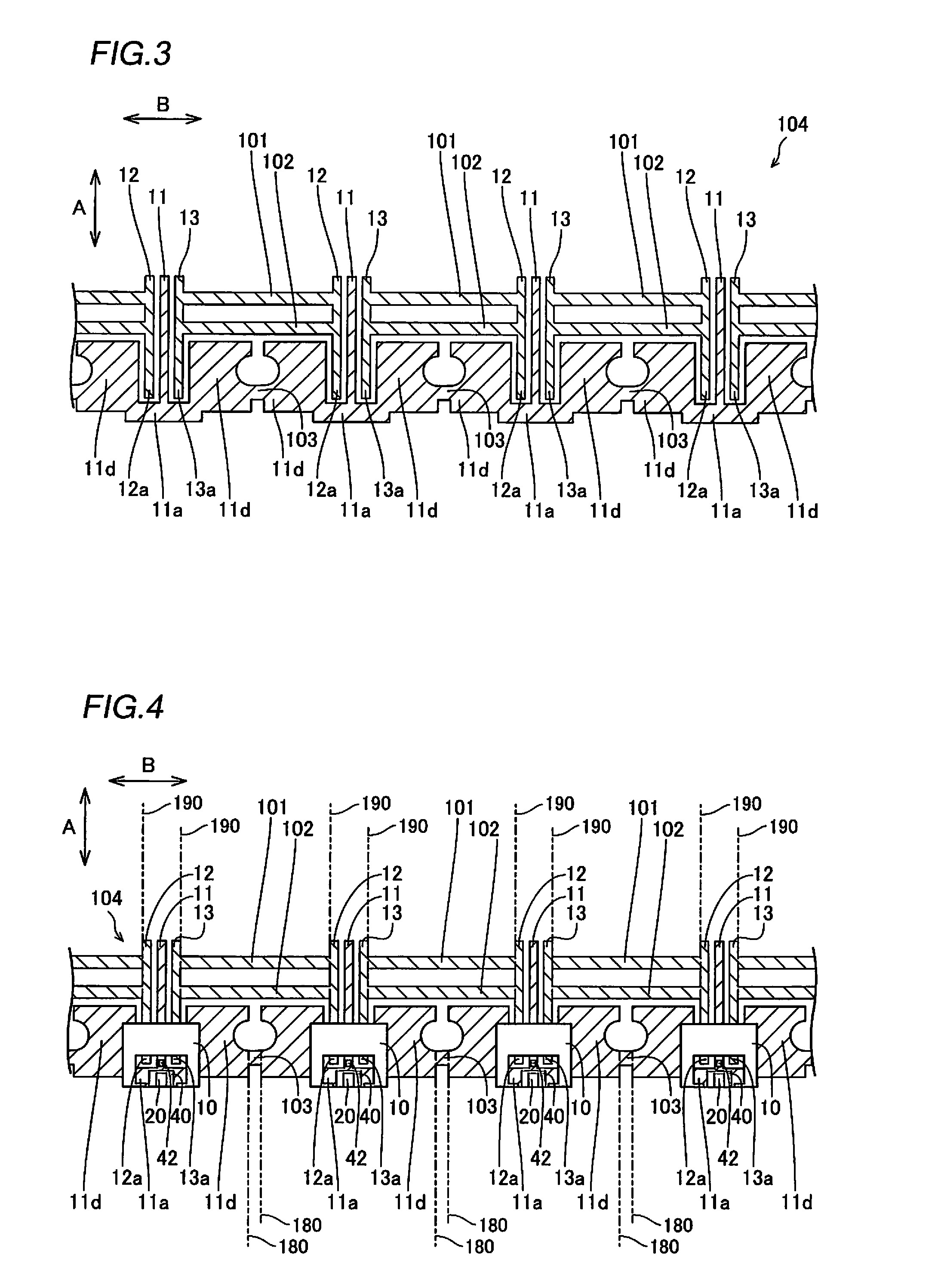

Semiconductor laser apparatus and optical apparatus

InactiveUS20120033695A1Improve sealingPromote absorptionSolid-state devicesSemiconductor lasersPolyvinyl alcoholSemiconductor chip

This semiconductor laser apparatus includes a package constituted by a plurality of members, having sealed space inside and a semiconductor laser chip arranged in the sealed space, while surfaces of the members located in the sealed space are covered with a covering agent made of an ethylene-polyvinyl alcohol copolymer.

Owner:SANYO ELECTRIC CO LTD

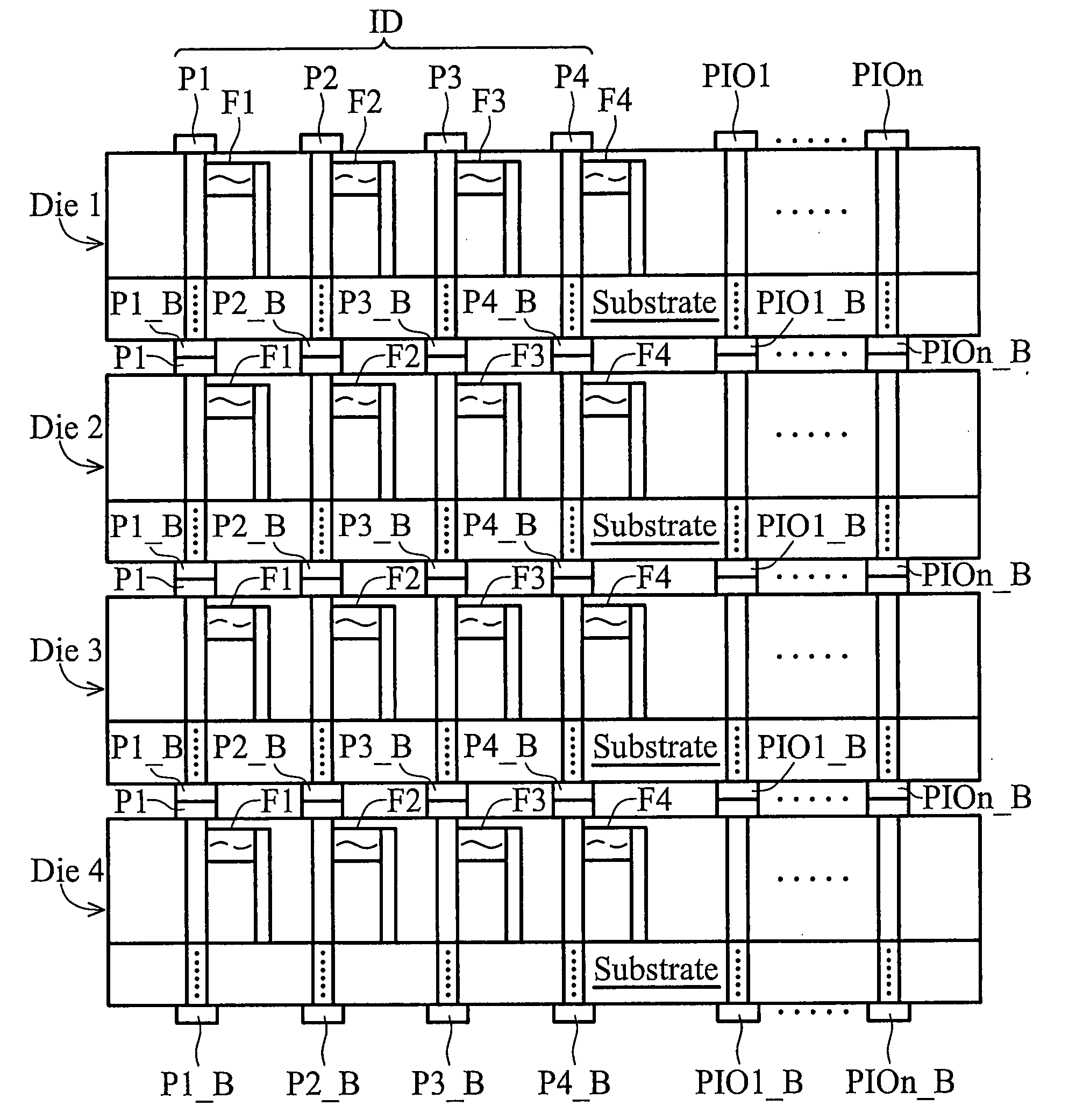

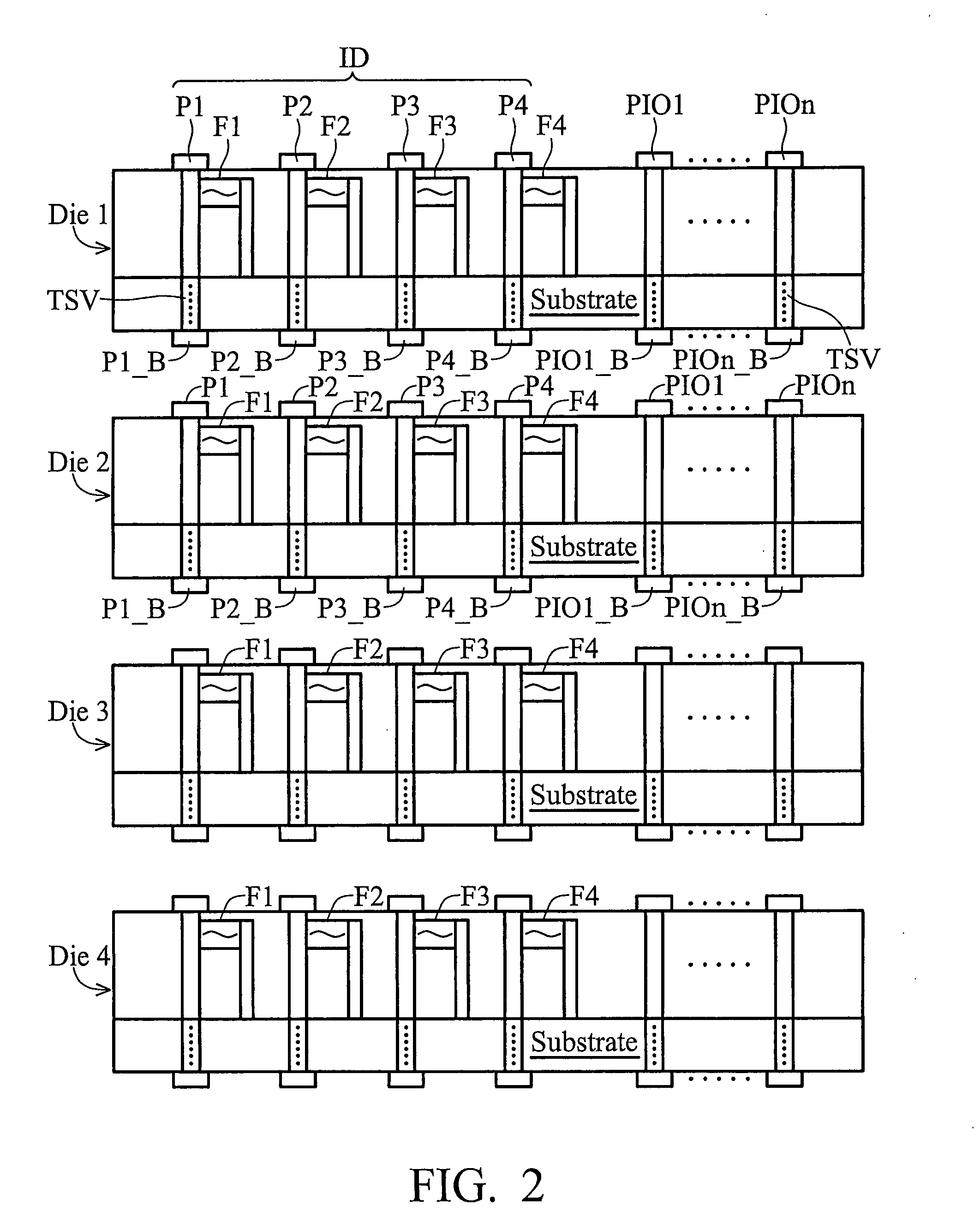

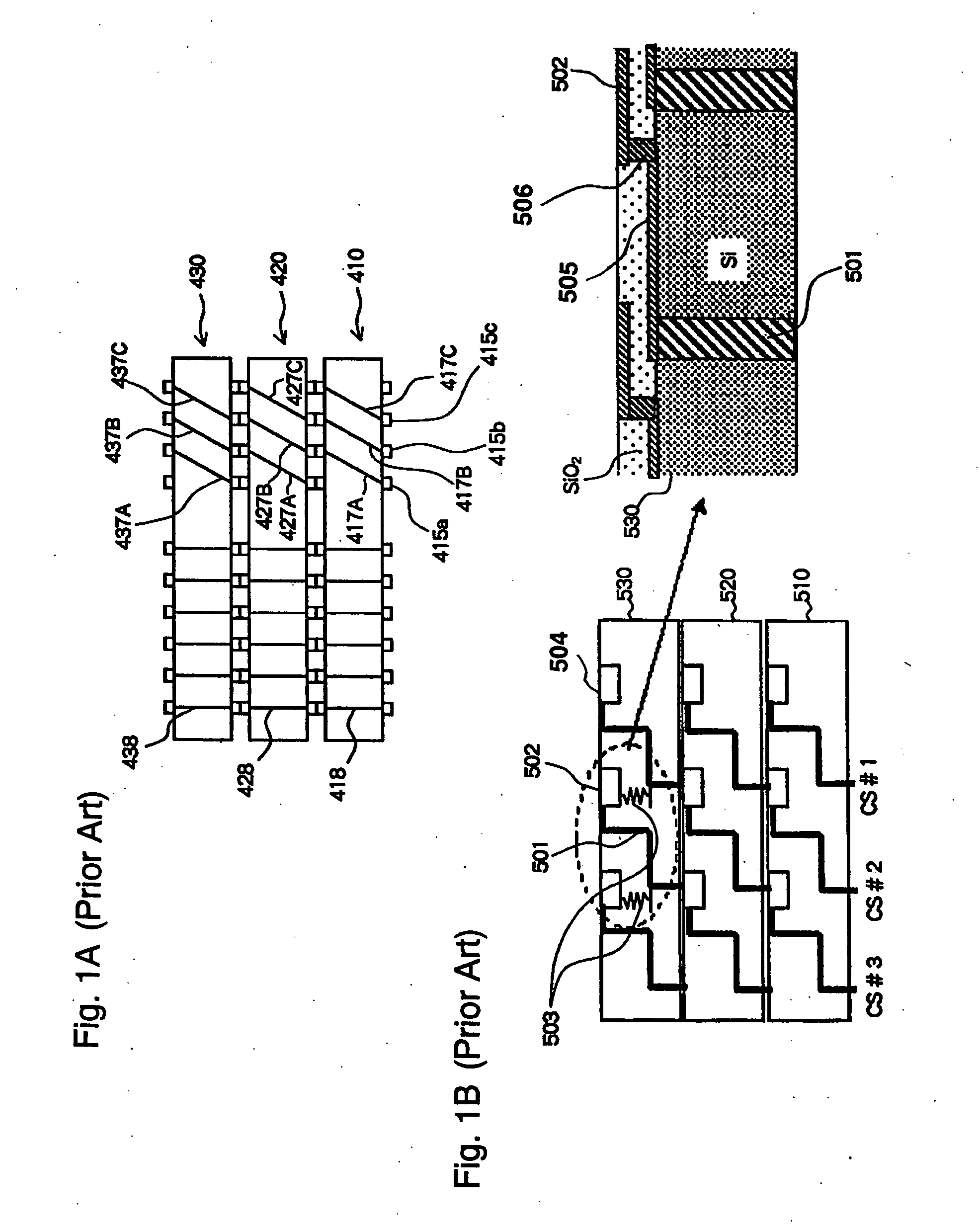

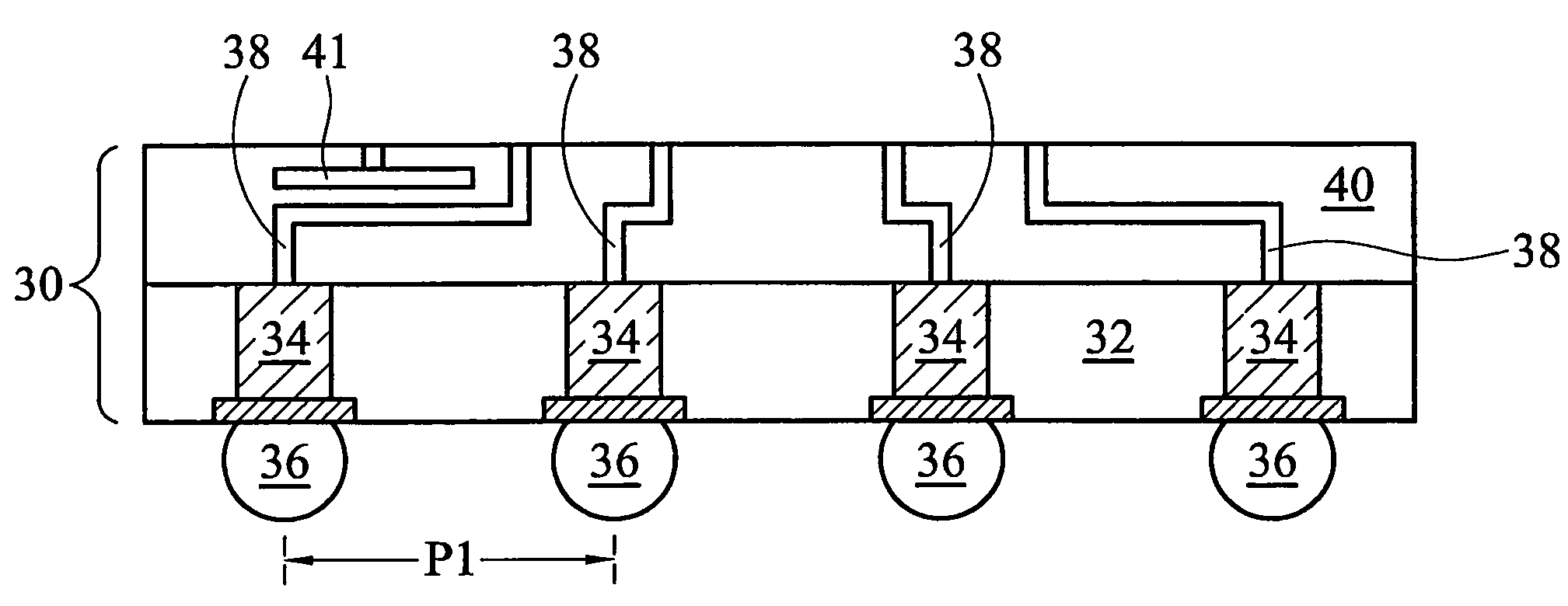

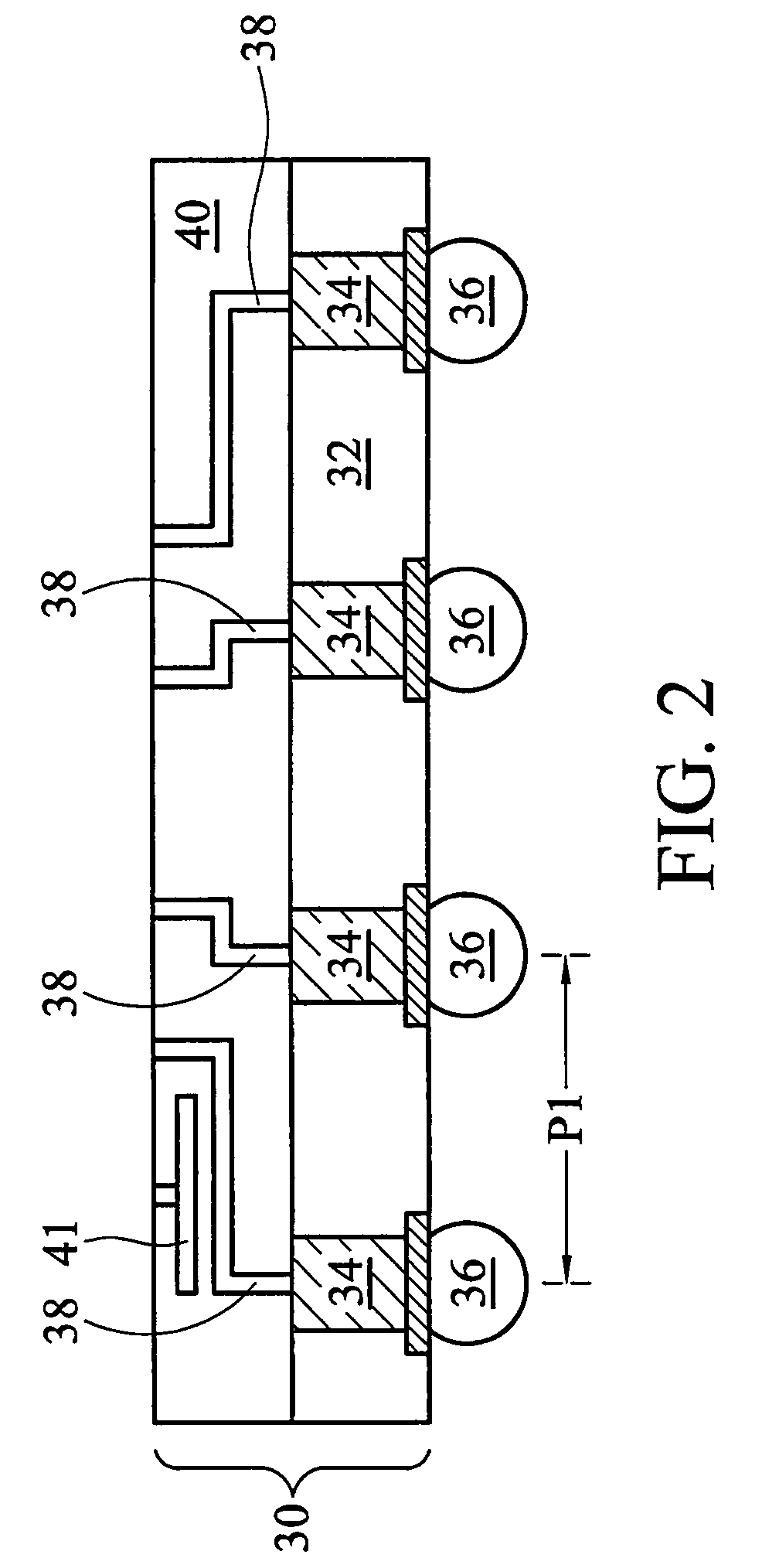

Design techniques for stacking identical memory dies

ActiveUS20080220565A1Reduce designReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor structure

A semiconductor structure includes a first semiconductor die and a second semiconductor die identical to the first semiconductor die. The first semiconductor die includes a first identification circuit; and a first plurality of input / output (I / O) pads on the surface of the first semiconductor die. The second semiconductor die includes a second identification circuit, wherein the first and the second identification circuits are programmed differently from each other; and a second plurality of I / O pads on the surface of the second semiconductor die. Each of the first plurality of I / O pads is vertically aligned to and connected to one of the respective second plurality of I / O pads. The second semiconductor die is vertically aligned to and bonded on the first semiconductor die.

Owner:TRENCHANT BLADE TECH LLC

Stack type semiconductor package and method of fabricating the same

InactiveUS20080017968A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A stack type semiconductor package, and a method of fabricating the same are provided. The stack type semiconductor package may include a lower unit package and an upper unit package. The lower unit package may include a substrate, and a semiconductor chip on an upper surface of the substrate. A bump may be on an upper surface of the substrate, and a protecting layer, covering the semiconductor chip, may be formed. The protecting layer may include a via hole partially exposing the bump. The upper unit package may be on the protecting layer, and may include an internal connection solder ball on a lower surface of the upper unit package. The internal connection solder ball may be inserted into the via hole and connected to the bump.

Owner:SAMSUNG ELECTRONICS CO LTD

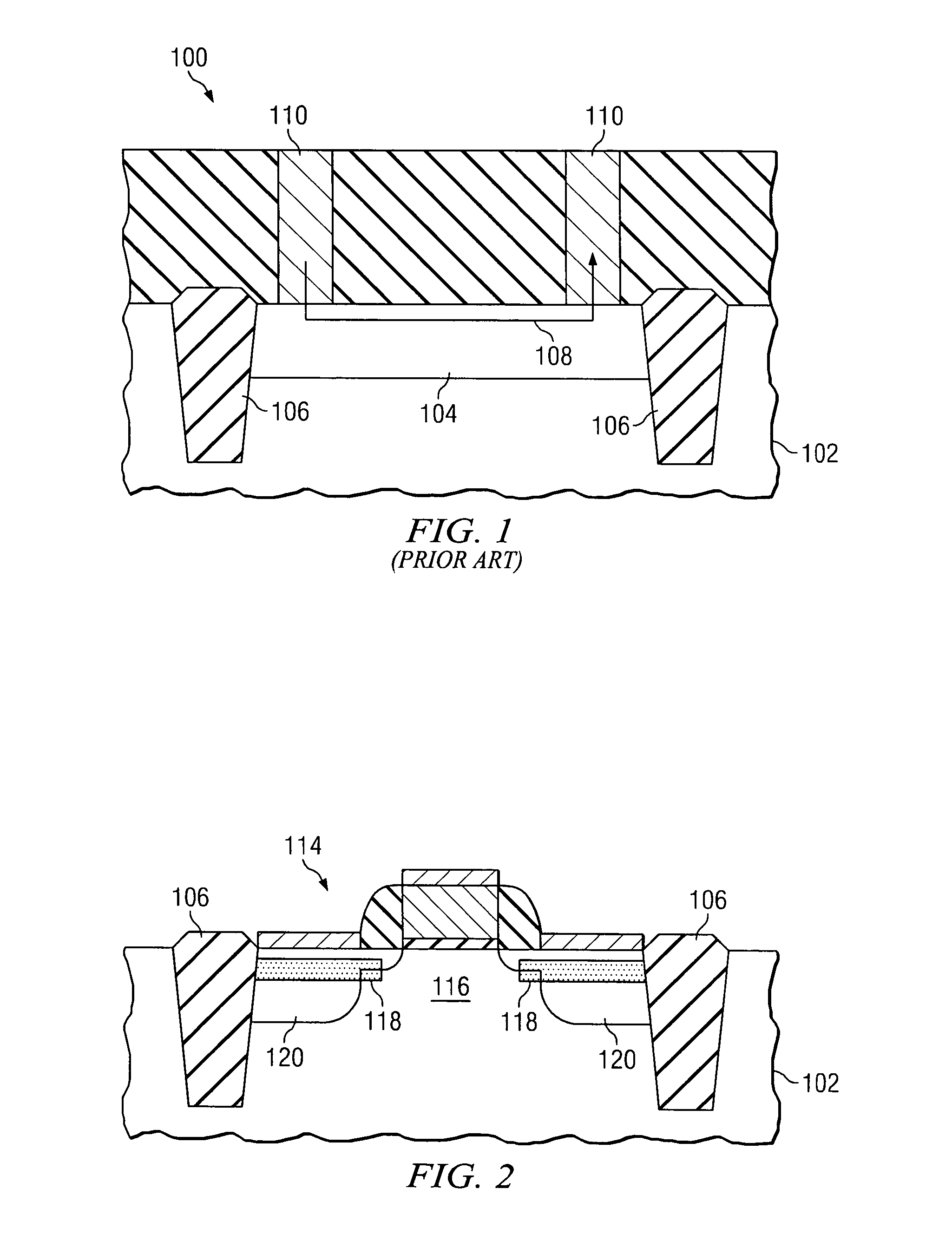

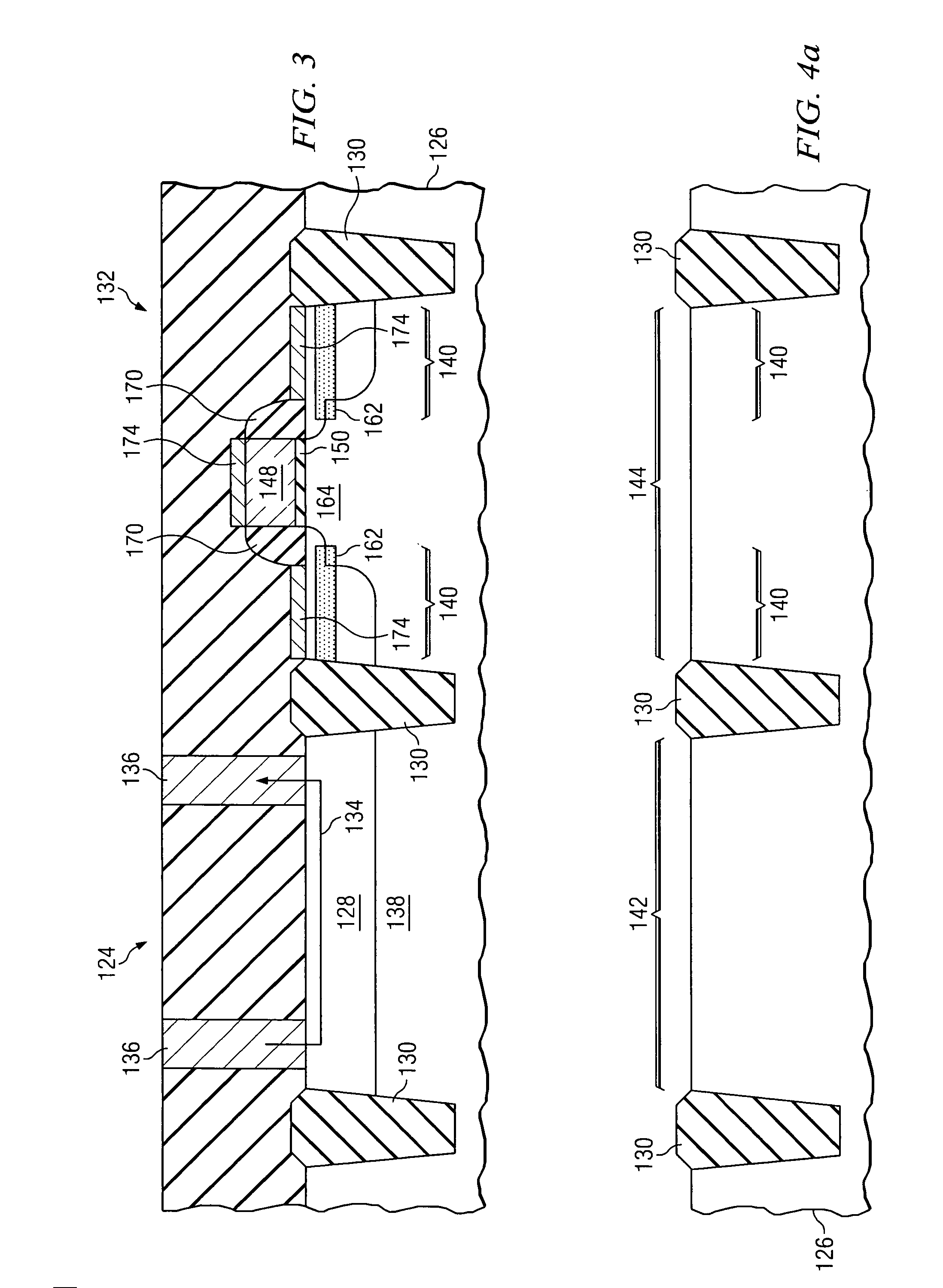

Structure and method of a strained channel transistor and a second semiconductor component in an integrated circuit

A semiconductor chip includes a semiconductor substrate 126, in which first and second active regions are disposed. A resistor 124 is formed in the first active region and the resistor 124 includes a doped region 128 formed between two terminals 136. A strained channel transistor 132 is formed in the second active region. The transistor includes a first and second stressor 141, formed in the substrate oppositely adjacent a strained channel region 143.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device with base support structure

InactiveUS20050280156A1TransistorSemiconductor/solid-state device detailsDevice materialSemiconductor chip

An apparatus includes a semiconductor chip with a base support structure having a surface and an opposed surface. At least one device structure extends from the surface of the base support structure. A first conductive region is coupled to the base support structure. At least a portion of the first conductive region extends below the opposed surface.

Owner:BESANG

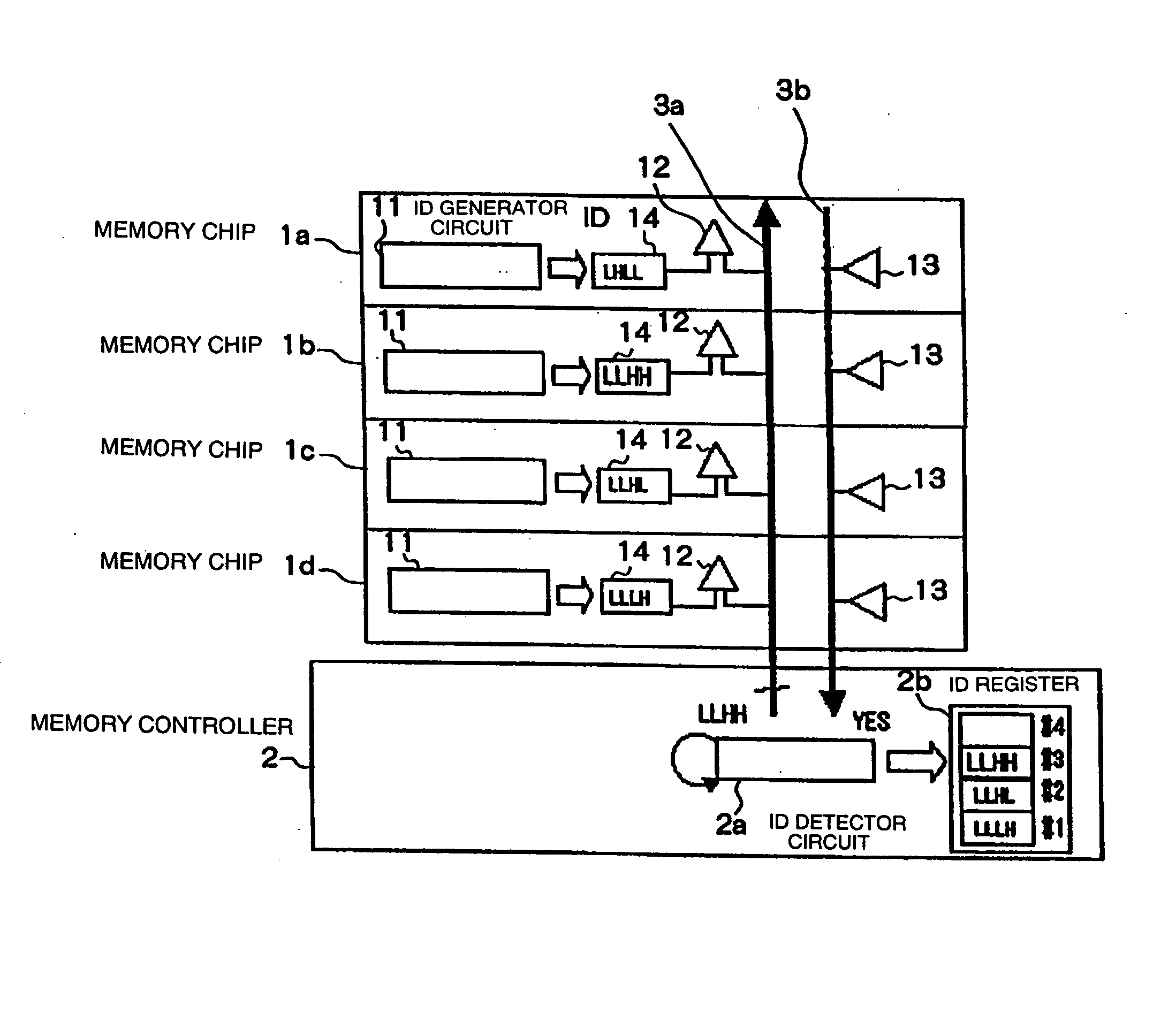

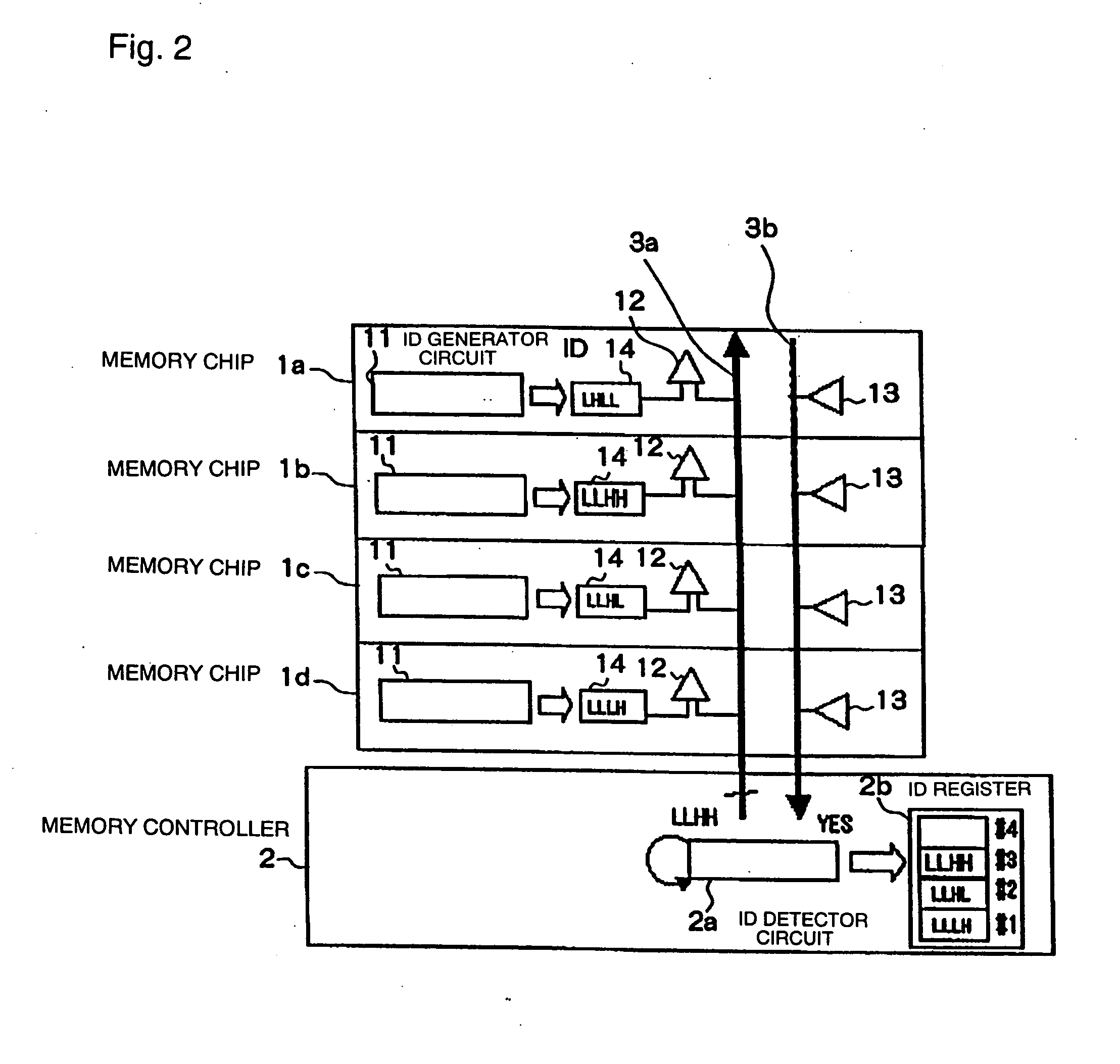

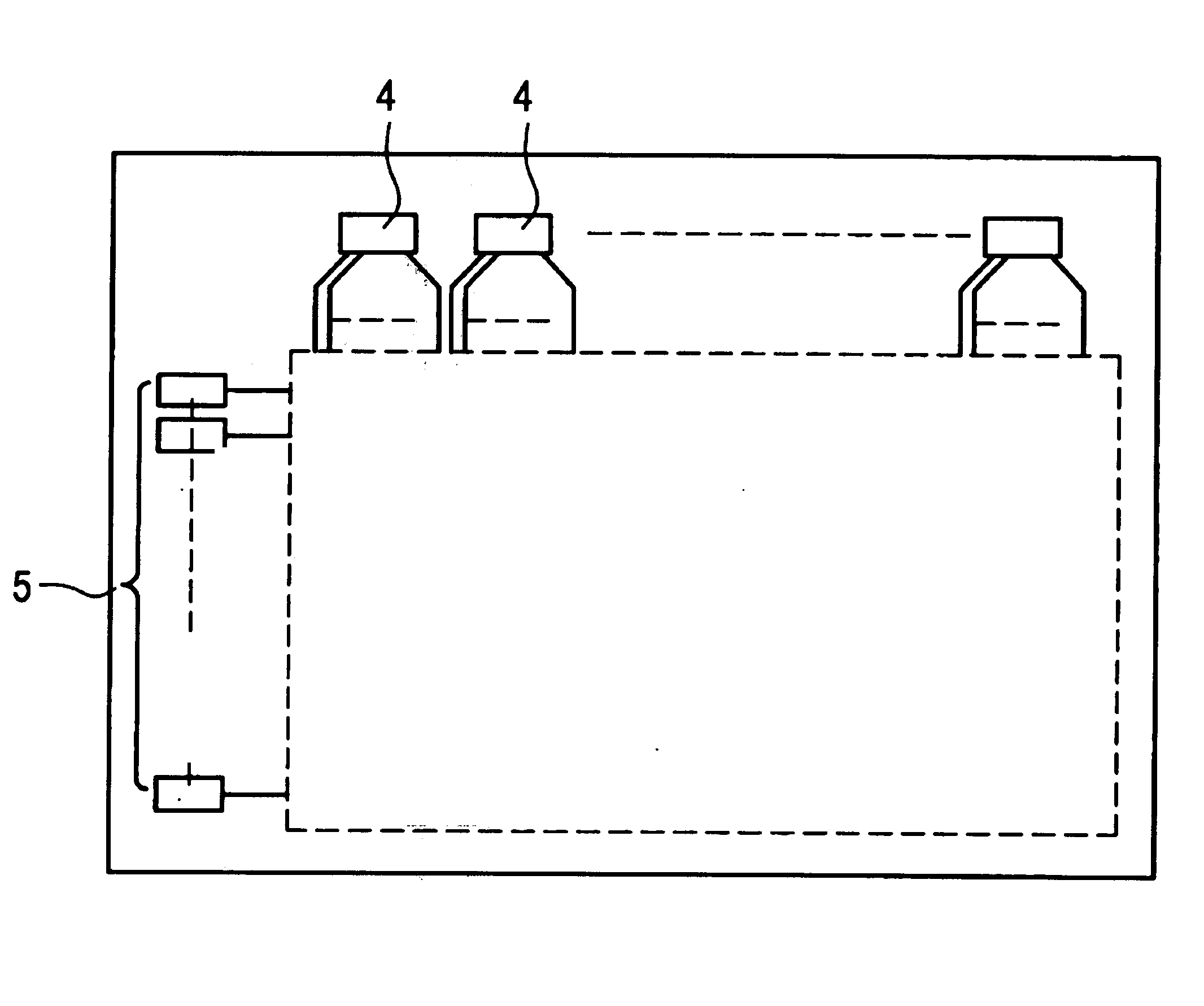

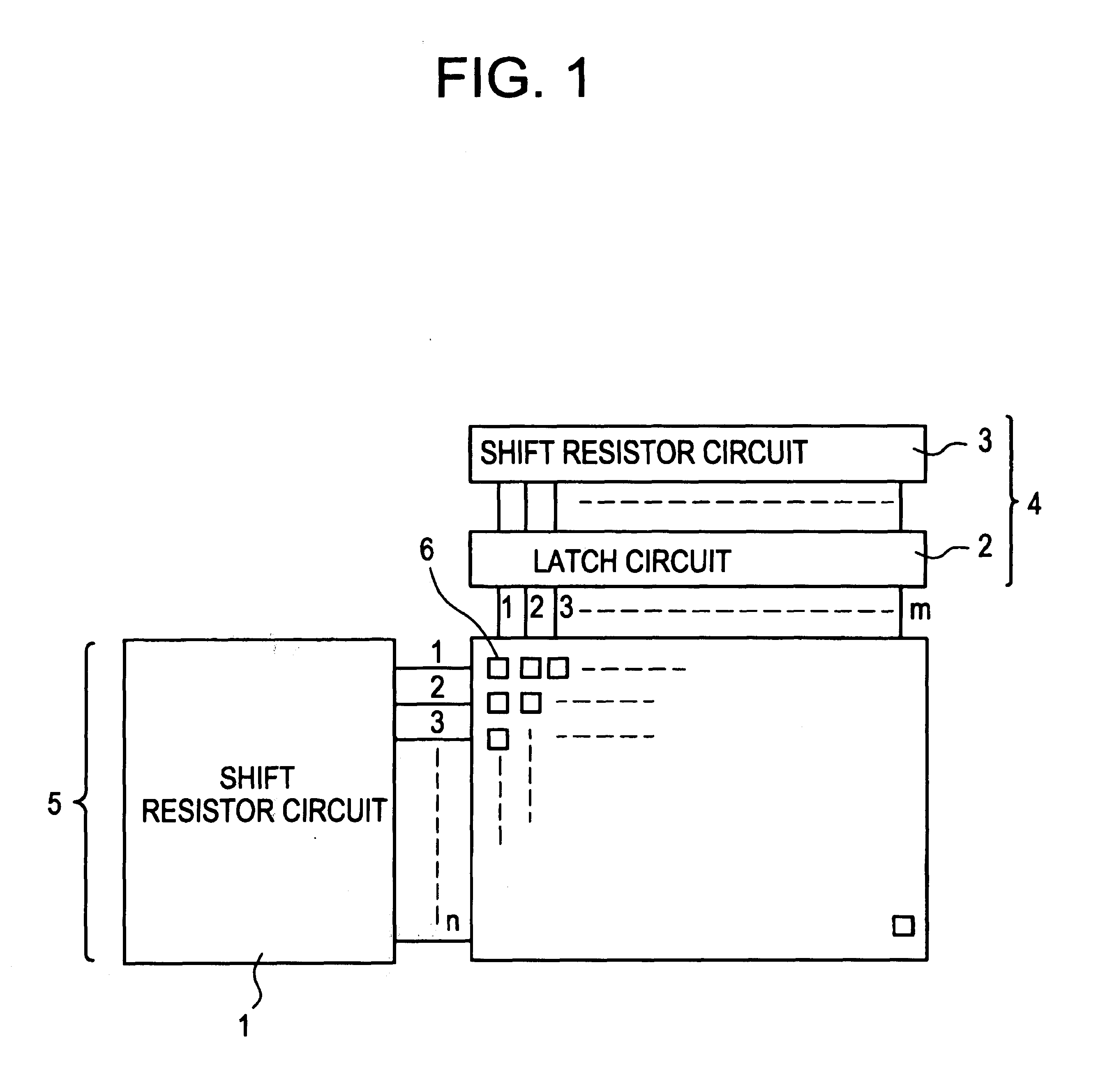

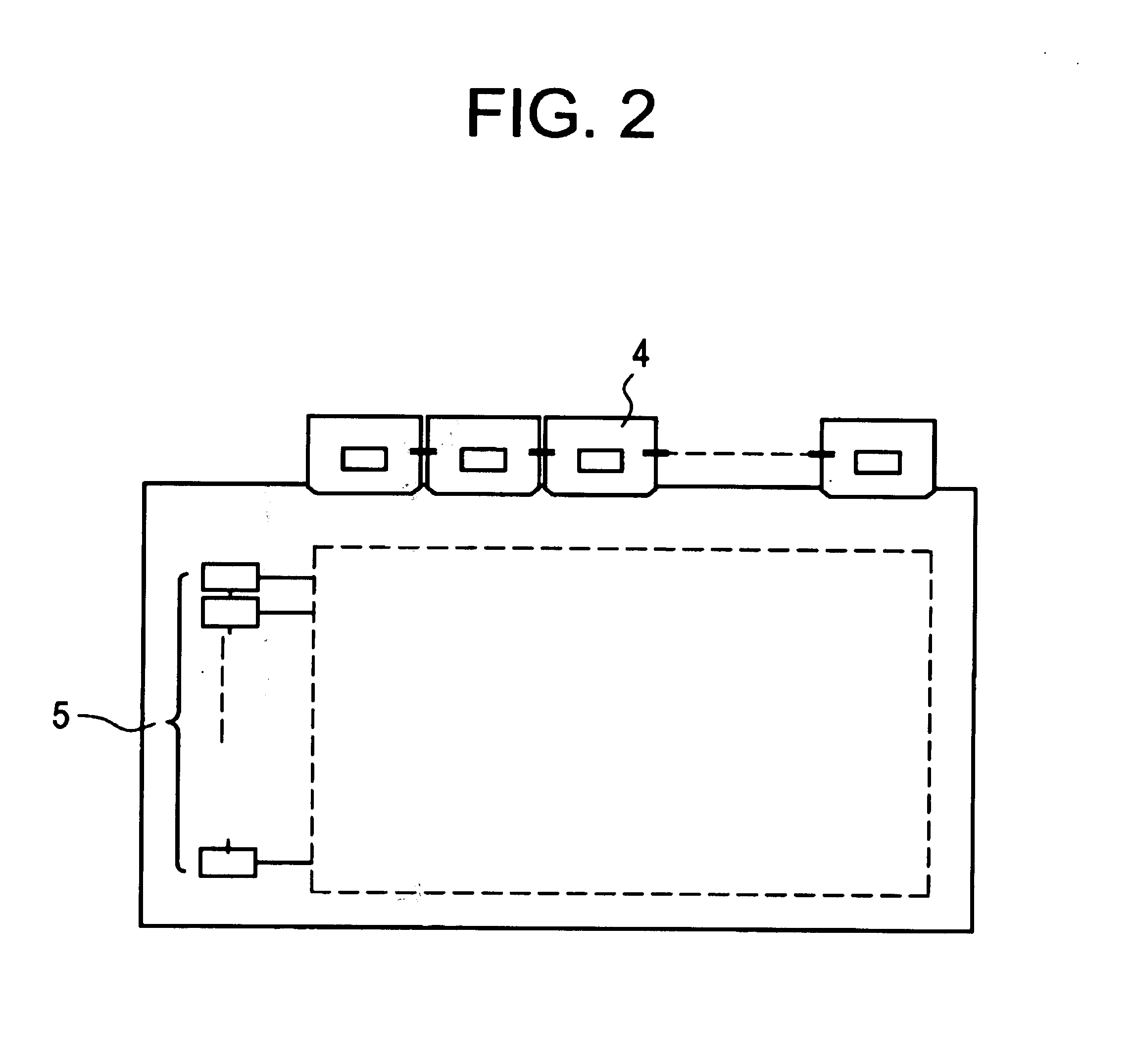

Stacked semiconductor device and semiconductor chip control method

InactiveUS20050082664A1Semiconductor/solid-state device detailsSolid-state devicesMemory chipDetector circuits

Each of stacked memory chips has an ID generator circuit for generating identification information in accordance with its manufacturing process. Since the memory chip manufacturing process implies process variations, the IDs generated by the respective ID generator circuits are different from one another even though the ID generator circuits are identical in design. A memory controller instructs an ID detector circuit to detect the IDs of the respective memory chips, and individually controls the respective memory chips based on the detected IDs.

Owner:ELPIDA MEMORY INC

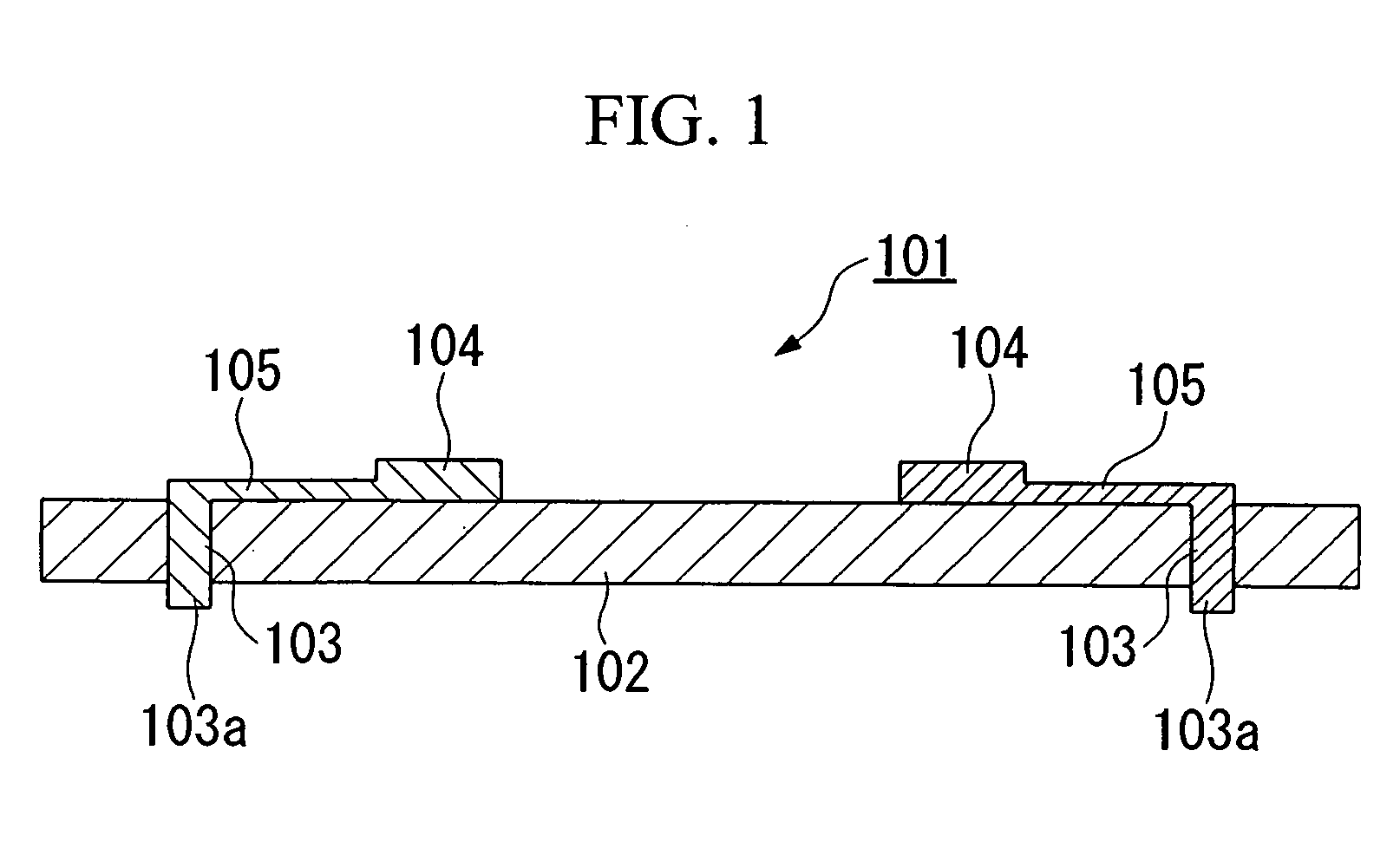

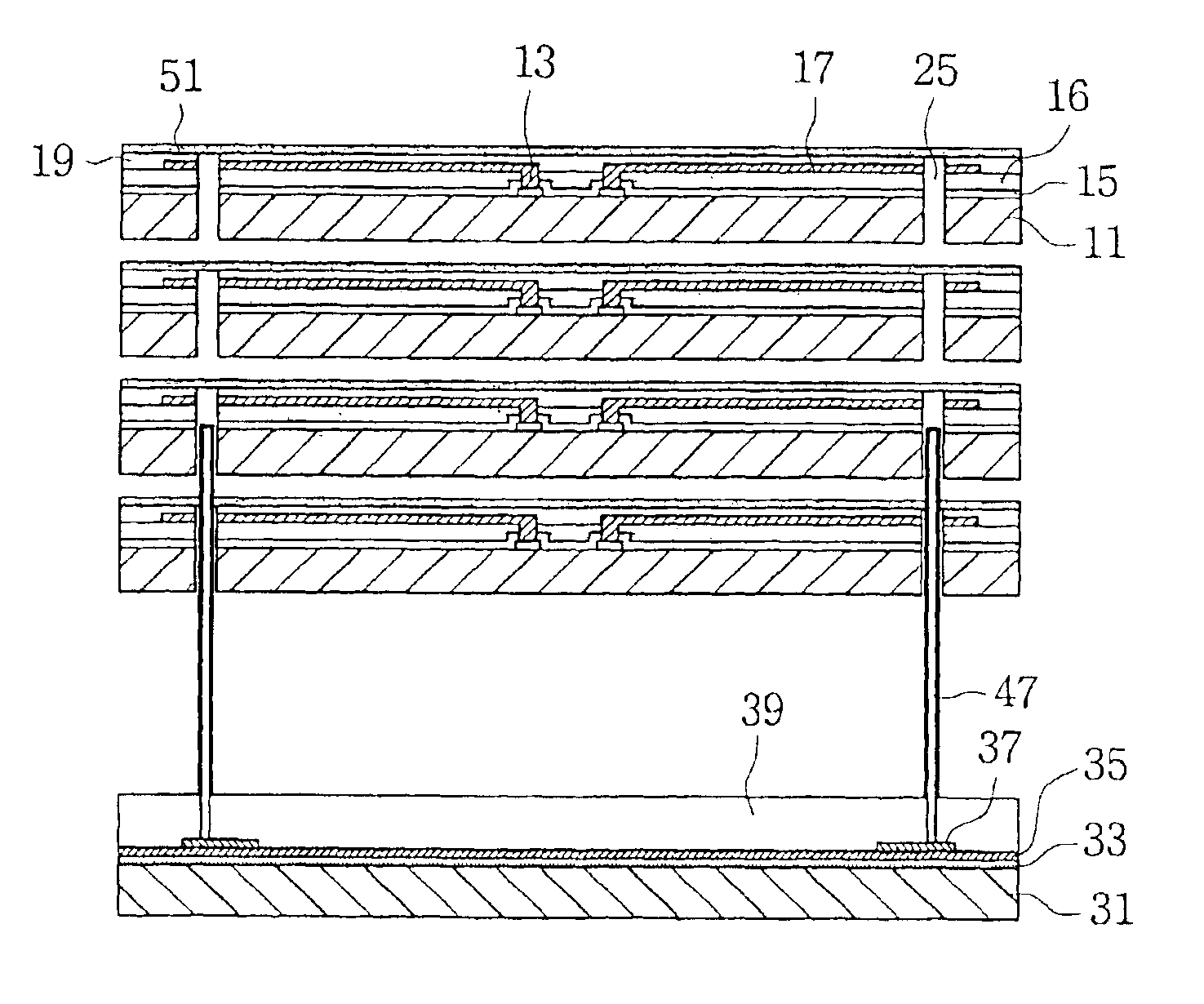

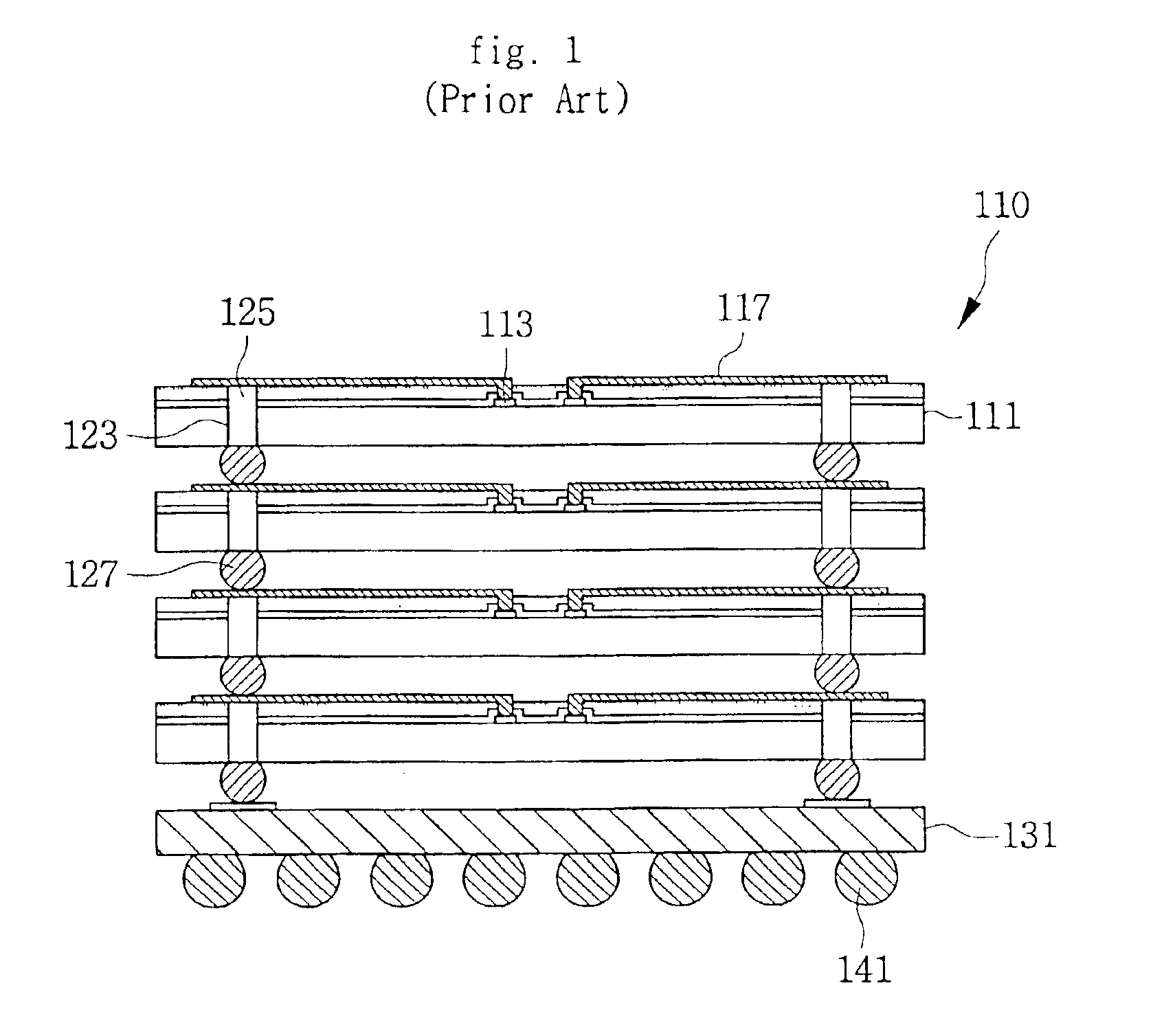

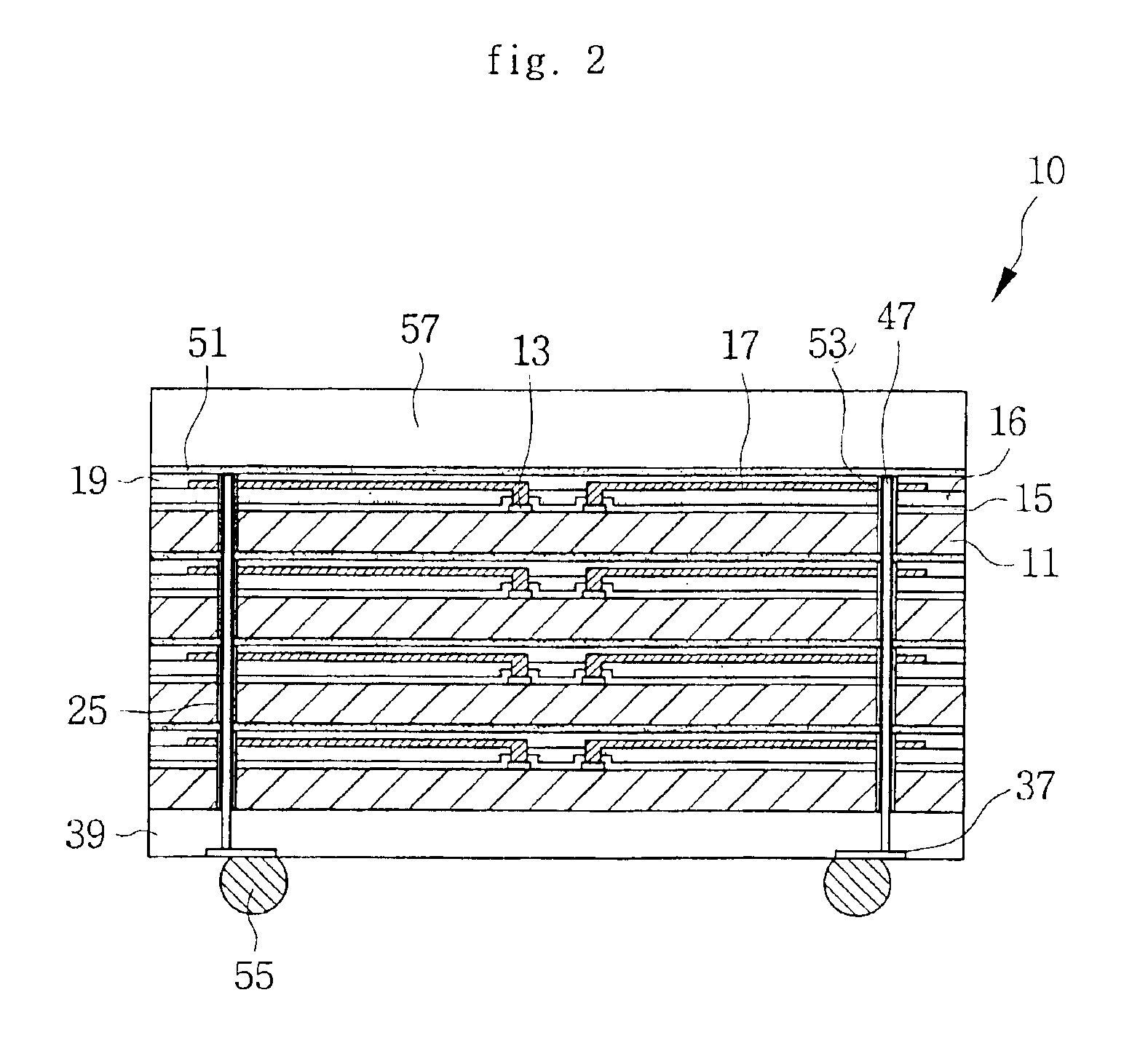

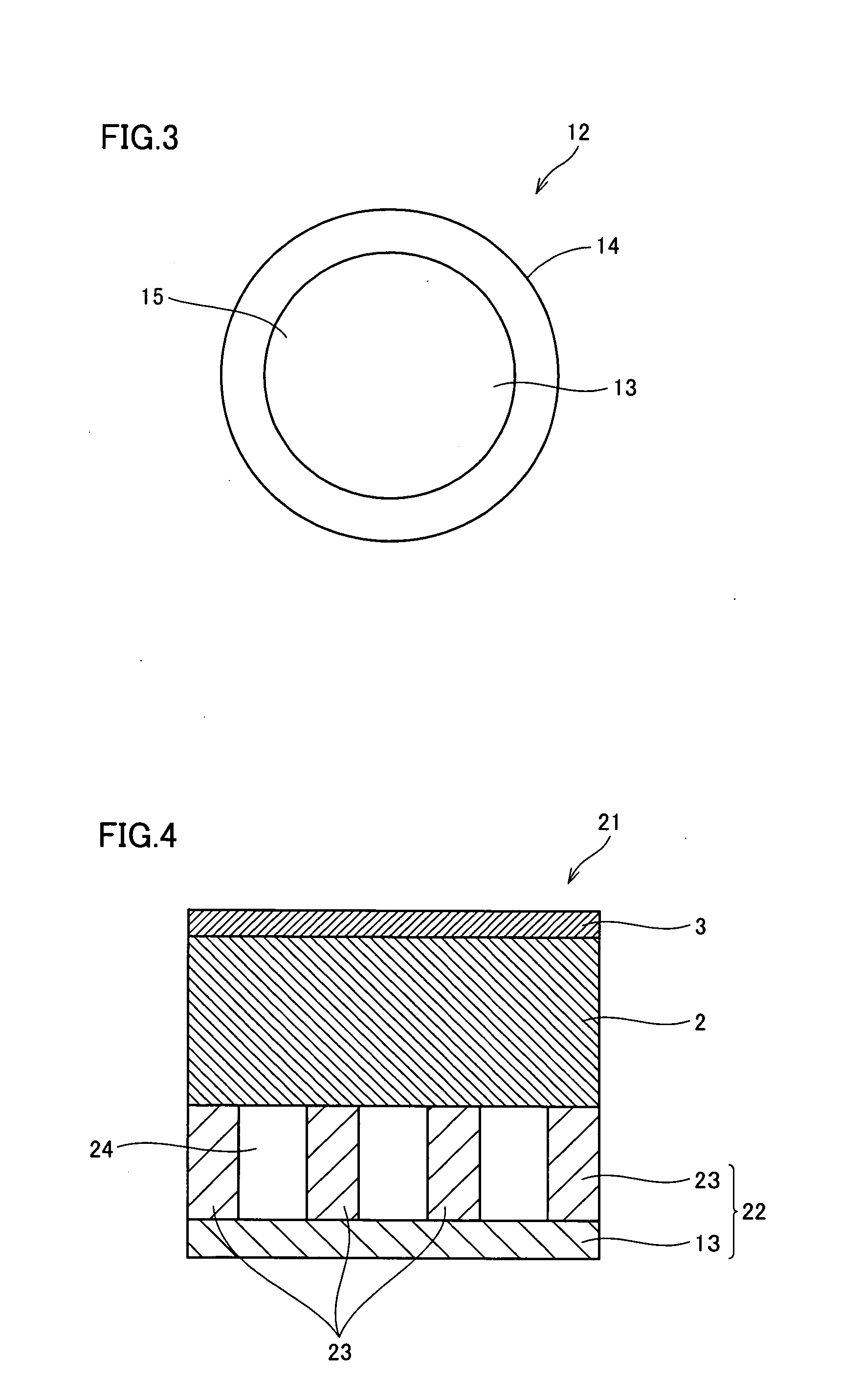

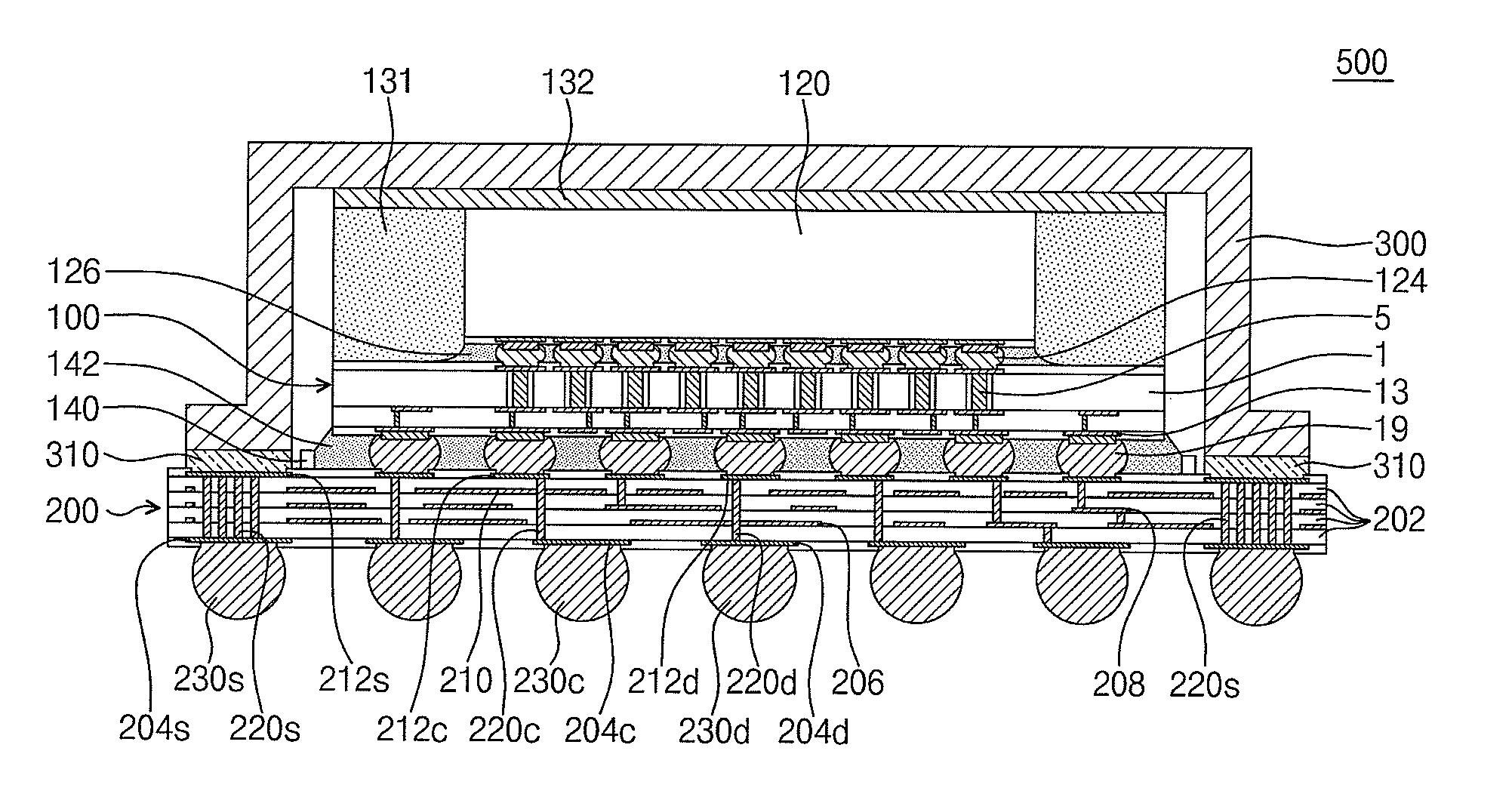

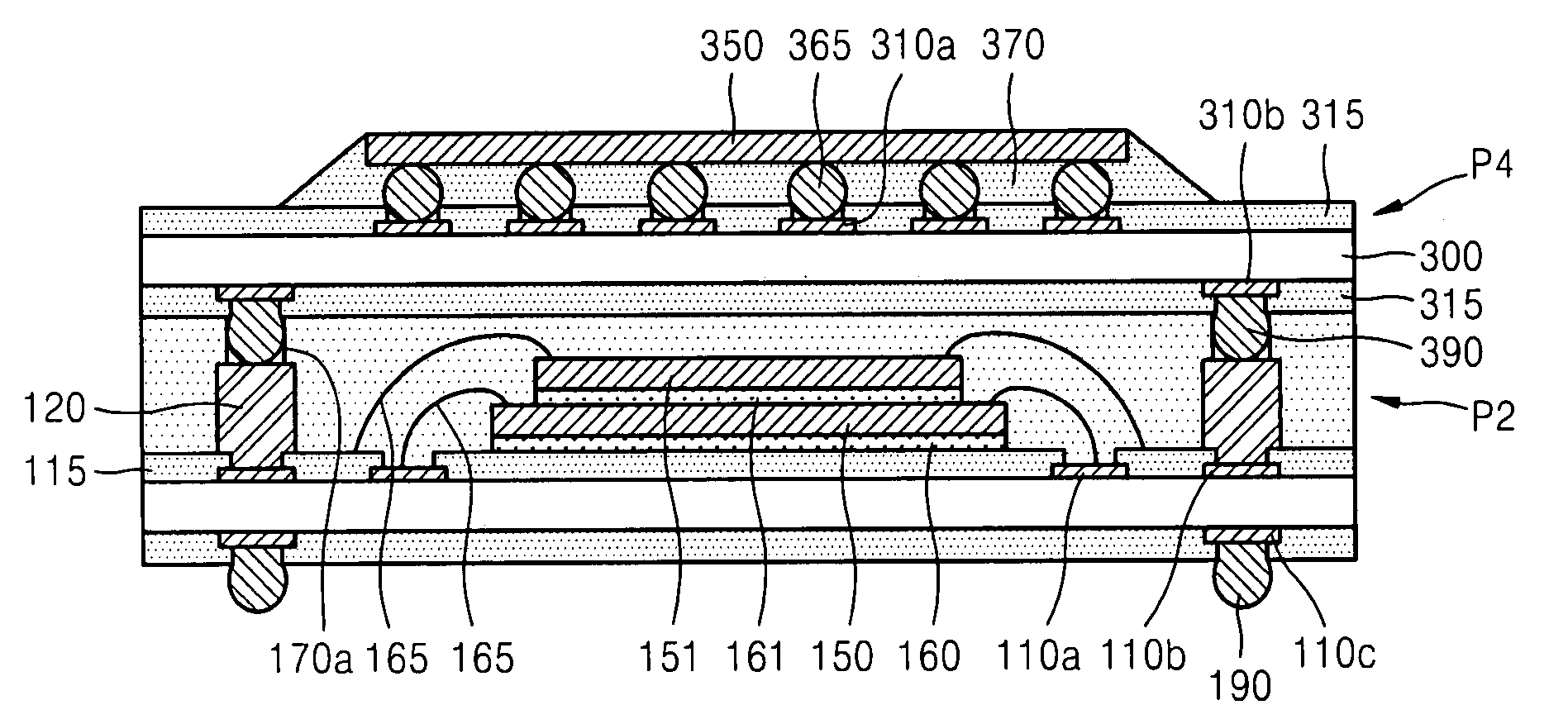

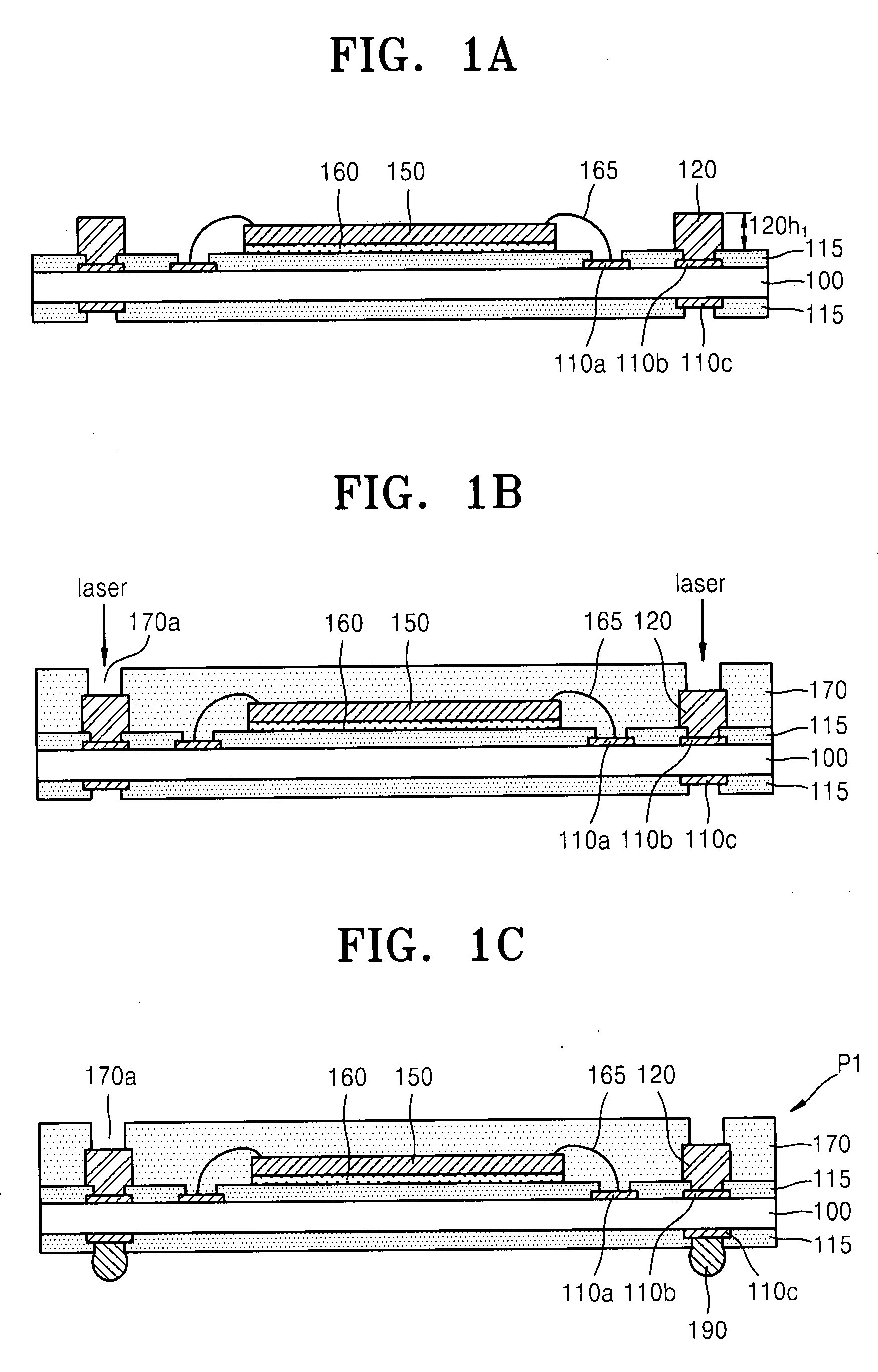

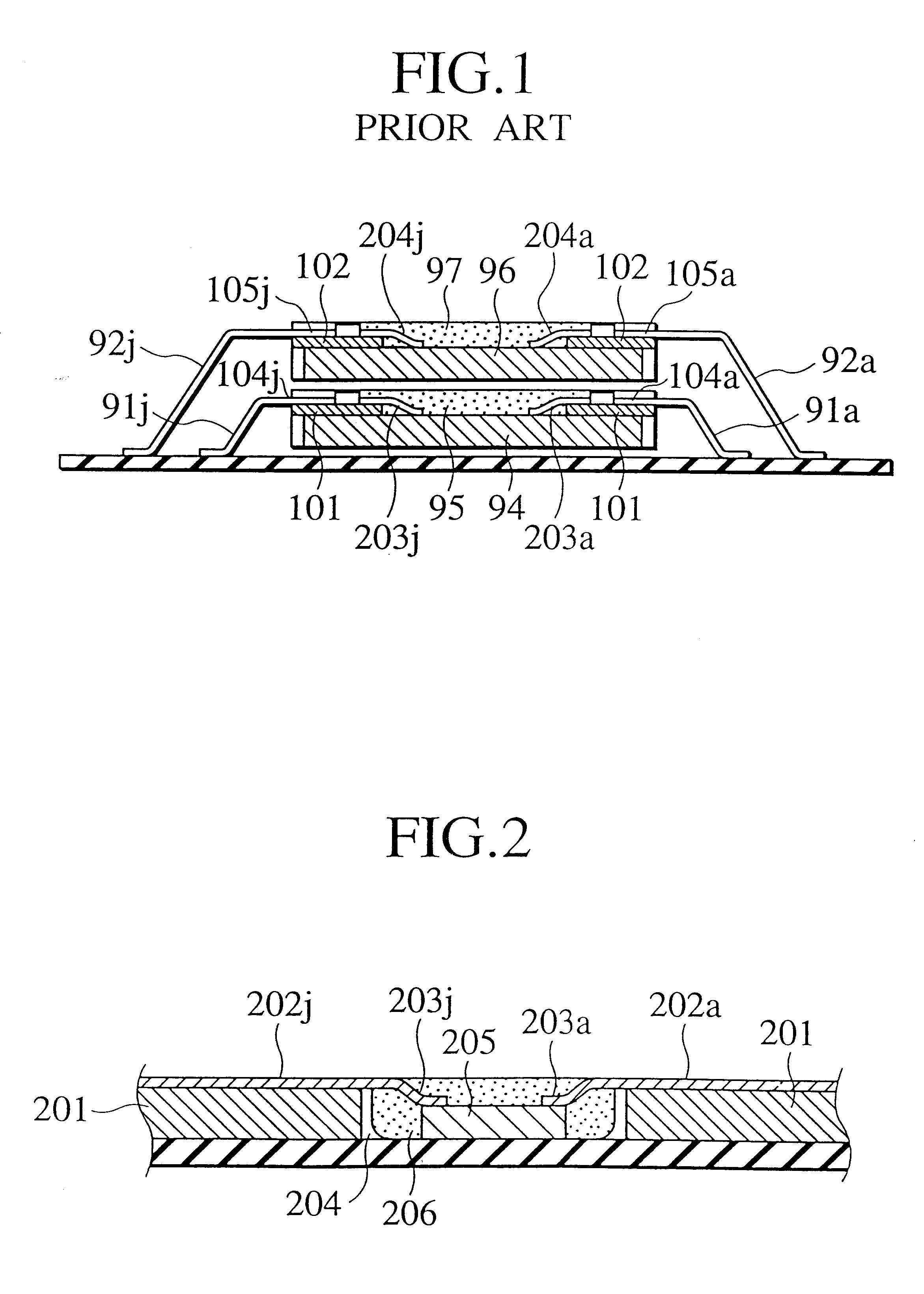

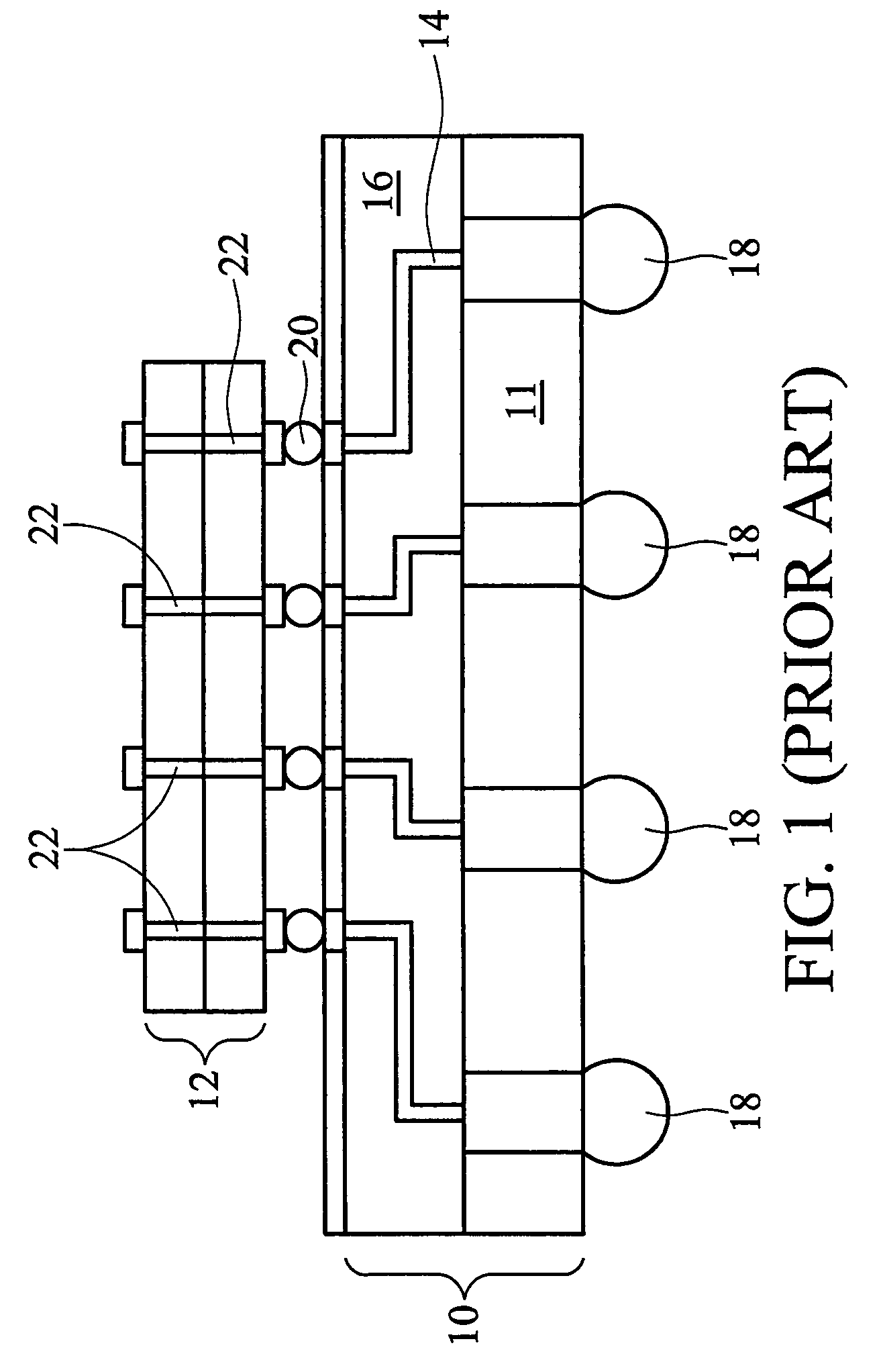

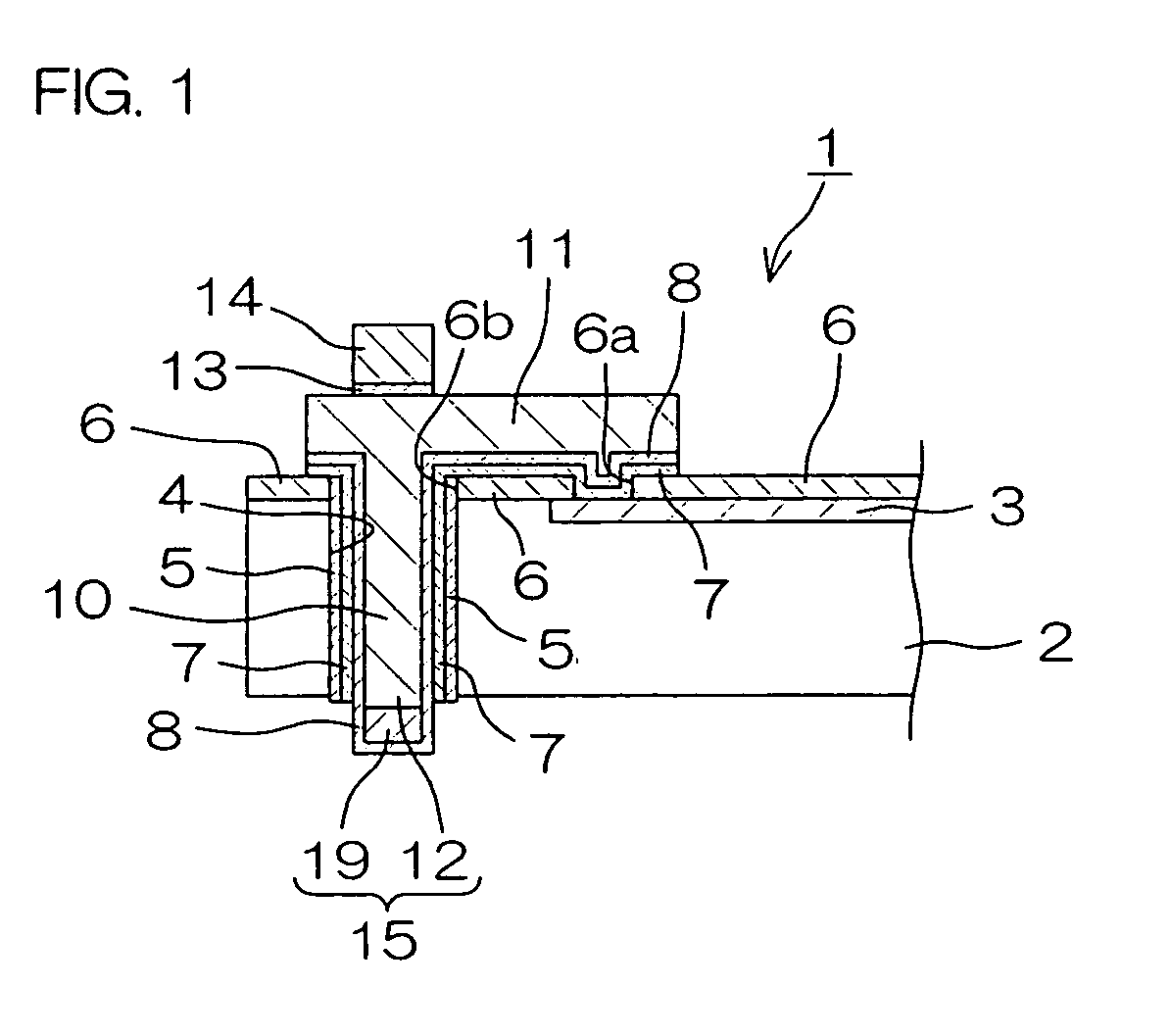

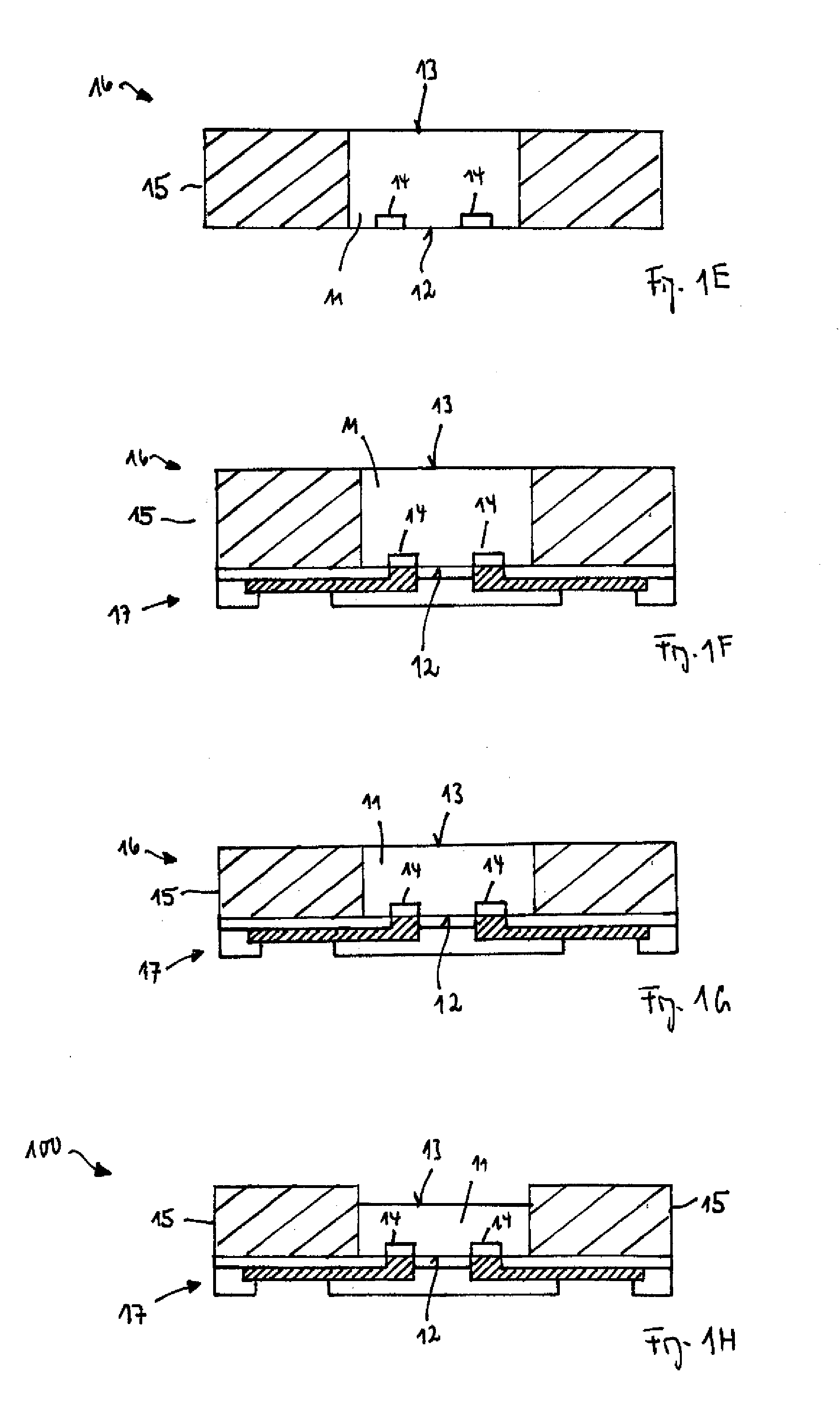

Package having very thin semiconductor chip, multichip module assembled by the package, and method for manufacturing the same

InactiveUS6239496B1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor package

A semiconductor package of this invention has an insulating substrates, wiring layers disposed on the surface of the insulating substrate, a semiconductor chip disposed in a device hole provided in the insulating substrate, inner-joint-conductors for connecting at least part of the bonding pads on the surface of the semiconductor chip to the corresponding inner-joint-conductors and connection lands connected to the wiring layers. The device hole is provided so that it goes through the center of the insulating substrate. The semiconductor chip is thinner than the insulating substrate. Then, this semiconductor chip is disposed in the device hole such that a bottom thereof is flush with a bottom plane of the insulating substrate. Further, this invention provides a MCM in which plural pieces of the thin semiconductor packages are laminated. In the MCM, the semiconductor packages are laminated such that top and bottom faces of the thin silicon chip are inverted. Predetermined connection lands are electrically connected to each other through a connecting conductor. This MCM has a high mechanical strength in its stacked structure and there is a low possibility that crack may occur in the package due to stress in the bending direction.

Owner:KK TOSHIBA

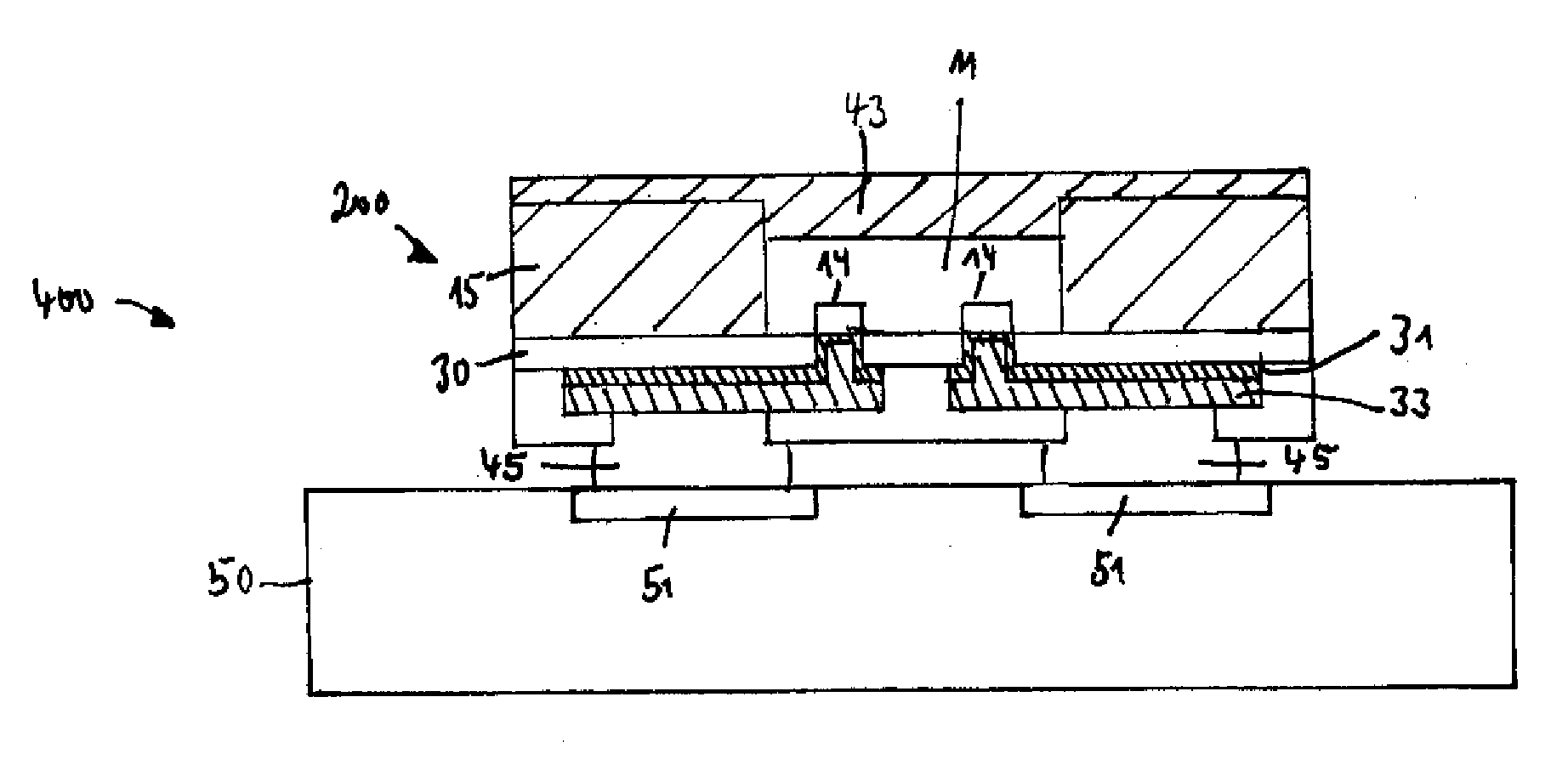

Low-cost and ultra-fine integrated circuit packaging technique

ActiveUS7576435B2Improved feasibility of formingReduce bondingSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor chip

A semiconductor package structure and the methods for forming the same are provided. The semiconductor package structure includes an interposer; a first plurality of bonding pads on a side of the interposer; a semiconductor chip; and a second plurality of bonding pads on a side of the semiconductor chip. The first and the second plurality of bonding pads are bonded through metal-to-metal bonds.

Owner:ADVANCED MFG INNOVATIONS INC

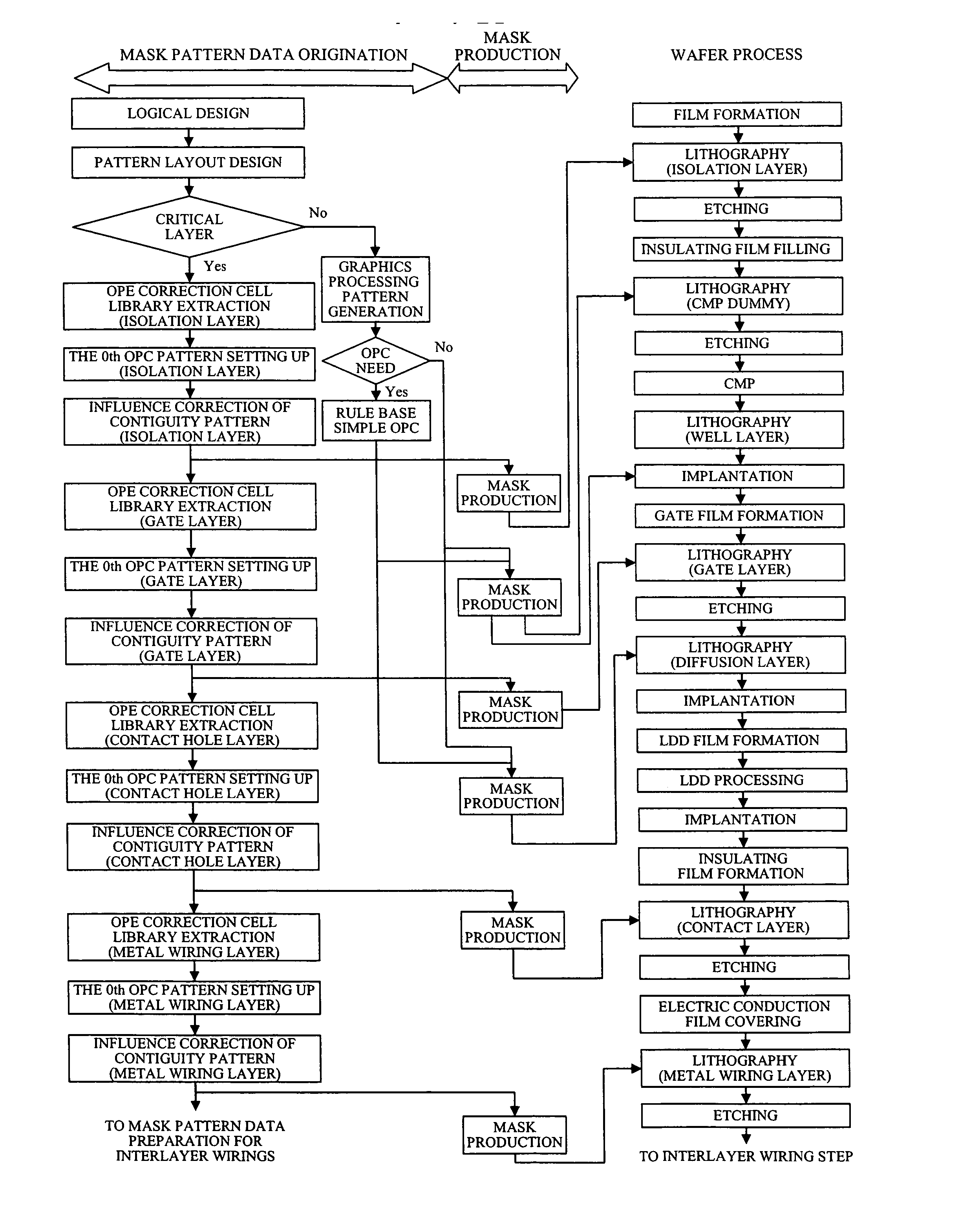

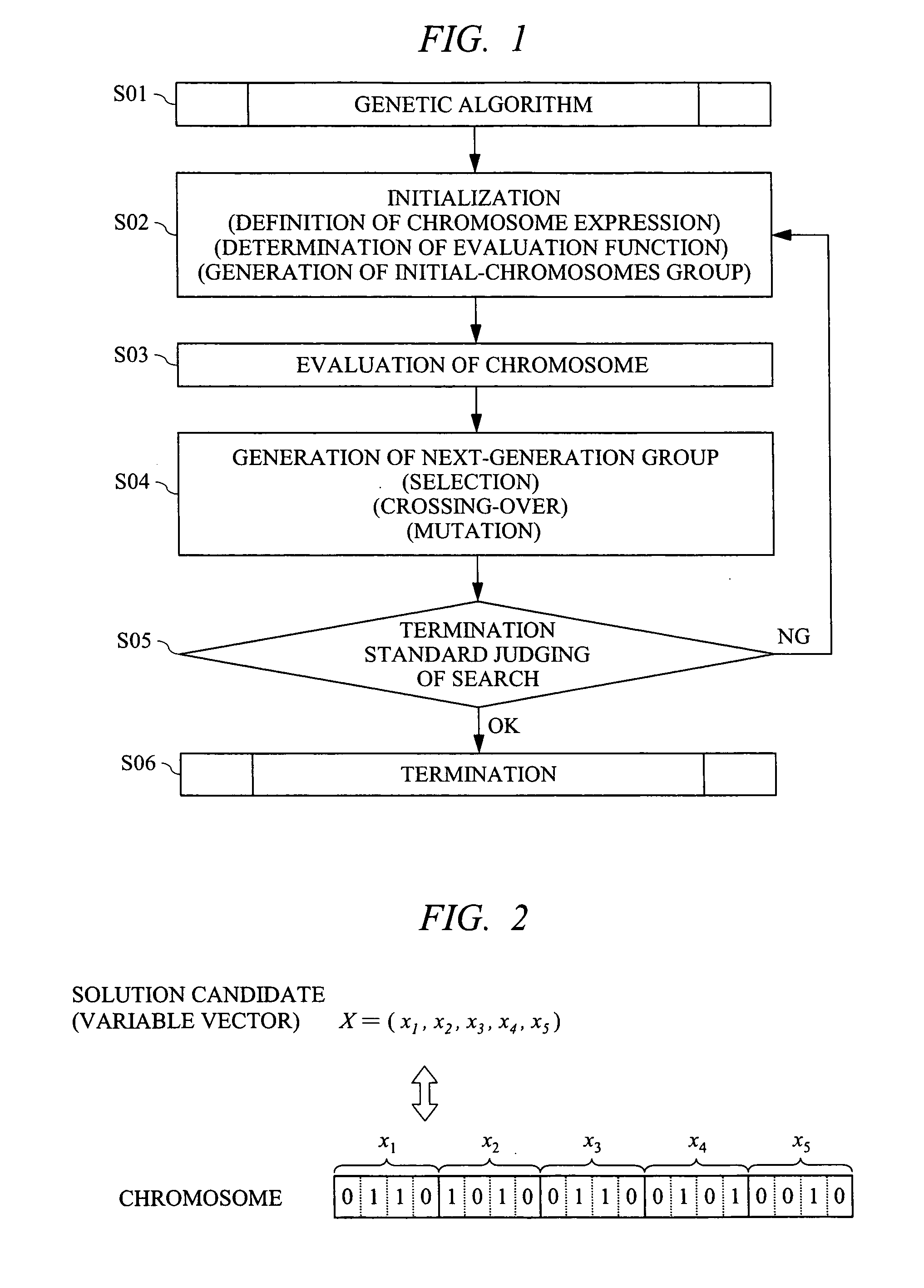

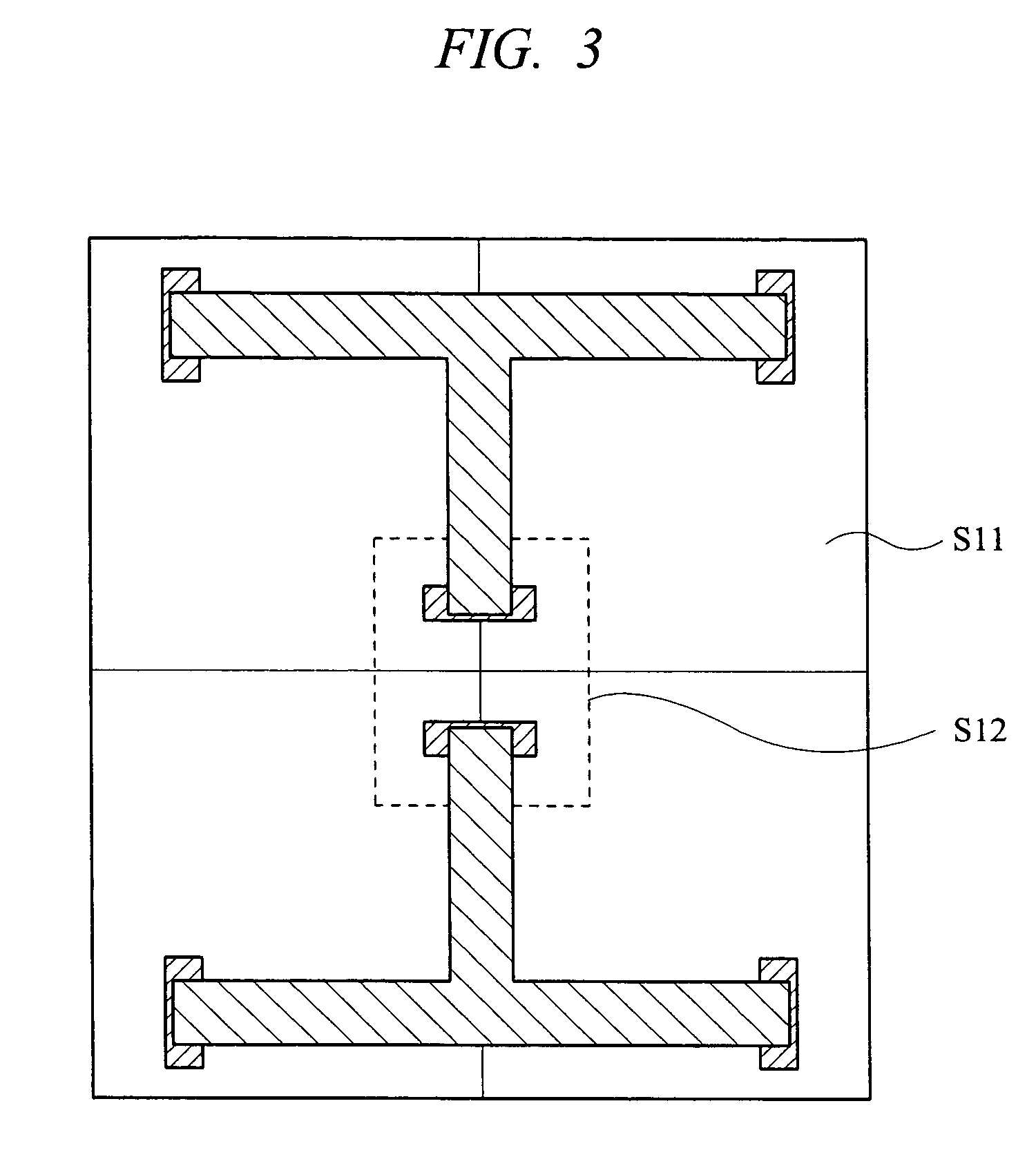

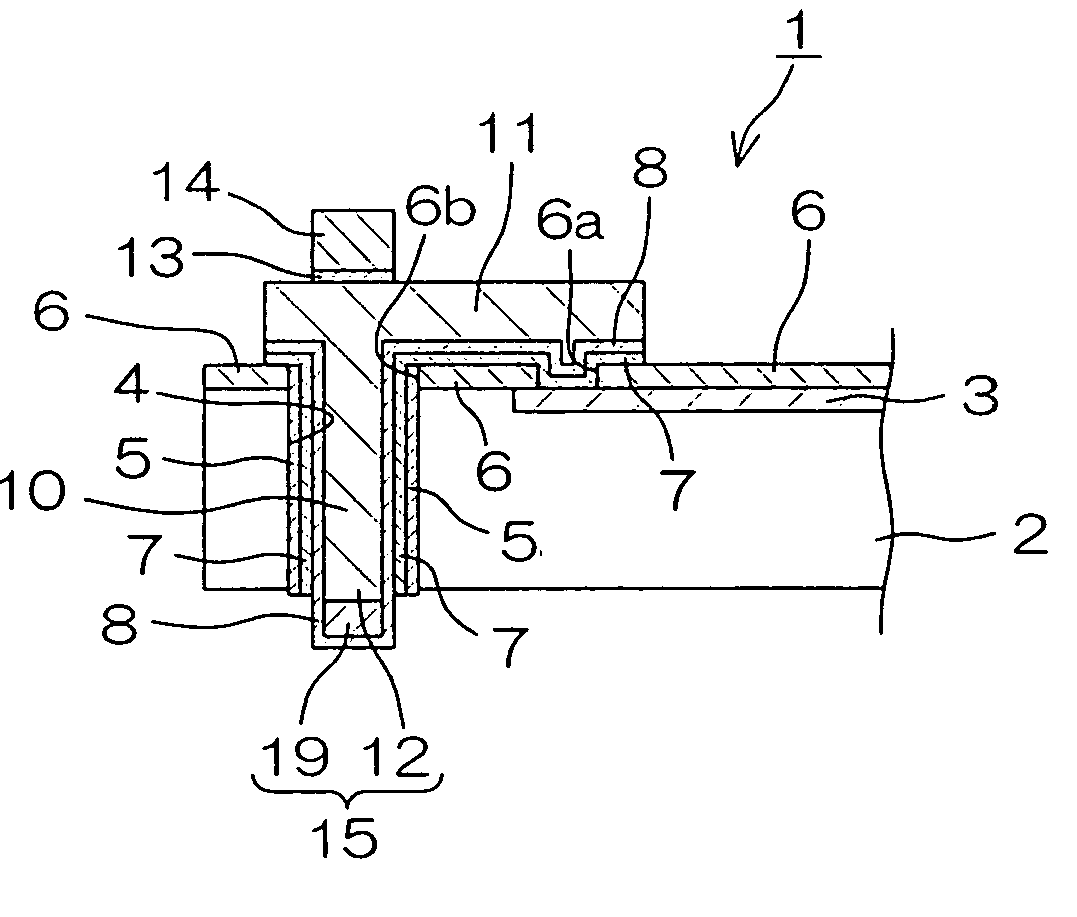

Mask pattern design method and manufacturing method of semiconductor device

InactiveUS20070074145A1Extended processing timeLower manufacturing requirementsOriginals for photomechanical treatmentSpecial data processing applicationsDevice materialSemiconductor chip

To a cell library pattern which makes the basic constitution of a semiconductor circuit pattern, OPC processing is performed beforehand, and a semiconductor chip is produced using this cell library pattern. Since it is influenced by the pattern of the cell arranged to the circumference and the pattern arranged around other cells at this time, correction processing (optimization processing) is performed. The part of this correction processing is a portion in which a pattern faces between cell boundaries in the inside of the region specified from the cell boundary, and proximity effect correction is performed by making the width, the length, and the position of this portion into variables. Or proximity effect correction is performed by making a polygon into a variable. Or sizing is done and proximity effect correction is performed.

Owner:RENESAS TECH CORP

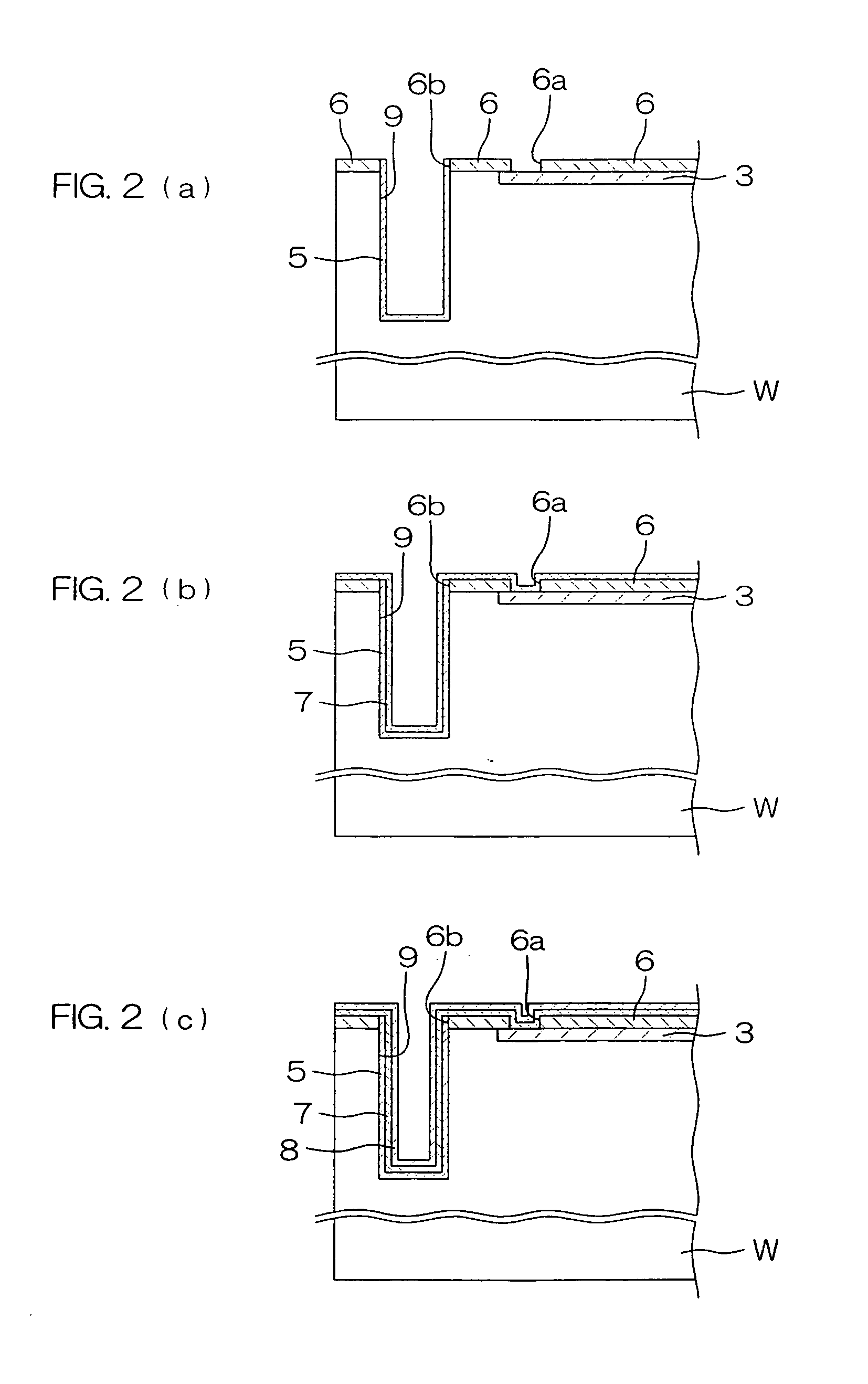

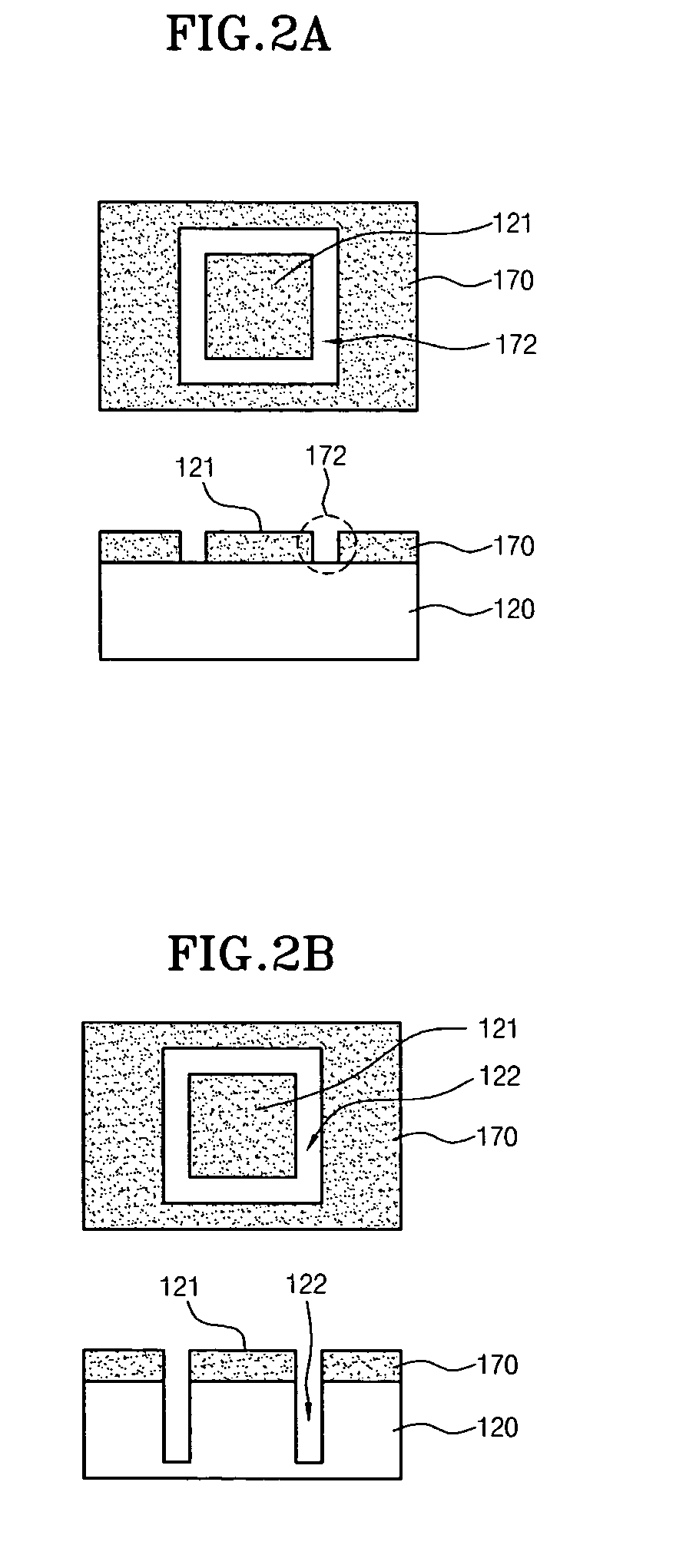

Semiconductor chip and manufacturing method for the same, and semiconductor device

ActiveUS20050151228A1Improve reliabilityThe connection is tight and firmSemiconductor/solid-state device detailsSolid-state devicesDevice formSemiconductor chip

The invention provides a semiconductor chip manufacturing method including the steps of: forming a concave portion extended in the thickness direction of a semiconductor substrate which has a front surface and a rear surface and has a function device formed on the front surface, from the front surface; forming an oxidation preventive film made of an inert first metal material by supplying the first metal material onto the inner wall surface of the concave portion; supplying a second metal material containing a metal which is oxidized more easily than the first metal material to the inside of the concave portion after the step of forming the oxidation preventive film; electrically connecting the second metal material supplied to the inside of the concave portion and the function device; and thinning the semiconductor substrate so that the thickness thereof becomes thinner than the depth of the concave portion by removing the semiconductor substrate from the rear surface while leaving the oxidation preventive film.

Owner:KIOXIA CORP +3

Semiconductor device and manufacturing process therefor

InactiveUS20050263869A1Improve reliabilityHigh practicabilitySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologySurface layer

To provide a very-low-cost and short-TAT connection structure superior in connection reliability in accordance with a method for three-dimensionally connecting a plurality of semiconductor chips at a shortest wiring length by using a through-hole electrode in order to realize a compact, high-density, and high-function semiconductor system. The back of a semiconductor chip is decreased in thickness up to a predetermined thickness through back-grinding, a hole reaching a surface-layer electrode is formed at a back position corresponding to a device-side external electrode portion through dry etching, a metallic deposit is applied to the sidewall of the hole and the circumference of the back of the hole, a metallic bump (protruded electrode) of another semiconductor chip laminated on the upper side is deformation-injected into the through-hole by compression bonding, and the metallic bump is geometrically caulked and electrically connected to the inside of a through-hole formed in an LSI chip. It is possible to realize a unique connection structure having a high reliability in accordance with the caulking action using the plastic flow of a metallic bump in a very-low-cost short-TAT process and provide a three-dimensional inter-chip connection structure having a high practicability.

Owner:RENESAS TECH CORP

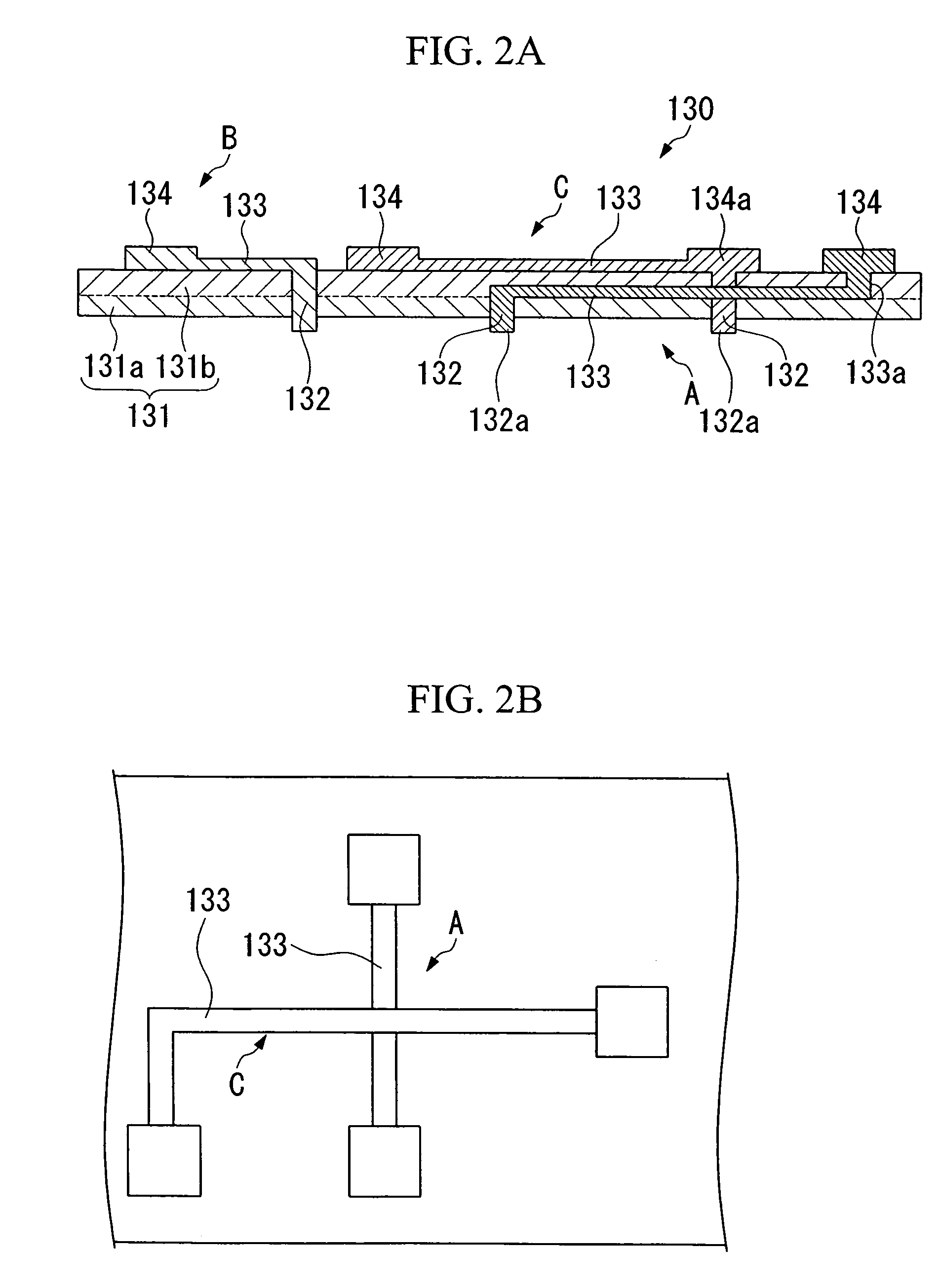

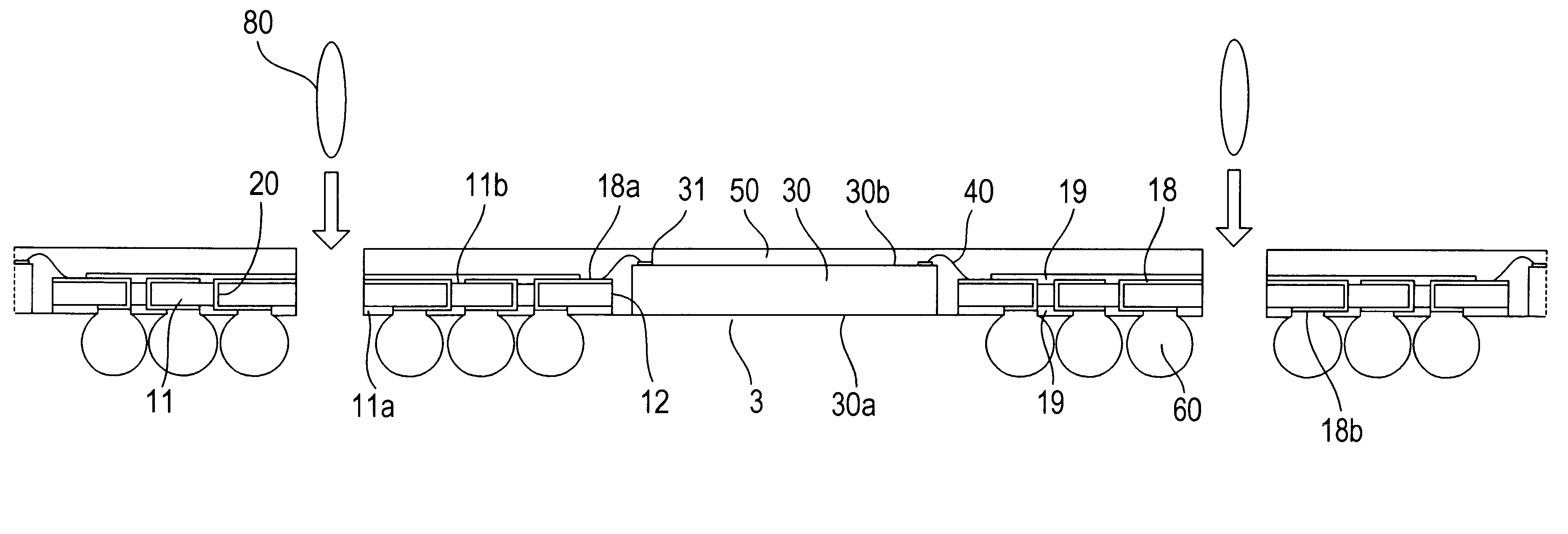

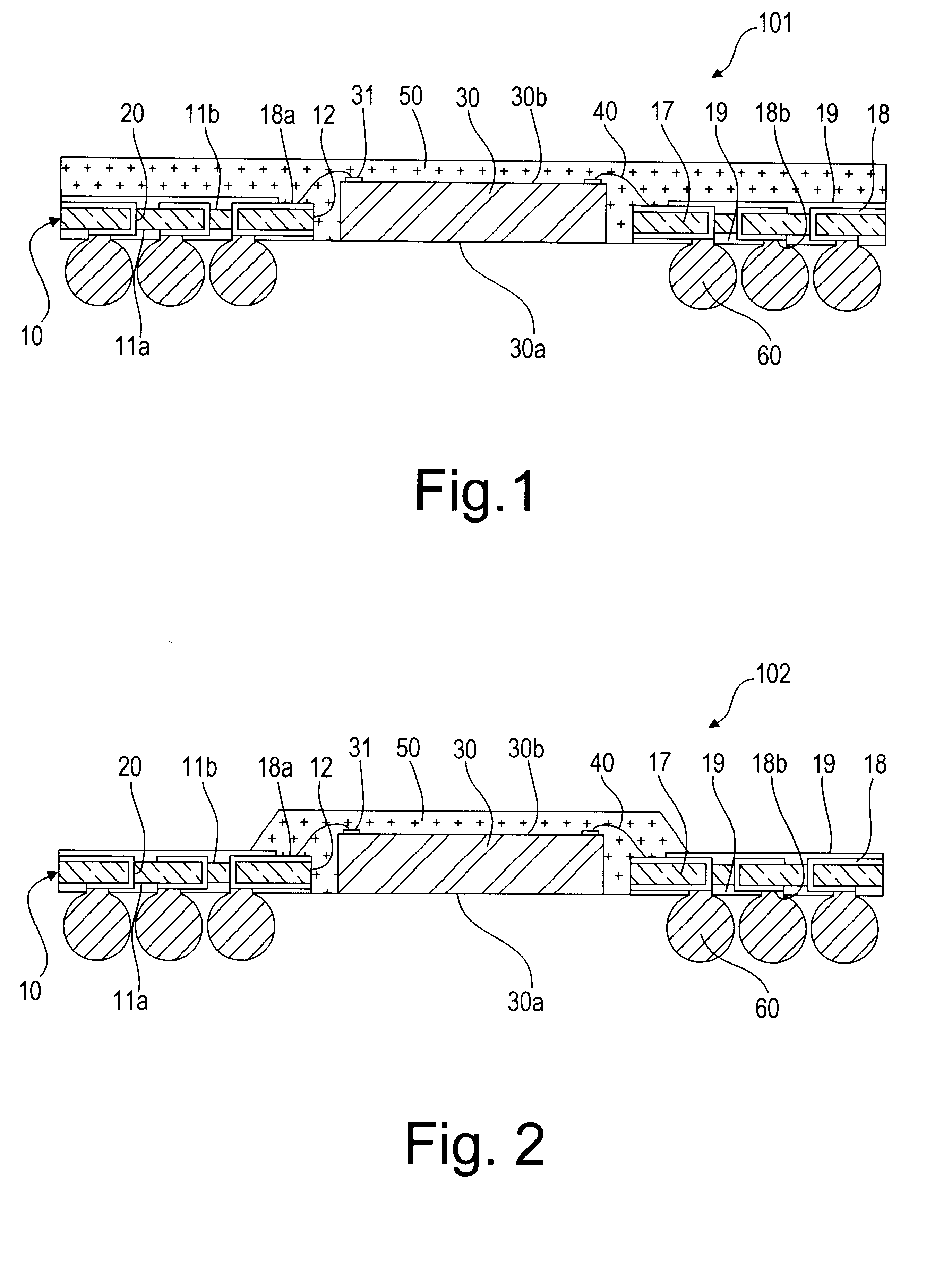

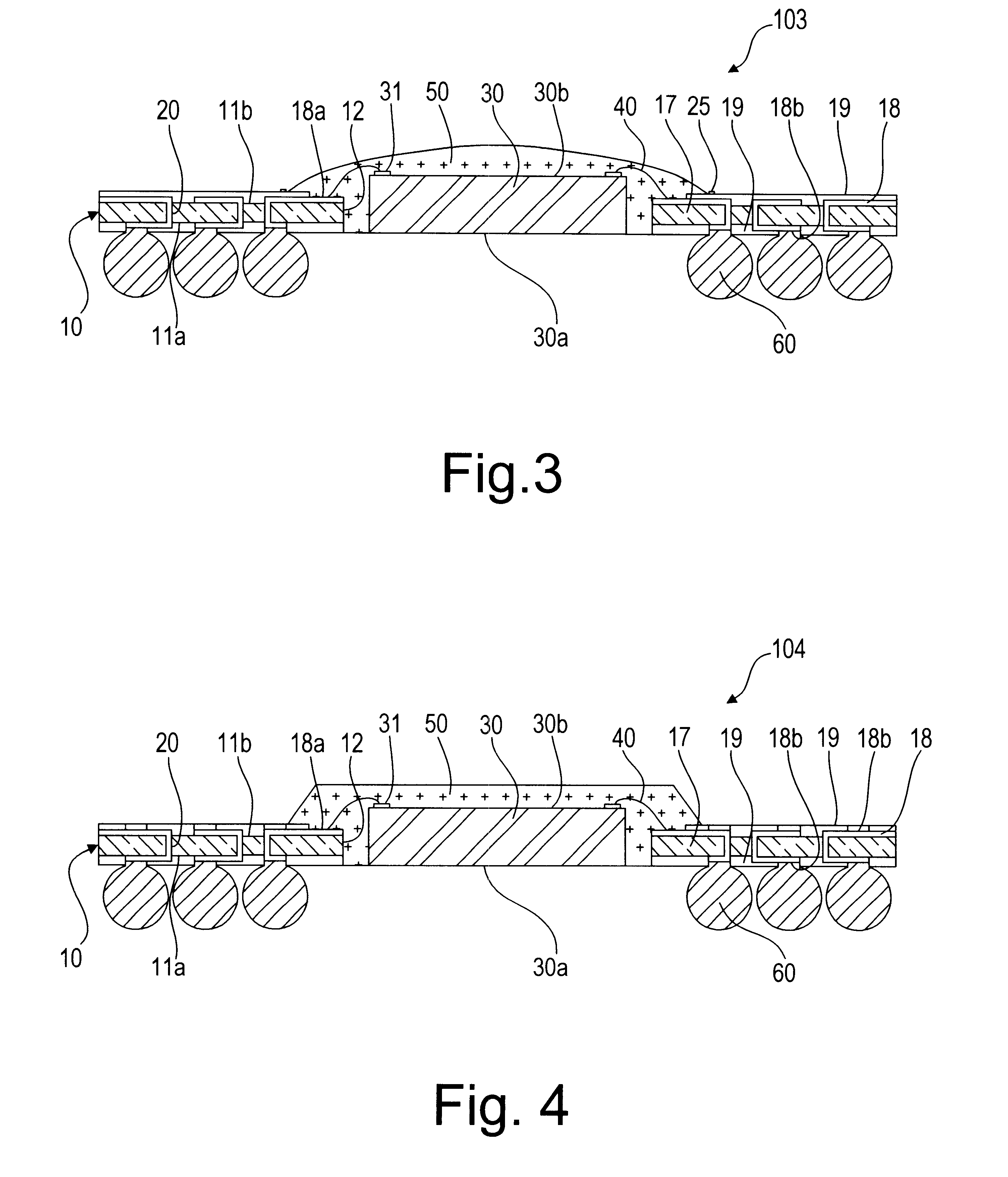

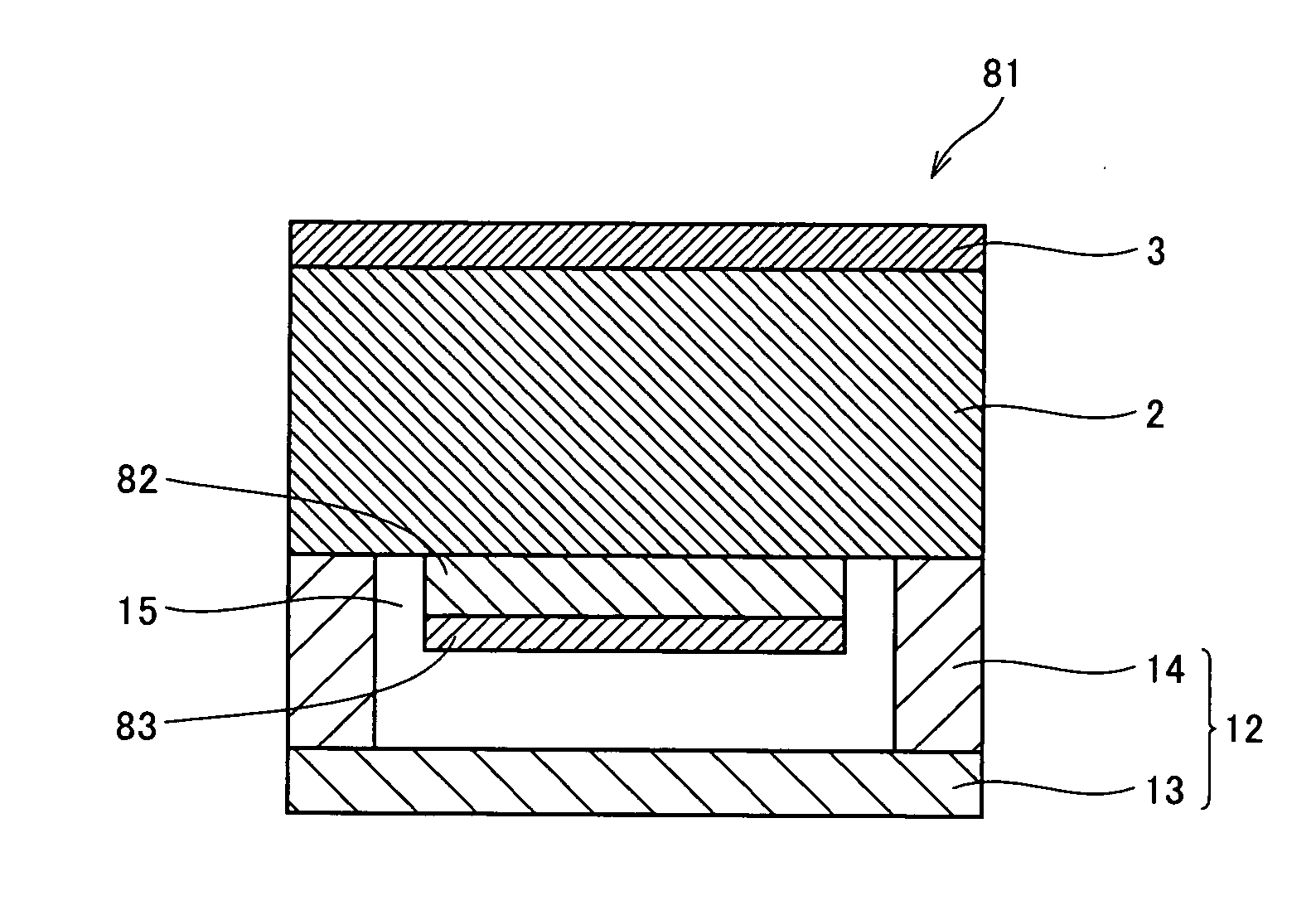

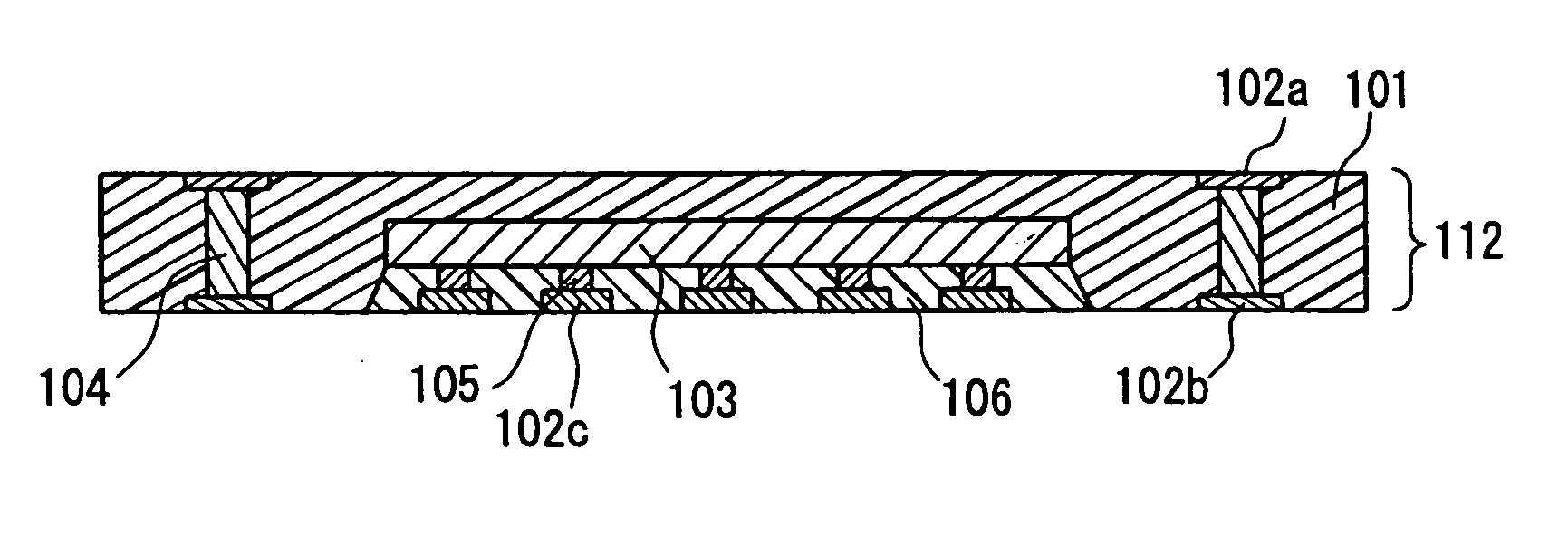

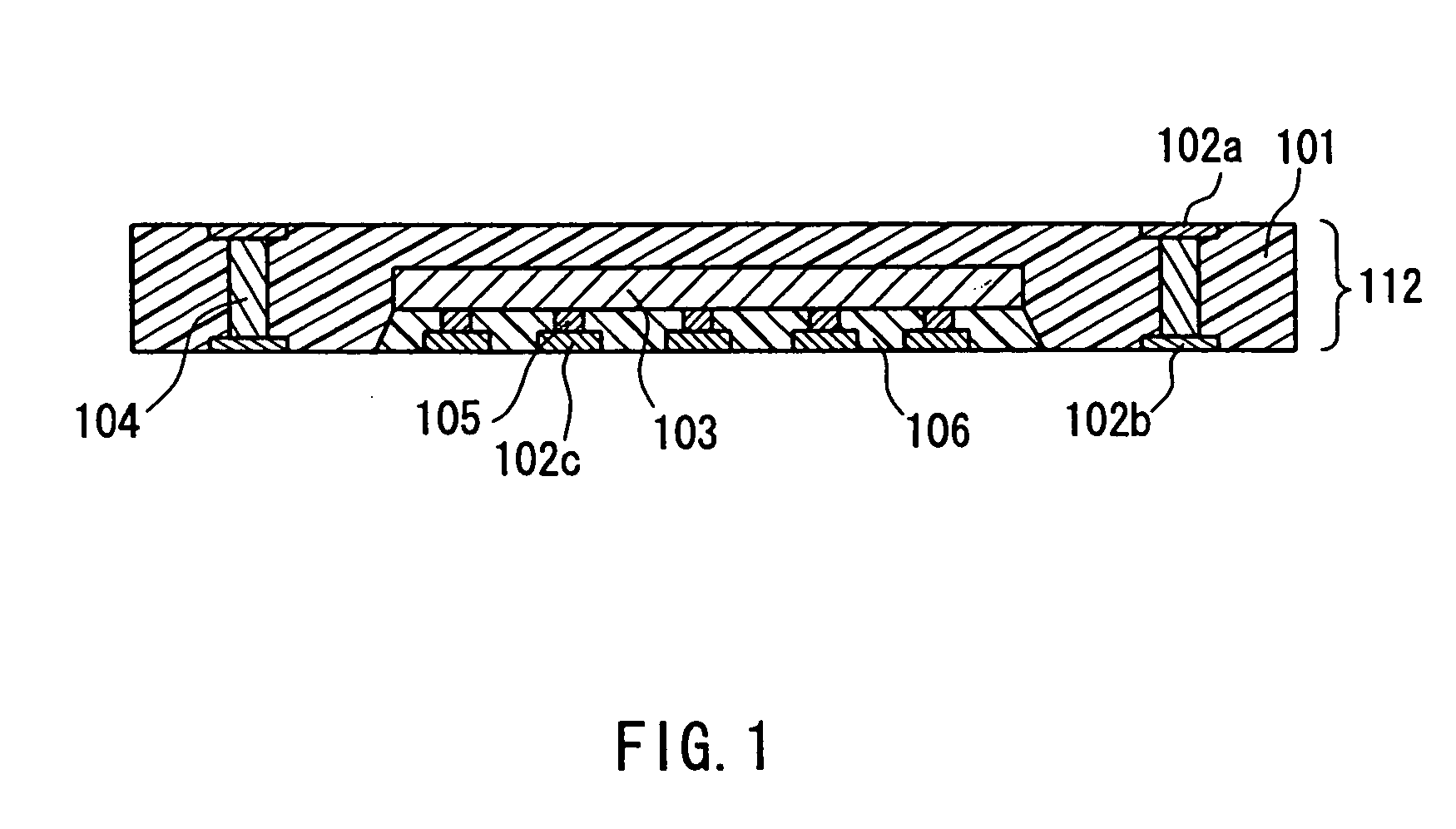

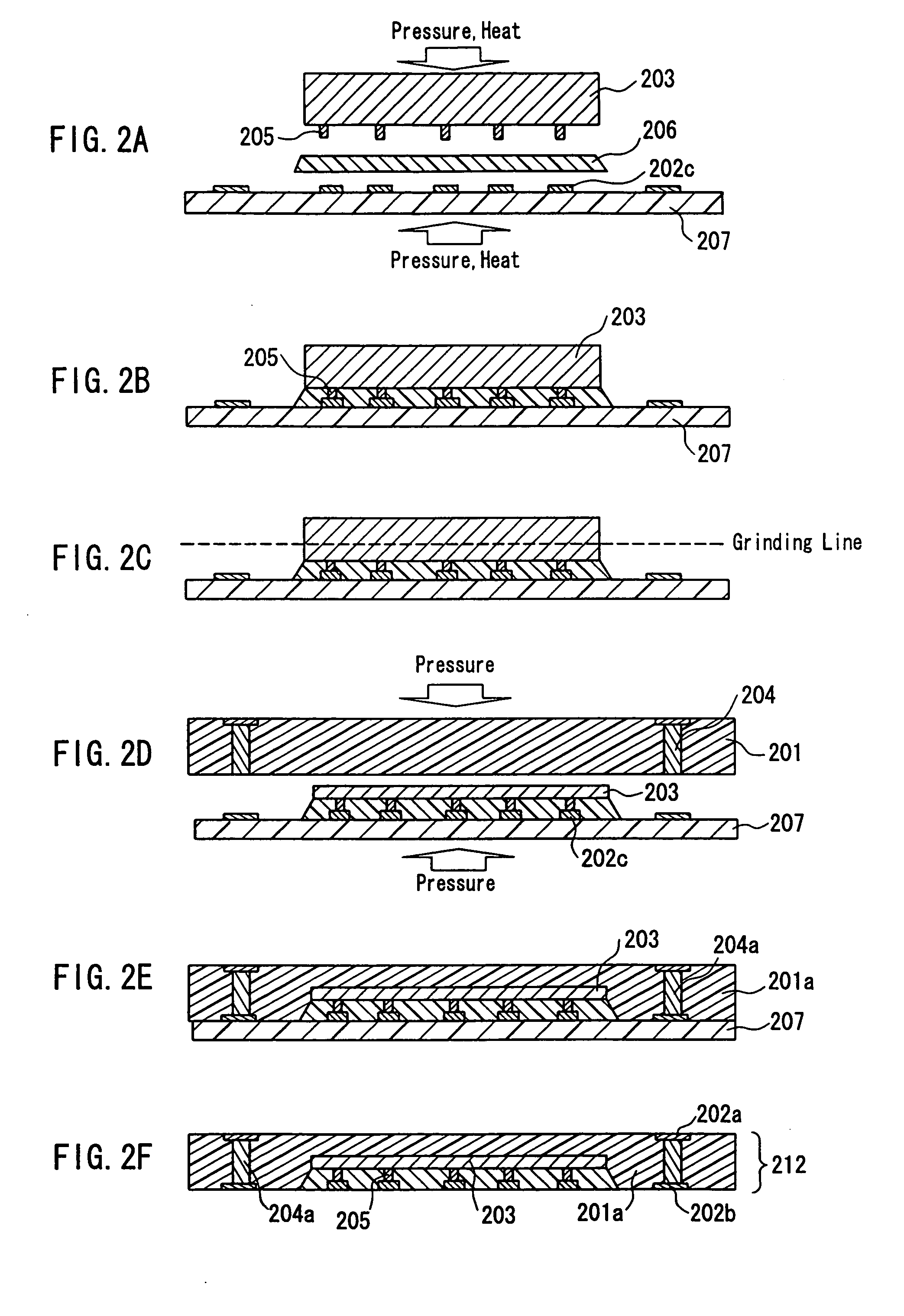

Circuit component built-in module with embedded semiconductor chip and method of manufacturing

InactiveUS20040145044A1Improve Noise PerformanceSemiconductor/solid-state device detailsSolid-state devicesHigh densityMiniaturization

A circuit component built-in module includes: a first electrical insulating substrate made of a mixture containing an inorganic filler and a thermosetting resin; a plurality of wiring patterns formed at least on a principal surface of the first electrical insulating substrate; a semiconductor chip incorporated in the first electrical insulating substrate and connected electrically with the wiring patterns; and inner vias electrically connecting the plurality of wiring patterns with one another, the inner vias passing through the first electrical insulating substrate. In the circuit component built-in module, the semiconductor chip has a thickness of not less than 30 mum and not more than 100 mum, and has a non-wired surface ground, and the circuit component built-in module has a thickness in a range of not less than 80 mum and not more than 200 mum. With this configuration, the high-performance and compact-size circuit component built-in module in which circuit components are mounted at a high density is provided so as to be used suitably in various types of electronic information devices.

Owner:PANASONIC CORP

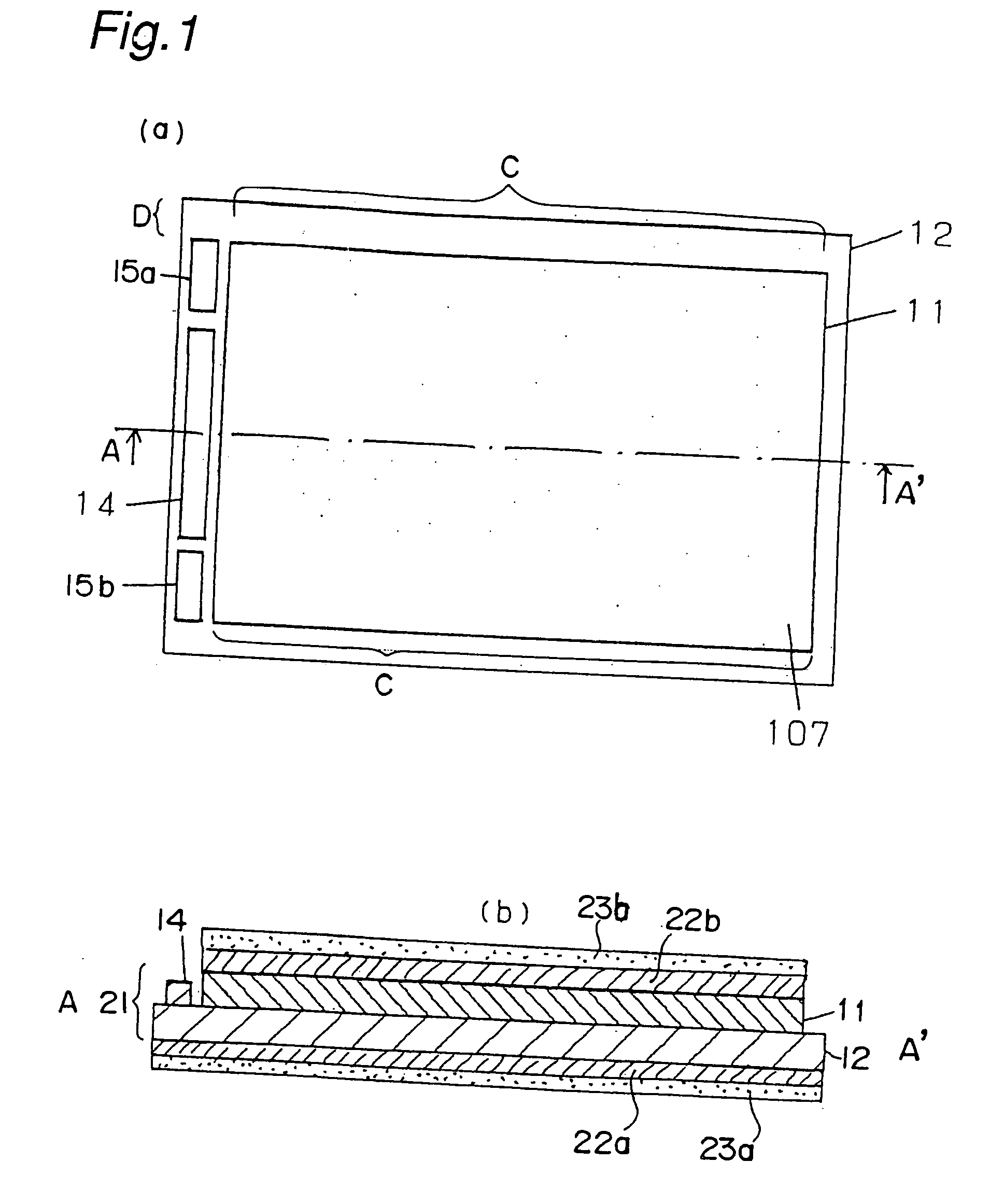

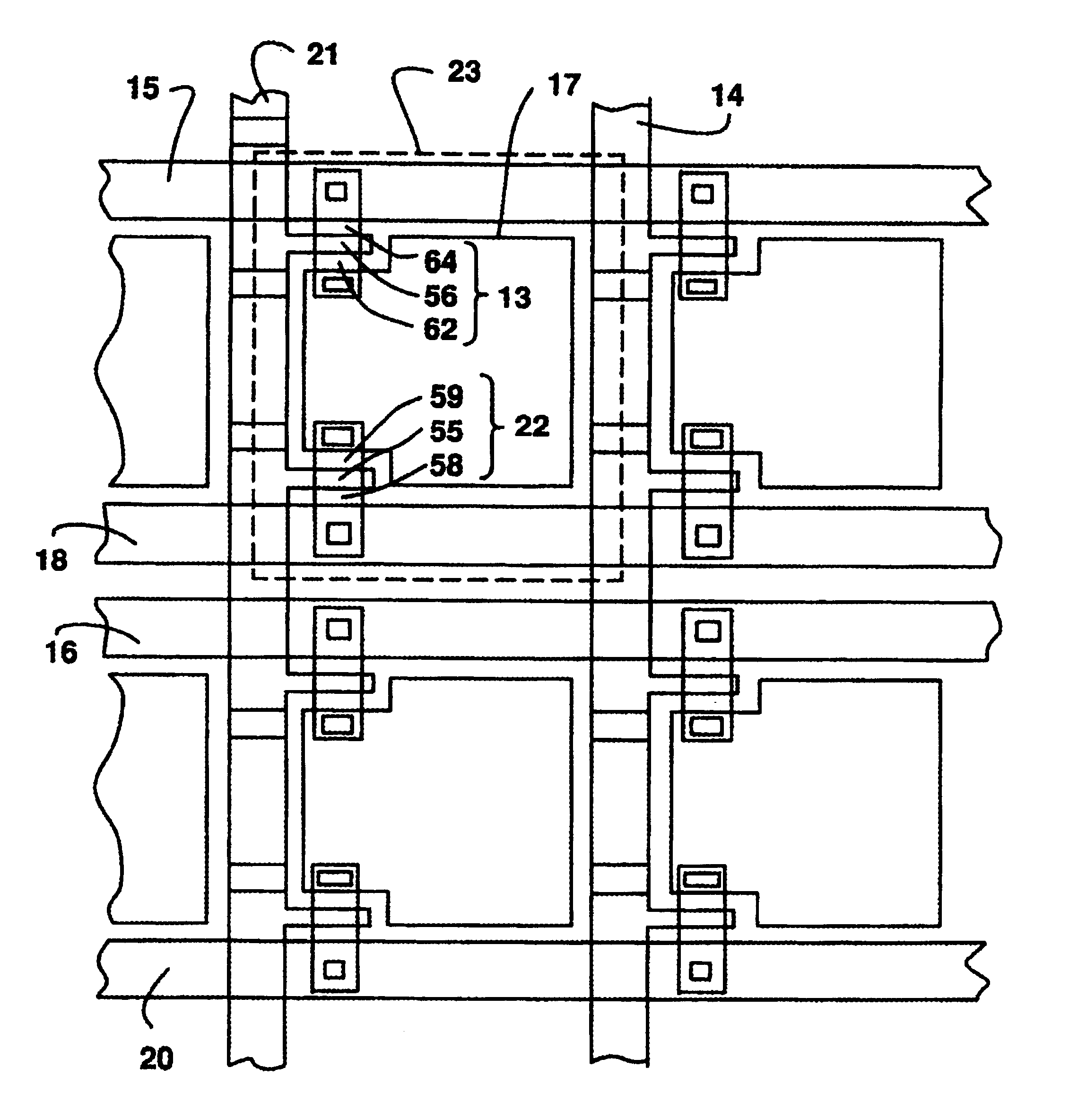

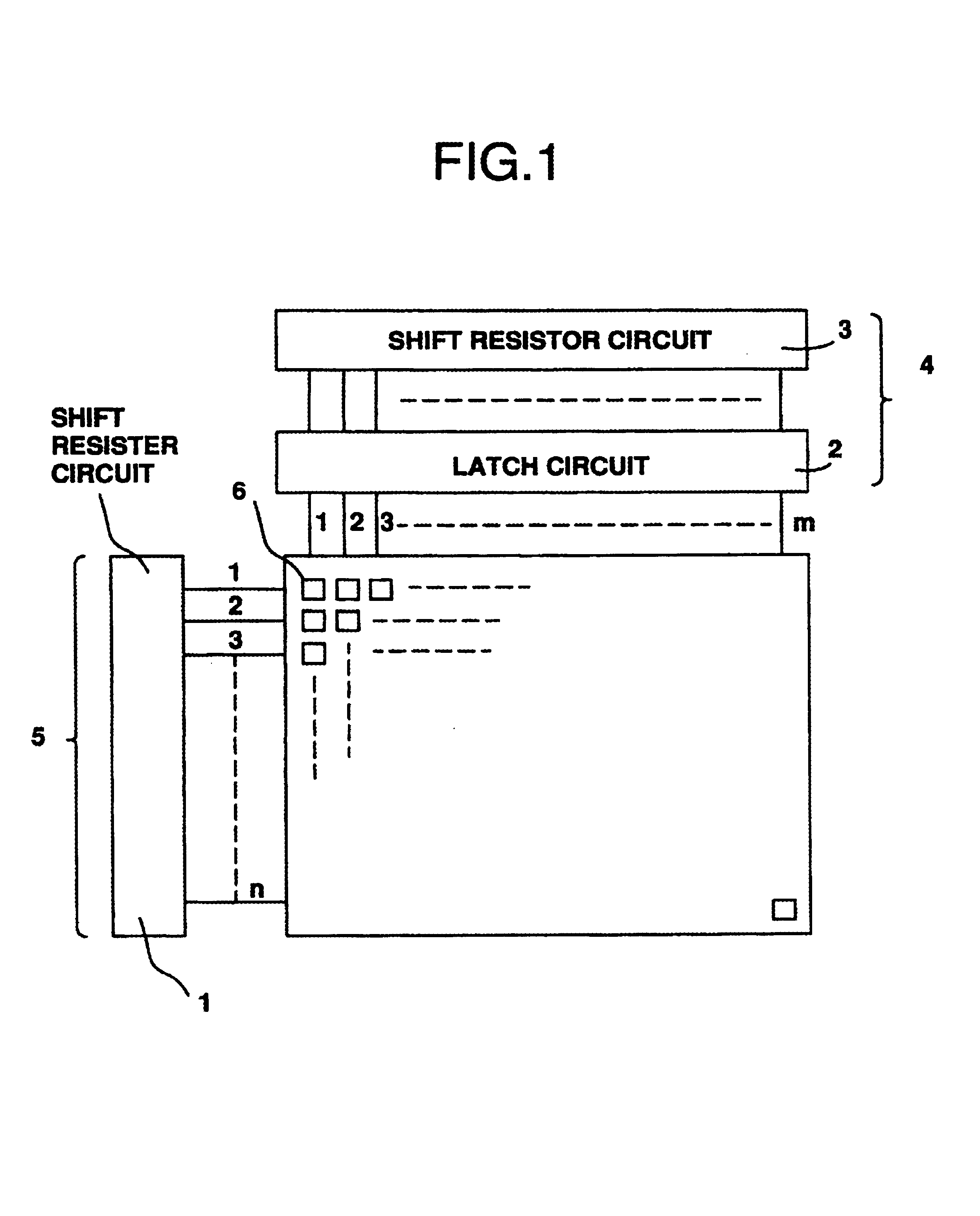

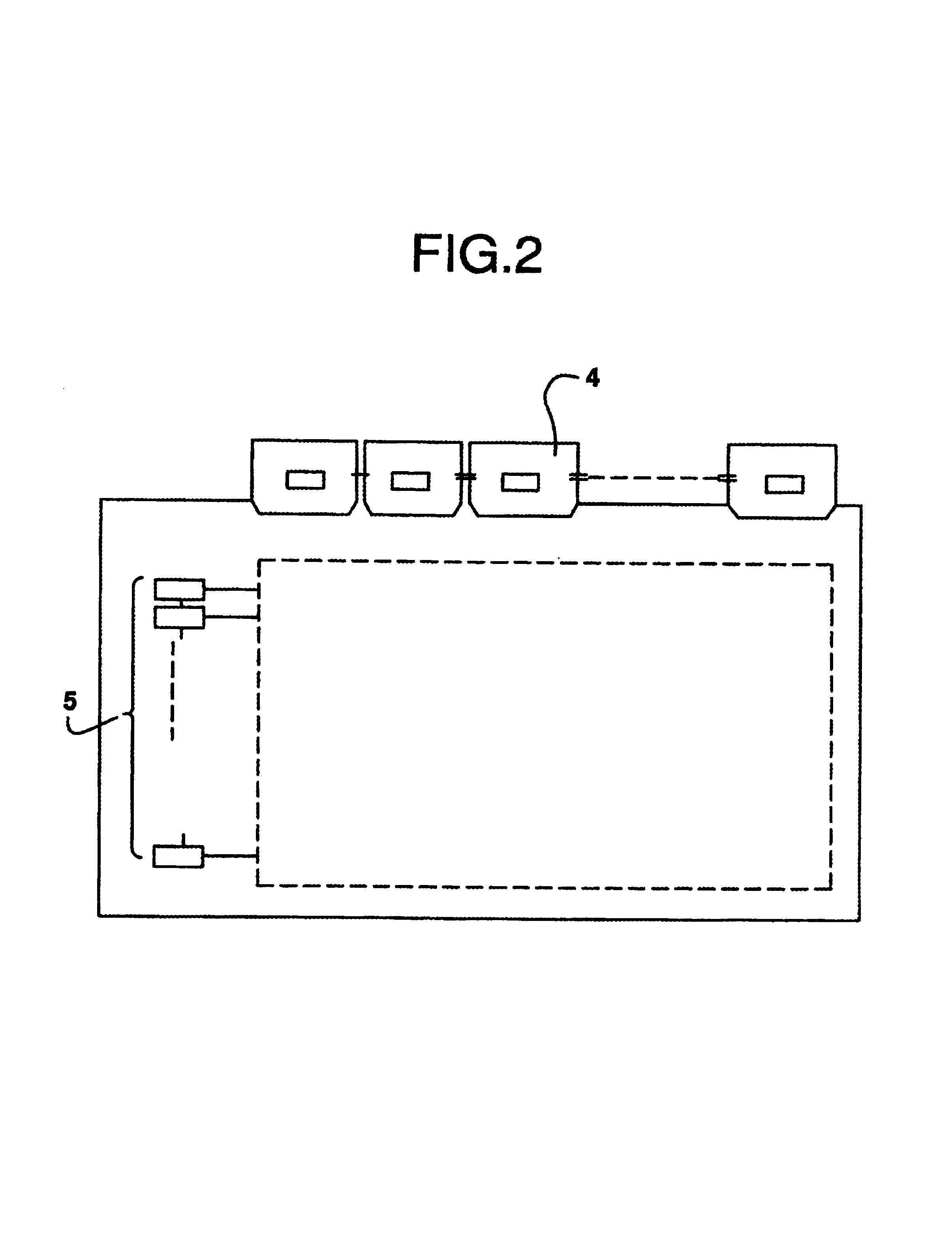

Electro-optical device and method for manufacturing the same

InactiveUS7115902B1High carrier mobilityDegree of improvementSolid-state devicesSemiconductor devicesLiquid-crystal displaySemiconductor chip

An electro-optical device and a method for manufacturing the same are disclosed. The device comprises a pair of substrates and an electro-optical modulating layer (e.g. a liquid crystal layer having sandwiched therebetween, said pair of substrates consisting of a first substrate having provided thereon a plurality of gate wires, a plurality of source (drain) wires, and a pixel matrix comprising thin film transistors, and a second substrate facing the first substrate, wherein, among the peripheral circuits having established on the first substrate and being connected to the matrix wirings for the X direction and the Y direction, only a part of said peripheral circuits is constructed from thin film semiconductor devices fabricated by the same process utilized for an active device, and the rest of the peripheral circuits is constructed from semiconductor chips. The liquid crystal display device according to the present invention is characterized by that the peripheral circuits are not wholly fabricated into thin film transistors, but only those portions having a simple device structure, or those composed of a small number of devices, or those comprising an IC not easily available commercially, or those comprising an expensive integrated circuit, are fabricated by thin film transistors. According to the present invention, an electro-optical device is provided at an increased production yield with a reduced production cost.

Owner:SEMICON ENERGY LAB CO LTD

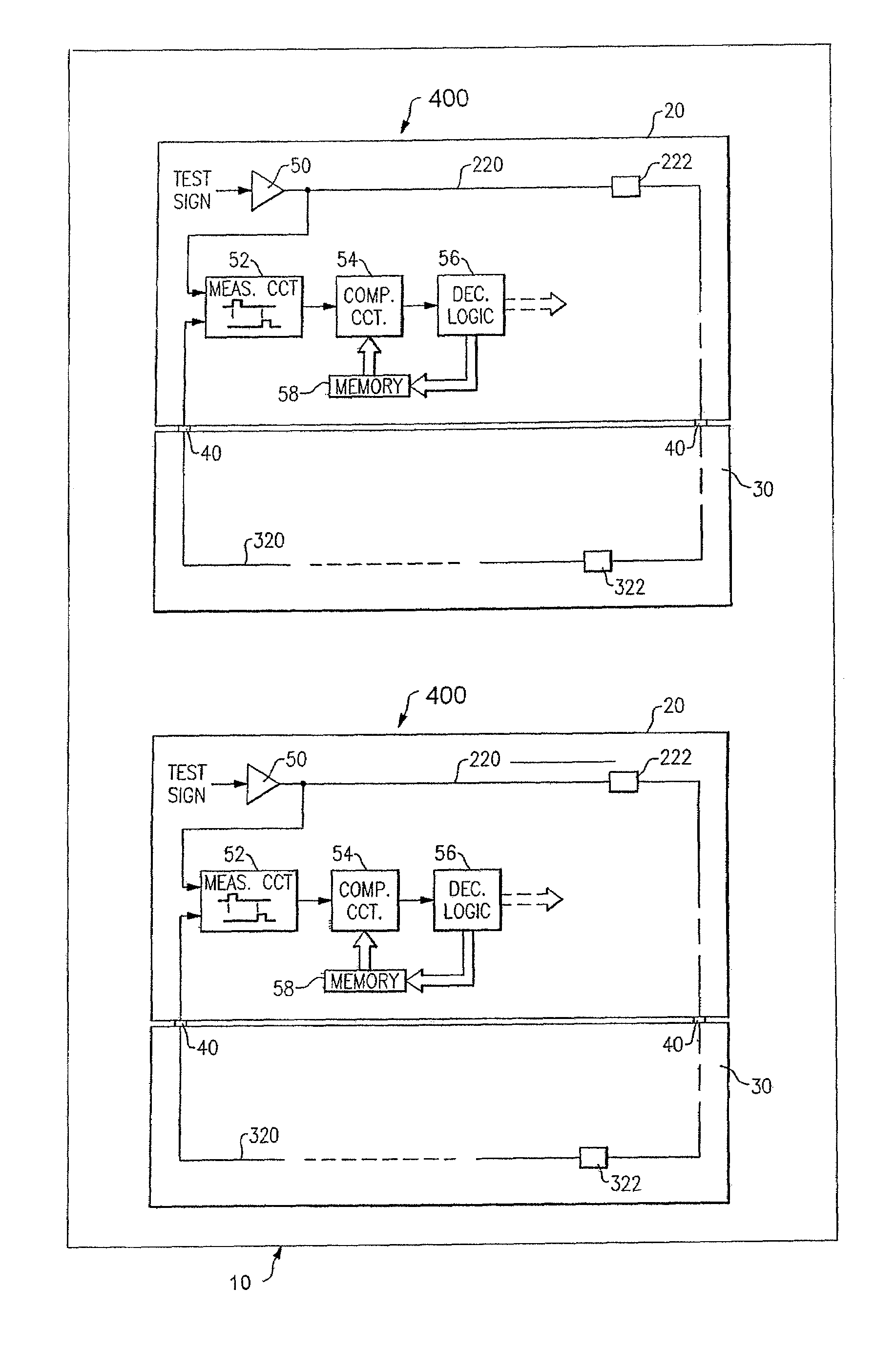

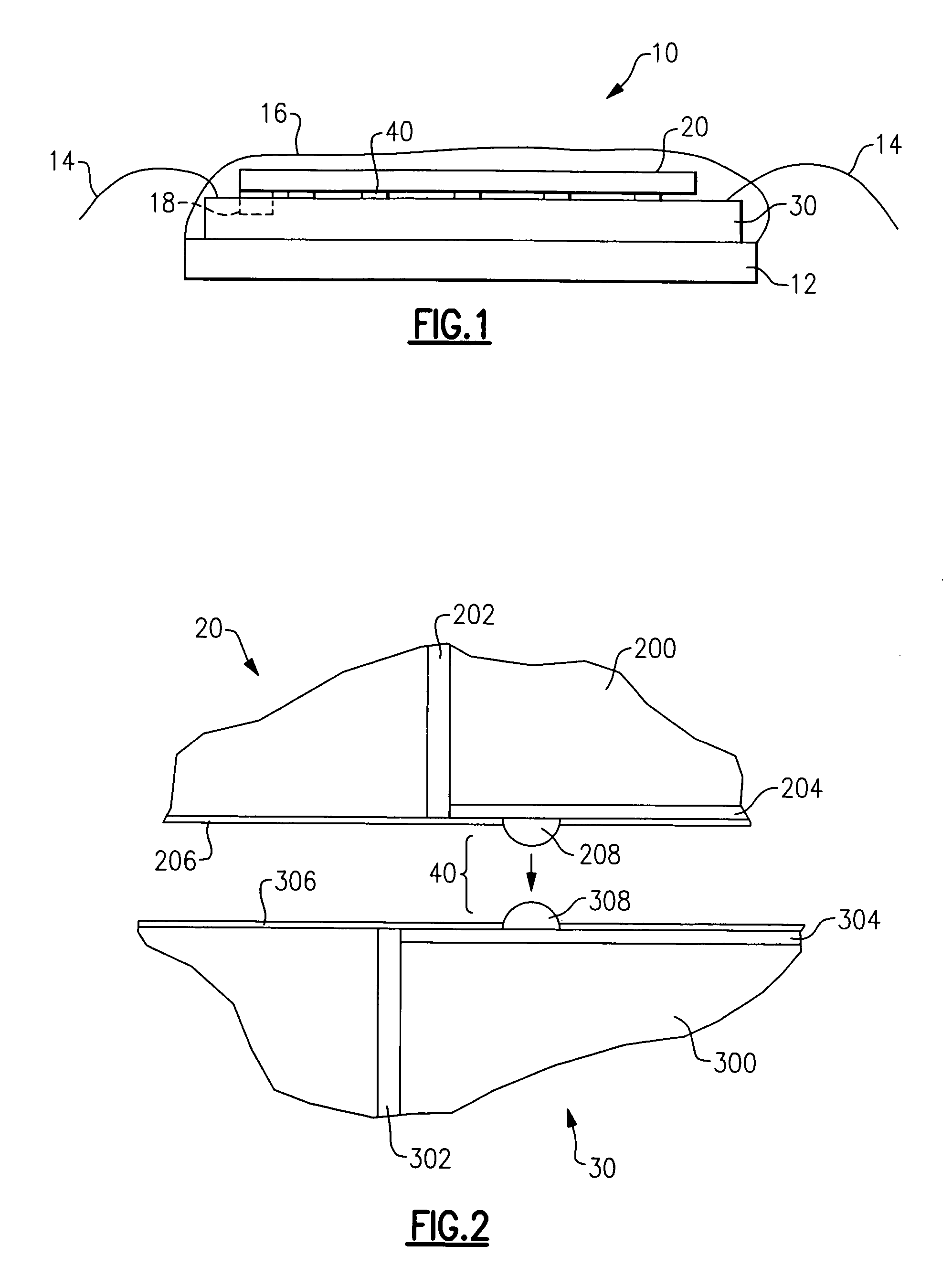

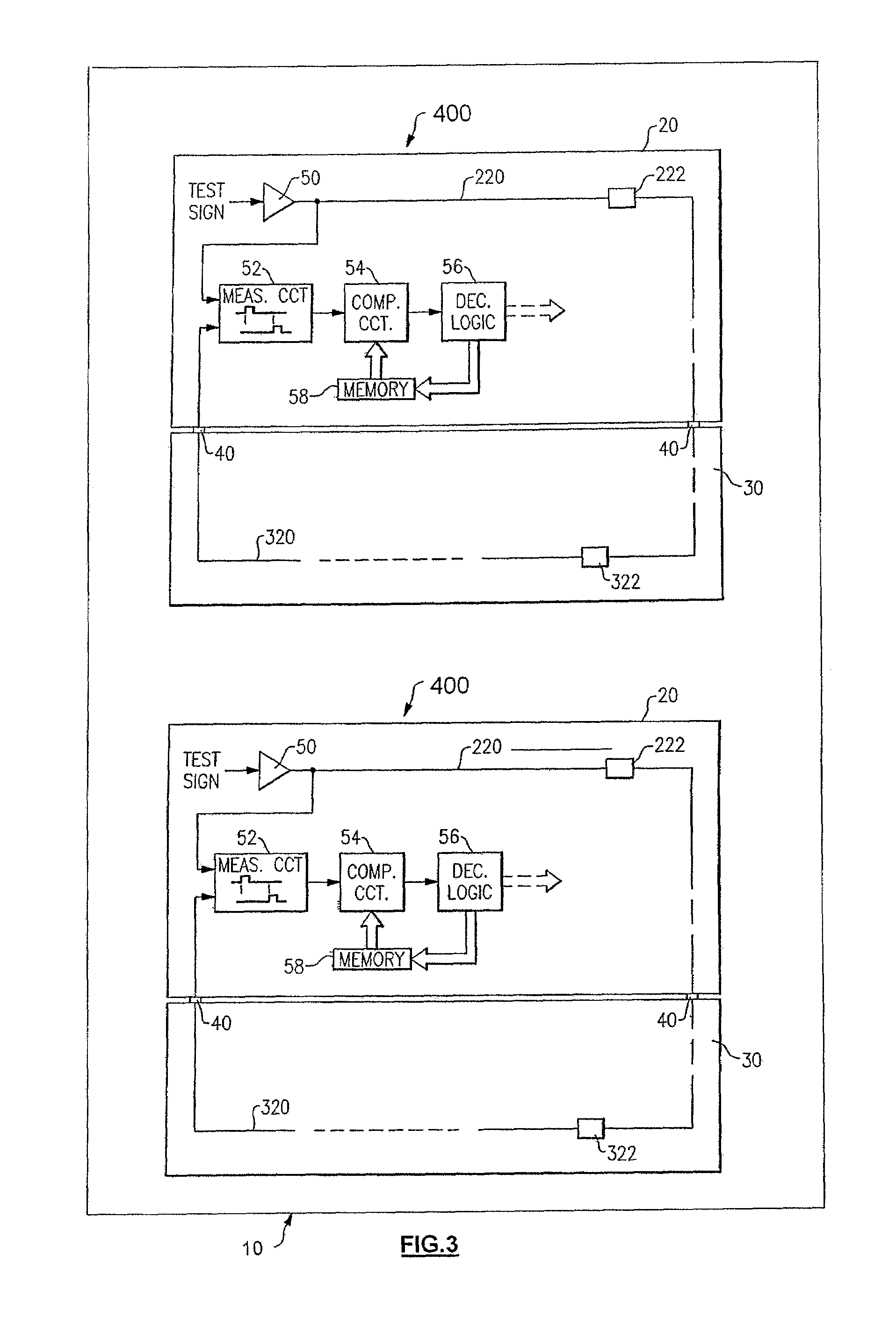

Stacked chip security

InactiveUS7557597B2Semiconductor/solid-state device testing/measurementElectronic circuit testingSemiconductor chipInterconnection

The present invention is directed to an integrated circuit module device. The device includes a first semiconductor chip having a first circuit layer and at least one first interconnection element disposed on a first chip surface. The at least one first interconnection element is electrically coupled to the first circuit layer. A second semiconductor chip includes a second circuit layer and at least one second interconnection element disposed on a second chip surface. The at least one second interconnection element is electrically coupled to the second circuit layer. The at least one first interconnection element is connected to the at least one second interconnection element to establish electrical continuity between the first circuit layer and the second circuit layer. The first surface is adjoined to the second surface. At least one ring delay circuit includes a first ring delay path partially disposed on the first circuit layer and a second ring delay path partially disposed on the second circuit layer. The first ring delay path and the second ring delay path form a signal path having a predetermined measurement signature. The ring delay circuit compares the predetermined measurement signature to a test measurement signature.

Owner:INT BUSINESS MASCH CORP

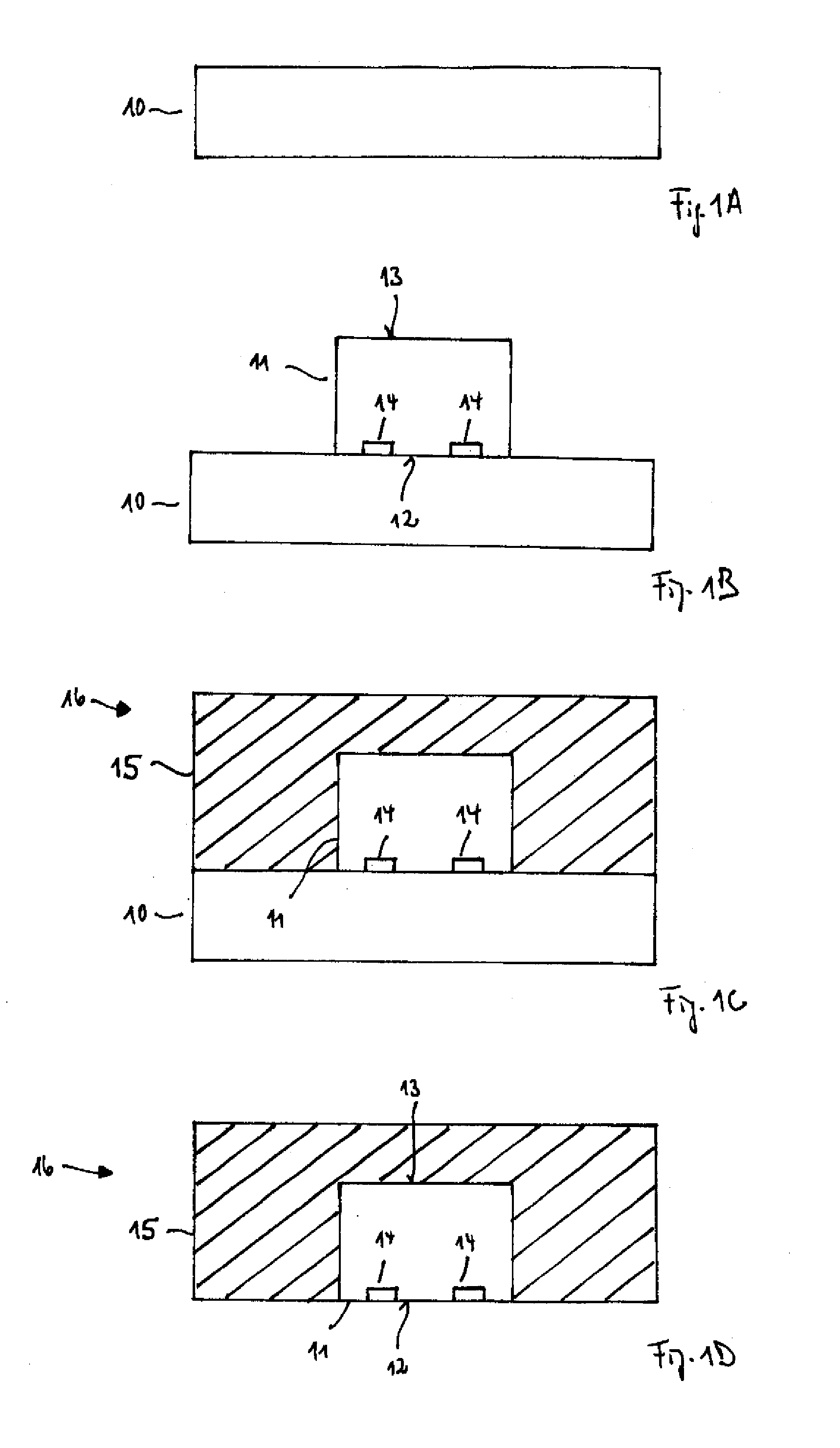

Semiconductor Device and Method of Manufacturing a Semiconductor Device Including Grinding Steps

ActiveUS20130049205A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsContact pad

A method of manufacturing a device includes providing a semiconductor chip having a first face and a second face opposite to the first face with a contact pad arranged on the first face. The semiconductor chip is placed on a carrier with the first face facing the carrier. The semiconductor chip is encapsulated with an encapsulation material. The carrier is removed and the semiconductor material is removed from the second face of the first semiconductor chip without removing encapsulation material at the same time.

Owner:INTEL CORP

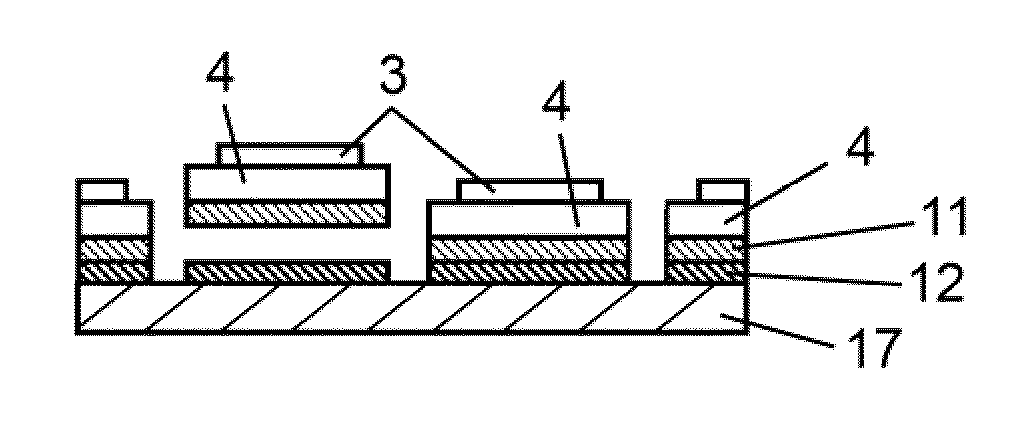

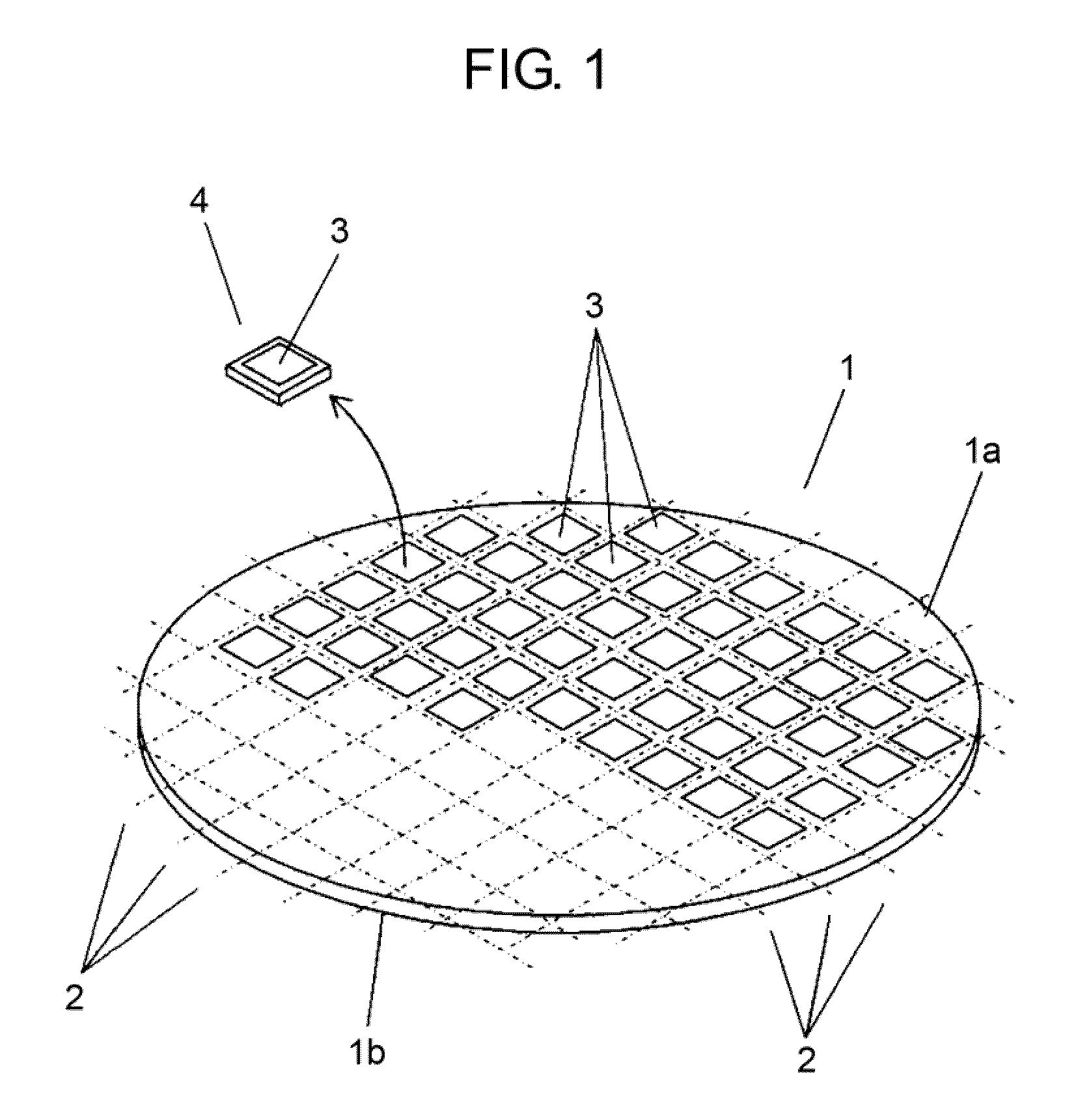

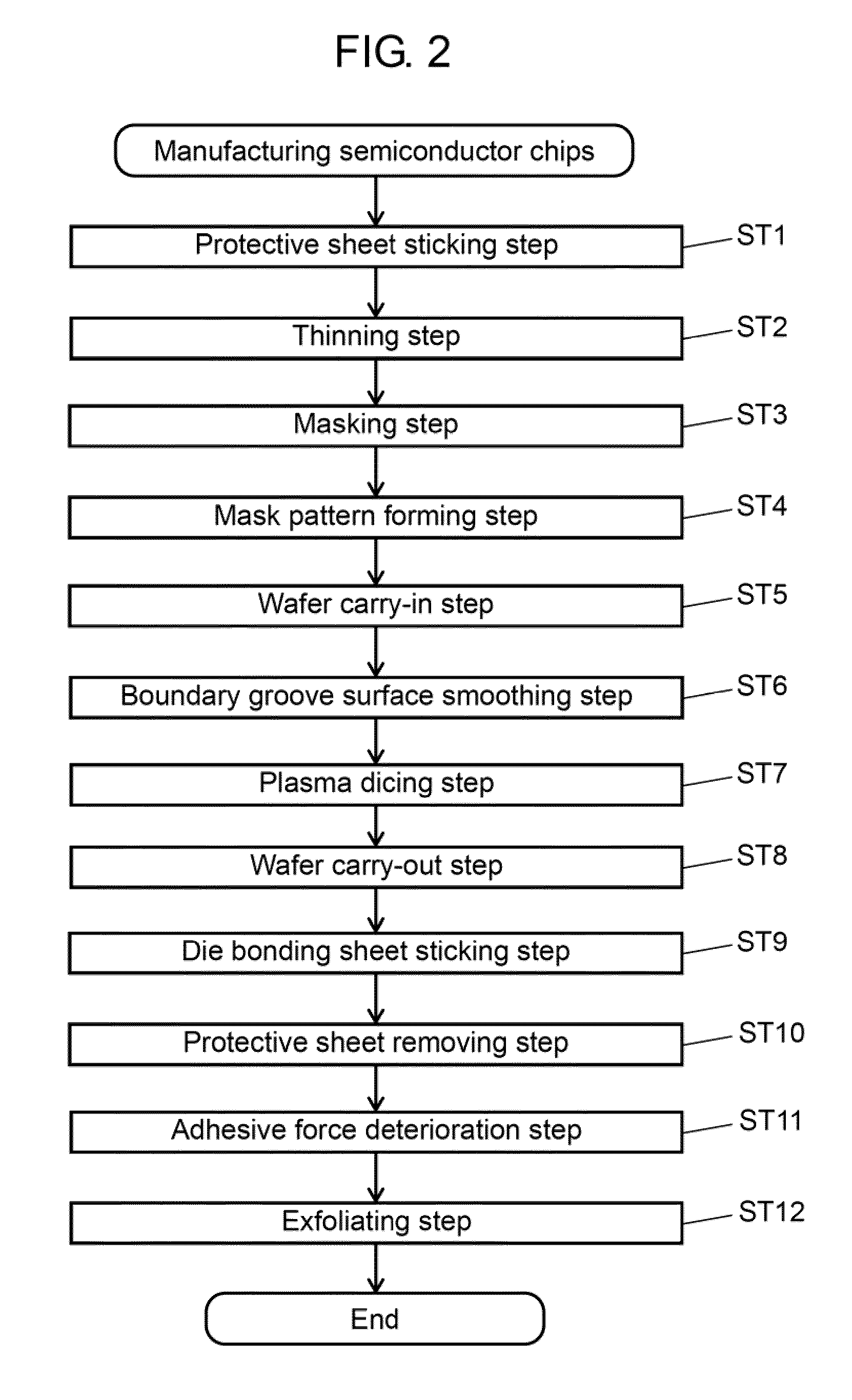

Plasma dicing apparatus and method of manufacturing semiconductor chips

InactiveUS20100048001A1Improve workabilityFacilitates carrying a semiconductor waferSemiconductor/solid-state device testing/measurementElectric discharge tubesSemiconductor chipVacuum chamber

A plasma dicing apparatus in which a semiconductor wafer with a protective sheet stuck thereonto covering the entire circuit-forming surface and with an etching-resistant mask member stuck on the back surface opposite to the circuit-forming surface is mounted on a mounting stage; plasma etching is performed using the mask member as a mask; and the semiconductor wafer is diced into plural semiconductor chips. The plasma dicing apparatus includes a ring-shaped frame member retaining the outer circumference of the mask member extending off the outer circumference of the semiconductor wafer. The mounting stage is composed of a wafer supporting part supporting a semiconductor wafer and a frame member supporting part supporting the frame member. This facilitates carrying a semiconductor wafer into and out of the vacuum chamber.

Owner:PANASONIC CORP

Electro-optical device

InactiveUS7067844B2High carrier mobilityDegree of improvementTransistorStatic indicating devicesLiquid-crystal displaySemiconductor chip

An electro-optical device is disclosed. The device comprises a pair of substrates and an electro-optical modulating layer (e.g. a liquid crystal layer) having sandwiched therebetween, said pair of substrates consisting of a first substrate having provided thereon a plurality of gate wires, a plurality of source (drain) wires, and a pixel matrix comprising thin film transistors, and a second substrate facing the first substrate, wherein, among the peripheral circuits having established on the first substrate and being connected to the matrix wiring for the X direction and the Y direction, only a part of said peripheral circuits is constructed from thin film semiconductor devices fabricated by the same process utilized for an active device, and the rest of the peripheral circuits are constructed from semiconductor chips. The liquid crystal display device according to the present invention is characterized in that the peripheral circuits are not wholly fabricated into thin film transistors, but only those portions having a simple device structure, or those composed of a small number of devices, or those comprising an IC not easily available commercially, or those comprising an expensive integrated circuit, are fabricated by thin film transistors. According to the present invention, an electro-optical device is provided at an increased production yield with a reduced production cost.

Owner:SEMICON ENERGY LAB CO LTD

Stack package having guard ring which insulates through-via interconnection plug and method for manufacturing the same

ActiveUS7525186B2Avoid crackingAvoid disconnectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A stack package comprises a substrate having a circuit pattern; at least two semiconductor chips stacked on the substrate, having a plurality of through-via interconnection plugs and a plurality of guard rings which surround the respective through-via interconnection plugs, and connected with each other by the medium of the through-via interconnection plugs; a molding material for molding an upper surface of the substrate including the stacked semiconductor chips; and solder balls mounted to a lower surface of the substrate.

Owner:SK HYNIX INC

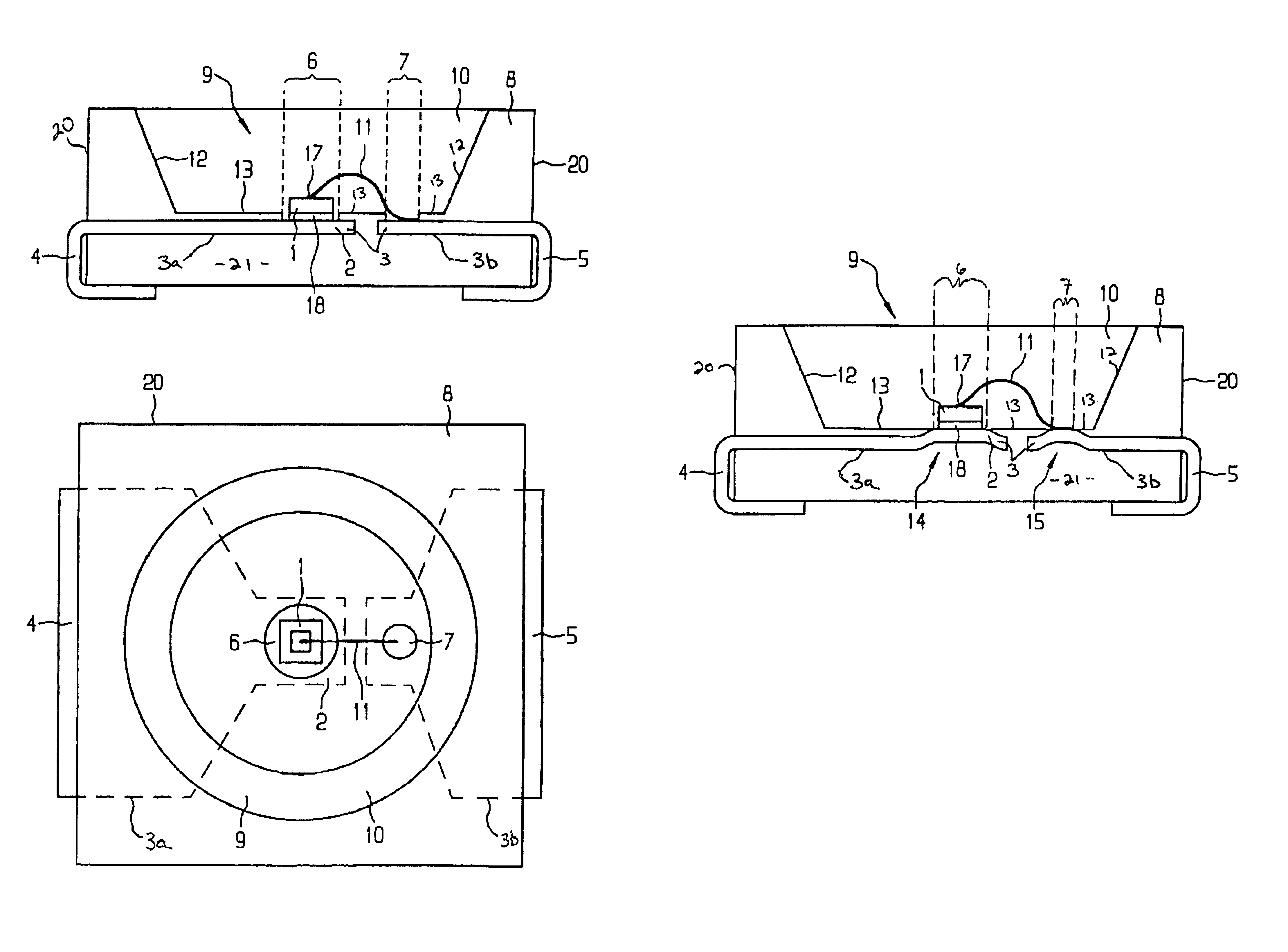

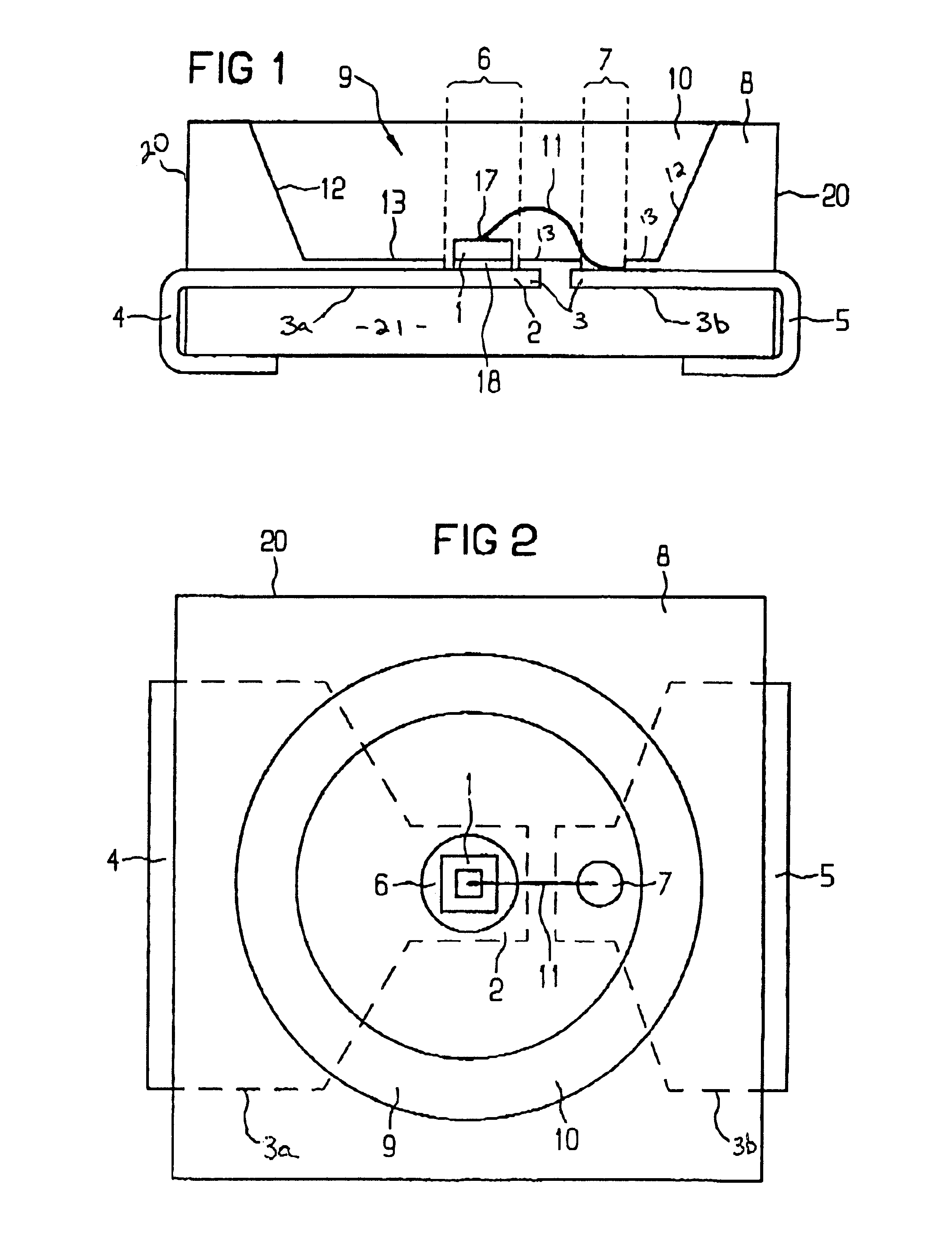

Diode housing

InactiveUS6624491B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

A housing accommodating a semiconductor chip is set out. The housing and chip may be used for sending and / or receiving radiation. Popular applications of the housing may be in light emitting diodes. The housing includes a conductor strip that is punched into two electrically isolated portions. The housing further includes a cavity extending inwards from the top of the housing. The conductor portions include respective areas that are exposed at the bottom of the cavity. The semiconductor chip is bonded to one of the exposed areas and a wire bonds the chip to the second exposed area. The conductor portions also terminate in exposed electrodes, which allow for electrical connection of the chip with external devices. A window is formed in the cavity and the walls of the housing that form the cavity may be made of a reflective material. The electrodes remain unexposed to the window but for any residual areas about the chip and bonding wire within the first and second exposed areas. By minimizing the area of the conductor exposed to the window, delamination brought about by the different thermal expansions of the window and conductor are minimized and / or eliminated. Likewise, with a reflective housing covering the base of the cavity that accommodates the window, internal radiation reflection is increased over that which was achieved with an exposed conductor.

Owner:OSRAM GMBH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com