Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2809 results about "Memory chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A memory chip is an integrated circuit made out of millions of capacitors and transistors that can store data or can be used to process code. Memory chips can hold memory either temporarily through random access memory (RAM), or permanently through read only memory (ROM).

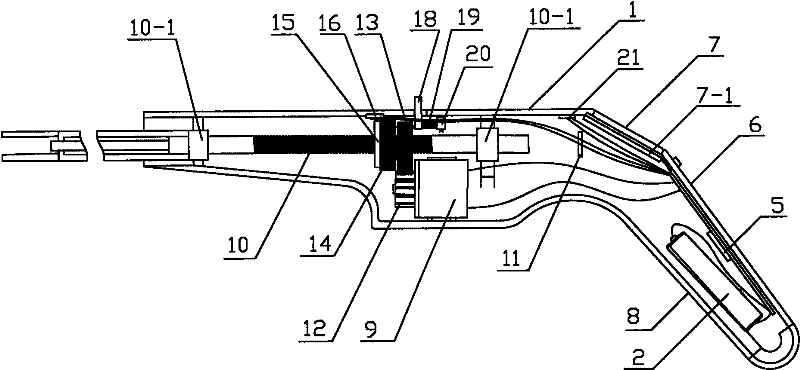

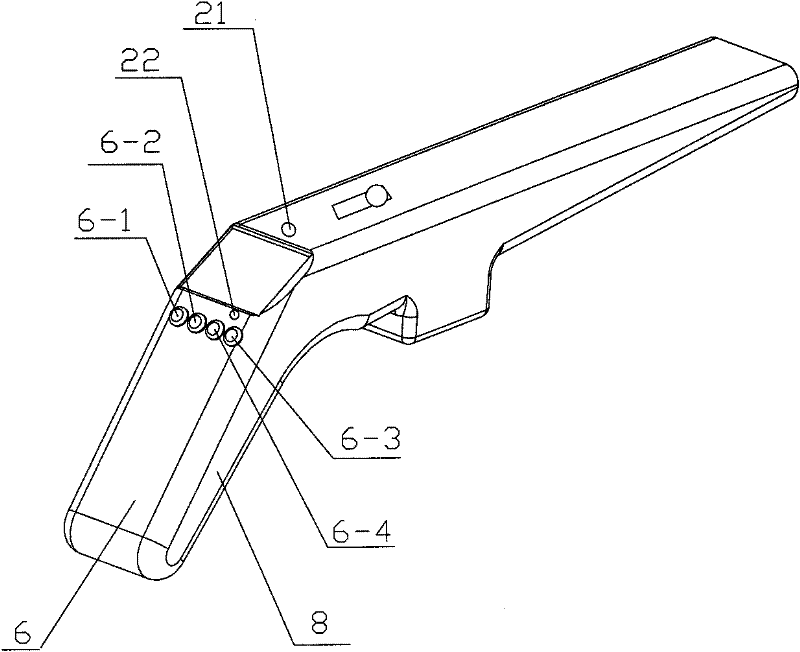

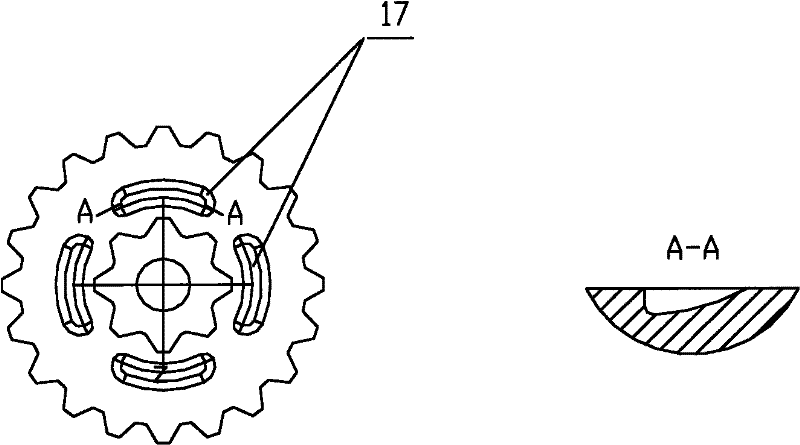

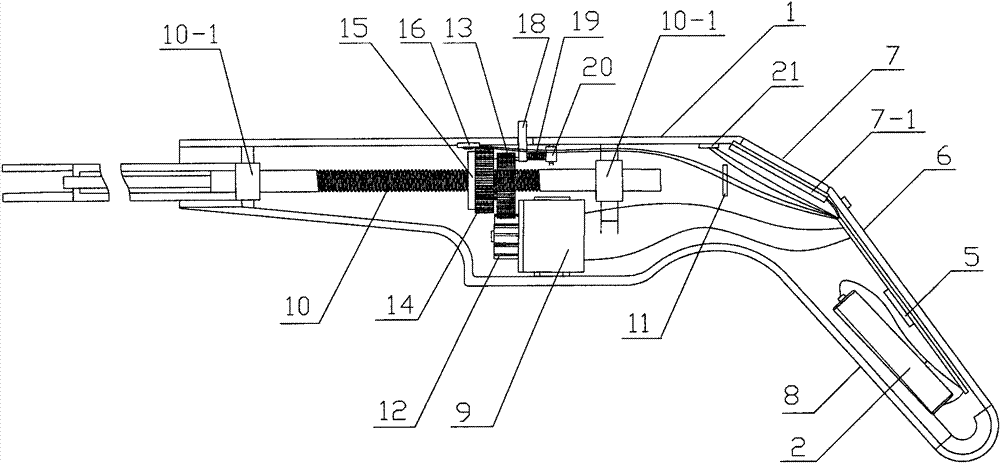

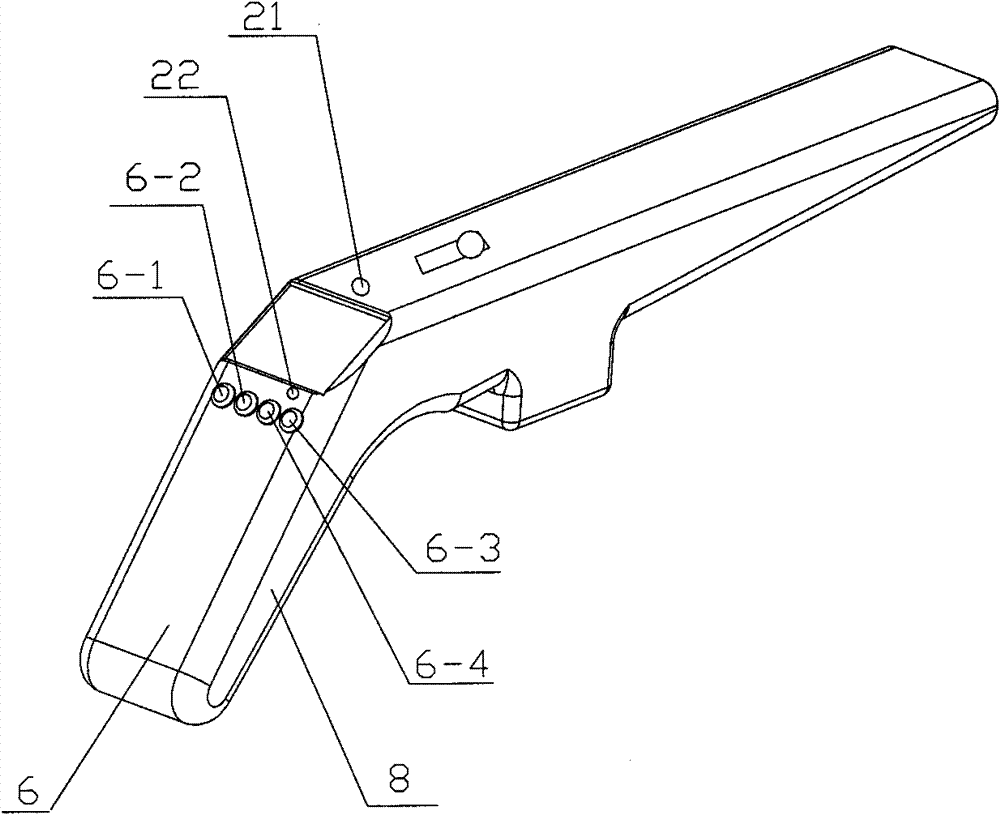

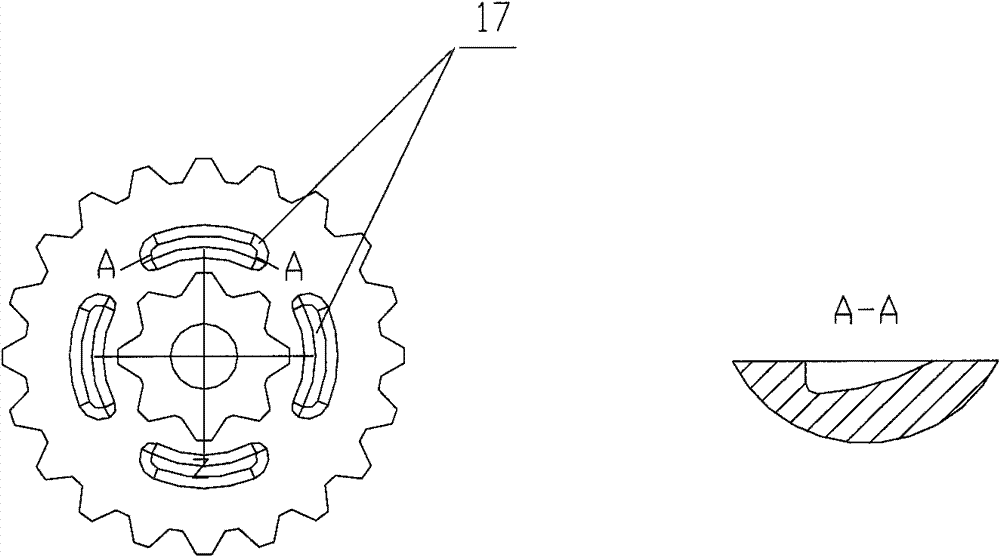

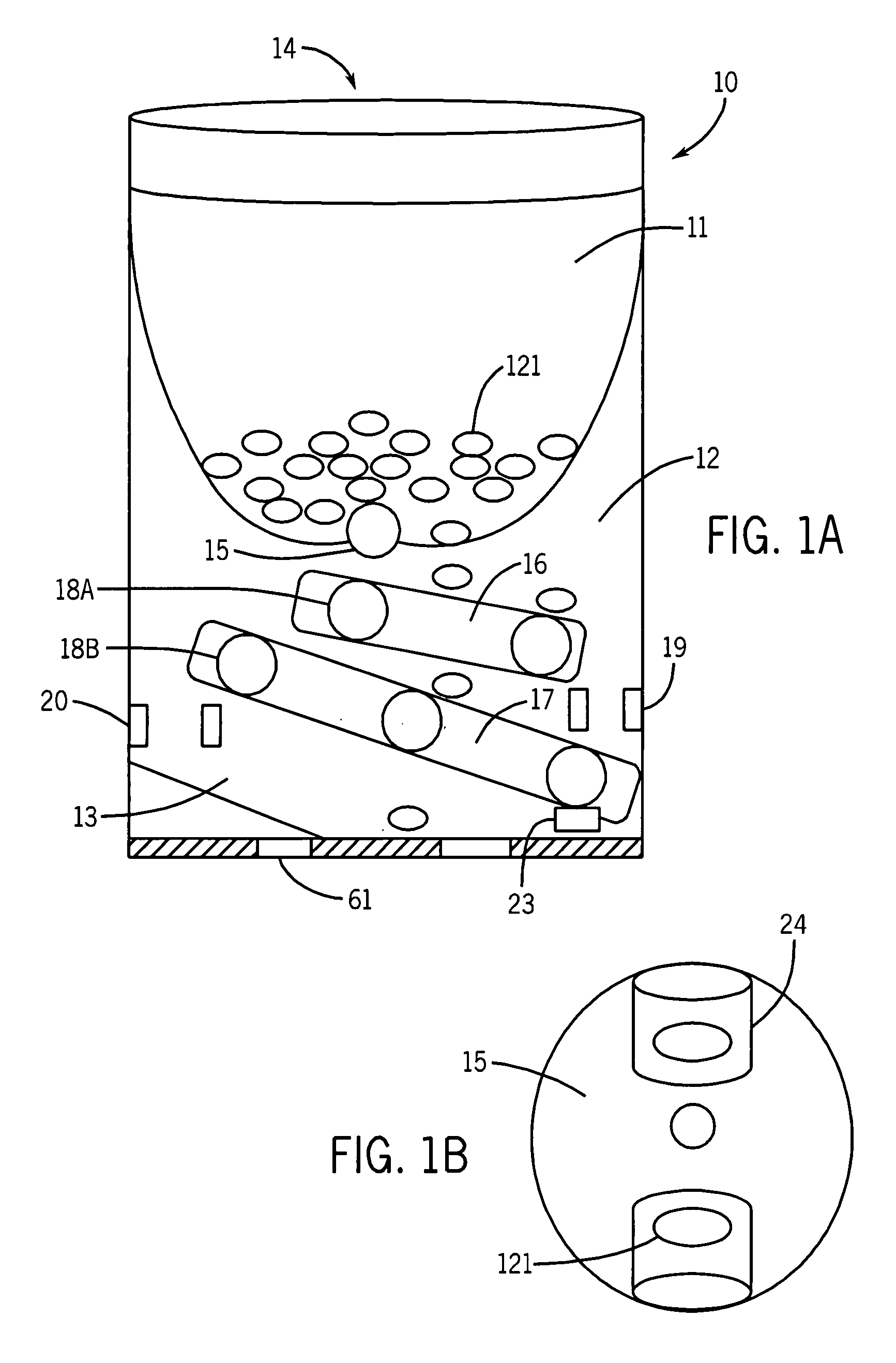

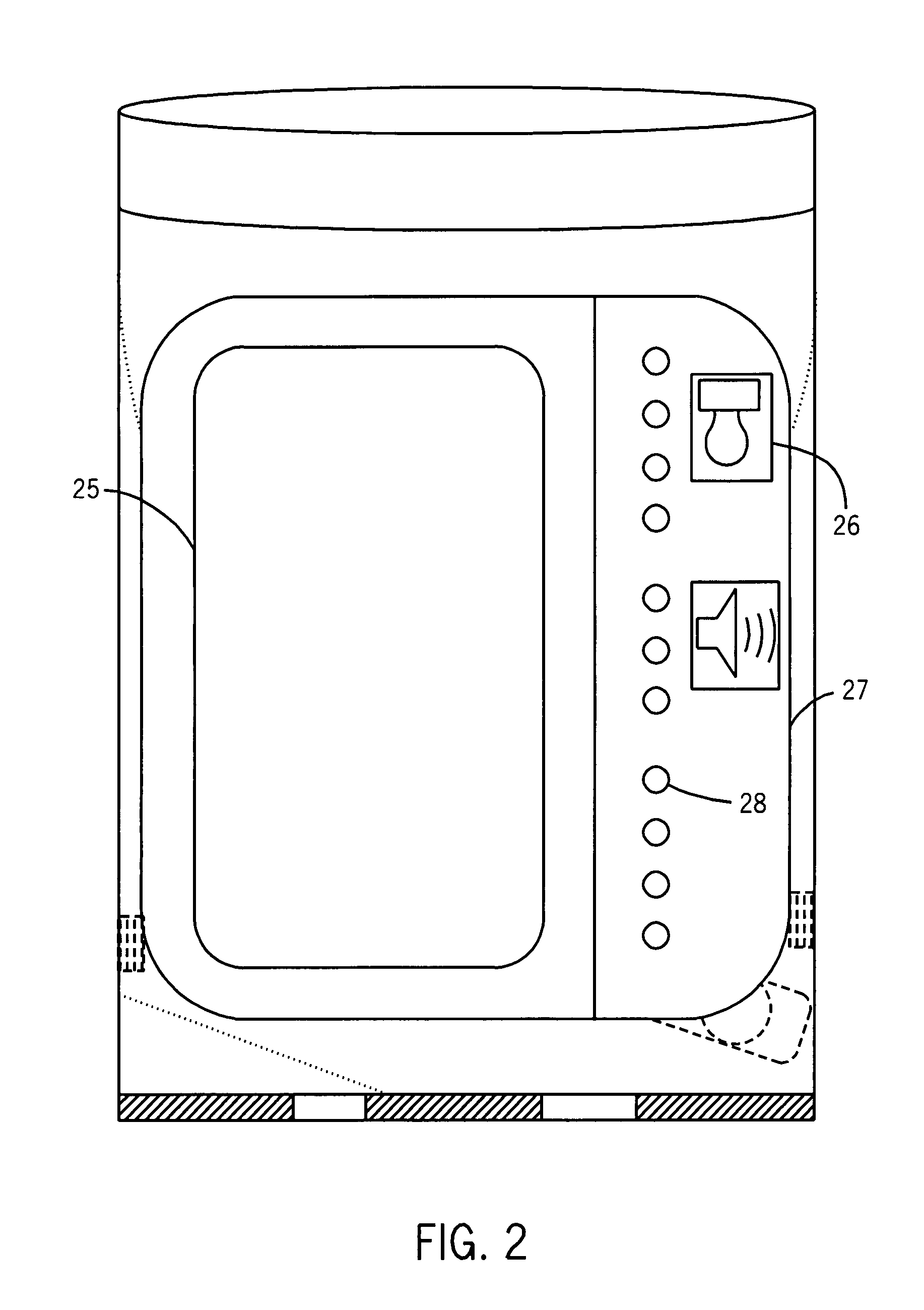

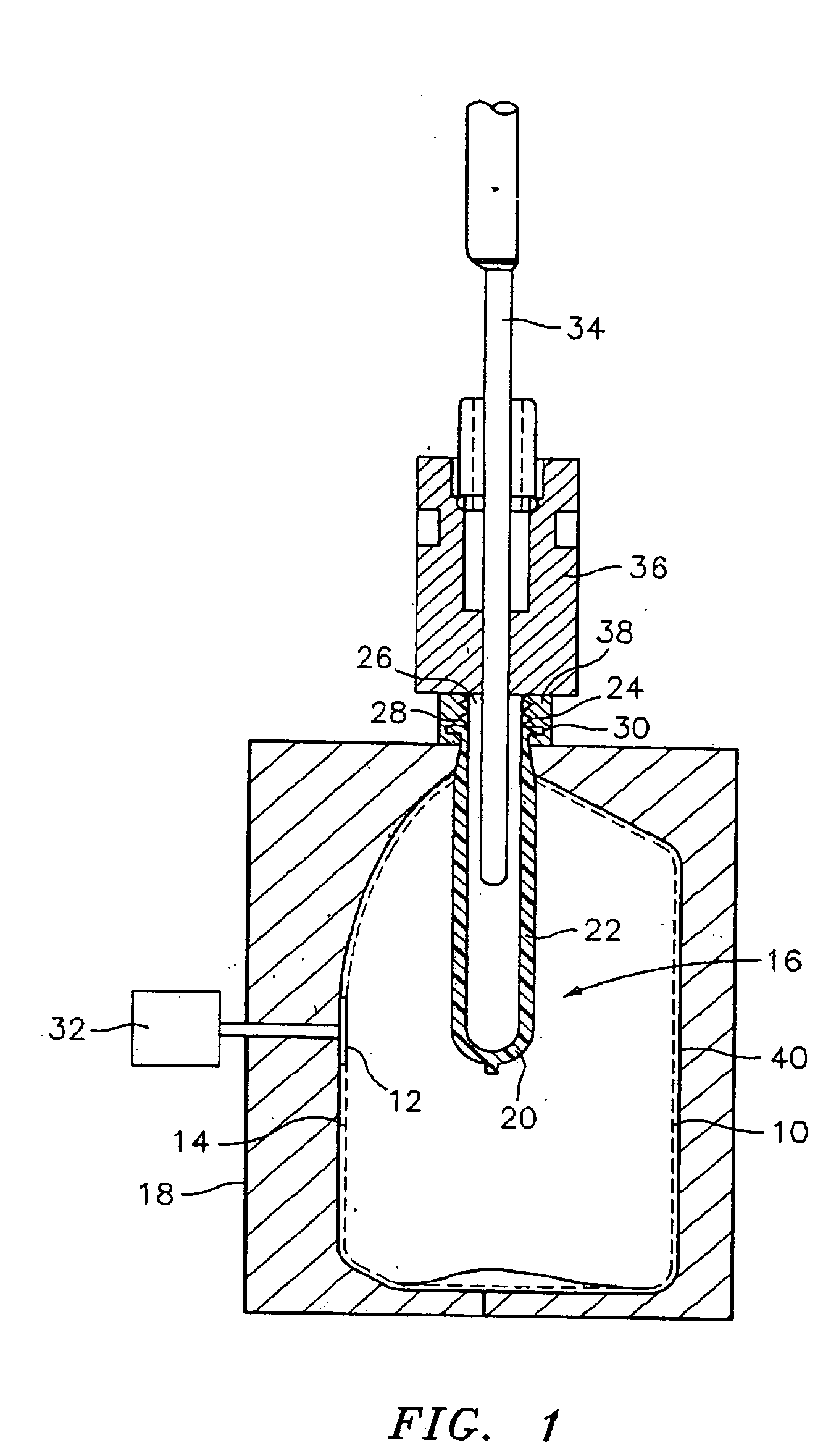

Numerically controlled surgical stapling apparatus

ActiveCN102228387AAccurate operationOperational securityNumerical controlSurgical staplesElectricityMemory chip

The invention relates to a numerically controlled surgical stapling apparatus comprising a clamping assembly, a housing and a main body assembly arranged in the housing. An electric driving device is arranged in the main body assembly. The stapling apparatus is characterized by further comprising a numerical control device which comprises a control board, a display screen and a sensing device, wherein at least one memory chip and a control chip are arranged on the control board; and the display screen is capable of displaying the values of operation parameters and clock information. The electric driving device is capable of receiving a signal produced by the numerical control device and drives a nail magazine to move toward a nail anvil until a predetermined closing gap, and further causes a suturing nail to reach a predetermined forming height after firing the suturing nail. The numerically controlled surgical stapling apparatus provided in the invention is capable of performing accurate and safe control on the transmission steps and the operation actions and also of clearly displaying the operation parameters so that a doctor can know the whole surgery process; therefore, human-machine conversation is made possible.

Owner:B J ZH F PANTHER MEDICAL EQUIP

Numerically controlled surgical stapling apparatus

ActiveCN102228387BAccurate operationOperational securitySurgical staplesNumerical controlMemory chipElectricity

The invention relates to a numerically controlled surgical stapling apparatus comprising a clamping assembly, a housing and a main body assembly arranged in the housing. An electric driving device is arranged in the main body assembly. The stapling apparatus is characterized by further comprising a numerical control device which comprises a control board, a display screen and a sensing device, wherein at least one memory chip and a control chip are arranged on the control board; and the display screen is capable of displaying the values of operation parameters and clock information. The electric driving device is capable of receiving a signal produced by the numerical control device and drives a nail magazine to move toward a nail anvil until a predetermined closing gap, and further causes a suturing nail to reach a predetermined forming height after firing the suturing nail. The numerically controlled surgical stapling apparatus provided in the invention is capable of performing accurate and safe control on the transmission steps and the operation actions and also of clearly displaying the operation parameters so that a doctor can know the whole surgery process; therefore, human-machine conversation is made possible.

Owner:B J ZH F PANTHER MEDICAL EQUIP

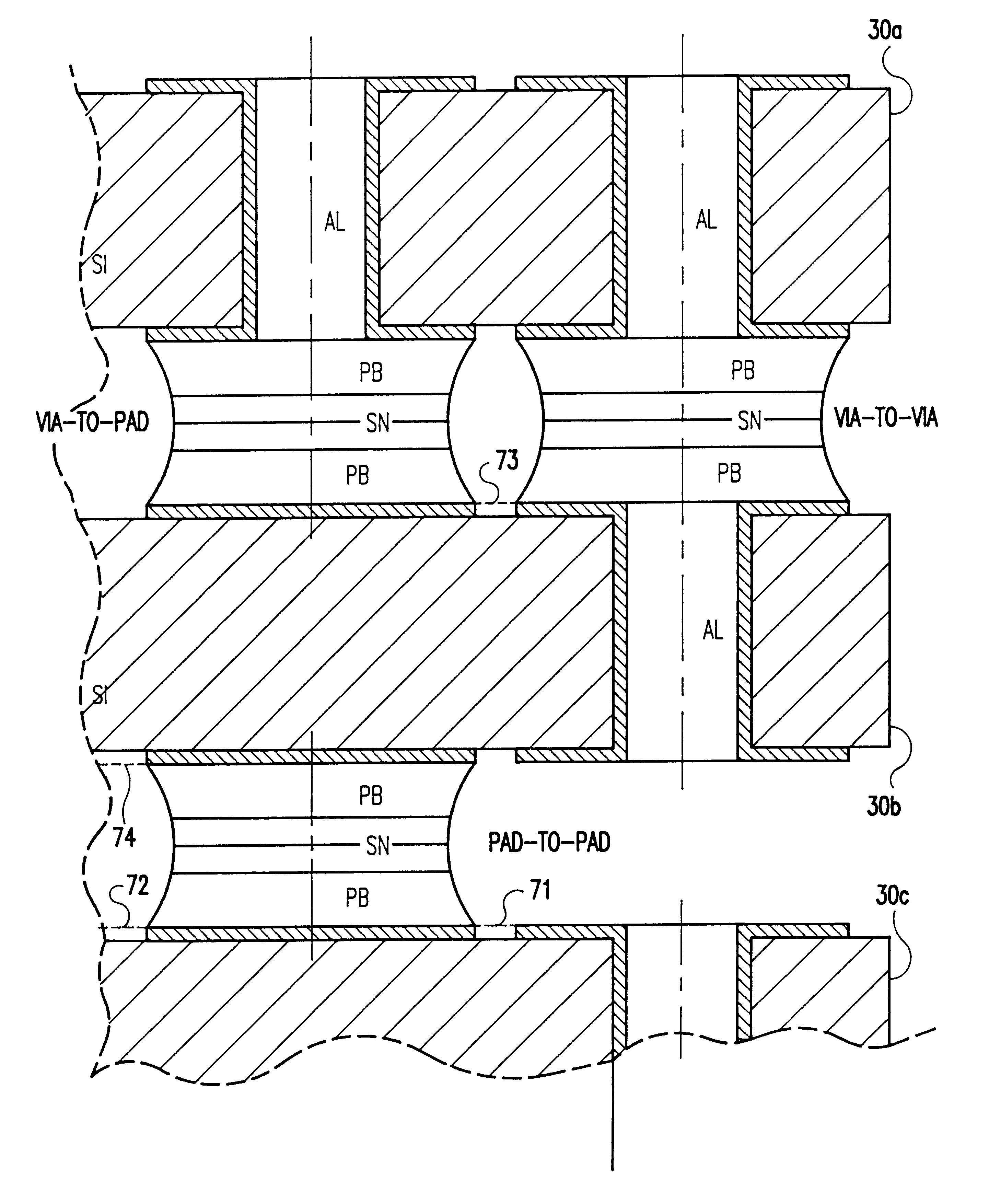

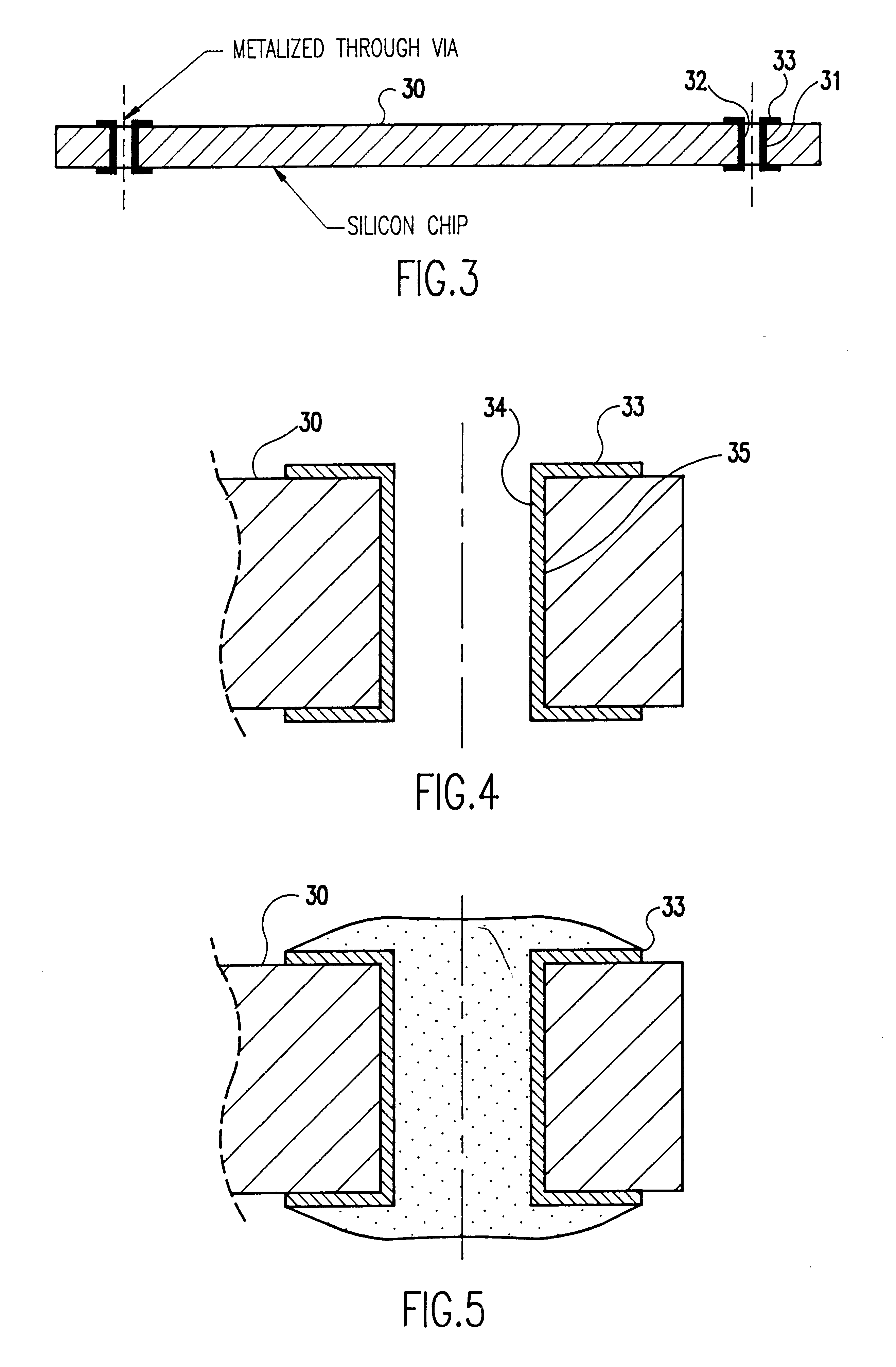

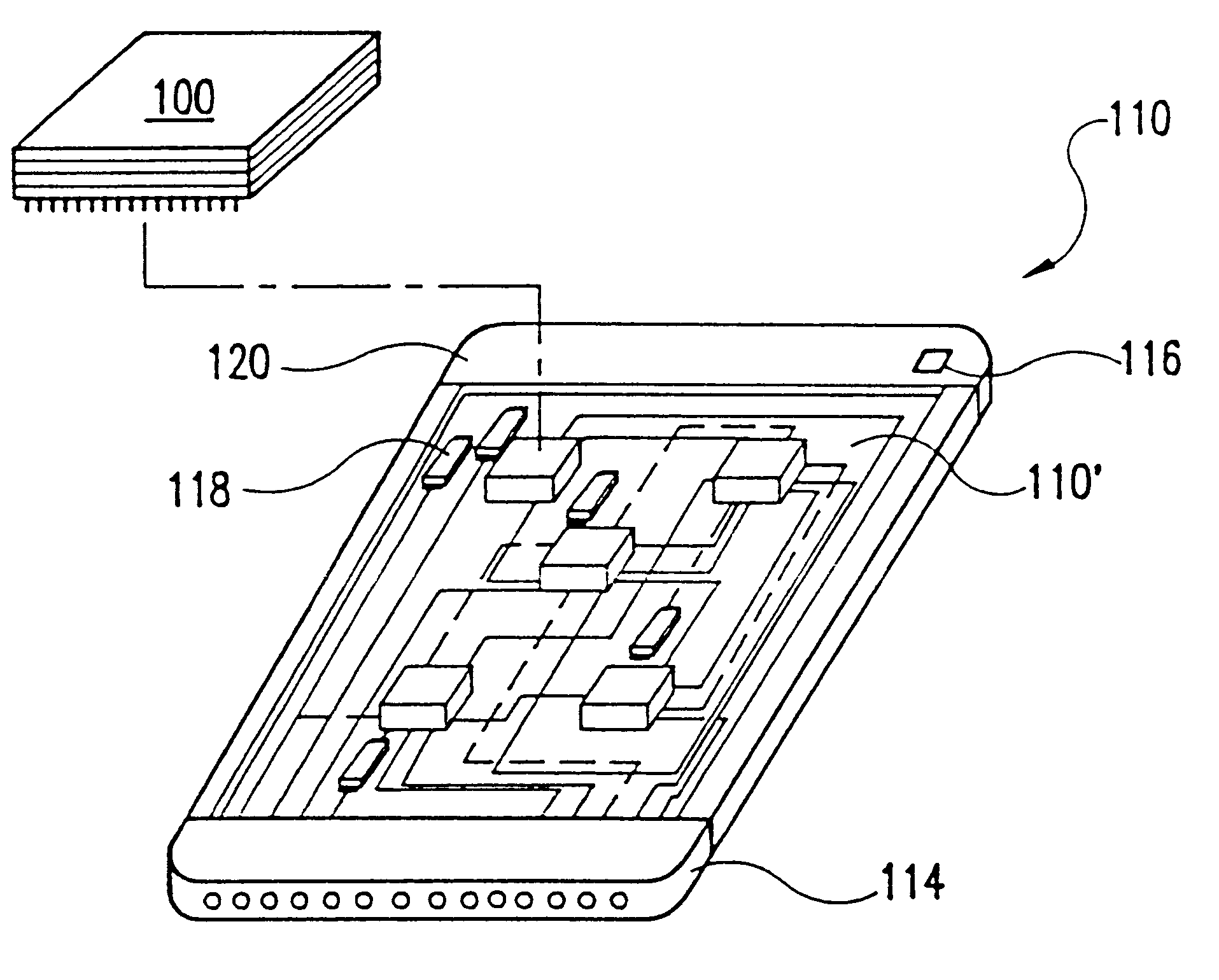

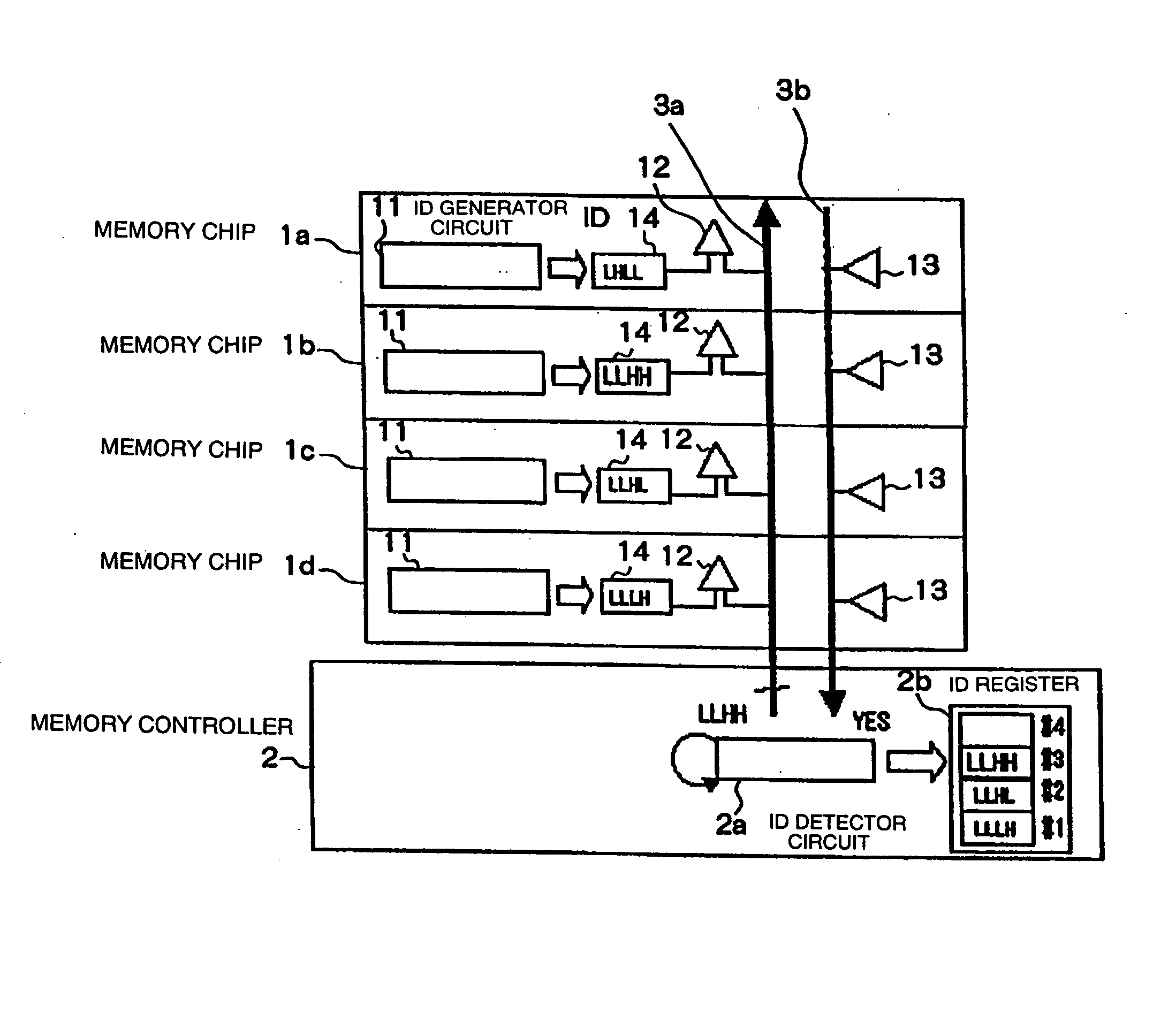

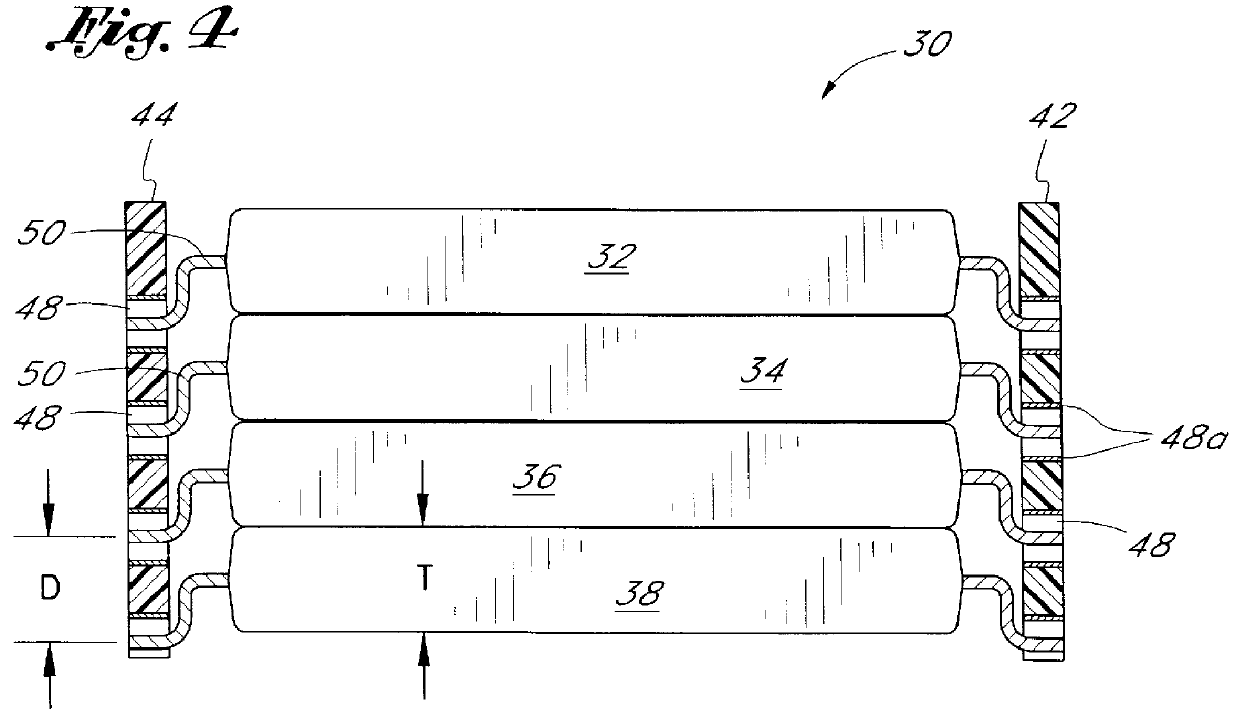

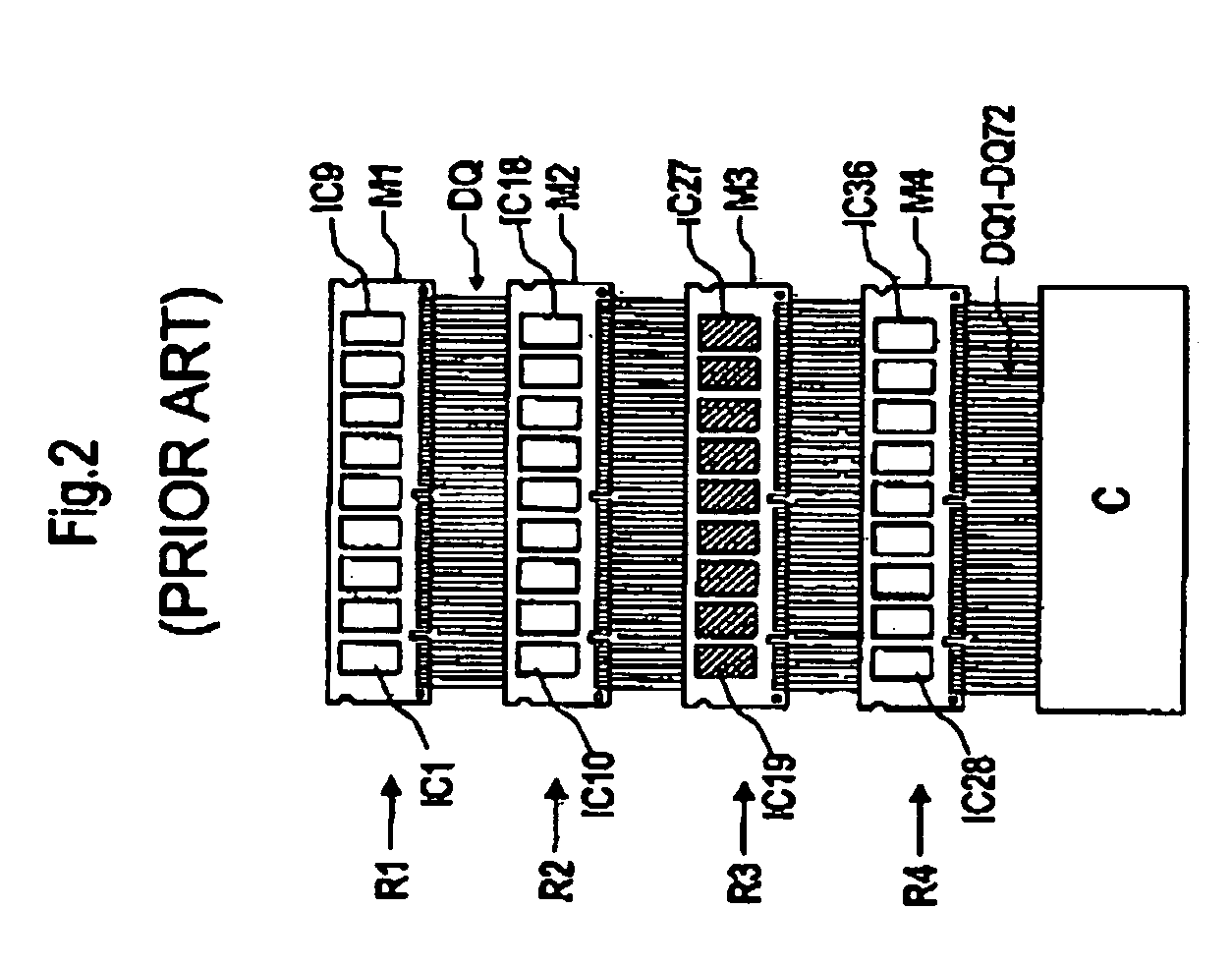

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

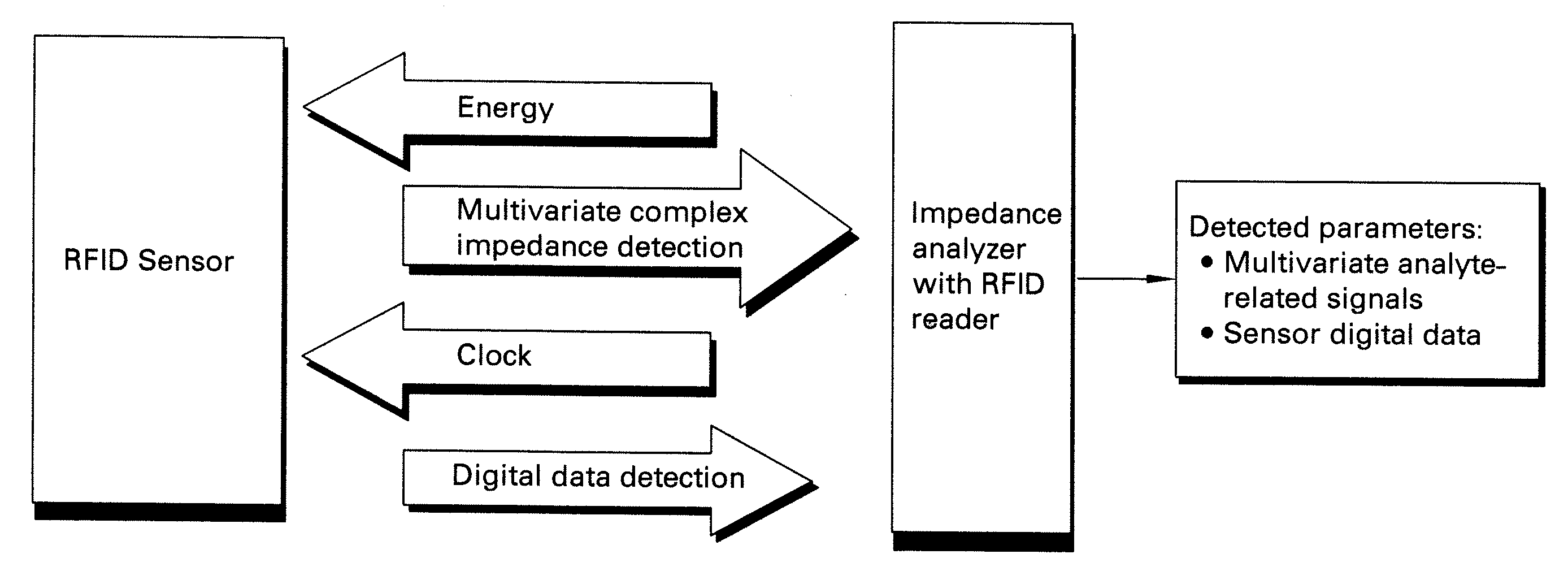

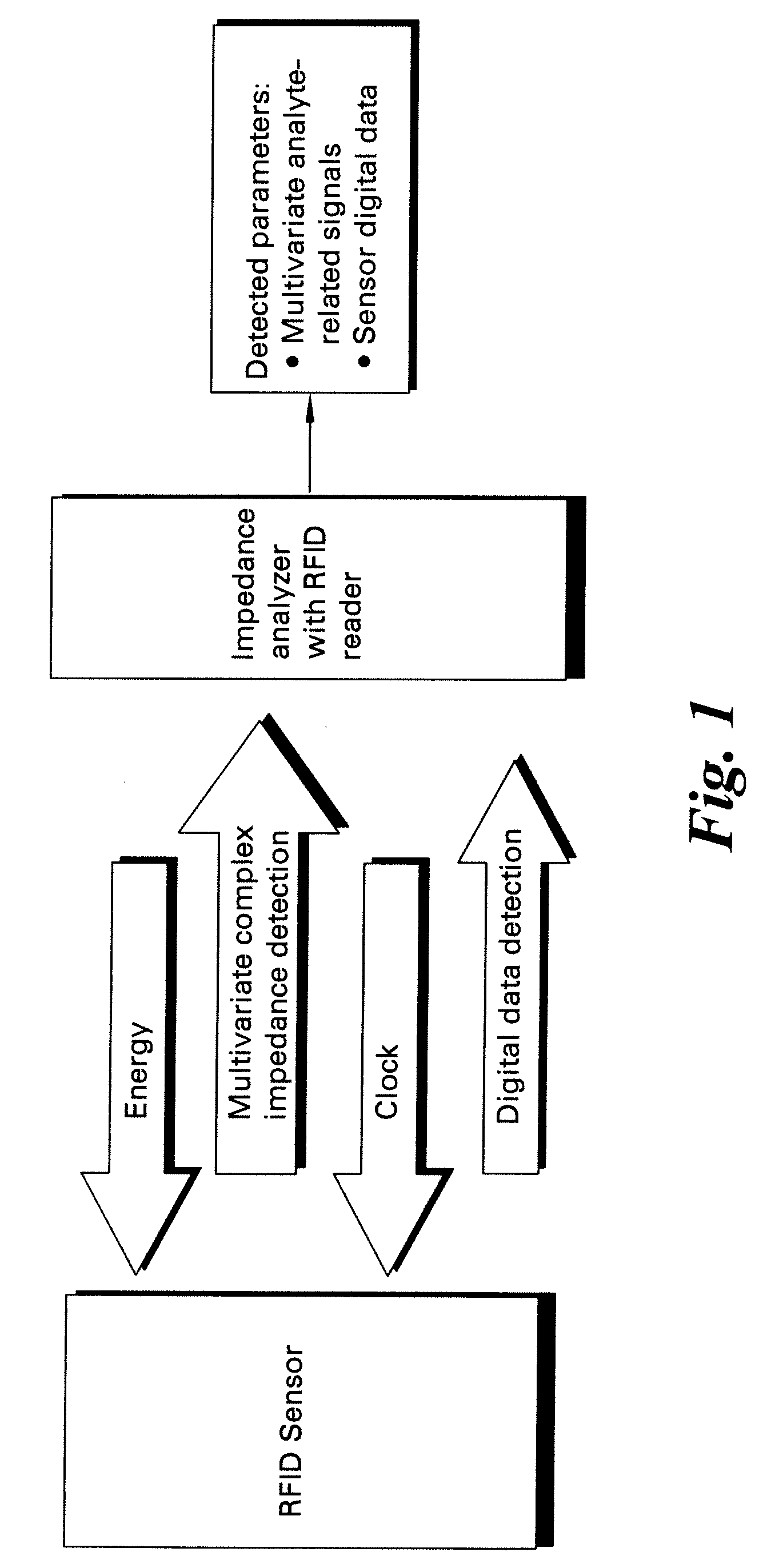

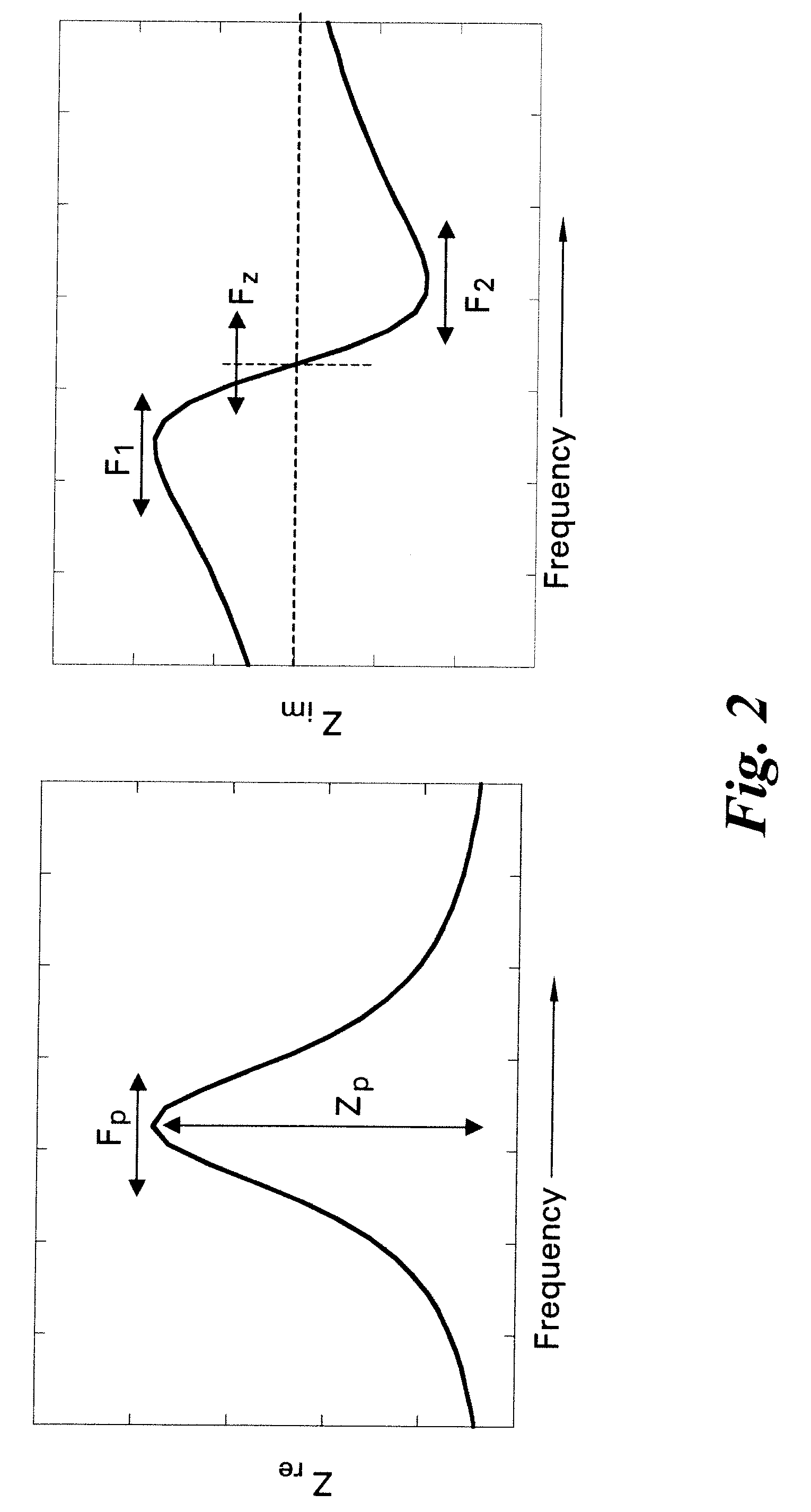

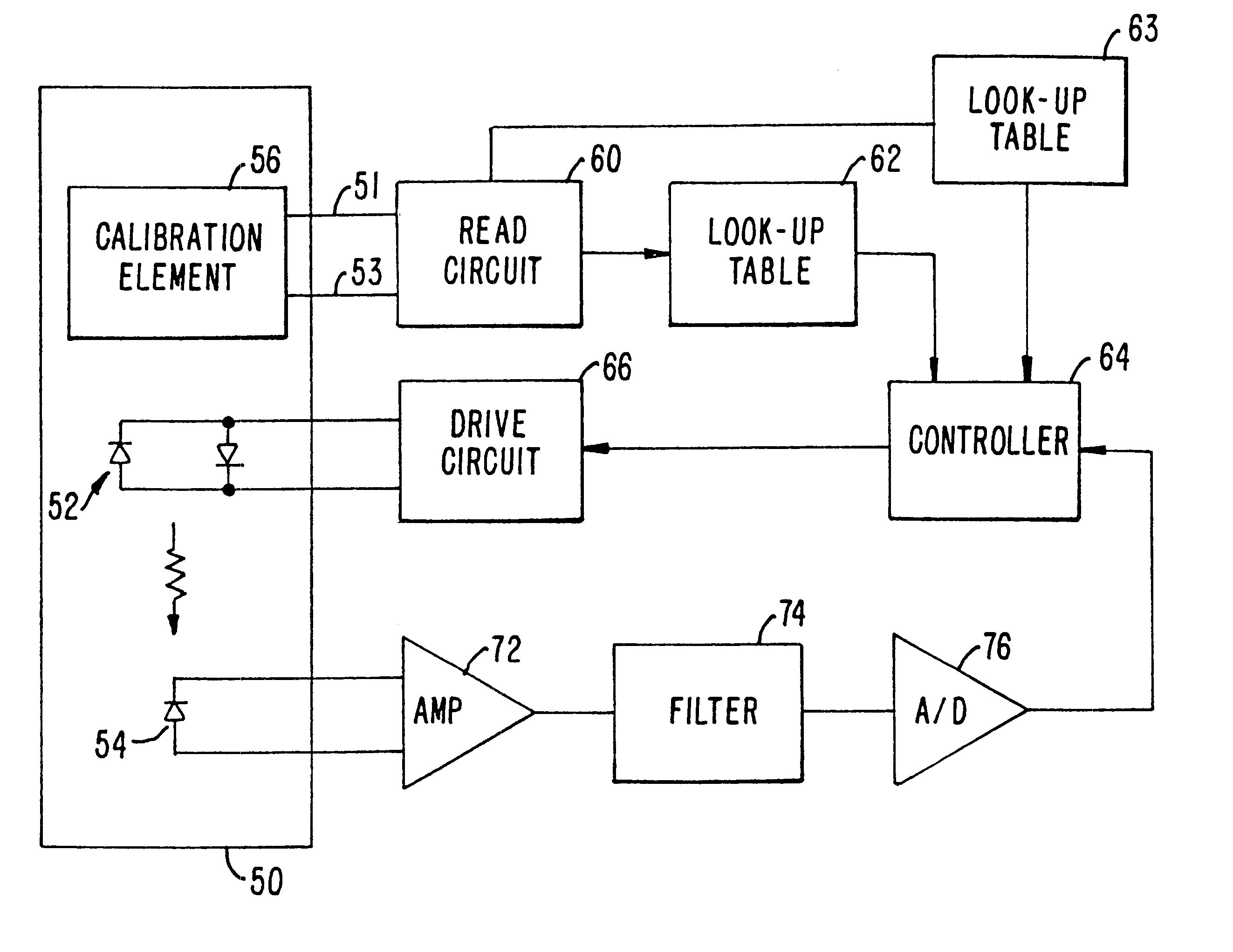

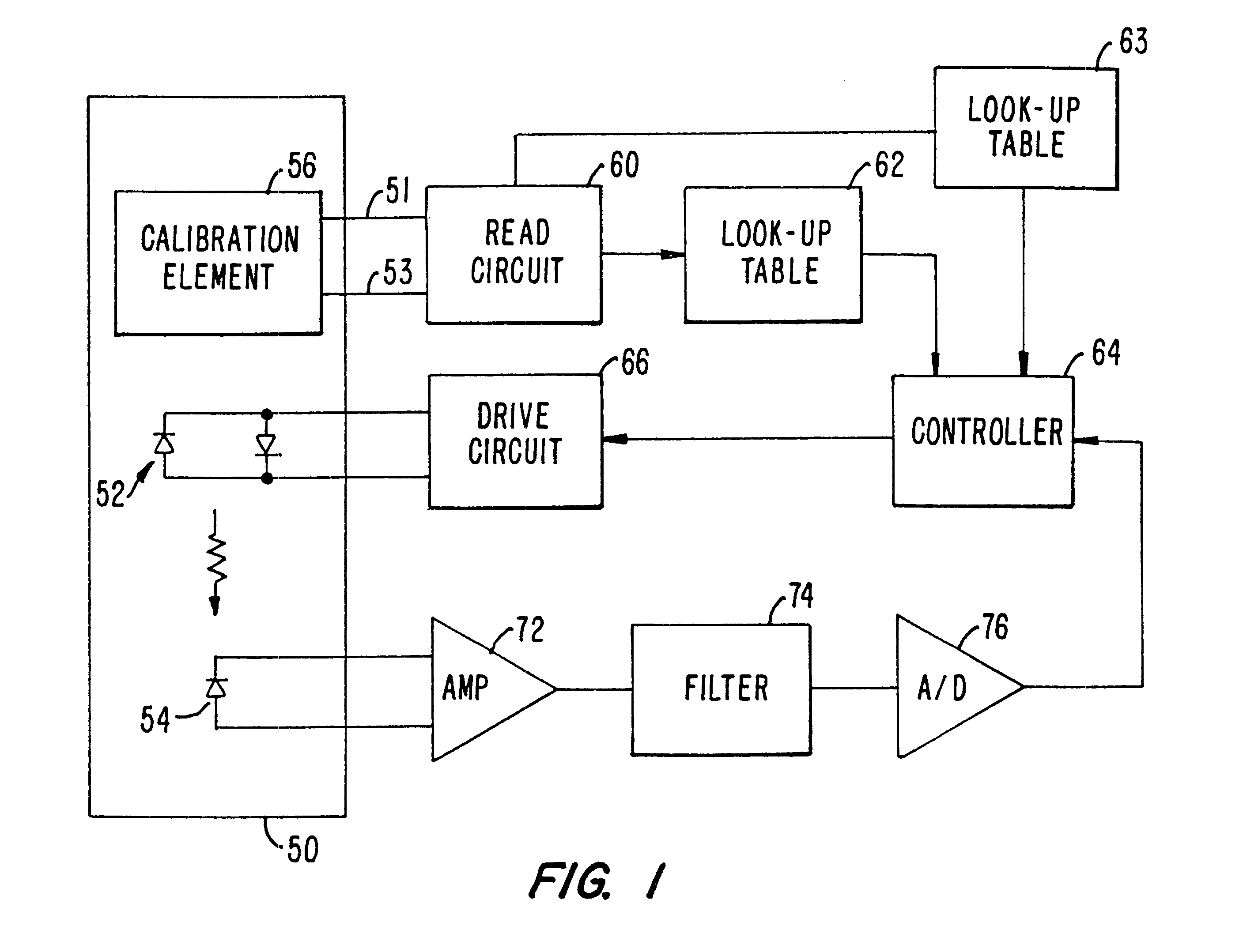

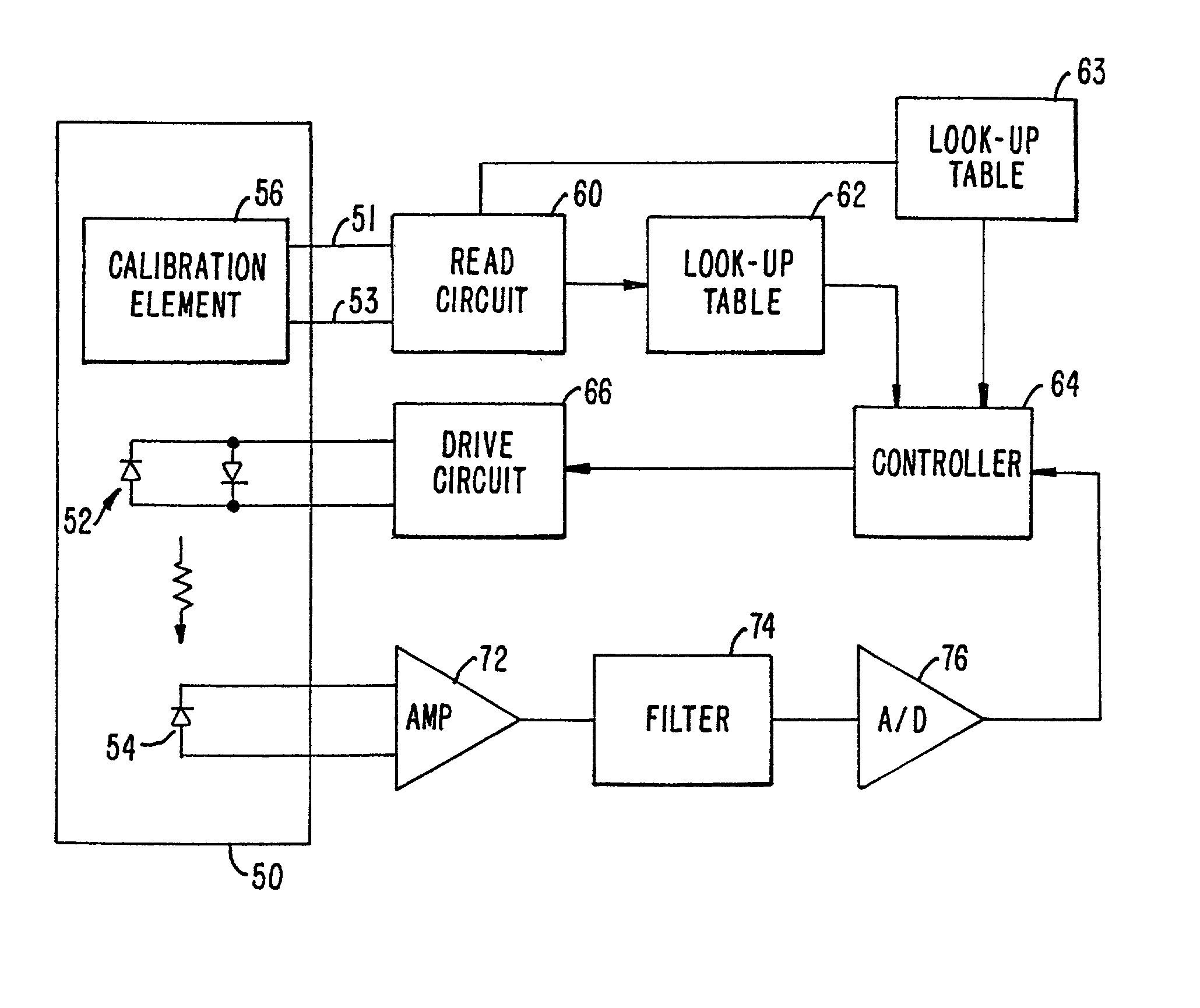

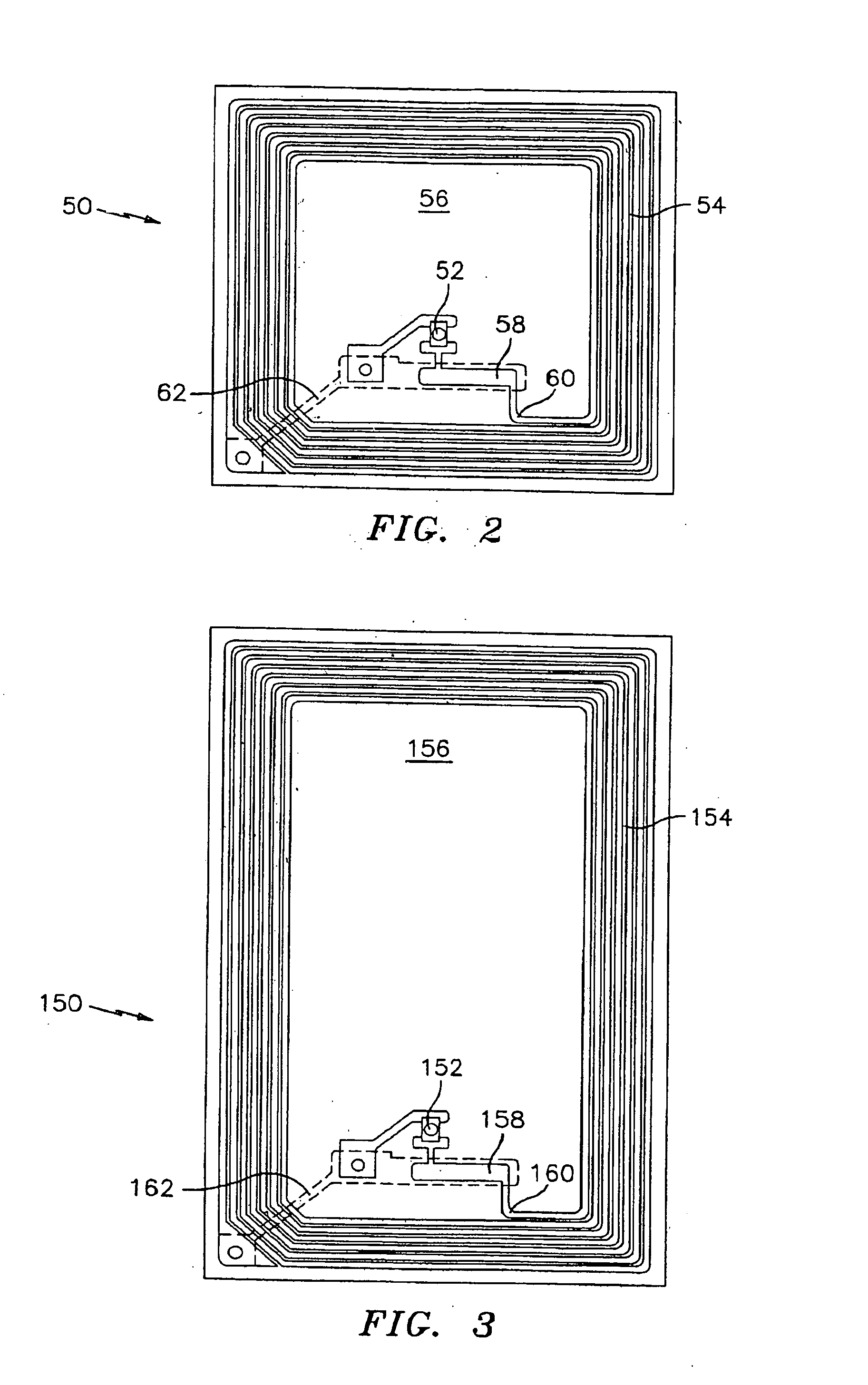

Methods and systems for calibration of RFID sensors

ActiveUS20090278685A1Testing sensing arrangementsGas analyser calibrationMemory chipComplex impedance spectra

Methods and systems for calibration of RFID sensors used in manufacturing and monitoring systems are provided. The methods include measuring impedance of an RFID sensor antenna, relating the measurement of impedance to one or more parameters (such as physical, chemical and biological properties), computing one or more analytical fit coefficients, and storing the one or more analytical fit coefficients on a memory chip of the RFID sensor. Measuring impedance of the RFID sensor may comprise measuring complex impedance which involves measuring complex impedance spectrum, phase angle and magnitude of the impedance, at least one of frequency of the maximum of the real part of the complex impedance, magnitude of the real part of the complex impedance, zero-reactance frequency, resonant frequency of the imaginary part of the complex impedance, and antiresonant frequency of the imaginary part of the complex impedance. Also provided are manufacturing or monitoring systems comprised of an RFID sensor wherein the RFID sensor comprises, a memory chip, an antenna, and a sensing film wherein analytical fit coefficients are stored on the memory chip to allow calibration of the RFID sensor. Also provided are manufacturing or monitoring systems comprised of an RFID sensor wherein the RFID sensor comprises, a memory chip, an antenna, and a complementary sensor attached to the antenna where the complementary sensor in a pre-calibrated fashion predictably affects the impedance of the antenna.

Owner:WESTINGHOUSE AIR BRAKE TECH CORP

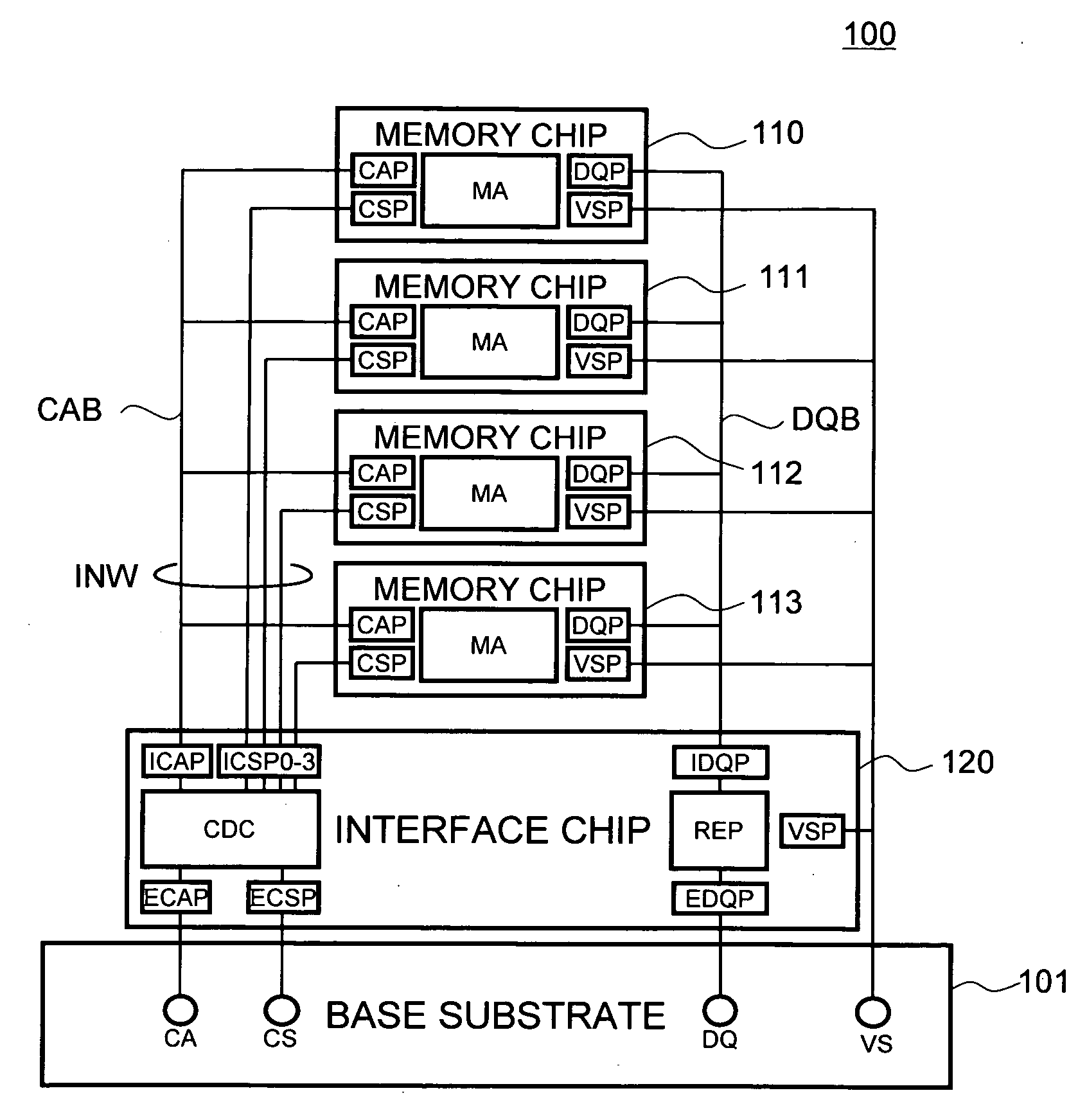

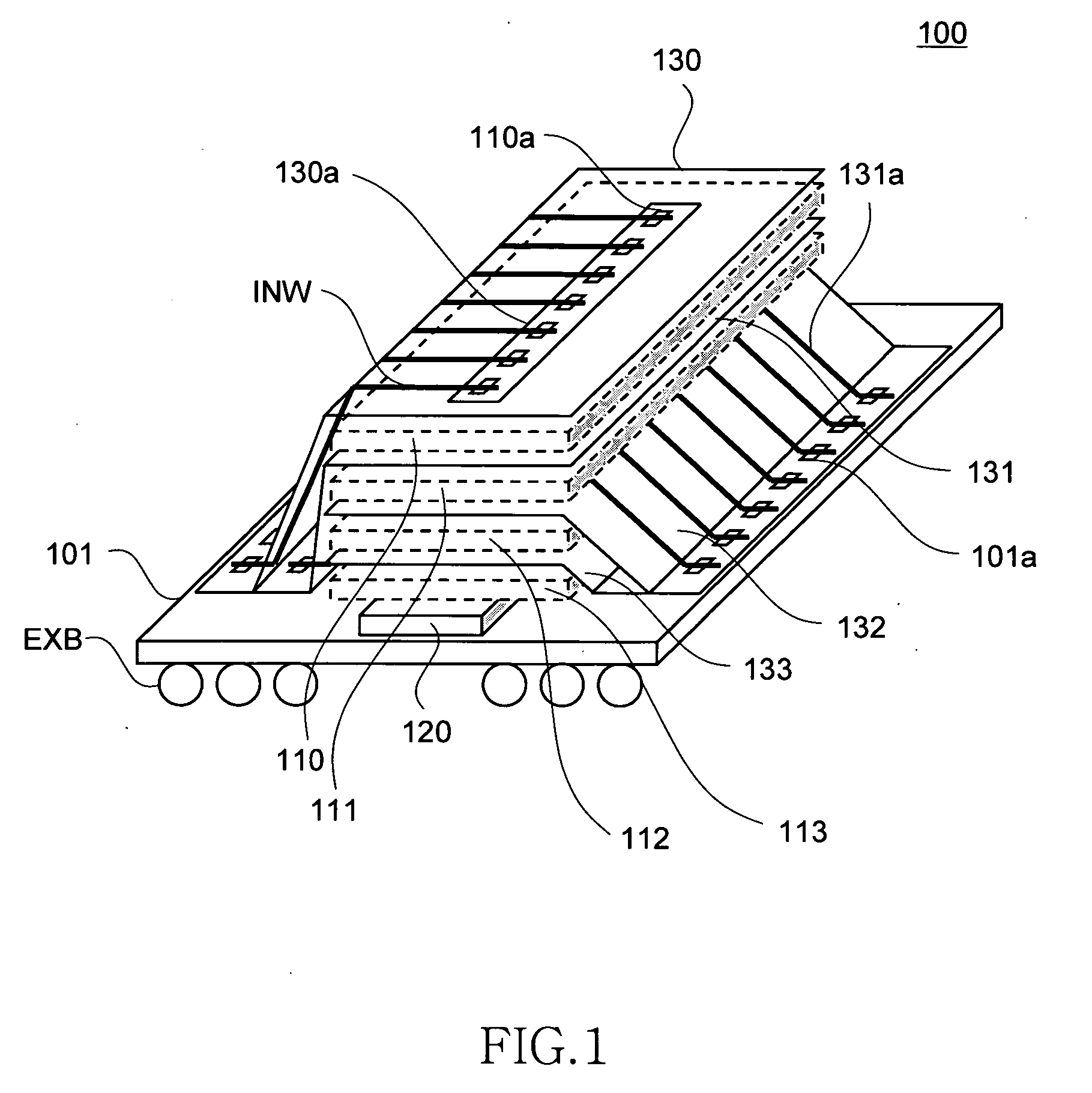

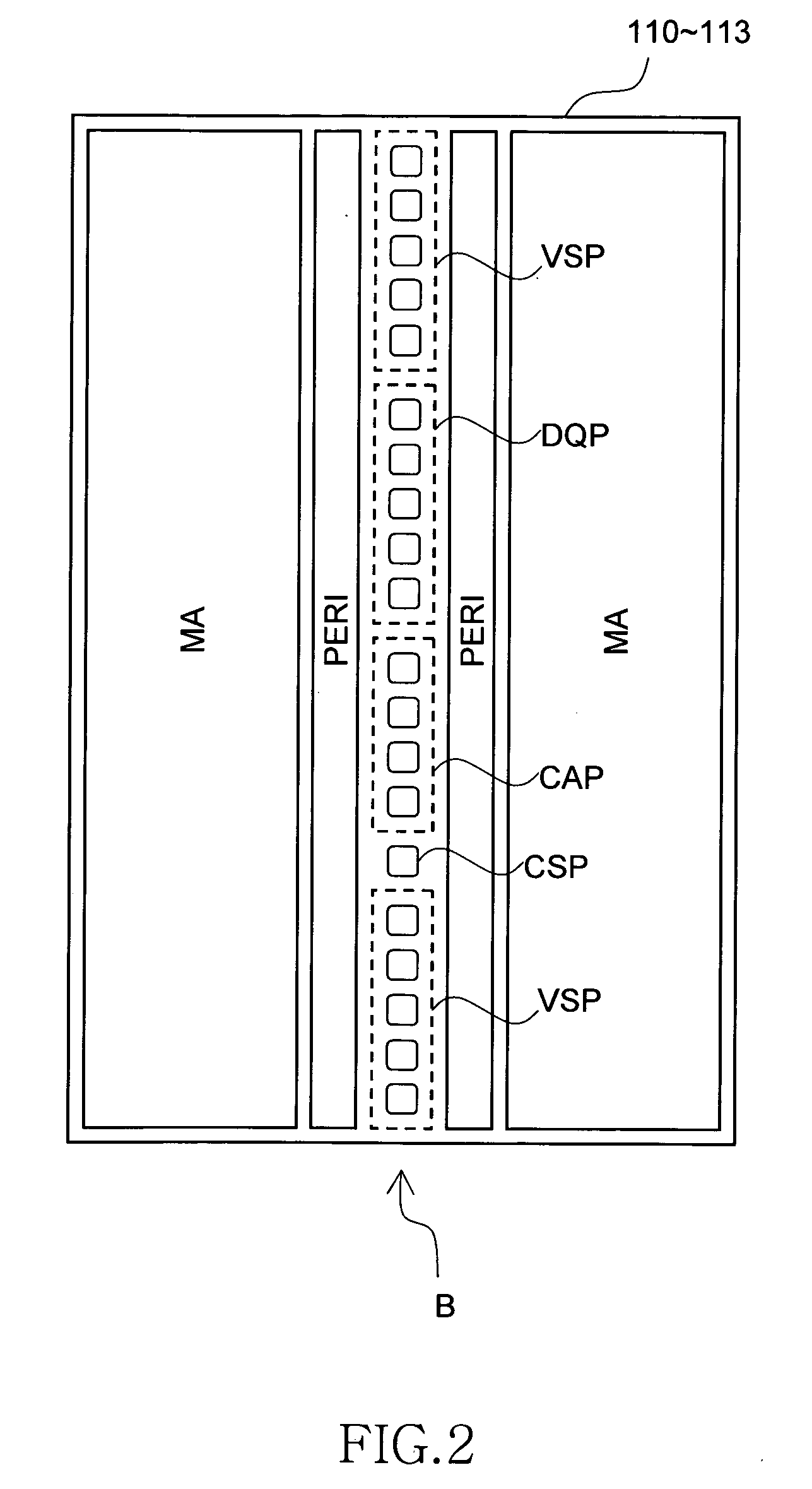

Semiconductor storage device having a plurality of stacked memory chips

ActiveUS20060233012A1Reduce in quantityReduction in wiring capacitanceSemiconductor/solid-state device detailsSolid-state devicesMemory chipChip select

A semiconductor storage employs a base substrate (101) having a command / address external terminal group (CA), a data input / output external terminal group (DQ), and a single chip select external terminal (CS), and also comprises a plurality of memory chips (110) to (113) mounted on a base substrate (101), each of which can individually carry out read and write operations. The terminals (CA), (DQ), and (CS) are connected to an interface chip (120). The interface chip (120) has a chip select signal generation circuit that can individually activate a plurality of memory chips (110) to (113) on the basis of an address signal fed by way of the terminal (CA) and on the basis of a chip select signal fed by way of the terminal (CS).

Owner:LONGITUDE LICENSING LTD

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

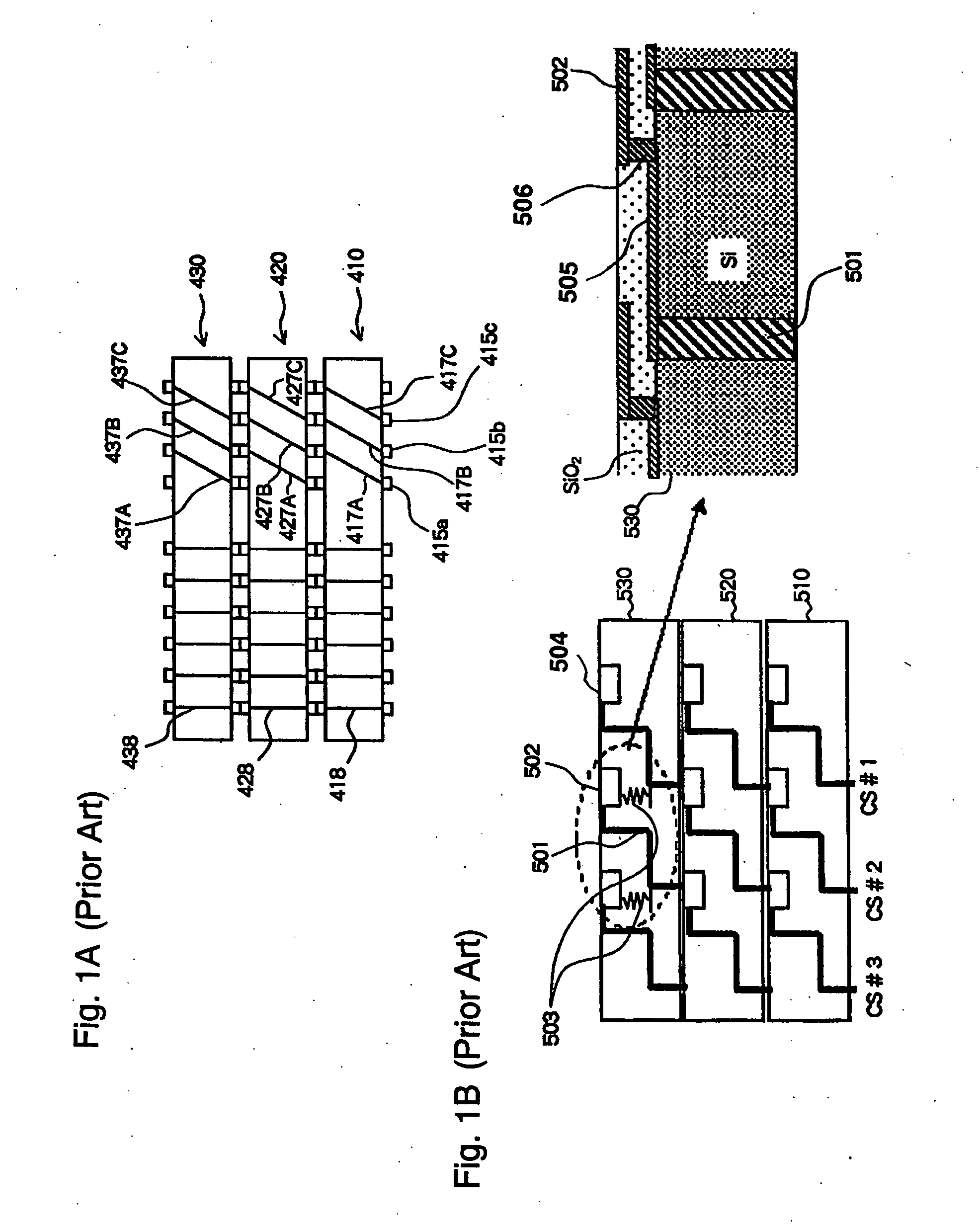

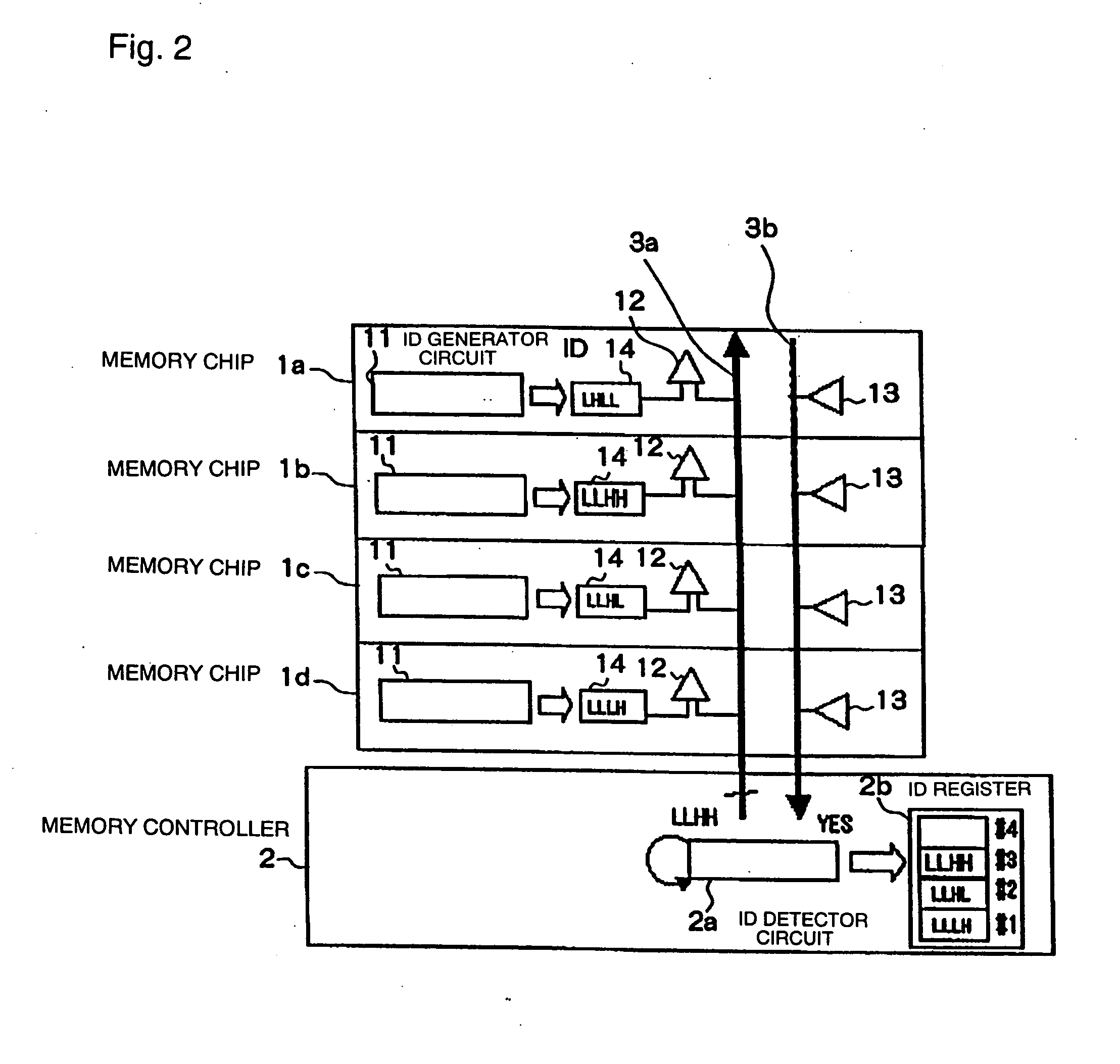

Stacked semiconductor device and semiconductor chip control method

InactiveUS20050082664A1Semiconductor/solid-state device detailsSolid-state devicesMemory chipDetector circuits

Each of stacked memory chips has an ID generator circuit for generating identification information in accordance with its manufacturing process. Since the memory chip manufacturing process implies process variations, the IDs generated by the respective ID generator circuits are different from one another even though the ID generator circuits are identical in design. A memory controller instructs an ID detector circuit to detect the IDs of the respective memory chips, and individually controls the respective memory chips based on the detected IDs.

Owner:ELPIDA MEMORY INC

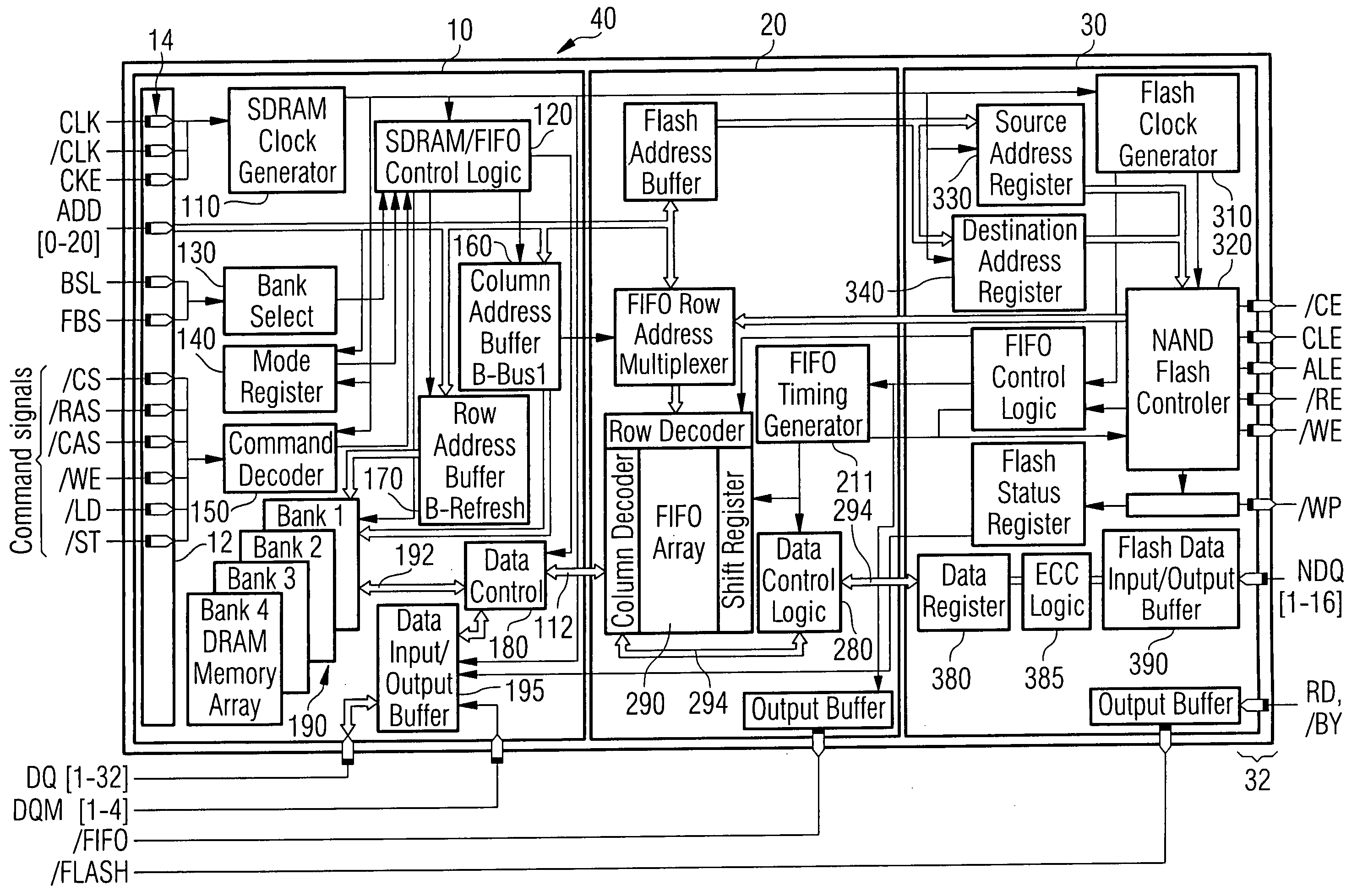

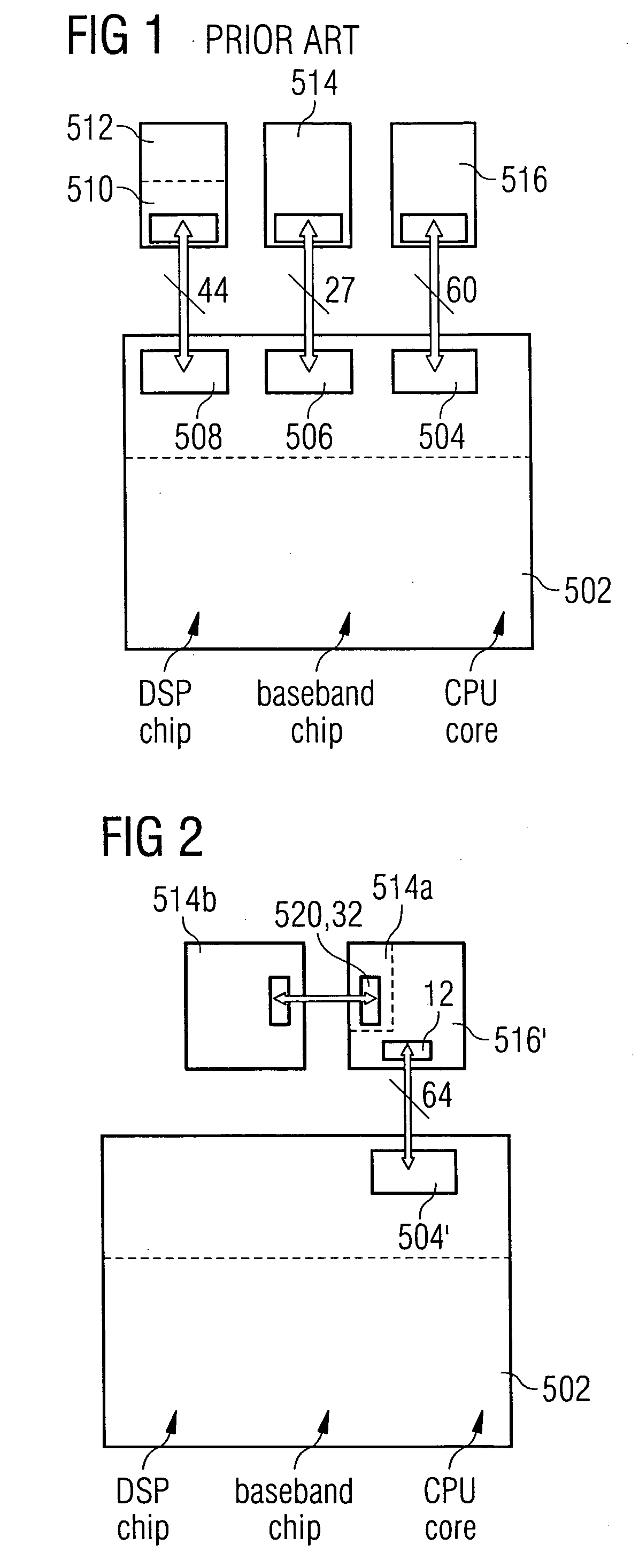

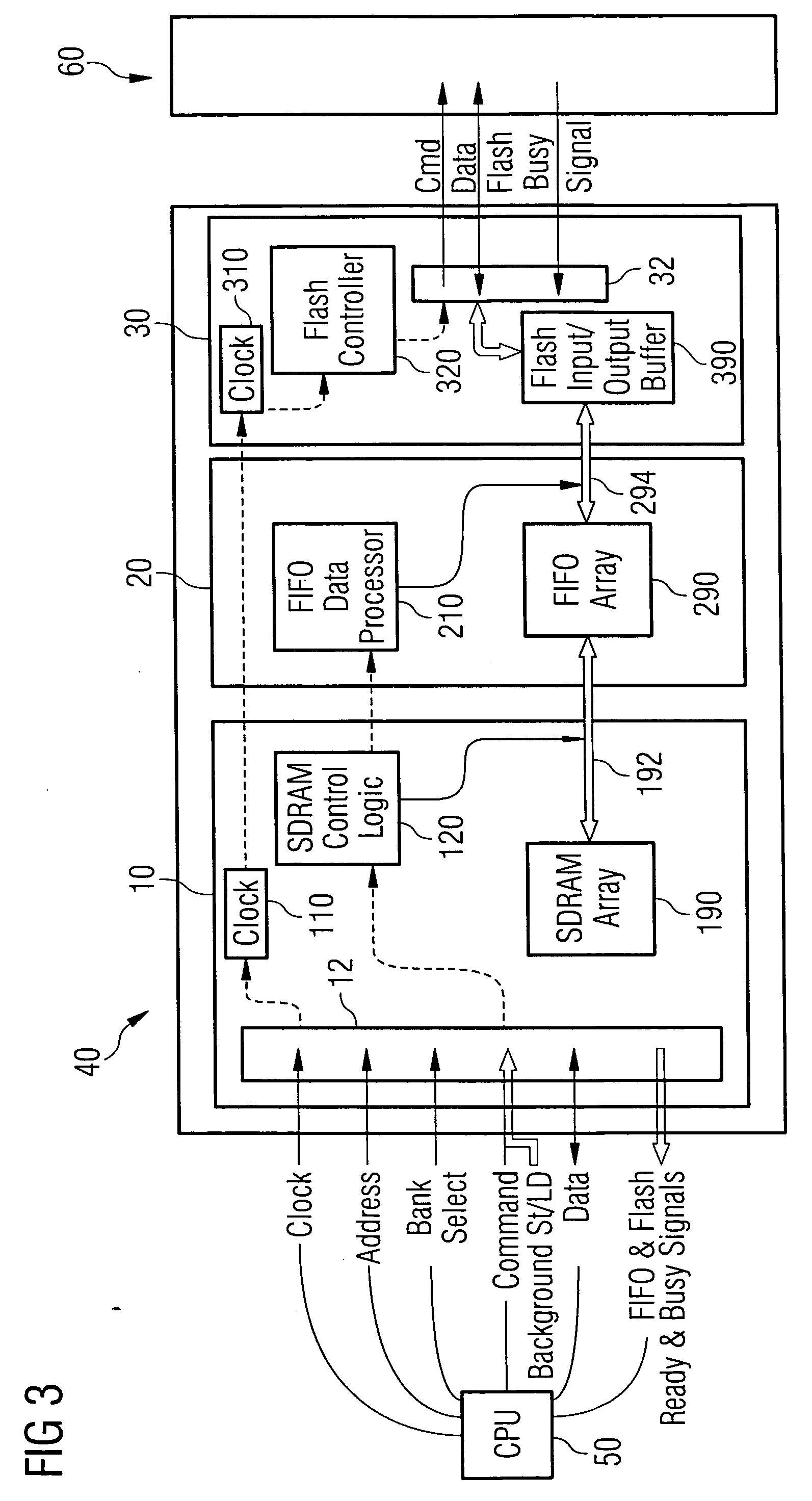

DRAM chip device well-communicated with flash memory chip and multi-chip package comprising such a device

An SDRAM memory chip device comprises a non-volatile memory controller for operating a non-volatile memory, e.g., a NAND-flash, and a FIFO memory buffer. The FIFO memory buffer serves to operate background store and load operations between a FIFO buffer array and the non-volatile memory, while a host system such as a CPU exchanges data with the SDRAM work memory. The SDRAM memory chip device, therefore, has at least two additional pins as compared with conventional SDRAM standard for generating a set of additional commands. These commands are employed by the FIFO memory buffer to manage the data transfer between the FIFO buffer and each of the non-volatile memory and the volatile SDRAM memory. Two further pins reflecting the flash memory status provide appropriate issuance of load or store signals by the host system.

Owner:INFINEON TECH AG

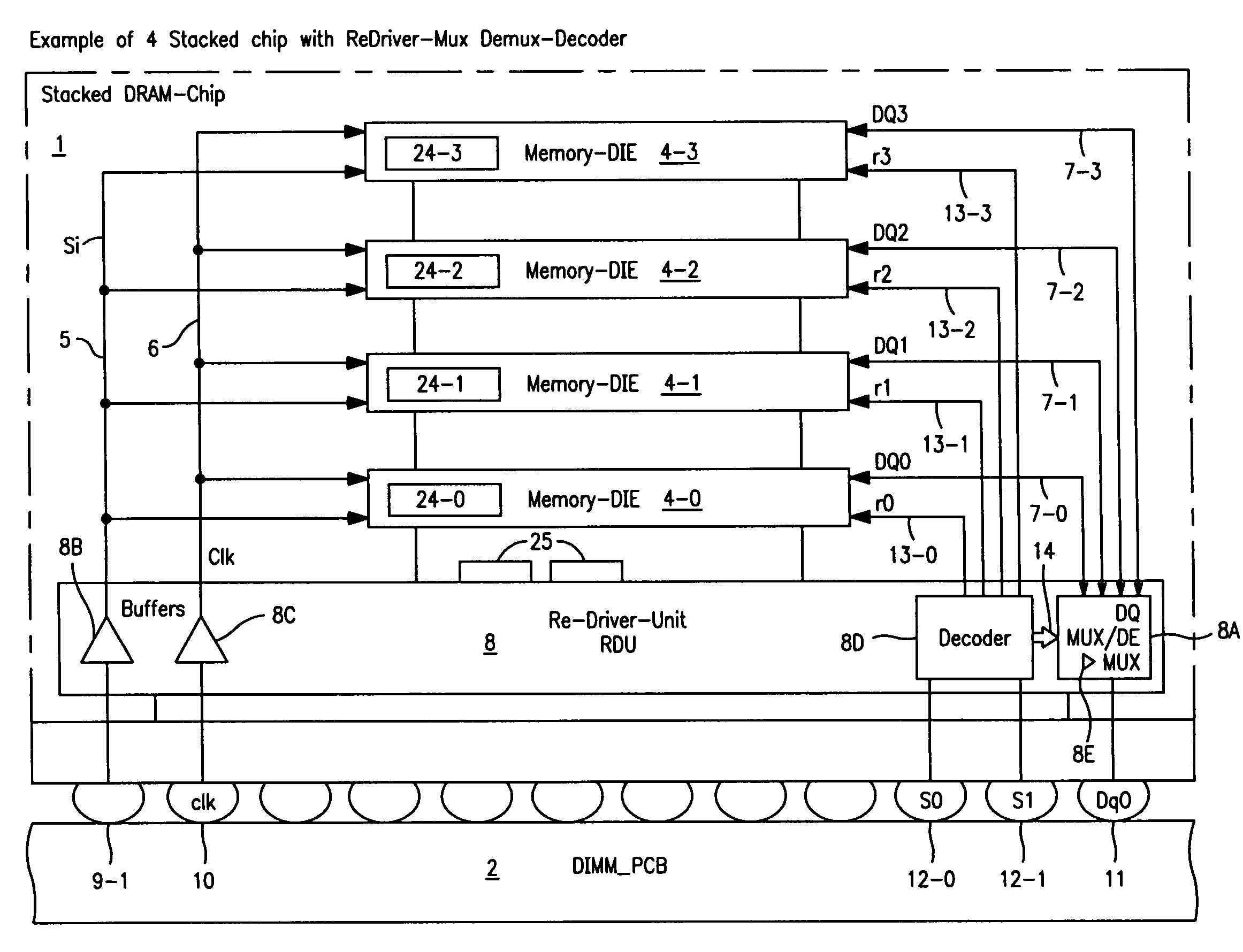

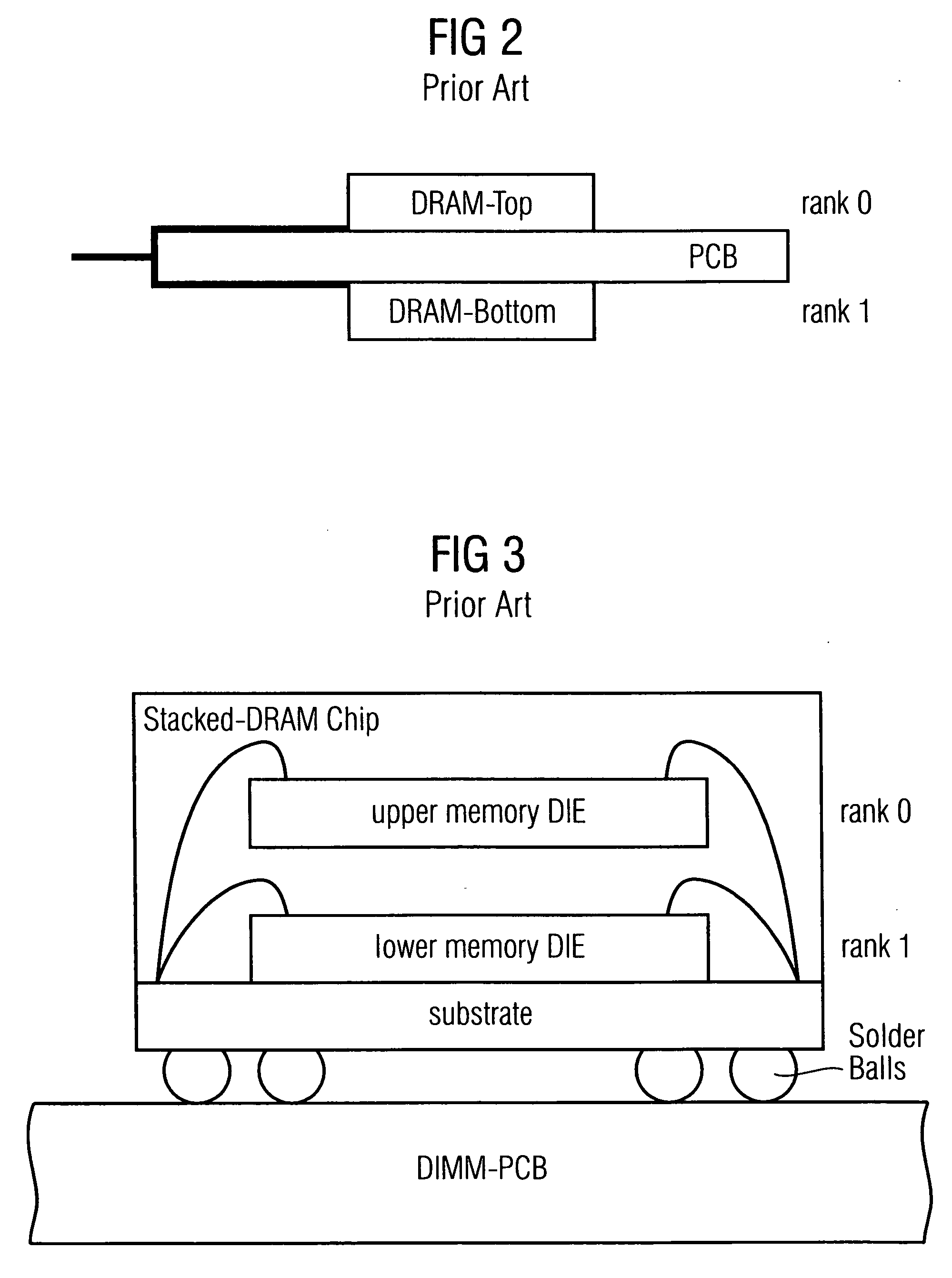

Stacked DRAM memory chip for a dual inline memory module (DIMM)

ActiveUS7200021B2Increase the number ofSmall sizeSemiconductor/solid-state device detailsNanoinformaticsInternal memoryMemory chip

A stacked DRAM memory chip for a Dual In Line Memory Module (DIMM) is disclosed. According to one aspect, the DRAM memory chip comprises at least four stacked DRAM memory dies. Further, the memory dies are each selectable by a corresponding internal memory rank signal. Each memory die comprises an array of memory cells. A common internal address bus is provided for addressing the memory cells and is connected to all stacked DRAM memory dies. Internal data buses are provided for writing data into the memory cells and reading data out of the memory cells of the DRAM memory dies. An integrated redriving unit comprises buffers for all internal address lines provided for driving external address signals applied to address pads of the DRAM memory chip. A multiplexer / demultiplexer switches the internal data lines of the selected DRAM memory die. A memory rank decoder selects a corresponding memory die.

Owner:POLARIS INNOVATIONS LTD

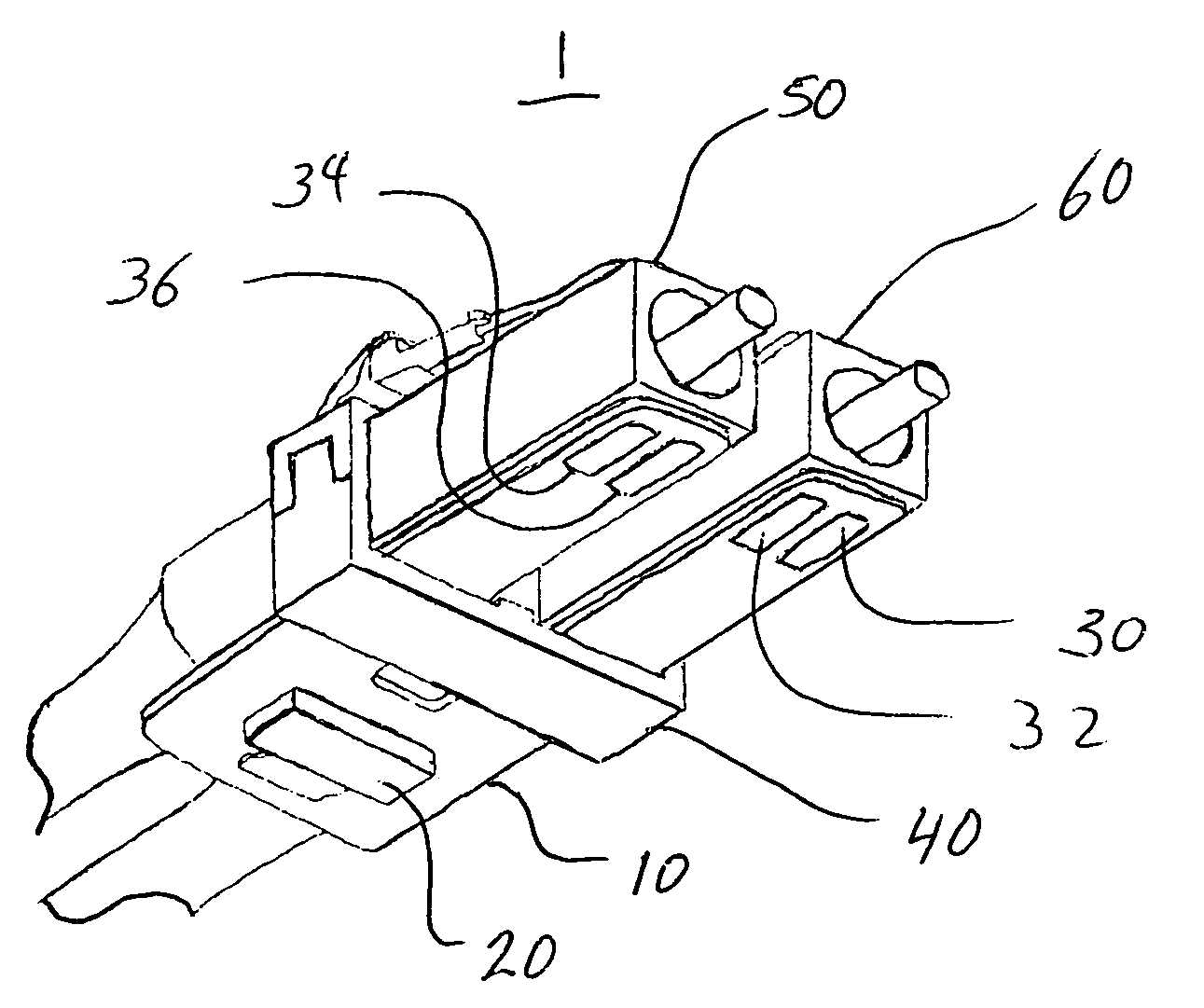

Oximeter sensor with digital memory storing data

InactiveUS6628975B1Improve abilitiesImprove performanceDiagnostic recording/measuringSensorsMemory chipDigital storage

Owner:TYCO HEALTHCARE GRP LP

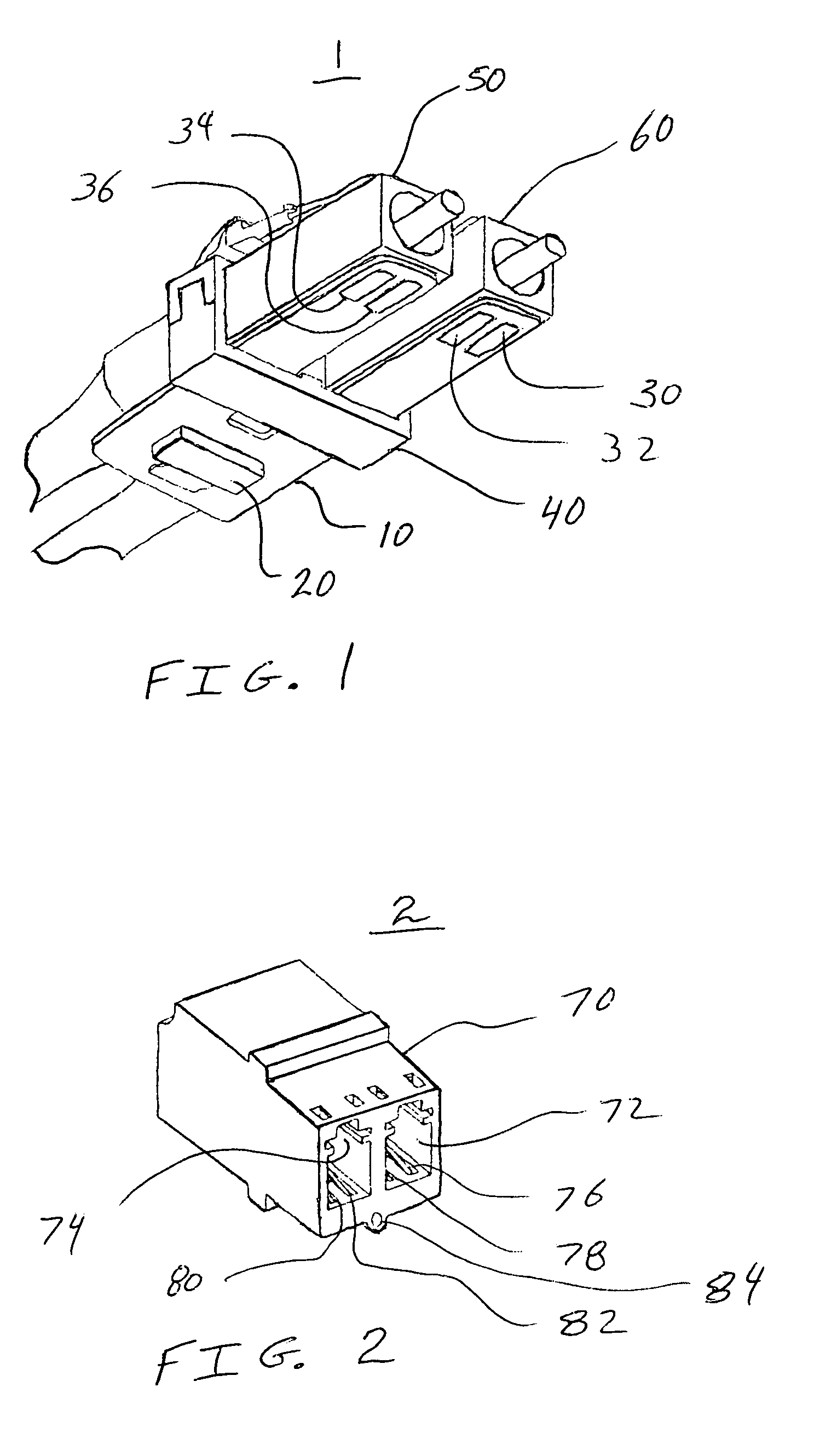

Transceiver/fiber optic connector adaptor with patch cord ID reading capability

The device includes a first optical connector, a second optical connector, a flexible substrate, a first electrical connector, a second electrical connector, a memory chip, and a clip. The first electrical connector is attached to the flexible substrate. The second electrical connector is attached to the flexible substrate. The memory chip is attached to the flexible substrate. A clip retains the first optical connector and the second optical connector adjacent to the flexible substrate.

Owner:STRATOS INT

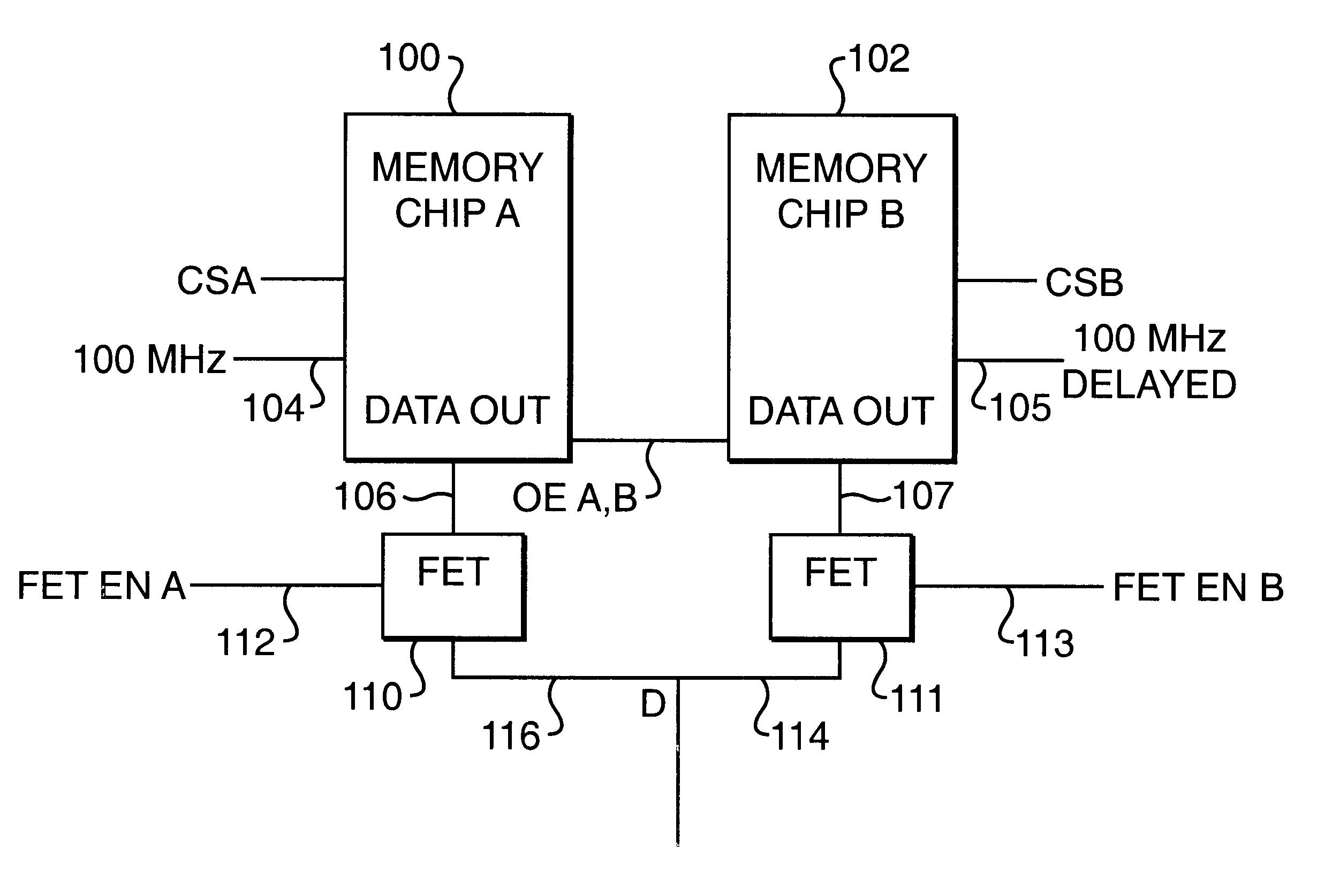

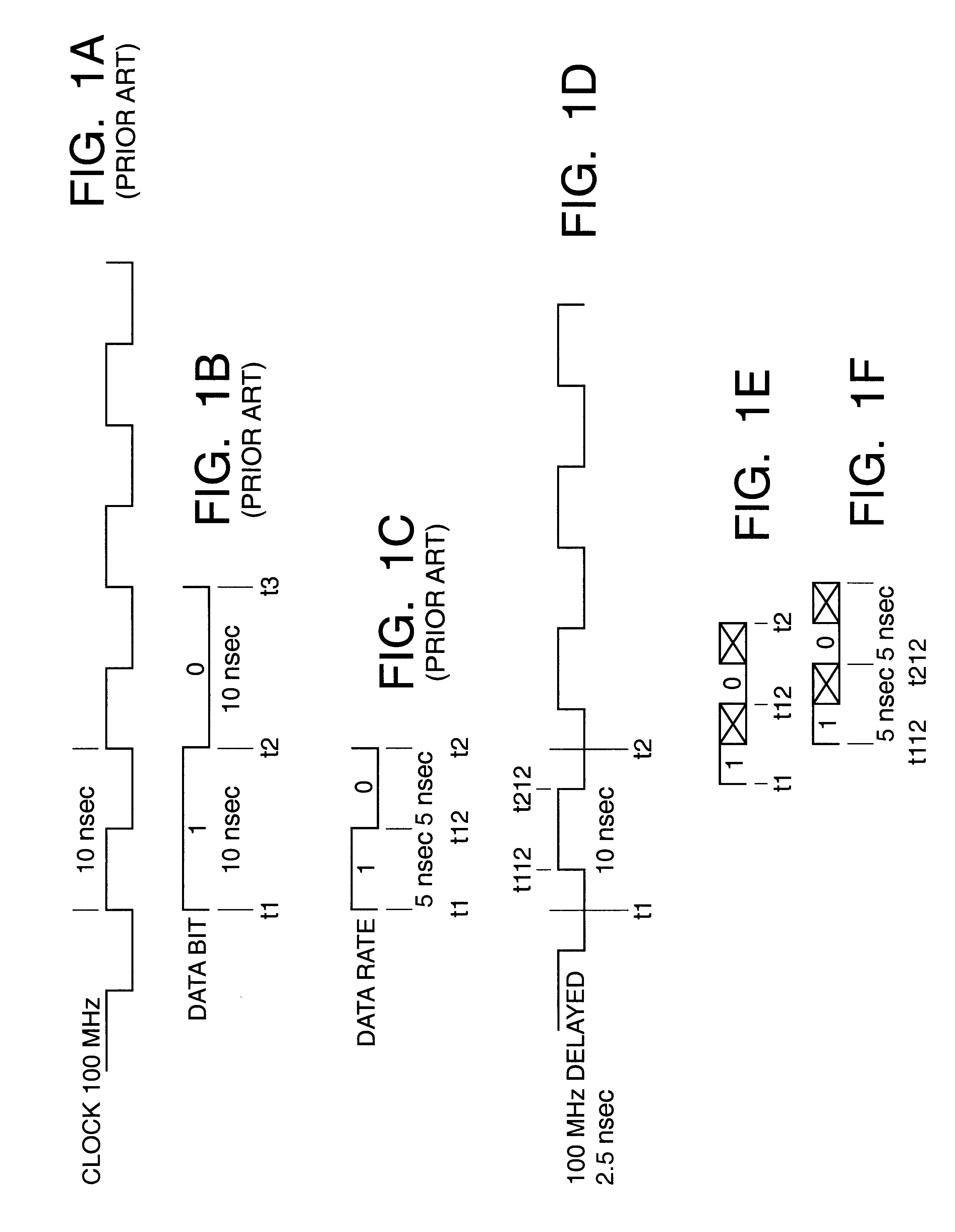

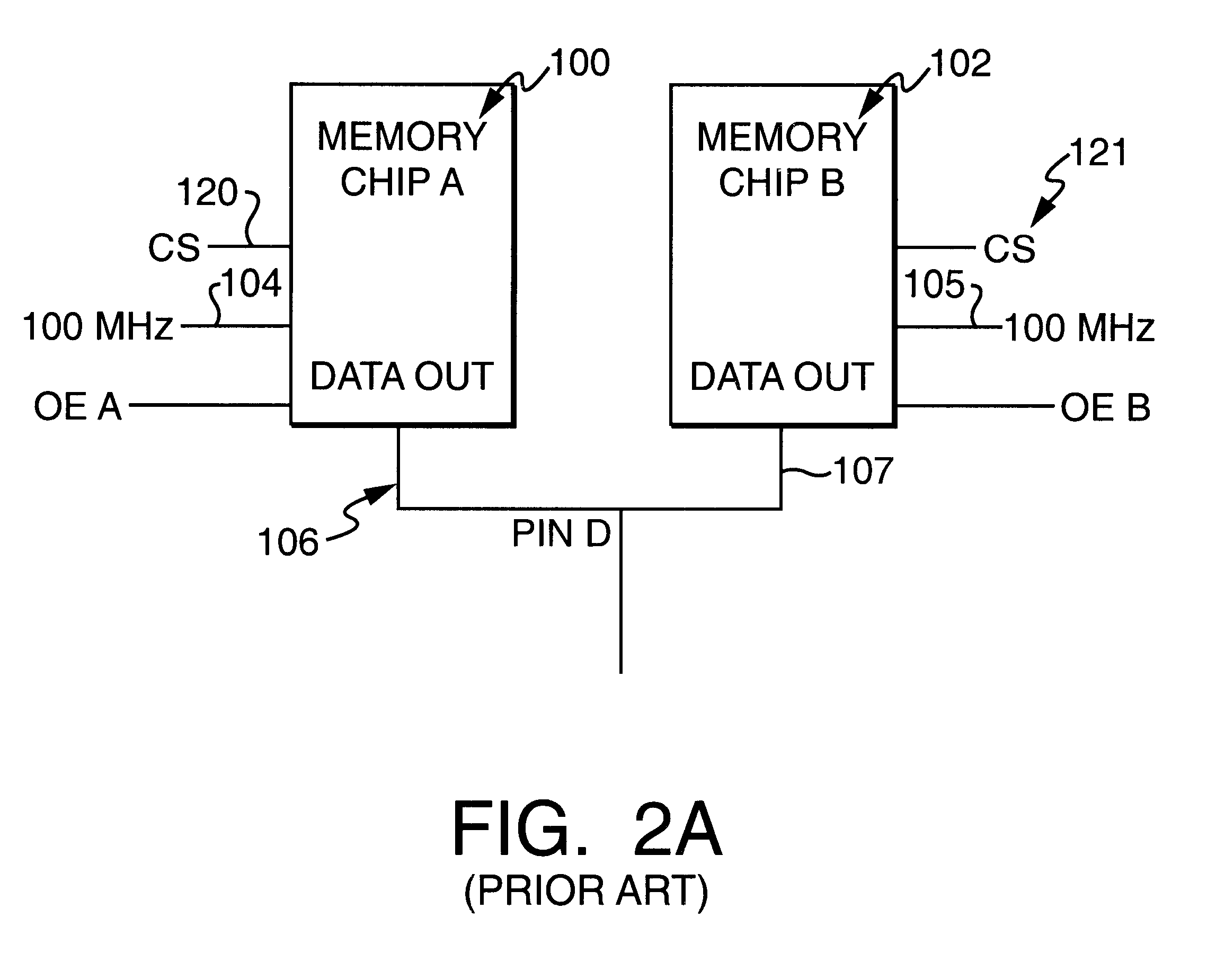

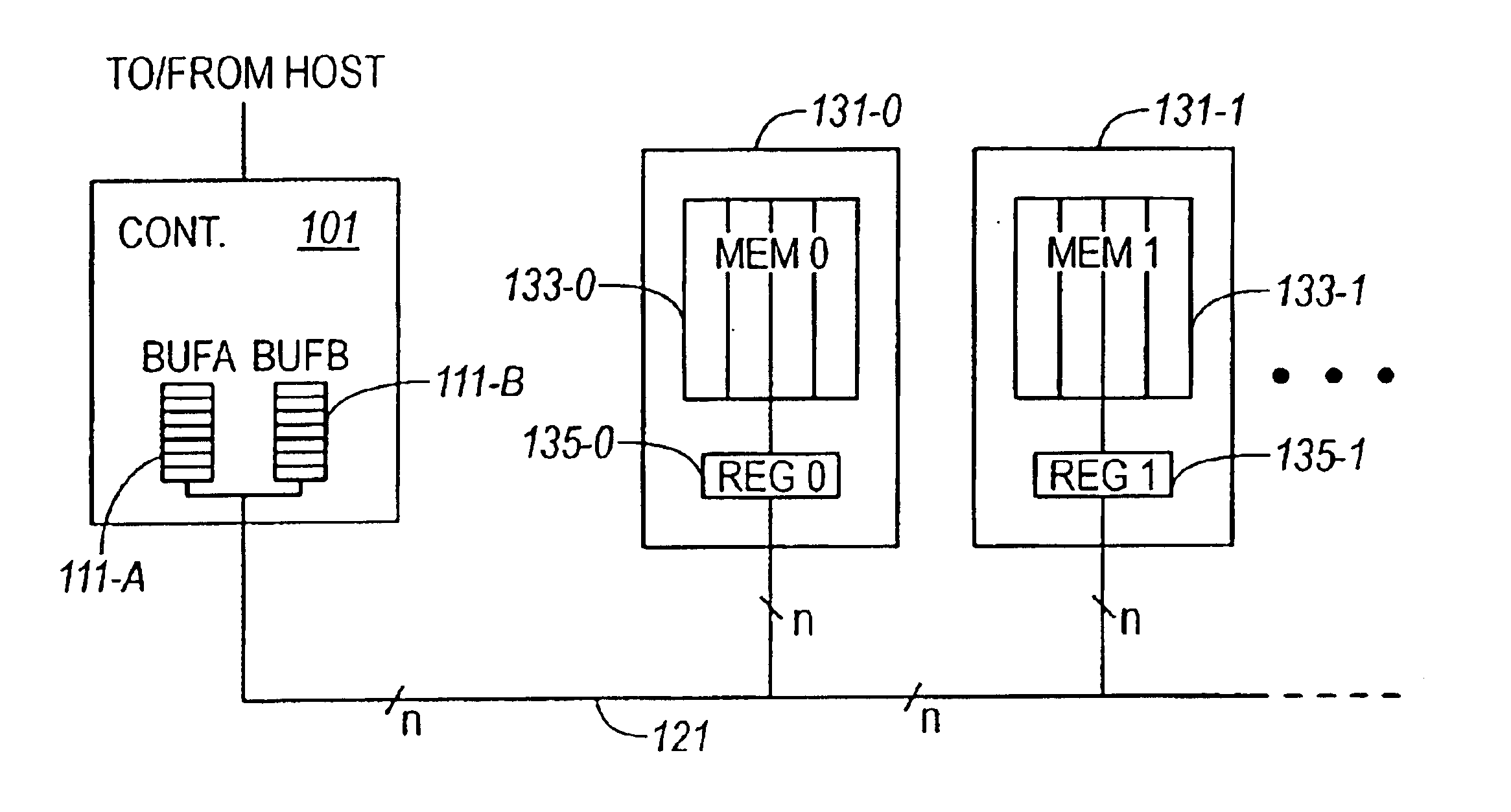

Memory system using FET switches to select memory banks

A computer memory system provides a double data rate (DDR) memory output while requiring memory chips with only half the frequency limit of the prior art DDR memory chips. The system contains a first memory bank having data lines and a second memory bank having data lines. The first and second memory banks are associated with first and second clock signals, respectively, where the second clock signal is delayed from the first clock signal such that the data lines of the first memory bank are connected to a data bus in synchronism with the first clock signal while the data lines of the second memory bank are connected with the data bus in synchronism with the second clock signal. In one embodiment, a first FET switch connects the data lines of the first memory bank with the data bus and a second FET switch connects the data lines of the second memory bank with the data bus. The second FET switch is connected to the data bus at a time delayed from the beginning after the start of each clock cycle of the second clock signal. As a result, the data bus is never connected to the data lines of both memory banks at the same time, but rather, the data bus is alternately connected with the first memory bank and then the second memory bank.

Owner:FOOTHILLS IP LLC

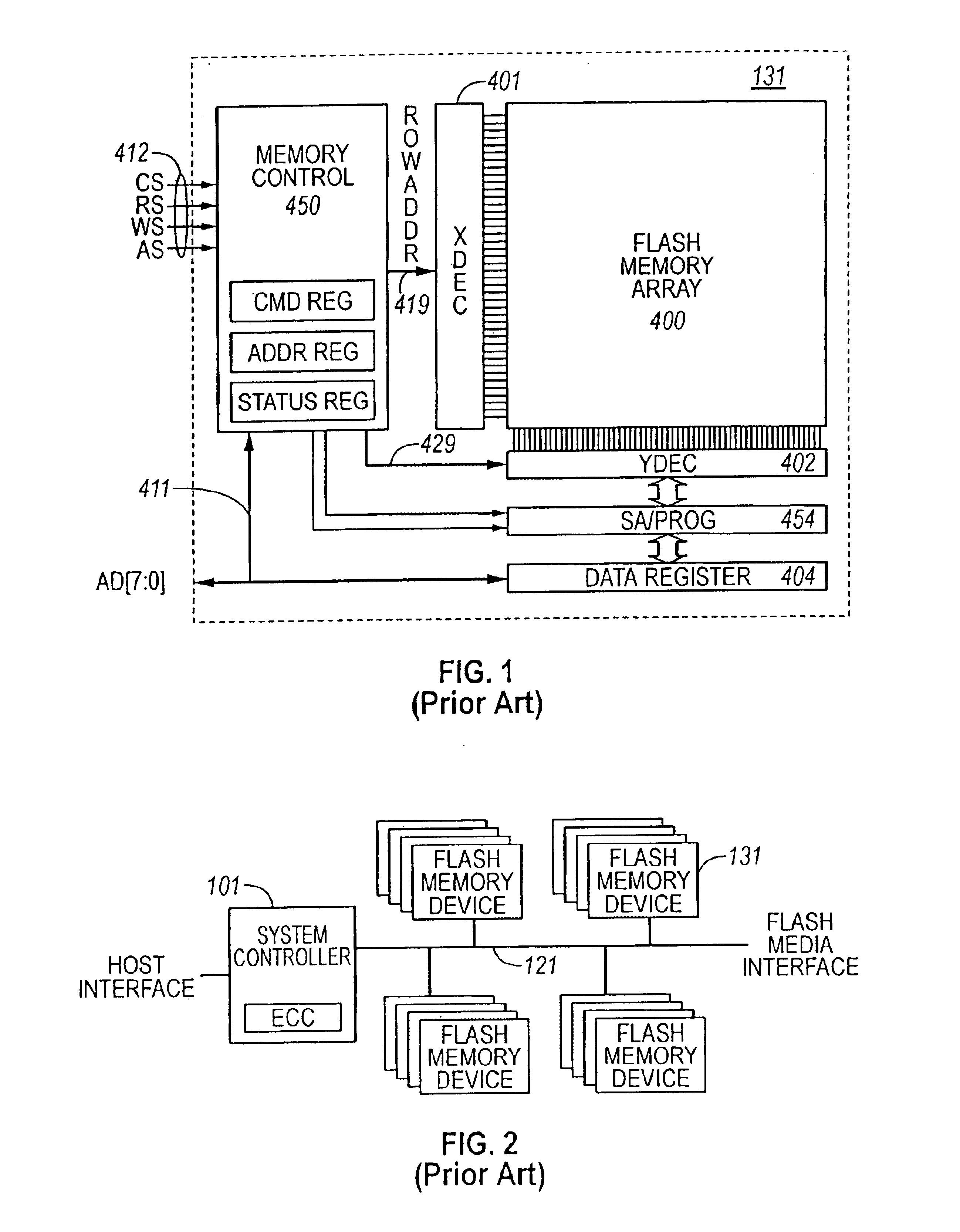

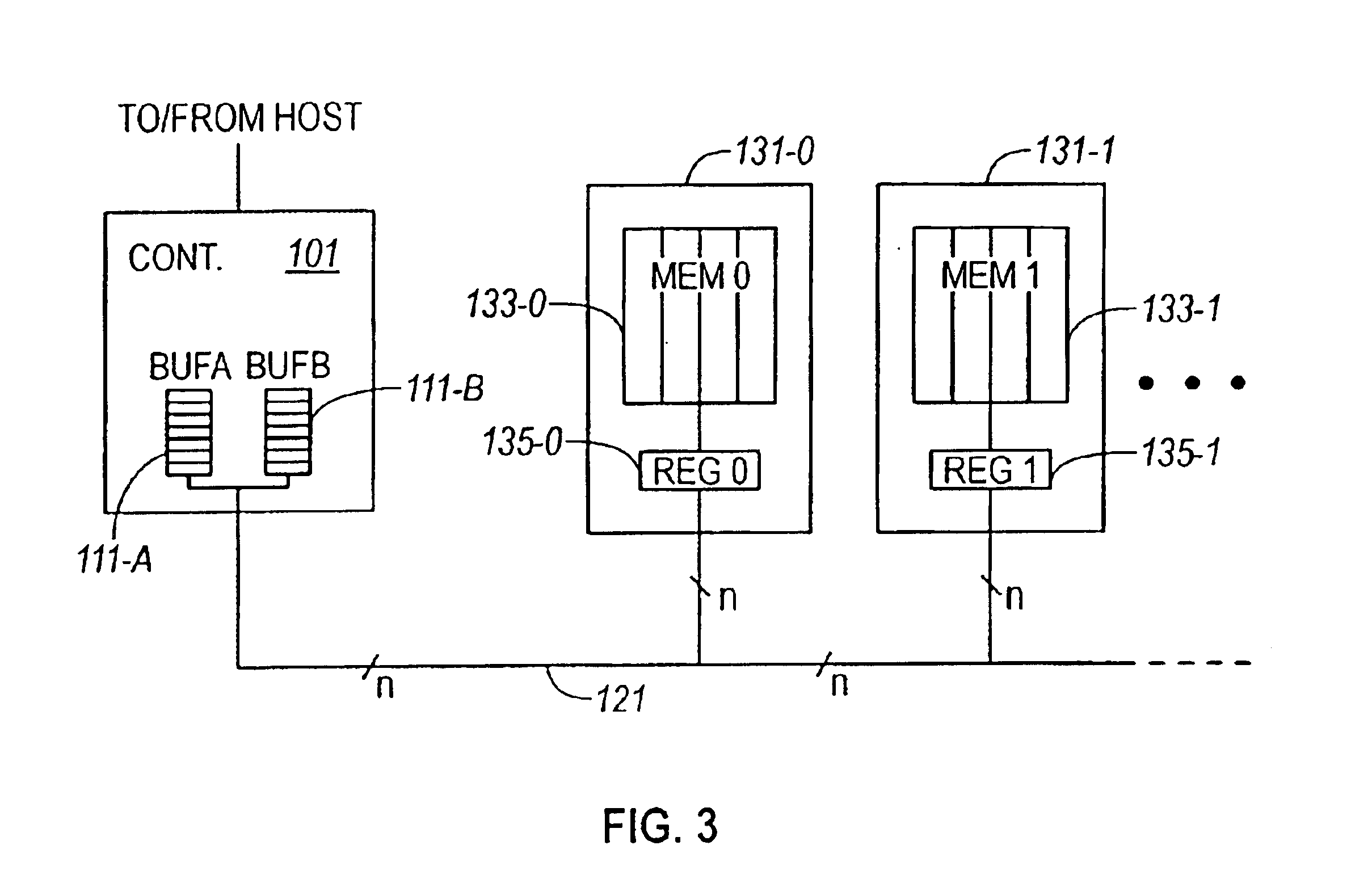

Pipelined parallel programming operation in a non-volatile memory system

InactiveUS6871257B2High degree of parallelismEasy to liftRead-only memoriesDigital storageMemory chipHigh rate

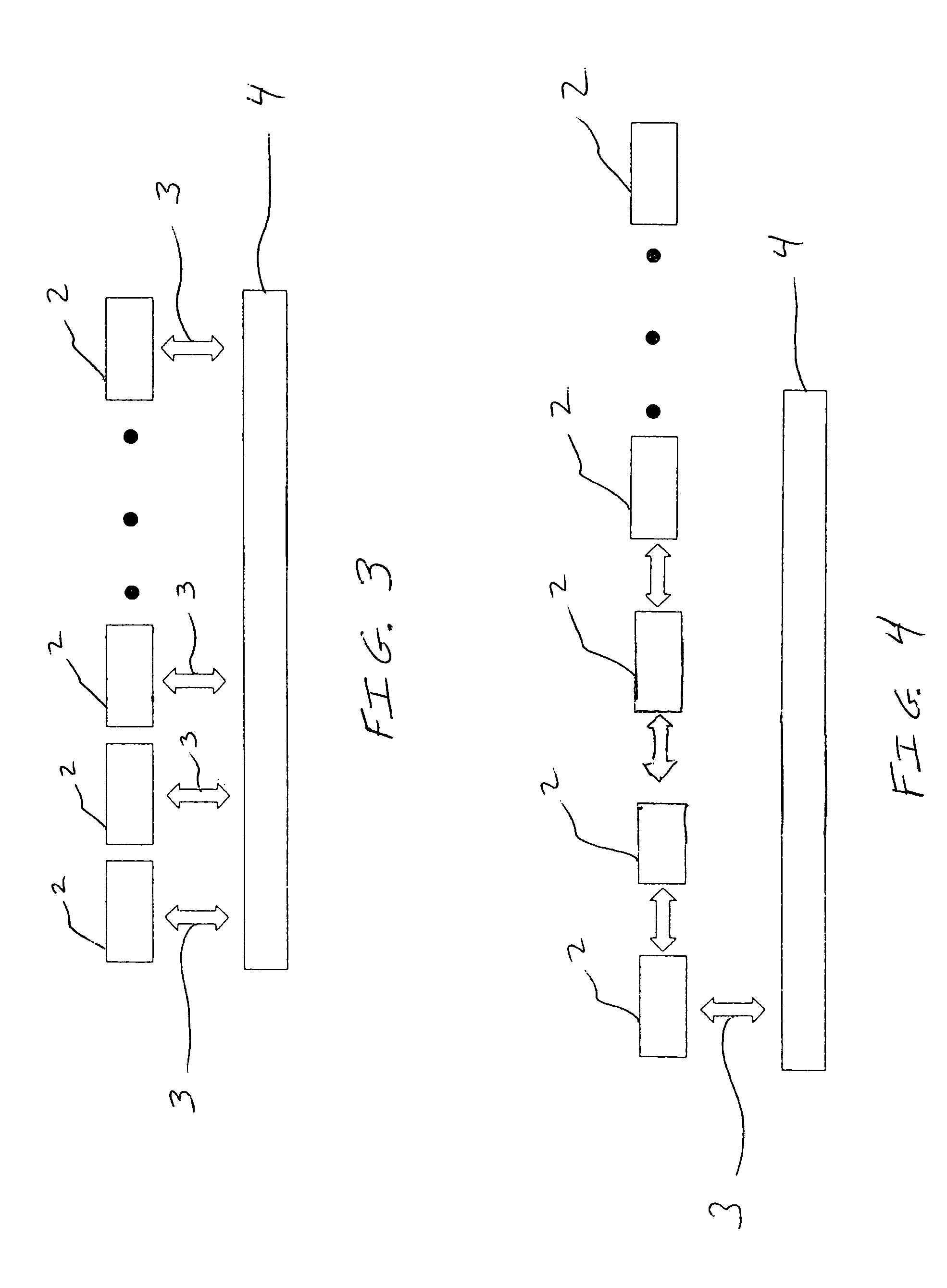

The present invention allows for an increase in programming parallelism in a non-volatile memory system without incurring additional data transfer latency. Data is transferred from a controller to a first memory chip and a programming operation is caused to begin. While that first memory chip is busy performing that program operation, data is transferred from the controller to a second memory chip and a programming operation is caused to begin in that chip. Data transfer can begin to the first memory chip again once it has completed its programming operation even though the second chip is still busy performing its program operation. In this manner high parallelism of programming operation is achieved without incurring the latency cost of performing the additional data transfers. Two sets of embodiments are presented, one that preserves the host data in a buffer until successful programming of that data is confirmed and one that does not require that success be achieved and that does not preserve the data thus achieving a higher rate of data programming throughput.

Owner:SANDISK TECH LLC

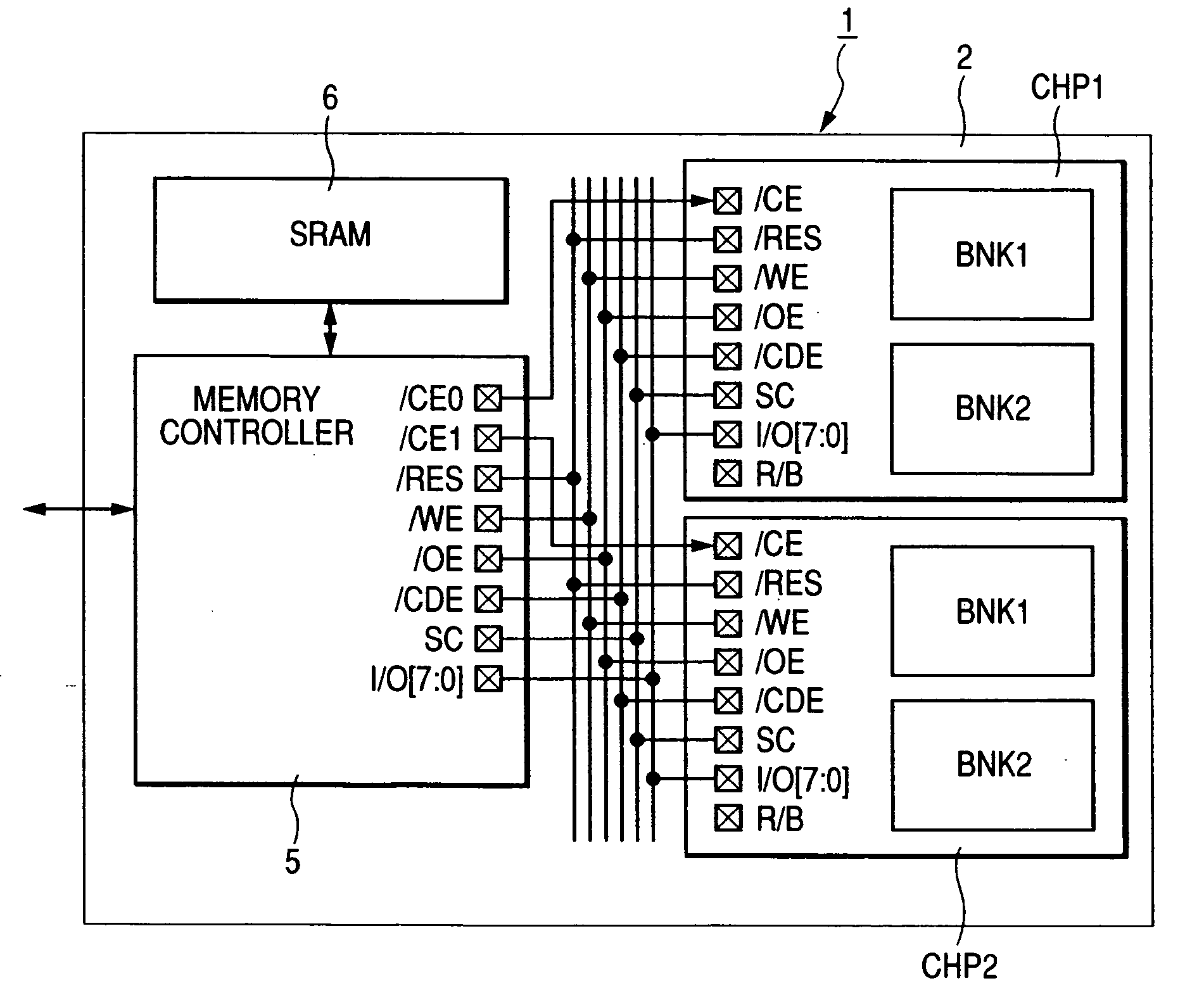

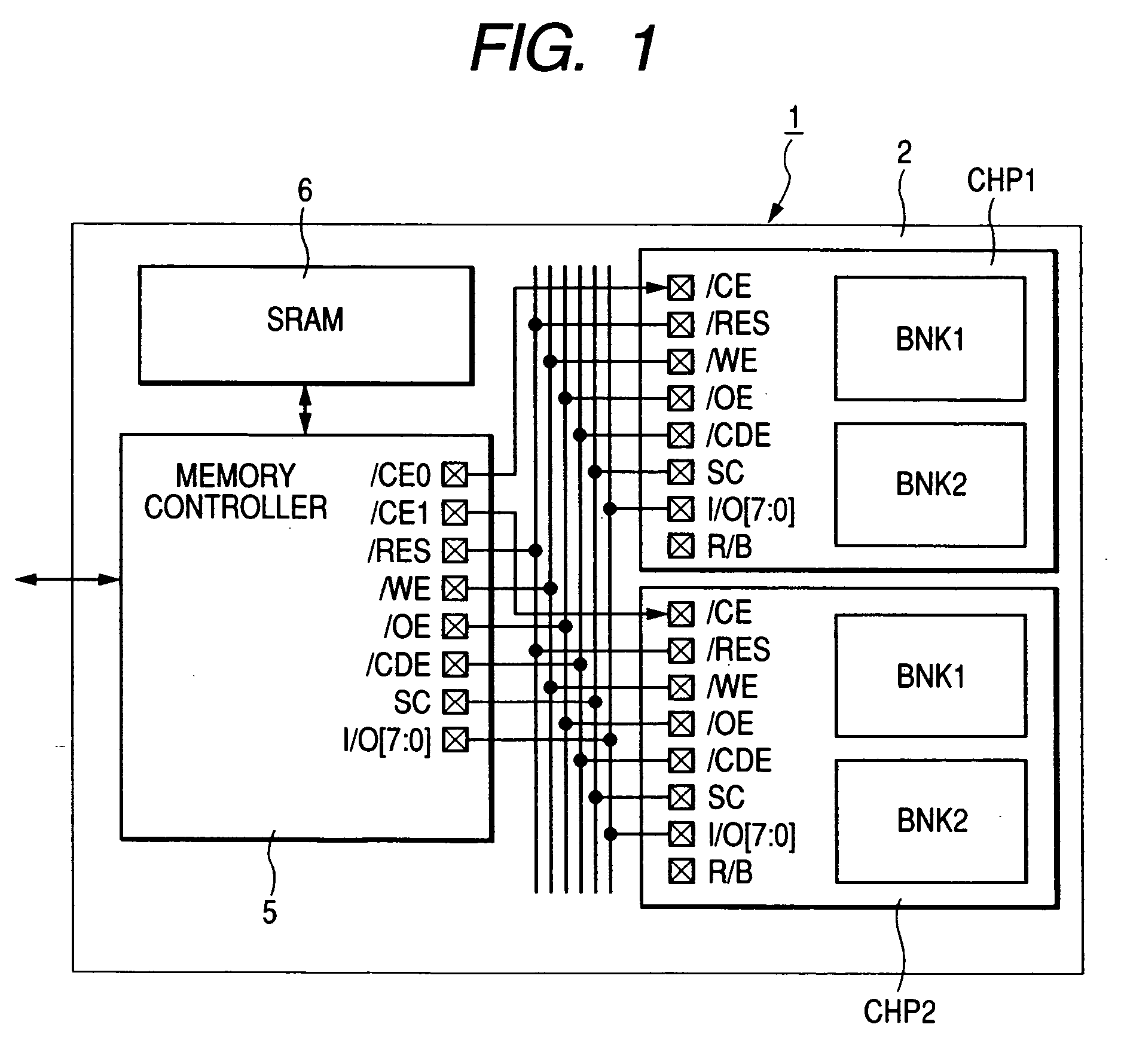

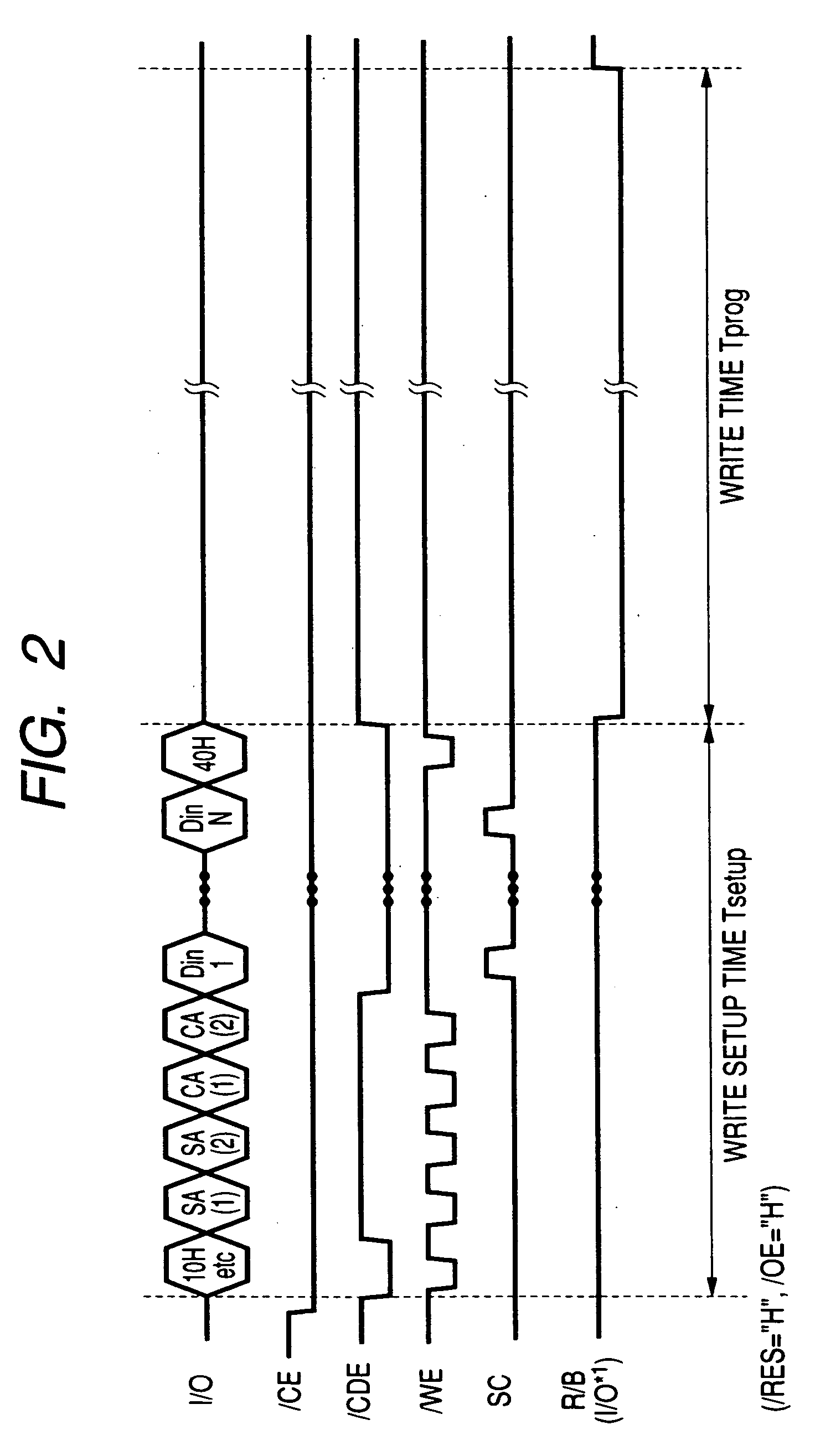

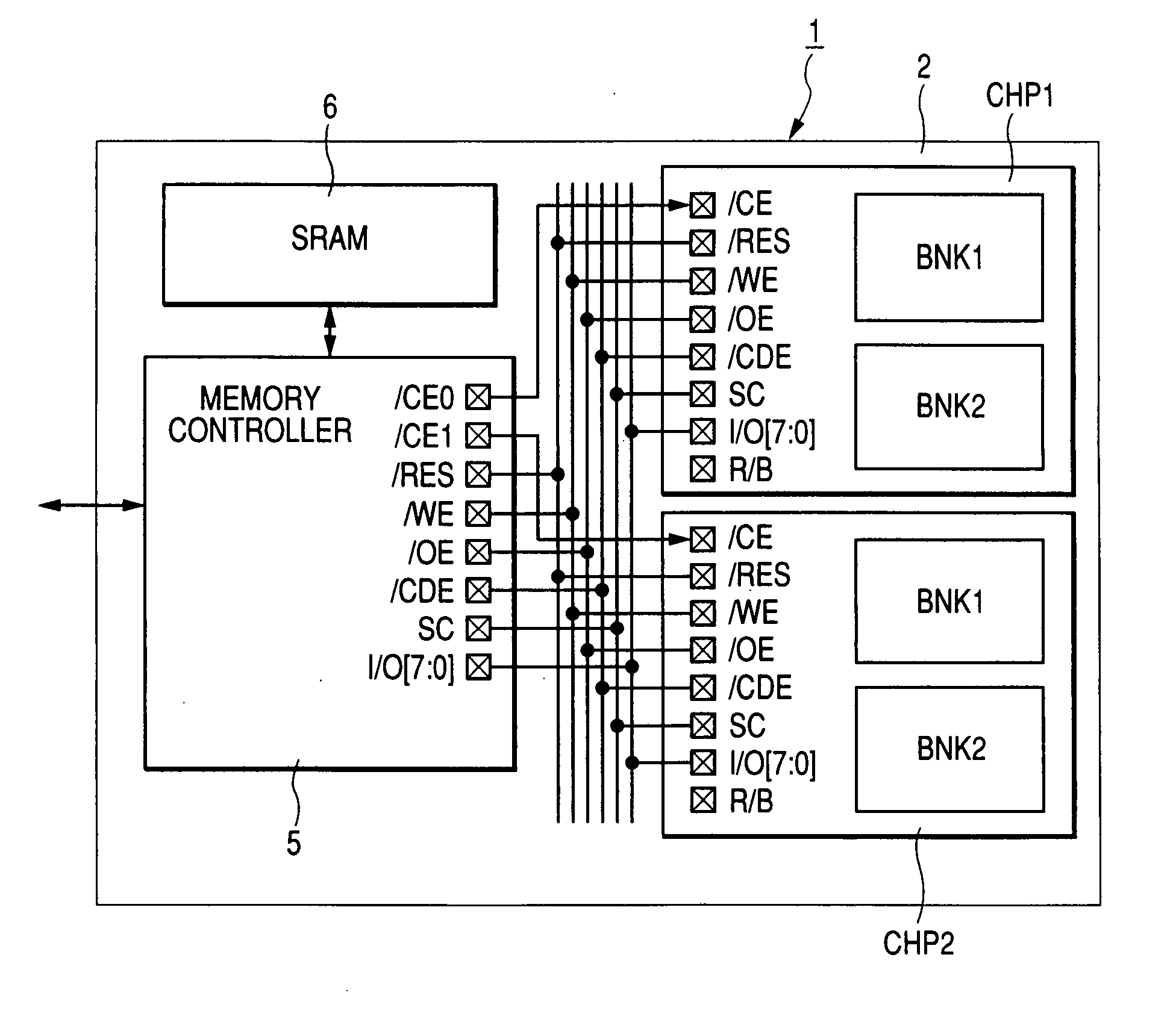

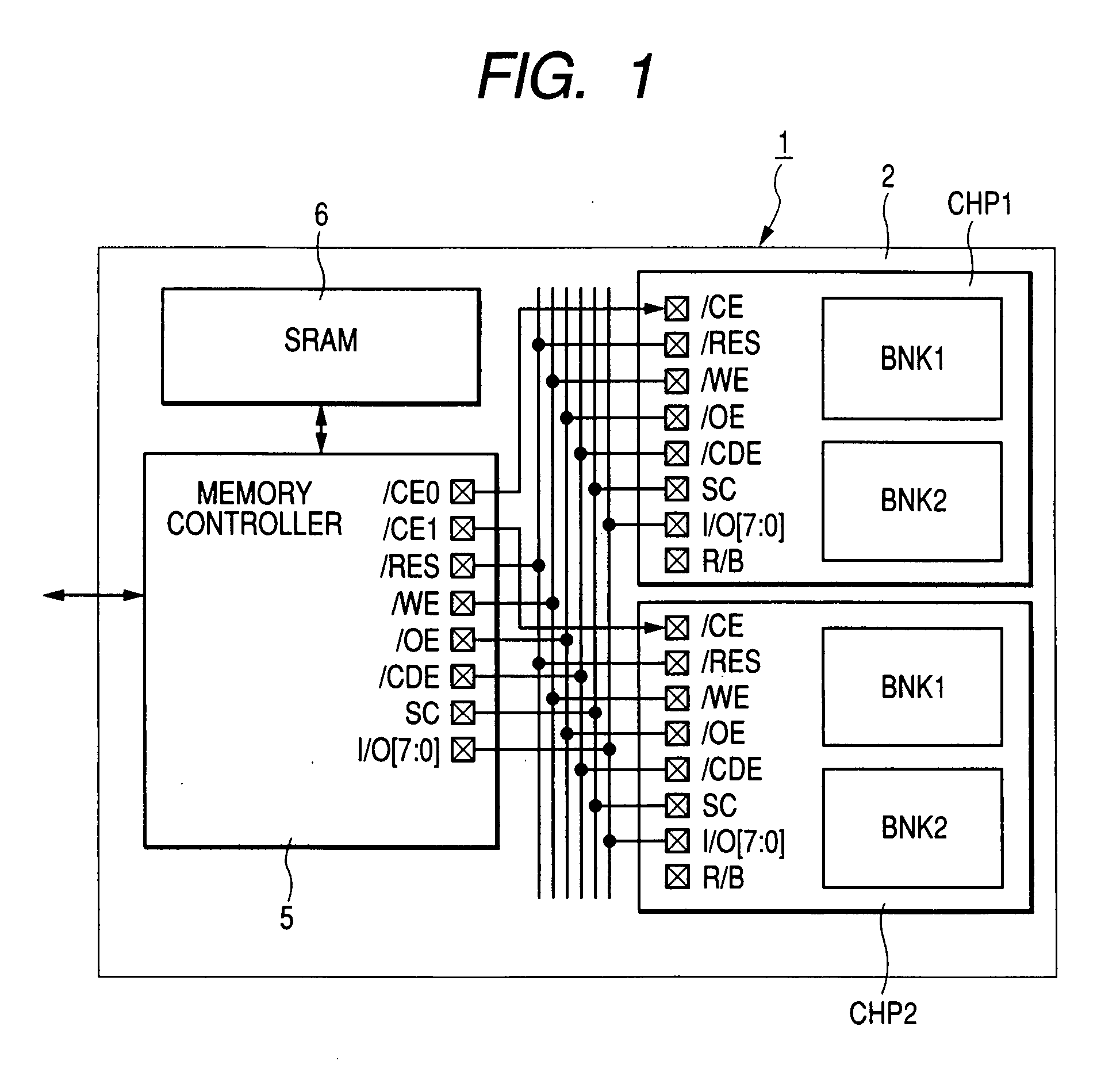

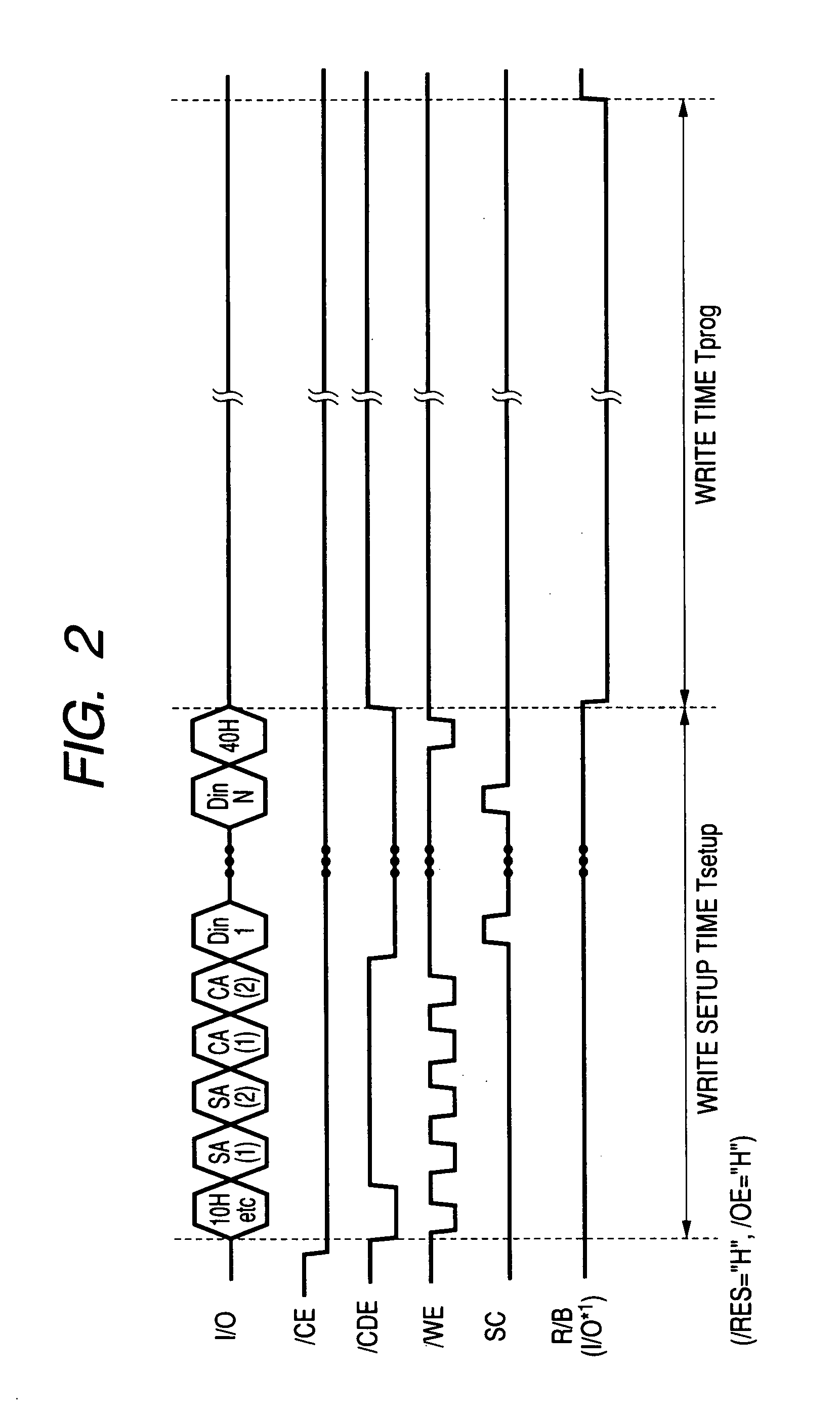

Memory system and memory card

InactiveUS20050015539A1Increase costIncrease speedMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:RENESAS ELECTRONICS CORP

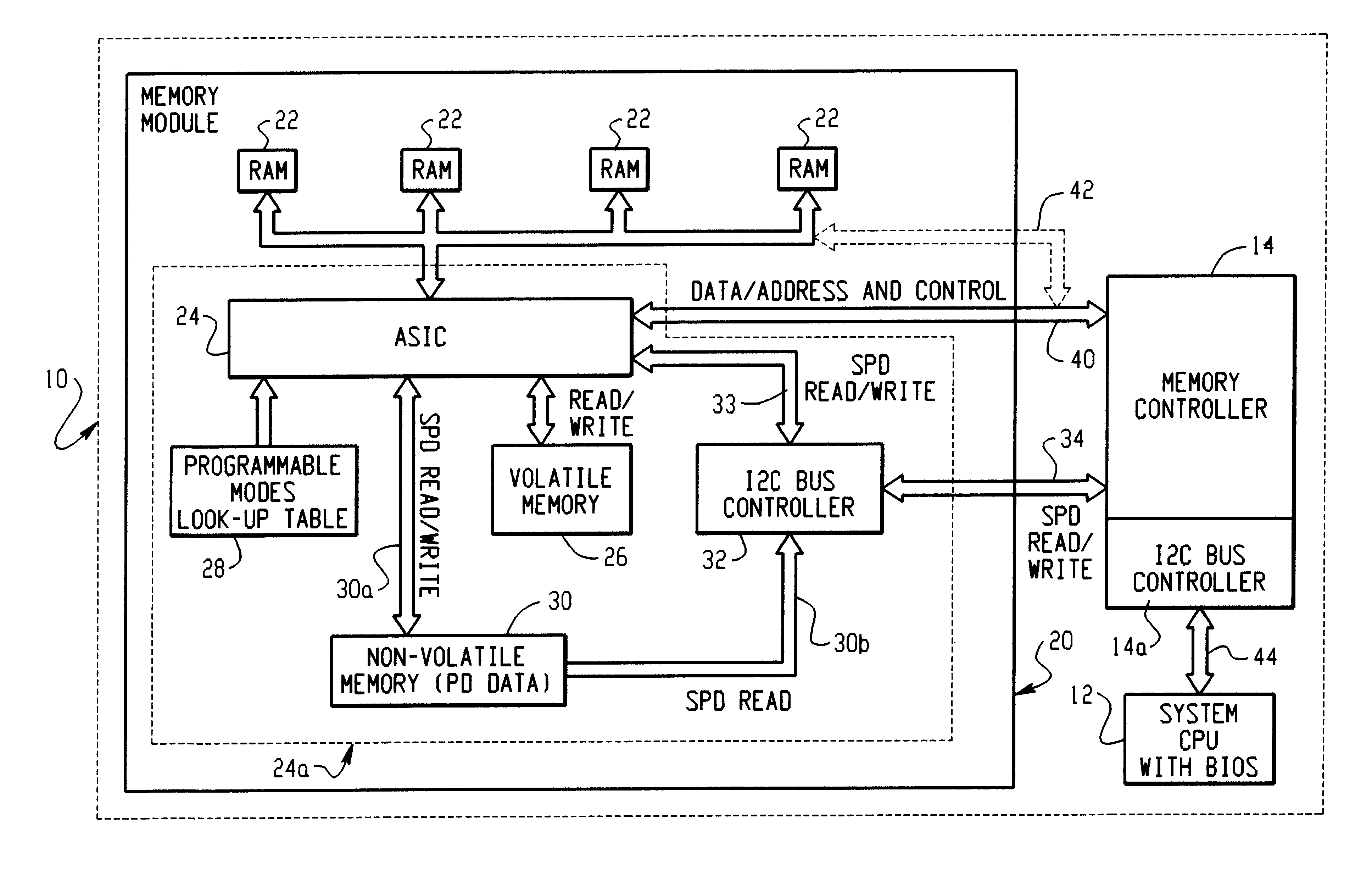

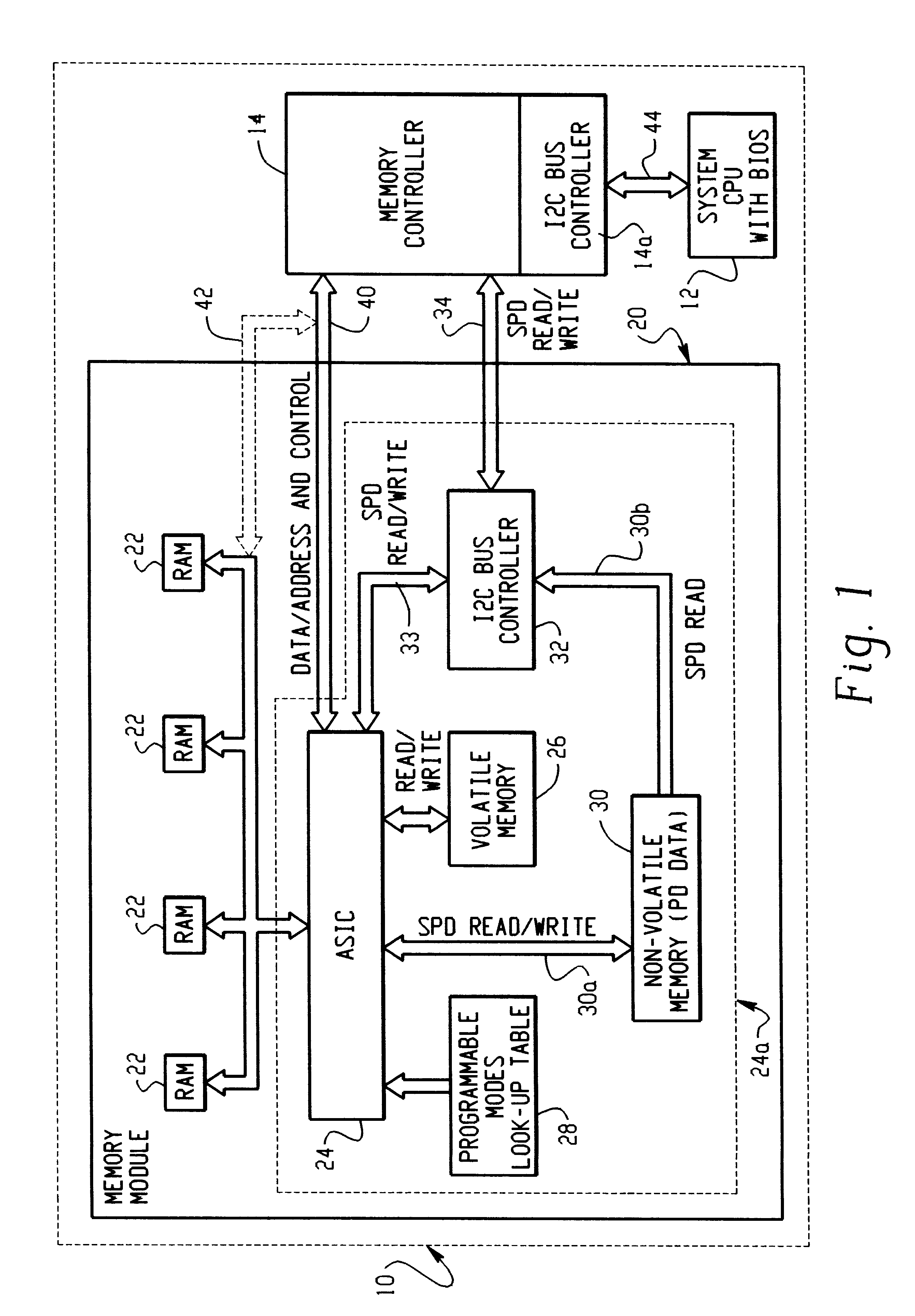

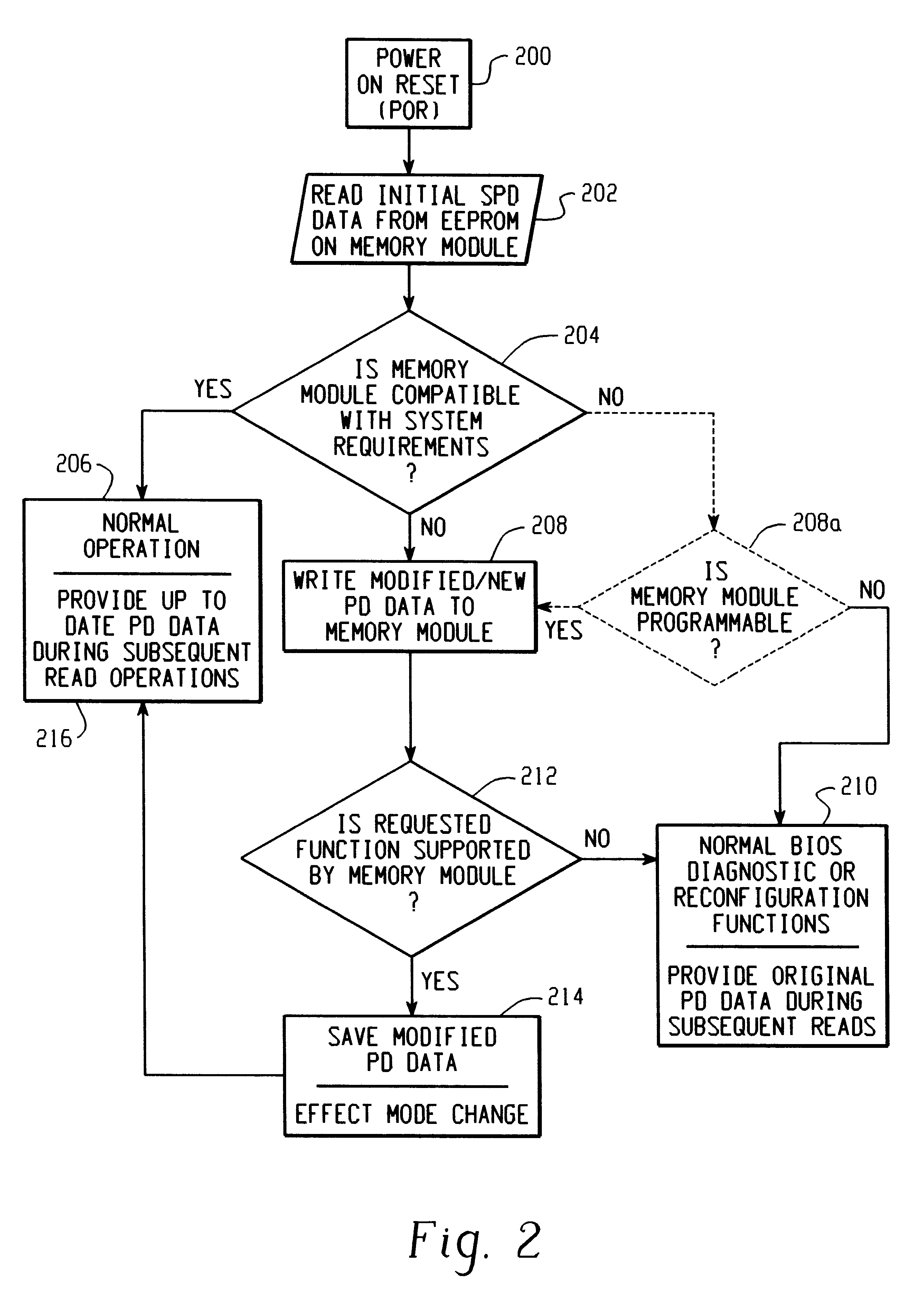

Dynamic configuration of memory module using modified presence detect data

A memory module includes a plurality of memory chips on the module; first logic for configuring the memory module to operate in a selectable mode; second logic for storing initial presence detect (PD) data; and third logic for storing modified PD data that corresponds to a requested mode of operation of the memory module received from a system controller.

Owner:IBM CORP

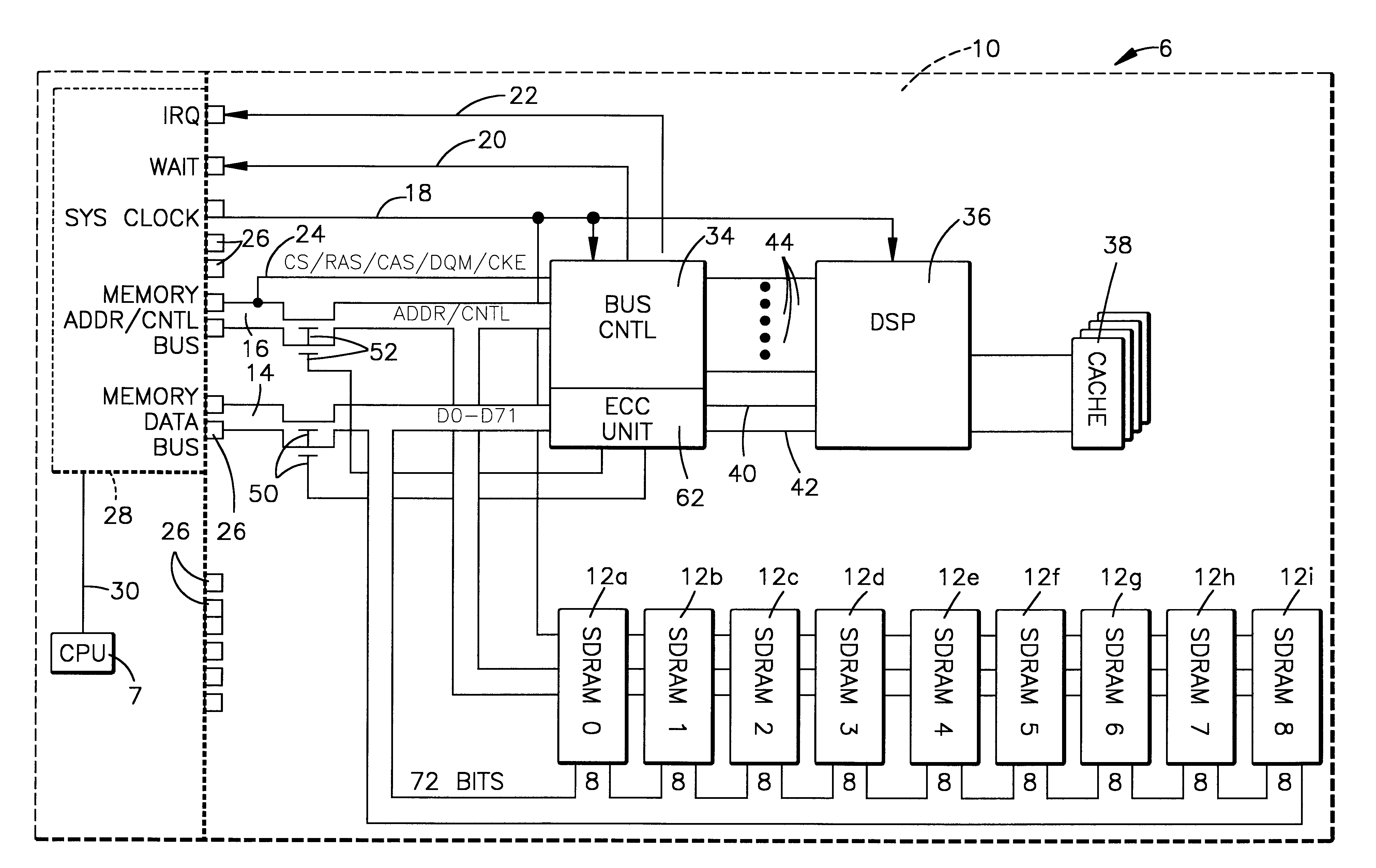

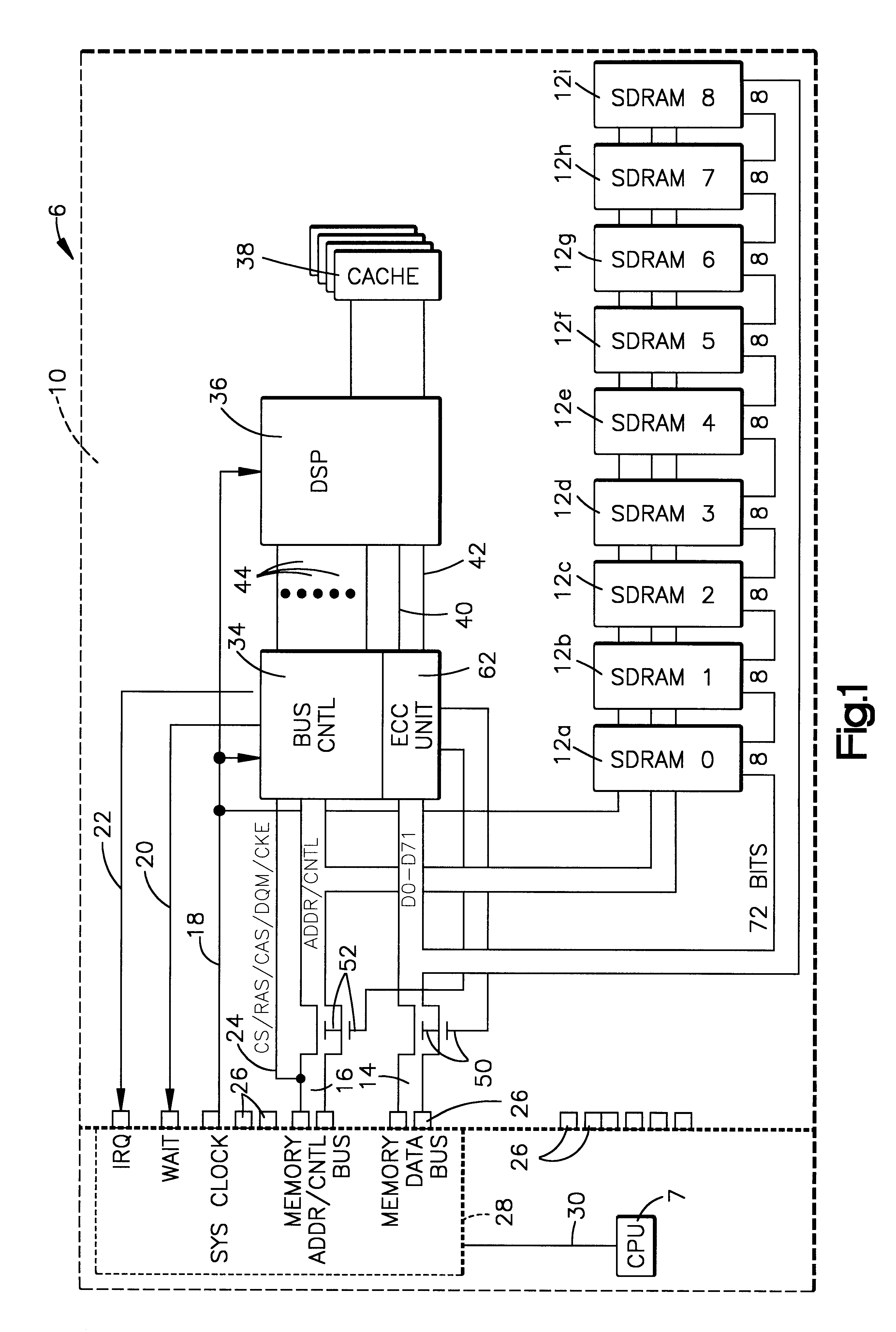

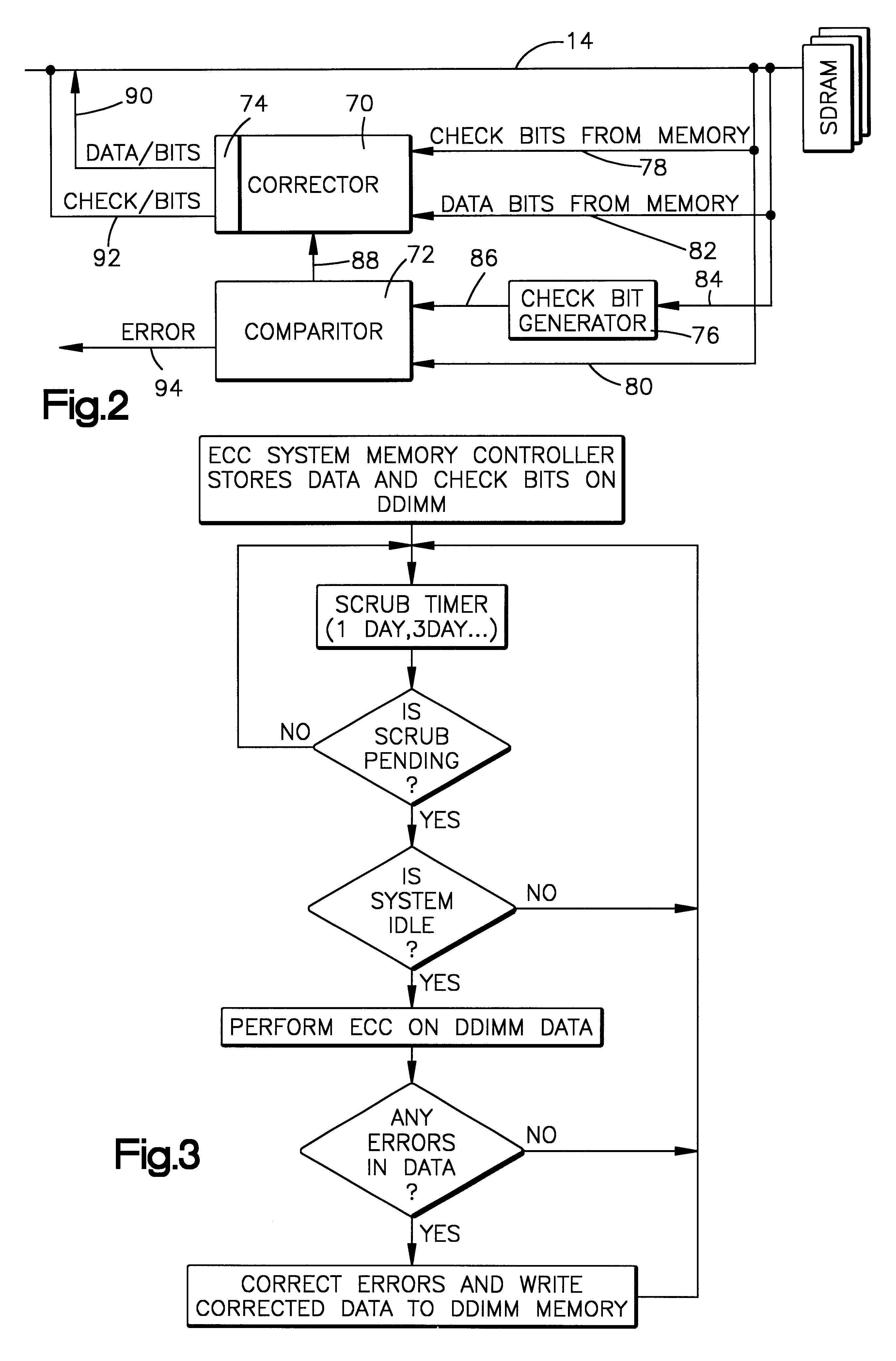

On-board scrubbing of soft errors memory module

A memory module for attachment to a computer system having a memory bus and a method of using the memory module for error correction by scrubbing soft errors on-board the module is provided. The module includes a printed circuit card with memory storage chips on the card to store data bits and associated ECC check bits. Tabs are provided on the circuit card to couple the card to the memory bus of the computer system. Logic circuitry selectively operatively connects and disconnects the memory chip and the memory bus. A signal processor is connected in circuit relationship with the memory chips. The logic circuitry selectively permits the signal processor to read the stored data bits and associated check bits from the memory chips, recalculate the check bits from the read stored data bits, compare the recalculated check bits with the stored check bits, correct all at least one bit errors in the store data bits and stored associated check bits and re-store the correct data bits and associated check bits in the memory chips. When the memory chips and the memory bus are disconnected, single bit soft errors occurring during storage of the data bits and check bits are corrected periodically before the data is read from the memory chips to the data bus on a read operation.

Owner:IBM CORP

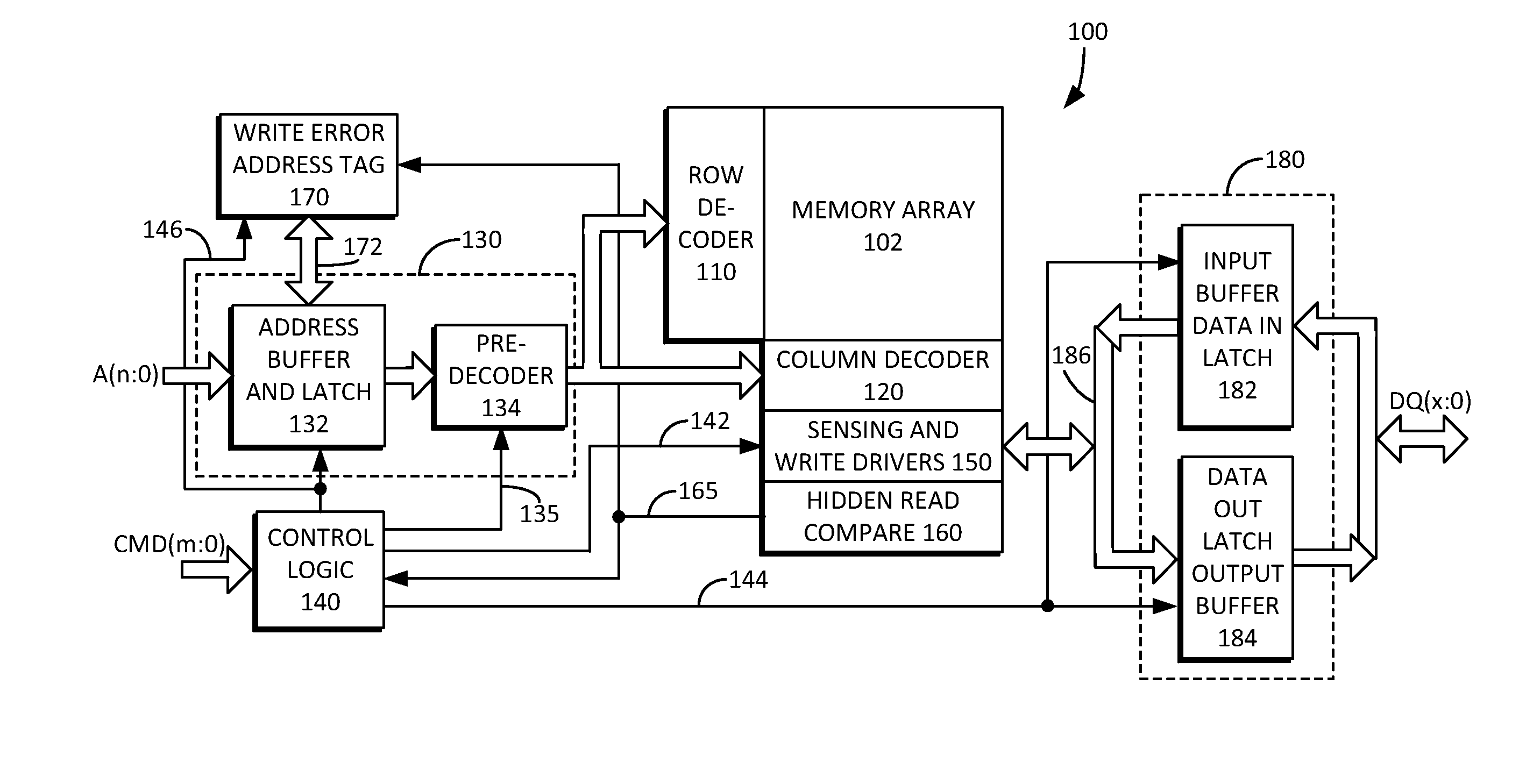

Method and system for providing a smart memory architecture

ActiveUS20140157065A1High rateHigh error rateError detection/correctionDigital computer detailsMemory chipSmart memory

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The system may include a smart memory controller capable of performing a bit error rate built-in self test. The smart memory control may include bit error rate controller logic configured to control the bit error rate built-in self test. A write error rate test pattern generator may generate a write error test pattern for the bit error rate built-in self test. A read error rate test pattern generator may generate a read error test pattern for the built-in self test. The smart memory controller may internally generate an error rate timing pattern, perform built-in self test, measure the resulting error rate, automatically adjust one or more test parameters based on the measured error rate, and repeat the built-in self test using the adjusted parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

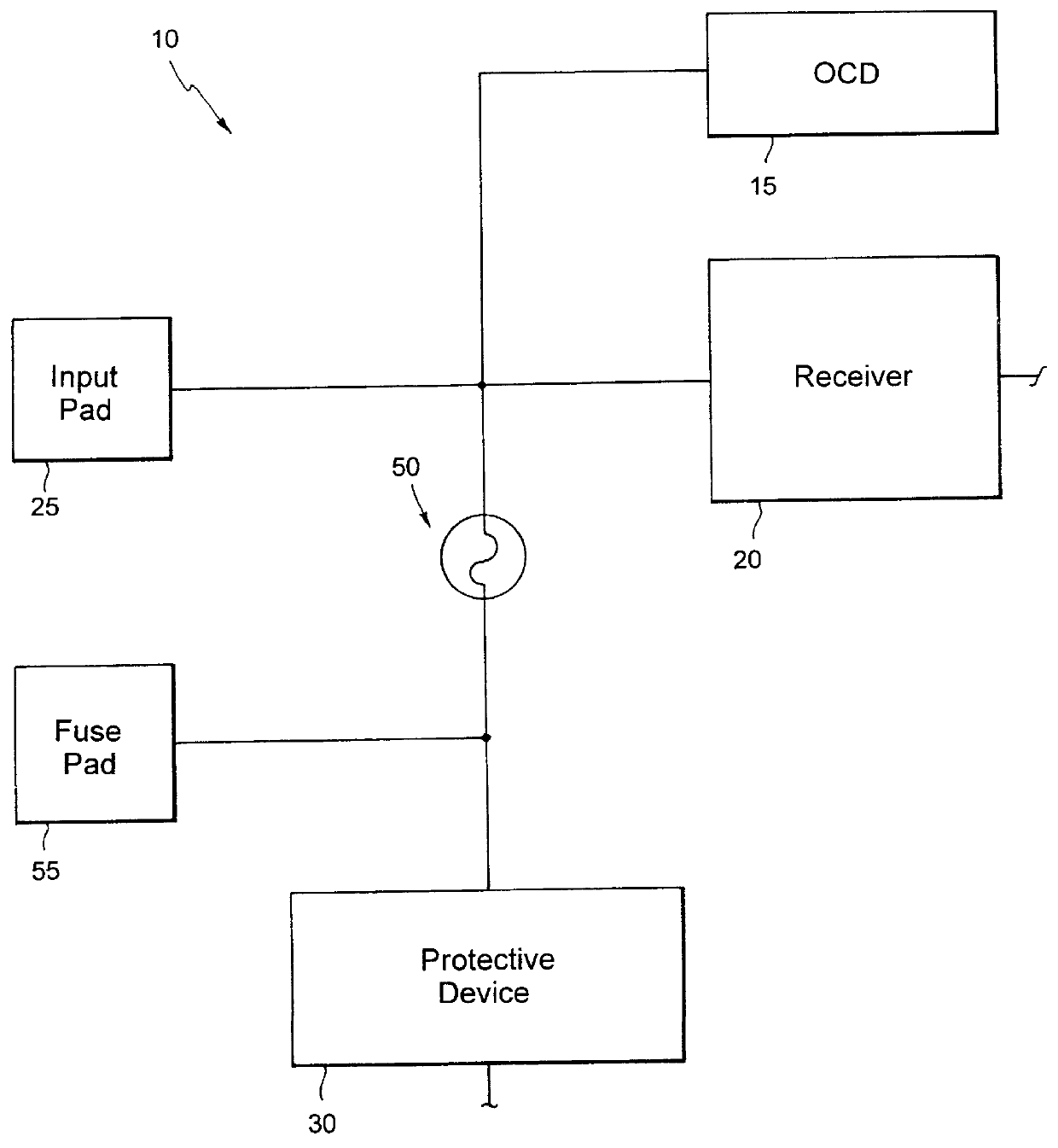

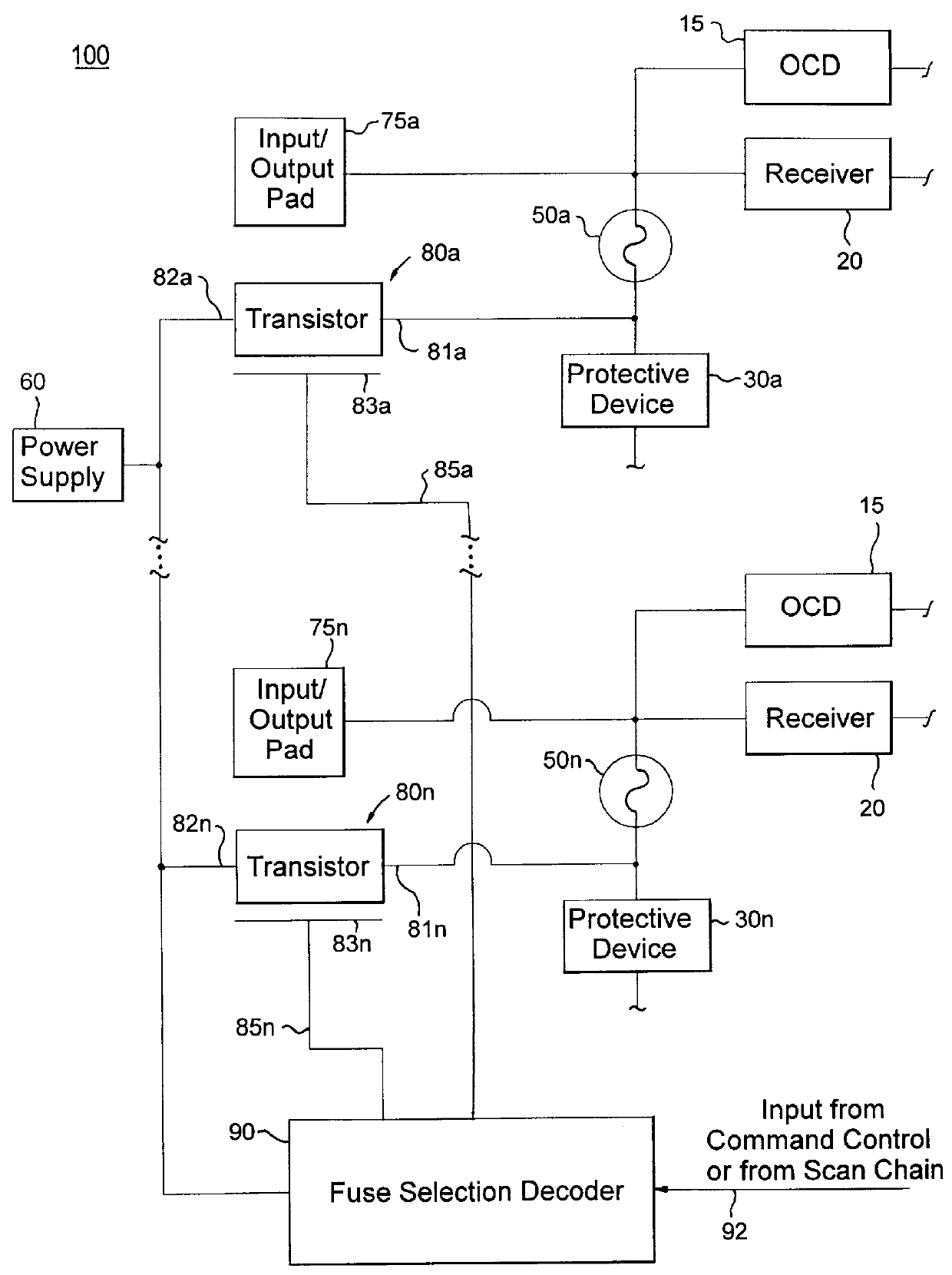

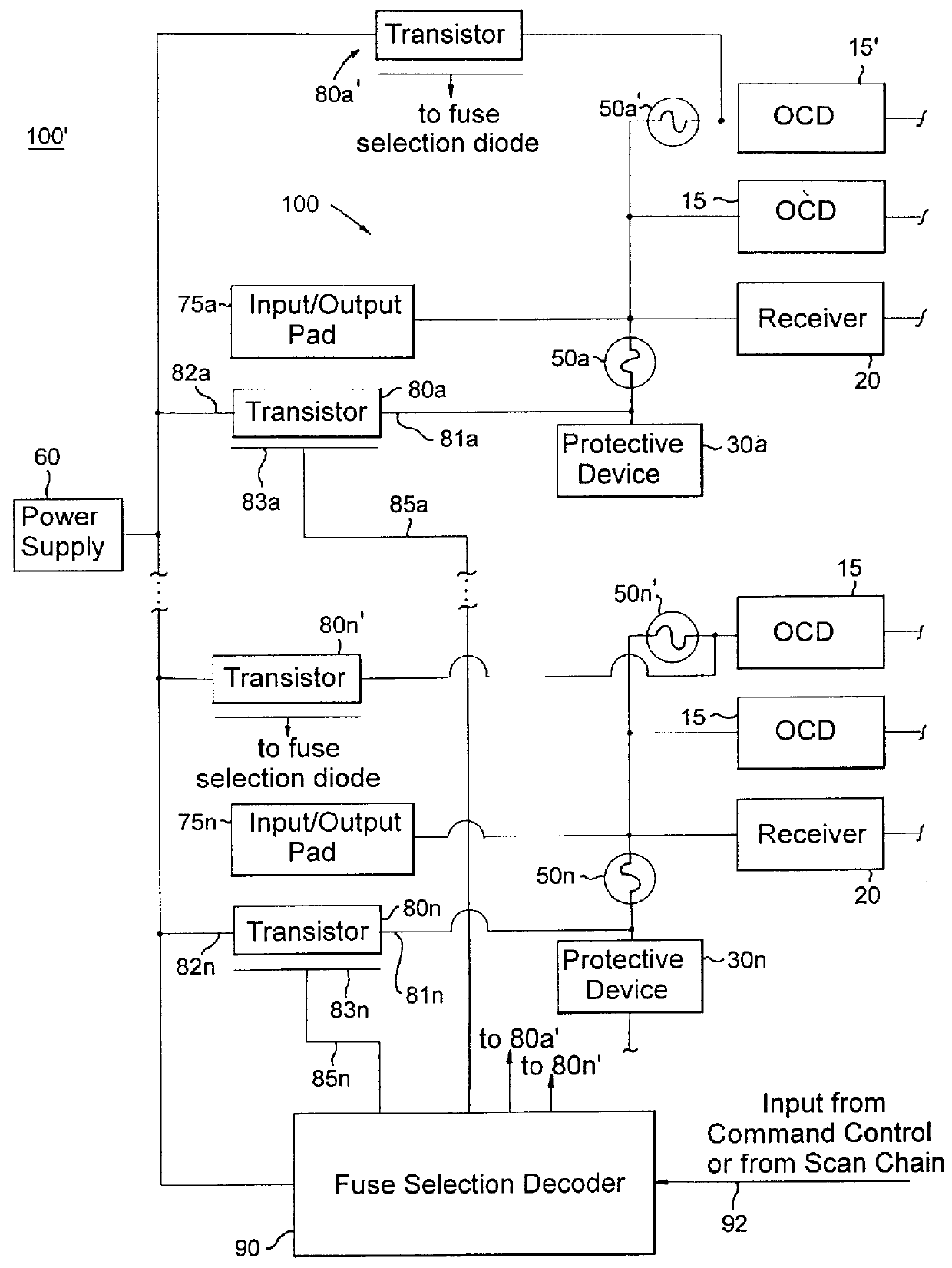

Impedance control using fuses

InactiveUS6141245ALower latencyHigher-bandwidth operationSemiconductor/solid-state device detailsSolid-state devicesMemory chipElectricity

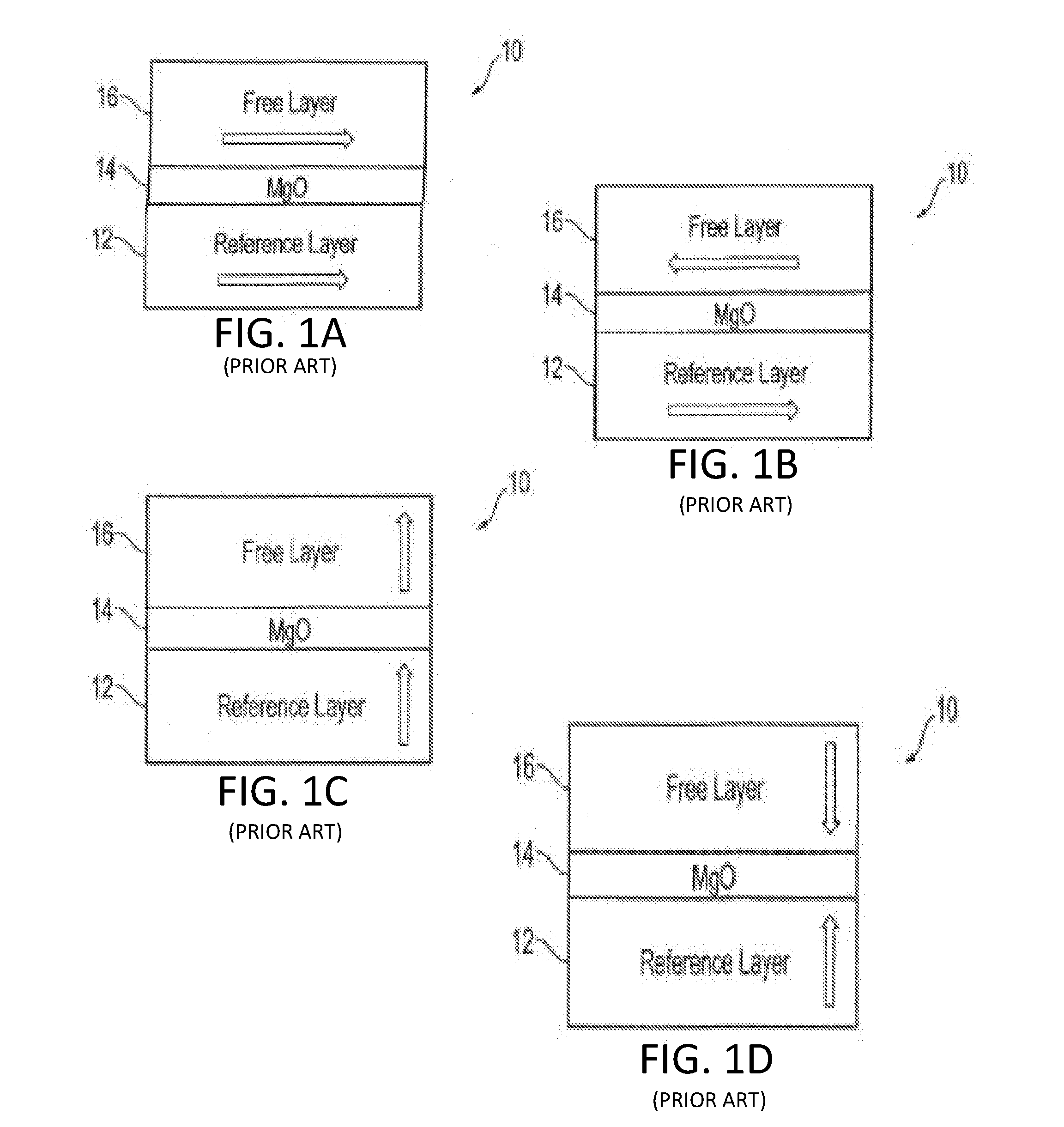

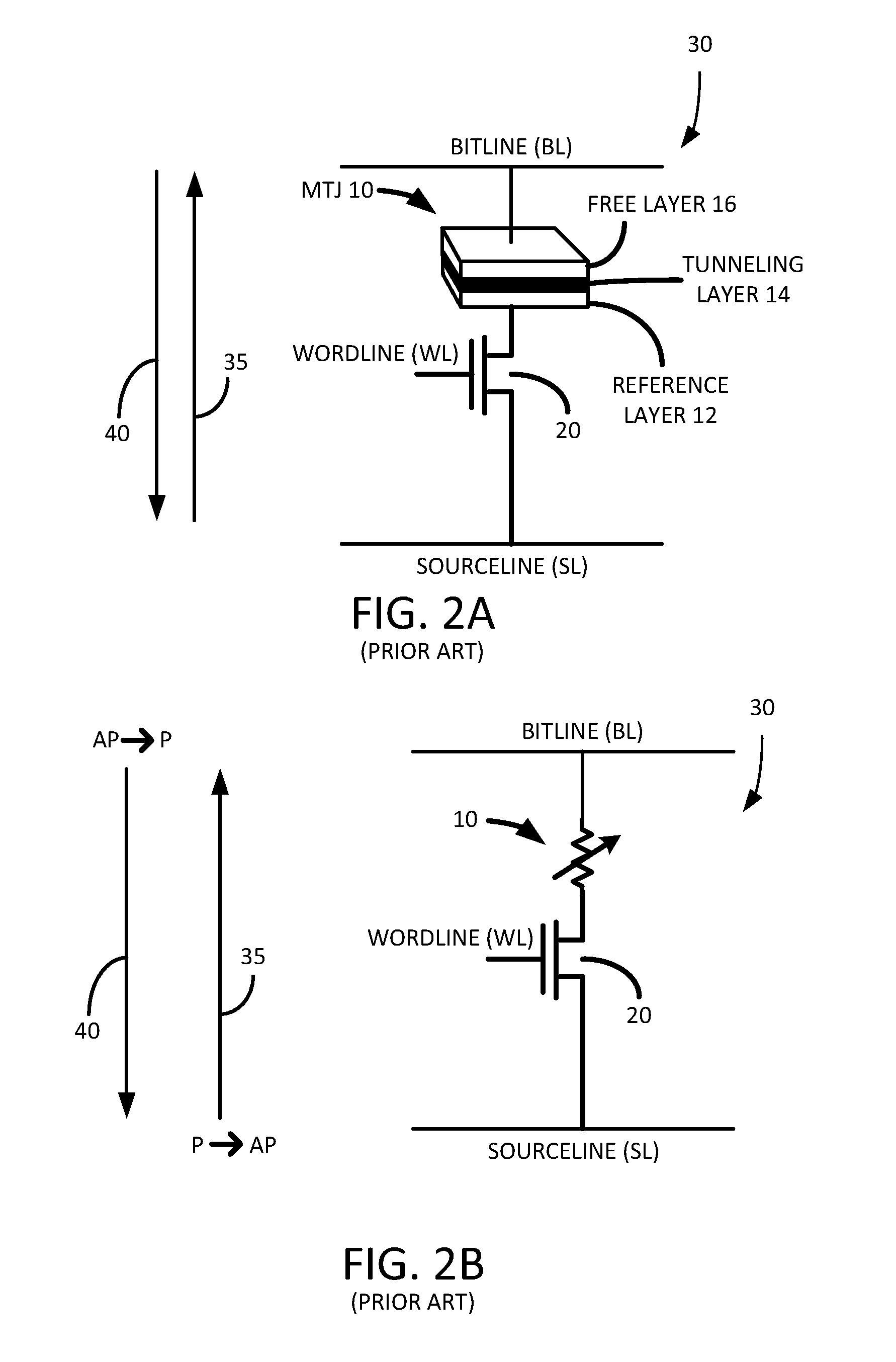

A system and method for reducing impedance loading of semiconductor integrated circuit devices implementing protective device structures that contributes to impedance loading at an I / O pad connection. The method comprises providing a fuse device between the I / O pad connection and the protective device; connecting a current source device associated with each fuse device in the integrated circuit, the current source device connected to one end of the fuse device; providing fuse selection circuit for activating current flow through a selected fuse device between the current source and the I / O connection, the current flow being of an amount sufficient for blowing the fuse and disconnecting the protective device from the circuit structure, thereby reducing impedance loading at the I / O connection. Such a system and method is employed in a memory system comprising integrated circuit chips disposed in a stacked relation, with each chip including: a layer of active circuitry formed at a first layer of each chip; a plurality of through conducting structures disposed substantially vertically through each chip for enabling electronic connection with active circuitry at the first layer; second conducting device disposed at an end of the through conducting structure at an opposite side of a chip for connection with a corresponding through conductive structure of an adjacent stacked chip, the stacked chip structure formed by aligning one or more through conducting structures and second conducting devices of adjacent chips, whereby a chip of the stack is electronically connected to active circuitry formed on other chips of the stack. The stacked chip structure is ideal for reducing data access latency in memory systems employing memory chips such as DRAM.

Owner:MARVELL ASIA PTE LTD

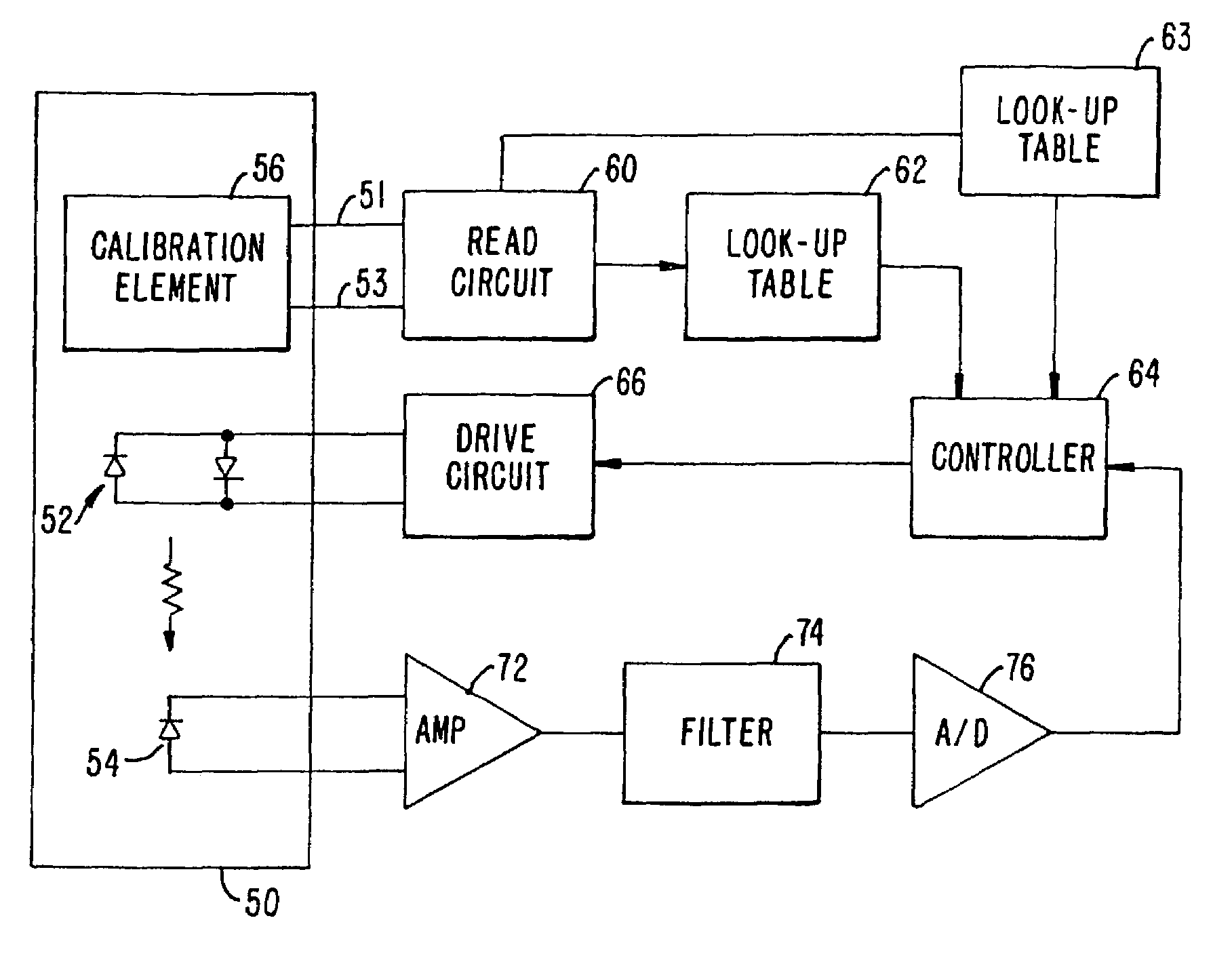

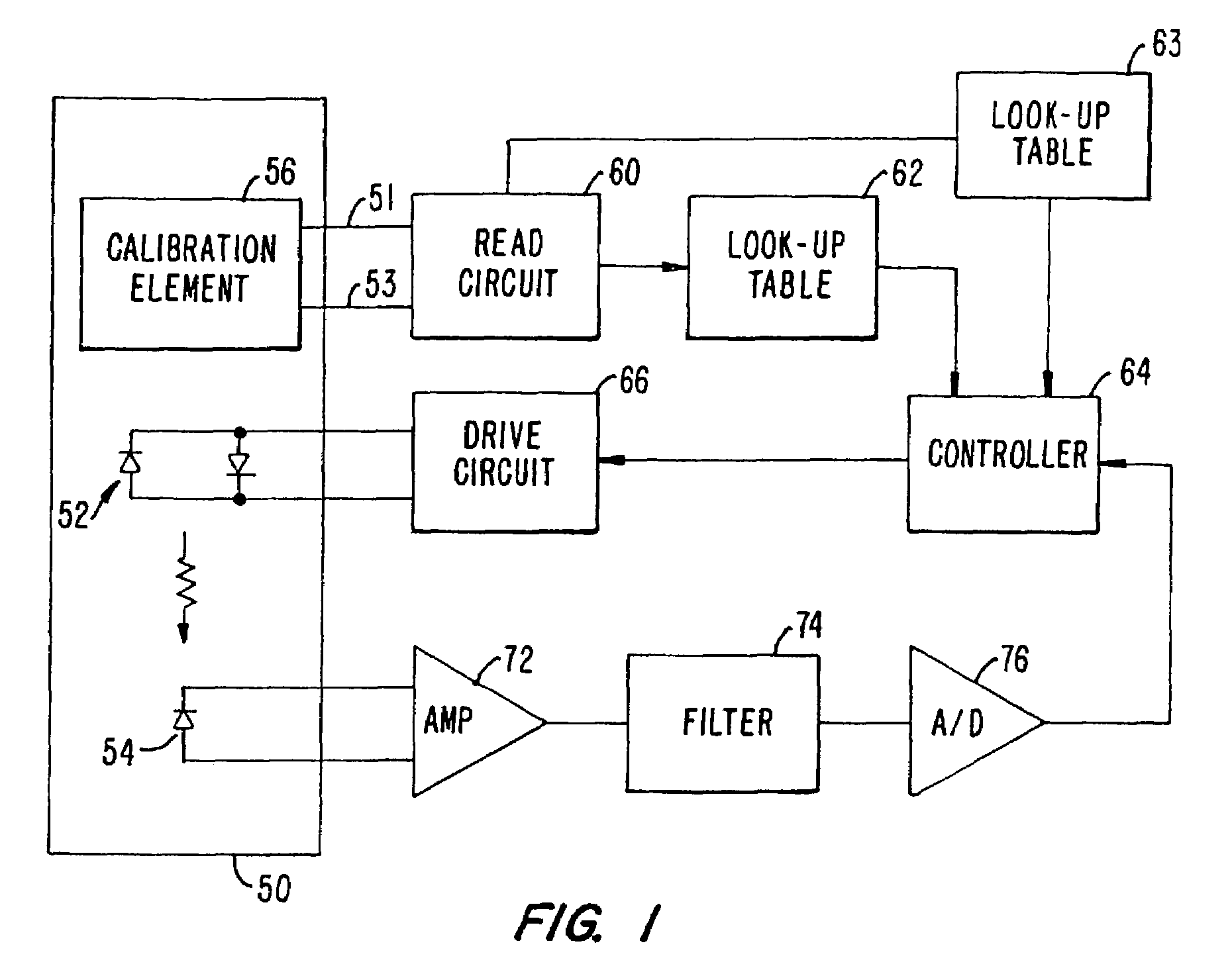

Oximeter sensor with digital memory recording sensor data

InactiveUS20020038081A1Improve abilitiesEvaluation of blood vesselsSensorsMemory chipDriving current

The present invention provides a memory chip for use in an oximeter sensor, or an associated adapter or connector circuit. The memory chip allows the storing of different data to provide enhanced capabilities for the oximeter sensor. In addition to providing unique data to store in such a memory, the invention describes unique uses of data stored in such a memory. The data stored in the memory chip may include information relating to use of the oximeter sensor. For example, the memory chip may encode a sensor model identification that can be displayed on a display screen when the sensor is connected to an oximeter monitor. The memory may also encode a range of operating parameters such as light levels over which the sensor can function or a maximum drive current. The operating parameters are read and interpreted by a controller circuit to control the pulse oximetry system.

Owner:TYCO HEALTHCARE GRP LP

Memory system and memory card

InactiveUS20070198770A1Rise in cost is suppressedRequirement for numberMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:HORII TAKASHI +2

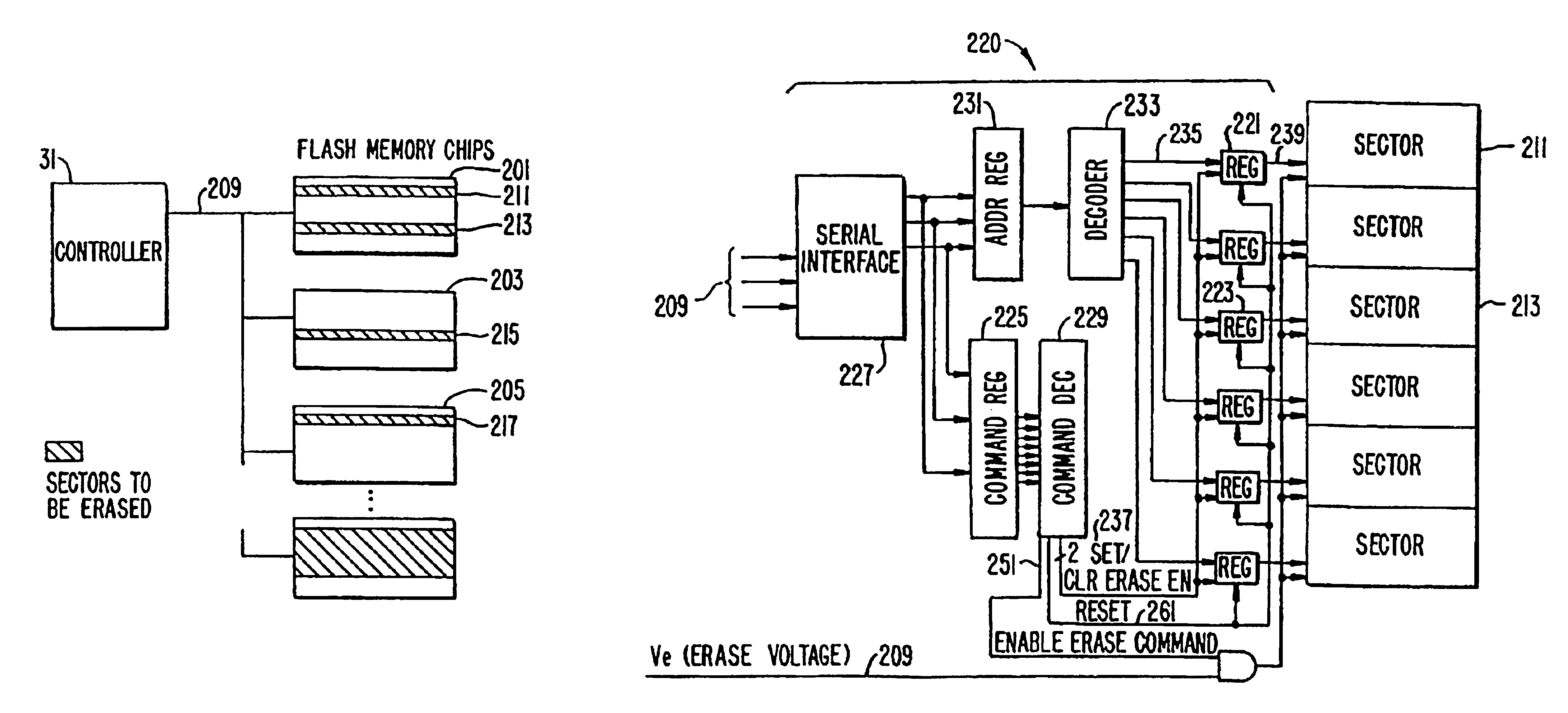

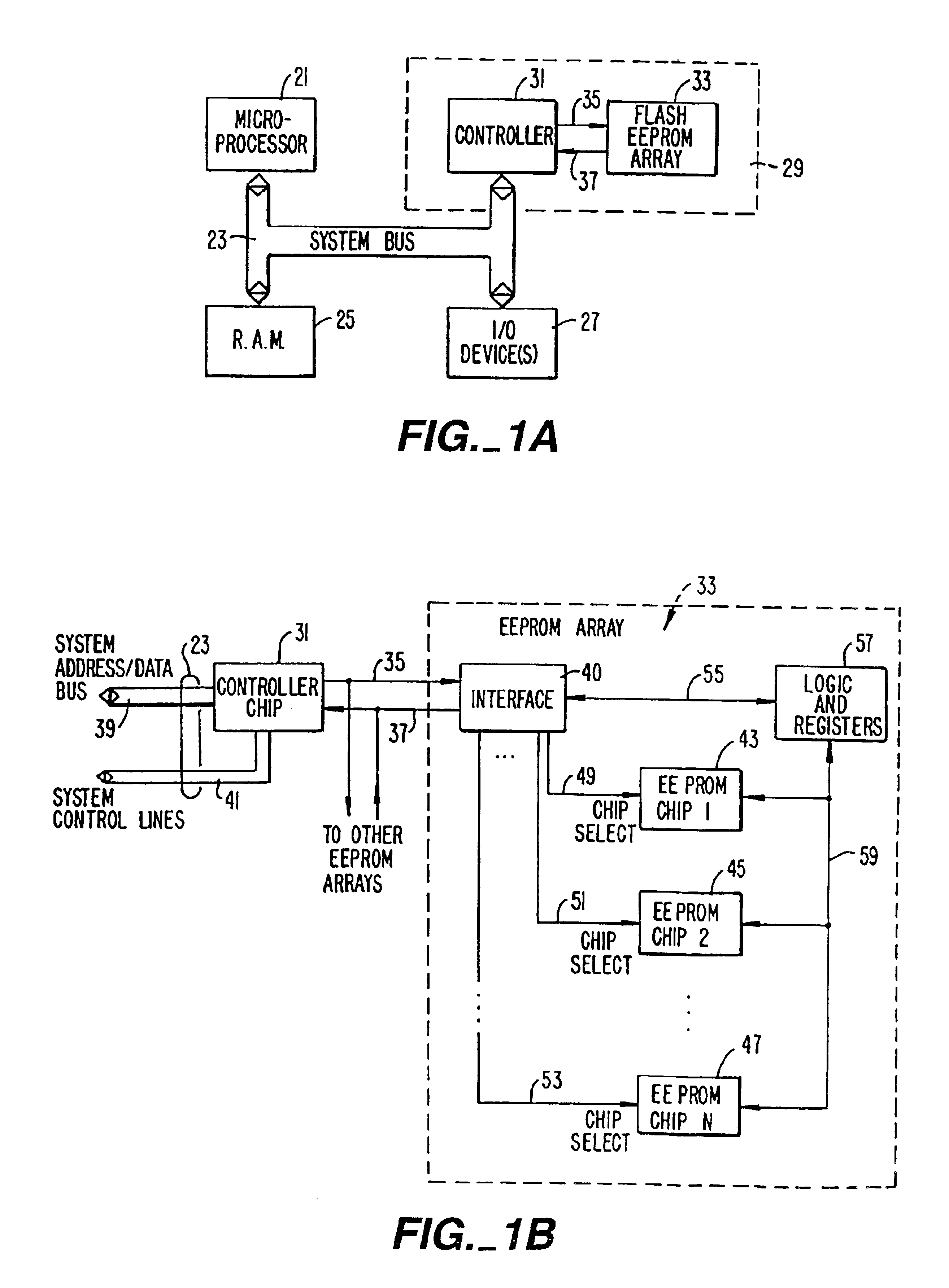

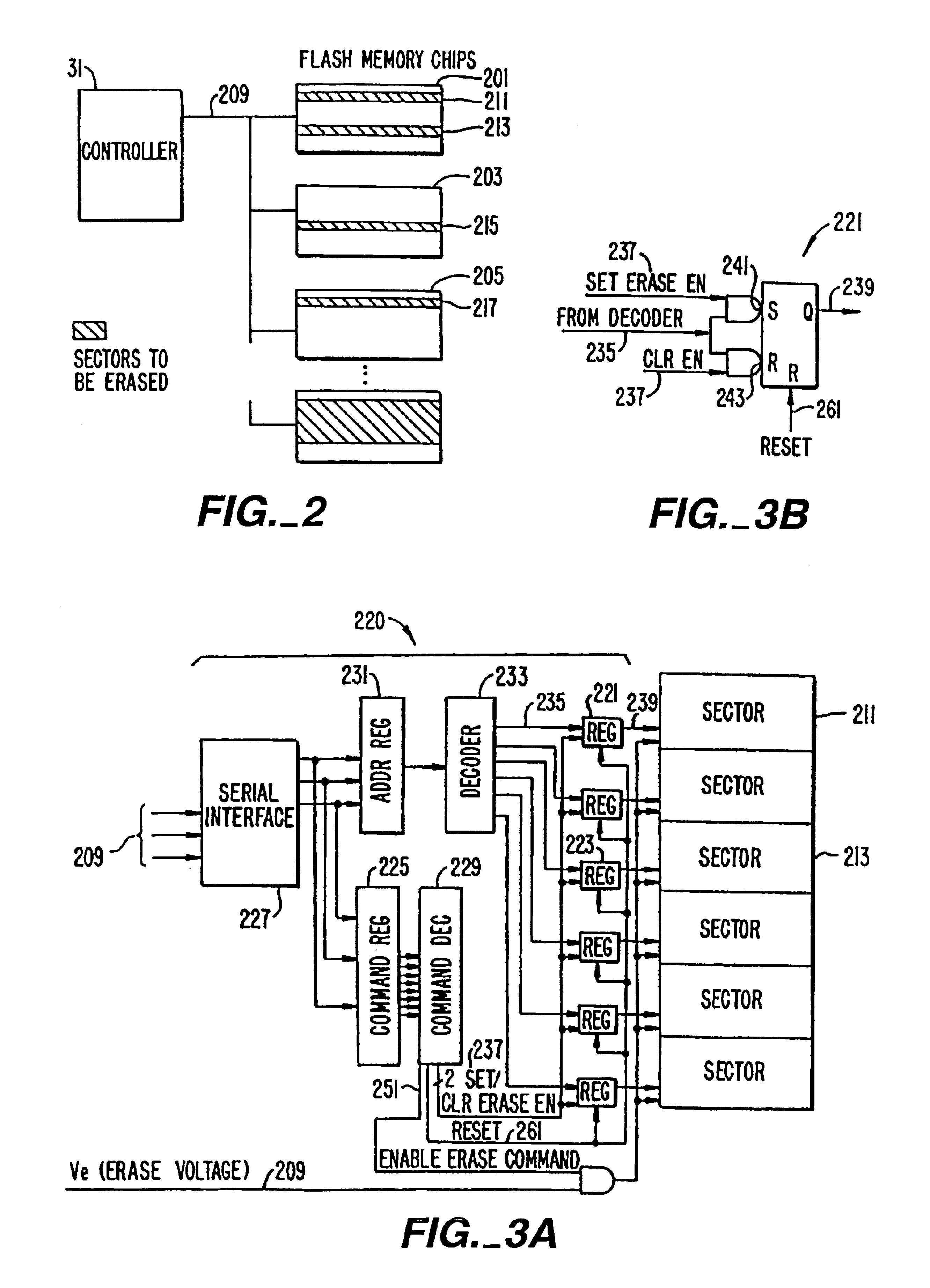

Flash EEprom system

InactiveUS6914846B2Minimize the numberAnti agingMemory architecture accessing/allocationTransistorMemory chipControl circuit

A system of Flash EEprom memory chips with controlling circuits serves as non-volatile memory such as that provided by magnetic disk drives. Improvements include selective multiple sector erase, in which any combinations of Flash sectors may be erased together. Selective sectors among the selected combination may also be de-selected during the erase operation. Another improvement is the ability to remap and replace defective cells with substitute cells. The remapping is performed automatically as soon as a defective cell is detected. When the number of defects in a Flash sector becomes large, the whole sector is remapped. Yet another improvement is the use of a write cache to reduce the number of writes to the Flash EEprom memory, thereby minimizing the stress to the device from undergoing too many write / erase cycling.

Owner:SANDISK TECH LLC

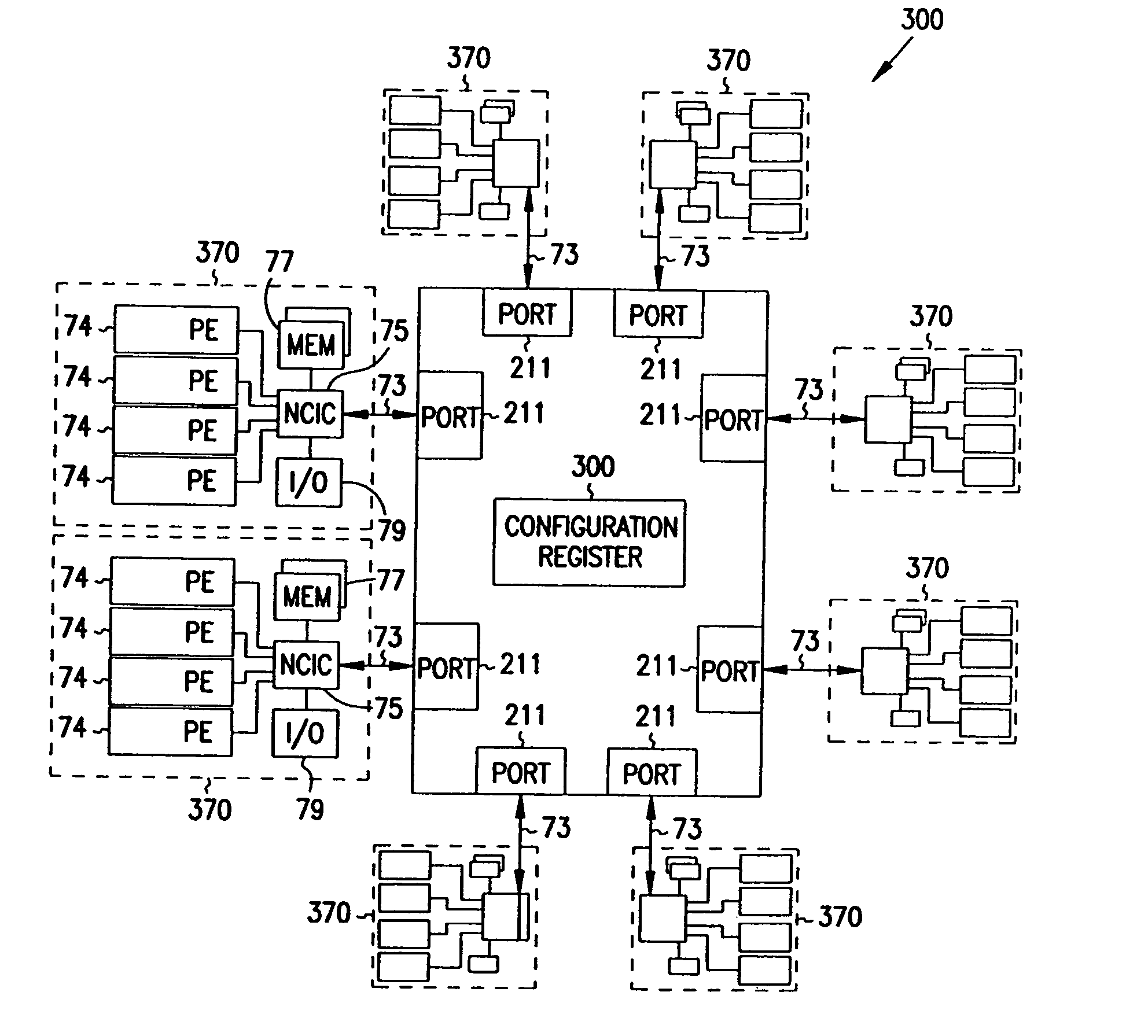

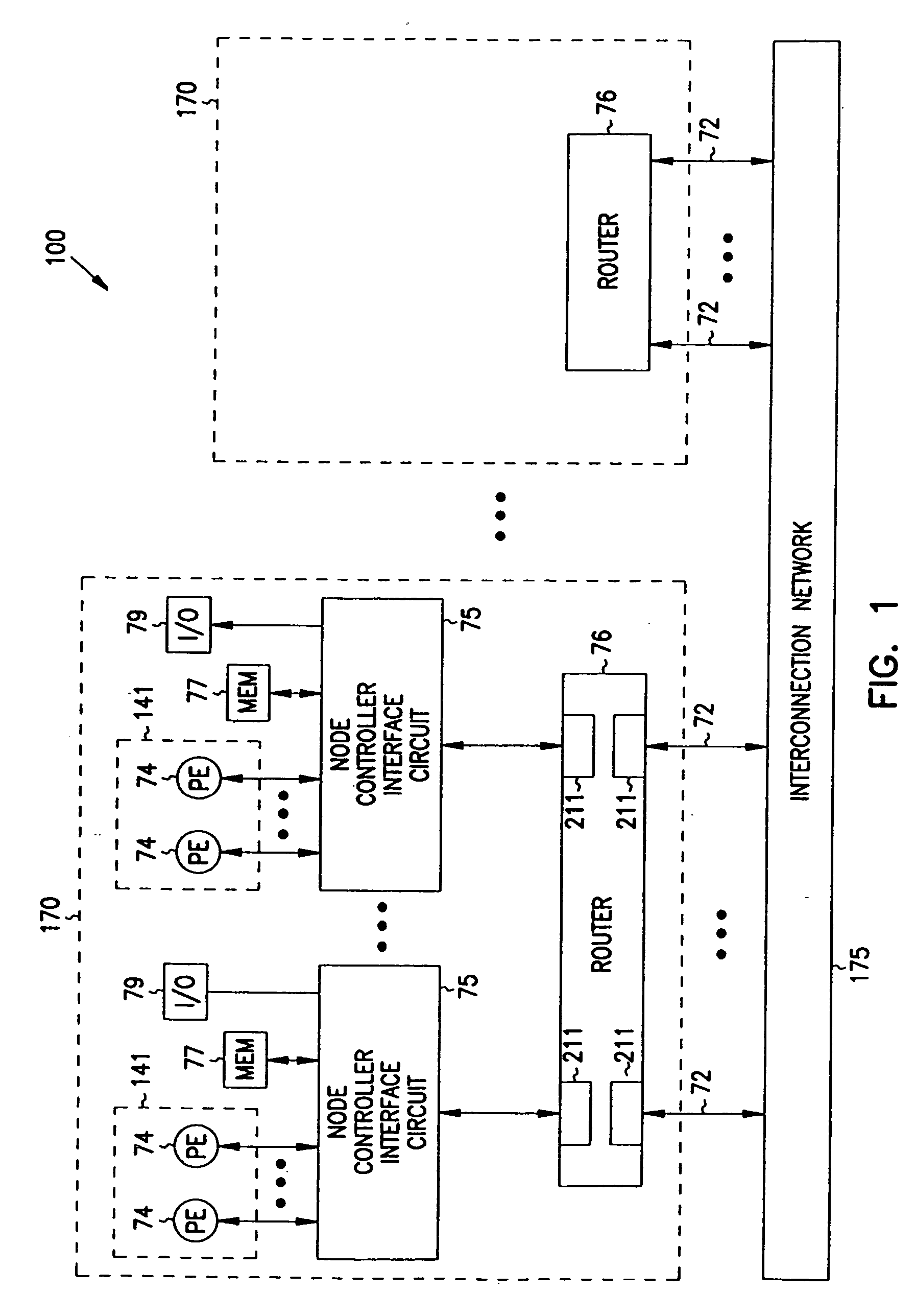

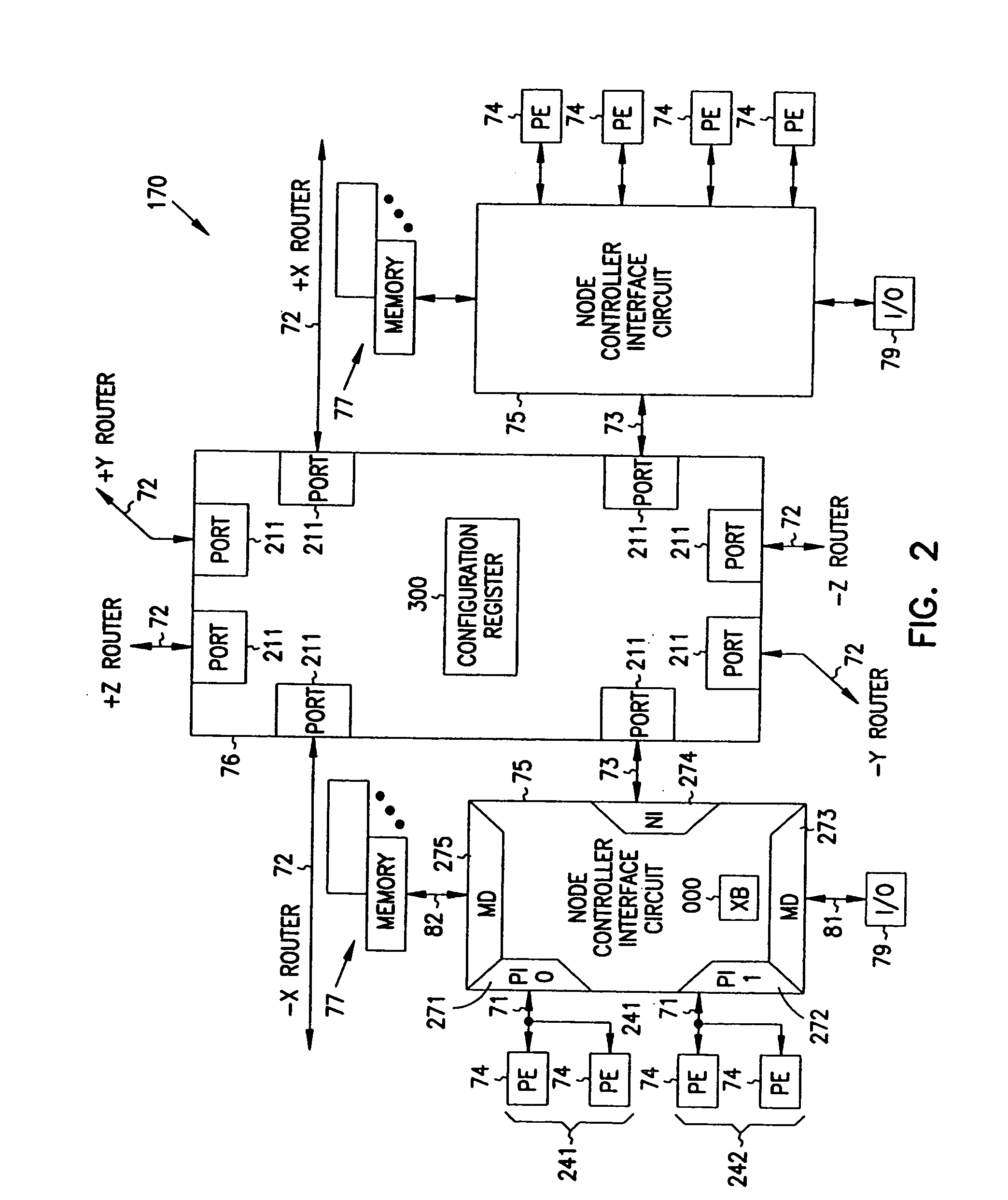

Multiprocessor node controller circuit and method

InactiveUS20050053057A1Ease of parallel processingImprove welfareMultiplex system selection arrangementsMemory adressing/allocation/relocationMemory addressCrossbar switch

Improved method and apparatus for parallel processing. One embodiment provides a multiprocessor computer system that includes a first and second node controller, a number of processors being connected to each node controller, a memory connected to each controller, a first input / output system connected to the first node controller, and a communications network connected between the node controllers. The first node controller includes: a crossbar unit to which are connected a memory port, an input / output port, a network port, and a plurality of independent processor ports. A first and a second processor port connected between the crossbar unit and a first subset and a second subset, respectively, of the processors. In some embodiments of the system, the first node controller is fabricated onto a single integrated-circuit chip. Optionally, the memory is packaged on plugable memory / directory cards wherein each card includes a plurality of memory chips including a first subset dedicated to holding memory data and a second subset dedicated to holding directory data. Further, the memory port includes a memory data port including a memory data bus and a memory address bus coupled to the first subset of memory chips, and a directory data port including a directory data bus and a directory address bus coupled to the second subset of memory chips. In some such embodiments, the ratio of (memory data space) to (directory data space) on each card is set to a value that is based on a size of the multiprocessor computer system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

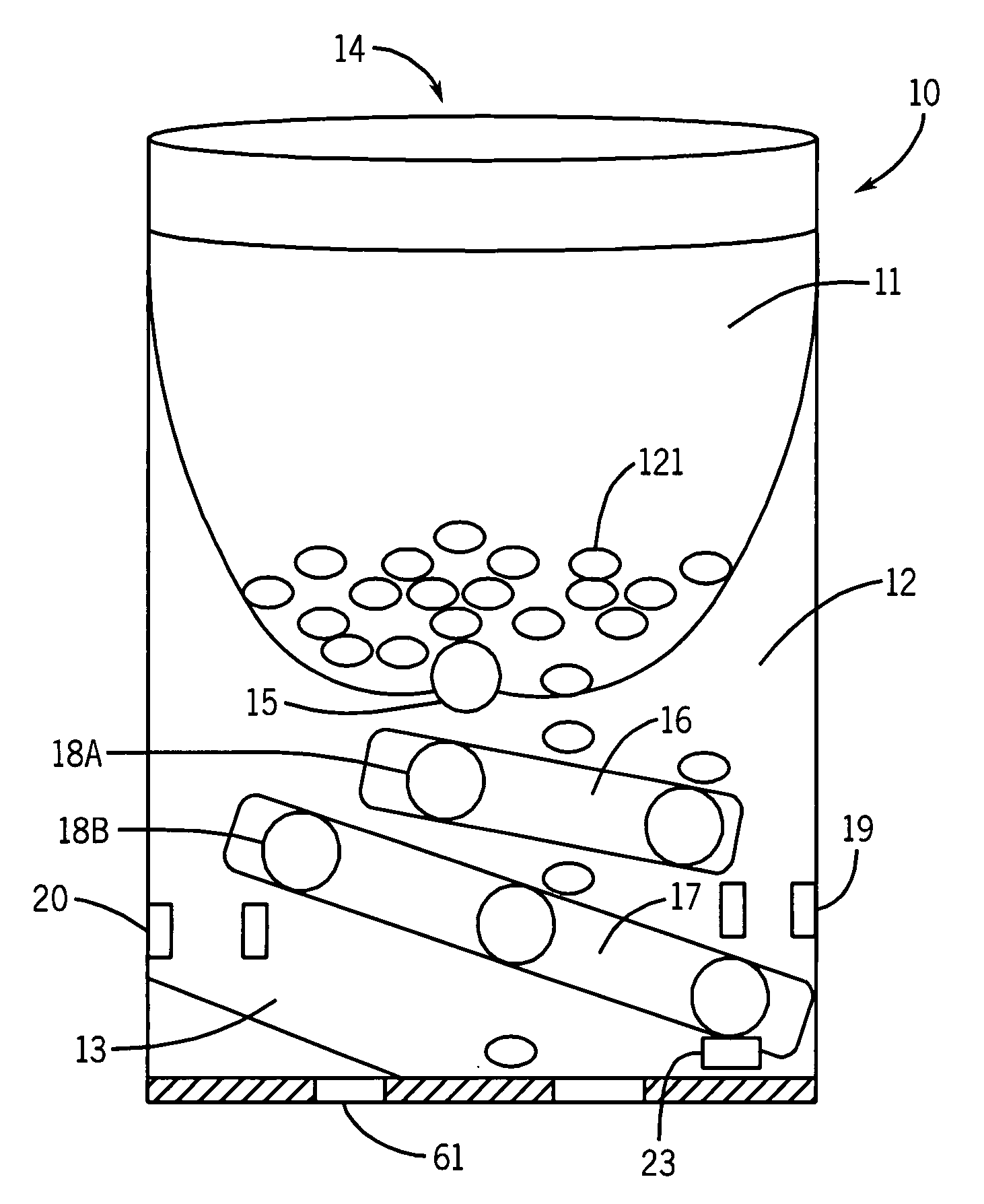

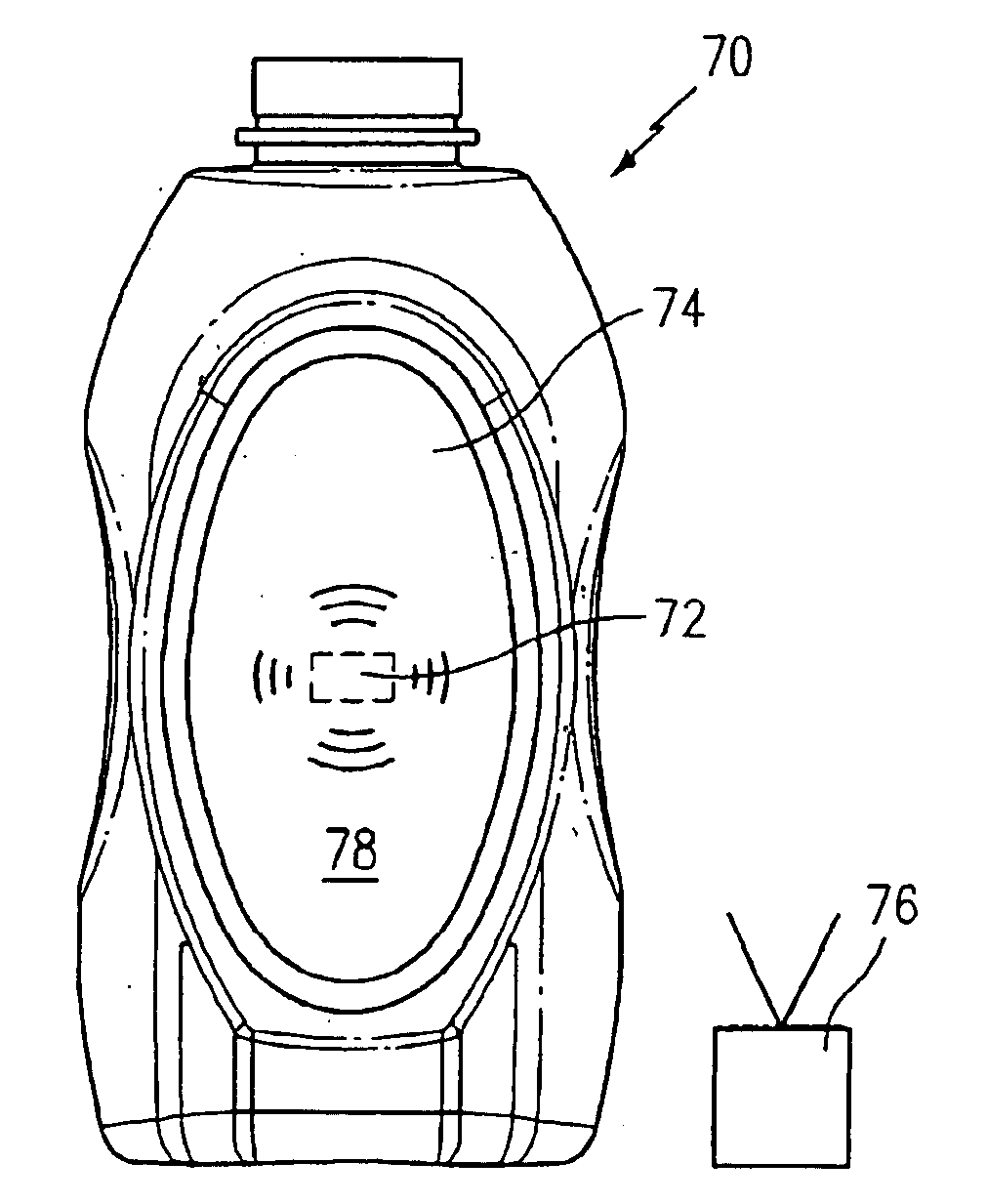

Smart medicine container

InactiveUS7269476B2Prevent misuse of prescription medicationsAssembly is accurate and reliableDrug and medicationsCoin-freed apparatus detailsDiseaseGlucose meter device

Owner:RATNAKAR NITESH

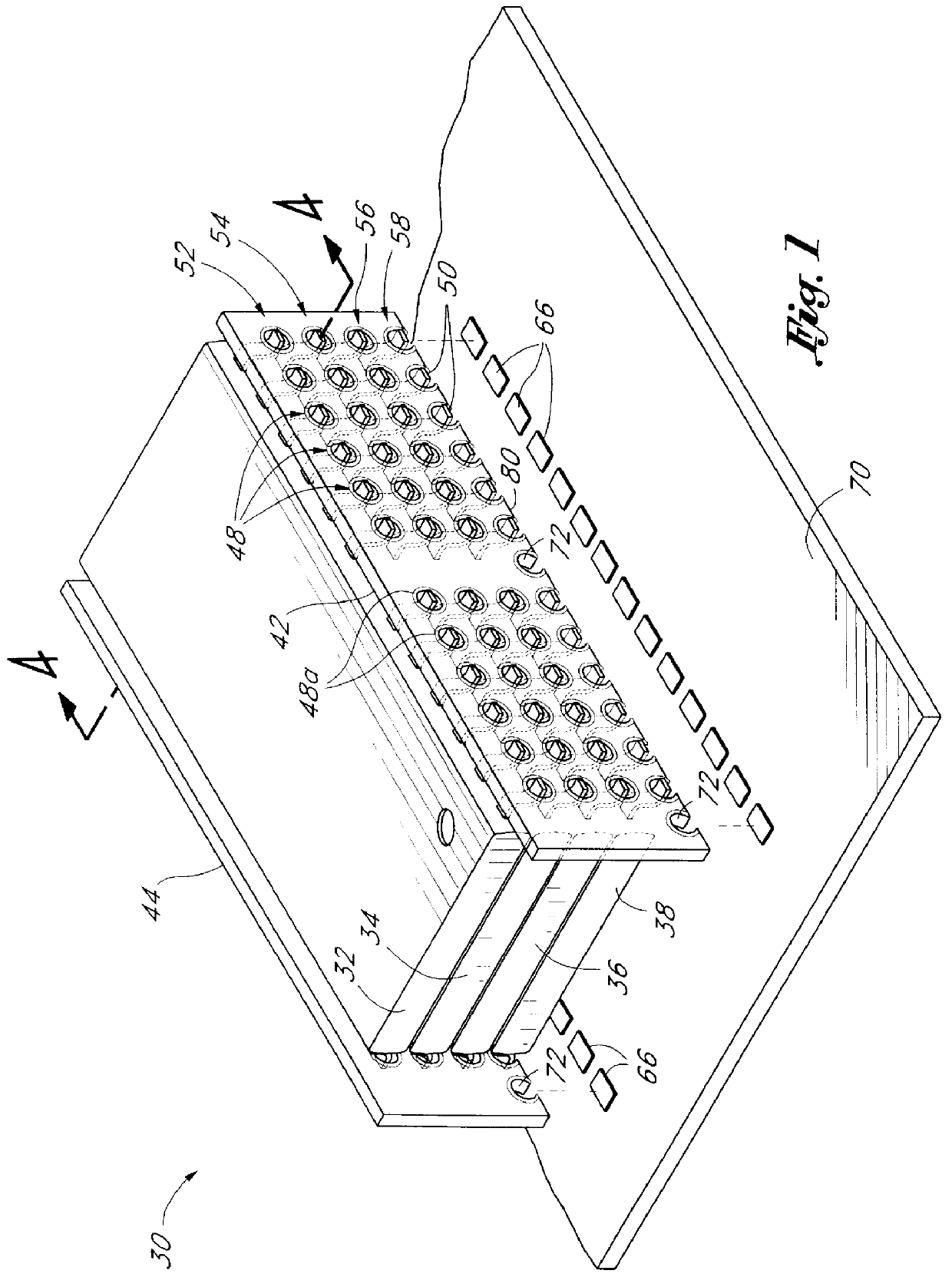

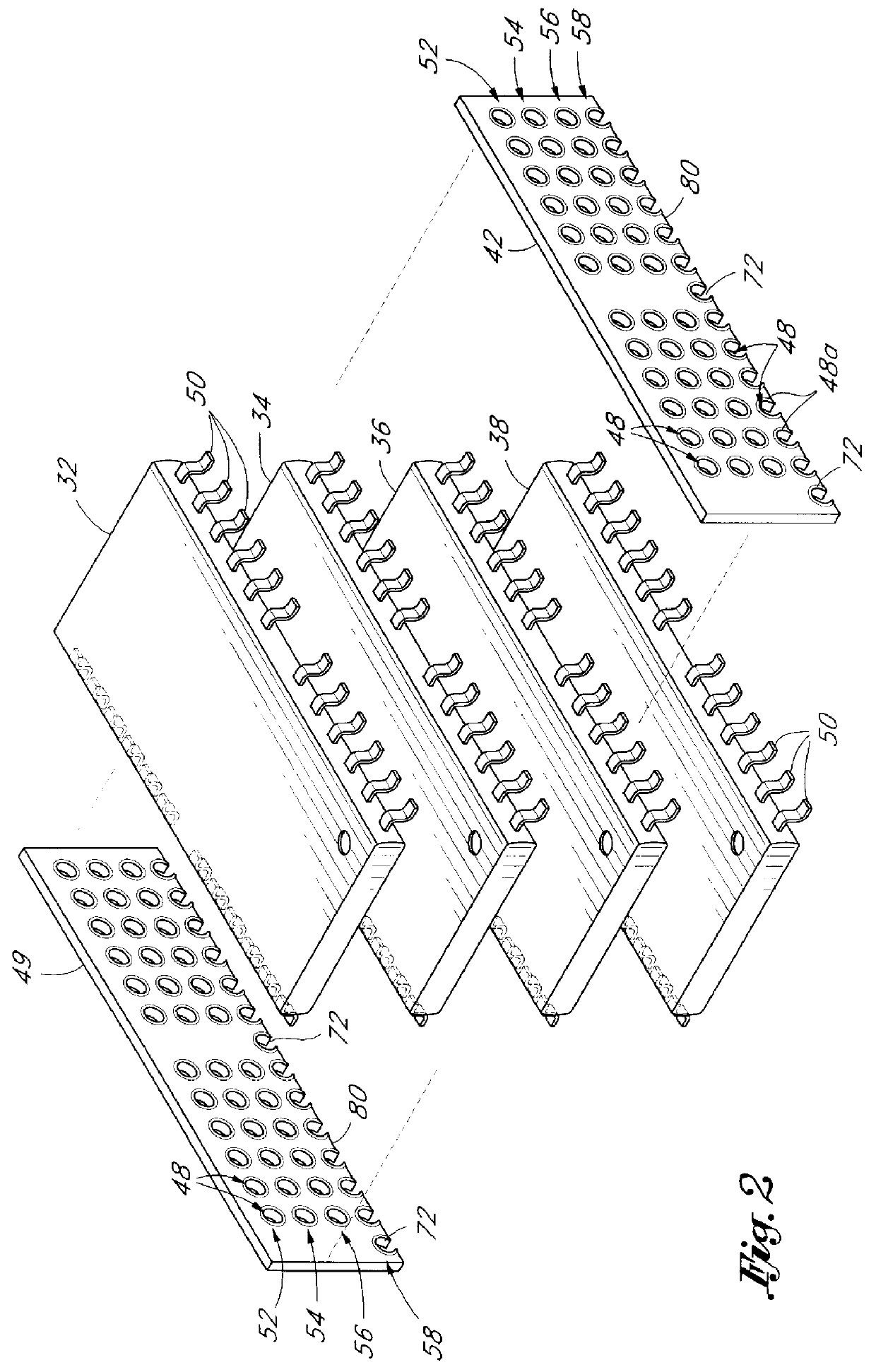

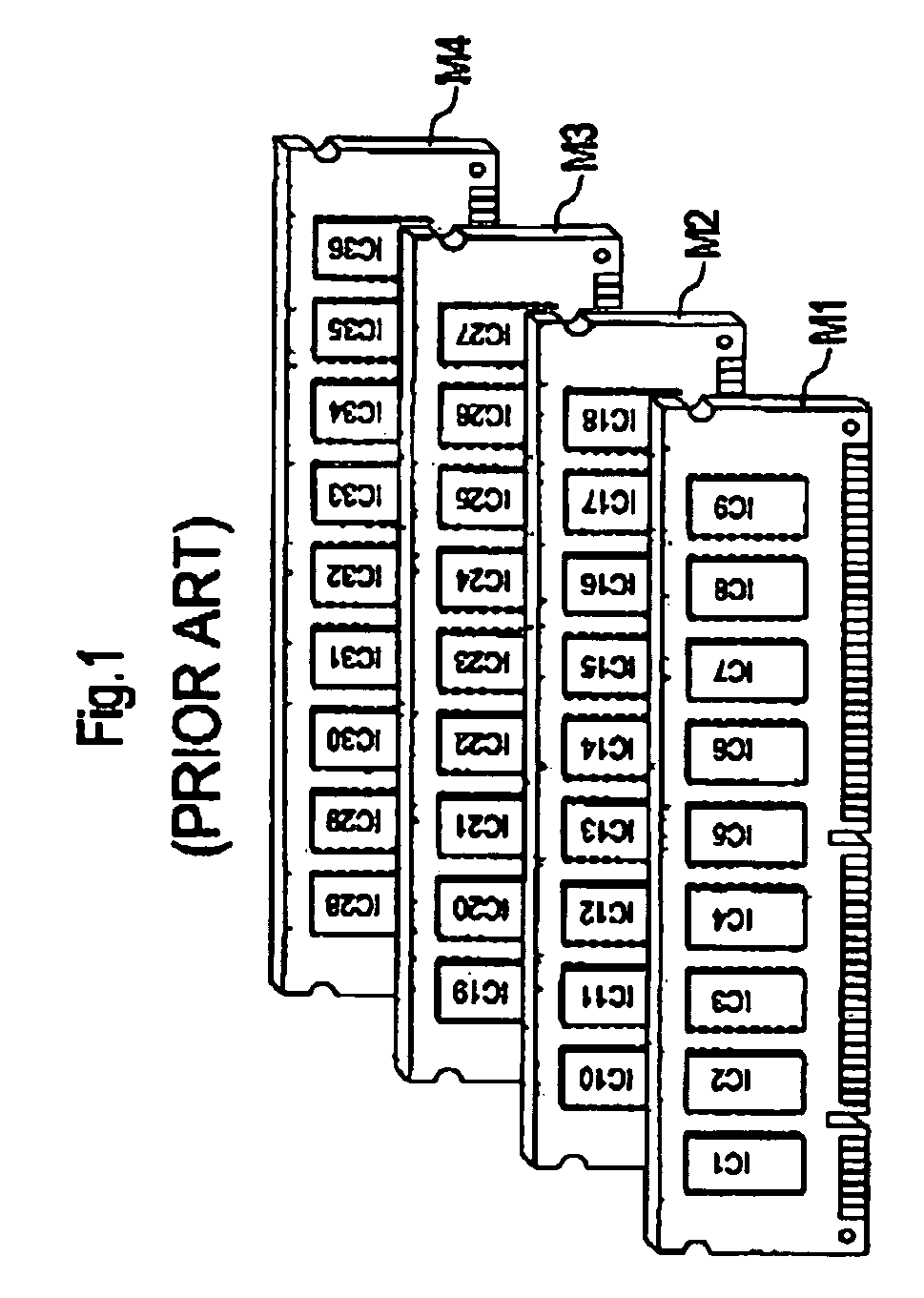

Apparatus for stacking semiconductor chips

InactiveUSRE36916E1Low profileHigh densitySemiconductor/solid-state device detailsSolid-state devicesMemory chipSurface mounting

A multi-chip memory module comprises multiple standard, surface-mount-type memory chips stacked on top of each other, and a pair of printed circuit boards mounted on opposite sides of the memory chips to electrically interconnect the memory chips. Each printed circuit board has vias that are positioned to form multiple rows, with each row of vias used to connect the printed circuit board to a respective memory chip. The vias falling along the bottom-most row of each printed circuit board are also exposed and are used to surface mount the multi-chip module to pads of a memory board.

Owner:HGST TECH SANTA ANA

Oximeter sensor with digital memory recording sensor data

The present invention provides a memory chip for use in an oximeter sensor, or an associated adapter or connector circuit. The memory chip allows the storing of different data to provide enhanced capabilities for the oximeter sensor. In addition to providing unique data to store in such a memory, the invention describes unique uses of data stored in such a memory. The data stored in the memory chip may include information relating to use of the oximeter sensor. For example, the memory chip may encode a sensor model identification that can be displayed on a display screen when the sensor is connected to an oximeter monitor. The memory may also encode a range of operating parameters such as light levels over which the sensor can function or a maximum drive current. The operating parameters are read and interpreted by a controller circuit to control the pulse oximetry system.

Owner:COVIDIEN LP

Application of radio frequency identification

InactiveUS20050068182A1Easy to getElectric signal transmission systemsDigital data processing detailsMemory chipEngineering

Improved plastic article having an integral radio frequency identification (RFID) as an integral, permanent part of the article. The RFID can be molded onto an article; as a memory chip-antenna combination molded onto a desired location on an article.

Owner:PLASTIPAK PACKAGING

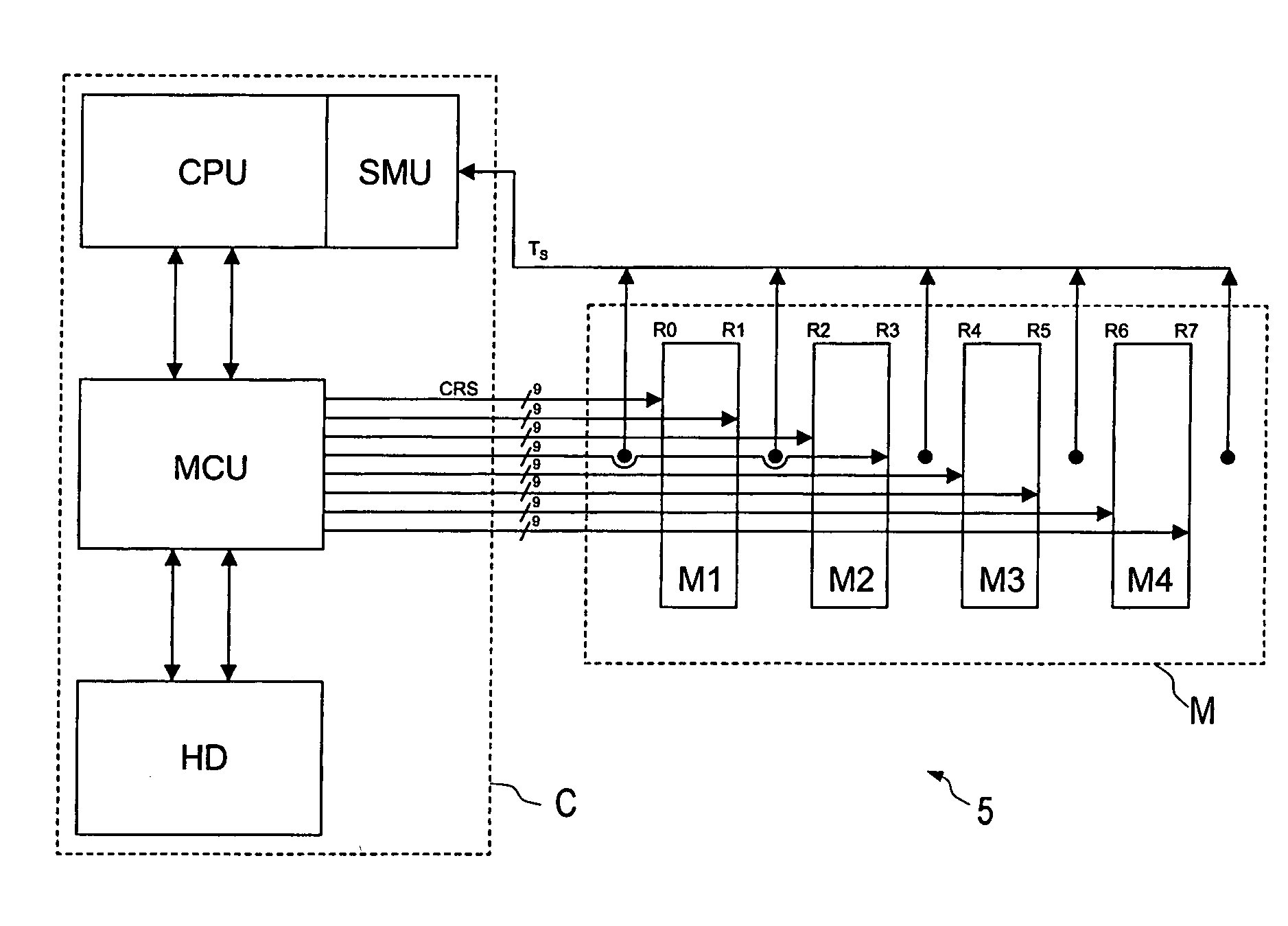

Method for controlling semiconductor chips and control apparatus

InactiveUS6986118B2Increase choiceEasy to operateDigital computer detailsData resettingMemory chipSemiconductor chip

The invention relates to a method for operating semiconductor chips, particularly memory chips, which are arranged in groups on modules which are connected to a common data bus wherein each semiconductor chip on each module is connected to at least one data line in the common data bus comprising the following method steps:a) selecting a group of semiconductor chips from the semiconductor chips arranged on the modules based on a prescribed selection criterion independently of module, the selected group of semiconductor chips using data lines in the common data bus over the entire bus width;b) activating the semiconductor chips in the selected group; andc) performing data interchange between the data lines in the common data bus and the selected group of semiconductor chips.

Owner:POLARIS INNOVATIONS

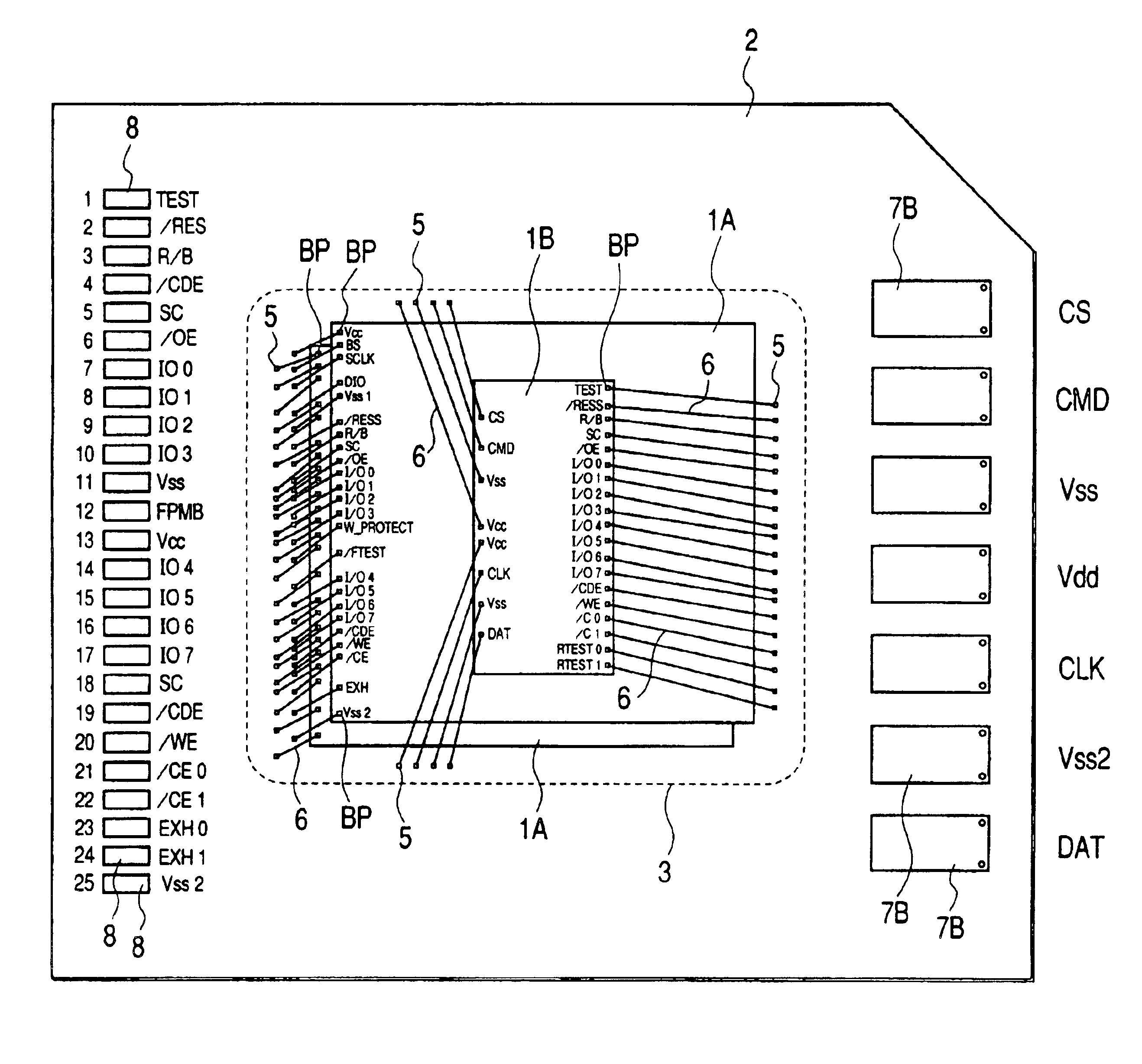

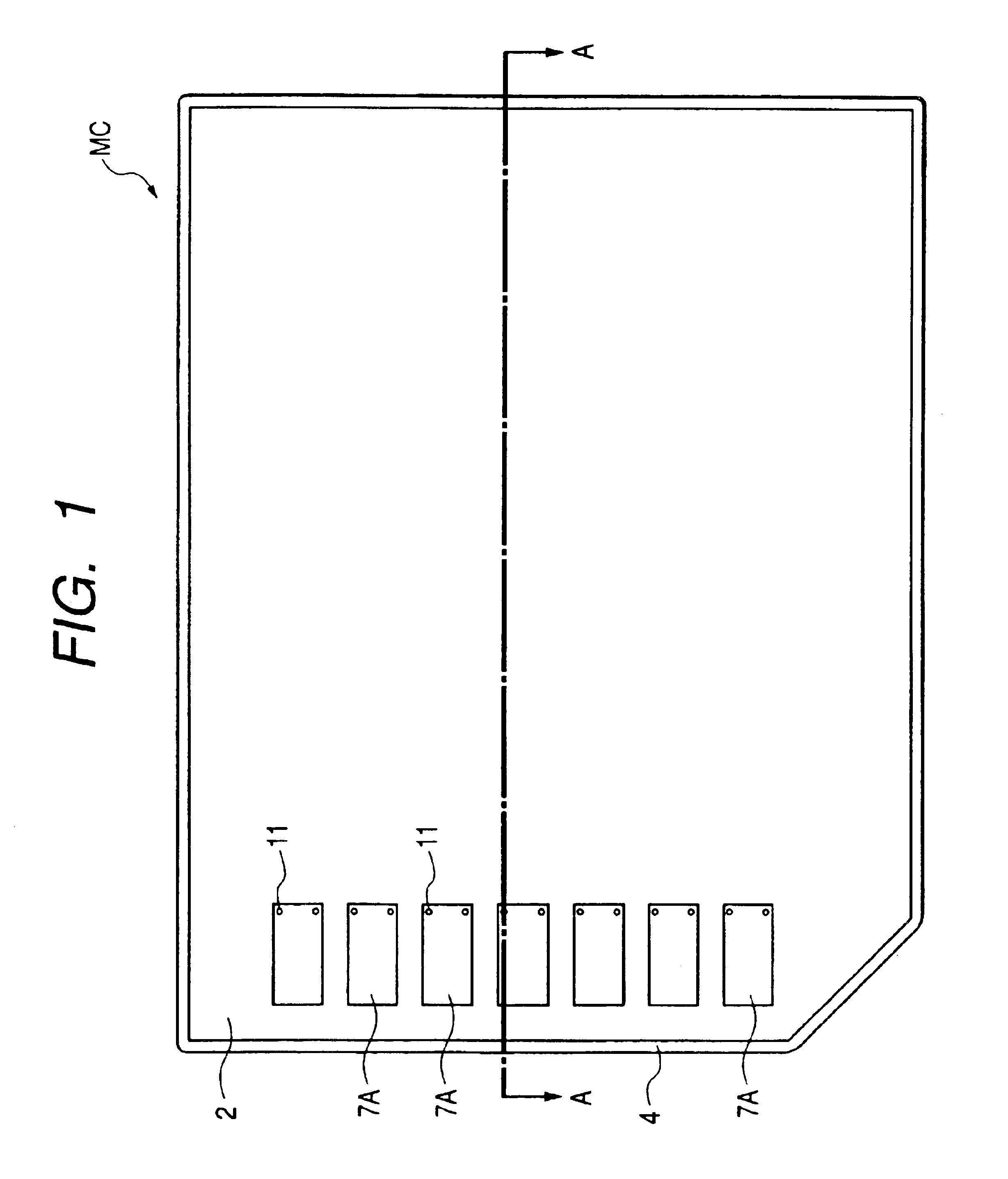

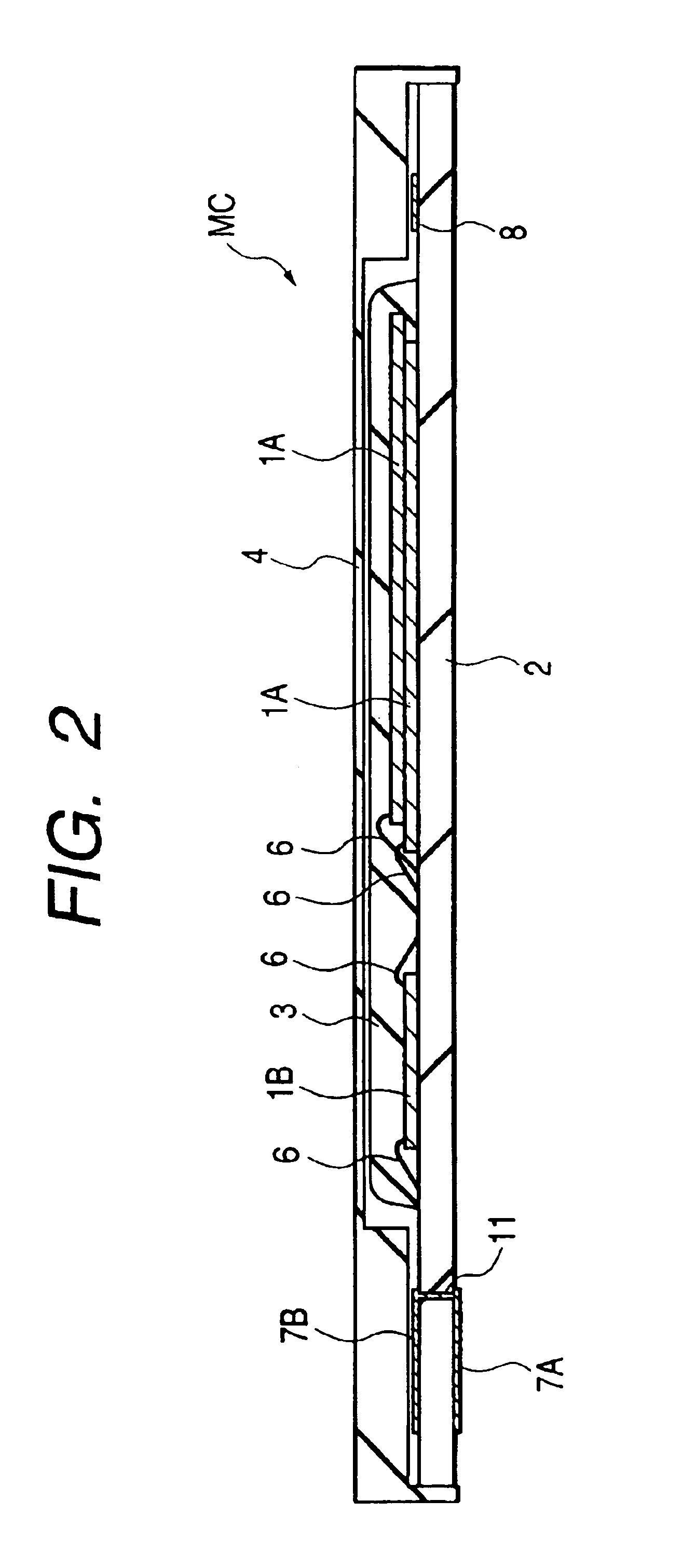

Semiconductor device and a method of manufacturing the same

InactiveUS7061105B2Reduce distanceIncrease in loop heightSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMemory chipSemiconductor

Two memory chips mounted over a base substrate have the same external size and a flash memory of the same memory capacity formed thereon. These memory chips are mounted over the base substrate with one of them being overlapped with the upper portion of the other one, and they are stacked with their faces being turned in the same direction. The bonding pads BP of one of the memory chips are disposed in the vicinity of the bonding pads BP of the other memory chip. In addition, the upper memory chip is stacked over the lower memory chip in such a way that the upper memory chip is slid in a direction (X direction) parallel to the one side of the lower memory chip and in a direction (Y direction) perpendicular thereto in order to prevent partial overlapping of it with the bonding pads BP of the lower memory chip.

Owner:LONGITUDE LICENSING LTD

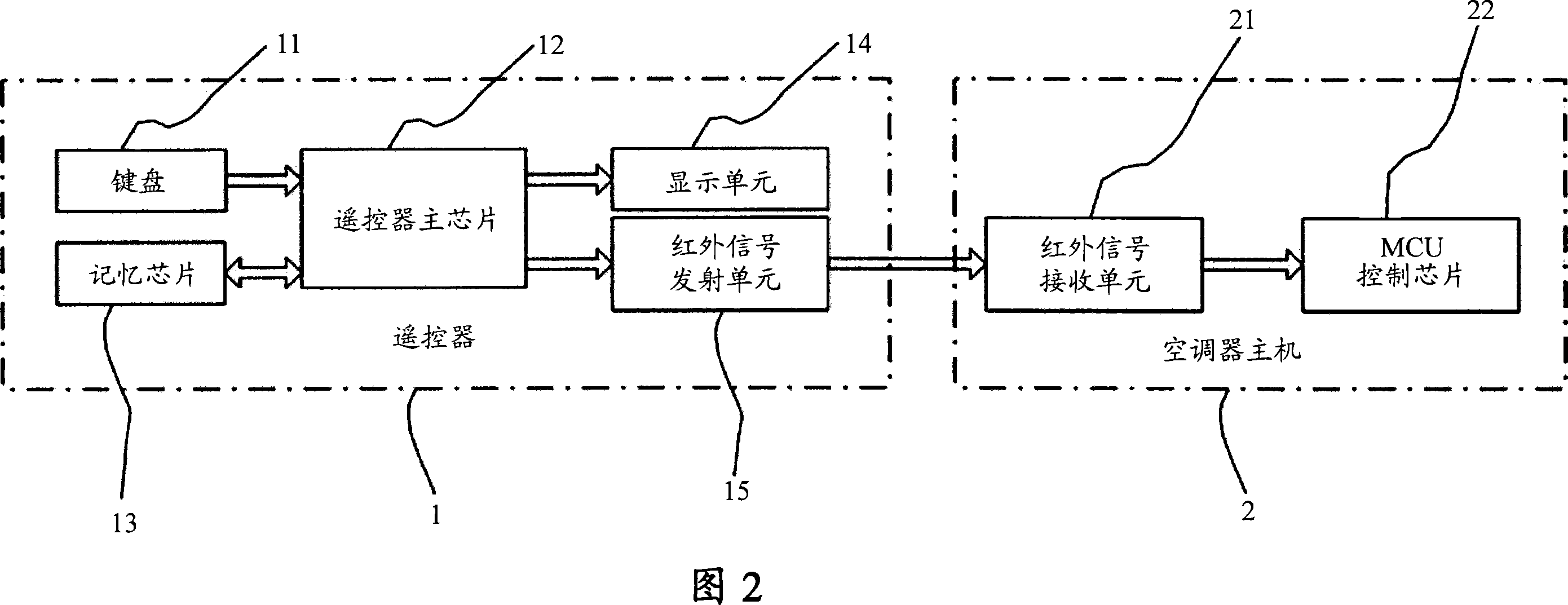

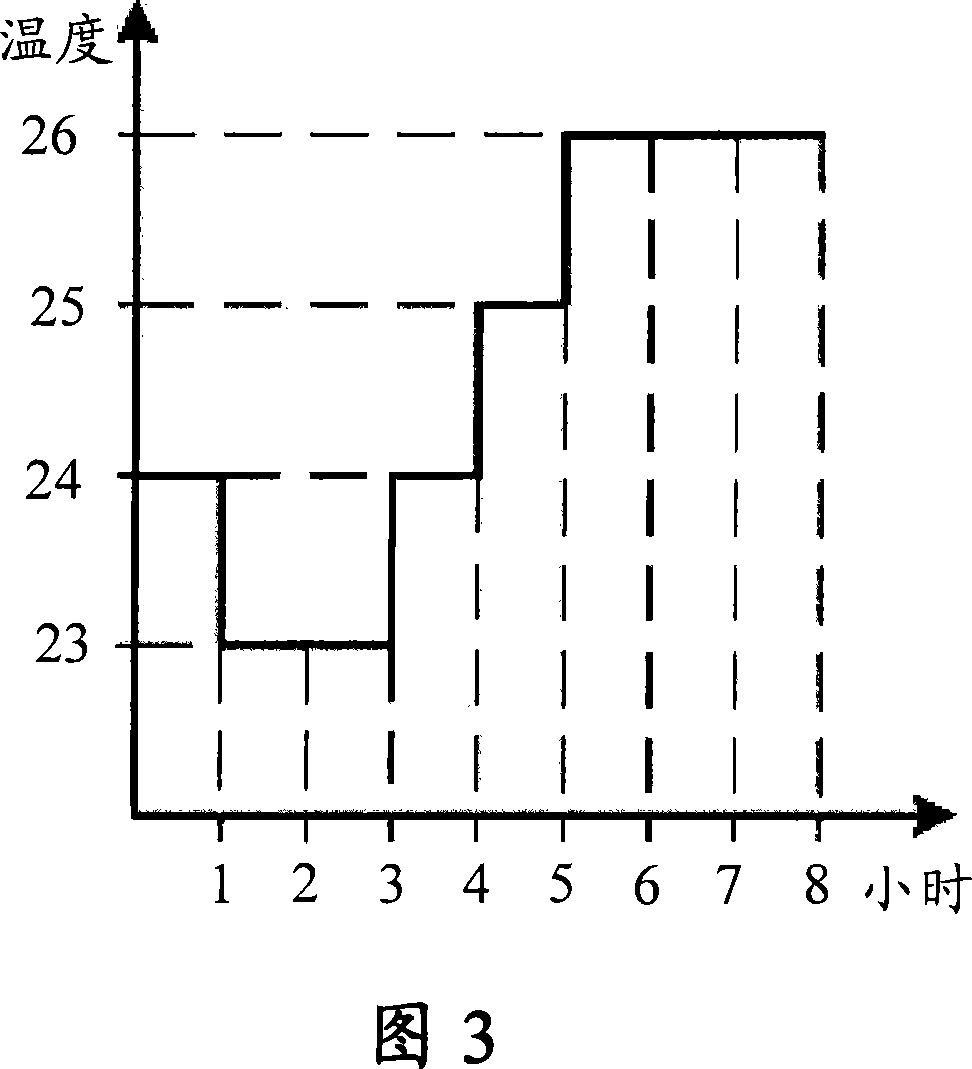

Air-conditioning unit operating according to user-defined curve and control method therefor

The invention discloses an air condition work by the custom curve operation and the controlling method. The air condition includes the main machine which includes the custom curve accepting unit to accept the user defined curve data which determines the relation between the air condition temperature and the time; the controlling unit connected with the custom curve accepting unit which controls the air condition temperature in the different time. The user can set the custom curve by the report controller keyboard. The custom curve data is stored in the report controller memory chip. It transforms the custom curve data to the infrared signal accepting unit of the main machine. The MCU controlling chip can control the air condition operation according to the custom curve. The air condition can work according to the custom temperature and time to satisfy the user comfort.

Owner:GREE ELECTRIC APPLIANCE INC OF ZHUHAI

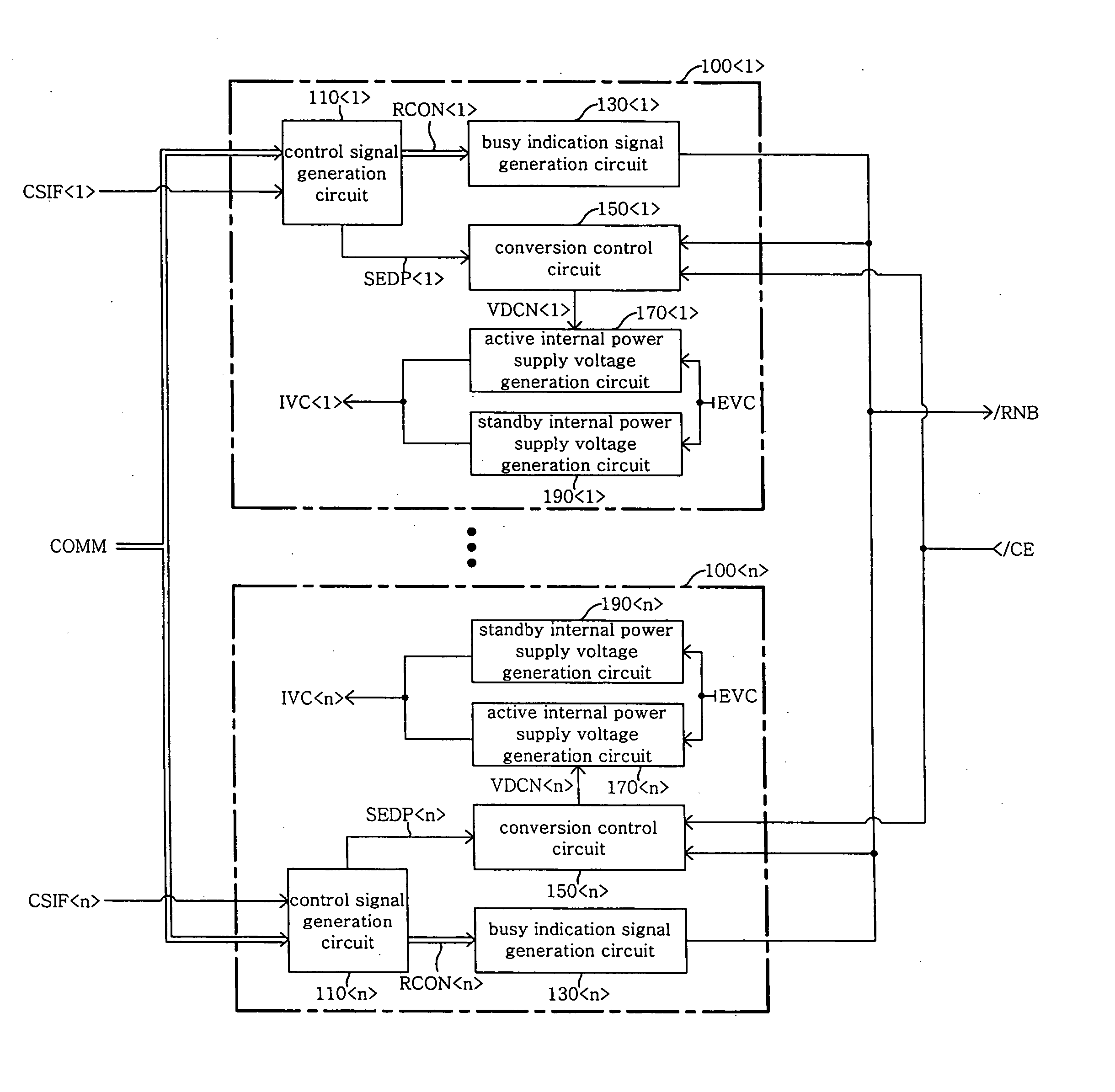

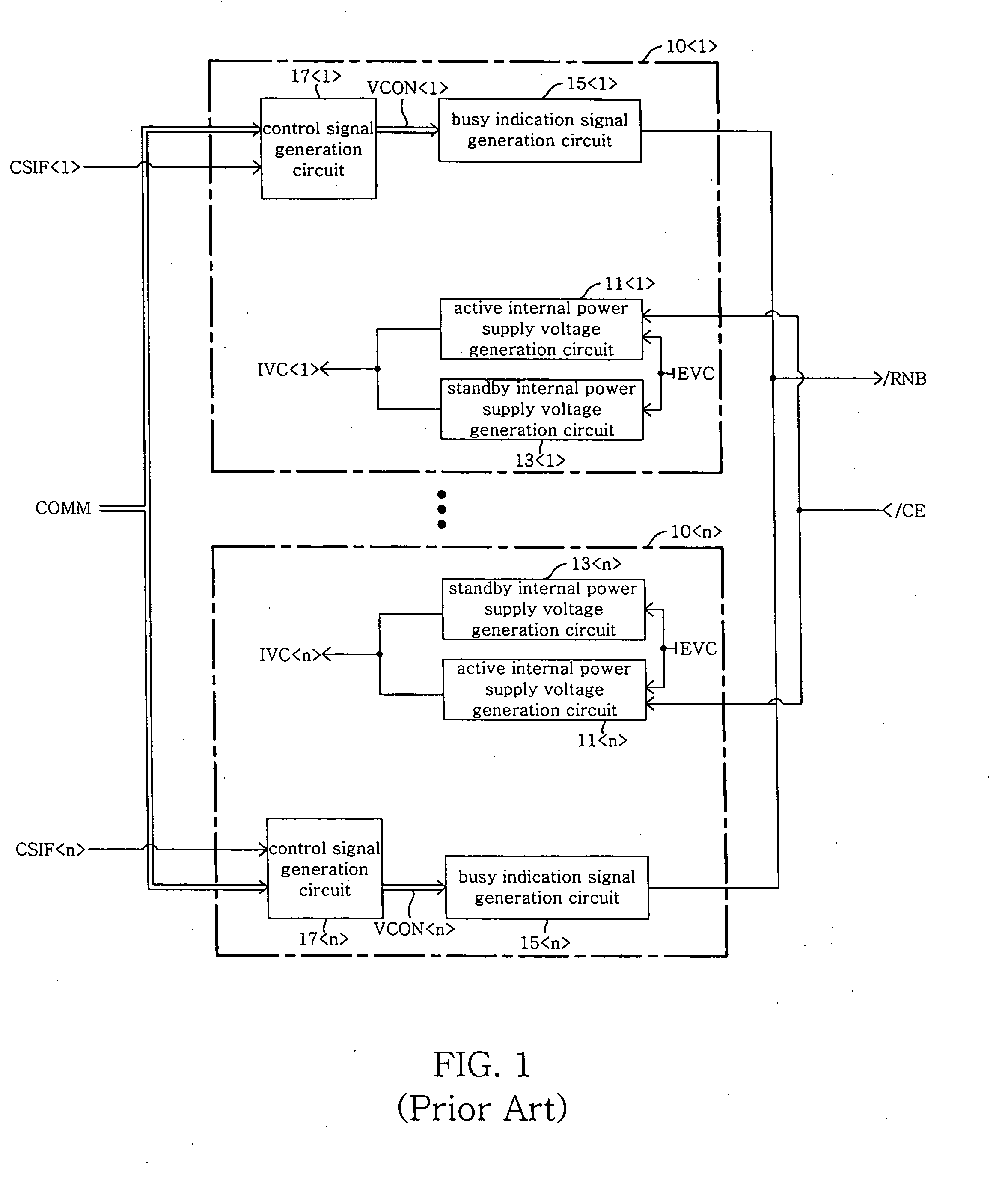

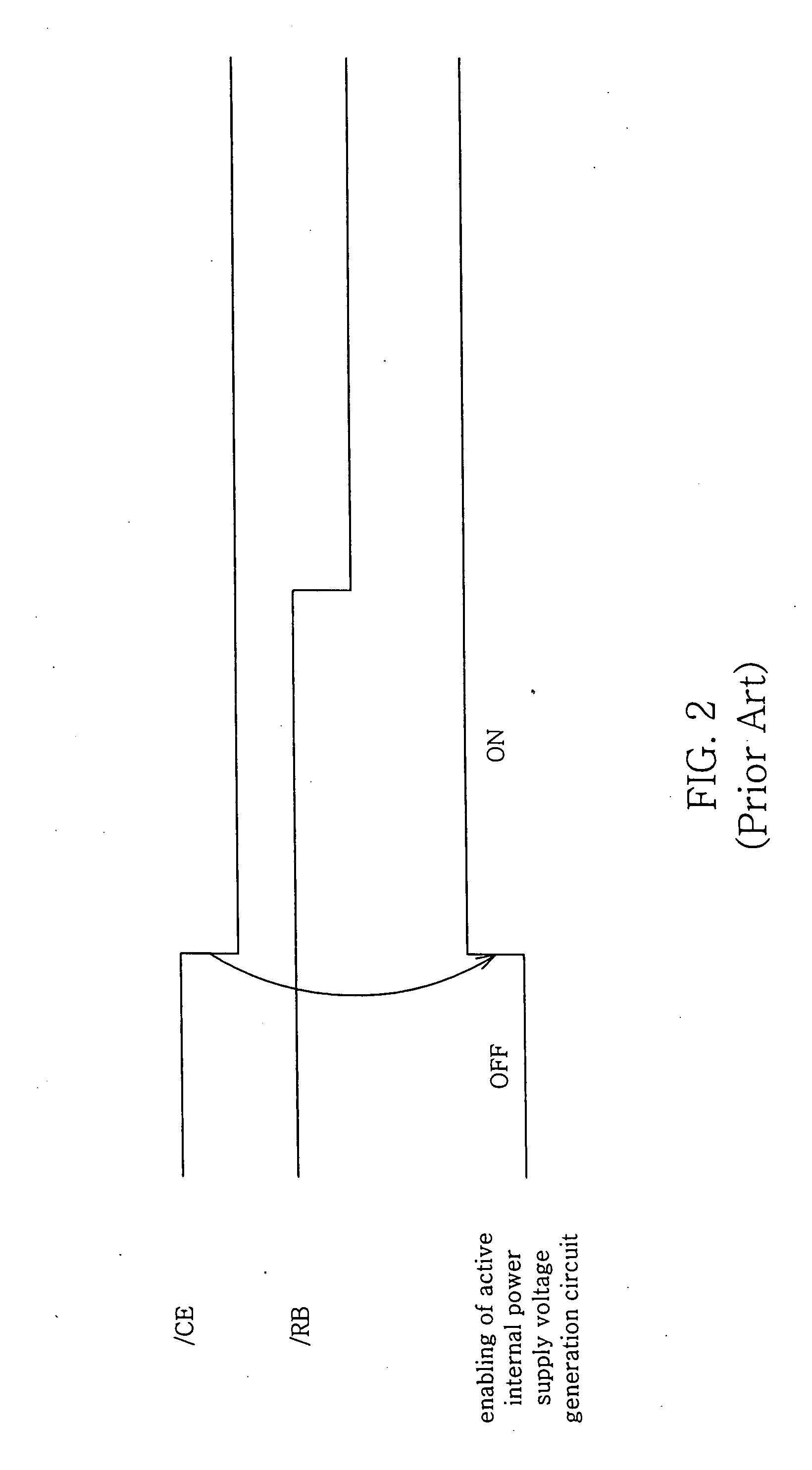

Multi-chip semiconductor memory device having internal power supply voltage generation circuit for decreasing current consumption

A multi-chip semiconductor memory device may comprise of a plurality of memory chips sharing a predetermined chip enable signal. Each of the plurality of memory chips may comprise of an active internal power supply generation circuit configured to convert an external power supply voltage into an internal power supply voltage and to be disabled in response to deactivation of a predetermined drive control signal. Each of the plurality of memory chips may also comprise of a conversion control circuit for generating the drive control signal, wherein the drive control signal is deactivated in an interval in which any of the plurality of memory chips is in an active interval.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com