Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

14229results about "Static storage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

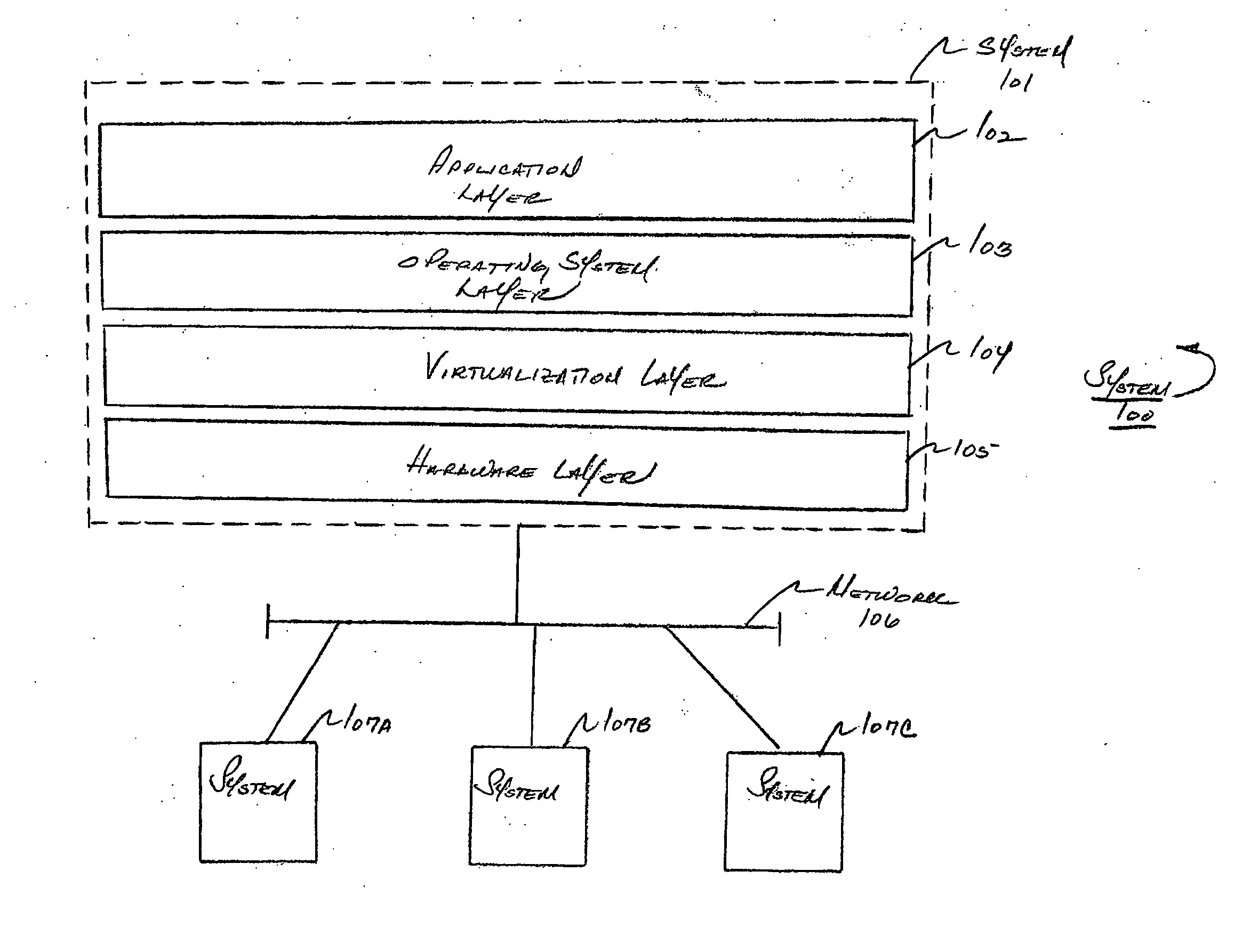

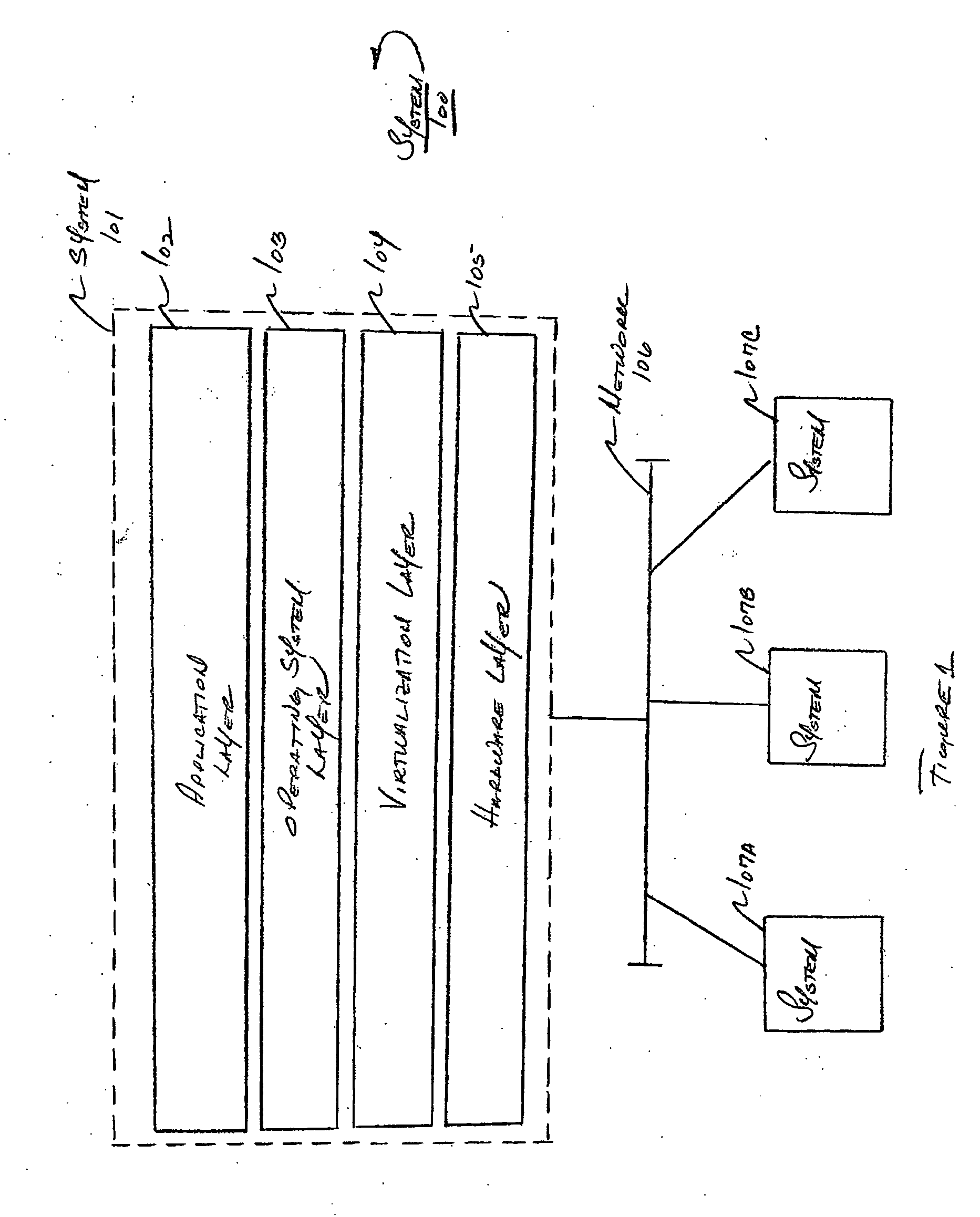

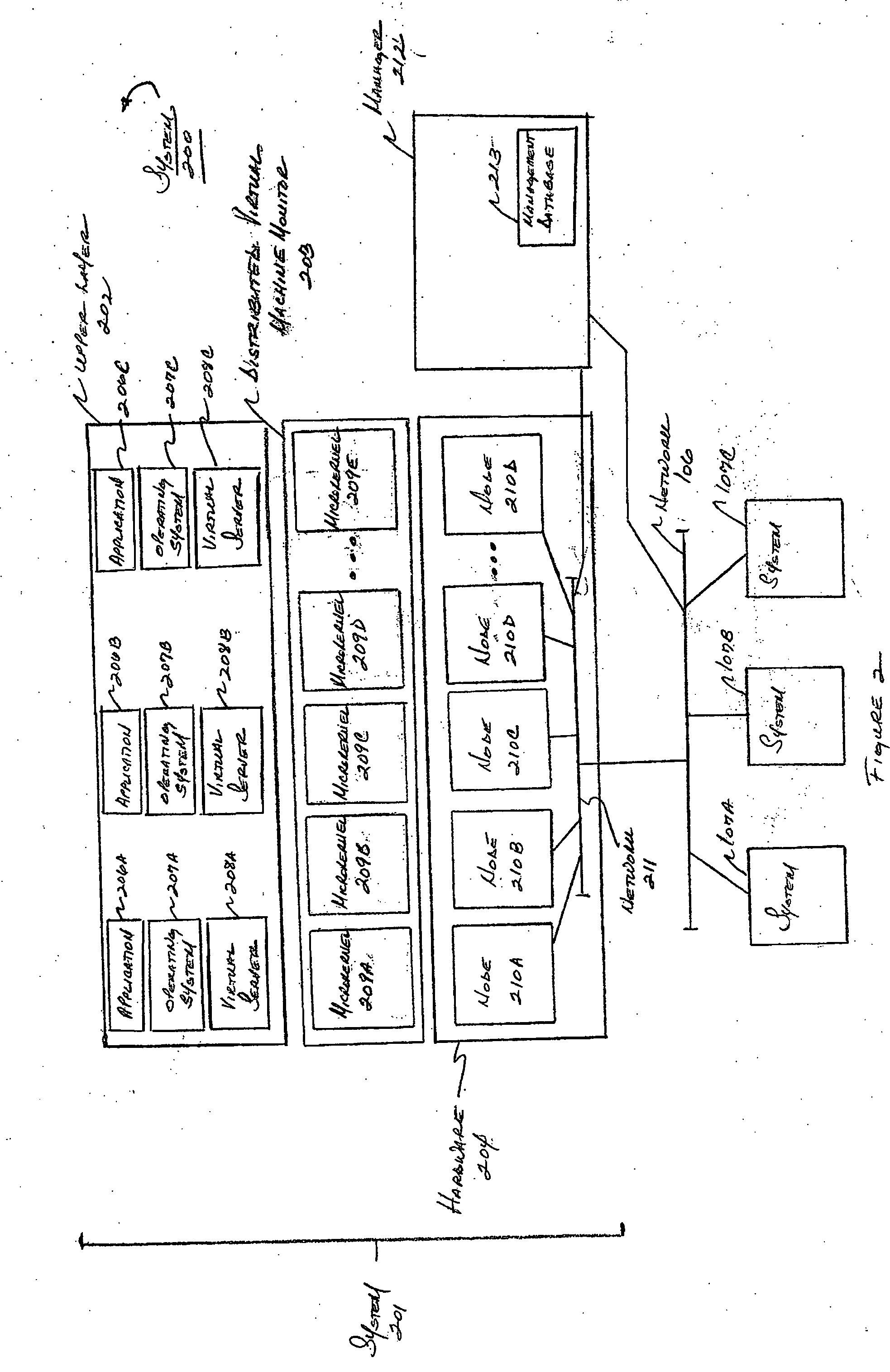

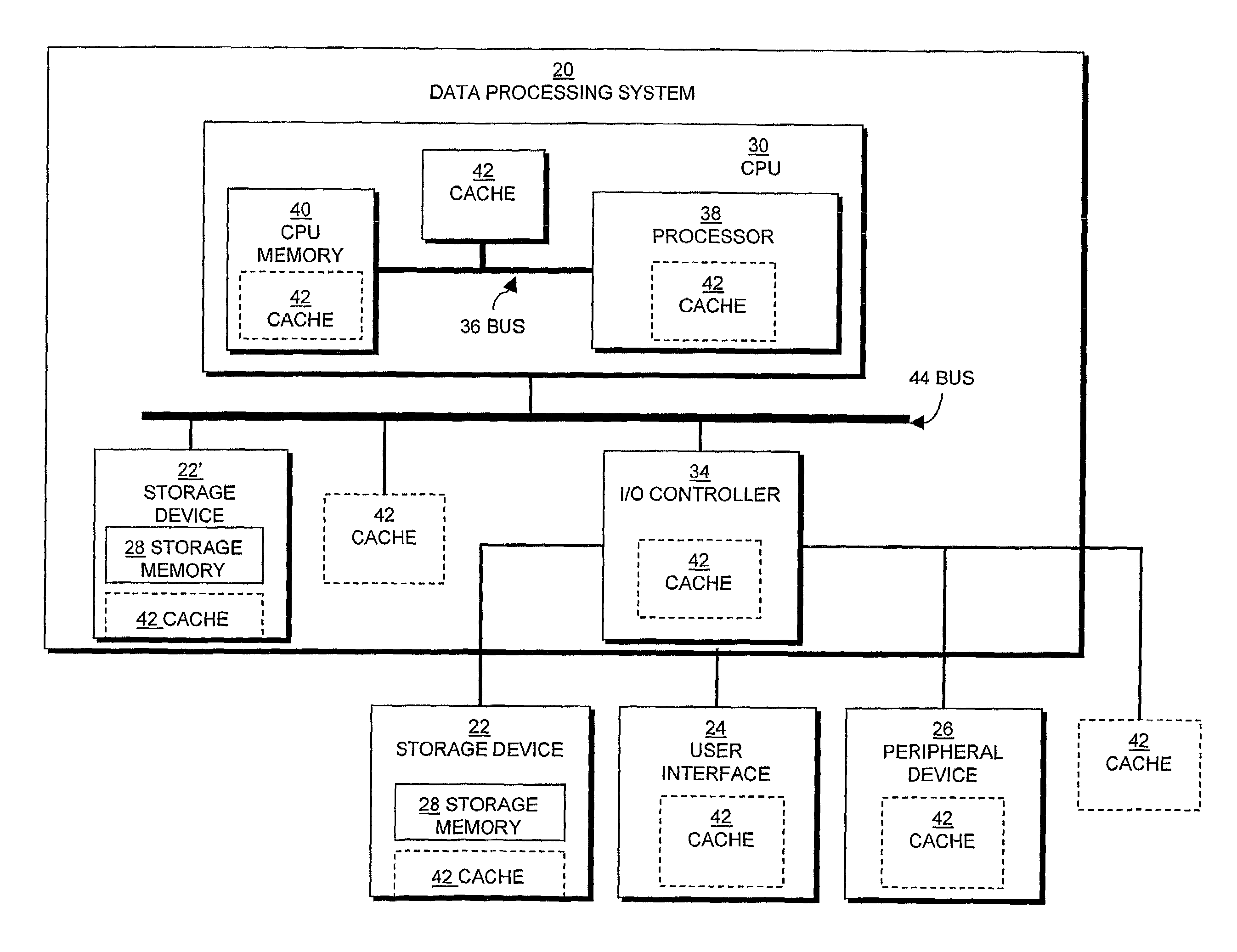

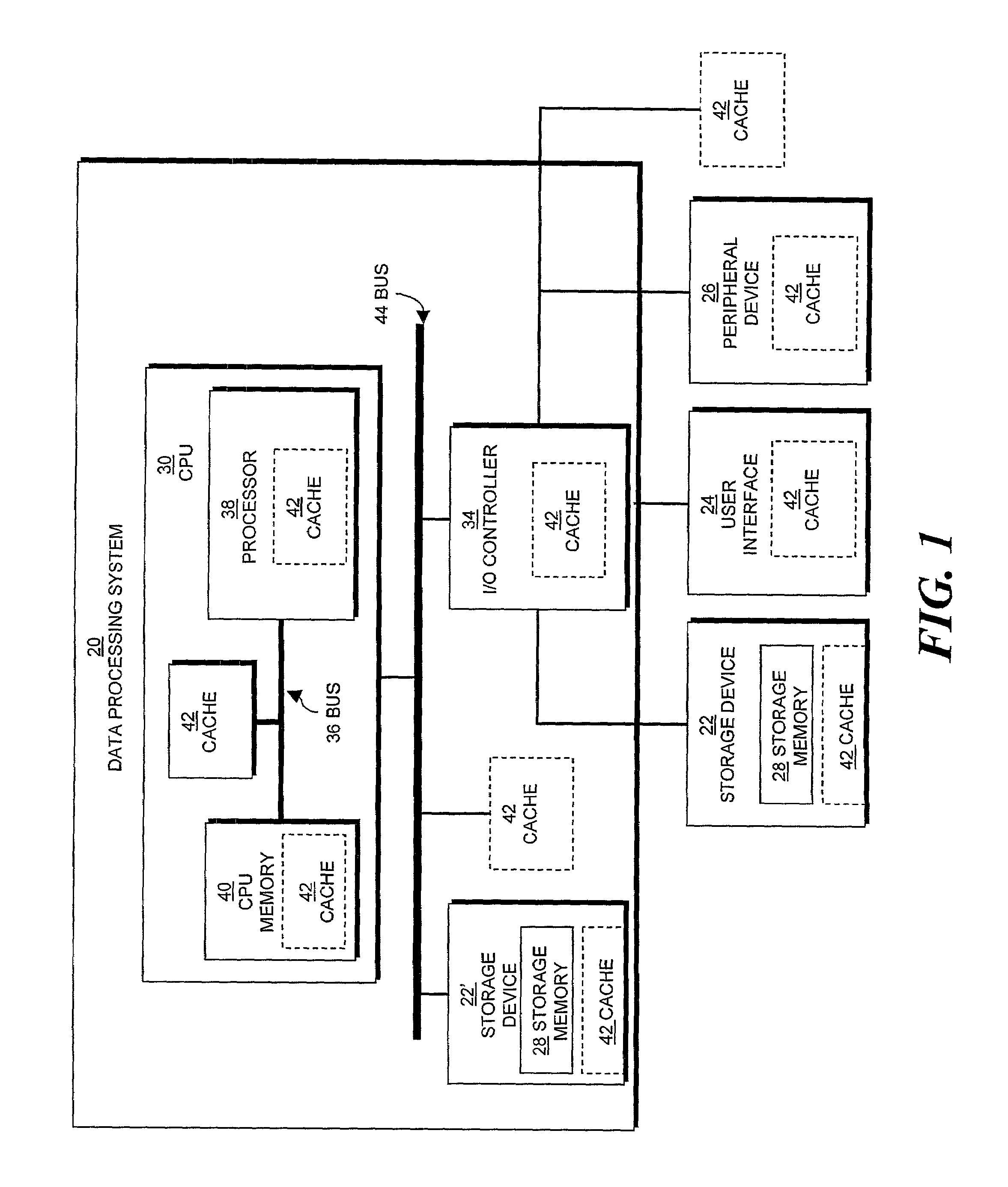

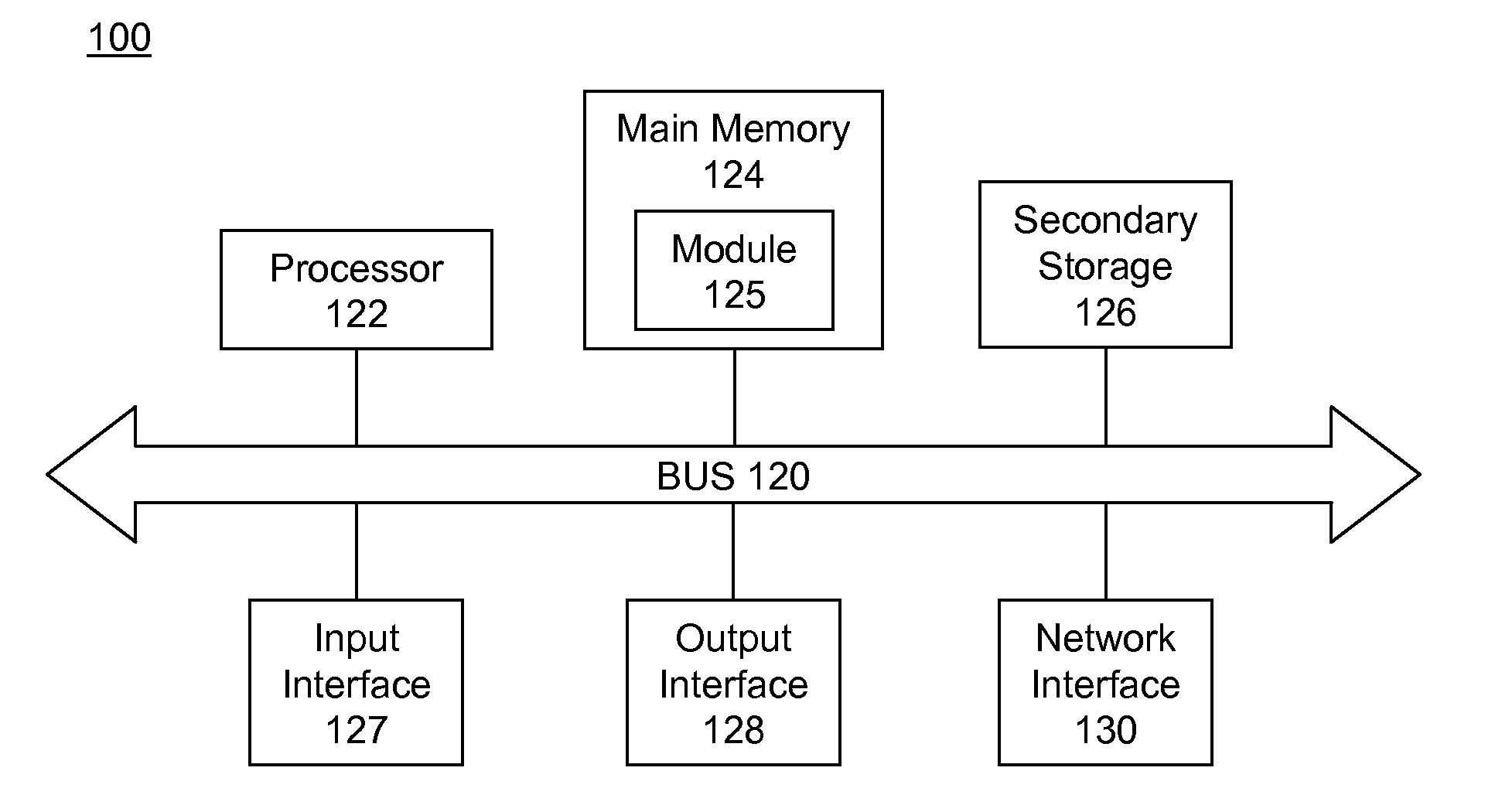

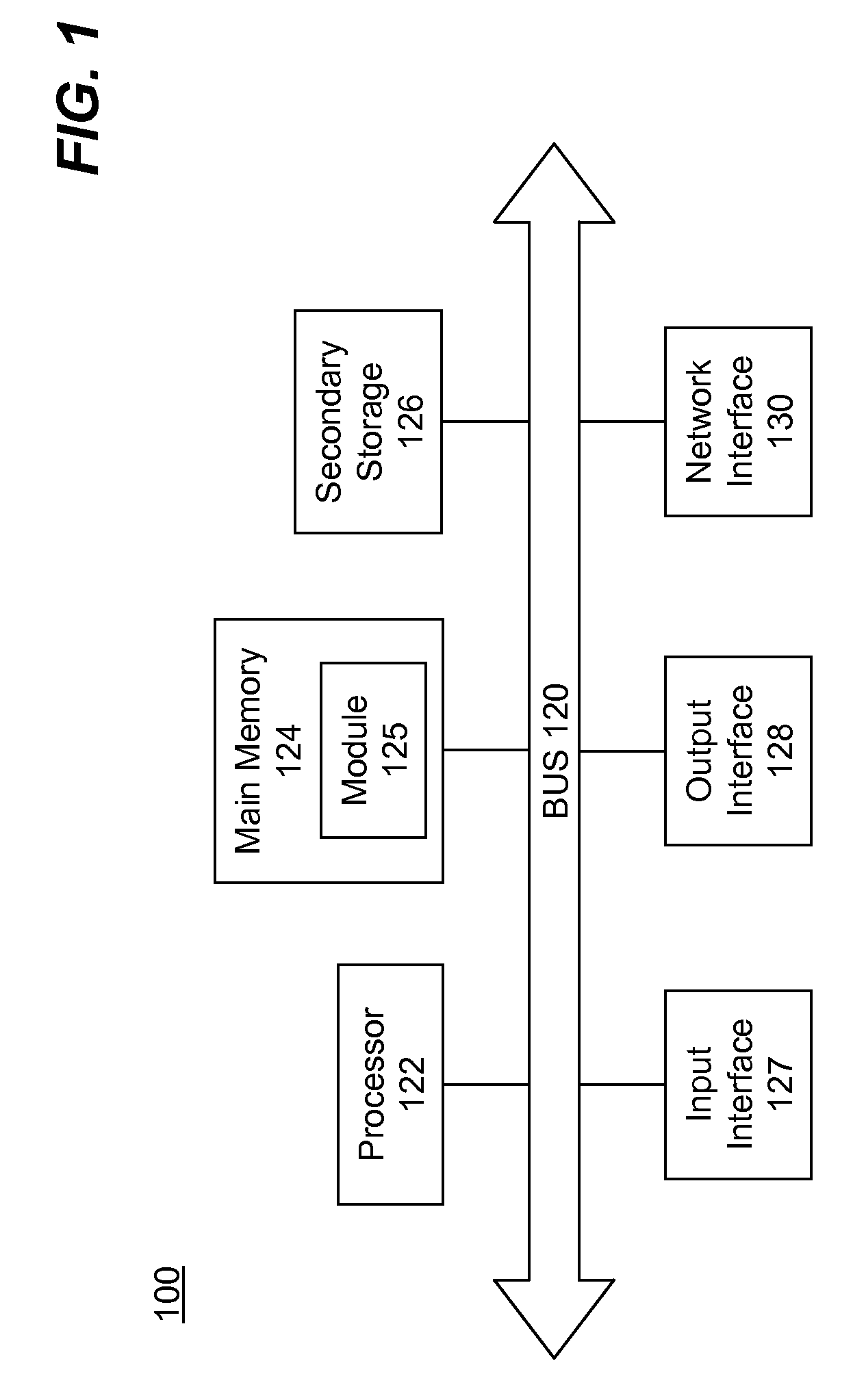

Method and apparatus for providing virtual computing services

InactiveUS20050044301A1Easy to manageLow costResource allocationMemory adressing/allocation/relocationVirtualizationOperational system

A level of abstraction is created between a set of physical processors and a set of virtual multiprocessors to form a virtualized data center. This virtualized data center comprises a set of virtual, isolated systems separated by a boundary referred as a partition. Each of these systems appears as a unique, independent virtual multiprocessor computer capable of running a traditional operating system and its applications. In one embodiment, the system implements this multi-layered abstraction via a group of microkernels, each of which communicates with one or more peer microkernel over a high-speed, low-latency interconnect and forms a distributed virtual machine monitor. Functionally, a virtual data center is provided, including the ability to take a collection of servers and execute a collection of business applications over a compute fabric comprising commodity processors coupled by an interconnect. Processor, memory and I / O are virtualized across this fabric, providing a single system, scalability and manageability. According to one embodiment, this virtualization is transparent to the application, and therefore, applications may be scaled to increasing resource demands without modifying the application.

Owner:ORACLE INT CORP

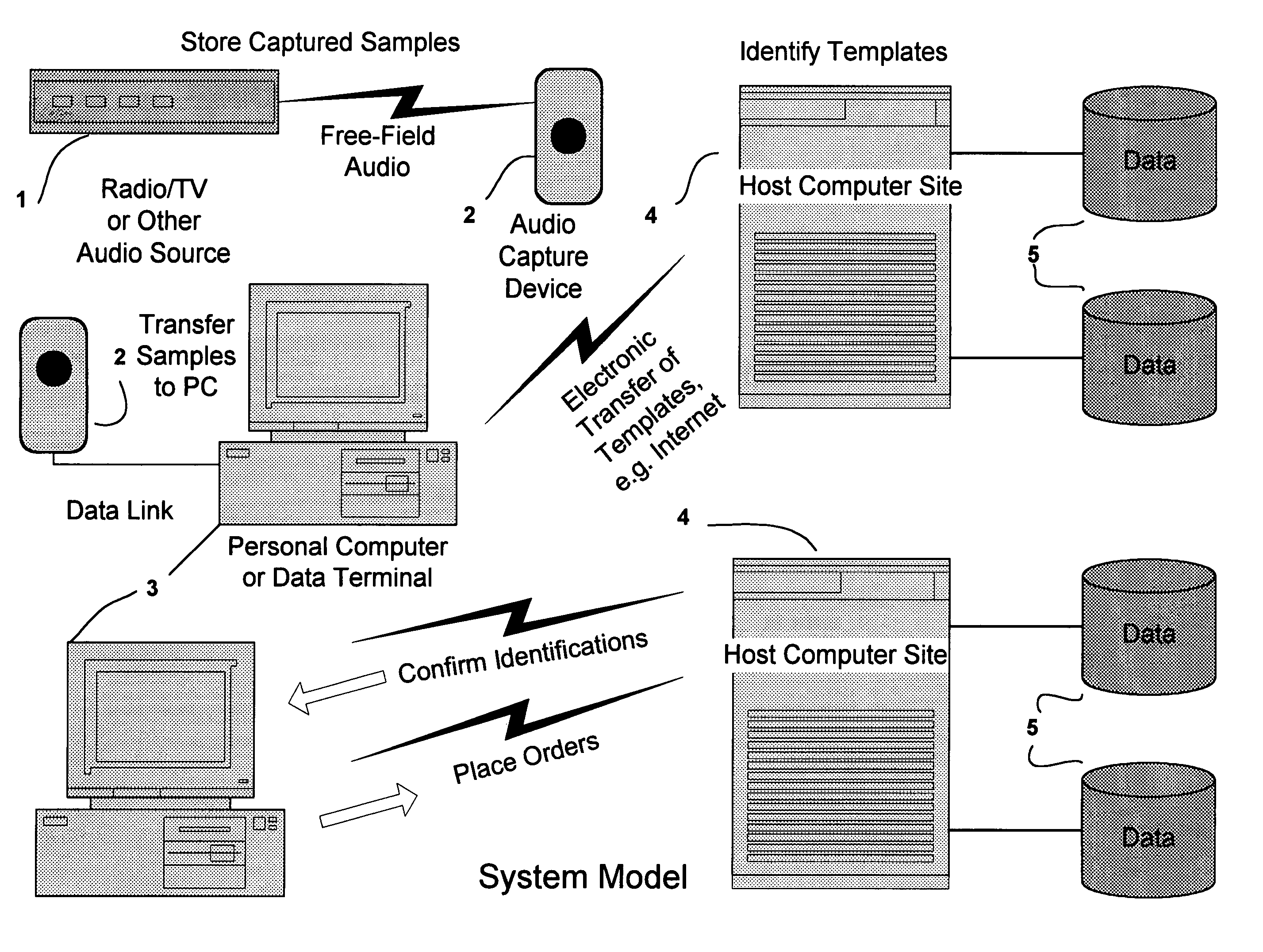

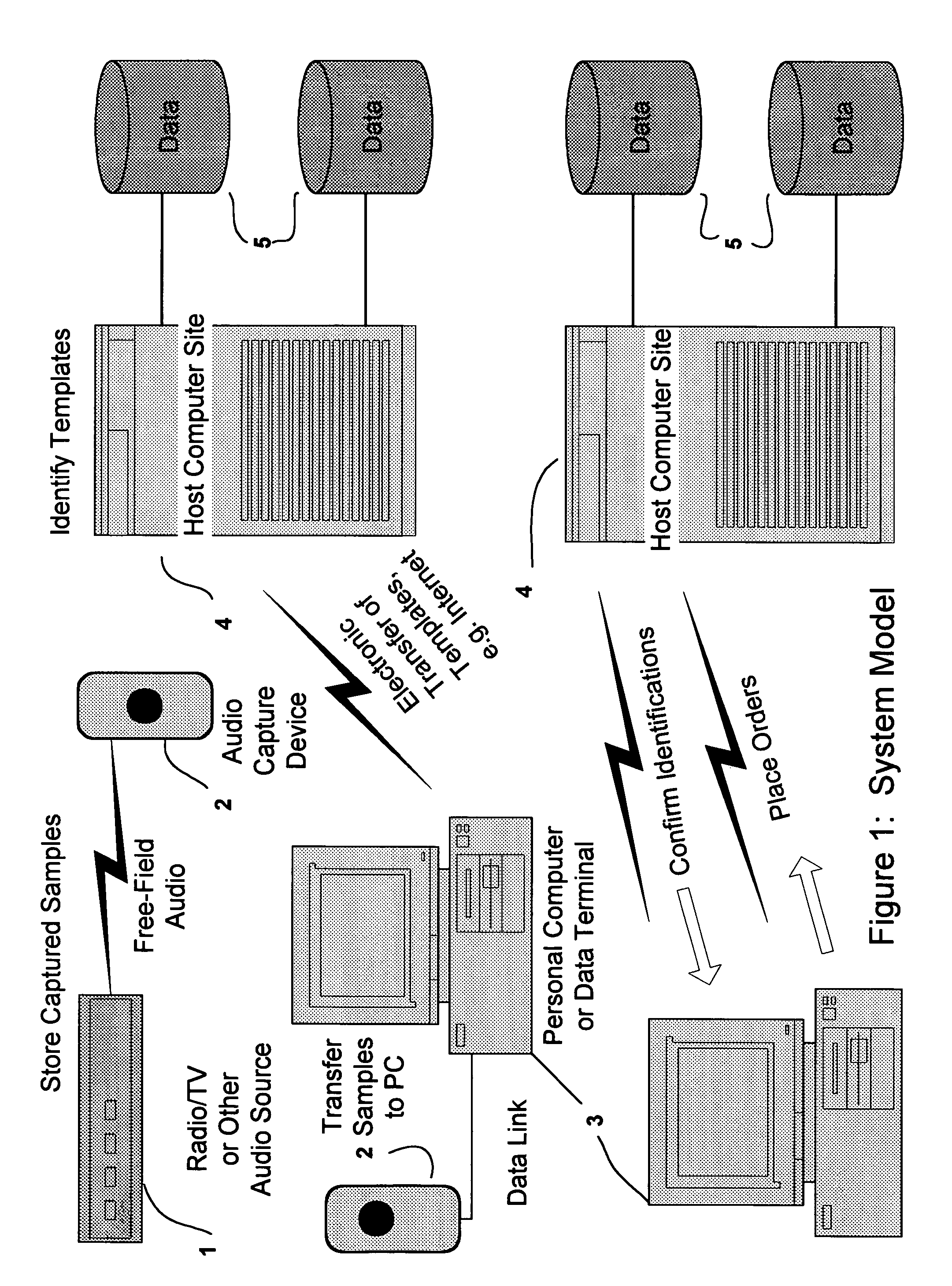

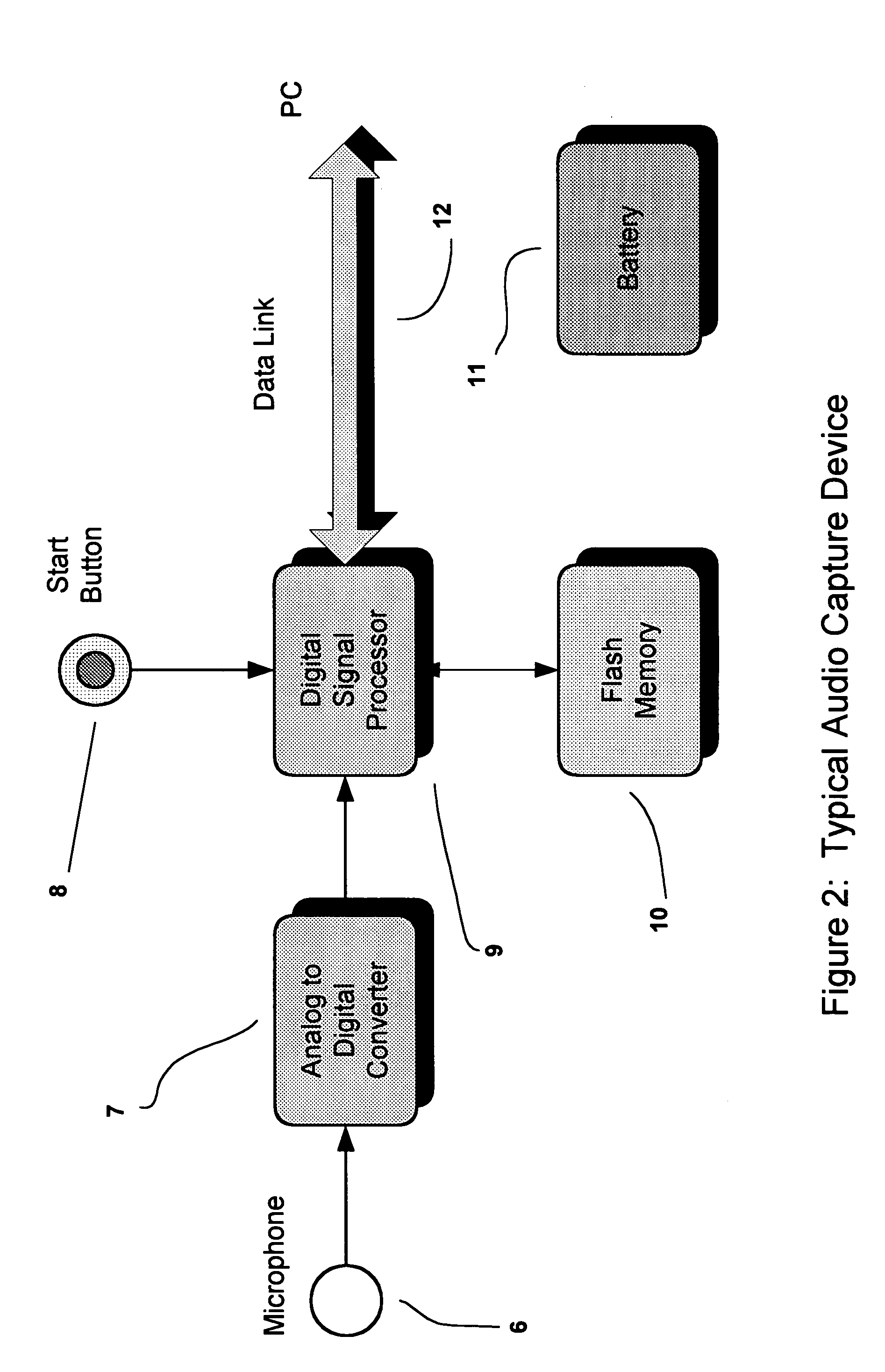

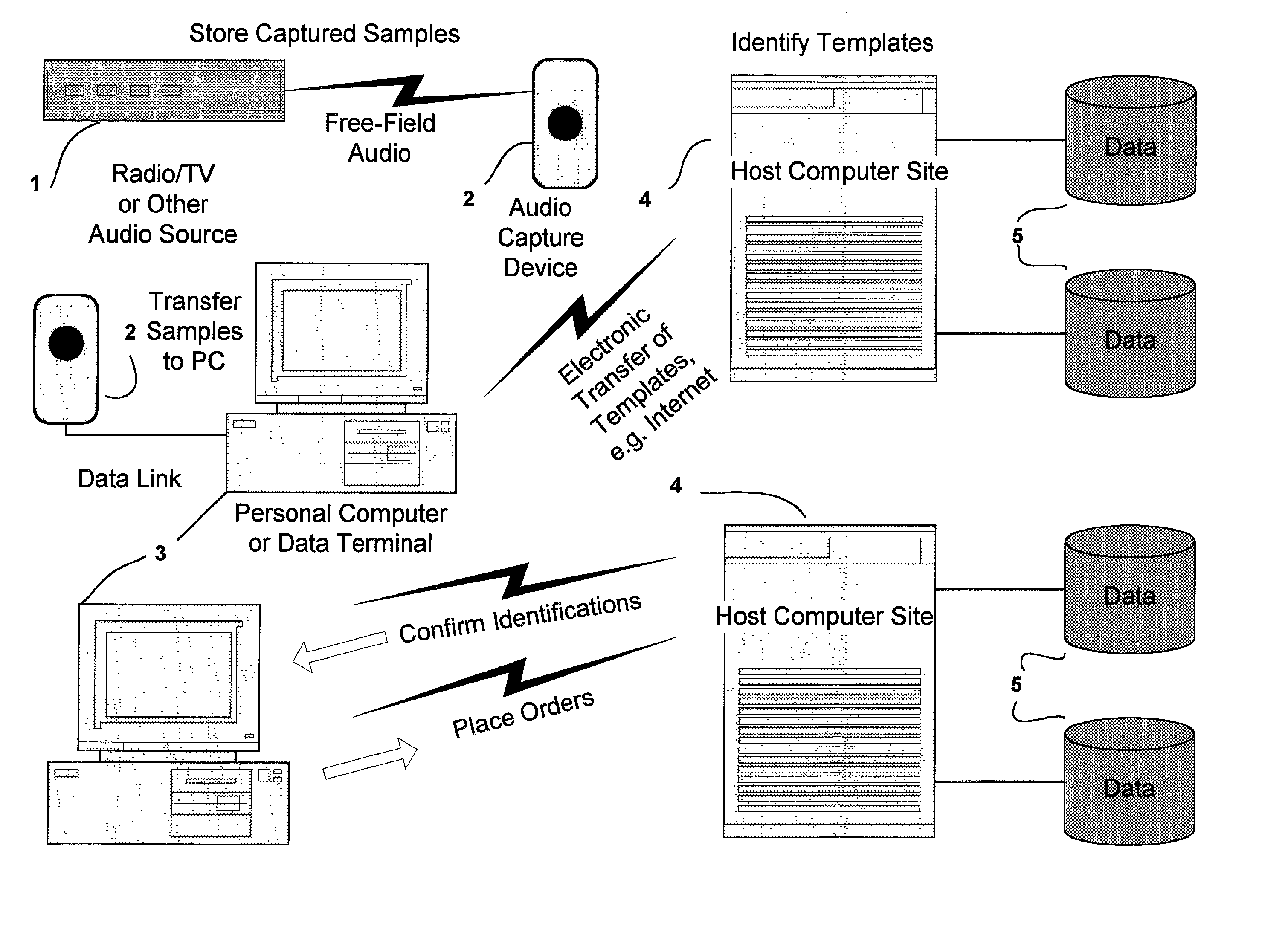

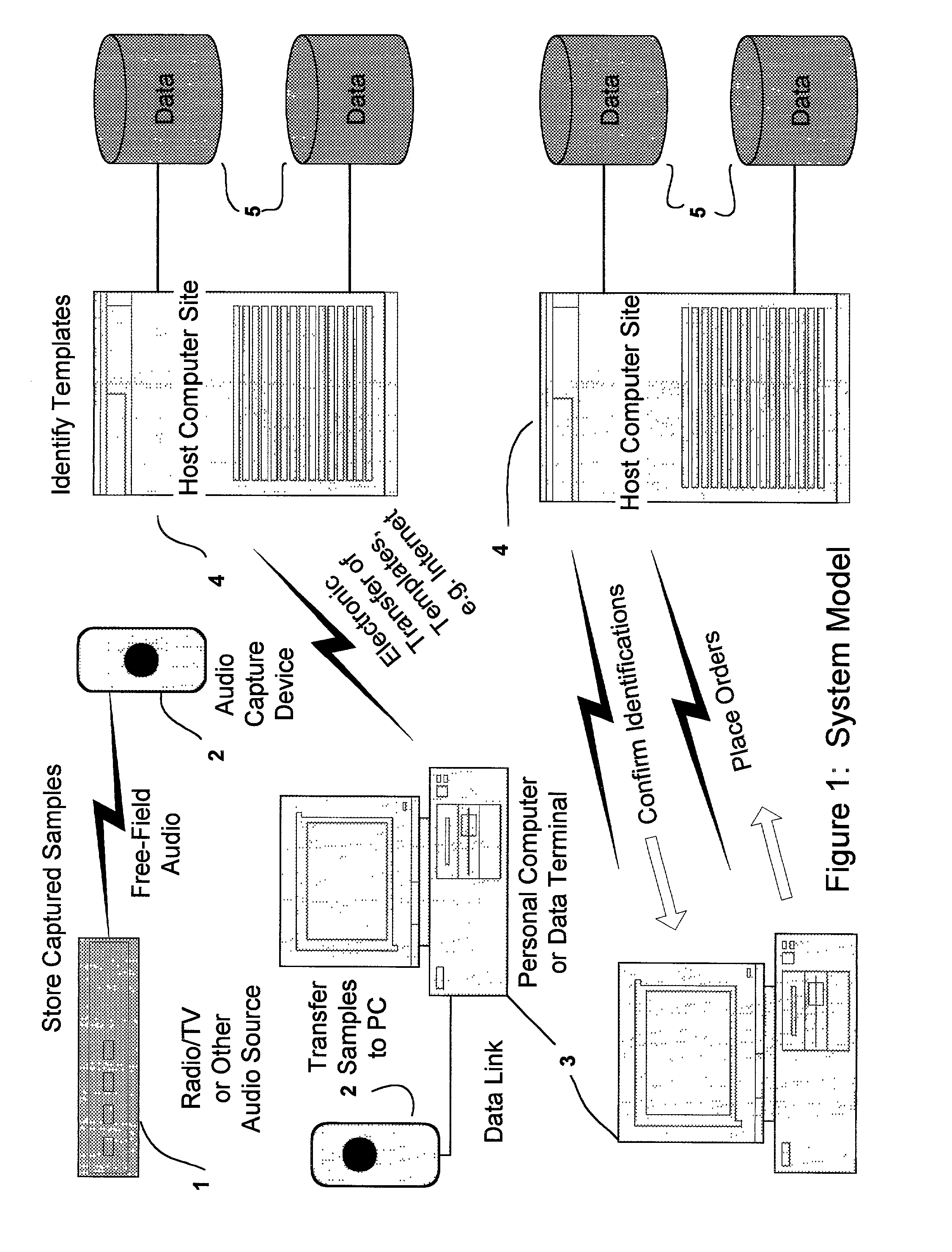

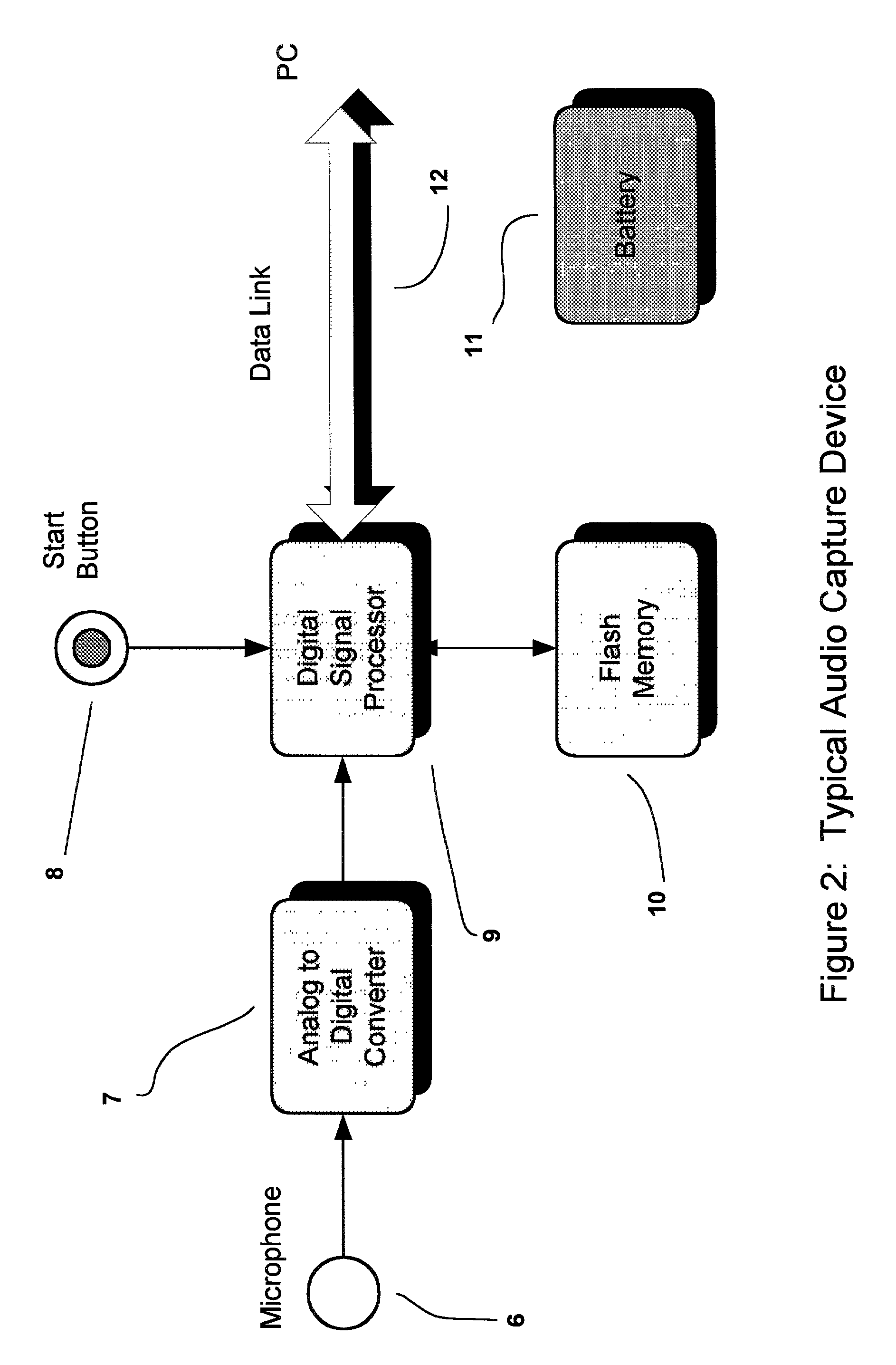

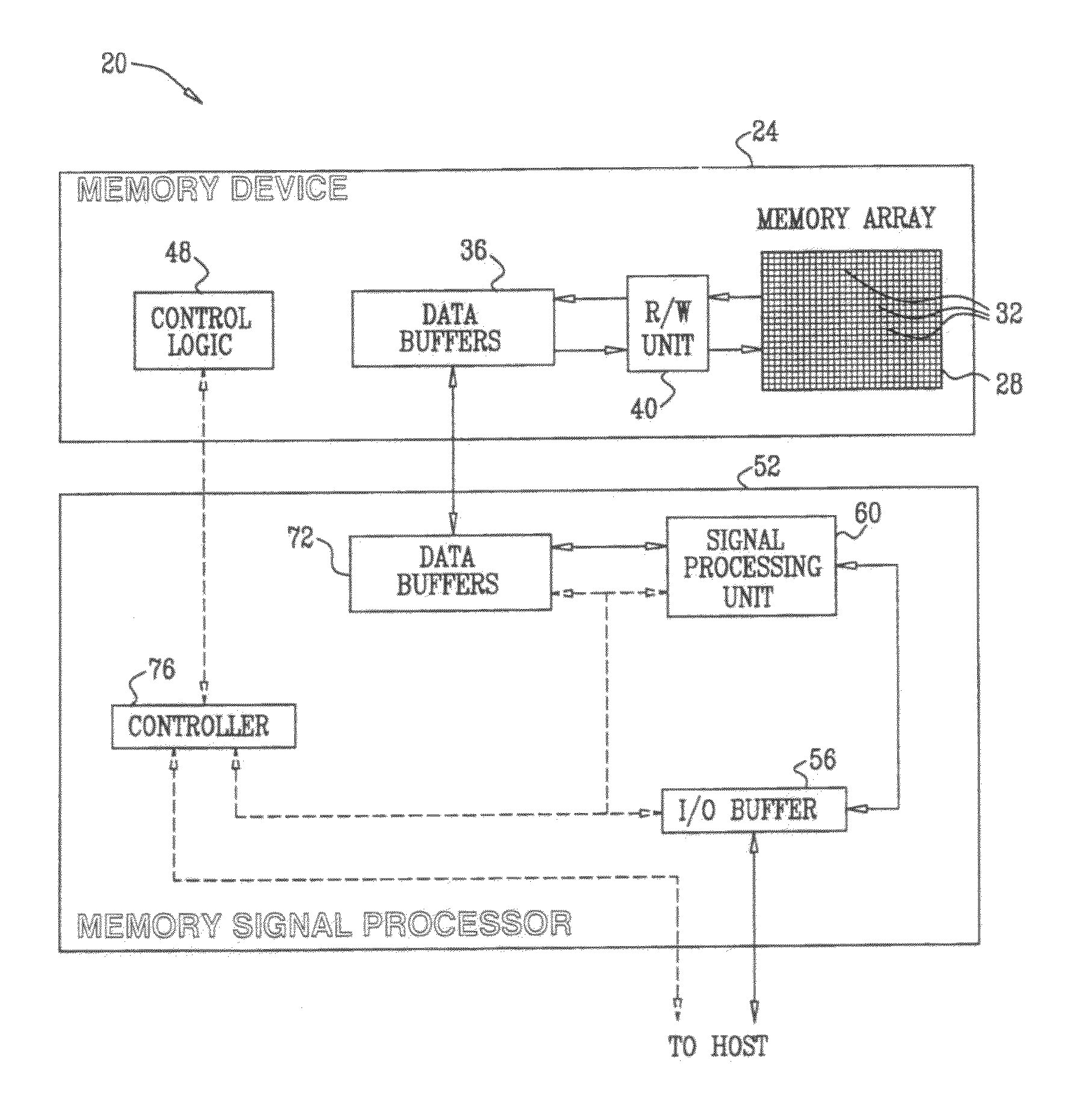

Audio identification system and method

InactiveUS7174293B2Facilitate interactive acceptance and processingImprove accuracySpeech recognitionStatic storageThe InternetEngineering

A method and system for direct audio capture and identification of the captured audio. A user may then be offered the opportunity to purchase recordings directly over the Internet or similar outlet. The system preferably includes one or more user-carried portable audio capture devices that employ a microphone, analog to digital converter, signal processor, and memory to store samples of ambient audio or audio features calculated from the audio. Users activate their capture devices when they hear a recording that they would like to identify or purchase. Later, the user may connect the capture device to a personal computer to transfer the audio samples or audio feature samples to an Internet site for identification. The Internet site preferably uses automatic pattern recognition techniques to identify the captured samples from a library of recordings offered for sale. The user can then verify that the sample is from the desired recording and place an order online. The pattern recognition process uses features of the audio itself and does not require the presence of artificial codes or watermarks. Audio to be identified can be from any source, including radio and television broadcasts or recordings that are played locally.

Owner:ICEBERG IND

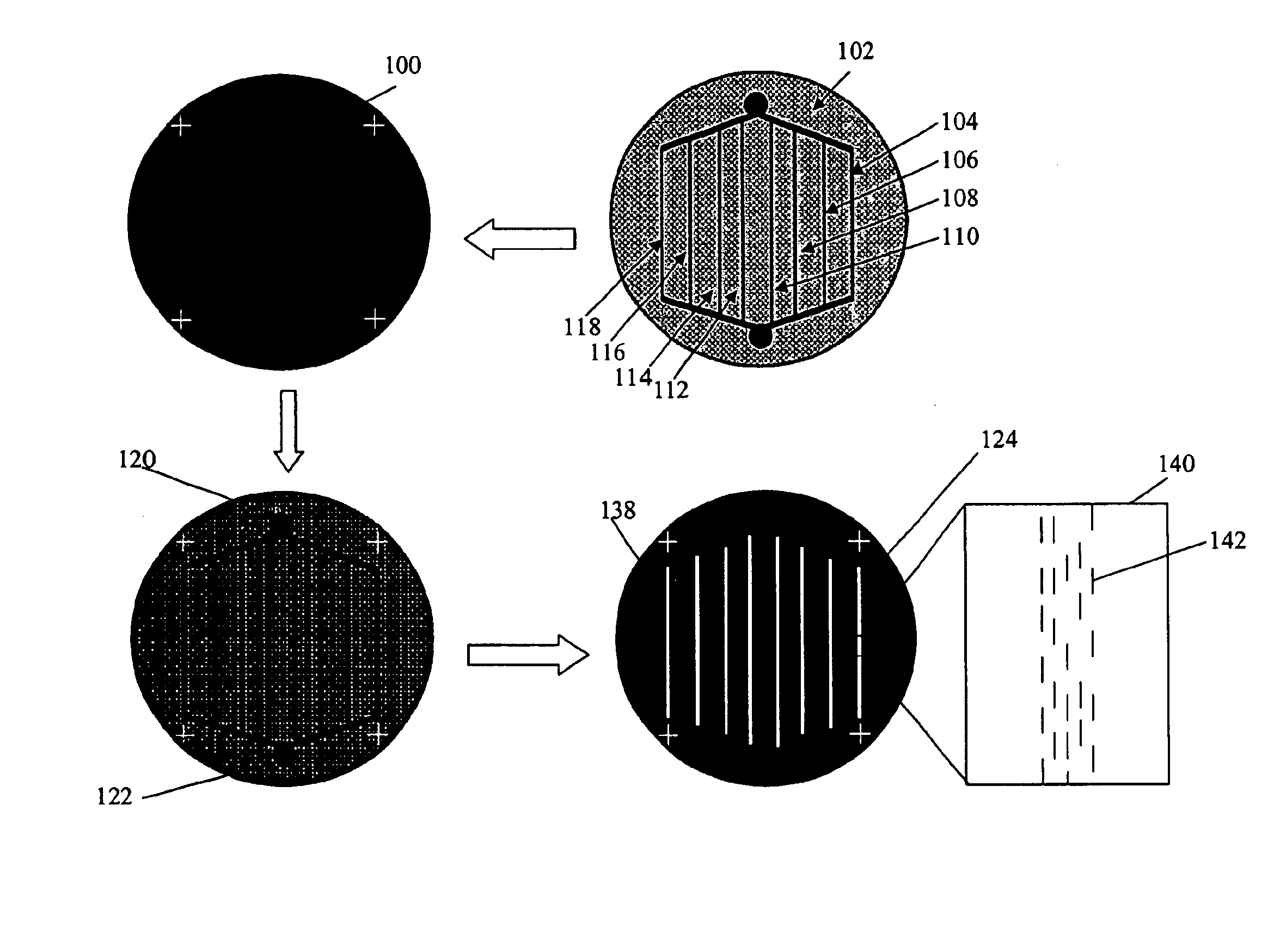

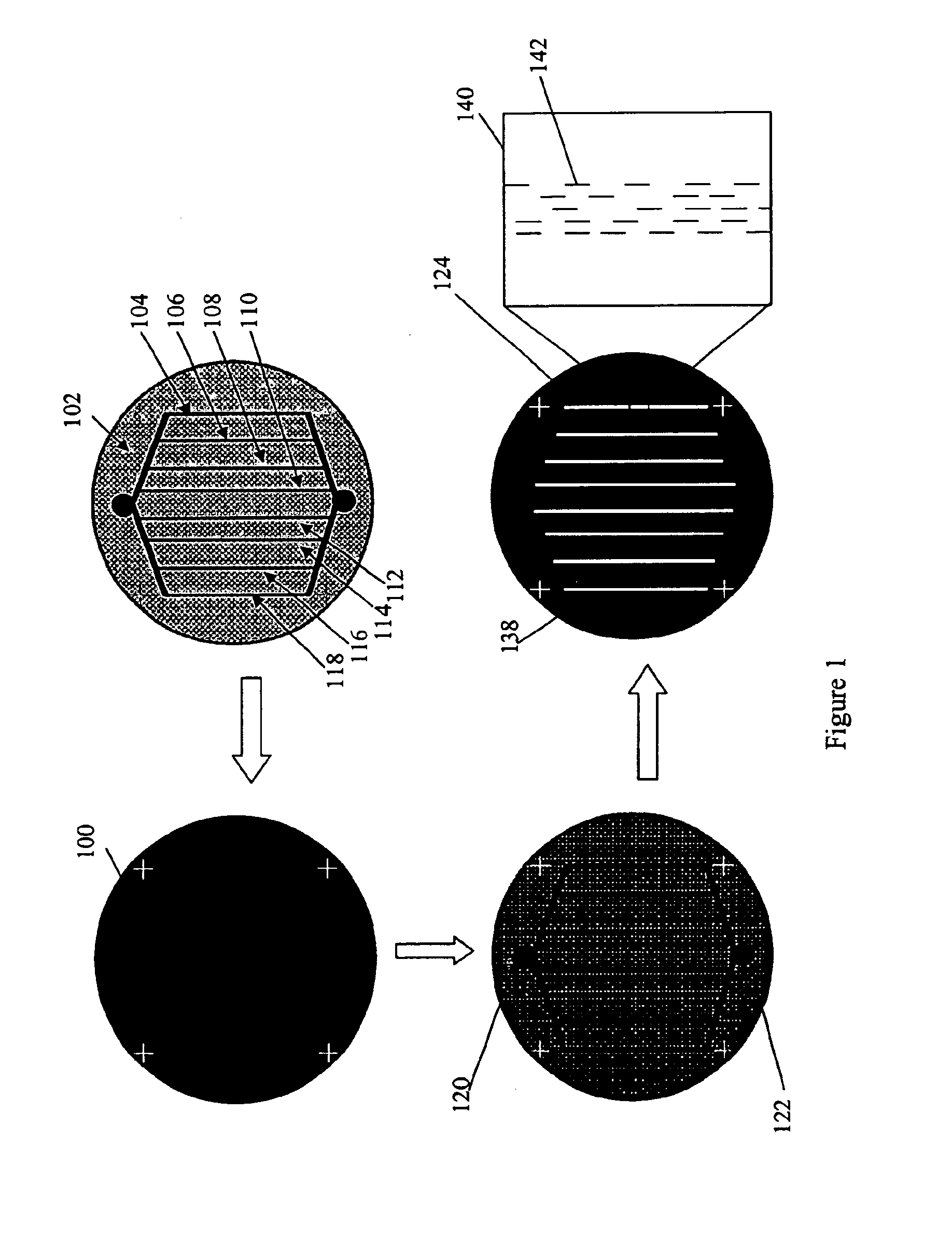

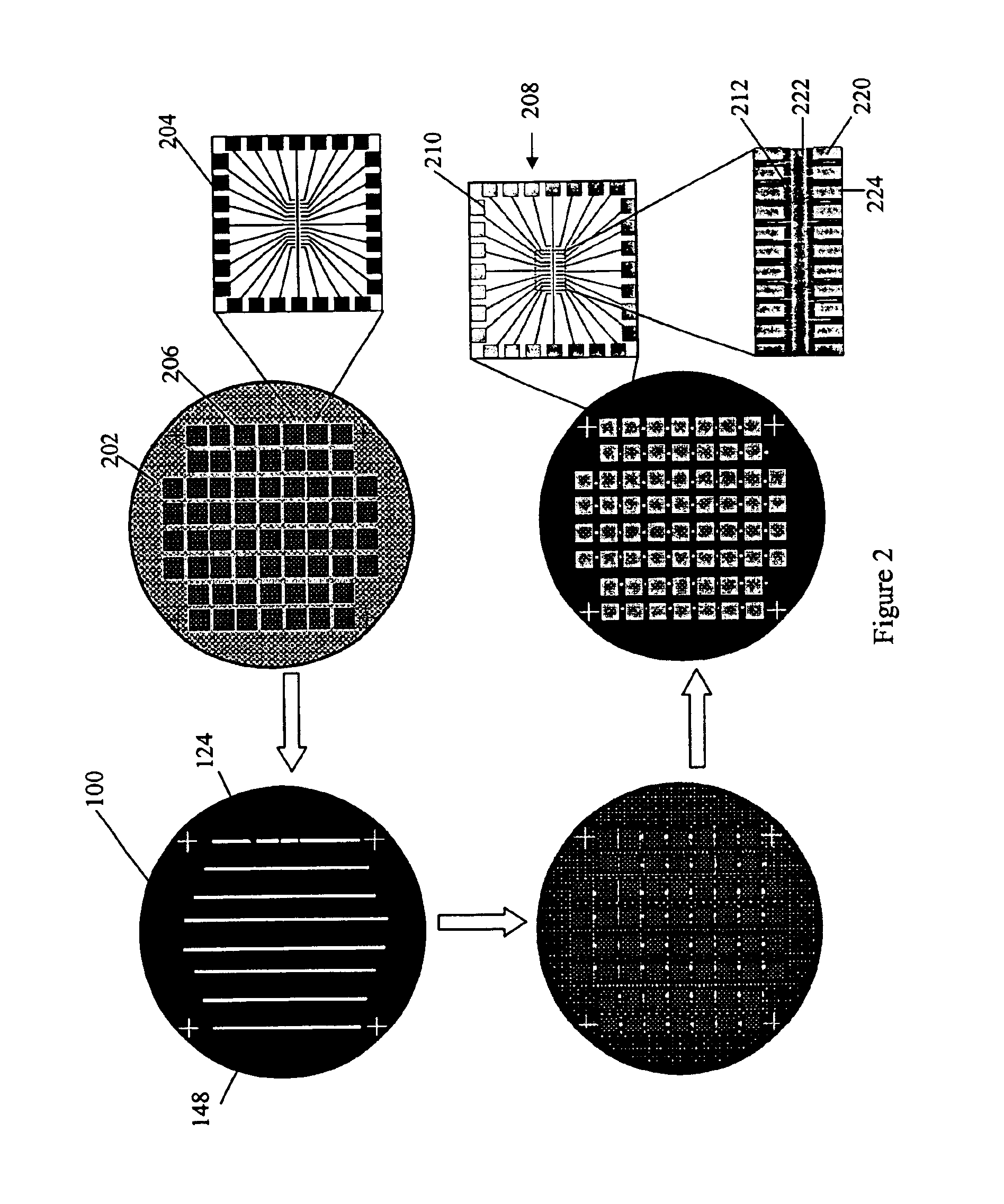

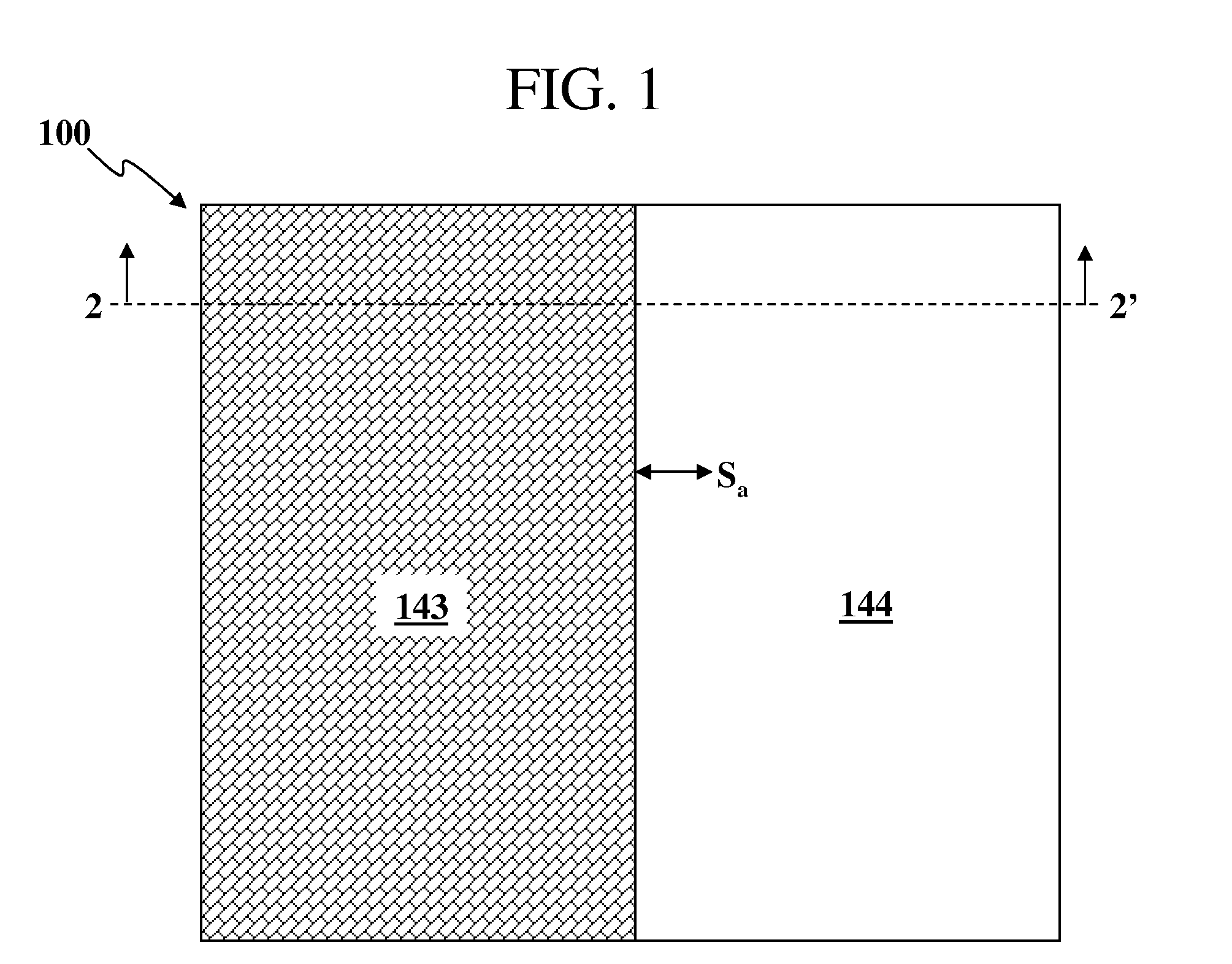

Methods of positioning and/or orienting nanostructures

Methods of positioning and orienting nanostructures, and particularly nanowires, on surfaces for subsequent use or integration. The methods utilize mask based processes alone or in combination with flow based alignment of the nanostructures to provide oriented and positioned nanostructures on surfaces. Also provided are populations of positioned and / or oriented nanostructures, devices that include populations of positioned and / or oriented nanostructures, systems for positioning and / or orienting nanostructures, and related devices, systems and methods.

Owner:ONED MATERIAL INC

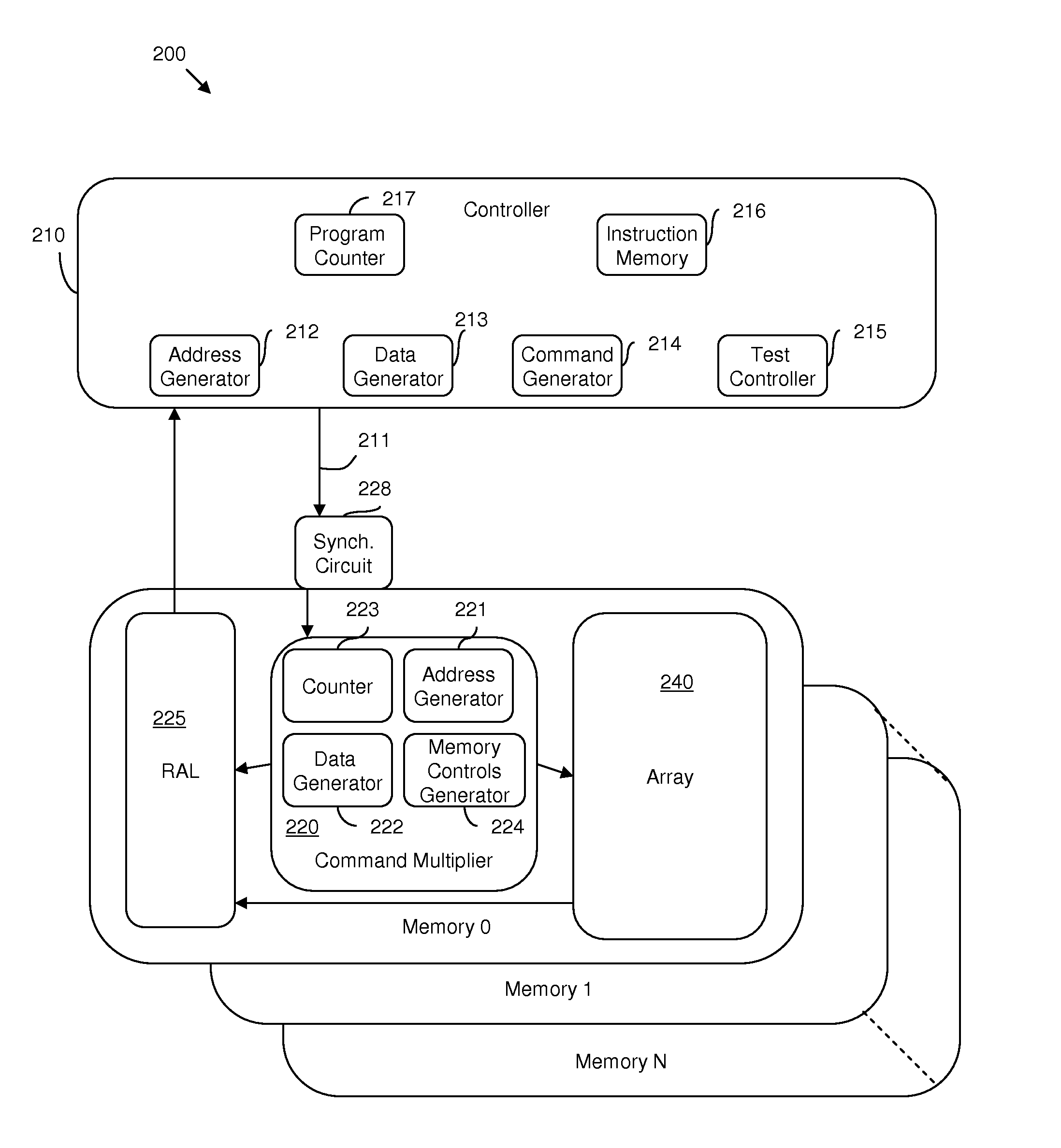

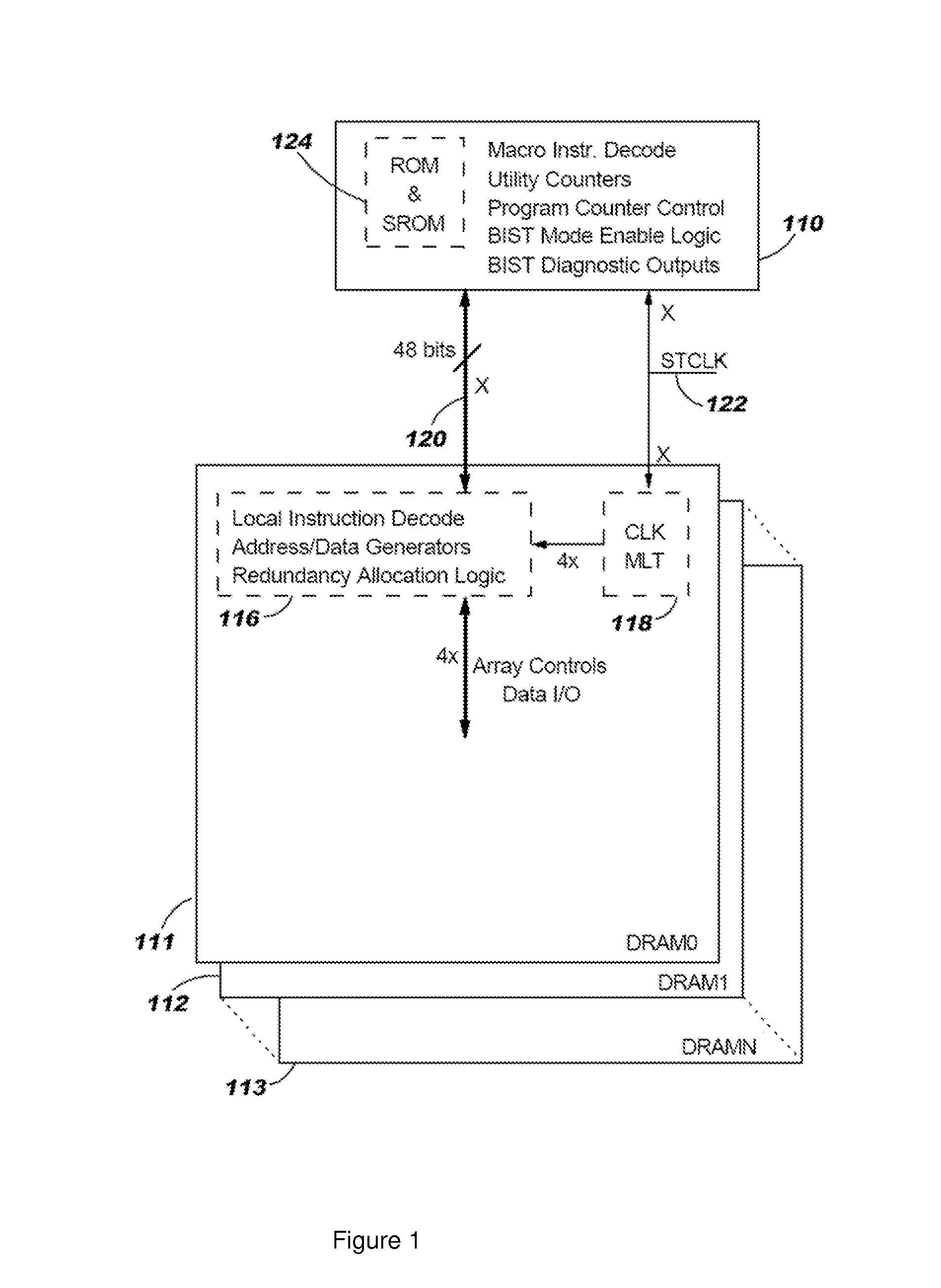

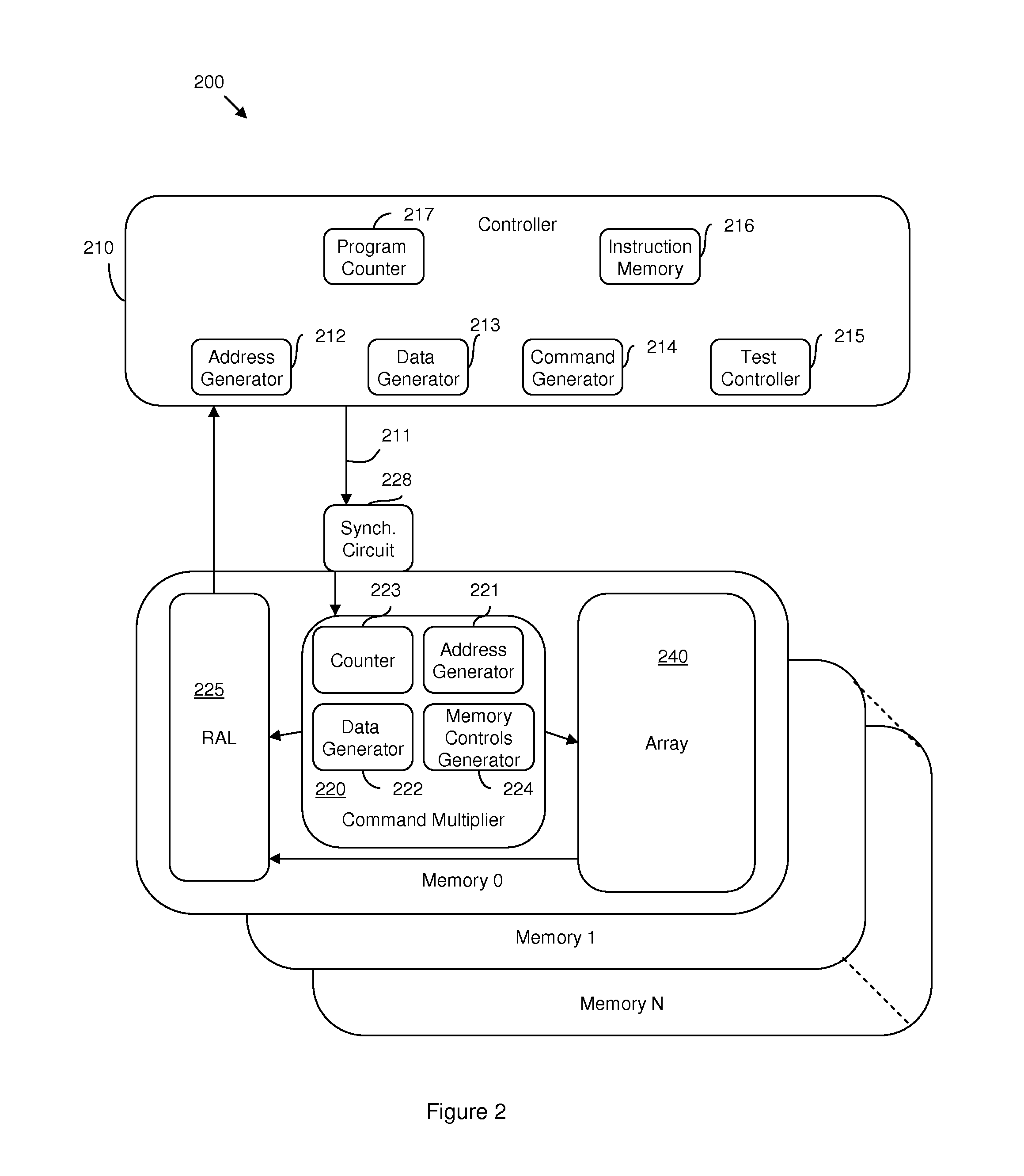

Hybrid built-in self test (BIST) architecture for embedded memory arrays and an associated method

ActiveUS20080178053A1Reduce frequencyMore test pattern flexibilityElectronic circuit testingFunctional testingSpecific testNormal mode

Disclosed are embodiments of a built-in self-test (BIST) architecture that incorporates a standalone controller that operates at a lower frequency to remotely perform test functions common to a plurality of embedded memory arrays. The architecture also incorporates command multipliers that are associated with the embedded memory arrays and that selectively operate in one of two different modes: a normal mode or a bypass mode. In the normal mode, instructions from the controller are multiplied so that memory array-specific test functions can be performed locally at the higher operating frequency of each specific memory array. Whereas, in the bypass mode, multiplication of the instructions is suspended so that memory array-specific test functions can be performed locally at the lower operating frequency of the controller. The ability to vary the frequency at which test functions are performed locally, allows for more test pattern flexibility.

Owner:META PLATFORMS INC

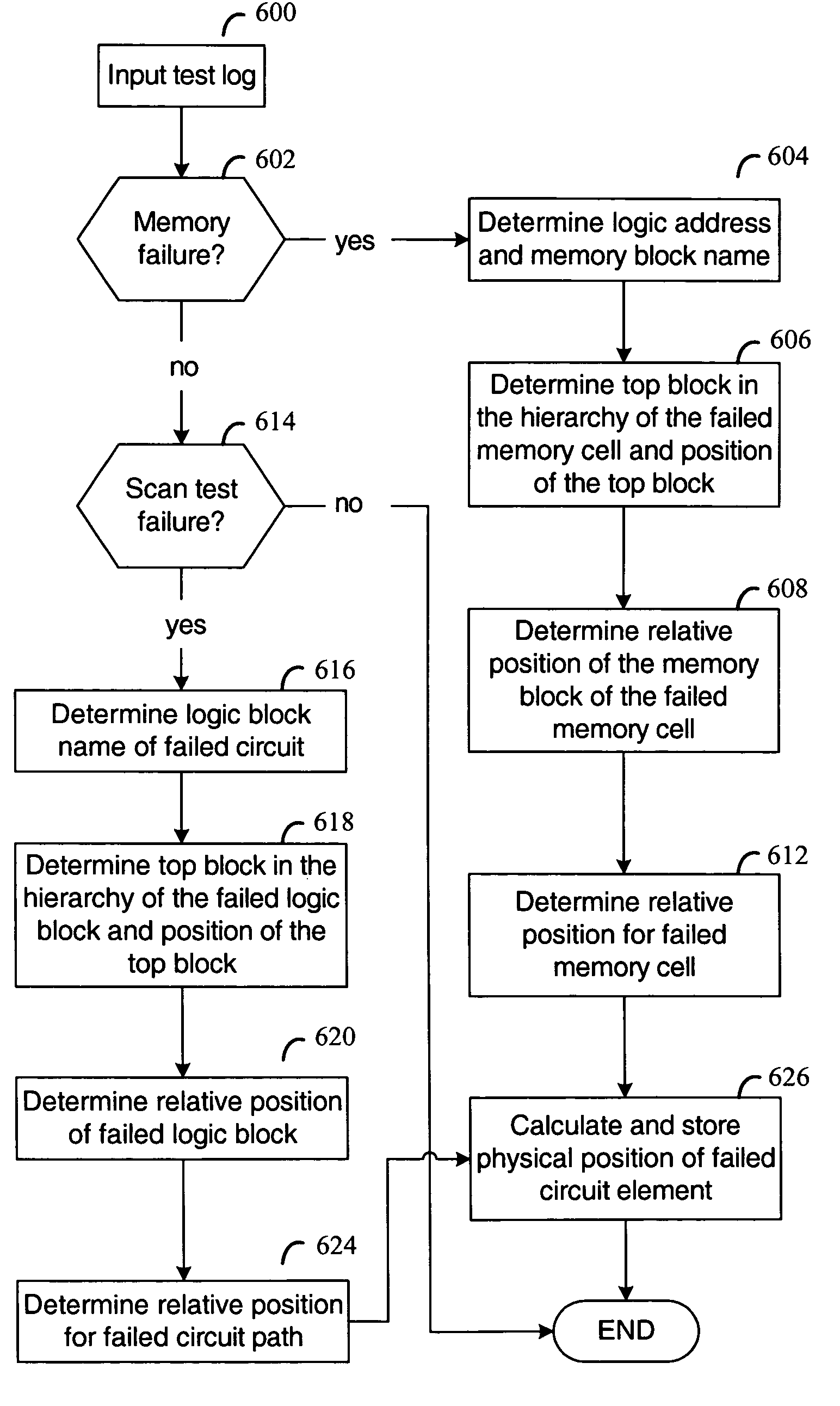

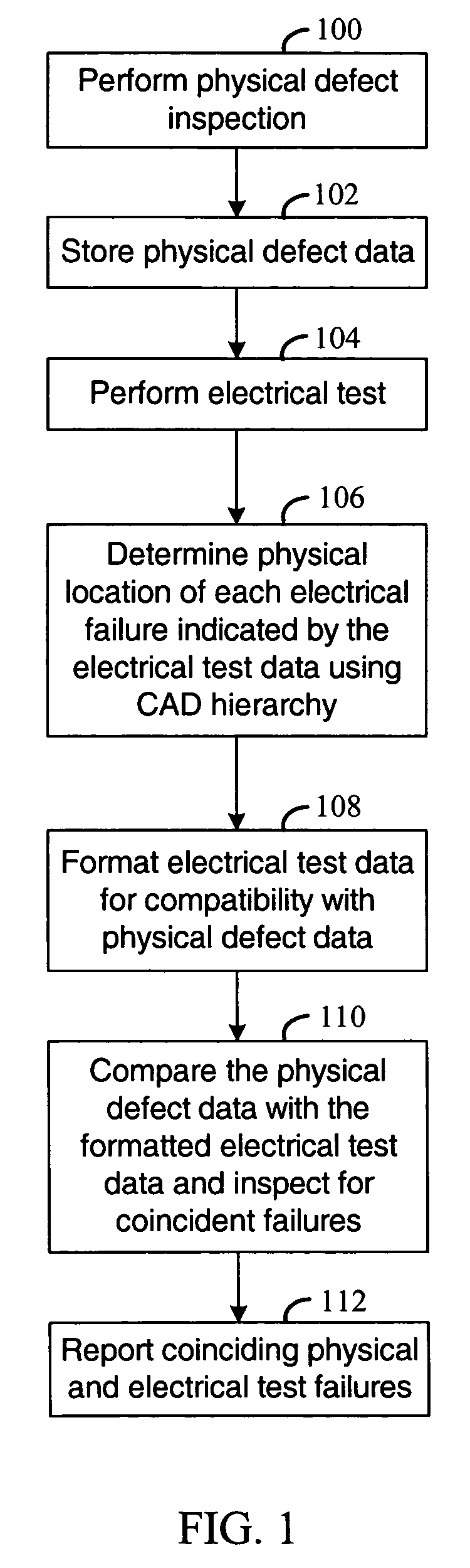

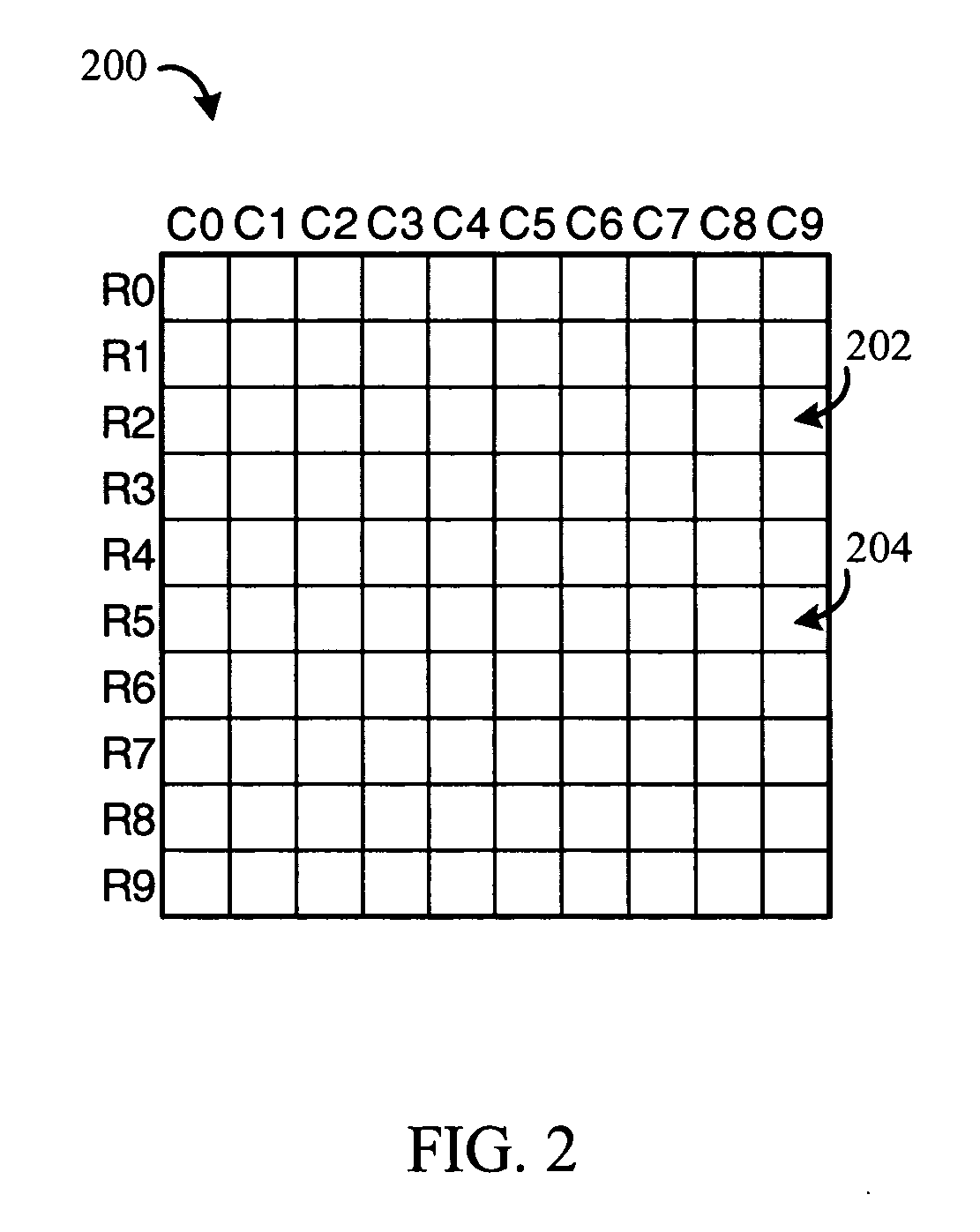

Correlation of electrical test data with physical defect data

ActiveUS6950771B1Improve yield analysisEasy to analyzeResistance/reactance/impedenceElectronic circuit testingData setDesign testing

Method and apparatus are disclosed for analyzing defect data produced in testing a semiconductor chip from a logic design. In various embodiments, input for processing is a first inspection data set that identifies a first set of physical locations that are associated with defects detected during fabrication of the chip. Also input is a second test data set that includes one or more identifiers associated with failing circuitry in the chip. A second set of physical locations is determined from the one or more identifiers of failing circuitry, hierarchical relationships between blocks of the design, and placement information associated with the blocks. Each of the one or more identifiers is associated with at least one of the blocks. Correspondences are identified between physical locations in the first inspection data set and the second set of physical locations.

Owner:XILINX INC

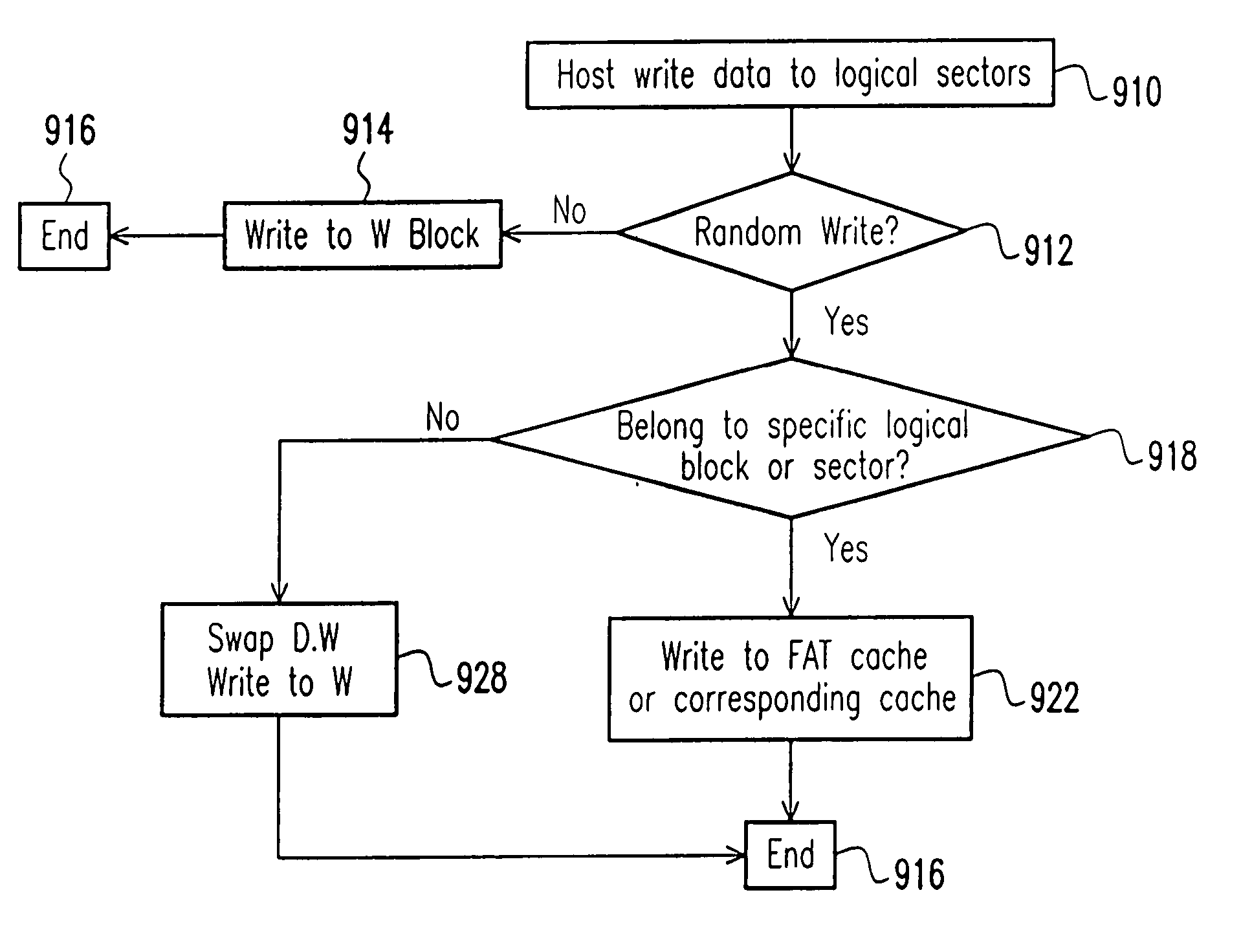

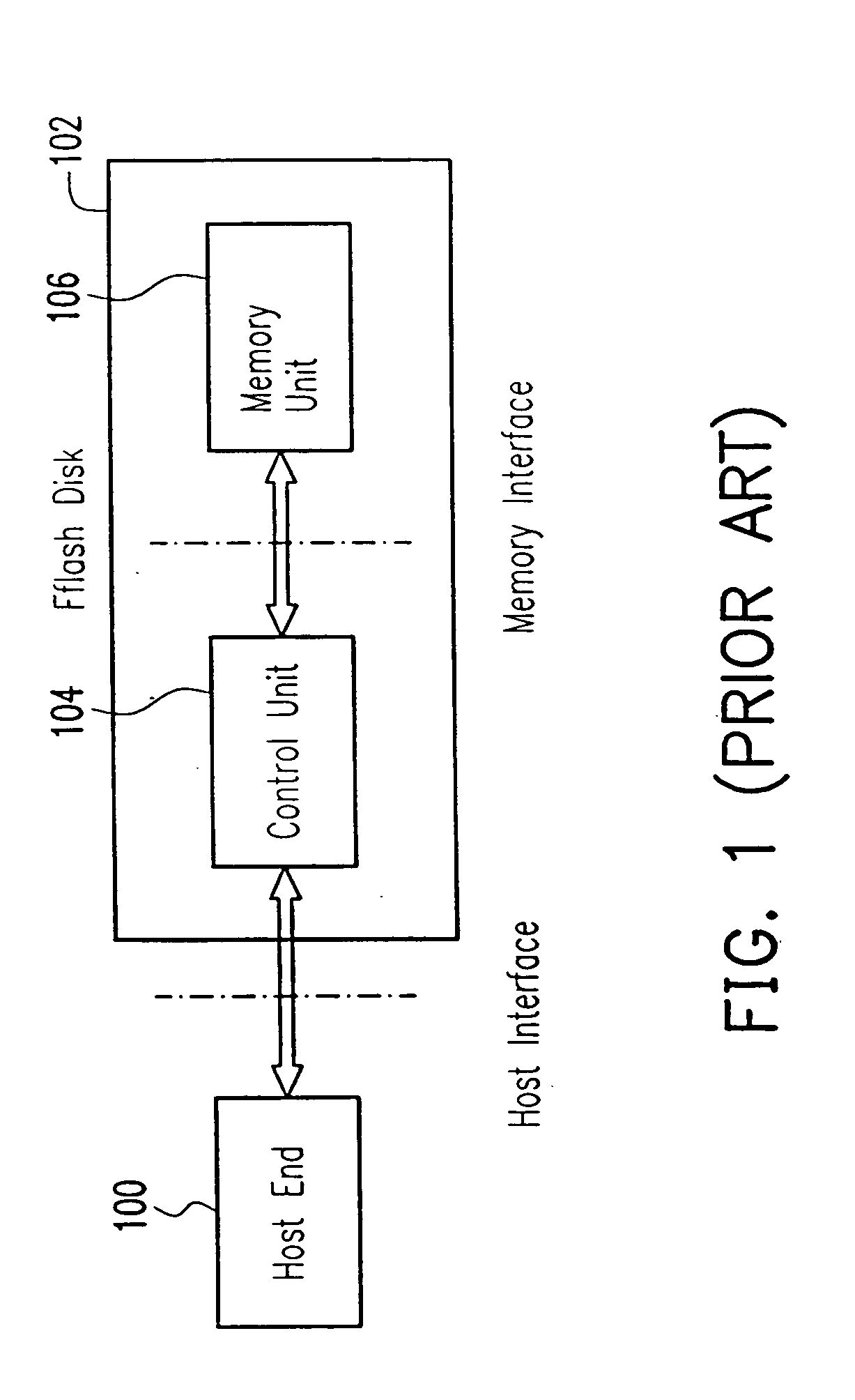

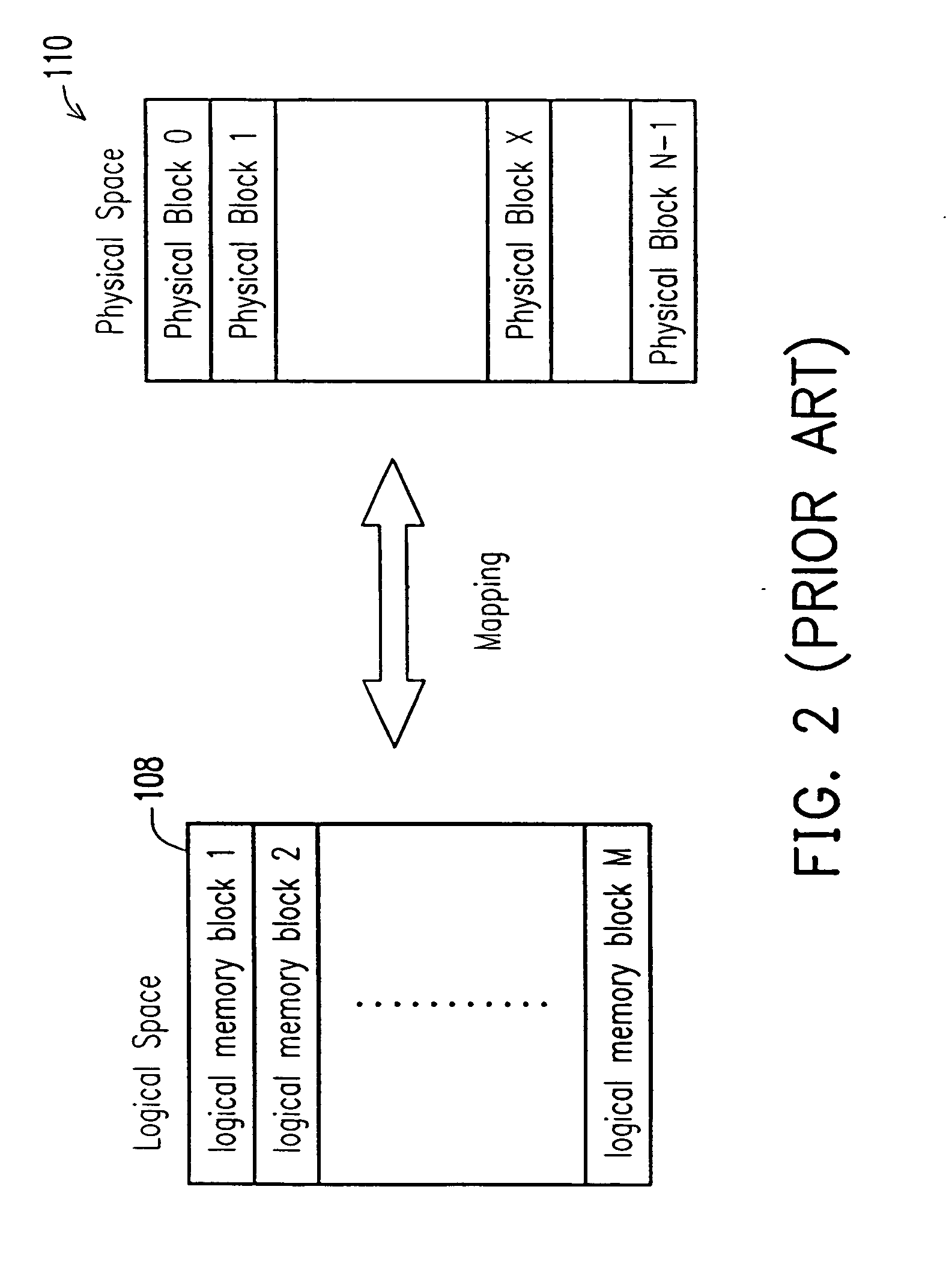

Nonvolatile memory unit with specific cache

InactiveUS20050015557A1Reduce frequencyAvoid actionMemory architecture accessing/allocationInput/output to record carriersOperating systemVolatile memory

The invention provides a method for organizing a writing operation to a nonvolatile memory. The method comprises setting a specific cache area, into which a specific data belonging to a specific group of logical blocks is to be written. It is determined whether or not the writing operation is a random write. If the writing operation is the random write, then the following steps are performed: determining whether or not the writing operation is to write a data that is belonging to the specific group of logical blocks; and writing the data into the specific cache area if the data is belonging to the specific group of logical blocks. As a result, a swap action between a data block and a writing block can be avoided during a random write operation. A storage structure in a nonvolatile memory device are organized to perform the forgoing writing operation.

Owner:SOLID STATE SYST

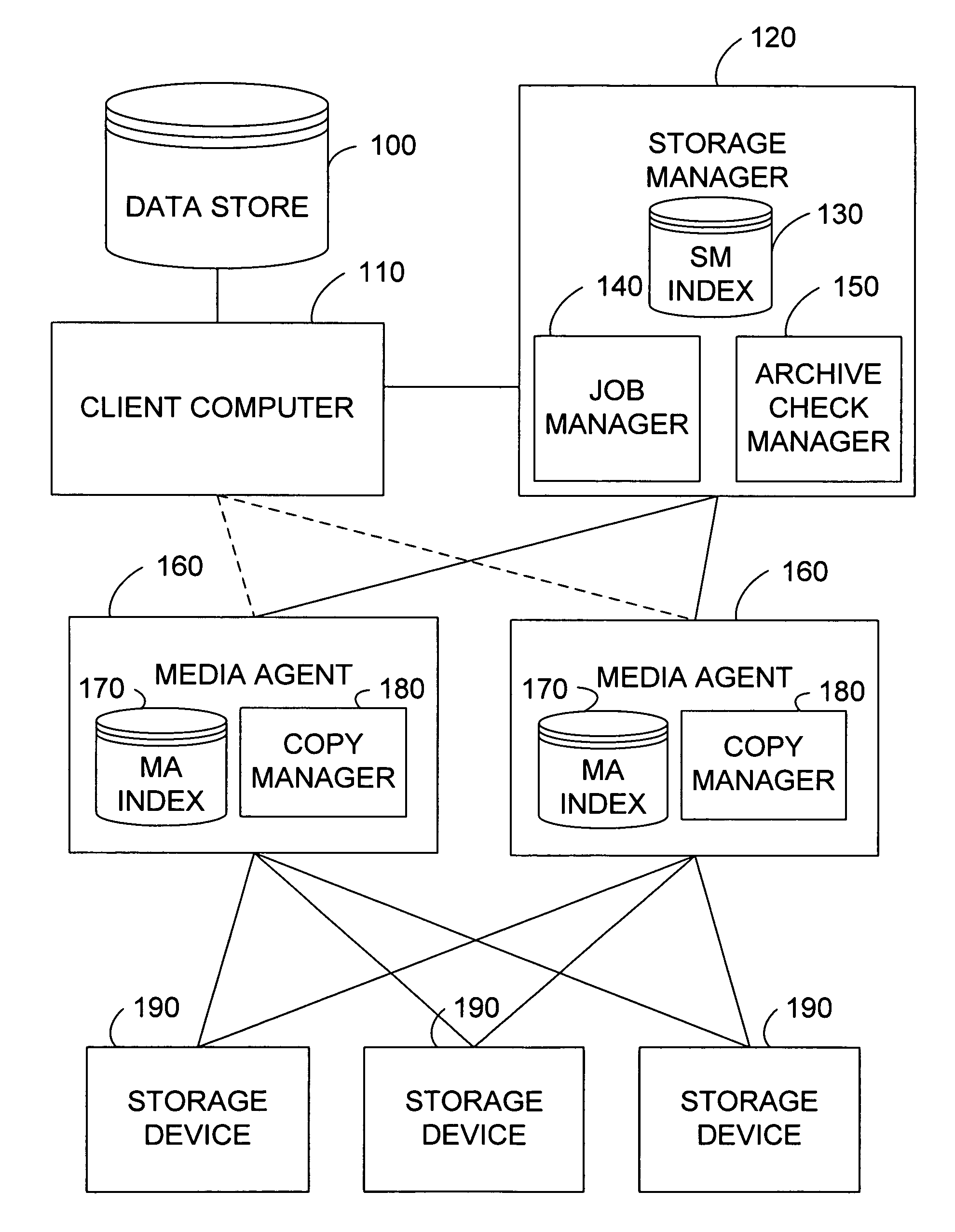

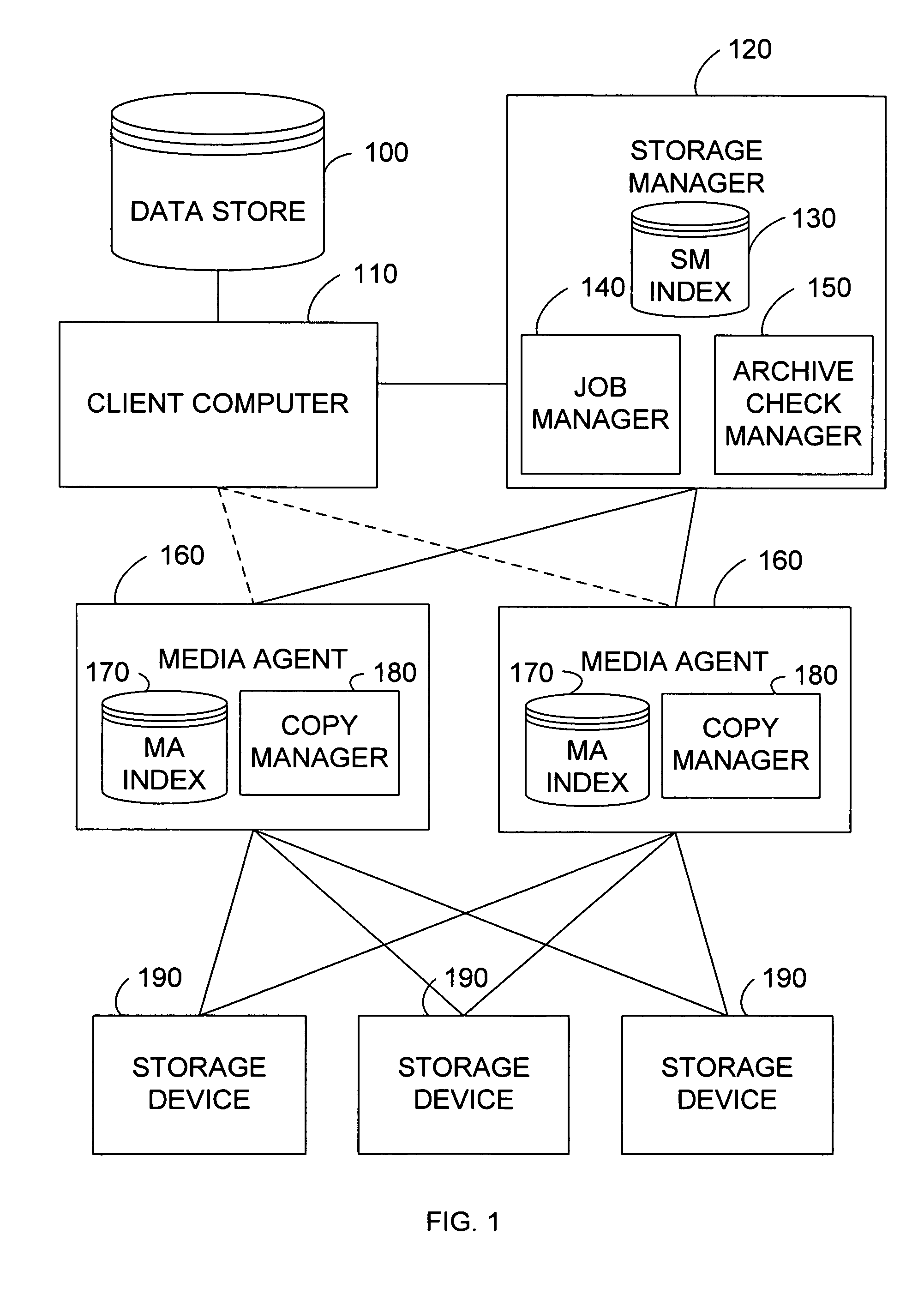

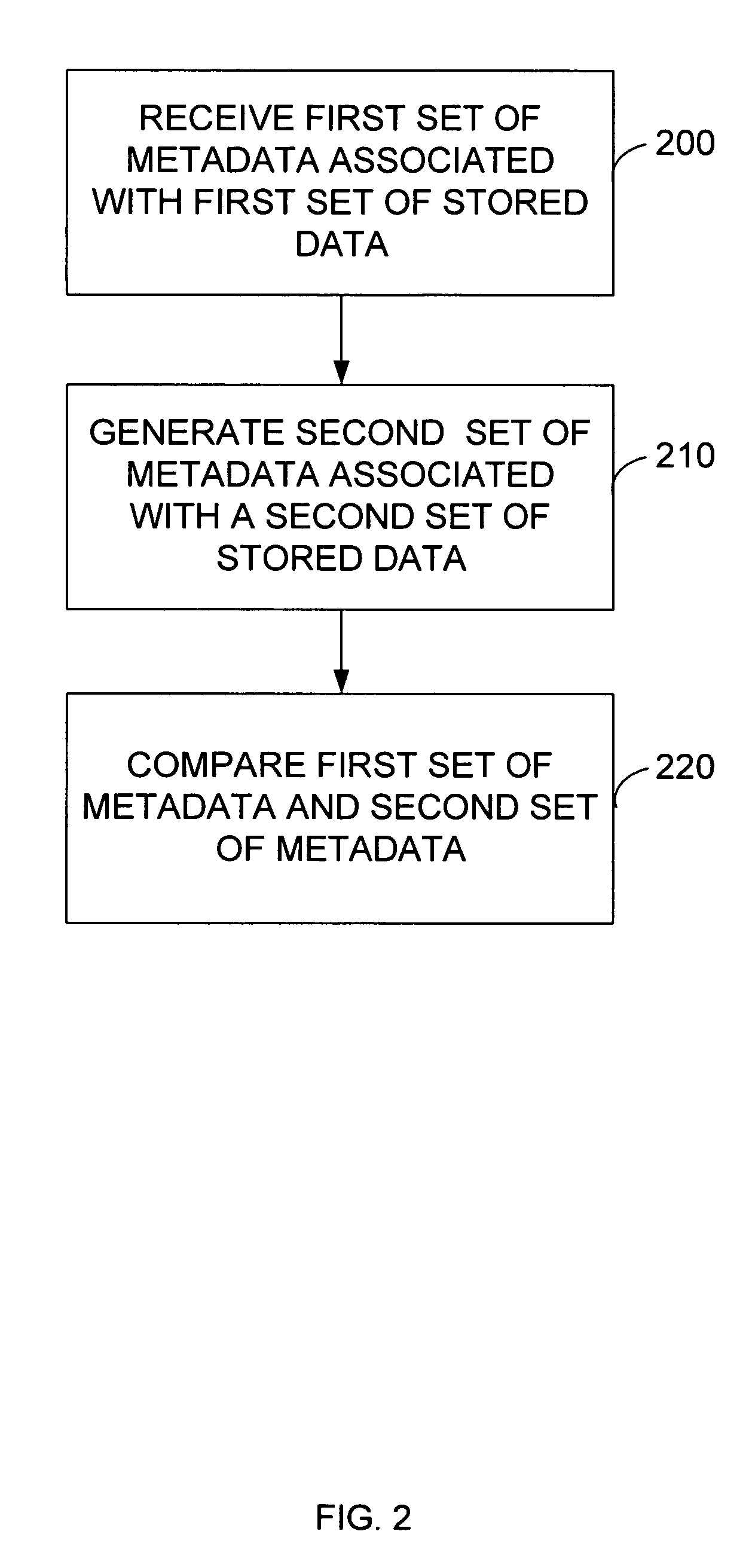

Stored data reverification management system and method

ActiveUS7613748B2Data processing applicationsDigital data information retrievalManagement systemDatabase

A system and method are provided for verifying data copies and reverifying the copies over the life span of media according to a verification policy. Characteristics of media and use of media are tracked to provide metrics which may be used to dynamically reevaluate and reassign verification policies to optimize media usage. Copies that fail verification operations may be repaired by repeating a storage operation for recent copies or by substituting a close temporal copy of the failed copy.

Owner:COMMVAULT SYST INC

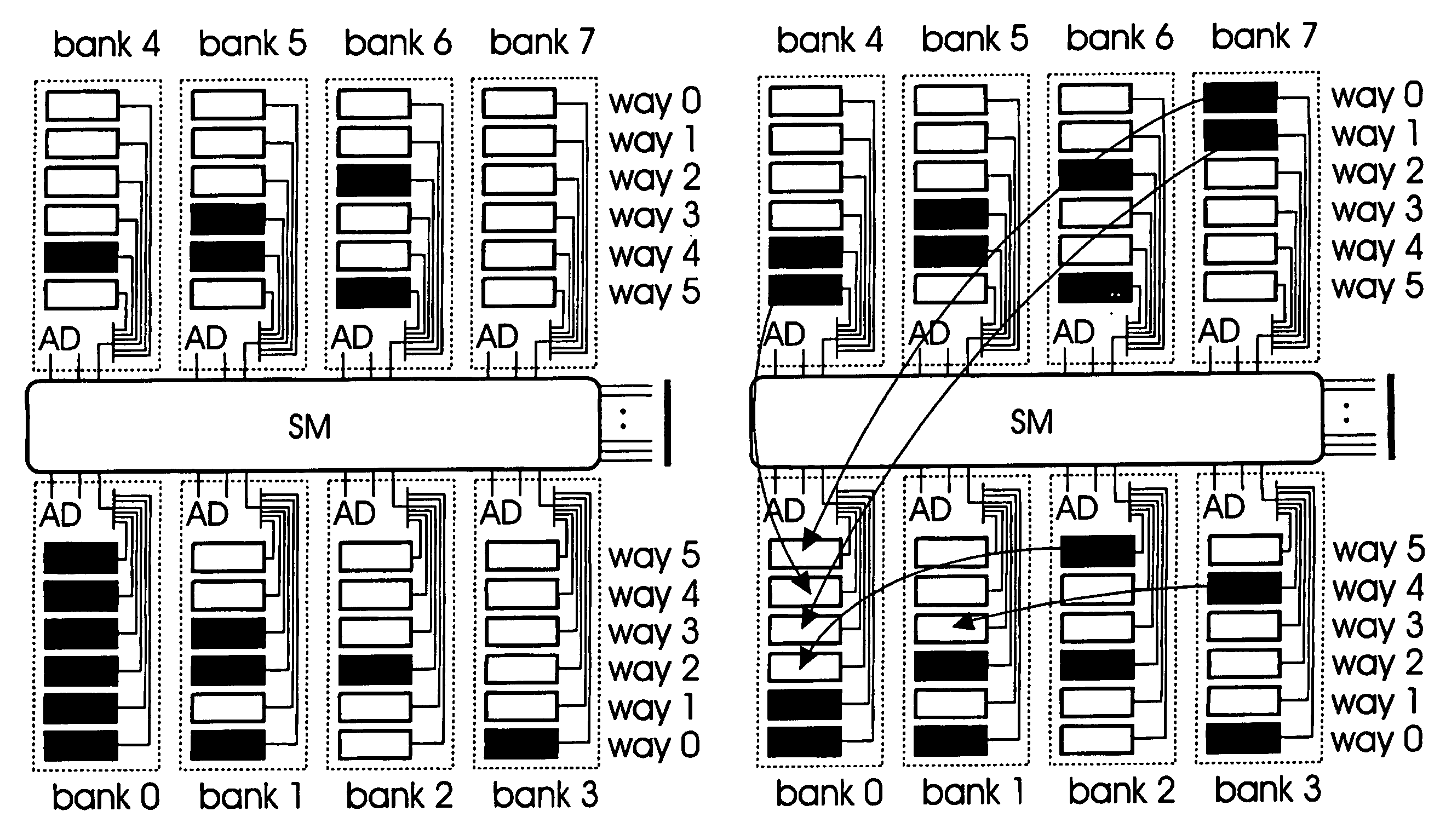

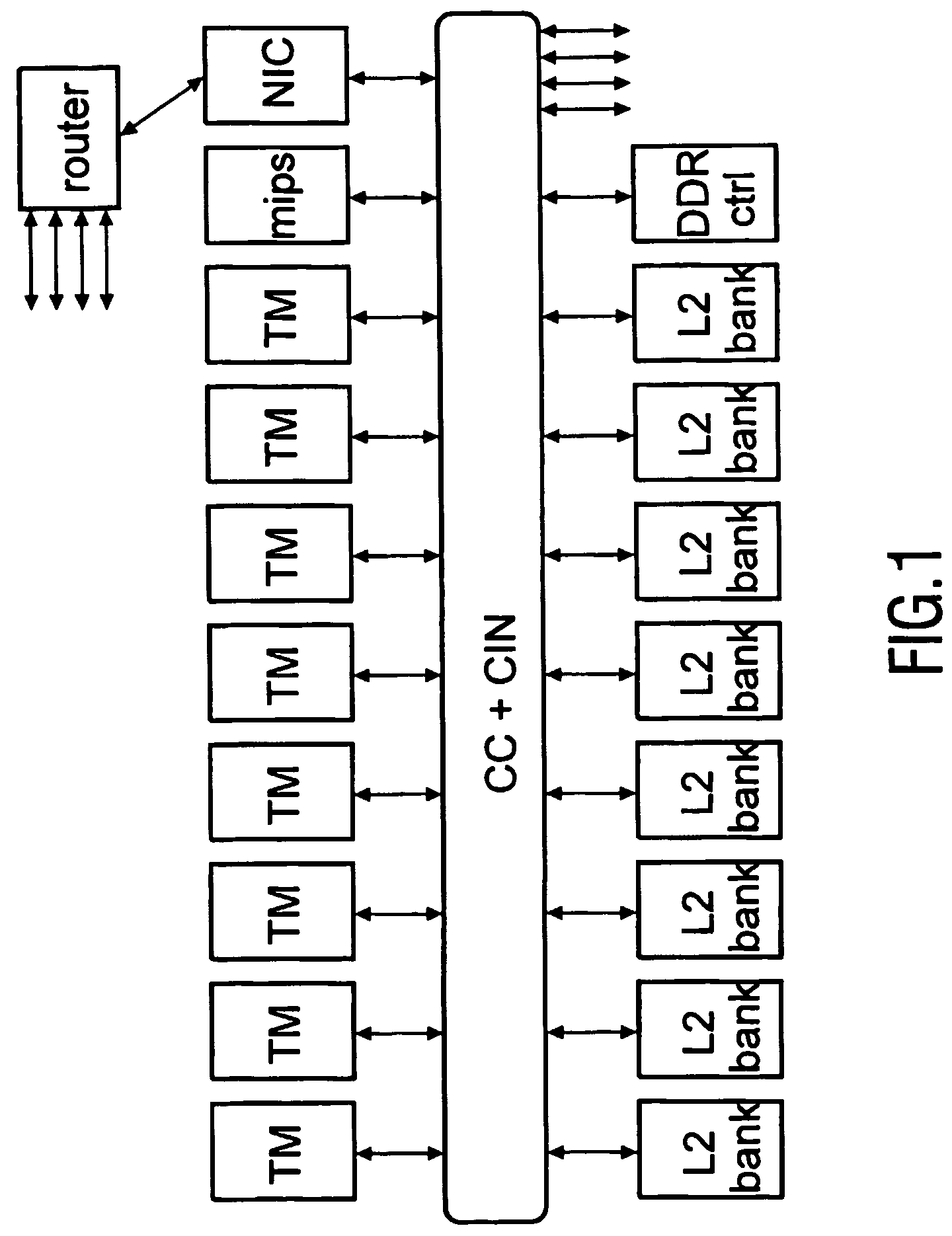

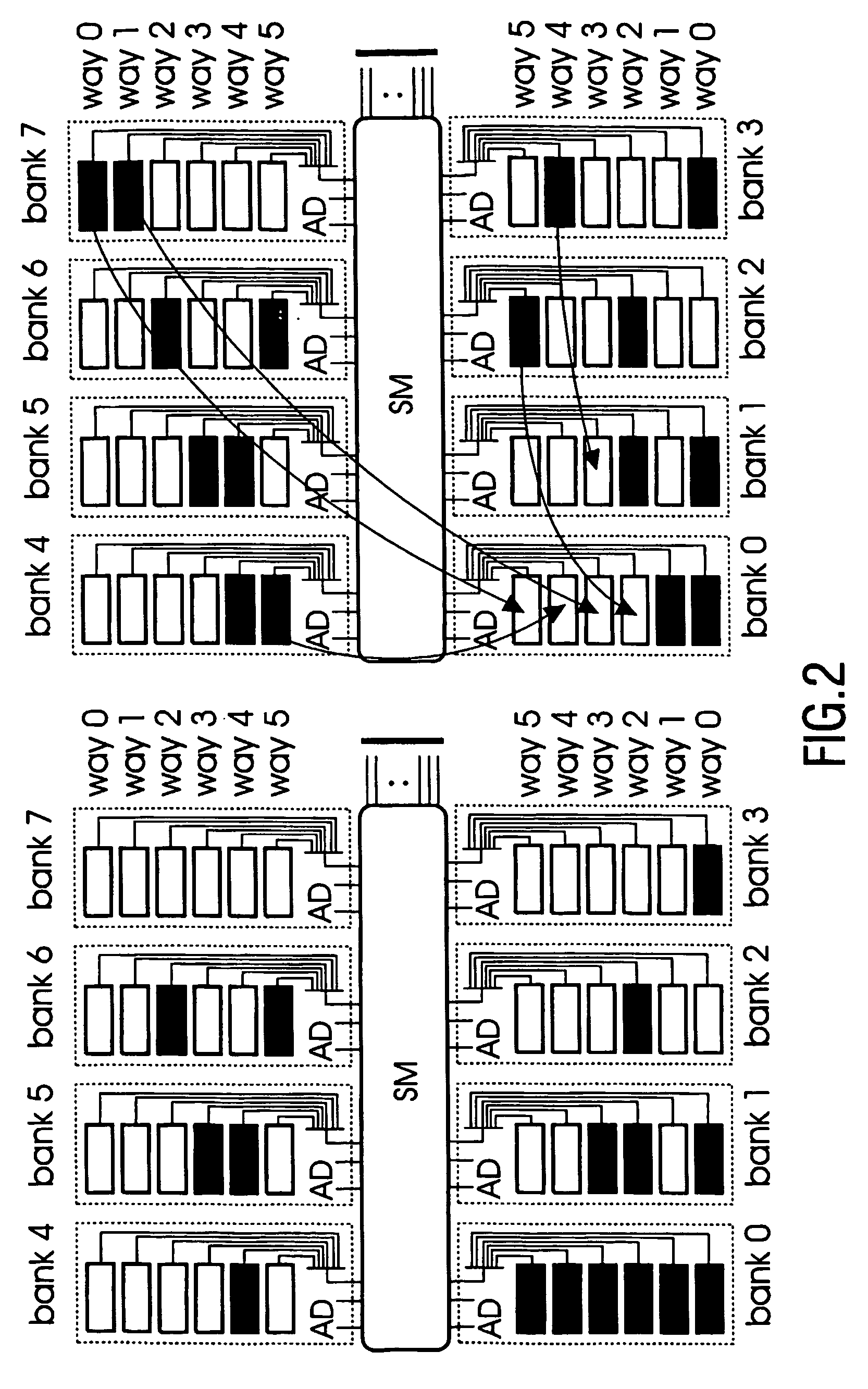

Intergrated circuit and a method of cache remapping

InactiveUS7827372B2Improve overall utilizationRapid cachingError detection/correctionMemory adressing/allocation/relocationParallel computingIntegrated circuit

An integrated circuit is provided with at least one processing unit (TM), a cache memory (L2 BANK) having a plurality of memory modules, and remapping means (RM) for performing an unrestricted remapping within said plurality of memory modules. Accordingly, faulty modules can be remapped without limitations in order to optimise the utilization of the memory modules by providing an even distribution of the faulty modules.

Owner:NYTELL SOFTWARE LLC

Audio identification system and method

A method and system for direct audio capture and identification of the captured audio. A user may then be offered the opportunity to purchase recordings directly over the Internet or similar outlet. The system preferably includes one or more user-carried portable audio capture devices that employ a microphone, analog to digital converter, signal processor, and memory to store samples of ambient audio or audio features calculated from the audio. Users activate their capture devices when they hear a recording that they would like to identify or purchase. Later, the user may connect the capture device to a personal computer to transfer the audio samples or audio feature samples to an Internet site for identification. The Internet site preferably uses automatic pattern recognition techniques to identify the captured samples from a library of recordings offered for sale. The user can then verify that the sample is from the desired recording and place an order online. The pattern recognition process uses features of the audio itself and does not require the presence of artificial codes or watermarks. Audio to be identified can be from any source, including radio and television broadcasts or recordings that are played locally.

Owner:ICEBERG IND

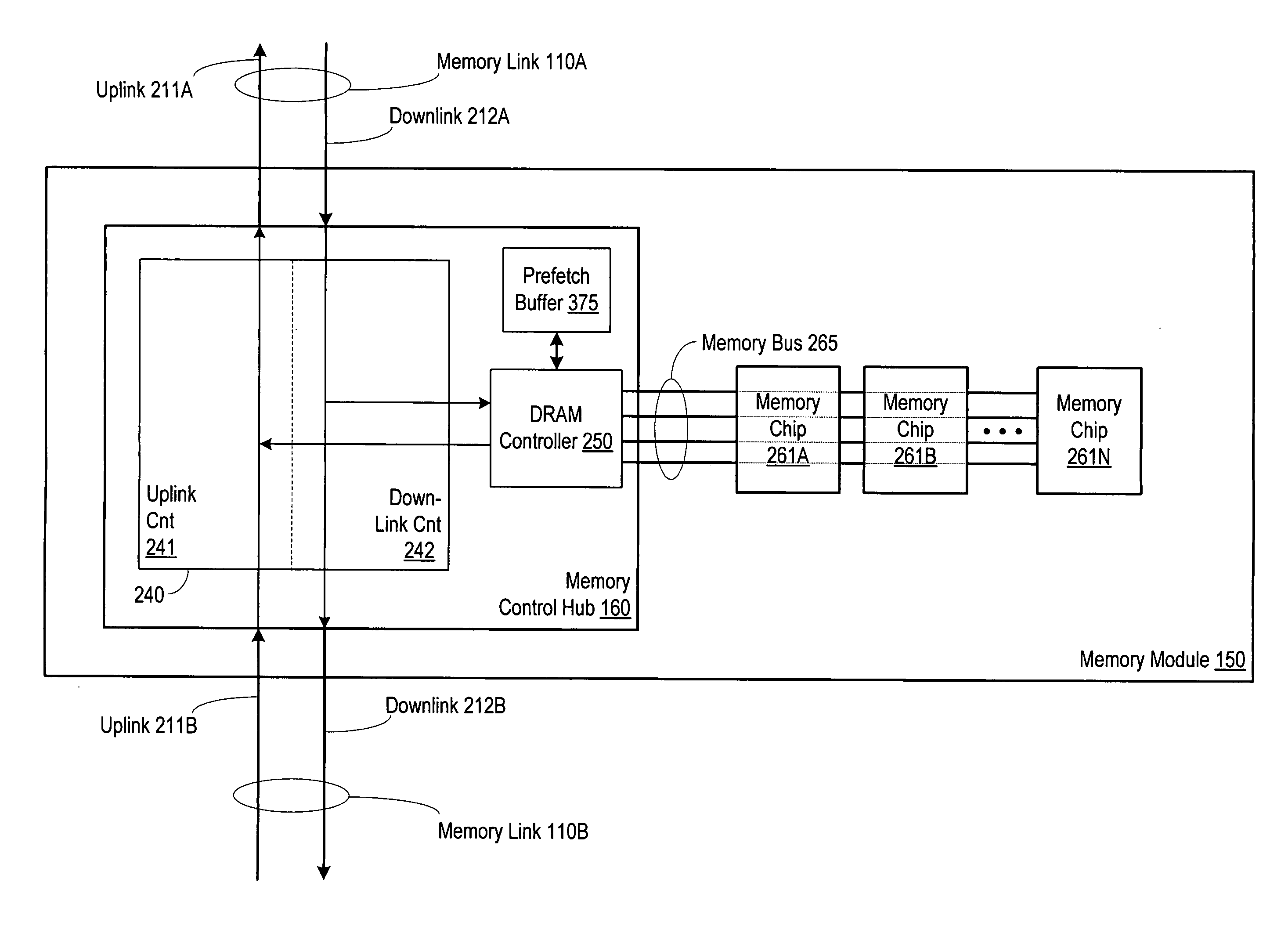

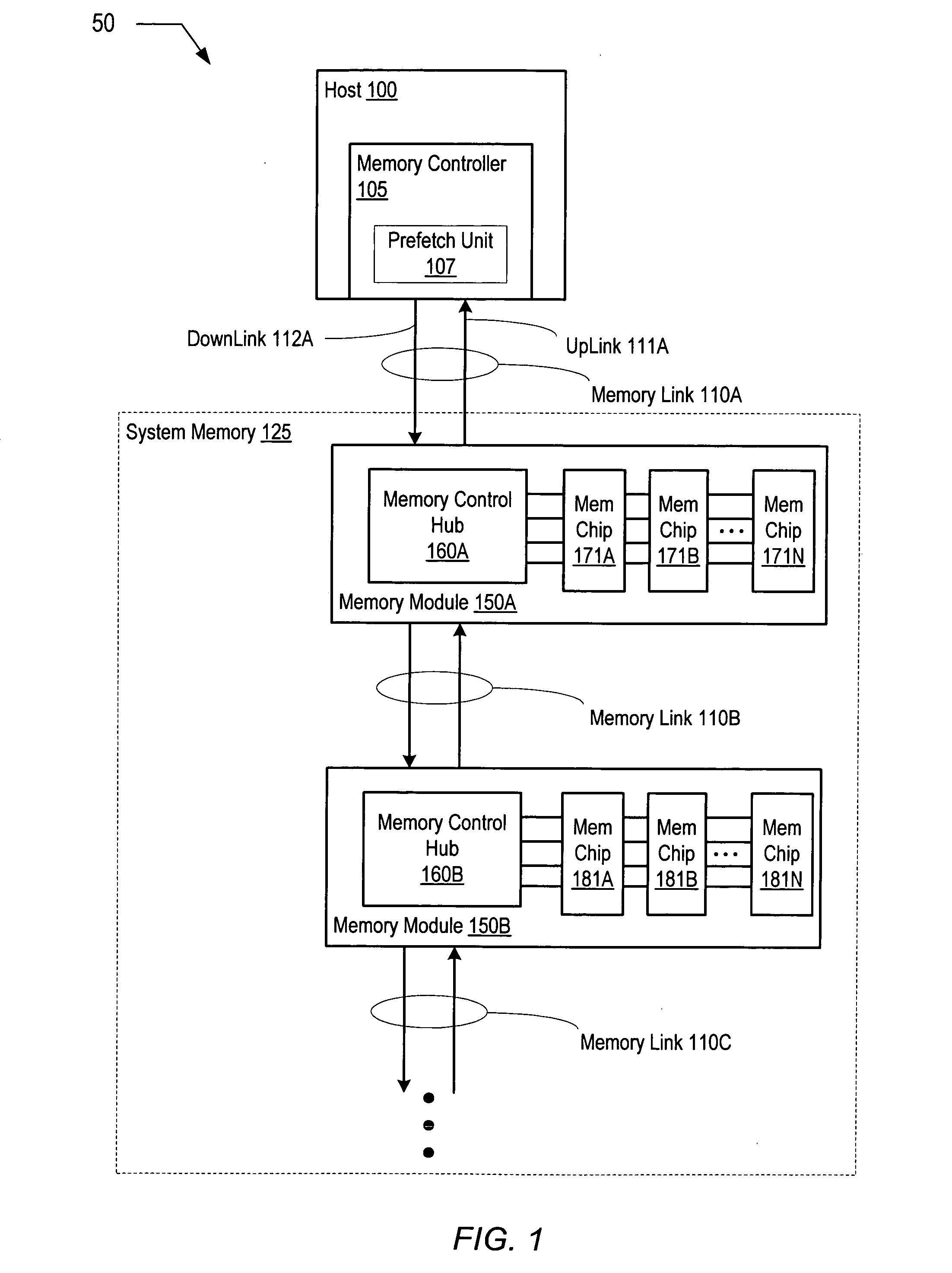

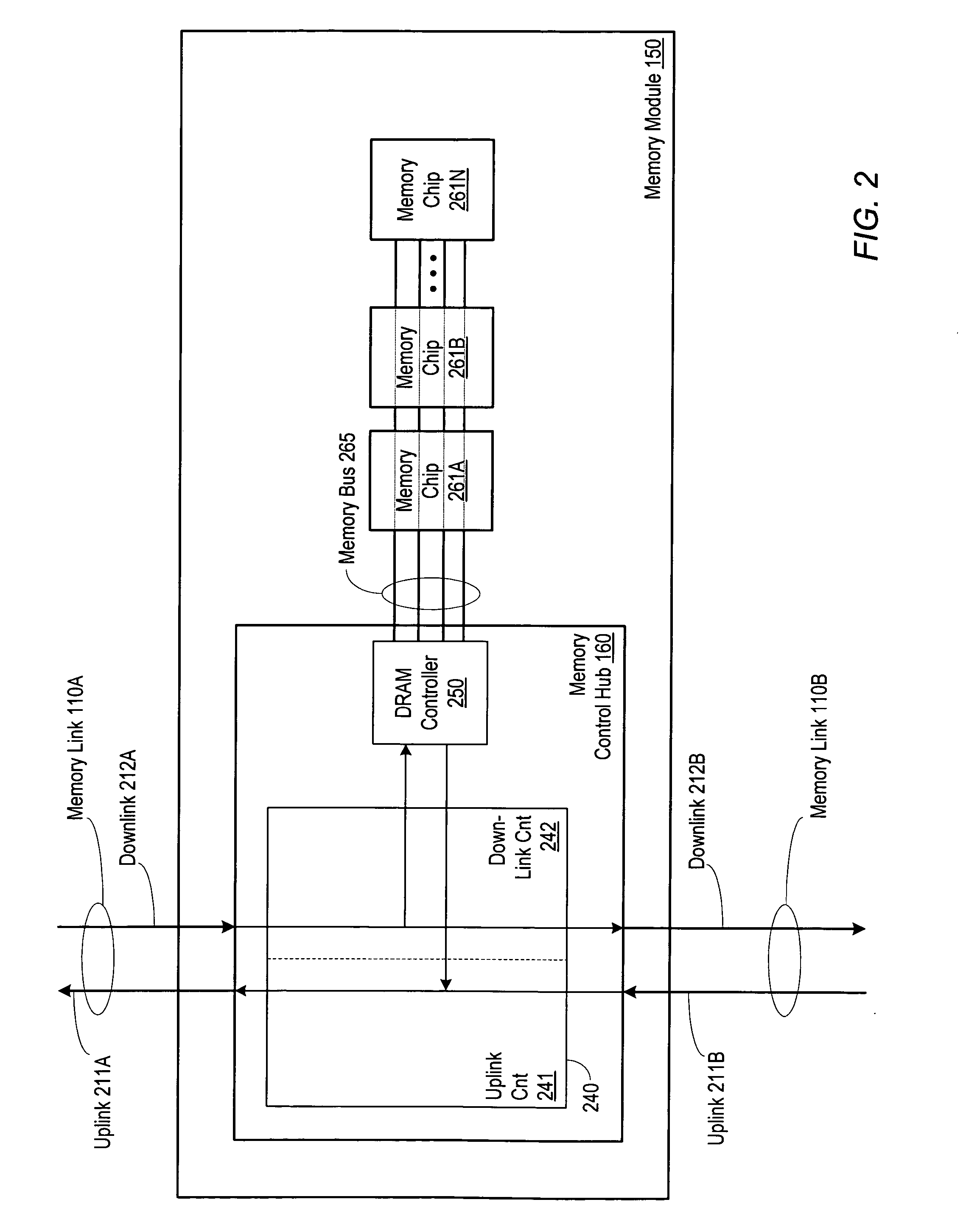

Prefetch mechanism for use in a system including a host connected to a plurality of memory modules via a serial memory interconnect

InactiveUS20050071542A1Memory architecture accessing/allocationStatic storageMemory controllerData storing

A system includes a host coupled to a serially connected chain of memory modules. In one embodiment, the host includes a memory controller that may be configured to issue a memory read request for data stored within the memory modules. The memory controller may further request that data be prefetched from the memory modules by encoding prefetch information within the memory read request. The memory controller may also be configured to issue a memory write request to write data to the memory modules and to selectively request that one or more pages of memory within a given one of the memory modules remain open by encoding the prefetch information within the memory write request.

Owner:ADVANCED MICRO DEVICES INC

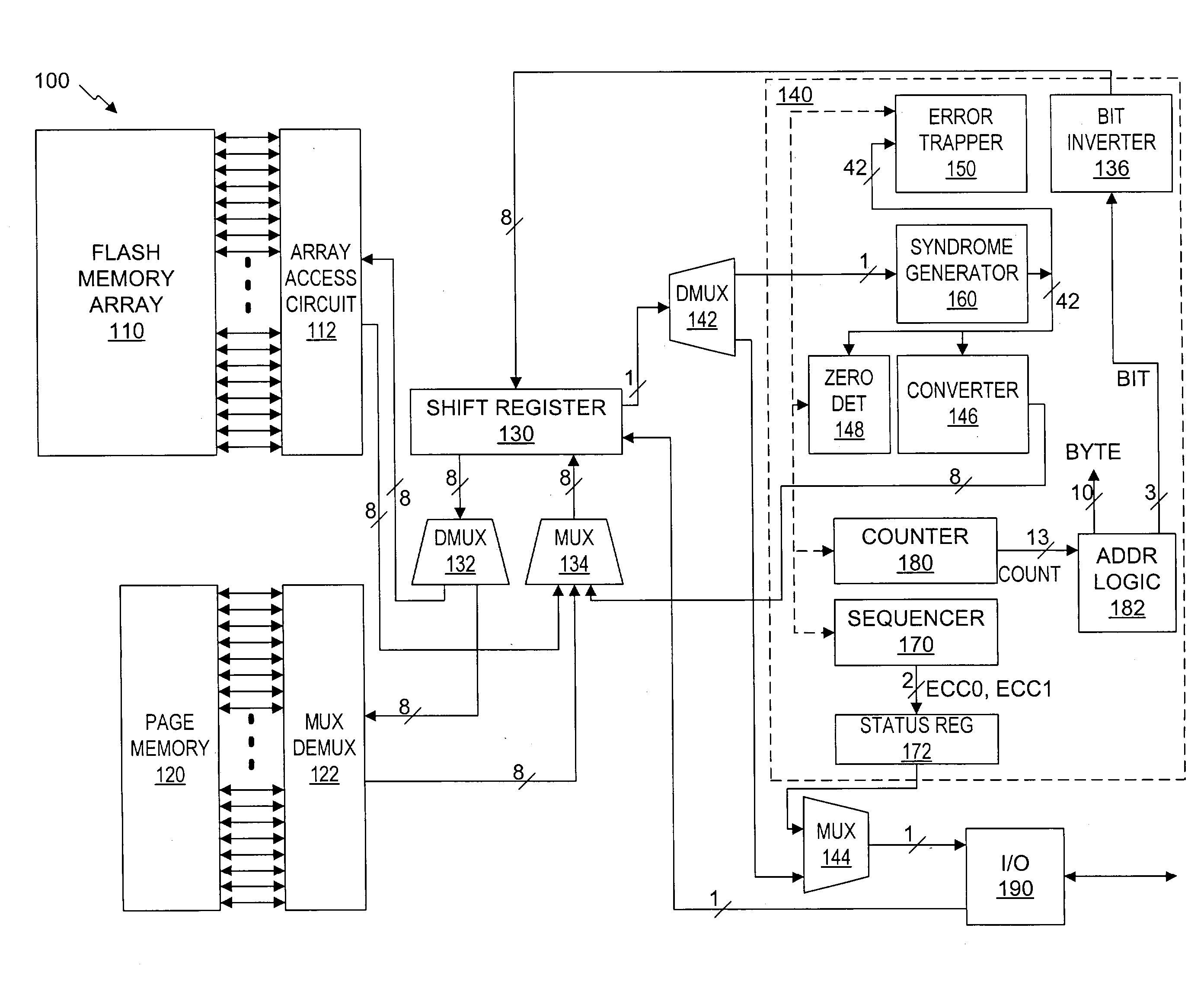

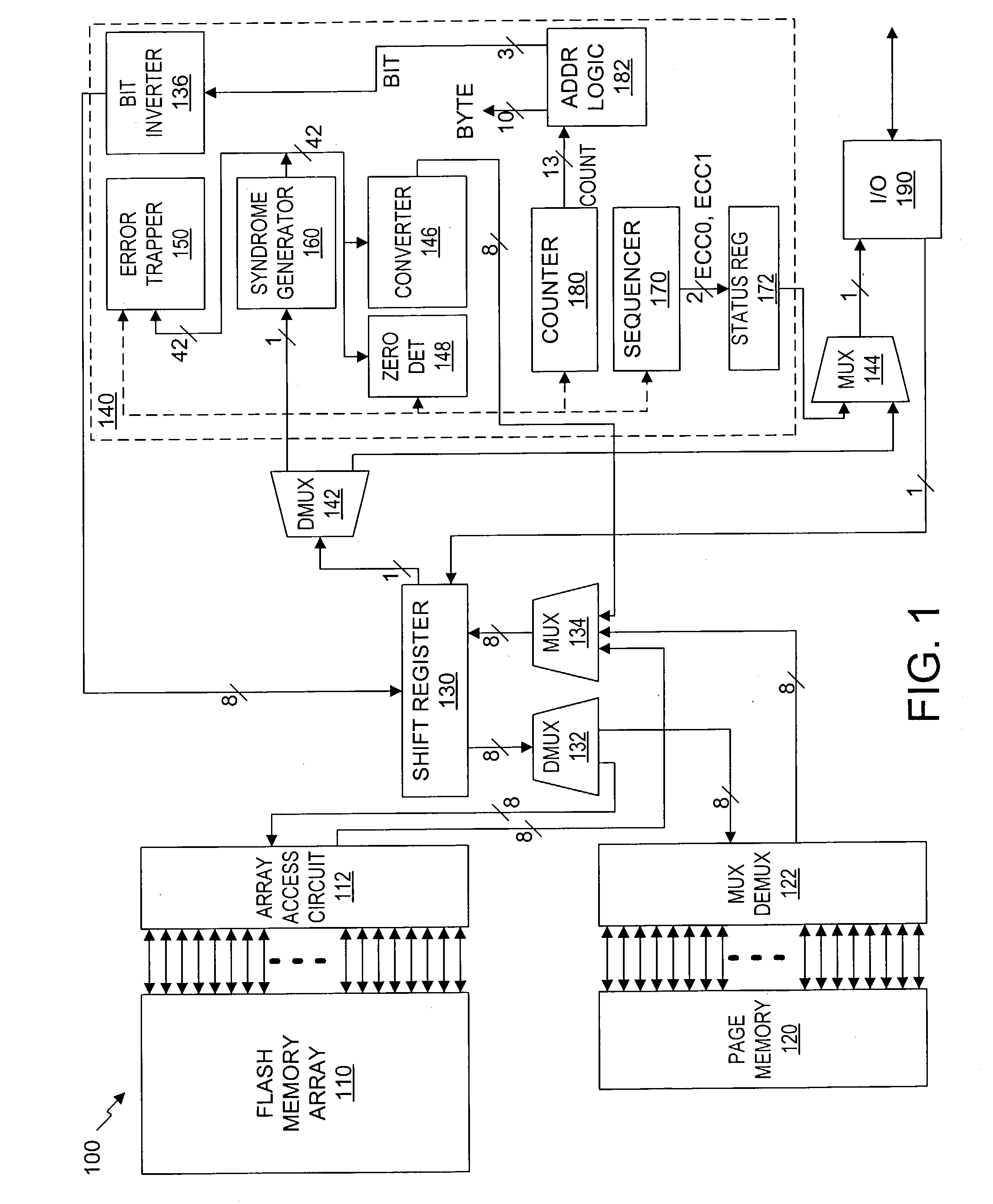

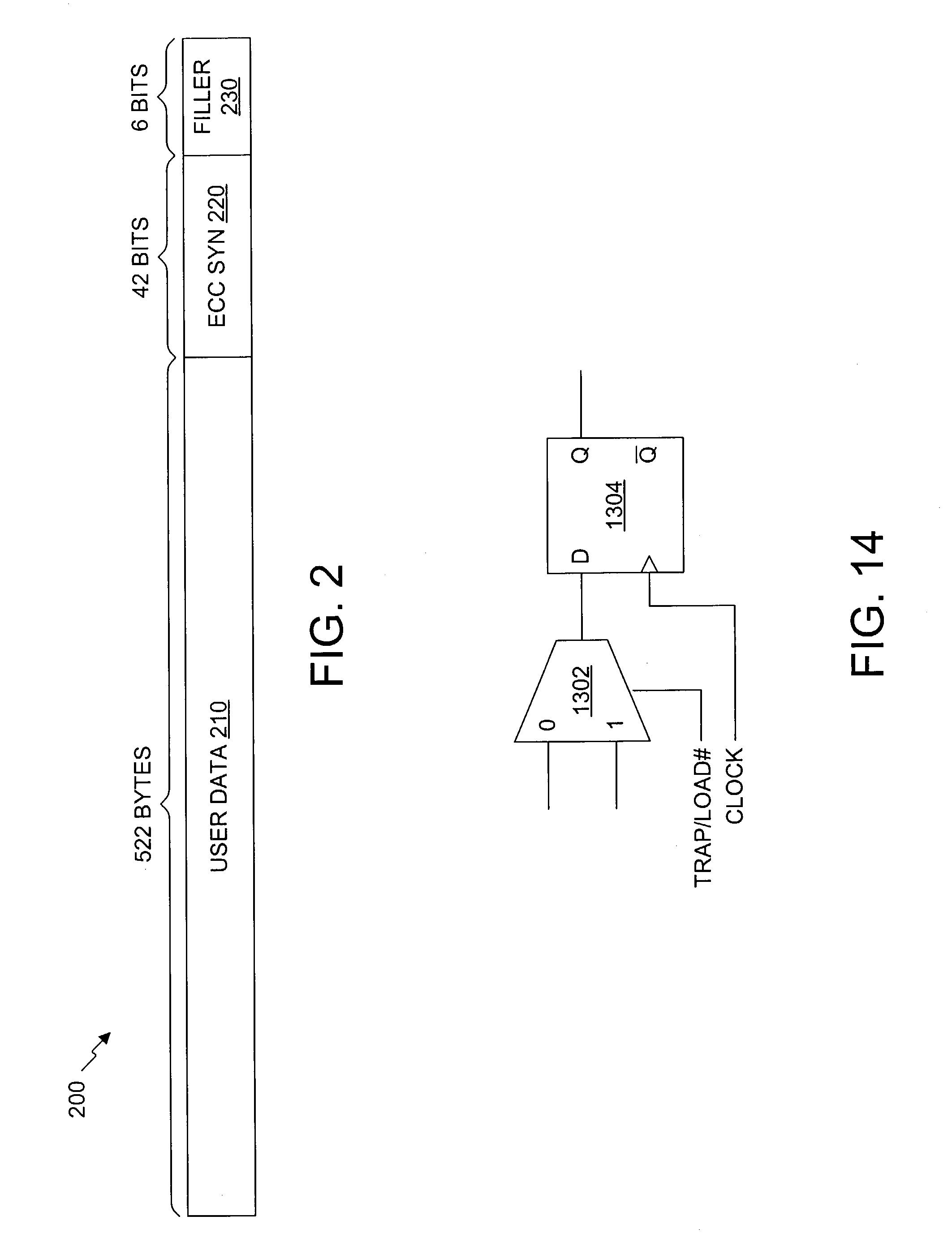

Serial flash integrated circuit having error detection and correction

InactiveUS20040153902A1Static storageRedundant data error correctionCorrection codeIntegrated circuit

A serial flash integrated circuit is provided with an integrated error correction coding ("ECC") system that is used with an integrated volatile page memory for fast automatic data correction. The ECC code has the capability of correcting any one or two bit errors that might occur on a page of the flash memory array. One bit corrections are done automatically in hardware during reads or transfer to the page memory, while two-bit corrections are handled in external software, firmware or hardware. The ECC system uses a syndrome generator for generating both write and read syndromes, and an error trapper to identify the location of single bit errors using very little additional chip space. The flash memory array may be refreshed from the page memory to correct any detected errors. Data status is made available to the application prior to the data. The use of the ECC is optional.

Owner:WINBOND ELECTRONICS CORP

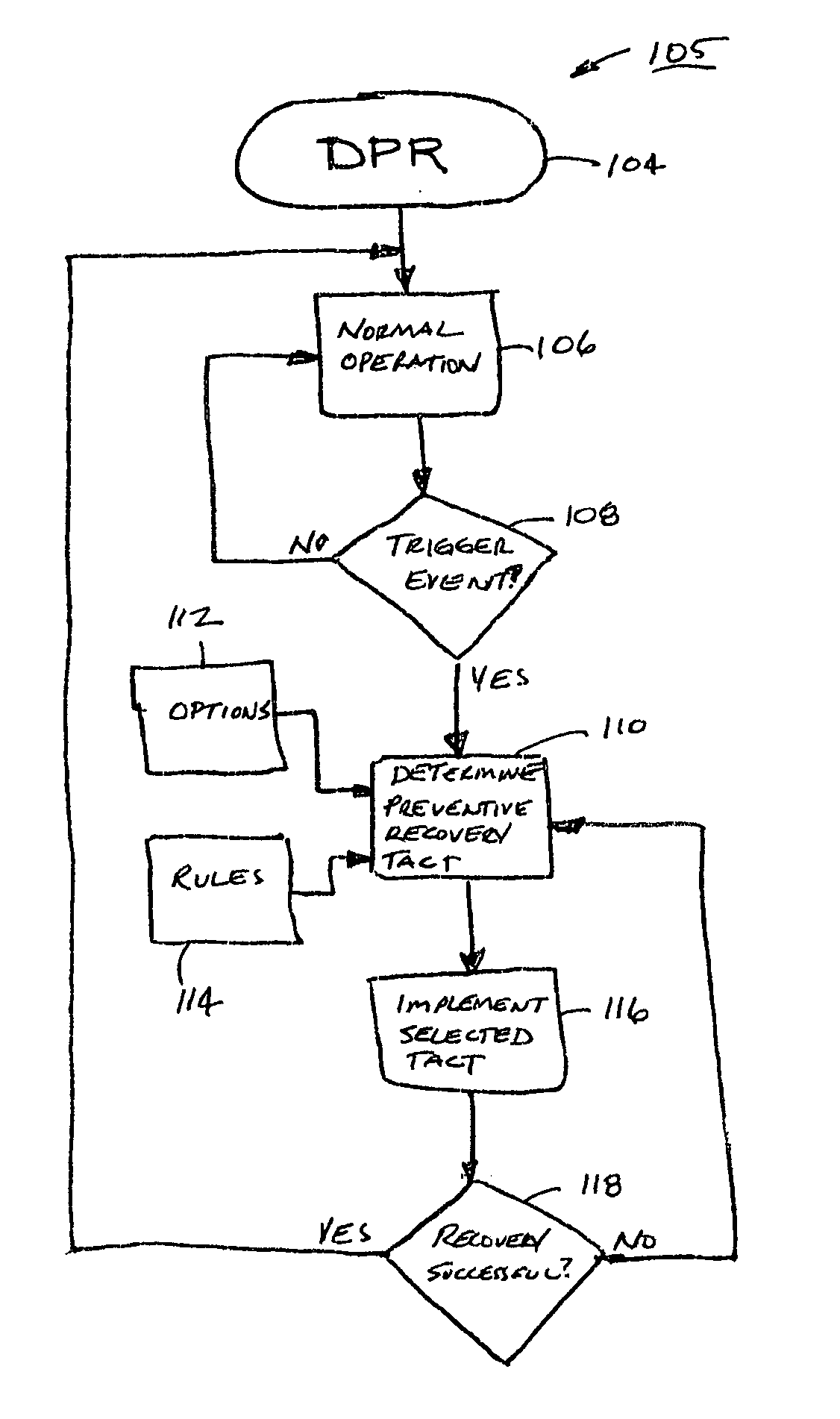

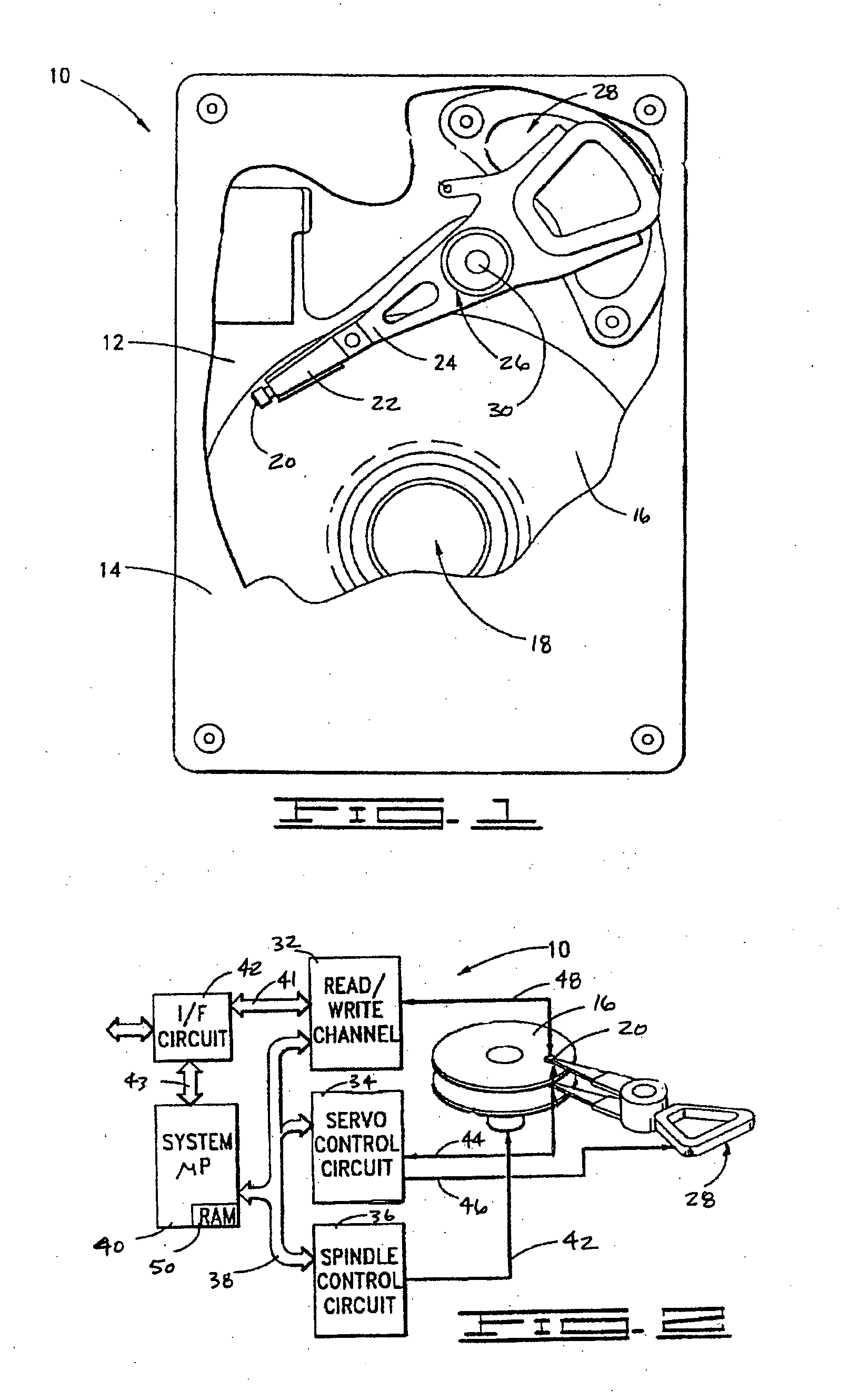

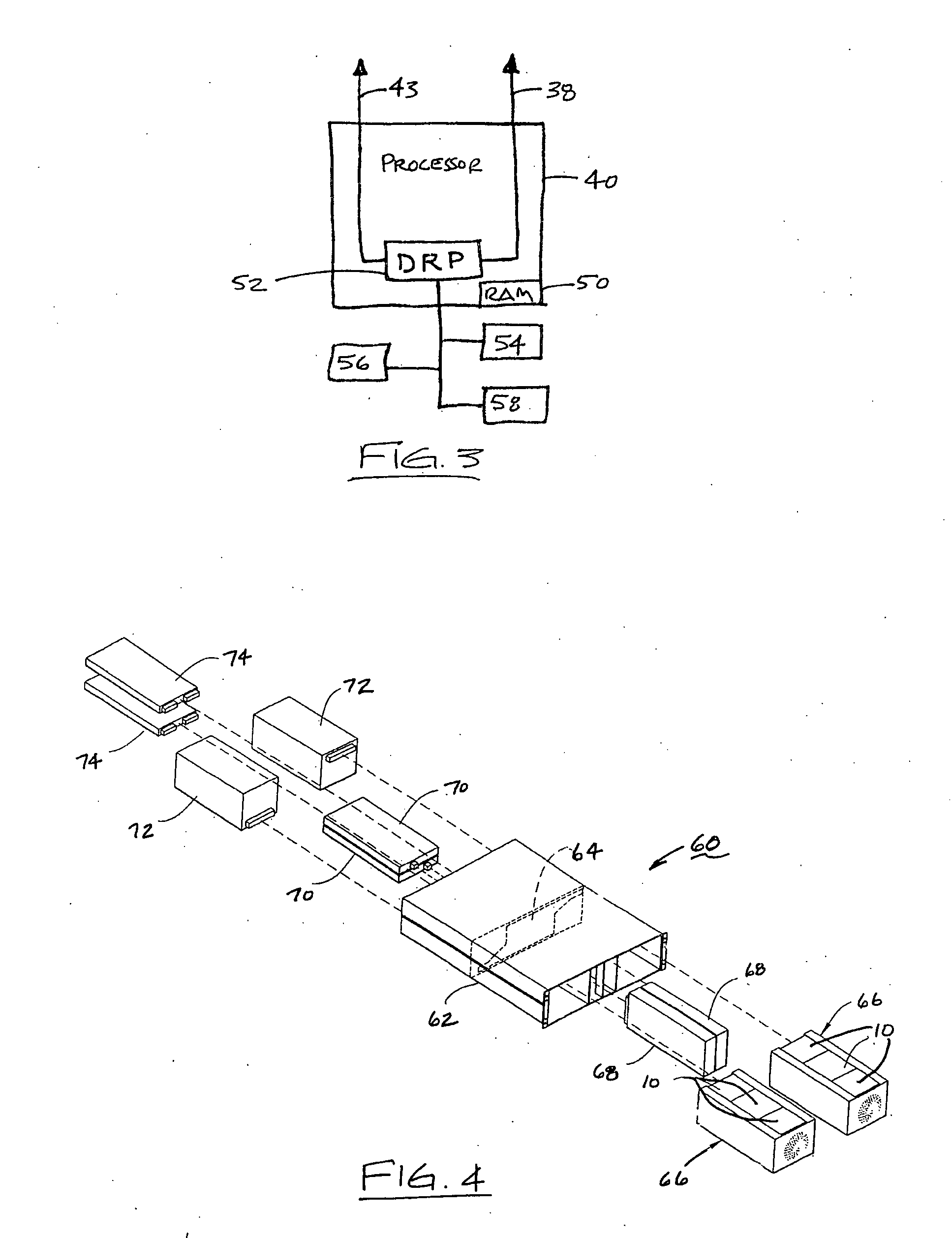

Deterministic preventive recovery from a predicted failure in a distributed storage system

A data storage subsystem in a distributed storage system having a plurality of predictive failure analyzing data storage devices. The subsystem furthermore has a circuit that is responsive to a predicted failure indication by a data storage device in relation to predetermined rules stored in memory for deterministically initiating a preventive recovery either by a data recovery procedure in the data storage device or by a fault tolerance storage arrangement in the subsystem.

Owner:SEAGATE TECH LLC

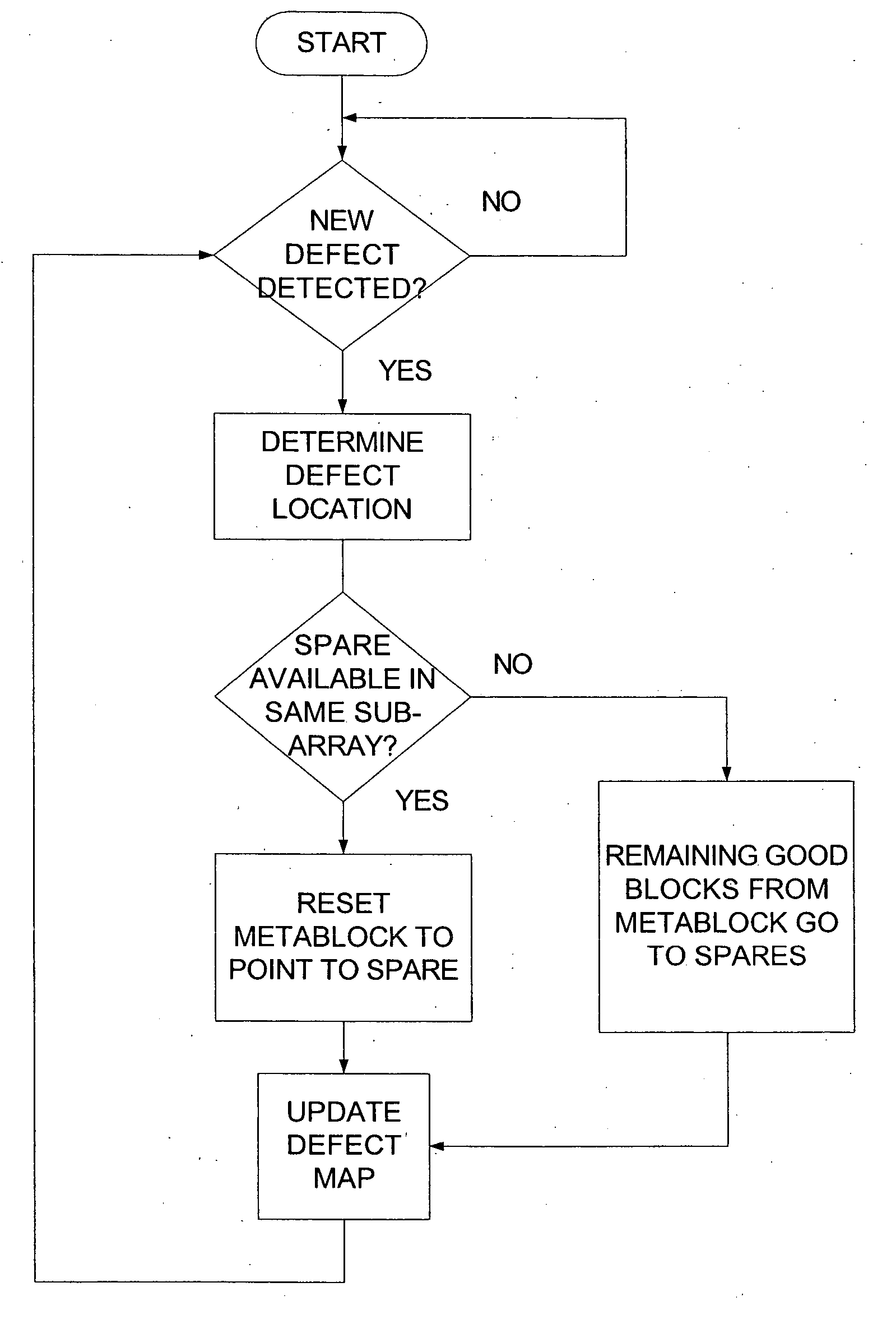

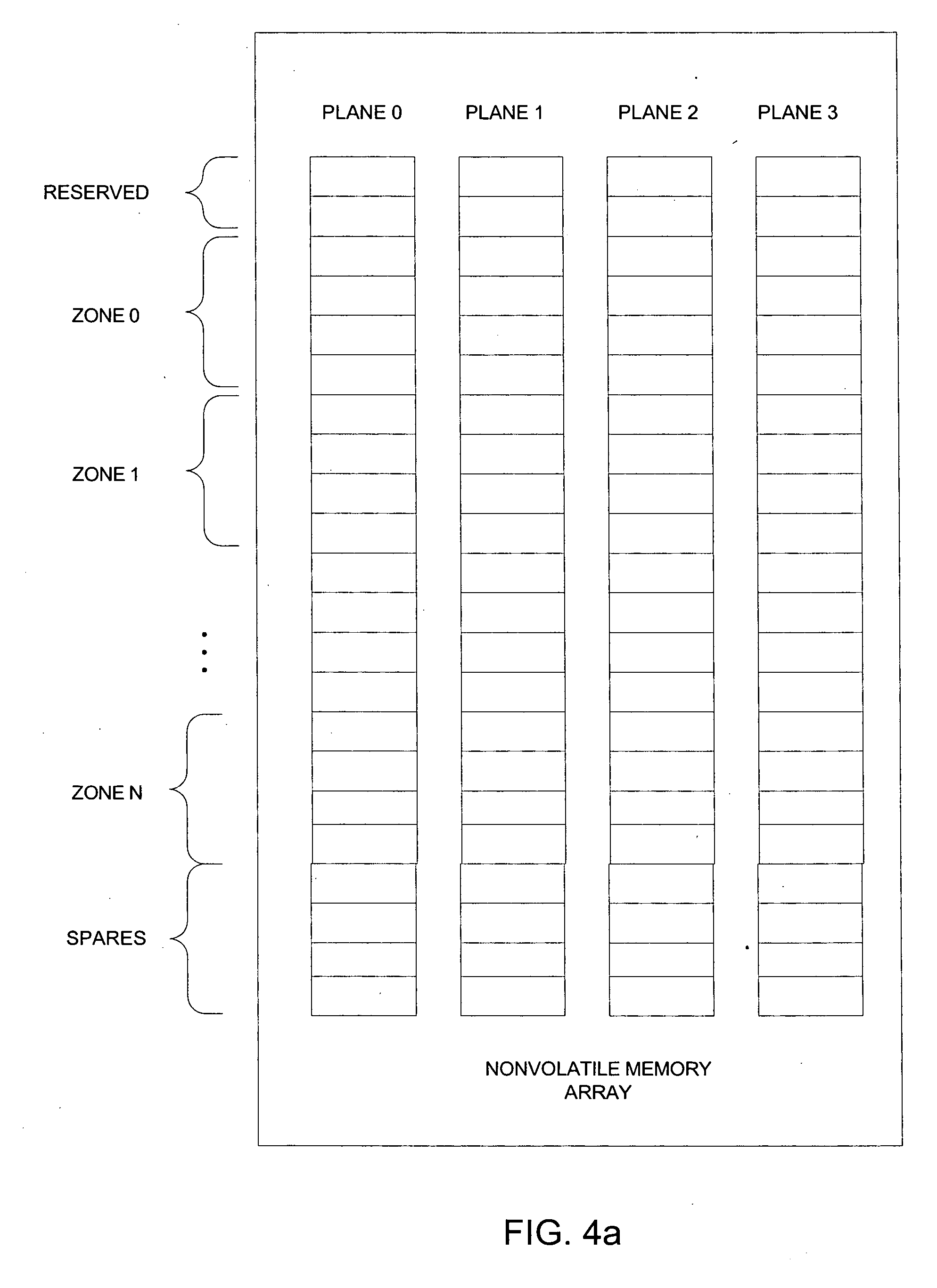

Adaptive deterministic grouping of blocks into multi-block units

InactiveUS20050144516A1Overcome limitationsMemory architecture accessing/allocationInput/output to record carriersSelf adaptiveLogic structure

The present invention presents techniques for the linking of physical blocks of a non-volatile memory into composite logical structures or “metablocks”. After determining an initial linking of good physical blocks into metablocks, a record of the linking is maintained in the non-volatile memory where it can be readily accessed when needed. In one set of embodiments, the initially linking is deterministically formed according to an algorithm and can be optimized according to the pattern of any bad blocks in the memory. As additional bad blocks arise, the linking is updated using by replacing the bad blocks in a linking with good blocks, preferably in the same sub-array of the memory as the block that they are replacing.

Owner:SANDISK TECH LLC

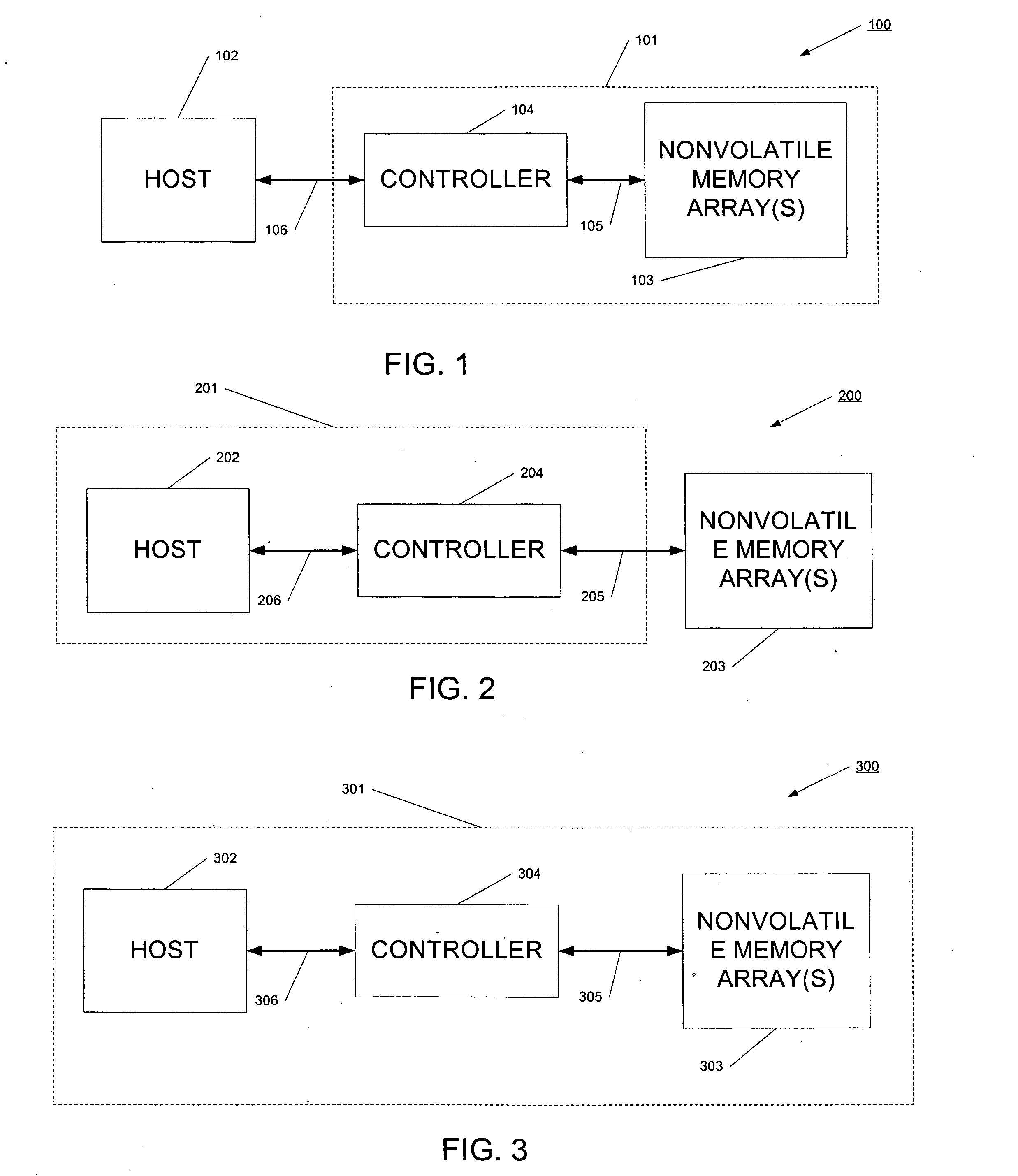

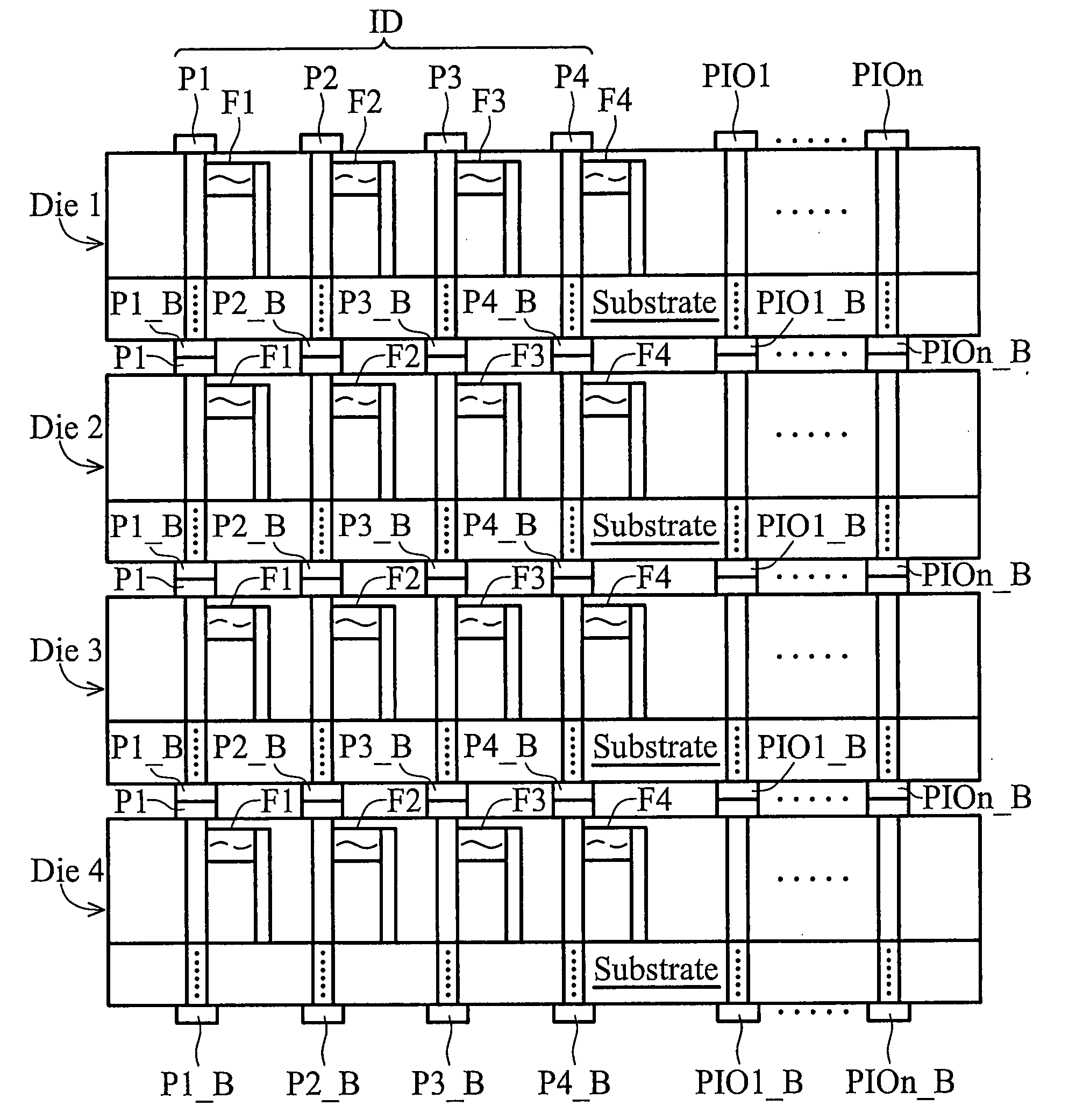

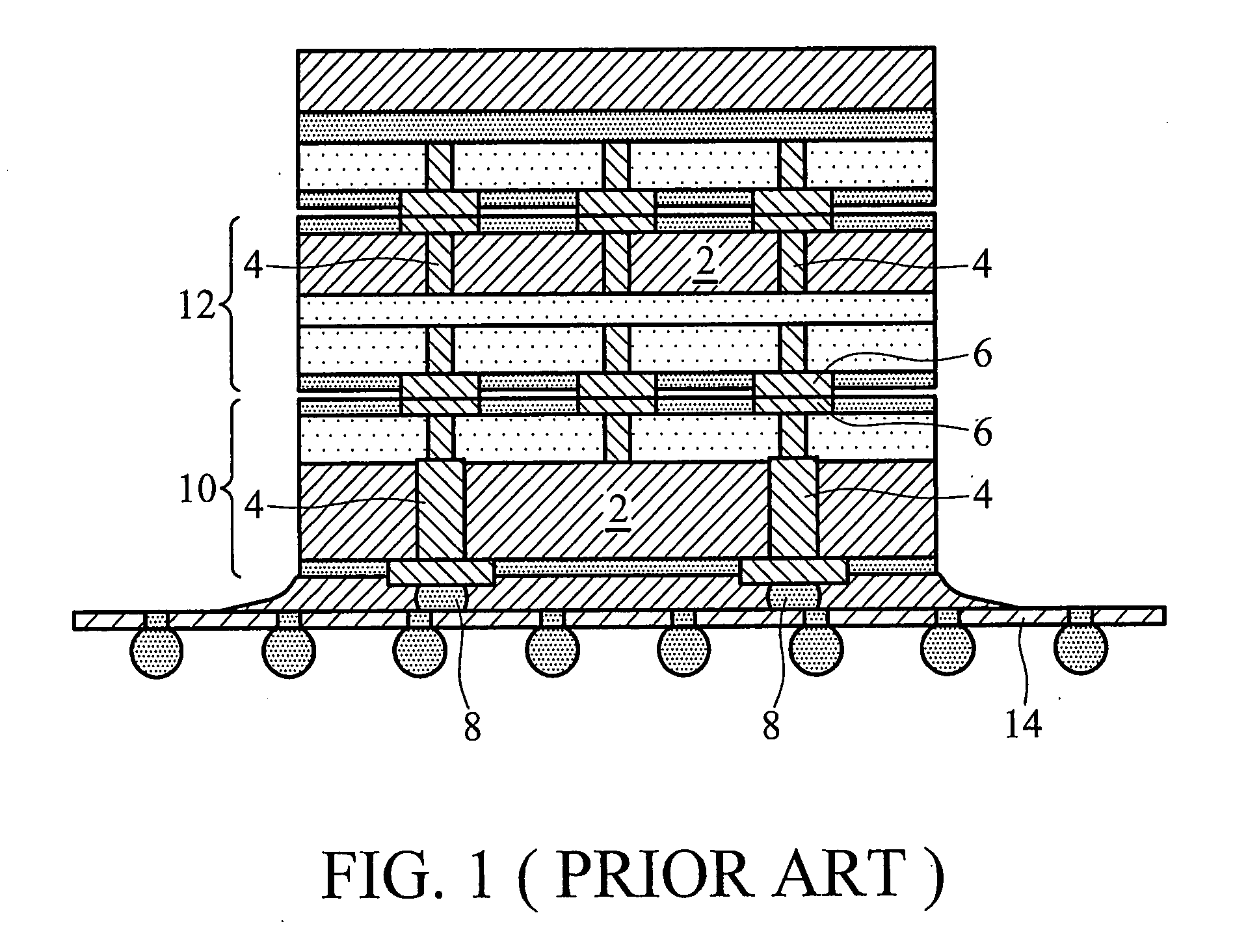

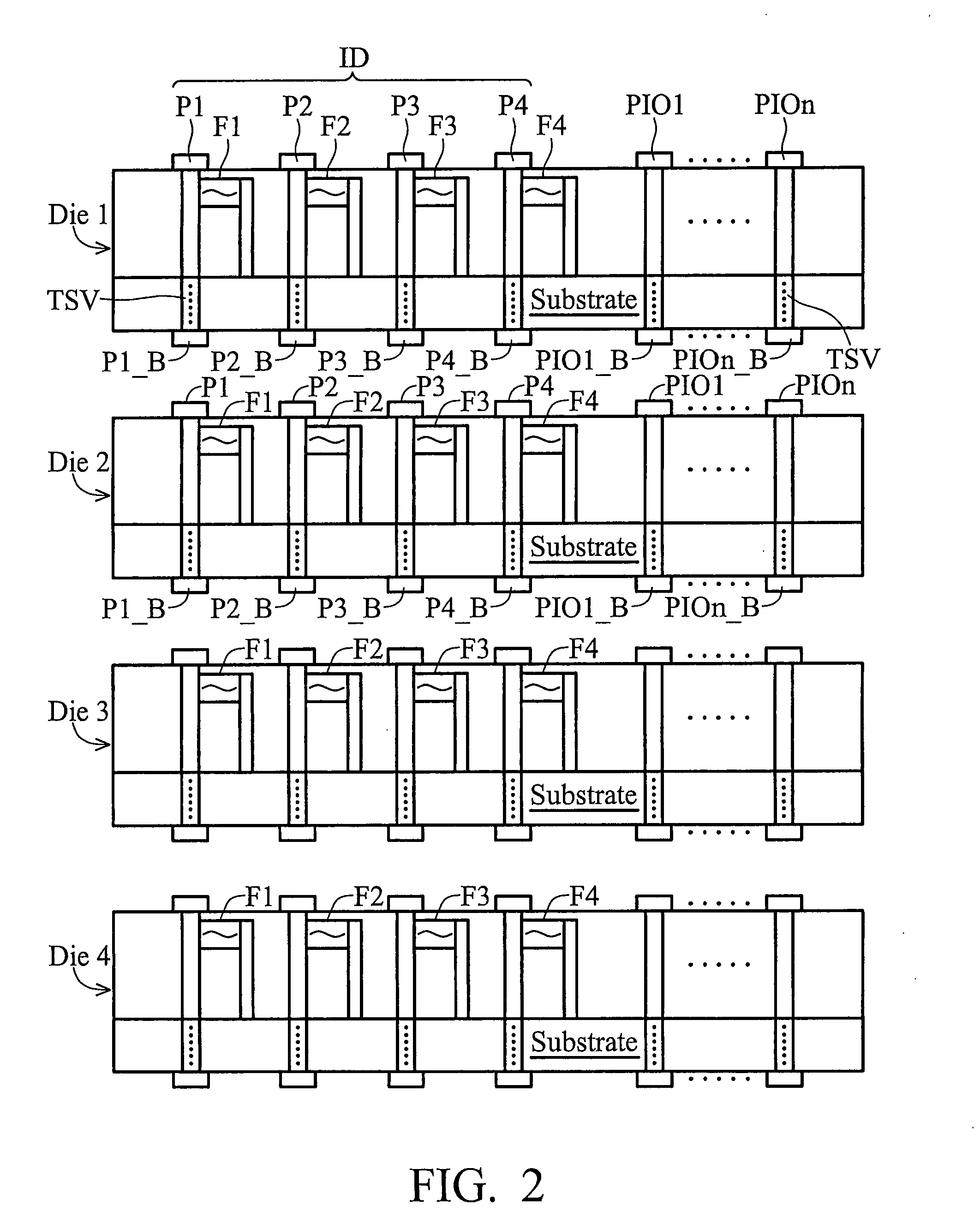

Design techniques for stacking identical memory dies

ActiveUS20080220565A1Reduce designReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor structure

A semiconductor structure includes a first semiconductor die and a second semiconductor die identical to the first semiconductor die. The first semiconductor die includes a first identification circuit; and a first plurality of input / output (I / O) pads on the surface of the first semiconductor die. The second semiconductor die includes a second identification circuit, wherein the first and the second identification circuits are programmed differently from each other; and a second plurality of I / O pads on the surface of the second semiconductor die. Each of the first plurality of I / O pads is vertically aligned to and connected to one of the respective second plurality of I / O pads. The second semiconductor die is vertically aligned to and bonded on the first semiconductor die.

Owner:TRENCHANT BLADE TECH LLC

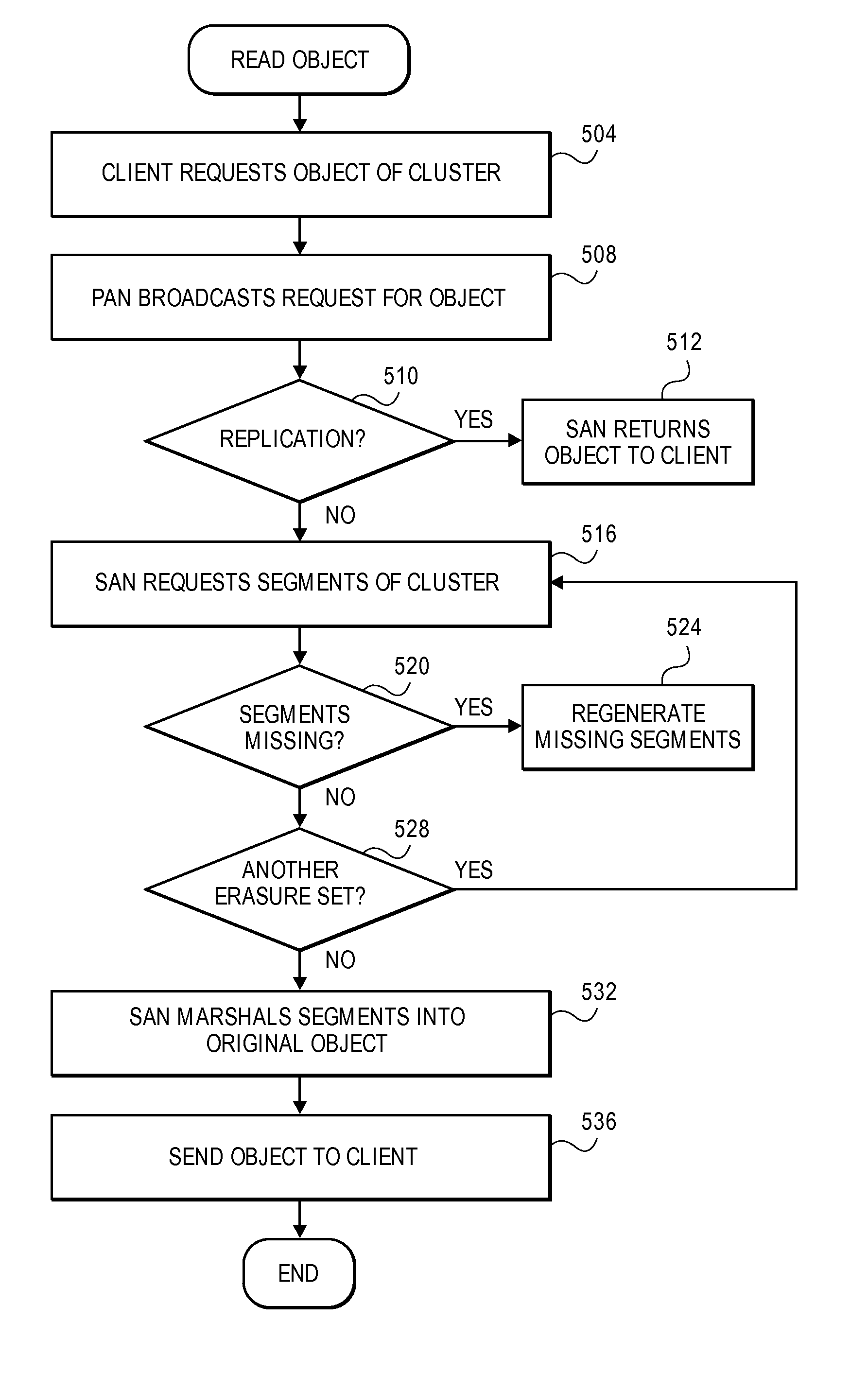

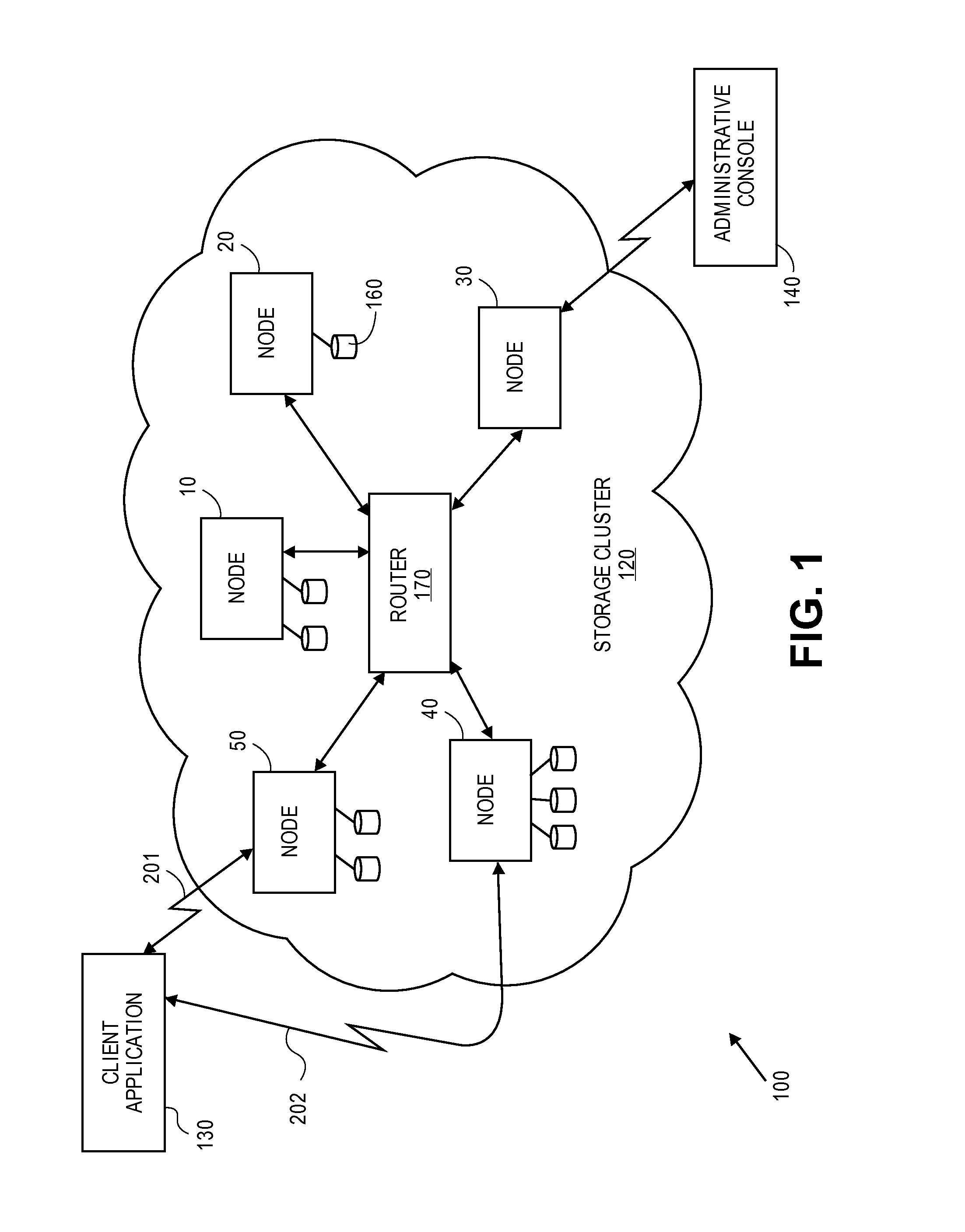

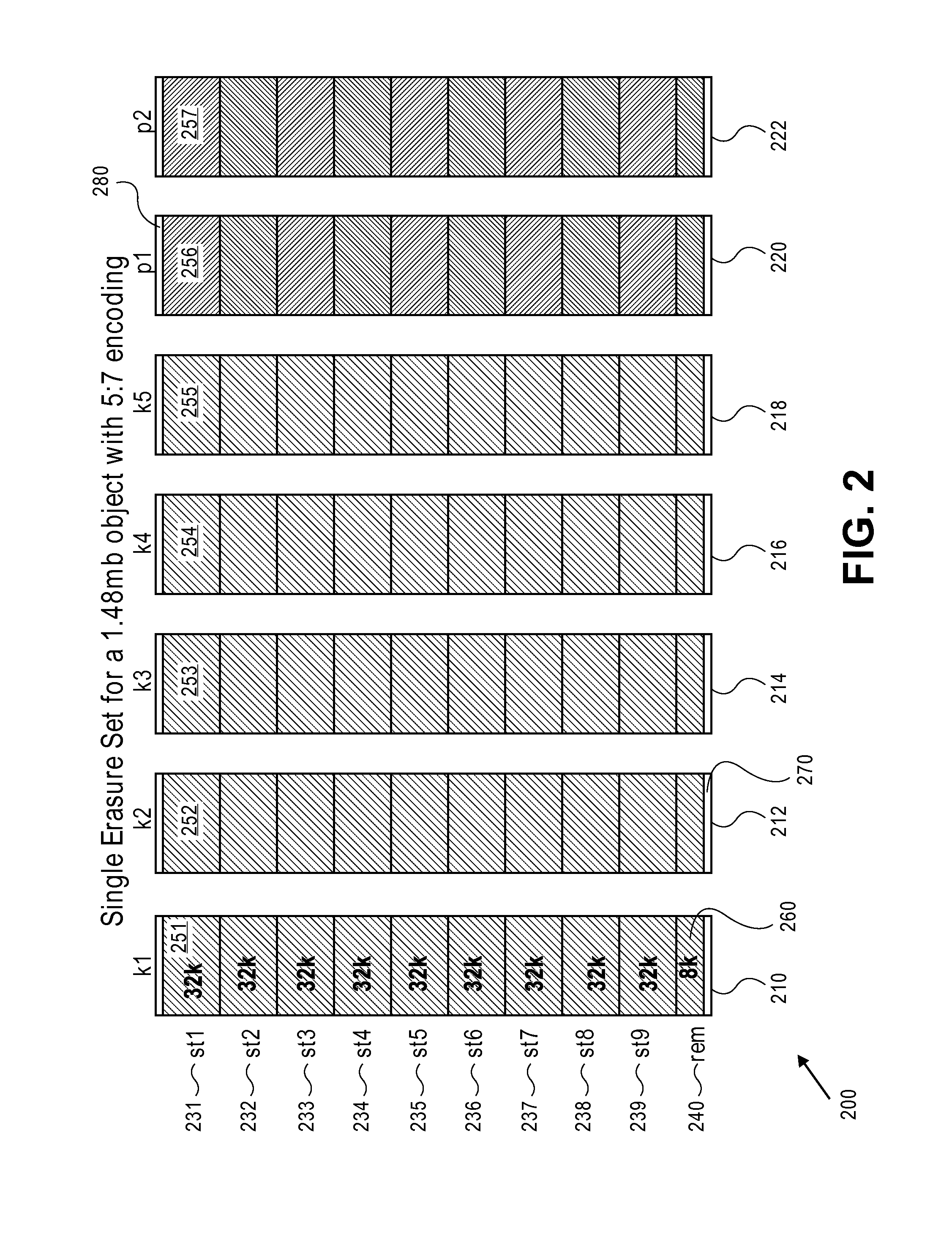

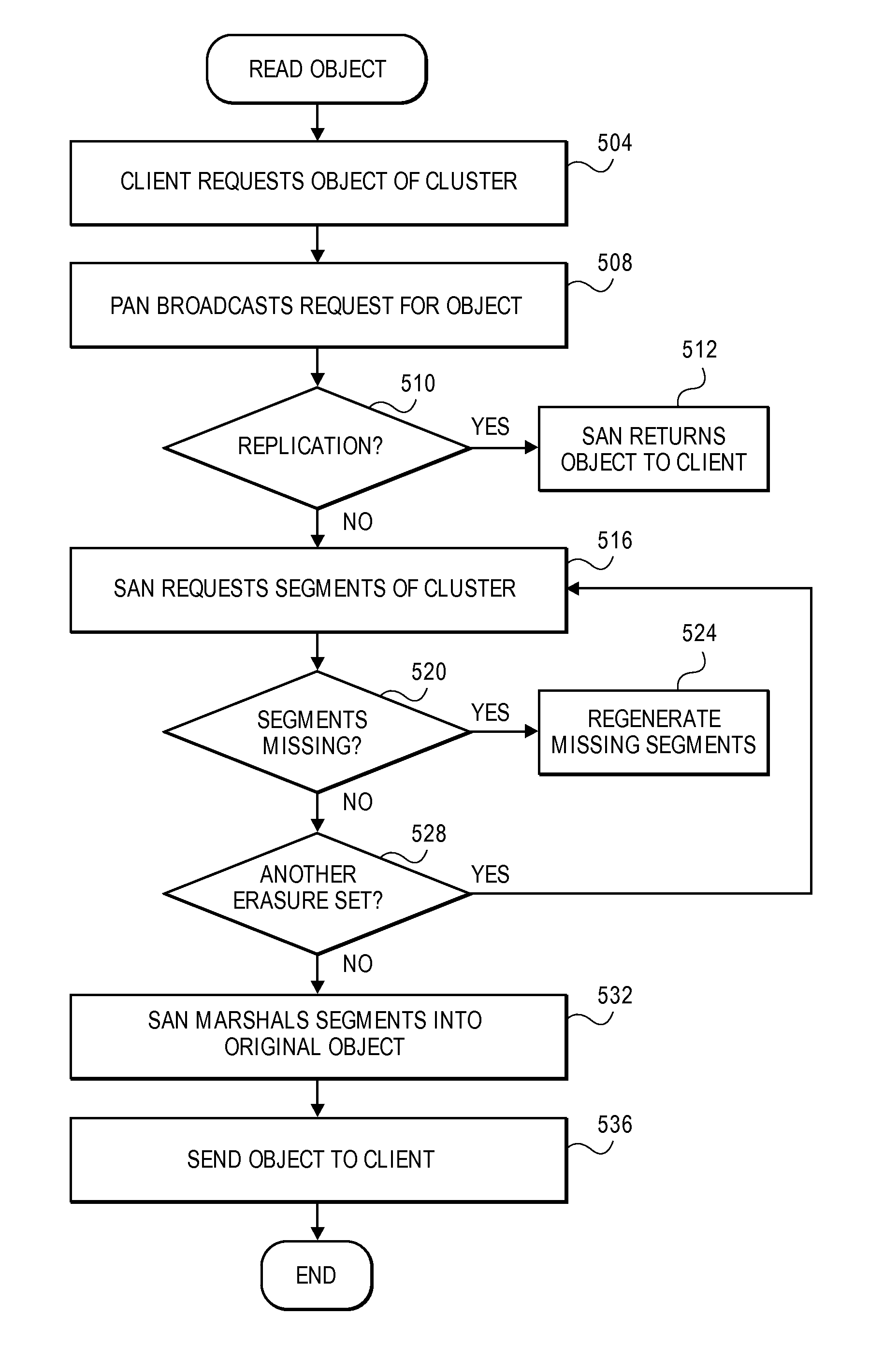

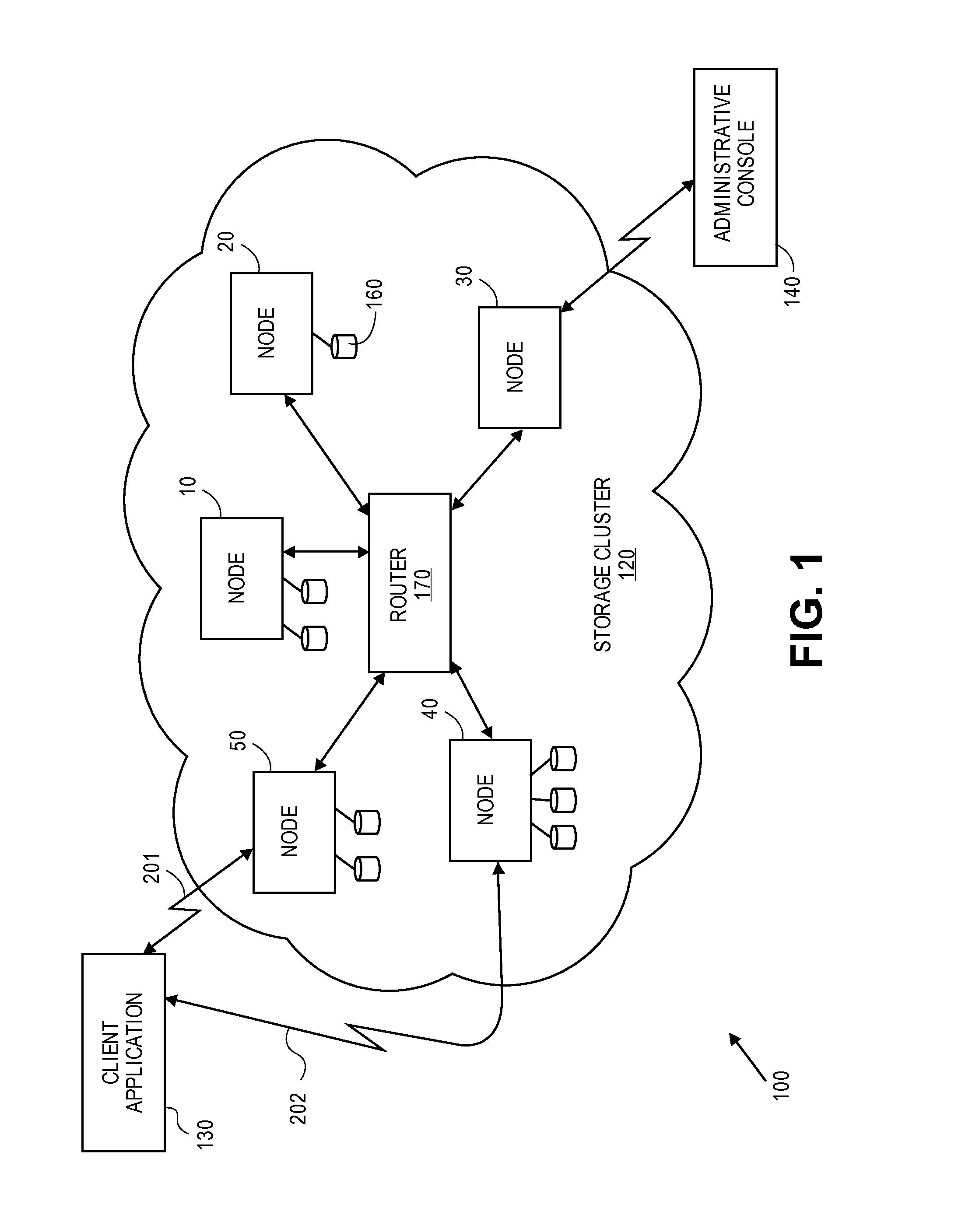

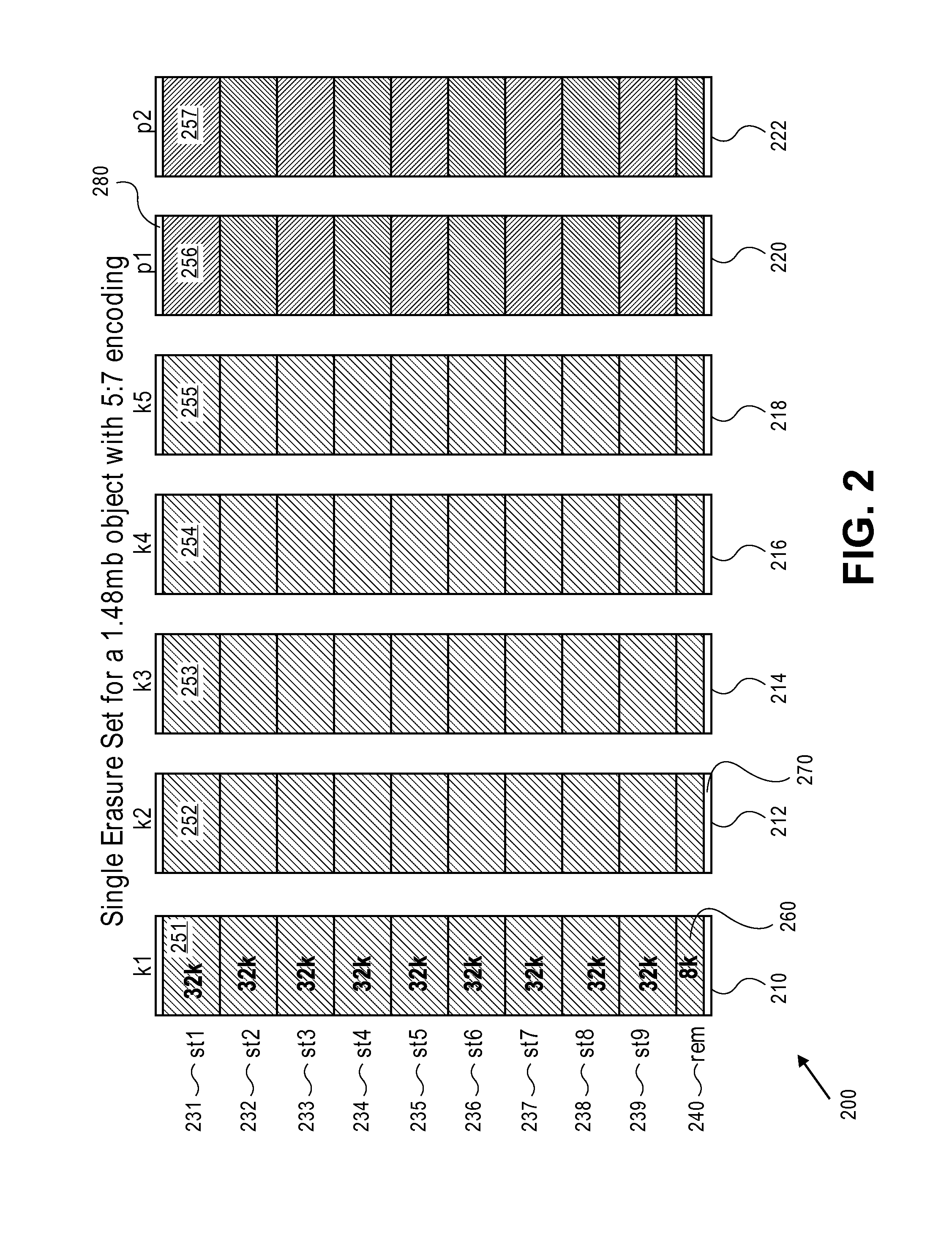

Erasure coding and replication in storage clusters

ActiveUS20130339818A1Error correction/detection using block single space codingCode conversionUnique identifierOperating system

A cluster receives a request to store an object using replication or erasure coding. The cluster writes the object using erasure coding. A manifest is written that includes an indication of erasure coding and a unique identifier for each segment. The cluster returns a unique identifier of the manifest. The cluster receives a request from a client that includes a unique identifier. The cluster determines whether the object has been stored using replication or erasure coding. If using erasure coding, the method reads a manifest. The method identifies segments within the cluster using unique segment identifiers of the manifest. Using these unique segment identifiers, the method reconstructs the object. A persistent storage area of another disk is scanned to find a unique identifier of a failed disk. If using erasure coding, a missing segment previously stored on the disk is identified. The method locates other segments. Missing segments are regenerated.

Owner:DATACORE SOFTWARE

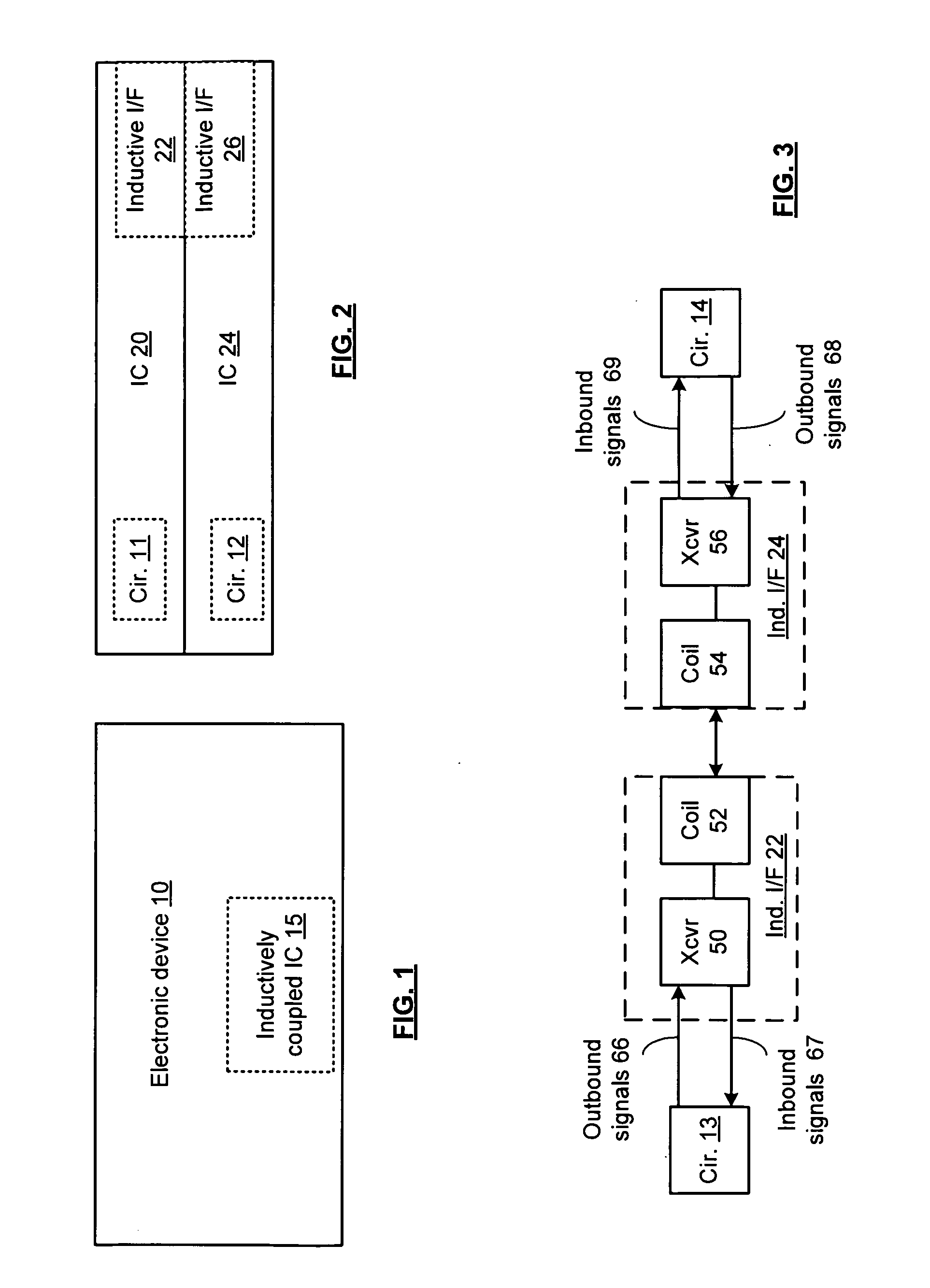

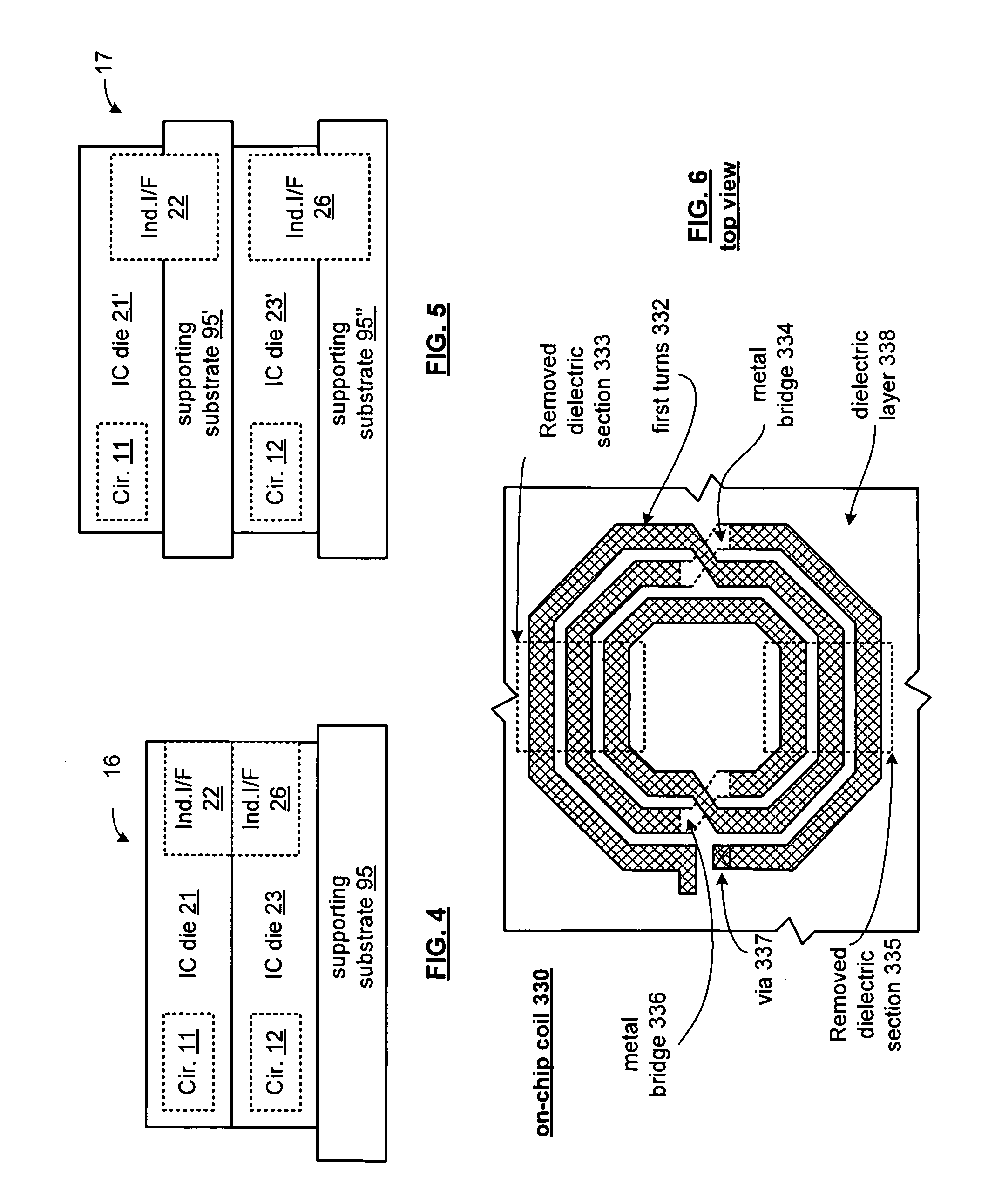

Integrated circuit with millimeter wave and inductive coupling and methods for use therewith

ActiveUS20090218407A1Near-field transmissionSemiconductor/solid-state device detailsEngineeringMillimetre wave

A circuit includes a plurality of integrated circuits or dies having corresponding circuits, the plurality of integrated circuits or dies include a first plurality of integrated circuits or dies having corresponding millimeter wave interfaces and a second plurality of integrated circuits or dies having corresponding inductive interfaces. The first plurality of integrated circuits or dies communicate first signals therebetween via the corresponding millimeter wave interfaces and the second plurality of integrated circuits or dies communicate second signals therebetween via the corresponding inductive interfaces.

Owner:AVAGO TECH INT SALES PTE LTD

Erasure coding and replication in storage clusters

ActiveUS8799746B2Error correction/detection using block single space codingCode conversionUnique identifierOperating system

Owner:DATACORE SOFTWARE

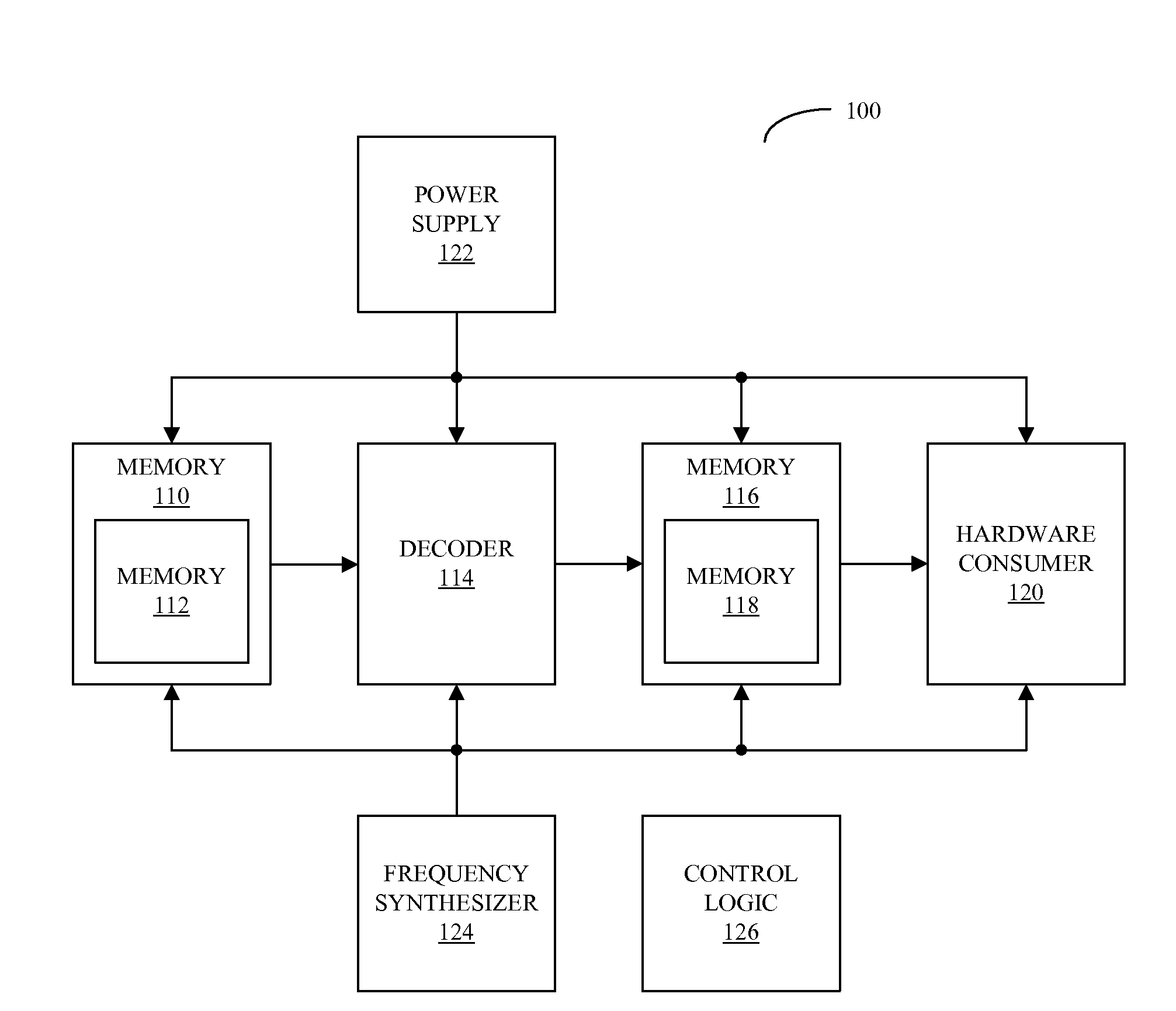

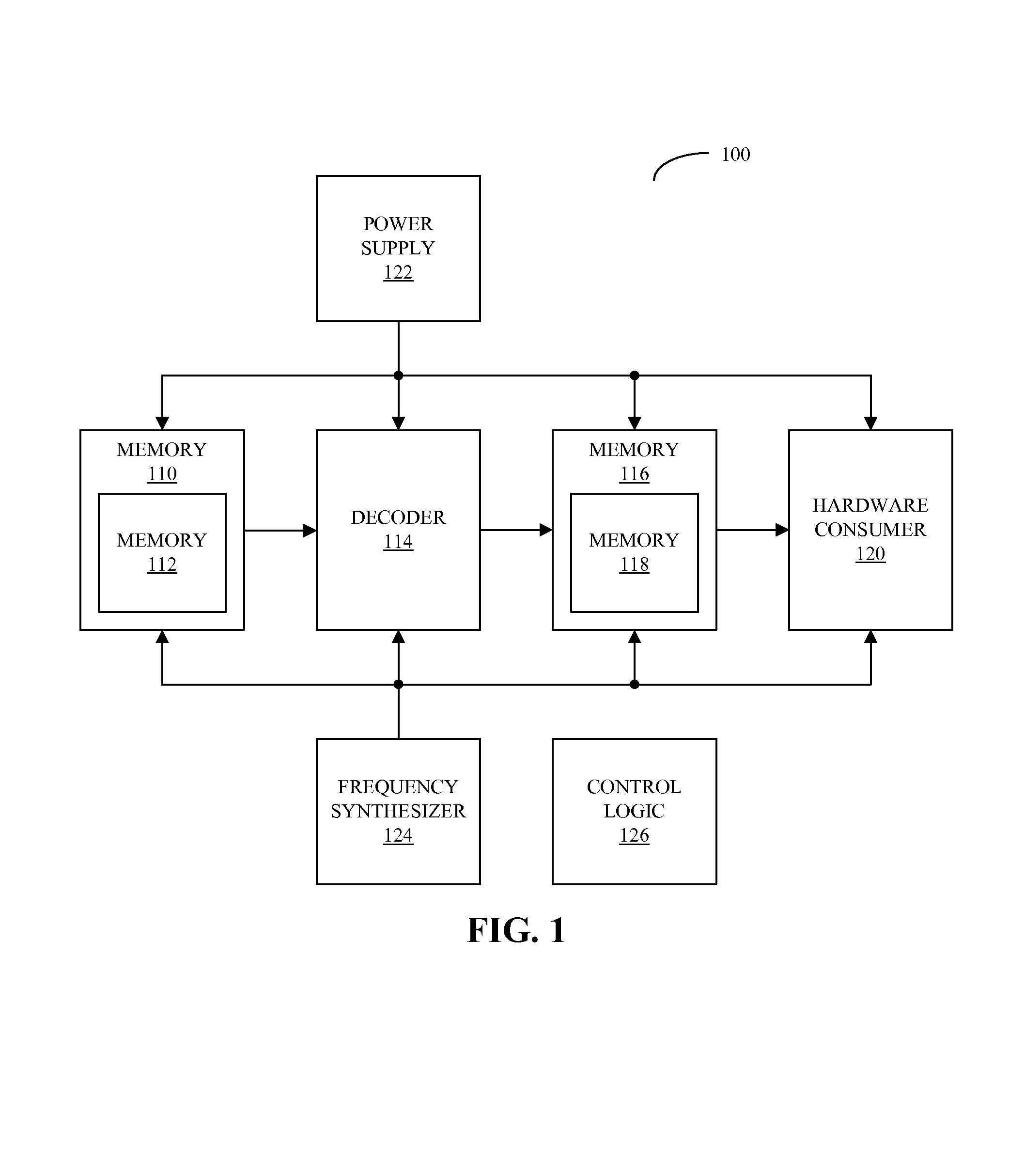

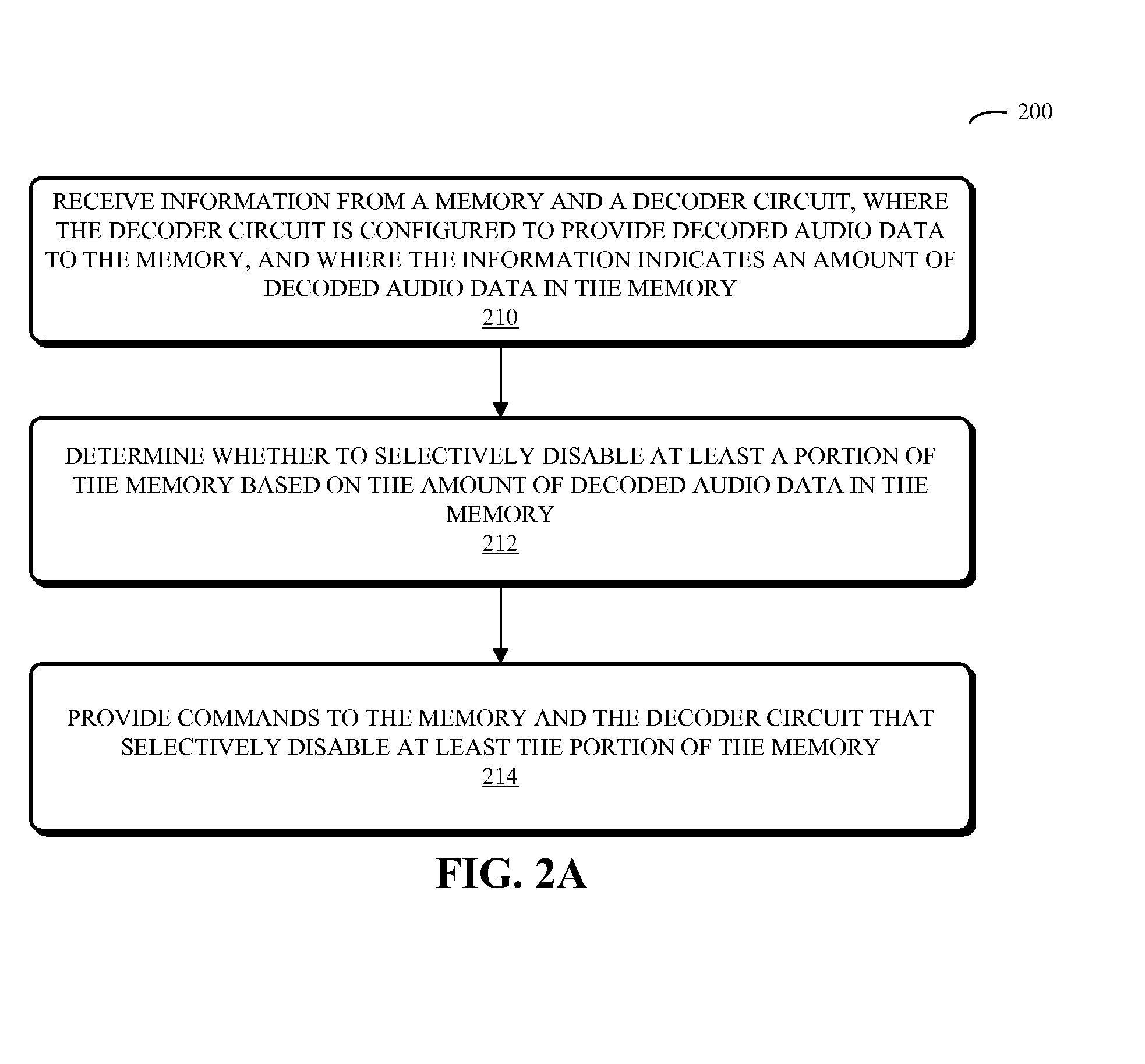

Power-gating media decoders to reduce power consumption

ActiveUS20090003115A1Reduce power consumptionEnergy efficient ICTDigital data processing detailsElectricityHemt circuits

Embodiments of a system that reduces power consumption by power-gating media decoders are described. During operation of the system, a decoder circuit receives encoded audio data and outputs corresponding decoded audio data to a memory, which is electrically coupled to the decoder circuit. Moreover, control logic, which is electrically coupled to the memory and the decoder circuit, provides commands to the memory and the decoder circuit that selectively disable at least a portion of the memory based on an amount of decoded audio data in the memory.

Owner:APPLE INC

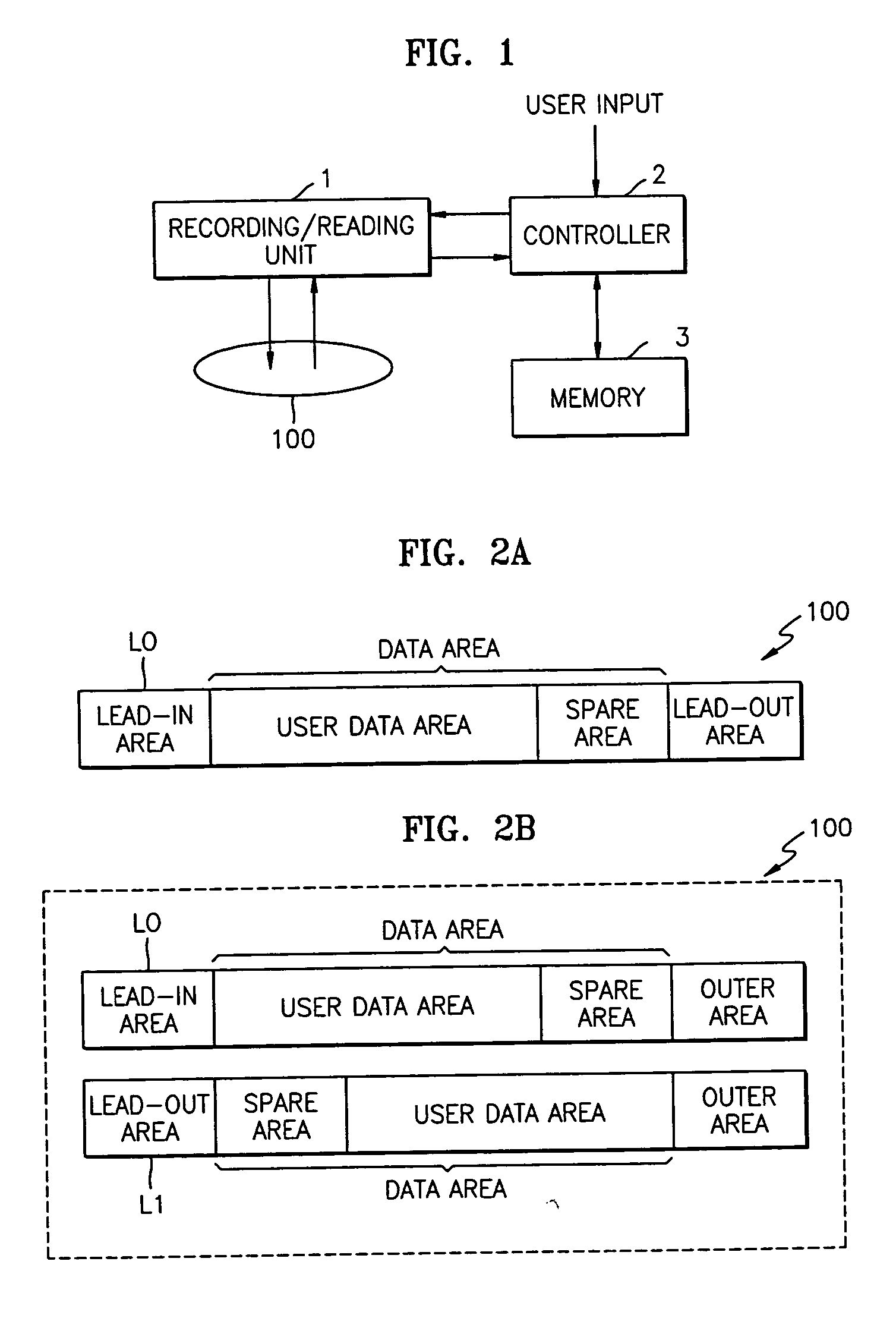

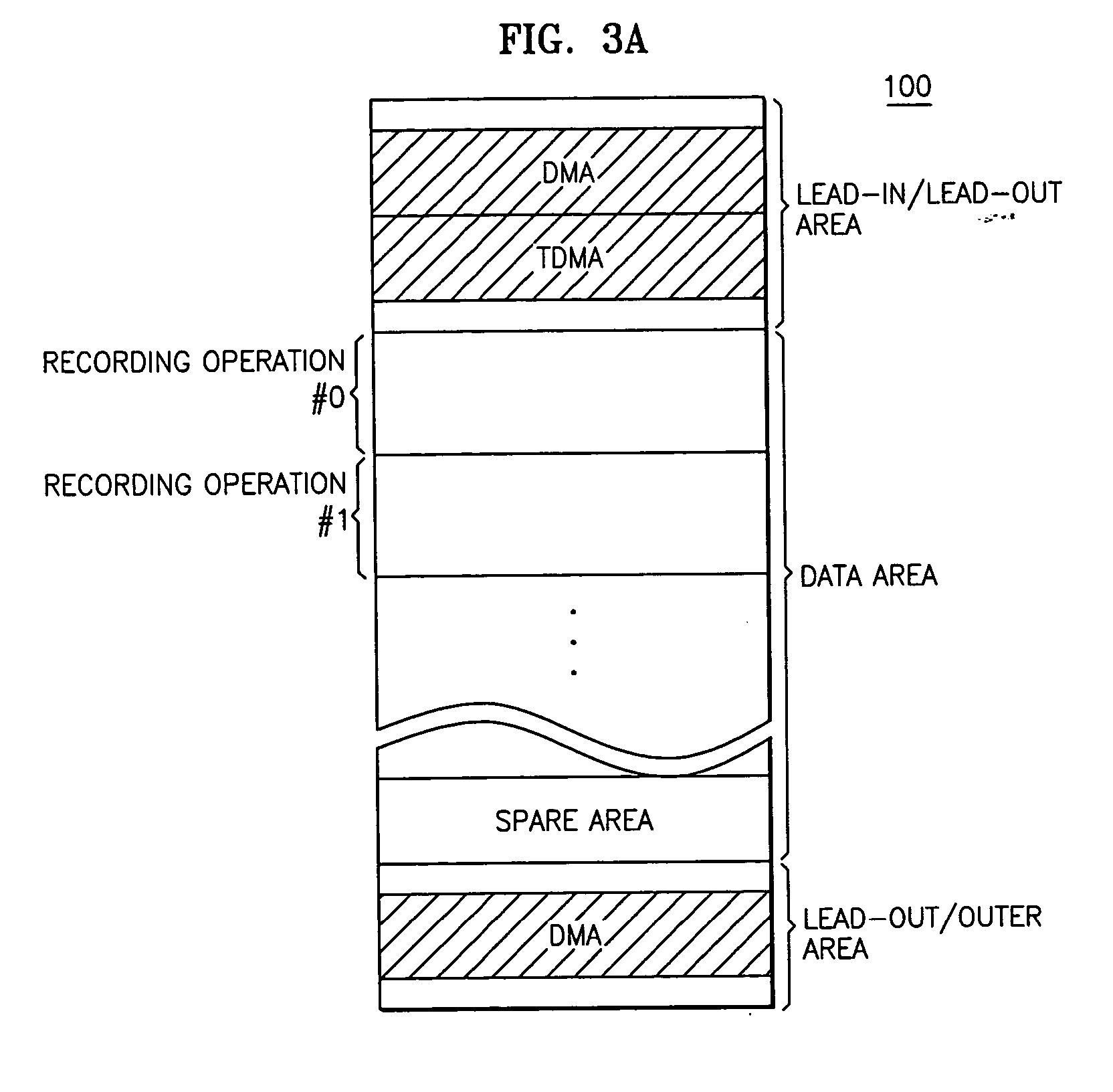

Method of and apparatus for managing disc defects using temporary defect management information (TDFL) and temporary defect management information (TDDS), and disc having the TDFL and TDDS

ActiveUS20040076096A1Combination recordingRecord information storageComputer hardwareManagement area

A disc having an updatable defect management area used by an apparatus for managing defects on the disc, the disc including a user data area which includes user data, a spare area that is a substitute area for a defect existing in the user data area, and an area in which are recorded an address of data that is last recorded in the user data area and an address of a replacement data recorded in the spare area. Accordingly, the disc defect management method and apparatus are applicable to a recordable disc such as a write-once disc while effectively using a defect management area of the disc.

Owner:SAMSUNG ELECTRONICS CO LTD

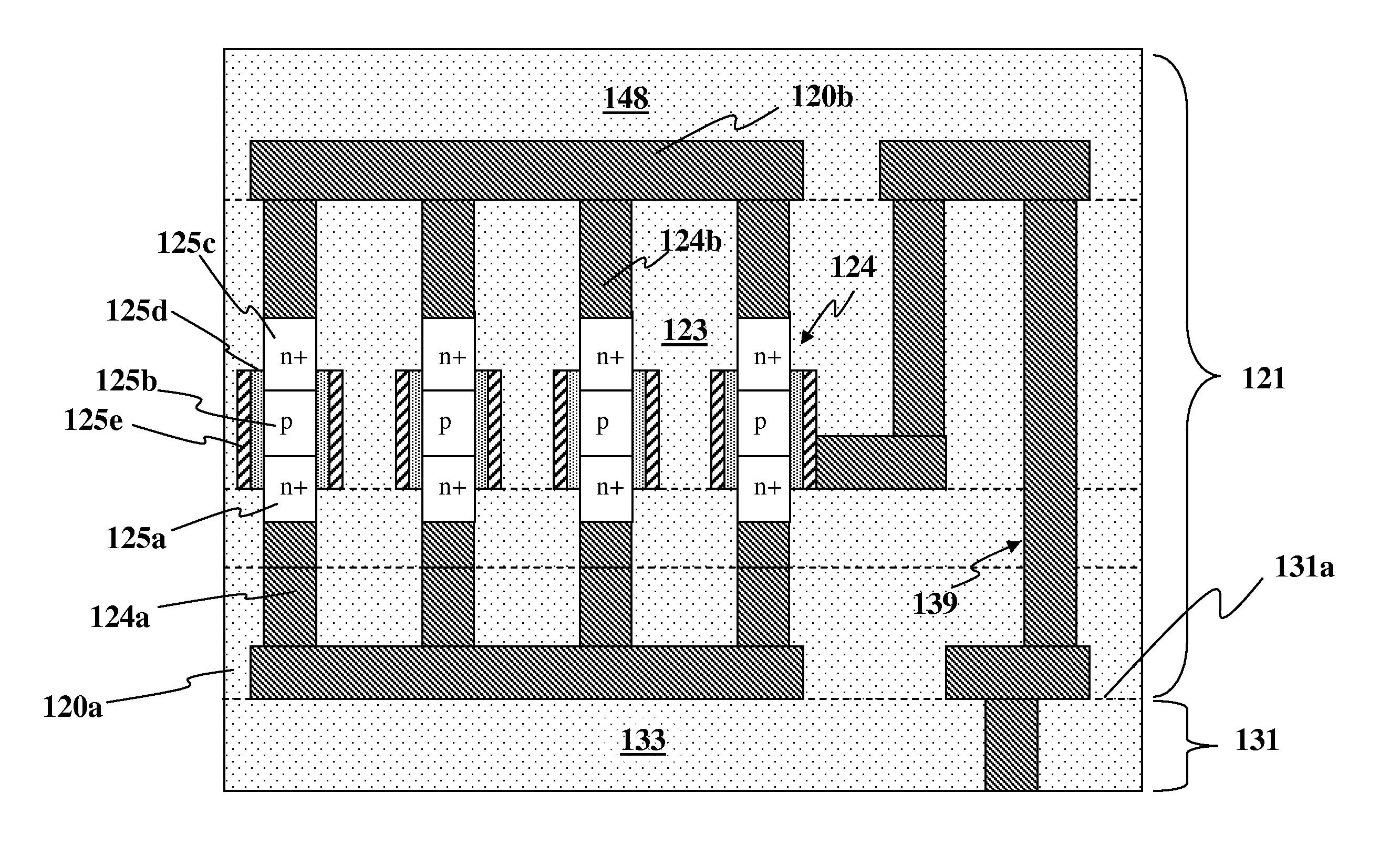

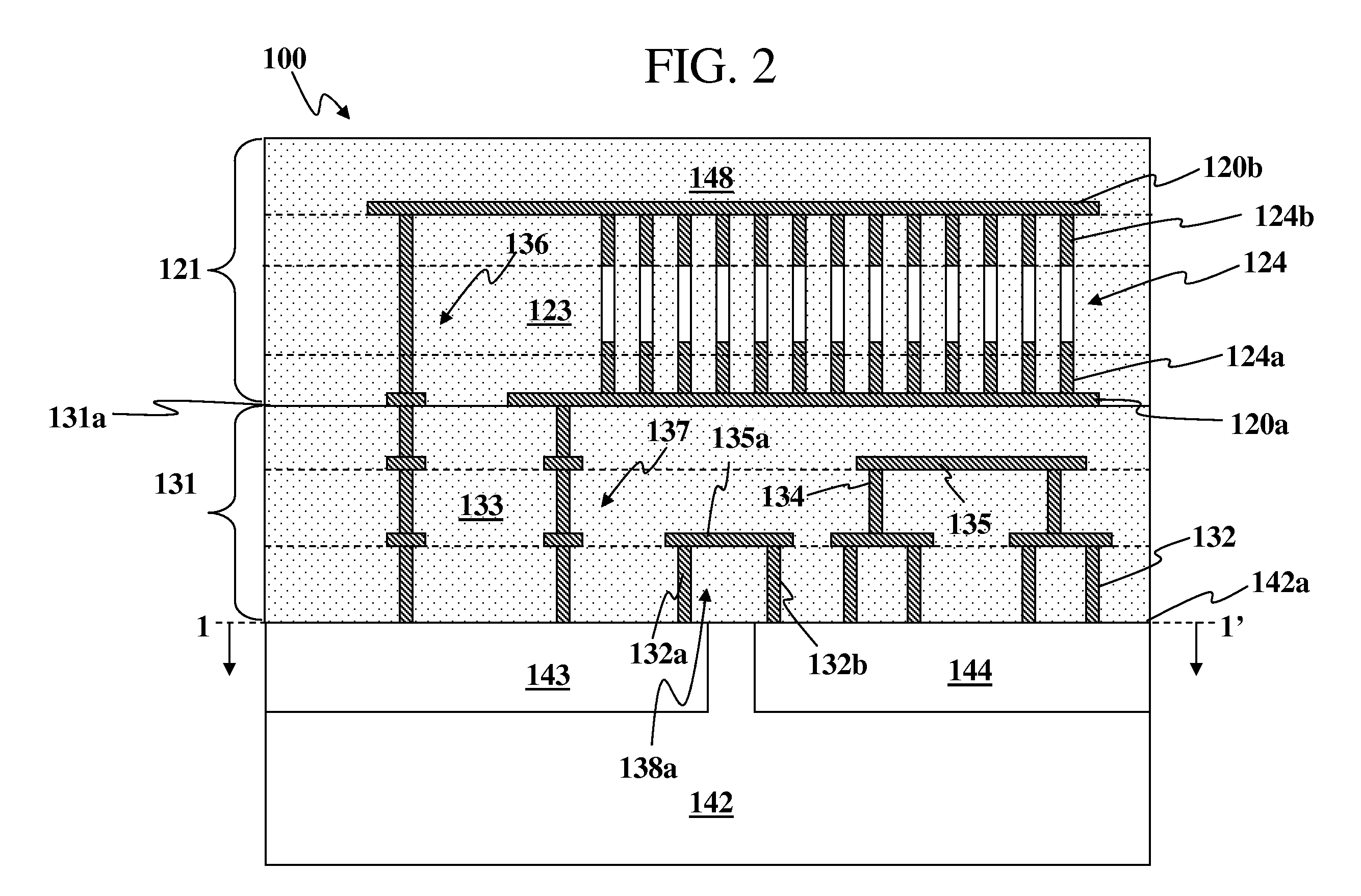

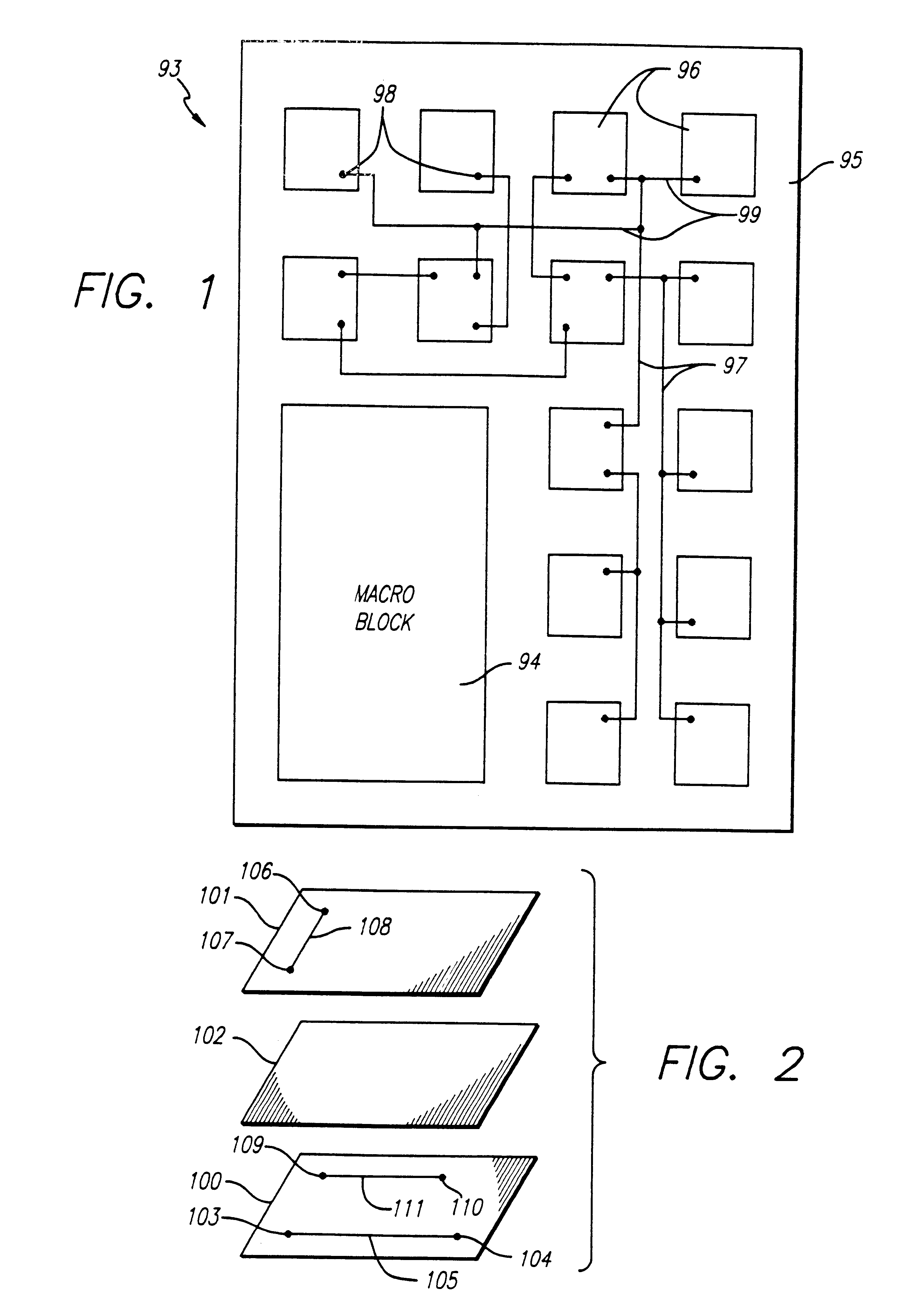

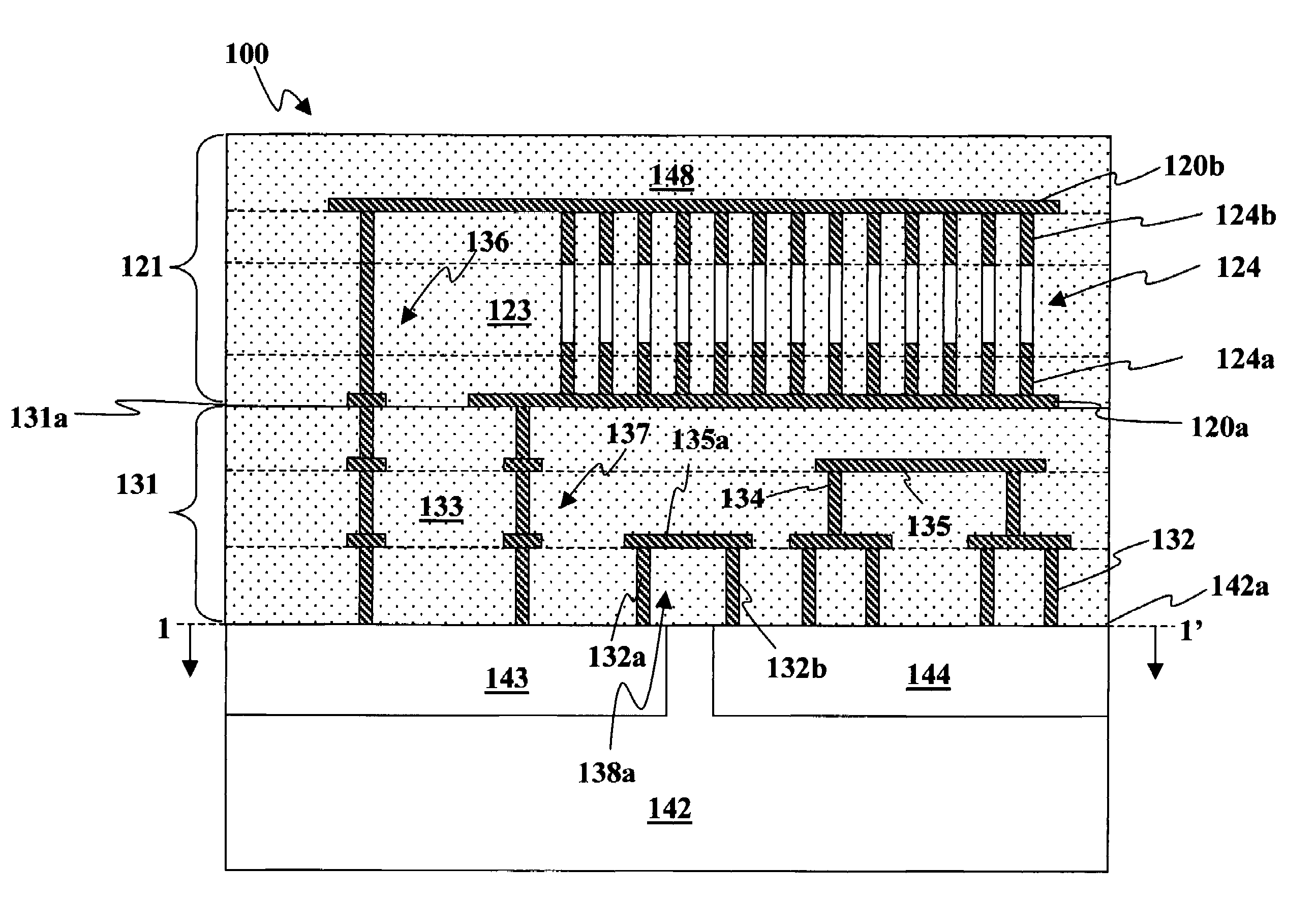

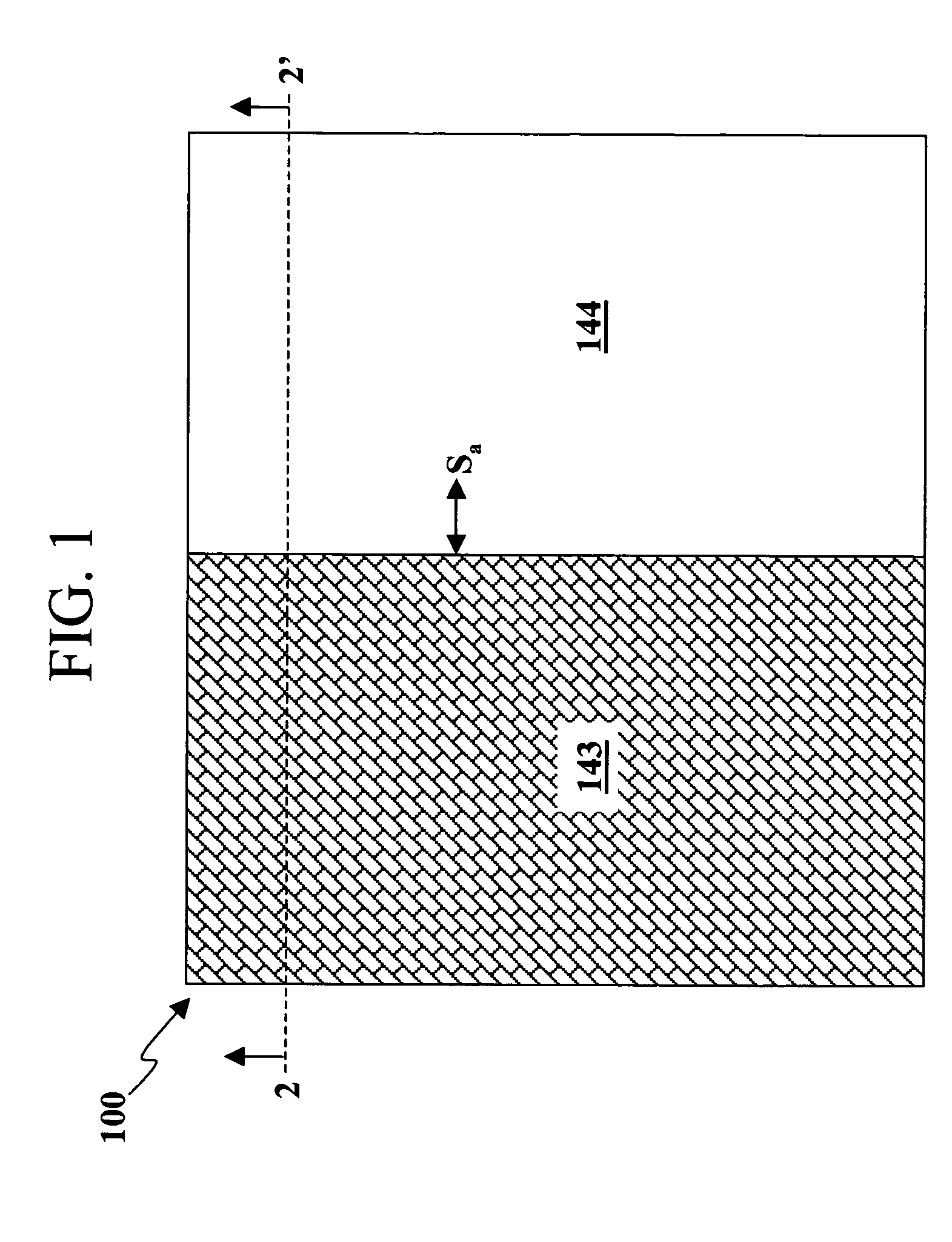

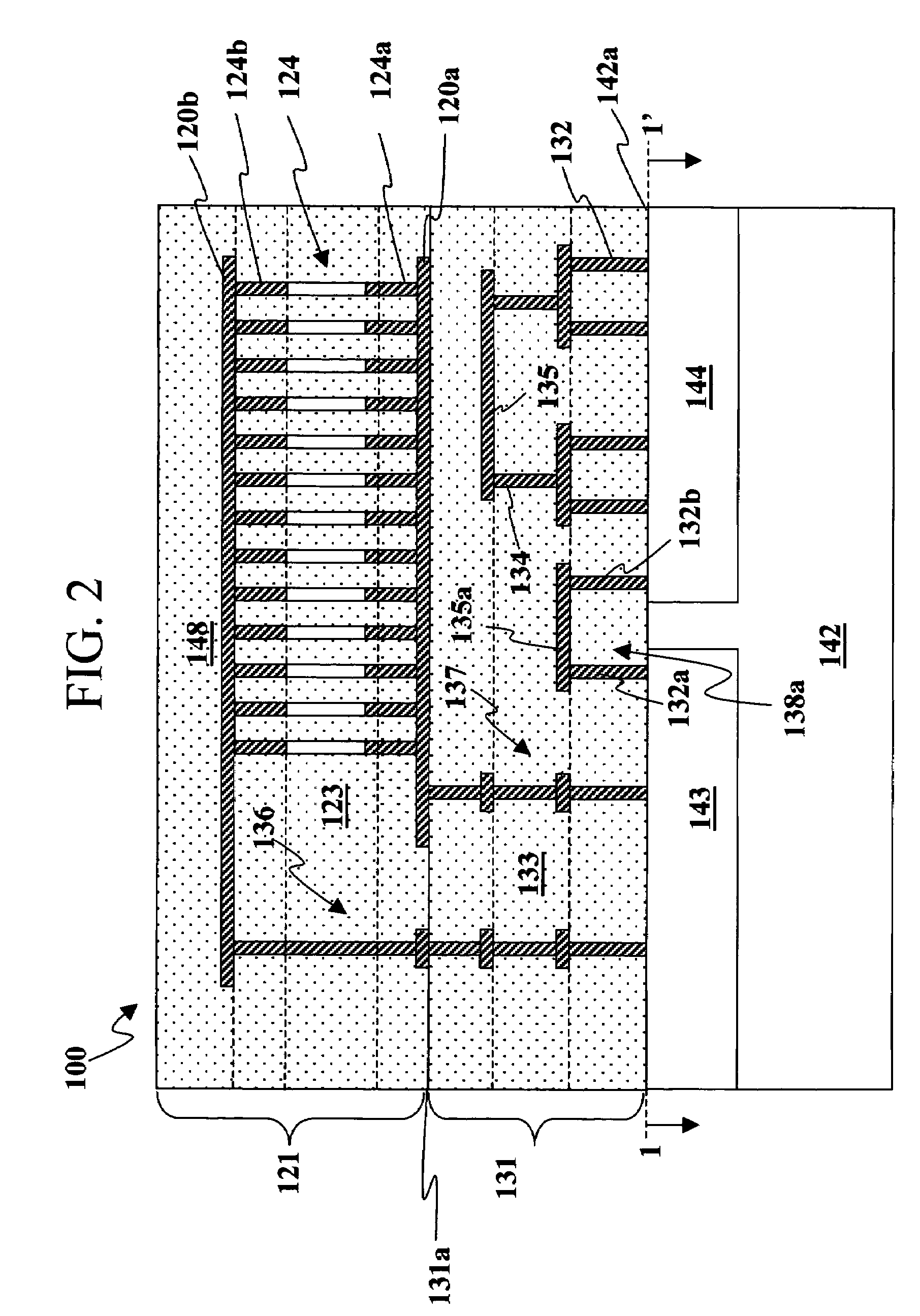

Electronic circuit with embedded memory

InactiveUS20080048327A1Semiconductor/solid-state device detailsSolid-state devicesMemory circuitsSemiconductor

Owner:BESANG

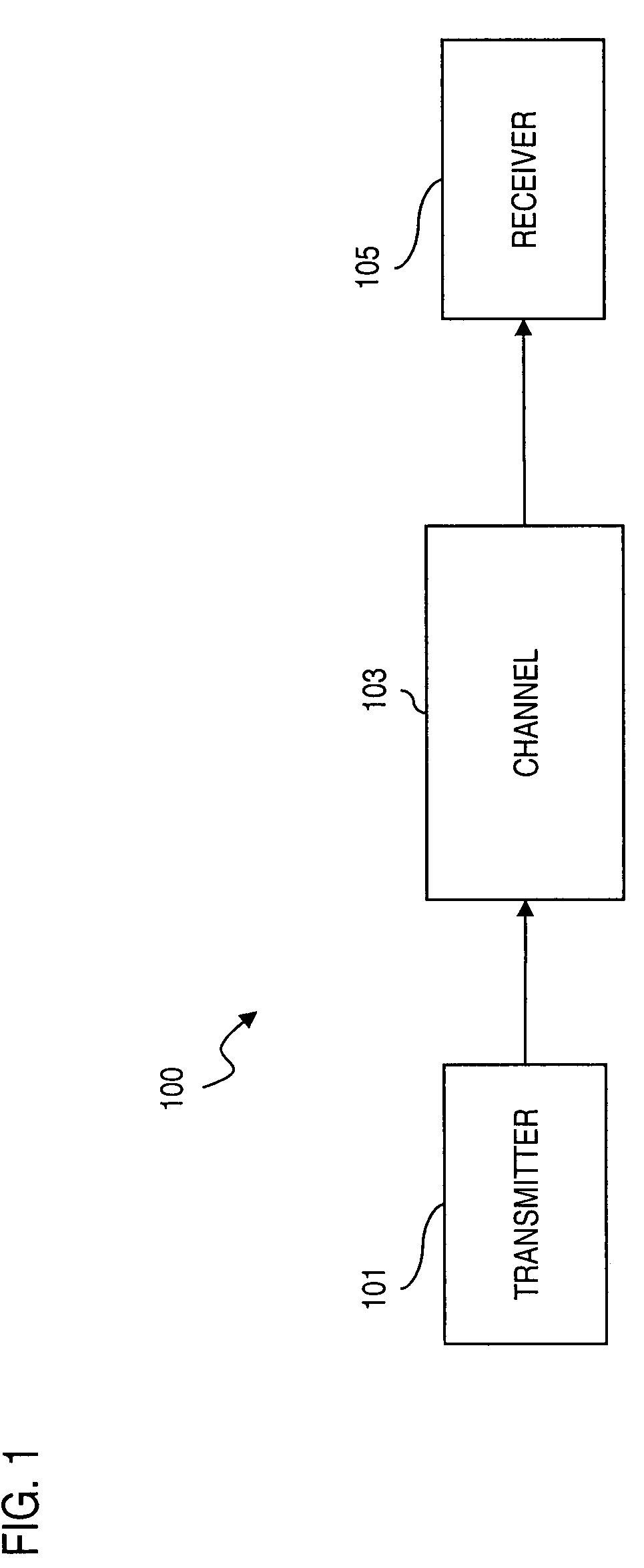

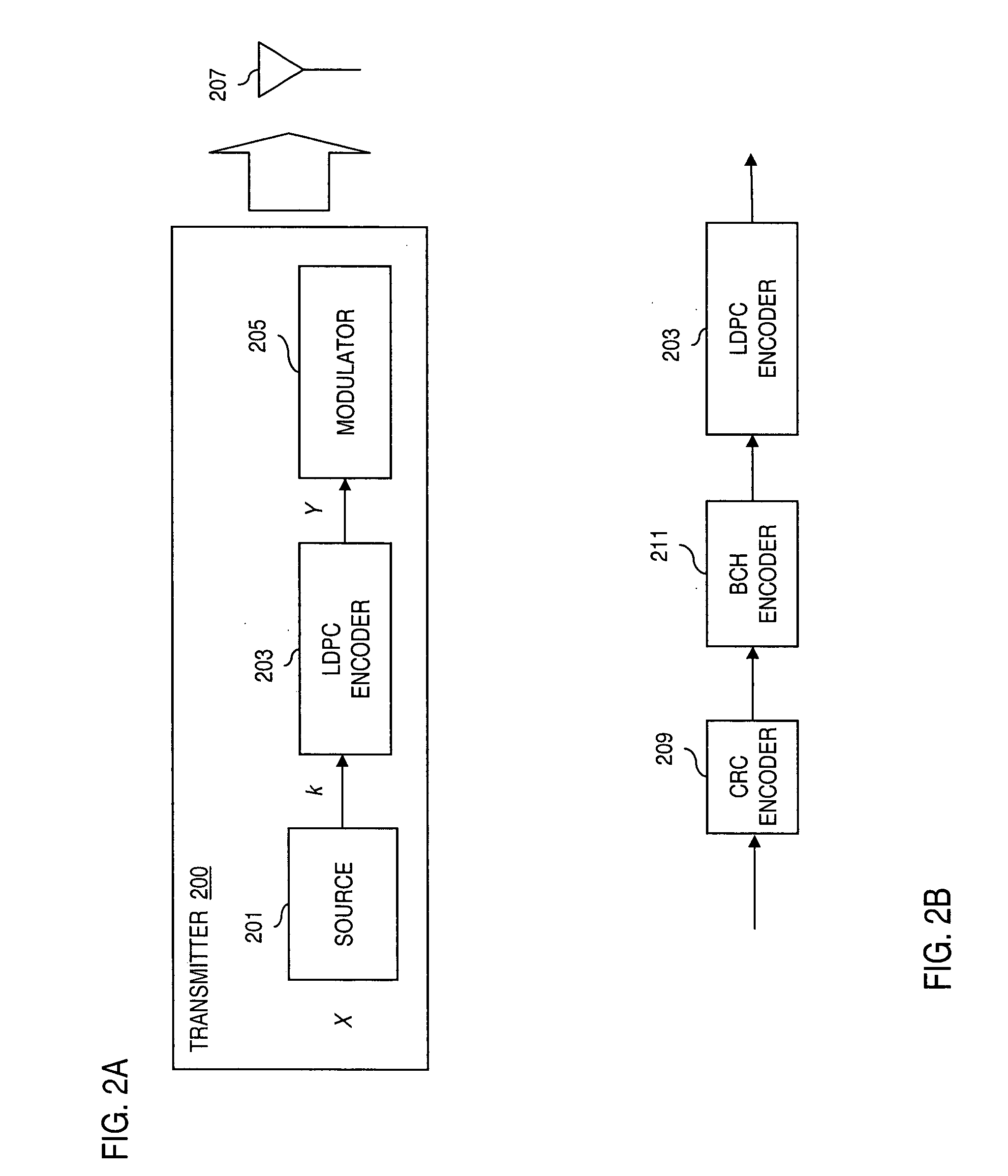

Method and system for providing low density parity check (LDPC) encoding

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

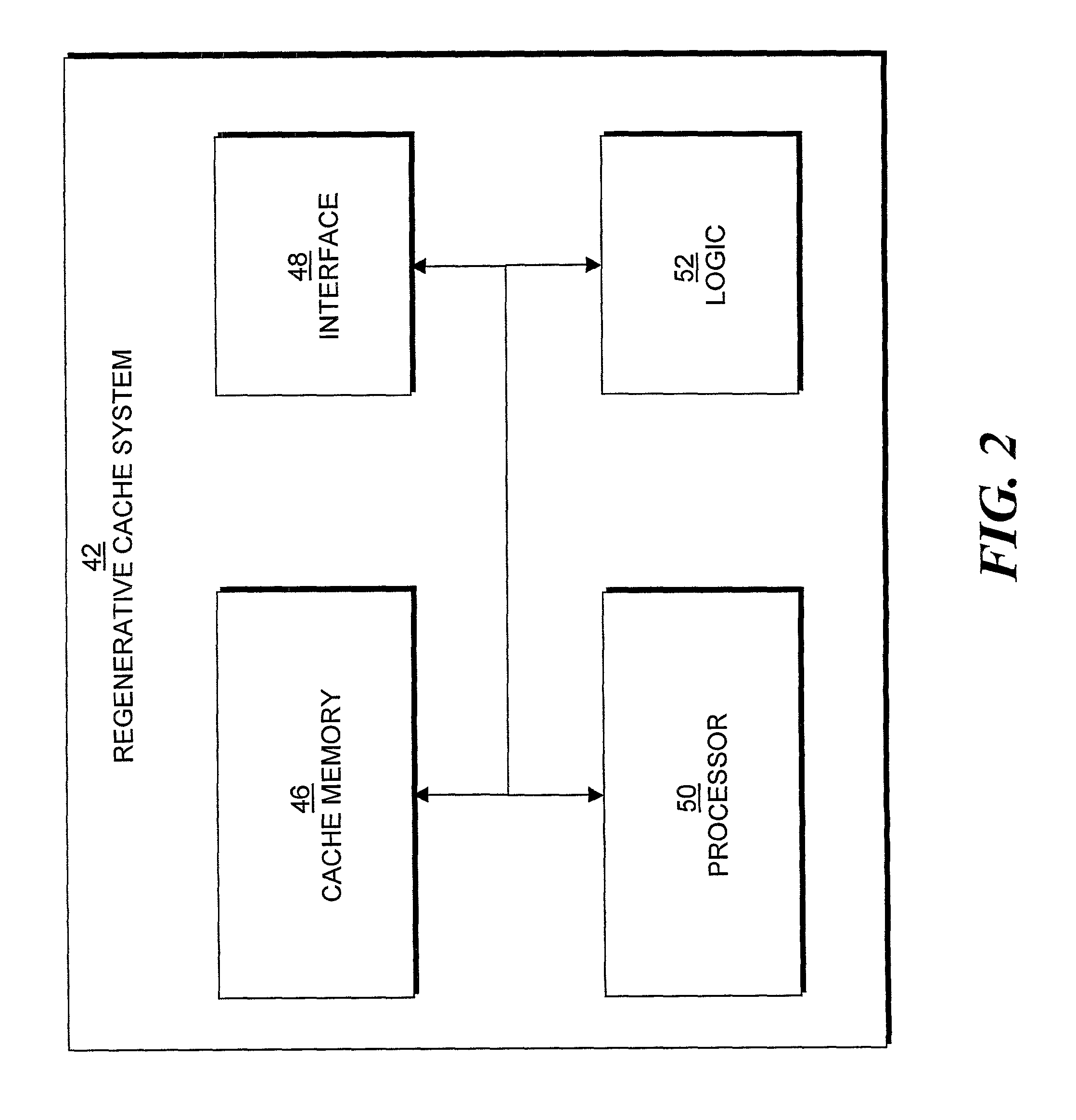

Cache system and method for generating uncached objects from cached and stored object components

InactiveUS7006099B2Memory architecture accessing/allocationImage memory managementExternal storageParallel computing

Methods and apparatus for constructing objects within a cache system thereby allowing the cache system to respond to requested objects that are not initially available within the cache system. One embodiment of the invention caches image files, where the images are divided into components and stored in a format that allows identification and access to the components. The cache system determines that an object, such as an image file, is missing from the cache memory, locates sufficient components from the cache memory and / or external storage, and constructs the object from the located components.

Owner:AWARE INC

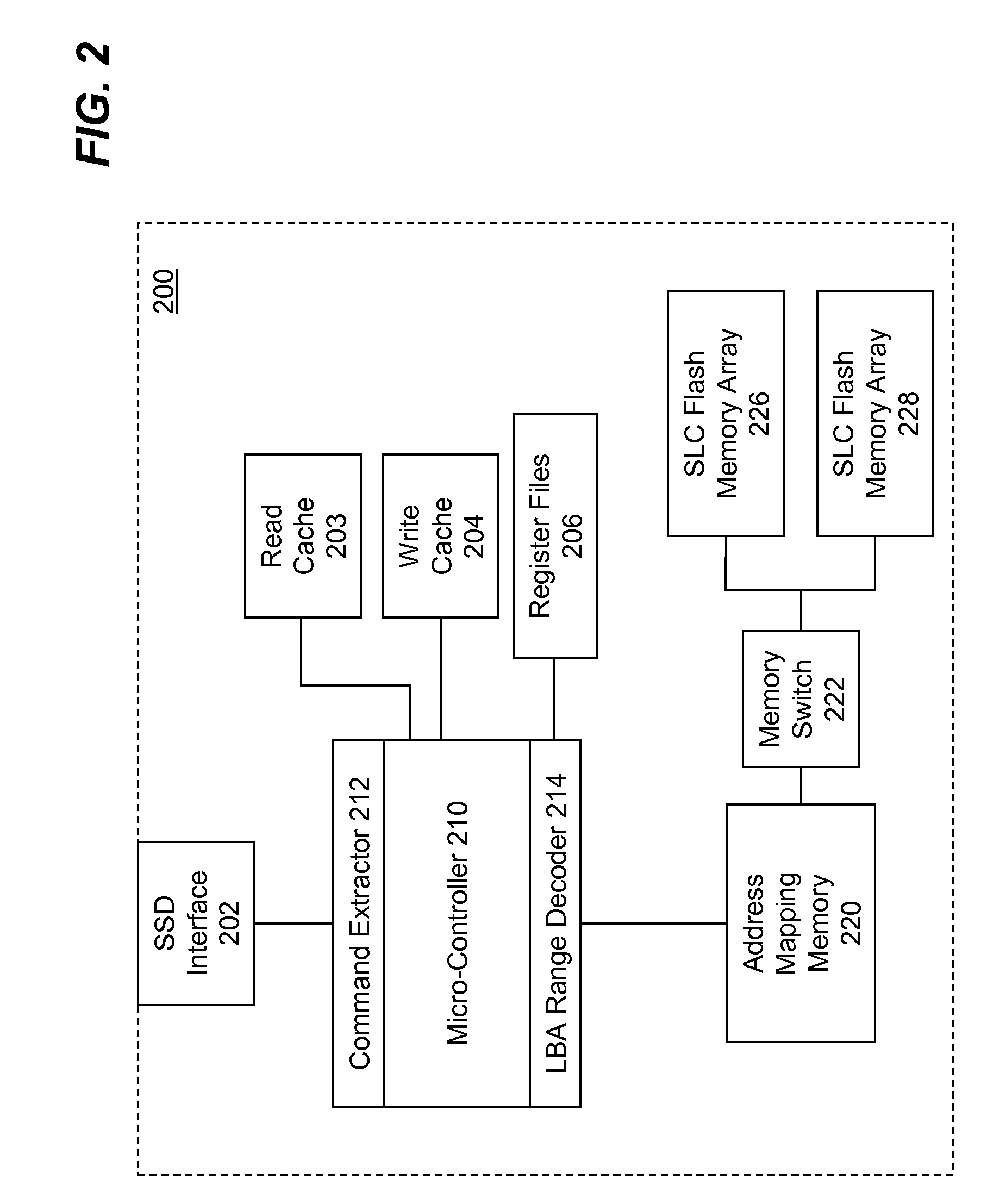

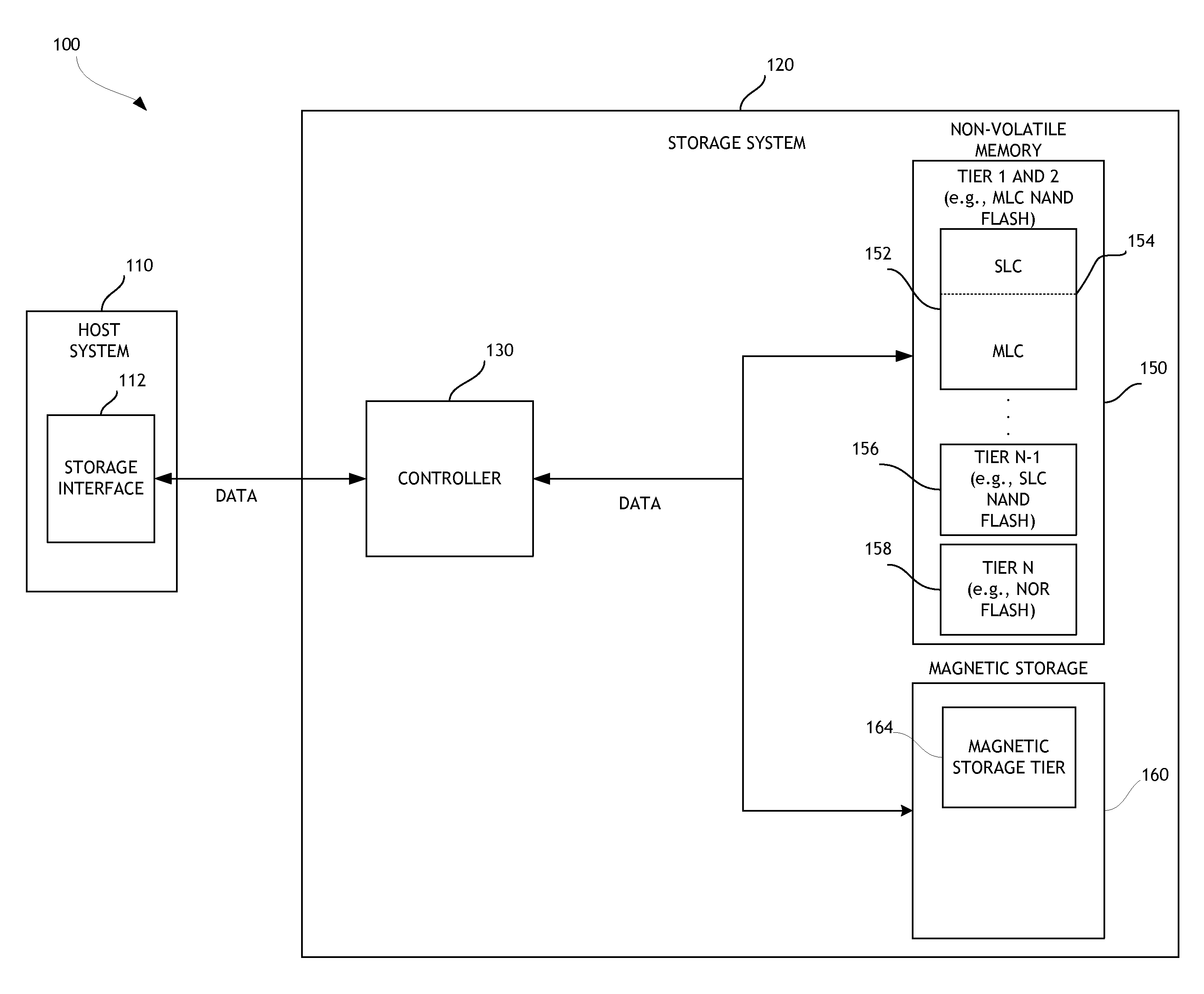

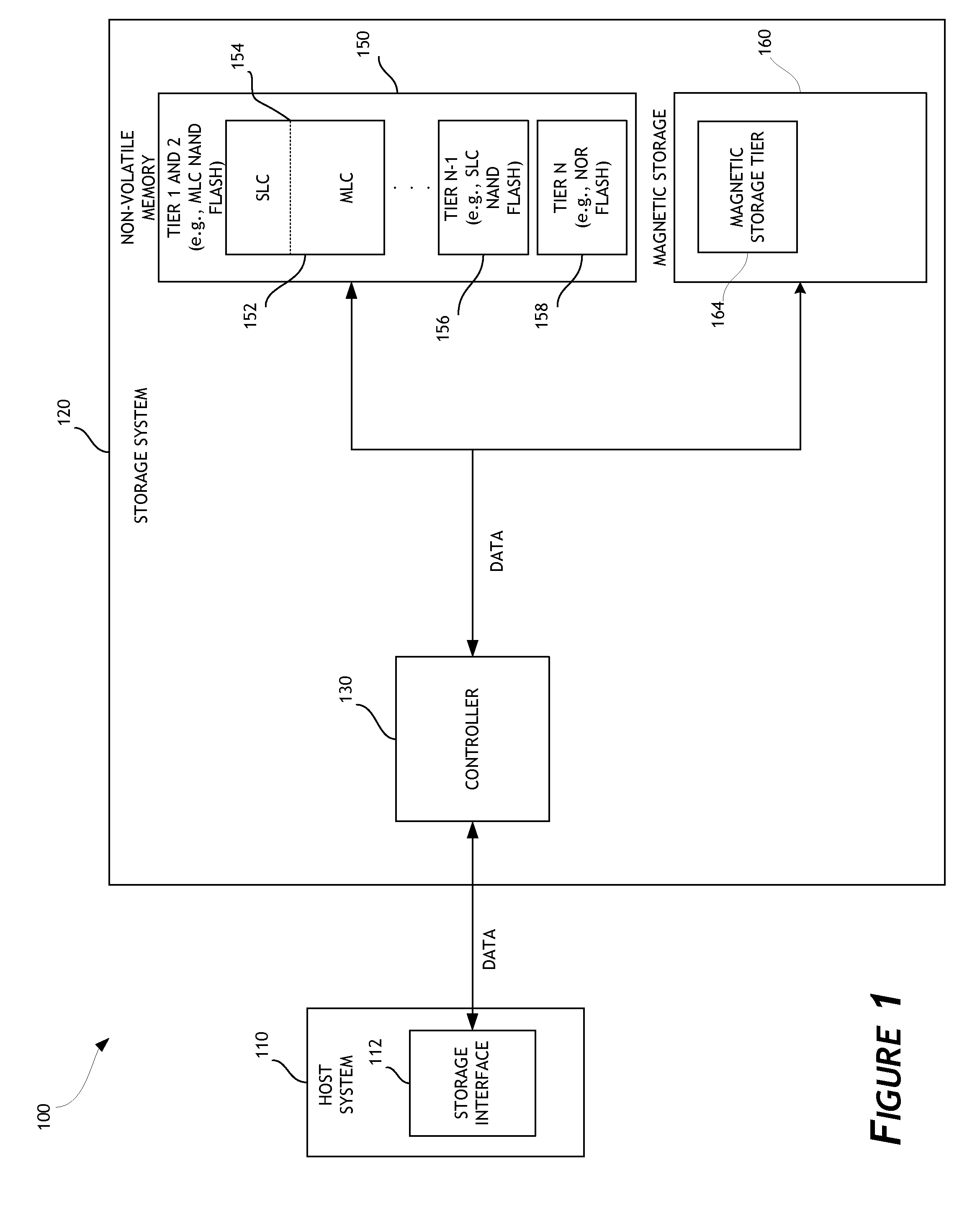

Hybrid SSD Using A Combination of SLC and MLC Flash Memory Arrays

InactiveUS20080215800A1Reduce manufacturing costAcceptable levelMemory architecture accessing/allocationInternal/peripheral component protectionData fileSingle level

Hybrid solid state drives (SSD) using a combination of single-level cell (SLC) and multi-level cell (MLC) flash memory arrays are described. According to one aspect of the present invention, a hybrid SSD is built using a combination SLC and MLC flash memory arrays. The SSD also includes a micro-controller to control and coordinate data transfer from a host computing device to either the SLC flash memory array of the MLC flash memory array. A memory selection indicator is determined by triaging data file based on one or more criteria, which include, but is not limited to, storing system files and user directories in the SLC flash memory array and storing user files in the MLC flash memory array; or storing more frequent access files in the SLC flash memory array, while less frequent accessed files in the MLC flash memory array.

Owner:SUPER TALENT TECH CORP

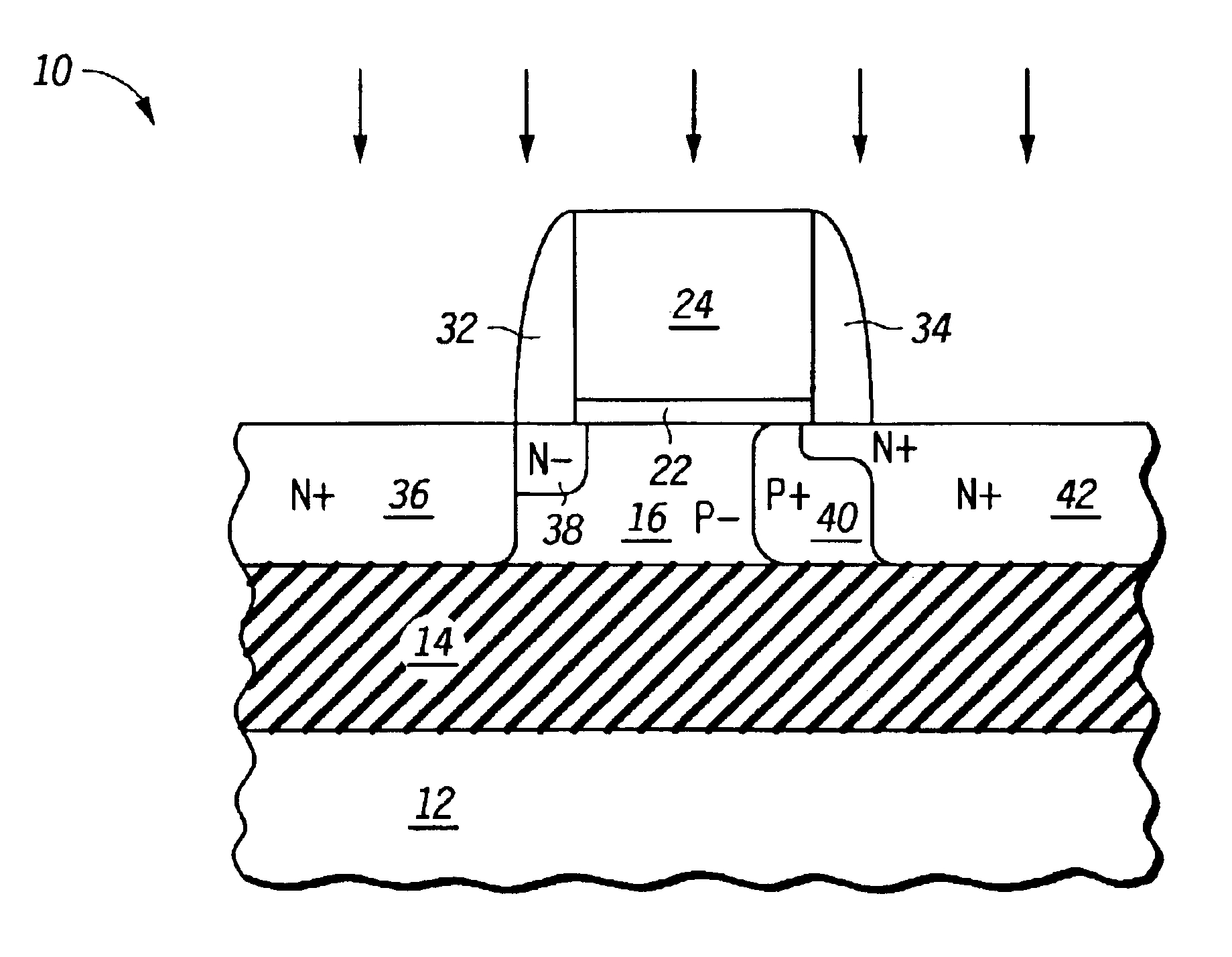

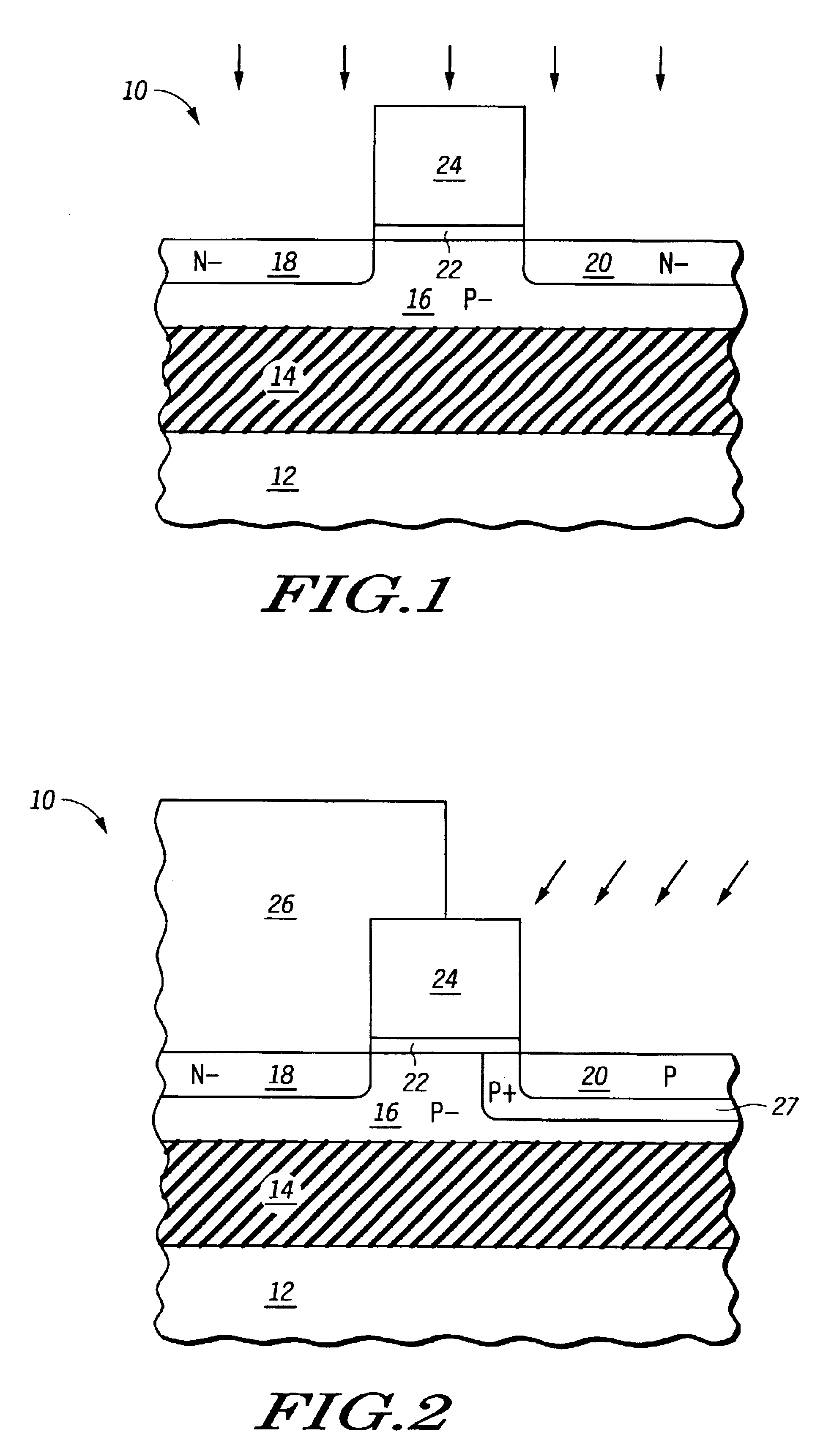

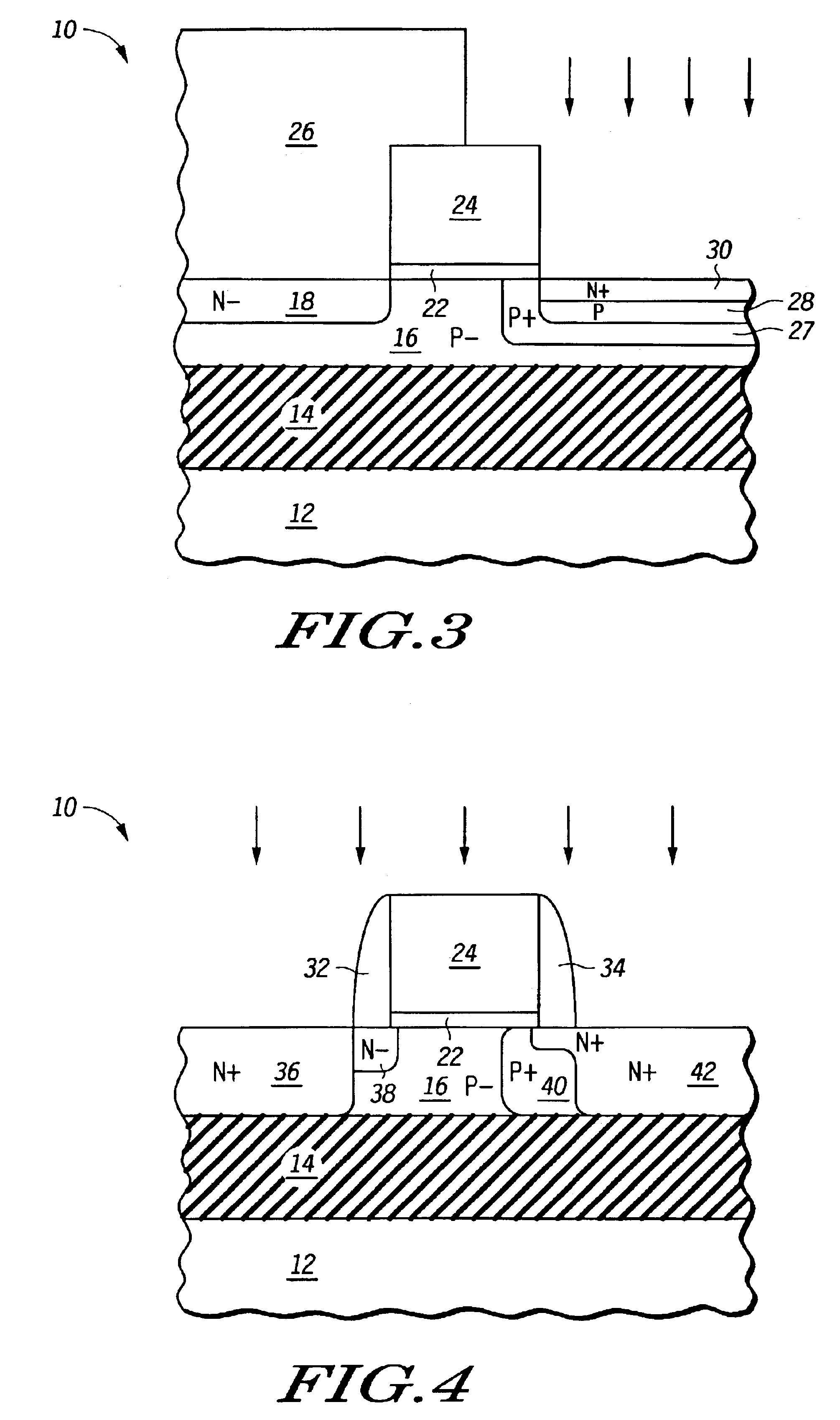

One transistor DRAM cell structure and method for forming

A single transistor DRAM cell is formed in a SOI substrate so that the DRAM cells are formed in bodies that are electrically isolated from each other. Each cell has doped regions that act as source and drain contacts. Between the drain contact and the body is a region, which aids in impact ionization and thus electron / hole formation during programming that is the same conductivity type as the body but of a higher concentration than the body. Adjacent to the source contact and to the body is a region, which aids in diode current during erase, that is the same conductivity type as the source contact but of a lower concentration than the source contact.

Owner:III HLDG 12 LLC

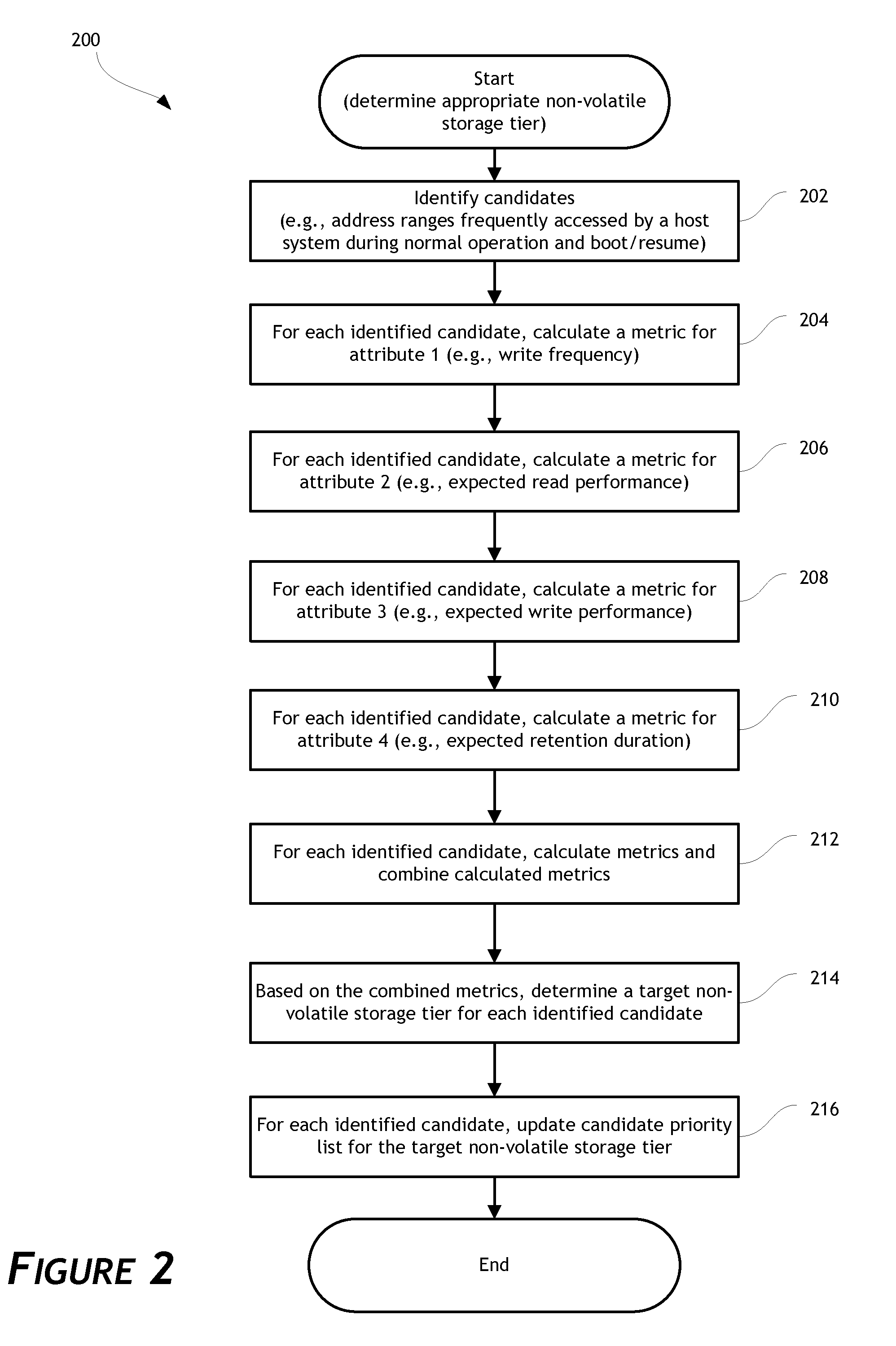

Disk drive data caching using a multi-tiered memory

ActiveUS20130132638A1Limit usable lifeReduce dataMemory architecture accessing/allocationEnergy efficient ICTSingle levelComputer science

A disk drive is disclosed that utilizes multi-tiered solid state memory for caching data received from a host. Data can be stored in a memory tier that can provide the required performance at a low cost. For example, multi-level cell (MLC) memory can be used to store data that is frequently read but infrequently written. As another example, single-level cell (SLC) memory can be used to store data that is frequently written. Improved performance, reduced costs, and improved power consumption can thereby be attained.

Owner:WESTERN DIGITAL TECH INC

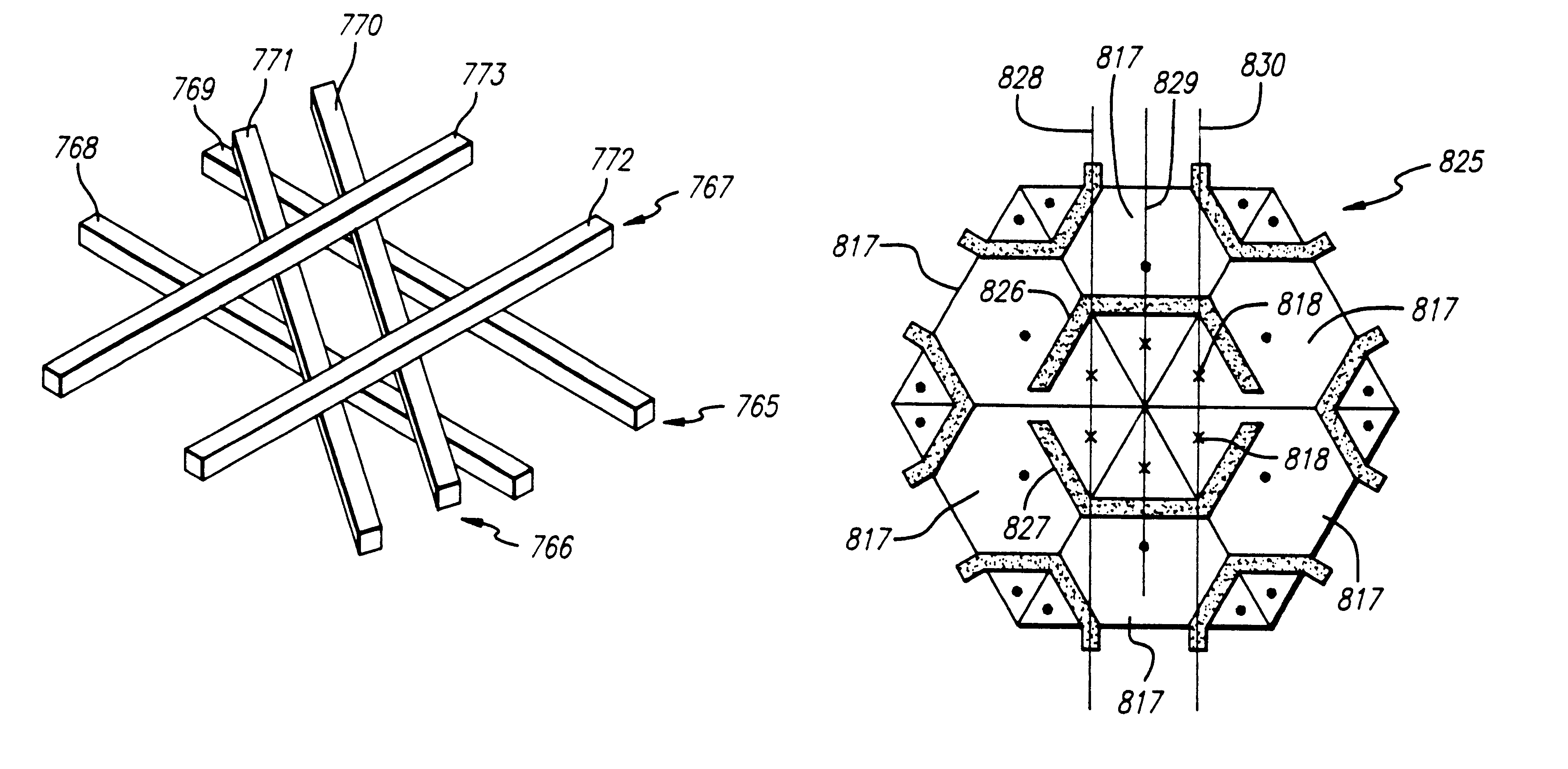

Hexagonal architecture

InactiveUS6407434B1Reduce total wirelength interconnect congestionReduce the numberTransistorSemiconductor/solid-state device detailsCapacitanceElectrical conductor

Several inventions are disclosed. A cell architecture using hexagonal shaped cells is disclosed. The architecture is not limited to hexagonal shaped cells. Cells may be defined by clusters of two or more hexagons, by triangles, by parallelograms, and by other polygons enabling a variety of cell shapes to be accommodated. Polydirectional non-orthogonal three layer metal routing is disclosed. The architecture may be combined with the tri-directional routing for a particularly advantageous design. In the tri-directional routing arraingement, electrical conductors for interconnecting terminals of microelectronic cells of an integrated circuit preferrably extend in three directions that are angularly displaced from each other by 60°. The conductors that extend in the three directions are preferrably formed in three different layers. A method of minimizing wire length in a semiconductor device is disclosed. A method of minimizing intermetal capacitance in a semiconductor device is disclosed. A novel device called a "tri-ister" is disclosed. Triangular devices are disclosed, including triangular NAND gates, triangular AND gates, and triangular OR gates. A triangular op amp and triode are disclosed. A triangular sense amplifier is disclosed. A DRAM memory array and an SRAM memory array, based upon triangular or parallelogram shaped cells, are disclosed, including a method of interconnecting such arrays. A programmable variable drive transistor is disclosed. CAD algorithms and methods are disclosed for designing and making semiconductor devices, which are particularly applicable to the disclosed architecture and tri-directional three metal layer routing.

Owner:BELL SEMICON LLC

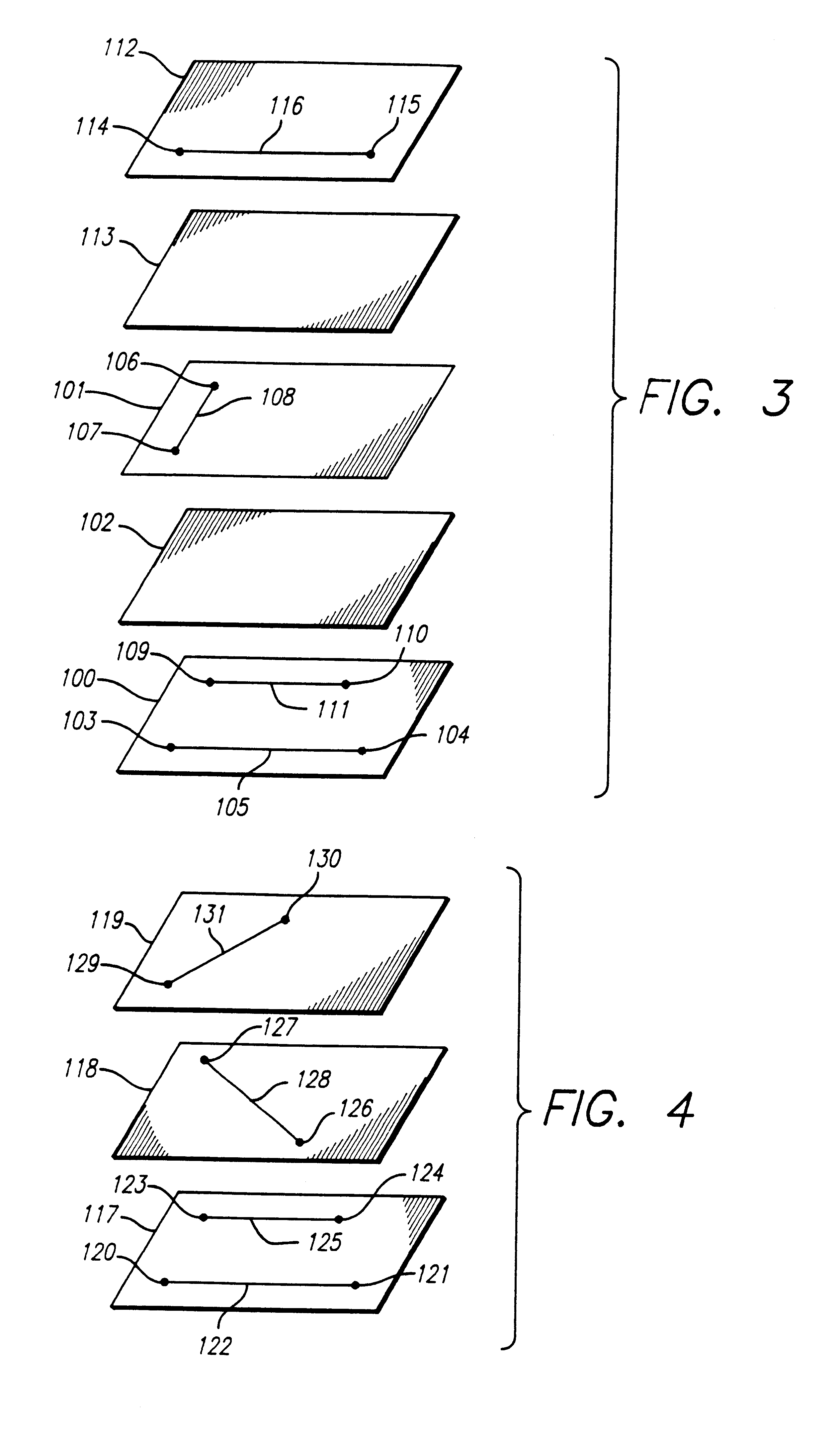

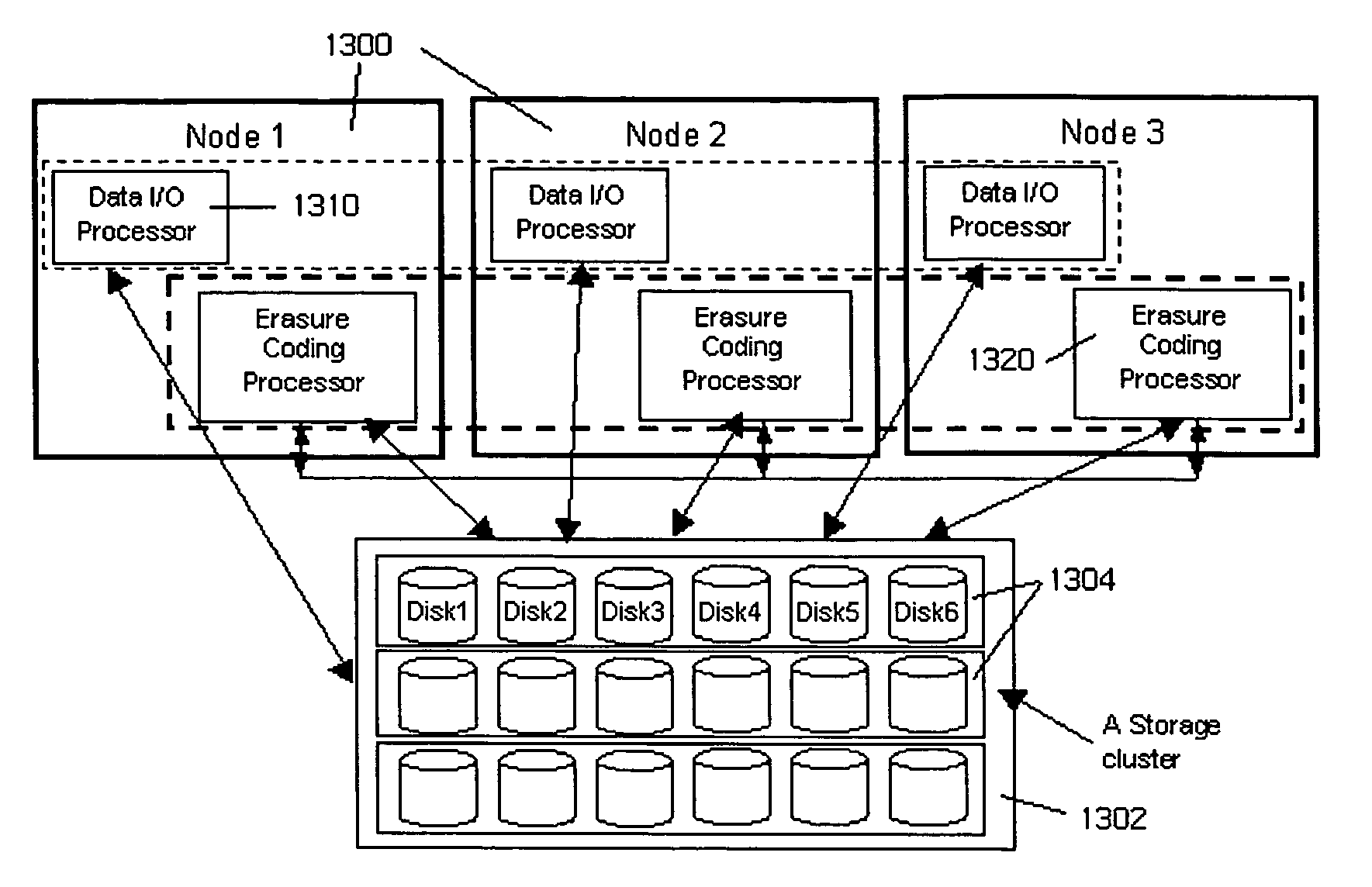

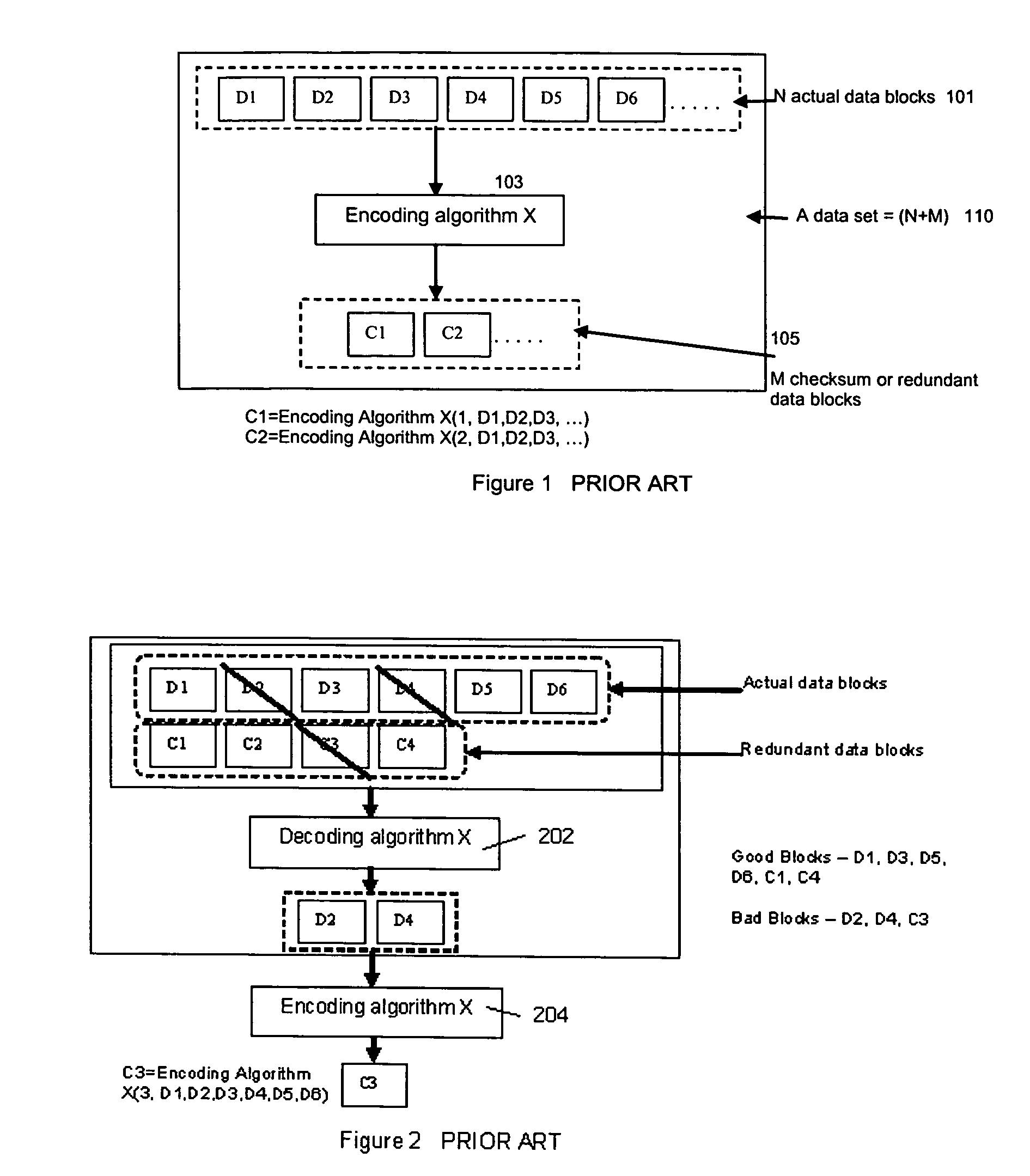

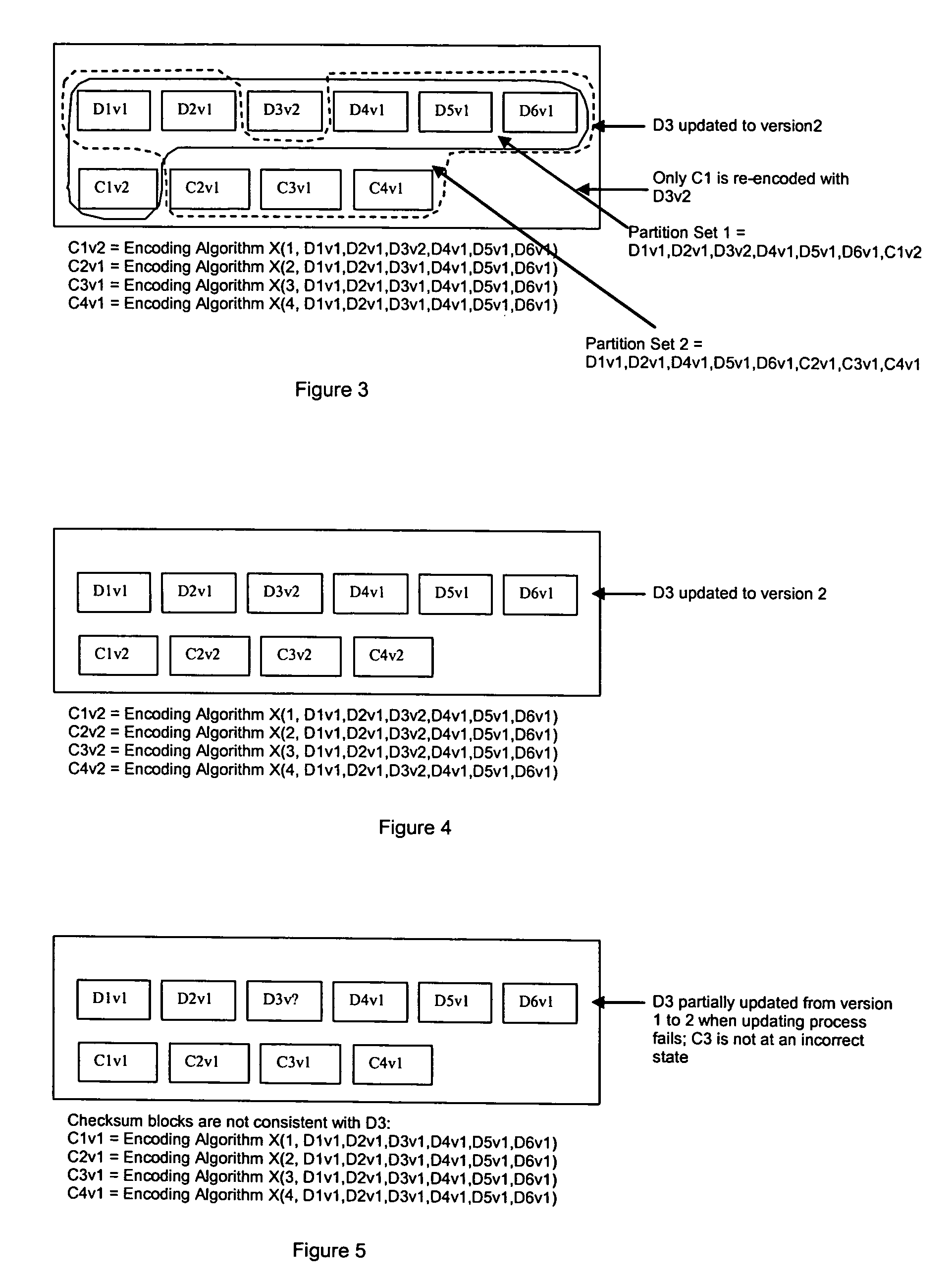

Method for lock-free clustered erasure coding and recovery of data across a plurality of data stores in a network

ActiveUS7681105B1Maintain data consistencyEffective applicationError detection/correctionCode conversionData storingData store

The present invention provides a distributed clustering method to allow multiple active instances of consistency management processes that apply the same encoding scheme to be cooperative and function collectively. The techniques described herein facilitate an efficient method to apply an erasure encoding and decoding scheme across dispersed data stores that receive constant updates. The technique can be applied on many forms of distributed persistent data stores to provide failure resiliency and to maintain data consistency and correctness.

Owner:QUEST SOFTWARE INC

Electronic circuit with embedded memory

InactiveUS7633162B2Semiconductor/solid-state device detailsSolid-state devicesMemory circuitsSemiconductor

Owner:BESANG

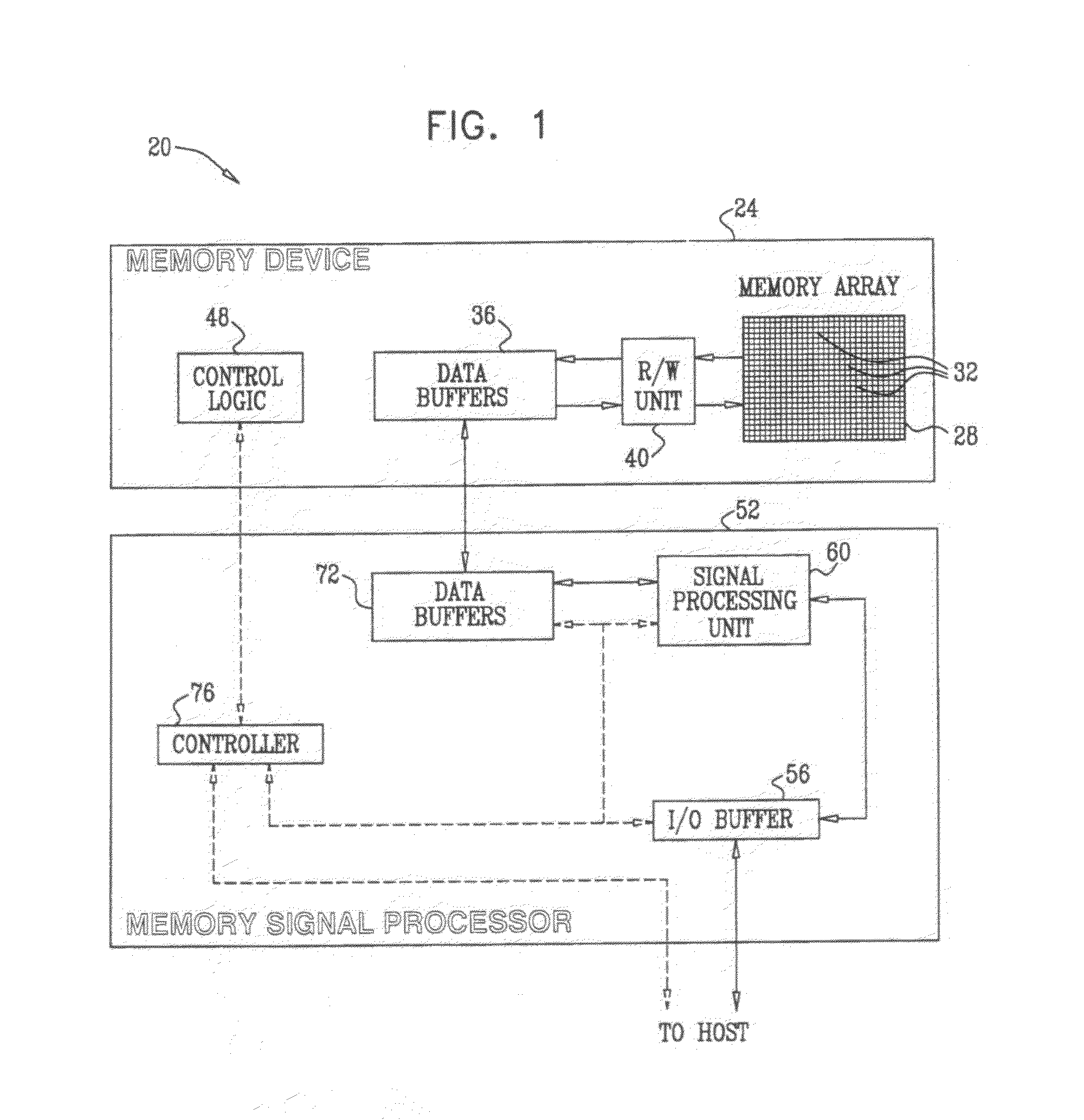

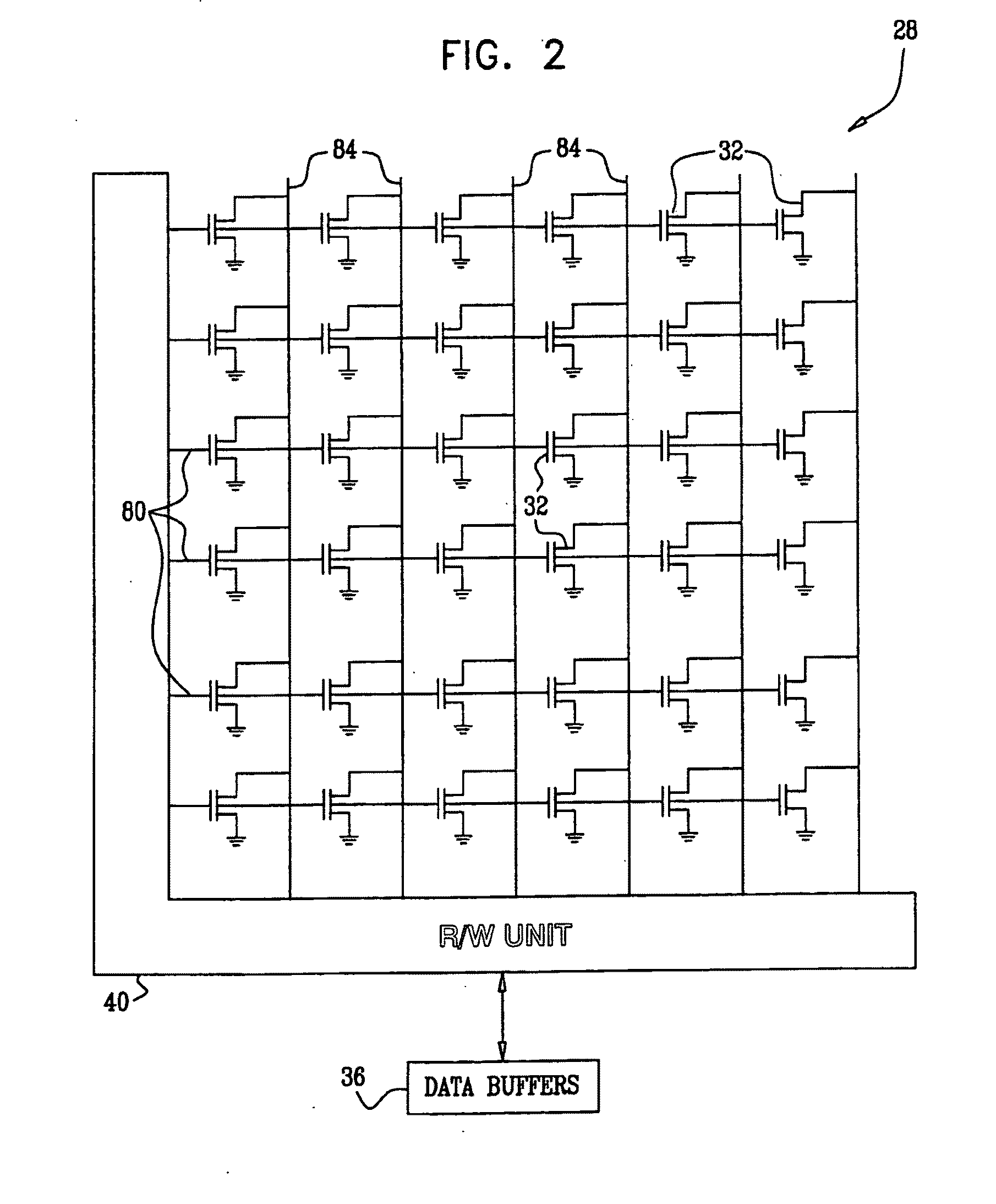

Automatic defect management in memory devices

ActiveUS20100115376A1Code conversionError correction/detection using block codesAlternative methodsComputer science

A method for storing data in a memory (28) that includes analog memory cells (32) includes identifying one or more defective memory cells in a group of the analog memory cells. An Error Correction Code (ECC) is selected responsively to a characteristic of the identified defective memory cells. The data is encoded using the selected ECC and the encoded data is stored in the group of the analog memory cells. In an alternative method, an identification of one or more defective memory cells among the analog memory cells is generated. Analog values are read from the analog memory cells in which the encoded data were stored, including at least one of the defective memory cells. The analog values are processed using an ECC decoding process responsively to the identification of the at least one of the defective memory cells, so as to reconstruct the data.

Owner:APPLE INC

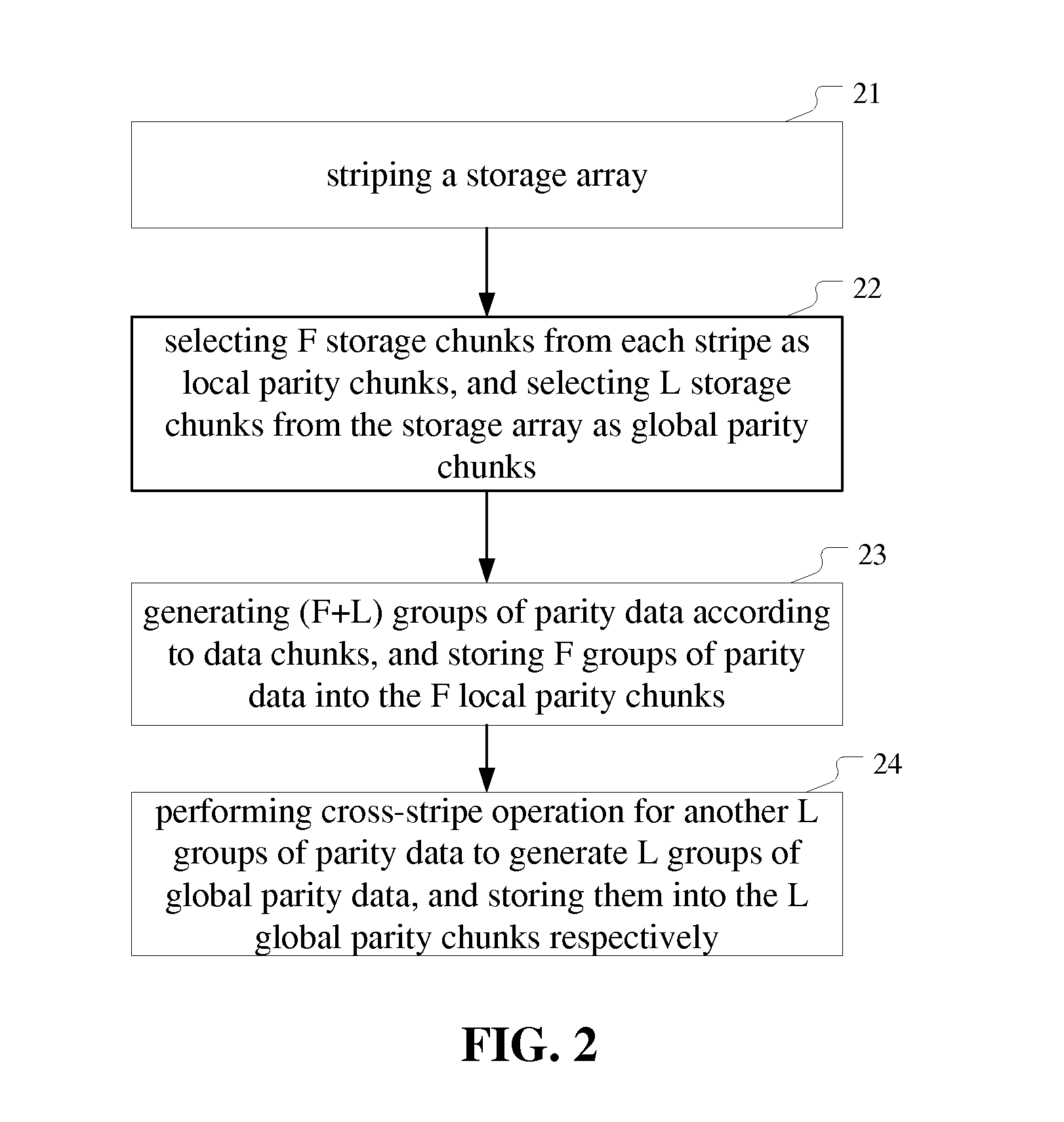

Managing a storage array

ActiveUS20140040702A1Easy to manageError capabilityCode conversionError correction/detection using interleaving techniquesFault toleranceErasure code

The present invention provides a method and apparatus of managing a storage array. The method comprises: striping the storage array to form a plurality of stripes; selecting F storage chunks from each stripe as local parity chunks, and selecting another L storage chunks from the storage array as global parity chunks; performing (F+L) fault tolerant erasure coding on all data chunks in a stripe to generate (F+L) groups of parity data, and storing F groups of parity data therein into the F local parity chunks; performing cross-stripe operation on another L groups of parity data to generate L groups of global parity data, and storing them into the L global parity chunks, respectively. The apparatus corresponds to the method. With the invention, a plurality of errors in the storage array can be detected and / or recovered to improve fault tolerance and space utilization of the storage array.

Owner:IBM CORP

Popular searches

Software simulation/interpretation/emulation Marketing Special data processing applications Nanoinformatics Bulk negative resistance effect devices Forming microstructural systems Microstructural device assembly Microelectromechanical systems Patterned record carriers Metal/metal-oxides/metal-hydroxide catalysts

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com