Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3014 results about "Correction code" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An error-correcting code (ECC) or forward error correction (FEC) code is a process of adding redundant data, or parity data, to a message, such that it can be recovered by a receiver even when a number of errors (up to the capability of the code being used) were introduced, either during the process of transmission, or on storage.

Method for recovering from errors in flash memory

ActiveUS20070091677A1Satisfies needRead-only memoriesDigital storageVoltage referenceCorrection code

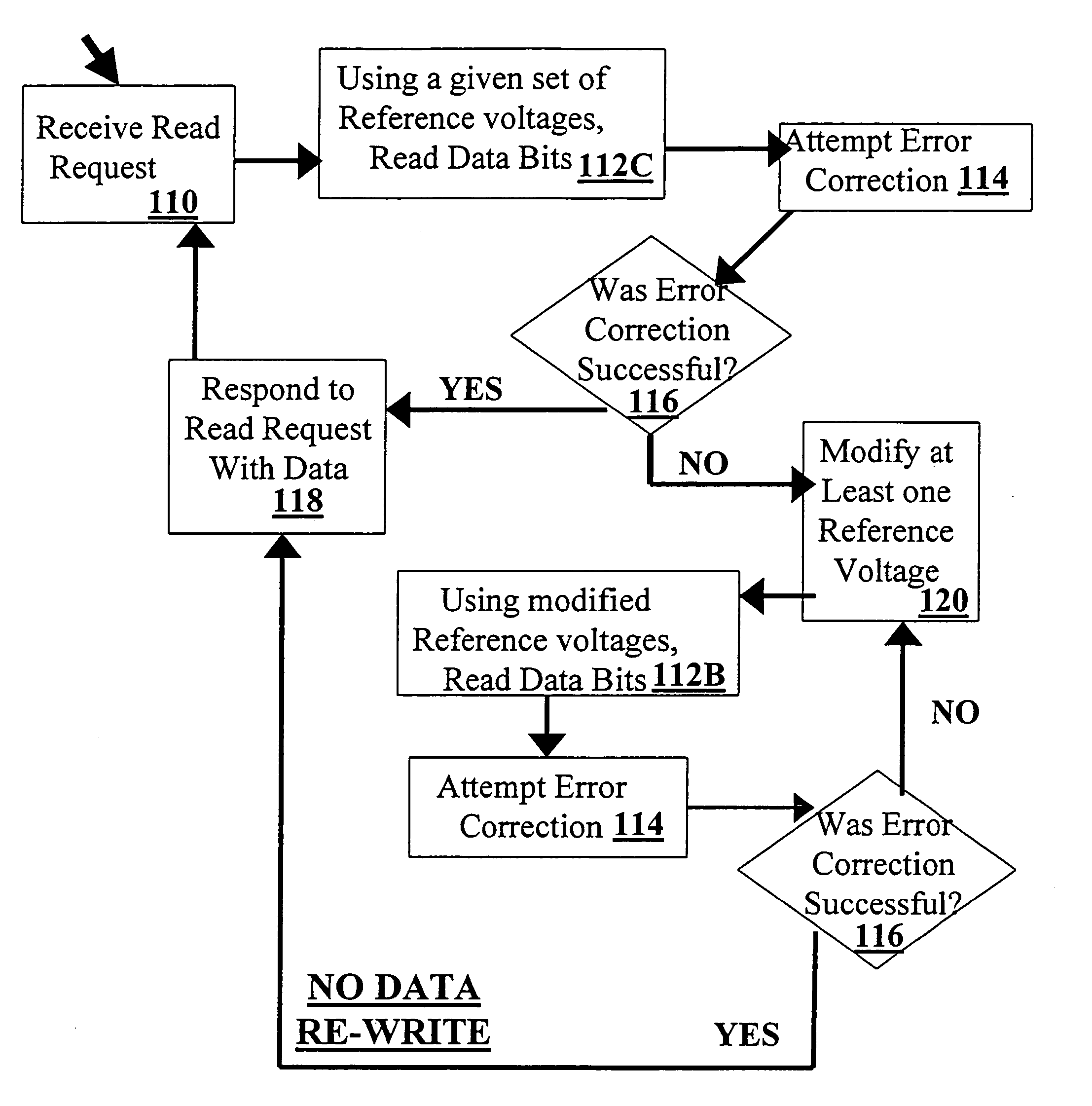

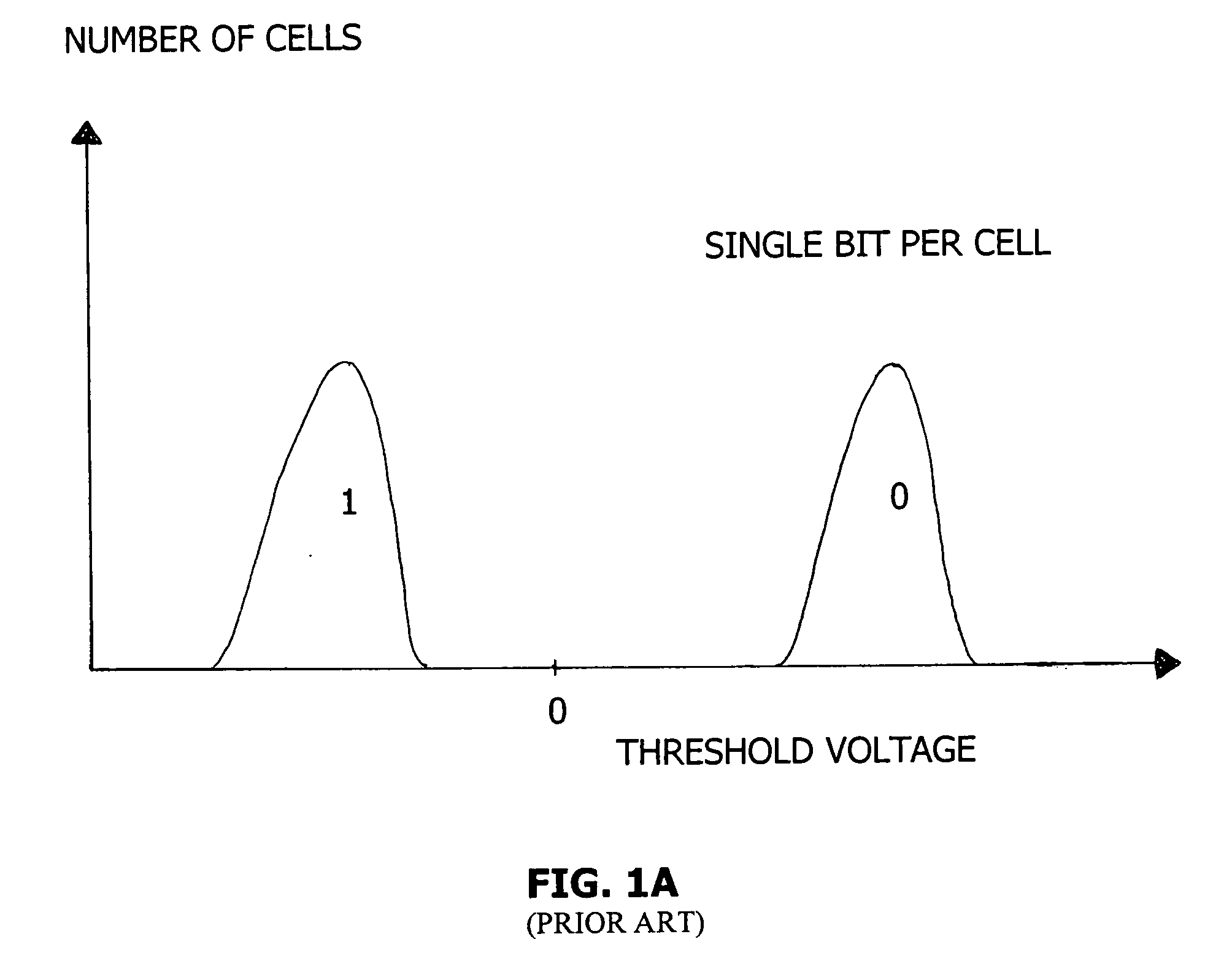

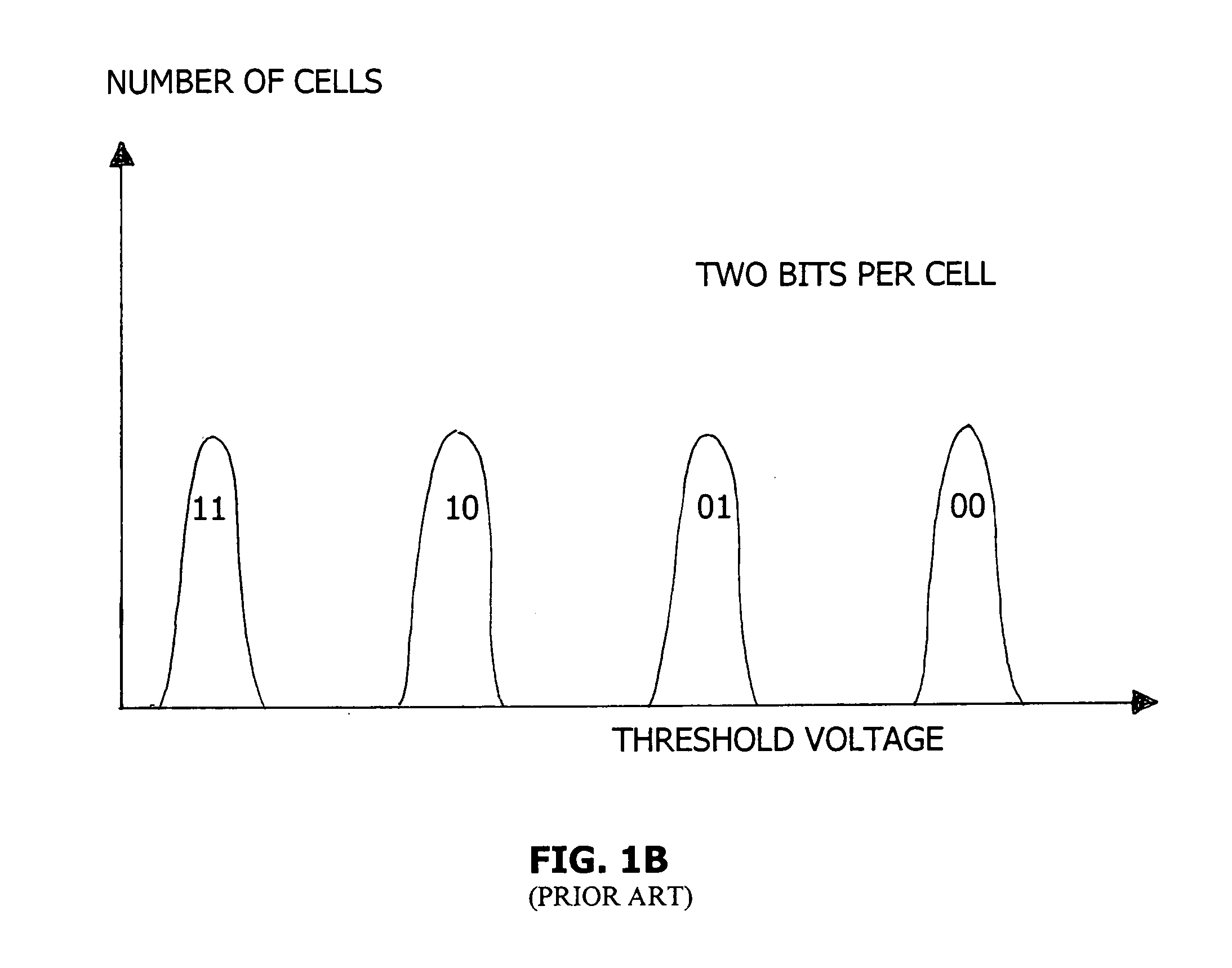

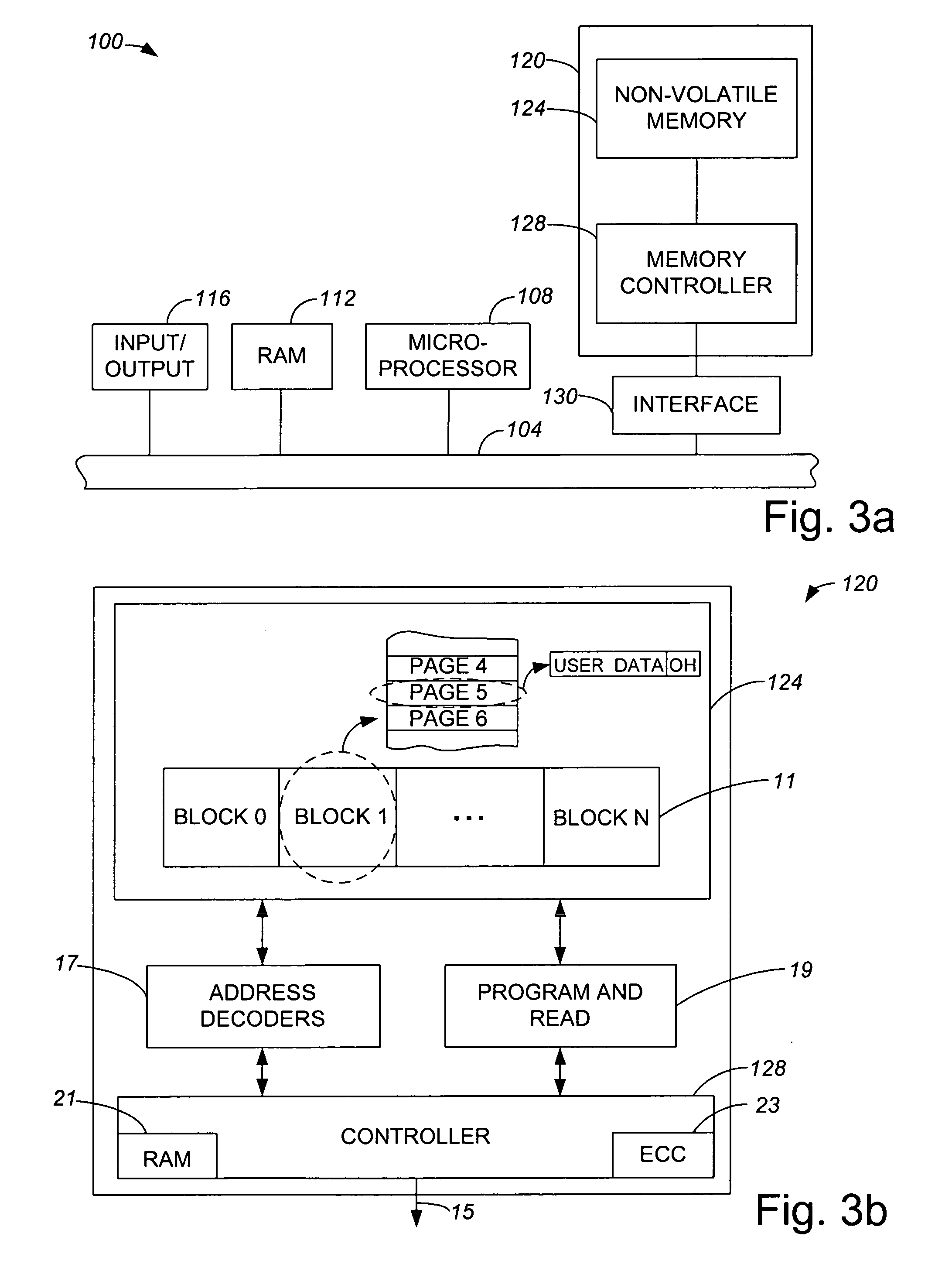

Methods, devices and computer readable code for reading data from one or more flash memory cells, and for recovering from read errors are disclosed. In some embodiments, in the event of an error correction failure by an error detection and correction module, the flash memory cells are re-read at least once using one or more modified reference voltages, for example, until a successful error correction may be carried out. In some embodiments, after successful error correction a subsequent read request is handled without re-writing data (for example, reliable values of the read data) to the flash memory cells in the interim. In some embodiments, reference voltages associated with a reading where errors are corrected may be stored in memory, and retrieved when responding to a subsequent read request. In some embodiments, the modified reference voltages are predetermined reference voltages. Alternatively or additionally, these modified reference voltages may be determined as needed, for example, using randomly generated values or in accordance with information provided by the error detection and correction module. Methods, devices and computer readable code for reading data for situations where there is no error correction failure are also provided.

Owner:WESTERN DIGITAL ISRAEL LTD

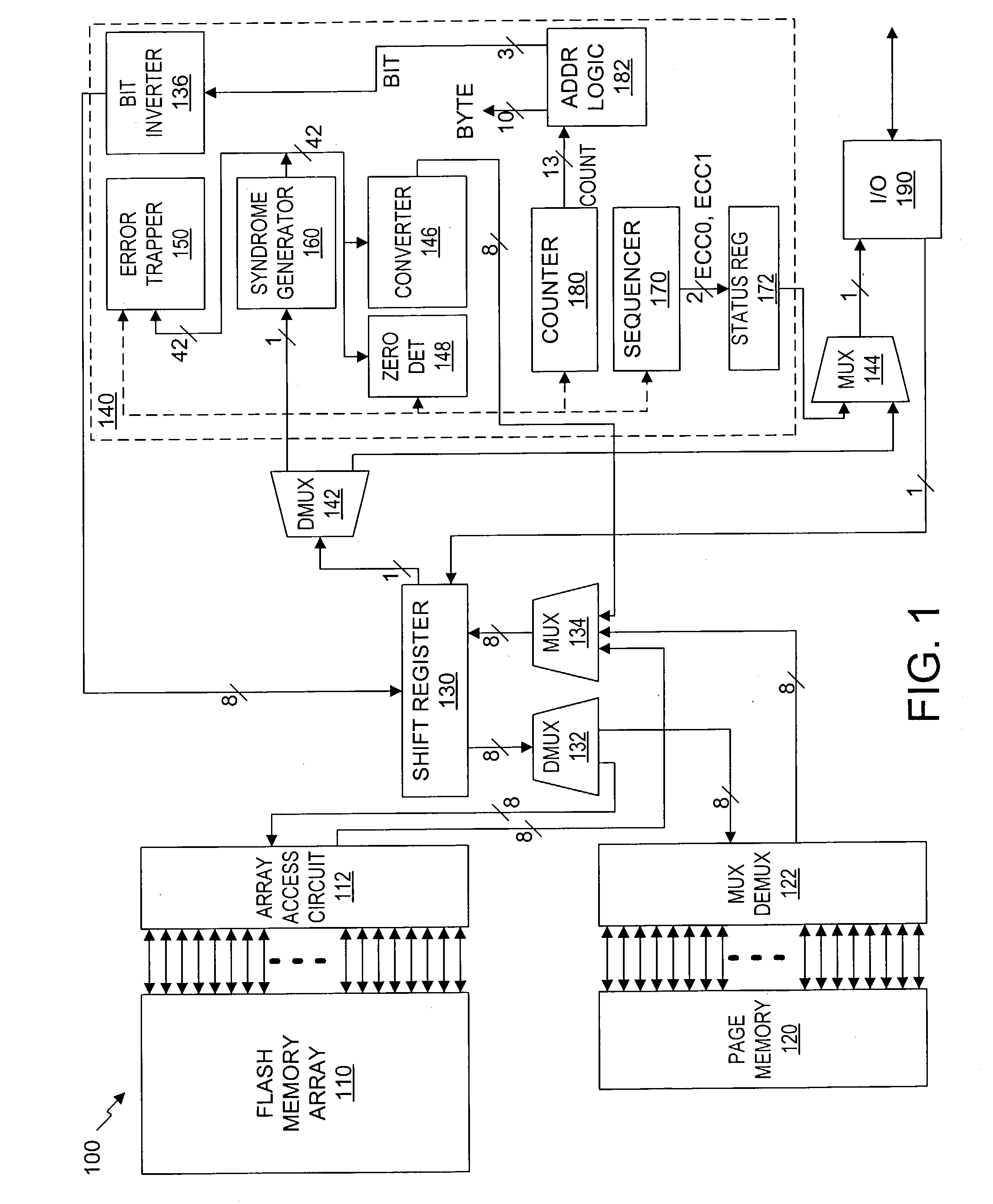

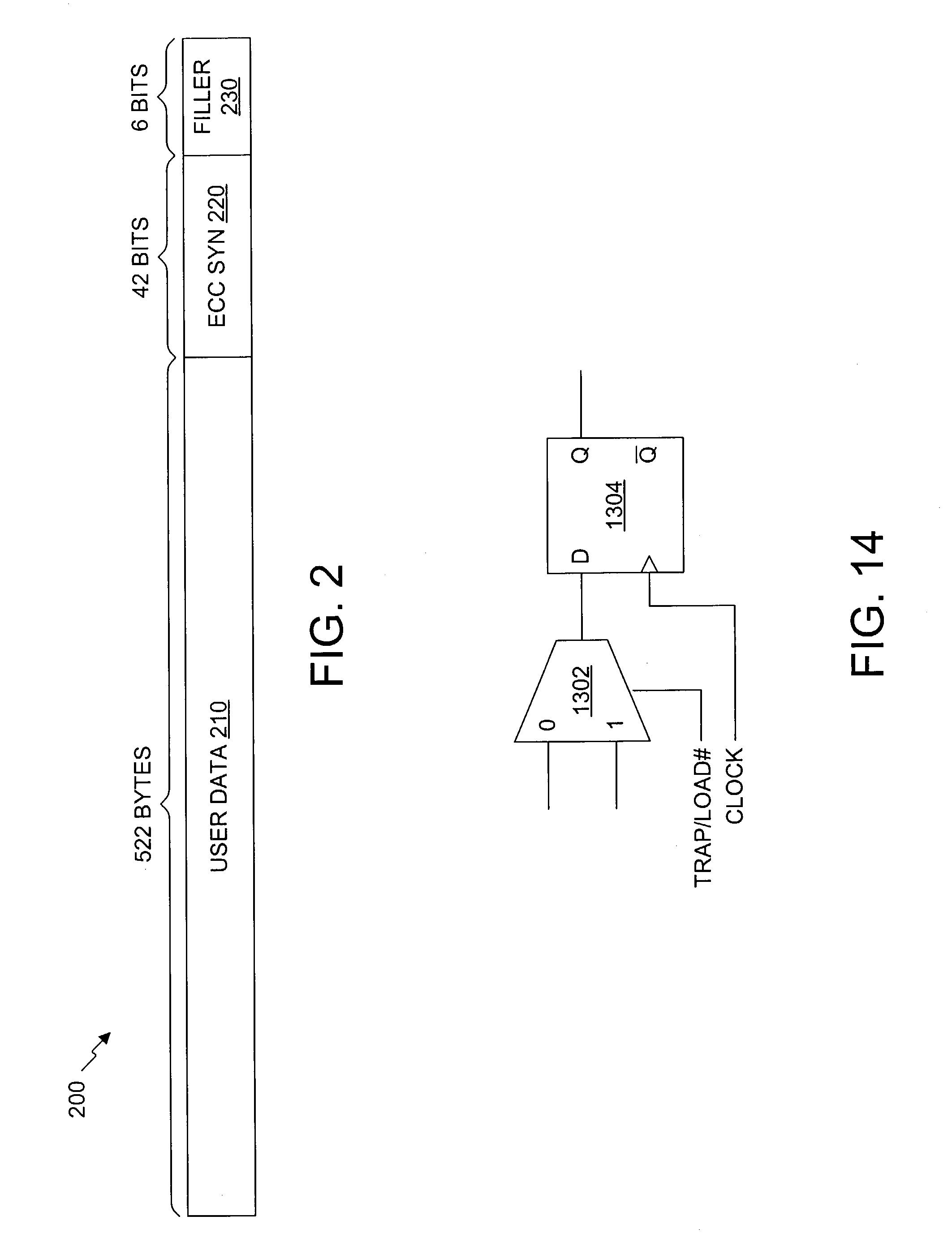

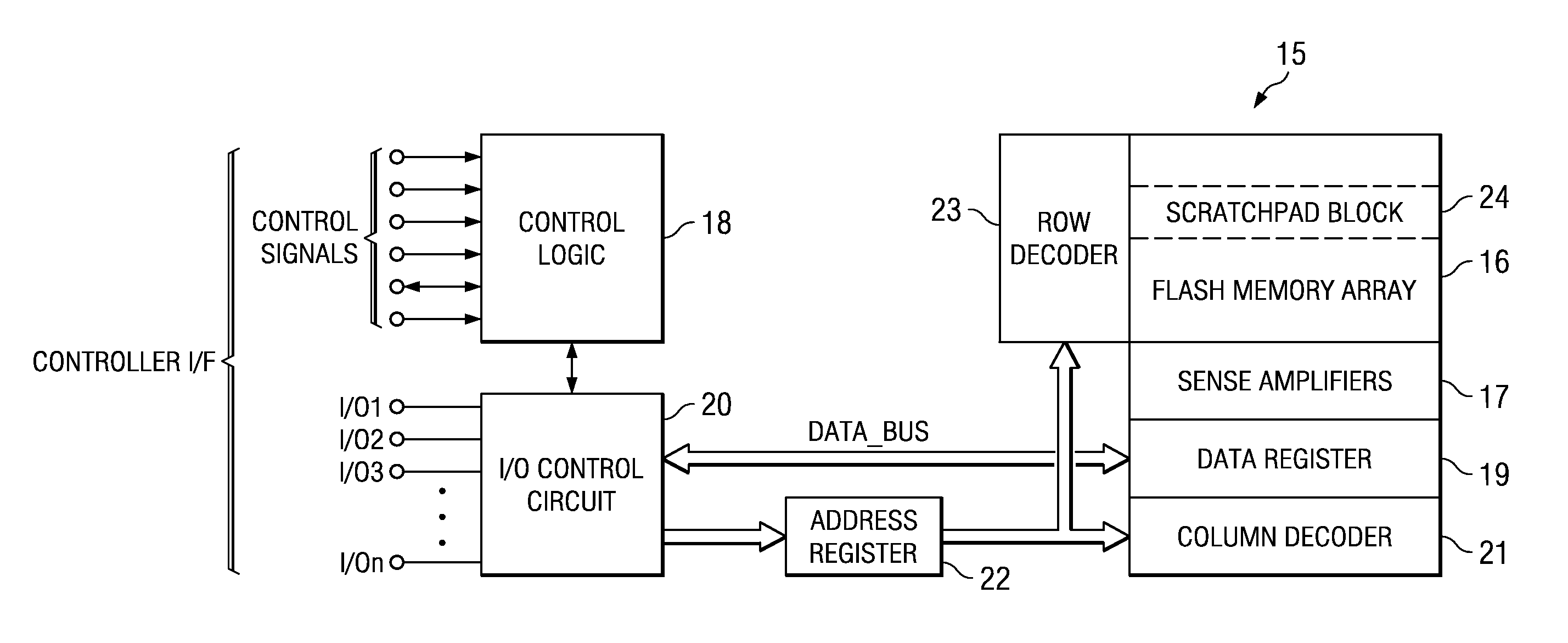

Serial flash integrated circuit having error detection and correction

InactiveUS20040153902A1Static storageRedundant data error correctionCorrection codeIntegrated circuit

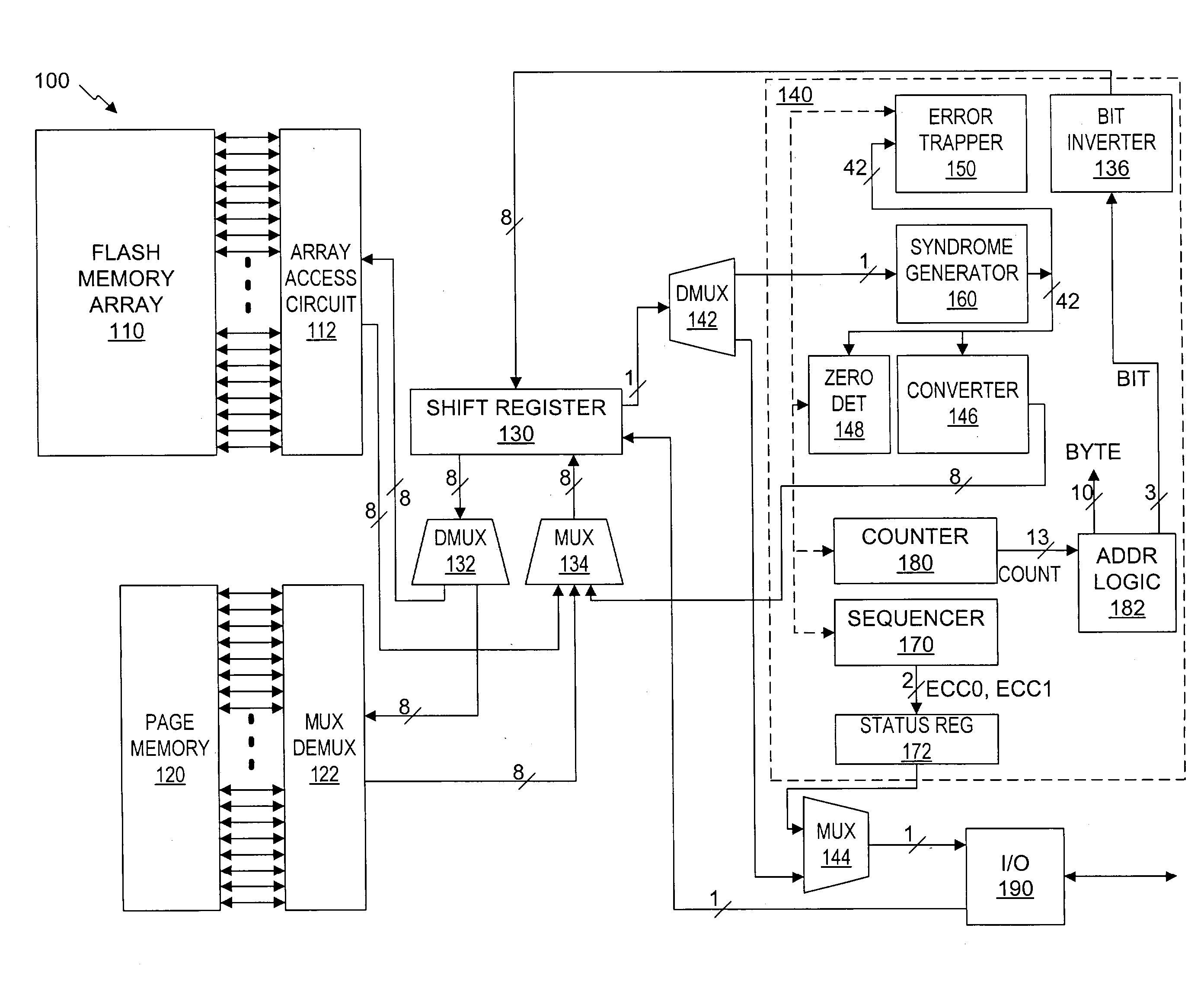

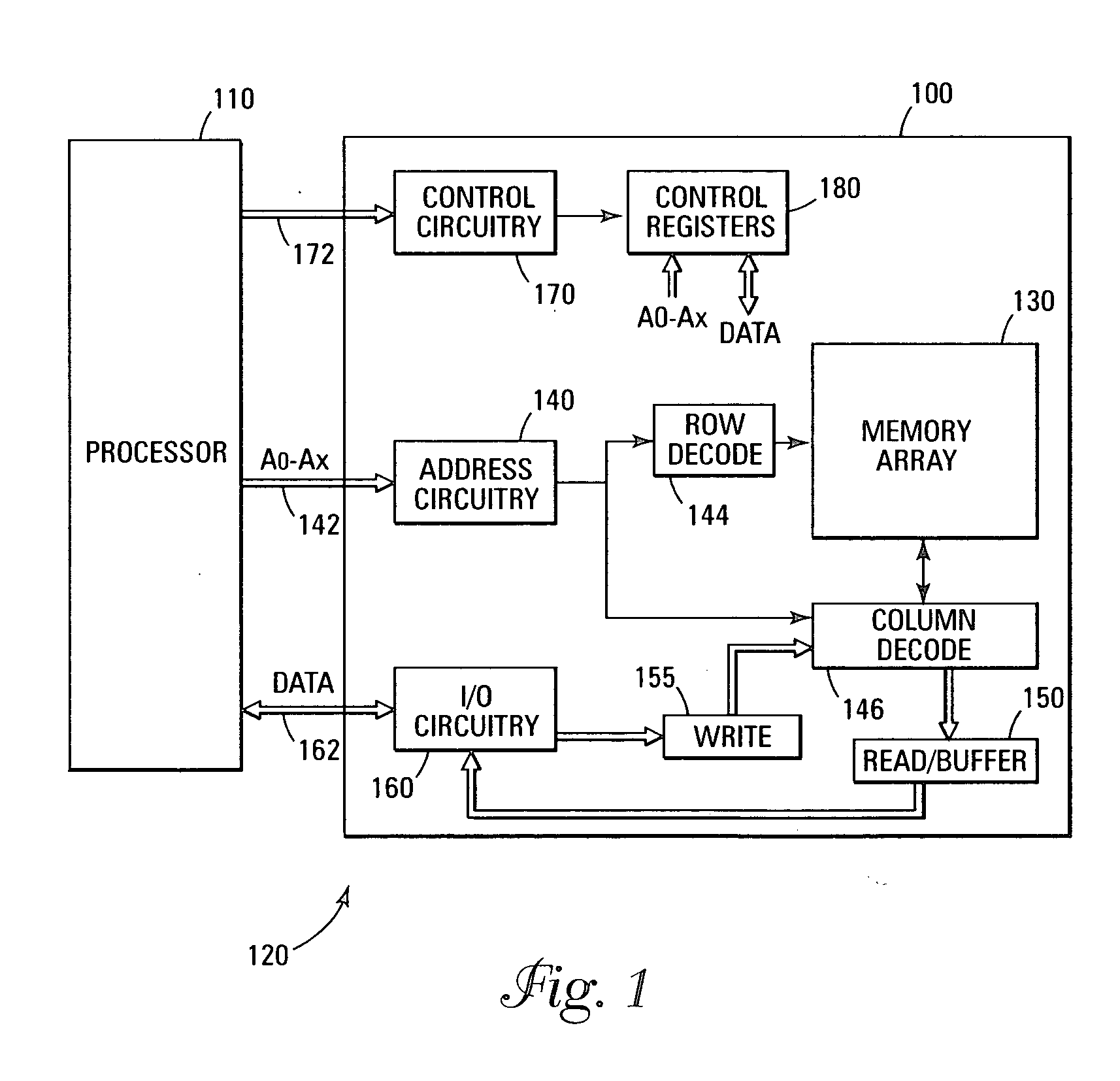

A serial flash integrated circuit is provided with an integrated error correction coding ("ECC") system that is used with an integrated volatile page memory for fast automatic data correction. The ECC code has the capability of correcting any one or two bit errors that might occur on a page of the flash memory array. One bit corrections are done automatically in hardware during reads or transfer to the page memory, while two-bit corrections are handled in external software, firmware or hardware. The ECC system uses a syndrome generator for generating both write and read syndromes, and an error trapper to identify the location of single bit errors using very little additional chip space. The flash memory array may be refreshed from the page memory to correct any detected errors. Data status is made available to the application prior to the data. The use of the ECC is optional.

Owner:WINBOND ELECTRONICS CORP

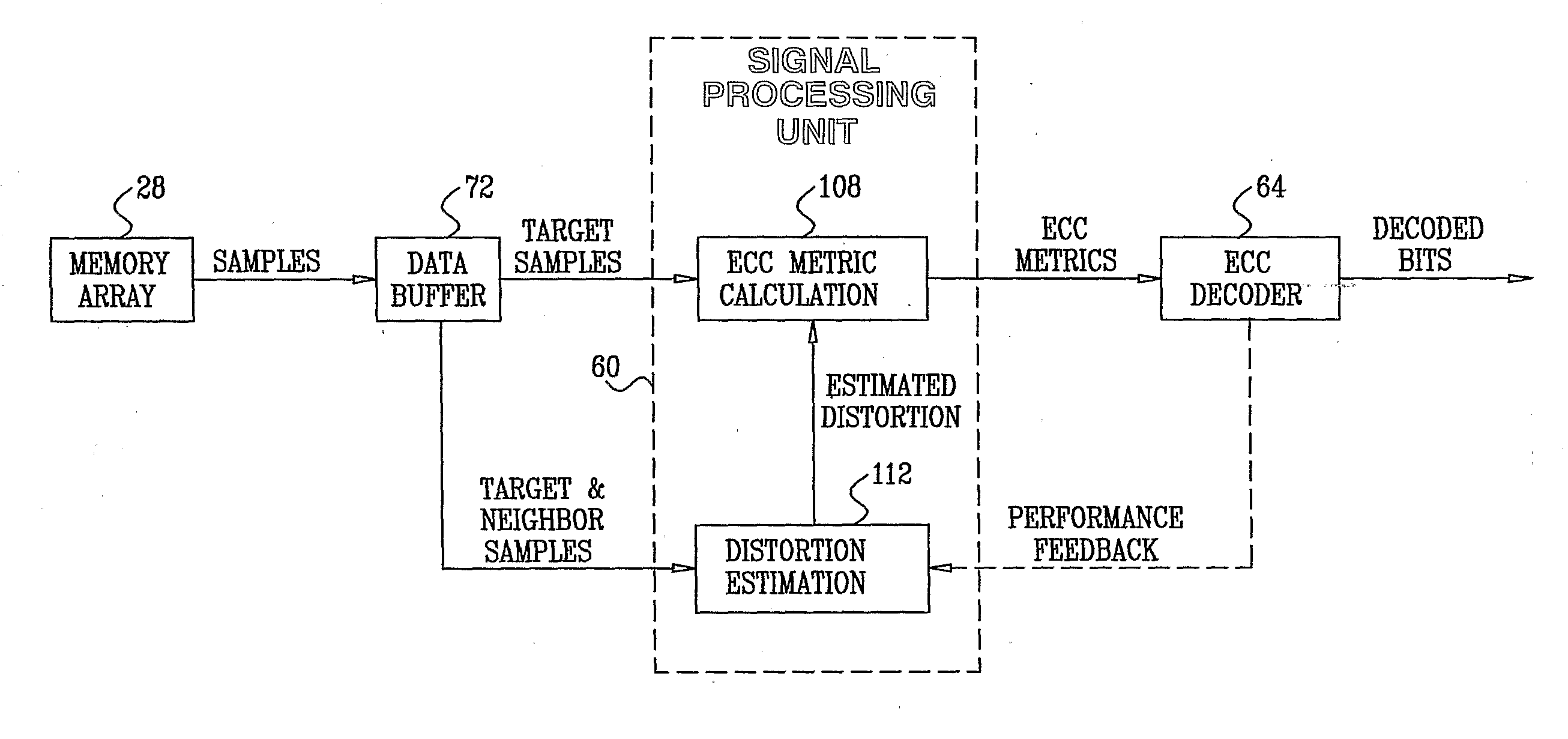

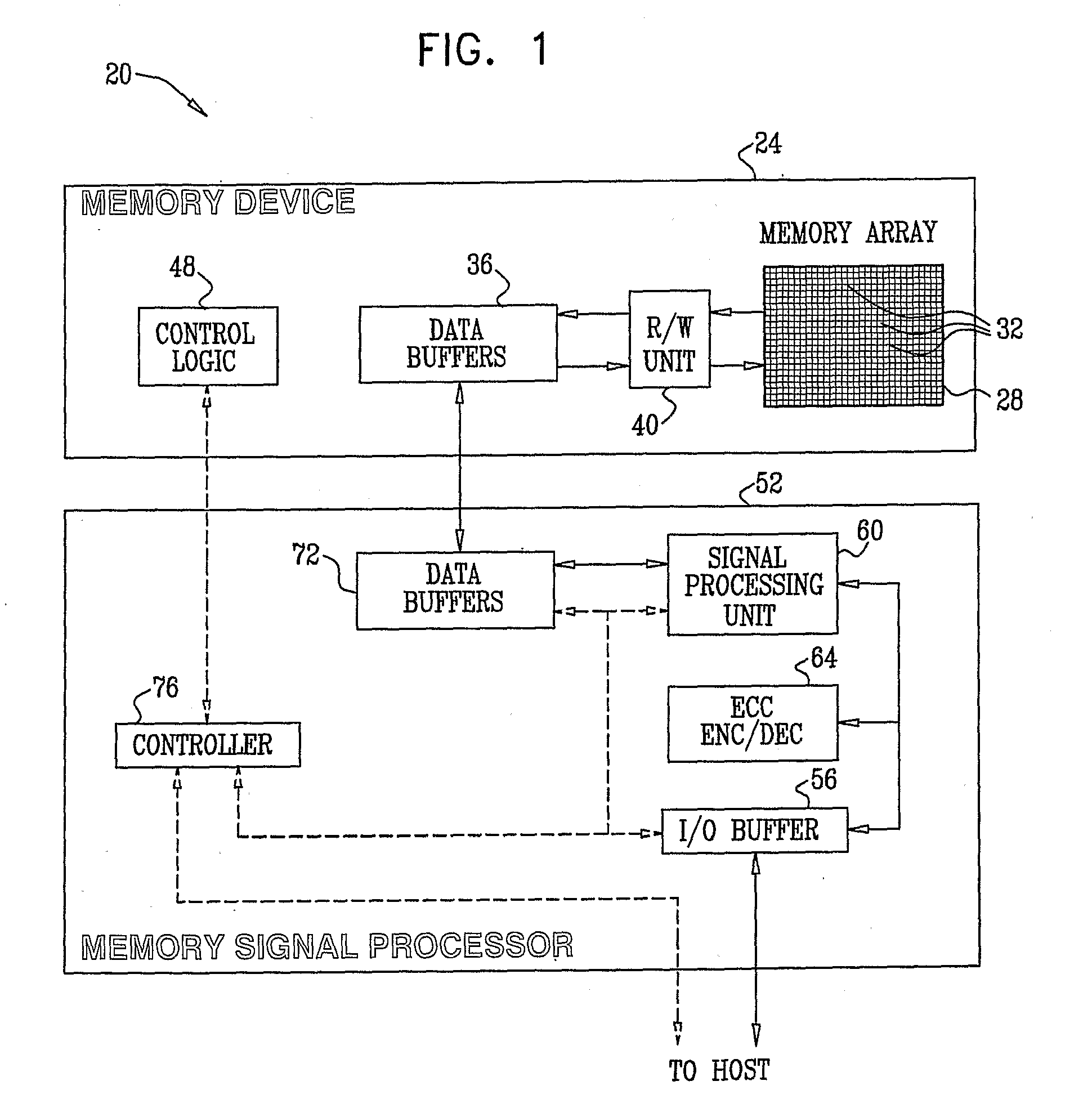

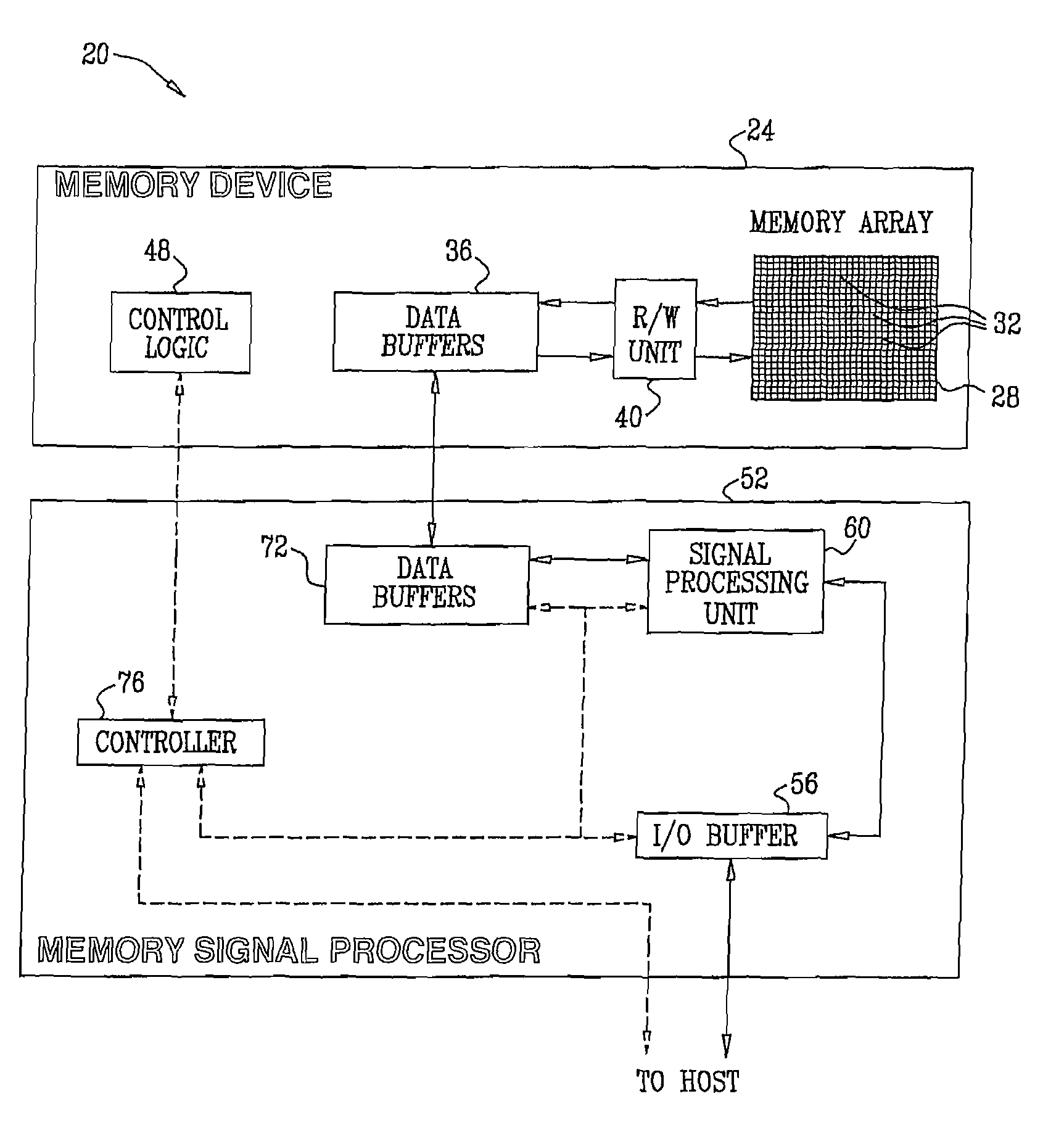

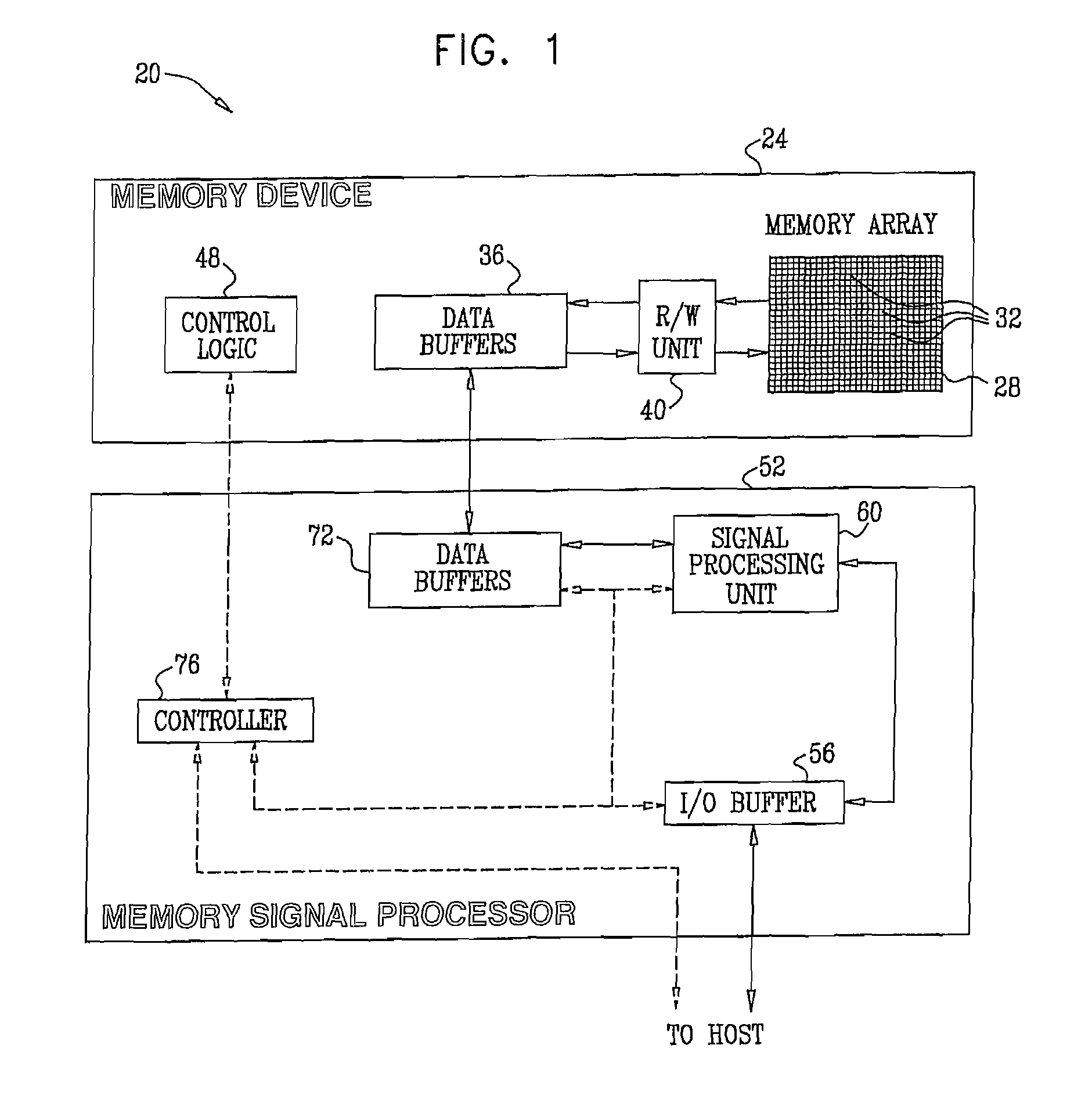

Combined distortion estimation and error correction coding for memory devices

ActiveUS20090024905A1Improve performanceData representation error detection/correctionError detection/correctionCalculation errorDistortion

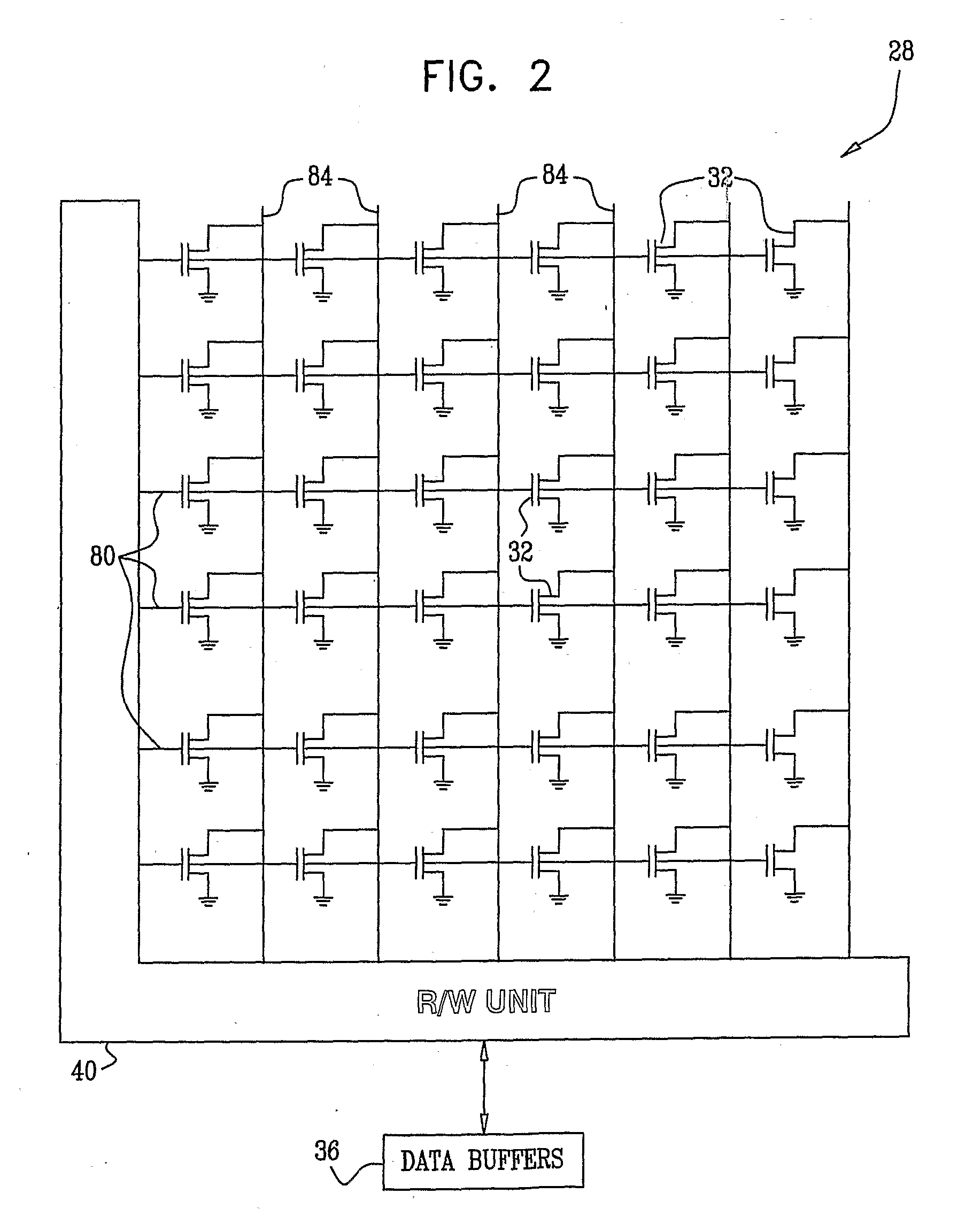

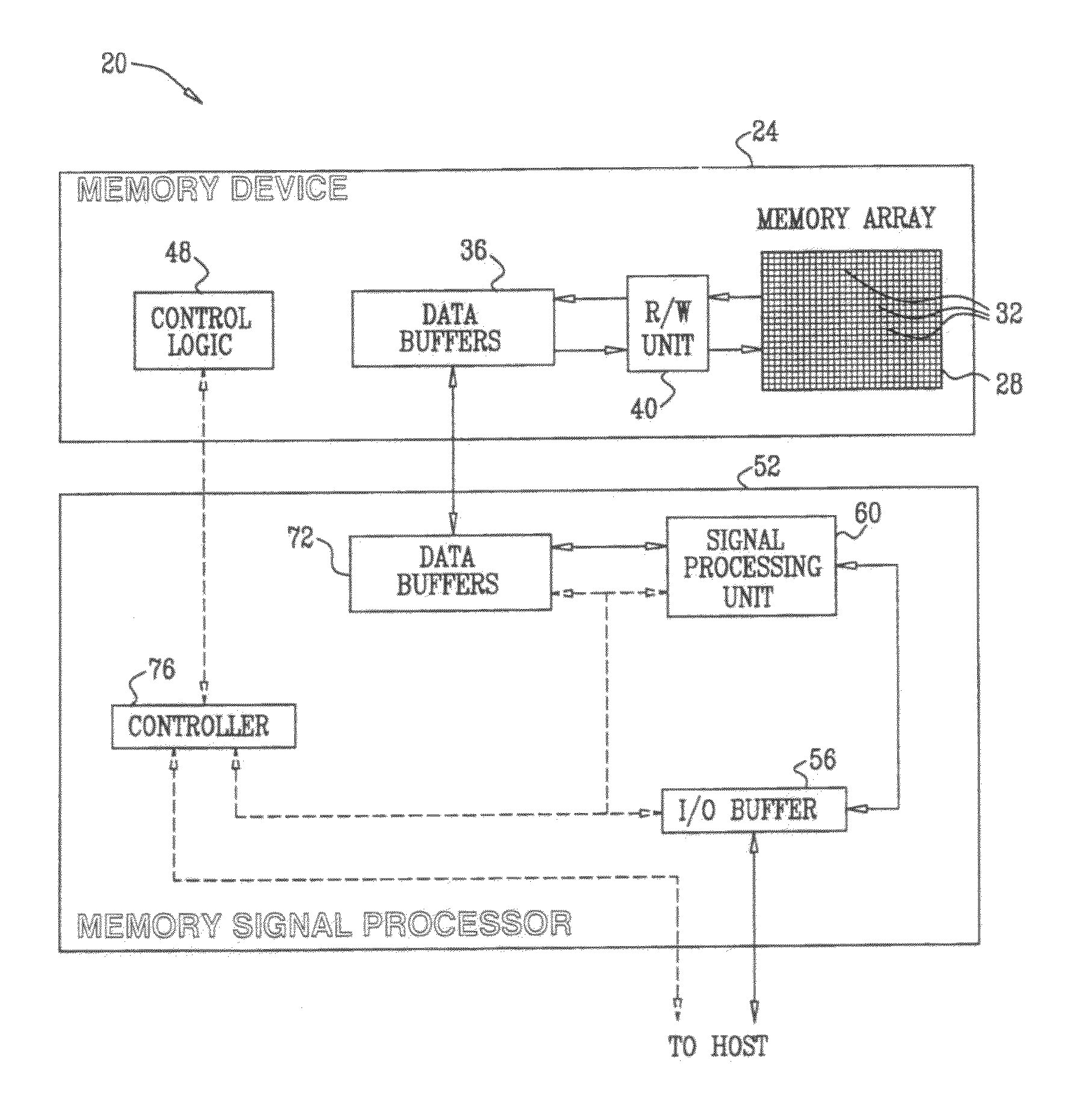

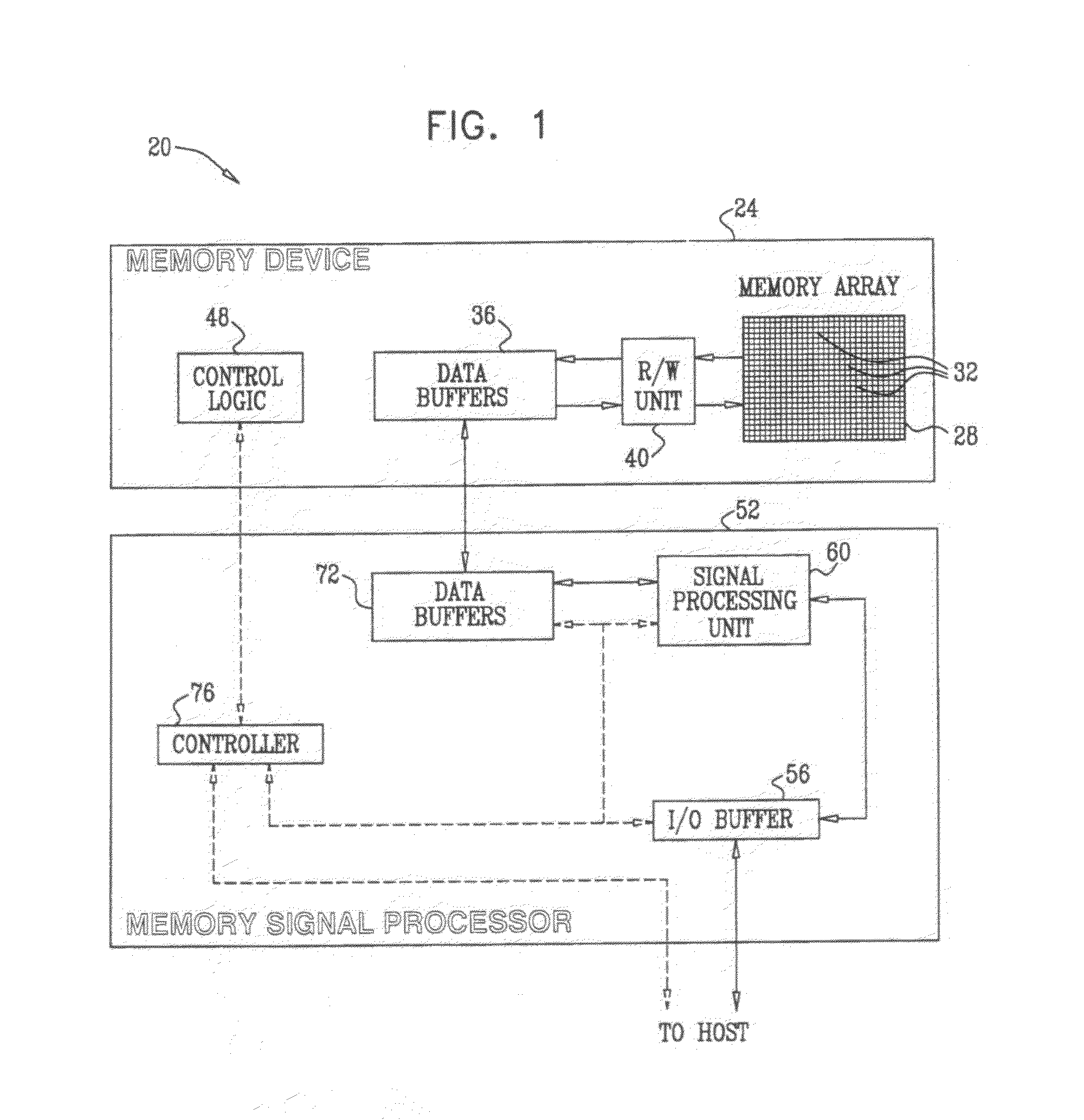

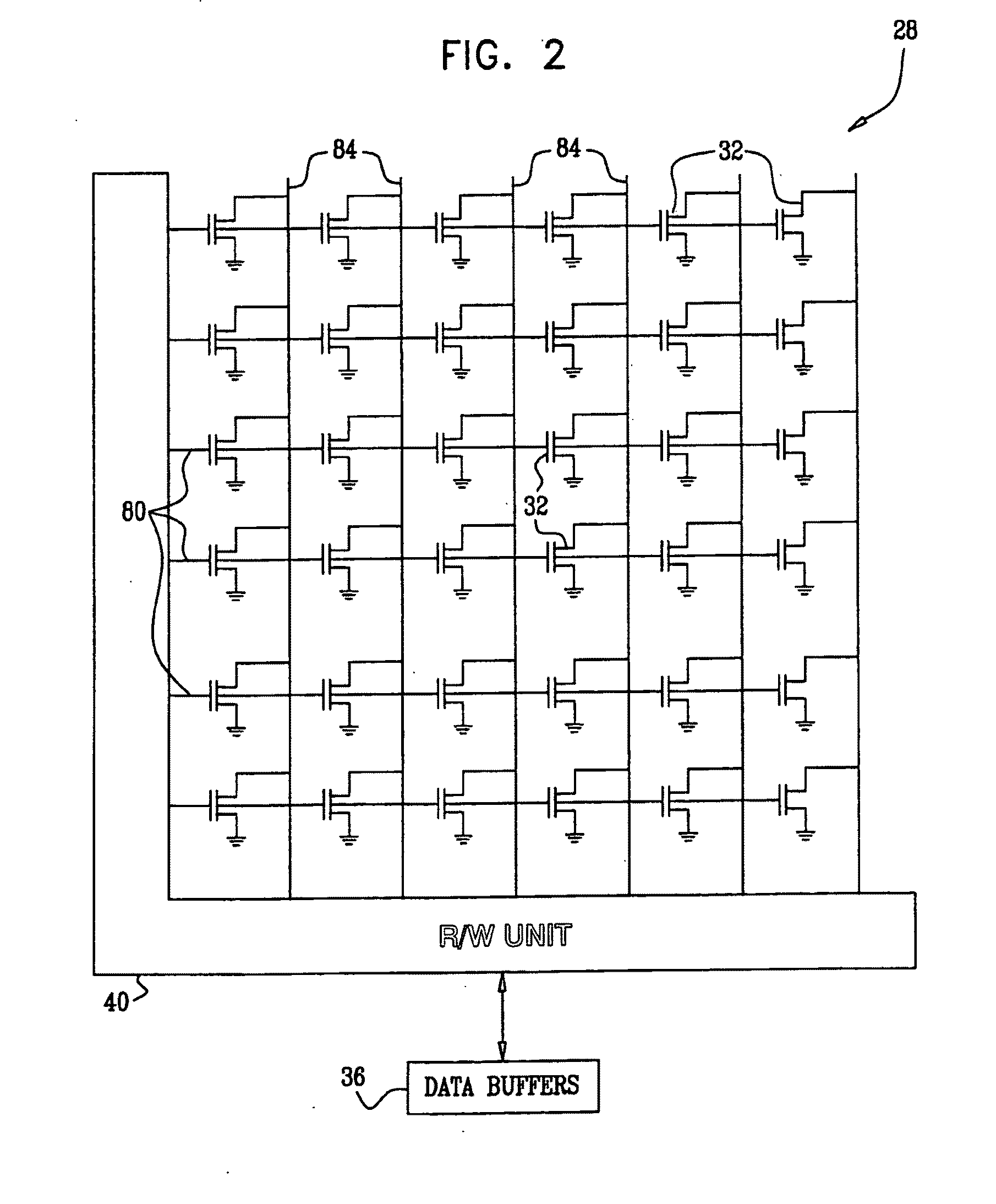

A method for operating a memory device (24) includes encoding data using an Error Correction Code (ECC) and storing the encoded data as first analog values in respective analog memory cells (32) of the memory device. After storing the encoded data, second analog values are read from the respective memory cells of the memory device in which the encoded data were stored. At least some of the second analog values differ from the respective first analog values. A distortion that is present in the second analog values is estimated. Error correction metrics are computed with respect to the second analog values responsively to the estimated distortion. The second analog values are processed using the error correction metrics in an ECC decoding process, so as to reconstruct the data.

Owner:APPLE INC

Emerging bad block detection

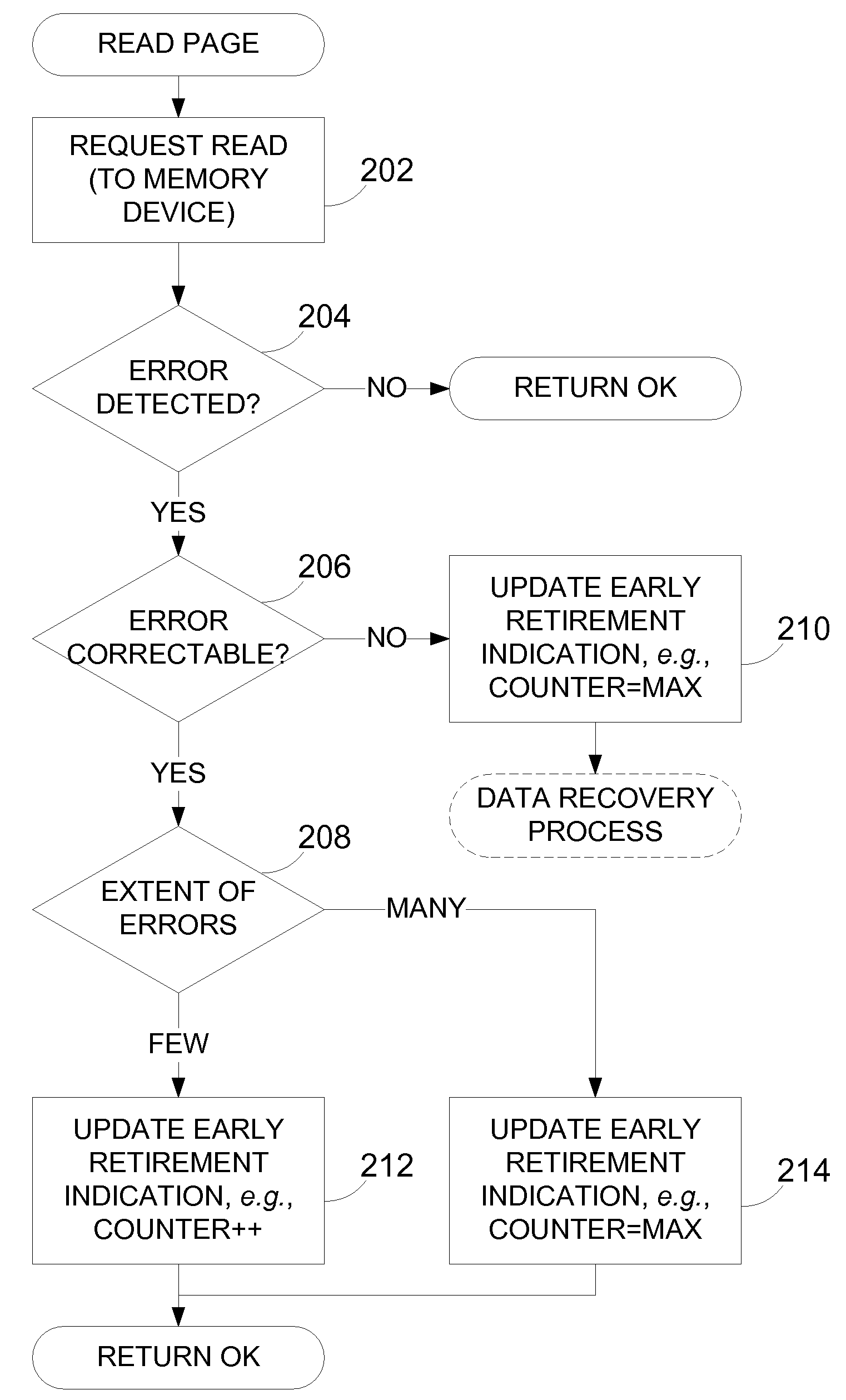

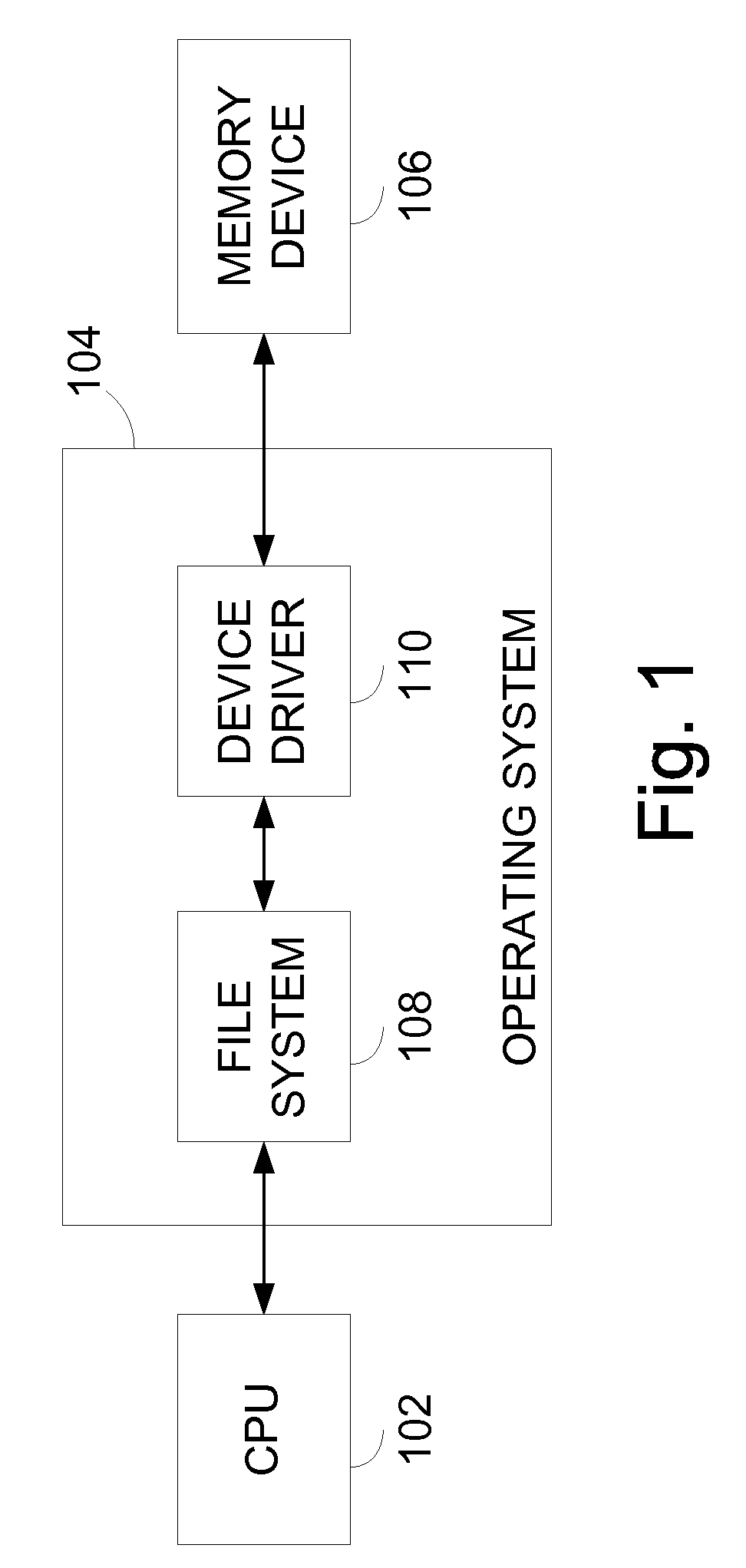

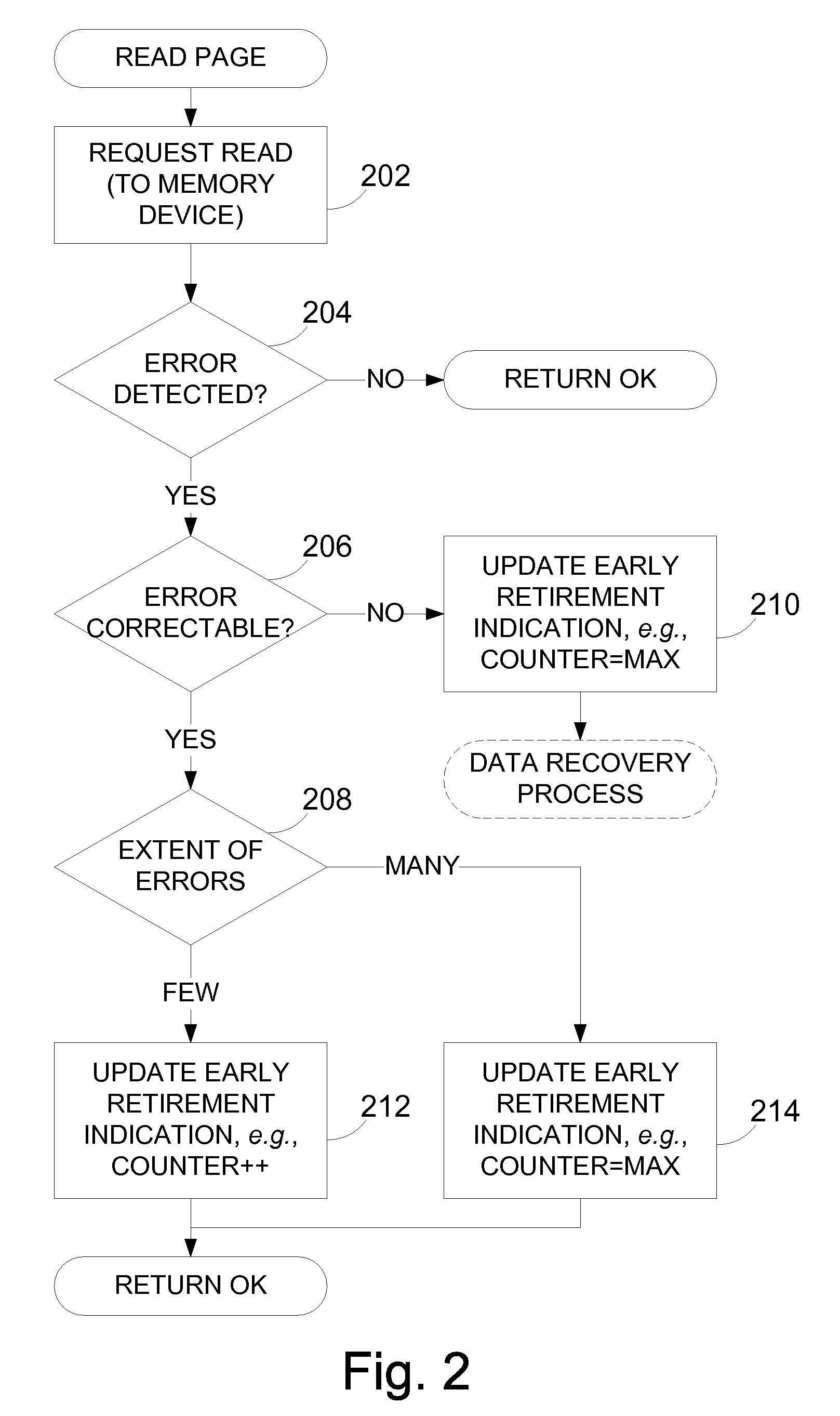

Apparatus and methods, such as those that read data from non-volatile integrated circuit memory devices, such as NAND flash. For example, disclosed techniques can be embodied in a device driver of an operating system. Errors are tracked during read operations. If sufficient errors are observed during read operations, the block is then retired when it is requested to be erased or a page of the block is to be written. One embodiment is a technique to recover data from uncorrectable errors. For example, a read mode can be changed to a more reliable read mode to attempt to recover data. One embodiment further returns data from the memory device regardless of whether the data was correctable by decoding of error correction code data or not.

Owner:MICRON TECH INC

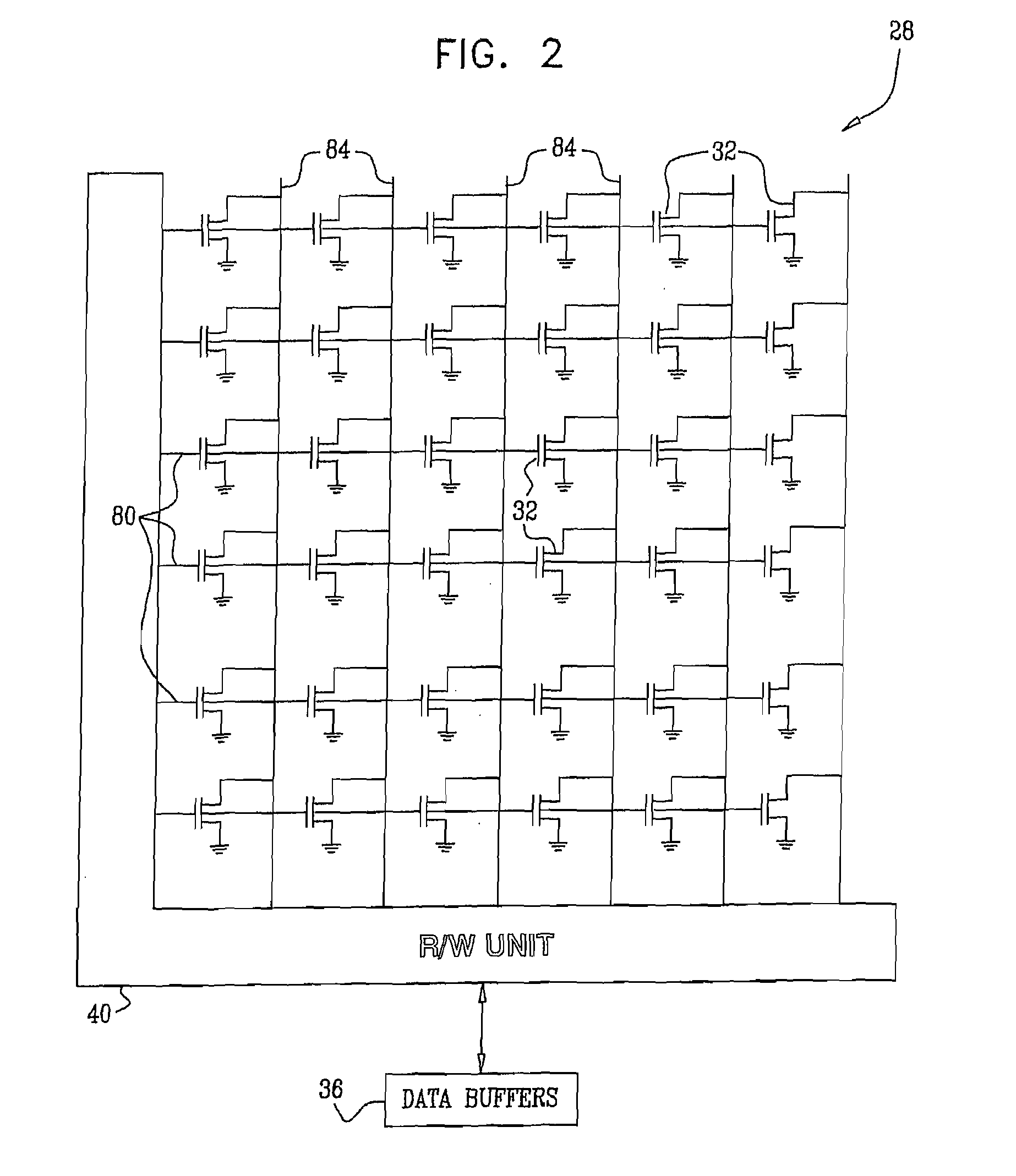

Automatic defect management in memory devices

ActiveUS20100115376A1Code conversionError correction/detection using block codesAlternative methodsComputer science

A method for storing data in a memory (28) that includes analog memory cells (32) includes identifying one or more defective memory cells in a group of the analog memory cells. An Error Correction Code (ECC) is selected responsively to a characteristic of the identified defective memory cells. The data is encoded using the selected ECC and the encoded data is stored in the group of the analog memory cells. In an alternative method, an identification of one or more defective memory cells among the analog memory cells is generated. Analog values are read from the analog memory cells in which the encoded data were stored, including at least one of the defective memory cells. The analog values are processed using an ECC decoding process responsively to the identification of the at least one of the defective memory cells, so as to reconstruct the data.

Owner:APPLE INC

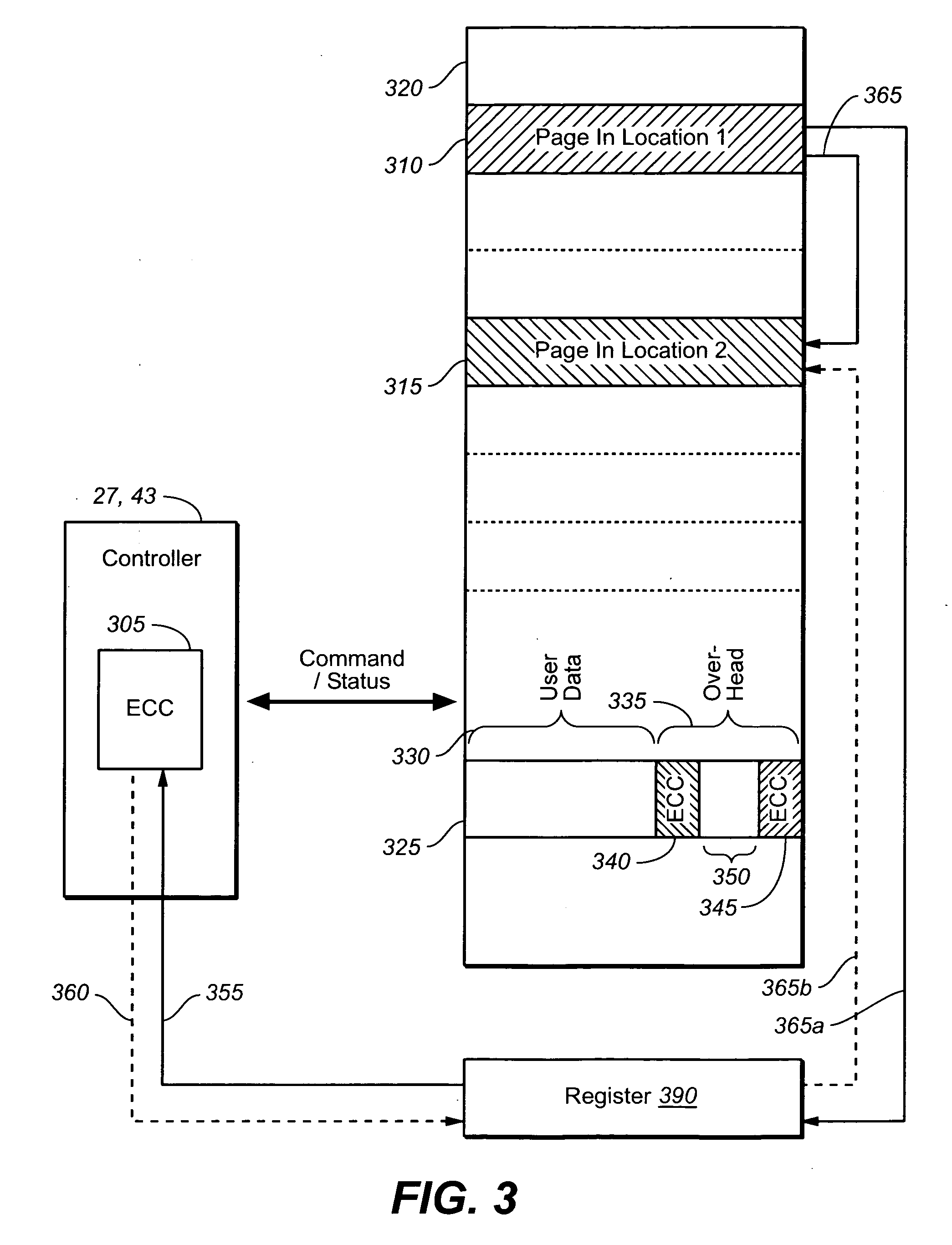

Method and apparatus for managing the integrity of data in non-volatile memory system

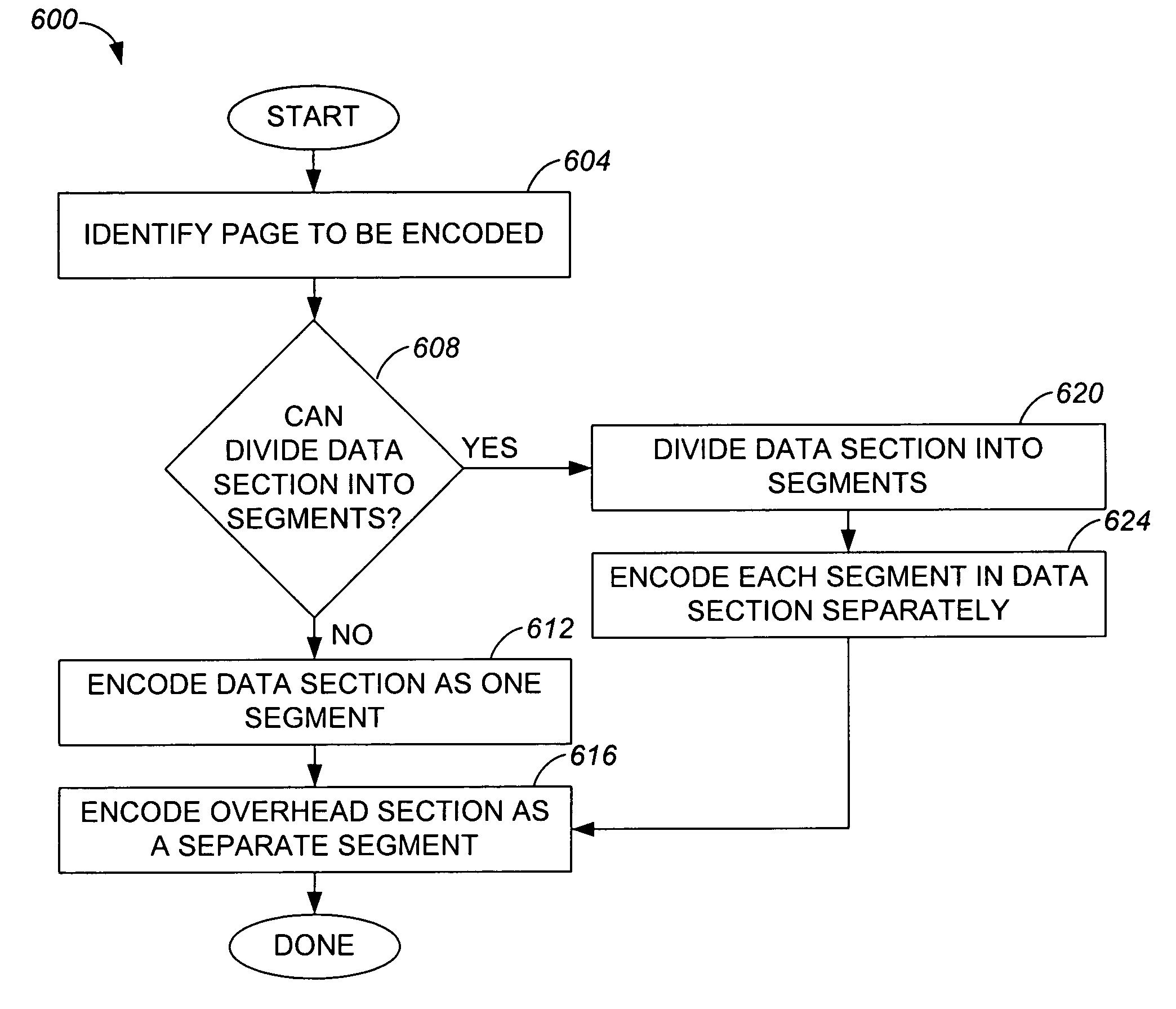

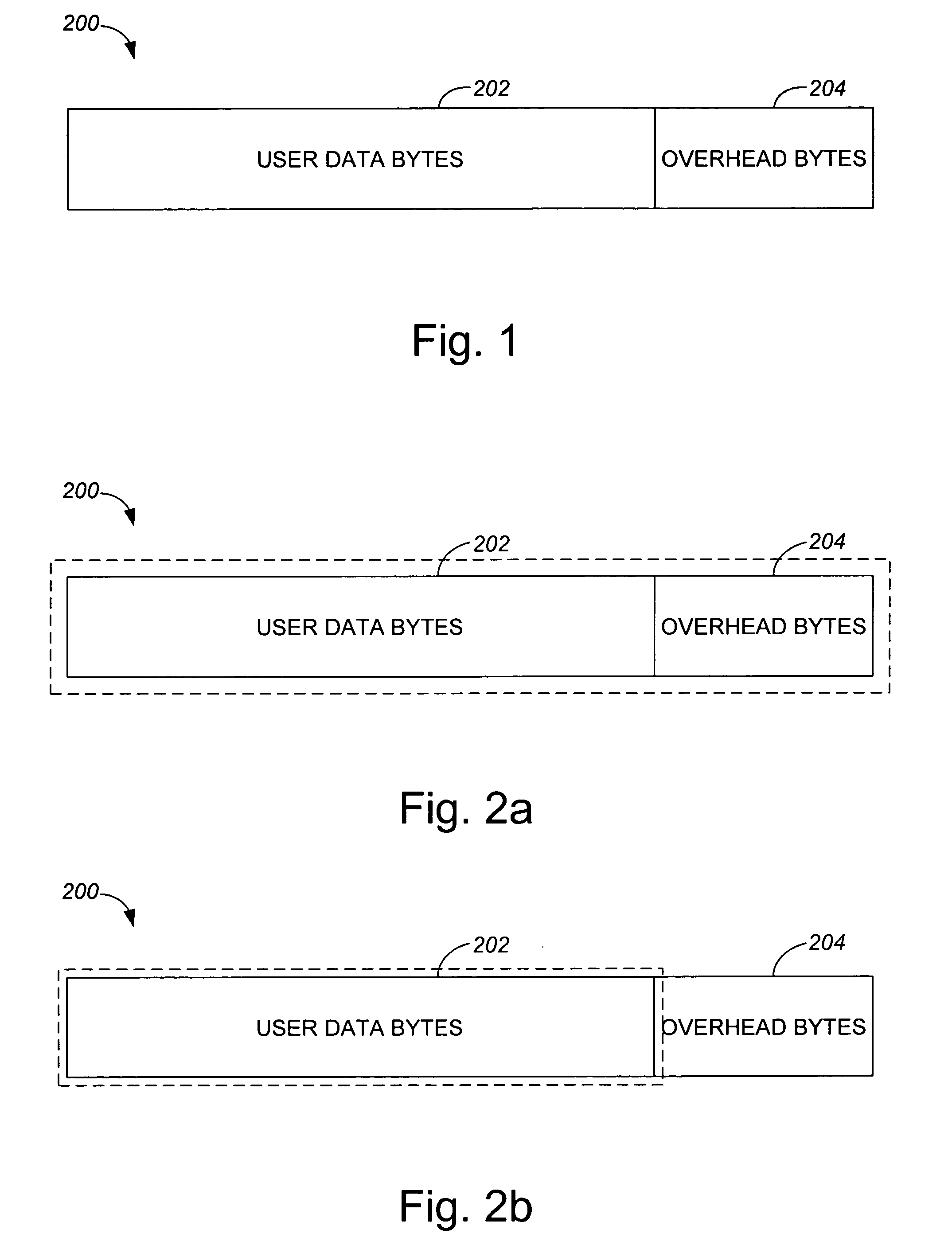

Methods and apparatus for encoding data associated with a page by dividing the page into segments and separately encoding the segments using extended error correction code (ECC) calculations are disclosed. According to one aspect of the present invention, a method for encoding data associated with a page which has a data area and an overhead area within a non-volatile memory of a memory system includes dividing at least a part of the page into at least two segments of the data, the at least two segments of the data including a first segment and a second segment, and performing ECC calculations on the first segment to encode the first segment. The method also includes performing the ECC calculations on the second segment to encode the second segment substantially separately from the first segment.

Owner:SANDISK TECH LLC

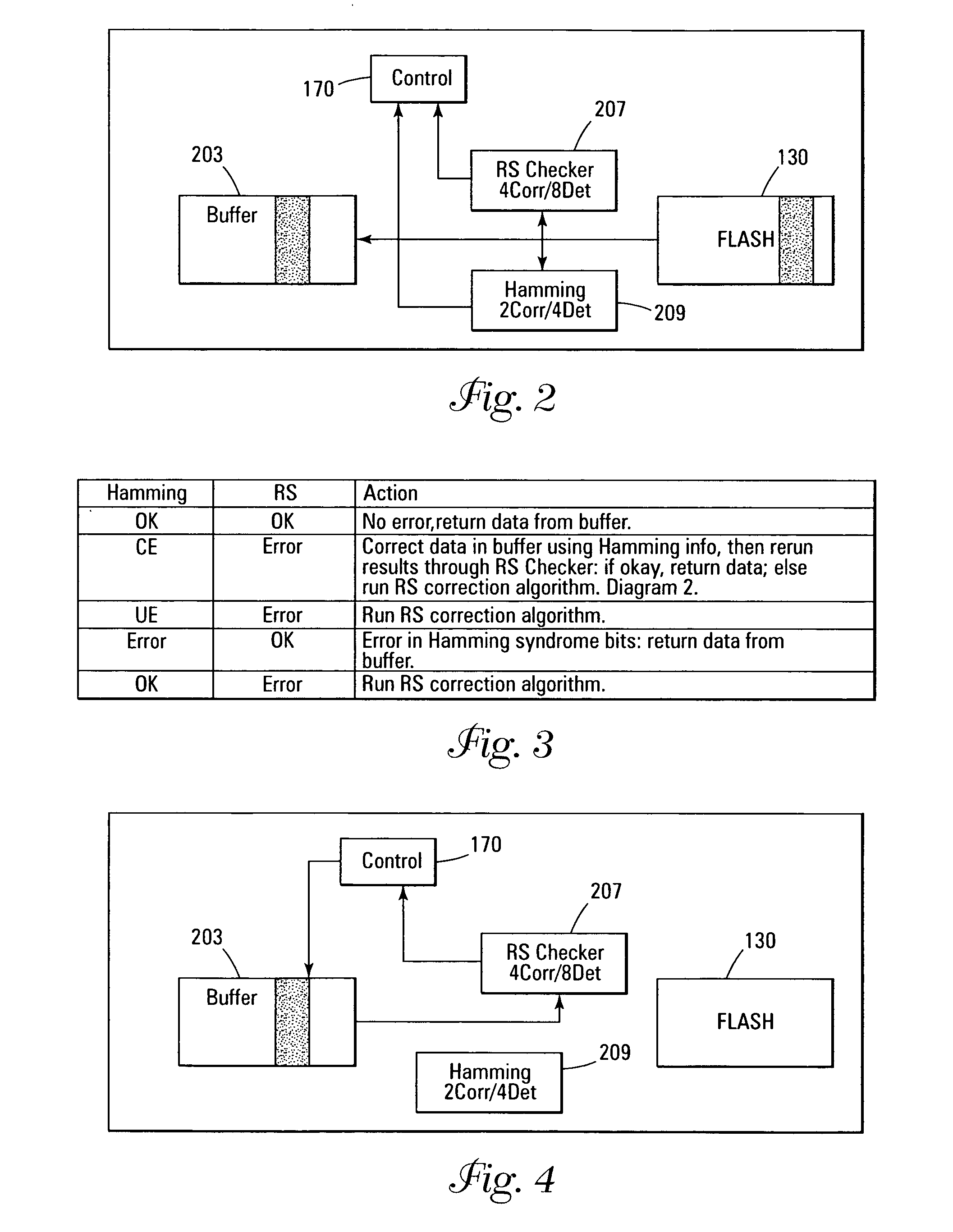

Error detection and correction scheme for a memory device

ActiveUS20050172207A1Code conversionError correction/detection by combining multiple code structuresHamming codeCorrection code

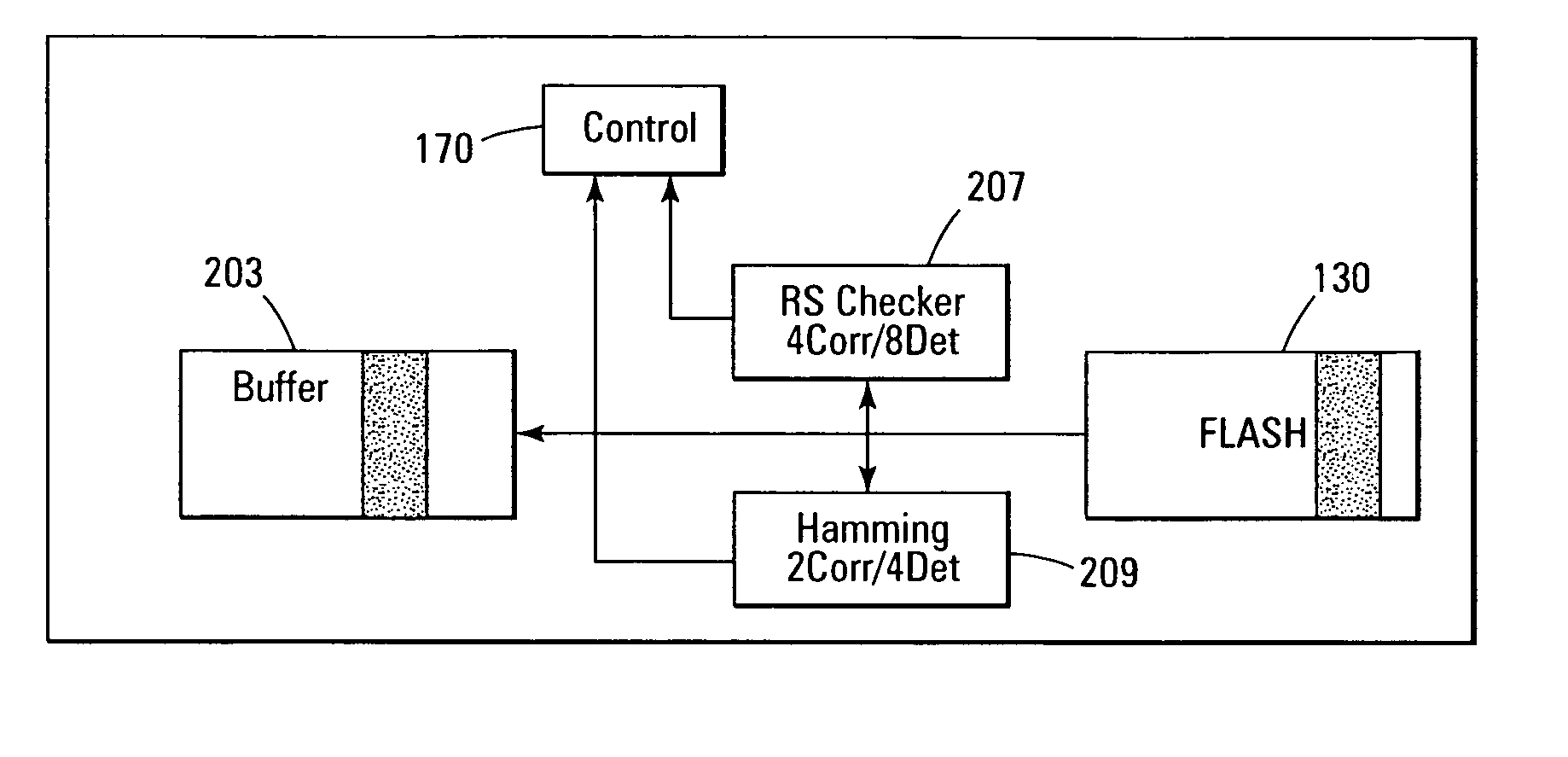

Data is read from a memory array. Before being stored in a data buffer, a Hamming code detection operation and a Reed-Solomon code detection operation are operated in parallel to determine if the data word has any errors. The results of the parallel detection operations are communicated to a controller circuit. If an error is present that can be corrected by the Hamming code correction operation, this is performed and the Reed-Solomon code detection operation is performed on the corrected word. If the error is uncorrectable by the Hamming code, the Reed-Solomon code correction operation is performed on the word.

Owner:MICRON TECH INC

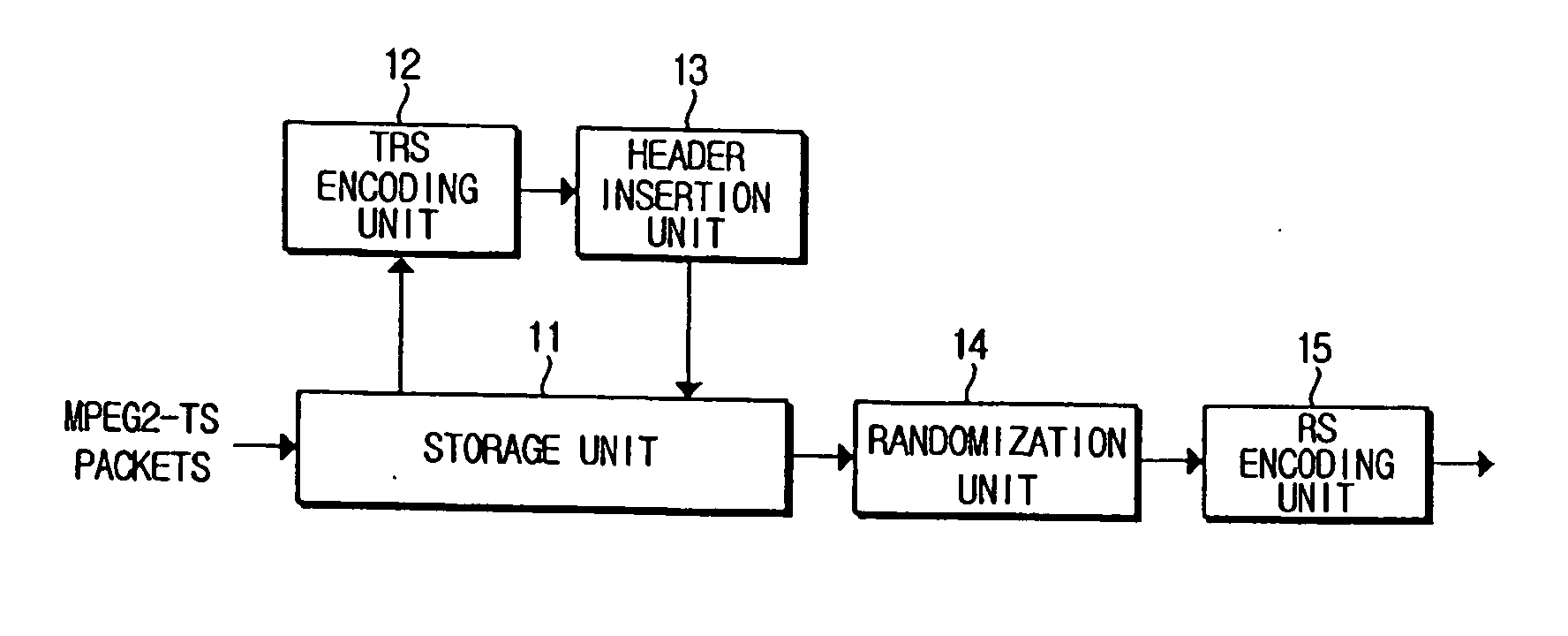

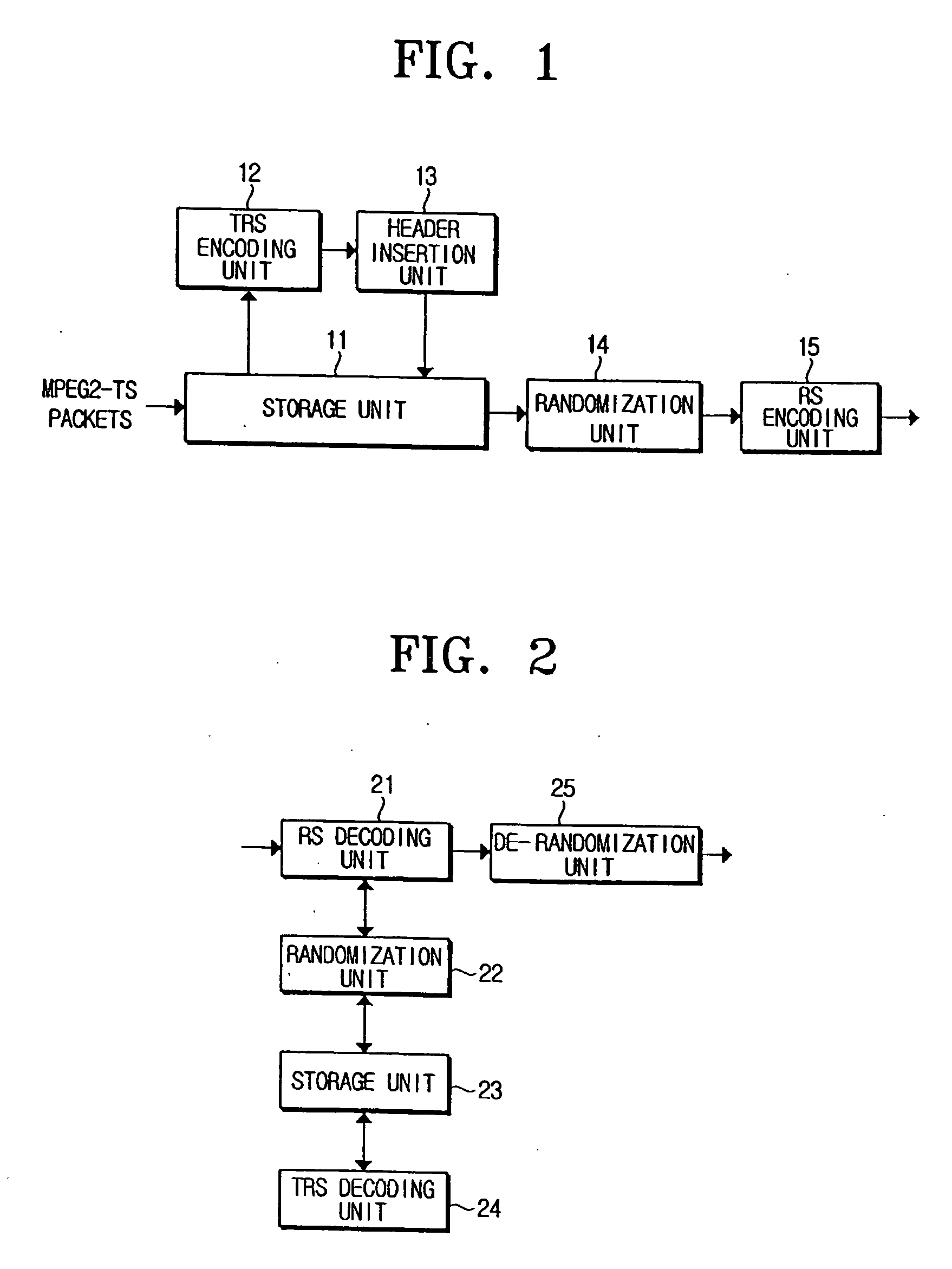

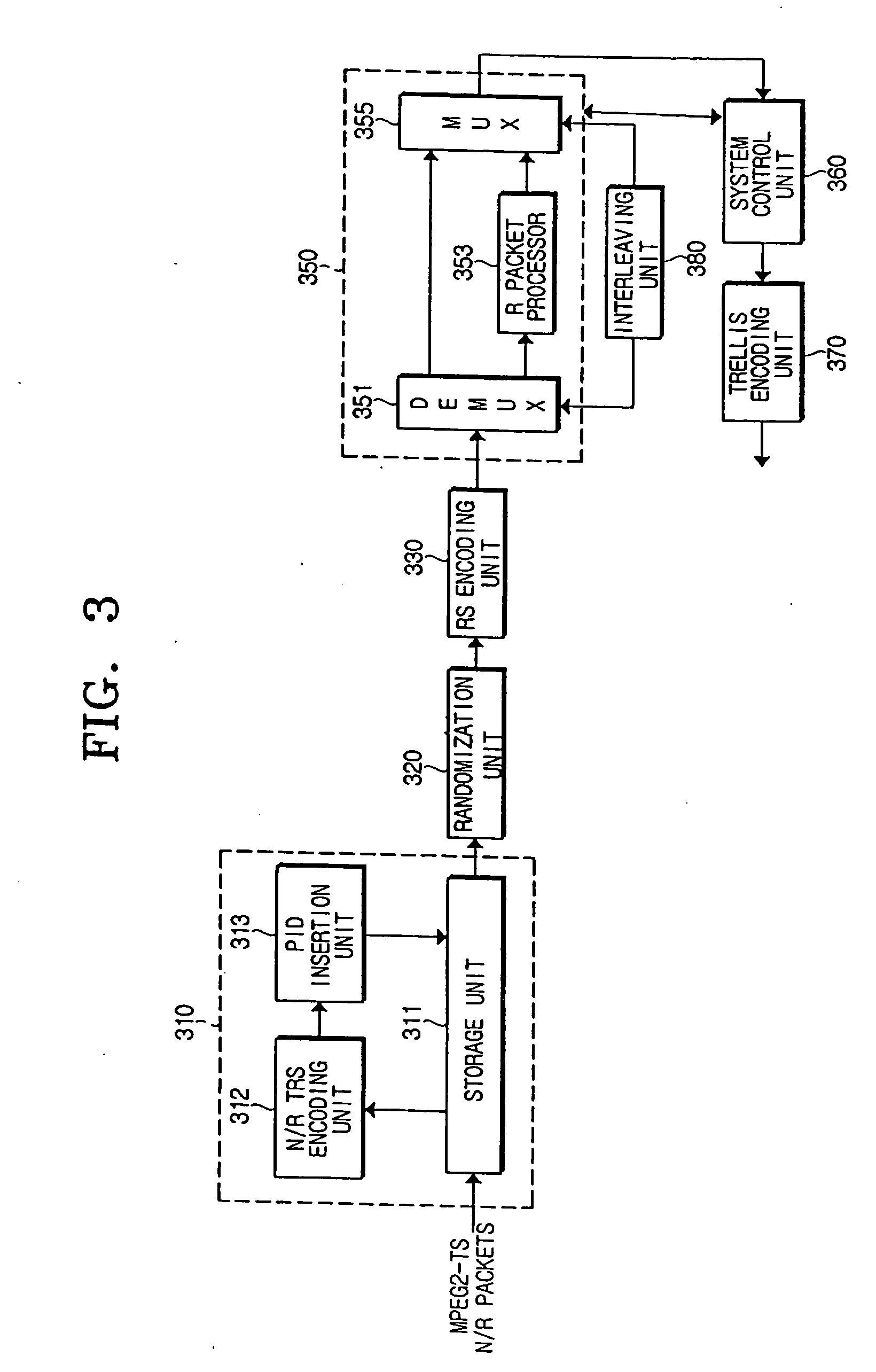

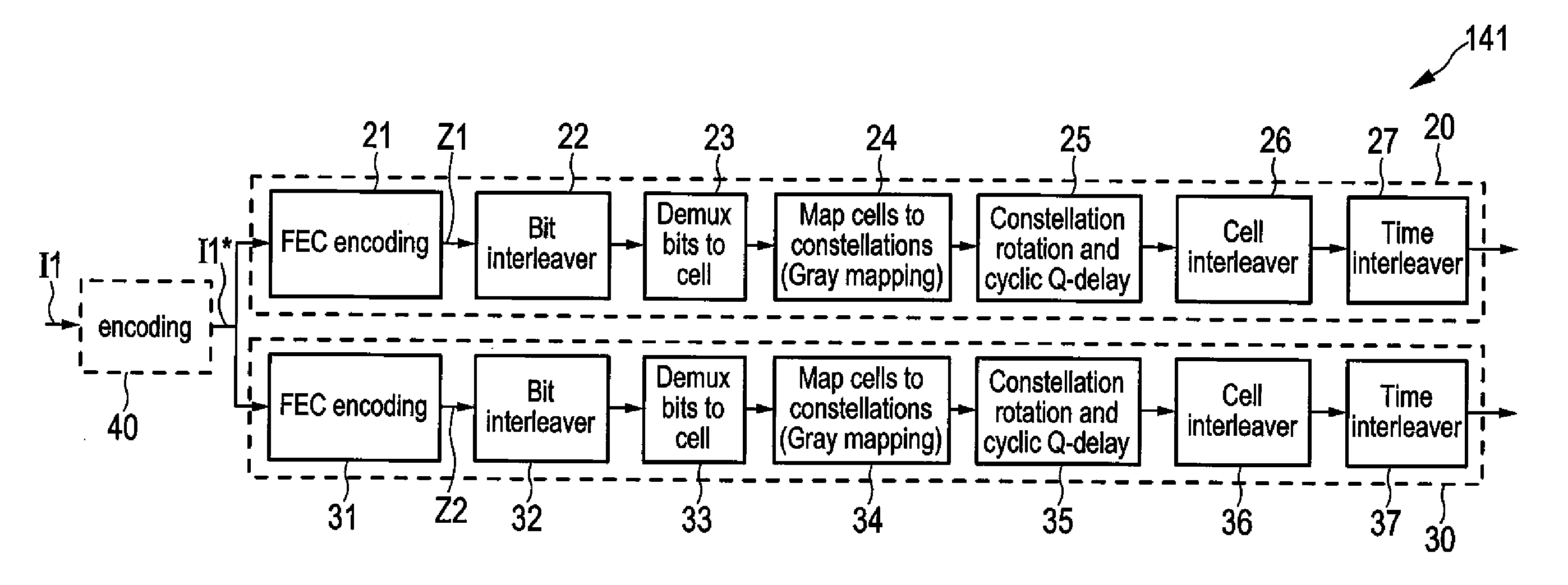

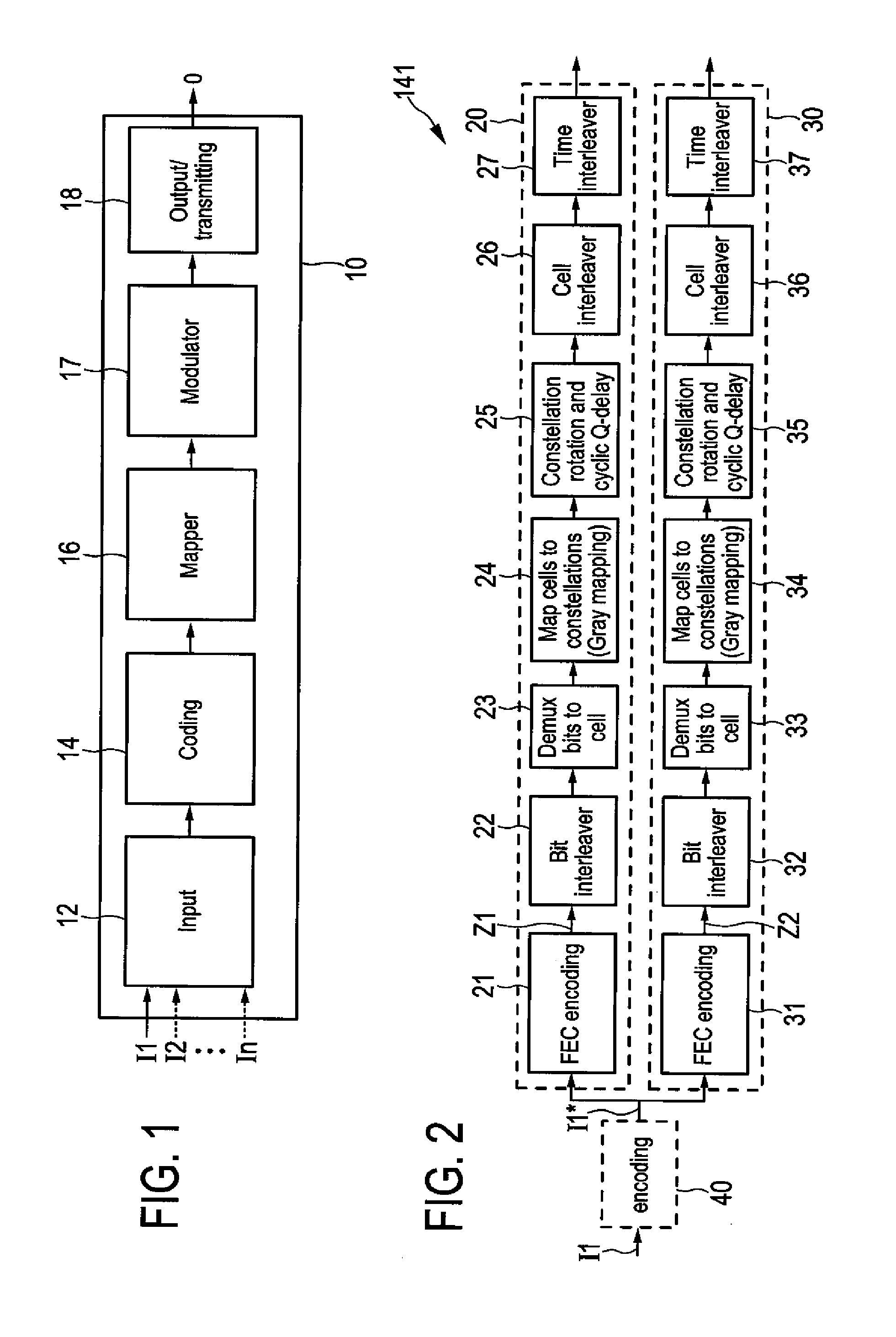

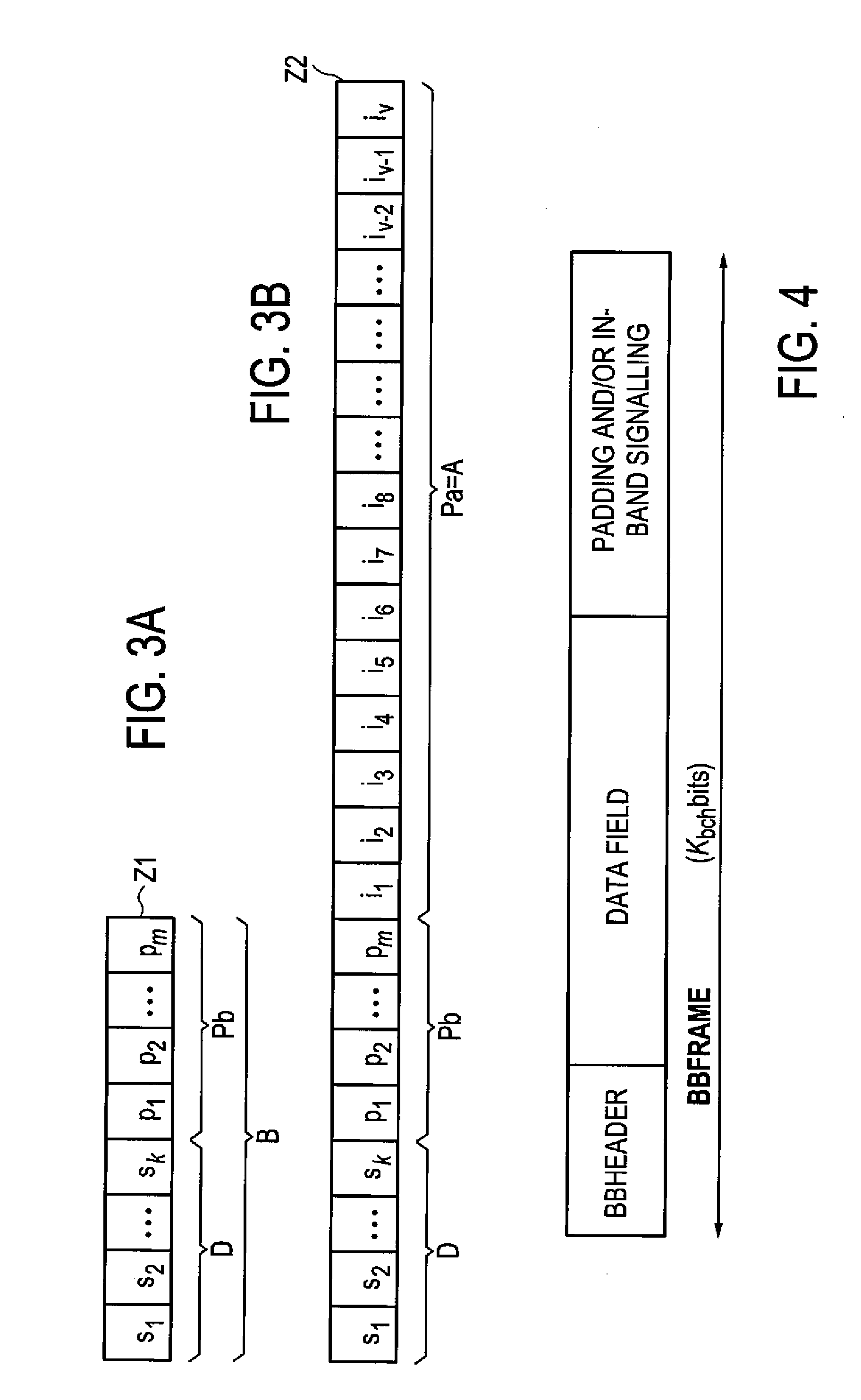

Robust error correction encoding/deconding apparatus and method of digital dual-stream broadcast reception/transmission system

ActiveUS20050097428A1Data representation error detection/correctionPulse modulation television signal transmissionTransfer systemControl data

An error correction encoding and / or decoding apparatus and method of a digital dual-stream broadcast transmission and / or reception system. An error correction encoding apparatus includes a TRS encoding part to apply the transversal encoding to normal data packets and robust data packets and to append parity packets to the normal data packet and robust data packet, a randomization unit to randomize the data packets and the parity packets according to a predetermined pattern, an RS encoding unit to append parities to the randomized data packets and parity packets, a packet format unit to split the data packets and the parity packets into normal data and robust data and to process the normal and robust data, and a system control unit to control the packet format unit. Accordingly, a robust error correction encoding apparatus can be provided for the digital dual-stream broadcast transmission system to which Transversal Reed-Solomon (TRS) encoding is applied.

Owner:SAMSUNG ELECTRONICS CO LTD

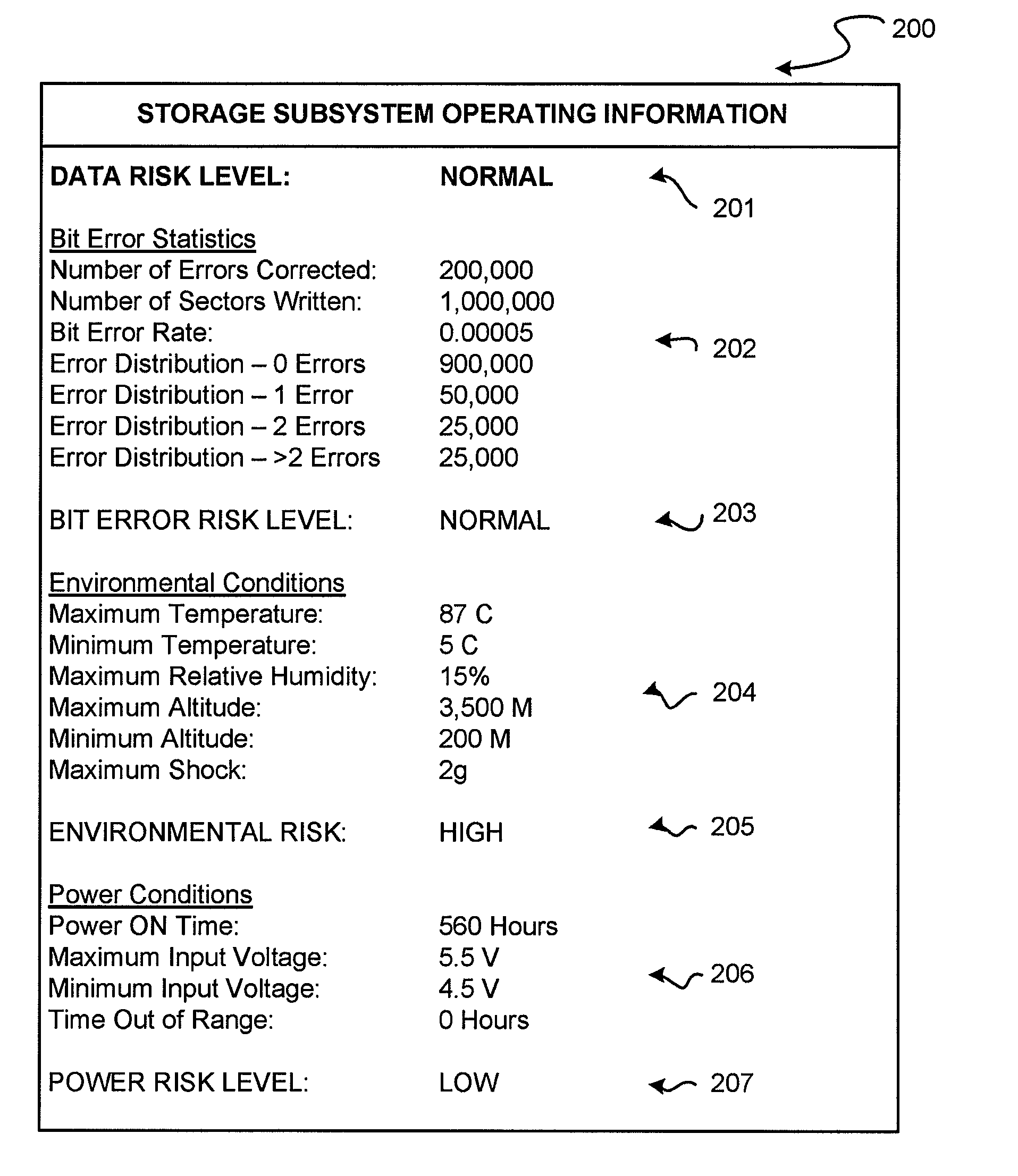

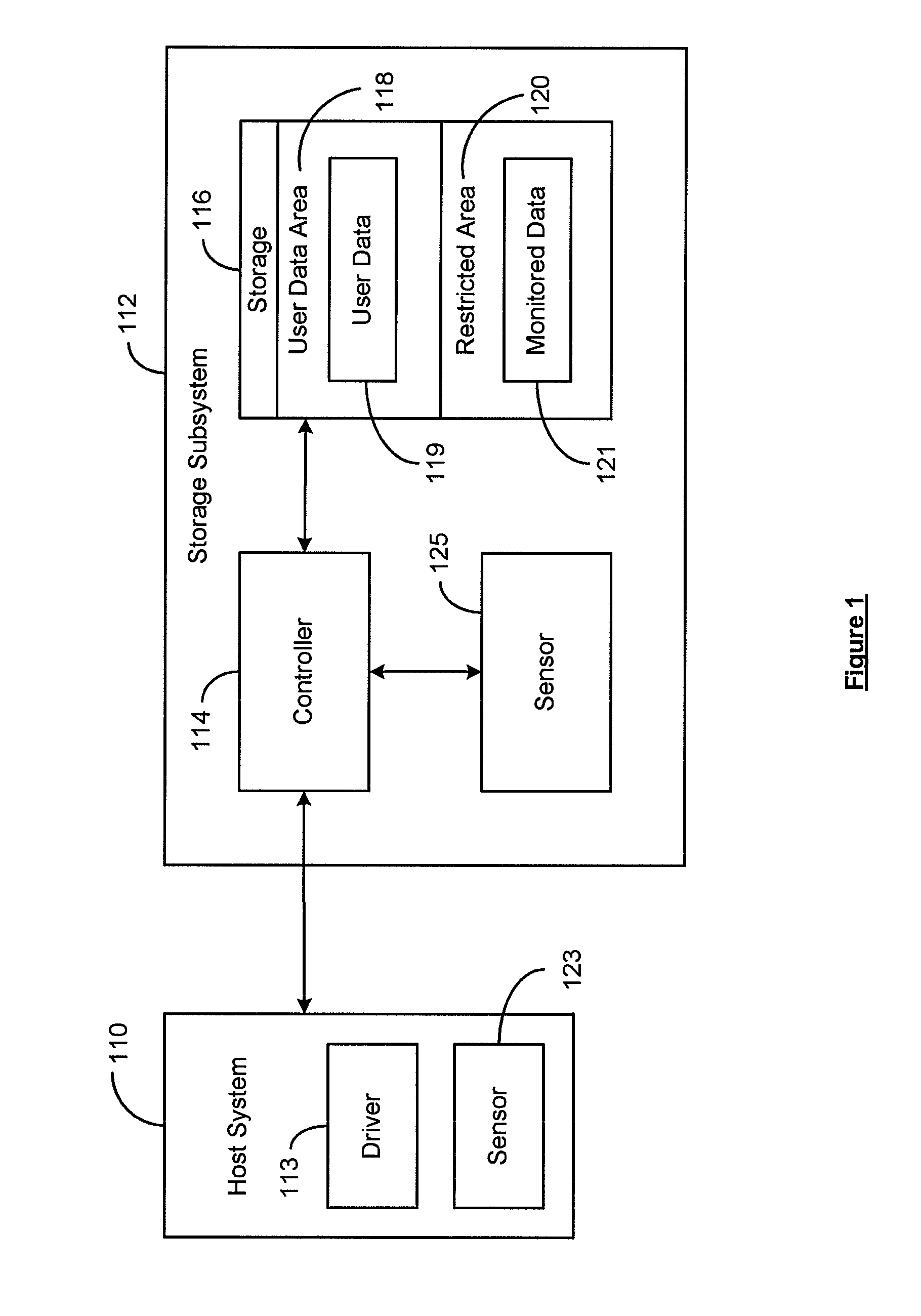

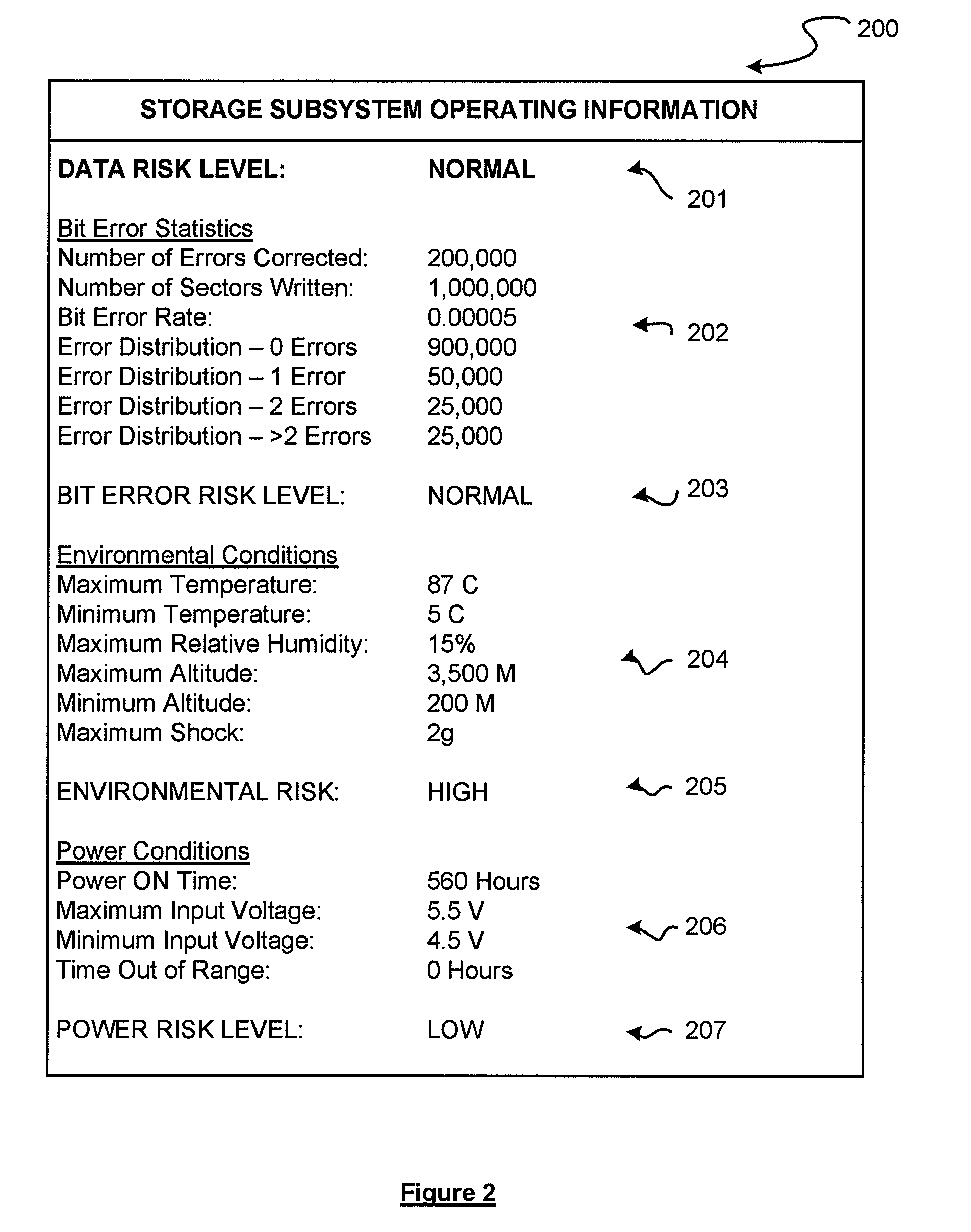

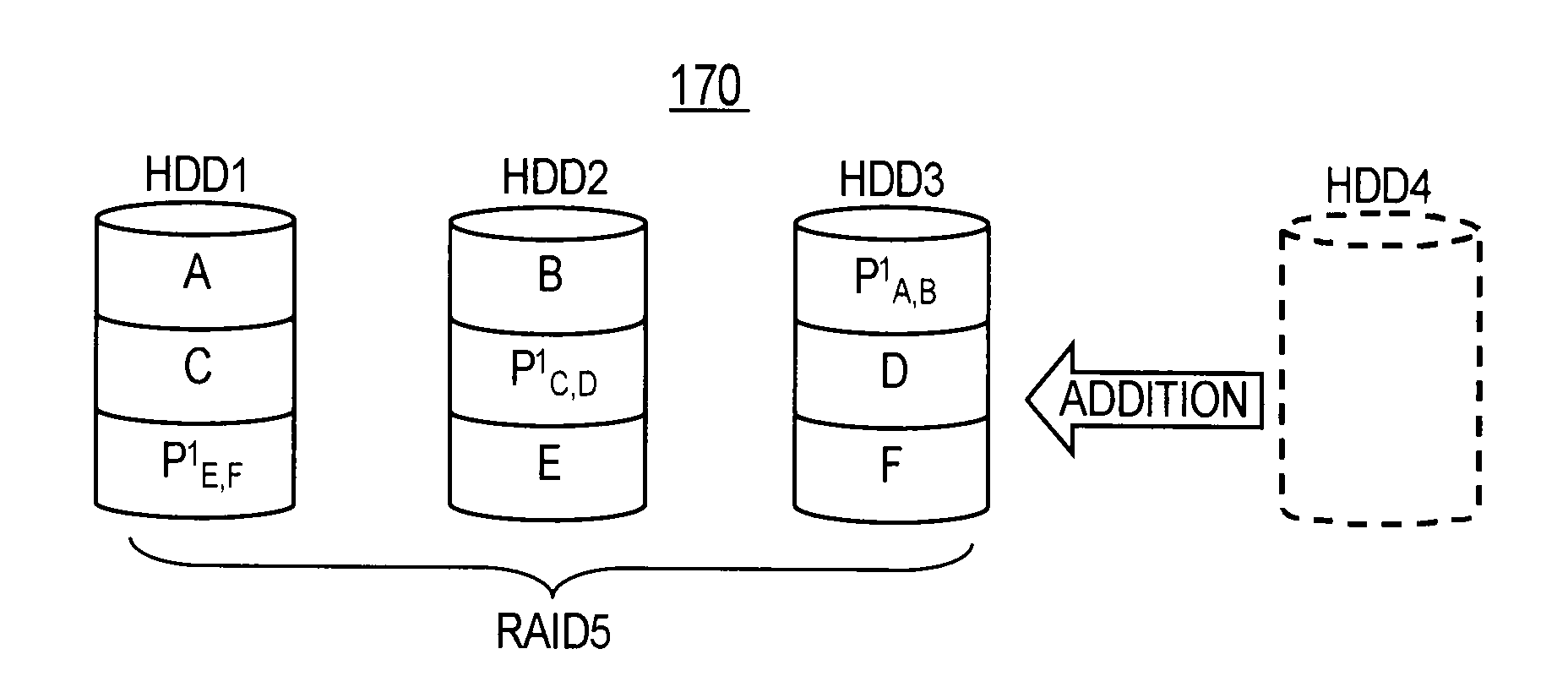

Solid state storage subsystem that maintains and provides access to data reflective of a failure risk

Owner:WESTERN DIGITAL TECH INC

Storage apparatus and control method therefor

Owner:BUFFALO CORP LTD

Arabic spell checking technique

ActiveUS9037967B1Natural language translationSpecial data processing applicationsStatistical modelCorrection code

An Arabic spelling error detection and correction method for identifying real word spelling errors. The method uses a corpus of Arabic text alongside n-gram statistical techniques to detect erroneous words within the text. After identifying the erroneous word the method uses a dictionary formed from the corpus of Arabic text to retrieve candidate correction word to replace the erroneous word with. Using n-gram statistical models candidate correction words are generated and ranked in order of highest probable correction for the word. The generated and ranked correction words are assessed and the best correction word is selected. A final assessment of the correction is conducted and if the result is positive then erroneous word is replaced with the highest statistical correction.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

Error recovery storage along a nand-flash string

ActiveUS20090013233A1Error prevention/detection by using return channelError correction/detection using convolutional codesConvolutional codeData storing

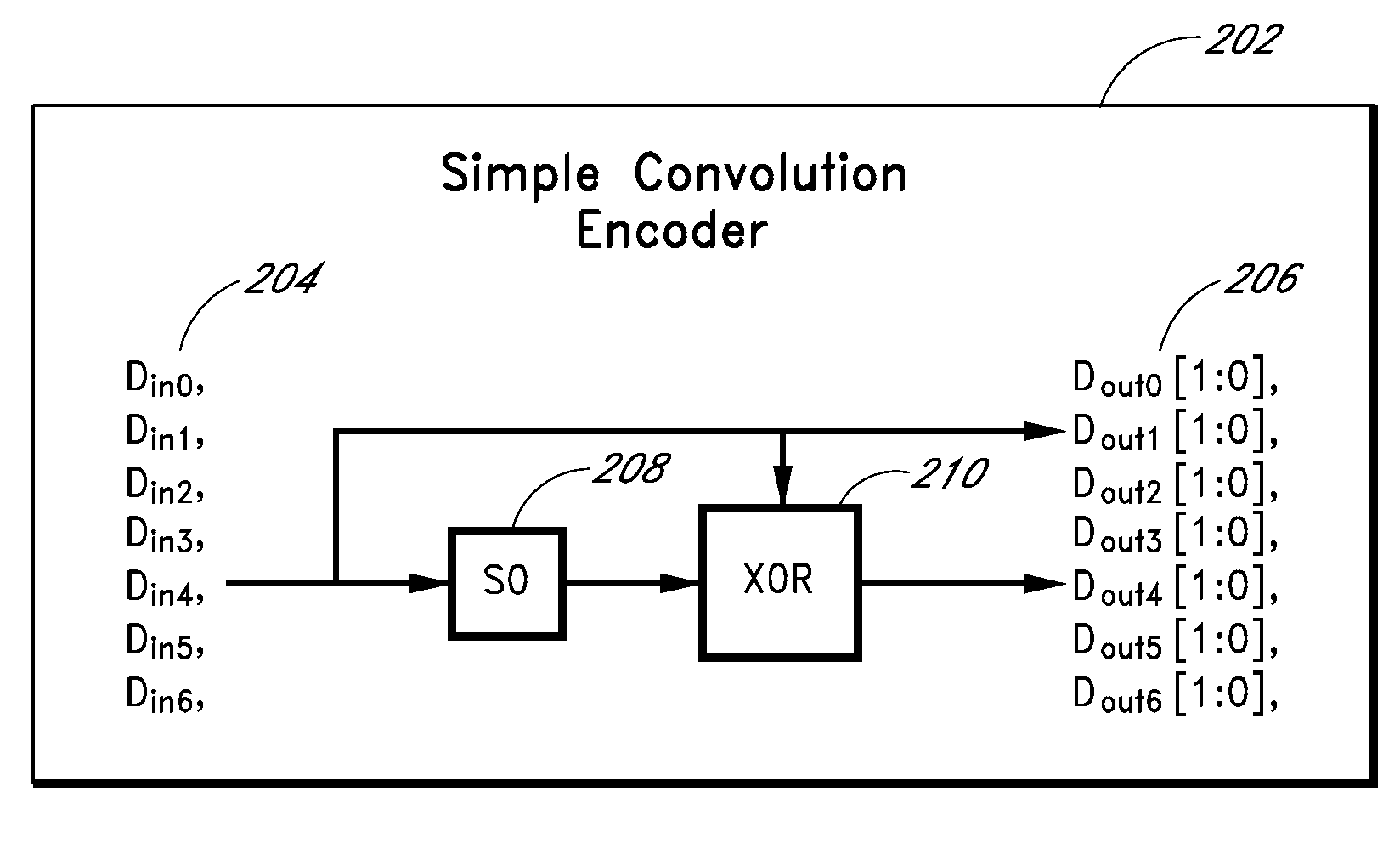

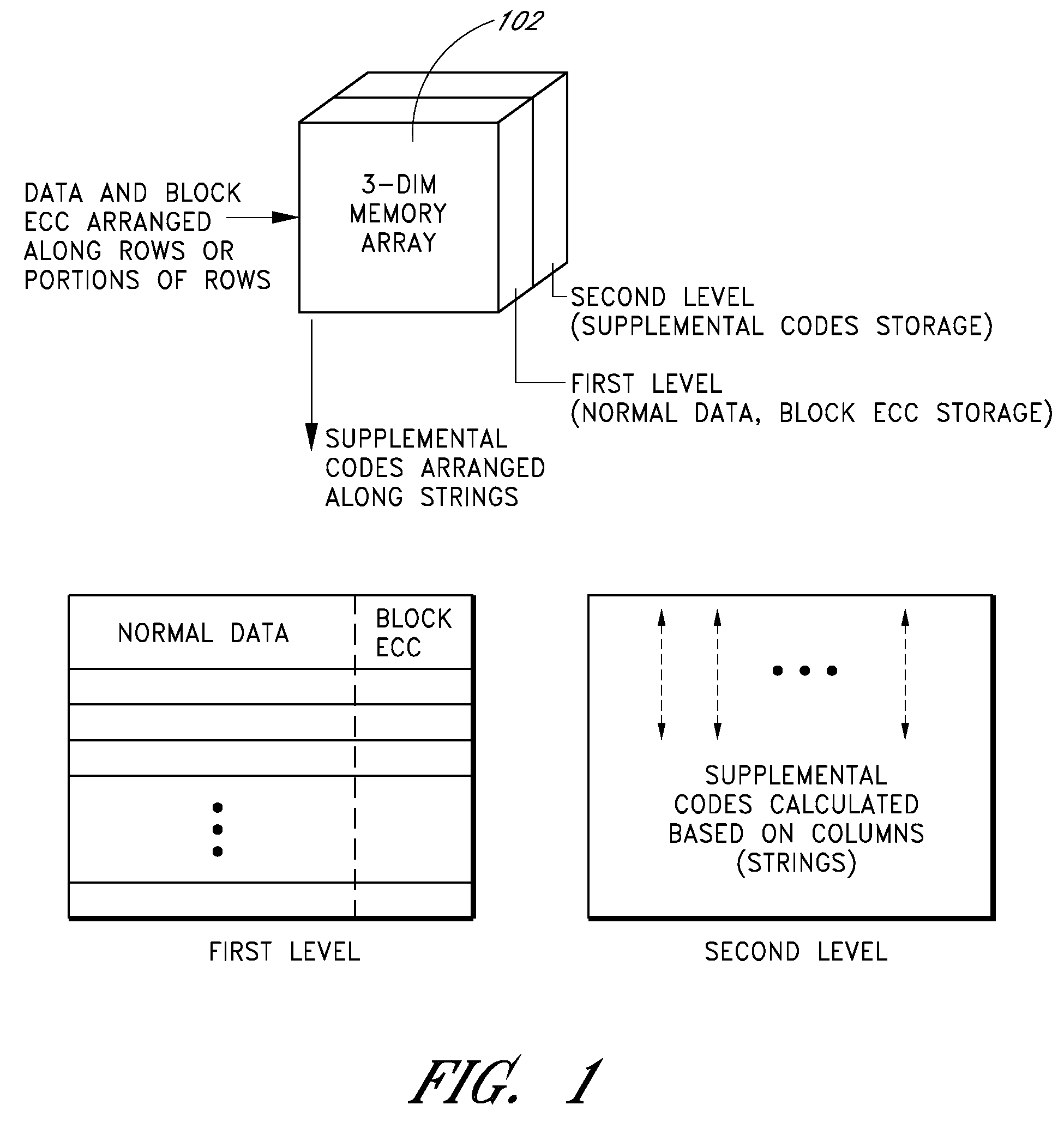

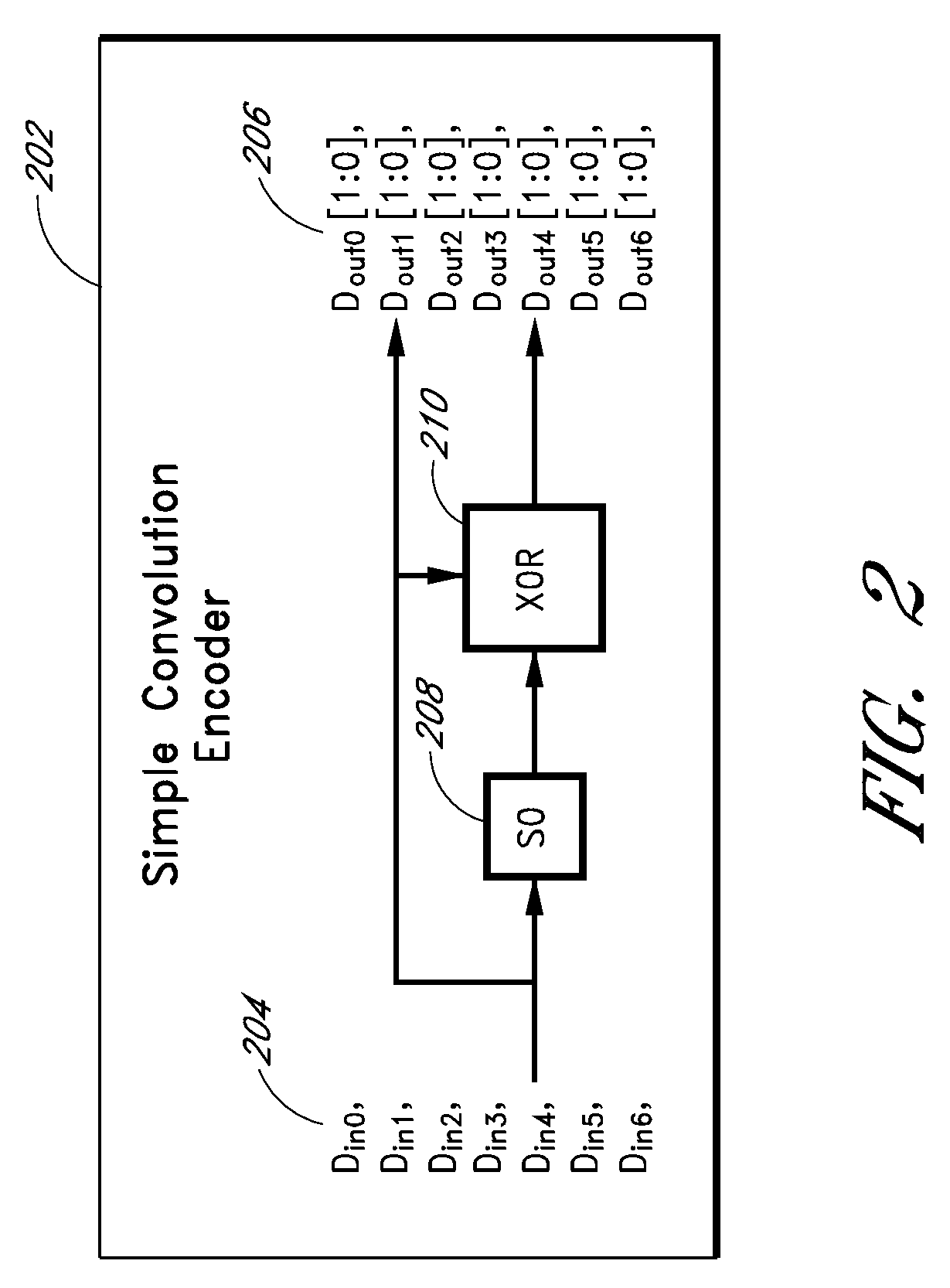

Apparatus and methods store error recovery data in different dimensions of a memory array. For example, in one dimension, block error correction codes (ECC) are used, and in another dimension, supplemental error correction codes, such as convolutional codes, are used. By using separate dimensions, the likelihood that a defect affects both error recovery techniques is lessened, thereby increasing the probability that error recovery can be performed successfully. In one example, block error correction codes are used for data stored along rows, and this data is stored in one level of multiple-level cells of the array. Supplemental error correction codes are used for data stored along columns, such as along the cells of a string, and the supplemental error correction codes are stored in a different level than the error correction codes.

Owner:MICRON TECH INC

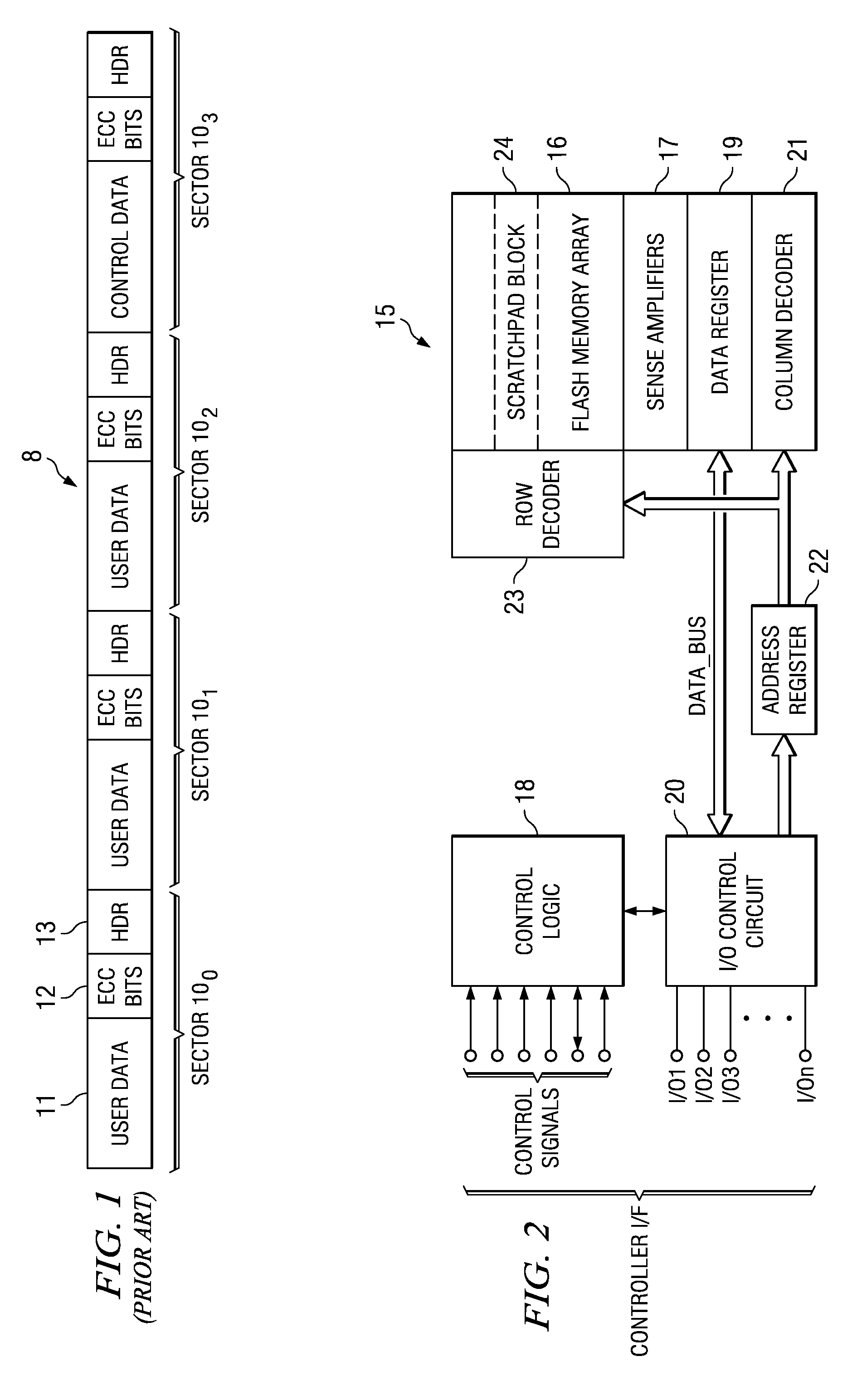

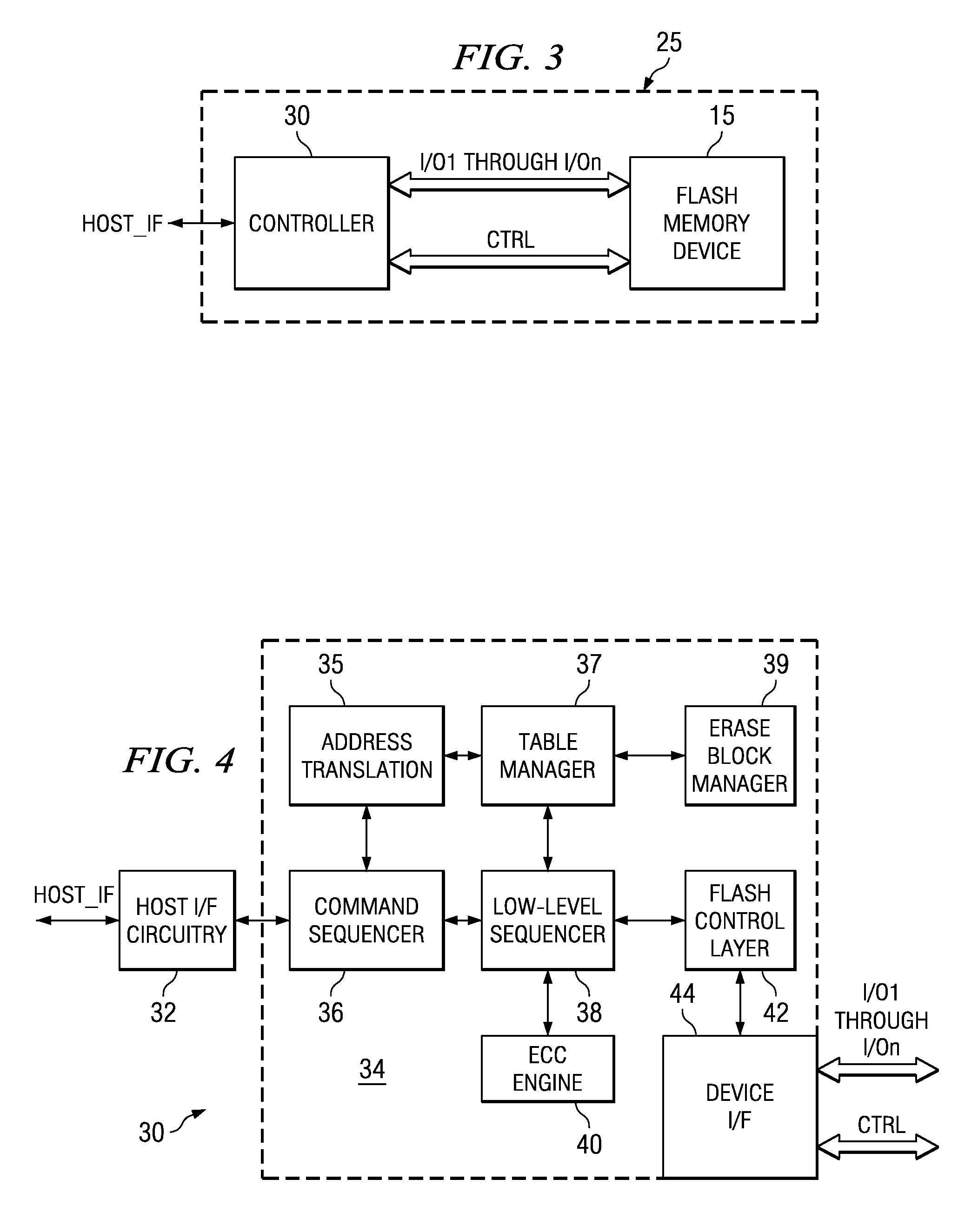

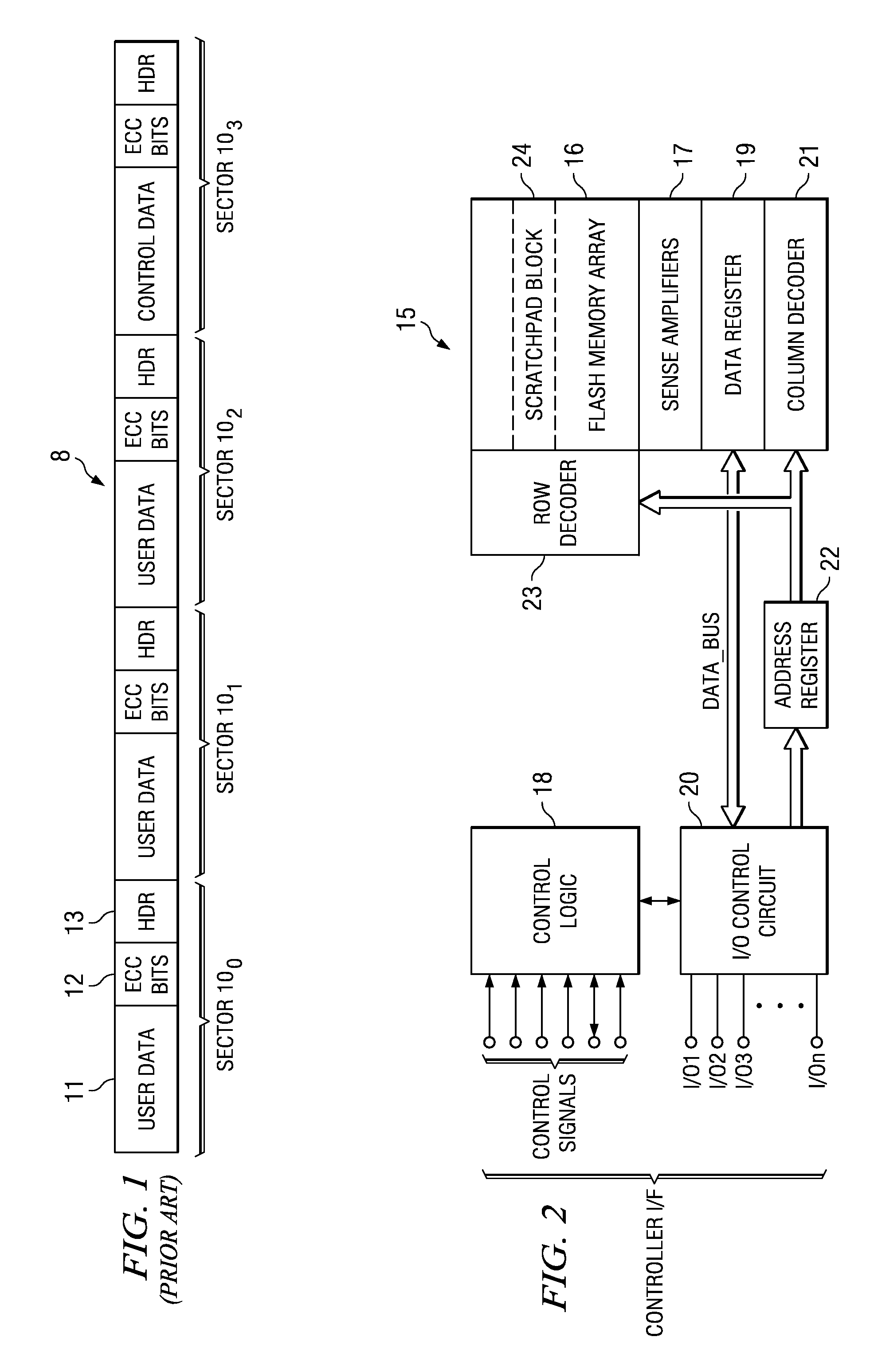

Method of Error Correction Coding for Multiple-Sector Pages in Flash Memory Devices

InactiveUS20070300130A1Efficient error correctionError detection/correctionRead-only memoriesControl dataDependability

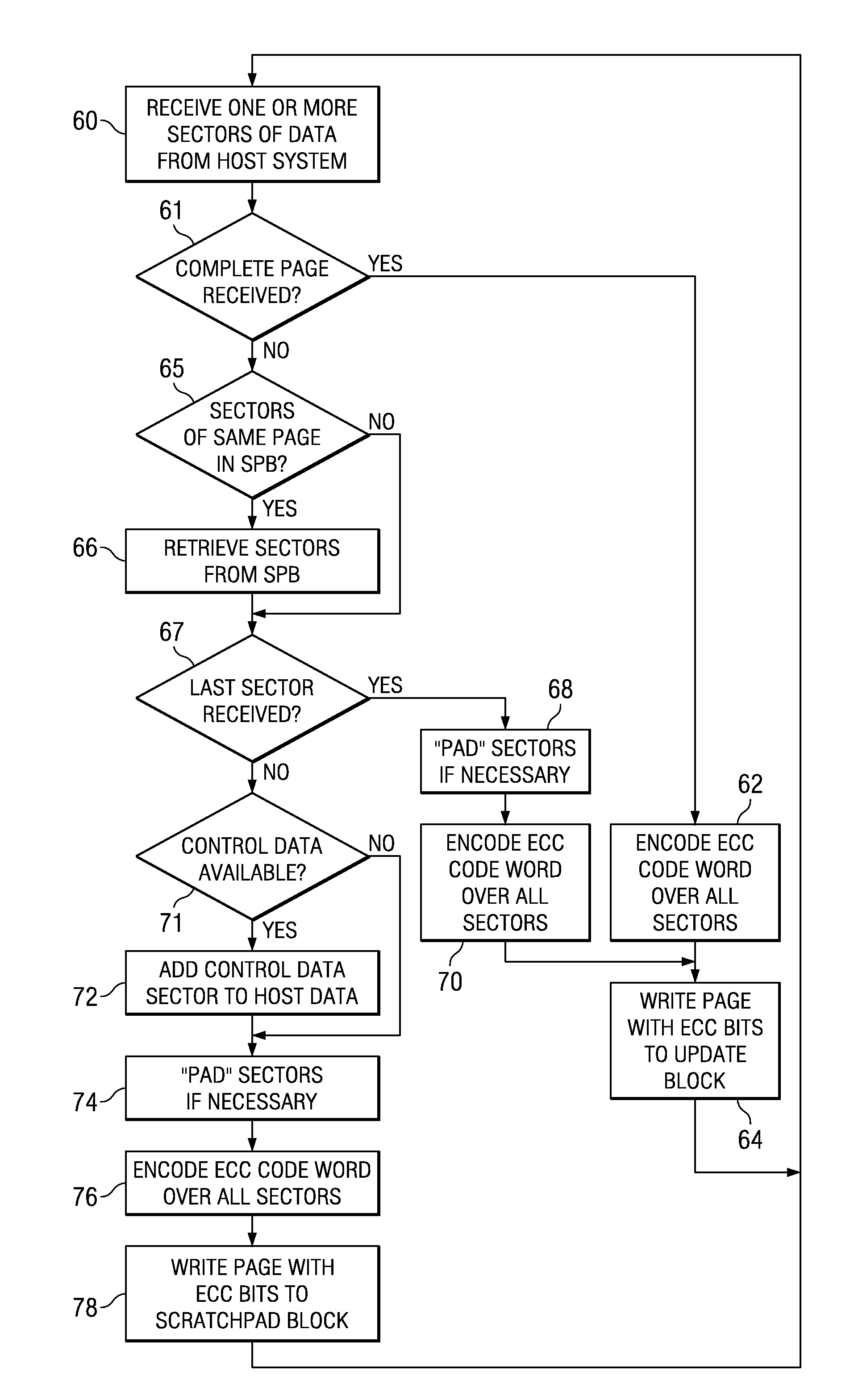

A flash memory system, including a flash memory device and a controller, and having improved efficiency error correction coding (ECC), is disclosed. Each page in the flash memory device has the capacity to store multiple sectors' worth of data. However, partial page programming (i.e., followed by a later write to fill the page) is prohibited for reliability reasons. A scratchpad block within the flash memory device is designed, and stores both user data and control data. ECC efficiency is improved by encoding the ECC, or parity, bits over the entire data block corresponding to the user and control data in the page. Retrieval of a particular sector of data requires reading and decoding of the entire page. Especially for codes such as Reed-Solomon and BCH codes, the larger data block including multiple sectors' data improves the error correction capability, and thus enables either fewer redundant memory cells in each page or improved error correction.

Owner:SANDISK TECH LLC

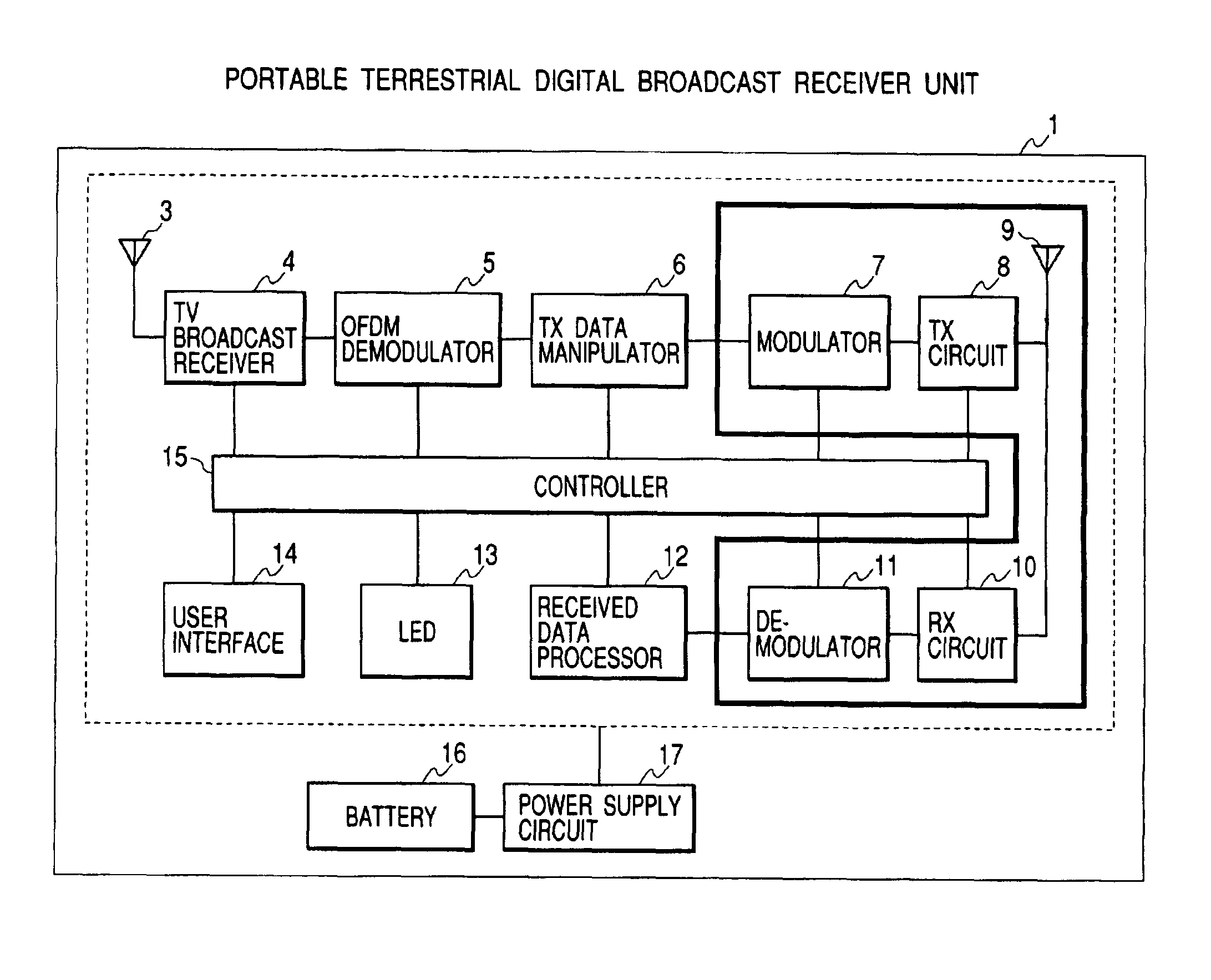

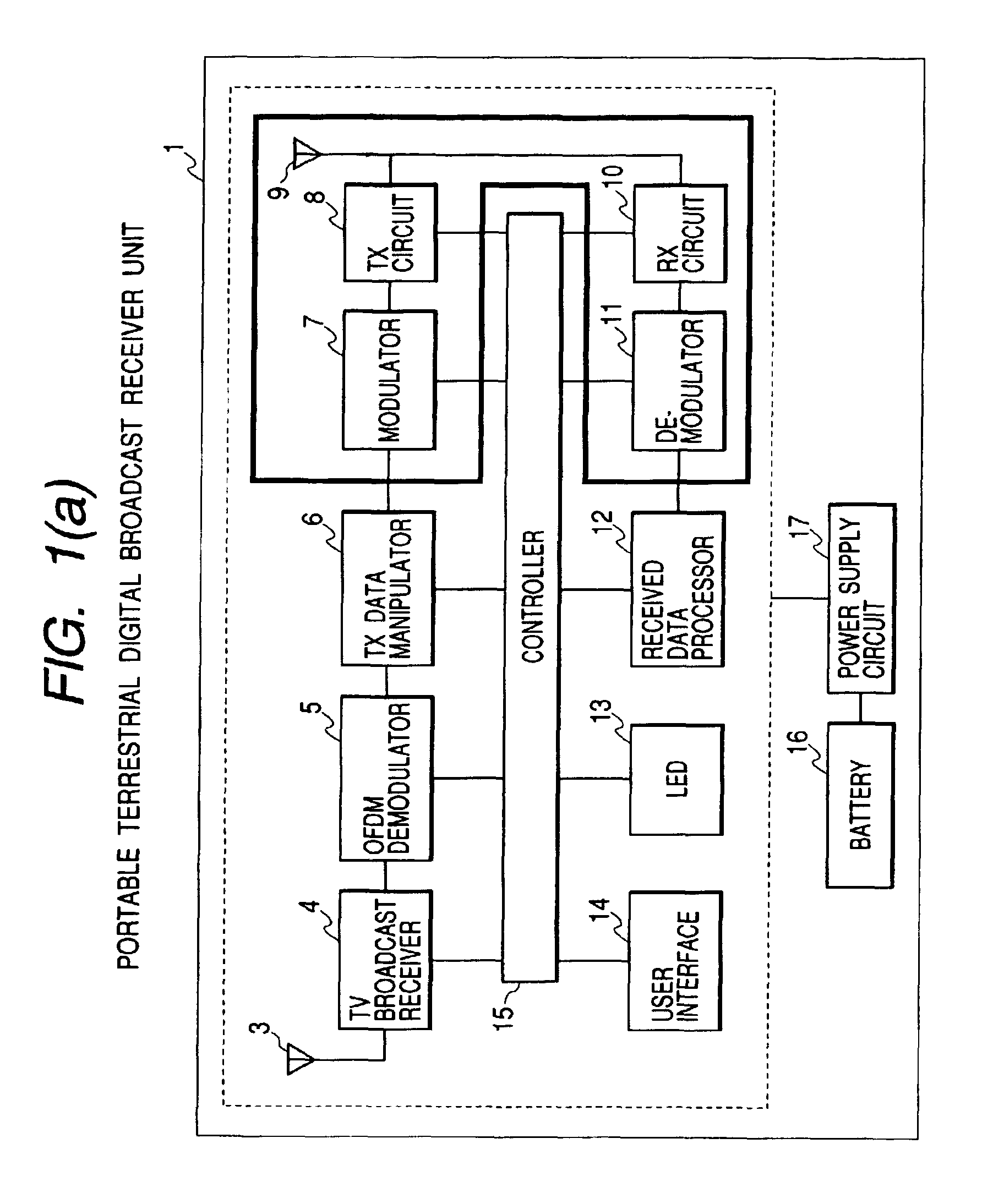

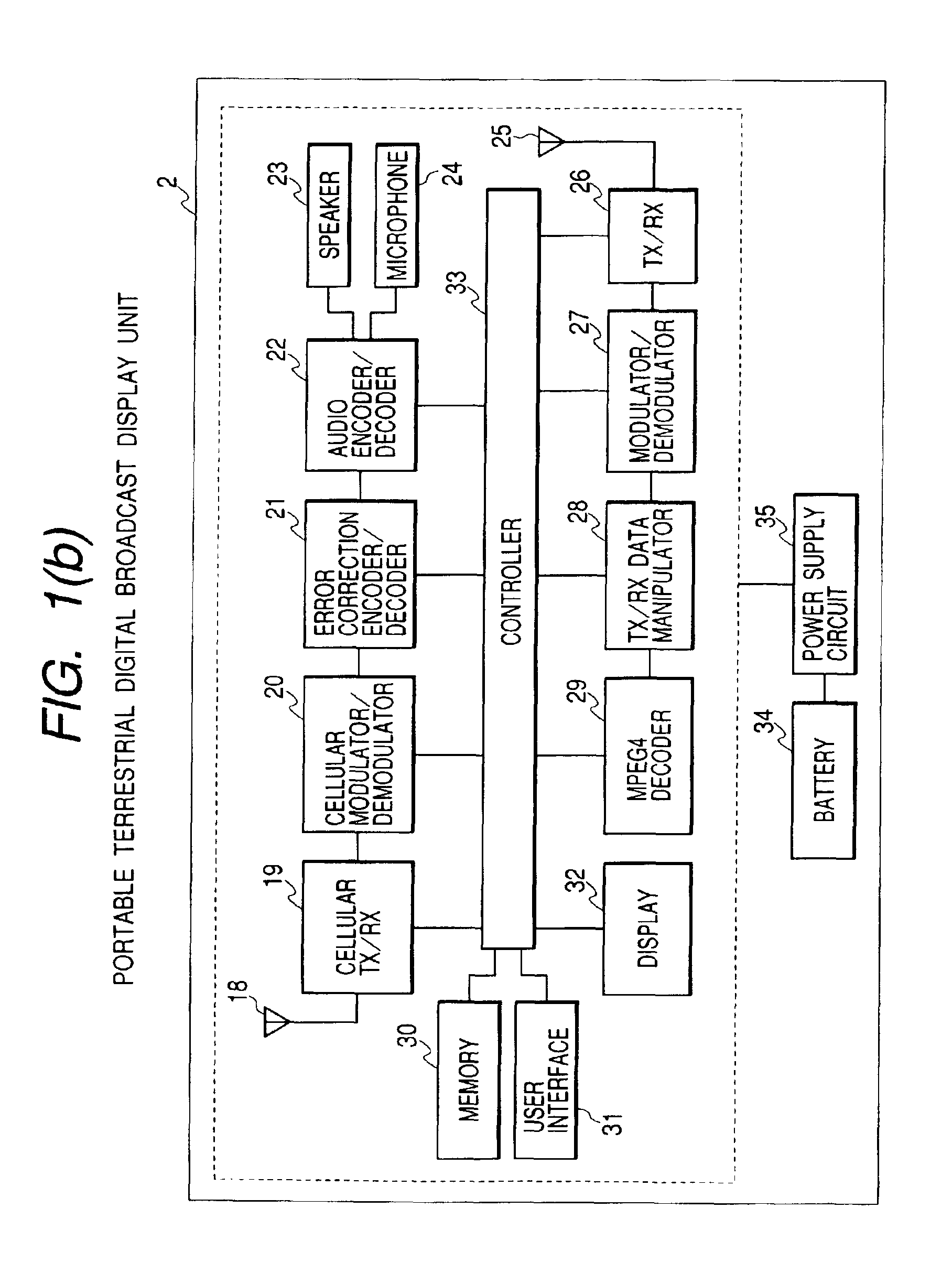

Digital broadcast channel reception system and method and portable terminal for use in such system

ActiveUS6952595B2Battery consumption increaseReduce waiting timeTelevision system detailsBroadcast specific applicationsComputer hardwareBroadcast channels

A digital broadcast channel reception system and a portable terminal allow watching a digital broadcast on the terminal. In the examples, a receiver unit for receiving digital broadcasts transmits video data to a display unit, using its TX data manipulator, modulator, TX circuit, and antenna. The TX data manipulator manipulates the output from an OFDM demodulator into data to transmit from the TX circuit and appends error correction codes to the data. The modulator modulates the output from the TX data manipulator. A display unit for digital broadcast display receives video data transmitted from the receiver unit, using its antenna, TX / RX section, and modulator / demodulator. After error correction codes in the received signals are decoded by a TX / RX data manipulator, video data is extracted. After the video data is decoded by a MPEG4 decoder, a picture is output on the display.

Owner:MAXELL HLDG LTD

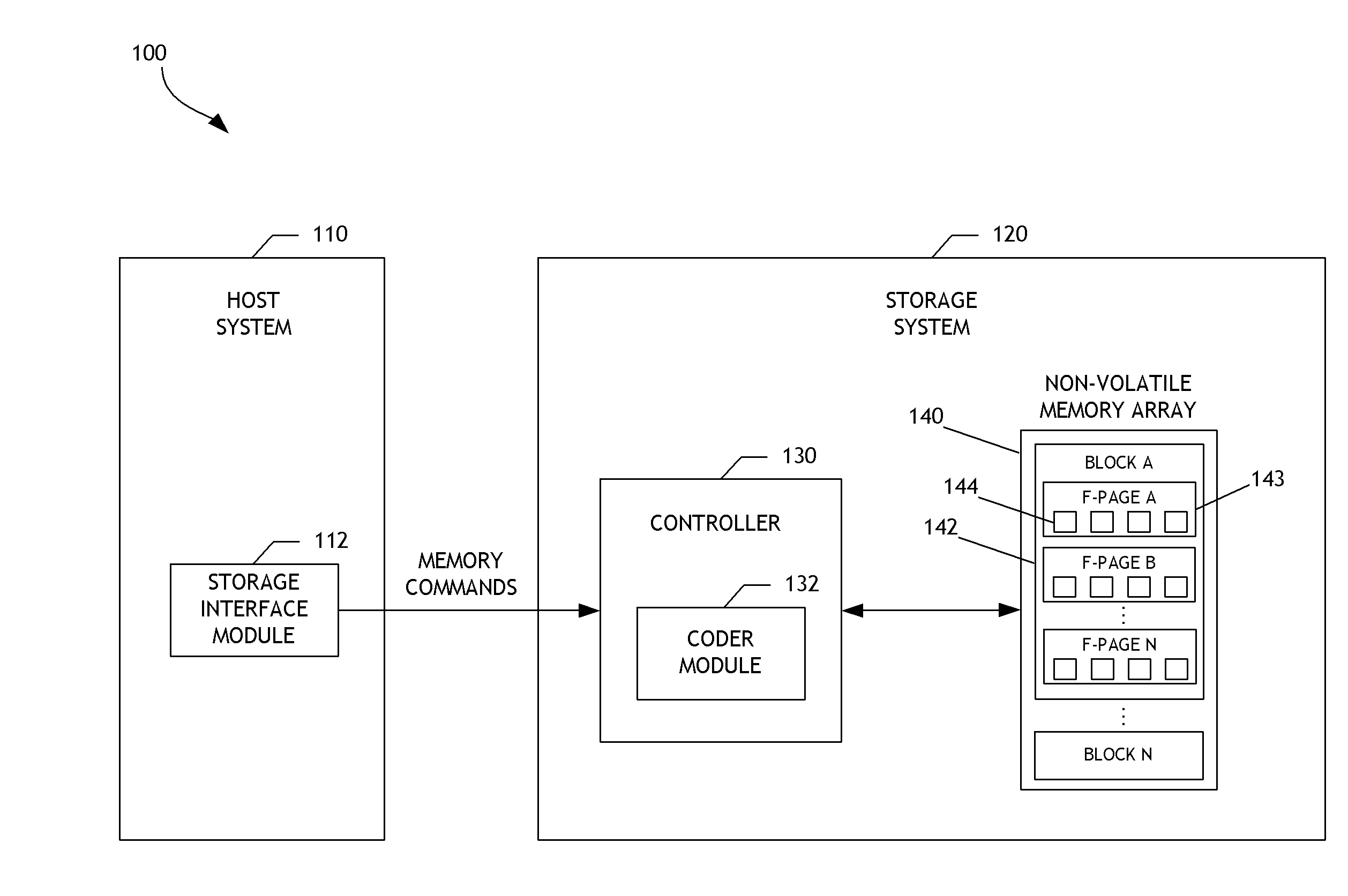

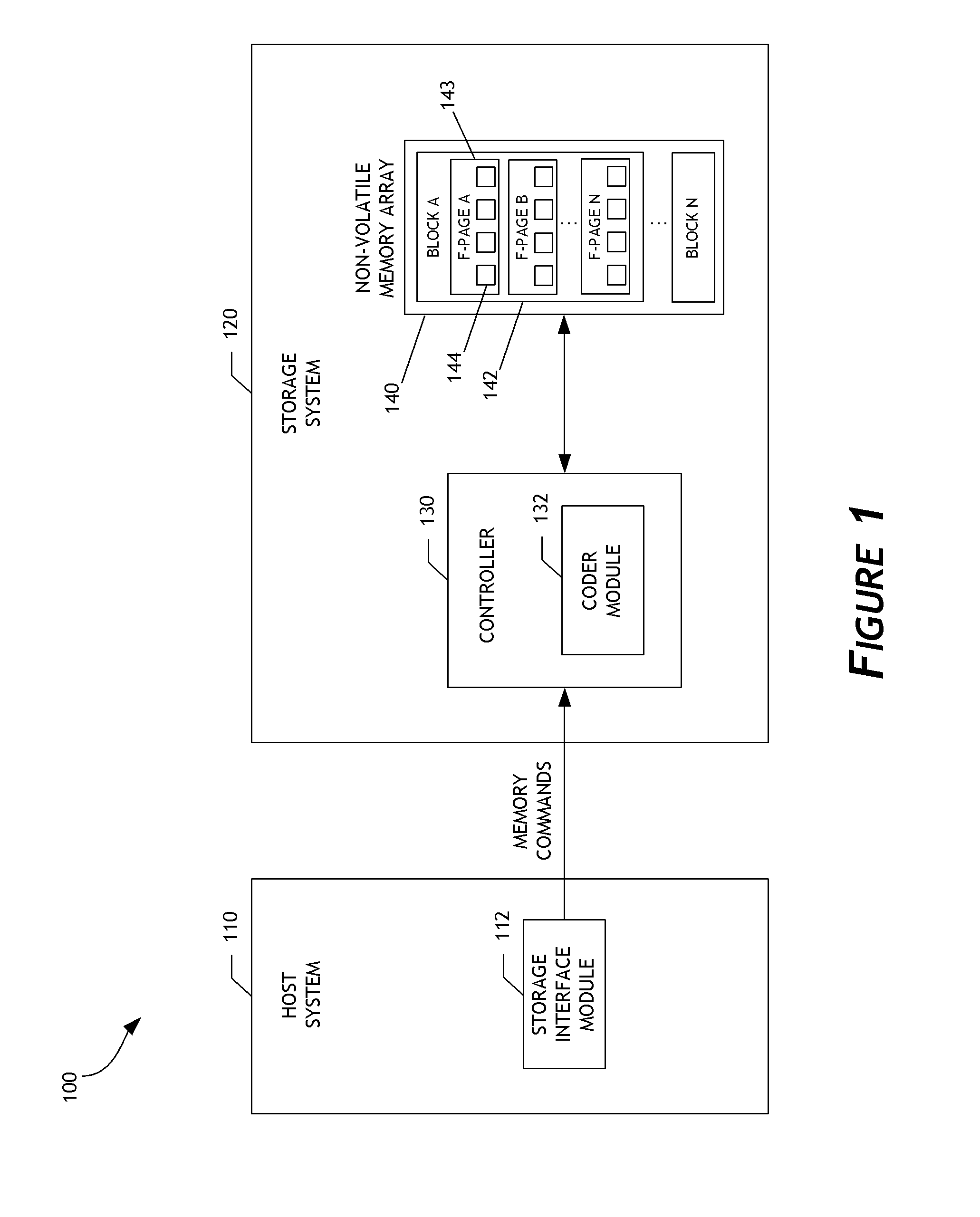

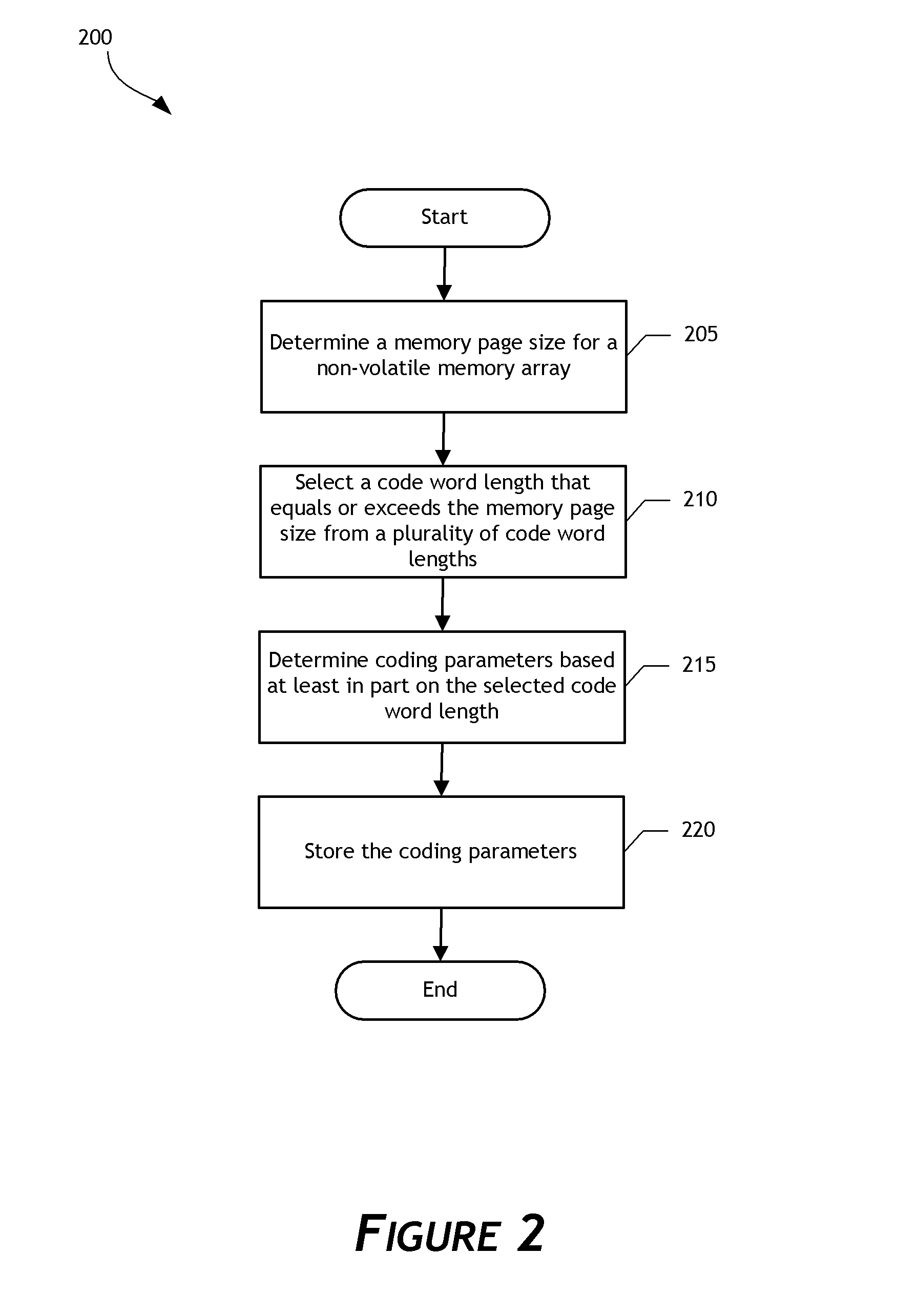

Adaptive error correction codes for data storage systems

ActiveUS20140115427A1Error detection/correctionUnequal/adaptive error protectionConcatenated error correction codeData encoding

A data storage system configured to adaptively code data is disclosed. In one embodiment, a data storage system controller determines a common memory page size, such as an E-page size, for a non-volatile memory array. Based on the common memory page size, the controller selects a low-density parity-check (LDPC) code word length from a plurality of pre-defined LDPC code word lengths. The controller determines LDPC coding parameters for coding data written to or read from the memory array based on the selected LDPC code word length. By using the plurality of pre-defined LDPC code word lengths, the data storage system can support multiple non-volatile memory page formats, including memory page formats in which the common memory page size does not equal any LDPC code word length of the plurality of pre-defined LDPC code word lengths. Flexibility and efficiency of data coding can thereby be achieved.

Owner:WESTERN DIGITAL TECH INC

Error Correction Coding for Multiple-Sector Pages in Flash Memory Devices

ActiveUS20070271494A1Memory architecture accessing/allocationError detection/correctionControl dataDependability

A flash memory system, including a flash memory device and a controller, and having improved efficiency error correction coding (ECC), is disclosed. Each page in the flash memory device has the capacity to store multiple sectors' worth of data. However, partial page programming (i.e., followed by a later write to fill the page) is prohibited for reliability reasons. A scratchpad block within the flash memory device is designed, and stores both user data and control data. ECC efficiency is improved by encoding the ECC, or parity, bits over the entire data block corresponding to the user and control data in the page. Retrieval of a particular sector of data requires reading and decoding of the entire page. Especially for codes such as Reed-Solomon and BCH codes, the larger data block including multiple sectors' data improves the error correction capability, and thus enables either fewer redundant memory cells in each page or improved error correction.

Owner:SANDISK TECH LLC

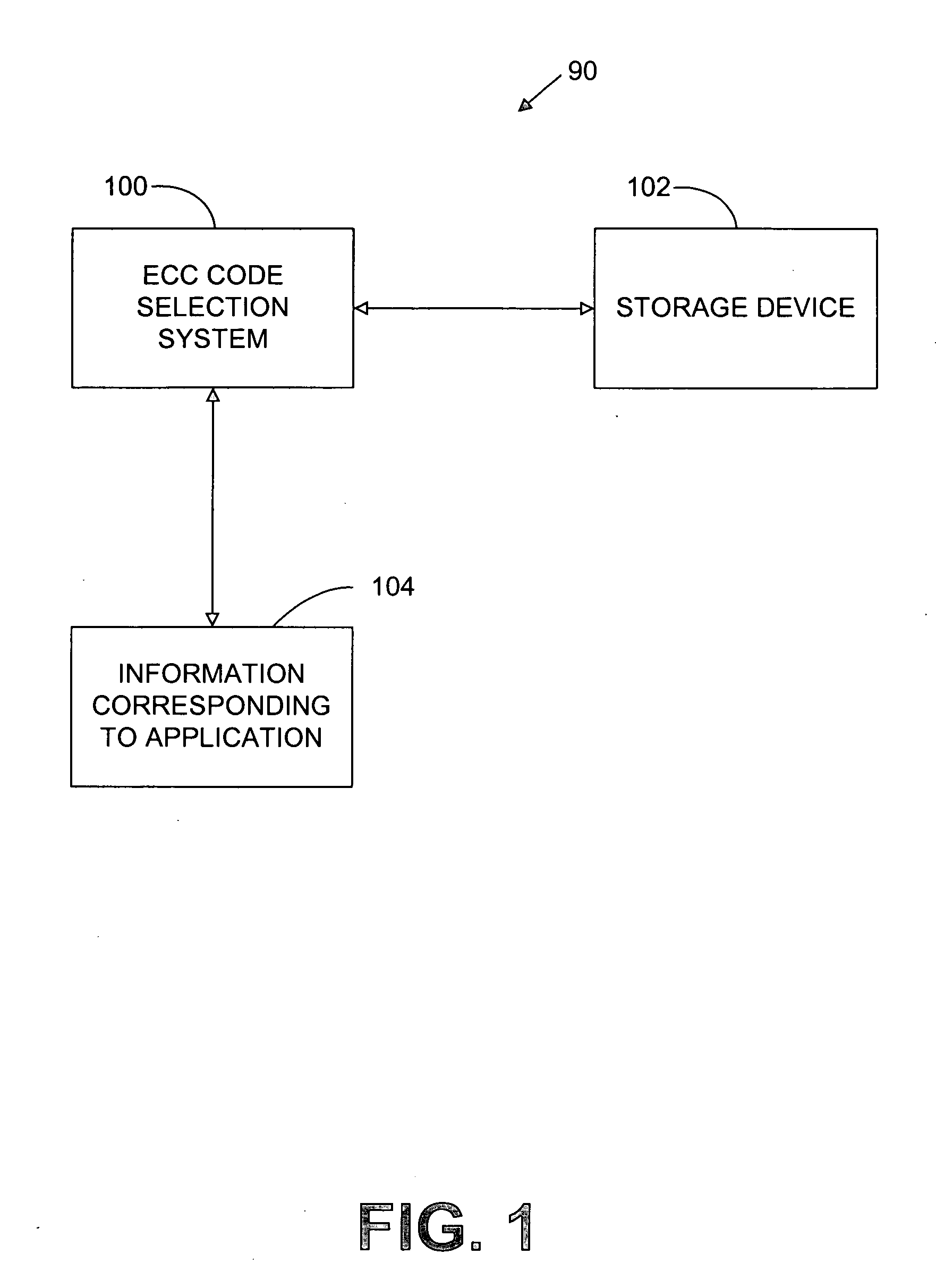

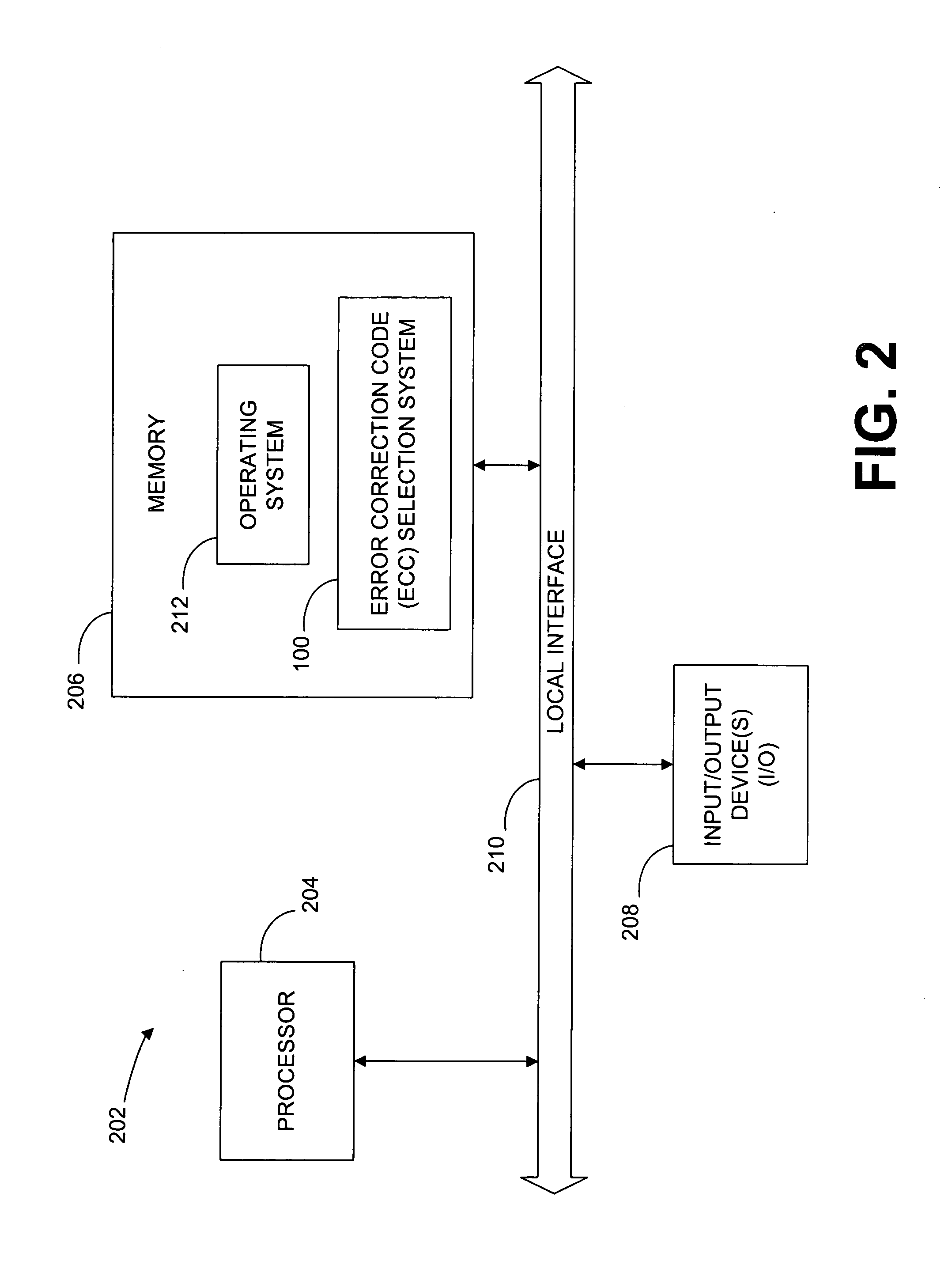

System and method for configuring a solid-state storage device with error correction coding

A system for configuring solid-state storage devices comprises a solid-state storage device and an error correction code (ECC) selection system. The ECC selection system is configured to automatically select a set of error correction code based on an error rate of the storage device. The ECC selection system is further configured to install the selected set of error correction code in the solid-state storage device.

Owner:SK HYNIX INC

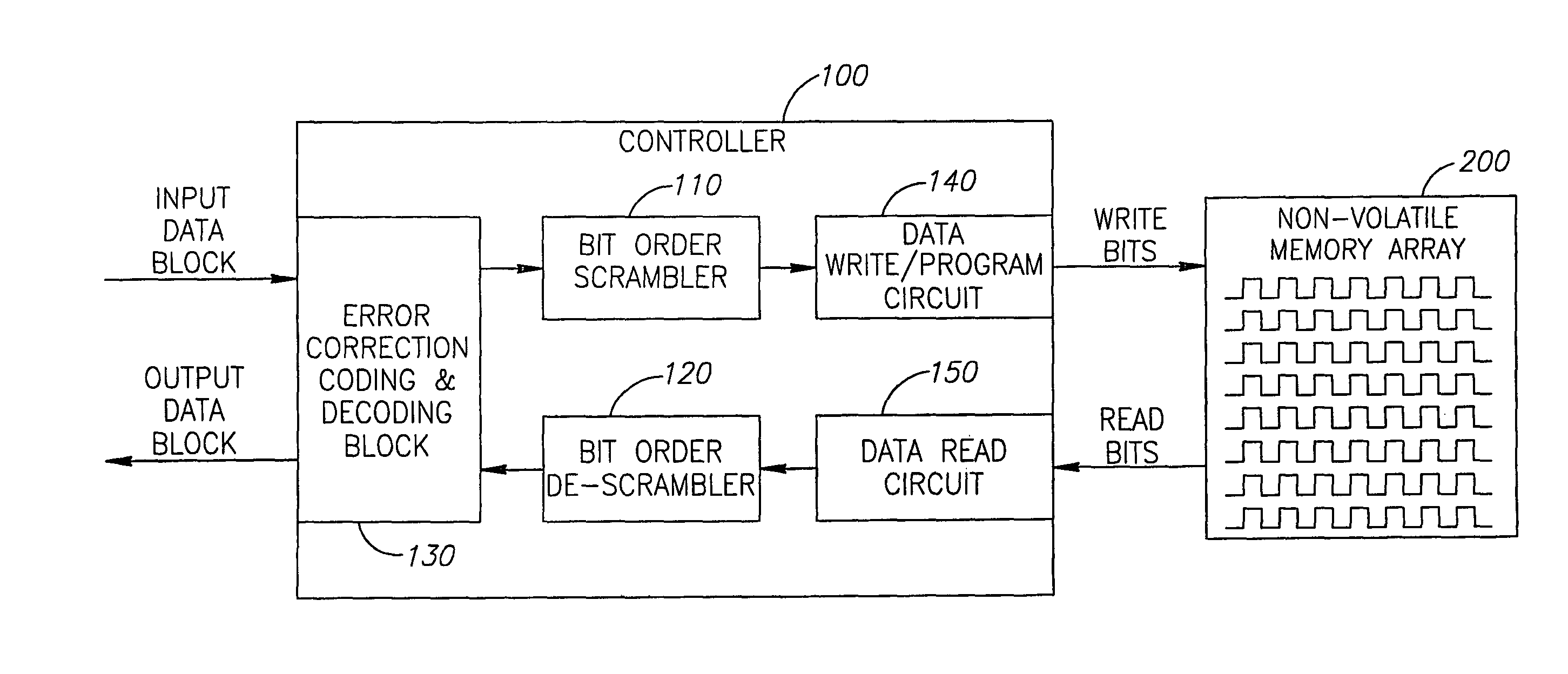

Circuit, system and method for encoding data to be stored on a non-volatile memory array

The present invention is a method, circuit and system for storing bits on a Non-Volatile Memory (“NVM”) array. According to some embodiments of the present invention, a bit scrambling block may rearrange the received block of bits according to a spreading pattern. An error correction code block may generate an error correction code (“ECC”) based on either the original block of bits or based on the rearranged block of bits, and a data storing circuit may store in the NVM array the ECC and the block of bits from which the ECC was not derived.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of Error Correction Code on Solid State Disk to Gain Data Security and Higher Performance

An electronic data storage device having a Reed Solomon (RS) decoder including a syndrome calculator block responsive to information including data and overhead and operative to generate a syndrome, in accordance with an embodiment of the present invention. The electronic data storage device further includes a root finder block coupled to receive said syndrome and operative to generate at least two roots, said RS decoder for processing said two roots to generate at least one error address identifying a location in said data wherein said error lies; and an erasure syndrome calculator block responsive to said information and operative to generate an erasure syndrome, said RS decoder responsive to said information identifying a disk crash, said RS decoder for processing said erasure syndrome to generate an erasure error to recover the data in said disk crash.

Owner:SUPER TALENT ELECTRONICS

Memory with embedded error correction codes

A memory has one bus for data, addresses, and commands. A data register is coupled to the bus to store the data written to and read from the memory, a command register is coupled to the bus for receiving memory commands, and an address register is coupled to the bus to address the memory. The memory also includes an Error Correction Code circuit for calculating an ECC. The memory is configured to be responsive to external commands for controlling the operation of the ECC circuit for reading or writing of the ECC that are separate from external commands controlling reads or writes of the memory data. The memory may also include a status register that stores information regarding the passing or failing of the ECC.

Owner:STMICROELECTRONICS SRL +1

Transmitter and receiver for broadcasting data and providing incremental redundancy

ActiveUS20120272117A1Increase probabilityImprove robustnessError prevention/detection by using return channelCode conversionData streamBroadcast data

A transmitter for broadcasting data in a broadcasting system that improves the decoding quality, if needed, comprises a data input, and an encoder for error correction code encoding the input data words into codewords, a codeword comprising a basic codeword portion and an auxiliary codeword portion, wherein said encoder is adapted for generating said basic codeword portion from an input data word according to a first code and for generating said auxiliary codeword portion from an input data word according to a second code, said basic codeword portion being provided for regular decoding and said auxiliary codeword portion being provided as incremental redundancy if regular decoding of the codeword by use of the basic codeword portion is erroneous. Further, the transmitter comprises a data mapper for mapping the codewords onto frames of a transmitter output data stream, and a transmitter unit for transmitting said transmitter output data stream.

Owner:SATURN LICENSING LLC

Reading memory cells using multiple thresholds

A method for operating a memory (28) includes storing data, which is encoded with an Error Correction Code (ECC), in analog memory cells (32) of the memory by writing respective analog input values selected from a set of nominal values to the analog memory cells. The stored data is read by performing multiple read operations that compare analog output values of the analog memory cells to different, respective read thresholds so as to produce multiple comparison results for each of the analog memory cells. At least two of the read thresholds are positioned between a pair of the nominal values that are adjacent to one another in the set of the nominal values. Soft metrics are computed responsively to the multiple comparison results. The ECC is decoded using the soft metrics, so as to extract the data stored in the analog memory cells.

Owner:APPLE INC

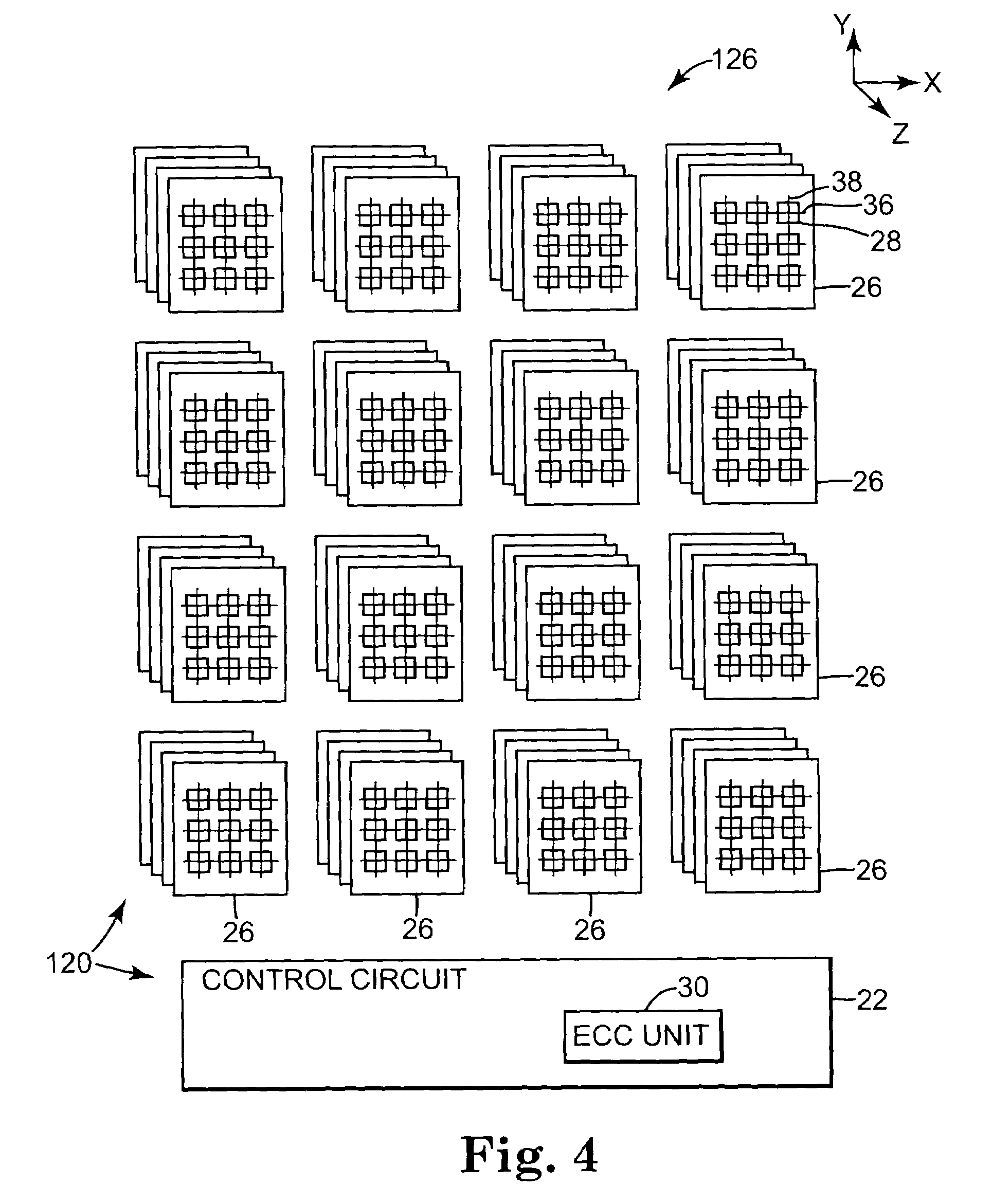

Magnetic memory with error correction coding

Embodiments of the present invention are implemented in memory systems. In one embodiment, the memory comprises an array of memory cells and a control circuit. The control circuit is configured to read error correction coded data from the array of memory cells, provide error correction code decoding to selected error correction coded data and discard unused error correction code parity data of unselected error correction coded data.

Owner:SAMSUNG ELECTRONICS CO LTD

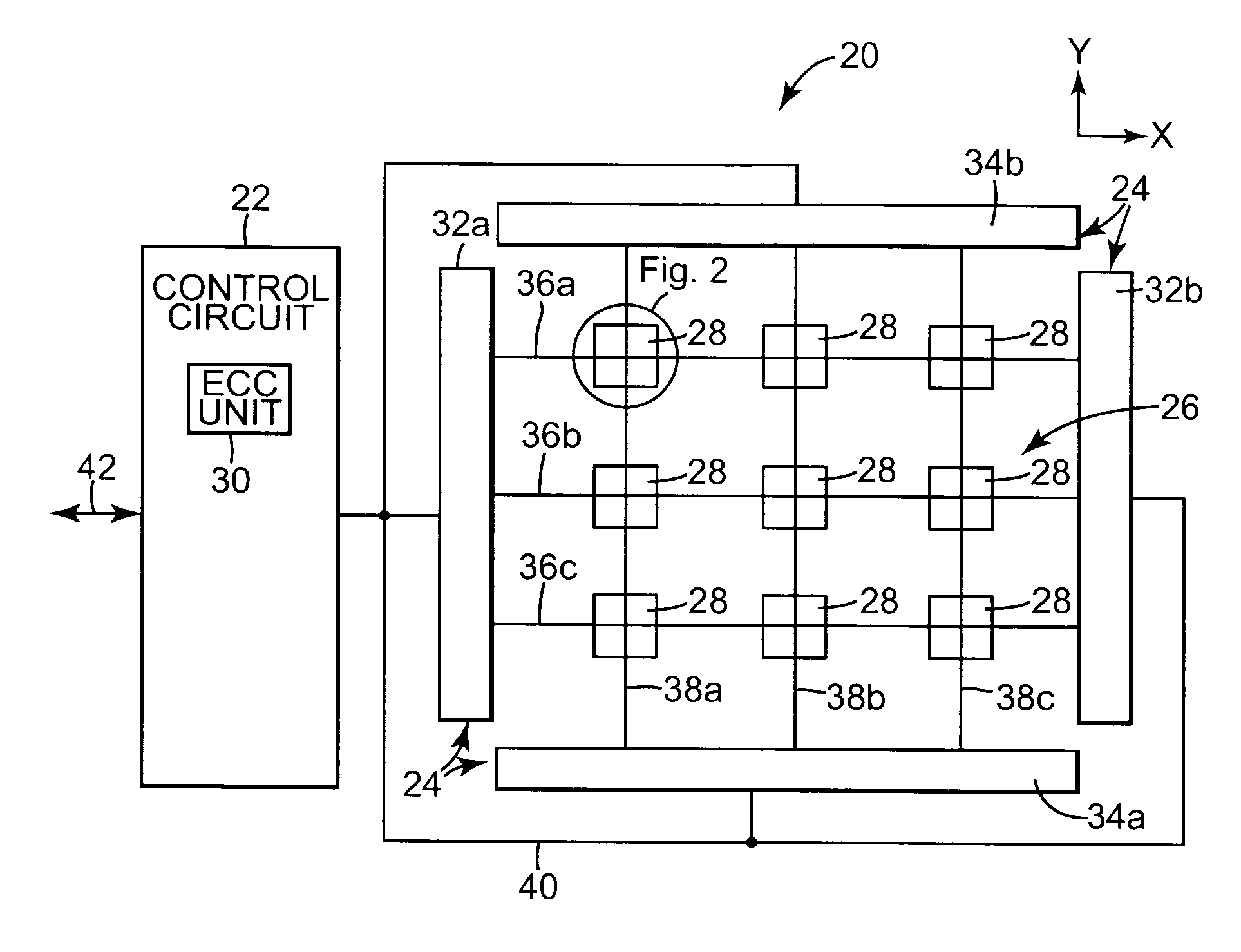

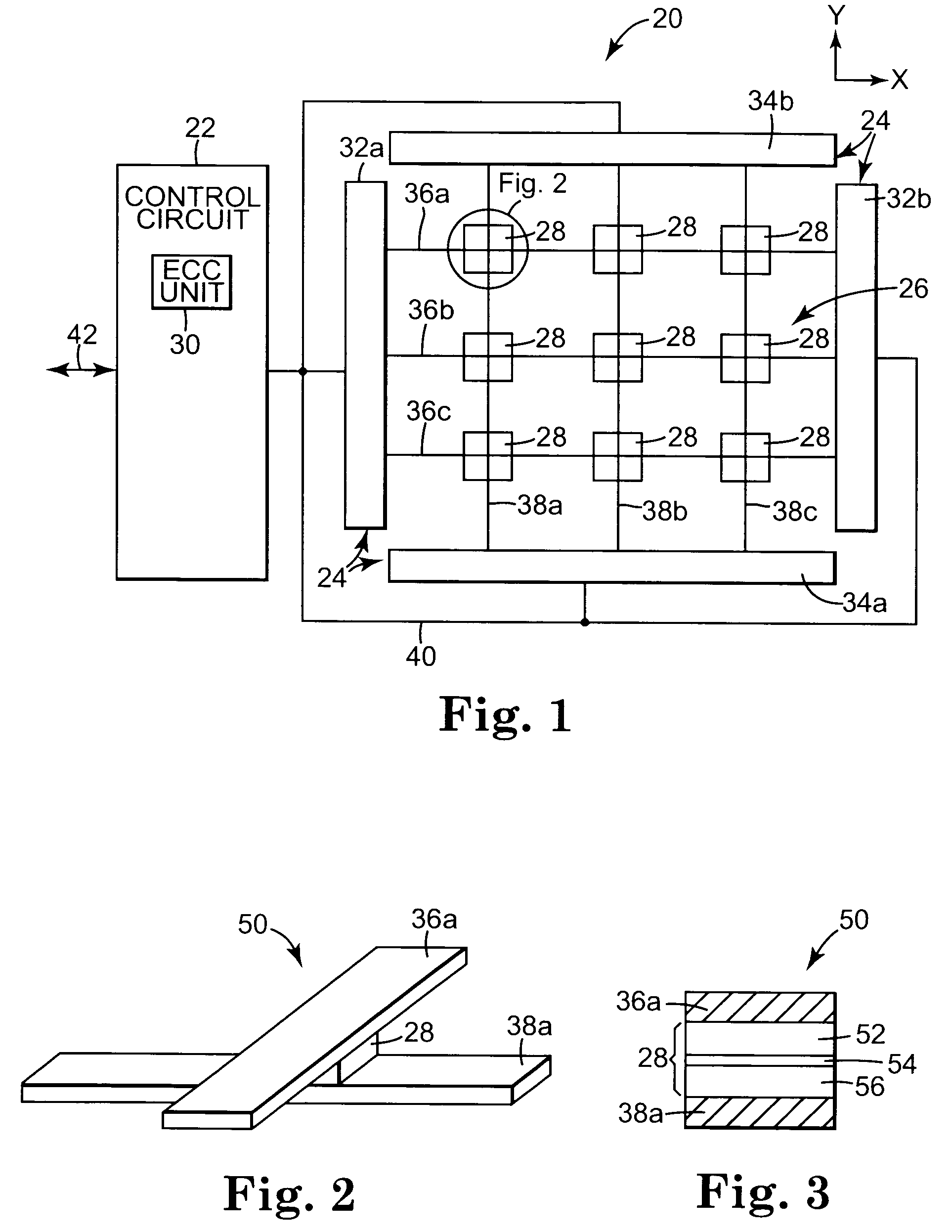

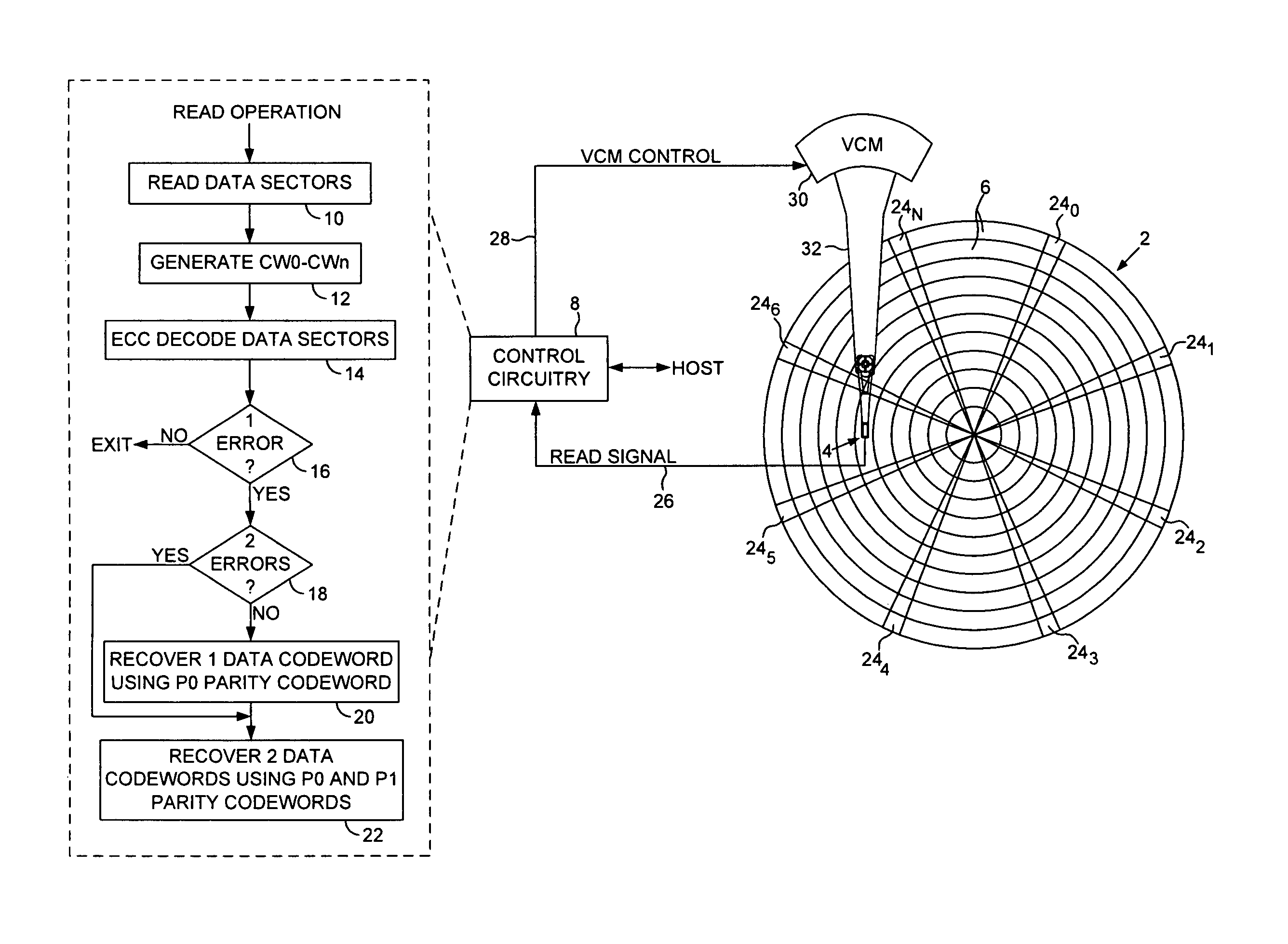

Disk drive recovering multiple codewords in data sectors using progressively higher order parity codewords

A disk drive is disclosed comprising a disk and a head actuated over the disk. The disk comprises a plurality of tracks, wherein each track comprises a plurality of data sectors including a parity sector, the parity sector comprising at least a P0 parity codeword and a P1 parity codeword. A plurality of data sectors are read from the disk (including the parity sector) to generate a plurality of data codewords CW0-CWn. The data sectors are decoded using an error correction code (ECC) decoder. When a single data codeword in CW0-CWn is unrecoverable using the ECC decoder, the single data codeword is recovered using the P0 parity codeword. When two data codewords in CW0-CWn are unrecoverable using the ECC decoder, the two data codewords are recovered using the P0 and P1 parity codewords.

Owner:WESTERN DIGITAL TECH INC

Hybrid implementation for error correction codes within a non-volatile memory system

ActiveUS20040083333A1Memory loss protectionMemory adressing/allocation/relocationCorrection codeVolatile memory

Methods and apparatus for using different error correction code algorithms to encode and to decode contents of blocks within a non-volatile memory are disclosed. According to one aspect of the present invention, a method for storing data within a non-volatile memory includes identifying a first block into which the data is to be stored, and obtaining an indicator associated with the first block. A determination may then be made regarding whether the indicator indicates that the data is to be encoded using a first algorithm. The data is encoded using the first algorithm when it is determined that the data is to be encoded using the first algorithm, after which point the data encoded using the first algorithm is written into the first block.

Owner:SANDISK TECH LLC

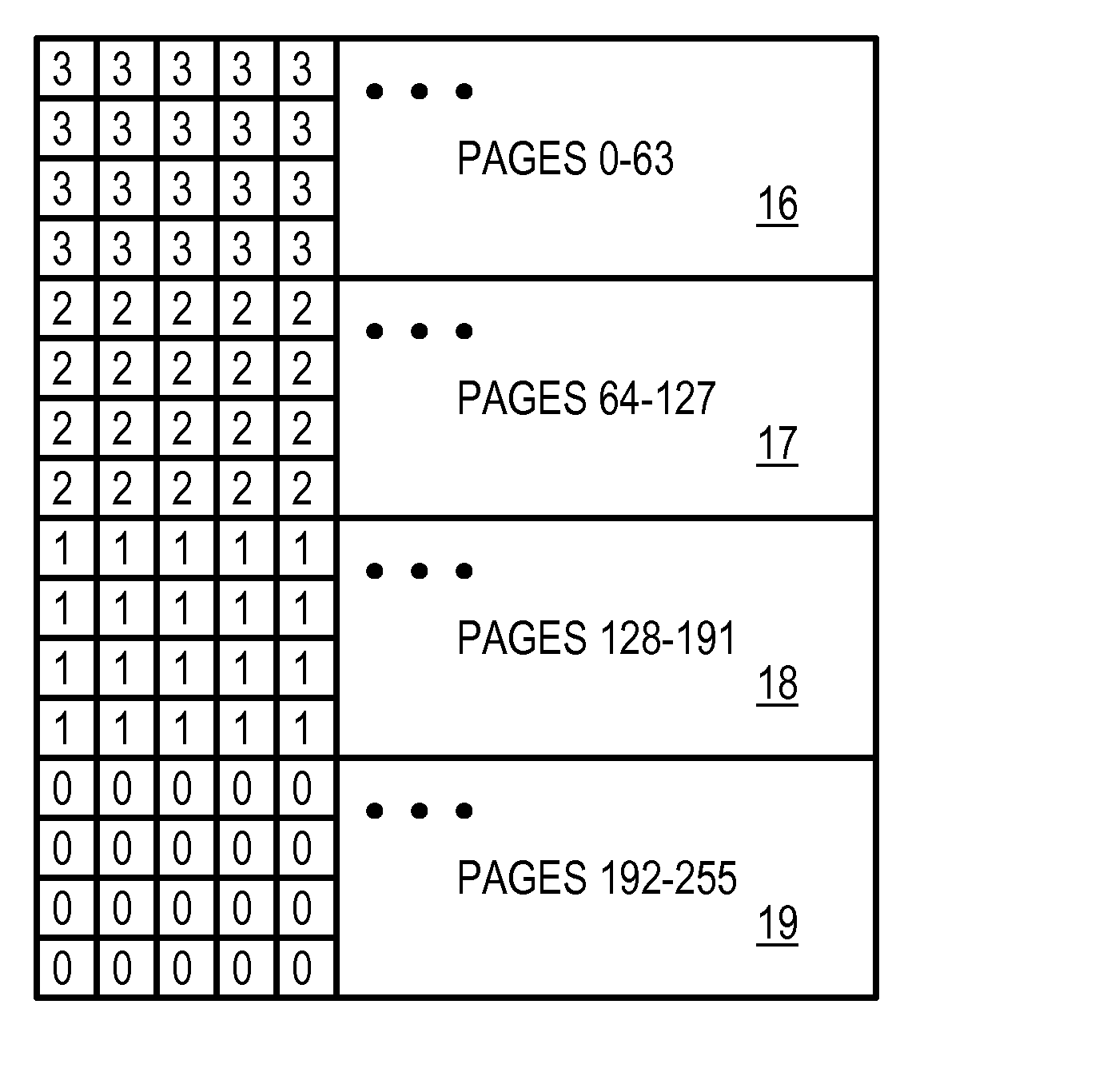

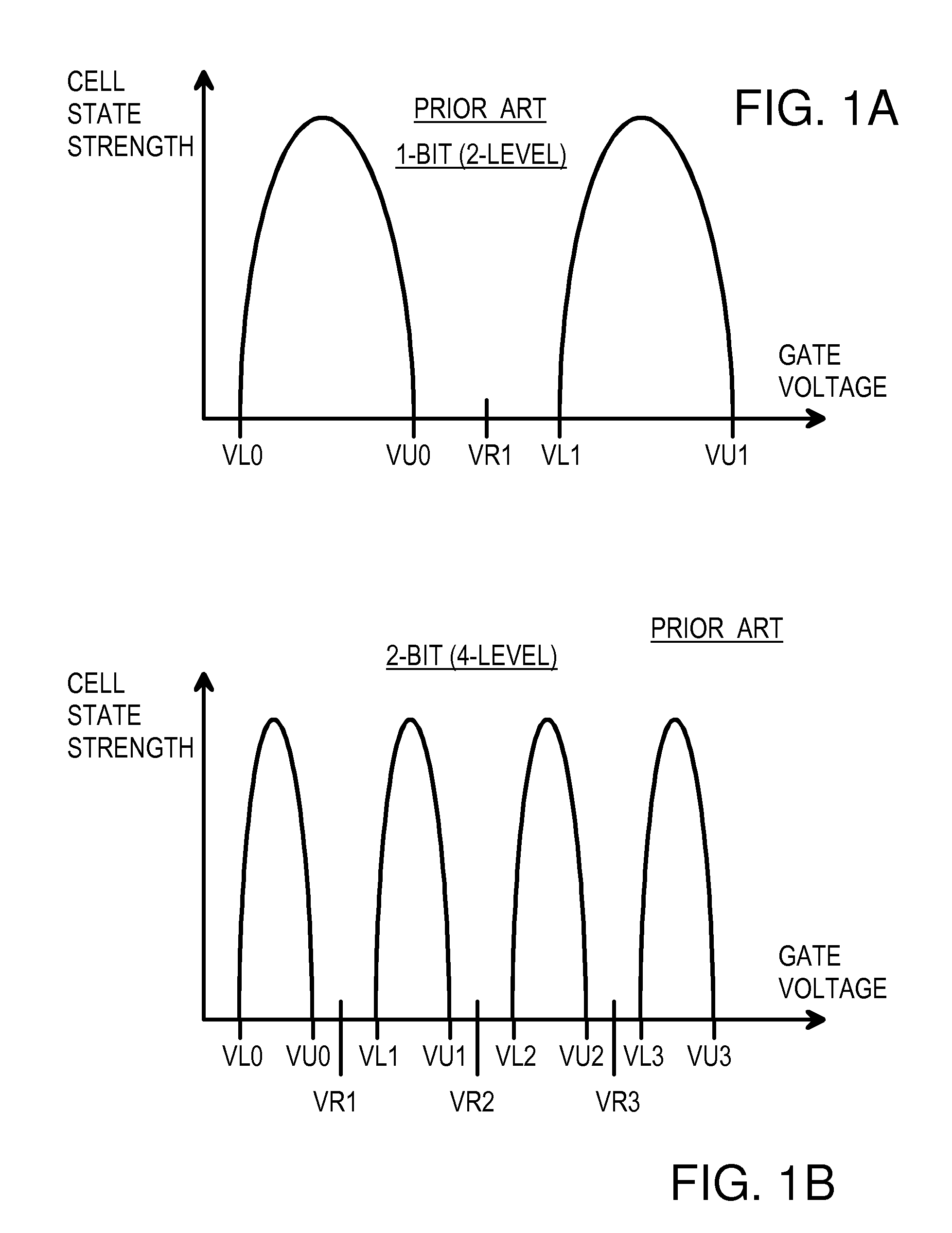

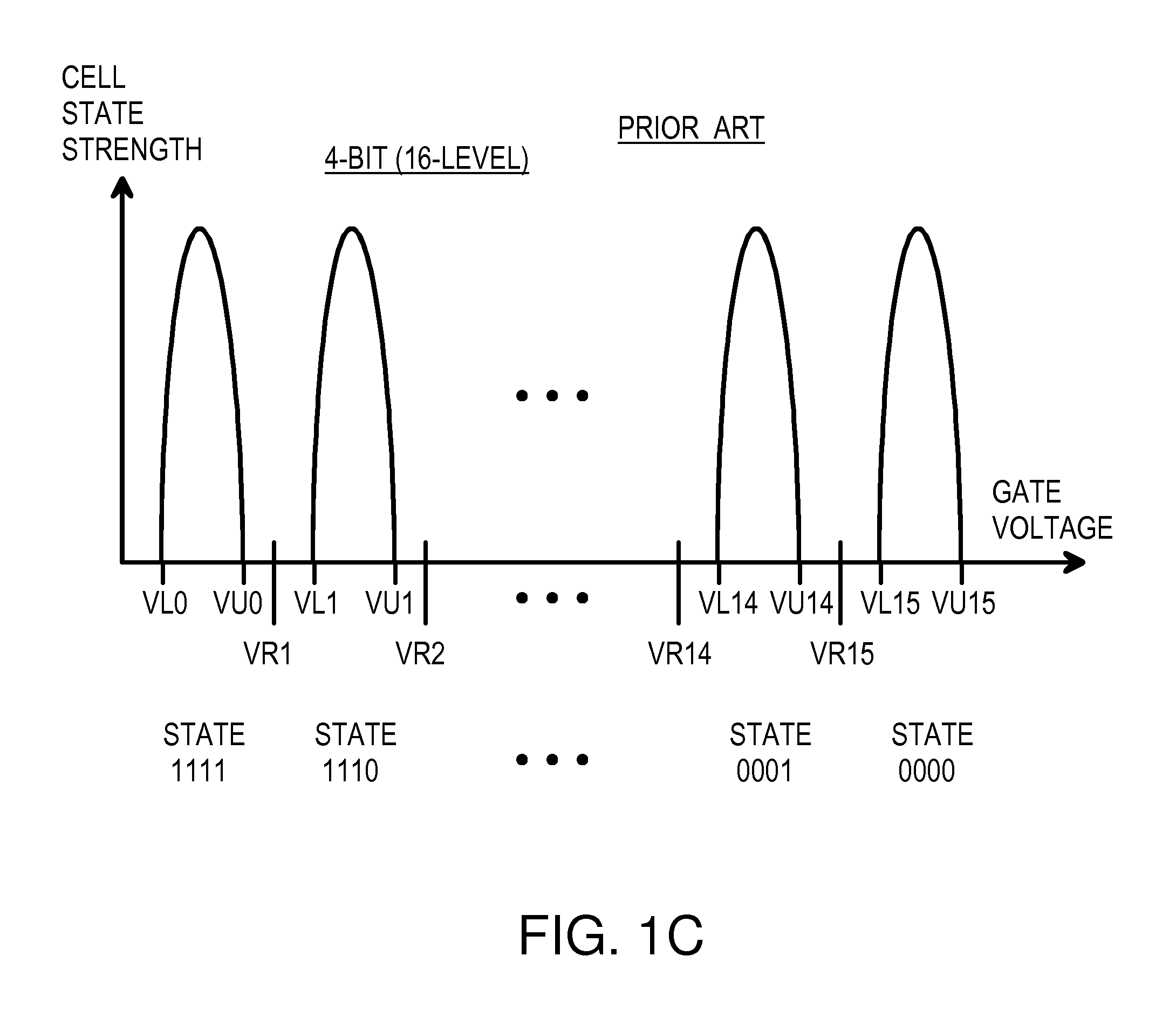

Cell-Downgrading and Reference-Voltage Adjustment for a Multi-Bit-Cell Flash Memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

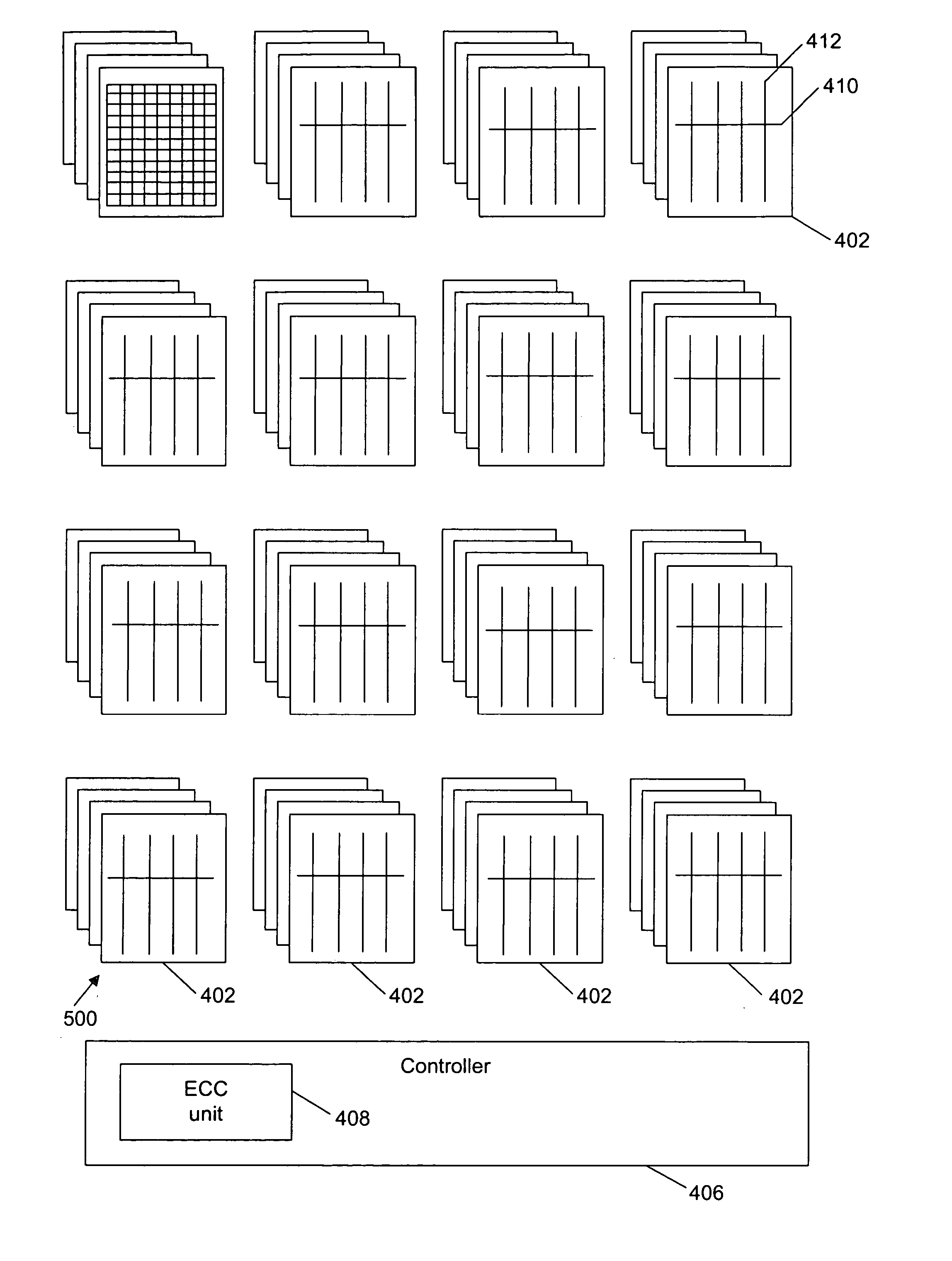

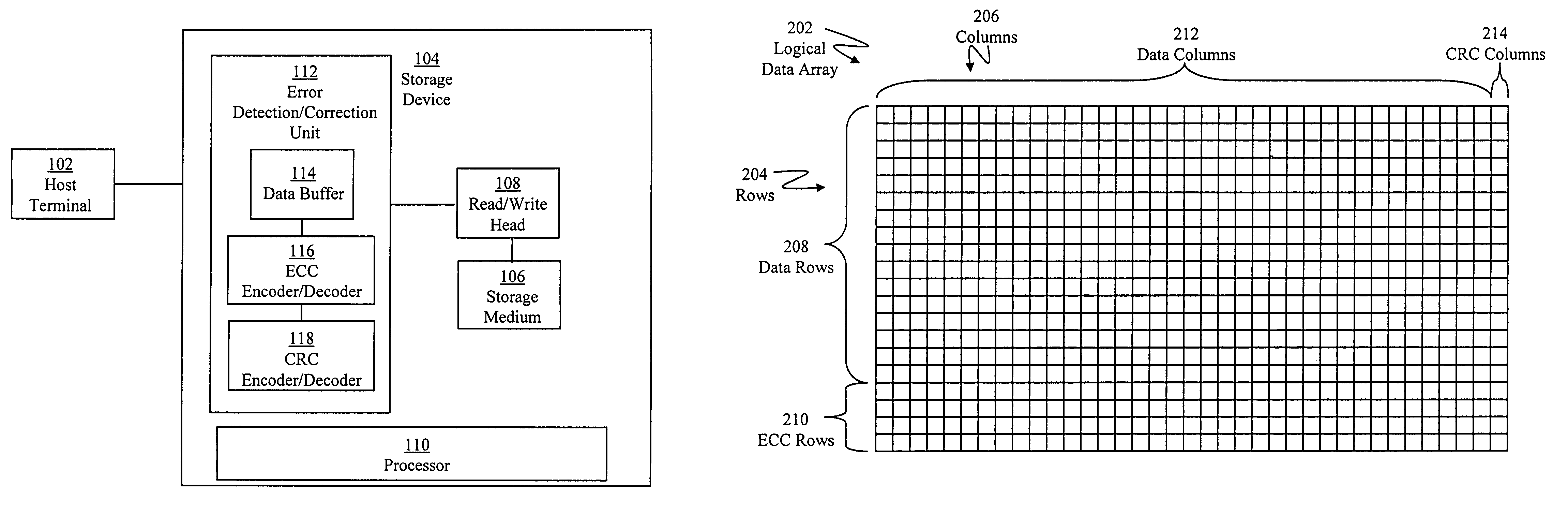

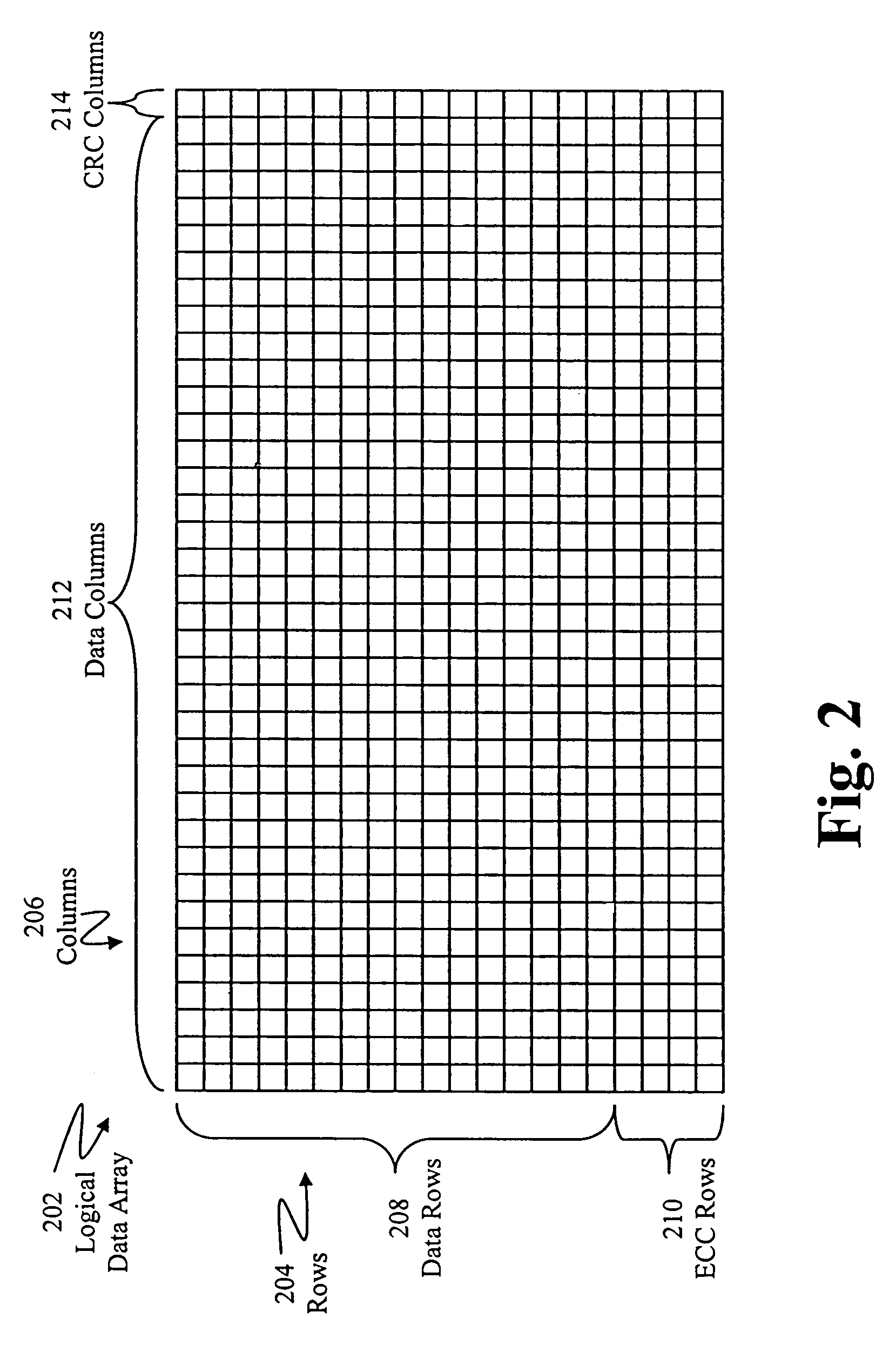

Extended error correction codes

Errors in data retrieved from a storage medium are verified by retrieving a plurality of data blocks from the storage medium. A data set having data from multiple data blocks is selected, where the data set includes a plurality of rows corresponding to the data bocks and a row has data from a data block corresponding to the row. One or more error correction codes (ECCs) are retrieved from the storage medium, where the one or more ECCs correspond to the data set. A plurality of check sums are retrieved from the storage medium, where a check sum corresponds to a data block. Data blocks retrieved from the storage medium having errors are identified using the check sums corresponding to the data blocks. When the number of data blocks identified as having errors is greater than the number of ECCs for the data set, a first set of rows in the data set corresponding to the data blocks identified as having errors is selected, where the number of rows in the first set of rows is equal to the number of ECCs for the data set and less than the number of data blocks identified as having errors. Data for the first set of rows are generated using the ECCs for the data set, and the rows corresponding to the data blocks identified as having errors are verified based on the generated data for the first set of rows.

Owner:QUANTUM CORP

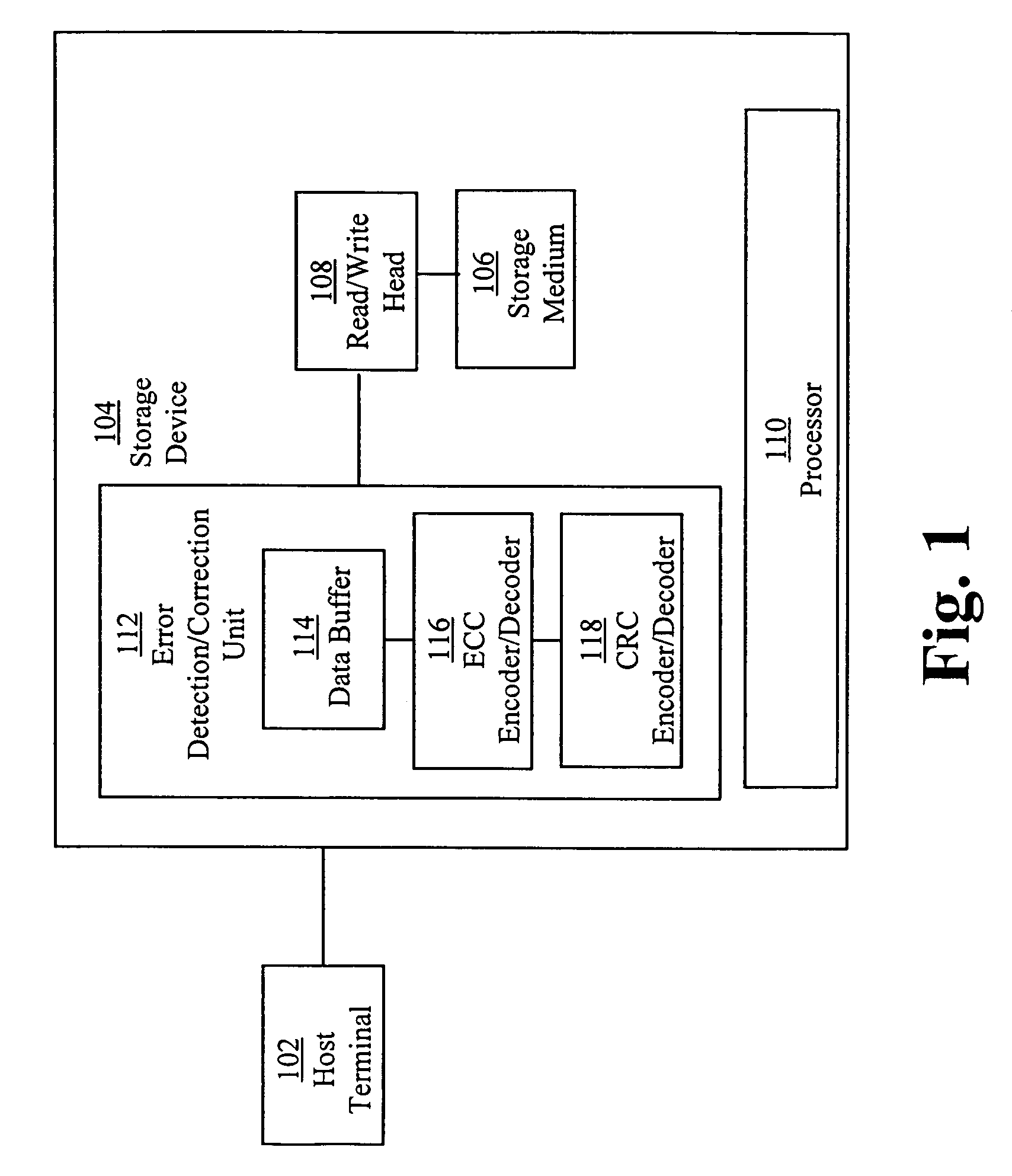

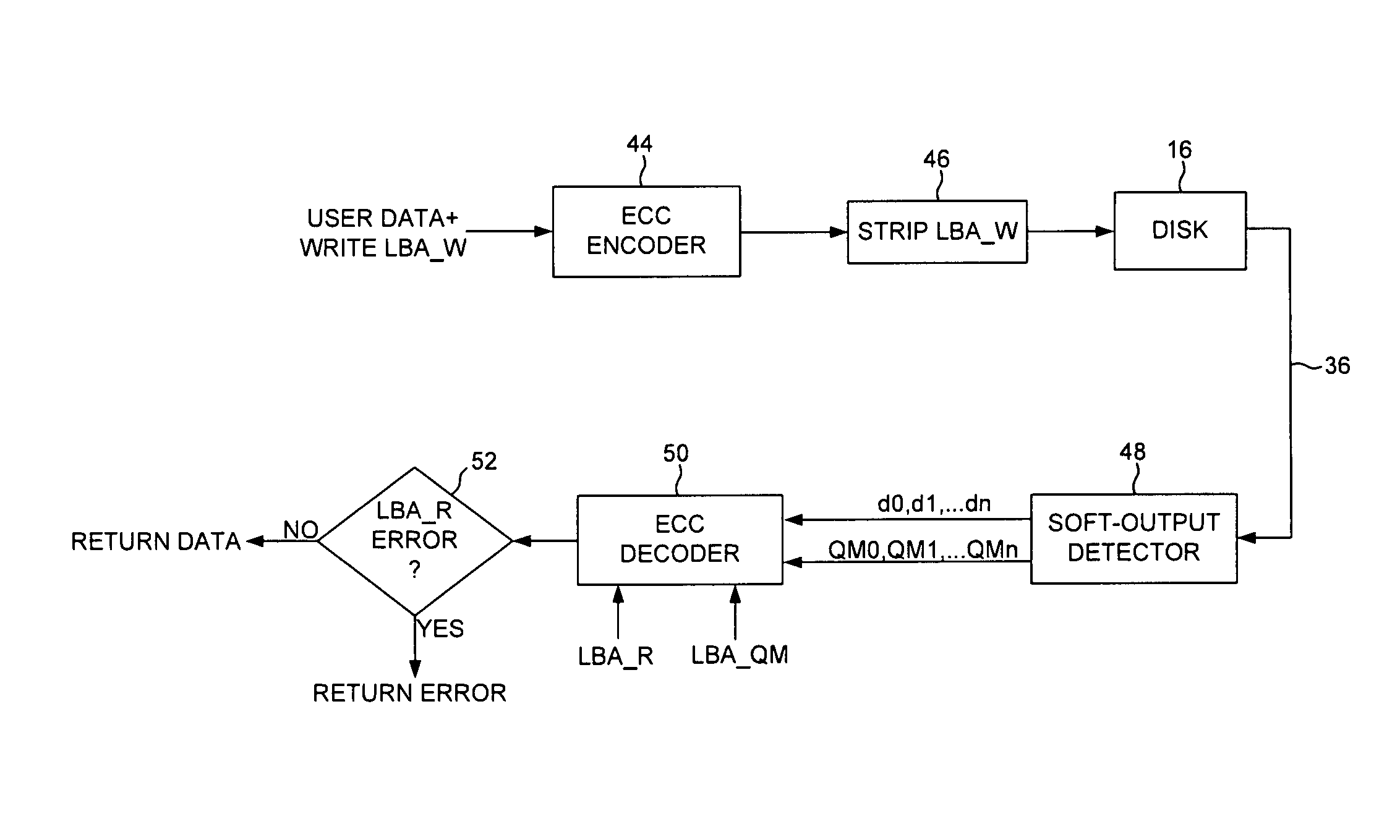

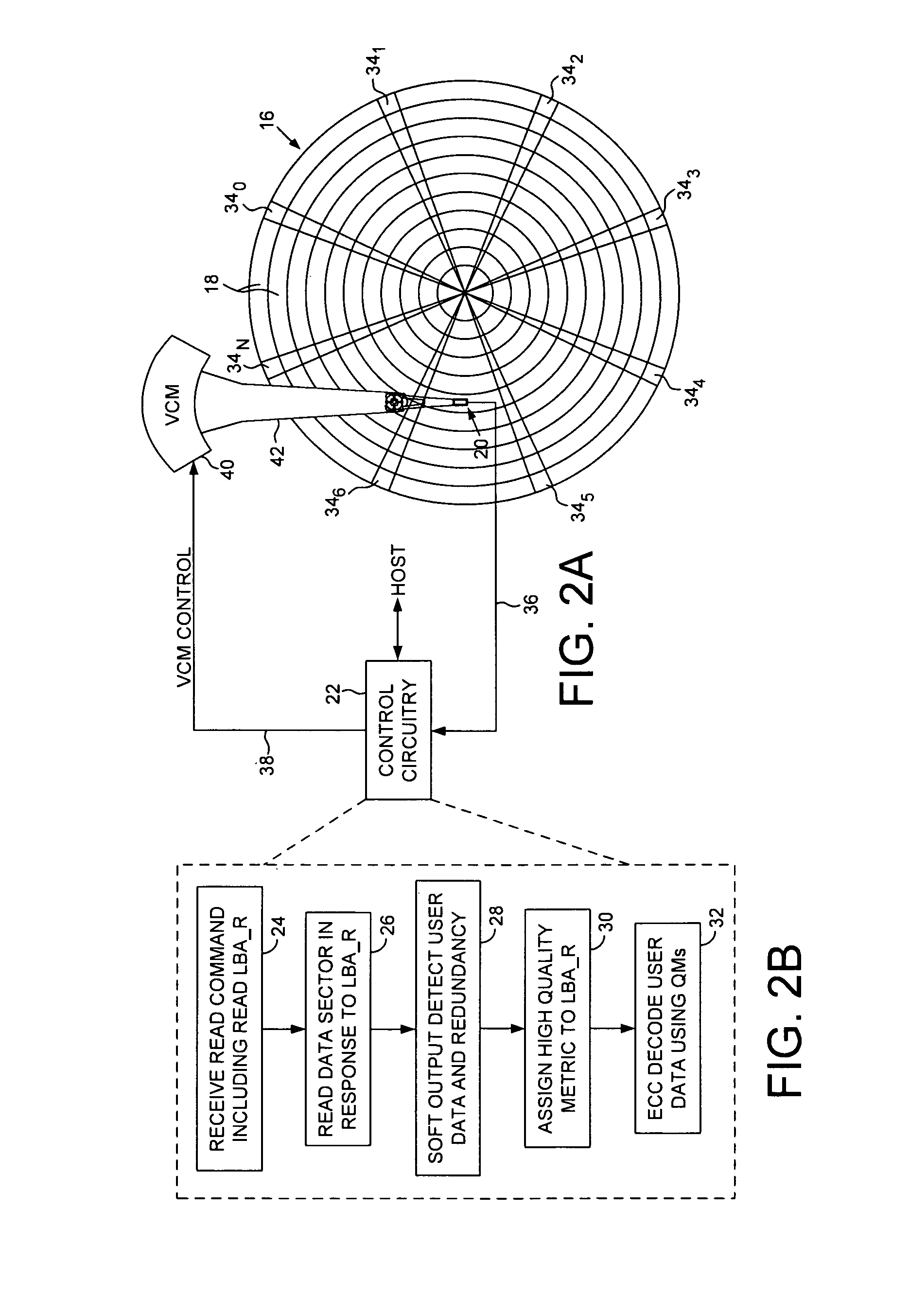

Data storage device employing high quality metrics when decoding logical block address appended to a data sector

ActiveUS8413010B1Data representation error detection/correctionCode conversionLogical block addressingCorrection code

A data storage device is disclosed that receives a read command from a host, wherein the read command comprises a read logical block address (LBA_R). A target data sector is read in response to the LBA_R to generate a read signal. The read signal is processed to detect user data and redundancy data using a soft-output detector that outputs quality metrics for the user data and redundancy data. A high quality metric is assigned to the LBA_R, and errors are corrected in the user data using an error correction code (ECC) decoder in response to the quality metrics output by the soft-output detector and the quality metrics assigned to the LBA_R.

Owner:WESTERN DIGITAL TECH INC

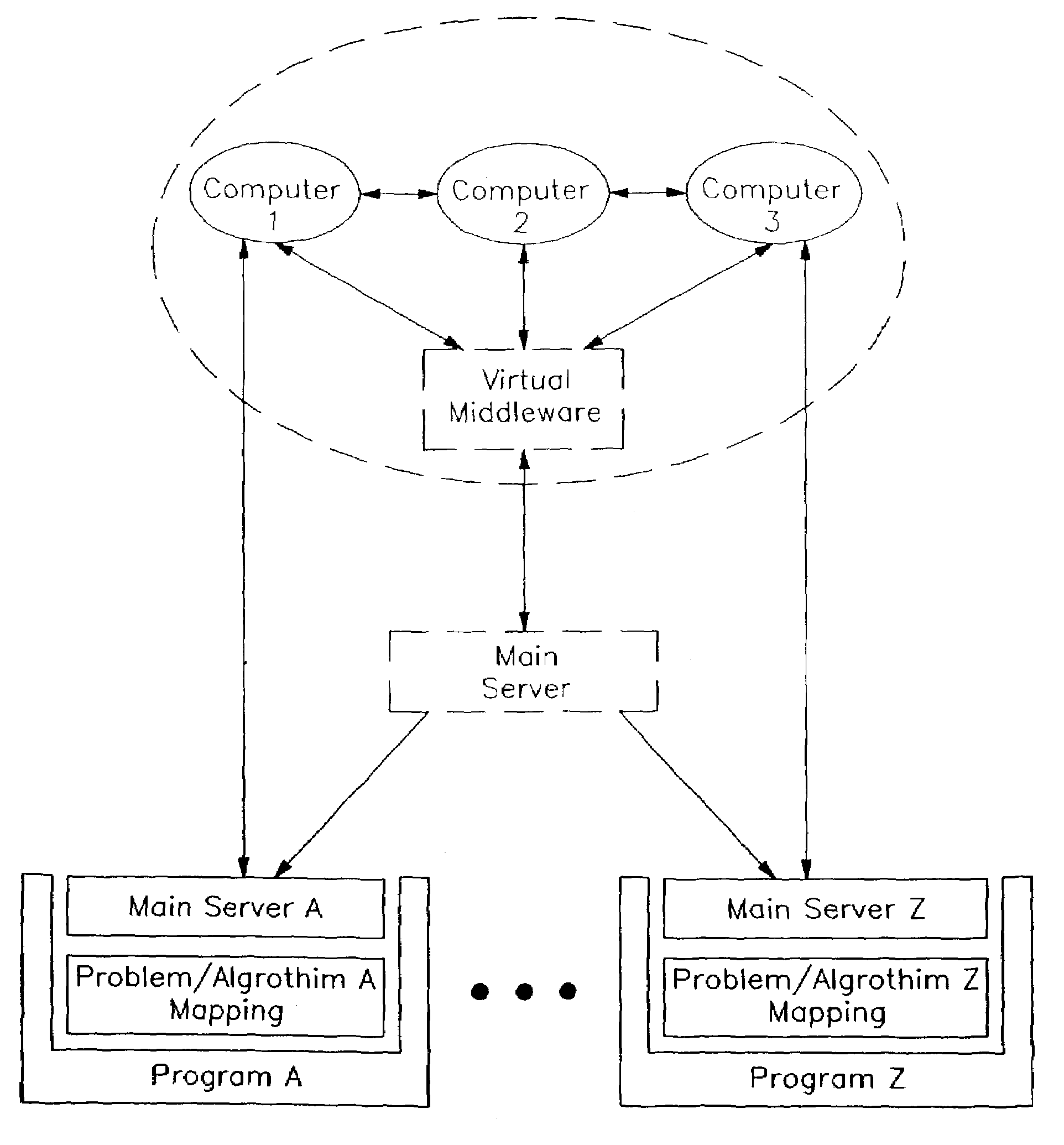

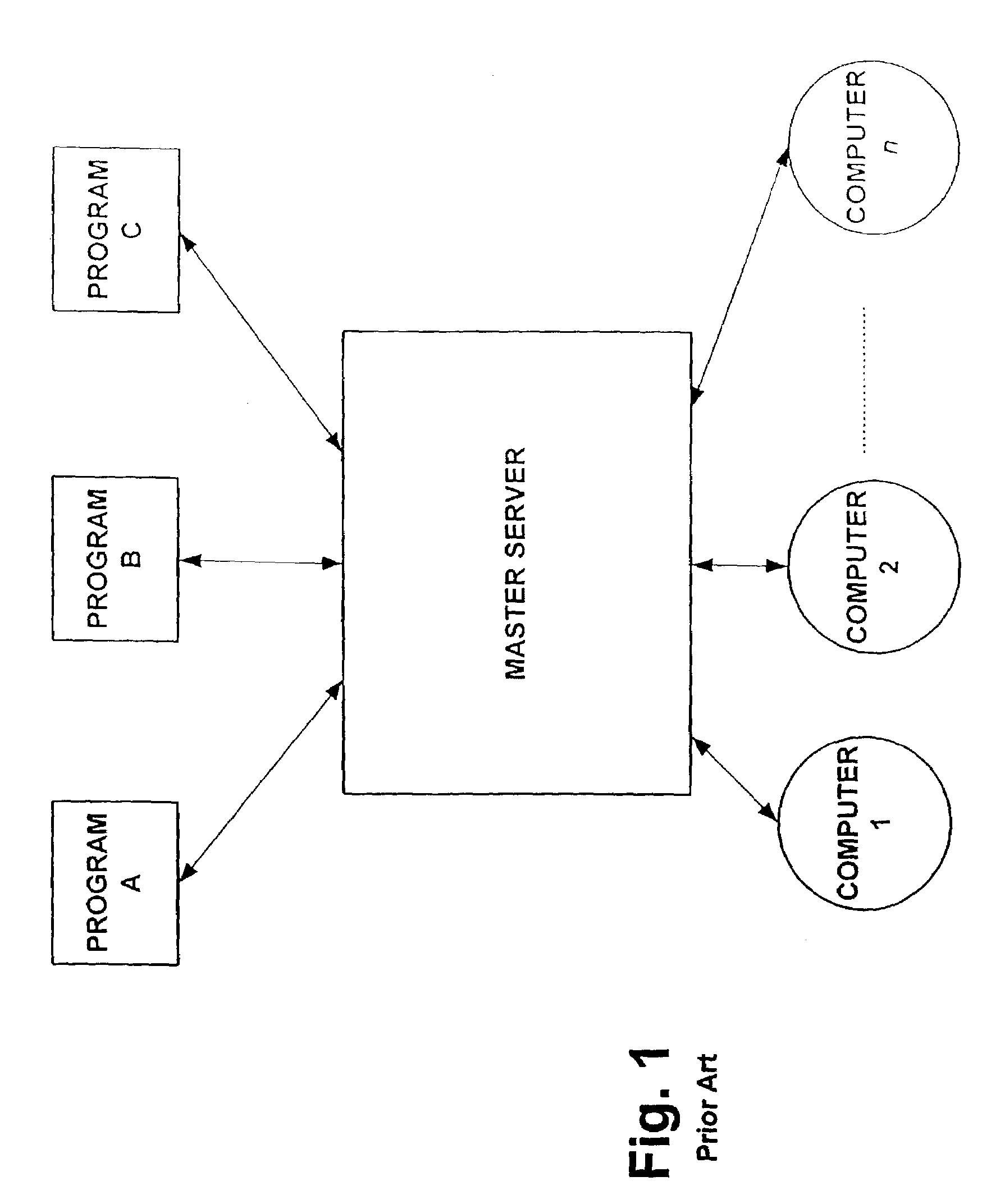

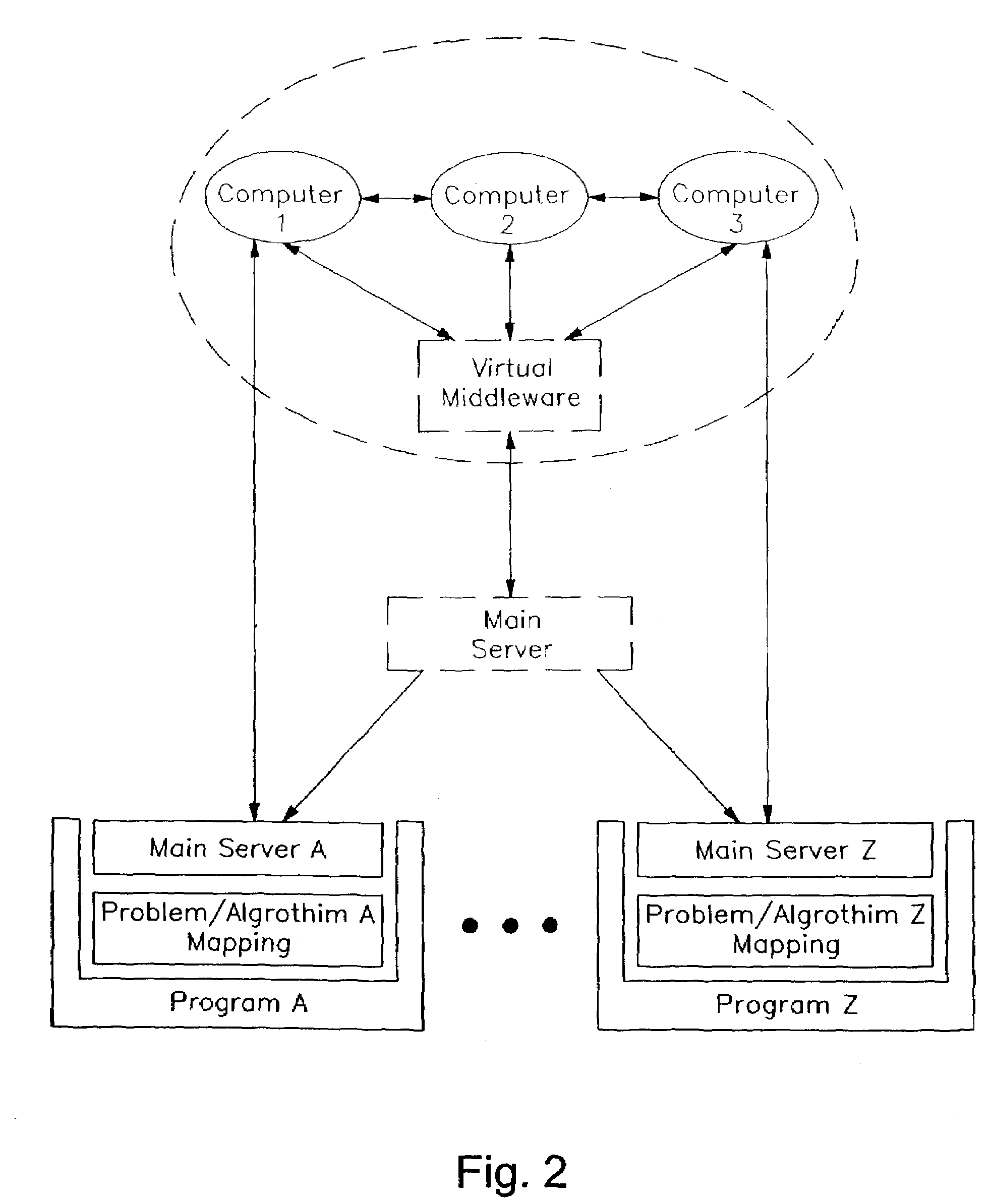

Parallel computing system, method and architecture

InactiveUS7174381B2Easy to implementResource allocationSoftware engineeringParallel computingApplication software

A parallel or computing system and method make use of a plurality of adapters each affording a specific type of processing algorithm. At each point in an application, an adapter is identified, to parallelize that portion of the application. The process involves associating an appropriate adapter with the application portion, parsing the application portion to define tasks that may be distributed over the available computers. Combined with the parallelized program is a software server that is designed to cooperate with the adapters to control and supervise distributed processing functions. Such functions include mapping, load balancing, and error detection and correction. Also included are functions that cause the results of the computing to be coordinated in real-time and returned appropriately, according to the application. In addition to the parallelized program and server, an application created by the present invention is provided with the functionality of virtual middleware, which interfaces with and controls existing forms of middleware.

Owner:SIMTONE CORP (US)

Method for copying data in reprogrammable non-volatile memory

ActiveUS20060156189A1Improve performanceMemory architecture accessing/allocationError detection/correctionPresent methodSelection criterion

The present invention presents methods for improving data relocation operations. In one aspect, rather than check the quality of the data based on its associated error correction code (ECC) in every relocation operation, it is determined whether to check ECC based on predetermined selection criteria, and if ECC checking is not selected, causing the memory to perform an on-chip copy the data from a first location to a second location. If ECC checking is selected, the data is transferred to the controller and checked; when an error is found, a correction operation is performed and when no error is found, an on-chip copy is performed. The predetermined selection criteria may comprise a sampling mechanism, which may be random based or deterministic. In another aspect, data transfer flags are introduced to indicate data has been corrected and should be transferred back to the memory. A further aspect considers the header and user data separately if each has a distinct associated ECC.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com