Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5620 results about "Memory cell" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

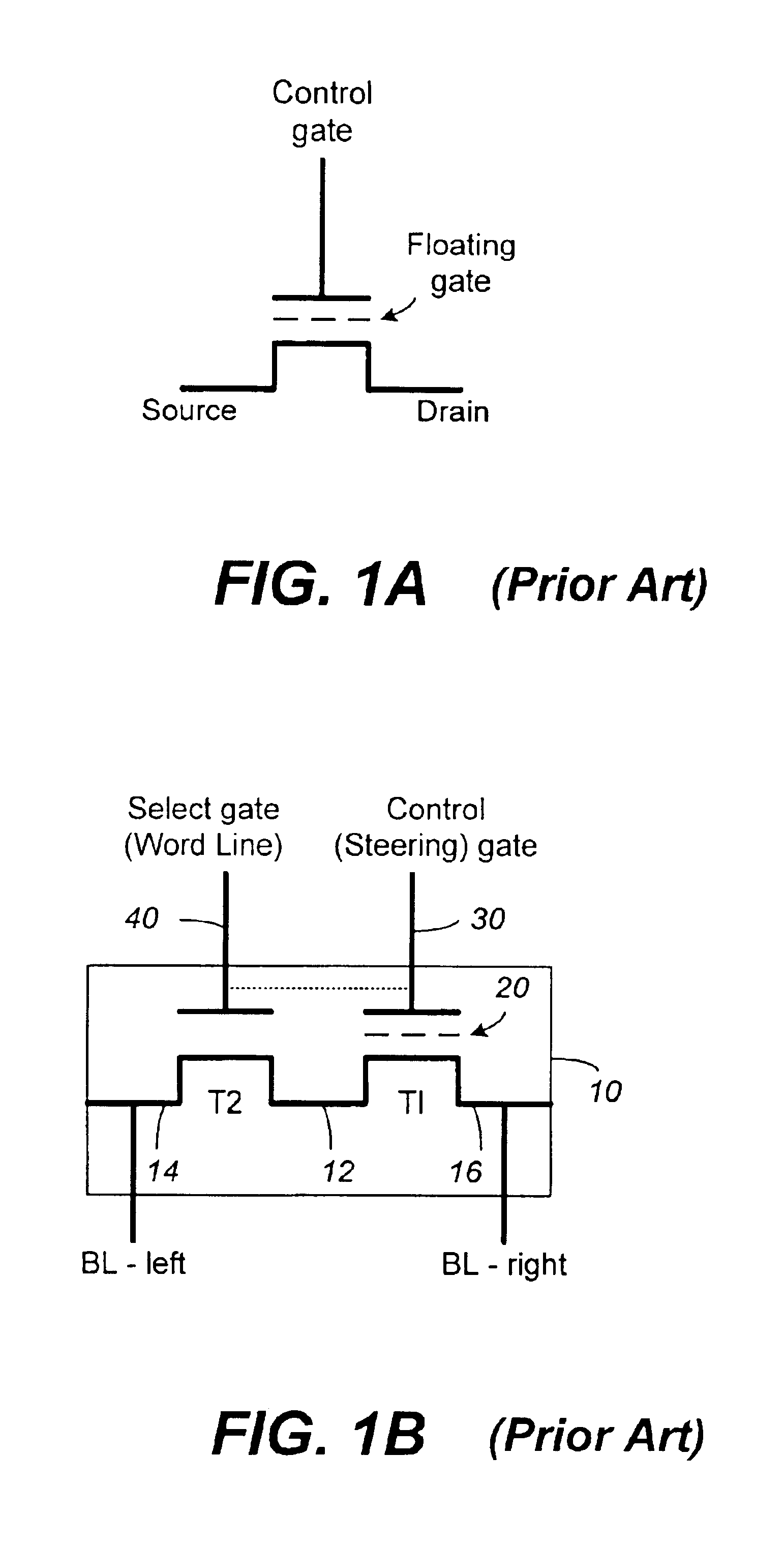

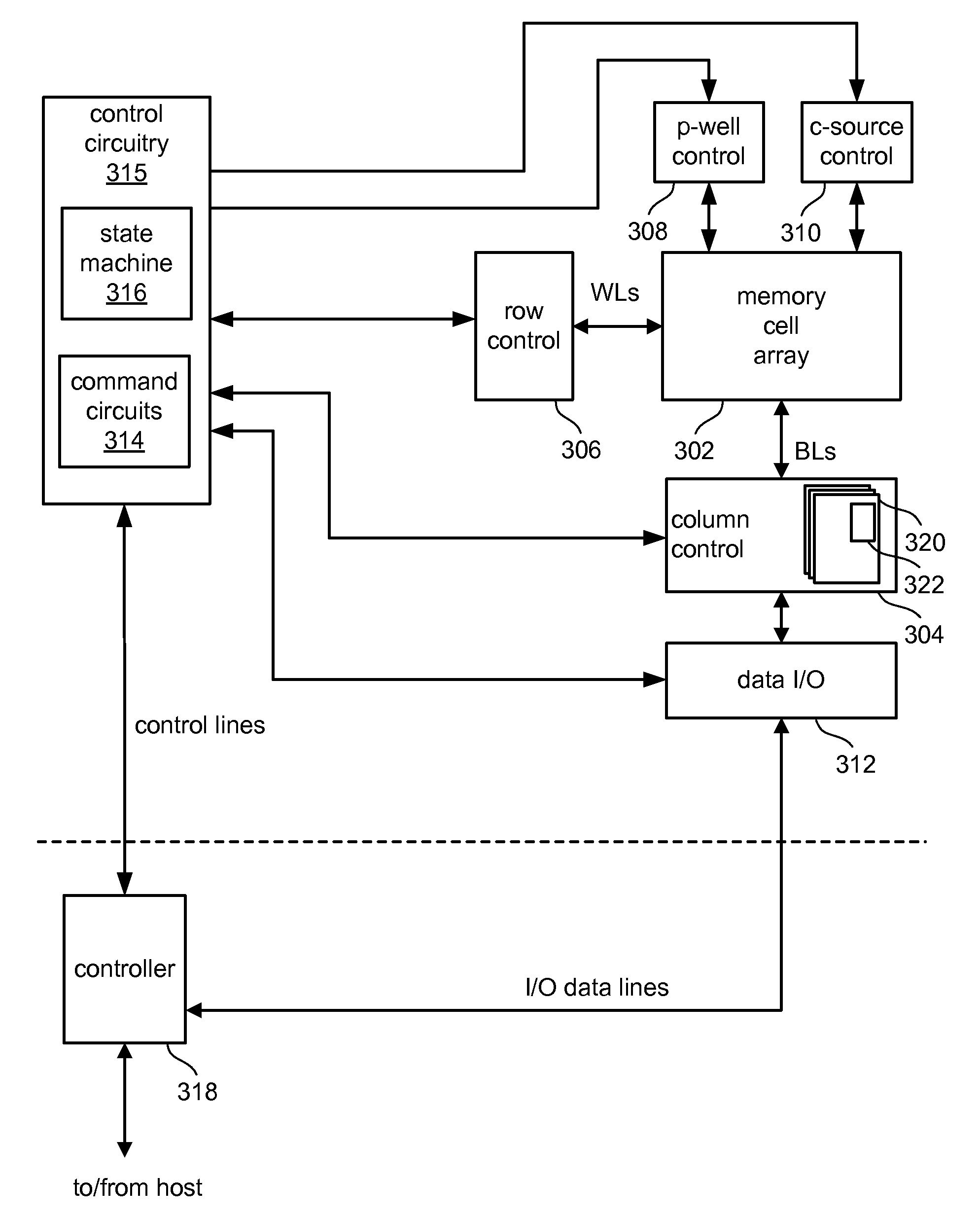

The memory cell is the fundamental building block of computer memory. The memory cell is an electronic circuit that stores one bit of binary information and it must be set to store a logic 1 (high voltage level) and reset to store a logic 0 (low voltage level). Its value is maintained/stored until it is changed by the set/reset process. The value in the memory cell can be accessed by reading it.

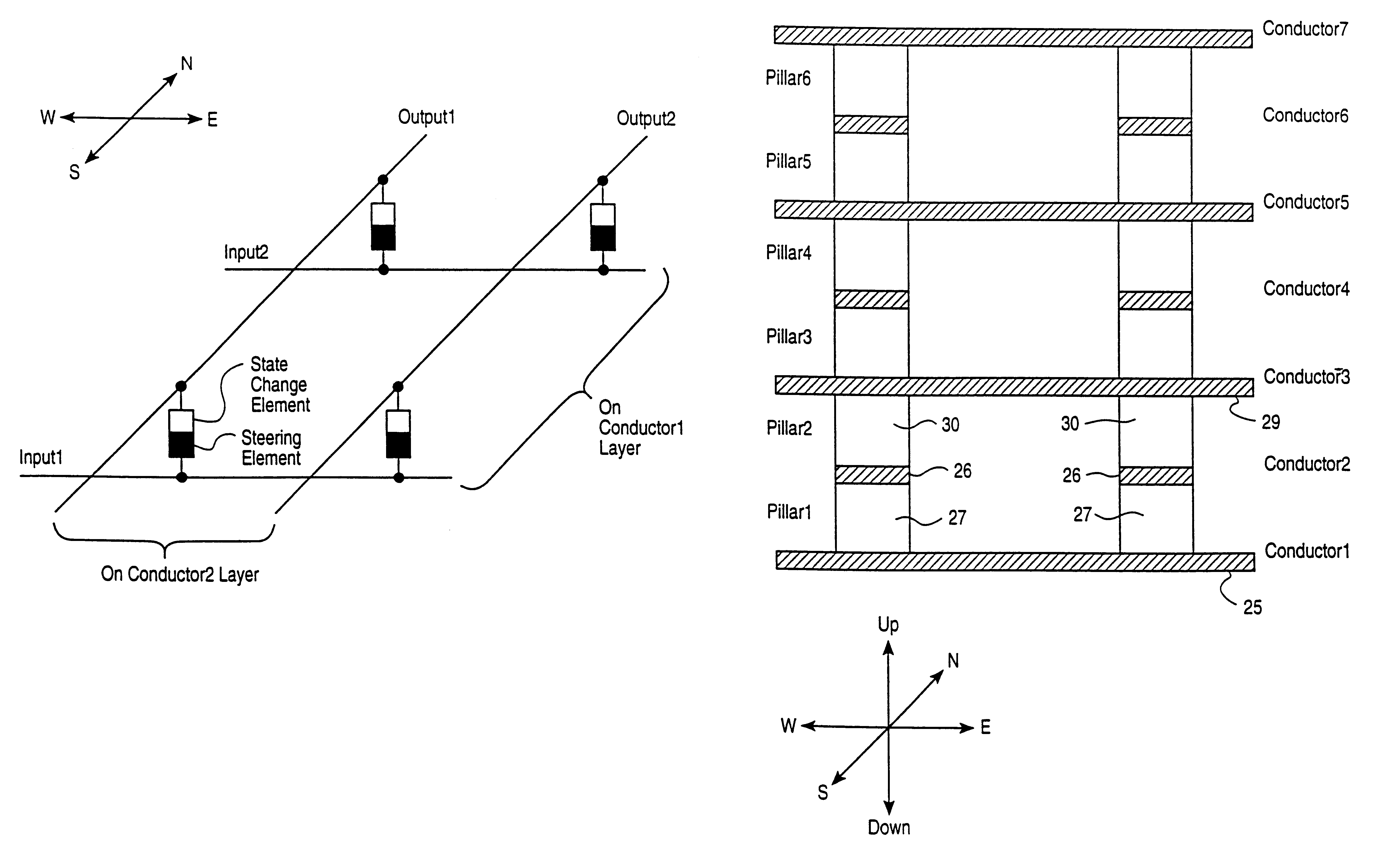

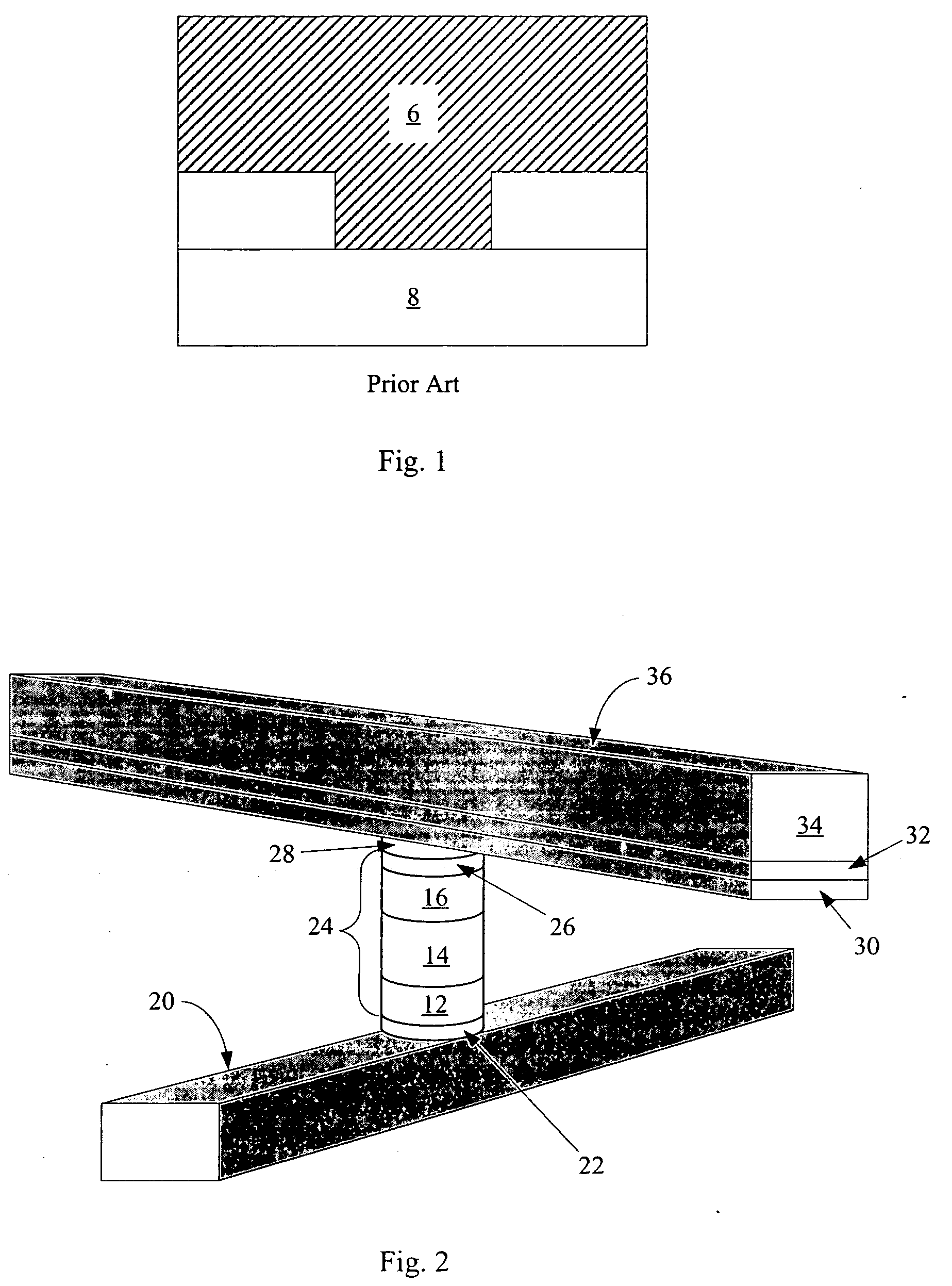

Vertically stacked field programmable nonvolatile memory and method of fabrication

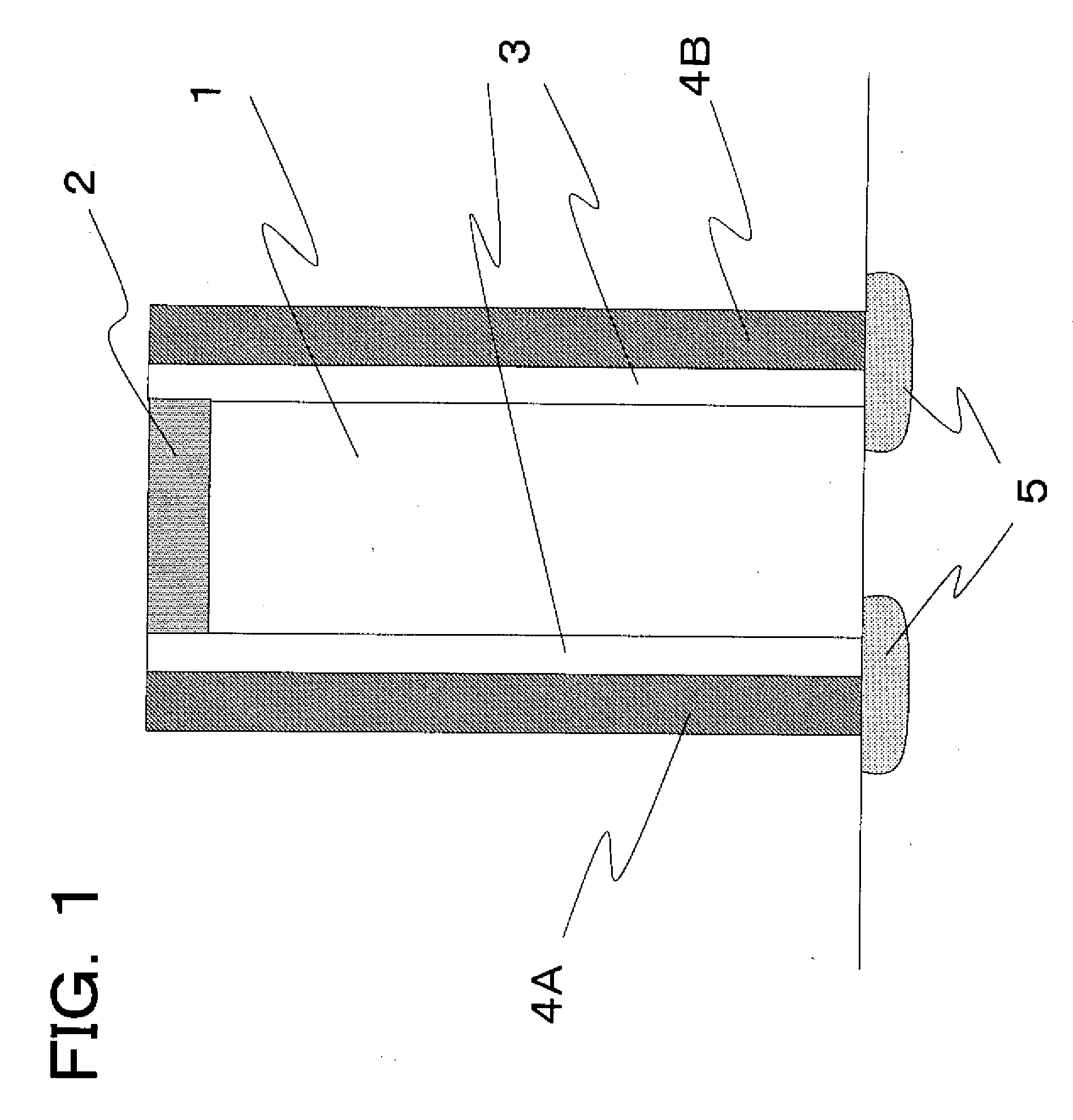

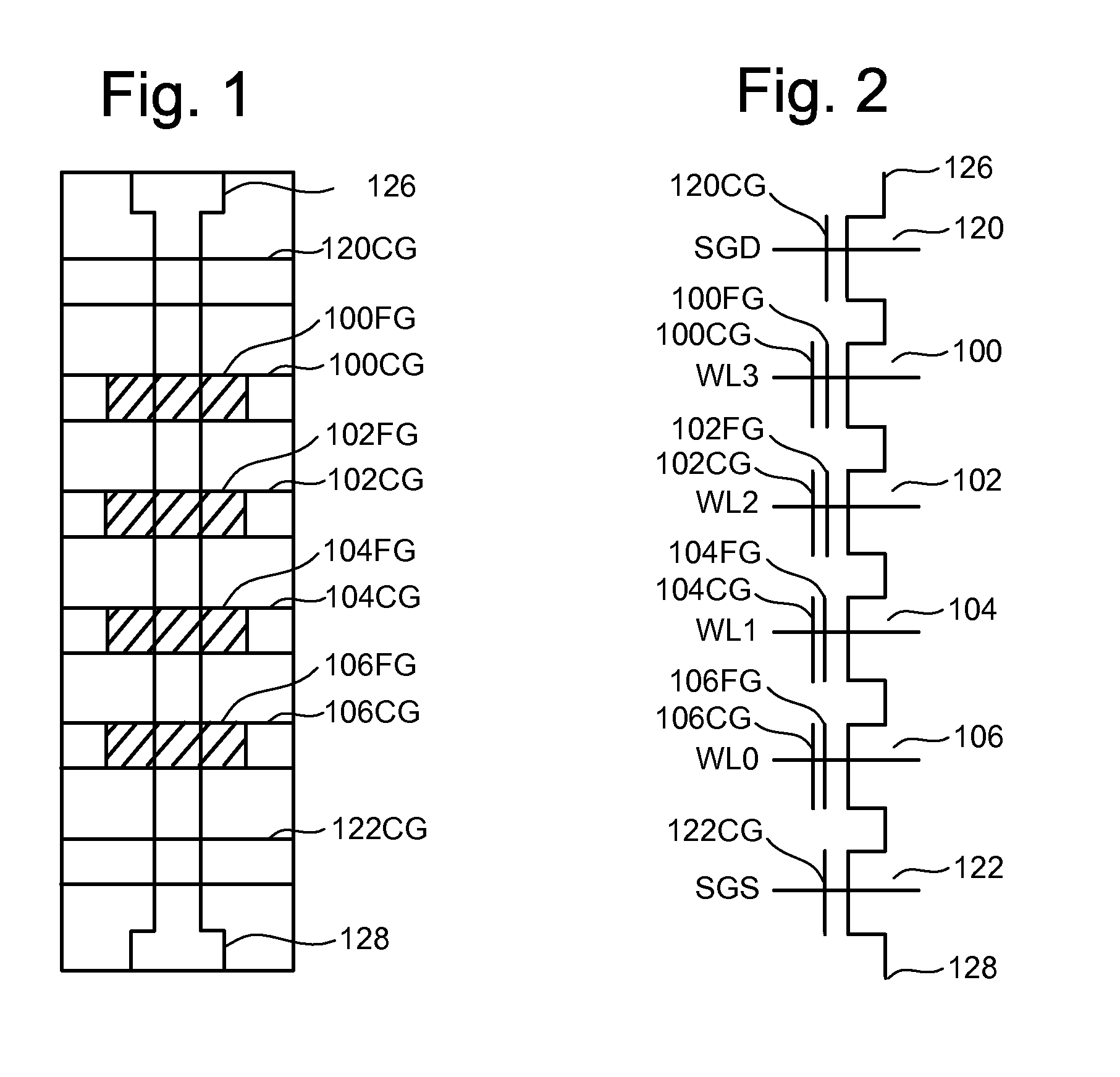

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

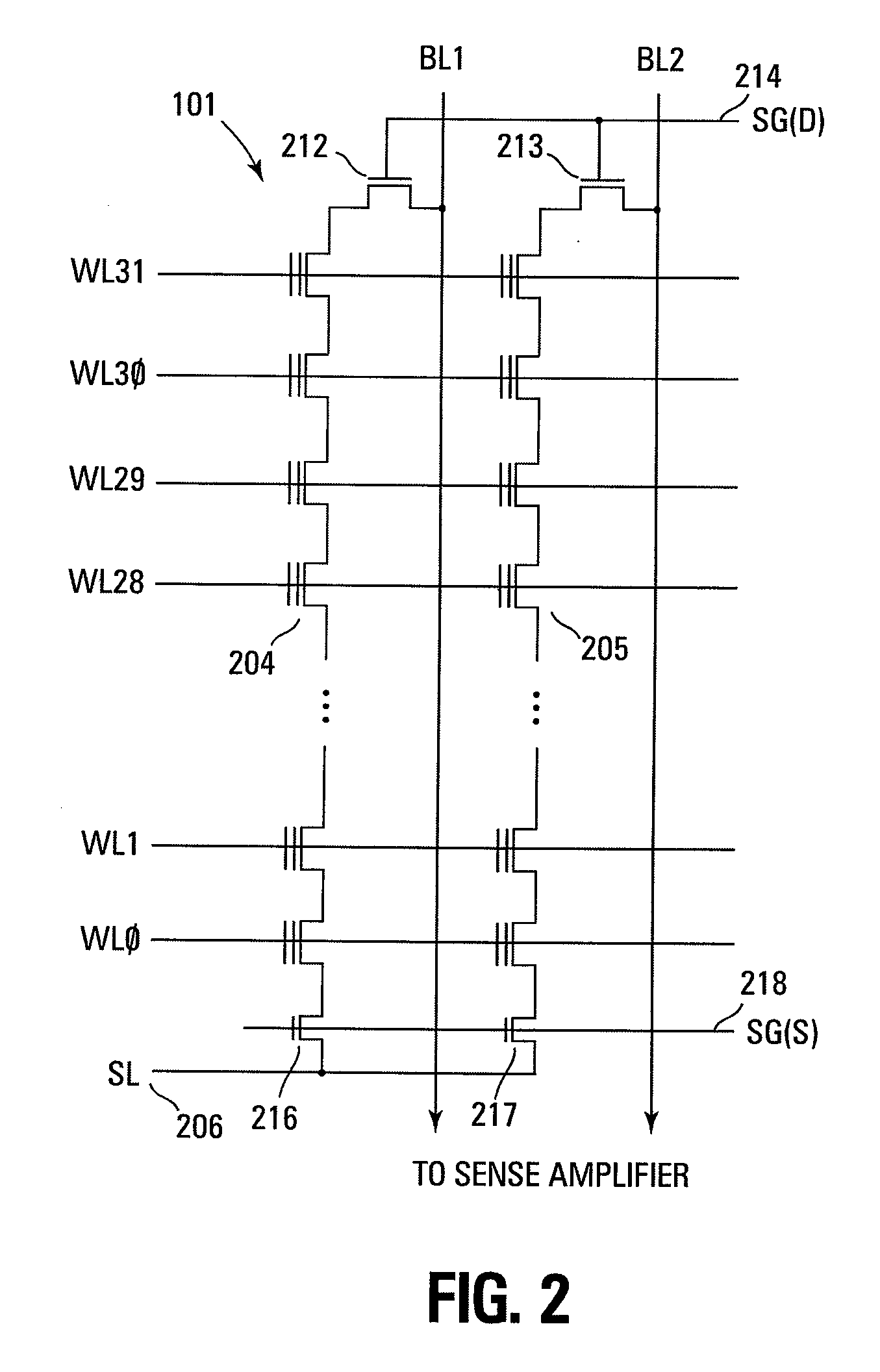

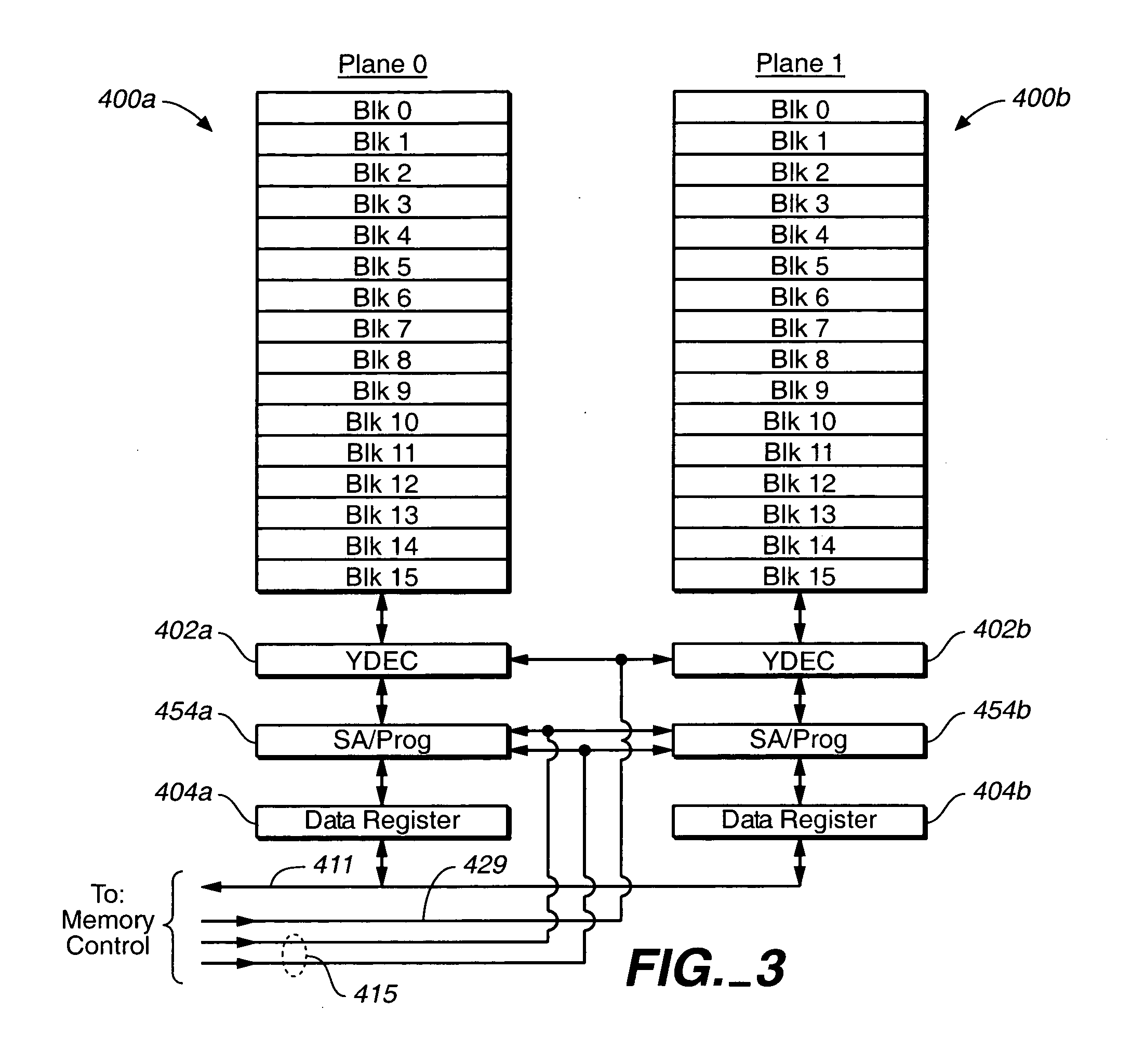

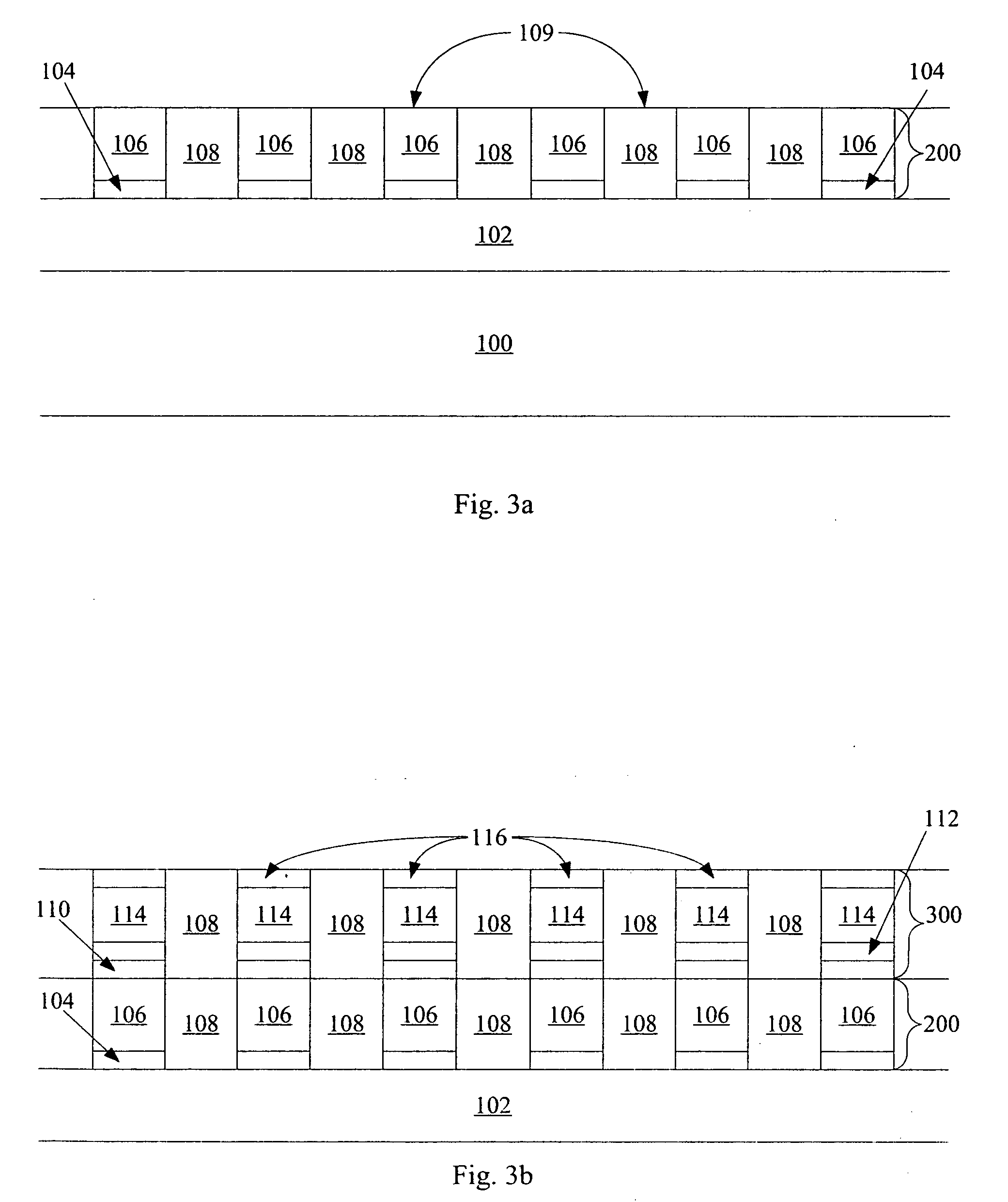

Non-volatile memory and method with reduced neighboring field errors

InactiveUS6987693B2Large capacityImprove performanceRead-only memoriesDigital storageNon-volatile memoryParallel programing

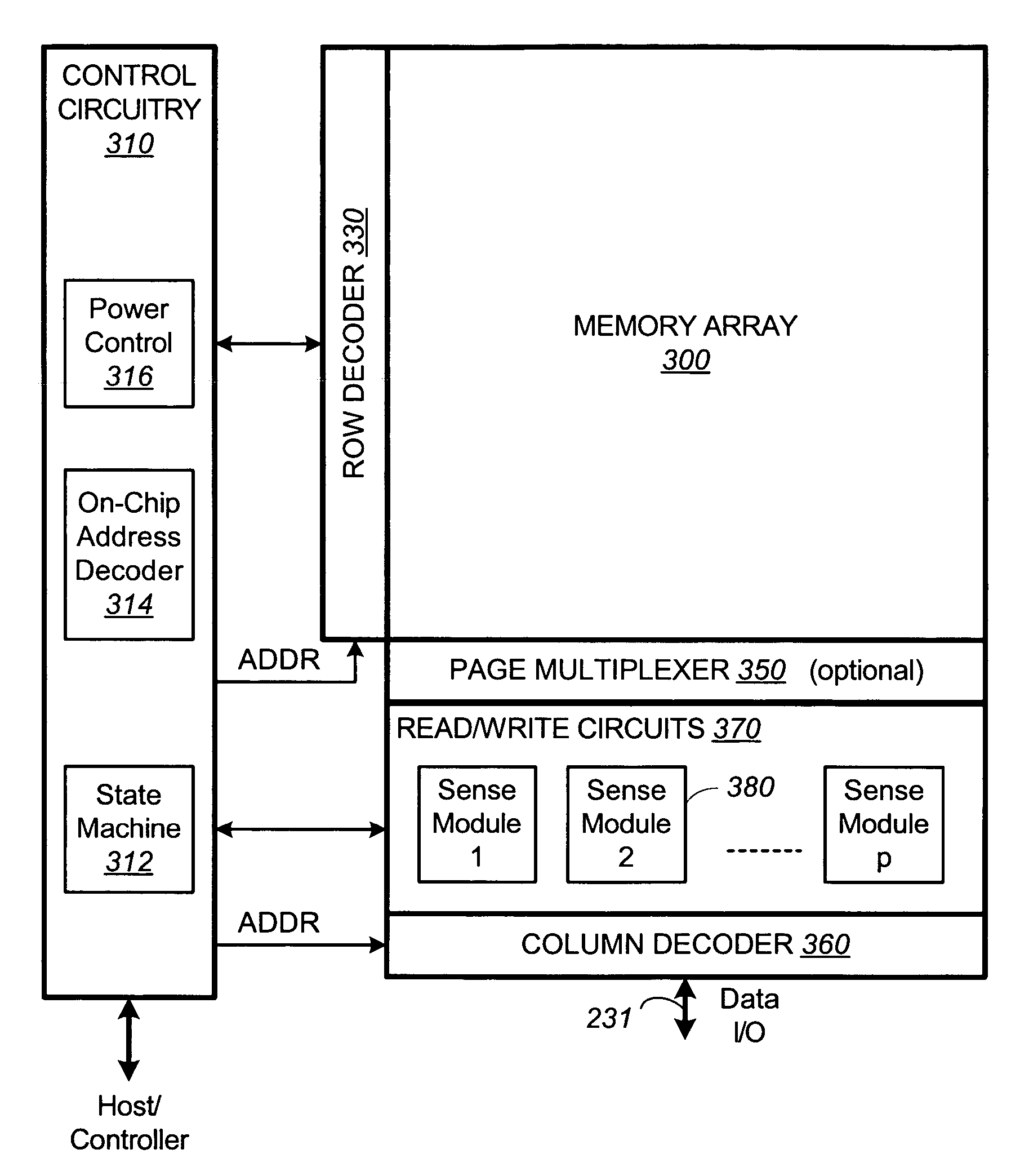

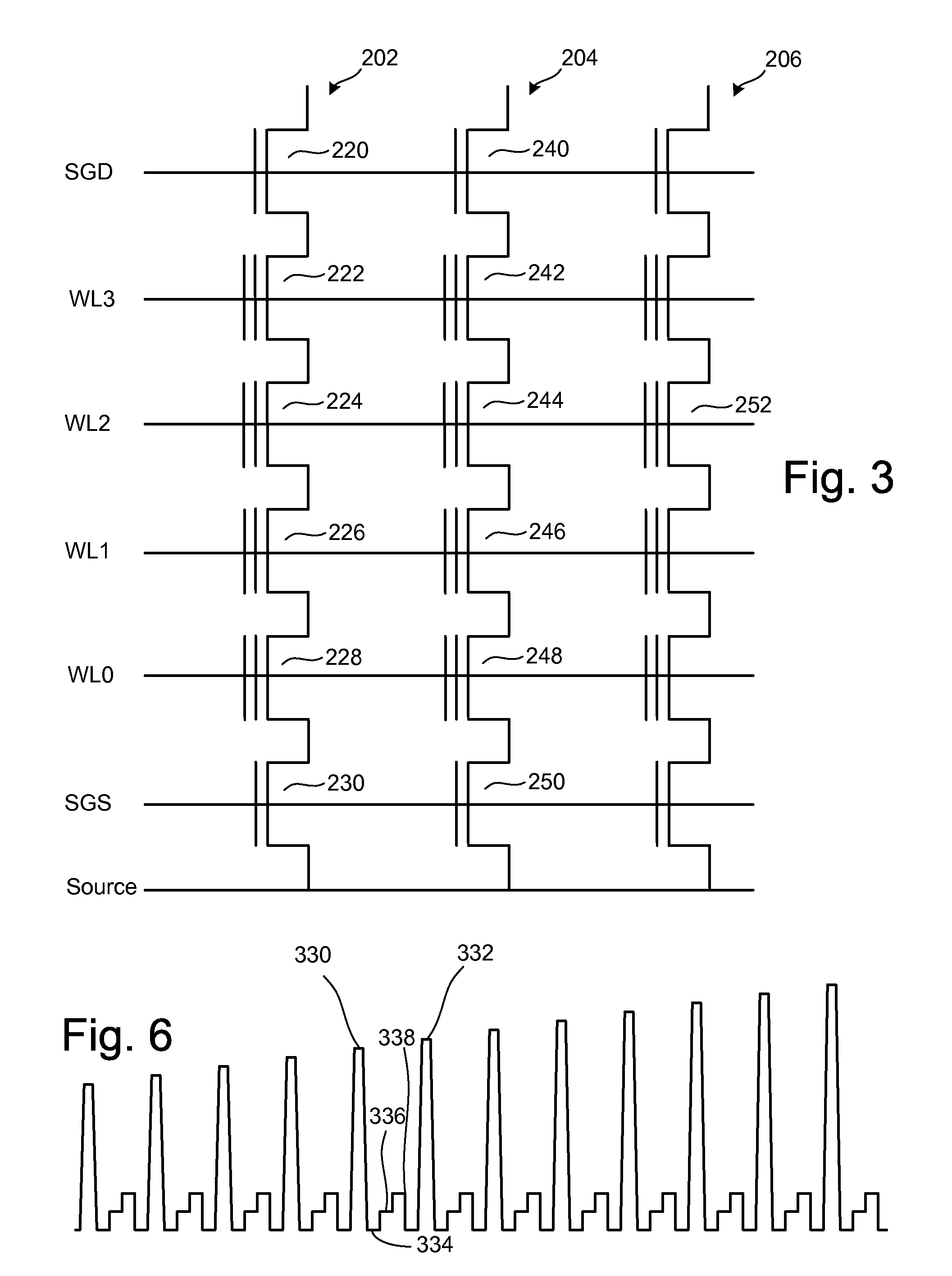

A memory device and a method thereof allow programming and sensing a plurality of memory cells in parallel in order to minimize errors caused by coupling from fields of neighboring cells and to improve performance. The memory device and method have the plurality of memory cells linked by the same word line and a read / write circuit is coupled to each memory cells in a contiguous manner. Thus, a memory cell and its neighbors are programmed together and the field environment for each memory cell relative to its neighbors during programming and subsequent reading is less varying. This improves performance and reduces errors caused by coupling from fields of neighboring cells, as compared to conventional architectures and methods in which cells on even columns are programmed independently of cells in odd columns.

Owner:SANDISK TECH LLC

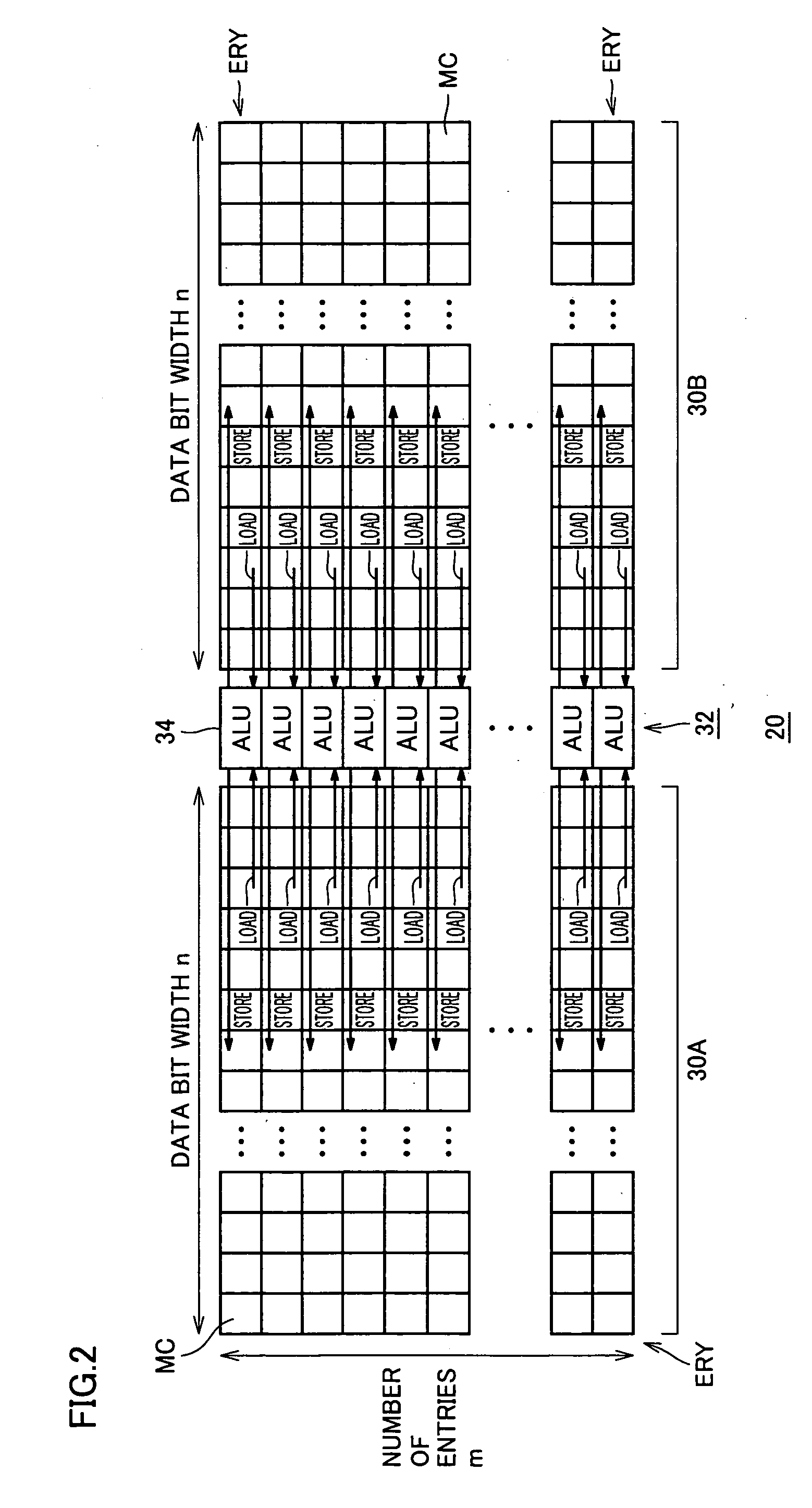

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

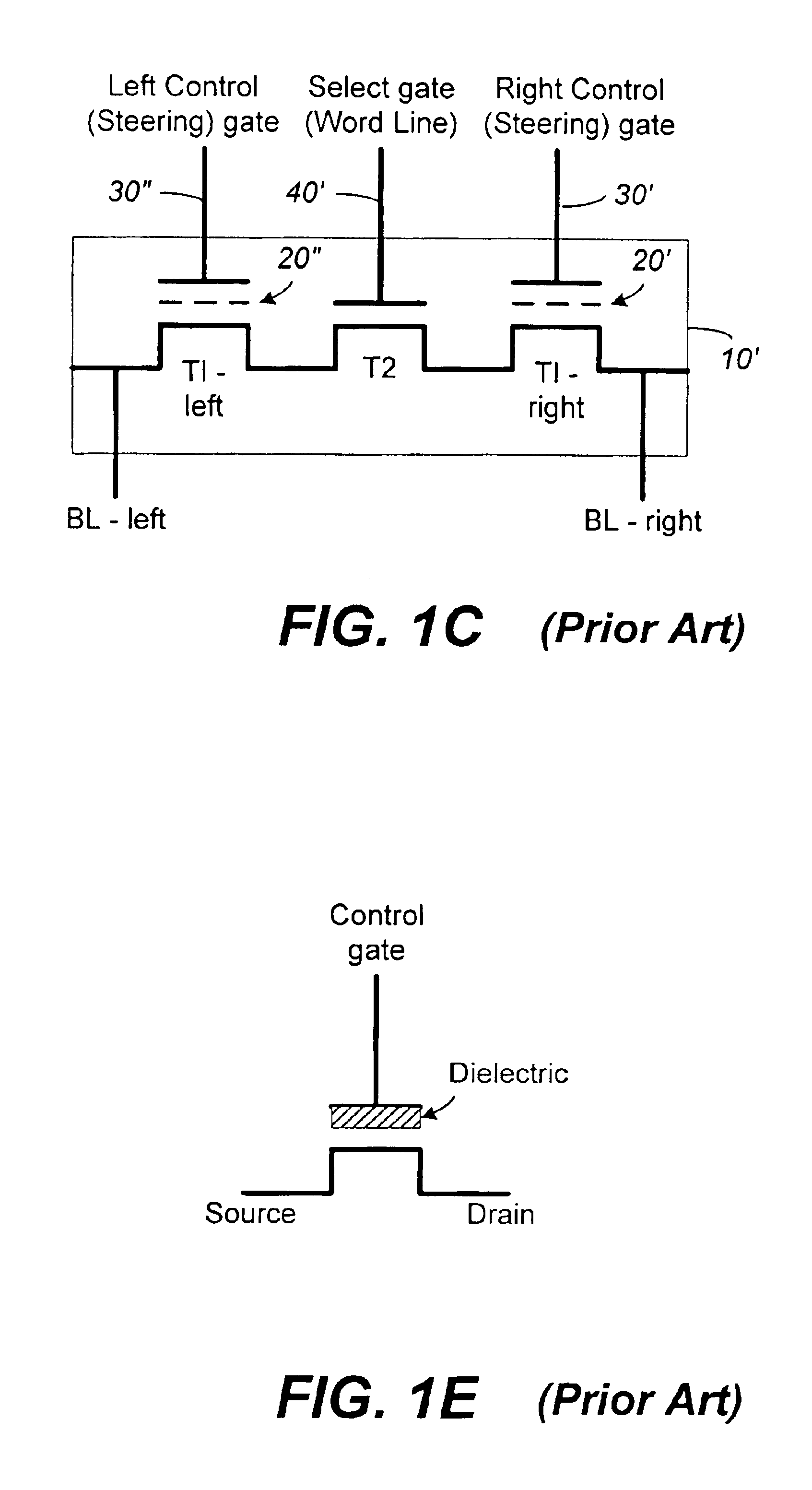

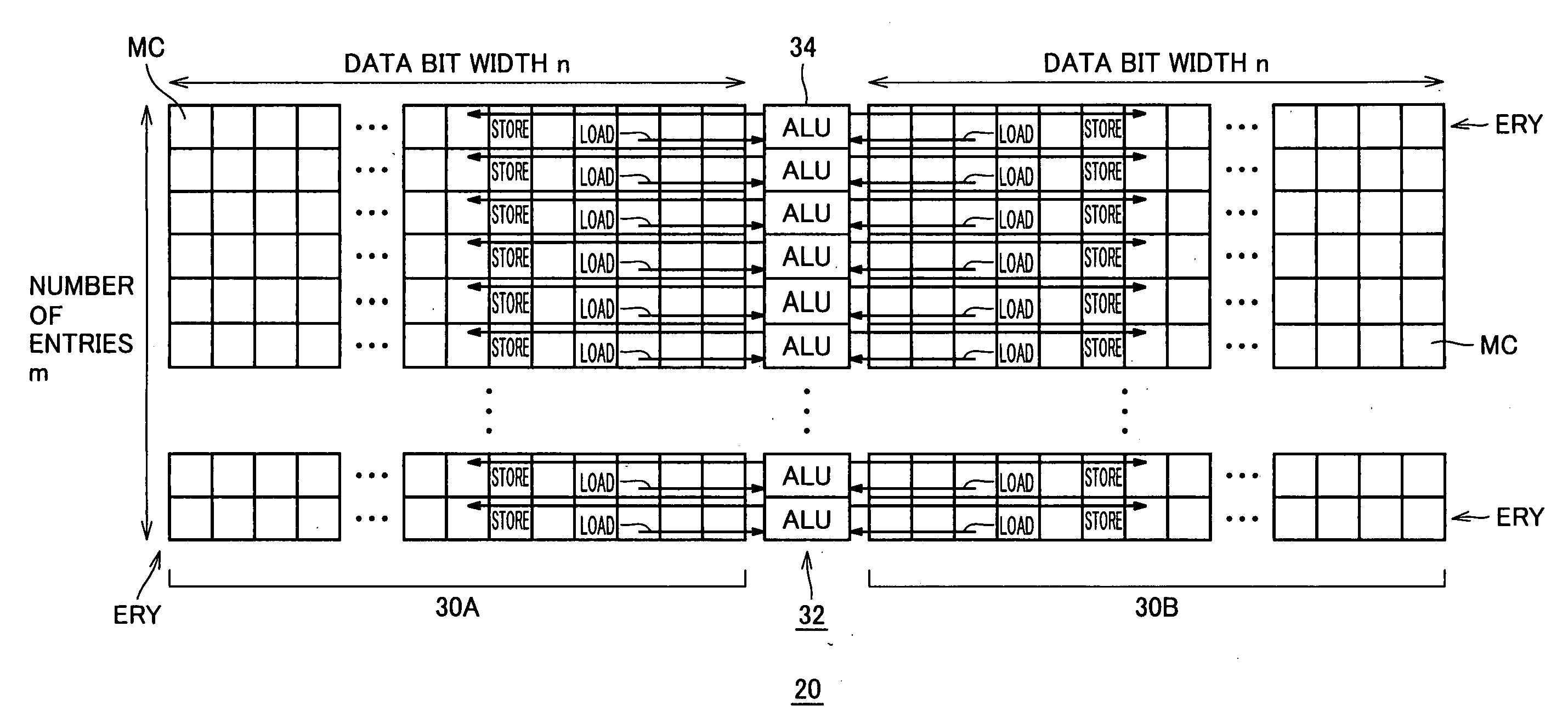

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

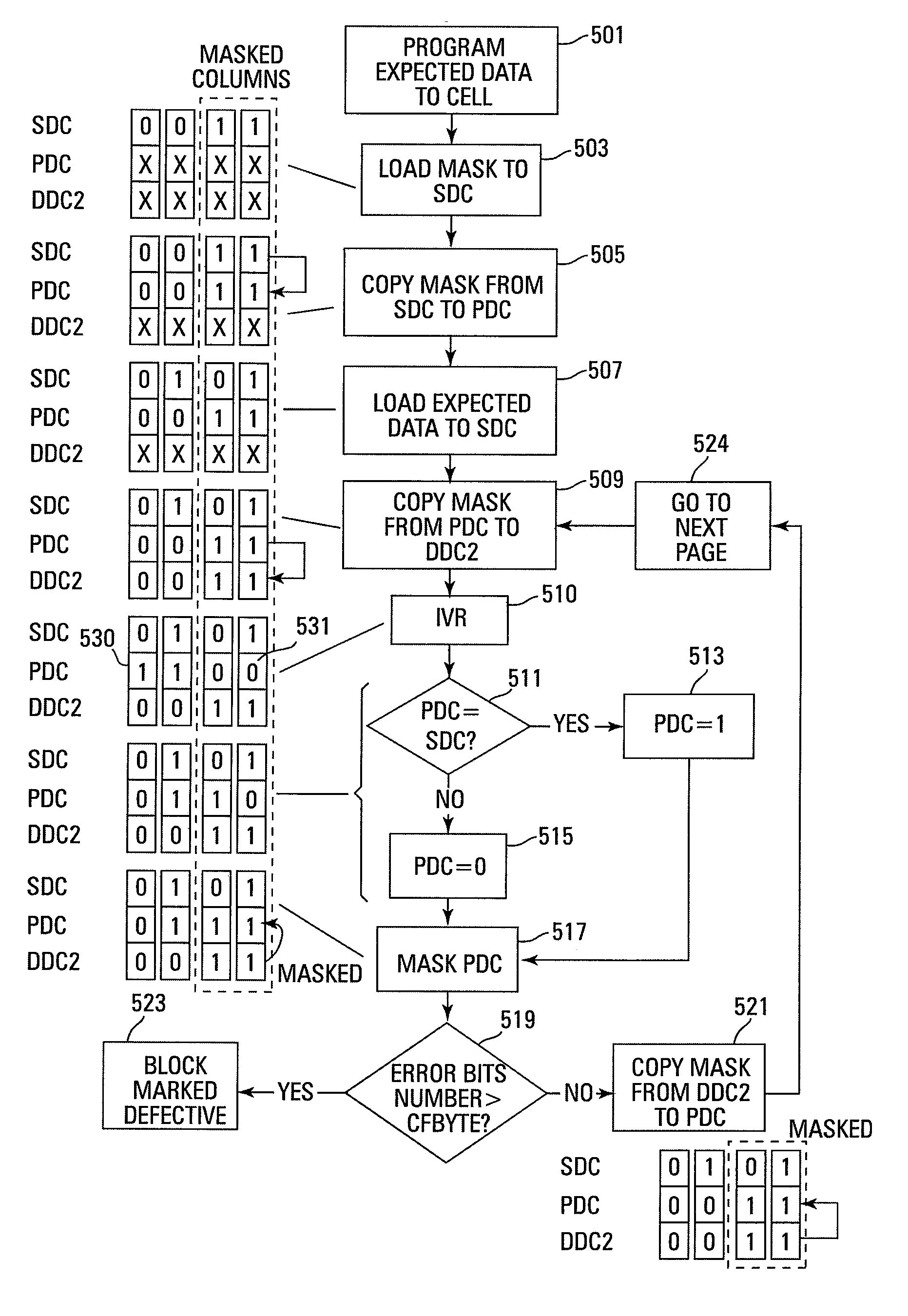

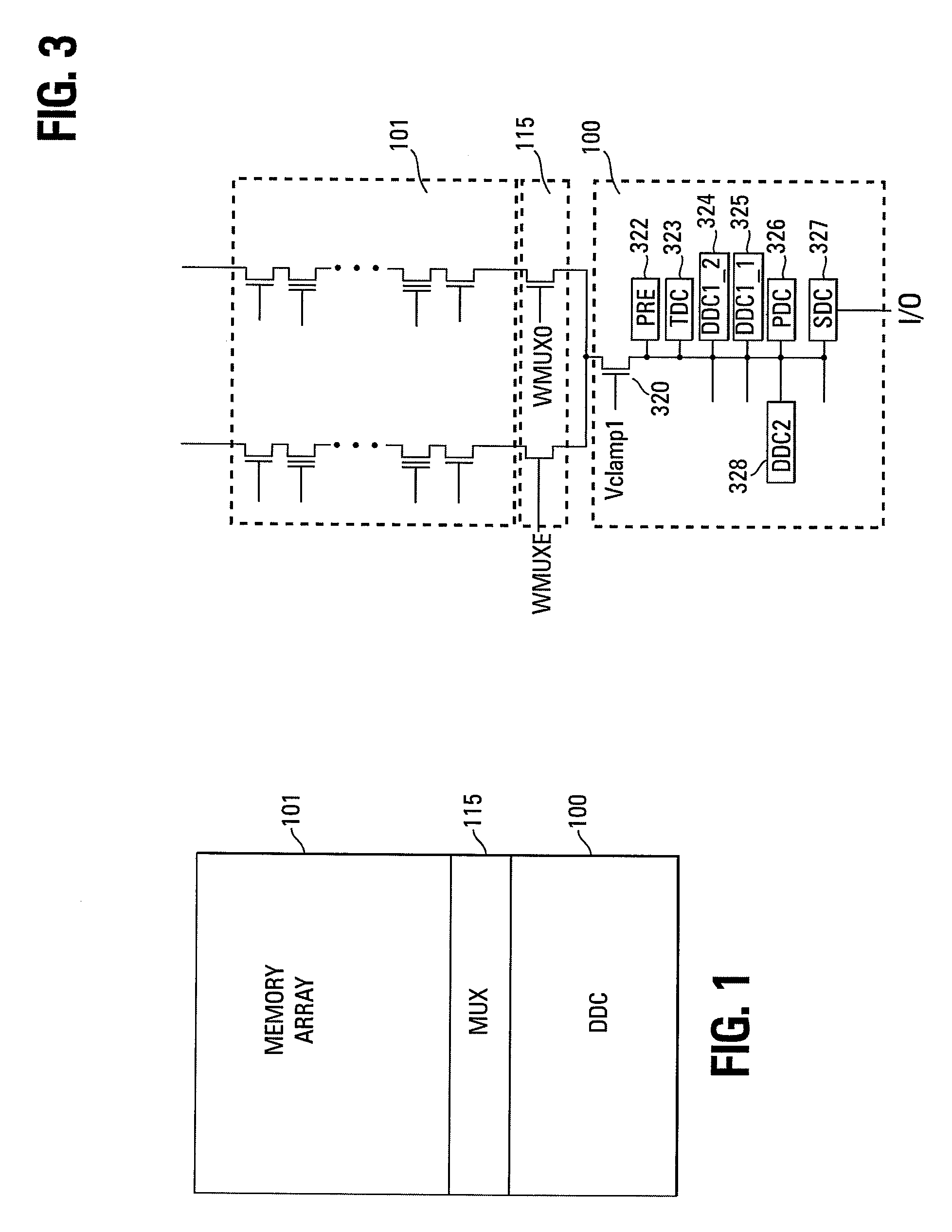

Small unit internal verify read in a memory device

Methods for small unit internal verify read operation and a memory device are disclosed. In one such method, expected data is programmed into a grouping of columns of memory cells (e.g., memory block). Mask data is loaded into a third dynamic data cache of three dynamic data caches. The expected data is loaded into a second data cache. After a read operation of programmed columns of memory cells, the read data is compared to the expected data and error bit indicators are stored in the second data cache in the error bit locations. The second data cache is masked with the mask data so that only those error bits that are unmasked are counted. If the number of unmasked error bit indicators is greater than a threshold, the memory block is marked as unusable.

Owner:MICRON TECH INC

Semiconductor memory apparatus and test circuit therefor

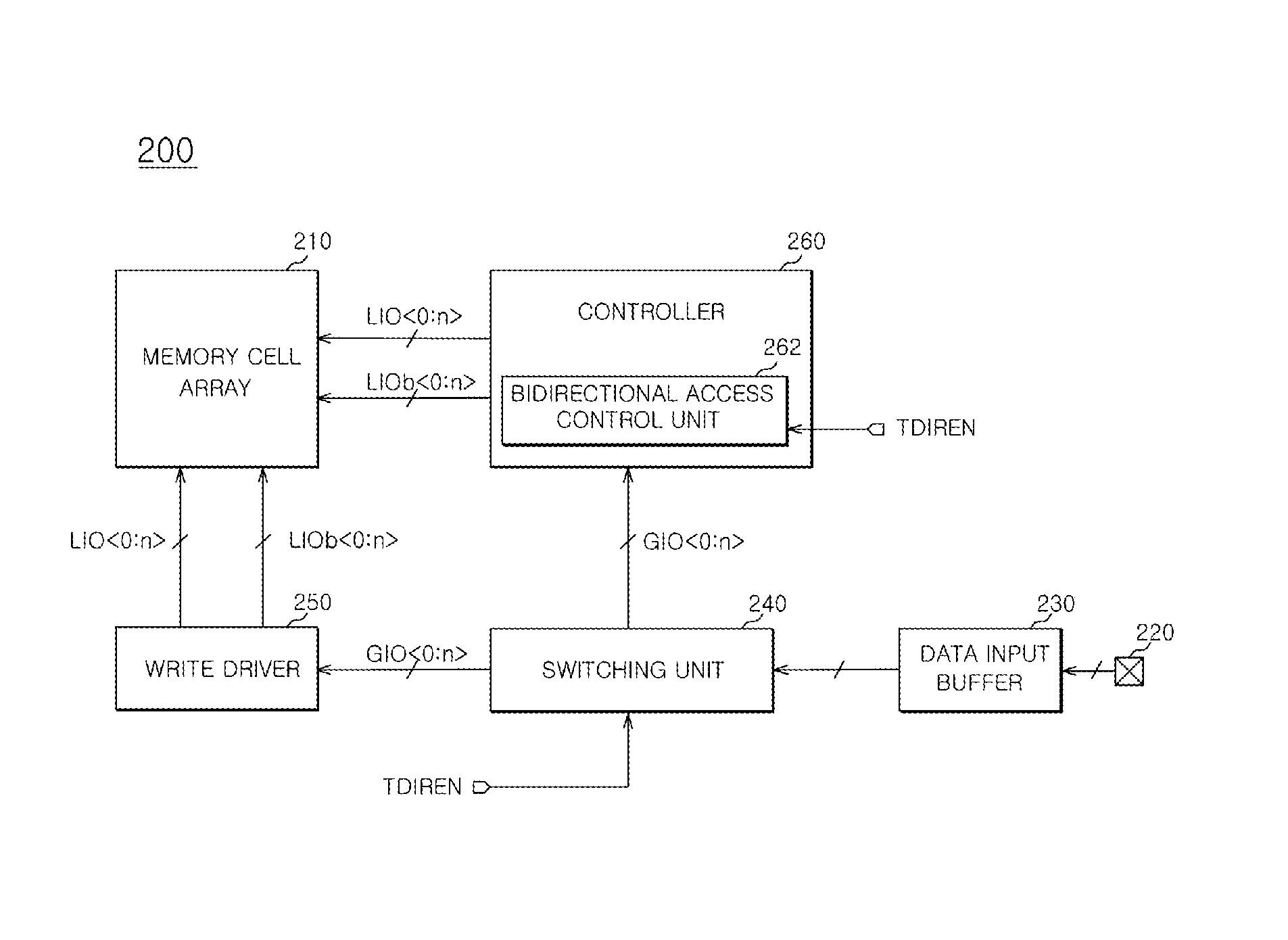

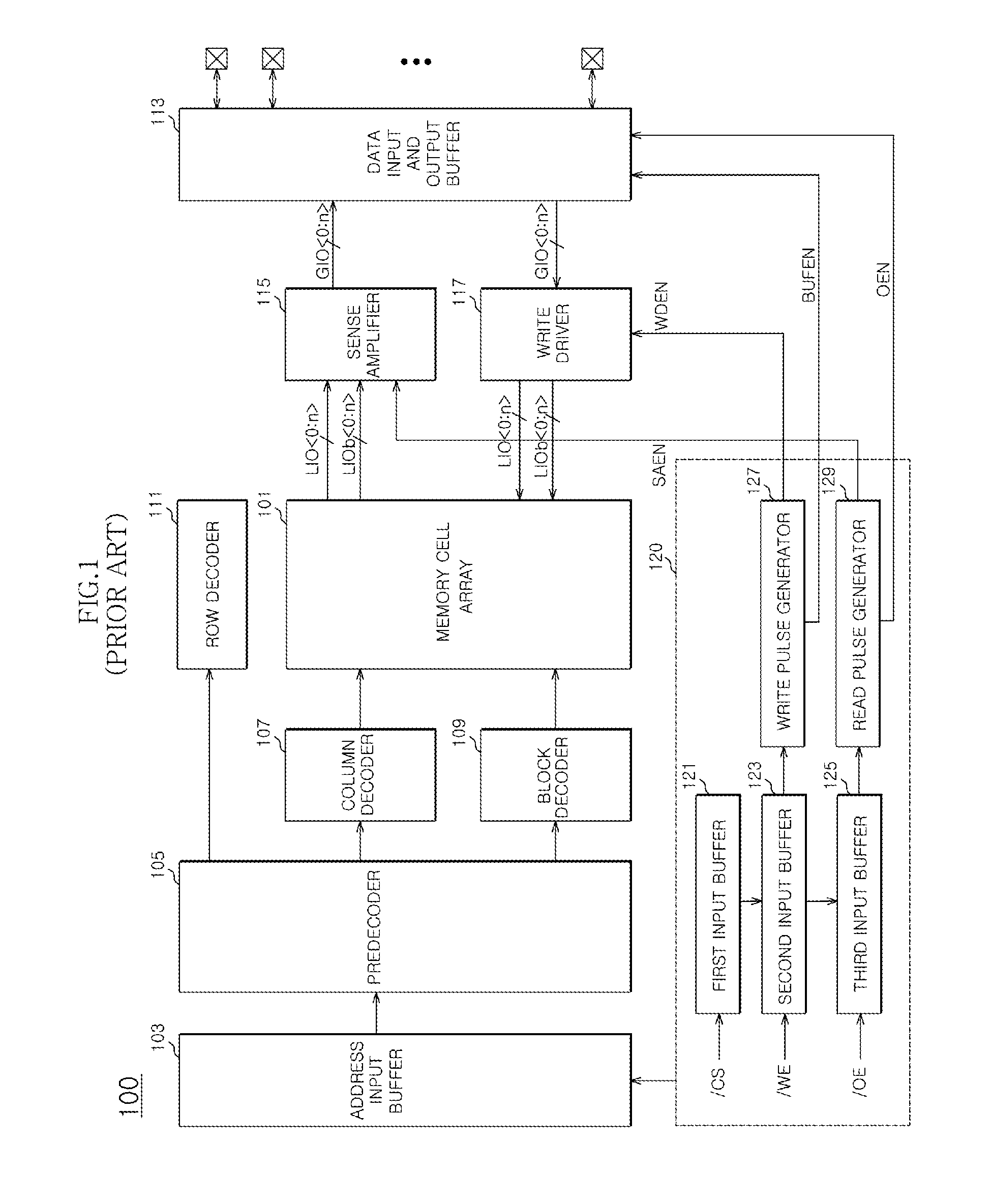

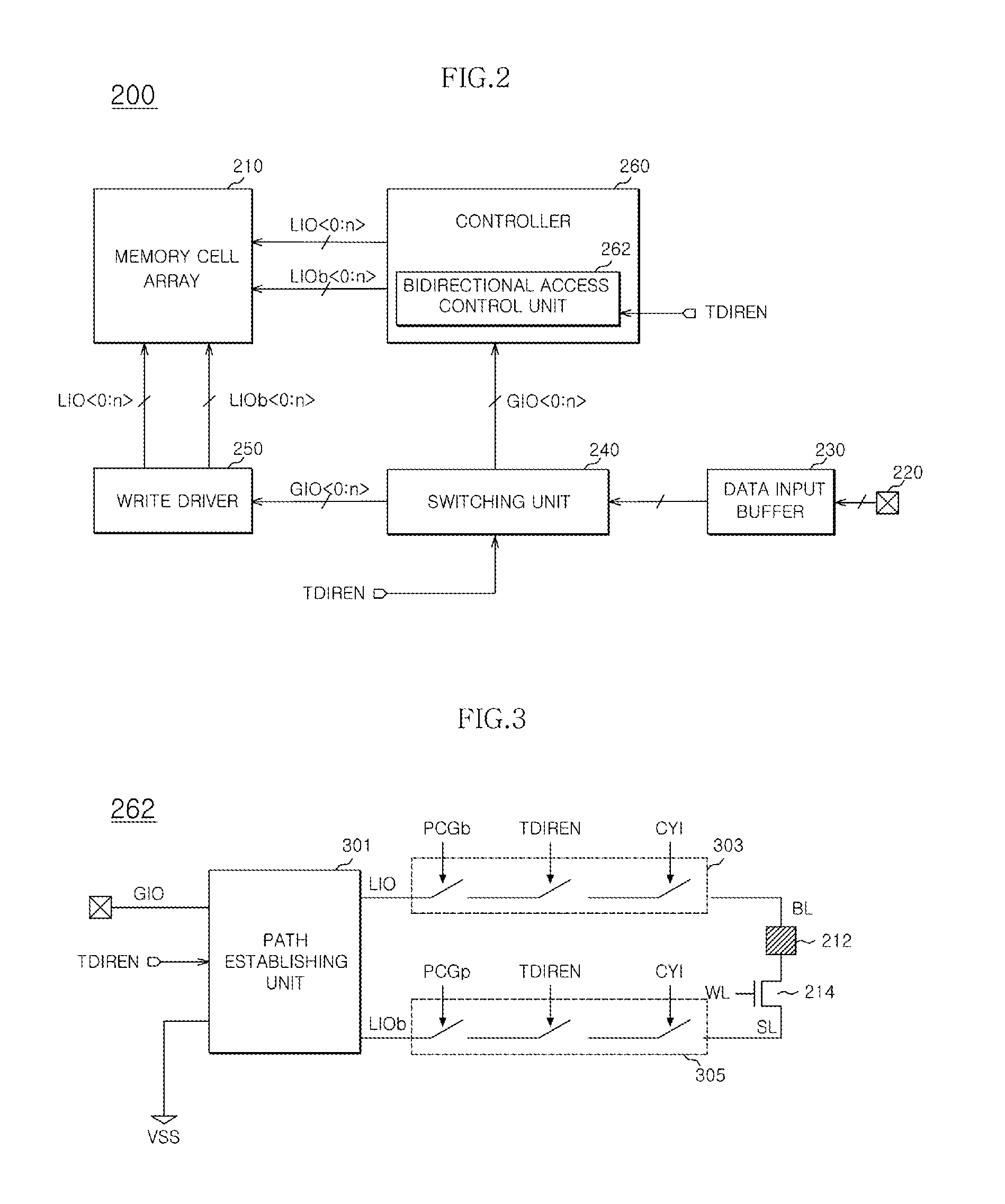

Disclosed is a semiconductor memory apparatus, including: a memory cell array configured to include a plurality of memory cells; a switching unit configured to be coupled to data input and output pads and control a data transfer path of data applied to the data input and output pads in response to a test mode signal; a write driver configured to drive data transferred from the switching unit and write the data in the memory cell array at a normal mode; and a controller configured to transfer the data from the switching unit to the memory cell at a test mode.

Owner:SK HYNIX INC

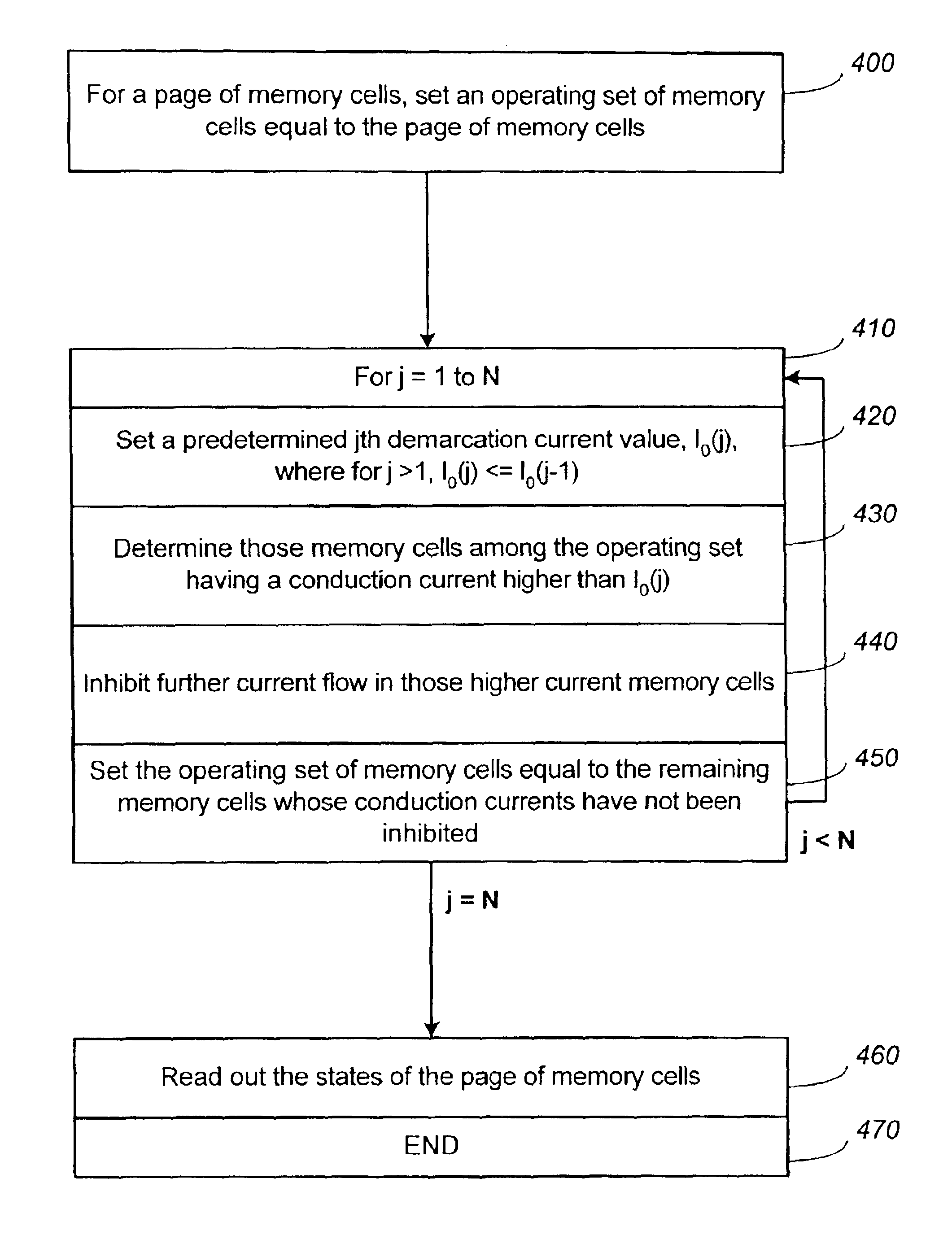

Memory sensing circuit and method for low voltage operation

InactiveUS7046568B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineAudio power amplifier

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

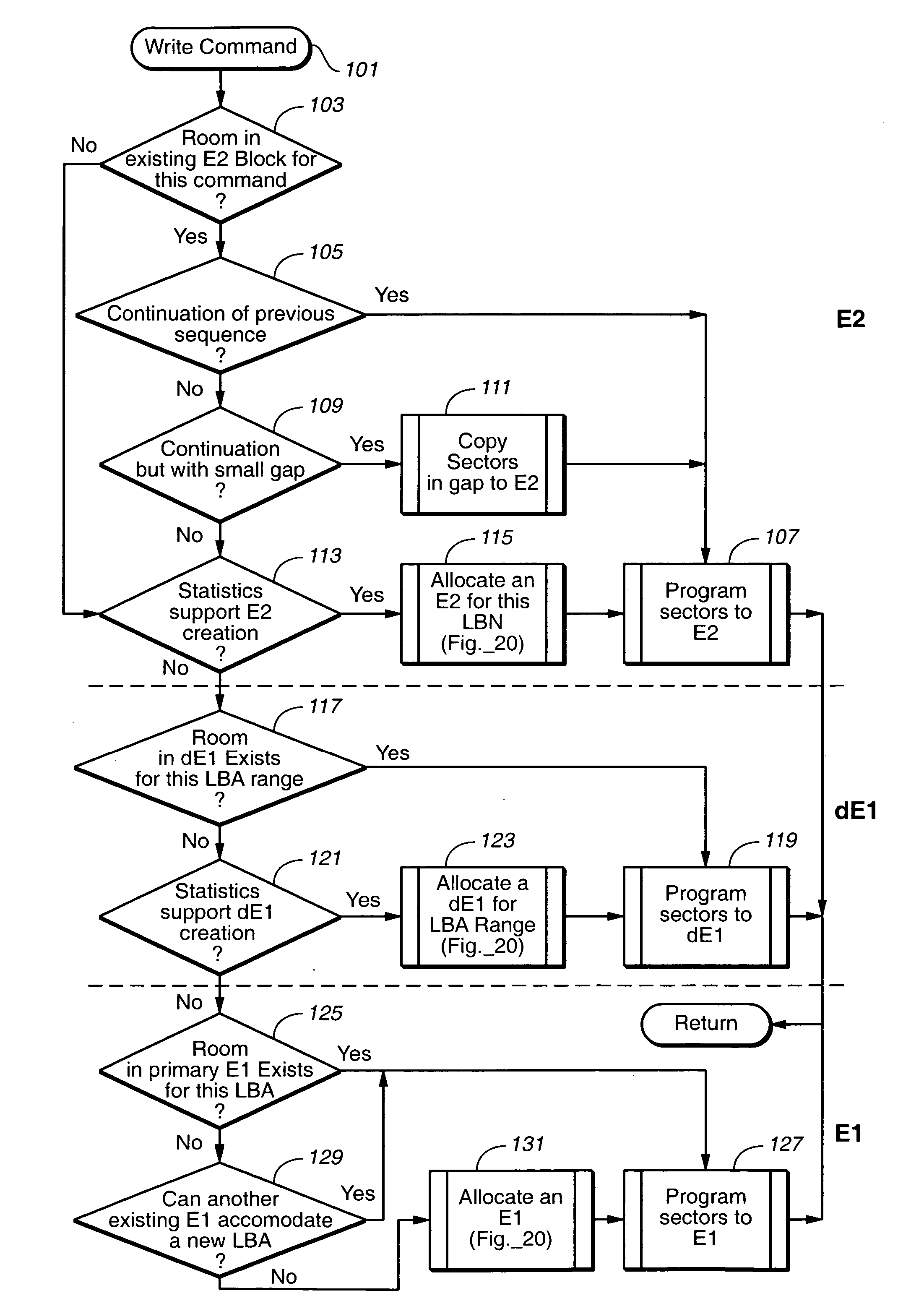

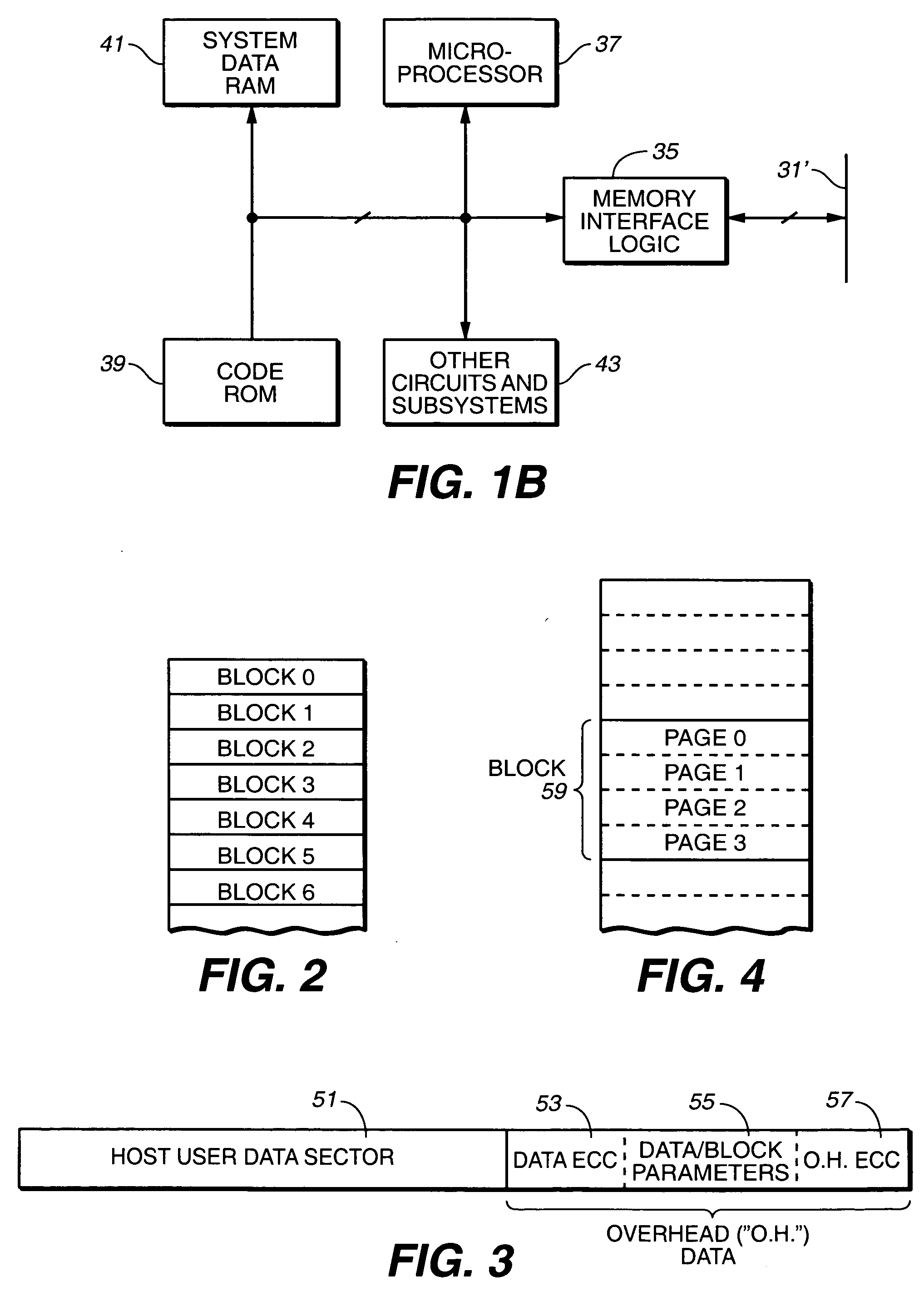

Management of non-volatile memory systems having large erase blocks

ActiveUS20050144358A1Reduce amountImprove system performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationOriginal dataTerm memory

A non-volatile memory system of a type having blocks of memory cells erased together and which are programmable from an erased state in units of a large number of pages per block. If the data of only a few pages of a block are to be updated, the updated pages are written into another block provided for this purpose. Updated pages from multiple blocks are programmed into this other block in an order that does not necessarily correspond with their original address offsets. The valid original and updated data are then combined at a later time, when doing so does not impact on the performance of the memory. If the data of a large number of pages of a block are to be updated, however, the updated pages are written into an unused erased block and the unchanged pages are also written to the same unused block. By handling the updating of a few pages differently, memory performance is improved when small updates are being made. The memory controller can dynamically create and operate these other blocks in response to usage by the host of the memory system.

Owner:SANDISK TECH LLC

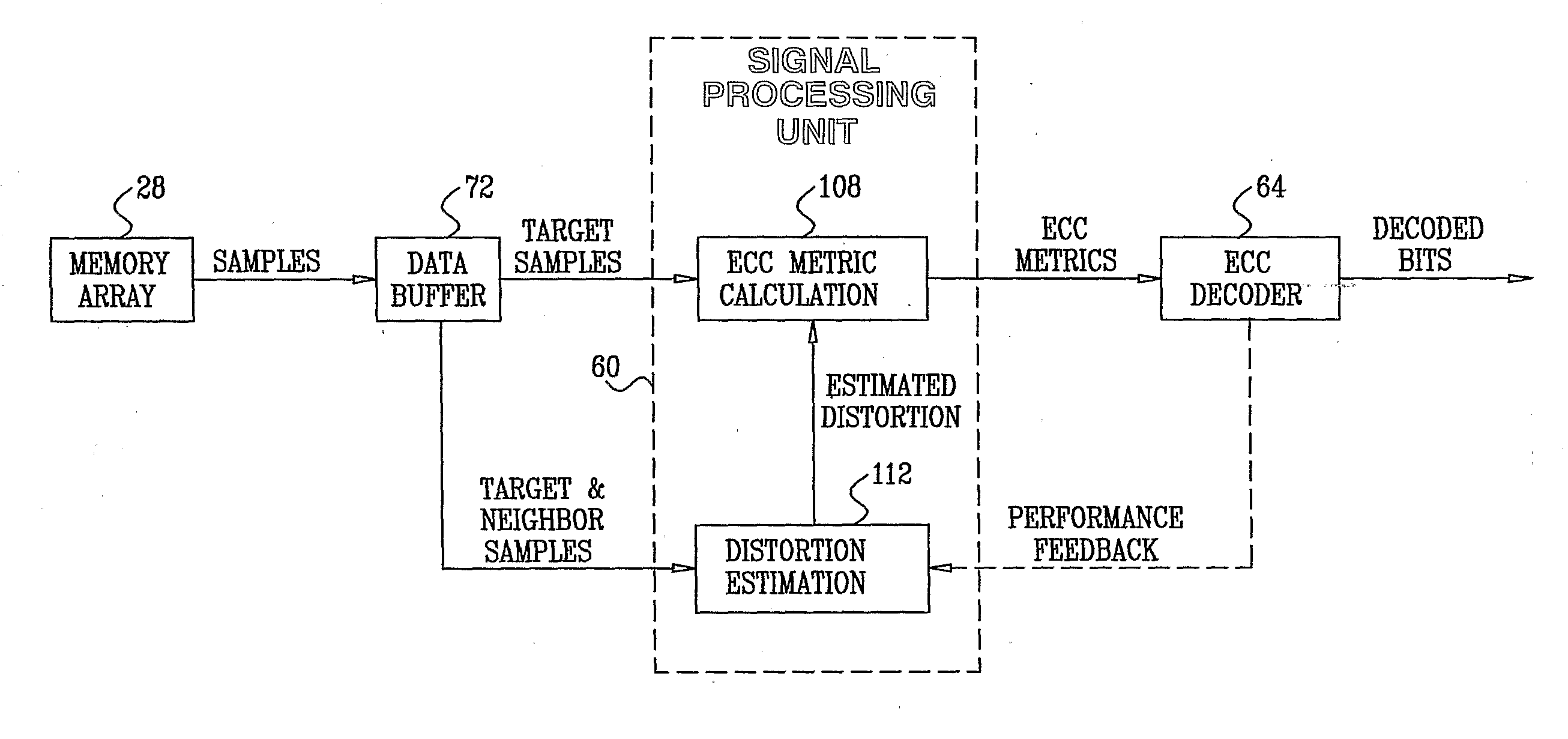

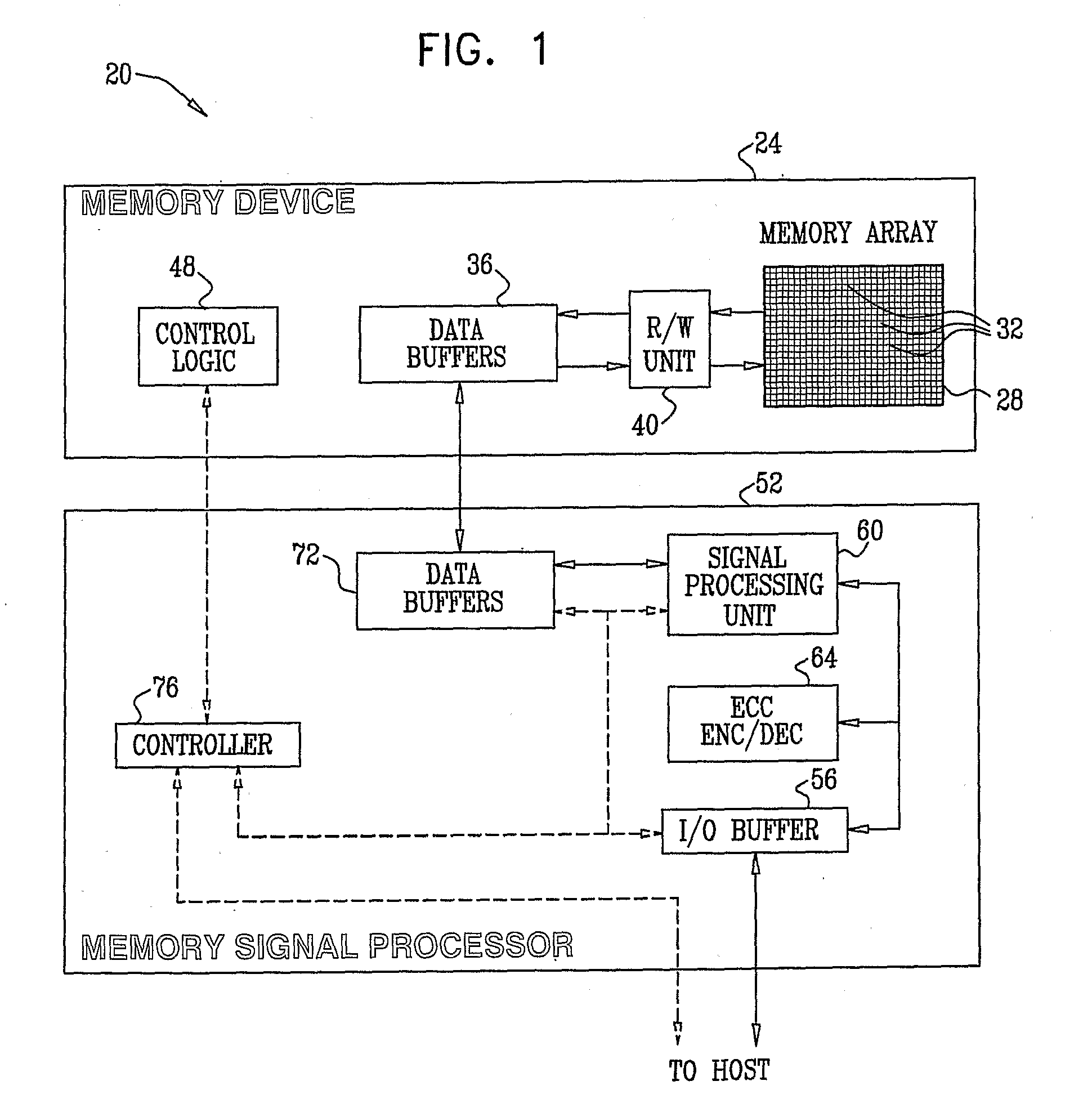

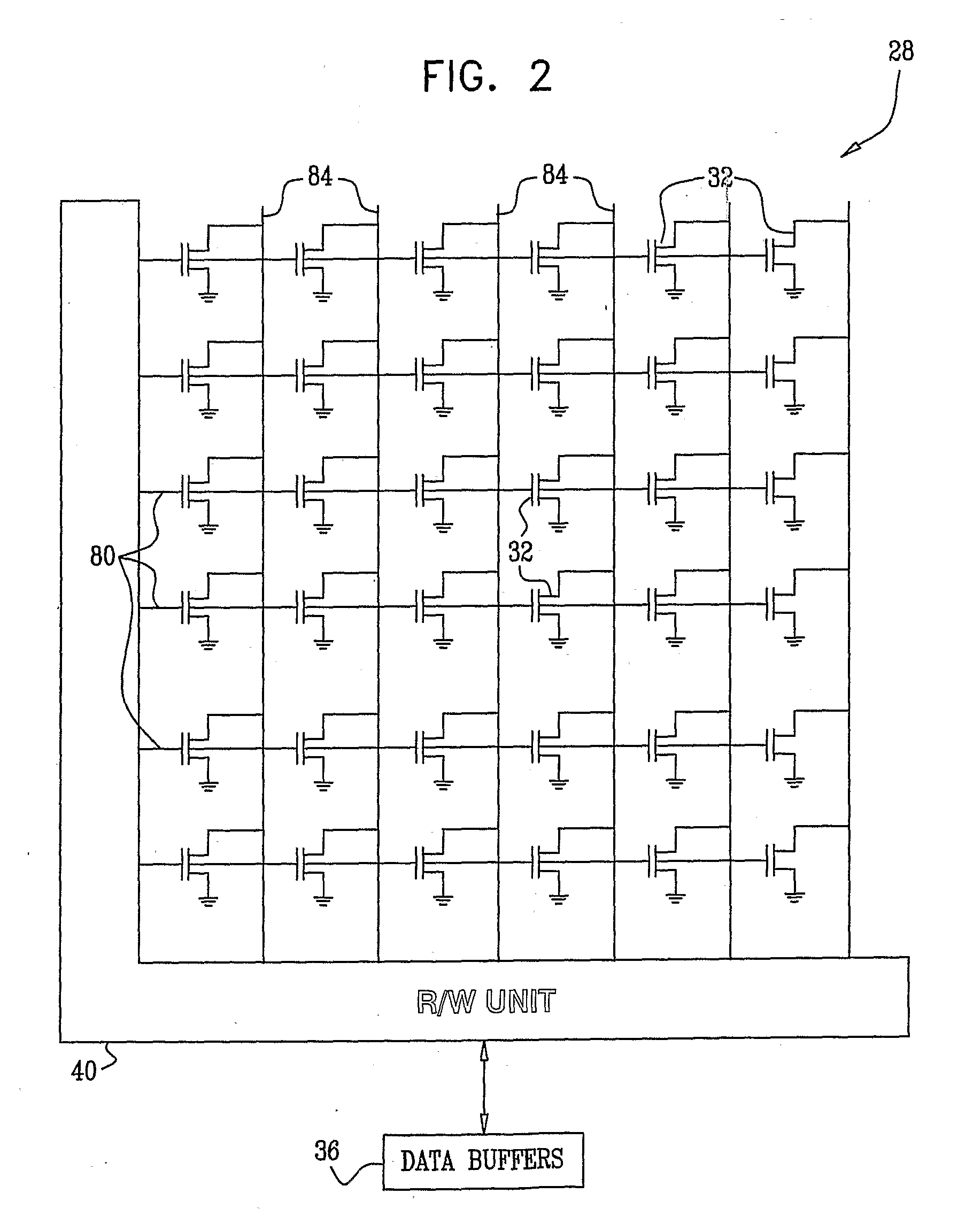

Combined distortion estimation and error correction coding for memory devices

ActiveUS20090024905A1Improve performanceData representation error detection/correctionError detection/correctionCalculation errorDistortion

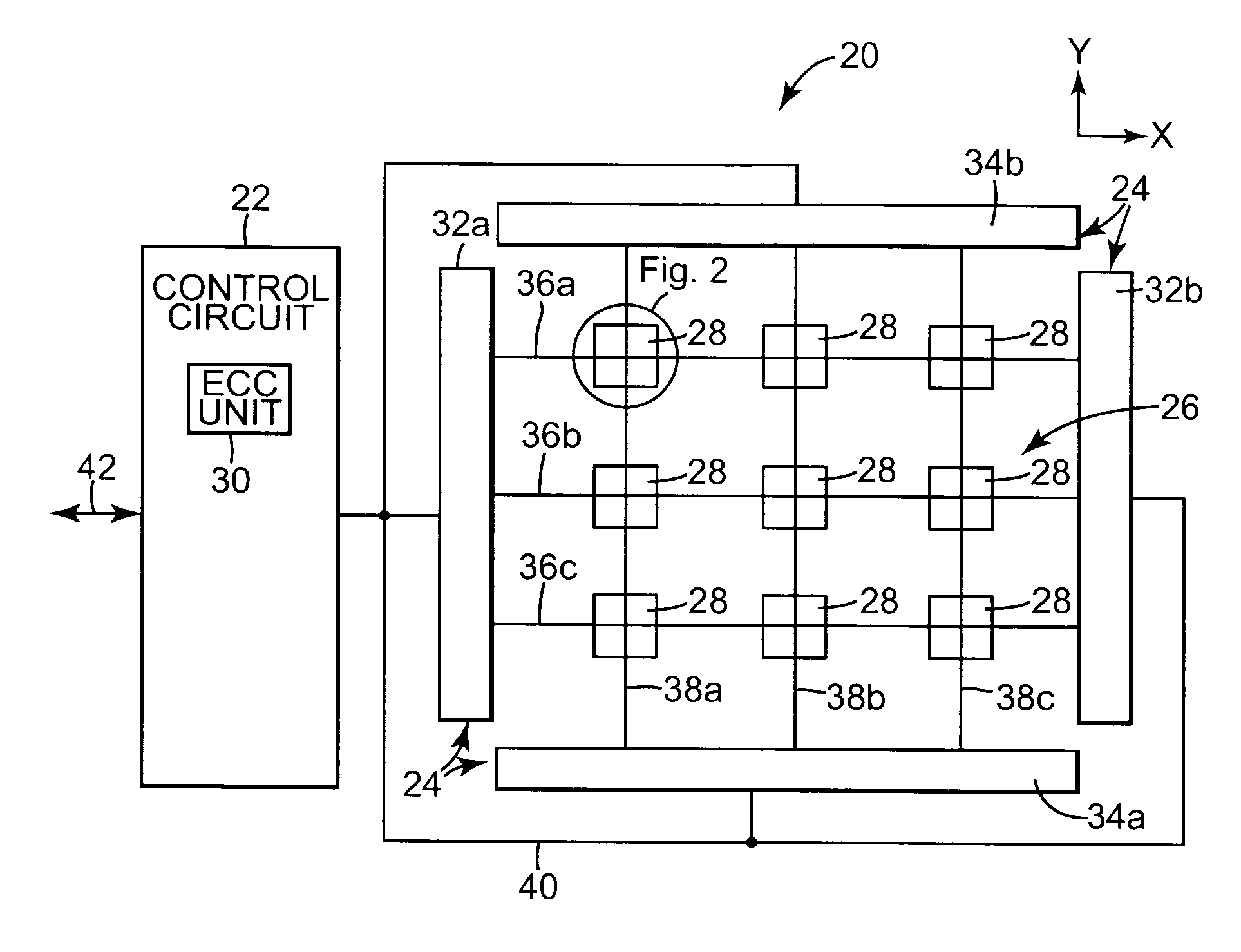

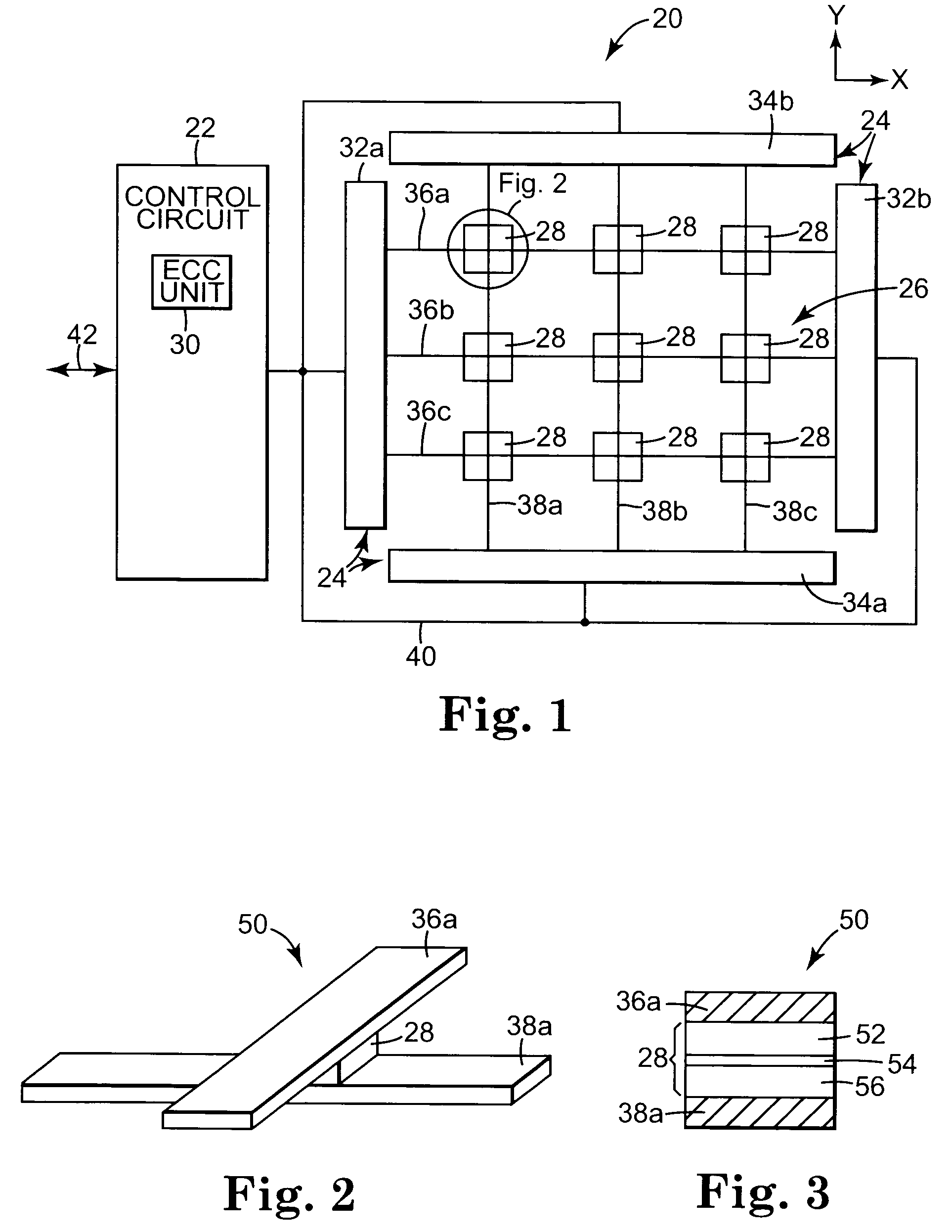

A method for operating a memory device (24) includes encoding data using an Error Correction Code (ECC) and storing the encoded data as first analog values in respective analog memory cells (32) of the memory device. After storing the encoded data, second analog values are read from the respective memory cells of the memory device in which the encoded data were stored. At least some of the second analog values differ from the respective first analog values. A distortion that is present in the second analog values is estimated. Error correction metrics are computed with respect to the second analog values responsively to the estimated distortion. The second analog values are processed using the error correction metrics in an ECC decoding process, so as to reconstruct the data.

Owner:APPLE INC

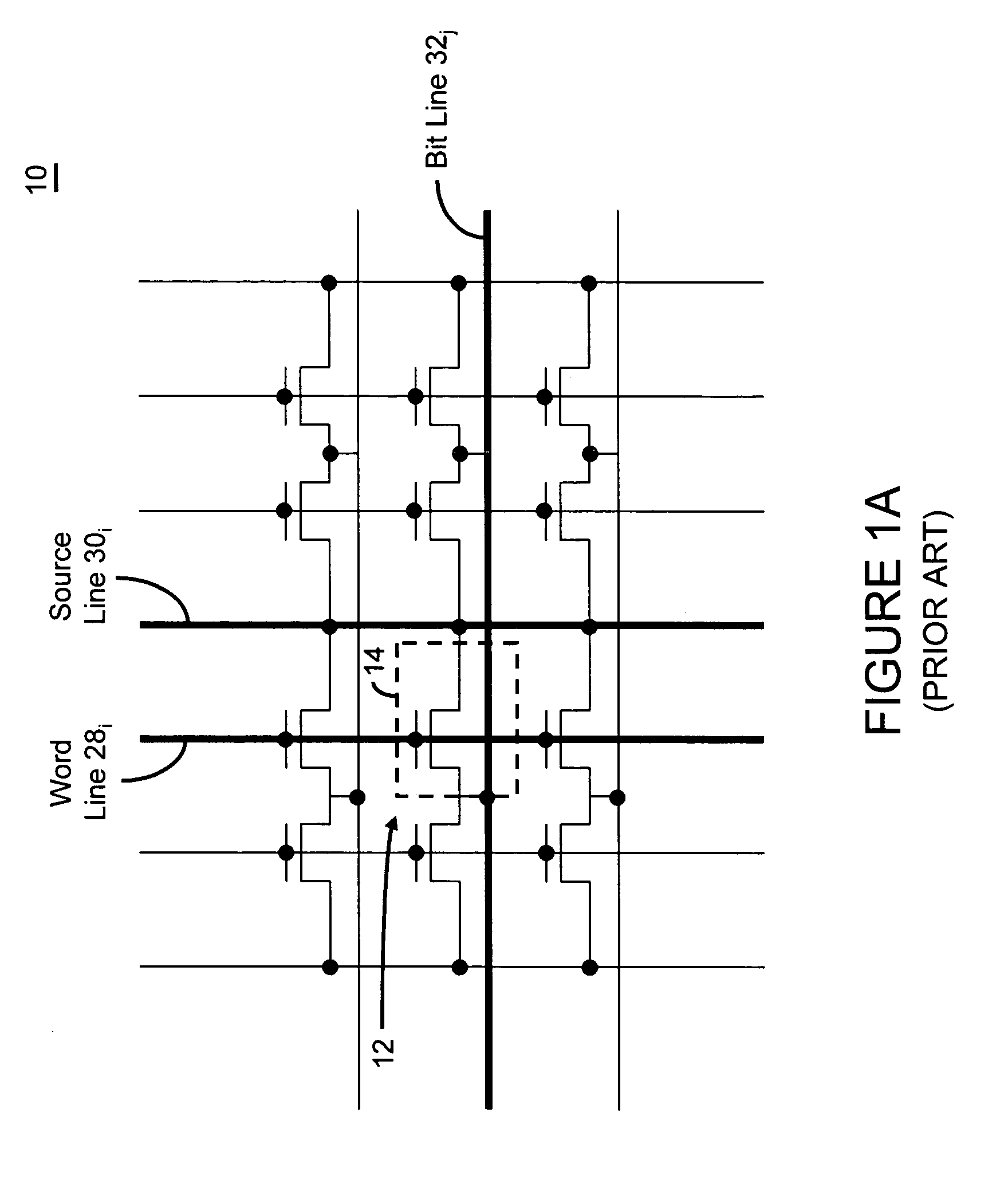

Memory array organization and related test method particularly well suited for integrated circuits having write-once memory arrays

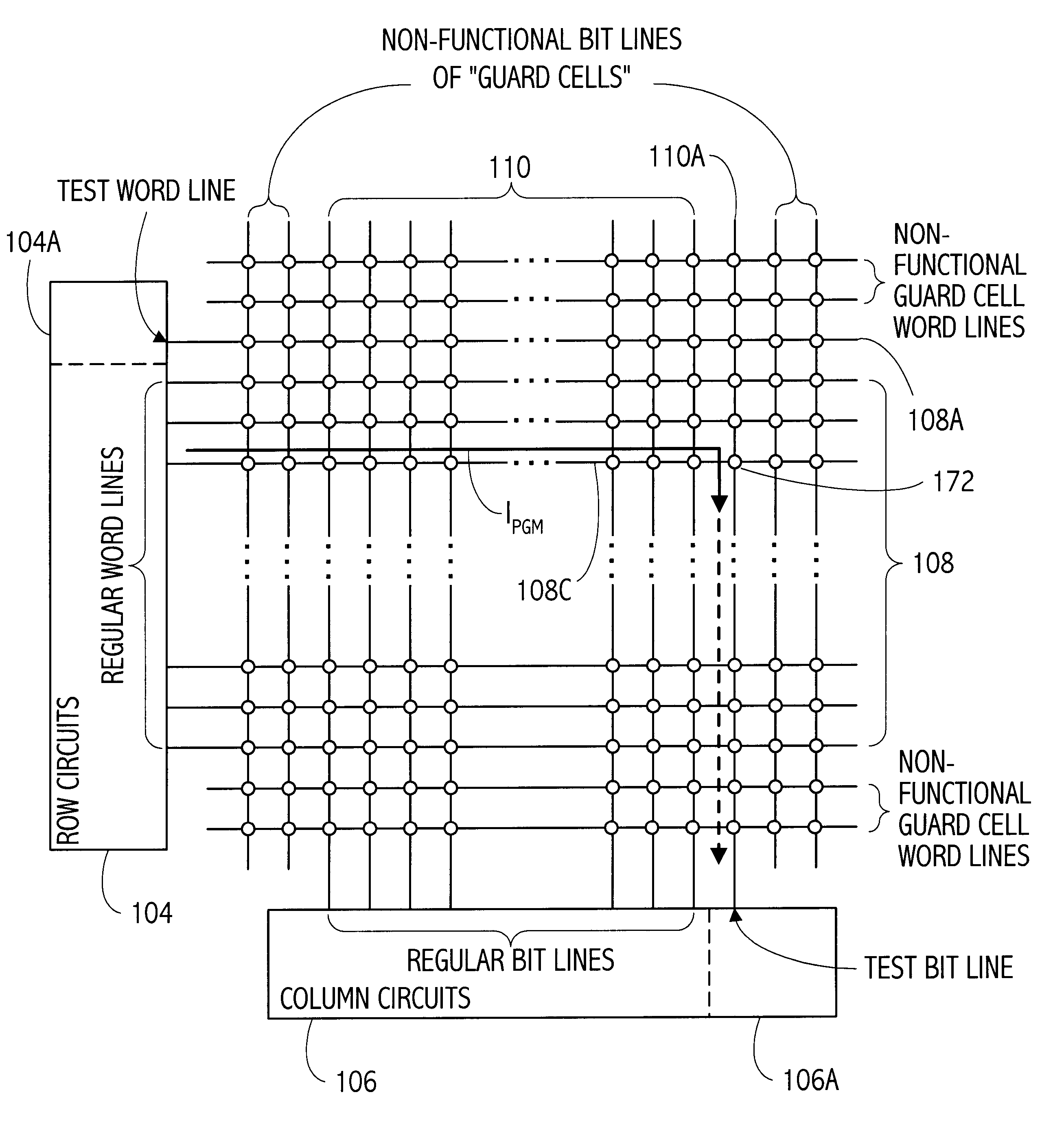

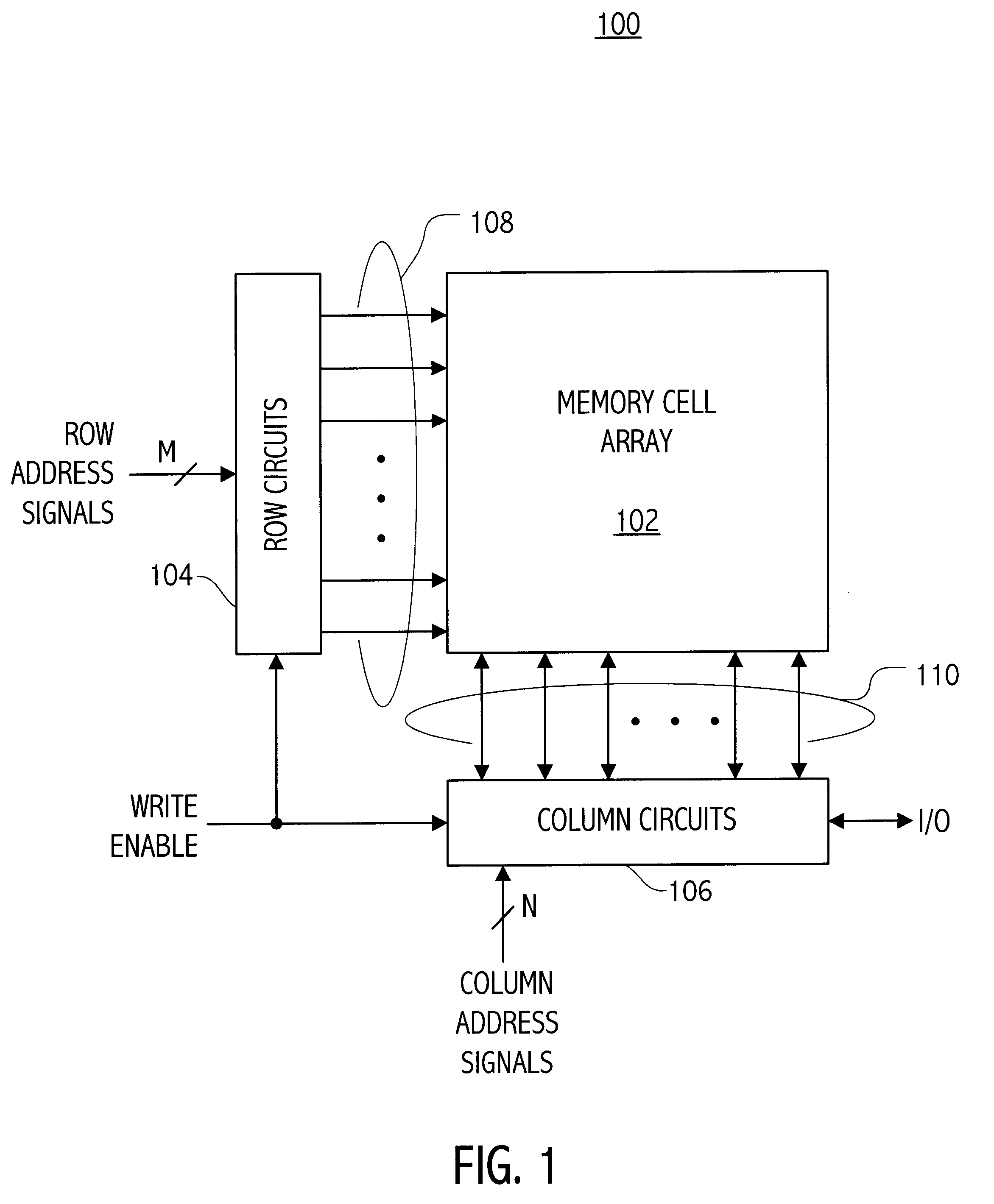

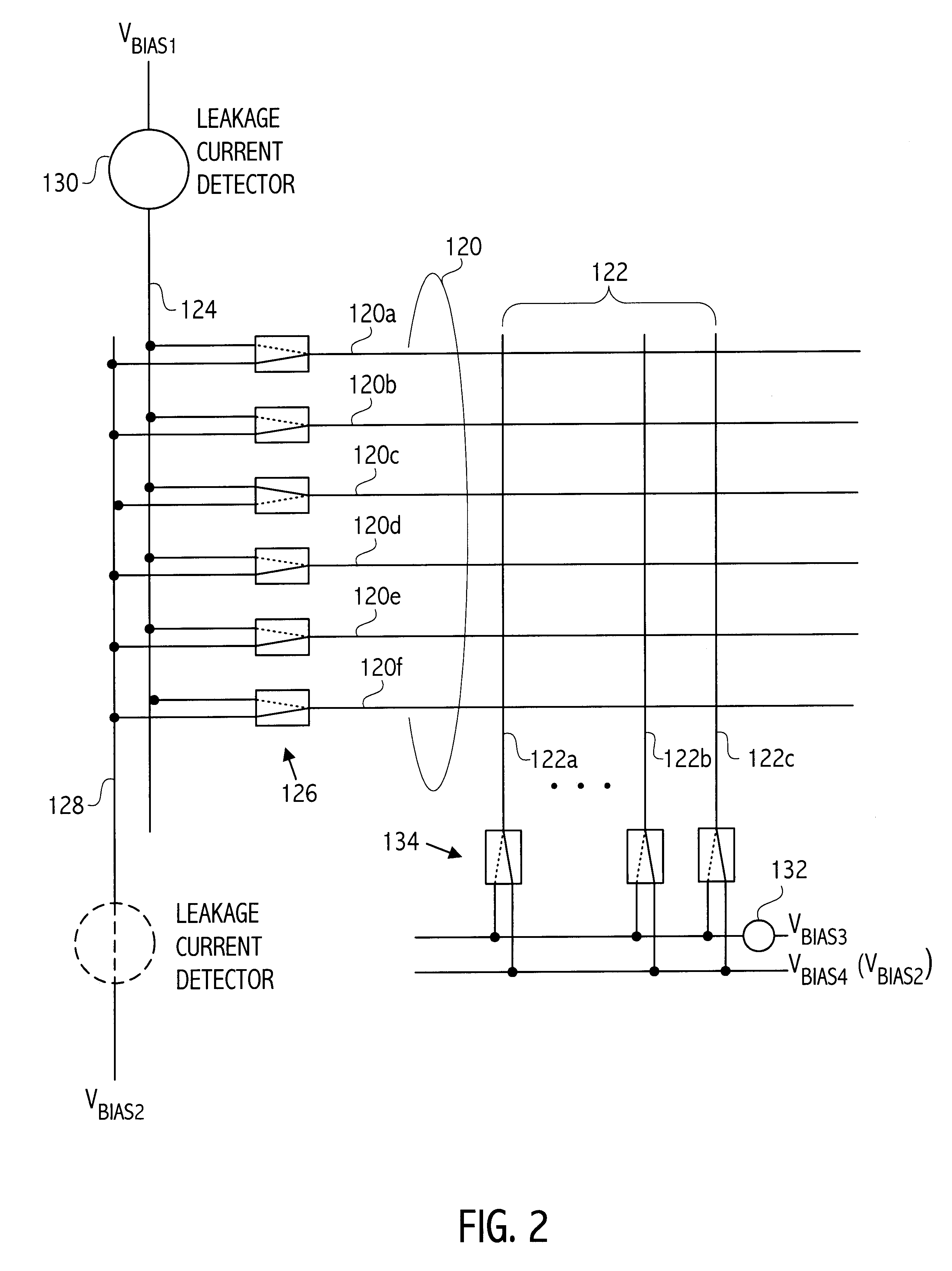

In a preferred integrated circuit embodiment, a write-once memory array includes at least one test bit line which provides a respective test memory cell at the far end of each respective word line relative to its word line driver, and further includes at least one test word line which provides a respective test memory cell at the far end of each respective bit line relative to its bit line driver. An intra-layer short between word lines may be detected, such as during manufacturing testing, by biasing adjacent word lines to different voltages and detecting whether any leakage current flowing from one to another exceeds that normally accounted for by the memory cells and other known circuits. Intra-layer bit line shorts and inter-layer word line and bit line shorts may also be similarly detected. An "open" in a word line or bit line may be detected by trying to program the test memory cell at the far end of each such word line or bit line. If successfully programmed, the continuity of each word line and bit line is assured, and the programming circuitry for each word line and bit line is also known to be functional.

Owner:SANDISK TECH LLC

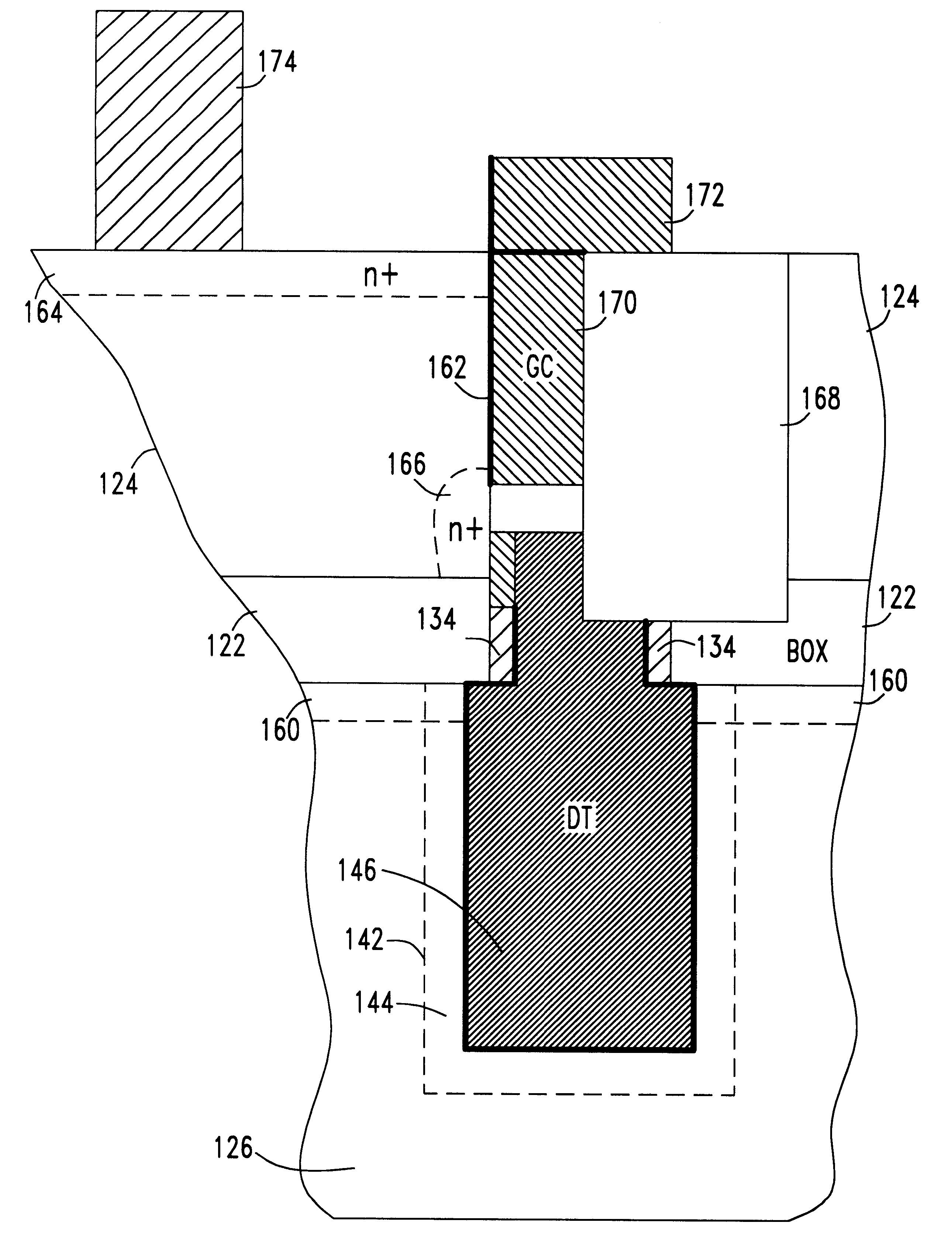

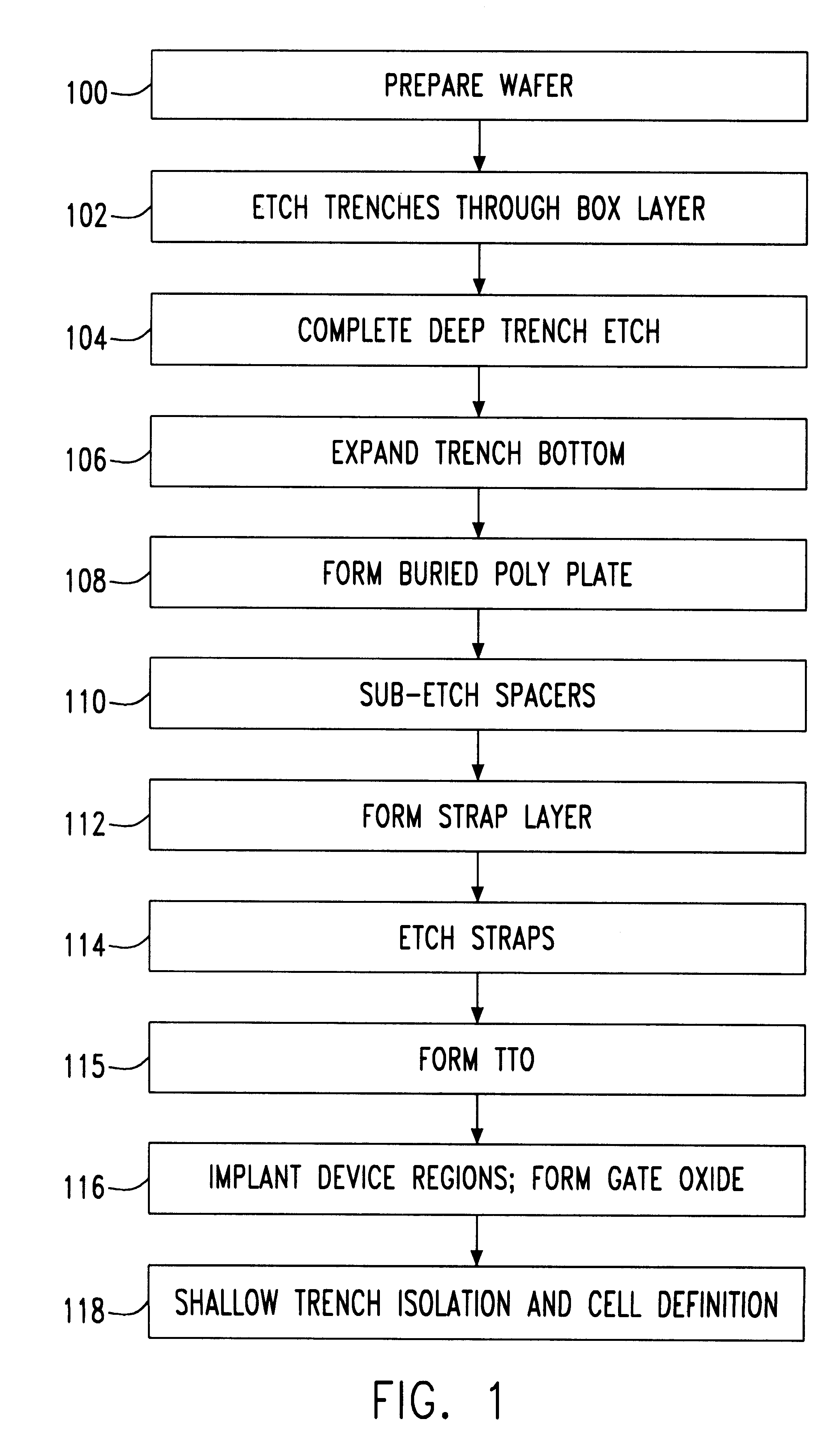

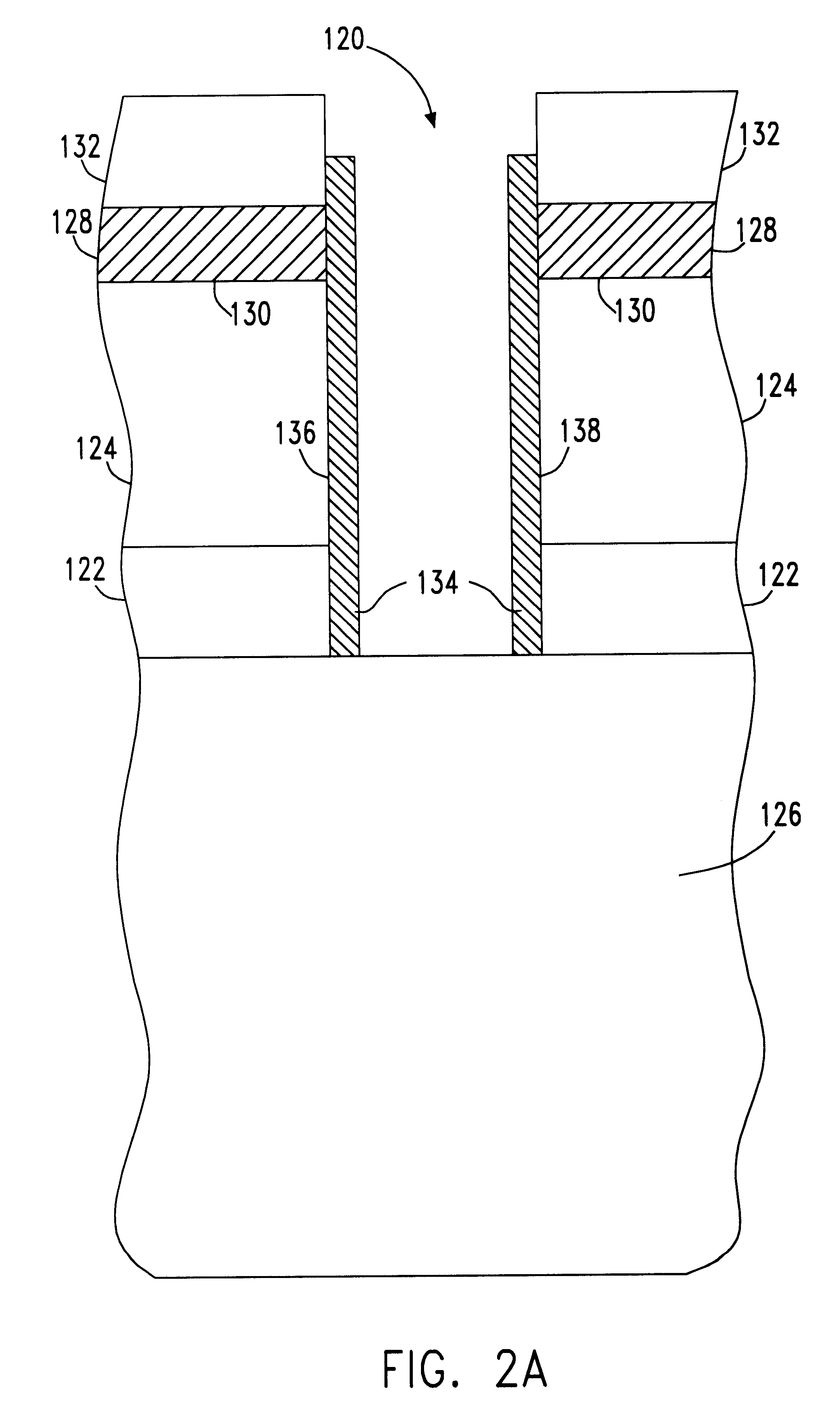

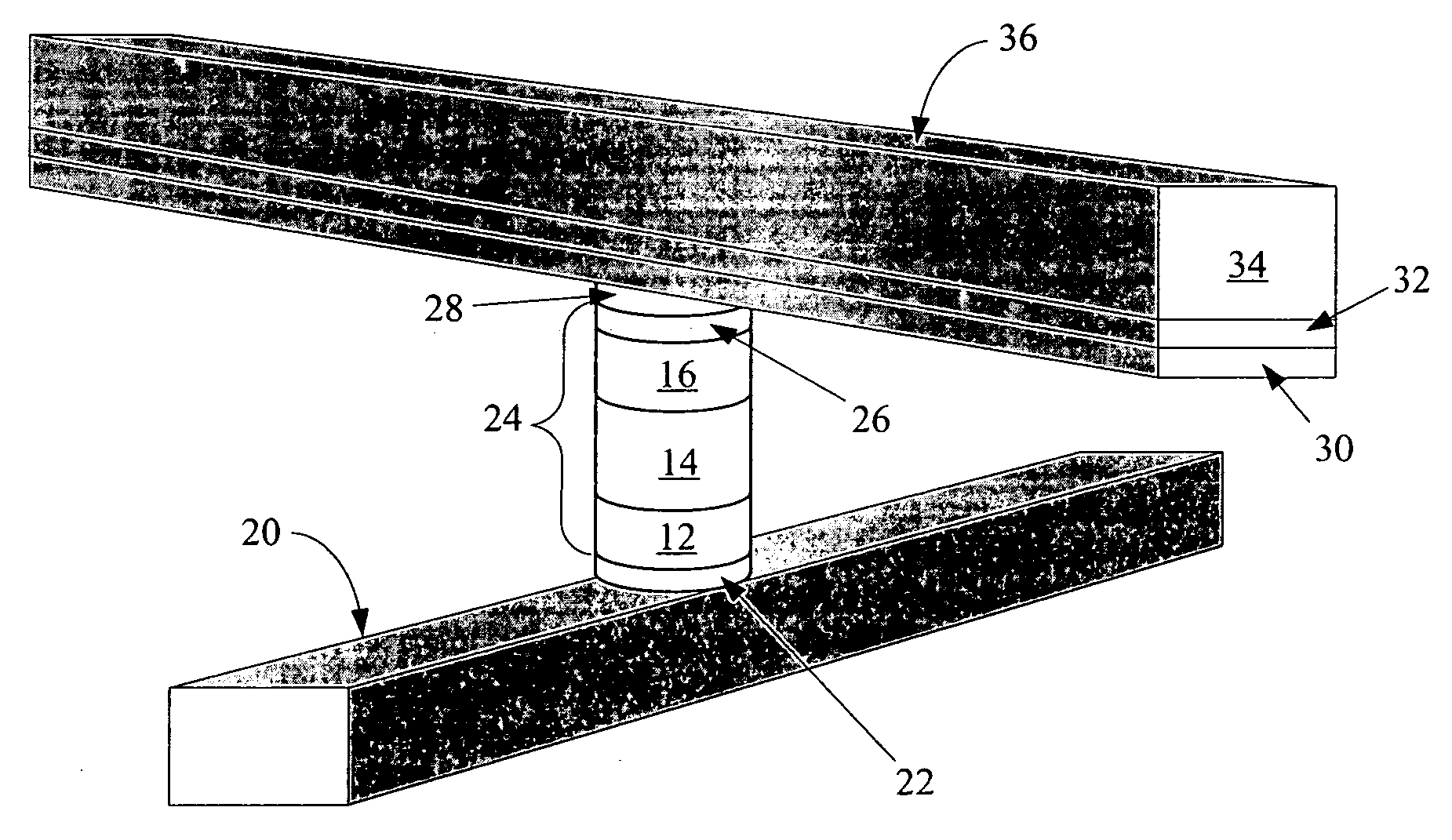

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

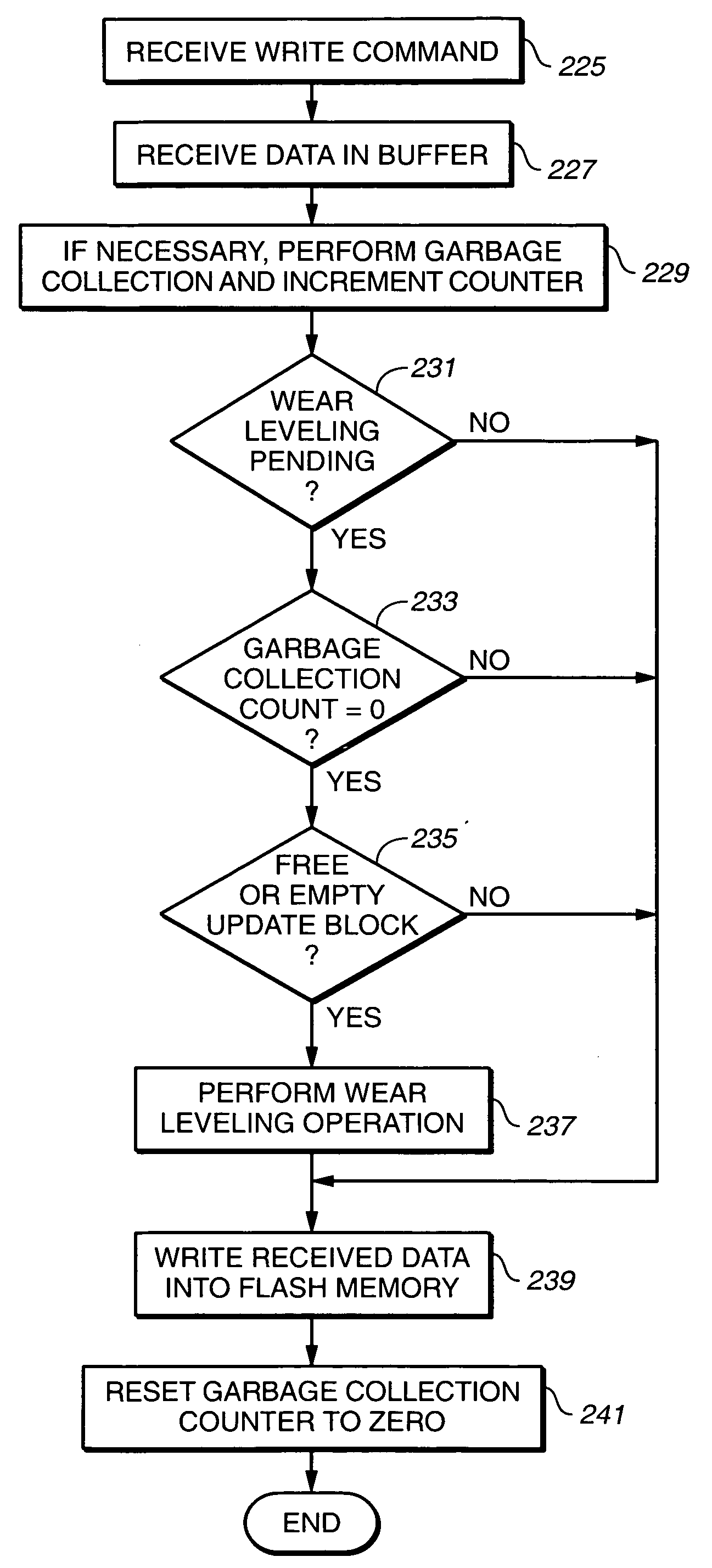

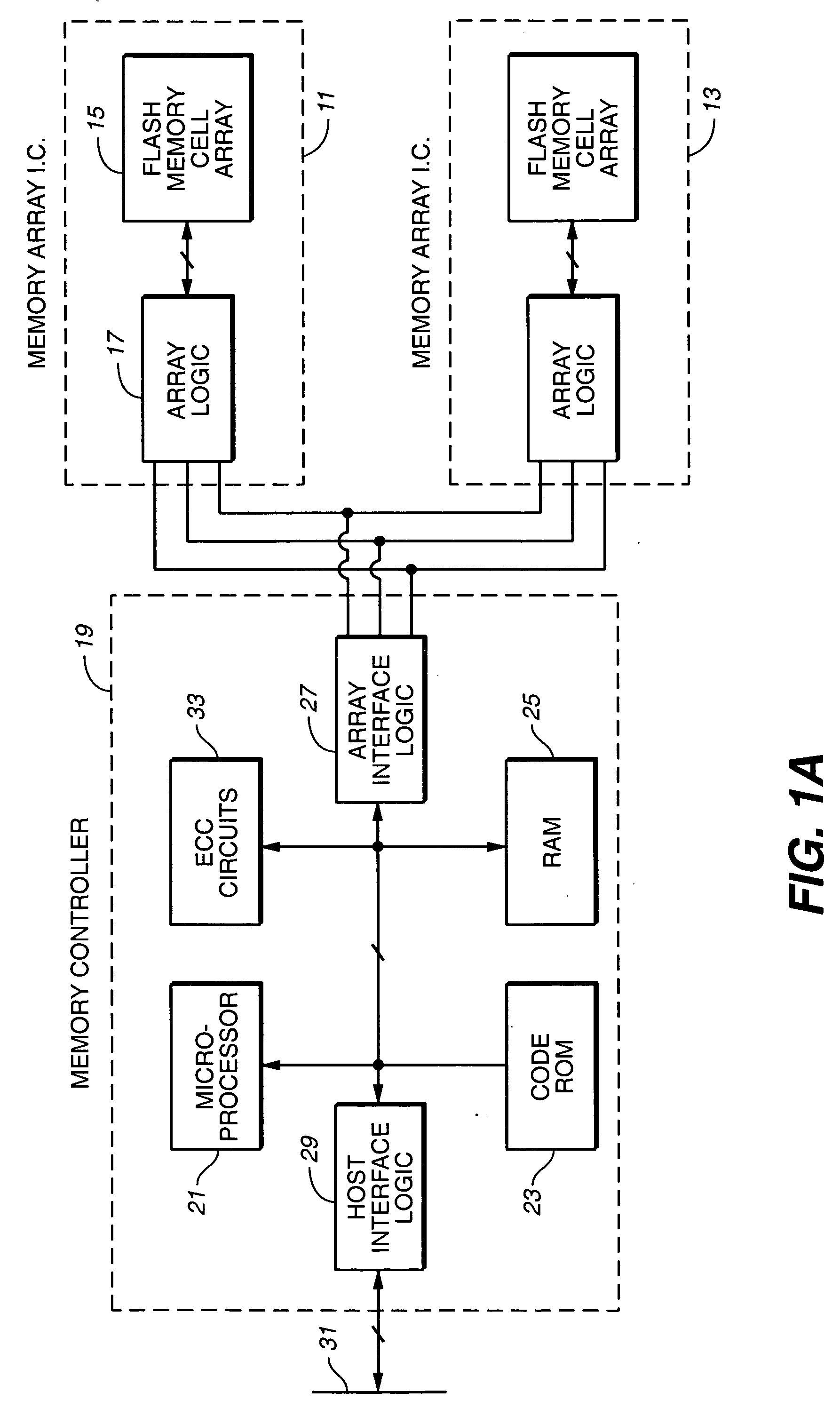

Scheduling of housekeeping operations in flash memory systems

ActiveUS20060161728A1Good performanceMemory architecture accessing/allocationRead-only memoriesEEPROMHousekeeping

A re-programmable non-volatile memory system, such as a flash EEPROM system, having its memory cells grouped into blocks of cells that are simultaneously erasable is operated to perform memory system housekeeping operations in the foreground during execution of a host command, wherein the housekeeping operations are unrelated to execution of the host command. Both one or more such housekeeping operations and execution of the host command are performed within a time budget established for executing that particular command. One such command is to write data being received to the memory. One such housekeeping operation is to level out the wear of the individual blocks that accumulates through repetitive erasing and re-programming.

Owner:SANDISK TECH LLC

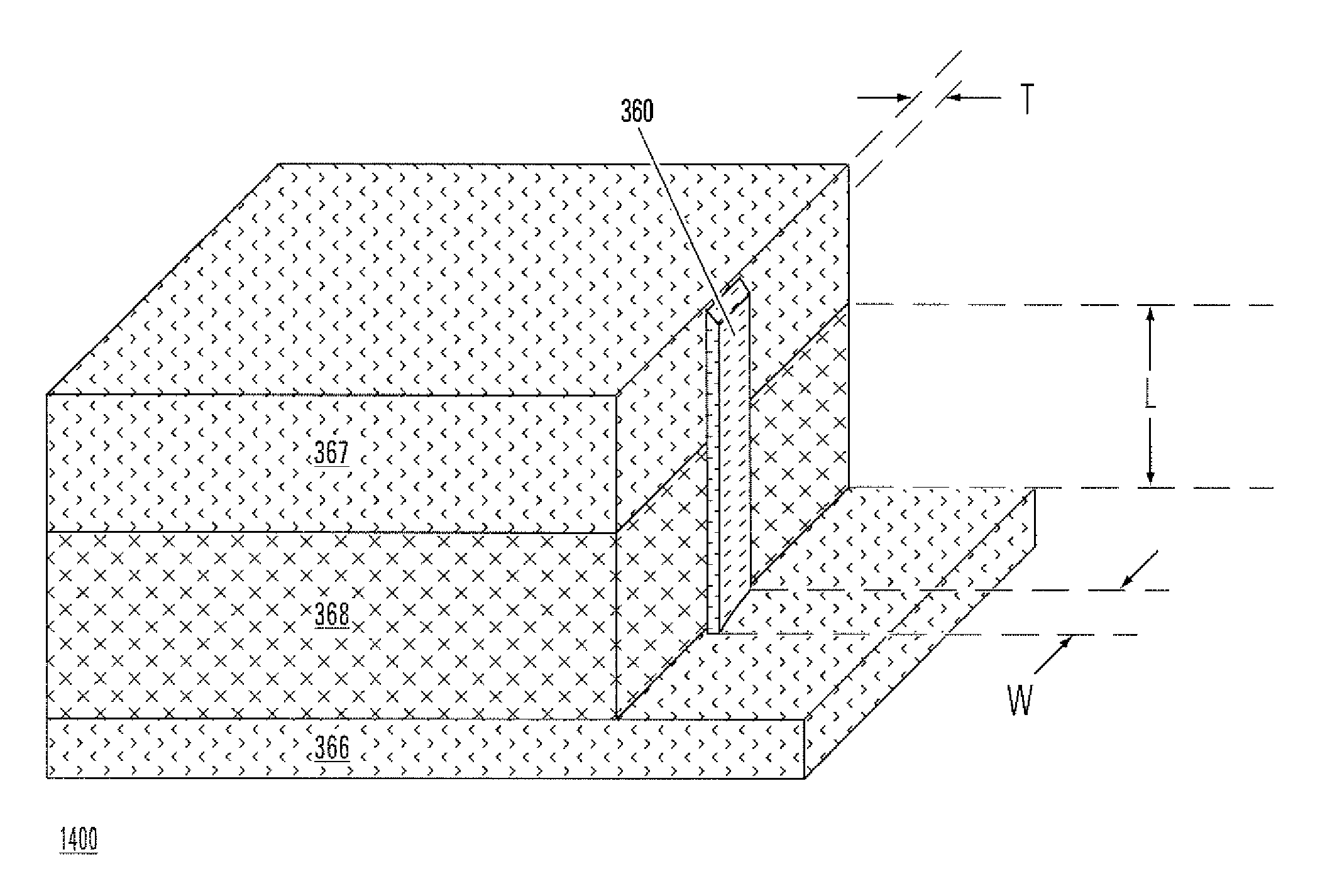

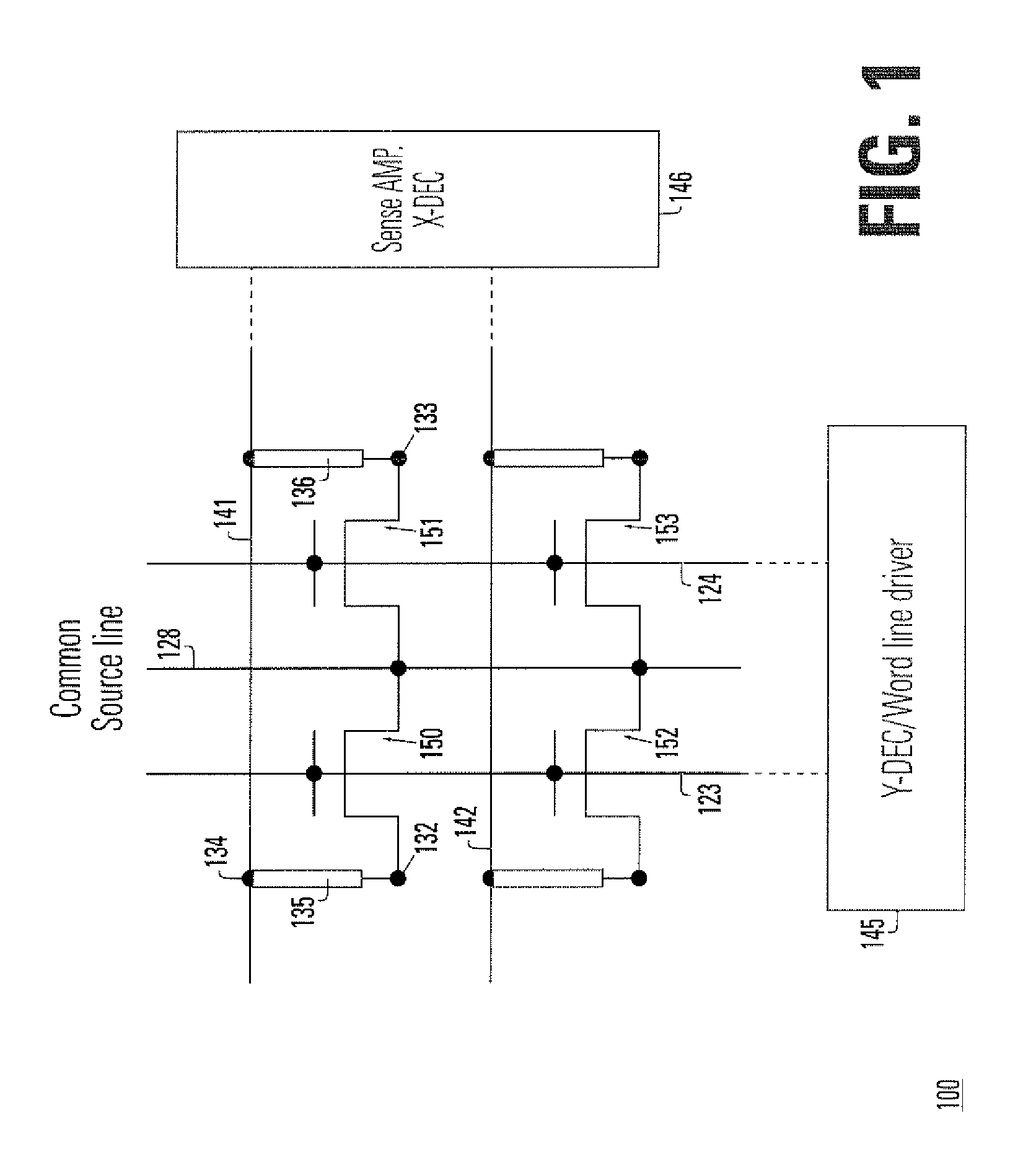

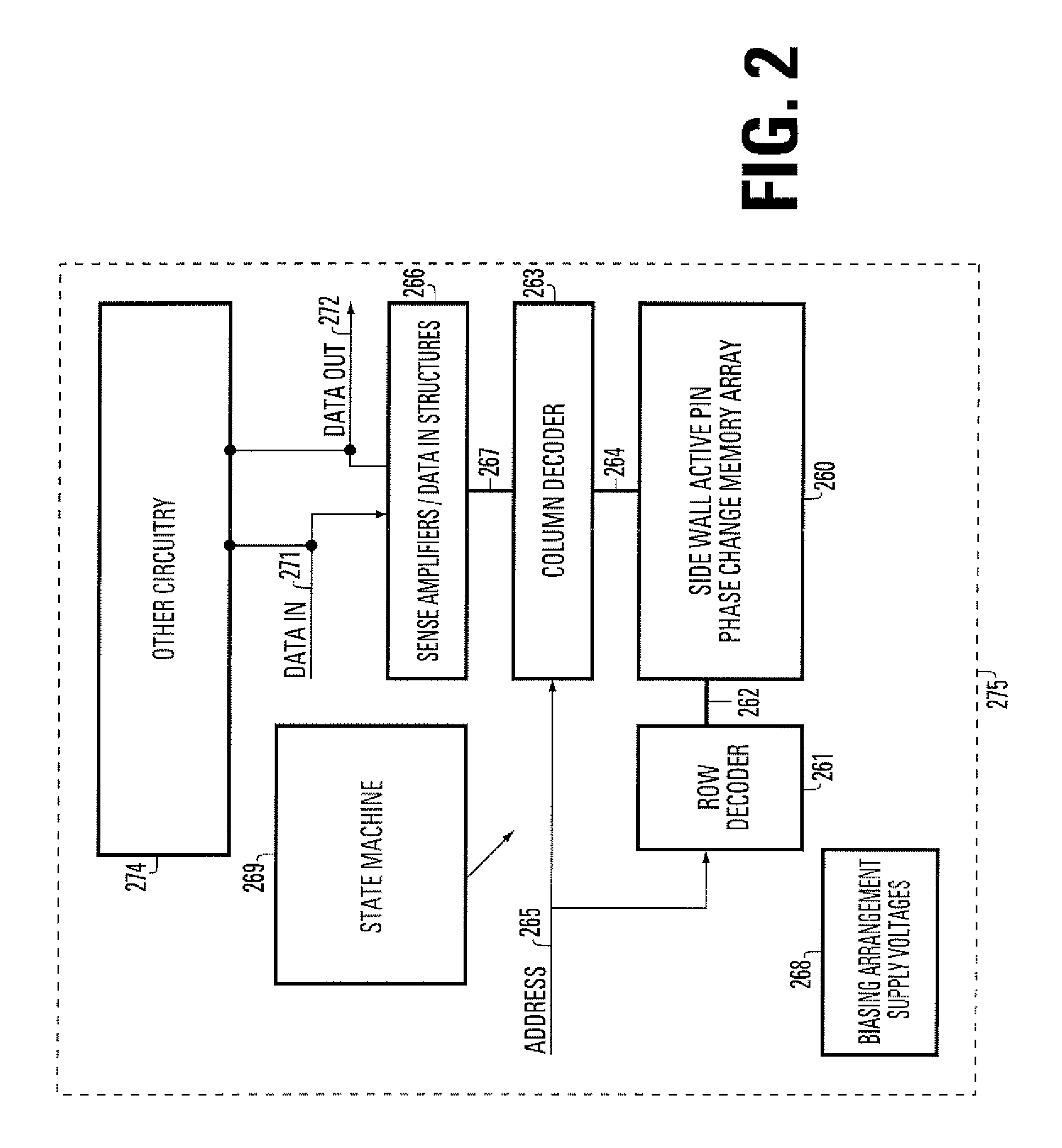

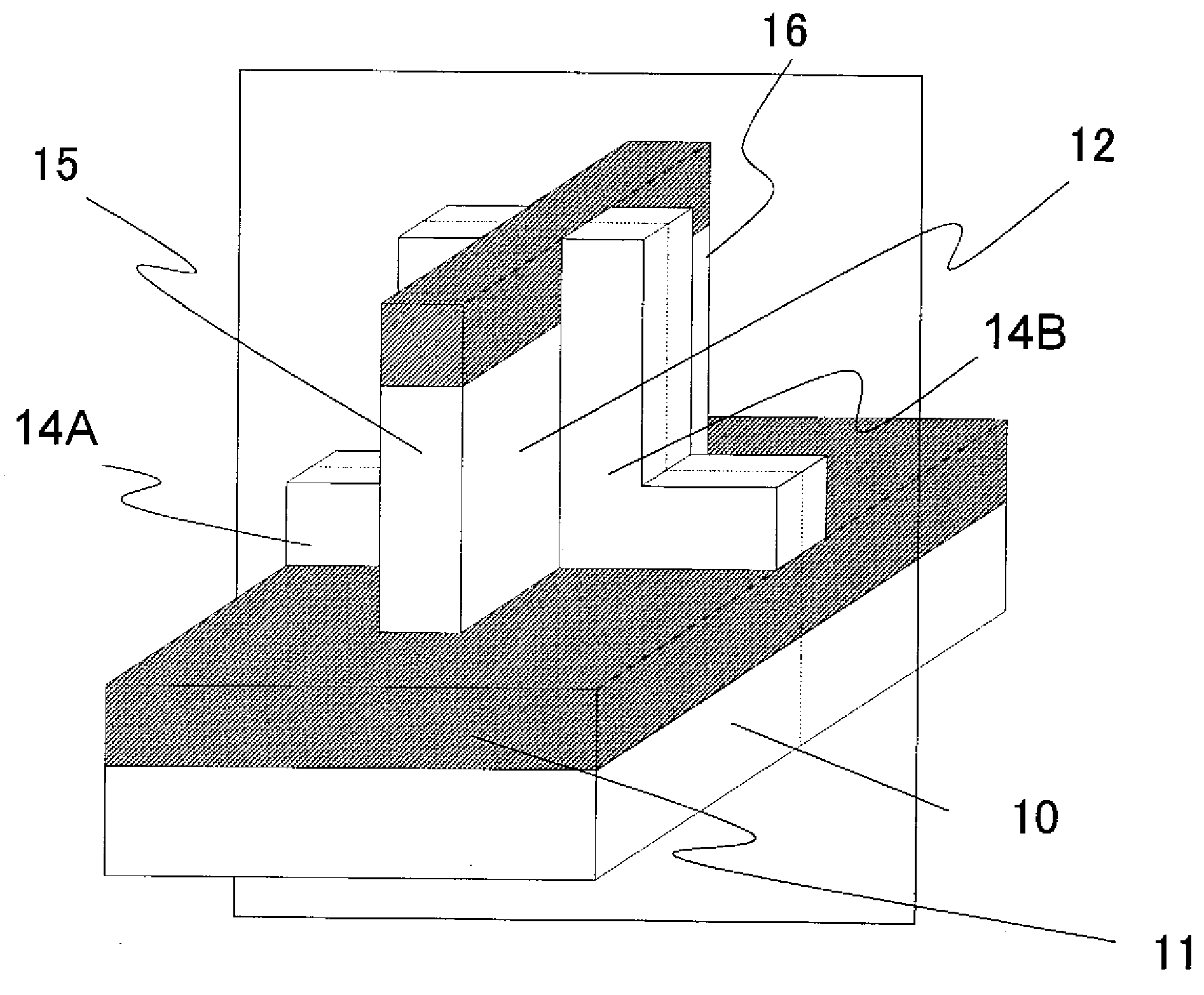

Vertical Side Wall Active Pin Structures in a Phase Change Memory and Manufacturing Methods

ActiveUS20070176261A1Reduce electrical currentLow resistivitySolid-state devicesSemiconductor devicesEngineeringPhase-change material

A programmable resistor memory, such as a phase change memory, with a memory element comprising narrow vertical side wall active pins is described. The side wall active pins comprise a programmable resistive material, such as a phase change material. In a first aspect of the invention, a method of forming a memory cell is described which comprises forming a stack comprising a first electrode having a principal surface with a perimeter, an insulating layer overlying a portion of the principal surface of the first electrode, and a second electrode vertically separated from the first electrode and overlying the insulating layer. Side walls on the insulating layer and on the second electrode are positioned over the principle surface of the first electrode with a lateral offset from the perimeter of the first electrode.

Owner:MACRONIX INT CO LTD

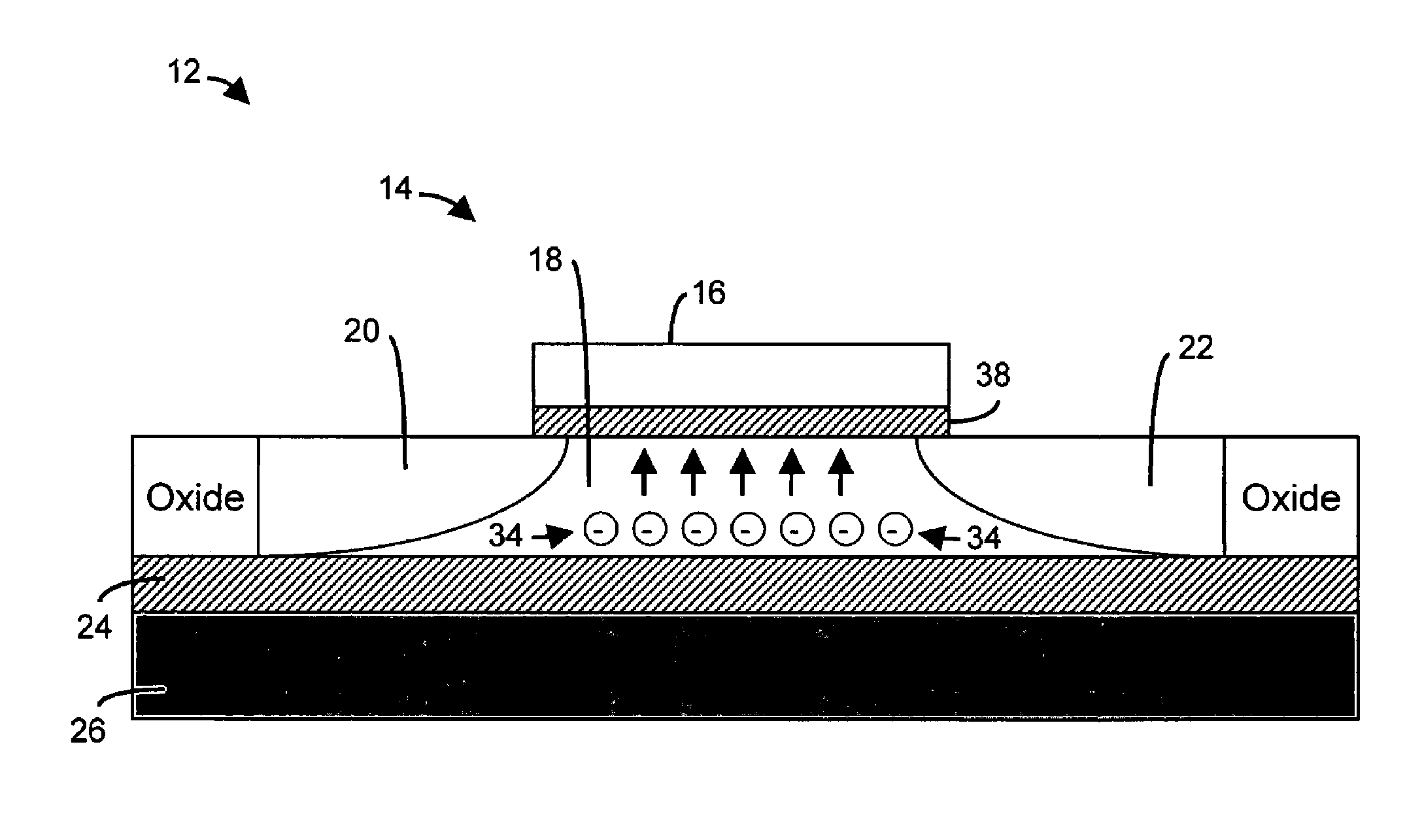

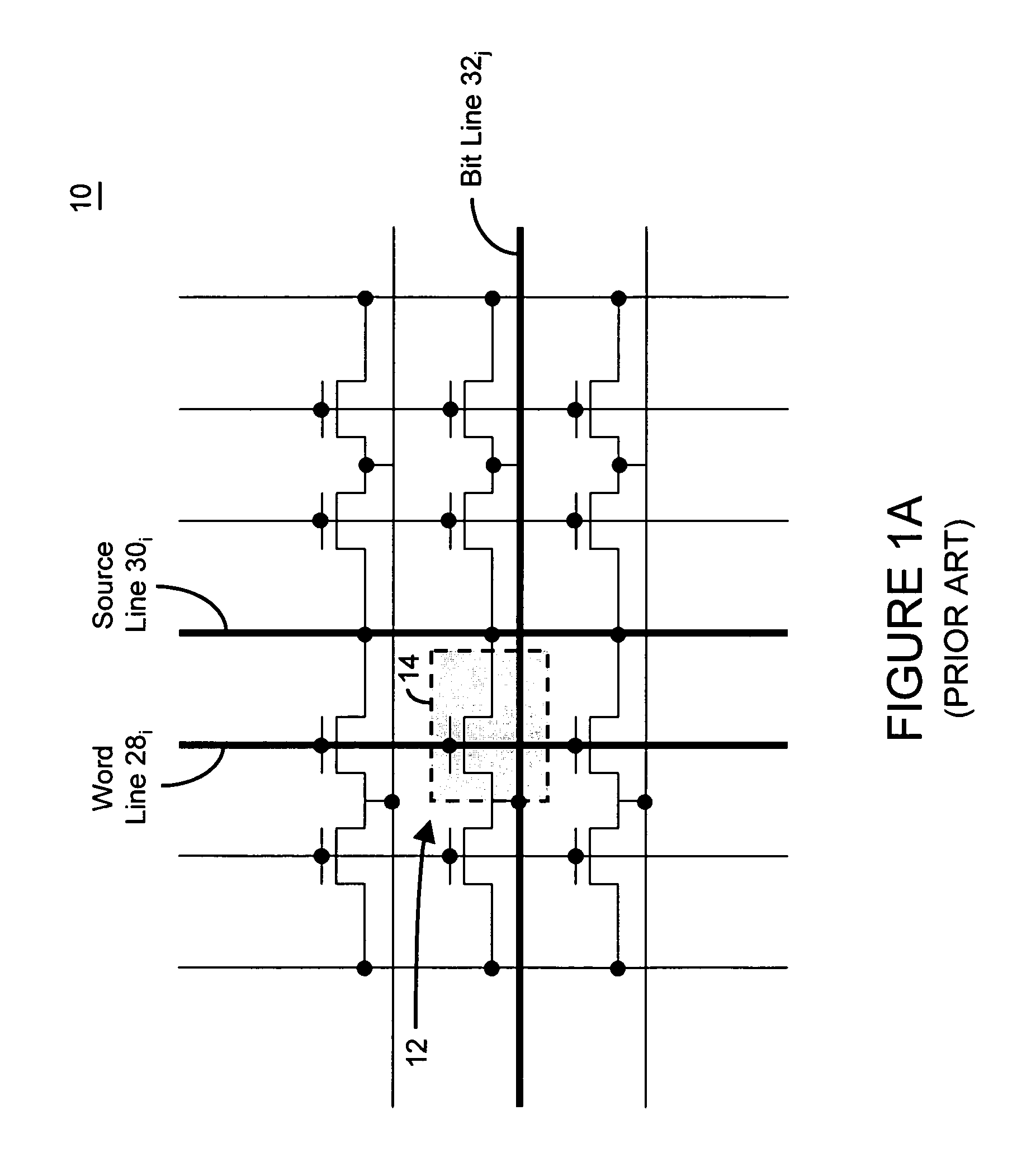

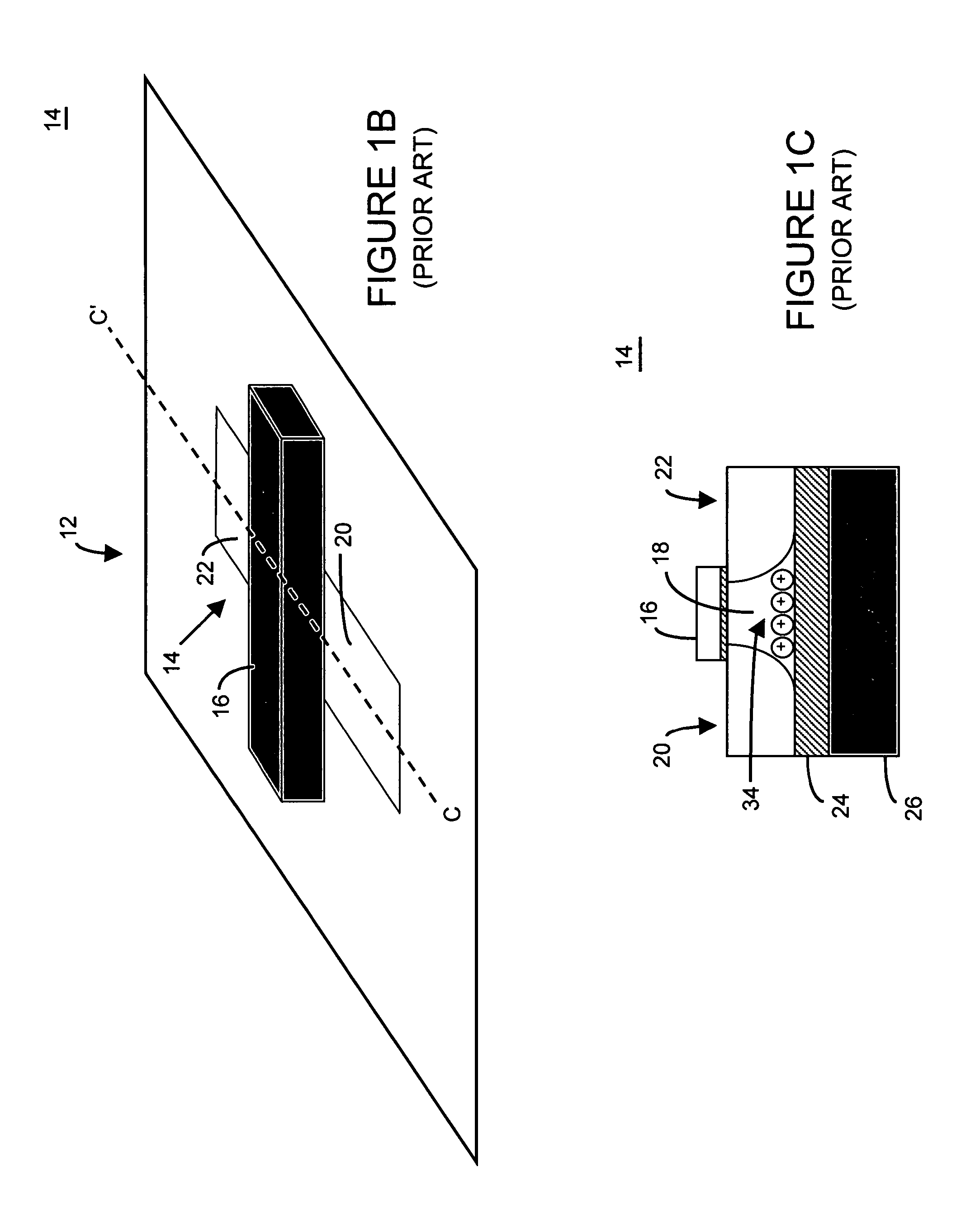

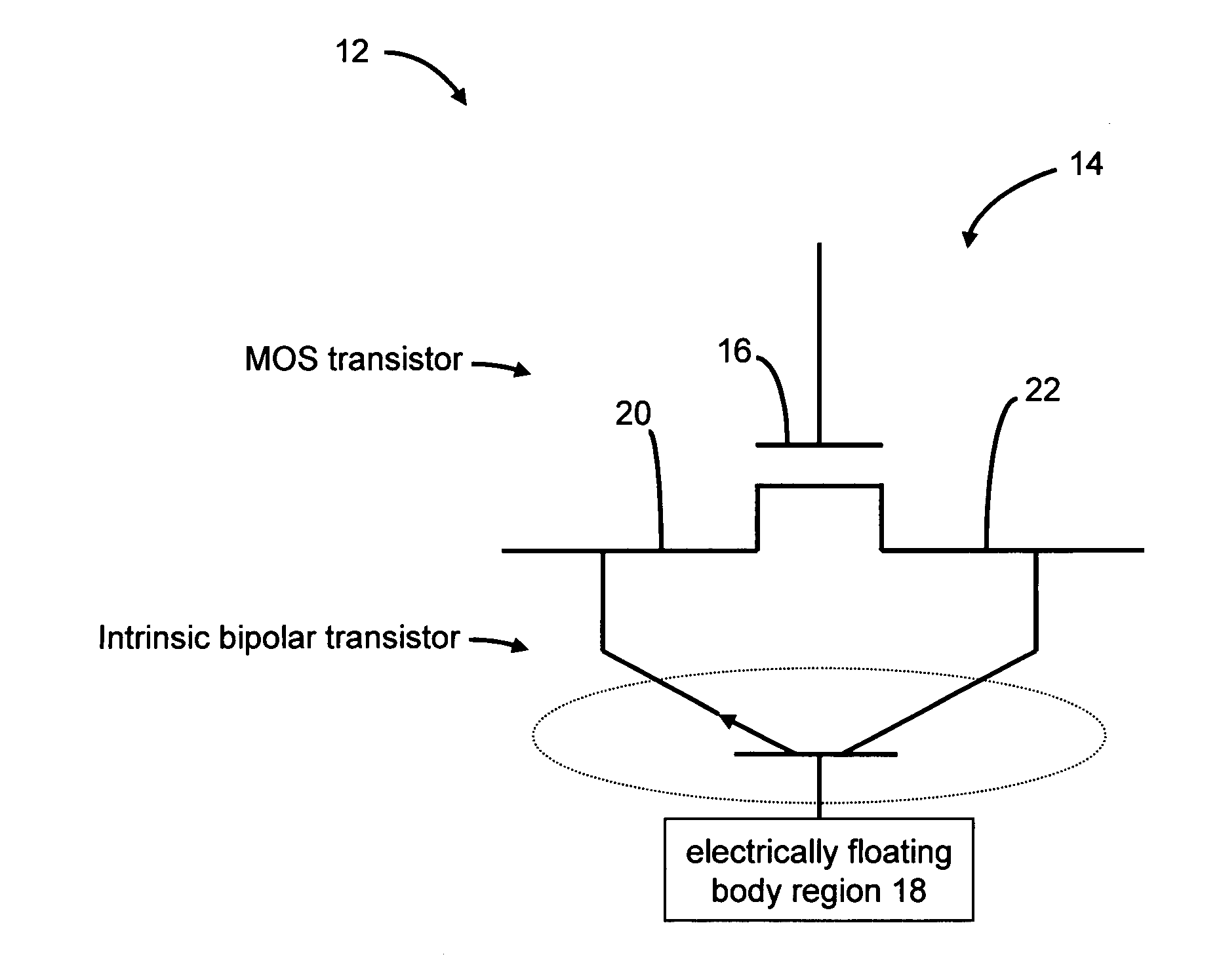

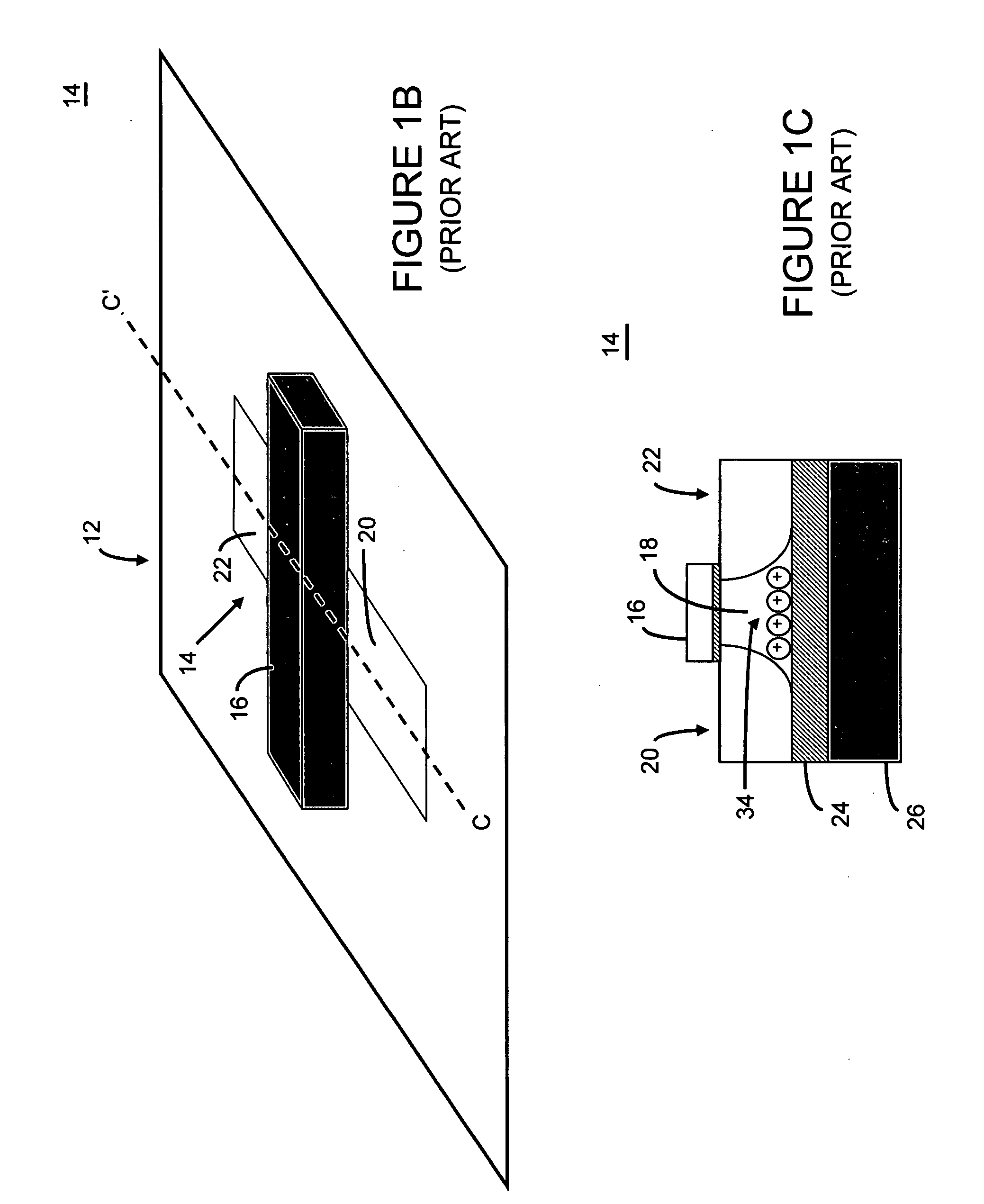

Memory cell having an electrically floating body transistor and programming technique therefor

A memory cell comprising an electrically floating body transistor including a source region, a drain region, a body region disposed therebetween, wherein the body region is electrically floating, and a gate disposed over the body region and separated therefrom by a gate dielectric. The memory cell includes a first data state representative of a first charge in the body region and a second data state representative of a second charge in the body region wherein the second charge is substantially provided by removing carriers from the body region through the gate. Thus, a memory cell may be programmed to a logic low by, for example, causing, forcing and / or inducing carriers in the floating body of the transistor to tunnel through or traverse the gate dielectric to the gate of the electrically floating body transistor (and, in many array configurations, the word line of a memory cell array).

Owner:MICRON TECH INC

Non-volatile memory cell comprising a dielectric layer and a phase change material in series

The invention provides for a nonvolatile memory cell comprising a dielectric material in series with a phase change material, such as a chalcogenide. Phase change is achieved in chalcogenide memories by thermal means. Concentrating thermal energy in a relatively small volume assists this phase change. By applying high voltage across a dielectric layer, dielectric breakdown occurs, forming a low-resistance rupture region traversing the dielectric layer. This rupture region can serve to concentrate thermal energy in a phase-change memory cell. In a preferred embodiment, such a cell can be used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

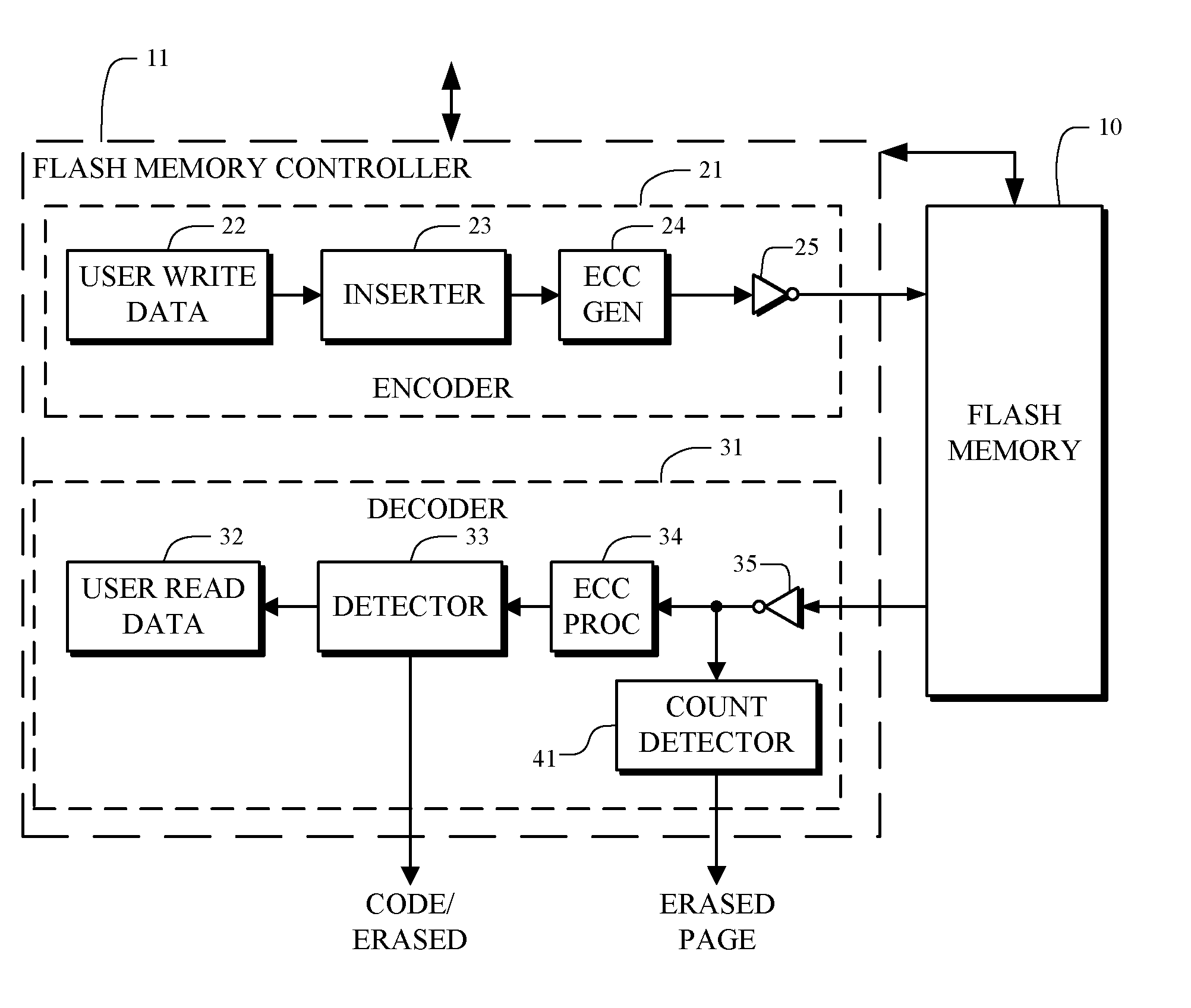

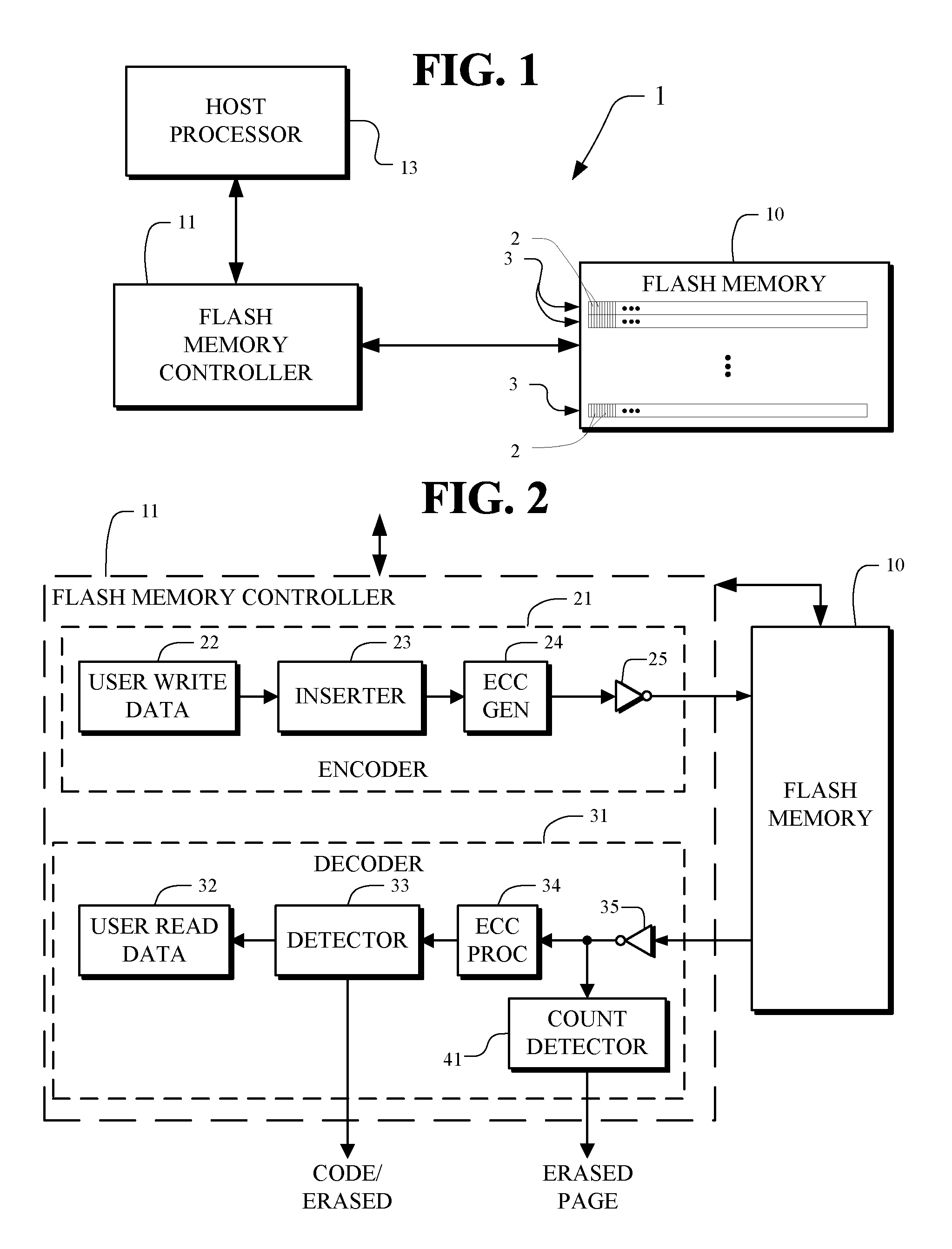

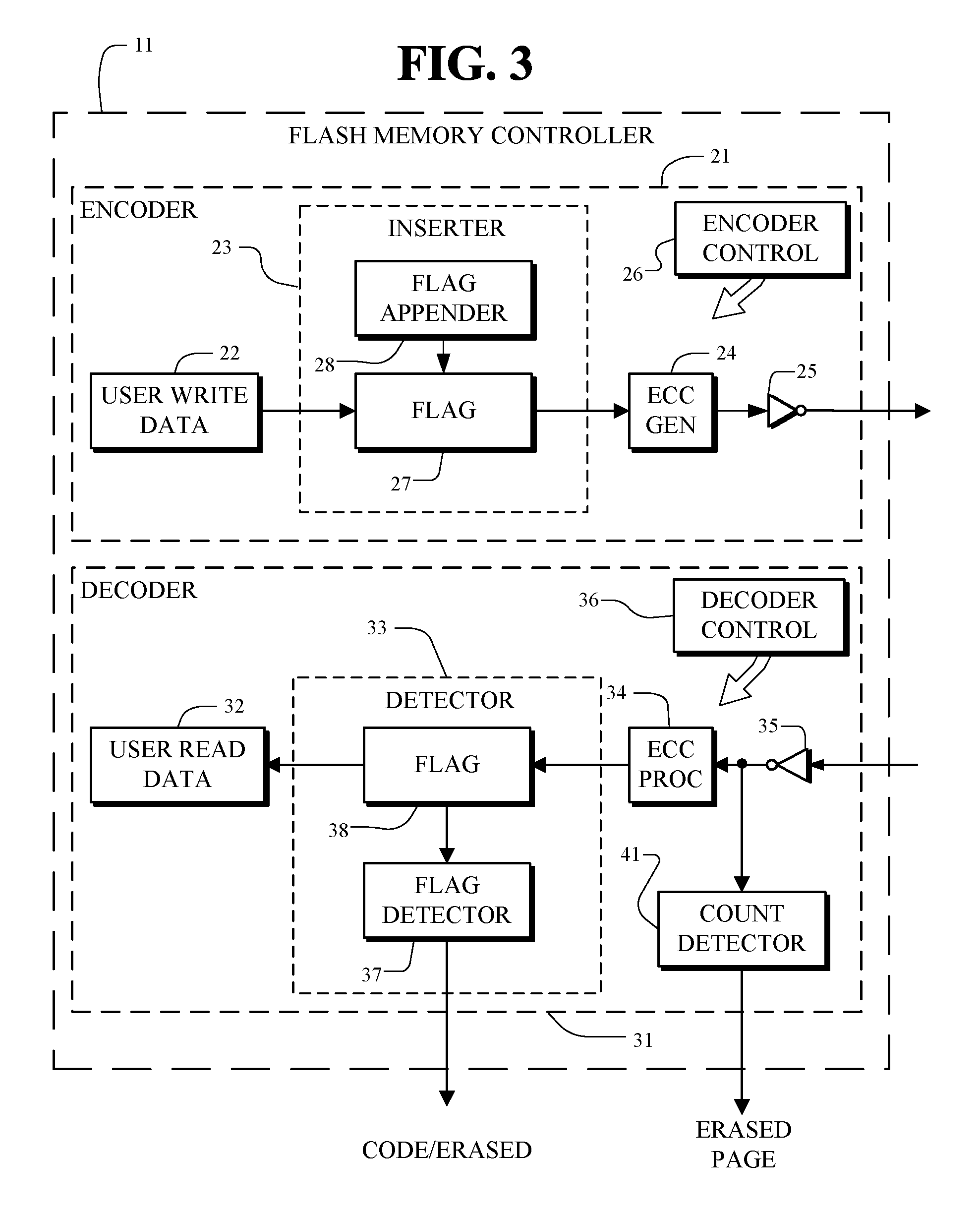

Erased page detection

A memory device and method, such as a flash memory device and method, includes a memory having a plurality of nonvolatile memory cells for storing stored values of user data. The memory device and method includes a memory controller for controlling the memory. The memory controller includes an encoder for encoding user write data for storage of code values as the stored values in the memory. The encoder includes an inserter for insertion of an indicator as part of the stored values for use in determining when the stored values are or are not in an erased state. The memory controller includes a decoder for reading the stored values from the memory to form user read data values when the stored values are not in the erased state.

Owner:MARVELL ASIA PTE LTD

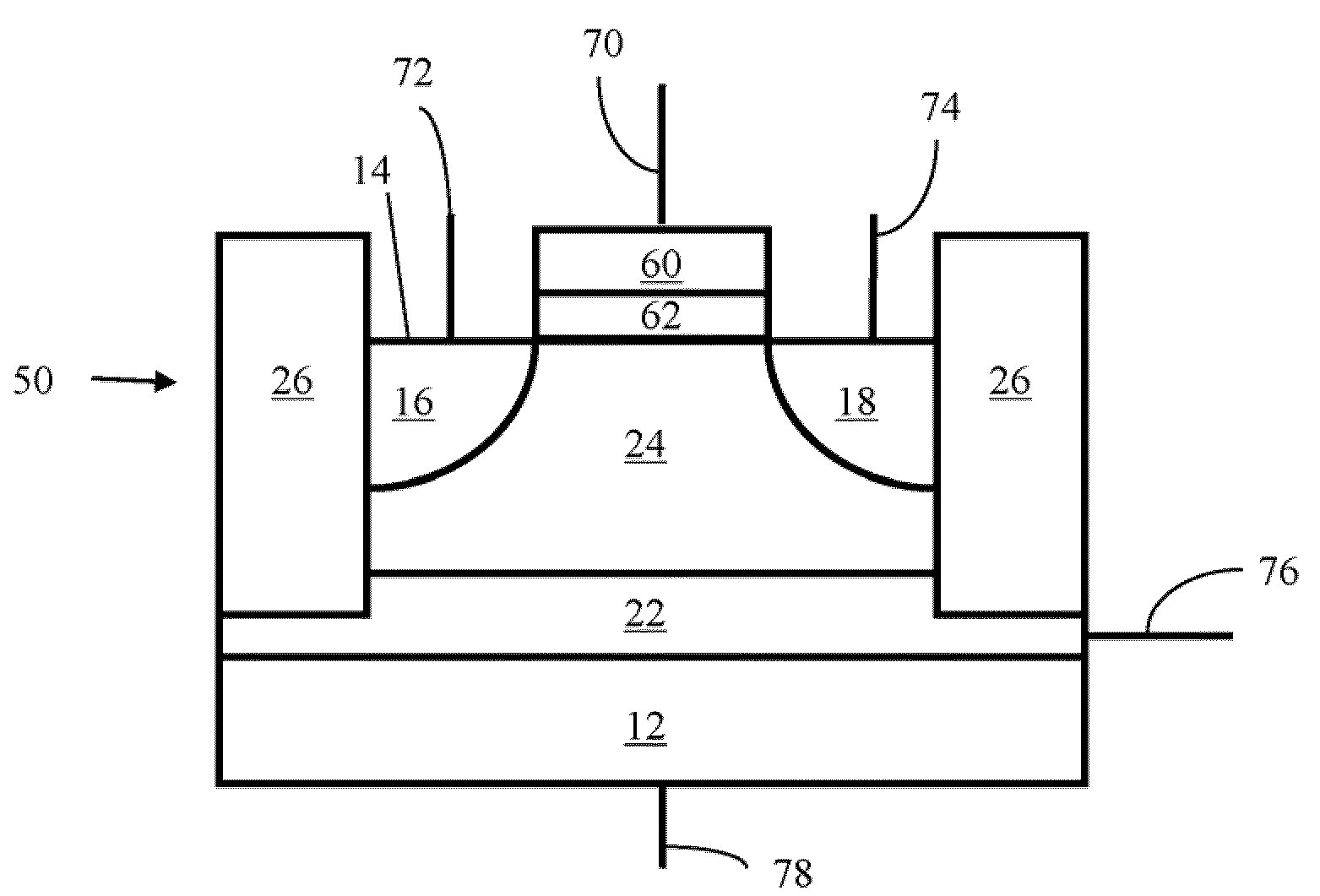

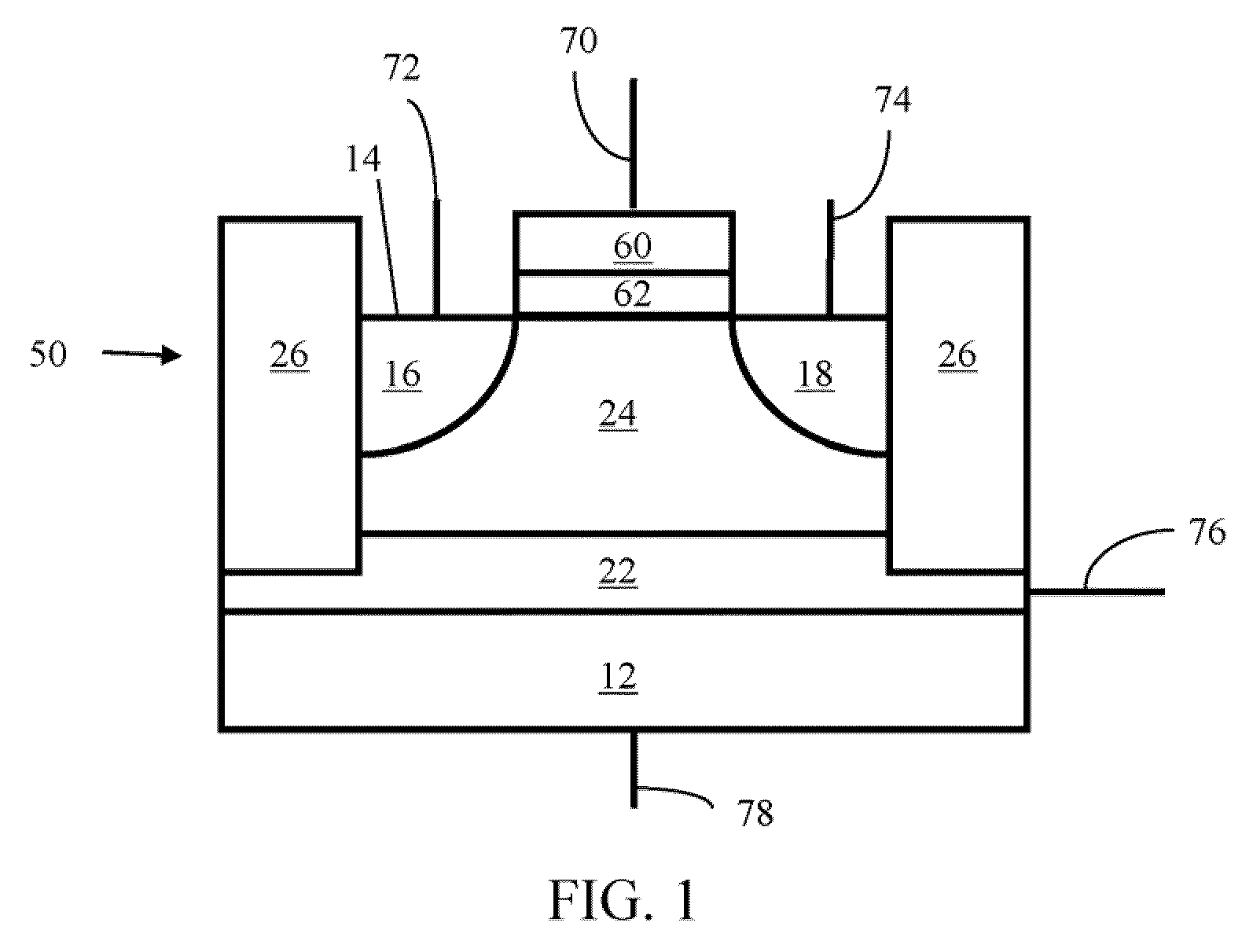

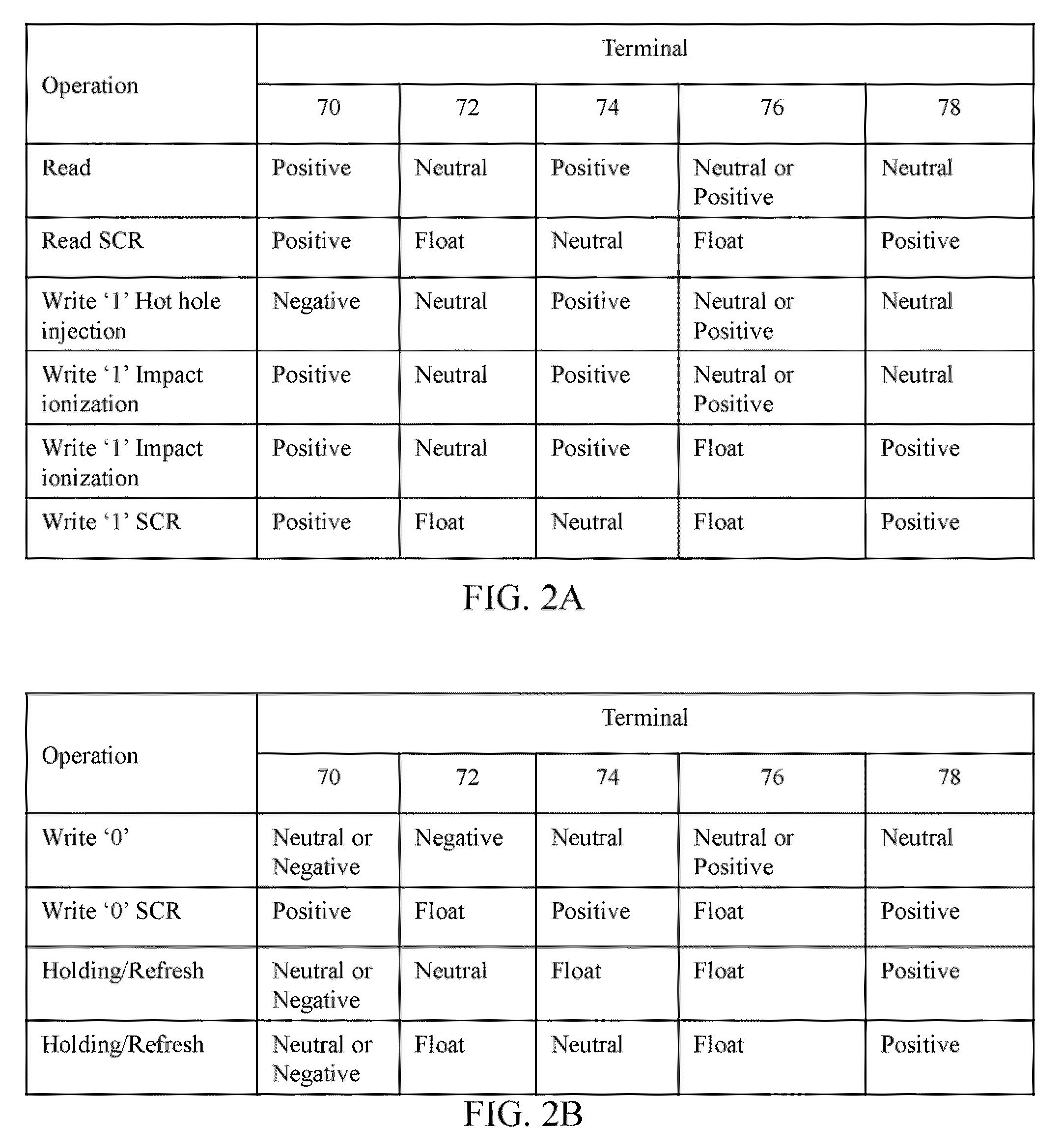

Method of operating semiconductor memory device with floating body transistor using silicon controlled rectifier principle

Methods of operating semiconductor memory devices with floating body transistors, using a silicon controlled rectifier principle are provided, as are semiconductor memory devices for performing such operations. A method of maintaining the data state of a semiconductor dynamic random access memory cell is provided, wherein the memory cell comprises a substrate being made of a material having a first conductivity type selected from p-type conductivity type and n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type; a second region having the second conductivity type, the second region being spaced apart from the first region; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; and a gate positioned between the first and second regions and adjacent the body region. The memory cell is configured to store a first data state which corresponds to a first charge in the body region in a first configuration, and a second data state which corresponds to a second charge in the body region in a second configuration. The method includes: providing the memory cell storing one of the first and second data states; and applying a positive voltage to a substrate terminal connected to the substrate beneath the buried layer, wherein when the body region is in the first state, the body region turns on a silicon controlled rectifier device of the cell and current flows through the device to maintain configuration of the memory cell in the first memory state, and wherein when the memory cell is in the second state, the body region does not turn on the silicon controlled rectifier device, current does not flow, and a blocking operation results, causing the body to maintain the second memory state.

Owner:ZENO SEMICON

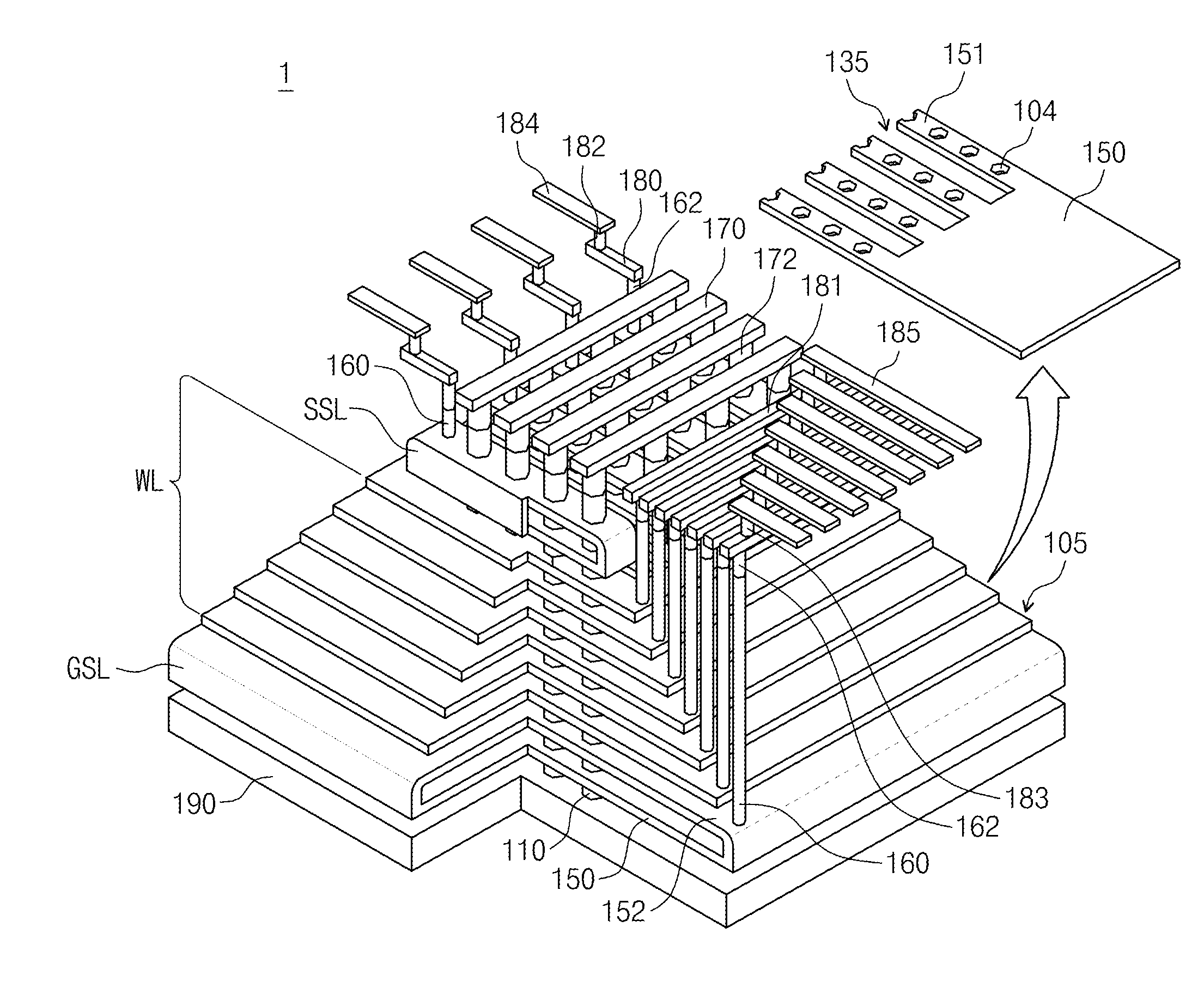

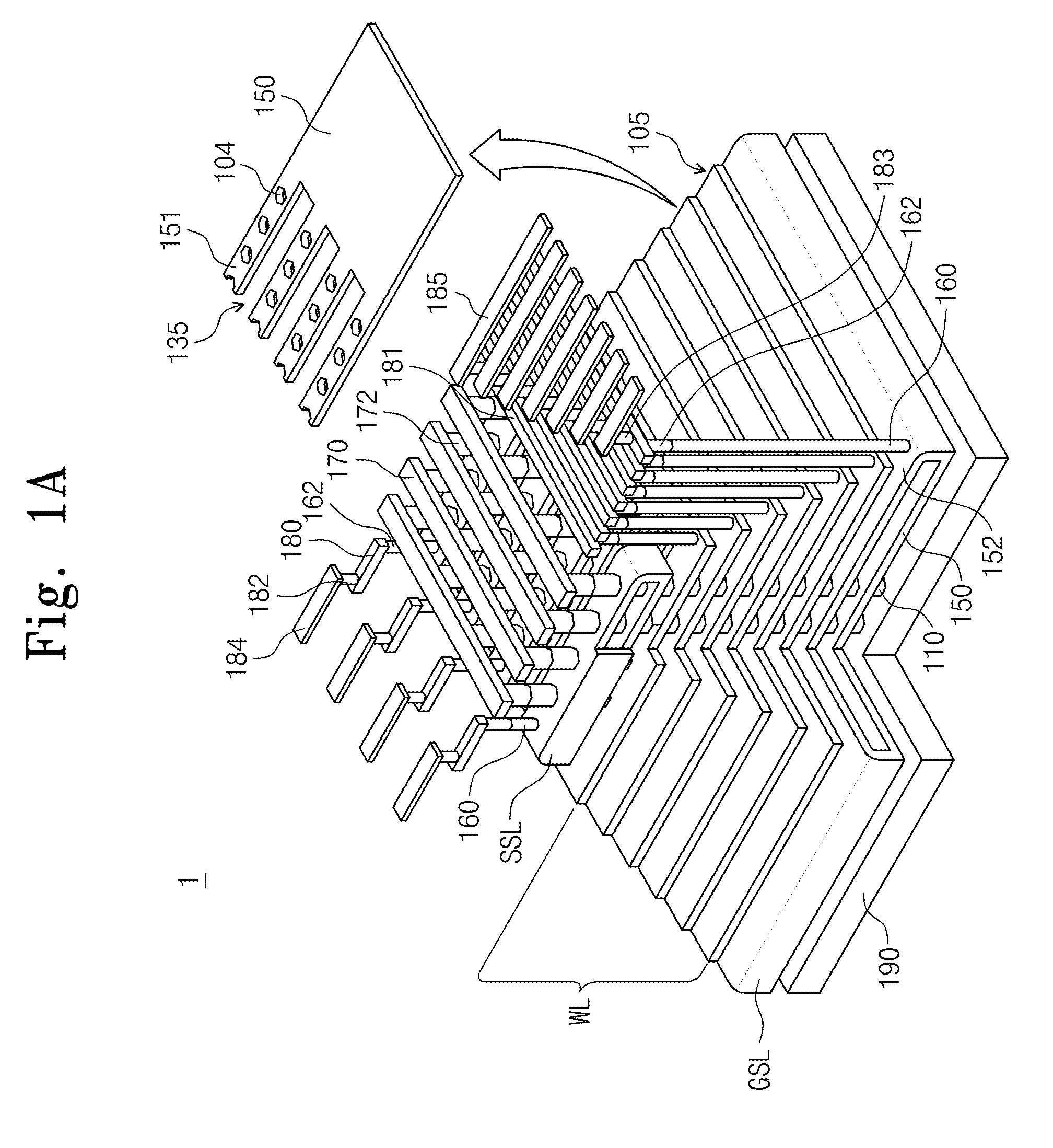

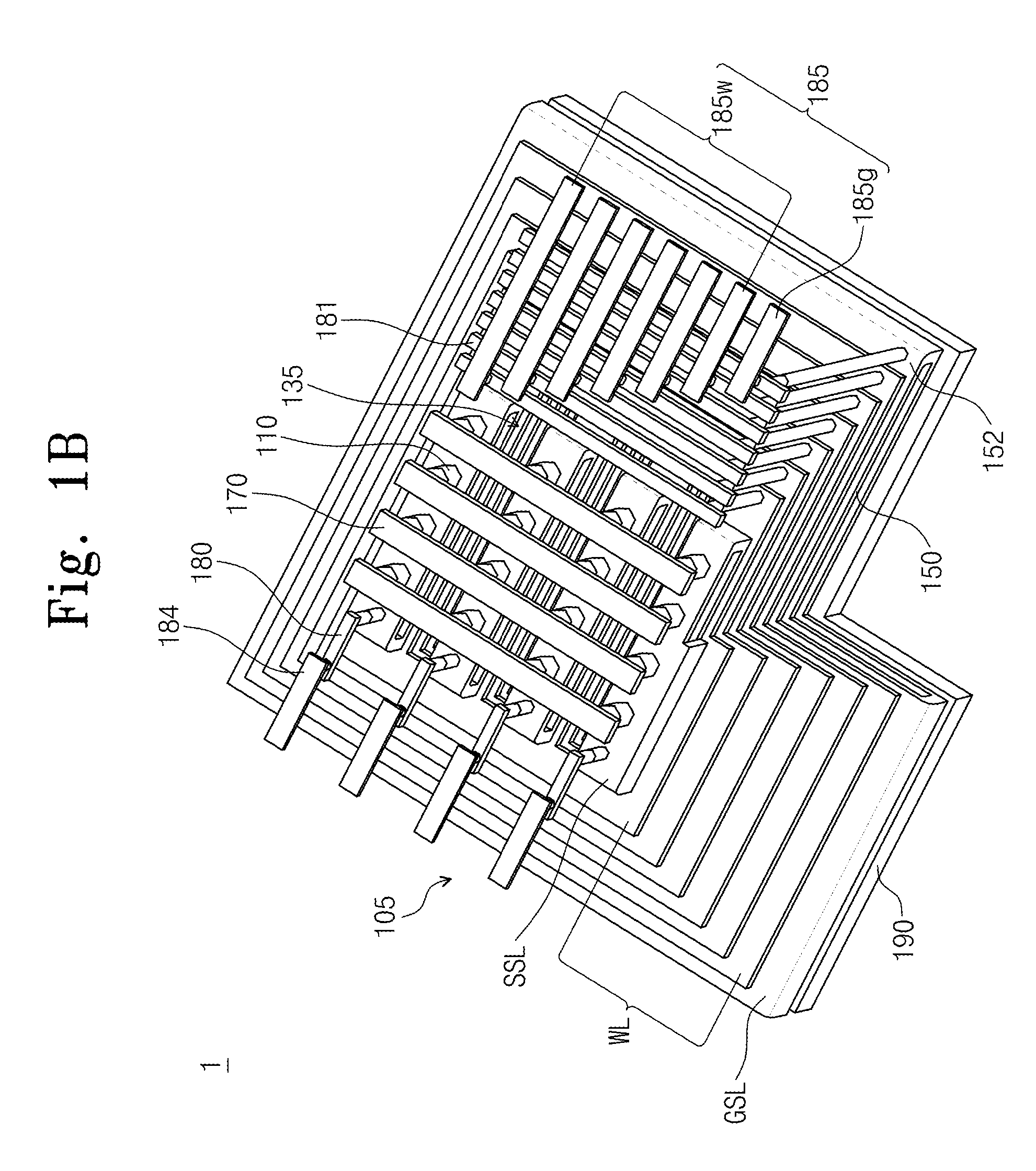

3D semiconductor devices and methods of fabricating same

ActiveUS20120119287A1Fabrication yield can be improvedPrevent and minimize process errorSolid-state devicesSemiconductor/solid-state device manufacturingMemory cellDevice material

A three dimensional (3D) semiconductor device includes; a vertical channel extending from a lower end proximate a substrate to an upper end and connecting a plurality of memory cells, and a cell array comprising the plurality of cells, wherein the cell array is arranged in a gate stack of layers having a stair-stepped structure disposed on the substrate. The gate stack includes a lower layer including a lower select line coupled to a lower non-memory transistor proximate the lower end, upper layers including conductive lines respectively coupled to an upper non-memory transistor proximate the upper end and connected as a single conductive piece to form an upper select line, and intermediate layers respectively including a word line and coupled to a cell transistor, wherein the intermediate layers are disposed between the lower select line and the upper select line.

Owner:SAMSUNG ELECTRONICS CO LTD

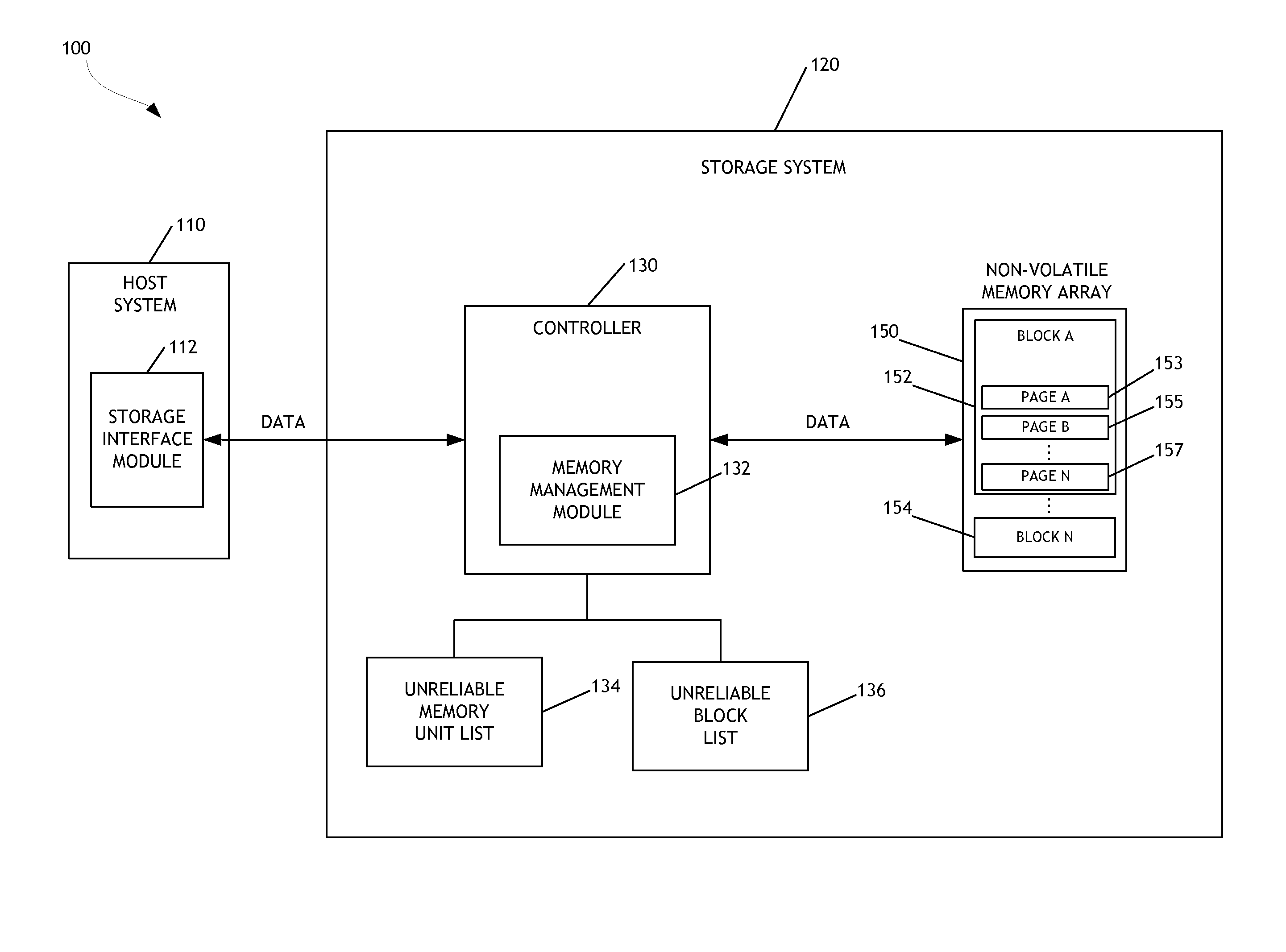

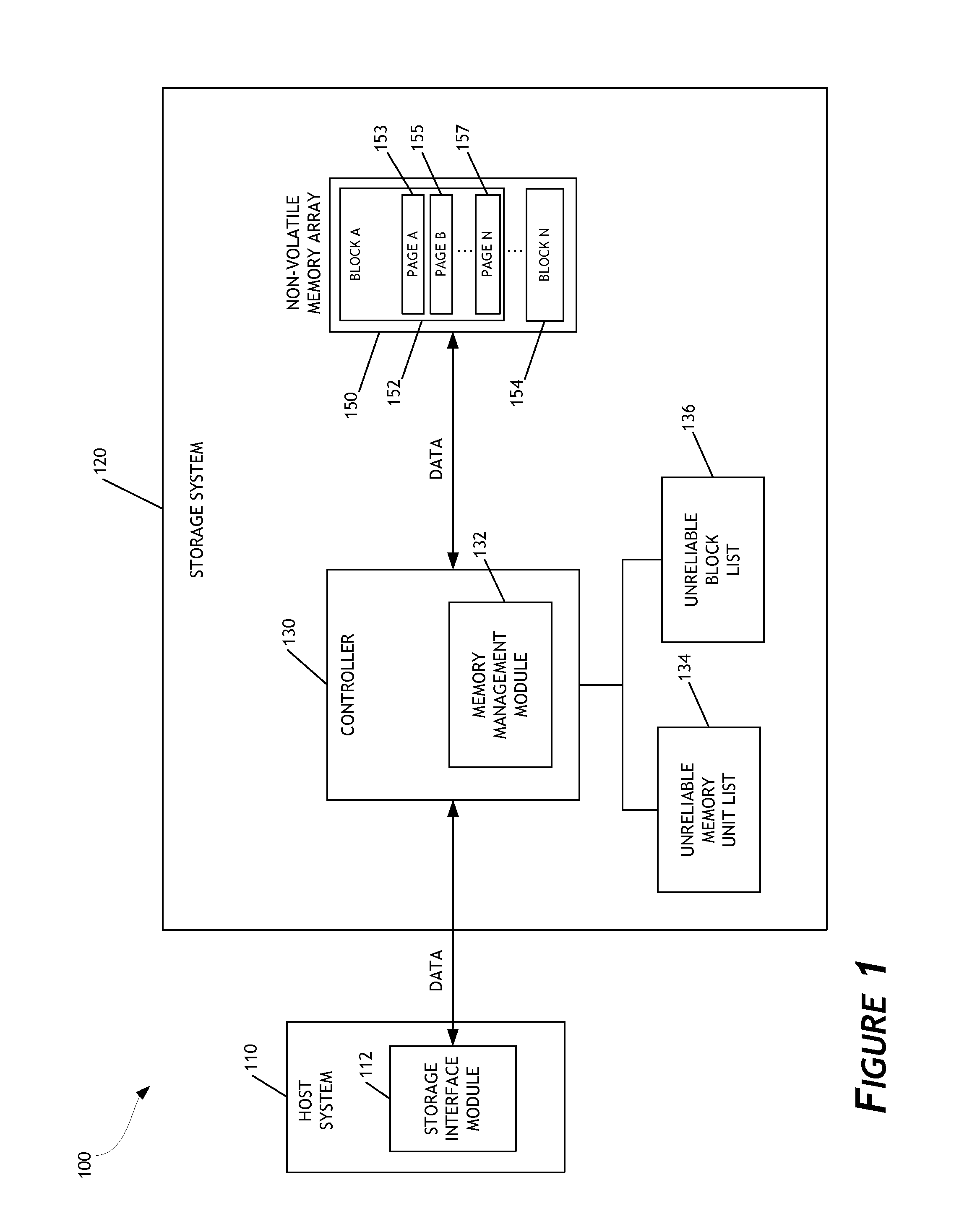

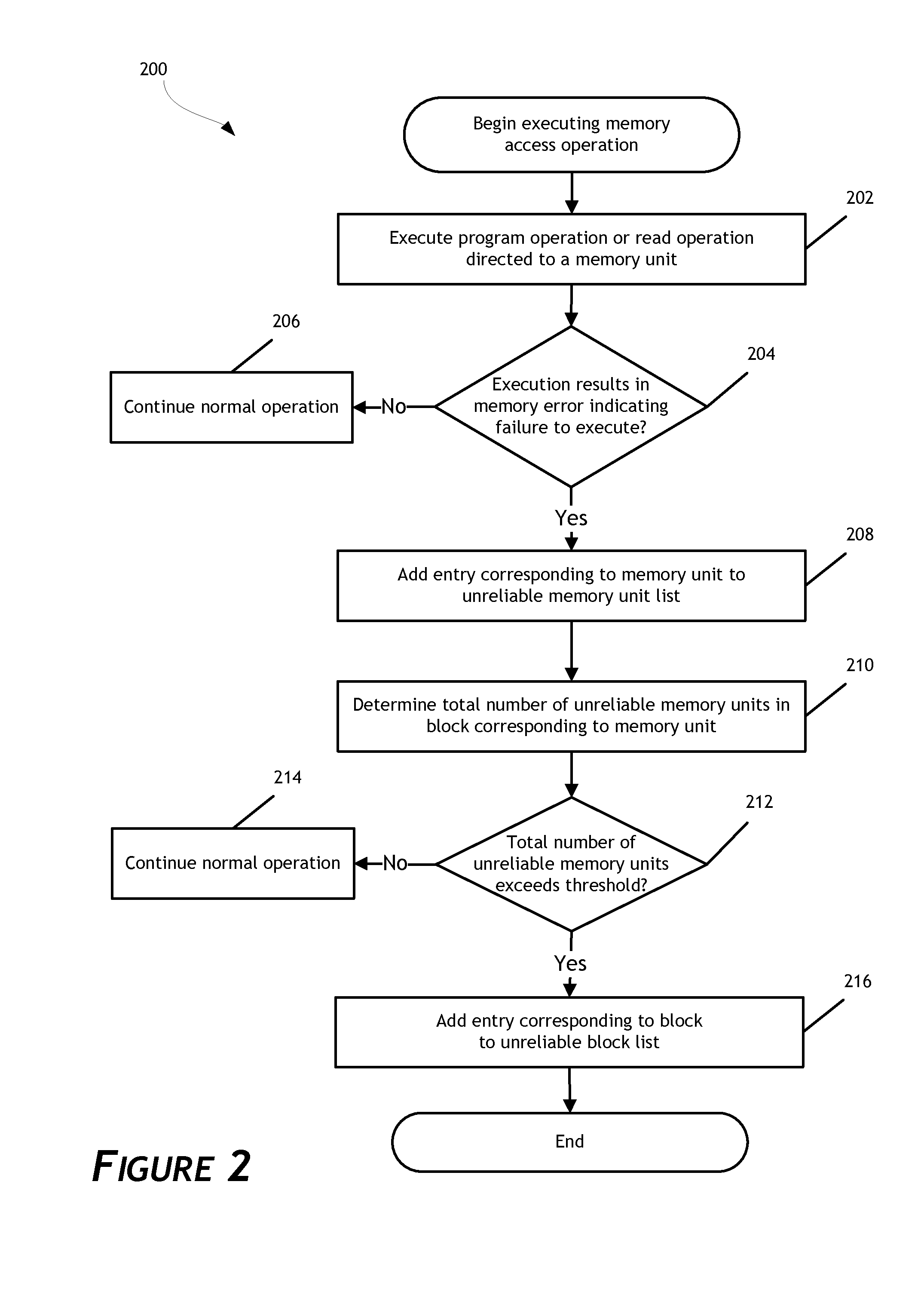

Managing unreliable memory in data storage systems

A data storage system configured to manage unreliable memory units is disclosed. In one embodiment, the data storage system maintains an unreliable memory unit list designating memory units in a non-volatile memory array as reliable or unreliable. The unreliable memory unit list facilitates management of unreliable memory at a granularity level finer than the granularity of a block of memory. The data storage system can add entries to the unreliable memory unit list as unreliable memory units are discovered. Further, the data storage system can continue to perform memory access operations directed to reliable memory units in blocks containing other memory units determined to be unreliable. As a result, the operational life of the data storage system is extended.

Owner:WESTERN DIGITAL TECH INC

Thin film memory, array, and operation method and manufacture method therefor

A memory cell which is formed on a fully depleted SOI or other semiconductor thin film and which operates at low voltage without needing a conventional large capacitor is provided as well as a memory cell array. The semiconductor thin film is sandwiched between first and second semiconductor regions which face each other across the semiconductor thin film and which have a first conductivity type. A third semiconductor region having the opposite conductivity type is provided in an extended portion of the semiconductor thin film. From the third semiconductor region, carriers of the opposite conductivity type are supplied to and accumulated in the semiconductor thin film portion to change the gate threshold voltage of a first conductivity type channel that is induced by a first conductive gate voltage in the semiconductor thin film between the first and second semiconductor regions through an insulating film.

Owner:HAYASHI YUTAKA +1

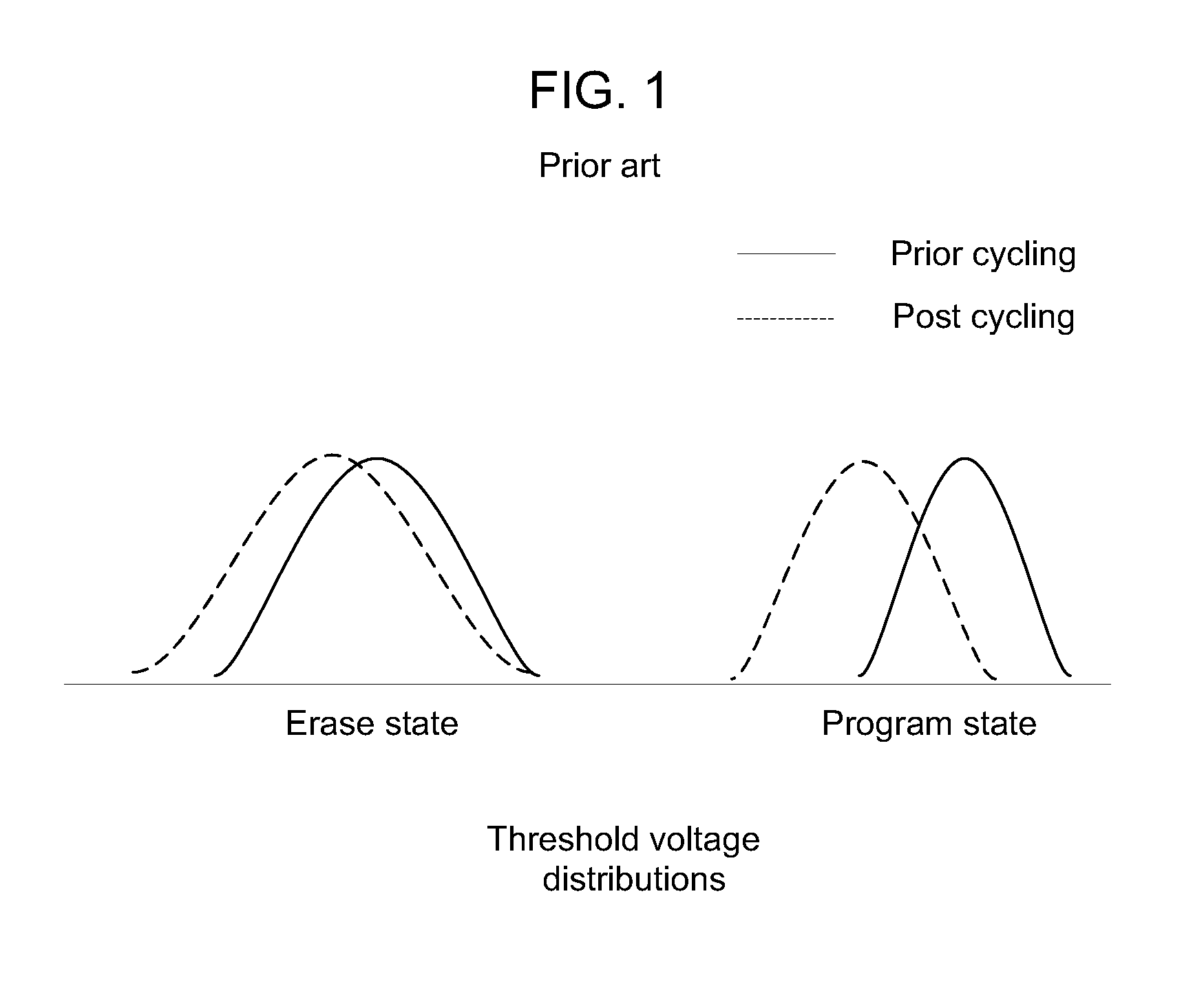

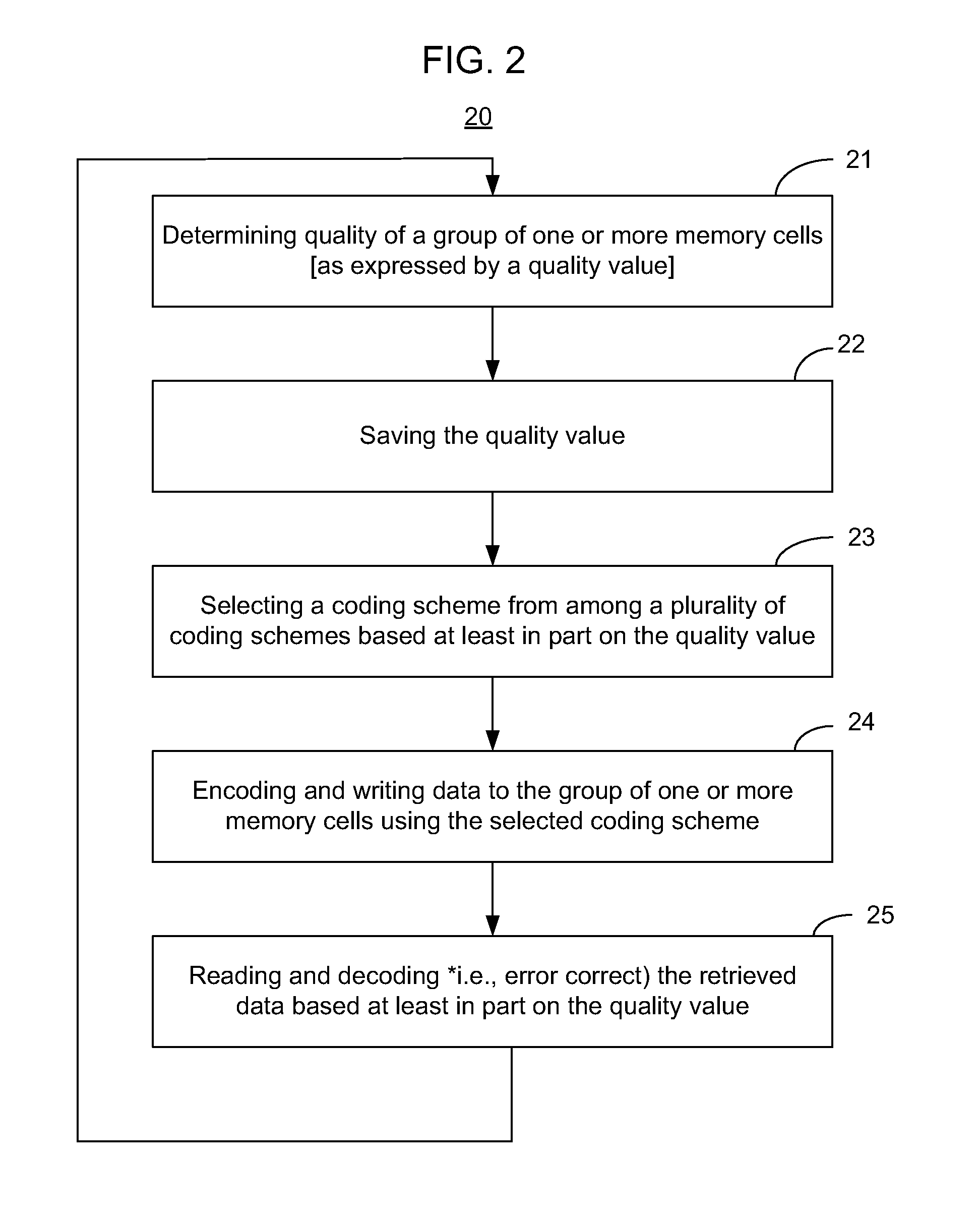

Adaptive systems and methods for storing and retrieving data to and from memory cells

ActiveUS20080086677A1Error correction capabilityEasy to processInput/output to record carriersMemory loss protectionParallel computingData encoding

Adaptive systems and methods that may help assure the reliability of data retrieved from memory cells are described herein. The systems may include a memory device including a plurality of memory cells, a data quality monitoring block, and an adaptive data encoding block, the data quality monitoring block and the adaptive data encoding block both being operatively coupled to the memory device. The data quality monitoring block may be configured to determine a quality value of a group of one or more memory cells included in the memory device, the determined quality value being indicative of a quality of the group of one or more memory cells. The adaptive data encoding block may be configured to select a coding scheme from a plurality of coding schemes to encode data to be written to the group of one or more memory cells in the memory device, the selection of the coding scheme being based at least in part on the determined quality value of the group of one or more memory cells.

Owner:MARVELL ASIA PTE LTD

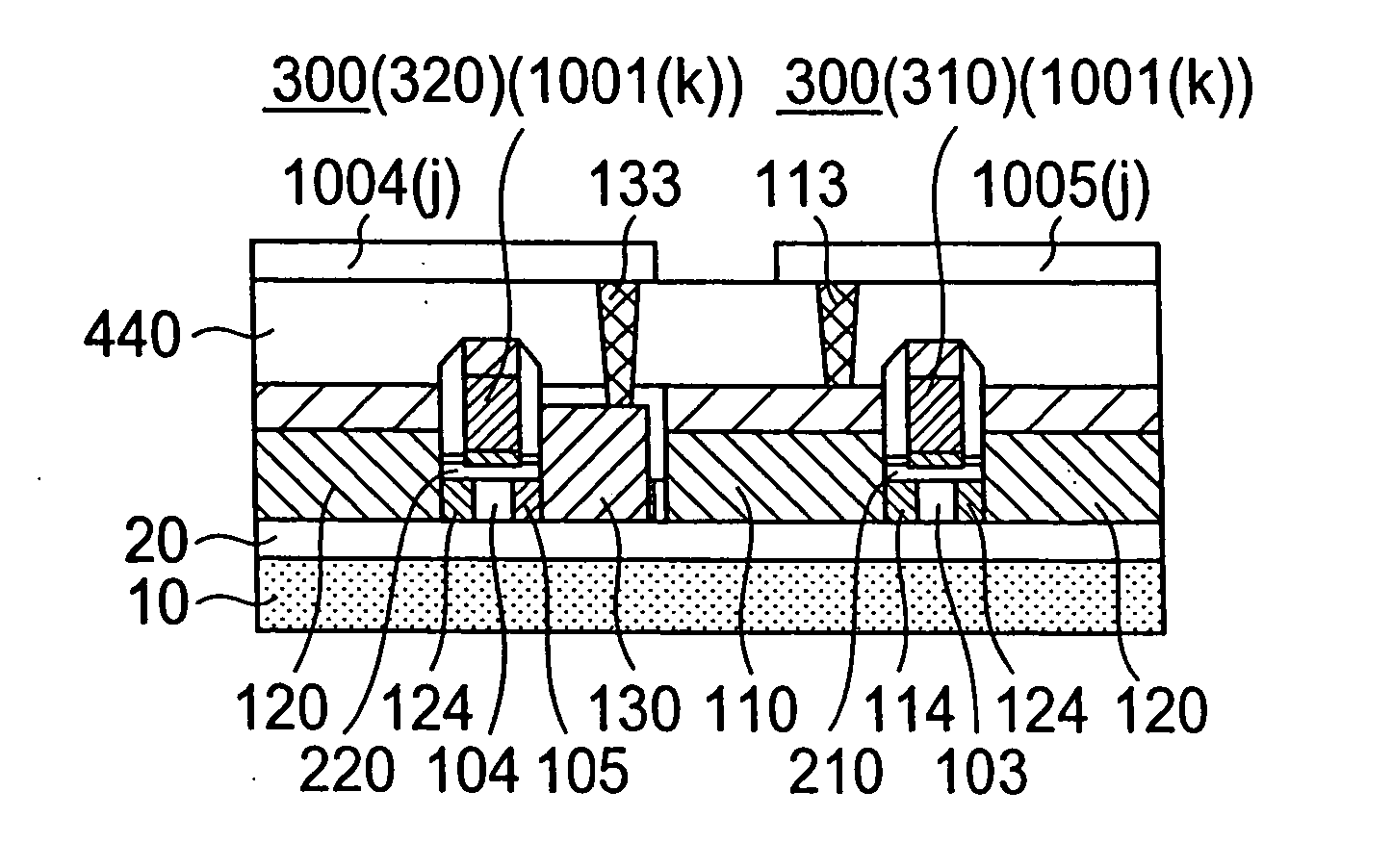

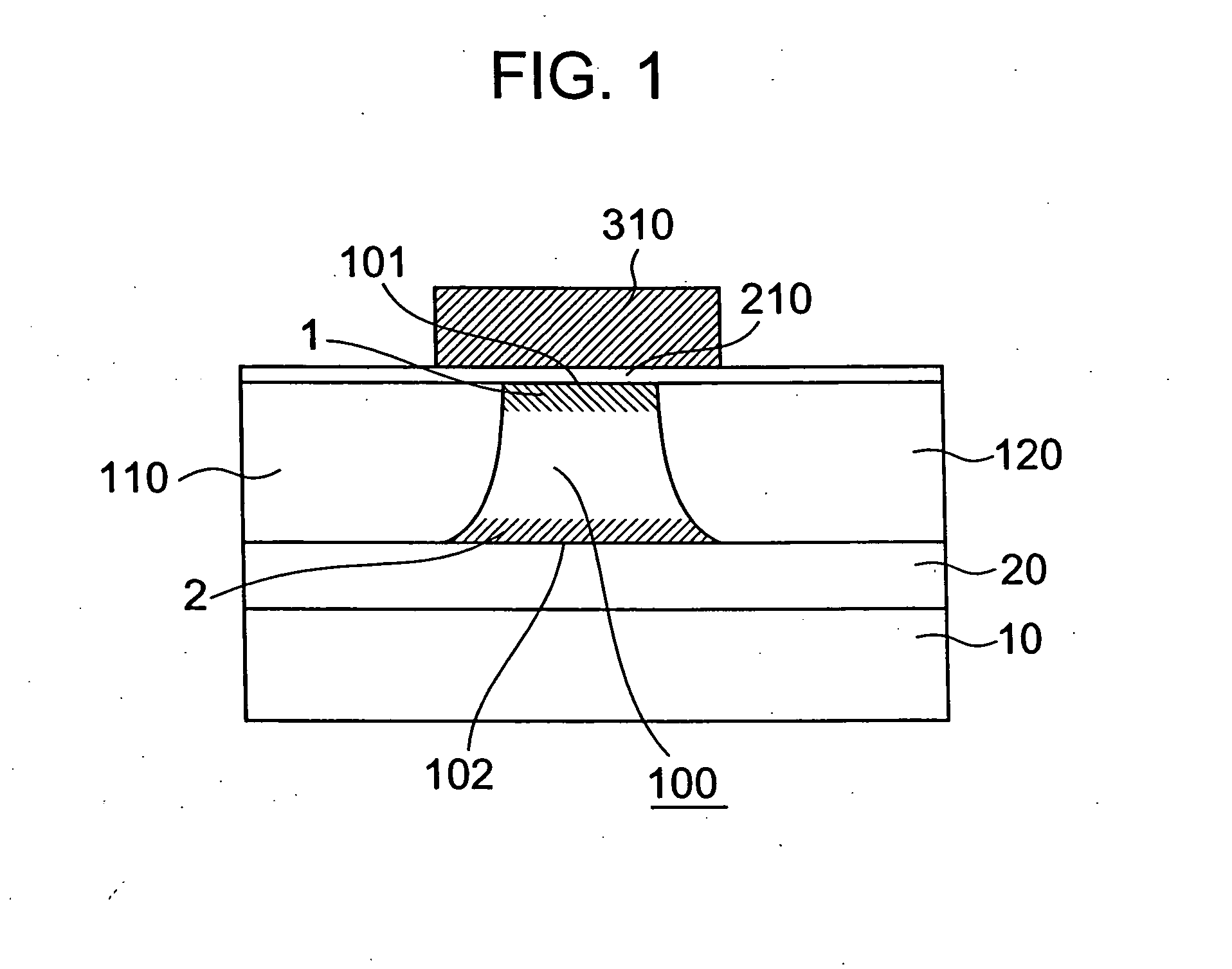

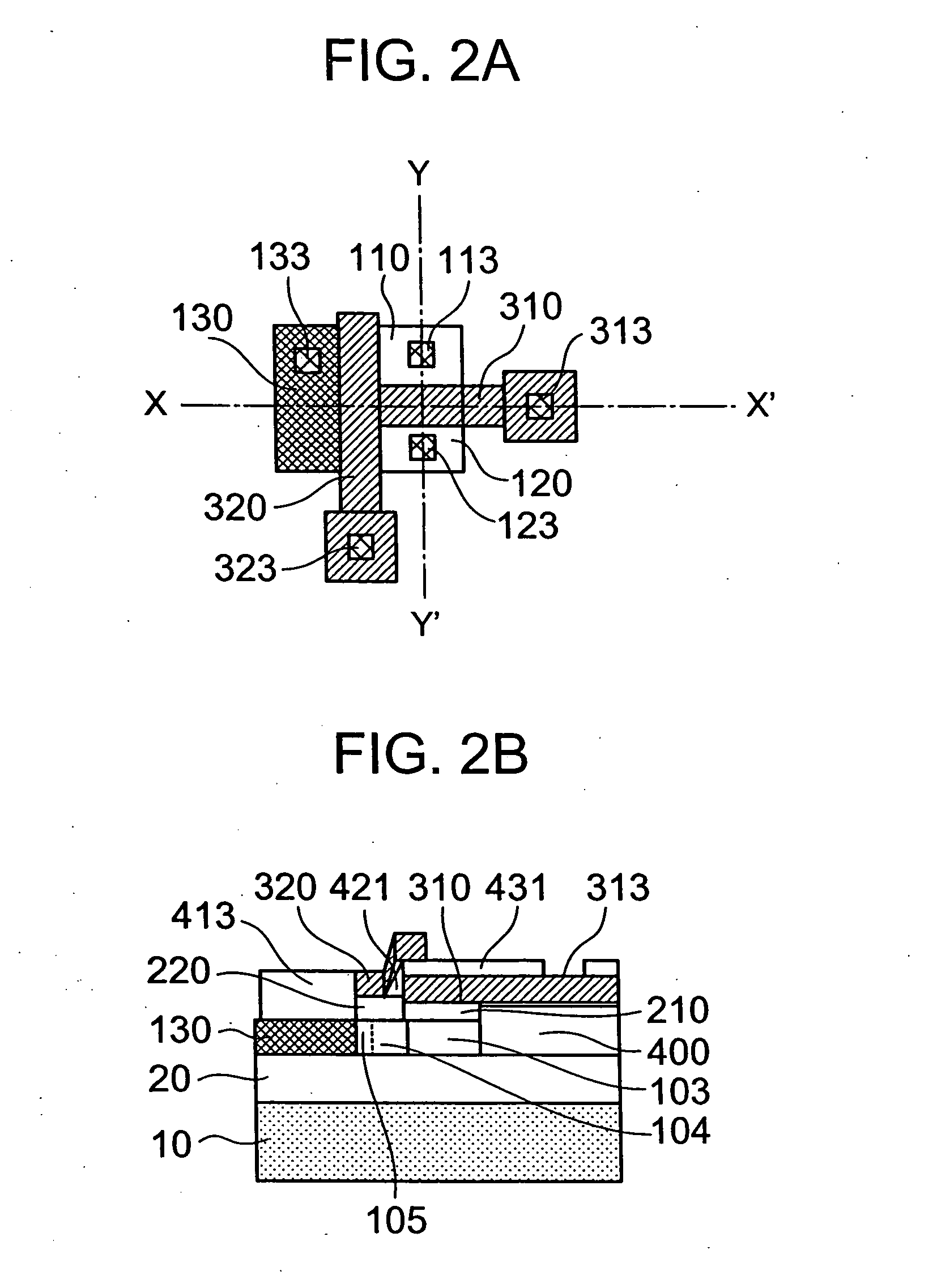

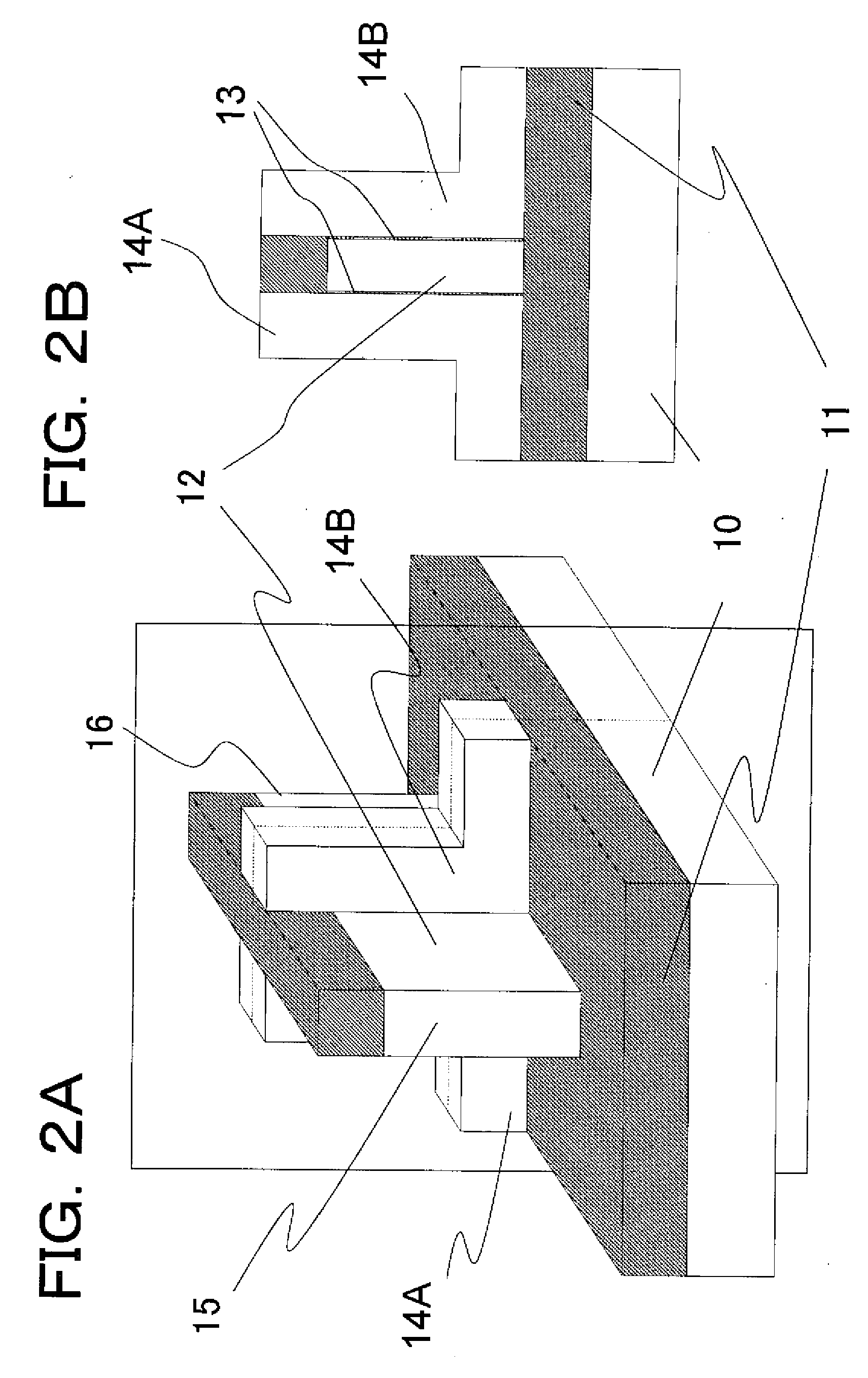

Memory cell array, method of producing the same, and semiconductor memory device using the same

A memory cell array includes isolated semiconductor regions formed on a supporting insulating substrate, memory cells formed in the respective semiconductor regions, and insulating regions formed so as to insulate the memory cells. Each memory cell formed in a semiconductor region includes a source region, a drain region, a front gate region formed on a gate insulating film formed on one of side surfaces of the semiconductor region such that the source region and the drain region are separated from each other by the front gate region, and a back gate region formed on a gate insulating film formed on an opposite side surface of the semiconductor region such that the source region and the drain region are separated from each other by the back gate region. Each memory cell shares the back gate region with a memory cell adjacent in a row direction.

Owner:FUJITSU LTD

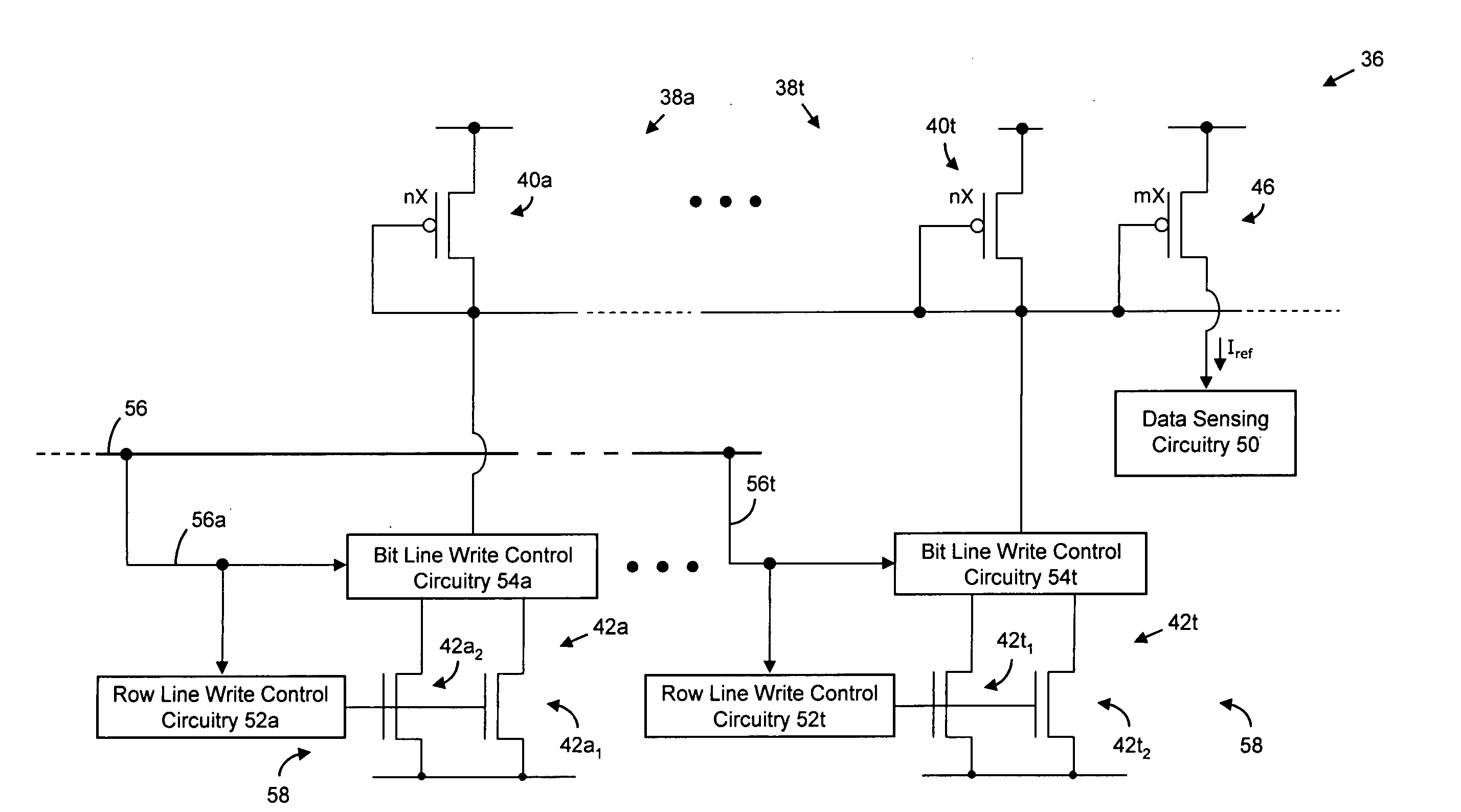

Method and circuitry to generate a reference current for reading a memory cell, and device implementing same

There are many inventions disclosed herein. In one aspect, the present inventions are directed to methods and circuitry to control, adjust, determine and / or modify the absolute and / or relative positioning or location (i.e., absolute or relative amount) of reference current which is employed by sensing circuitry to sense the data state of a memory cell during a read operation of one or more memory cells. The control, adjustment, determination and / or modification of the reference current levels may be implemented using many different, distinct and / or diverse techniques and circuitry, including both analog and digital techniques and circuitry.

Owner:MICRON TECH INC

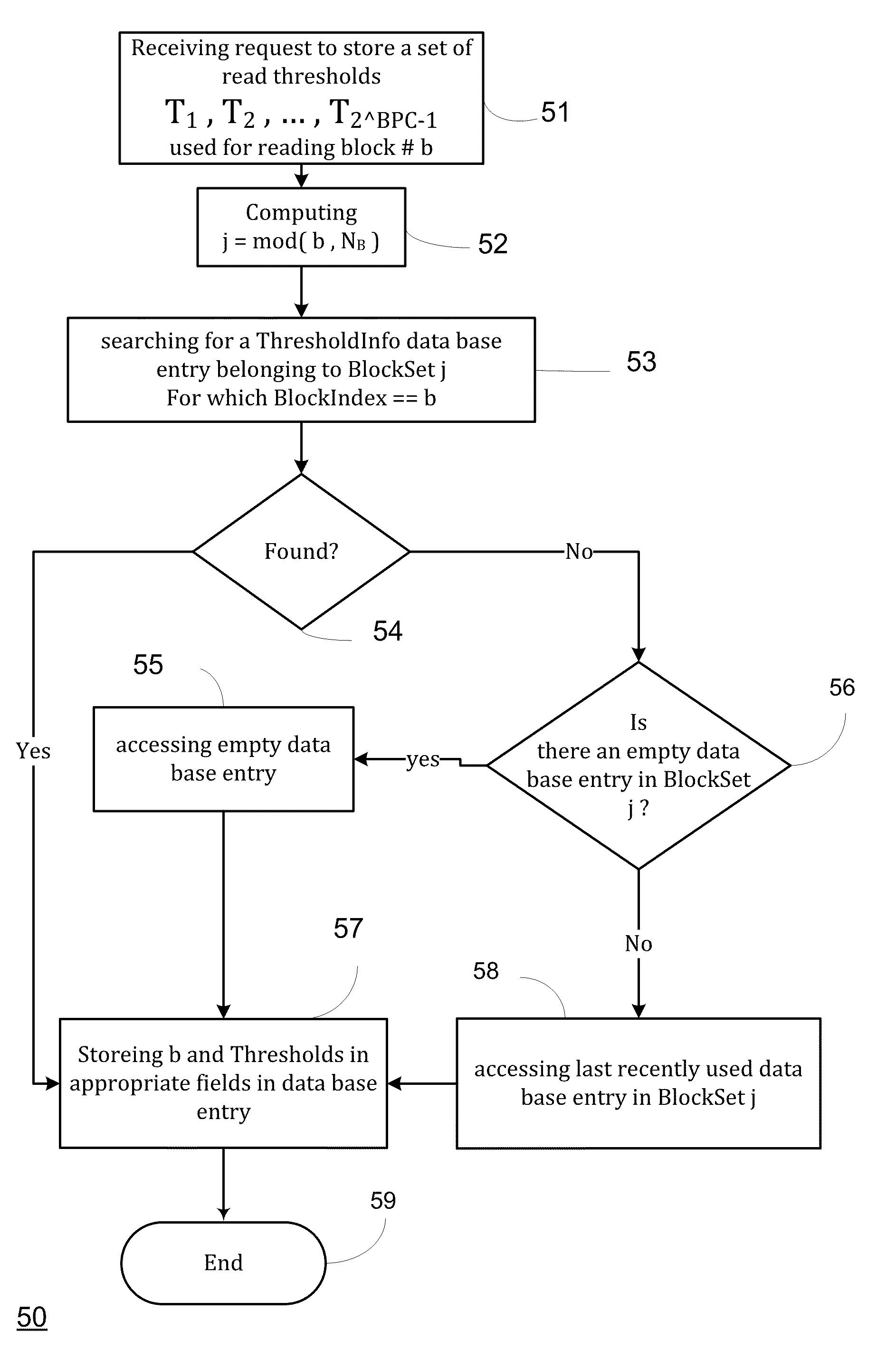

Systems and methods for storing, retrieving, and adjusting read thresholds in flash memory storage system

A method, system and computer-readable medium are provided for reading information from a memory unit. A read instruction may be received to read information from a set of memory cells in the memory unit. A data structure storing sets of read thresholds may be searched for a set of read thresholds based on one or more characteristic value(s) of the set of memory cells. If the set of read thresholds is found, the set of memory cells may be read to execute the read instruction using the found set of read thresholds. The set of read thresholds may be thresholds which were previously used to successfully read a set of cells having the same or similar characteristic value(s).

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

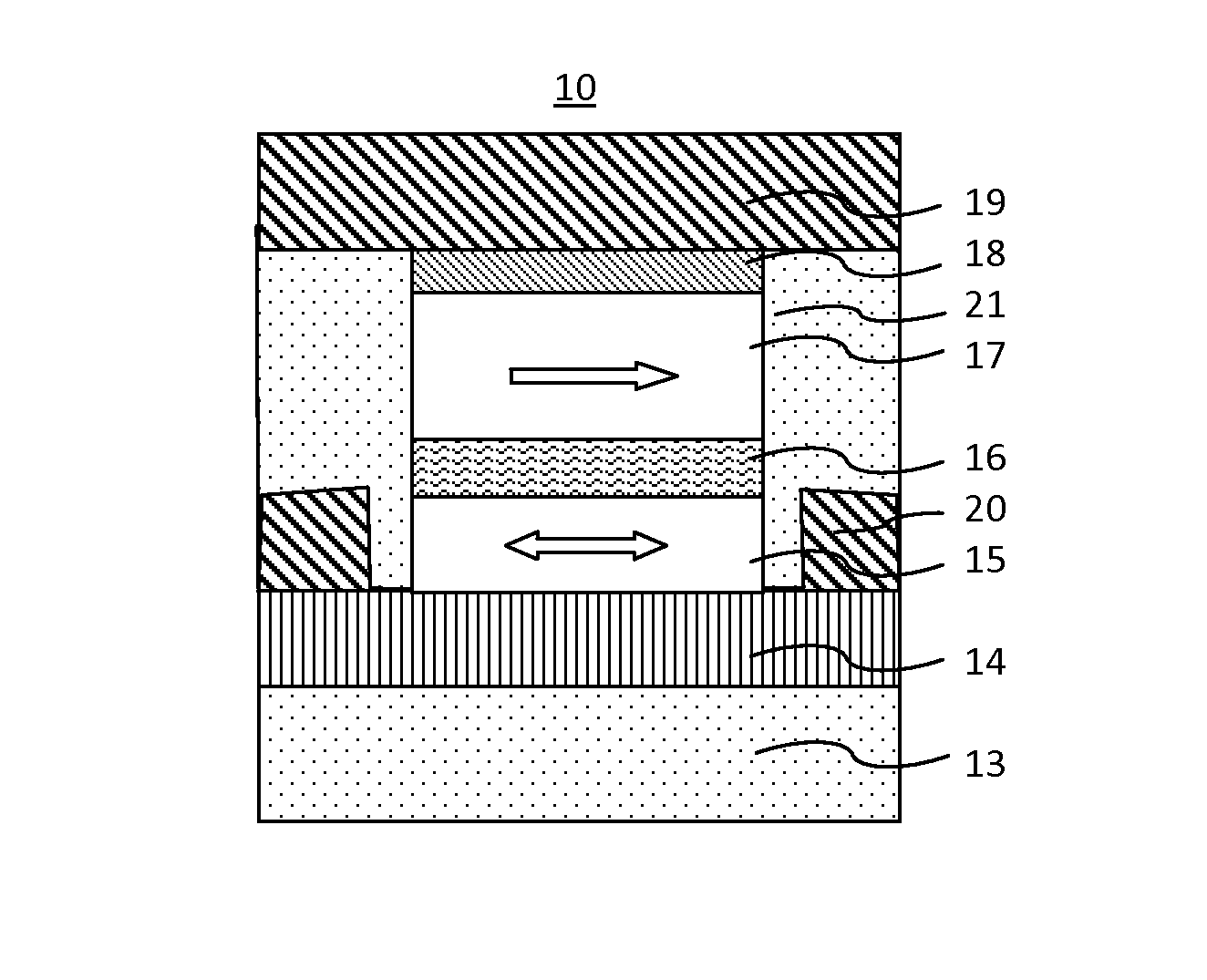

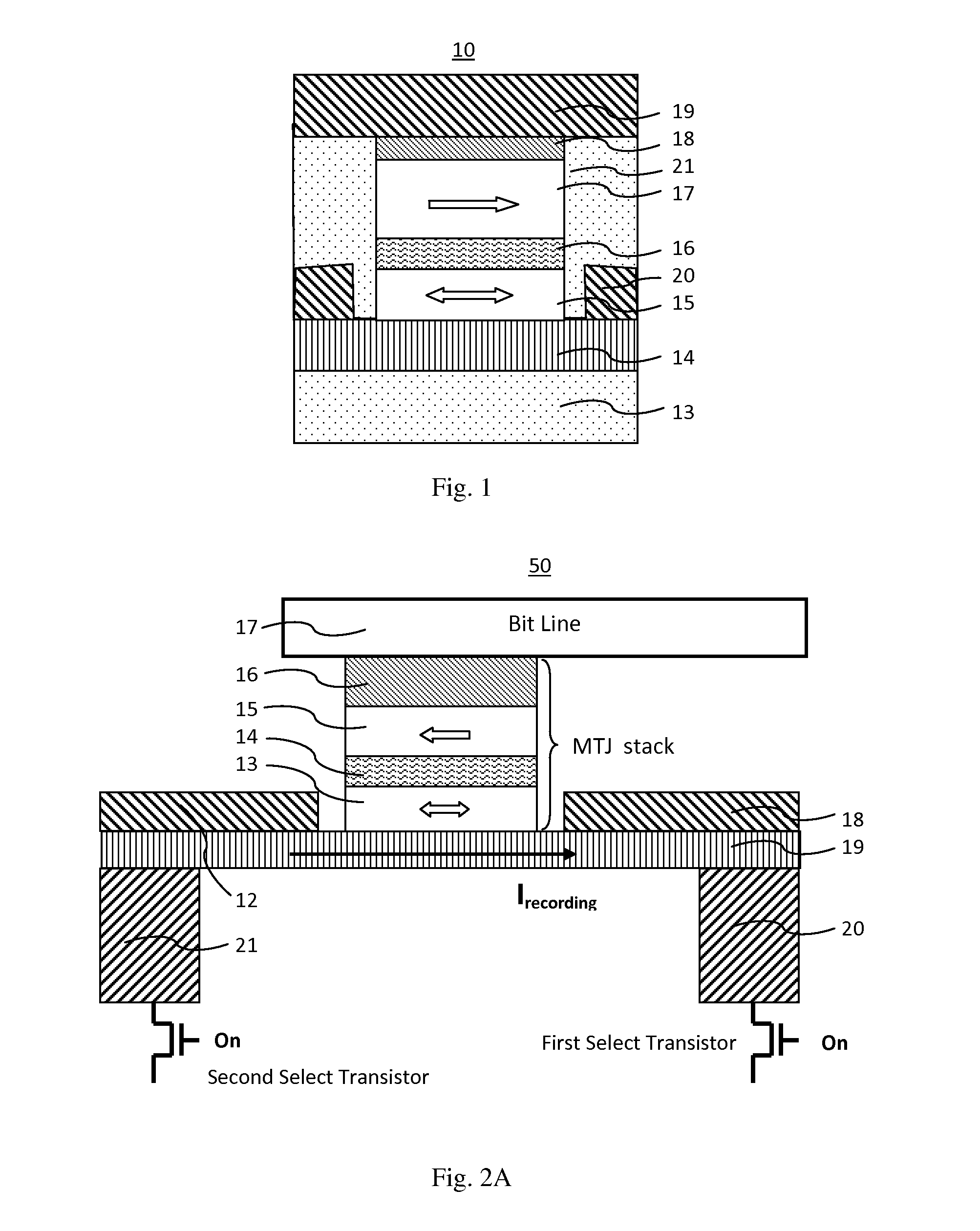

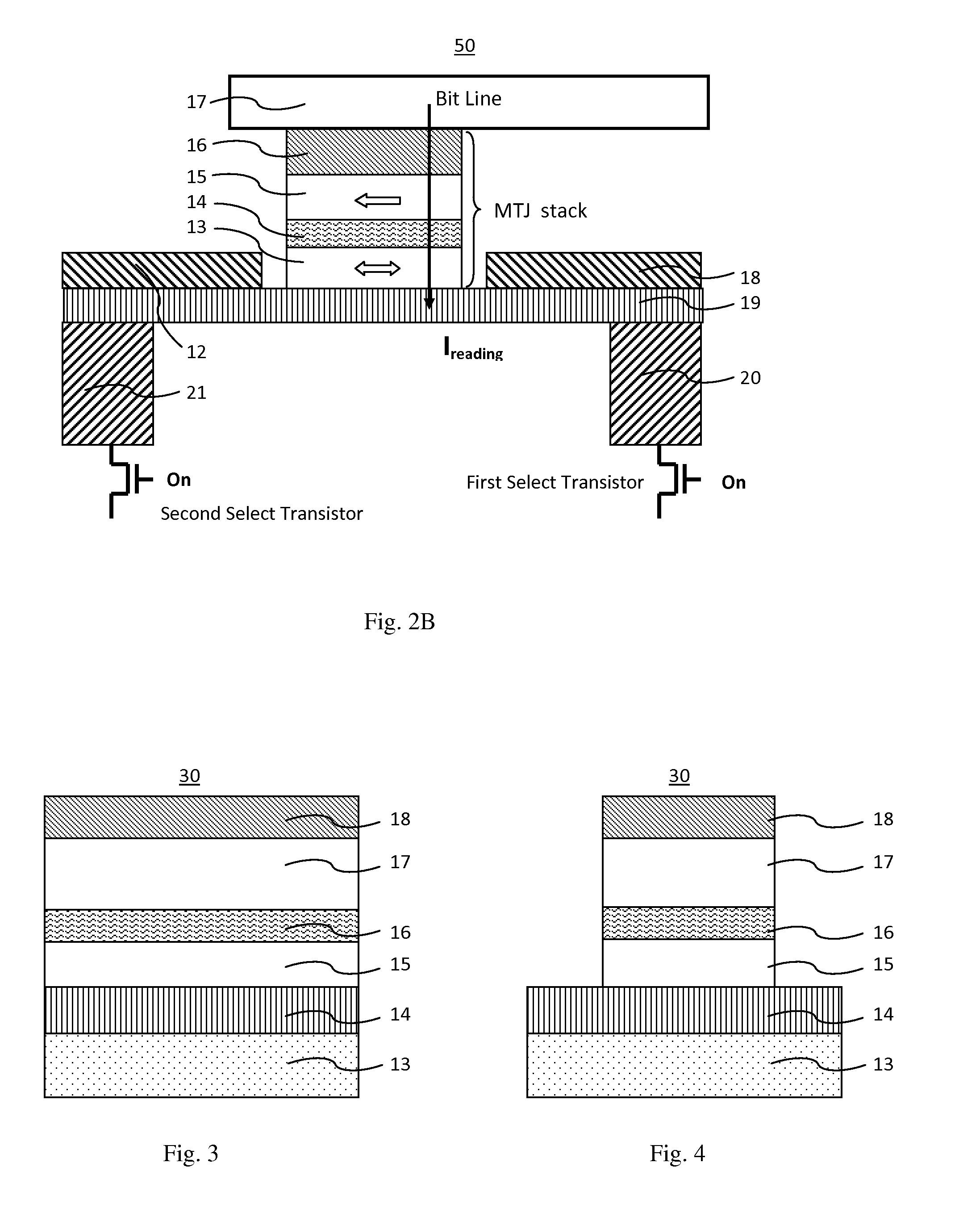

MRAM having spin hall effect writing and method of making the same

InactiveUS20140252439A1Easy to switchEasy to reverseSemiconductor/solid-state device manufacturingGalvano-magnetic device detailsMagnetic reluctanceRecording layer

A spin-transfer-torque magnetoresistive memory comprises apparatus and method of manufacturing a three terminal magnetoresistive memory element having highly conductive bottom electrodes overlaid on top of a SHE-metal layer in the regions outside of an MTJ stack. The memory cell comprises a bit line positioned adjacent to selected ones of the plurality of magnetoresistive memory elements to supply a reading current across the magnetoresistive element stack and two highly conductive bottom electrodes overlaid and electrically contacting on top of a SHE-metal layer in the outside of an MTJ region and to supply a bi-directional spin Hall effect recording current, and accordingly to switch the magnetization of the recording layer. Thus magnetization of a recording layer can be readily switched or reversed to the direction in accordance with a direction of a current along the SHE-metal layer by applying a low write current.

Owner:T3MEMORY

Programming Differently Sized Margins and Sensing with Compensations at Select States for Improved Read Operations in Non-Volatile Memory

ActiveUS20070291556A1Good effectWider marginRead-only memoriesDigital storageMemory cellSoftware engineering

Non-volatile memory read operations compensate for floating gate coupling when the apparent threshold voltage of a memory cell may have shifted. A memory cell of interest can be read using a reference value based on a level of charge read from a neighboring memory cell. Misreading the neighboring cell may have greater effects in particular programming methodologies, and more specifically, when reading the neighboring cell for particular states or charge levels in those methodologies. In one embodiment, memory cells are programmed to create a wider margin between particular states where misreading a neighboring cell is more detrimental. Further, memory cells are read in one embodiment by compensating for floating gate coupling based on the state of a neighboring cell when reading at certain reference levels but not when reading at other reference levels, such as those where a wider margin has been created.

Owner:SANDISK TECH LLC

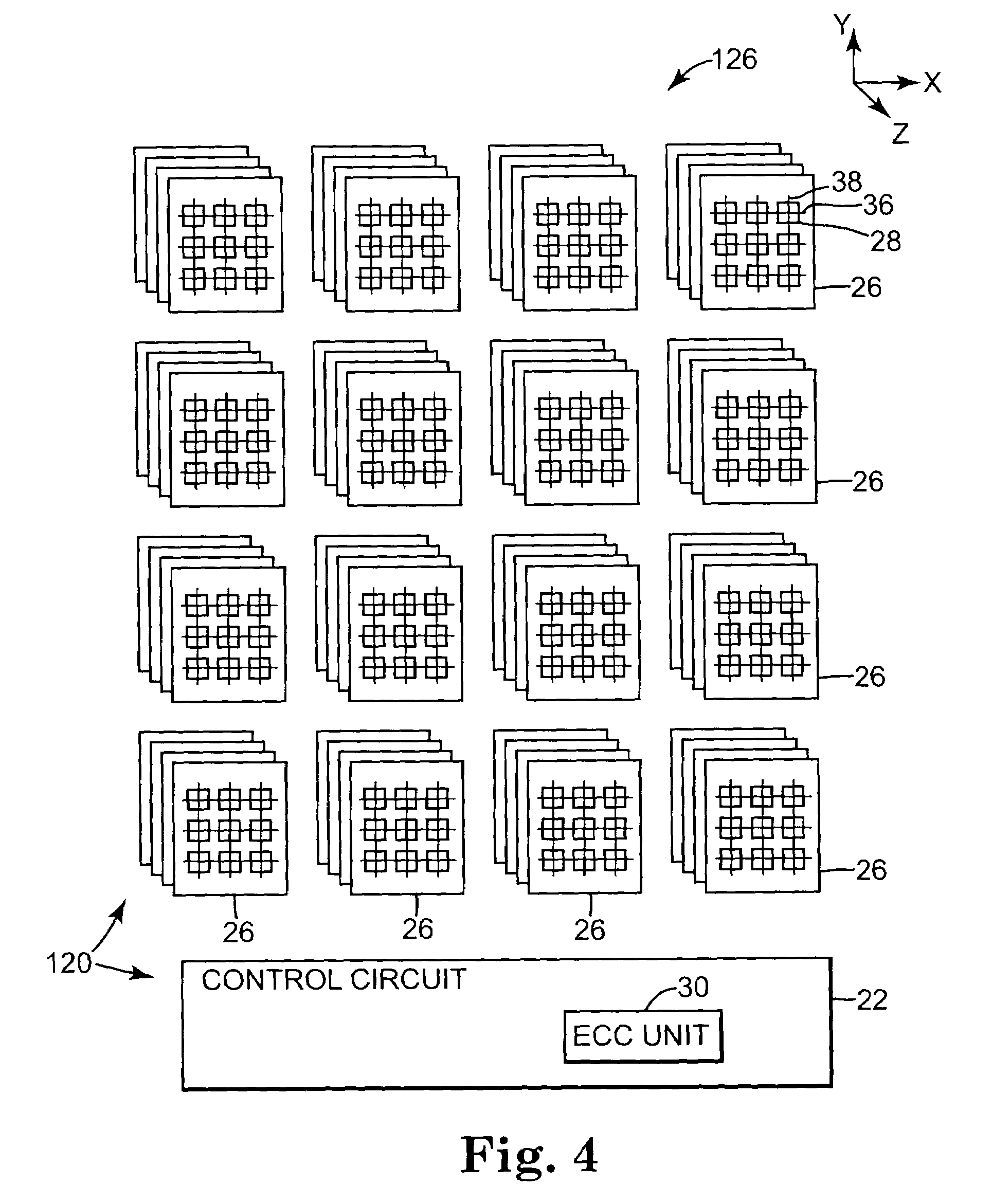

Magnetic memory with error correction coding

Embodiments of the present invention are implemented in memory systems. In one embodiment, the memory comprises an array of memory cells and a control circuit. The control circuit is configured to read error correction coded data from the array of memory cells, provide error correction code decoding to selected error correction coded data and discard unused error correction code parity data of unselected error correction coded data.

Owner:SAMSUNG ELECTRONICS CO LTD

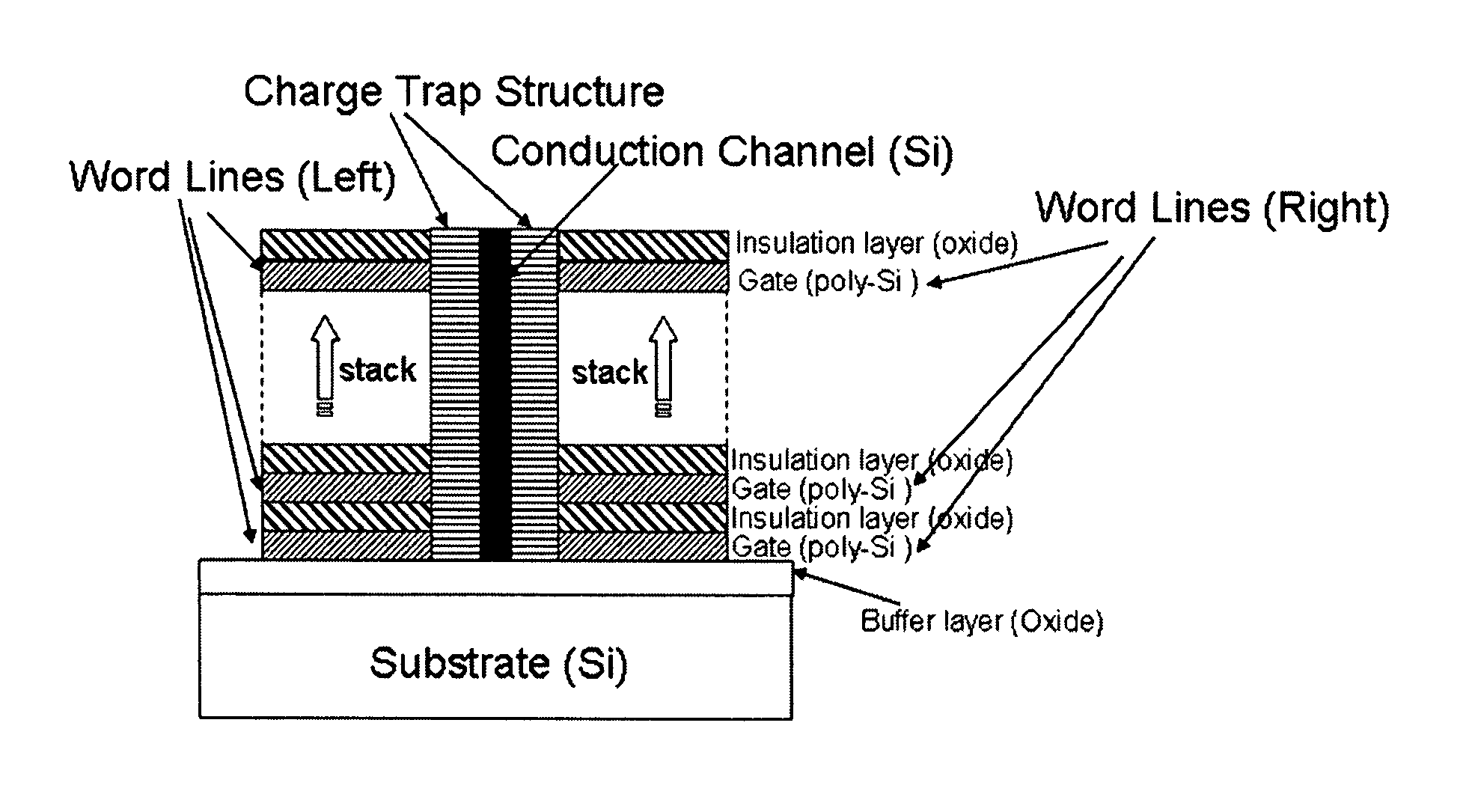

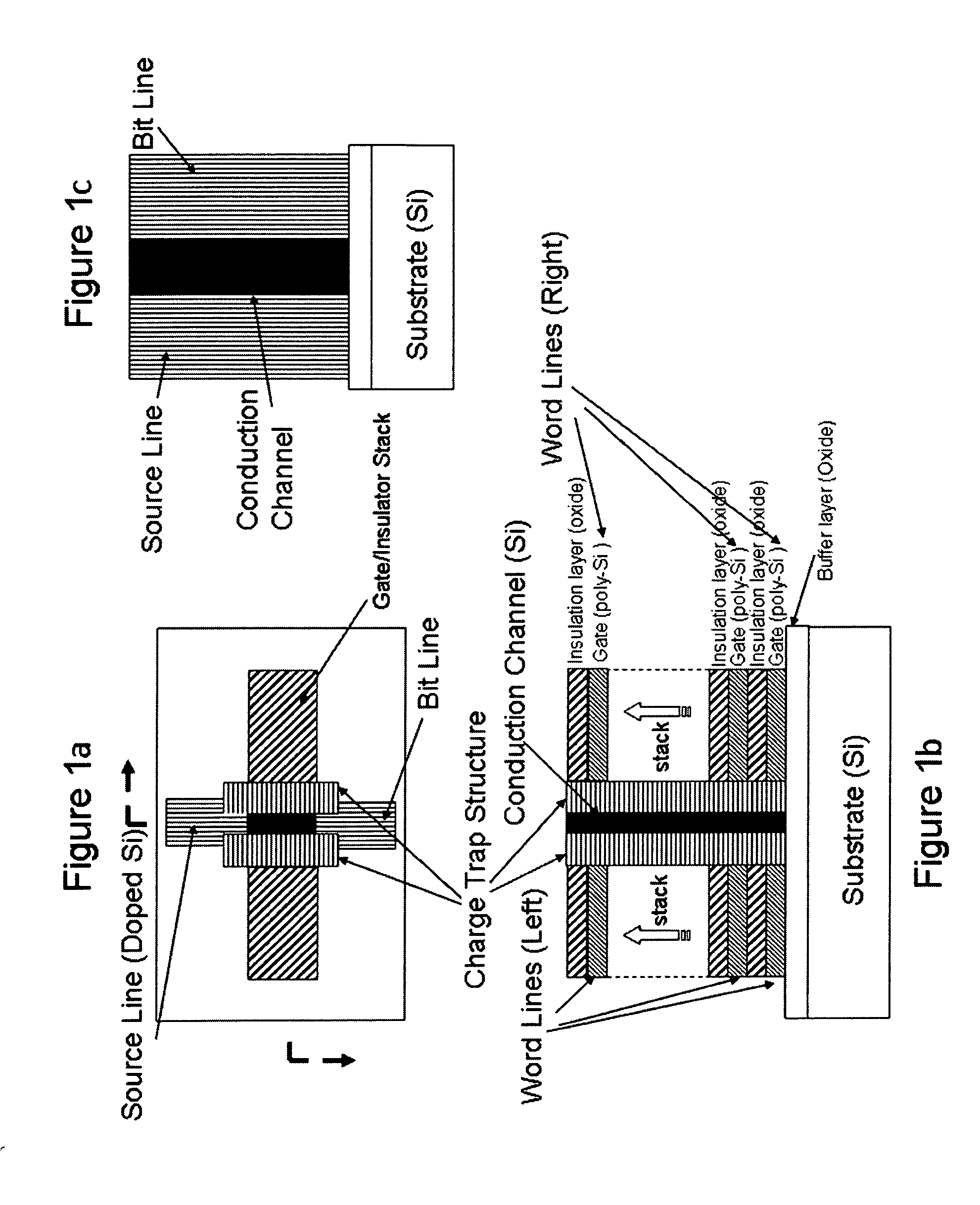

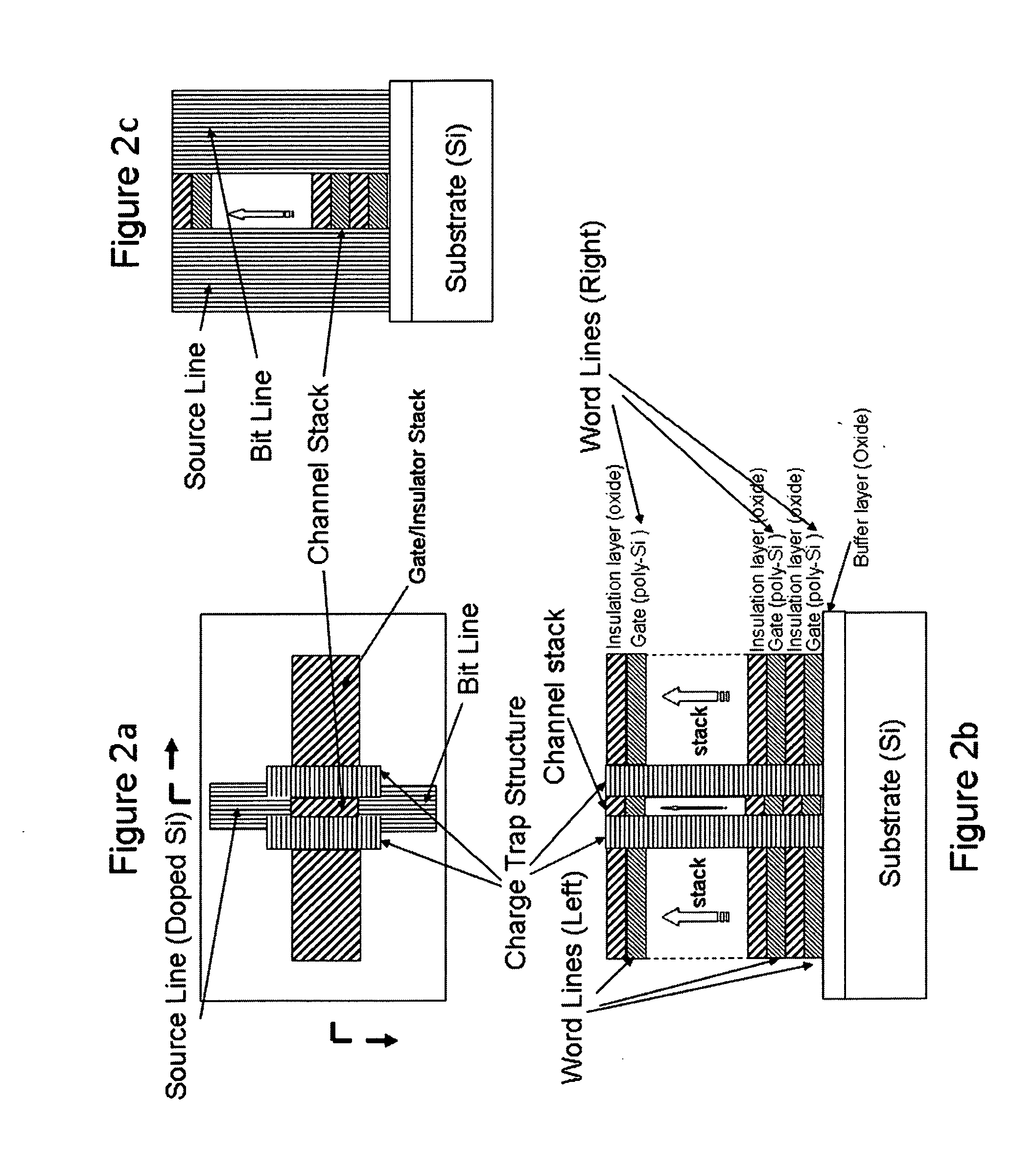

Three-dimensional non-volatile nor-type flash memory

ActiveUS20160086970A1High storage densitySolid-state devicesSemiconductor devicesElectricityEngineering

The present invention provides a design of three-dimensional non-volatile NOR flash memory devices consisting of arrays of basic NOR memory group in which individual memory cells (field-effect-transistors) are stacked along a direction (or directions) either out of or parallel to the plane of the substrate and electrically connected in parallel to achieve high storage densities approaching 1 TB with lower manufacturing cost. Offering full random access to every individual memory cells and also capability of parallel programming / erasing in blocks of memory cells, such three-dimensional non-volatile NOR flash memory can be widely used for both executable-code storage and mass data storage applications.

Owner:PENG HAIBING

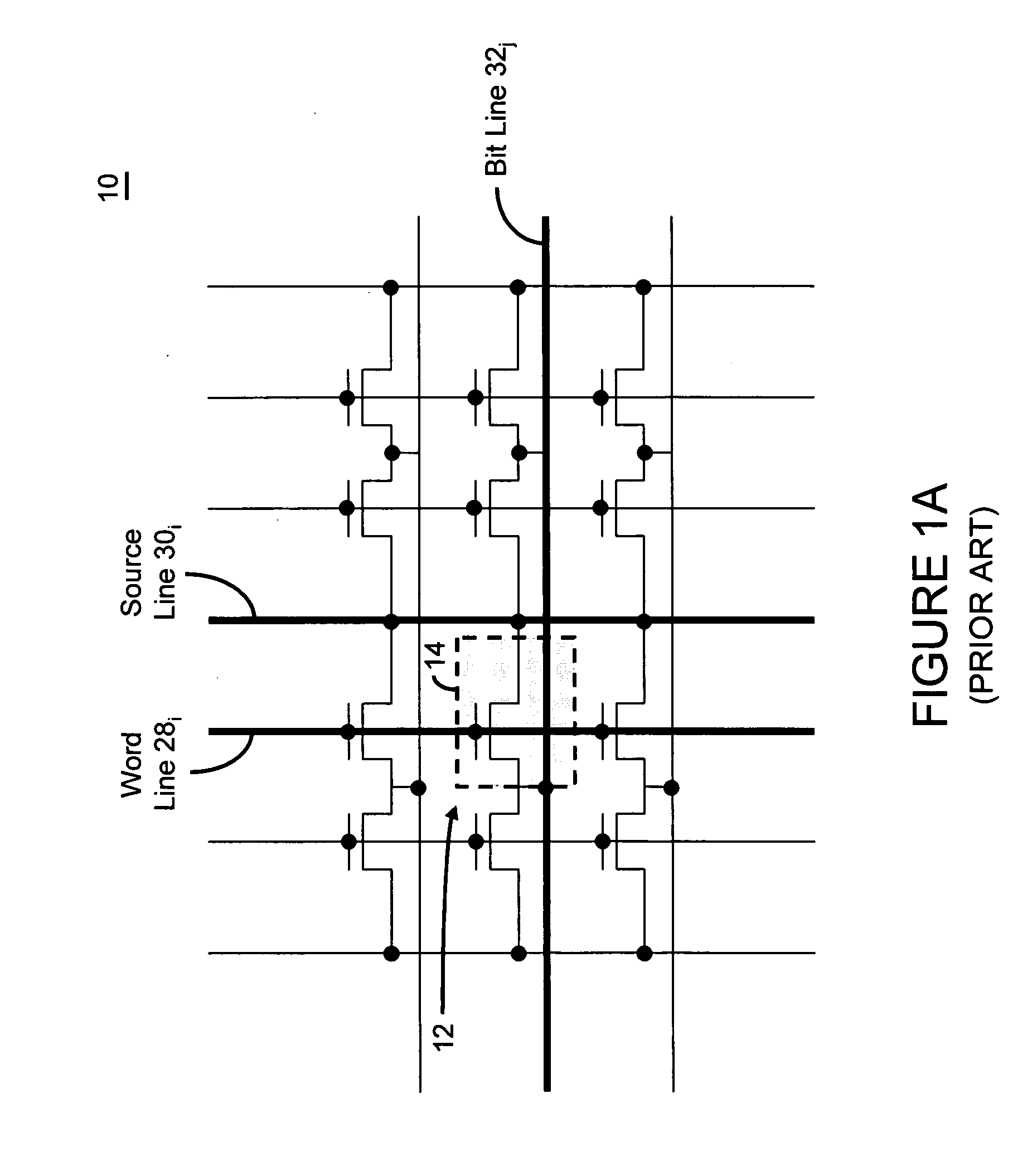

Bipolar reading technique for a memory cell having an electrically floating body transistor

A technique of sampling, sensing, reading and / or determining the data state of a memory cell of a memory cell array (for example, a memory cell array having a plurality of memory cells which consist of an electrically floating body transistor). In one embodiment, the present inventions are directed to a memory cell, having an electrically floating body transistor, and / or a technique of reading the data state in such a memory cell. In this regard, the present inventions employ the intrinsic bipolar transistor current to read and / or determine the data state of the electrically floating body memory cell (for example, whether the electrically floating body memory cell is programmed in a State “0” and State “1”). During the read operation, the data state is determined primarily by or sensed substantially using the bipolar current responsive to the read control signals and significantly less by the interface channel current component, which is negligible relatively to the bipolar component. The bipolar transistor current may be very sensitive to the floating body potential due to the high gain of the intrinsic bipolar transistor. As such, the programming window obtainable with the bipolar reading technique may be considerably higher (for example, up two orders of magnitude higher) than the programming window employing a conventional reading technique (which is based primarily on the interface channel current component.

Owner:MICRON TECH INC

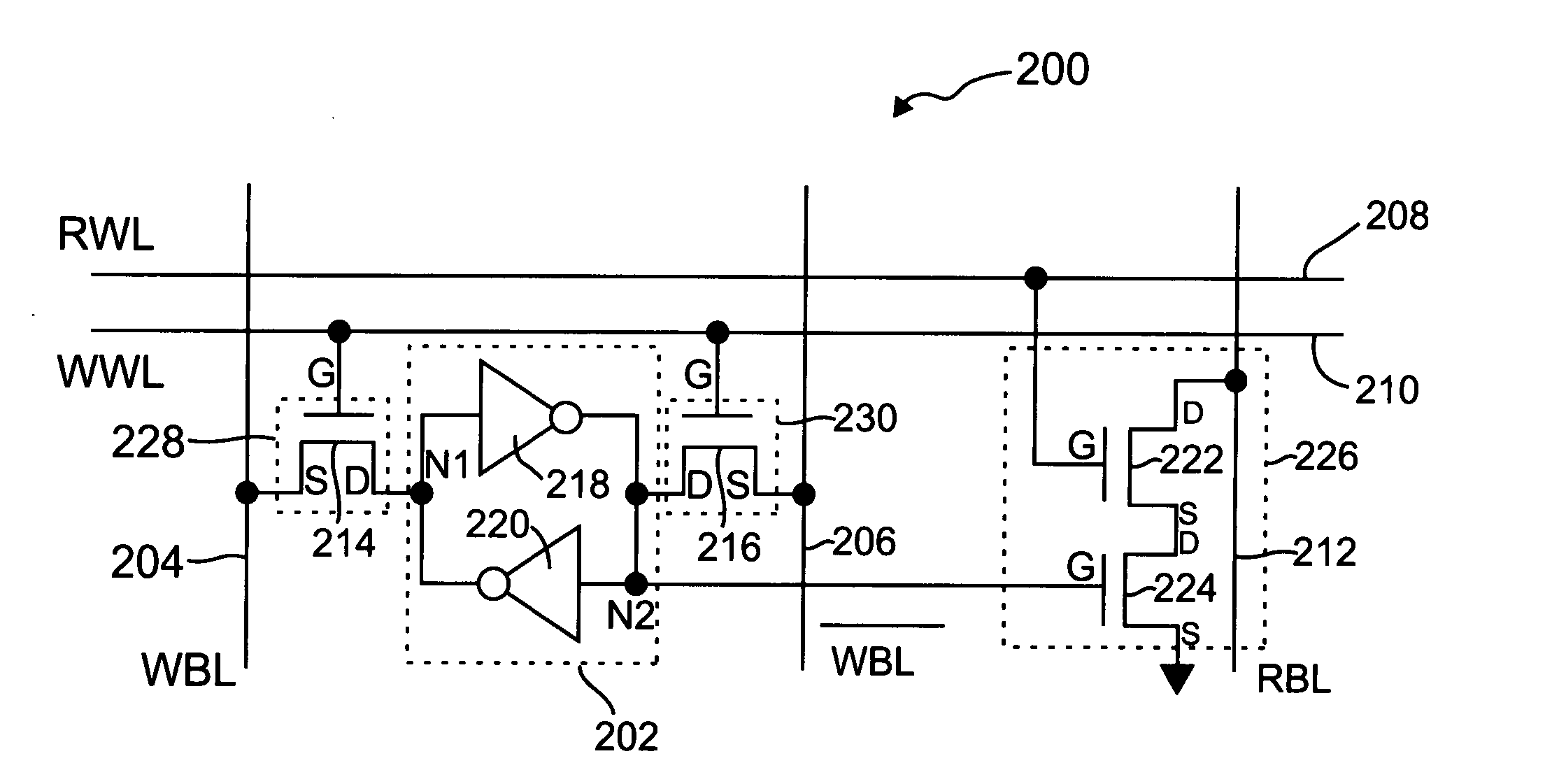

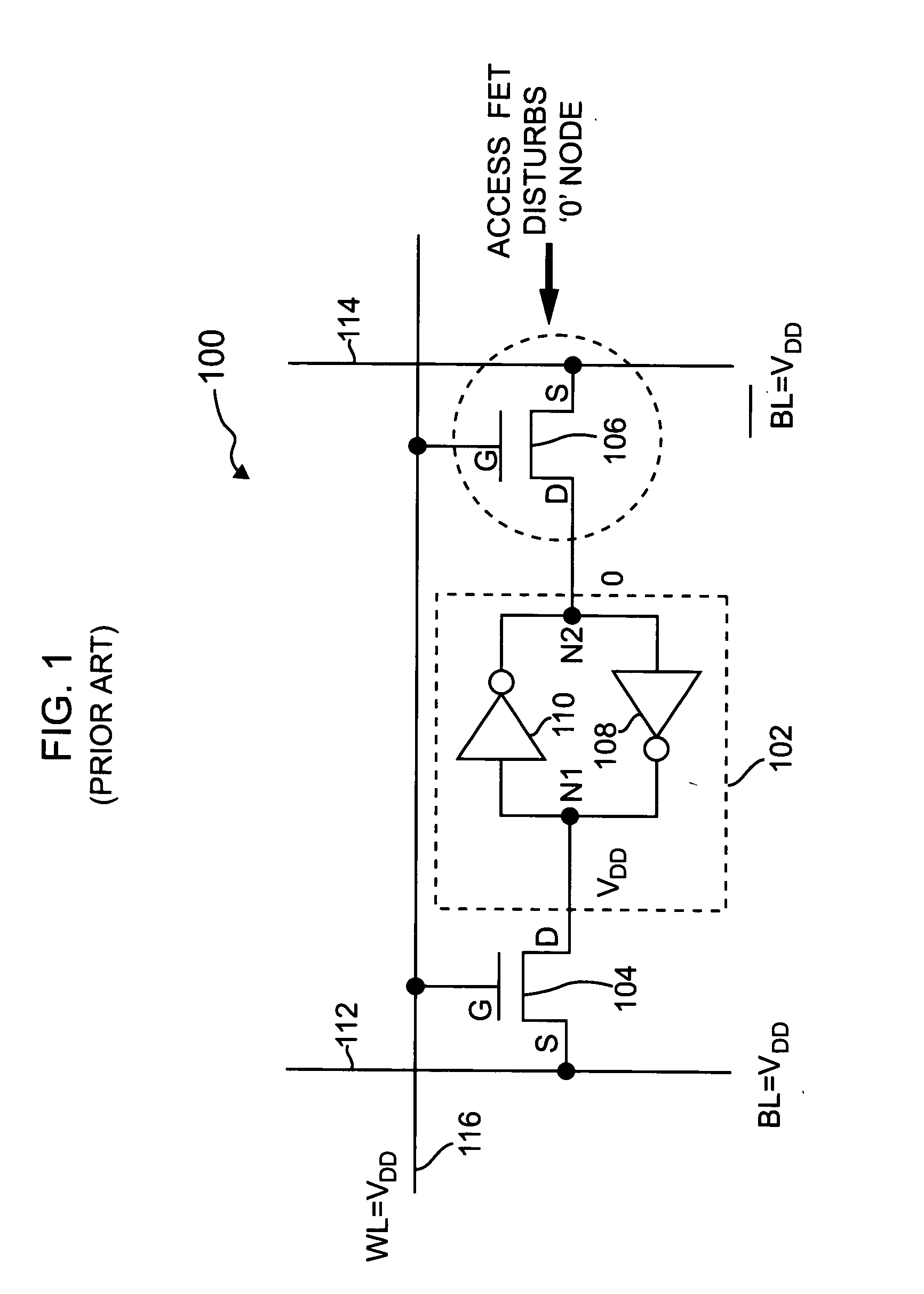

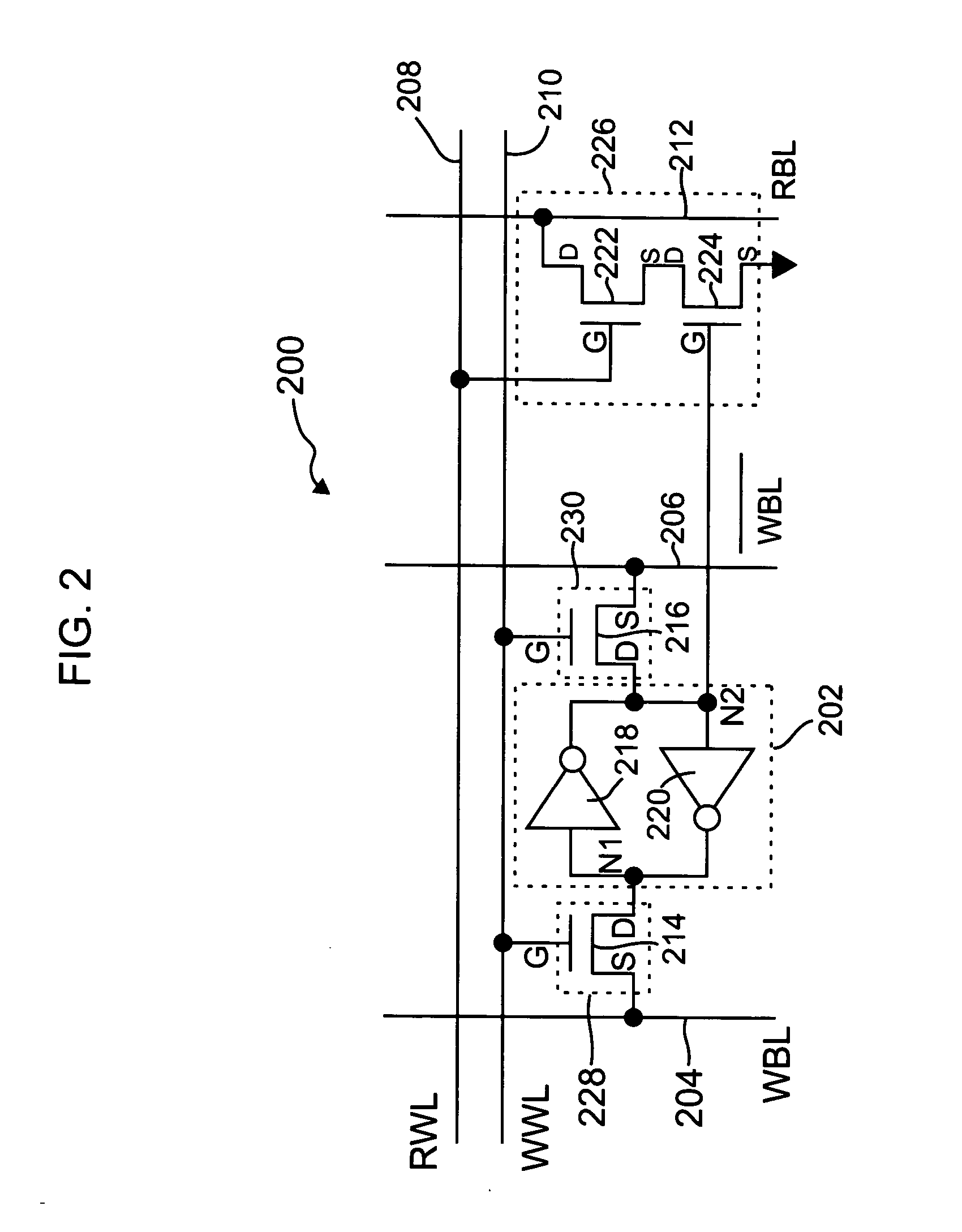

Memory cell having improved read stability

ActiveUS20060146638A1Virtually eliminates disturbs of the memory cellTransistorSolid-state devicesHigh impedanceStorage cell

A memory cell for use in a memory array includes a storage element for storing a logical state of the memory cell, a write circuit and a read circuit. The write circuit is operative to selectively connect a first node of the storage element to at least a first write bit line in the memory array in response to a write signal for selectively writing the logical state of the memory cell. The read circuit includes a substantially high impedance input node connected to the storage element and an output node connectable to a read bit line of the memory array. The read circuit is configured to generate an output signal at the output node which is representative of the logical state of the storage element in response to a read signal applied to the read circuit. The memory cell is configured such that the write circuit is disabled during a read operation of the memory cell so as to substantially isolate the storage element from the first write bit line during the read operation. A strength of at least one transistor device in the storage element is separately optimized relative to a strength of at least one transistor device in the write circuit and / or the read circuit.

Owner:MICROSOFT TECH LICENSING LLC

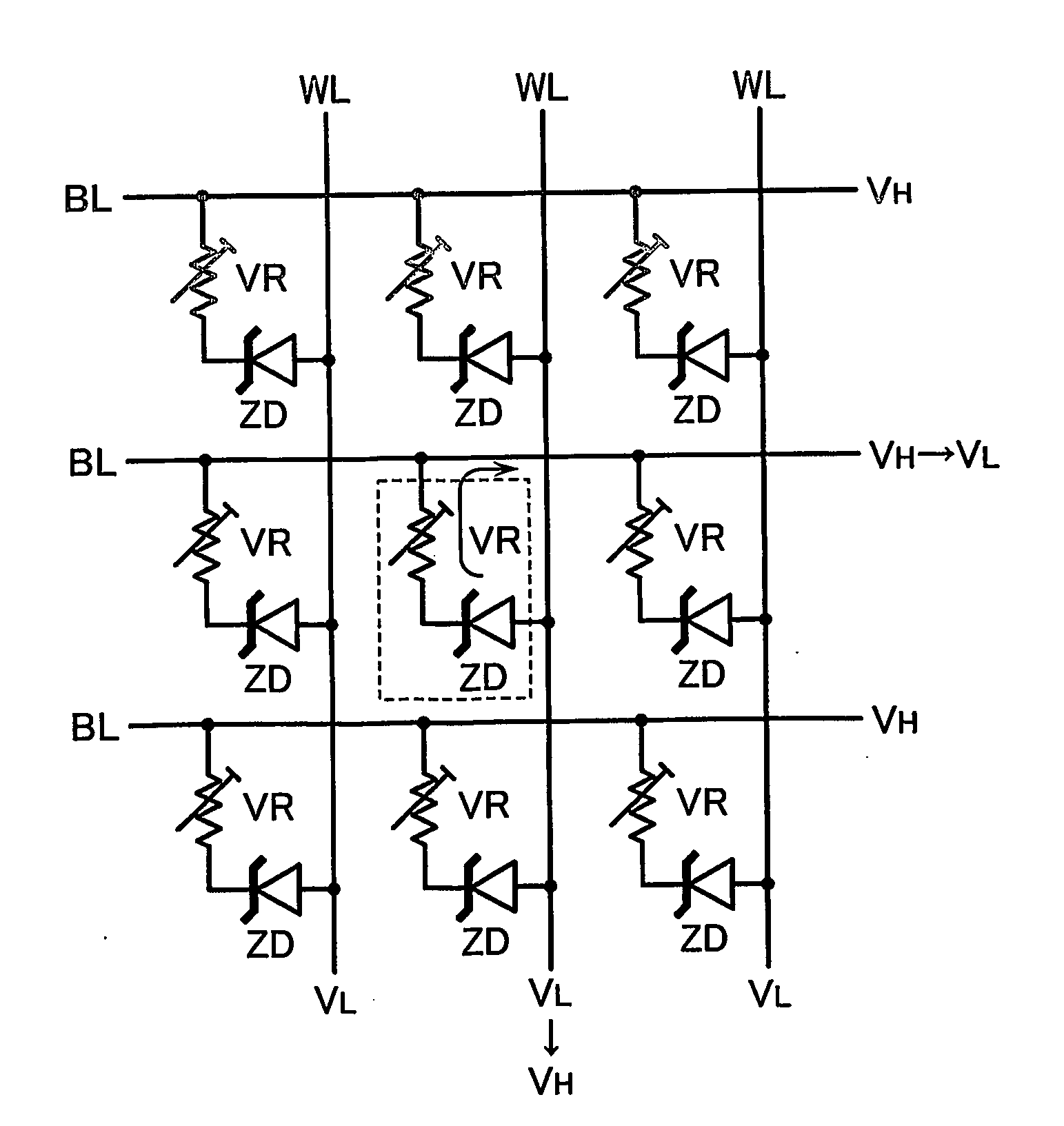

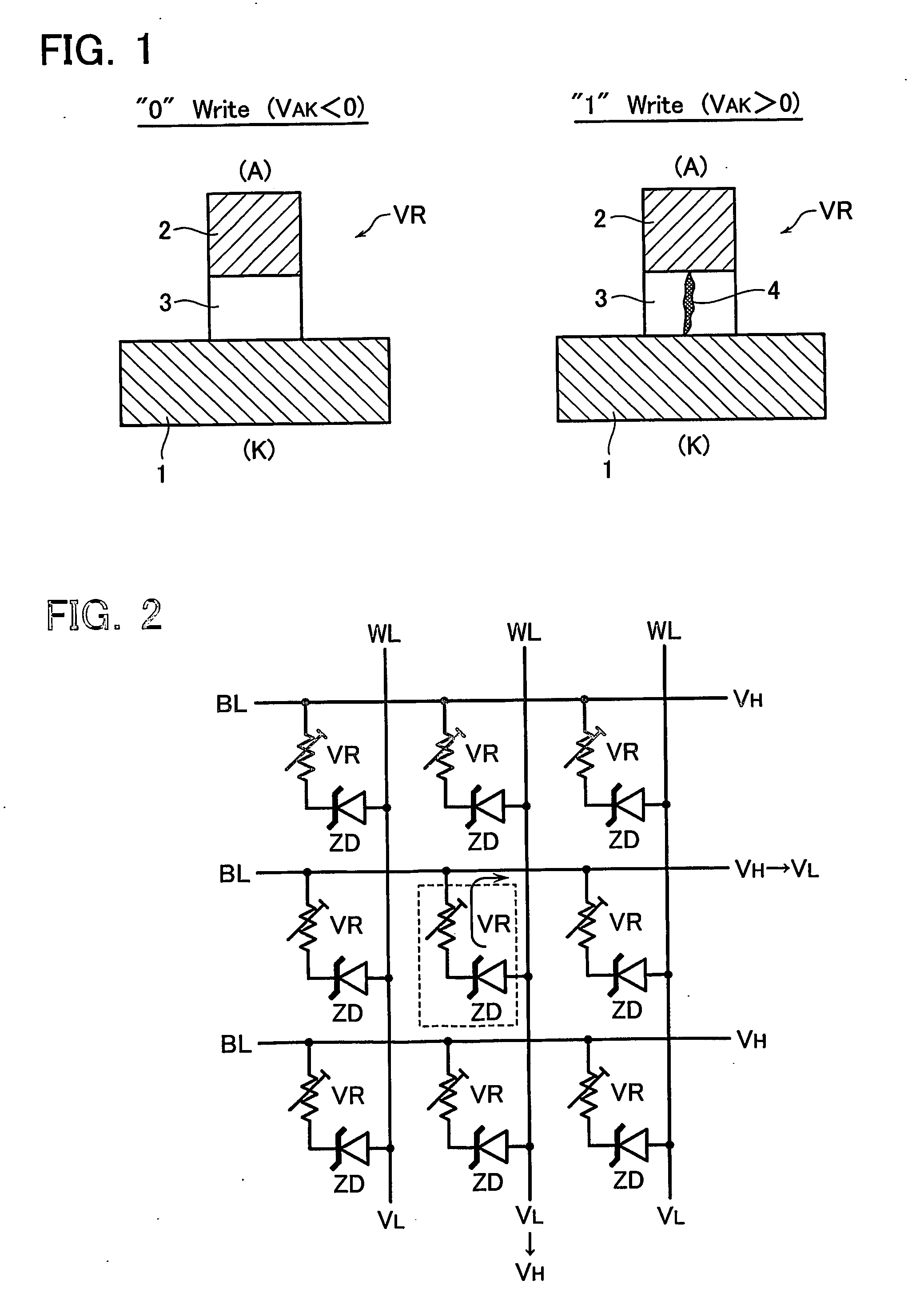

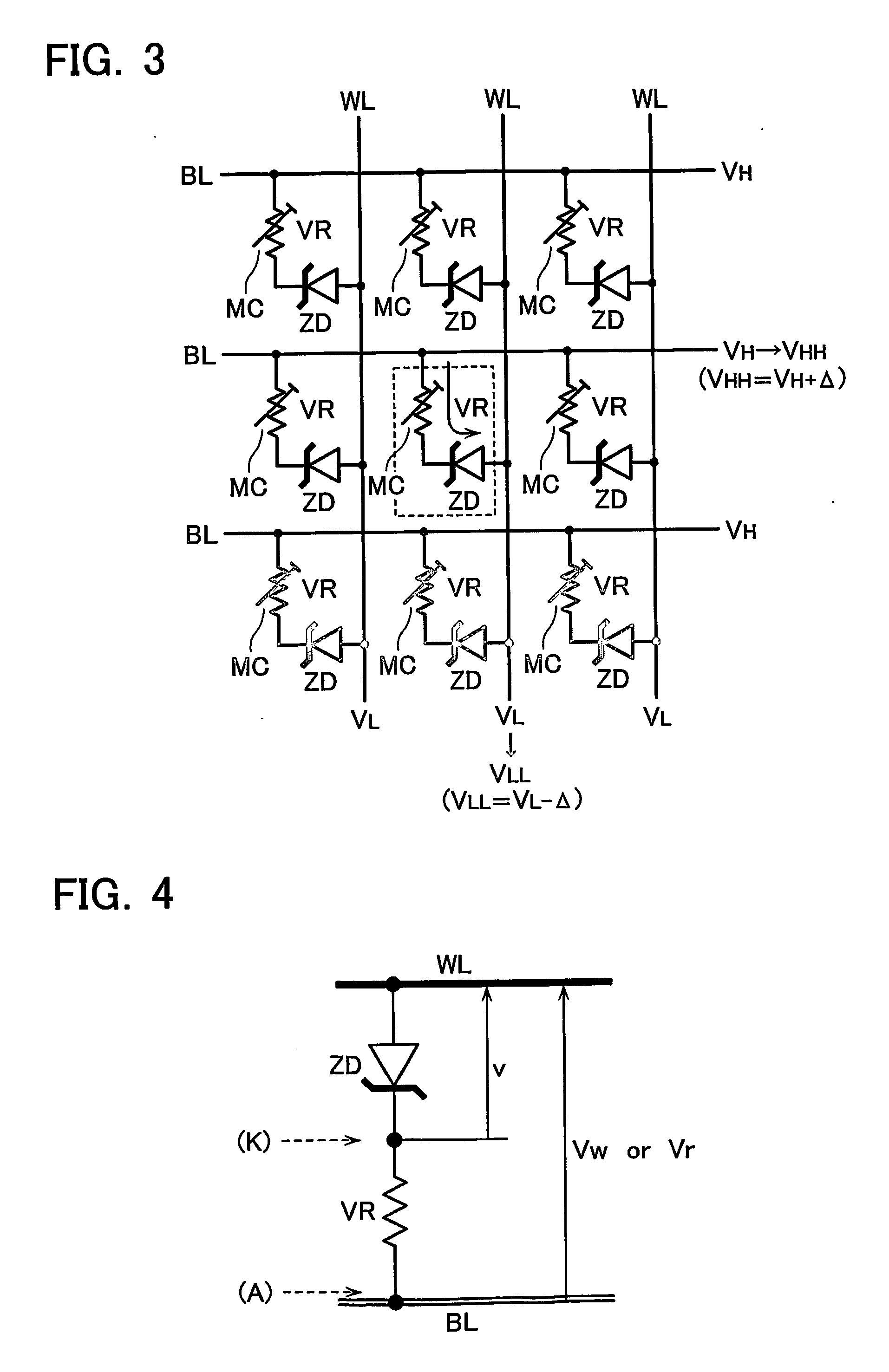

Programmable resistance memory device

programmable resistance memory device includes: a semiconductor substrate; at least one cell array, in which memory cells are arranged, formed above the semiconductor substrate, each the memory cell having a stack structure of a programmable resistance element and an access element, the programmable resistance element storing a high resistance state or a low resistance state determined due to the polarity of voltage application in a non-volatile manner, the access element having such a resistance value in an off-state in a certain voltage range that is ten times or more as high as that in a select state; and a read / write circuit formed on the semiconductor substrate as underlying the cell array for data reading and data writing in communication with the cell array.

Owner:KIOXIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com