Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

56536 results about "Audio power amplifier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An audio power amplifier (or power amp) is an electronic amplifier that amplifies low-power electronic audio signals such as the signal from radio receiver or electric guitar pickup to a level that is high enough for driving loudspeakers or headphones. Audio power amplifiers are found in all manner of sound systems including sound reinforcement, public address and home audio systems and musical instrument amplifiers like guitar amplifiers. It is the final electronic stage in a typical audio playback chain before the signal is sent to the loudspeakers.

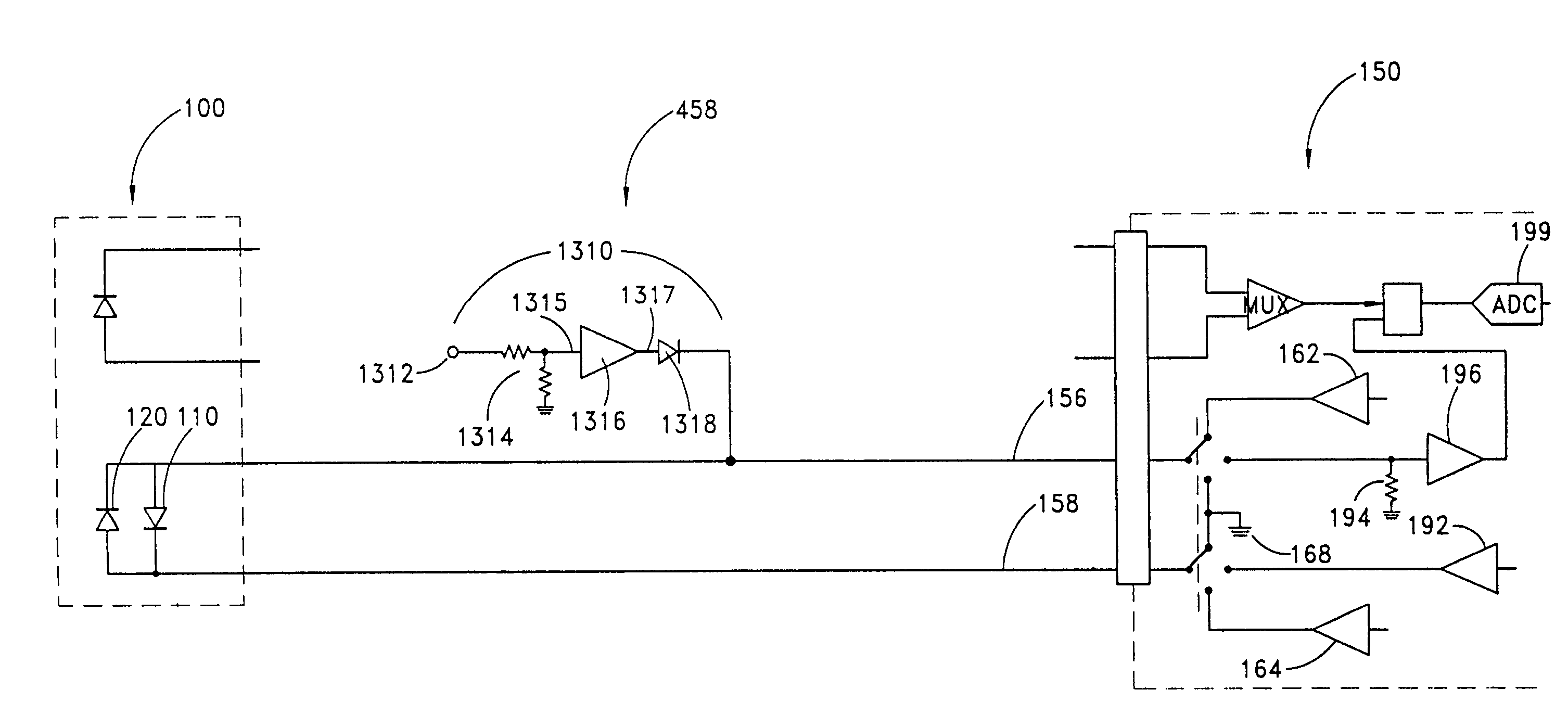

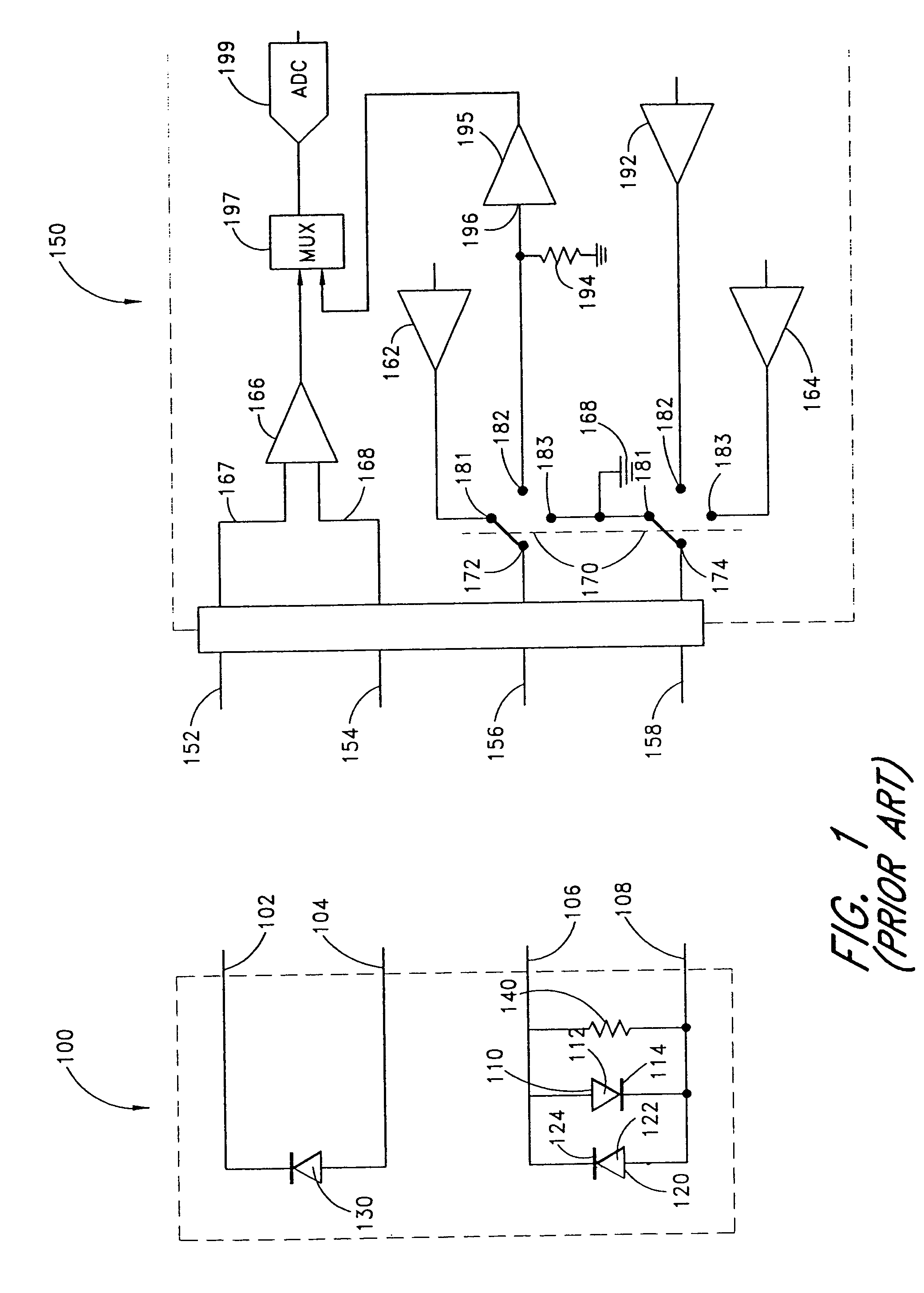

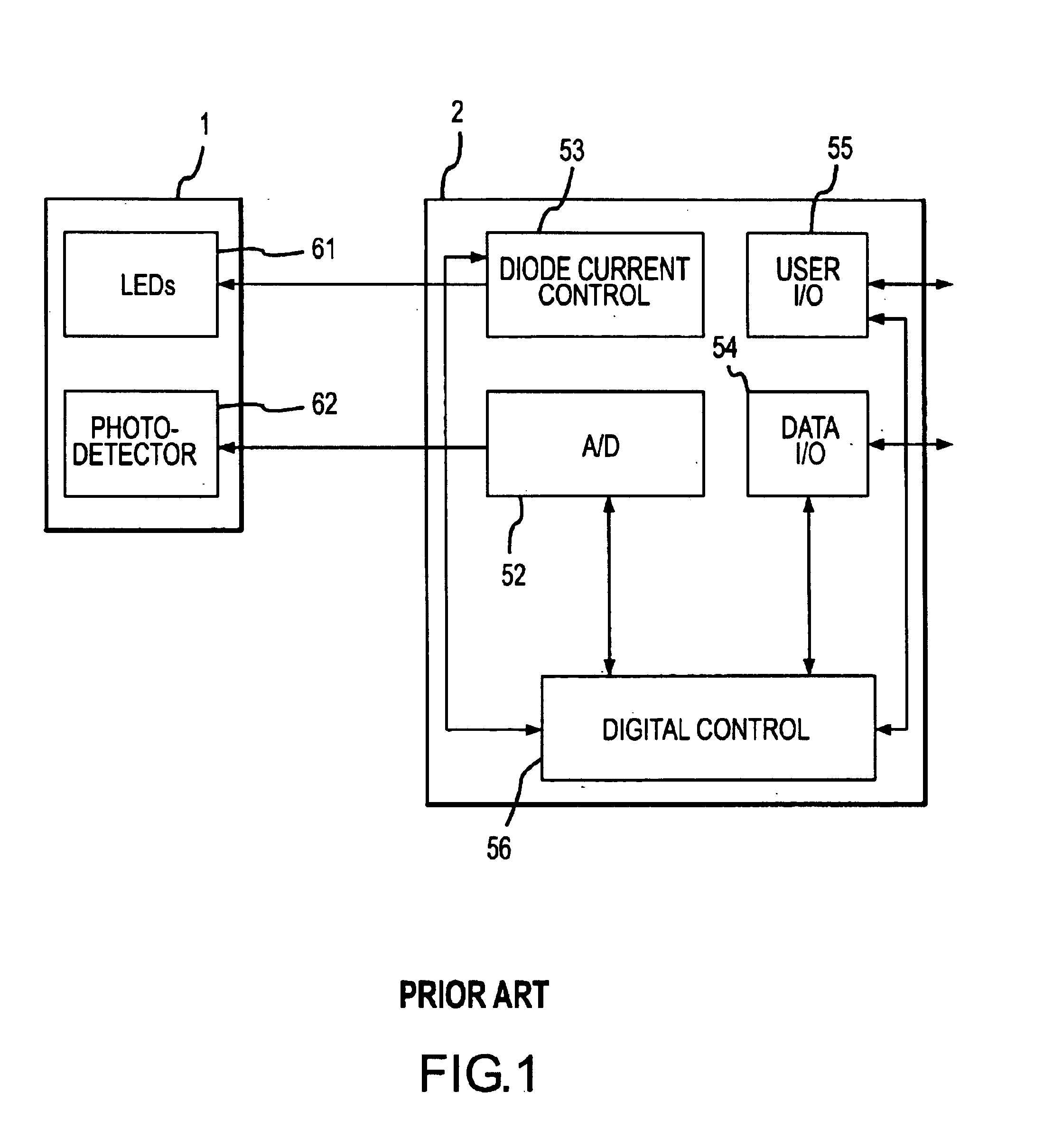

Pulse oximetry sensor adaptor

InactiveUS6993371B2Avoid complex processCost of very criticalDiagnostic recording/measuringSensorsAudio power amplifierPulse oximetry

An adapter allows the interconnection of a sensor originating from one manufacturer to be coupled with conventionally incompatible monitors originating from other manufacturers to form a properly functioning pulse oximetry system. The adapter matches a sensor driver in a monitor to the current requirements and light source configuration of a sensor. The adapter also matches a sensor's light detector signal level to the dynamic range requirements of a monitor preamplifier. Further, the adapter provides compatible sensor calibration, sensor type and security information to a monitor. The adapter may have a self-contained power source or it may derive power from the monitor, allowing both passive and active adapter components. The adapter is particular suited as an adapter cable, replacing a conventional patient cable or sensor cable as the interconnection between a sensor to a monitor in a pulse oximetry system.

Owner:JPMORGAN CHASE BANK NA

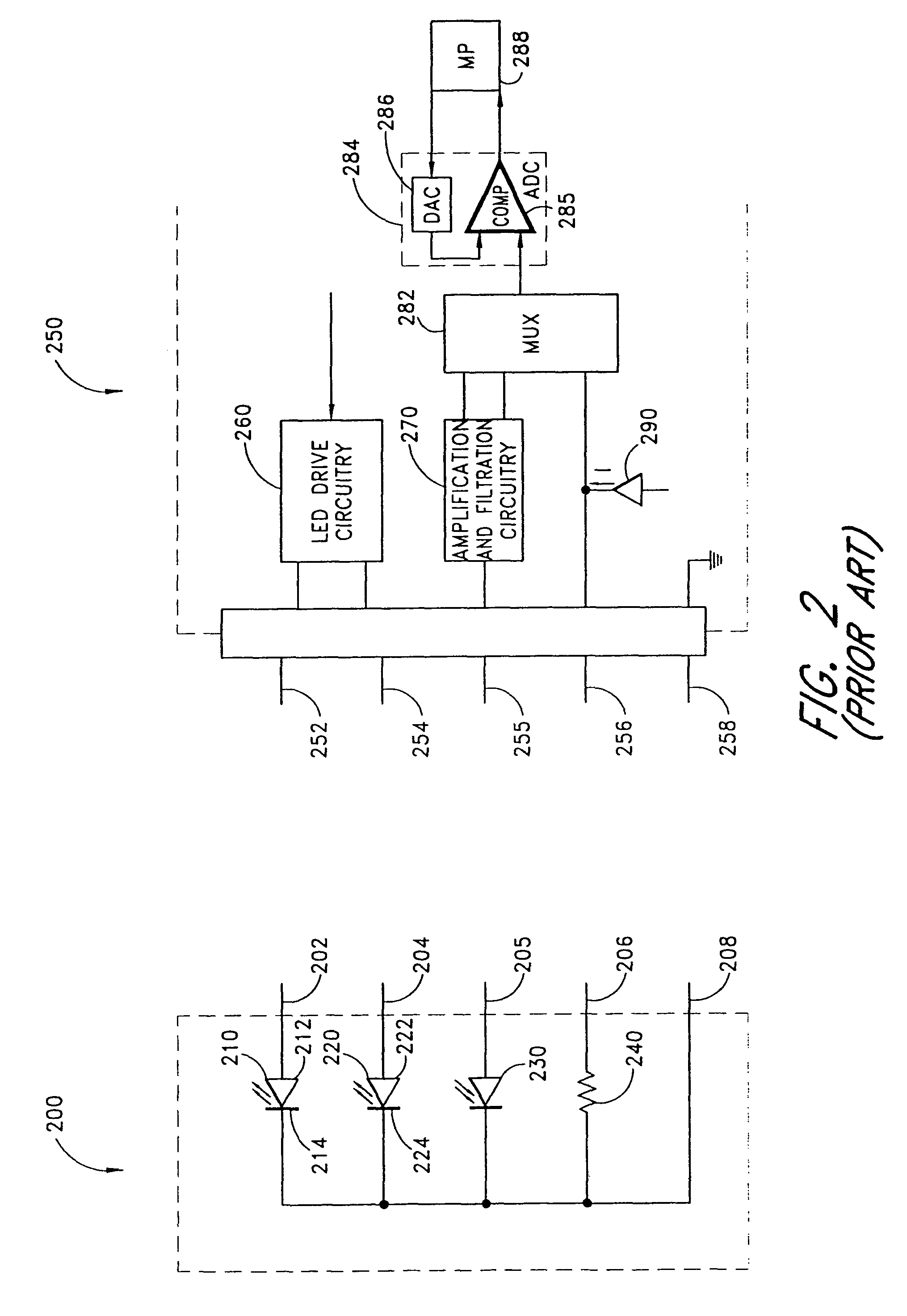

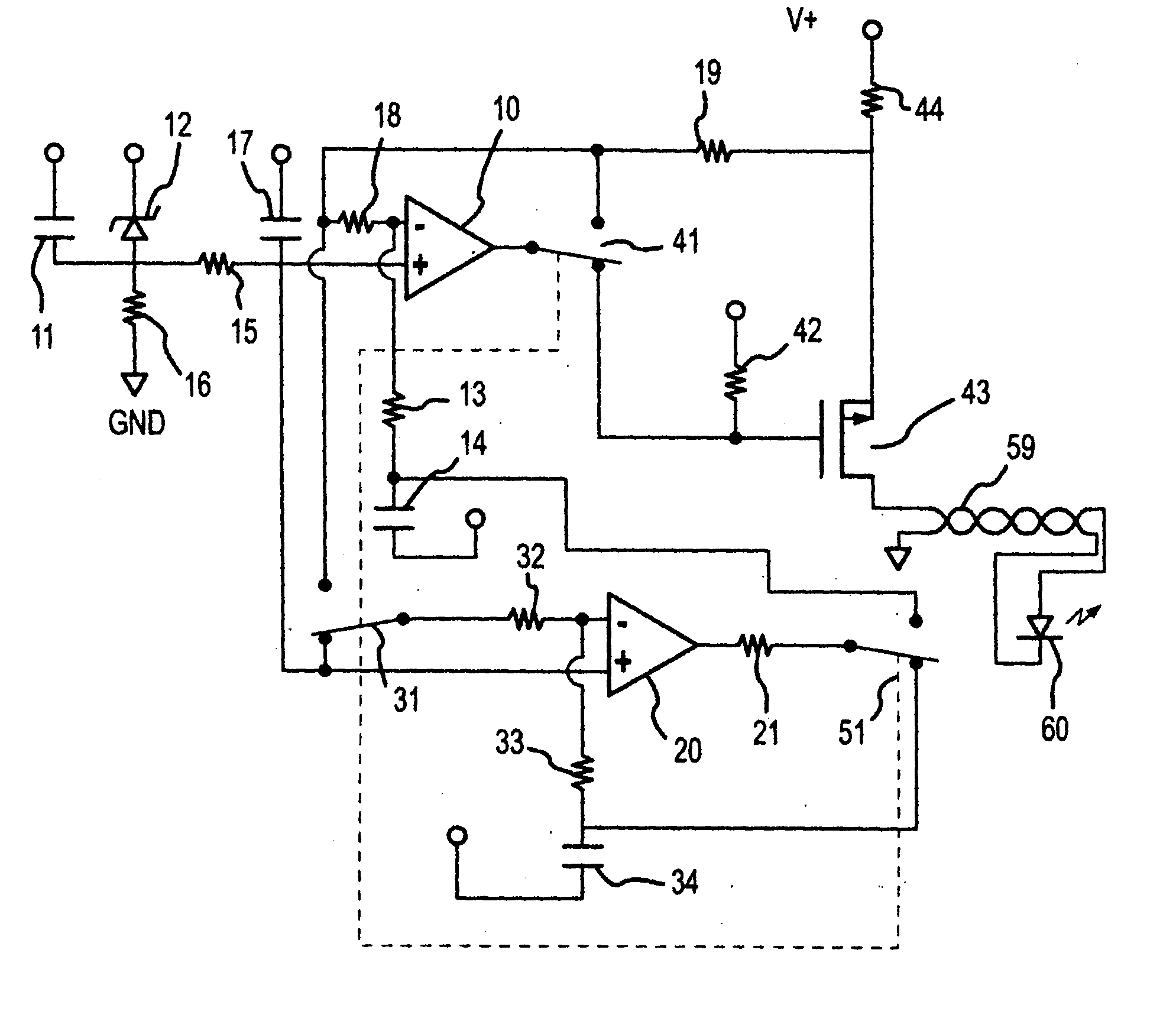

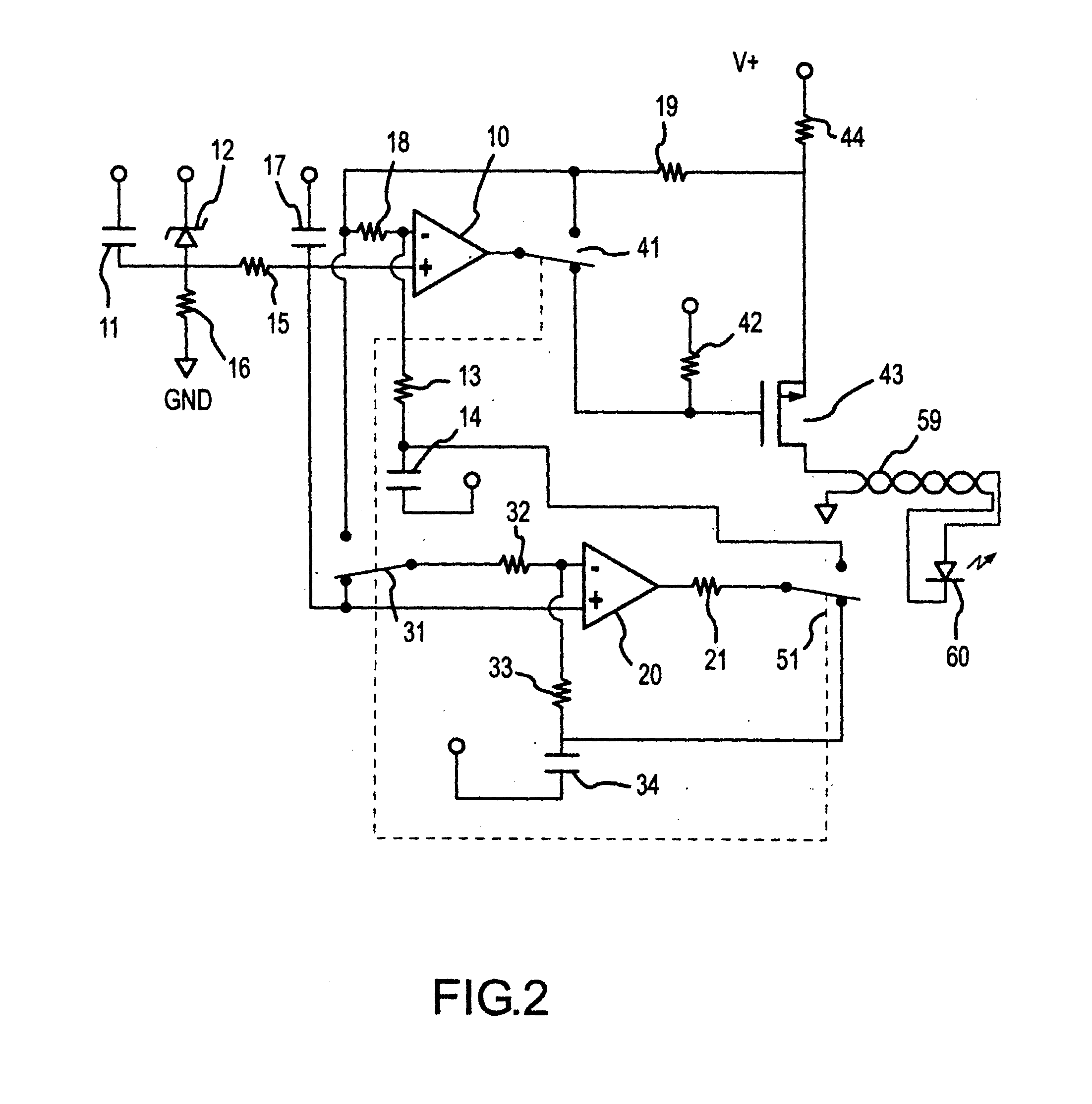

Oximeter with nulled op-amp current feedback

InactiveUS6720734B2Eliminating low frequency driftEasy to detectElectric light circuit arrangementDiagnostic recording/measuringDriving currentLight flashes

A method of producing a diode drive current in an oximeter includes sensing at least a part of a current passing through the diode and converting the sensed current to a sensed voltage, inputting the sensed voltage to a feedback amplifier for stabilizing the current passing through the diode, and eliminating an offset voltage across inputs of the feedback amplifier. A pulse oximeter includes a diode for emitting light flashes, a feedback amplifier having inputs, a feedback capacitor, and an output, the feedback amplifier stabilizing a current passing through the diode, a nulling amplifier having inputs, a nulling capacitor, and an output, the nulling amplifier charging and discharging the feedback capacitor until the inputs of the feedback amplifier are at a same voltage. The operation may include synchronizing an elimination of input offset voltages of the feedback and nulling amplifiers with on or off state of diode current.

Owner:DATEX OHMEDA

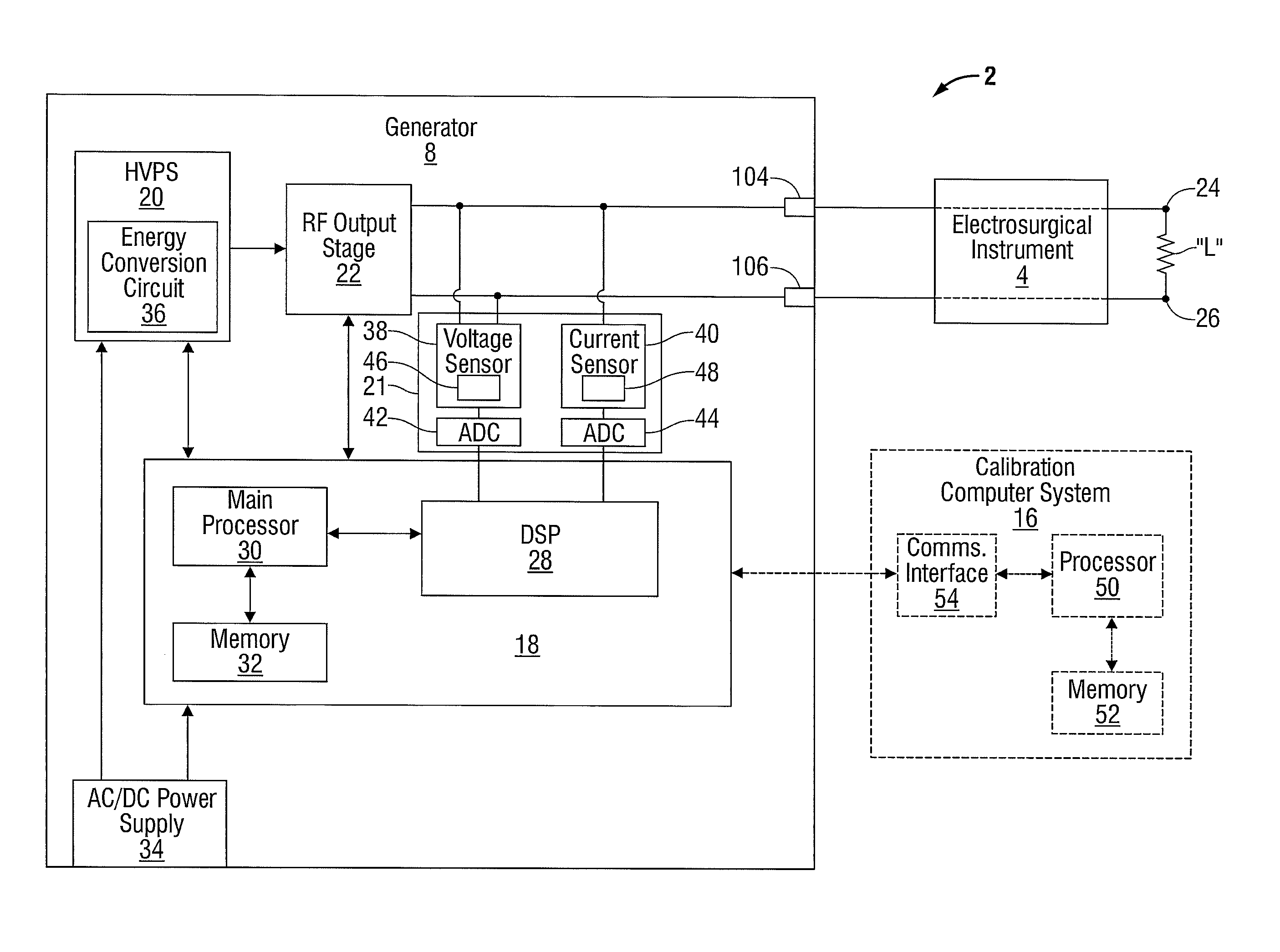

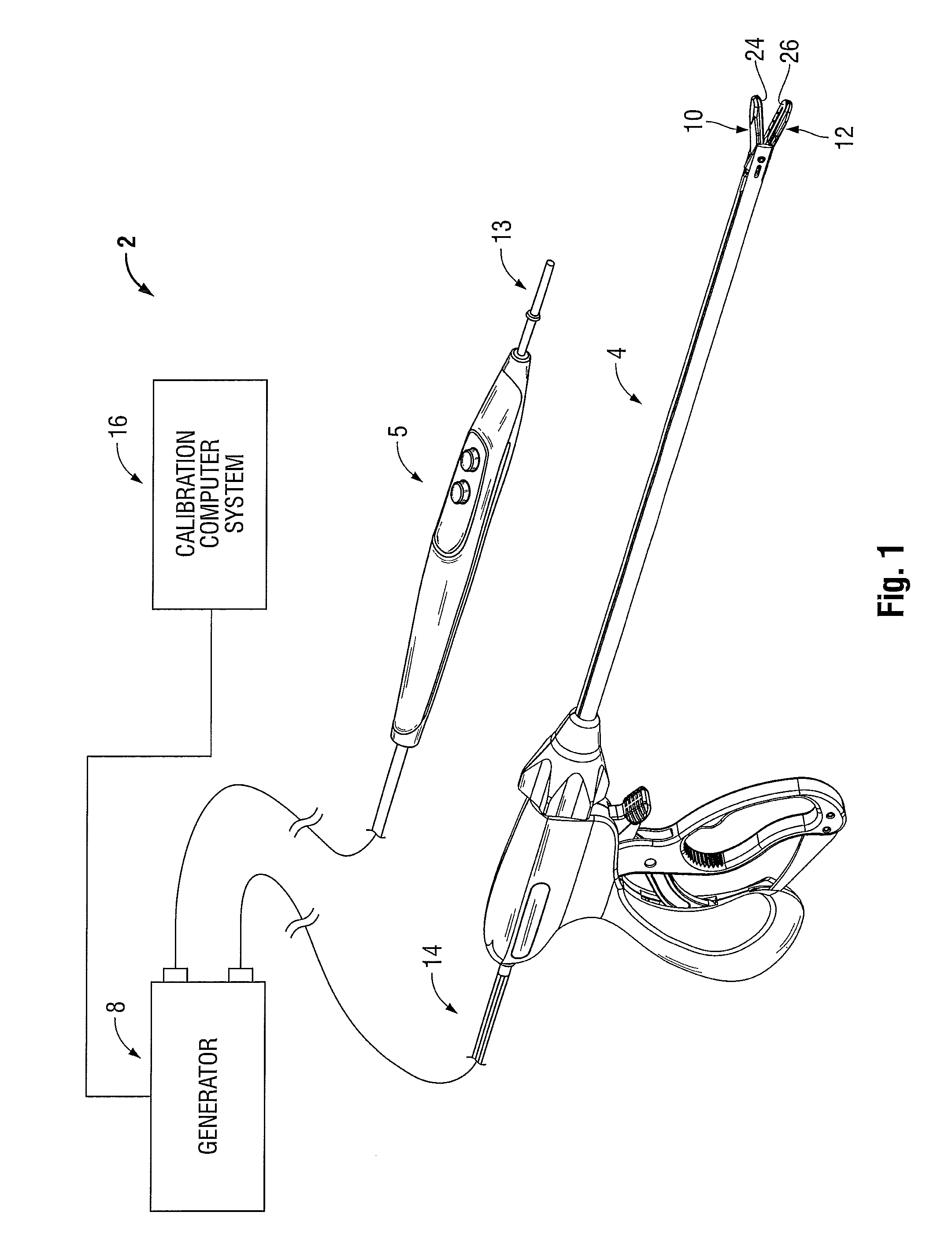

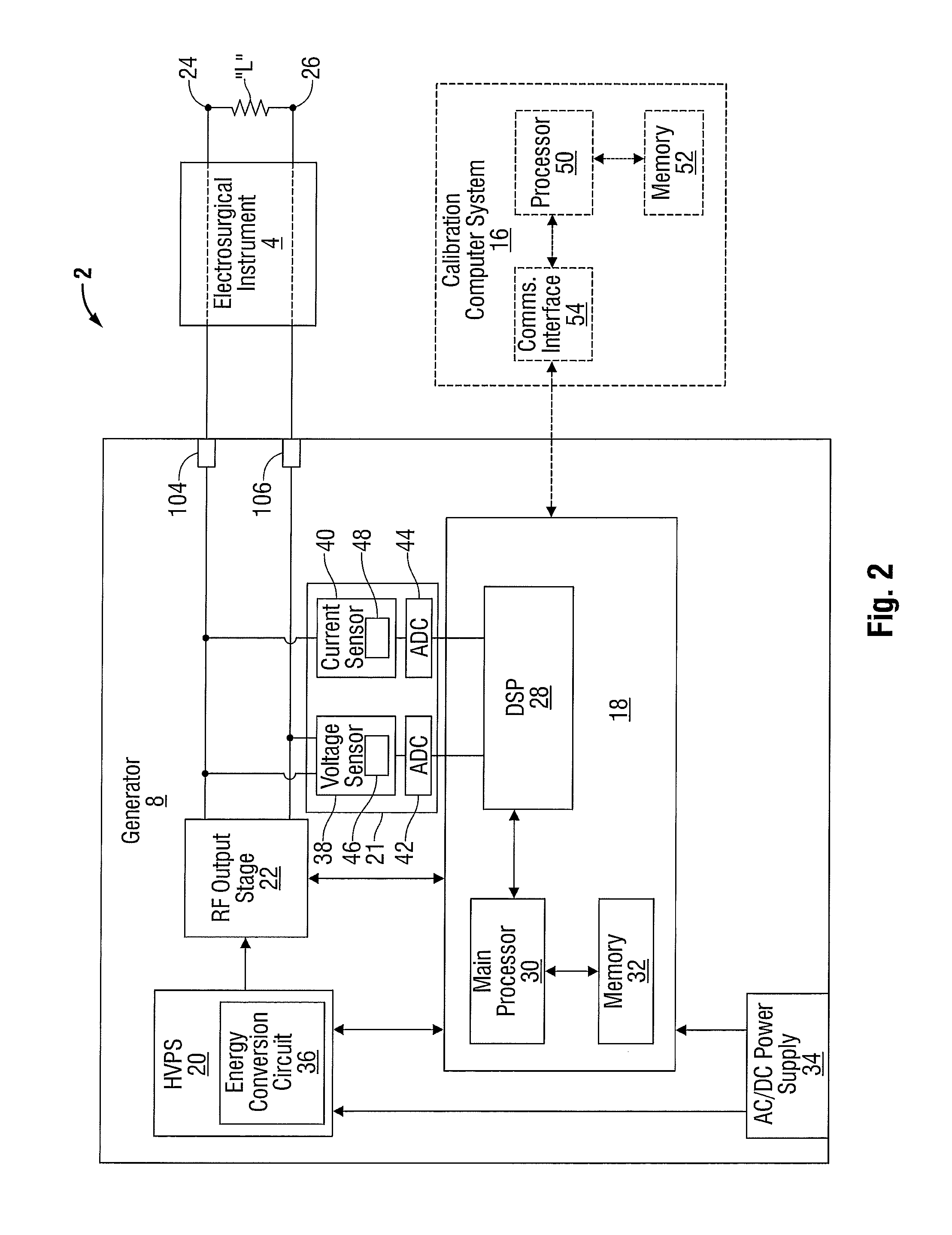

Electrosurgical generator

An electrosurgical system for performing an electrosurgical procedure is provided and includes an electrosurgical generator and a calibration computer system. The electrosurgical generator includes one or more processors and a measurement module including one or more log amps that are in operative communication with the processor. The calibration computer system configured to couple to a measurement device and is configured to measure parameters of an output signal generated by the electrosurgical generator. The calibration computer system is configured to compile the measured parameters into one or more data look-up tables and couple to the electrosurgical generator for transferring the data look-up table(s) to memory of the electrosurgical generator. The microprocessor is configured to receive an output from the log amp(s) and access the data look-up table(s) from memory to execute one or more control algorithms for controlling an output of the electrosurgical generator.

Owner:COVIDIEN LP

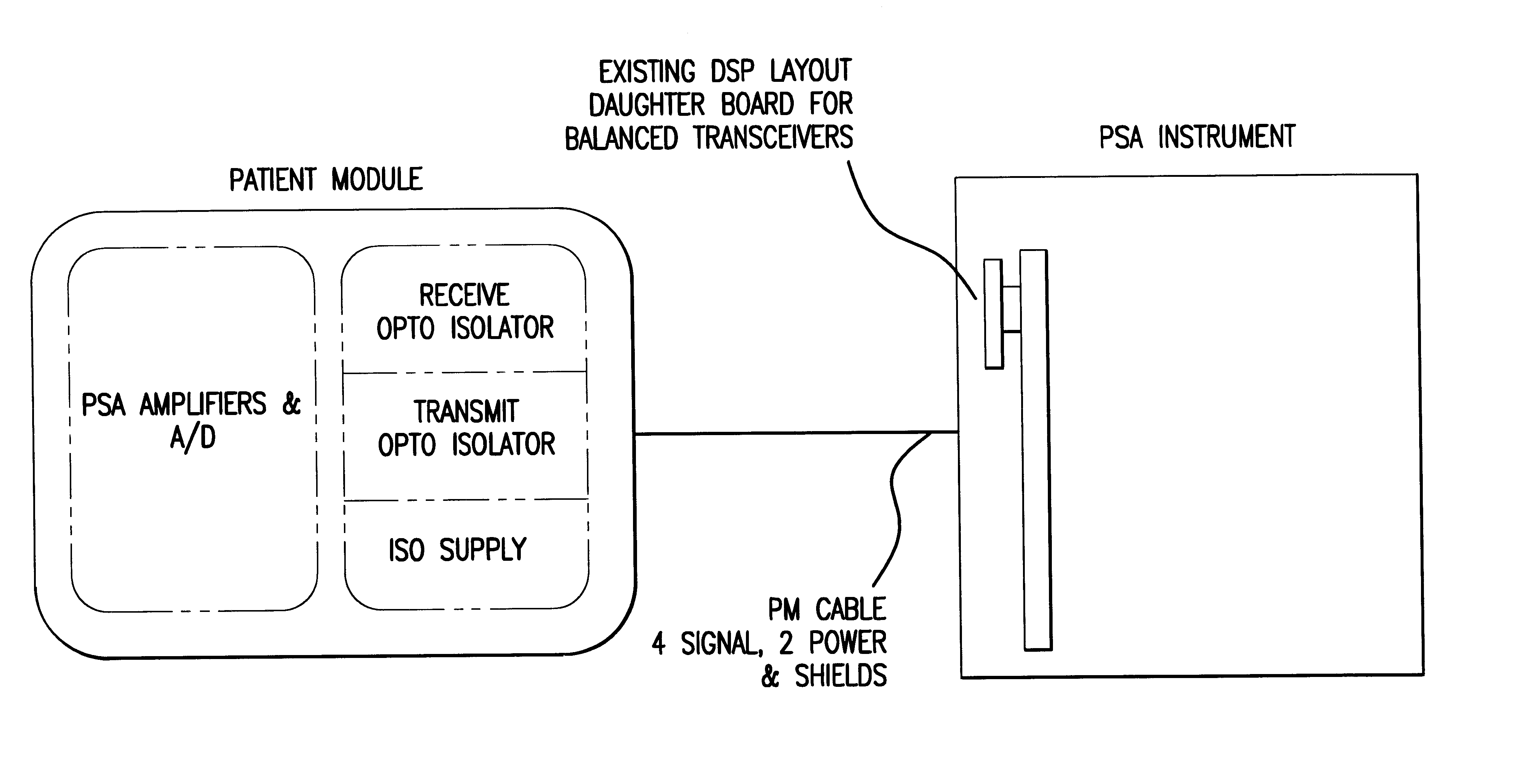

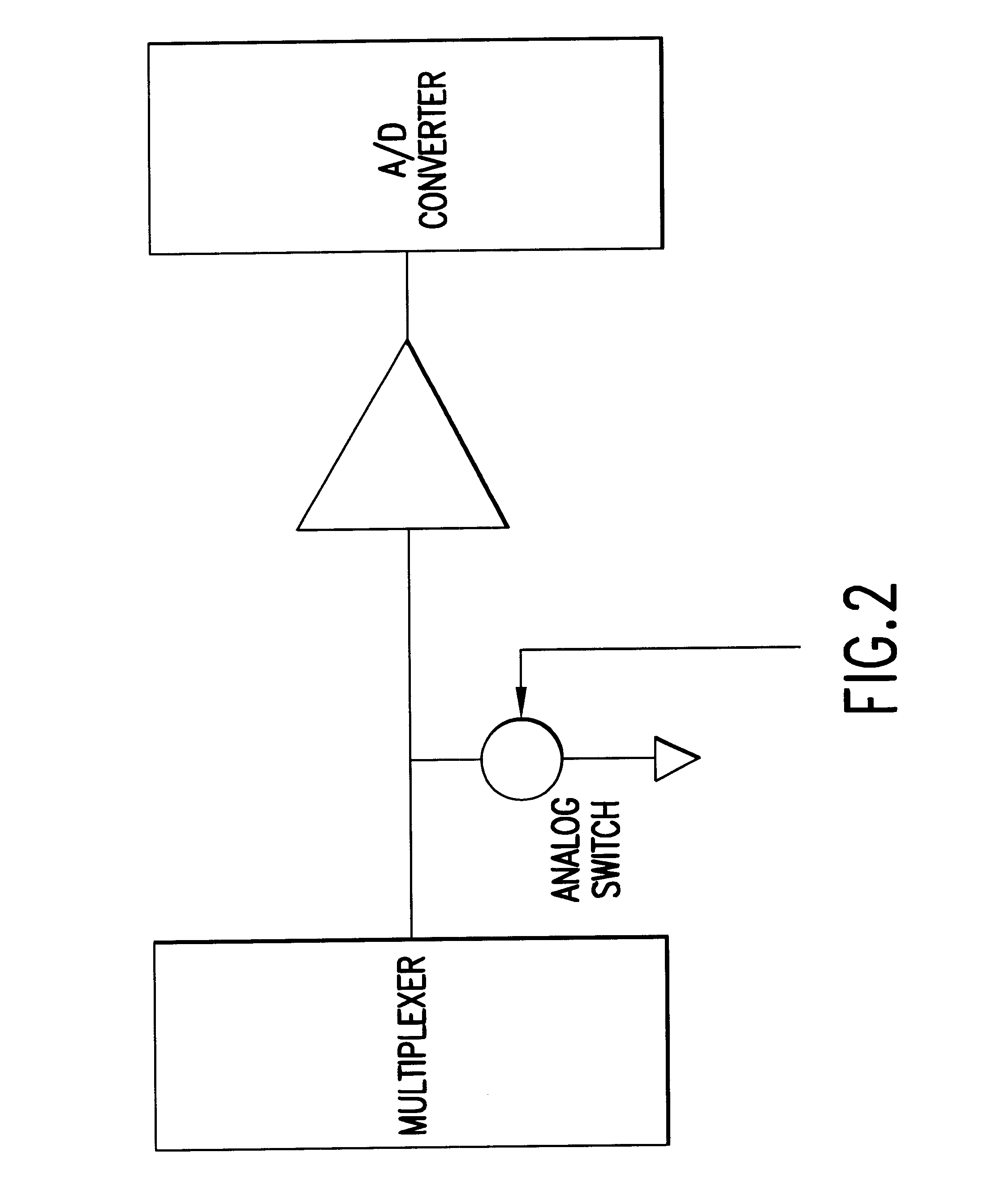

Module for acquiring electroencephalograph signals from a patient

InactiveUS6430437B1Good techniqueEliminate artifactsElectroencephalographyPloughsAudio power amplifierMultiplexer

A patient module comprising an 8 channel EEG pre-amplifier whose signal acquisition and processing characteristics are optimized for use in the operating room and intensive care unit. This patient module comprises at least an optimized multistage input filter, an optimized input stage circuit topography, ultra-isolation, oversampling, a multiplexer inter-sample charge dump, and high performance low-frequency-enhanced shielding.

Owner:JPMORGAN CHASE BANK NA

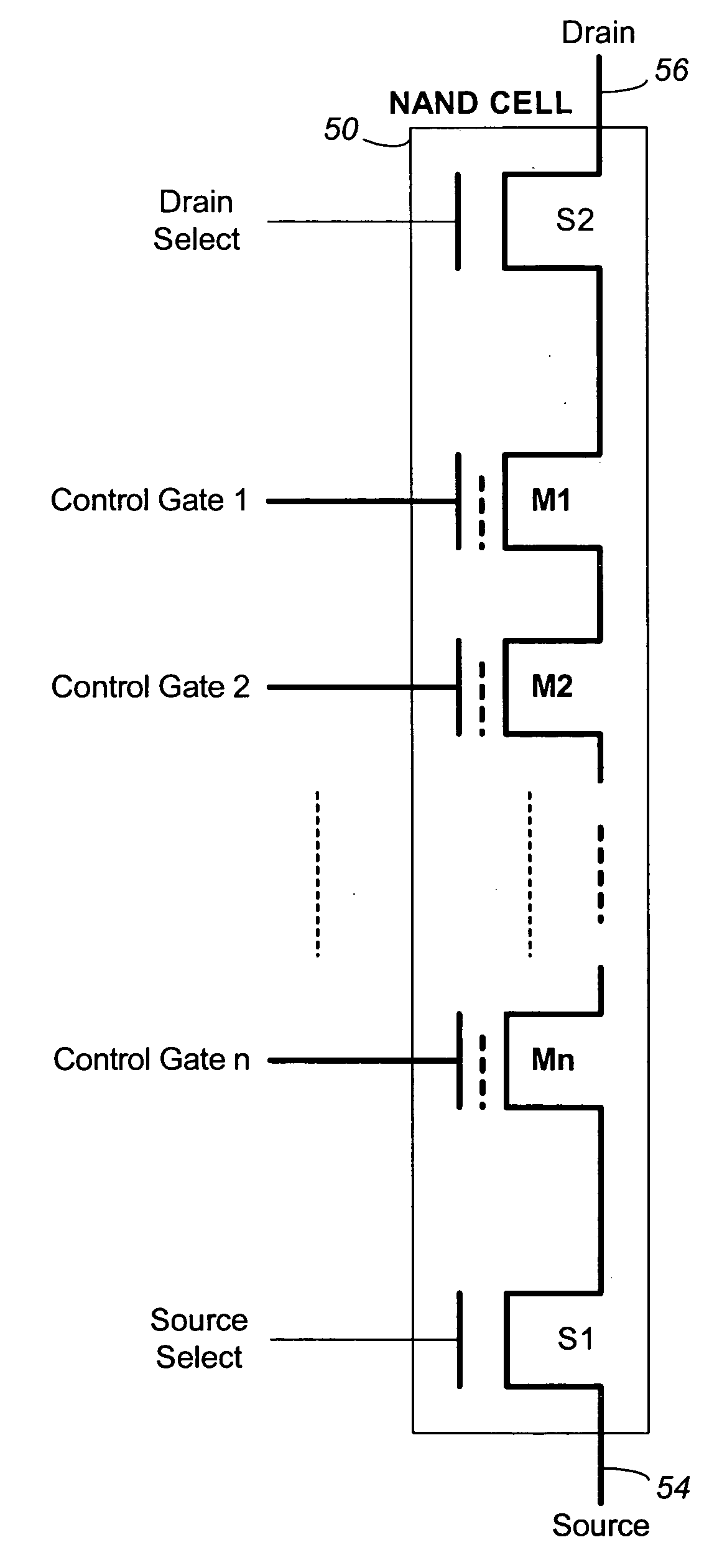

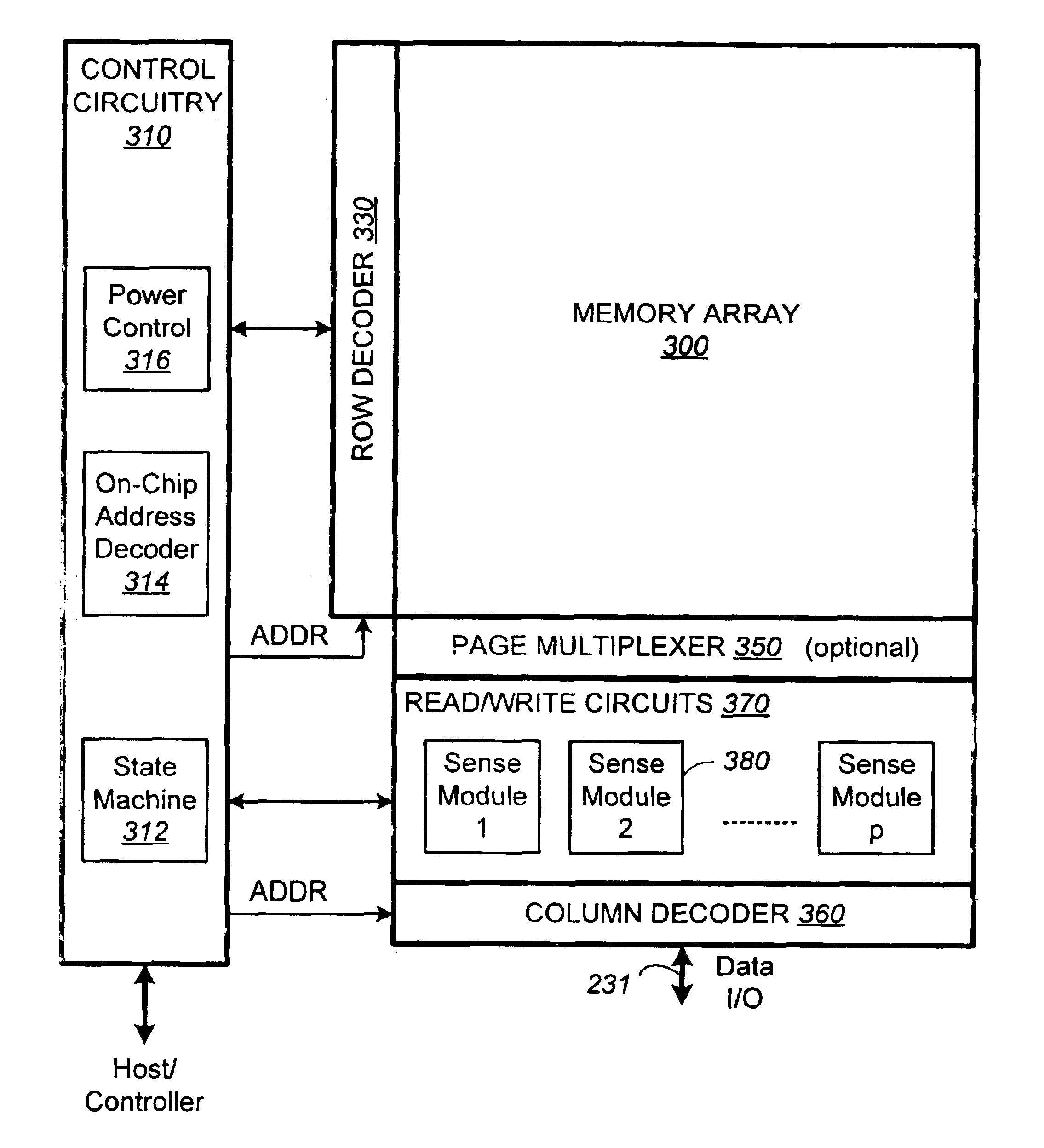

Non-volatile memory and method with shared processing for an aggregate of read/write circuits

InactiveUS20060140007A1Maximum versatilityMinimal componentRead-only memoriesDigital storageAudio power amplifierAssociative processor

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. The multiple read / write circuits are organized into a bank of similar stacks of components. Redundant circuits such as a processor for processing data among stacks each associated with multiple memory cells are factored out. The processor is implemented with an input logic, a latch and an output logic. The input logic can transform the data received from either the sense amplifier or the data latches. The output logic further processes the transformed data to send to either the sense amplifier or the data latches or to a controller. This provides an infrastructure with maximum versatility and a minimum of components for sophisticated processing of the data sensed and the data to be input or output.

Owner:SANDISK TECH LLC

Front-end signal compensation

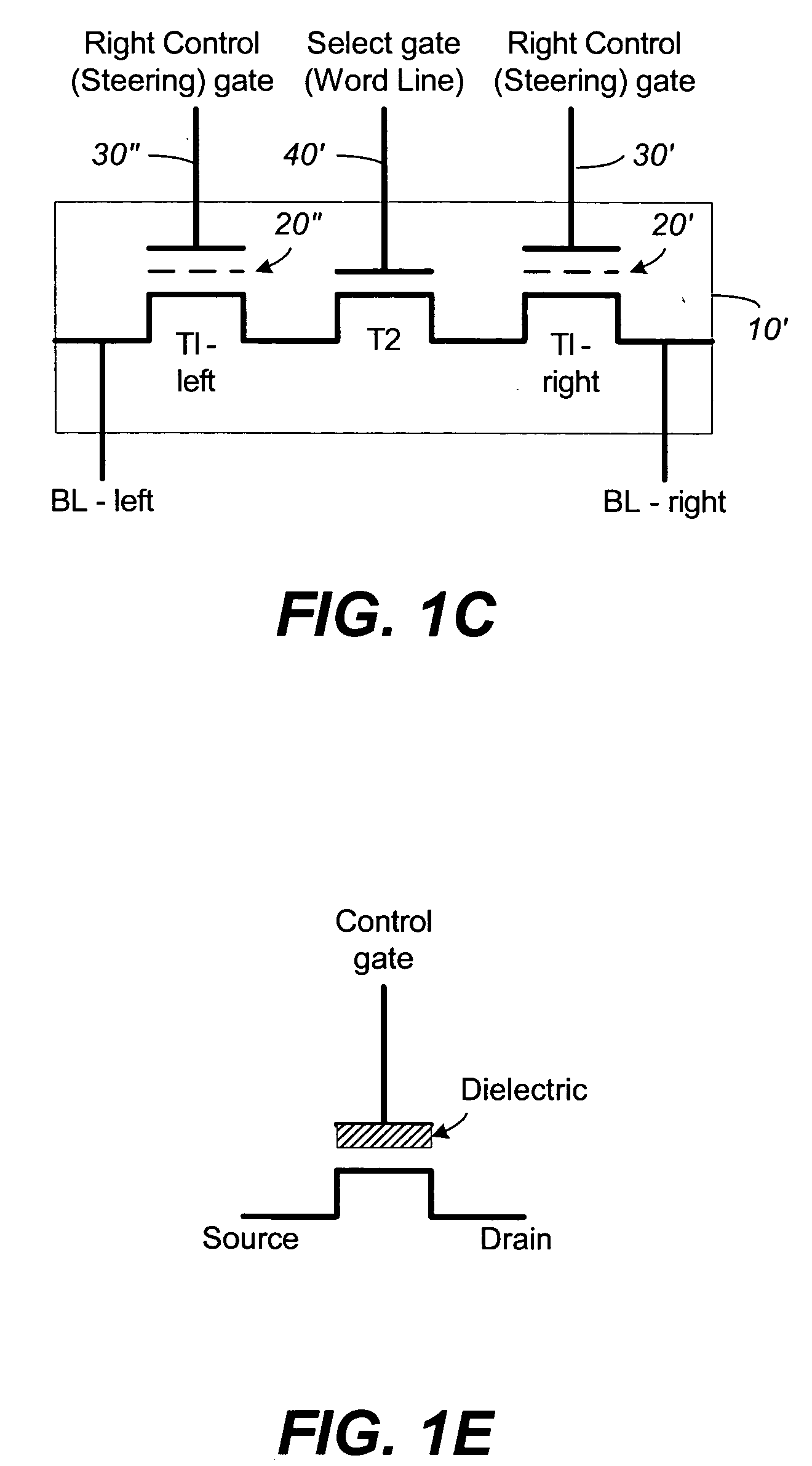

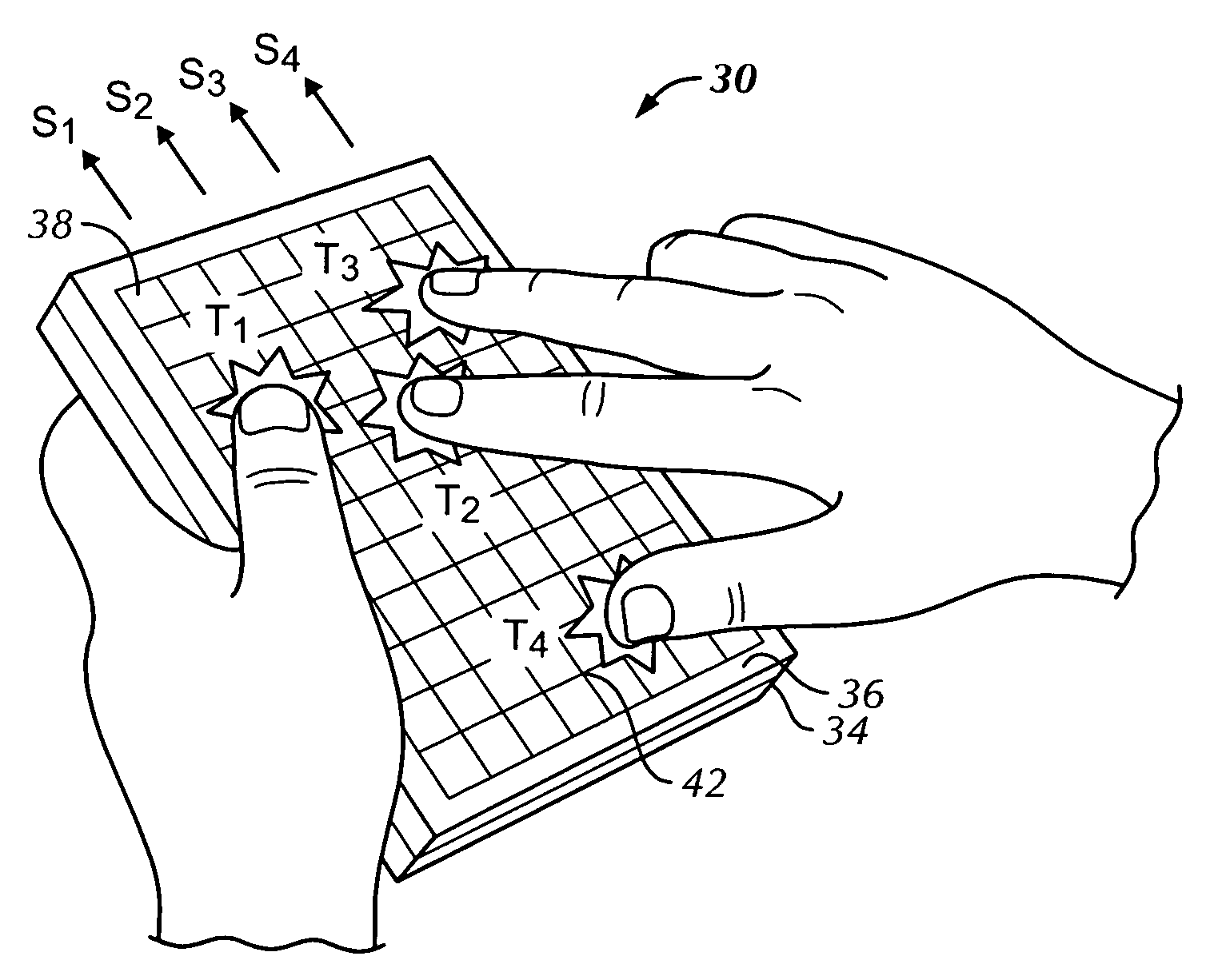

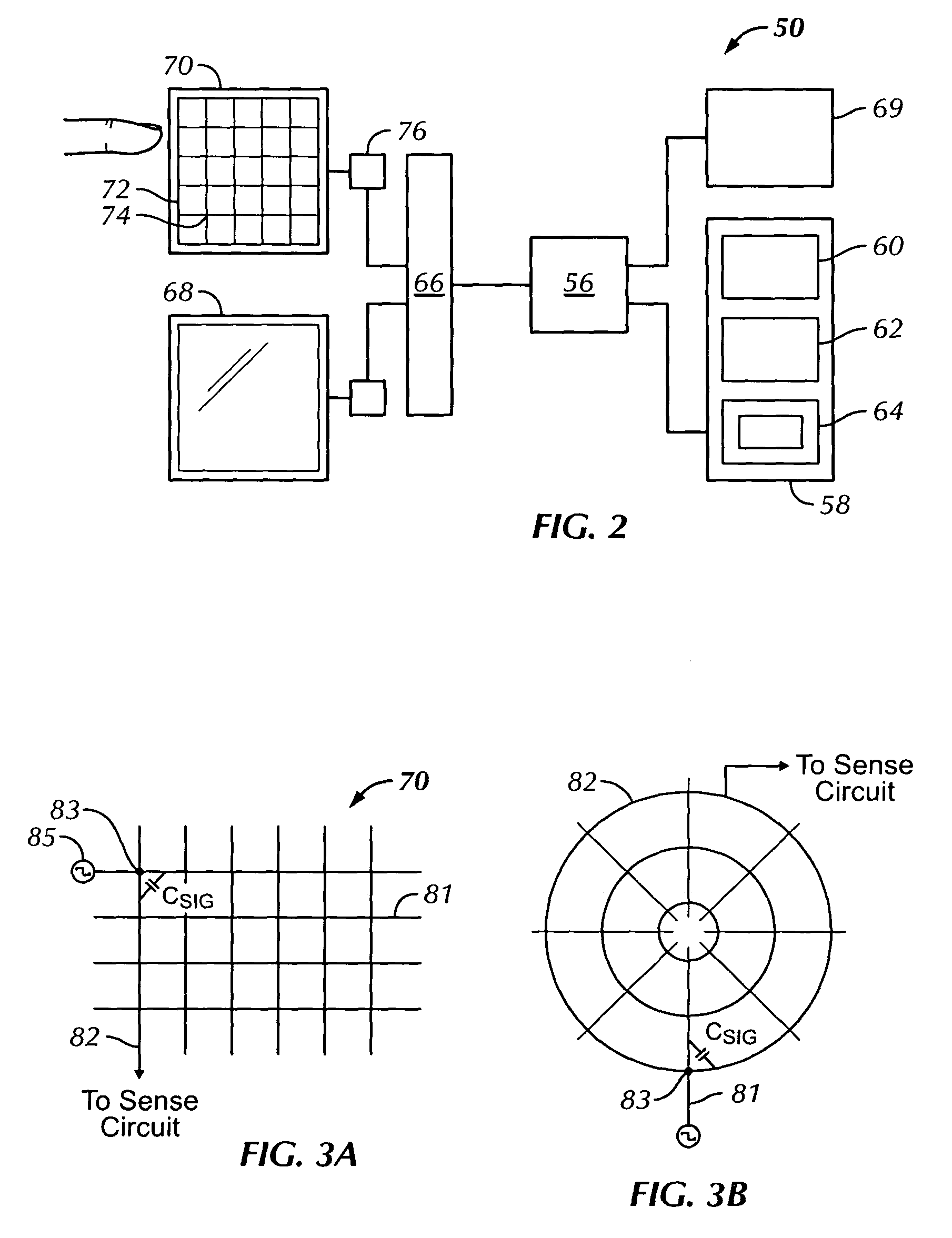

A touch surface device having improved sensitivity and dynamic range is disclosed. In one embodiment, the touch surface device includes a touch-sensitive panel having at least one sense node for providing an output signal indicative of a touch or no-touch condition on the panel; a compensation circuit, coupled to the at least one sense node, for generating a compensation signal that when summed with the output signal removes an undesired portion of the output signal so as to generated a compensated output signal; and an amplifier having an inverting input coupled to the output of the compensation circuit and a non-inverting input coupled to a known reference voltage.

Owner:APPLE INC

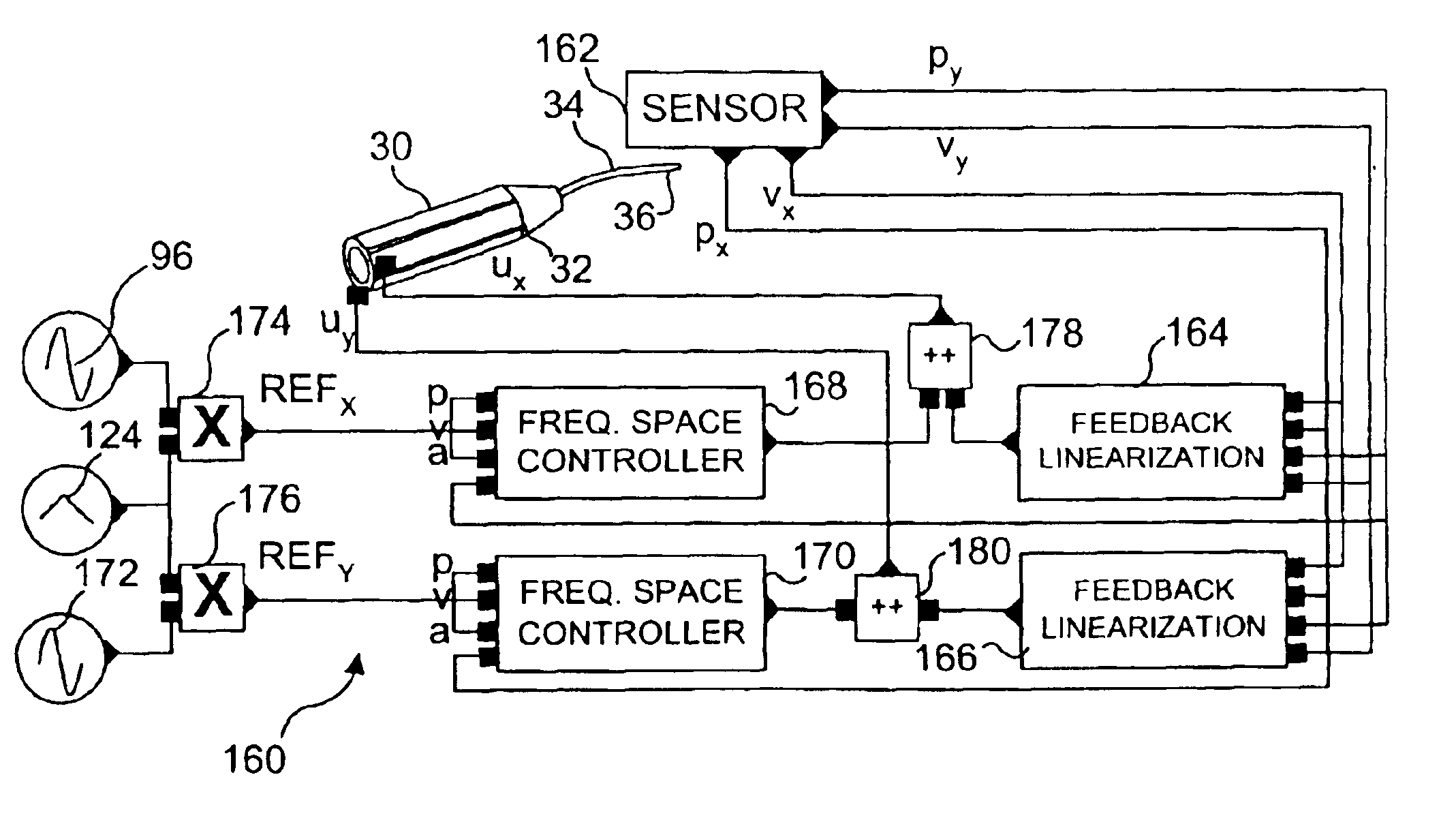

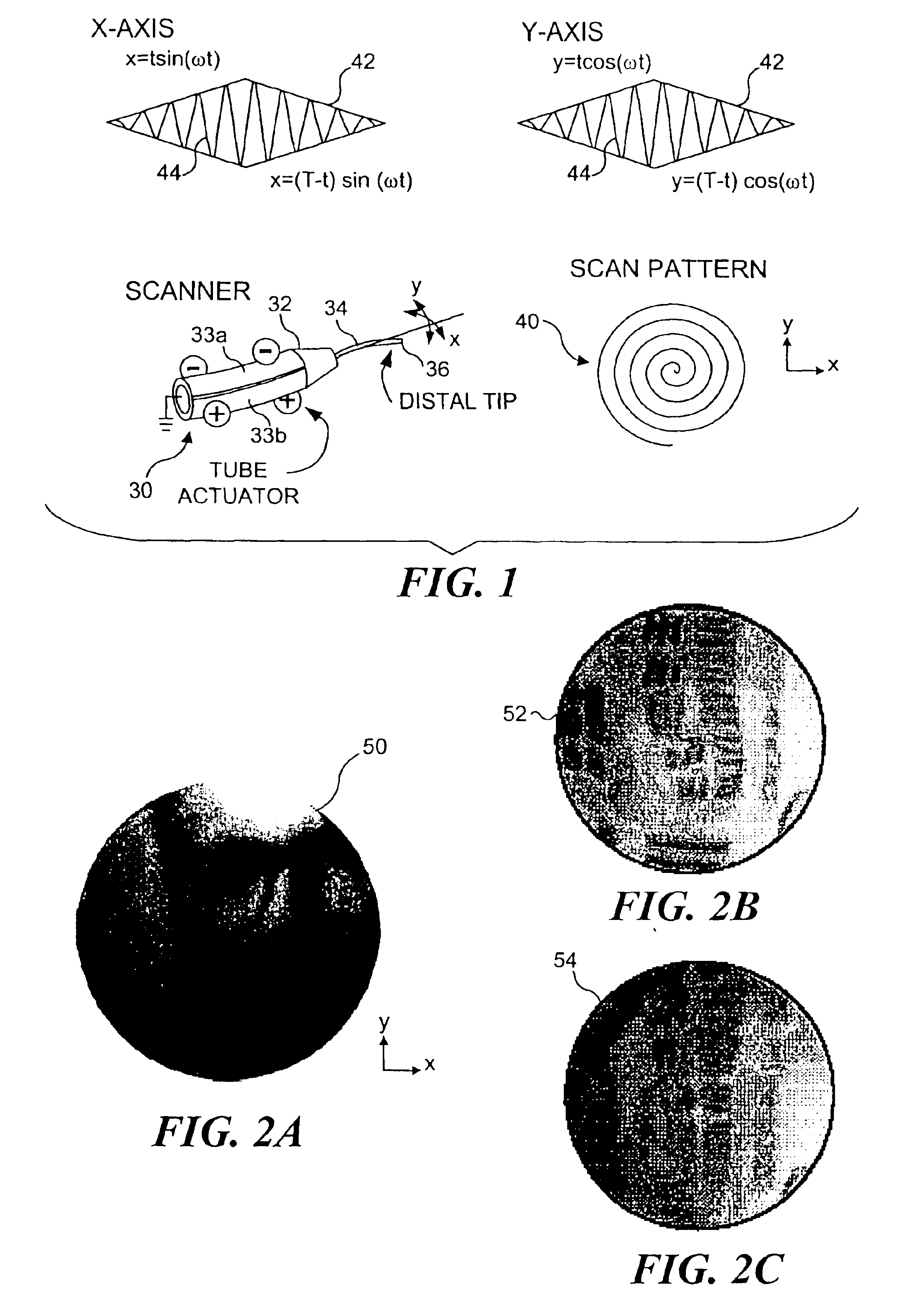

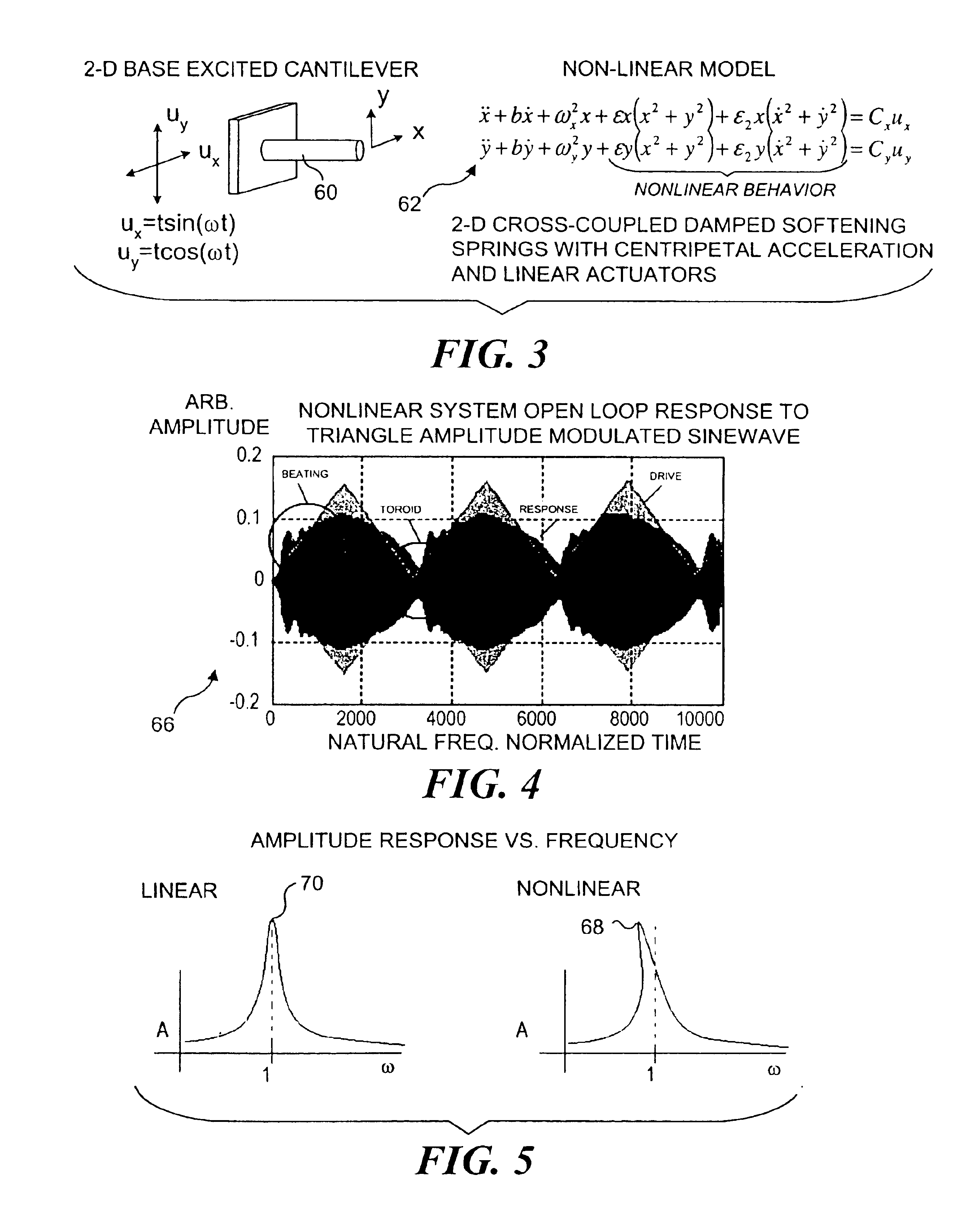

Control of an optical fiber scanner

InactiveUS6845190B1Remove nonlinear behaviorRobust cancellationSurgeryEndoscopesOptical scannersPhotodetector

Controls for an optical scanner, such as a single fiber scanning endoscope (SFSE) that includes a resonating optical fiber and a single photodetector to produce large field of view, high-resolution images. A nonlinear control scheme with feedback linearization is employed in one type of control to accurately produce a desired scan. Open loop and closed loops controllers are applied to the nonlinear optical scanner of the SFSE. A closed loop control (no model) uses either phase locked loop and PID controllers, or a dual-phase lock-in amplifier and two PIDs for each axis controlled. Other forms of the control that employ a model use a frequency space tracking control, an error space tracking control, feedback linearizing controls, an adaptive control, and a sliding mode control.

Owner:UNIV OF WASHINGTON

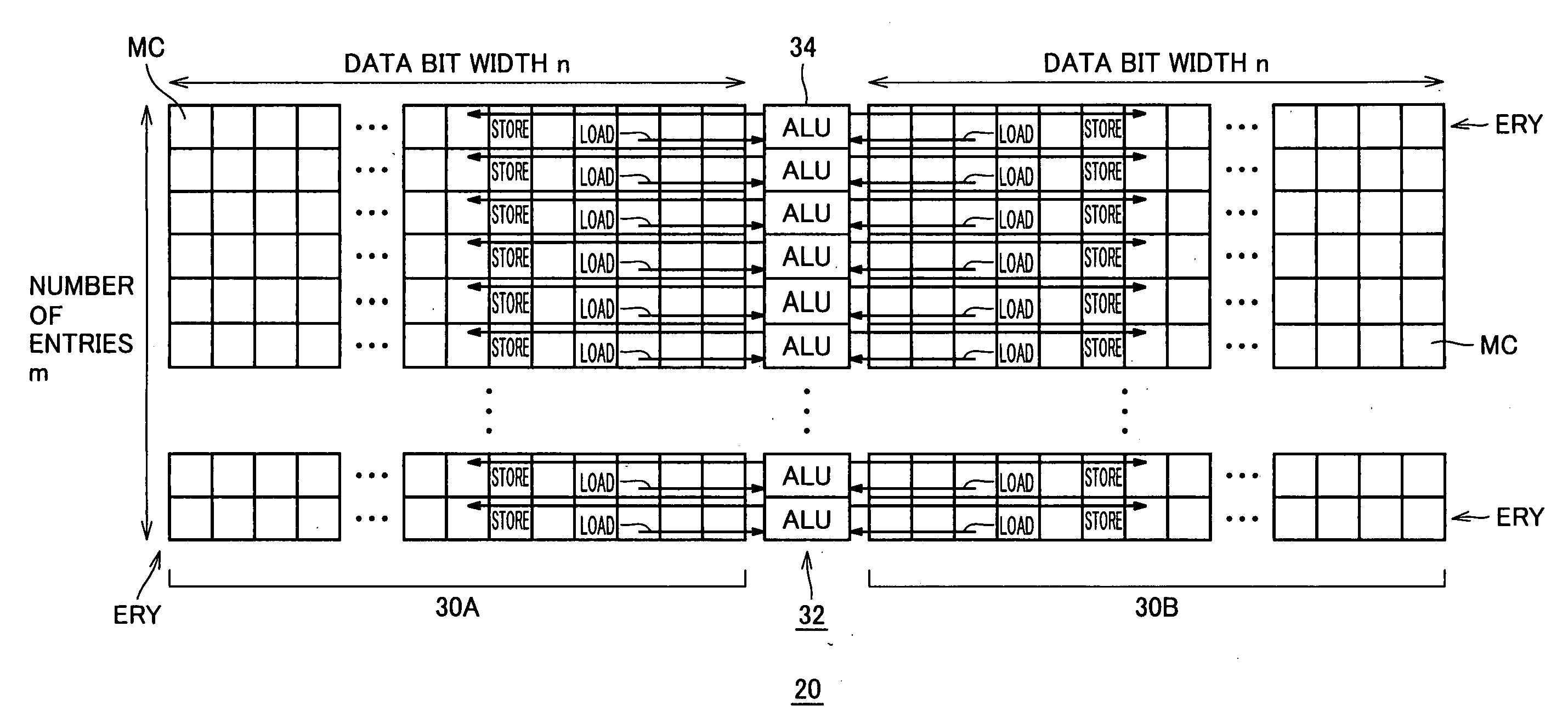

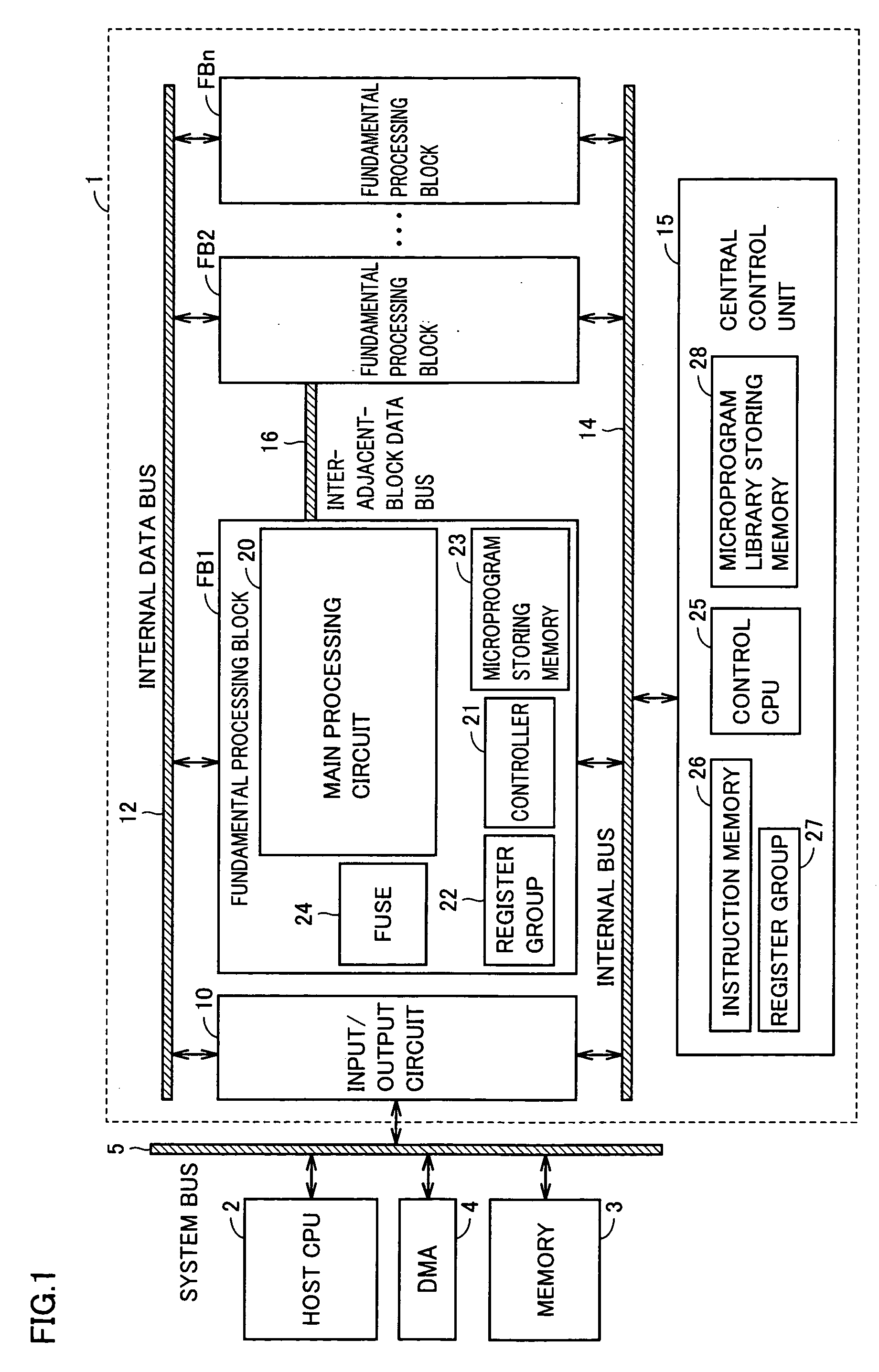

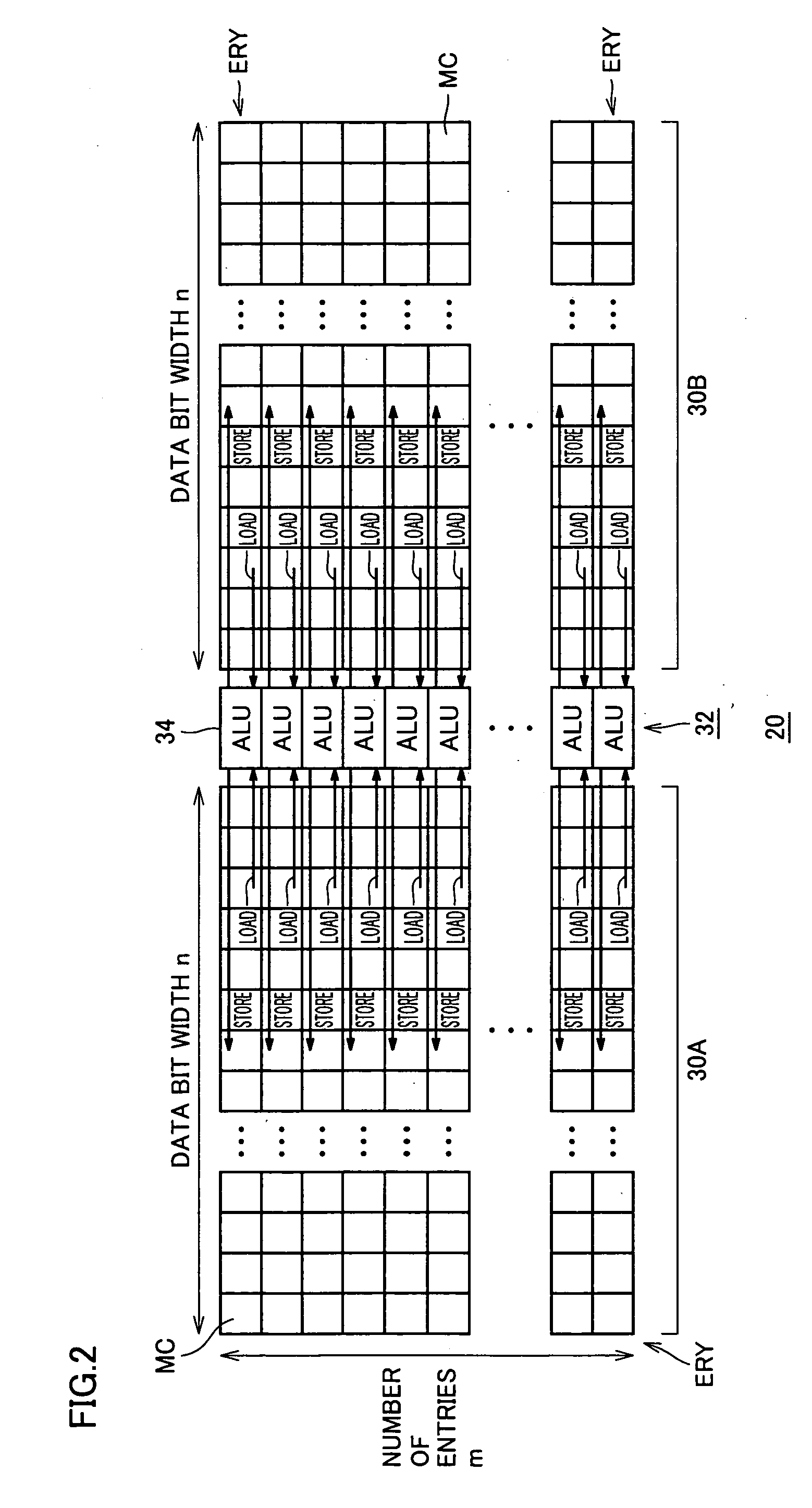

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

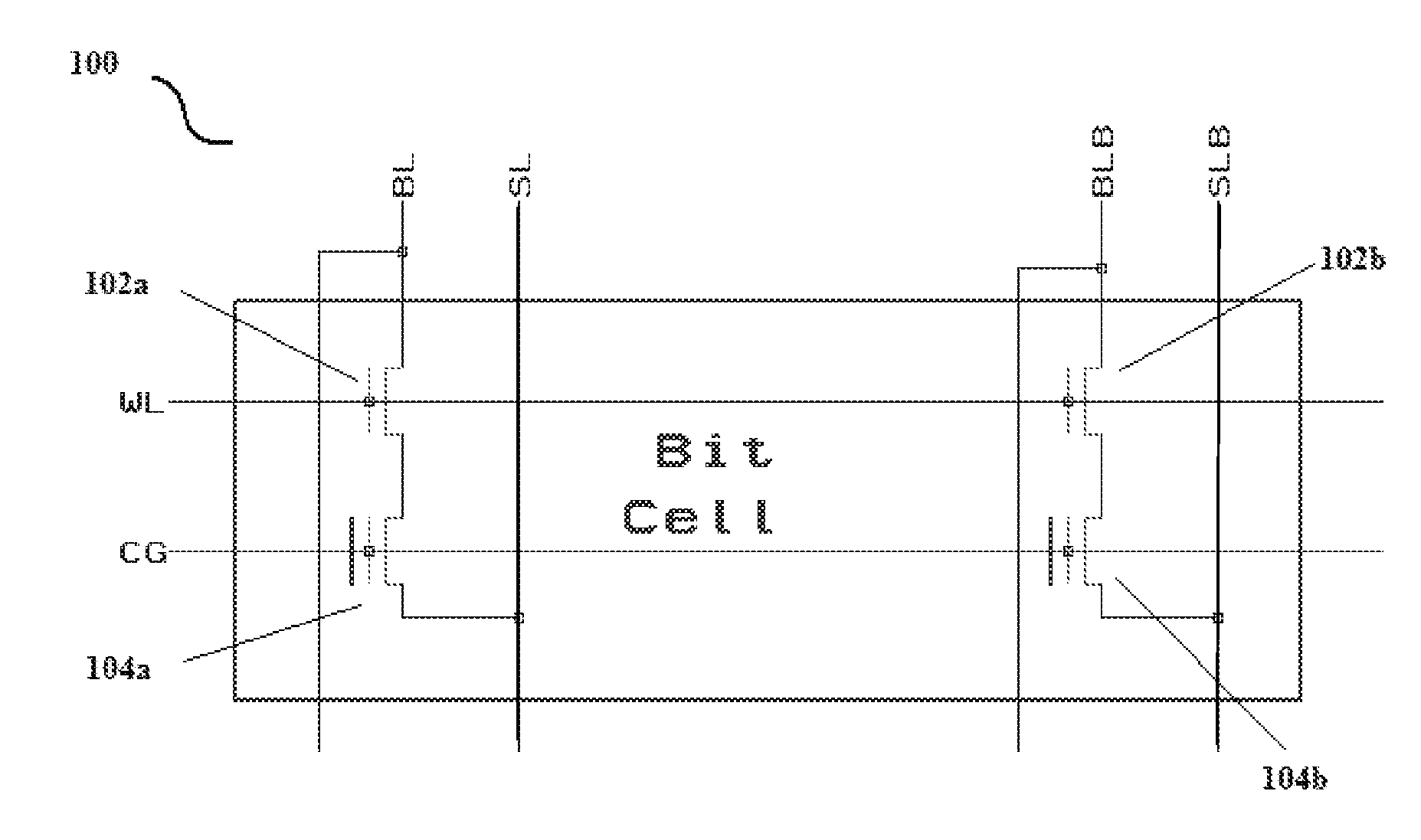

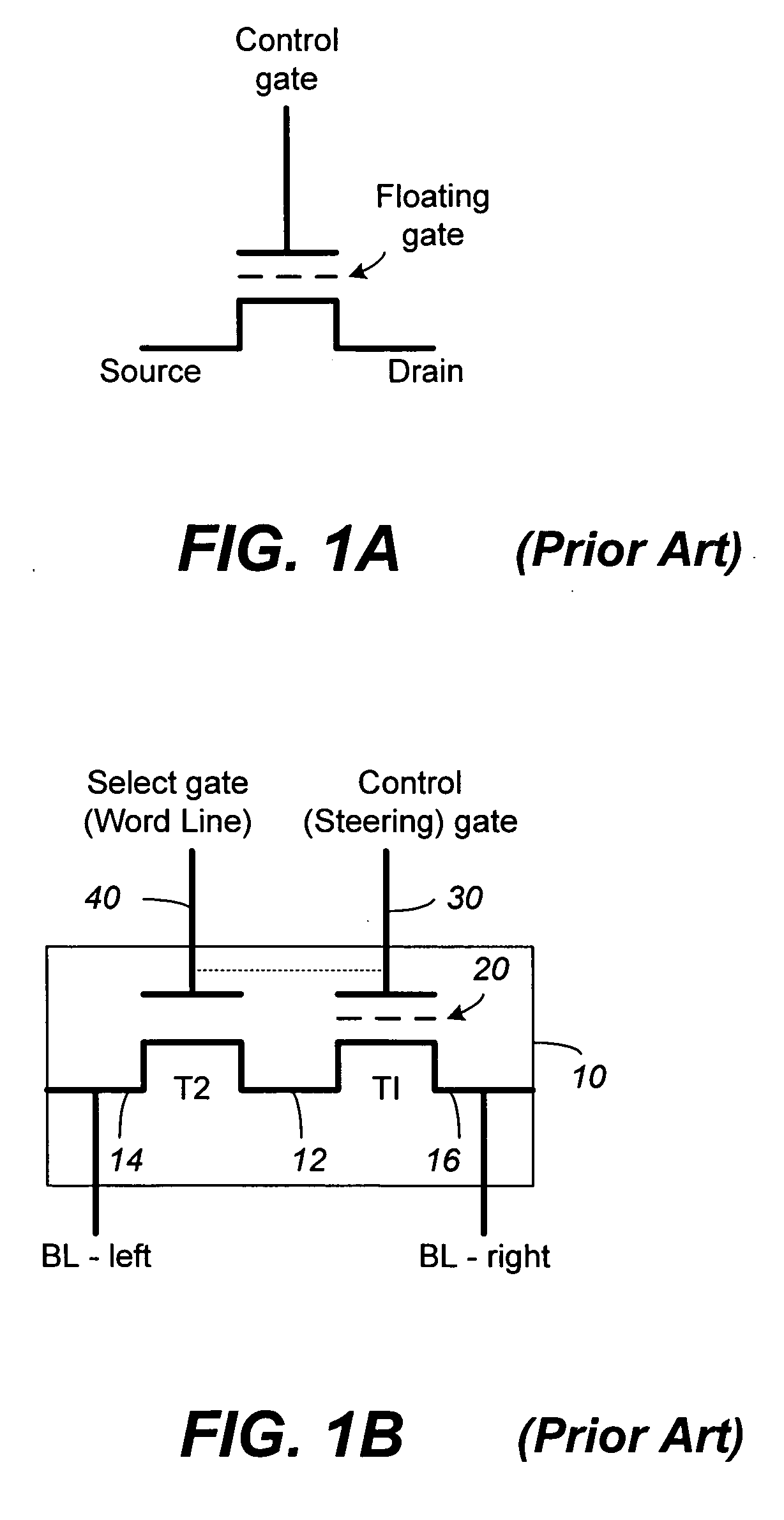

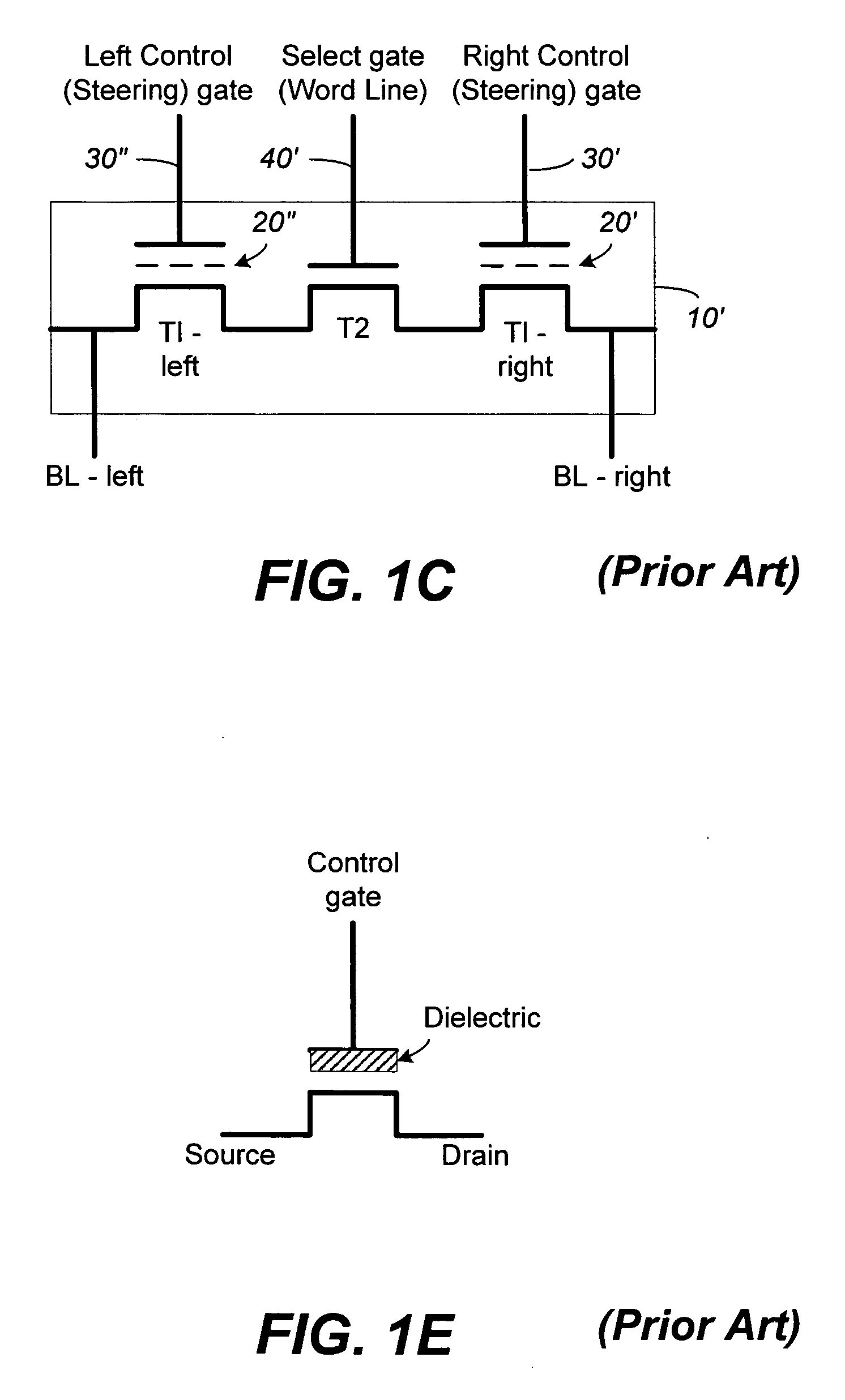

Dram-like nvm memory array and sense amplifier design for high temperature and high endurance operation

InactiveUS20110267883A1Improve threshold voltage sensing marginLarge silicon areaRead-only memoriesDigital storageBit lineAudio power amplifier

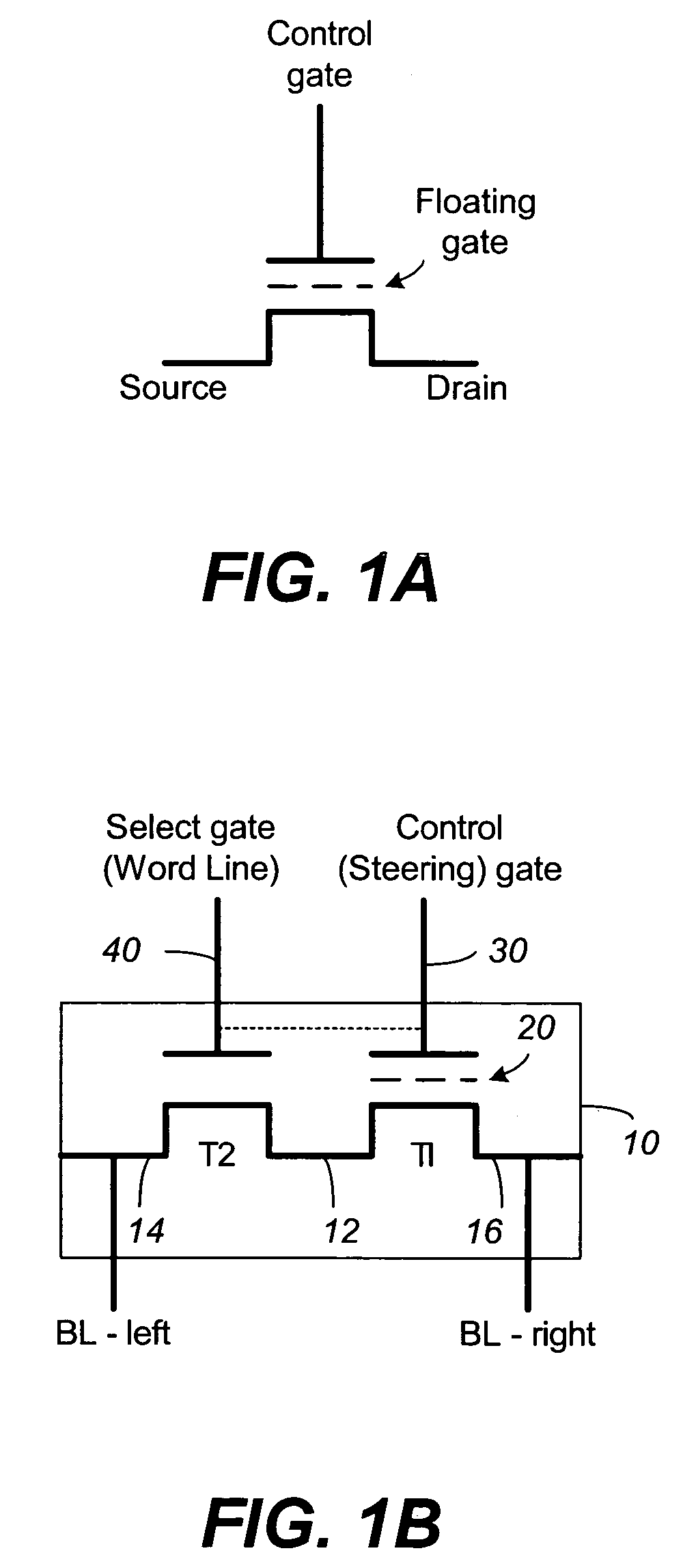

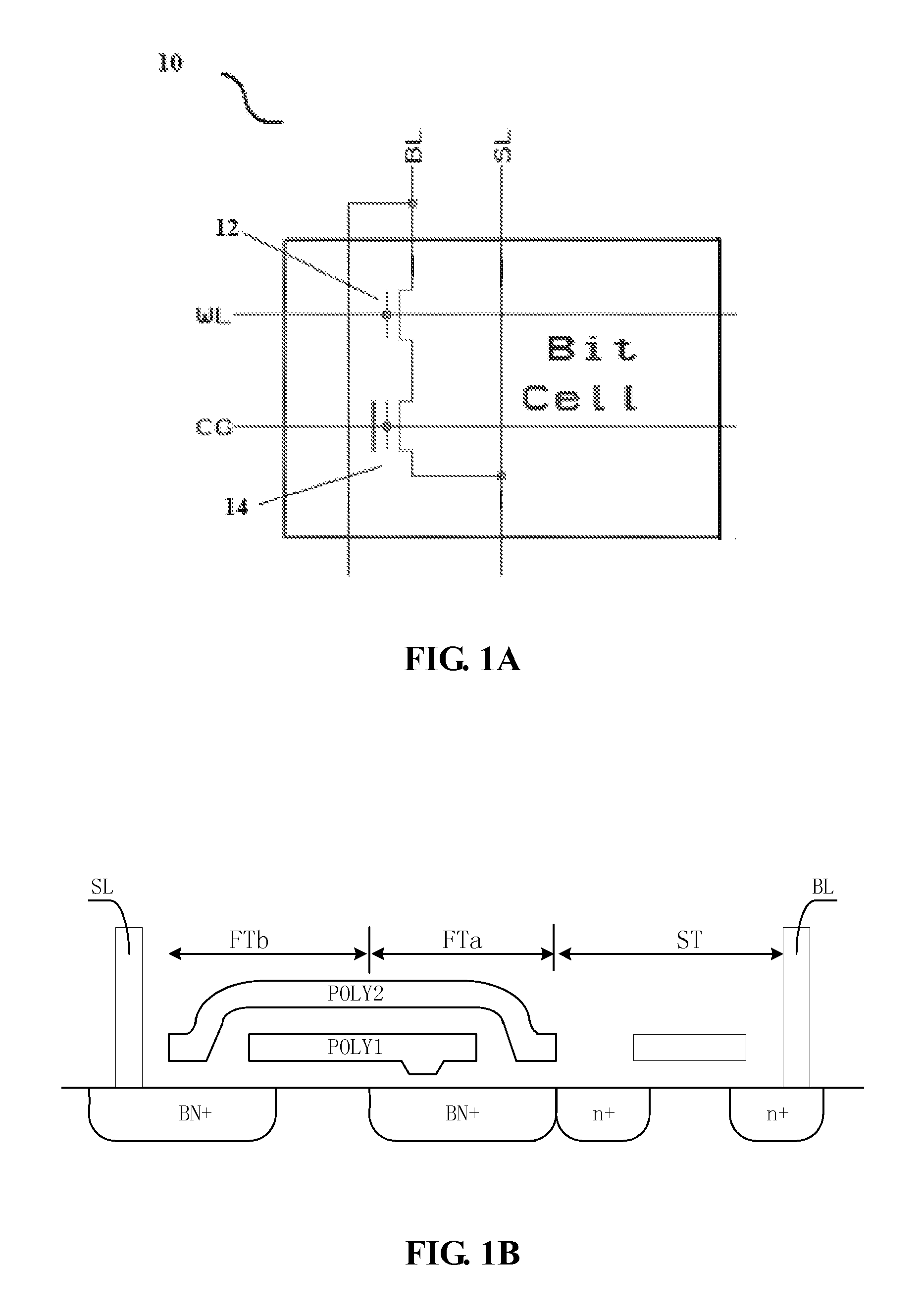

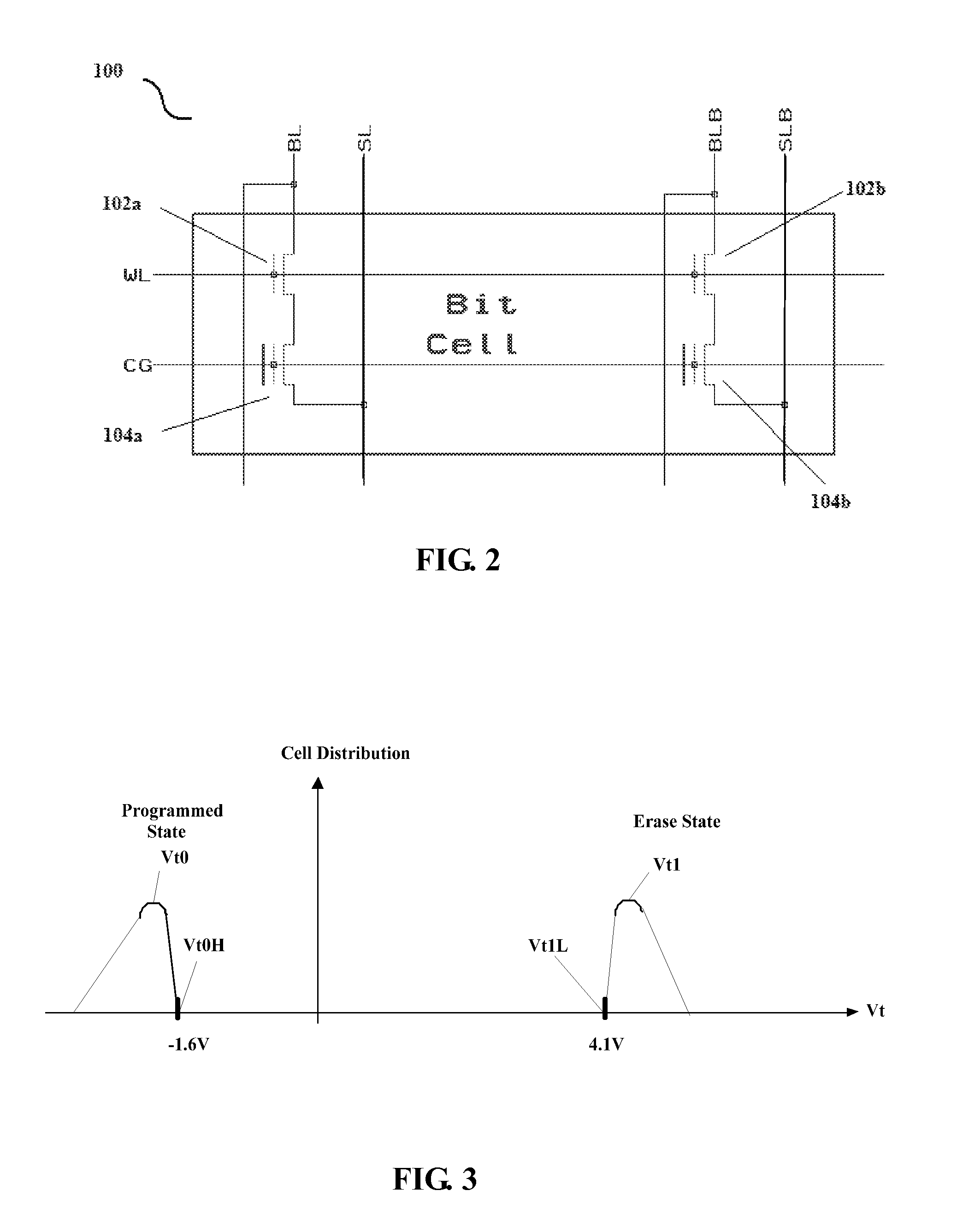

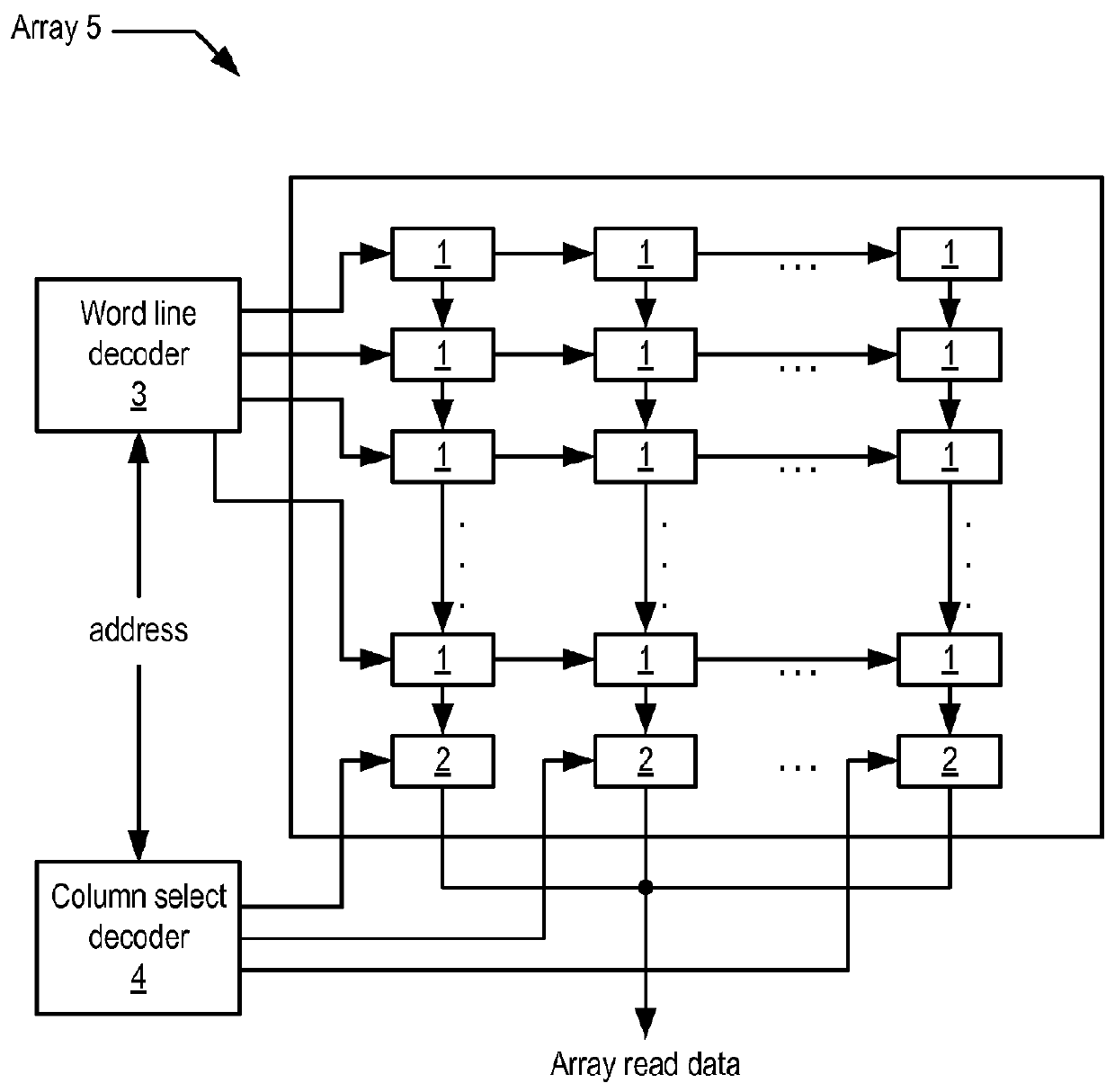

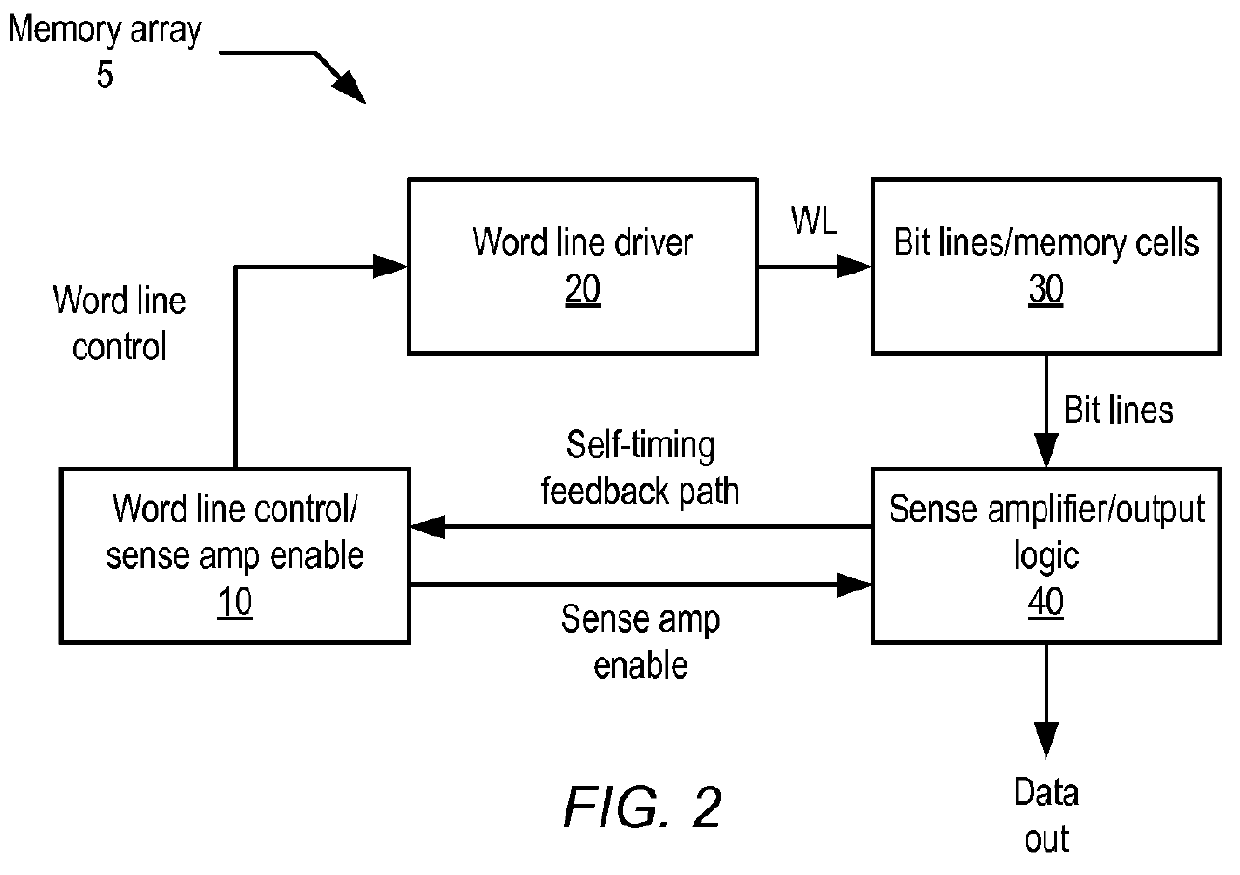

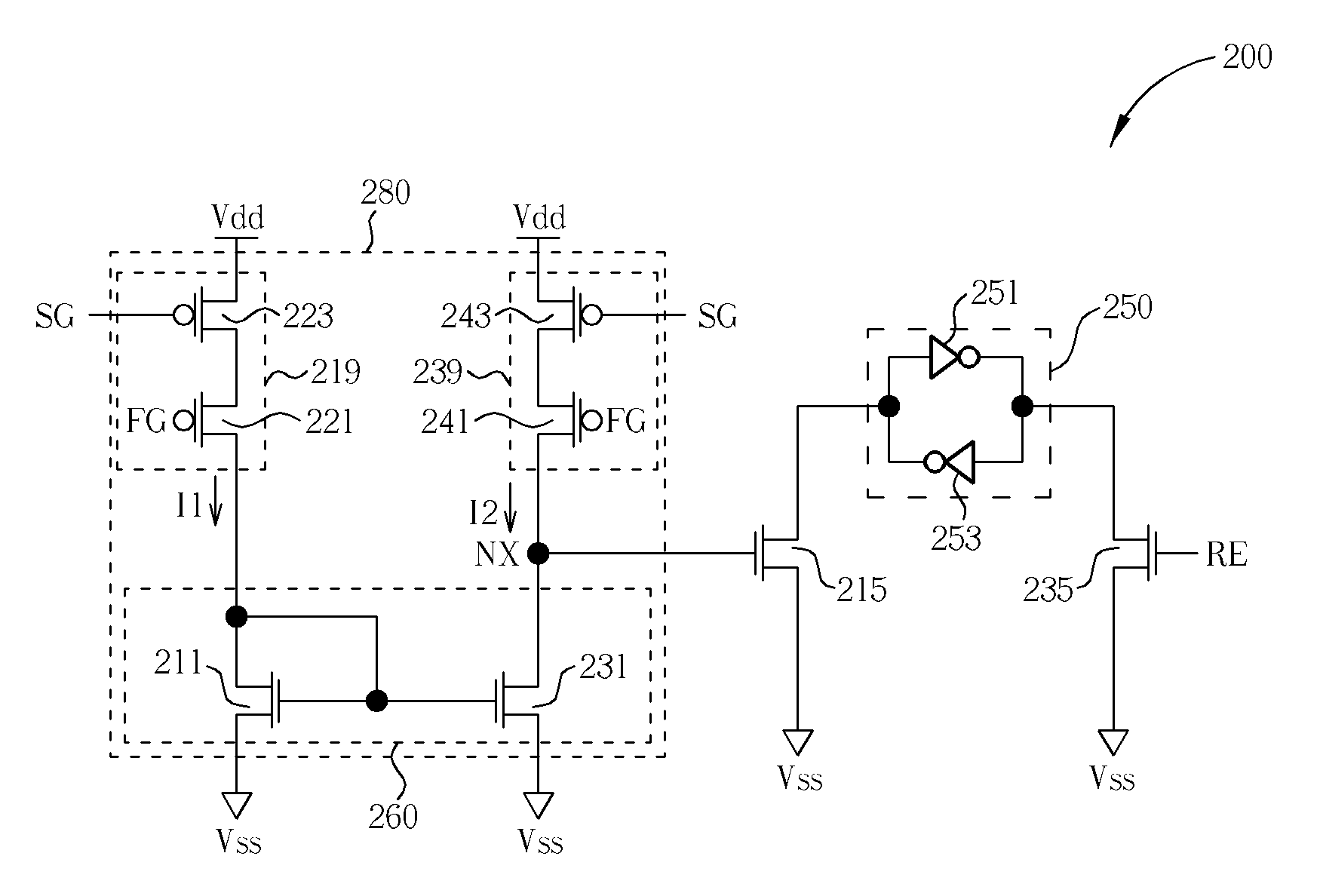

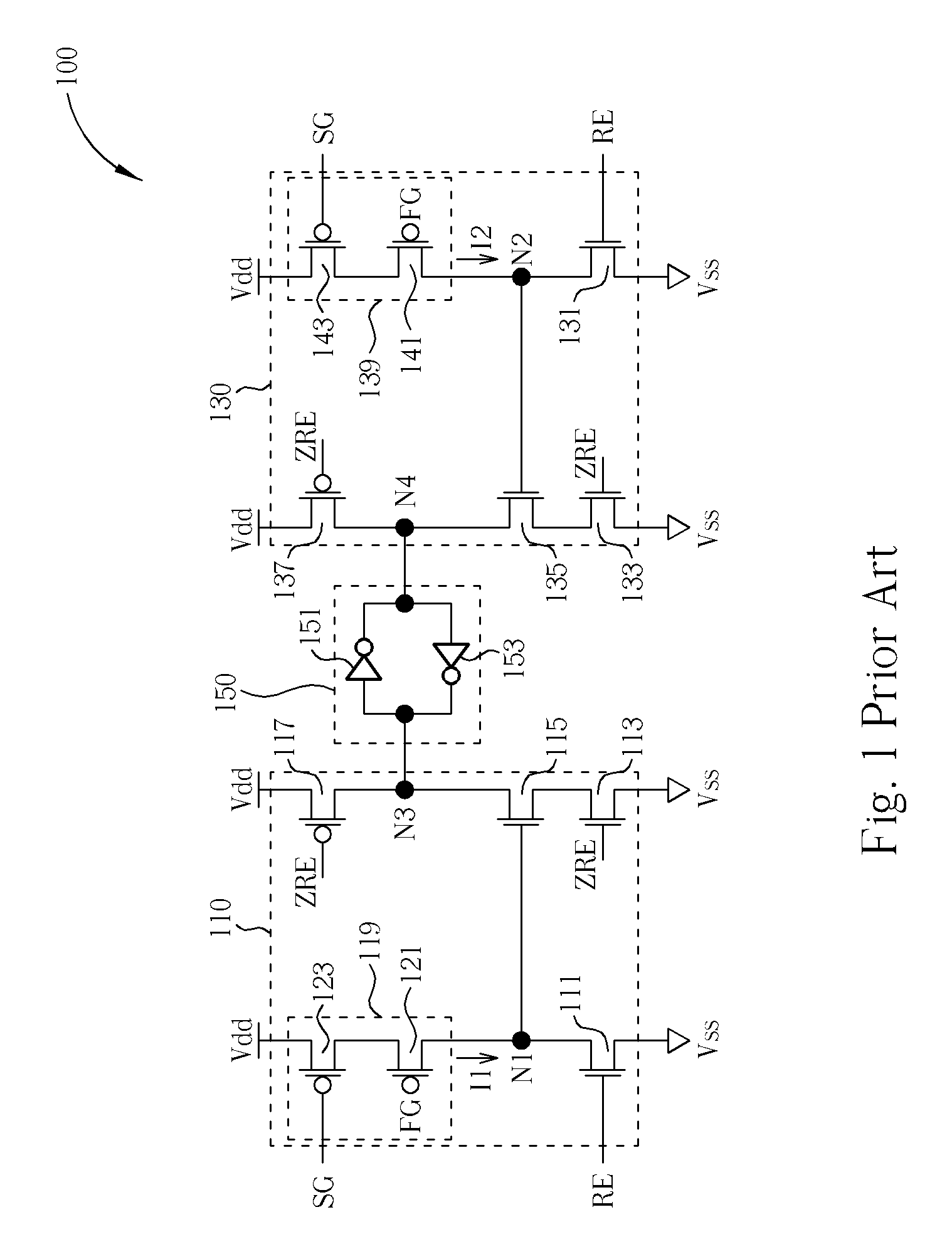

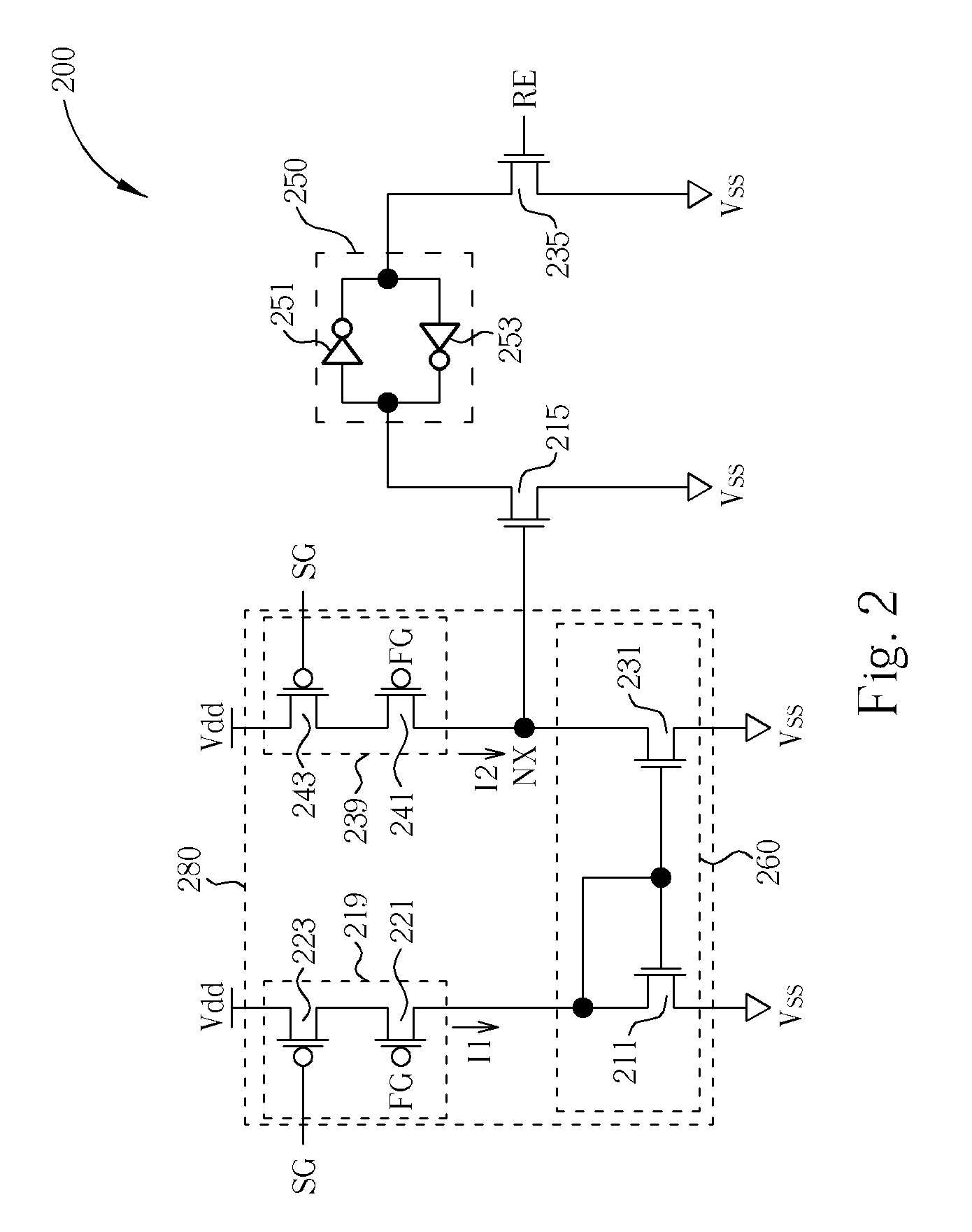

A DRAM-like non-volatile memory array includes a cell array of non-volatile cell units with a DRAM-like cross-coupled latch-type sense amplifier. Each non-volatile cell unit has two non-volatile cell devices with respective bit lines and source lines running in parallel and laid out perpendicular to the word line associated with the non-volatile cell unit. The two non-volatile cell devices are programmed with erased and programmed threshold voltages as a pair for storing a single bit of binary data. The two bit lines of each non-volatile cell unit are coupled through a Y-decoder and a latch device to the two respective inputs of the latch-type sense amplifier which provides a large sensing margin for the cell array to operate properly even with a narrowed threshold voltage gap. Each non-volatile cell device may be a 2 T FLOTOX-based EEPROM cell, a 2 T flash cell, 11 T flash cell or a 1.5 T split-gate flash cell.

Owner:APLUS FLASH TECH

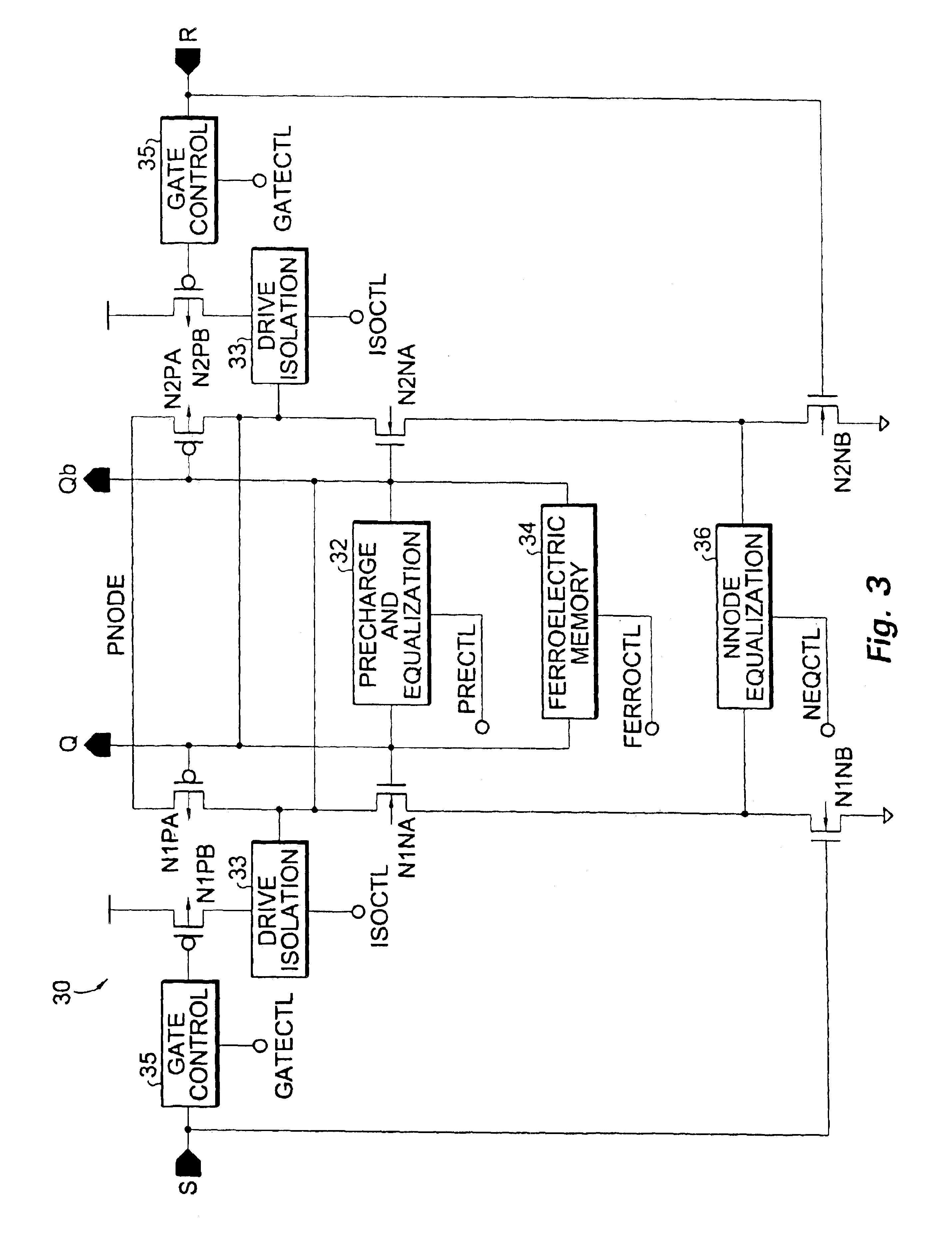

Sense amplifier and sense amplifier latch having common control

A sense amplifier of a memory array may be provided to amplify data presented from storage cells of the memory array. Additionally, a sense amplifier latch may be provided to store data received from the sense amplifier. The sense amplifier may be enabled for operation by a sense amplifier enable signal that is distinct from a clock signal. Moreover, the latch enable signal of the sense amplifier latch may be controlled by the sense amplifier enable signal, such that the sense amplifier latch opens in response to activation of the sense amplifier and closes in response to deactivation of the sense amplifier.

Owner:APPLE INC

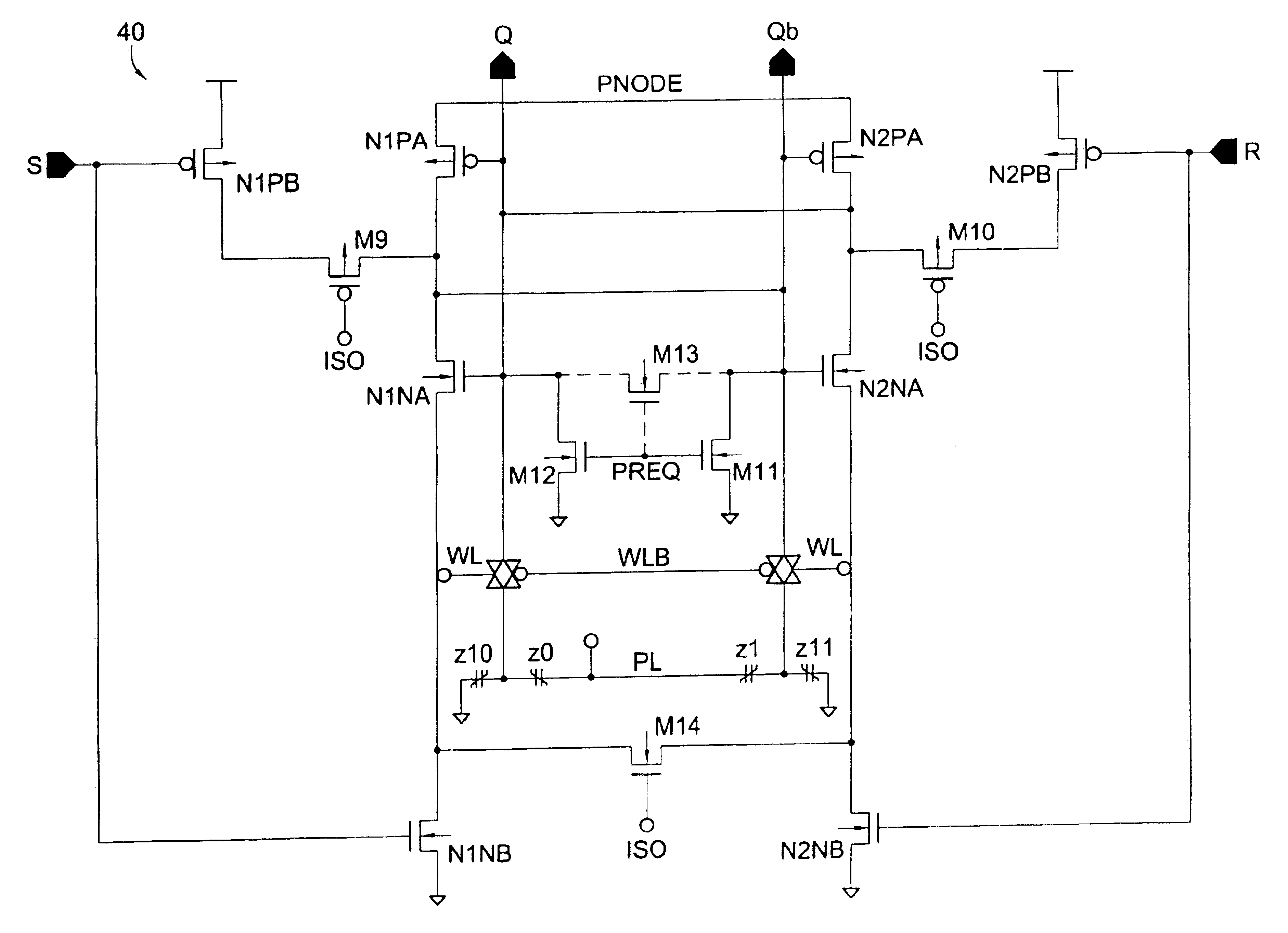

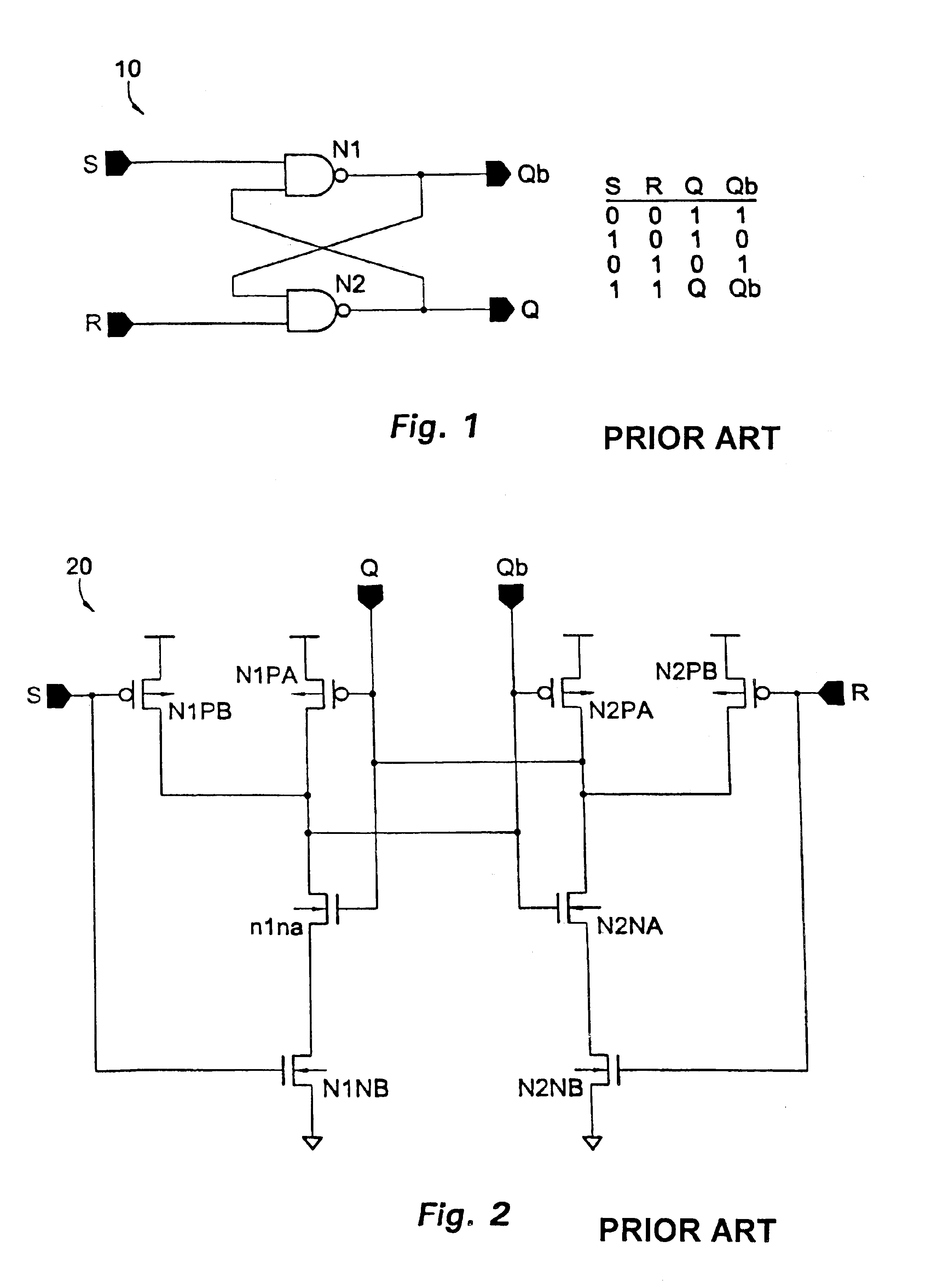

Ferroelectric non-volatile logic elements

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

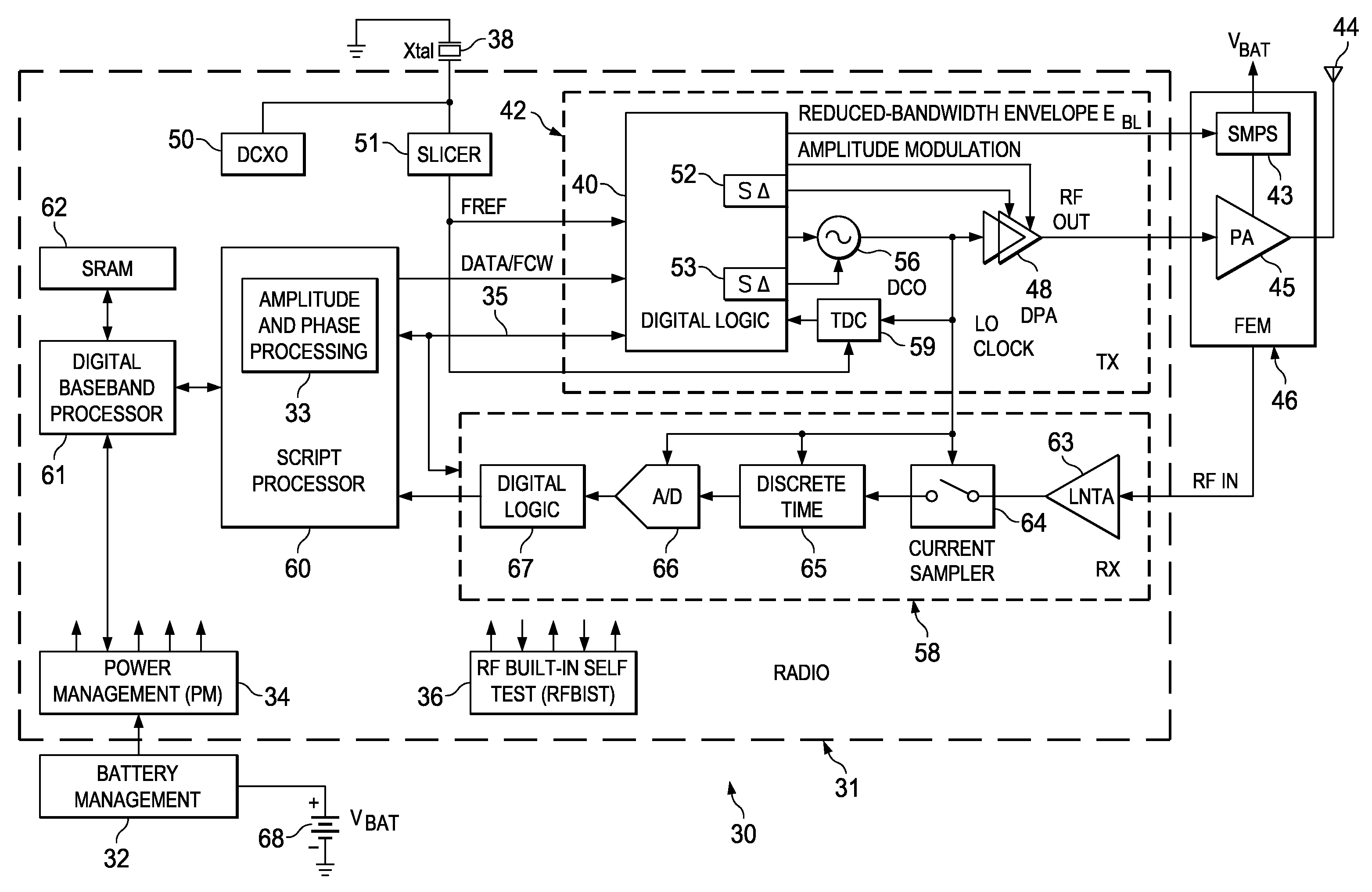

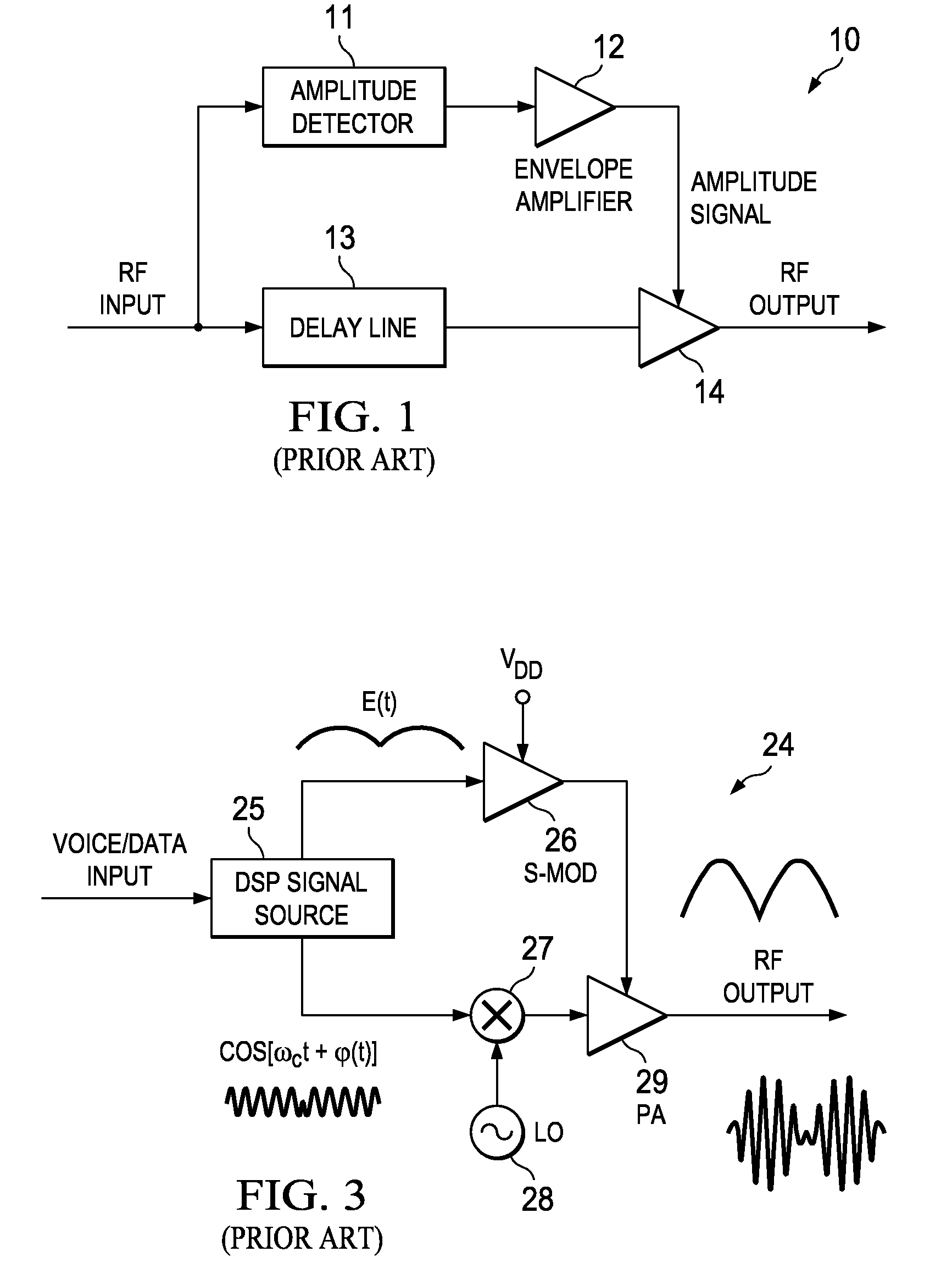

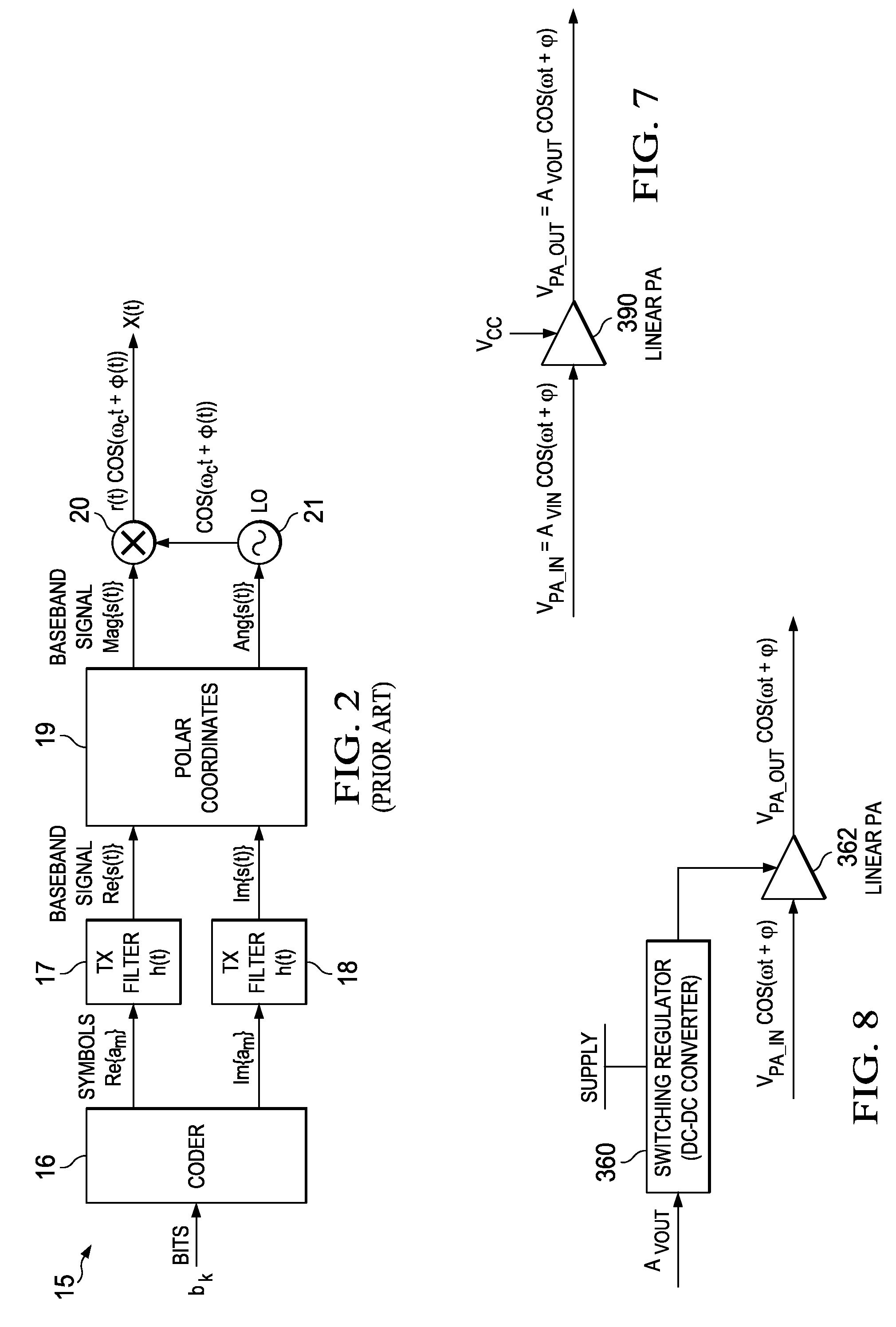

High efficiency digital transmitter incorporating switching power supply and linear power amplifier

InactiveUS20090004981A1Improve efficiencyAttenuation bandwidthResonant long antennasPower amplifiersDigital signal processingDc current

A novel apparatus and method of improving the power efficiency of a digital transmitter for non-constant-amplitude modulation schemes. The power efficiency improvement mechanism of the invention leverages the high efficiency of a switched-mode power supply (SMPS) that supplies the high DC current to the transmitter's power amplifier, while compensating for its limitations using predistortion. The predistortion may be achieved using any suitable technique such as digital signal processing, hardware techniques, etc. A switched mode power supply (i.e. switching regulator) is used to provide a slow form (i.e. reduced bandwidth) of envelope tracking (based on a narrower bandwidth distorted version of the envelope waveform) such that the switching regulator can use a lower switching rate corresponding to the lower bandwidth, thereby obtaining high efficiency in the switching regulator. The resulting AM-AM and AM-PM distortions in the power amplifier are compensated through predistortion of the digital amplitude modulating signal which dictates the envelope at the PA input. Similarly, the phase modulation is also compensated prior to the PA, such that once it undergoes the distortion in the PA, the end result is sufficiently close to the desired phase.

Owner:TEXAS INSTR INC

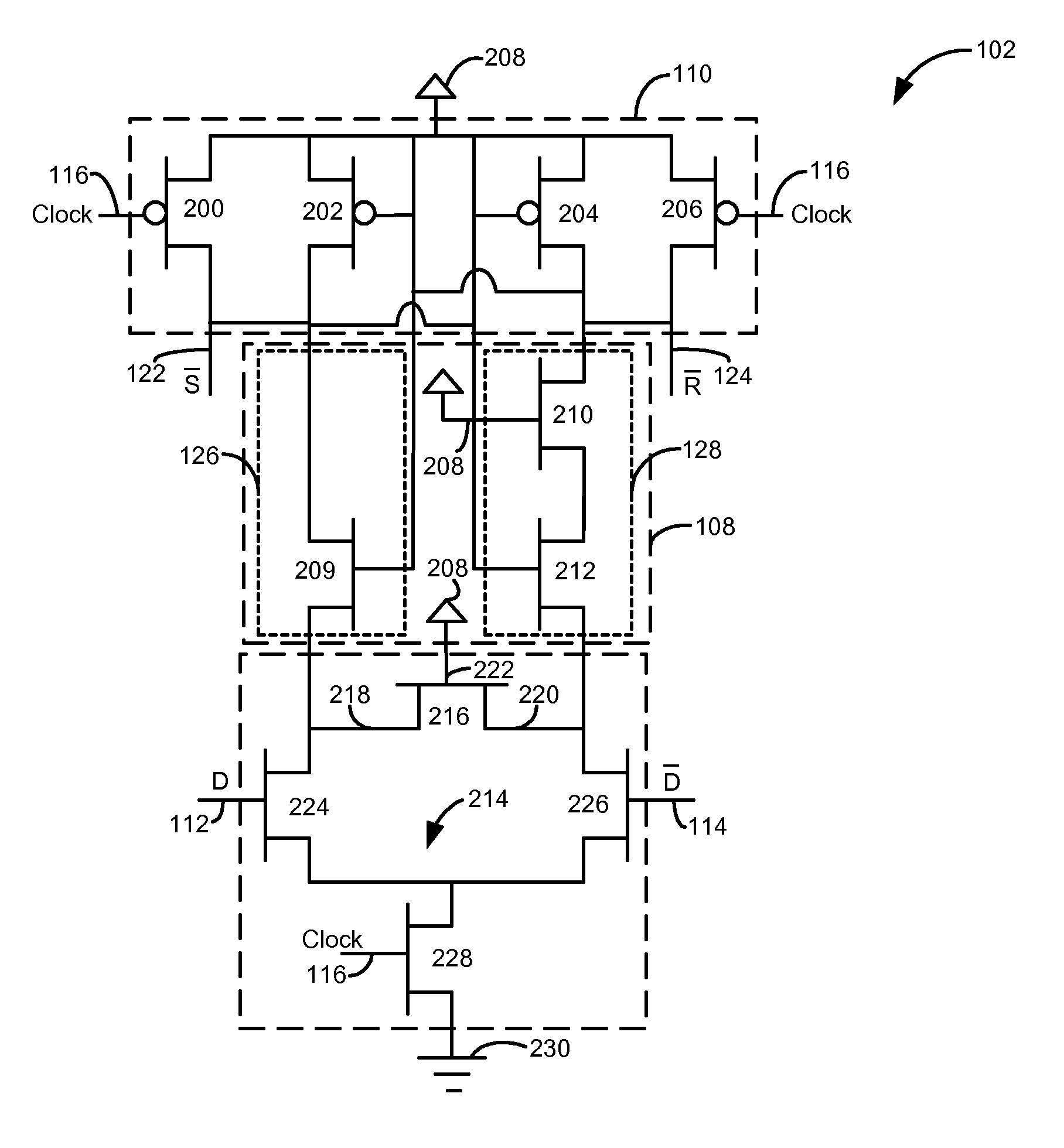

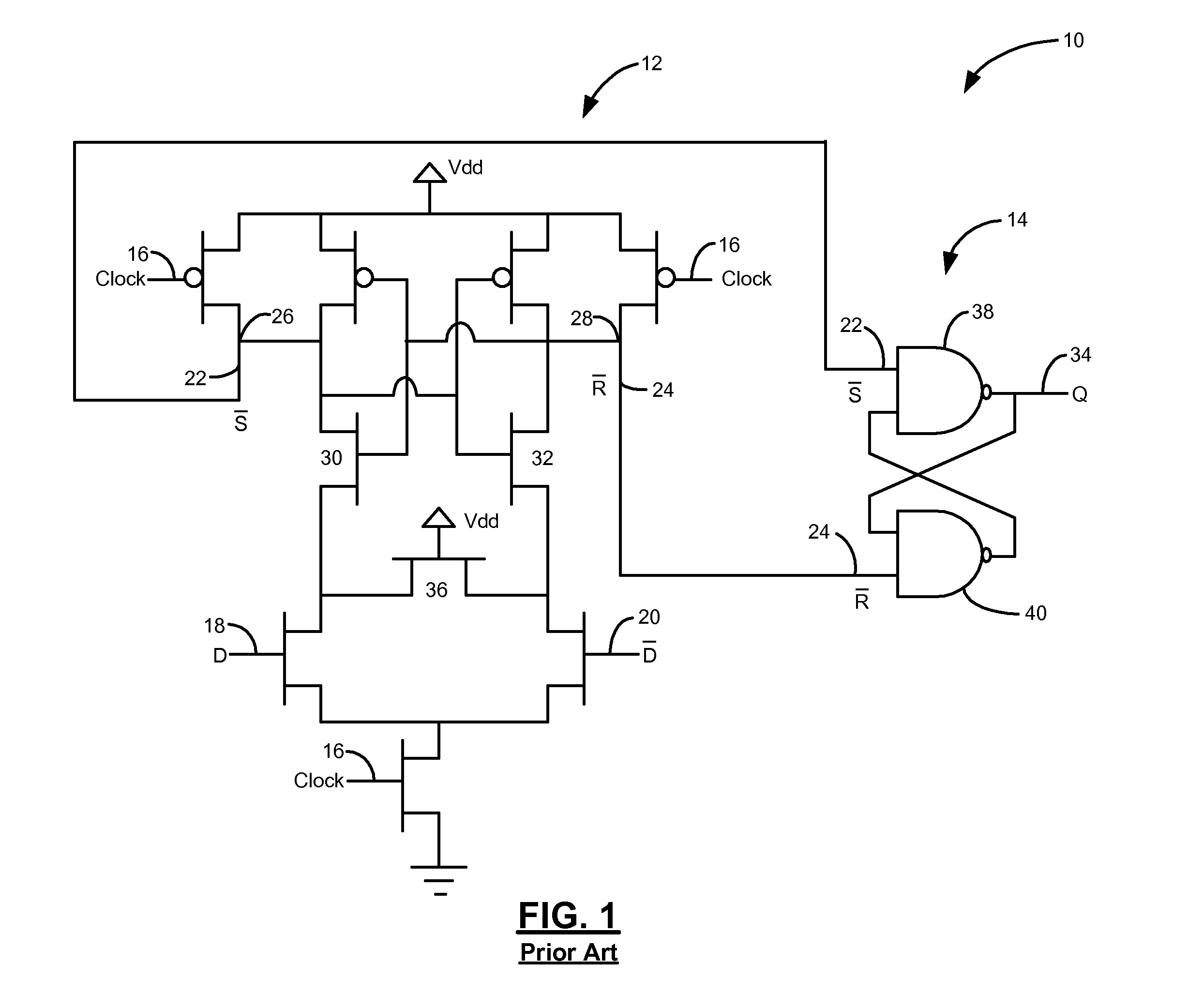

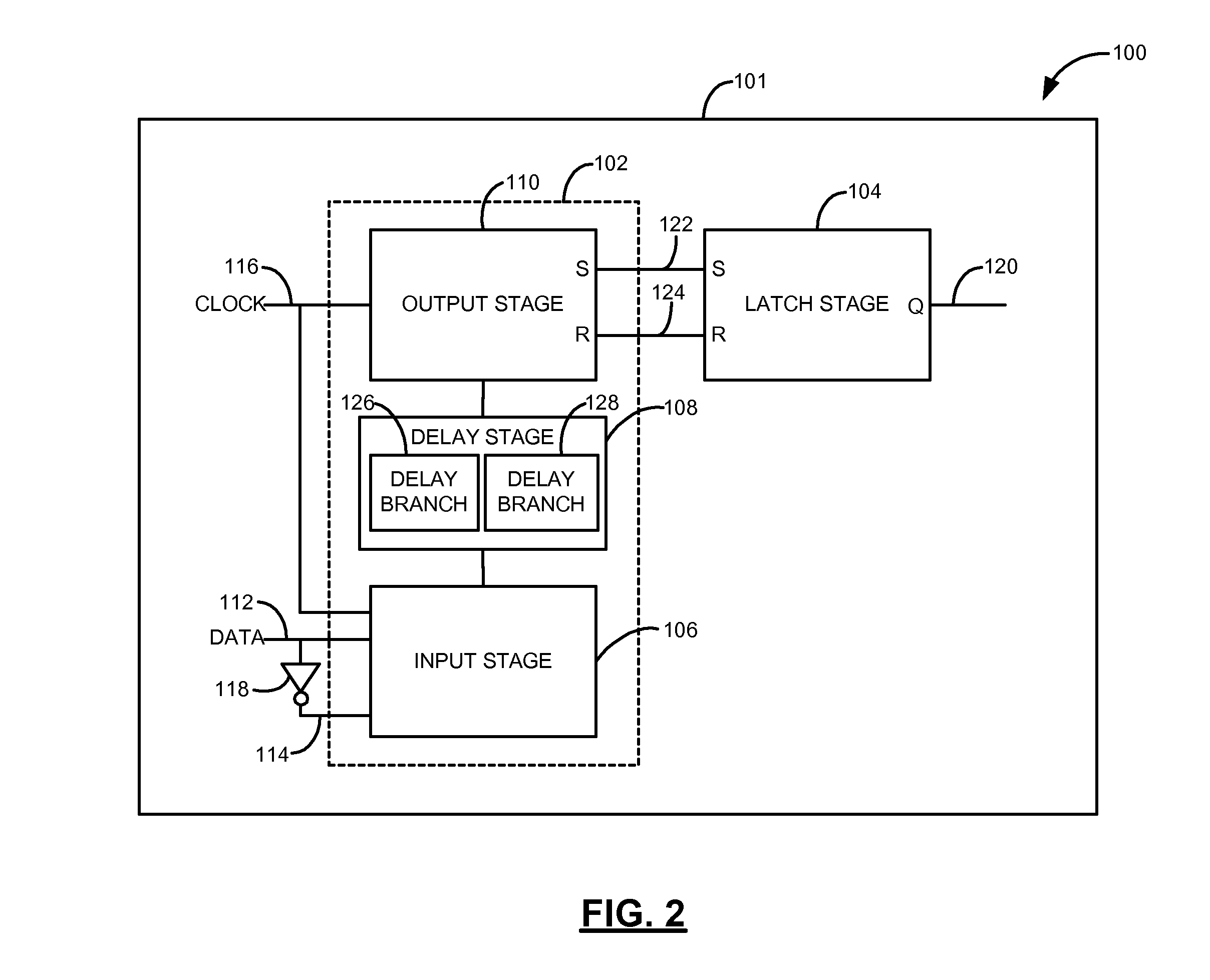

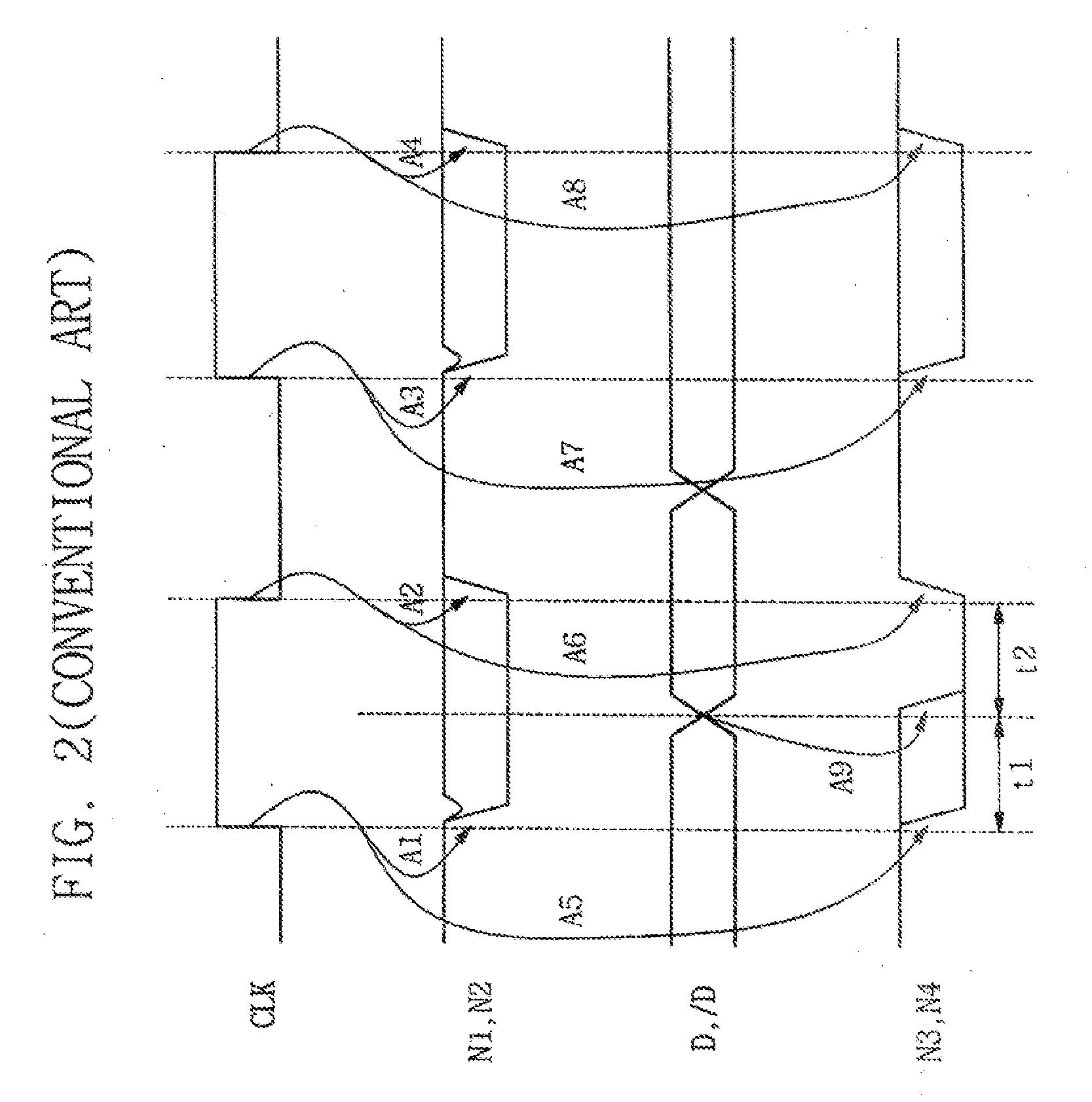

Sense amplifier based flip-flop

A circuit includes an input stage, an output stage, and a delay stage. The input stage is operative to receive a clock signal and a first and second input signal. The output stage is operative to receive the clock signal. The output stage is also operative to generate a first and second output signal based on the clock signal and the first and second input signals. The delay stage is operatively coupled to the input and output stages. The delay stage includes a first and second branch. The second branch includes at least one more delay element than the first branch.

Owner:ATI TECH INC

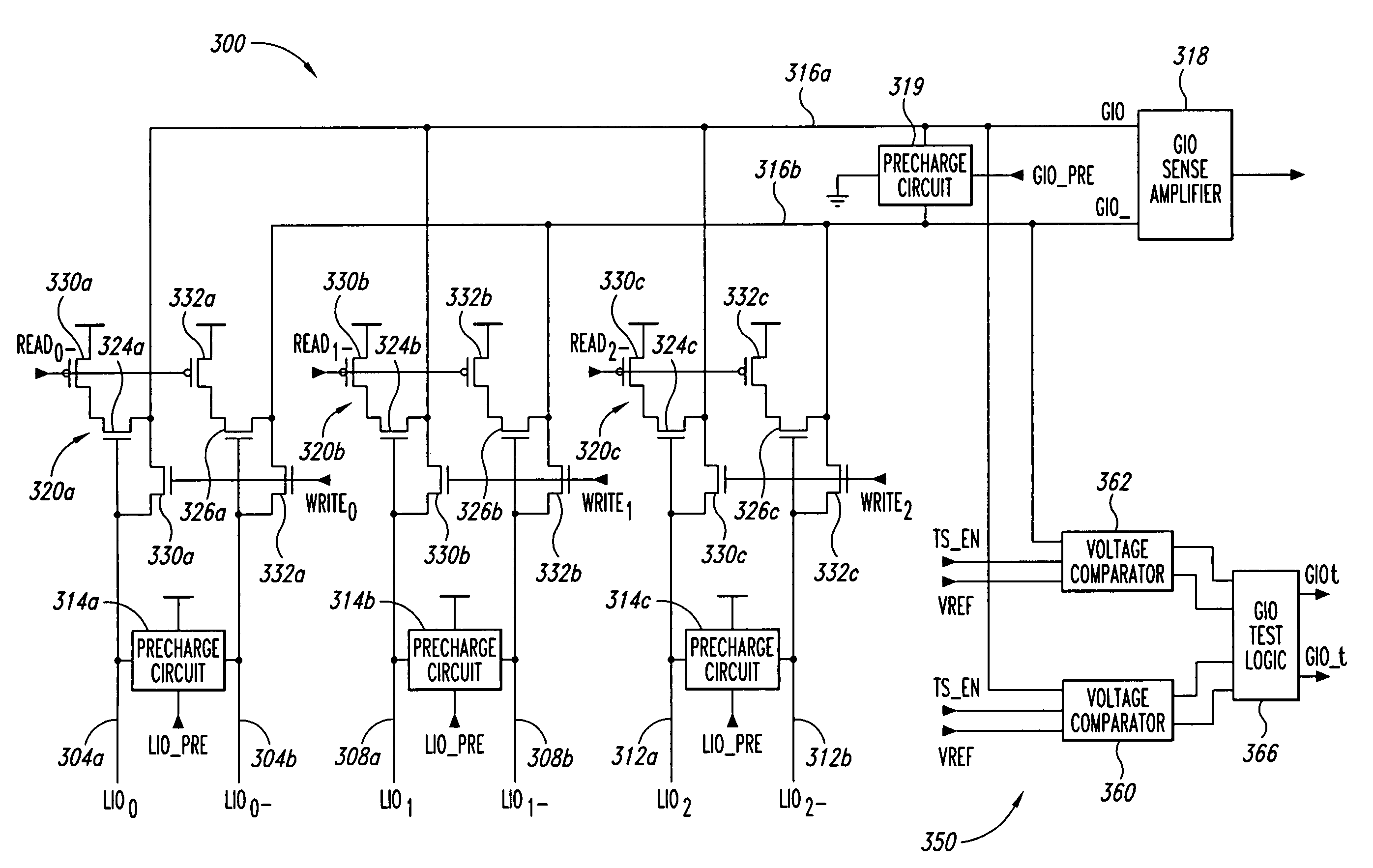

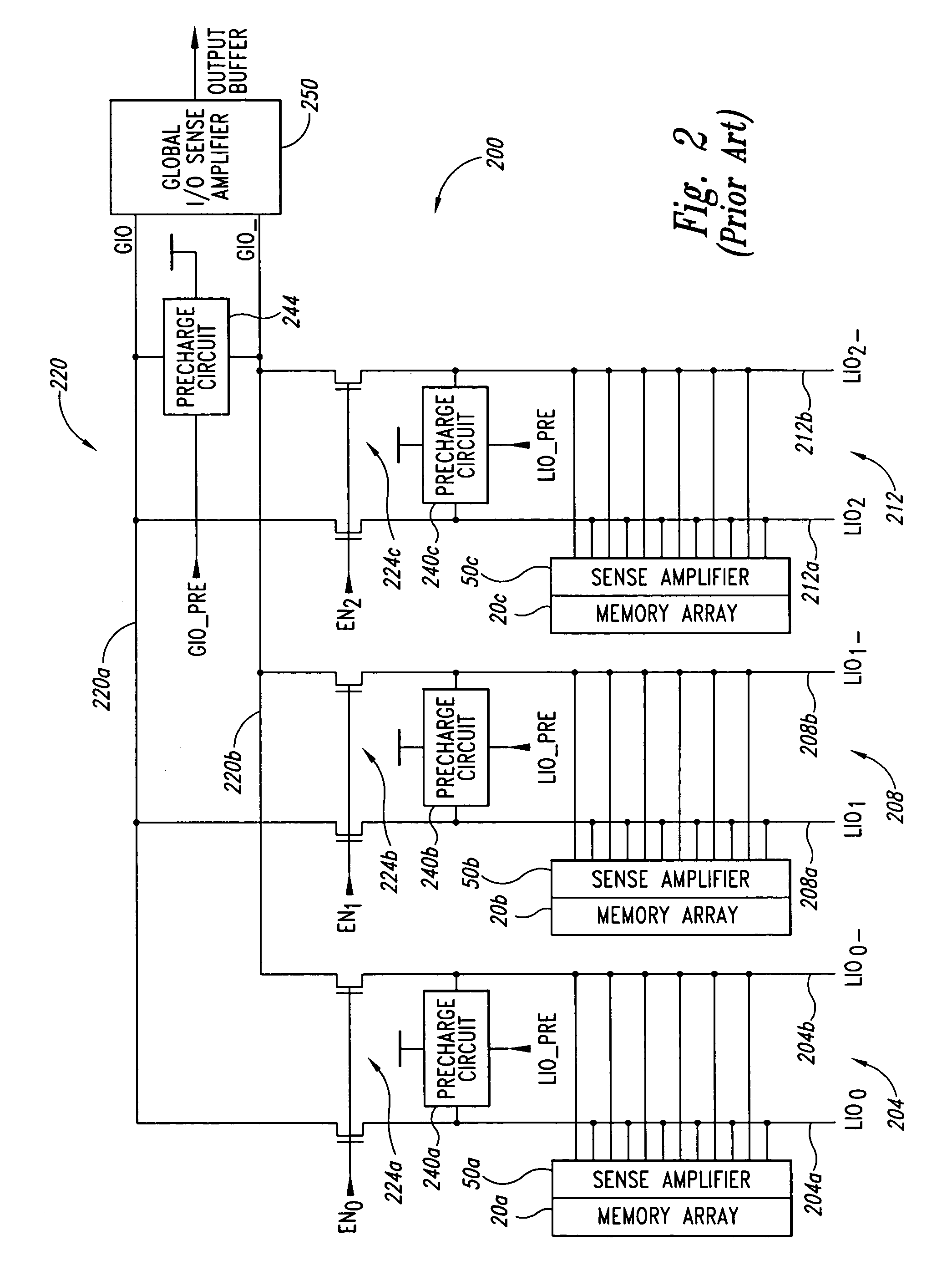

Data path having grounded precharge operation and test compression capability

A data path for coupling data between a memory cell and an input / output (IO) line sense amplifier. An IO line coupling circuit is coupled to a pair of global data lines and a pair of local data lines to couple and decouple each of the global data lines to and from a voltage supply based on the voltage levels of the local data lines for the memory read operation. For the memory write operation, the IO line coupling circuit couples and decouples each of the global data lines to and from a respective one of the local data lines. The data path also includes a first precharge circuit coupled to the global data lines to couple the global data lines to ground to precharge the signal lines prior to a memory read or write operation, and can further include a test compression circuit coupled to the global data lines.

Owner:MOSAID TECH

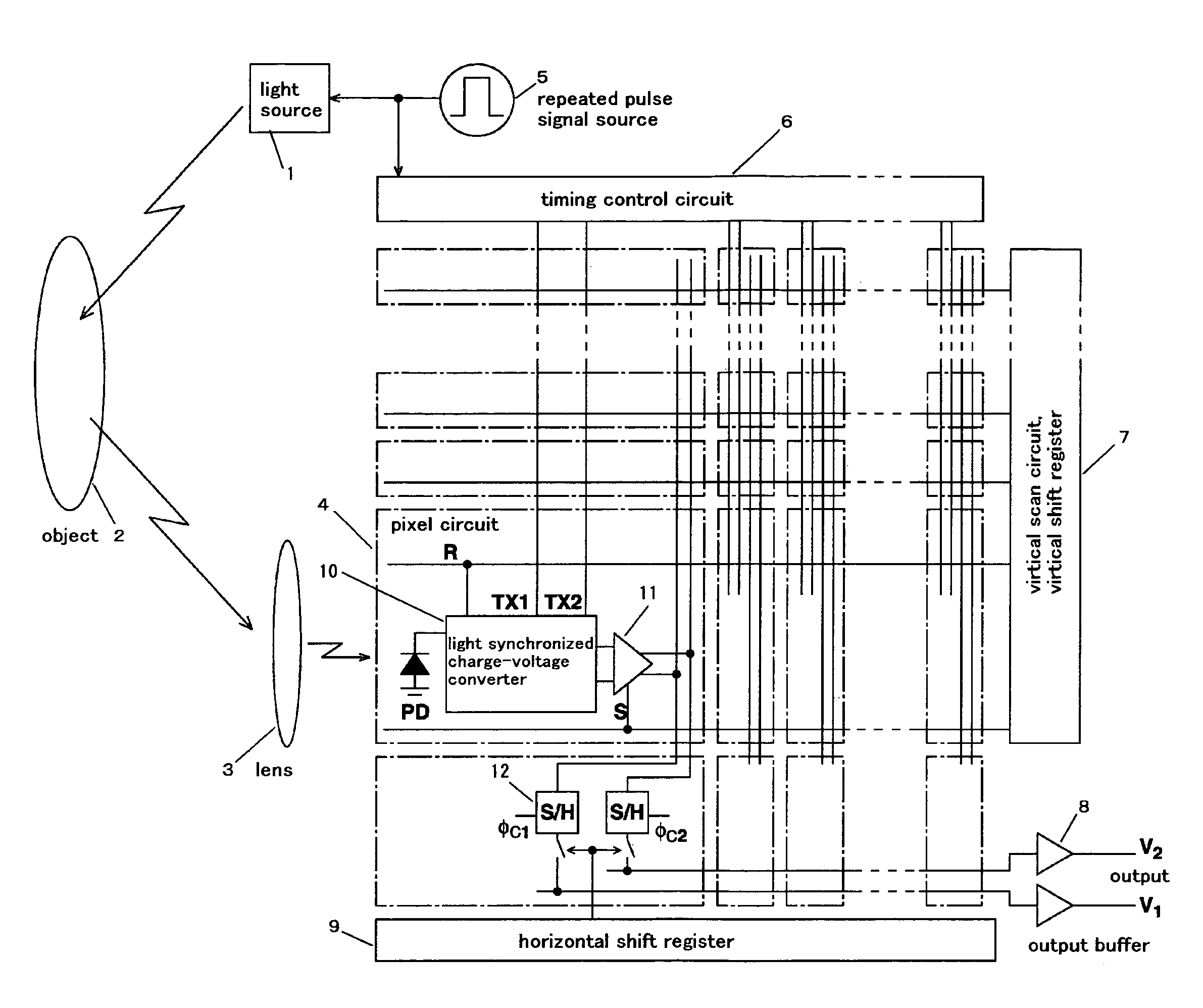

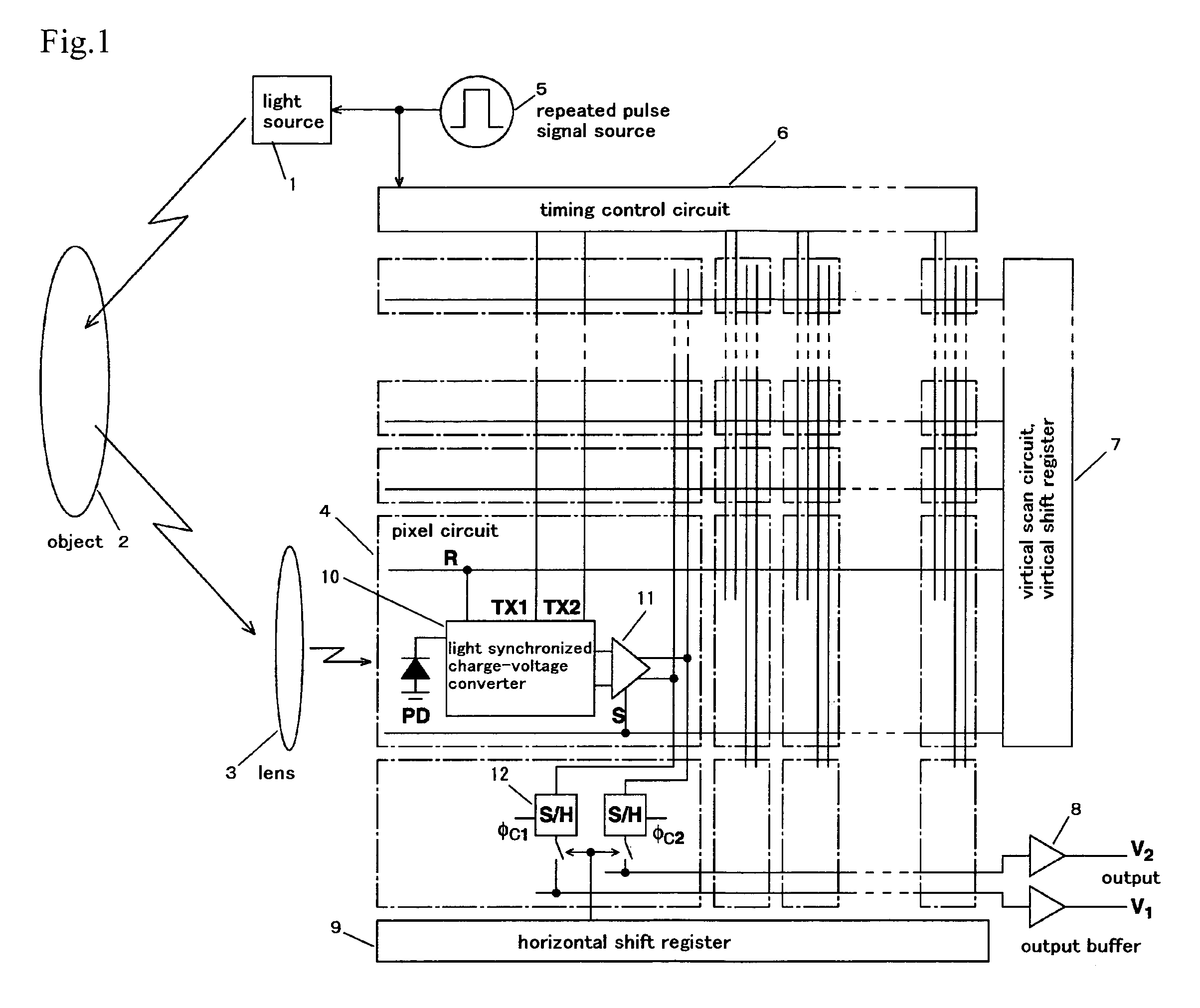

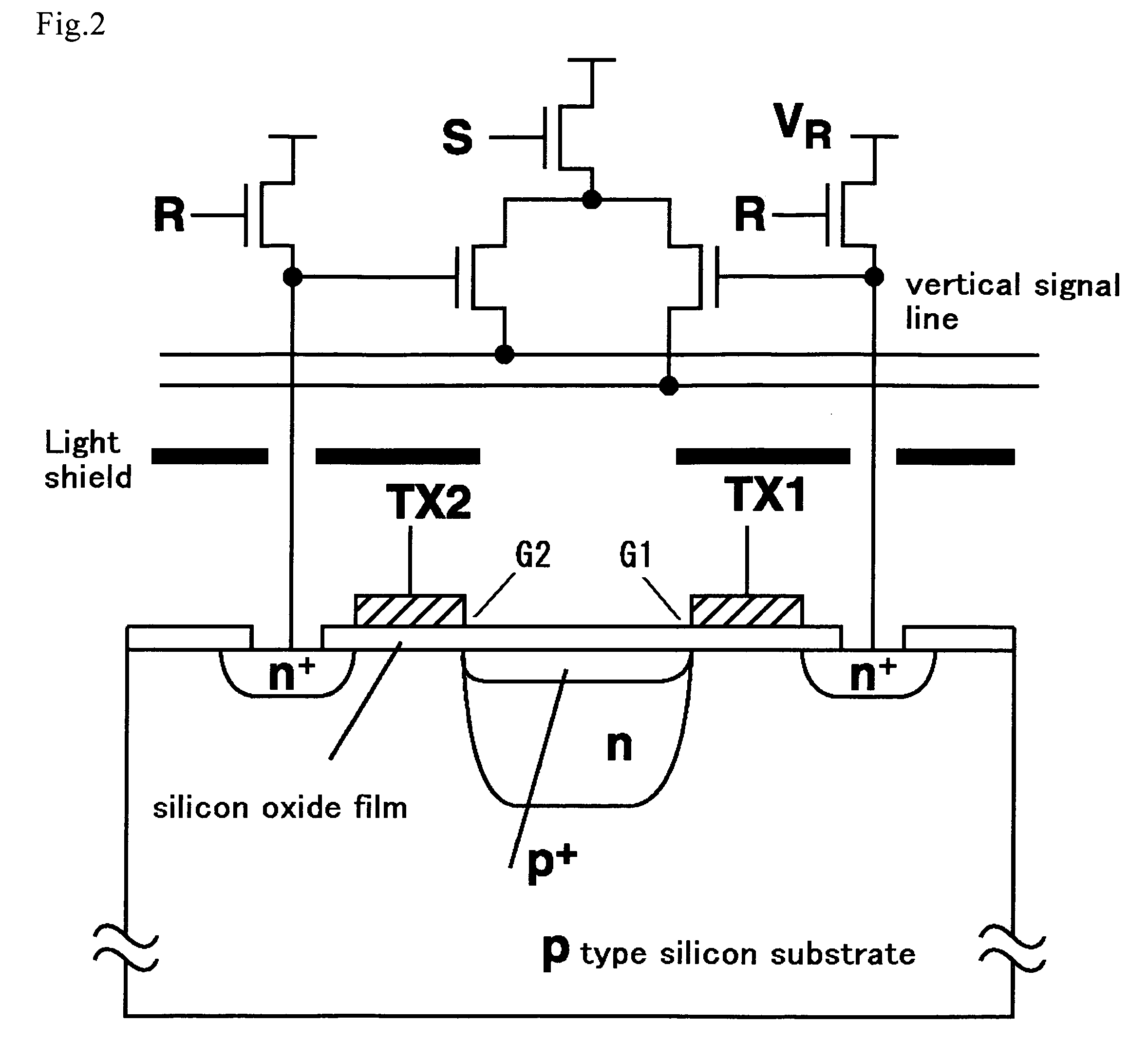

Distance image sensor

ActiveUS7436496B2High sensitivityEnhanced charge transferTelevision system detailsOptical rangefindersAudio power amplifierDelayed time

A distance image sensor for removing the background light and improving the charge transfer efficiency in a device for measuring the distance to an object by measuring the time-of-flight of the light.In a distance image sensor for determining the signals of two charge storage nodes which depend on the delay time of the modulated light, a signal by the background light is received from the third charge storage node or the two charge storage nodes in a period when the modulated light does not exist, and is subtracted from the signal which depends on the delay time of the two charge storage nodes, so as to remove the influence of the background. Also by using a buried diode as a photo-detector, and using an MOS gate as gate means, the charge transfer efficiency improves. The charge transfer efficiency is also improved by using a negative feedback amplifier where a capacitor is disposed between the input and output.

Owner:NAT UNIV CORP SHIZUOKA UNIV

Sense amplifier circuit having current mirror architecture

A sense amplifier circuit for use in a semiconductor memory device has complemented logic states at opposite sides of the latch circuit in the sense amplifier circuit determinate all the time in operation. The sense amplifier circuit takes advantage of a current mirror circuit for ascending or descending a voltage level at the gate of a transistor by charge accumulation or charge dissipation, which turns on or off the transistor so as to control the logic states at opposite sides of the latch circuit in the sense amplifier circuit.

Owner:EMEMORY TECH INC

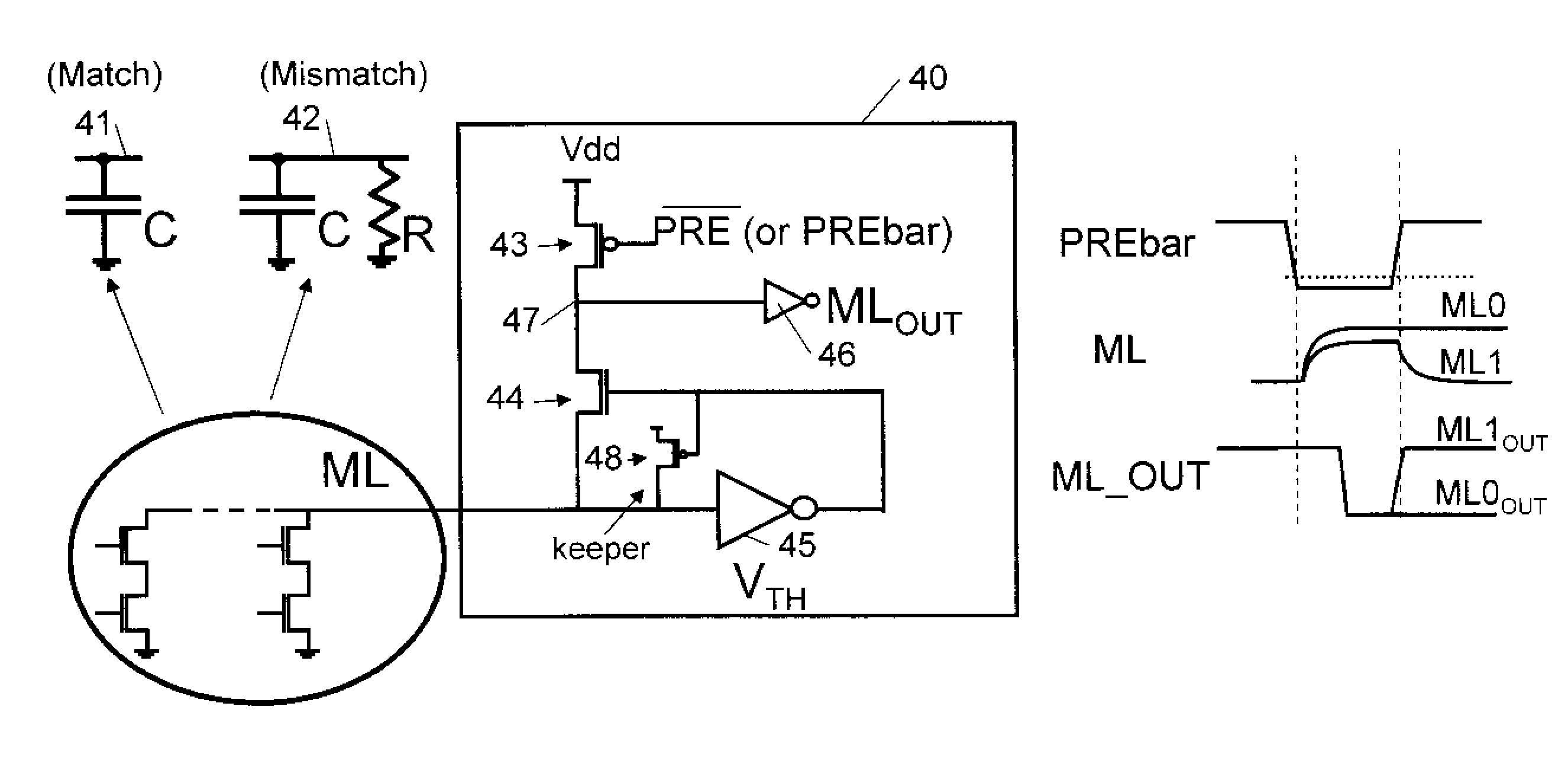

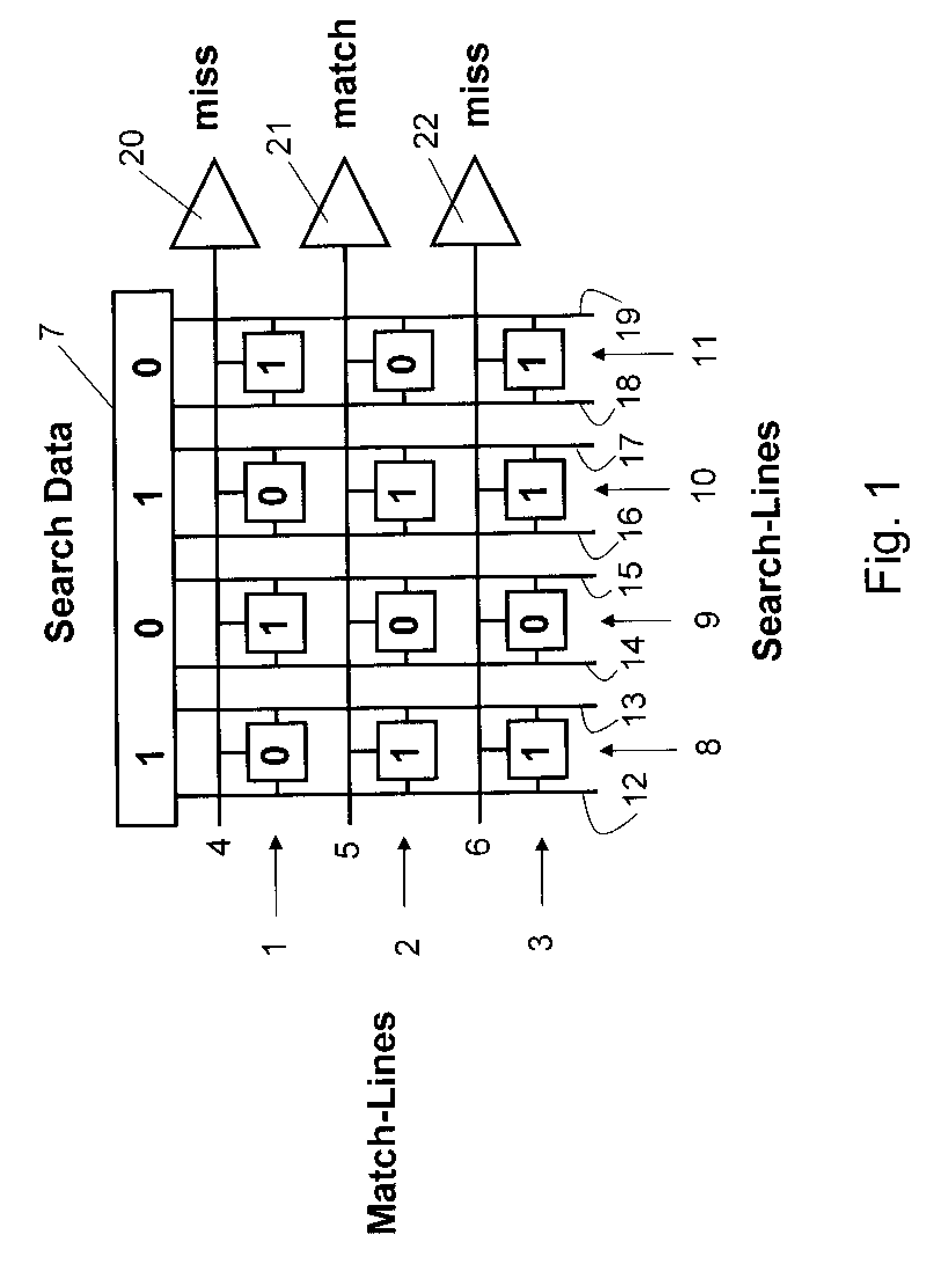

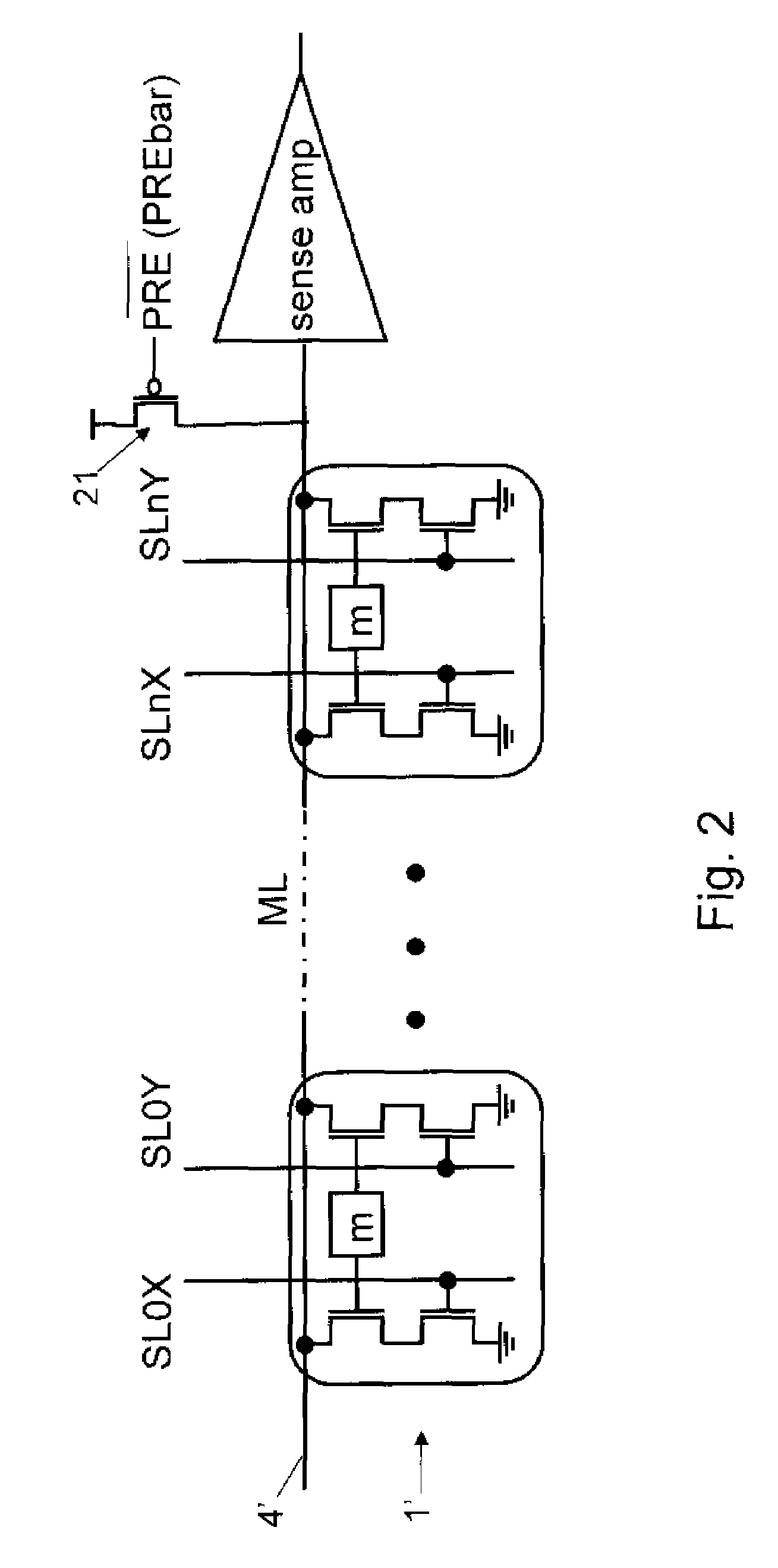

Self-Referenced Match-Line Sense Amplifier For Content Addressable Memories

ActiveUS20080025073A1Reduce the impactReduce impactCurrent/voltage measurementDigital storageAudio power amplifierComputer science

A content addressable memory (CAM) device and process for searching a CAM. The CAM device includes a plurality of CAM cells, match-lines (MLs), search lines, and ML sense amplifiers. The ML sense amplifiers are capable of self-calibration to their respective thresholds to reduce effects of random device variation between adjacent sense amplifiers.

Owner:MARVELL ASIA PTE LTD

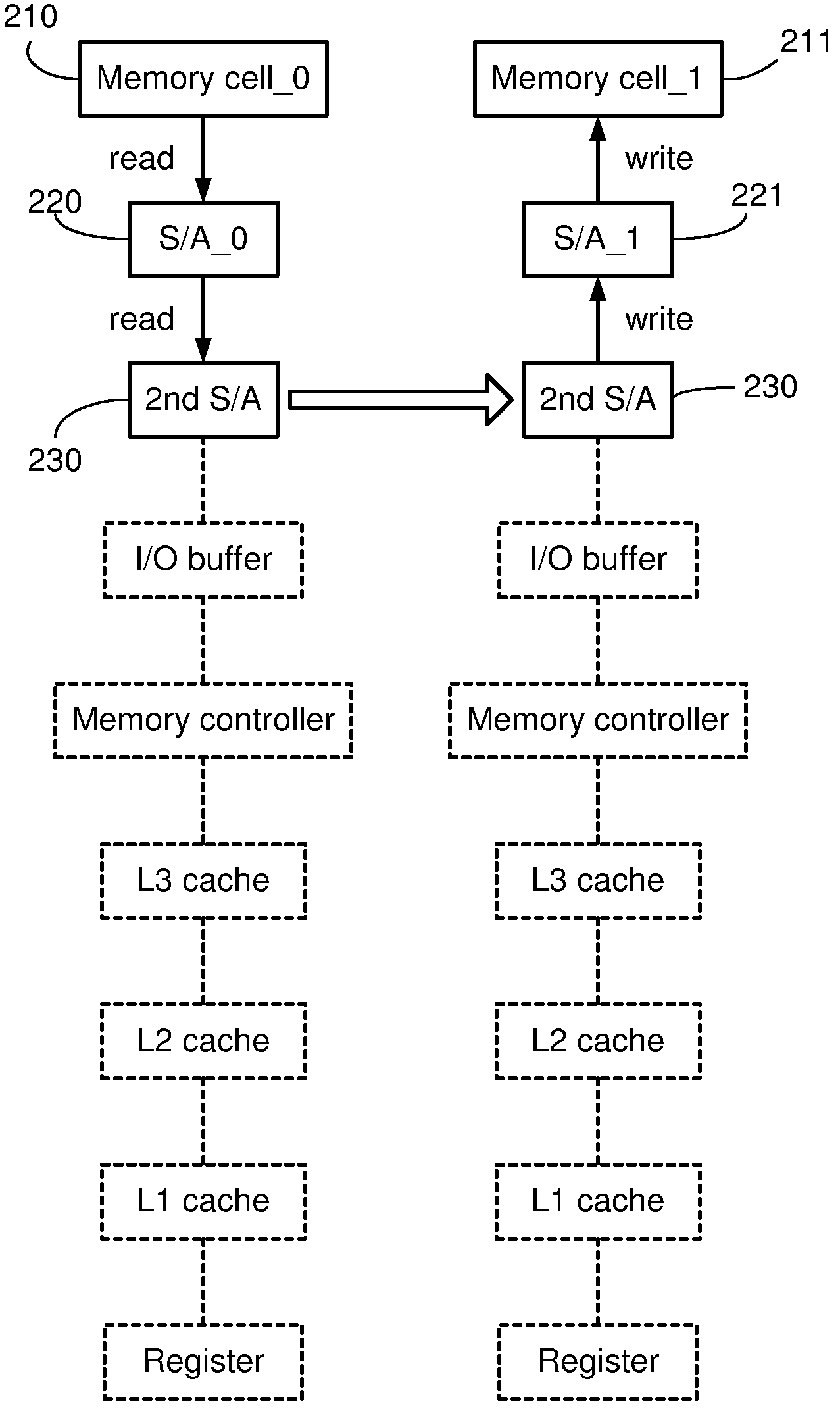

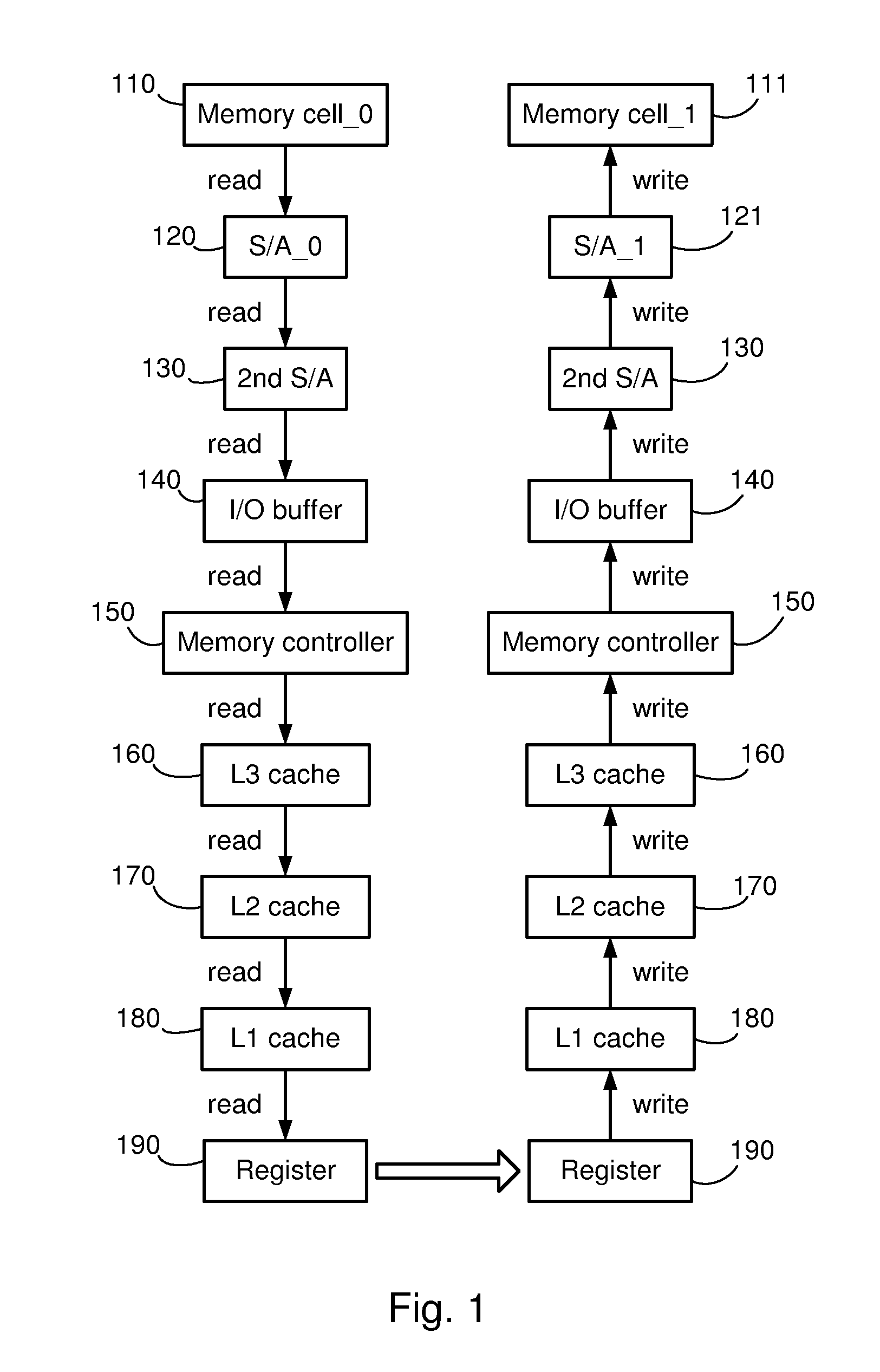

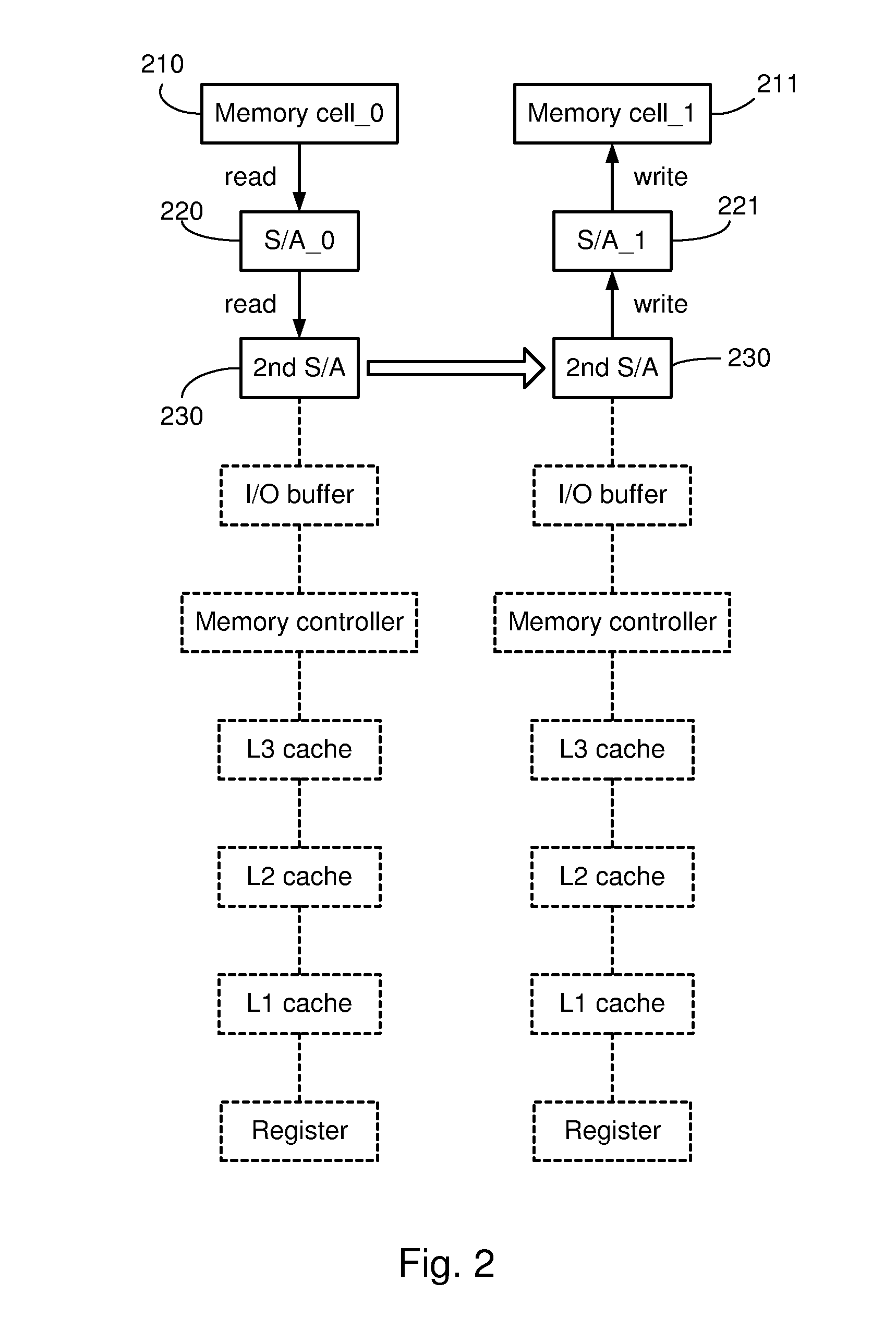

Systems and methods for data transfers between memory cells

Systems and methods for reducing the latency of data transfers between memory cells by enabling data to be transferred directly between sense amplifiers in the memory system. In one embodiment, a memory system uses a conventional DRAM memory structure having a pair of first-level sense amplifiers, a second-level sense amplifier and control logic for the sense amplifiers. Each of the sense amplifiers is configured to be selectively coupled to a data line. In a direct data transfer mode, the control logic generates control signals that cause the sense amplifiers to transfer data from a first one of the first-level sense amplifiers (a source sense amplifier) to the second-level sense amplifier, and from there to a second one of the first-level sense amplifiers (a destination sense amplifier.) The structure of these sense amplifiers is conventional, and the operation of the system is enabled by modified control logic.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

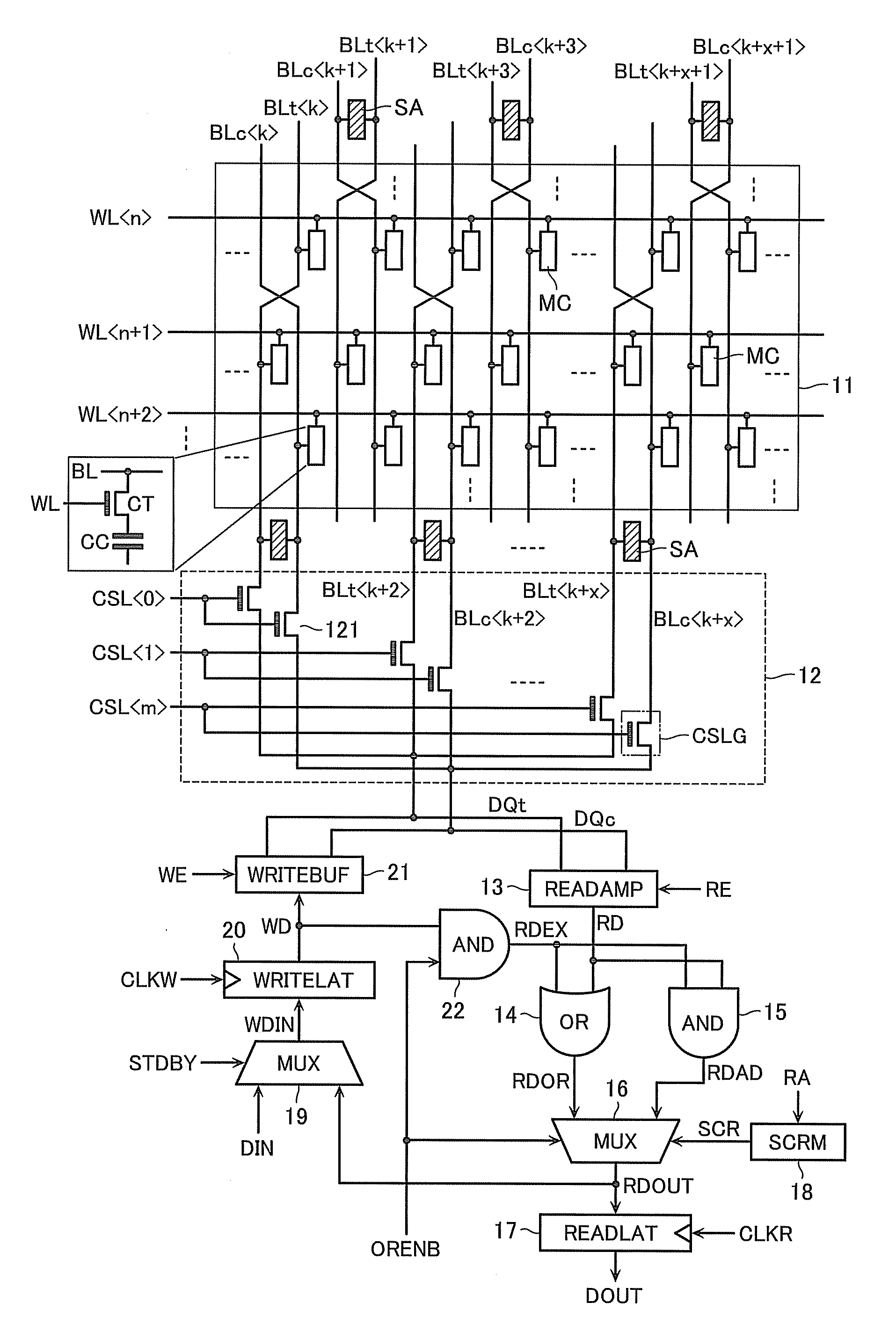

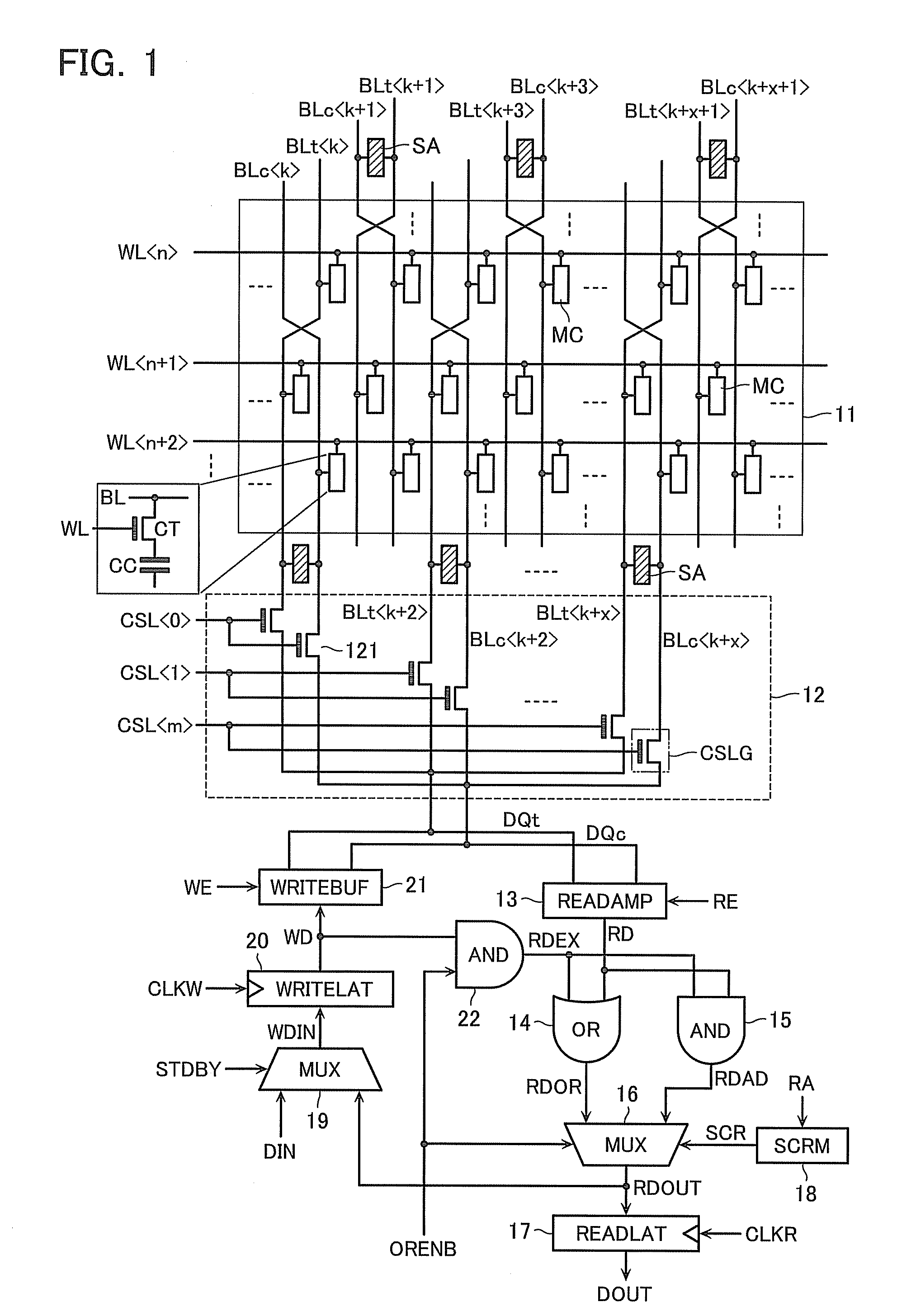

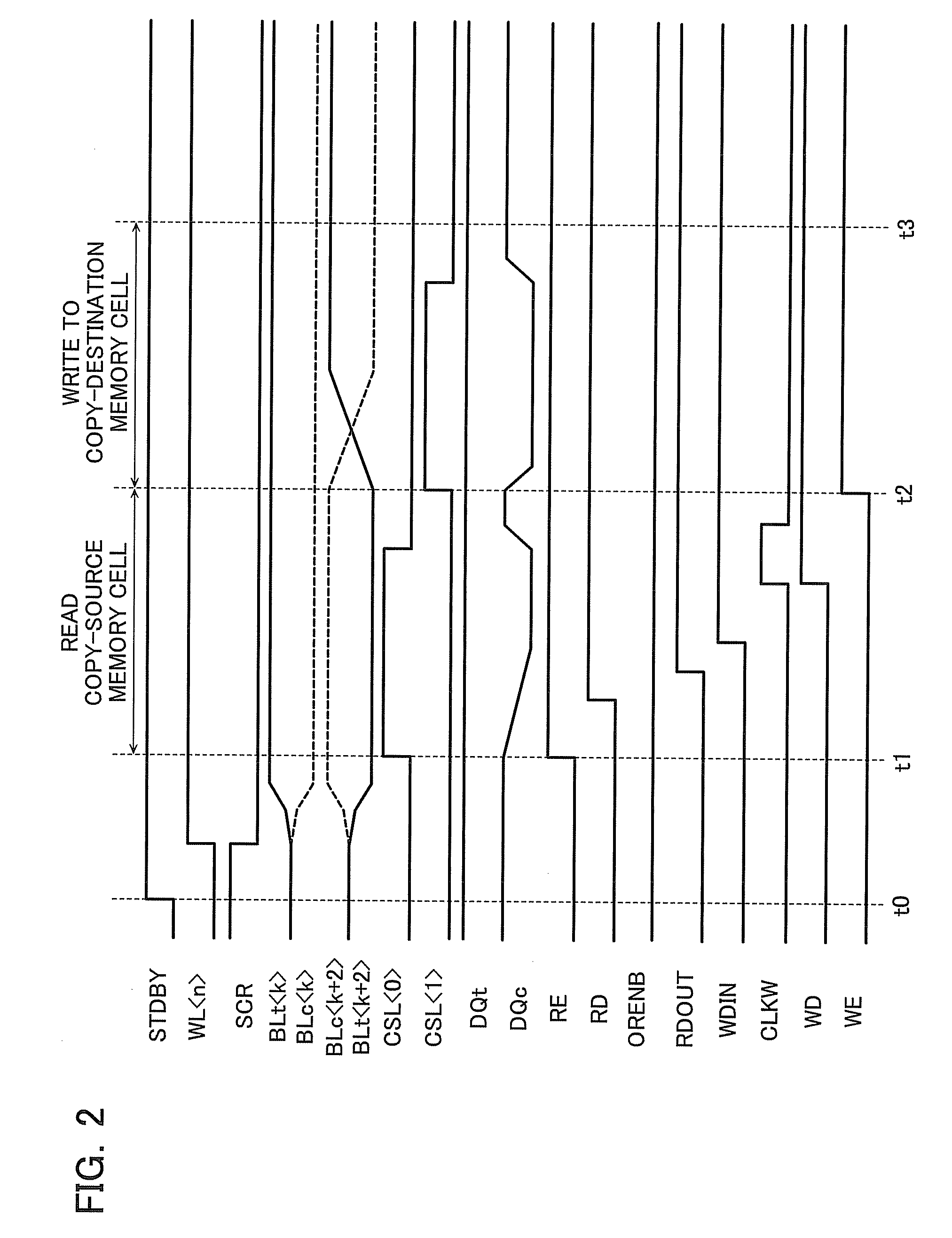

Semiconductor memory device

A sense amplifier circuit senses and amplifies a signal read from memory cells arranged at intersections of word-lines and bit-lines. A write circuit reads first data held in a first memory cell of the memory cells, and writes second data corresponding to the first data in a second memory cell different from the first memory cell. A data latch circuit holds data read from the first memory cell. A logic operation circuit performs a logic operation using data read from the second memory cell and data held in the data latch circuit as input values and outputs third data as an operation value. A write-back circuit writes the third data back to the first memory cell.

Owner:KIOXIA CORP

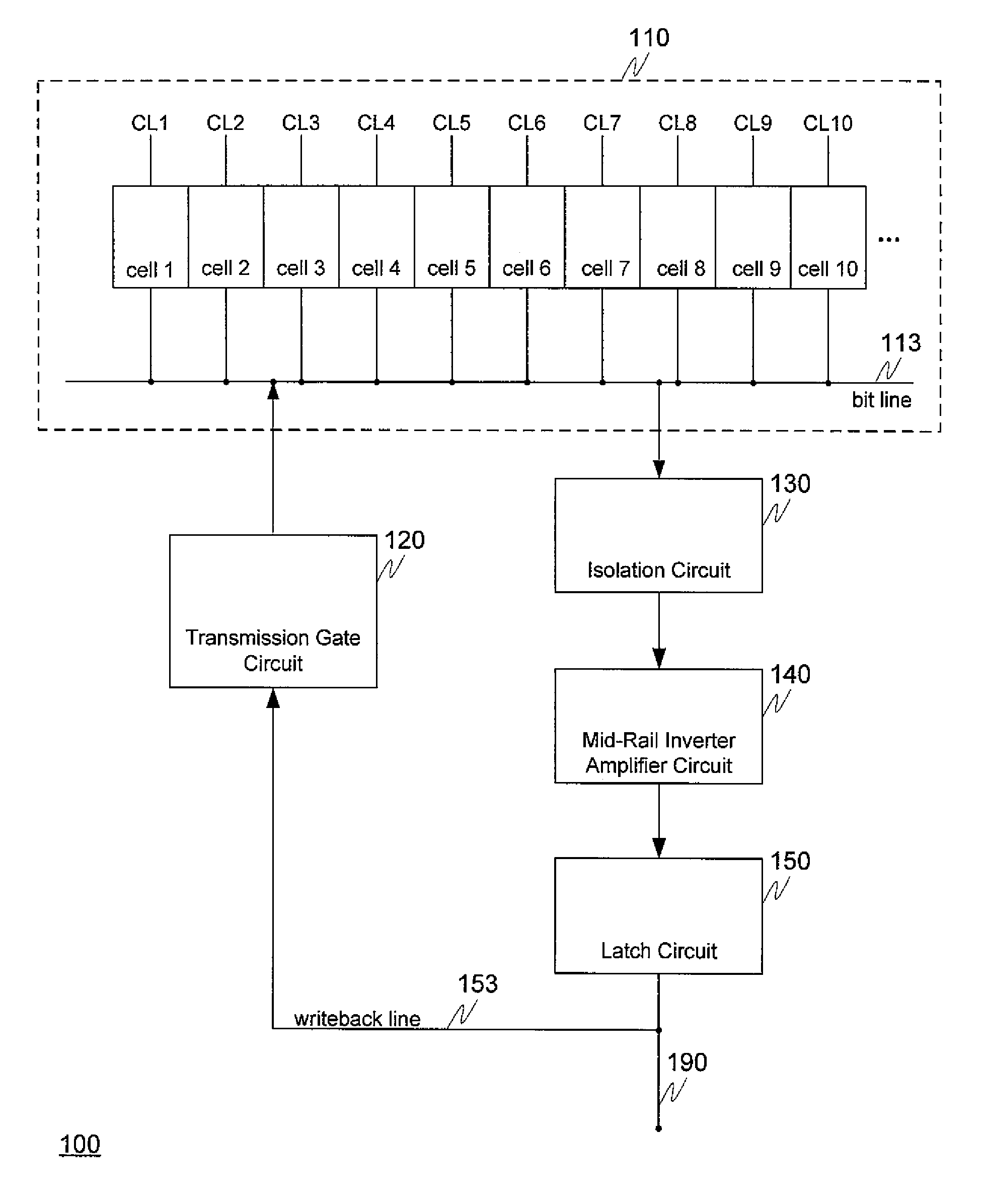

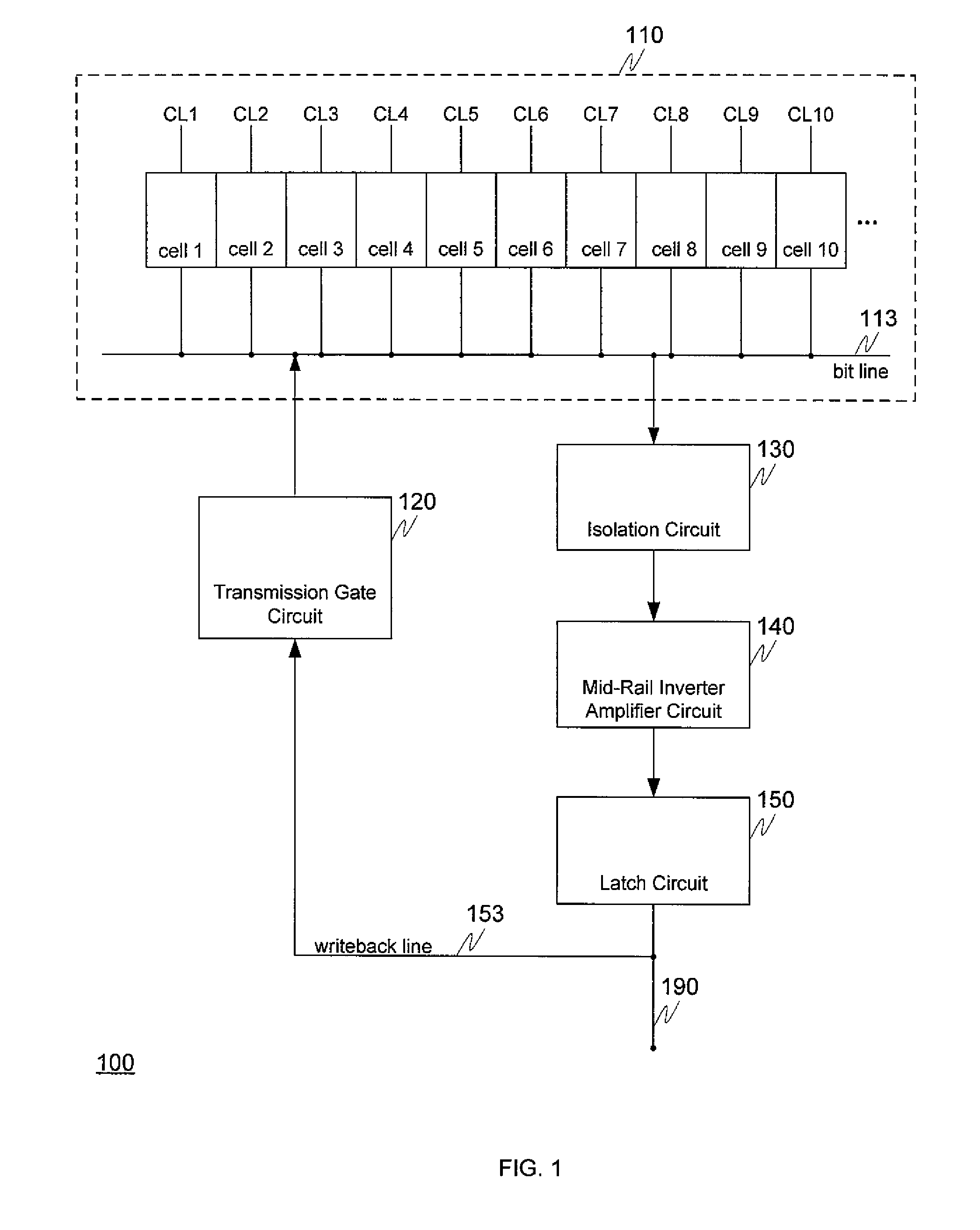

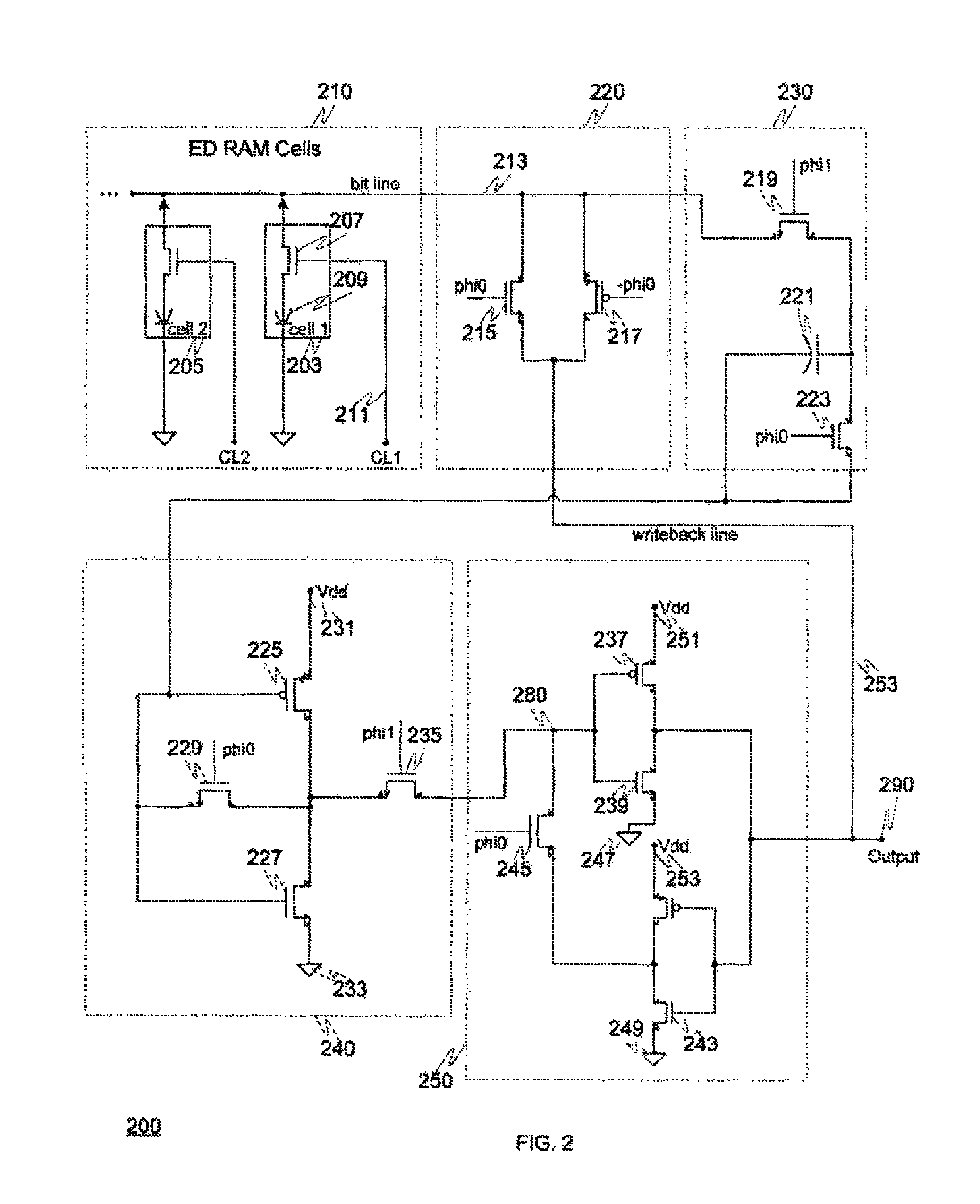

High performance eDRAM sense amplifier

Embedded dynamic random access memory (eDRAM) sense amplifier circuitry in which a bit line connected to each of a first plurality of eDRAM cells is controlled by cell control lines tied to each of the cells. During a READ operation the eDRAM cell releases its charge indicating its digital state. The digital charge propagates through the eDRAM sense amplifier circuitry to a mid-rail amplifier inverter circuit which amplifies the charge and provides it to a latch circuit. The latch circuit, in turn, inverts the charge to correctly represent at its output the logical value stored in the eDRAM cell being read, and returns the charge through the eDRAM sense amplifier circuitry to replenish the eDRAM cell.

Owner:INT BUSINESS MASCH CORP

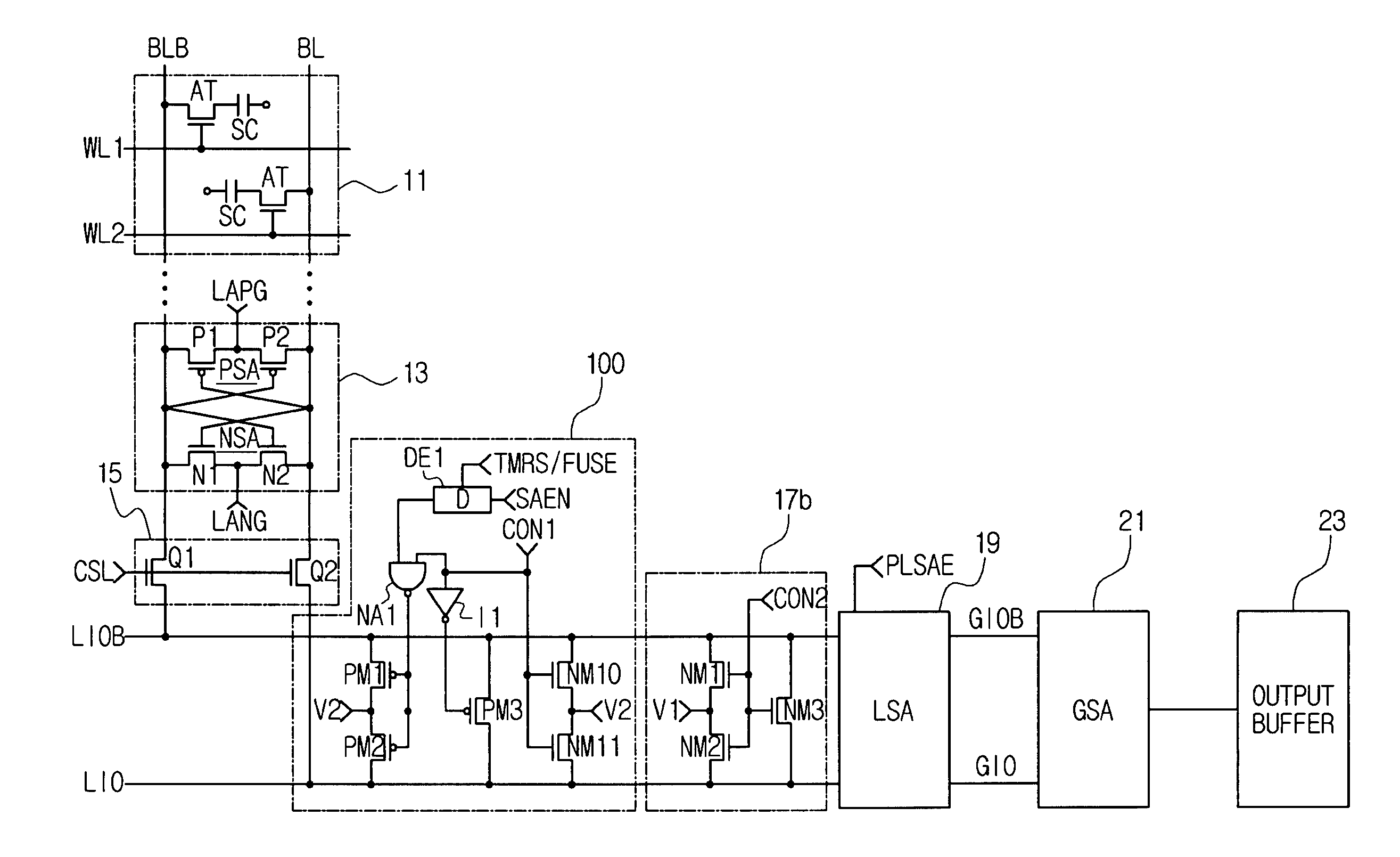

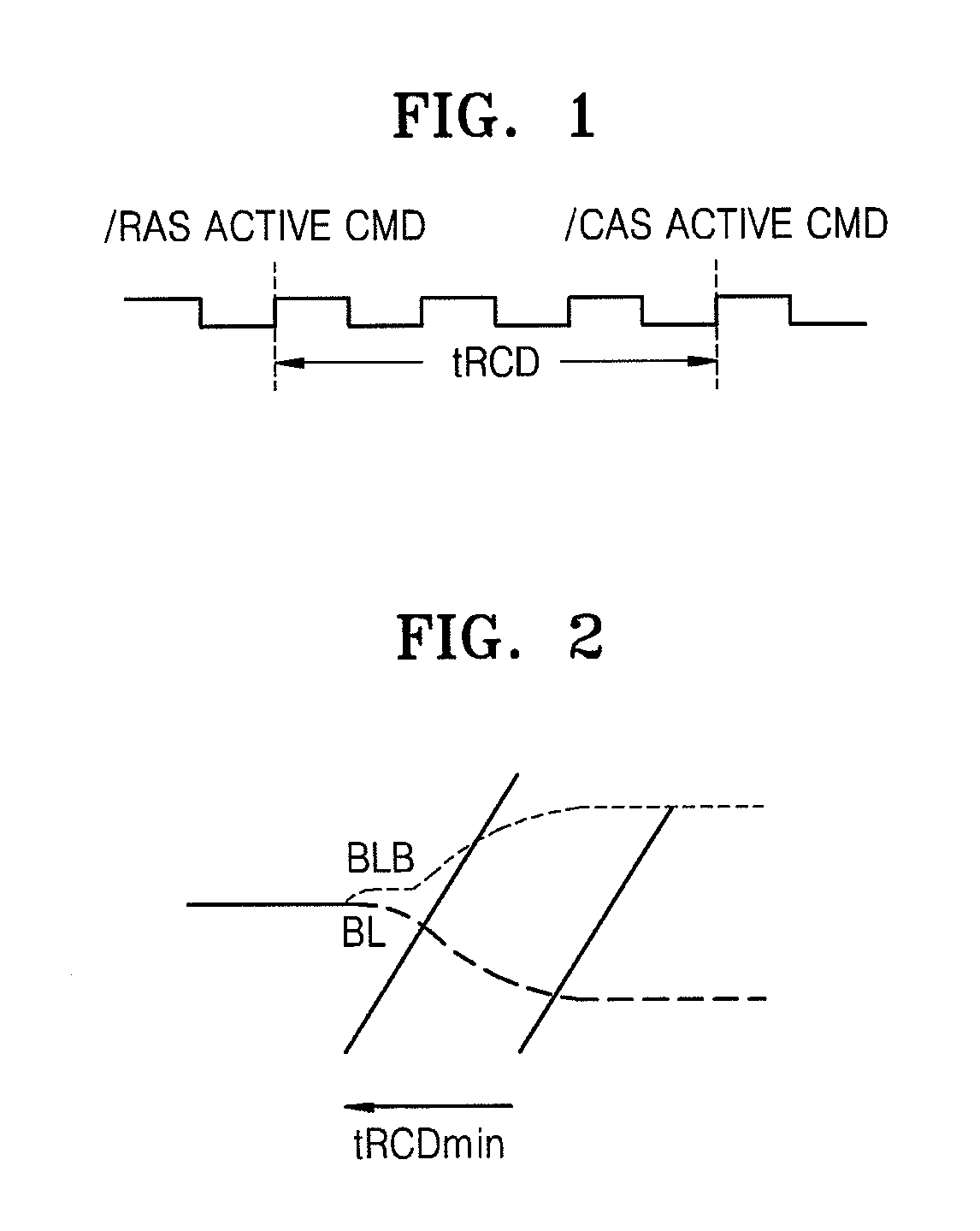

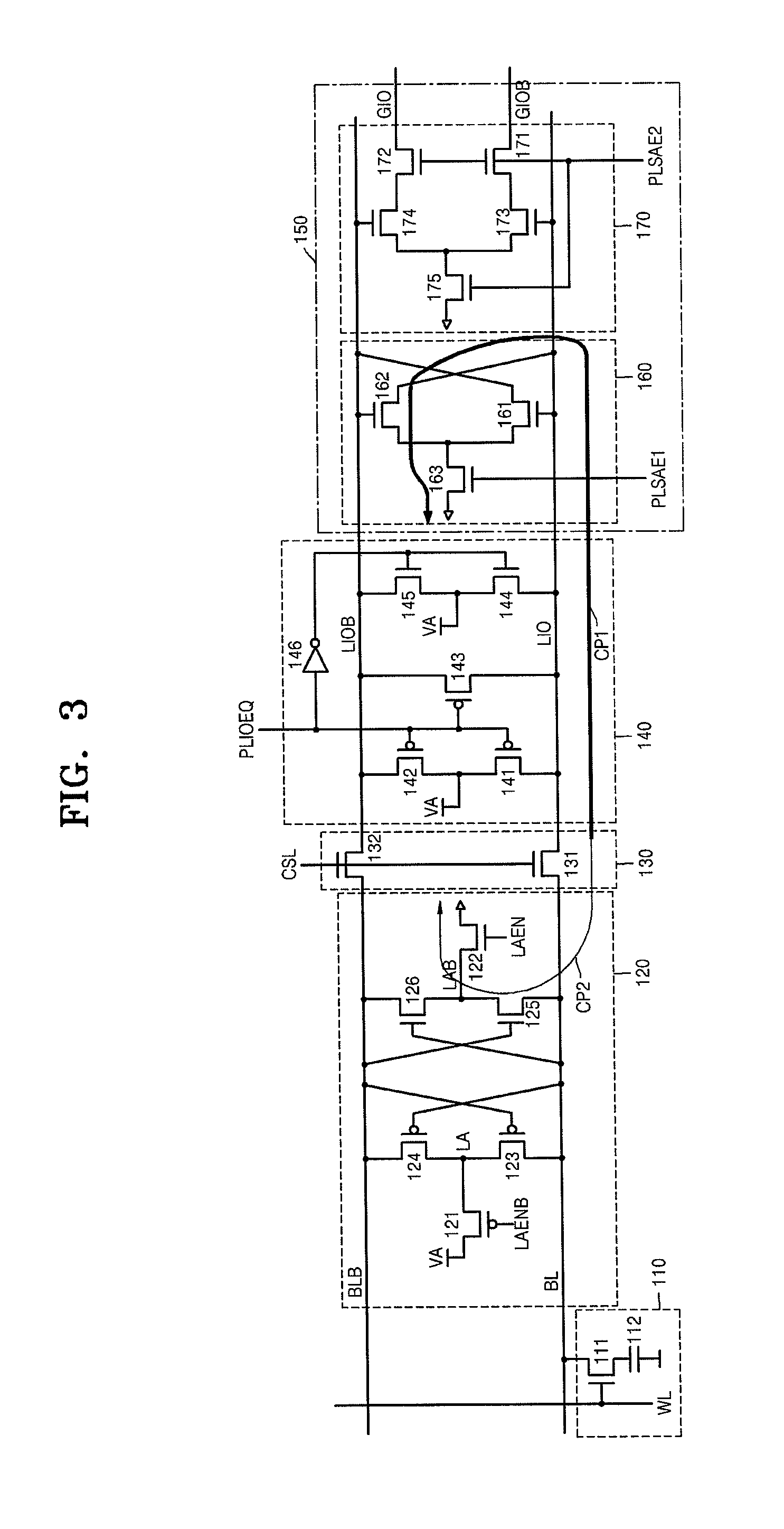

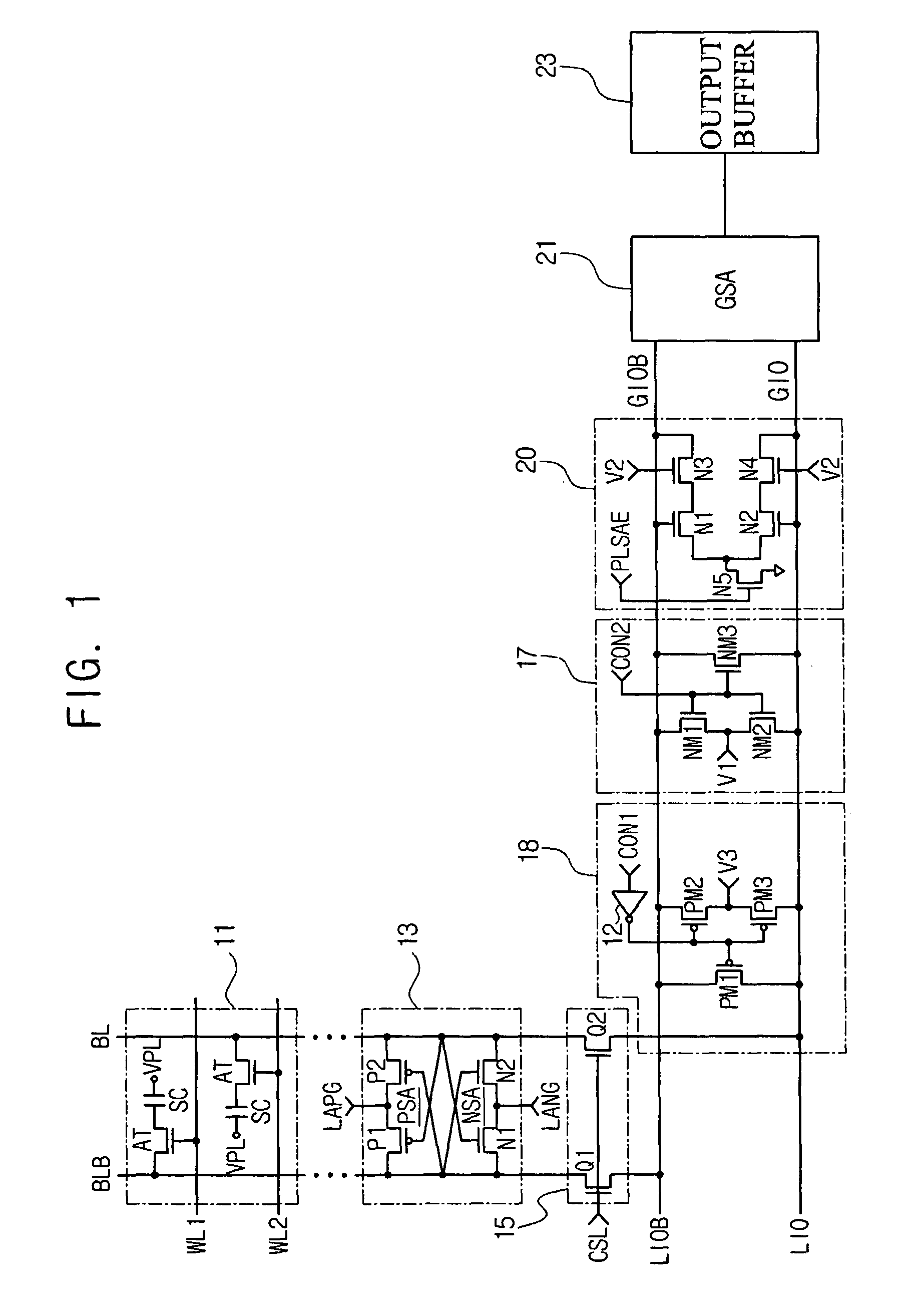

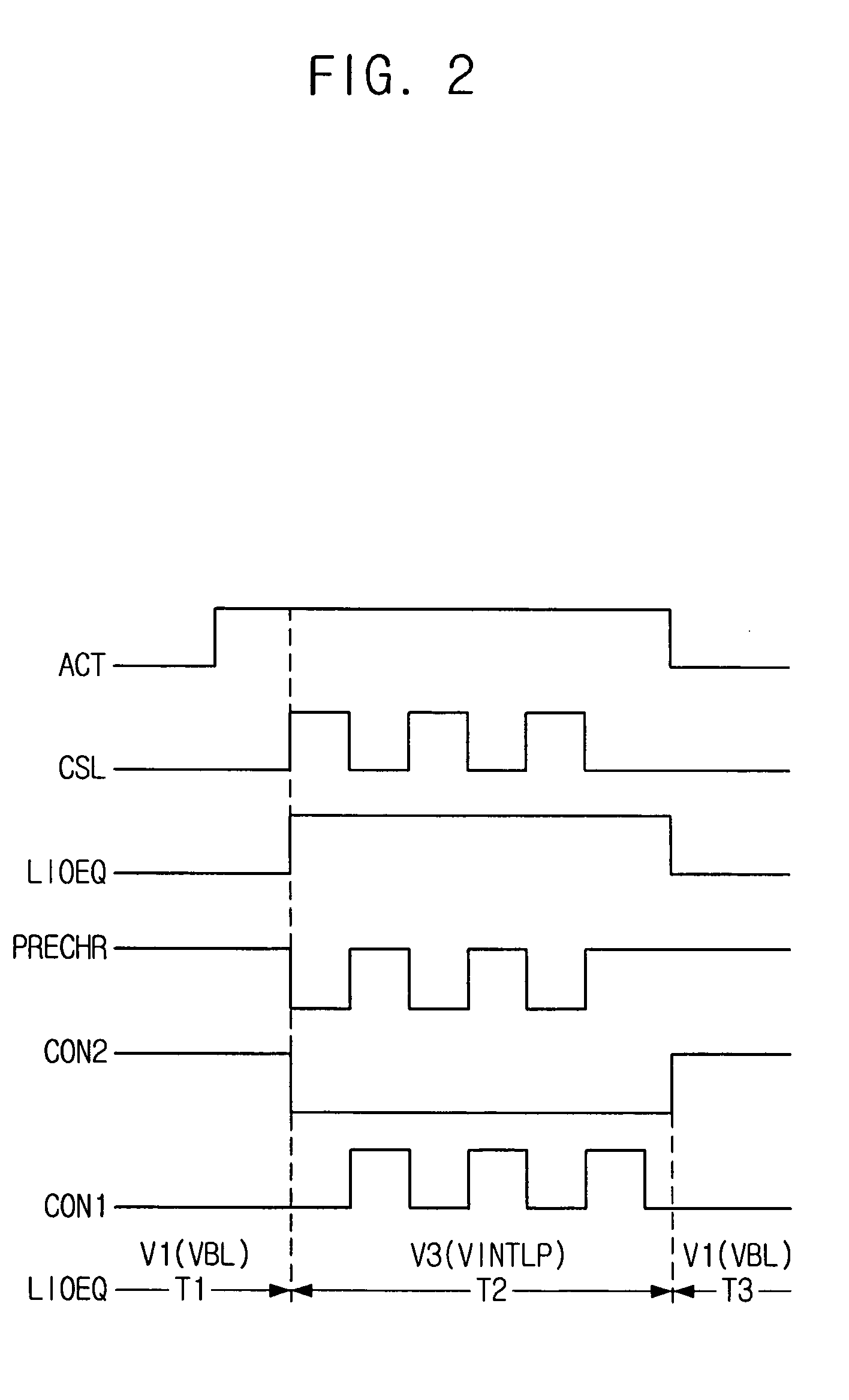

Semiconductor memory device adopting improved local input/output line precharging scheme

A semiconductor memory device capable of preventing or minimizing bit line disturbance and performing a low-voltage high-speed operation includes a read data path circuit including a bit line sense amplifier, a local input / output line sense amplifier, a column selecting unit to operationally connect bit lines connected to the bit line sense amplifier to local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal, and a local input / output line precharging unit to precharge the pair of local input / output lines by a first precharging unit, equalizing the pair of local input / output lines by an equalizing unit, and to precharge the local input / output lines by a second precharging unit following an elapsed time after the bit line sense amplifier is activated, while the column selection is deactivated.

Owner:SAMSUNG ELECTRONICS CO LTD

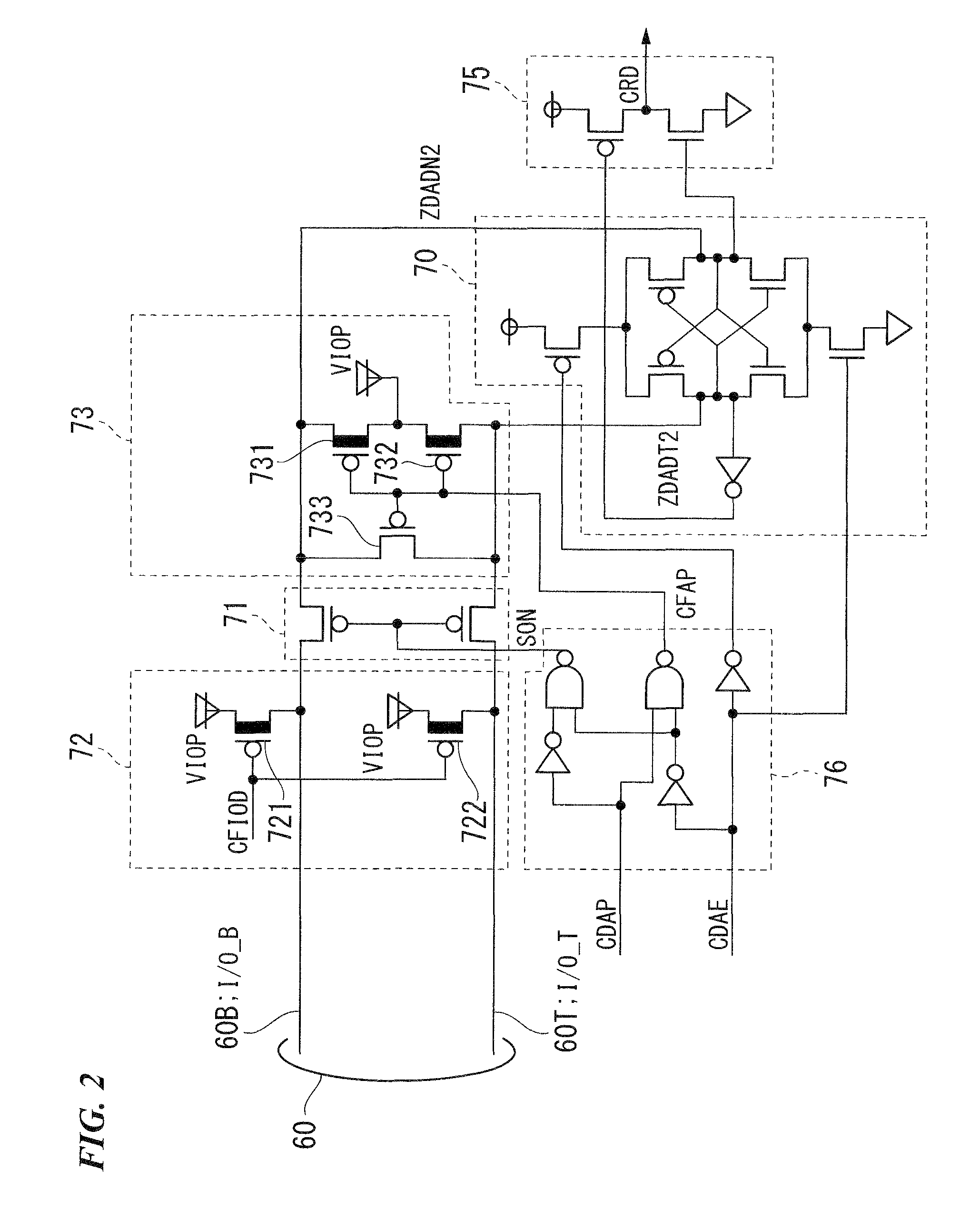

Semiconductor device

A semiconductor device includes a column decoder that generates a column selecting signal that selects any of a plurality of bit line pairs to which memory cells are connected according to a column address that is input; a bit line selecting switch that connects by the column selecting signal any of a plurality of bit line pairs and a data I / O line pair that outputs data that has been read from a memory cell to the outside; a data amplifier that amplifies a voltage differential of a data I / O line pair and outputs data that has been read to an output buffer; a data I / O line switch that is provided in the data I / O lines; an I / O line precharge circuit that precharges a data I / O line pair that is not on the side of the data amplifier; and an amplifier precharge circuit that precharges a data I / O line pair that is on the side of the data amplifier.

Owner:LONGITUDE LICENSING LTD

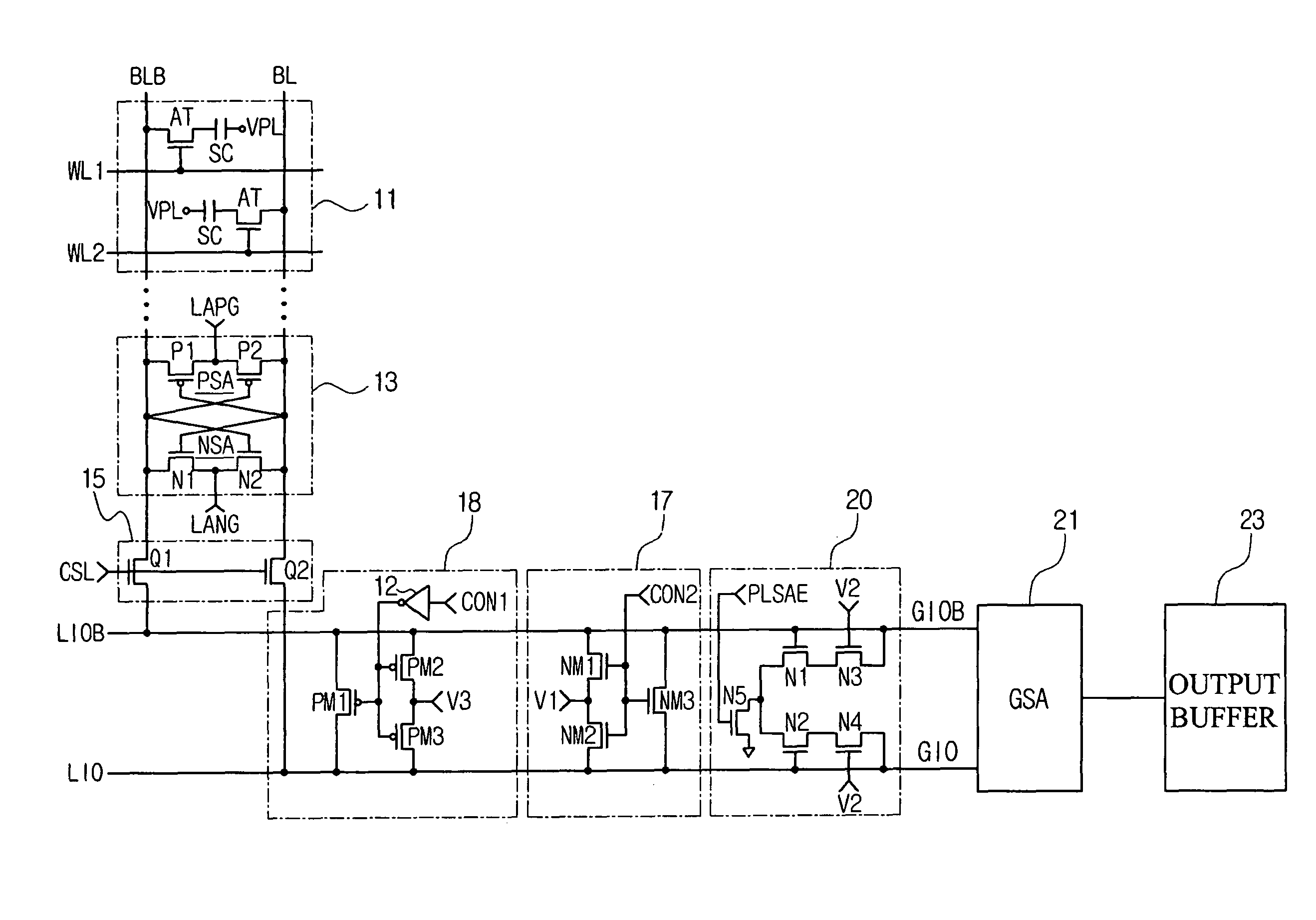

Semiconductor memory device

A semiconductor memory device includes a bitline sensing amp detecting and amplifying data of a pair of bitlines from a memory cell, a column selecting unit transmitting the data of the pair of bitlines to a pair of local datalines in response to a column selecting signal, a dataline precharging unit precharging the pair of local datalines to a precharging voltage level in response to a precharging signal, and a dataline sensing amp detecting and amplifying data transmitted to the pair of local datalines. The dataline sensing amp includes a charge sync unit discharging the pair of local datalines at the precharging voltage level in response to a first dataline sensing enabling signal and data of the pair of local datalines, and a data sensing unit transmitting data of the pair of local datalines to a pair of global datalines in response to a second dataline sensing enabling signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device having improved local input/output line precharge scheme

ActiveUS8213248B2Preventing bit line disturbanceRun at high speedDigital storageBit lineDatapath circuits

A data path circuit of a semiconductor memory device includes: a bit line sense amplifier driven by a first power supply voltage; a local input / output line sense amplifier; a column selecting unit operatively connecting a pair of bit lines connected to the bit line sense amplifier and a pair of local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal; and a local input / output line precharge unit precharging the pair of local input / output lines with a second power supply voltage different from the first power supply voltage during a period for which the column selection signal is in an inactive state.

Owner:SAMSUNG ELECTRONICS CO LTD

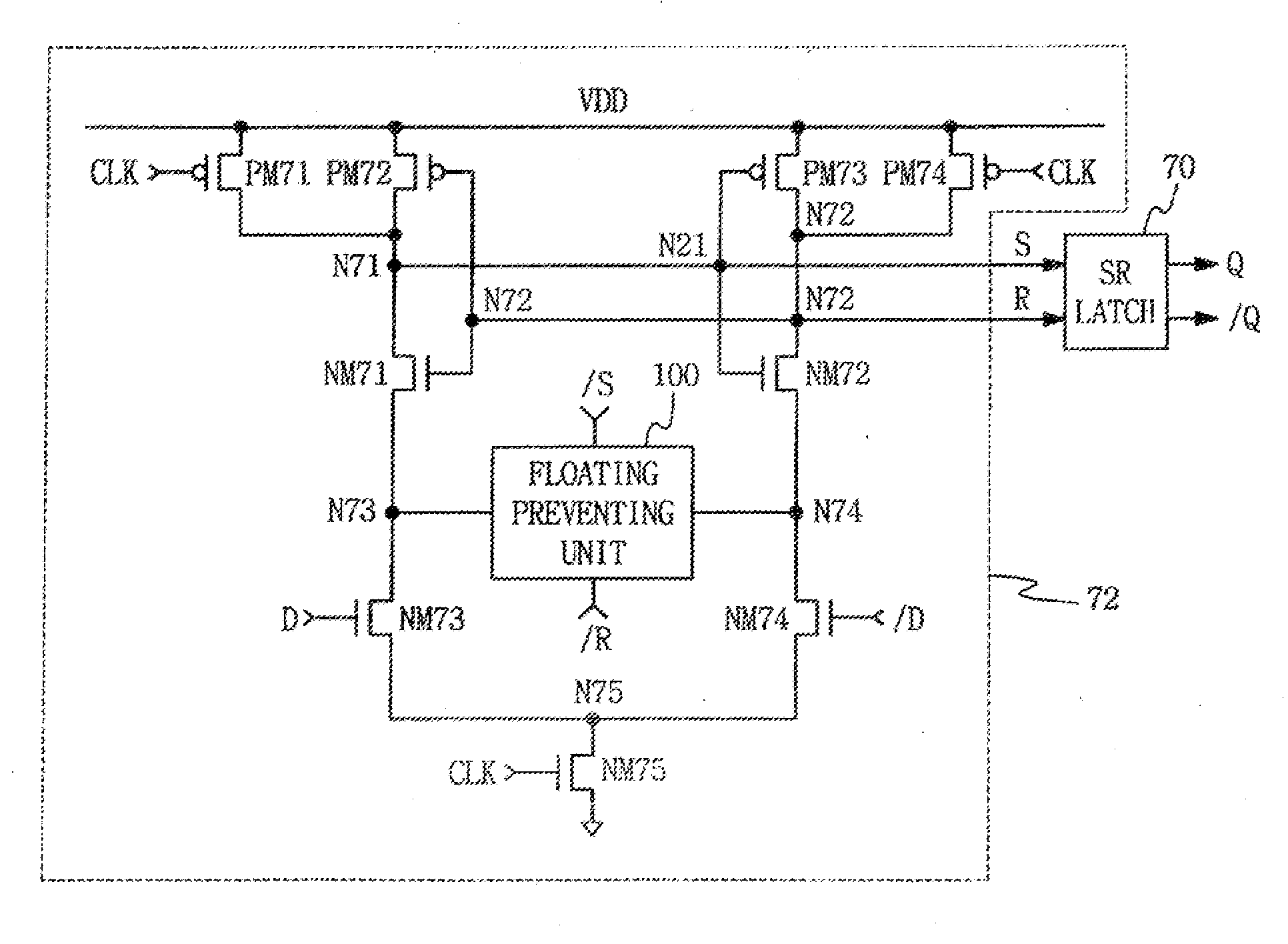

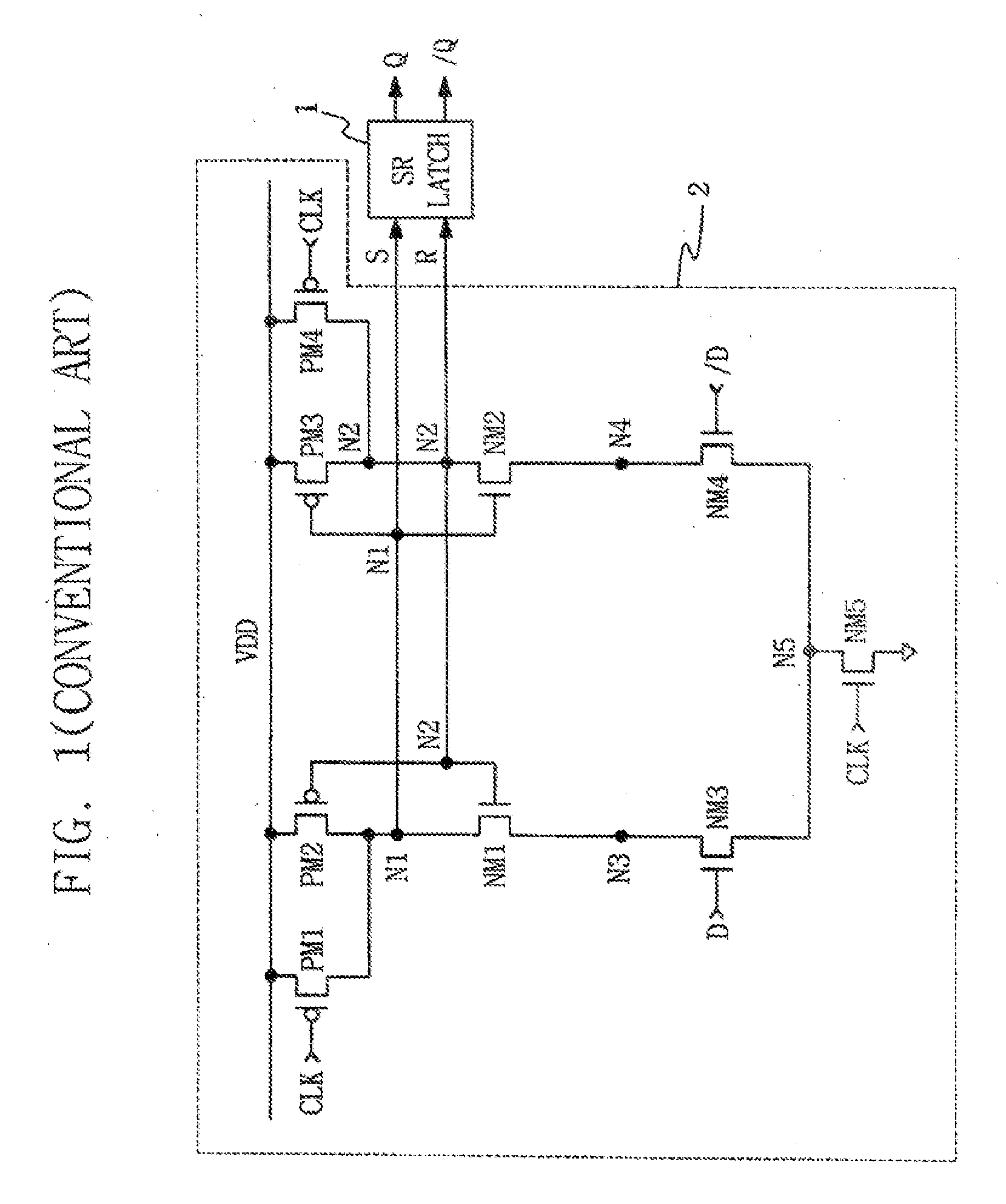

Sense amplifier circuit and sense amplifier-based flip-flop having the same

ActiveUS20070285131A1Reducing signal delay timePrevent degradation of outputCurrent/voltage measurementDigital storageAudio power amplifierControl delay

A sense amplifier-based flip-flop includes a first latch, a second latch, a floating reduction unit, an input signal applying unit, a ground switch and a delay reduction unit. The first latch outputs a signal to a first output terminal pair, and outputs an evaluation signal pair corresponding to an input single pair to the first output terminal pair. The second latch latches the evaluation signal pair and outputs the evaluation signal pair to a second output terminal pair. The floating reduction unit is controlled by signals of the first output terminal pair and is operationally connected between current passing nodes of the first latch to prevent the first output terminal pair from floating. The input signal applying unit is disposed between the current passing nodes and a ground terminal, and receives the input signal pair. The ground switch is disposed between the input signal applying unit and the ground terminal, and is controlled by the clock signal. The delay reduction unit is disposed between the input signal applying unit and the ground switch, and reduces a signal delay from when the clock signal to when the evaluation signal pair is output from the second output terminal pair.

Owner:SAMSUNG ELECTRONICS CO LTD

Reference sense amplifier for non-volatile memory

InactiveUS20060158947A1Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierReference current

One or more sense amplifiers for sensing the conduction current of non-volatile memory is controlled by signals that are timed by a reference sense amplifier having similar characteristics and operating conditions. In one aspect, a sensing period is determined by when the reference sense amplifier sensing a reference current detects an expected state. In another aspect, an integration period for an amplified output is determined by when the reference sense amplifier outputs an expected state. When these determined timings are used to control the one or more sense amplifiers, environment and systemic variations are tracked.

Owner:SANDISK TECH LLC

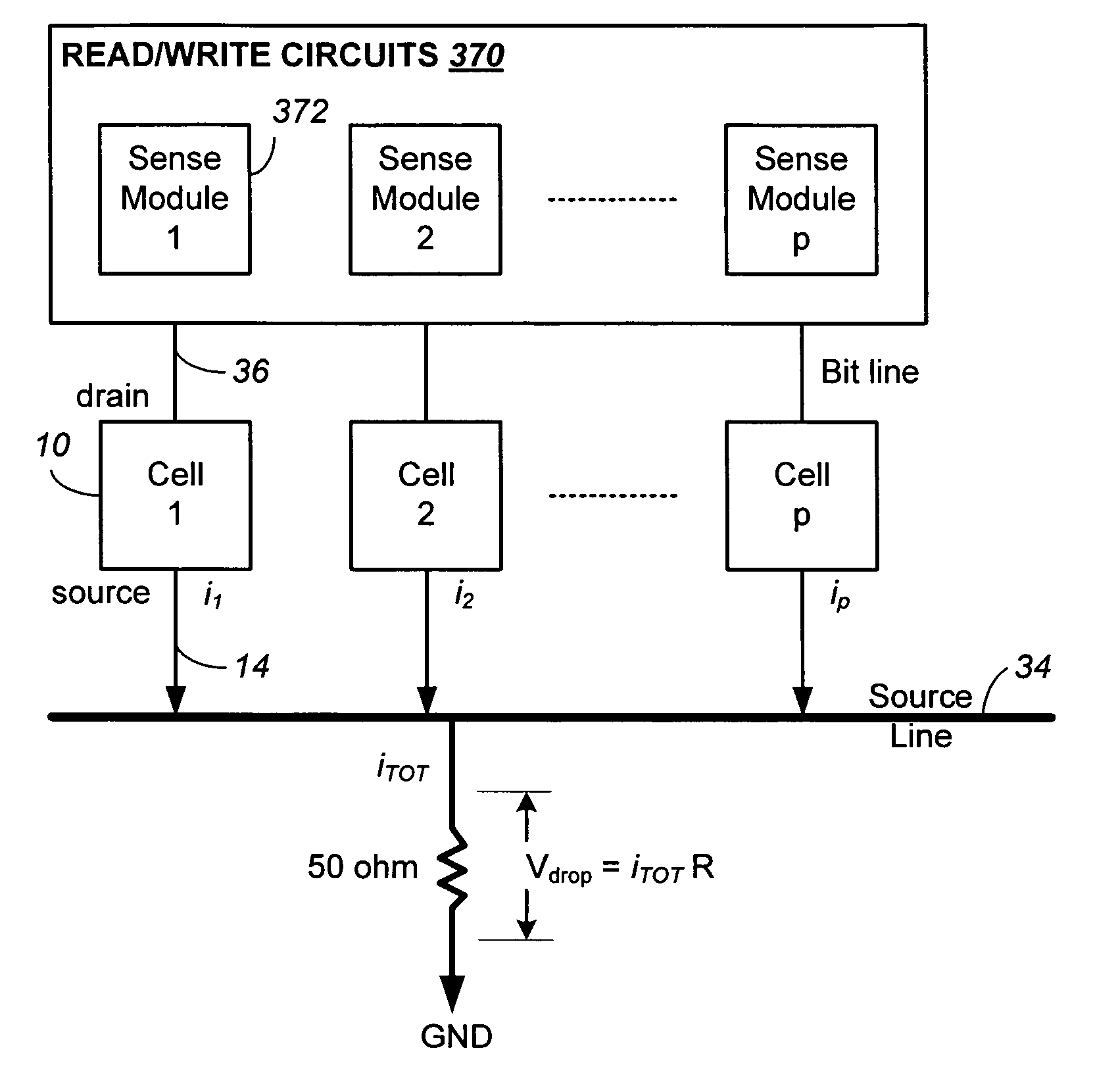

Non-volatile memory and method with improved sensing

InactiveUS7023736B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierMultiple pass

A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In particular, the identified memory cells are shut down after all sensing in the current pass have been completed. In this way the shutting down operation does not disturb the sensing operation. Sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells. In another aspect of sensing improvement, a reference sense amplifier is employed to control multiple sense amplifiers to reduce their dependence on power supply and environmental variations.

Owner:SANDISK TECH LLC

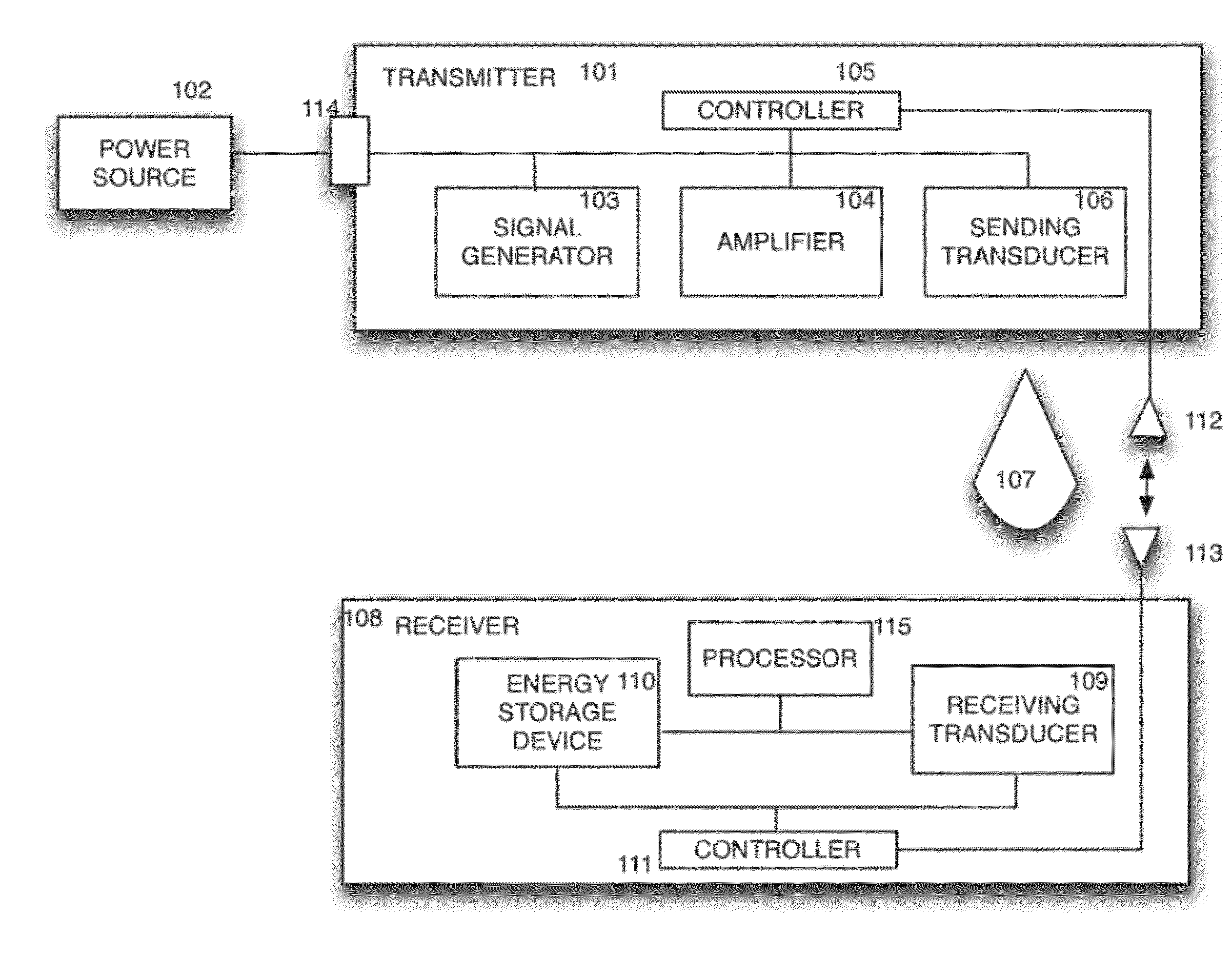

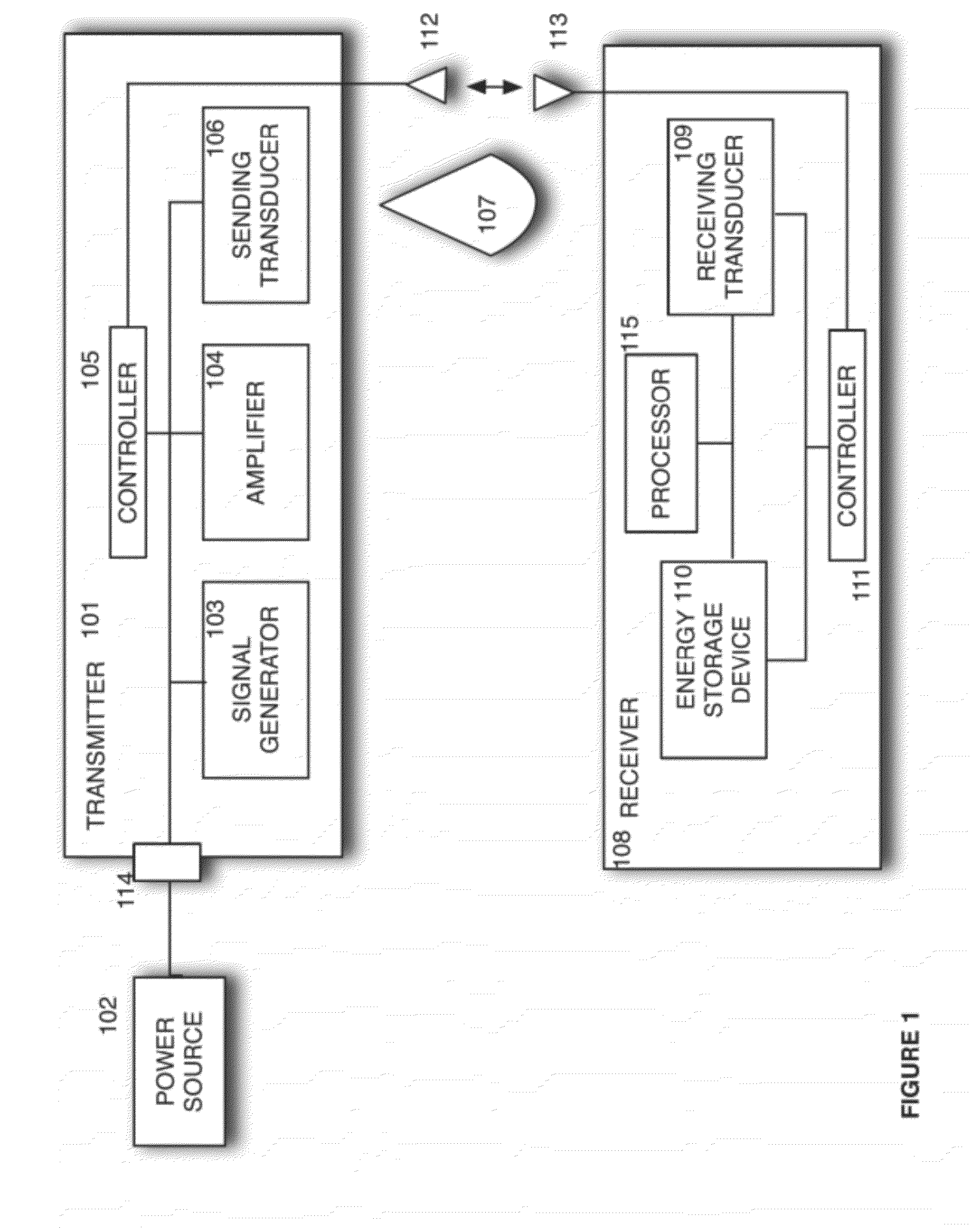

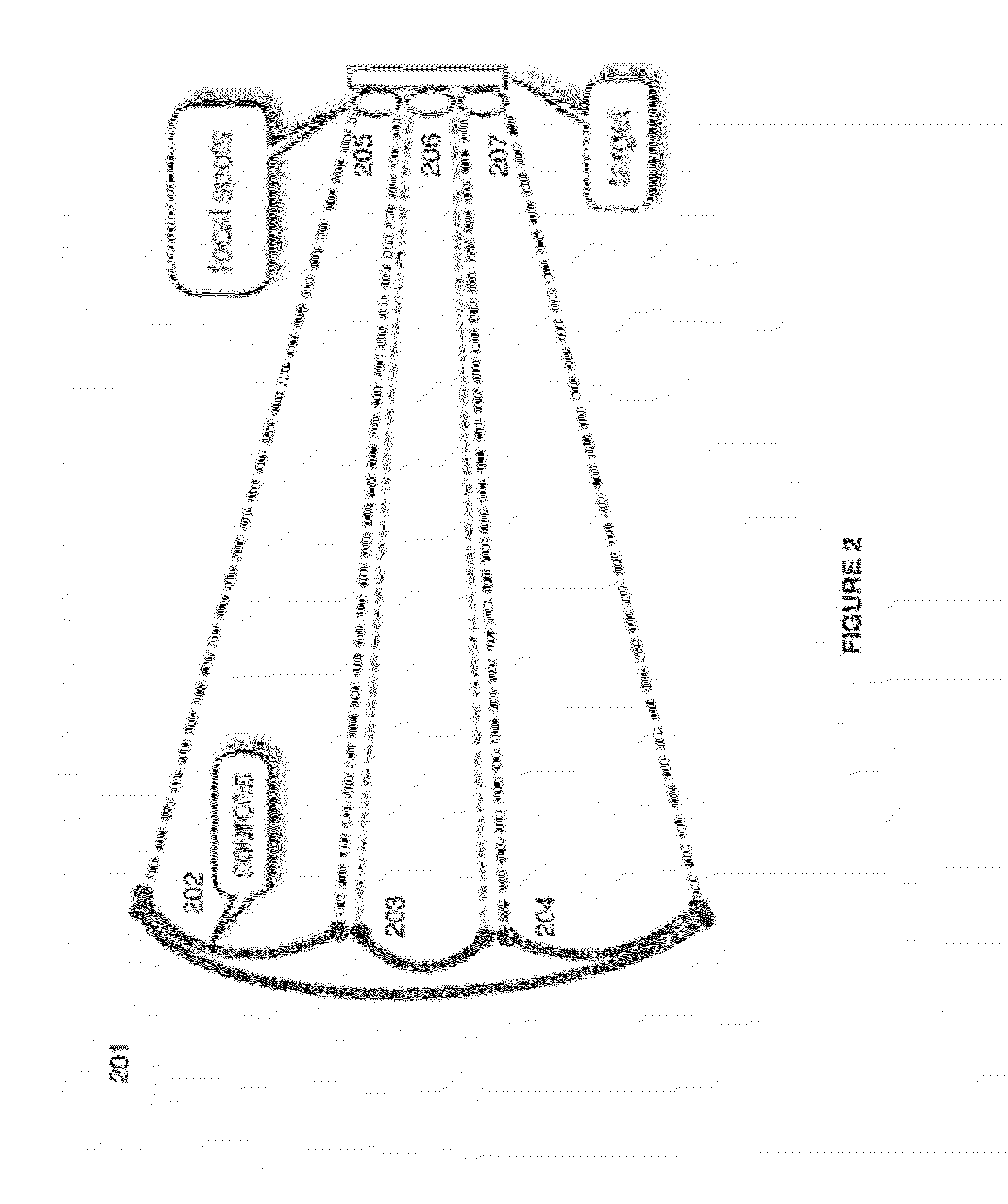

Sender communications for wireless power transfer

A signal generator generates an electrical signal that is sent to an amplifier, which increases the power of the signal using power from a power source. The amplified signal is fed to a sender transducer to generate ultrasonic waves that can be focused and sent to a receiver. The receiver transducer converts the ultrasonic waves back into electrical energy and stores it in an energy storage device, such as a battery, or uses the electrical energy to power a device. In this way, a device can be remotely charged or powered without having to be tethered to an electrical outlet.

Owner:UBEAM

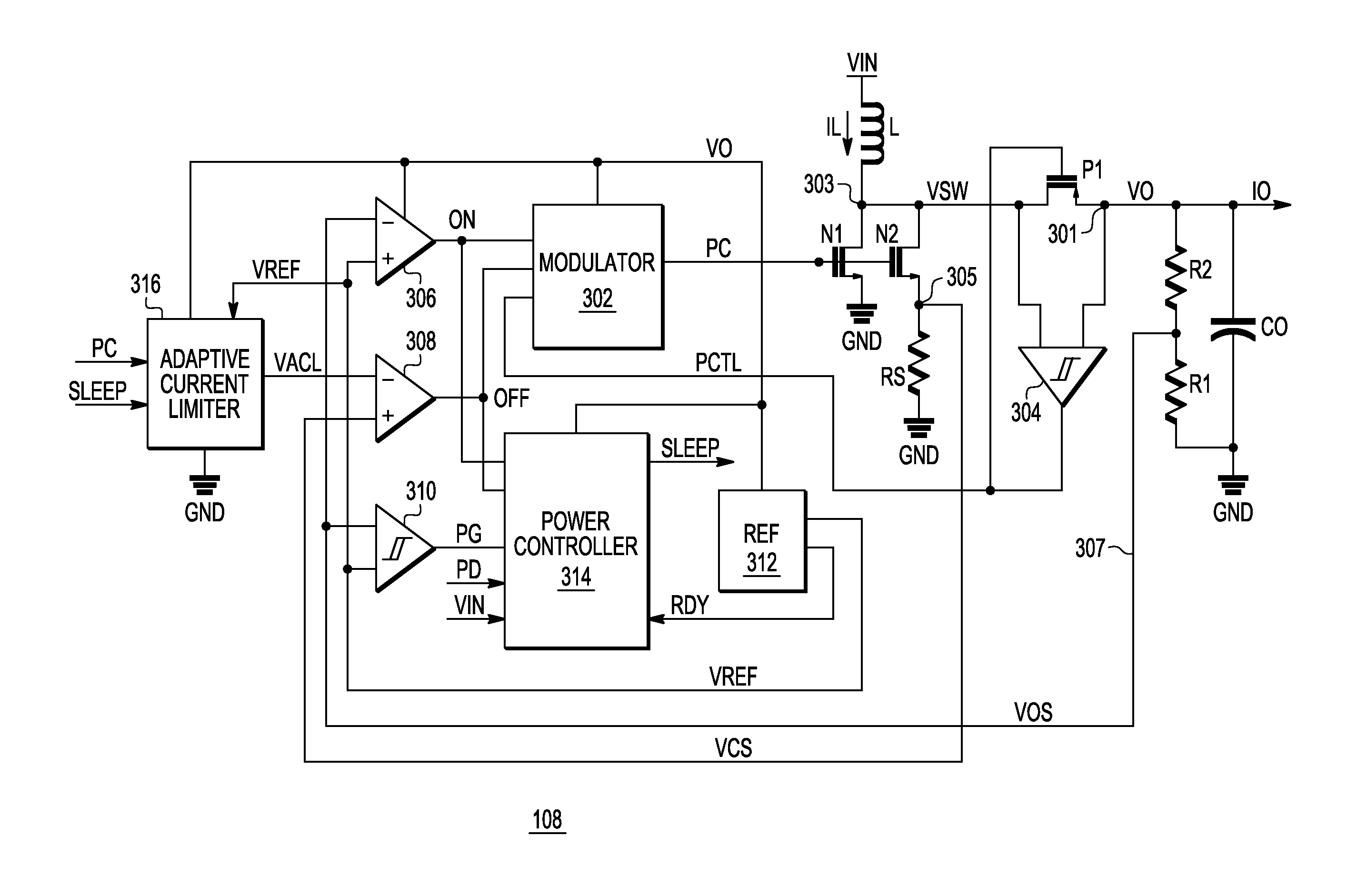

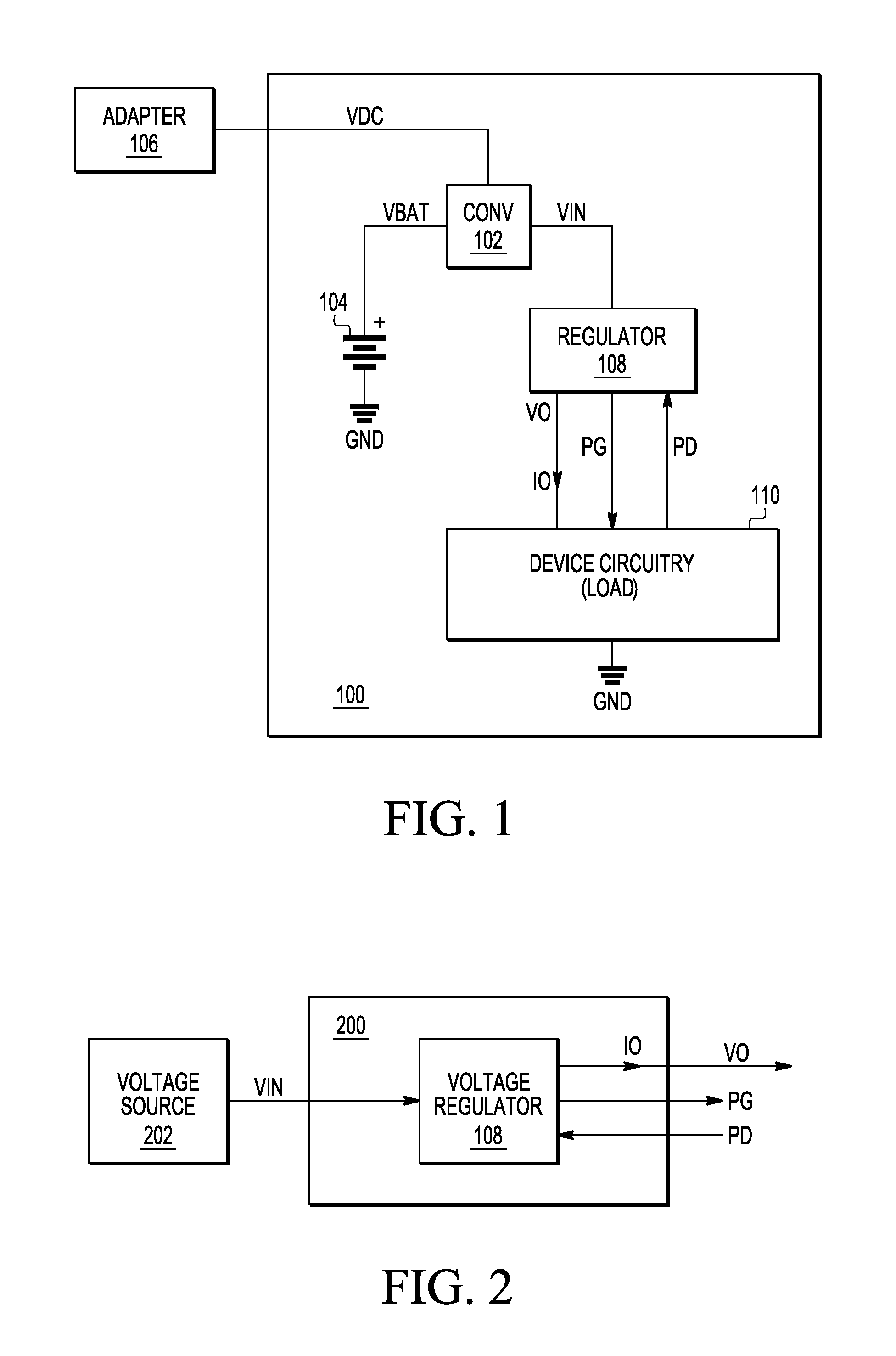

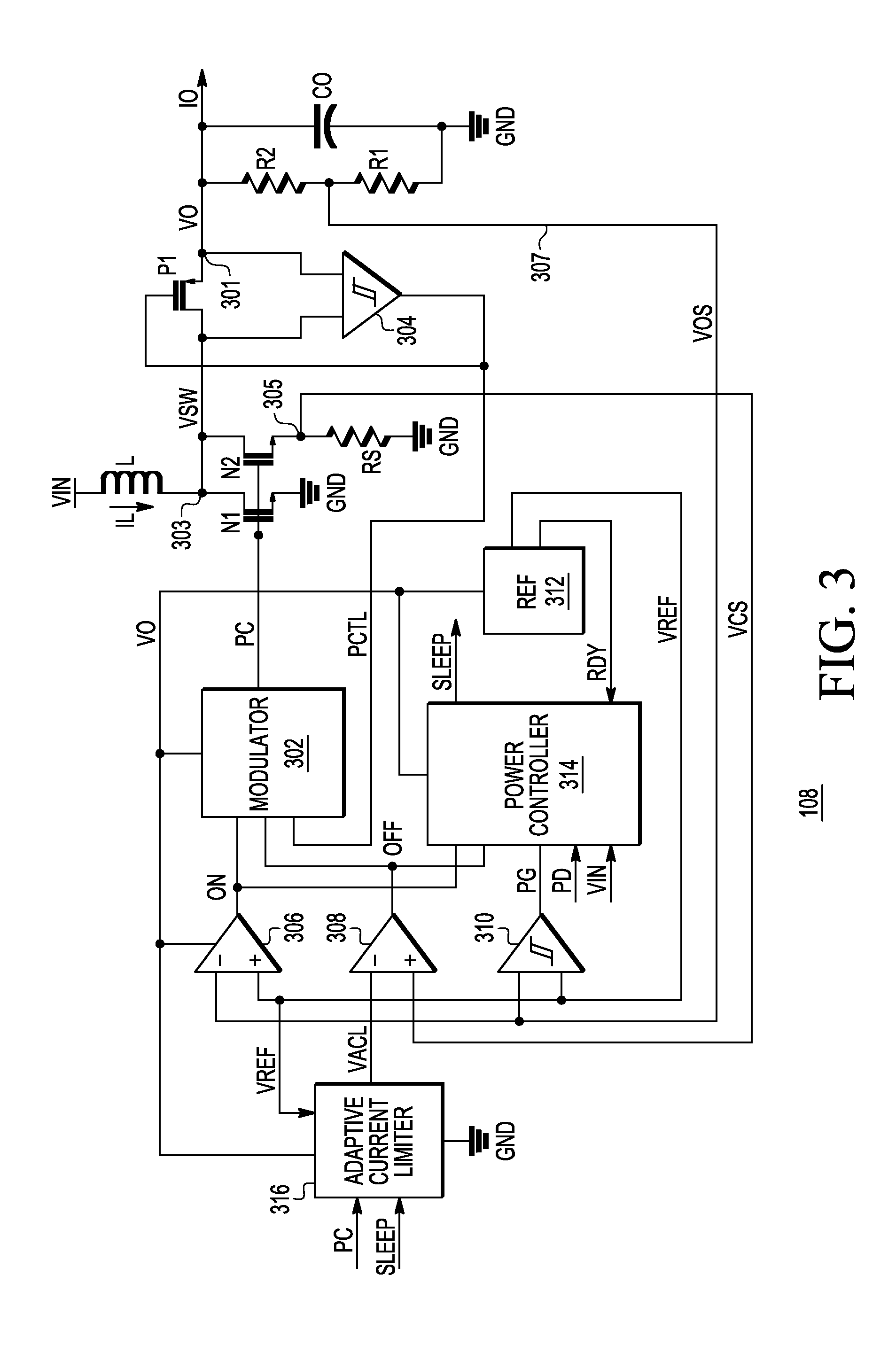

System and method for adaptive current limit of a switching regulator

ActiveUS9099922B2Efficient power electronics conversionDc-dc conversionControl signalReference current

Owner:SILICON LAB INC

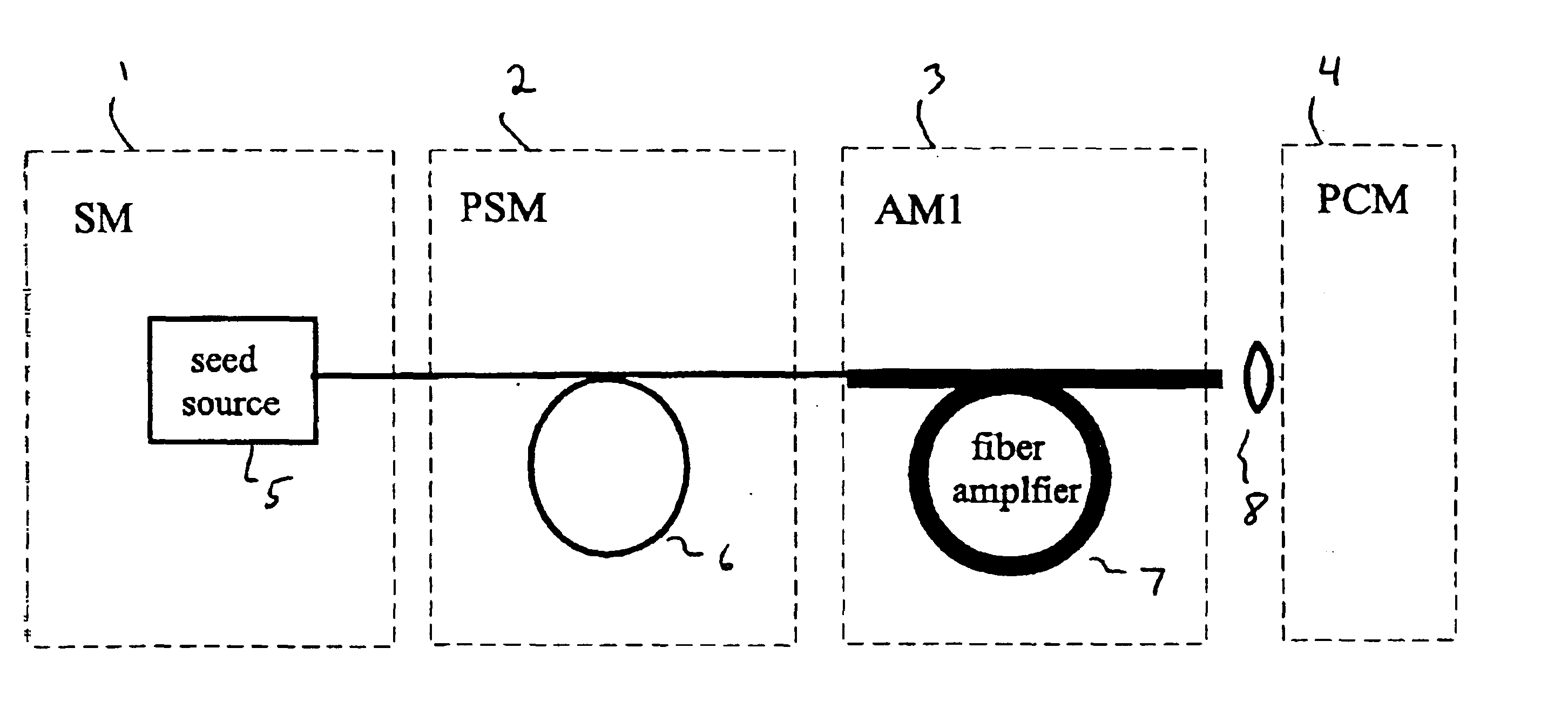

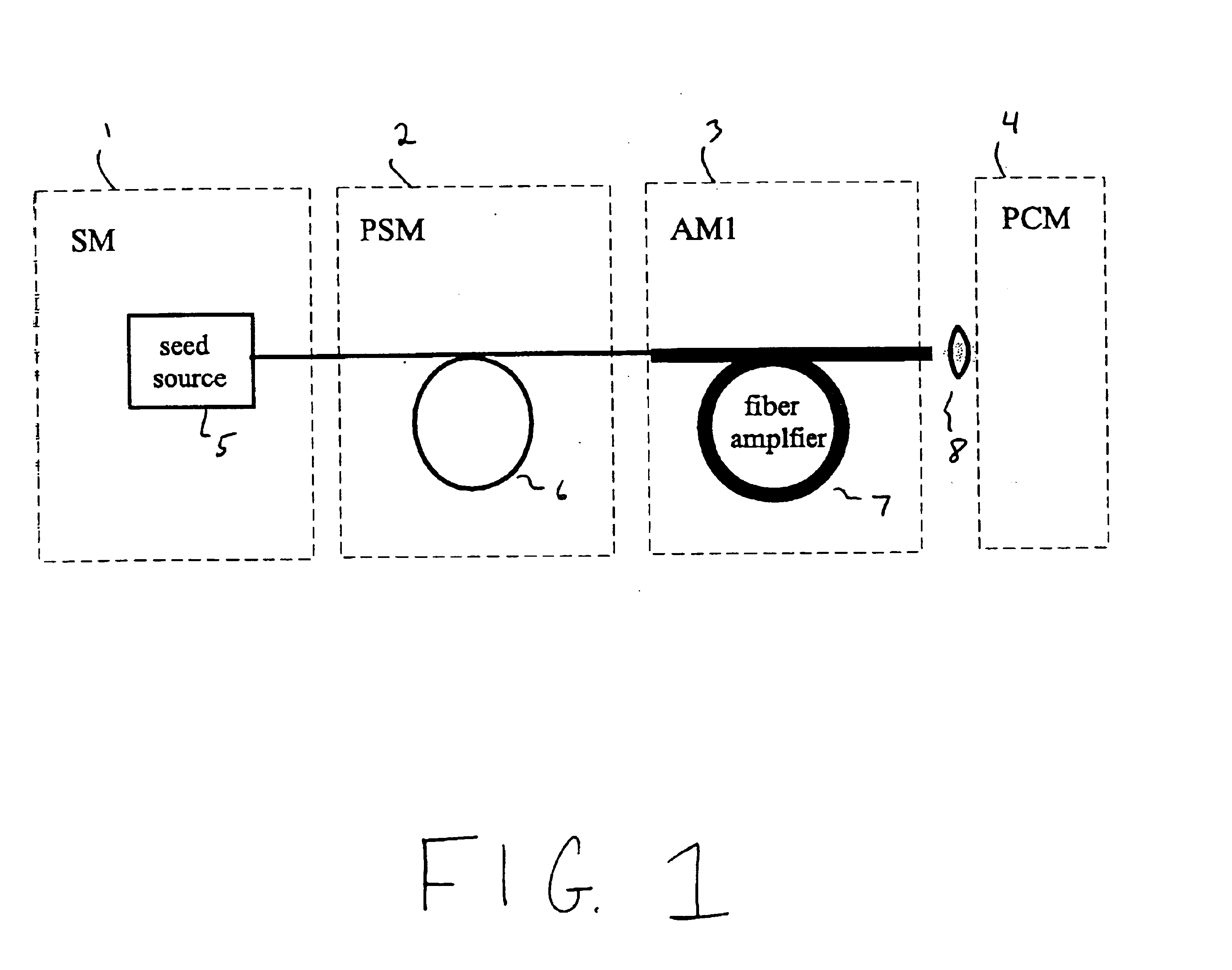

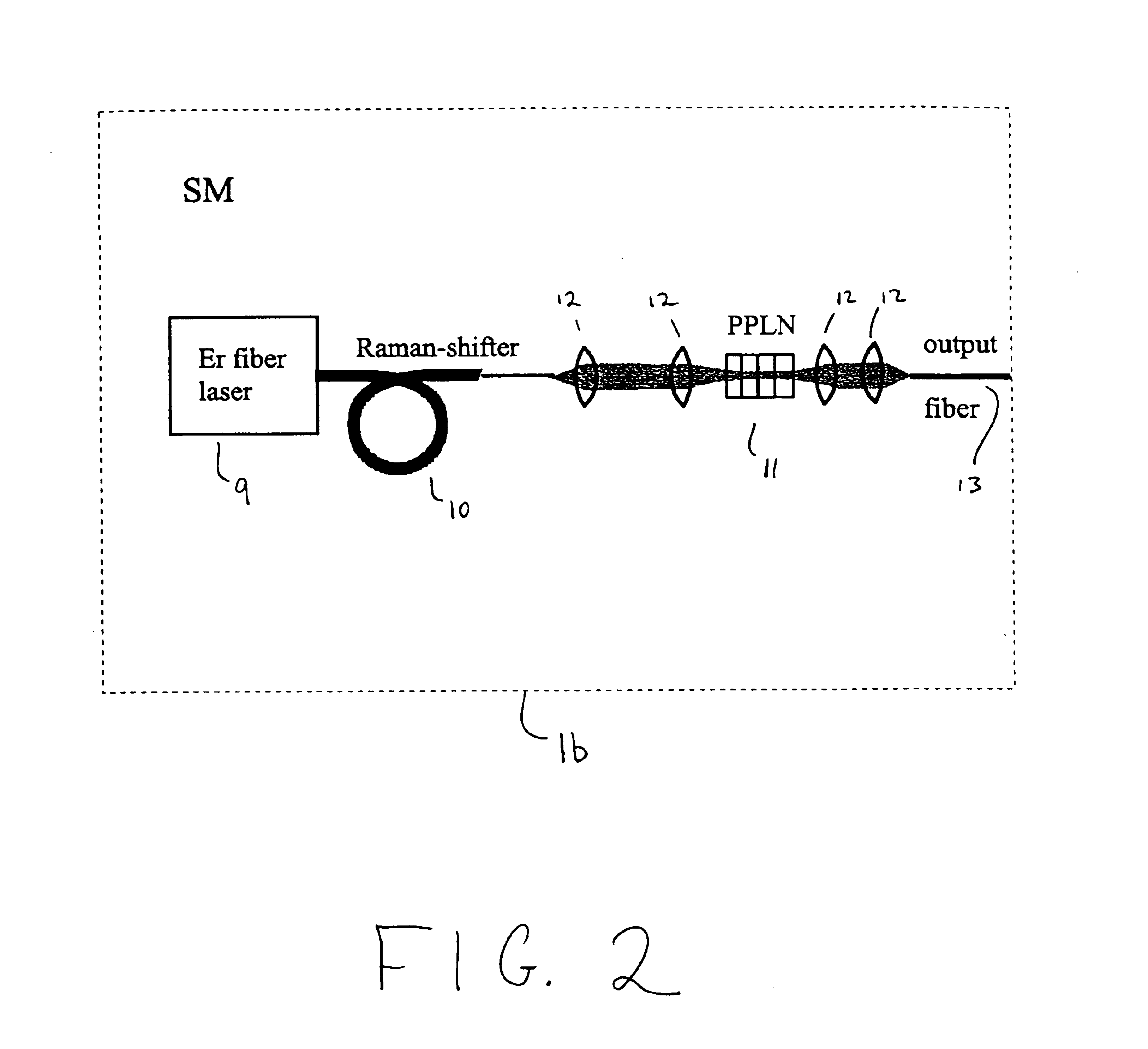

Modular, high energy, widely-tunable ultrafast fiber source

InactiveUS6885683B1High peak and high average powerReduce noiseCladded optical fibreLaser using scattering effectsNonlinear optical crystalHigh peak

A modular, compact and widely tunable laser system for the efficient generation of high peak and high average power ultrashort pulses. Modularity is ensured by the implementation of interchangeable amplifier components. System compactness is ensured by employing efficient fiber amplifiers, directly or indirectly pumped by diode lasers. Peak power handling capability of the fiber amplifiers is expanded by using optimized pulse shapes, as well as dispersively broadened pulses. After amplification, the dispersively stretched pulses can be re-compressed to nearly their bandwidth limit by the implementation of another set of dispersive delay lines. To ensure a wide tunability of the whole system, Raman-shifting of the compact sources of the ultrashort pulses in conjunction with frequency-conversion in nonlinear optical crystals can be implemented, or an Anti-Stokes fiber in conjunction with fiber amplifiers and Raman-shifters are used.

Owner:IMRA AMERICA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com