Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4895 results about "Current mirror" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

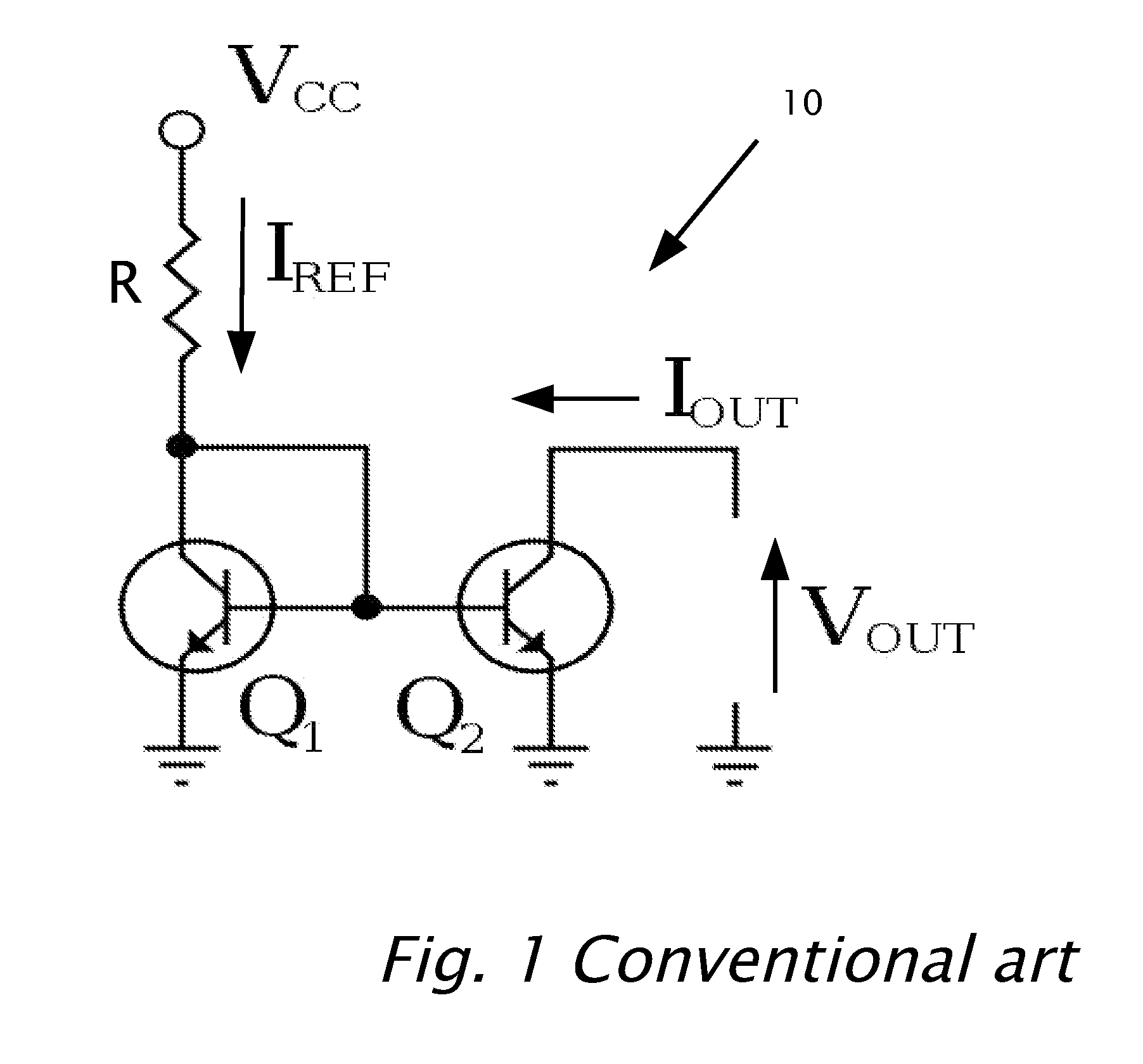

Inventor

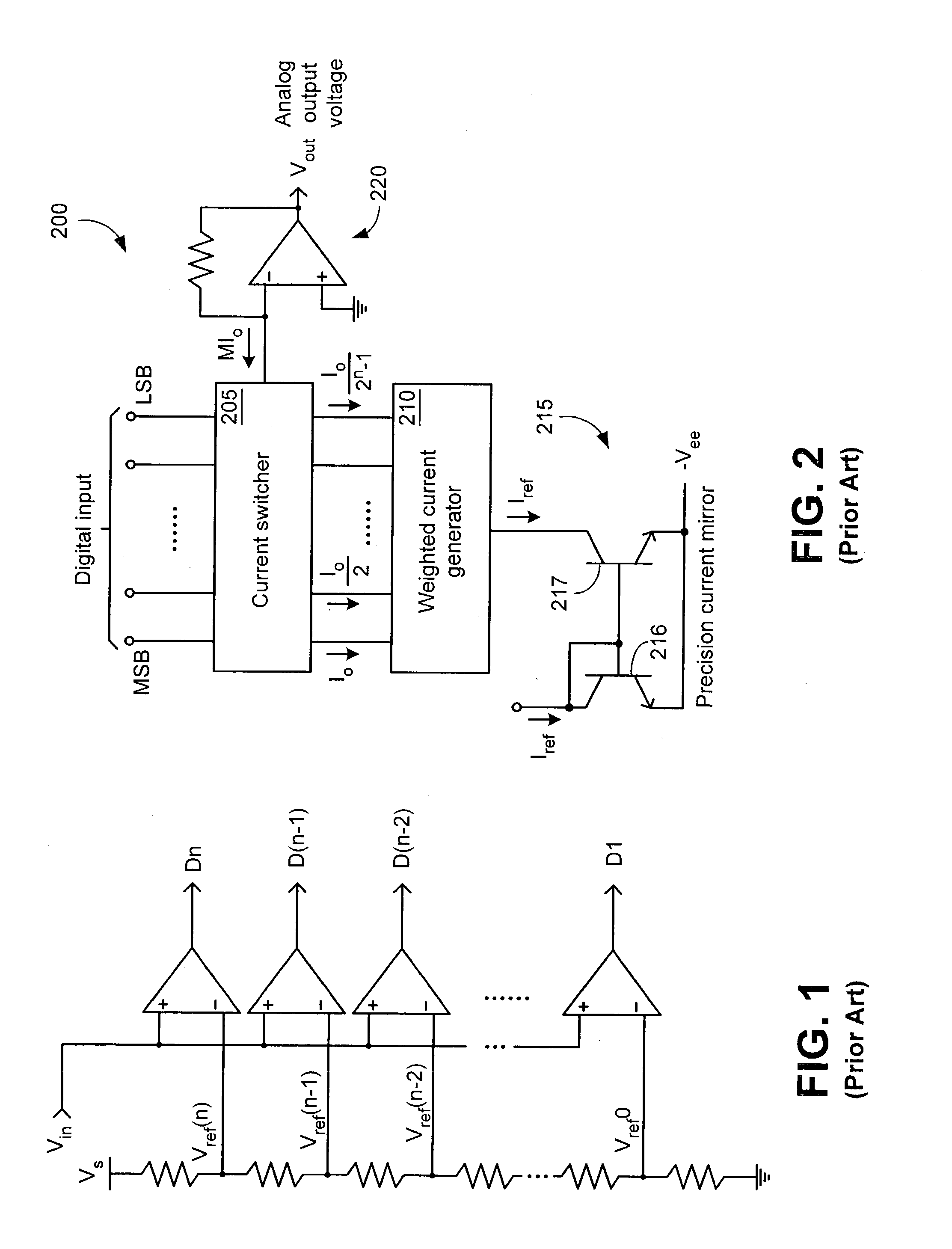

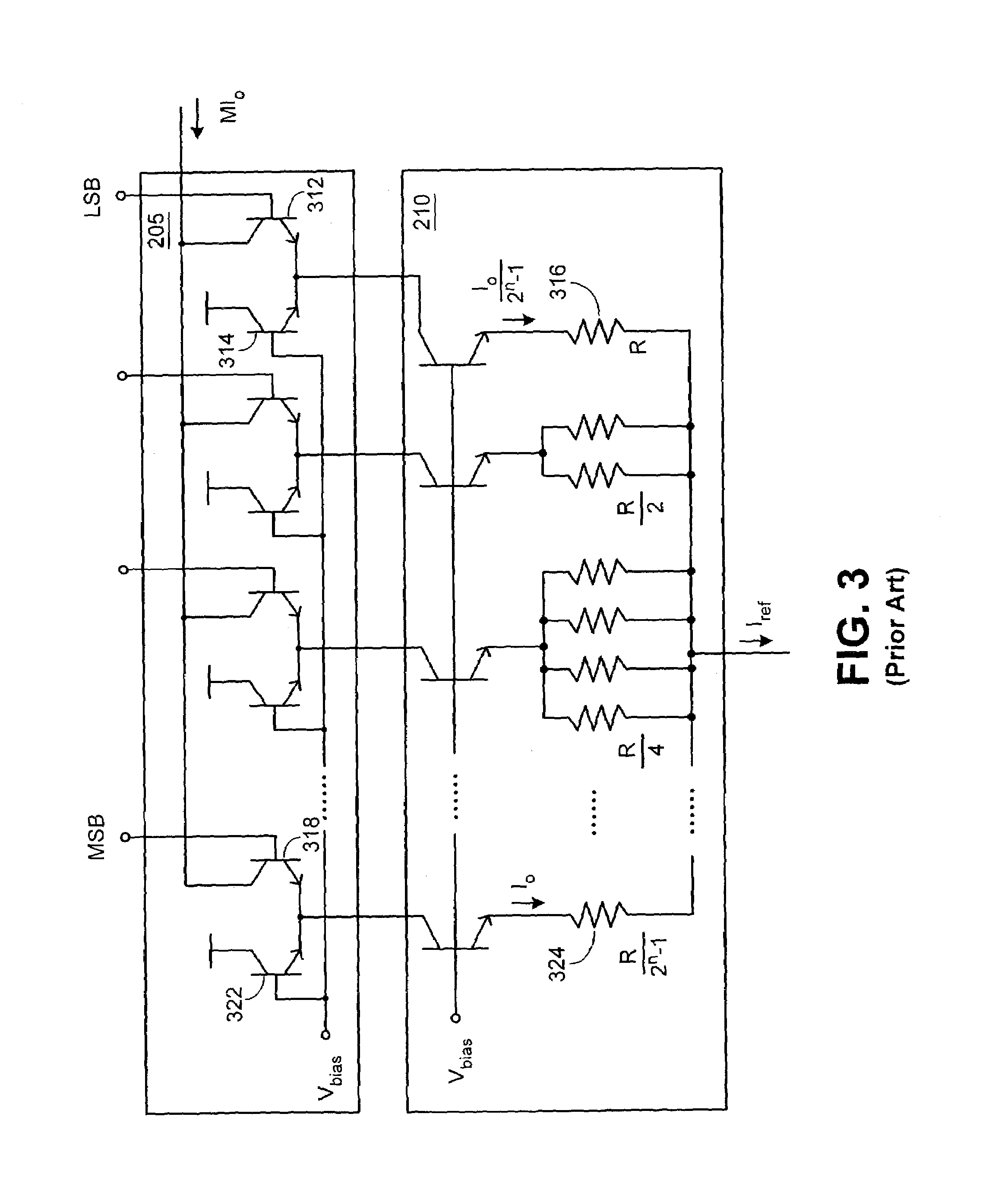

A current mirror is a circuit designed to copy a current through one active device by controlling the current in another active device of a circuit, keeping the output current constant regardless of loading. The current being "copied" can be, and sometimes is, a varying signal current. Conceptually, an ideal current mirror is simply an ideal inverting current amplifier that reverses the current direction as well. Or it can consist of a current-controlled current source (CCCS). The current mirror is used to provide bias currents and active loads to circuits. It can also be used to model a more realistic current source (since ideal current sources don't exist).

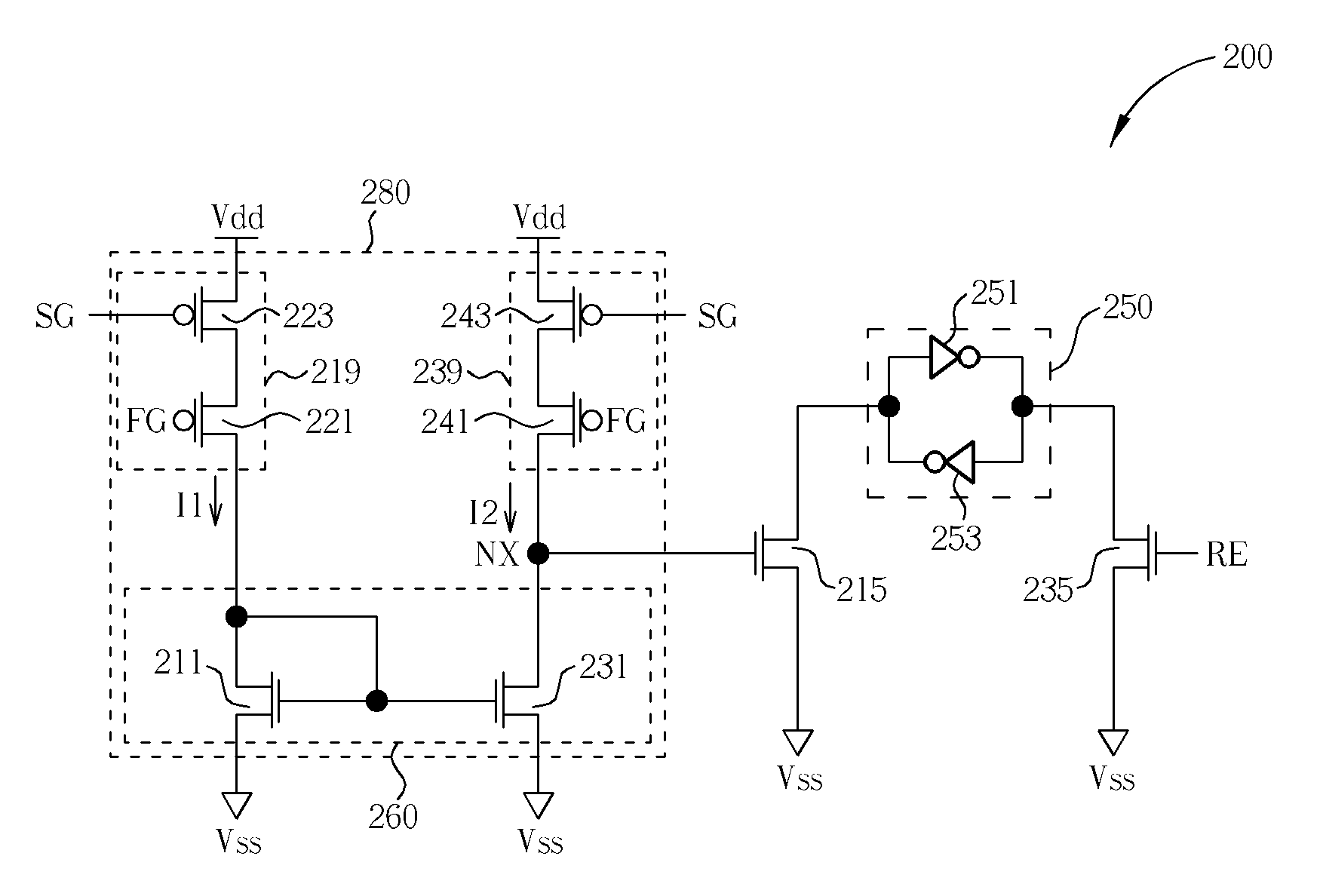

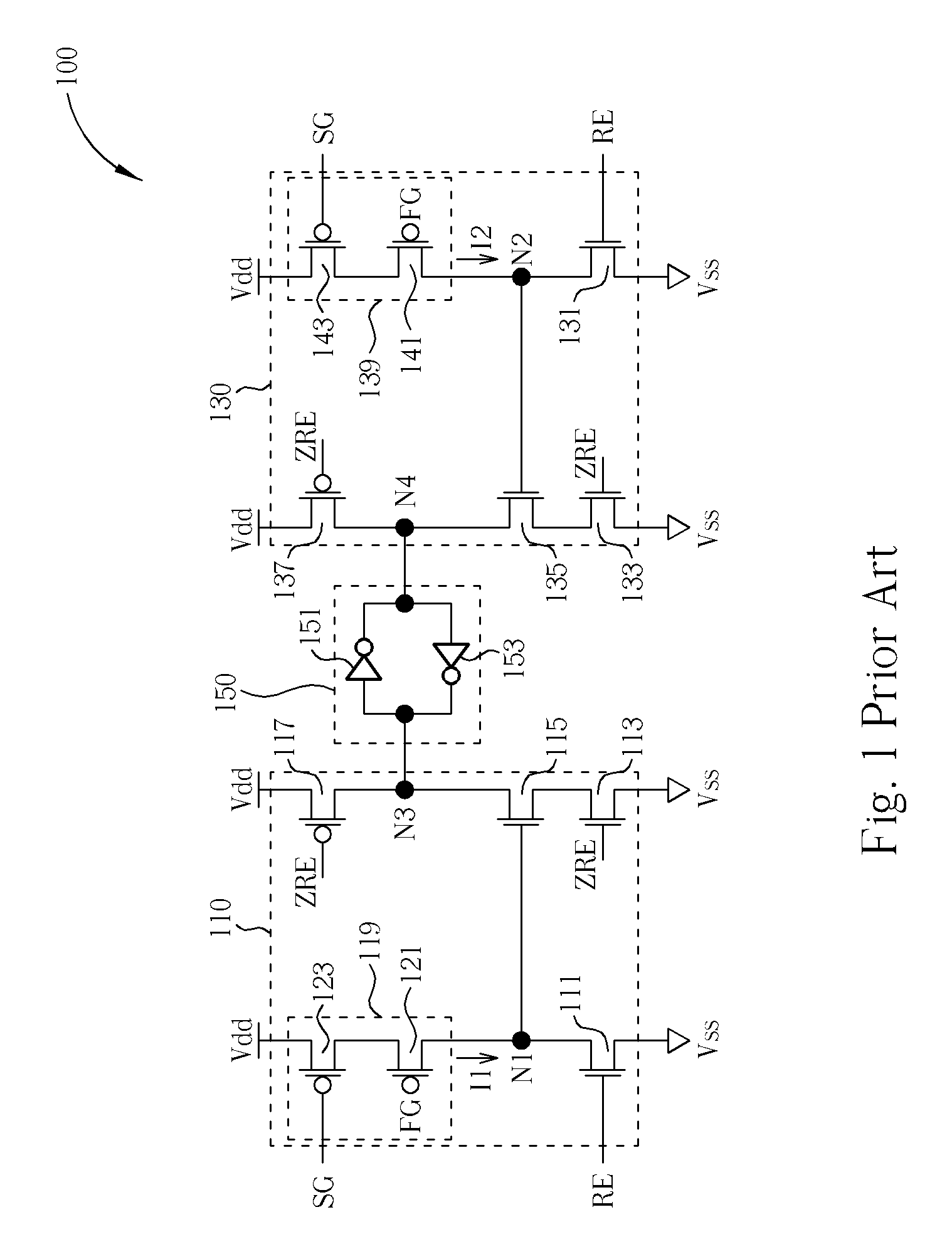

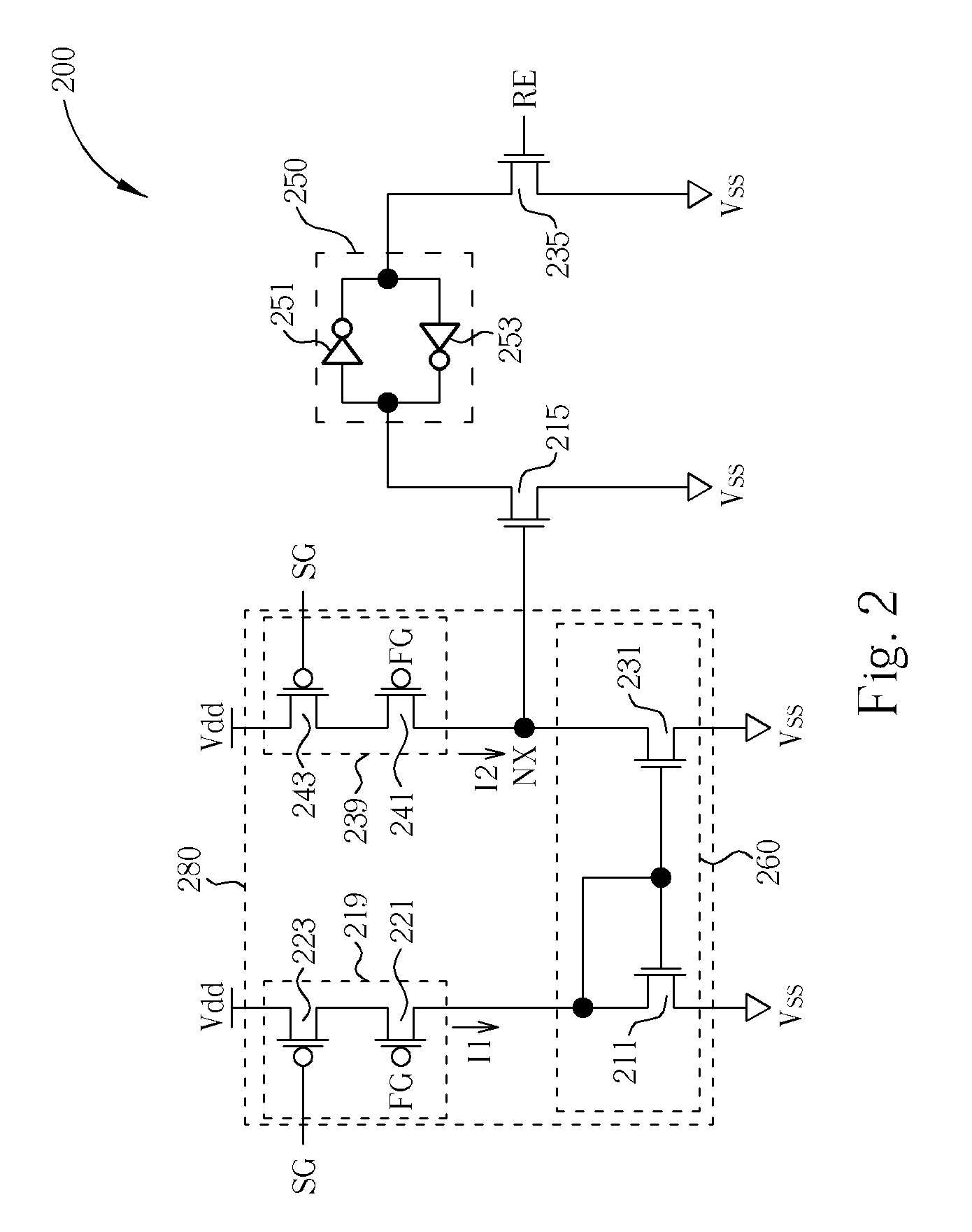

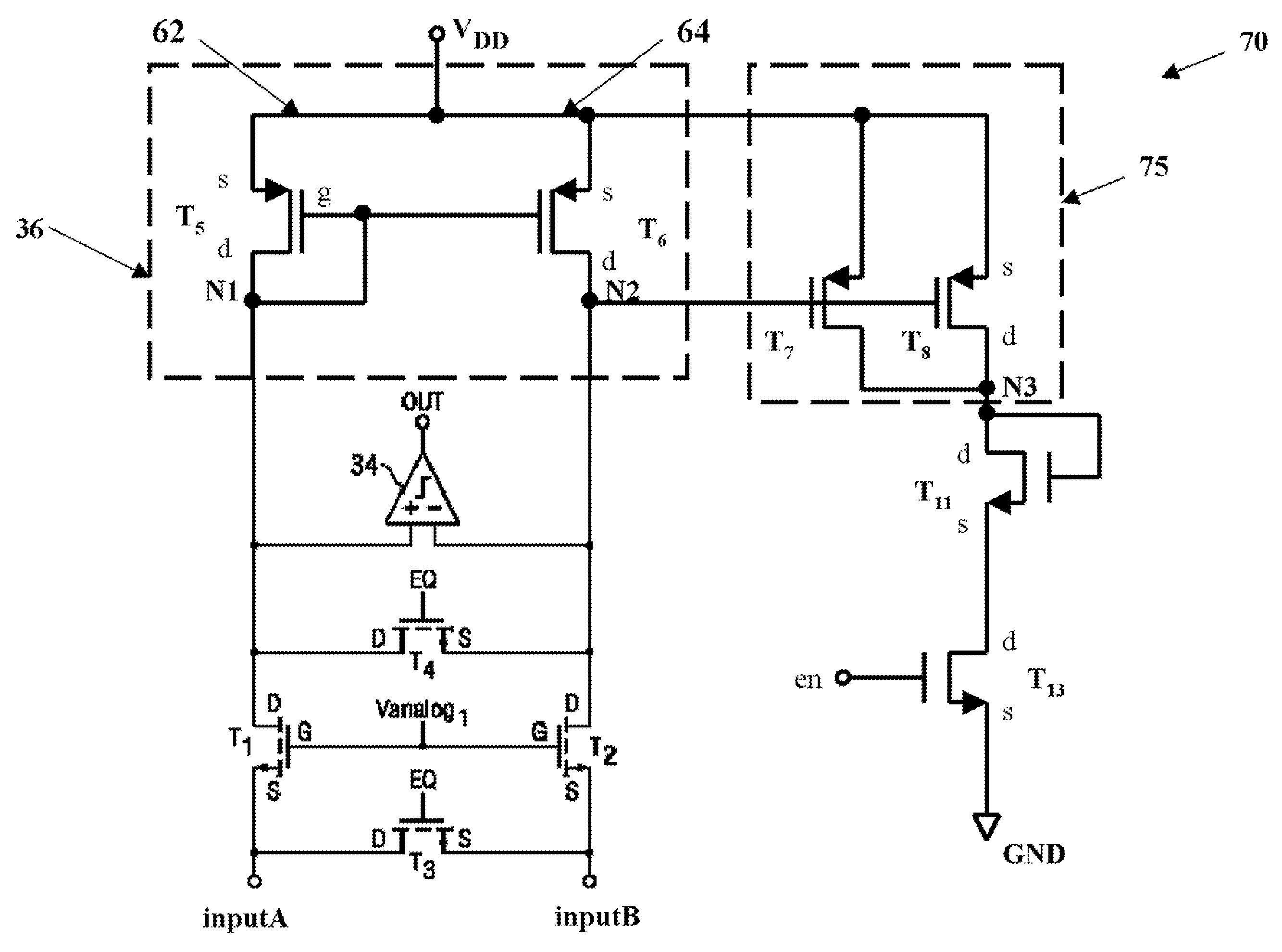

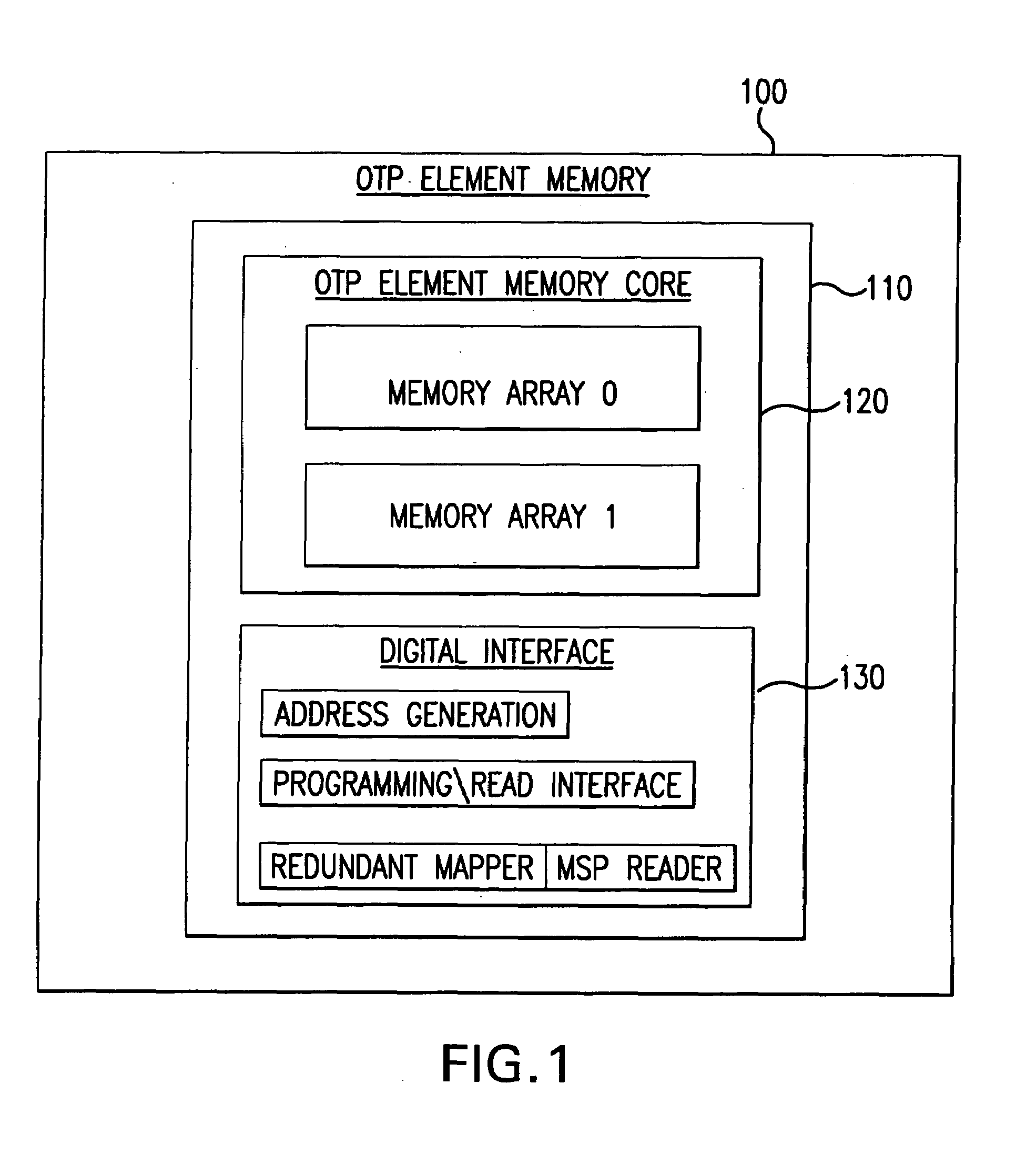

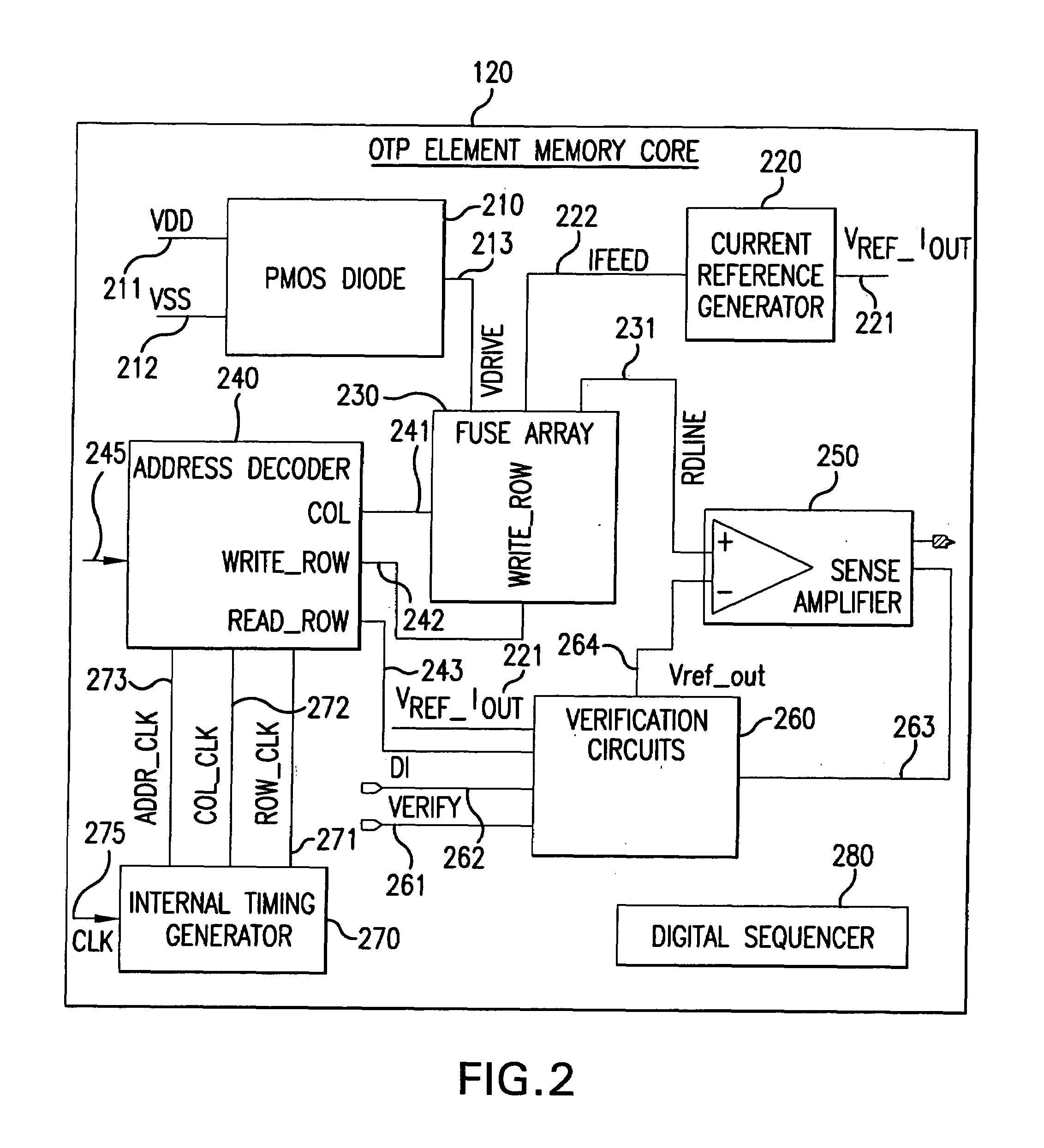

Sense amplifier circuit having current mirror architecture

A sense amplifier circuit for use in a semiconductor memory device has complemented logic states at opposite sides of the latch circuit in the sense amplifier circuit determinate all the time in operation. The sense amplifier circuit takes advantage of a current mirror circuit for ascending or descending a voltage level at the gate of a transistor by charge accumulation or charge dissipation, which turns on or off the transistor so as to control the logic states at opposite sides of the latch circuit in the sense amplifier circuit.

Owner:EMEMORY TECH INC

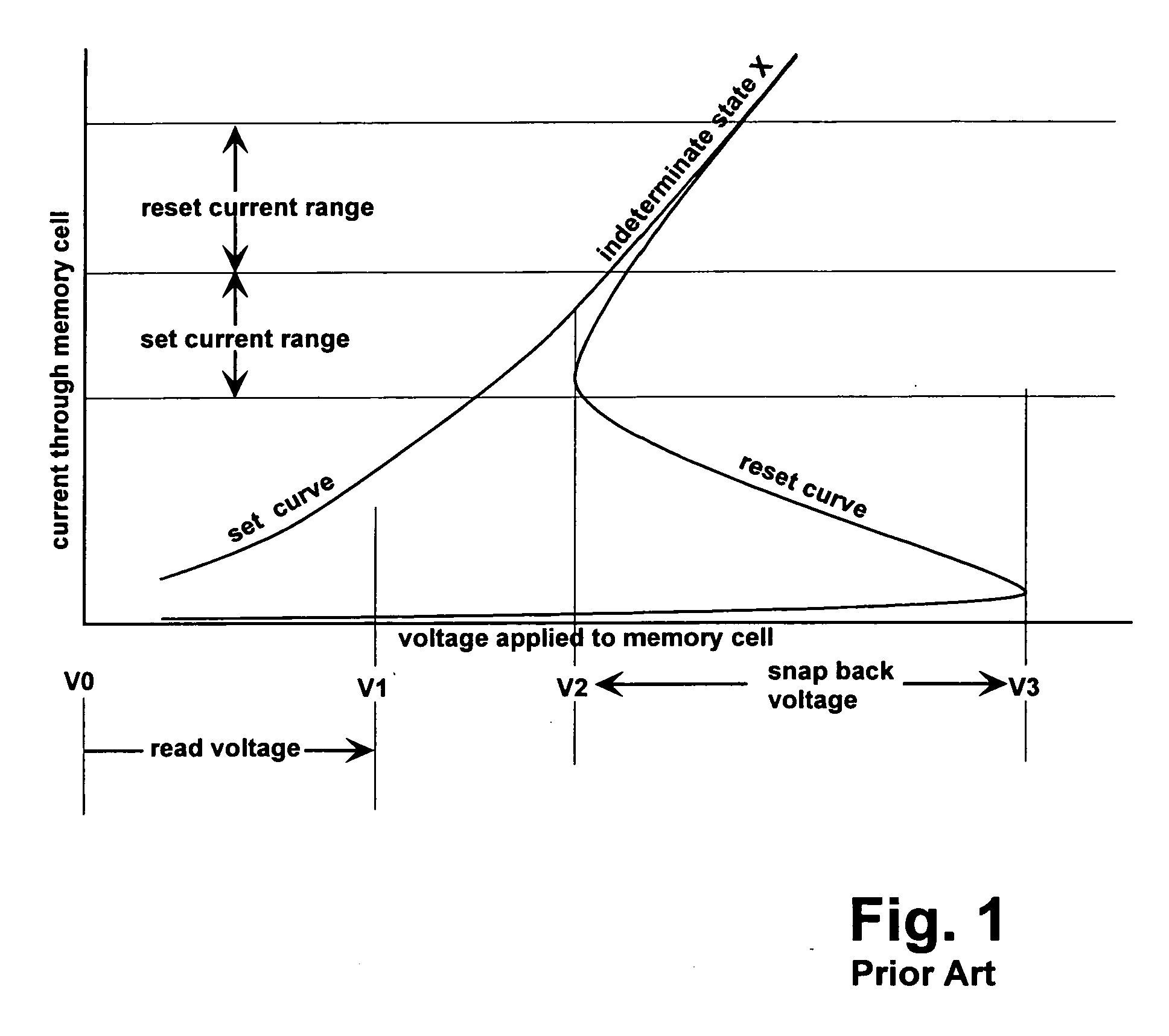

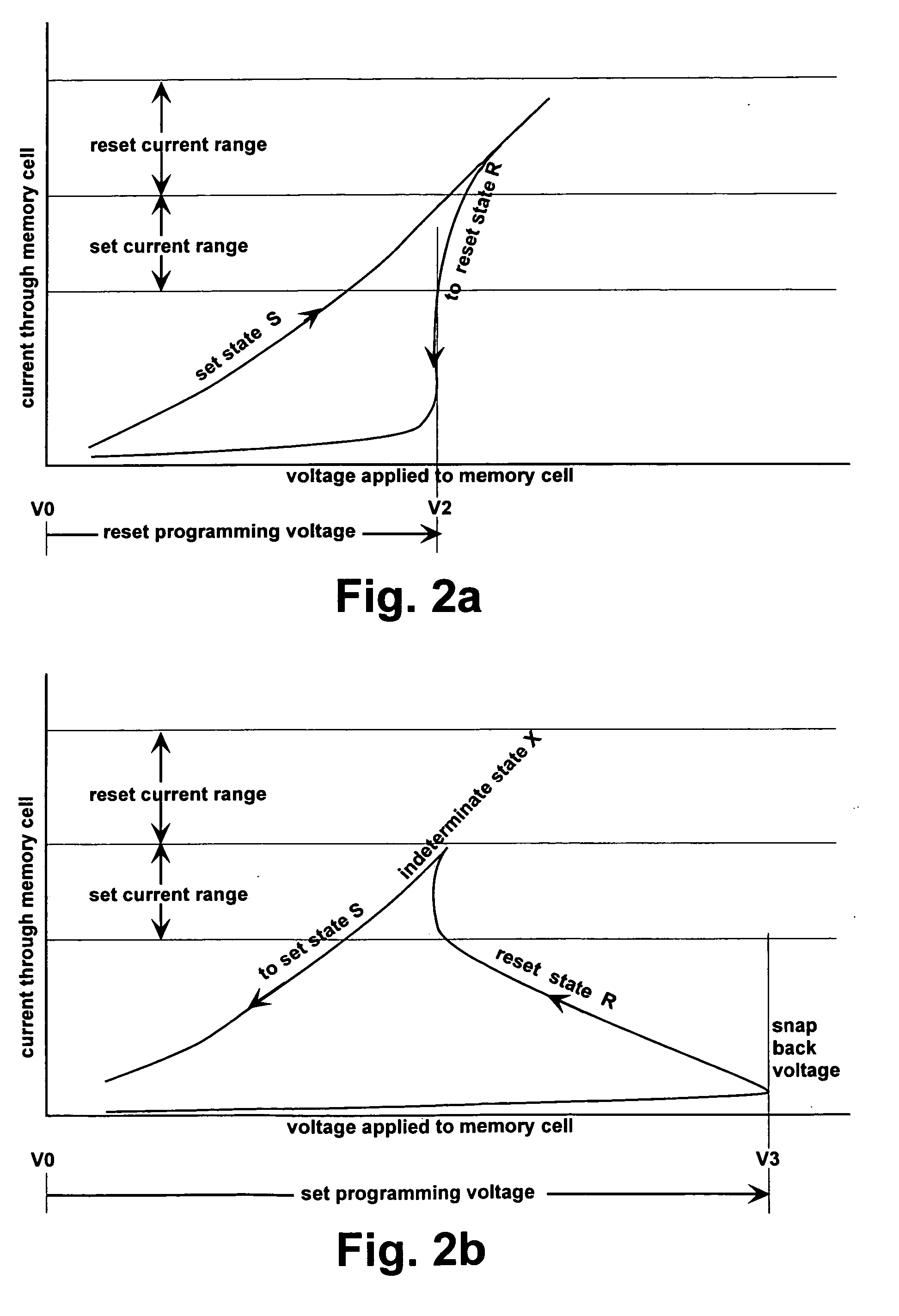

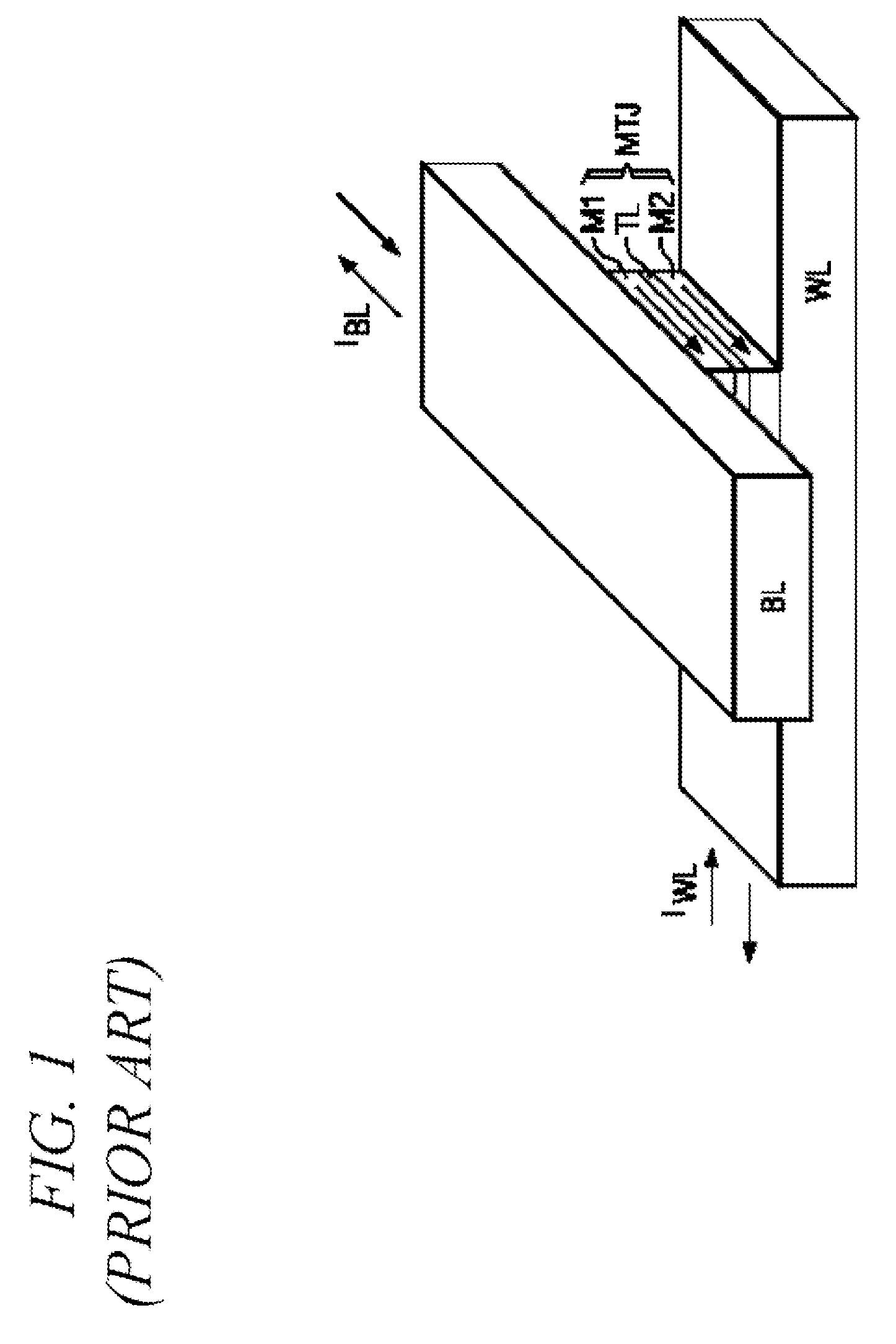

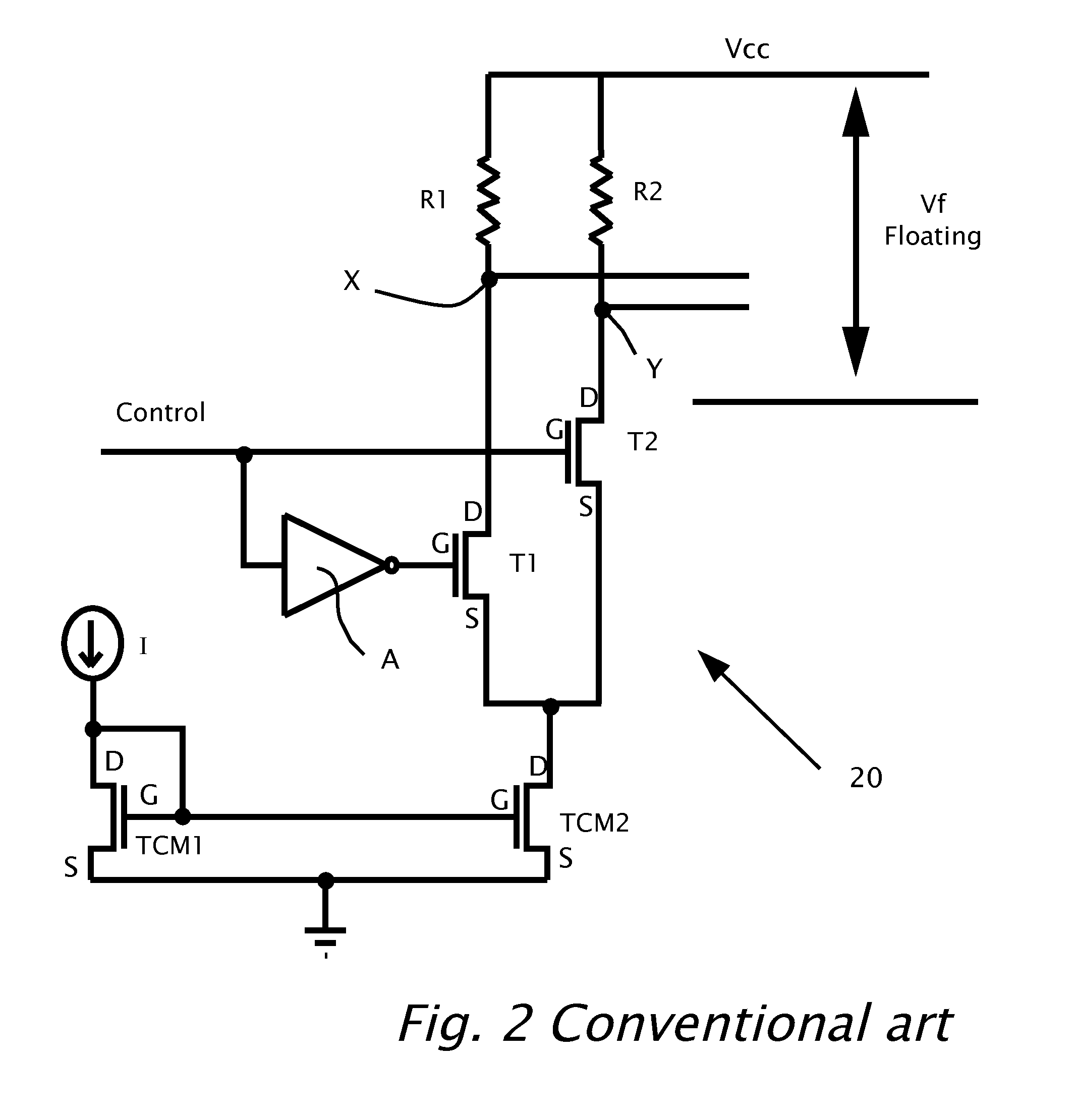

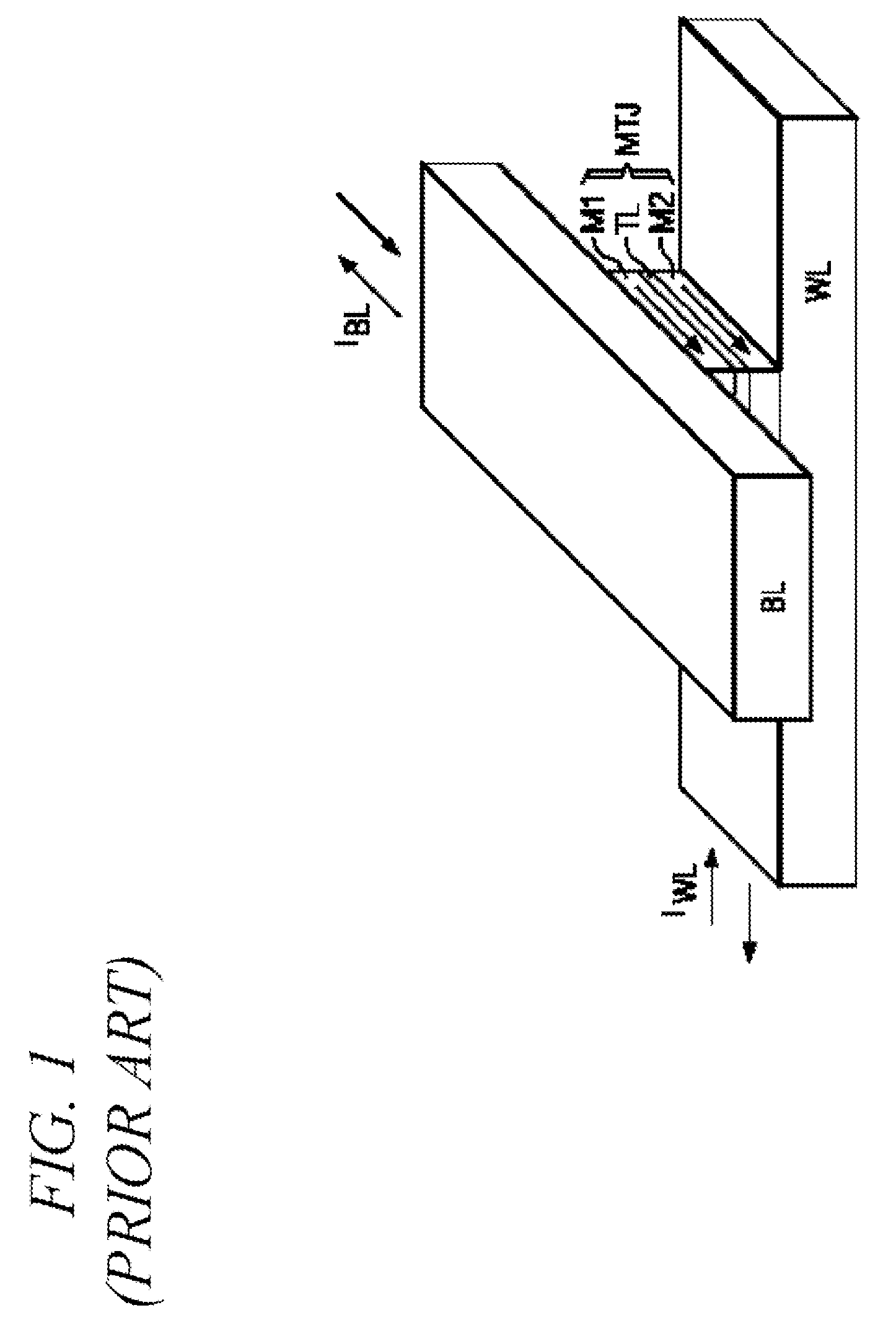

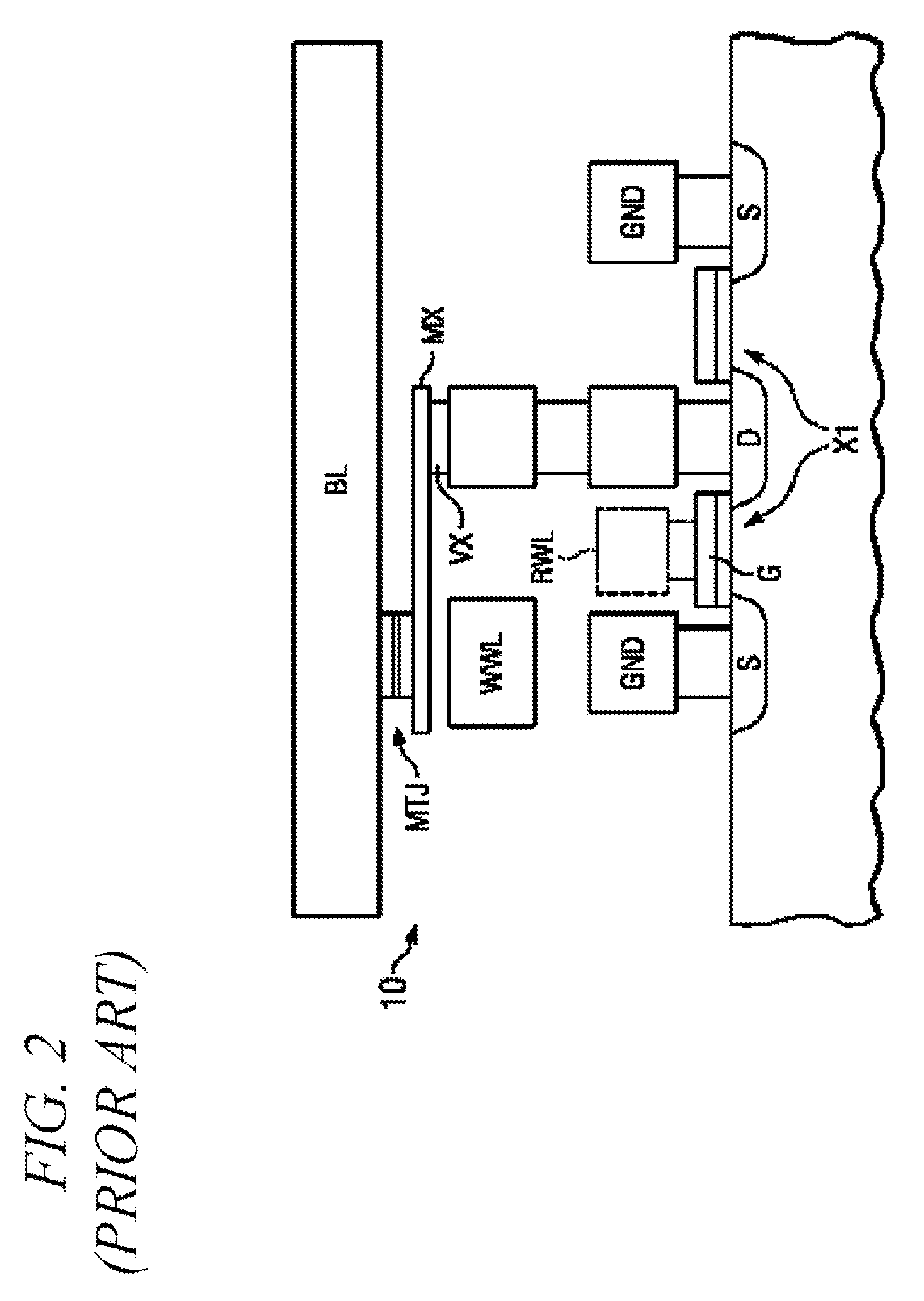

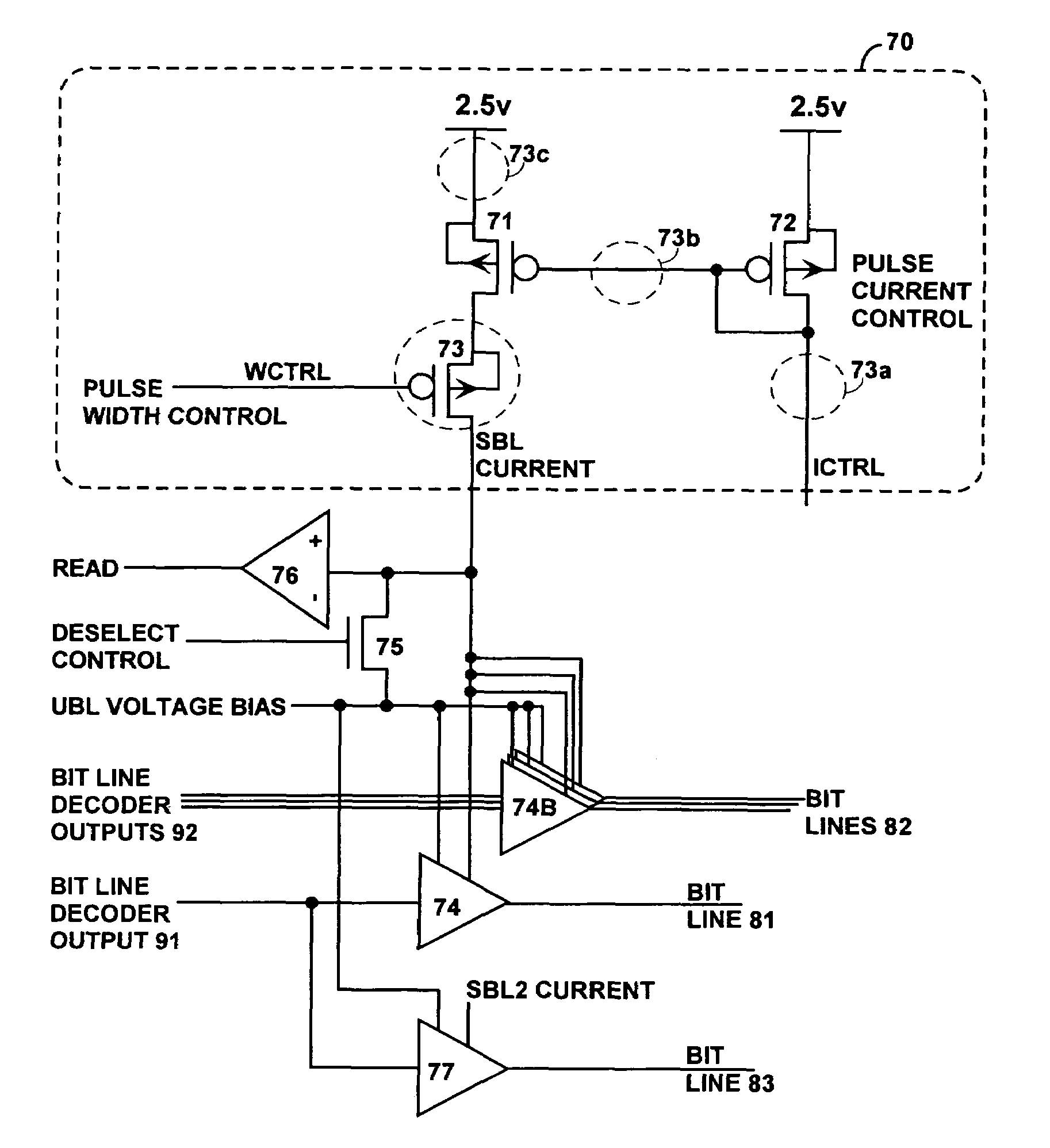

Structure and method for biasing phase change memory array for reliable writing

ActiveUS20060157679A1Minimize leakage currentReduce the possibilitySolid-state devicesDigital storageBit linePhase-change memory

A memory array having memory cells comprising a diode and a phase change material is reliably programmed by maintaining all unselected memory cells in a reverse biased state. Thus leakage is low and assurance is high that no unselected memory cells are disturbed. In order to avoid disturbing unselected memory cells during sequential writing, previously selected word and bit lines are brought to their unselected voltages before new bit lines and word lines are selected. A modified current mirror structure controls state switching of the phase change material.

Owner:SANDISK TECH LLC

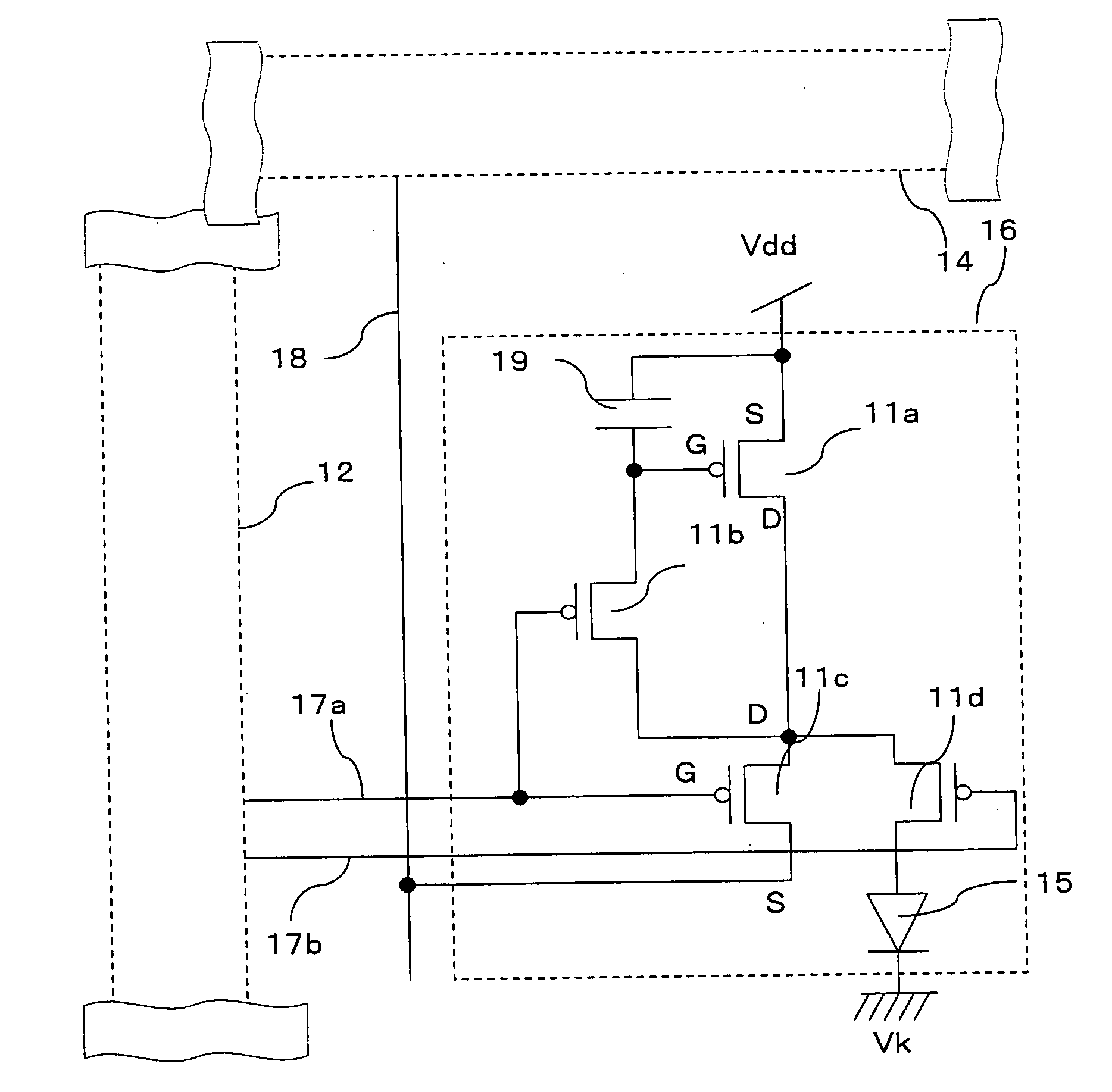

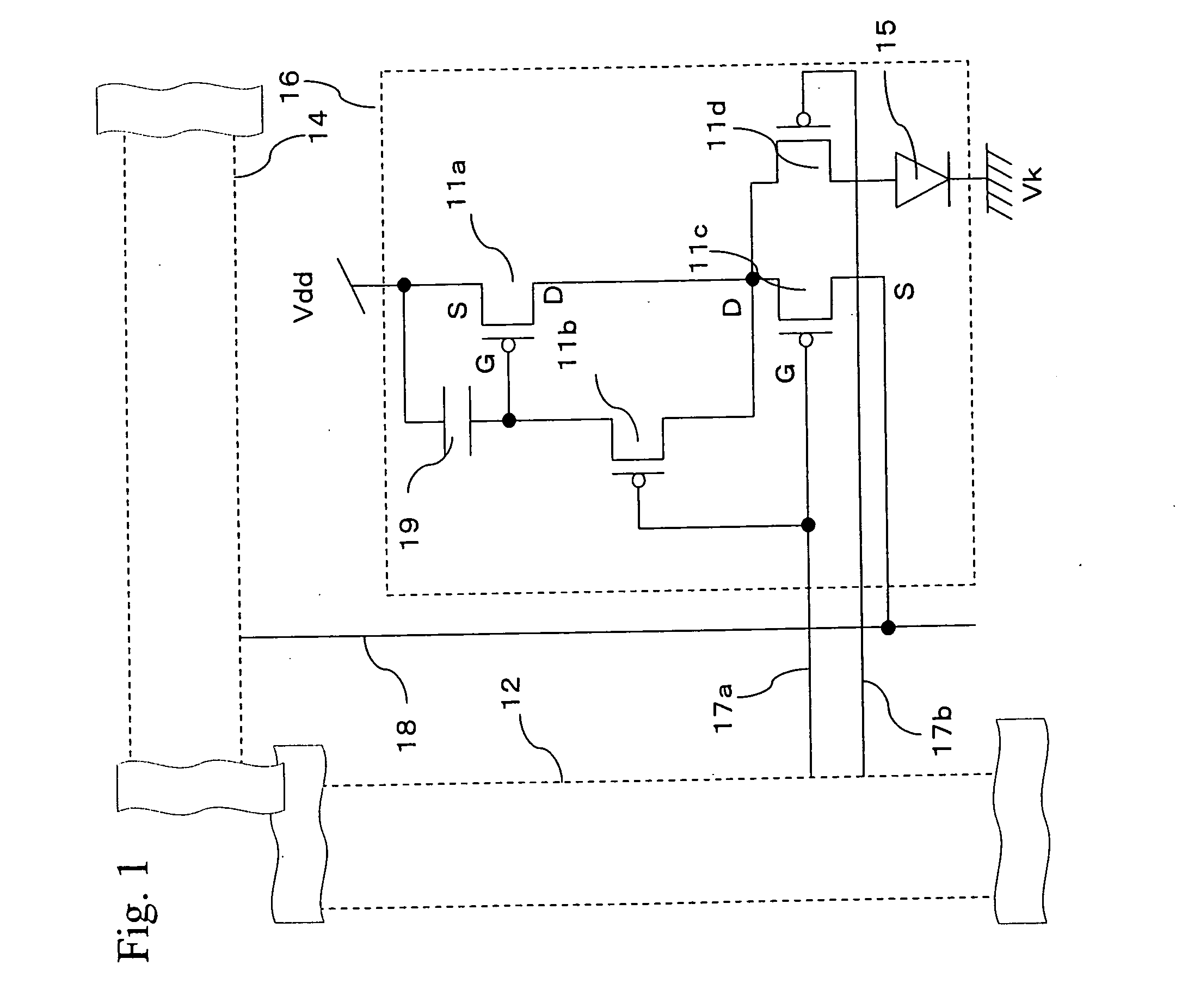

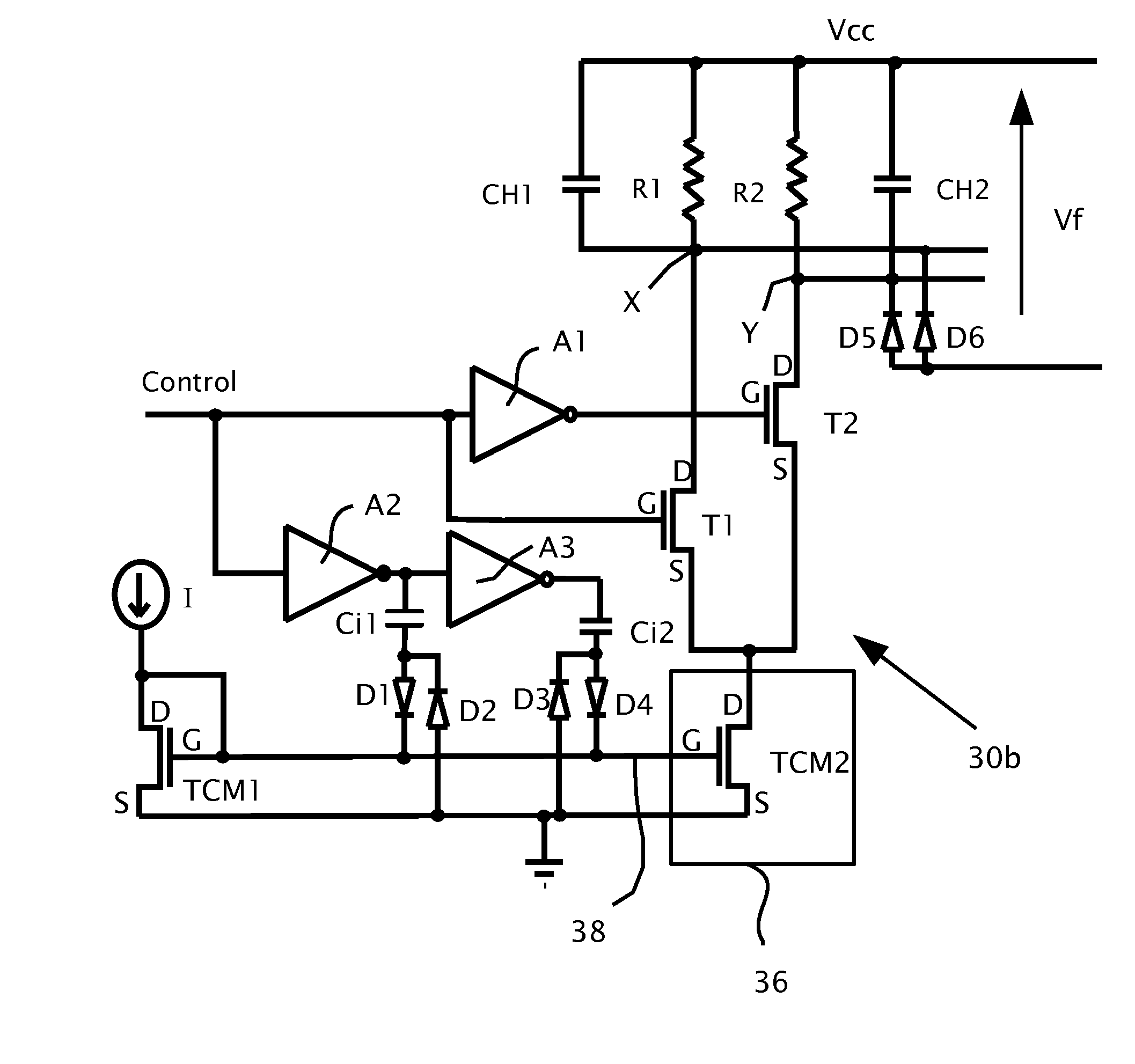

Method and apparatus for controlling light emitting diodes

InactiveUS6864641B2Electroluminescent light sourcesSemiconductor lamp usageEngineeringLight-emitting diode

A light emitting code (“LED”) circuit includes a plurality of light emitting diodes connected in a hybrid parallel-series configuration, and a current regulating circuit that includes a current regulating element connected to a first chain of the plurality of chains of LEDS, and a plurality of current mirroring elements, each current mirroring element being connected to a respective chain of the plurality of chains of LEDs.

Owner:VISTEON GLOBAL TECH INC

Drive circuit for el display panel

InactiveUS20050180083A1Static indicating devicesElectroluminescent light sourcesReference currentEngineering

Owner:TOSHIBA MATSUSHITA DISPLAY TECH

Drive method of el display apparatus

ActiveUS20050168490A1Electrical apparatusElectroluminescent light sourcesDriving currentReference current

To provide a drive method capable of maintaining gradation display performance regardless of screen display brightness. Reference numeral 491R denotes a regulator used to control reference current for red (R). By adjusting a reference current for R linearly, it is possible to linearly vary a current flowing through a transistor 472a which constitutes a current mirror with a transistor 471R. This changes a current flowing through a transistor 472b which has received a current-based delivery from the transistor 472a in a transistor group 521a. This in turn causes changes to a transistor 473a in a transistor group 521b which constitutes a current mirror with the transistor 472b, resulting in changes to a transistor 473b which has received a current-based delivery from the transistor 473a. Thus, since drive current of the unit transistor 484 changes, programming current can be changed linearly. Reference numeral 491G denotes a regulator used to control reference current for green (G) and reference numeral 491B denotes a regulator used to control reference current for blue (B). By adjusting 491R, 491G, and 491B, it is possible to adjust white balance easily and change screen brightness easily. Besides, gradation display performance is maintained at any screen brightness.

Owner:JAPAN DISPLAY CENT INC

Integrated Circuit, Method of Operating an Integrated Circuit, Method of Manufacturing an Integrated Circuit, Memory Module, Stackable Memory Module

InactiveUS20080002481A1Improve performanceIncrease speedCurrent/voltage measurementDigital storageCapacitanceAudio power amplifier

An integrated circuit has a current sense amplifier that includes a voltage comparator having a first input, a second input and an output; a first clamping device coupled between the first input of the voltage comparator and a first input signal node, a second clamping device coupled between the second input of the voltage comparator and a second input signal node, a current mirror having a first side and a second side, the current mirror first side including a first transistor coupled between a voltage source and the first clamping device and the current mirror second side including a second transistor coupled between the voltage source and the second clamping device, and a sensing scheme including an actively balanced capacitance coupled to the source and drain of the second transistor.

Owner:POLARIS INNOVATIONS

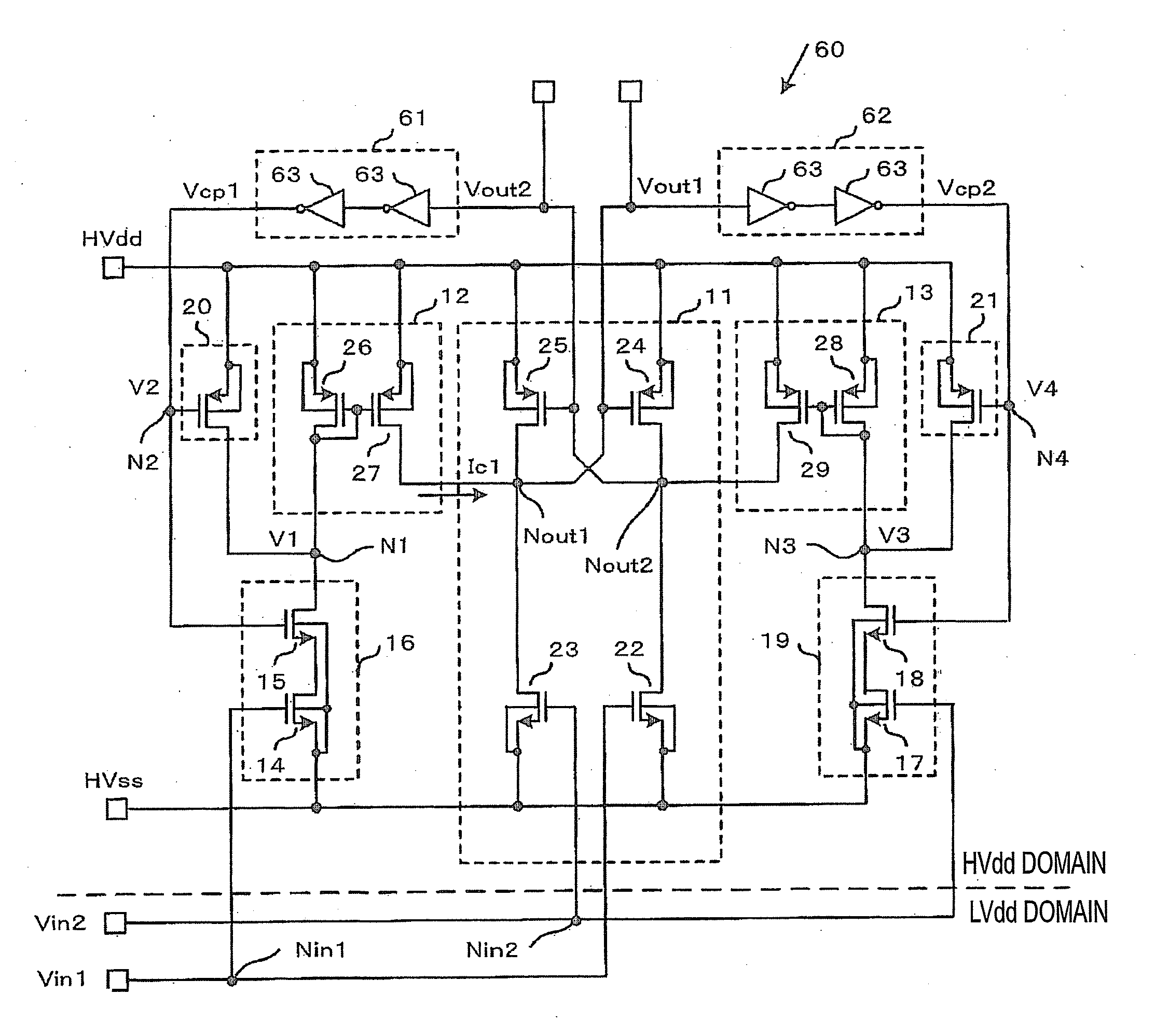

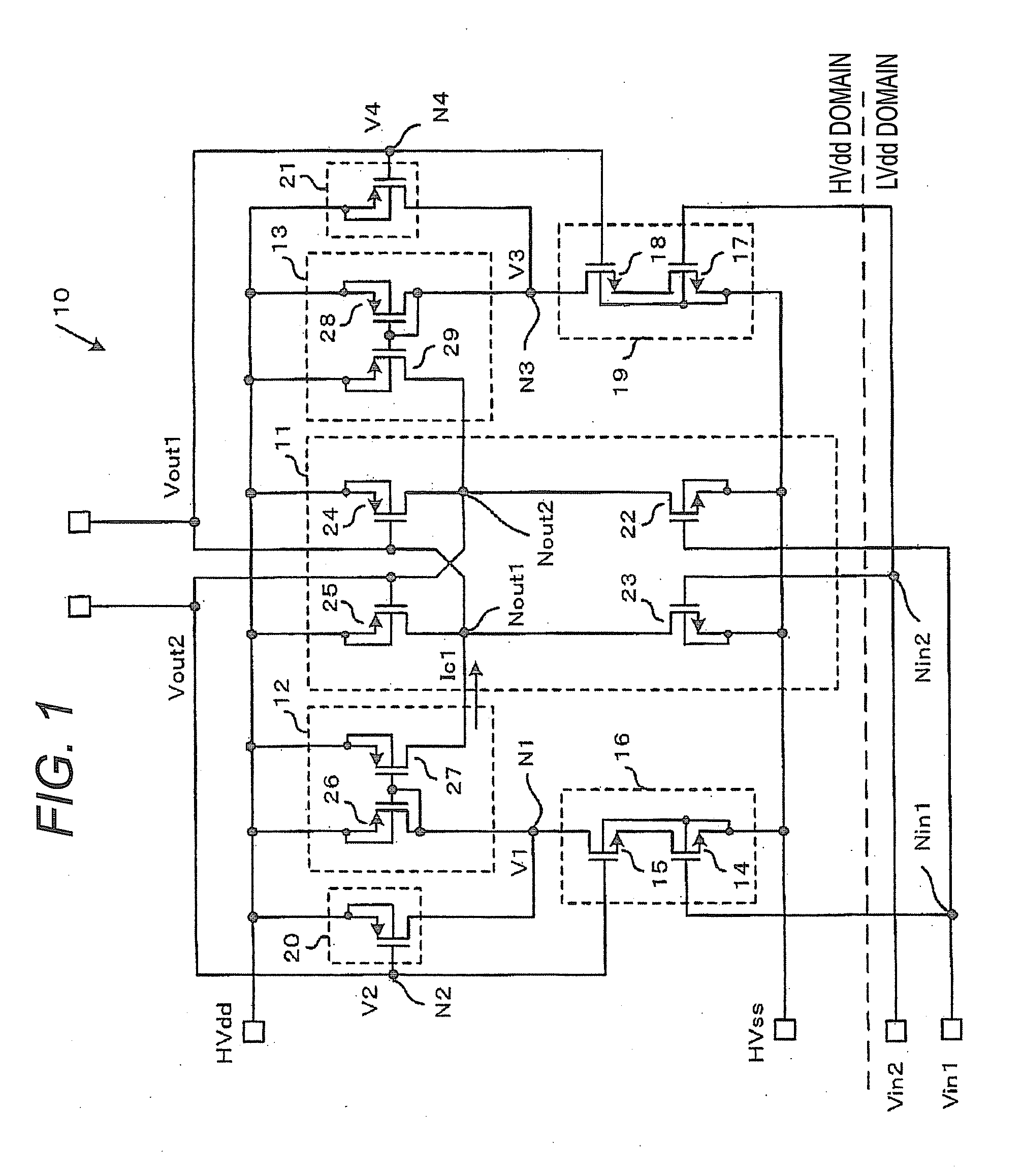

Semiconductor integrated device

InactiveUS20090224817A1Pulse automatic controlElectric pulse generatorSemiconductorIntegrated devices

According to an aspect of the present invention, there is provided a semiconductor integrated device including: a level-shifting circuit including: a first and a second input nodes; and a first and a second output nodes; a first current mirror circuit connected with the first output node; a second current mirror circuit connected with the second output node; a first switch circuit series-connected with an input-side of first current mirror circuit; a second switch circuit series-connected with an input-side of the second current mirror circuit; a fifth switching element parallel-connected with the input-side of the first current mirror circuit; and a sixths switching element parallel-connected with the input-side of the second current mirror circuit.

Owner:KK TOSHIBA

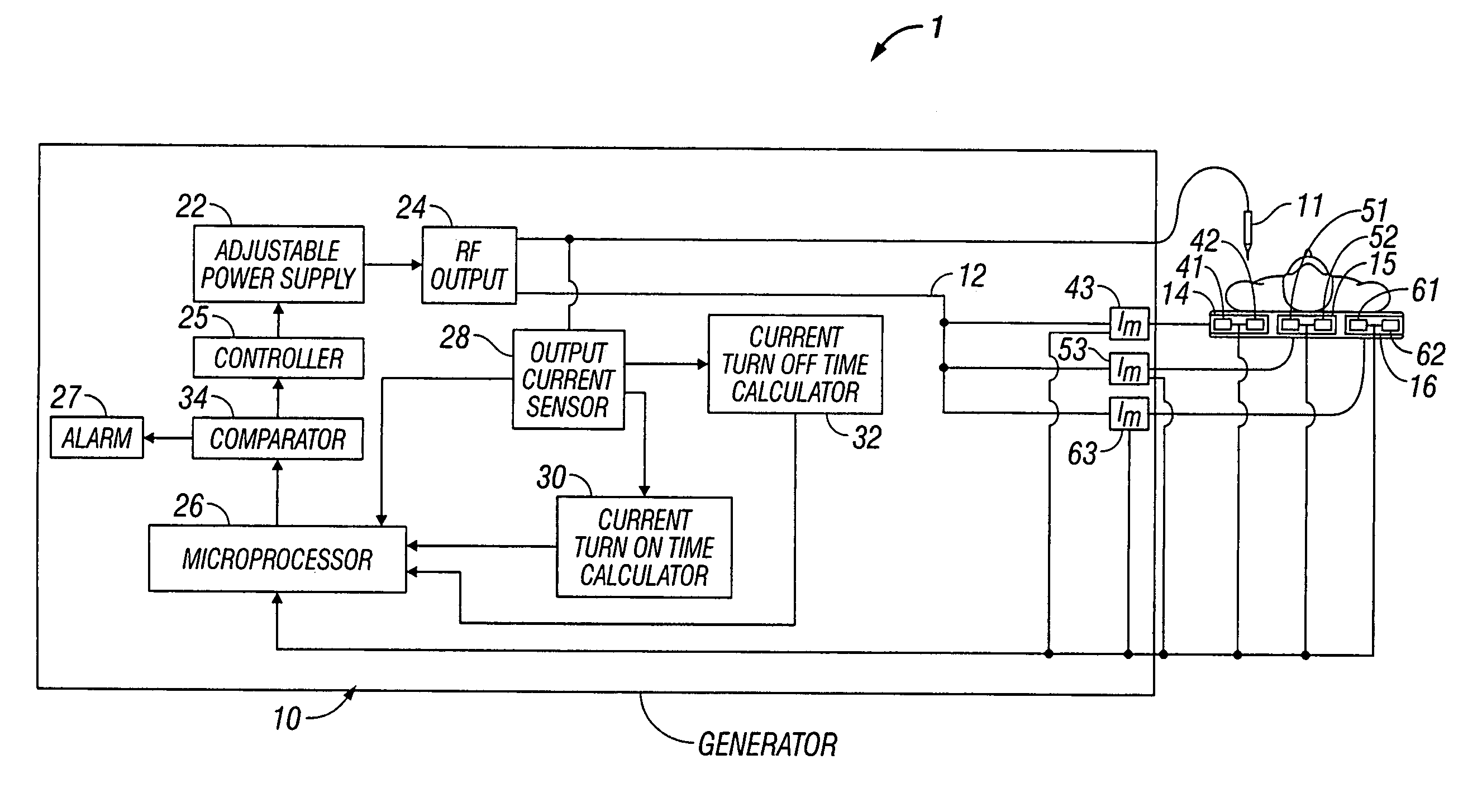

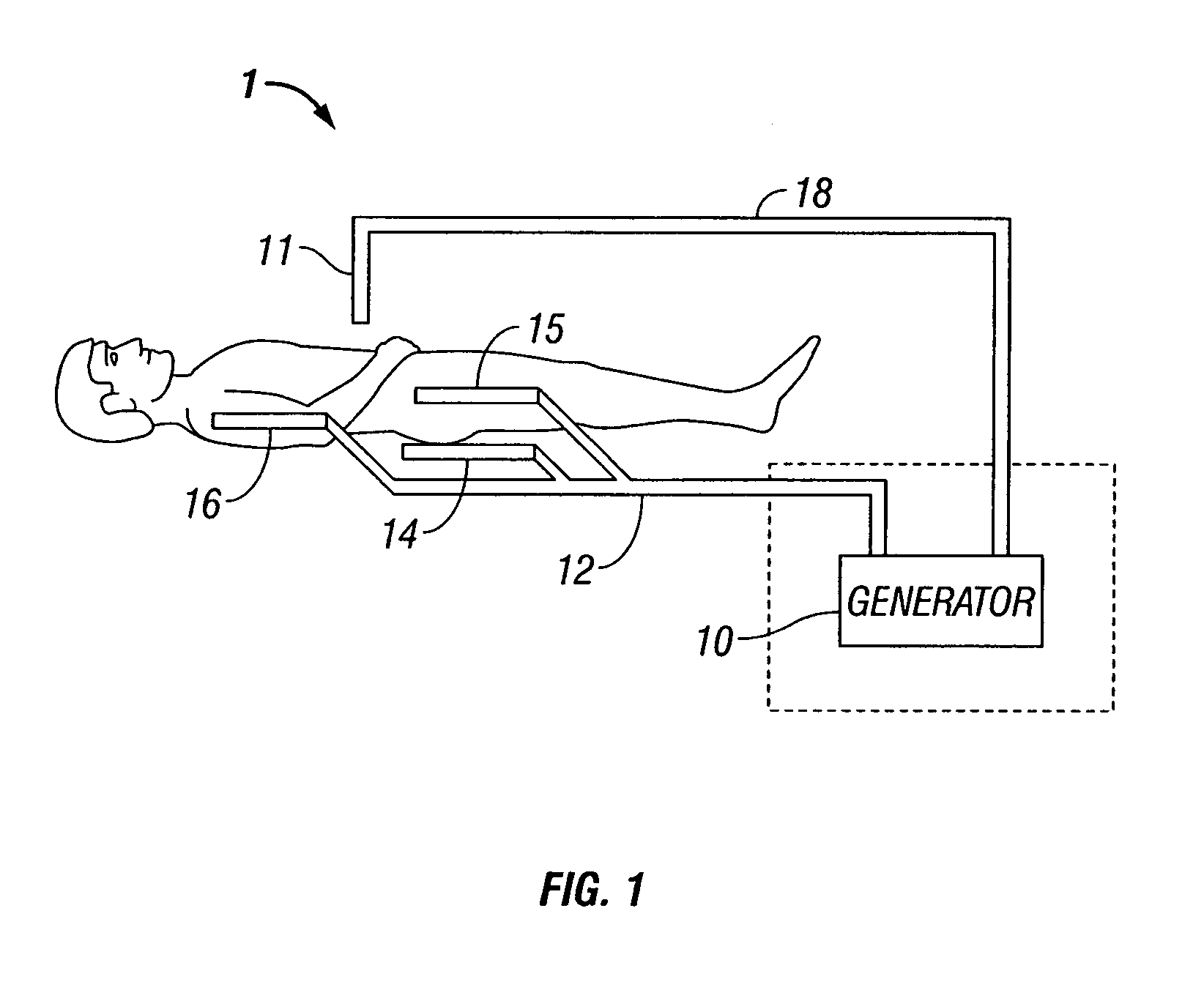

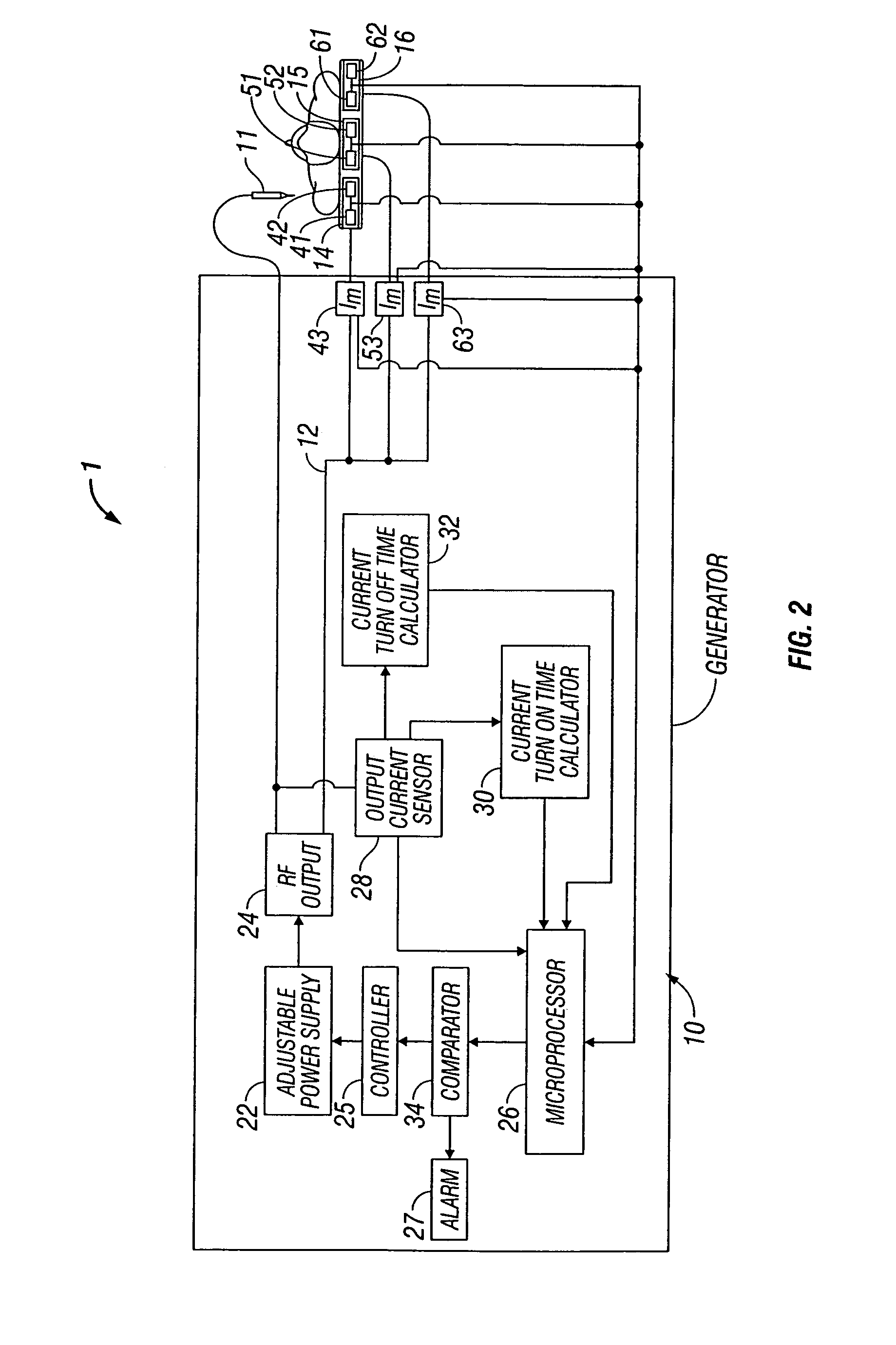

System and method for return electrode monitoring

ActiveUS7637907B2Reduce probabilityAccurate attachmentSurgical instruments for heatingPower flowCurrent mirror

A system for monitoring a plurality of return electrodes is disclosed. The system includes a plurality of return electrodes adhered to a patient and adapted to couple to an electrosurgical generator configured to generate an electrosurgical current. The system also includes a current monitor connected in series with each of the plurality of the return electrodes to measure a current signal passing therethrough and a processor coupled to each of the current monitors. The processor is configured to determine a desired current ratio and an actual current ratio for each of the plurality of the return electrodes as a function of the current passing through each of the plurality of the return electrodes. The processor is further configured to compare the desired current ratio and the actual current ratio.

Owner:COVIDIEN AG

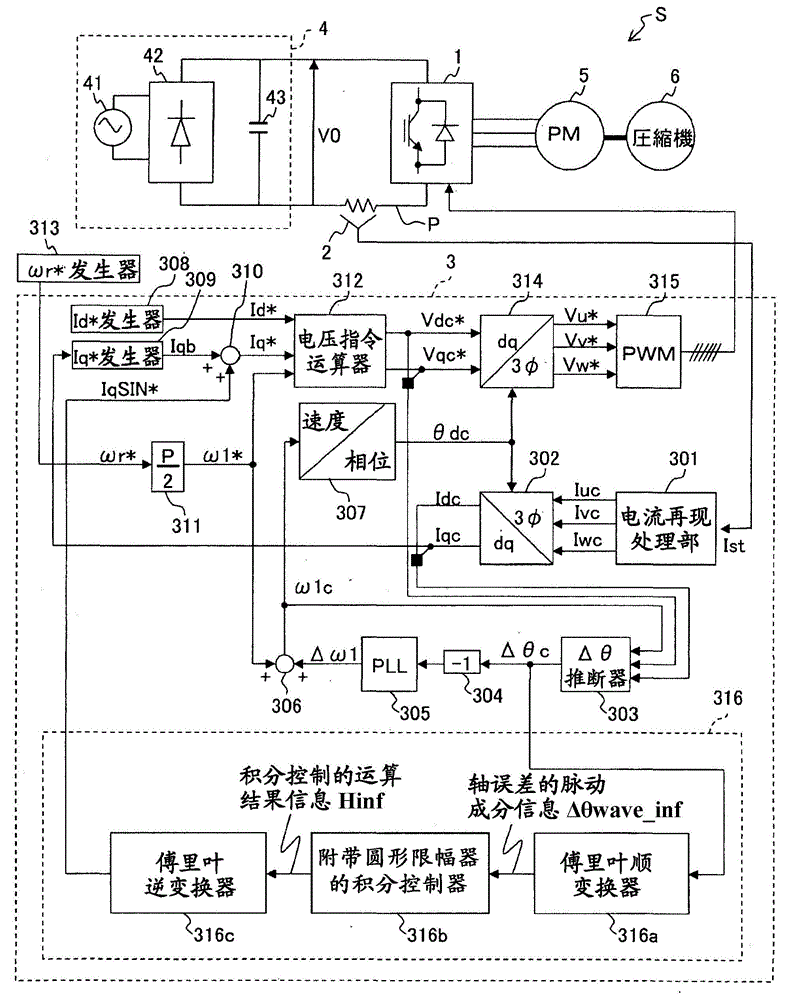

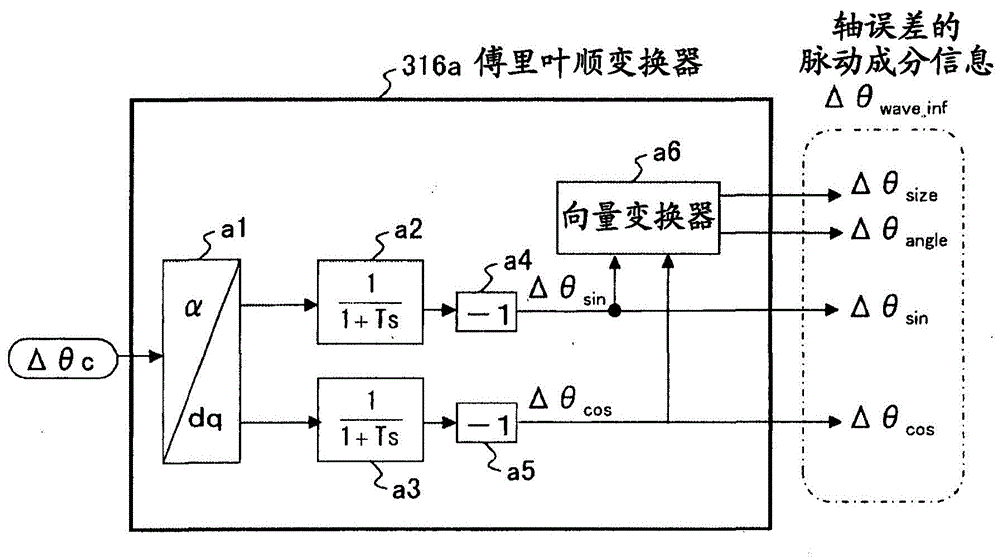

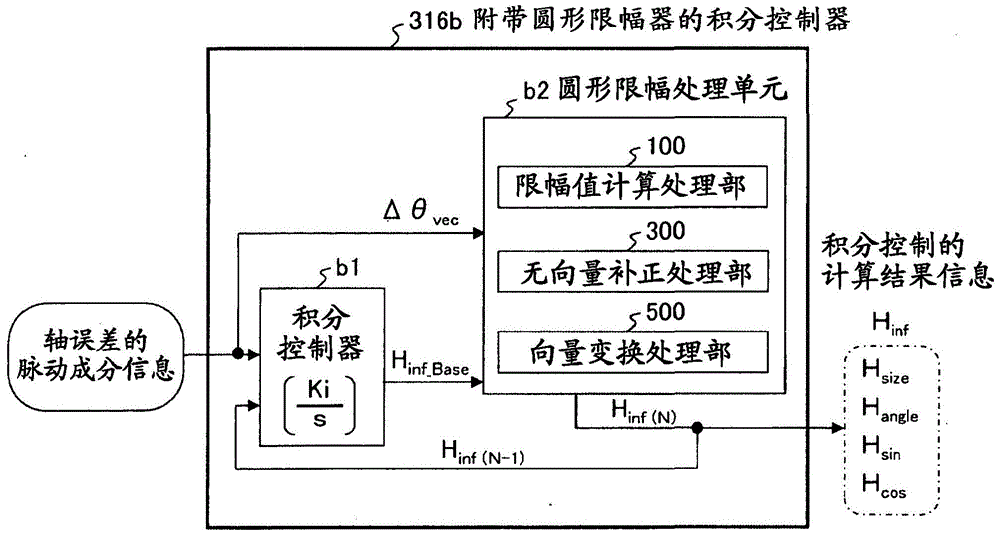

Motor control device

ActiveCN104038127ASuppression of pulsating torqueVector control systemsDynamo-electric converter controlCurrent sensorIntegral controller

A motor control device capable of suitably inhibiting the pulsating torque of an alternating-current motor is provided. The motor control device comprises an axis error inference machine (30) which infers an axis error based on a current value of an inverter, detected by a current sensor (2); a Fourier rectification machine (316a) which extracts an axis error vector from the time-base changes of the axis error; an integral control machine (316b) additionally provided with a circular amplitude limiter, which is used to calculate a correction current vector for offsetting the pulsating torque, wherein a circle with a set amplitude limiting value serving as the radius is used as the base for limiting the movement of the correction current vector, and the integral control machine (316b) additionally provided with the circular amplitude limiter performs the circular amplitude limiting for limiting the movement of the correction current vector so as to enable the deflection angle of the correction current vector to be close to the deflection angle of the axis error vector.

Owner:HITACHI JOHNSON CONTROLS AIR CONDITIONING INC

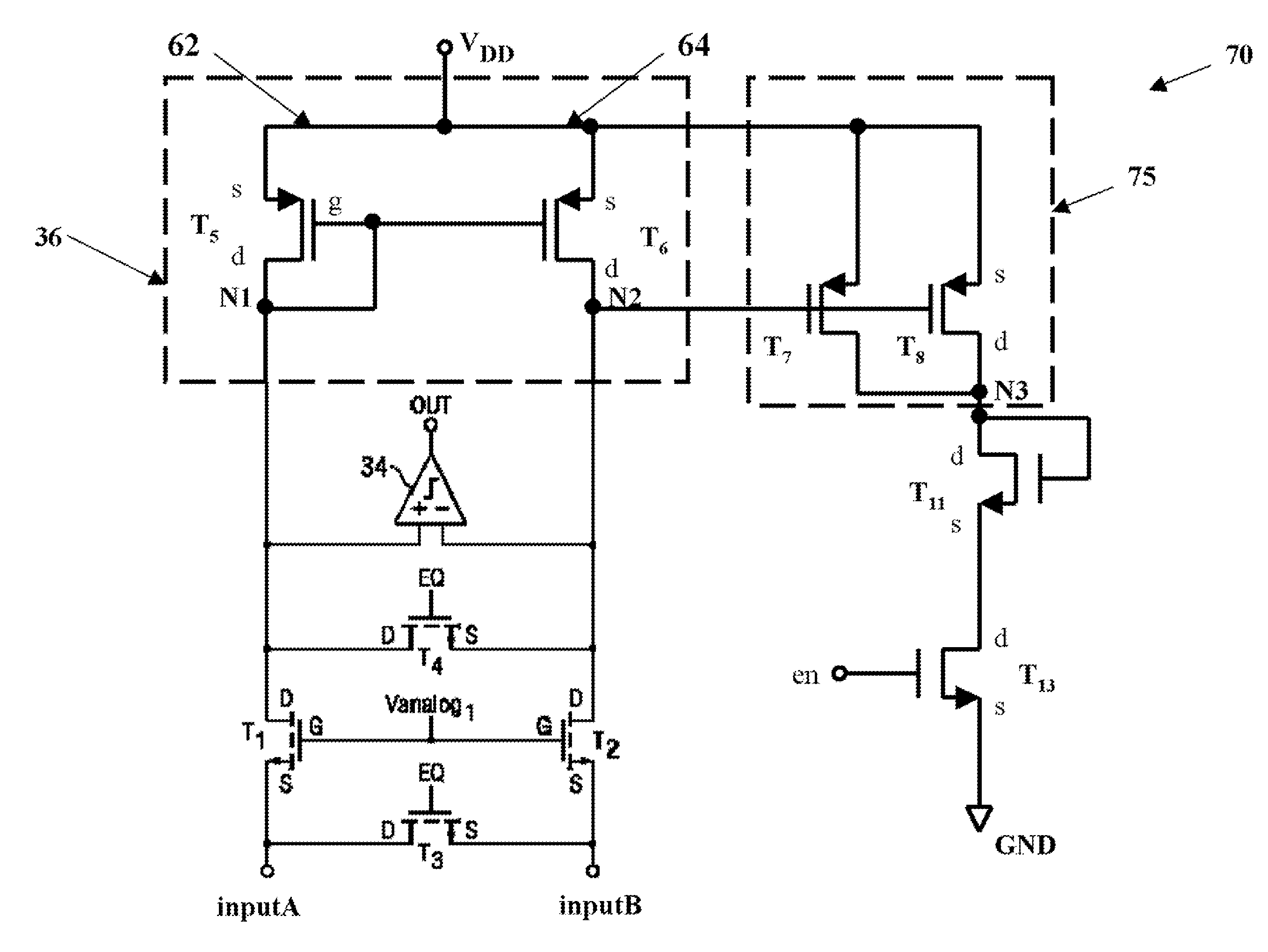

Fast Voltage Level Shifter Circuit

ActiveUS20110181340A1Pulse automatic controlLogic circuits coupling/interface using field-effect transistorsField-effect transistorLevel converter

A voltage level shifting circuit with an input terminal and an output terminal. The level shifting circuit has a field-effect transistor (FET) switch with a gate attached to the input terminal, a drain attached to the output terminal and a source attached to a current changing mechanism. The current changing mechanism includes a current mirror circuit having an output connected between the source and an electrical earth. The output of the current mirror circuit is preferably adapted to change a current flowing between the drain and the source based on an input voltage applied to the gate.

Owner:SOLAREDGE TECH LTD

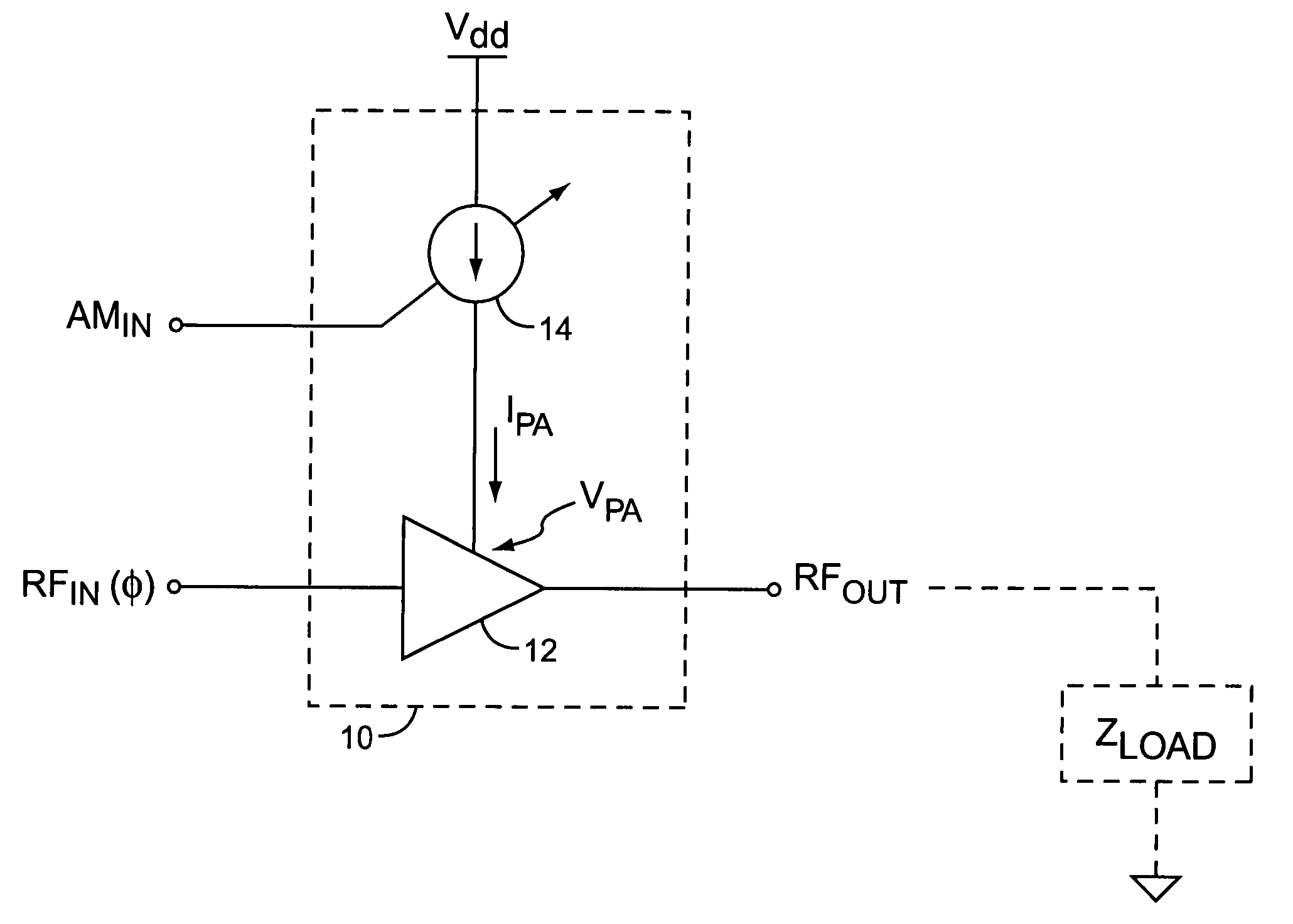

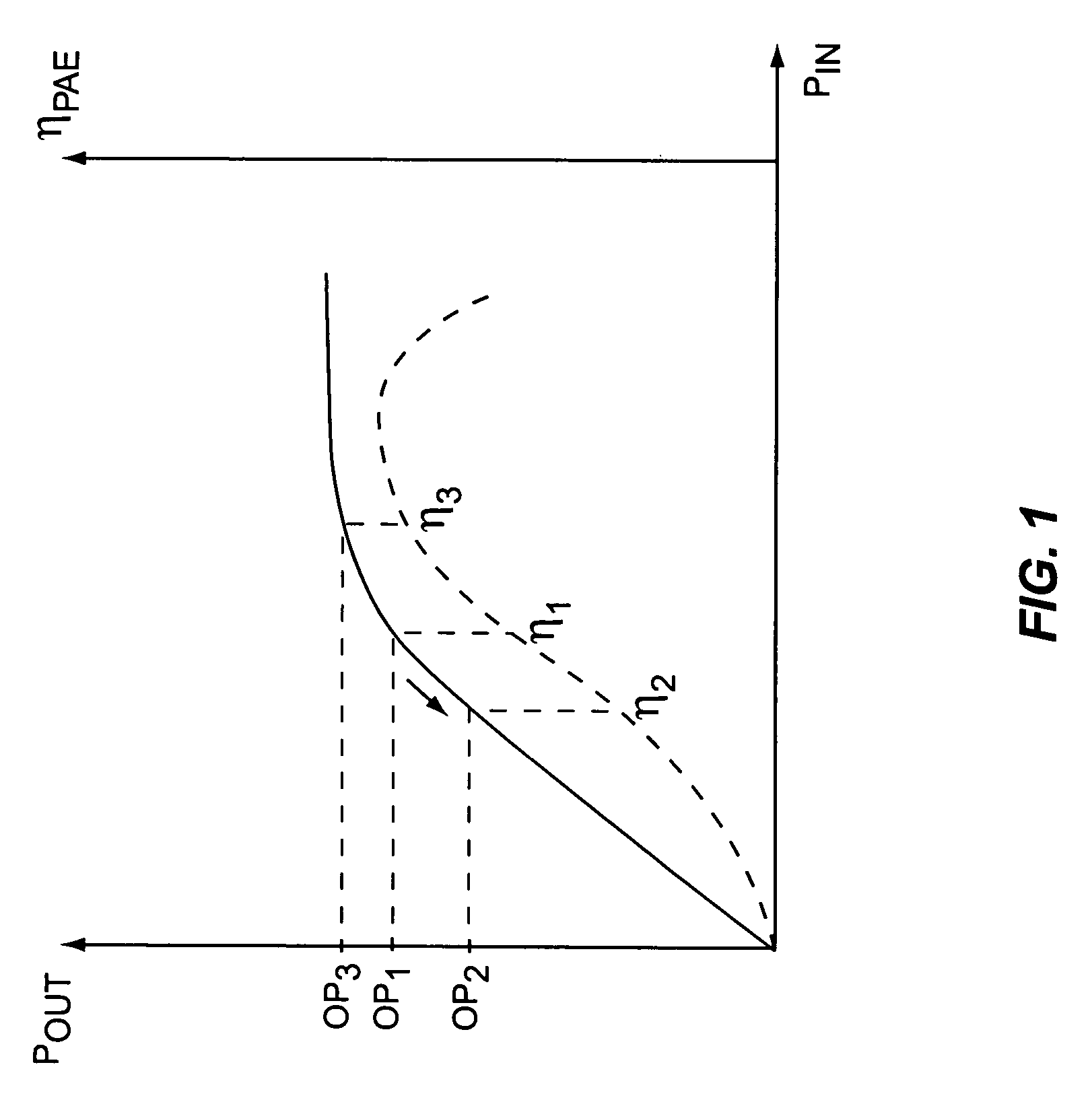

System and method for current-mode amplitude modulation

InactiveUS20050032488A1Efficient and linear amplificationHighly linear envelope modulationSimultaneous amplitude and angle modulationAmplifier modifications to reduce non-linear distortionAntenna impedanceAudio power amplifier

An amplifier circuit includes a power amplifier biased for saturated mode operation, and a controllable current source to provide supply current to the power amplifier. The controllable current source effects desired amplitude modulation of the output signal from the power amplifier by modulating the supply current it provides responsive to an amplitude information signal. In one or more embodiments, the current source includes a circuit that is configured to adjust one or more transmitter operating parameters responsive to detecting changes in the effective DC resistance of the power amplifier. For example, the circuit may generate a compensation signal that reduces the effective DC resistance responsive to detecting that the effective DC resistance has undesirably increased. By way of non-limiting examples, such compensation may be effected by changing a current mirror, an amplifier-to-antenna impedance matching, an amplifier bias or device size, or imposing some form of transmit signal back-off.

Owner:ERICSSON INC

Integrated circuit, method of operating an integrated circuit, method of manufacturing an integrated circuit, memory module, stackable memory module

InactiveUS7433253B2Design and efficient manufactureAccurate balanceCurrent/voltage measurementDigital storageCapacitanceEngineering

An integrated circuit has a current sense amplifier that includes a voltage comparator having a first input, a second input and an output; a first clamping device coupled between the first input of the voltage comparator and a first input signal node, a second clamping device coupled between the second input of the voltage comparator and a second input signal node, a current mirror having a first side and a second side, the current mirror first side including a first transistor coupled between a voltage source and the first clamping device and the current mirror second side including a second transistor coupled between the voltage source and the second clamping device, and a sensing scheme including an actively balanced capacitance coupled to the source and drain of the second transistor.

Owner:POLARIS INNOVATIONS LTD

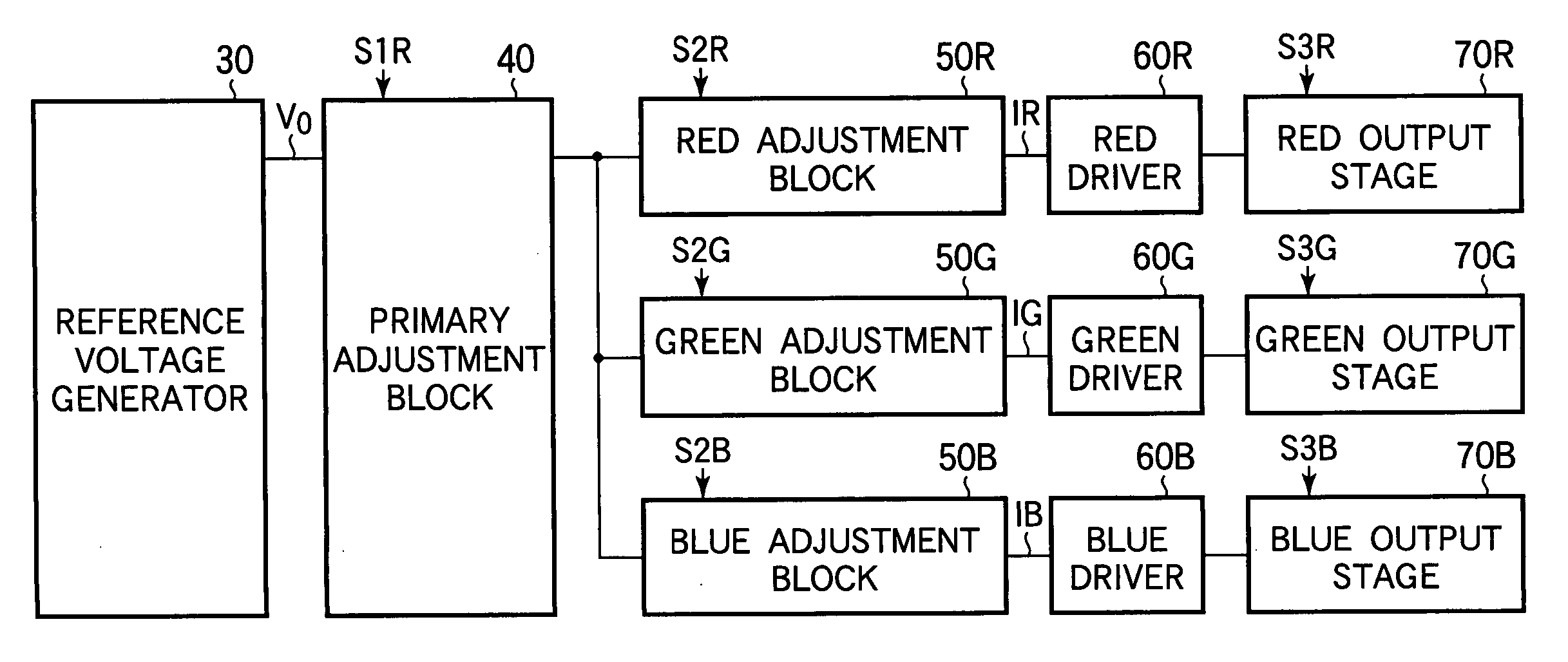

Color balancing circuit for a display panel

InactiveUS20060023002A1Effective balanceSewerage structuresElectrical apparatusDriving currentEngineering

A color balancing circuit for a flat panel display such as an electroluminescent display generates a primary current that can be varied to adjust the overall brightness of the display. Three currents related to the primary current by selectable ratios are generated, by current mirror circuits, for example; the ratios can be individually varied to adjust the color balance. Driving currents are generated from the three adjusted currents, by mirroring the adjusted currents, for example, and are used to drive display elements that emit light in the three primary colors. Image brightness and color balance can accordingly be adjusted separately, even though both are adjusted by adjusting the driving current. Circuit size is reduced in that the same primary current is used for all three primary colors.

Owner:LAPIS SEMICON CO LTD

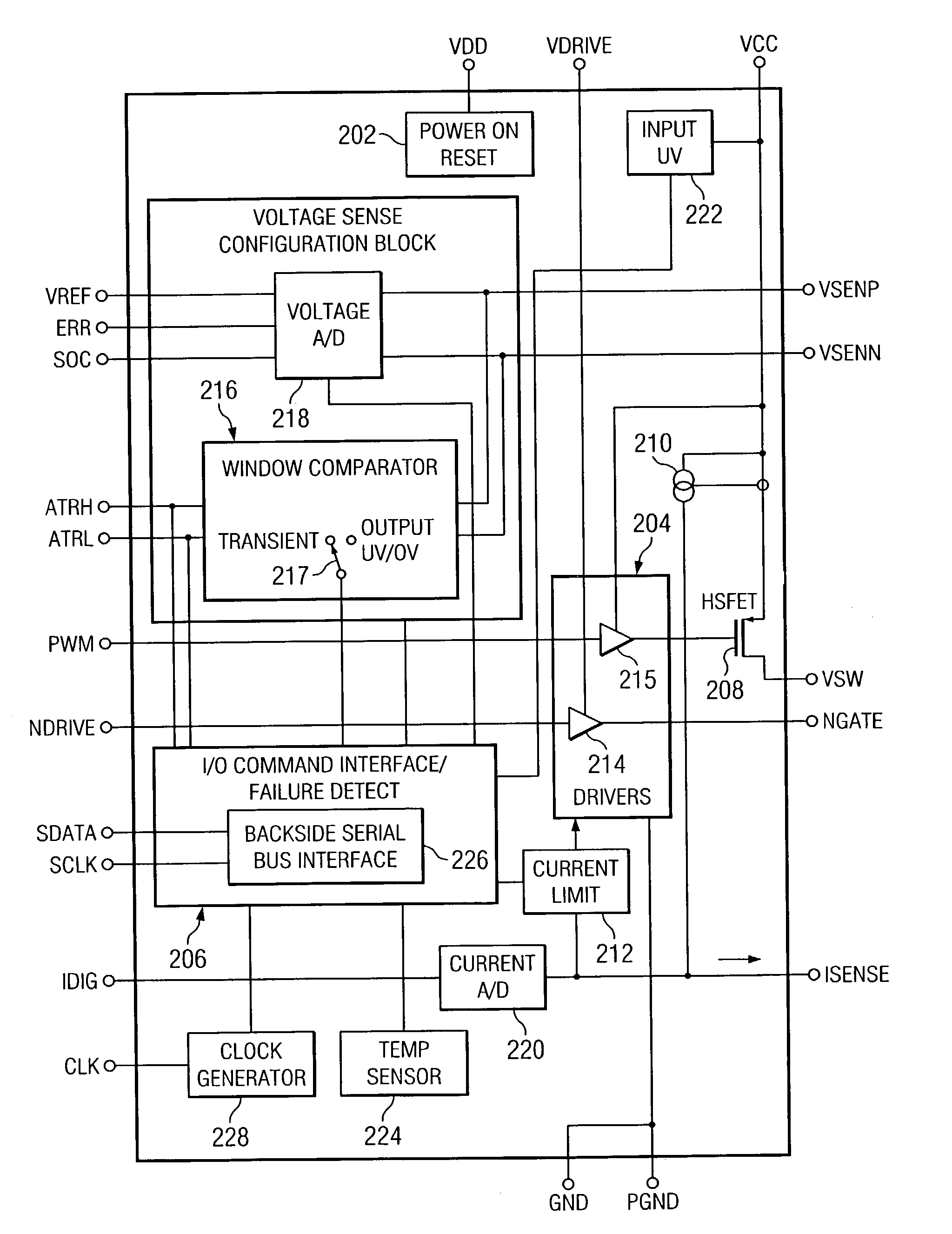

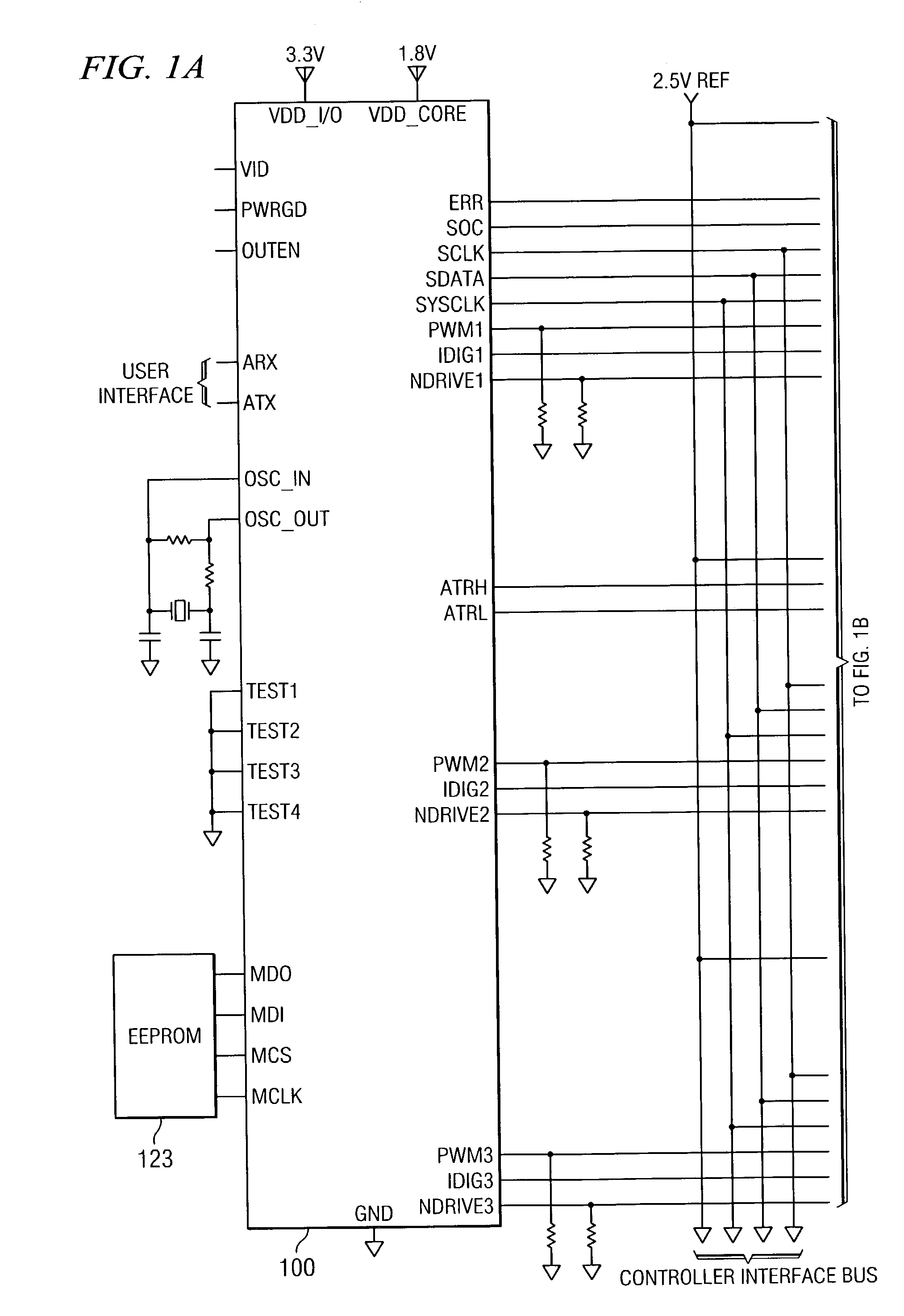

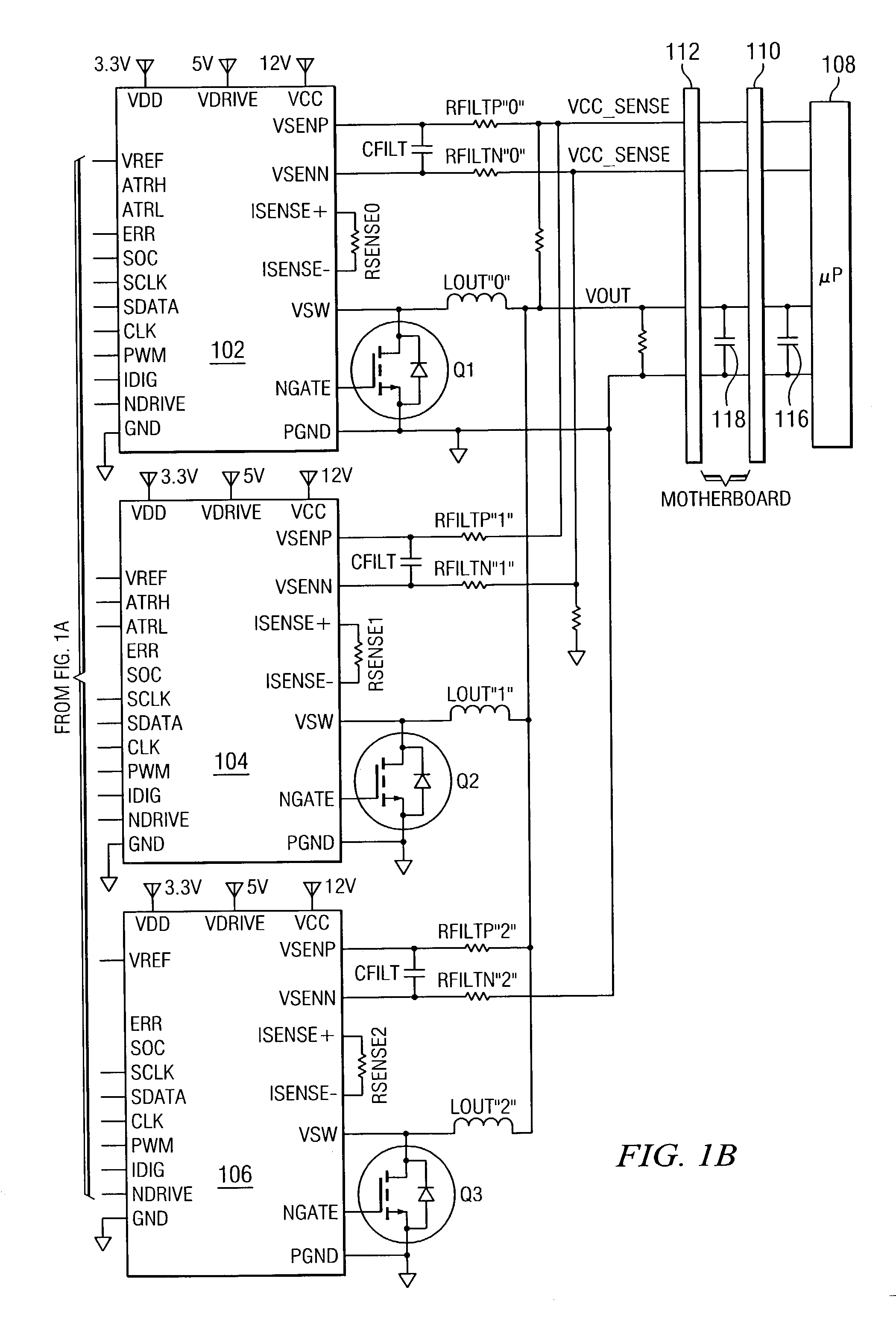

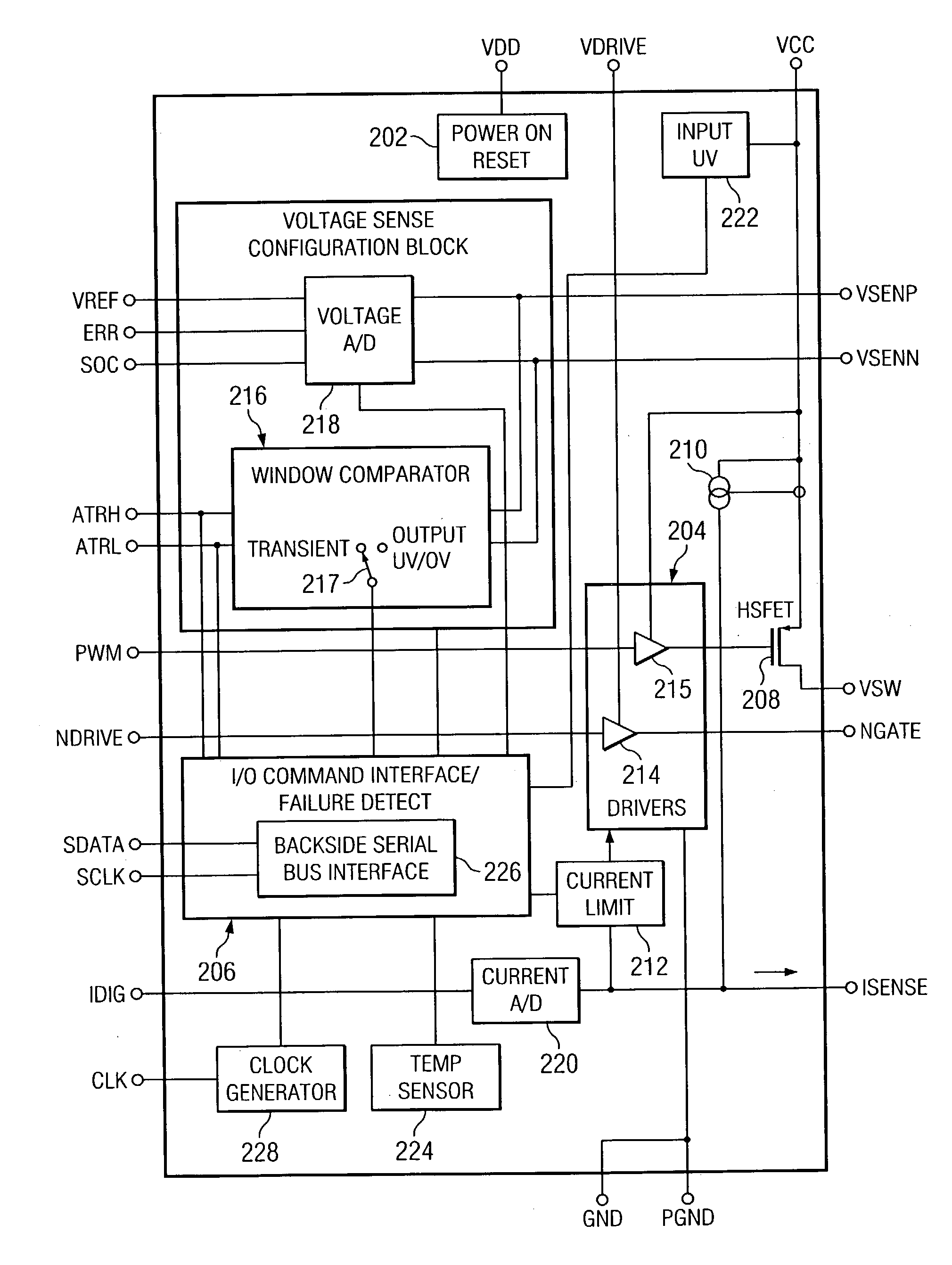

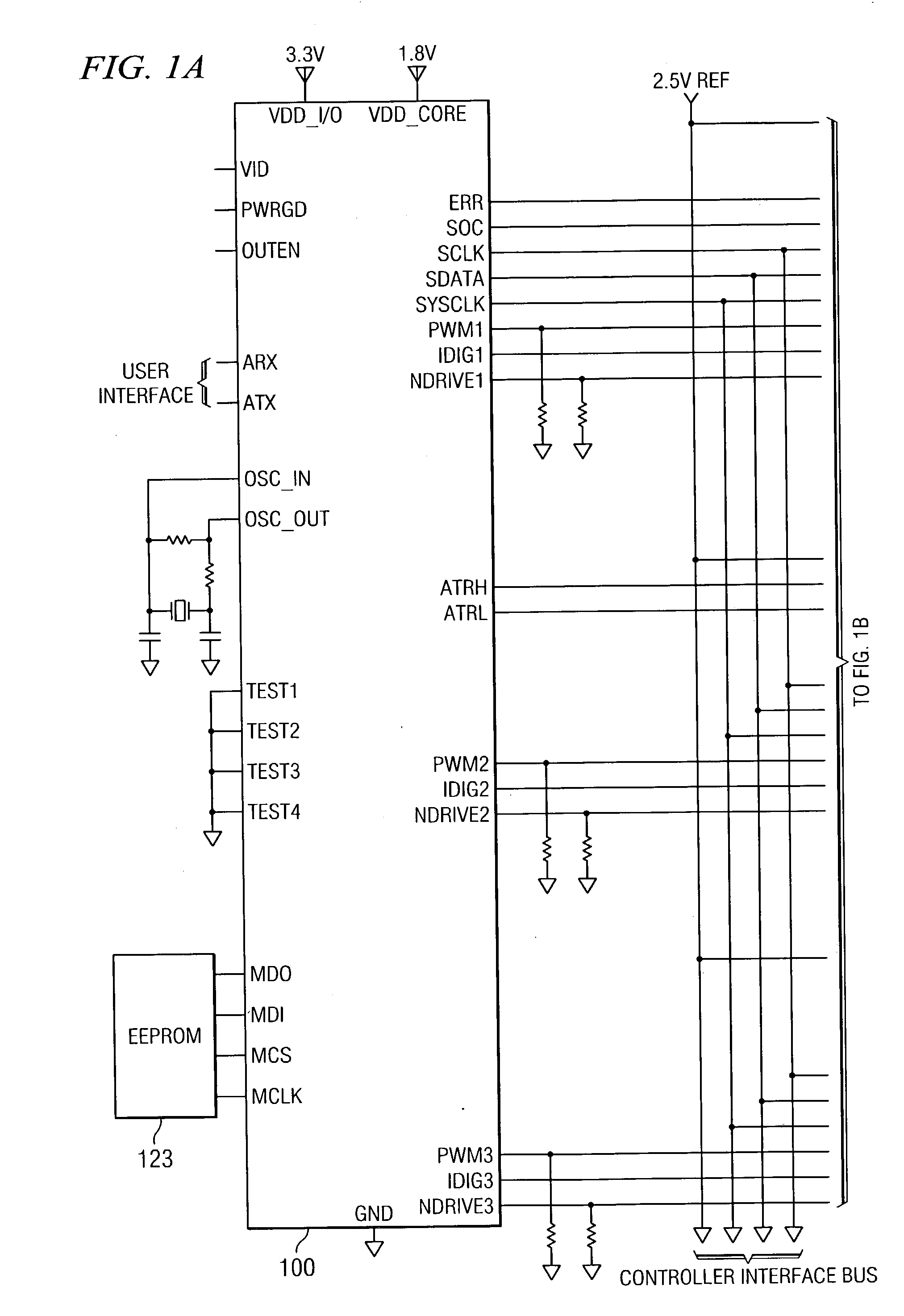

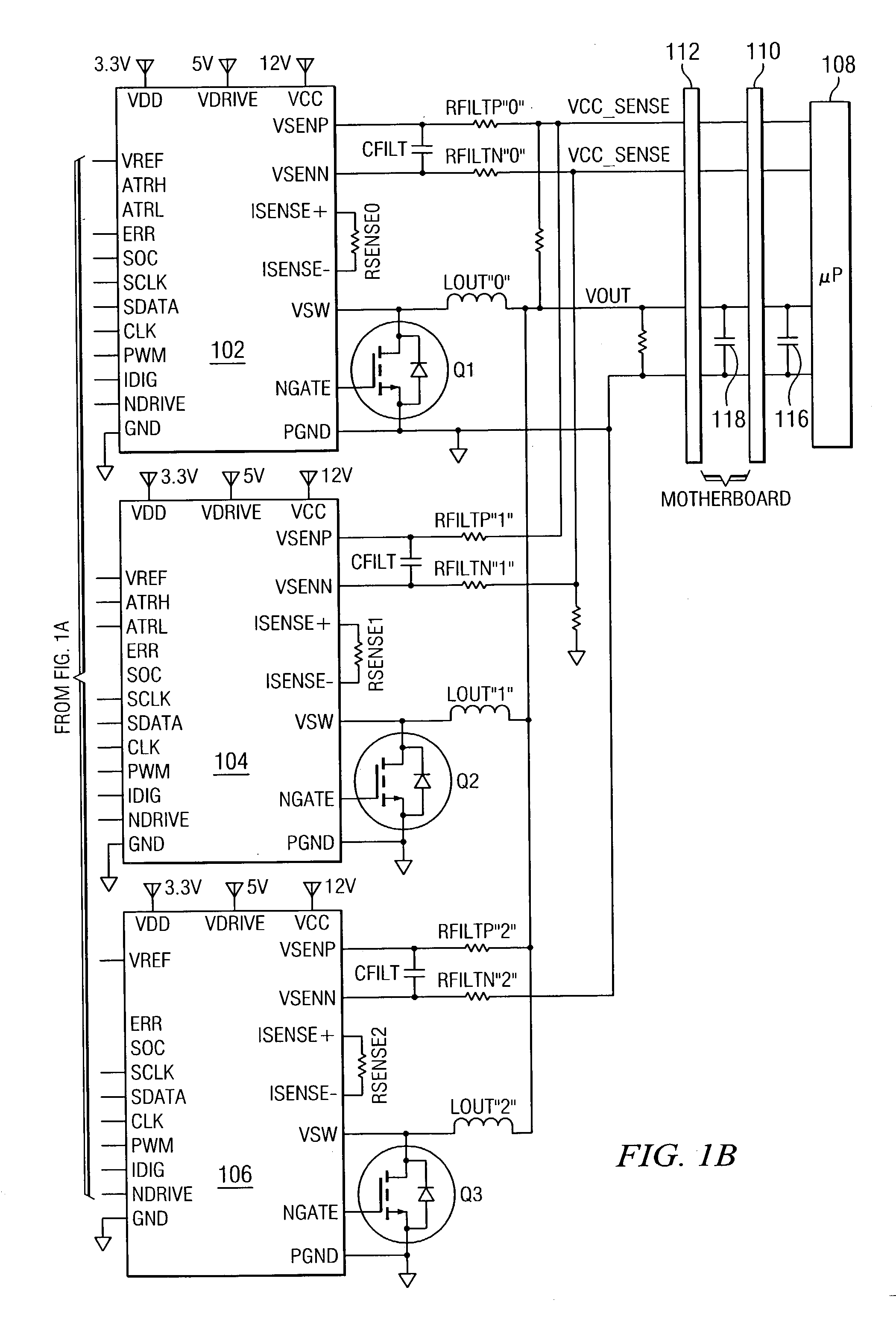

Digitally controlled voltage regulator

ActiveUS7023672B2Easy to customizePrecise power controlEfficient power electronics conversionDc-dc conversionControl signalOptimal control

Disclosed is a digitally controlled multi-phase voltage regulator system providing regulated power to electronic components that have variable power requirements. Power is supplied by one or more power integrated circuits (IC) each having a high side power switch controlled by pulse width modulated signals and a low side power switch. The power IC senses voltage at the load and has an on-chip current mirror for generating a current that is a ratio of current delivered to the load. The power IC also has current limiting and on-chip temperature sensing components. The voltage and current information is digitized and provided to a control integrated circuit (IC). The control IC receives this digitized information as well as user provided parameters and, in the regulation mode of operation, provides digitized pulse width modulated control signals to the power IC. In an active transient response mode of operation, the control IC provides signals to turn either the high side switches or low side switches ON. Fault detection circuitry identifies over voltage, under voltage, and excessive temperatures. All communications between the control IC and the power IC are digital providing high bandwidth, optimal control frequency response, noise immunity and efficient active transient response.

Owner:INFINEON TECH AUSTRIA AG

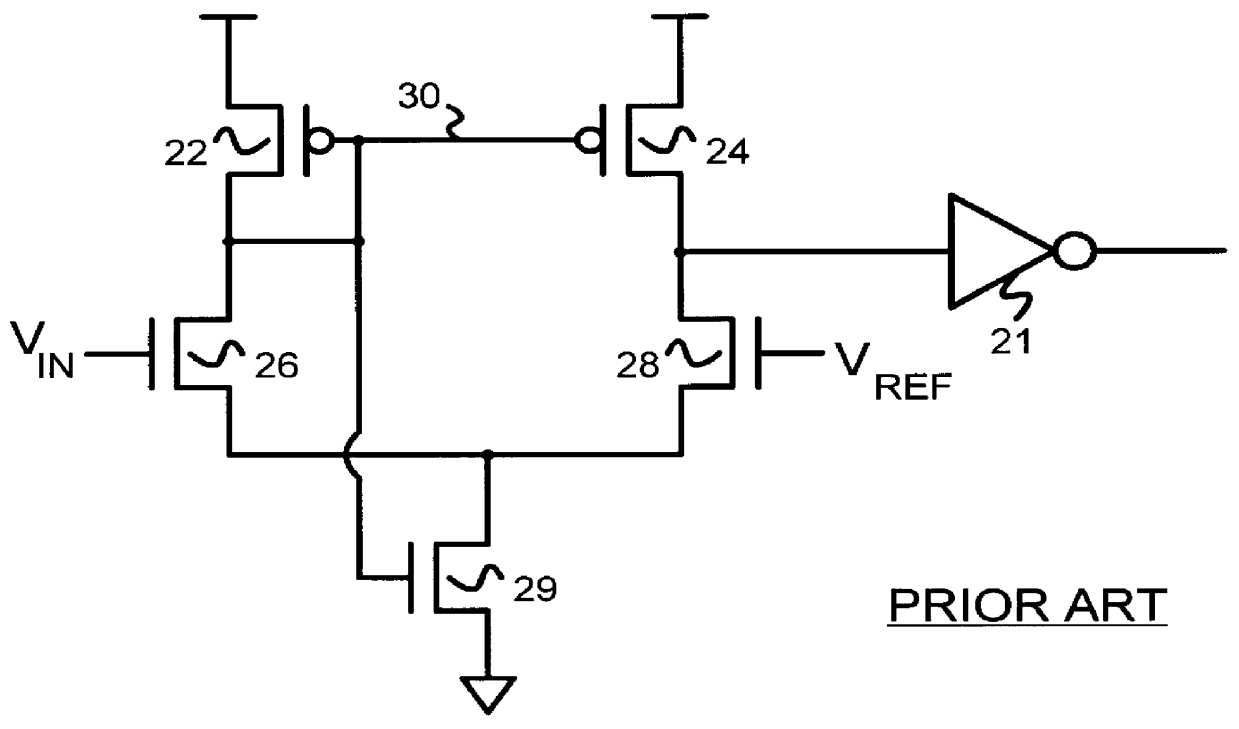

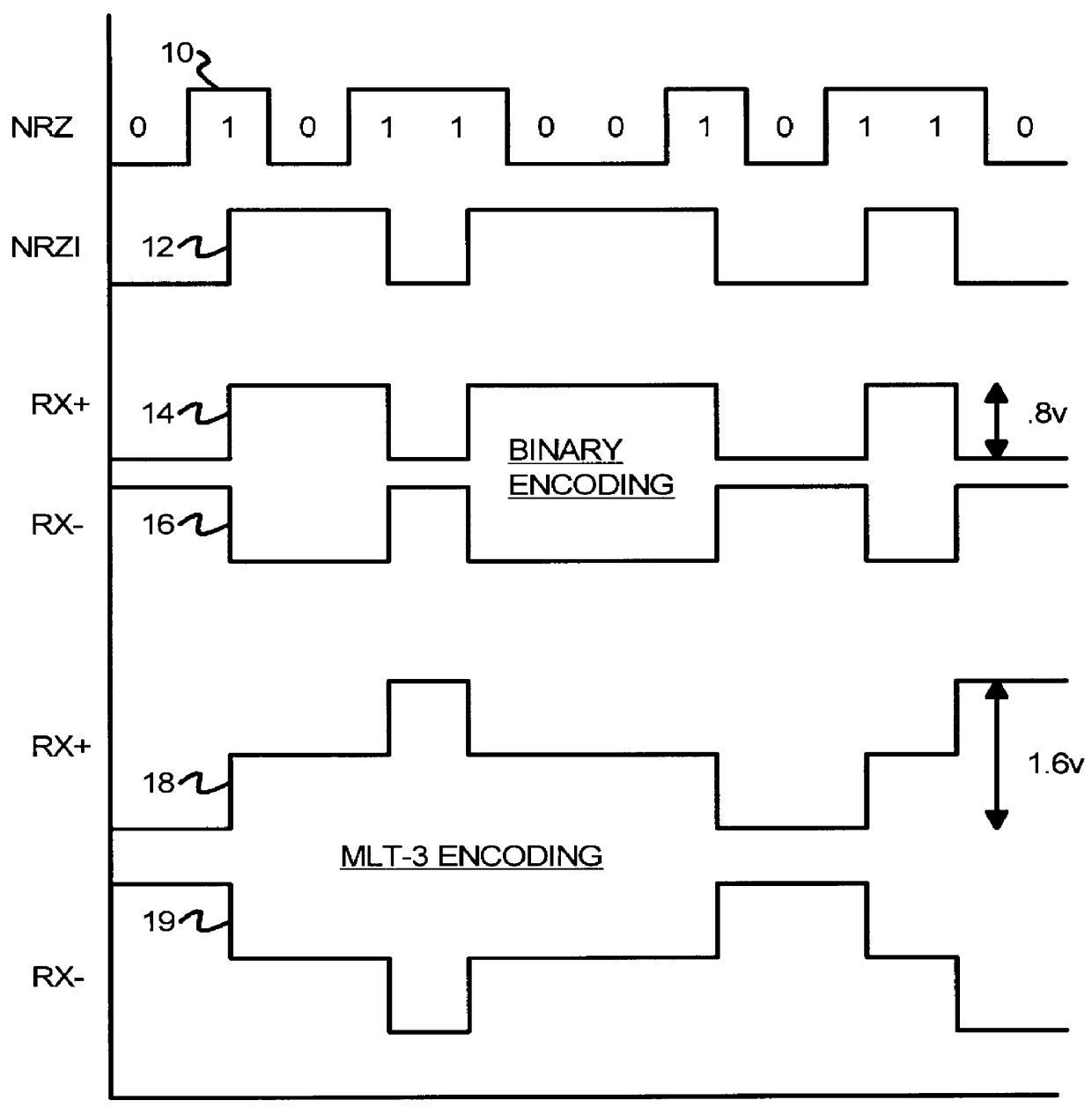

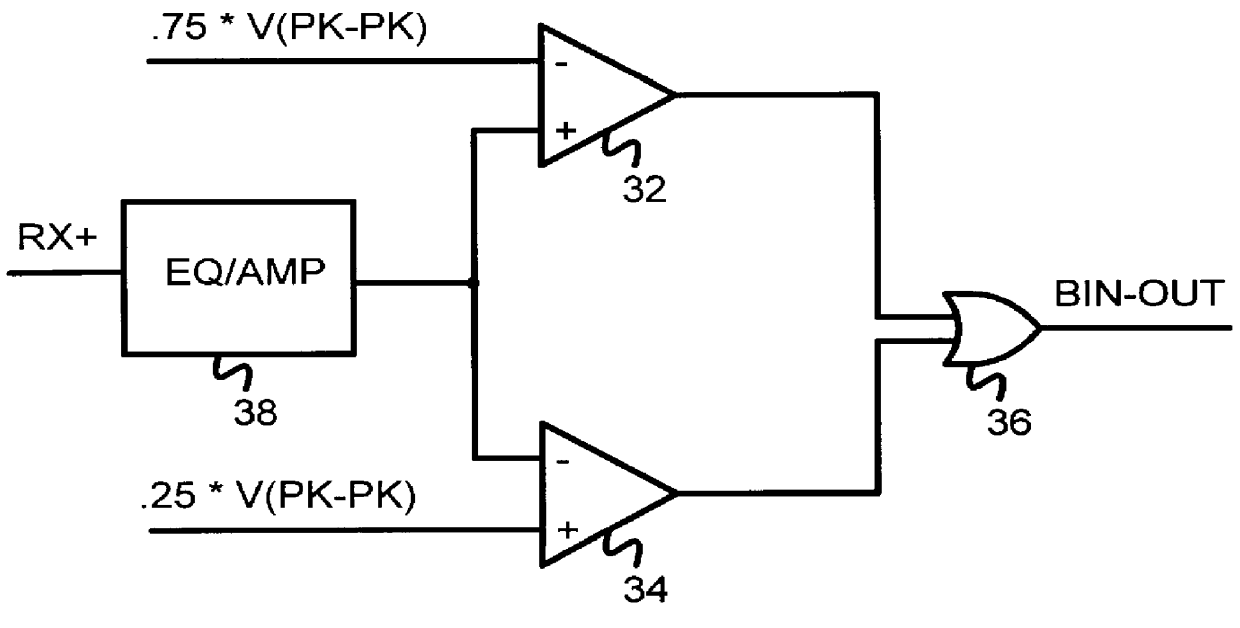

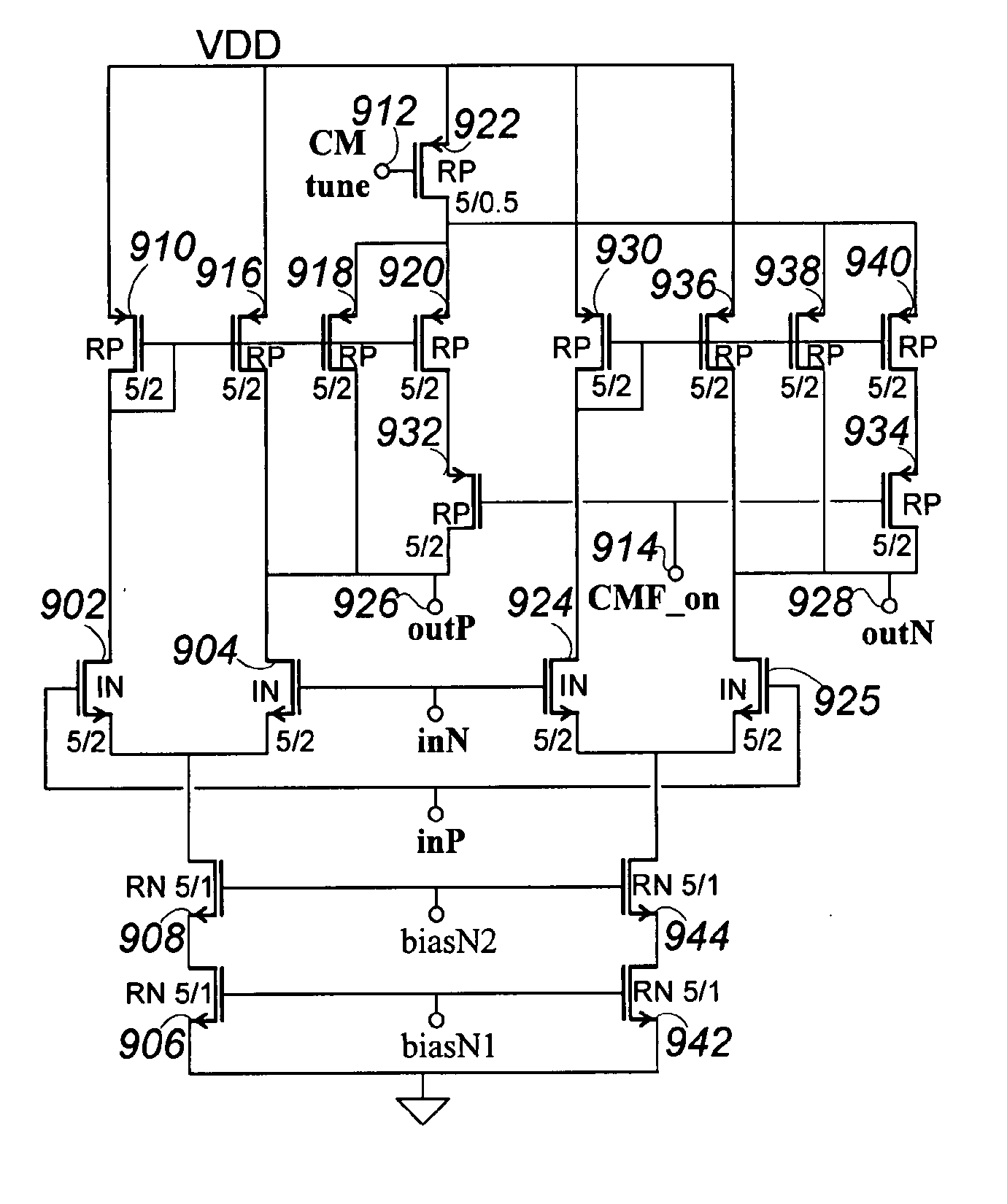

Self-biasing CMOS PECL receiver with wide common-mode range and multi-level-transmit to binary decoder

InactiveUS6049229AReduced Power RequirementsSimplify interconnect routingLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsThree levelEmitter-coupled logic

A pseudo-emitter-coupled-logic (PECL) receiver has a wide common-mode range. Two current-mirror CMOS differential amplifiers are used. One amplifier has n-channel differential transistors and a p-channel current mirror, while the second amplifier has p-channel differential transistors and an n-channel current mirror. When the input voltages approach power or ground, one type of differential transistor continues to operate even when the other type shuts off. The outputs of the two amplifiers are connected together and each amplifier receives the same differential input signals. The tail-current transistor is self-biased using the current-mirror's gate-bias. This self biasing of each amplifier eliminates the need for an additional voltage reference and allows each amplifier to adjust its biasing over a wide input-voltage range. Thus the common-mode input range is extended using self biasing and complementary amplifiers. The complementary self-biased comparators can be used for receiving binary or multi-level-transition (MLT) inputs by selecting different voltage references for threshold comparison. Using the same reference on both differential inputs eliminates a second reference for multi-level inputs having three levels. Thus binary and MLT inputs can be detected and decoded by the same decoder.

Owner:DIODES INC

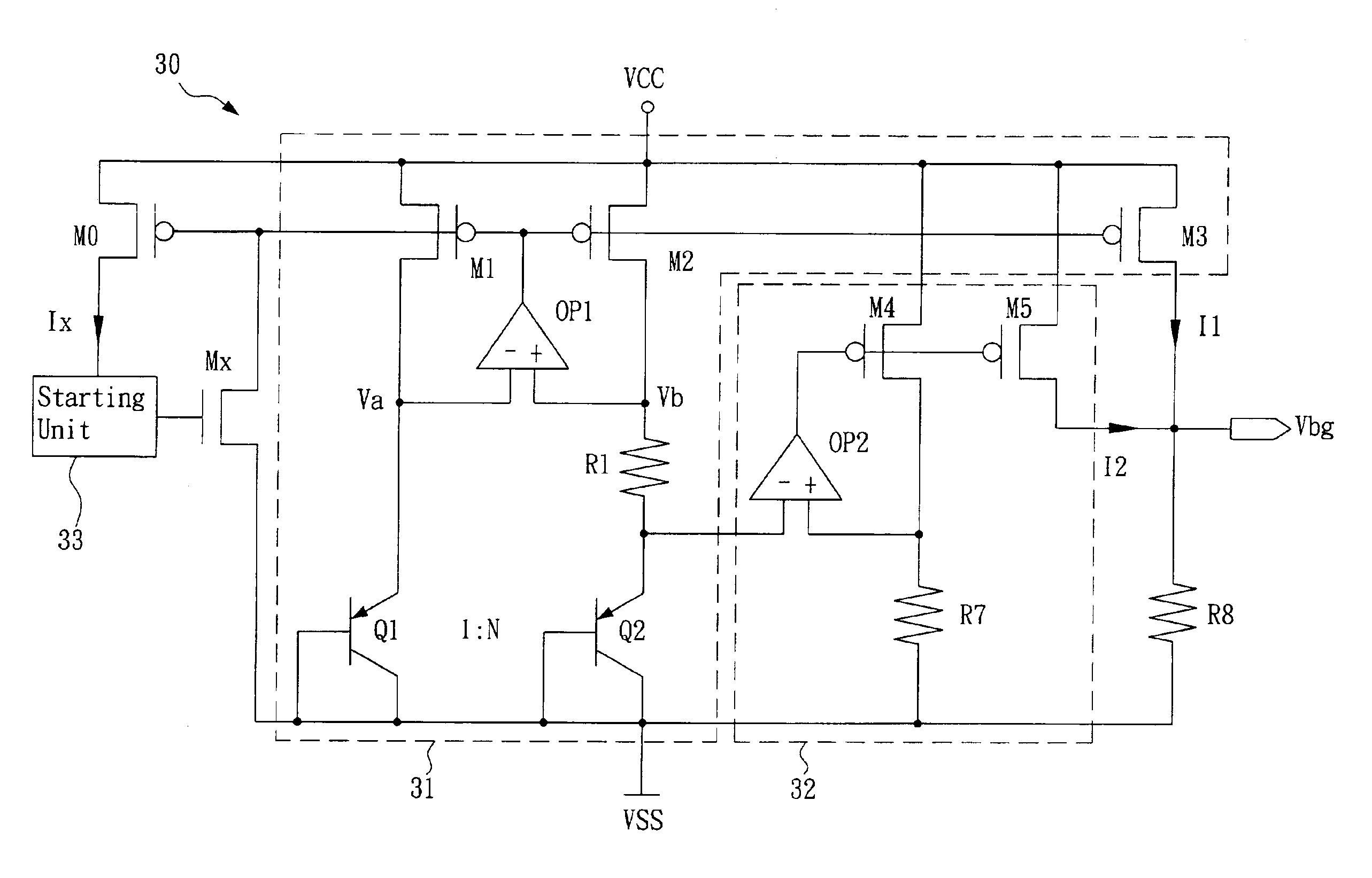

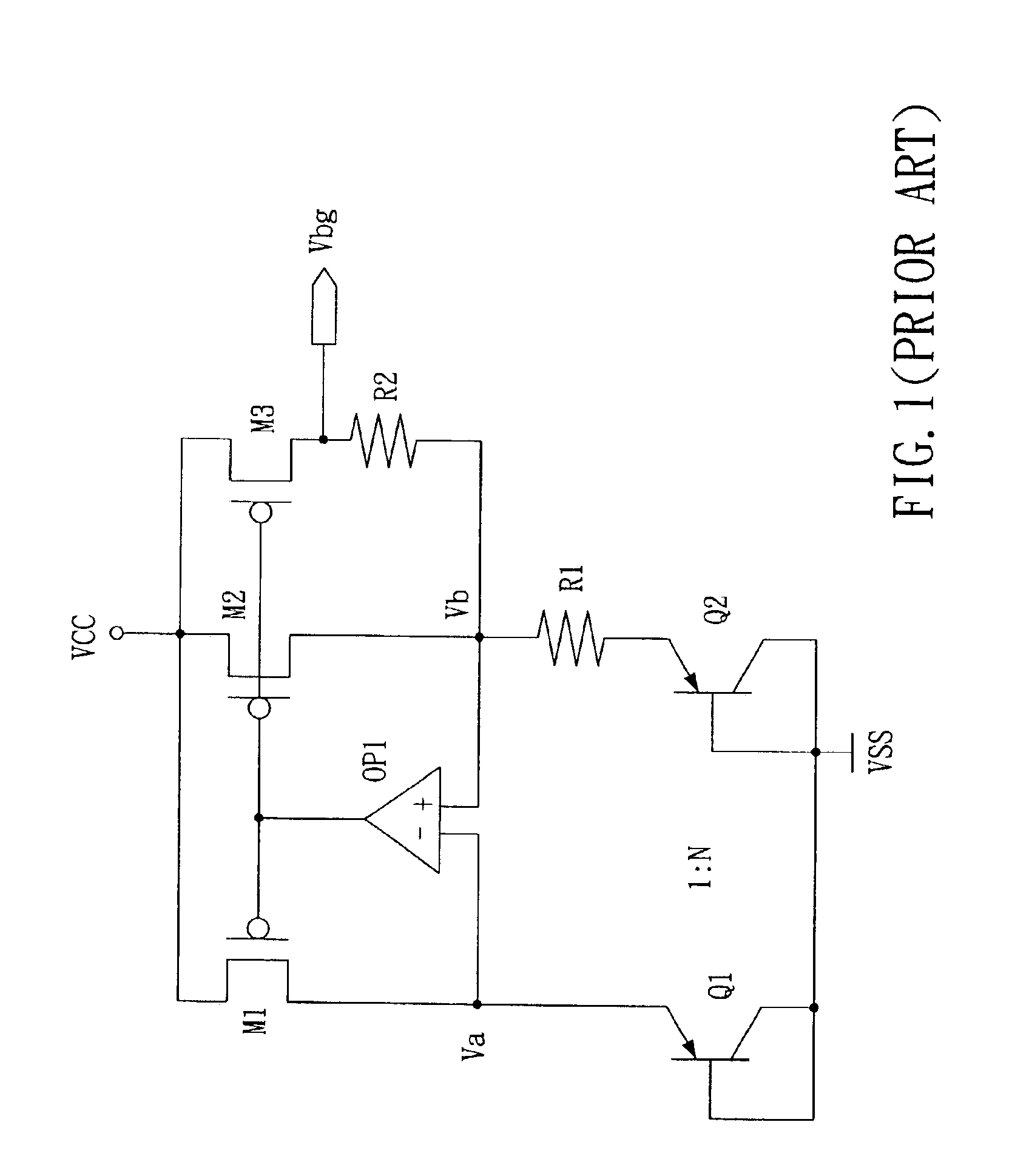

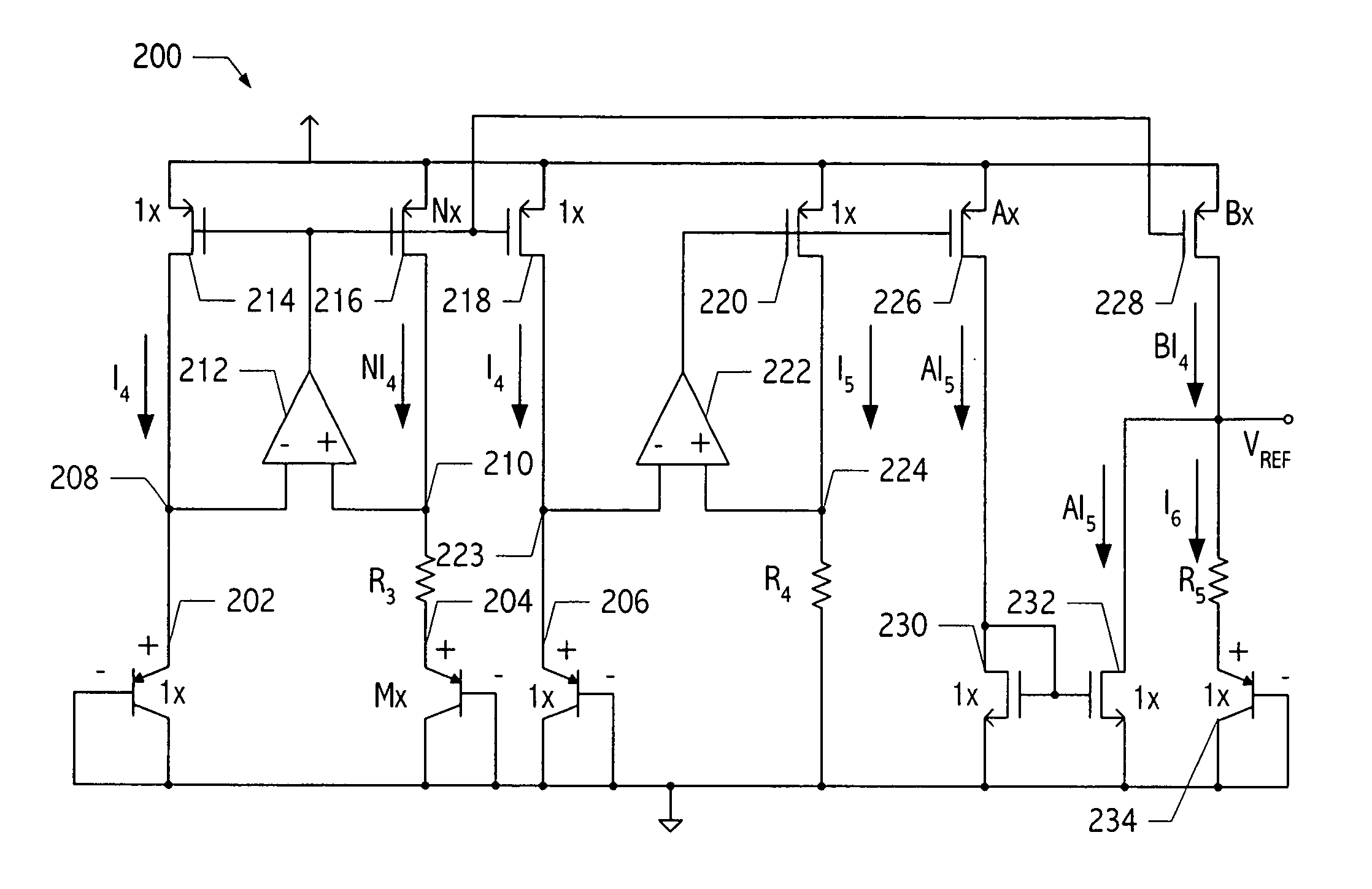

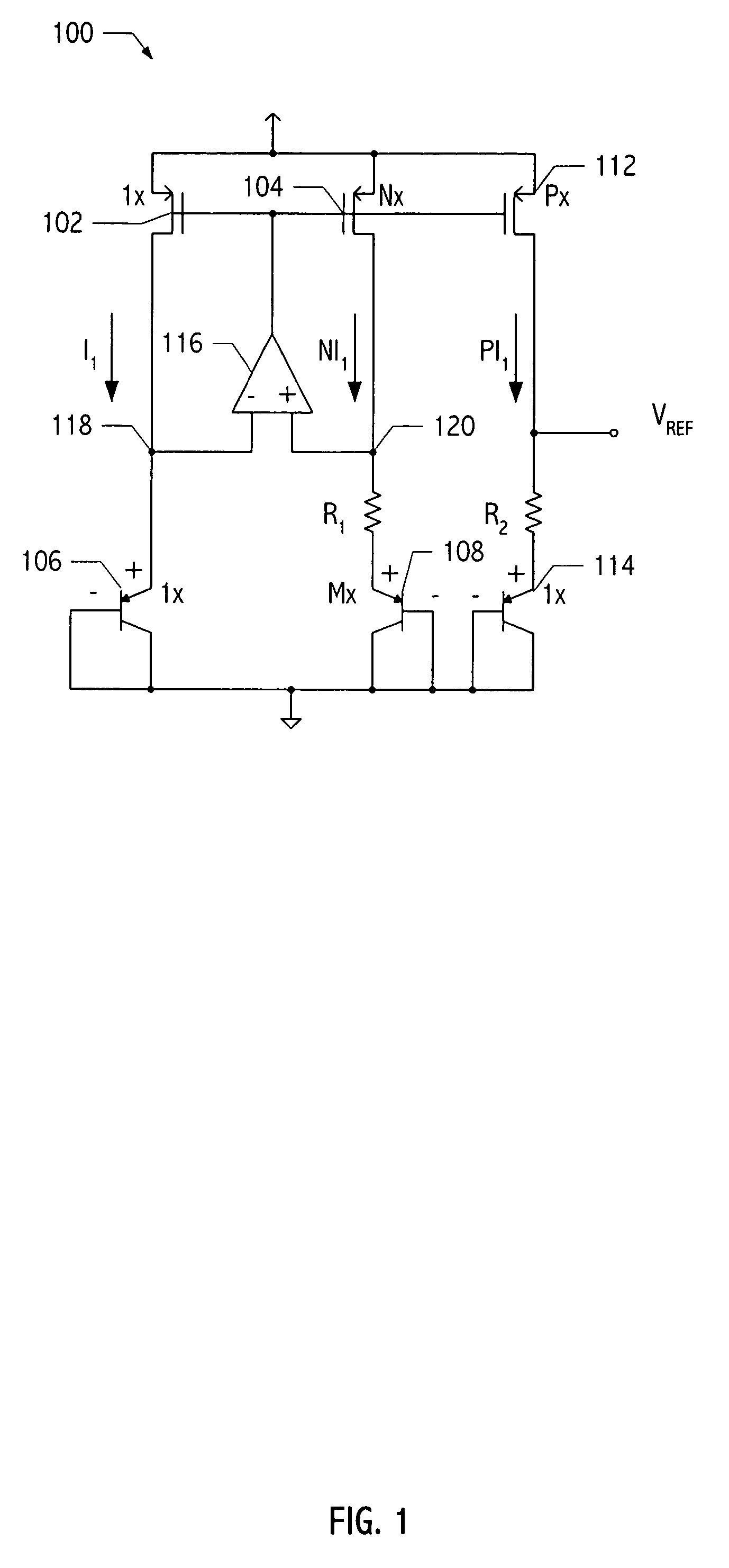

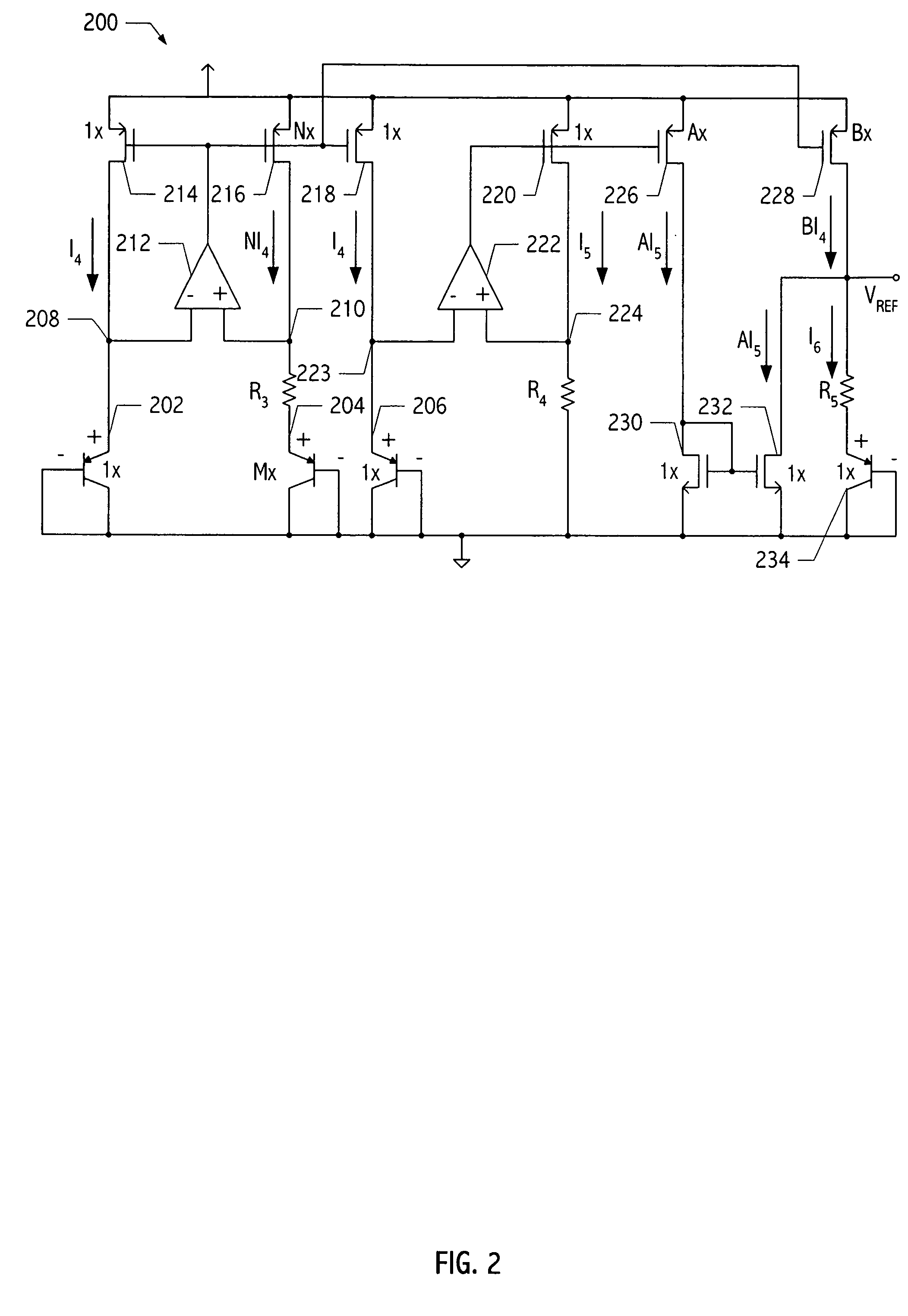

Fast start-up low-voltage bandgap voltage reference circuit

A fast start-up low-voltage bandgap voltage reference circuit is disclosed. The bandgap voltage reference circuit includes: a first current generator, which is implemented by a self-bias unit and a current mirror for generating a first reference current with positive temperature coefficient; a second current generator, which is connected to a point with negative temperature coefficient in the first current generator to generate a second reference current with negative temperature coefficient; and a resistor for converting the first reference current and the second reference current into a low-voltage bandgap voltage independent of temperature. Because the bandgap voltage reference circuit of the invention uses the resistor to convert the first reference current and the second reference current into voltage, the circuit can provide low-voltage bandgap voltage.

Owner:REALTEK SEMICON CORP

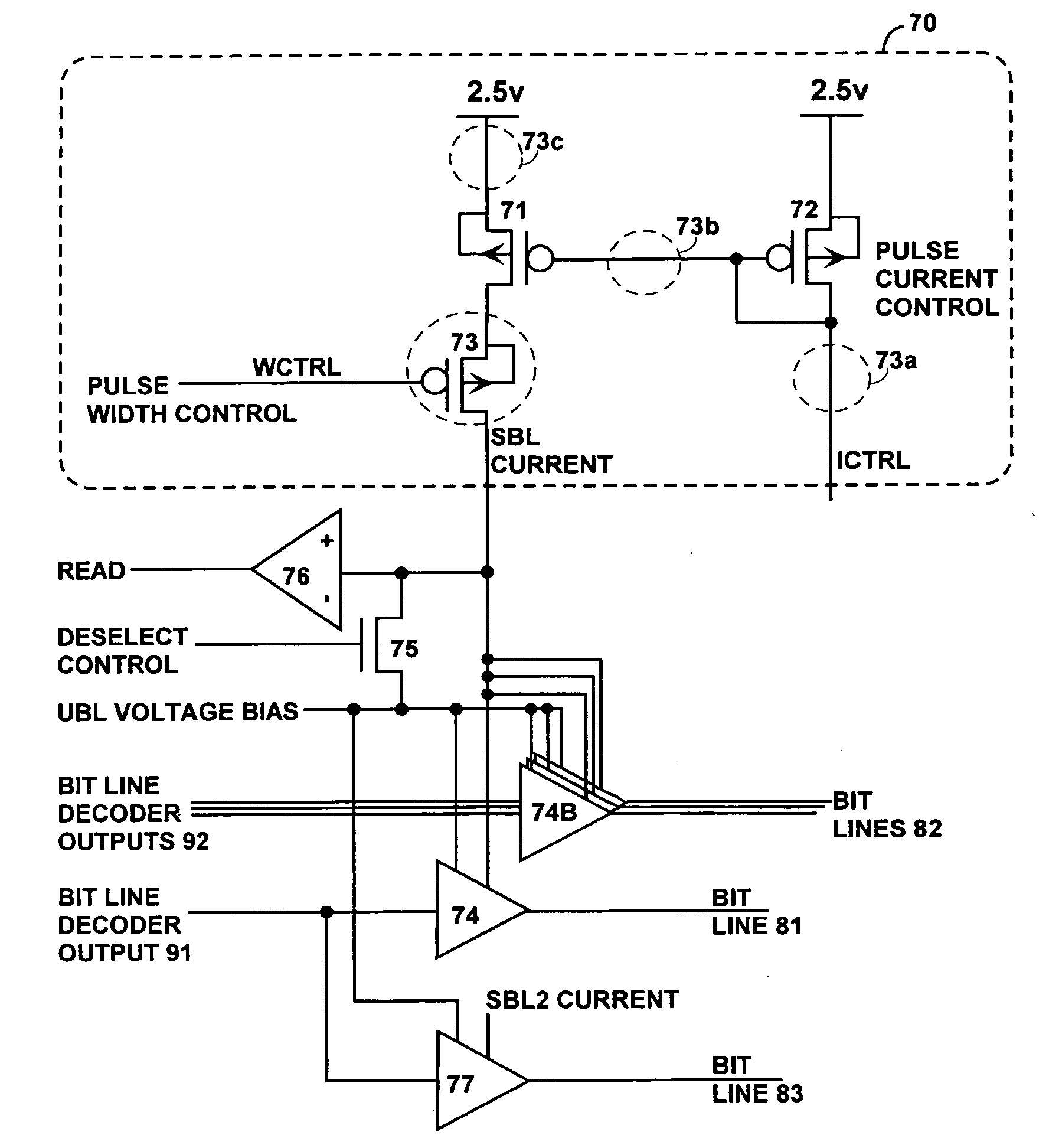

Structure and method for biasing phase change memory array for reliable writing

ActiveUS7307268B2Reduce the possibilityMinimize leakage currentSolid-state devicesDigital storageBit linePhase-change memory

A memory array having memory cells comprising a diode and a phase change material is reliably programmed by maintaining all unselected memory cells in a reverse biased state. Thus leakage is low and assurance is high that no unselected memory cells are disturbed. In order to avoid disturbing unselected memory cells during sequential writing, previously selected word and bit lines are brought to their unselected voltages before new bit lines and word lines are selected. A modified current mirror structure controls state switching of the phase change material.

Owner:SANDISK TECH LLC

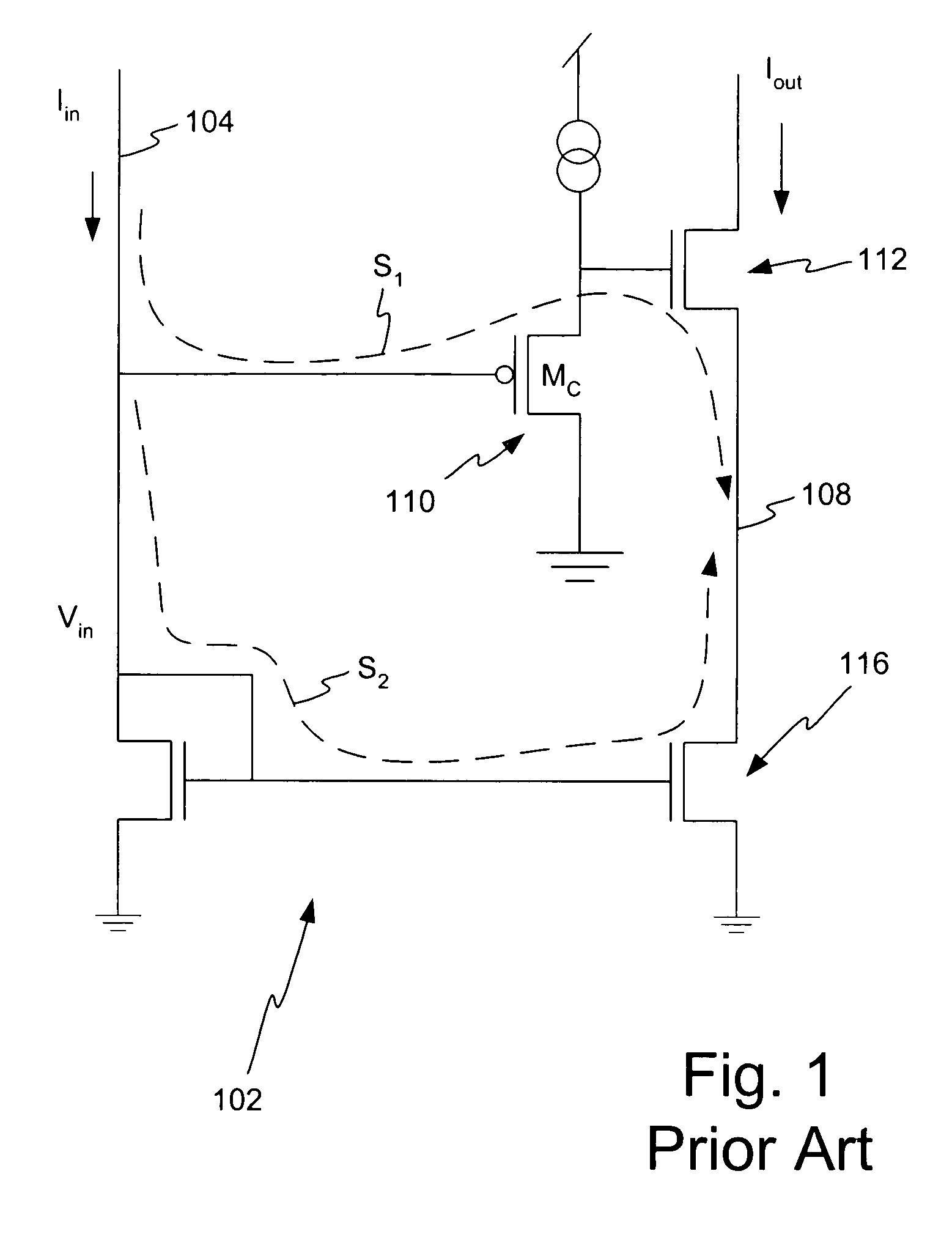

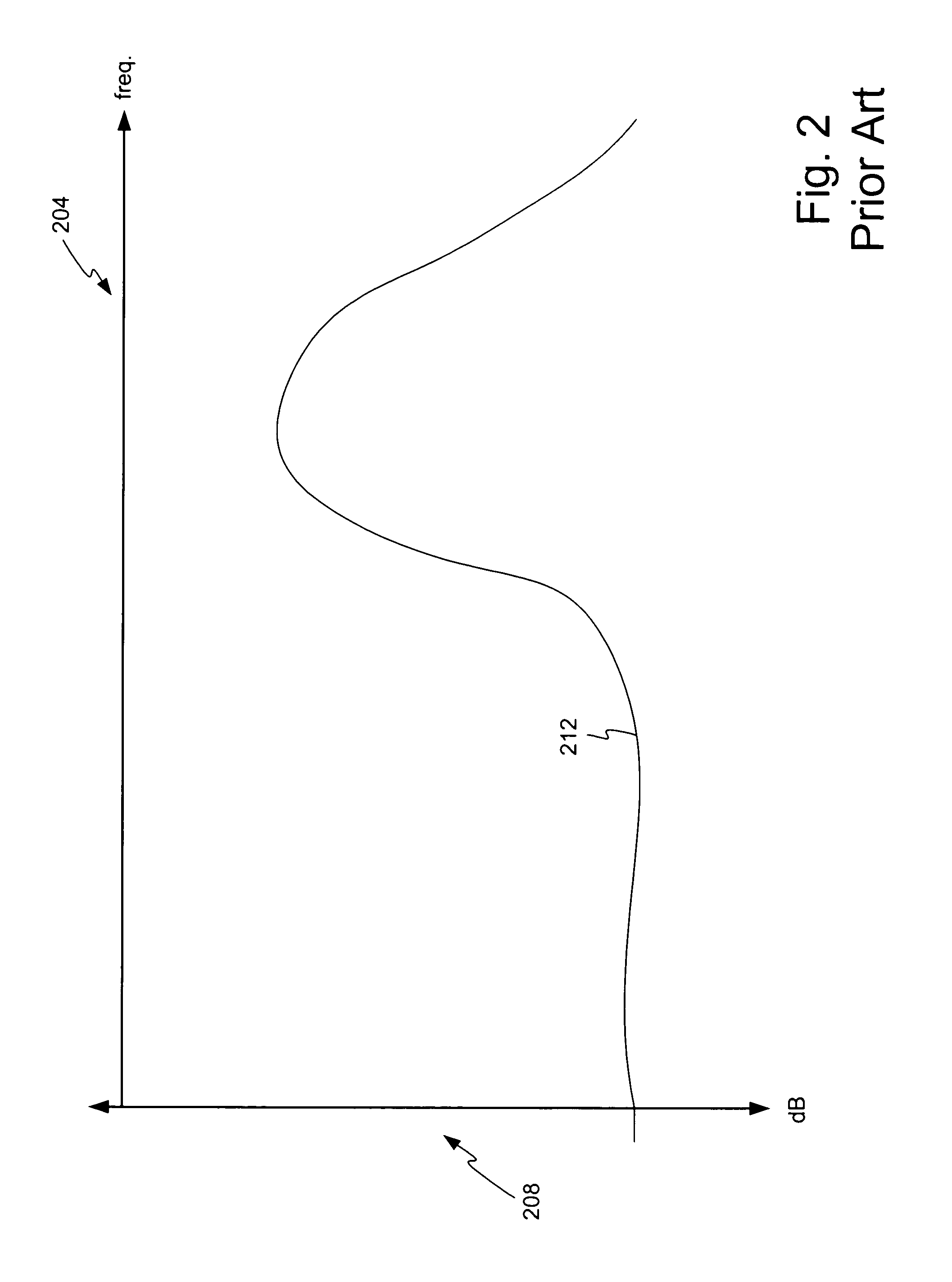

Method and apparatus for increasing the linearity and bandwidth of an amplifier

ActiveUS20050083130A1Amplifier modifications to reduce non-linear distortionElectric variable regulationCascodeEngineering

A method and apparatus is disclosed for improving high frequency performance of an amplifier, such as for example, a current mirror. In one embodiment, a delay element is introduced in a current mirror signal path to account for signal propagation delay that may exist in one or more alternative signal paths. The delay element maintains desired phase alignment at a cascade node of the current mirror thereby establishing, in one embodiment, the cascode node (Vc) in an AC ground state. To extend current mirror high frequency capability an embodiment is disclosed having cross-coupled capacitors, active elements, or one or more other devices configured to provide positive feedback to one or more current mirror inputs. The positive feedback may be selectively configured to increase the operational bandwidth of the current mirror.

Owner:MARVELL ASIA PTE LTD

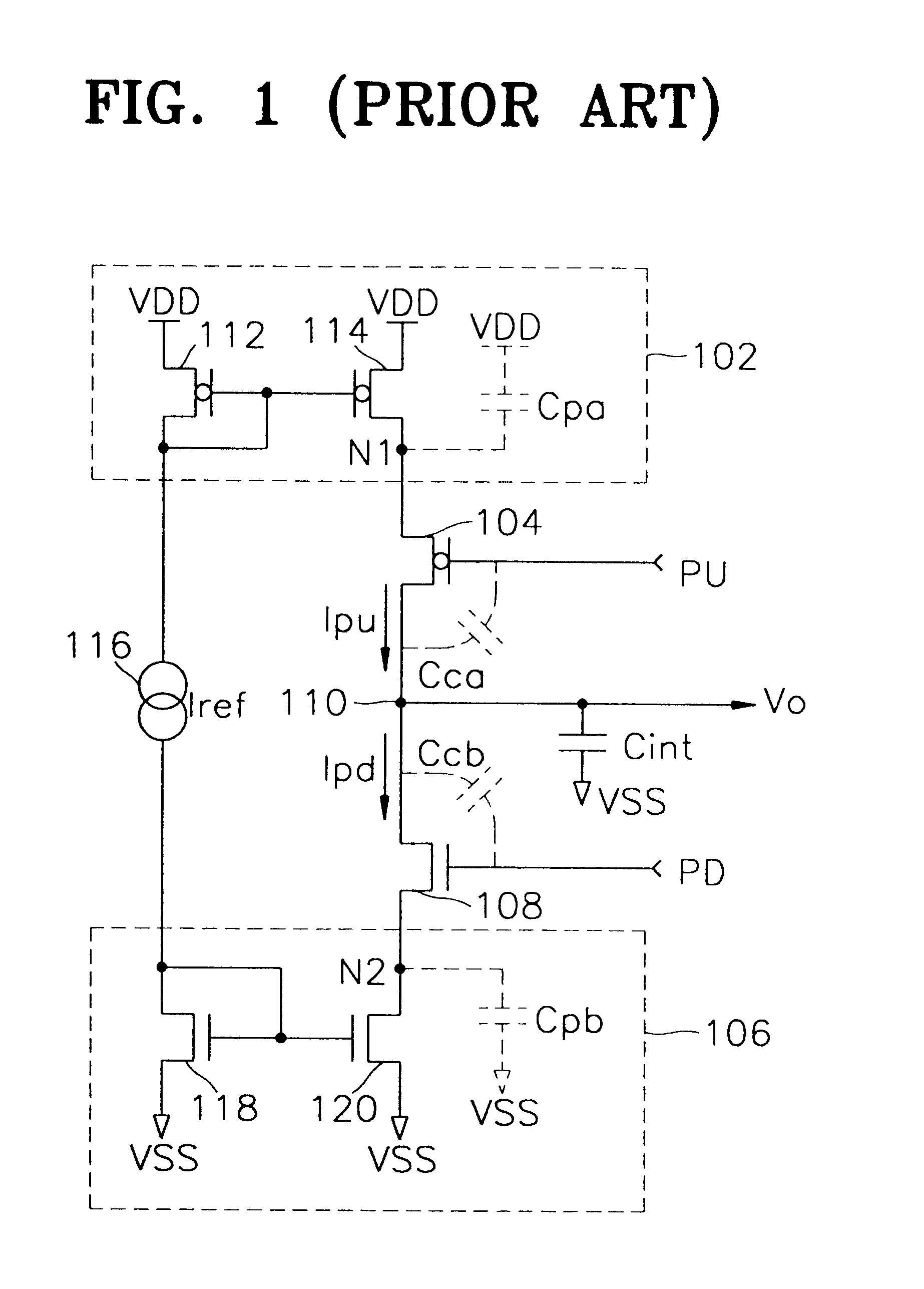

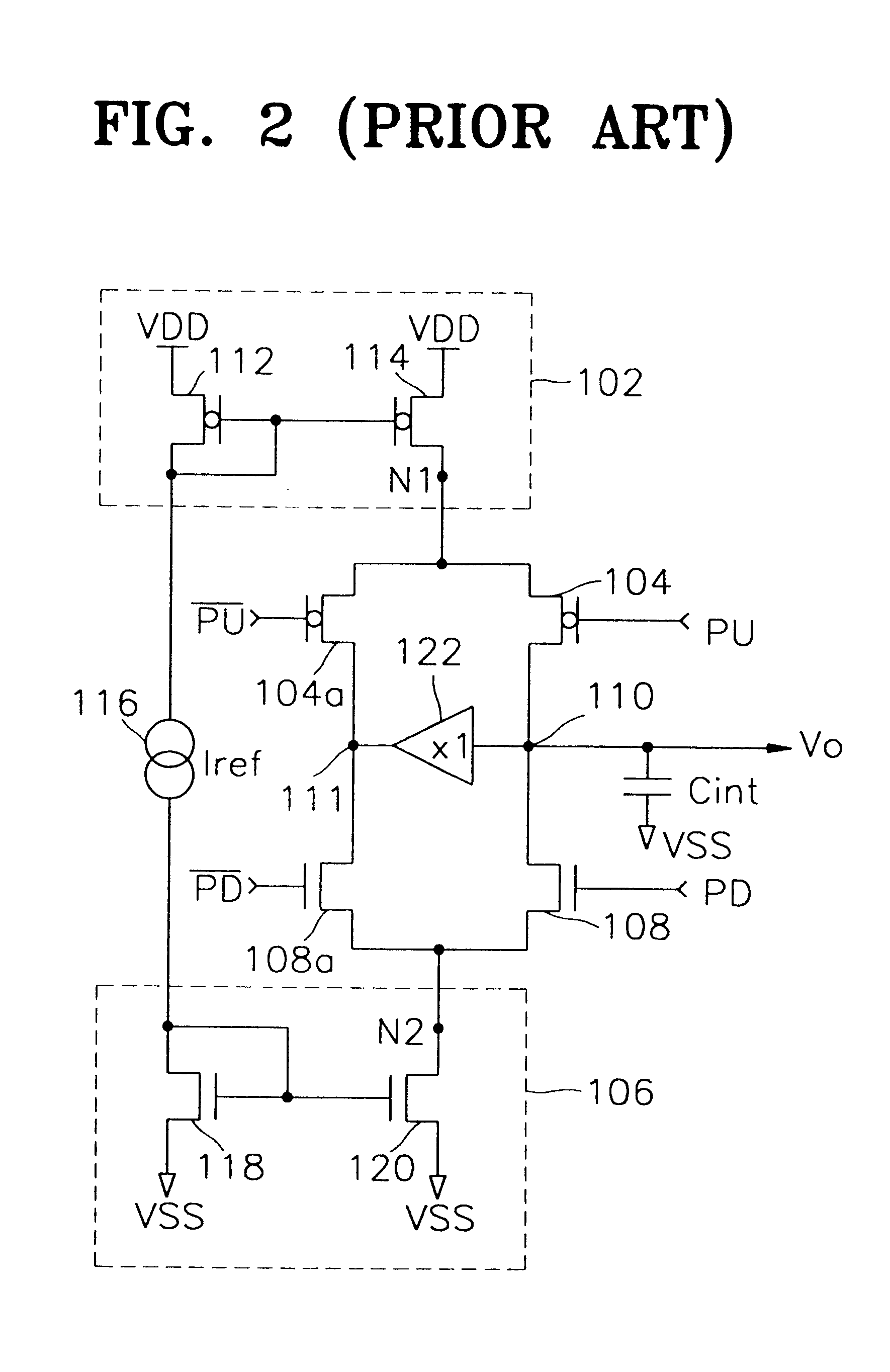

Charge pump circuit

InactiveUS6535051B2Pulse automatic controlElectric variable regulationCharge injectionControl signal

A charge pump circuit capable of preventing coupling and charge injection without increasing a layout area and power consumption is provided. The charge pump circuit includes a pull-up current source, a pull-down current source, a first switching device, and a second switching device. The pull-up current source sources pump-up current to the output node. The pull-down current source includes a current mirror and sinks pump-down current from the output node. In particular, the first switching device is connected between a supply voltage node and the pull-up current source and is switched in response to a pump-up control signal. The second switching device is connected between the second current source and a ground voltage node and is switched in response to a pump-down control signal. The current pump circuit may further include a first dummy capacitor one end of which is connected to a junction between the first switching device and the first current source and a second dummy capacitor one end of which is connected to a junction between the second switching device and the second current source.

Owner:SAMSUNG ELECTRONICS CO LTD

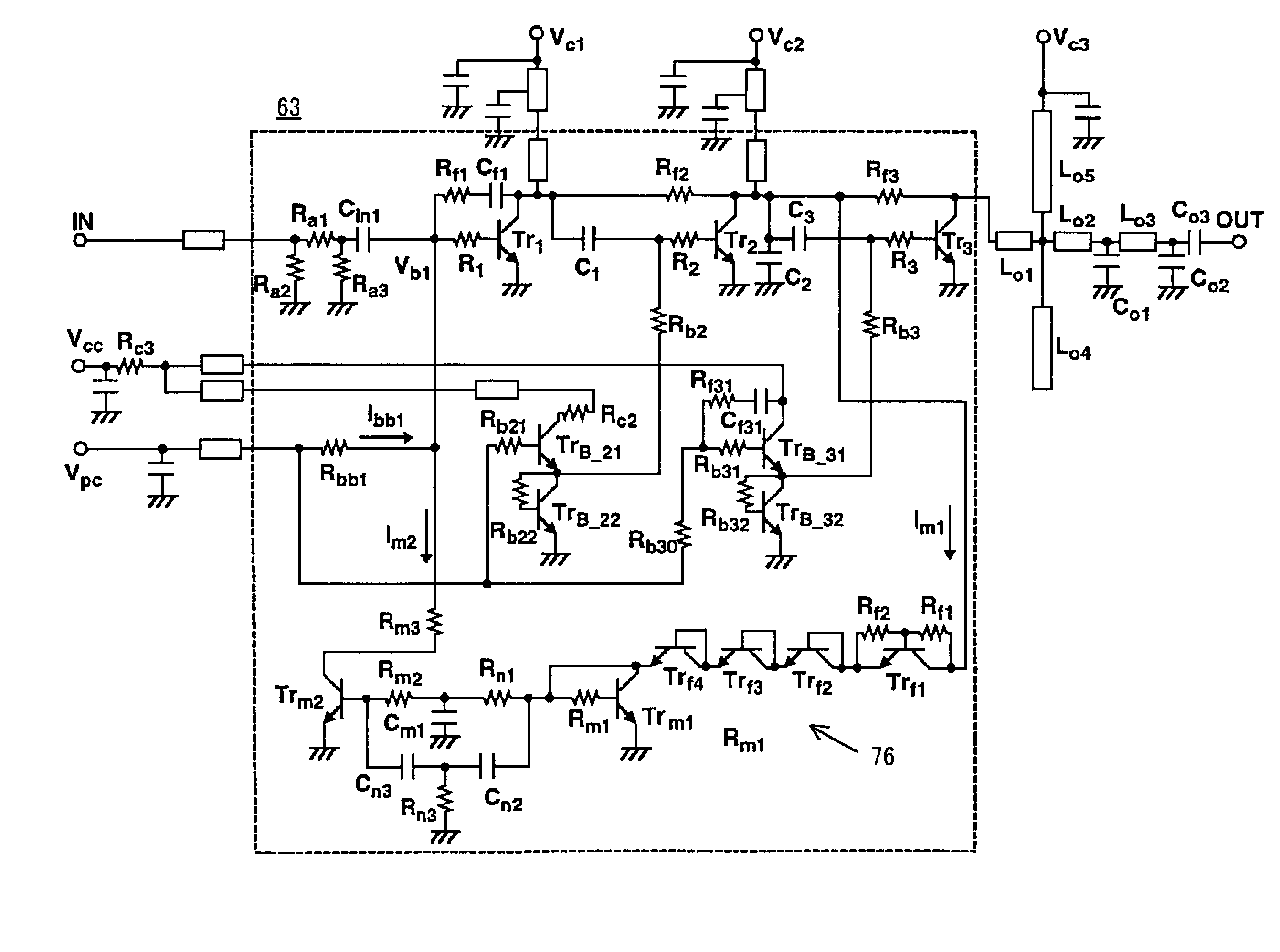

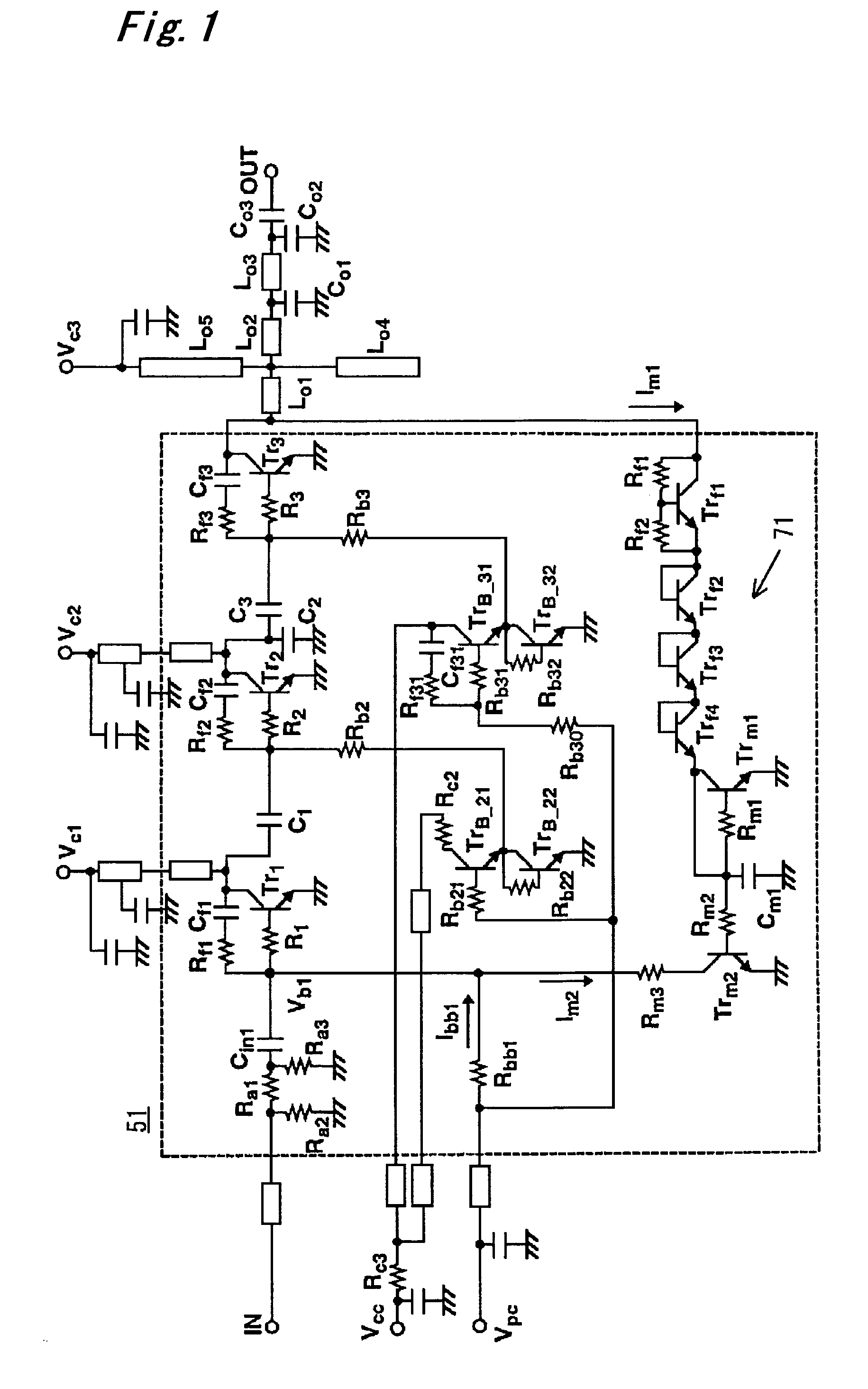

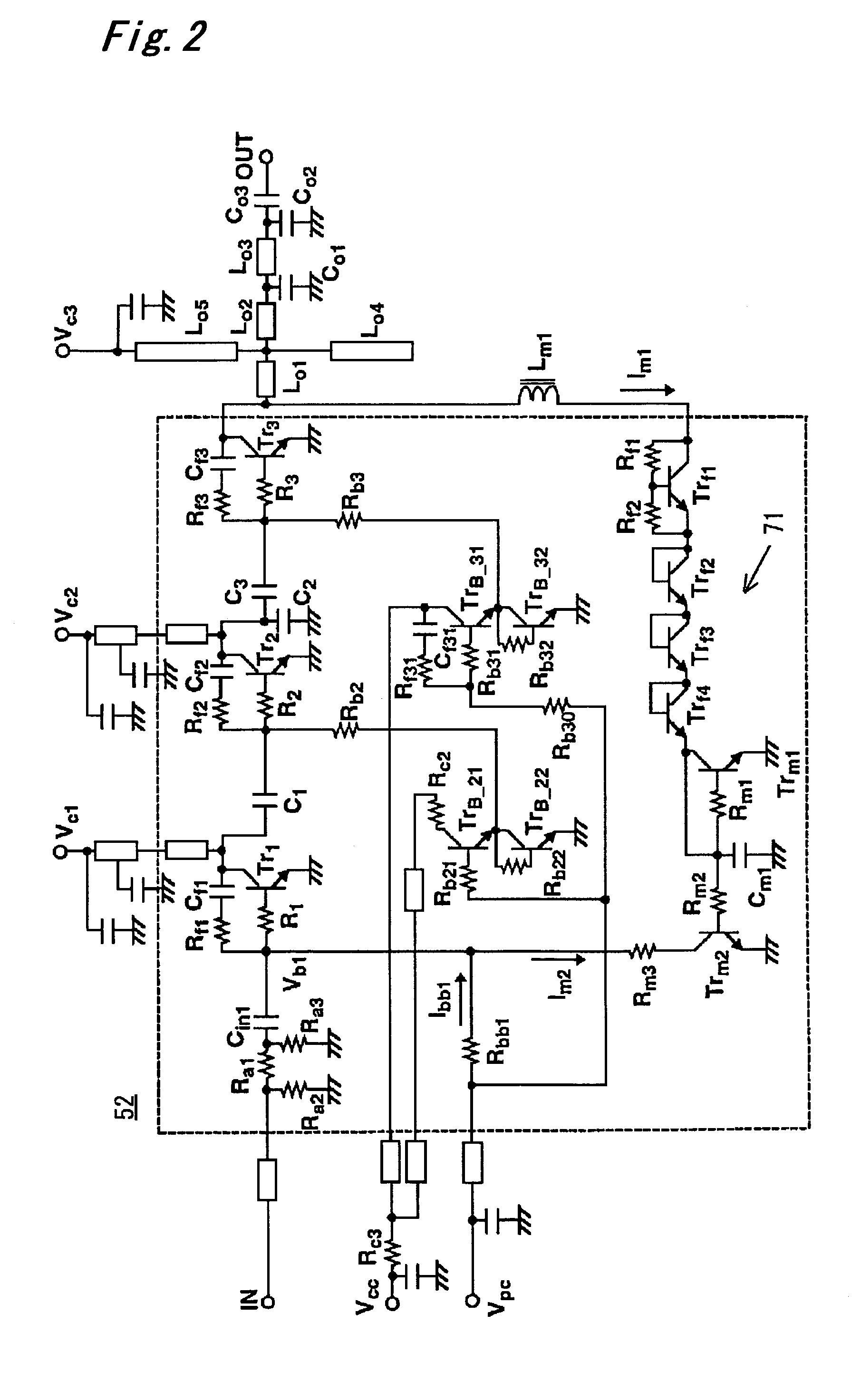

Low bias current/temperature compensation current mirror for linear power amplifier

InactiveUS6937102B2Gain controlAmplifier modifications to reduce temperature/voltage variationAudio power amplifierLinear power amplifier

A power amplifier circuit whose performance is optimized by operating its stages in substantially close to a Class B mode by reducing quiescent current during low driver signal levels. As the driver signal amplitude increases, the operation of the amplifier is configured to dynamically adjust to be in a Class AB mode, thereby increasing the power efficiency of the overall circuit at kiw drive levels. A further enhancement to the power amplifier circuit includes a temperature compensation circuit to adjust the bias of the amplifier so as to stabilize the performance in a wide temperature range.

Owner:SKYWORKS SOLUTIONS INC

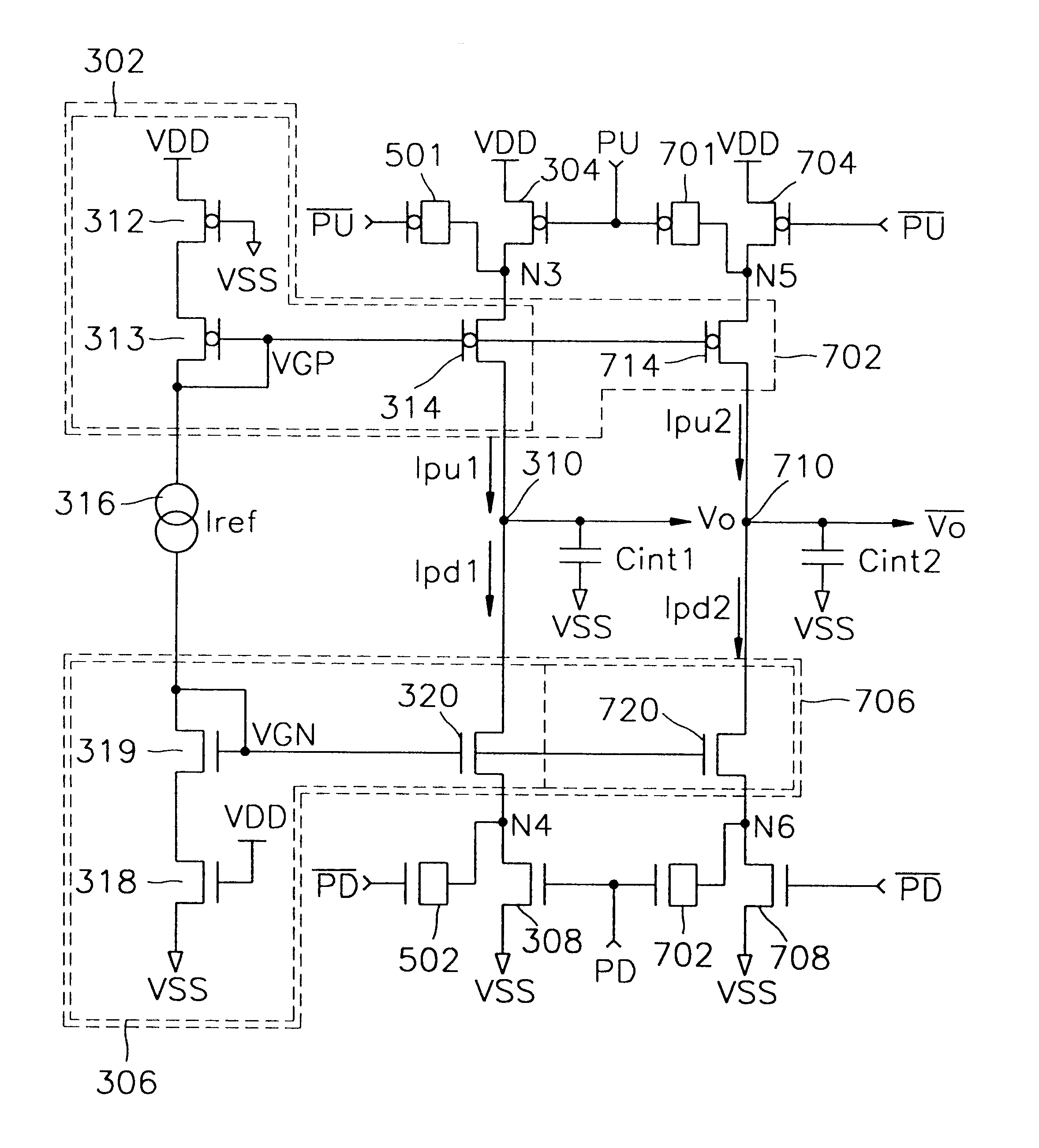

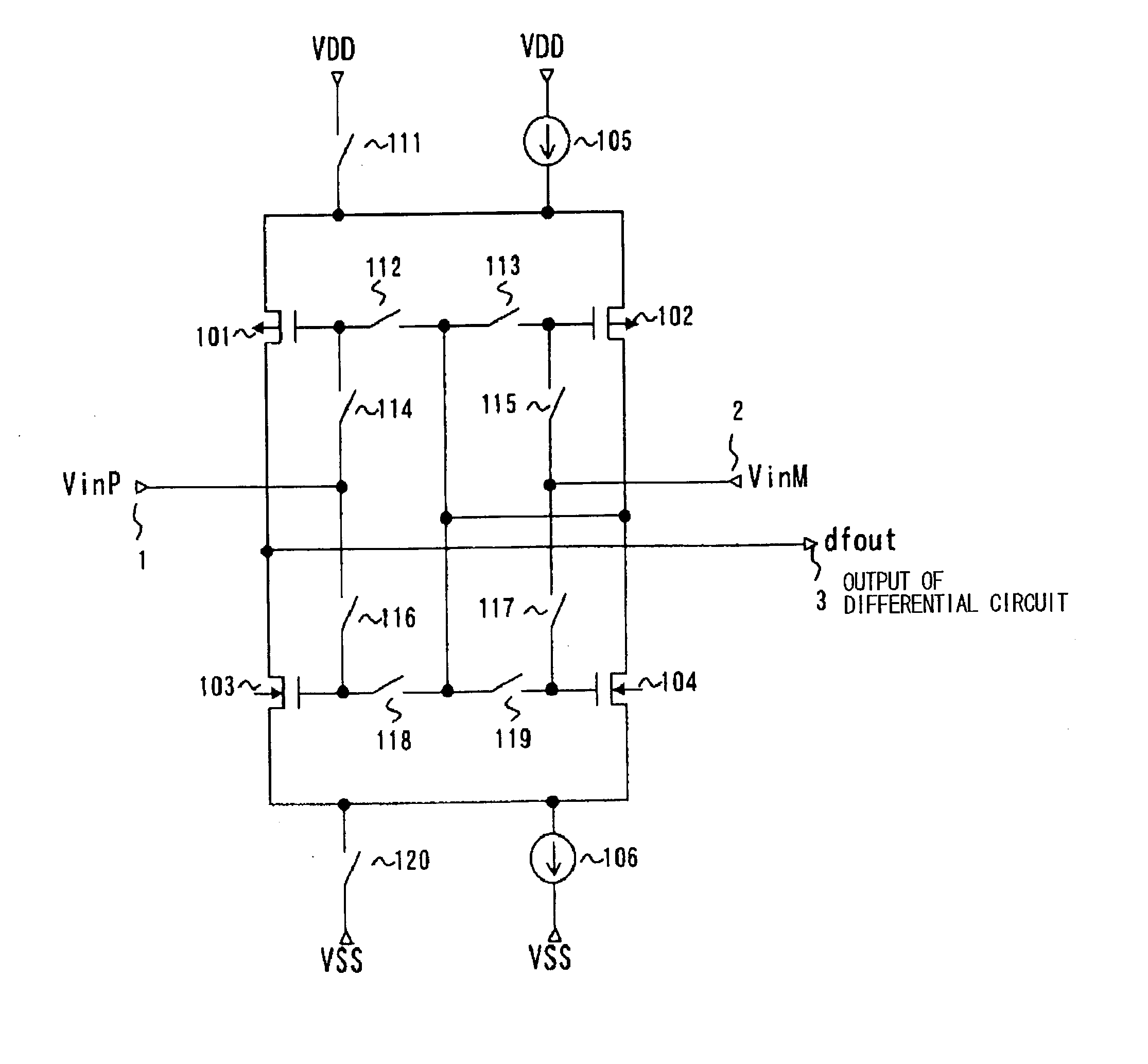

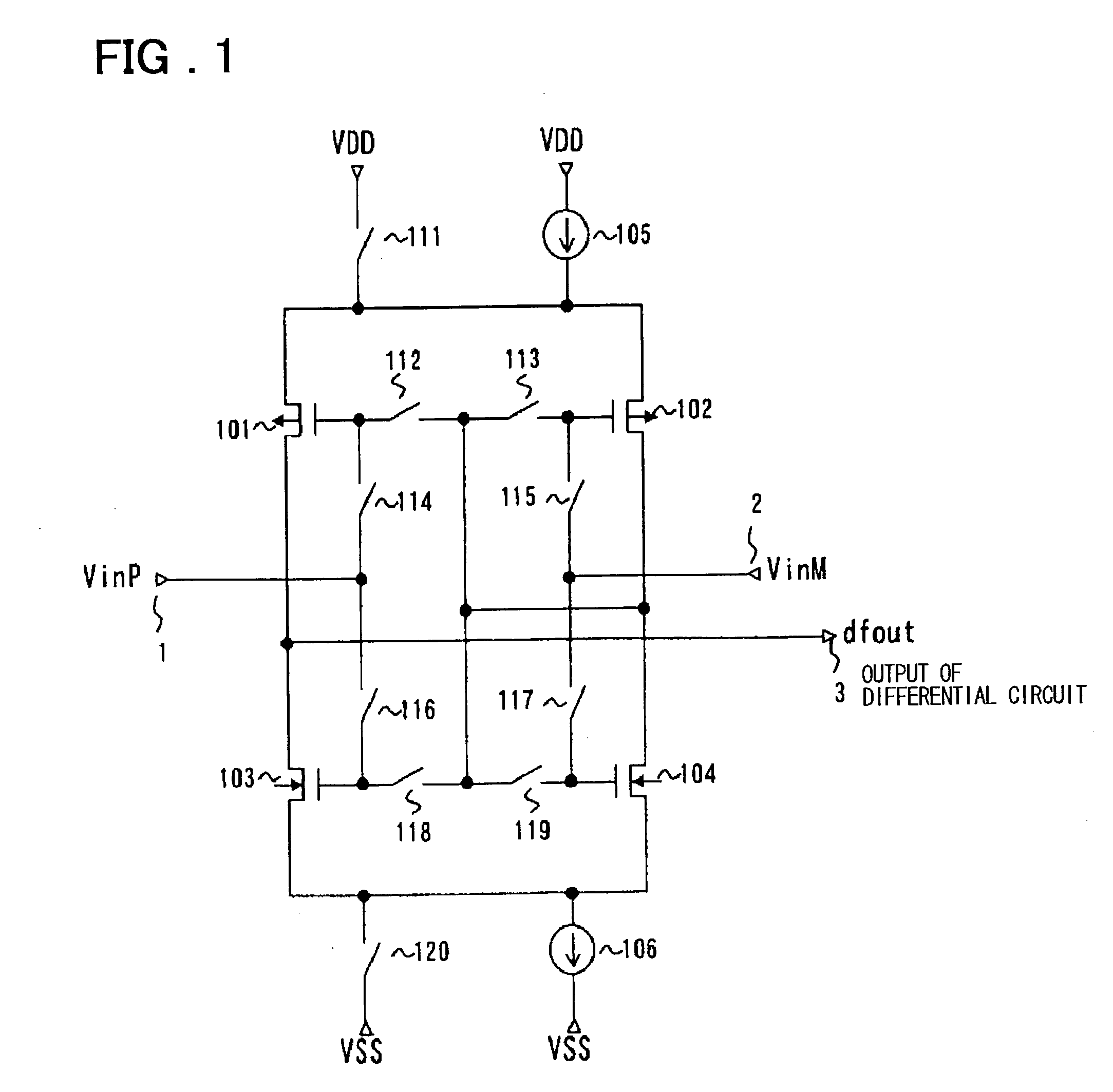

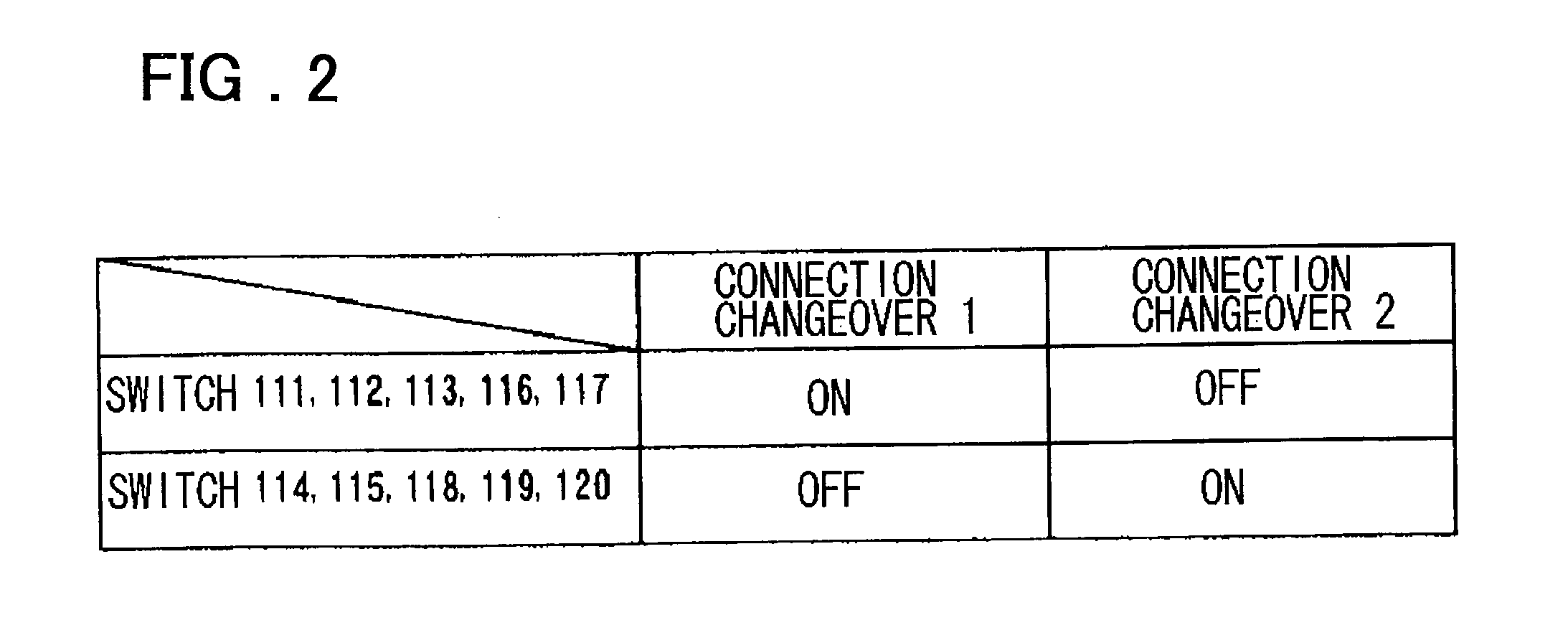

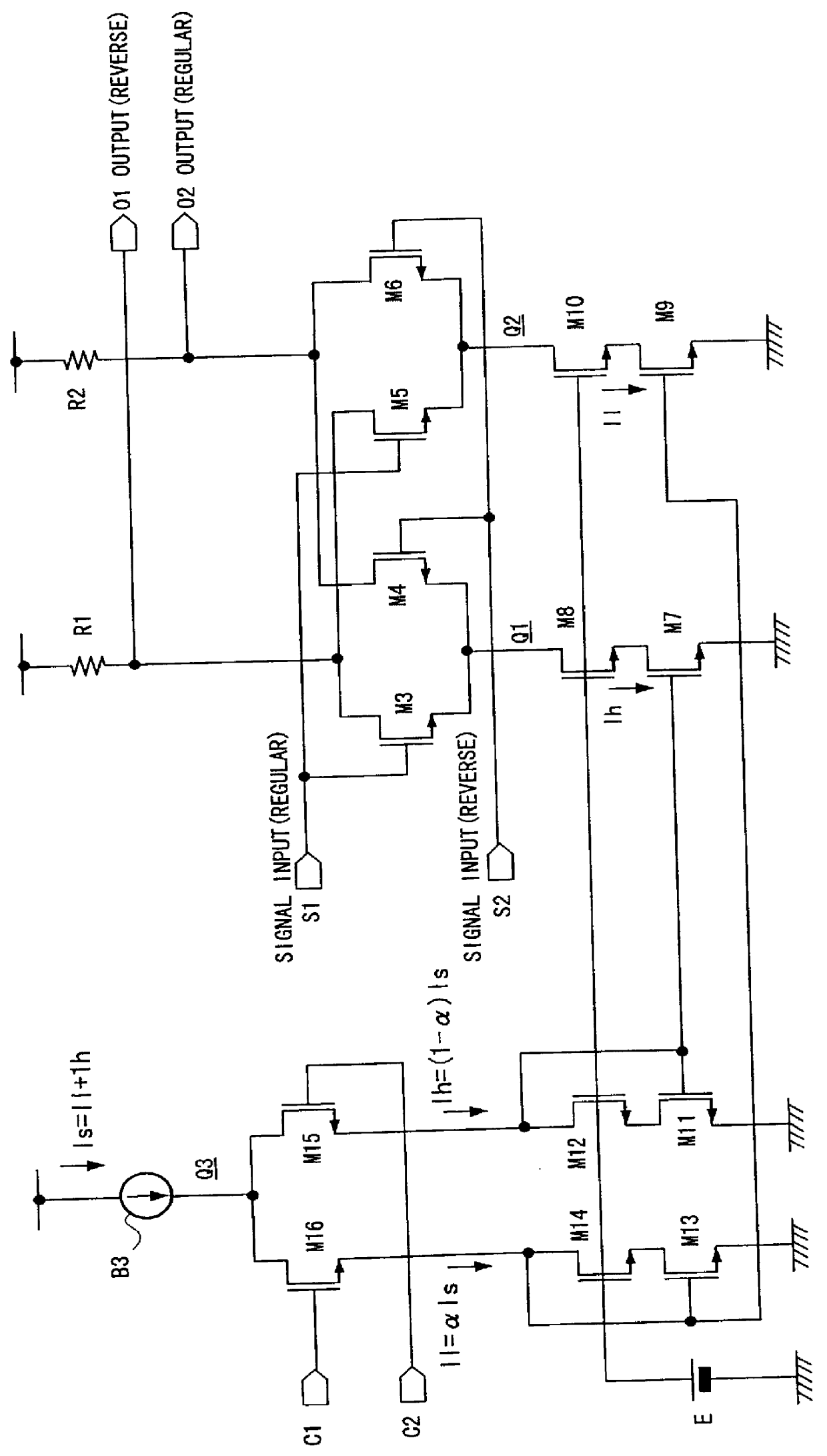

Differential circuit, amplifier circuit, driver circuit and display device using those circuits

ActiveUS20030160749A1Reduce power consumptionReducing amplitude difference deviationStatic indicating devicesGated amplifiersDriver circuitAudio power amplifier

A differential circuit and an amplifier circuit for reducing an amplitude difference deviation, performing a full-range drive, and consuming less power are disclosed. The circuit includes a first pair of p-type transistors and a second pair of n-type transistors. A first current source and a first switch are connected in parallel between the sources of the first pair of transistors, which are tied together, and a power supply VDD. A second current source and a second switch are connected in parallel between the sources of the second pair of transistors, which are tied together, and a power supply VSS. The circuit further includes connection changeover means that performs the changeover of first and second pairs between a differential pair that receives differential input voltages and a current mirror pair that is the load of the differential pair. When one of the two pairs is the differential pair, the other is the current mirror pair. In a differential amplifier circuit, there is provided an added transistor connected in parallel to a transistor, which is one transistor of a differential pair transistors, whose control terminal is a non-inverting input terminal. The added transistor has a control terminal for receiving a control voltage which is set so that, when an input voltage applied to the non-inverting input terminal is in a range in which the transistor whose control terminal is the non-inverting input terminal is turned off, the added transistor is turned on.

Owner:RENESAS ELECTRONICS CORP

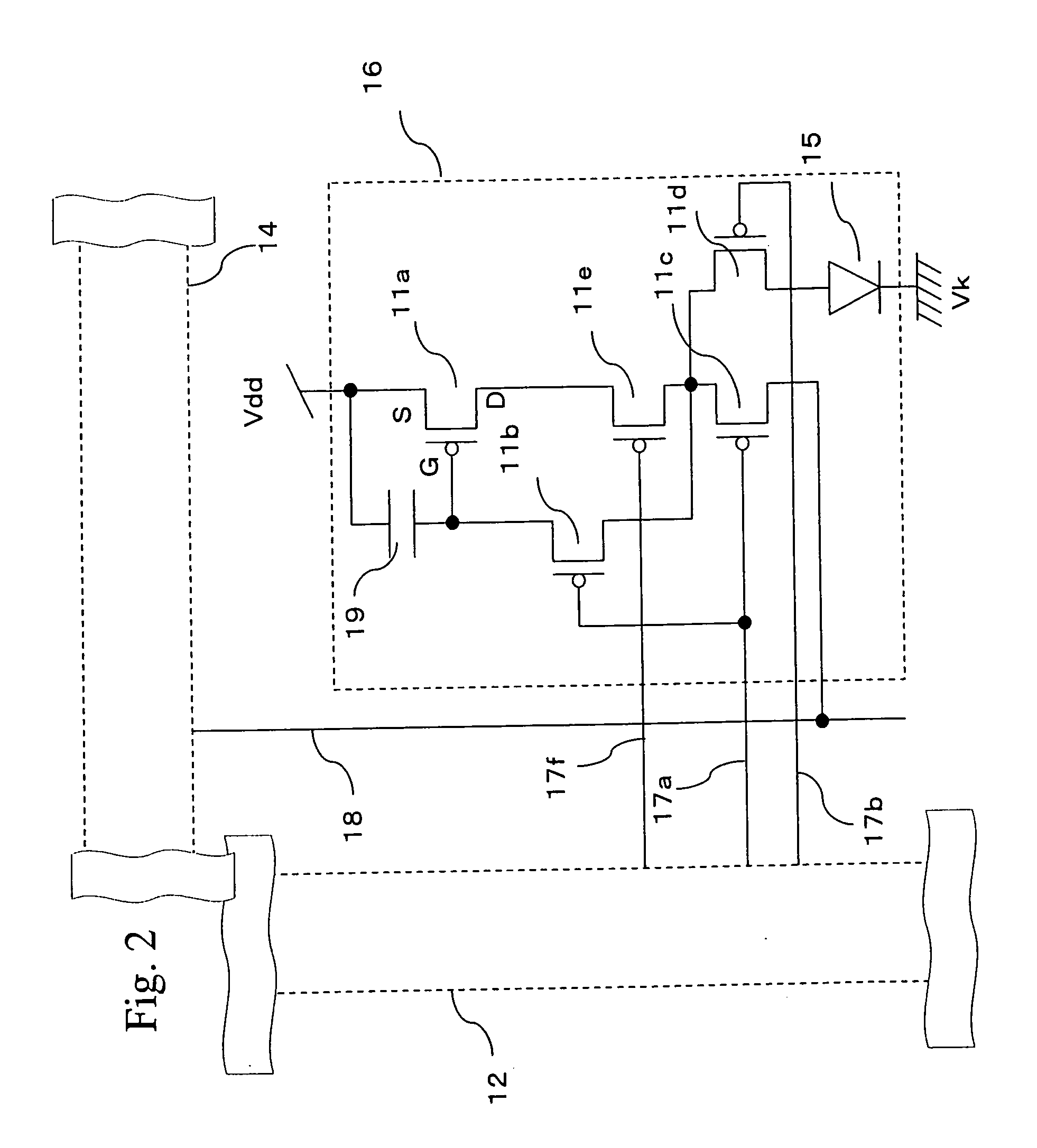

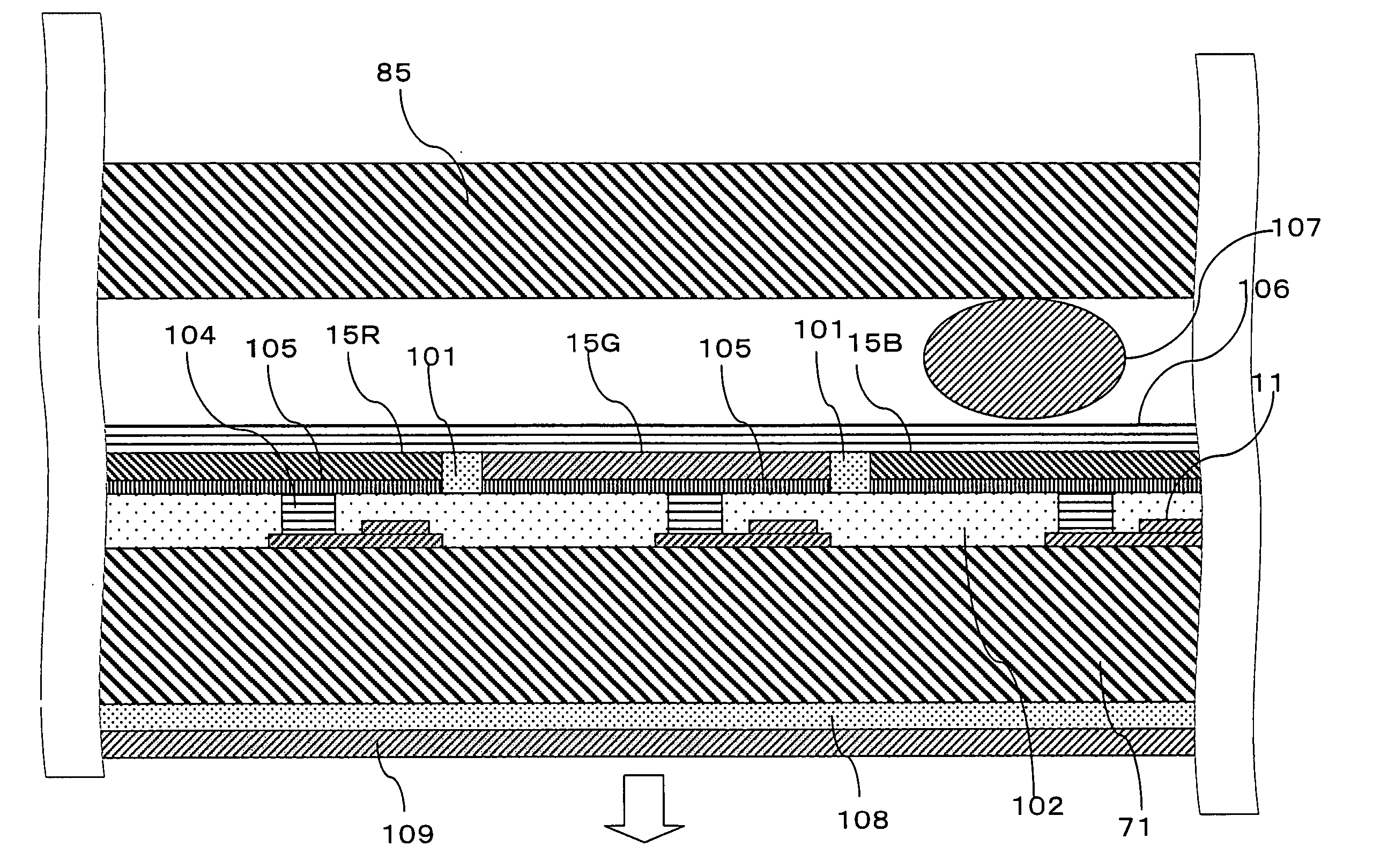

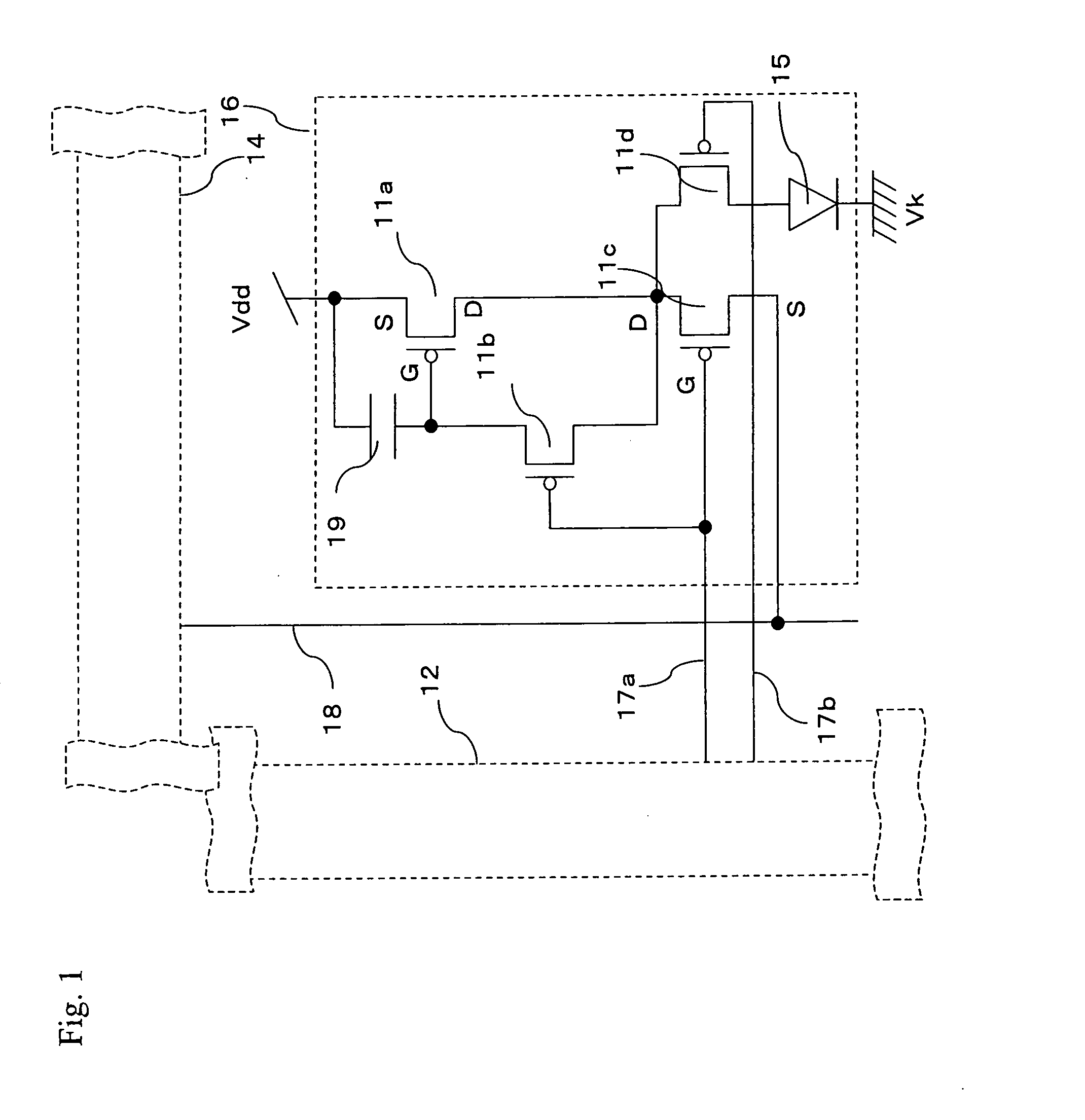

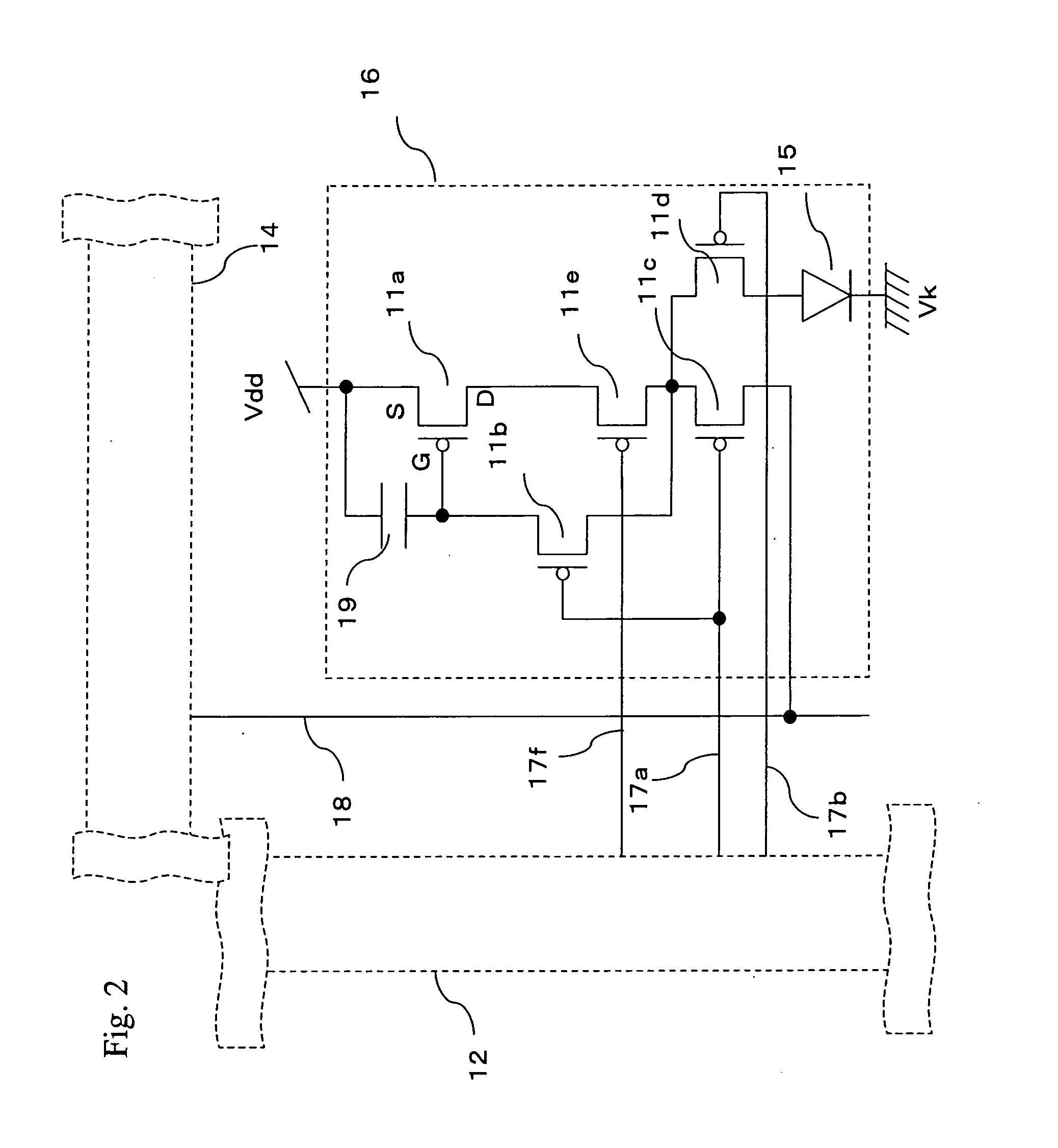

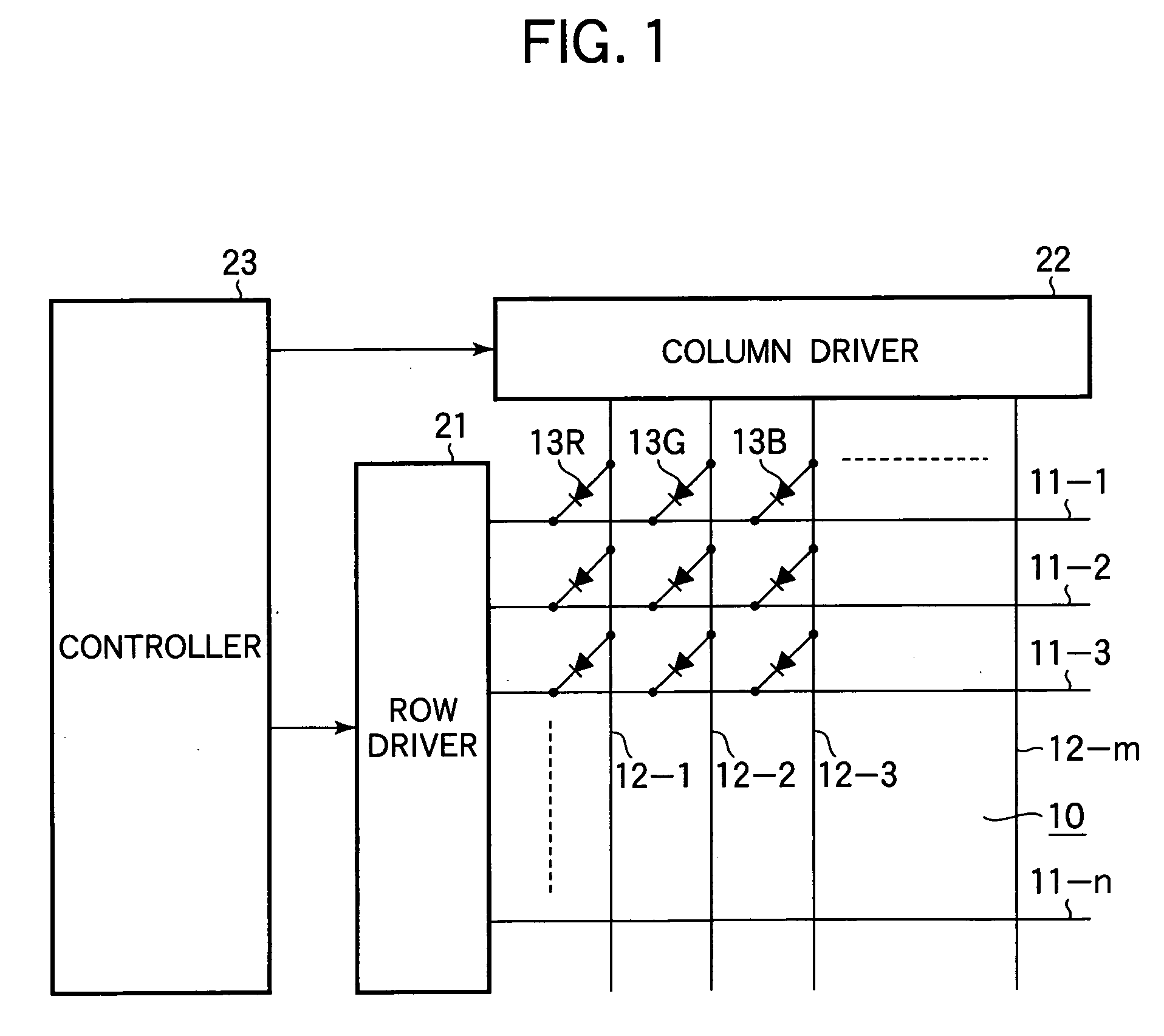

Image display apparatus and drive method

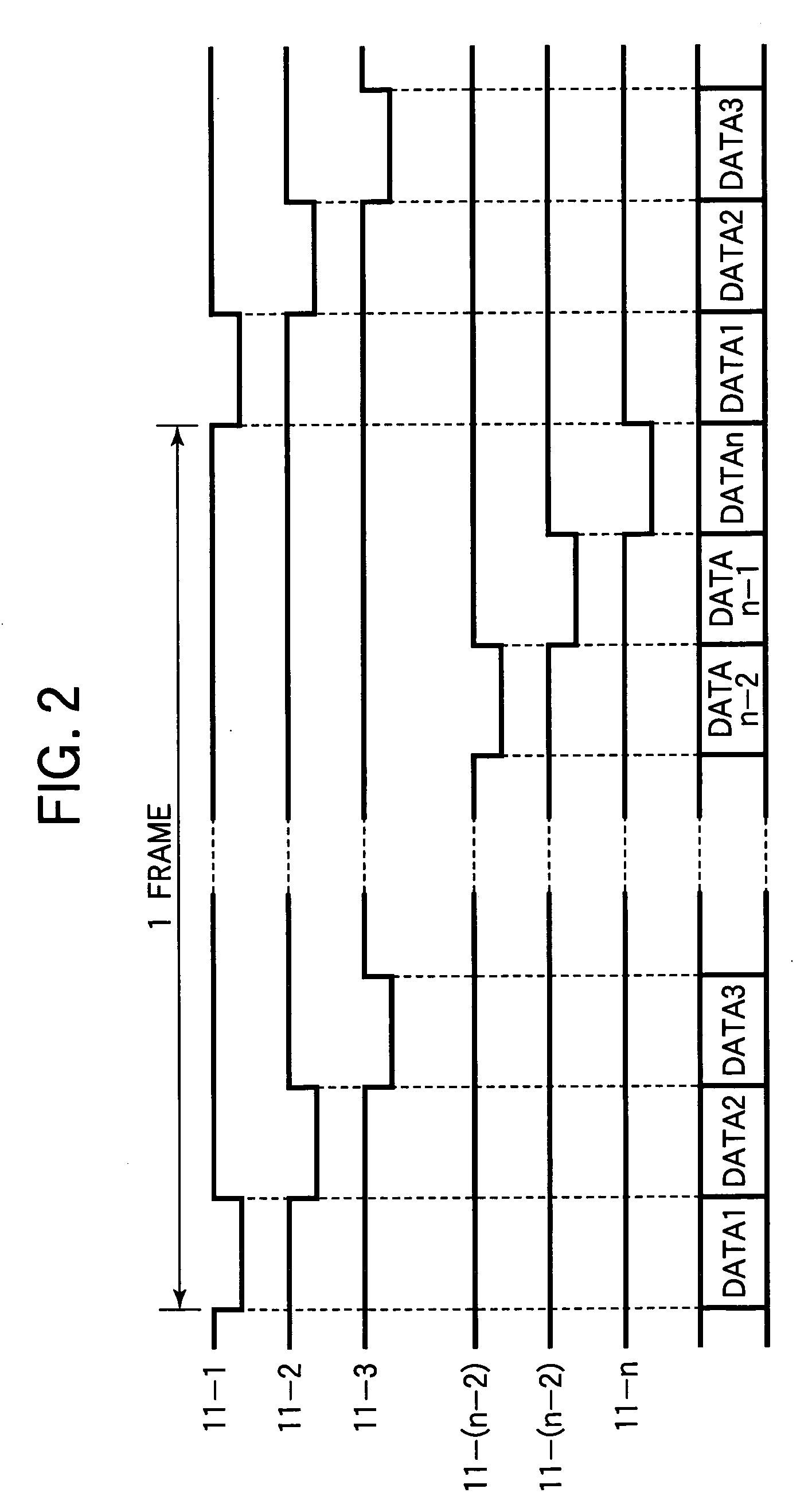

InactiveUS7042426B2Improve the level ofHigh resolutionStatic indicating devicesSolid-state devicesComputer graphics (images)Scan line

Disclosed is an image display apparatus having, in every pixel, a light-emitting element such as an organic electro-luminescence (EL) element of which the brightness is controlled by a current. The image display apparatus includes transistors that form a current mirror in the pixel and using a pixel structure having two scan lines, so as to select pixels of at least two rows simultaneously, distribute the current applied to the data line to the pixel for recording display information and the adjacent pixel, and record the display information on the pixel of no more than one row among the selected pixels. This drastically increases the current for driving the data line and decreases the size of the transistors that form the current mirror in the pixel.

Owner:SAMSUNG SDI CO LTD

Digitally controlled voltage regulator

ActiveUS20040150928A1Easy to customizePrecise power controlEfficient power electronics conversionDc-dc conversionControl signalOptimal control

Disclosed is a digitally controlled multi-phase voltage regulator system providing regulated power to electronic components that have variable power requirements. Power is supplied by one or more power integrated circuits (IC) each having a high side power switch controlled by pulse width modulated signals and a low side power switch. The power IC senses voltage at the load and has an on-chip current mirror for generating a current that is a ratio of current delivered to the load. The power IC also has current limiting and on-chip temperature sensing components. The voltage and current information is digitized and provided to a control integrated circuit (IC). The control IC receives this digitized information as well as user provided parameters and, in the regulation mode of operation, provides digitized pulse width modulated control signals to the power IC. In an active transient response mode of operation, the control IC provides signals to turn either the high side switches or low side switches ON. Fault detection circuitry identifies over voltage, under voltage, and excessive temperatures. All communications between the control IC and the power IC are digital providing high bandwidth, optimal control frequency response, noise immunity and efficient active transient response.

Owner:INFINEON TECH AUSTRIA AG

Programmable gain current amplifier

ActiveUS20060103463A1Increase currentSimple structureGain controlGated amplifiersAmplifierCurrent mirror

A programmable gain current amplifier is provided, including a transistor pair, a plurality of differential pairs, and a control device. The transistor pair receives an input current. Each differential pairs connecting with each other in parallel is connected to the transistor pair to form a differential current mirror for amplifying the input current. The control device adjusts the output polarity of the current mirror, thereby obtaining a predetermined gain between the output of the current mirror and the input current. Therefore, amplification of the input current at a programmable gain is realized.

Owner:IND TECH RES INST

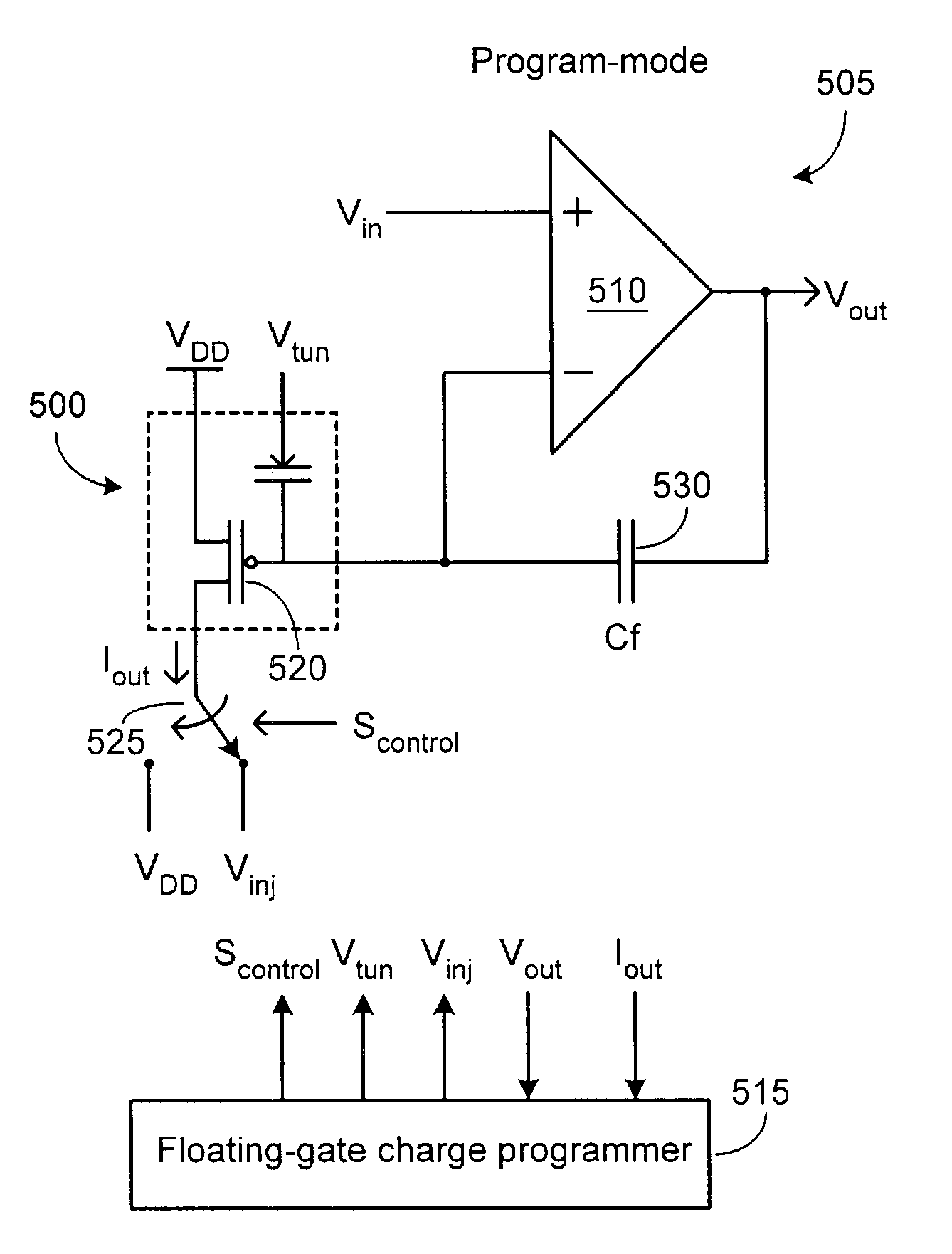

Floating-gate reference circuit

InactiveUS7034603B2Electric signal transmission systemsElectric analogue storesReference currentComparators circuits

Systems and methods are discussed for using a floating-gate MOSFET as a programmable reference circuit. One example of the programmable reference circuit is a programmable voltage reference source, while a second example of a programmable reference circuit is a programmable reference current source. The programmable voltage reference source and / or the reference current source may be incorporated into several types of circuits, such as comparator circuits, current-mirror circuits, and converter circuits. Comparator circuits and current-mirror circuits are often incorporated into circuits such as converter circuits. Converter circuits include analog-to-digital converters and digital-to-analog converters.

Owner:GEORGIA TECH RES CORP

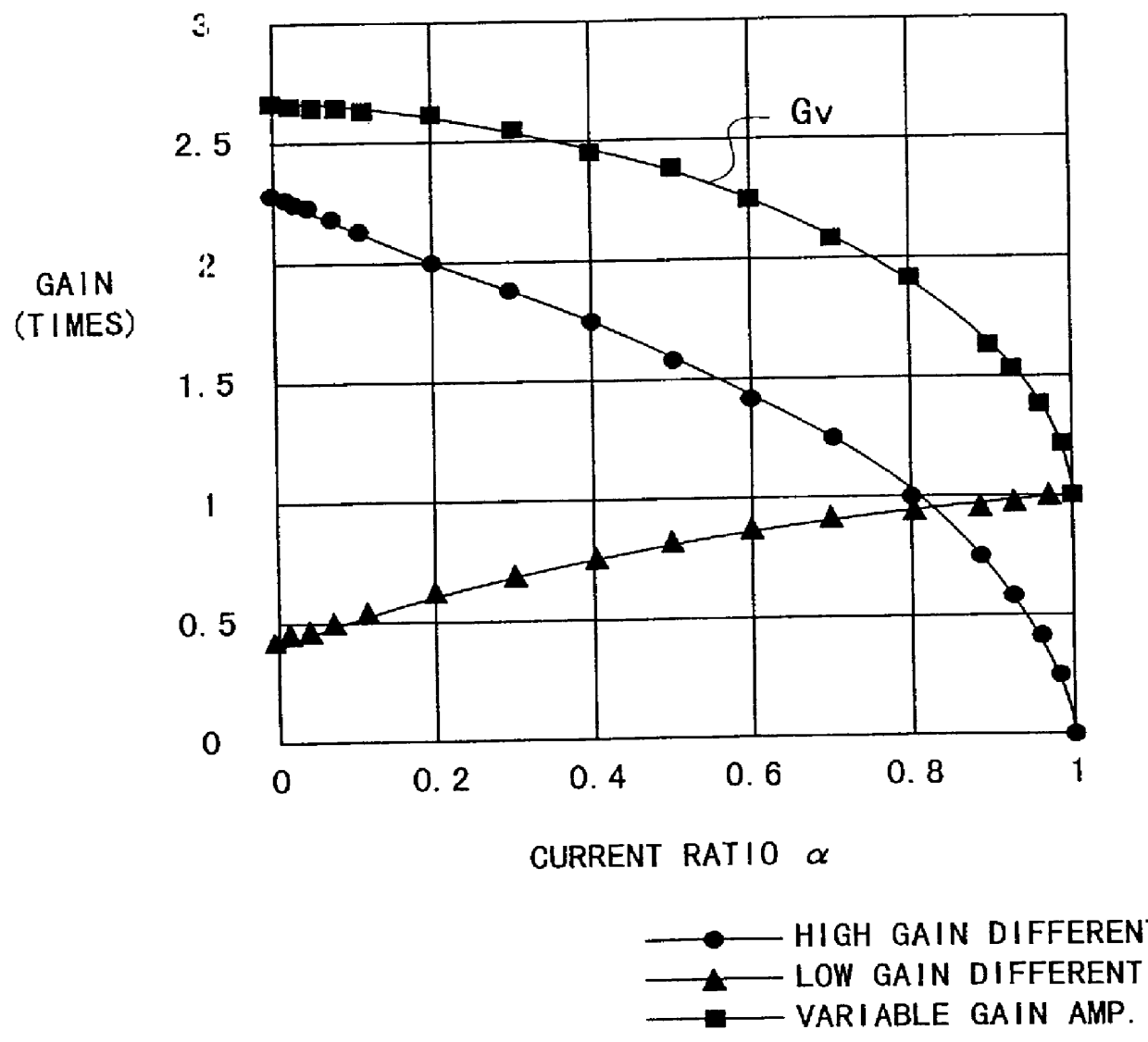

Variable gain amplifier

InactiveUS6163215AComputations using contact-making devicesGain controlAudio power amplifierVariable-gain amplifier

In a variable gain amplifier controlling a gain by using differential amplifiers with a gain control signal, a gain switchover differential amplifier or a bias circuit which composes a current mirror with the gain switchover differential amplifier is connected between a high and a low gain differential amplifier for the same bias current which are mutually connected to share load resistances for the same output polarity and a bias current source common to both of the differential amplifiers, to perform switchover operations of the high and the low differential amplifier by a gain control signal, and a current source which flows a fixed offset current through at least the low one of the high and the low differential amplifier is provided.

Owner:FUJITSU LTD

Voltage reference generator circuit subtracting CTAT current from PTAT current

ActiveUS7224210B2Dc network circuit arrangementsElectric variable regulationEngineeringVoltage reference

A voltage reference generator generates a stable reference voltage that is less than the bandgap voltage of silicon for power supply voltages less than 2V, yet provides sufficient voltage headroom to operate a current mirror. In one embodiment, the voltage reference generator has a power supply rejection ratio of at least 60 dB and has comparable noise performance as compared to traditional bandgap cirucits. These advantages are achieved by subtracting a current proportional to a complement of an absolute temperature from a current proportional to the absolute temperature to generate a voltage having a positive temperature coefficient, which is then added to a voltage that is a complement of the absolute temperature to achieve a voltage that has a low temperature coefficient.

Owner:SKYWORKS SOLUTIONS INC

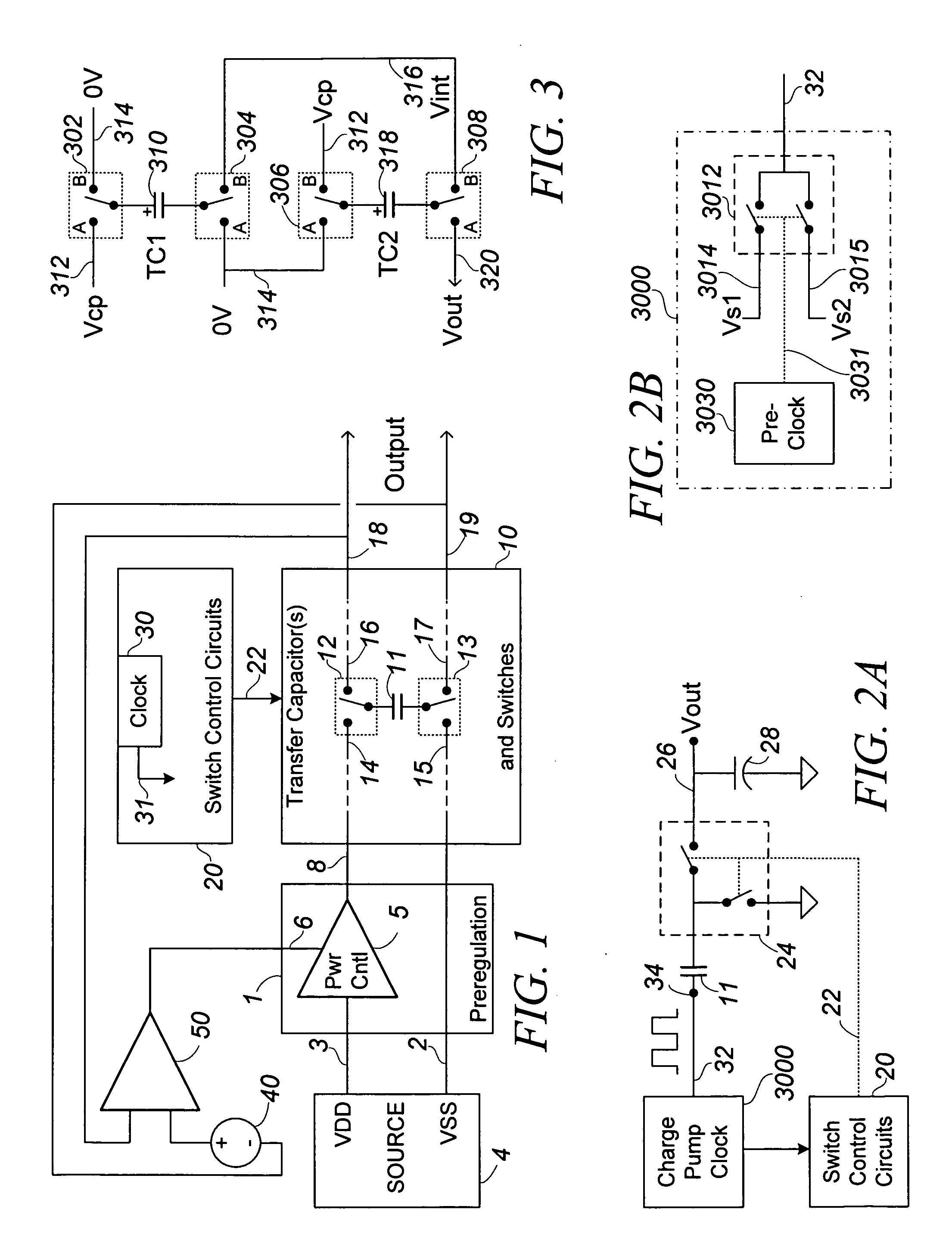

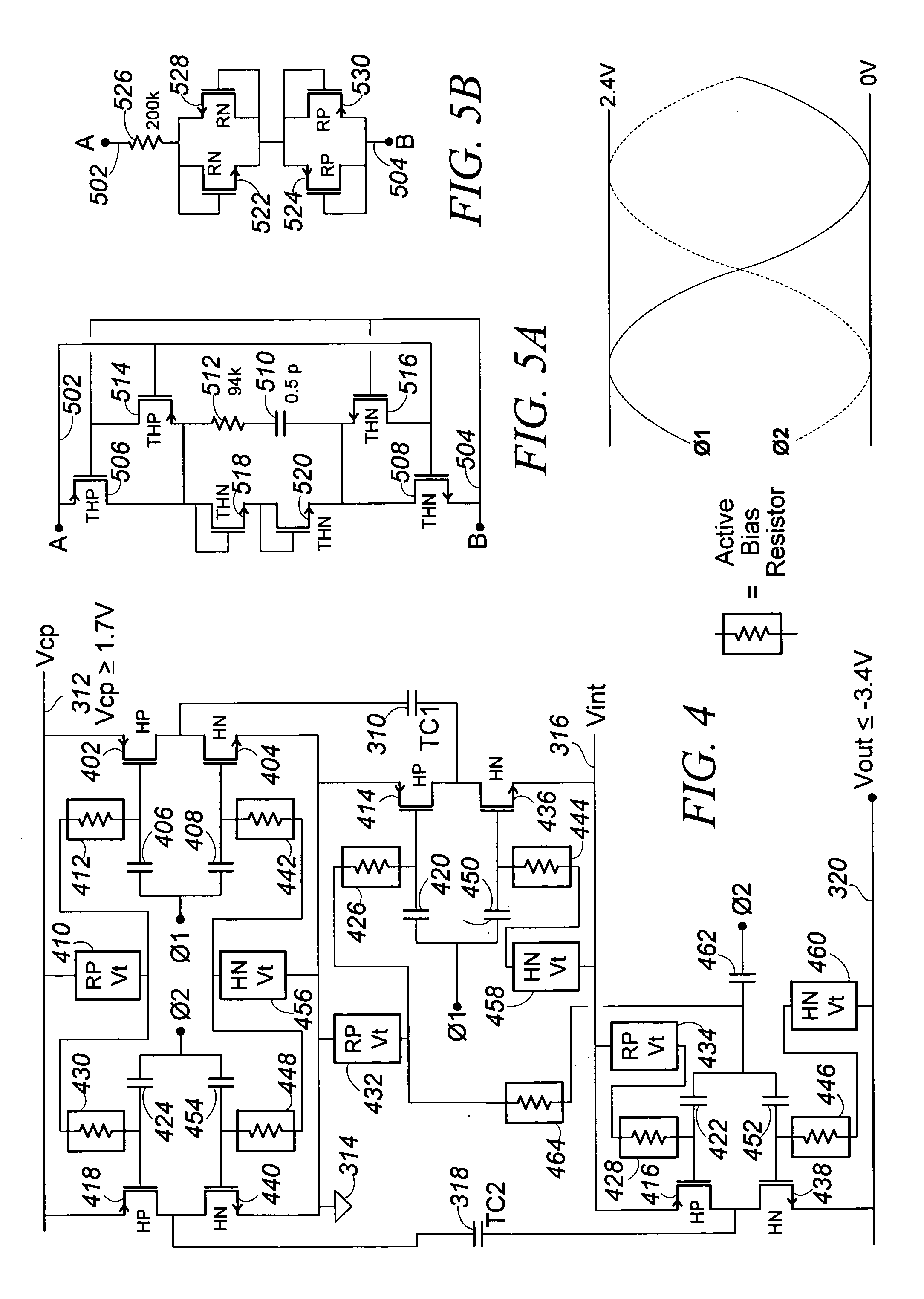

Low-Noise High Efficiency Bias Generation Circuits and Method

ActiveUS20110156819A1Reduce voltageAvoid problemsAmplifier modifications to reduce noise influenceActive element networkLow noiseCapacitance

A bias generation method or apparatus defined by any one or any practical combination of numerous features that contribute to low noise and / or high efficiency biasing, including: having a charge pump control clock output with a waveform having limited harmonic content or distortion compared to a sine wave; having a ring oscillator to generating a charge pump clock that includes inverters current limited by cascode devices and achieves substantially rail-to-rail output amplitude; having a differential ring oscillator with optional startup and / or phase locking features to produce two phase outputs suitably matched and in adequate phase opposition; having a ring oscillator of less than five stages generating a charge pump clock; capacitively coupling the clock output(s) to some or all of the charge transfer capacitor switches; biasing an FET, which is capacitively coupled to a drive signal, to a bias voltage via an “active bias resistor” circuit that conducts between output terminals only during portions of a waveform appearing between the terminals, and / or wherein the bias voltage is generated by switching a small capacitance at cycles of said waveform. A charge pump for the bias generation may include a regulating feed back loop including an OTA that is also suitable for other uses, the OTA having a ratio-control input that controls a current mirror ratio in a differential amplifier over a continuous range, and optionally has differential outputs including an inverting output produced by a second differential amplifier that optionally includes a variable ratio current mirror controlled by the same ratio-control input. The ratio-control input may therefore control a common mode voltage of the differential outputs of the OTA. A control loop around the OTA may be configured to control the ratio of one or more variable ratio current mirrors, which may particularly control the output common mode voltage, and may control it such that the inverting output level tracks the non-inverting output level to cause the amplifier to function as a high-gain integrator.

Owner:PSEMI CORP

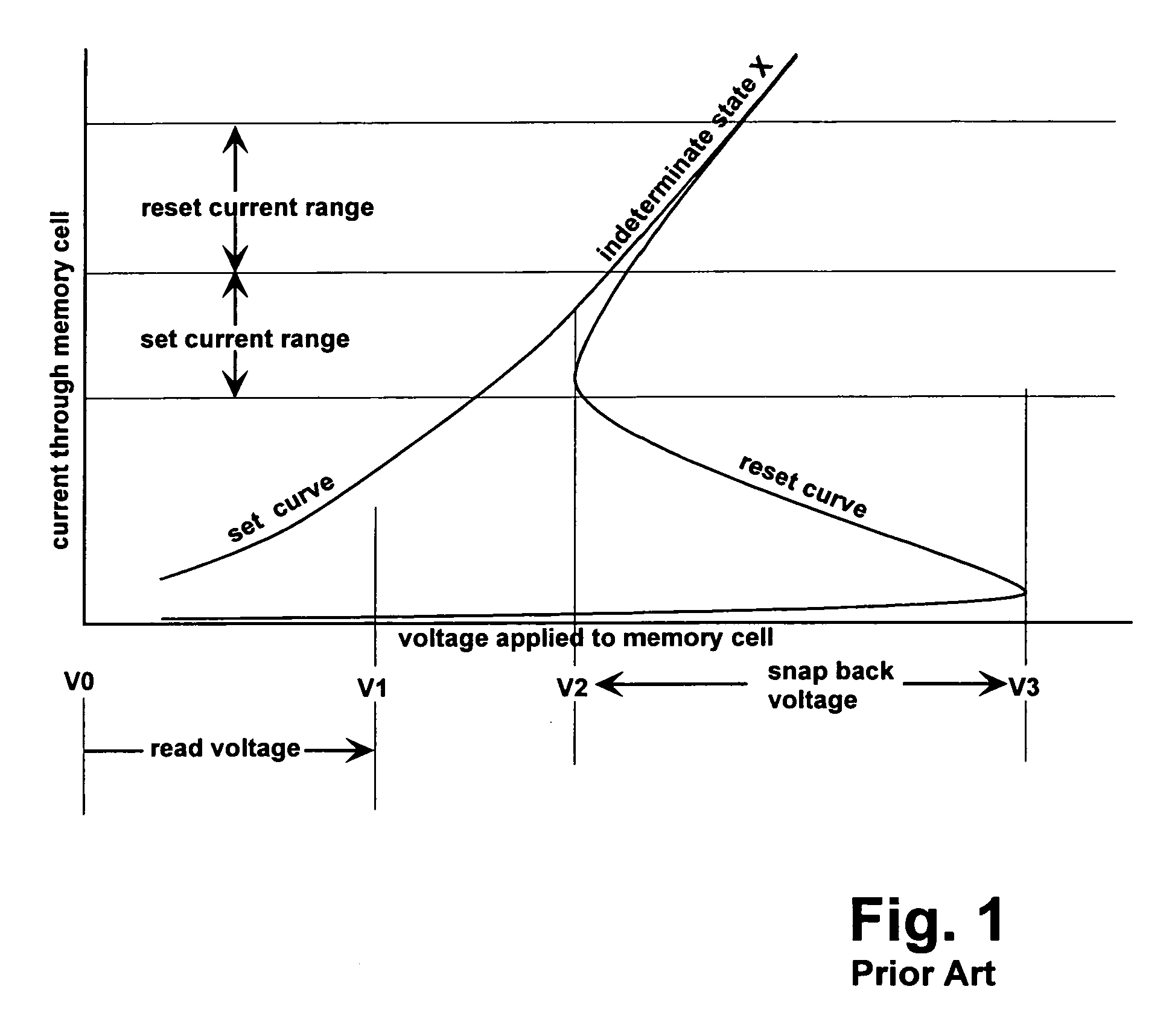

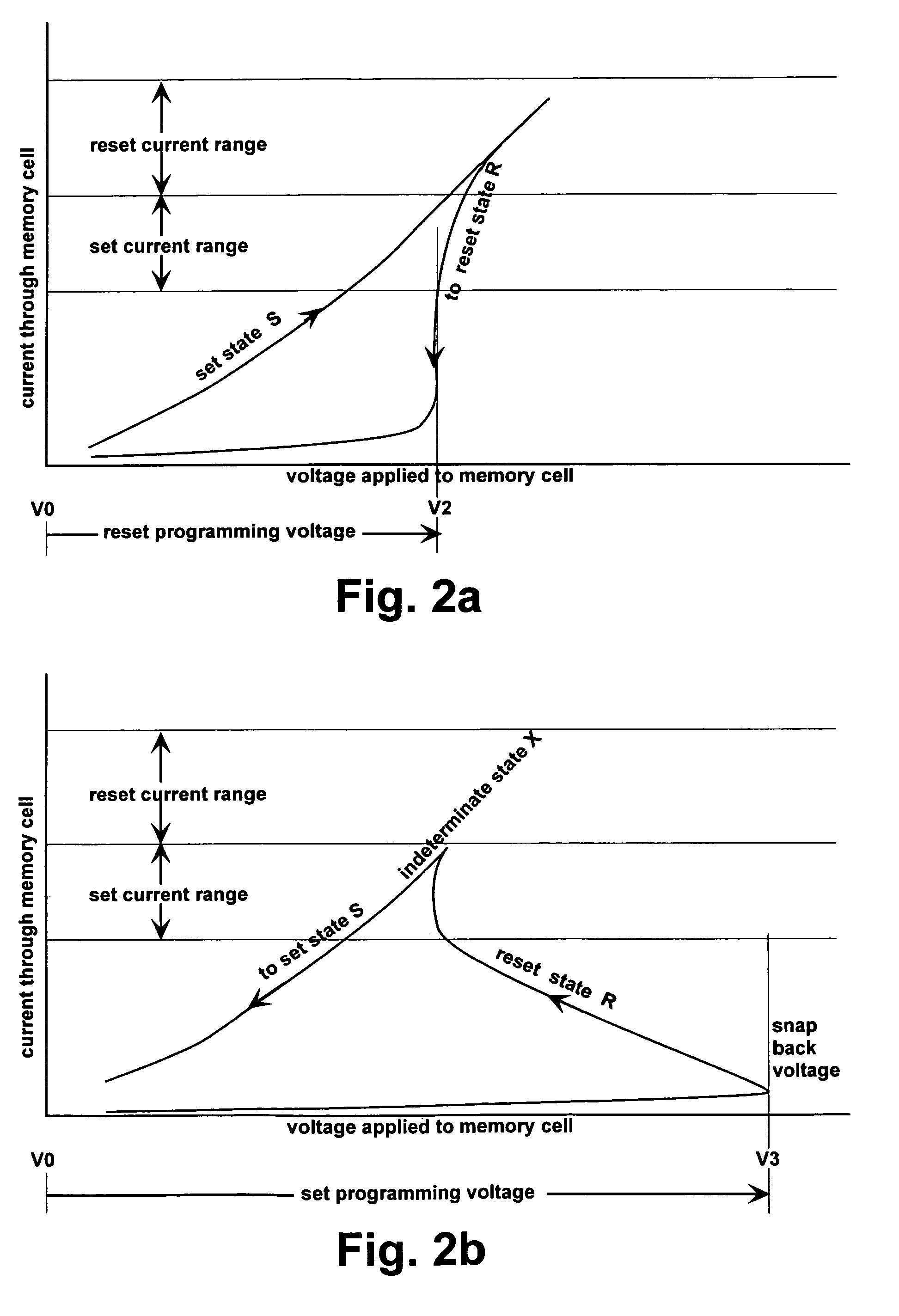

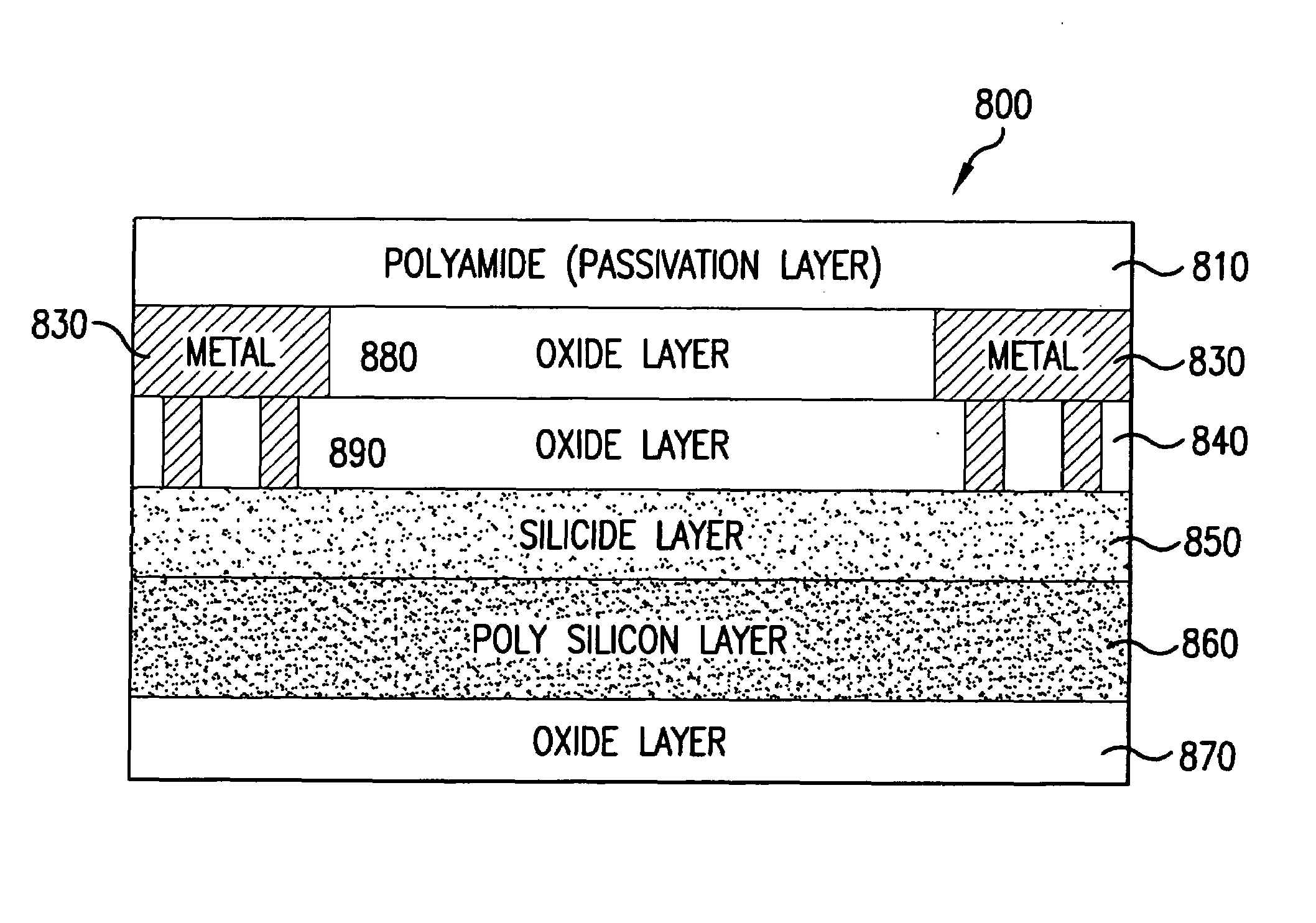

System and method for programming a memory cell

InactiveUS7211843B2Improve reliabilityGood repeatabilitySemiconductor/solid-state device detailsSolid-state devicesTime segmentEngineering

The present invention relates to systems and methods for programming a memory cell. More specifically, the present invention relates to a controlled application of current to a memory cell over a controlled time period. The invention utilizes a current mirror configuration having a first transistor and a second transistor, wherein the second transistor is coupled to the memory cell. Programming of the memory cell includes applying a voltage to the first transistor, whereby a first current is generated in the first transistor. A gate of the second transistor is coupled to the first transistor, whereby a second current is generated in the second transistor. The second current is proportional to the first current. The second current is provided to the memory cell, whereby the second current programs the memory cell.

Owner:AVAGO TECH INT SALES PTE LTD

Output overvoltage protection circuit for power amplifier

ActiveUS7145397B2Reduce outputBias of the first-stage transistorPower amplifiersEmergency protective circuit arrangementsOvervoltageAudio power amplifier

Disclosed is an output overvoltage protection circuit for a power amplifier having a plurality of stages, which comprises a monitor circuit for monitoring an output overvoltage of an output transistor in the final stage of the power amplifier and allowing a current to flow therethrough in response to the monitored output overvoltage, and a current mirror circuit for supplying a current proportional to the current from the monitor circuit in such a manner that the base bias of the first-stage transistor of the power amplifier is reduced in response to the current supplied from the current mirror circuit, to reduce the output of the final-stage output transistor.

Owner:MURATA MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com