Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

22538 results about "Chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital communications, a chip is a pulse of a direct-sequence spread spectrum (DSSS) code, such as a Pseudo-random Noise (PN) code sequence used in direct-sequence code division multiple access (CDMA) channel access techniques. In a binary direct-sequence system, each chip is typically a rectangular pulse of +1 or –1 amplitude, which is multiplied by a data sequence (similarly +1 or –1 representing the message bits) and by a carrier waveform to make the transmitted signal.

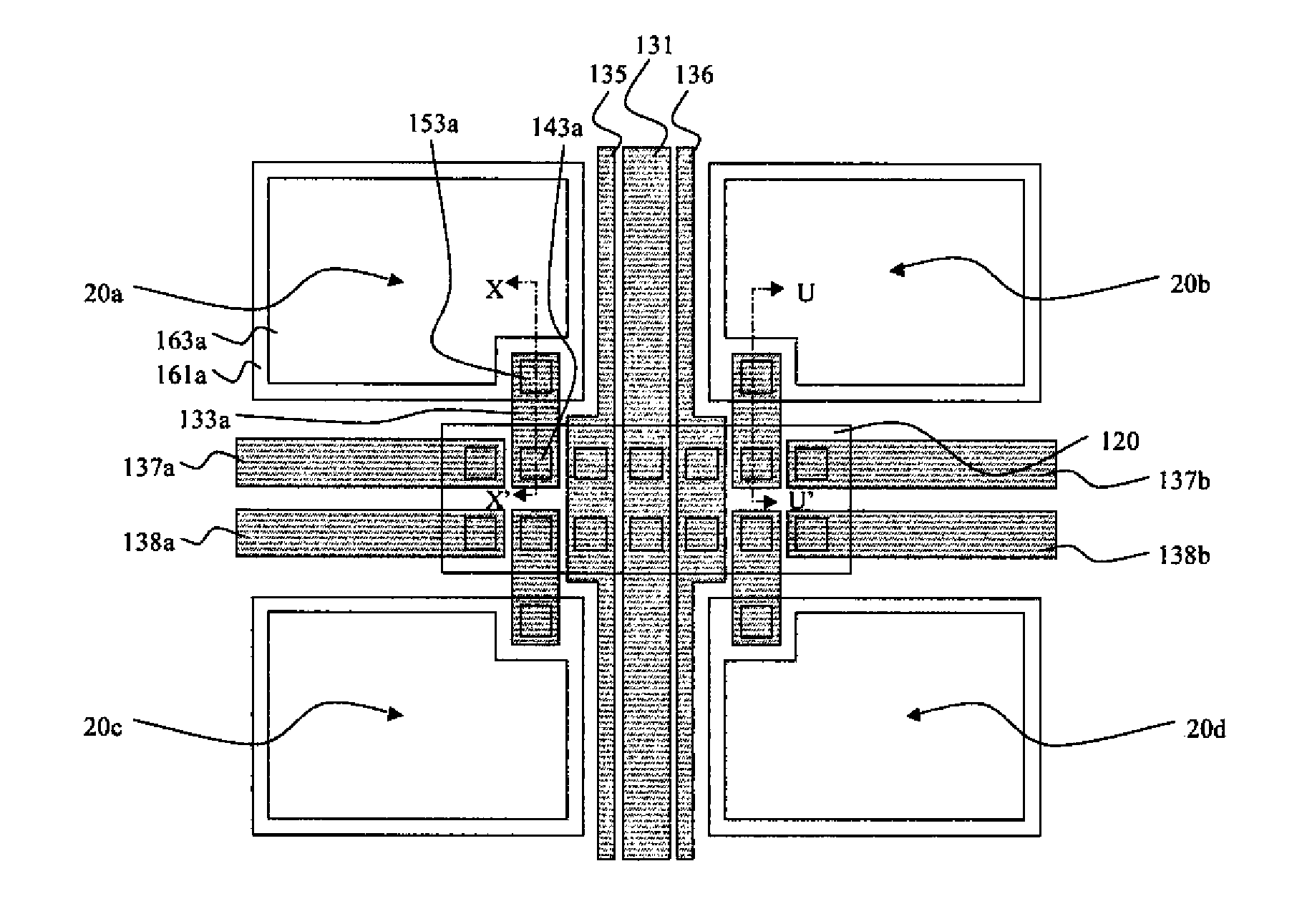

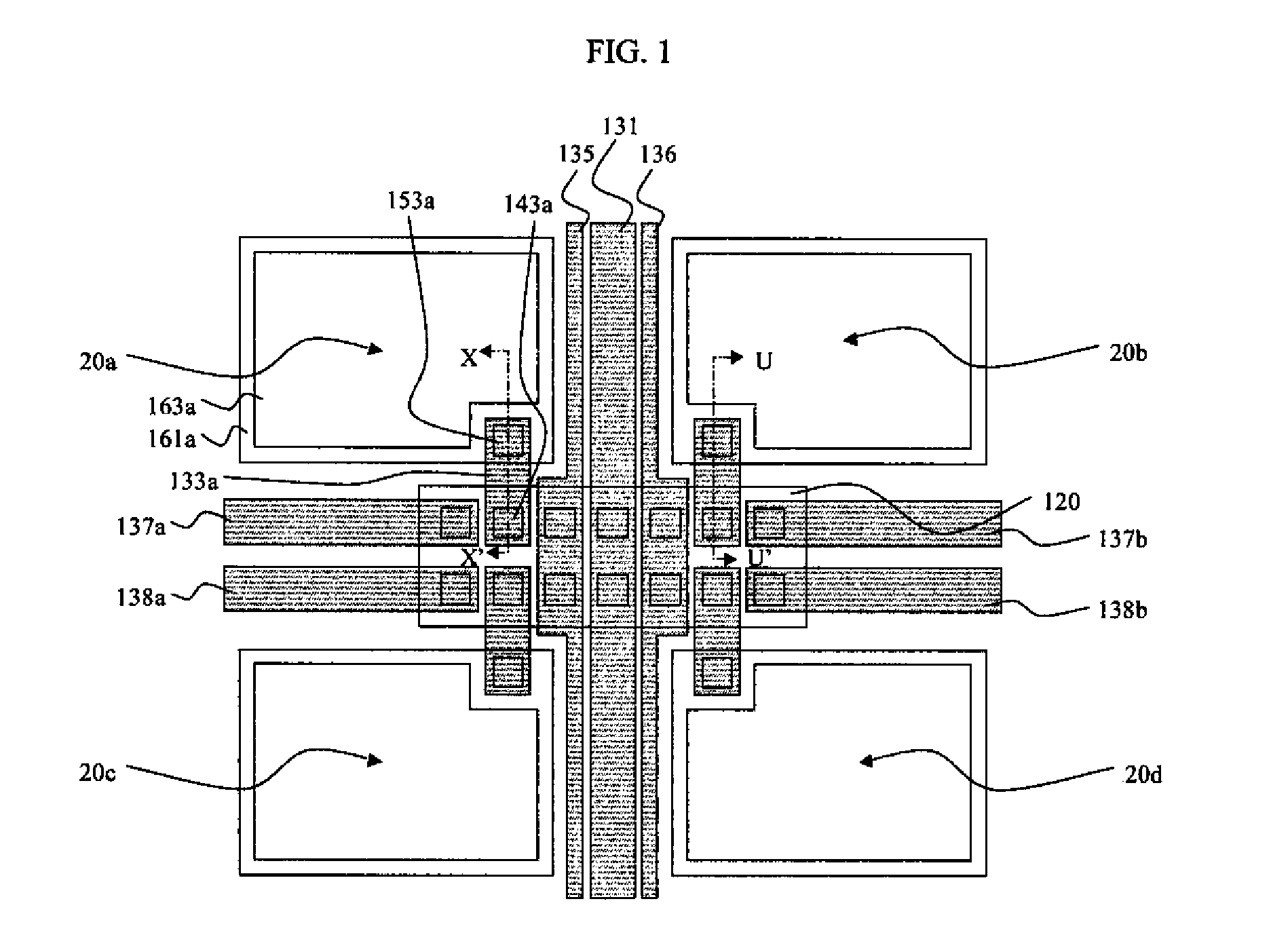

OLED device with embedded chip driving

ActiveUS7999454B2Small sizeReduce thicknessDischarge tube luminescnet screensElectroluminescent light sourcesHemt circuitsElectric current flow

An electroluminescent device having a plurality of current driven pixels arranged in rows and columns, such that when current is provided to a pixel it produces light, including each pixel having first and second electrodes and current responsive electroluminescent media disposed between the first and second electrodes; at least one chiplet having a thickness less than 20 micrometers; including transistor drive circuitry for controlling the operation of at least four pixels, the chiplet being mounted on a substrate and having connection pads; a planarization layer disposed over at least a portion of the chiplet; a first conductive layer over the planarization layer and connected to at least one of the connection pads; and a structure for providing electrical signals through the first conductive layer and at least one of the connection pads of the chiplet so that the transistor drive circuitry of the chiplet controls current to the four pixels.

Owner:X DISPLAY CO TECH LTD +1

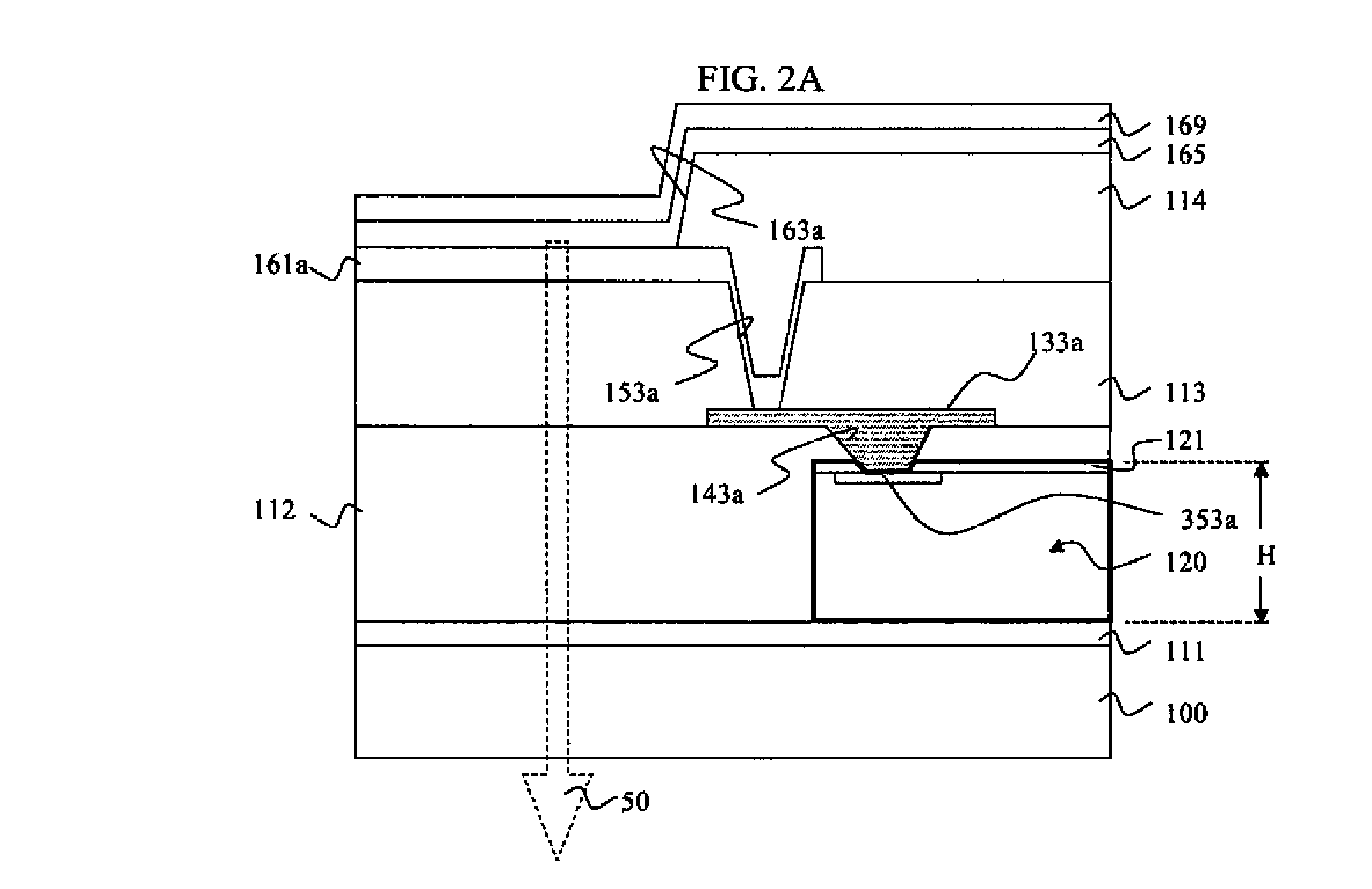

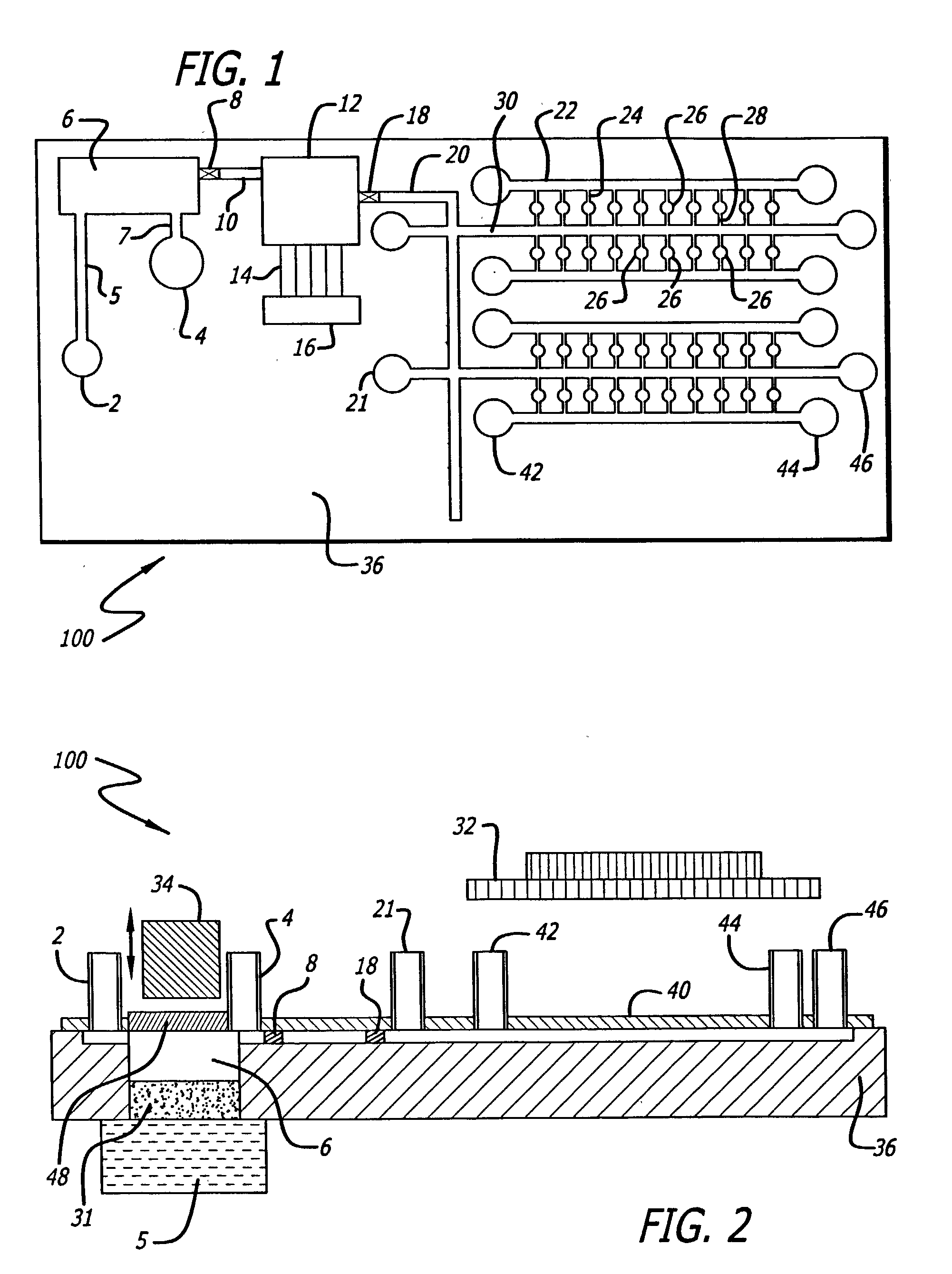

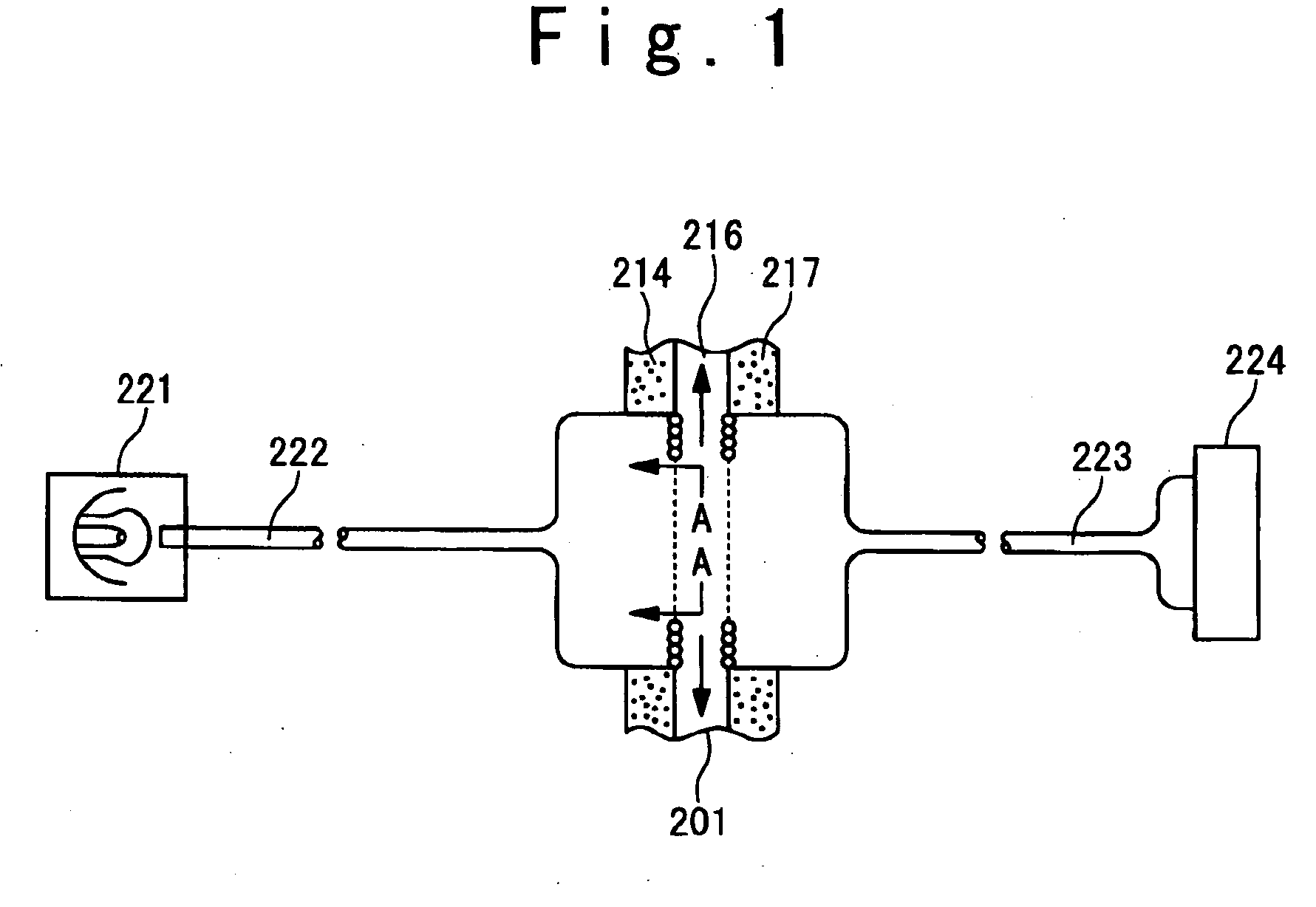

Sample preparation integrated chip

InactiveUS20030138941A1Facilitates introduction flowNon-conducive to conductionBioreactor/fermenter combinationsHeating or cooling apparatusAnalytical chemistryMicroarray

The present invention relates to an apparatus comprising a substrate having at least one assay station. The at least one assay station has at least a first assay station channel and at least a second assay station channel and the first and second assay station channels each separately being in communication with the at least one assay station. The apparatus has an arrangement of at least first and second multipurpose channels in communication with the first and second assay station channels, respectively. The first multipurpose channel and first assay station channel have internal surface characteristics conducive to conduction of a sample solution therethrough. There is at least one sample fluid inlet in communication with the at least first multipurpose channel, and at least one isolation-medium inlet in communication with the at least first and second multipurpose channels. The at least one second multipurpose channel has an internal surface portion non-conducive to conduction of said sample solution.

Owner:NANYANG TECH UNIV +1

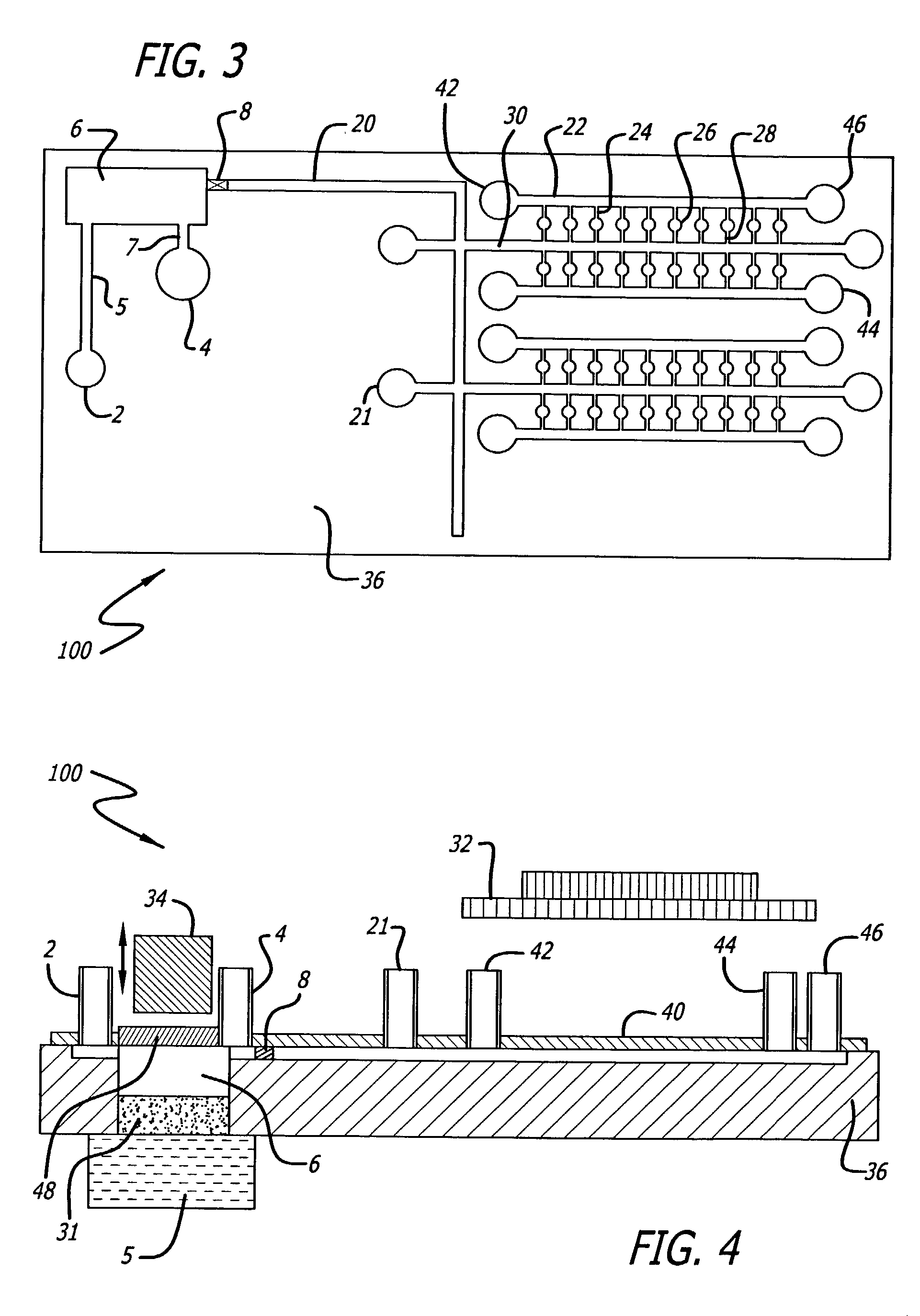

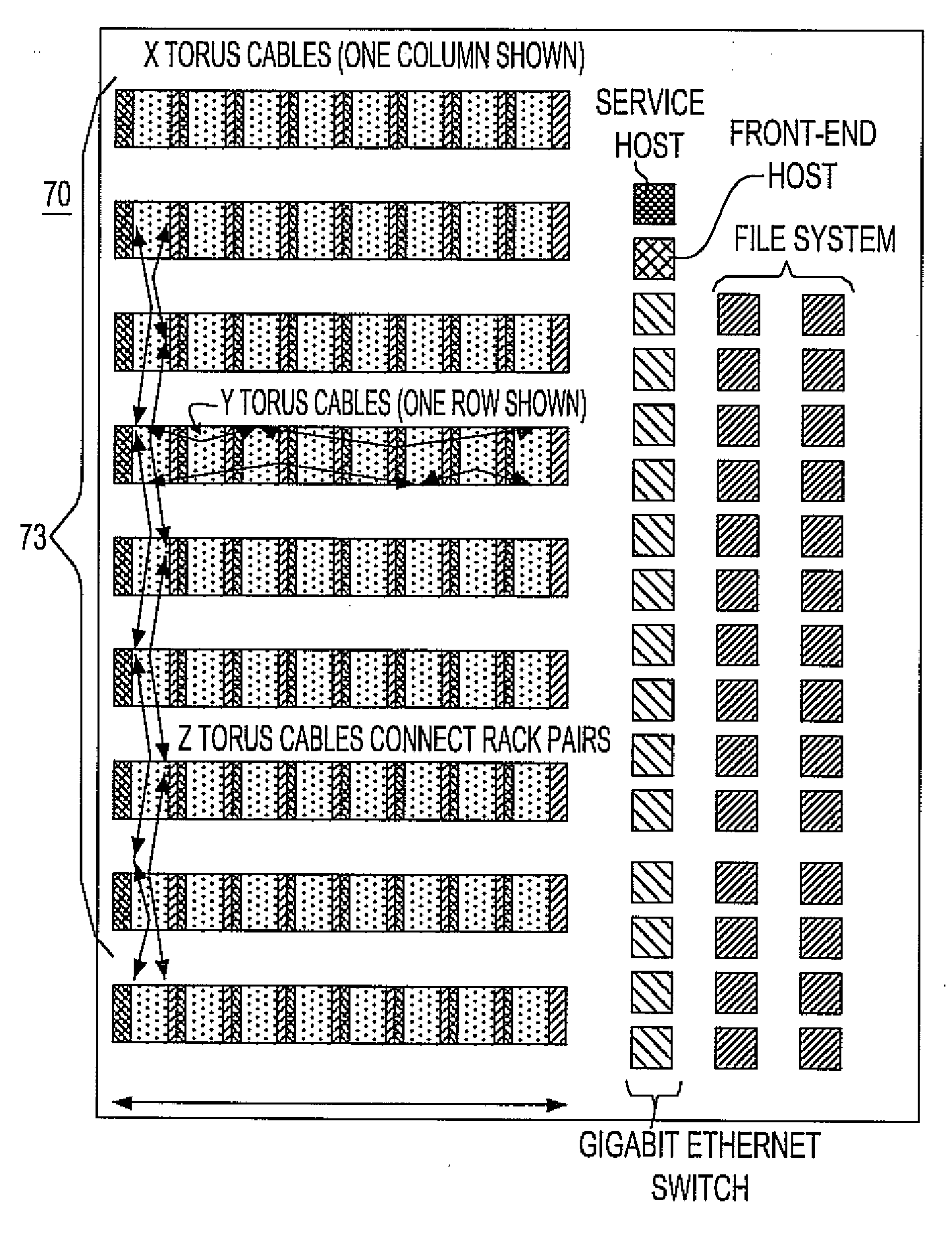

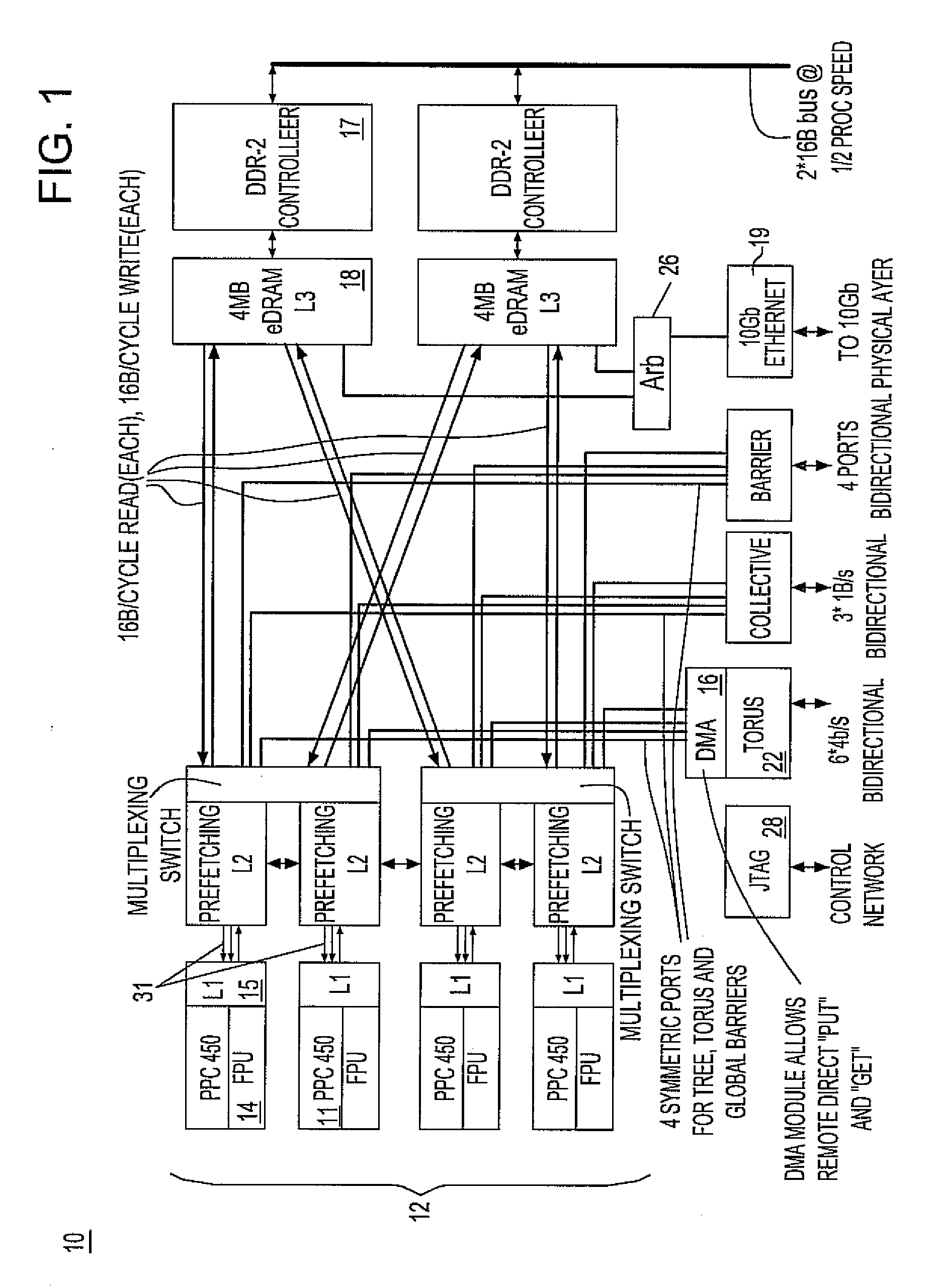

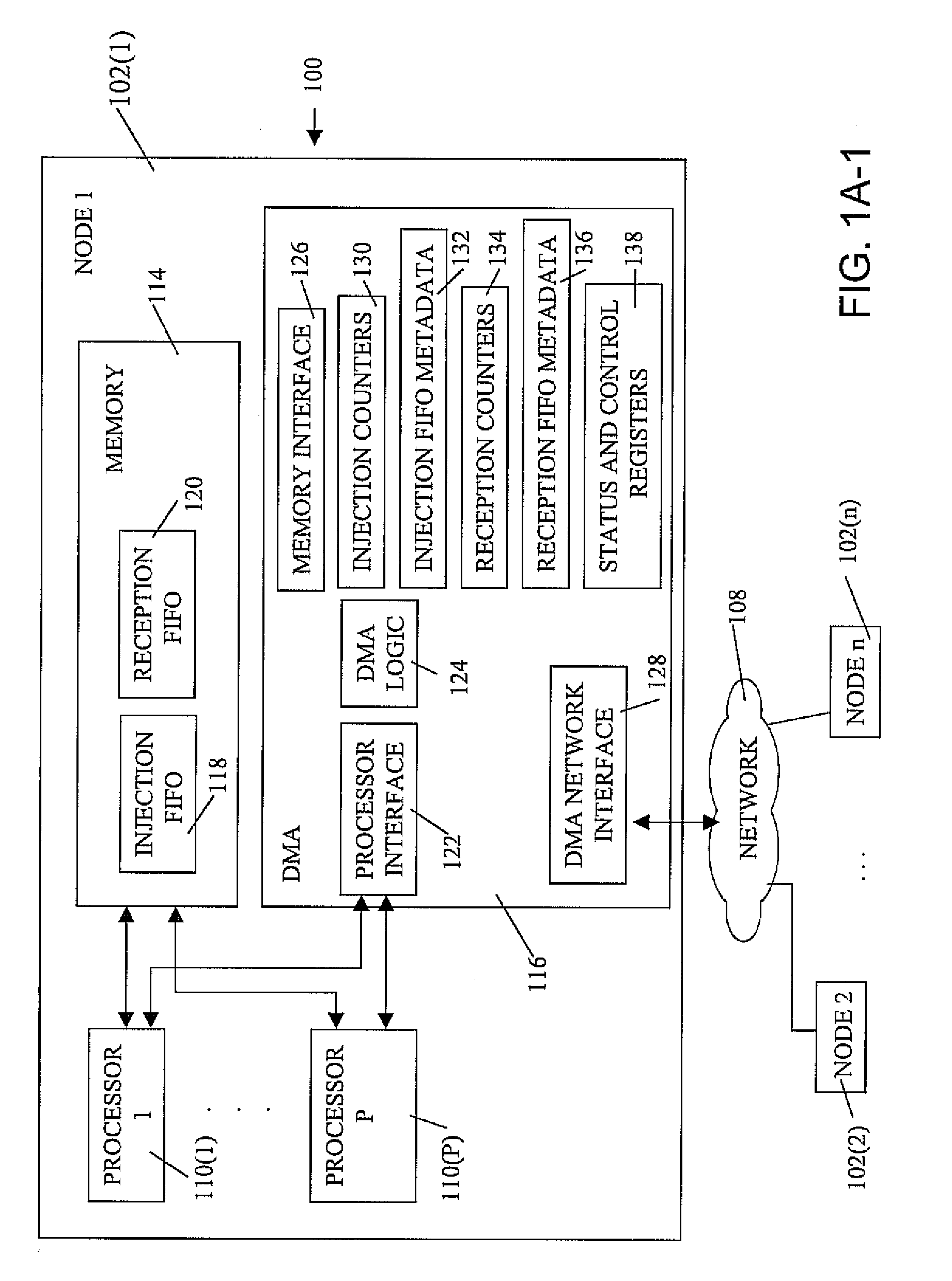

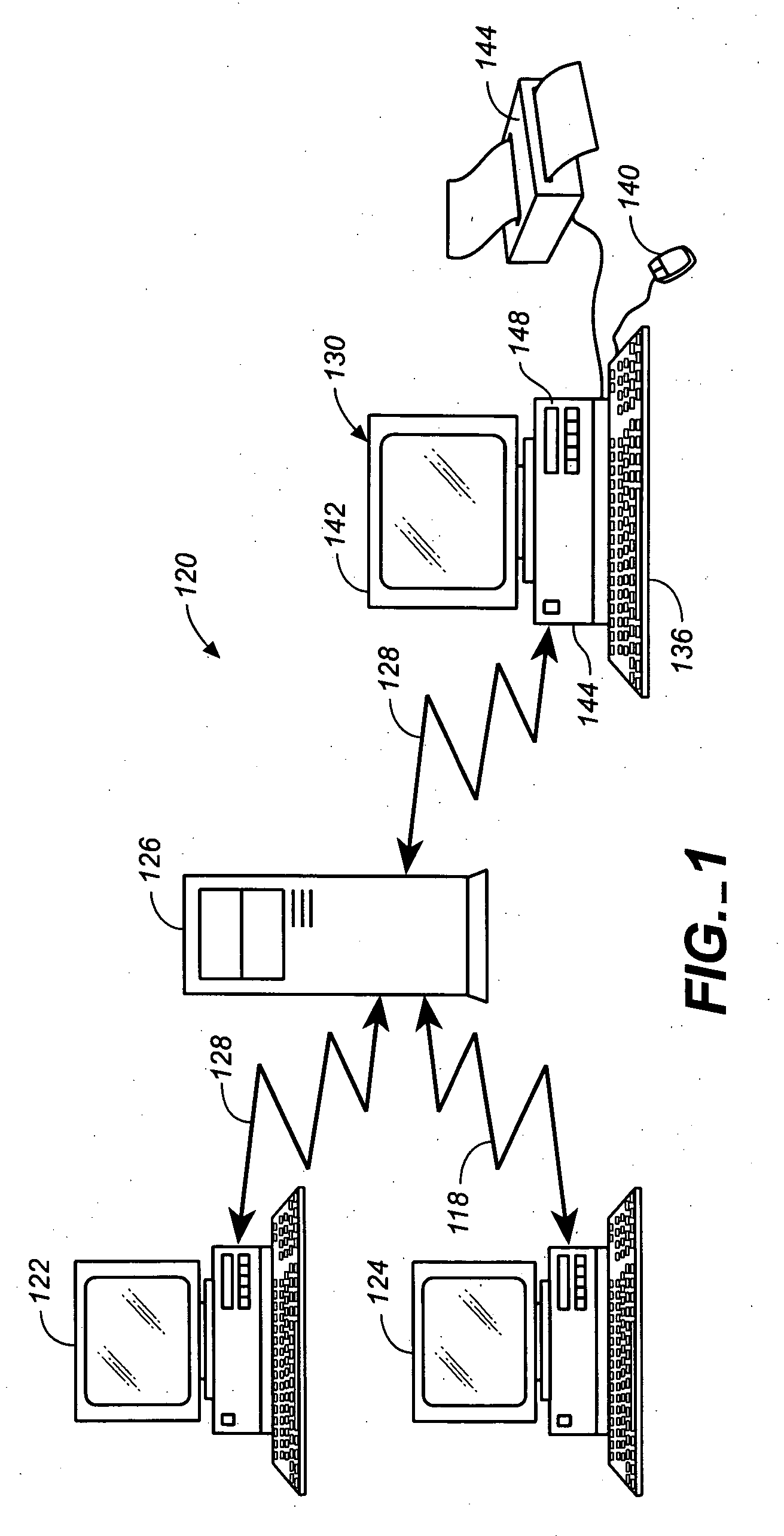

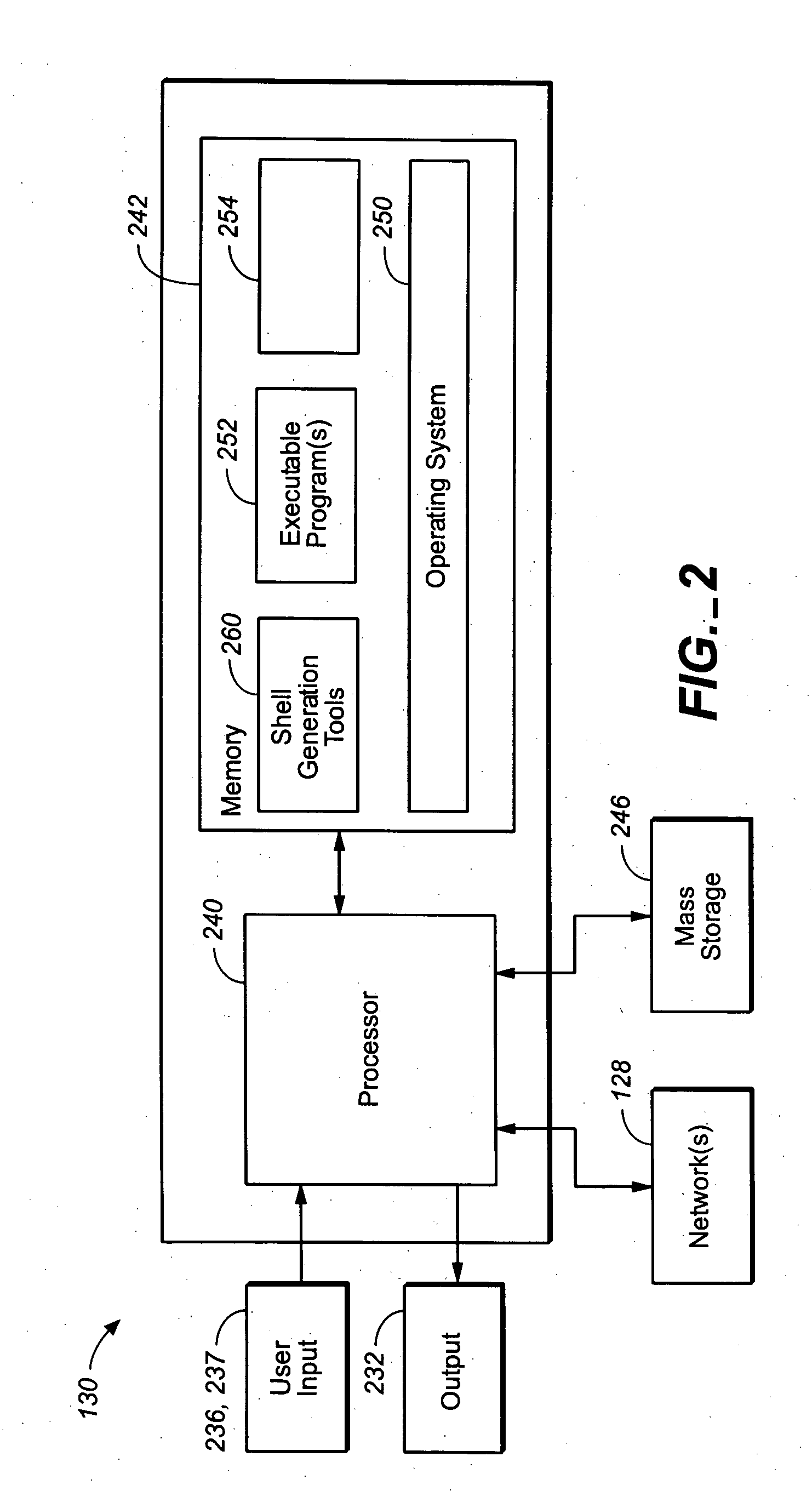

Ultrascalable petaflop parallel supercomputer

InactiveUS20090006808A1Massive level of scalabilityUnprecedented level of scalabilityProgram control using stored programsArchitecture with multiple processing unitsMessage passingPacket communication

A novel massively parallel supercomputer of petaOPS-scale includes node architectures based upon System-On-a-Chip technology, where each processing node comprises a single Application Specific Integrated Circuit (ASIC) having up to four processing elements. The ASIC nodes are interconnected by multiple independent networks that optimally maximize the throughput of packet communications between nodes with minimal latency. The multiple networks may include three high-speed networks for parallel algorithm message passing including a Torus, collective network, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. Novel use of a DMA engine is provided to facilitate message passing among the nodes without the expenditure of processing resources at the node.

Owner:IBM CORP

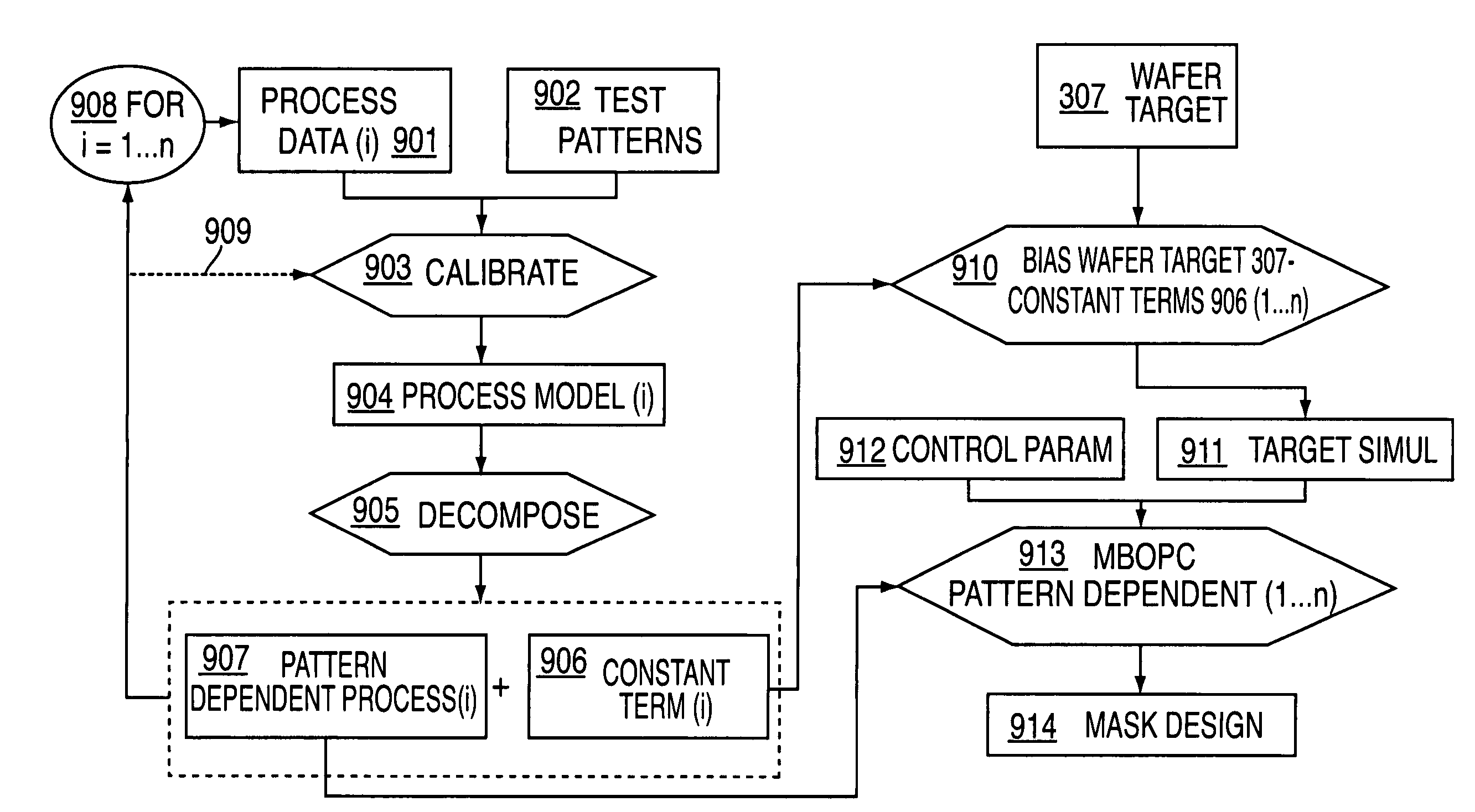

Method for improving optical proximity correction

ActiveUS7350183B2Improve variationDefect minimizationPhotomechanical apparatusOriginals for photomechanical treatmentLine widthComputer science

Owner:GLOBALFOUNDRIES U S INC

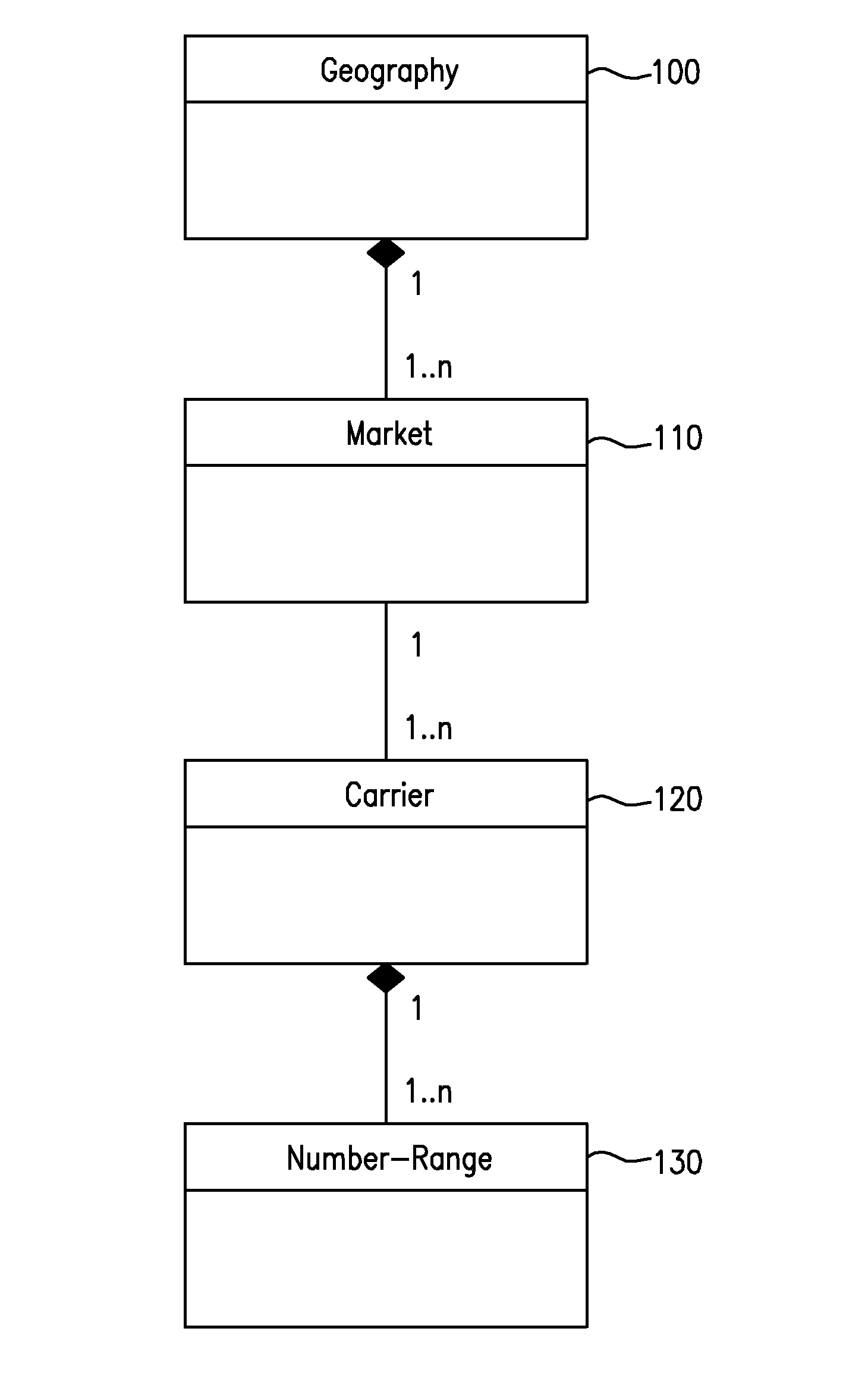

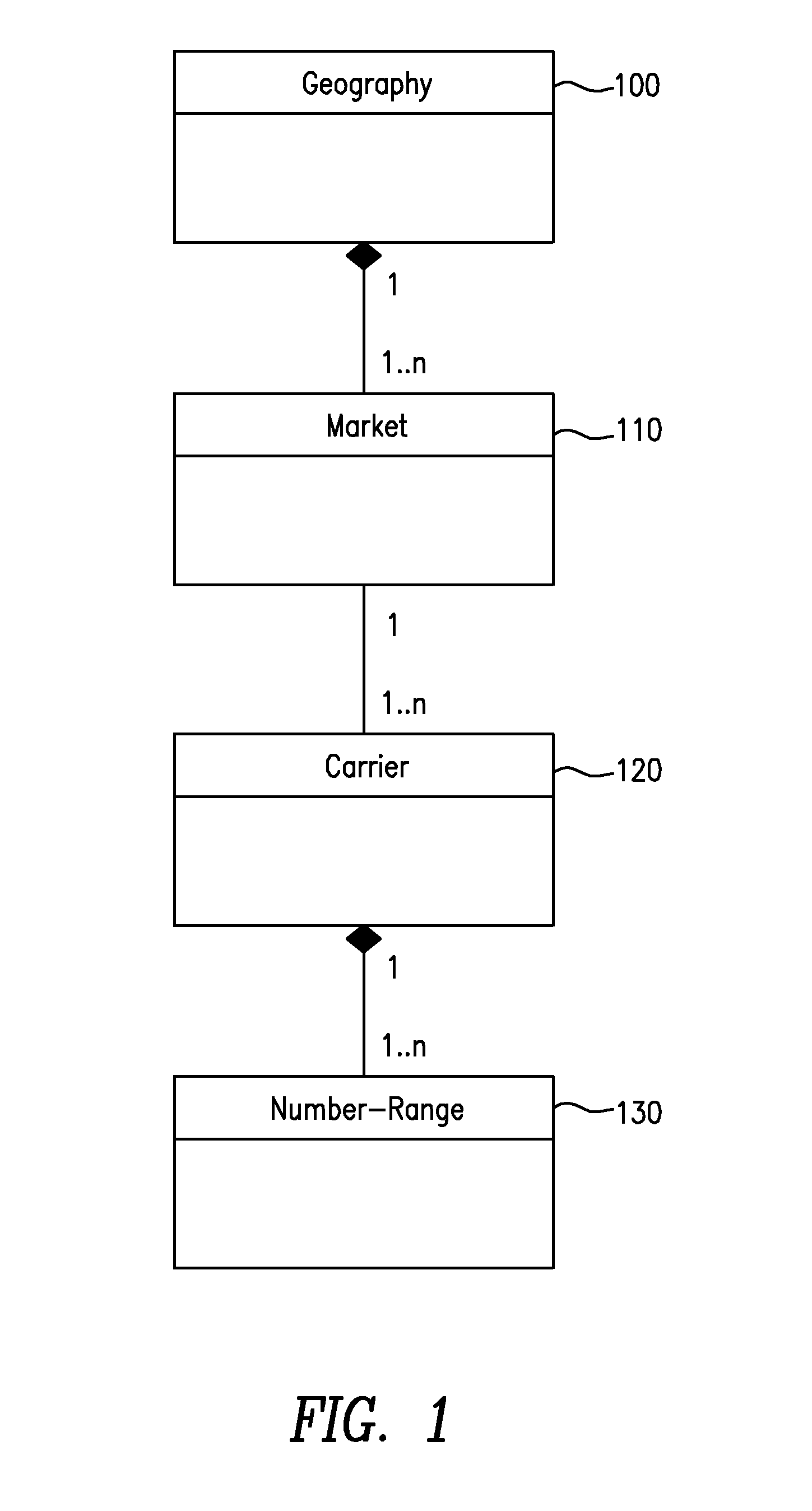

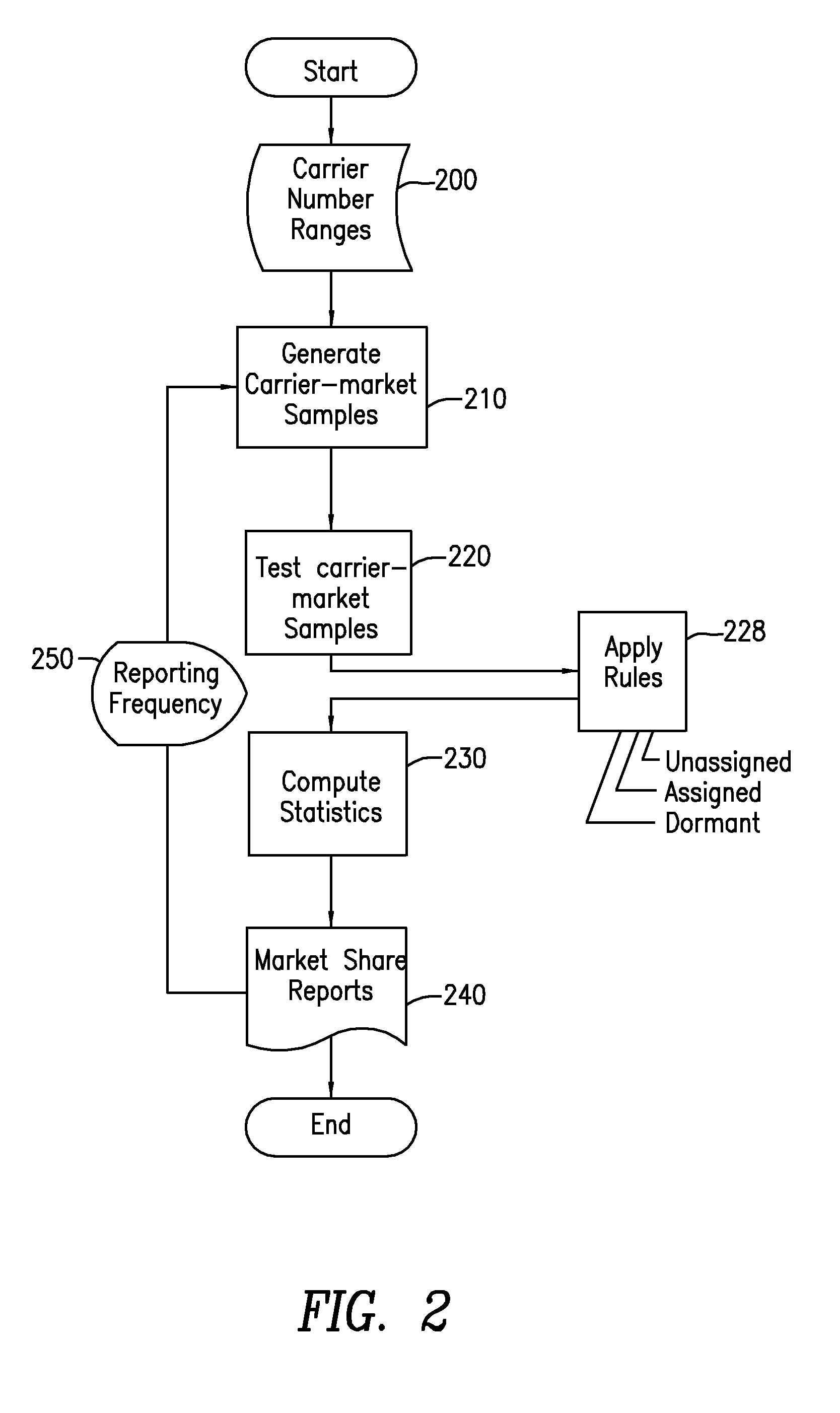

Method and apparatus for determining whether a cellular phone chip is dormant

InactiveUS20100167689A1Supervisory/monitoring/testing arrangementsWireless networksService provisionCellular telephone

Methods and systems are provided for determining whether a cellular telephone chip is dormant. Determinations are drawn from testing telephone numbers associated with chips and data collected is used to generate statistics. Methods are provided for determining the percentage of a wireless service provider's subscriber-base that consists of abandoned, or non-revenue-generating, customers.

Owner:MOBILE SCI

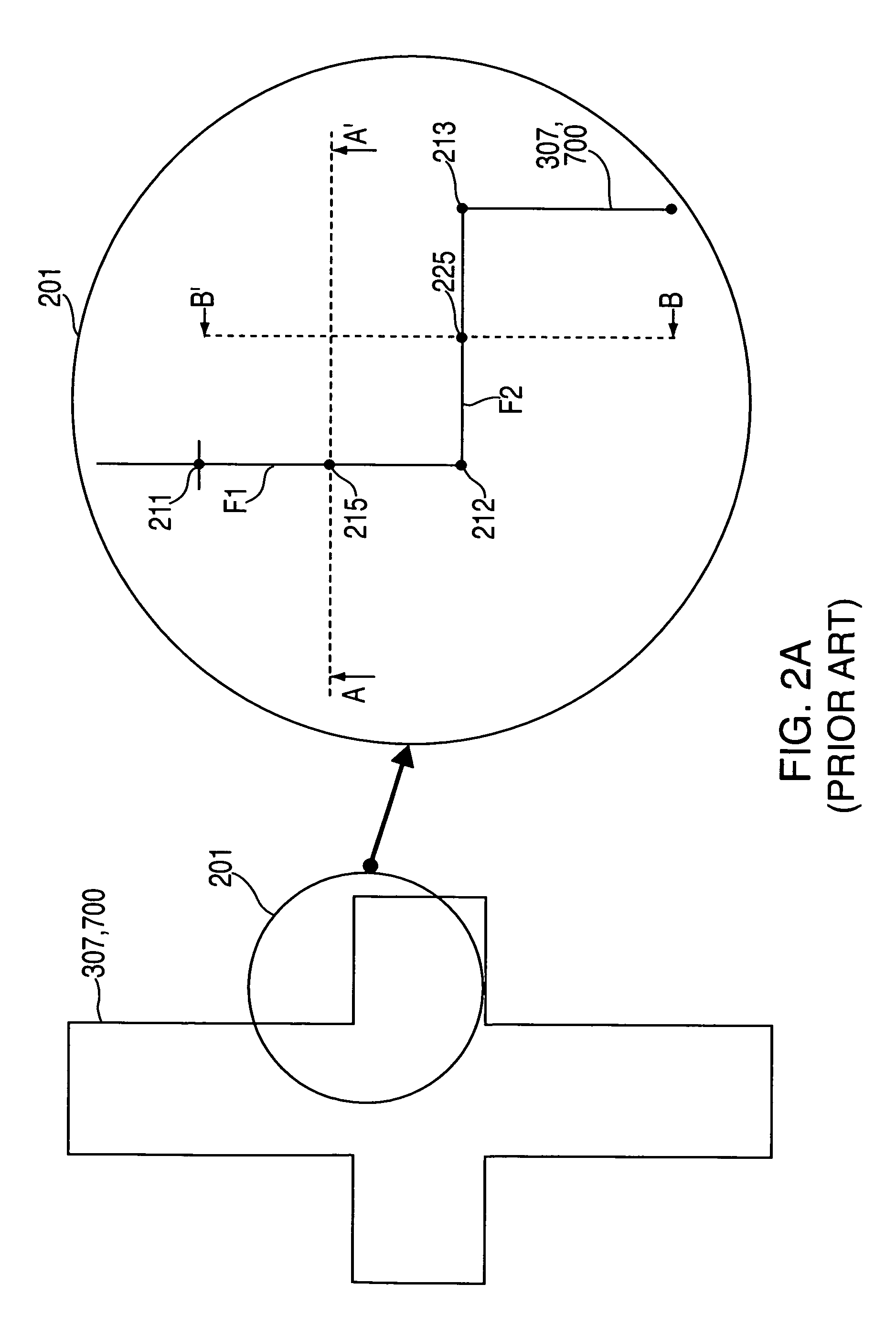

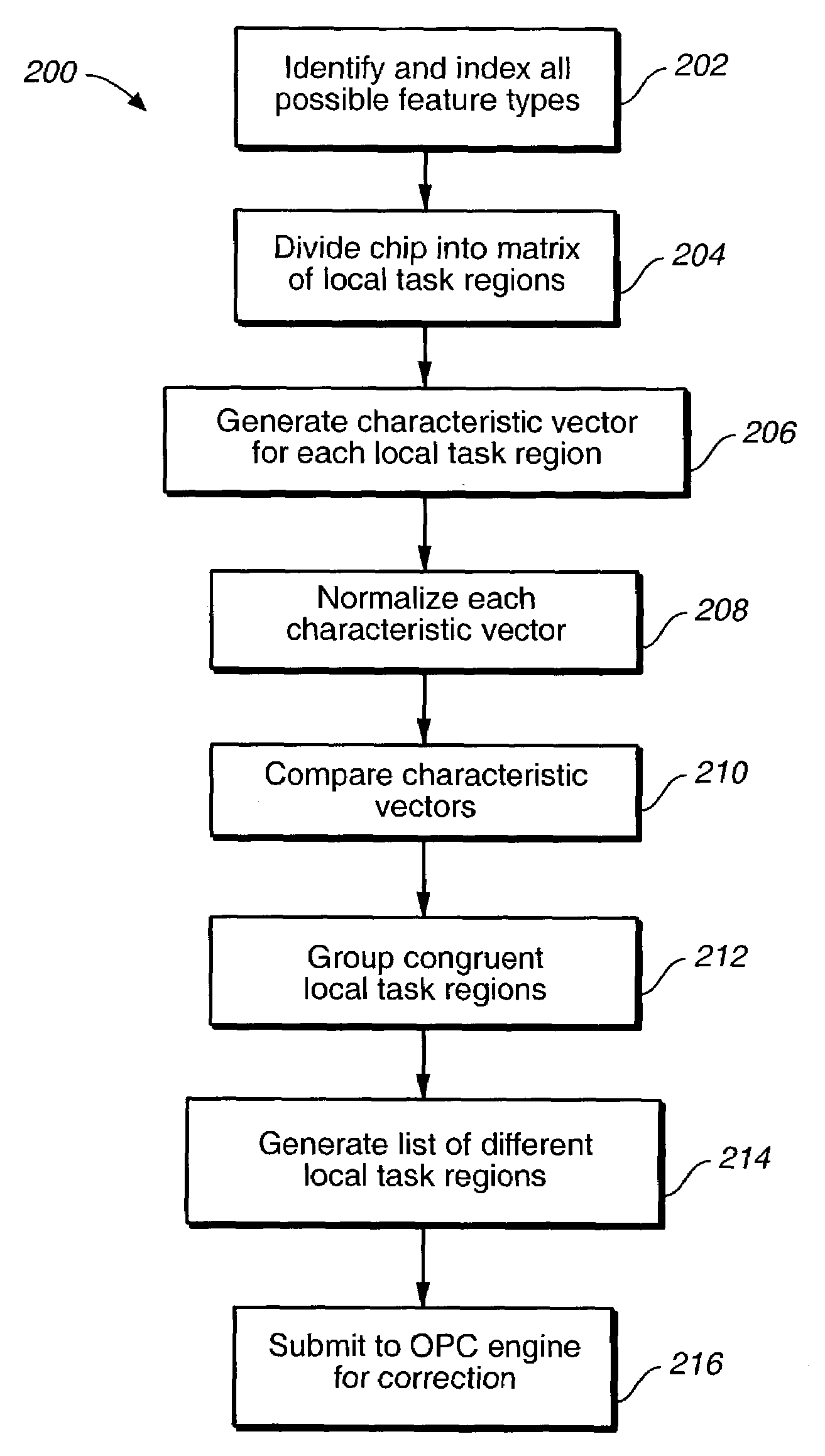

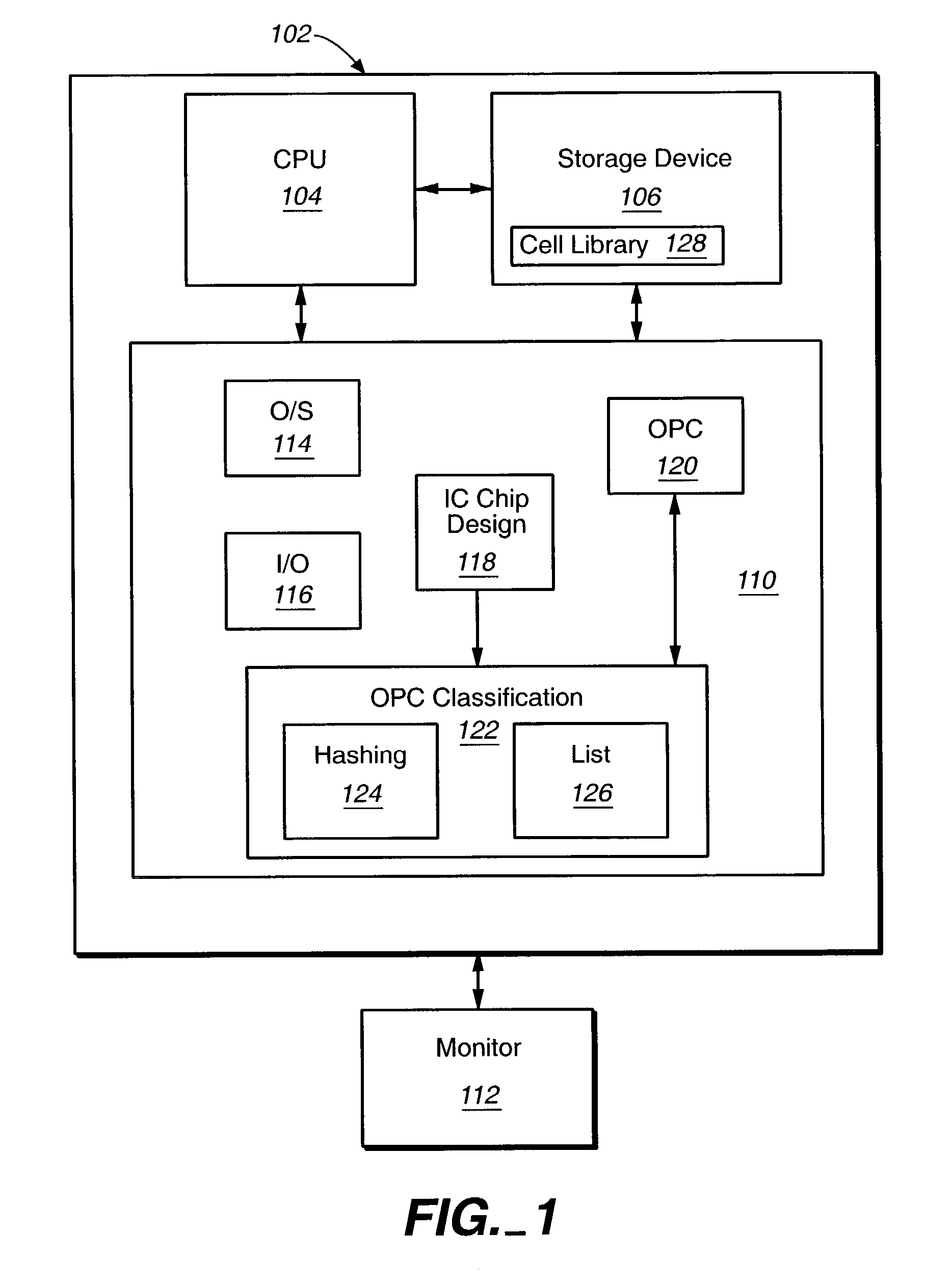

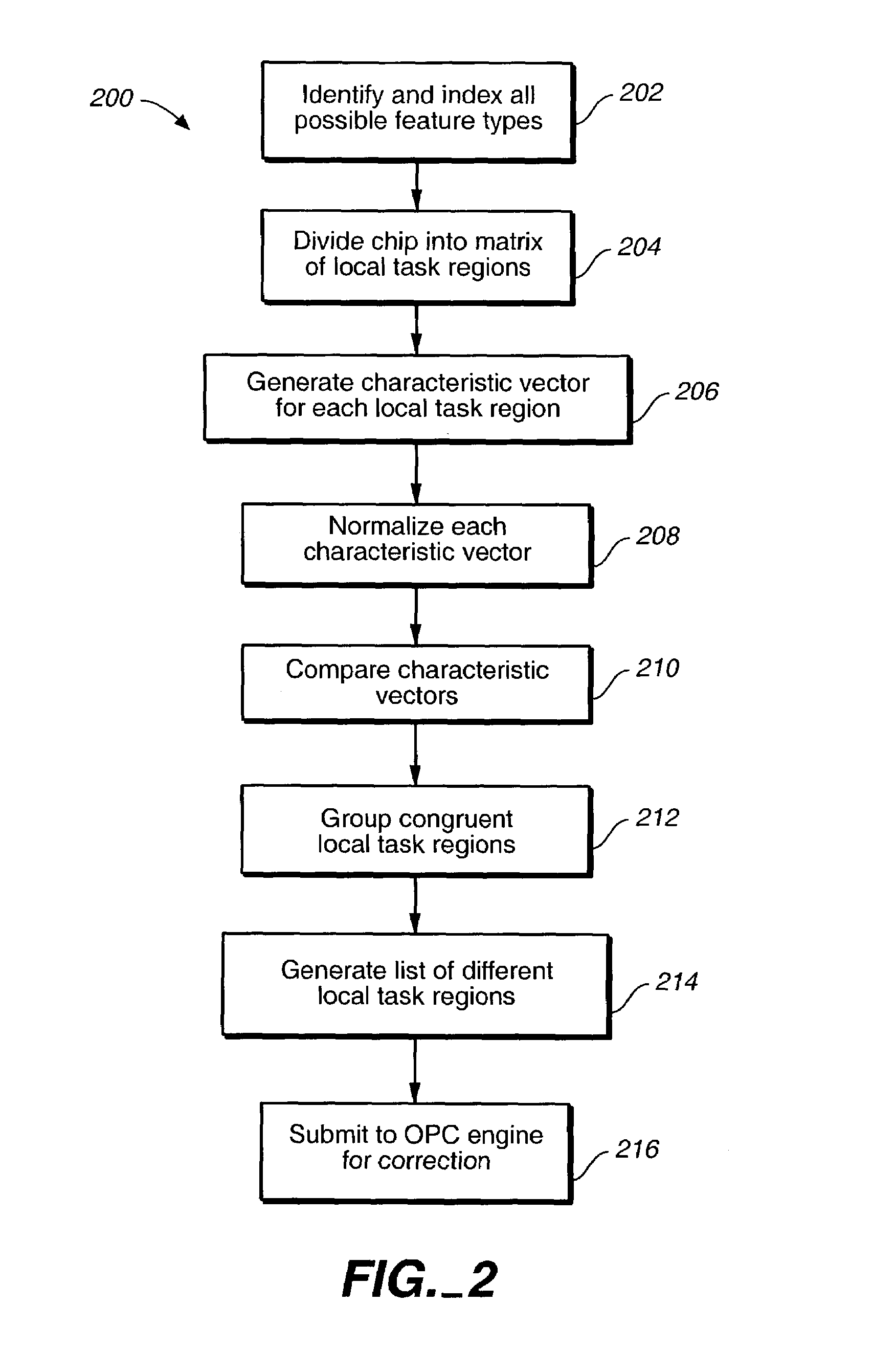

Method and system for classifying an integrated circuit for optical proximity correction

InactiveUS7093228B2Significant resource and timeReduce numberPhotomechanical exposure apparatusMicrolithography exposure apparatusIntegrated circuitOptical proximity correction

A method and system for performing optical proximity correction (OPC) on an integrated circuit (IC) chip design is disclosed. The system and method of the present invention includes dividing the IC chip into a plurality of local task regions, identifying congruent local task regions, classifying congruent local task regions into corresponding groups, and performing OPC for each group of congruent local task regions.By identifying and grouping congruent local task regions in the IC chip, according to the method and system disclosed herein, only one OPC procedure (e.g., evaluation and correction) needs to be performed per group of congruent local task regions. The amount of data to be evaluated and the number of corrections performed is greatly reduced because OPC is not performed on repetitive portions of the IC chip design, thereby resulting in significant savings in computing resources and time.

Owner:BELL SEMICON LLC

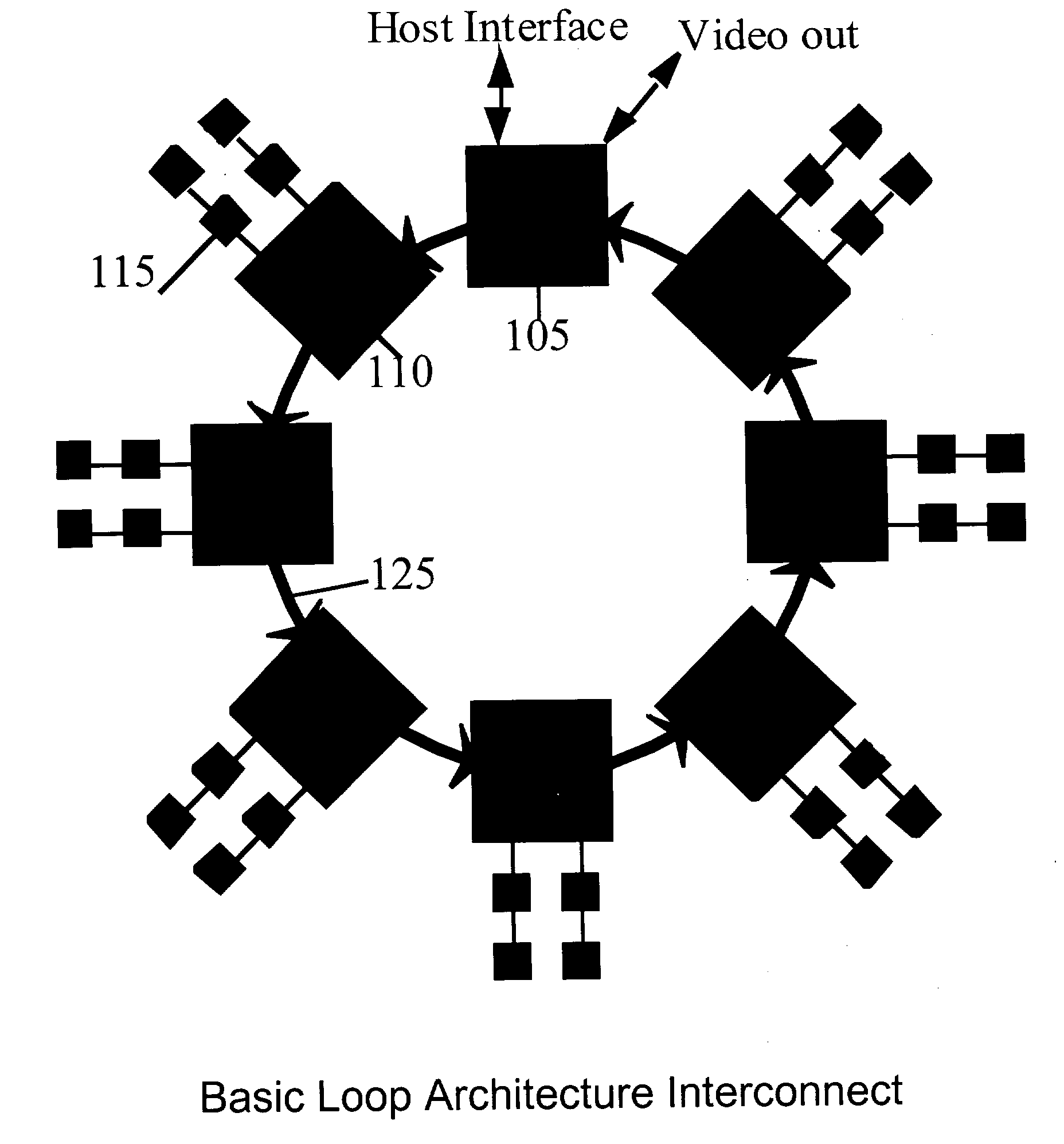

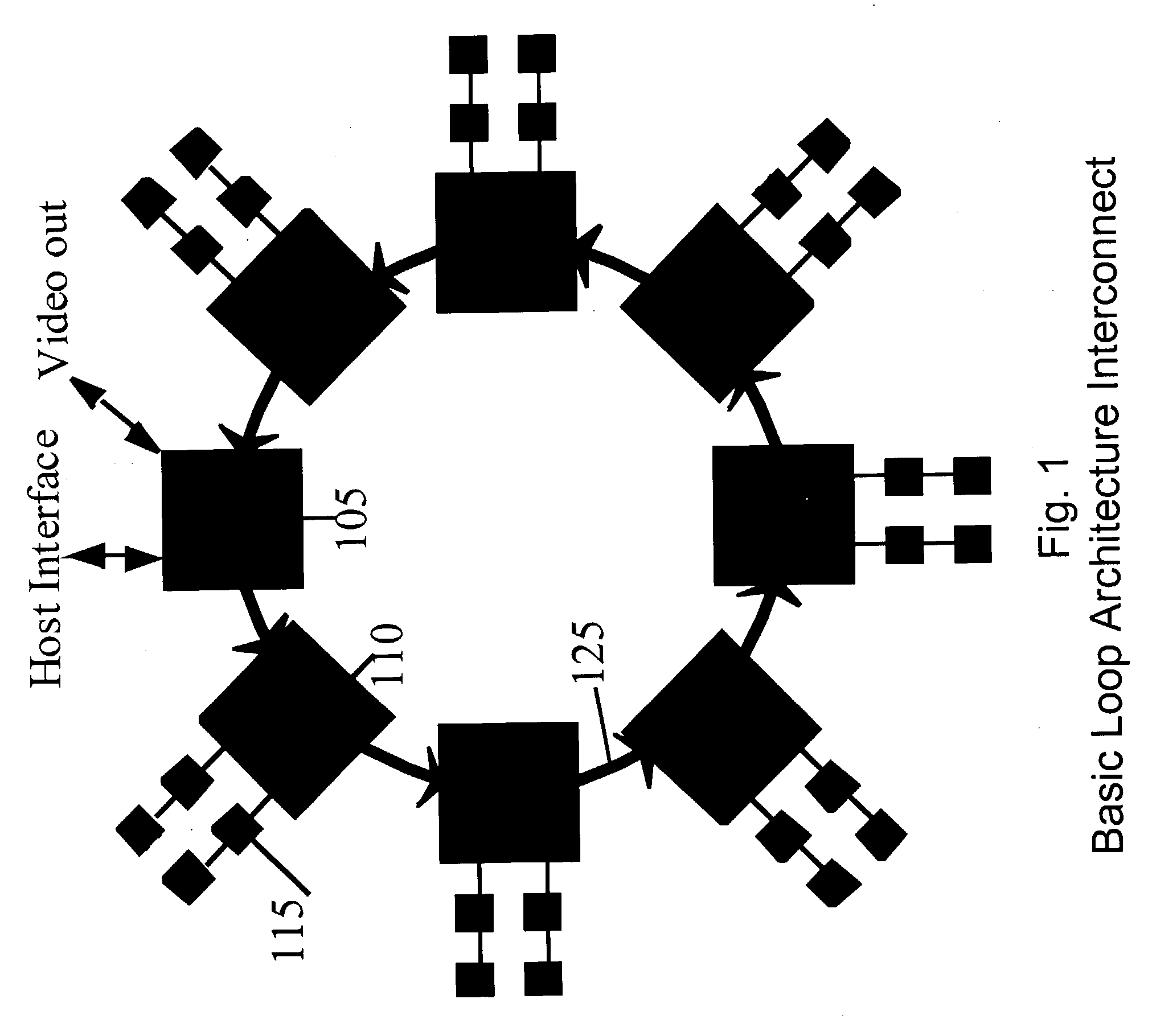

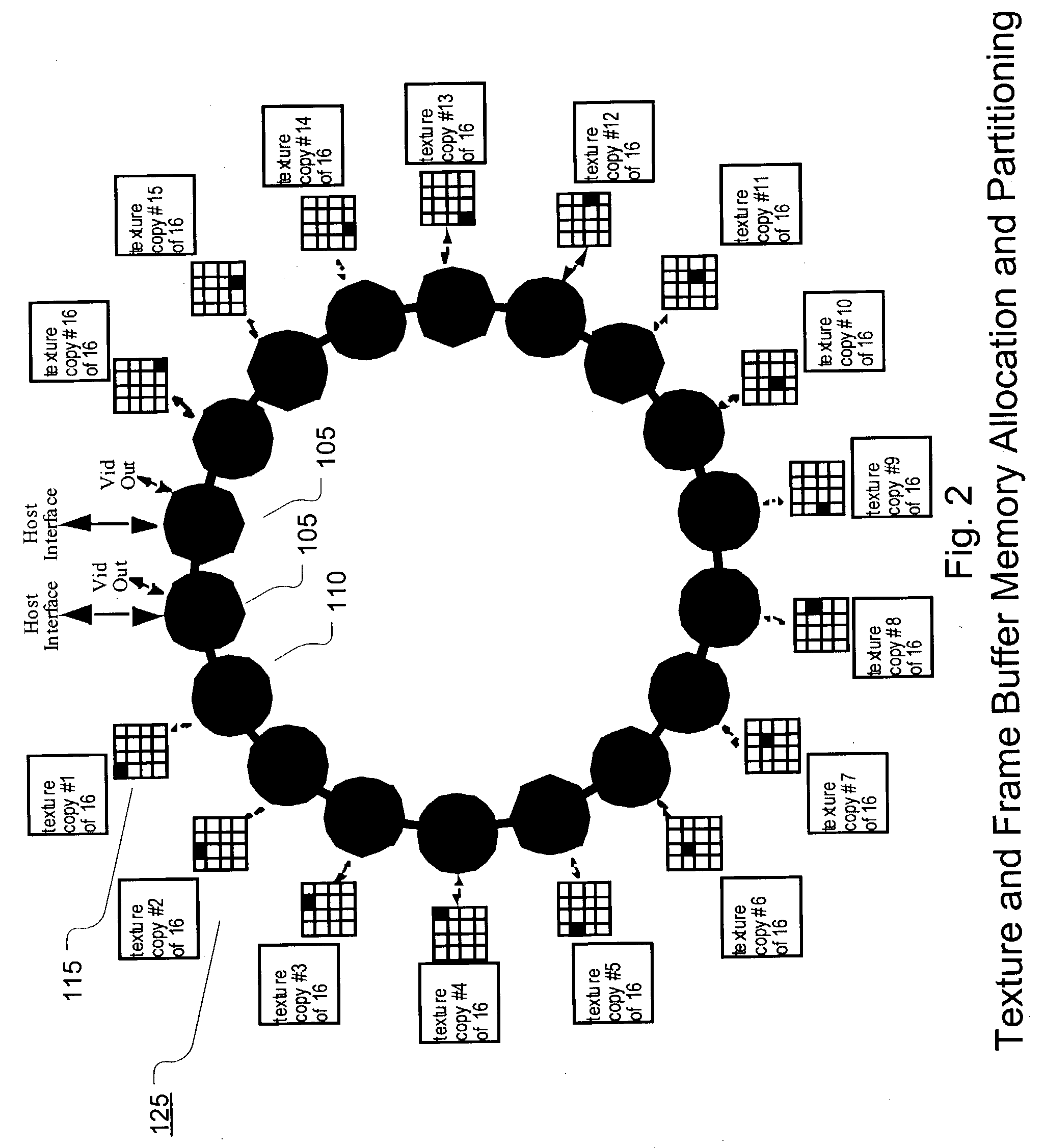

Scalable high performance 3d graphics

InactiveUS20040012600A1Minimizes cost and riskEasy to scaleImage enhancementImage memory managementGraphicsHigh bandwidth

A high-speed ring topology. In one embodiment, two base chip types are required: a "drawing" chip, LoopDraw, and an "interface" chip, LoopInterface. Each of these chips have a set of pins that supports an identical high speed point to point unidirectional input and output ring interconnect interface: the LoopLink. The LoopDraw chip uses additional pins to connect to several standard memories that form a high bandwidth local memory sub-system. The LoopInterface chip uses additional pins to support a high speed host computer host interface, at least one video output interface, and possibly also additional non-local interconnects to other LoopInterface chip(s).

Owner:DEERING MICHAEL F +2

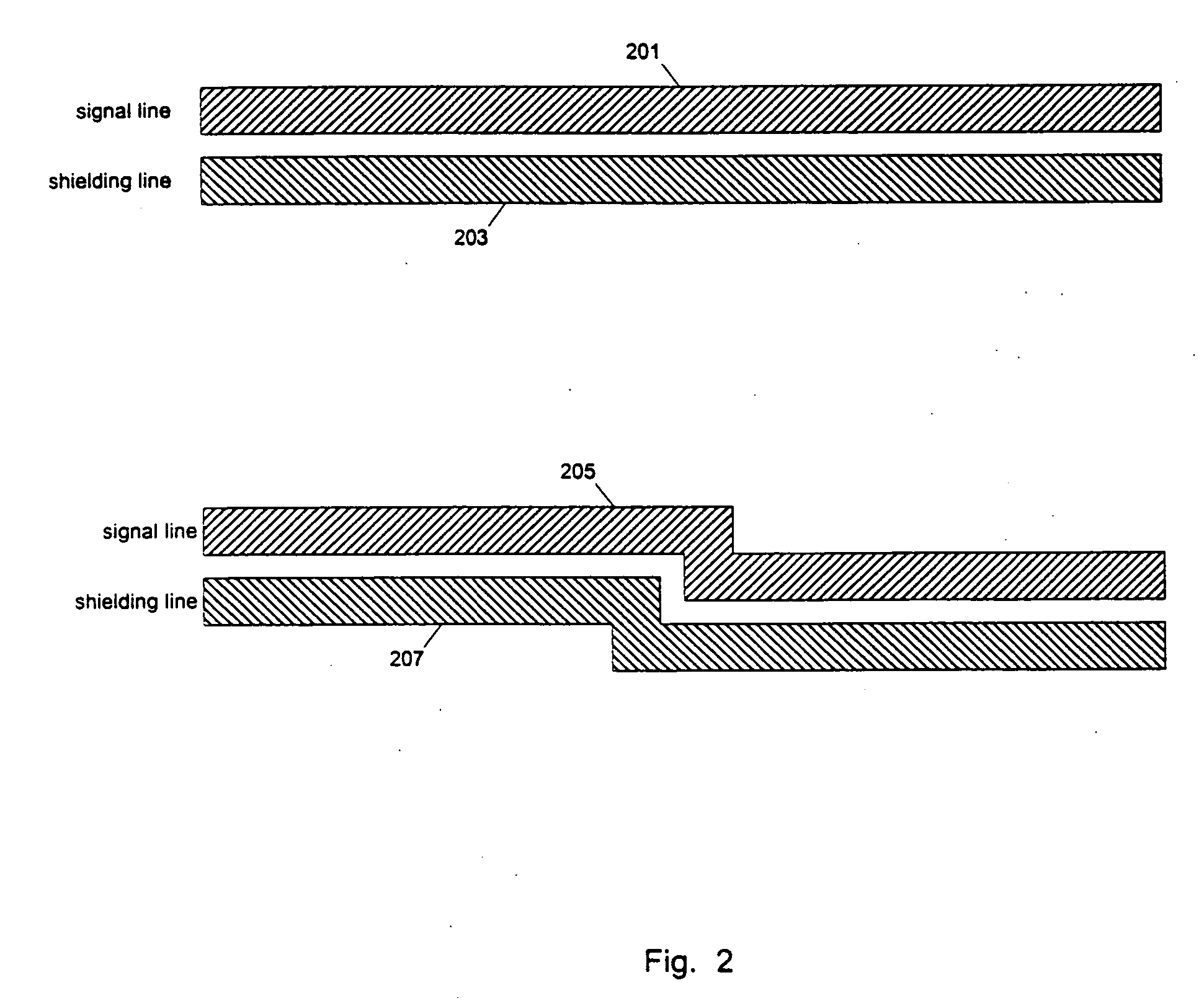

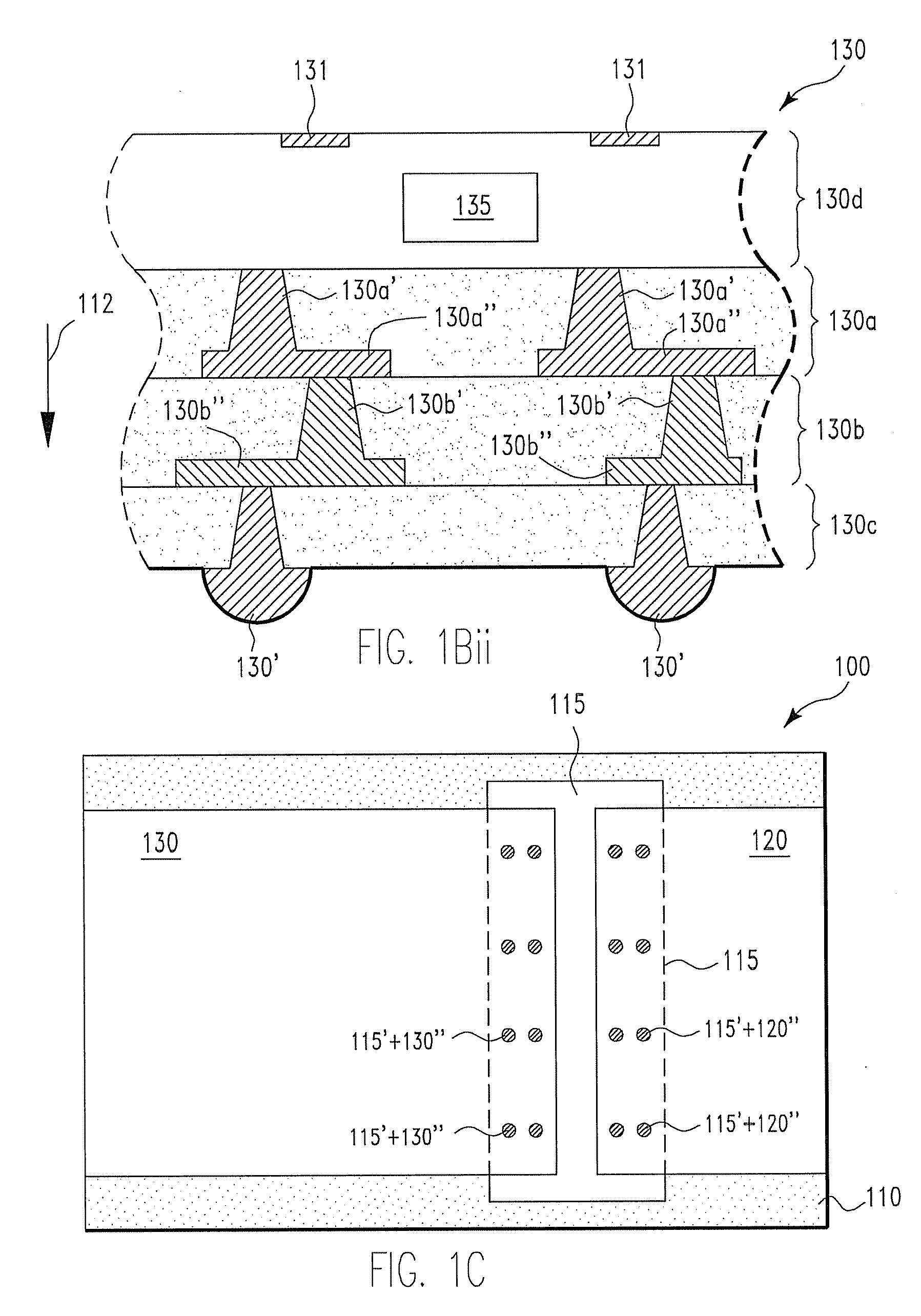

Integrated circuit devices and methods and apparatuses for designing integrated circuit devices

ActiveUS20060095872A1Reduce temperature changesSemiconductor/solid-state device detailsAnalogue computers for electric apparatusCapacitanceCapacitive coupling

Methods and apparatuses to design an Integrated Circuit (IC) with a shielding of wires. In at least one embodiment, a shielding mesh of at least two reference voltages (e.g., power and ground) is used to reduce both the capacitive coupling and the inductive coupling in routed signal wires in IC chips. In some embodiments, a type of shielding mesh (e.g., a shielding mesh with a window surrounded by a power ring, or a window with a parser set of shielding wires) is selected to make more routing area available in locally congested areas. In other embodiments, the shielding mesh is used to create or add bypass capacitance. Other embodiments are also disclosed.

Owner:SYNOPSYS INC

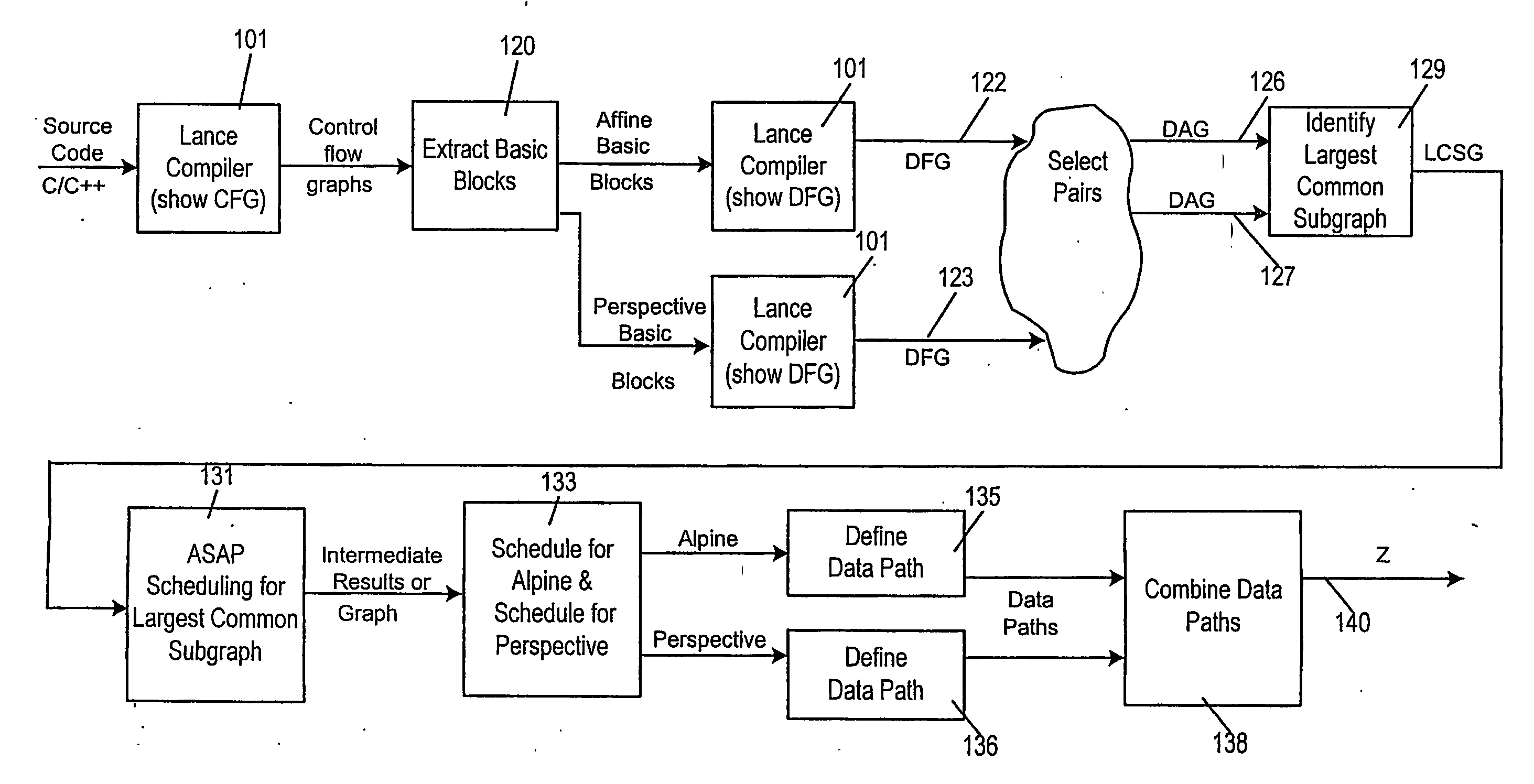

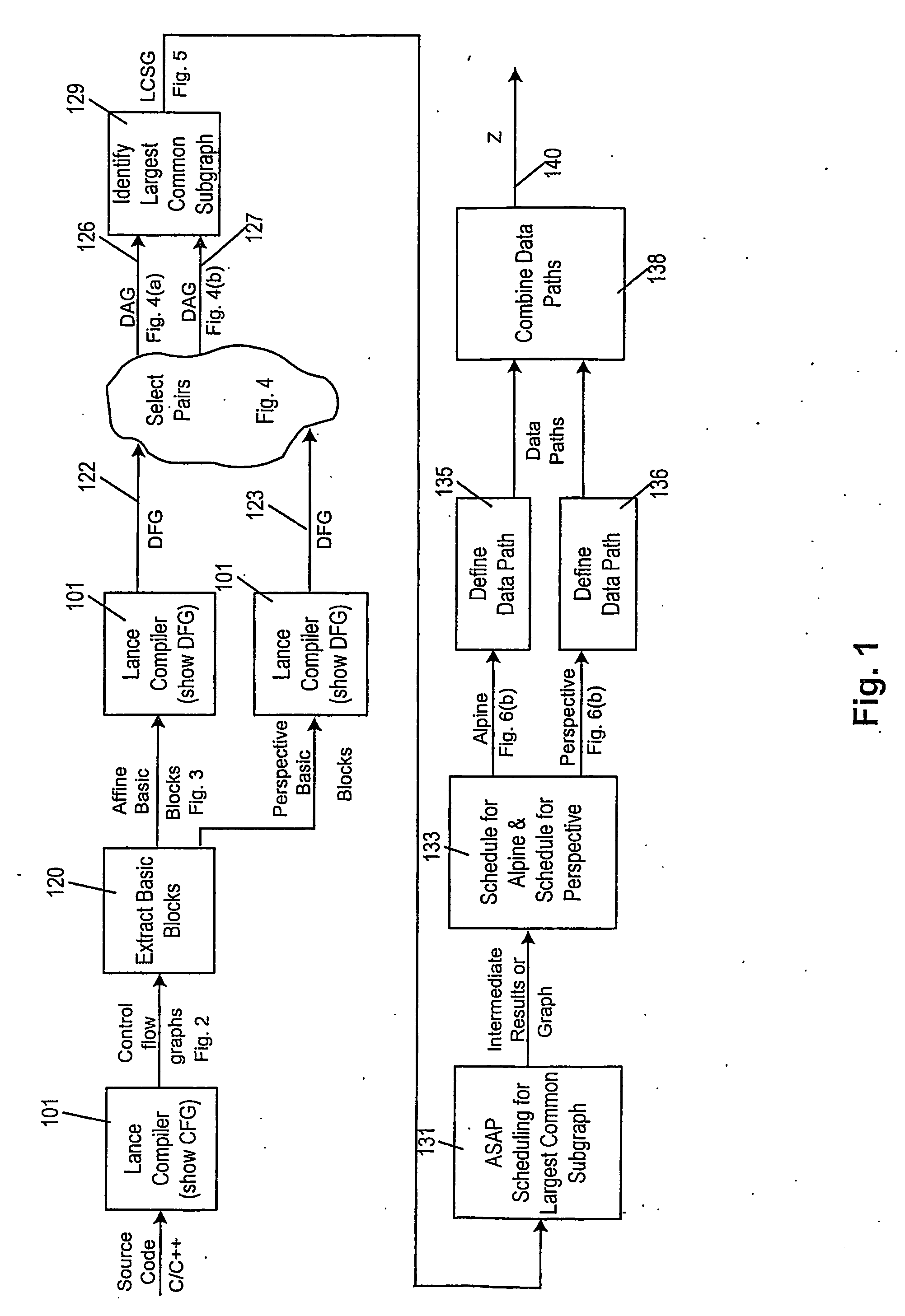

Reconfigurable processing

ActiveUS20070198971A1Reduce signal delayReduce areaEnergy efficient ICTSoftware engineeringPathPingComputer architecture

A method of producing a reconfigurable circuit device for running a computer program of moderate complexity such as multimedia processing. Code for the application is compiled into Control Flow Graphs representing distinct parts of the application to be run. From those Control Flow Graphs are extracted basic blocks. The basic blocks are converted to Data Flow Graphs by a compiler utility. From two or more Data Flow Graphs, a largest common subgraph is determined. The largest common subgraph is ASAP scheduled and substituted back into the Data Flow Graphs which also have been scheduled. The separate Data Flow Graphs containing the scheduled largest common subgraph are converted to data paths that are then combined to form code for operating the application. The largest common subgraph is effected in hardware that is shared among the parts of the application from which the Data Flow Graphs were developed. Scheduling of the overall code is effected for sequencing, providing fastest run times and the code is implemented in hardware by partitioning and placement of processing elements on a chip and design of the connective fabric for the design elements.

Owner:ARIZONA STATE UNIVERSITY

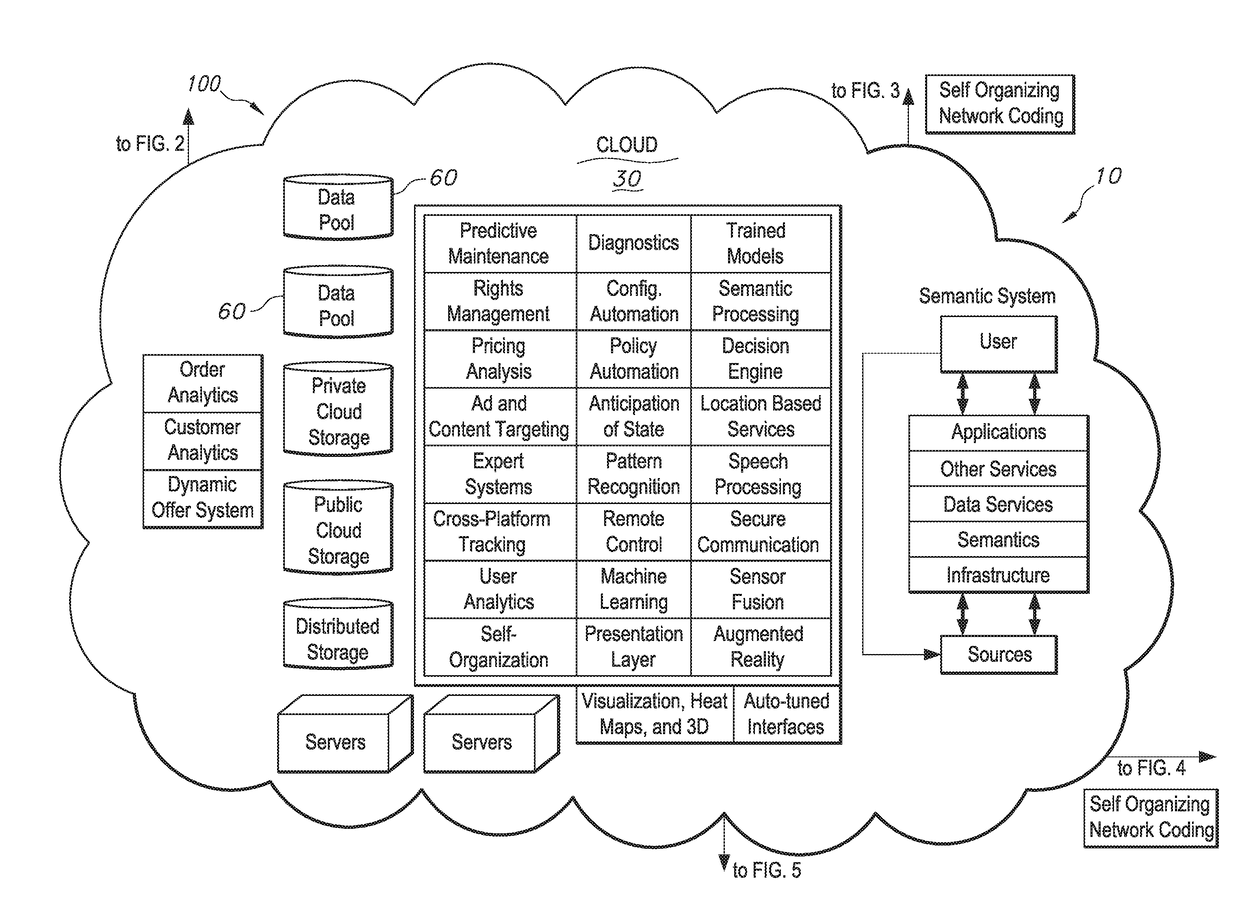

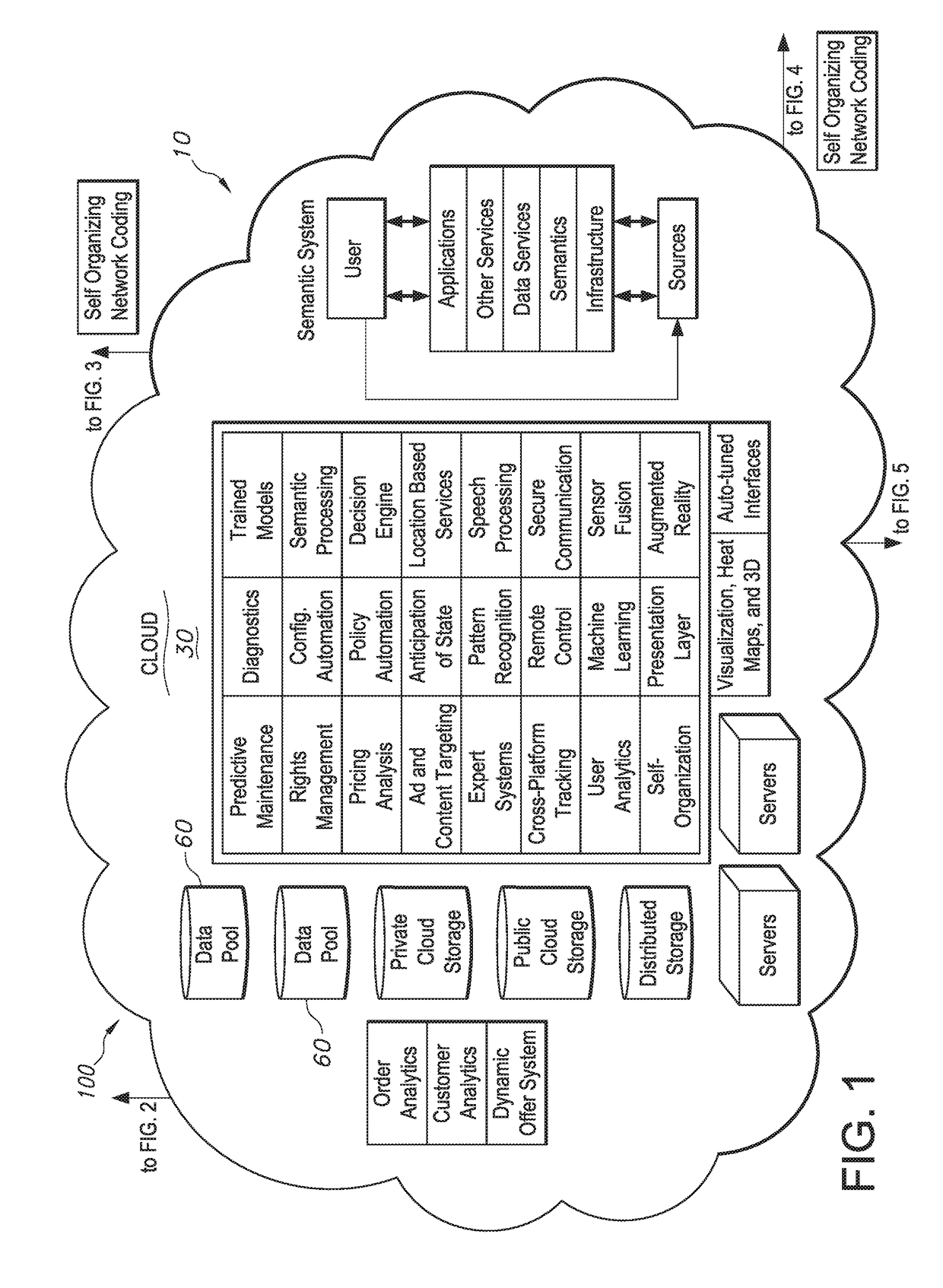

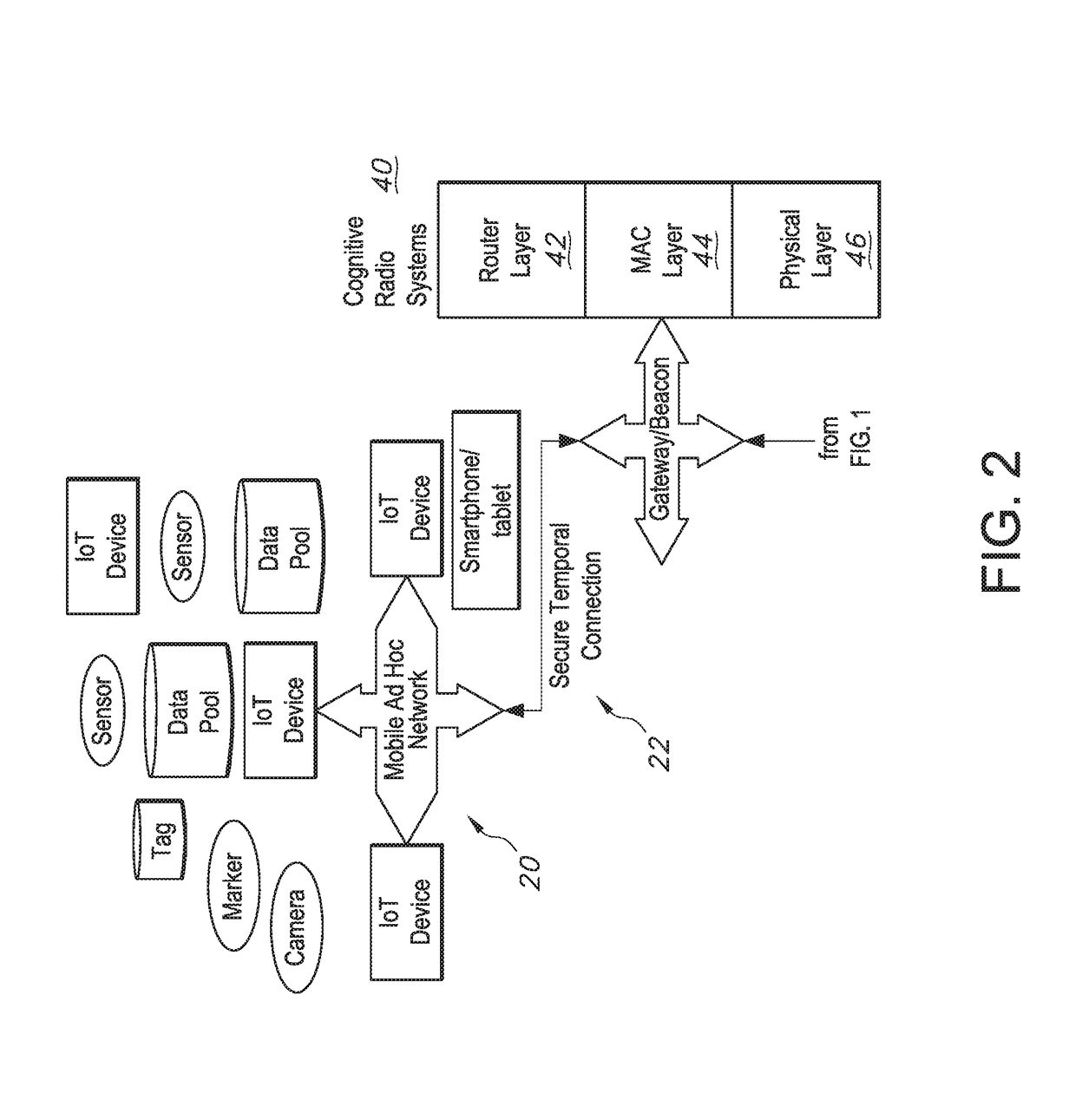

Methods and systems for the industrial internet of things

ActiveUS20180188704A1Improve signal-to-noise ratioLow sampling rateVibration measurement in solidsMachine part testingData streamData acquisition

The system generally includes a crosspoint switch in the local data collection system having multiple inputs and multiple outputs including a first input connected to the first sensor and a second input connected to the second sensor. The multiple outputs include a first output and a second output configured to be switchable between a condition in which the first output is configured to switch between delivery of the first sensor signal and the second sensor signal and a condition in which there is simultaneous delivery of the first sensor signal from the first output and the second sensor signal from the second output. Each of multiple inputs is configured to be individually assigned to any of the multiple outputs. Unassigned outputs are configured to be switched off producing a high-impedance state. The local data collection system includes multiple multiplexing units and multiple data acquisition units receiving multiple data streams from multiple machines in the industrial environment. The local data collection system includes distributed complex programmable hardware device (CPLD) chips each dedicated to a data bus for logic control of the multiple multiplexing units and the multiple data acquisition units that receive the multiple data streams from the multiple machines in the industrial environment. The local data collection system is configured to manage data collection bands.

Owner:STRONG FORCE IOT

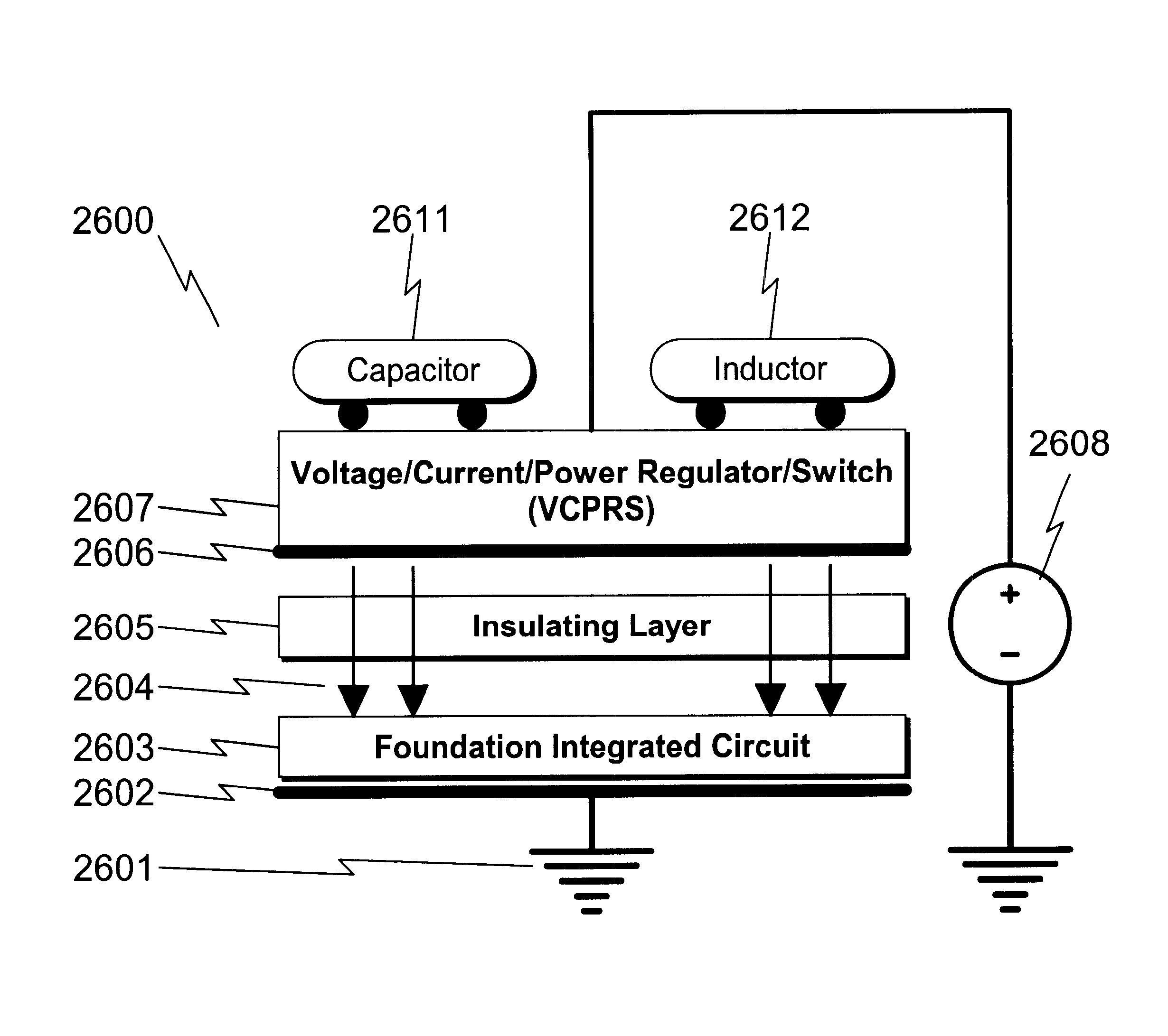

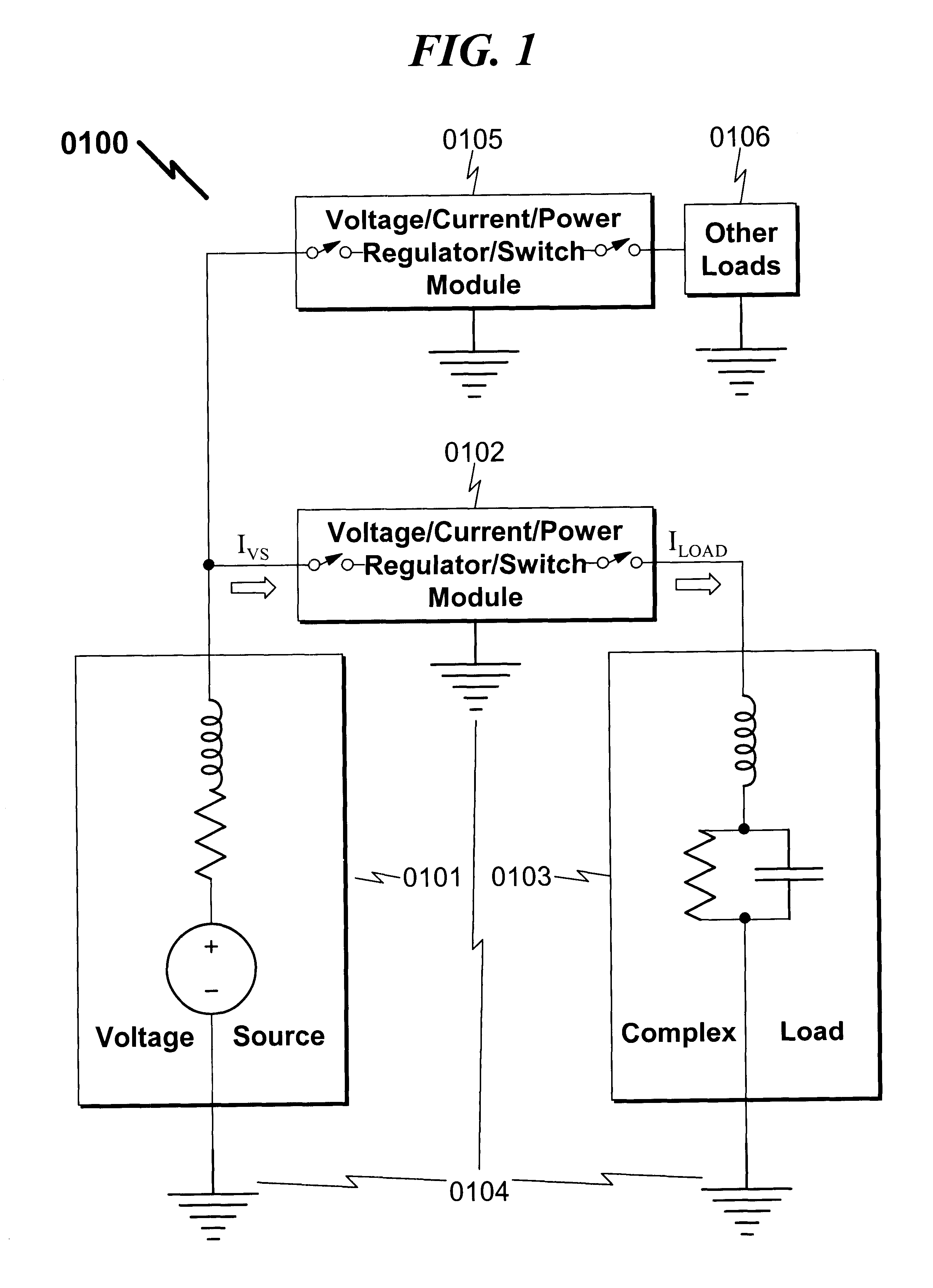

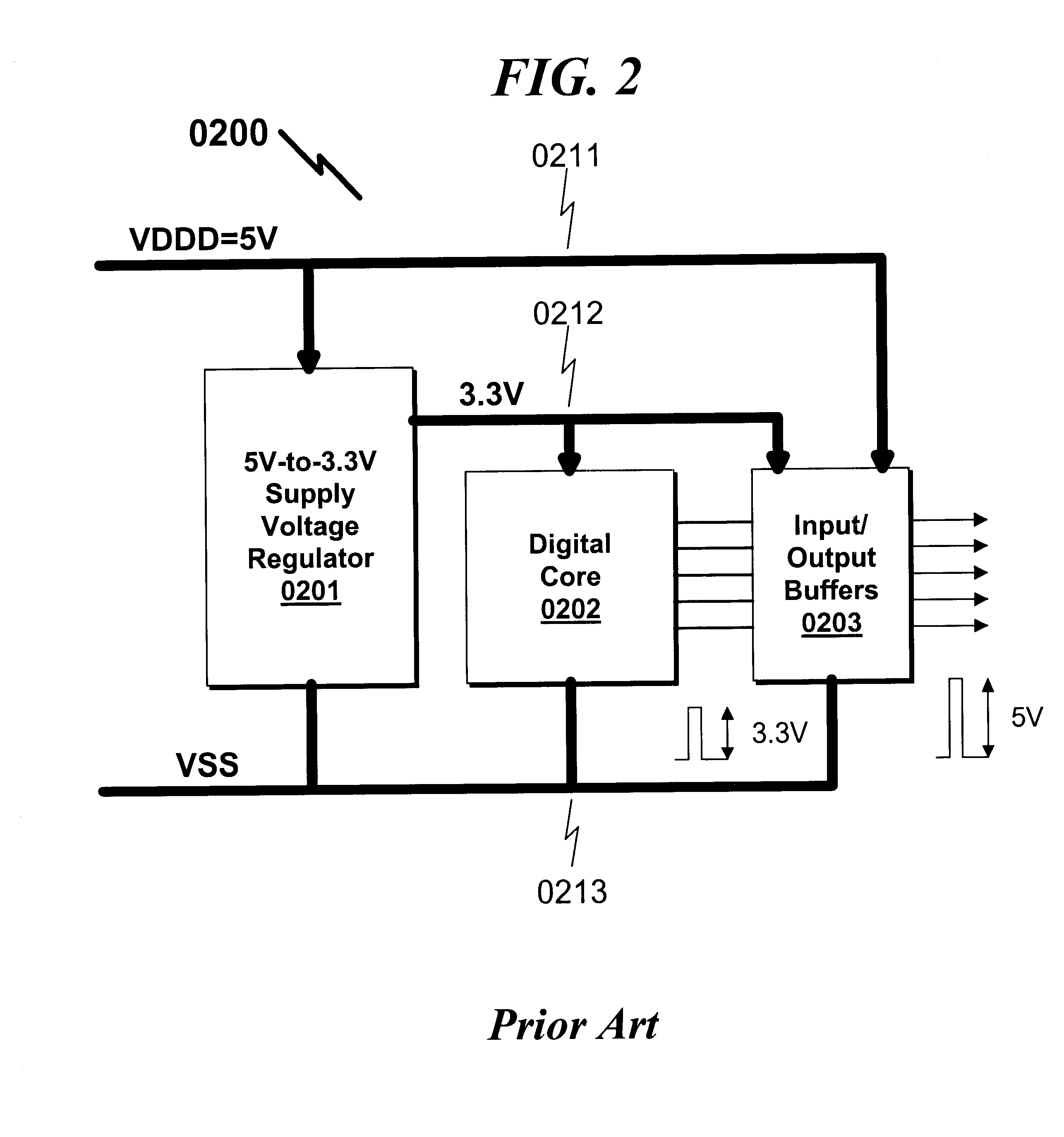

Integrated voltage/current/power regulator/switch system and method

InactiveUS6396137B1Minimal noiseGood PSRRSemiconductor/solid-state device detailsDc-dc conversionPower applicationPower capability

An integrated voltage / current / power regulator / switch (VCPRS) system and method are disclosed in which regulator / switch circuitry is vertically integrated on top of an existing integrated circuit. The present invention does not require additional integrated circuit chip area for the regulator pass device as is required in the prior art, and by virtue of its construction provides a significantly reduced on-resistance as compared to all prior art implementations. The present invention both stabilizes the power supply for large area integrated circuits and permits individual areas of the integrated circuit to have switched power capability, a highly desirable feature in low power and battery power applications. The present invention permits an increase in the power supply rejection ratio (PSRR) for digital, analog, and especially mixed-signal integrated circuit designs by permitting various circuit blocks to have localized power regulation that is obtained from a common power supply plane within the integrated circuit framework. Finally, the present invention appears to be the only economically practical method of addressing the power supply regulation requirements of modern and future integrated microprocessor designs.

Owner:KLUGHART KEVIN MARK

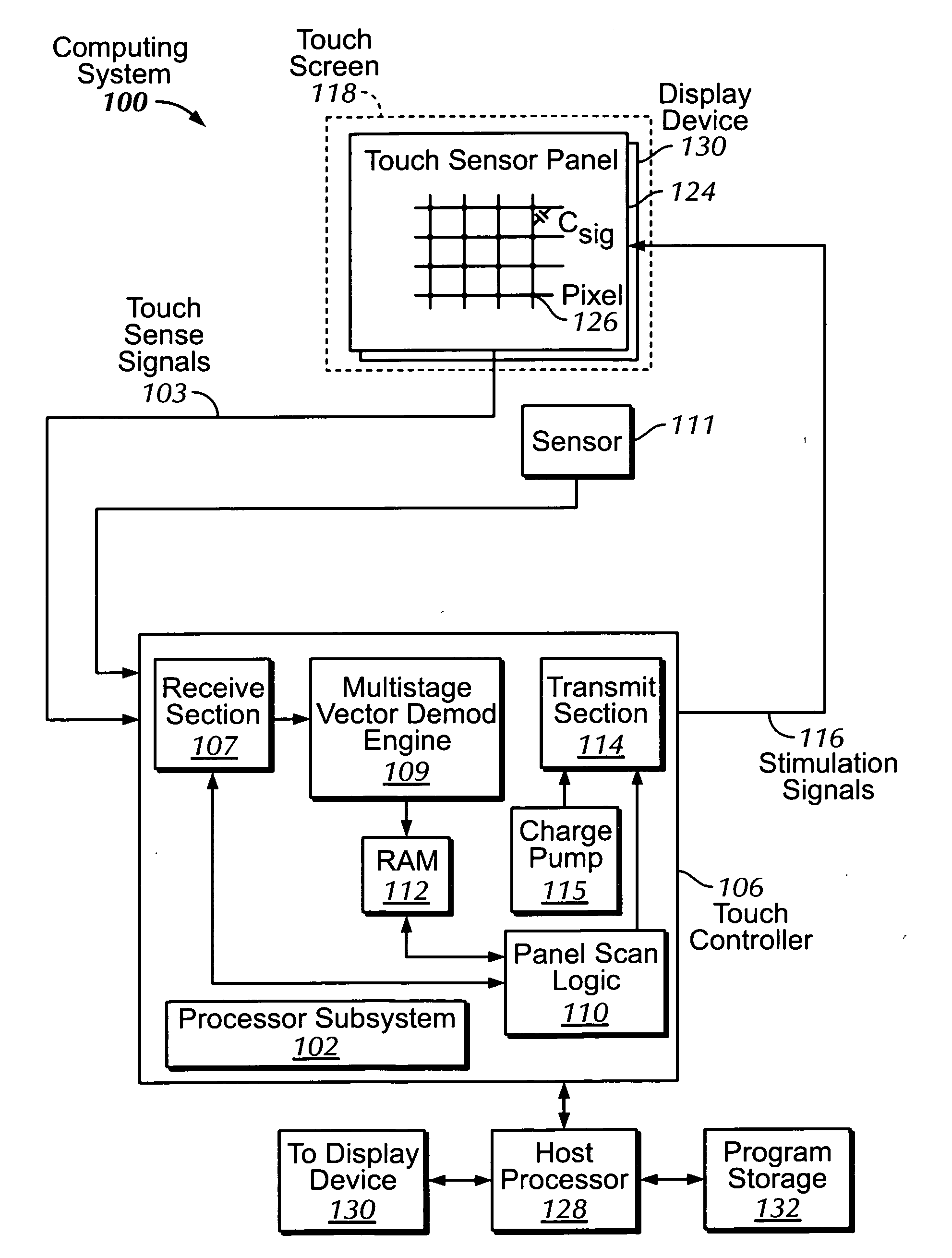

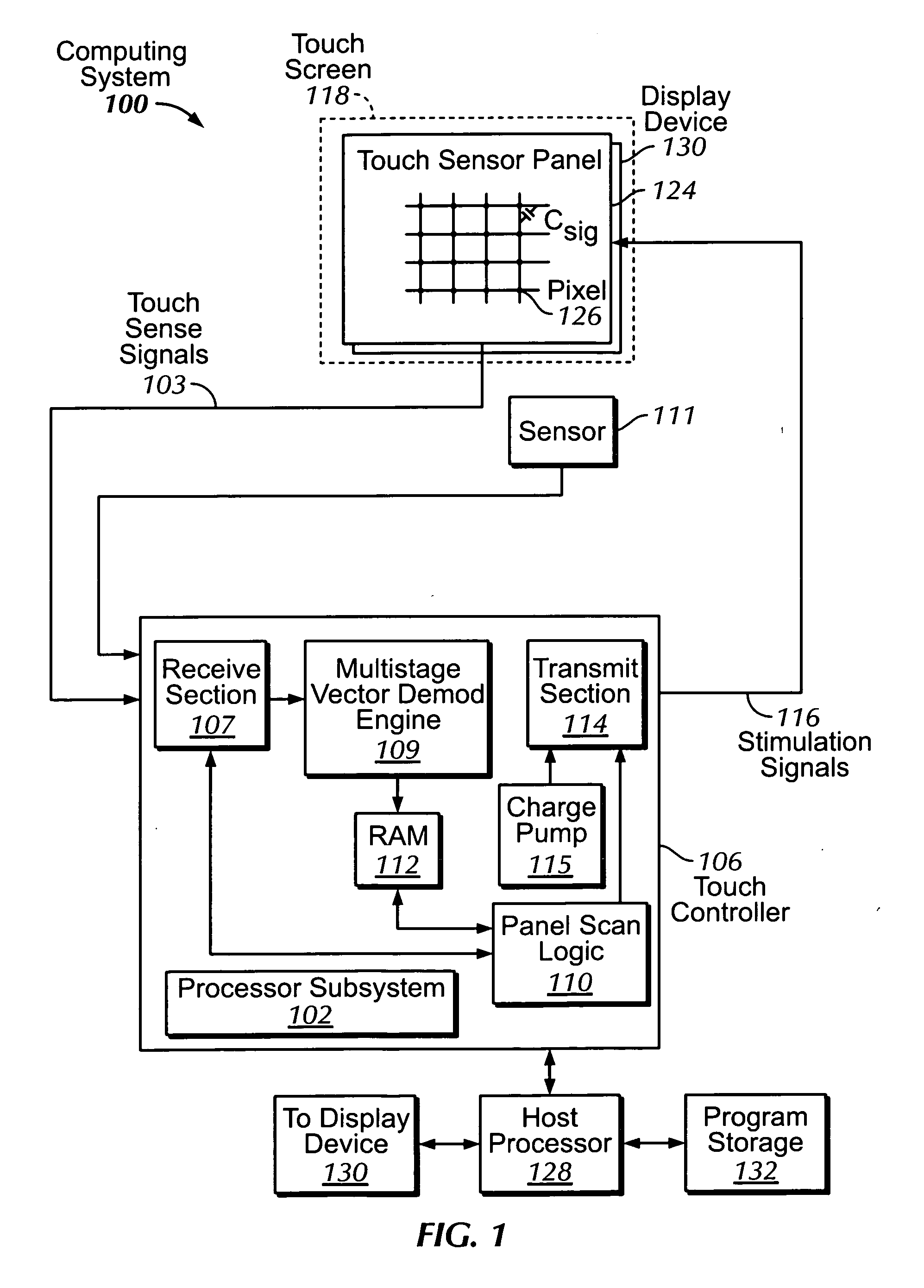

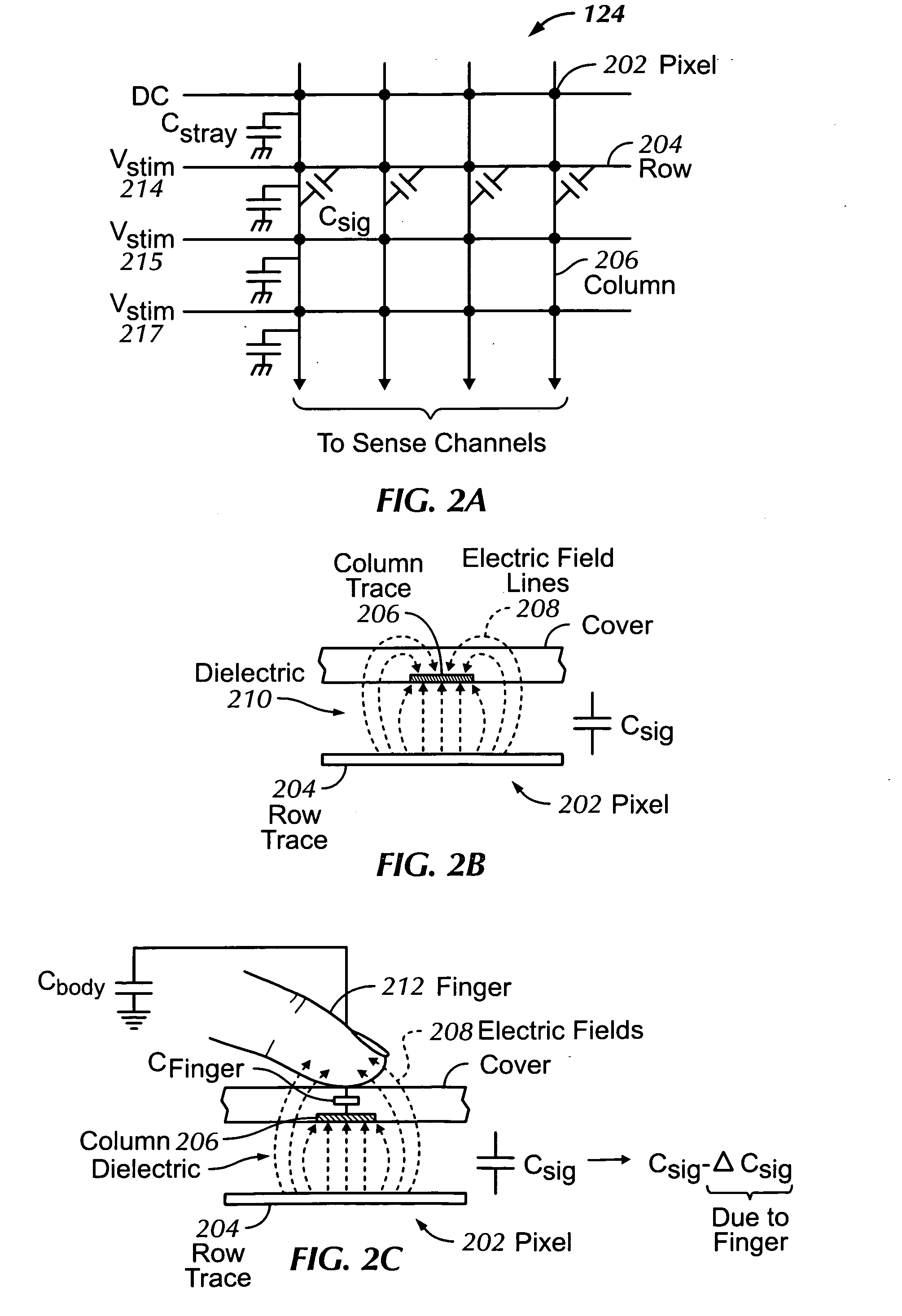

Single-chip multi-stimulus sensor controller

ActiveUS20100059295A1Transmission systemsCathode-ray tube indicatorsSingle chipFrequency demodulation

A multi-stimulus controller for a multi-touch sensor is formed on a single integrated circuit (single-chip). The multi-stimulus controller includes a transmit oscillator, a transmit signal section that generates a plurality of drive signals based on a frequency of the transmit oscillator, a plurality of transmit channels that transmit the drive signals simultaneously to drive the multi-touch sensor, a receive channel that receives a sense signal resulting from the driving of the multi-touch sensor, a receive oscillator, and a demodulation section that demodulates the received sense signal based on a frequency of the receive oscillator to obtain sensing results, the demodulation section including a demodulator and a vector operator.

Owner:APPLE INC

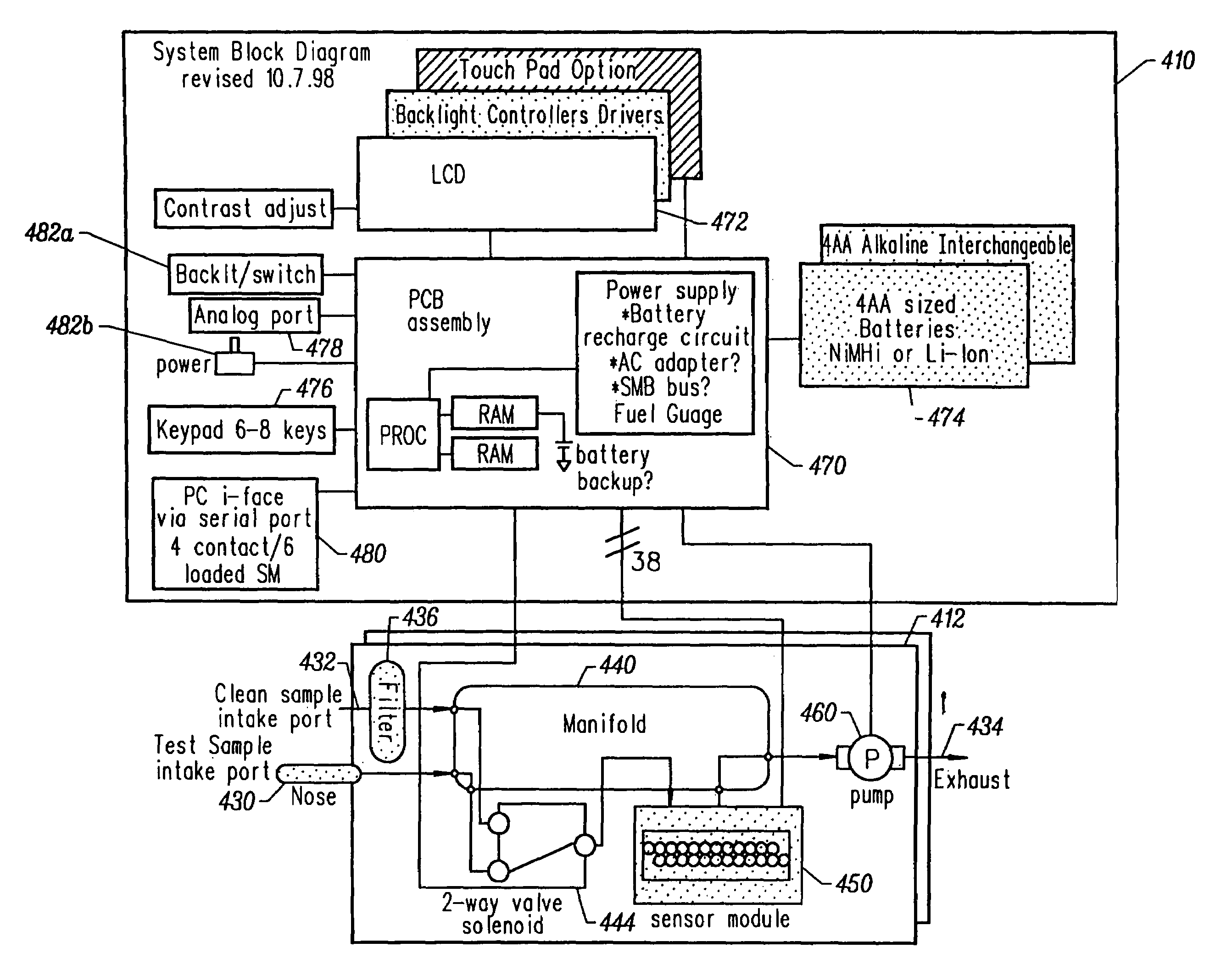

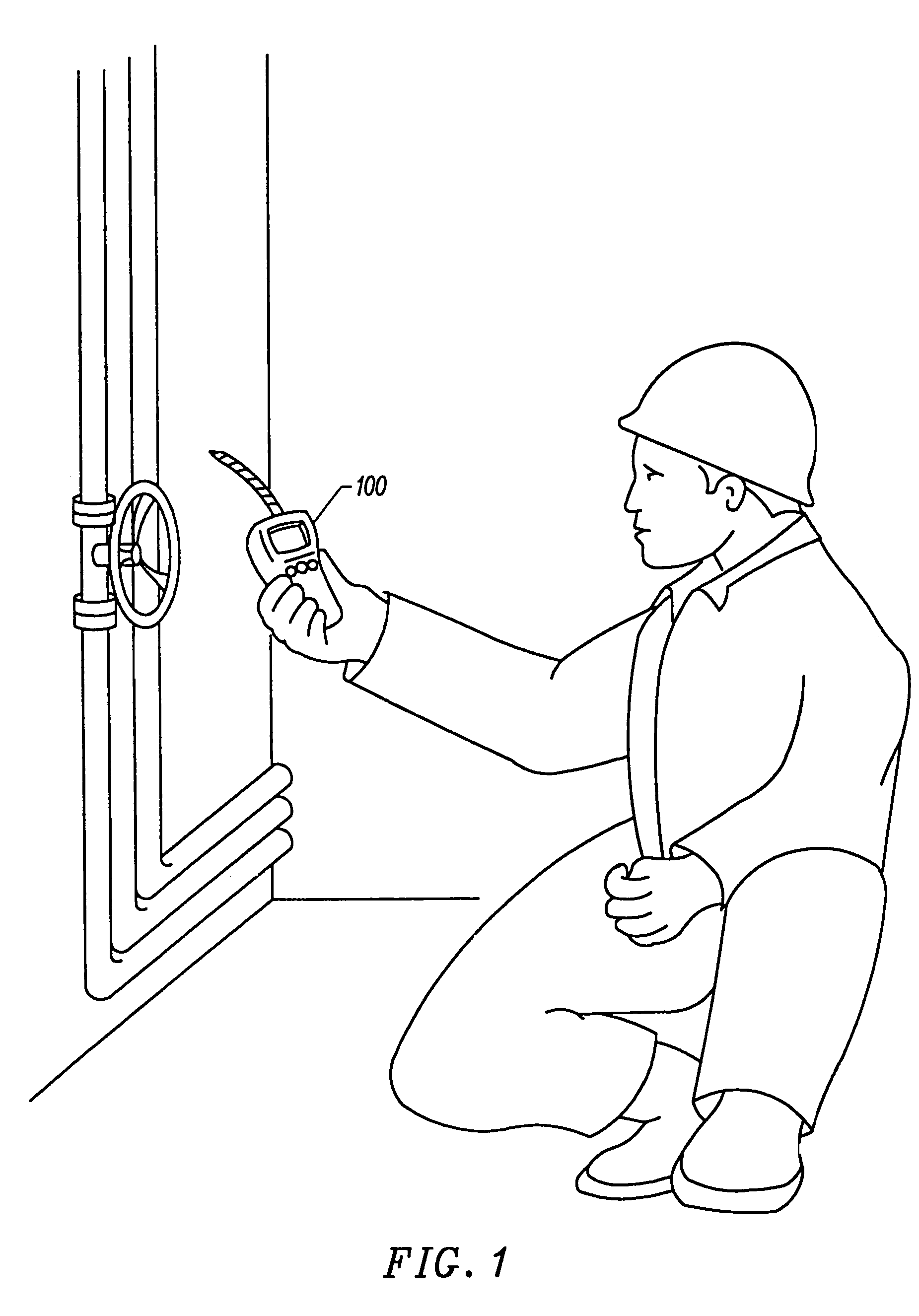

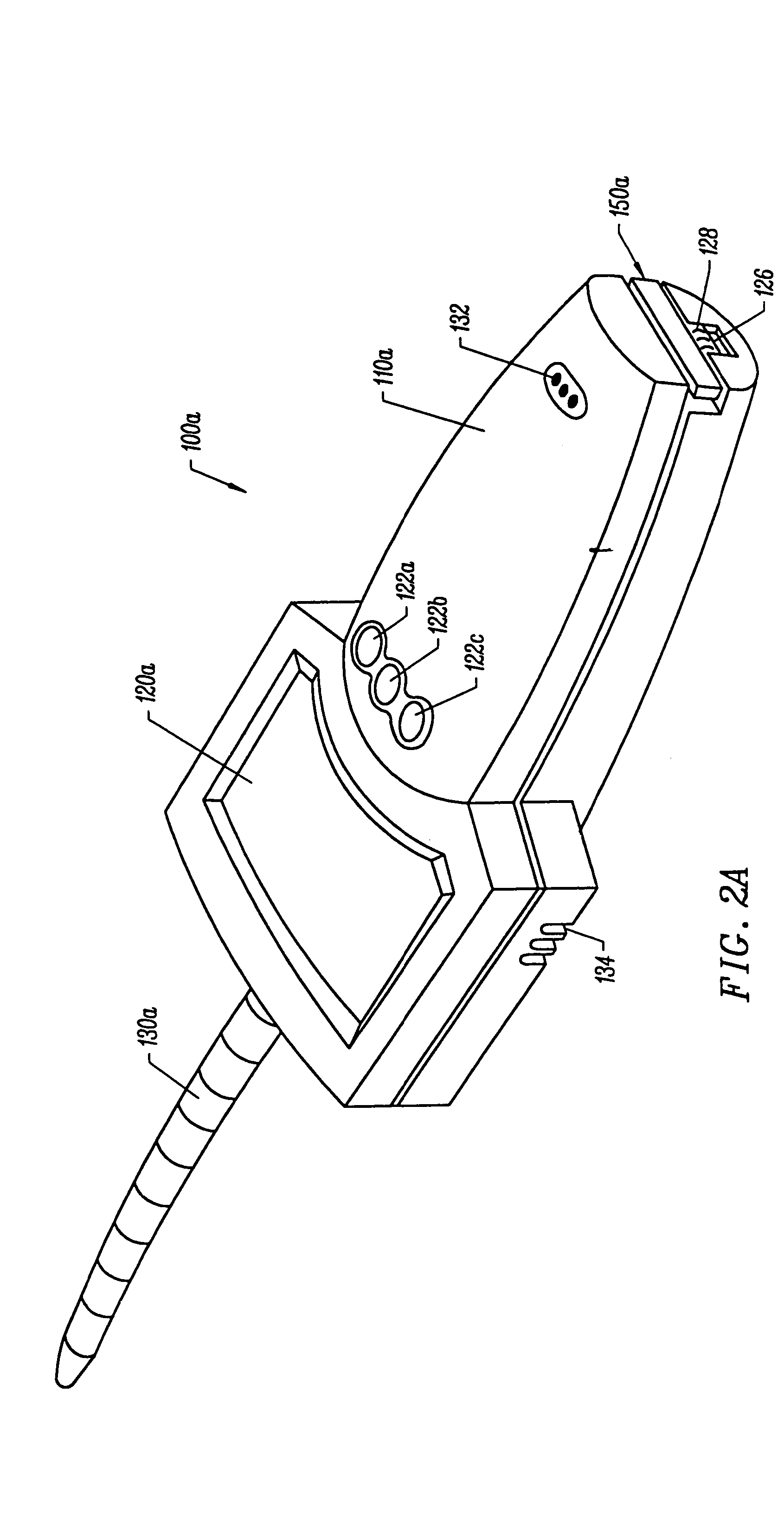

Apparatus, systems and methods for detecting and transmitting sensory data over a computer network

InactiveUS7089780B2Increase profitImprove performanceAnalysing fluids using sonic/ultrasonic/infrasonic wavesMaterial analysis by electric/magnetic meansElectrical resistance and conductanceThe Internet

A vapor sensing device that is sufficiently small and lightweight to be handheld, and also modular so as to allow the device to be conveniently adapted for use in sensing the presence and concentration of a wide variety of specified vapors. The device provides these benefits using a sensor module that incorporates a sample chamber and a plurality of sensors located on a chip releasably carried within or adjacent to the sample chamber. Optionally, the sensor module can be configured to be releasably plugged into a receptacle formed in the device. Vapors are directed to pass through the sample chamber, whereupon the sensors provide a distinct combination of electrical signals in response to each. The sensors of the sensor module can take the form of chemically sensitive resistors having resistances that vary according to the identity and concentration of an adjacent vapor. These chemically sensitive resistors can each be connected in series with a reference resistor, between a reference voltage and ground, such that an analog signal is established for each chemically sensitive resistor. The resulting analog signals are supplied to an analog-to-digital converter, to produce corresponding digital signals. These digital signals are appropriately analyzed for vapor identification. The device can then subsequently transmit the digital signals over a computer network, such as the Internet, for analysis at a remote location.

Owner:SMITHS DETECTION

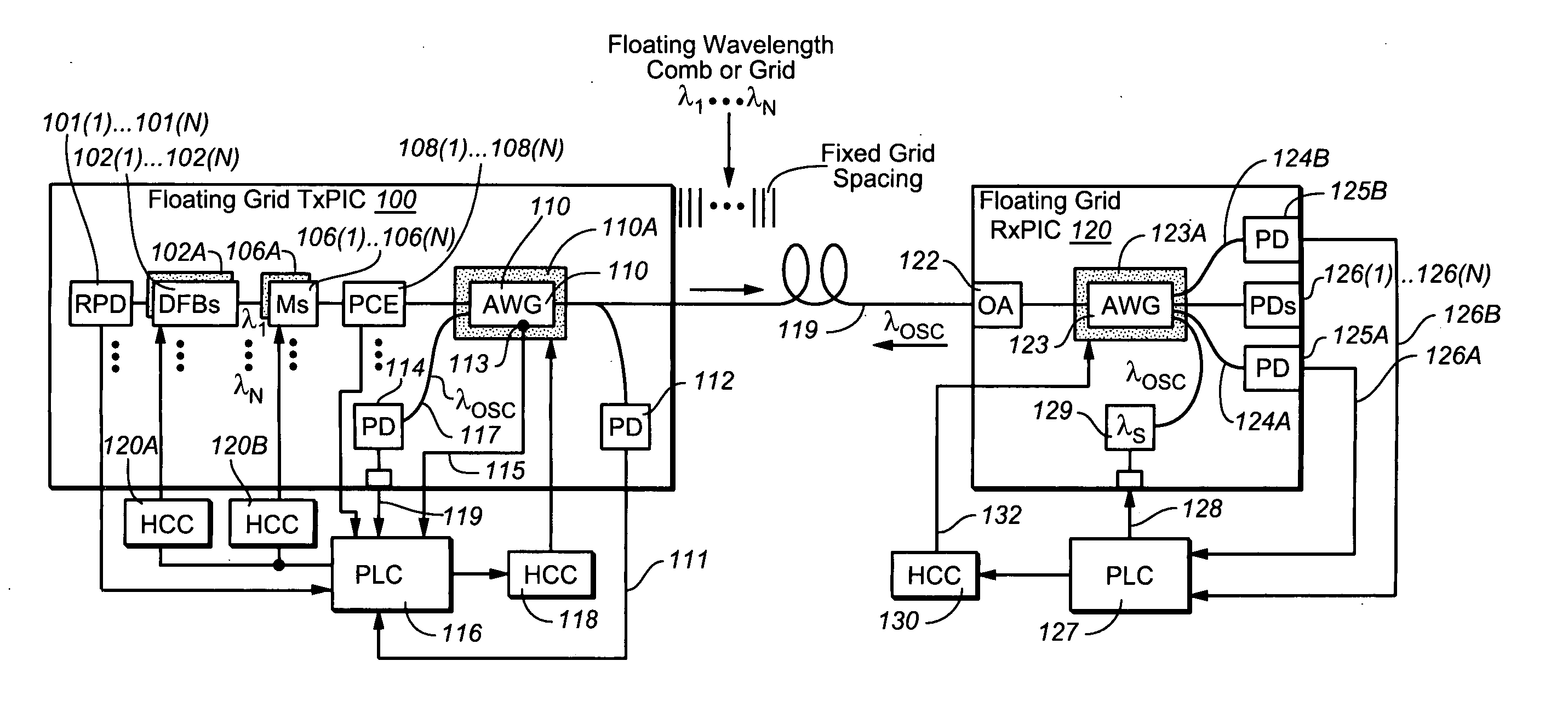

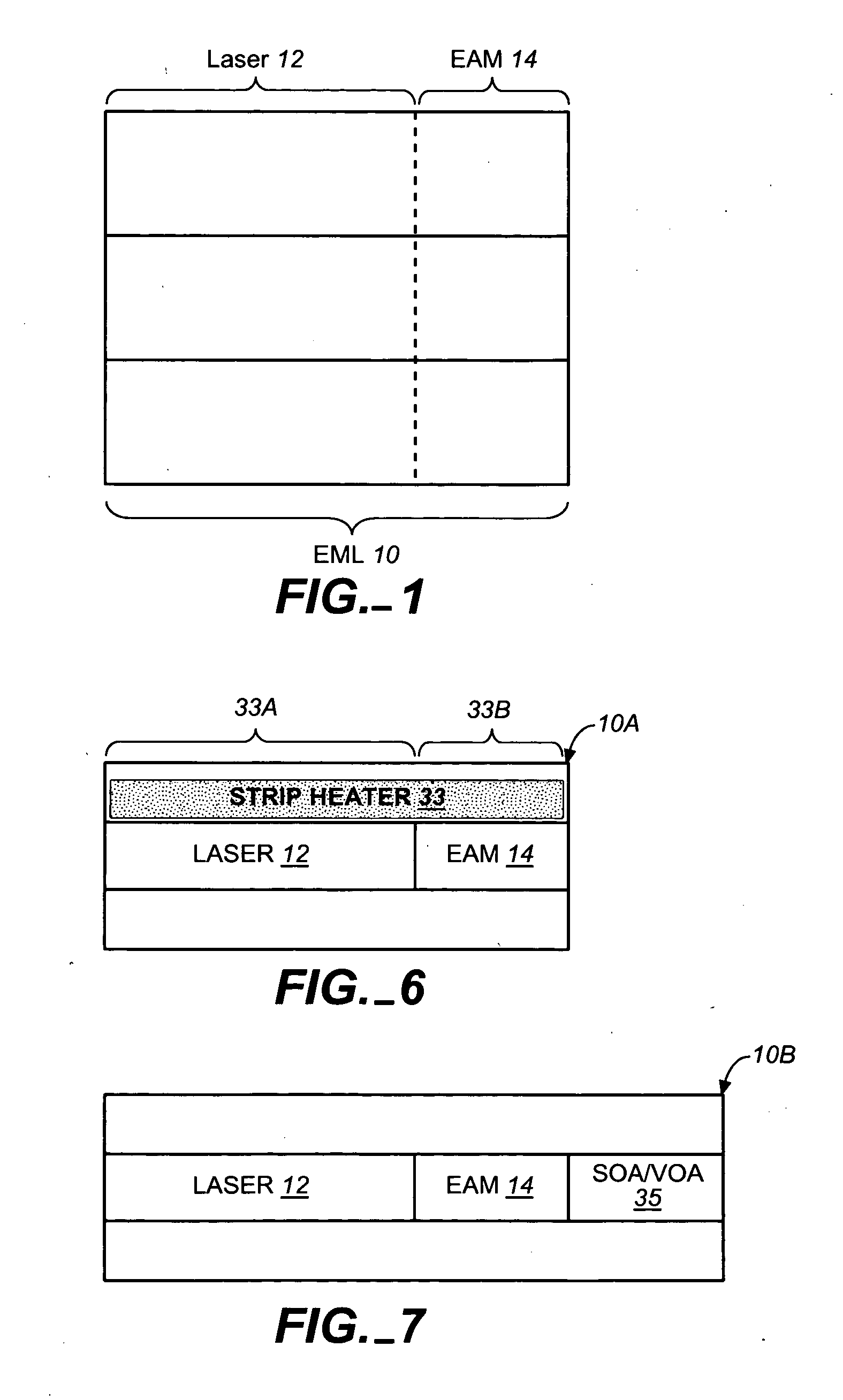

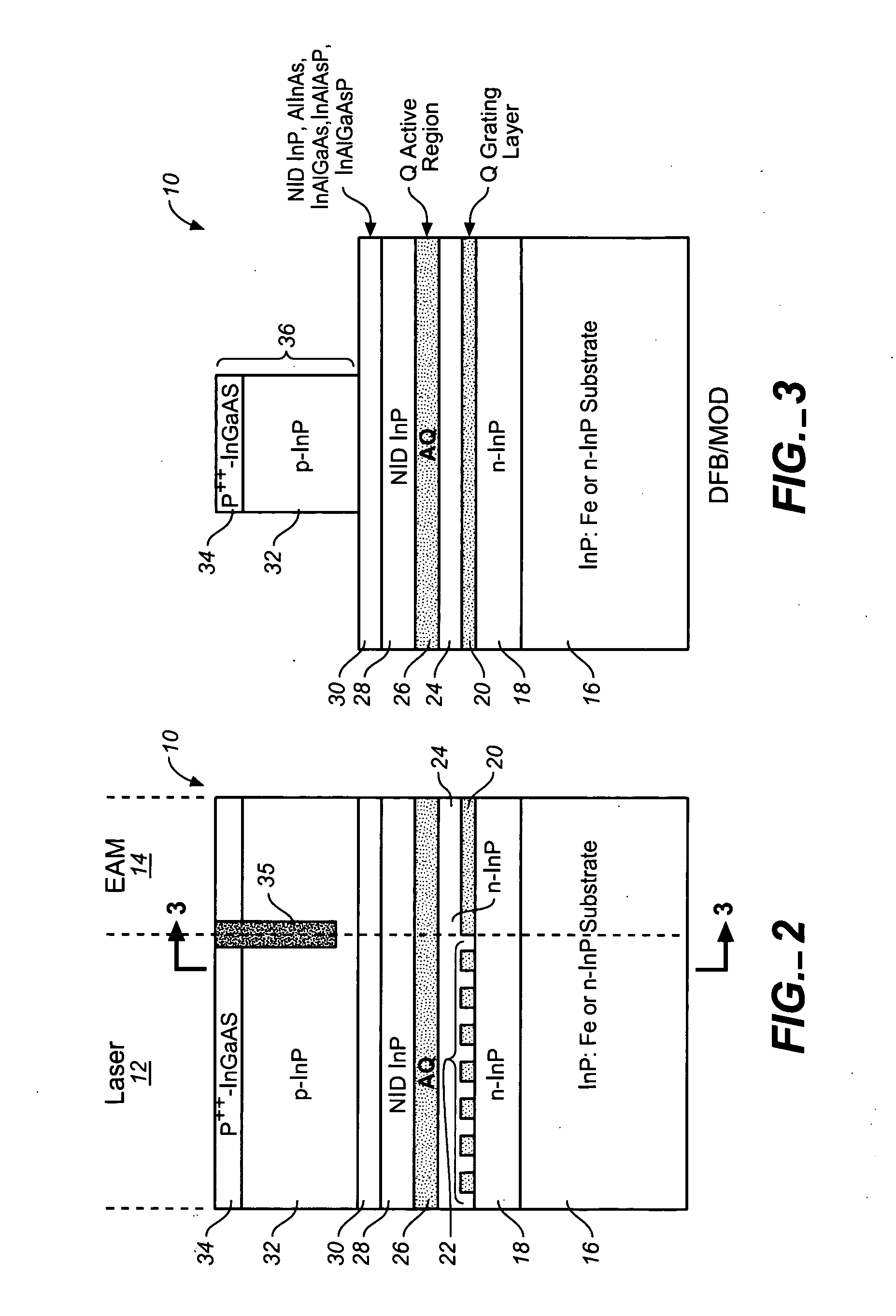

Coolerless photonic integrated circuits (PICs) for WDM transmission networks and PICs operable with a floating signal channel grid changing with temperature but with fixed channel spacing in the floating grid

ActiveUS20050249509A1Requirements for a hermetically sealed package are substantially relievedEasy to controlLaser optical resonator constructionSemiconductor laser arrangementsElectro-absorption modulatorHermetic packaging

A coolerless photonic integrated circuit (PIC), such as a semiconductor electro-absorption modulator / laser (EML) or a coolerless optical transmitter photonic integrated circuit (TxPIC), may be operated over a wide temperature range at temperatures higher then room temperature without the need for ambient cooling or hermetic packaging. Since there is large scale integration of N optical transmission signal WDM channels on a TxPIC chip, a new DWDM system approach with novel sensing schemes and adaptive algorithms provides intelligent control of the PIC to optimize its performance and to allow optical transmitter and receiver modules in DWDM systems to operate uncooled. Moreover, the wavelength grid of the on-chip channel laser sources may thermally float within a WDM wavelength band where the individual emission wavelengths of the laser sources are not fixed to wavelength peaks along a standardized wavelength grid but rather may move about with changes in ambient temperature. However, control is maintained such that the channel spectral spacing between channels across multiple signal channels, whether such spacing is periodic or aperiodic, between adjacent laser sources in the thermally floating wavelength grid are maintained in a fixed relationship. Means are then provided at an optical receiver to discover and lock onto floating wavelength grid of transmitted WDM signals and thereafter demultiplex the transmitted WDM signals for OE conversion.

Owner:INFINERA CORP

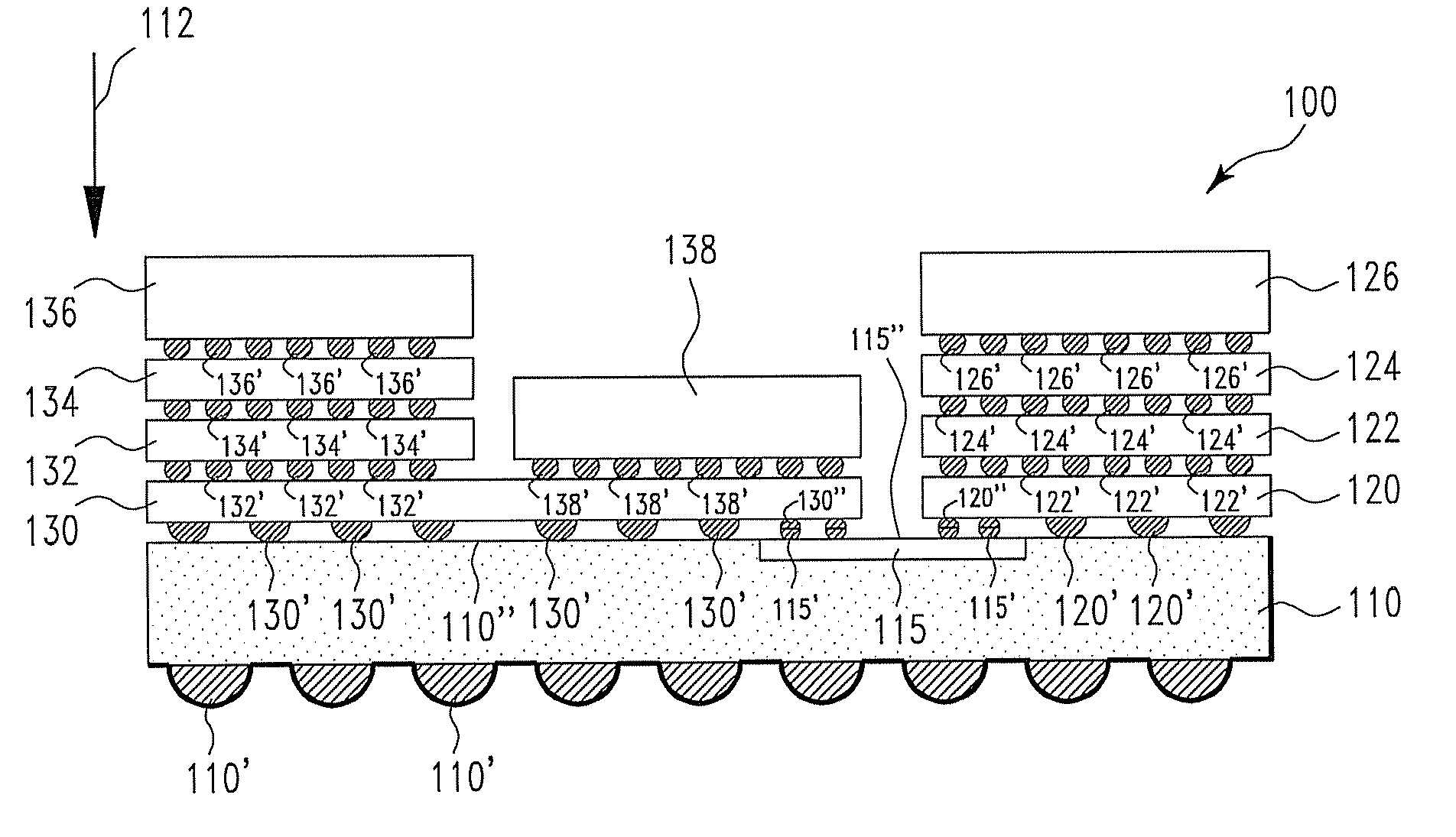

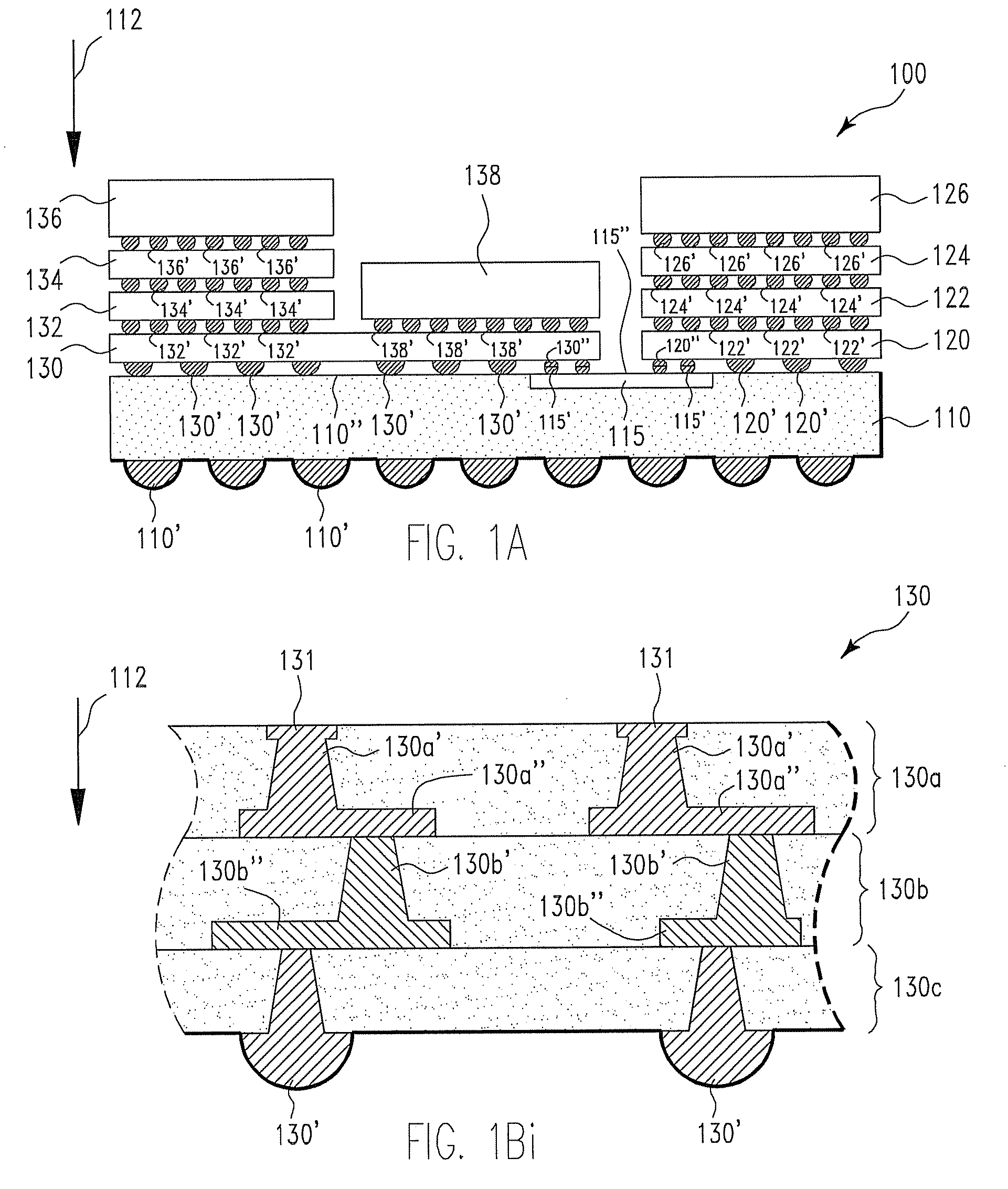

Bridges for interconnecting interposers in multi-chip integrated circuits

ActiveUS20090267238A1Semiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A structure and a method for forming the same. The structure includes a substrate, a first interposer on the substrate, a second interposer on the substrate, and a first bridge. The first and second interposers are electrically connected to the substrate. The first bridge is electrically connected to the first and second interposers.

Owner:GLOBALFOUNDRIES US INC

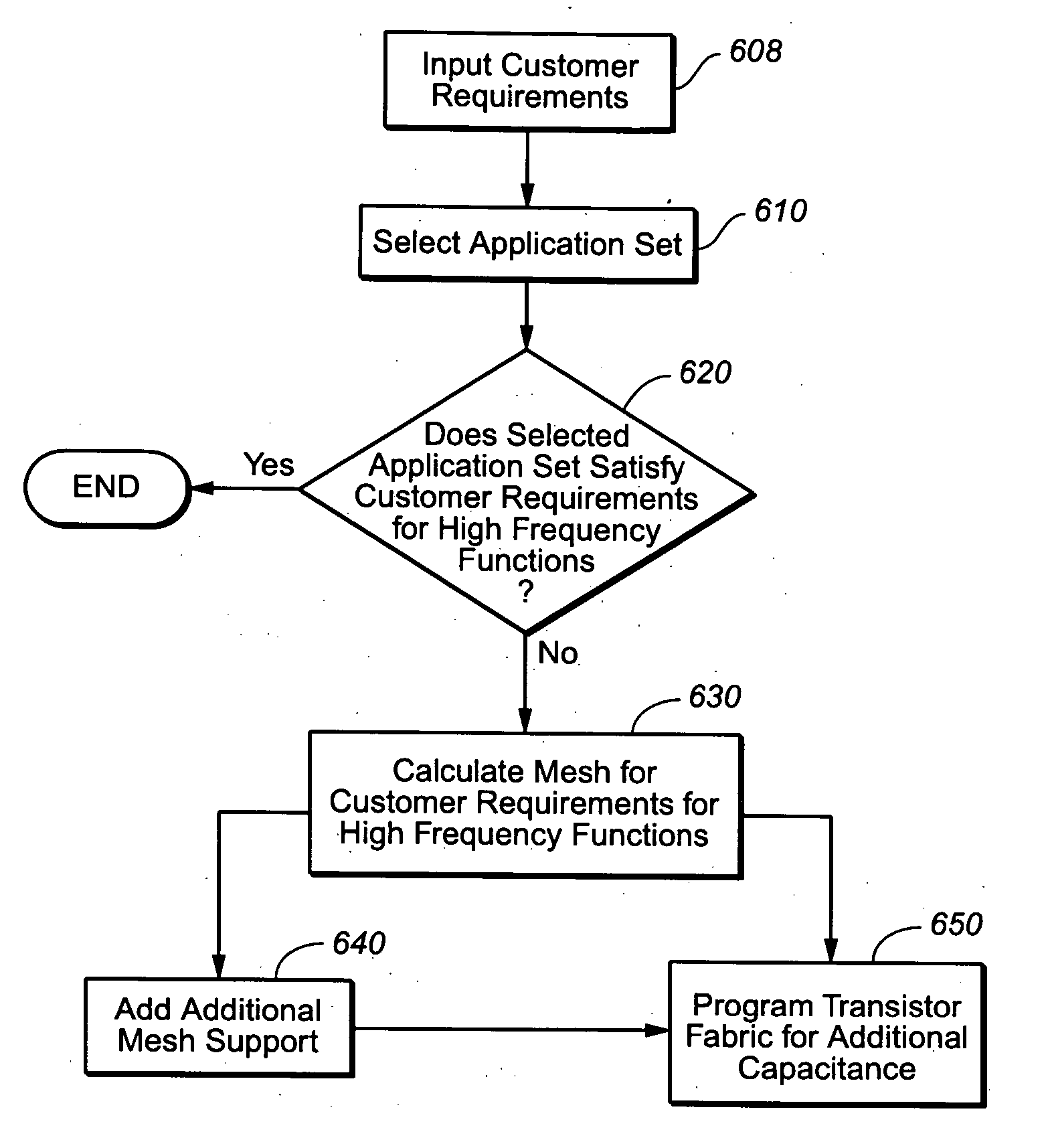

Power mesh for multiple frequency operation of semiconductor products

InactiveUS20060123376A1Decoupling capacitanceIncrease speedComputer programmed simultaneously with data introductionCAD circuit designCapacitanceTransceiver

The design of integrated circuits, i.e., semiconductor products, is made easier with a semiconductor platform having versatile power mesh that is capable of supporting simultaneous operations having different frequencies on the semiconductor product; e.g., higher frequency operations may be embedded as diffused blocks within the lower layers or may be programmed from a configurable transistor fabric above the diffused layers. Preferably the power mesh is located above the layers having the operations requiring the different frequencies, and may be fixed in an application set given to a chip designer or may be configurable by the designer her / himself. For example, to support high speed communications adjacent an embedded high speed data transceiver, the transistor fabric may be programmed as a data link layer having higher performance requirements than the rest of the integrated circuit. The data link layer may be connected to one of the localized grids of the versatile power mesh which may have an increased density and / or wider strap width of a power / ground grid. Additional decoupling capacitance can be embedded in the lower layers of the semiconductor product and / or can be programmed from the configurable transistors fabric.

Owner:AVAGO TECH INT SALES PTE LTD

Compact millimeter wave packages with integrated antennas

ActiveUS20100327068A1Simultaneous aerial operationsSemiconductor/solid-state device detailsEngineeringIntegrated antenna

A radio-frequency integrated circuit chip package has at least one integrated antenna. The package includes at least one generally planar ground plane formed with at least one slot therein. A first substrate structure has an outer surface and an inner surface. The at least one generally planar ground plane is formed on the outer surface of the first substrate structure. At least one feed line is spaced inwardly from the ground plane and parallel thereto. The at least one feed line has an inner surface and an outer surface and is a transmission line formed on the inner surface of the first substrate structure with the outer surface of the at least one feed line adjacent the inner surface of the first substrate structure. At least one radio frequency chip is coupled to the feed line and the ground plane. A second substrate structure, spaced inwardly from the feed line, defines a chip-receiving cavity. The chip is located in the chip-receiving cavity. The inner surface of the at least one feed line borders the chip-receiving cavity. An antenna patch may be provided. Planar phased array embodiments, assemblies with motherboards and heat sinks, and fabrication techniques are also disclosed.

Owner:GLOBALFOUNDRIES US INC +1

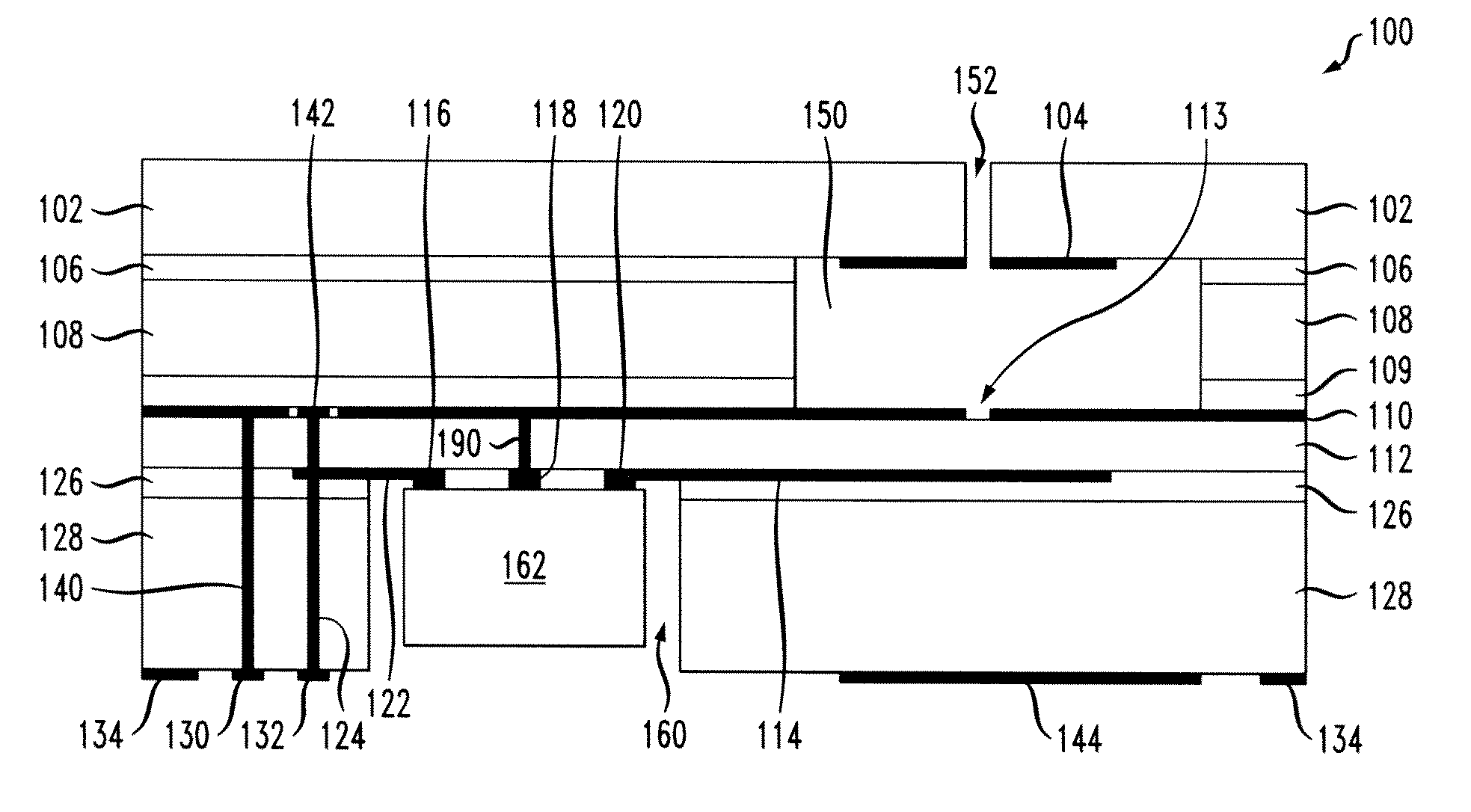

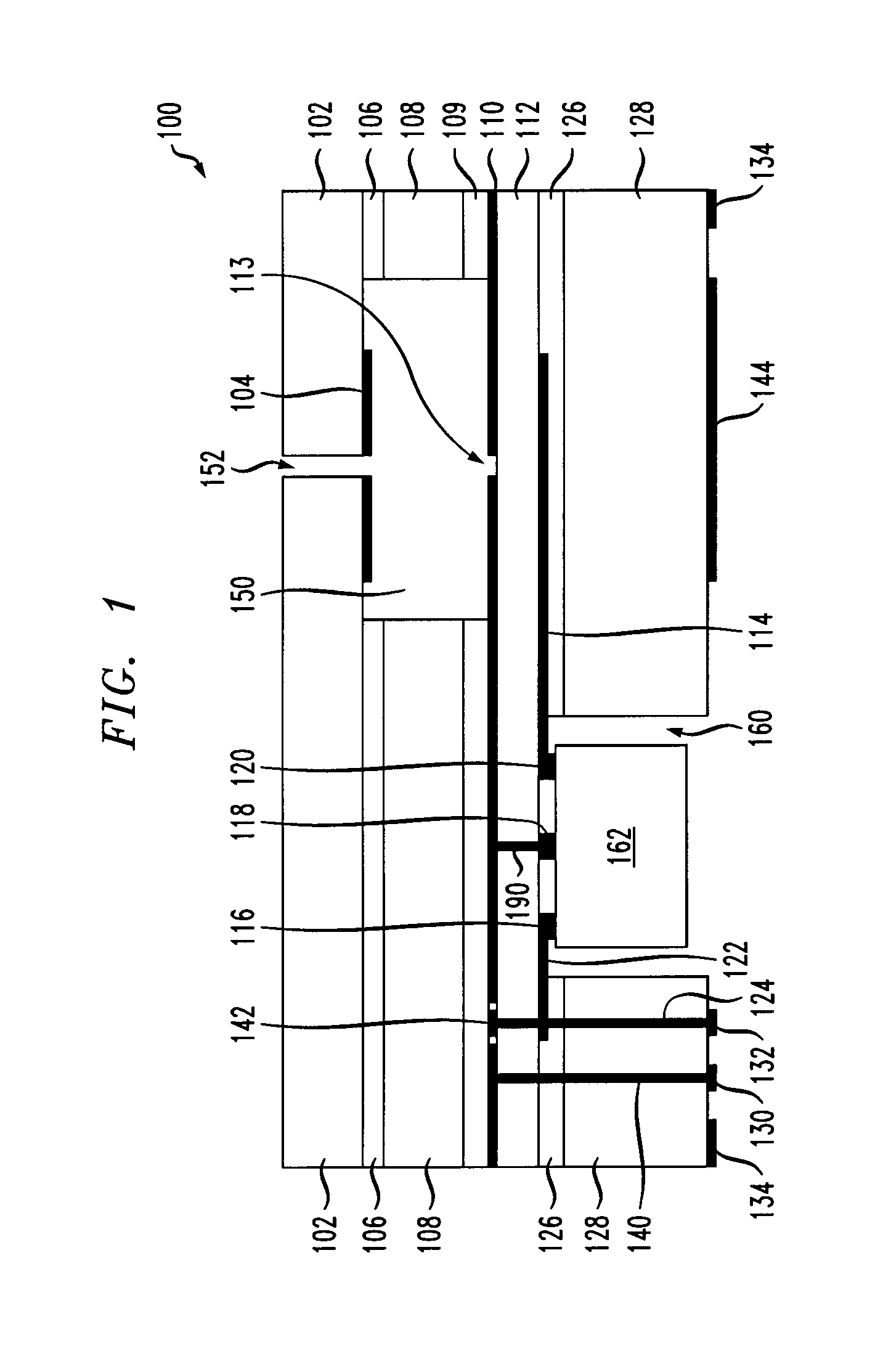

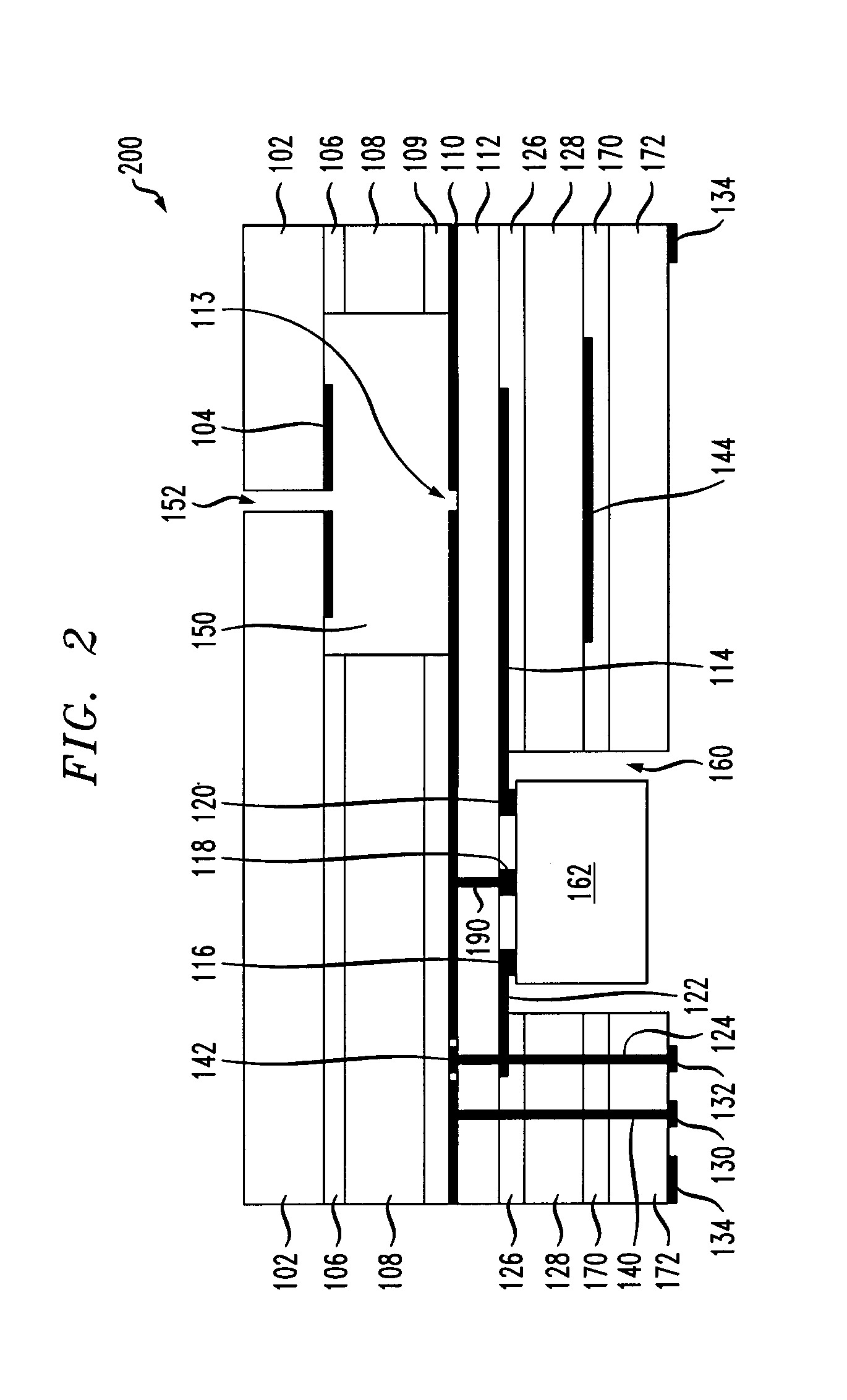

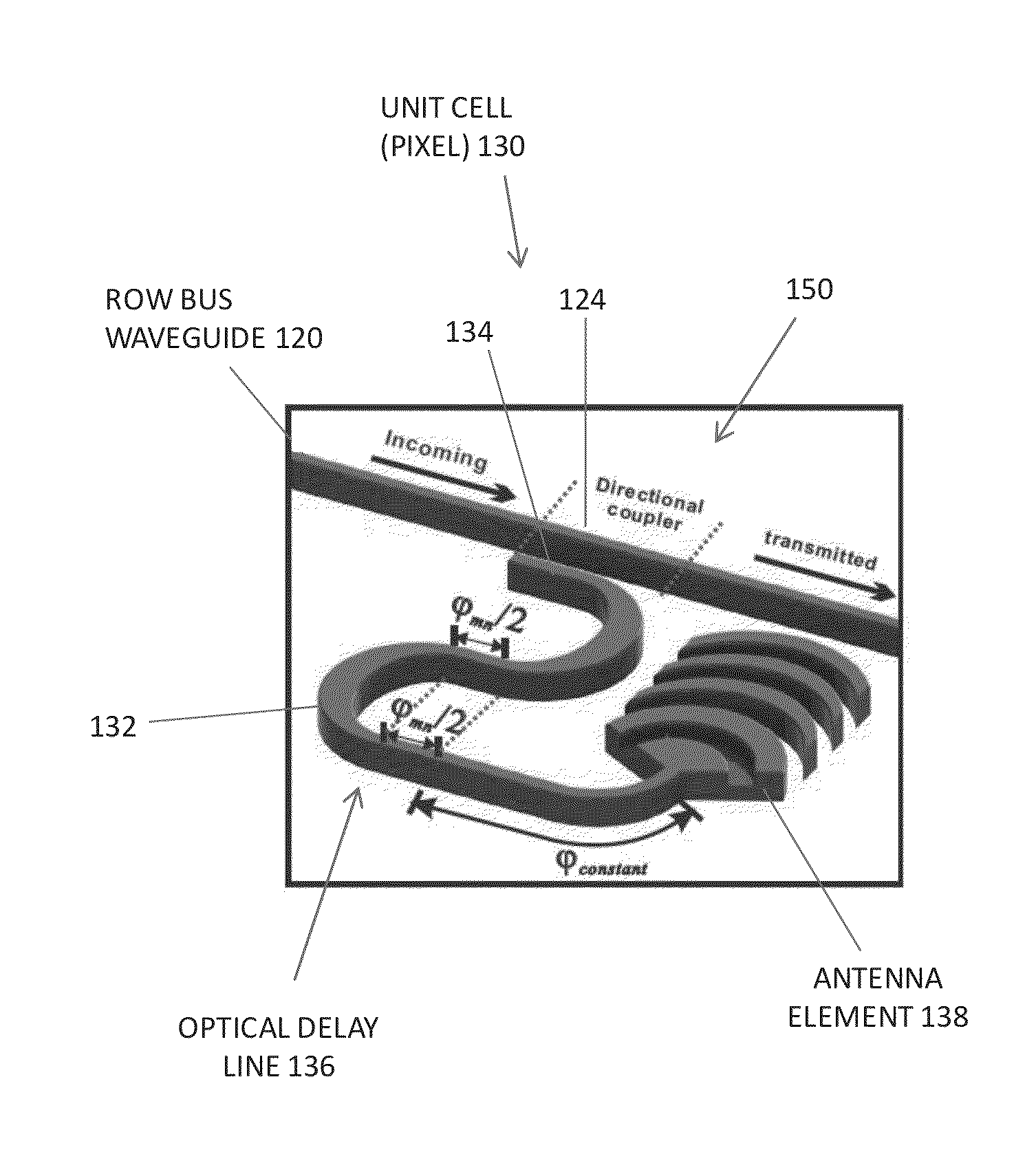

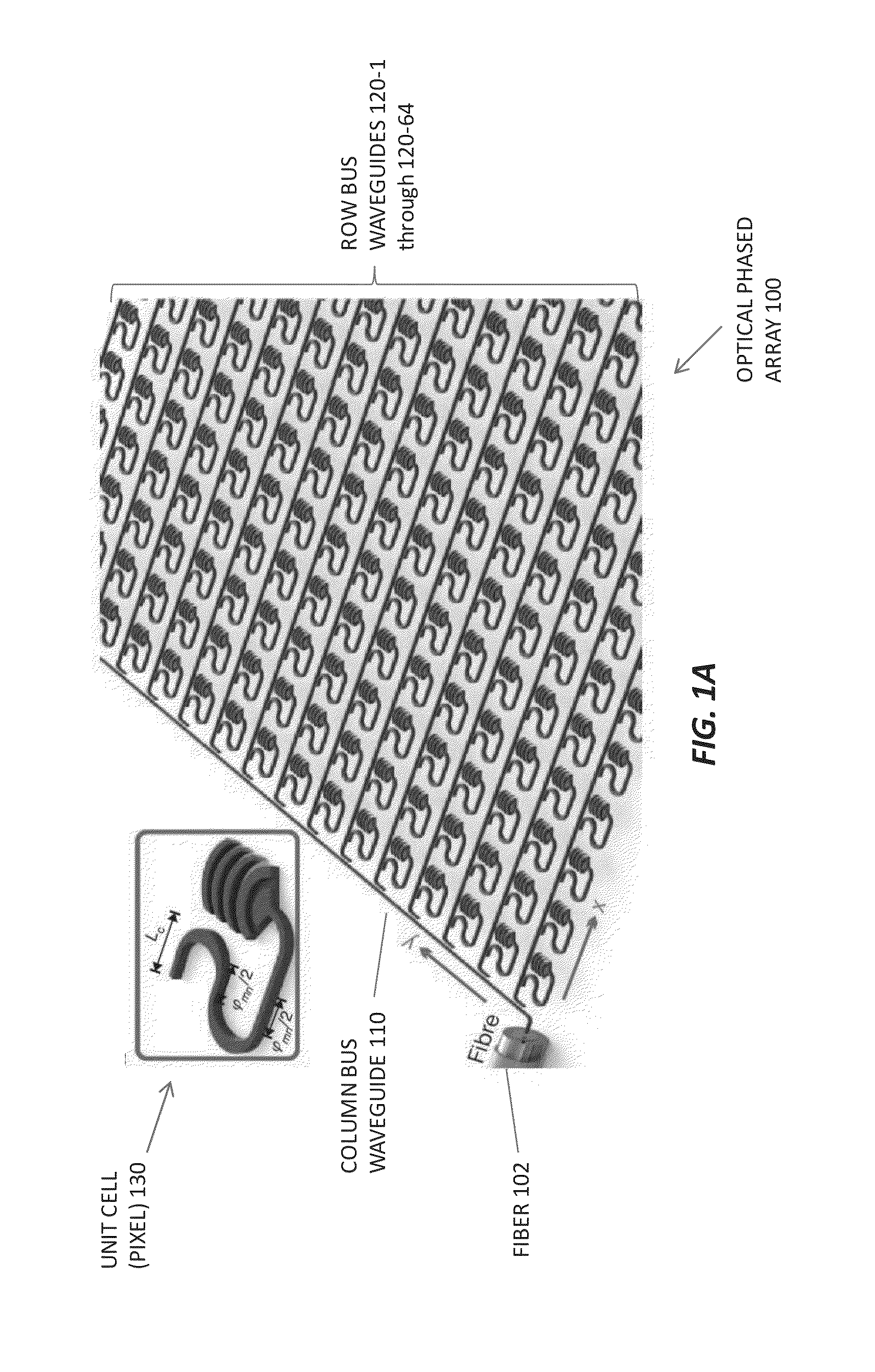

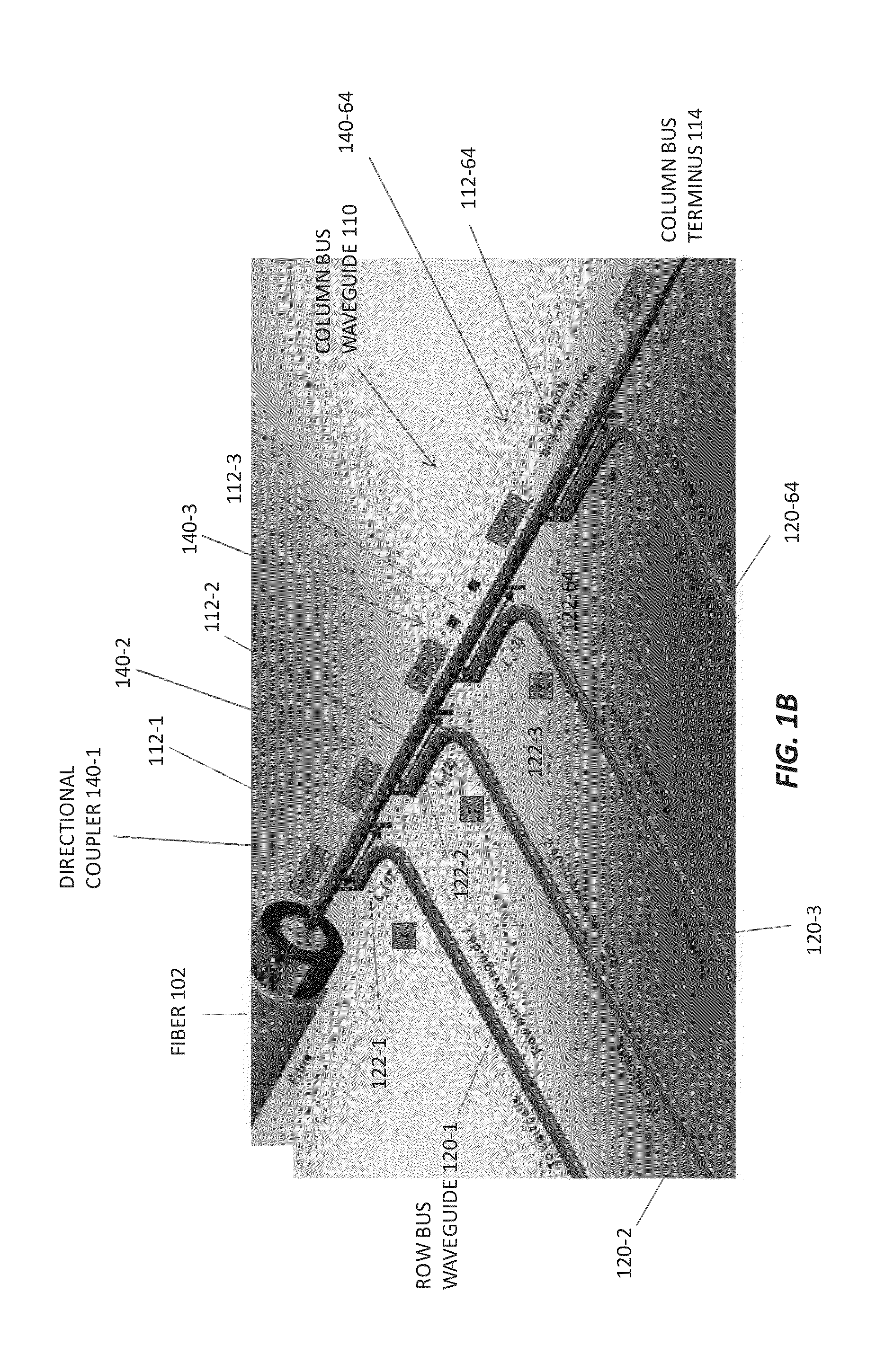

Optical phased arrays

ActiveUS20140192394A1Compensate for such errorCoupling light guidesNon-linear opticsPhysicsOxide semiconductor

An optical phased array formed of a large number of nanophotonic antenna elements can be used to project complex images into the far field. These nanophotonic phased arrays, including the nanophotonic antenna elements and waveguides, can be formed on a single chip of silicon using complementary metal-oxide-semiconductor (CMOS) processes. Directional couplers evanescently couple light from the waveguides to the nanophotonic antenna elements, which emit the light as beams with phases and amplitudes selected so that the emitted beams interfere in the far field to produce the desired pattern. In some cases, each antenna in the phased array may be optically coupled to a corresponding variable delay line, such as a thermo-optically tuned waveguide or a liquid-filled cell, which can be used to vary the phase of the antenna's output (and the resulting far-field interference pattern).

Owner:MASSACHUSETTS INST OF TECH

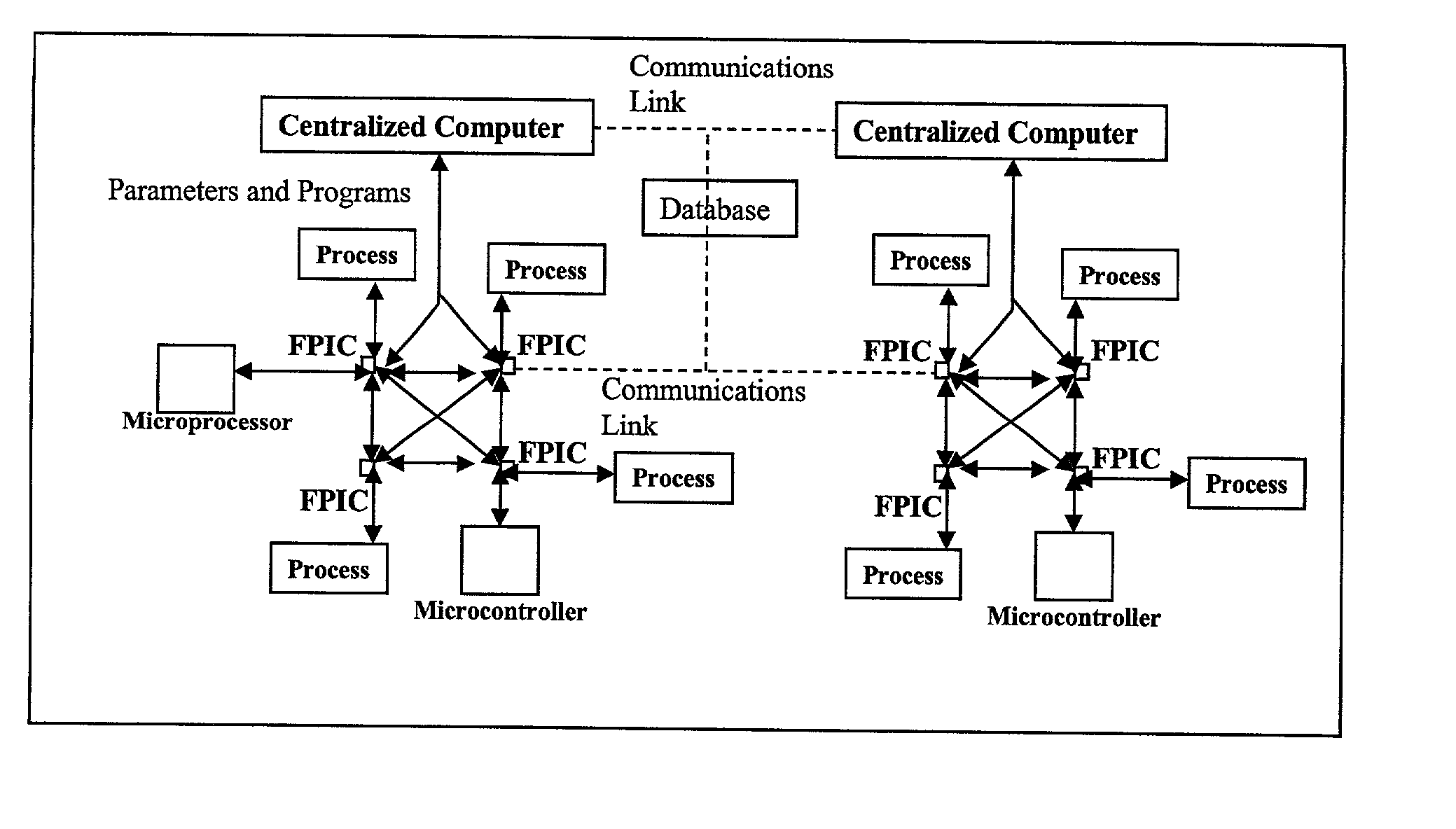

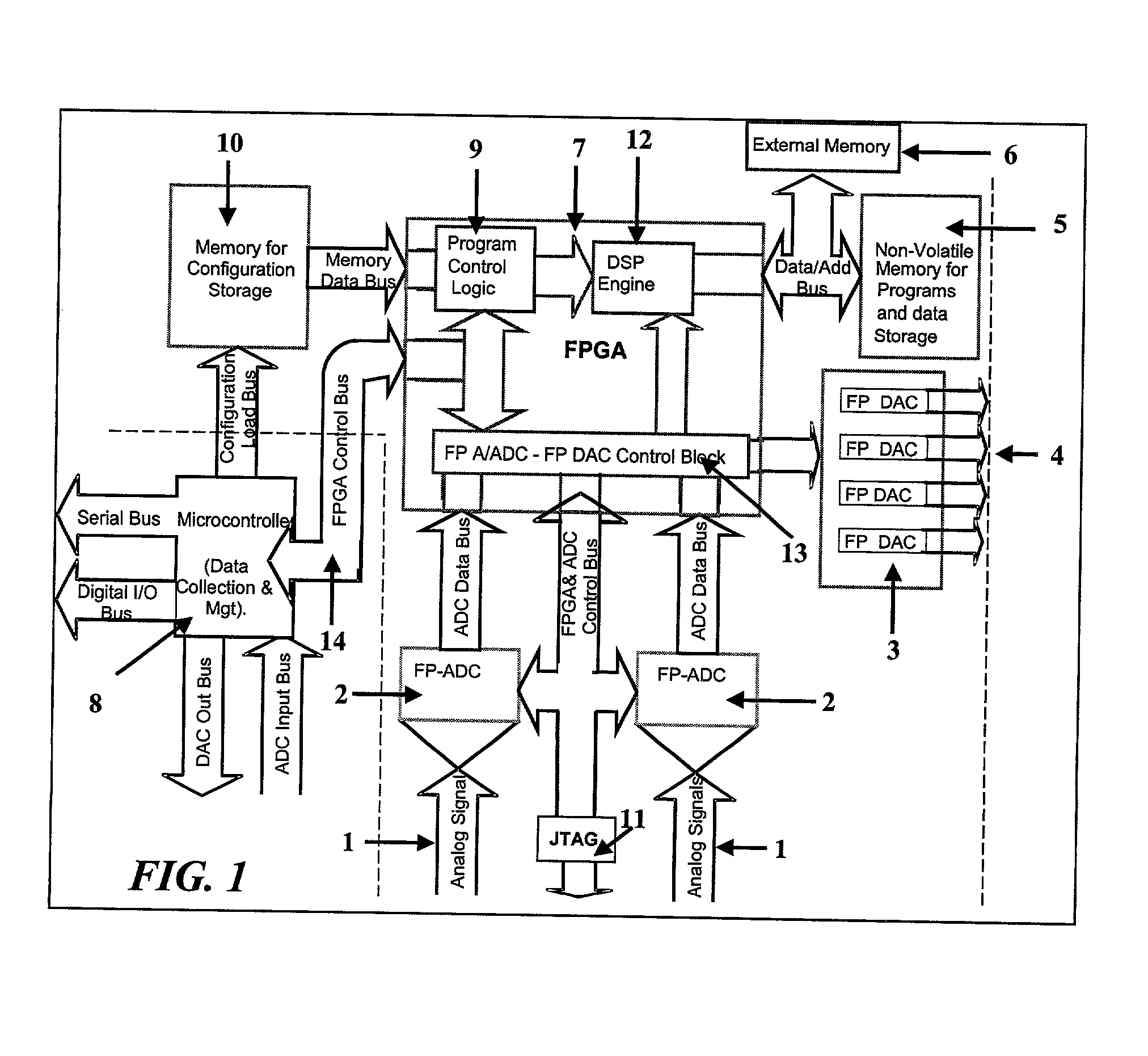

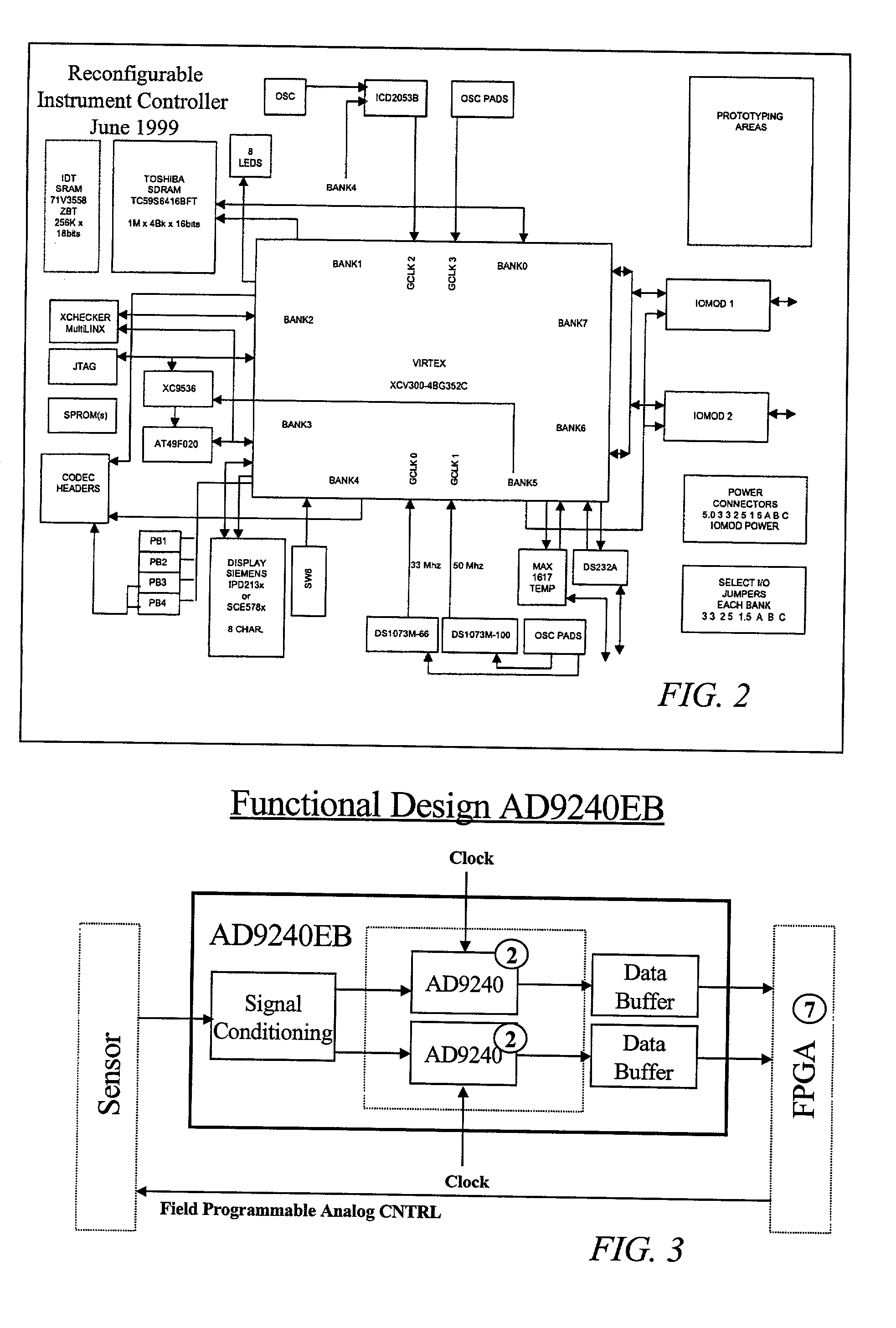

High performance hybrid micro-computer

The Field Programmable Instrument Controller (FPIC) is a stand-alone low to high performance, clocked or unclocked multi-processor that operates as a microcontroller with versatile interface and operating options. The FPIC can also be used as a concurrent processor for a microcontroller or other processor. A tightly coupled Multiple Chip Module design incorporates non-volatile memories, a large field programmable gate array (FPGA), field programmable high precision analog to digital converters, field programmable digital to analog signal generators, and multiple ports of external mass data storage and control processors. The FPIC has an inherently open architecture with in-situ reprogrammability and state preservation capability for discontinuous operations. It is designed to operate in multiple roles, including but not limited to, a high speed parallel digital signal processing; co-processor for precision control feedback during analog or hybrid computing; high speed monitoring for condition based maintenance; and distributed real time process control. The FPIC is characterized by low power with small size and weight.

Owner:BLEMEL KENNETH G

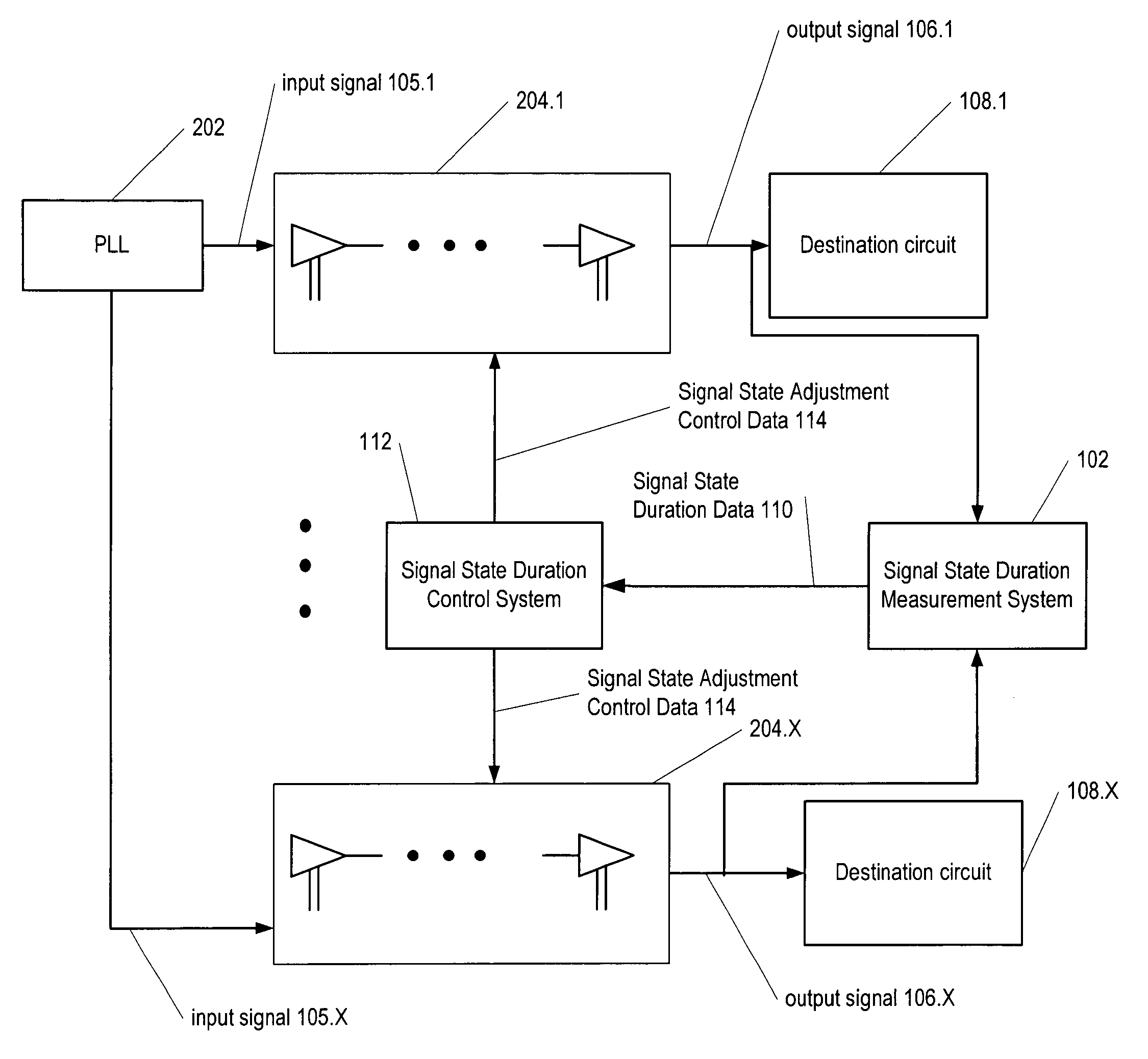

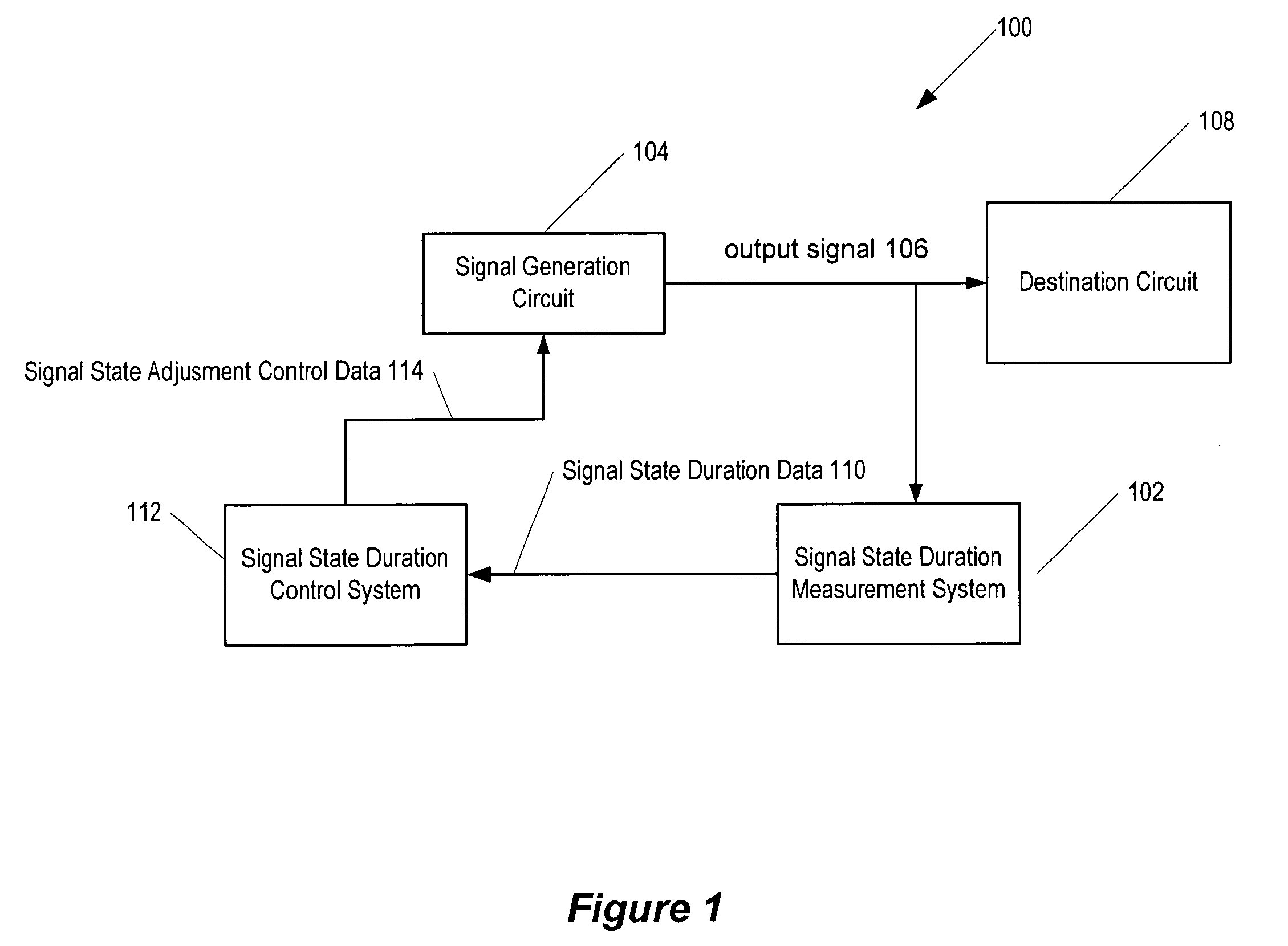

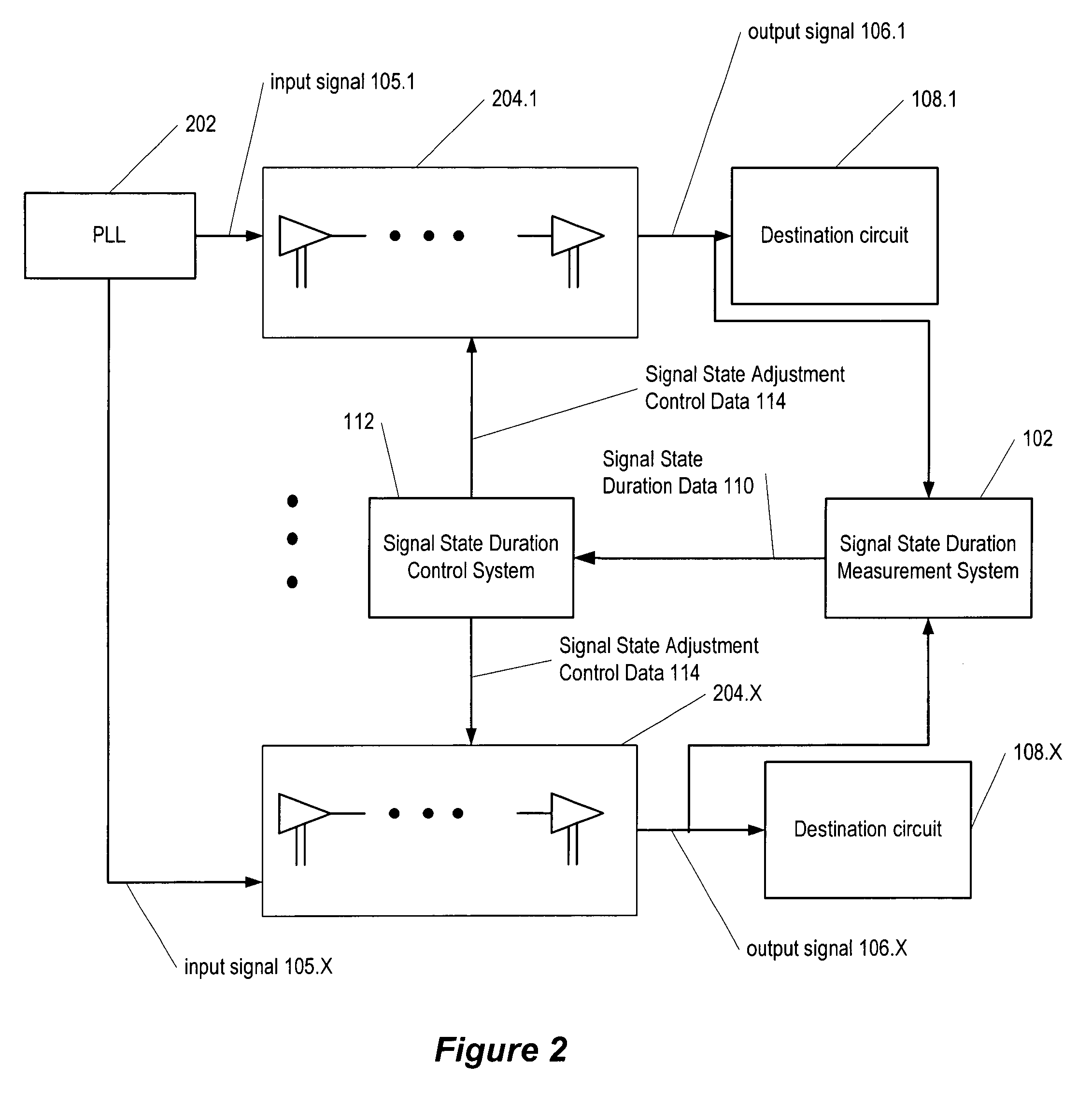

On-chip signal state duration measurement and adjustment

Signal state durations, such as the pulse-width, of on-chip signals are often critical to the successful operation of an integrated circuit. The signal state durations measured by on-chip technology provide signal state duration information to an on-chip signal state duration control system. The signal state duration control system uses the information to adjust the signal state duration of an on-chip signal. In one embodiment, the signal state duration of the on-chip signal is the pulse width of the on-chip signal. The signal duration measurement and adjustment system is, for example, useful for measuring the state duration of signals such as self-resetting signals, which are difficult to externally measure and adjust signal state durations using on-chip technology.

Owner:ORACLE INT CORP

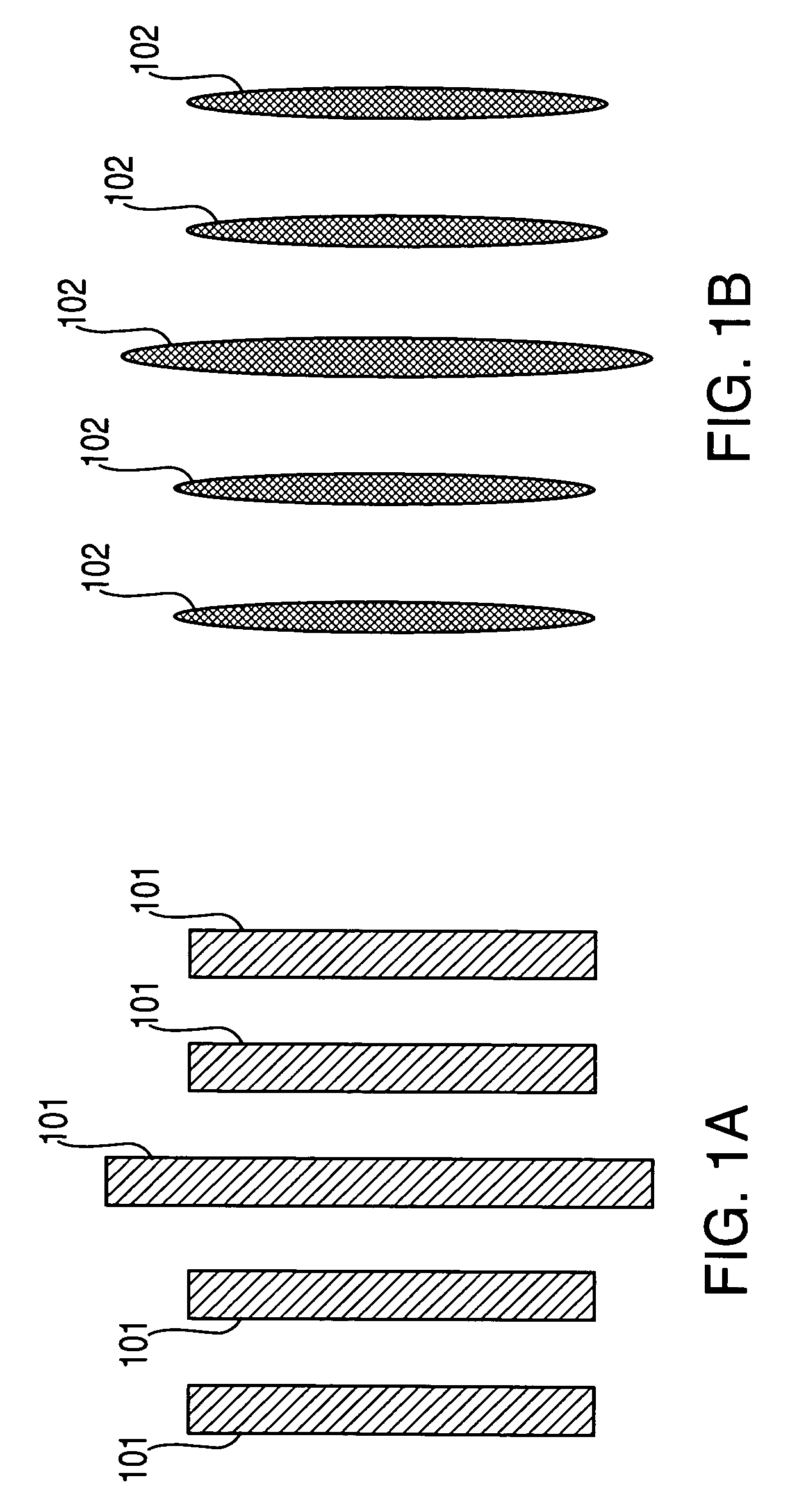

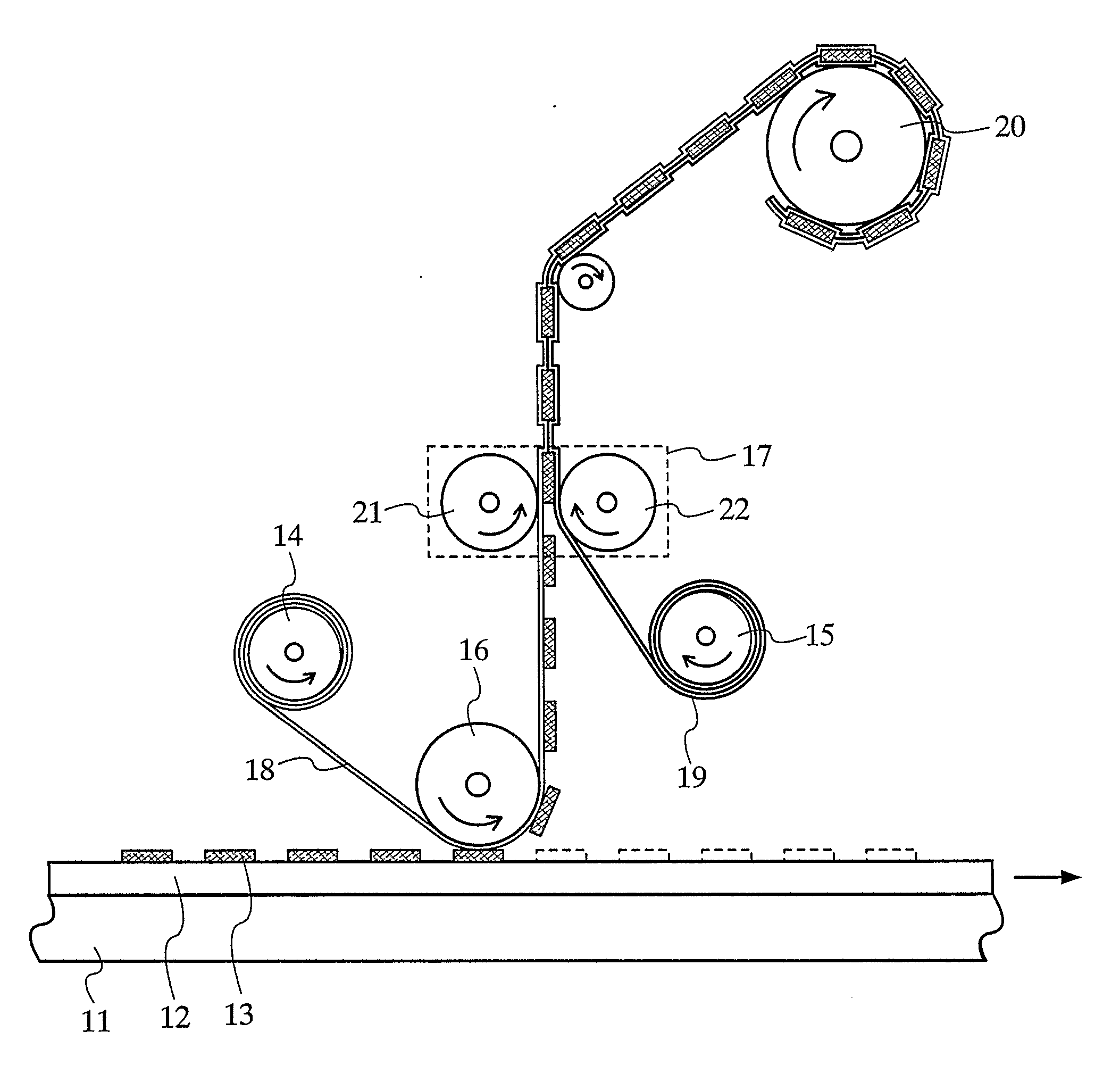

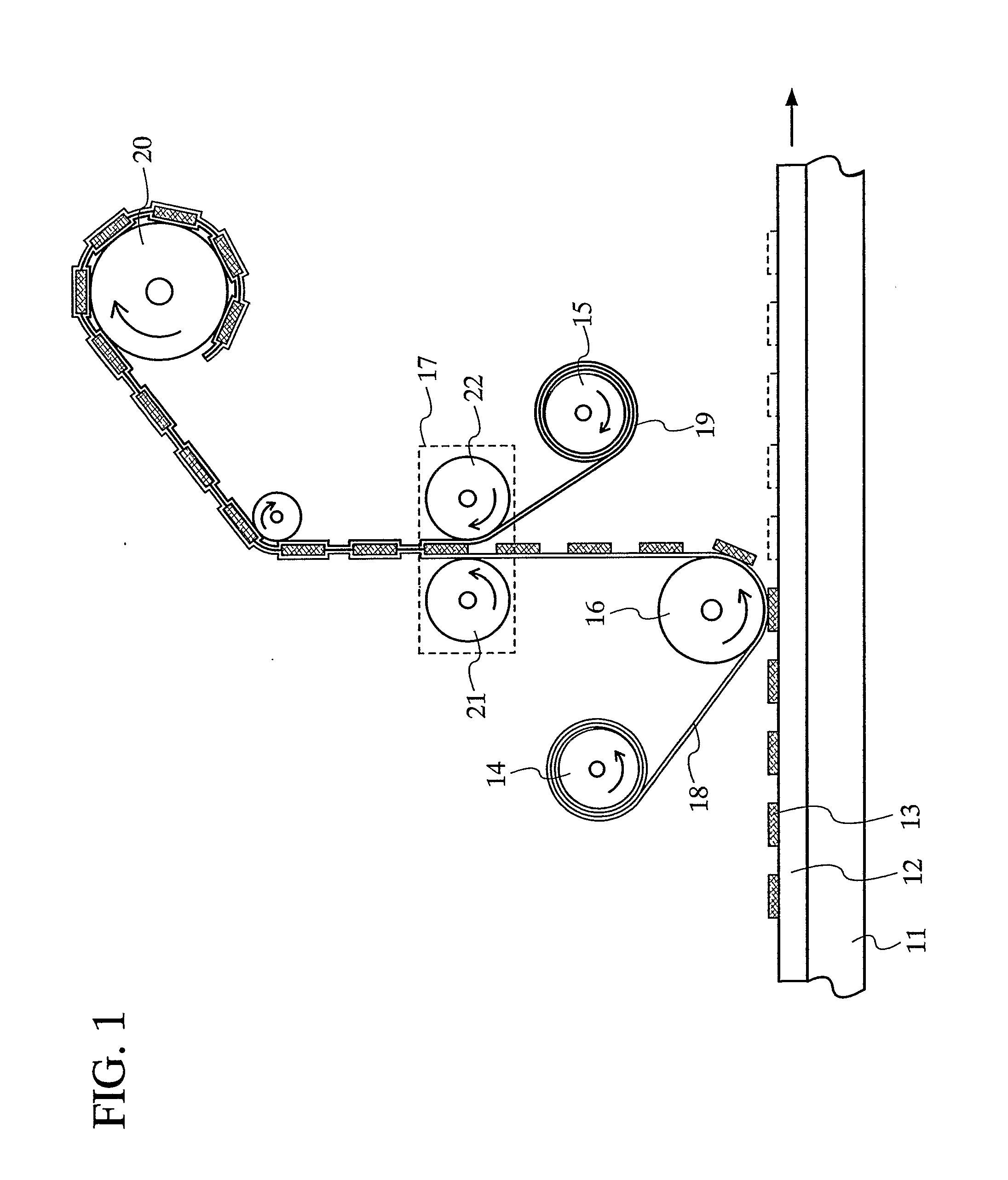

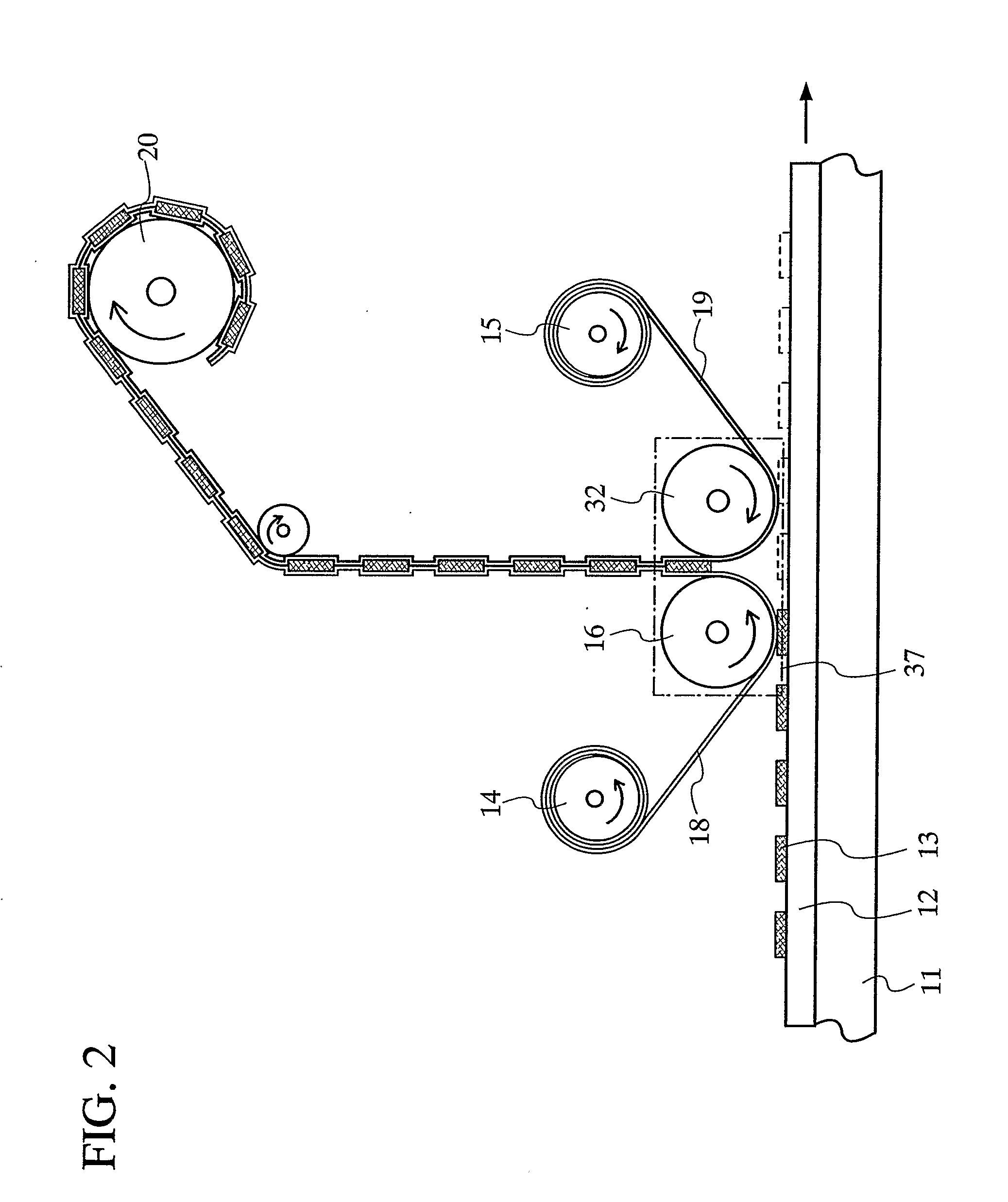

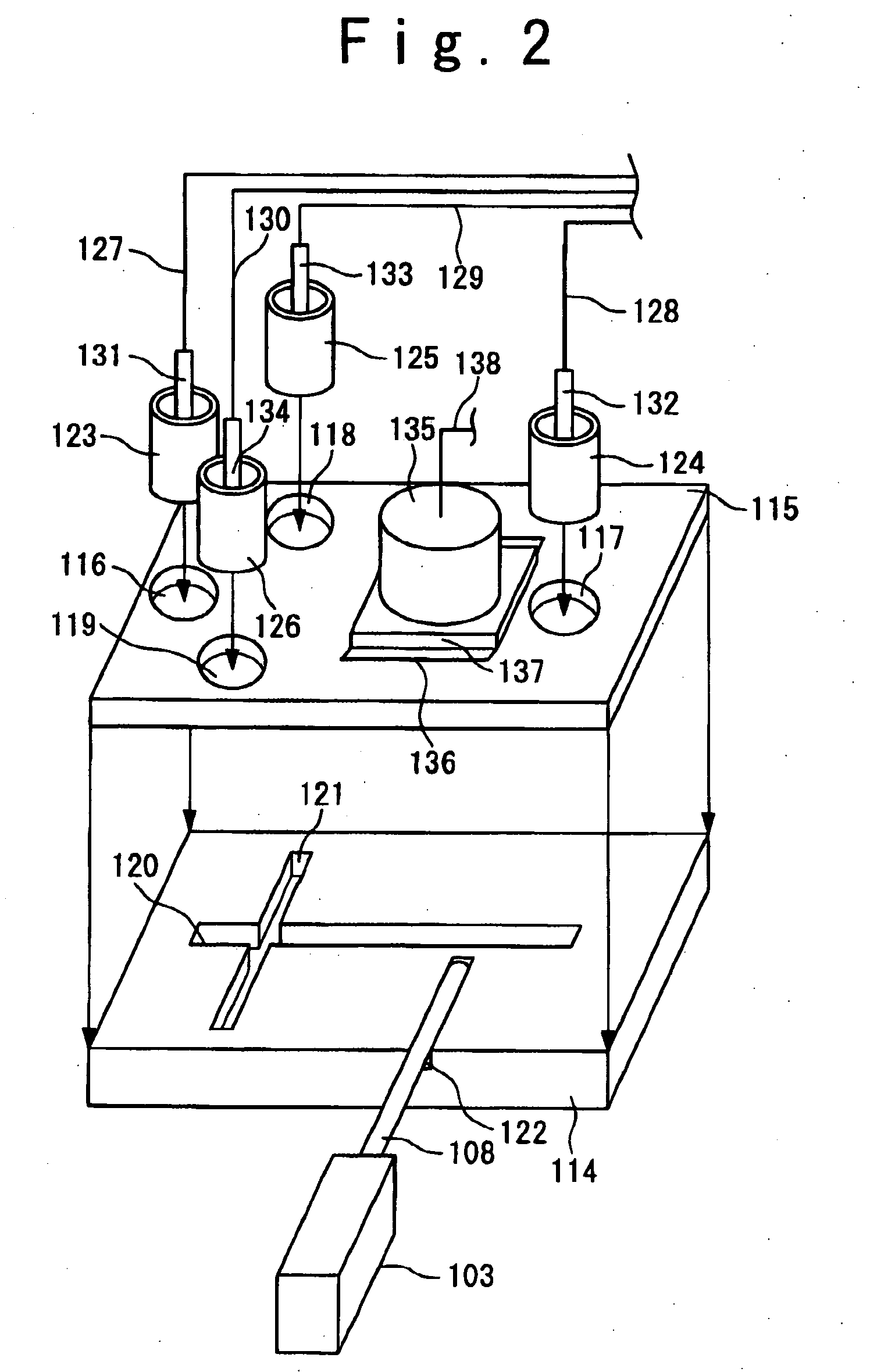

Laminating System

InactiveUS20080044940A1Increase productivityShorten production timePaper/cardboard wound articlesSemiconductor/solid-state device detailsEngineeringIntegrated circuit

It is an object of the invention to improve the production efficiency in sealing a thin film integrated circuit and to prevent the damage and break. Further, it is another object of the invention to prevent a thin film integrated circuit from being damaged in shipment and to make it easier to handle the thin film integrated circuit. The invention provides a laminating system in which rollers are used for supplying a substrate for sealing, receiving IC chips, separating, and sealing. The separation, sealing, and reception of a plurality of thin film integrated circuits can be carried out continuously by rotating the rollers; thus, the production efficiency can be extremely improved. Further, the thin film integrated circuits can be easily sealed since a pair of rollers opposite to each other is used.

Owner:SEMICON ENERGY LAB CO LTD

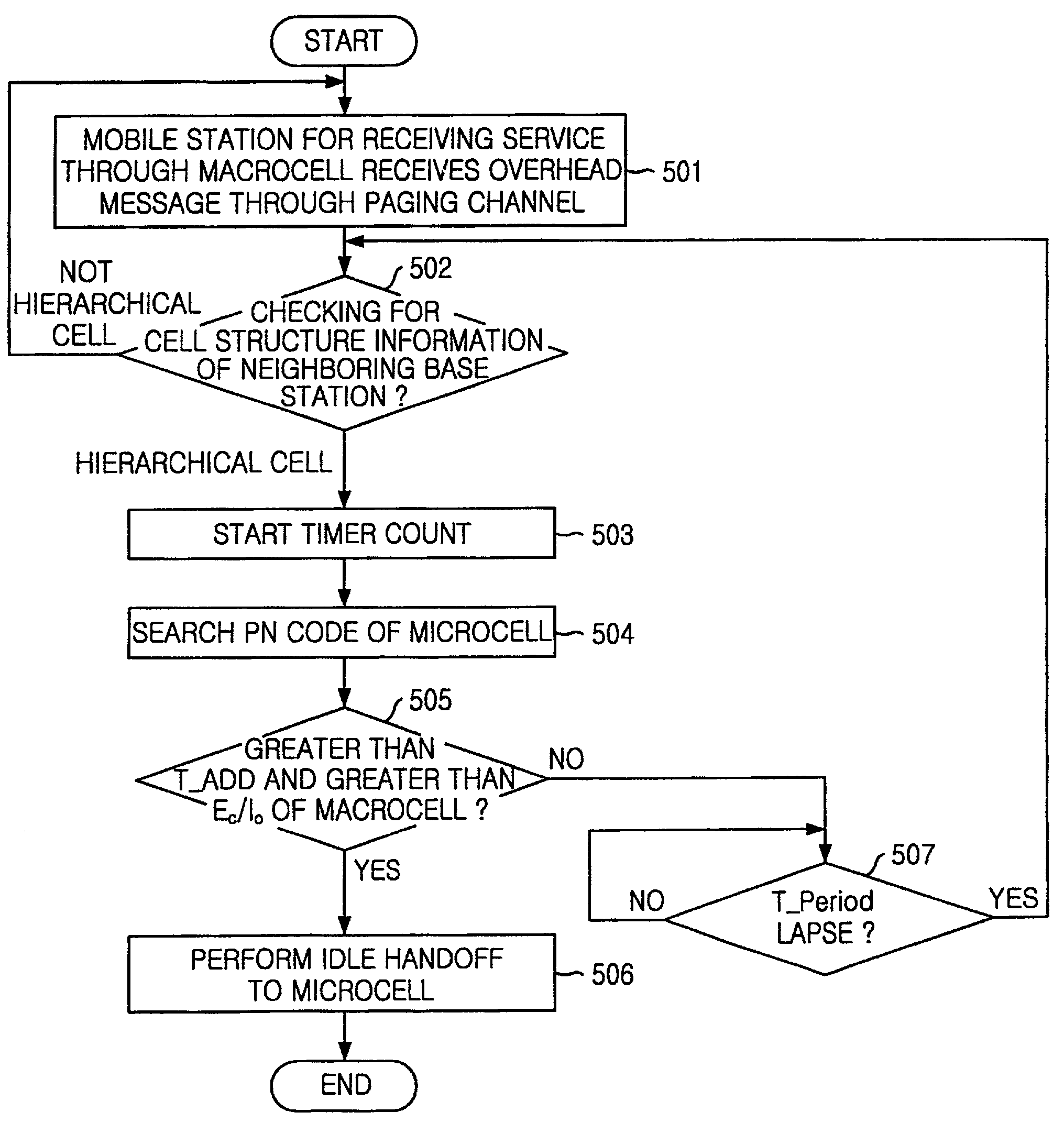

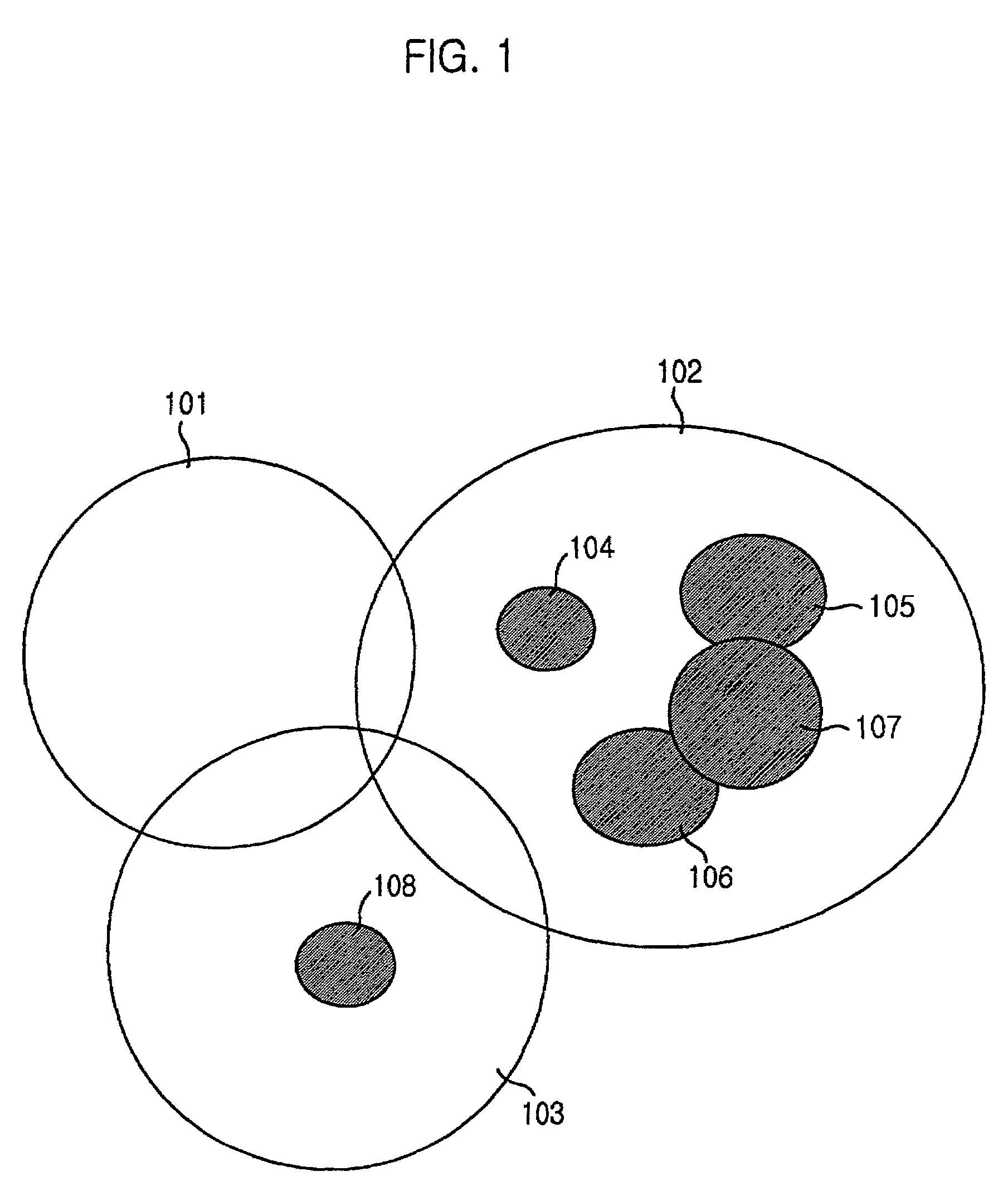

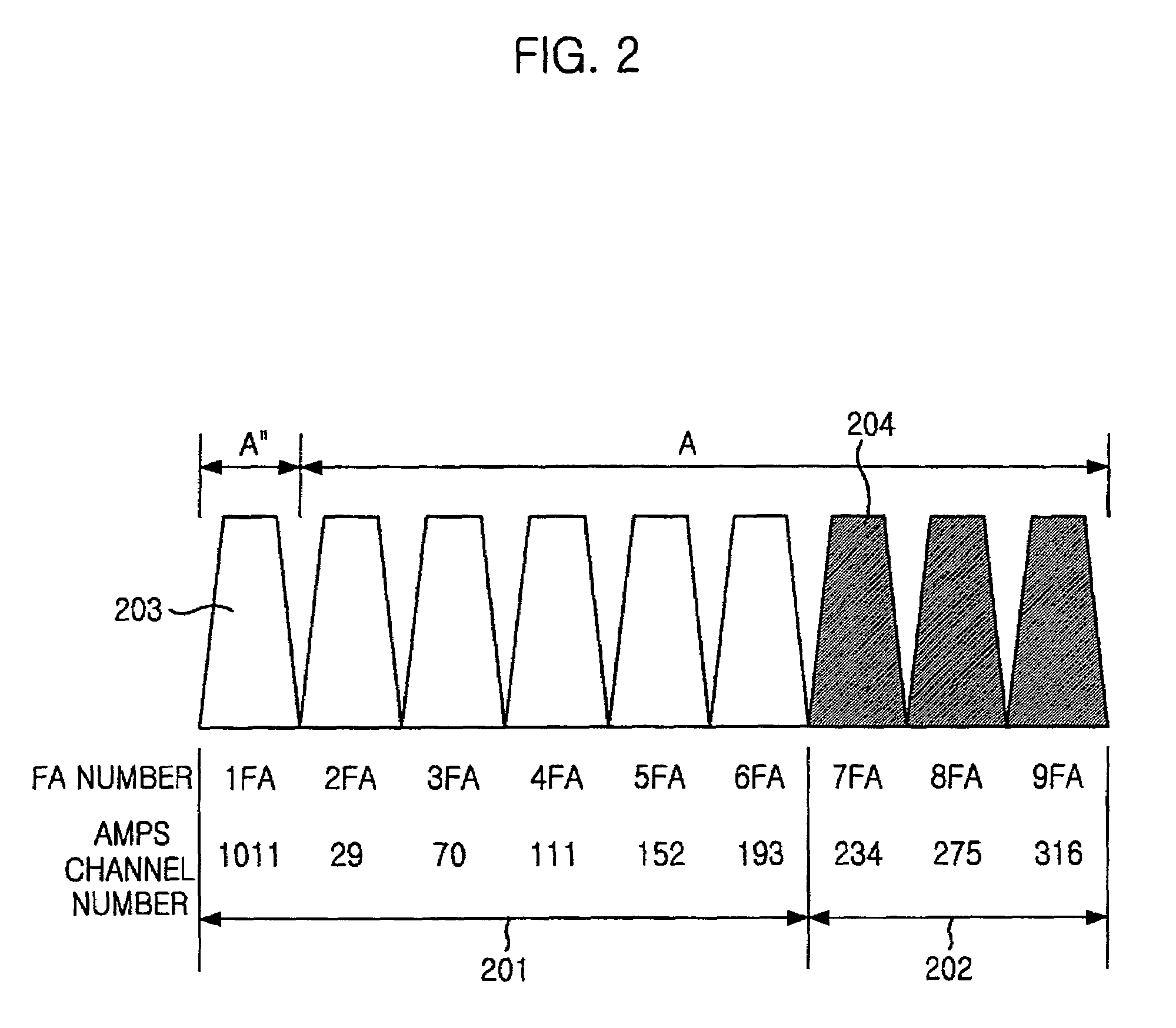

Method for carrying out handoff between macrocell and microcell in hierarchical cell structure

A method for carrying out an idle handoff from a macrocell to a microcell (picocell) in a hierarchical cell structure includes the steps of: a) allocating different frequency assignments (FA) to the macrocell and the microcell in a same service band, to construct the hierarchical cell structure; b) transmitting cell structure information of neighboring base stations and pseudo noise (PN) code from base station to mobile station; c) checking whether the mobile station is in the hierarchical cell by using the cell structure information of neighboring base station; and d) checking whether a value of the pseudo noise (PN) code is greater than T_ADD and greater than Ec / Io of the macrocell by periodically searching the pseudo noise (PN) code of the microcell, to carry out an idle handoff to the microcell, wherein the T_ADD represents a value of base station pilot strength required for the base station of neighboring set to be included in a candidate set, the Ec represents an pilot energy accumulated during one pseudo noise (PN) chip period, and the Io represents a total power spectrum density within a reception bandwidth.

Owner:SK TELECOM CO LTD

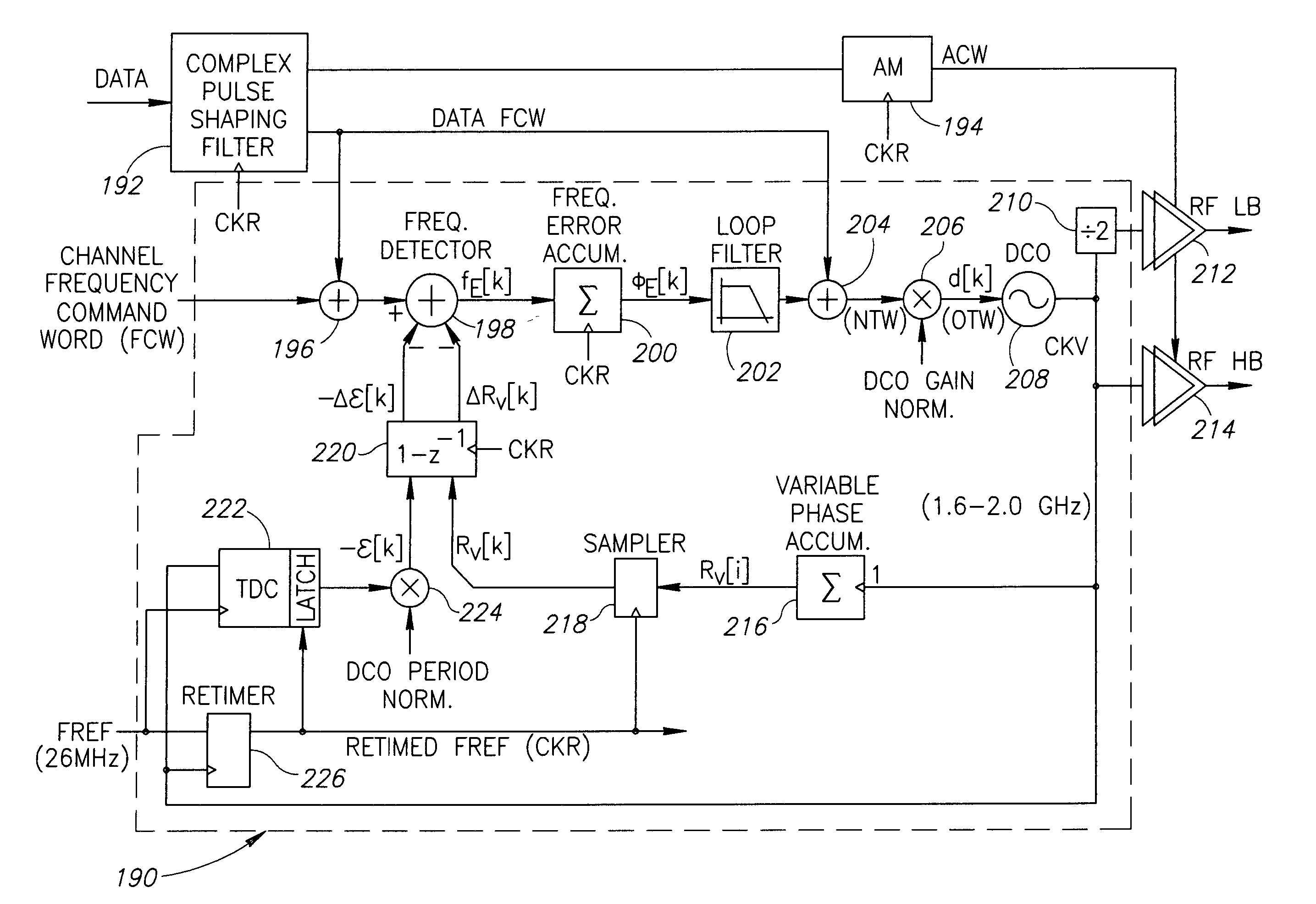

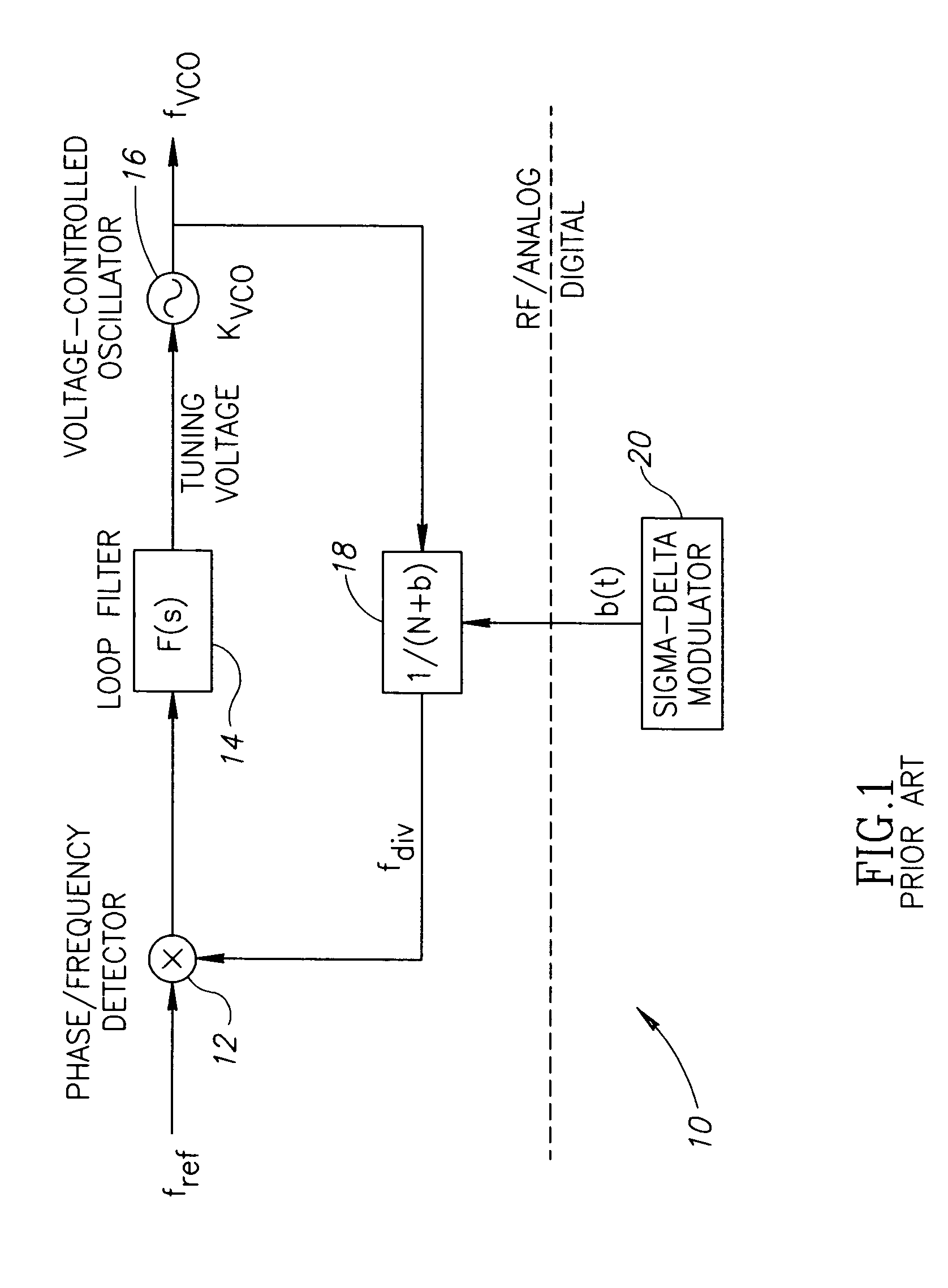

Apparatus for and method of noise suppression and dithering to improve resolution quality in a digital RF processor

InactiveUS20050186920A1Cancel noiseAvoid it happening againPulse automatic controlAngle modulationImage resolutionEngineering

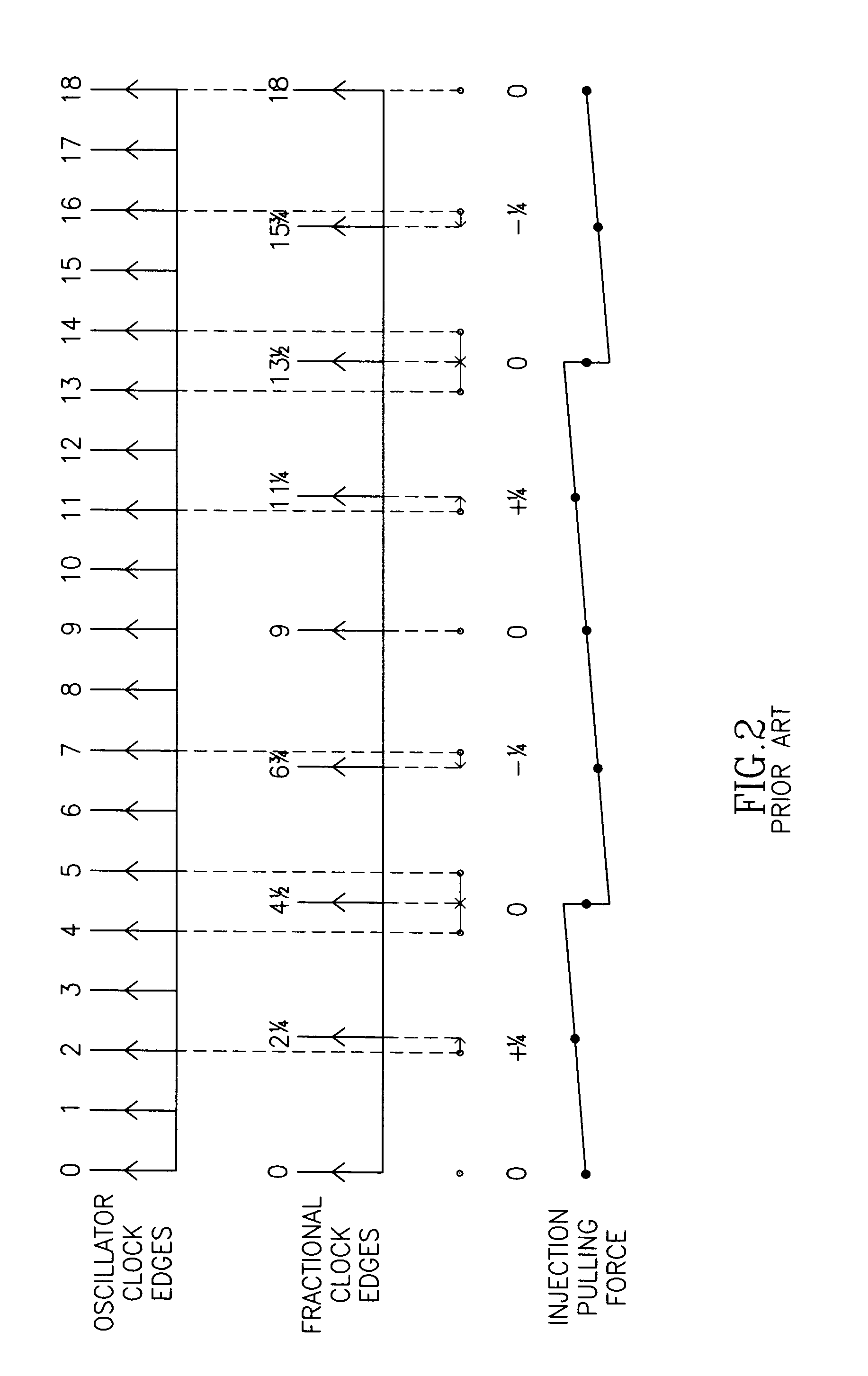

A novel apparatus for and a method of noise and spurious tones suppression in a digital RF processor (DRP). The invention is well suited for use in highly integrated system on a chip (SoC) radio solutions that incorporate a very large amount of digital logic circuitry. The noise suppression scheme eliminates the noise caused by various on chip interference sources transmitted through electromagnetic, power, ground and substrate paths. The noise suppression scheme permits an all digital PLL (ADPLL) to operate in such a way to avoid generating the spurs that would normally be generated from the injection pulling effect of interfering sources on the chip. The frequency reference clock is retimed to be synchronous to the RF oscillator clock and used to drive the entire digital logic circuitry of the DRP. This ensures that the different clock edges throughout the system will not exhibit mutual drift. A method of improving the resolution quality of a time to digital converter within the ADPLL is also taught. The method dithers the reference clock by passing it through a delay circuit that is controlled by a sigma-delta modulator. The dithered reference clock reduces the affect on the phase noise at the output of the ADPLL due to ill-behaved quantization of the TDC timing estimation.

Owner:TEXAS INSTR INC

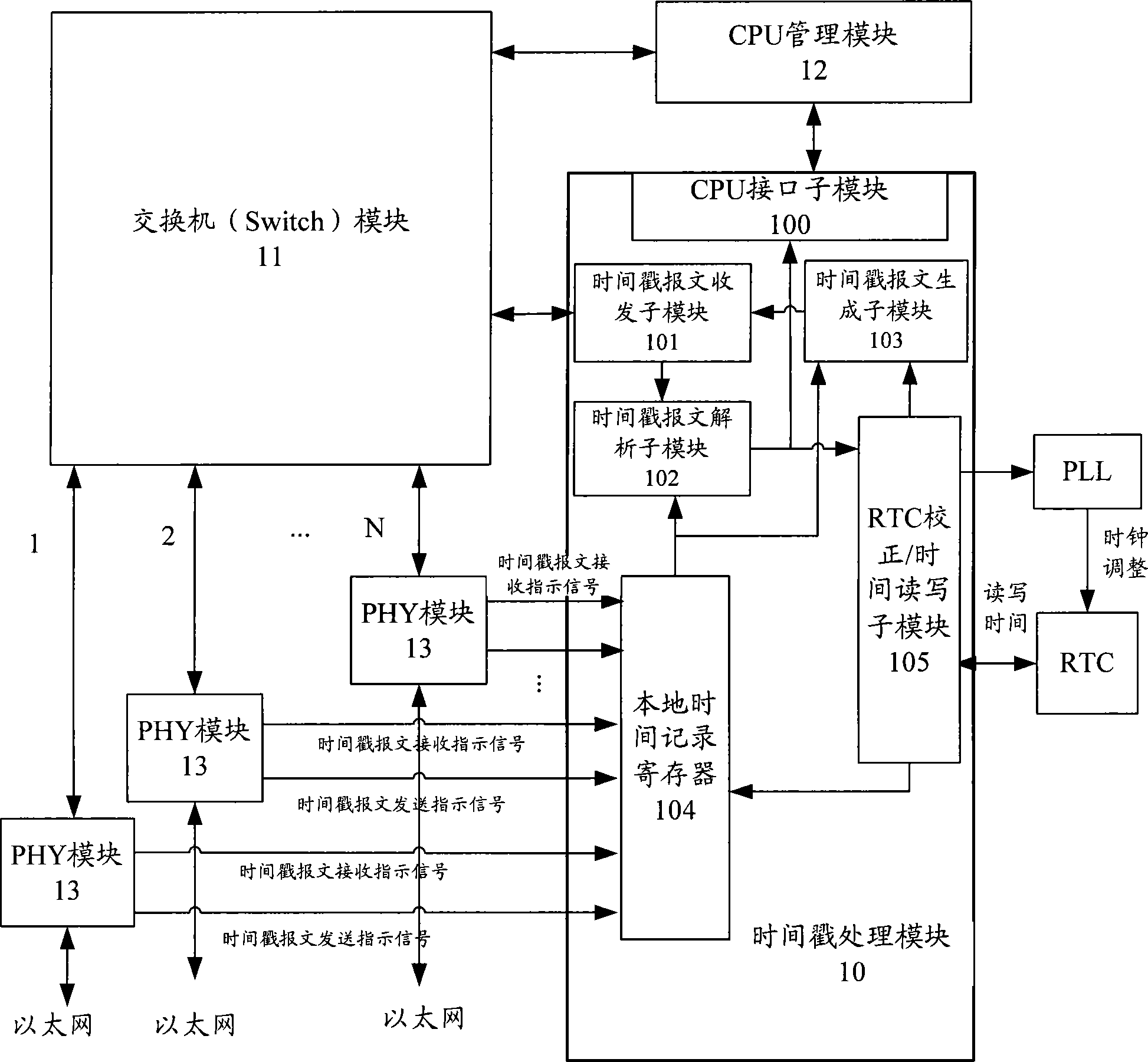

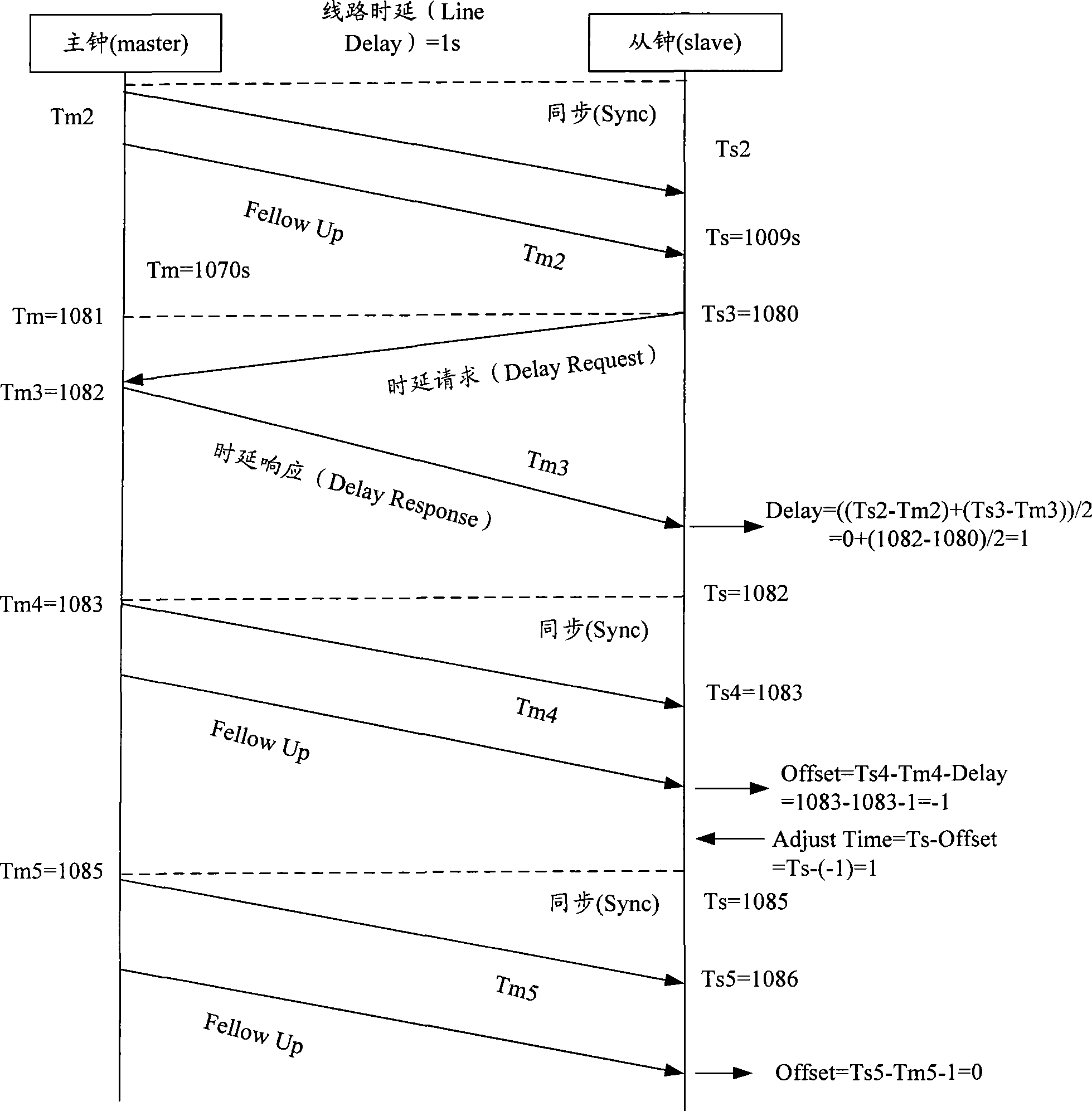

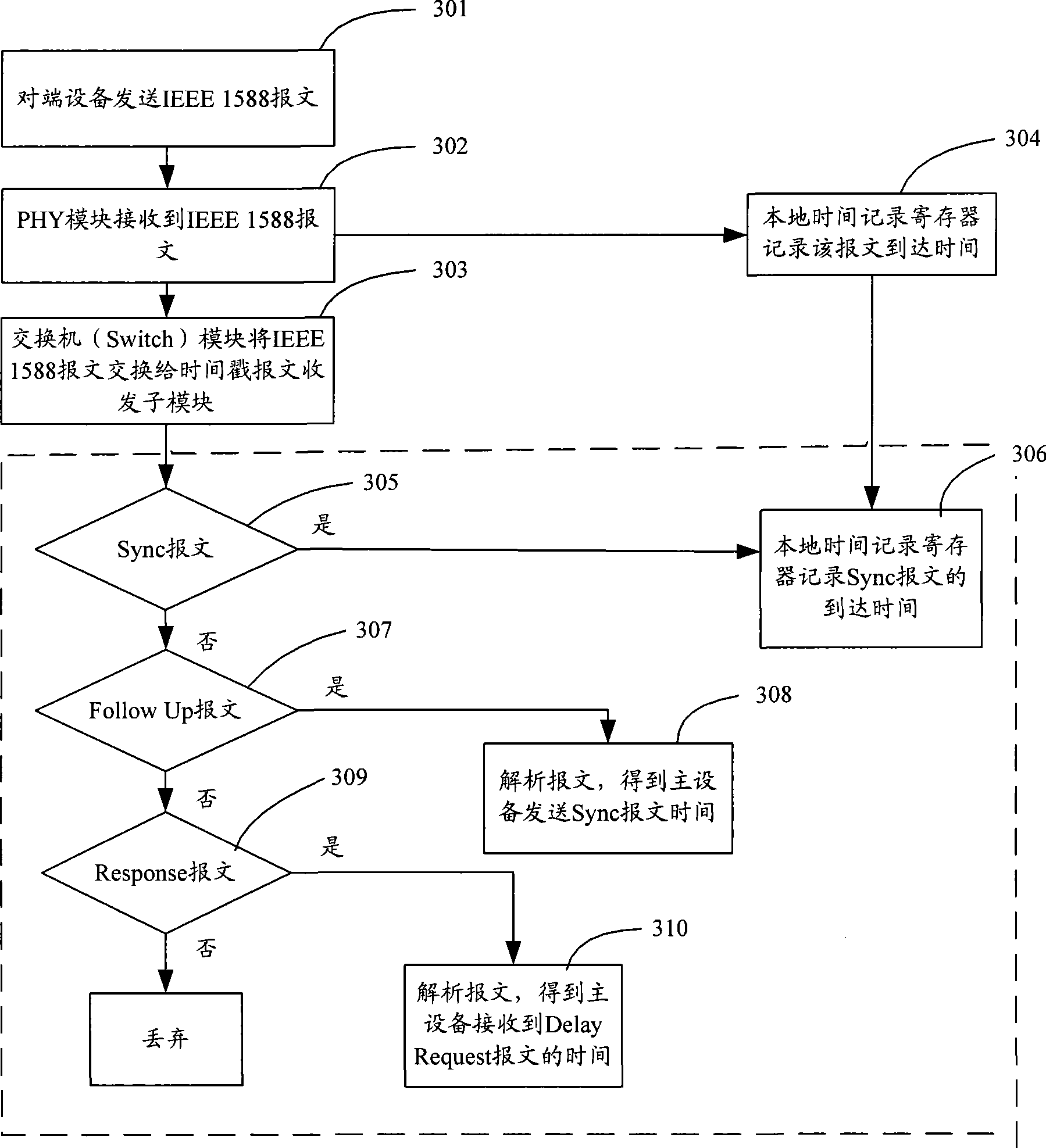

IEEE 1588 time synchronization system and implementation method thereof

ActiveCN101447861ASynchronized High Precision TimeGuaranteed real-timeTime-division multiplexSynchronising arrangementTime informationPHY

The invention discloses an IEEE 1588 time synchronization system. By adding a time-stamp processing module, a time-stamp message transceiving sub module, a time-stamp message resolving sub module, a time-stamp message generating sub module, a local time recording register, and an RTC correction / time read-write module in the module are used for combining peripheral components such as a switch module, a PHY and a real-time clock (RTC) module to form a hardware system. When in use, the high precision time synchronization requested by an IEEE 1588v2 protocol can be implemented by using the modes of one-to-one or one-to-many of master-slave synchronization. The invention also discloses a method for implementing the IEEE 1588 time synchronization, which can implement the function of the time synchronization system by processing the time information of master-slave devices in real time. The invention plays an active role in promoting Ethernet construction.

Owner:ZTE CORP

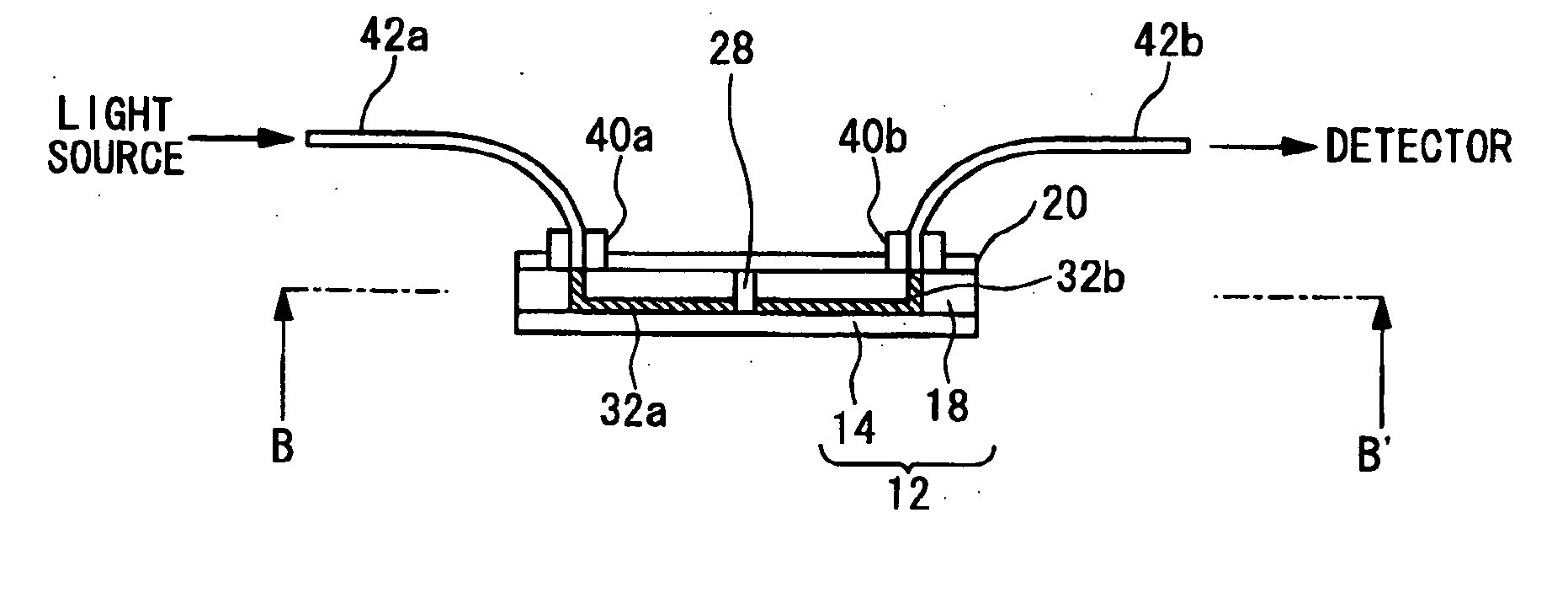

Microchip, method of manufacturing microchip, and method of detecting compositions

InactiveUS20050175273A1Improve accuracyHigh precision analysisRadiation pyrometryCladded optical fibrePhysicsRefractive index

A microchip includes a clad layer having a channel through which a sample flows, and an optical waveguide formed within the clad layer and having a higher refractive index than the clad layer. The optical waveguide is formed to act on the channel optically. Thus, the sample flowing in the channel can be analyzed with high accuracy even in the microchip having a fine structure.

Owner:NEC CORP

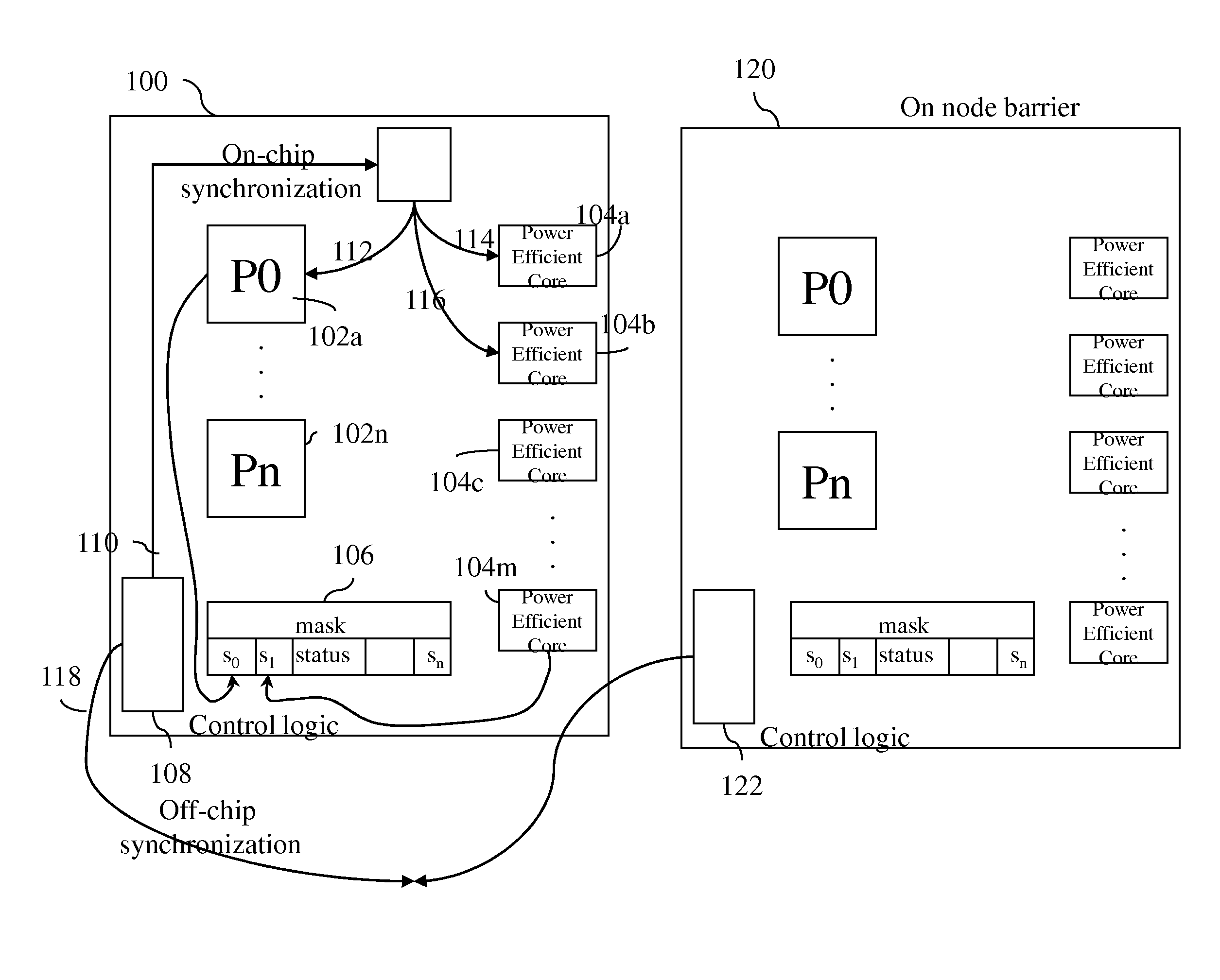

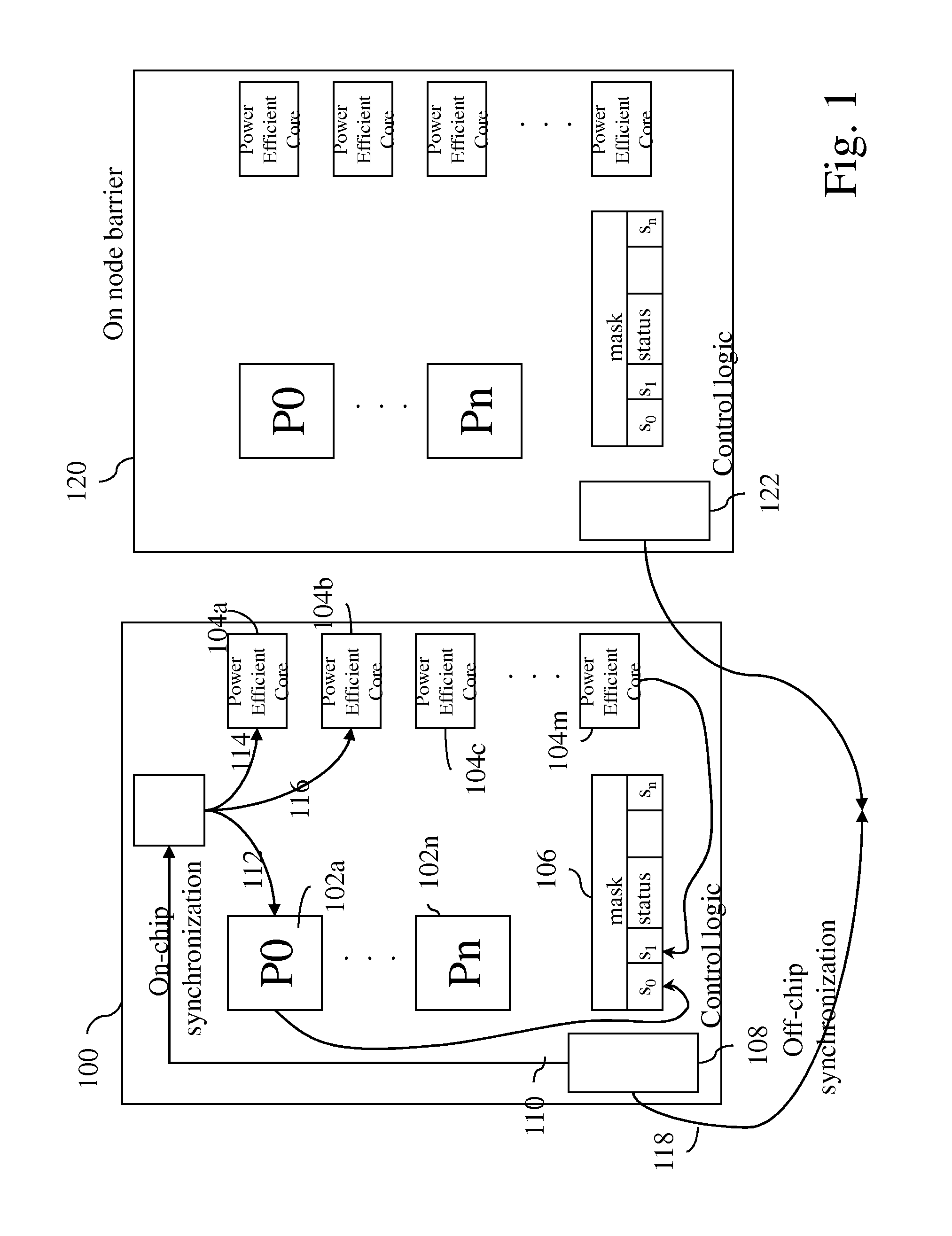

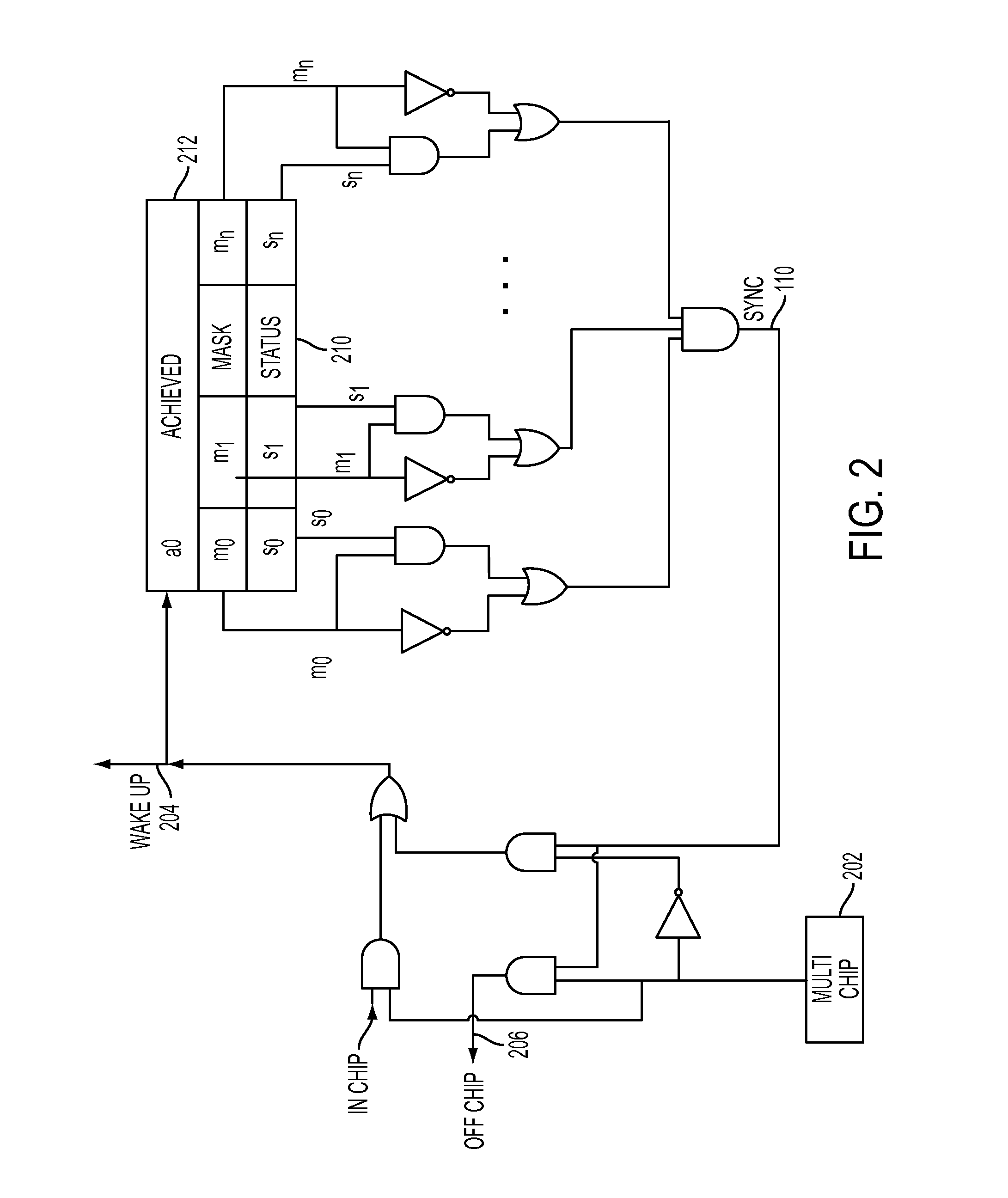

Method and apparatus for a hierarchical synchronization barrier in a multi-node system

A hierarchical barrier synchronization of cores and nodes on a multiprocessor system, in one aspect, may include providing by each of a plurality of threads on a chip, input bit signal to a respective bit in a register, in response to reaching a barrier; determining whether all of the plurality of threads reached the barrier by electrically tying bits of the register together and “AND”ing the input bit signals; determining whether only on-chip synchronization is needed or whether inter-node synchronization is needed; in response to determining that all of the plurality of threads on the chip reached the barrier, notifying the plurality of threads on the chip, if it is determined that only on-chip synchronization is needed; and after all of the plurality of threads on the chip reached the barrier, communicating the synchronization signal to outside of the chip, if it is determined that inter-node synchronization is needed.

Owner:IBM CORP

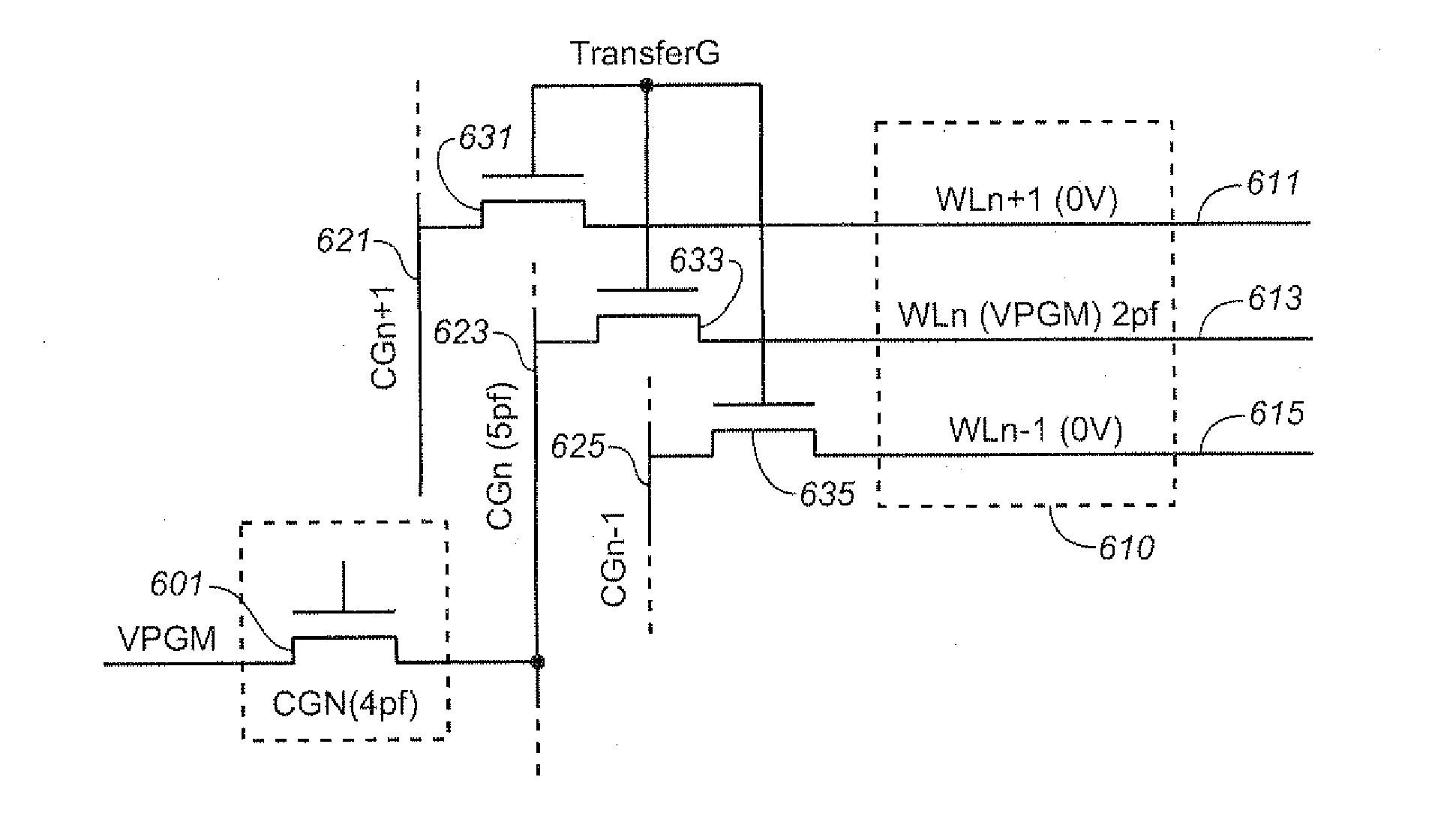

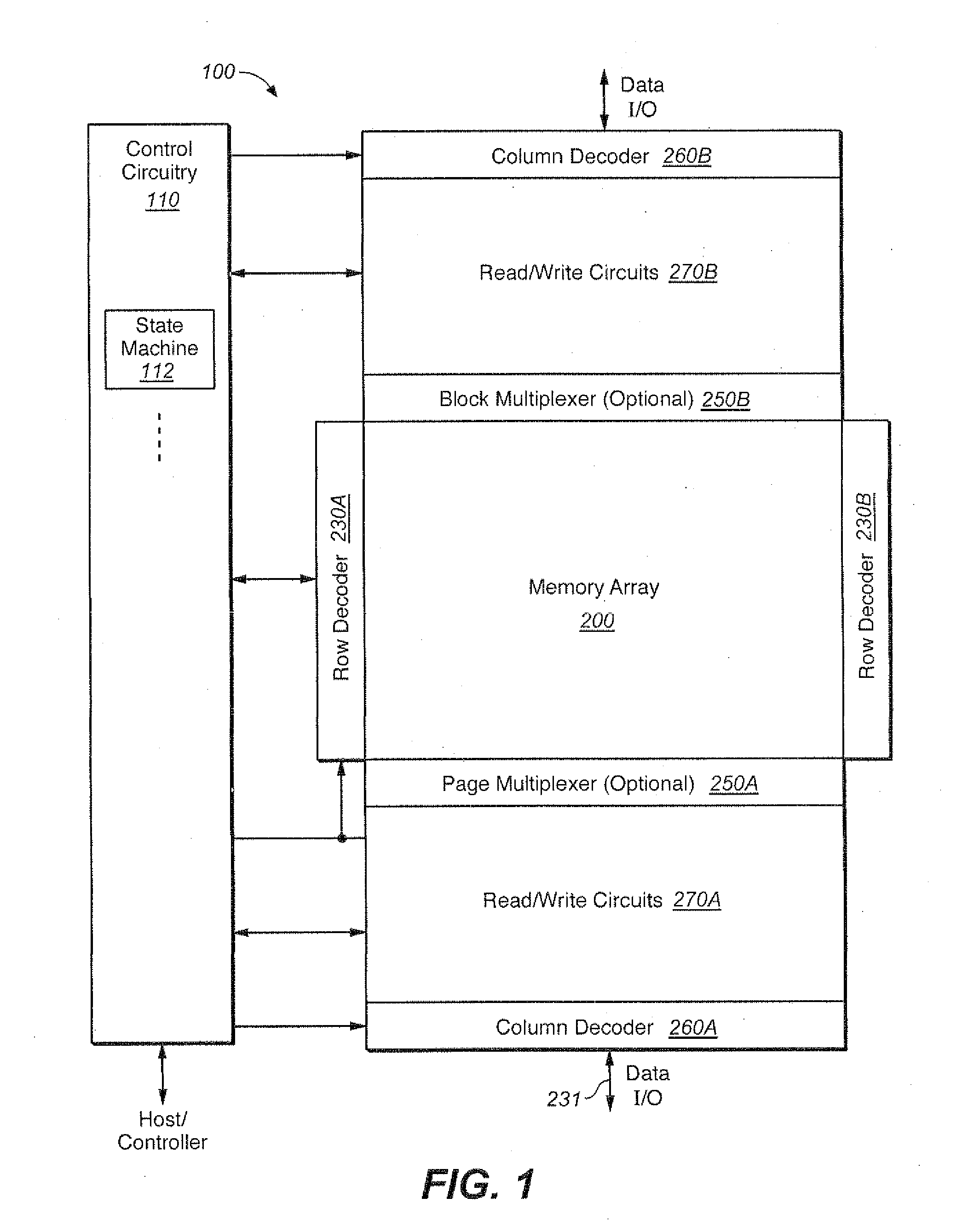

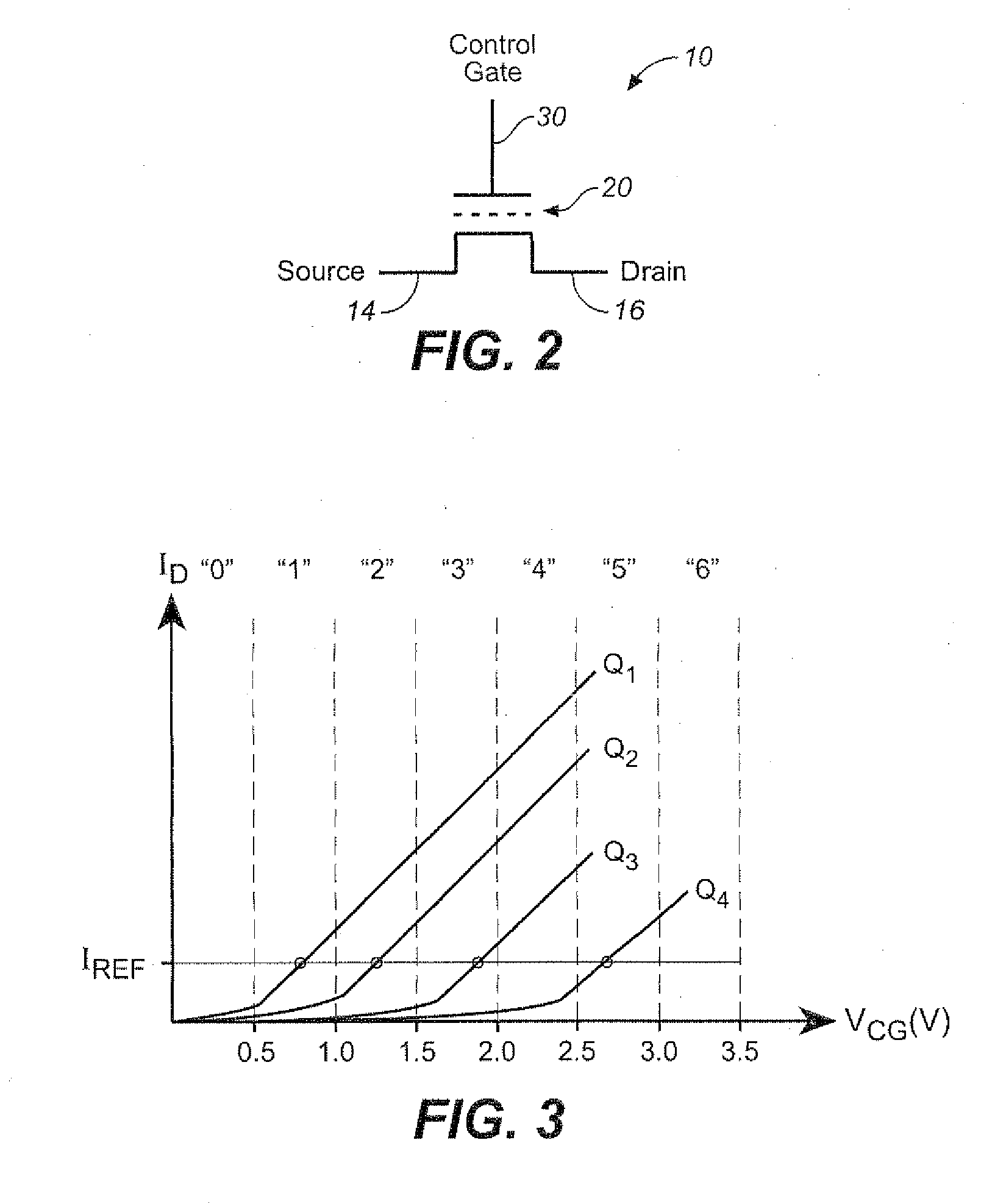

Detection of Word-Line Leakage in Memory Arrays: Current Based Approach

Techniques and corresponding circuitry are presented for the detection of wordline leakage in a memory array. In an exemplary embodiment, a capacitive voltage divider is used to translate the high voltage drop to low voltage drop that can be compared with a reference voltage to determine the voltage drop due to leakage. An on-chip self calibration method can help assure the accuracy of this technique for detecting leakage limit. In other embodiments, the current drawn by a reference array, where a high voltage is applied to the array with all wordlines non-selected, is compared to the current drawn by an array where the high voltage is applied and one or more selected wordlines. In these current based embodiments, the reference array can be a different array, or the same array as that one selected for testing.

Owner:SANDISK TECH LLC

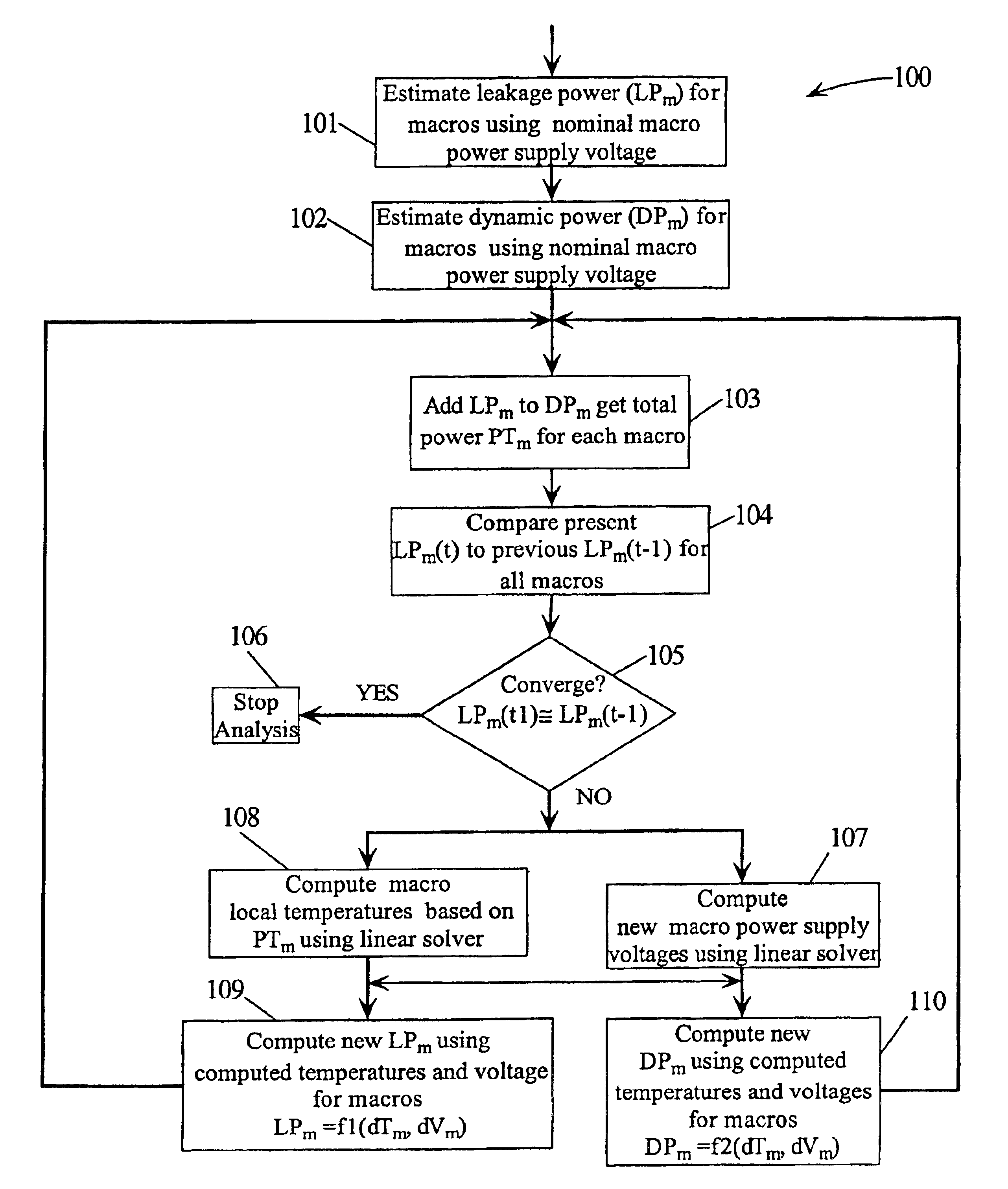

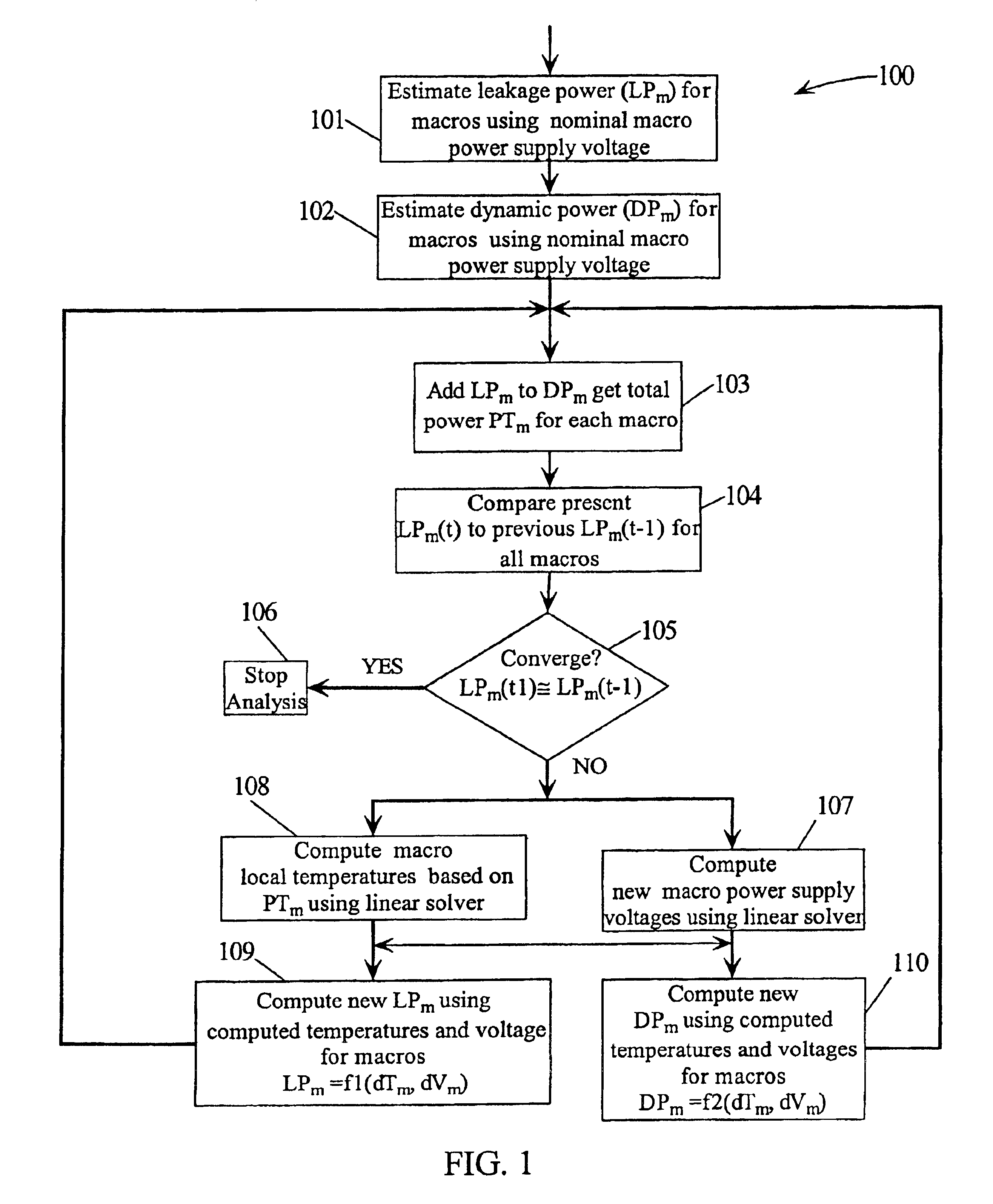

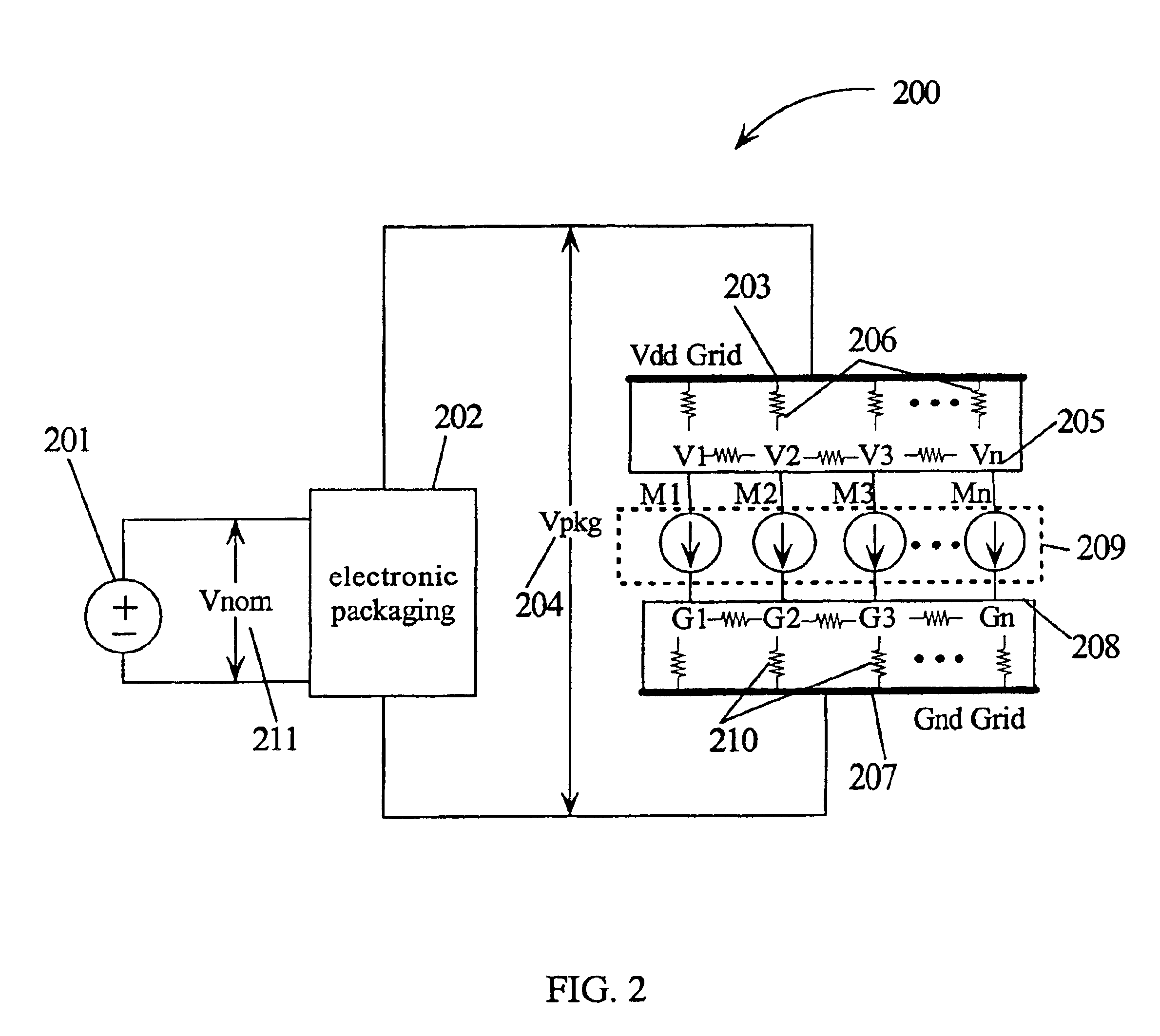

Method for determining the leakage power for an integrated circuit

InactiveUS6842714B1Electric devicesCurrent/voltage measurementElectrical resistance and conductanceElectric distribution network

A method for determining full chip leakage power first estimates leakage power and dynamic power for each circuit macro. The power supply voltage to each macro is first assumed to be nominal. The power dissipation for each macro is modeled as a current source whose value is the estimated power divided by the nominal power supply voltage. The power distribution network is modeled as a resistive grids. The thermal environment of the IC and its electronic package are modeled as multi dimensional grids of thermal elements. Algebraic multi-grid (AMG) methods are used to calculate updated circuit macro voltages and temperatures. The macro voltages and temperatures are updated and updated leakage and dynamic power dissipation are calculated. Iterations are continued until leakage power converges to a final value.

Owner:IBM CORP

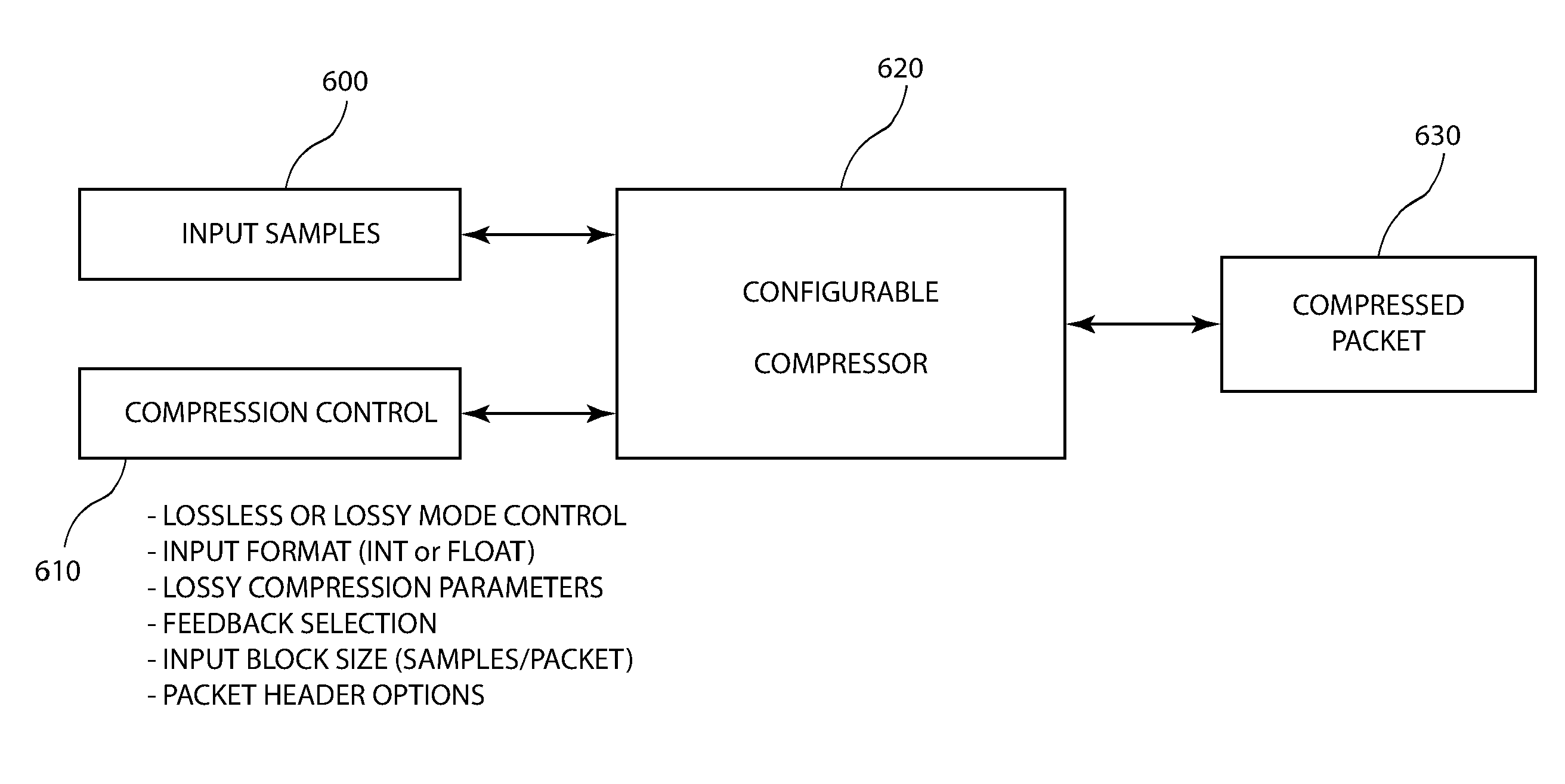

Enhanced multi-processor waveform data exchange using compression and decompression

InactiveUS20110078222A1Save resourcesReduce latencyDigital computer detailsCode conversionData transmissionMemory controller

Configurable compression and decompression of waveform data in a multi-core processing environment improves the efficiency of data transfer between cores and conserves data storage resources. In waveform data processing systems, input, intermediate, and output waveform data are often exchanged between cores and between cores and off-chip memory. At each core, a single configurable compressor and a single configurable decompressor can be configured to compress and to decompress integer or floating-point waveform data. At the memory controller, a configurable compressor compresses integer or floating-point waveform data for transfer to off-chip memory in compressed packets and a configurable decompressor decompresses compressed packets received from the off-chip memory. Compression reduces the memory or storage required to retain waveform data in a semiconductor or magnetic memory. Compression reduces both the latency and the bandwidth required to exchange waveform data. This abstract does not limit the scope of the invention as described in the claims.

Owner:ALTERA CORP

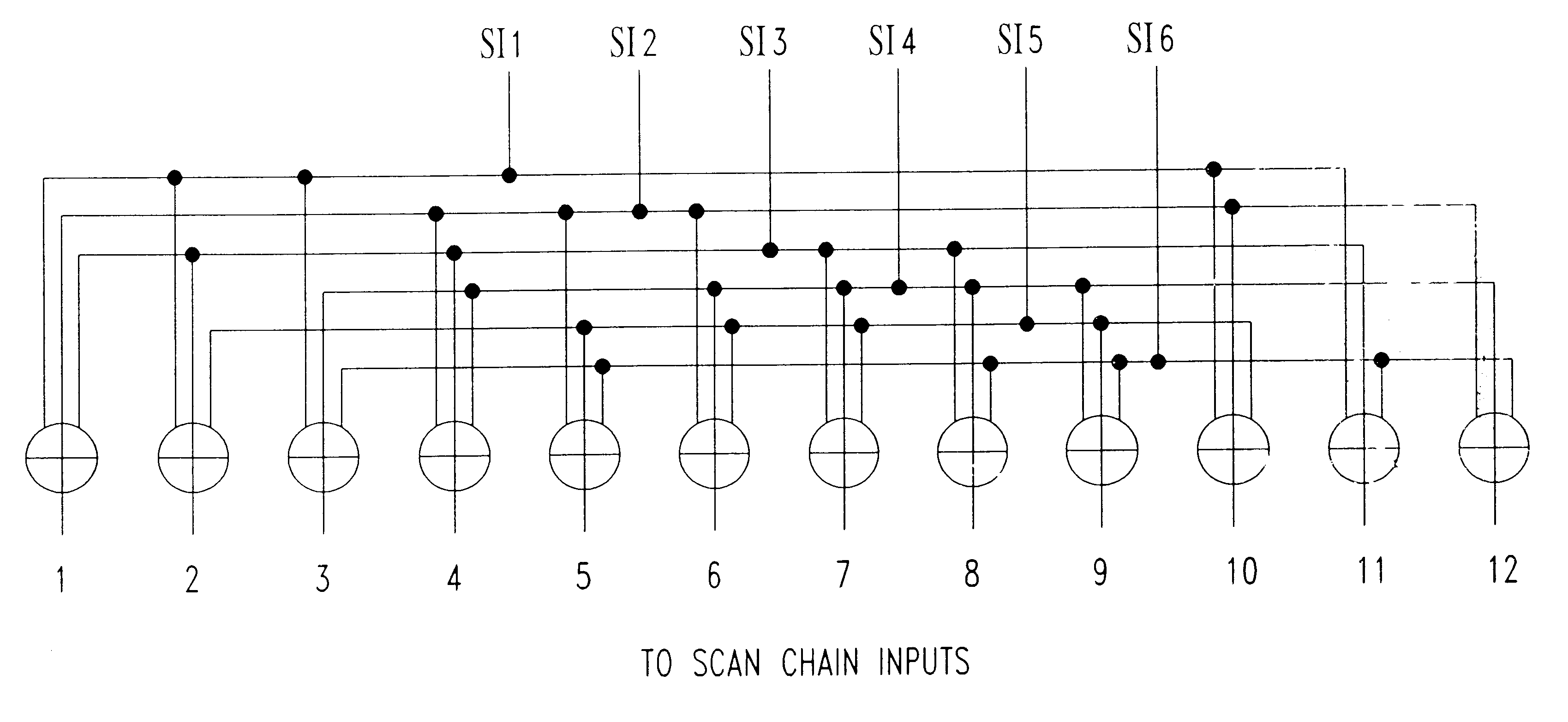

Real-time decoder for scan test patterns

InactiveUS6611933B1Cost-efficiently integratedForming accuratelyElectronic circuit testingError detection/correctionComputer hardwareTest efficiency

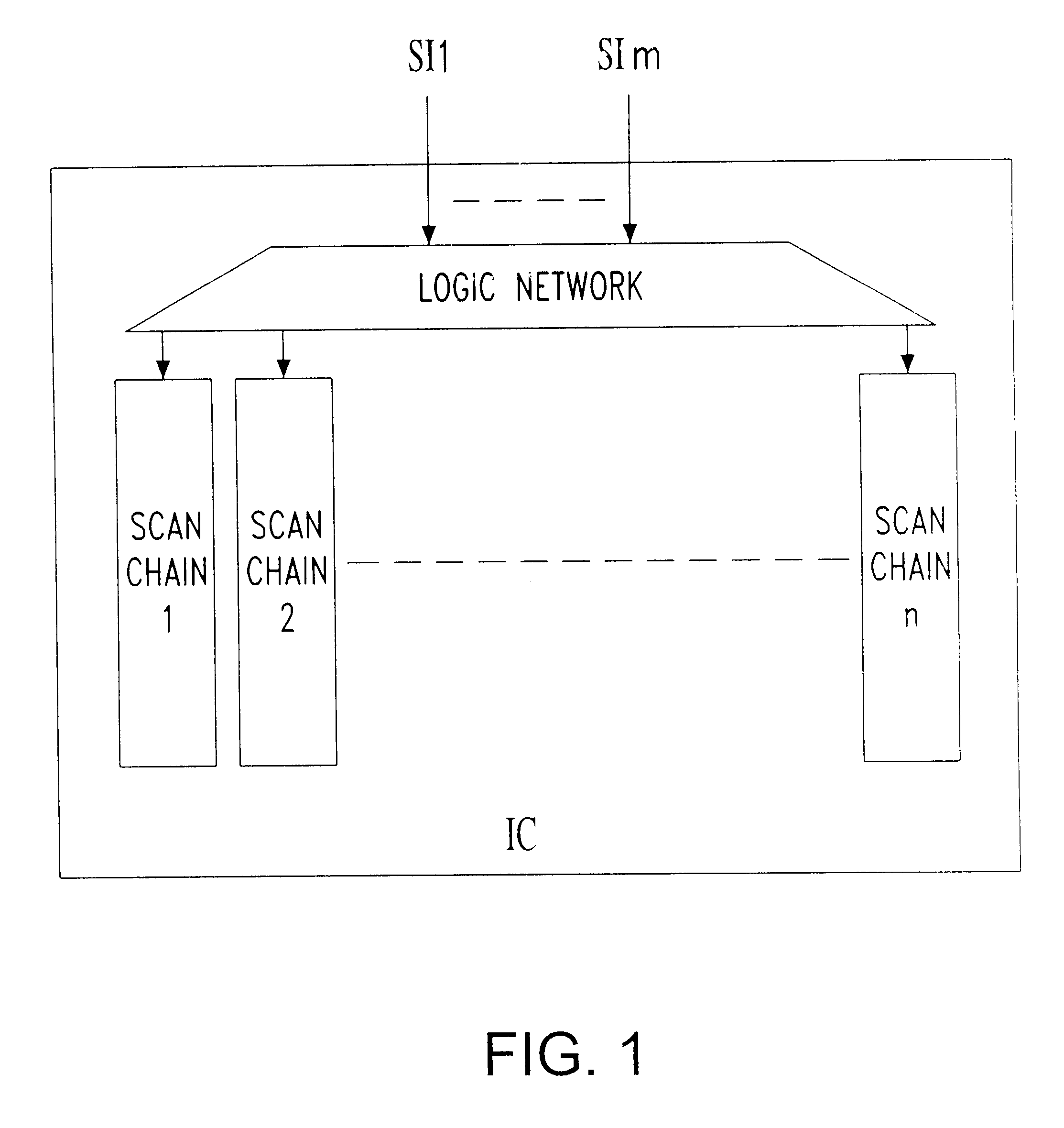

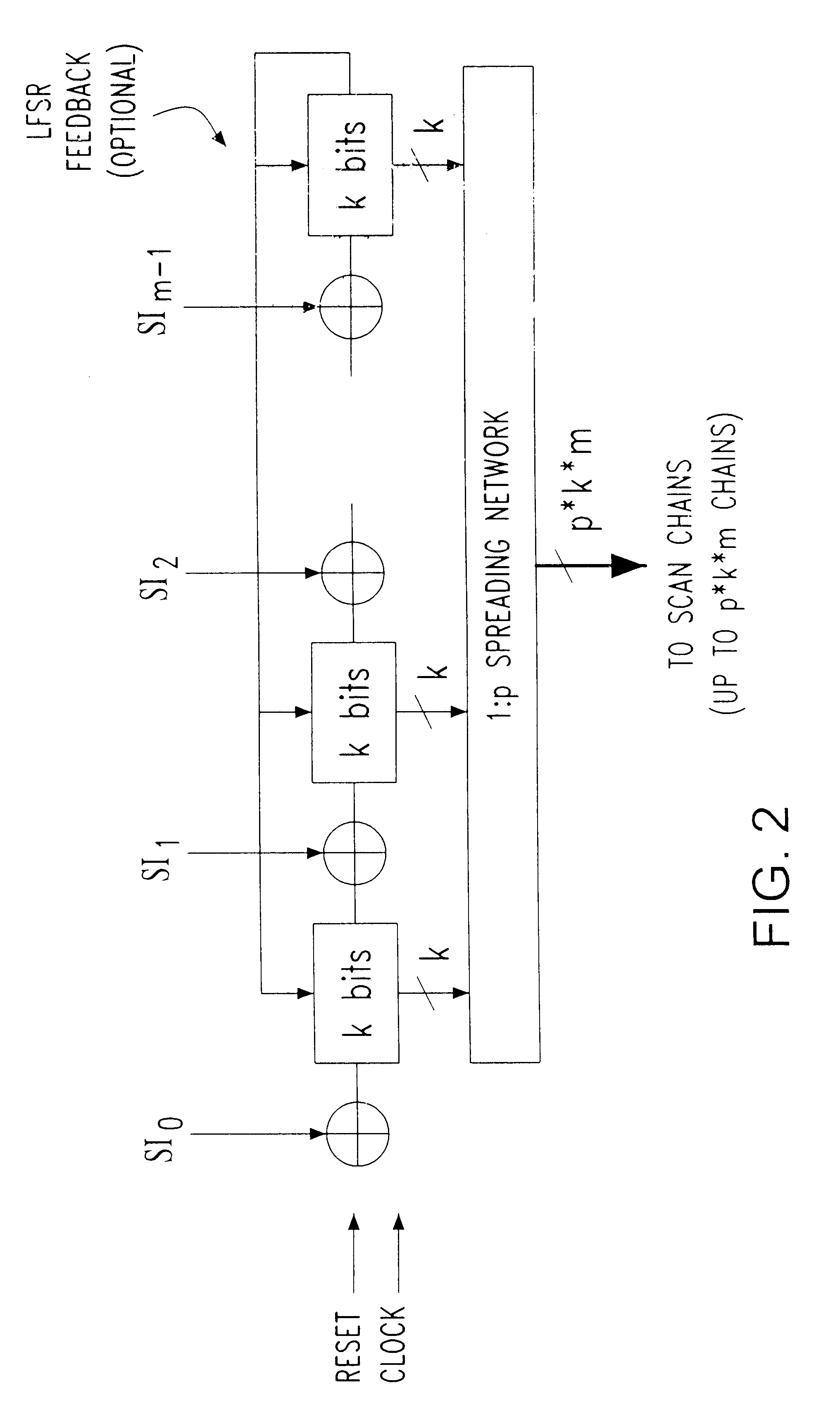

A method and apparatus for improving the efficiency of scan testing of integrated circuits is described. This efficiency is achieved by reducing the amount of required test stimulus source data and by increasing the effective bandwidth of the scan-load operation. The reduced test data volume and corresponding test time are achieved by integrating a real-time test data decoder or logic network into each integrated circuit chip. The apparatus, servicing a plurality of internal scan chains wherein the number of said internal scan chains exceeds the number of primary inputs available for loading data into the scan chains, includes: a) logic network positioned between the primary inputs and the inputs of the scan chains, the logic network expanding input data words having a width corresponding to the number of the primary inputs, and converting the input data words into expanded output data words having a width that corresponds to the number of the internal scan chains; and b) coupled to the internal scan chains, registers loaded with bit values provided by the expanded output data words while data previously loaded into the scan chains shifts forward within the scan chains by one bit position at a time; wherein a first plurality of the input data words supplied to the primary inputs produce a second plurality of expanded data words that are loaded into the internal scan chains to achieve an improved test coverage.

Owner:GOOGLE LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com