Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2275 results about "Interposer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An interposer is an electrical interface routing between one socket or connection to another. The purpose of an interposer is to spread a connection to a wider pitch or to reroute a connection to a different connection.

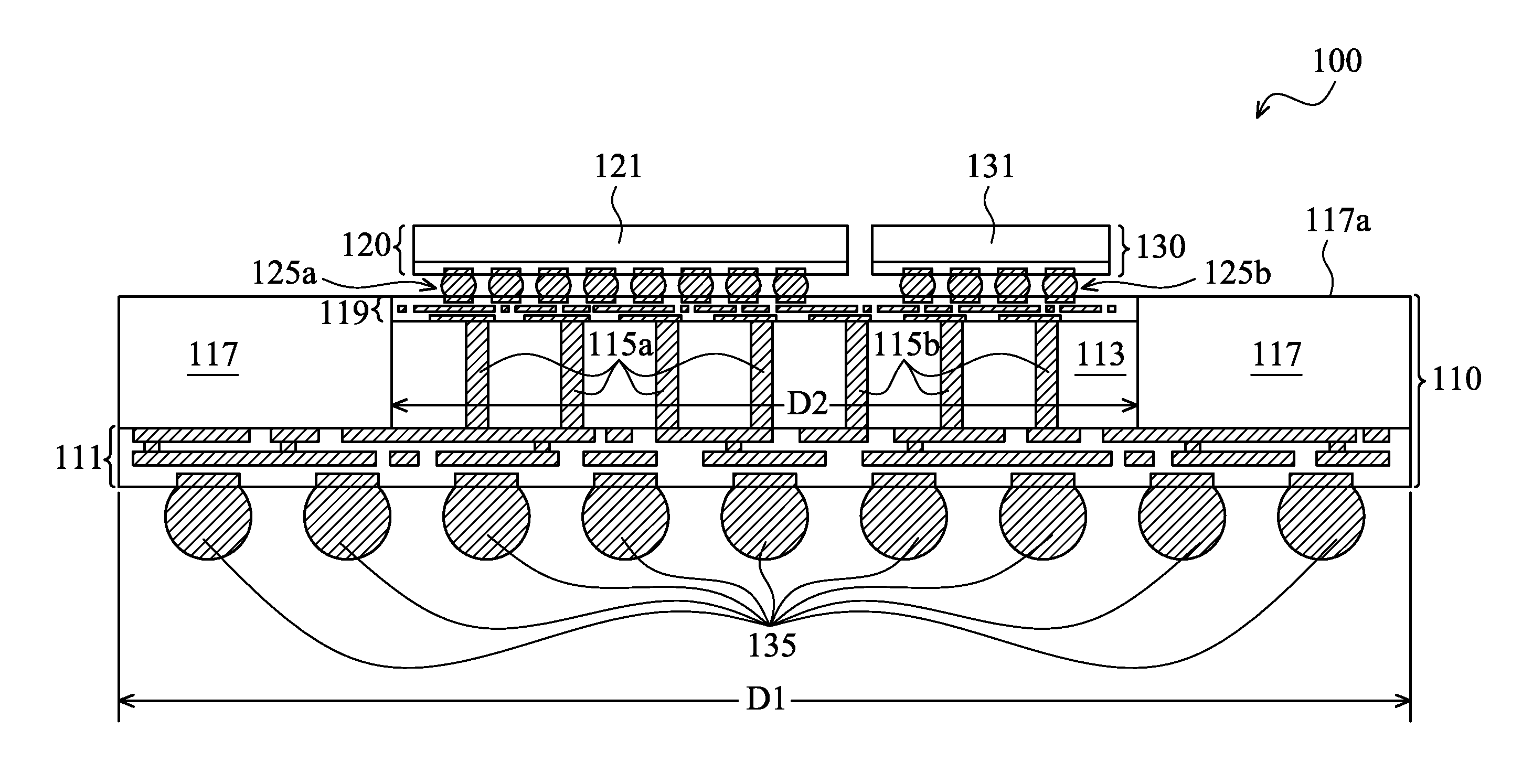

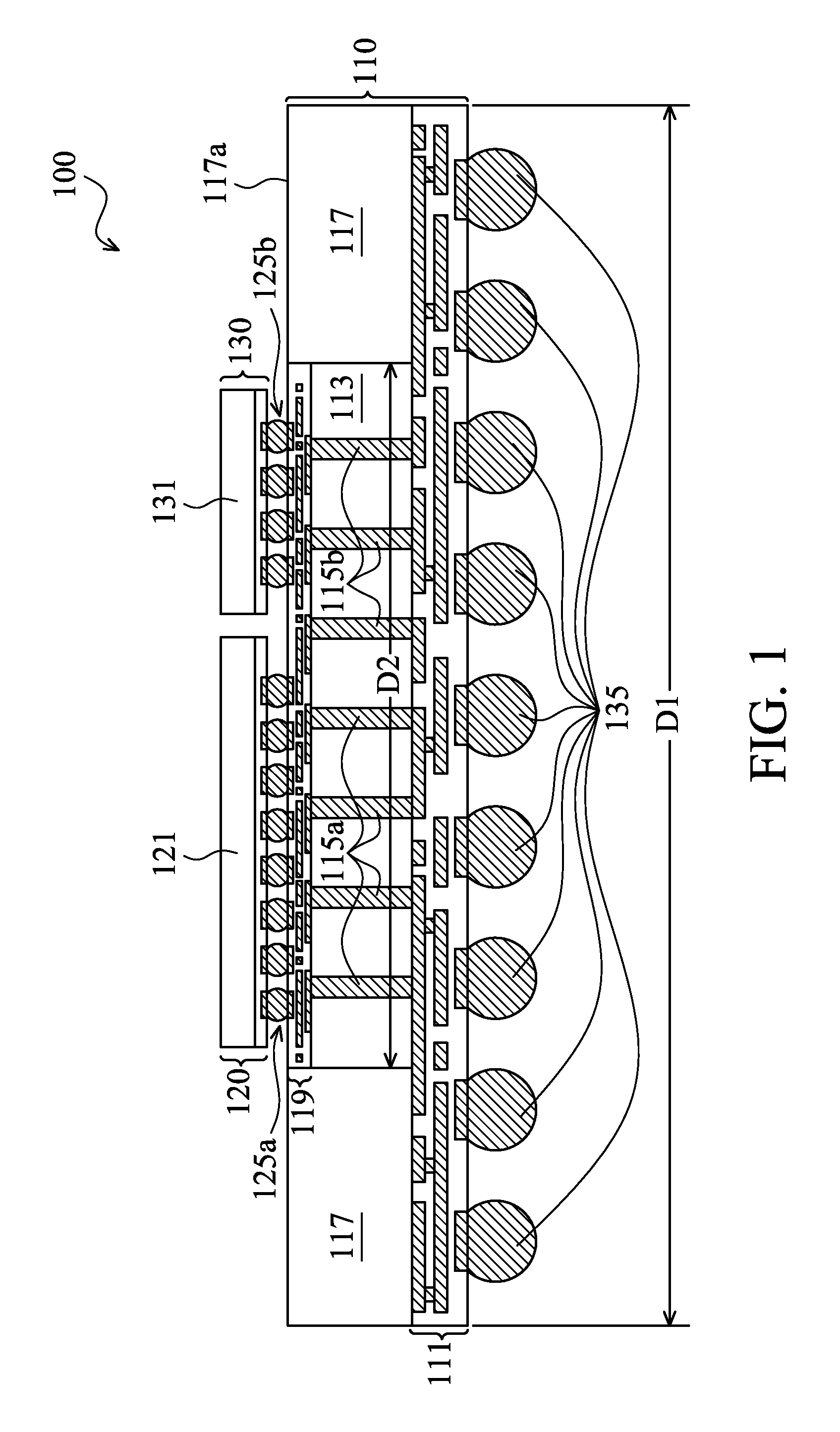

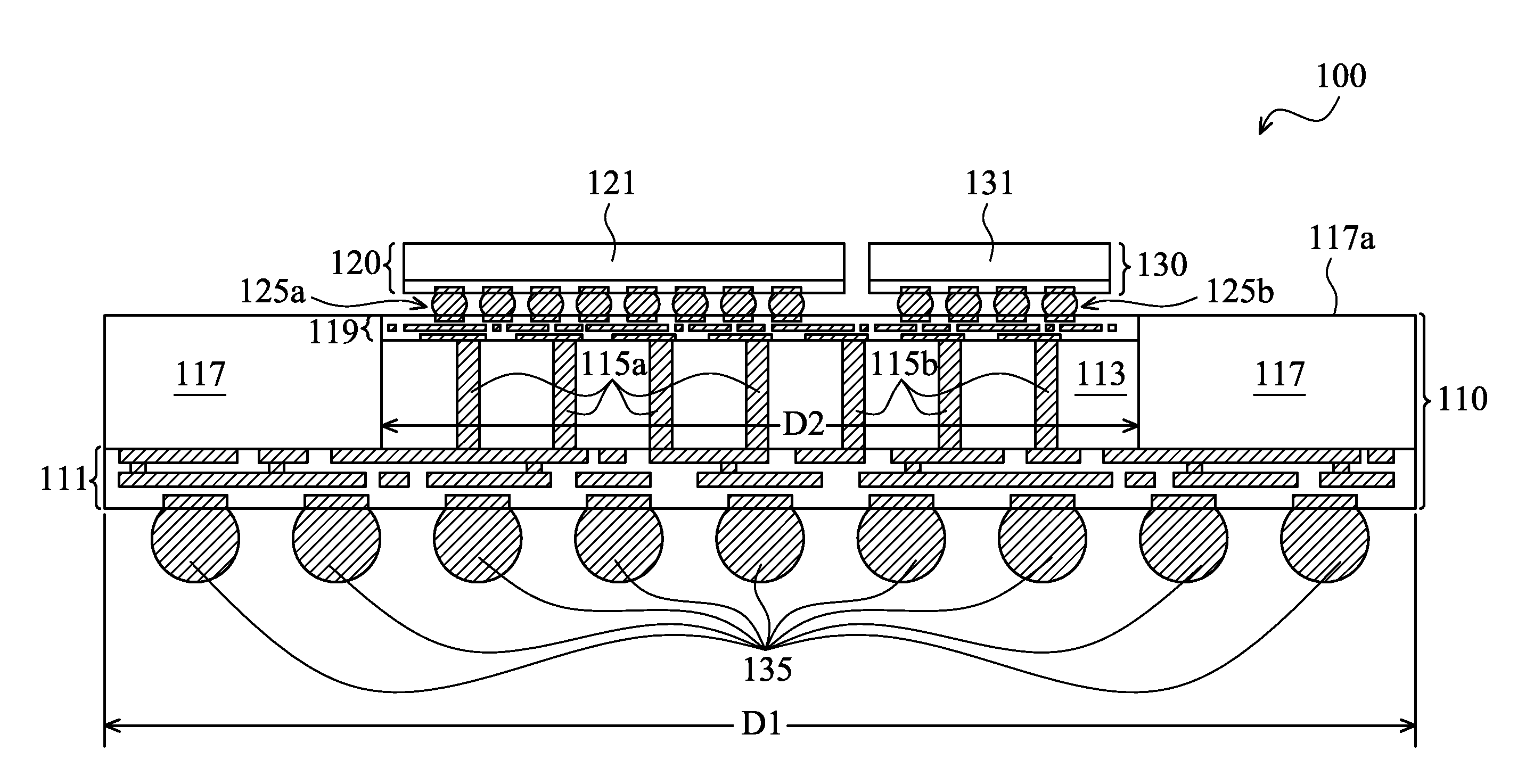

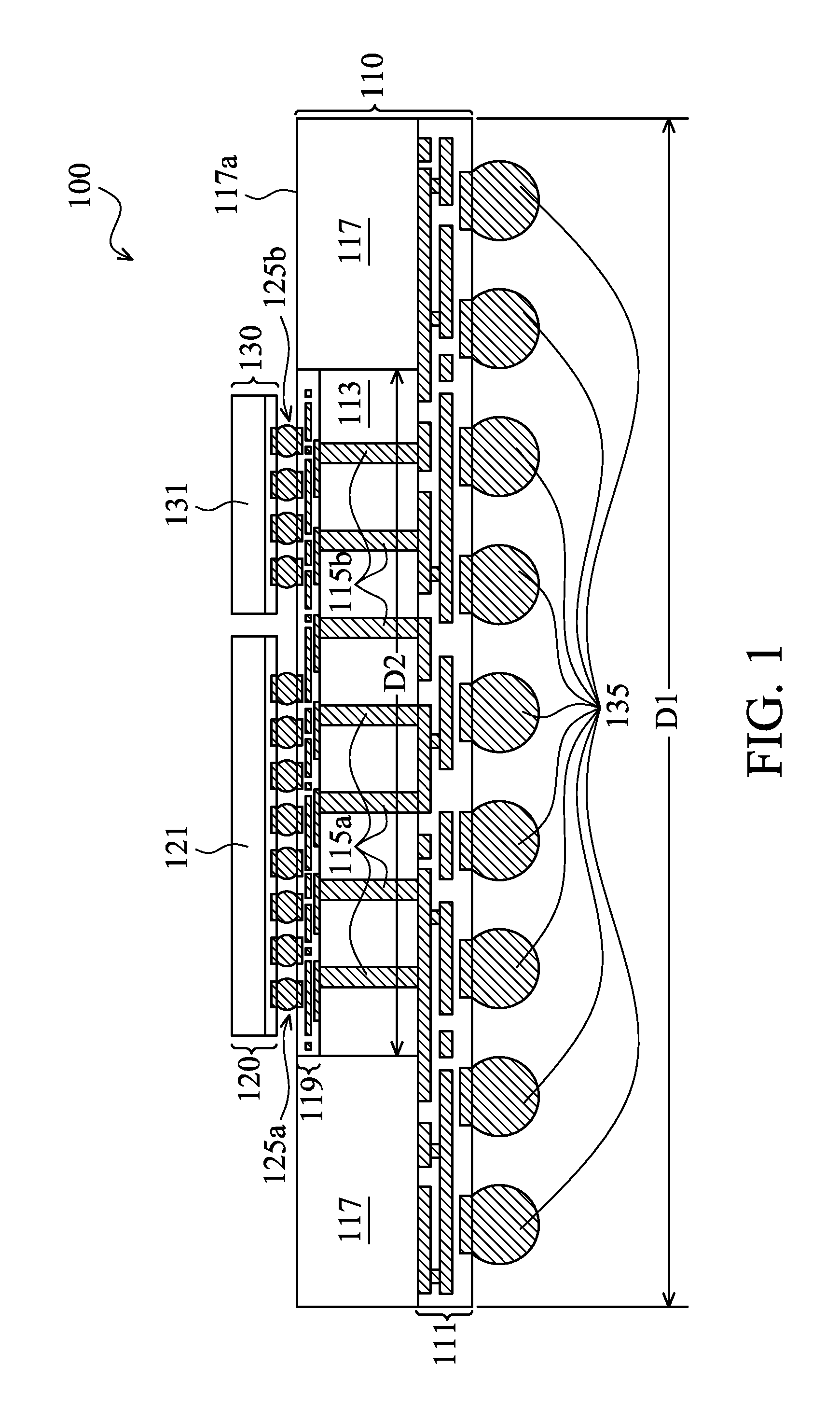

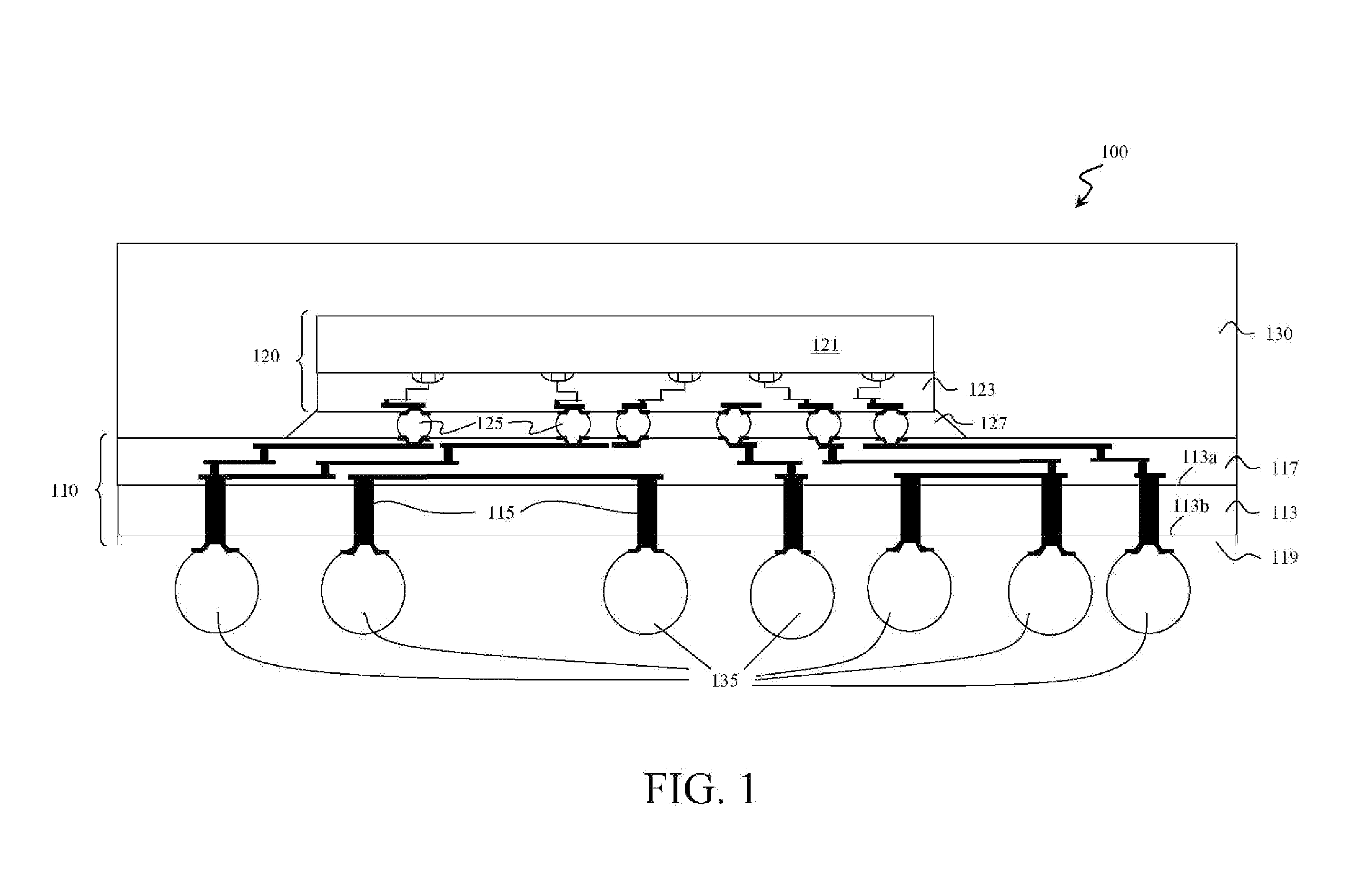

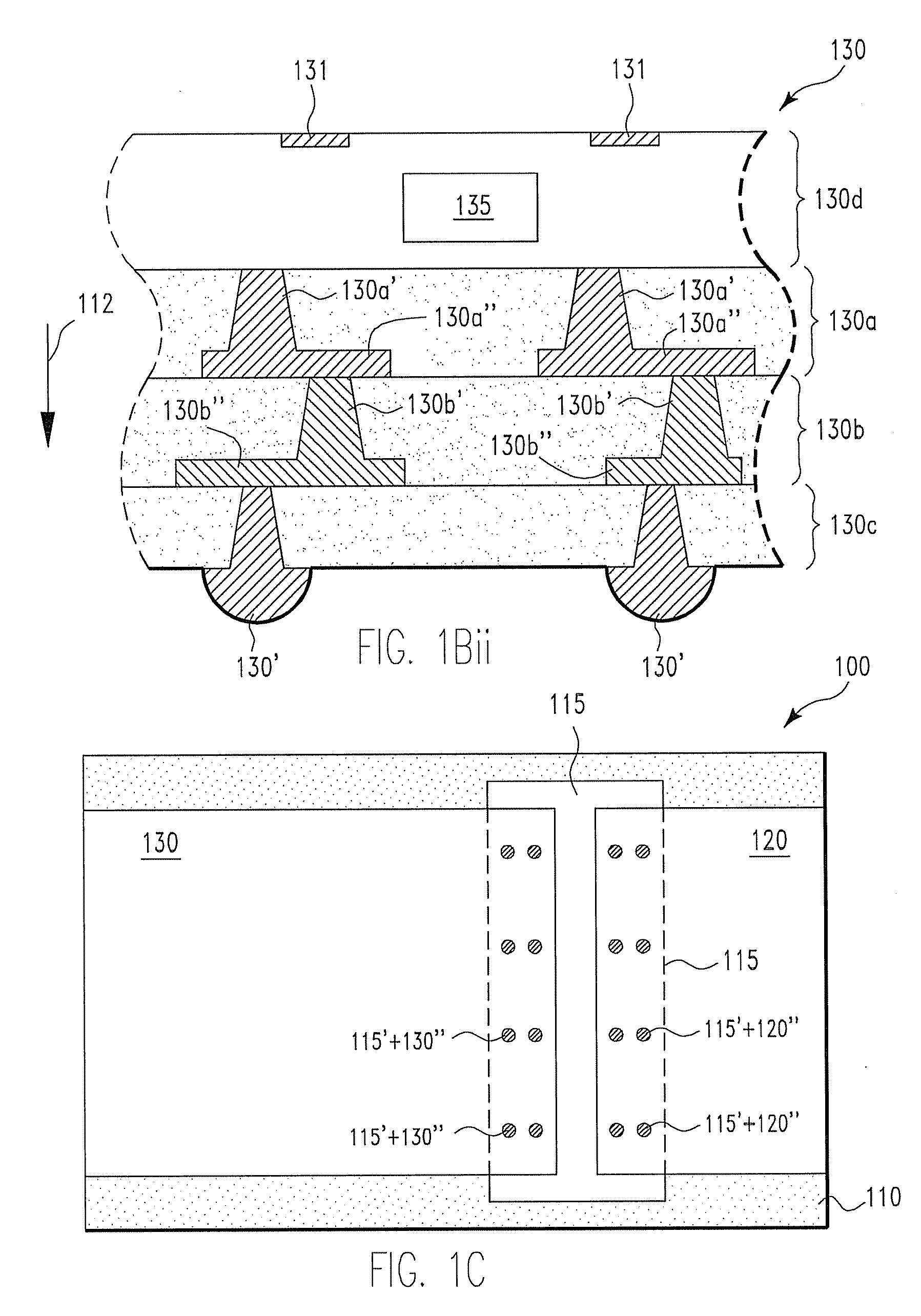

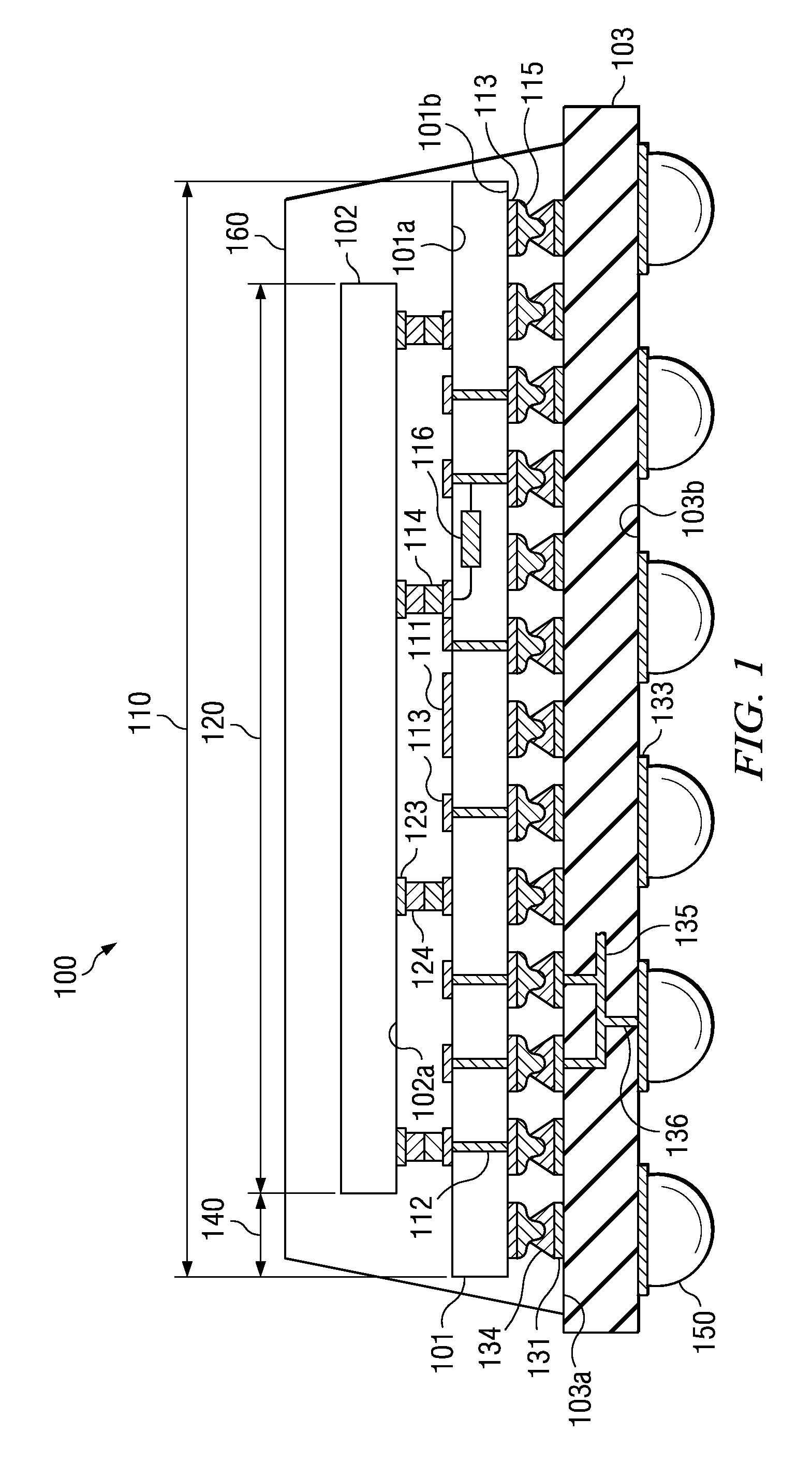

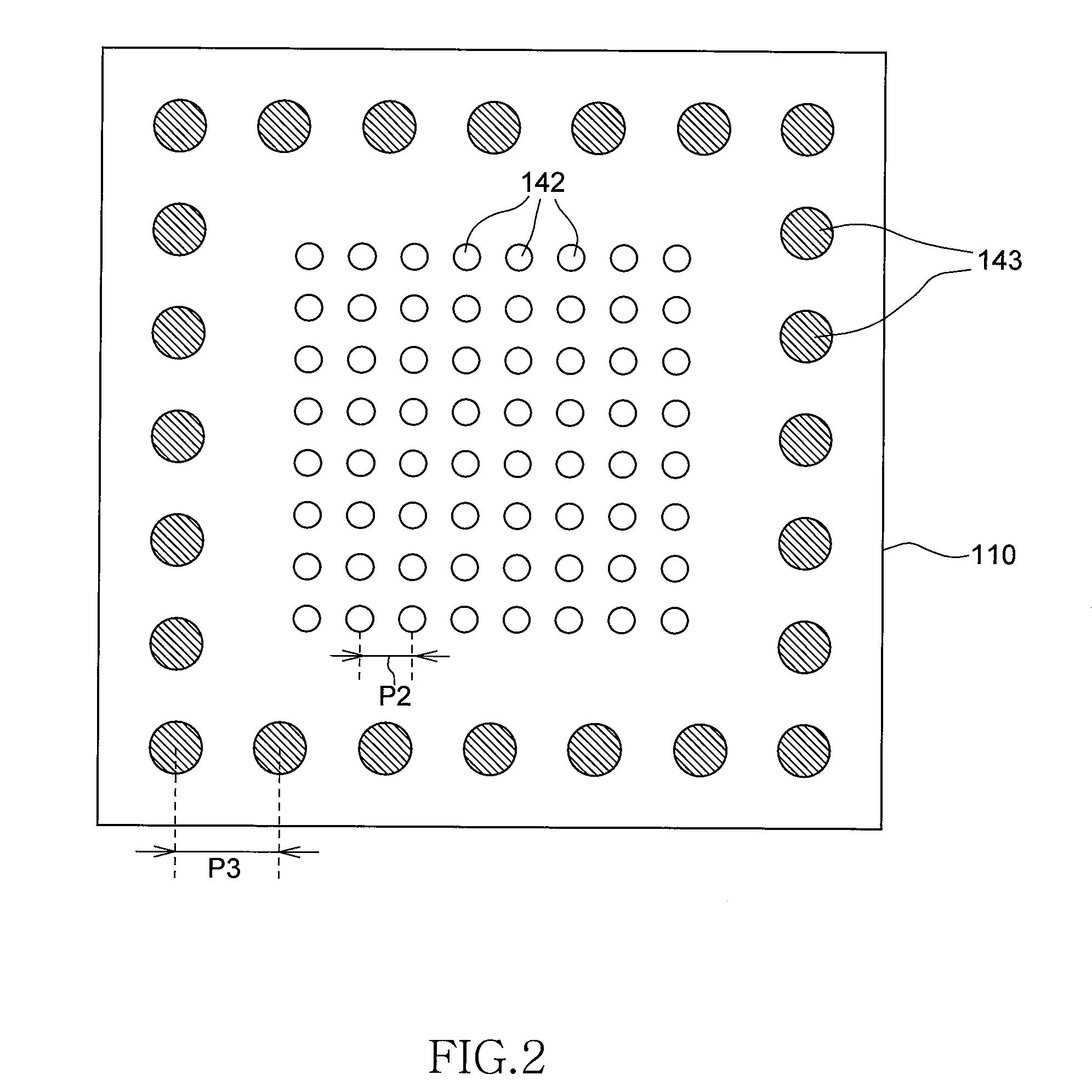

Package systems having interposers

A package system includes an integrated circuit disposed over an interposer. The interposer includes a first interconnect structure. A first substrate is disposed over the first interconnect structure. The first substrate includes at least one first through silicon via (TSV) structure therein. A molding compound material is disposed over the first interconnect structure and around the first substrate. The integrated circuit is electrically coupled with the at least one first TSV structure.

Owner:TAIWAN SEMICON MFG CO LTD

Package systems having interposers

ActiveUS20110291288A1Semiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A package system includes an integrated circuit disposed over an interposer. The interposer includes a first interconnect structure. A first substrate is disposed over the first interconnect structure. The first substrate includes at least one first through silicon via (TSV) structure therein. A molding compound material is disposed over the first interconnect structure and around the first substrate. The integrated circuit is electrically coupled with the at least one first TSV structure.

Owner:TAIWAN SEMICON MFG CO LTD

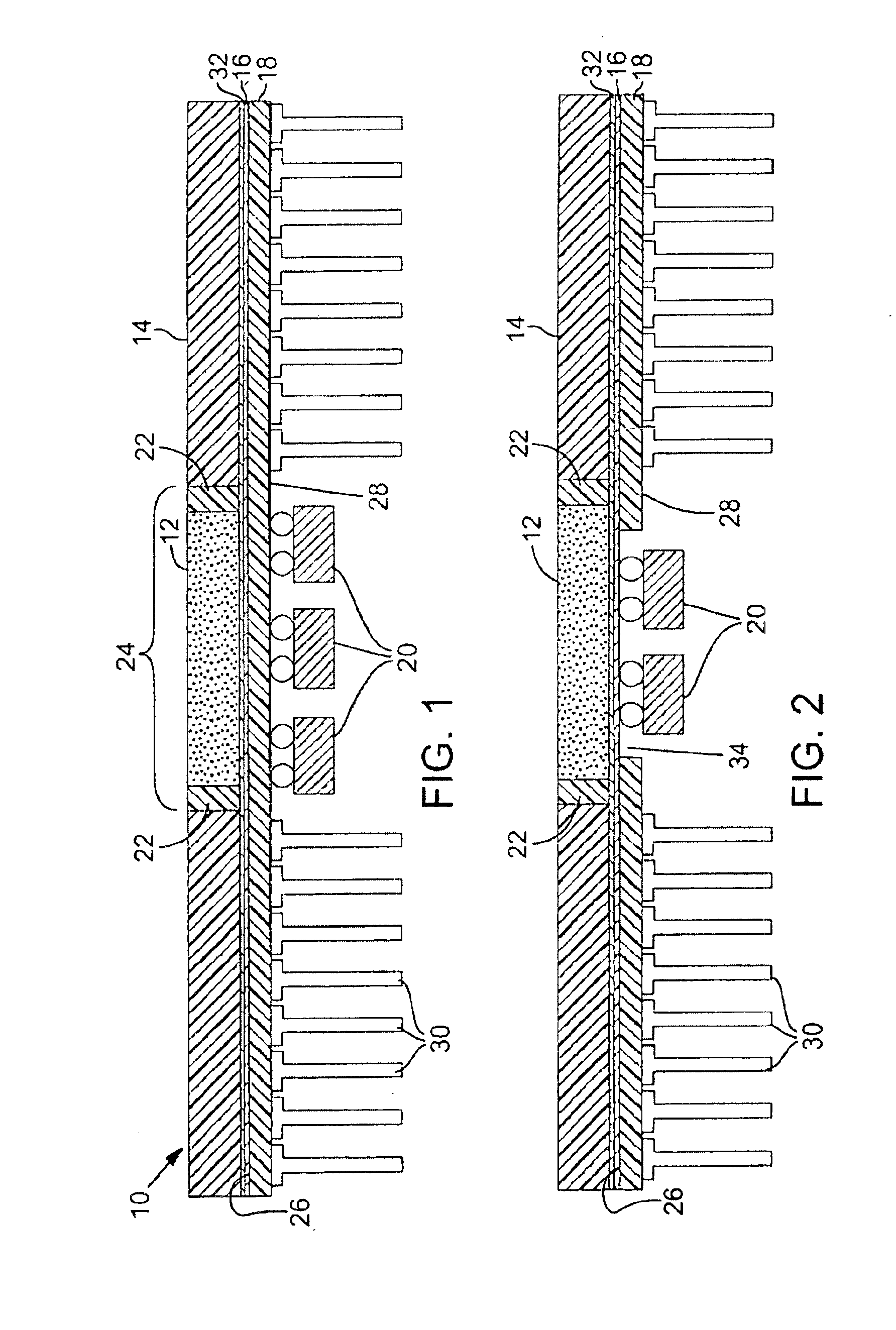

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

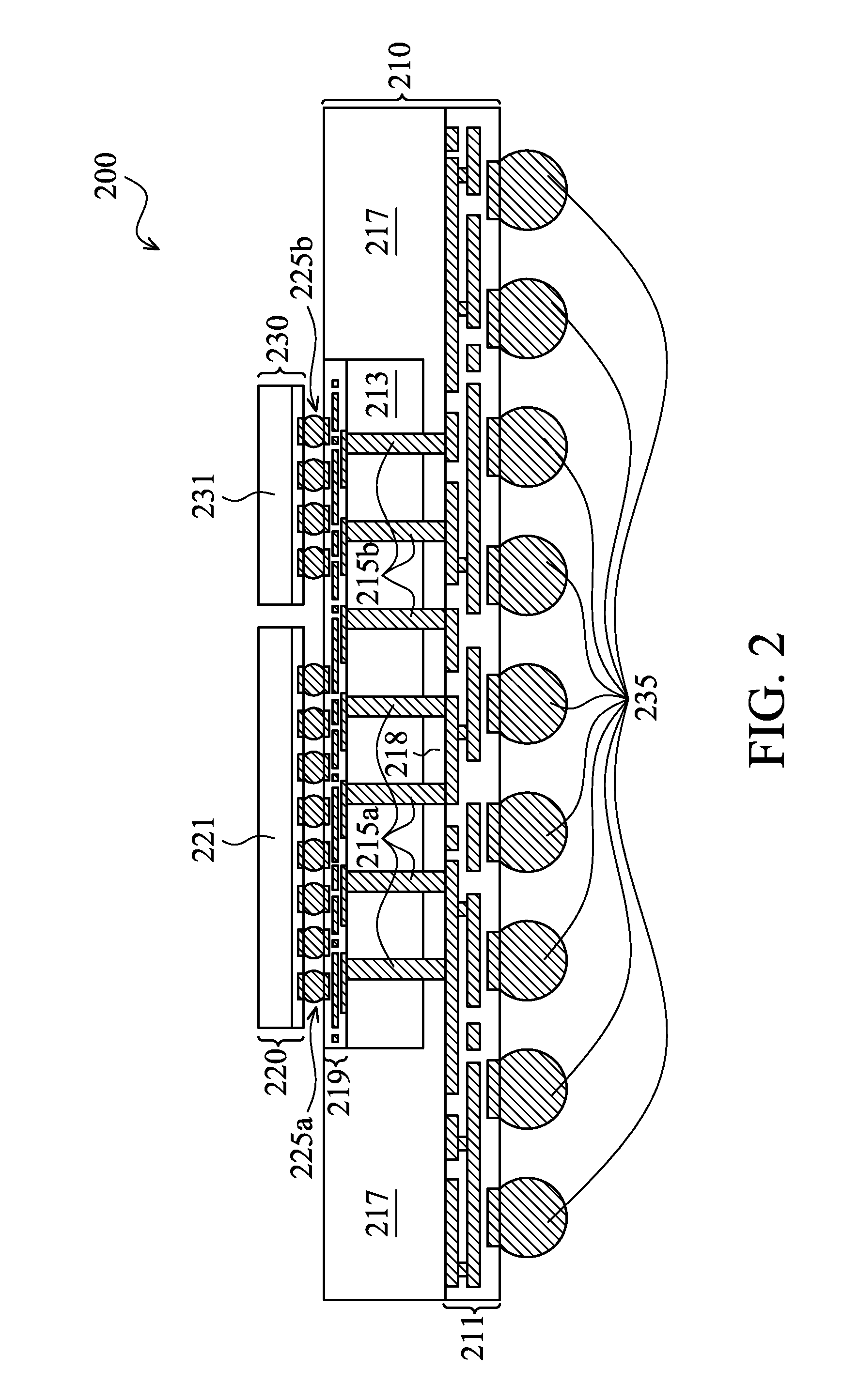

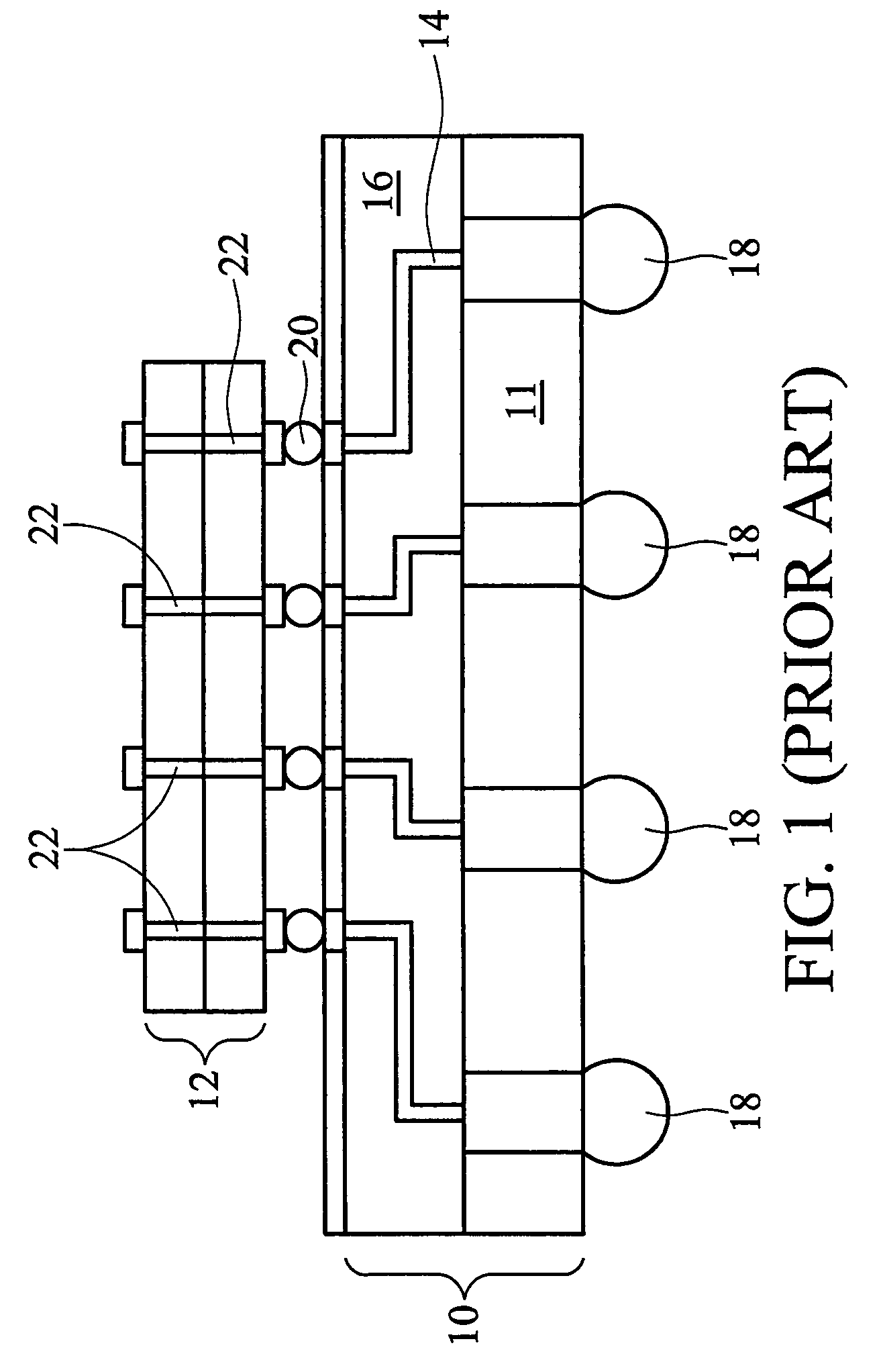

Stacked semiconductor packages and method for the fabrication thereof

ActiveUS6861288B2High densitySemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor package

A method for fabricating a stacked semiconductor package includes providing a substrate and mounting a first semiconductor device on the substrate. An interposer is supported above the first semiconductor device opposite the substrate. The interposer is electrically connected to the substrate. A second semiconductor device is then mounted on the interposer.

Owner:STATS CHIPPAC LTD

Low-cost and ultra-fine integrated circuit packaging technique

ActiveUS7576435B2Improved feasibility of formingReduce bondingSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor chip

A semiconductor package structure and the methods for forming the same are provided. The semiconductor package structure includes an interposer; a first plurality of bonding pads on a side of the interposer; a semiconductor chip; and a second plurality of bonding pads on a side of the semiconductor chip. The first and the second plurality of bonding pads are bonded through metal-to-metal bonds.

Owner:ADVANCED MFG INNOVATIONS INC

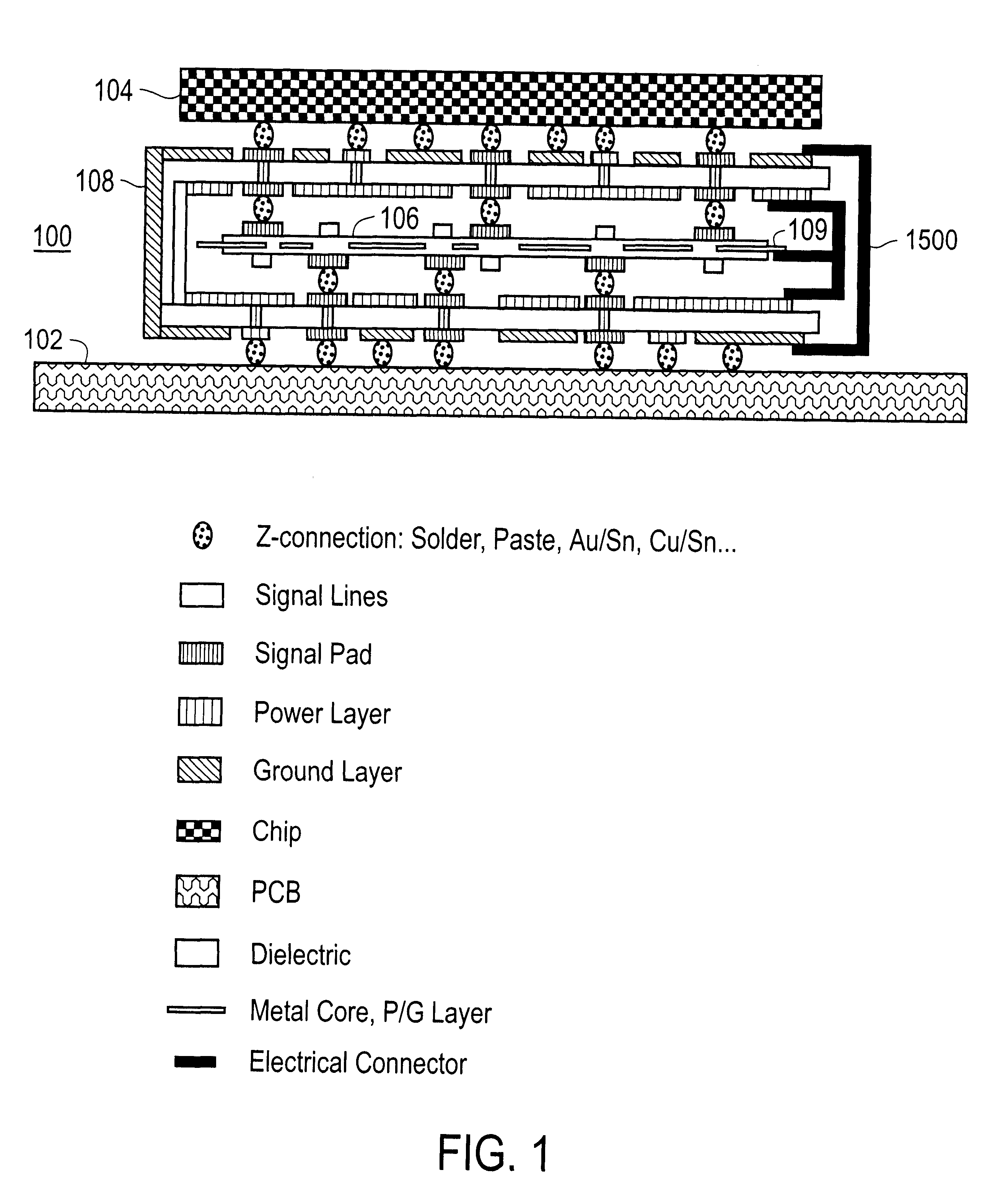

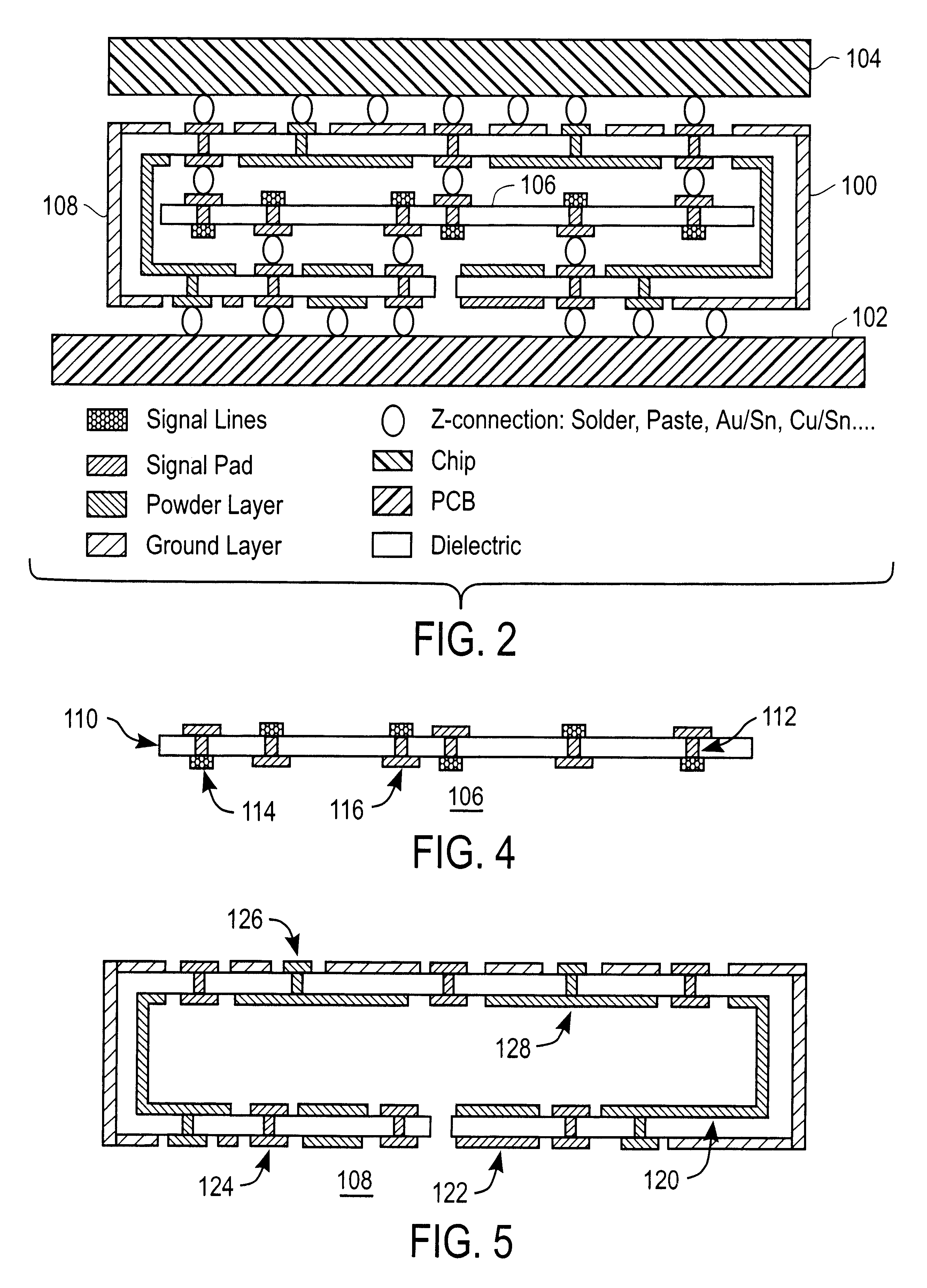

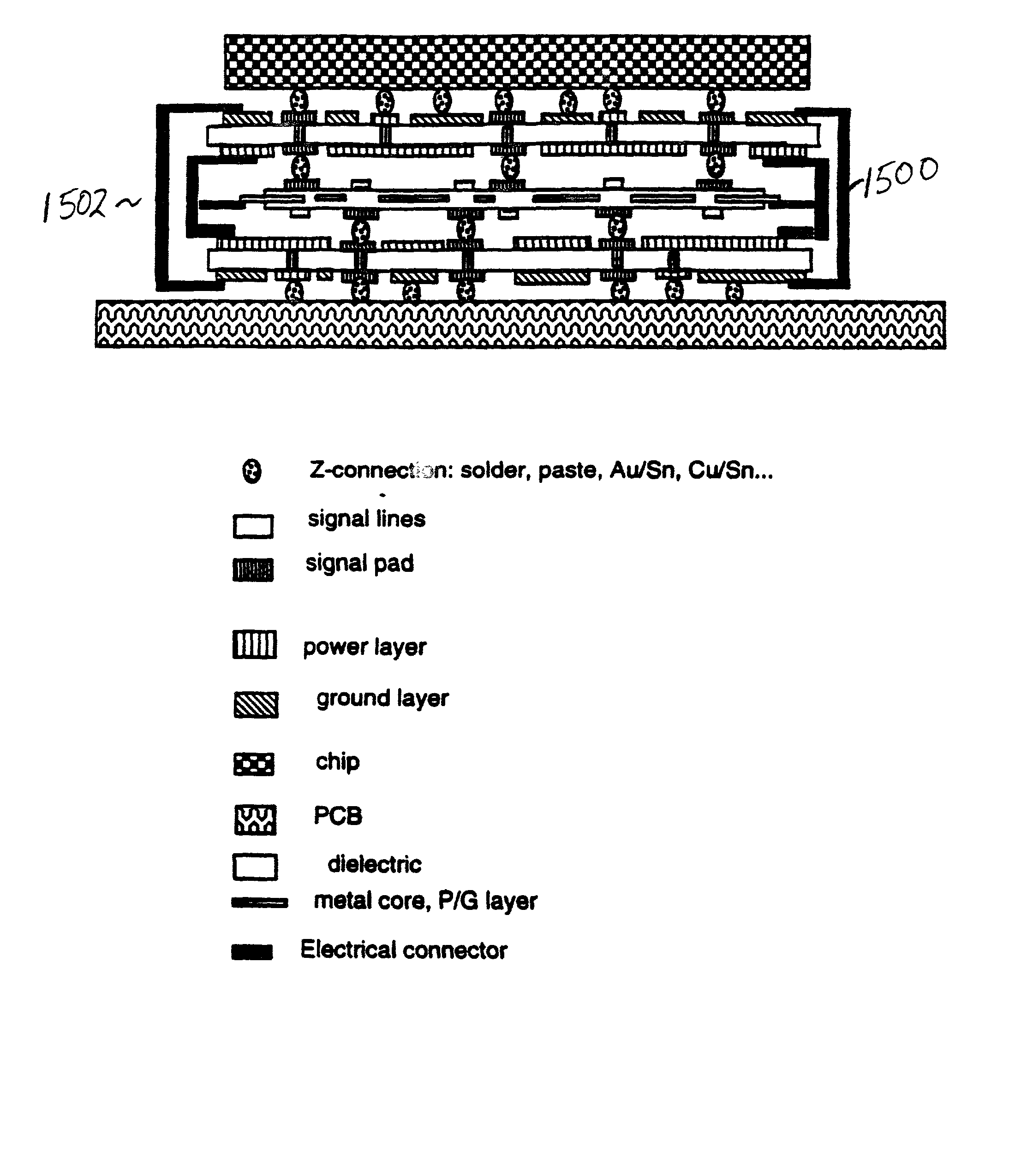

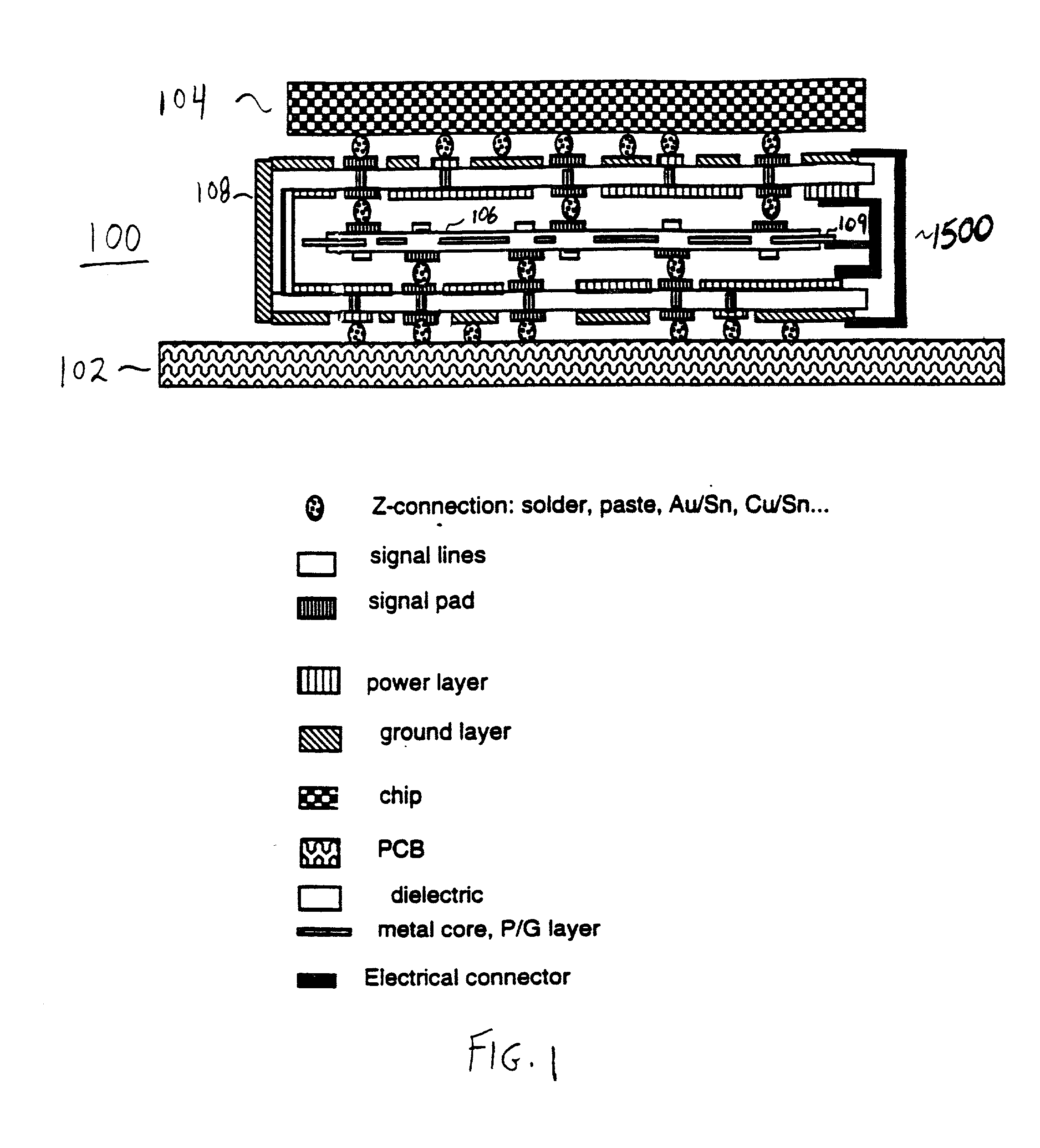

Composite interposer and method for producing a composite interposer

InactiveUS6521530B2Cross-talk/noise/interference reductionSemiconductor/solid-state device detailsEpoxyFilling materials

A composite interposer for providing power and signal connections between an integrated circuit chip or chips and a substrate. The interposer includes a signal core formed from a conductive power / ground plane positioned between two dielectric layers. A method for fabricating a composite interposer comprising disposing a silicon layer on a substrate, and selectively etching the silicon layer down to the substrate to develop silicon openings with a silicon profile, and to expose part of the substrate. Vias are formed through the exposed part of the substrate. The method additionally includes filling the vias and the silicon openings with a filler material (e.g., a high-aspect-ratio-capable photodefinable epoxy polymer) to form filled silicon openings and filled vias, forming first openings through the filled silicon openings and through the filled vias, forming second opening through filler material to expose semiconductor devices on the silicon layer, and interconnecting electrically, through the first openings and through the second openings, the exposed semiconductor devices with pads disposed against a bottom of the substrate.

Owner:FUJITSU LTD

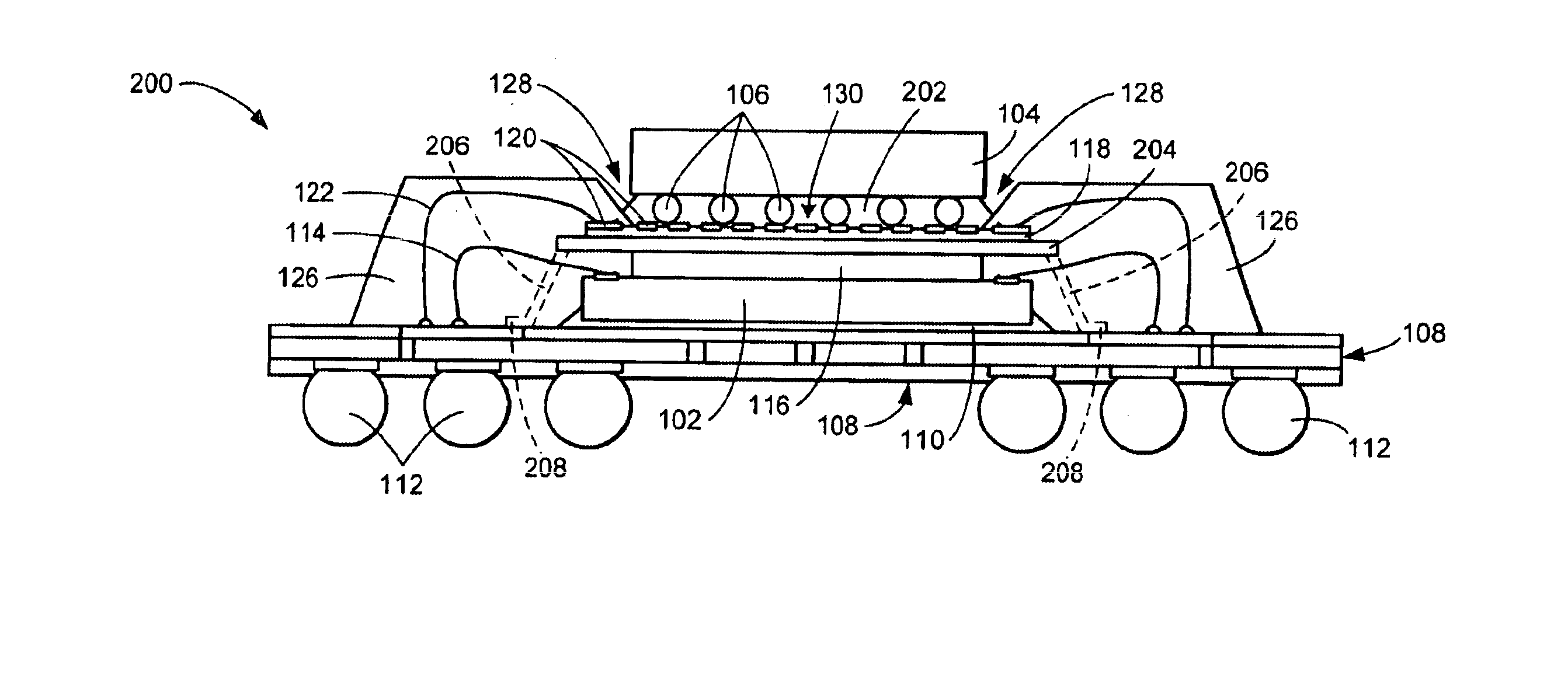

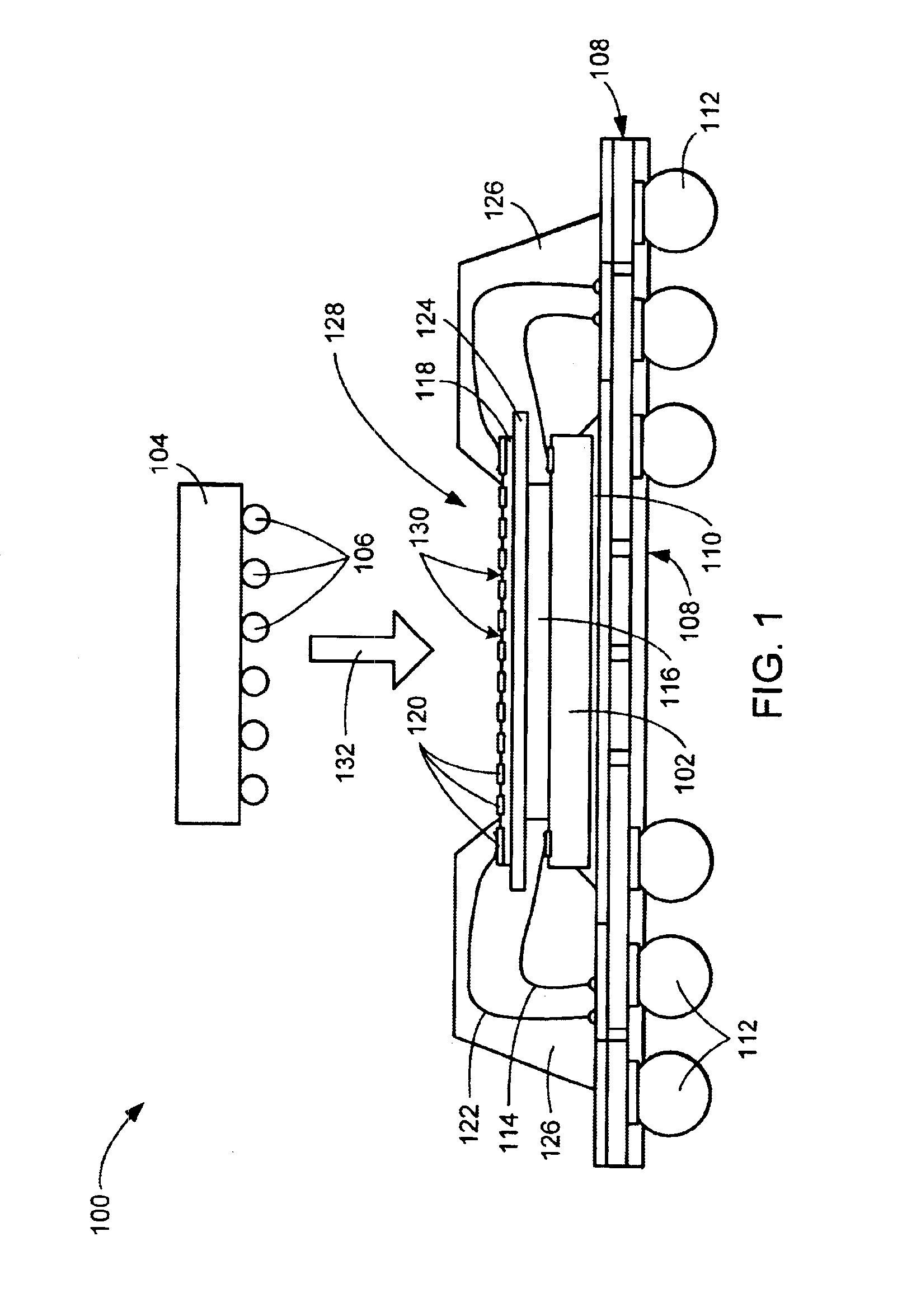

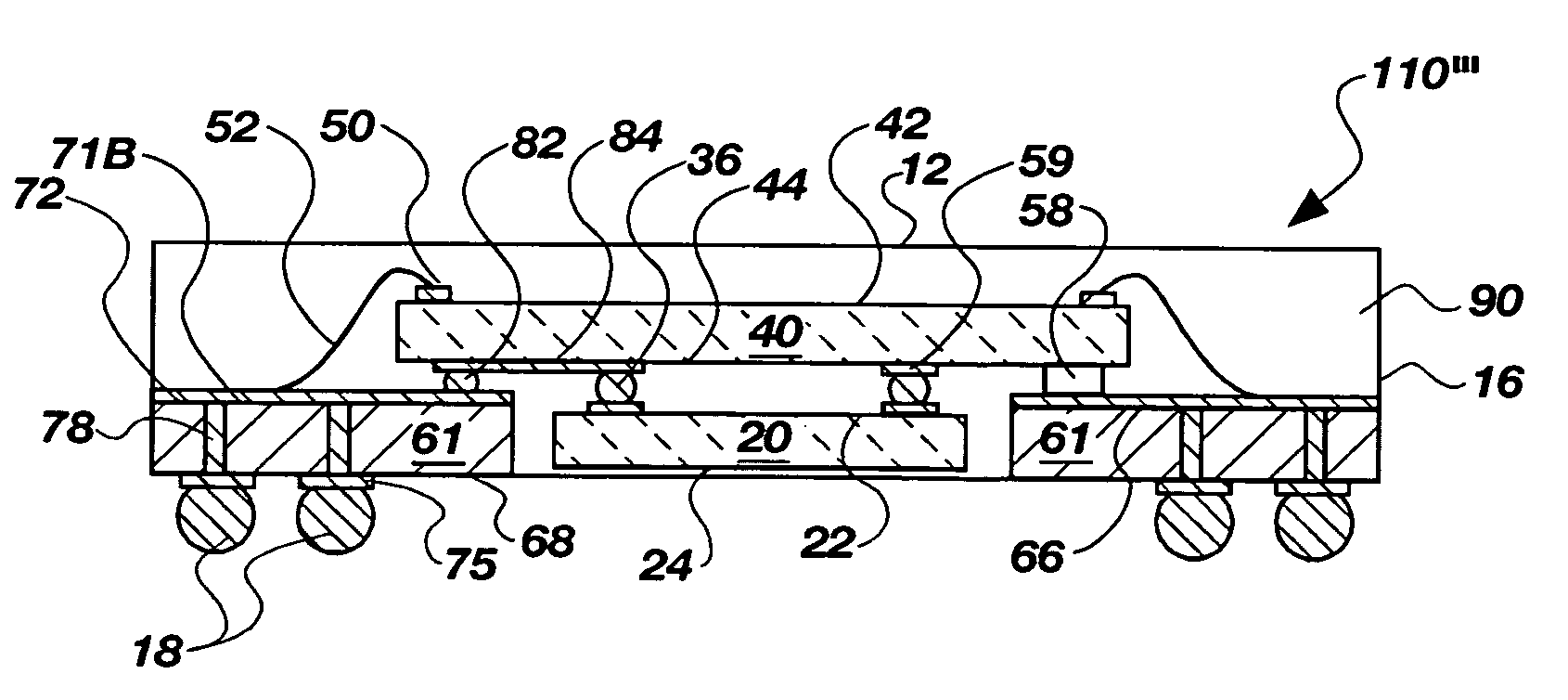

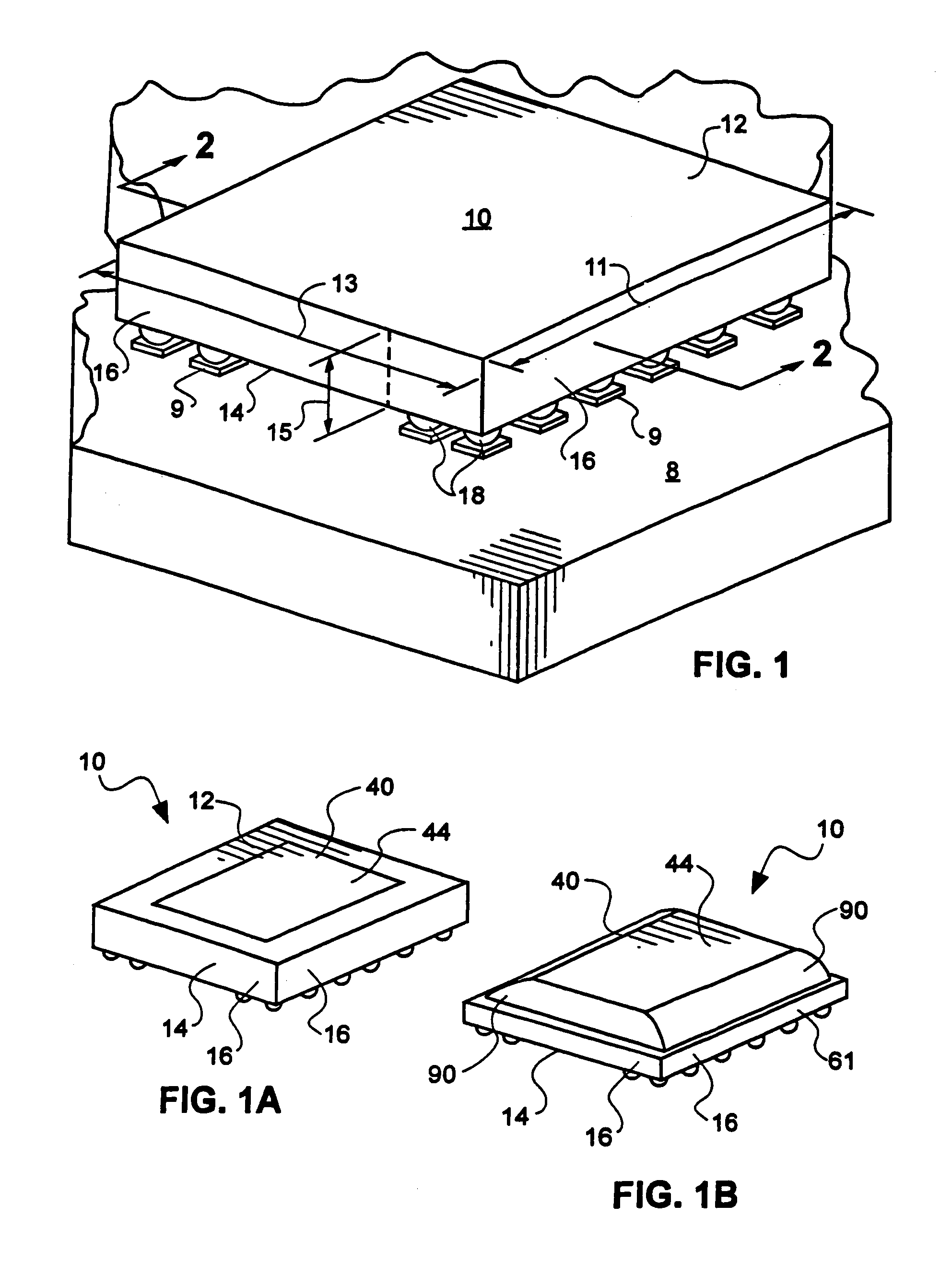

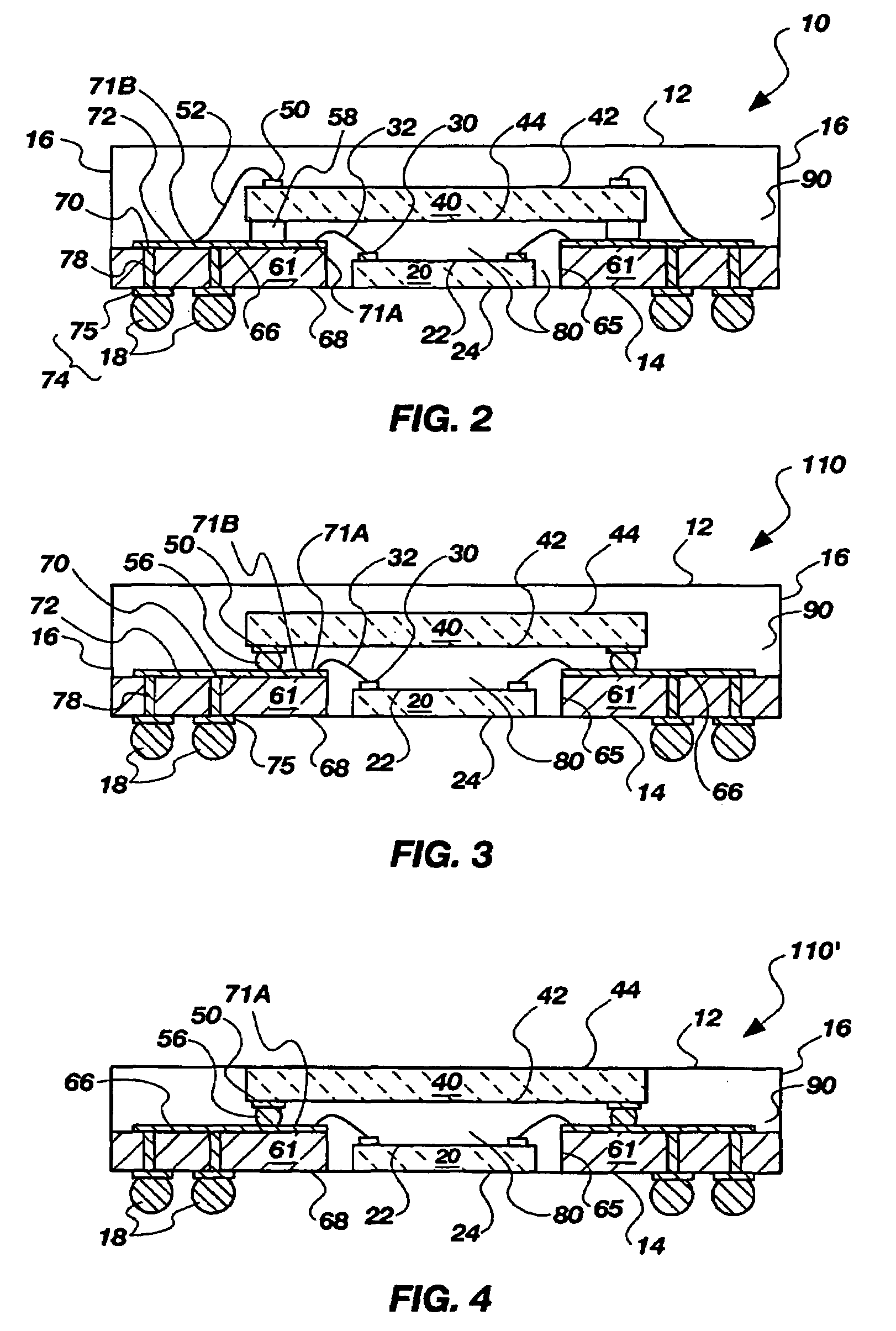

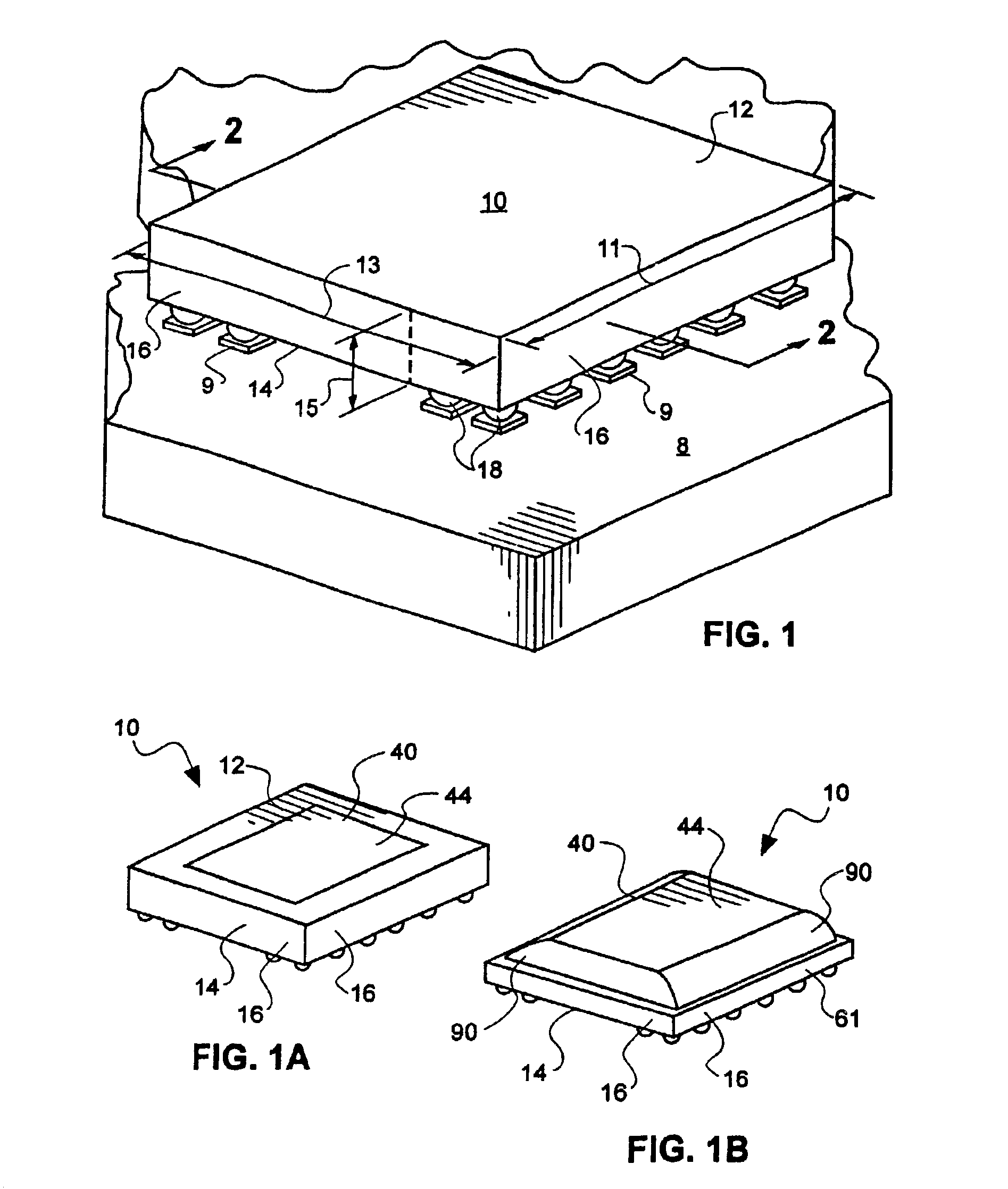

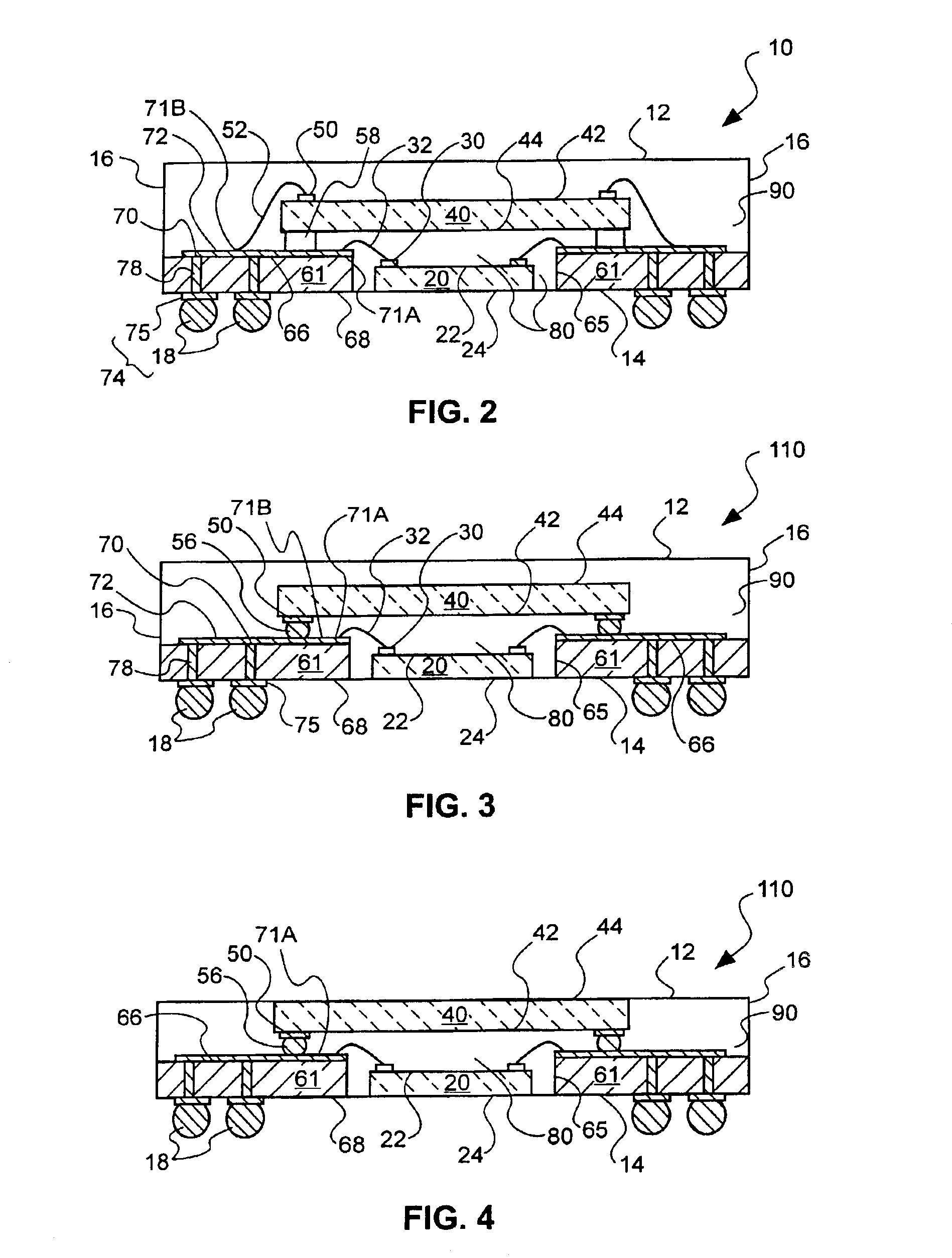

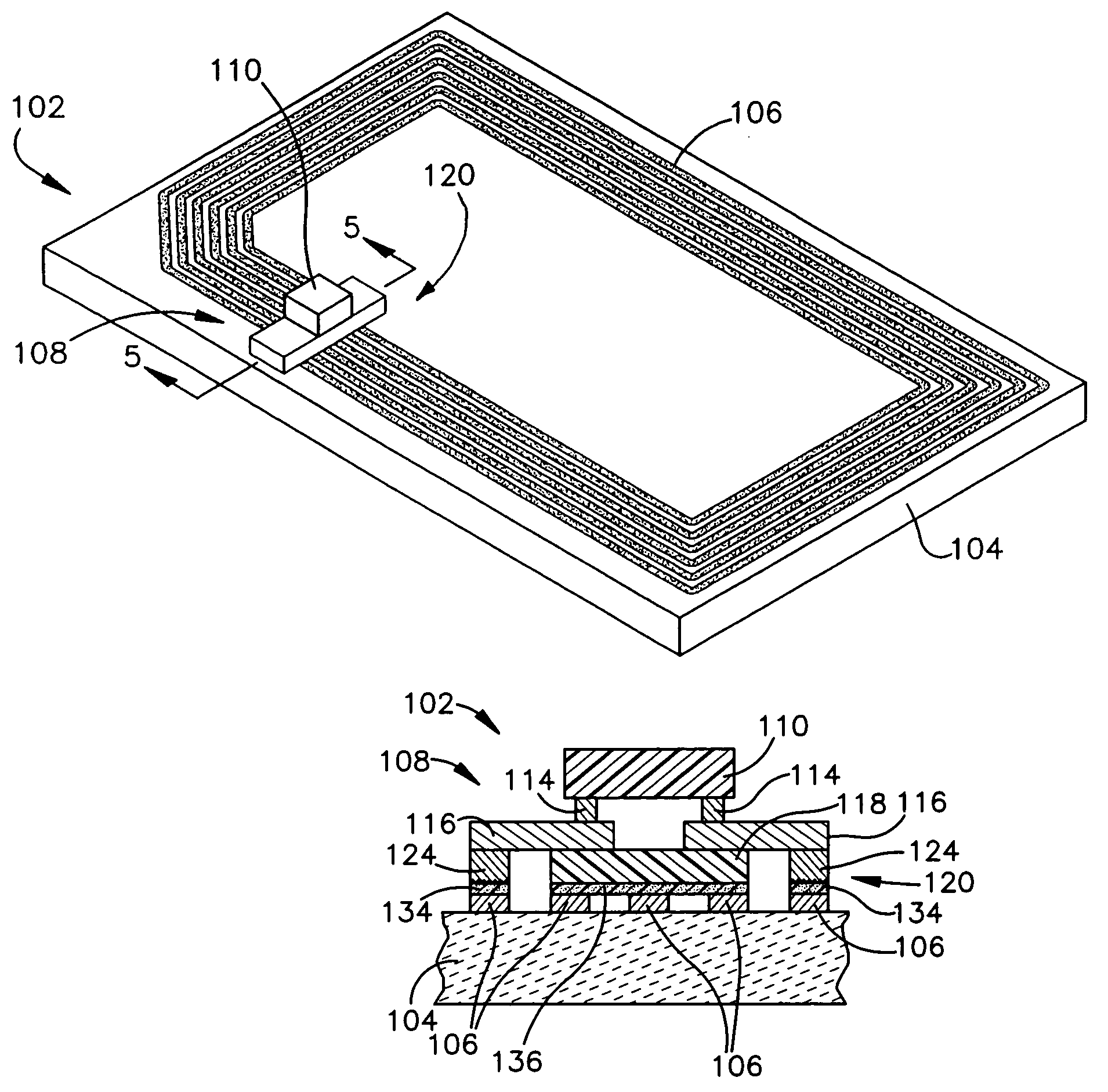

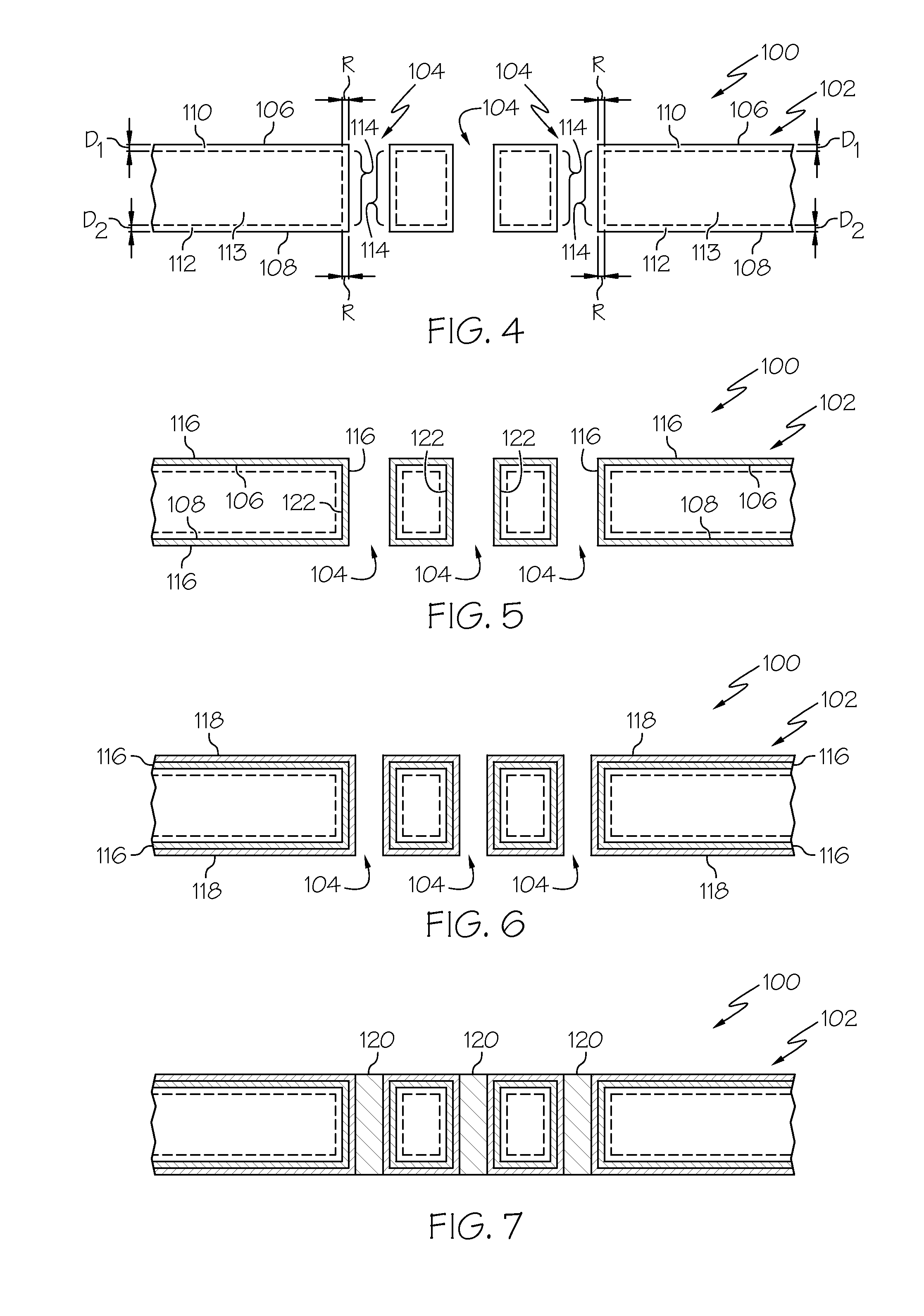

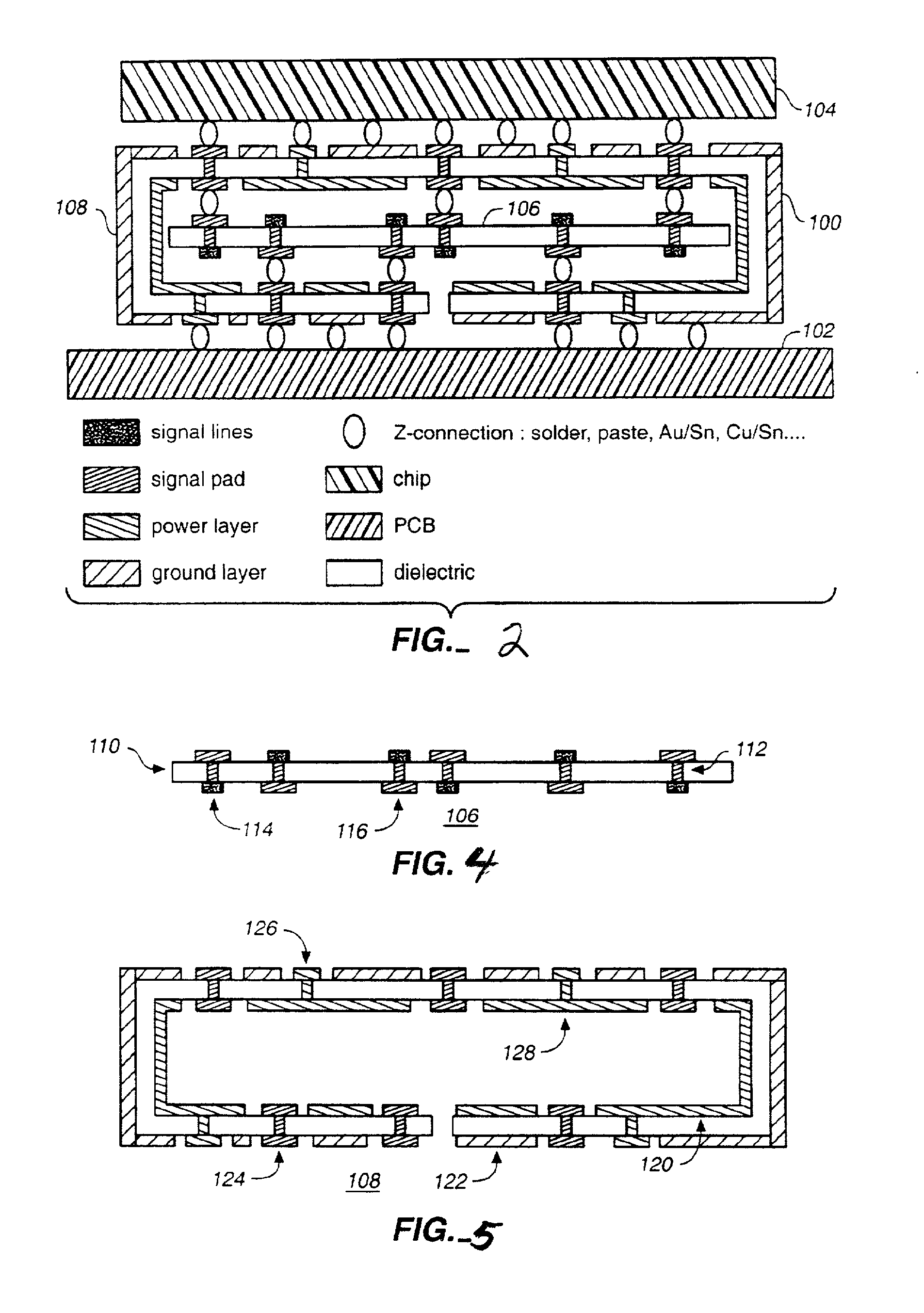

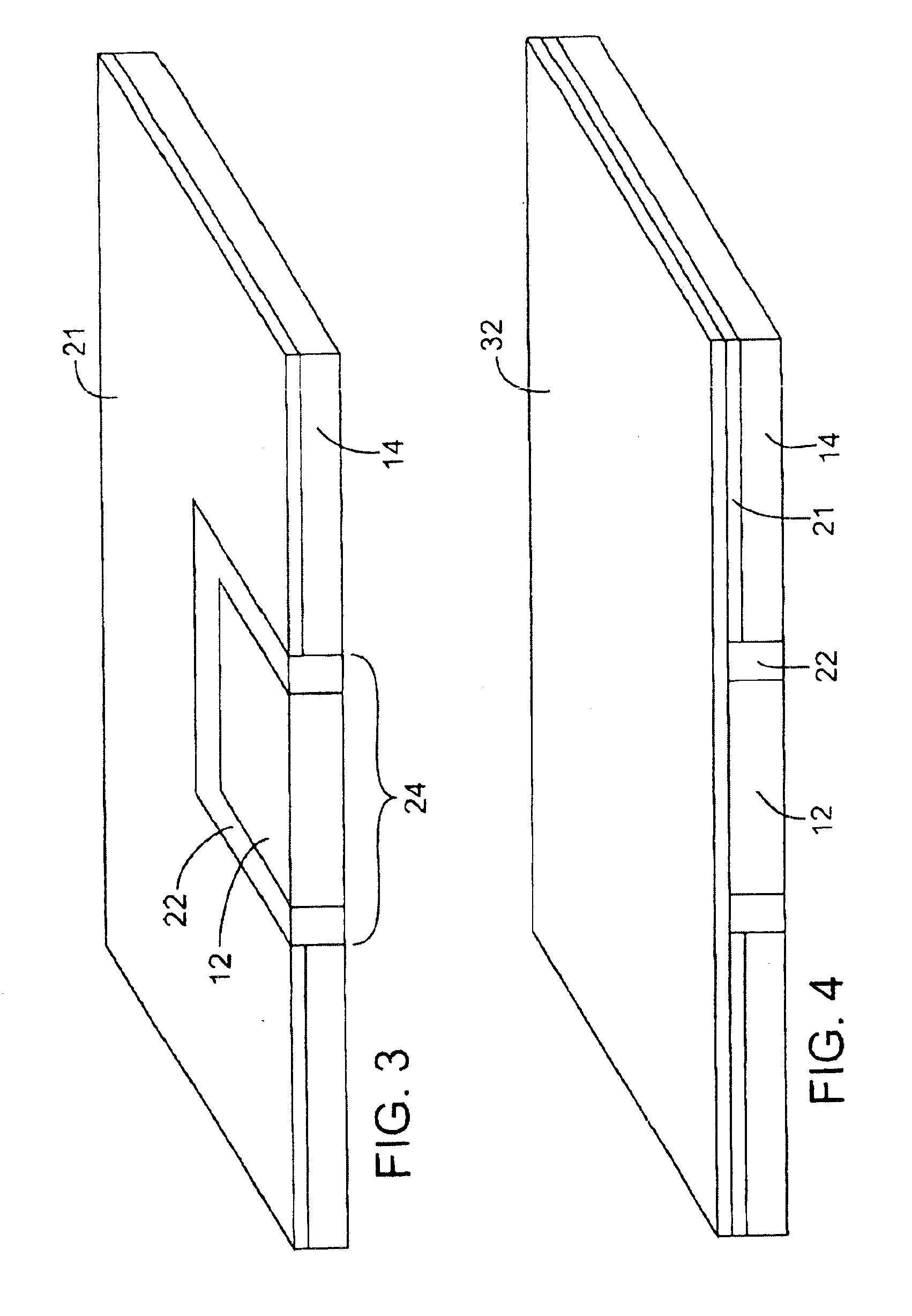

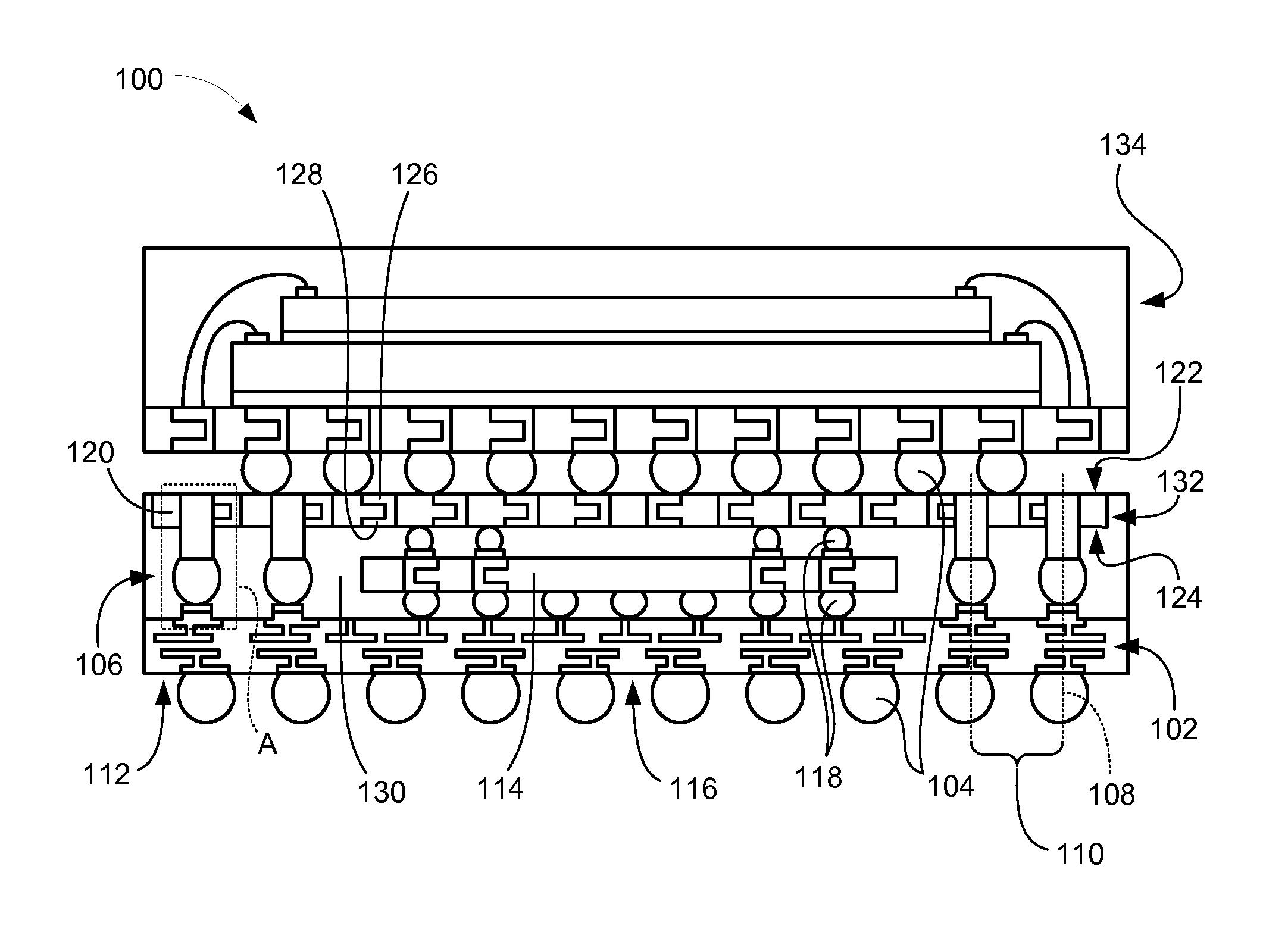

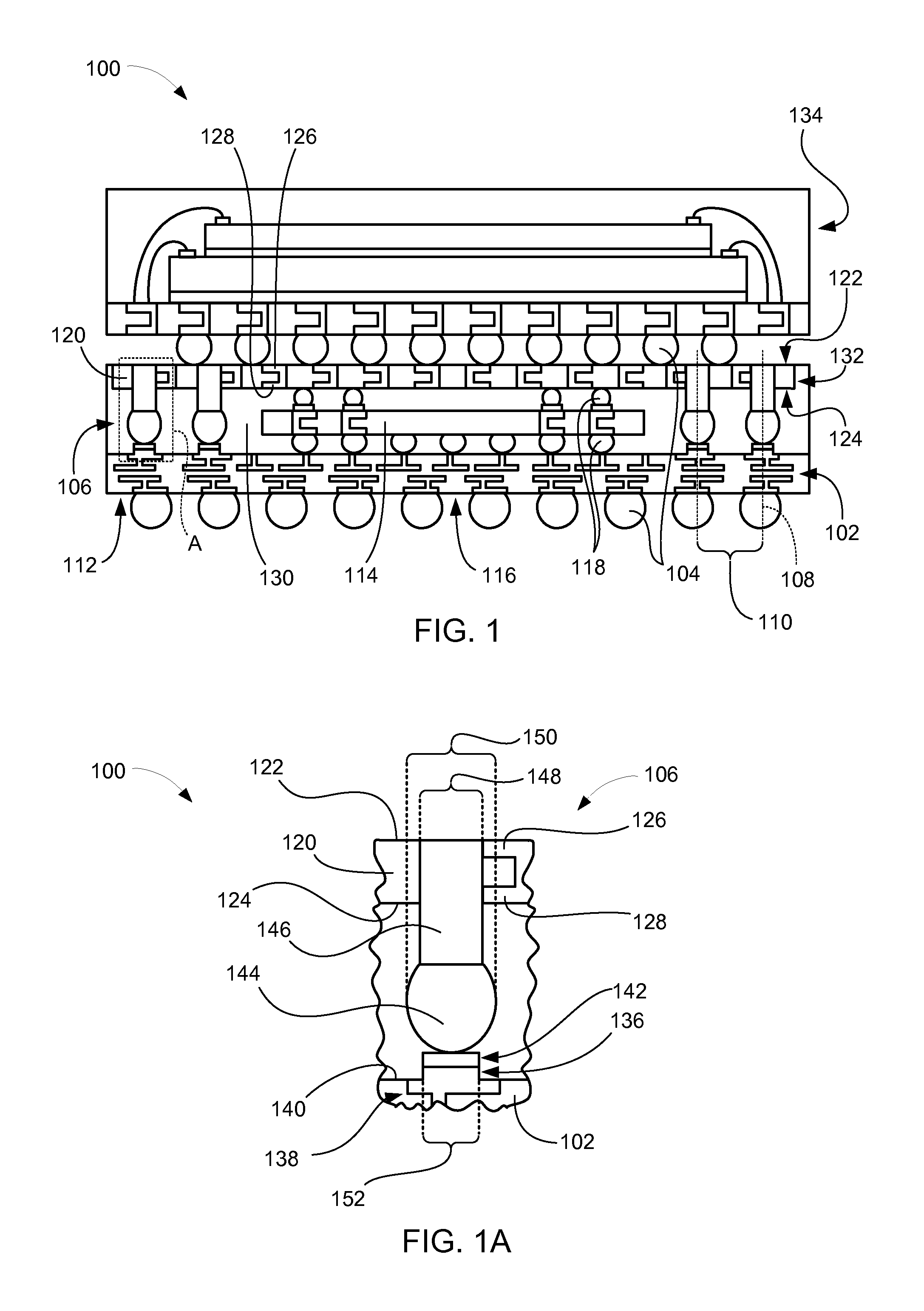

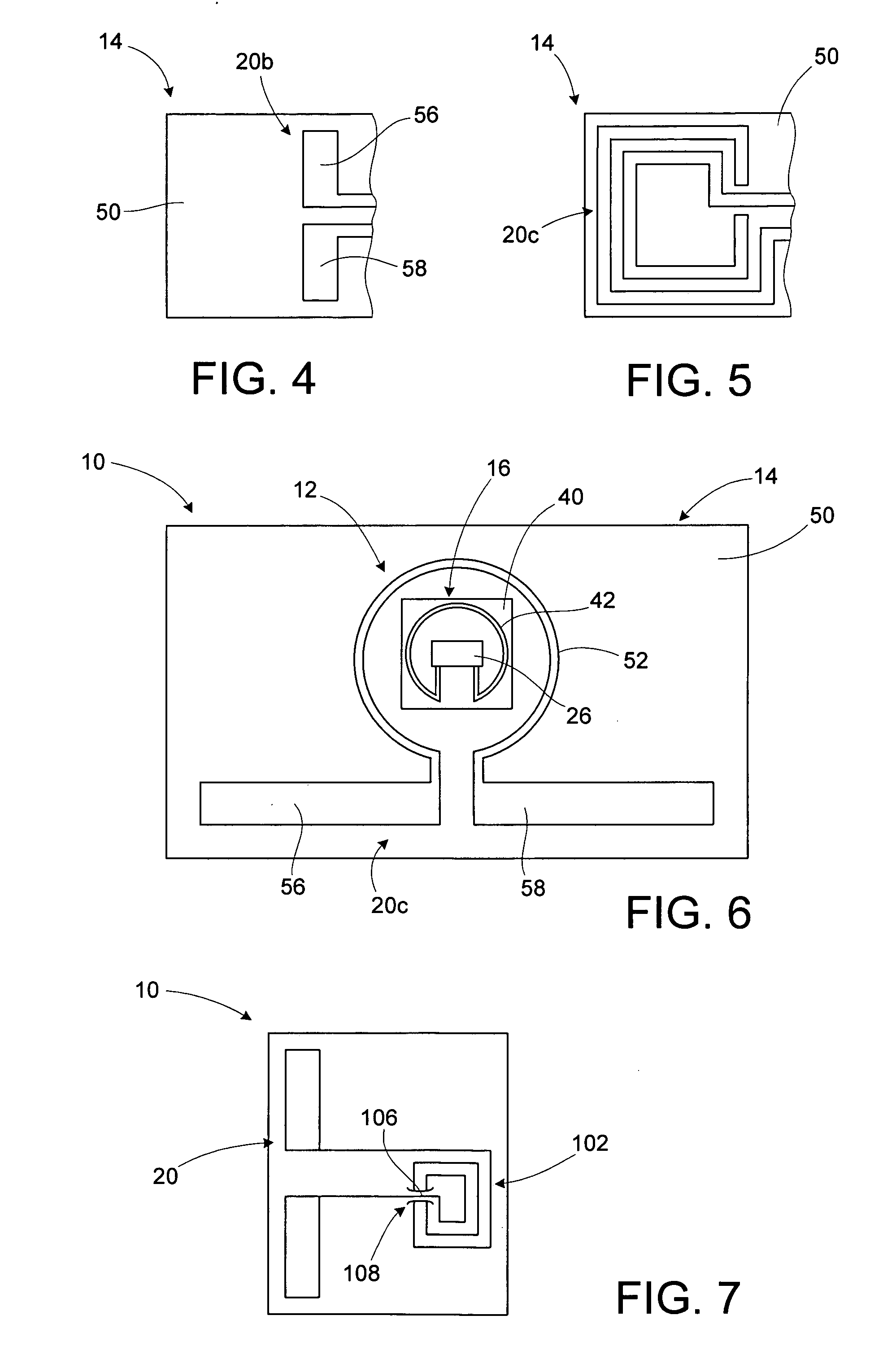

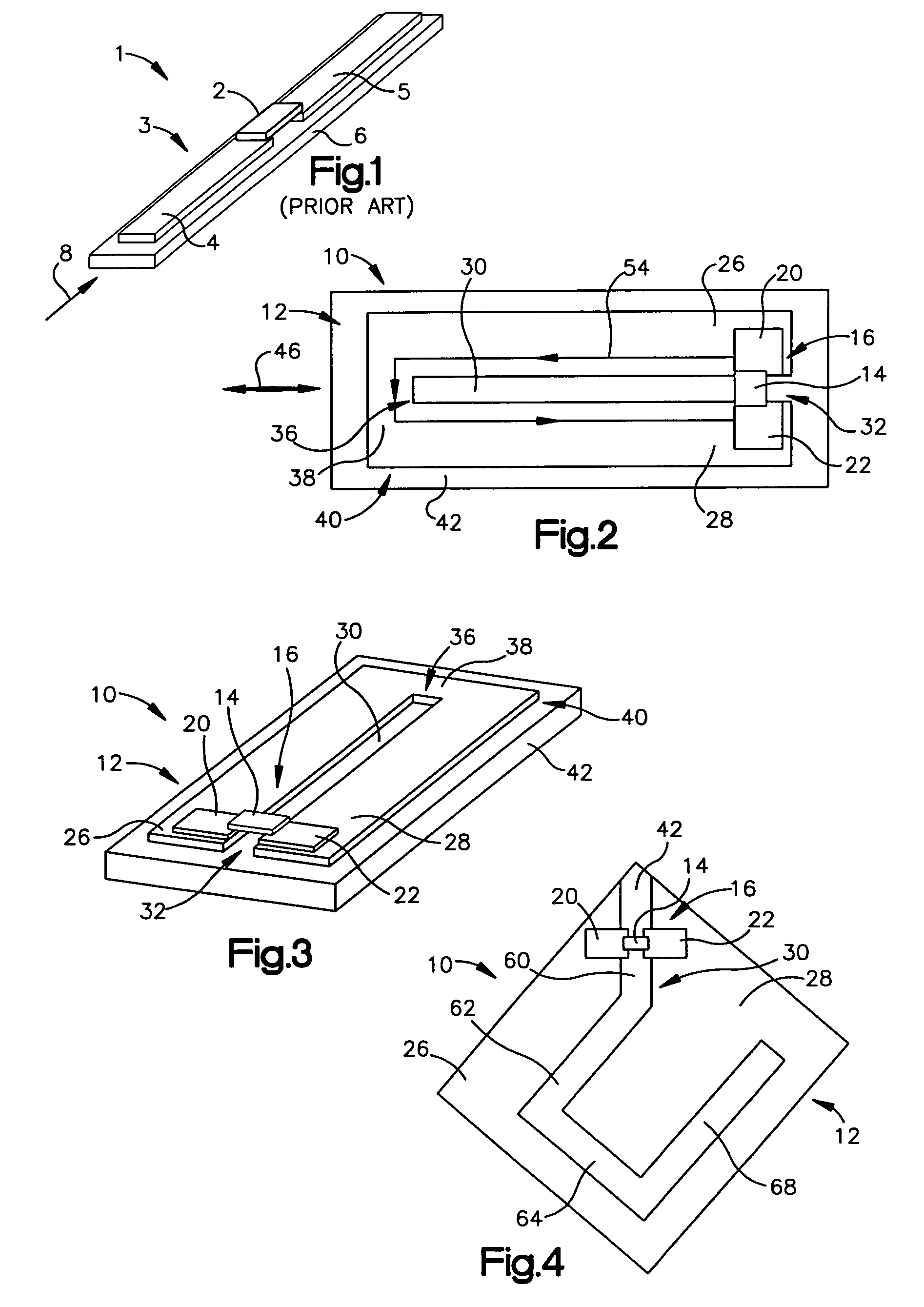

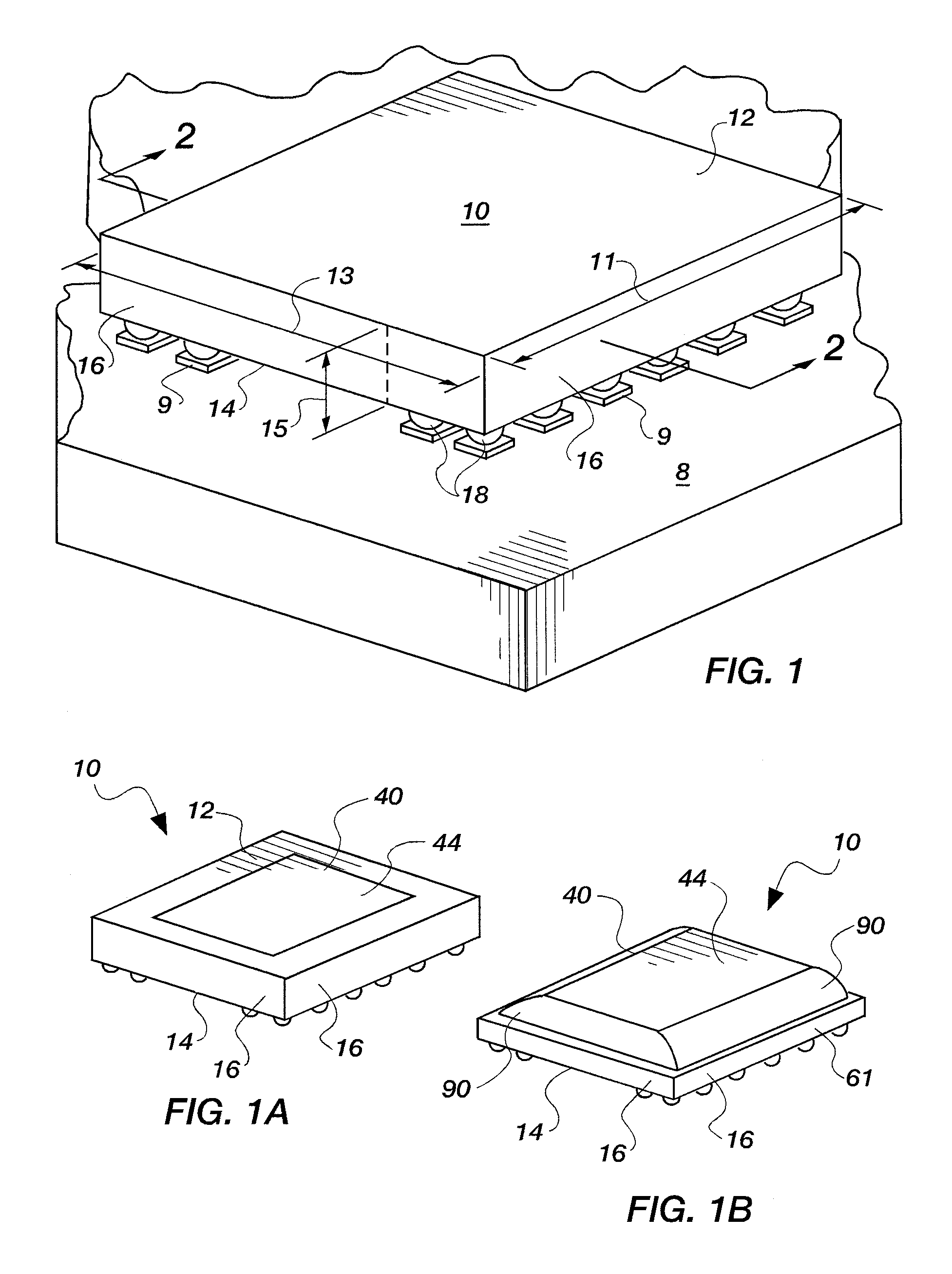

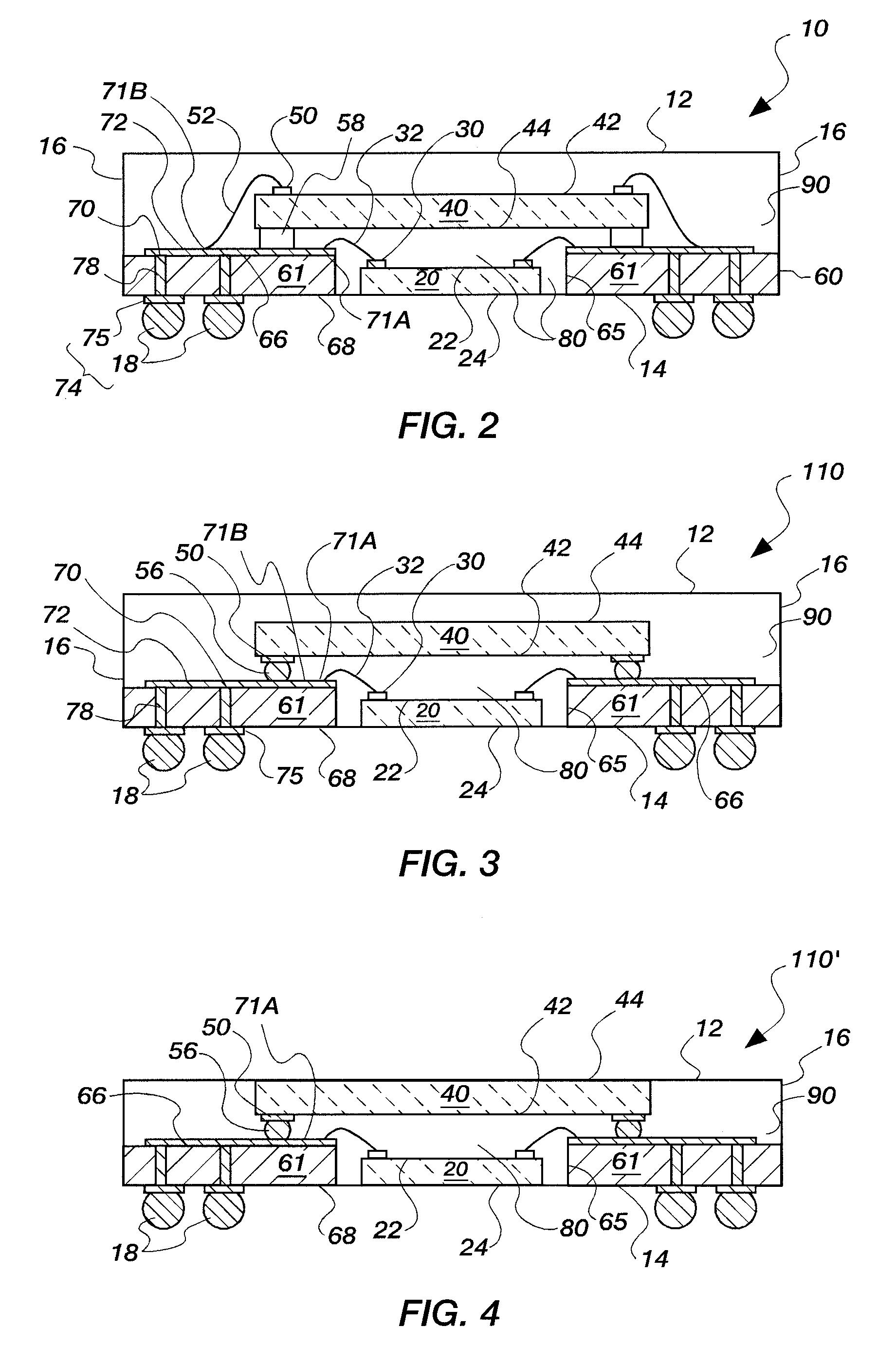

Methods for assembling multiple semiconductor devices

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

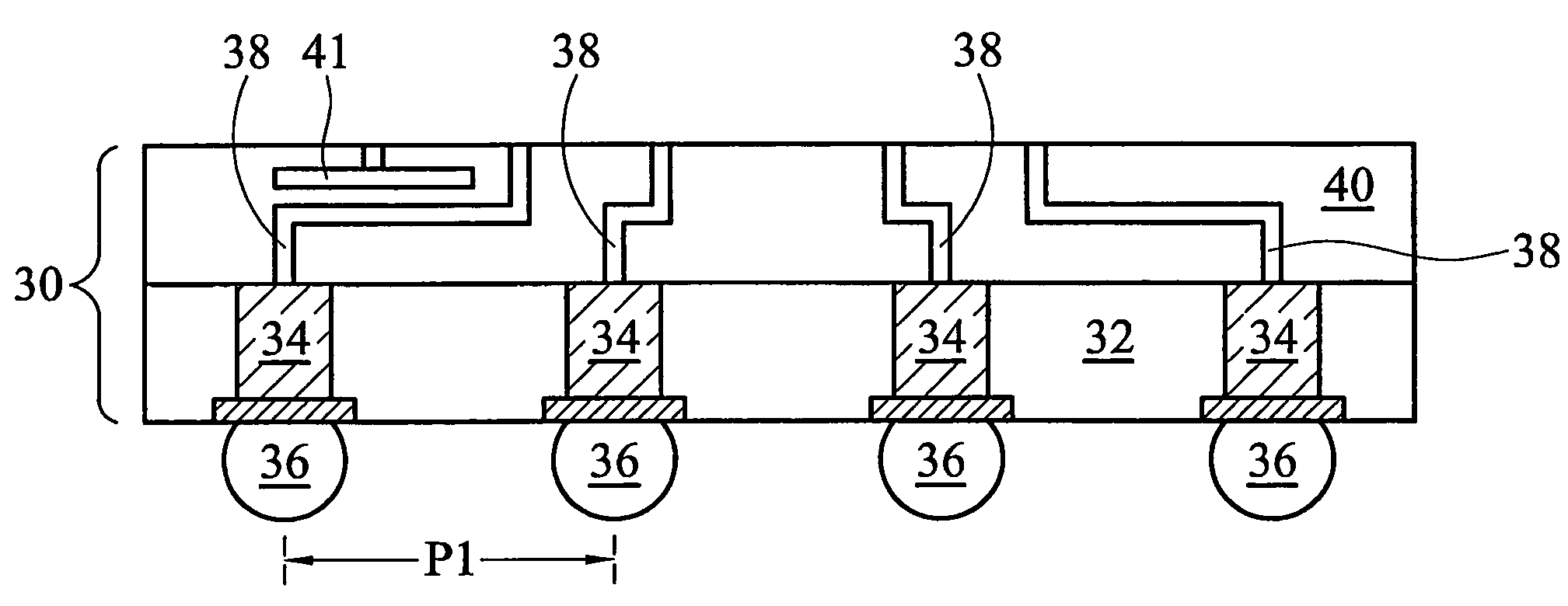

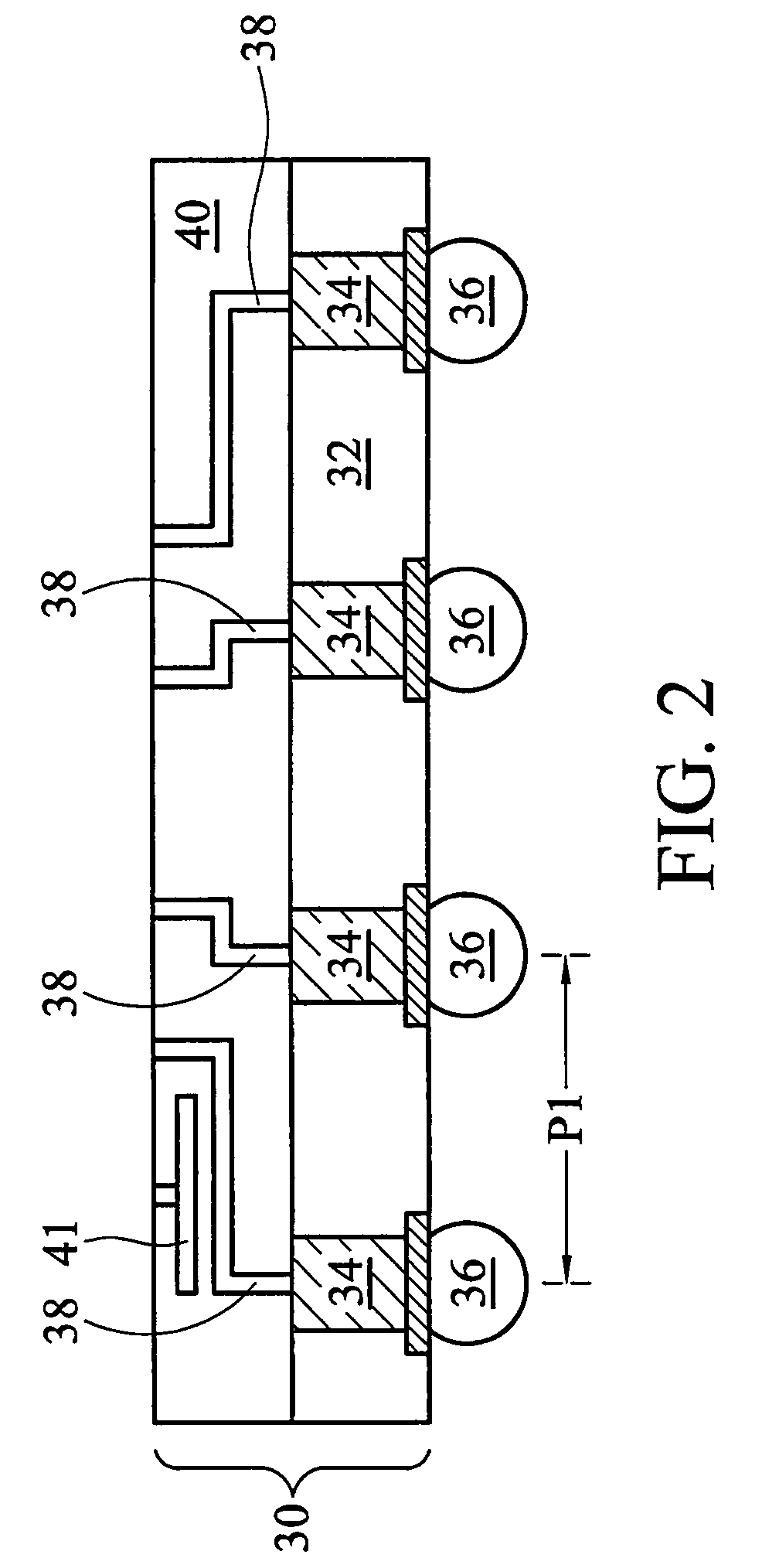

Semiconductor device assemblies and packages including multiple semiconductor devices and methods

InactiveUS6906415B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

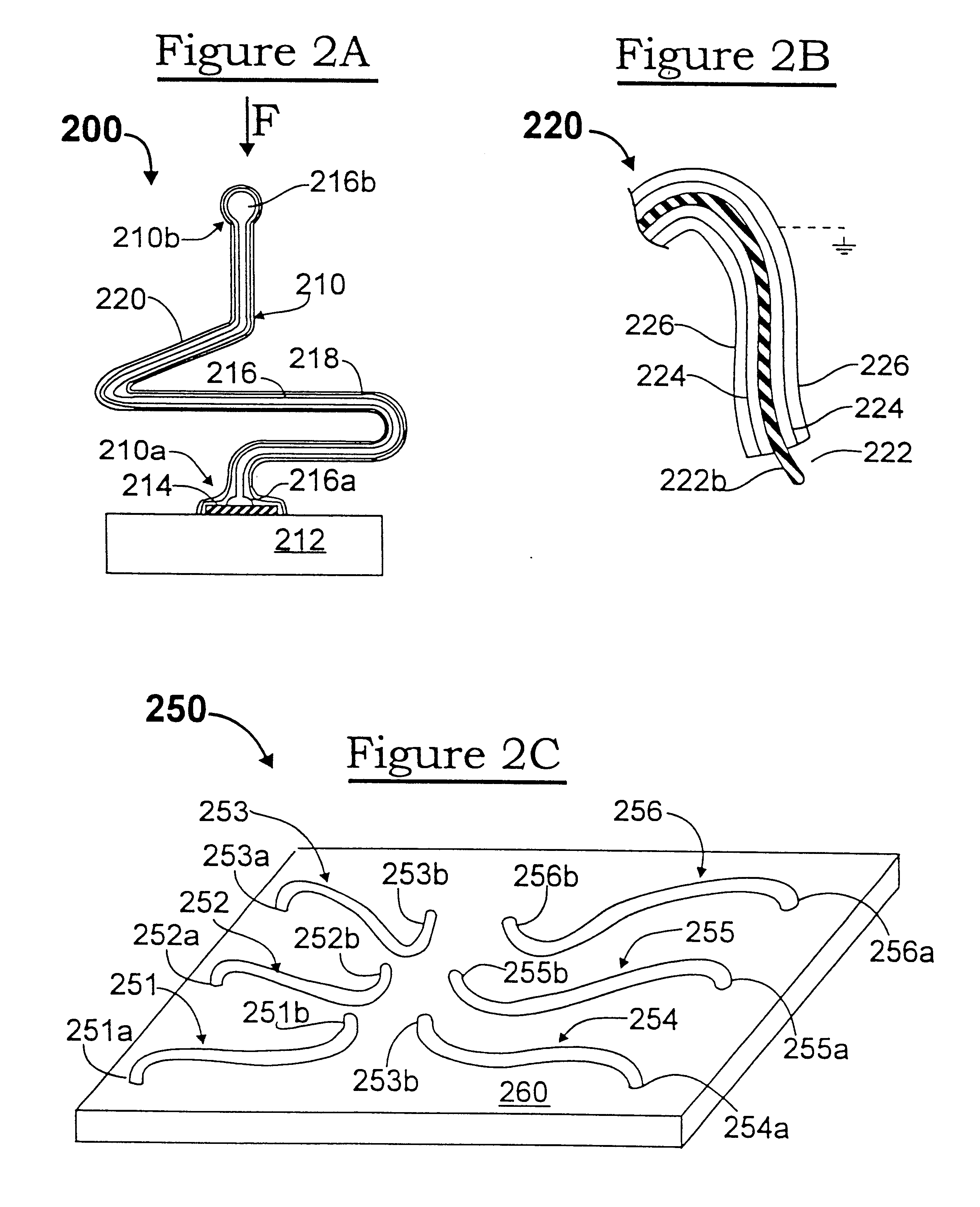

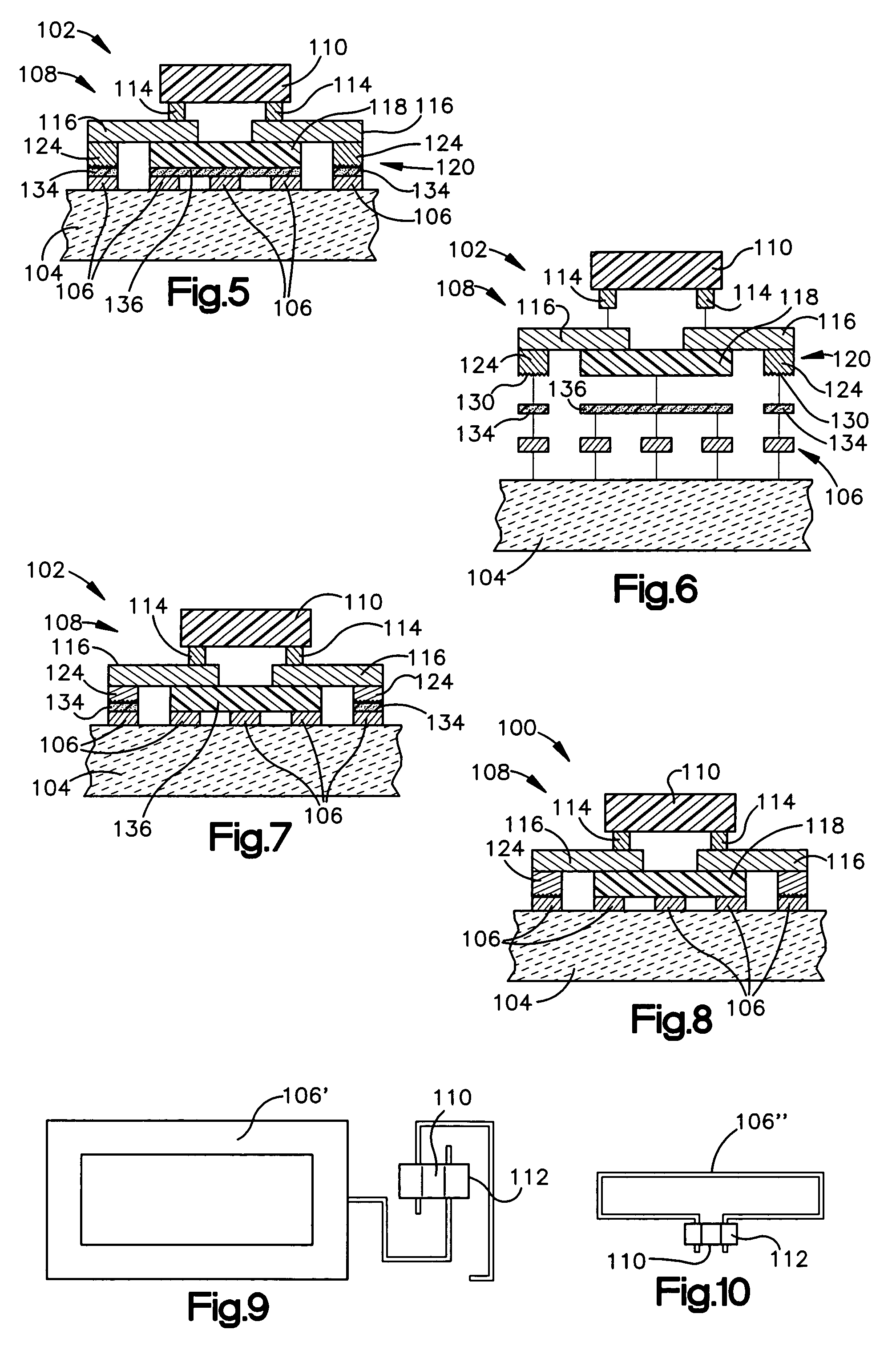

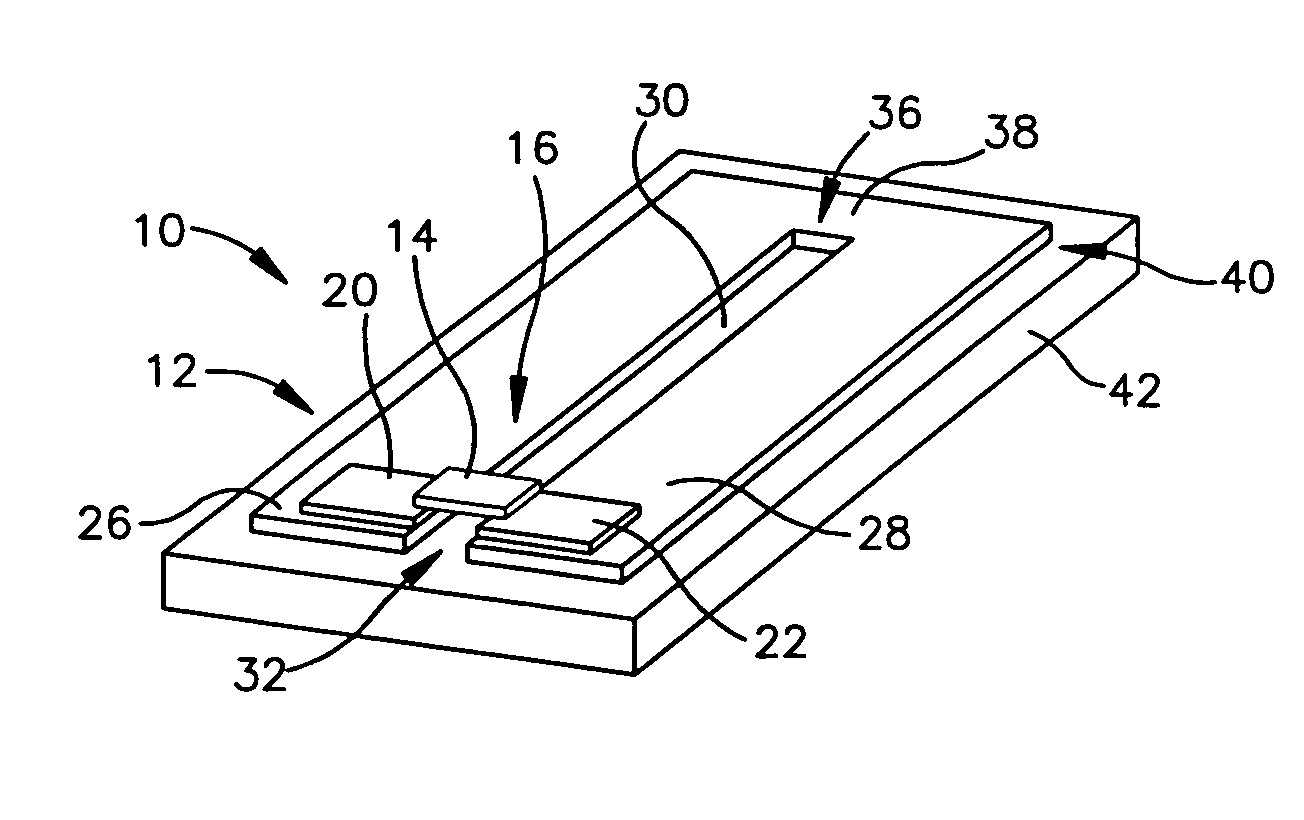

Probe card assembly and kit, and methods of using same

InactiveUS6246247B1Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly thereto (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are "stacked up" so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

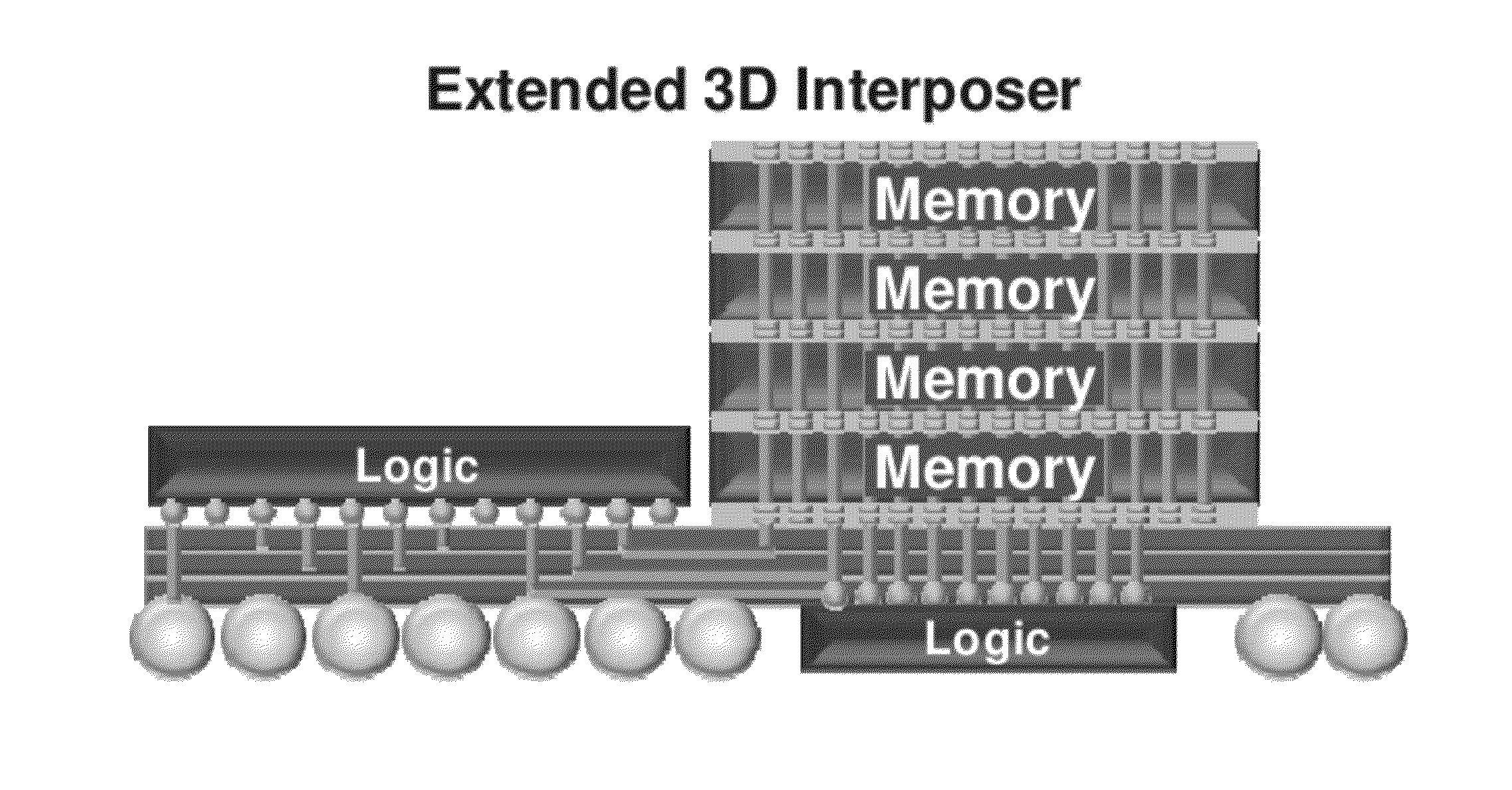

Ultra-thin interposer assemblies with through vias

ActiveUS20120106117A1Semiconductor/solid-state device detailsPrinted circuit aspectsGraphicsElectricity

A 3D interconnect structure comprising an ultra-thin interposer having a plurality of ultra-high density of through-via interconnections defined therein. The 3D interposer electrically connects first and second electronic devices in vertical dimension and has the same or similar through-via density as the first or second electronic devices it connects. The various embodiments of the interconnect structure allows 3D ICs to be stacked with or without TSVs and increases bandwidth between the two electronic devices as compared to other interconnect structures of the prior art. Further, the interconnect structure of the present invention is scalable, testable, thermal manageable, and can be manufactured at relatively low costs. Such a 3D structure can be used for a wide variety of applications that require a variety of heterogeneous ICs, such as logic, memory, graphics, power, wireless and sensors that cannot be integrated into single ICs.

Owner:GEORGIA TECH RES CORP

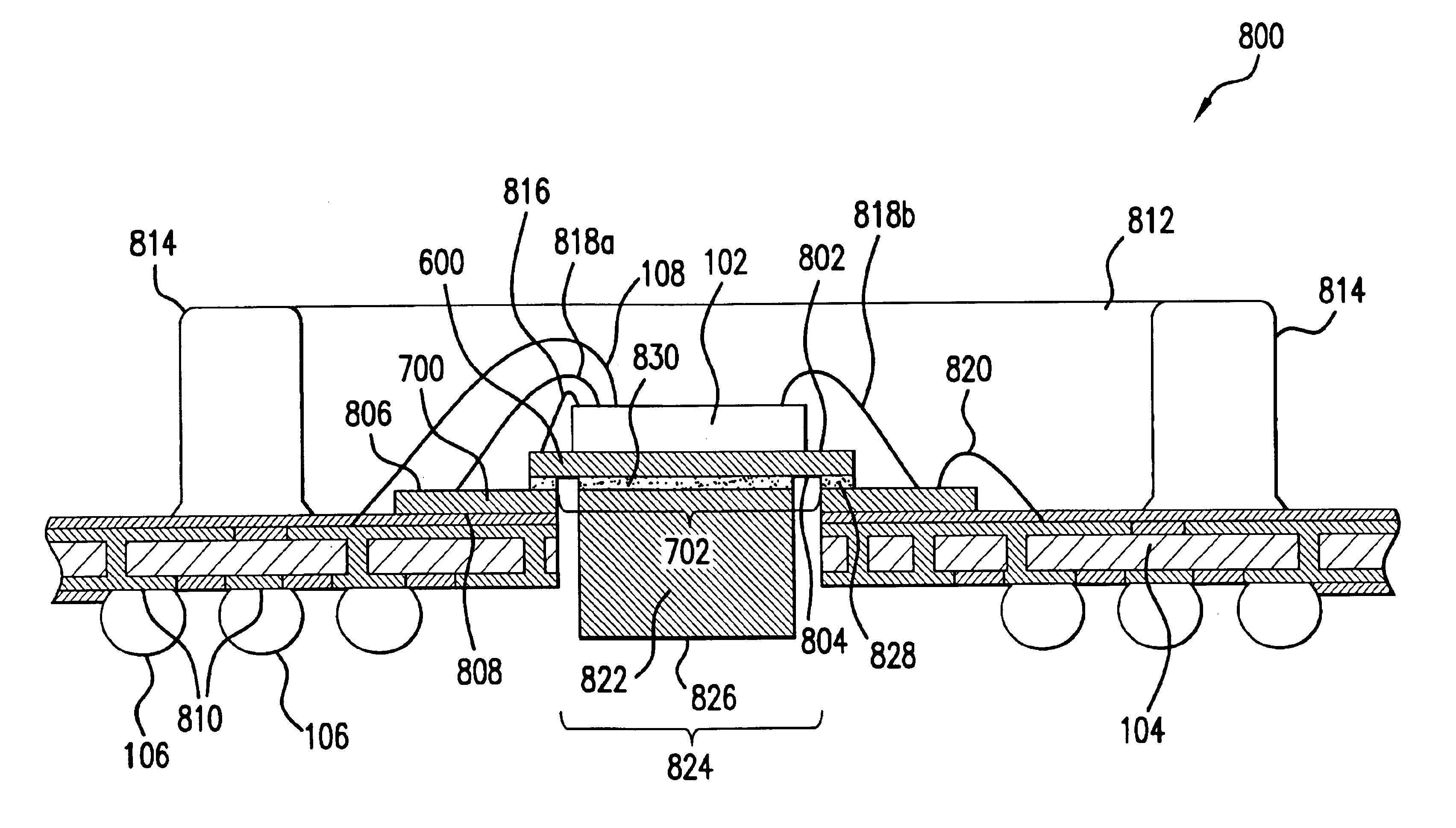

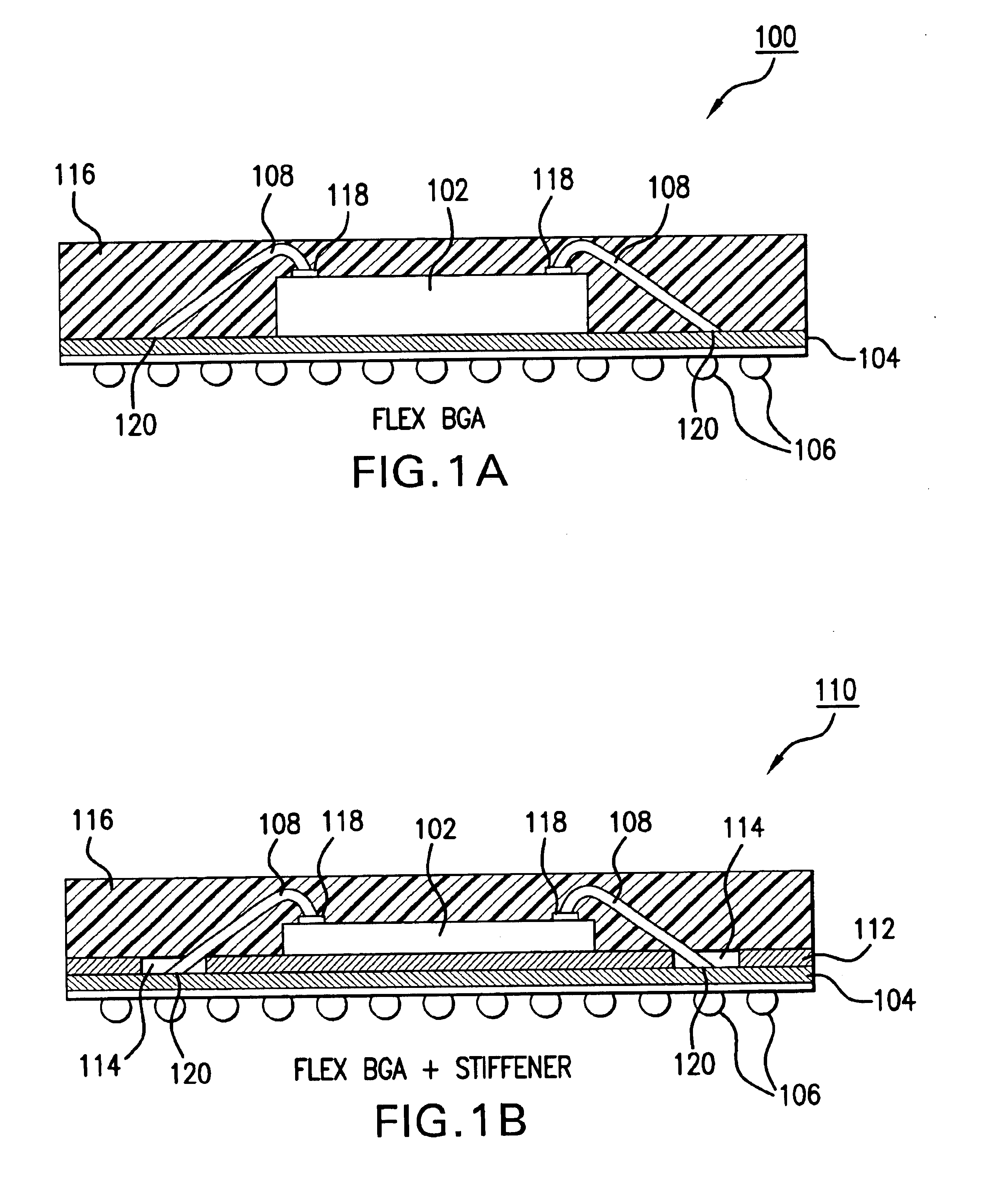

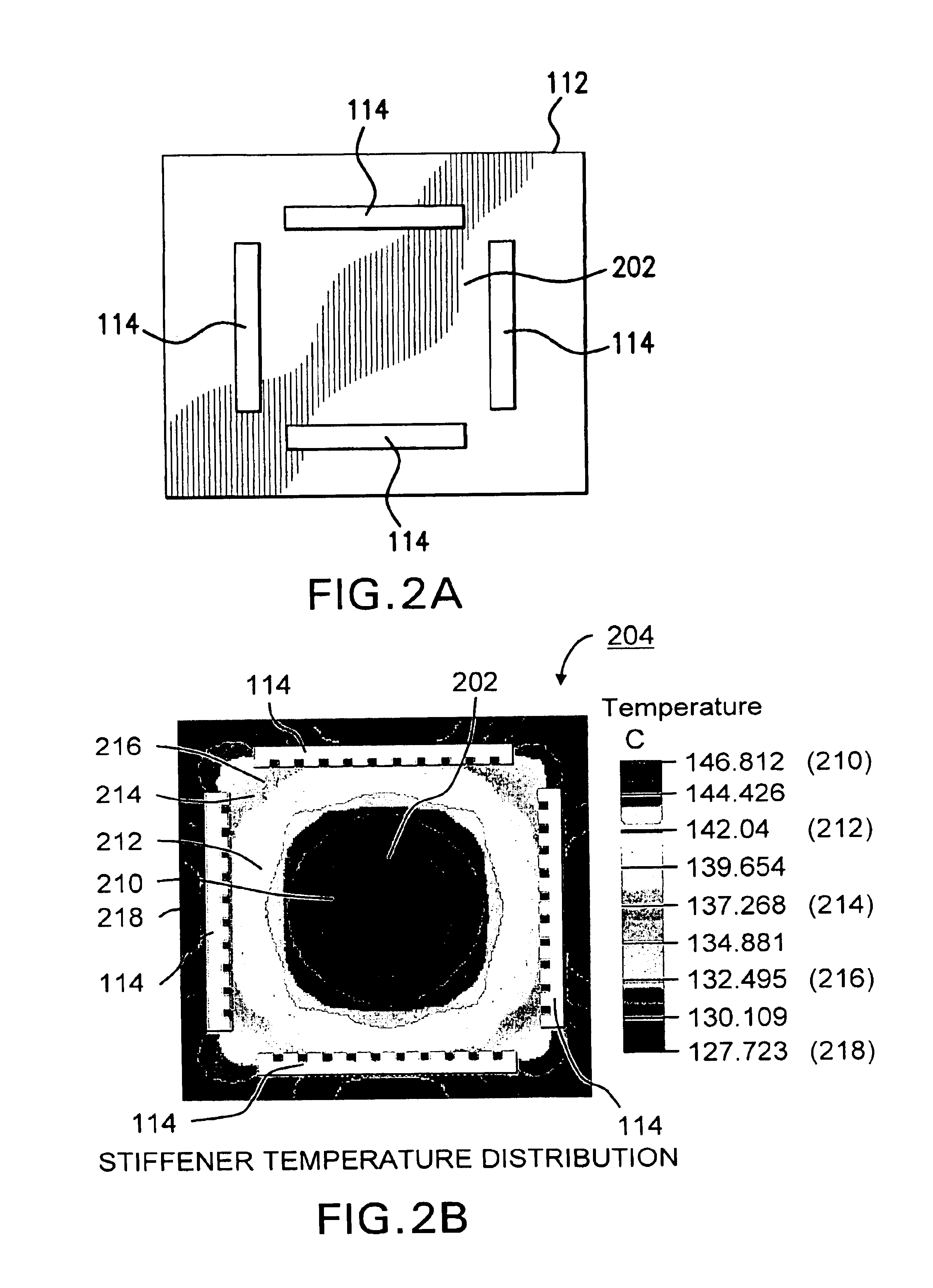

Ball grid array package with multiple interposers

InactiveUS6861750B2Increase stiffness/rigidityImprove heat transfer performanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsContact padPlanar substrate

Electrically, thermally and mechanically enhanced ball grid array (BGA) packages are described. An IC die is mounted to a first surface of a first stiffener. A peripheral edge portion of a second surface of the first stiffener is attached to a first surface of a second stiffener to cover an opening through the second stiffener that is open at the first surface and a second surface of the second stiffener. The second surface of the second stiffener is attached to a first surface of a substantially planar substrate that has a plurality of contact pads on the first surface of the substrate. The plurality of contact pads are electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

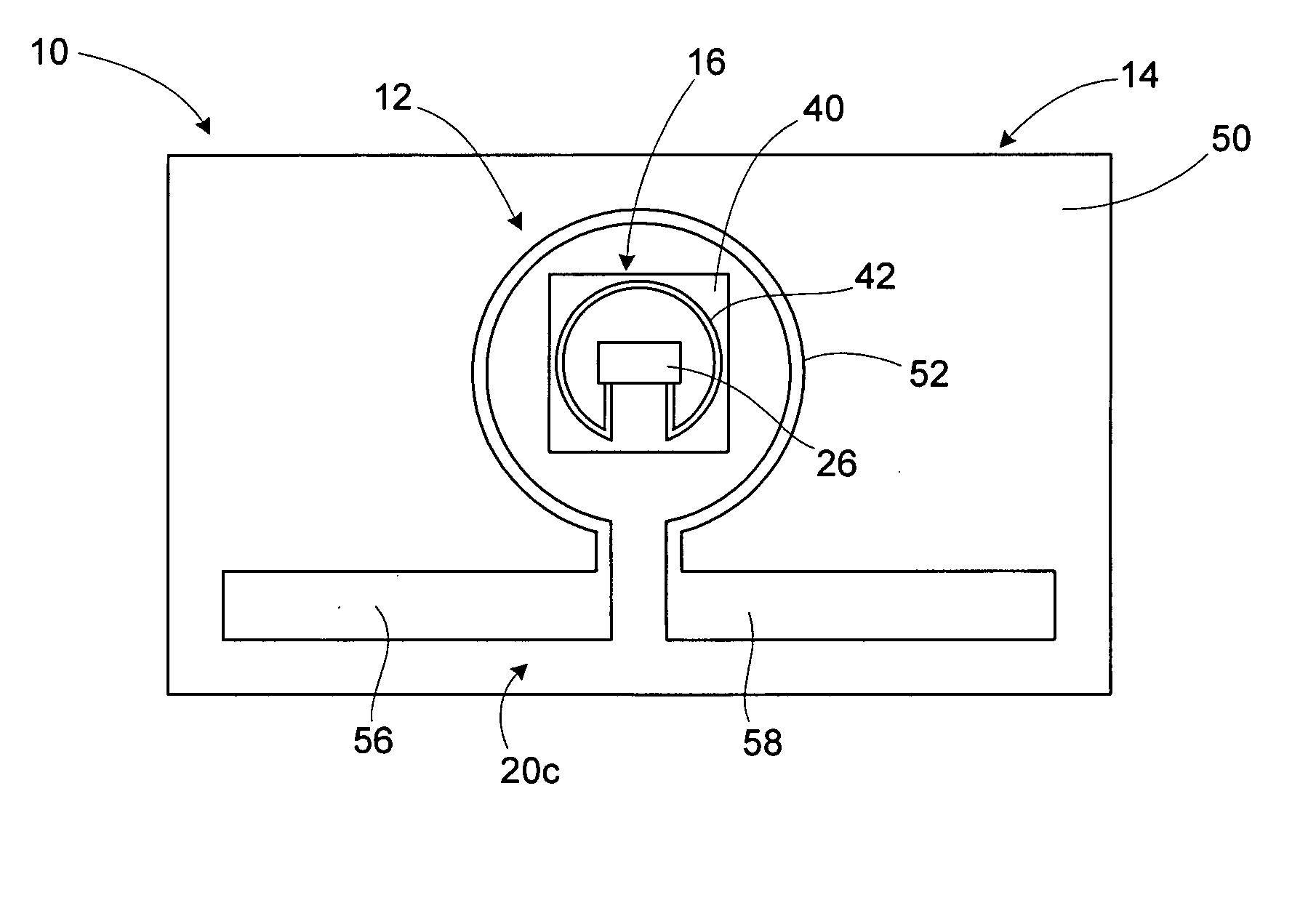

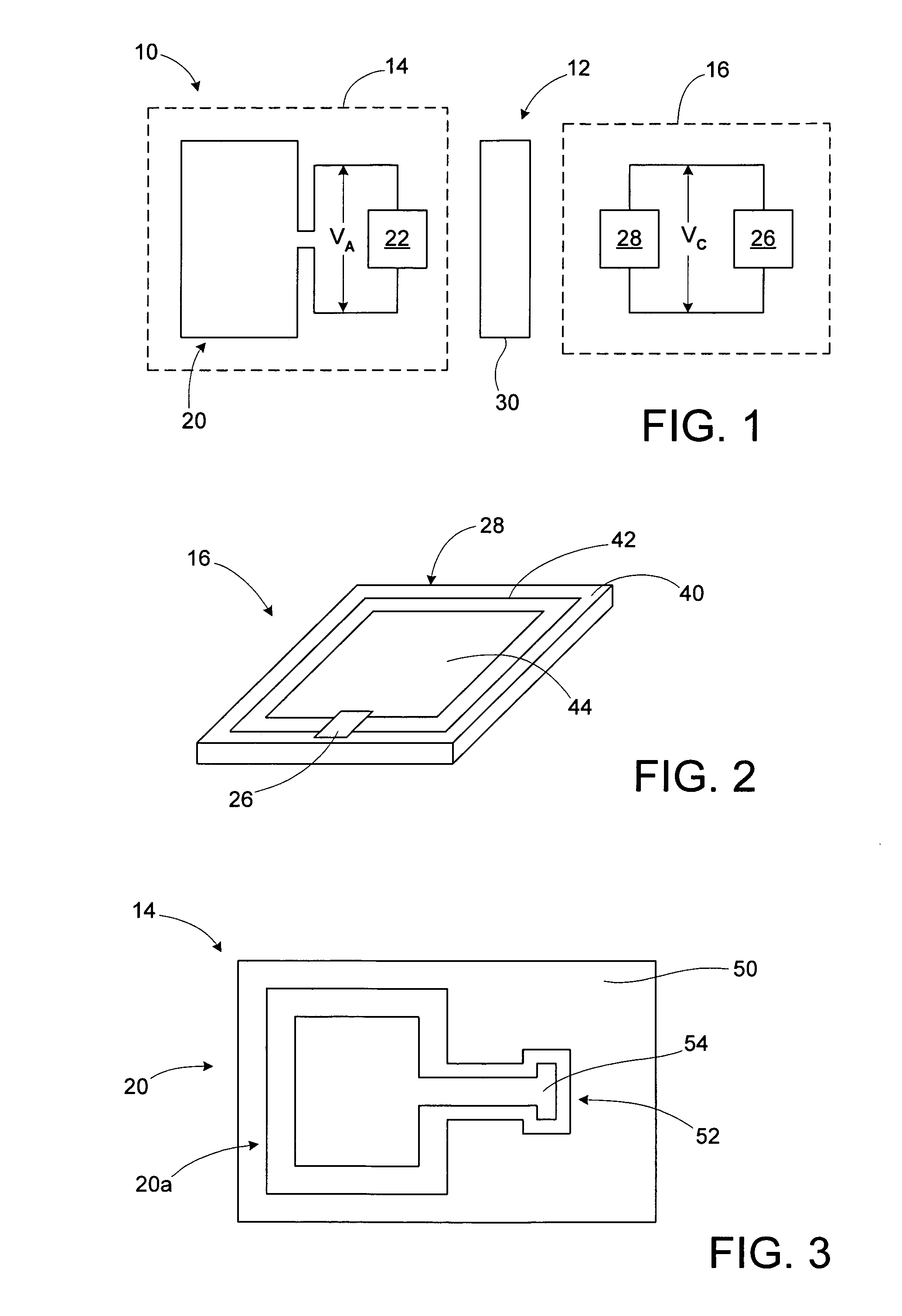

RFID device and method of forming

InactiveUS7102520B2Simultaneous aerial operationsAntenna supports/mountingsInterposerAntenna substrate

Owner:AVERY DENNISON CORP

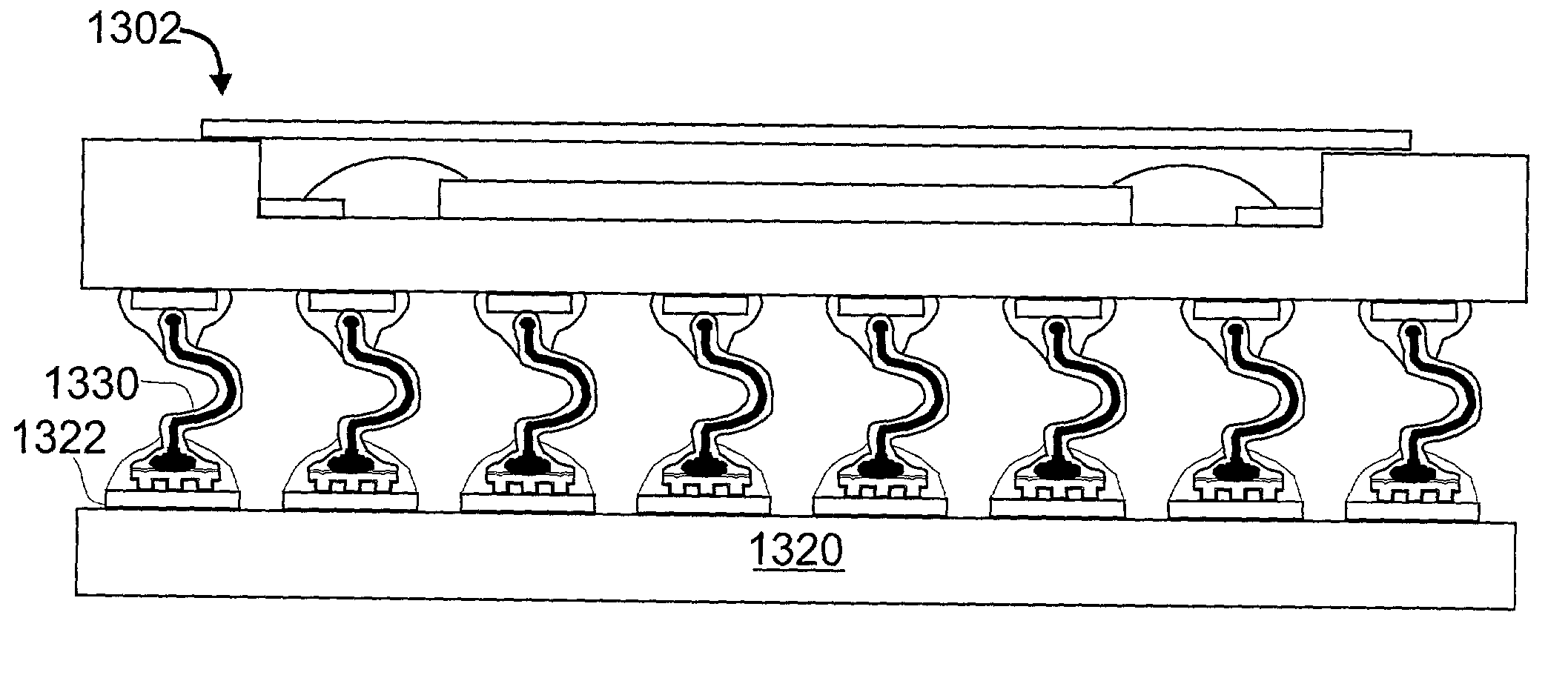

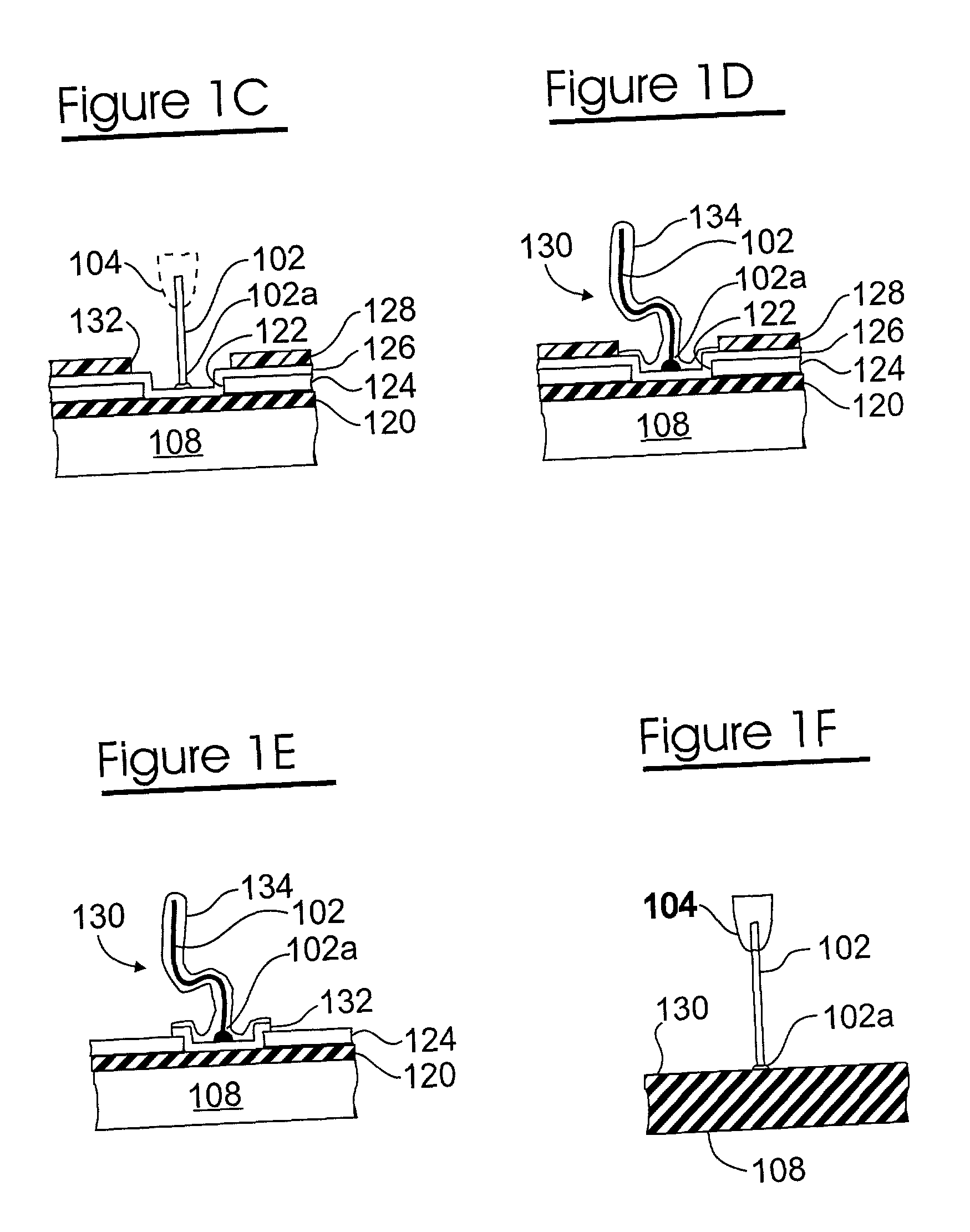

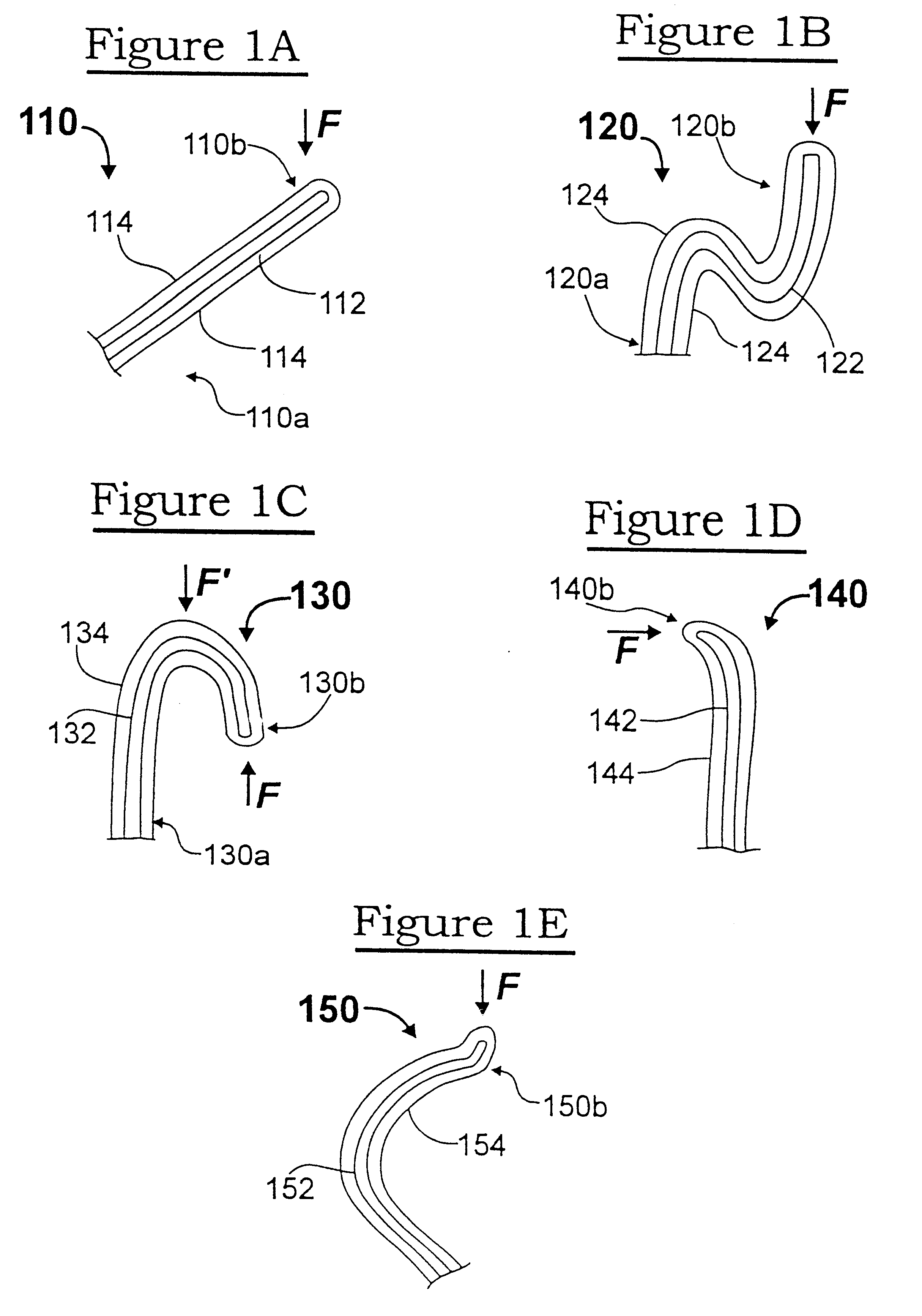

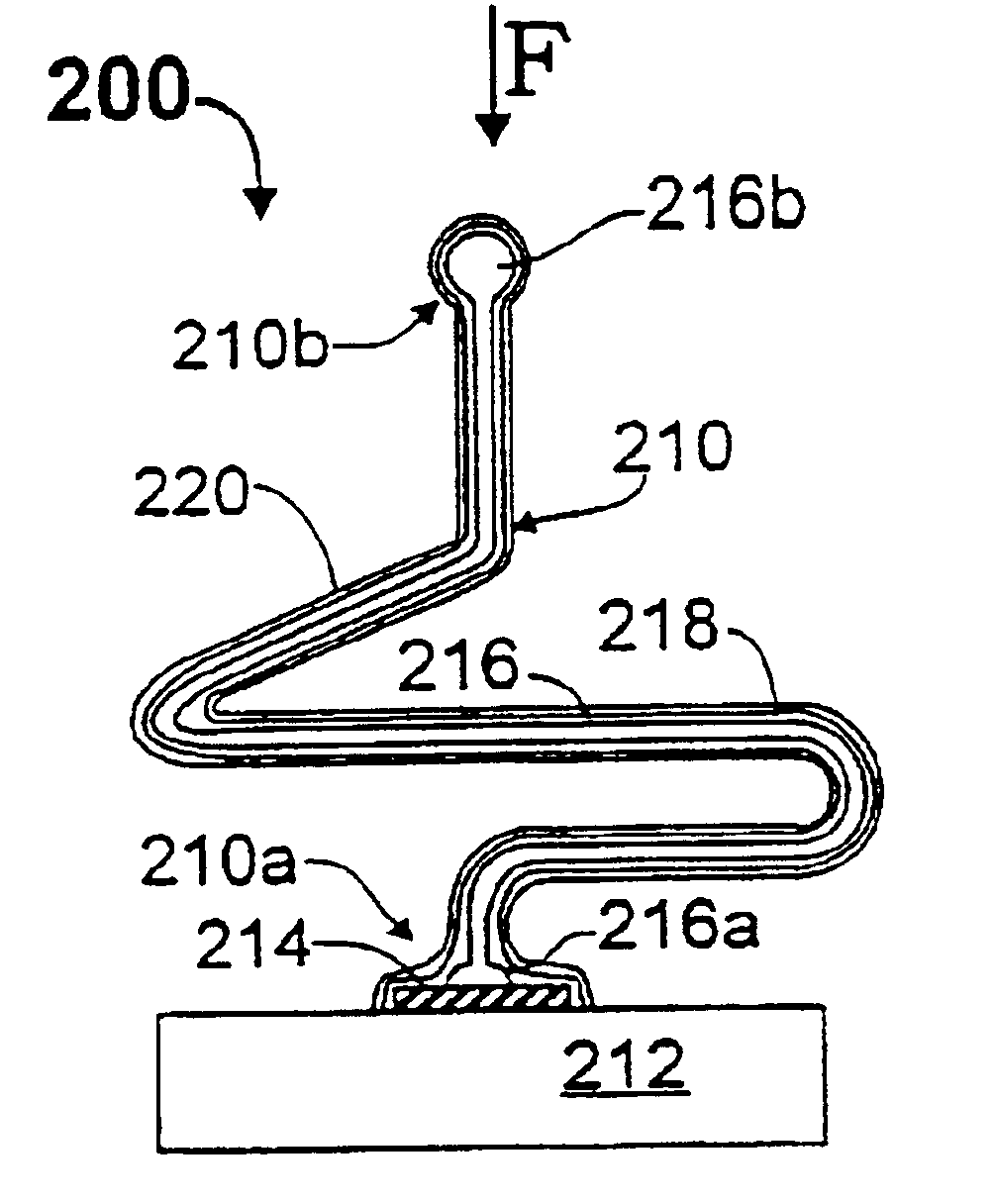

Method and apparatus for shaping spring elements

InactiveUS6836962B2Easy to disassembleEasy to manufactureElectrically conductive connectionsContact member assembly/disassemblyProbe cardCopper wire

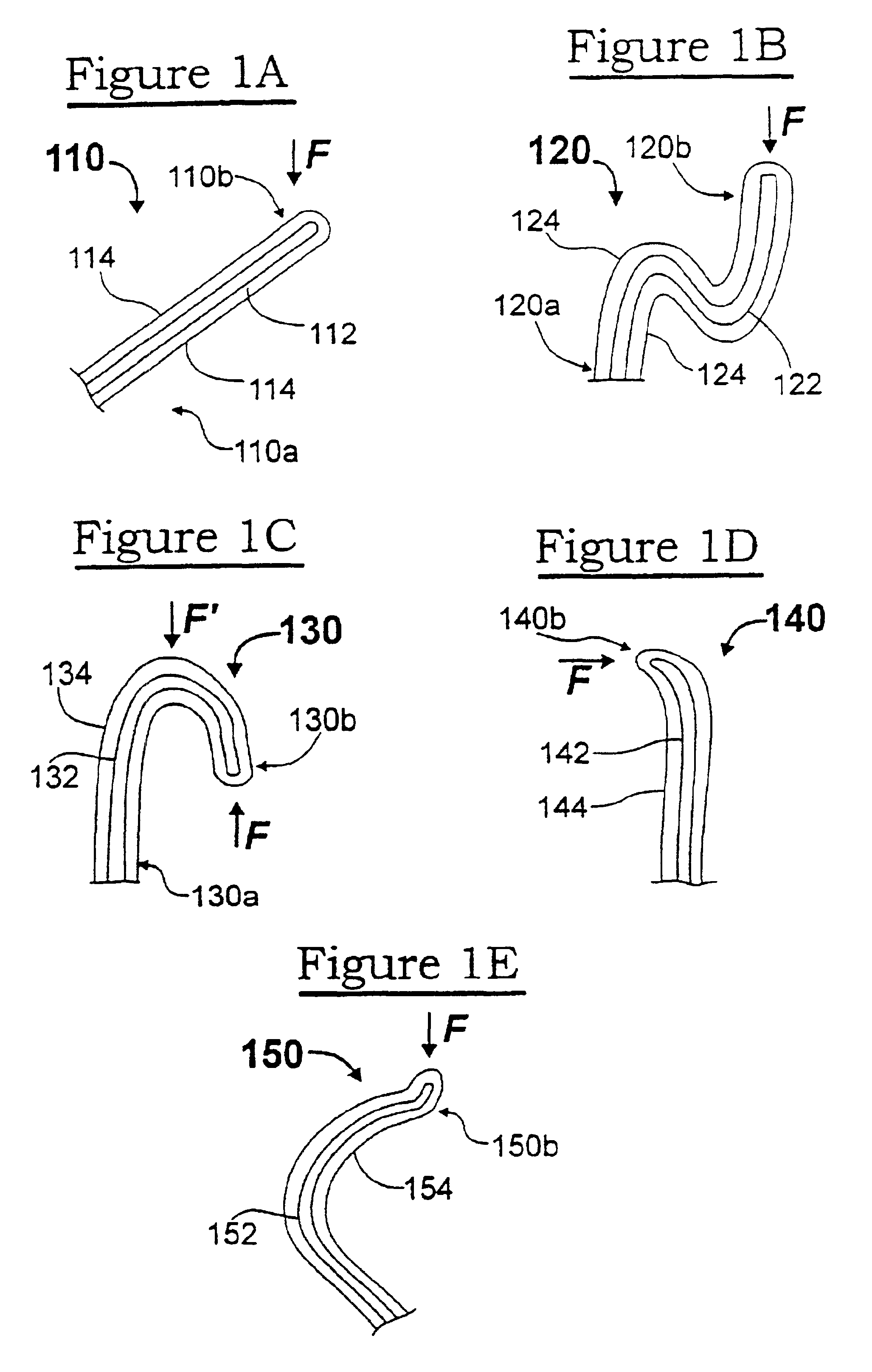

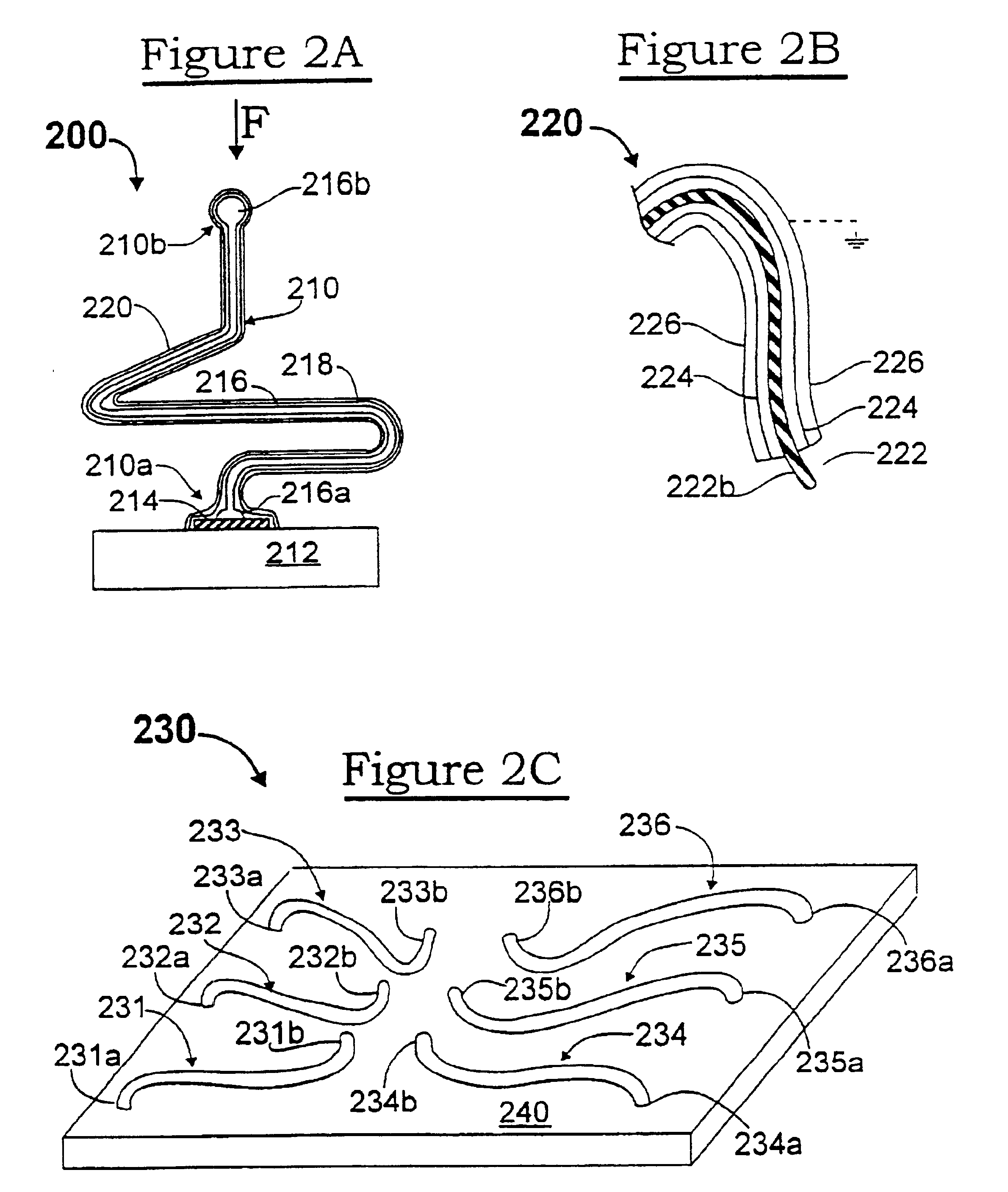

Interconnection elements for electronic components, exhibiting desirable mechanical characteristic (such as resiliency, for making pressure contacts) are formed by using a shaping tool (512) to shape an elongate core element (502) of a soft material (such as gold or soft copper wire) to have a springable shape (including cantilever beam, S-shape, U-shape), and overcoating the shaped core element with a hard material (such as nickel and its alloys), to impart to desired spring (resilient) characteristic to the resulting composite interconnection element. A final overcoat of a material having superior electrical qualities (e.g., electrical conductivity and / or solderability) may be applied to the composite interconnection element. The resulting interconnection elements may be mounted to a variety of electronic components, including directly to semiconductor dies and wafers (in which case the overcoat material anchors the composite interconnection element to a terminal (or the like) on the electronic component), may be mounted to support substrates for use as interposers and may be mounted to substrates for use as probe cards or probe card inserts. The shaping tool may be an anvil (622) and a die (624), and may nick or sever successive shaped portions of the elongate elements, and the elongate element may be of an inherently hard (springy) material. Methods of fabricating interconnection elements on sacrificial substrates are described. Methods of fabricating tip structures (258) and contact tips at the end of interconnection elements are also described.

Owner:FORMFACTOR INC

Glass Interposer Panels And Methods For Making The Same

InactiveUS20120048604A1Line/current collector detailsPrinted circuit detailsInterposerSecondary layer

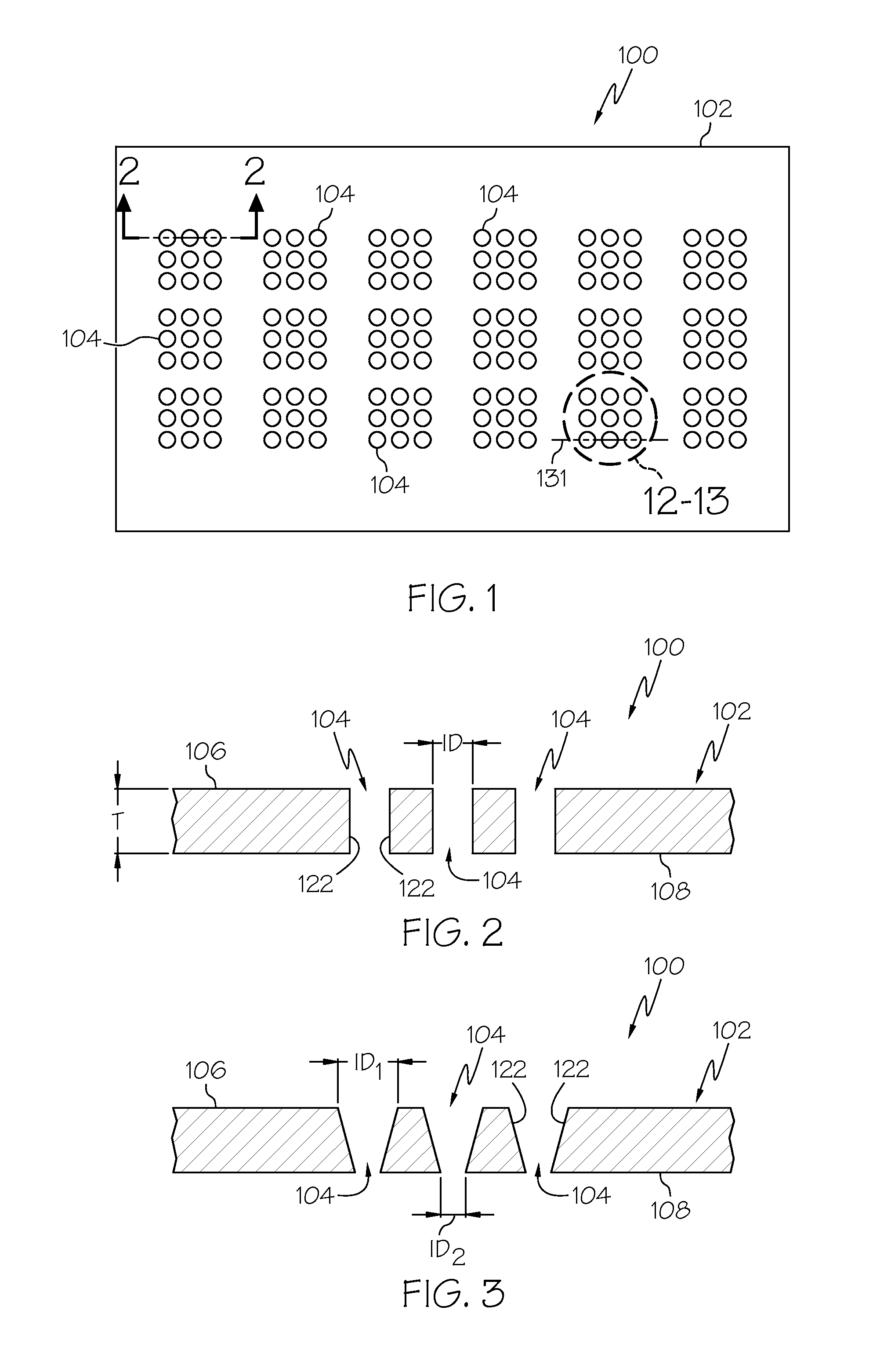

Glass interposer panels and methods for forming the same are described herein. The interposer panels include a glass substrate core formed from an ion-exchangeable glass. A first layer of compressive stress may extend from a first surface of the glass substrate into the thickness T of the glass substrate core to a first depth of layer D1. A second layer of compressive stress may be spaced apart from the first layer of compressive stress and extending from a second surface of the glass substrate core into the thickness T of the glass substrate core to a second depth of layer D2. A plurality of through-vias may extend through the thickness T of the glass substrate core. Each through-via is surrounded by an intermediate zone of compressive stress that extends from the first layer of compressive stress to the second layer of compressive stress adjacent to a sidewall of each through-via.

Owner:CORNING INC

Composite interposer and method for producing a composite interposer

InactiveUS20020076919A1Semiconductor/solid-state device detailsCross-talk/noise/interference reductionEpoxyDevice material

A composite interposer for providing power and signal connections between an integrated circuit chip or chips and a substrate. The interposer includes a signal core formed from a conductive power / ground plane positioned between two dielectric layers. A method for fabricating a composite interposer comprising disposing a silicon layer on a substrate, and selectively etching the silicon layer down to the substrate to develop silicon openings with a silicon profile, and to expose part of the substrate. Vias are formed through the exposed part of the substrate. The method additionally includes filling the vias and the silicon openings with a filler material (e.g., a high-aspect-ratio-capable photodefinable epoxy polymer) to form filled silicon openings and filled vias, forming first openings through the filled silicon openings and through the filled vias, forming second opening through filler material to expose semiconductor devices on the silicon layer, and interconnecting electrically, through the first openings and through the second openings, the exposed semiconductor devices with pads disposed against a bottom of the substrate.

Owner:FUJITSU LTD

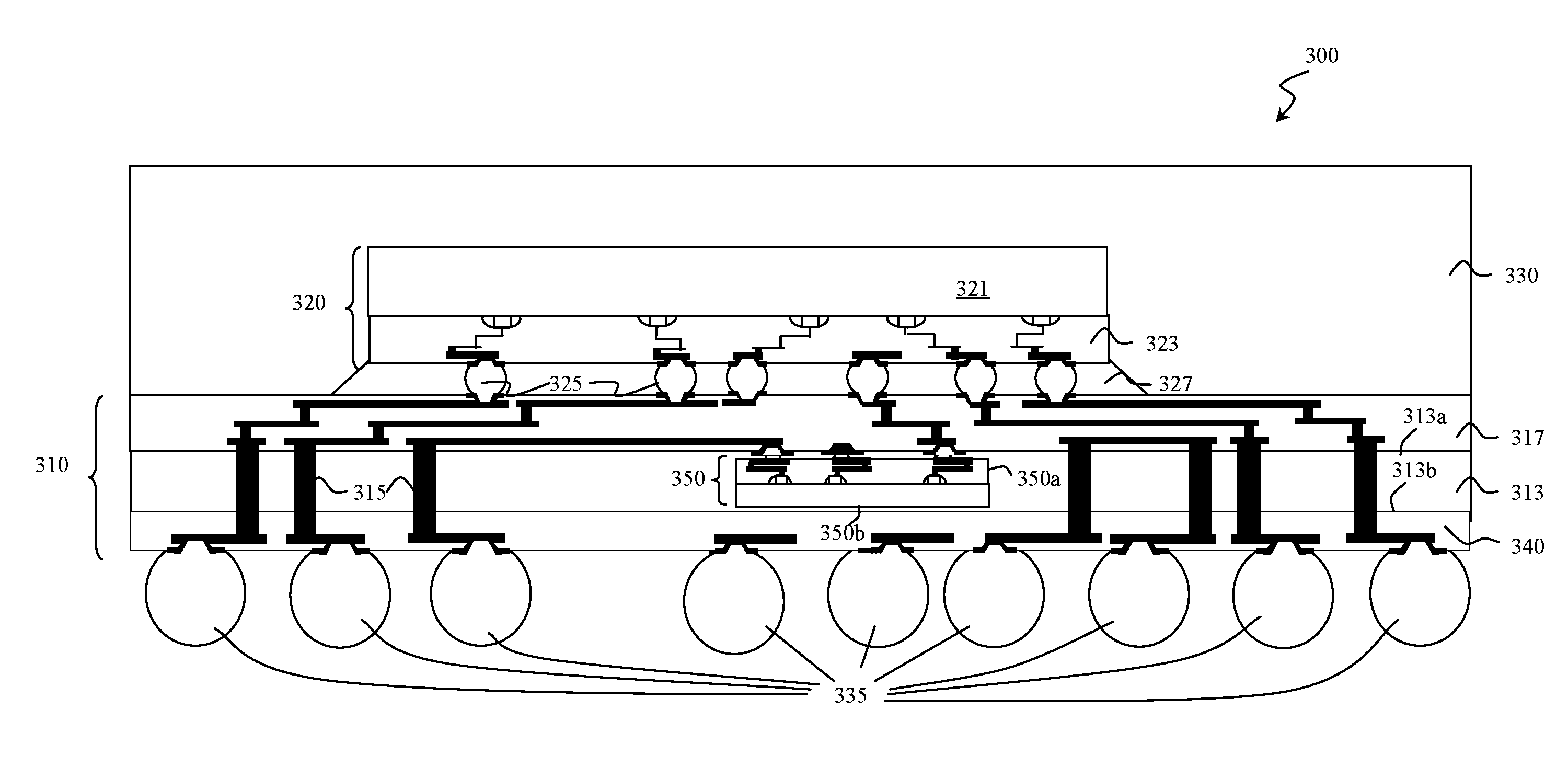

Package systems having interposers

ActiveUS20110285005A1Semiconductor/solid-state device detailsSolid-state devicesElectrical connectionInterposer

A package system includes a first integrated circuit disposed over an interposer. The interposer includes at least one molding compound layer including a plurality of electrical connection structures through the at least one molding compound layer. A first interconnect structure is disposed over a first surface of the at least one molding compound layer and electrically coupled with the plurality of electrical connection structures. The first integrated circuit is electrically coupled with the first interconnect structure.

Owner:TAIWAN SEMICON MFG CO LTD

High performance, low cost microelectronic circuit package with interposer

InactiveUS6888240B2Semiconductor/solid-state device detailsSolid-state devicesPin grid arrayInterposer

A low cost technique for packaging microelectronic circuit chips fixes a die within an opening in a package core. At least one metallic build up layer is then formed on the die / core assembly and a grid array interposer unit is laminated to the build up layer. The grid array interposer unit can then be mounted within an external circuit using any of a plurality of mounting technologies (e.g., ball grid array (BGA), land grid array (LGA), pin grid array (PGA), surface mount technology (SMT), and / or others). In one embodiment, a single build up layer is formed on the die / core assembly before lamination of the interposer.

Owner:INTEL CORP

Bridges for interconnecting interposers in multi-chip integrated circuits

ActiveUS20090267238A1Semiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A structure and a method for forming the same. The structure includes a substrate, a first interposer on the substrate, a second interposer on the substrate, and a first bridge. The first and second interposers are electrically connected to the substrate. The first bridge is electrically connected to the first and second interposers.

Owner:GLOBALFOUNDRIES US INC

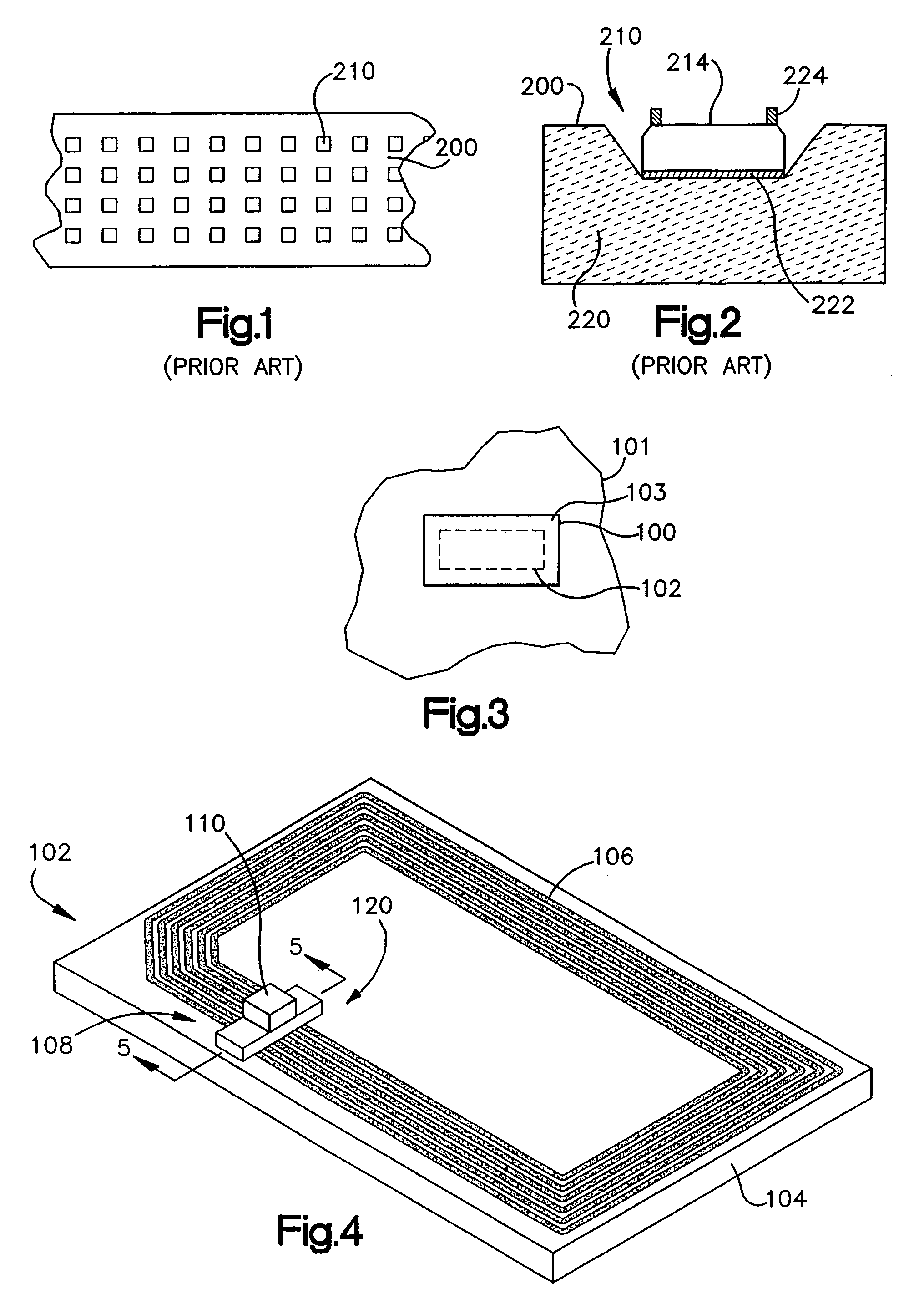

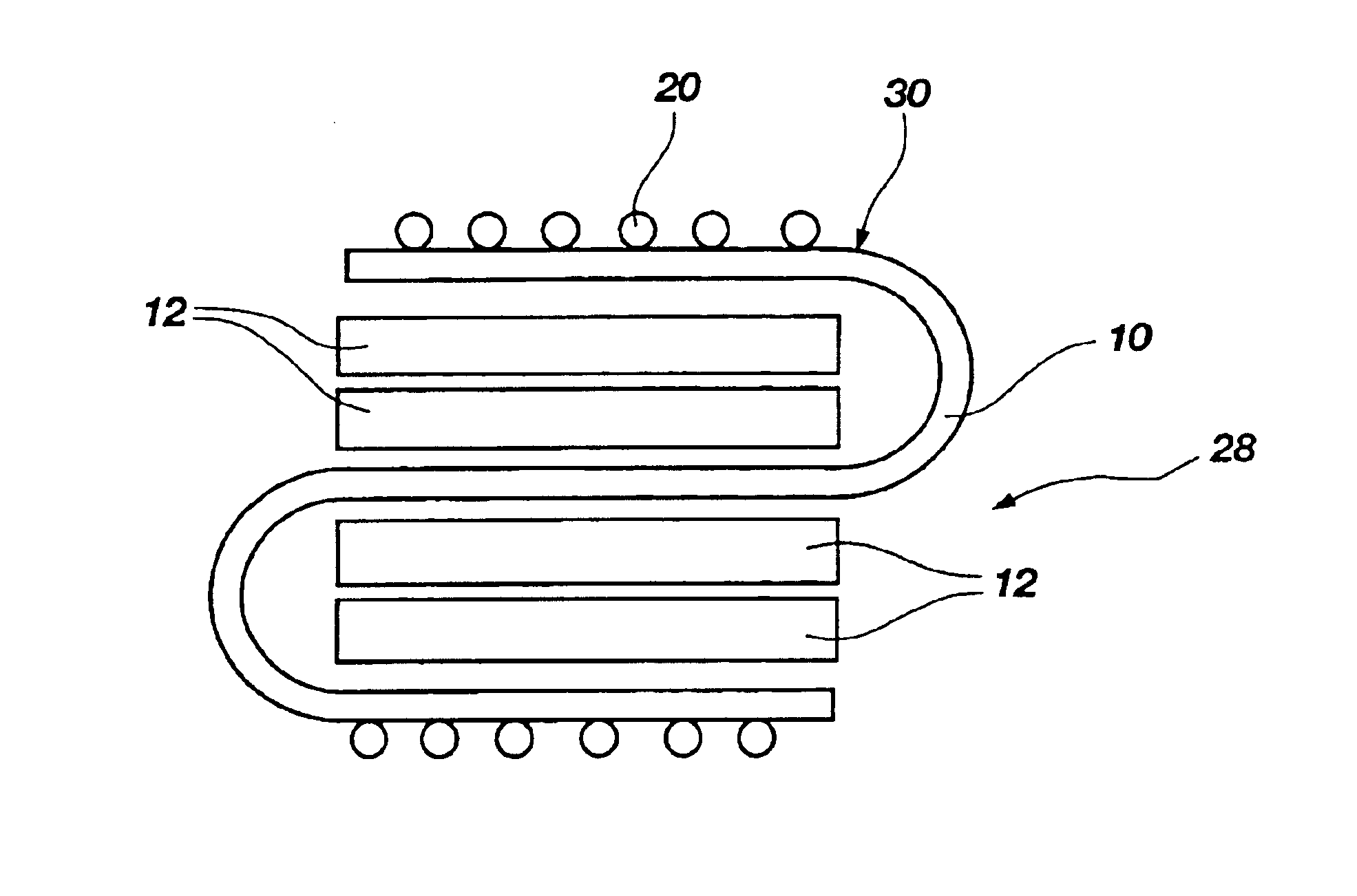

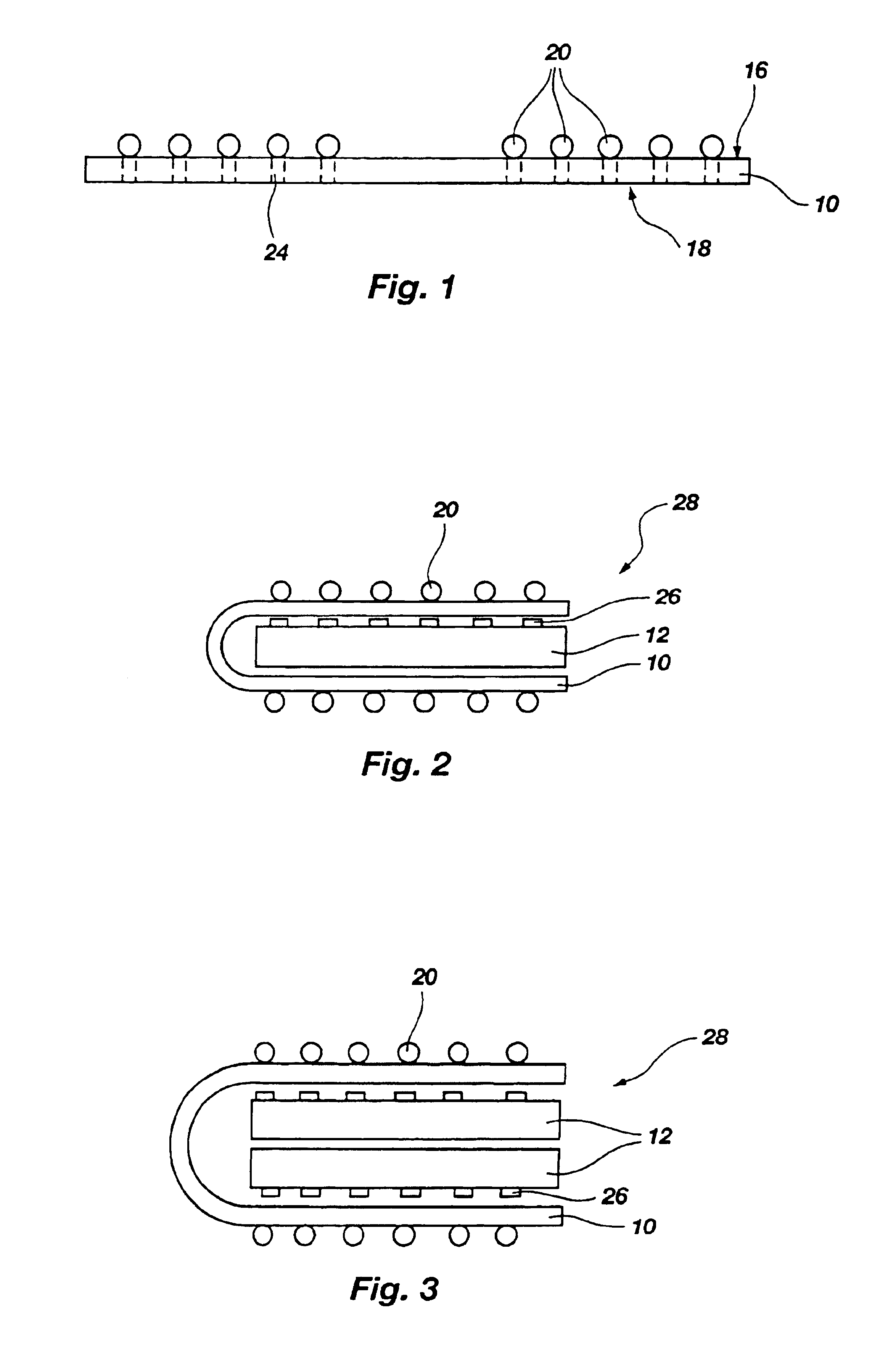

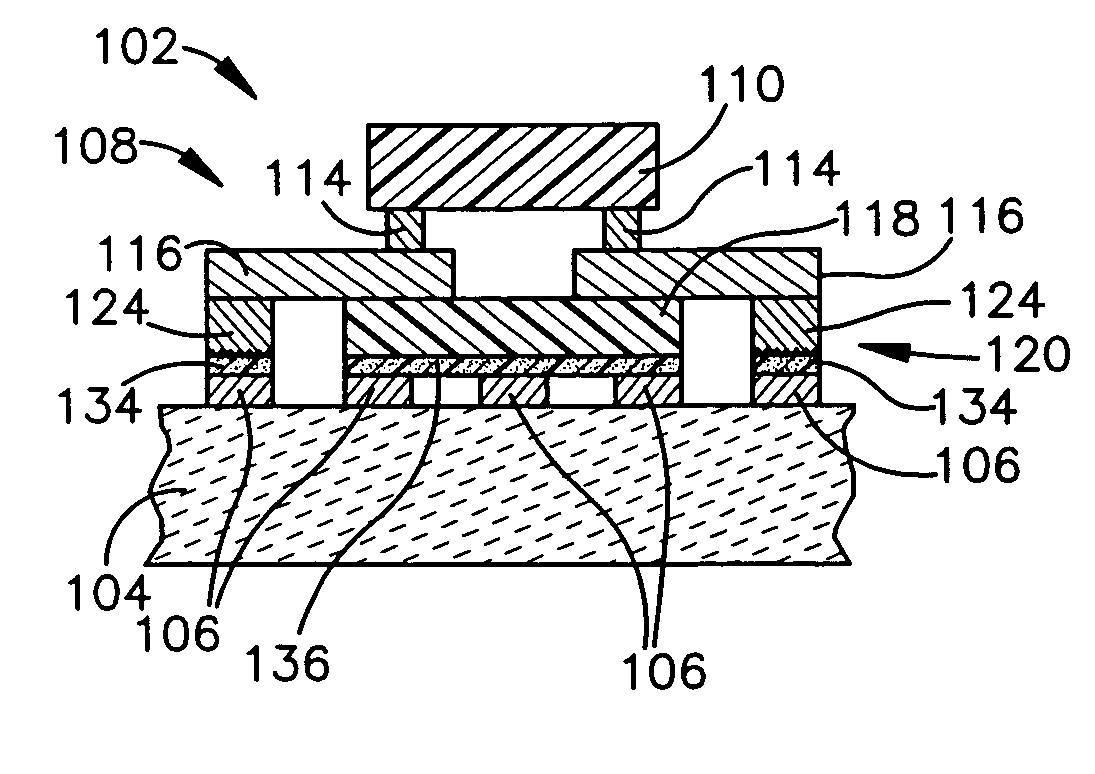

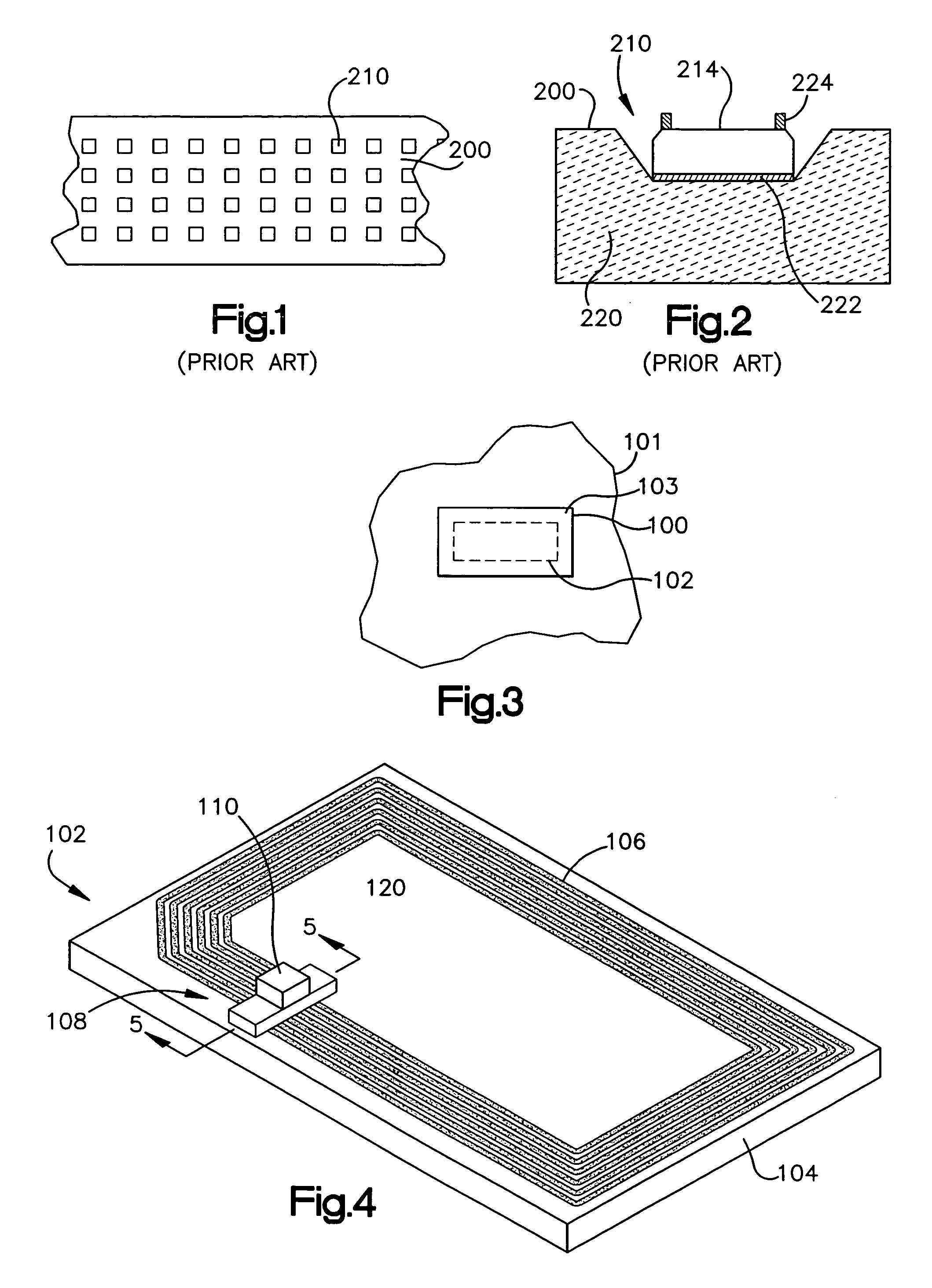

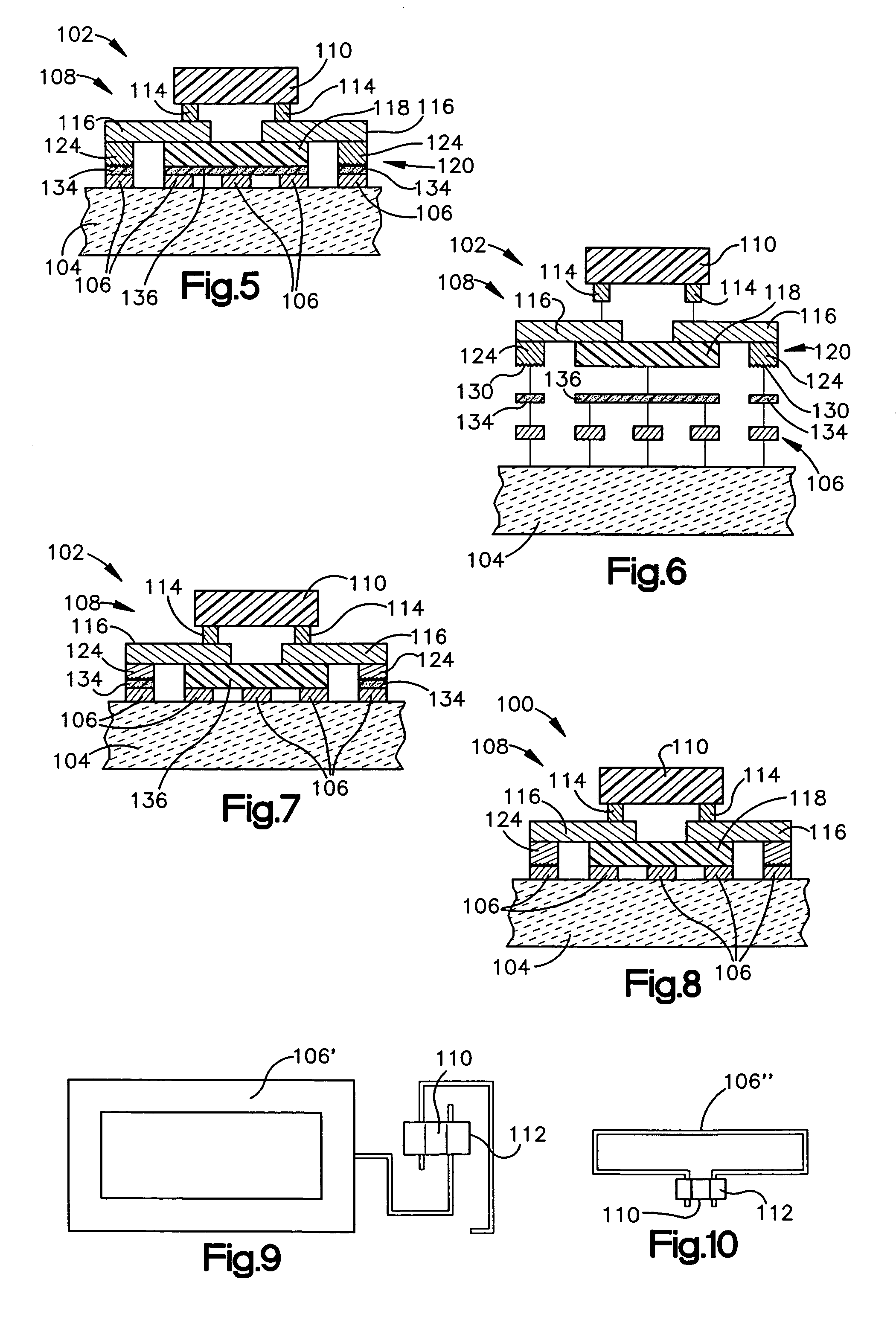

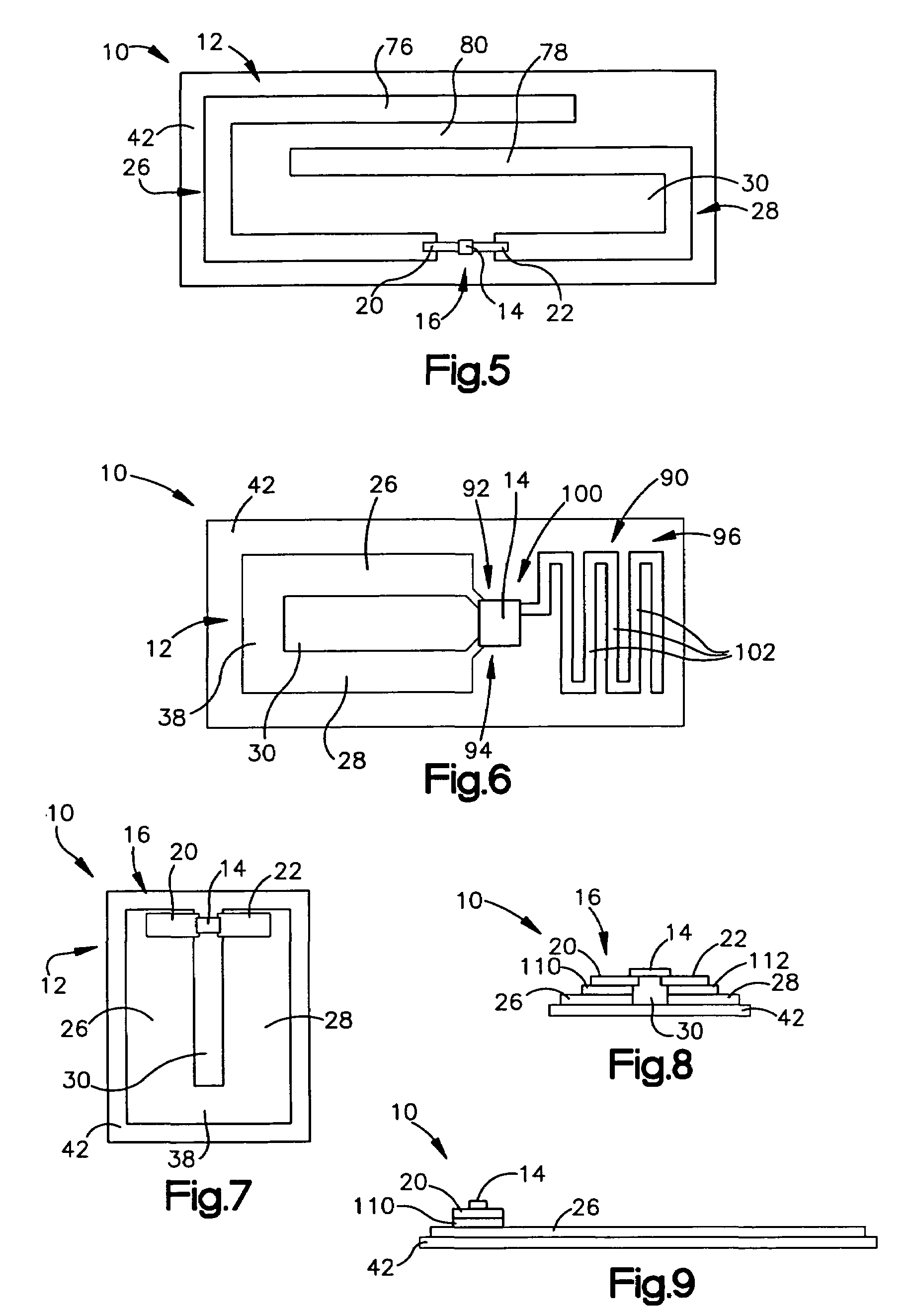

Folded interposer

InactiveUS6884653B2Efficient stackingWasted spaceSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densitySemiconductor package

A folded interposer used to achieve a high density semiconductor package is disclosed. The folded interposer is comprised of a thin, flexible material that can be folded around one or multiple semiconductor dice in a serpentine fashion. The semiconductor dice are then attached to a substrate through electrical contacts on the interposer. The folded interposer allows multiple semiconductor dice to be efficiently stacked in a high density semiconductor package by reducing the unused or waster space between stacked semiconductor dice. Vias extending through the folded interposer provide electrical communication between the semiconductor dice and the substrate. The present invention also relates to a method of packaging semiconductor dice in a high density arrangement and a method of forming the high density semiconductor package.

Owner:MICRON TECH INC

RFID device and method of forming

A radio frequency identification (RFID) inlay includes an electrical connection between a chip and an antenna. The electrical connection includes conductive interposer leads and a capacitive connection. The capacitive connection may involve putting the antenna and the interposer leads into close proximity, with dielectric pads therebetween, to allow capacitive coupling between the antenna and the interposer leads. The dielectric pads may include a non-conductive adhesive and a high dielectric material, such as a titanium oxide. The connections provide a convenient, fast, and effective way to operatively couple antennas and interposers. The RFID inlay may be part of an RFID lable or RFID tag.

Owner:AVERY DENNISON CORP

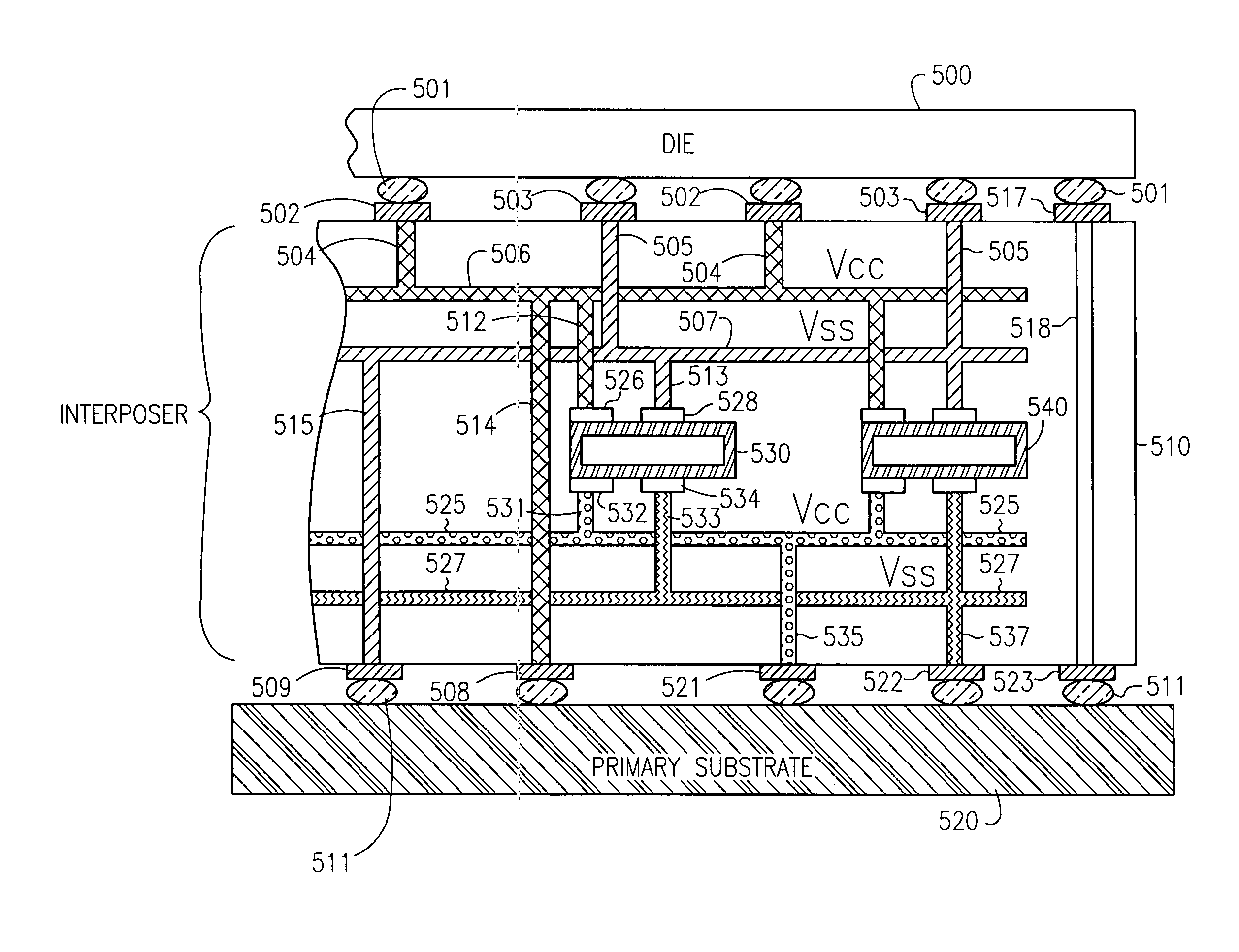

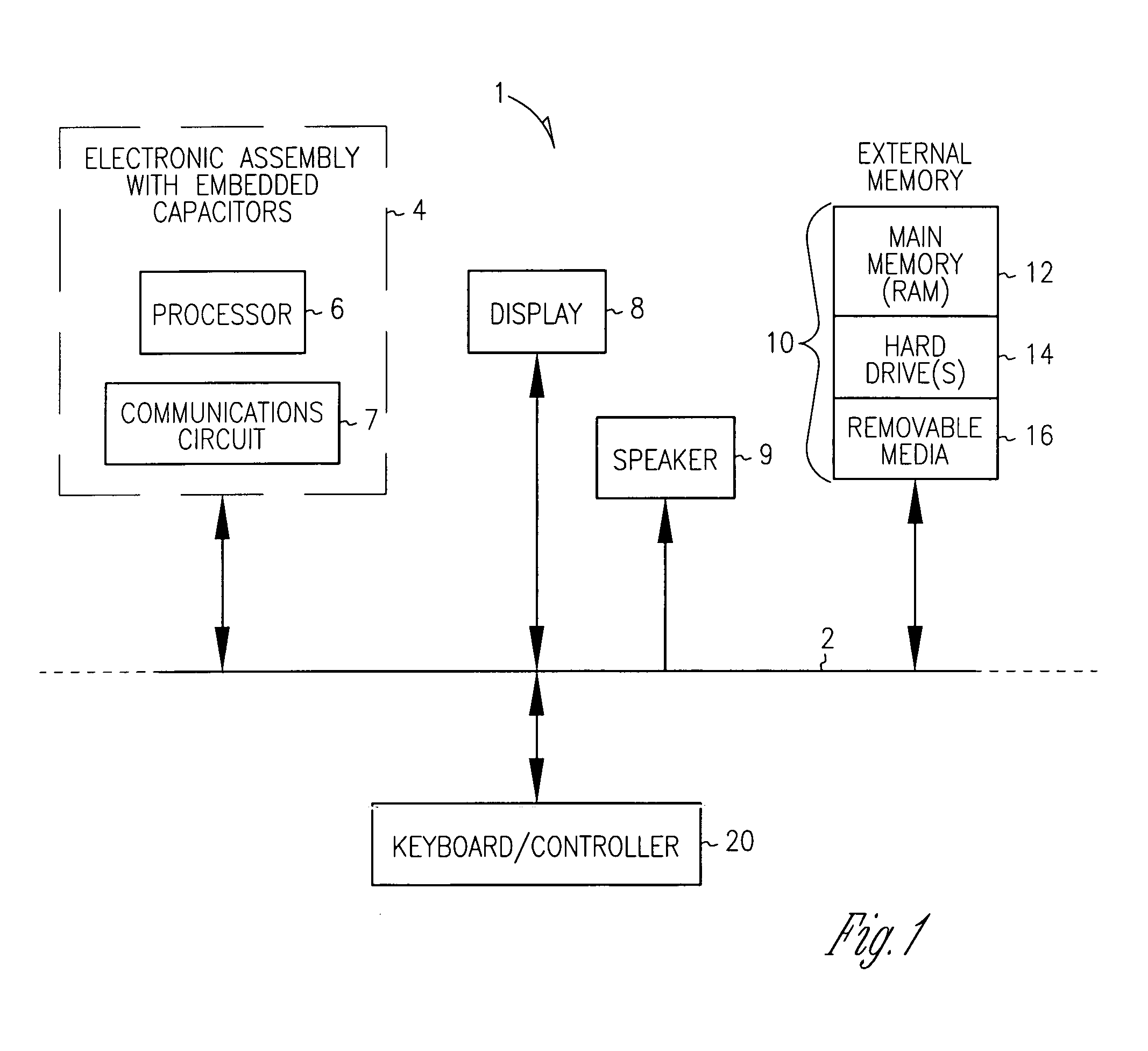

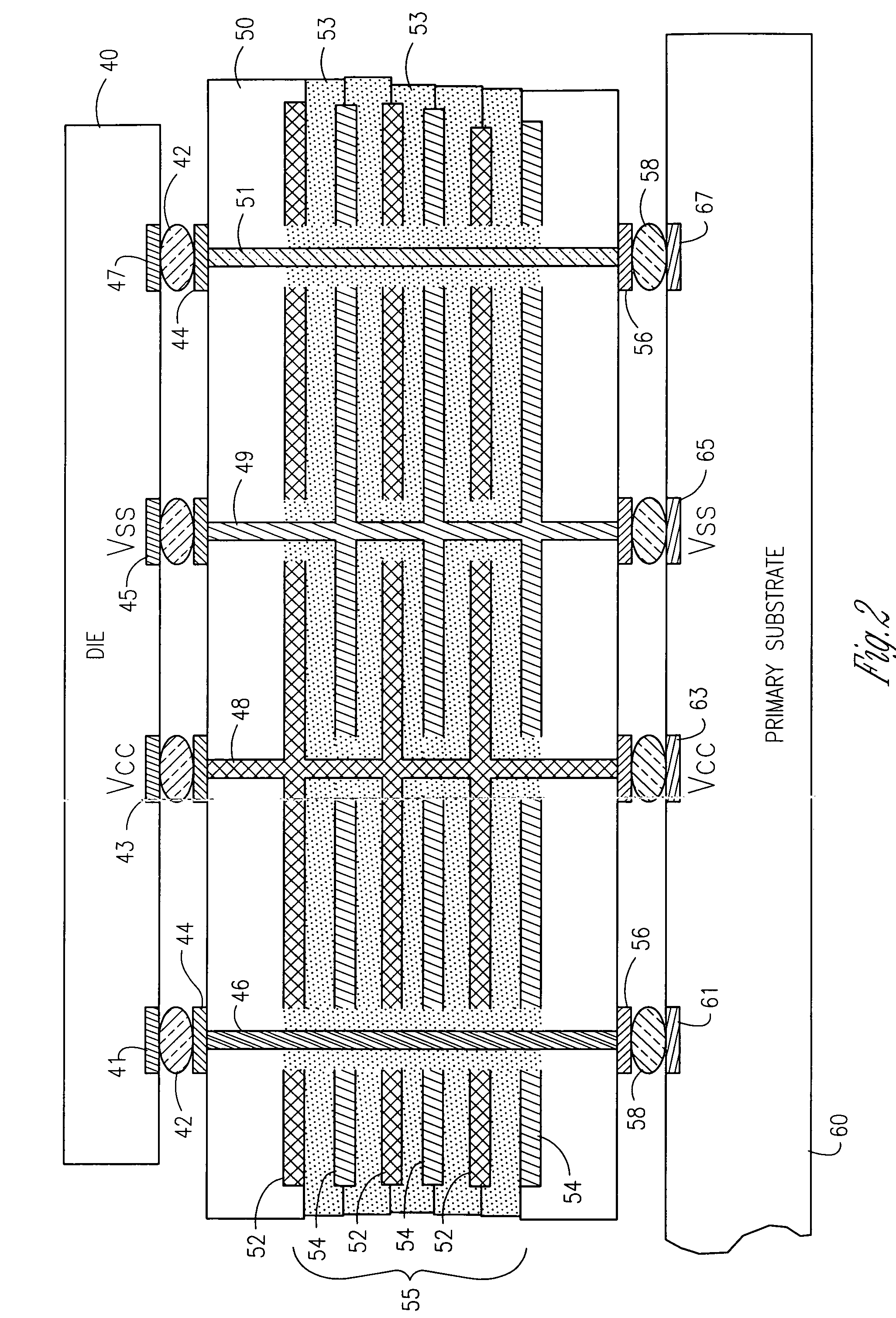

Electronic assemblies and systems comprising interposer with embedded capacitors

InactiveUS20060012966A1Semiconductor/solid-state device detailsSolid-state devicesData processing systemElectrical conductor

To reduce switching noise, the power supply terminals of an integrated circuit die are coupled to the respective terminals of at least one capacitor embedded in an interposer that lies between the die and a substrate. In an embodiment, the interposer is a multilayer ceramic structure that couples power and signal conductors on the die to corresponding conductors on the substrate. The capacitor is formed of at least one high permittivity layer and in an embodiment comprises several high permittivity layers interleaved with conductive layers. Alternatively, the capacitor can comprise at least one embedded discrete capacitor. Also described are an electronic system, a data processing system, and various methods of manufacture.

Owner:INTEL CORP

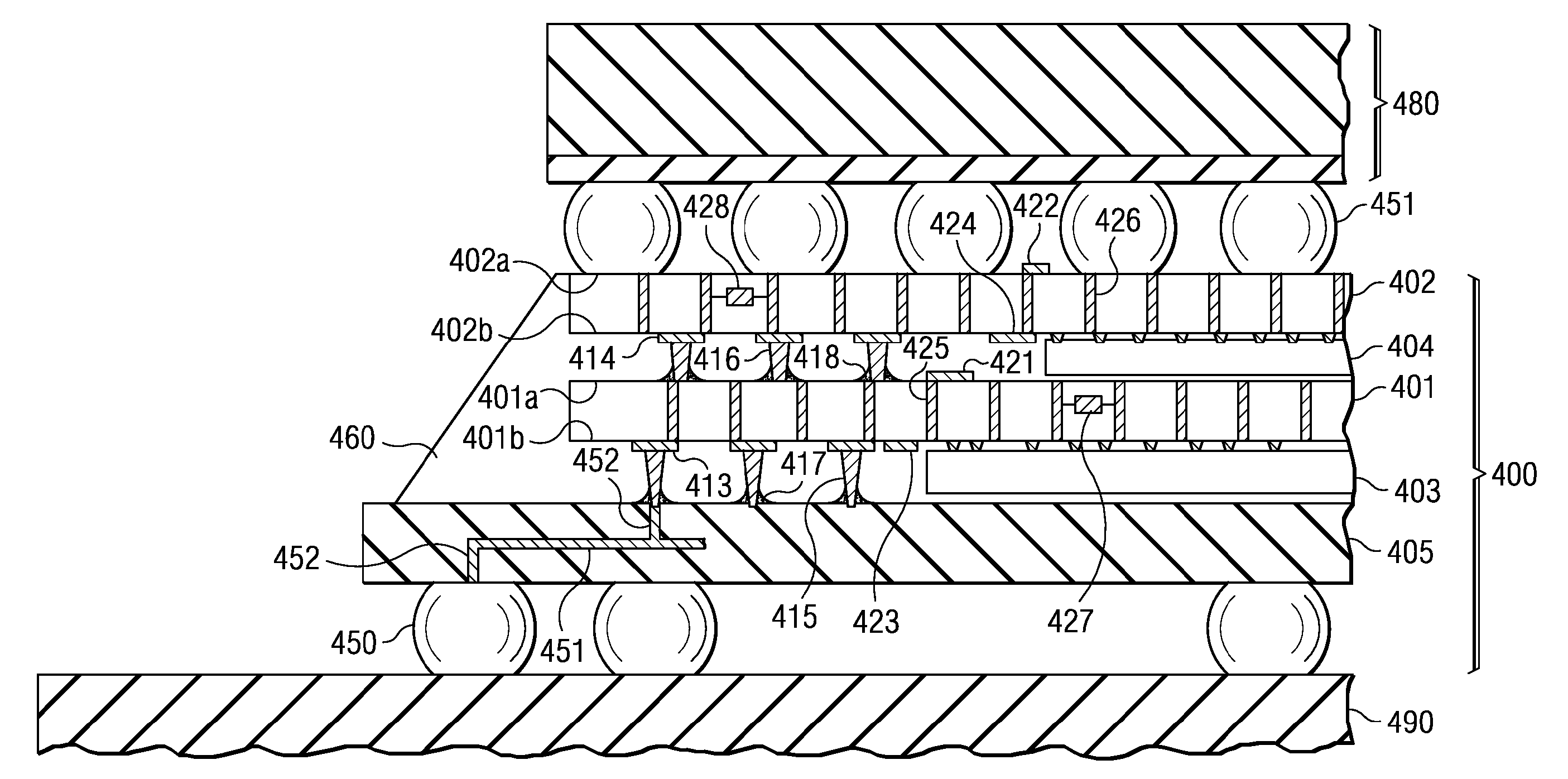

Integrated circuit packaging system with multipart conductive pillars and method of manufacture thereof

ActiveUS8217502B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipInterposer

A method of manufacture of an integrated circuit packaging system includes: providing a pillar ball; mounting an interposer having a first functional side and a second functional side over the pillar ball and a semiconductor chip; encapsulating the interposer, the pillar ball, and the semiconductor chip with an encapsulation; forming a via through the first functional side and the second functional side of the interposer, and through the encapsulation to expose a portion of the pillar ball; and filling the via with a pillar post.

Owner:STATS CHIPPAC LTD

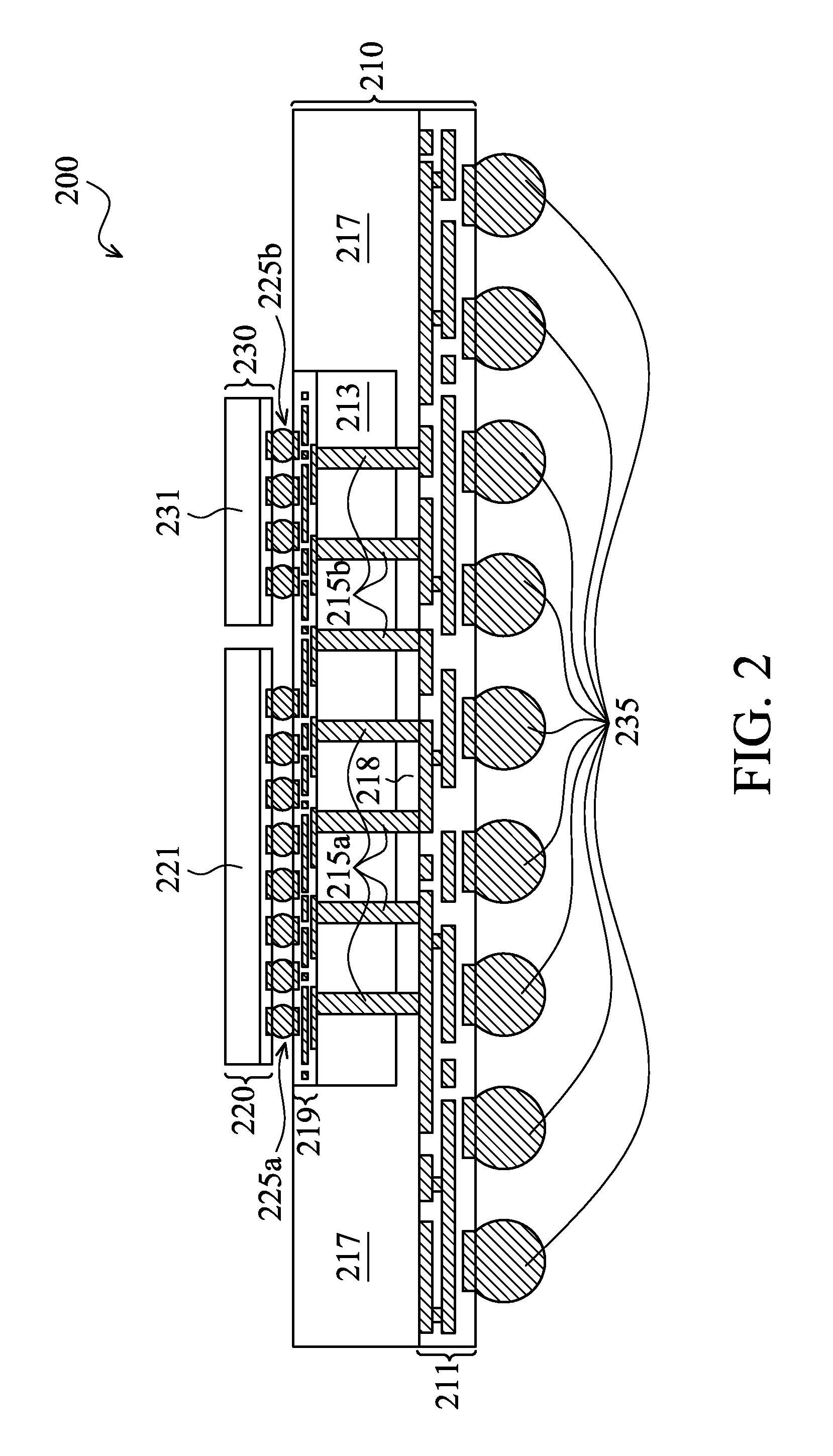

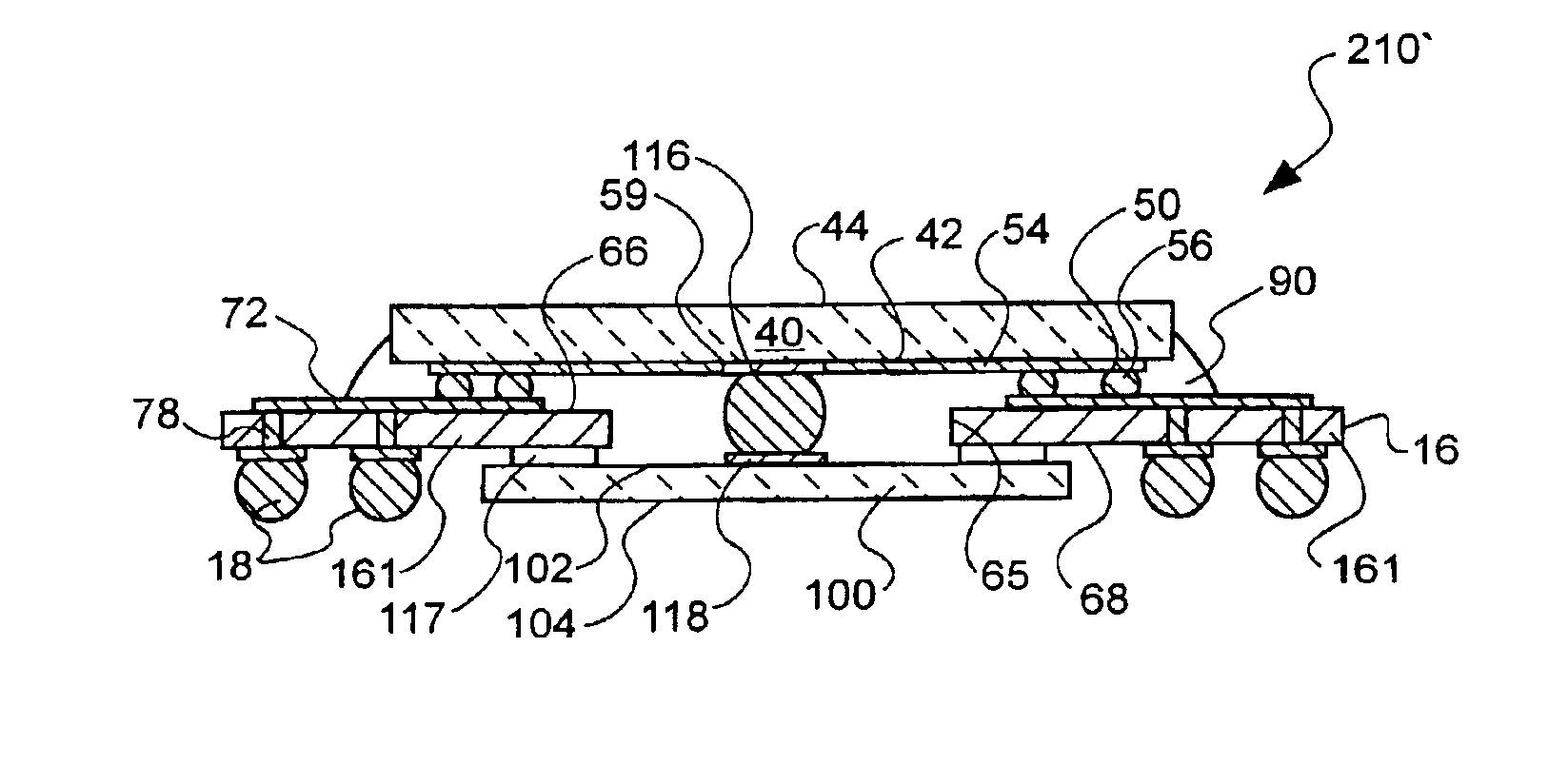

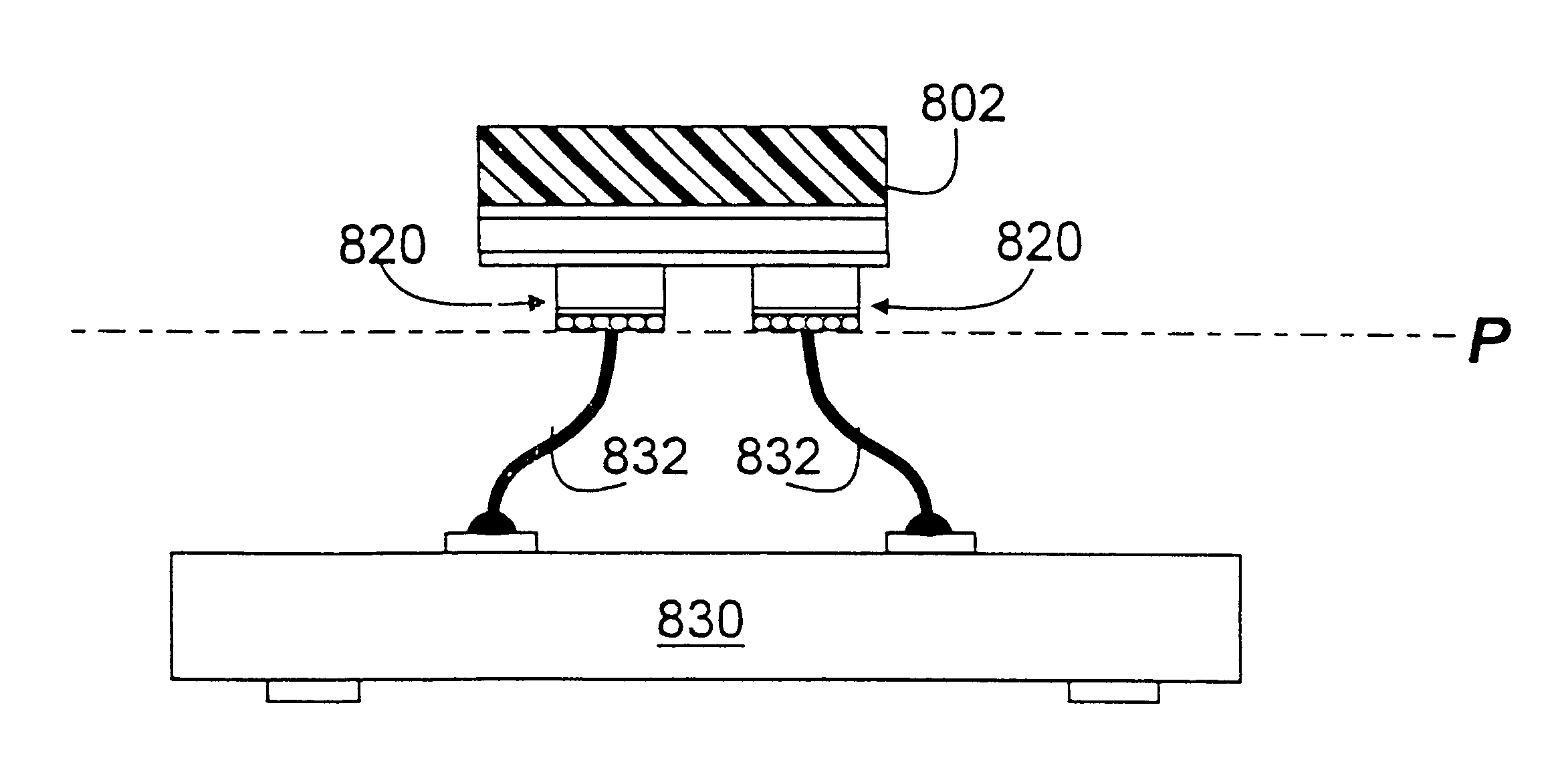

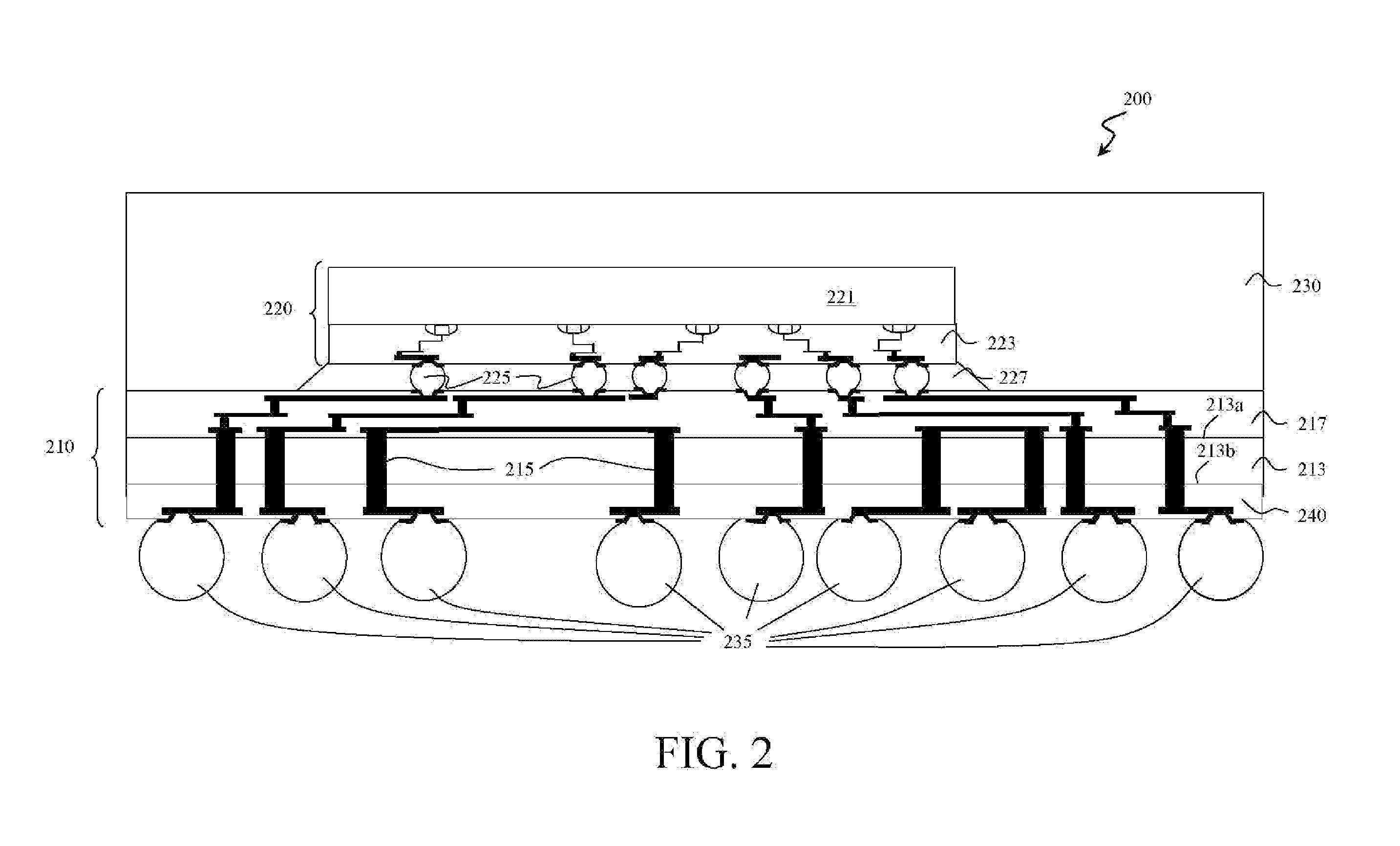

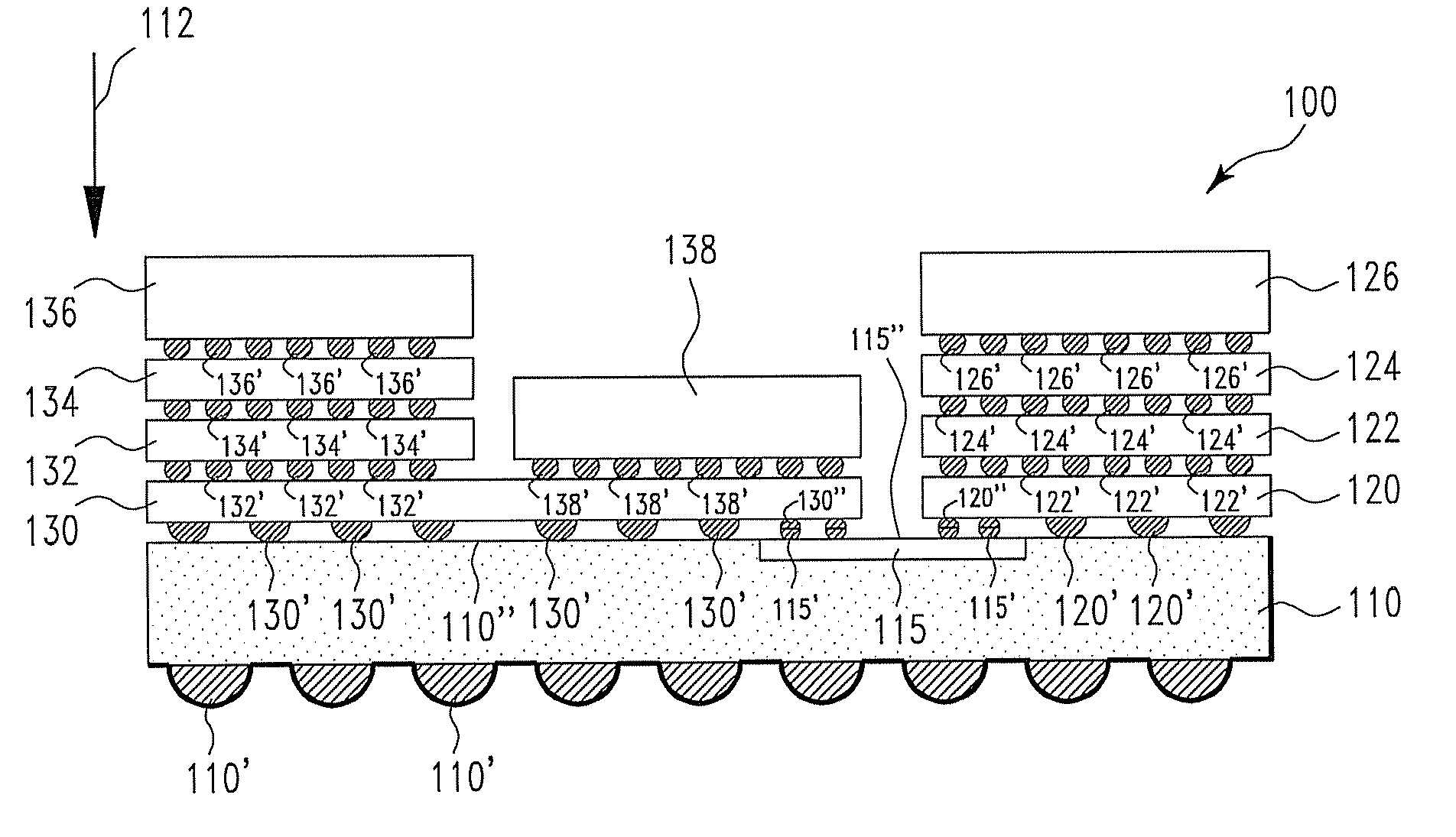

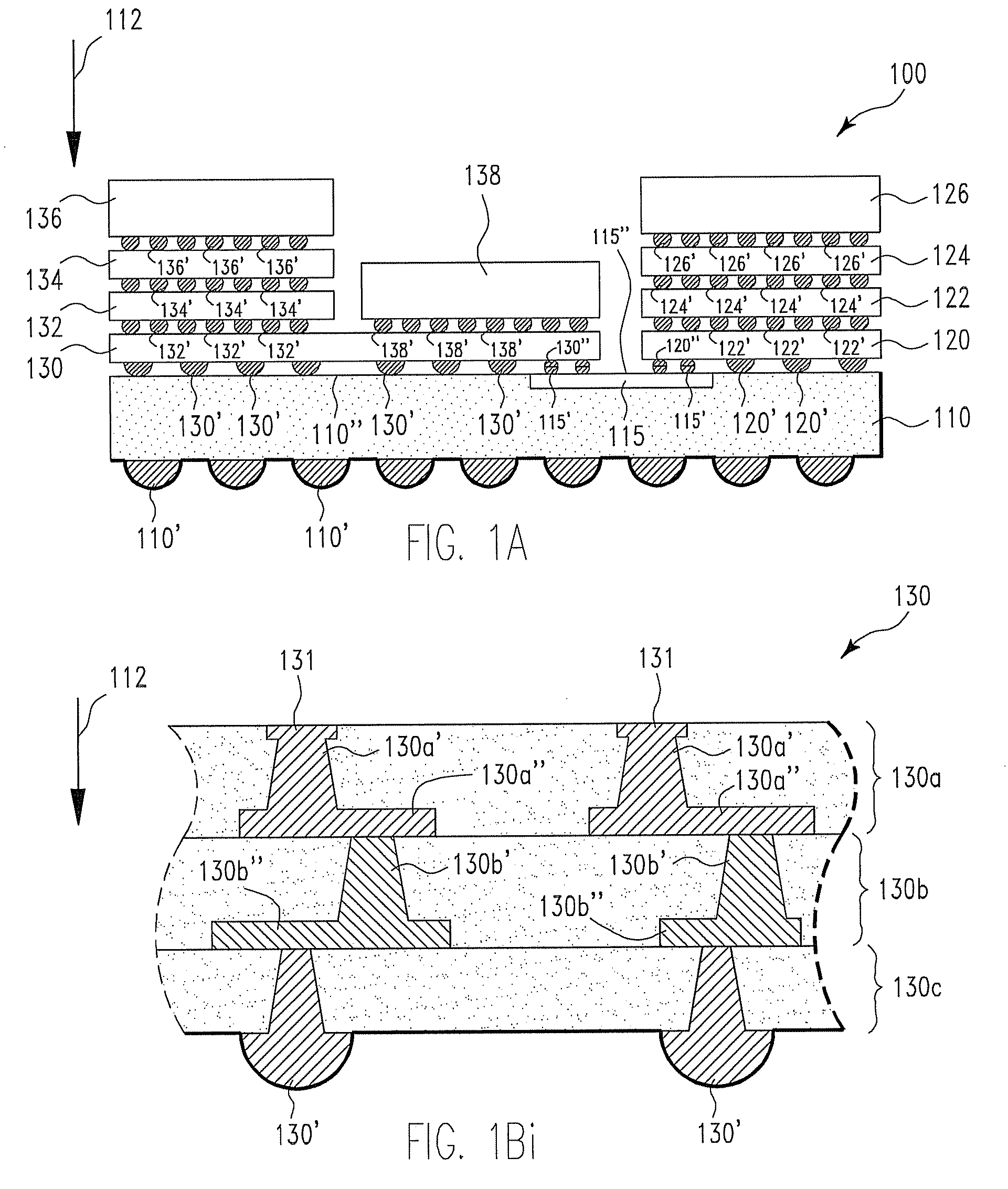

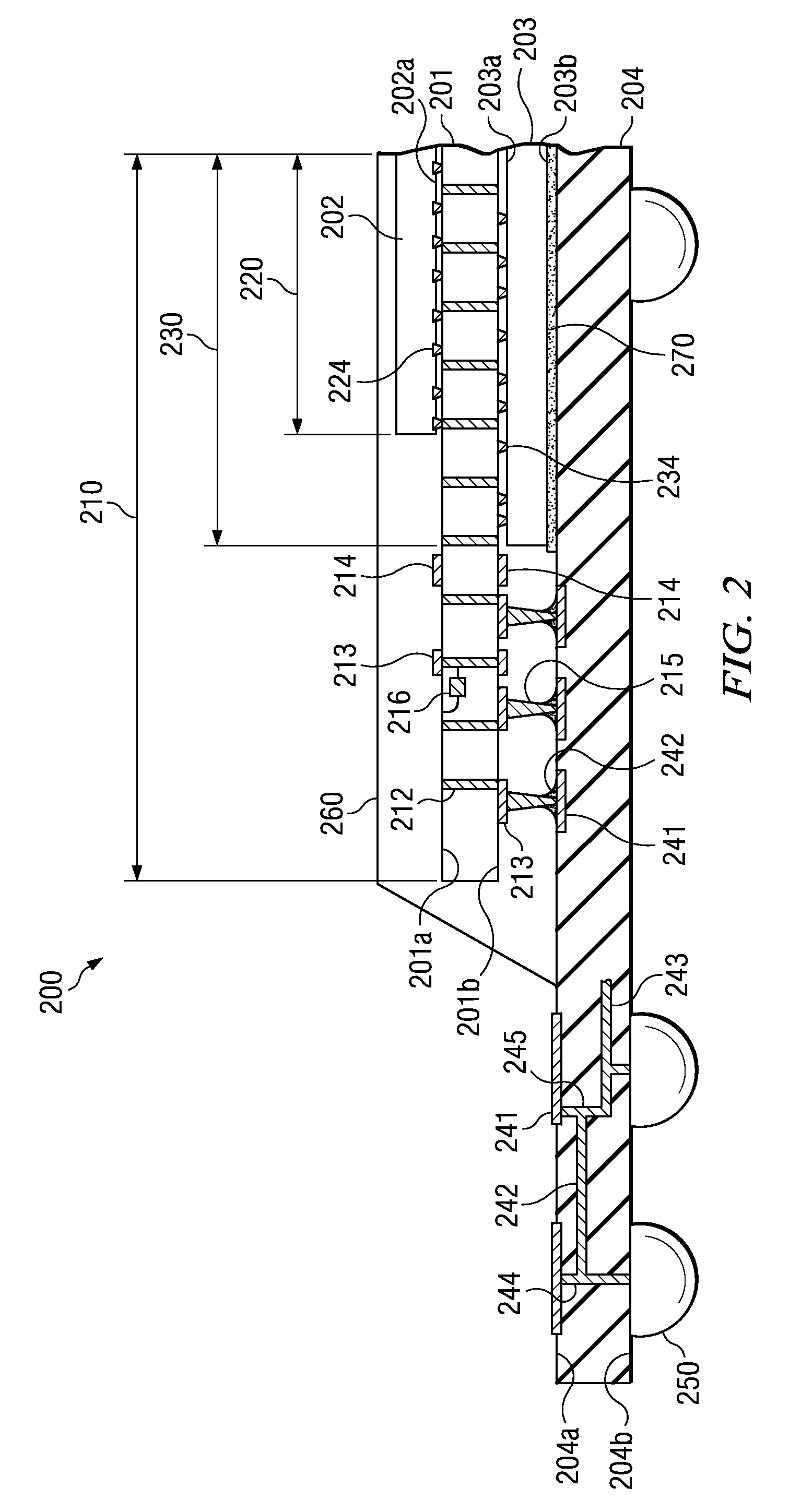

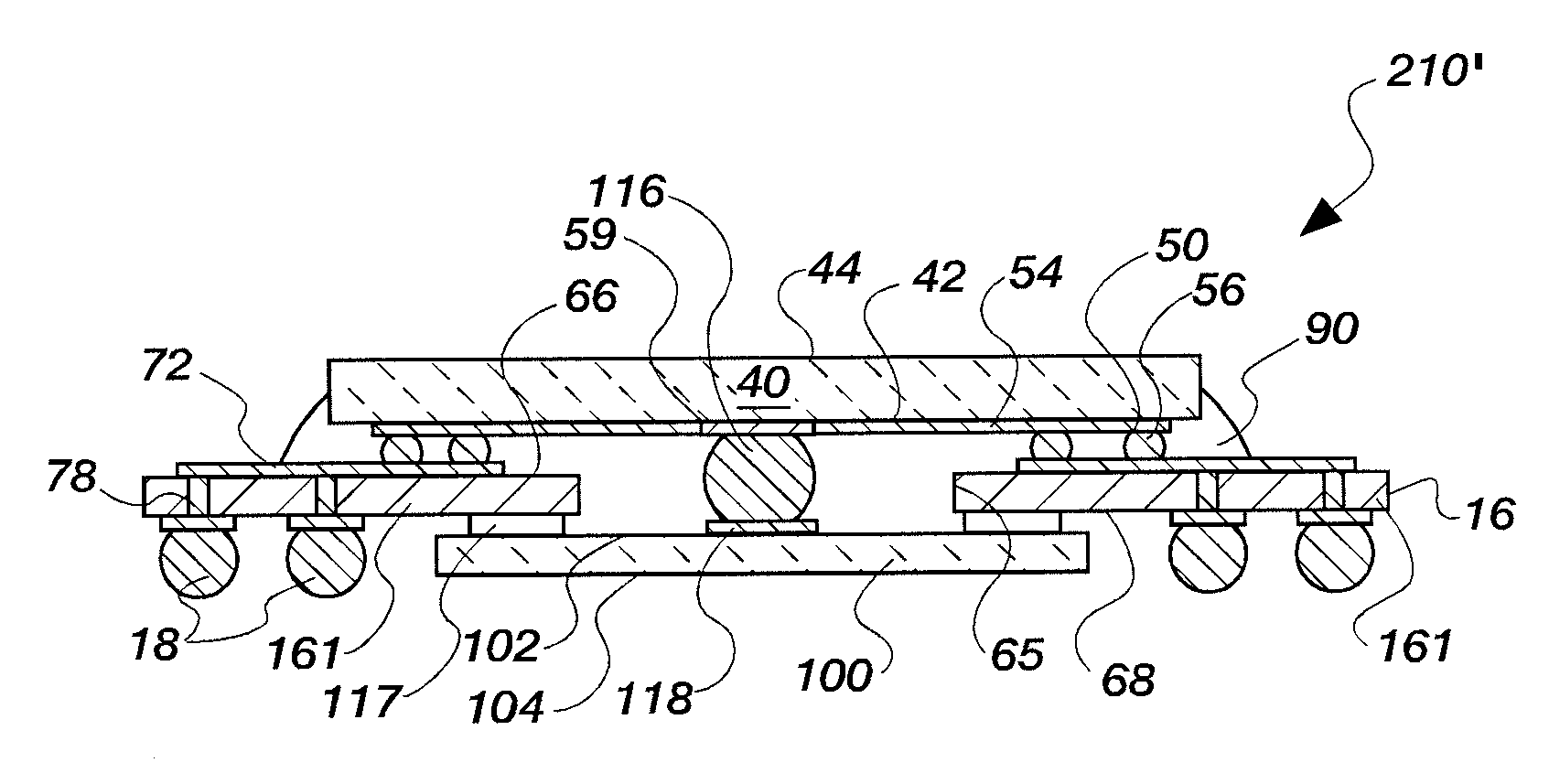

Packaged system of semiconductor chips having a semiconductor interposer

ActiveUS20070235850A1Increase powerIncrease speedSemiconductor/solid-state device detailsSolid-state devicesChip sizeInterposer

A semiconductor system (200) of one or more semiconductor interposers (201) with a certain dimension (210), conductive vias (212) extending from the first to the second surface, with terminals and attached non-reflow metal studs (215) at the ends of the vias. A semiconducting interposer surface may include discrete electronic components or an integrated circuit. One or more semiconductor chips (202, 203) have a dimension (220, 230) narrower than the interposer dimension, and an active surface with terminals and non-reflow metal studs (224, 234). One chip is flip-attached to the first interposer surface, and another chip to the second interposer surface, so that the interposer dimension projects over the chip dimension. An insulating substrate (204) has terminals and reflow bodies (242) to connect to the studs of the projecting interposer.

Owner:TEXAS INSTR INC

RFID device with magnetic coupling

An RFID device, such as an RFID tag or label, includes a magnetic coupler between an interposer or strap, and an antenna. The interposer or strap includes a transponder chip and an interposer magnetic coupling element that is operatively coupled to the transponder. An antenna portion magnetic coupling element is operatively coupled to the antenna. The magnetic coupling element s together constitute a magnetic coupler that is used to magnetically couple the transponder chip of the interposer to the RFID antenna. A high permeability material may be used to enhance the magnetic coupling between the magnetic coupling elements. The magnetic coupling elements single-turn conductive loops or multiple-turn coils. The magnetic coupler may function as a transformer, with the voltage across the antenna transformed to a different voltage across the transponder chip, and vice versa.

Owner:AVERY DENNISON CORP

RFID tag with enhanced readability

ActiveUS7298343B2Improve performanceSimultaneous aerial operationsAntenna supports/mountingsInterposerConductive materials

A radio frequency identification (RFID) device includes a conductive antenna structure having an elongated slot therein. Parts of the antenna structure on both sides of one end of the elongated slot are coupled to a wireless communication device, such as an RFID chip or interposer. On the opposite end of the elongated slot, parts of the antenna structure at both sides of the elongated slot are electrically coupled together, for instance by being coupled together by other conductive parts of the antenna structure. All of the parts of the antenna structure may be parts of a continuous unitary layer of conductive material. The antenna structure with the elongated slot therein may facilitate increased readability of the RFID device, particularly in directions out from the edges of the RFID device.

Owner:AVERY DENNISON CORP

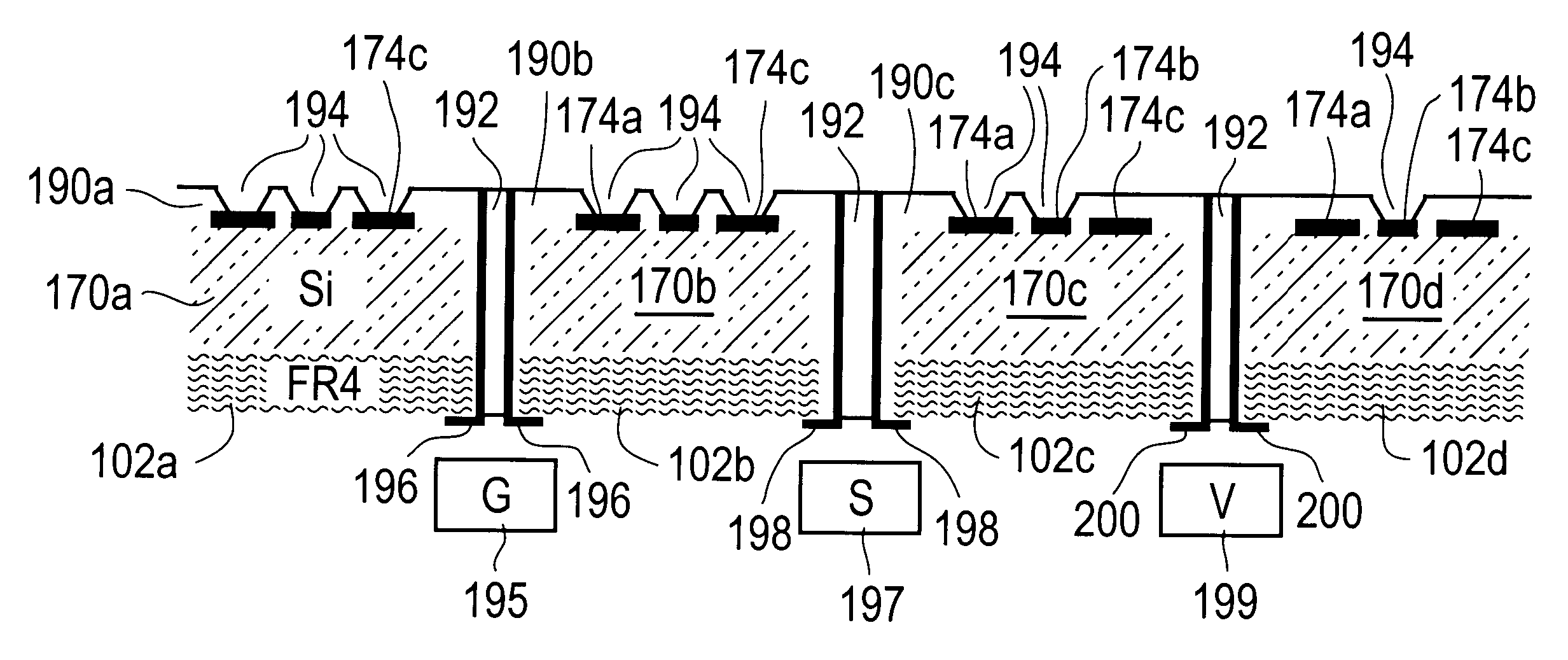

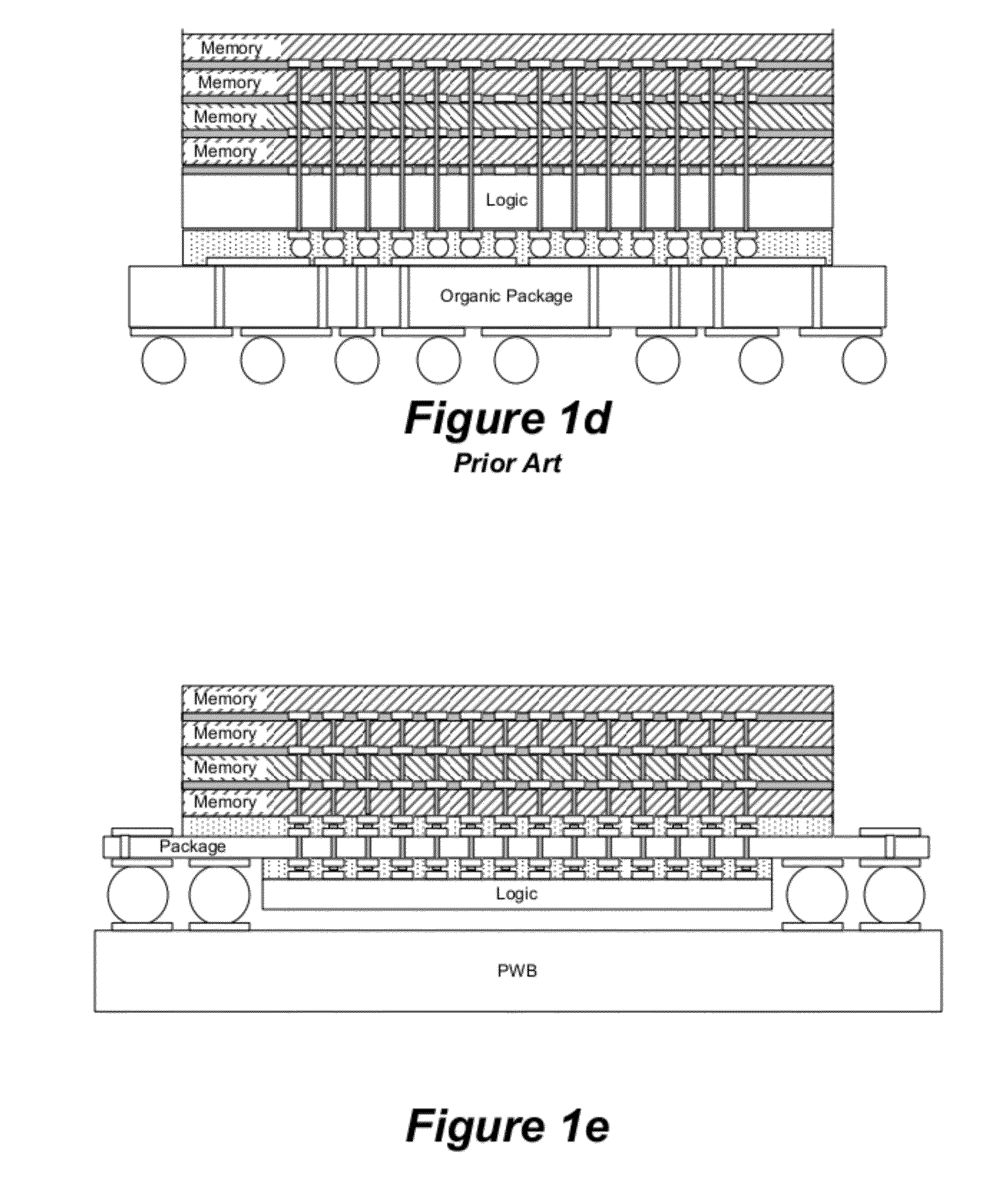

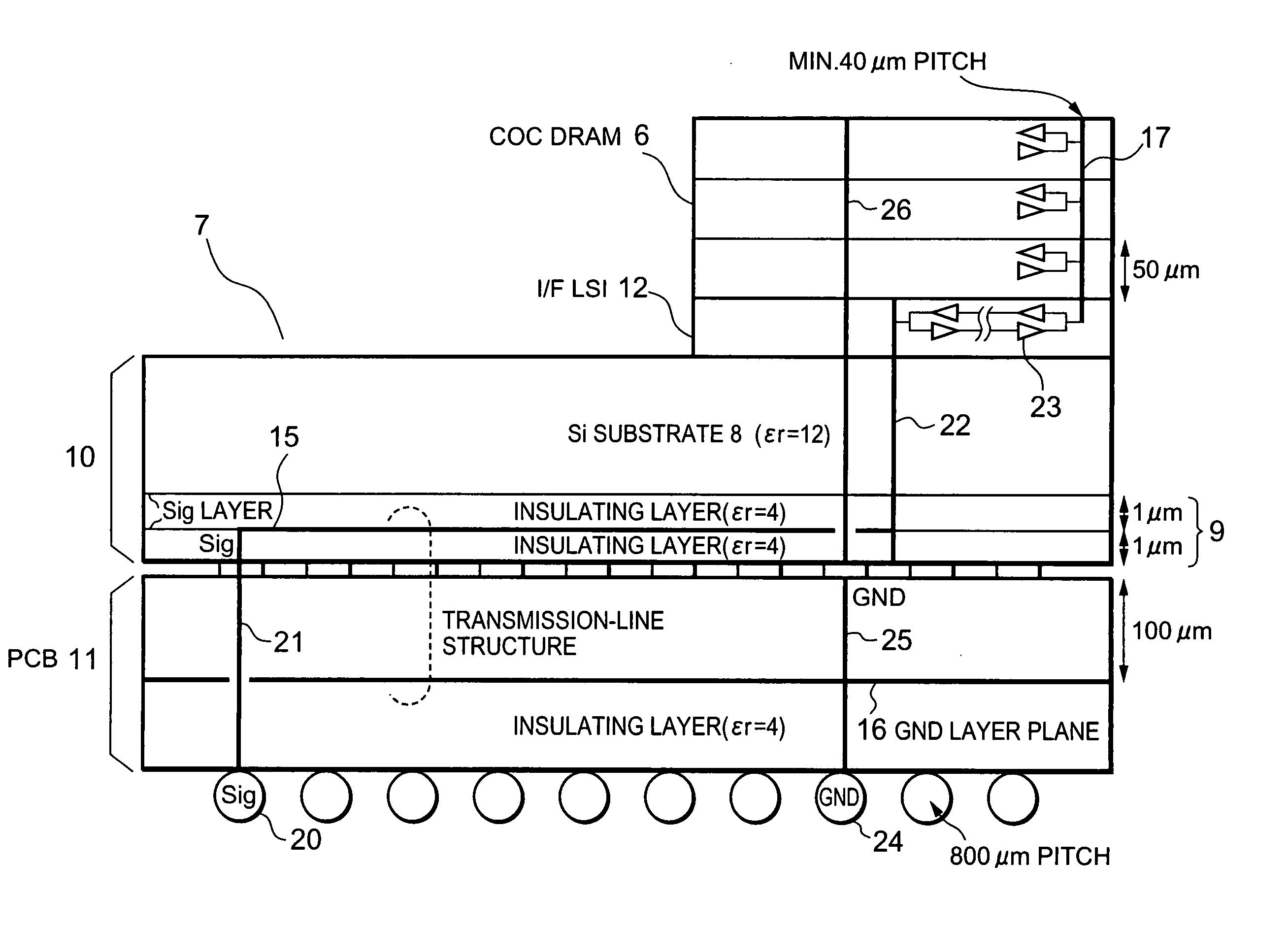

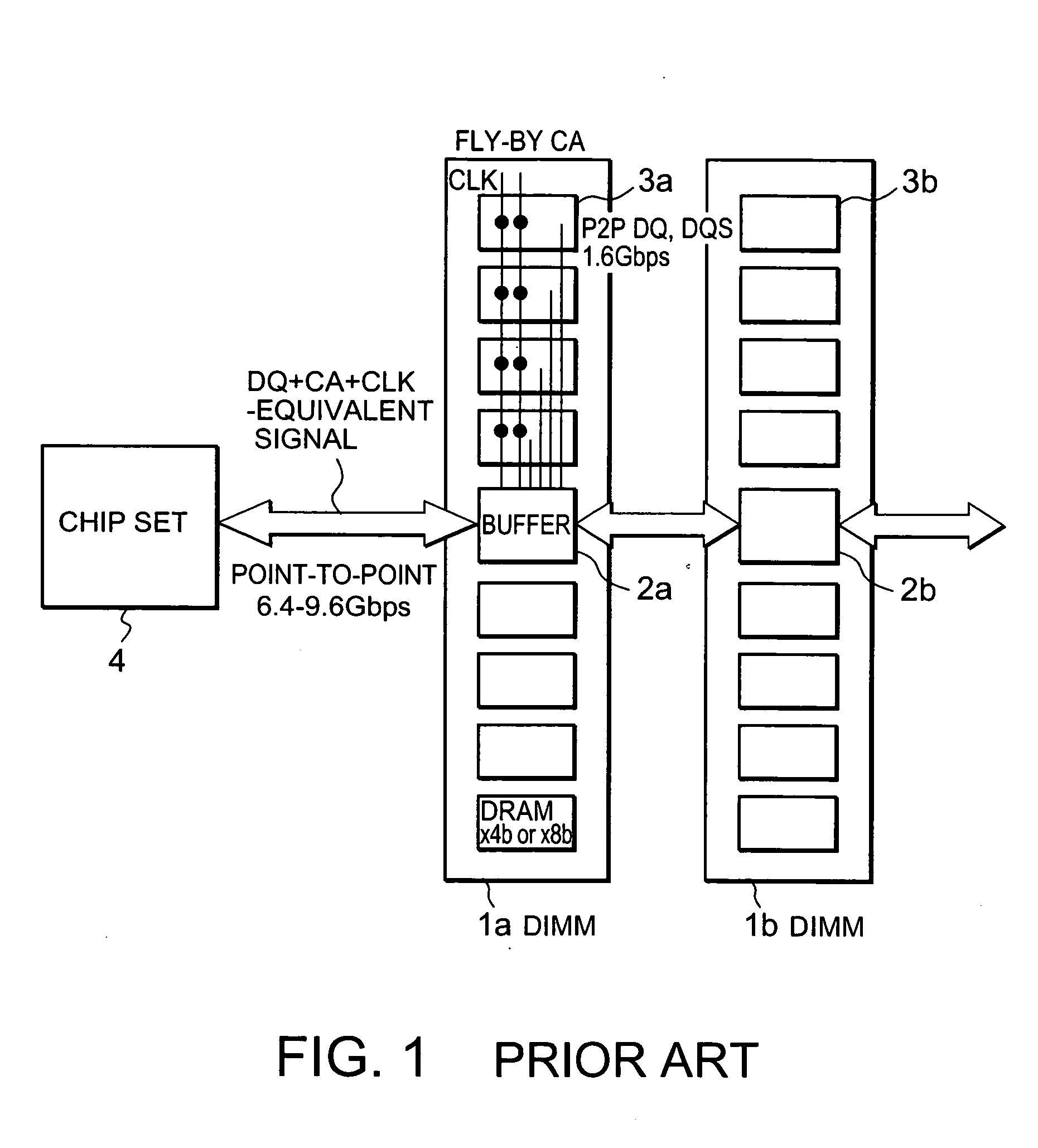

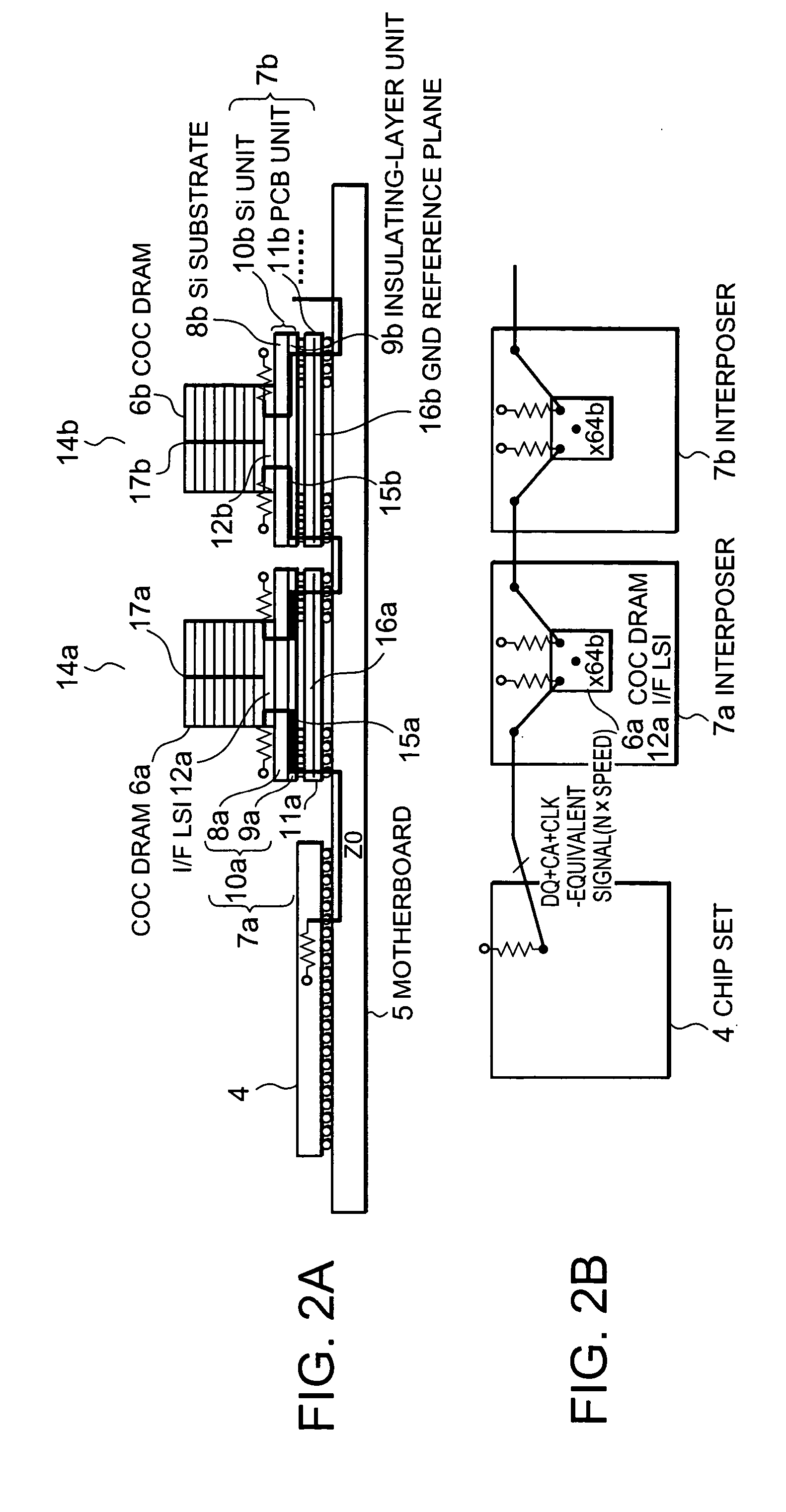

Semiconductor integrated circuit device

InactiveUS20050139977A1Easy impedance matchingReduce signalingTransistorSemiconductor/solid-state device detailsInterposerChipset

A COC DRAM including a plurality of stacked DRAM chips is mounted on a motherboard by using an interposer. The interposer includes a Si unit and a PCB. The Si unit includes a Si substrate and an insulating-layer unit in which wiring is installed. The PCB includes a reference plane for the wiring in the Si unit. The wiring topology between a chip set and the COC DRAM is the same for every signal. Accordingly, a memory system enabling a high-speed operation, low power consumption, and large capacity is provided.

Owner:PS4 LUXCO SARL

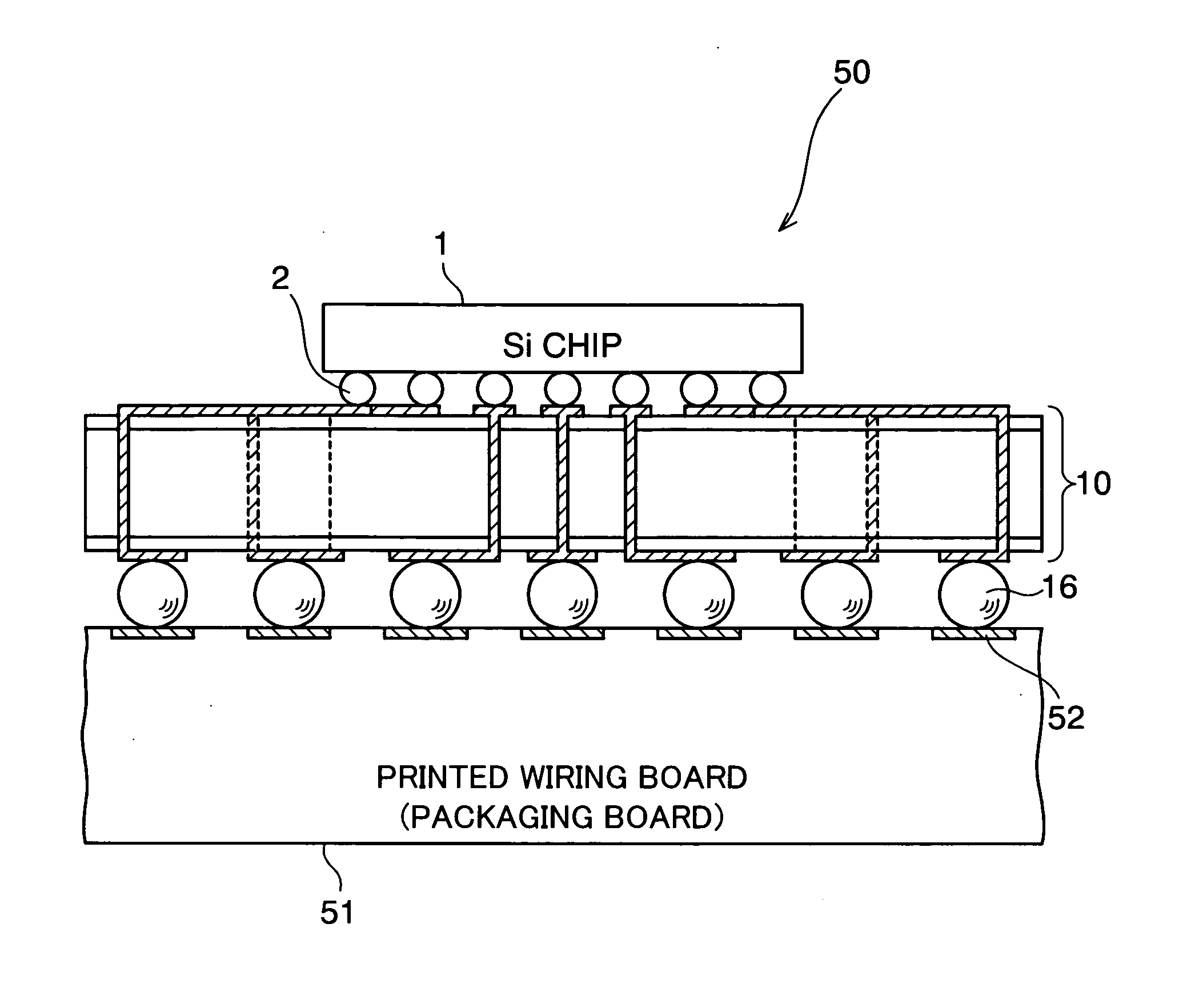

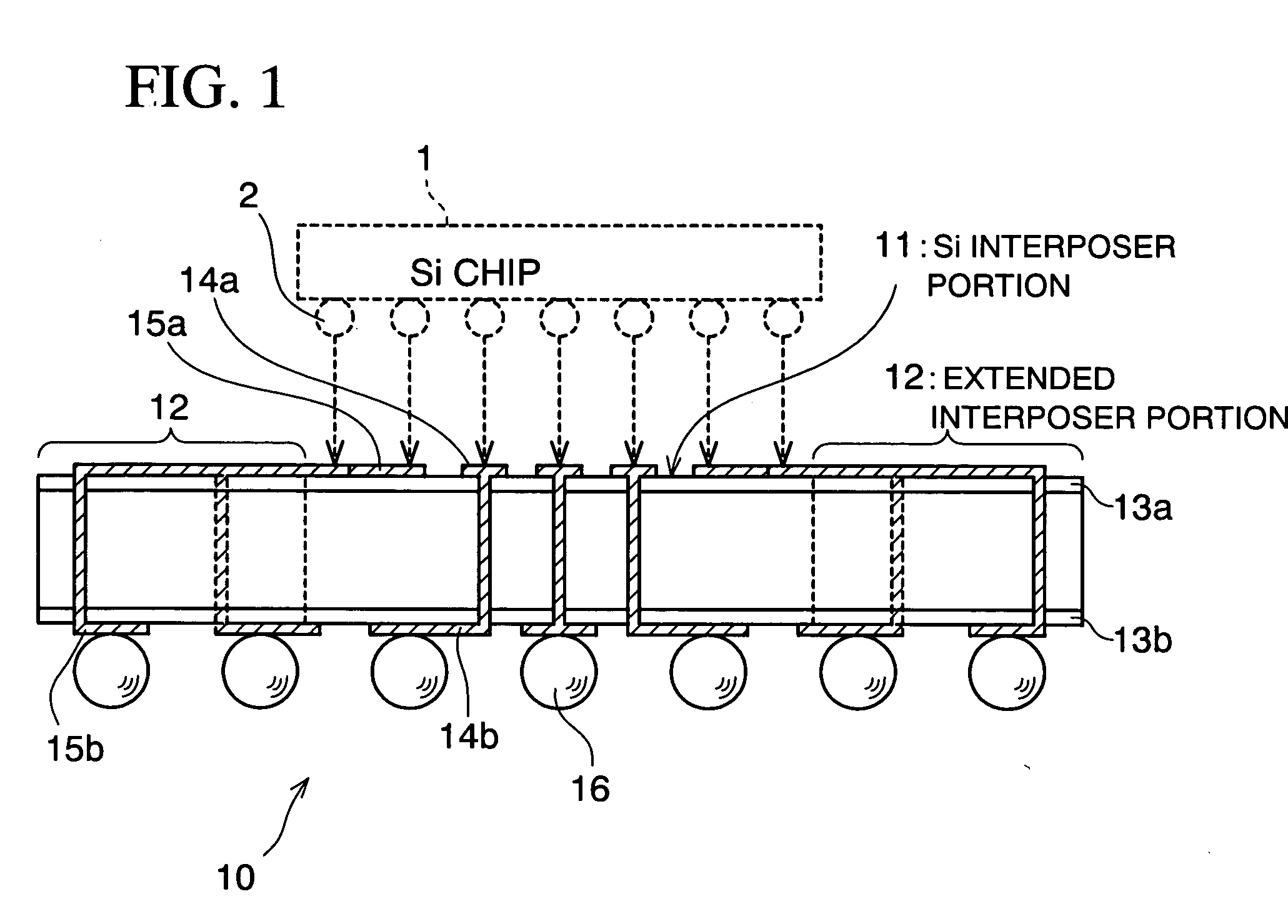

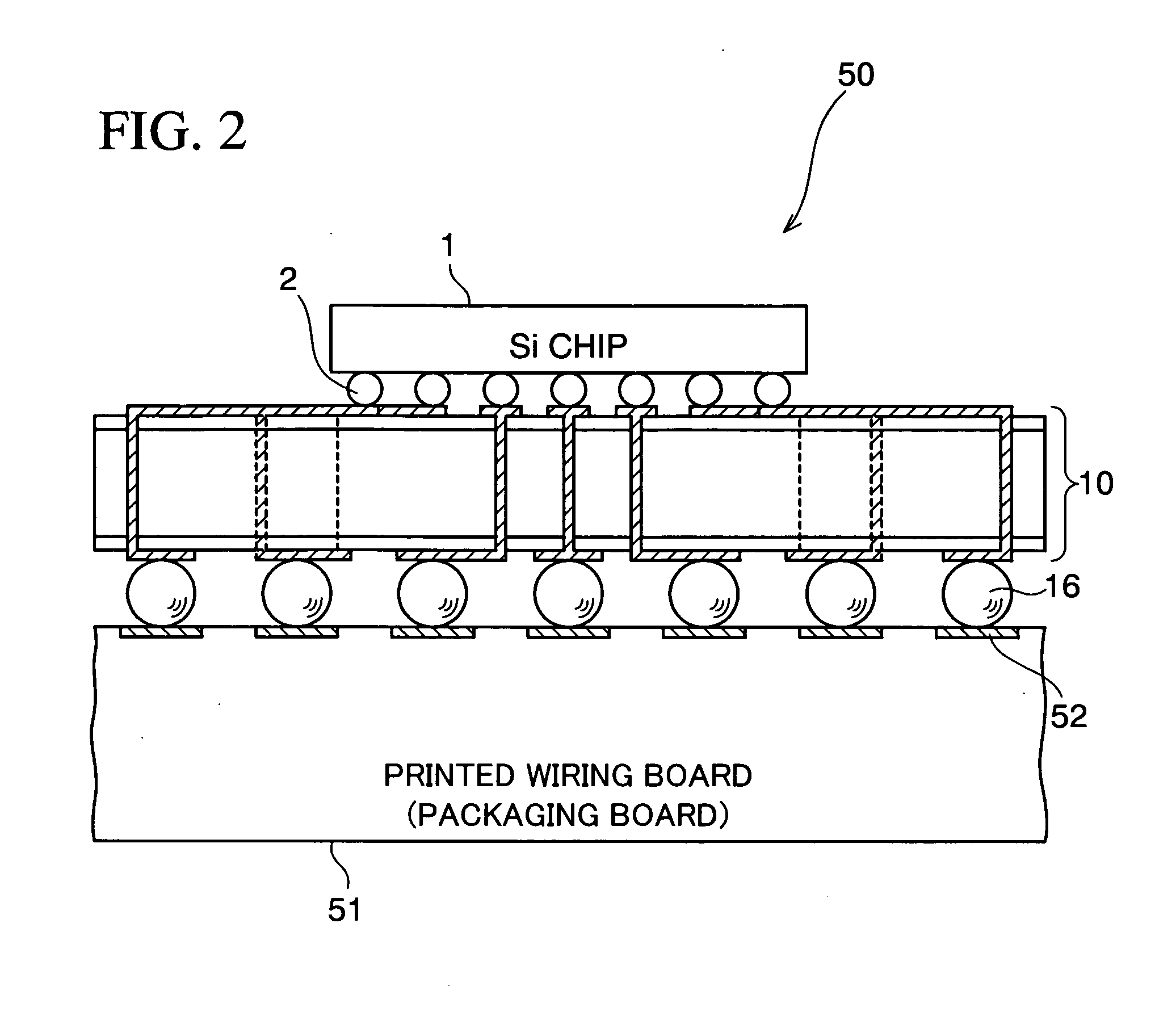

Interposer, method of fabricating the same, and semiconductor device using the same

ActiveUS20060001179A1Low costWell formedSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterposer

An interposer to be interposed between a semiconductor chip to be mounted thereon and a packaging board has an interposer portion made of a semiconductor and an interposer portion provided around the foregoing interposer portion integrally therewith. On both surfaces of the interposer portions, wiring patterns are formed via insulating layers. The wiring patterns are electrically connected via through holes formed at required positions in the interposer portions. The outer interposer portion is made of an insulator or a metal body. Further, external connection terminals are bonded to one surface of the interposer.

Owner:SHINKO ELECTRIC IND CO LTD

Semiconductor memory device and manufacturing method thereof

InactiveUS20090294990A1Easy to provideSuppression of Reliability DecreaseSemiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A semiconductor memory device has a plurality of core chips and an interface chip, whose specification can be easily changed, while suppressing the degradation of its reliability. The device has an interposer chip. First internal electrodes connected to core chips are formed on the first surface of the interposer chip. Second internal electrodes connected to an interface chip and third internal electrodes connected to external electrodes are formed on the second surface of the interposer chip. The interface chip can be mounted on the second surface of the interposer chip whenever desired. Therefore, the memory device can have any specification desirable to a customer, only if an appropriate interface chip is mounted on the interposer chip, as is demanded by the customer. Thus, the core chips do not need to be stocked in great quantities in the form of bare chips.

Owner:LONGITUDE LICENSING LTD

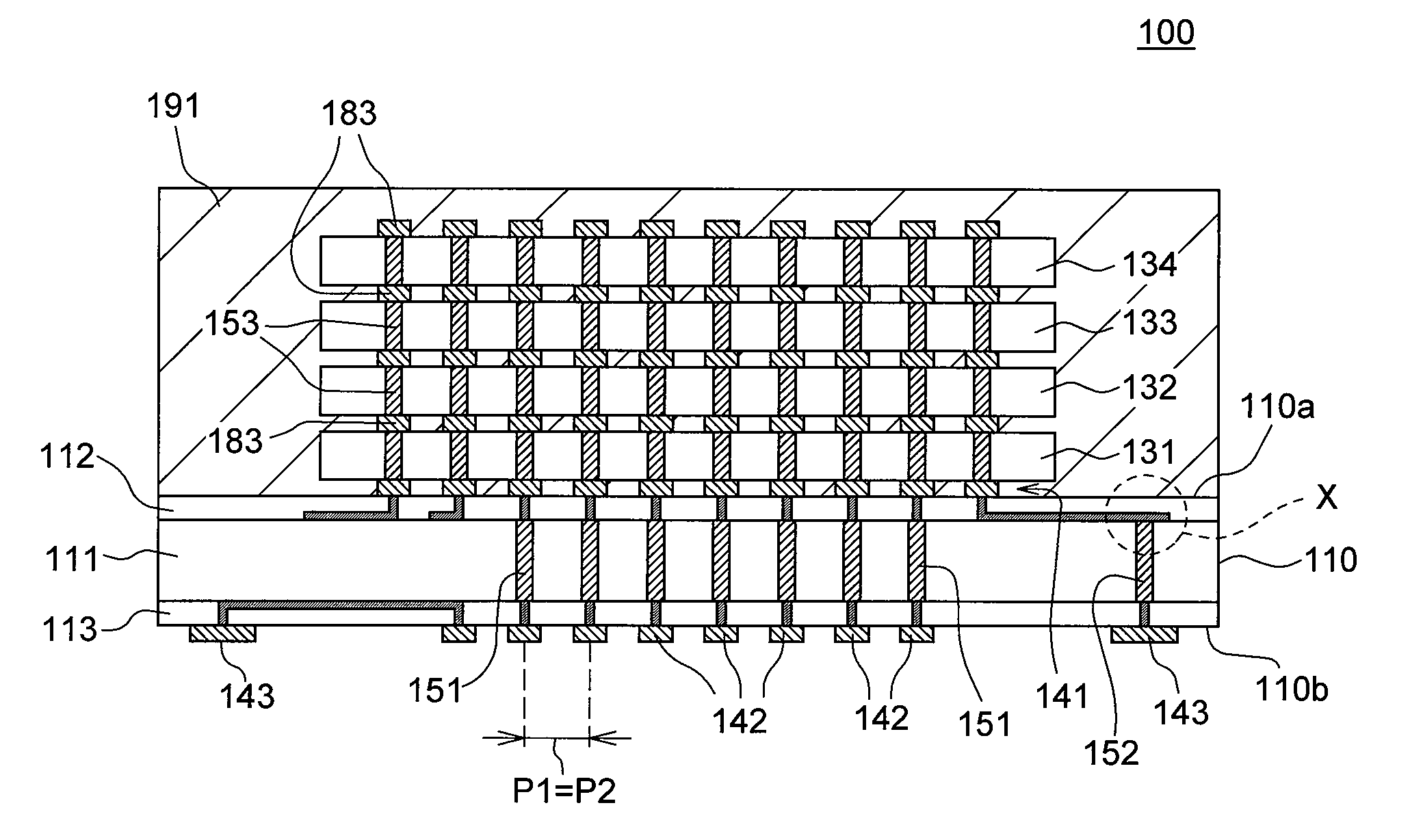

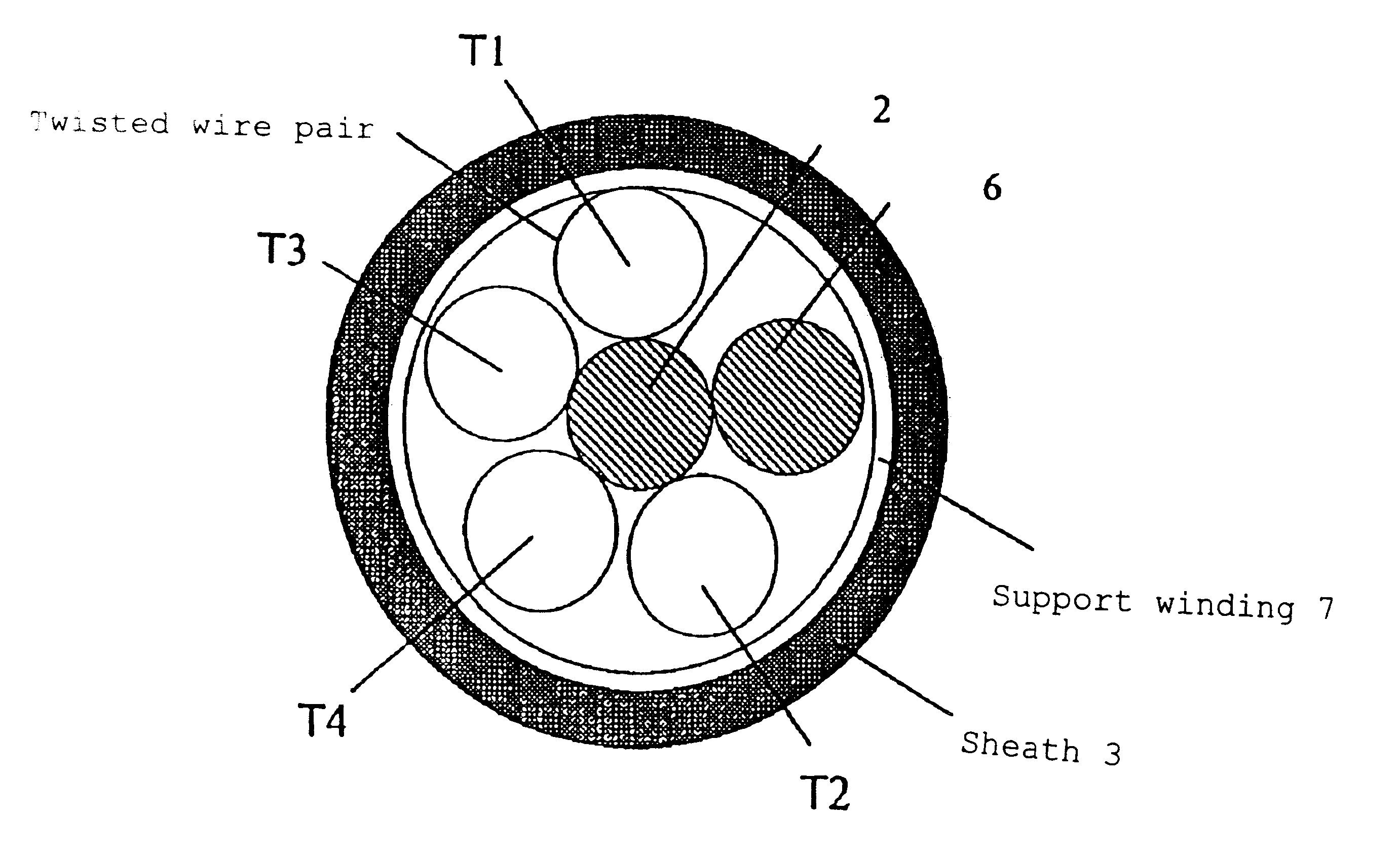

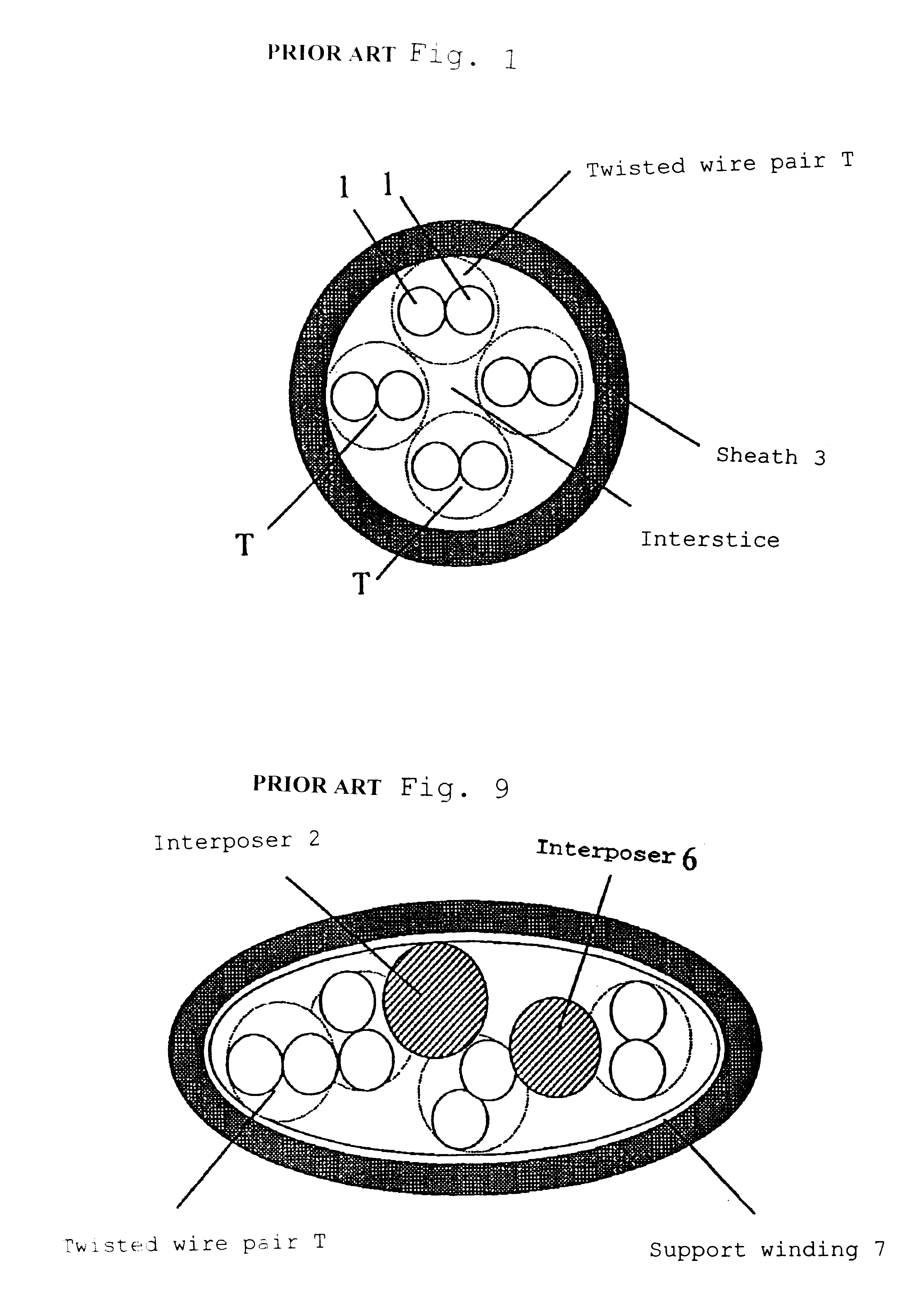

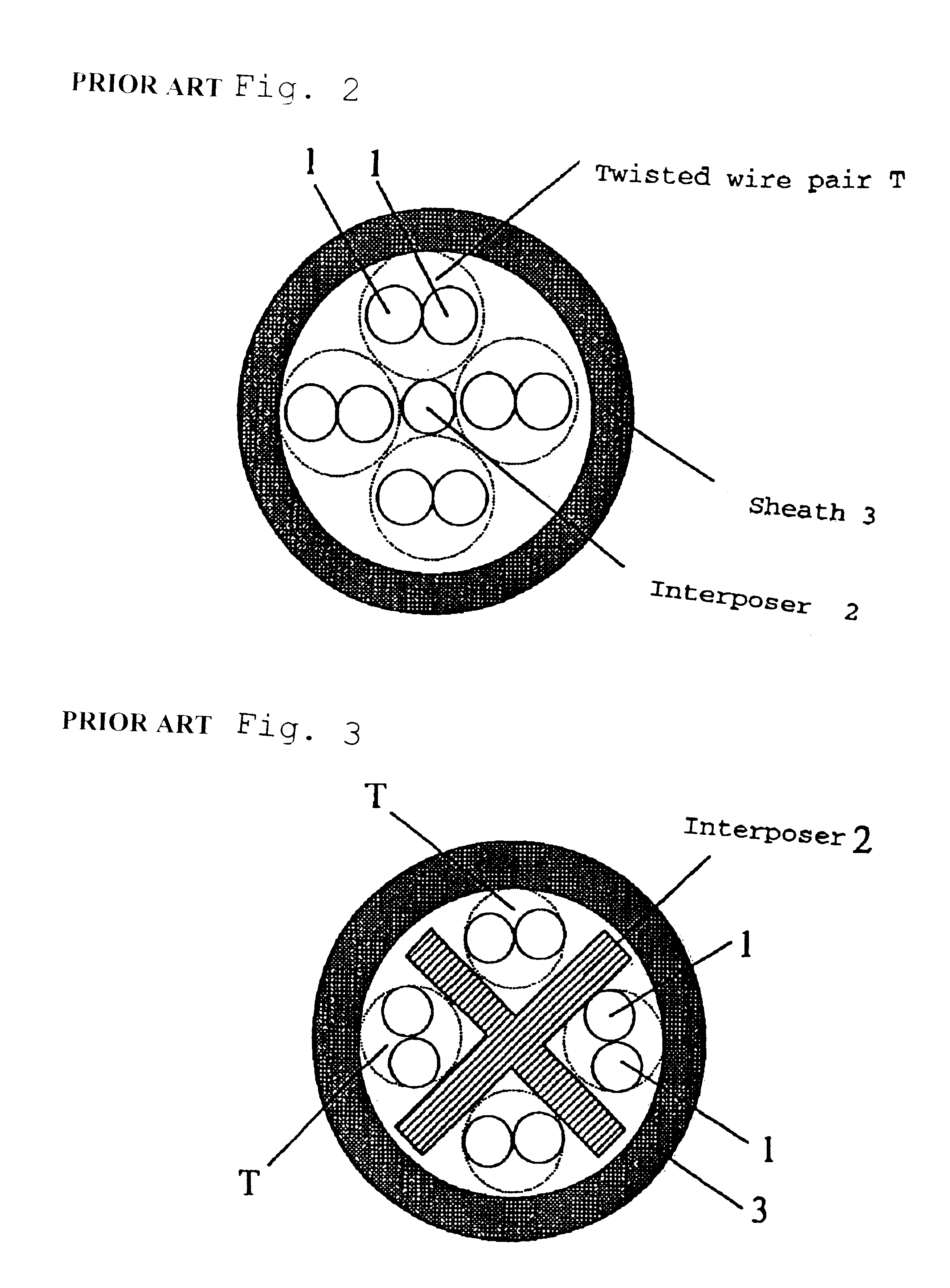

Communication cable

InactiveUS6300573B1Reduce the differenceIncrease spacingInsulated cablesPower cablesPolyolefinProximal point

A communication cable is provided that satisfies the requirement of Cat.6 for near-end cross talk wherein the difference between the maximum and minimum values of delay time among the four twisted wire pairs constituting the cable is within 25 ns / 100 m. The communication cable is made by entwining four twisted wire pairs (T1), (T2), (T3), (T4) made by twisting pairs of insulated wires made by covering electrically conductive wires by polyolefin thermoplastic resin with each pair being twisted with a twist pitch different from the others (pitch: P1<P2<P3<P4) and the inter-pair interposer (6) made of polyolefin thermoplastic resin, while being entwined with each wire pair, around a central interposer (2) made of polyolefin thermoplastic resin having cross sectional area of S1. Cross sectional area S1 of the central interposer (2) satisfies the relationship of inequality S1>=[{4.1 d / (1+{square root over (2)})}.0.35]2xpi, while the inter-pair interposer (6) that is entwined with the twisted wire pairs is located at such a position as adjoins the twisted wire pair (T1) having the least pitch P1 and does not adjoin the twisted wire pair (T4) having the largest pitch P4.

Owner:FURUKAWA ELECTRIC CO LTD

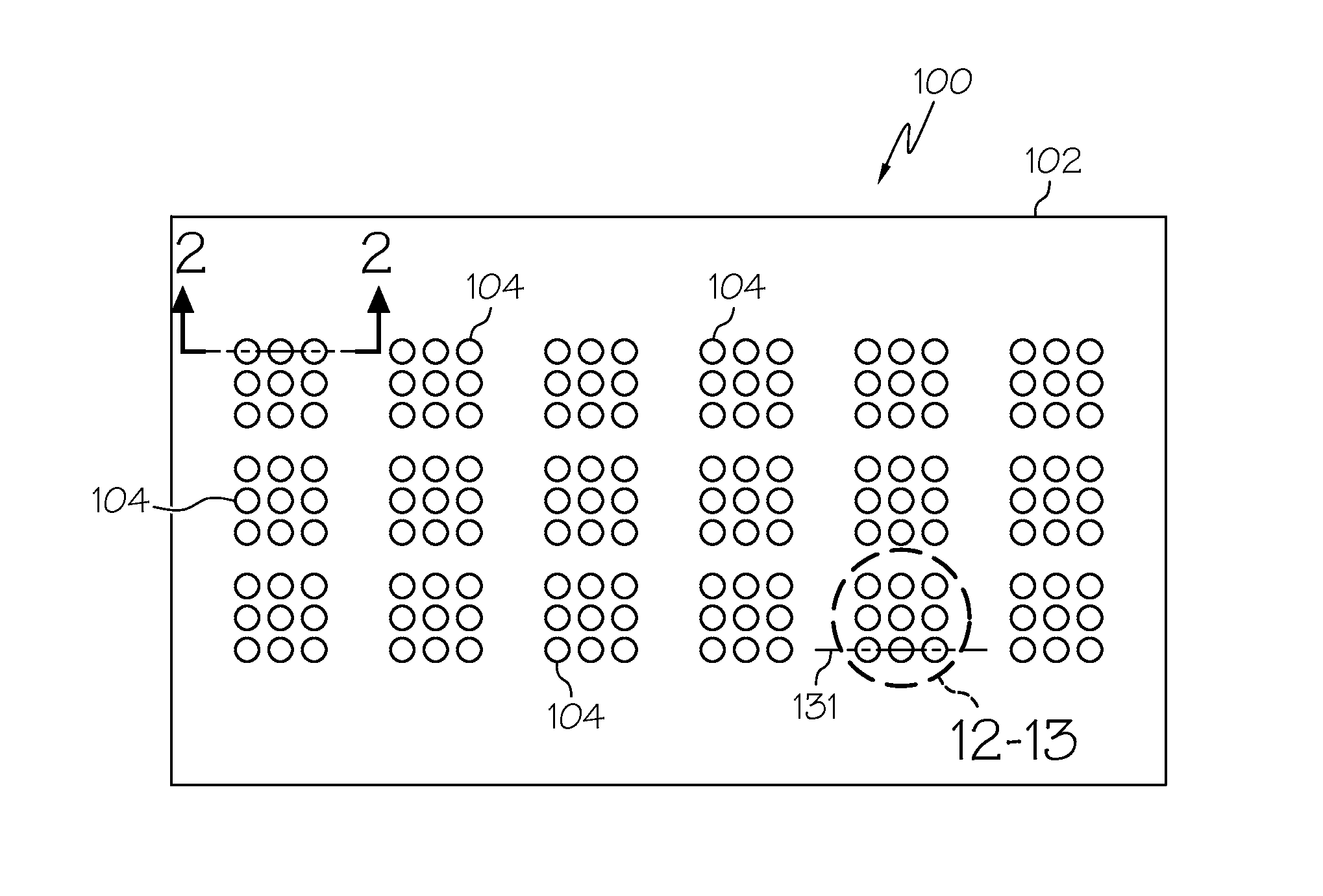

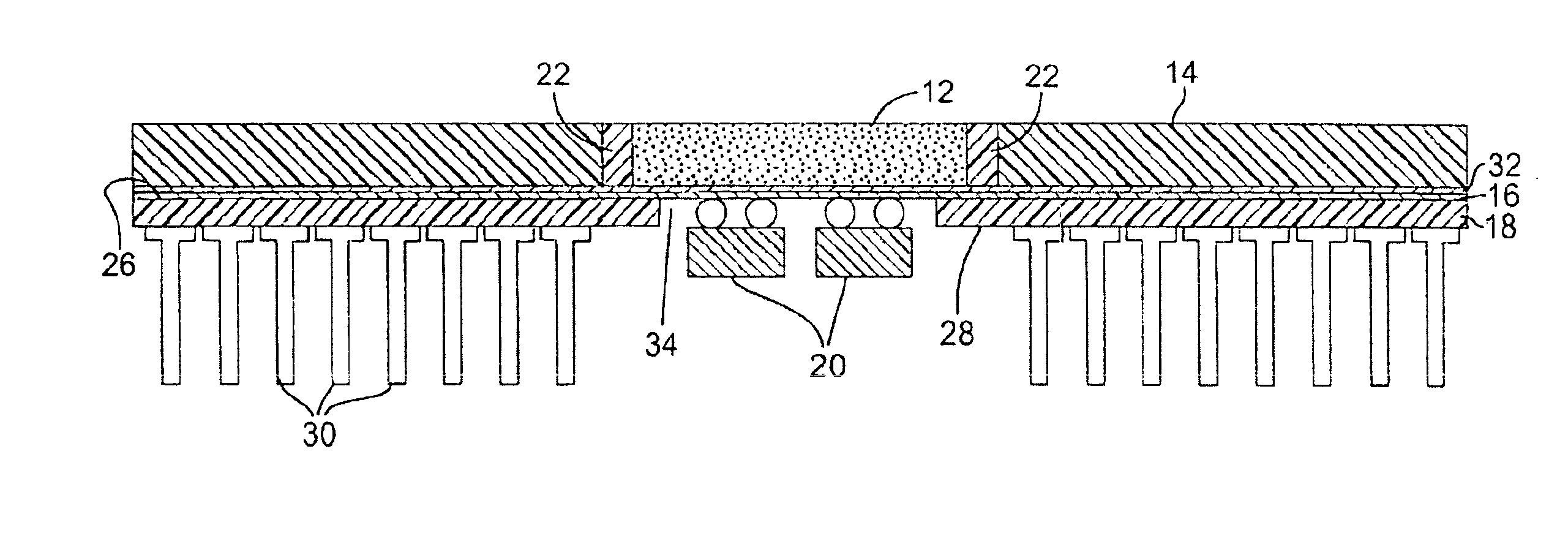

Semiconductor device assemblies and packages including multiple semiconductor device components

InactiveUS7573136B2Reduce area requirementsHelp positioningSemiconductor/solid-state device detailsSolid-state devicesContact padInterposer

A multidie semiconductor device assembly or package includes an interposer comprising a substrate with at least one receptacle therethrough. A plurality of semiconductor device components (e.g., semiconductor devices) may be assembled with the interposer. For example, at least one contact pad of a semiconductor device component adjacent to one surface of the interposer may be electrically connected to a corresponding contact pad of another semiconductor device component positioned adjacent to an opposite surface of the interposer. As another example, multiple semiconductor device components may be at least partially superimposed relative to one another and at least partially disposed within a receptacle of the interposer.

Owner:MICRON TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com