Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1258 results about "Chip size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

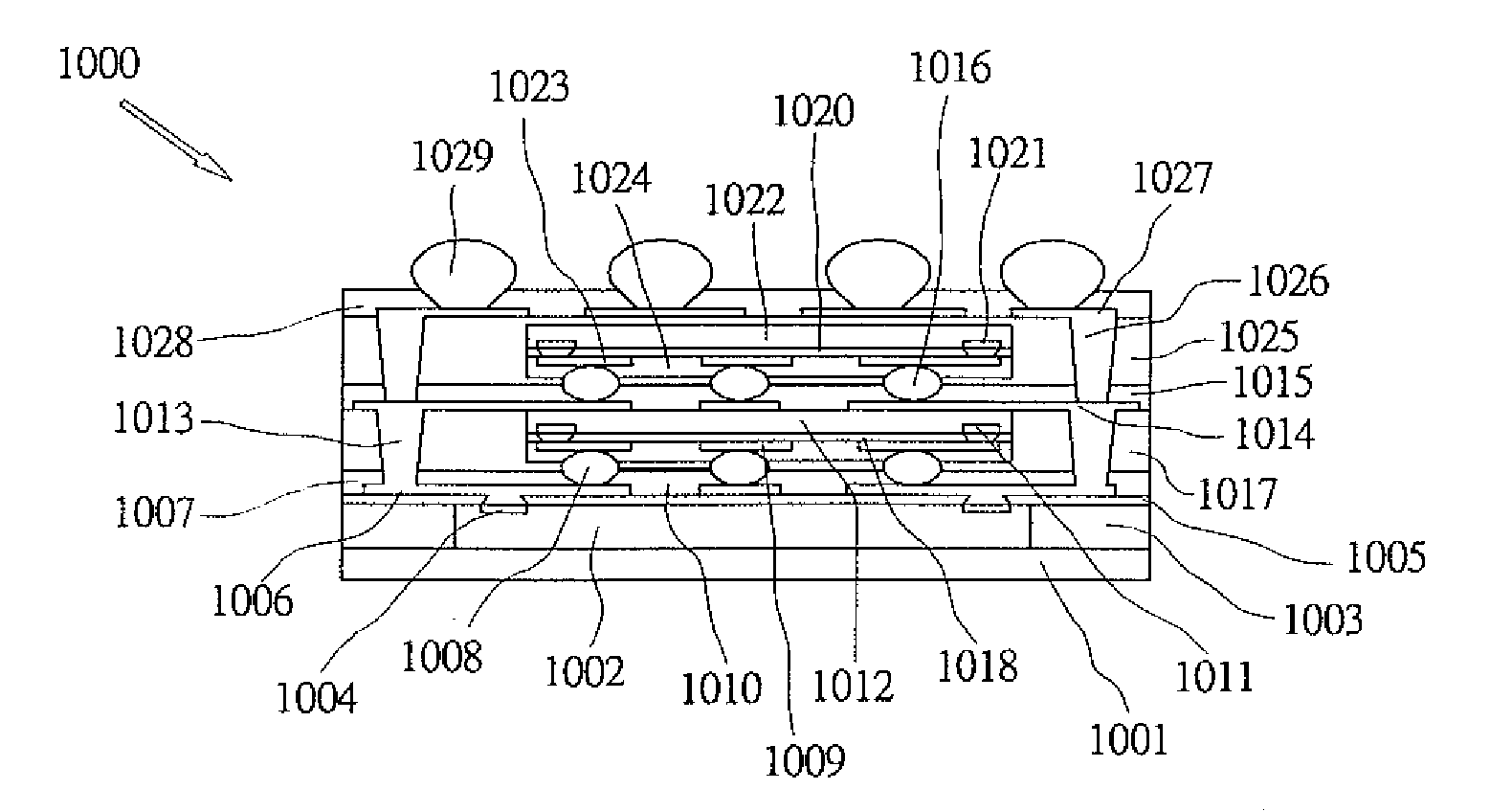

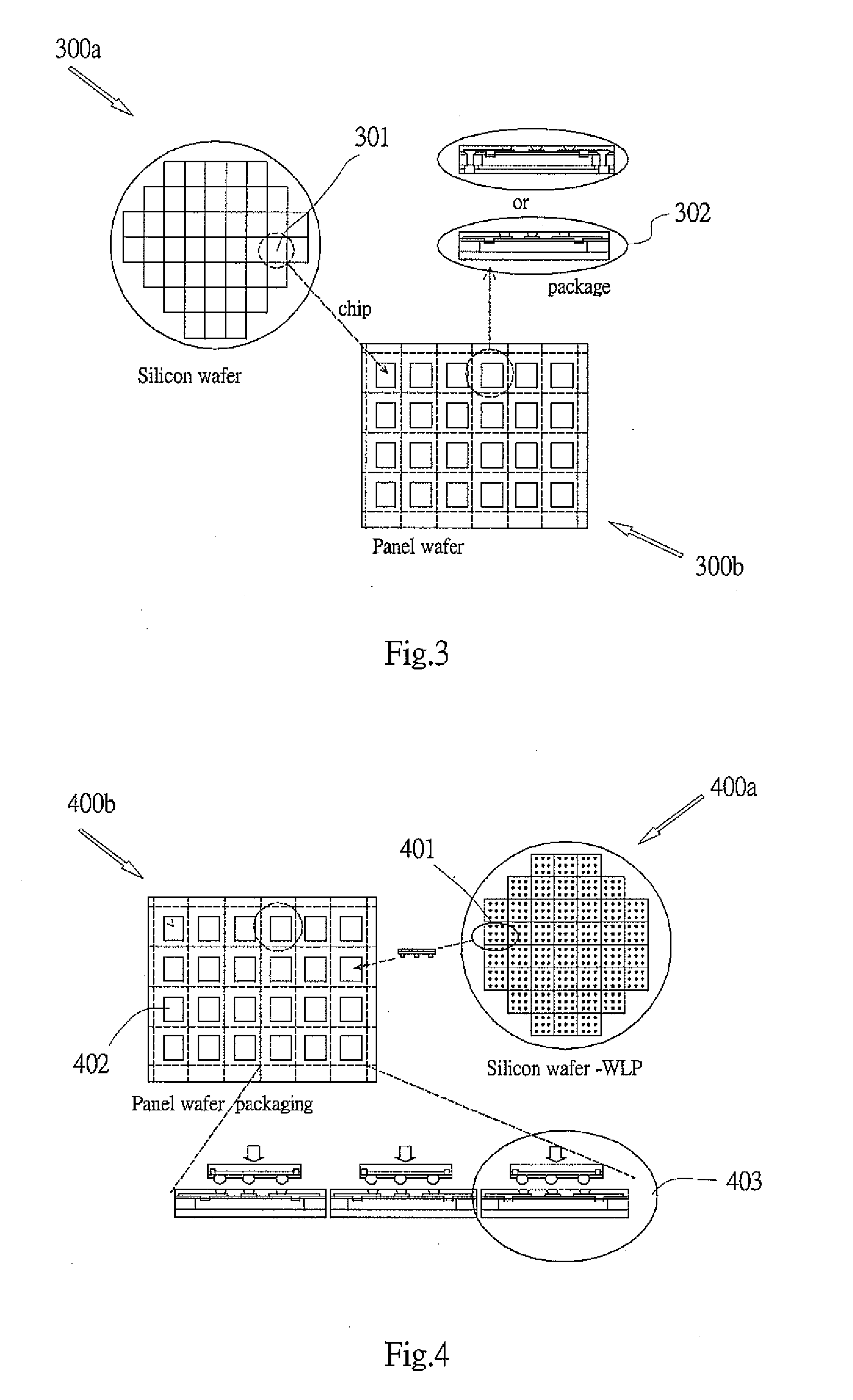

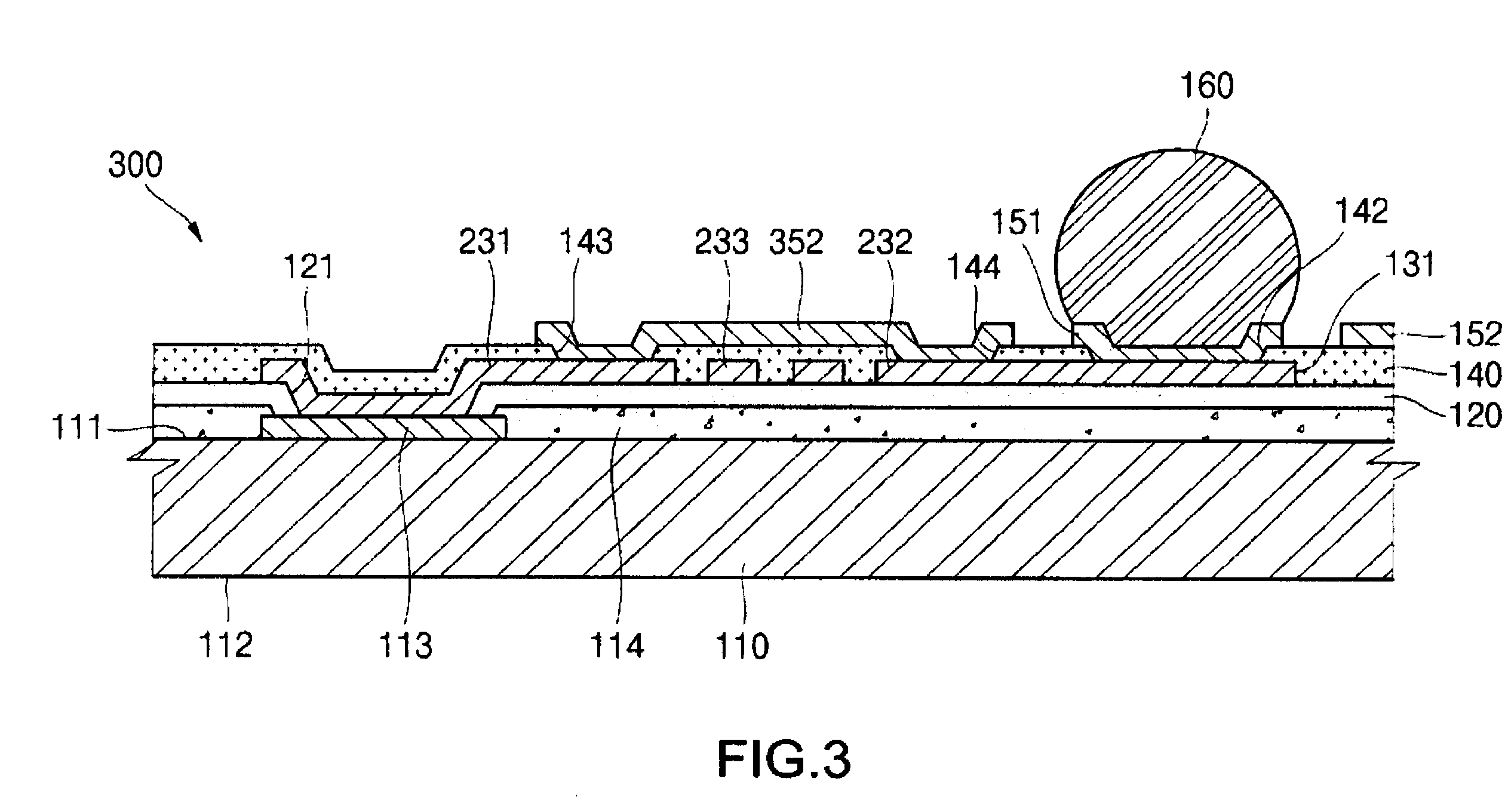

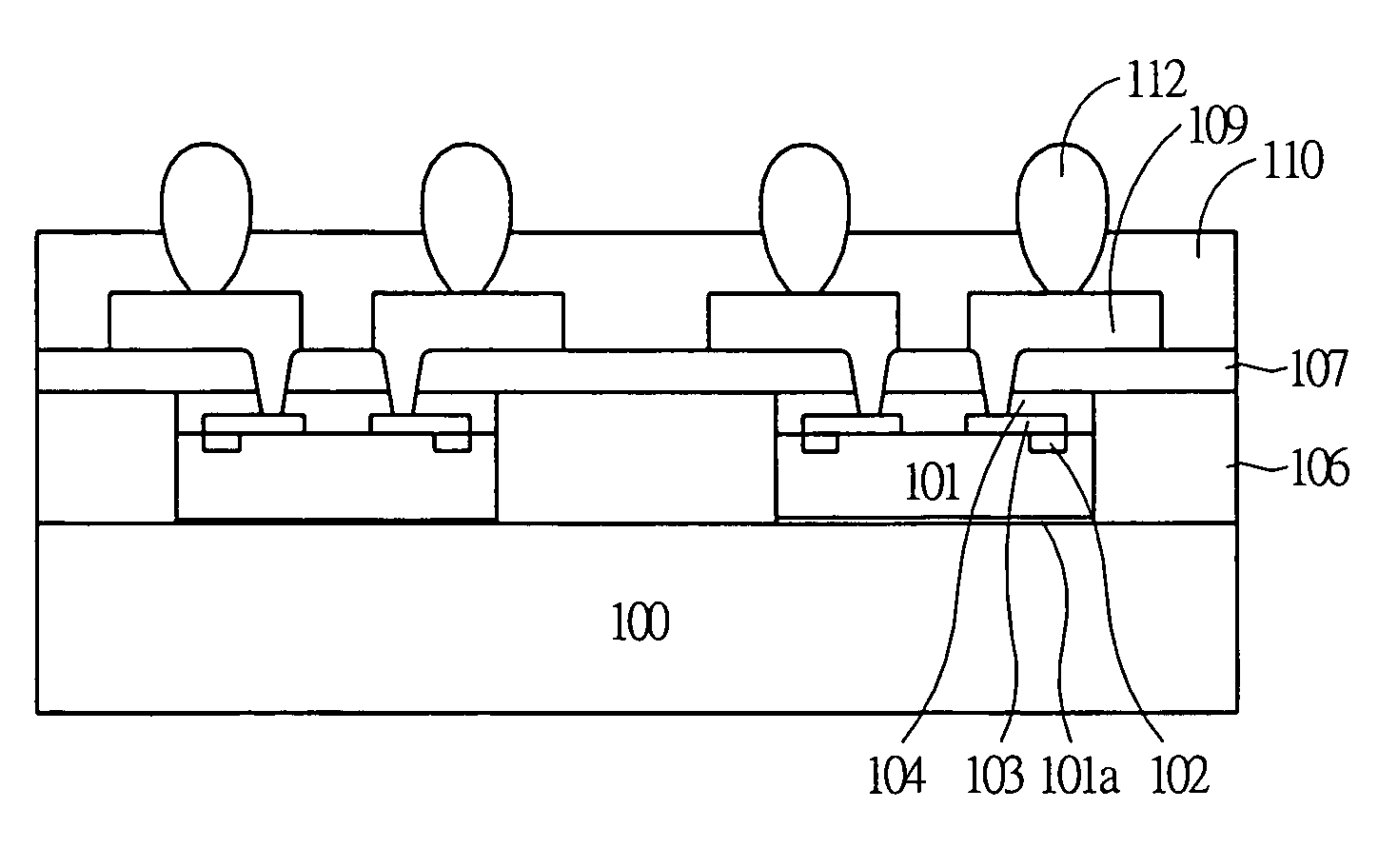

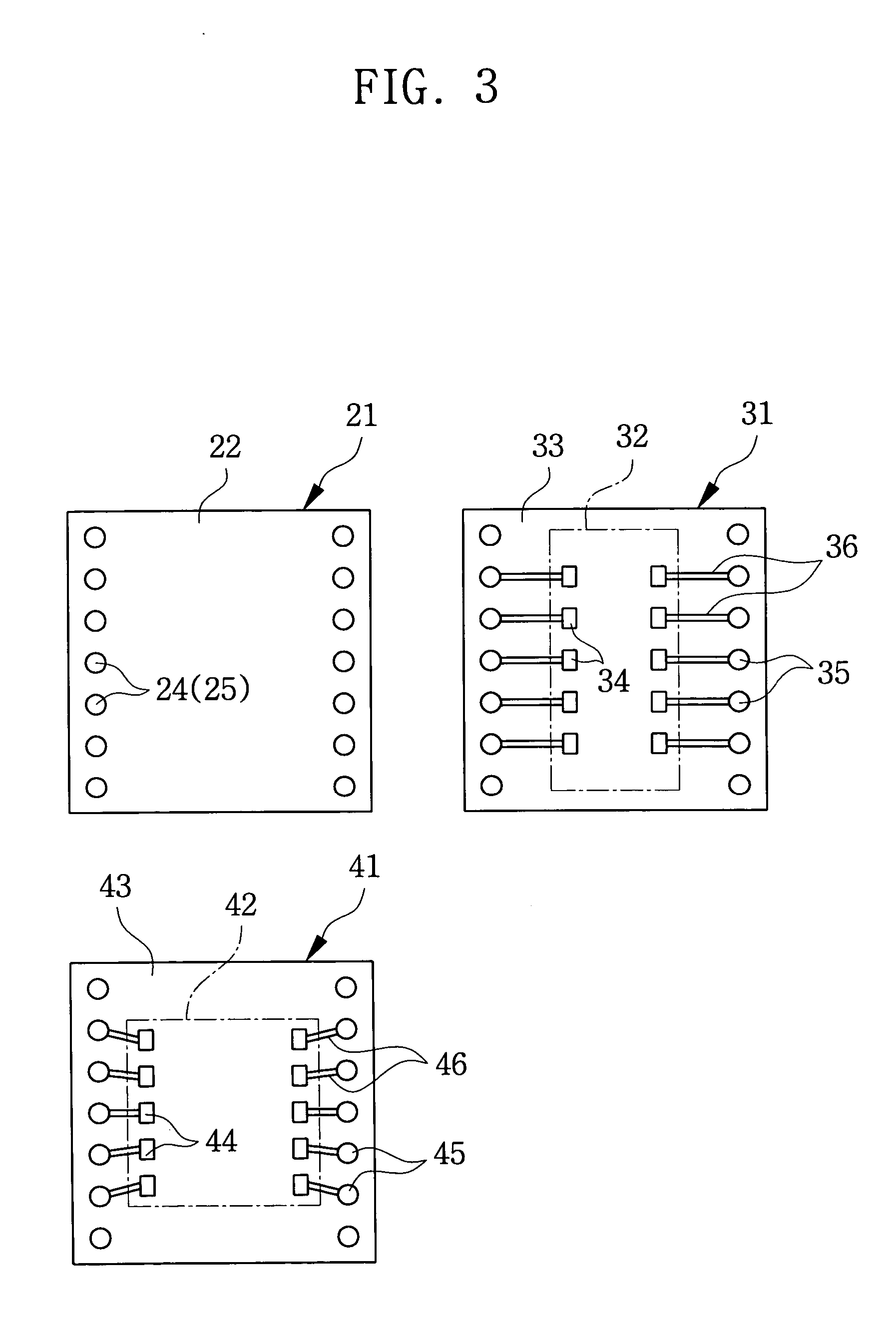

Wafer level stack structure for system-in-package and method thereof

ActiveUS7215033B2Semiconductor/solid-state device detailsSolid-state devicesChip sizeSystem in package

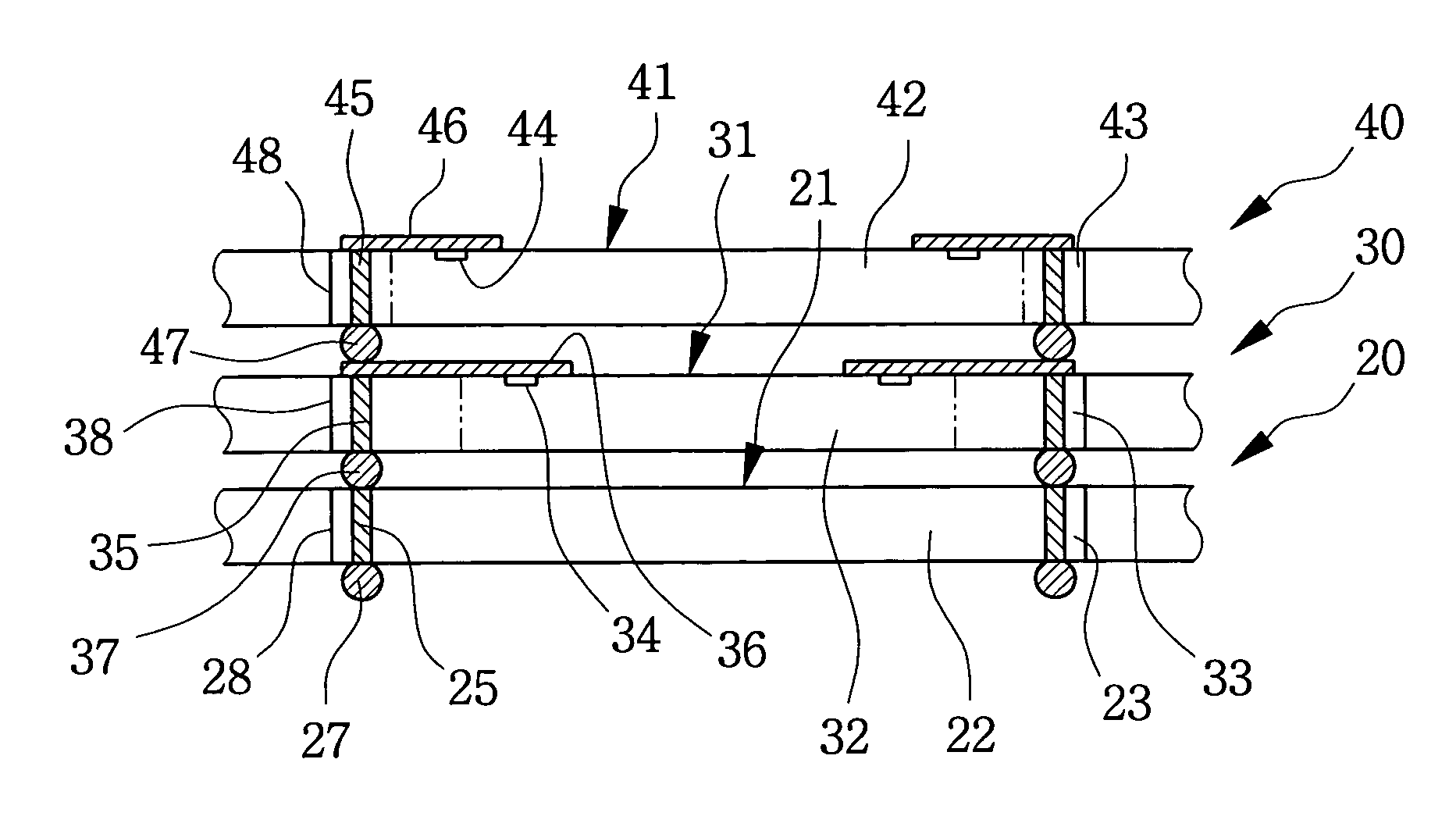

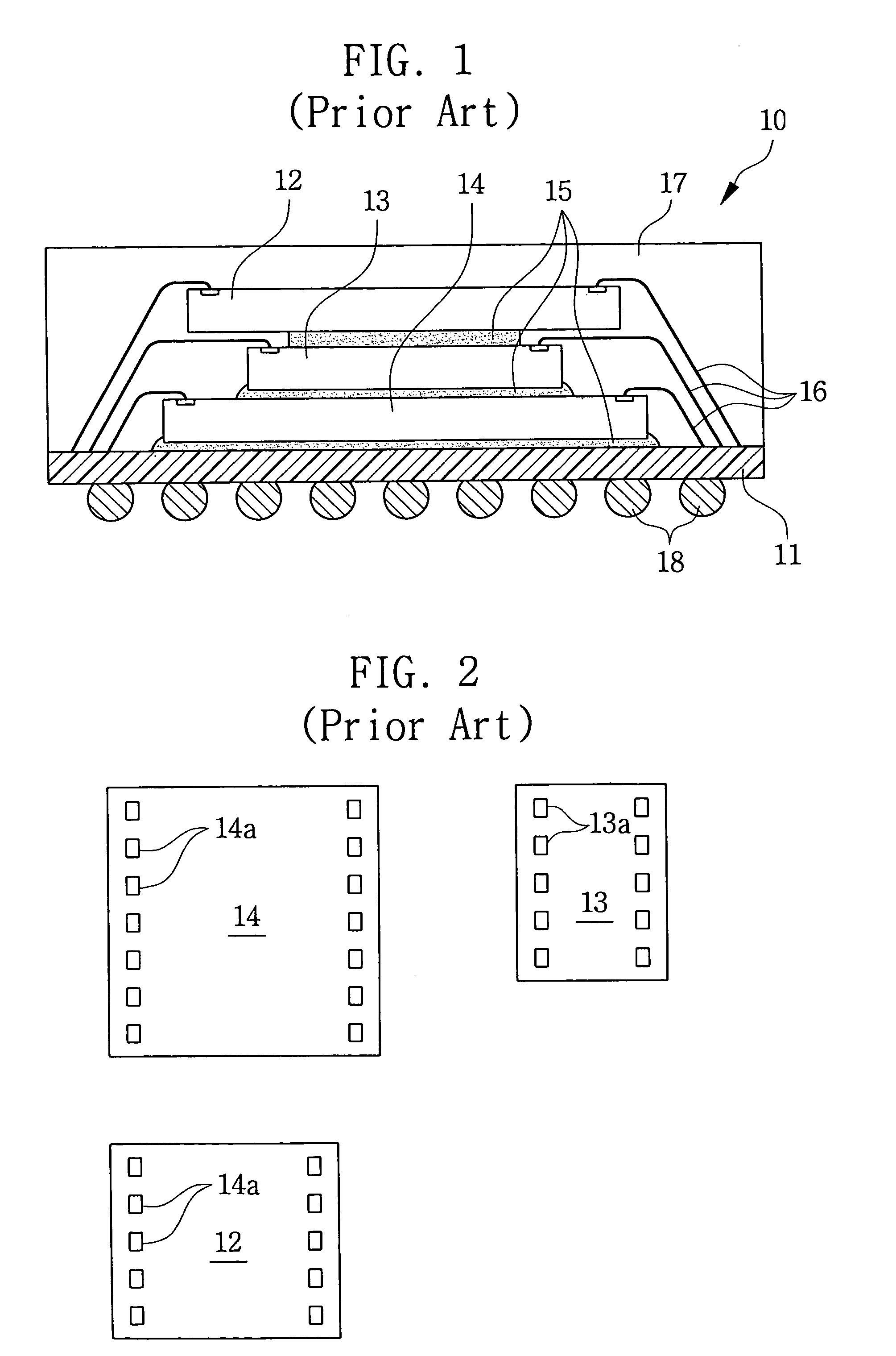

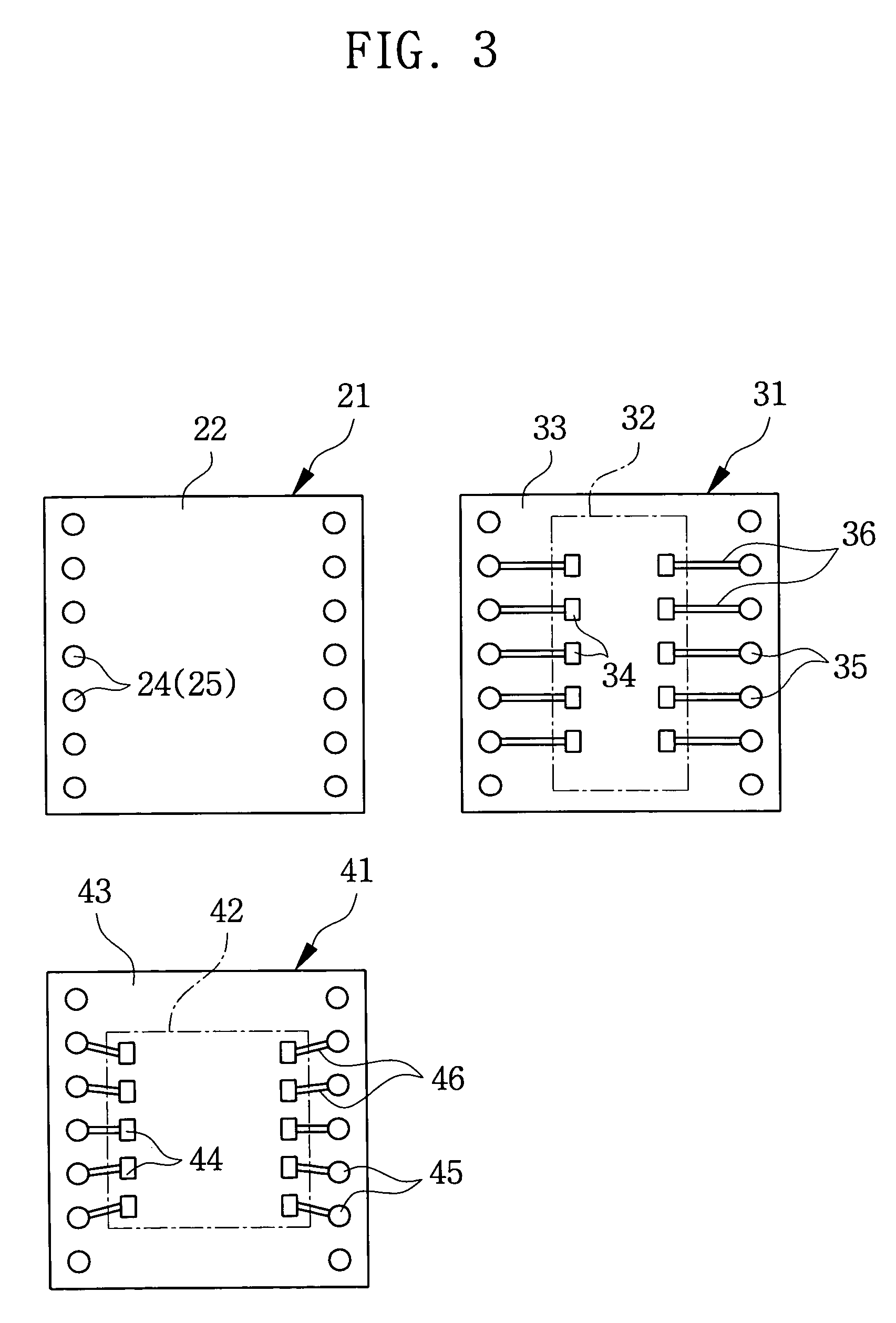

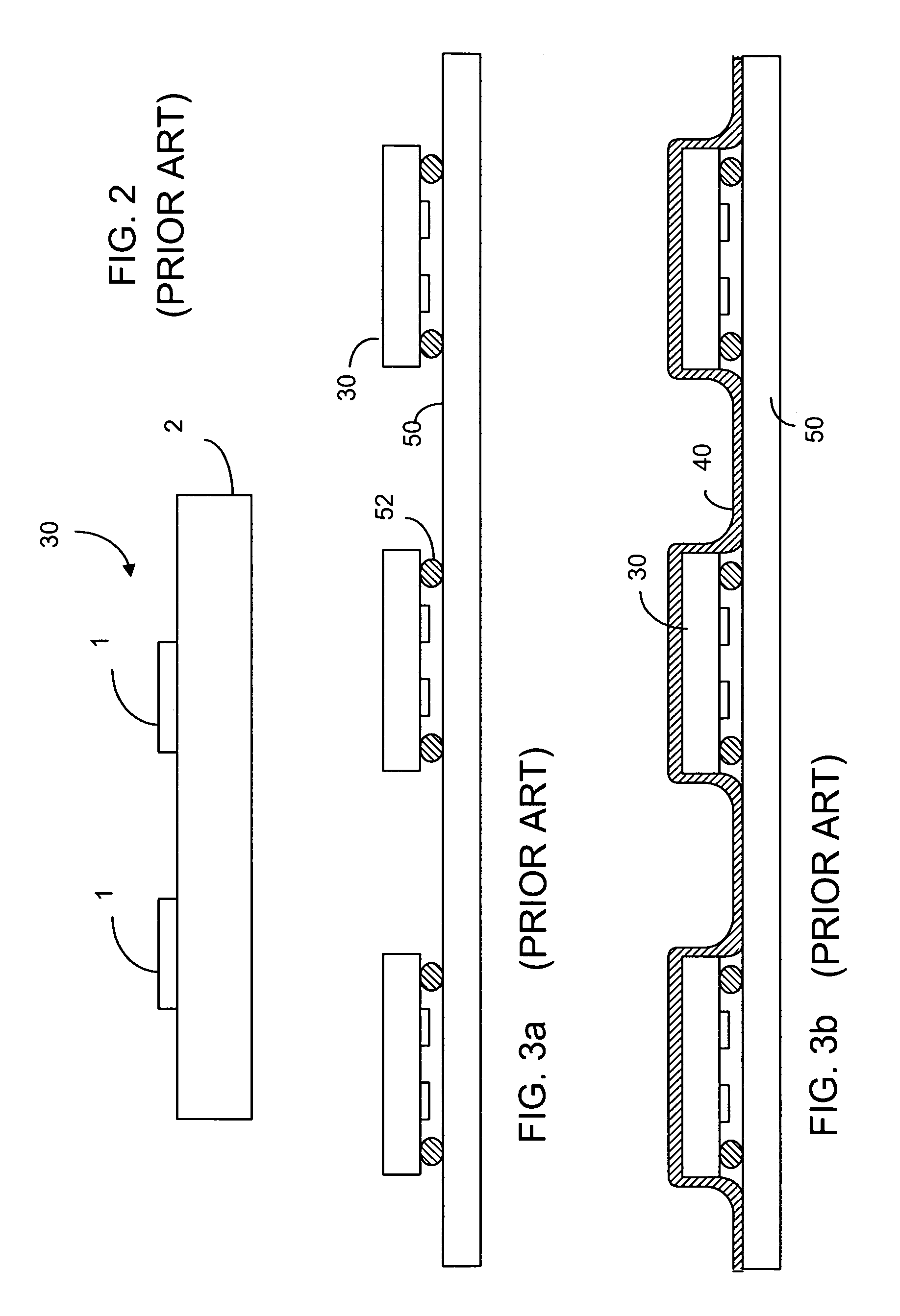

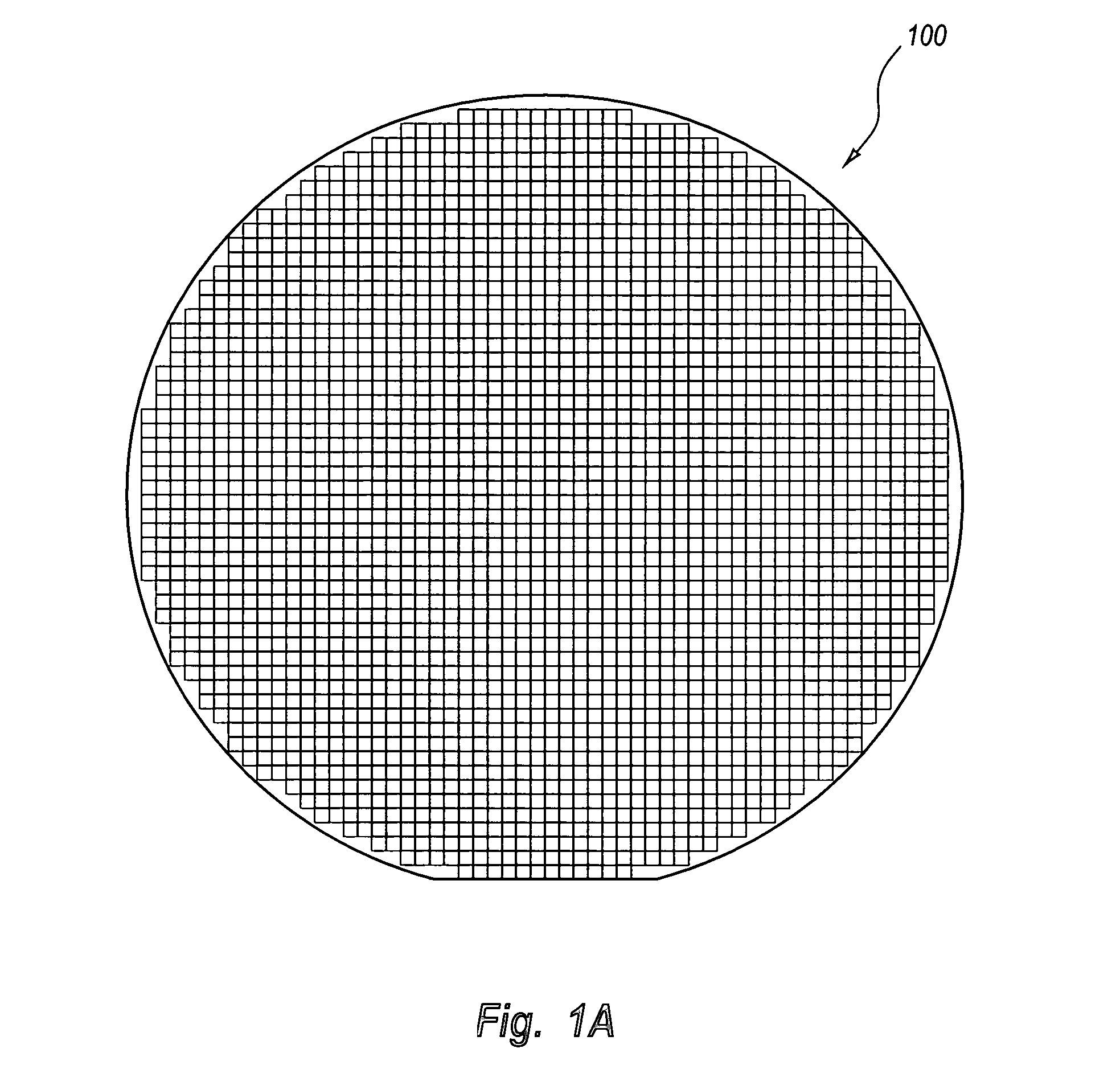

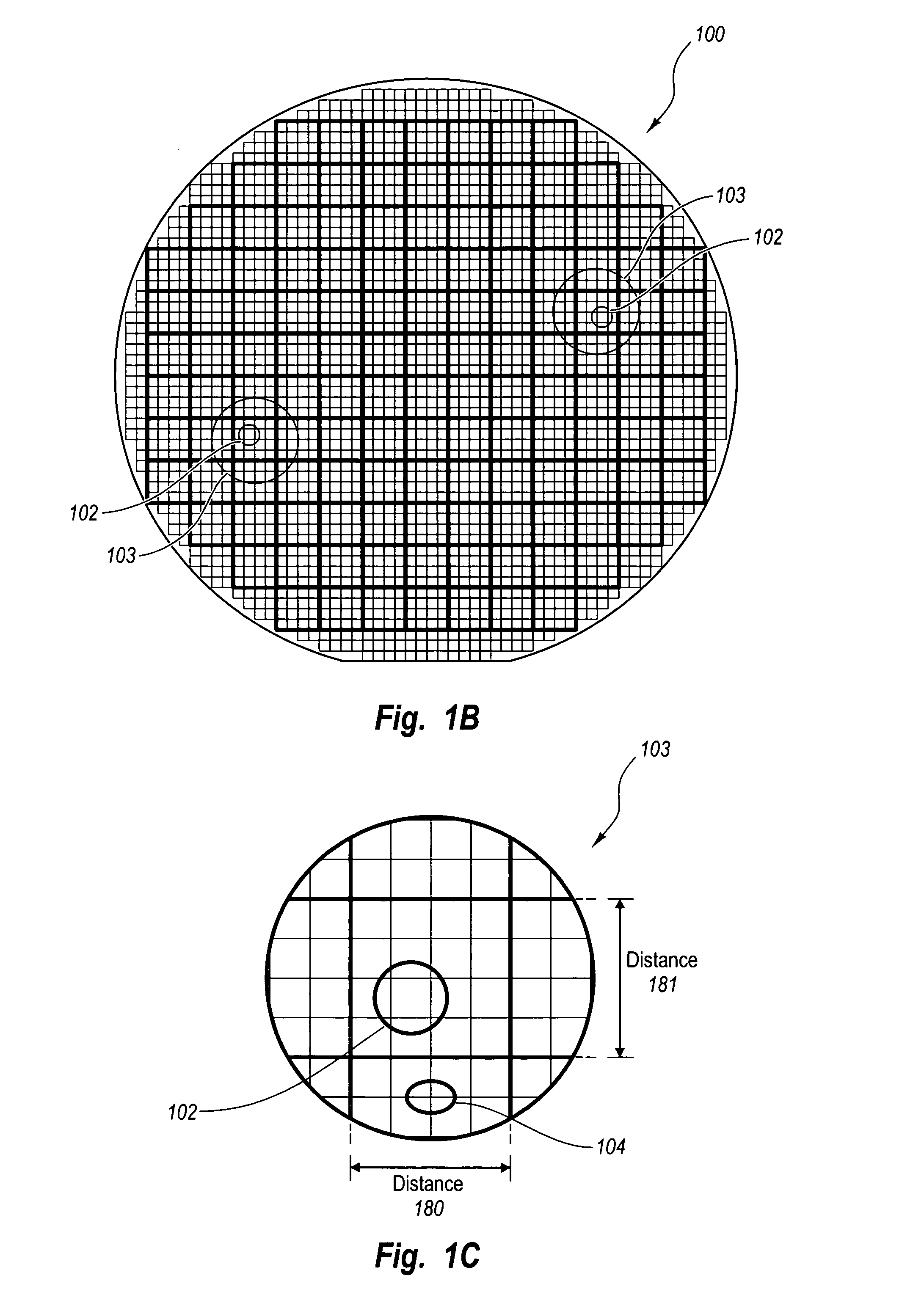

A wafer level stack structure, including a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, wherein the first wafer and the second wafer are stacked, and wherein the first wafer and the second wafer are coupled to each other. A method of forming a wafer level stack structure, including forming a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, forming a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, stacking the first wafer and the second wafer, and coupling the first wafer and the second wafer to each other. A system-in-package, including a wafer level stack structure including at least one first device chip with a first plurality of input / output (I / O) pads and at least one second device chip with a second plurality of I / O pads, and a common circuit board to which the wafer level stack structure is connected.

Owner:SAMSUNG ELECTRONICS CO LTD

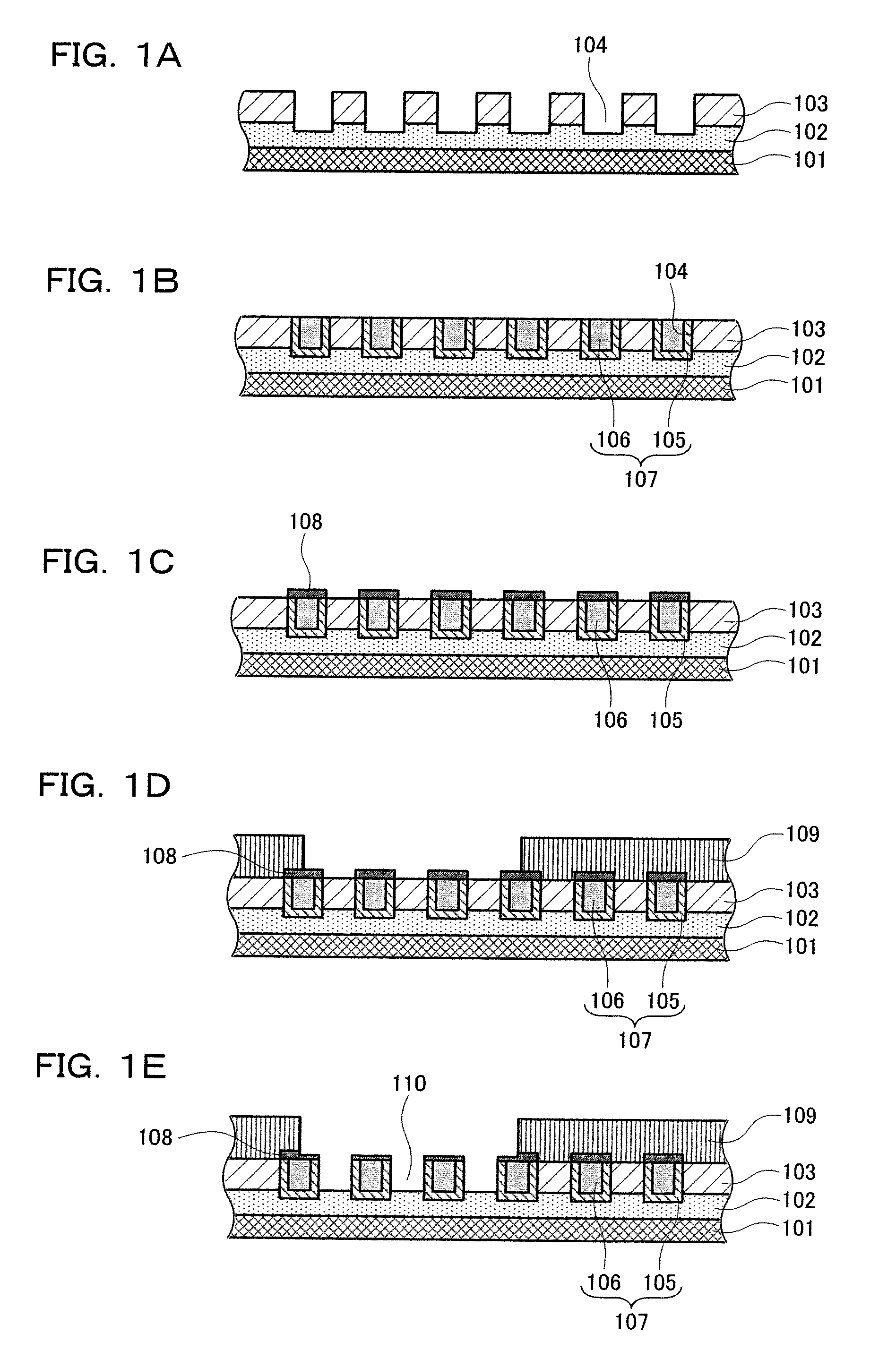

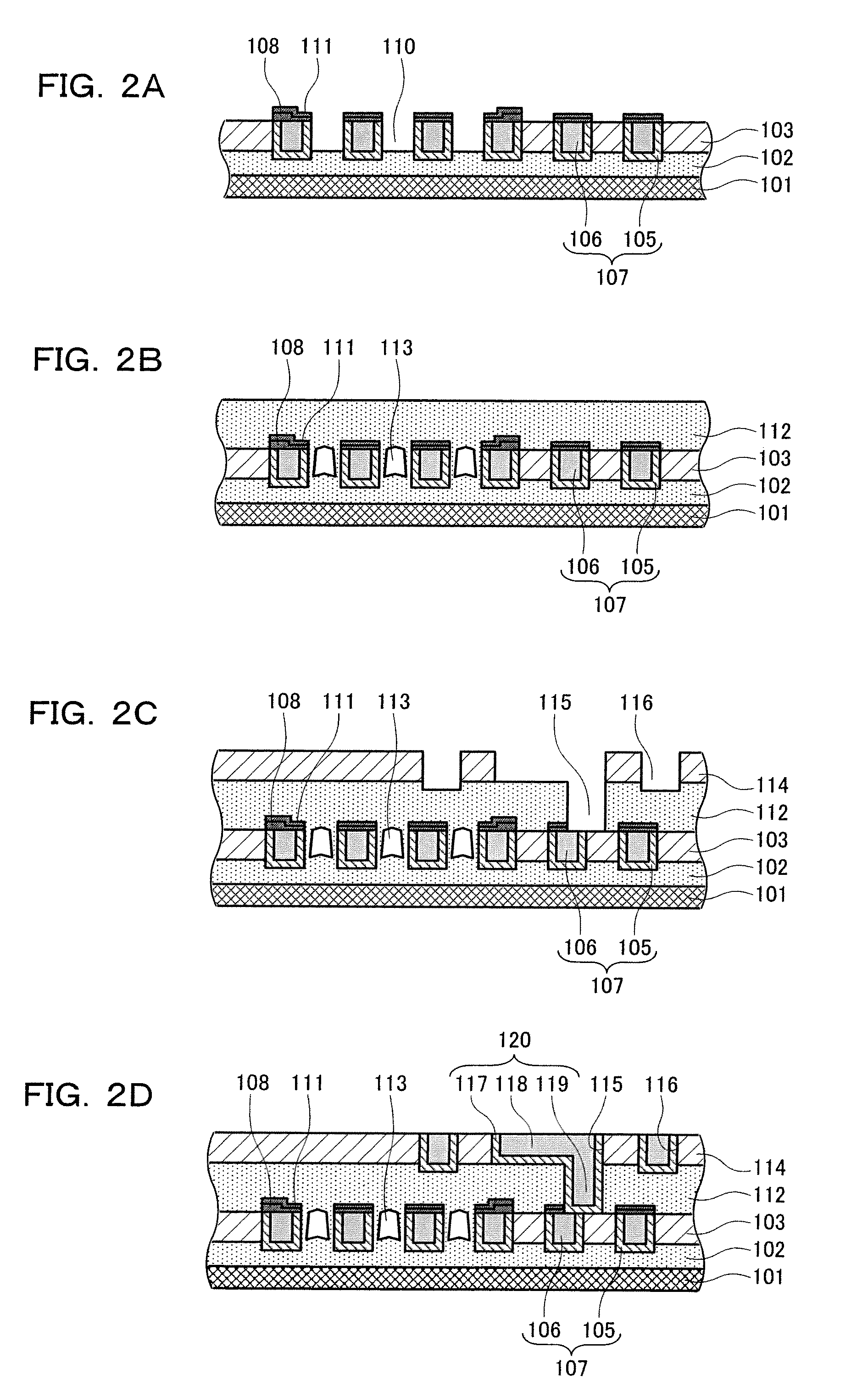

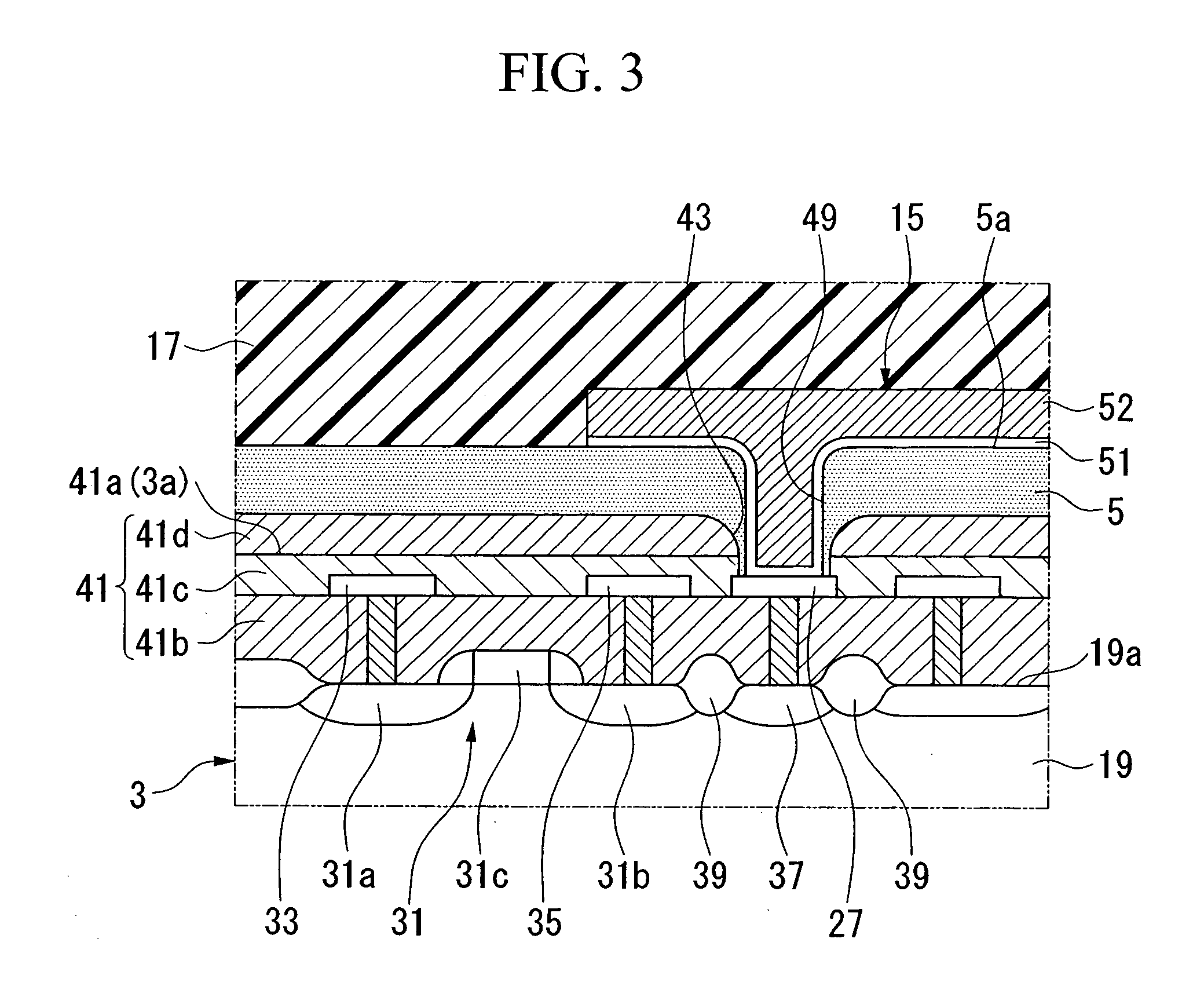

Method of manufacturing semiconductor device

ActiveUS20080299758A1Reduces yield and reliabilityReduce capacitySemiconductor/solid-state device detailsSolid-state devicesHigh densityDevice material

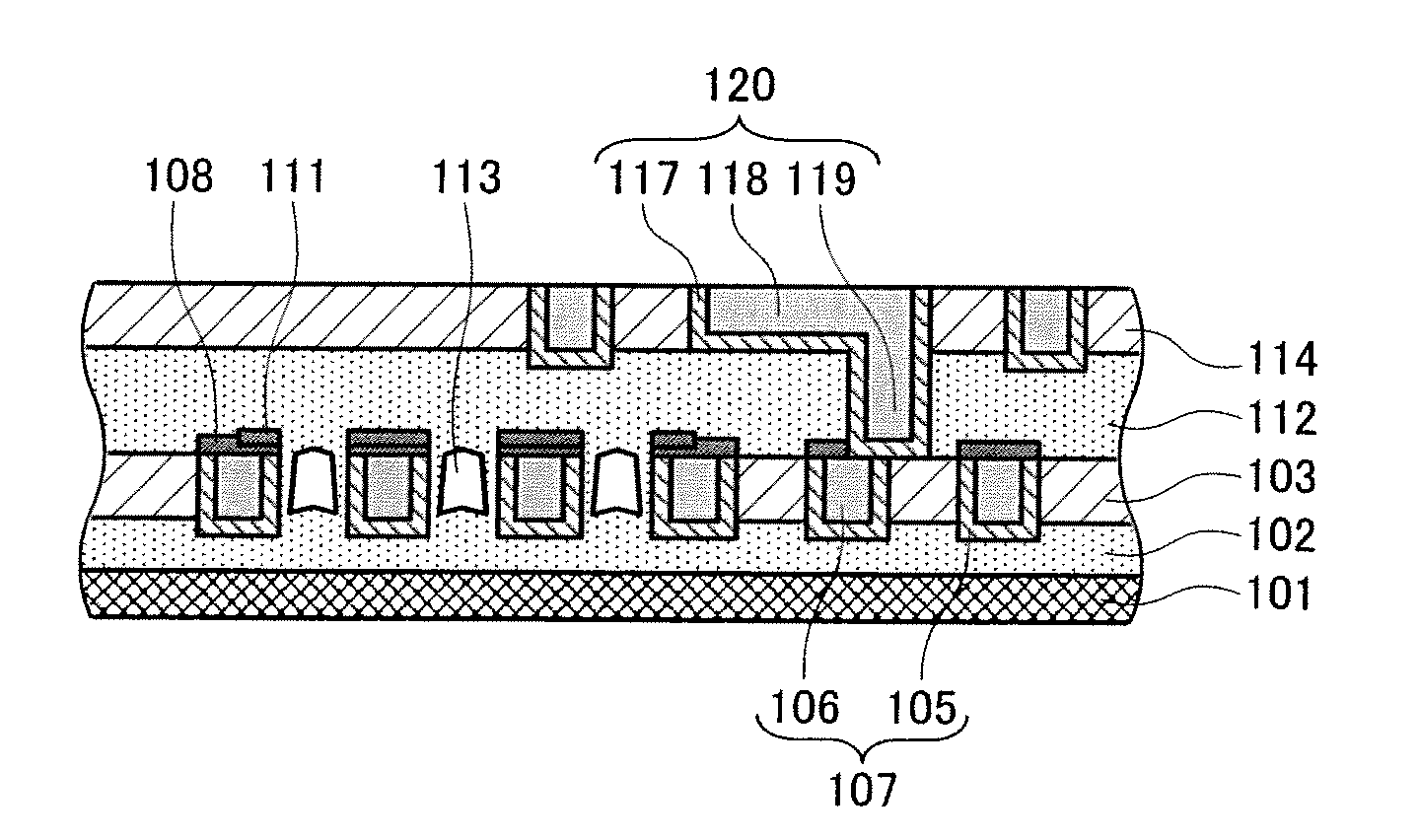

A high-density N-type diffusion layer 116 formed in a separation area 115 makes it possible to reduce a collector current flowing through a parasitic NPN transistor 102. Thus, a normal CMOS process can be used to provide a driving circuit and a data line driver which make it possible to improve resistance to possible noise occurring between adjacent terminals, while controlling a chip size.

Owner:PANNOVA SEMIC

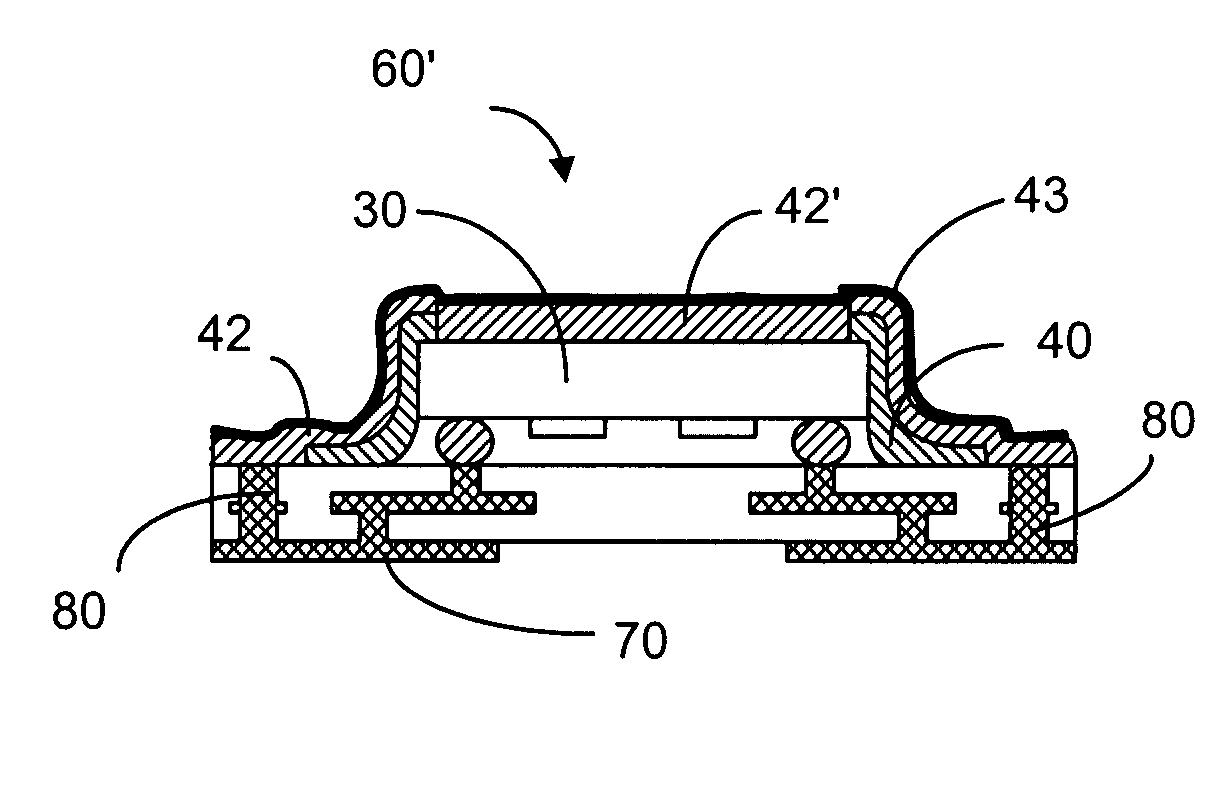

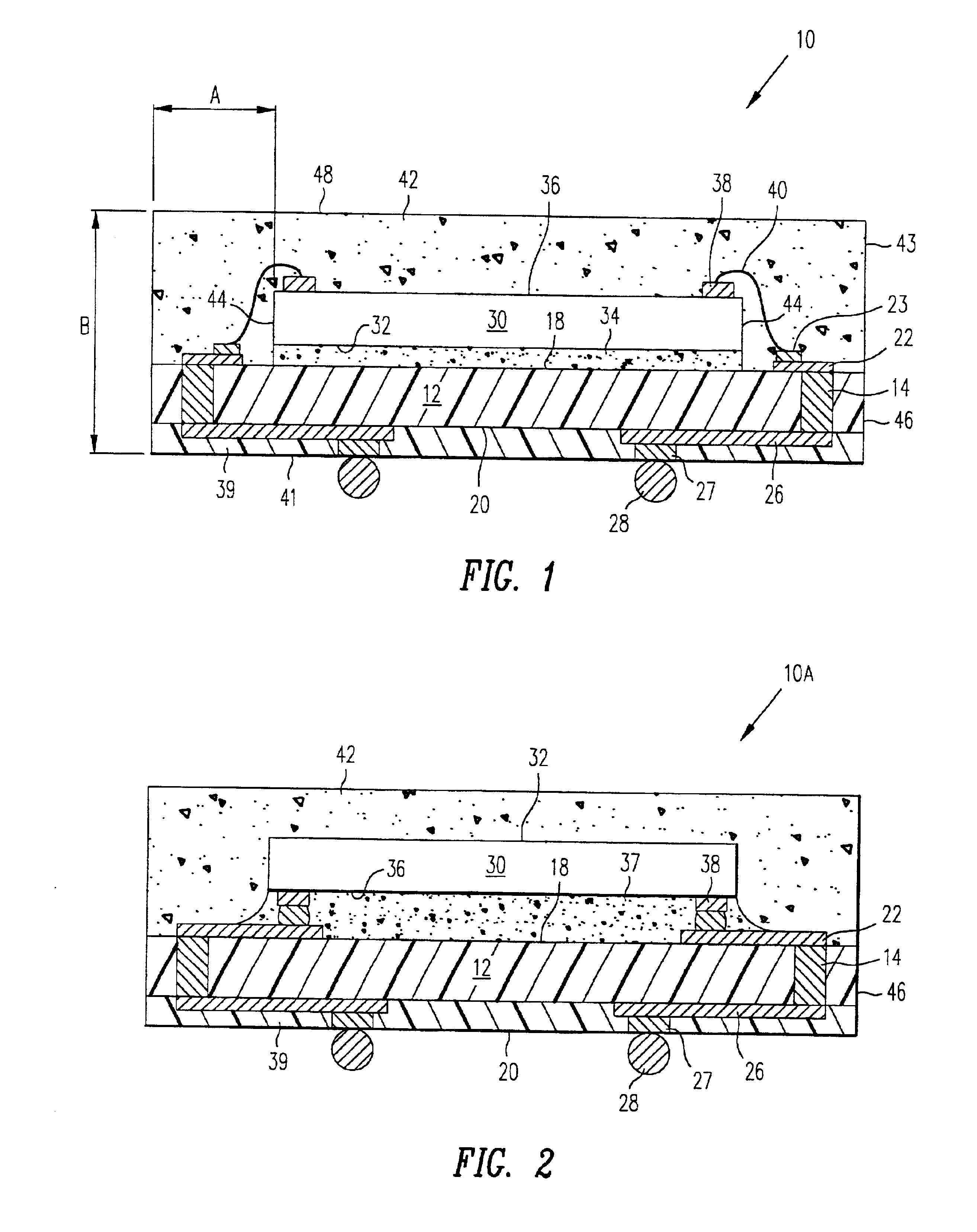

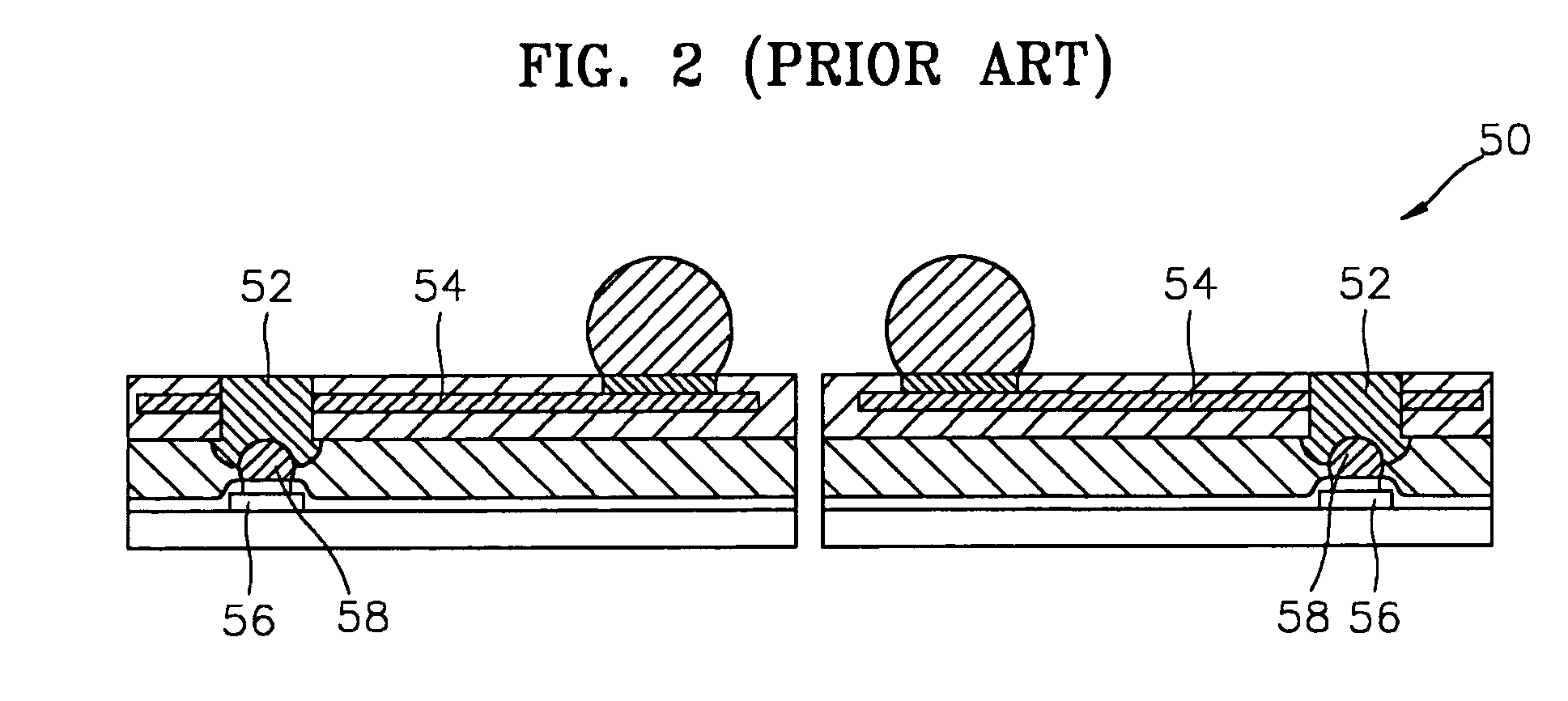

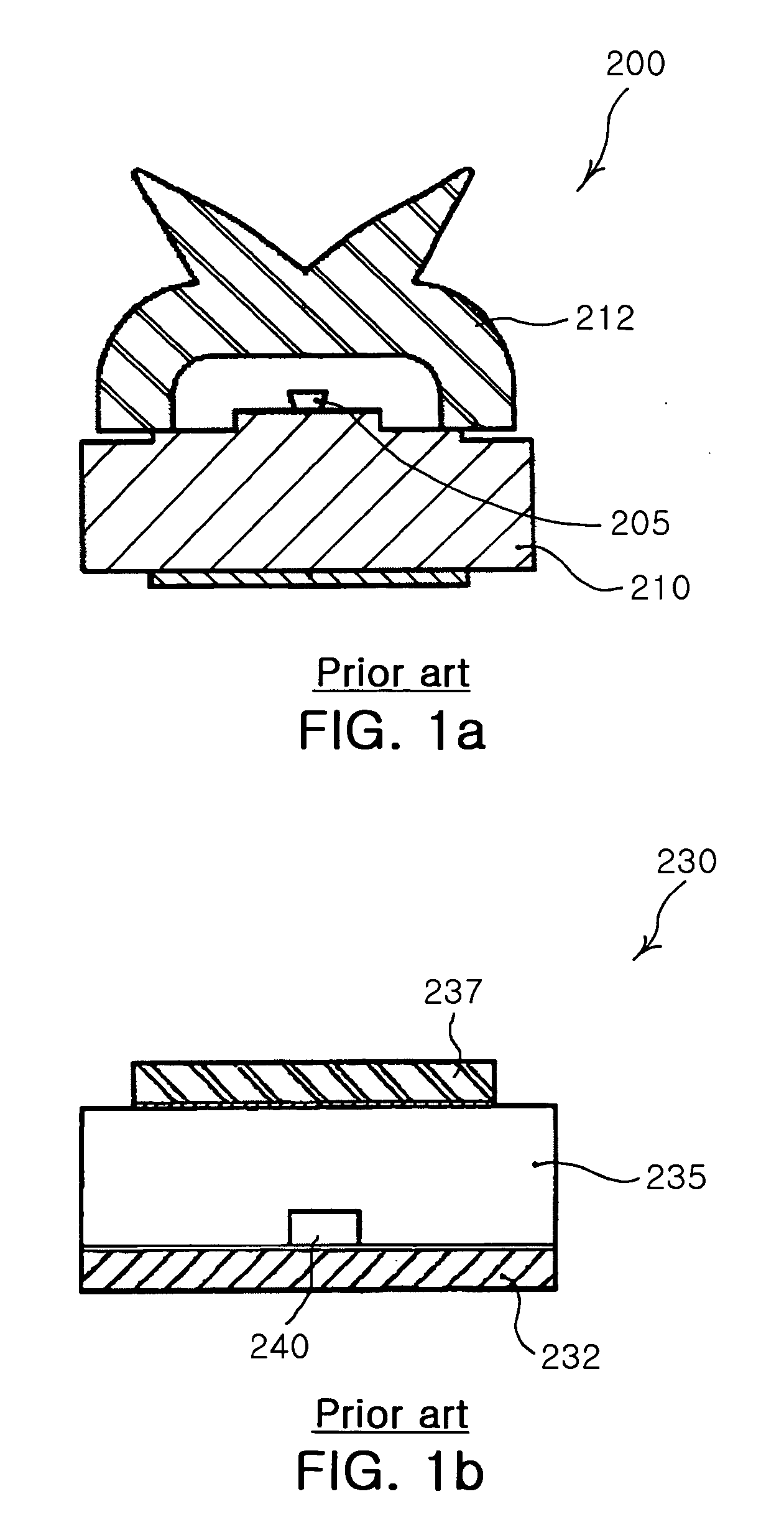

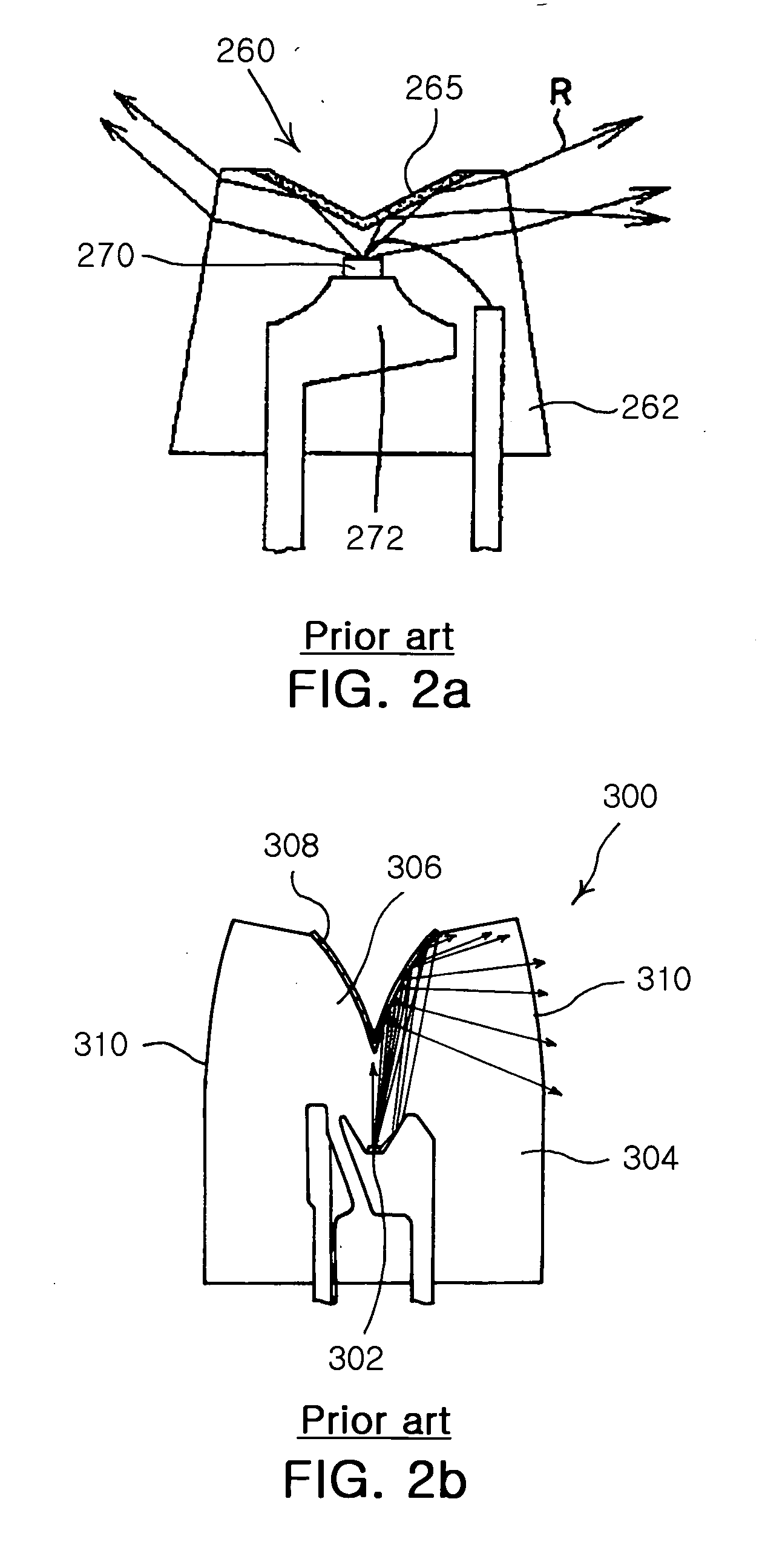

Encapsulated electronics device with improved heat dissipation

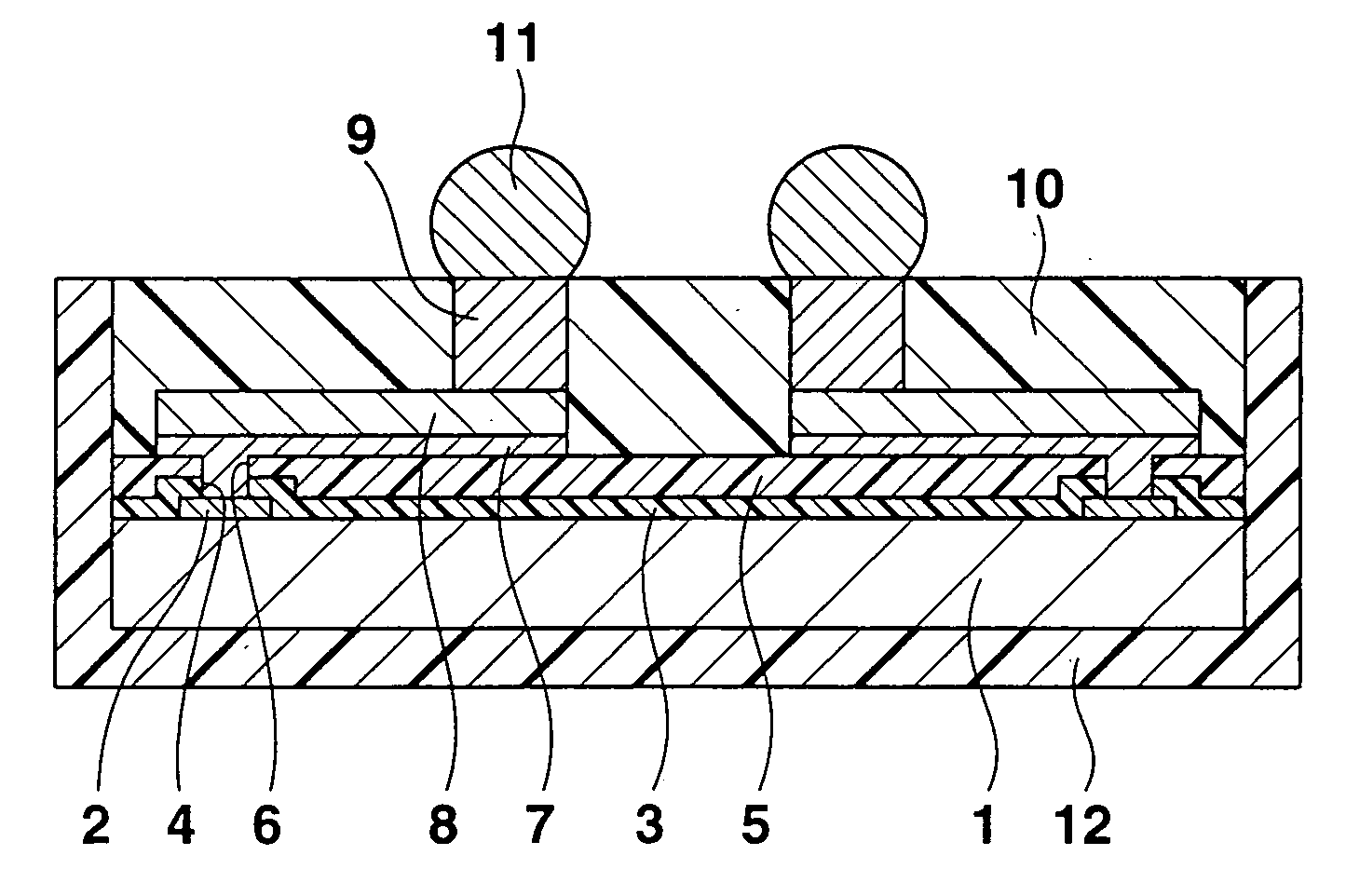

ActiveUS6992400B2Improve cooling effectImpedence networksSemiconductor/solid-state device detailsHermetic sealHeat conducting

A method for improving heat dissipation in an encapsulated electronic package usually referred to as a chip-size SAW package. The package comprises one or more acoustic-wave components fabricated on a die, which is disposed on an electrically non-conductive carrier separated by electrically conducting bumps. The top of the package is covered by a laminate and a hermetic seal layer. Heat dissipation can be improved by removing a part of the laminate and then depositing a layer of thermal conducting material on the package, and by providing one or more heat conducting paths through the carrier.

Owner:NOKIA CORP

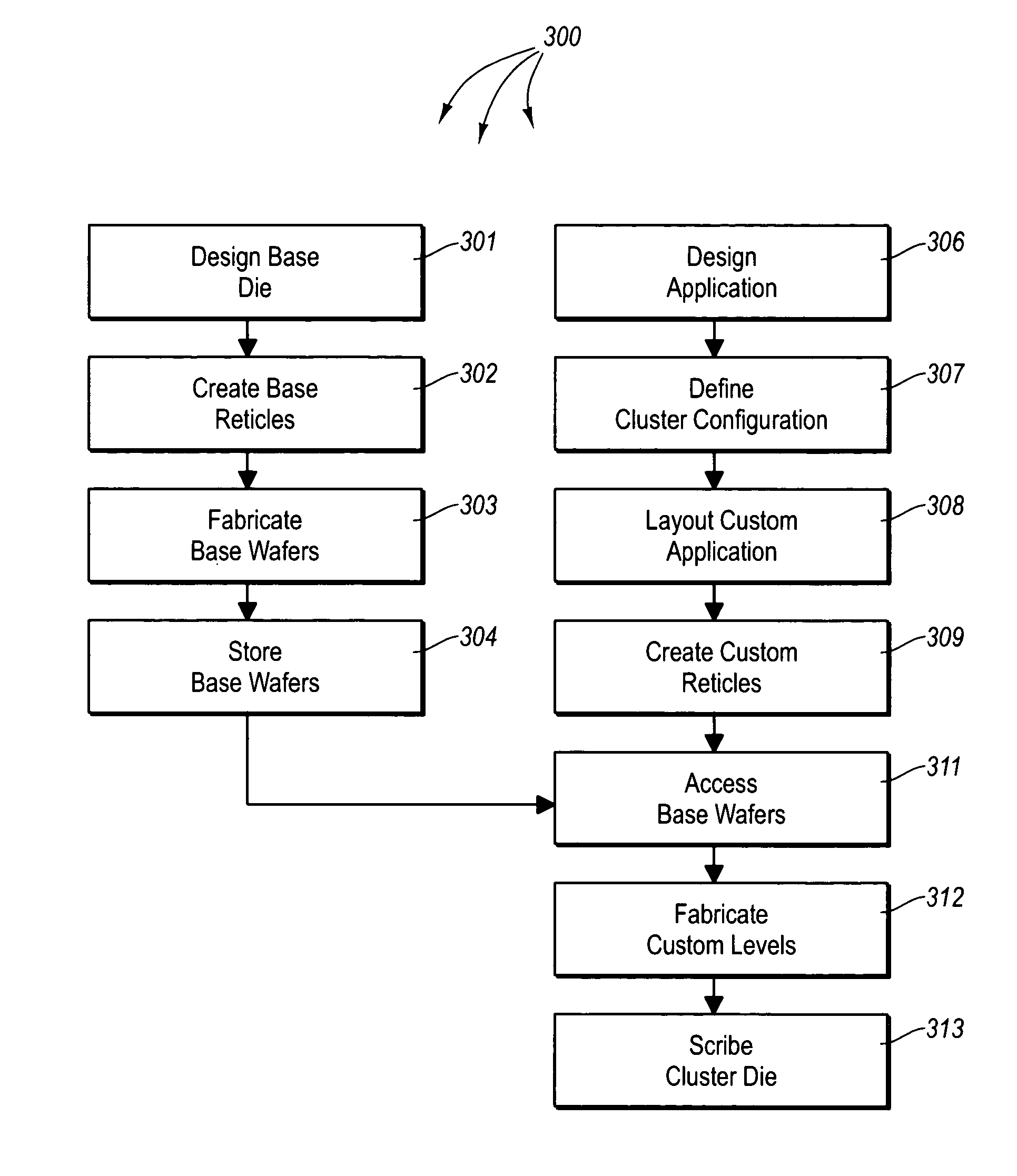

Structured ASIC device with configurable die size and selectable embedded functions

ActiveUS7337425B2Reduce the numberReduce tooling costsSemiconductor/solid-state device detailsSolid-state devicesGeneral purposeChip size

One embodiment of the present invention provides for a master or universal base and base tooling which addresses the general purpose Structured ASIC requirements. Another embodiment of the present invention provides for a common set of base tooling from which the master / universal base is created as well as additional custom bases with customized selection and quantity of embedded Platform ASIC functions. Embodiments can utilize conventional Structured ASIC architecture and processing and are compatible with traditional probing and packaging.

Owner:SEMICON COMPONENTS IND LLC

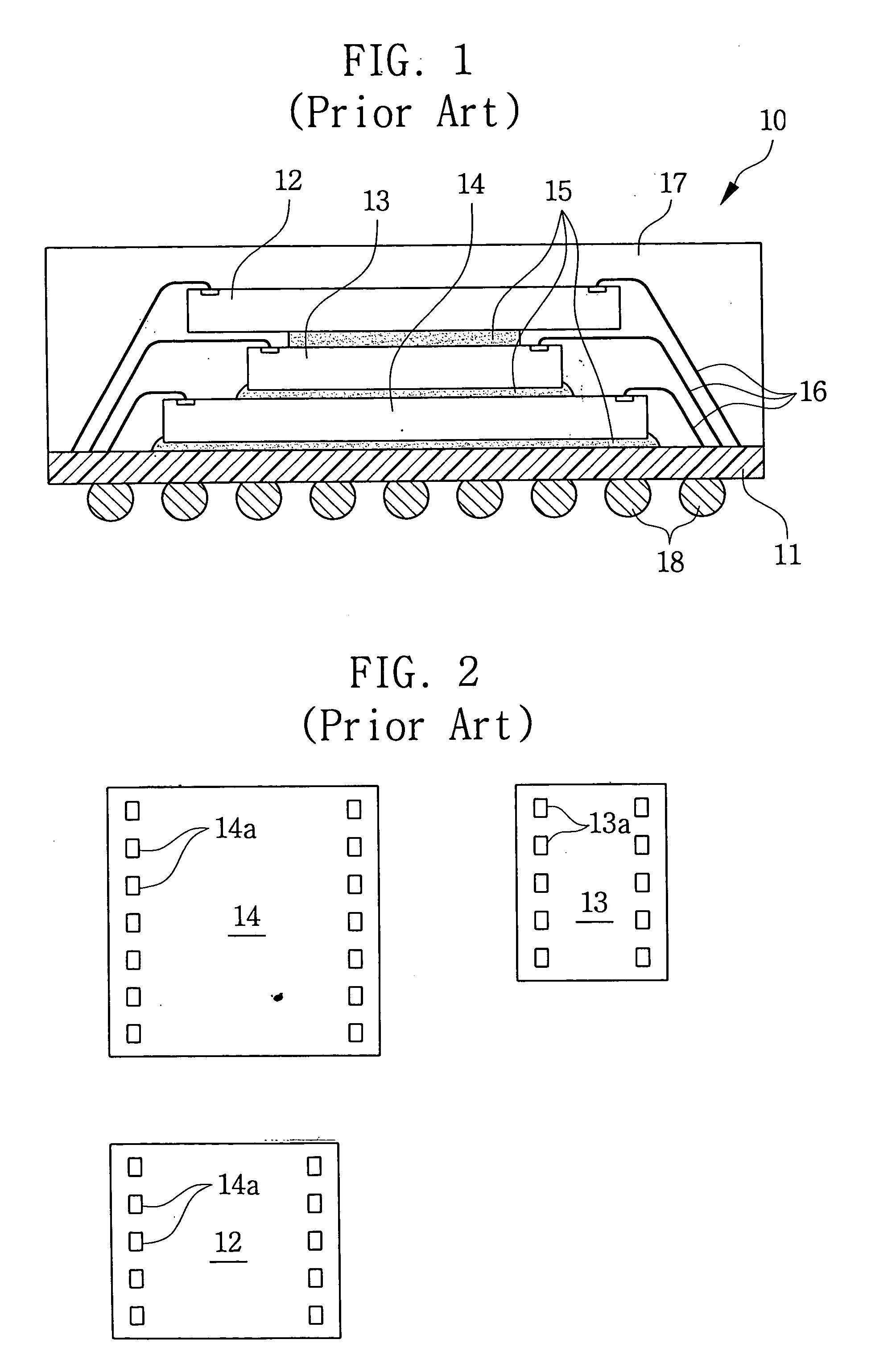

Multi-chip package structure and method of forming the same

InactiveUS20080136004A1Avoid problemsIncrease productionSemiconductor/solid-state device detailsSolid-state devicesChip sizeChip-scale package

To pick and place standard first chip size package on a base with a second chip for obtaining an appropriate stacking chip size package than the original chip size package. The package structure has a larger chip size package than the size of the traditional stacking package. Moreover, the terminal pins of the flip chip package may be located on peripheral of LGA package or on array of BGA package.

Owner:ADVANCED CHIP ENG TECH

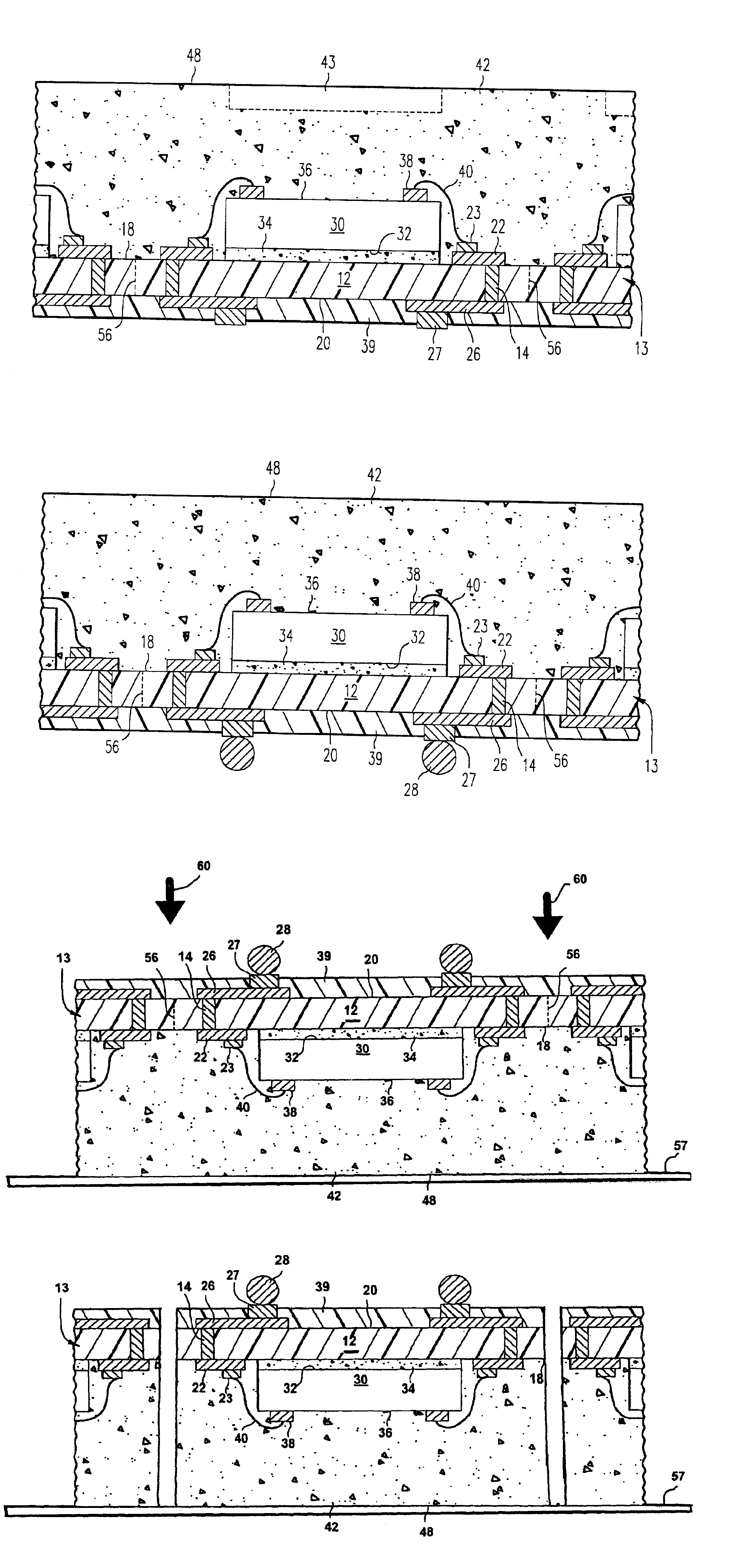

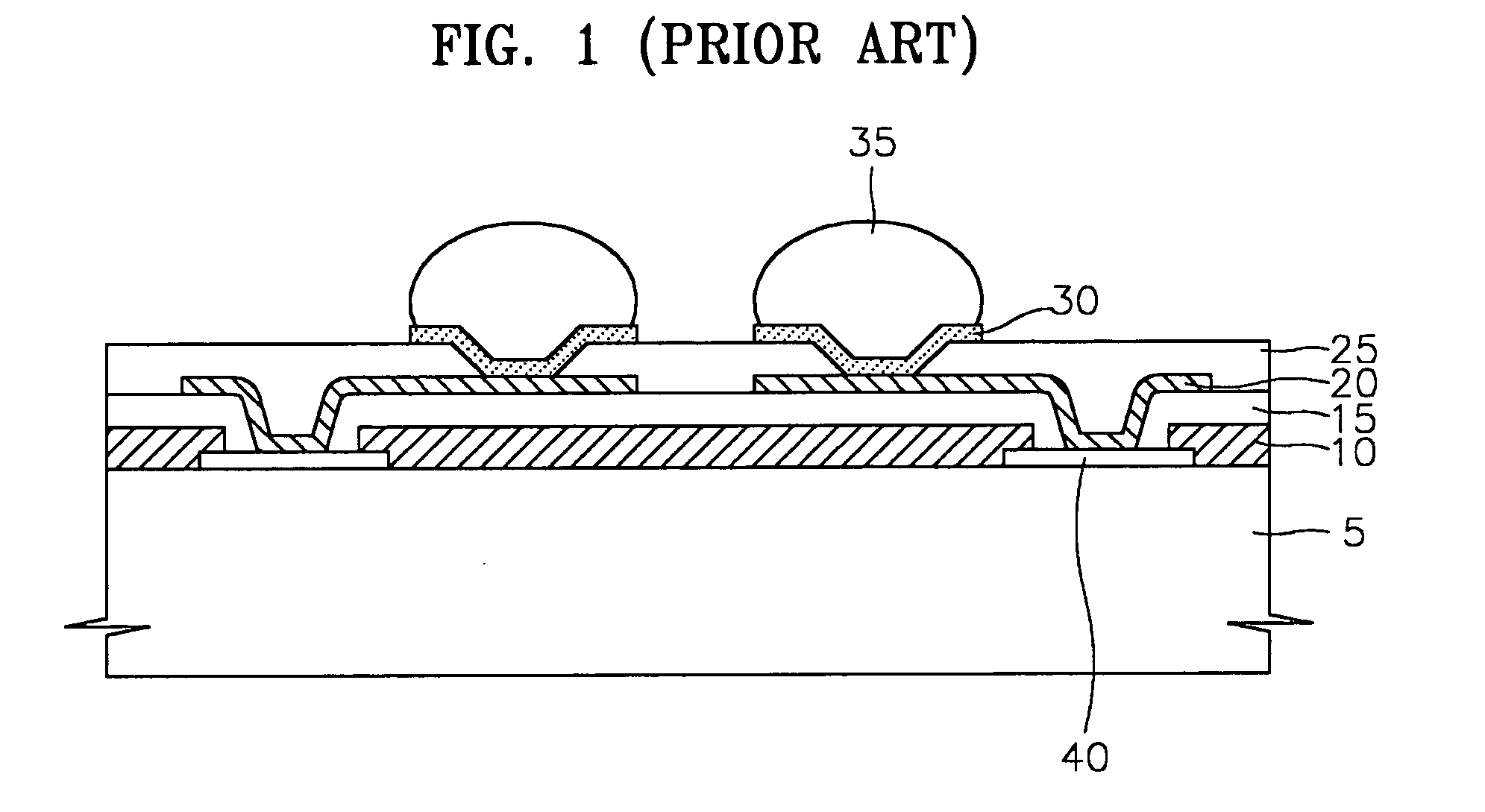

Method of making near chip size integrated circuit package

InactiveUS6962829B2Avoid radiationLow costPrinted circuit assemblingSemiconductor/solid-state device detailsChip sizeEngineering

A plurality of integrated circuit chip (IC chip) packages are fabricated simultaneously from a single insulating substrate having sections. In each section, an IC chip is attached. Bonding pads on the IC chip are electrically connected to first metallizations on a substrate first surface. The first metallizations, IC chip including bonding pads and first substrate surface are then encapsulated. Interconnection balls or pads are formed at substrate bonding locations on a substrate second surface, the interconnection pads or balls being electrically connected to corresponding first metallizations. The substrate and encapsulant are then cut along the periphery of each section to form the plurality of IC chip packages.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

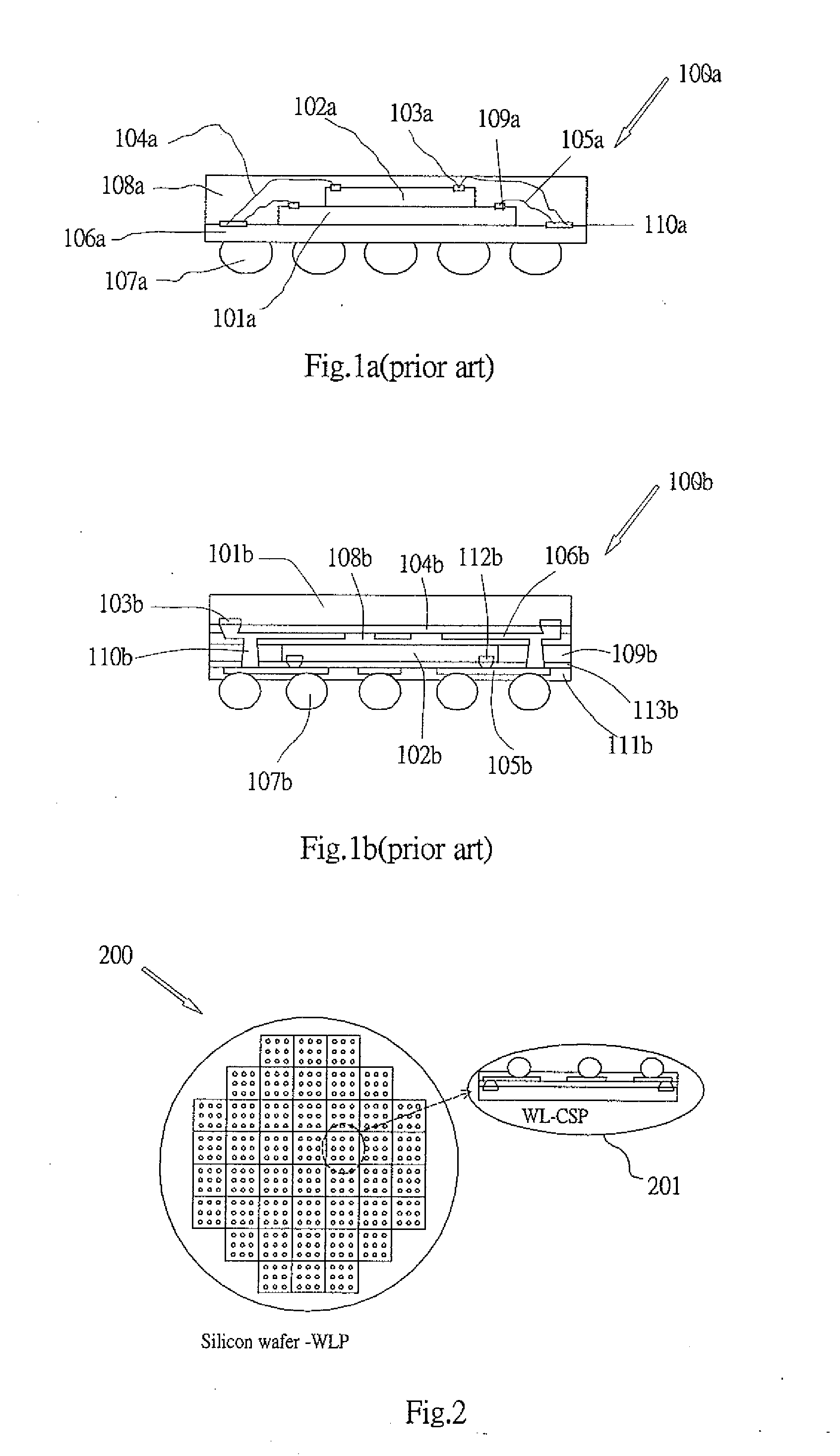

Method for manufacturing wafer level chip scale package using redistribution substrate

InactiveUS20060079019A1Increase widthIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringChip-scale package

The present invention provides a method for manufacturing a wafer level chip scale package using a redistribution substrate, which has patterned bump pairs connected by redistribution lines and formed on a transparent insulating substrate. The redistribution substrate is produced separately from a wafer and then bonded to the wafer. One part of each bump pair is in contact with a chip pad on the active surface of the wafer, and the other part coincides with one of holes formed in the wafer. Conductive lines are formed in the holes and on the non-active surface of the wafer. External connection terminals are formed on the conductive lines at the non-active surface.

Owner:EPWORKS

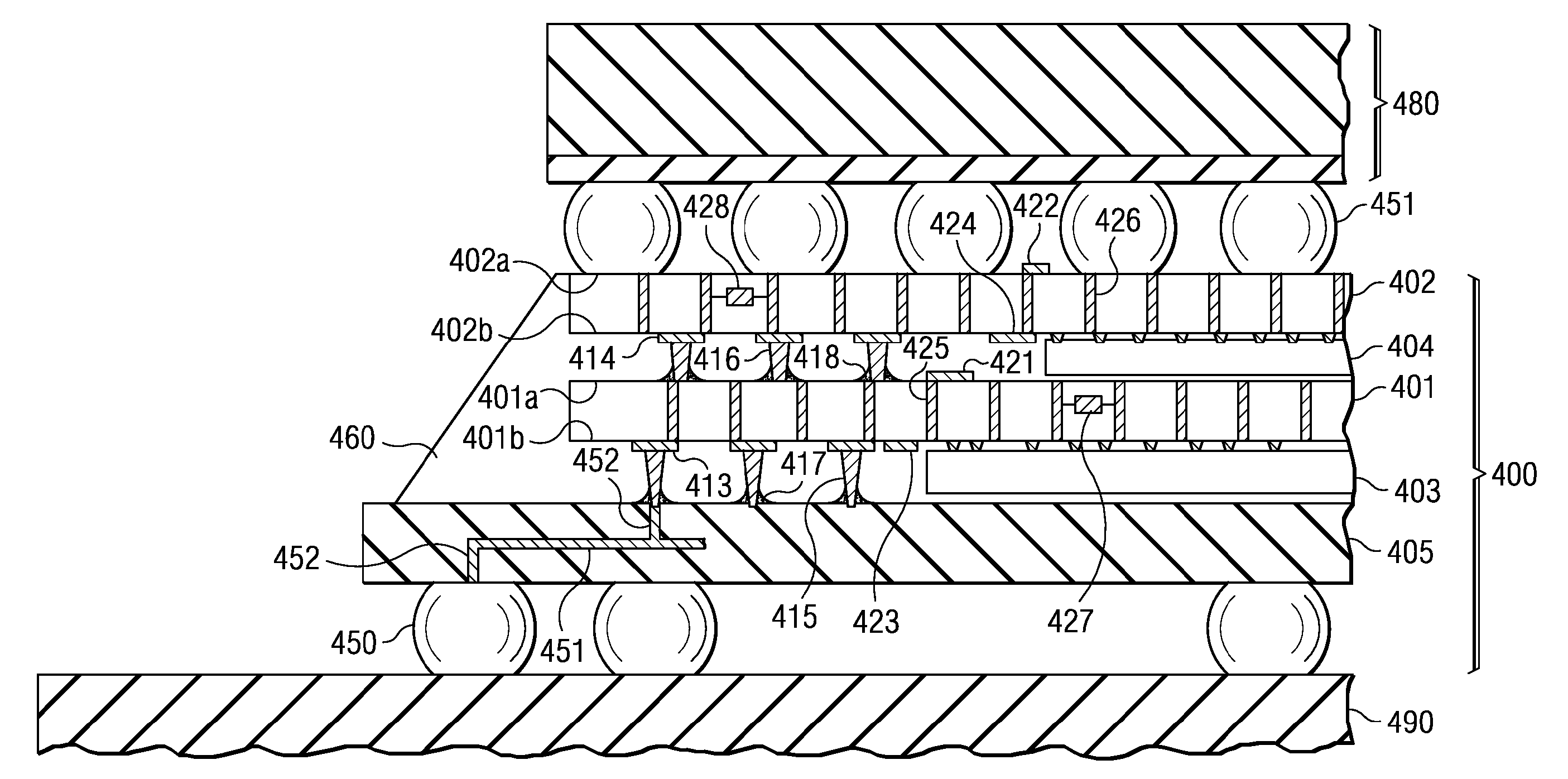

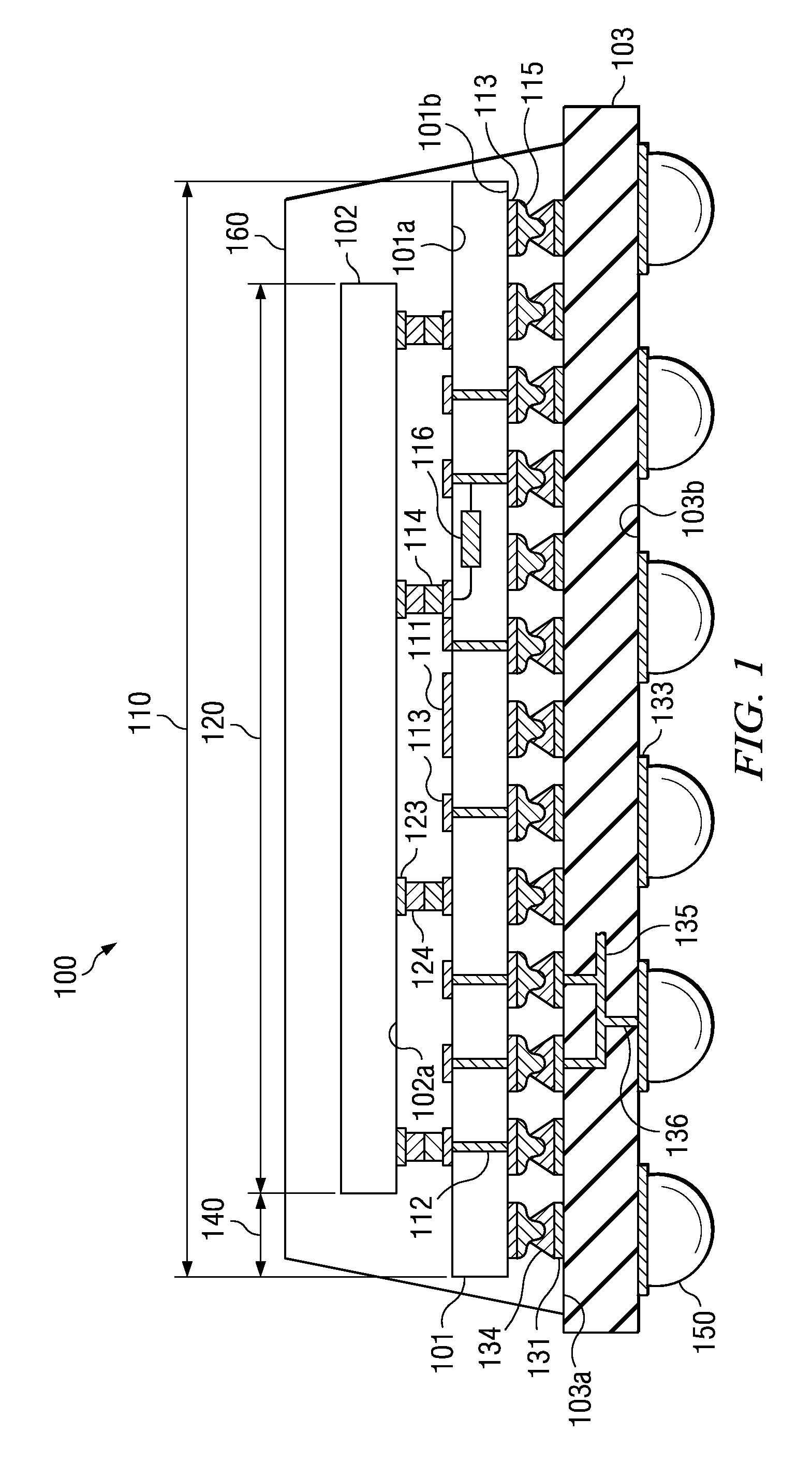

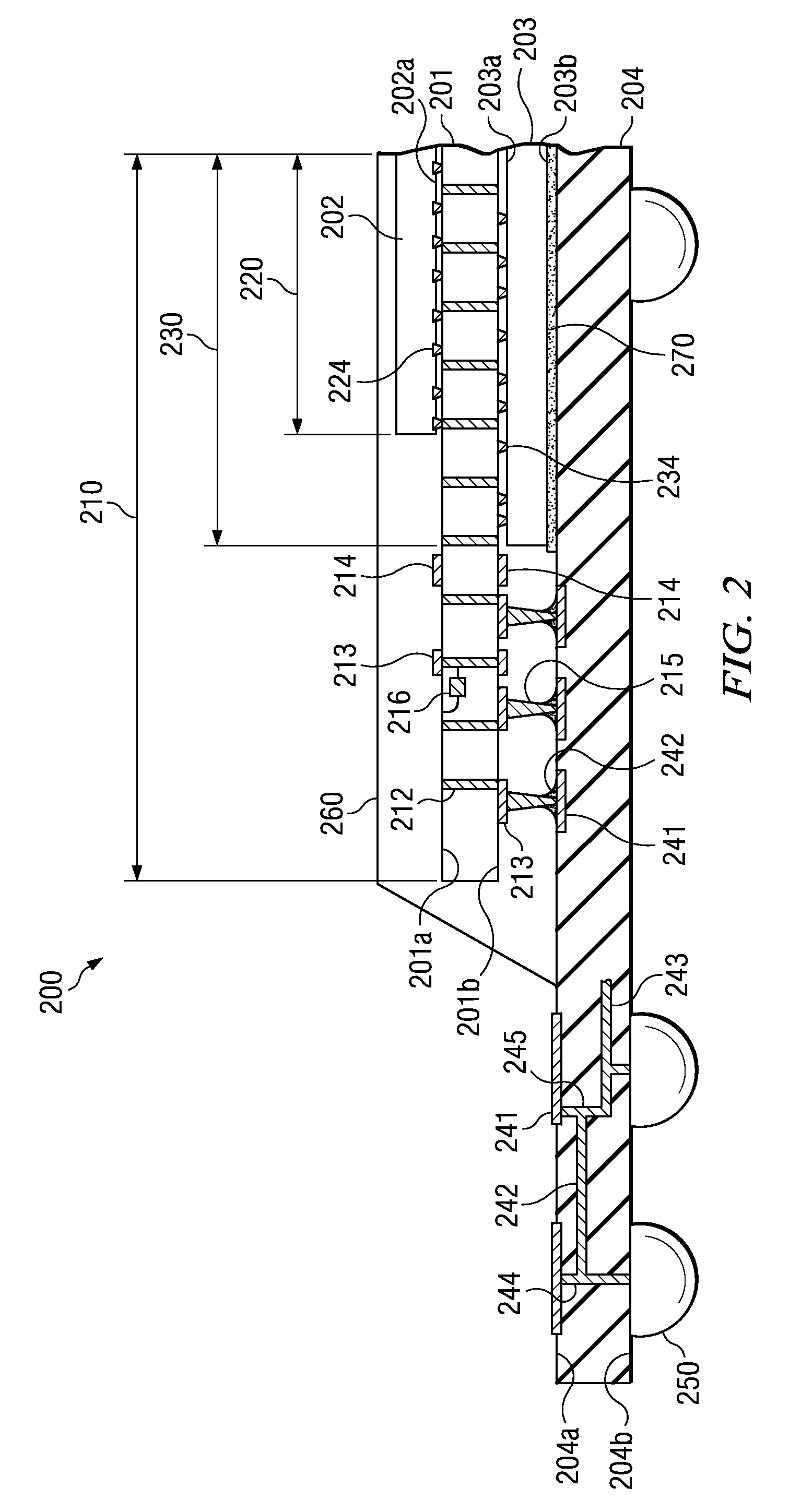

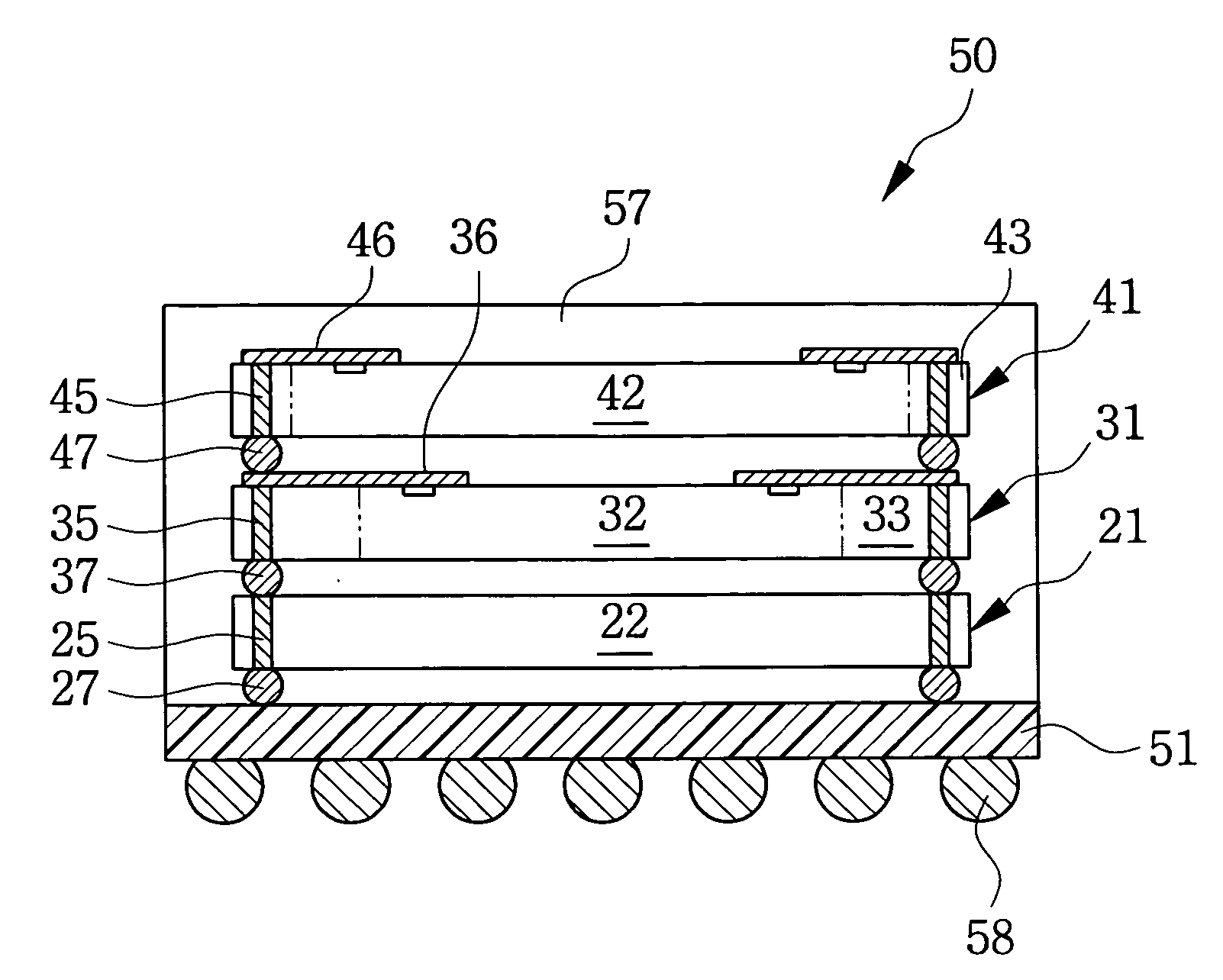

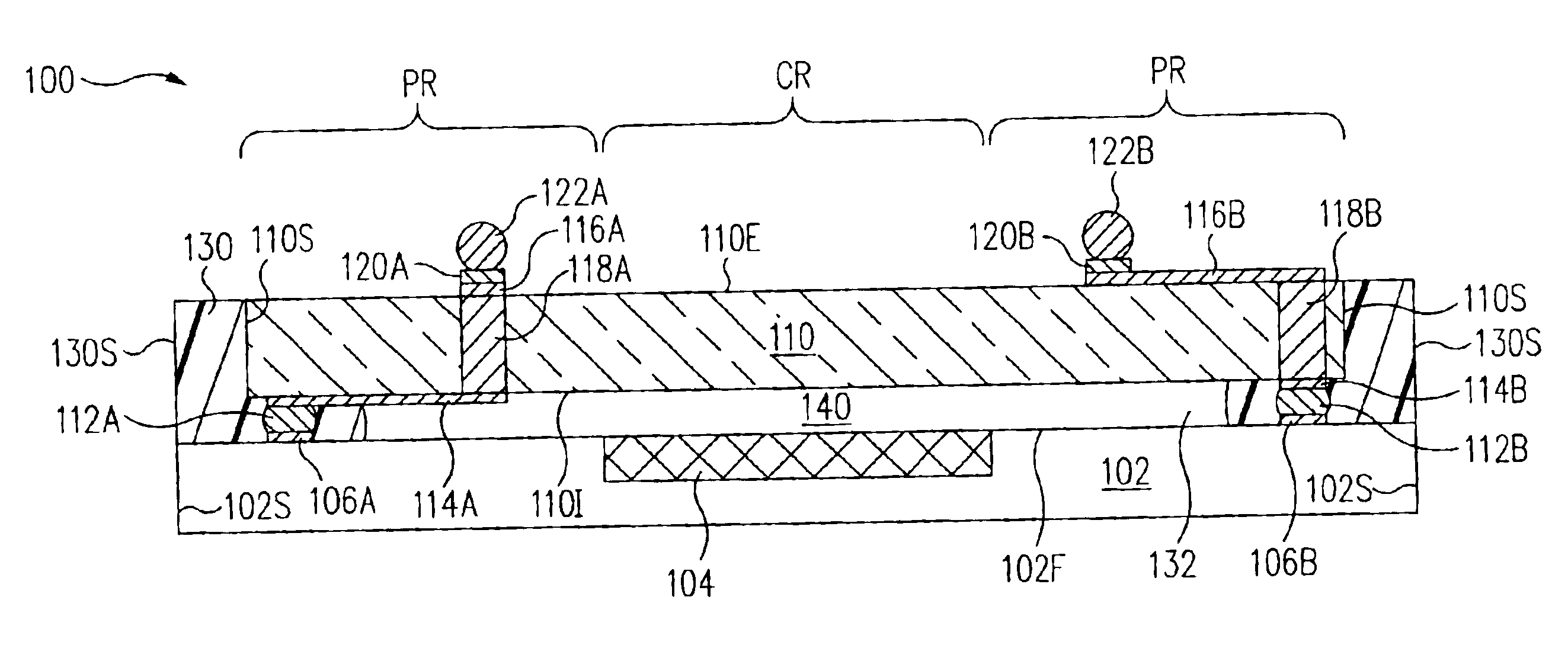

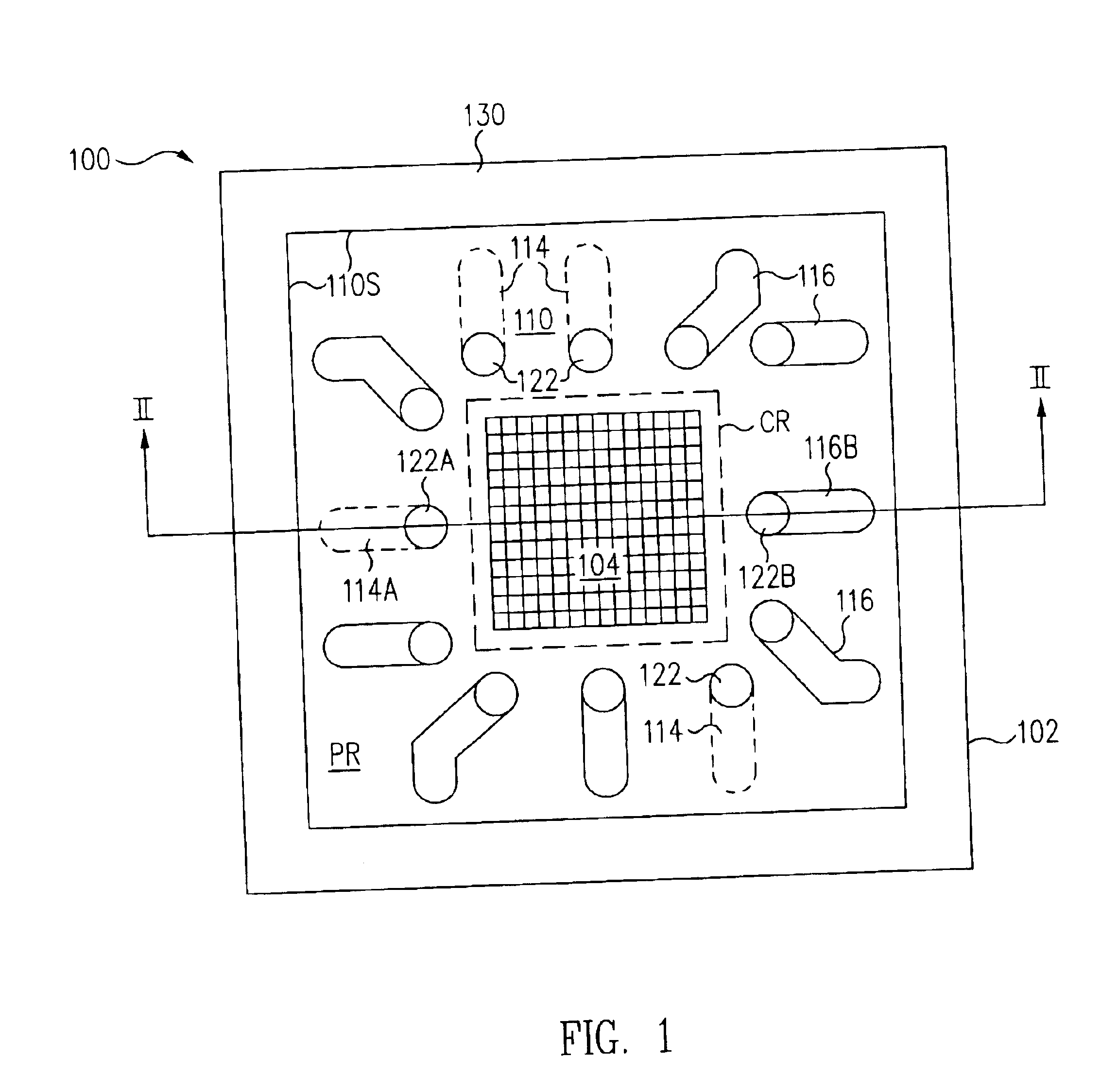

Packaged system of semiconductor chips having a semiconductor interposer

ActiveUS20070235850A1Increase powerIncrease speedSemiconductor/solid-state device detailsSolid-state devicesChip sizeInterposer

A semiconductor system (200) of one or more semiconductor interposers (201) with a certain dimension (210), conductive vias (212) extending from the first to the second surface, with terminals and attached non-reflow metal studs (215) at the ends of the vias. A semiconducting interposer surface may include discrete electronic components or an integrated circuit. One or more semiconductor chips (202, 203) have a dimension (220, 230) narrower than the interposer dimension, and an active surface with terminals and non-reflow metal studs (224, 234). One chip is flip-attached to the first interposer surface, and another chip to the second interposer surface, so that the interposer dimension projects over the chip dimension. An insulating substrate (204) has terminals and reflow bodies (242) to connect to the studs of the projecting interposer.

Owner:TEXAS INSTR INC

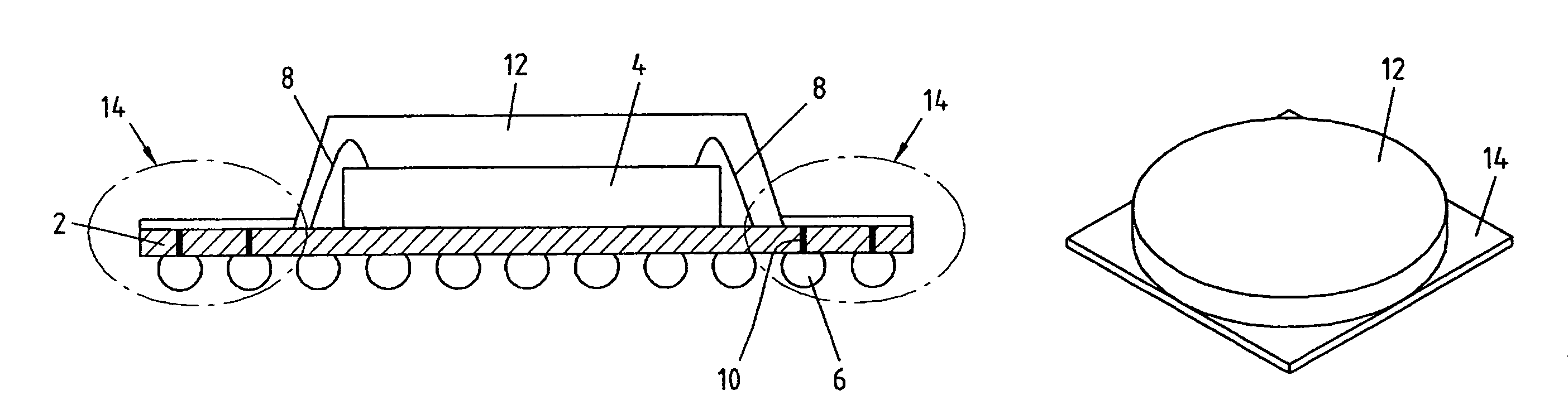

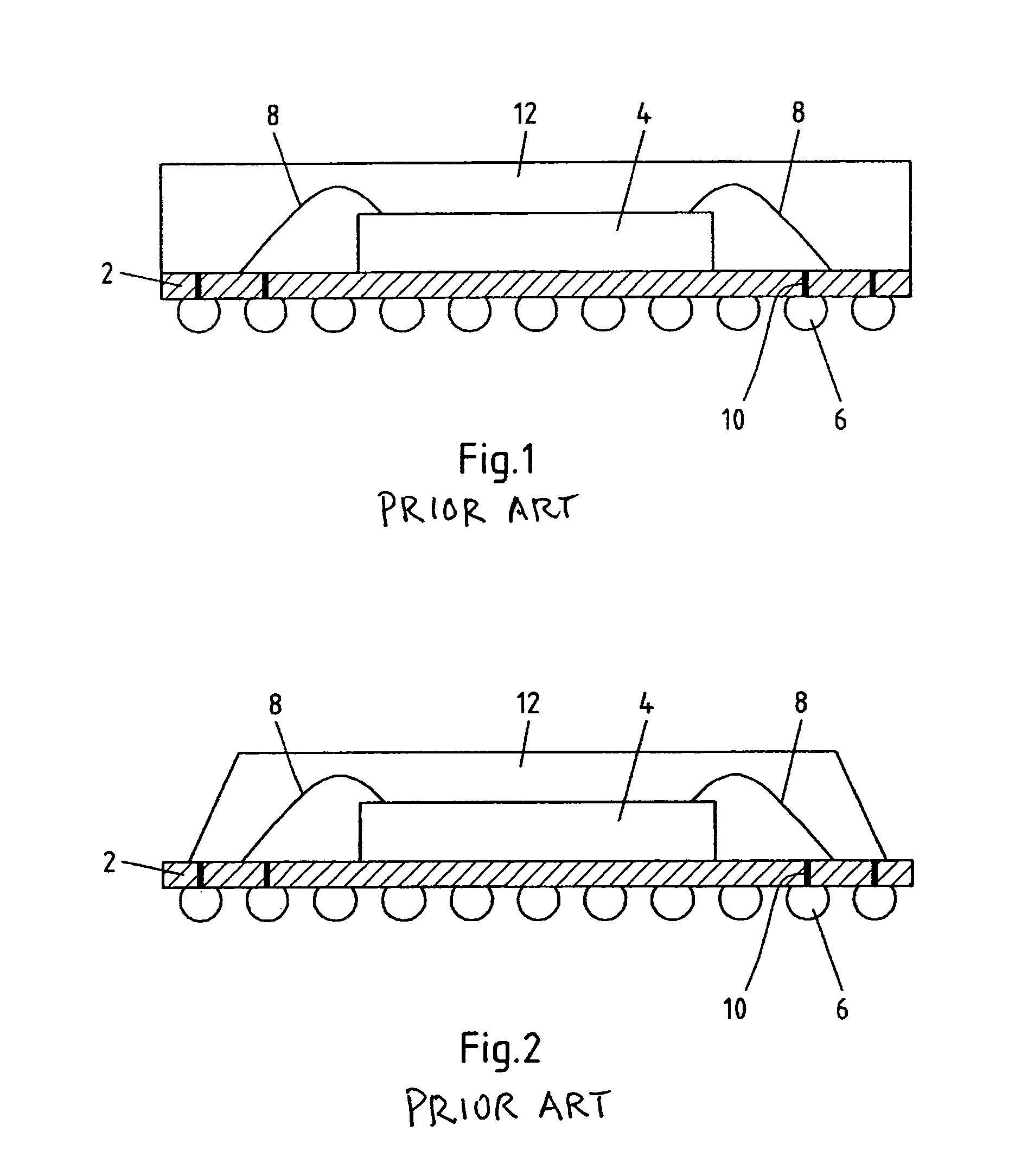

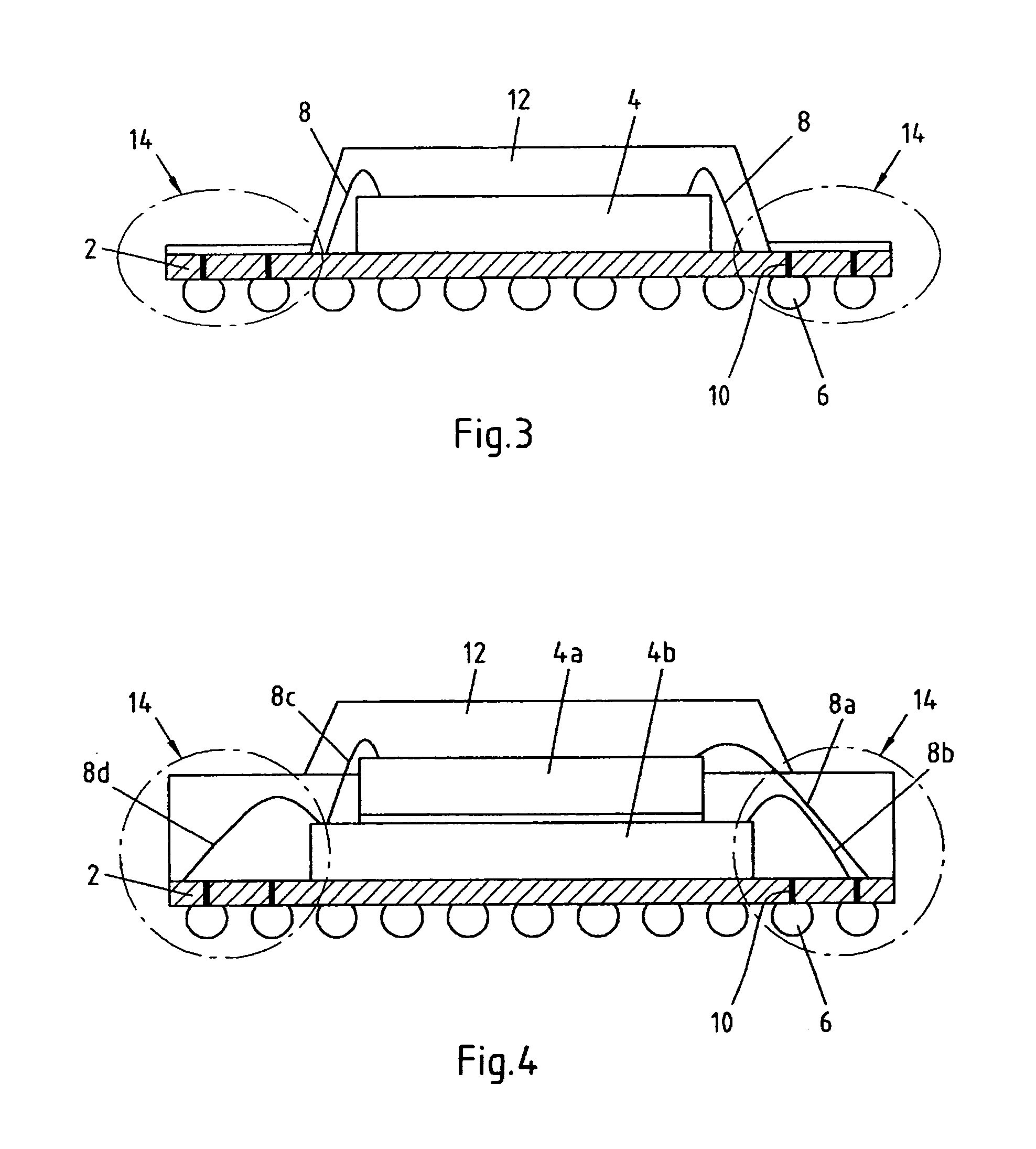

Integrated circuit package with optimized mold shape

InactiveUS7233057B2Reduce stiffnessIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesChip sizeInterconnection

The invention relates to an integrated circuit package, in particular an integrated chip size package or an integrated chip scale package, comprising a substrate carrying a die, and connection elements, interconnection elements, connecting pins of said die with said connection elements, and a mold encapsulating said die on said substrate. To increase reliability and to reduce failure due to deformation stress, the invention provides said mold with reduced stiffness at areas located substantially at one of said interconnection elements providing increased flexibility of said package at said areas compared to other areas of said package.

Owner:NOKIA CORP

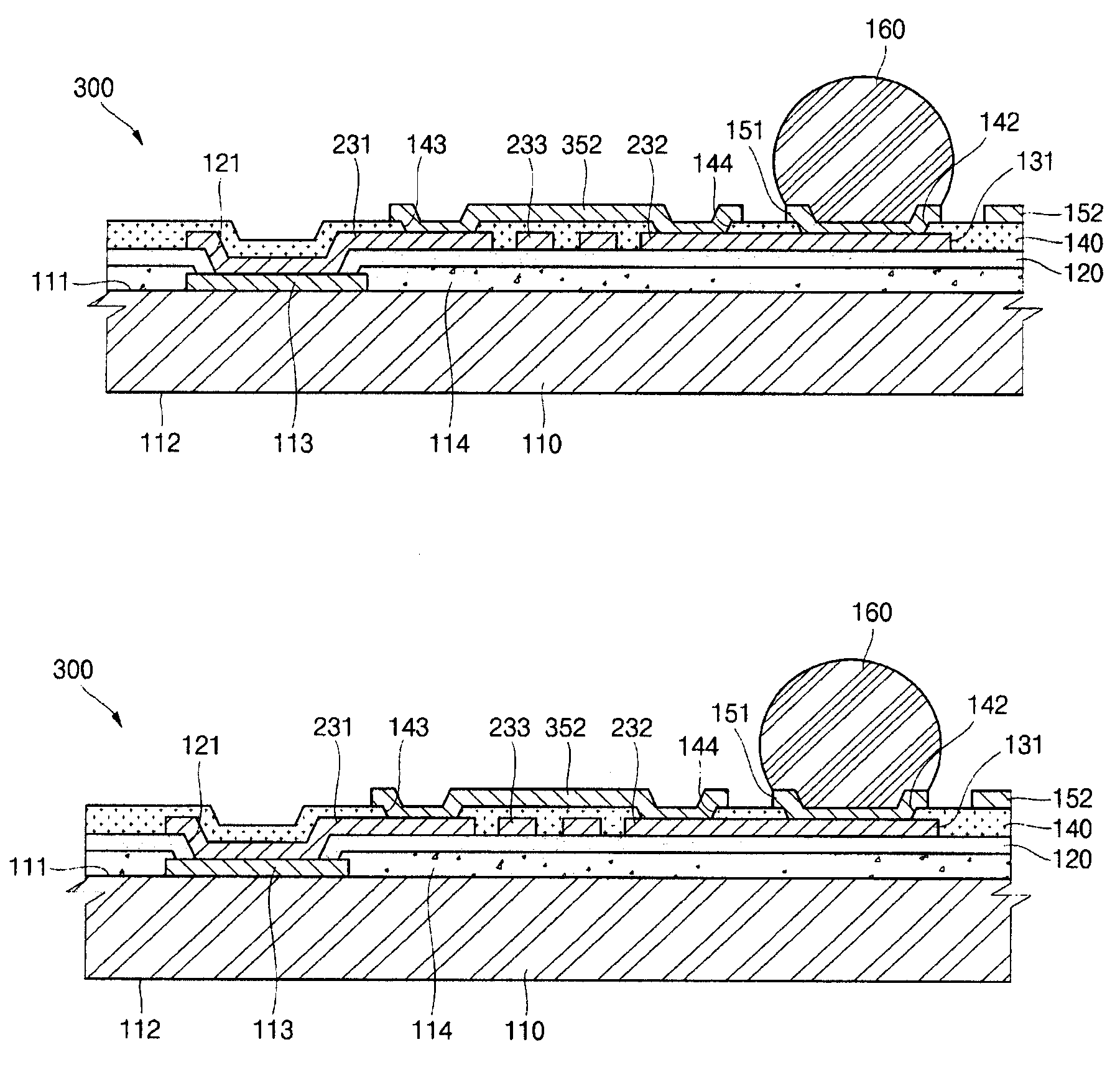

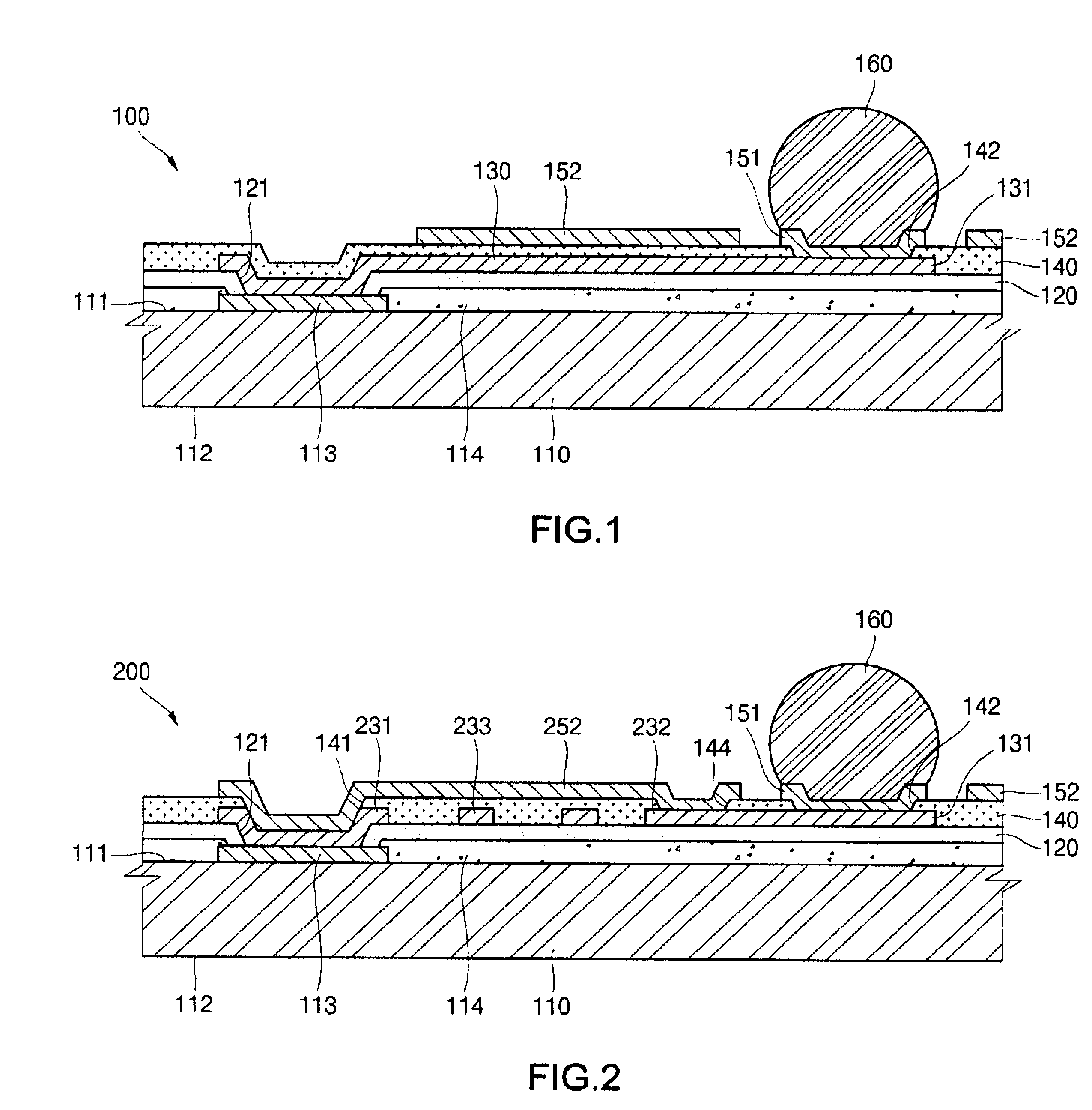

Wafer level chip size package having redistribution layers

ActiveUS7977783B1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A wafer level chip size package (WLCSP) and a method of manufacturing the same are disclosed. Lands are formed at the ends of redistribution layers. The redistribution layers excluding the lands and a first dielectric layer are covered with a second dielectric layer. After forming a first under bump metallurgy (UBM) layer on the land, a solder ball is reflowed to the first UBM layer. A second UBM layer is widely formed on the entire second dielectric layer that is the outer circumference of the first UBM layer and is connected to the redistribution layer through a via-hole. Therefore, the second UBM layer having a large area can be used as a ground plane or a power plane. In addition, the second UBM layer can electrically connect the redistribution layers physically separated from each other. Therefore, the plurality of redistribution layers can cross each other without being electrically shorted with each other.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Wafer-level chip scale package and method for fabricating and using the same

InactiveUS20050012225A1Address rising pricesSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A packaged semiconductor device (a wafer-level chip scale package) containing a conductive adhesive material as an electrical interconnect route between the semiconductor die and a patterned conductive substrate is described. The patterned conductive substrate acts not only as a substrate, but also as a redistribution layer that converts the dense pad layout of the die to a larger array configuration of the solder balls in the circuit board. Using the invention allows the formation of a lower priced chip scale package that also overcomes the restriction of the die size used in die-sized chip packages and the input-output pattern that can be required by the printed circuit board. Thus, the invention can provide a familiar pitch (i.e.,interface) to the printed circuit board for any small die.

Owner:SEMICON COMPONENTS IND LLC

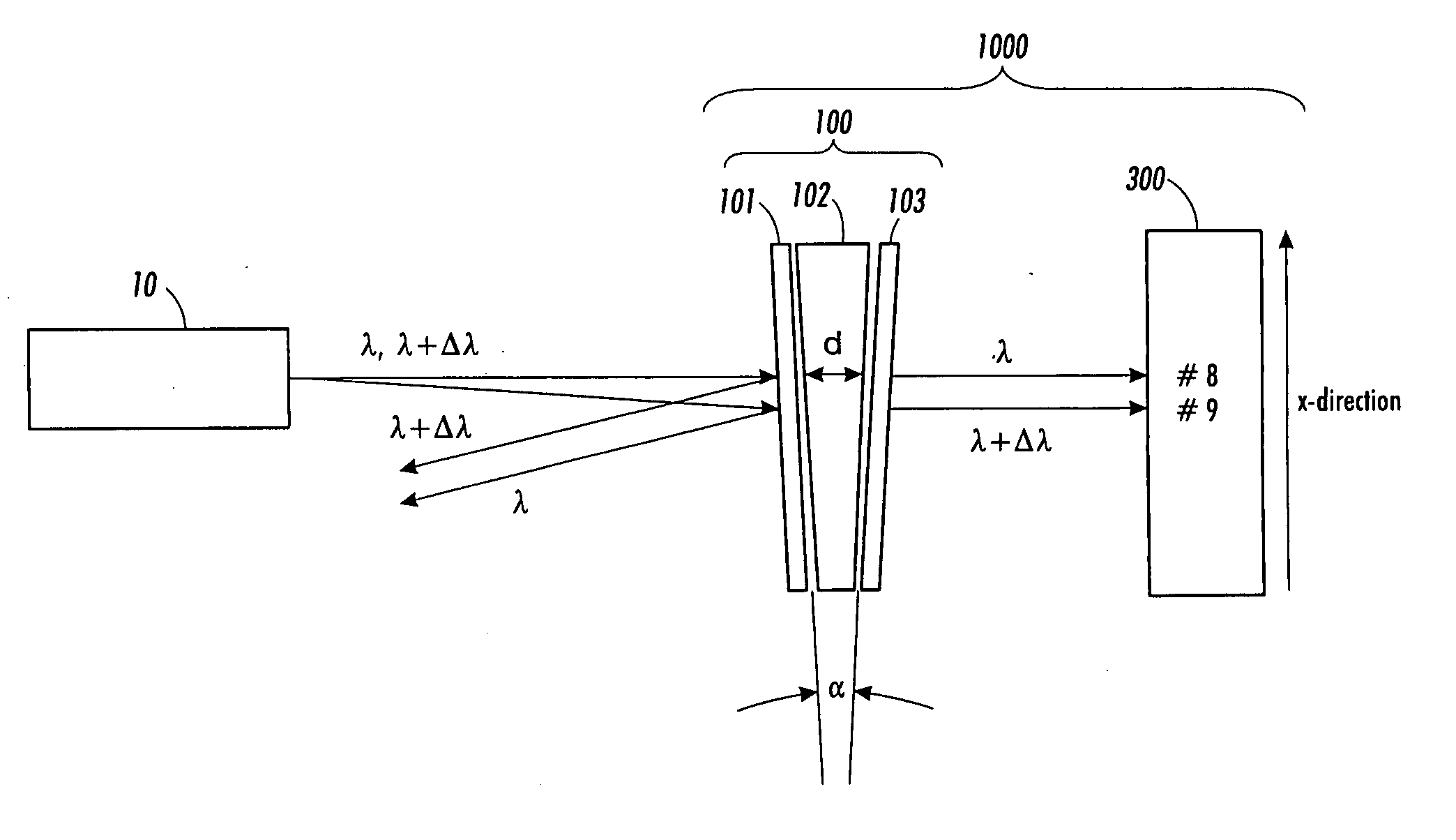

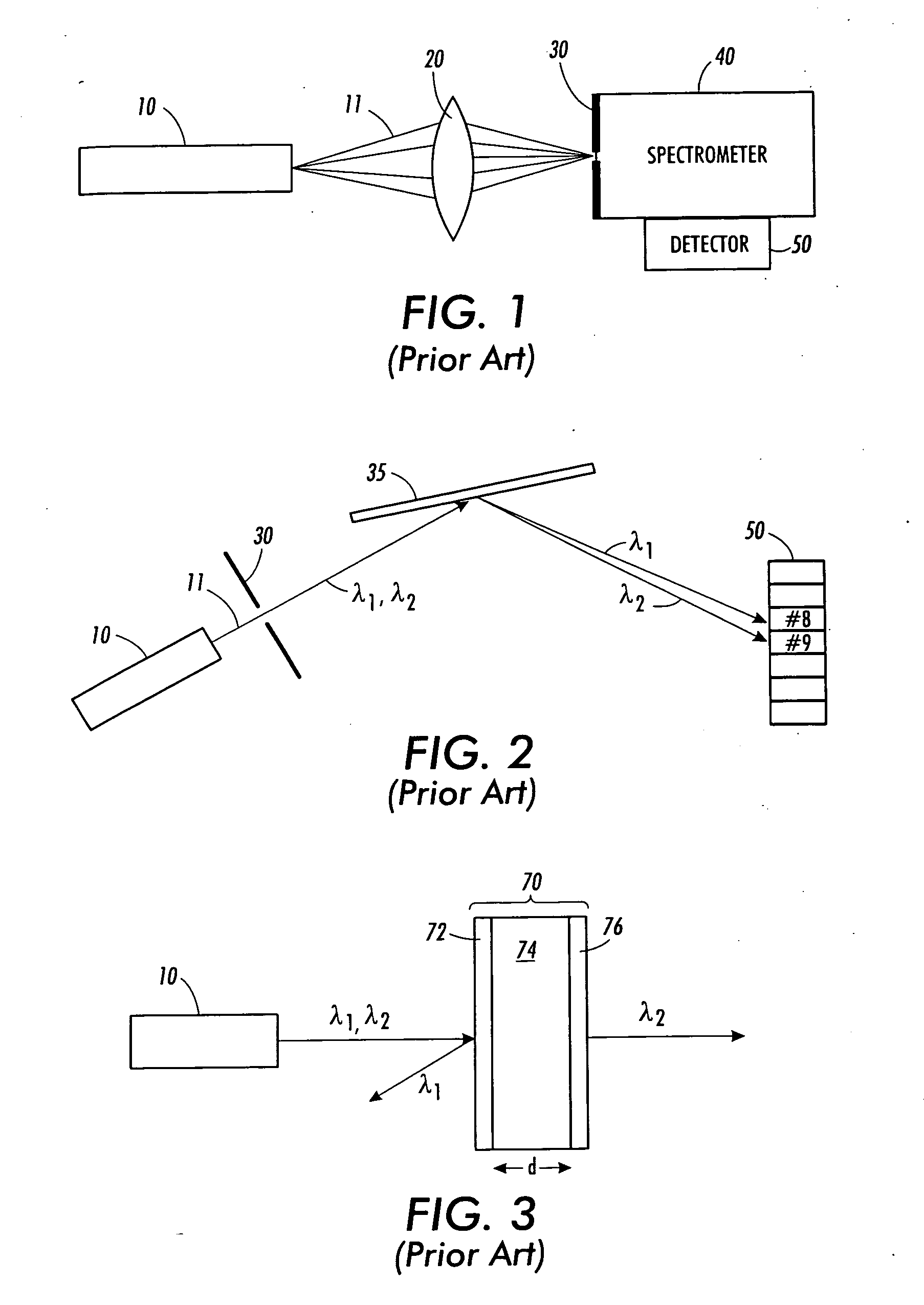

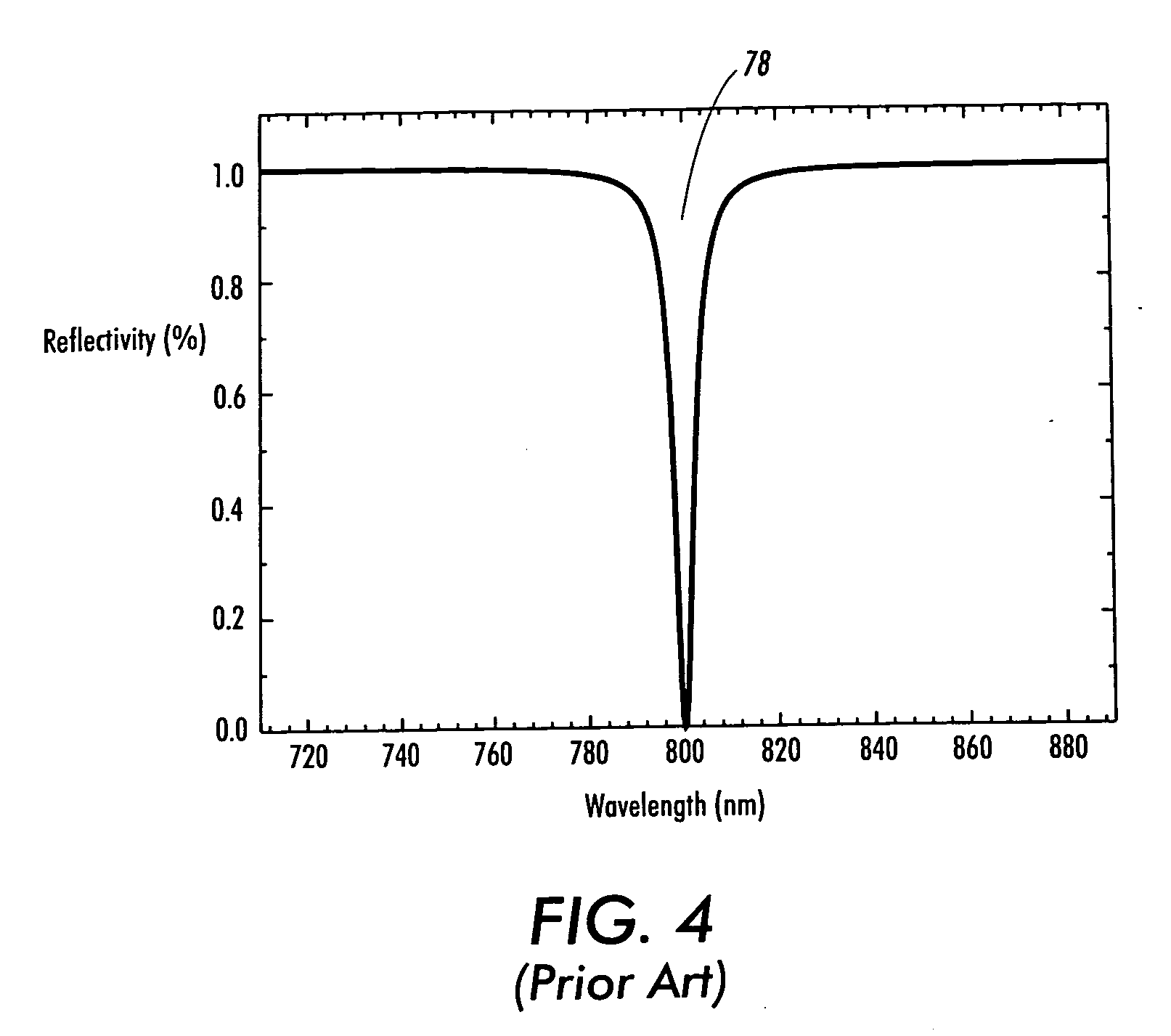

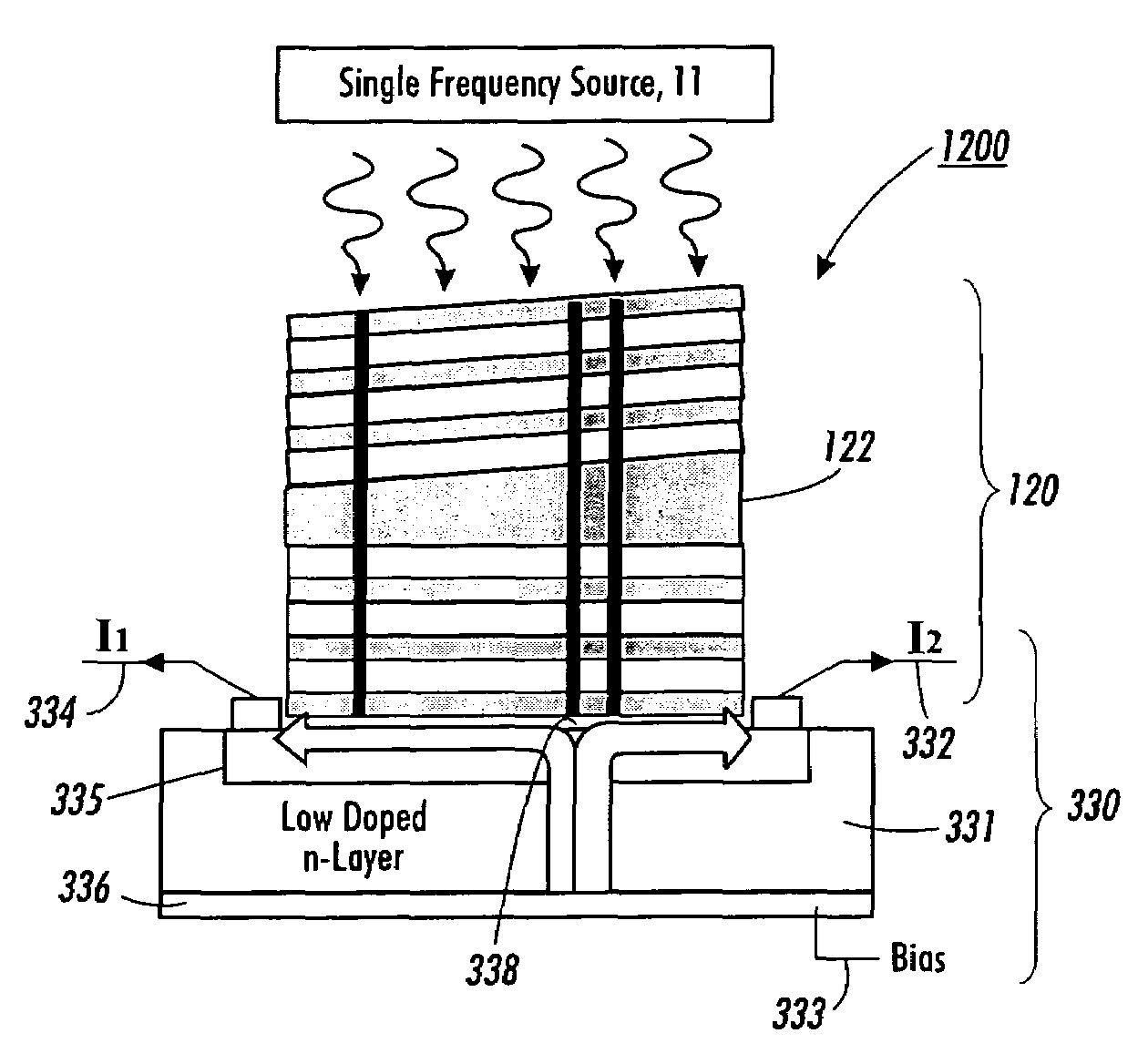

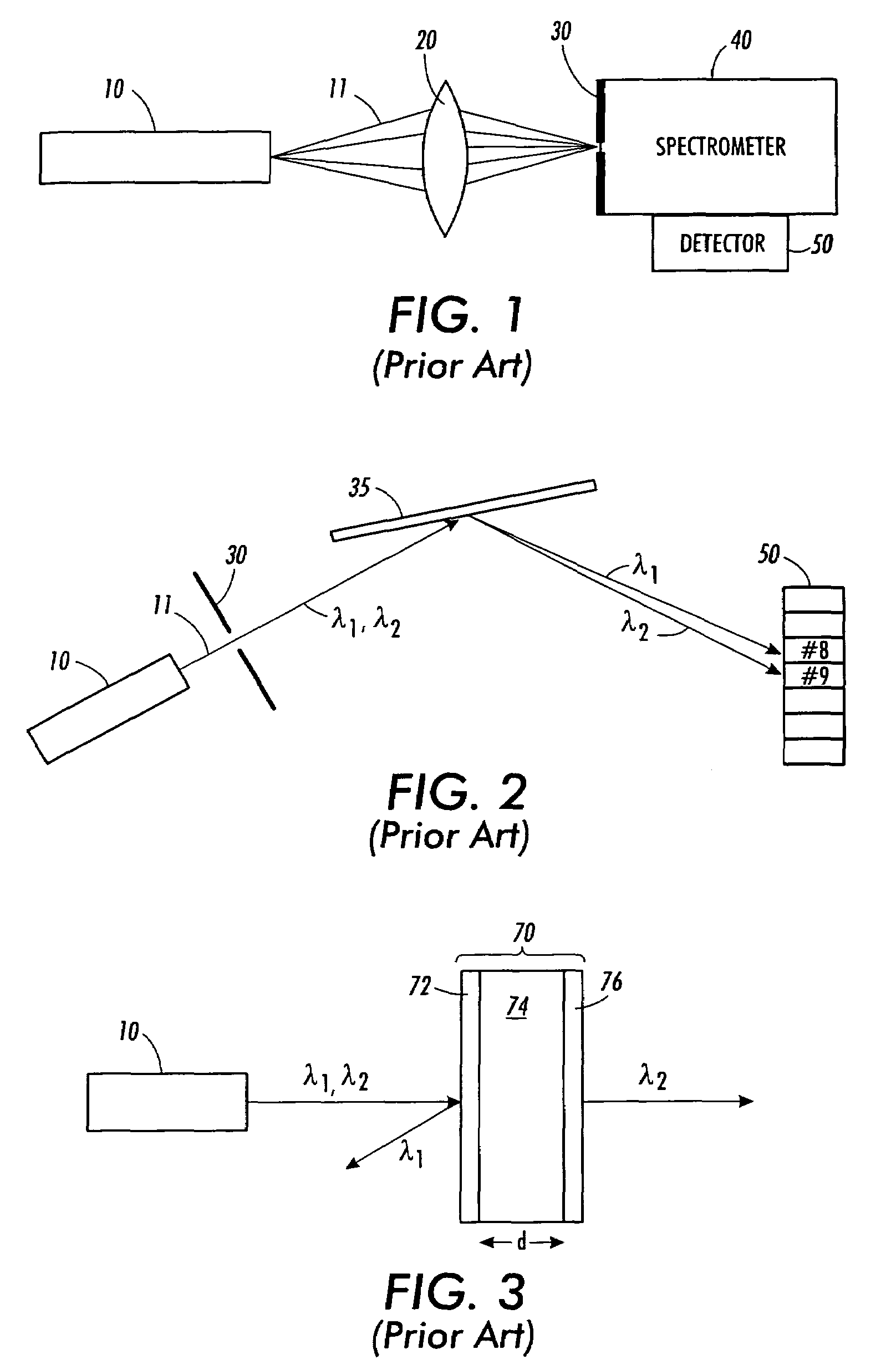

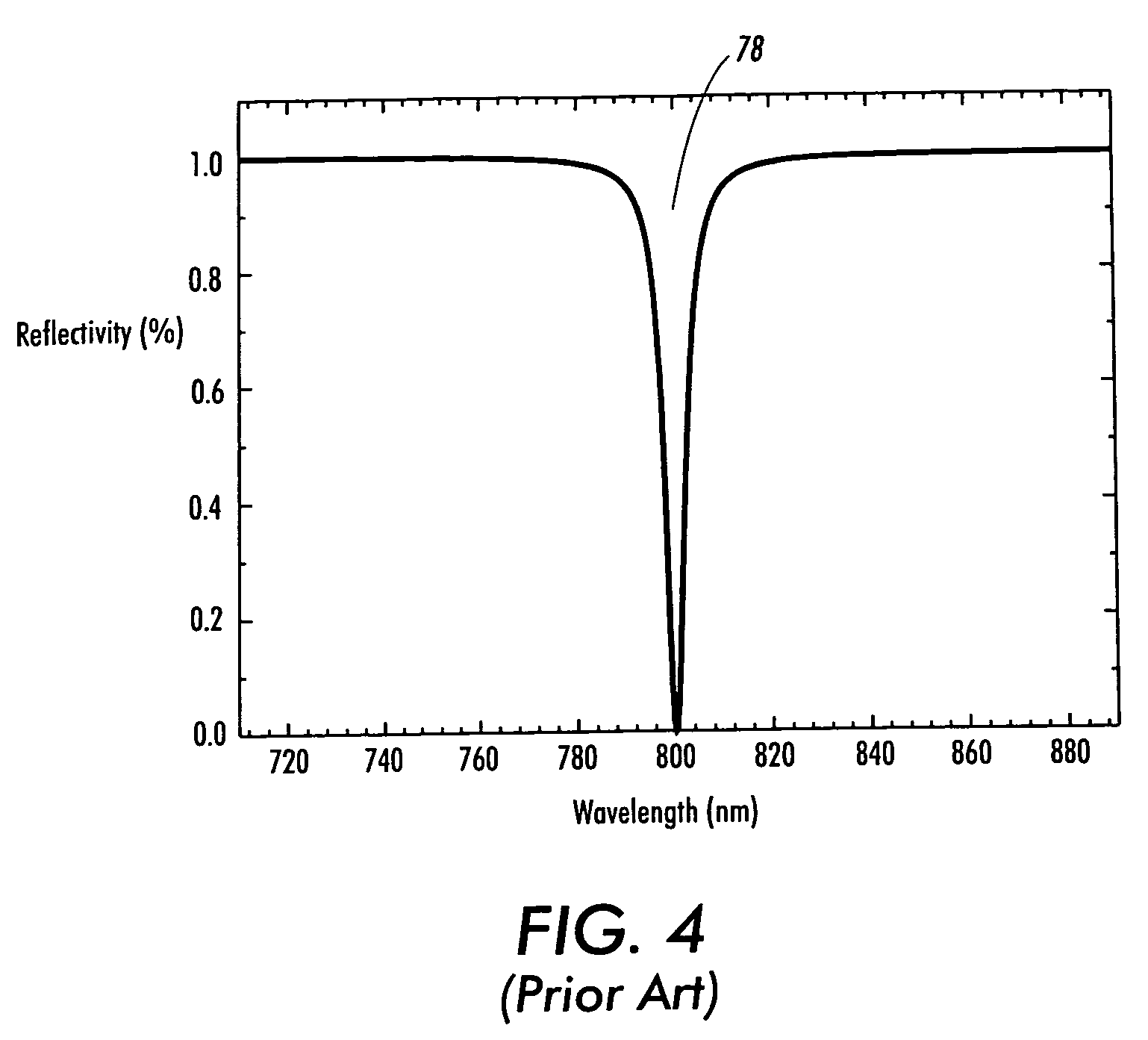

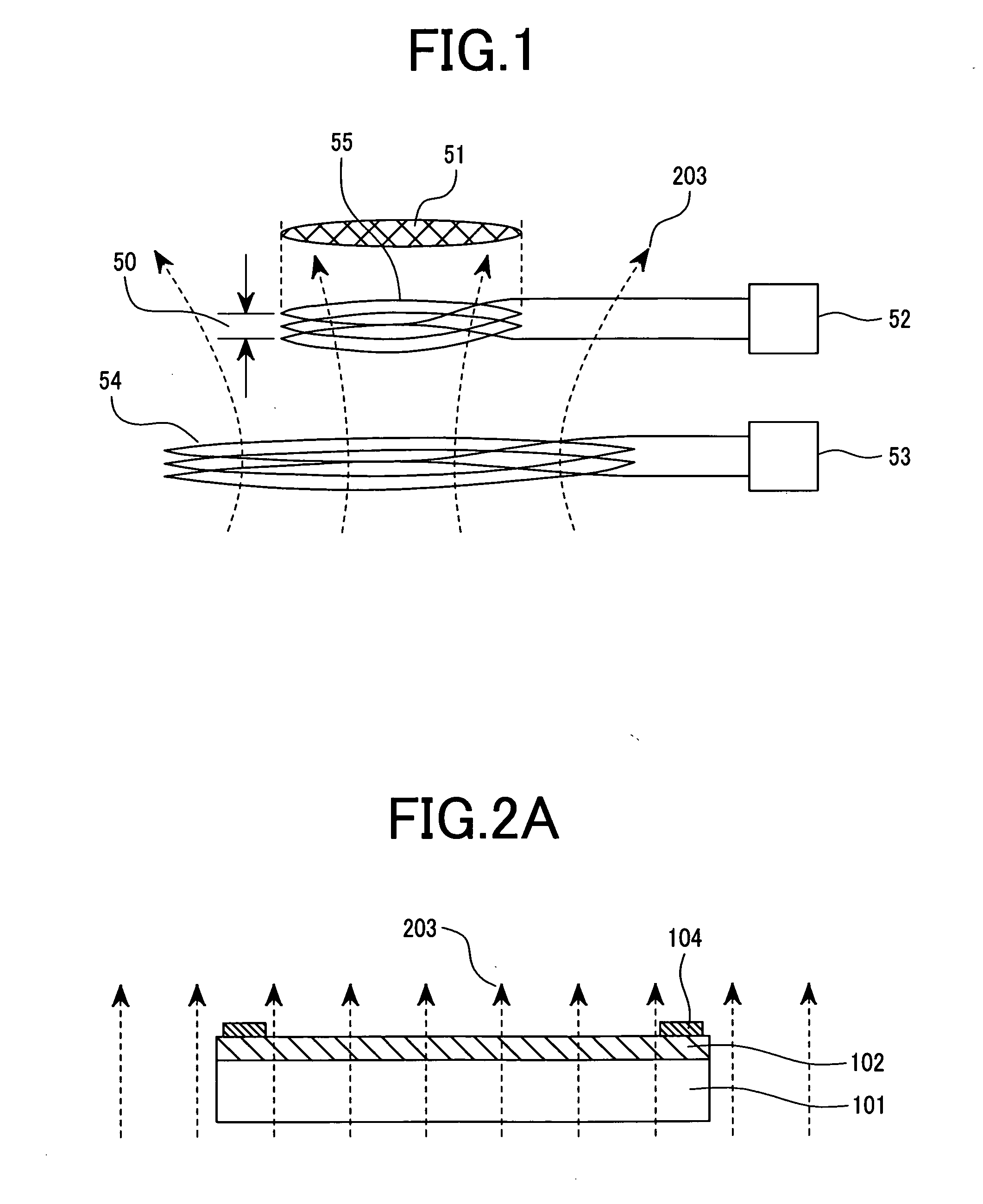

Chip-size wavelength detector

ActiveUS20060039009A1Good wavelength selectivityHigh selectivityOptical measurementsRadiation pyrometryChip sizeLength wave

A chip-size wavelength detector includes a film with laterally varying transmission properties and a position-sensitive detector. The film transmits a different wavelength as a function of lateral position across the film. The position of a spot of light transmitted through the film will shift, depending on the wavelength of the light. The shift is measured by the position-sensitive detector.

Owner:XEROX CORP

Chip-size package structure and method of the same

ActiveUS7238602B2Reduce contact resistanceLow costSemiconductor/solid-state device detailsSolid-state devicesChip sizeSolder ball

Owner:ADL ENERGY CORP

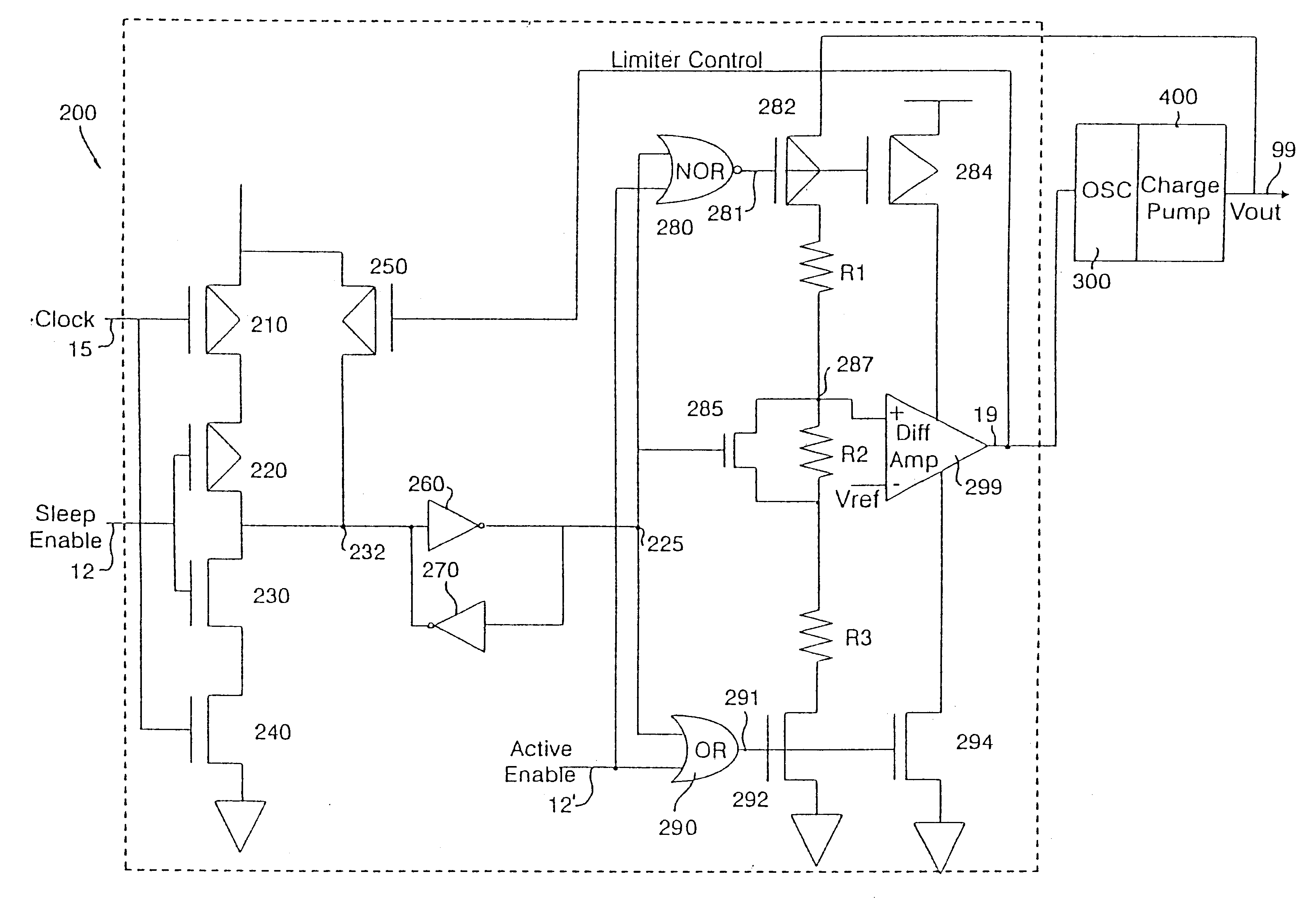

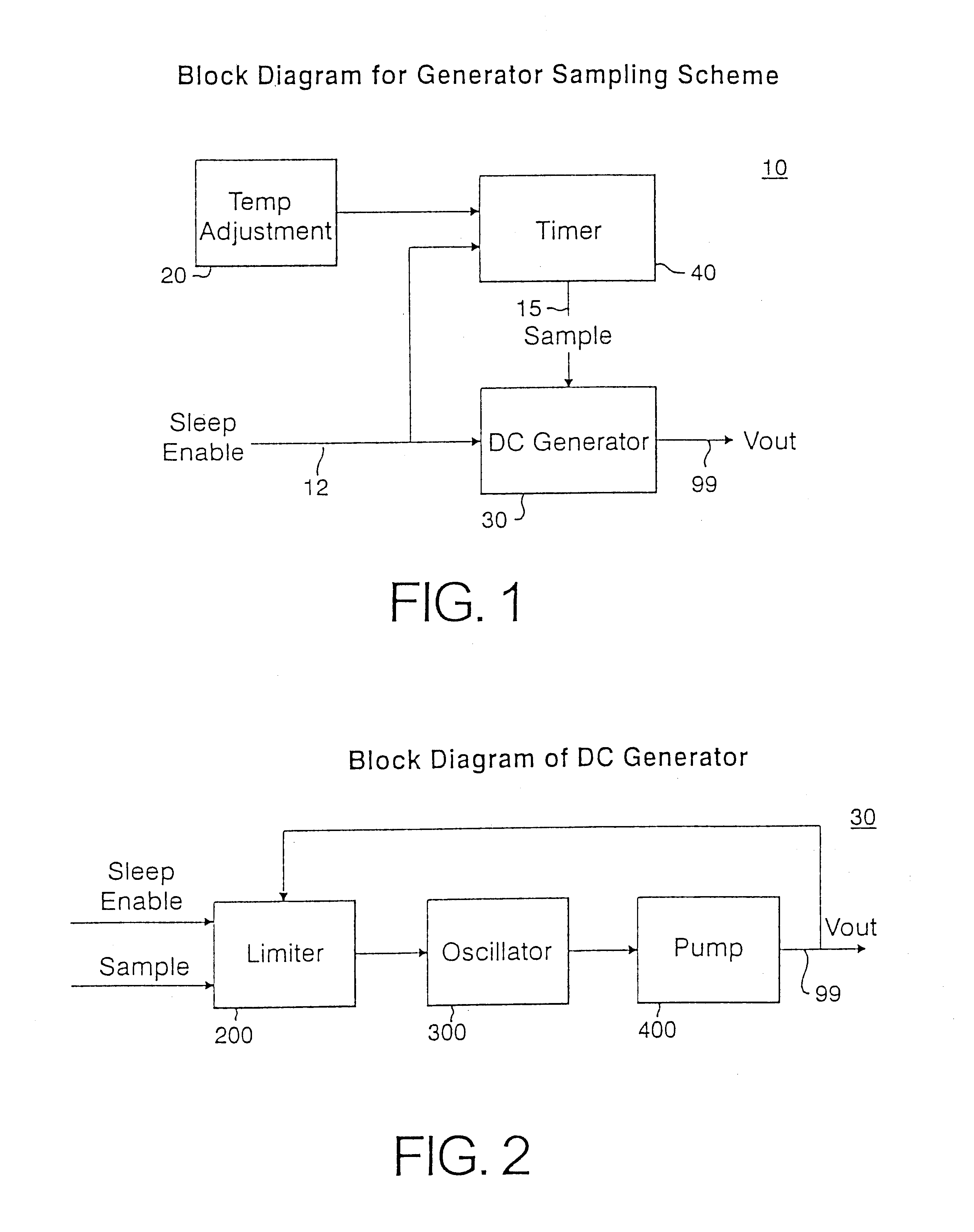

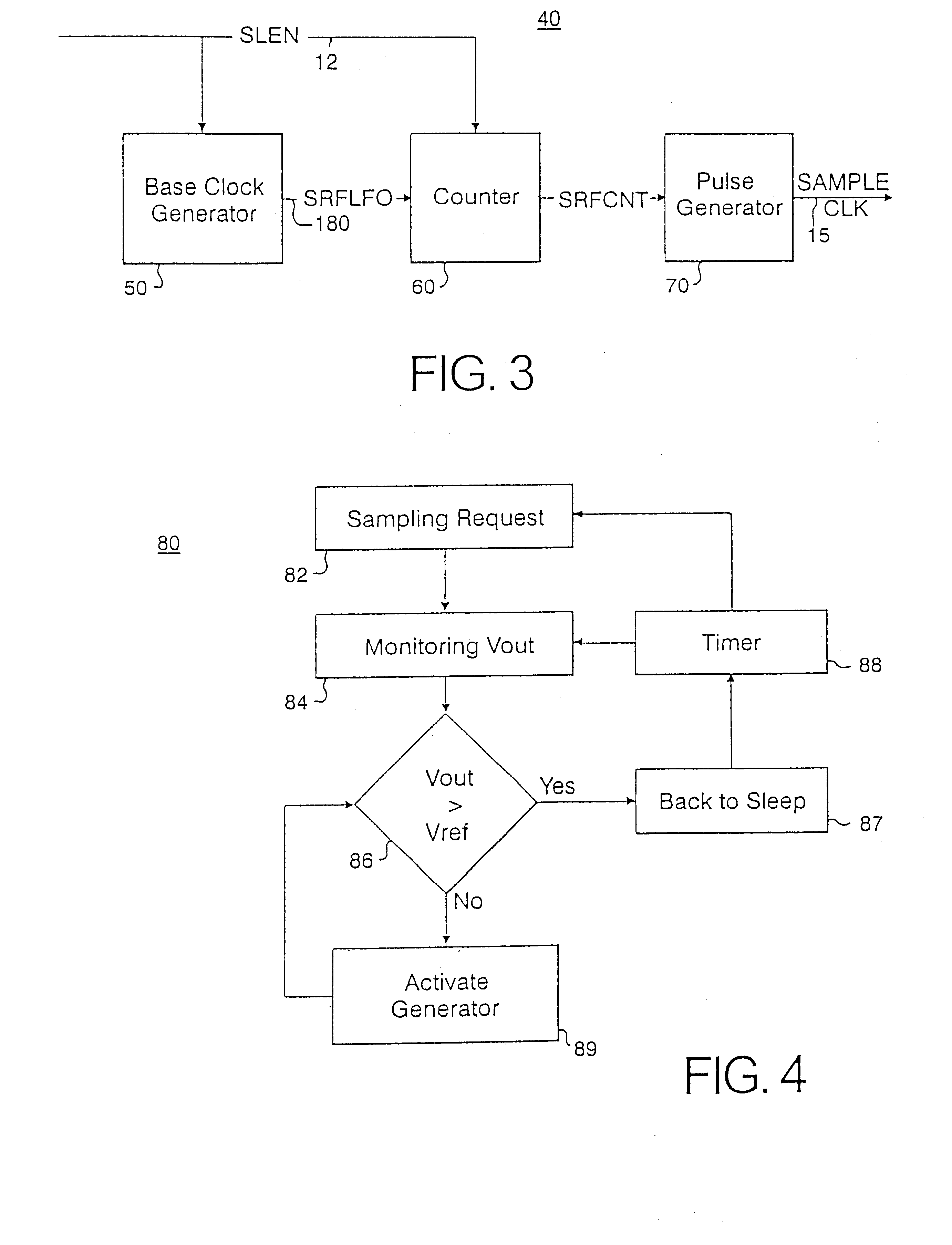

Self-refresh on-chip voltage generator

InactiveUS6411157B1Lower Level RequirementsReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingElectricityVoltage generator

A voltage control system and methodology for maintaining internally generated voltage levels in a semiconductor chip. The method comprises the steps of intermittently sampling an internal voltage supply level during a low power or "sleep" mode of operation; comparing the internal voltage supply level against a predetermined voltage reference level; and, activating a voltage supply generator for increasing the internal voltage supply level when the internal voltage supply level falls below the predetermined voltage reference level. The voltage supply generator is subsequently deactivated when the voltage supply level is restored to the predetermined voltage reference level. The sampling cycle may be appropriately tailored according to chip condition, chip temperature, and chip size. In one embodiment, the voltage control system and methodology is implemented in DRAM circuits during a refresh operation. The voltage levels that are suitable for sampling including DRAM band-gap reference voltage, boost wordline line voltage, wordline low voltage, bitline high voltage and bitline equalization voltages.

Owner:IBM CORP

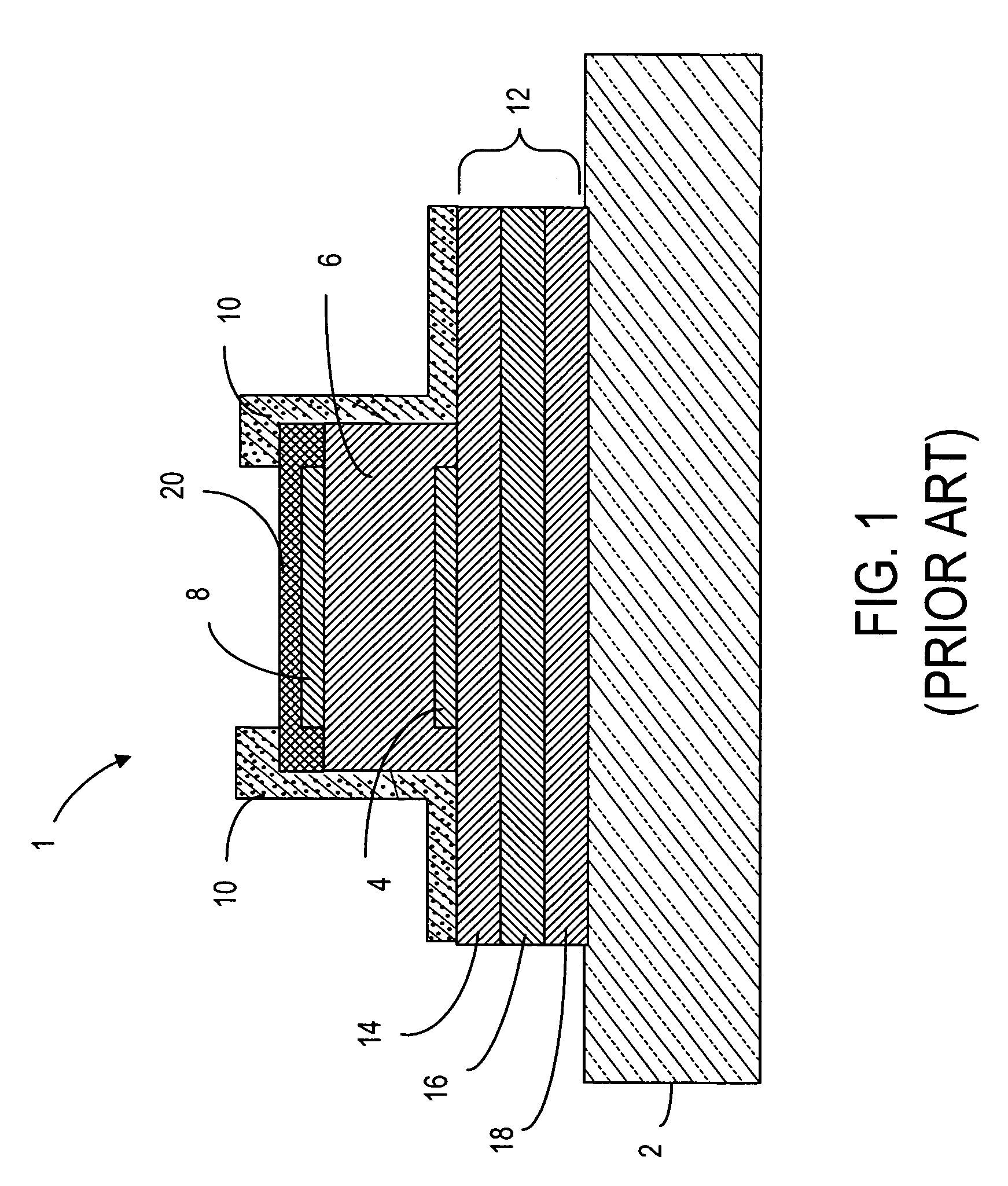

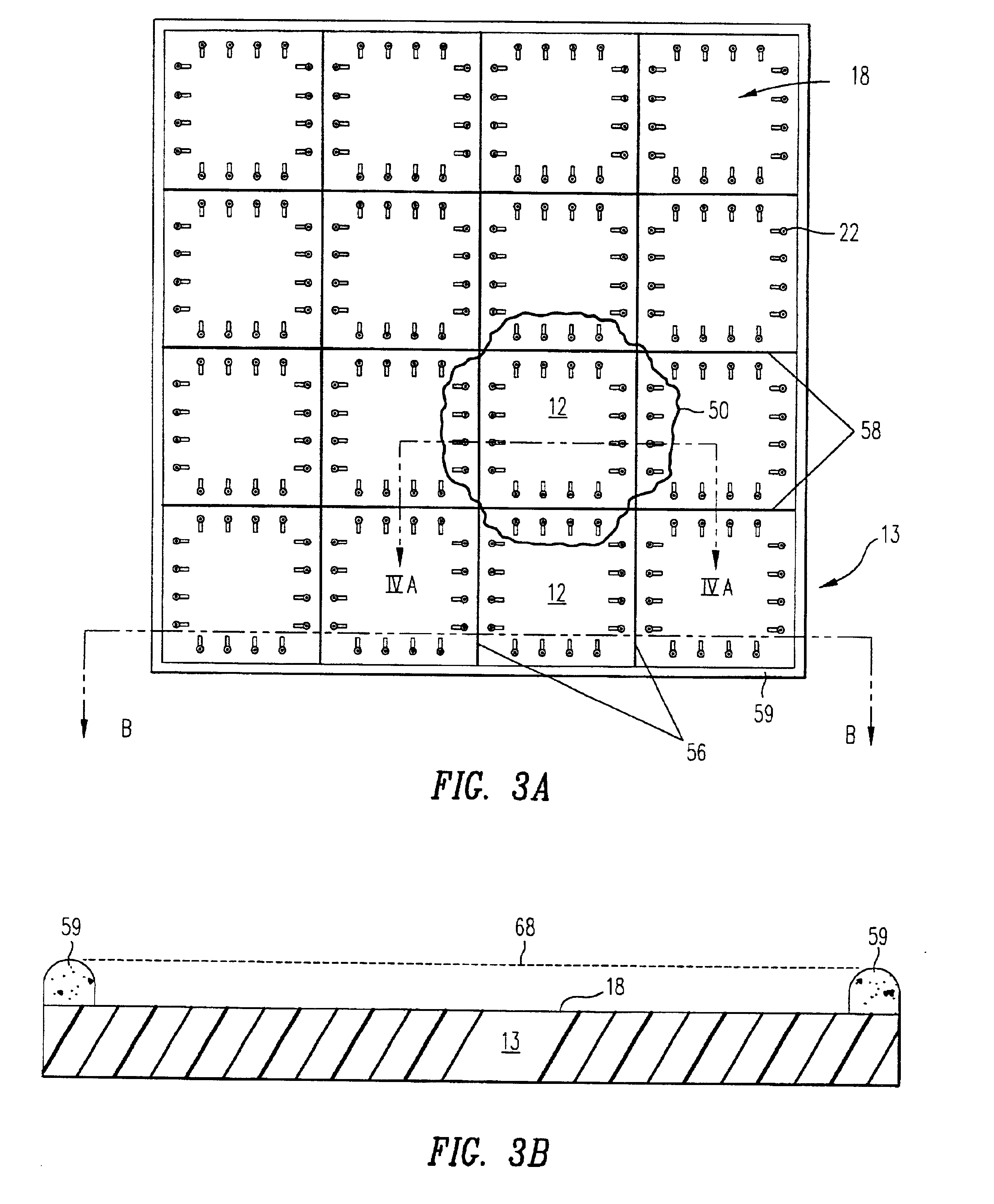

Fluxless assembly of chip size semiconductor packages

InactiveUS20050042838A1Semiconductor/solid-state device detailsSolid-state devicesChip sizeHermetic seal

A method for assembling semiconductor packages (10) includes forming corresponding pairs of conductive pads (14, 16, 20, 22) on respective surfaces of a die (12) and an interconnective substrate (18). Each pad in each pair includes an upper portion comprising at least one component of an electrically conductive eutectic alloy. Sharp, upstanding peaks (50, 58) are formed on at least one of the pads in each pair. The die and substrate are forcefully abutted and the pads heated until the sharp peaks penetrate through oxide films (52) on the respective opposing pads in each pair and contact the upper surface of the other pad therein, thereby initiating pad fusion. The pads are then cooled to solidify the molten portions thereof into an electrically conductive joint between each corresponding pair of pads and a hermetic seal around the periphery of the package.

Owner:AGNG

Semiconductor wafer and semiconductor device provided with columnar electrodes and methods of producing the wafer and device

InactiveUS7220657B2Improve reliabilitySemiconductor/solid-state device detailsSolid-state devicesChip sizeSolder ball

A semiconductor wafer provided with columnar electrodes which have plated nickel, palladium, and gold films successively formed at the top thereof, or have a plated solder film at their top. The semiconductor wafer can be preferably used for producing a chip-sized semiconductor device provided with columnar electrodes to which an external connection terminal, such as a solder ball, is to be bonded. Methods of producing the semiconductor wafer and device by use of plating are also disclosed.

Owner:SHINKO ELECTRIC IND CO LTD

Using position-sensitive detectors for wavelength determination

Owner:XEROX CORP

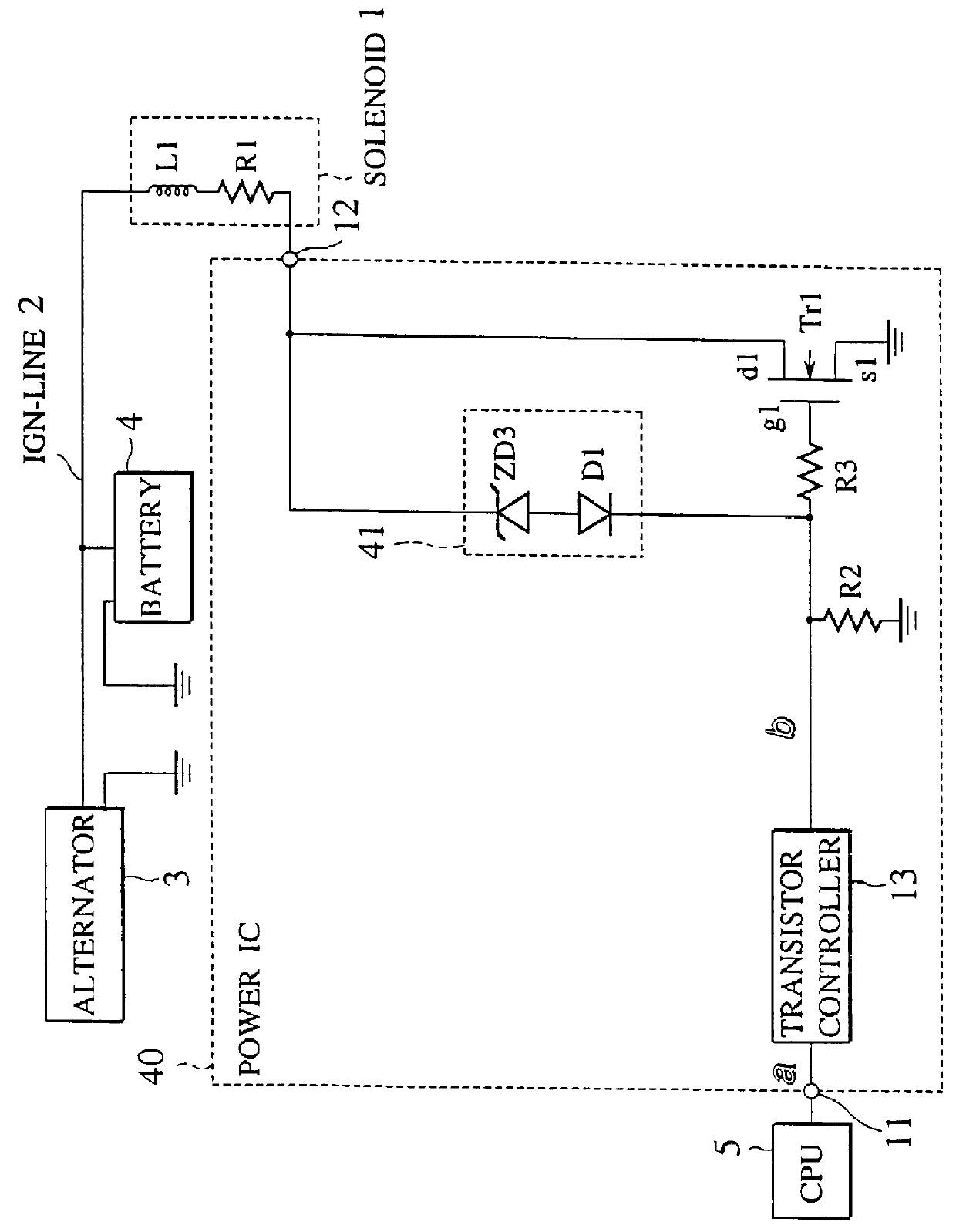

Integrated circuit having surge protection circuit

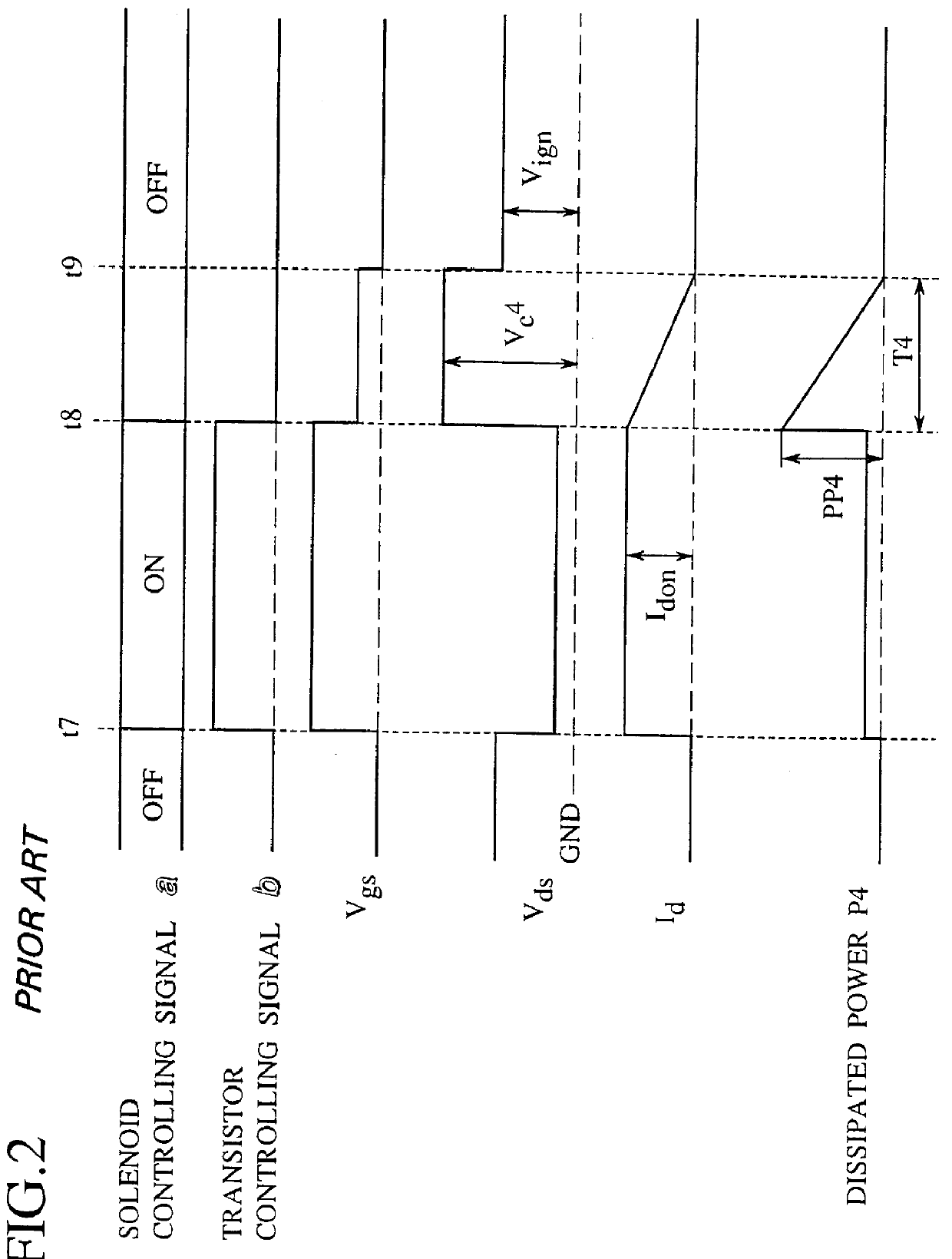

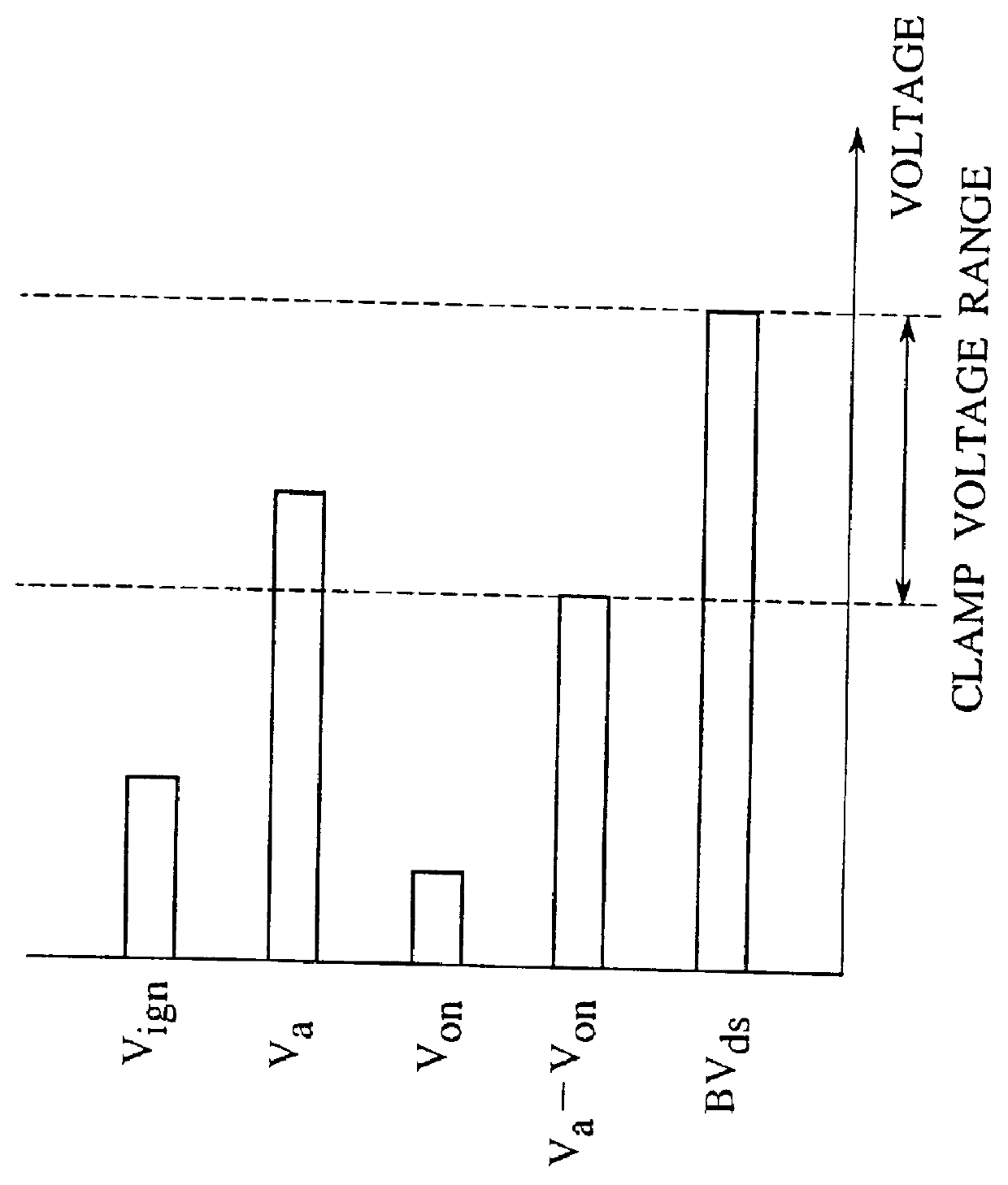

A trailing edge of a control signal of a transistor controller for controlling an output transistor is detected by an edge detector of a clamp controlling circuit. A surge voltage from a back electromotive voltage induced in an inductance L1 is absorbed from the output transistor, only for a given period immediately after the solenoid is turned off, by turning a switching transistor into an on-state by a timer to force a clamping circuit into conduction. At a normal operation, since the clamping circuit is cut off from an output terminal, the clamping voltage can be set in a manner to reduce to a normal voltage in an IGN-line. Therefore, a peak power value of a power loss caused by the surge voltage at the output transistor can be reduced, whereby generation of heat at the output transistor can be reduced. Therefore, the chip size of the power IC can be reduced.

Owner:NISSAN MOTOR CO LTD

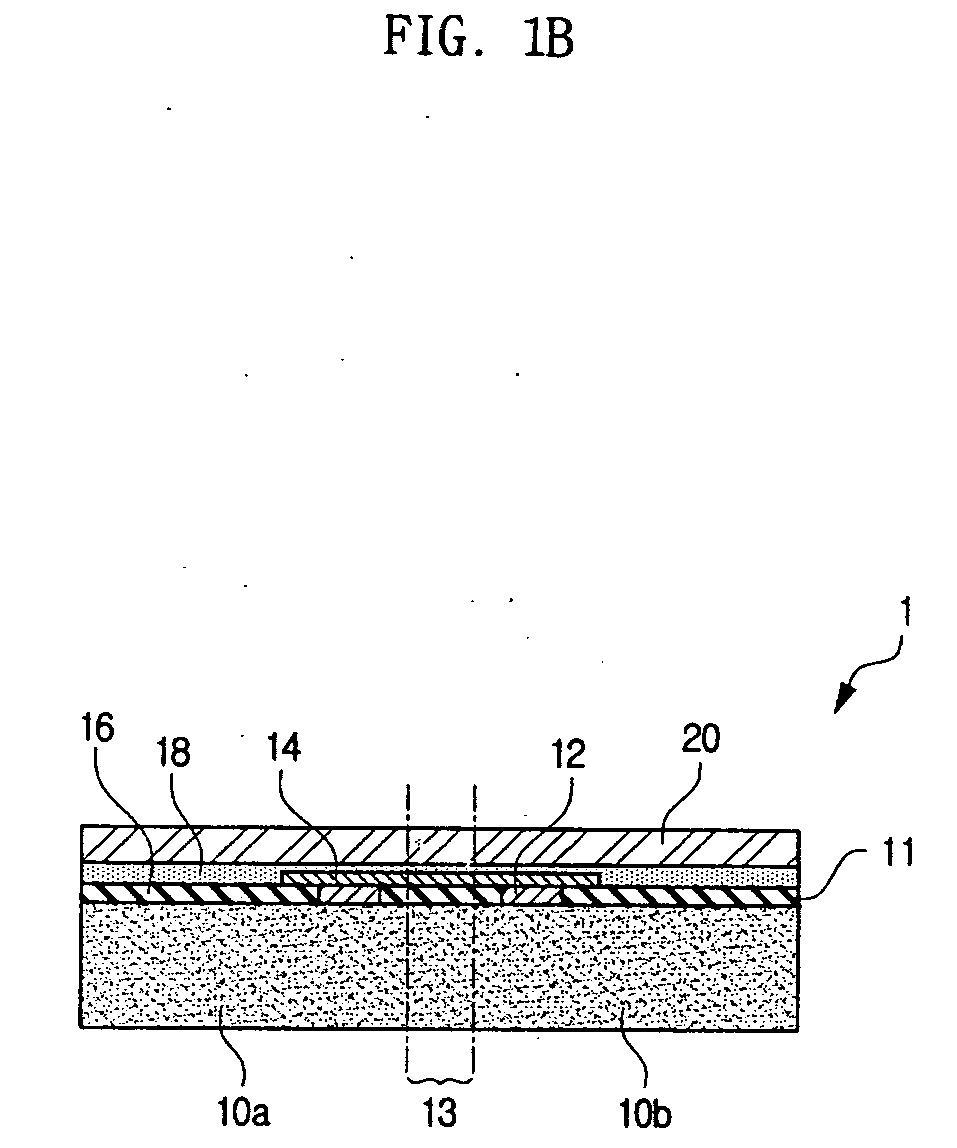

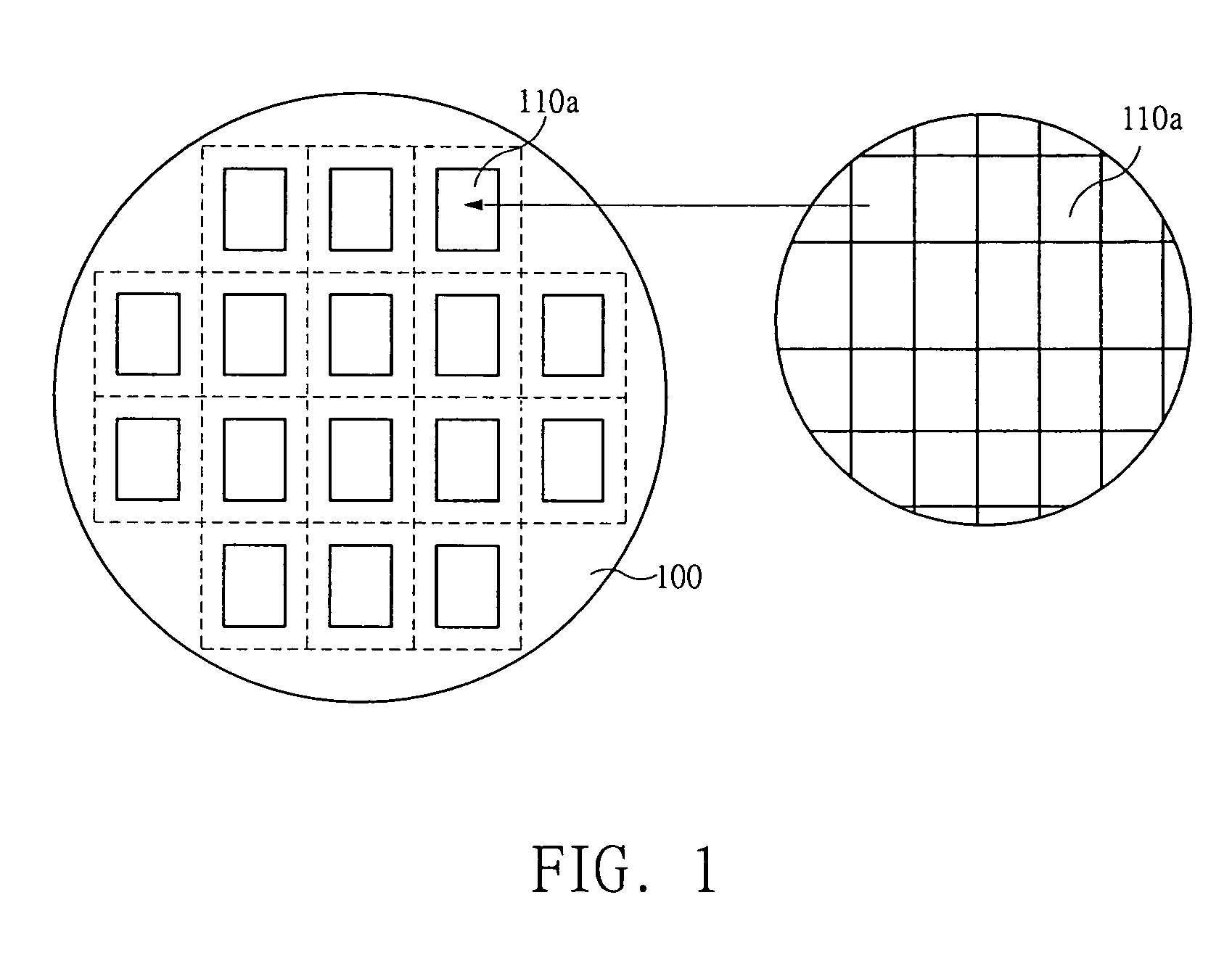

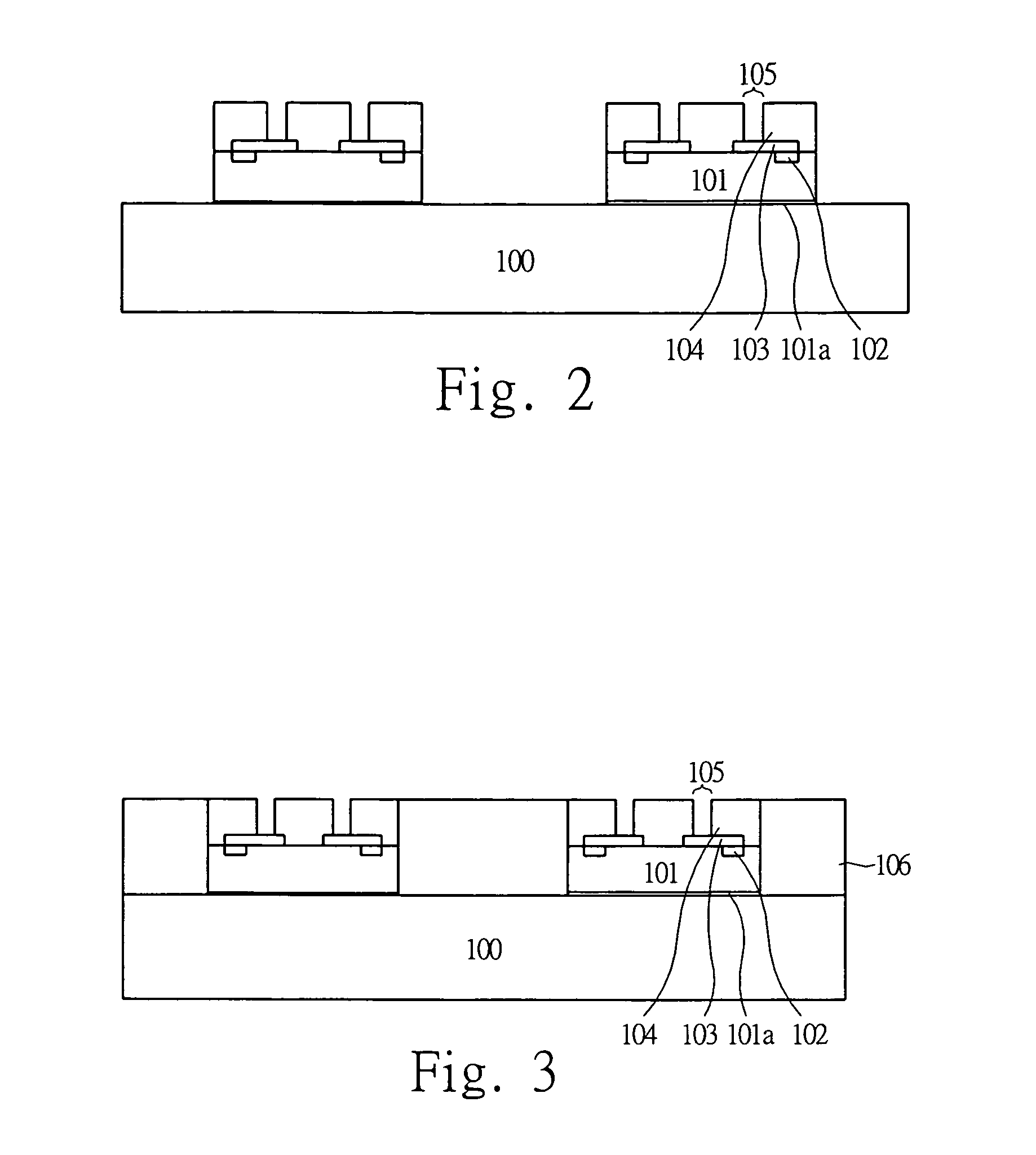

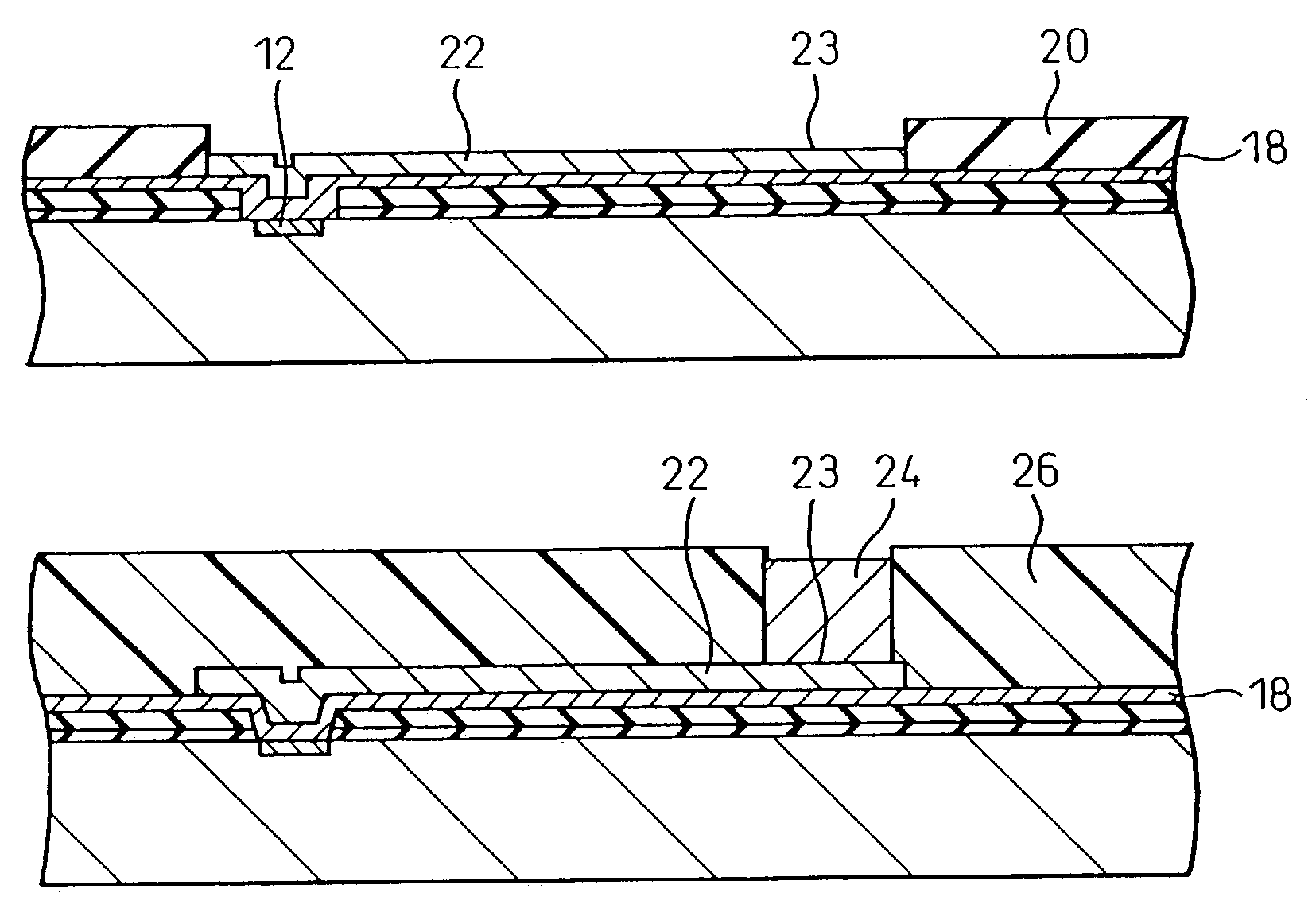

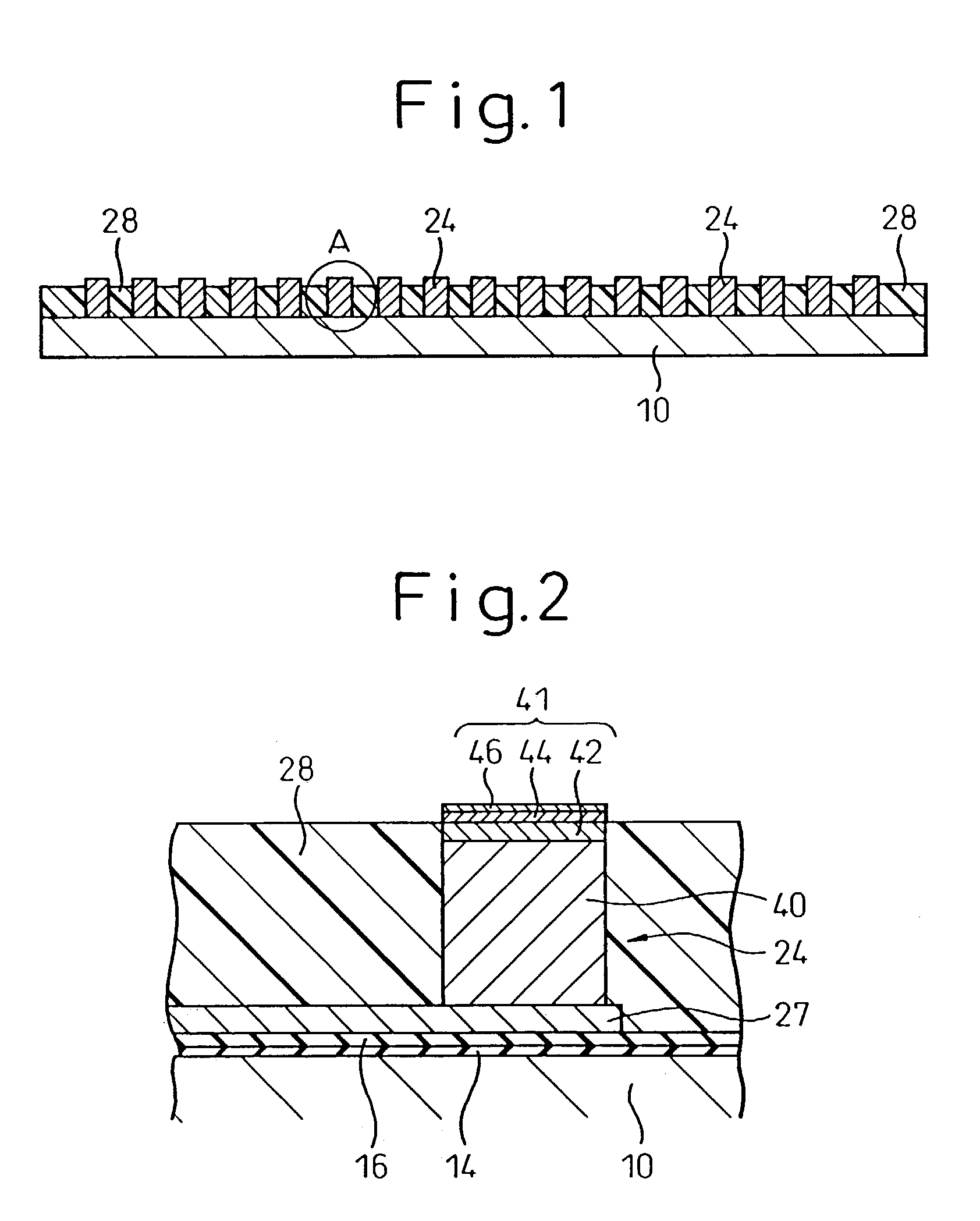

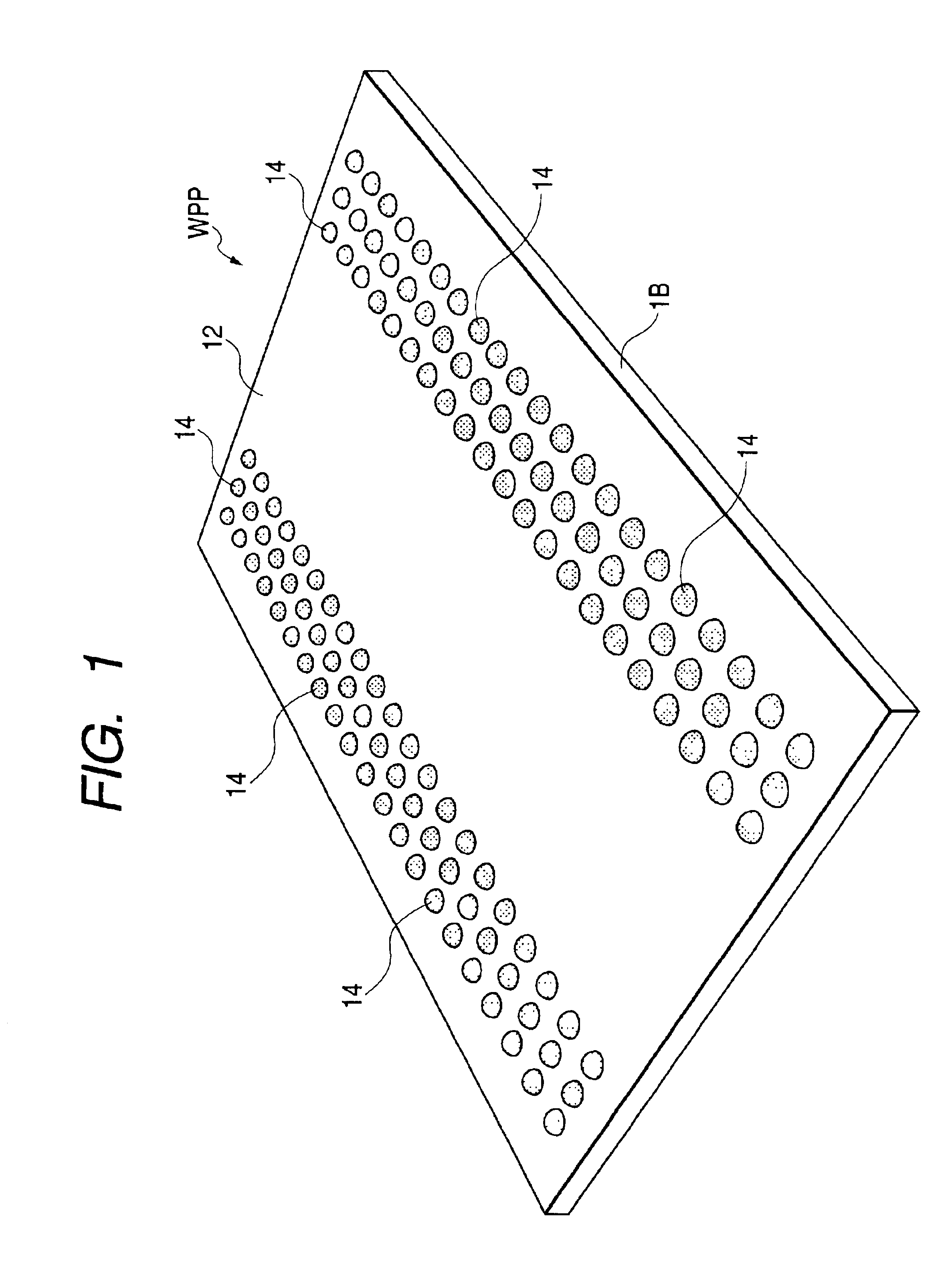

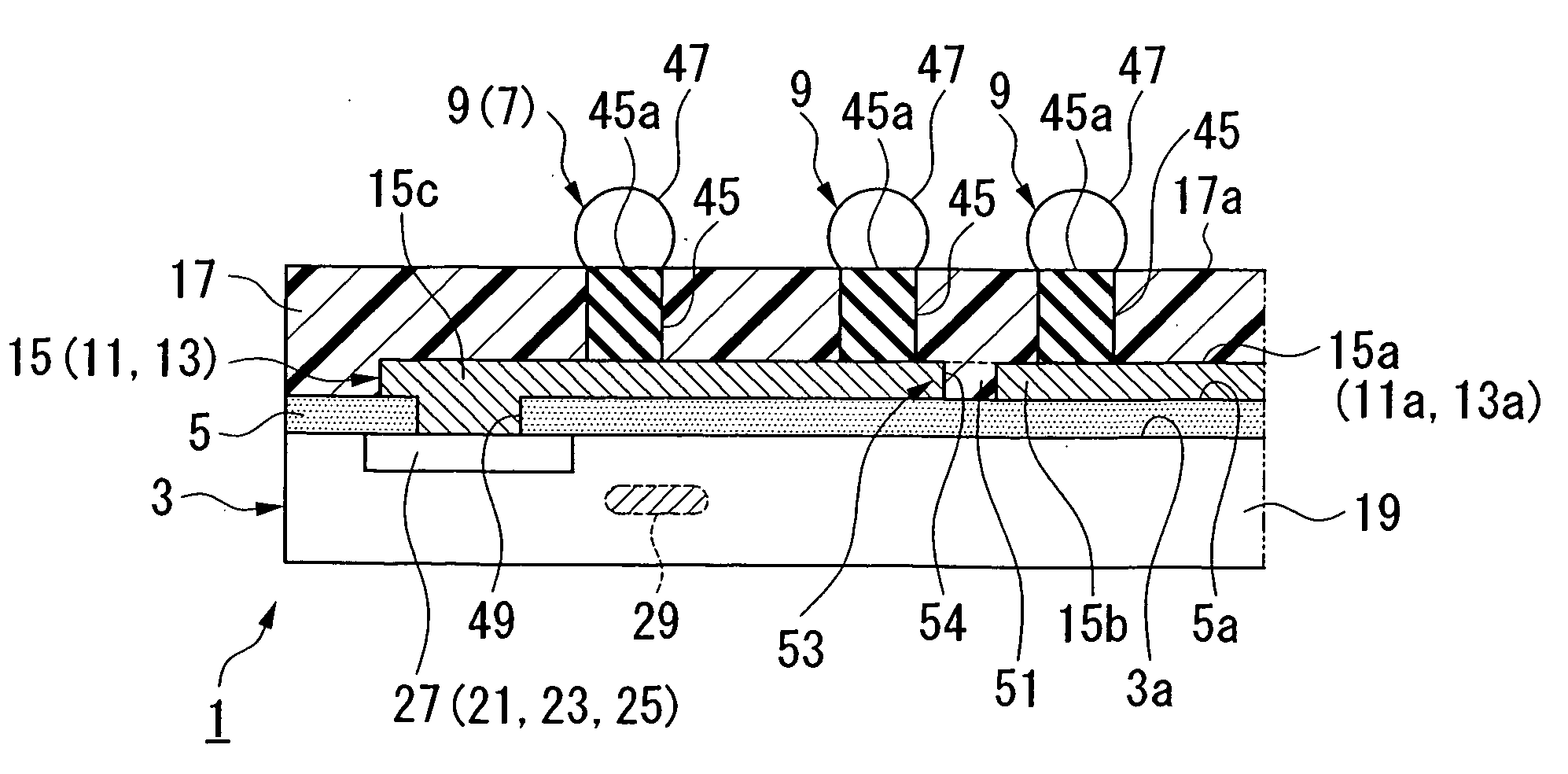

Wafer level stack structure for system-in-package and method thereof

ActiveUS20050104181A1Semiconductor/solid-state device detailsSolid-state devicesChip sizeSystem in package

A wafer level stack structure, including a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, wherein the first wafer and the second wafer are stacked, and wherein the first wafer and the second wafer are coupled to each other. A method of forming a wafer level stack structure, including forming a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, forming a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, stacking the first wafer and the second wafer, and coupling the first wafer and the second wafer to each other. A system-in-package, including a wafer level stack structure including at least one first device chip with a first plurality of input / output (I / O) pads and at least one second device chip with a second plurality of I / O pads, and a common circuit board to which the wafer level stack structure is connected. A method of forming a system-in-package for containing a wafer level stack structure, including forming a wafer level stack structure including at least one first device chip having a first plurality of input / output (I / O) pads and at least one second device chip having a second plurality of I / O pads, and forming a common circuit board to which the wafer level stack structure is connected.

Owner:SAMSUNG ELECTRONICS CO LTD

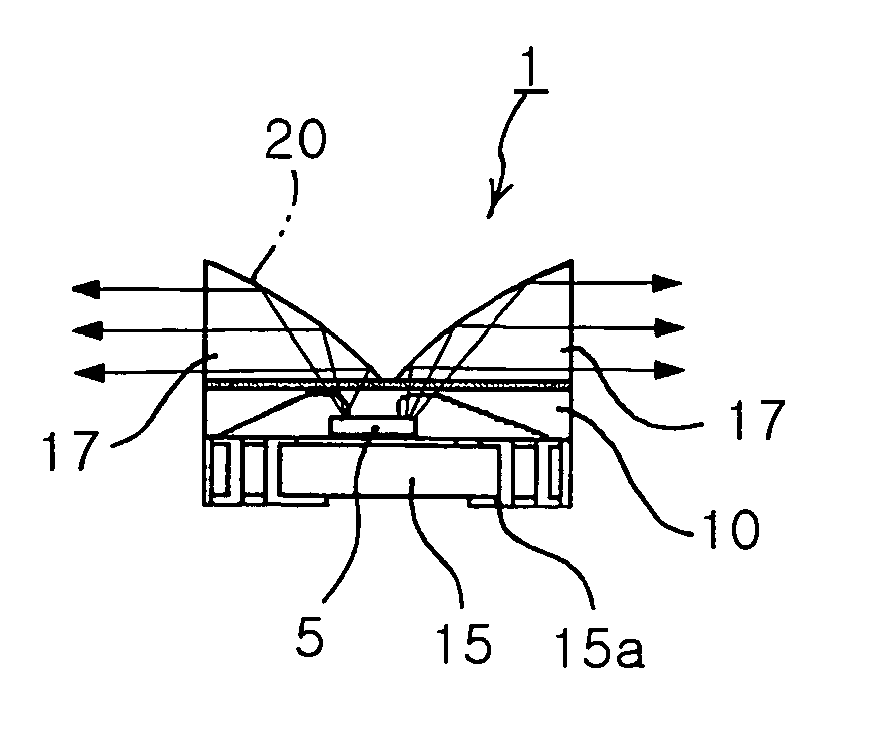

Side-emitting LED package and method of manufacturing the same

InactiveUS20060273337A1Effective reflectionEasy to manufactureSolid-state devicesSemiconductor devicesChip sizeEngineering

The invention relates to a side-emitting LED package and a manufacturing method thereof. The side-emitting LED package includes a substrate with an electrode formed thereon, and a light source disposed on the substrate and electrically connected to the electrode. The side-emitting LED package also includes a molded part having an upper surface with a center thereof depressed concavely, covering and protecting the substrate and the light source, and a reflection layer covering an entire upper surface of the molded part to reflect light sideward from the molded part which forms a light transmitting surface. The package is not restricted in the shape of the molded part and is not affected by the LED chip size, enabling a compact structure. The invention can also process a substrate by a PCB process, enabling mass-production.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

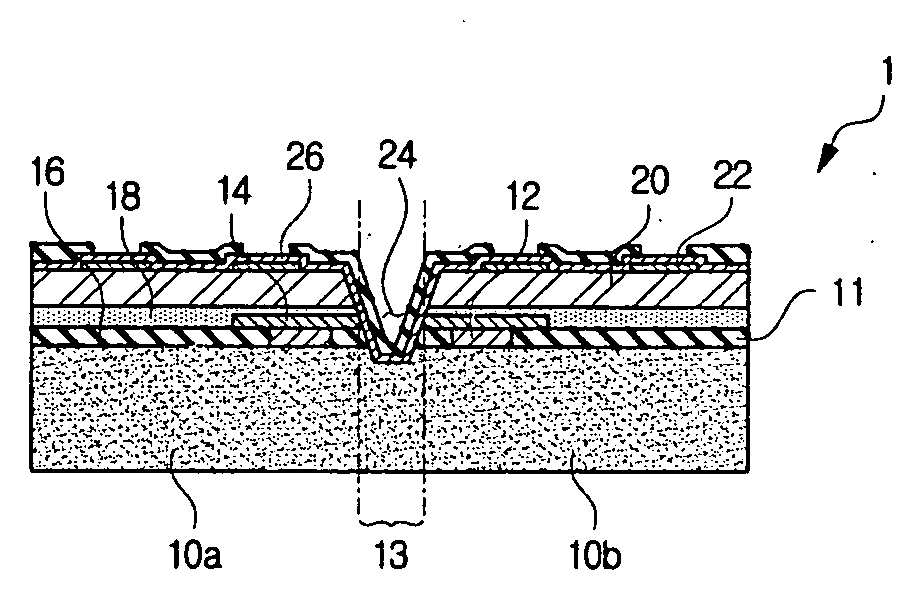

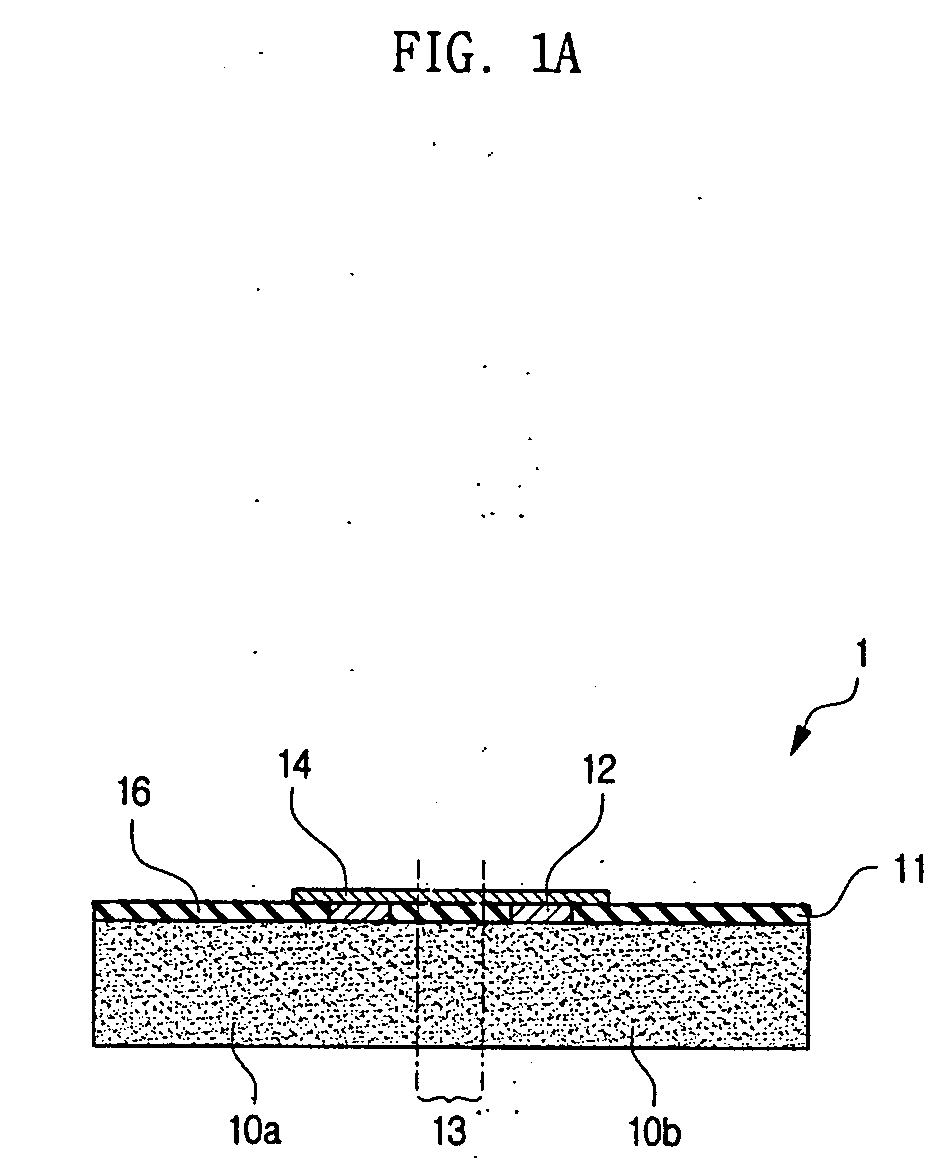

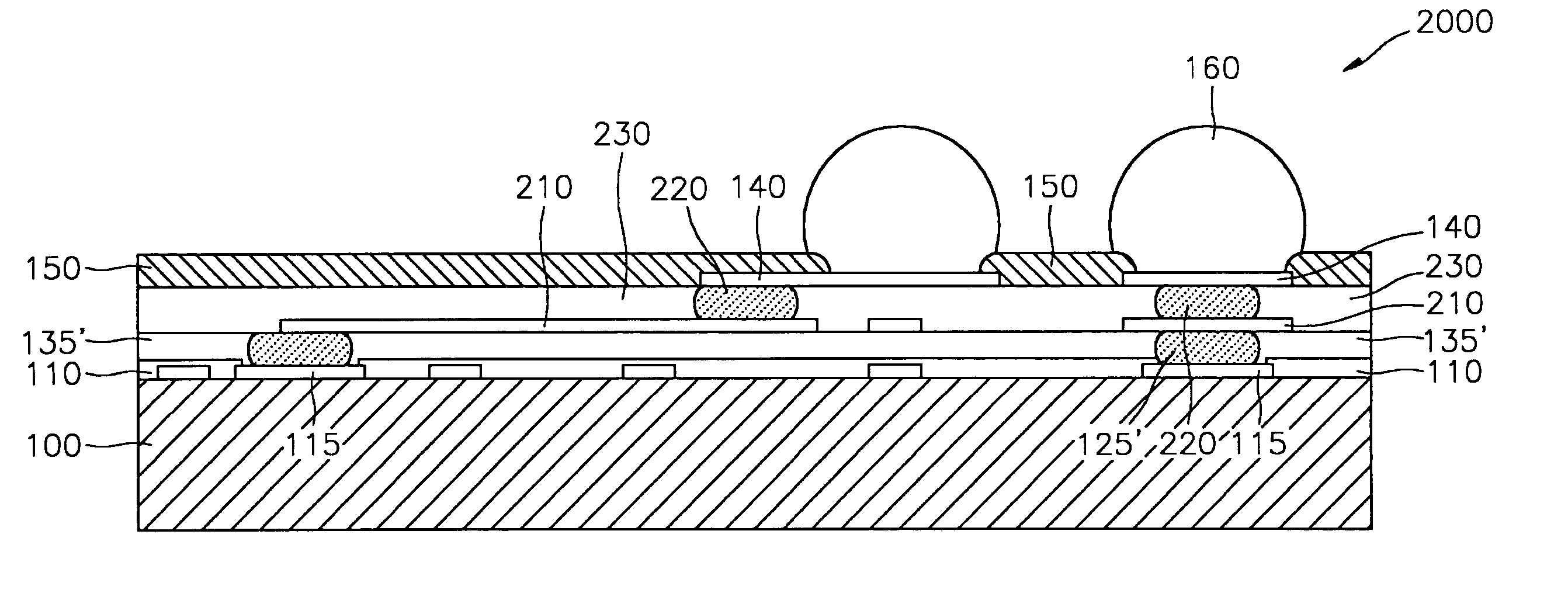

Semiconductor device packaged into chip size and manufacturing method thereof

InactiveUS20060060984A1Low costReduce methodSemiconductor/solid-state device detailsSolid-state devicesChip sizeEngineering

A semiconductor device includes a semiconductor substrate having an integrated circuit and at least one connection pad, and at least one external connection electrode electrically connected with the connection pad. A first sealing material is provided on the semiconductor substrate around the external connection electrode, each impurity concentration of an Na ion, a K ion, a Ca ion and Cl ion contained in the first sealing material being not greater than 10 ppm. A second sealing material is provided on at least one of a lower surface and a peripheral side surface of the semiconductor substrate, a total impurity concentration of an Na ion, a K ion, a Ca ion and a Cl ion contained in the second sealing material being not smaller than 100 ppm.

Owner:TERAMIKROS INC

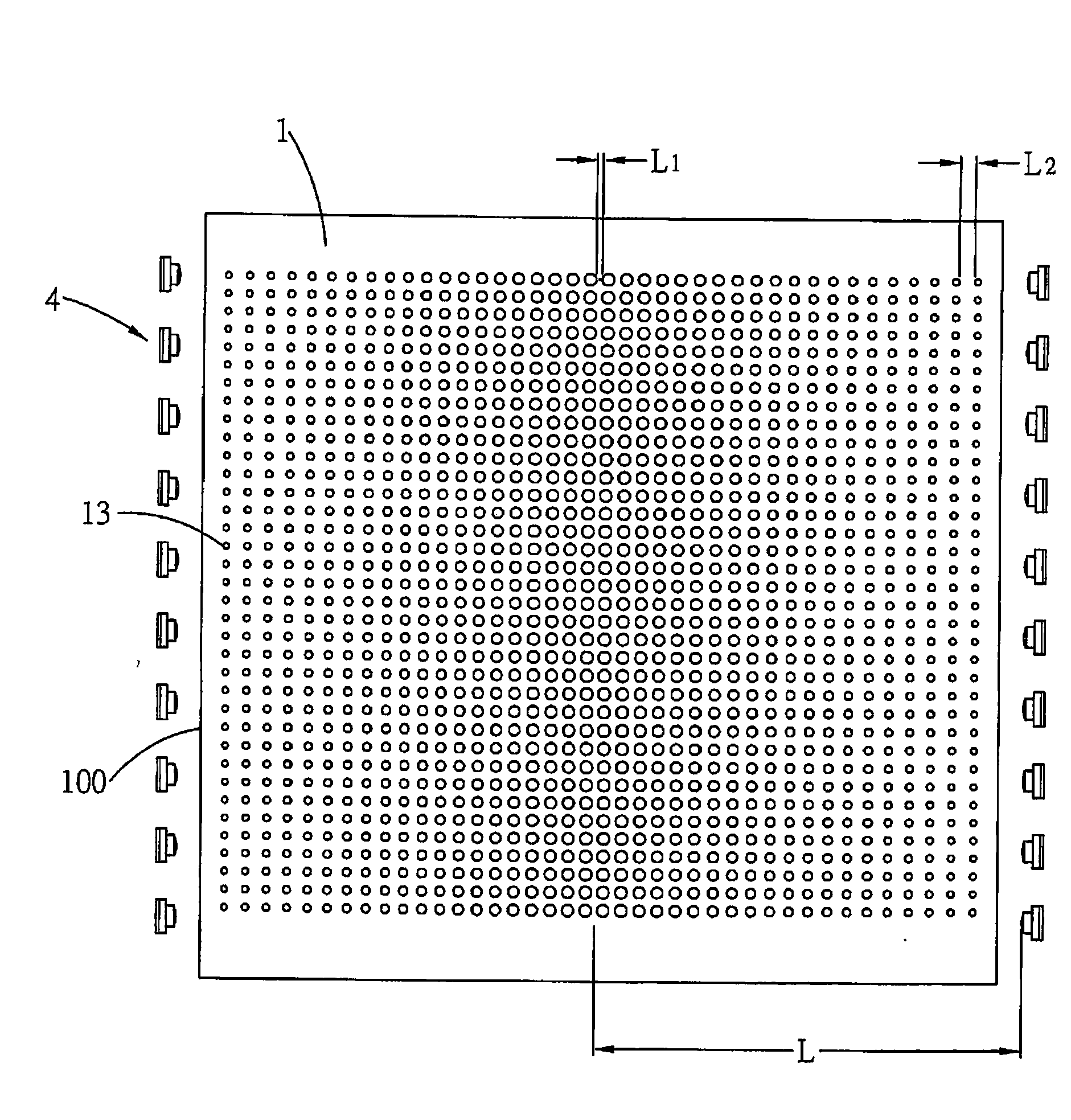

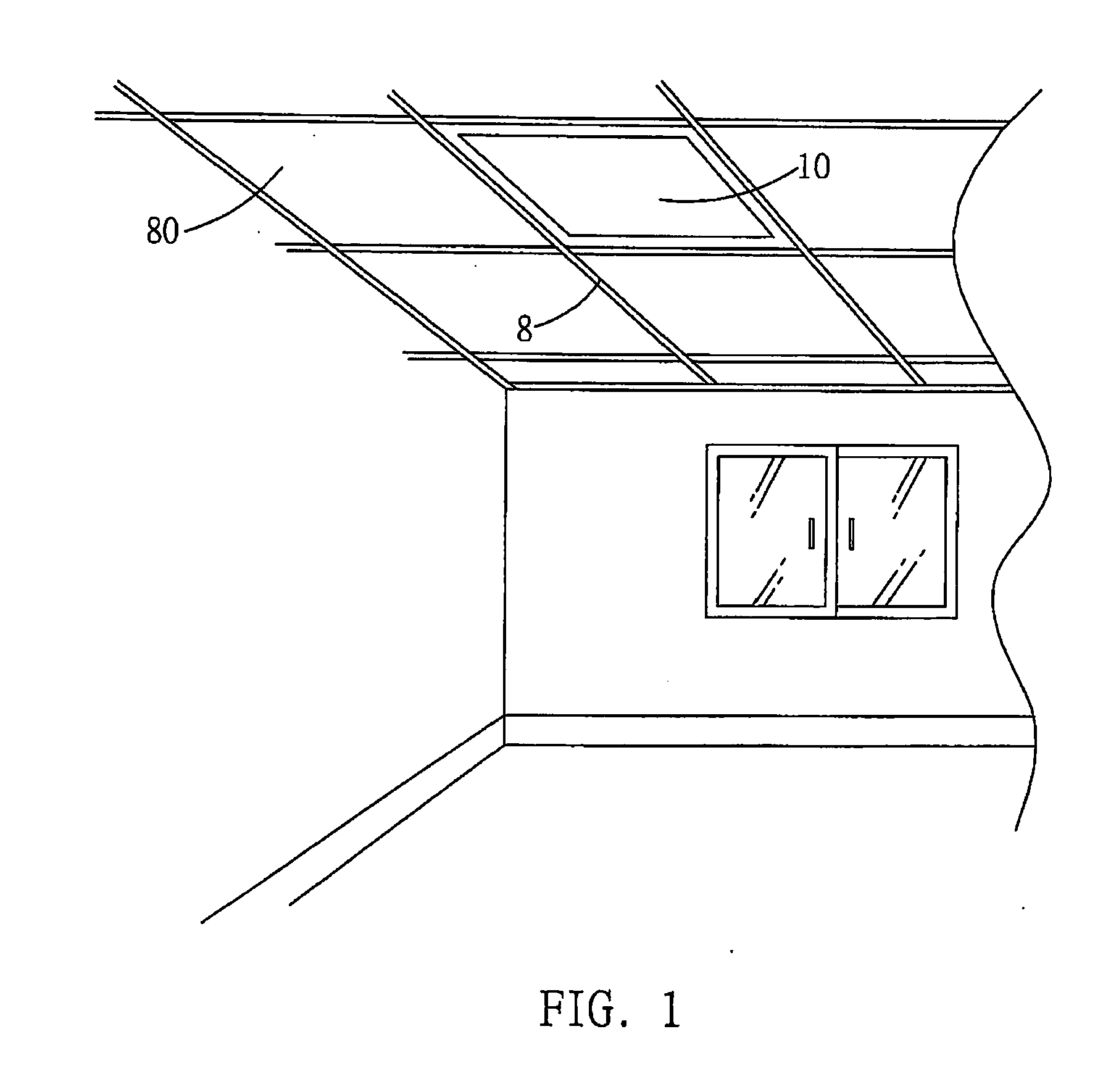

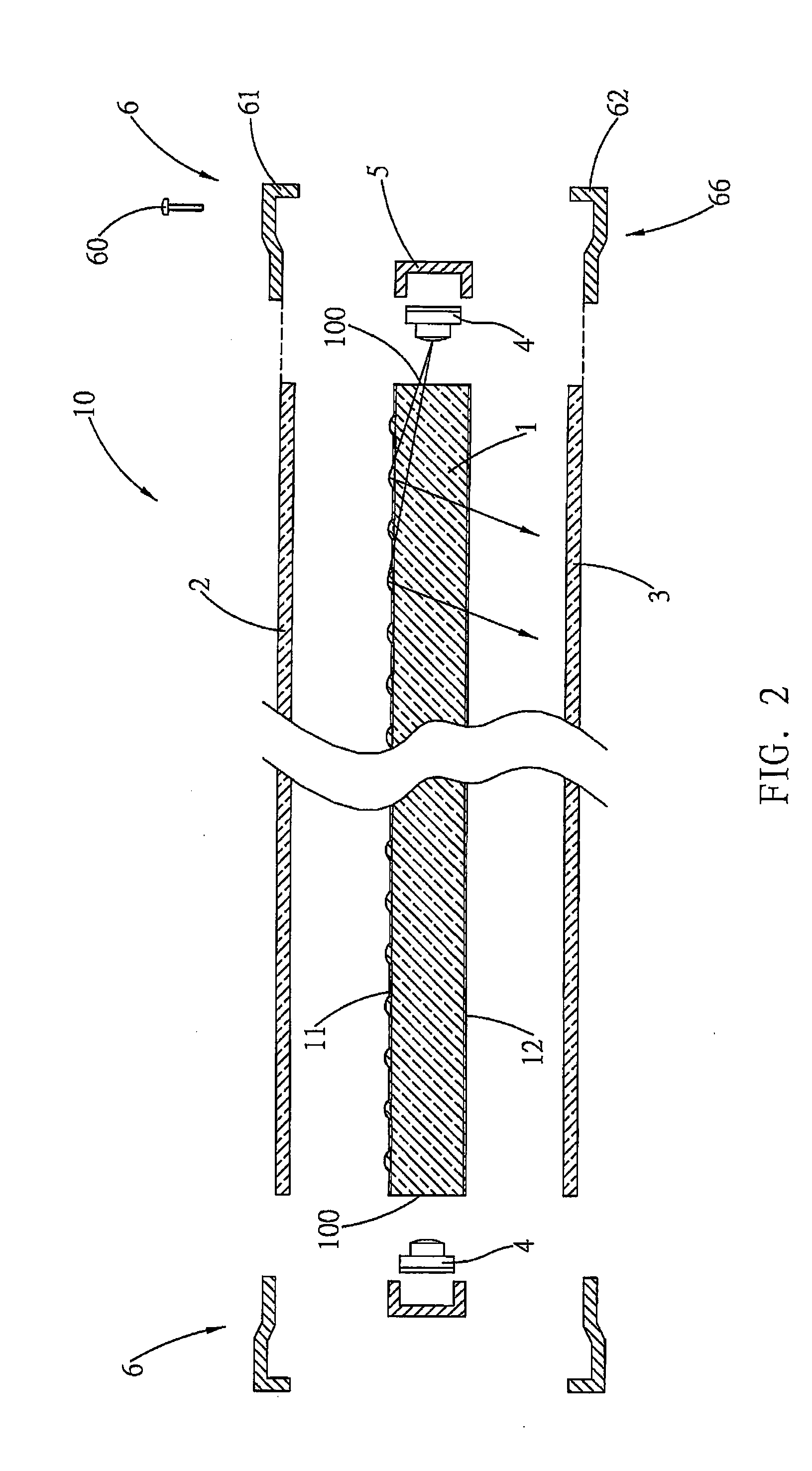

Refraction-type LED ceiling lamp

InactiveUS20100254121A1Effectively utilize lightUniform strengthPlanar light sourcesPoint-like light sourceFiberLight guide

A refraction-type LED ceiling lamp, especially a plate-type ceiling lamp which is used on an indoor ceiling, includes primarily a fiber light guide plate, a reflection surface of which is provided with multiple chip-shape reflection elements, distributed in arrays. A chip size of the reflection elements decreases gradually toward an entrance surface by a geometric series; whereas, a gap between the reflection elements increases gradually. A reflection curve of the reflection element allows light to be projected out uniformly and a required illumination angle to be achieved.

Owner:广东佳兆业佳云科技股份有限公司

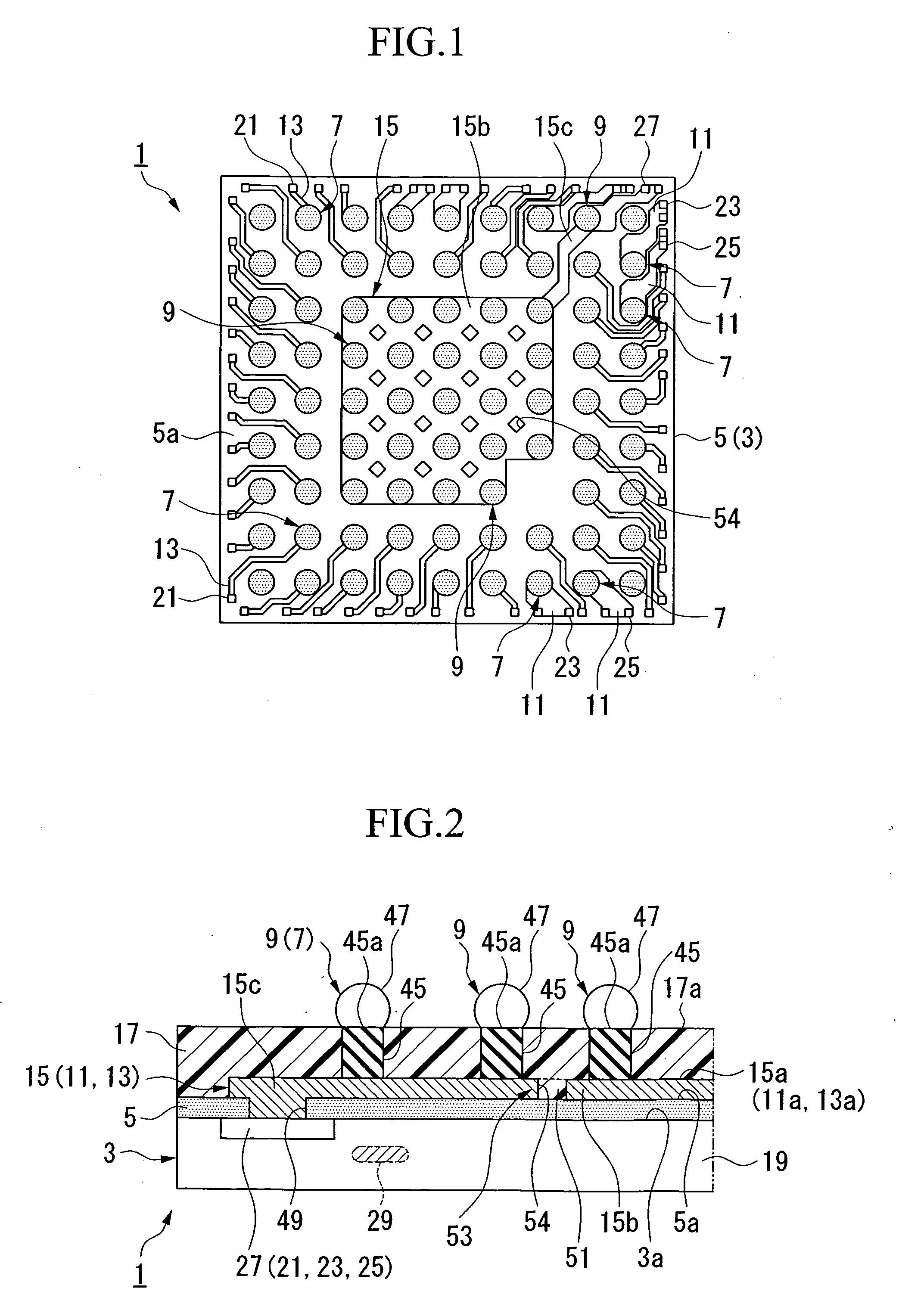

Wafer level chip size package having rerouting layers

InactiveUS6861742B2Reduce turnaround timeCost of wafer is decreasedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsChip sizeSemiconductor

A semiconductor integrated circuit device includes a semiconductor substrate, a circuit element formed on one major surface of the semiconductor substrate and constituting an integrated circuit having a plurality of functions or a plurality of characteristics, an internal connection terminal, connected to the integrated circuit, for selecting one of the plurality of functions or one of the characteristics in the integrated circuit, an insulating layer covering the internal connection terminal such that the internal connection terminal is selectively exposed, and an external connection terminal arranged on the insulating layer. One of the plurality of functions or one of the plurality of characteristics is selected by a connection state between the internal connection terminal and the external connection terminal.

Owner:RENESAS ELECTRONICS CORP

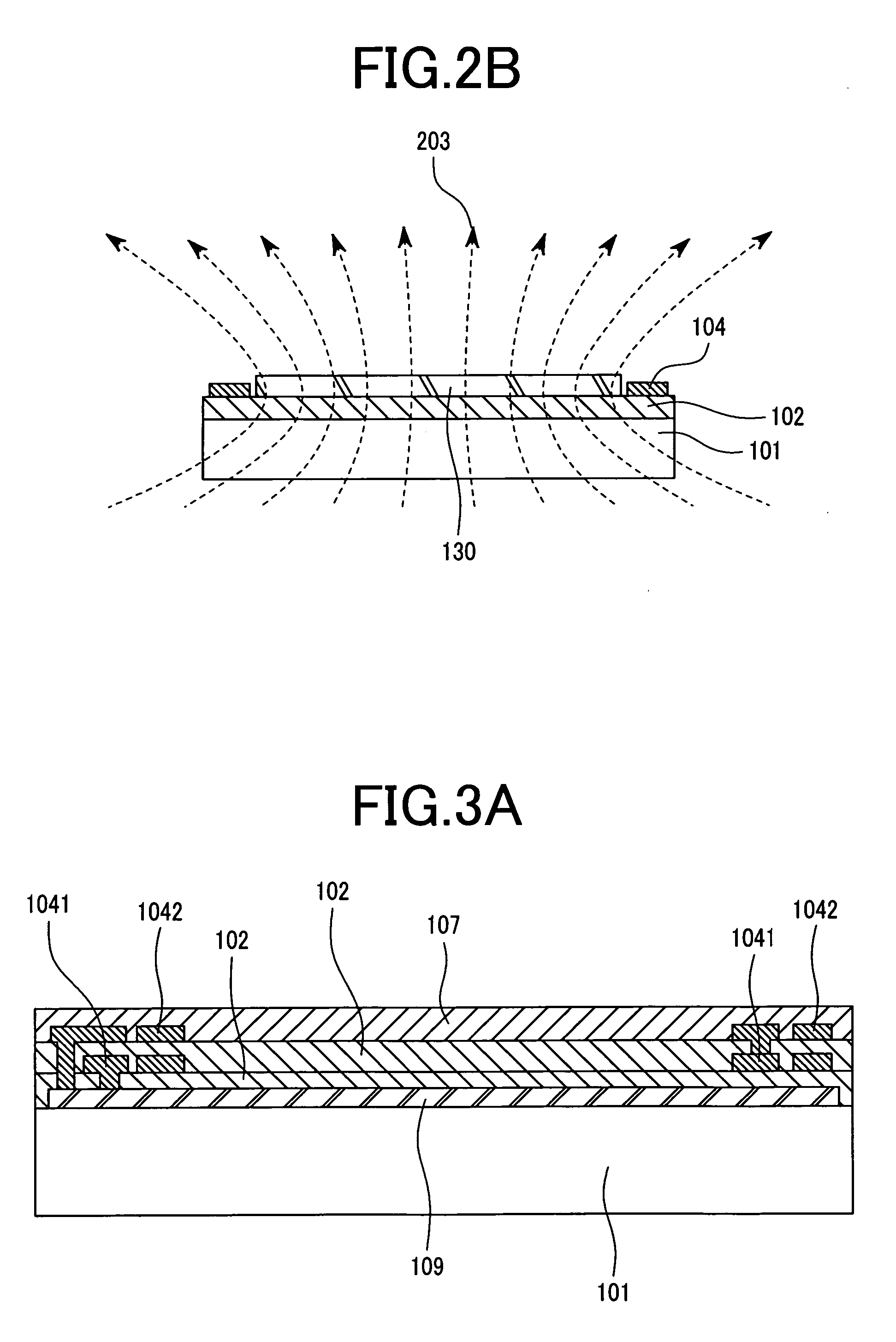

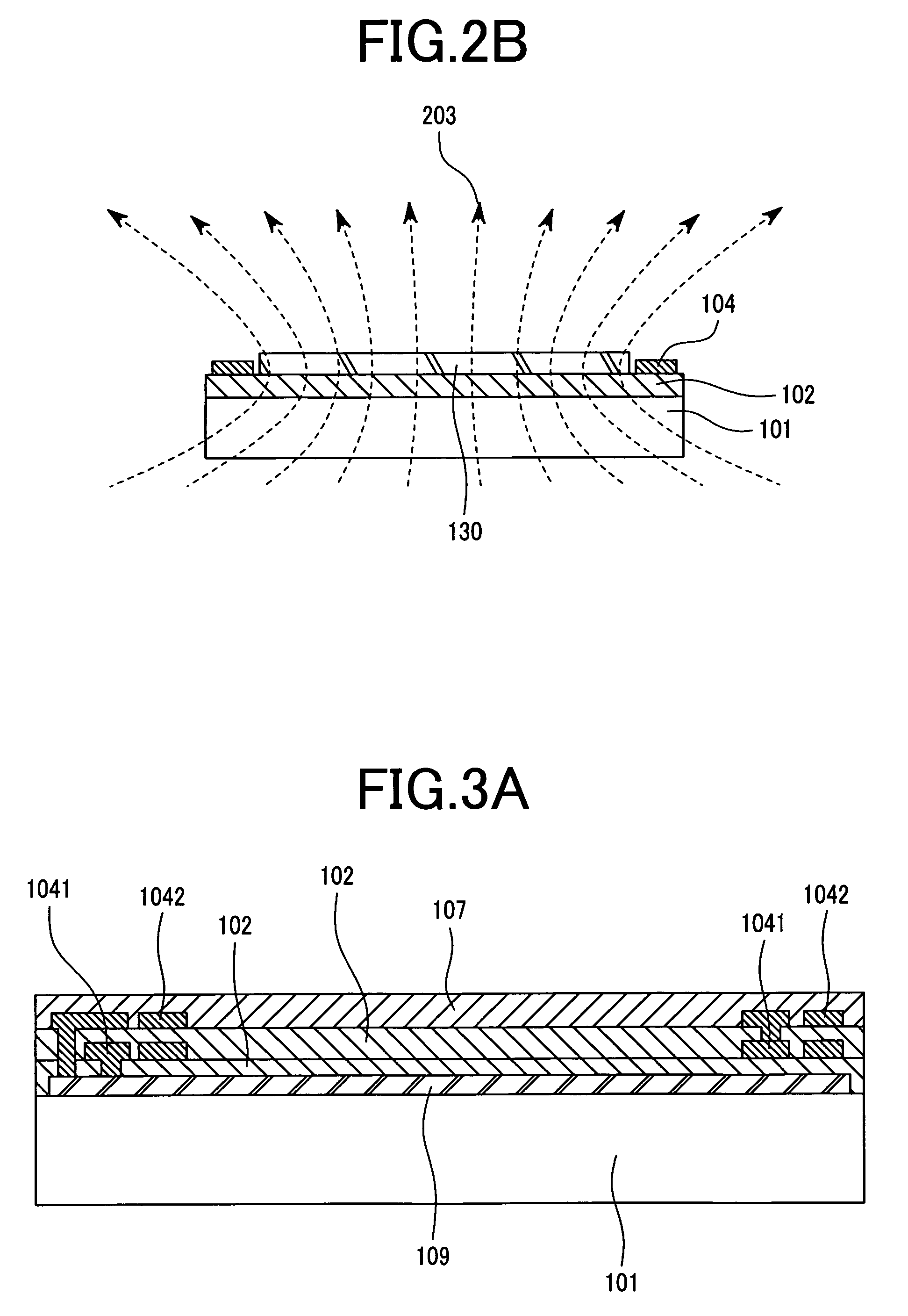

Semiconductor element and wafer level chip size package therefor

InactiveUS20050199995A1Efficiently dissipatedEasily discriminatedSemiconductor/solid-state device detailsSolid-state devicesChip sizeDevice material

A semiconductor device, encapsulated in a wafer level chip size package (WLCSP), includes a plurality of pad electrodes formed on the surface of a semiconductor chip, wherein a first insulating layer is formed on the surface of the semiconductor chip except the pad electrodes; a plurality of connection electrodes and at least one heat-dissipation electrode are formed on the surface of the first insulating layer; the pad electrodes and the connection electrodes are mutually connected via a first wiring portion; the heat-dissipation electrode is connected with a second wiring portion; and a second insulating layer is formed to enclose the electrodes and wiring portions, wherein the second wiring portion is arranged in proximity to a heating portion of the semiconductor chip and is formed on the surface of the first insulating layer except the prescribed region corresponding to the first wiring portion.

Owner:YAMAHA CORP

Flip chip on glass sensor package

InactiveUS6849916B1Rule out the possibilityLow and nonexistent dew pointTelevision system detailsSemiconductor/solid-state device detailsChip sizeComputer science

An image sensor package includes an image sensor having an active area and bond pads on a front surface of the image sensor. A window is mounted to the image sensor by flip chip bumps formed between the bond pads of the image sensor and interior traces on an interior surface of the window. The window has an area less than an area of the front surface of the image sensor. A bead is formed between the window and the front surface of the image sensor thus forming a sealed cavity in which the active area is located. The bead has sides coplanar with sides of the image sensor such that the image sensor package is chip size.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

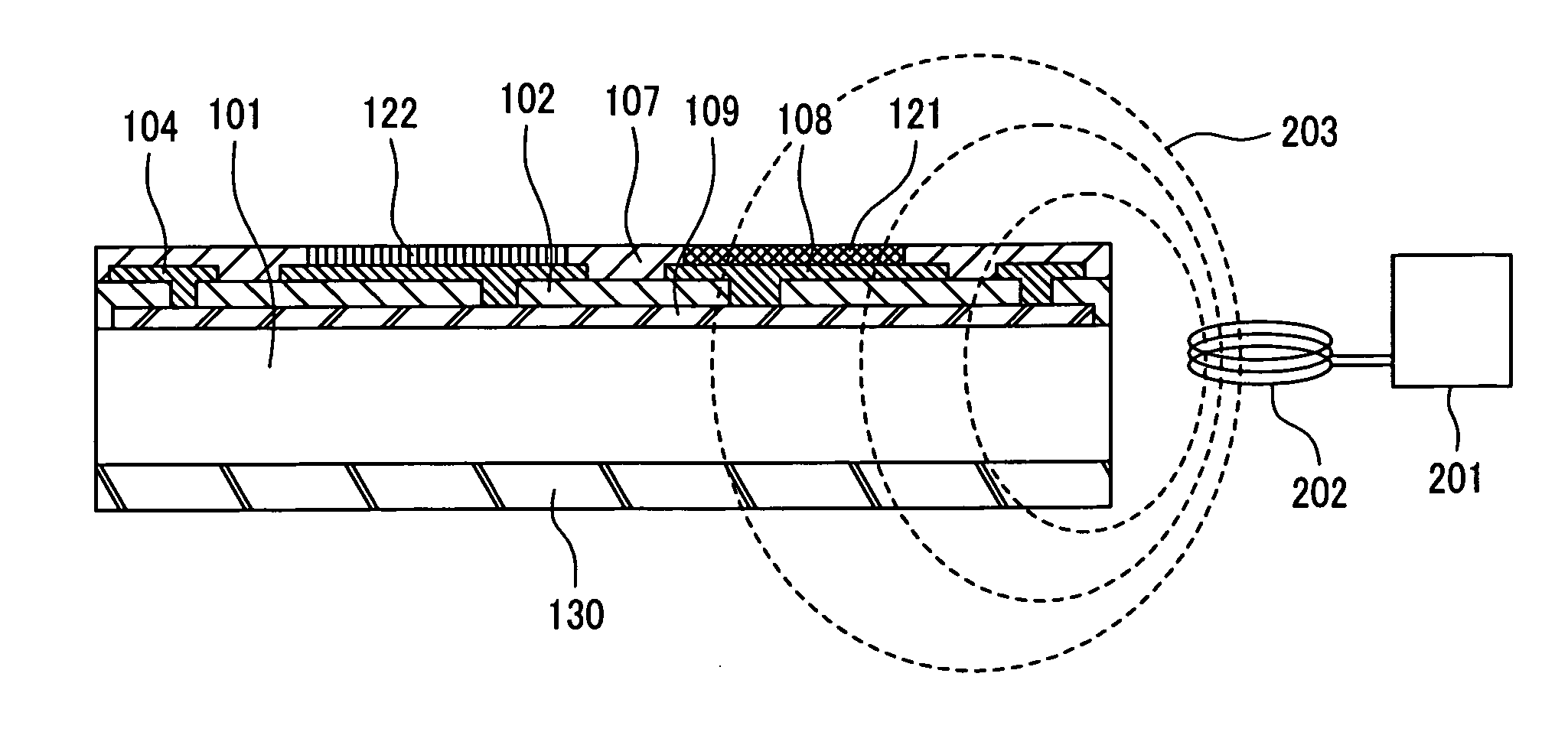

Semiconductor chip with coil antenna and communication system

InactiveUS20050173532A1Good communication characteristicsIncrease parasitic capacitanceLoop antennas with ferromagnetic coreAntenna supports/mountingsElectromagnetic couplingElectrical conductor

The present invention intends to prevent the communication distance from becoming shorter with a reduction in size of a coil antenna to the chip size and with a consequent decrease of an induced voltage. According to the present invention there is provided a semiconductor chip having a coil antenna and a circuit surface and adapted to transmit and receive signals by radio to and from an external device. The semiconductor chip has a configuration for increasing an electromagnetic coupling coefficient between the coil antenna and the external device. According to a concrete example thereof, a magnetic material is disposed, the coil antenna is formed by a stacked structure comprising plural conductor layers and insulating layers superimposed one on another, or the coil antenna is disposed outside an external form of a circuit of the semiconductor chip.

Owner:HITACHI LTD

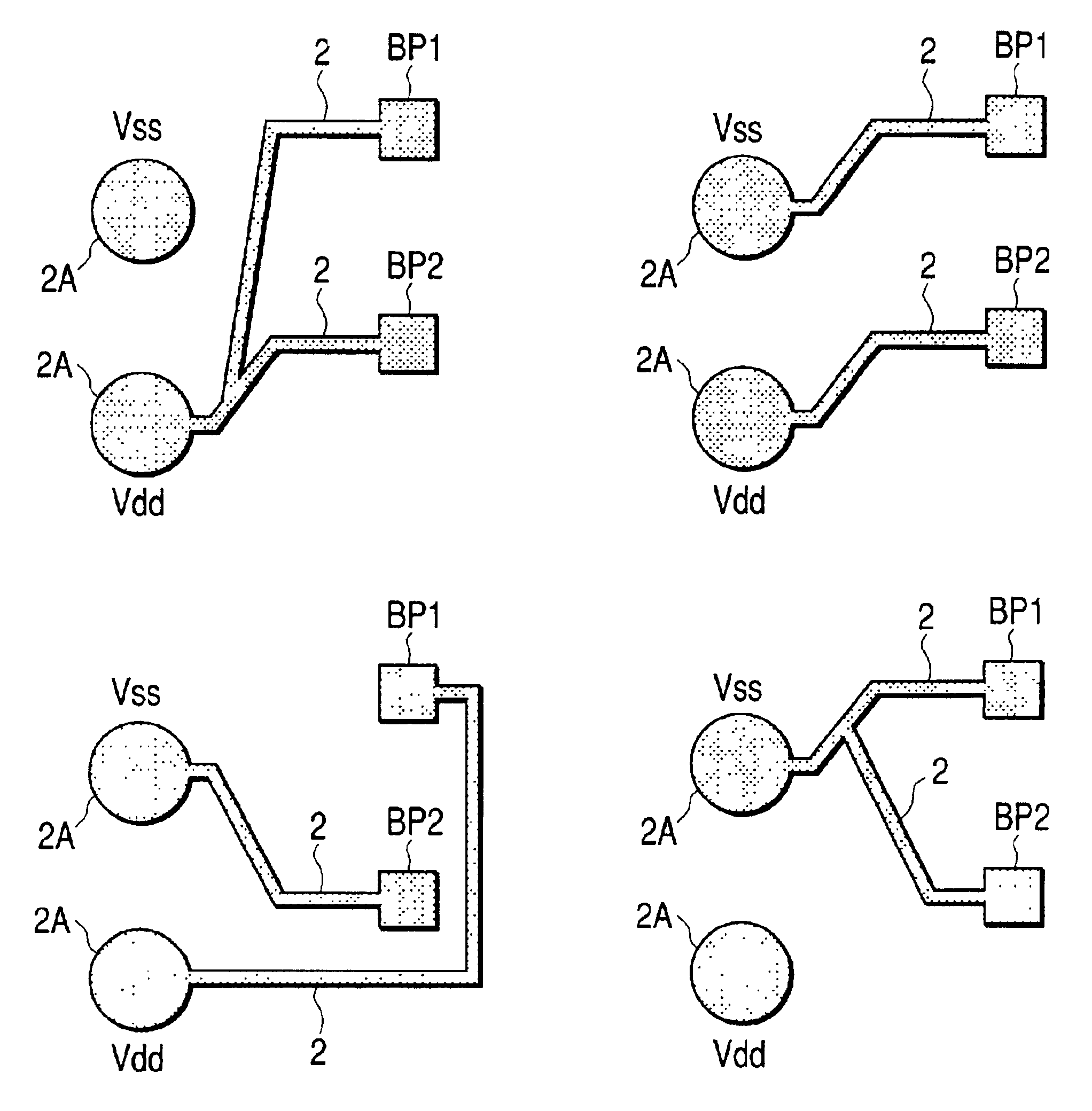

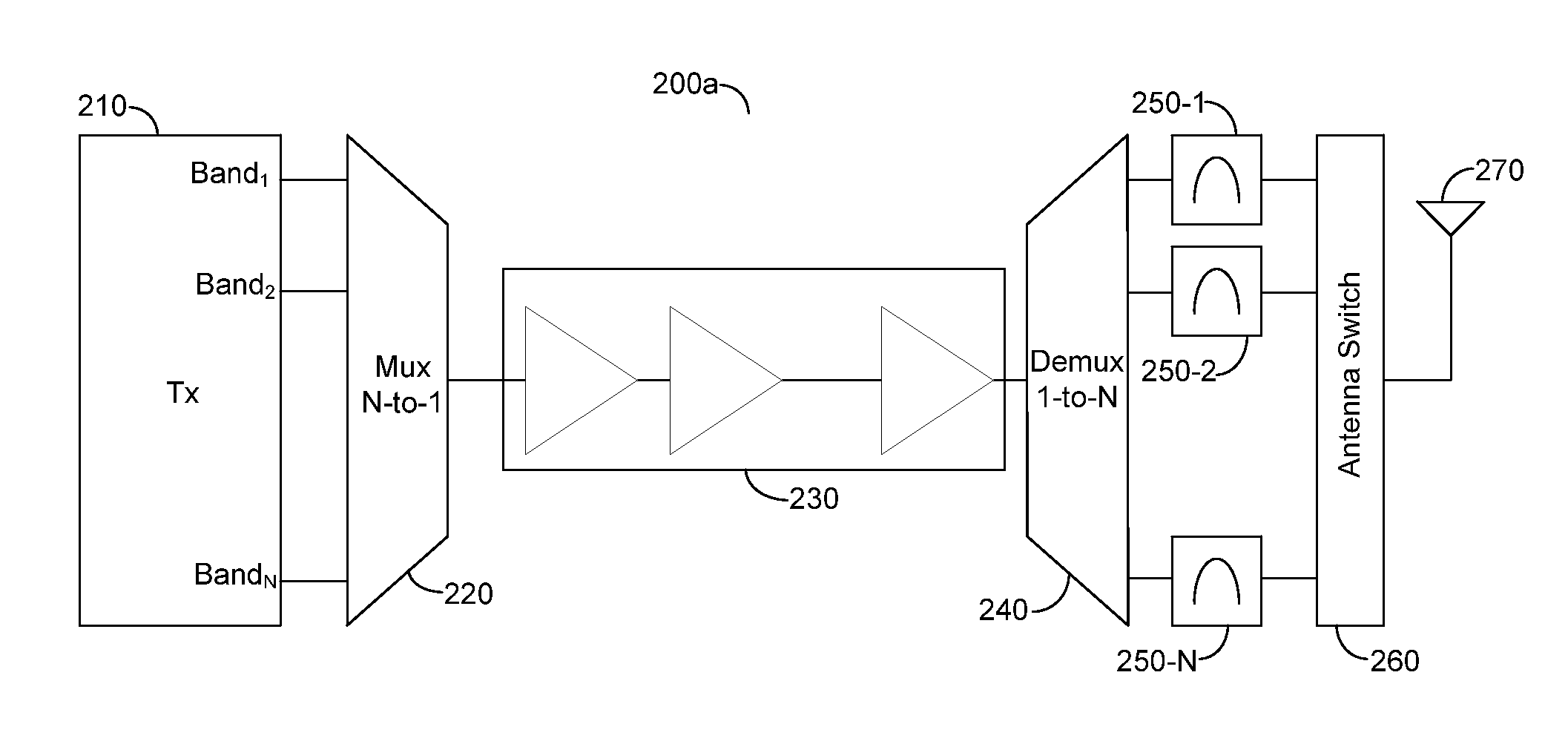

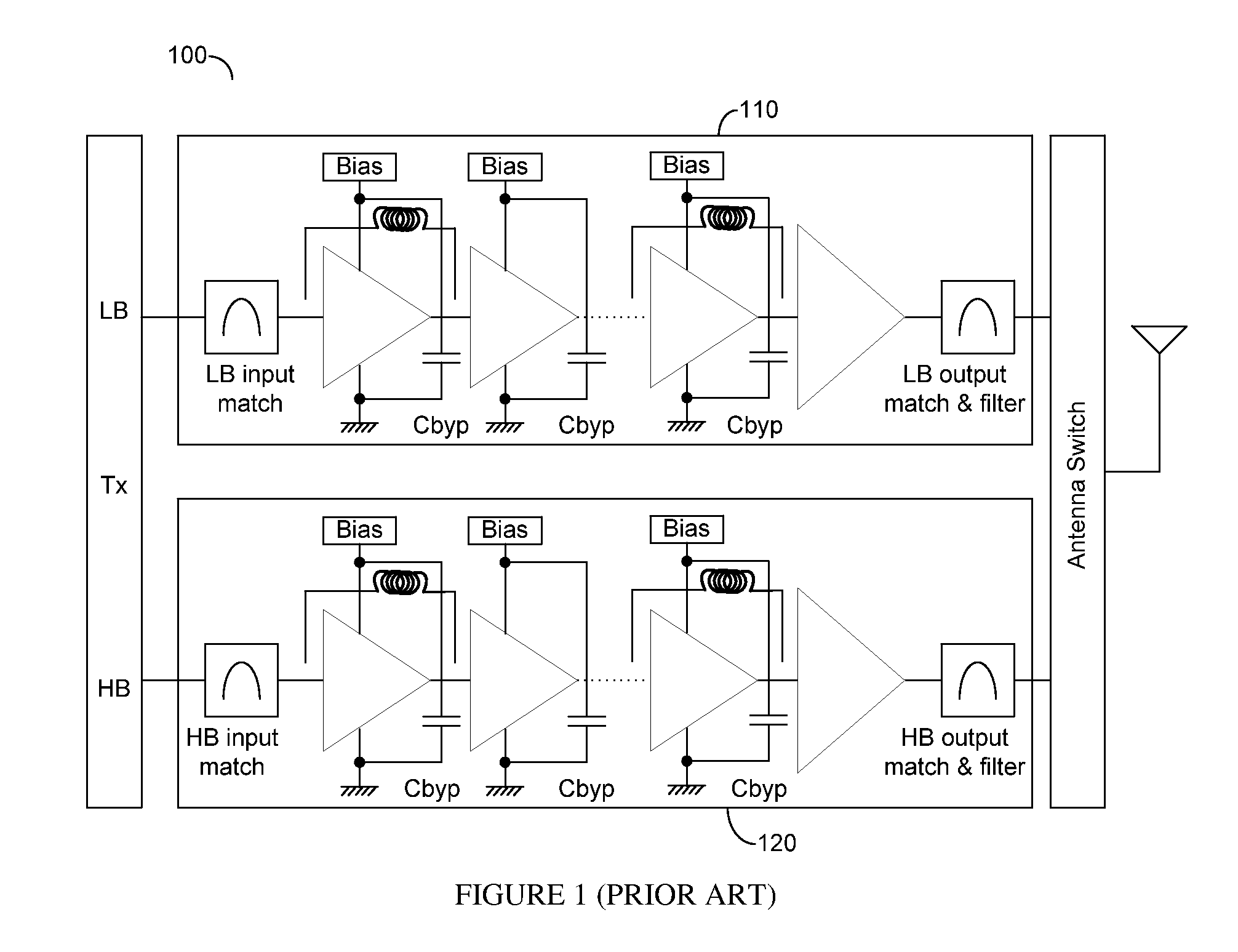

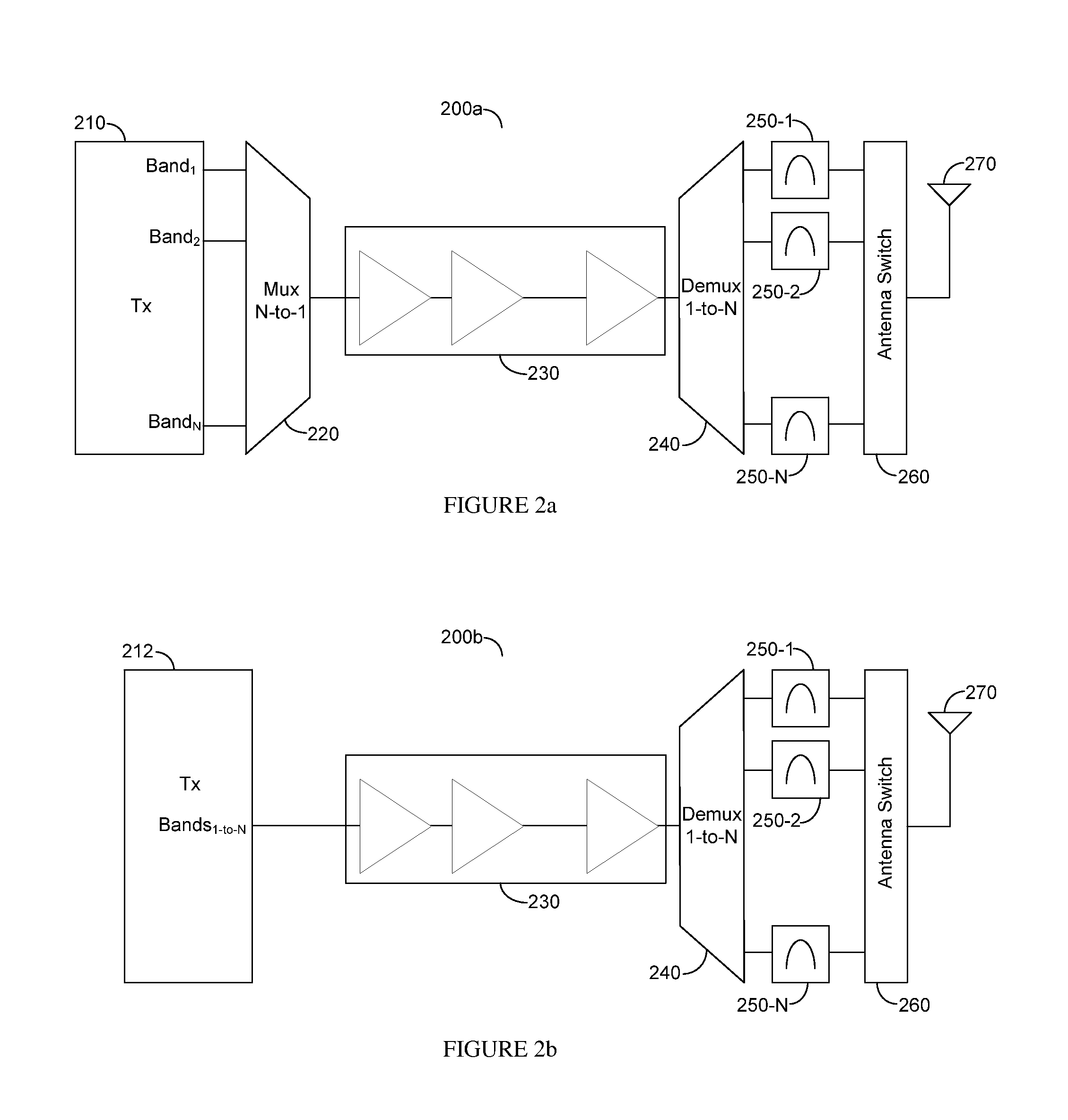

Multi-Band/Multi-Mode Power Amplifier with Signal Path Hardware Sharing

ActiveUS20140015603A1Amplifier modifications to reduce noise influencePower amplifiersMulti bandEnd stages

Existing multi-band / multi-mode (MB / MM) power amplifiers (PAs) use separate signal paths for the different covered frequency bands. This results in a large degree of hardware duplication and to a large die size and cost. Solutions that achieve hardware sharing between the different signal paths of MB / MM PAs are shown. Such sharing includes bias circuit and bypass capacitors sharing, as well as sharing front-end stages and the output stage of the PA. Signal multiplexing may be realized in the transmitter or at the PA front-end while the signal de-multiplexing can be realized either in the PA output stage or at the front-end of the output stage. Such circuits can be applied with saturated and linear MB / MM PAs with adjacent or non-adjacent bands.

Owner:QORVO INT PTE LTD

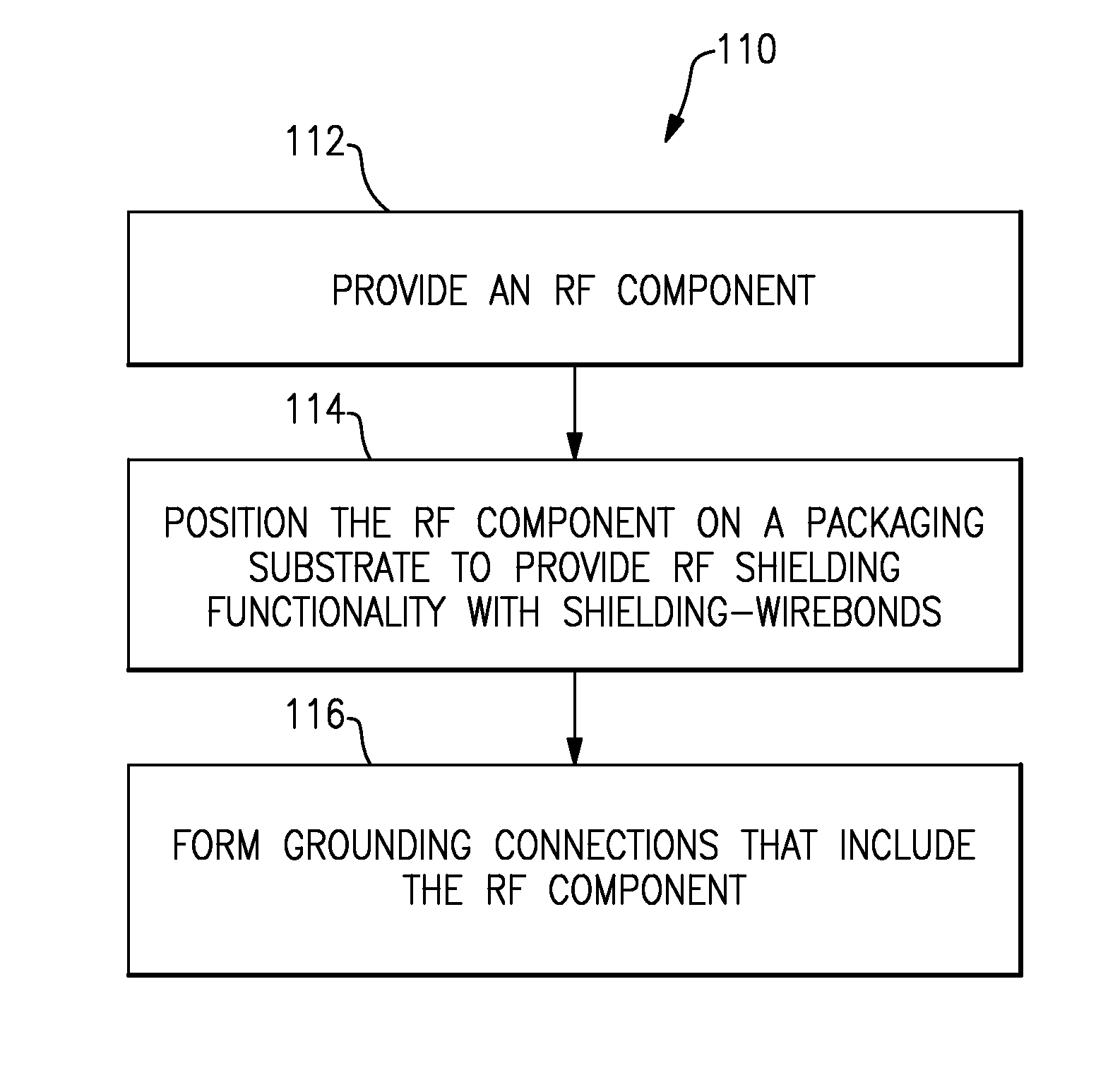

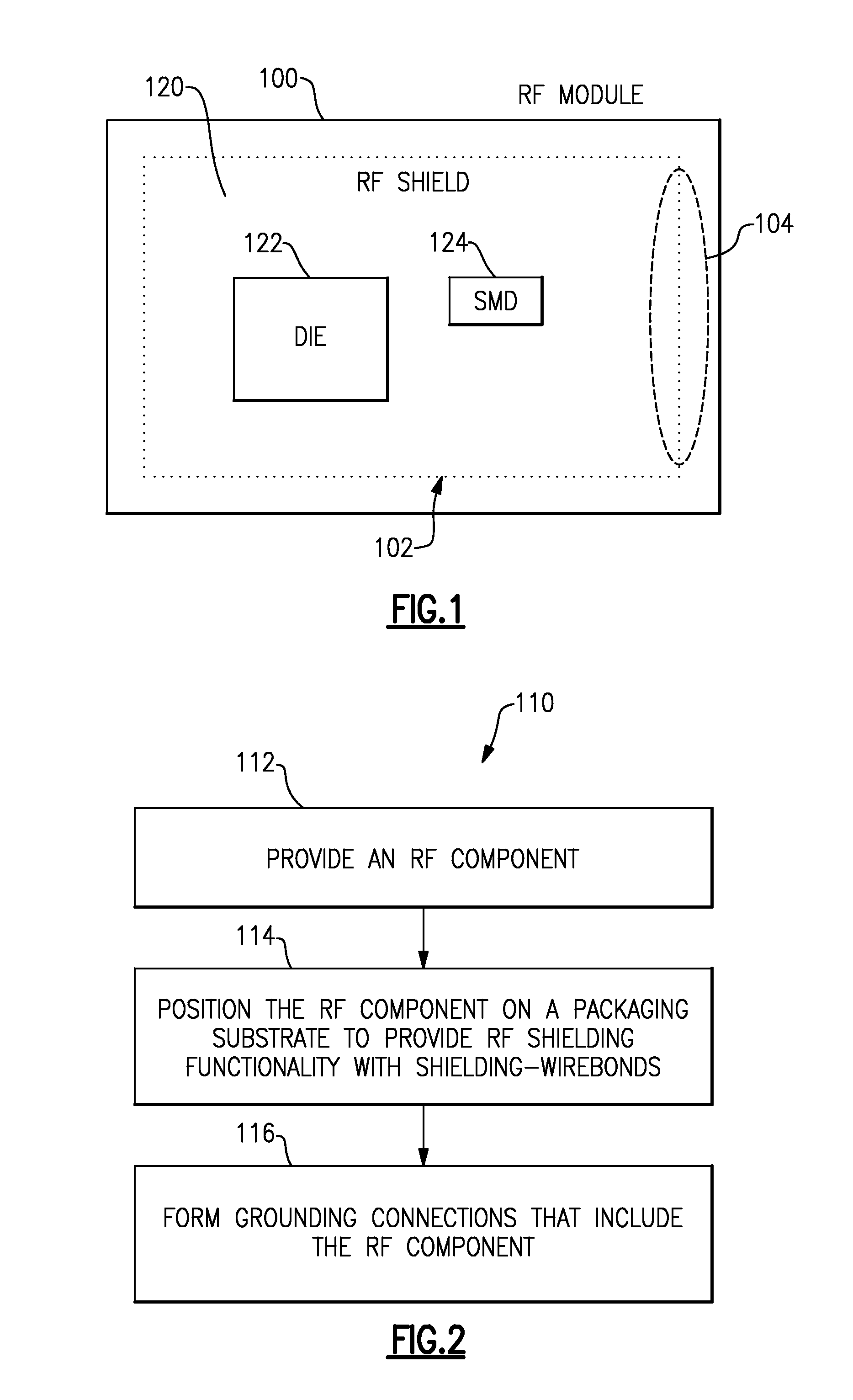

Apparatus and methods related to ground paths implemented with surface mount devices

ActiveUS20140308907A1Reduced lateral areaEasy to processMagnetic/electric field screeningSemiconductor/solid-state device detailsElectricityChip size

Disclosed are apparatus and methods related to ground paths implemented with surface mount devices to facilitate shielding of radio-frequency (RF) modules. In some embodiments, a module can include a packaging substrate configured to receive a plurality of components. The module can further include an RF component mounted on the packaging substrate and configured to facilitate processing of an RF signal. The module can further include an RF shield disposed relative to the RF component, with the RF shield being configured to provide shielding for the RF component. The RF shield can include at least one shielding-component configured to provide one or more electrical paths between a conductive layer on an upper surface of the module and a ground plane of the packaging substrate. The shielding-component can include a surface-mount device such as an RF filter implemented as a chip size surface acoustic wave (SAW) device (CSSD).

Owner:SKYWORKS SOLUTIONS INC

Semiconductor chip with coil antenna and communication system

InactiveUS7355270B2Coupling efficiency is improvedLoop antennas with ferromagnetic coreAntenna supports/mountingsElectromagnetic couplingCommunications system

The present invention intends to prevent the communication distance from becoming shorter with a reduction in size of a coil antenna to the chip size and with a consequent decrease of an induced voltage. According to the present invention there is provided a semiconductor chip having a coil antenna and a circuit surface and adapted to transmit and receive signals by radio to and from an external device. The semiconductor chip has a configuration for increasing an electromagnetic coupling coefficient between the coil antenna and the external device. According to a concrete example thereof, a magnetic material is disposed, the coil antenna is formed by a stacked structure comprising plural conductor layers and insulating layers superimposed one on another, or the coil antenna is disposed outside an external form of a circuit of the semiconductor chip.

Owner:HITACHI LTD

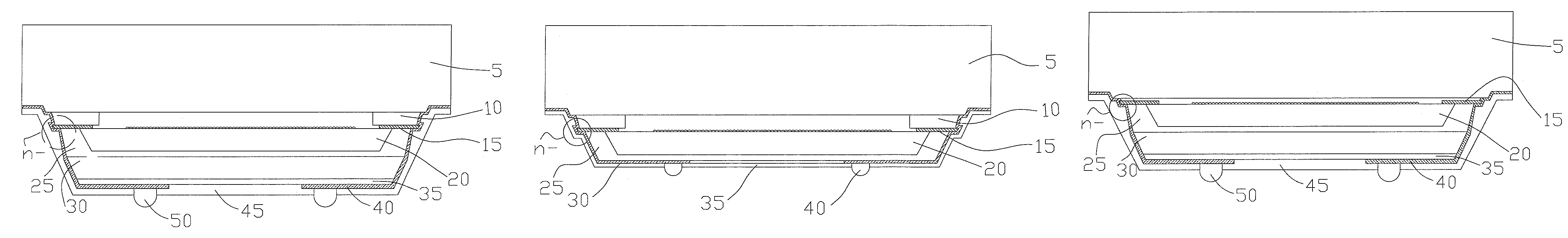

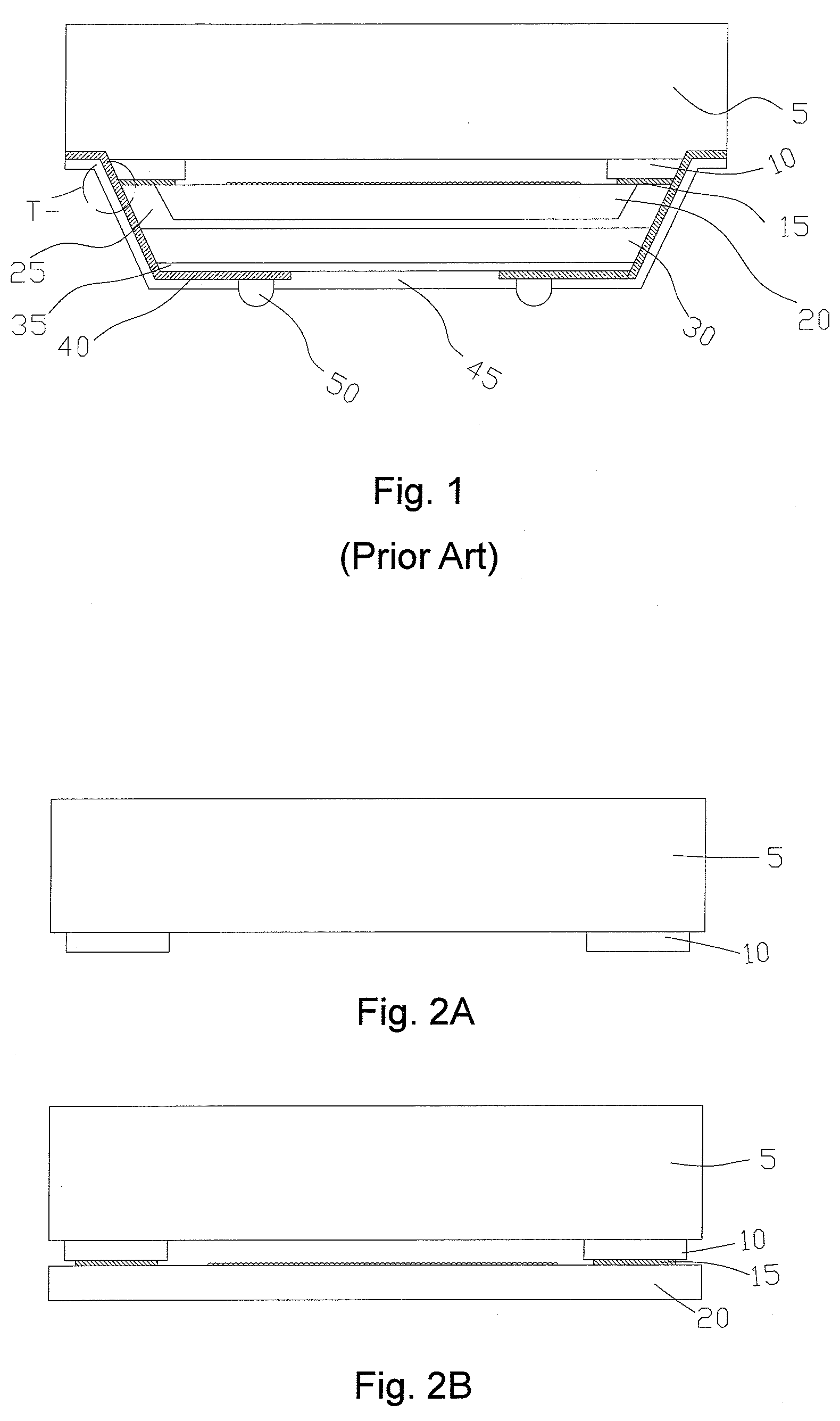

Wafer level chip size packaged chip device with an N-shape junction inside and method of fabricating the same

ActiveUS7394152B2Firmly connectedSemiconductor/solid-state device detailsSolid-state devicesChip sizeElectrical connection

The present invention provide a wafer level chip size packaged chip device with a N-shape junction at which external leads electrically connect to peripheral arrayed compatible pads and a method of fabricating the same. In the wafer level chip size package, with such an n-shape junction instead of a conventional T-shape junction observed in Shellcase type wafer level chip size package technology, electrical connections between compatible pads and external leads are more reliable due to larger connection area than the counterpart in the T-shape junction.

Owner:CHINA WAFER LEVEL CSP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com