Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

932 results about "Electrical interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

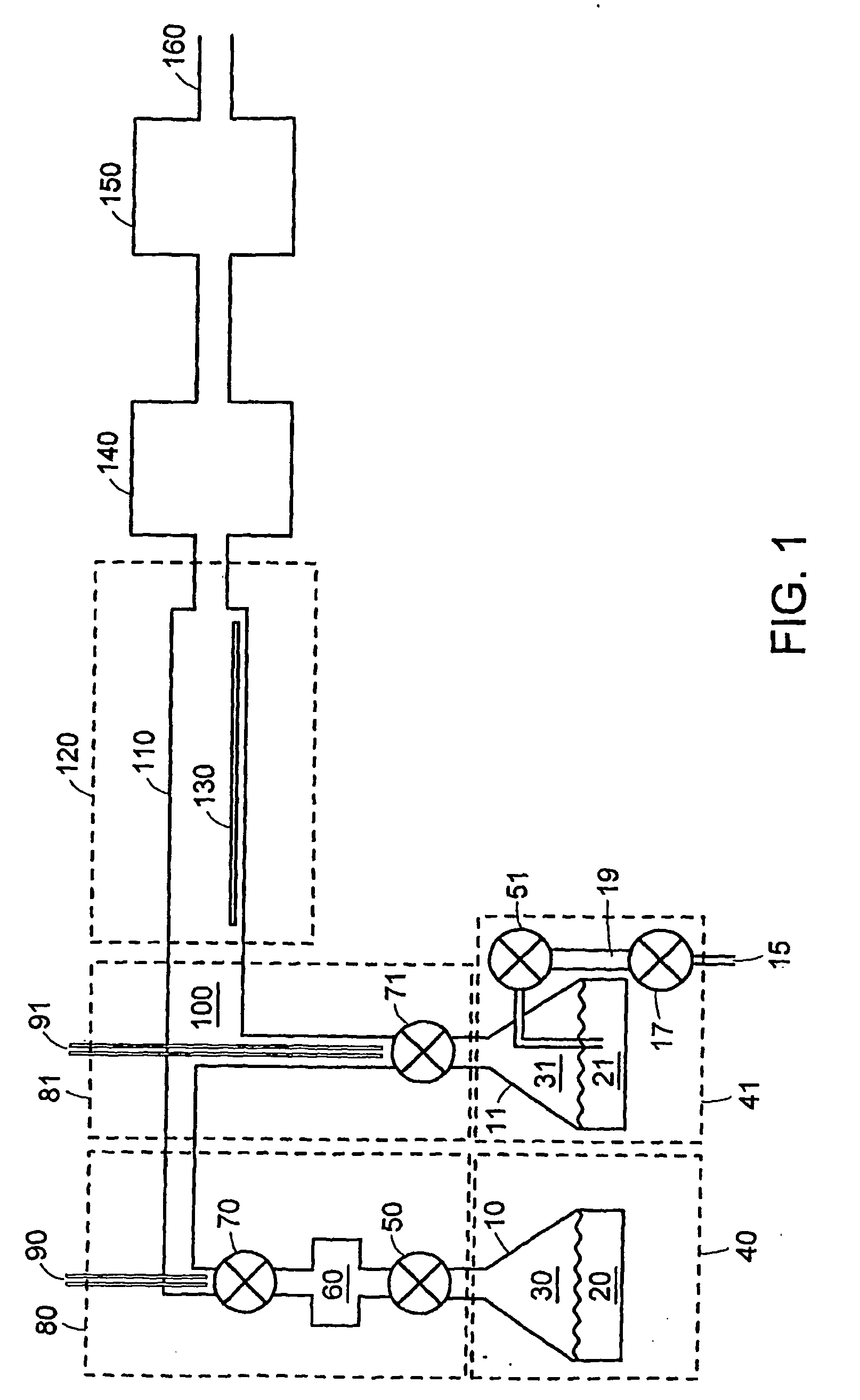

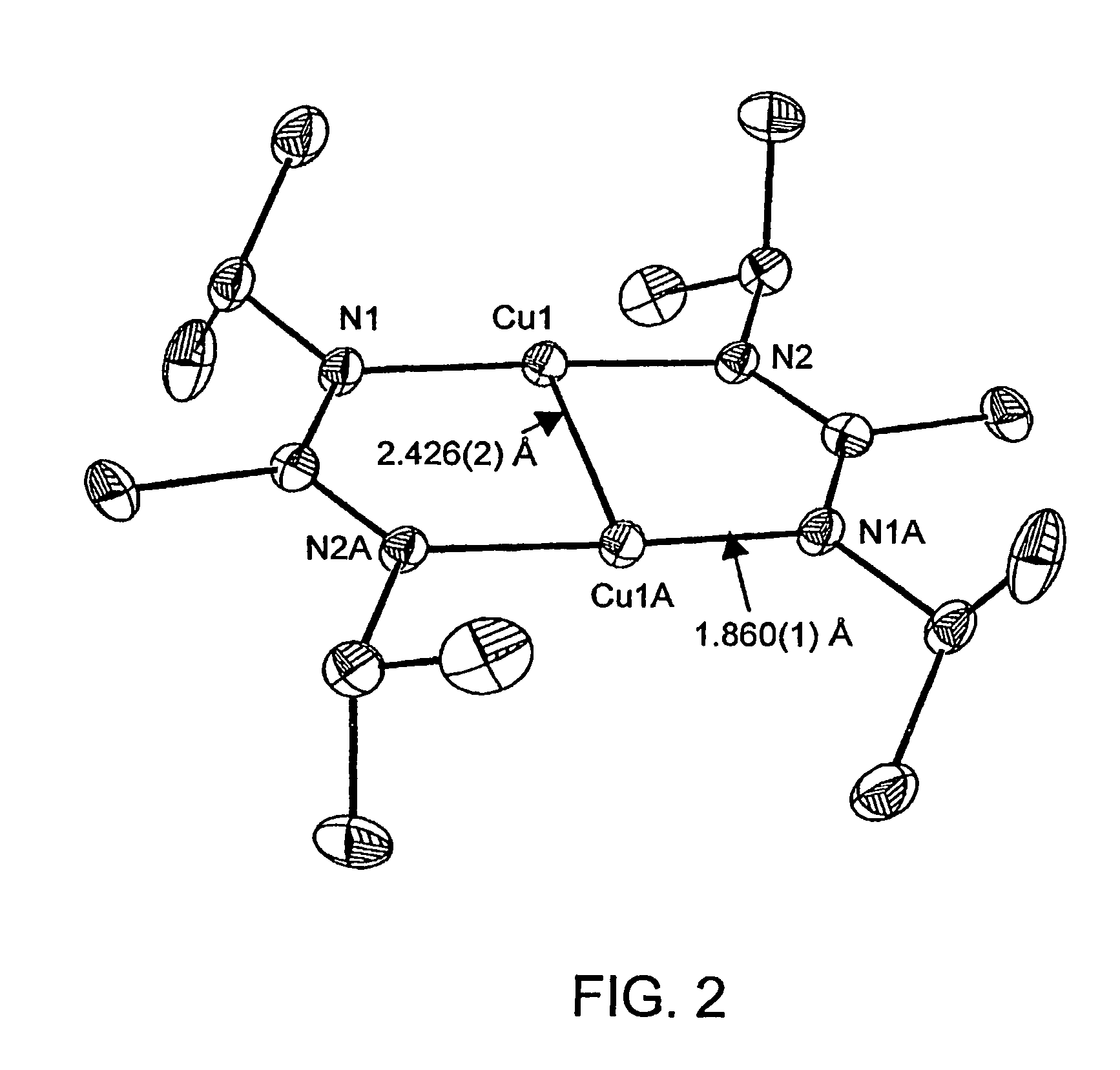

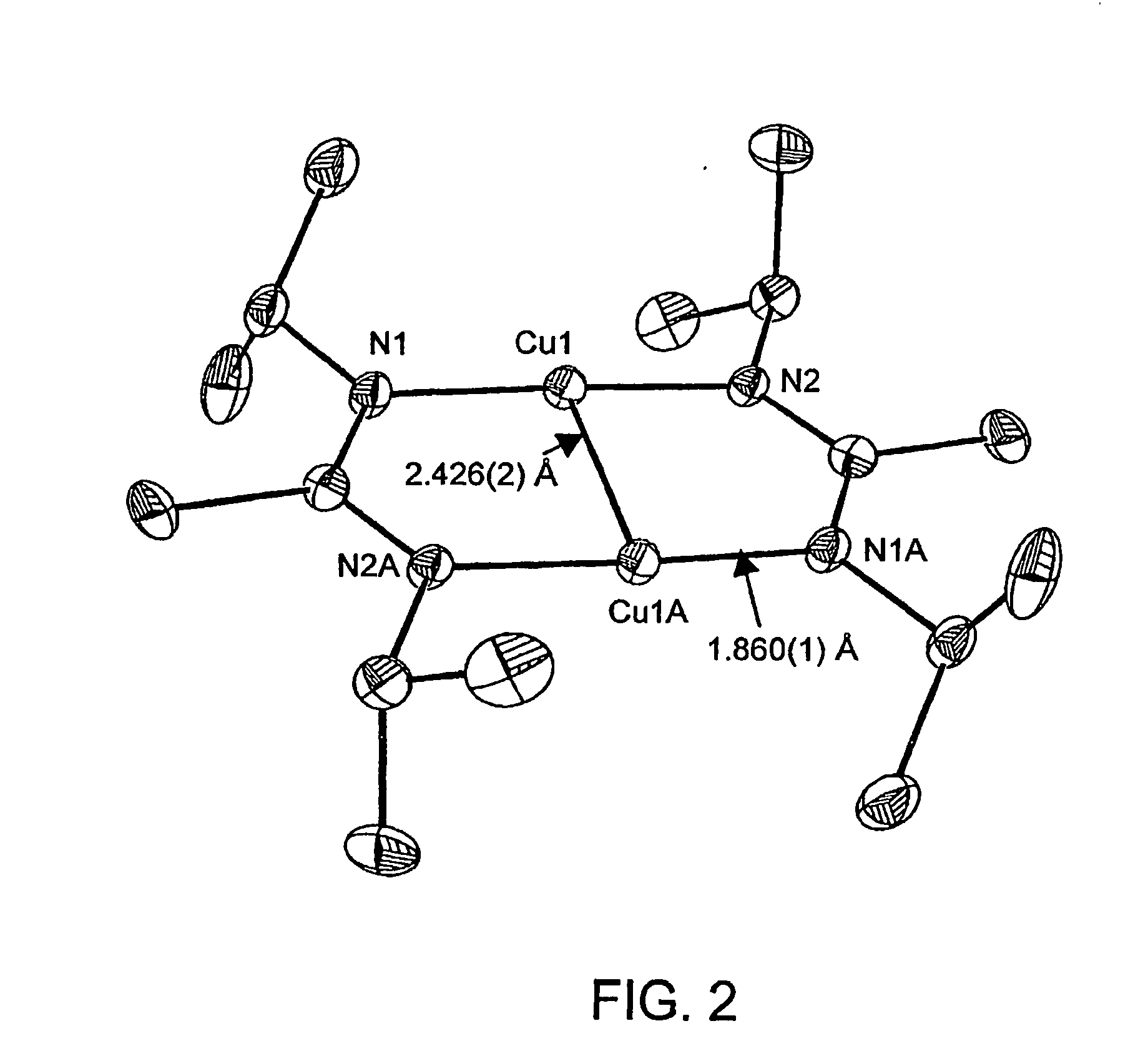

Atomic layer deposition using metal amidinates

ActiveUS20060141155A1Improve conductivityReduce the temperatureGroup 8/9/10/18 element organic compoundsGroup 5/15 element organic compoundsHydrogenWater vapor

Metal films are deposited with uniform thickness and excellent step coverage. Copper metal films were deposited on heated substrates by the reaction of alternating doses of copper(I) NN′-diisopropylacetamidinate vapor and hydrogen gas. Cobalt metal films were deposited on heated substrates by the reaction of alternating doses of cobalt(II) bis(N,N′-diisopropylacetamidinate) vapor and hydrogen gas. Nitrides and oxides of these metals can be formed by replacing the hydrogen with ammonia or water vapor, respectively. The films have very uniform thickness and excellent step coverage in narrow holes. Suitable applications include electrical interconnects in microelectronics and magnetoresistant layers in magnetic information storage devices.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

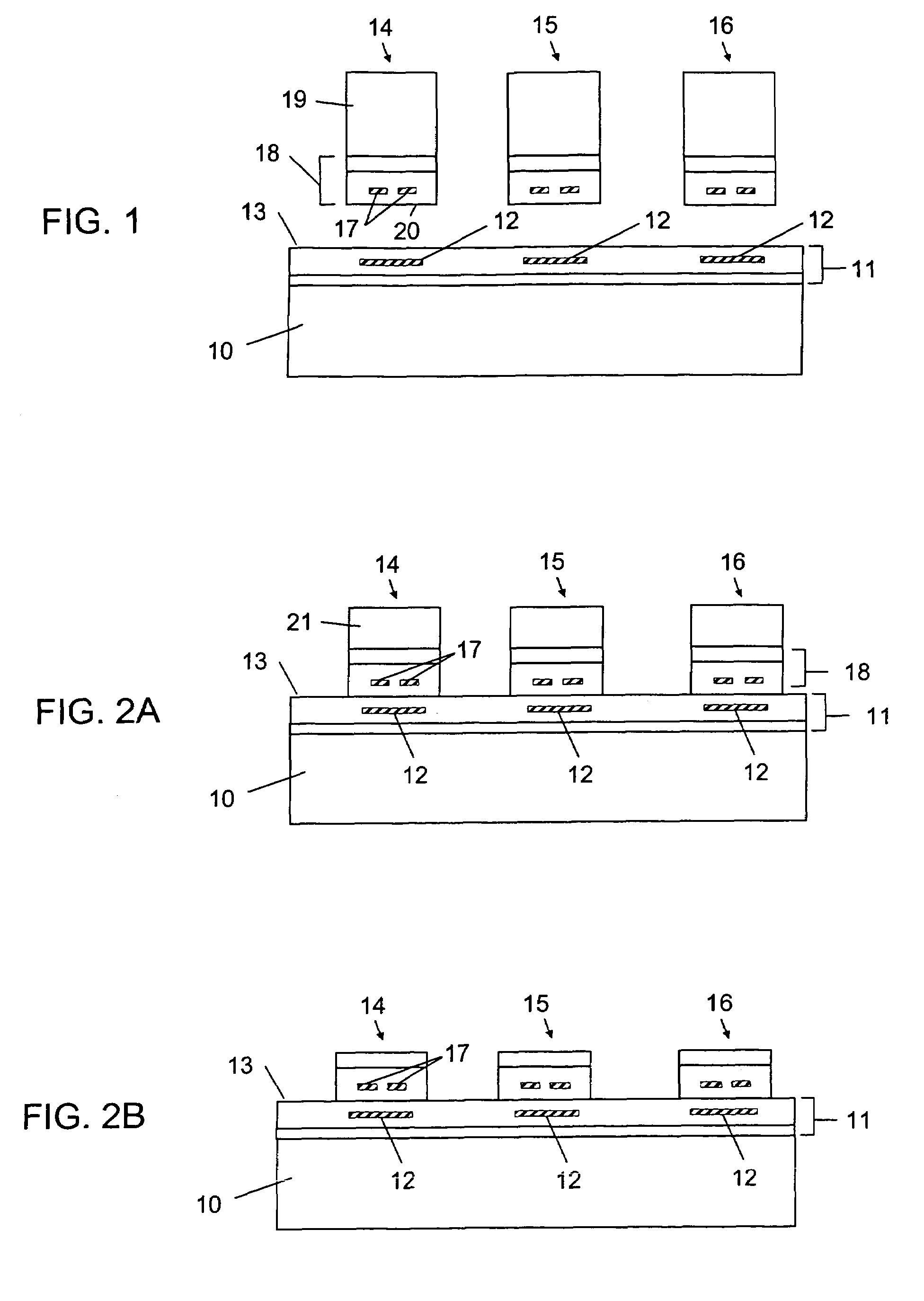

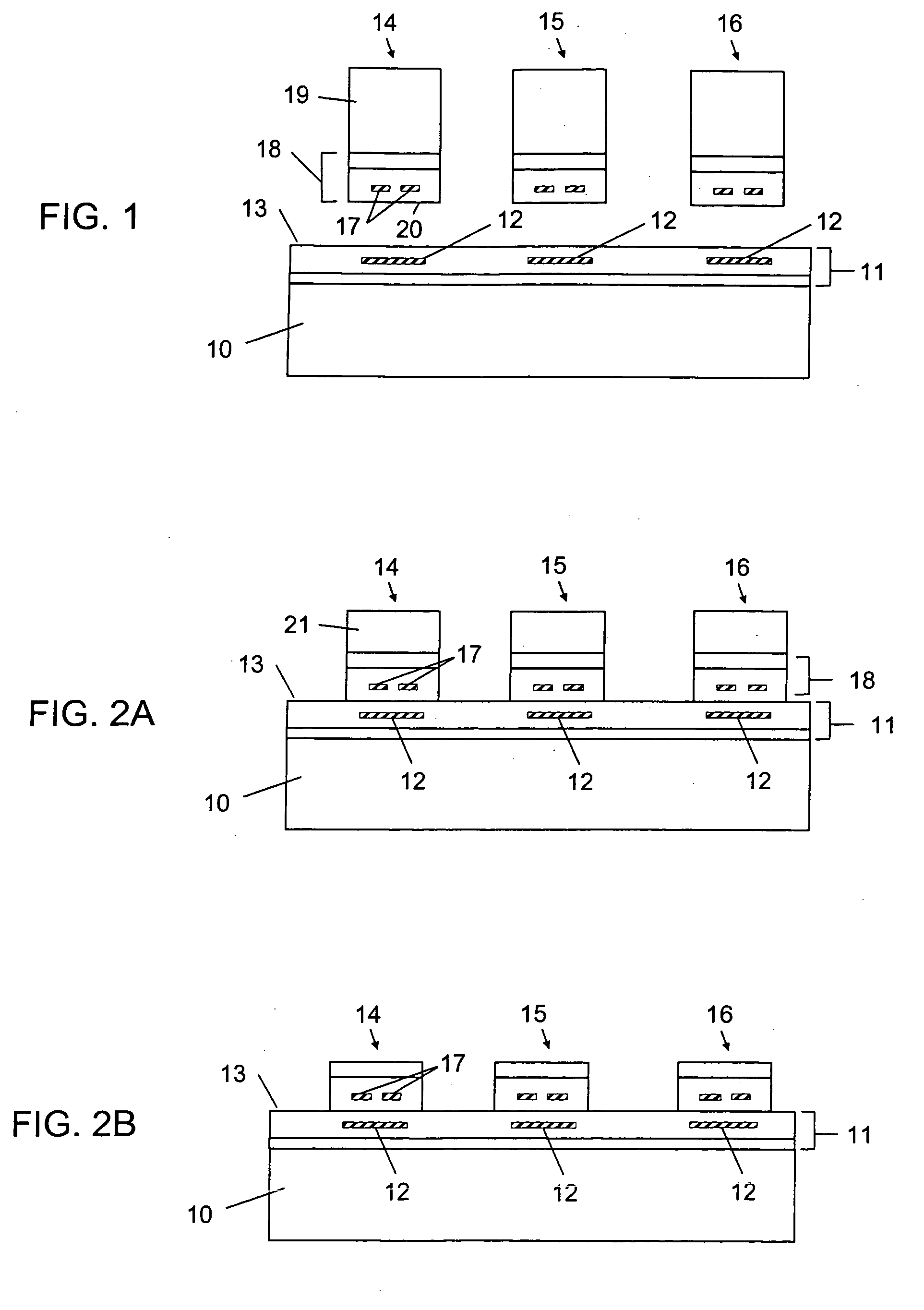

3D IC method and device

ActiveUS7485968B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductorElectrical interconnect

A method of three-dimensionally integrating elements such as singulated die or wafers and an integrated structure having connected elements such as singulated dies or wafers. Either or both of the die and wafer may have semiconductor devices formed therein. A first element having a first contact structure is bonded to a second element having a second contact structure. First and second contact structures can be exposed at bonding and electrically interconnected as a result of the bonding. A via may be etched and filled after bonding to expose and form an electrical interconnect to interconnected first and second contact structures and provide electrical access to this interconnect from a surface. Alternatively, first and / or second contact structures are not exposed at bonding, and a via is etched and filled after bonding to electrically interconnect first and second contact structures and provide electrical access to interconnected first and second contact structure to a surface. Also, a device may be formed in a first substrate, the device being disposed in a device region of the first substrate and having a first contact structure. A via may be etched, or etched and filled, through the device region and into the first substrate before bonding and the first substrate thinned to expose the via, or filled via after bonding.

Owner:INVENSAS BONDING TECH INC

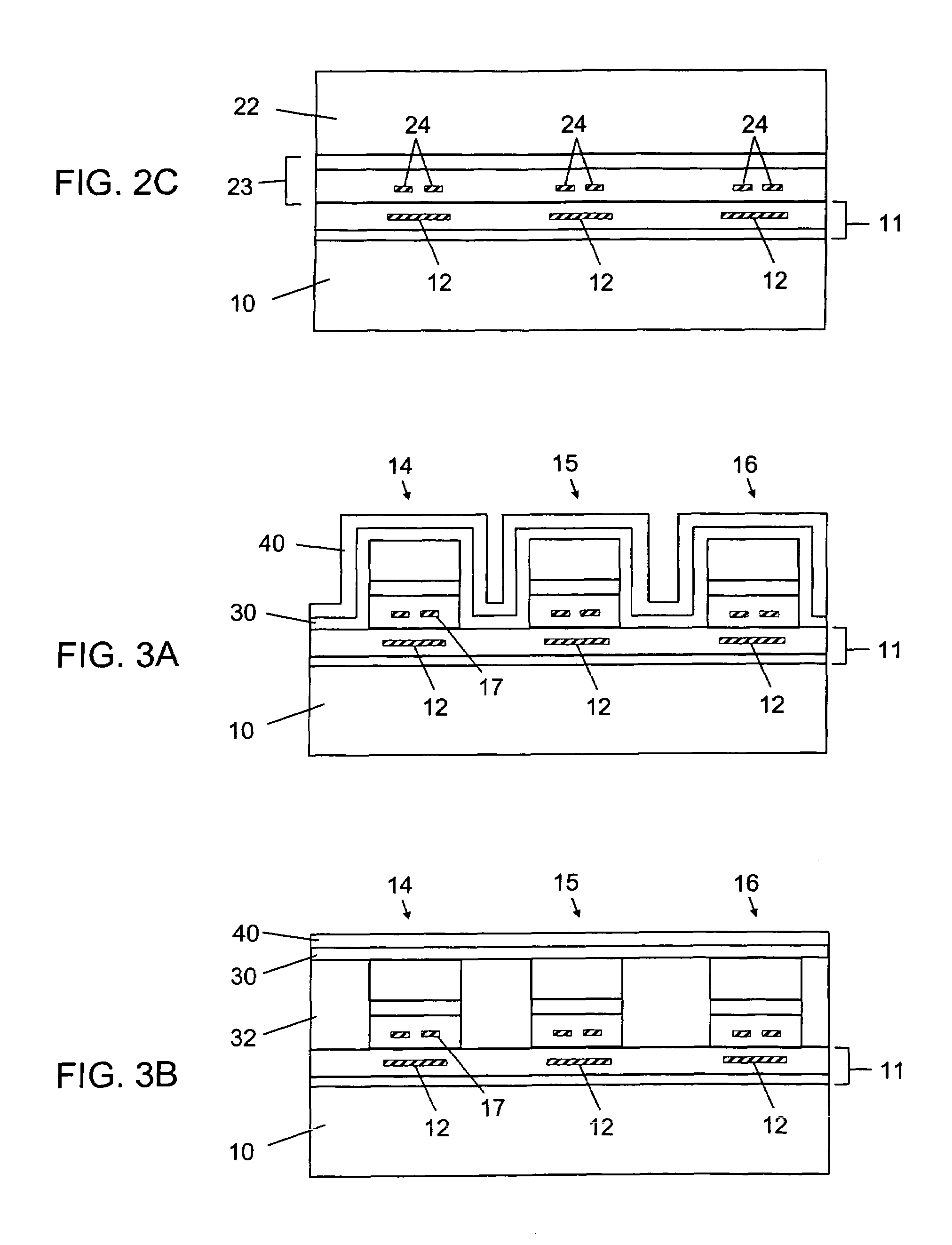

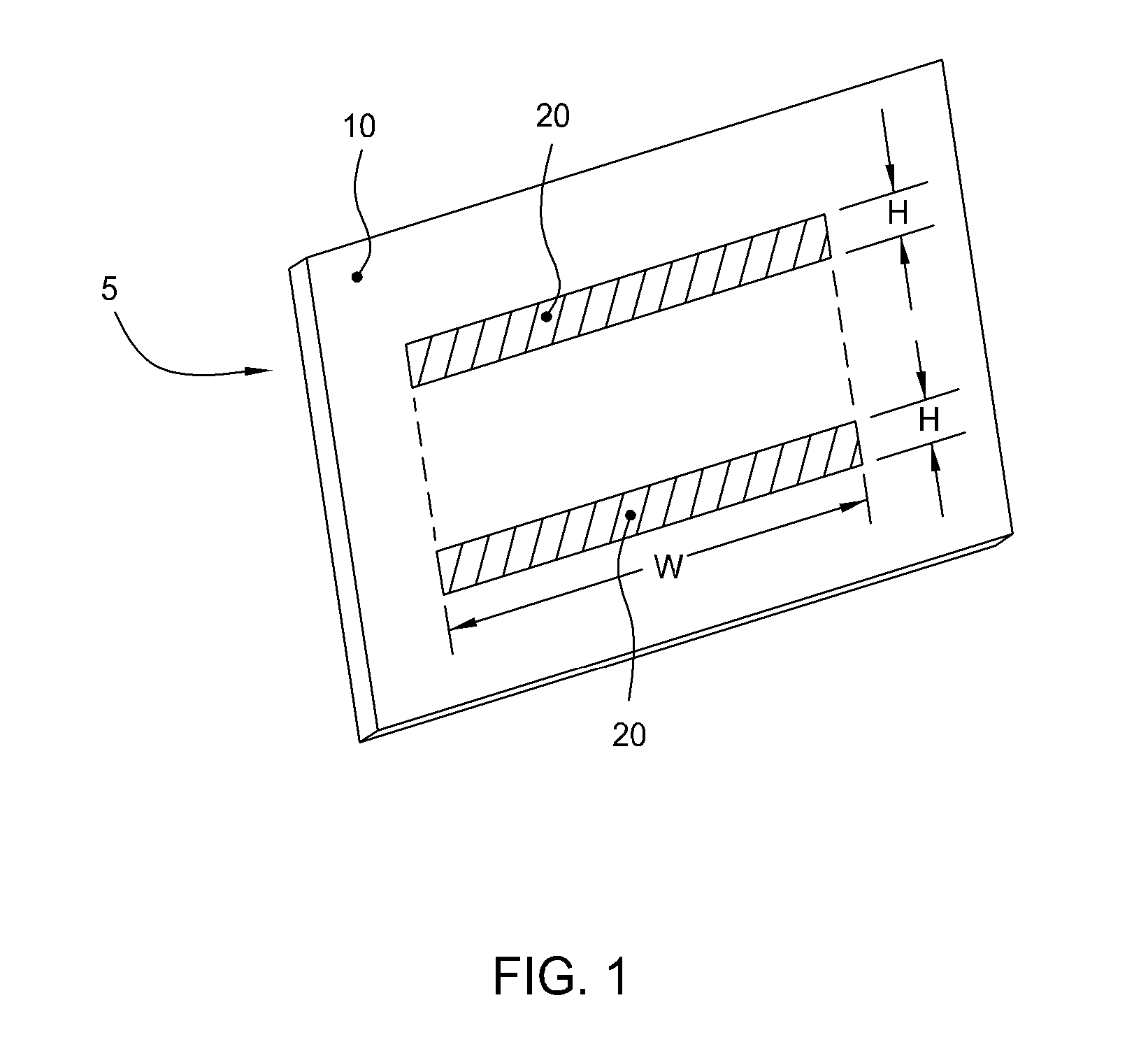

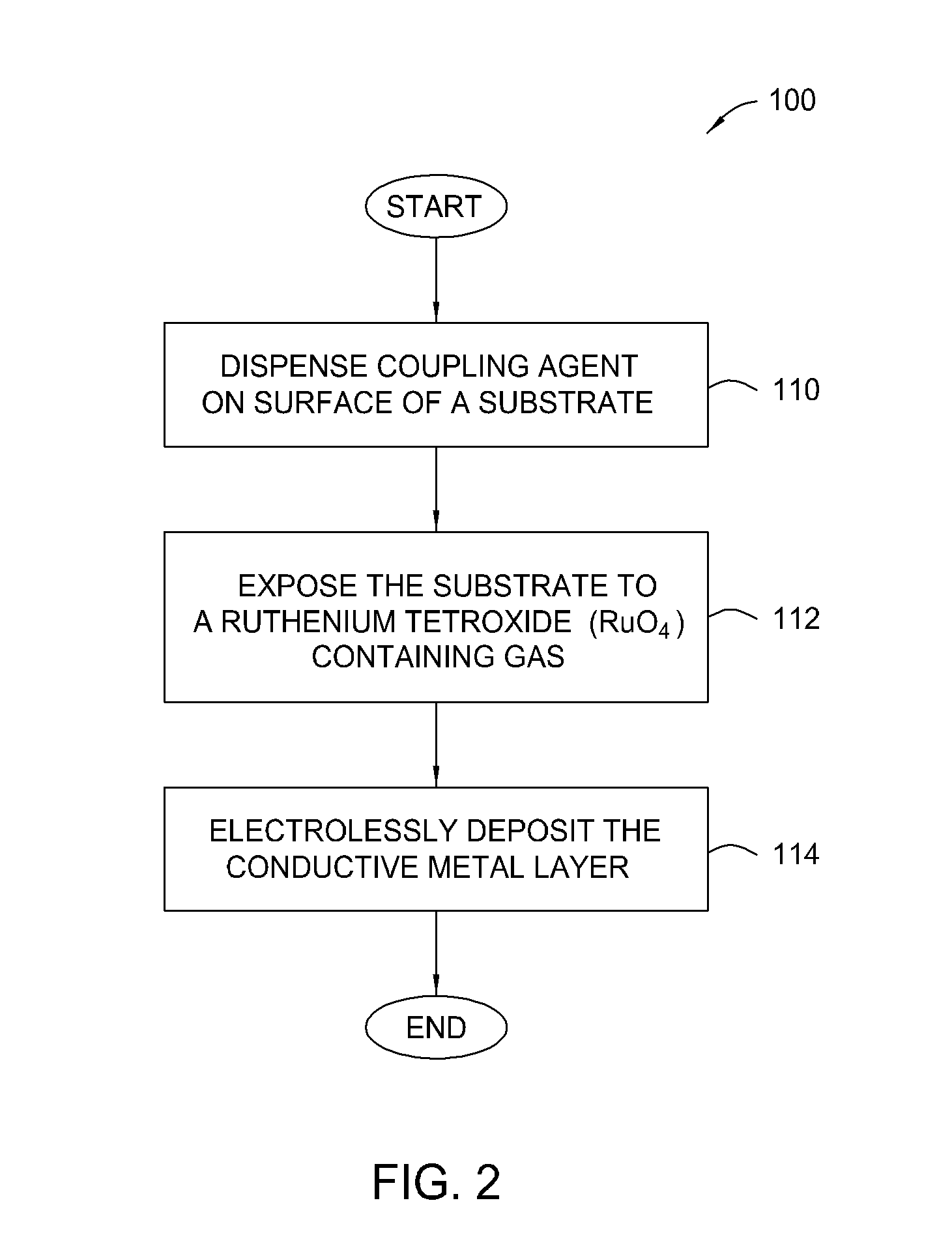

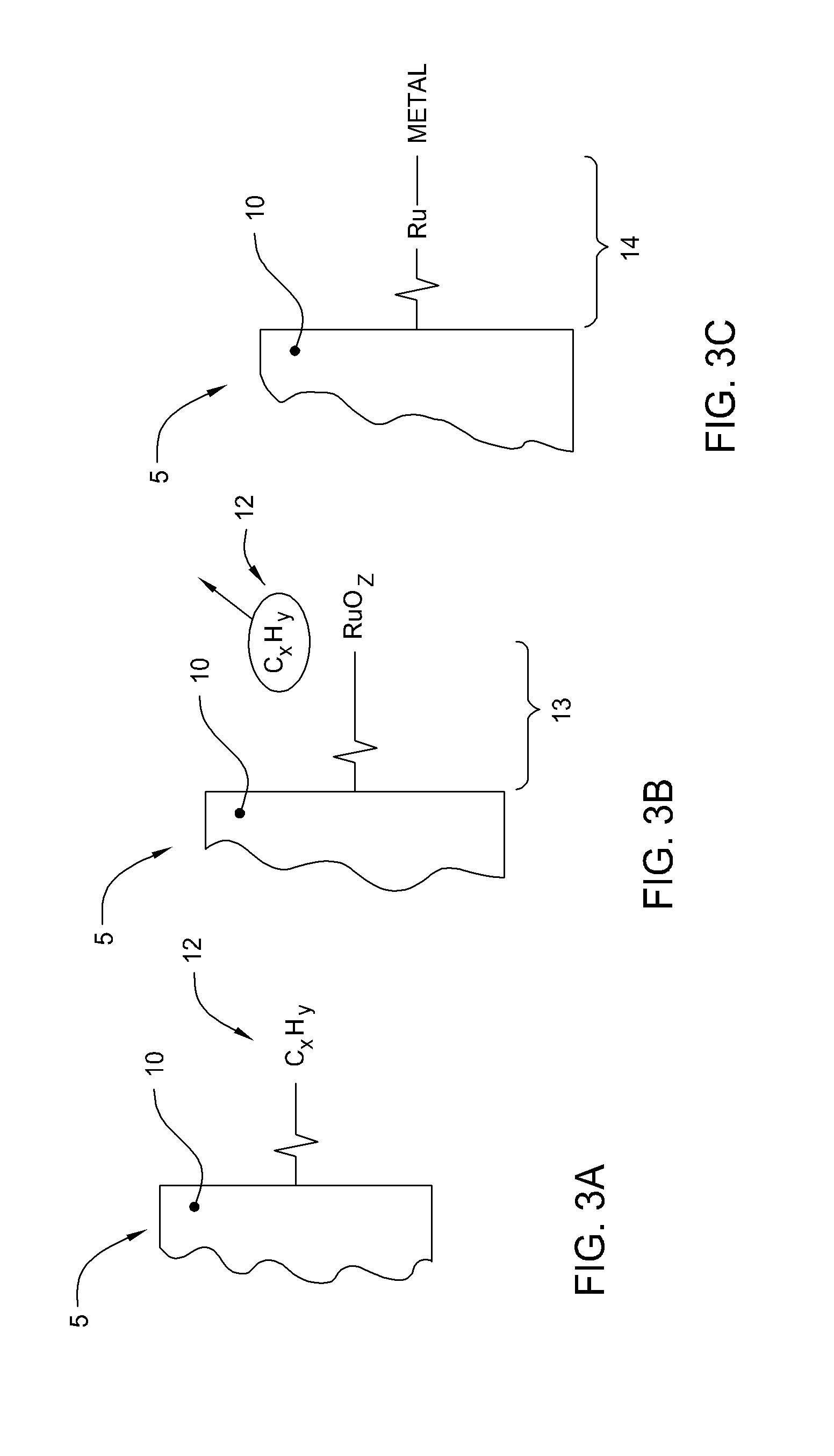

Patterned electroless metallization processes for large area electronics

The present invention generally provides an apparatus and method for selectively forming a metallized feature, such as an electrical interconnect feature, on a electrically insulating surface of a substrate. The present invention also provides a method of forming a mechanically robust, adherent, oxidation resistant conductive layer selectively over either a defined pattern or as a conformal blanket film. Embodiments of the invention also generally provide a new chemistry, process, and apparatus to provide discrete or blanket electrochemically or electrolessly platable ruthenium or ruthenium dioxide containing adhesion and initiation layers. In general, aspects of the present invention can be used for flat panel display processing, semiconductor processing, solar cell device processing, or any other substrate processing, being particularly well suited for the application of stable adherent coating on glass as well as flexible plastic substrates. This invention may be especially useful for the formation of electrical interconnects on the surface of flat panel display or solar cell type substrates where the line sizes are generally larger than semiconductor devices or where the formed feature are not generally as dense.

Owner:APPLIED MATERIALS INC

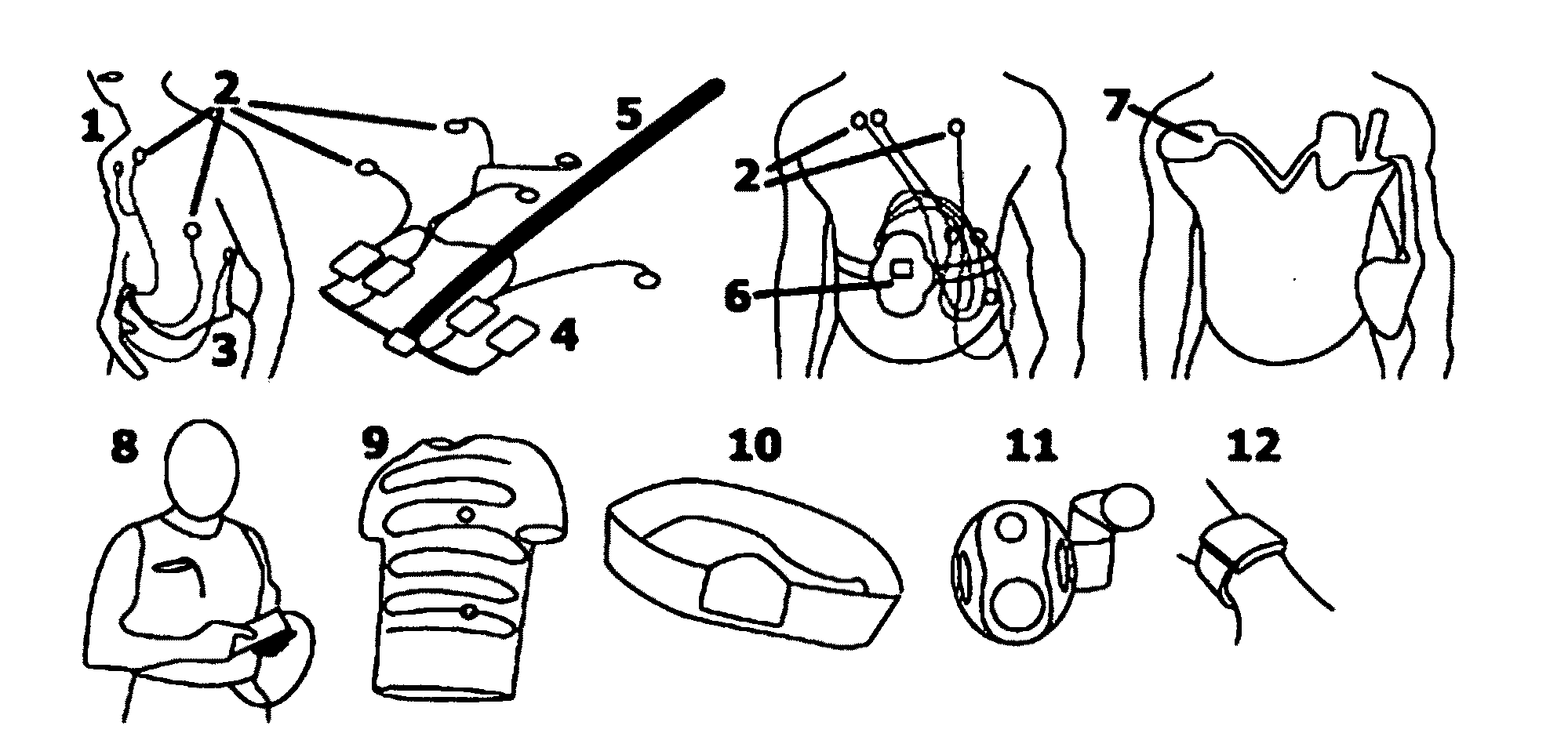

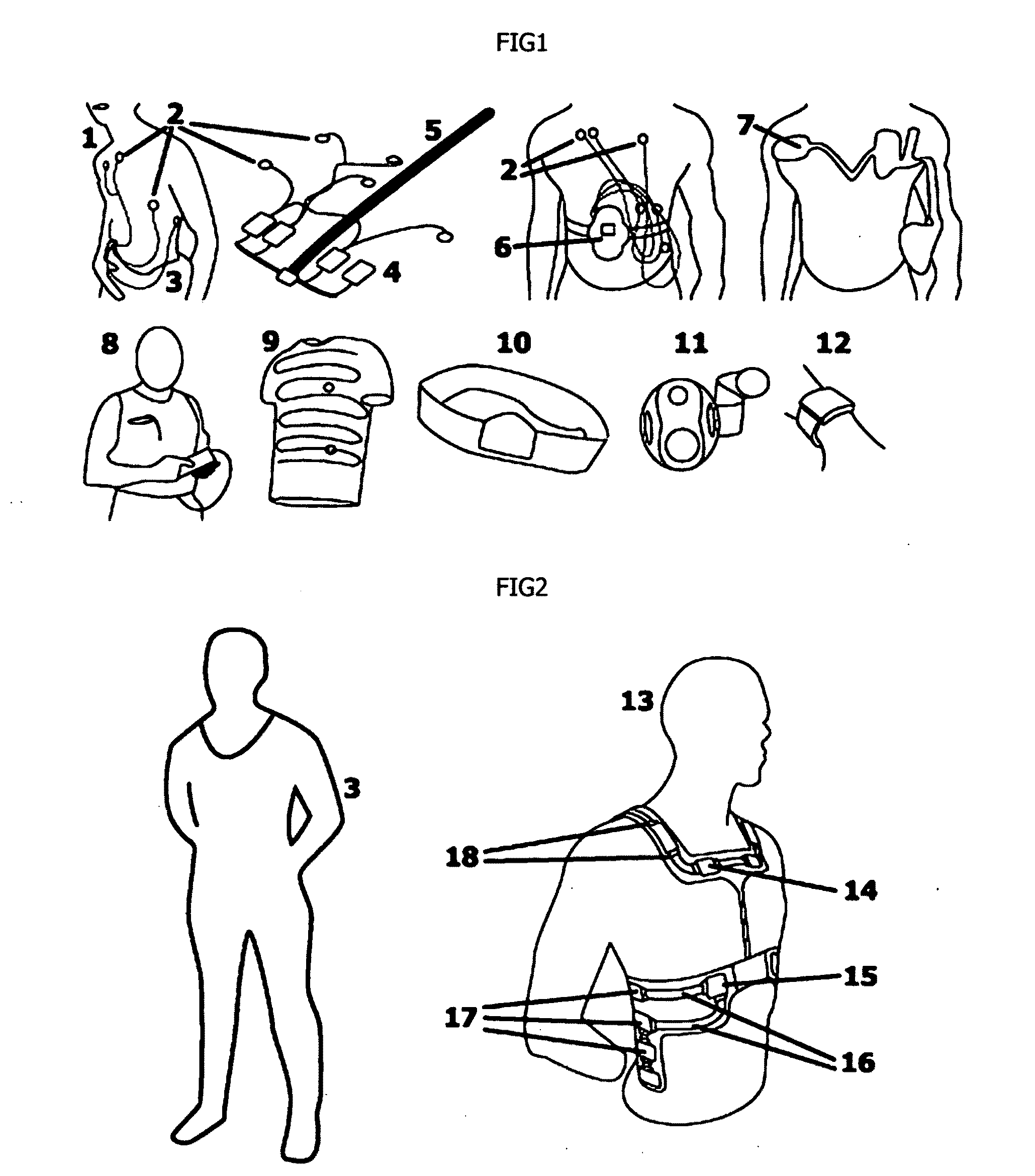

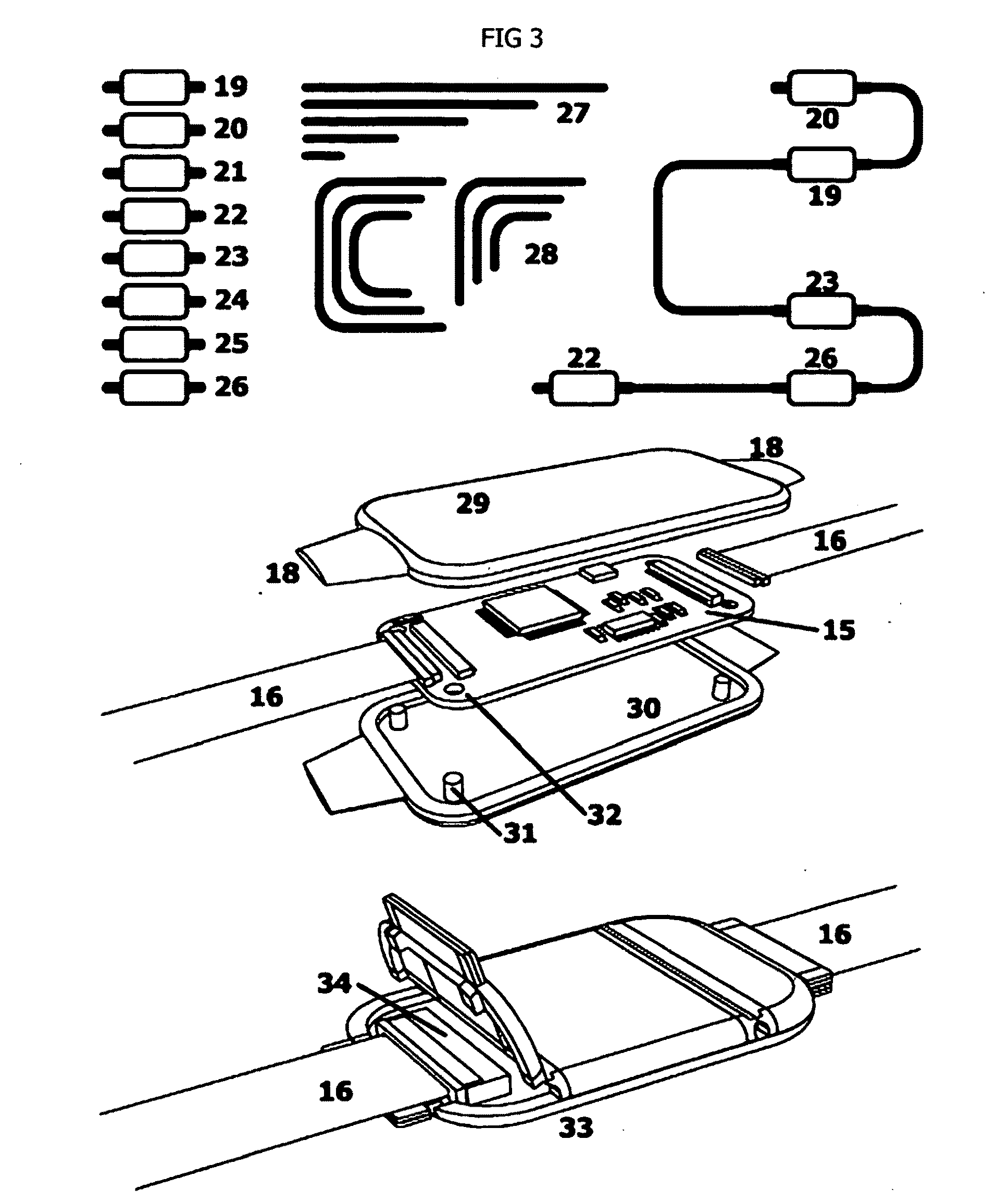

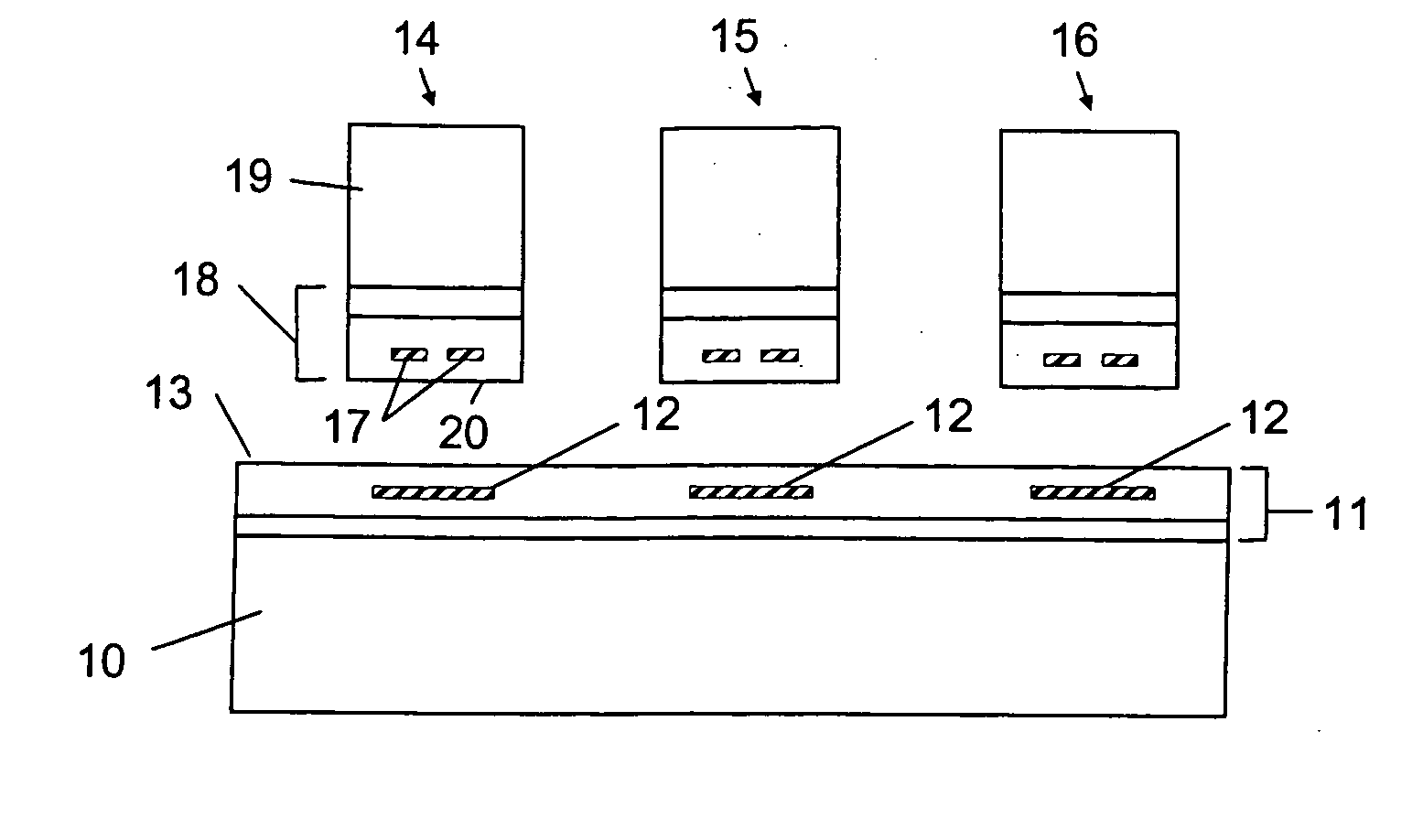

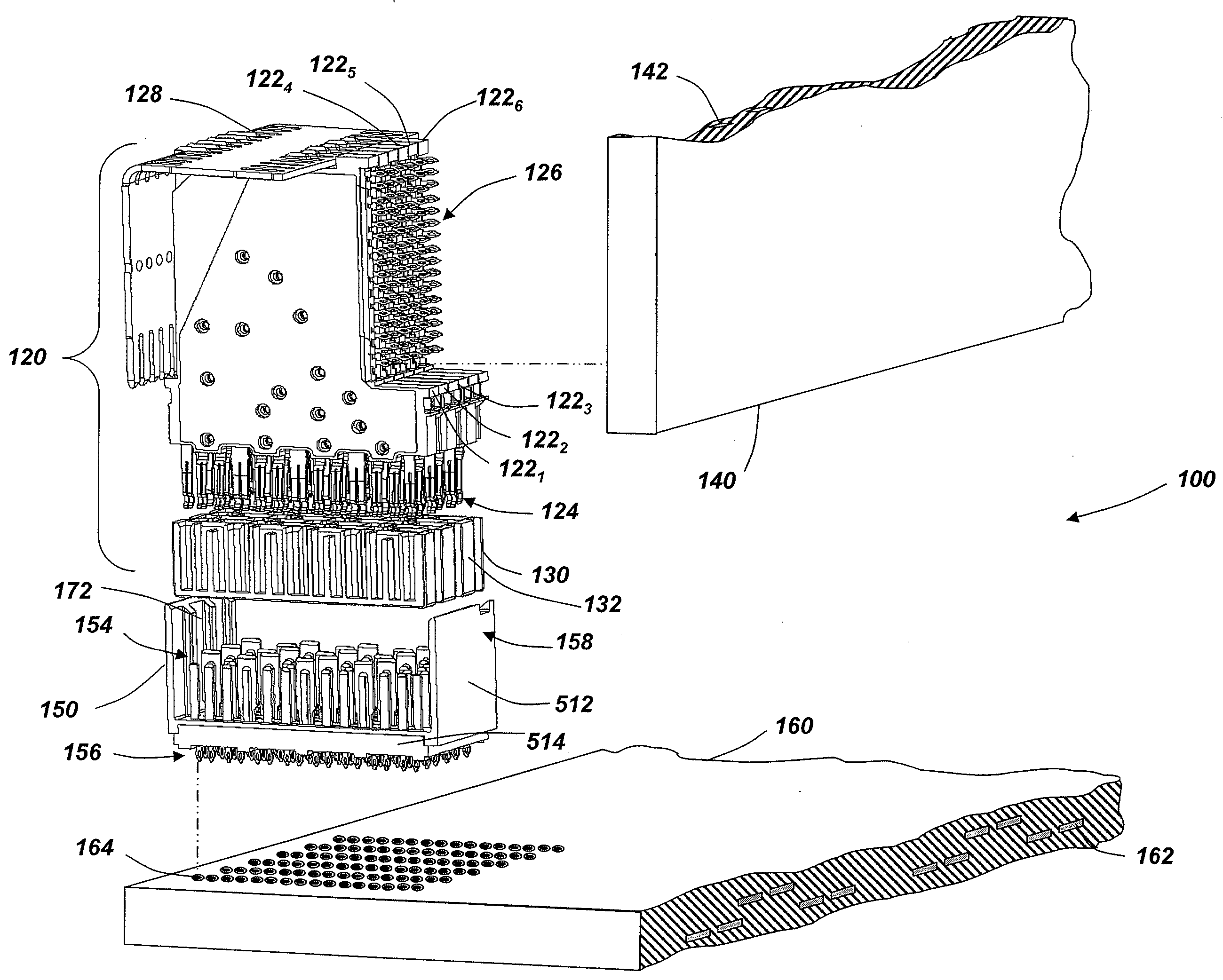

Wearable Electronic System

InactiveUS20090306485A1Easy to replaceAccurate placementElectrocardiographyCoupling device detailsElectricityElectronic systems

This document describes the design and control of a modular wearable electronic system that integrates an electrical interconnection harness, human body electrode modules, physiological sensor modules, electronic circuit modules, control software, and power supply modules into a single assembly. The design is intended to allow medical sensors and electronic circuits from different manufacturers to be connected into the system with relative ease. This system will enable a platform that can be expanded to incorporate many different kinds of physiological sensors and electronic circuits as and when they become available. It will also allow for different sizes of wearable electronic system to be constructed by simply changing the lengths and shapes of the electrical interconnections between the electrical modules.

Owner:BELL JONATHAN ARNOLD

Atomic layer deposition using metal amidinates

ActiveUS20090291208A1Good step coverageImprove conductivityGroup 8/9/10/18 element organic compoundsCopper organic compoundsHydrogenWater vapor

Metal films are deposited with uniform thickness and excellent step coverage. Copper metal films were deposited on heated substrates by the reaction of alternating doses of copper(I) NN′-diispropylacetamidinate vapor and hydrogen gas. Cobalt metal films were deposited on heated substrates b the reaction of alternating doses of cobalt(II) bis(N,N′-diispropylacetamidinate) vapor and hydrogen gas. Nitrides and oxides of these metals can be formed by replacing the hydrogen with ammonia or water vapor, respectively. The films have very uniform thickness and excellent step coverage in narrow holes. Suitable applications include electrical interconnects in microelectronics and magnetoresistant layers in magnetic information storage devices.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

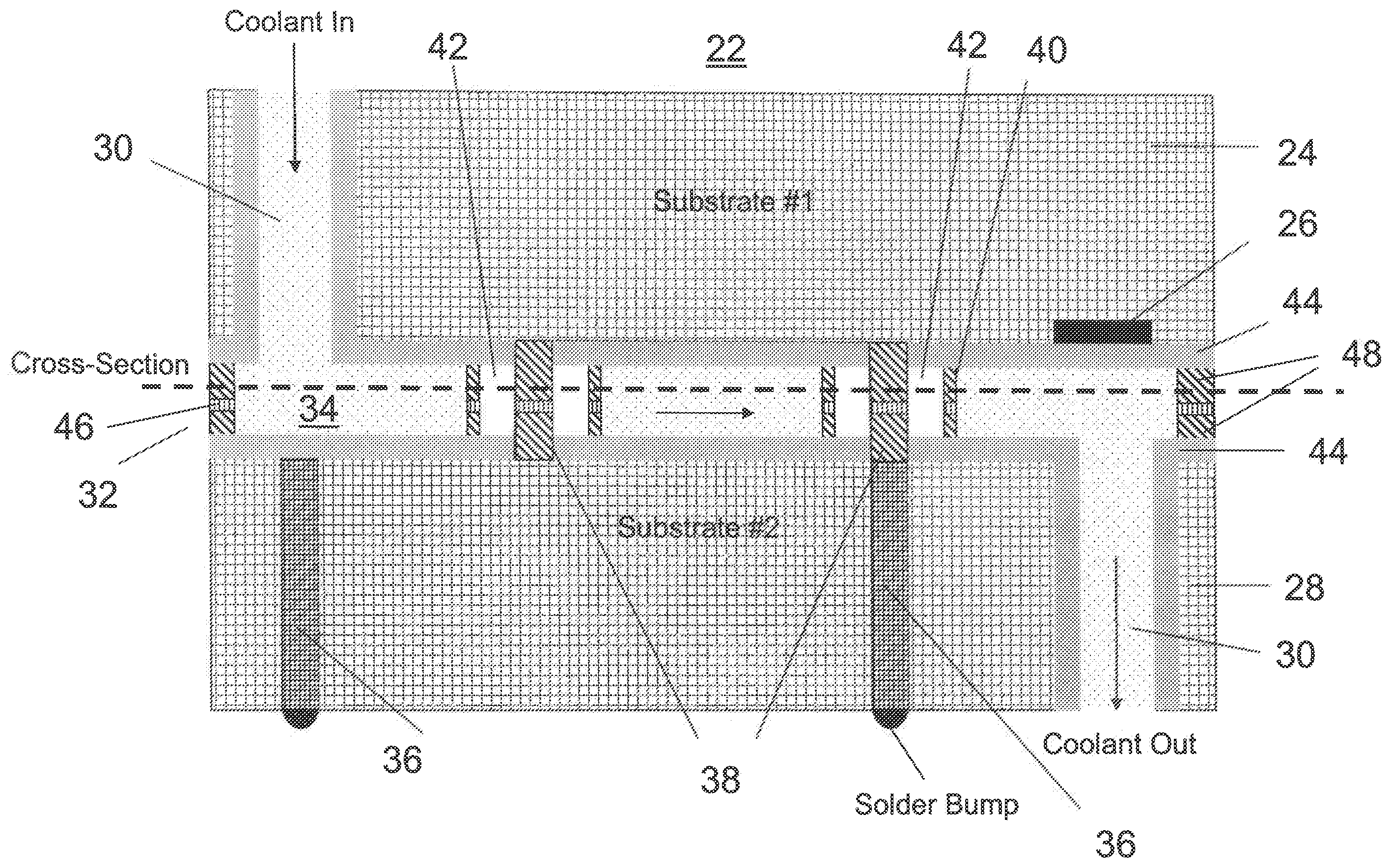

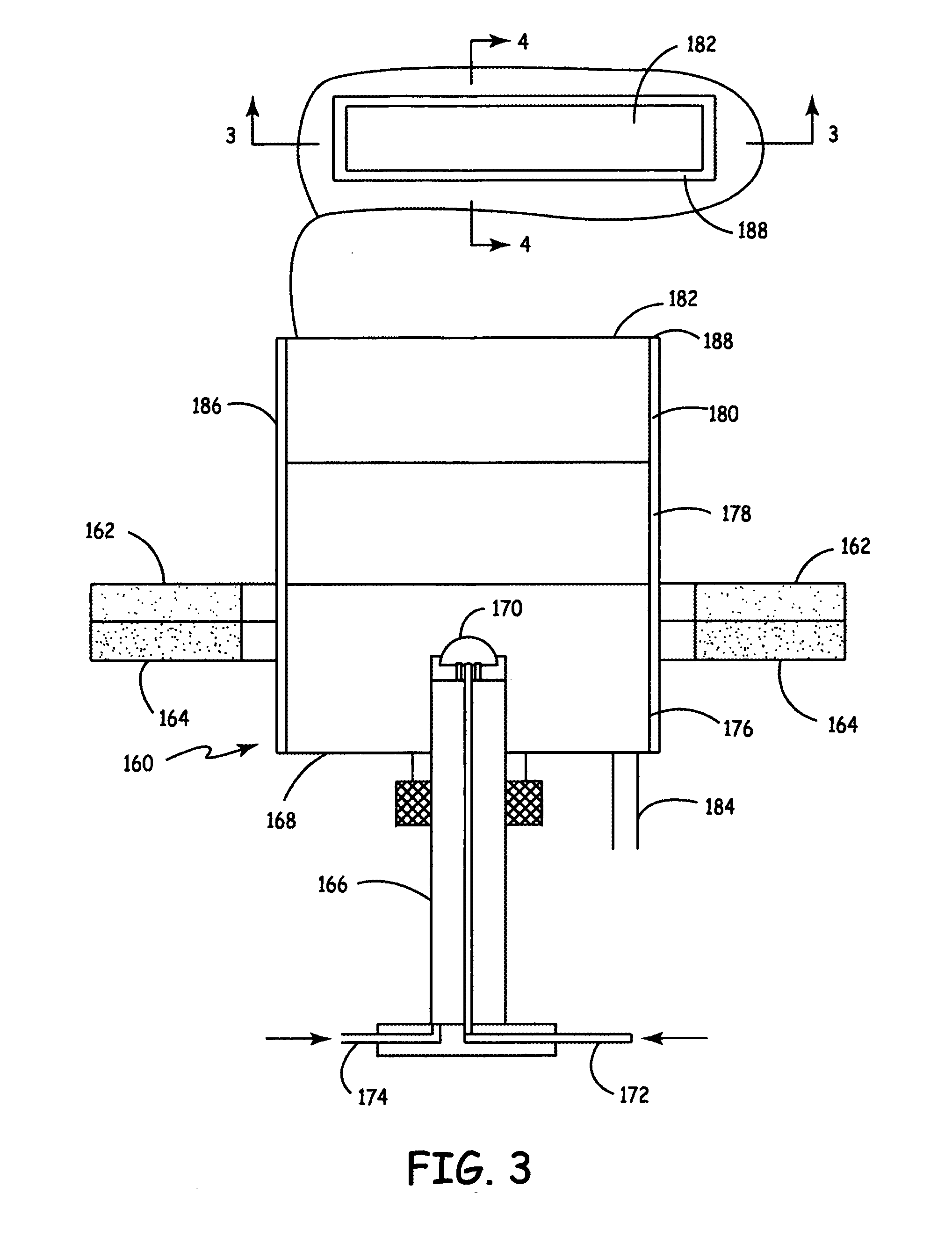

Structure and process for electrical interconnect and thermal management

ActiveUS20090057879A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical interconnect

A structure and method for thermal management of integrated circuits. The structure for thermal management of integrated circuits includes first and second substrates bonded together, at least one of the first and second substrates including at least one circuit element, an entrance through-hole having a length extending through a thickness of at least one of the first substrate and the second substrate, an exit through-hole having a length extending through a thickness of at least one of the first substrate and the second substrate, a bonding element forming a seal between the first and second substrates and forming a space between the first and second substrate, and a coolant channel formed in the space between the first and second substrates such that a fluid entering the entrance through-hole transits the coolant channel and the exit through-hole to provide cooling to the circuit element. The method supplies a fluid through the entrance through-hole, flows the fluid through the coolant channel between the first substrate and second substrates, and removes the fluid from the coolant channel through the exit through-hole.

Owner:MICROSS ADVANCED INTERCONNECT TECH LLC

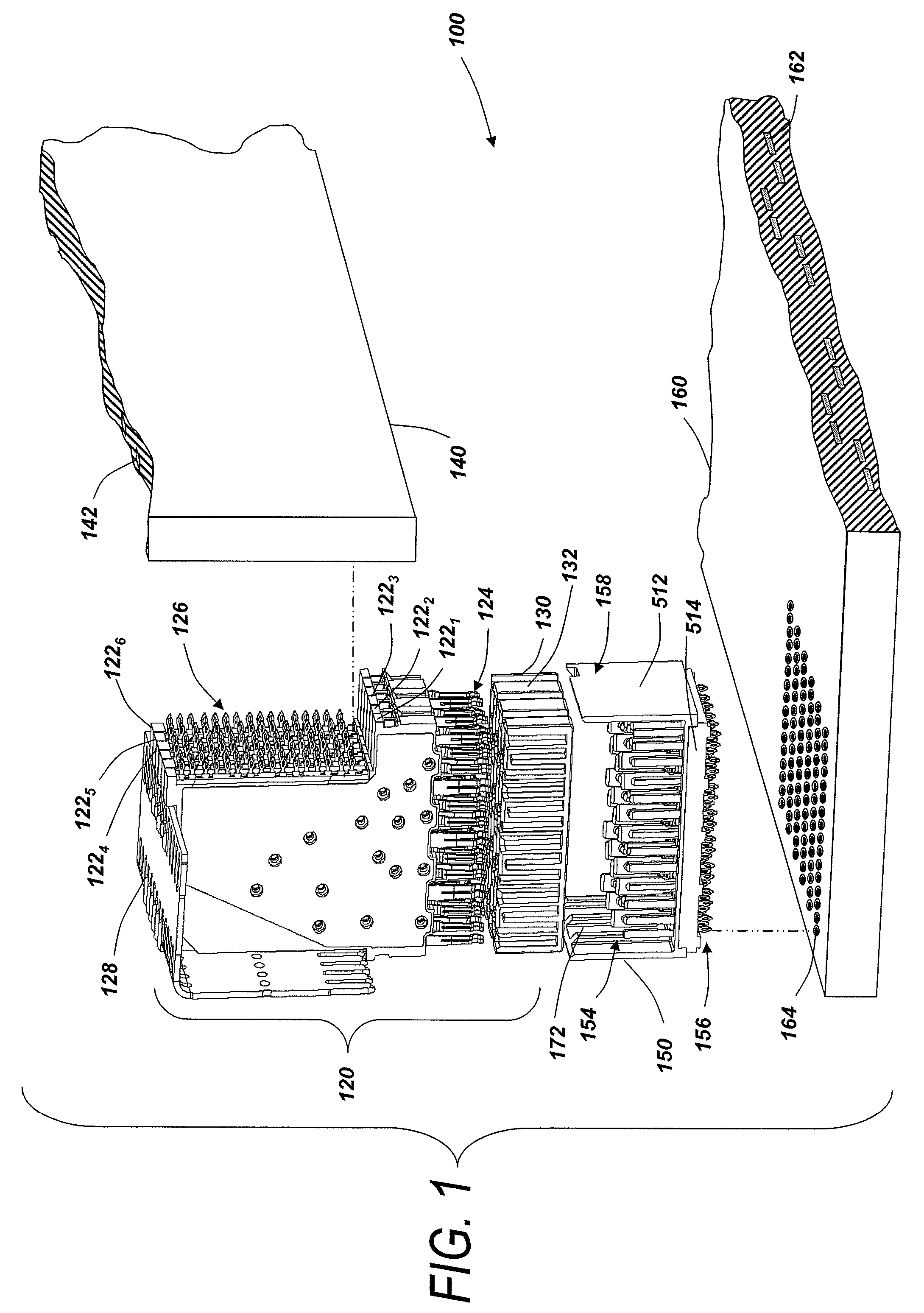

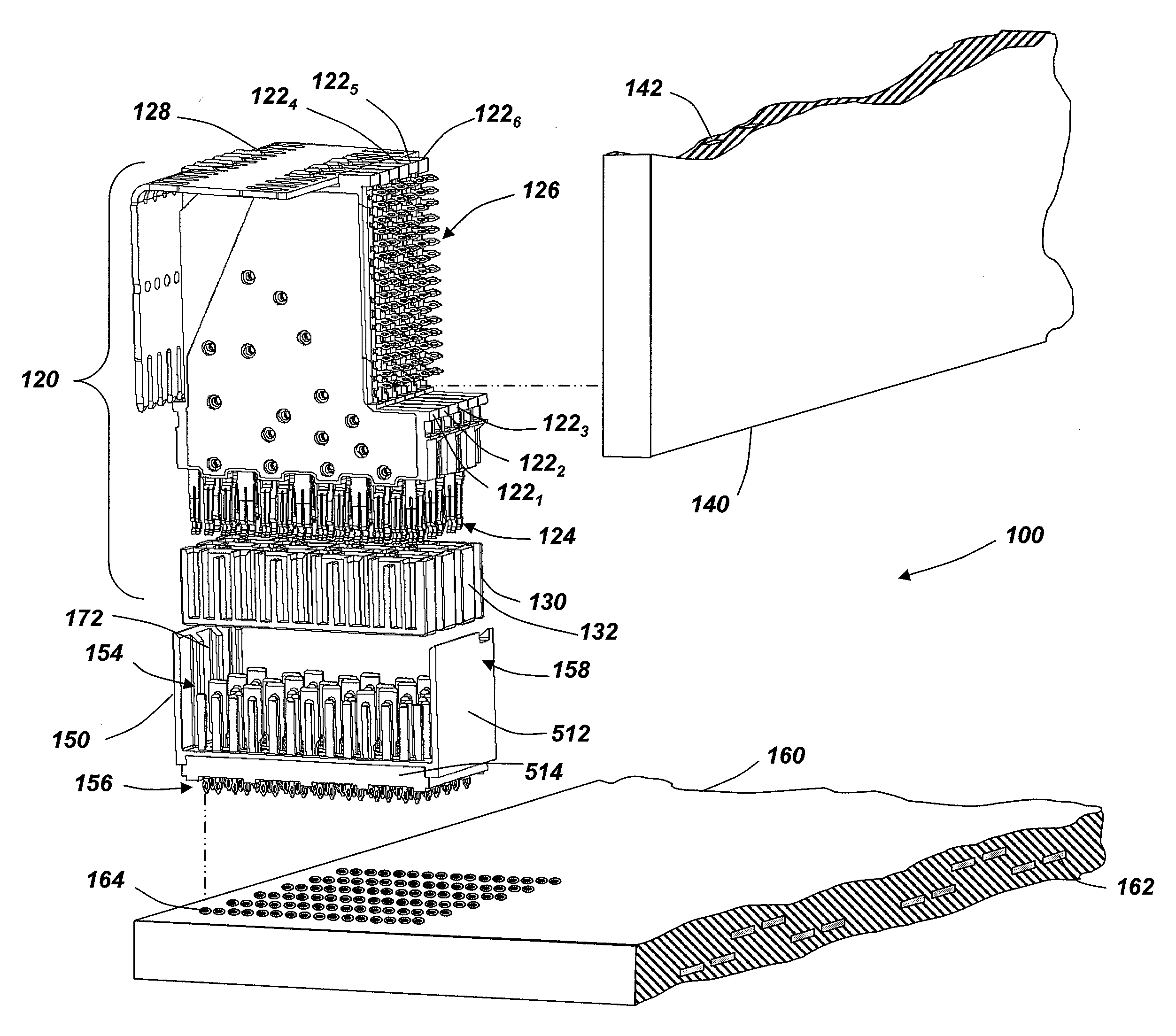

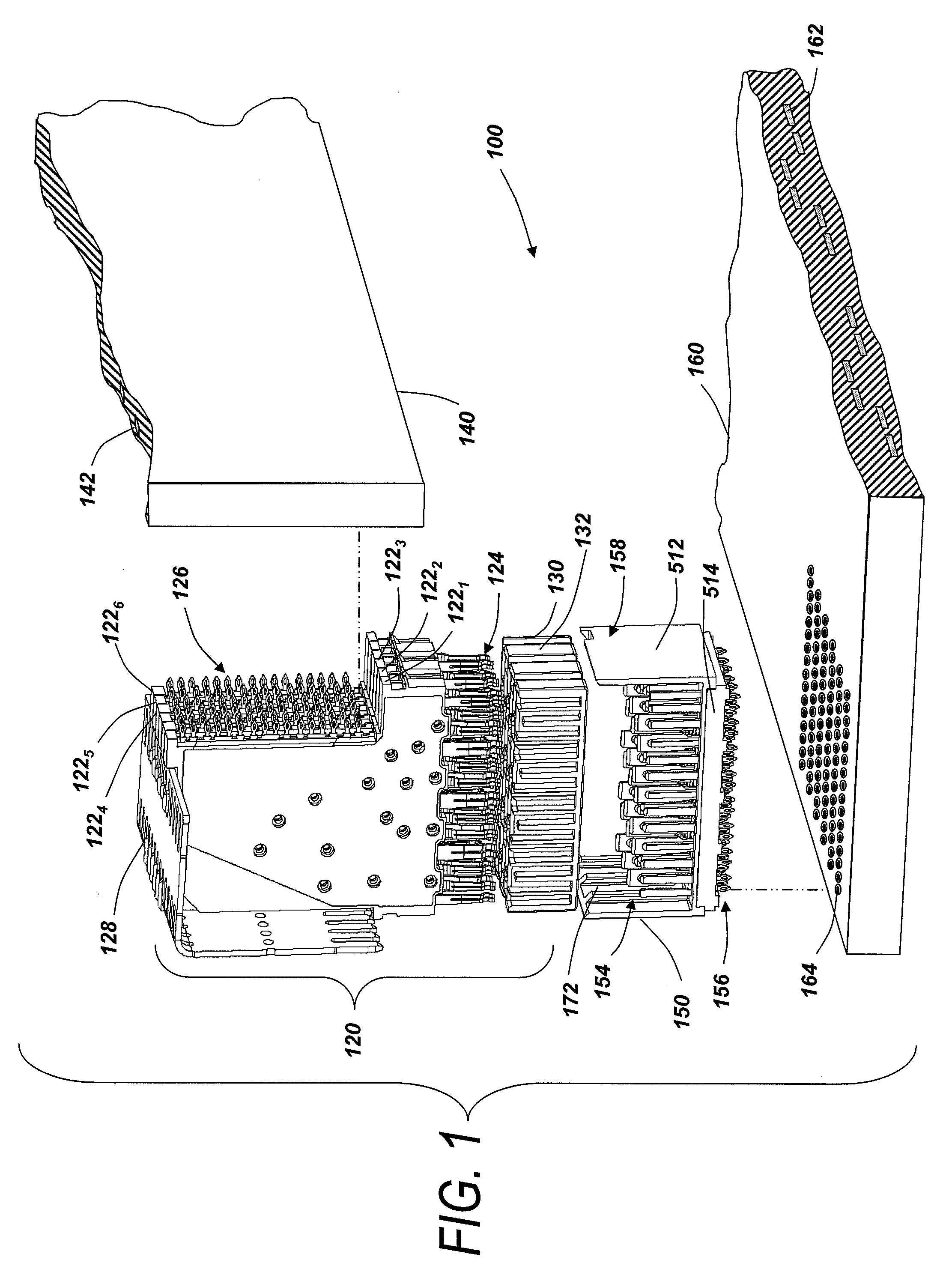

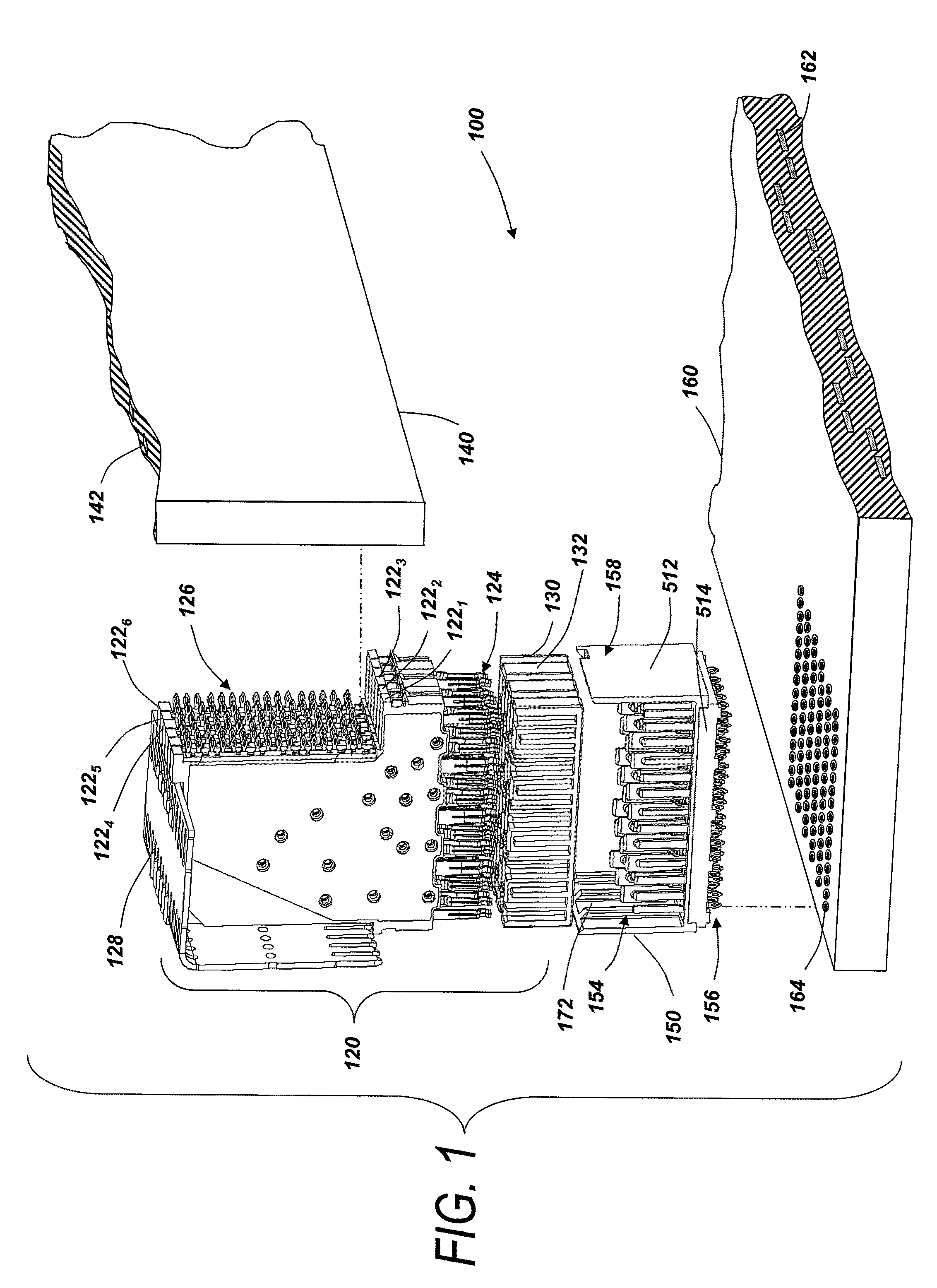

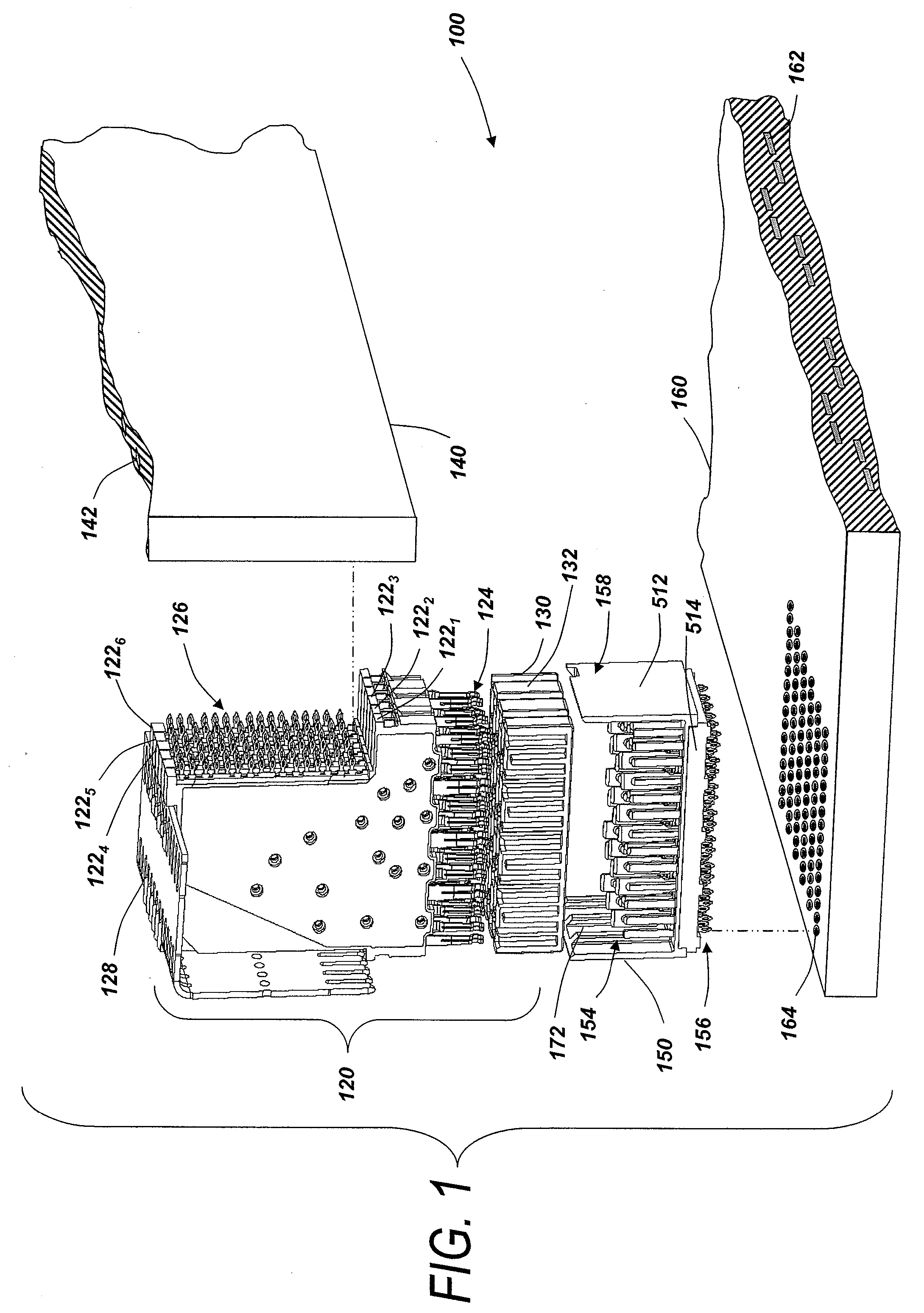

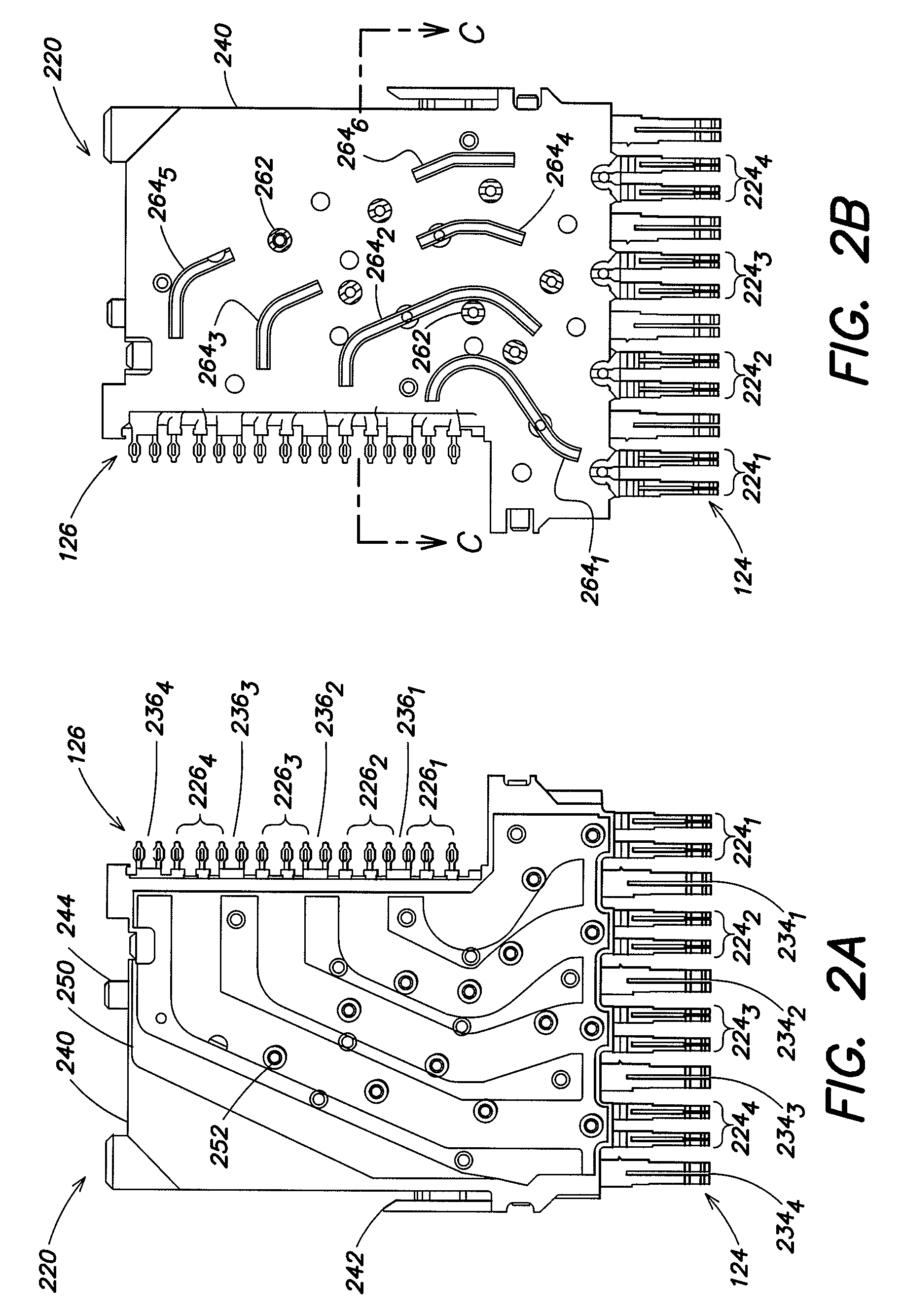

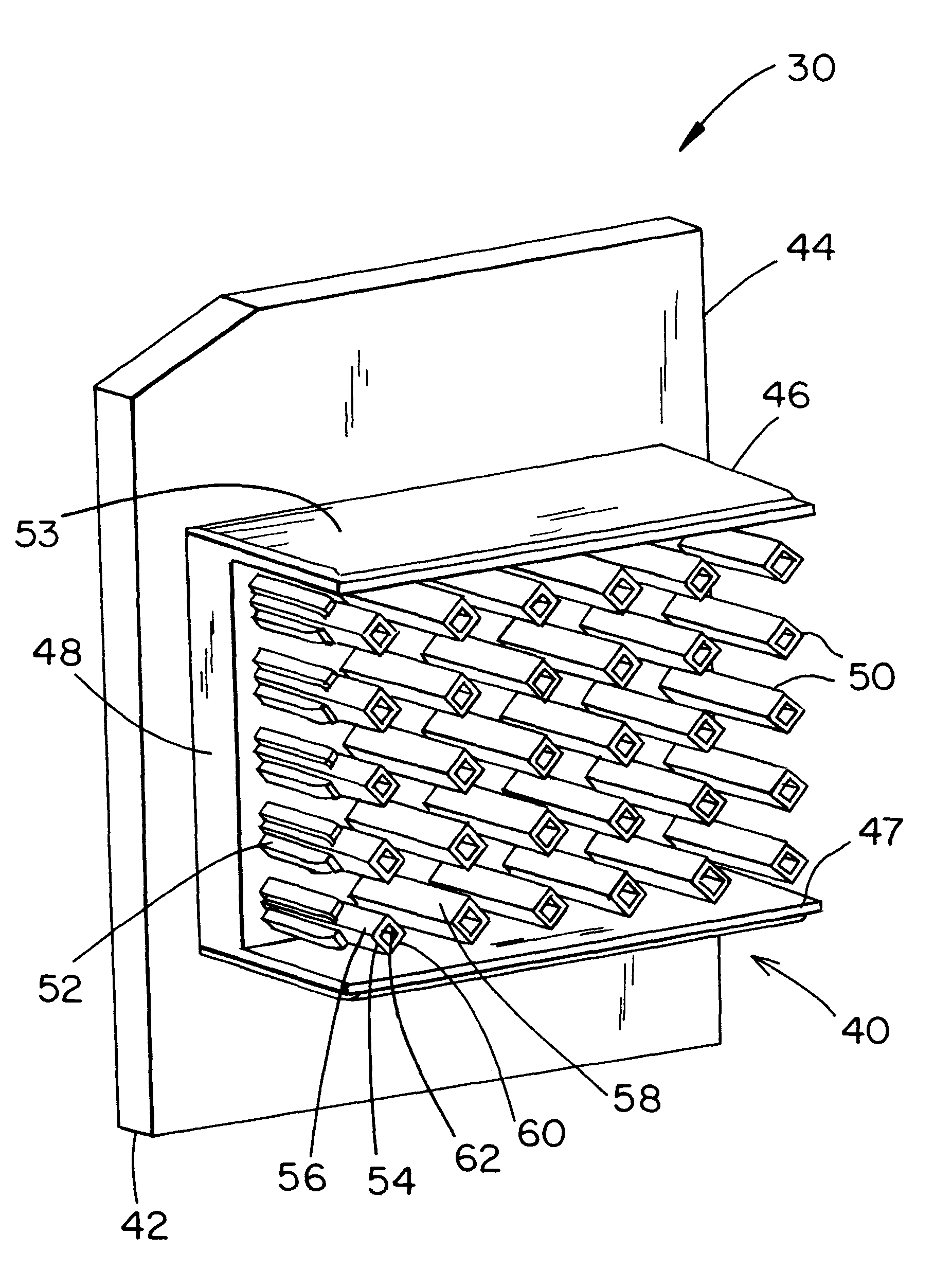

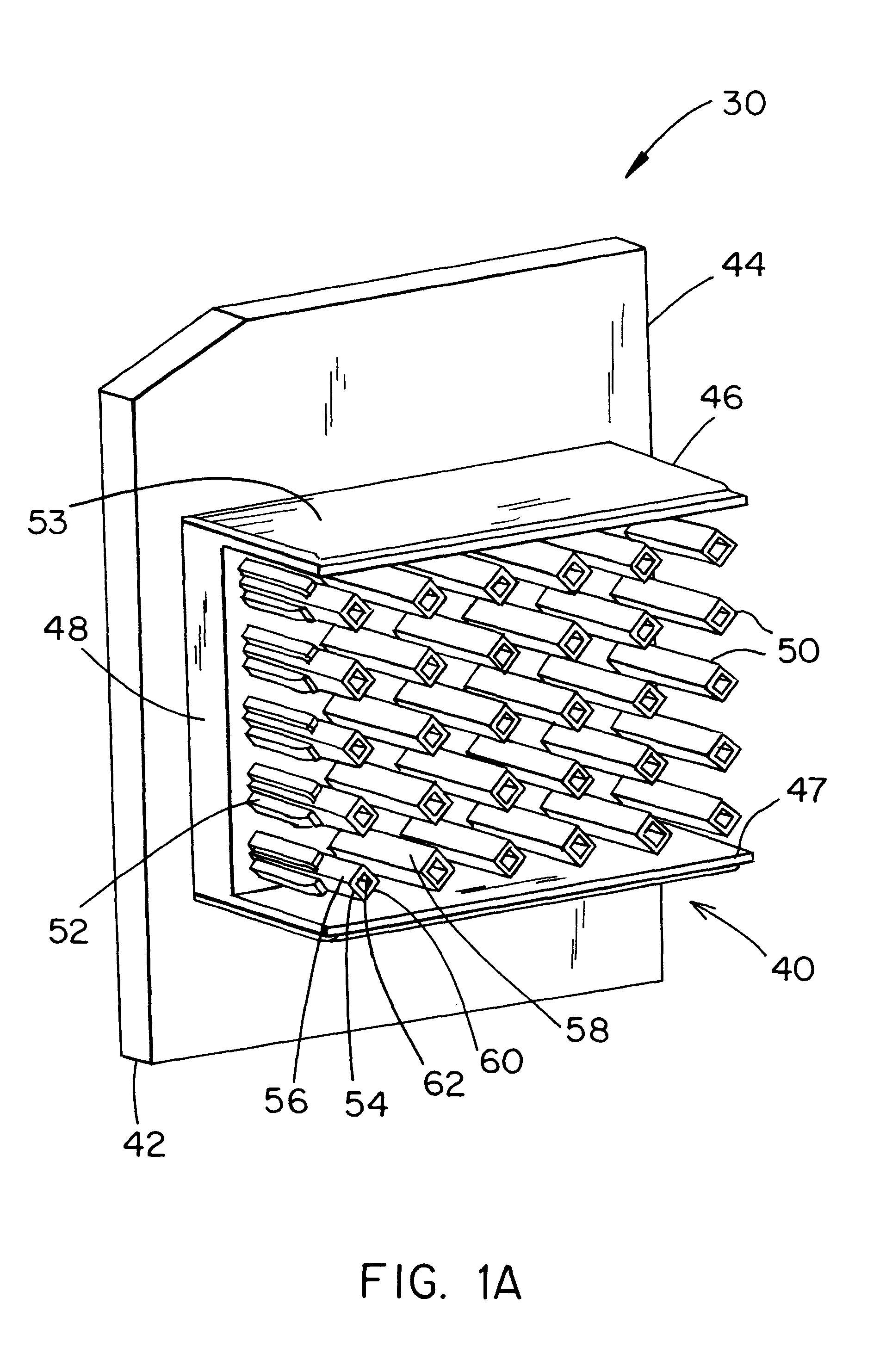

Electrical connector lead frame

An electrical interconnection system with high speed, differential electrical connectors. The connector is assembled from wafers containing columns of conductive elements, some of which form differential pairs. Each column may include ground conductors adjacent pairs of signal conductors. The ground conductors may be wider than the signal conductors, with ground conductors between adjacent pairs of signal conductors being wider than ground conductors positioned at an end of at least some of the columns. Each of the conductive elements may end in a mating contact portion positioned to engage a complementary contact element in a mating connector. The mating contact portions of the signal conductors in some of the pairs may be rotated relative to the columns. The printed circuit board to which the differential signal connector is mounted may be constructed with elongated antipads around pairs of signal conductors.

Owner:AMPHENOL CORP

3D IC method and device

ActiveUS20070037379A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A method of three-dimensionally integrating elements such as singulated die or wafers and an integrated structure having connected elements such as singulated dies or wafers. Either or both of the die and wafer may have semiconductor devices formed therein. A first element having a first contact structure is bonded to a second element having a second contact structure. First and second contact structures can be exposed at bonding and electrically interconnected as a result of the bonding. A via may be etched and filled after bonding to expose and form an electrical interconnect to interconnected first and second contact structures and provide electrical access to this interconnect from a surface. Alternatively, first and / or second contact structures are not exposed at bonding, and a via is etched and filled after bonding to electrically interconnect first and second contact structures and provide electrical access to interconnected first and second contact structure to a surface. Also, a device may be formed in a first substrate, the device being disposed in a device region of the first substrate and having a first contact structure. A via may be etched, or etched and filled, through the device region and into the first substrate before bonding and the first substrate thinned to expose the via, or filled via after bonding.

Owner:INVENSAS BONDING TECH INC

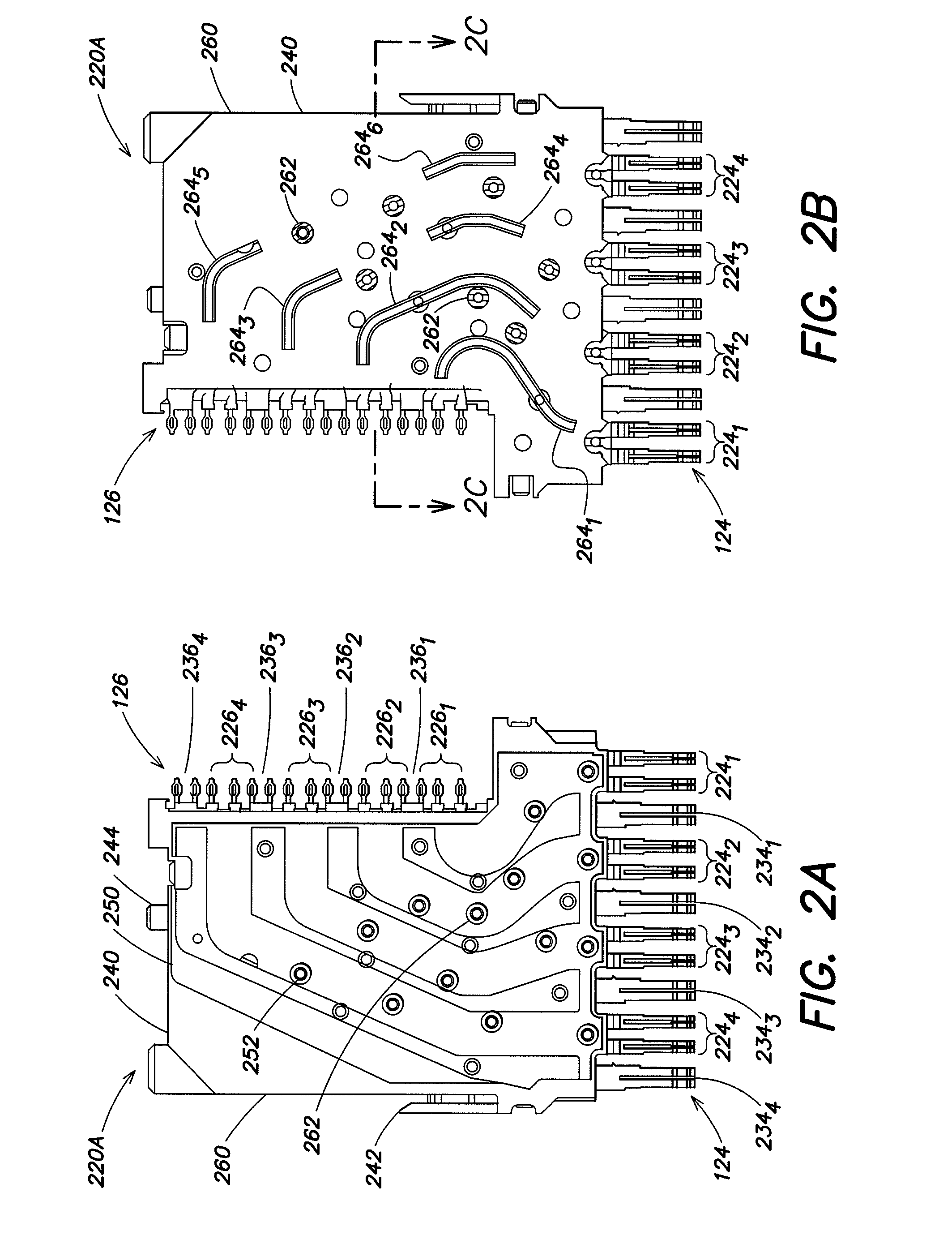

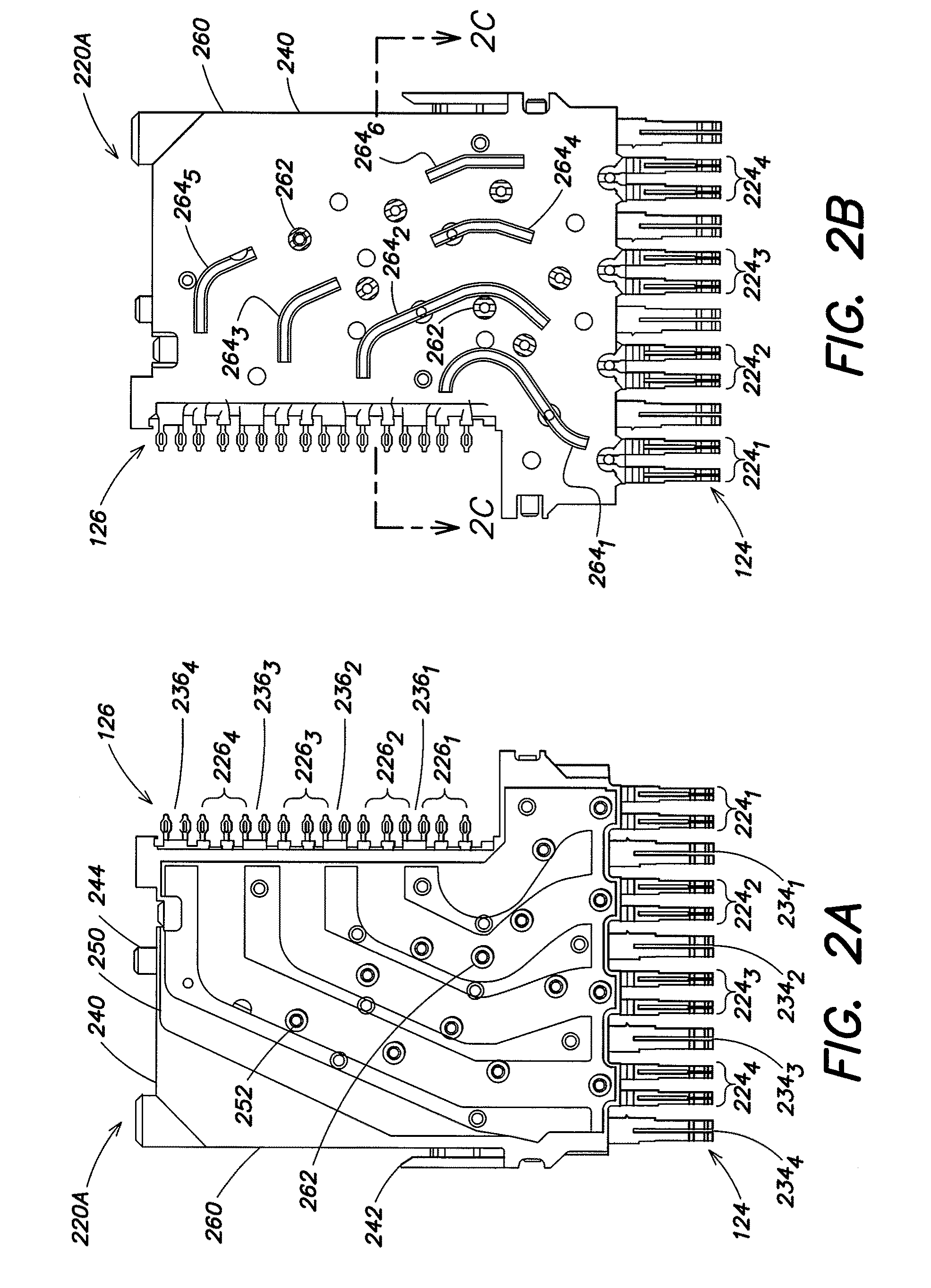

Differential electrical connector with skew control

ActiveUS20080246555A1Selective positioningCoupling devicesCoupling protective earth/shielding arrangementsElectrical conductorRegioselectivity

An electrical interconnection system with high speed, differential electrical connectors. The connector is assembled from wafers each containing a column of conductive elements, some of which form differential pairs. A housing for the wafer is formed with regions of higher and lower dielectric constant material. The regions of lower dielectric constant material are selectively positioned adjacent longer signal conductors of the differential pairs. The material may be preferentially placed along curved segments of the differential pair to reduce crosstalk in the connector while reducing skew.

Owner:AMPHENOL CORP

Module interface with optical and electrical interconnects

A module comprises an electrical device having at least one memory device. A plurality of electrical contacts provide electrical signals to the electrical device. The memory apparatus also includes an optical interface, and an optical-to-electrical signal converter is coupled to receive optical signals from the optical interface and provide electrical signals to the electrical device.

Owner:INTEL CORP

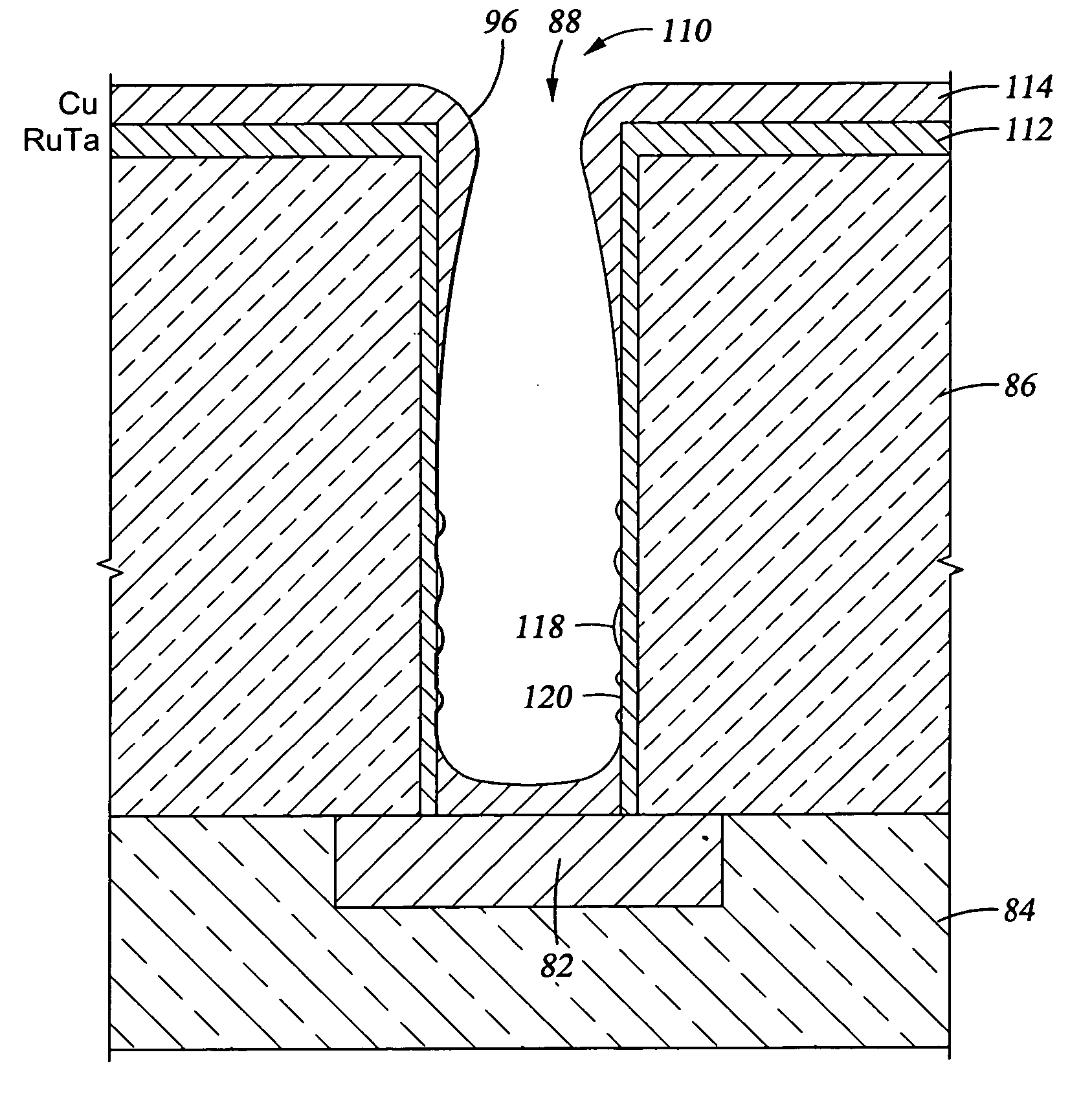

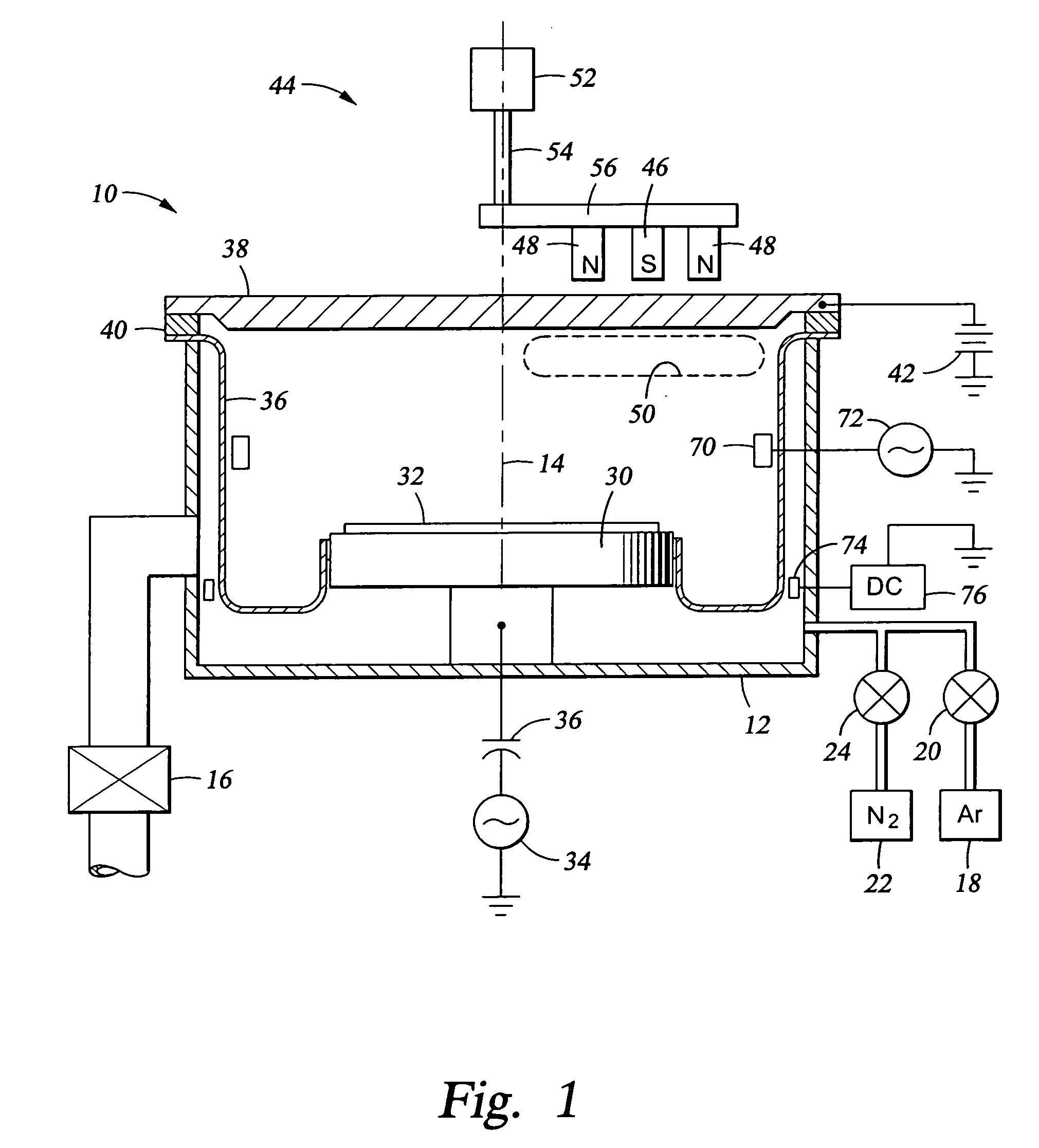

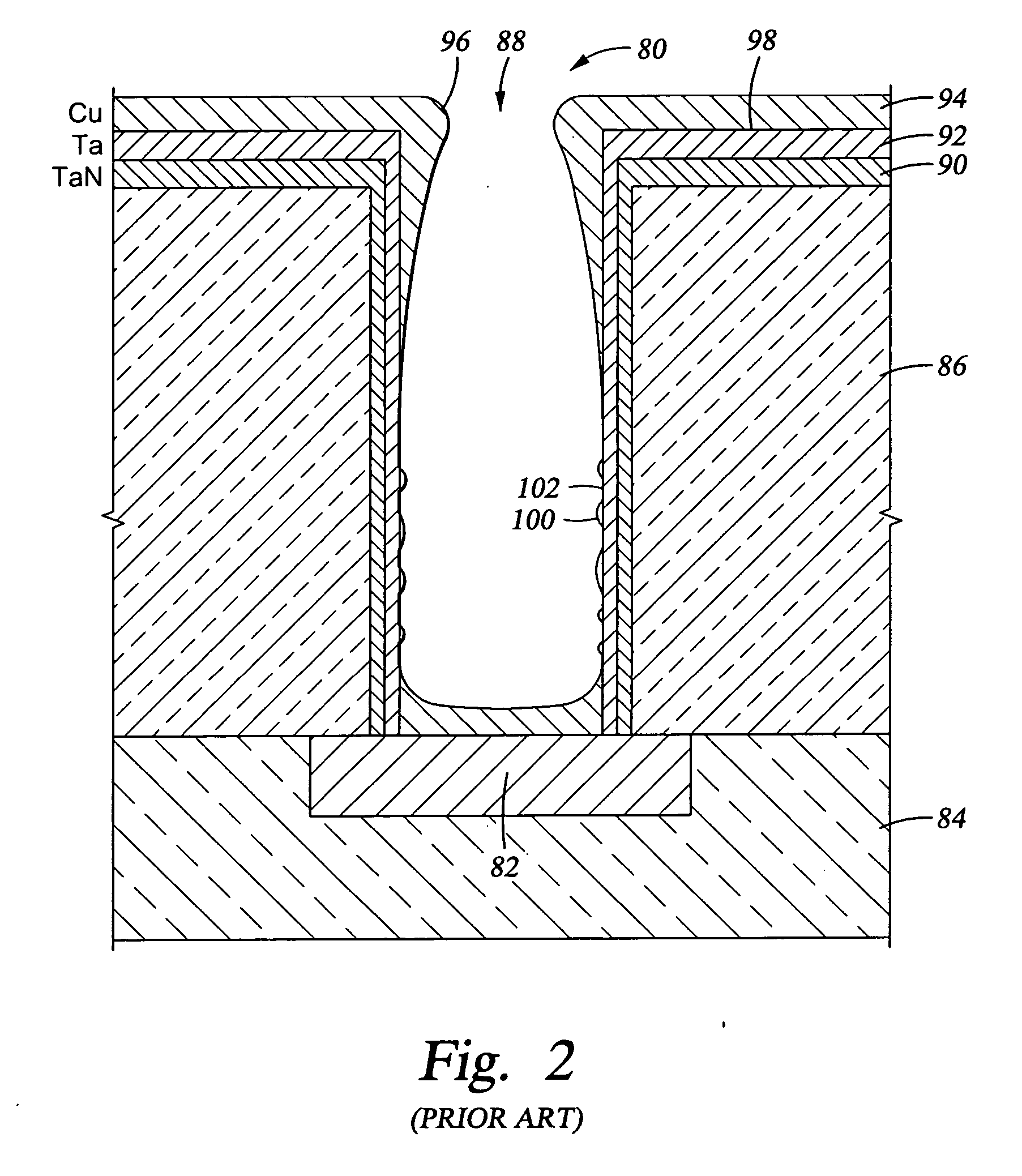

Integrated process for sputter deposition of a conductive barrier layer, especially an alloy of ruthenium and tantalum, underlying copper or copper alloy seed layer

InactiveUS20070059502A1Effective interfacial barrierGood suitSemiconductor/solid-state device detailsVacuum evaporation coatingMoisture barrierRefractory metals

A fabrication method and a product for the deposition of a conductive barrier or other liner layer in a vertical electrical interconnect structure. One embodiment includes within a a hole through a dielectric layer a barrier layer of RuTaN, an adhesion layer of RuTa, and a copper seed layer forming a liner for electroplating of copper. The ruthenium content is preferably greater than 50 at % and more preferably at least 80 at % but less than 95 at %. The barrier and adhesion layers may both be sputter deposited. Other platinum-group elements substitute for the ruthenium and other refractory metals substitute for the tantalum. Aluminum alloying into RuTa when annealed presents a moisture barrier. Copper contacts include different alloying fractions of RuTa to shift the work function to the doping type.

Owner:APPLIED MATERIALS INC

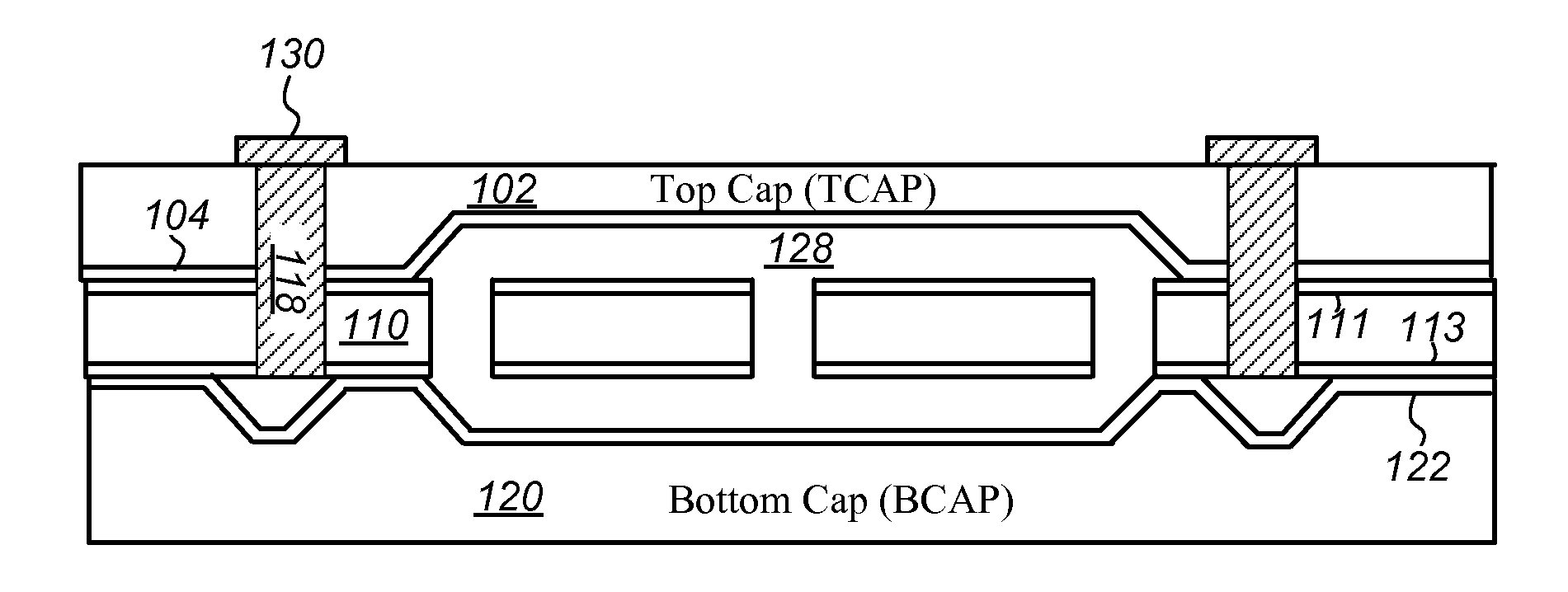

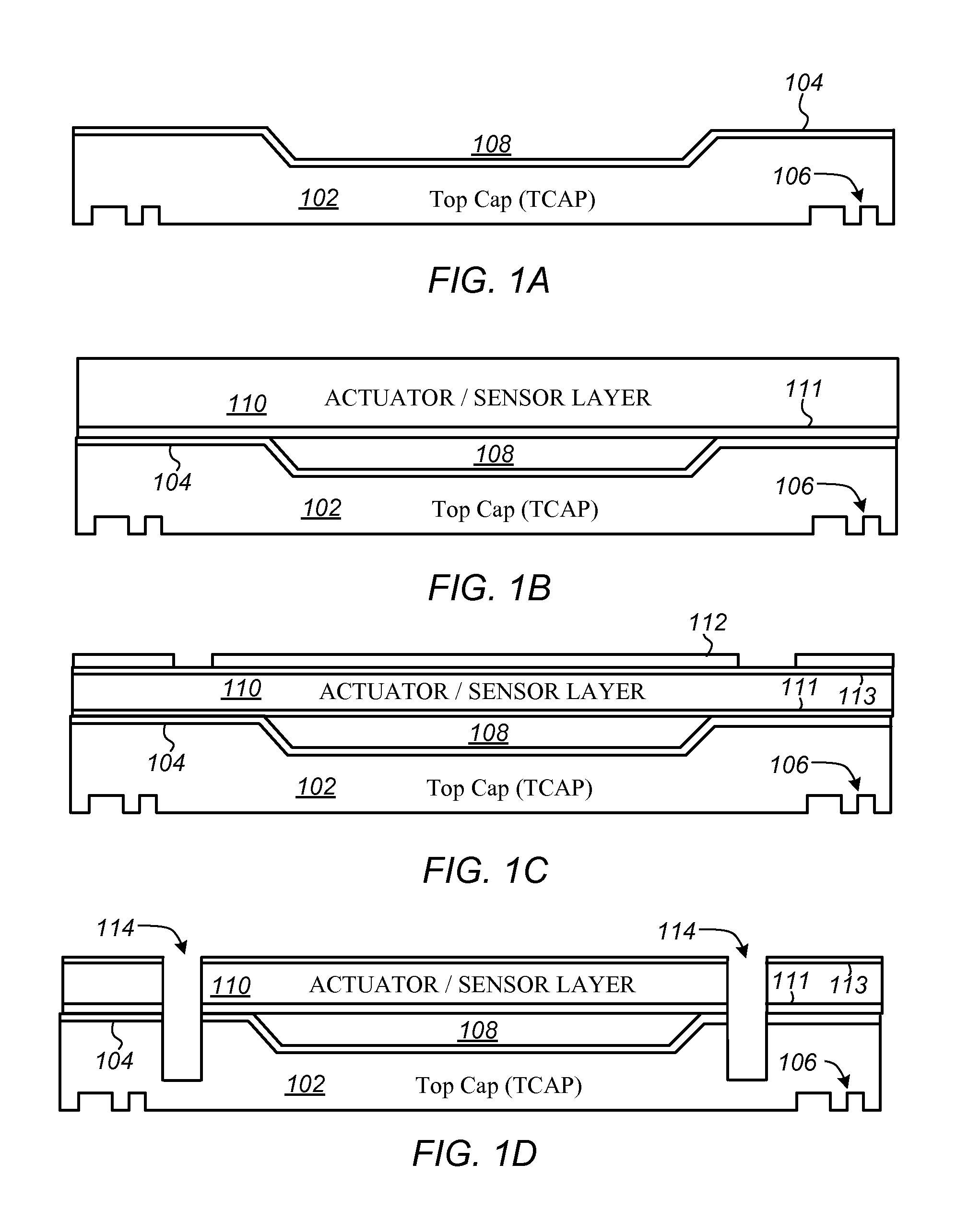

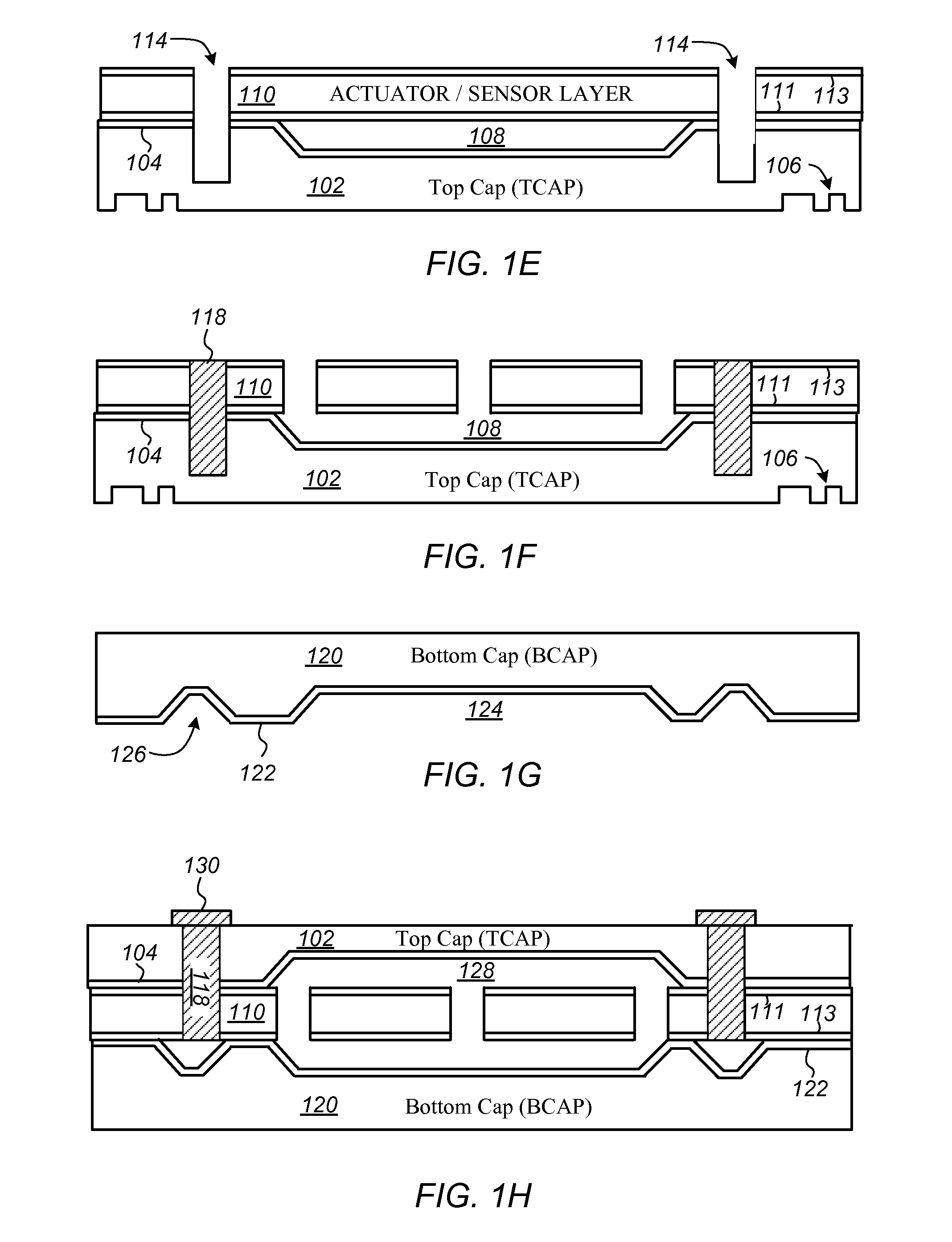

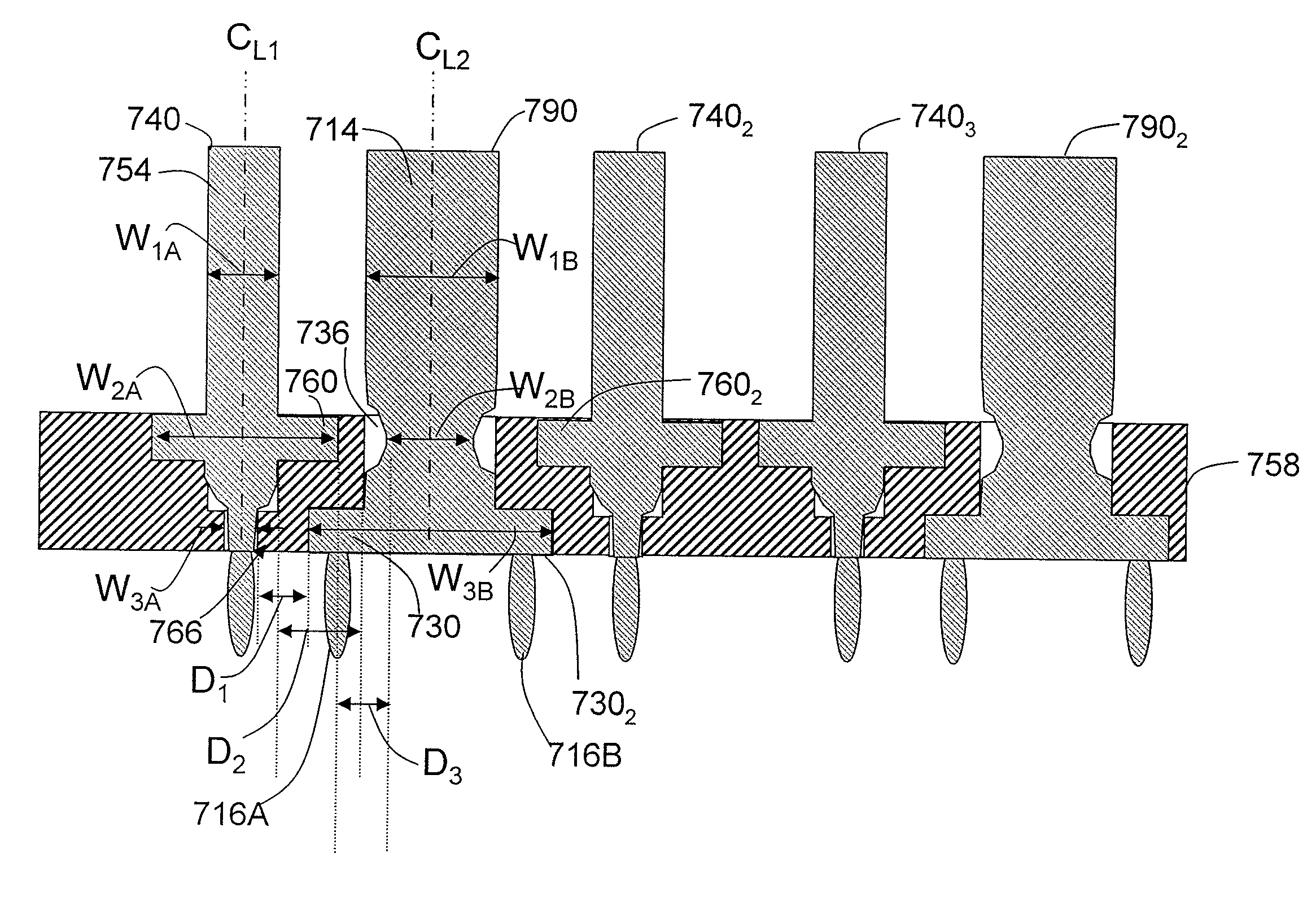

Wafer Level Structures and Methods for Fabricating and Packaging MEMS

ActiveUS20120142144A1Solid-state devicesSemiconductor/solid-state device manufacturingLevel structureHermetic seal

Methods of fabricating a Micro-Electromechanical System (MEMS) in a hermetically sealed cavity formed at a substrate level are provided. Generally, the method comprises: (i) forming a number of first open cavities in a surface of a first substrate and a number of second open cavities in a surface of a second substrate corresponding to the first open cavities; (ii) forming an actuator / sensor layer including a number of MEMS devices with electrically conductive regions therein; (iii) bonding the first substrate and the second substrate to the actuator / sensor layer so that at least one of the number of the first and second open cavities align with at least one of the number of MEMS devices to form a sealed cavity around the MEMS; and (iv) electrically connecting the electrically conductive regions of the MEMS device to a pad outside of the sealed cavity through an electrical interconnect. Other embodiments are also described.

Owner:INTEGRATED BIOSENSING TECH

Electrical connector with complementary conductive elements

ActiveUS7794240B2Improve signal integrityDesirable electrical propertyPrinted circuit assemblingCoupling device detailsElectrical connectorElectrical interconnect

Owner:AMPHENOL CORP

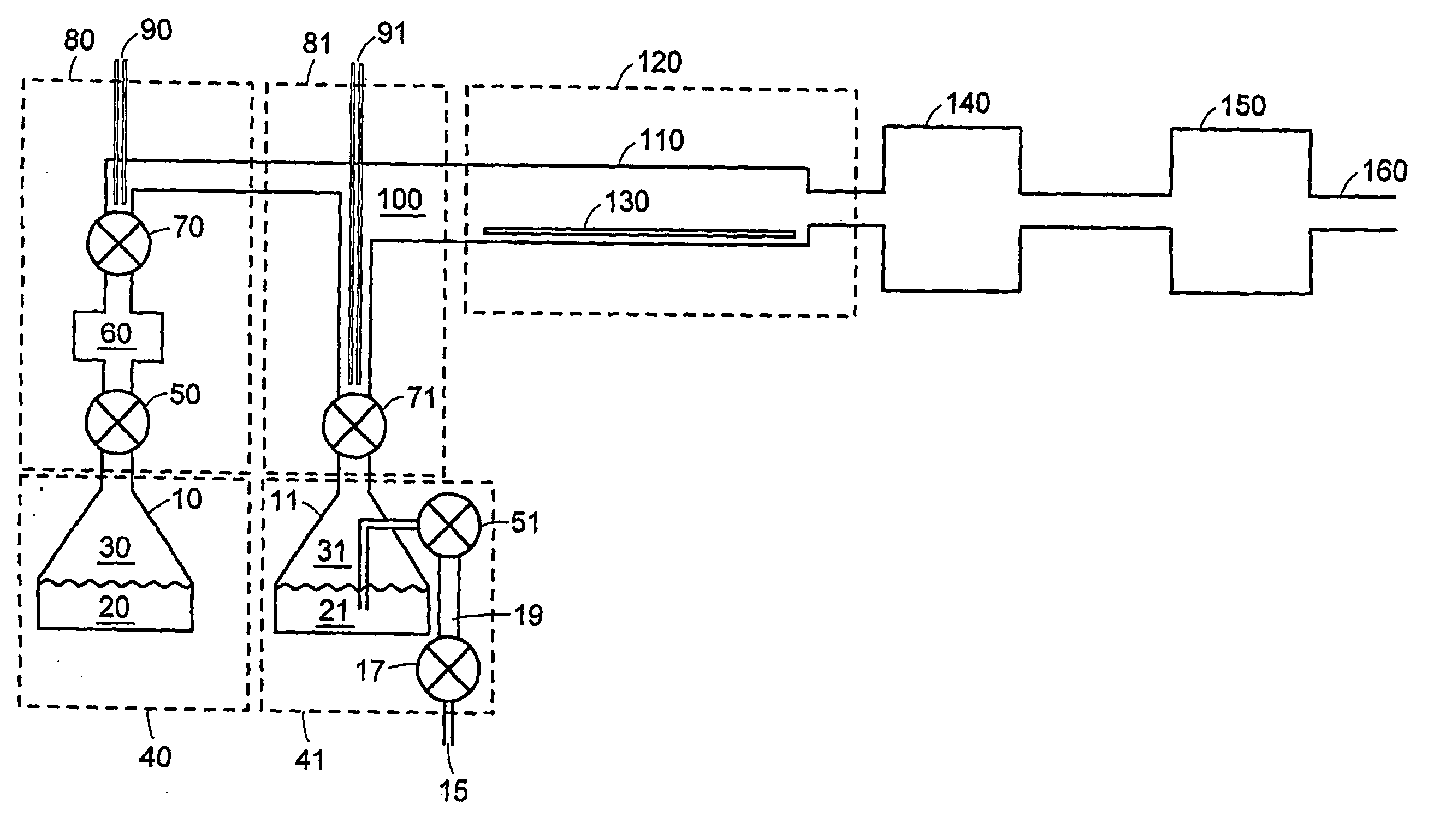

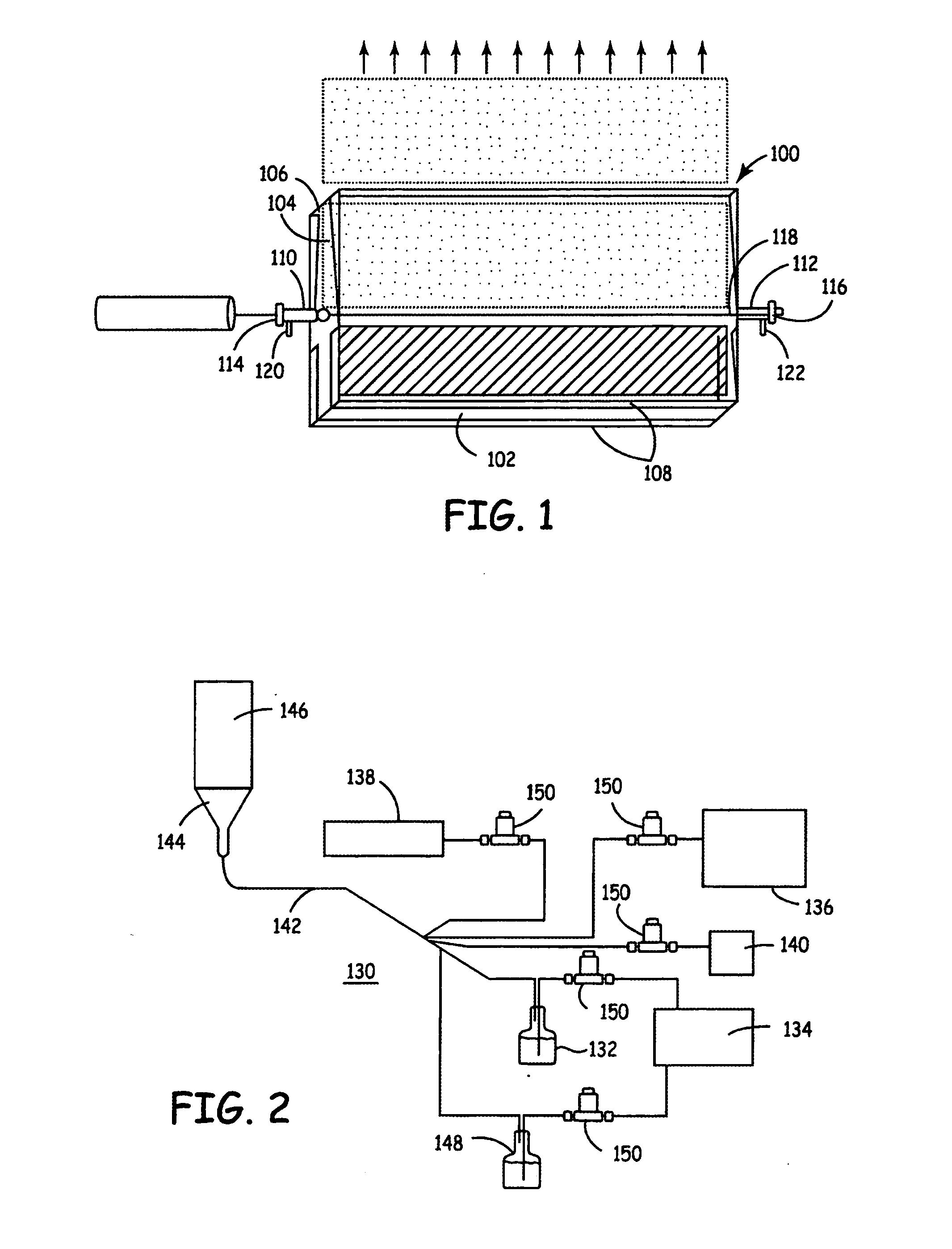

Reactive deposition for electrochemical cell production

Light reactive deposition can be adapted effectively for the deposition of one or more electrochemical cell components. In particular, electrodes, electrolytes, electrical interconnects can be deposited form a reactive flow. In some embodiments, the reactive flow comprises a reactant stream that intersects a light beam to drive a reaction within a light reactive zone to produce product that is deposited on a substrate. The approach is extremely versatile for the production of a range of compositions that are useful in electrochemical cells and fuel cell, in particular. The properties of the materials, including the density and porosity can be adjusted based on the deposition properties and any subsequent processing including, for example, heat treatments.

Owner:NANOGRAM

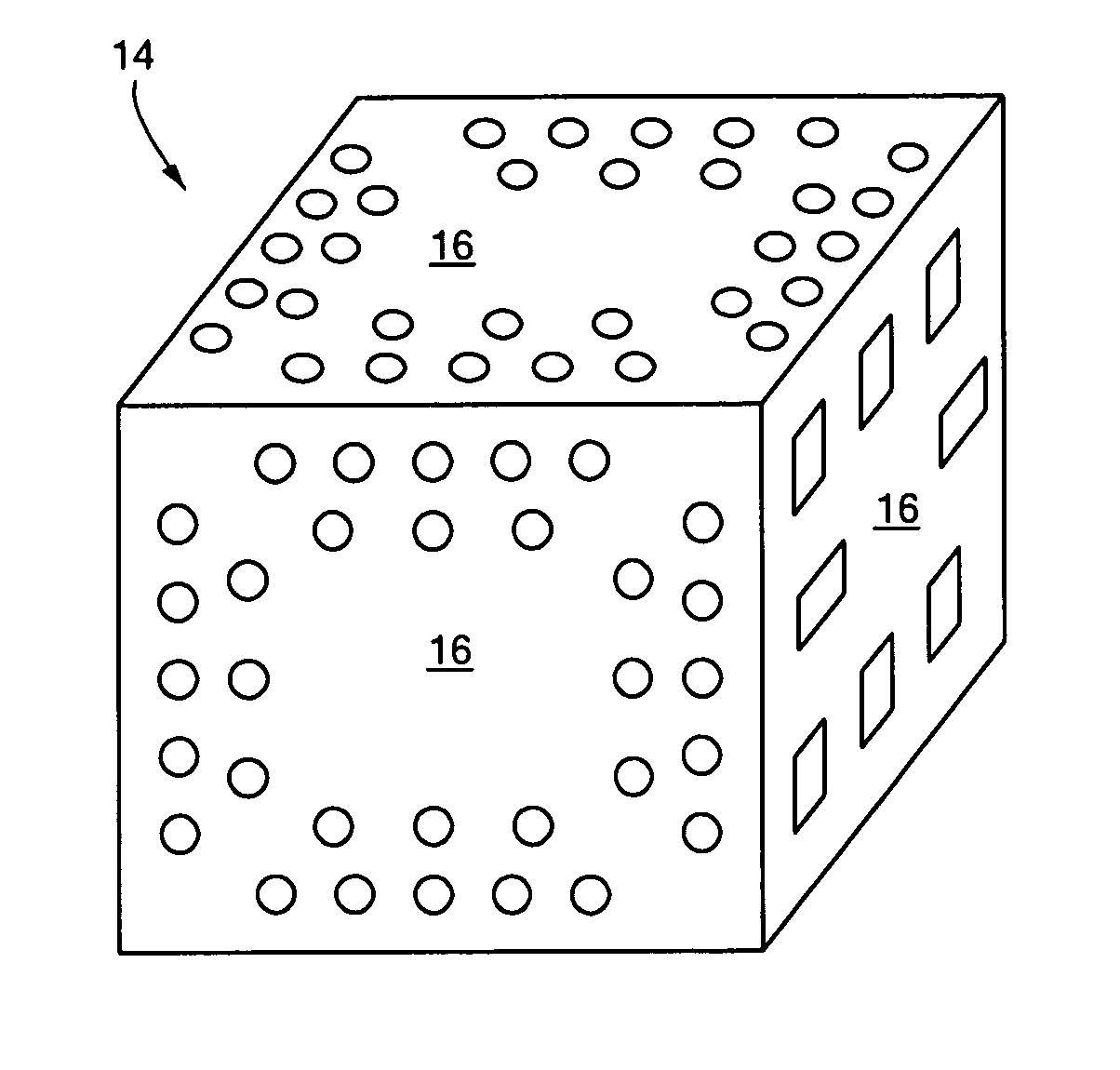

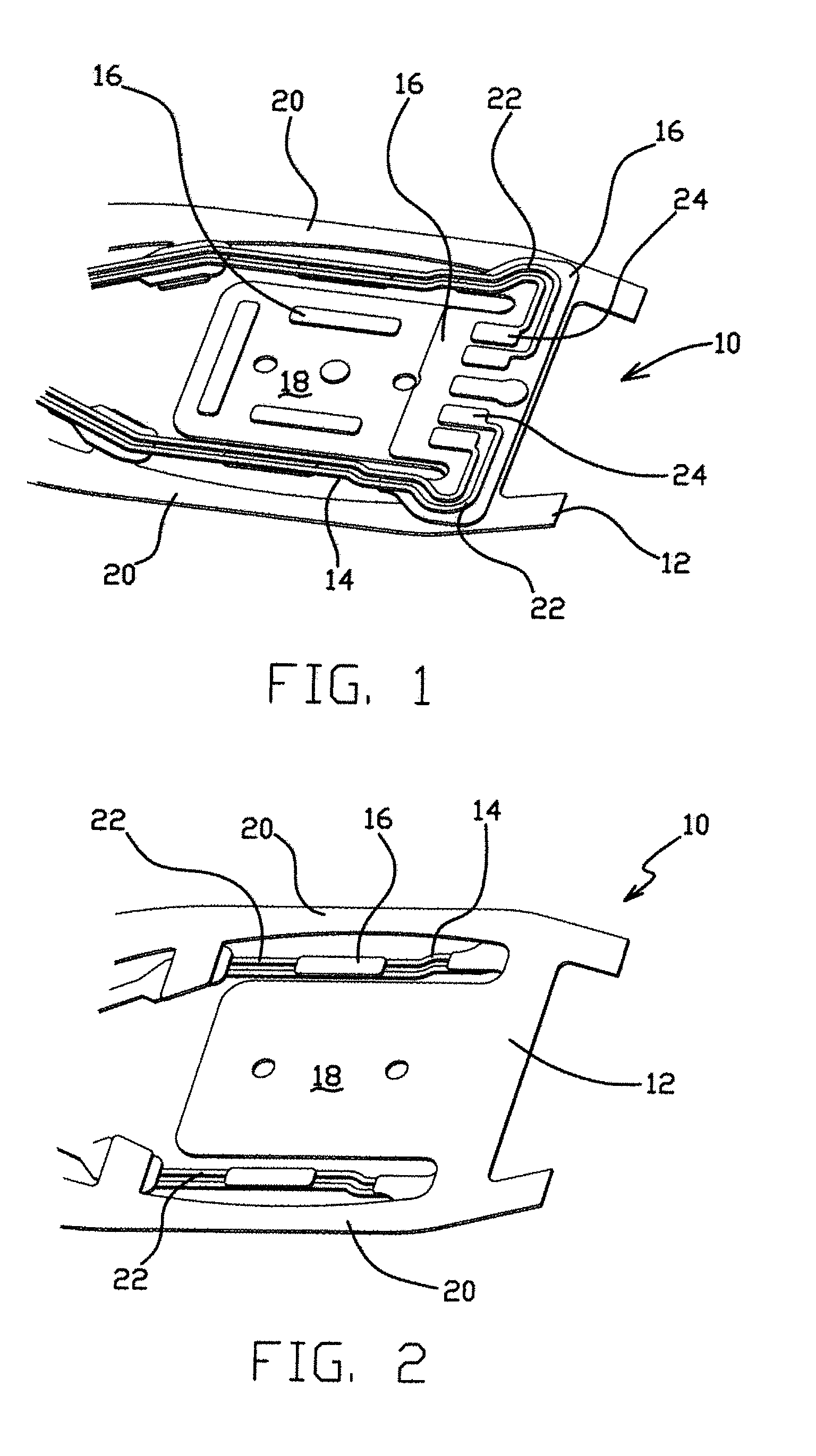

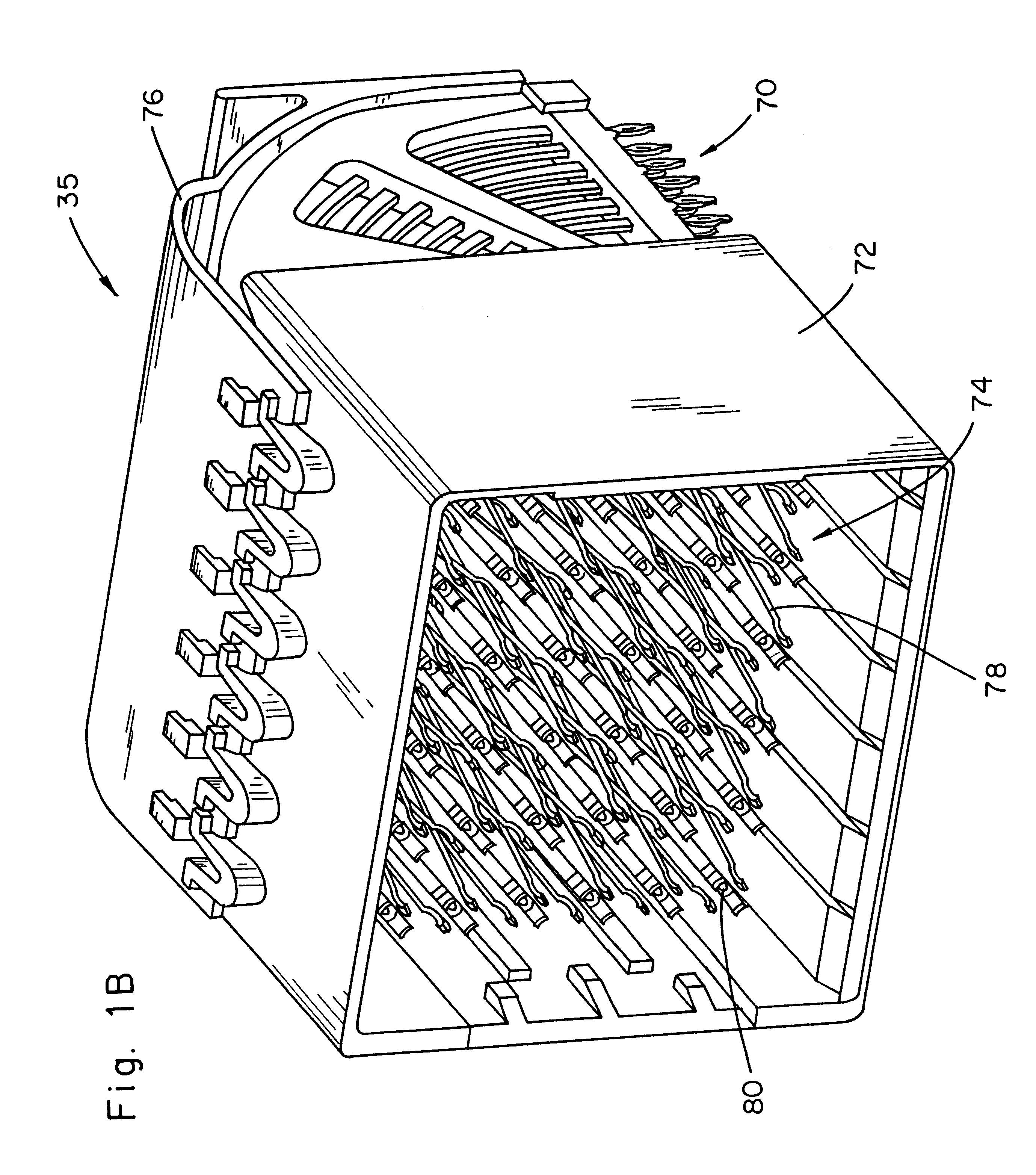

Multi-surface mounting member and electronic device

ActiveUS7040922B2Measurement apparatus componentsCoupling device detailsElectricityFlexible circuits

An electrical interconnect apparatus has a mounting member with a plurality of sides. The mounting member is formed from an insulator as a cuboid. Moreover, the mounting member also may be formed from a flexible circuit. Among other things, the plurality of sides includes an interface side. At least two of the plurality of sides are in electrical communication with the interface side.

Owner:ANALOG DEVICES INC

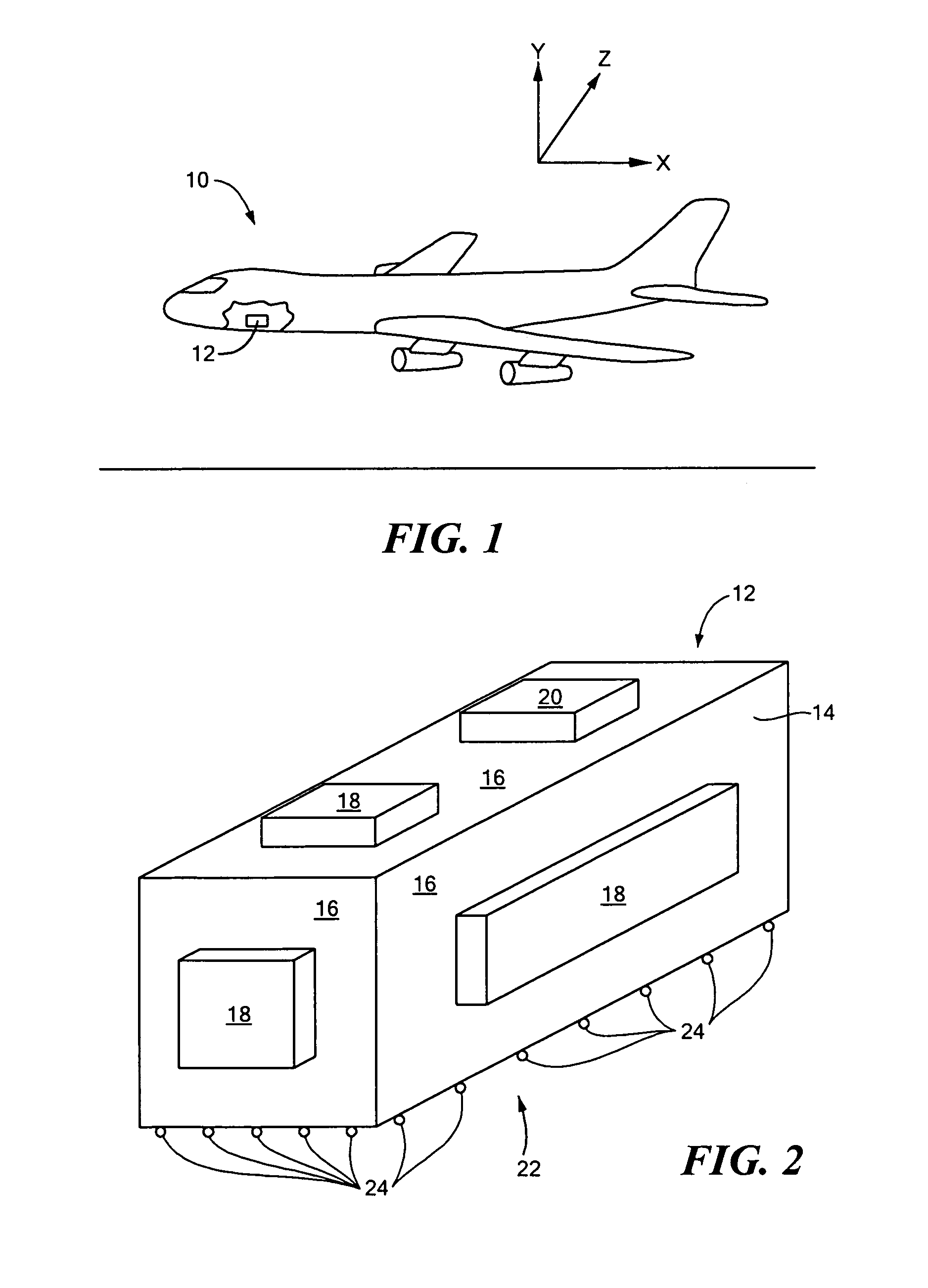

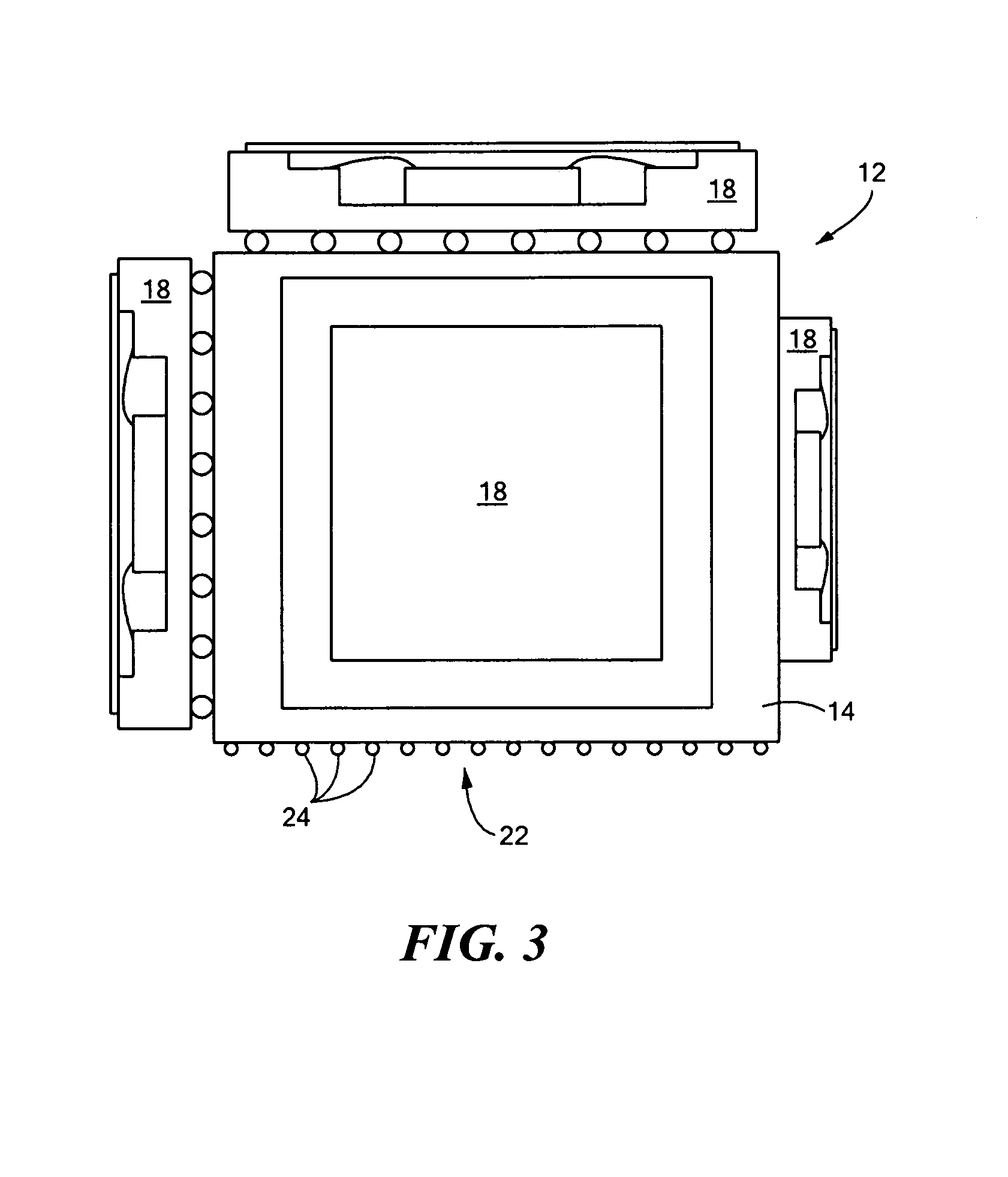

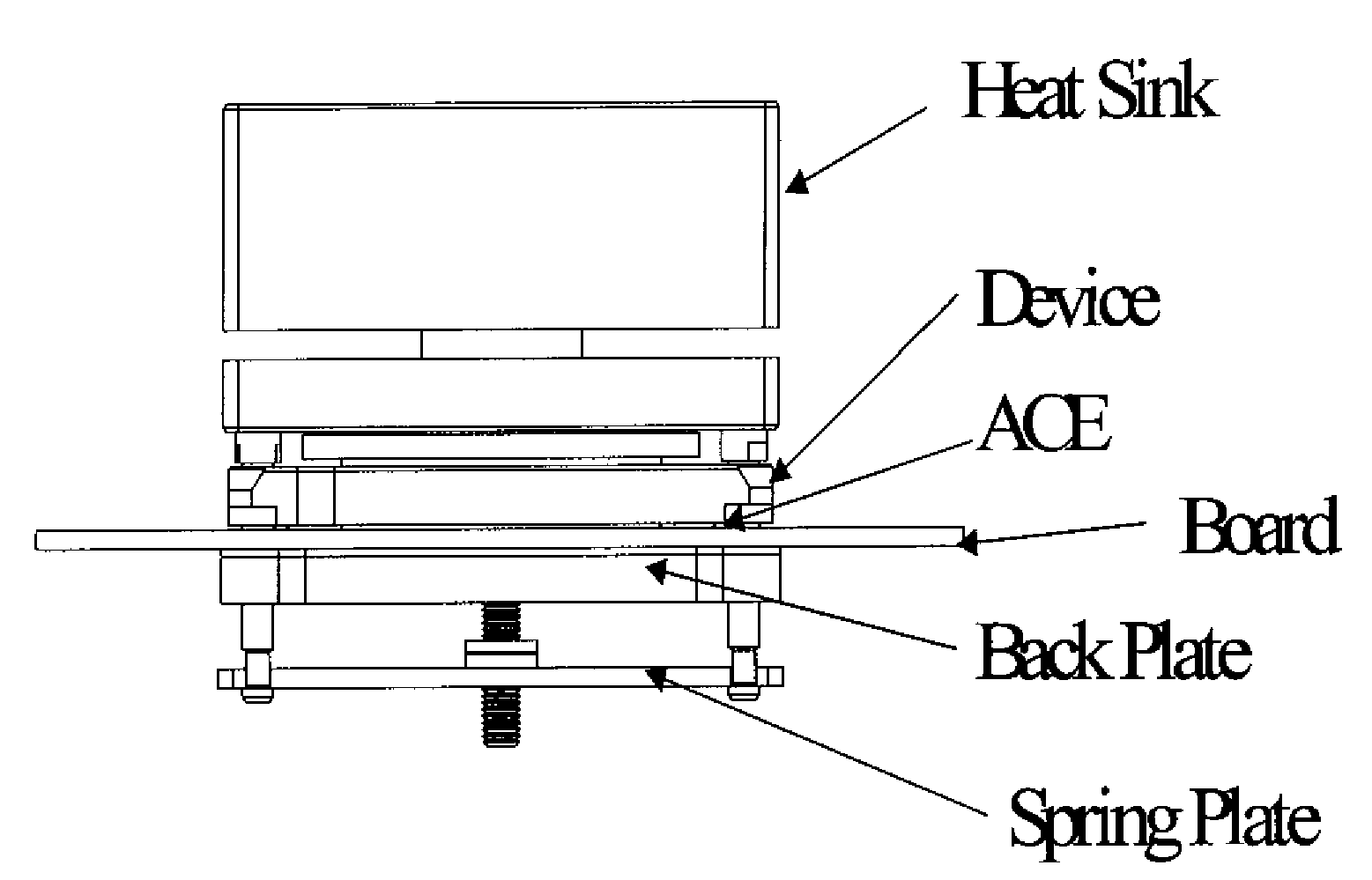

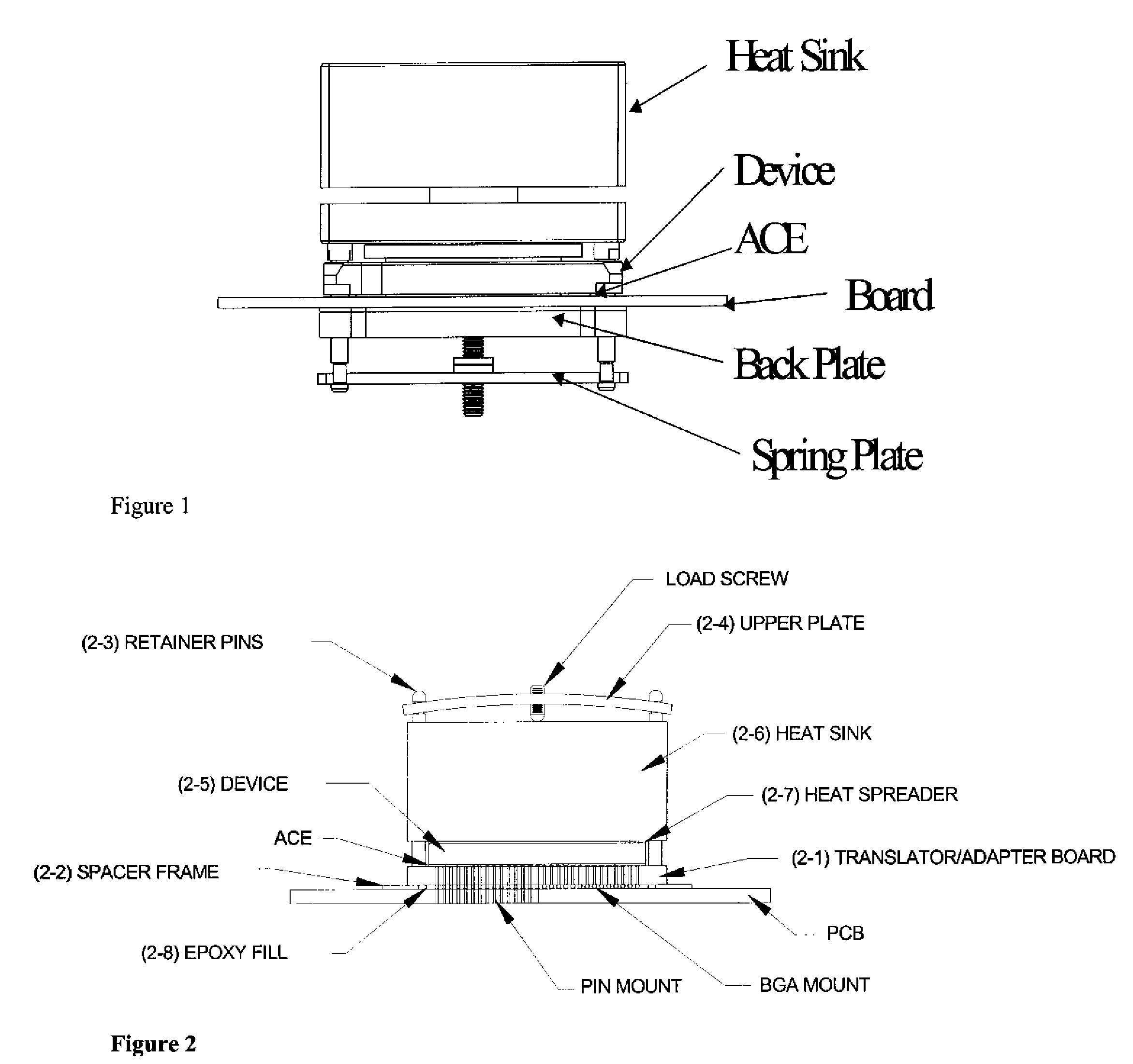

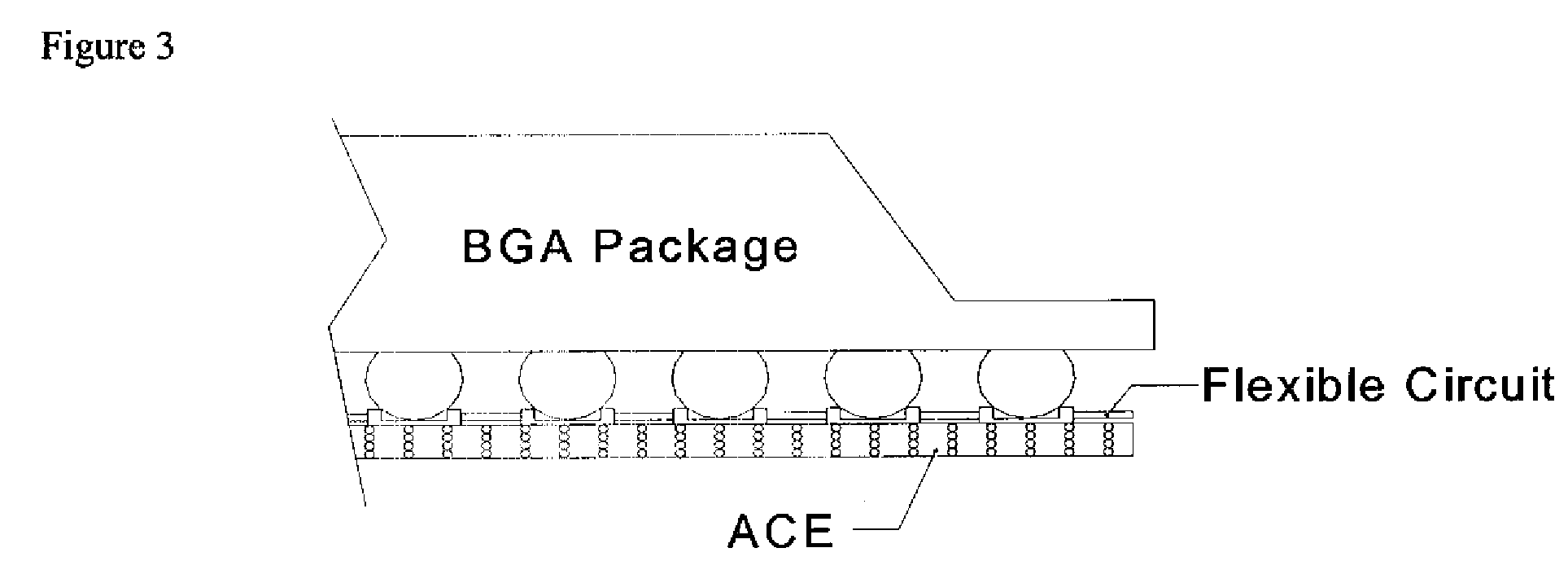

Separable electrical interconnect with anisotropic conductive elastomer for translating footprint

InactiveUS7249954B2Increase stiffnessPrinted circuit aspectsCoupling device detailsElastomerEngineering

A separable electrical connector for electrically interconnecting an electrical device to a substrate. In one embodiment, the connector includes an adapter board electrically connected to the substrate, the adapter board having electrical contacts on both sides, and a layer of ACE between the electrical device and the adapter board. A mechanical structure is used to apply a compressive force on the ACE through the adapter board and the electrical device. In another embodiment, the connector includes a translator board having electrical contacts on both sides and electrical circuits within to expand the footprint of the fine pitch electrical device to the coarser pitch of the substrate. The connector further includes a layer of ACE between the translator board and the substrate.

Owner:PARICON TECH

Metal amides of cyclic amines

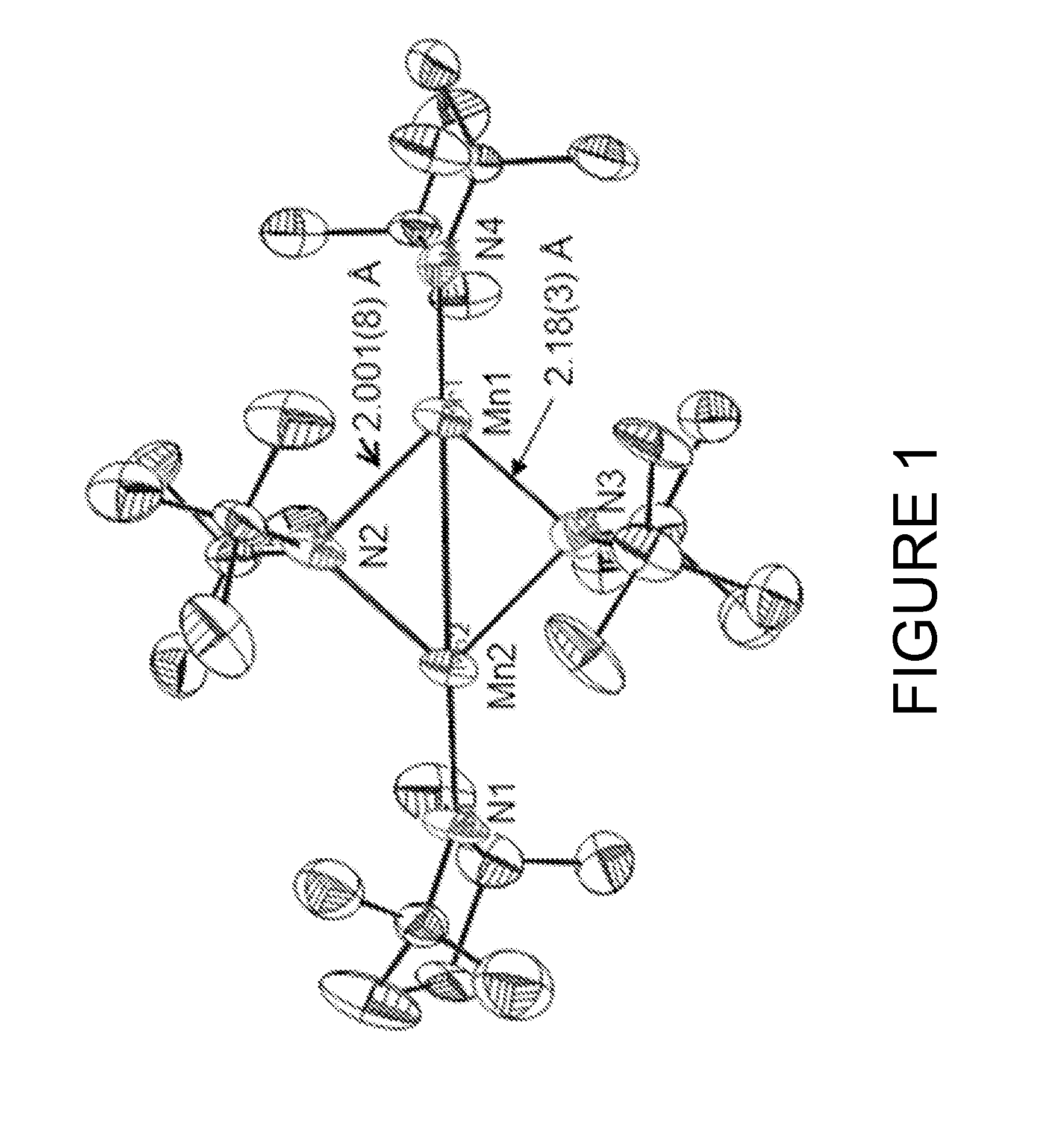

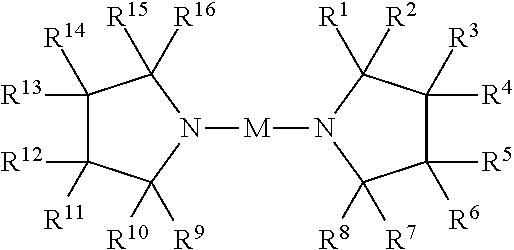

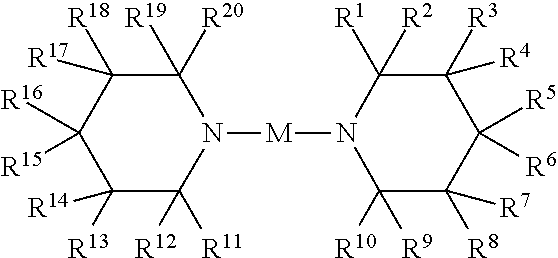

ActiveUS20160152649A1Improve thermal stabilityImprove conductivityIron group organic compounds without C-metal linkagesNickel organic compoundsGermanideMetal silicide

Compounds, and oligomers of the compounds, are synthesized with cyclic amine ligands attached to a metal atom. These compounds are useful for the synthesis of materials containing metals. Examples include pure metals, metal alloys, metal oxides, metal nitrides, metal phosphides, metal sulfides, metal selenides, metal tellurides, metal borides, metal carbides, metal silicides and metal germanides. Techniques for materials synthesis include vapor deposition (chemical vapor deposition and atomic layer deposition), liquid solution methods (sol-gel and precipitation) and solid-state pyrolysis. Suitable applications include electrical interconnects in microelectronics and magnetoresistant layers in magnetic information storage devices. The films have very uniform thickness and high step coverage in narrow holes.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

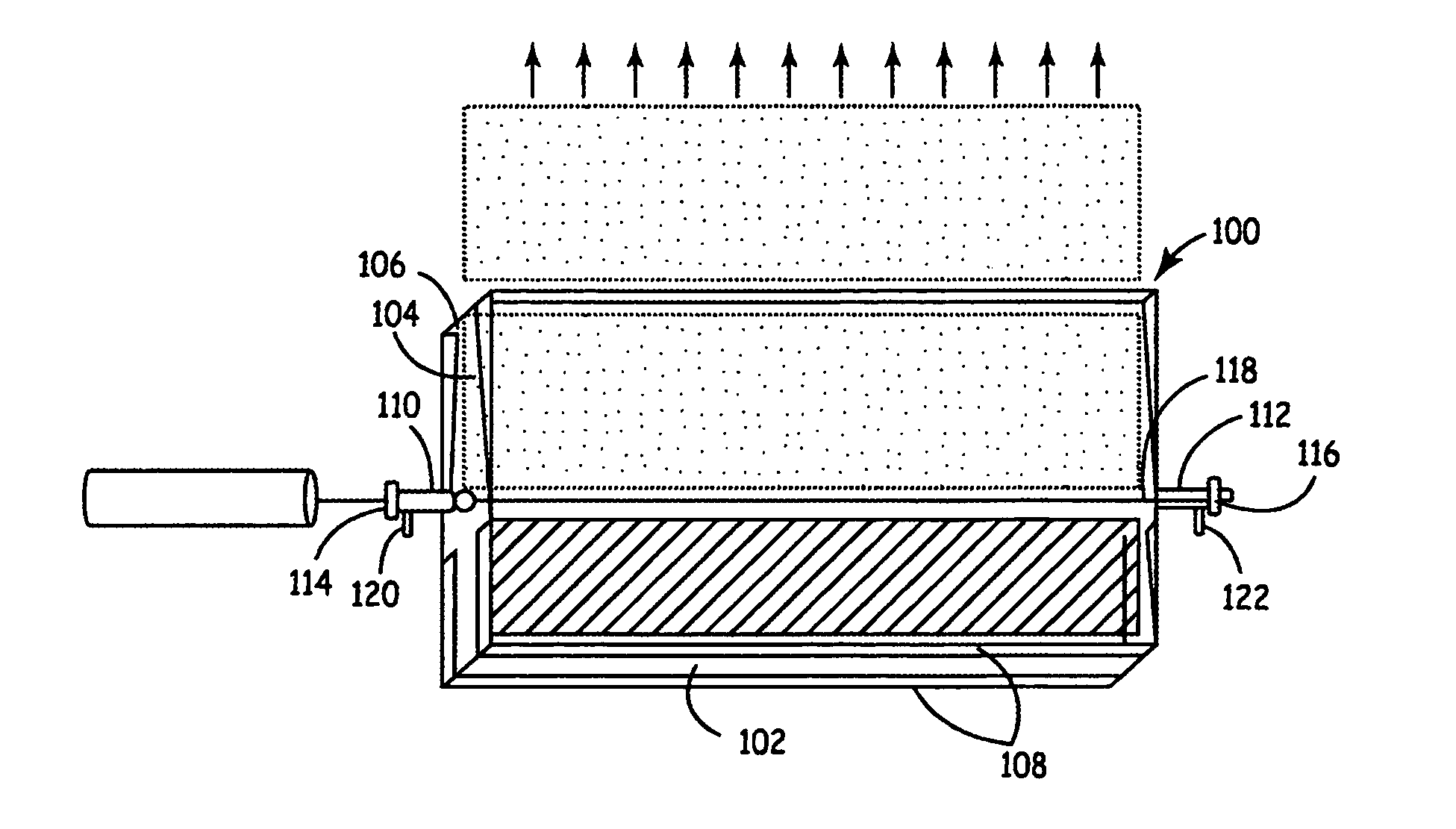

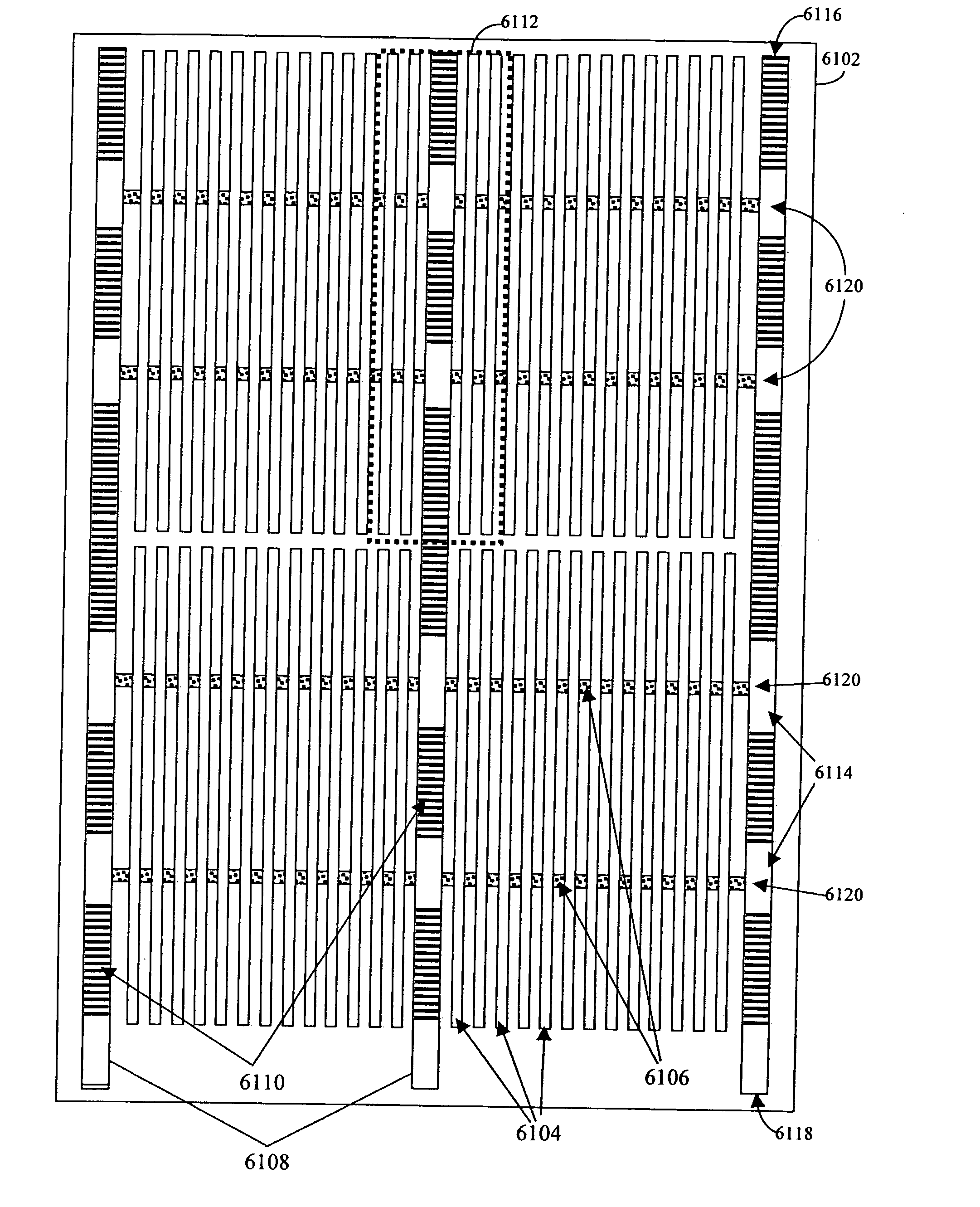

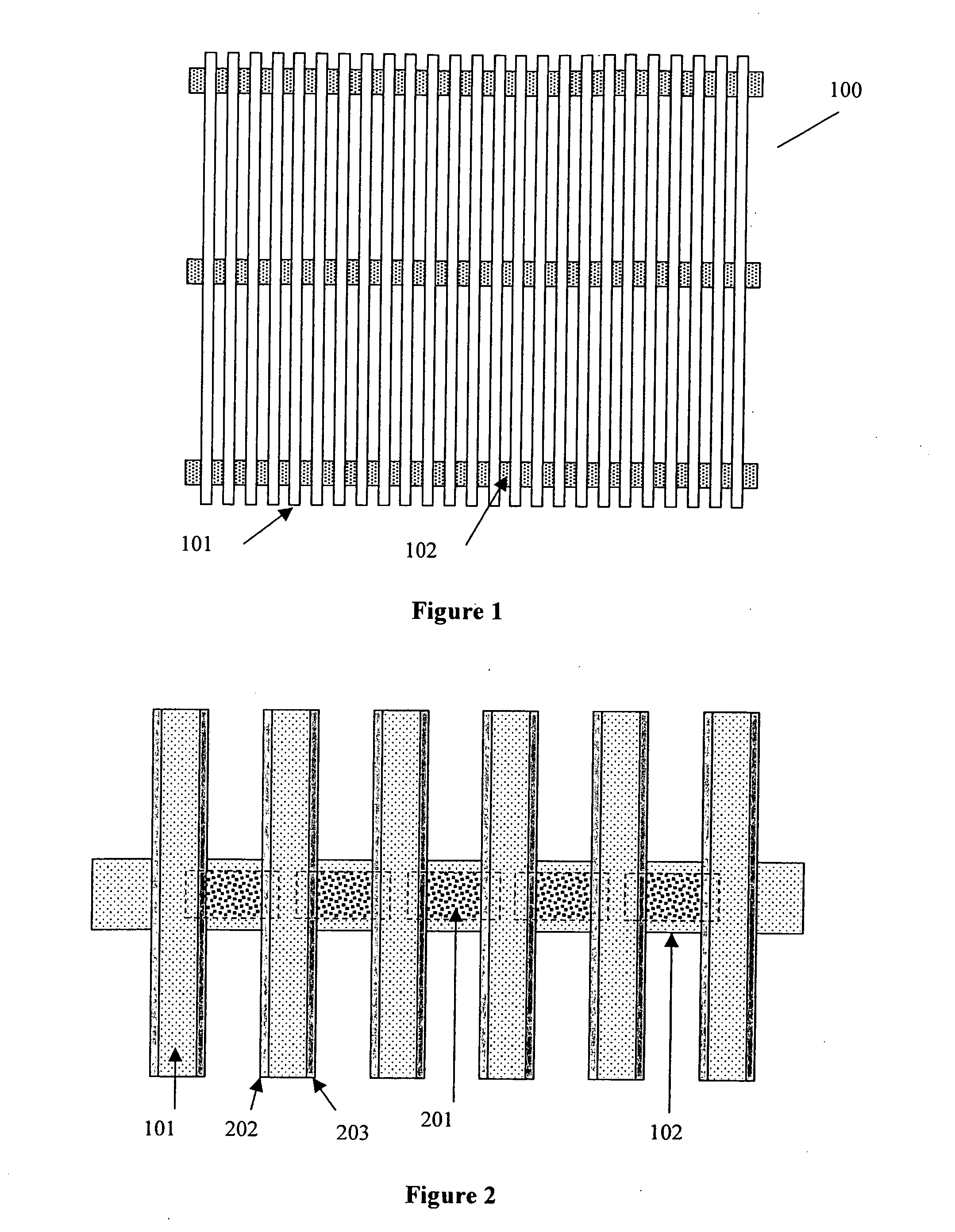

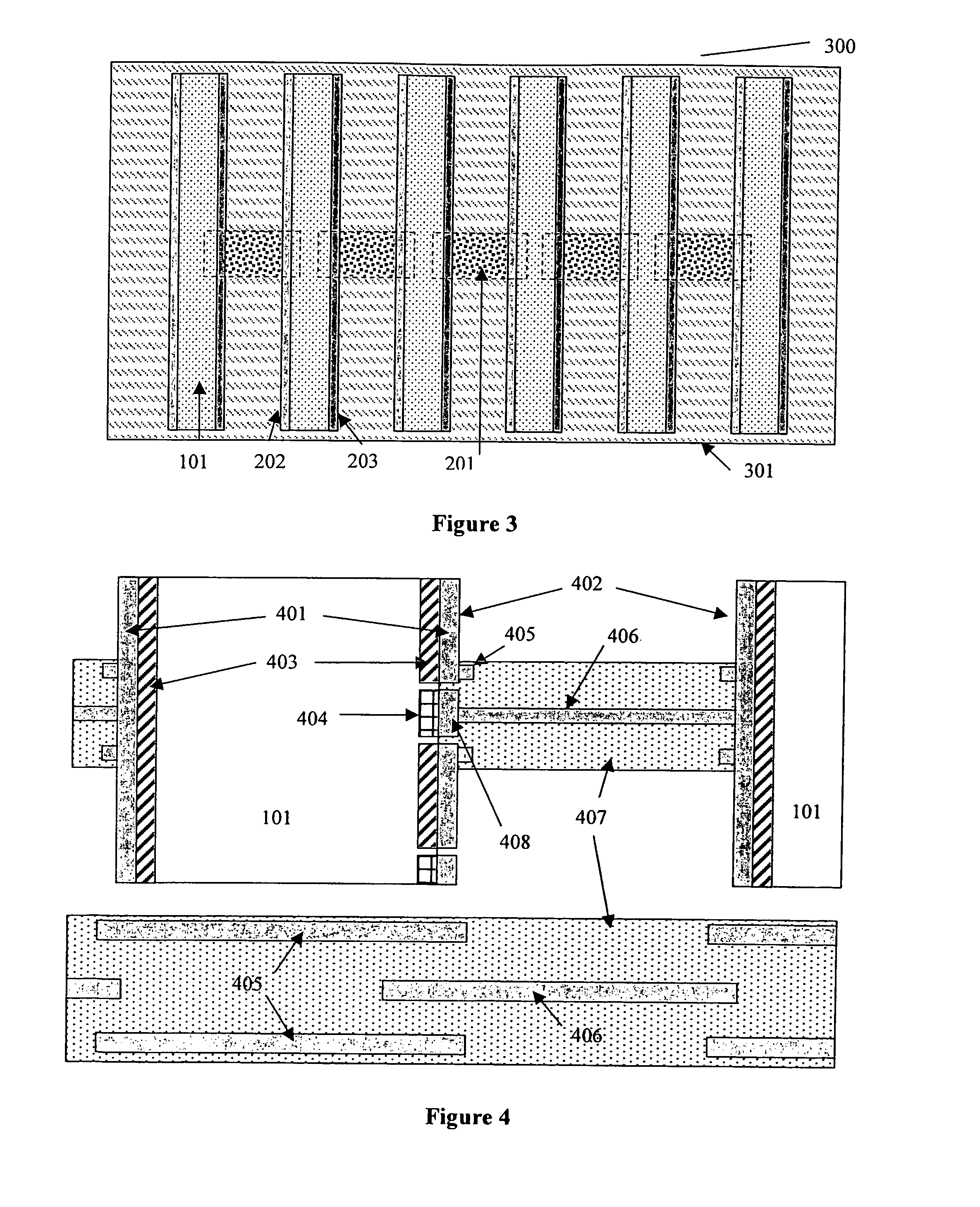

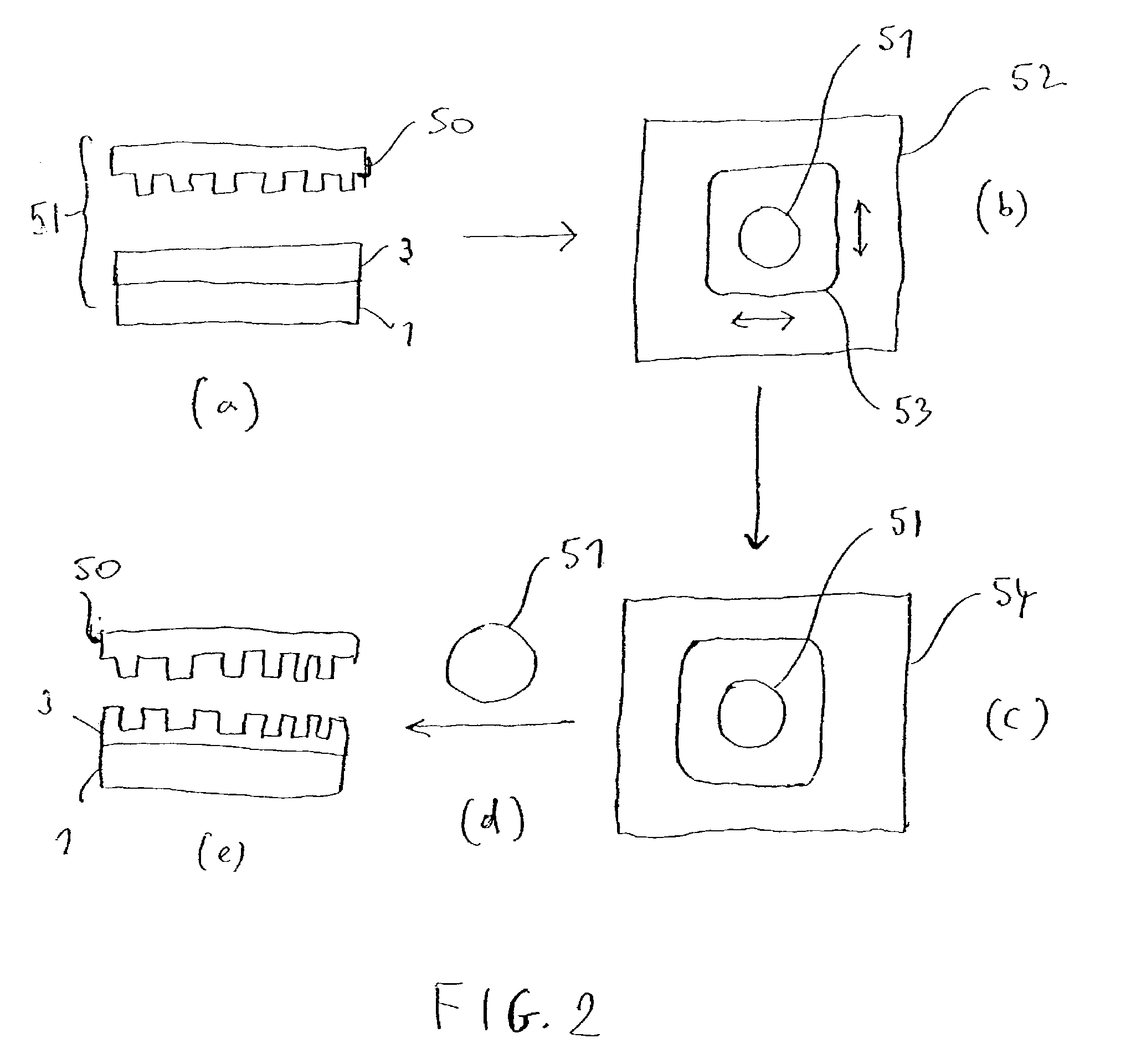

Solar Cell (Sliver) Sub-Module Formation

InactiveUS20080223429A1Provide mechanical stabilityAvoid damageLine/current collector detailsPV power plantsWaferingElectrical battery

A solar cell sub-module (100) for a photovoltaic device, including a plurality of elongate solar cells (slivers) (101) mounted in a structure that maintains the elongate solar cells in a longitudinally parallel and generally coplanar configuration, the structure providing one or more conductive pathways (201) electrically interconnecting the elongate solar cells (101). Also claimed are inventions related to releasing elongate substrate from a wafer frame; providing a plurality of mutually spaced elongate storage bins with a particular spacing; dispensing elongate solar cells into an alignment jig and attaching the cells to a substrate; engaging a length of electrical interconnect with an engagement tool having spaced engagement sections and applying a cutting tool; forming an electrical connection in a photovoltaic module with a conductor defining an indirect path between locations to compensate for thermal expansion; maintaining the solar cell orientation of sliver solar cells when releasing them from a wafer frame; engaging only opposing faces of elongate substrates, interconnected by a wafer frame, when releasing them; storing elongate substrate in a stacked configuration with a translation mechanism.

Owner:AUSTRALIEN NAT UNIV

Electrical connector lead frame

An electrical interconnection system with high speed, differential electrical connectors. The connector is assembled from wafers containing columns of conductive elements, some of which form differential pairs. Each column may include ground conductors adjacent pairs of signal conductors. The ground conductors may be wider than the signal conductors, with ground conductors between adjacent pairs of signal conductors being wider than ground conductors positioned at an end of at least some of the columns. Each of the conductive elements may end in a mating contact portion positioned to engage a complementary contact element in a mating connector. The mating contact portions of the signal conductors in some of the pairs may be rotated relative to the columns. The printed circuit board to which the differential signal connector is mounted may be constructed with elongated antipads around pairs of signal conductors.

Owner:AMPHENOL CORP

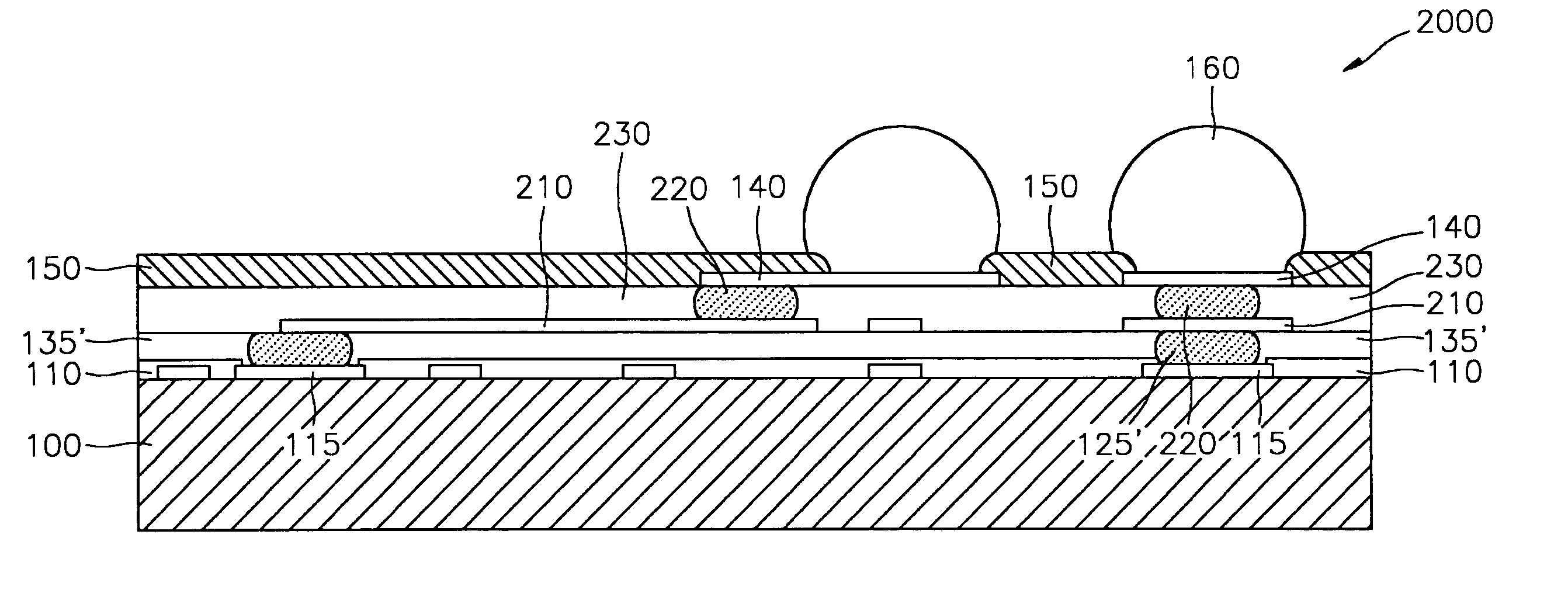

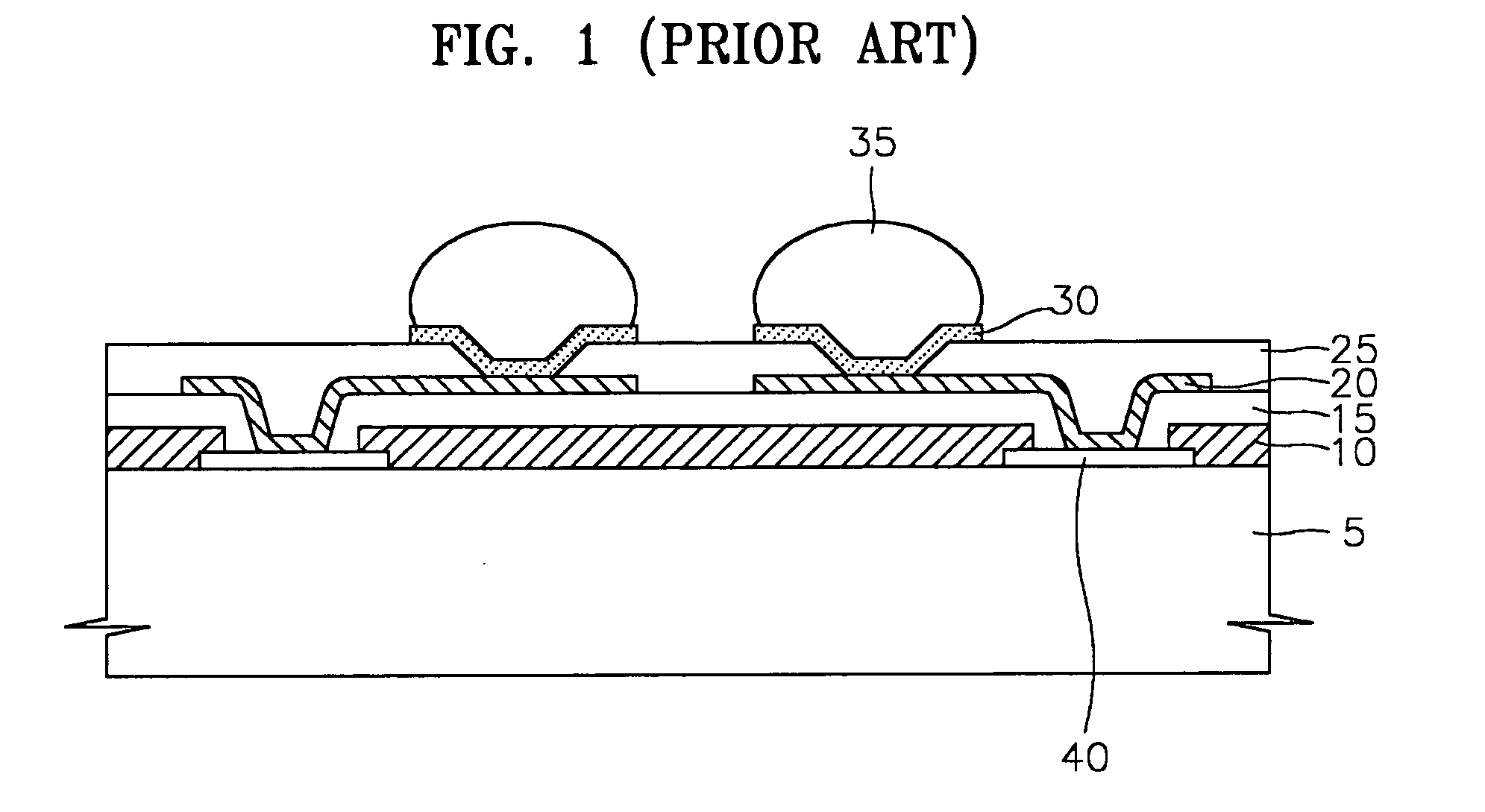

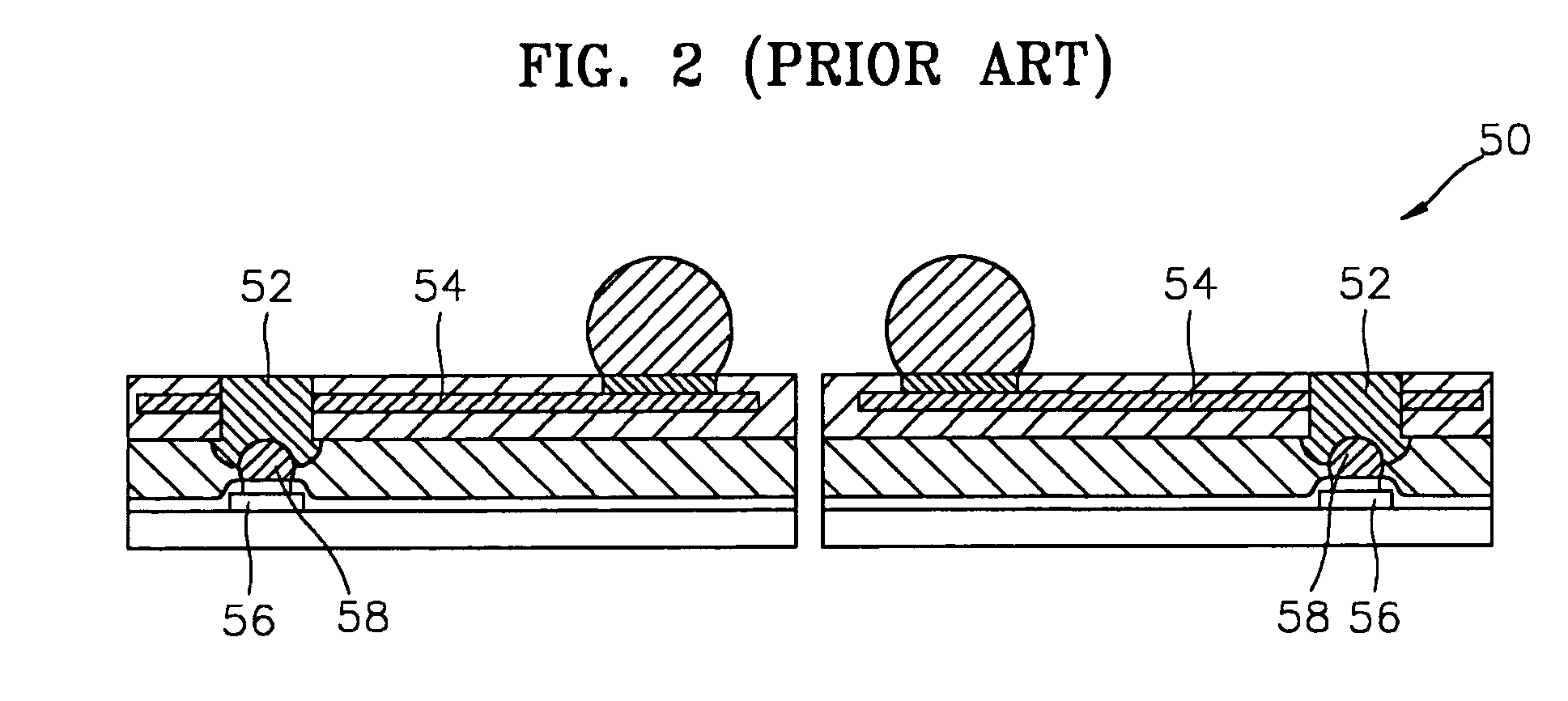

Wafer-level chip scale package and method for fabricating and using the same

InactiveUS20050012225A1Address rising pricesSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A packaged semiconductor device (a wafer-level chip scale package) containing a conductive adhesive material as an electrical interconnect route between the semiconductor die and a patterned conductive substrate is described. The patterned conductive substrate acts not only as a substrate, but also as a redistribution layer that converts the dense pad layout of the die to a larger array configuration of the solder balls in the circuit board. Using the invention allows the formation of a lower priced chip scale package that also overcomes the restriction of the die size used in die-sized chip packages and the input-output pattern that can be required by the printed circuit board. Thus, the invention can provide a familiar pitch (i.e.,interface) to the printed circuit board for any small die.

Owner:SEMICON COMPONENTS IND LLC

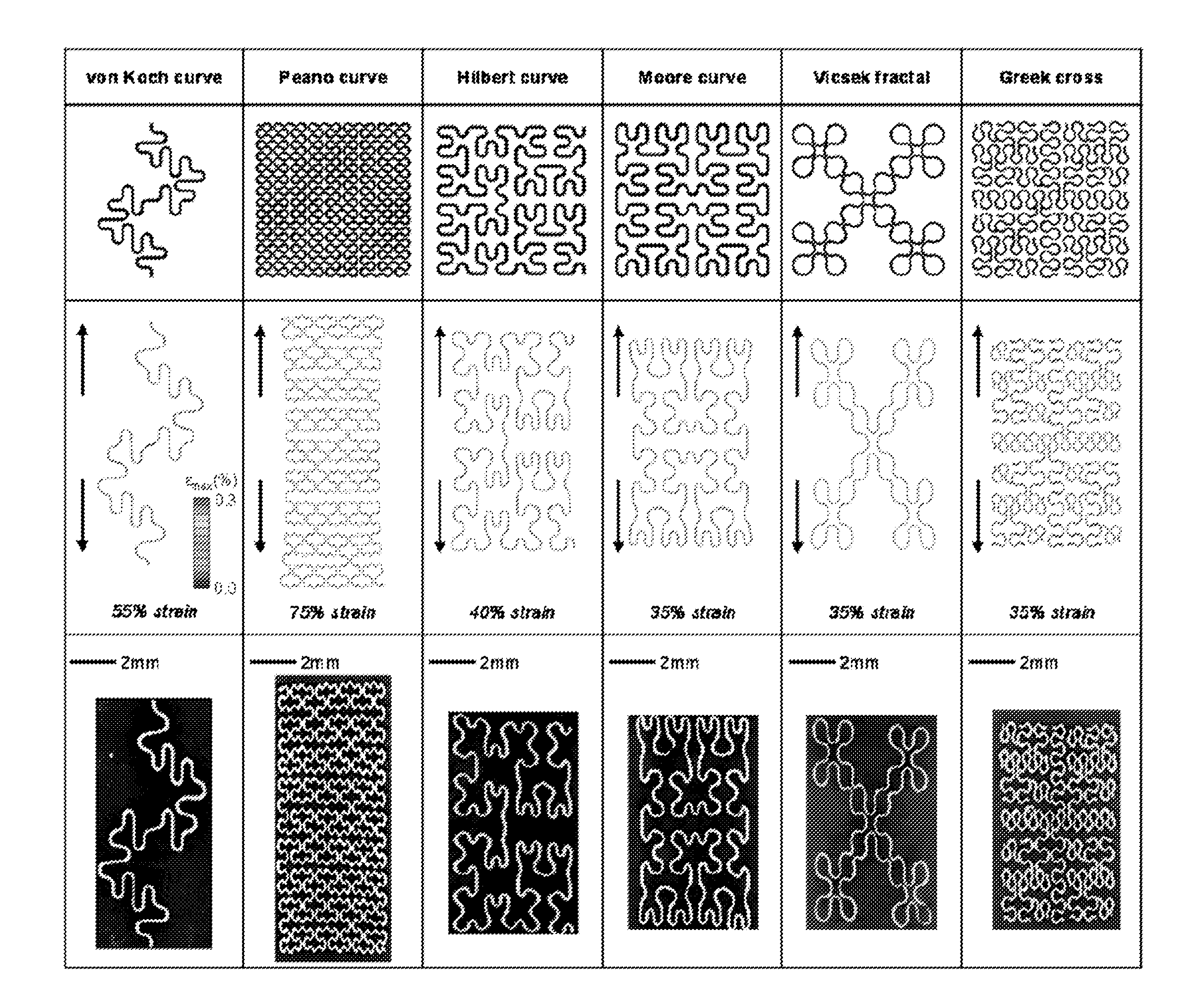

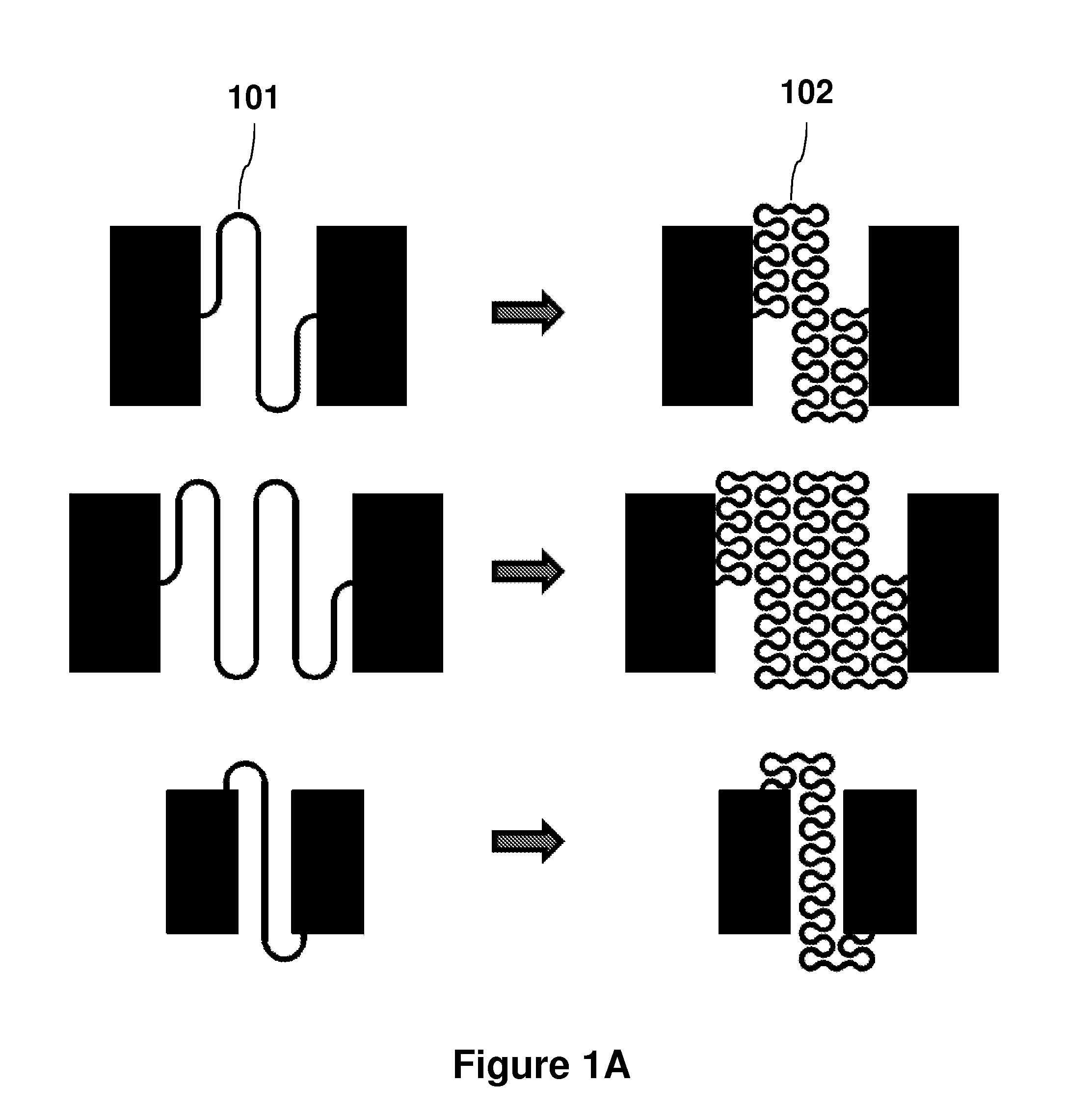

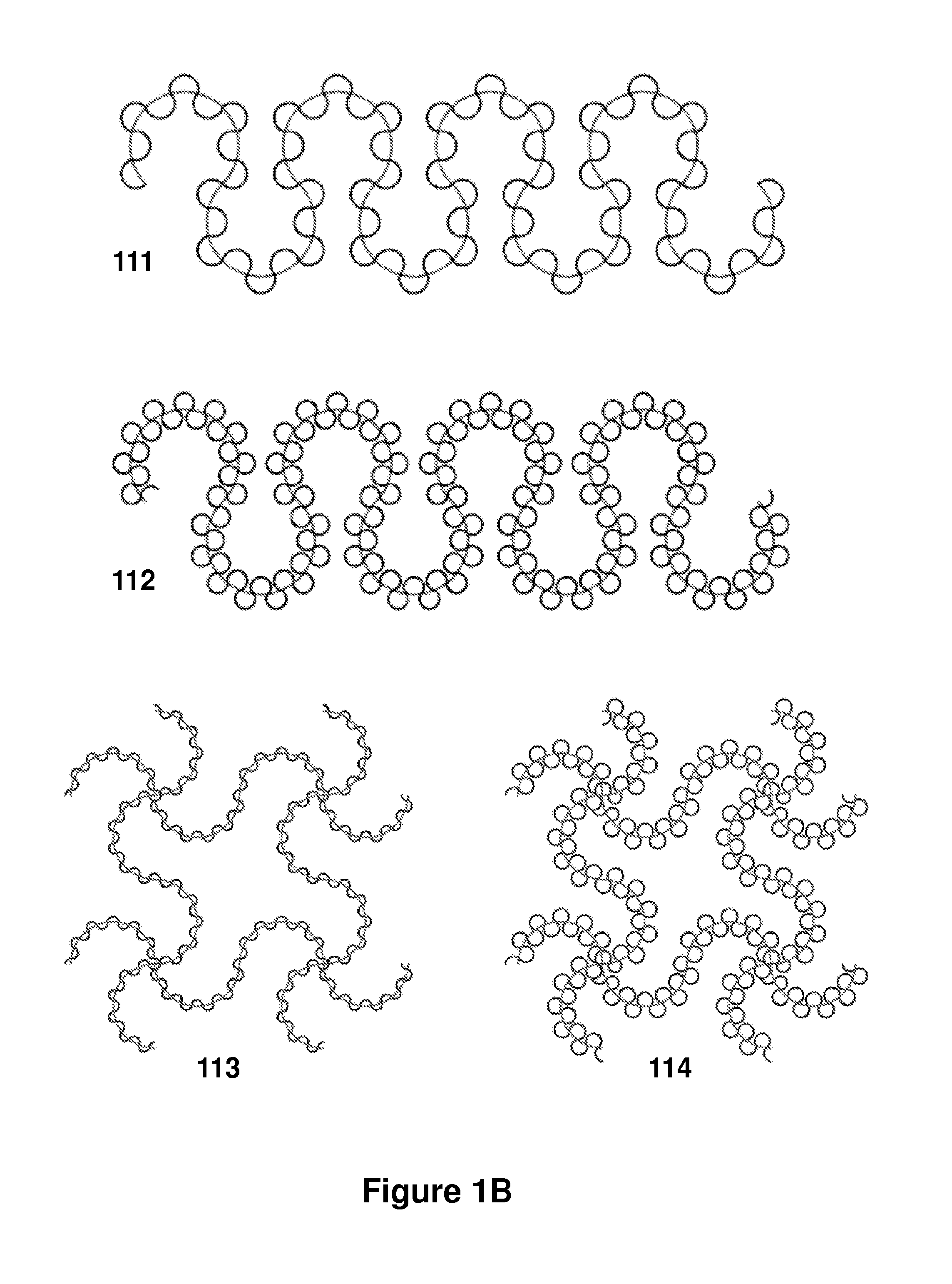

Self-similar and fractal design for stretchable electronics

ActiveUS20150380355A1Improve mechanical propertiesStretchabilityCircuit bendability/stretchabilitySemiconductor/solid-state device detailsElastomerStretchable electronics

The present invention provides electronic circuits, devices and device components including one or more stretchable components, such as stretchable electrical interconnects, electrodes and / or semiconductor components. Stretchability of some of the present systems is achieved via a materials level integration of stretchable metallic or semiconducting structures with soft, elastomeric materials in a configuration allowing for elastic deformations to occur in a repeatable and well-defined way. The stretchable device geometries and hard-soft materials integration approaches of the invention provide a combination of advance electronic function and compliant mechanics supporting a broad range of device applications including sensing, actuation, power storage and communications.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS +1

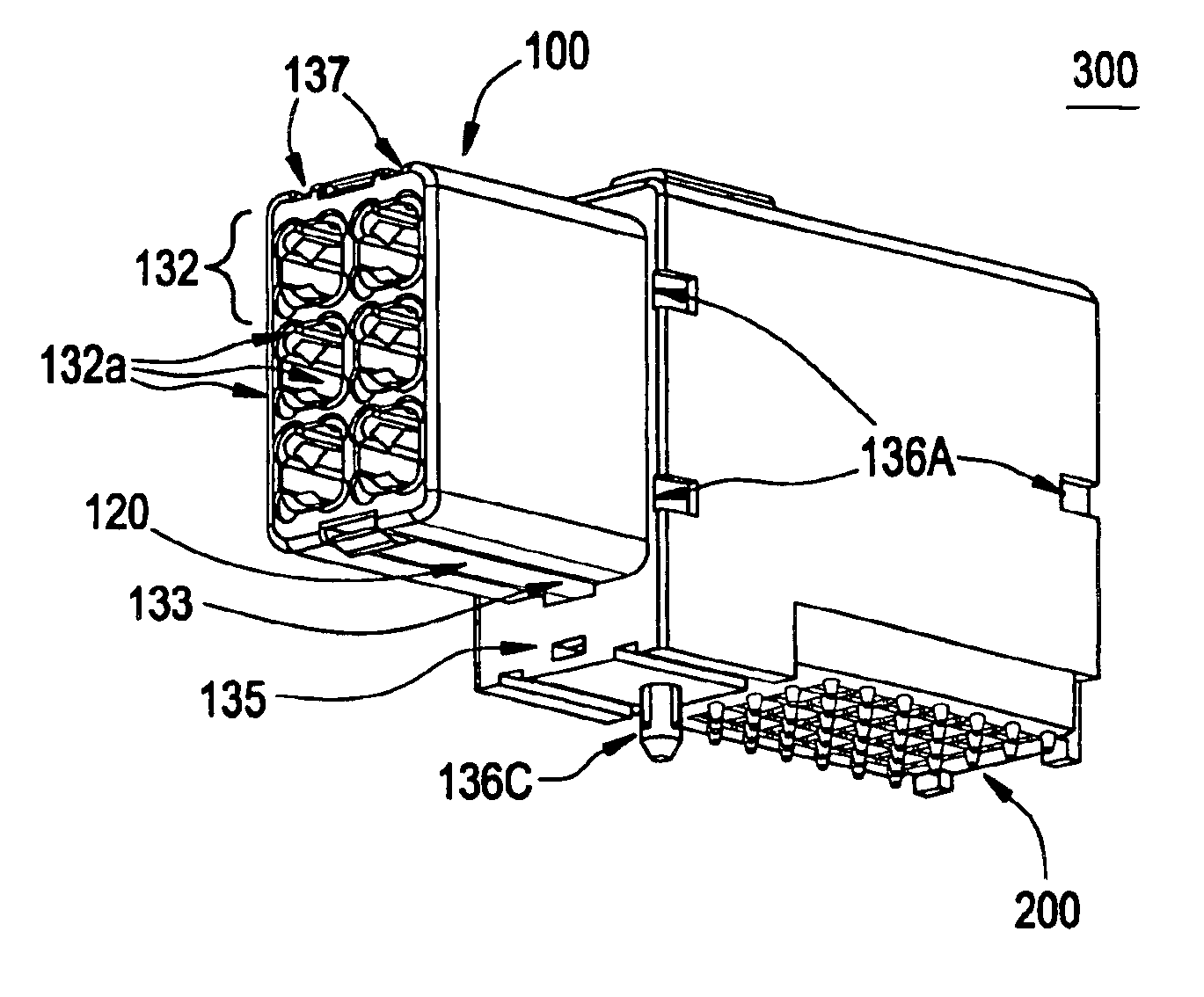

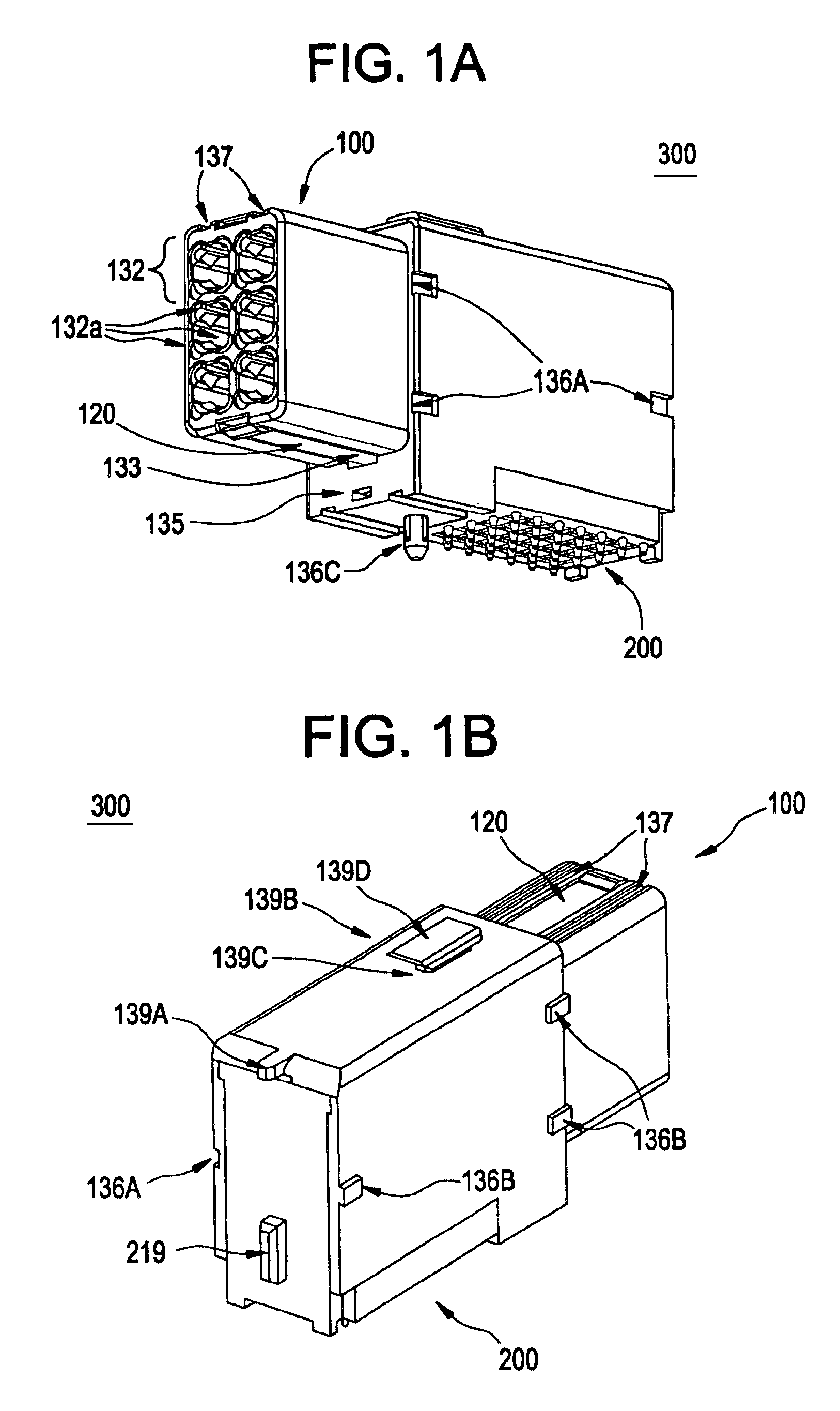

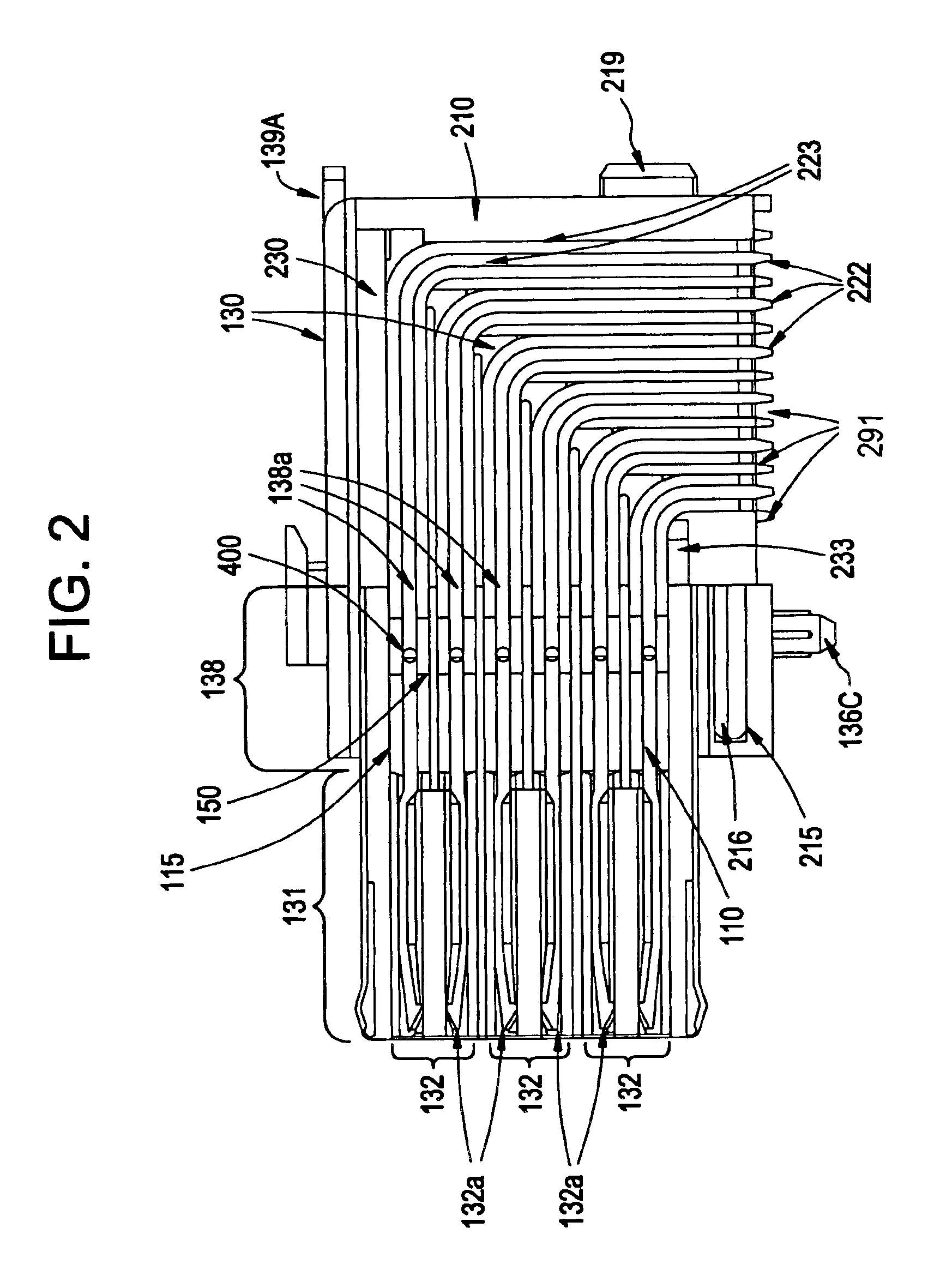

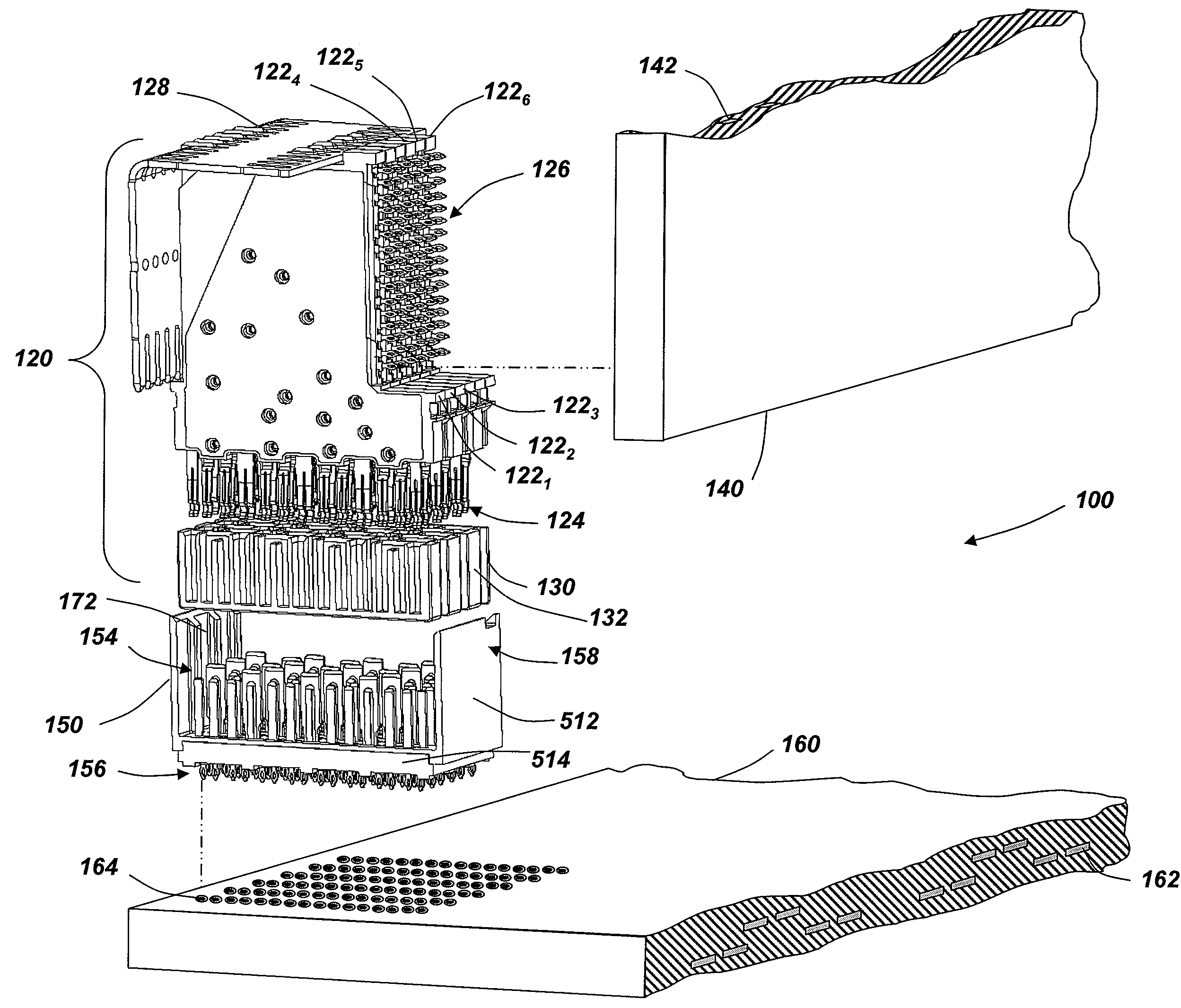

Modular coaxial electrical interconnect system having a modular frame and electrically shielded signal paths and a method of making the same

InactiveUS6905367B2Increasing signal speedEfficient space utilizationCoupling protective earth/shielding arrangementsModular connectorSurface projection

A modular connector assembly includes a modular frame having a first holes, second holes, and third holes formed at evenly spaced intervals. A plurality of modular interconnect components, fixable within the modular frame, have a back surface projection formed thereon. Each modular interconnect includes a contact housing made of electrically insulating material, an exterior of the contact housing comprising first and second side surfaces, a back surface, and a top surface. Contact signal pins are fixed within and electrically insulated from the contact housing.

Owner:SILICON BANDWIDTH

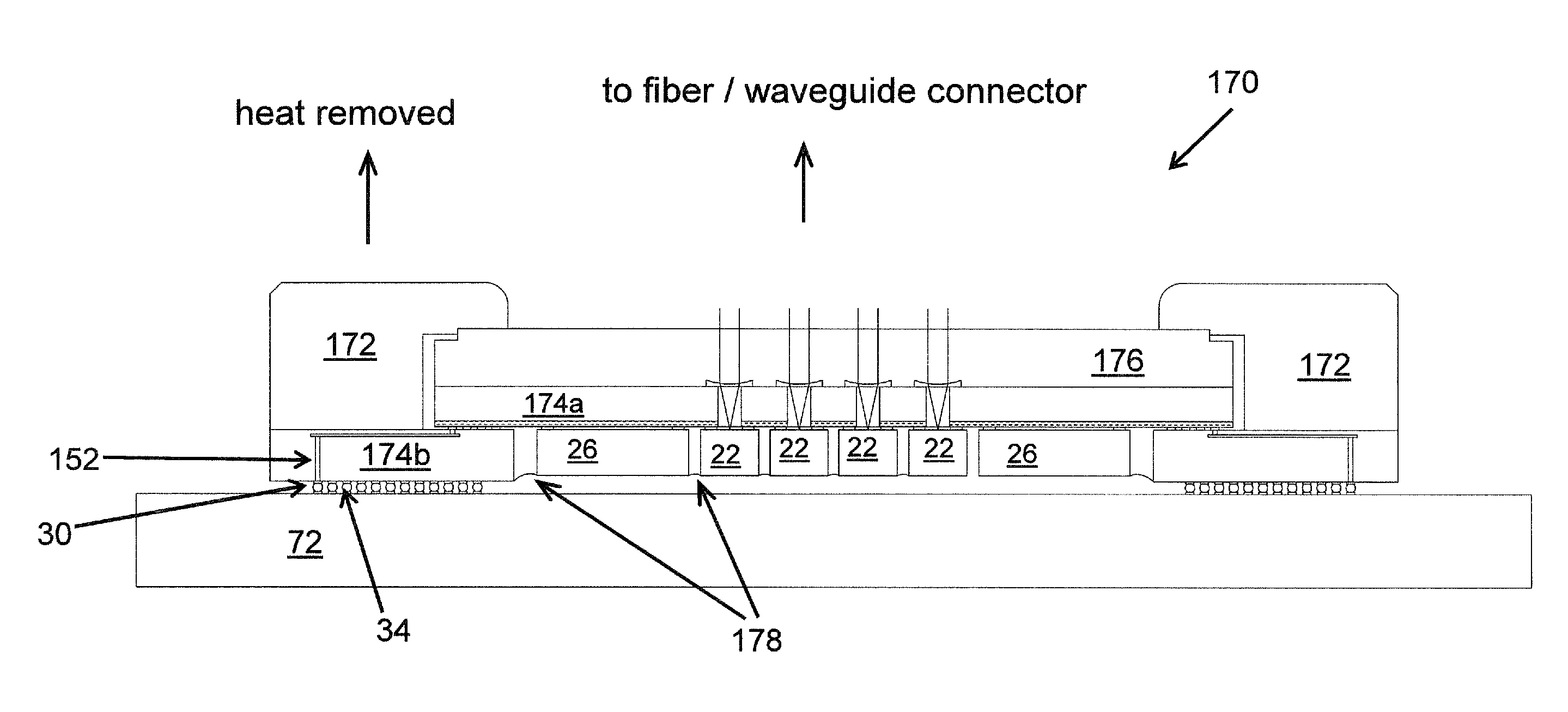

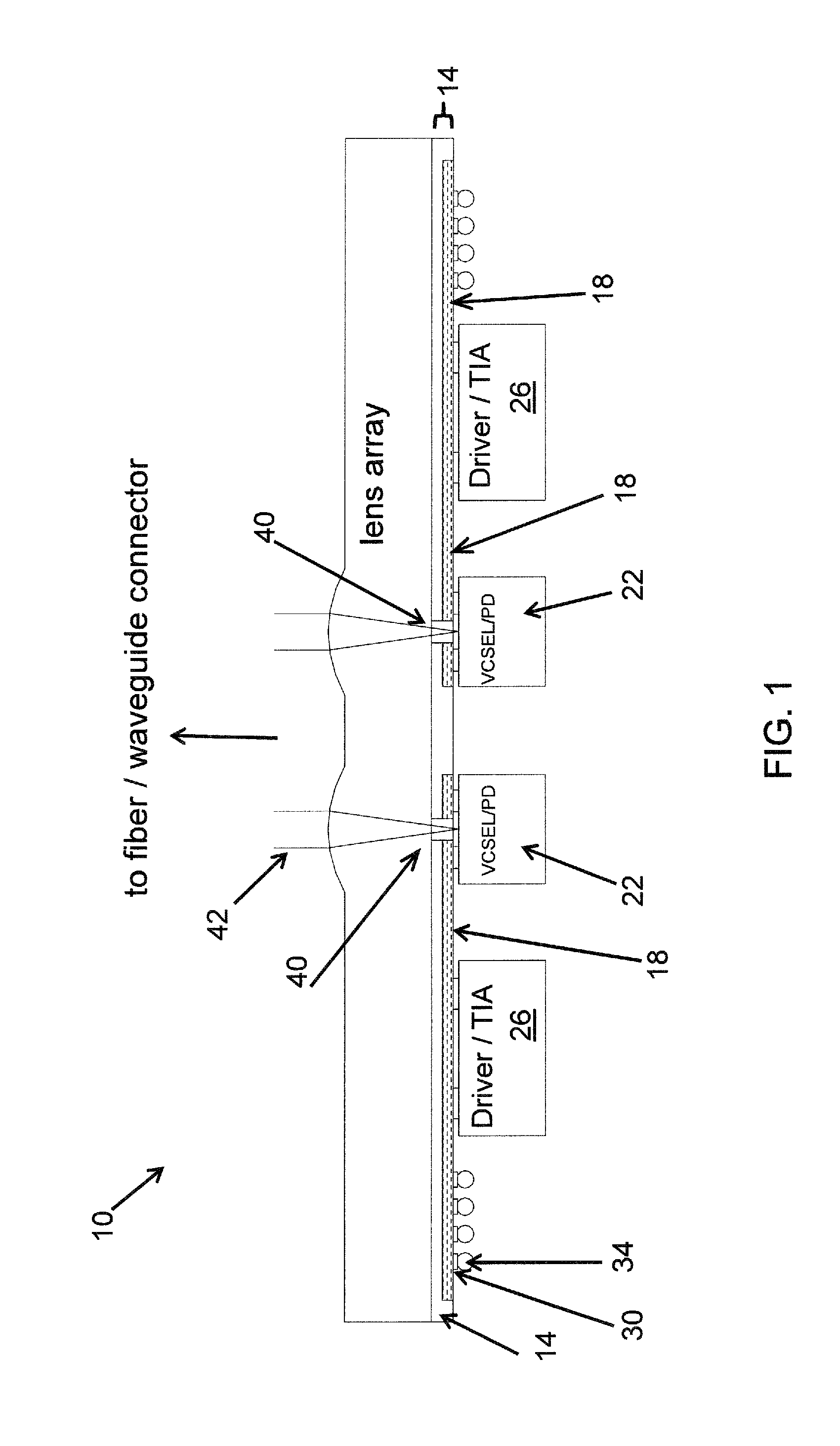

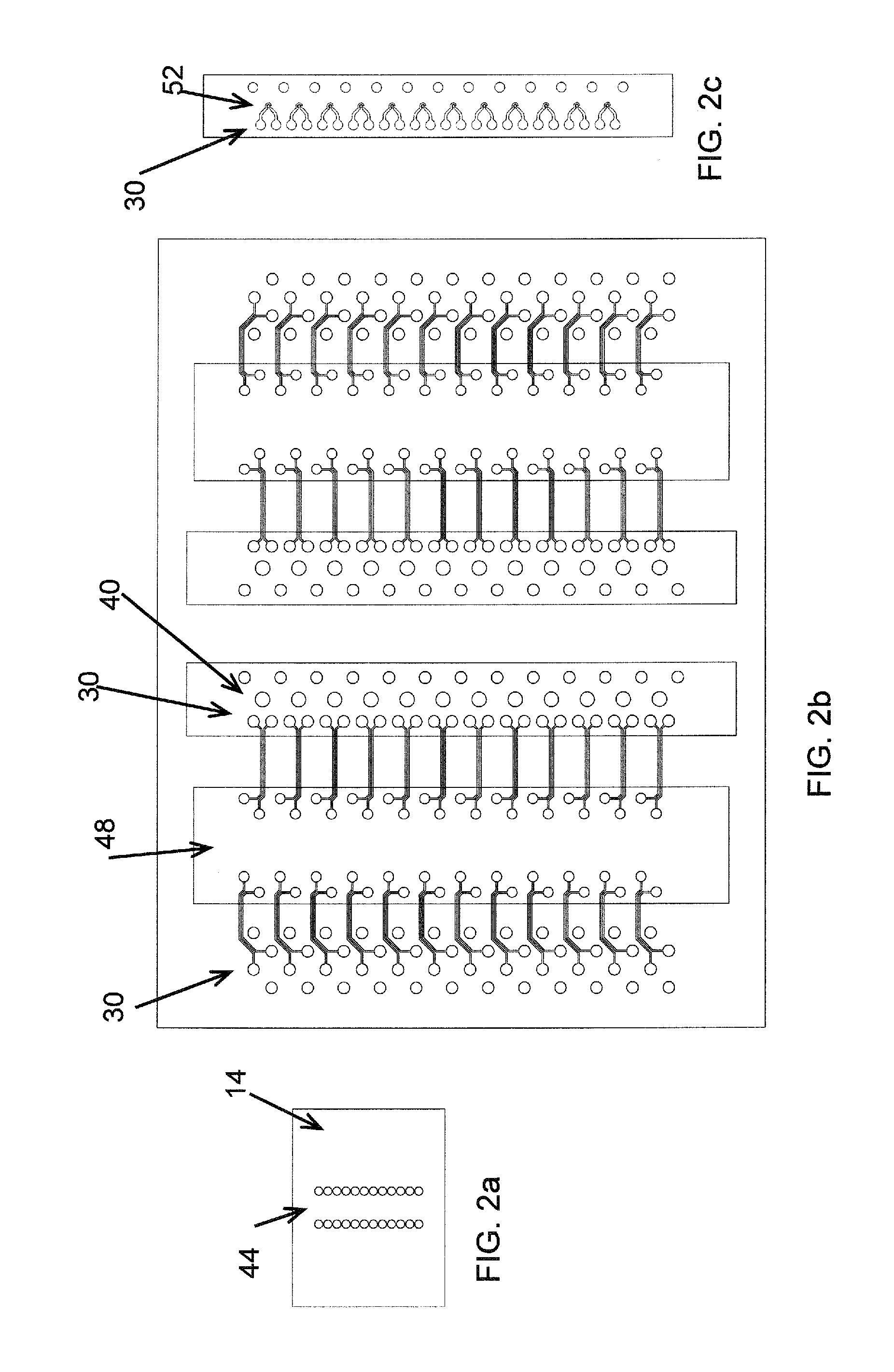

Silicon carrier optoelectronic packaging

ActiveUS20110044369A1Small sizeLow costLaser optical resonator constructionSemiconductor/solid-state device detailsOpto electronicOptical coupling

An optoelectronic (OE) package or system and method for fabrication is disclosed which includes a silicon layer with wiring. The silicon layer has an optical via for allowing light to pass therethrough. An optical coupling layer is bonded to the silicon layer, and the optical coupling layer includes a plurality of microlenses for focusing and or collimating the light through the optical via. A plurality of OE elements are coupled to the silicon layer and electrically communicating with the wiring. At least one of the OE elements positioned in optical alignment with the optical via for receiving the light. A carrier is interposed between electrical interconnect elements. The carrier is positioned between the wiring of the silicon layer and a circuit board and the carrier is electrically connecting first interconnect elements connected to the wiring of the silicon layer and second interconnect elements connected to the circuit board.

Owner:GLOBALFOUNDRIES US INC

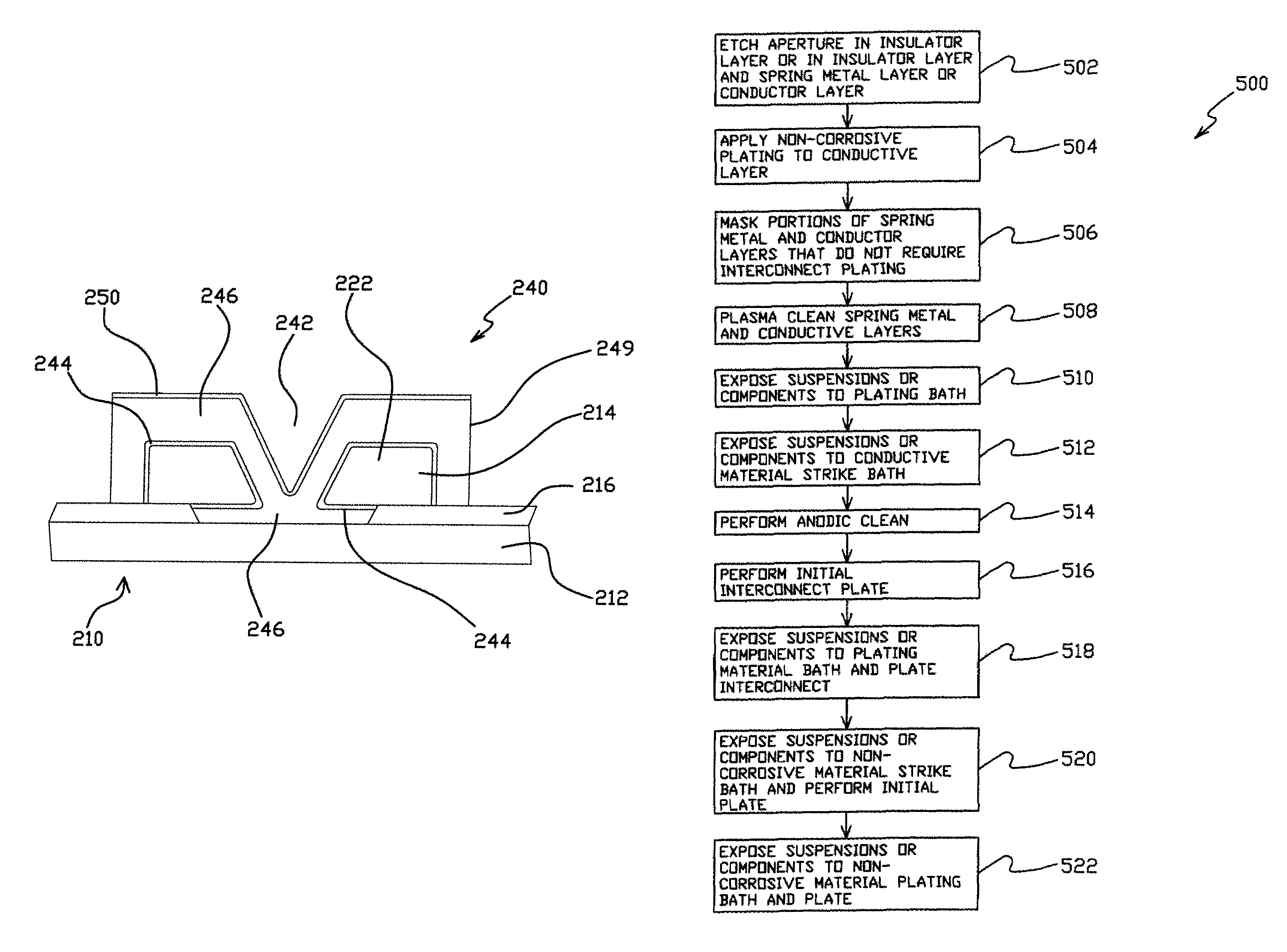

Plated ground features for integrated lead suspensions

ActiveUS7384531B1Quality improvementAnodisationElectrical connection between head and armConductive materialsElectroplating

A method for forming an electrical interconnect on an integrated lead suspension or suspension component of the type formed from a laminated sheet of material having a stainless steel layer, a conductive lead layer and an insulating layer separating the stainless steel and conductive lead layers. An aperture is formed through at least the insulating layer to expose the stainless steel layer at an interconnect site. An interconnect mask is applied around the interconnect site. Conductive material is electroplated onto the stainless steel layer at the interconnect site to form a plated interconnect. The mask is then removed. The method is used to form an interconnect bond pad on the same side of the stainless steel layer as the conductive lead layer in one embodiment. In another embodiment the aperture is formed through the insulator layer and the stainless steel layer, and conductive material is built up on the stainless steel layer during the electroplating step until it meets and plates onto the conductive lead layer to form a stainless steel side interconnect. In yet another embodiment the aperture is formed through the insulator layer and the conductive lead layer, and conductive material is built up on the stainless steel layer during the electroplating step until it meets and plates onto the conductive lead layer to form a conductive lead side interconnect.

Owner:HUTCHINSON TECH

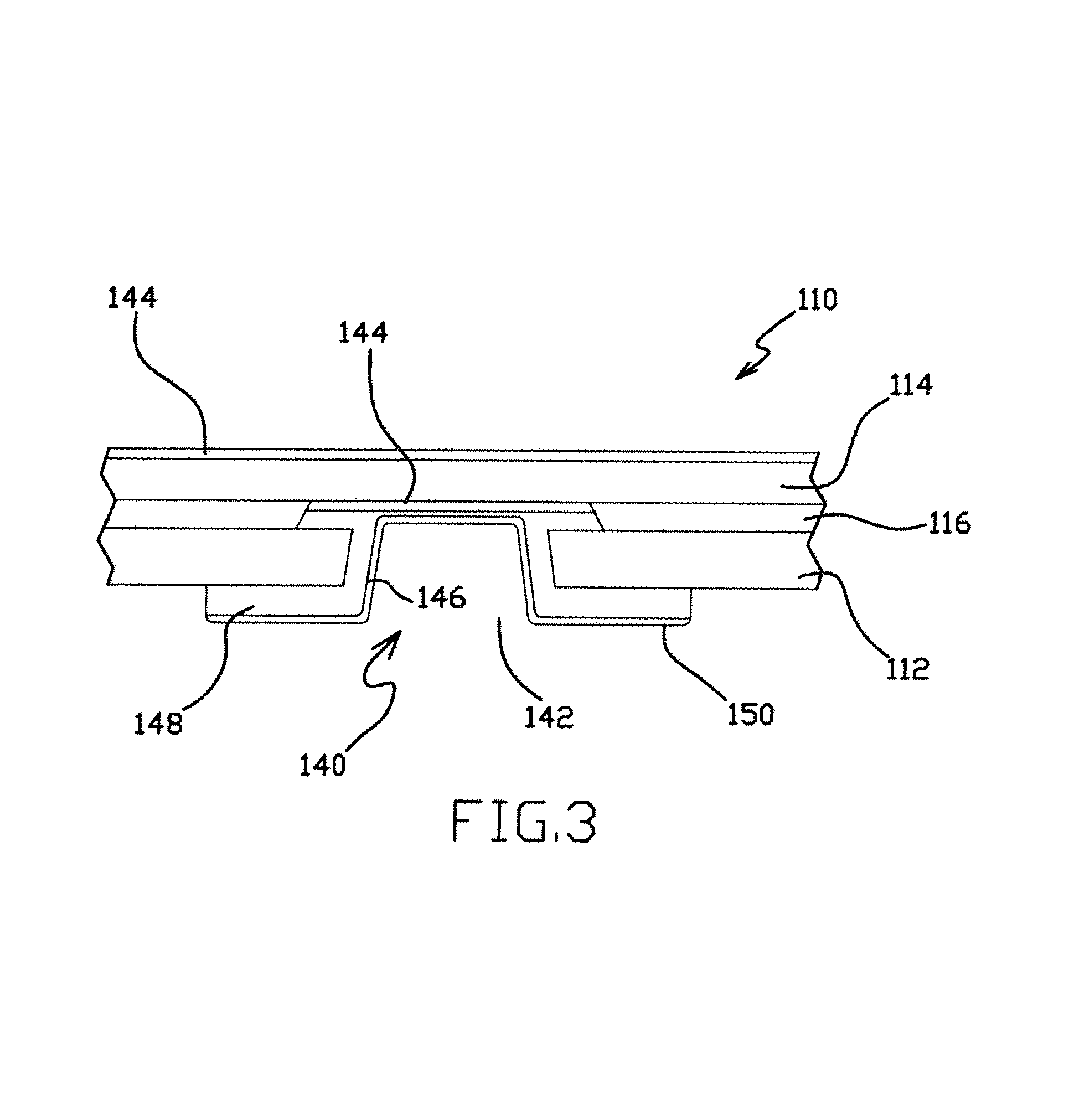

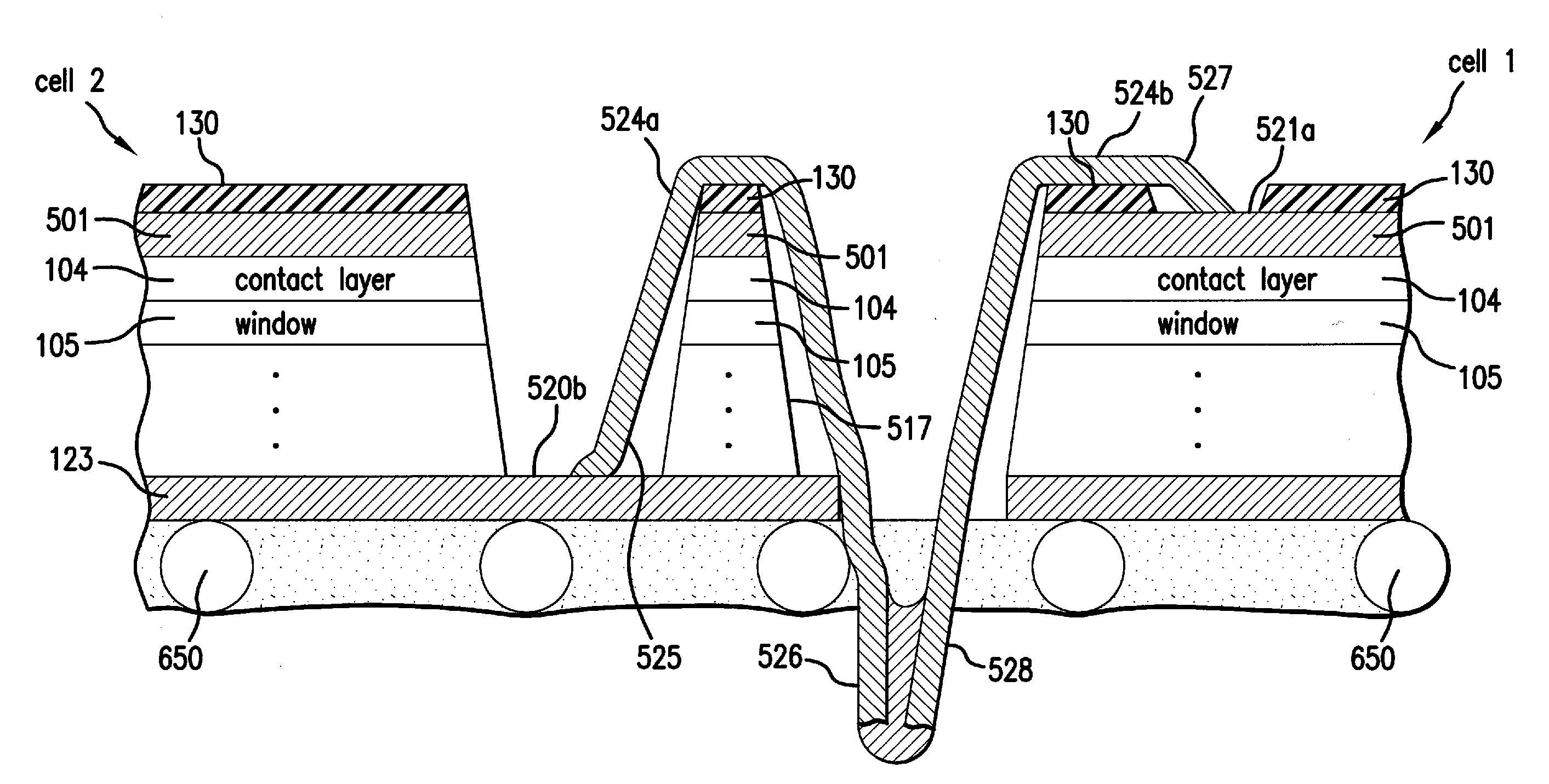

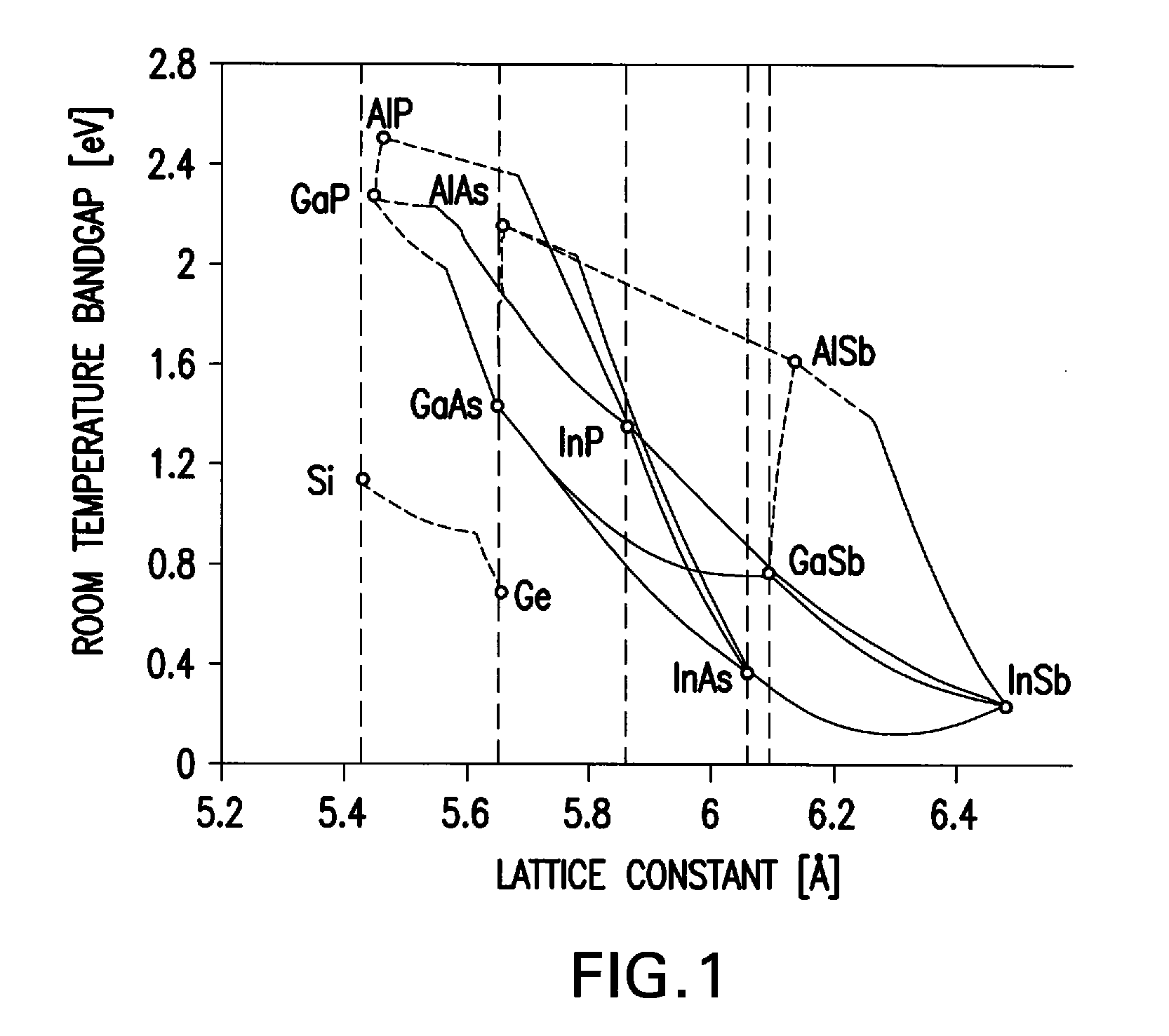

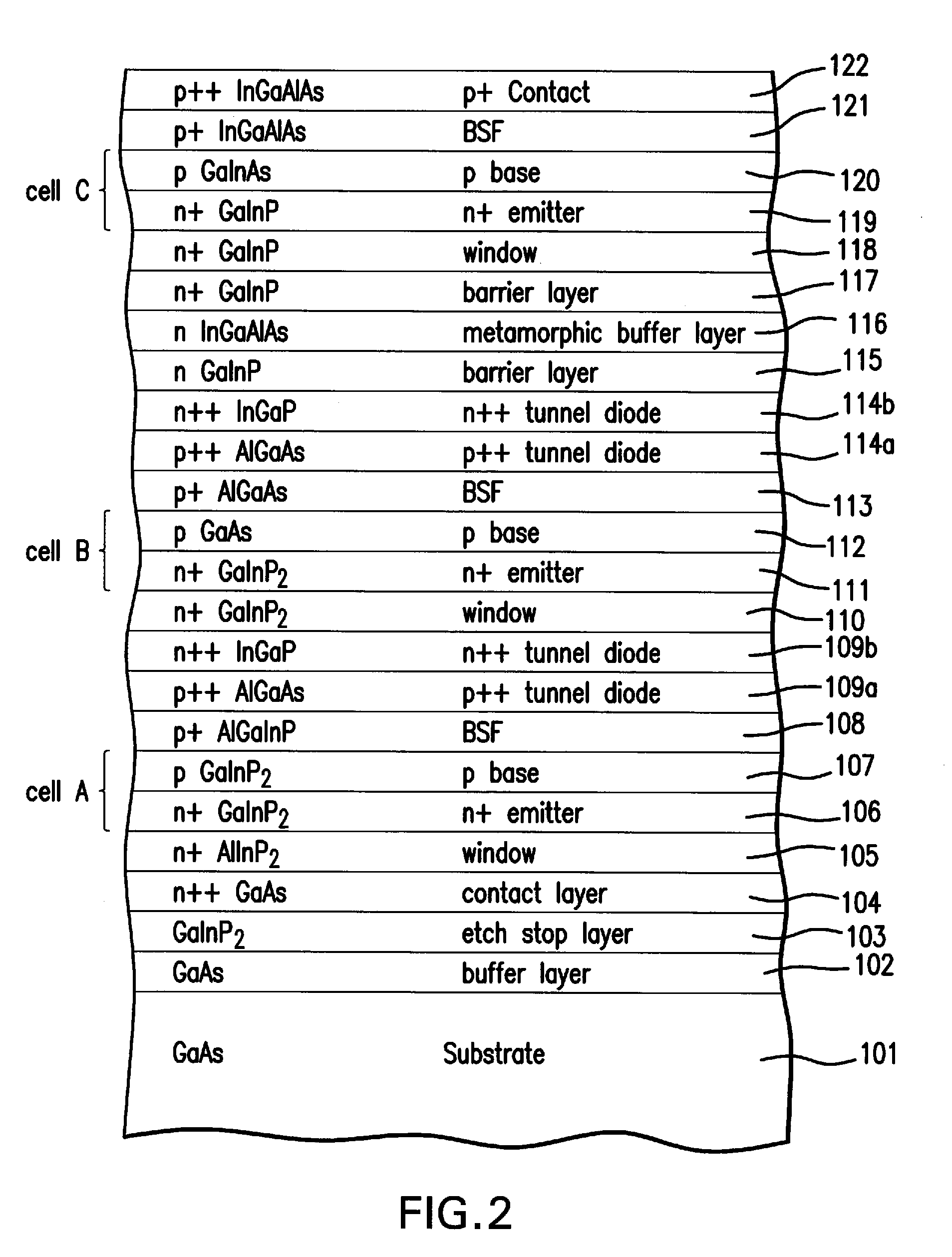

String Interconnection of Inverted Metamorphic Multijunction Solar Cells on Flexible Perforated Carriers

InactiveUS20100186804A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationContact padEngineering

A method of forming a multijunction solar cell string by providing a first multijunction solar cell including a contact pad disposed adjacent the top surface of the multijunction solar cell along a first peripheral edge thereof; providing a second multijunction solar cell disposed adjacent said first multijunction solar cell, having a top surface and a bottom surface, and including a cut-out extending from a second peripheral edge along the top surface of the second solar cell located adjacent the first peripheral edge of said first multijunction solar cell, and extending to a metal contact layer adjacent the bottom surface of said second multijunction solar cell to allow an electrical contact to be made to the metal contact layer; mounting said first and said second multijunction solar cells on a first side of a perforated carrier; attaching a first electrical interconnect to the contact pad of said first multijunction solar cell, the electrical interconnect extending through said perforated carrier; attaching a second electrical interconnect to the metal contact layer of said second multijunction solar cell, the electrical interconnect extending through said perforated carrier; and connecting said first electrical interconnect to said second electrical interconnect.

Owner:EMCORE SOLAR POWER

High density electrical interconnect system having enhanced grounding and cross-talk reduction capability

InactiveUS6179663B1High densityReduce eliminateElectric discharge tubesCouplings bases/casesElectricityGround contact

Disclosed is an electrical interconnect system using multiple grounding methods to reduce or prevent spurious signals from interfering with high density contacts carrying high speed transmissions. A first connector includes an insulative pillar partially surrounded by a plurality of signal contacts. A ground contact is at least partially located within the insulative pillar. A second connector includes a corresponding plurality of flexible signal contacts for mating with the signal contacts adjacent the insulative pillar. The second connector also includes a ground contact for receiving the ground contact of the first connector. The ground contacts provide a first method of providing a ground path to reduce spurious signals from entering the signal path. An electrically conducting shield is located outside the signal contacts when the first and the second connectors are mated. The first connector includes a member which provides a ground path between the first connector and the electrically conducting shield. Advantageously, the electrical interconnect system has two grounding methods which are particularly important in a high density electrical interconnect system where the contacts are closely spaced and susceptible to noise and other spurious signals.

Owner:WINCHESTER ELECTRONICS

Electrical connector with complementary conductive elements

ActiveUS20080248659A1Improve signal integrityEvenly spacedPrinted circuit assemblingCoupling device detailsElectricityEngineering

An electrical interconnection system with high speed, differential electrical connectors. The connectors are formed with columns of conductive elements, some of which carry signals some of which act as ground conductors. The conductive elements may contain projections to secure the conductive elements in a housing or to facilitate desirable current flow patterns. To avoid impedance discontinuities caused by the projections, adjacent conductive elements may be formed with complementary portions to provide a relatively uniform edge-to-edge spacing between signal and ground conductors along the length of the signal conductor. To manufacture such a connector in which both the signal and the ground conductive elements contain projections, the conductive elements carrying signals may be inserted into a housing from one side and the conductive elements acting as ground conductors may be inserted from an opposite side.

Owner:AMPHENOL CORP

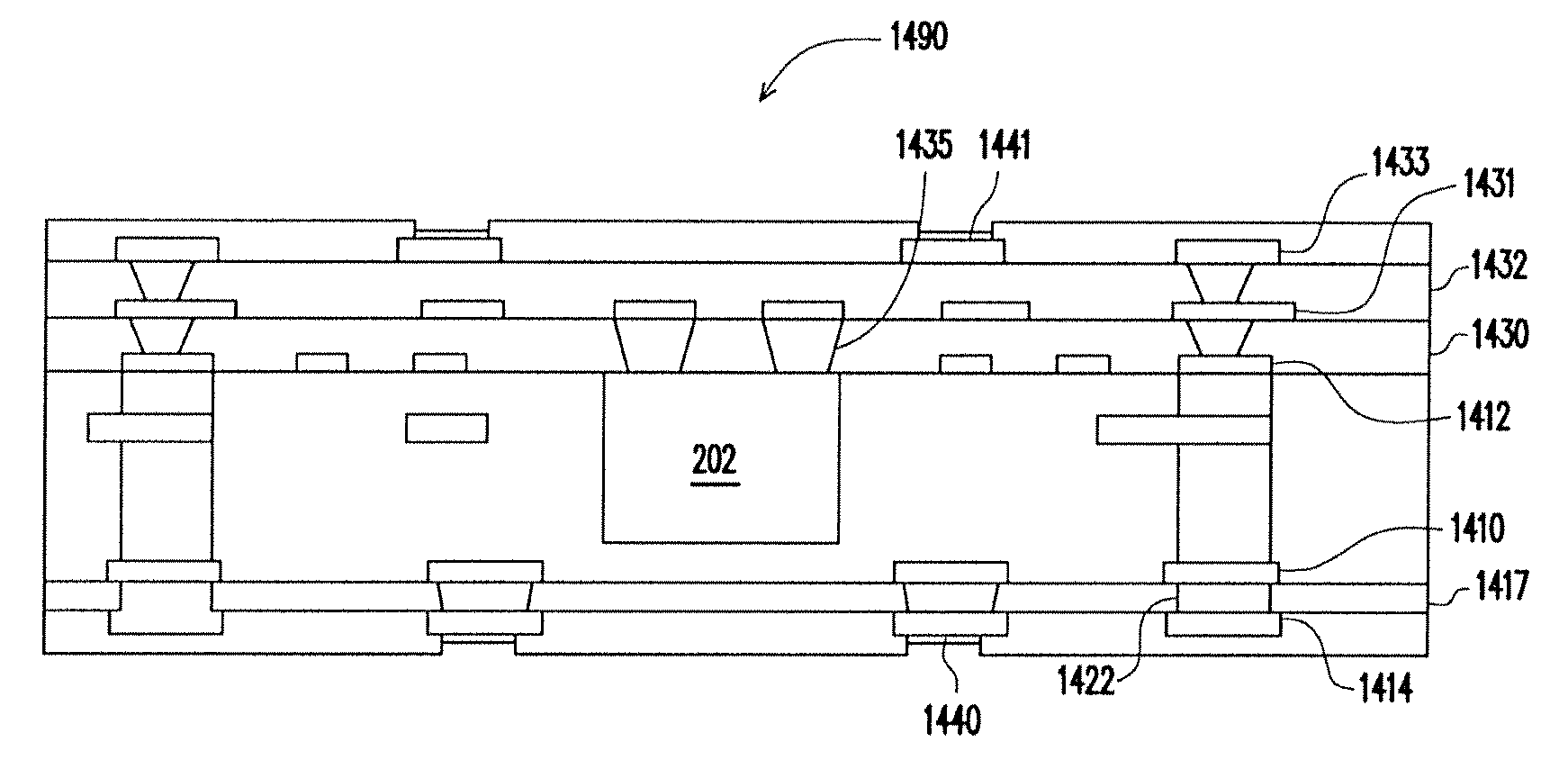

Embedded component device and manufacturing methods thereof

ActiveUS20120153493A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

An embedded component device includes an electronic component including an electrical contact, an upper patterned conductive layer, a dielectric layer between the upper patterned conductive layer and the electronic component, a first electrical interconnect, a lower patterned conductive layer, a conductive via, and a second electrical interconnect. The dielectric layer has a first opening exposing the electrical contact, and a second opening extending from the lower patterned conductive layer to the upper patterned conductive layer. The first electrical interconnect extends from the electrical contact to the upper patterned conductive layer, and fills the first opening. The second opening has an upper portion exposing the upper patterned conductive layer and a lower portion exposing the lower patterned conductive layer. The conductive via is located at the lower portion of the second opening. The second electrical interconnect fills the upper portion of the second opening.

Owner:ADVANCED SEMICON ENG INC

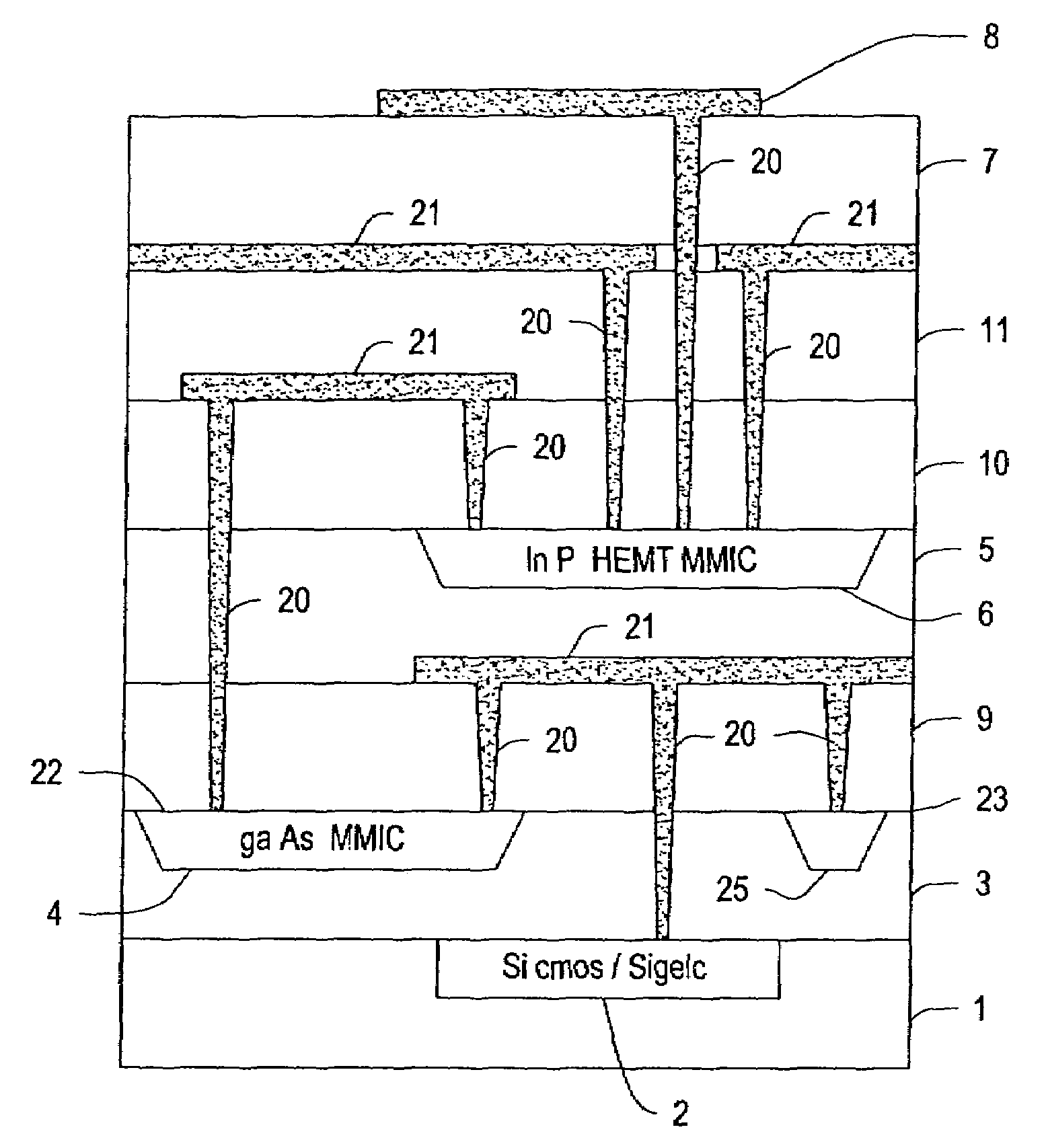

Process for assembling three-dimensional systems on a chip and structure thus obtained

InactiveUS7253091B2Function increaseEasy to manufactureSemiconductor/solid-state device detailsSolid-state devicesElectronic systemsEngineering

A method for assembling an electronic system with a plurality of layers. Recesses in formed in one or more dielectric layers and electronic components are positioned within the recesses. One or more layers containing the components are placed on a host substrate containing host circuits. Electrical interconnects are provided between and among the electronic components in the dielectric layers and the host circuits. The layers containing the components may also be provided by growing the electronic devices on a growth substrate. The growth substrate is then removed after the layer is attached to the host substrate.

Owner:HRL LAB

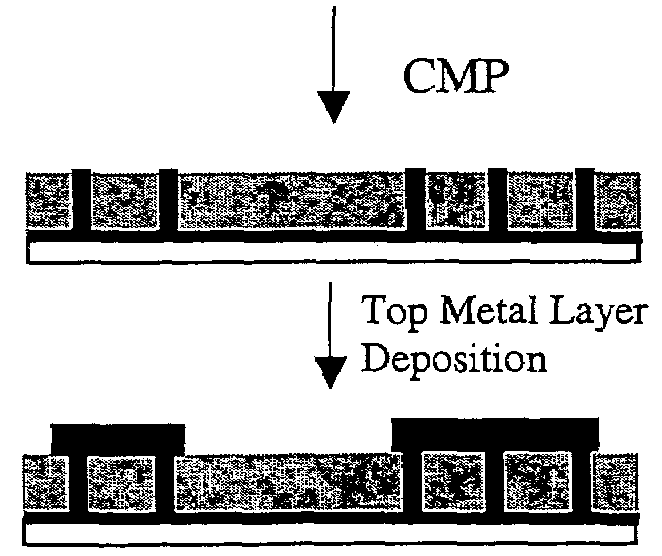

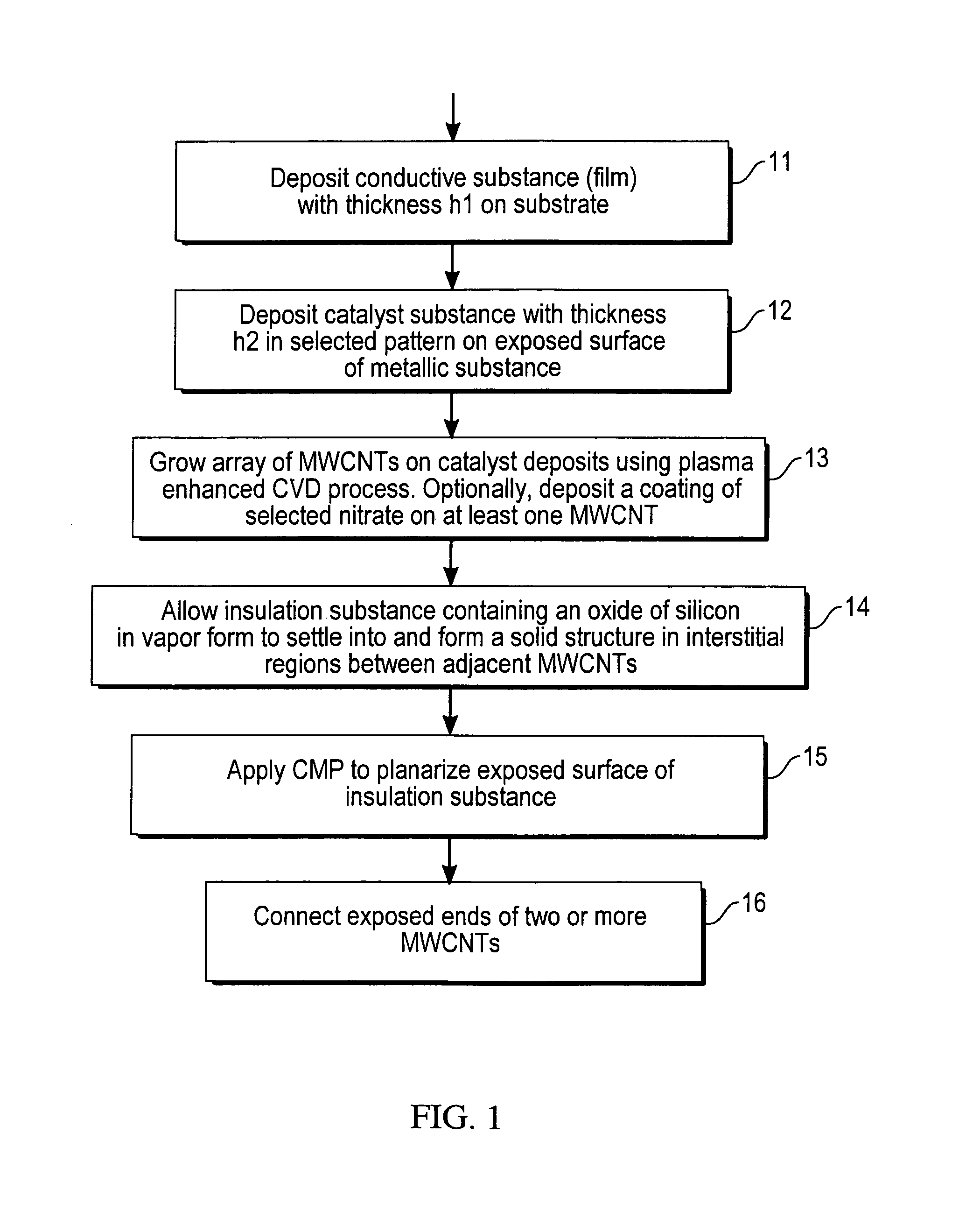

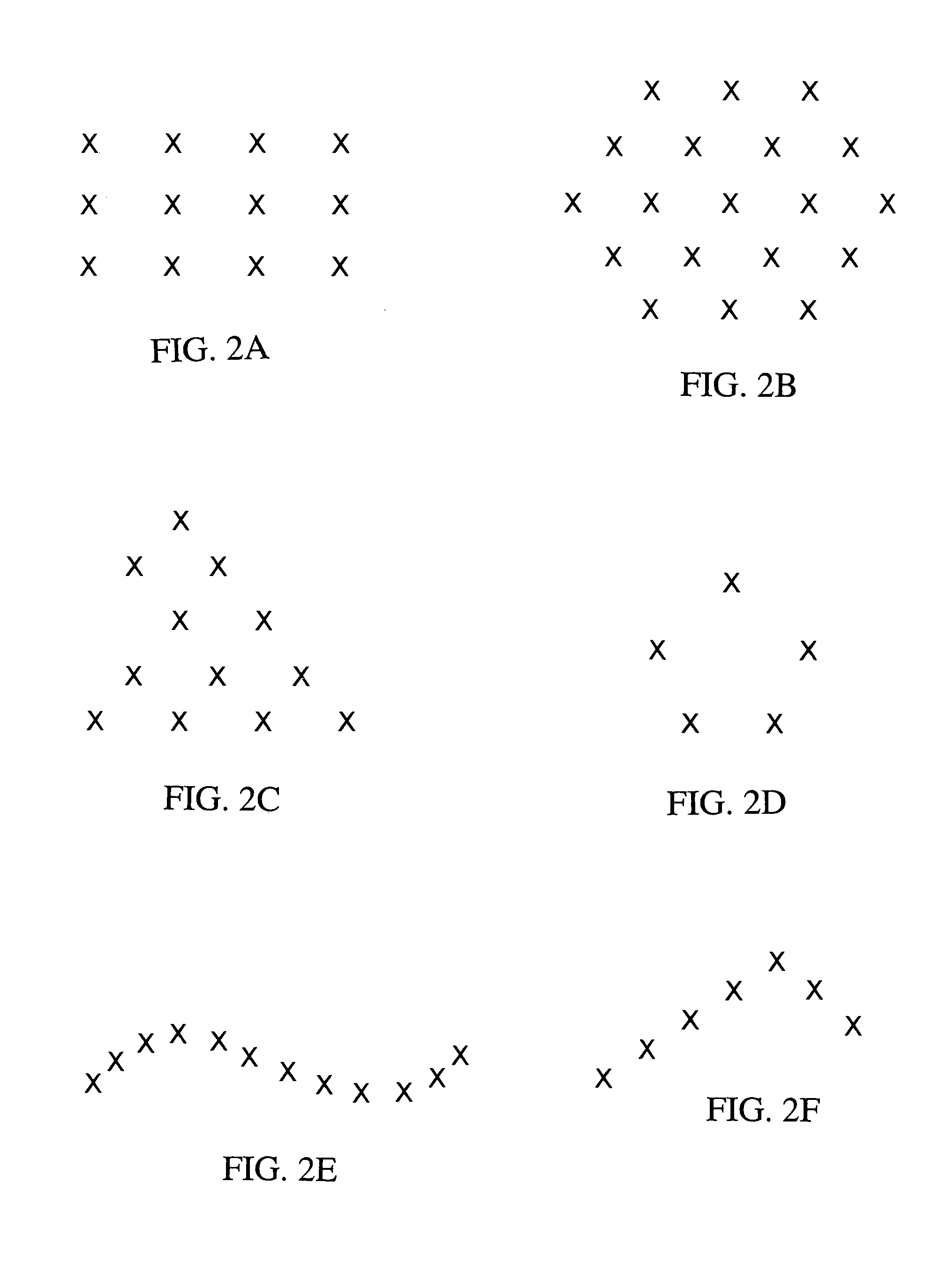

Carbon nanotube interconnect

InactiveUS7094679B1High density operationNanotechSemiconductor/solid-state device detailsHigh current densityCarbon nanotube

Method and system for fabricating an electrical interconnect capable of supporting very high current densities (106–1010 Amps / cm2), using an array of one or more carbon nanotubes (CNTs). The CNT array is grown in a selected spaced apart pattern, preferably with multi-wall CNTs, and a selected insulating material, such as SiOw or SiuNv, is deposited using CVD to encapsulate each CNT in the array. An exposed surface of the insulating material is planarized to provide one or more exposed electrical contacts for one or more CNTs.

Owner:NASA +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com