Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41791results about How to "High density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

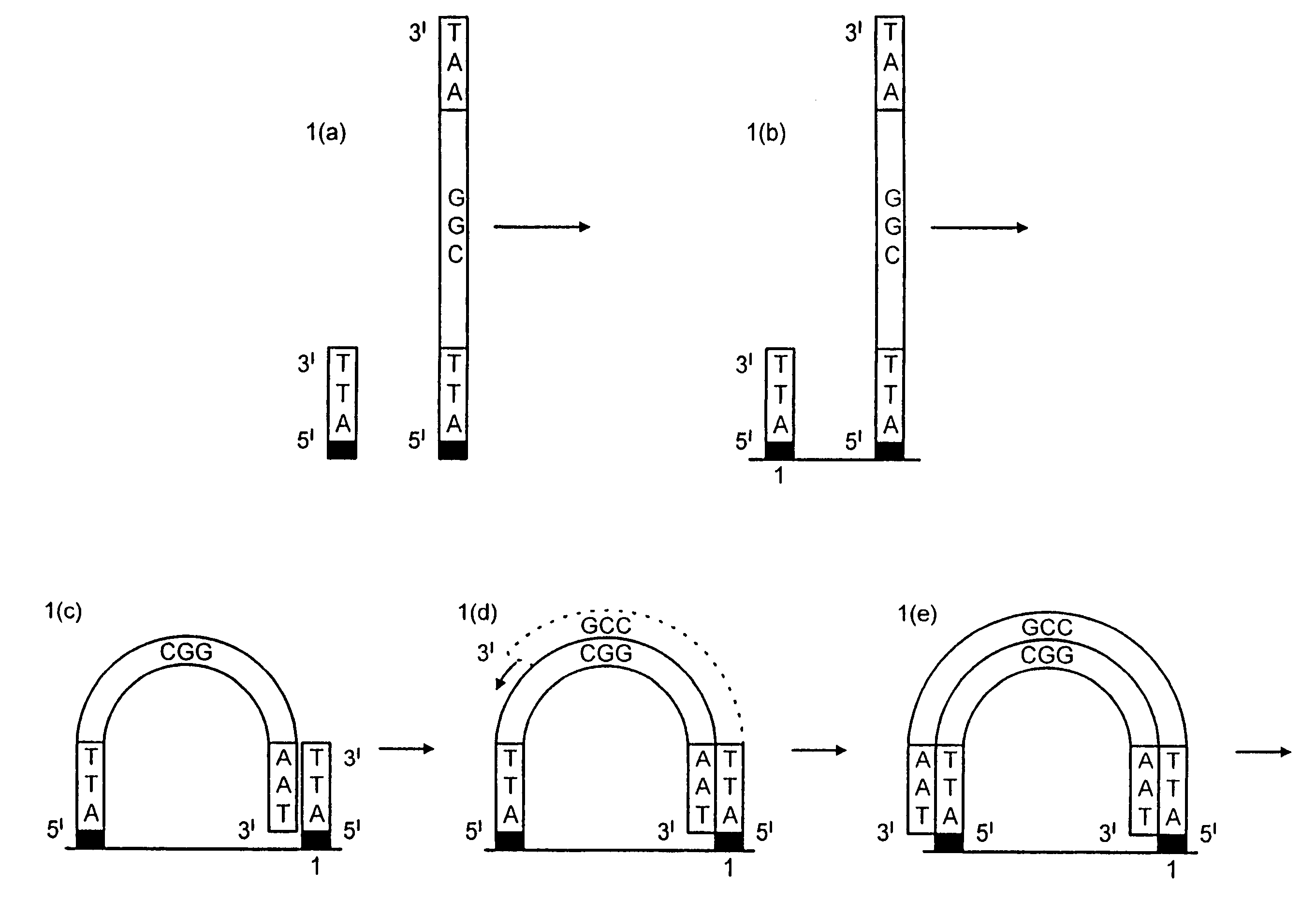

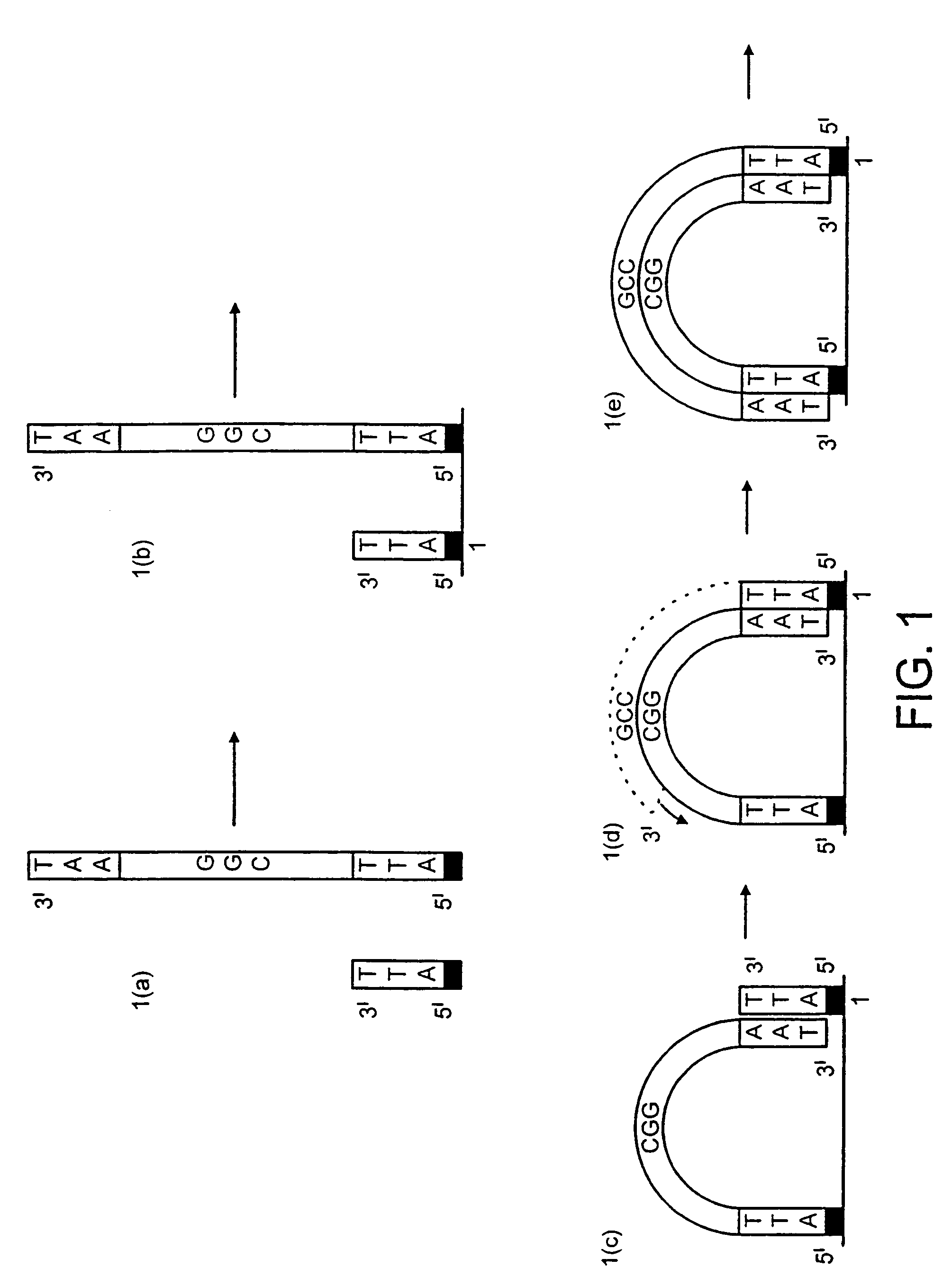

Methods of nucleic acid amplification and sequencing

InactiveUS7115400B1High densityBioreactor/fermenter combinationsBiological substance pretreatmentsOligonucleotideSequence determination

Owner:ILLUMINA INC

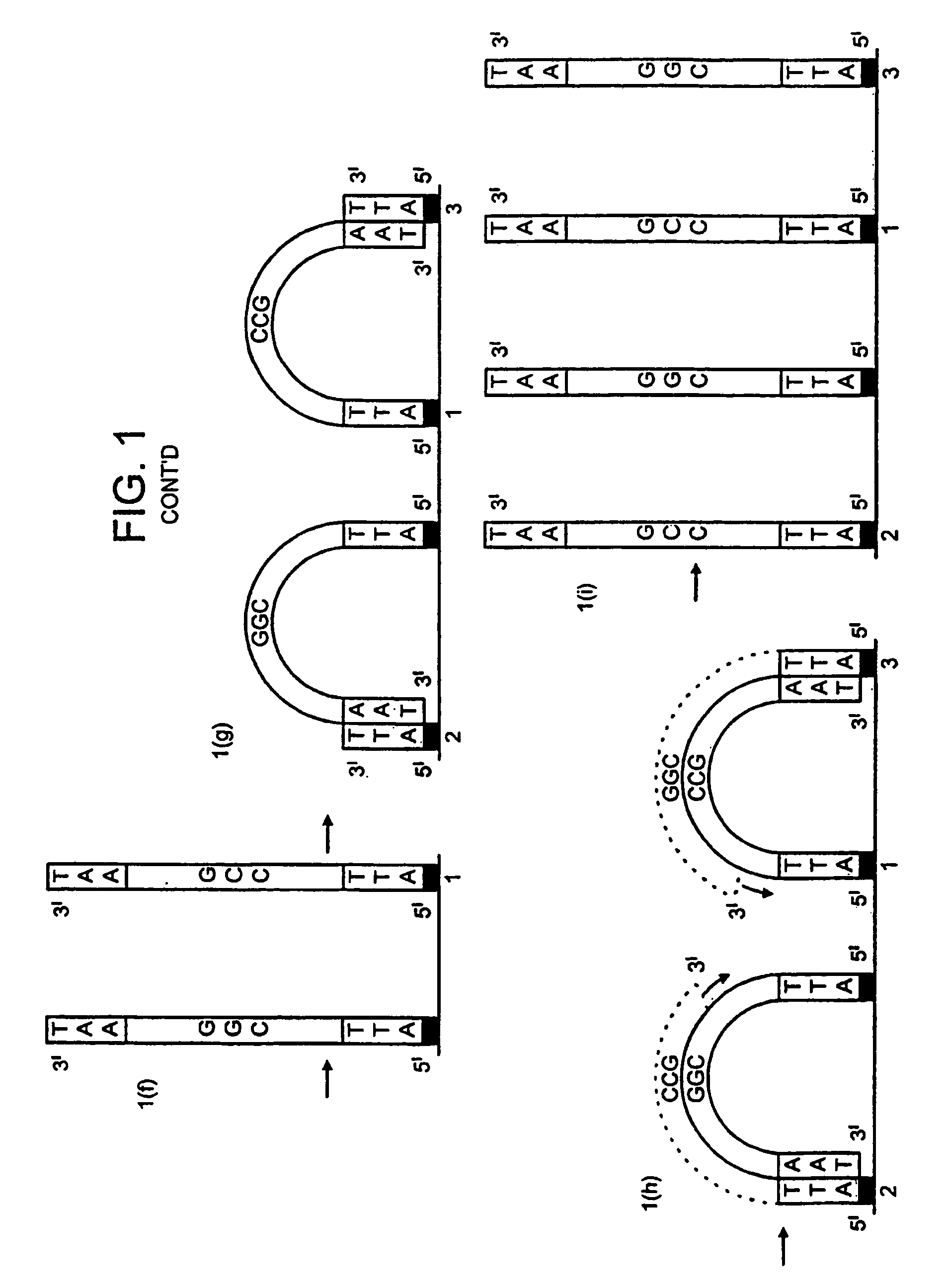

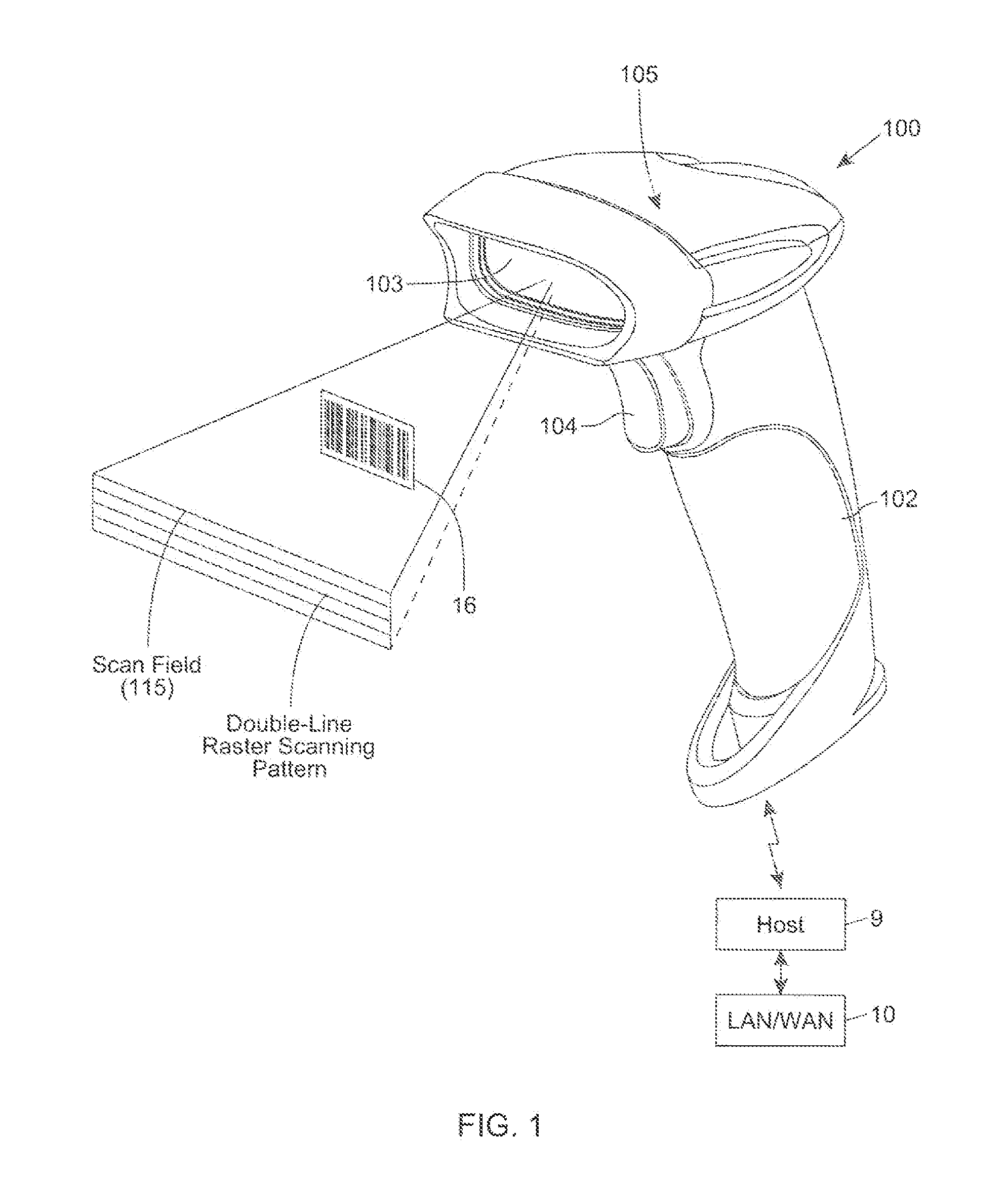

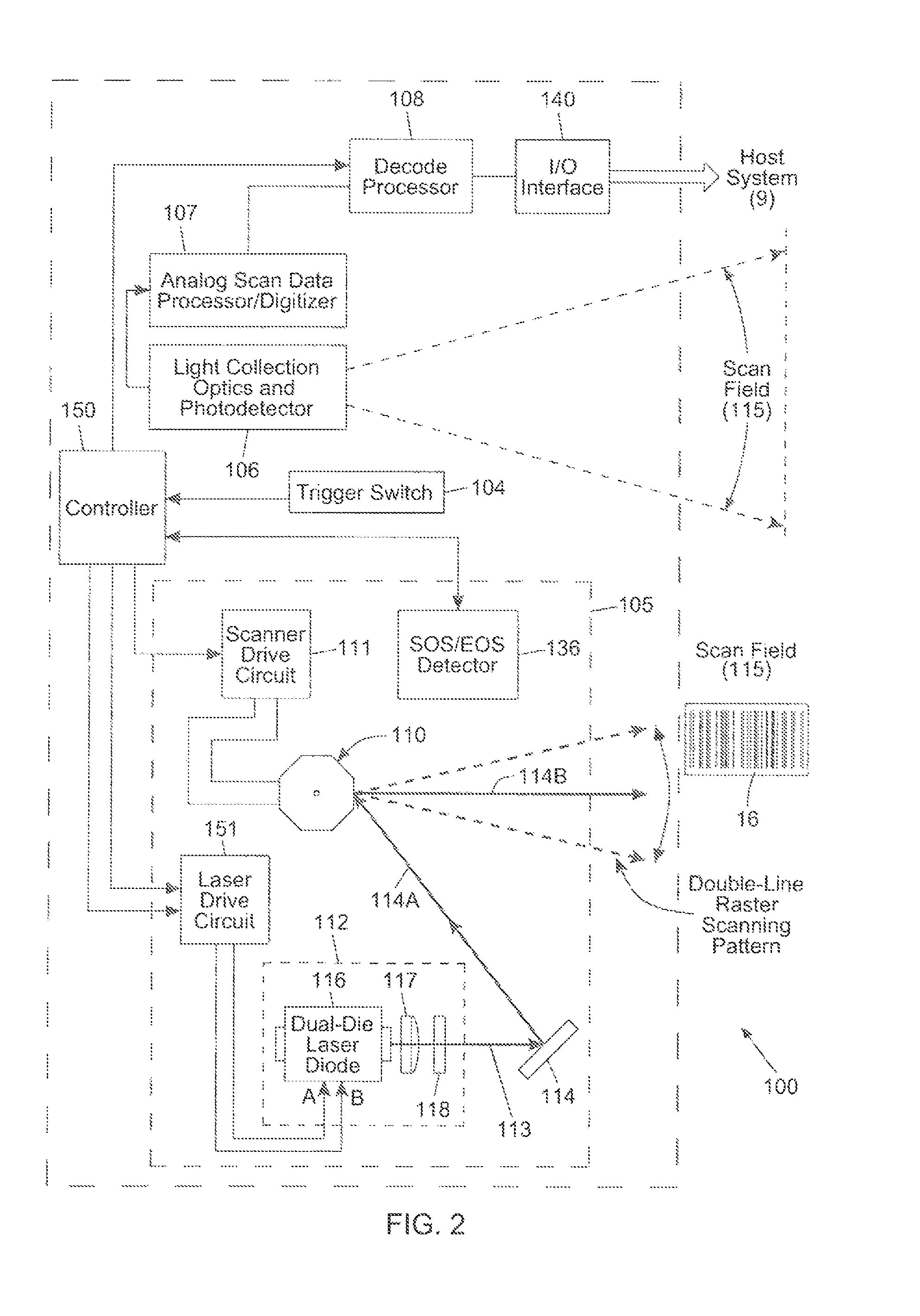

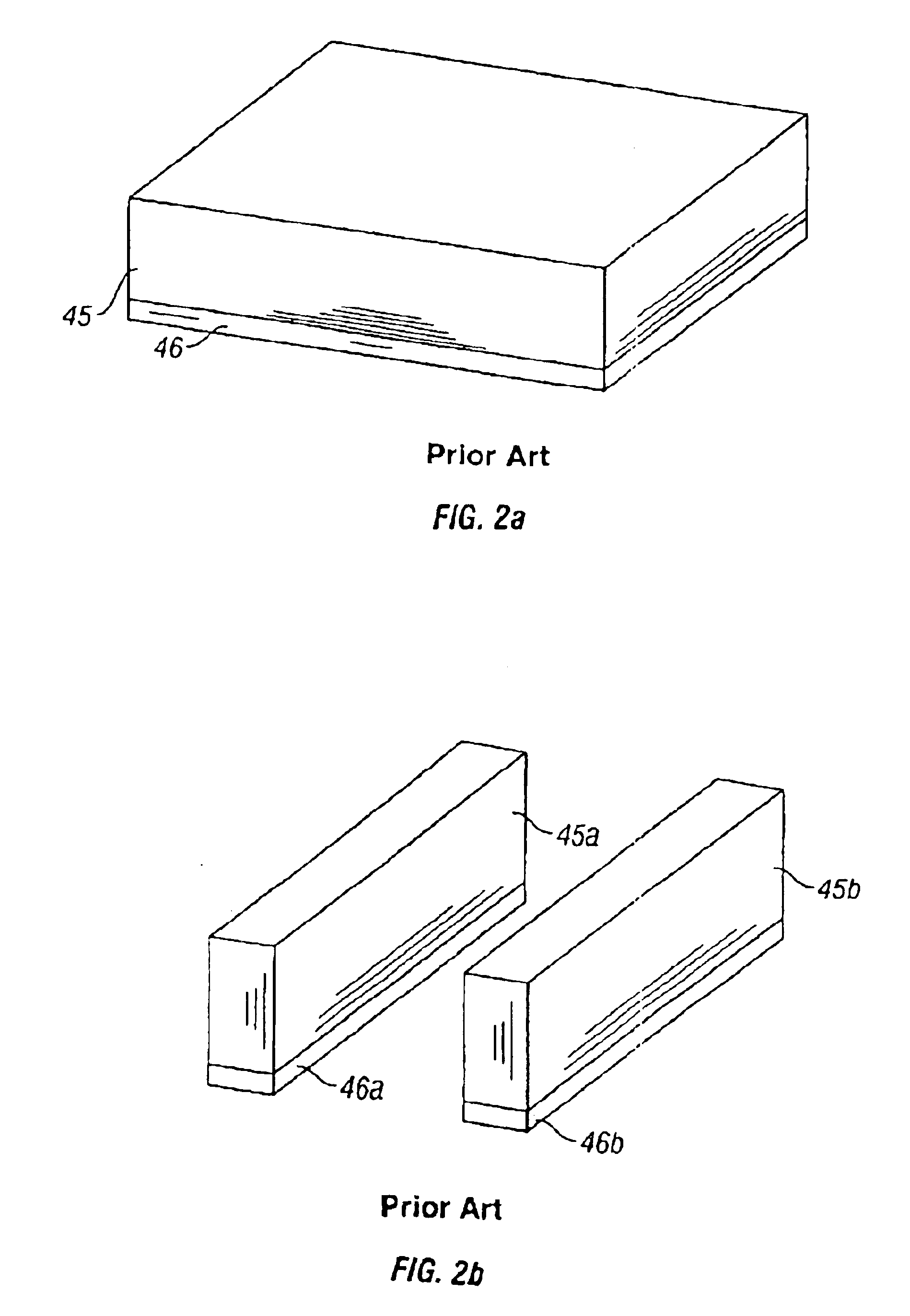

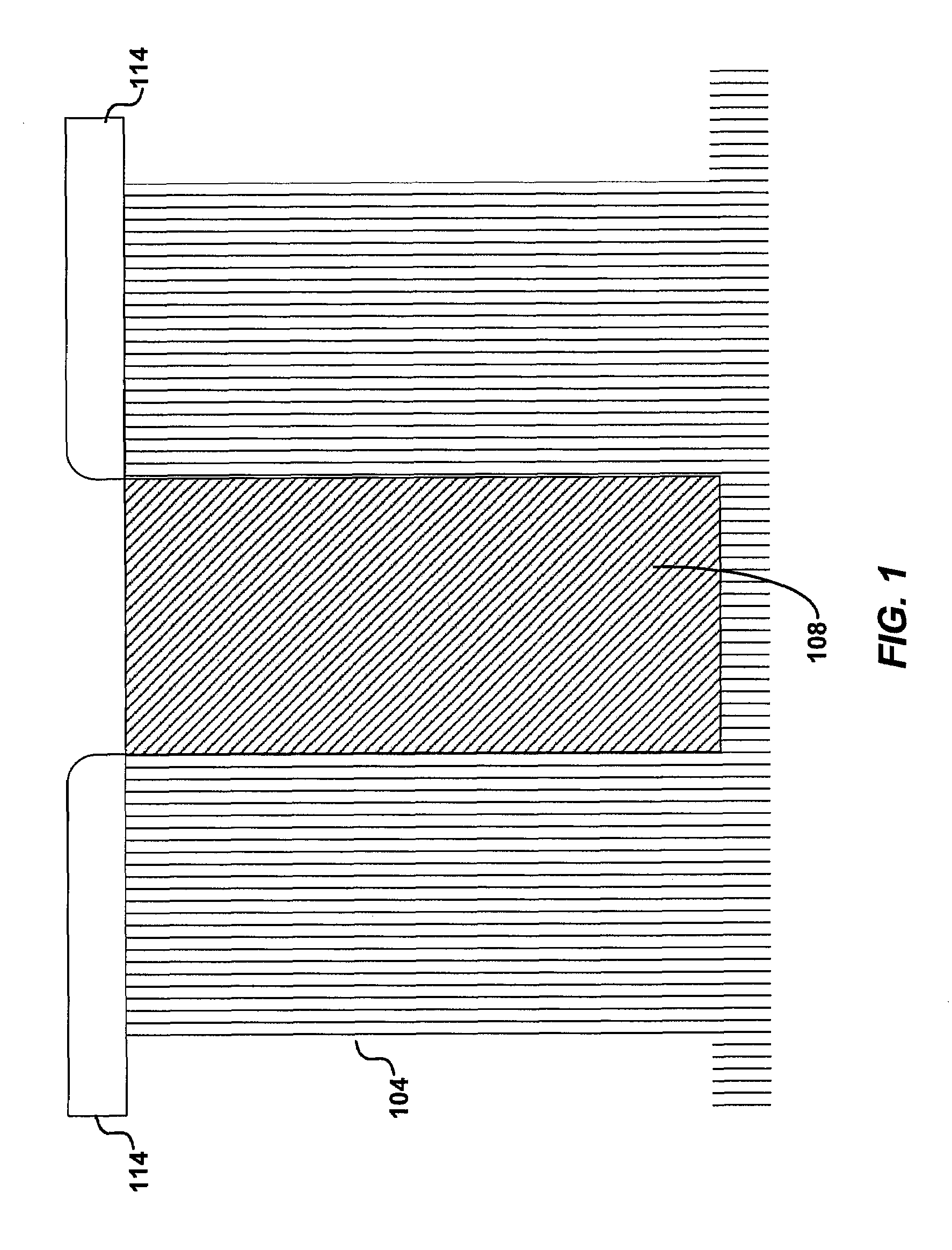

Method of and apparatus for multiplying raster scanning lines by modulating a multi-cavity laser diode

ActiveUS8678285B2Improve featuresHigh densityCharacter and pattern recognitionSensing by electromagnetic radiationGratingLaser scanning

A method of and apparatus for generating a multiple raster-type scanning pattern by modulating a multi-cavity laser diode in such a way that it sequentially generates different laser beams synchronously during different laser scanning cycles, while the output laser beams are directed incident upon a rotating polygonal laser scanning element. The system does not require additional moving parts beyond the rotating polygon scanning element so as to reduce complexity and simplify construction of the laser scanning mechanism.

Owner:METROLOGIC INSTR INC

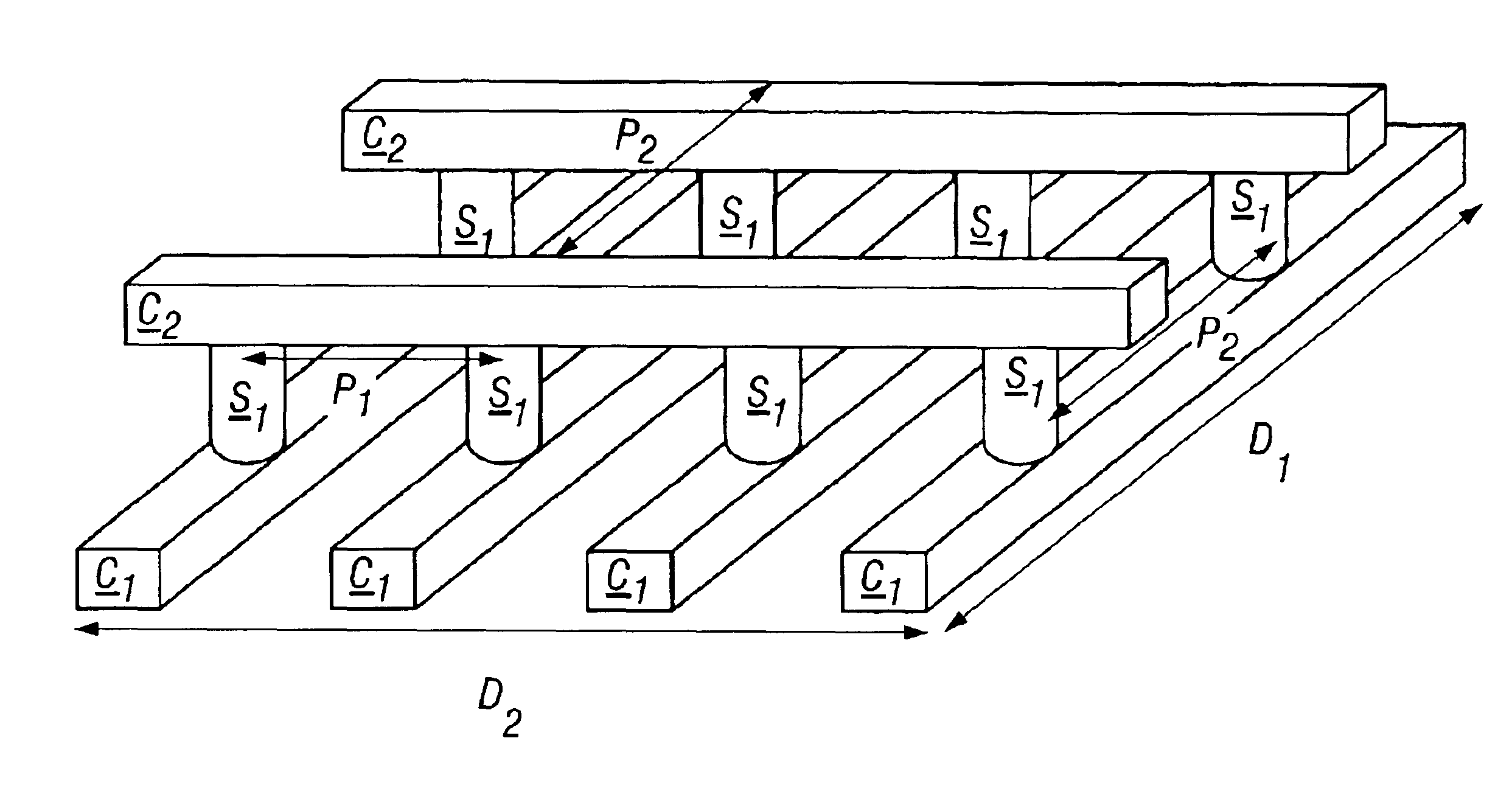

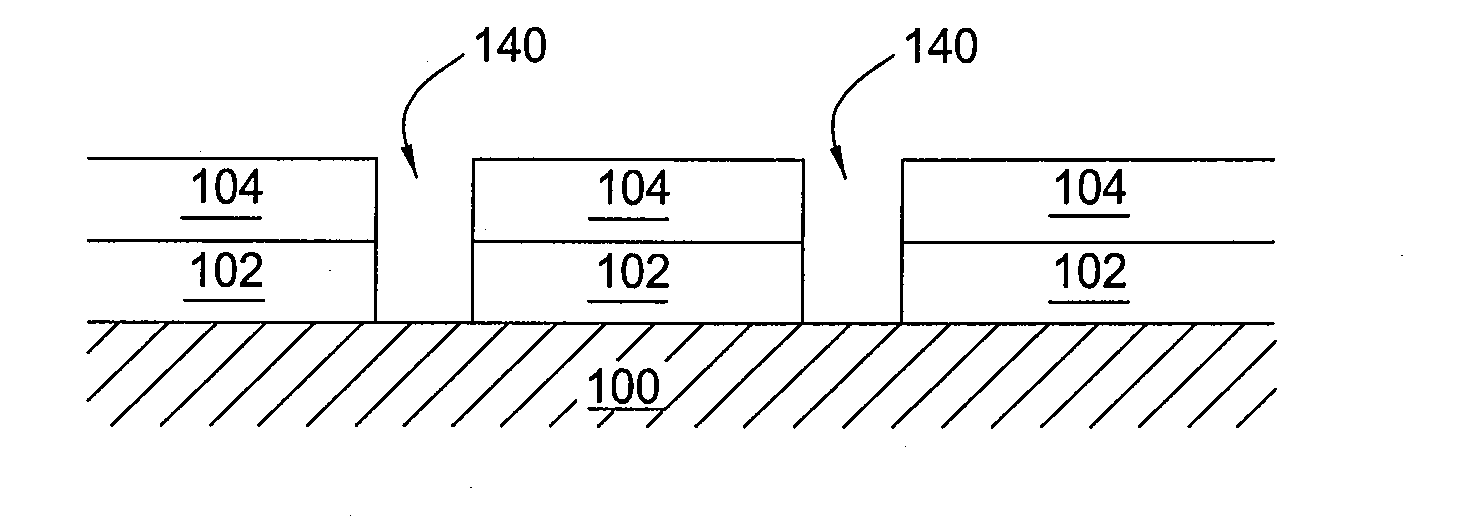

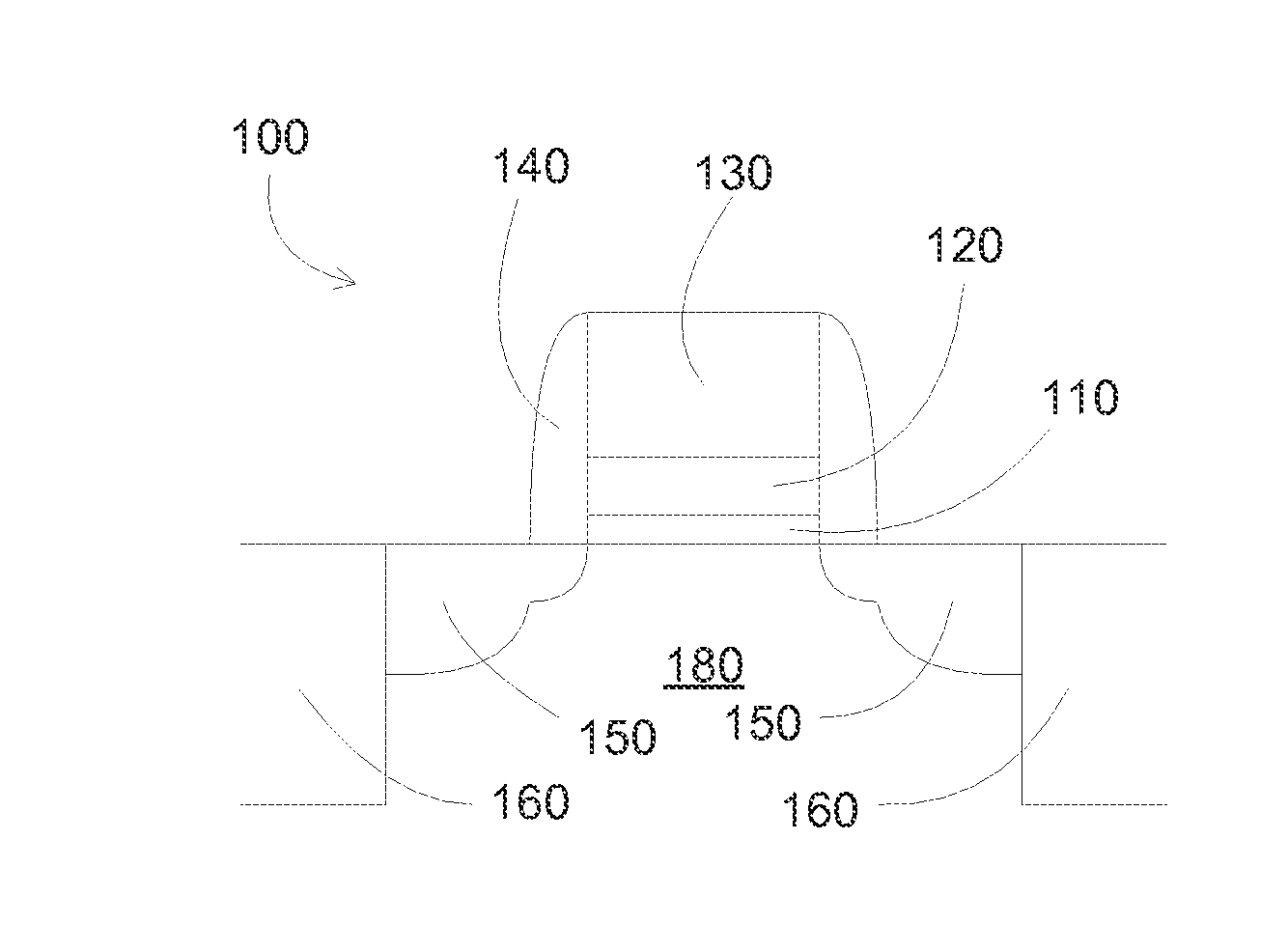

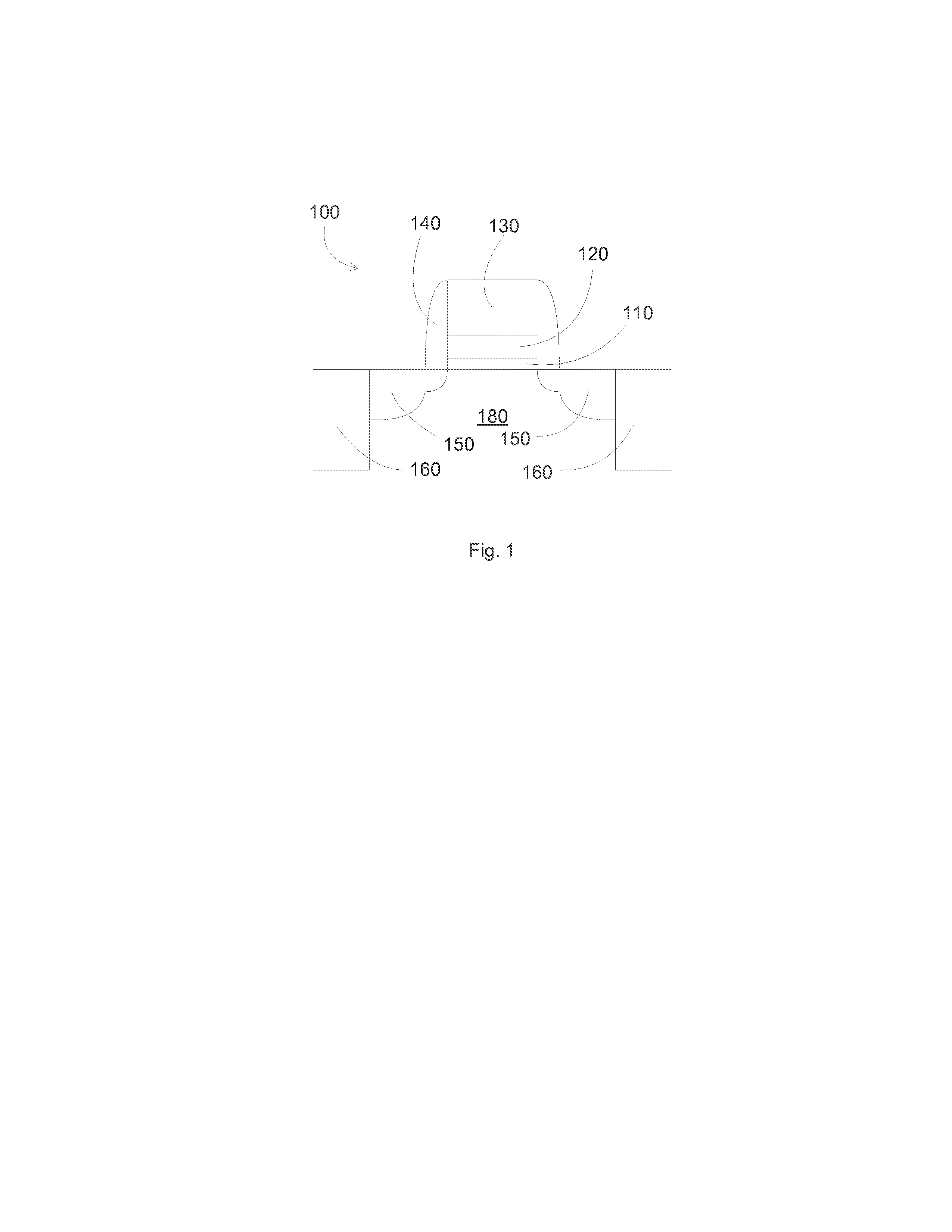

High-density three-dimensional memory cell

InactiveUS6952030B2High densityReduce the overall heightTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

A three dimensional monolithic memory comprising a memory cell allowing for increased density is disclosed. In the memory cell of the present invention, a bottom conductor preferably comprising tungsten is formed. Above the bottom conductor a semiconductor element preferably comprises two diode portions and an antifuse. Above the semiconductor element are additional conductors and semiconductor elements in multiple stones of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

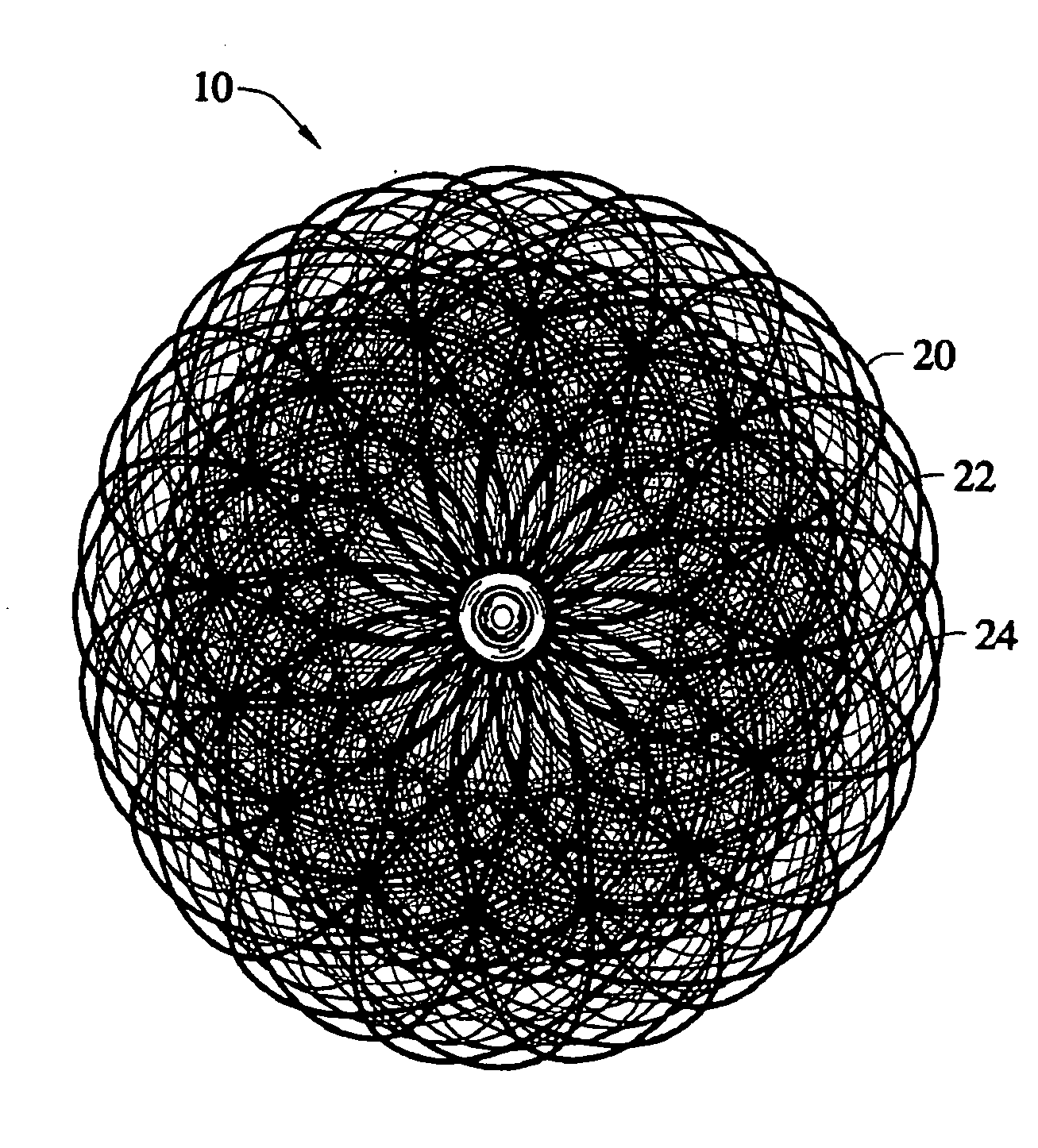

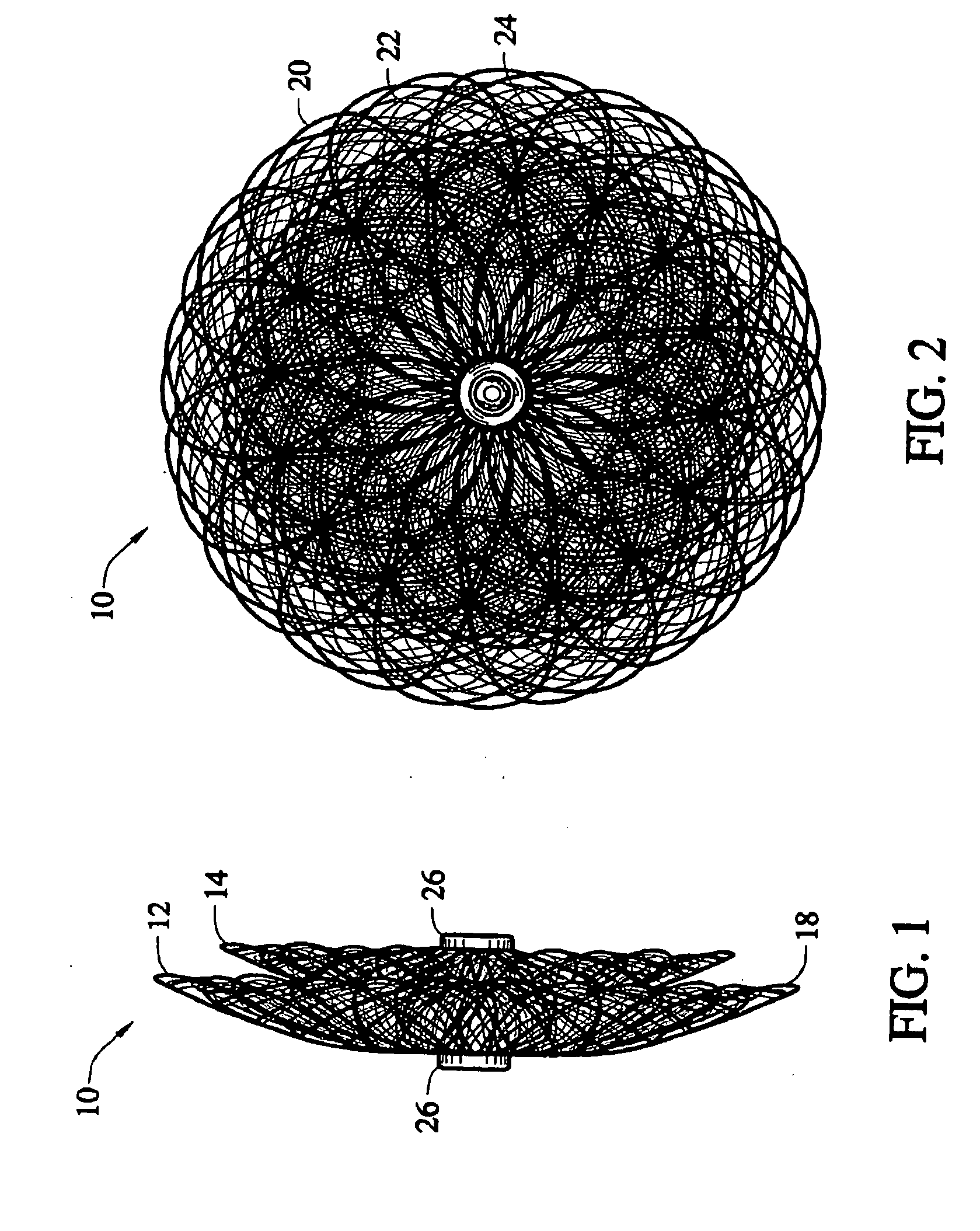

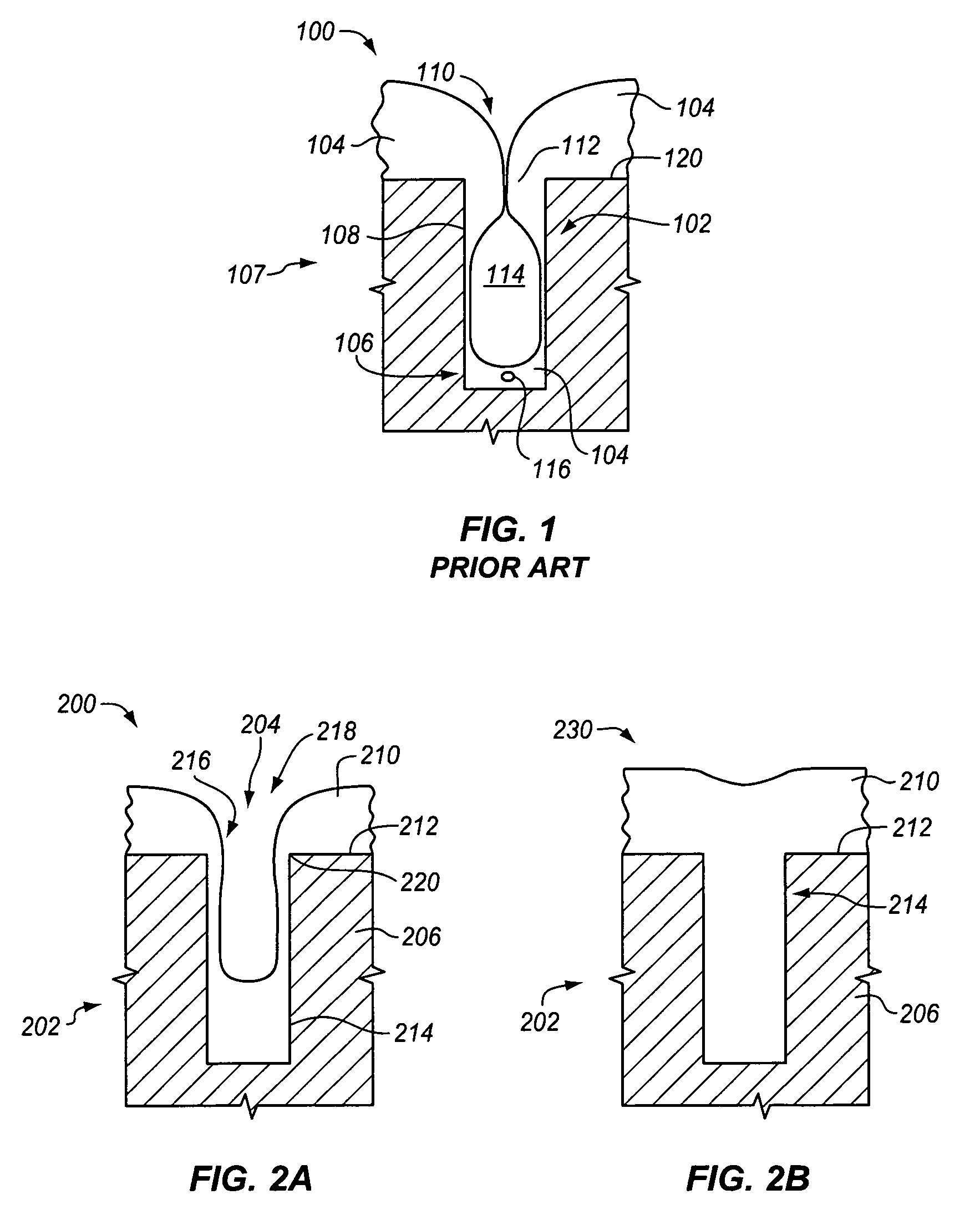

Multi-layer braided structures for occluding vascular defects

A collapsible medical device and associated methods of occluding an abnormal opening in, for example, a body organ, wherein the medical device is shaped from plural layers of a heat-treatable metal fabric. Each of the fabric layers is formed from a plurality of metal strands and the assembly is heat-treated within a mold in order to substantially set a desired shape of the device. By incorporating plural layers in the thus-formed medical device, the ability of the device to rapidly occlude an abnormal opening in a body organ is significantly improved.

Owner:ST JUDE MEDICAL CARDILOGY DIV INC

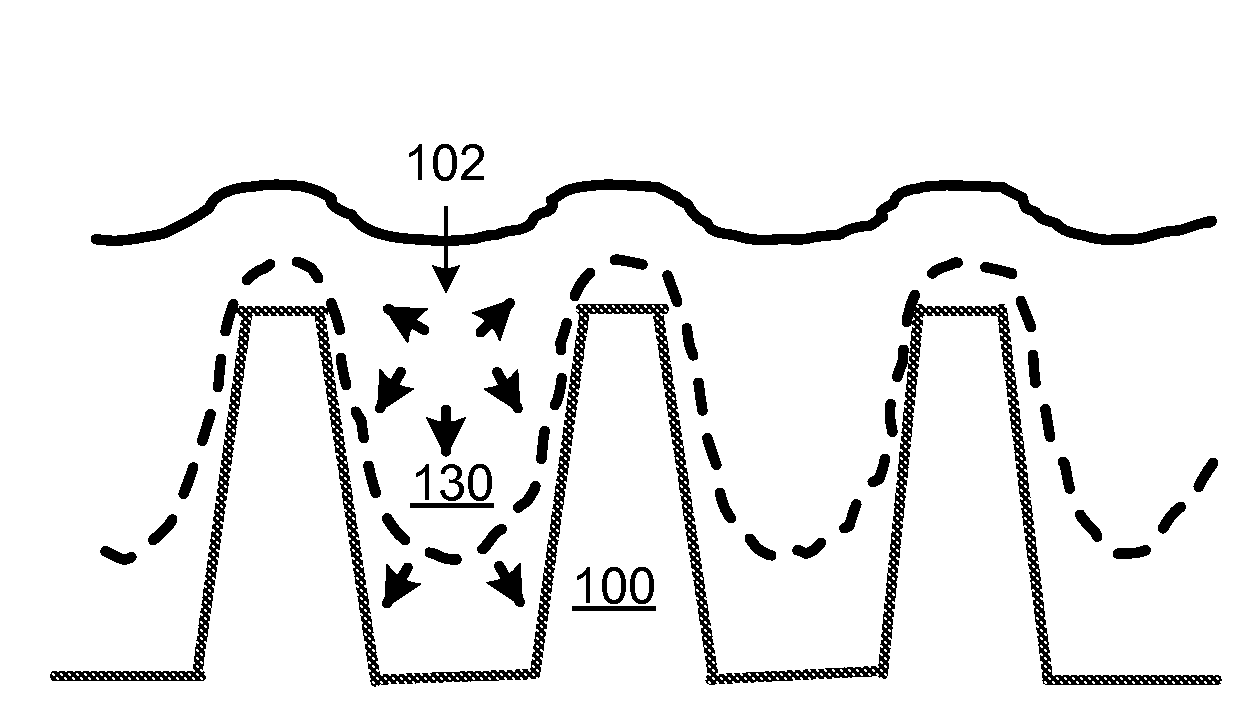

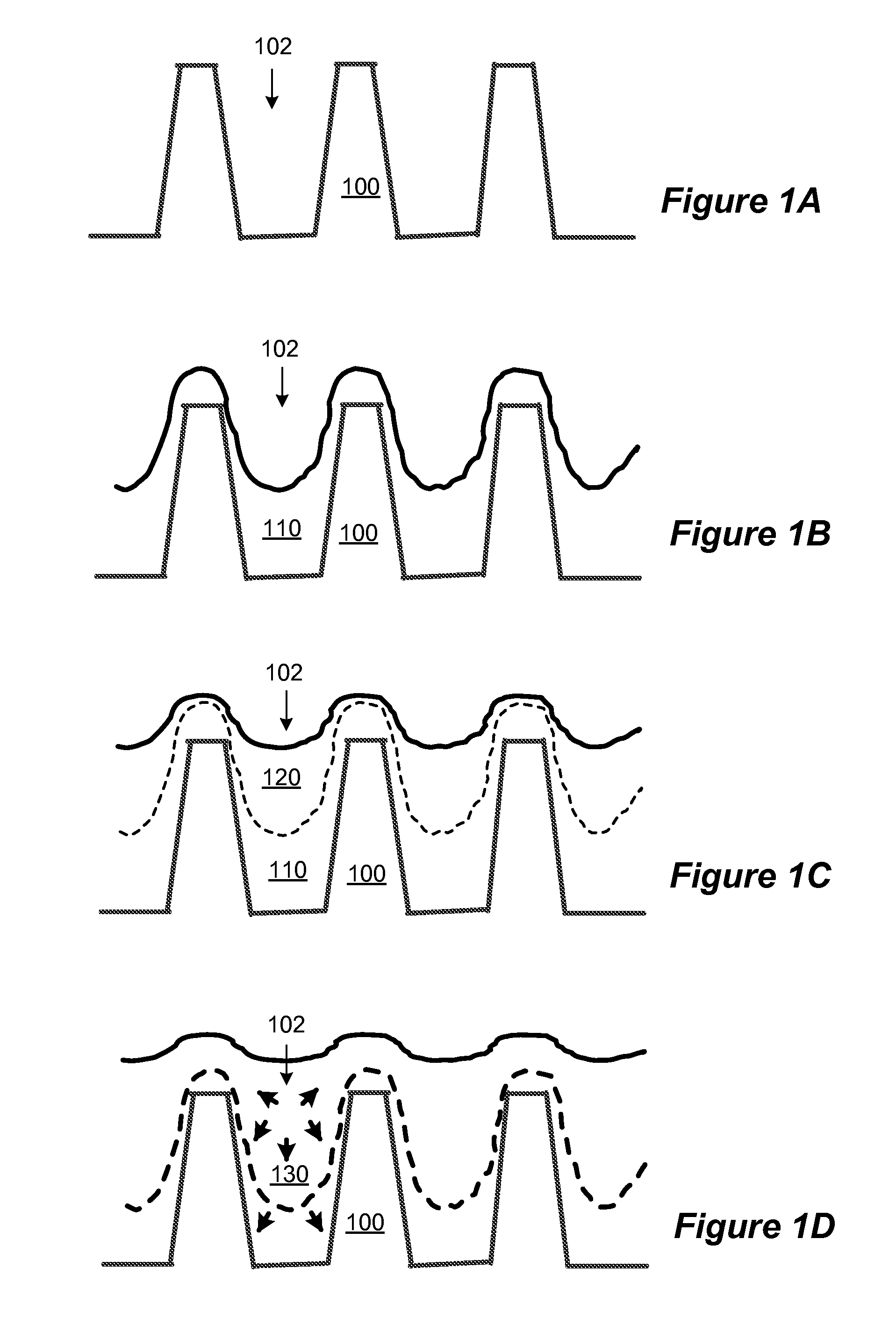

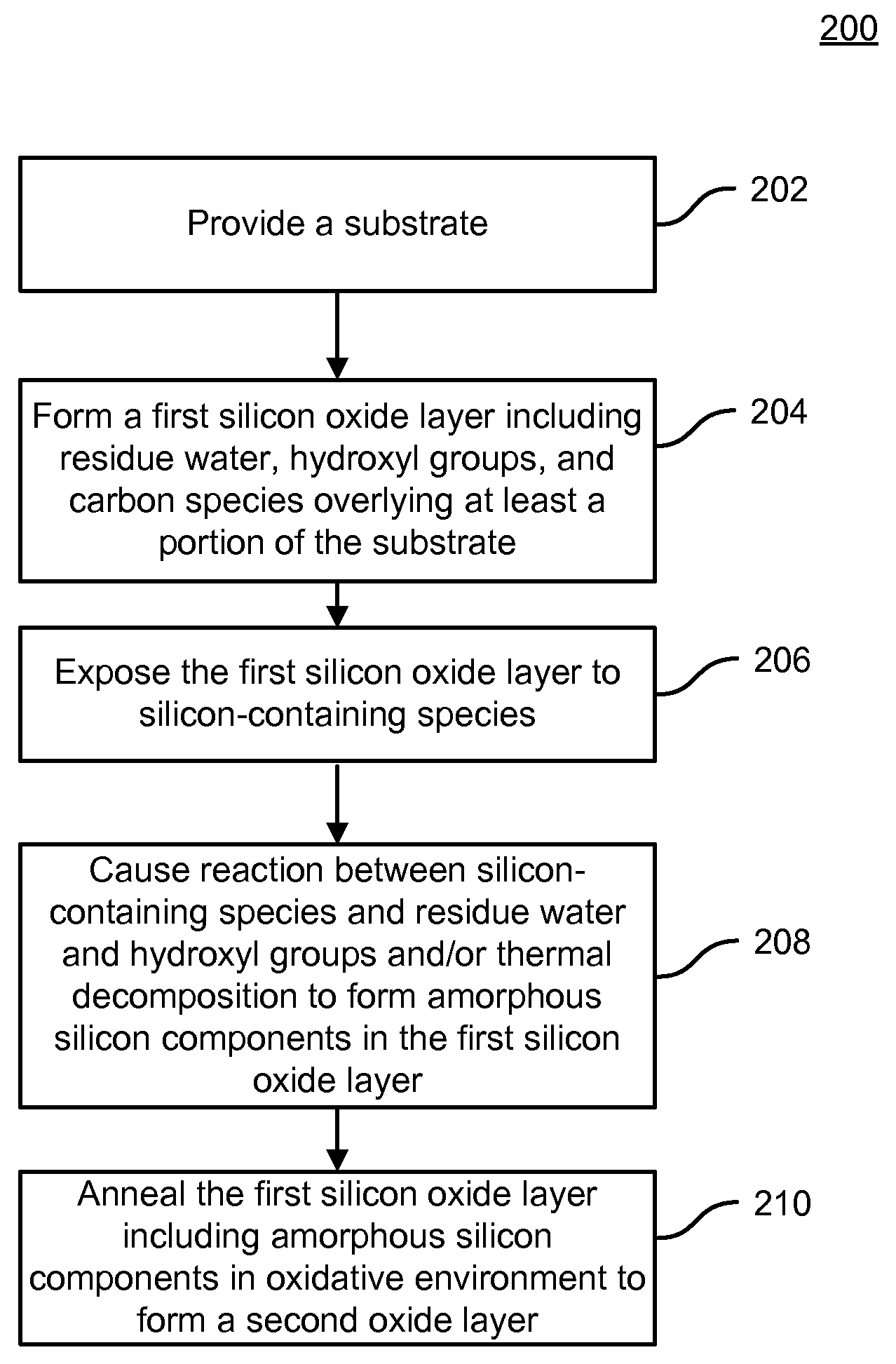

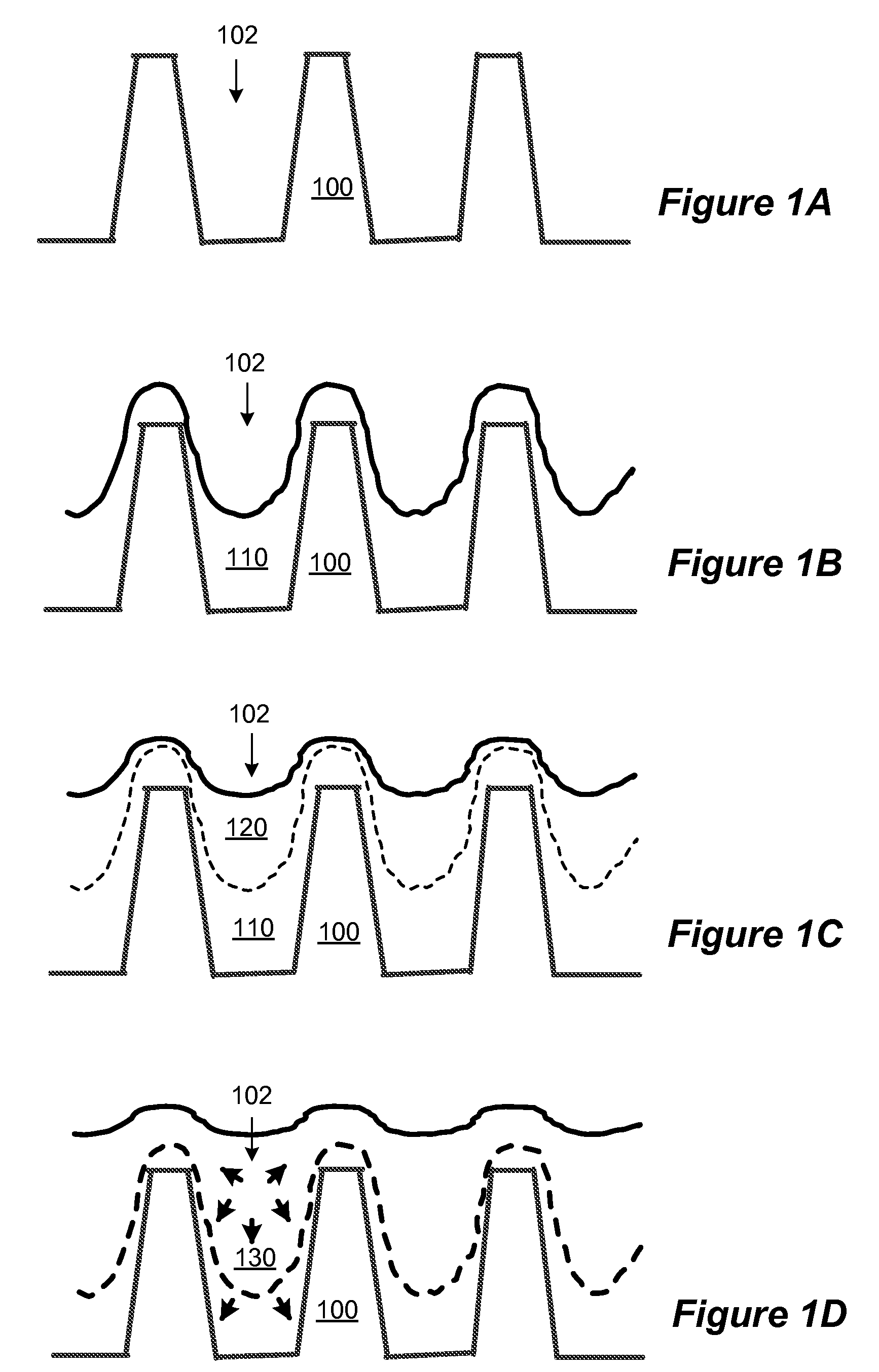

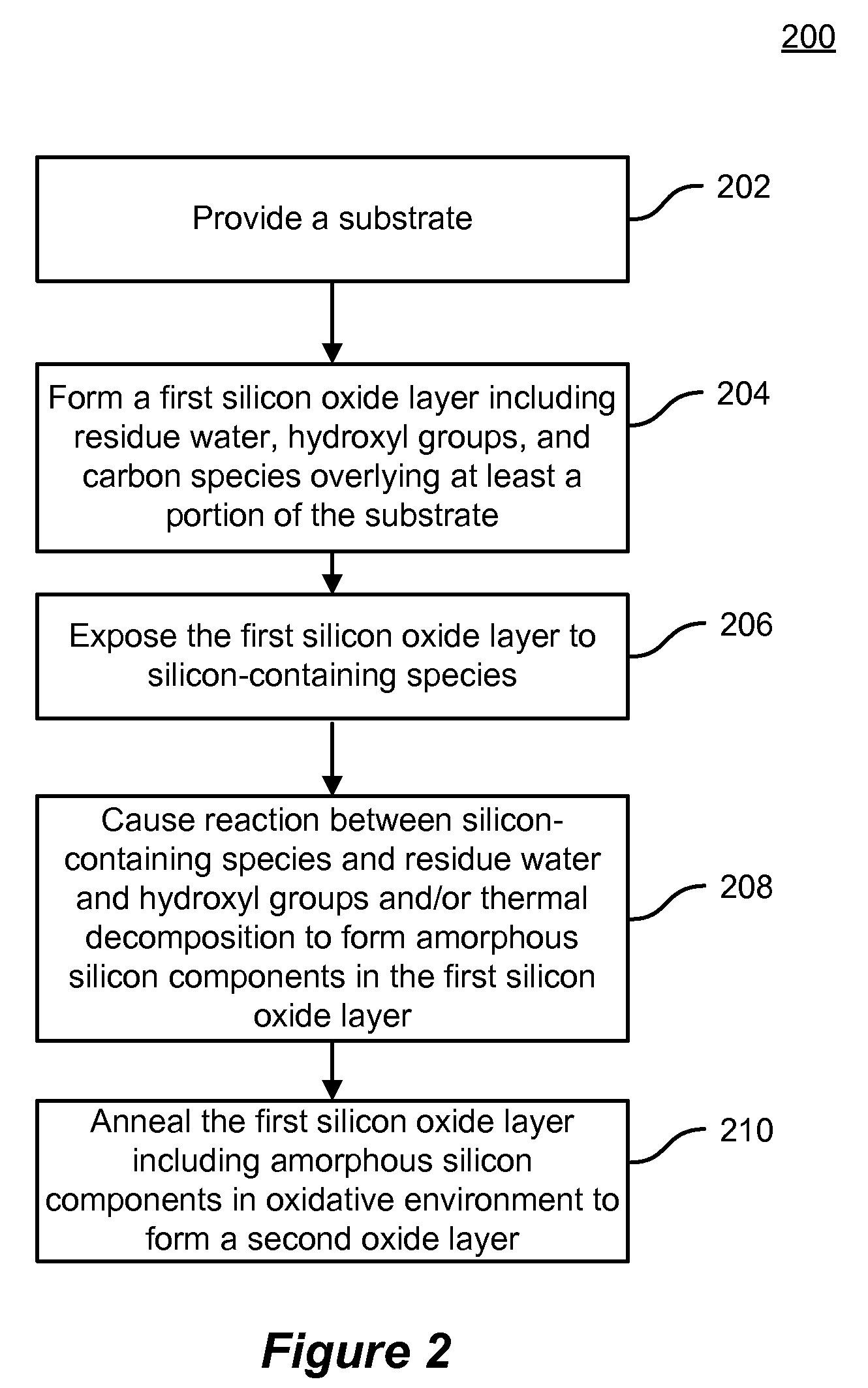

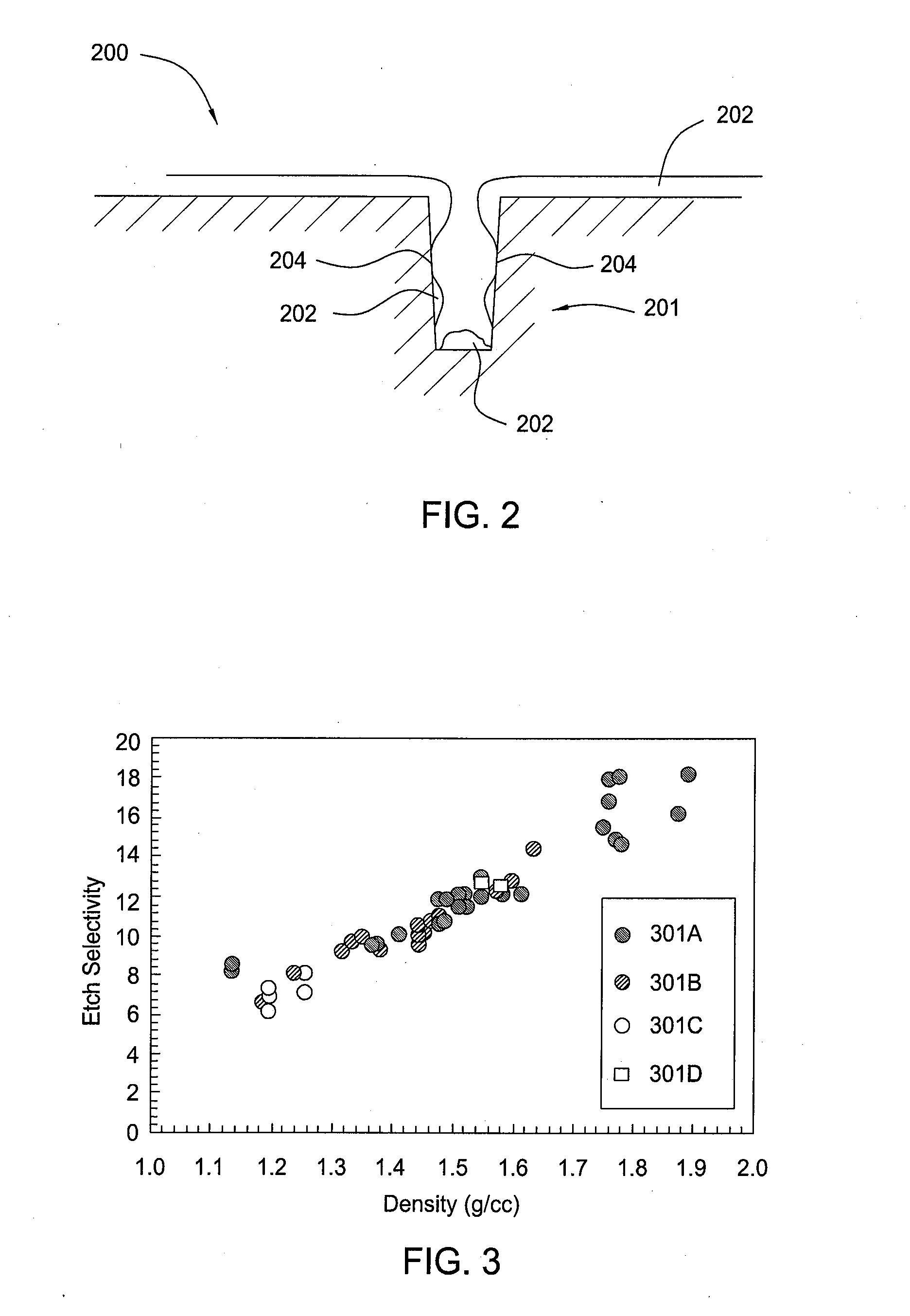

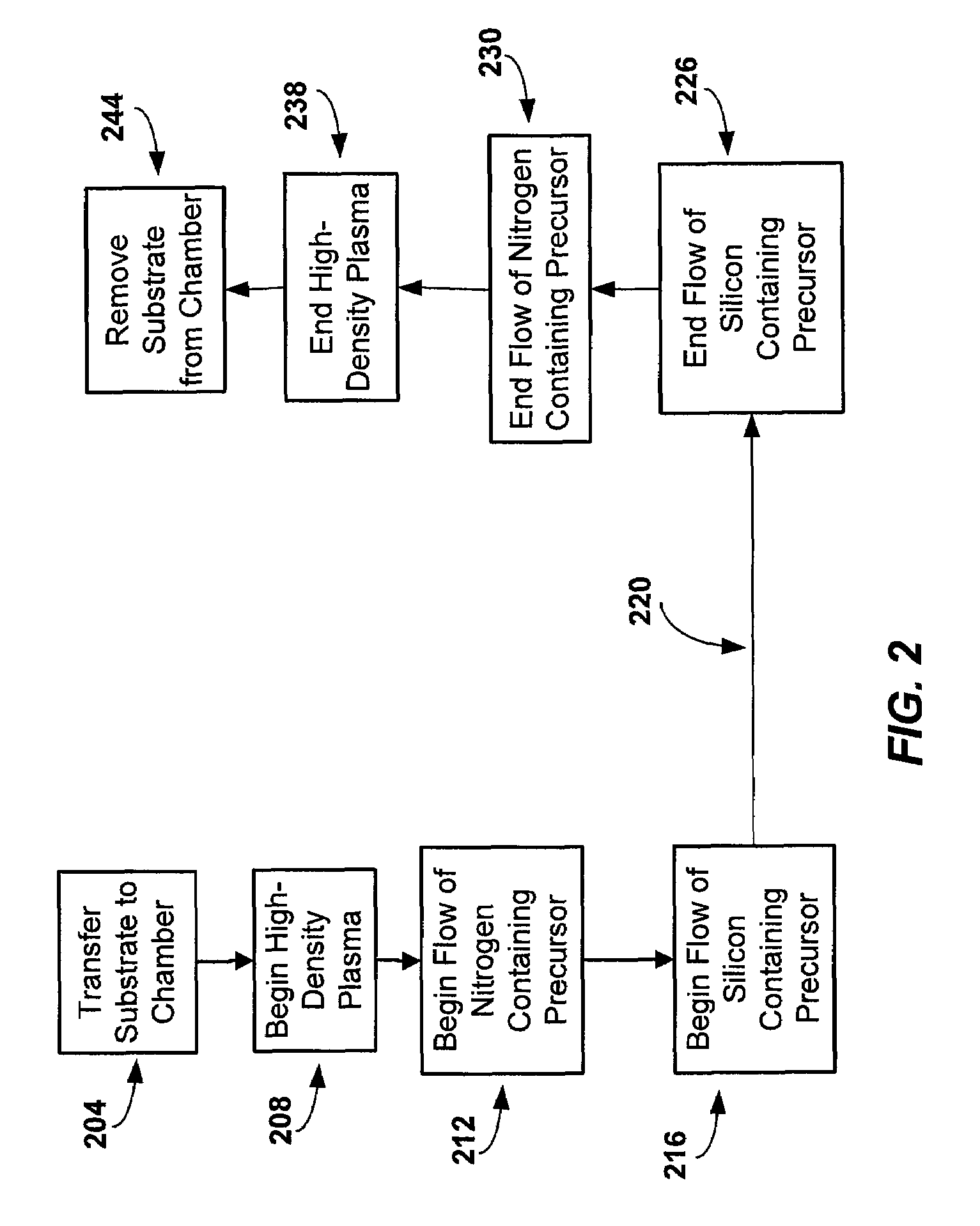

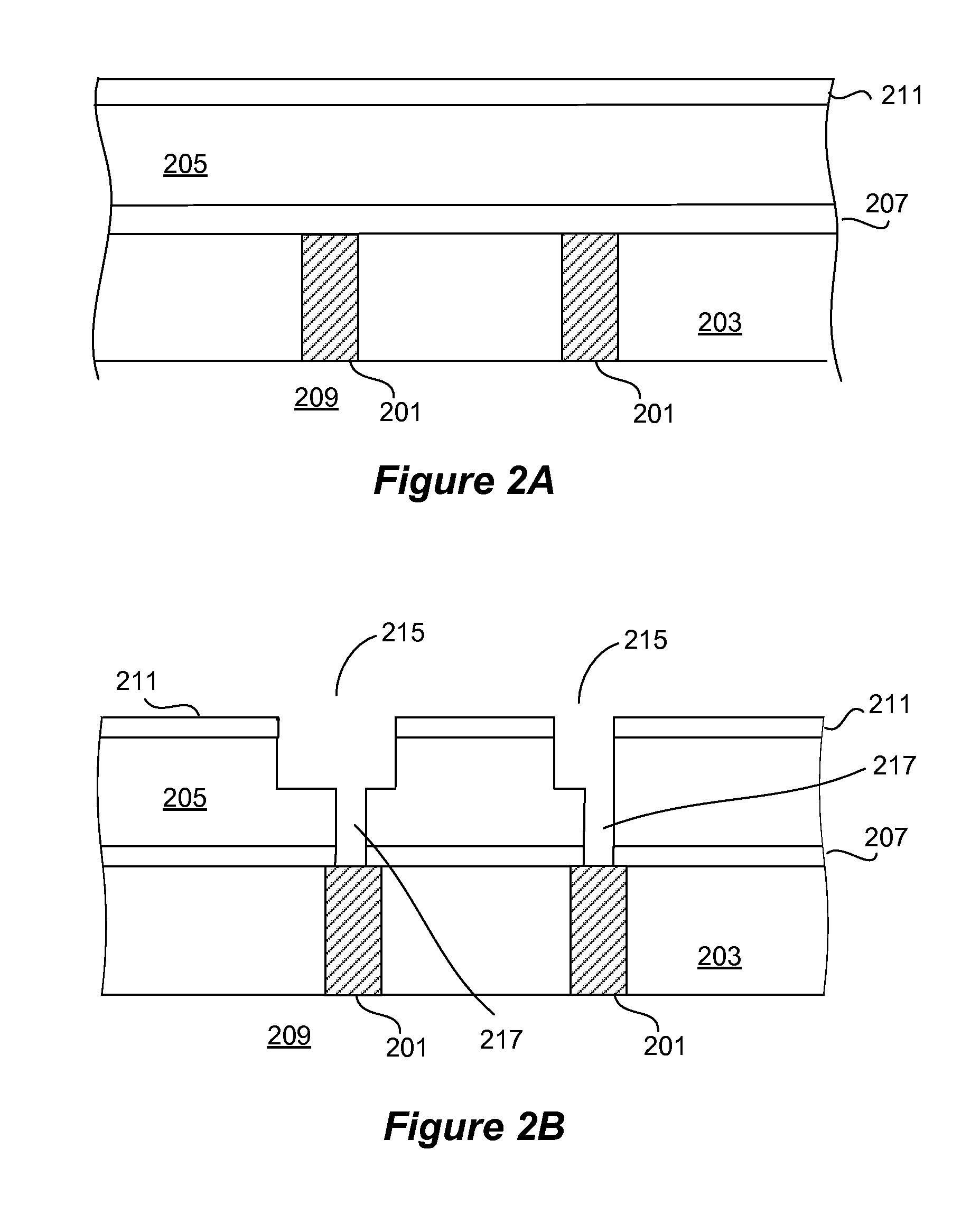

Method and system for improving dielectric film quality for void free gap fill

ActiveUS7541297B2Quality improvementHigh densitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingAmorphous siliconSilicon oxide

Owner:APPLIED MATERIALS INC

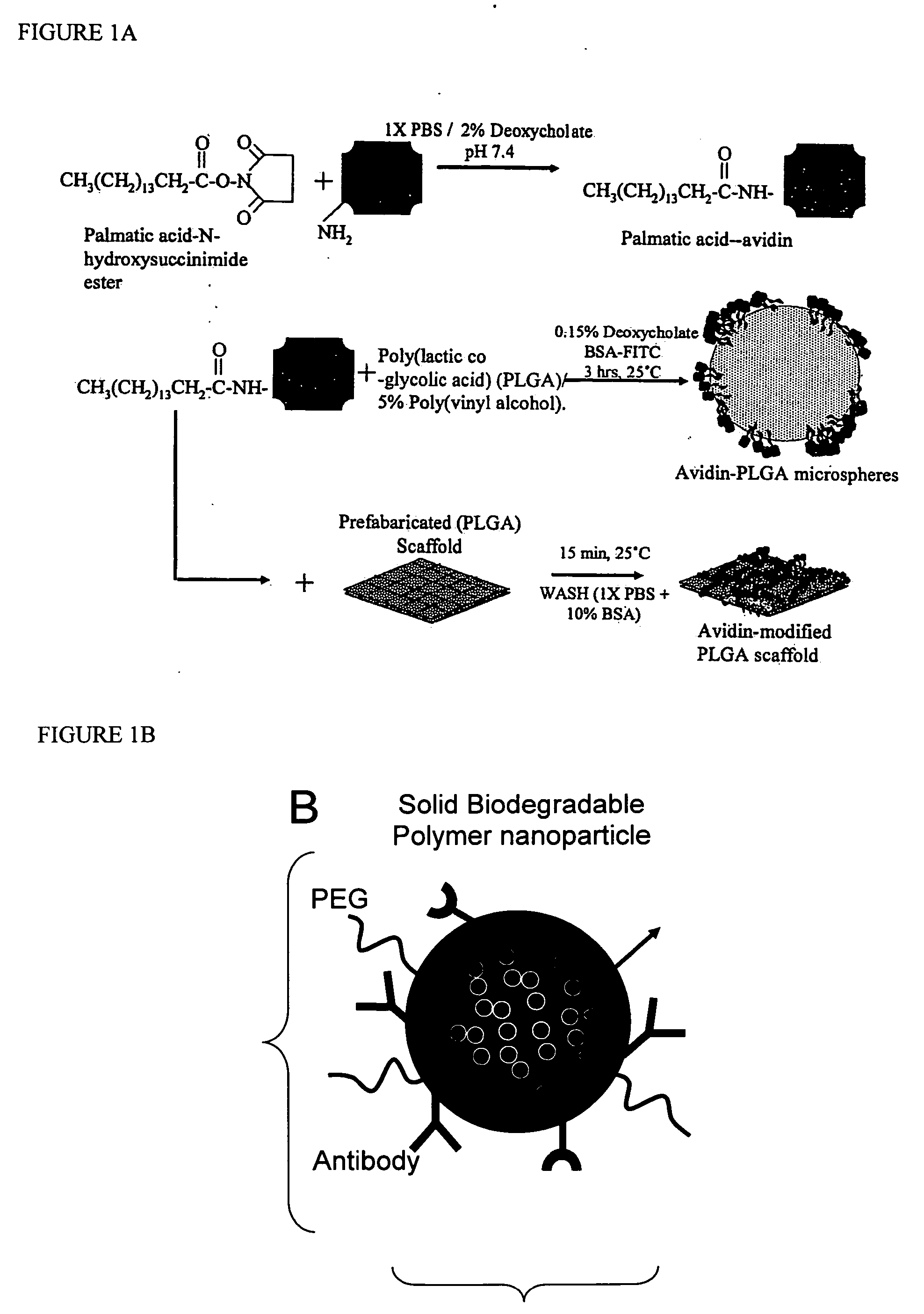

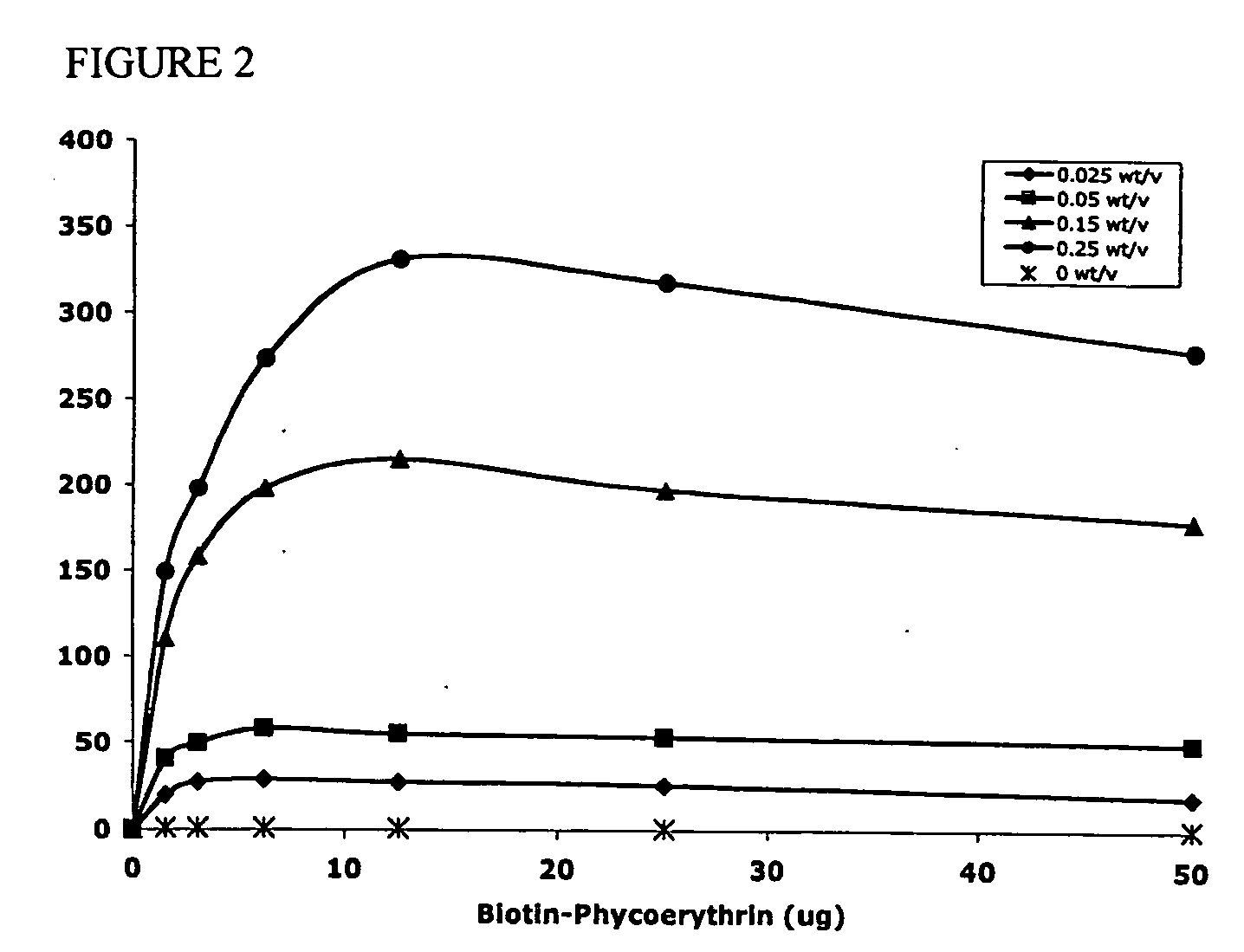

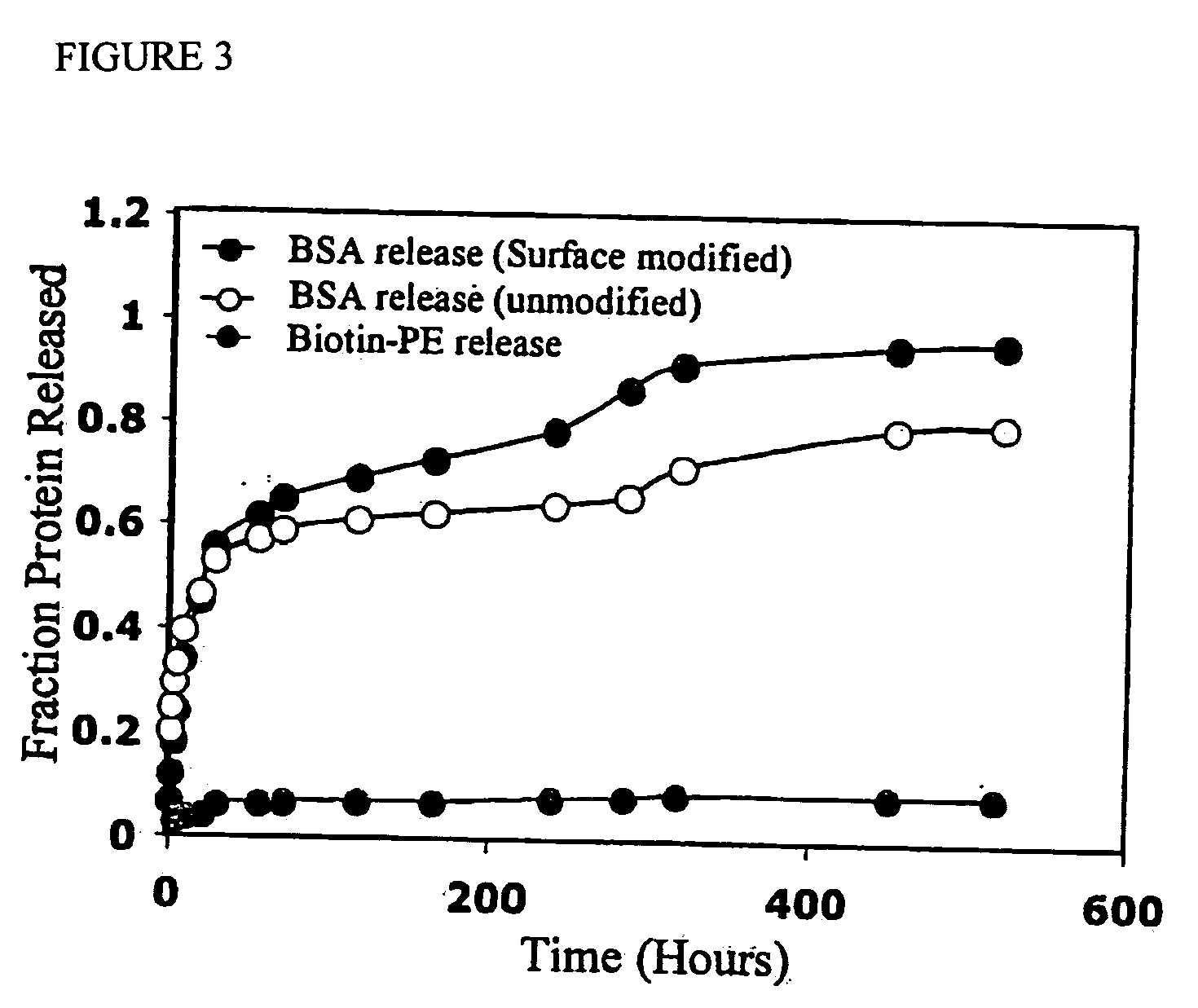

Targeted and high density drug loaded polymeric materials

ActiveUS20060002852A1Increase molecular densityHigh densityPowder deliveryBiocideAntigenWound dressing

Polymeric delivery devices have been developed which combine high loading / high density of molecules to be delivered with the option of targeting. As used herein, “high density” refers to microparticles having a high density of ligands or coupling agents, which is in the range of 1000-10,000,000, more preferably between 10,000 and 1,000,000 ligands per square micron of microparticle surface area. A general method for incorporating molecules into the surface of biocompatible polymers using materials with an HLB of less than 10, more preferably less than 5, such as fatty acids, has been developed. Because of its ease, generality and flexibility, this method has widespread utility in modifying the surface of polymeric materials for applications in drug delivery and tissue engineering, as well other other fields. Targeted polymeric microparticles have also been developed which encapsulate therapeutic compounds such as drugs, cellular materials or components, and antigens, and have targeting ligands directly bound to the microparticle surface. Preferred applications include use in tissue engineering matrices, wound dressings, bone repair or regeneration materials, and other applications where the microparticles are retained at the site of application or implantation. Another preferred application is in the use of microparticles to deliver anti-proliferative agents to the lining of blood vessels following angioplasty, transplantation or bypass surgery to prevent or decrease restenosis, and in cancer therapy. In still another application, the microparticles are used to treat or prevent macular degeneration when administered to the eye, where agents such as complement inhibitors are administered.

Owner:YALE UNIV

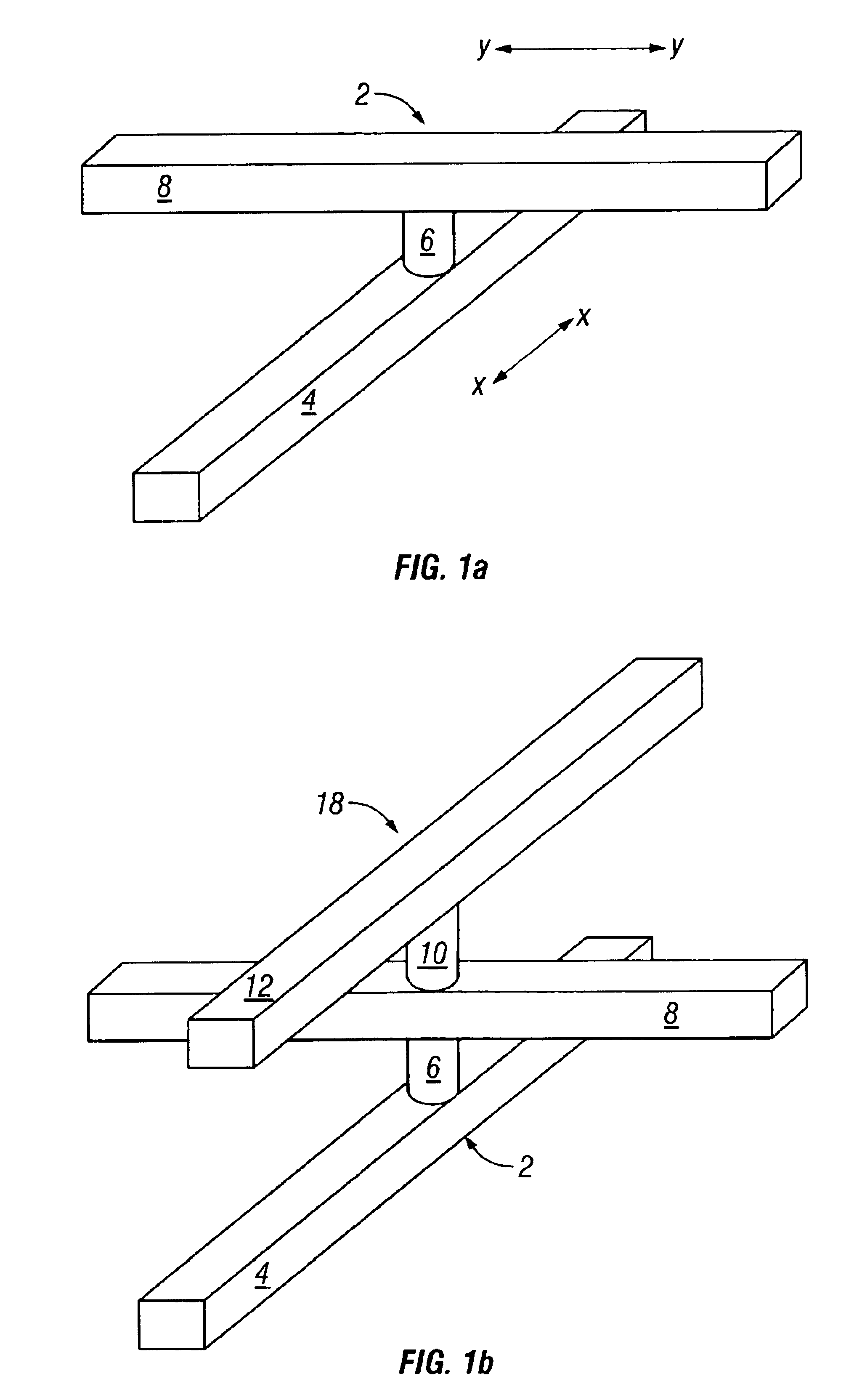

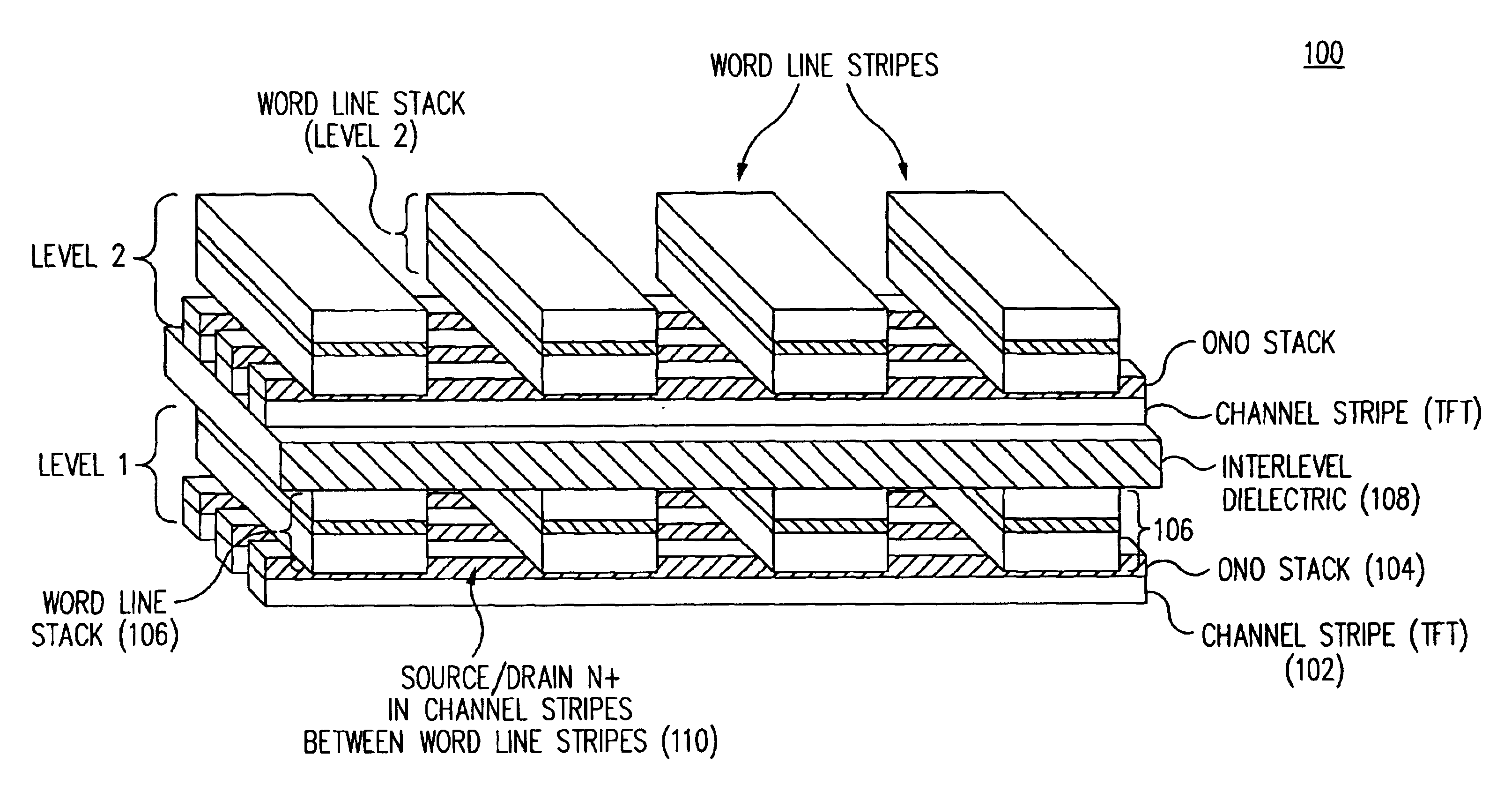

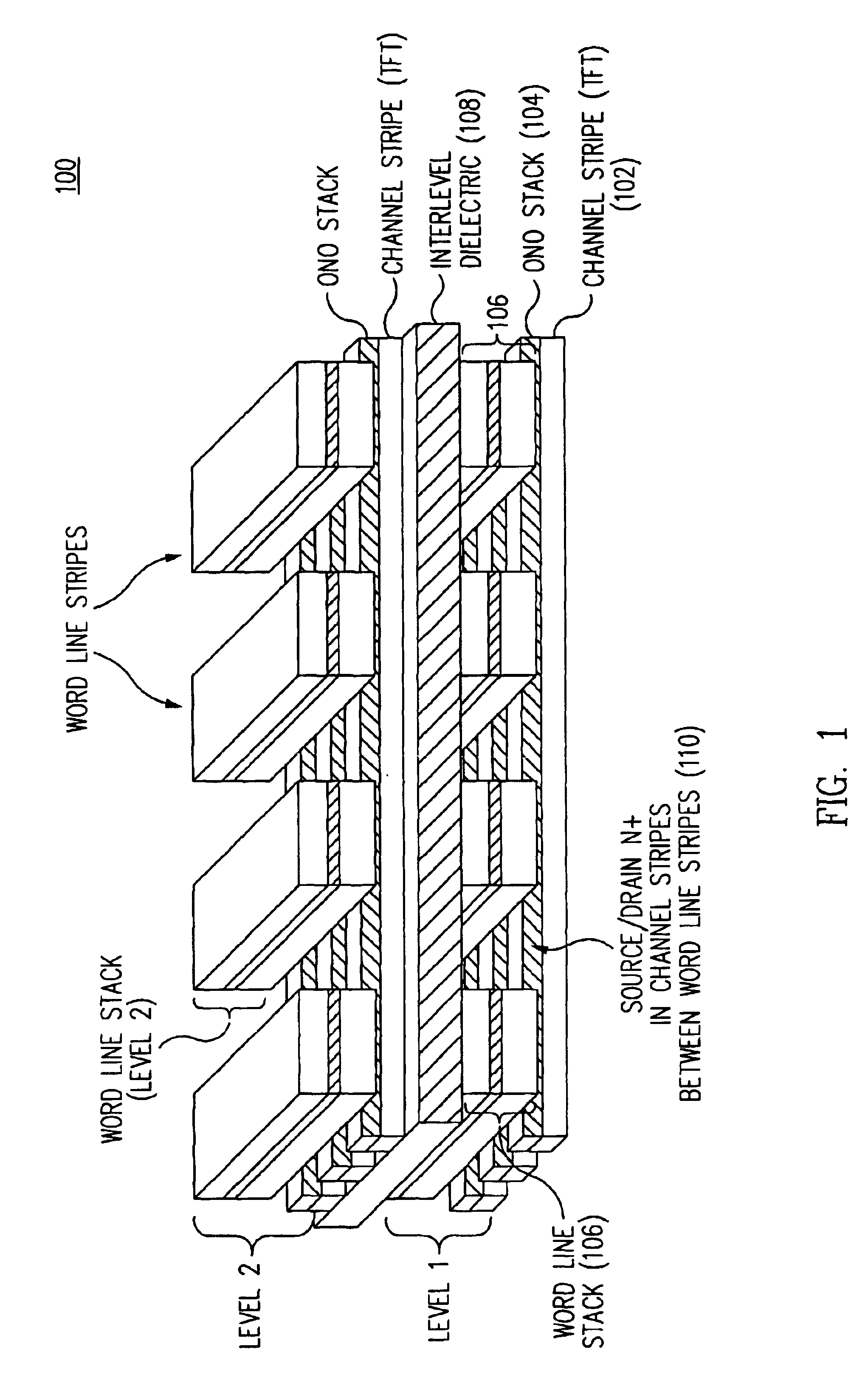

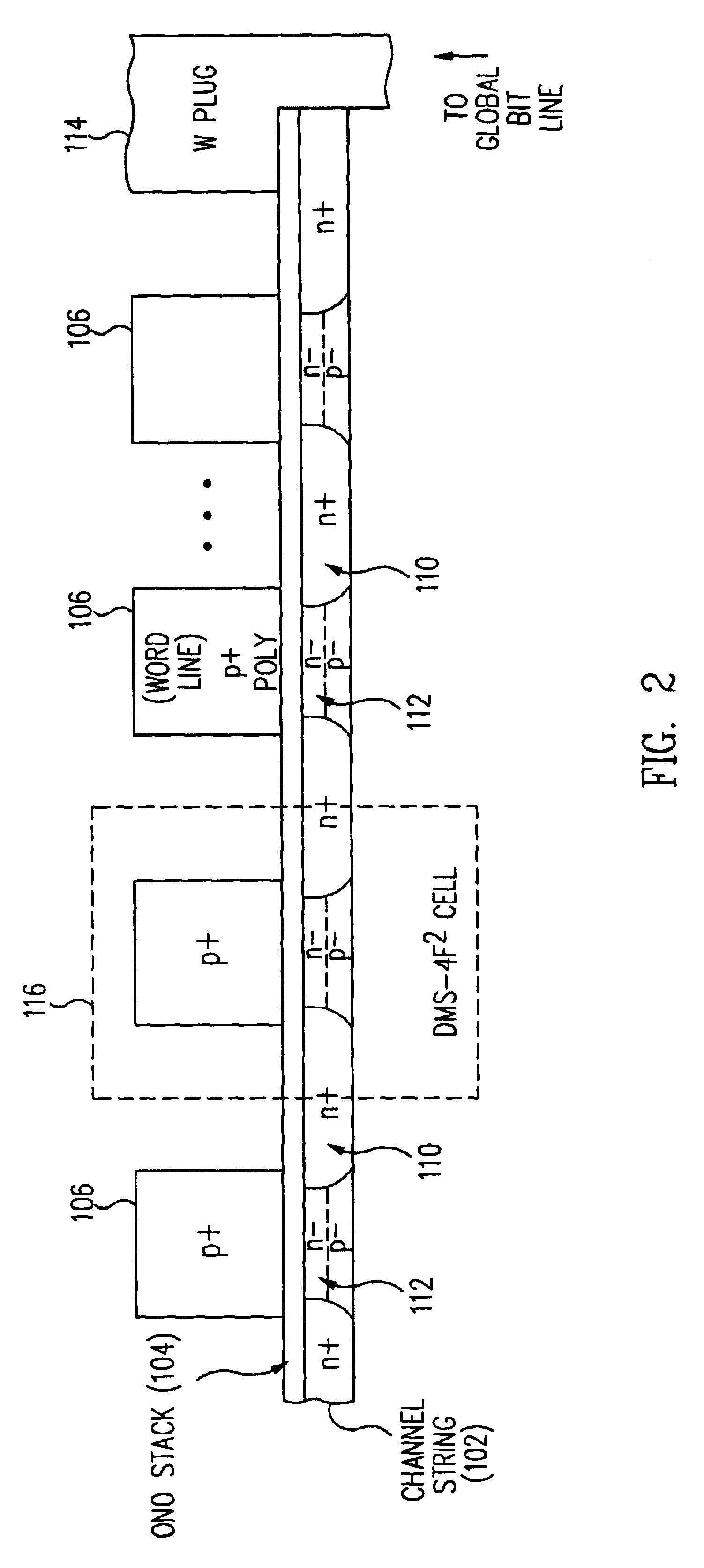

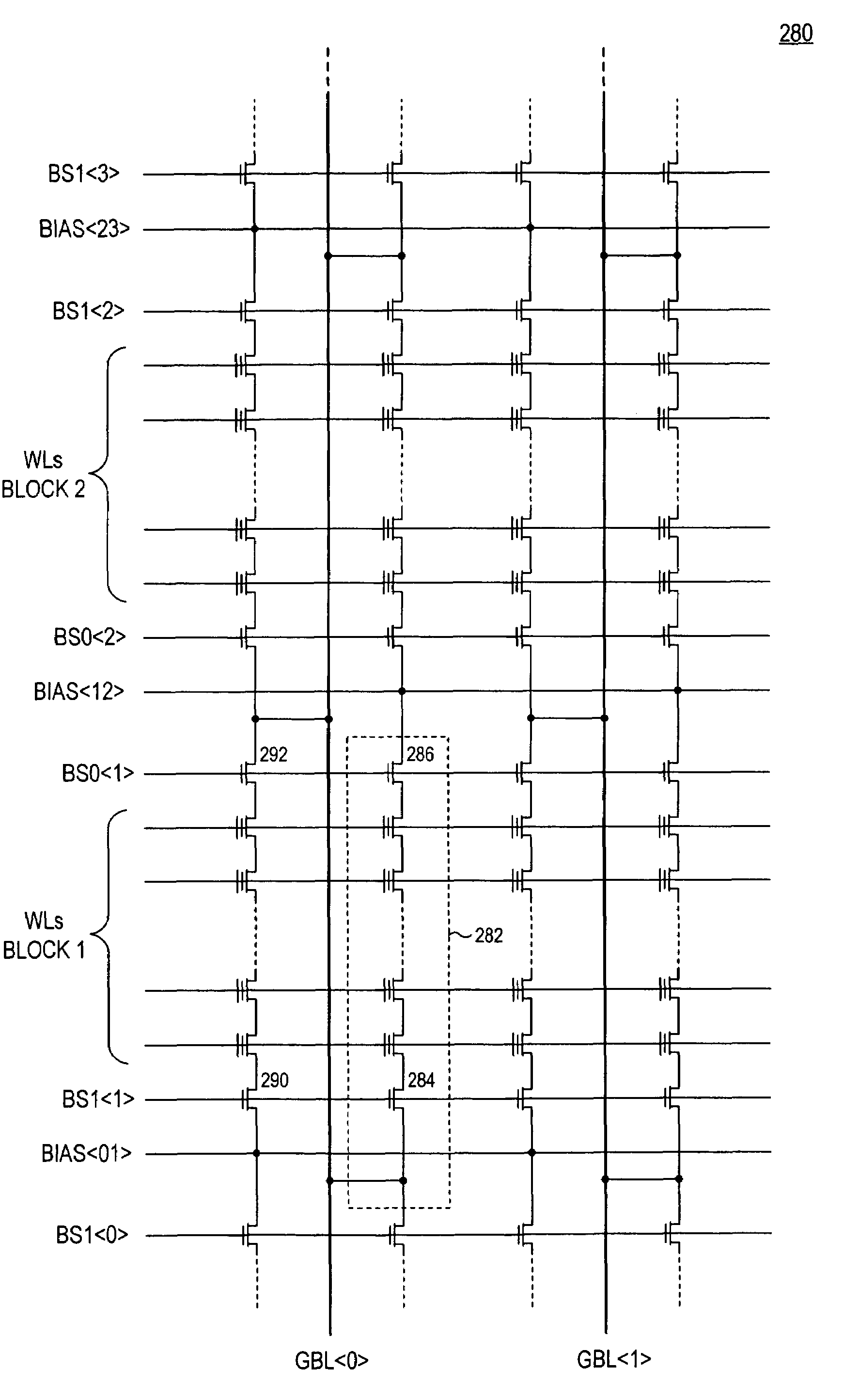

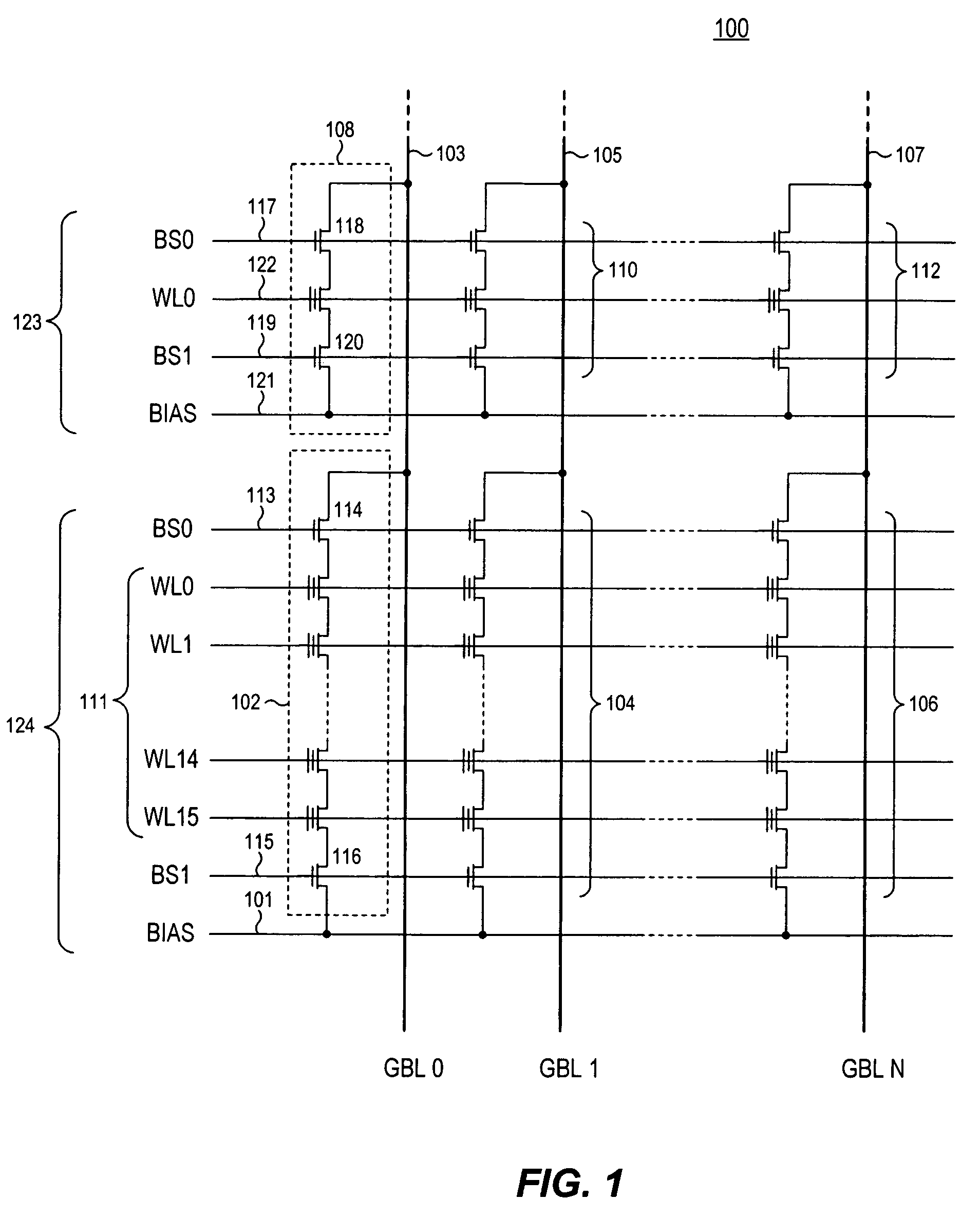

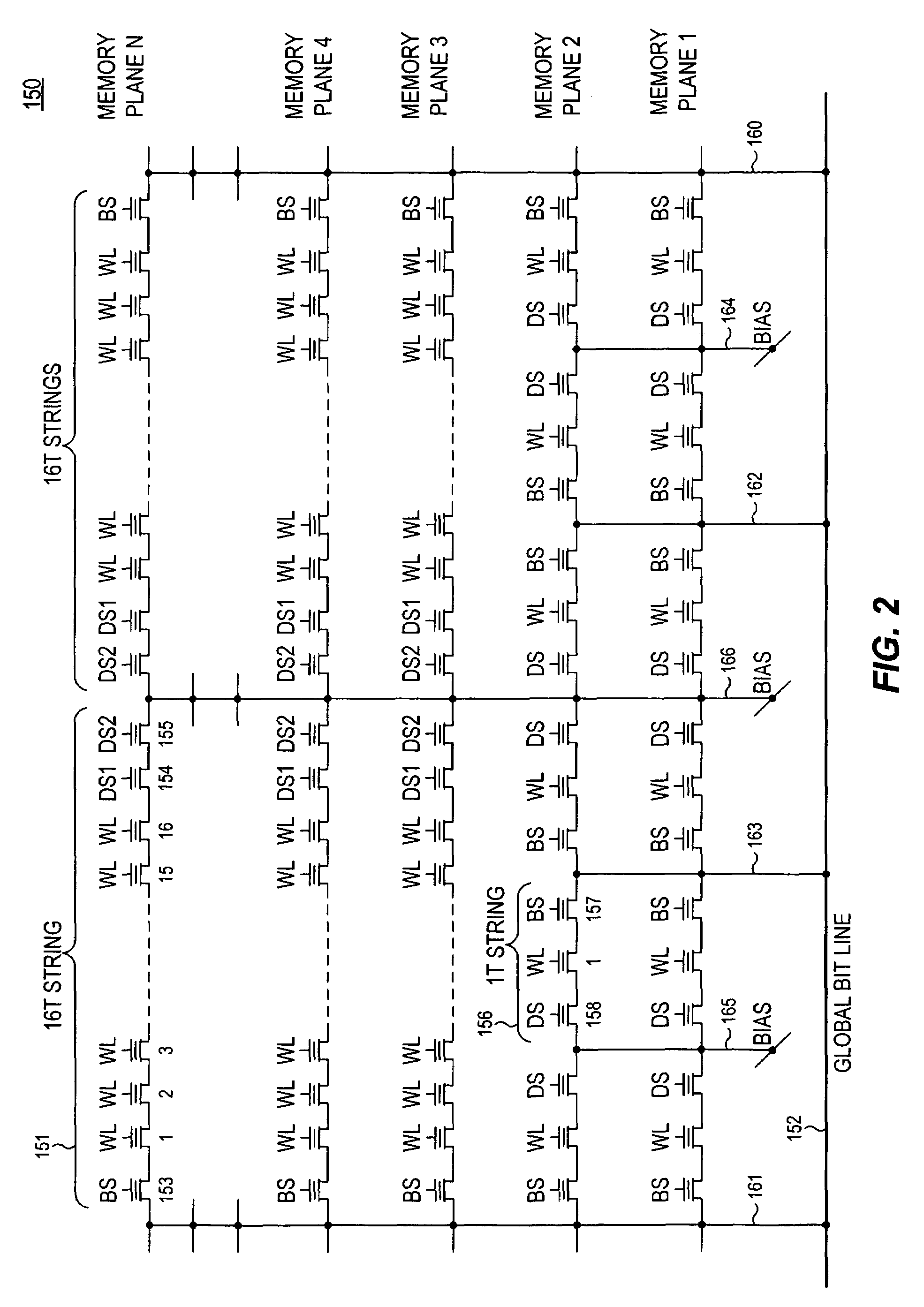

Method for fabricating programmable memory array structures incorporating series-connected transistor strings

InactiveUS7005350B2Reduce in quantityDense memory arraySolid-state devicesRead-only memoriesBit lineComputer architecture

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F2 memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

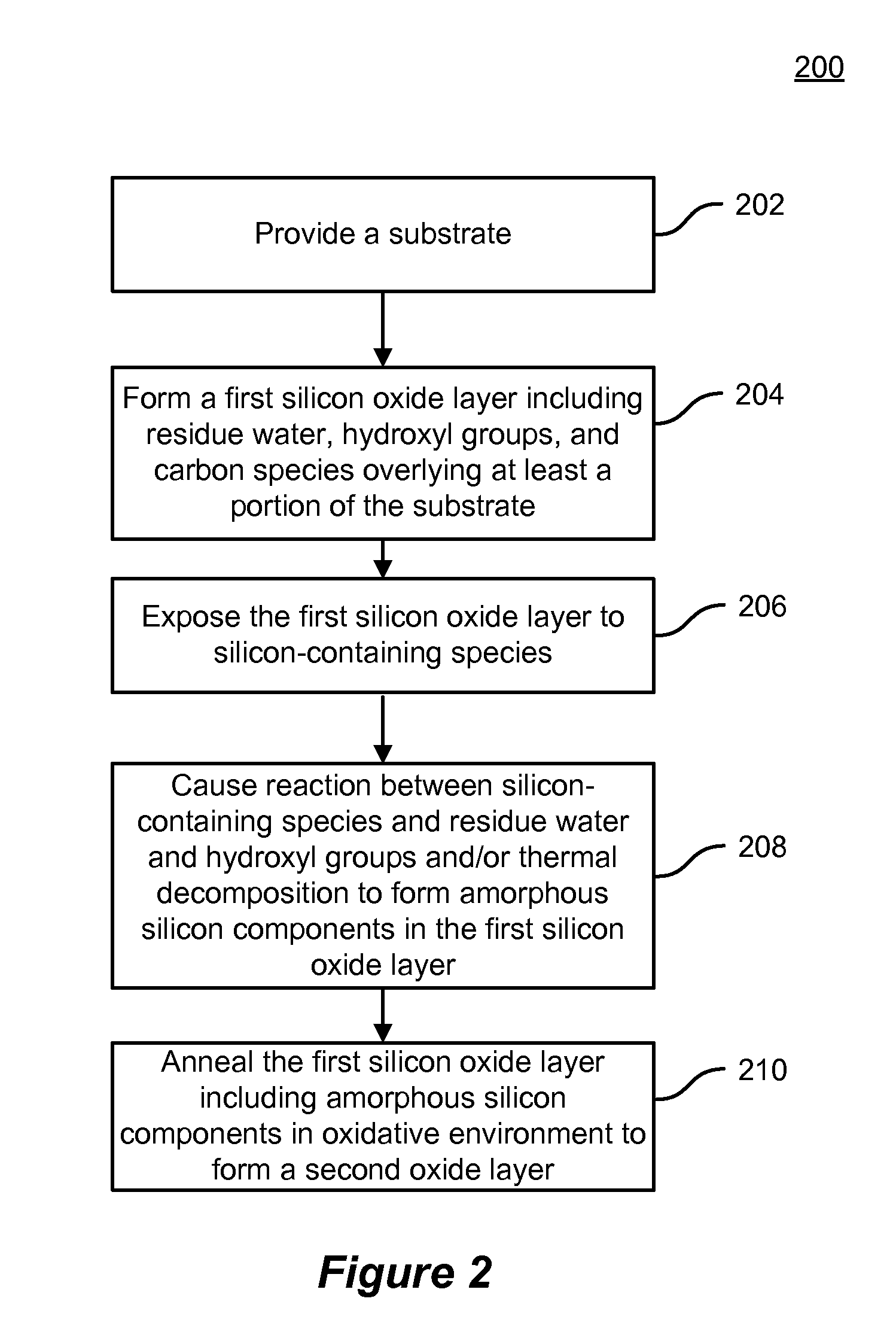

Method and system for improving dielectric film quality for void free gap fill

ActiveUS20090104789A1Quality improvementHigh densitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicon monoxideAmorphous silicon

A method of forming a silicon oxide layer on a substrate. The method includes providing a substrate and forming a first silicon oxide layer overlying at least a portion of the substrate, the first silicon oxide layer including residual water, hydroxyl groups, and carbon species. The method further includes exposing the first silicon oxide layer to a plurality of silicon-containing species to form a plurality of amorphous silicon components being partially intermixed with the first silicon oxide layer. Additionally, the method includes annealing the first silicon oxide layer partially intermixed with the plurality of amorphous silicon components in an oxidative environment to form a second silicon oxide layer on the substrate. At least a portion of amorphous silicon components are oxidized to become part of the second silicon oxide layer and unreacted residual hydroxyl groups and carbon species in the second silicon oxide layer are substantially removed.

Owner:APPLIED MATERIALS INC

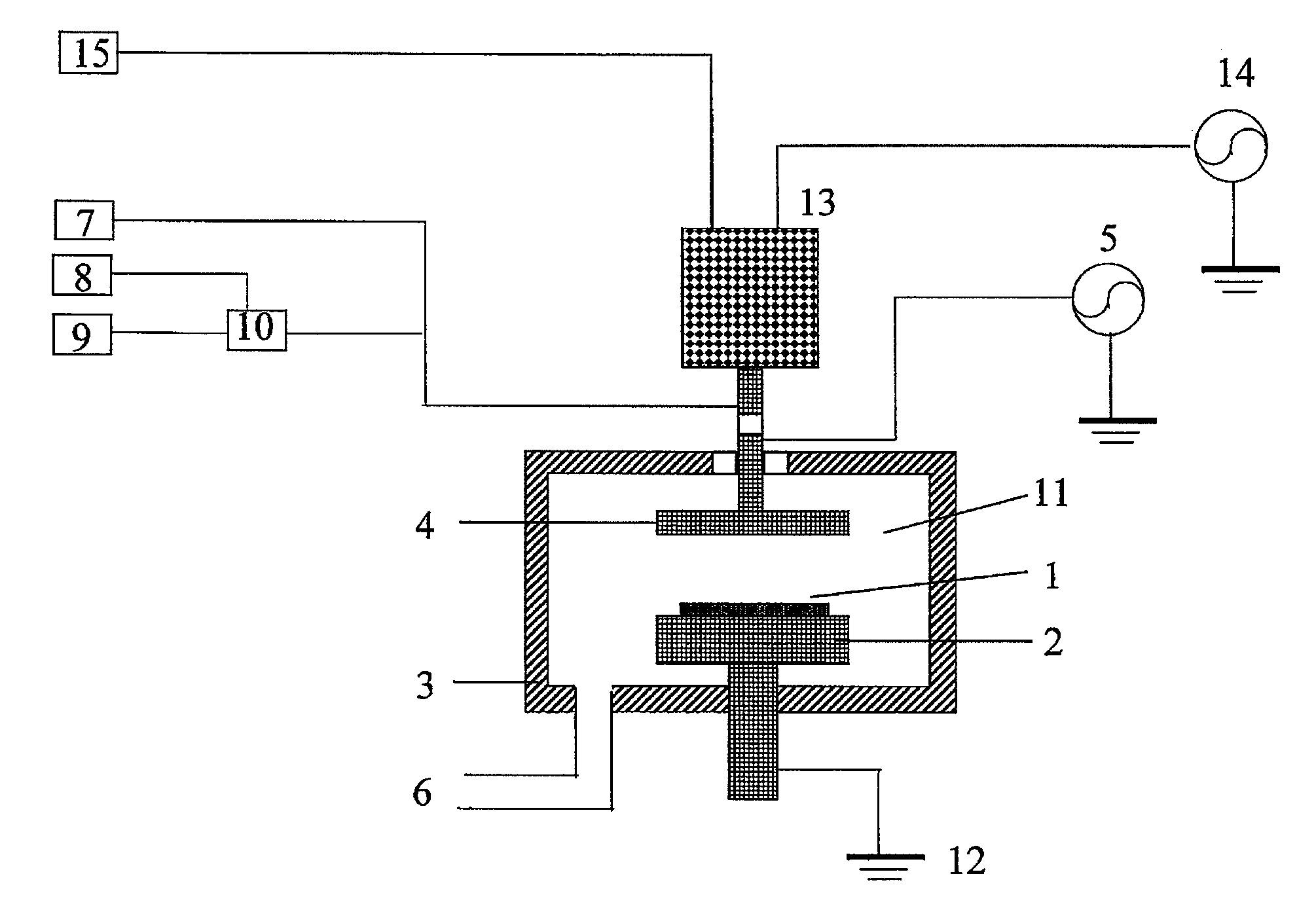

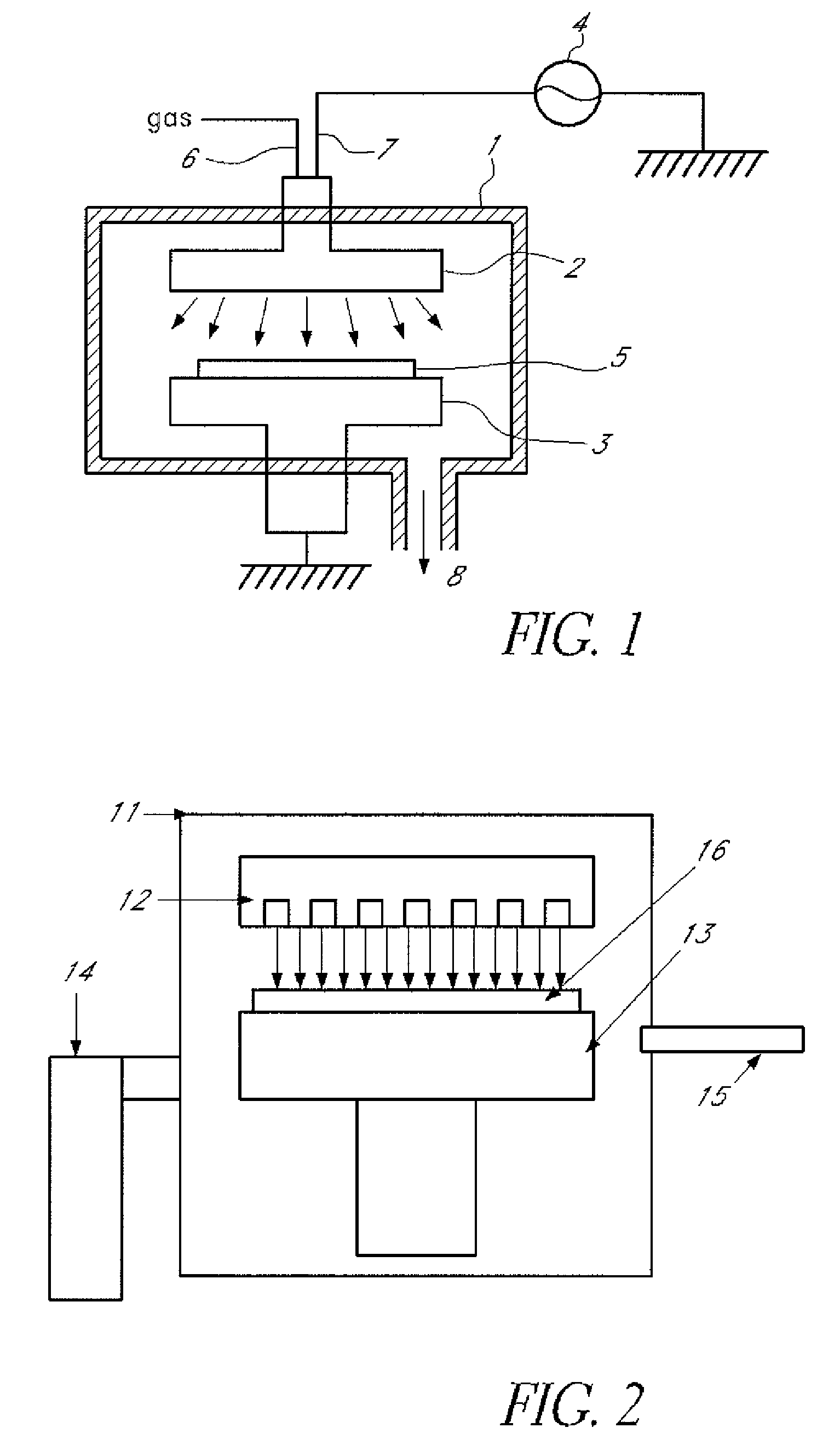

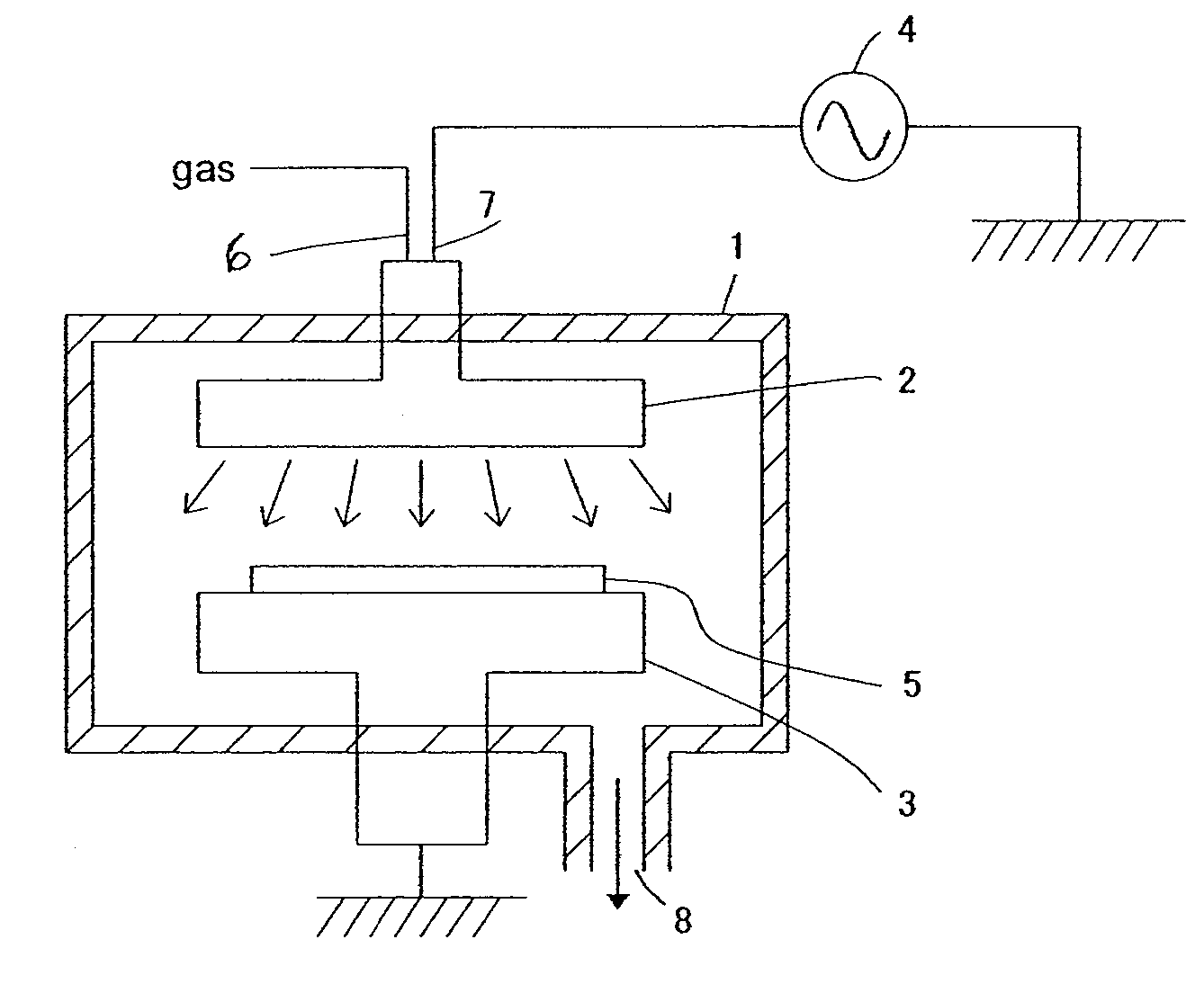

Method For Depositing an Amorphous Carbon Film with Improved Density and Step Coverage

ActiveUS20080003824A1High densityLower thermal budgetPretreated surfacesSemiconductor/solid-state device manufacturingCarbon layerKrypton

A method for depositing an amorphous carbon layer on a substrate includes the steps of positioning a substrate in a chamber, introducing a hydrocarbon source into the processing chamber, introducing a heavy noble gas into the processing chamber, and generating a plasma in the processing chamber. The heavy noble gas is selected from the group consisting of argon, krypton, xenon, and combinations thereof and the molar flow rate of the noble gas is greater than the molar flow rate of the hydrocarbon source. A post-deposition termination step may be included, wherein the flow of the hydrocarbon source and the noble gas is stopped and a plasma is maintained in the chamber for a period of time to remove particles therefrom.

Owner:APPLIED MATERIALS INC

Integrated circuit including memory array incorporating multiple types of NAND string structures

ActiveUS7177191B2High densityGood flexibilitySolid-state devicesRead-only memoriesDevice formParallel computing

Owner:SANDISK TECH LLC

Method for depositing an amorphous carbon film with improved density and step coverage

InactiveUS20080153311A1High densityLower thermal budgetSemiconductor/solid-state device manufacturingChemical vapor deposition coatingProduct gasMolecular physics

A method for depositing an amorphous carbon layer on a substrate includes the steps of positioning a substrate in a chamber, introducing a hydrocarbon source into the processing chamber, introducing a heavy noble gas into the processing chamber, and generating a plasma in the processing chamber. The heavy noble gas is selected from the group consisting of argon, krypton, xenon, and combinations thereof and the molar flow rate of the noble gas is greater than the molar flow rate of the hydrocarbon source. A post-deposition termination step may be included, wherein the flow of the hydrocarbon source and the noble gas is stopped and a plasma is maintained in the chamber for a period of time to remove particles therefrom.

Owner:APPLIED MATERIALS INC

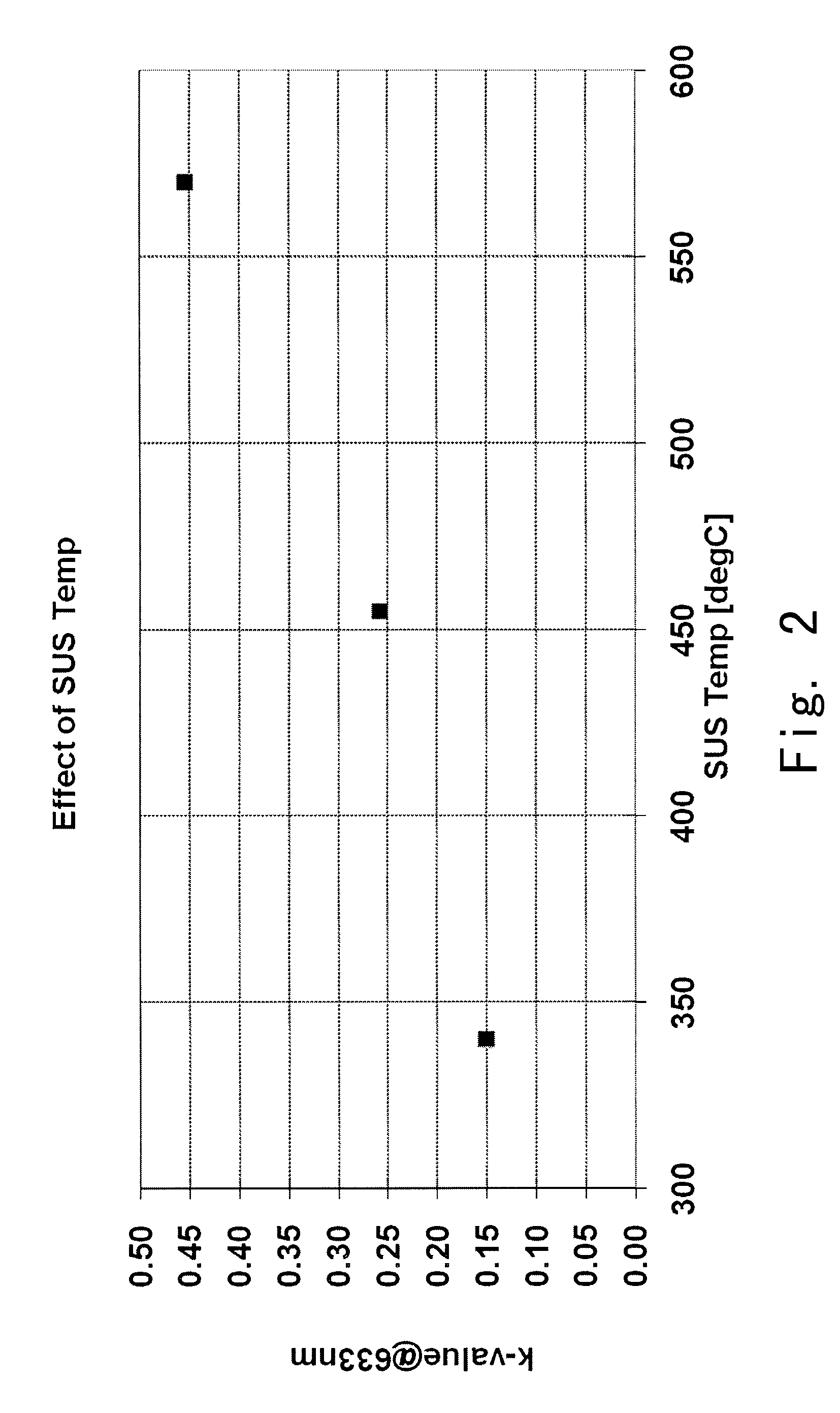

Method of forming a high transparent carbon film

ActiveUS7632549B2Improve featuresRich varietyLiquid surface applicatorsSemiconductor/solid-state device manufacturingCarbon filmProduct gas

A method of forming a transparent hydrocarbon-based polymer film on a substrate by plasma CVD includes: introducing a main gas consisting of a hydrocarbon gas (CαHβ, wherein α and β are natural numbers) and an inert gas at a flow ratio (R) of CαHβ / inert gas of 0.25 or less into a CVD reaction chamber inside which a substrate is placed; and forming a hydrocarbon-based polymer film on the substrate by plasma polymerization of the gas at a processing temperature (T) wherein T≦(−800R+500).

Owner:ASM JAPAN

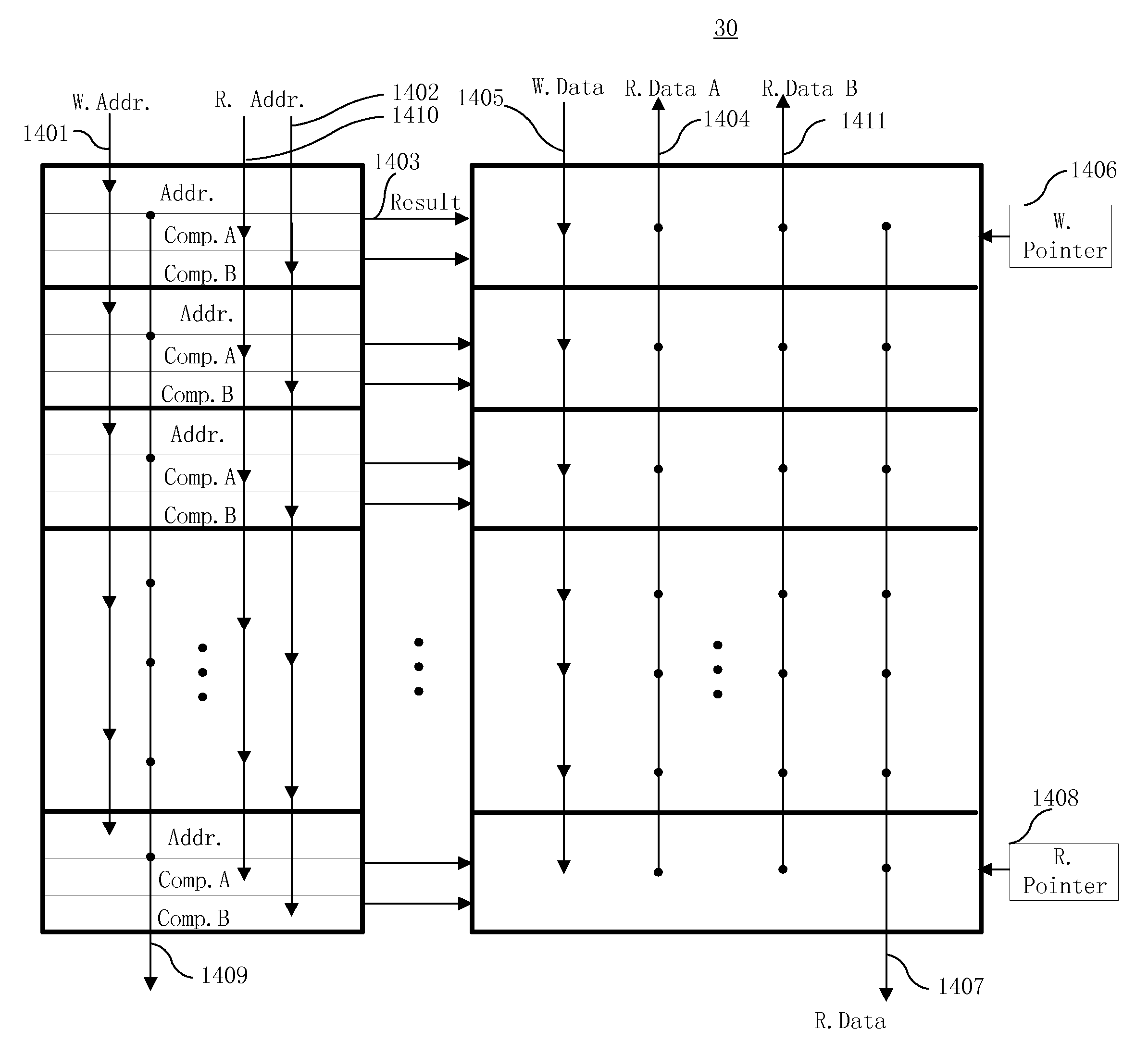

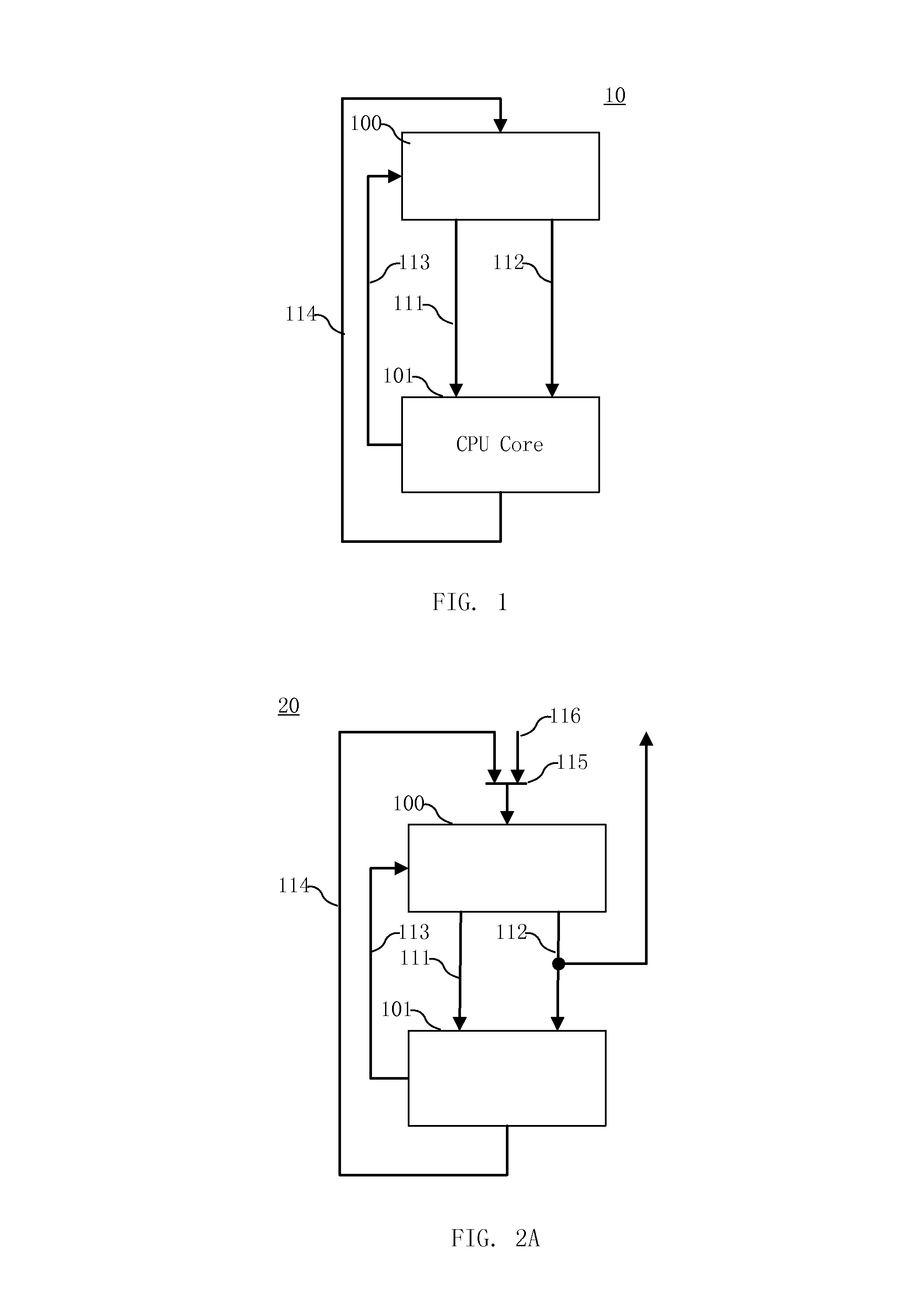

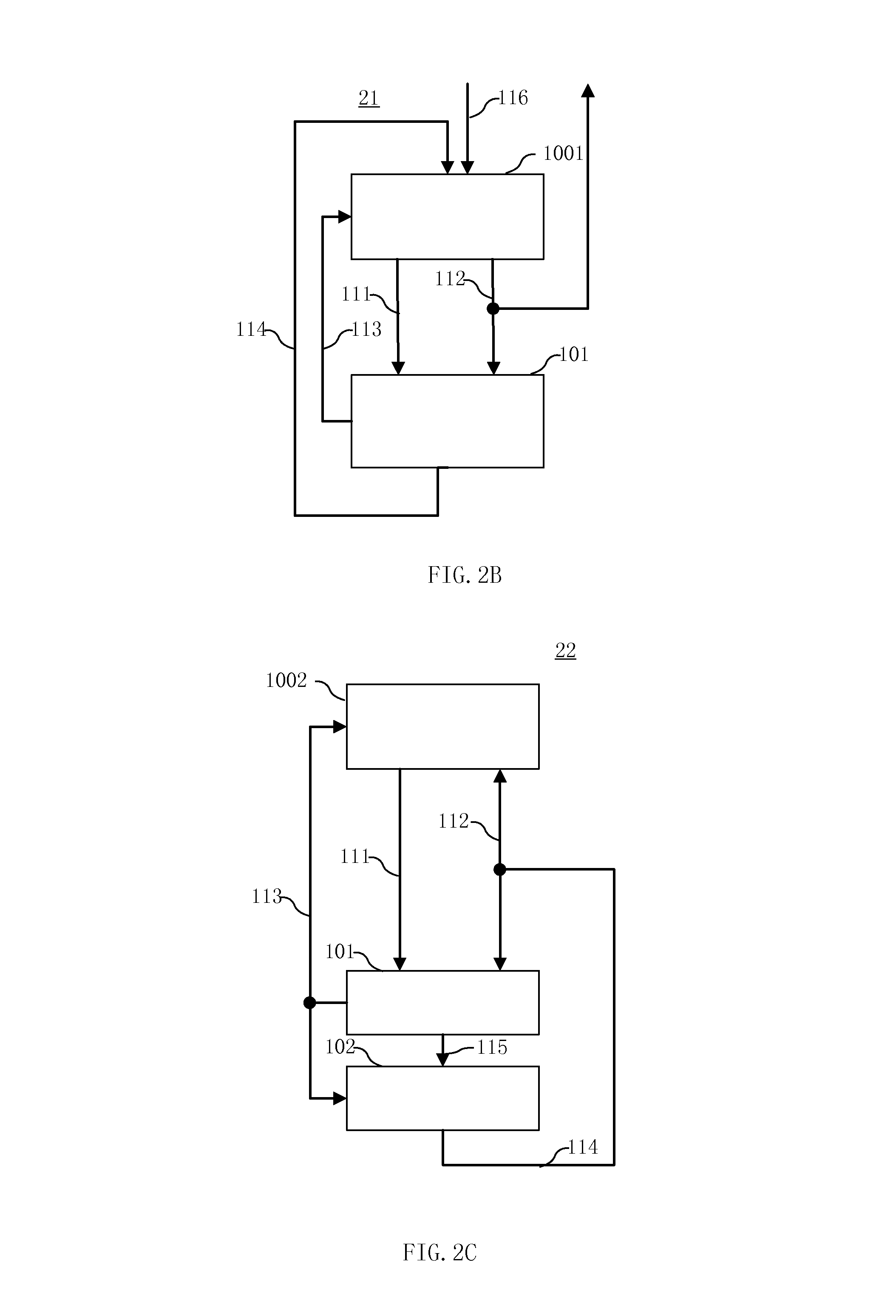

Processor-cache system and method

ActiveUS9047193B2Shorten the counting processEfficient and uniform structureEnergy efficient ICTRegister arrangementsAddress generation unitProcessor register

A digital system is provided. The digital system includes an execution unit, a level-zero (L0) memory, and an address generation unit. The execution unit is coupled to a data memory containing data to be used in operations of the execution unit. The L0 memory is coupled between the execution unit and the data memory and configured to receive a part of the data in the data memory. The address generation unit is configured to generate address information for addressing the L0 memory. Further, the L0 memory provides at least two operands of a single instruction from the part of the data to the execution unit directly, without loading the at least two operands into one or more registers, using the address information from the address generation unit.

Owner:SHANGHAI XINHAO MICROELECTRONICS

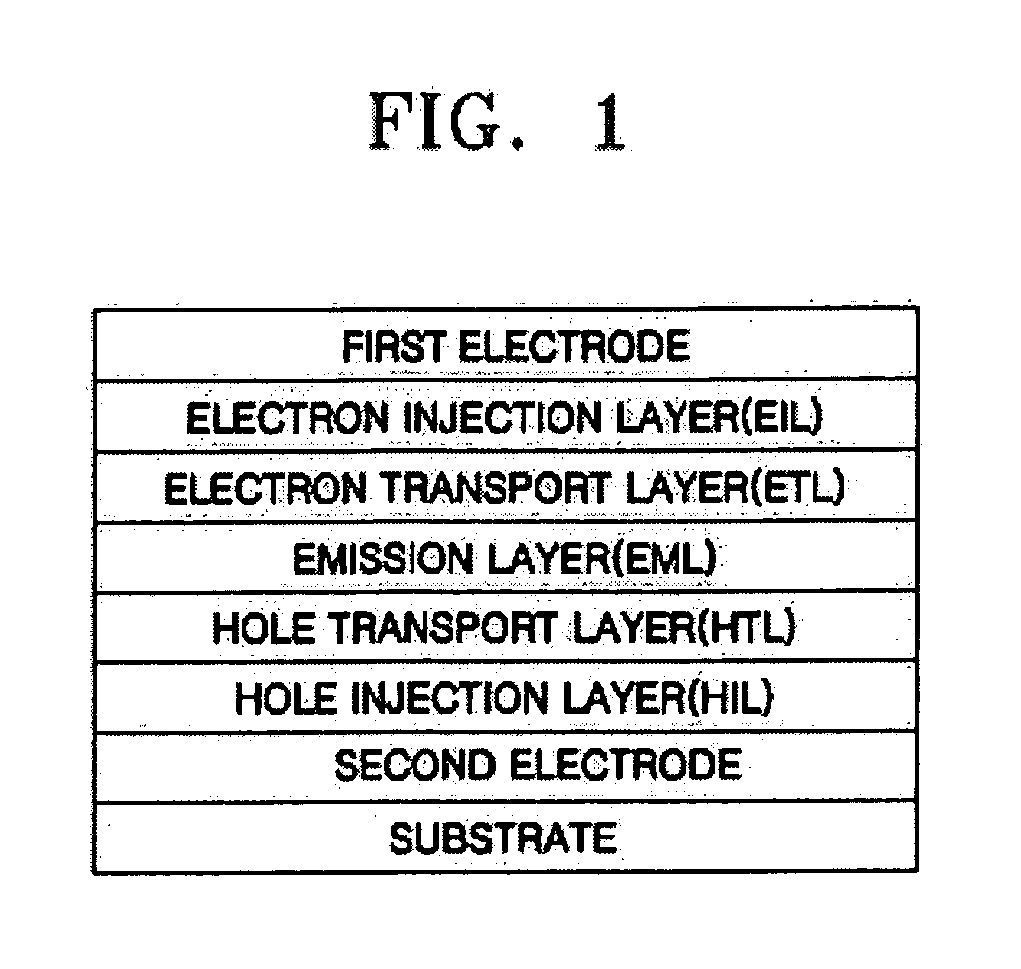

Fluorene-based compound and organic electroluminescent display device using the same

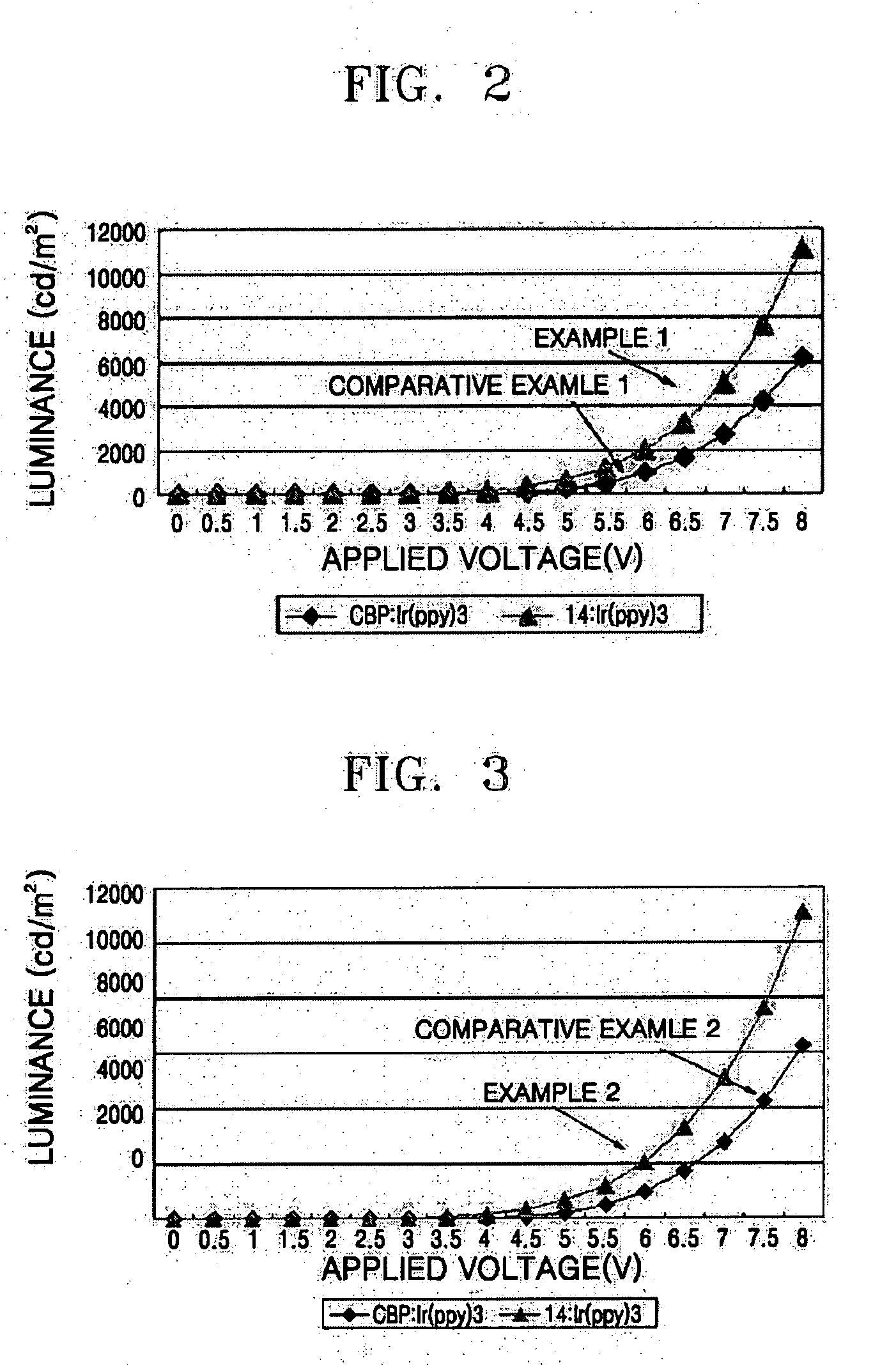

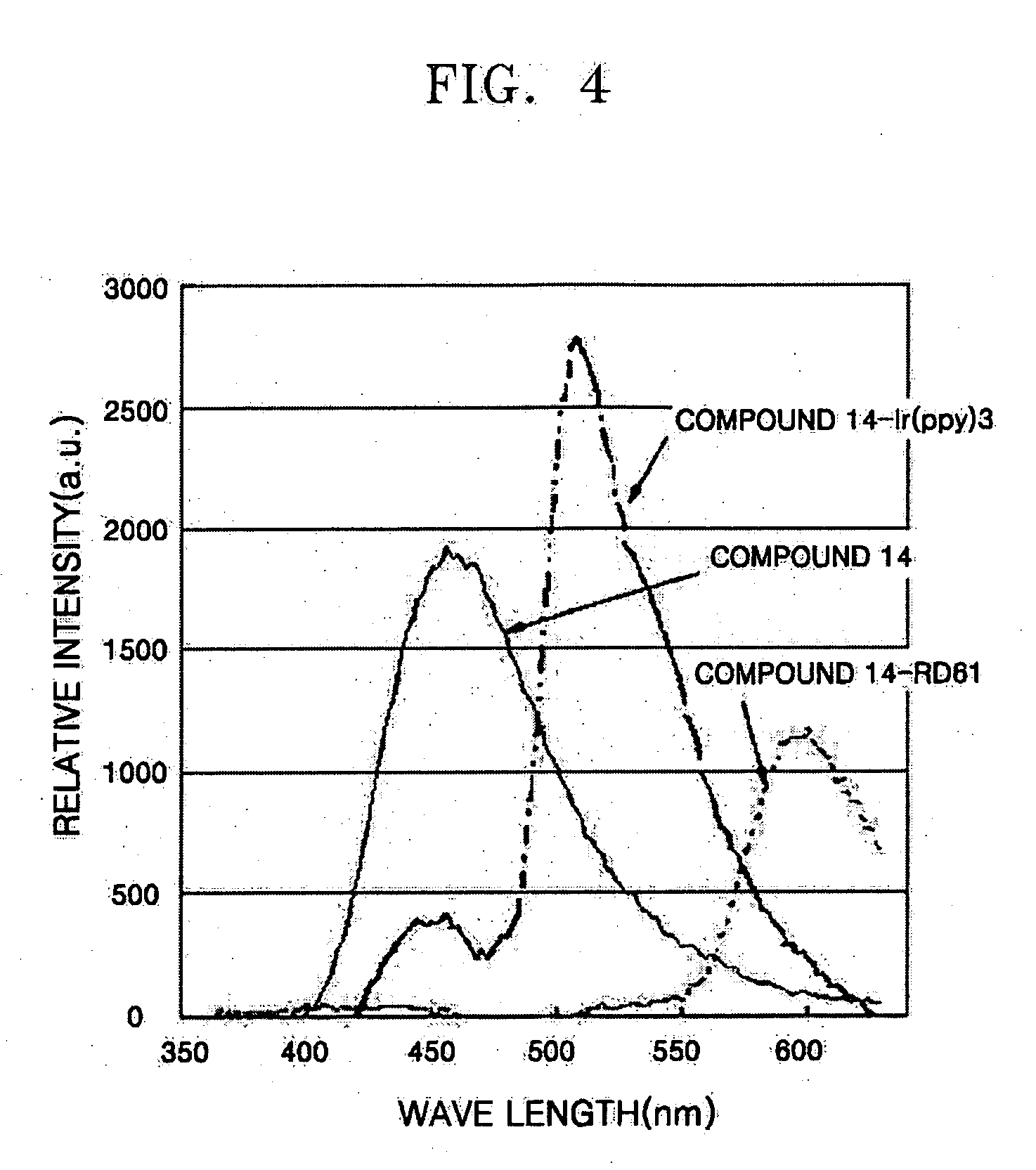

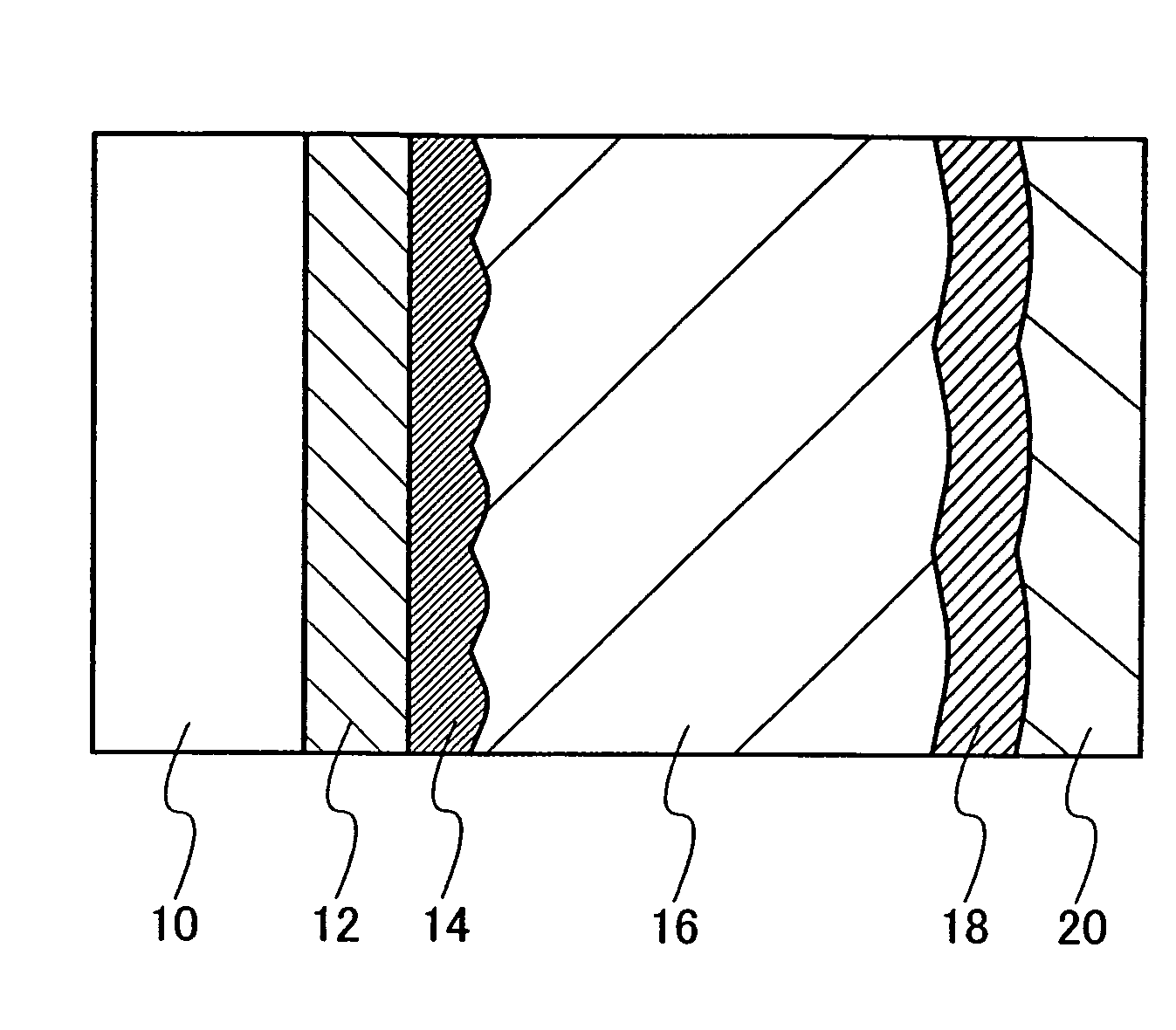

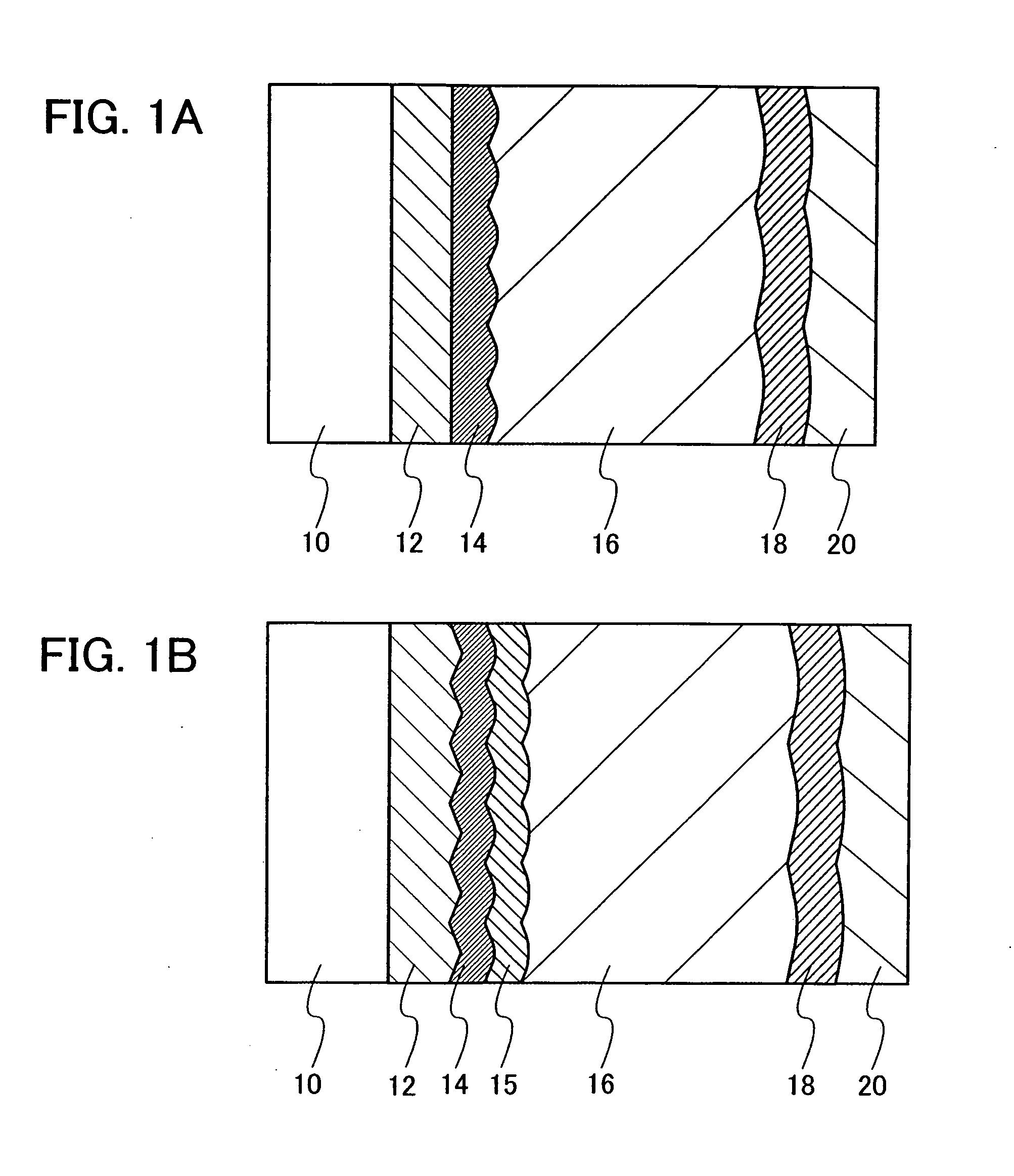

ActiveUS20050221124A1High charge transport performanceHigh glass transition temperatureDischarge tube luminescnet screensElectroluminescent light sourcesOrganic electroluminescenceFluorescence

The present invention relates to an organic electroluminescent (OEL) compound that comprises at least one fluorene derivative and at least one carbazole derivative. The compound has good electrical properties, light emitting properties and charge transport ability, and thus is suitable as a host material suitable for fluorescent and phosphorescent dopants of all colors including red, green, blue, white, etc., and as a charge transport material. An OEL display device that uses an organic layer that includes the OEL compound has a high efficiency, a low voltage, a high luminance, and a long lifespan because it has superior current density.

Owner:SAMSUNG DISPLAY CO LTD

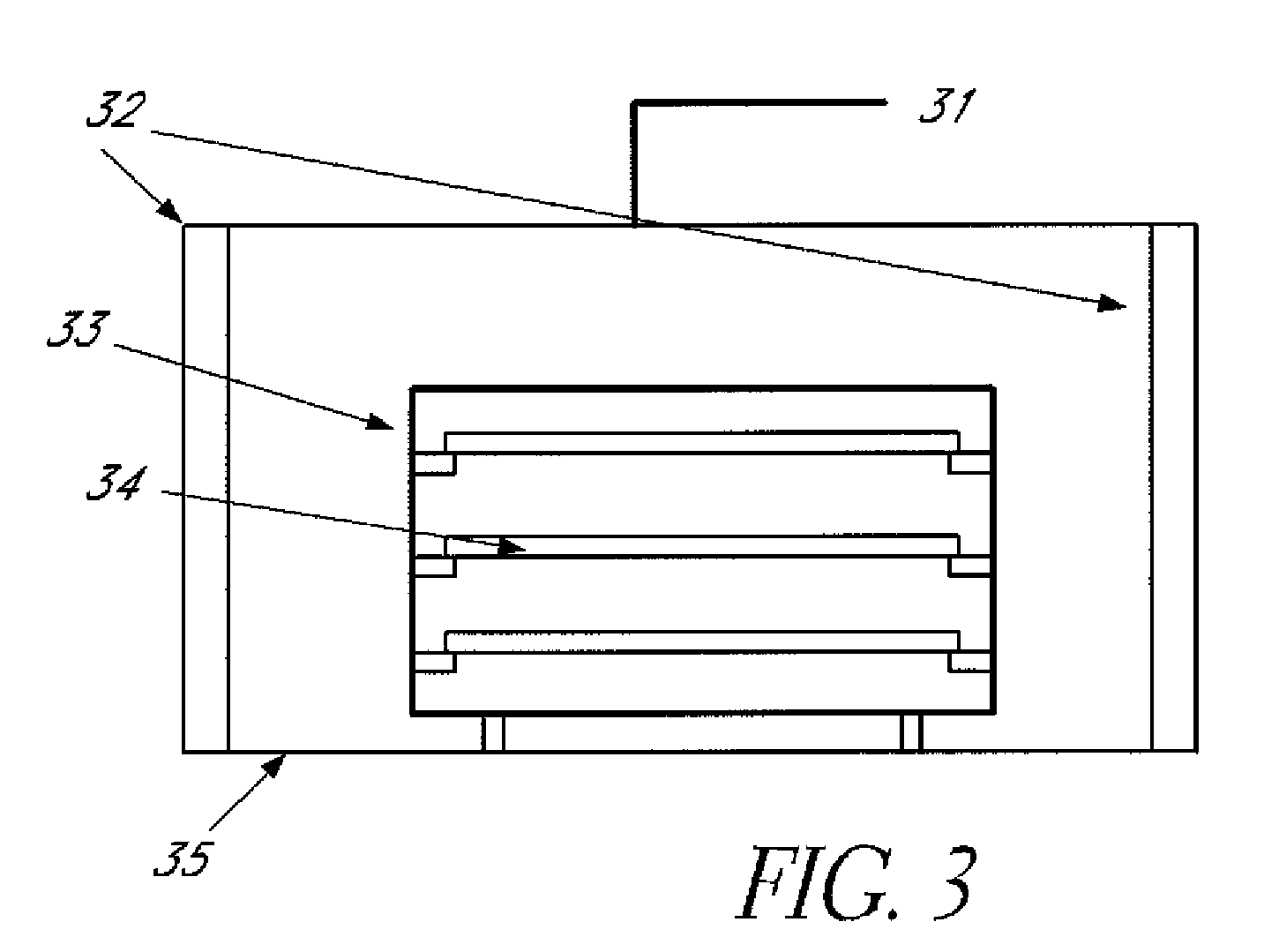

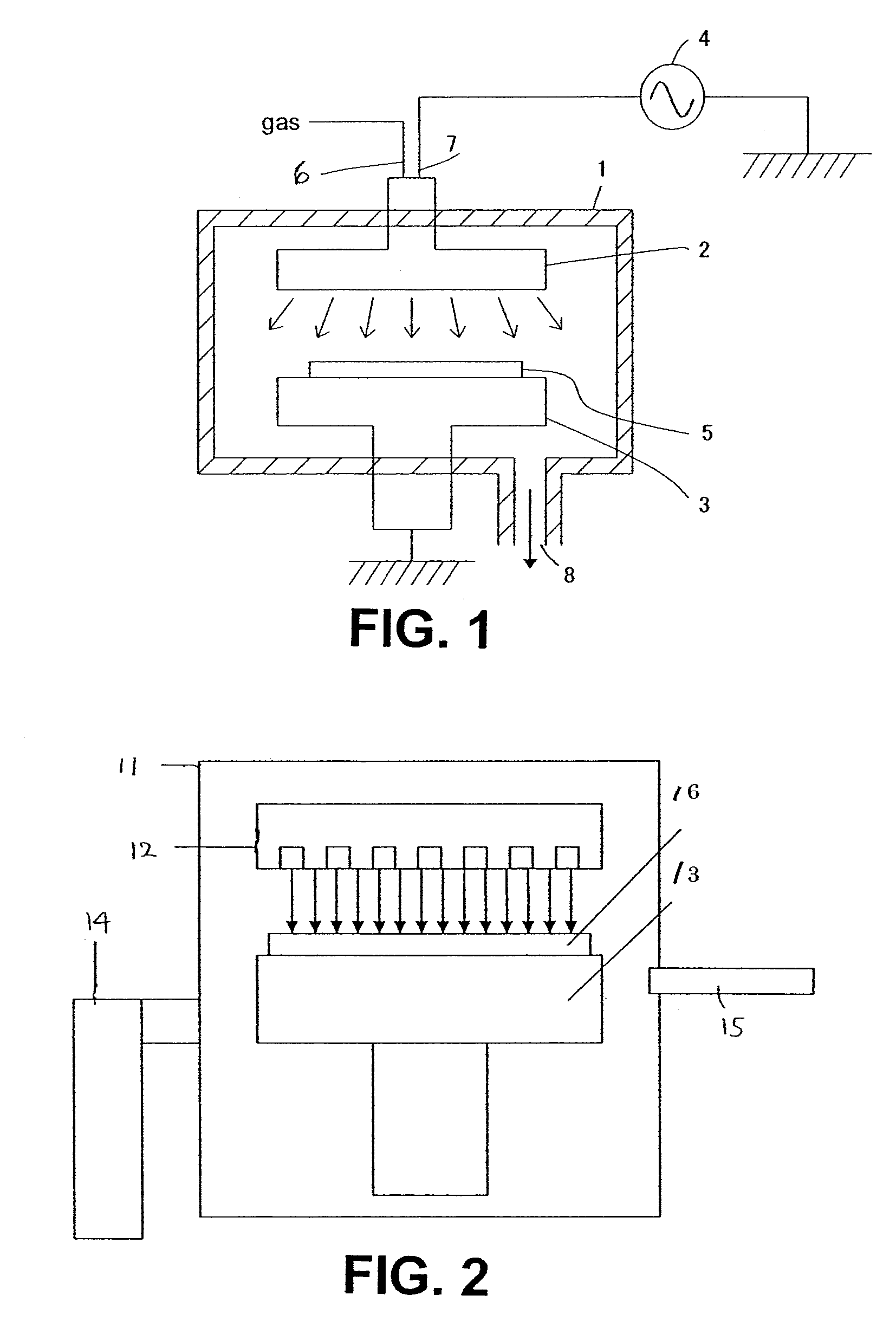

Method for manufacturing photoelectric conversion device

InactiveUS20090029503A1Quality improvementReduce deterioration rateFinal product manufactureSemiconductor/solid-state device manufacturingProduction rateMicrowave

To form a microcrystalline semiconductor with high quality which can be directly formed at equal to or less than 500° C. over a large substrate with high productivity without decreasing a deposition rate. In addition, to provide a photoelectric conversion device which employs the microcrystalline semiconductor as a photoelectric conversion layer. A reactive gas containing helium is supplied to a treatment chamber which is surrounded by a plurality of juxtaposed waveguides and a wall, the pressure in the treatment chamber is maintained at an atmospheric pressure or a subatmospheric pressure, microwave is supplied to a space sandwiched between the juxtaposed waveguides to generate plasma, and a photoelectric conversion layer of a microcrystalline semiconductor is deposited over a substrate which is placed in the treatment chamber.

Owner:SEMICON ENERGY LAB CO LTD

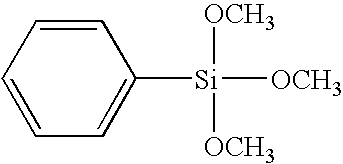

Method for forming dielectric film using siloxane-silazane mixture

ActiveUS8003174B2High densityHigh strengthPretreated surfacesSemiconductor/solid-state device manufacturingSilazaneMetallurgy

Owner:ASM JAPAN

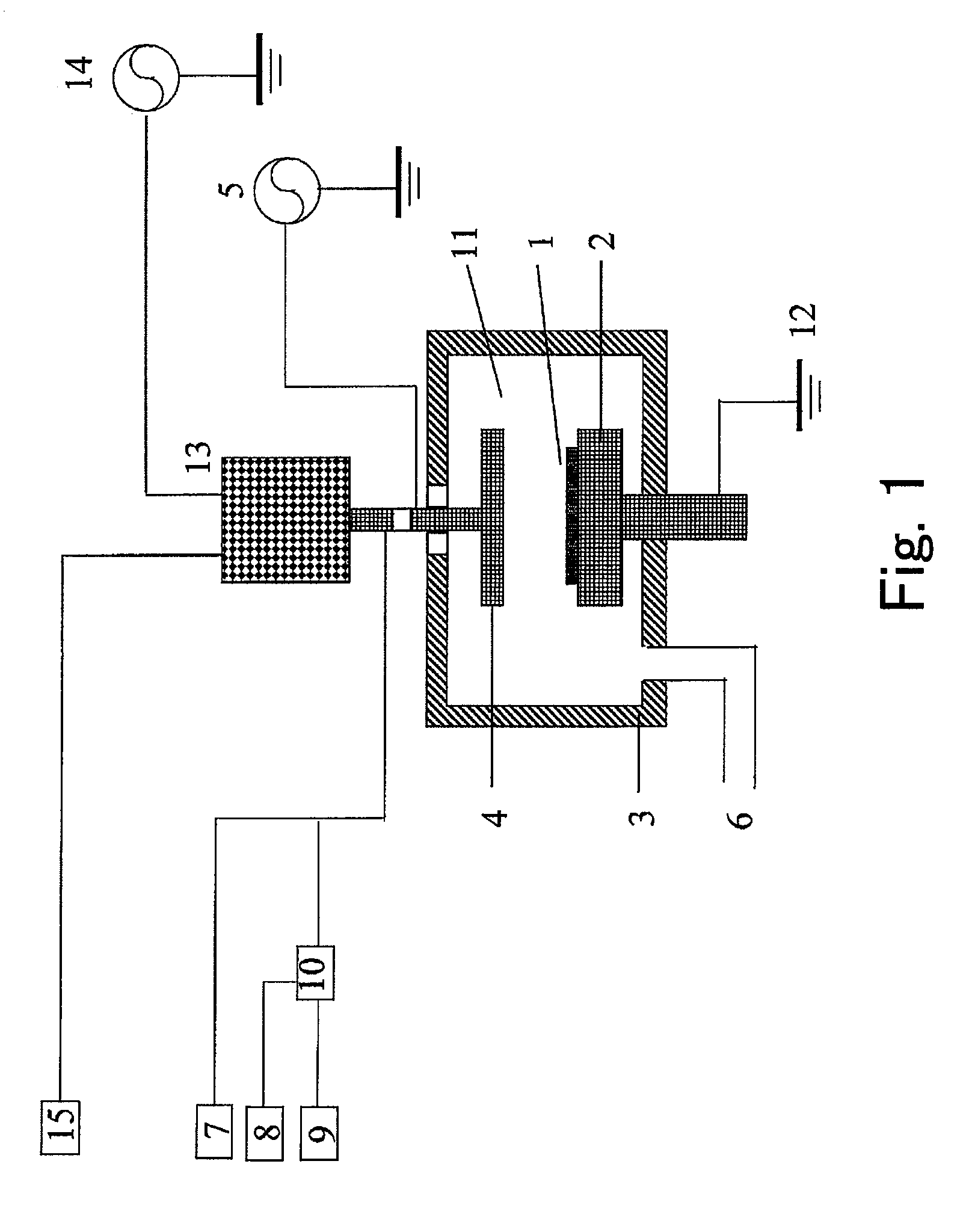

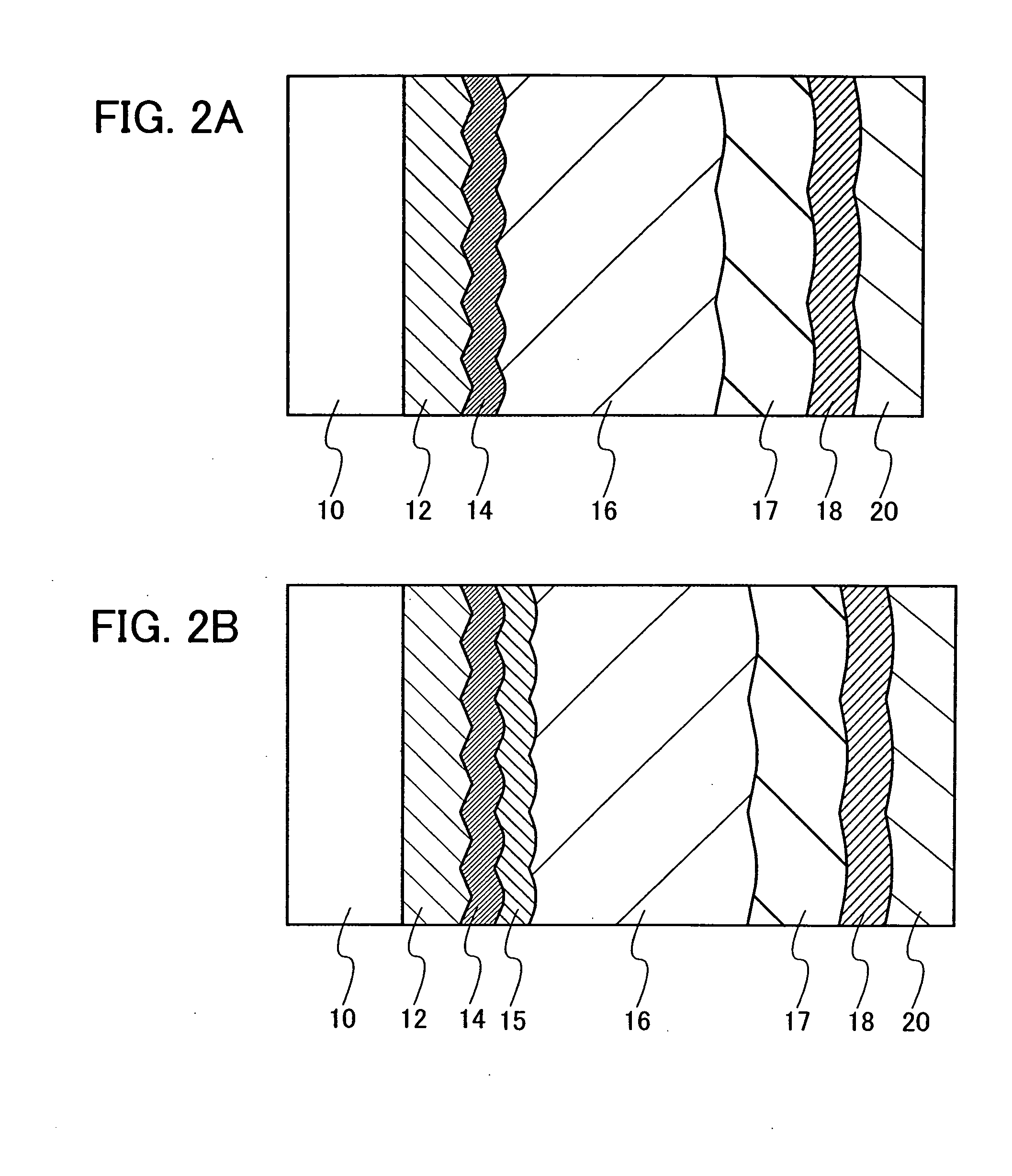

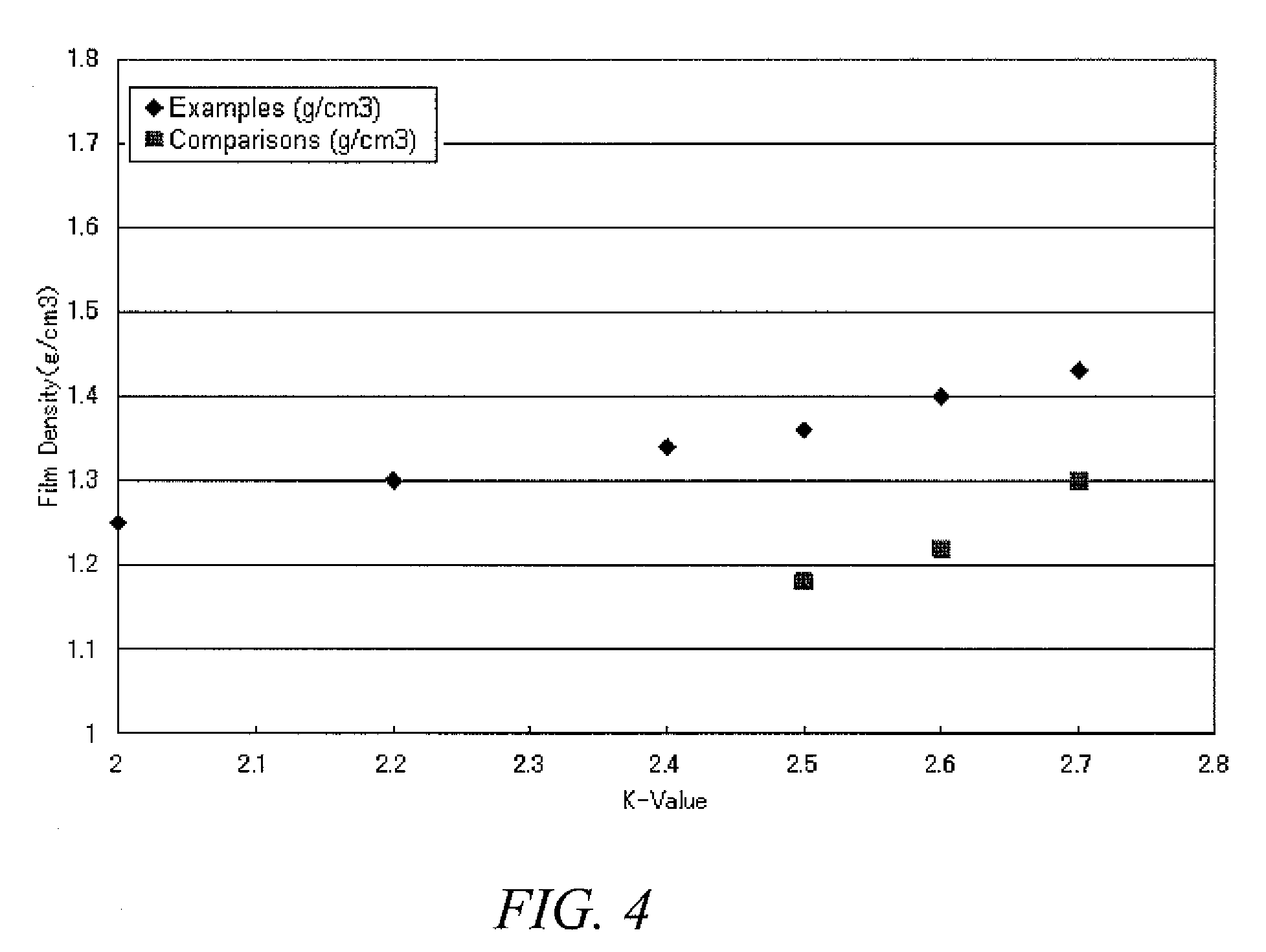

Method for forming insulation film having high density

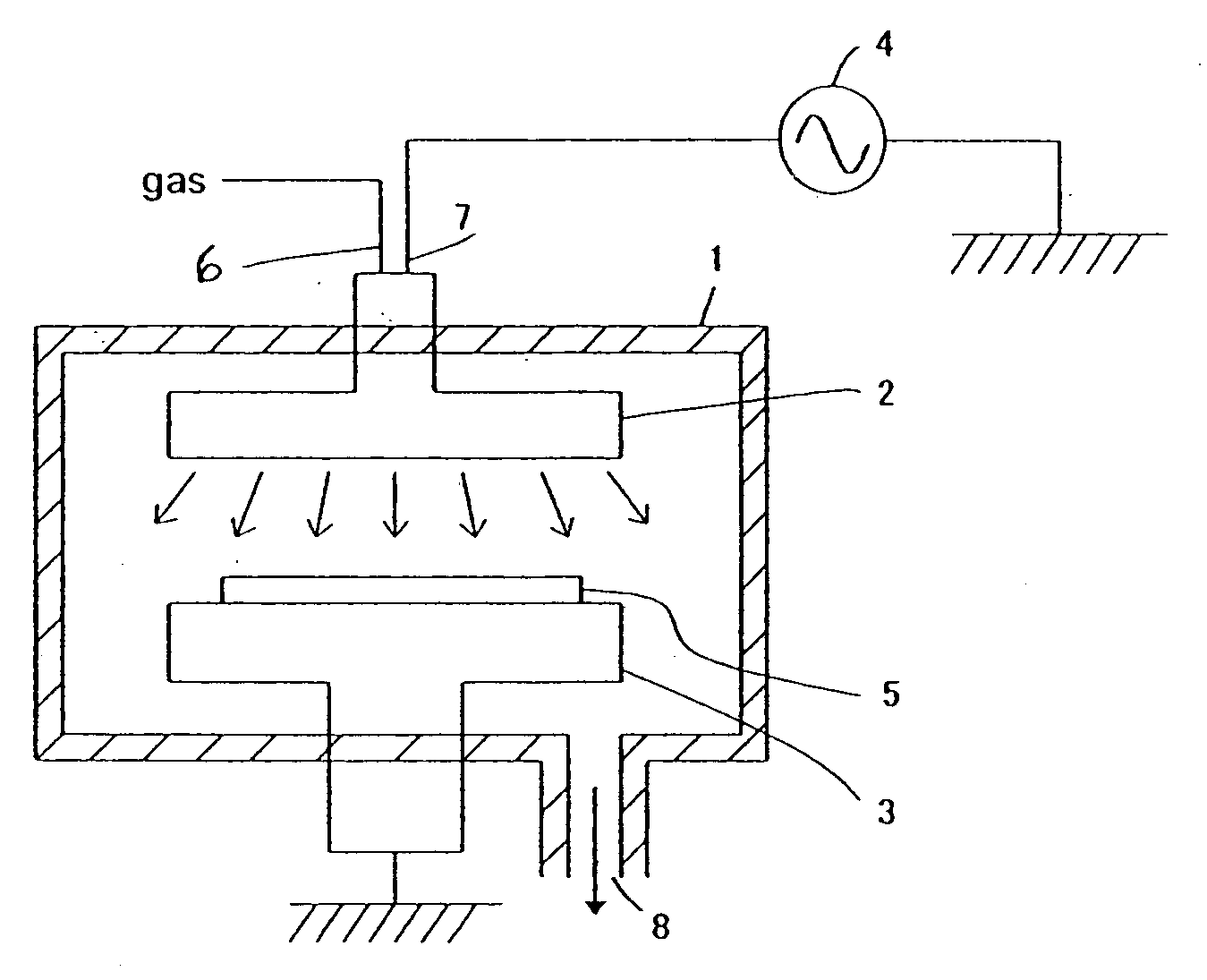

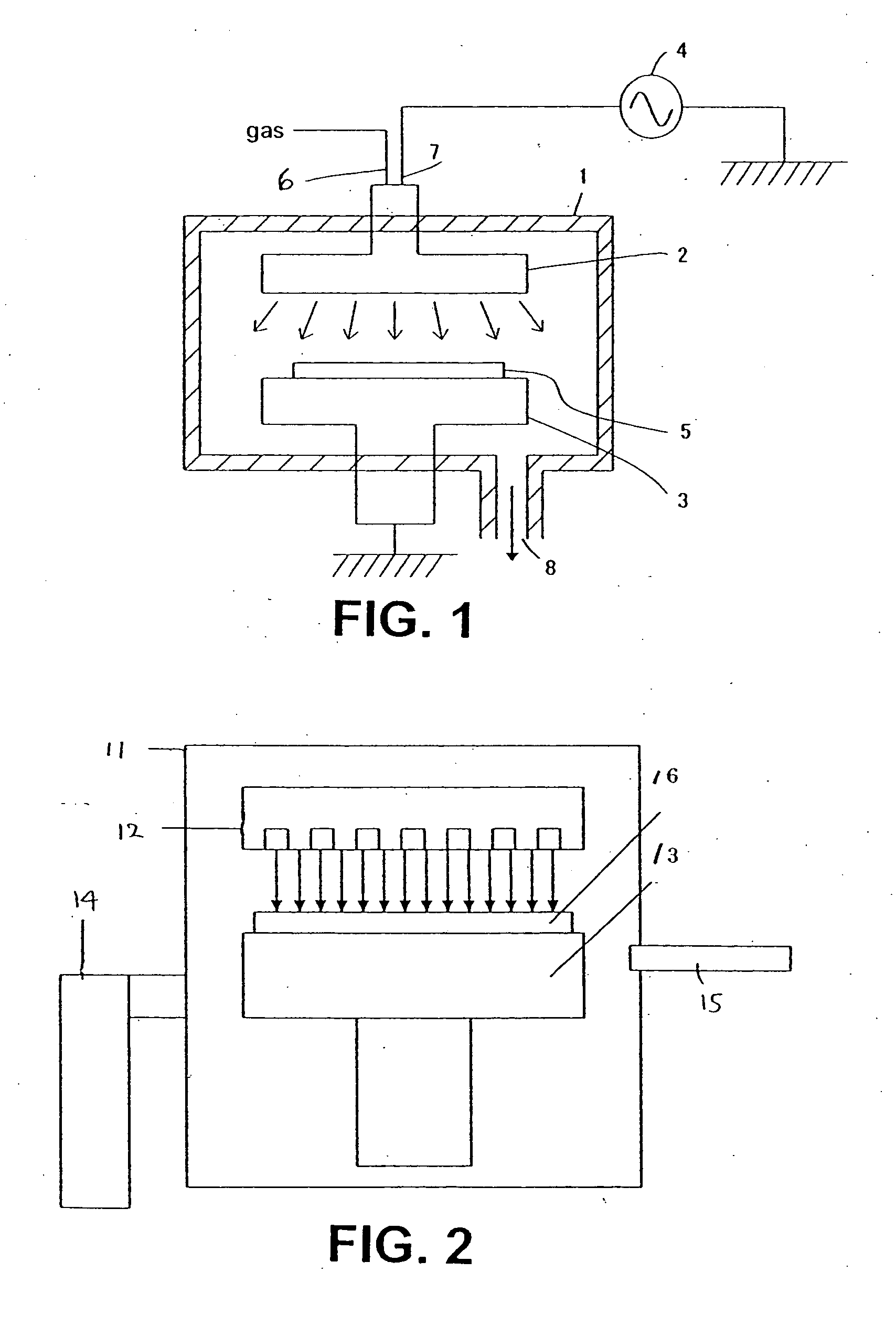

ActiveUS20080076266A1Good filling characteristicHigh aspect ratioSemiconductor/solid-state device manufacturingChemical vapor deposition coatingChemistryPlasma reaction

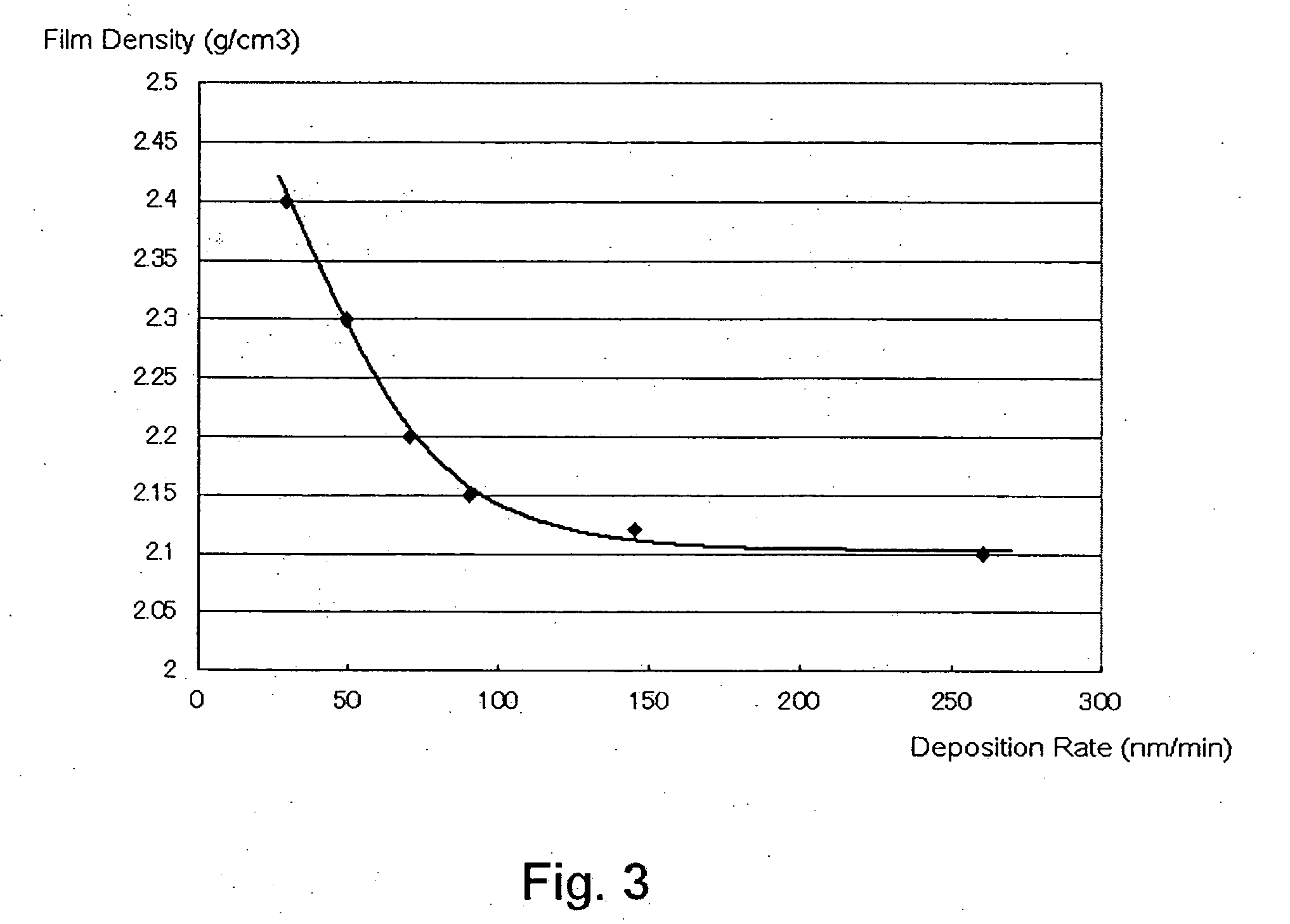

A method for forming an insulation film on a semiconductor substrate by plasma reaction includes: introducing into a reaction chamber a source gas of a silicon-containing hydrocarbon compound comprising in its molecule at least one Si—O bond and at least one bond selected from the group consisting of a Si—Si bond, Si—N bond, and Si—H bond; introducing into the reaction chamber an additive gas constituted by C, H, and optionally O; controlling a susceptor at a temperature of −50° C. to 50° C.; forming by plasma reaction an insulation film constituted by Si, O, H, and optionally N on an irregular surface of a substrate at a deposition rate of 100 nm / min or less; and heat-treating the substrate with the insulation film, thereby increasing a density of the insulation film to more than 2.1 g / cm3 as a result of the heat treatment.

Owner:ASM JAPAN

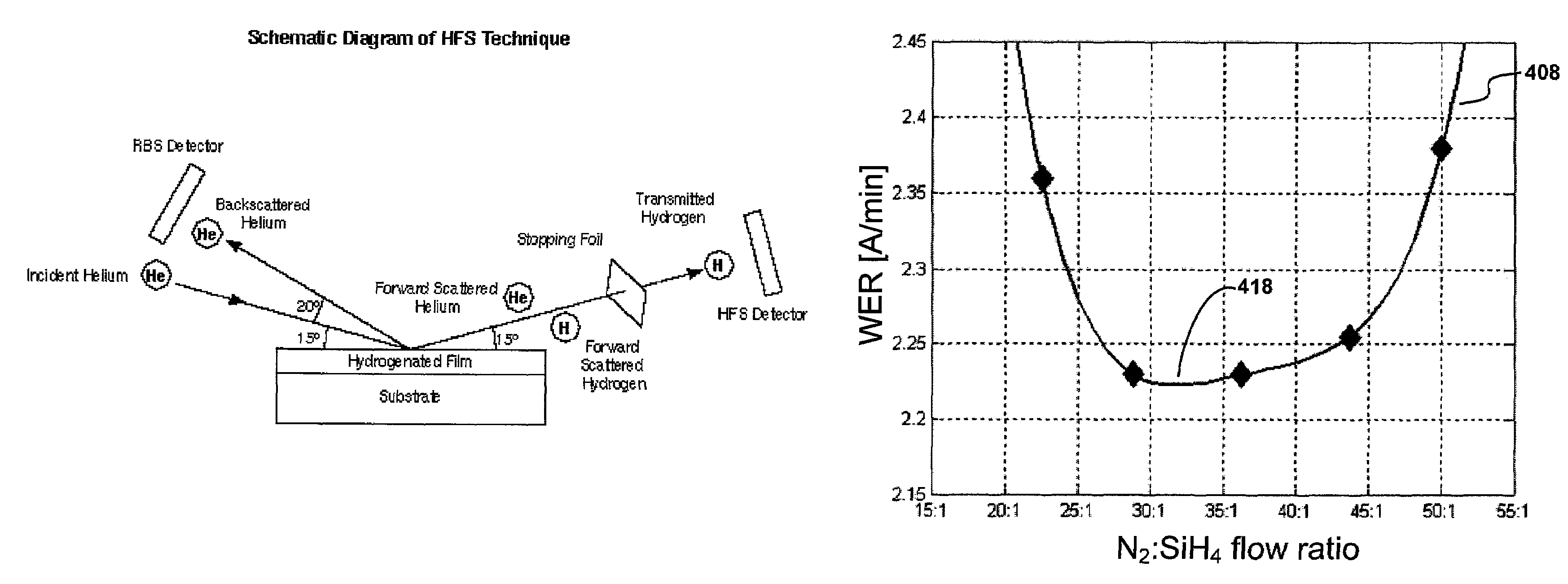

Low wet etch rate silicon nitride film

Owner:APPLIED MATERIALS INC

Methods of atomic layer deposition of hafnium oxide / erbium oxide bi-layer as advanced gate dielectrics

InactiveUS20130313656A1Improve electrical performanceFew defectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricHafnium

Provided is a two-step ALD deposition process for forming a gate dielectric involving an erbium oxide layer deposition followed by a hafnium oxide layer deposition. Hafnium oxide can provide a high dielectric constant, high density, large bandgap and good thermal stability. Erbium oxide can act as a barrier against oxygen diffusion, which can lead to increasing an effective oxide thickness of the gate dielectric and preventing hafnium-silicon reactions that may lead to higher leakage current.

Owner:INTERMOLECULAR

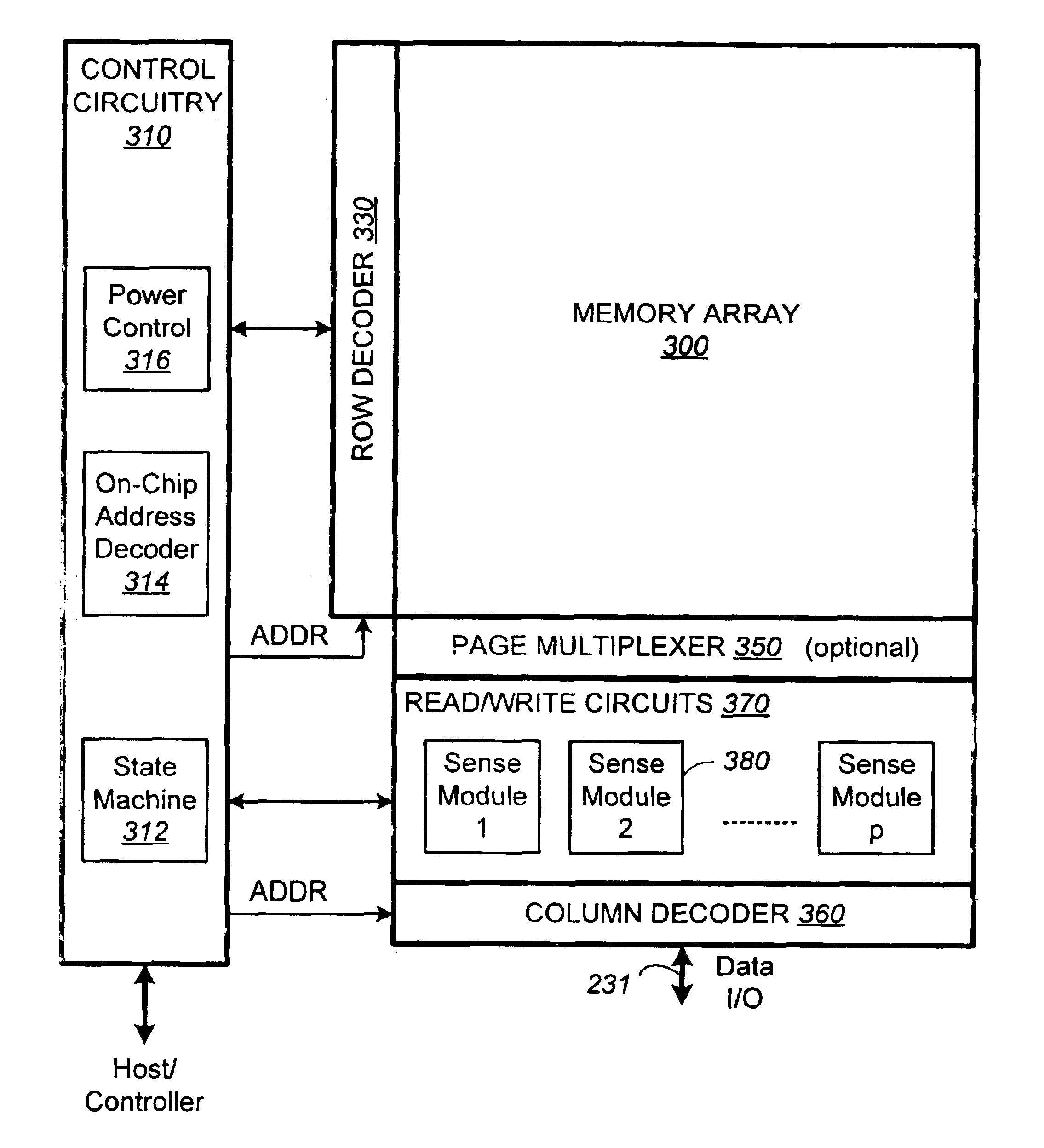

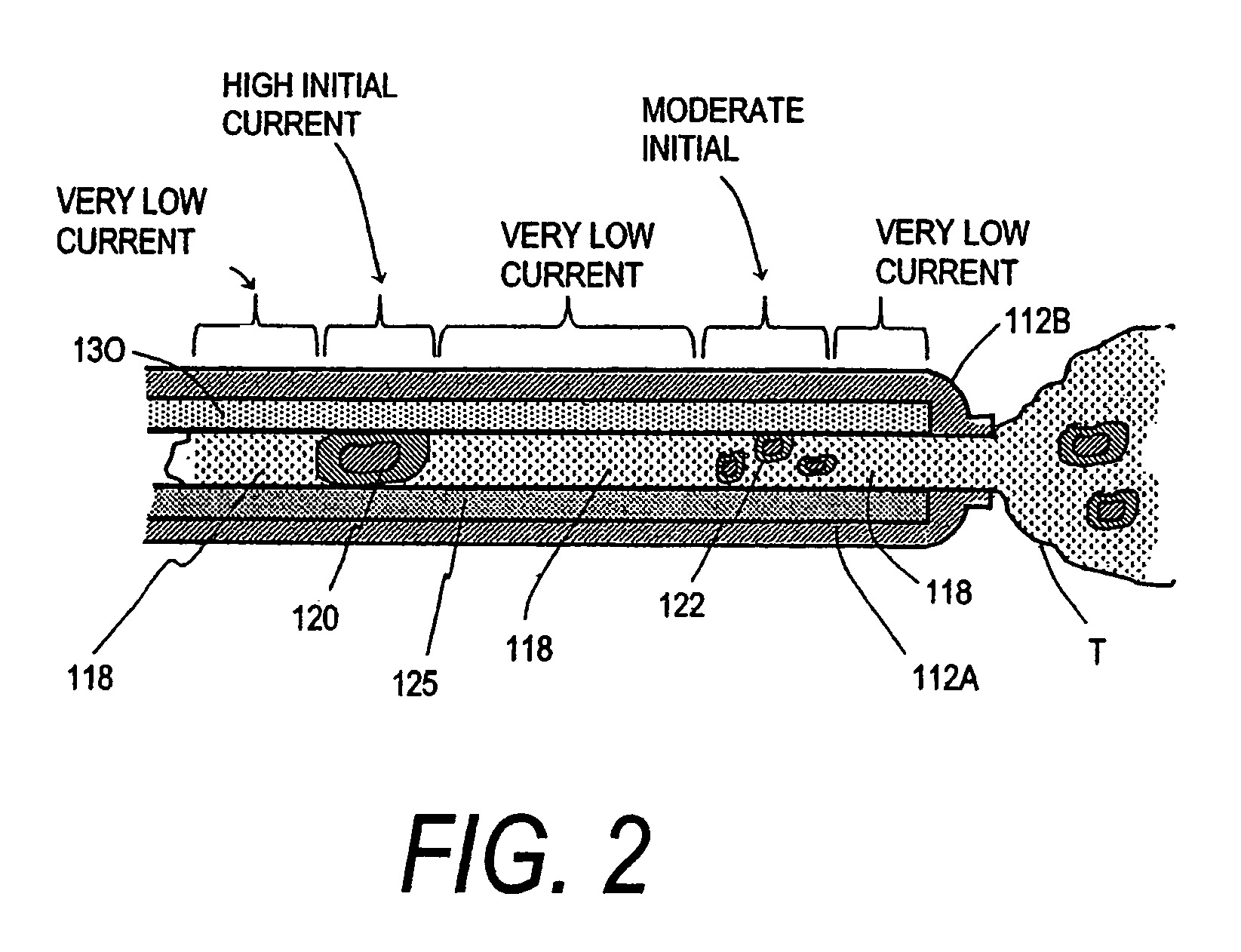

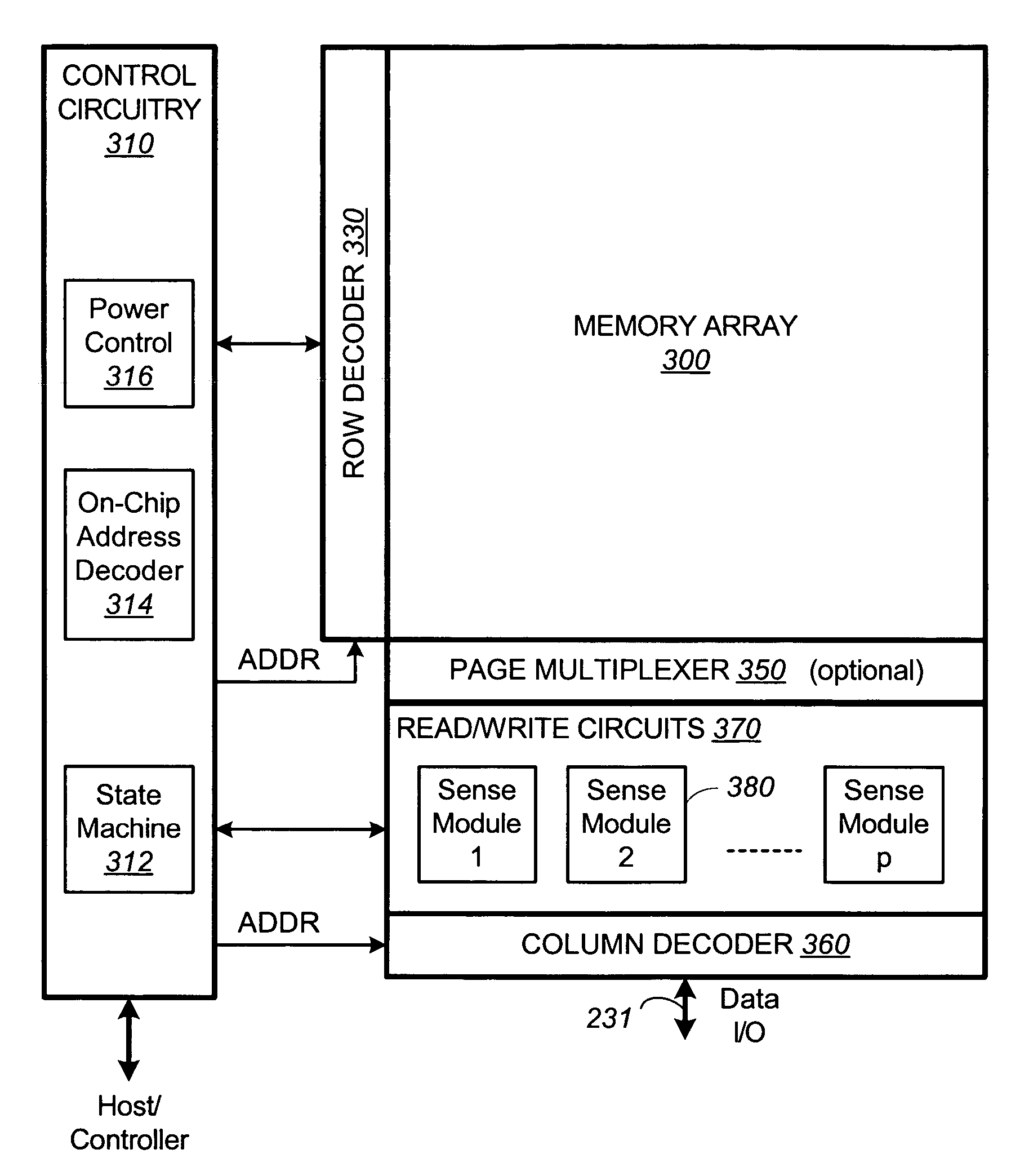

Non-volatile memory and method with improved sensing

InactiveUS7023736B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierMultiple pass

A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In particular, the identified memory cells are shut down after all sensing in the current pass have been completed. In this way the shutting down operation does not disturb the sensing operation. Sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells. In another aspect of sensing improvement, a reference sense amplifier is employed to control multiple sense amplifiers to reduce their dependence on power supply and environmental variations.

Owner:SANDISK TECH LLC

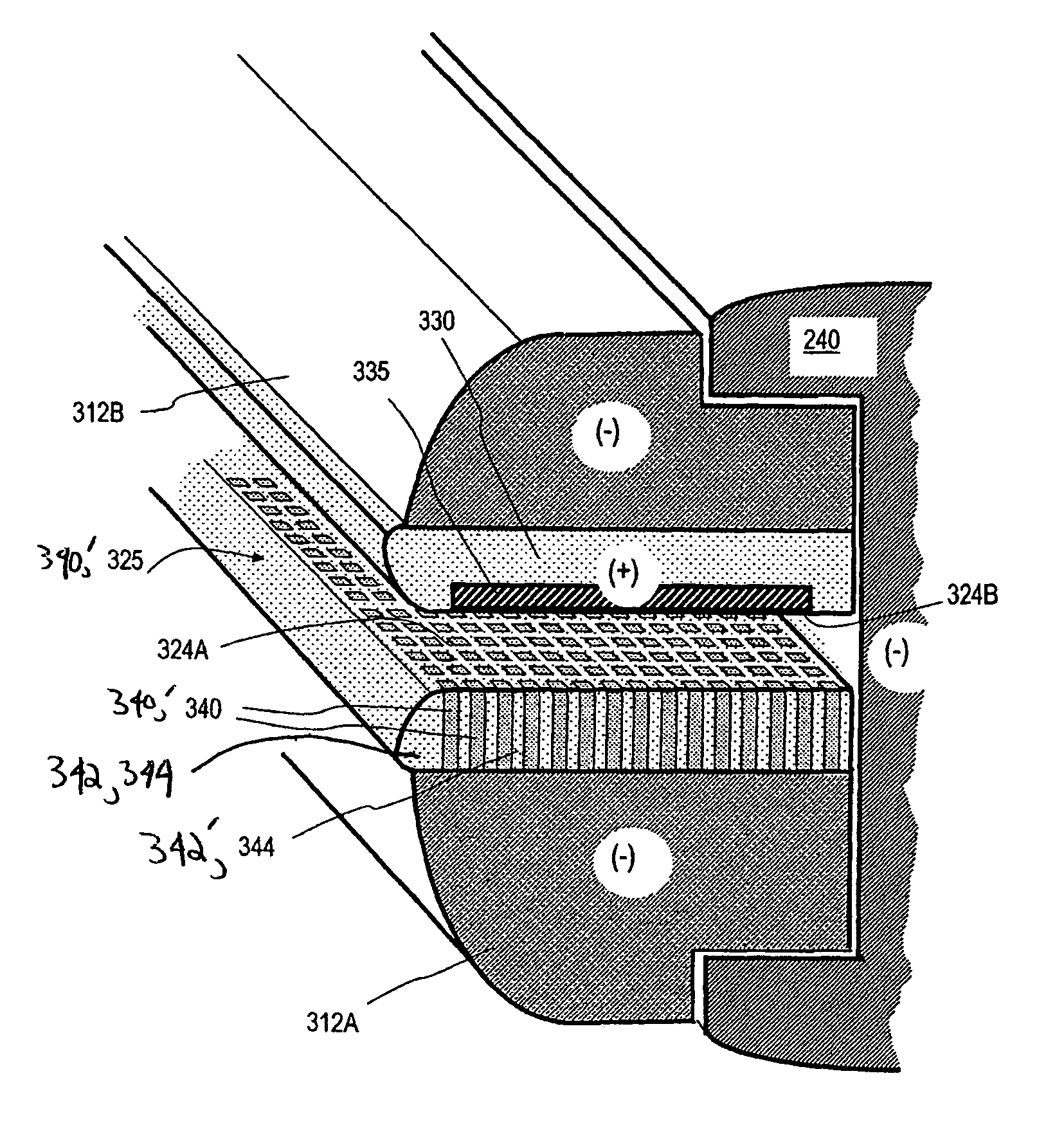

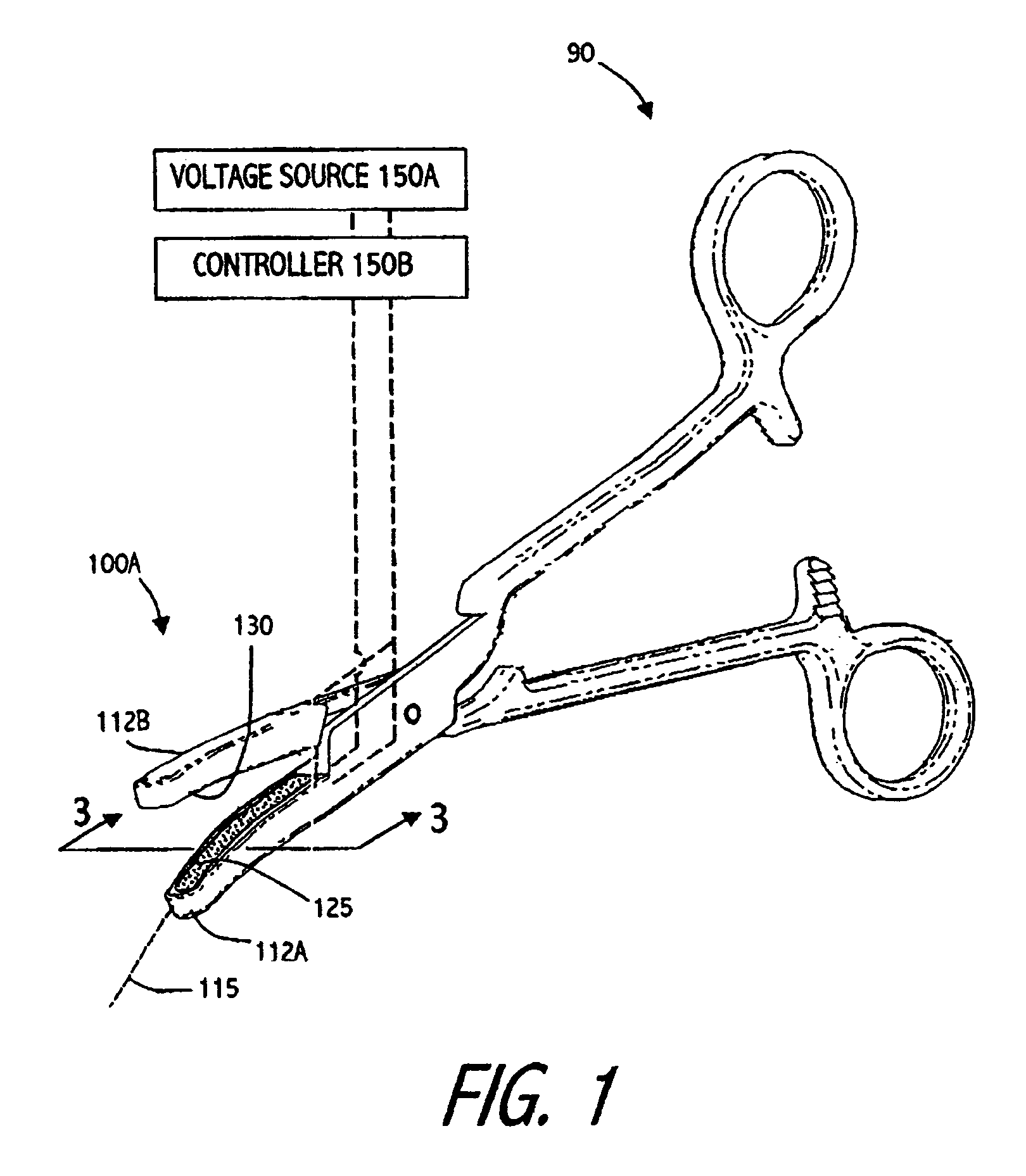

Electrosurgical instrument and method of use

ActiveUS7955331B2Effective “weld” in tissueAvoid flowSurgical instruments for heatingSurgical forcepsElectrical resistance and conductanceHigh intensity

A particular embodiment of the invention provides an electrosurgical working end for performing high strength welding of tissue comprising a body having a tissue contacting energy delivery surface. The body includes pixel portions and non-pixel portions distributed within the tissue contacting surface. The pixel portions comprise a positive temperature coefficient of resistance (PTCR) material with at least one pixel portion configured to switch Rf current on and off in the at least one pixel portion responsive to tissue temperature adjacent the at least one pixel portion. The pixel portions can be configured to be coupled to an Rf current source such as an Rf generator. The pixelated energy delivery surfaces are capable of highly localized modulation of Rf energy application to the engaged tissue to create high strength tissue welds.

Owner:ETHICON ENDO SURGERY INC

Memory sensing circuit and method for low voltage operation

InactiveUS7046568B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineAudio power amplifier

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

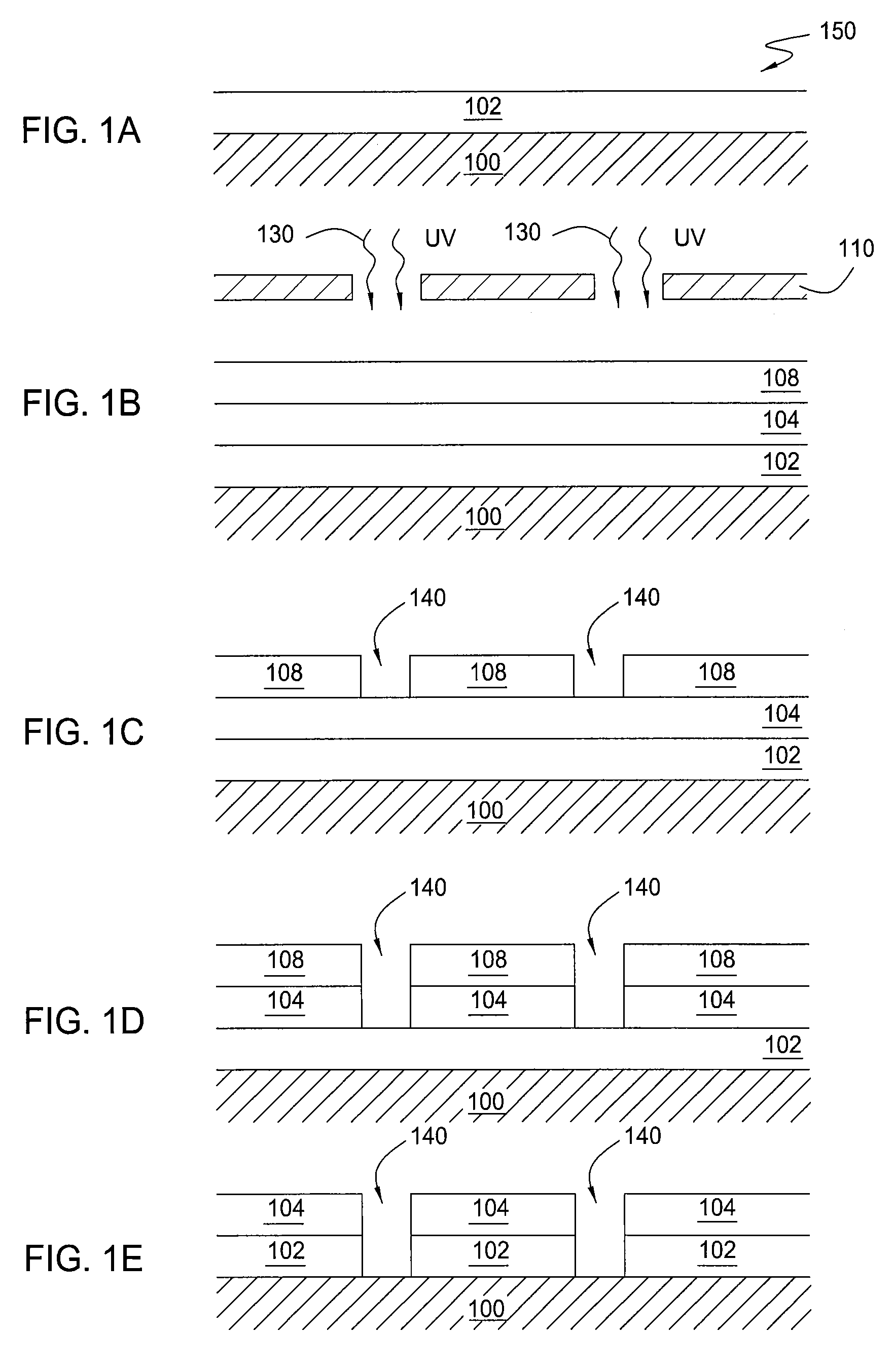

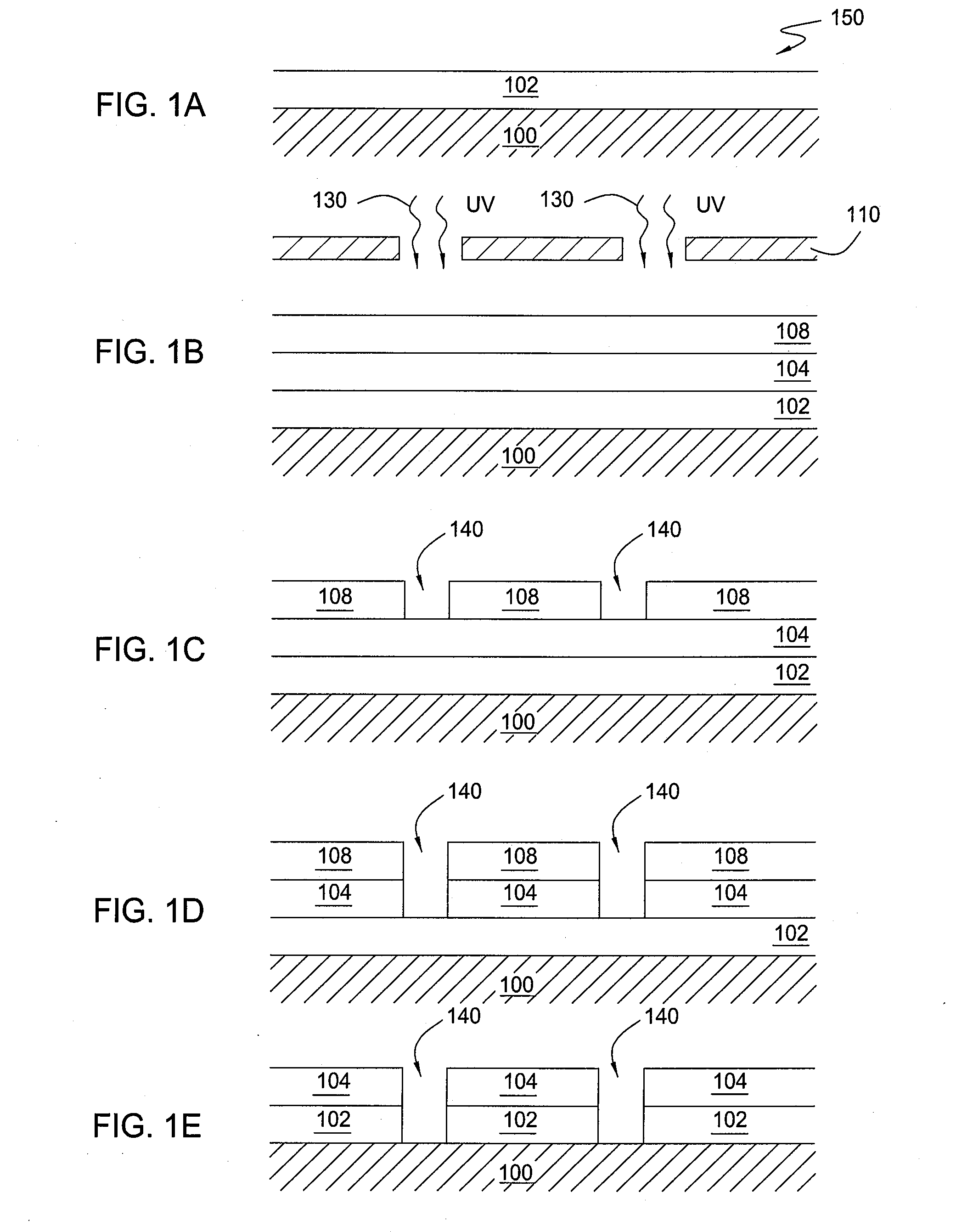

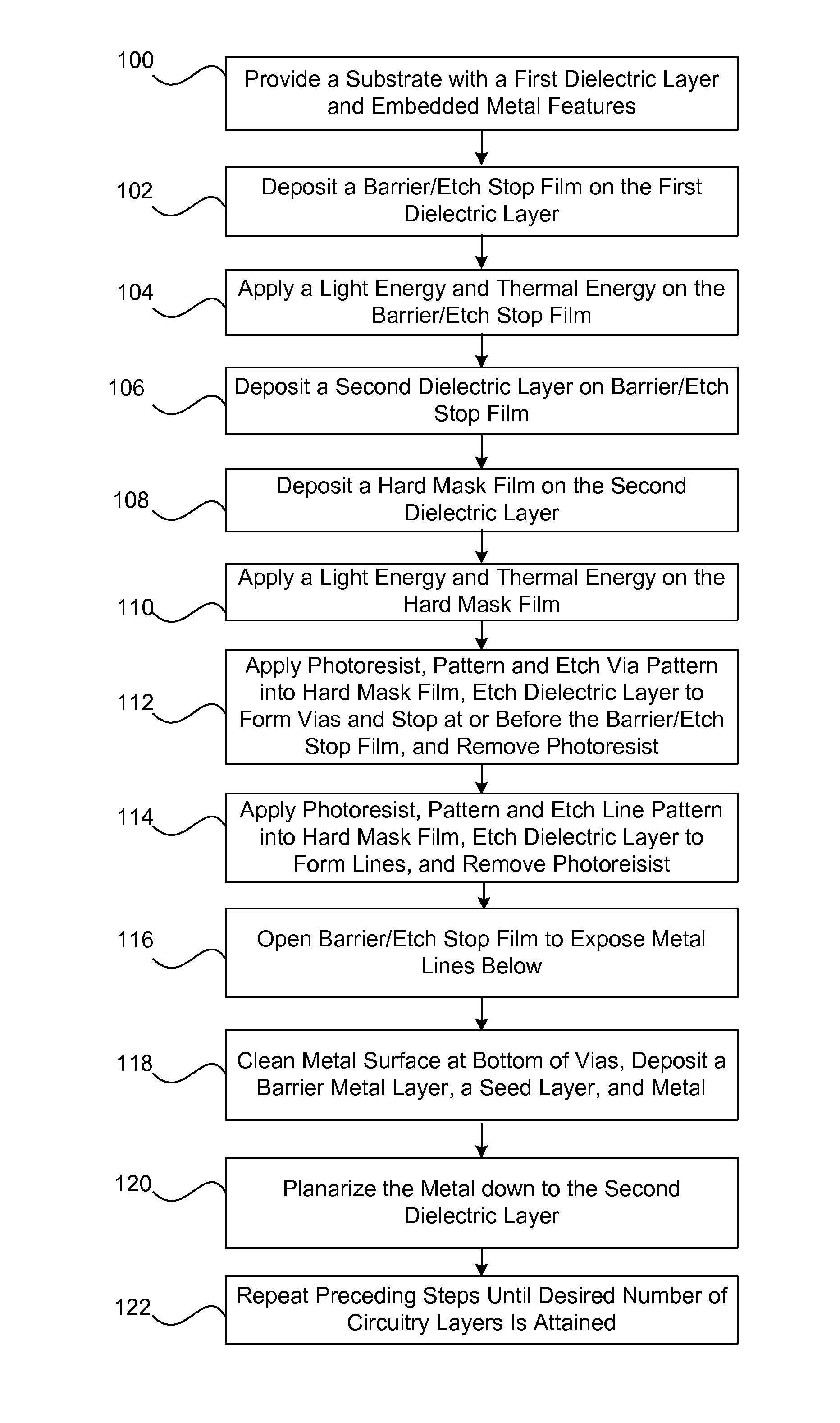

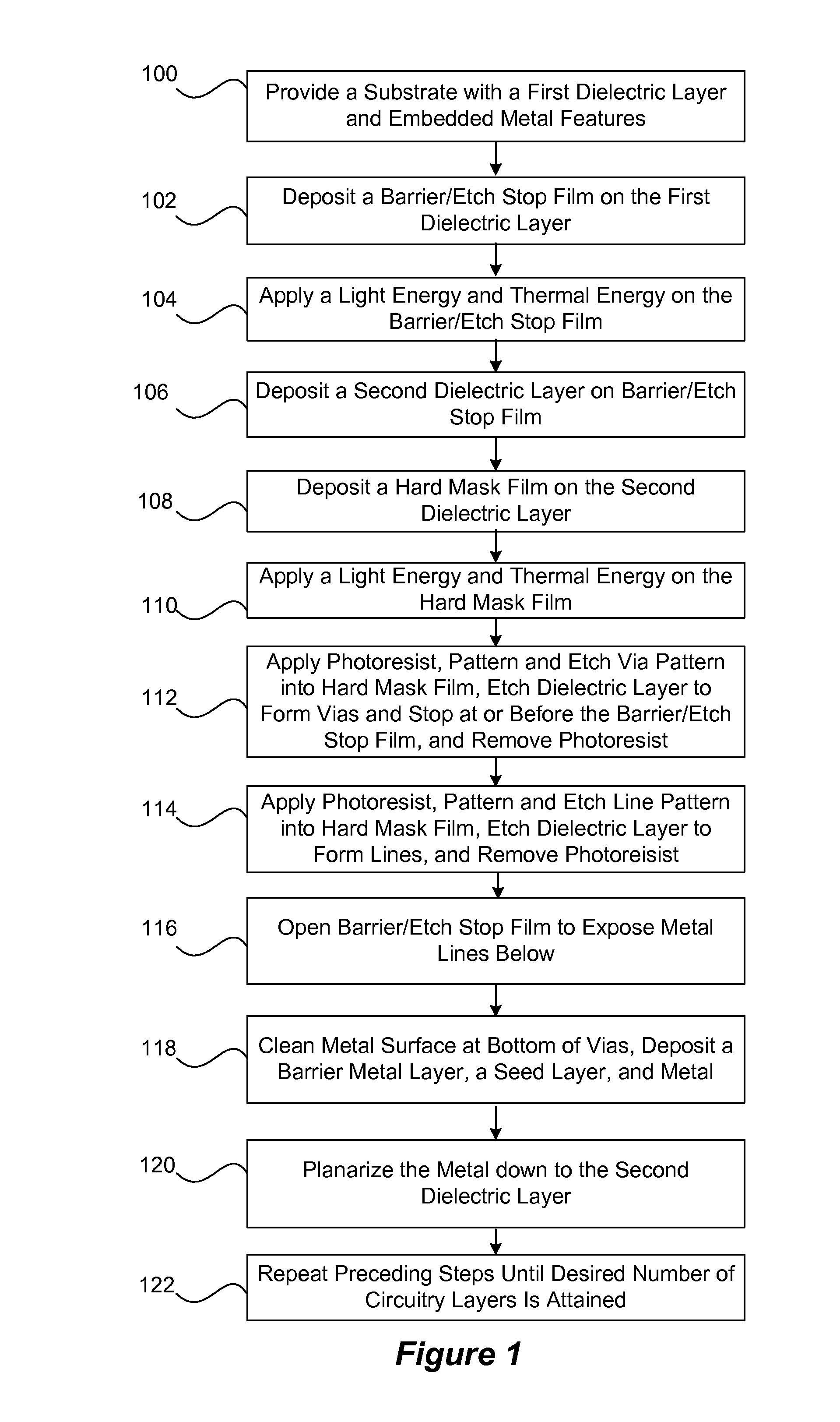

UV treatment of etch stop and hard mask films for selectivity and hermeticity enhancement

ActiveUS8242028B1Increase hermeticityHigh selectivitySemiconductor/solid-state device manufacturingThermal energyHydrogen

A method for the ultraviolet (UV) treatment of etch stop and hard mask film increases etch selectivity and hermeticity by removing hydrogen, cross-linking, and increasing density. The method is particularly applicable in the context of damascene processing. A method provides for forming a semiconductor device by depositing an etch stop film or a hard mask film on a substrate and exposing the film to UV radiation and optionally thermal energy. The UV exposure may be direct or through another dielectric layer.

Owner:NOVELLUS SYSTEMS

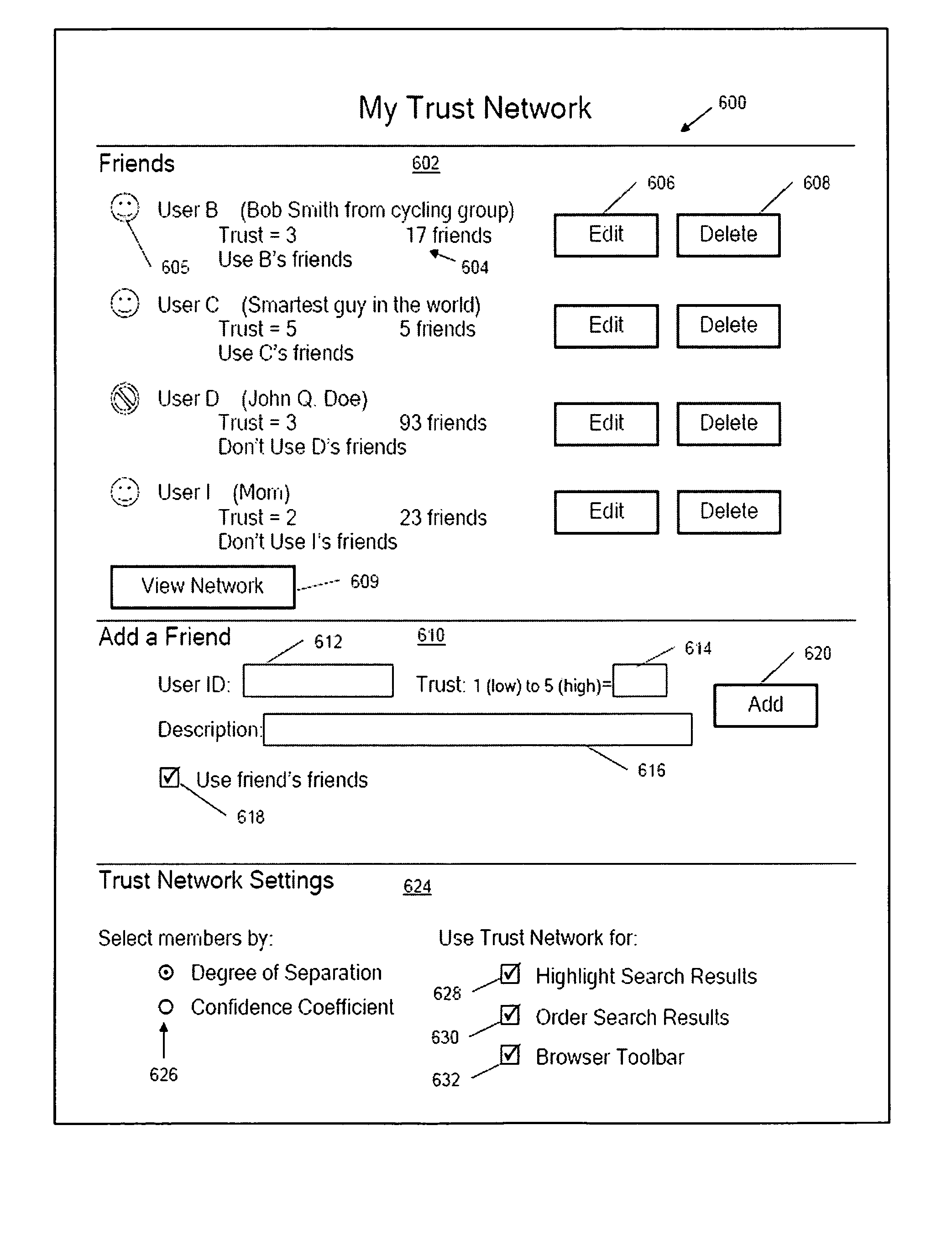

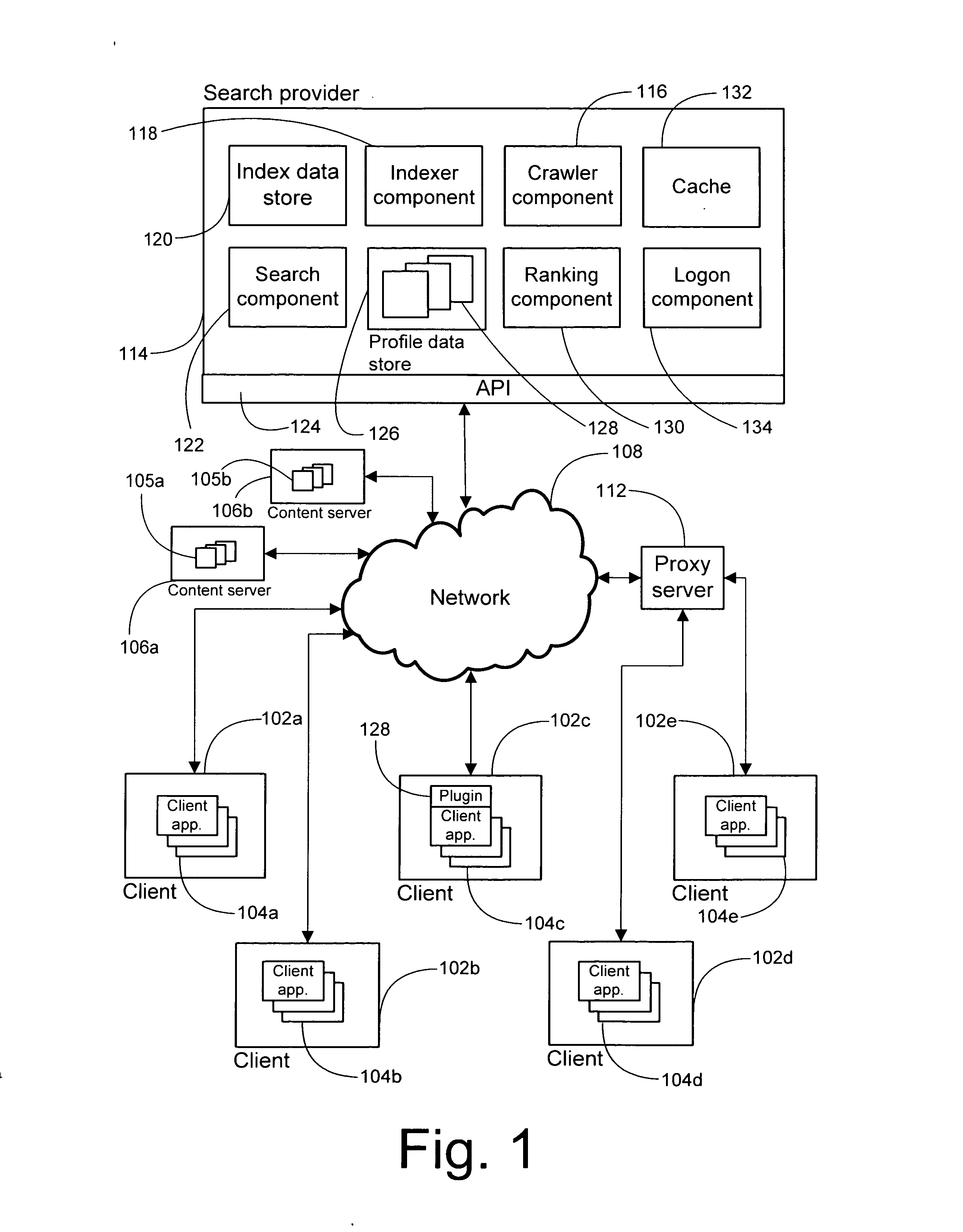

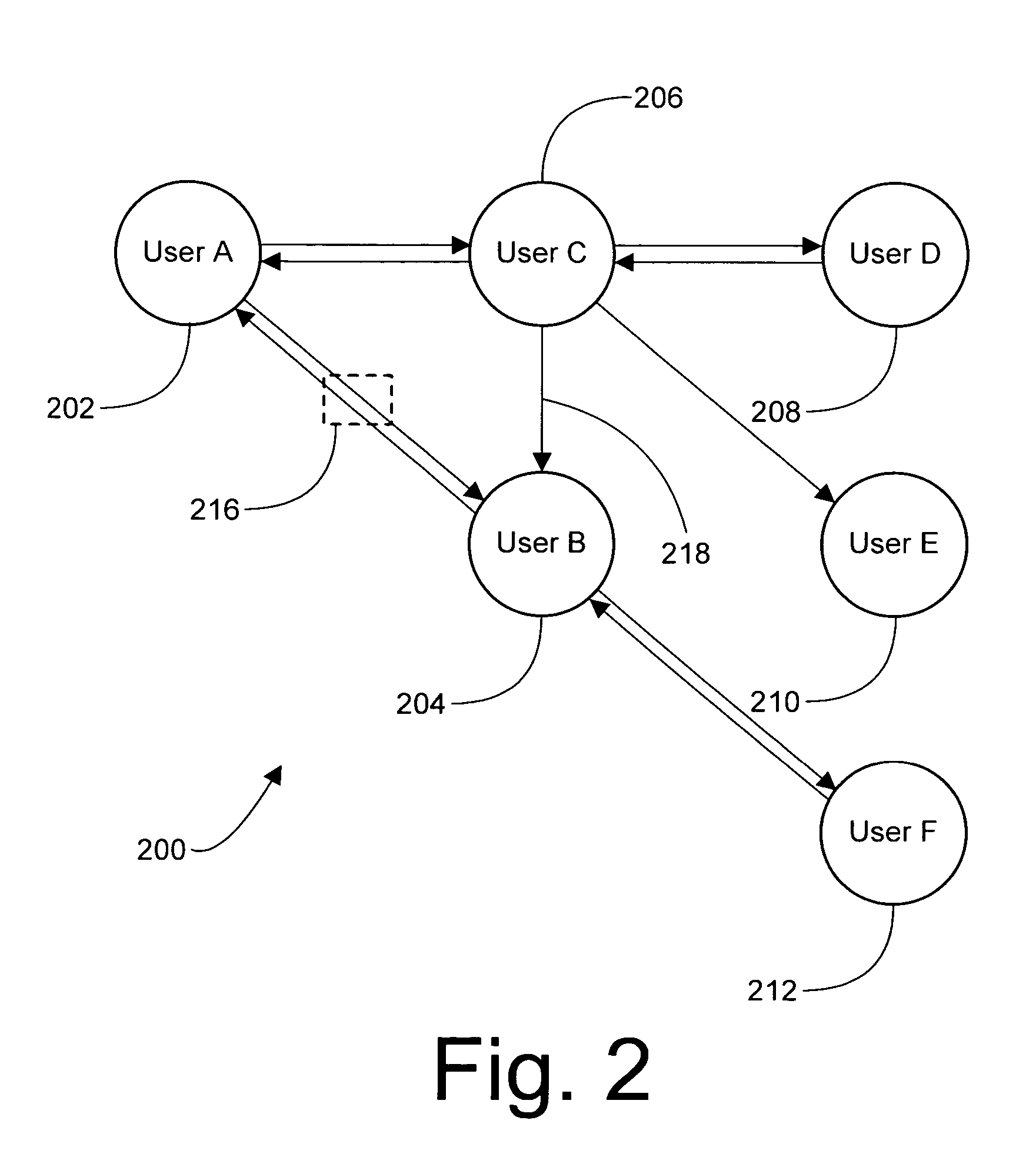

Search engine with augmented relevance ranking by community participation

ActiveUS20070112761A1Speed up searchPromote resultsData processing applicationsDigital data information retrievalCommunity participationResult set

Embodiments of the present invention provide systems and methods for ranking a result set. The method according to one embodiment comprises selecting an item from the result set, selecting a user profile from one or more user profiles and selecting one or more items of personalized information from the selected user profile. A rank is calculated for the item on the basis of the selected one or more items of personalized information and the selected item in the result set is ranked in accordance with the calculated rank.

Owner:R2 SOLUTIONS

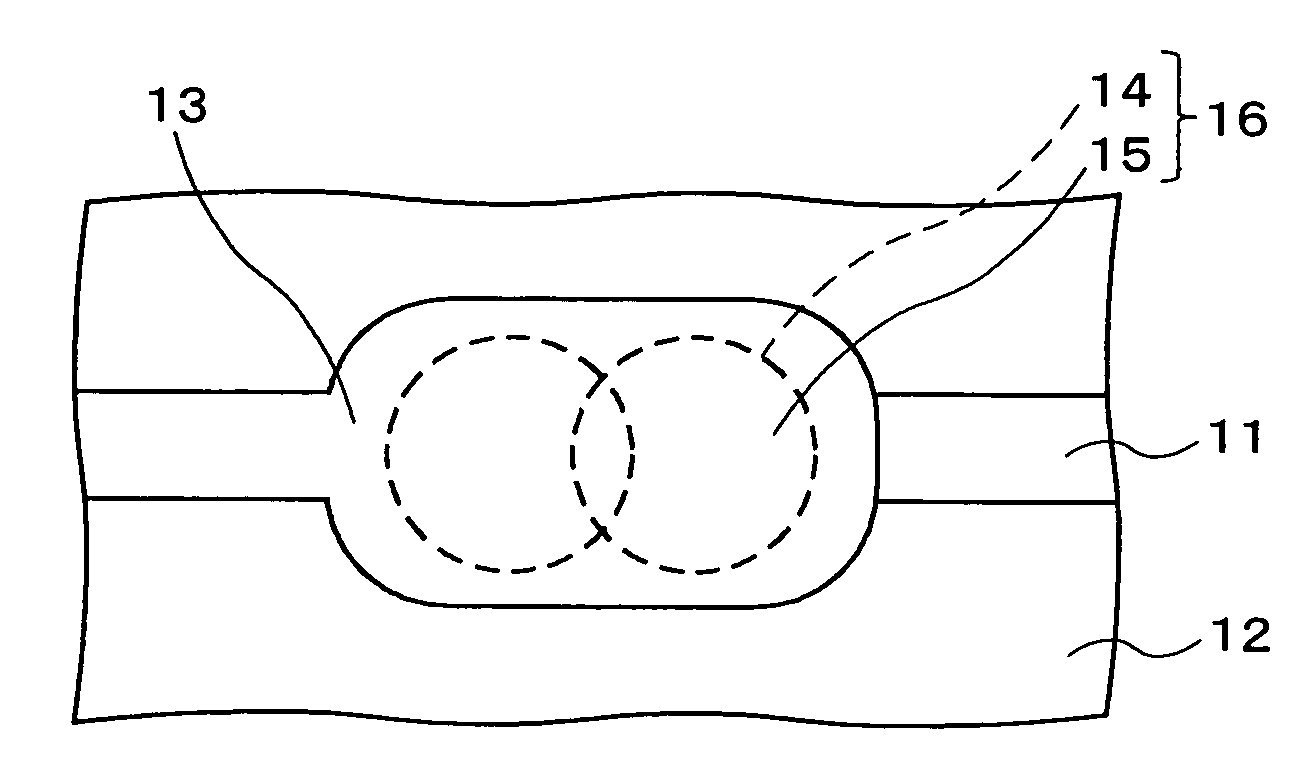

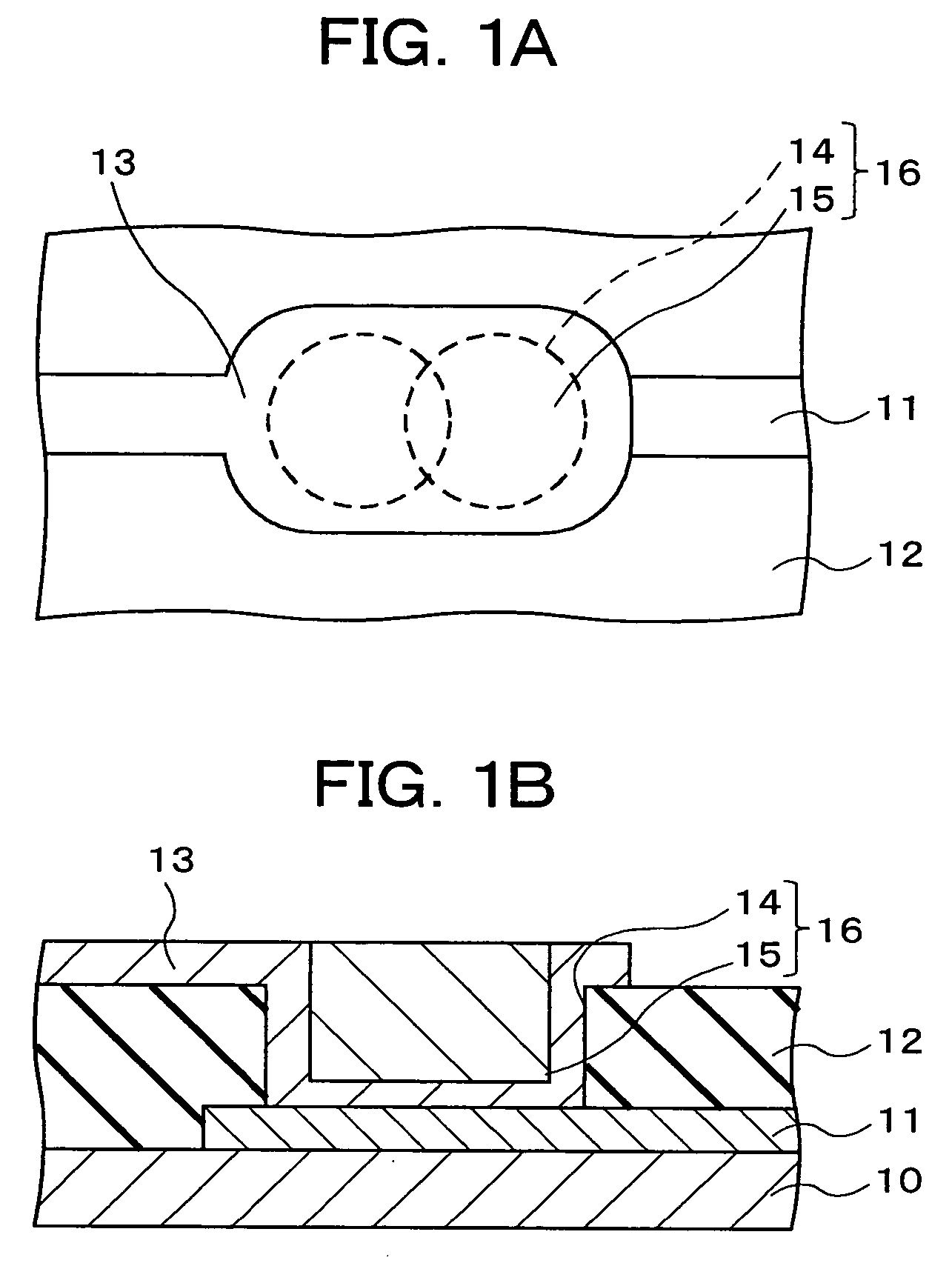

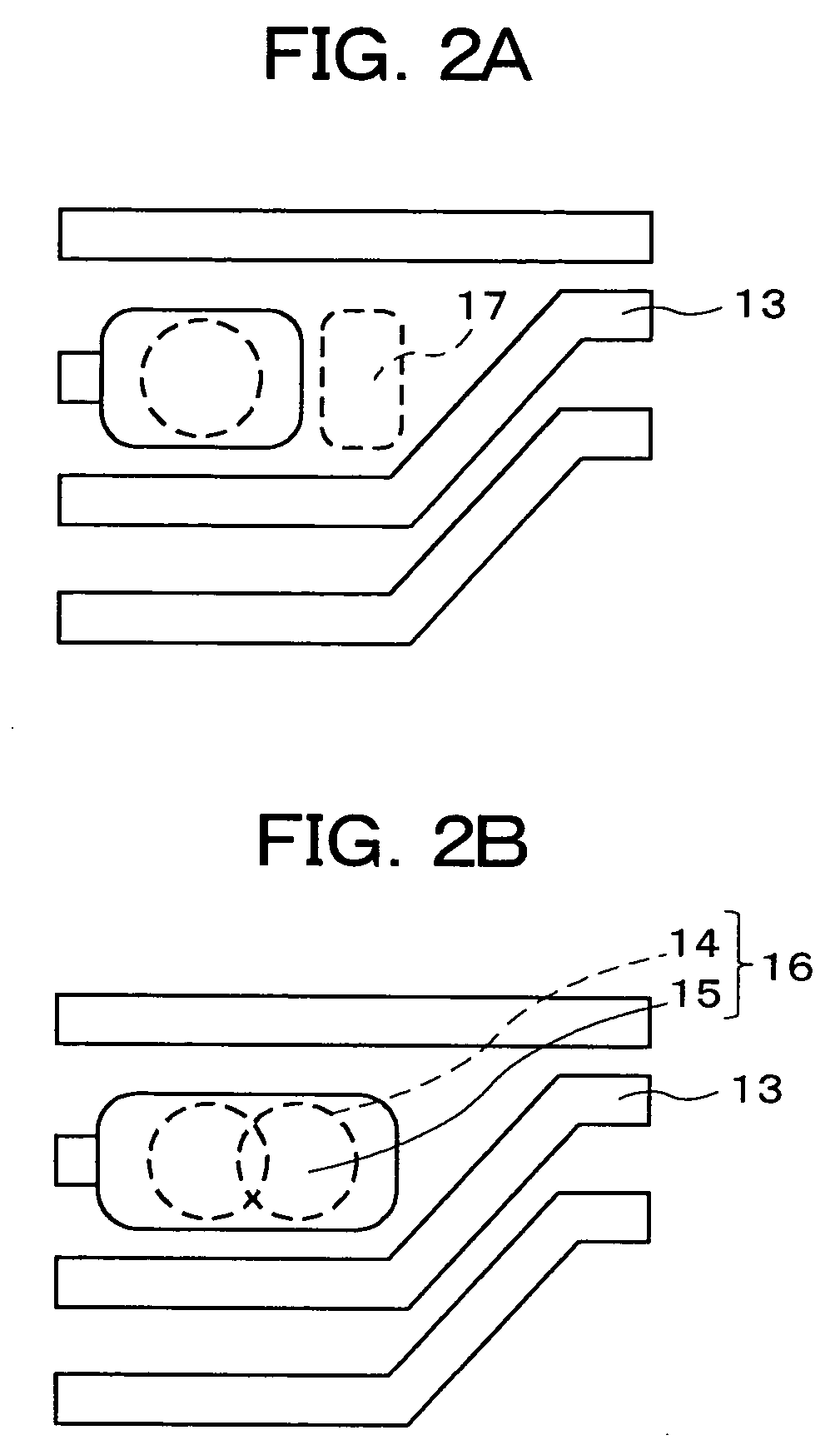

Wiring board and method for manufacturing the same

ActiveUS20060283629A1Easy to performIncrease cross-sectional areaPrinted electric component incorporationPrinted circuit aspectsEngineeringSemiconductor components

A wiring board for mounting a semiconductor element or electronic component having a plurality of wiring layers, an insulating layer provided between these wiring layers, and a via which is provided to the insulating layer and which electrically connects the wiring layers. In this wiring board, the cross-sectional shape of the via in the plane parallel to the wiring layers is obtained by the partial overlapping of a plurality of similar shapes (circles). Stable operation can be obtained in a semiconductor element by minimizing obstacles to increased density, effectively increasing the cross-sectional area of the via, and preventing the wiring resistance from increasing by making the cross-sectional shape of the via into a shape obtained by the partial overlapping of a plurality of similar shapes.

Owner:RENESAS ELECTRONICS CORP

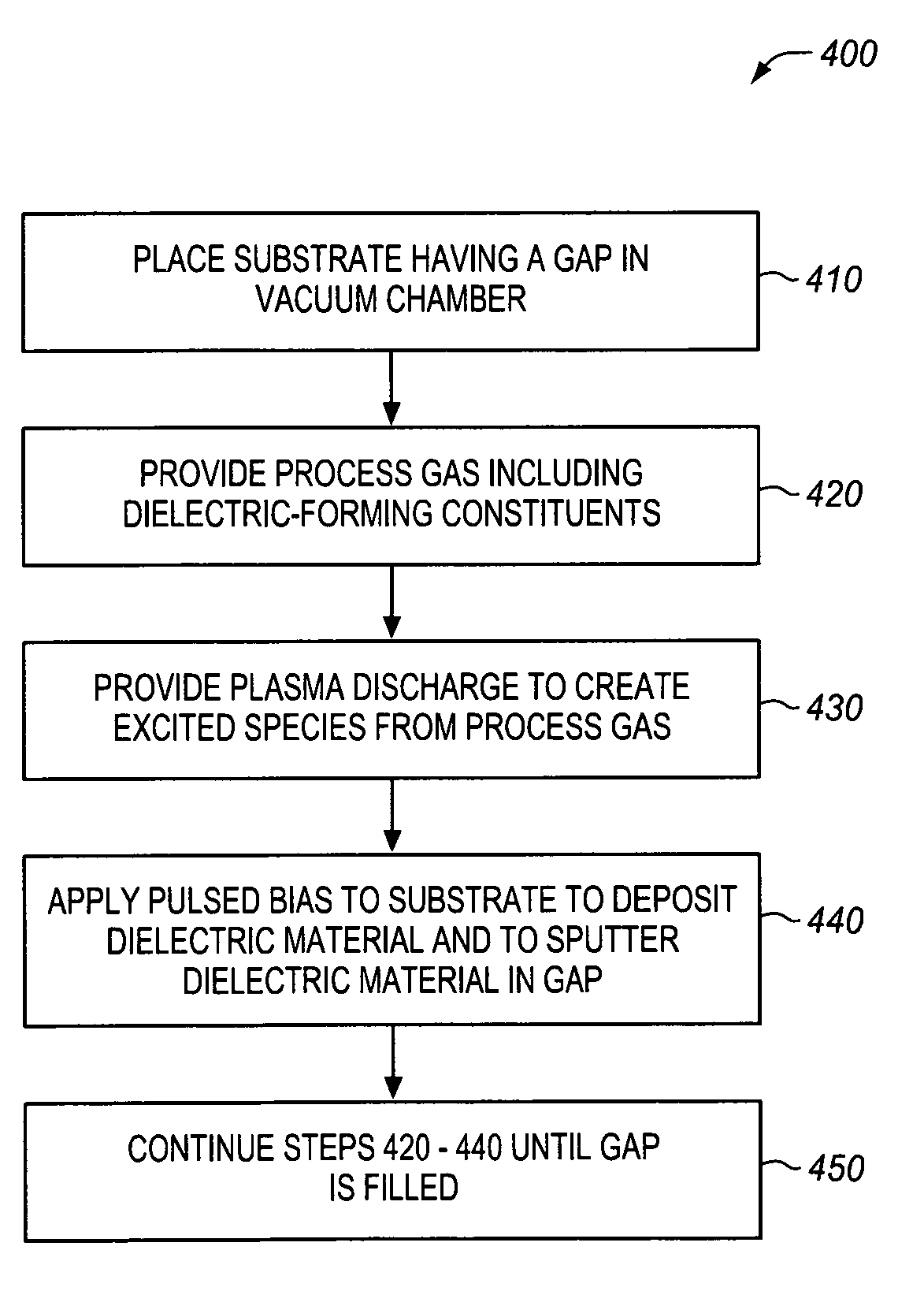

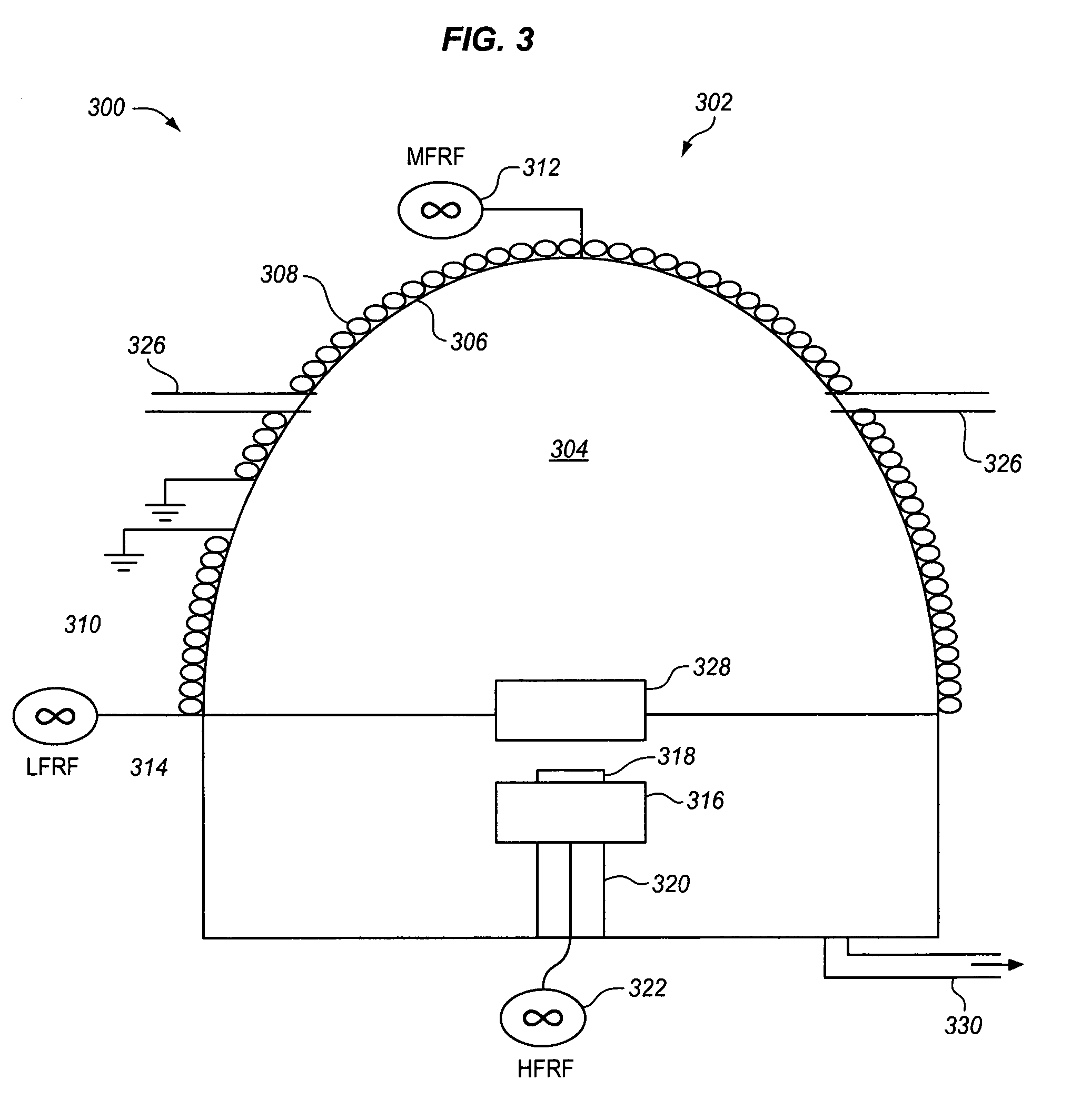

Pulsed bias having high pulse frequency for filling gaps with dielectric material

InactiveUS7514375B1High densityHigh fillingSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPulse frequencyPhysics

During bottom filling of high aspect ratio gaps and trenches in an integrated circuit substrate using HDP-CVD, a pulsed HF bias is applied to the substrate. In some embodiments, pulsed HF bias is applied to the substrate during etching operations. The pulsed bias typically has a pulse frequency in a range of about from 500 Hz to 20 kHz and a duty cycle in a range of about from 0.1 to 0.95.

Owner:NOVELLUS SYSTEMS

Method for forming insulation film

InactiveUS7354873B2Reduce distanceGood film densitySolid-state devicesSemiconductor/solid-state device manufacturingPlasma reactionResidence time

A method for forming an insulation film having filling property on a semiconductor substrate by plasma reaction includes: vaporizing a silicon-containing hydrocarbon having a Si—O bond compound to provide a source gas; introducing the source gas and a carrier gas without an oxidizing gas into a reaction space for plasma CVD processing; and forming an insulation film constituted by Si, O, H, and optionally C or N on a substrate by plasma reaction using a combination of low-frequency RF power and high-frequency RF power in the reaction space. The plasma reaction is activated while controlling the flow of the reaction gas to lengthen a residence time, Rt, of the reaction gas in the reaction space.

Owner:ASM JAPAN

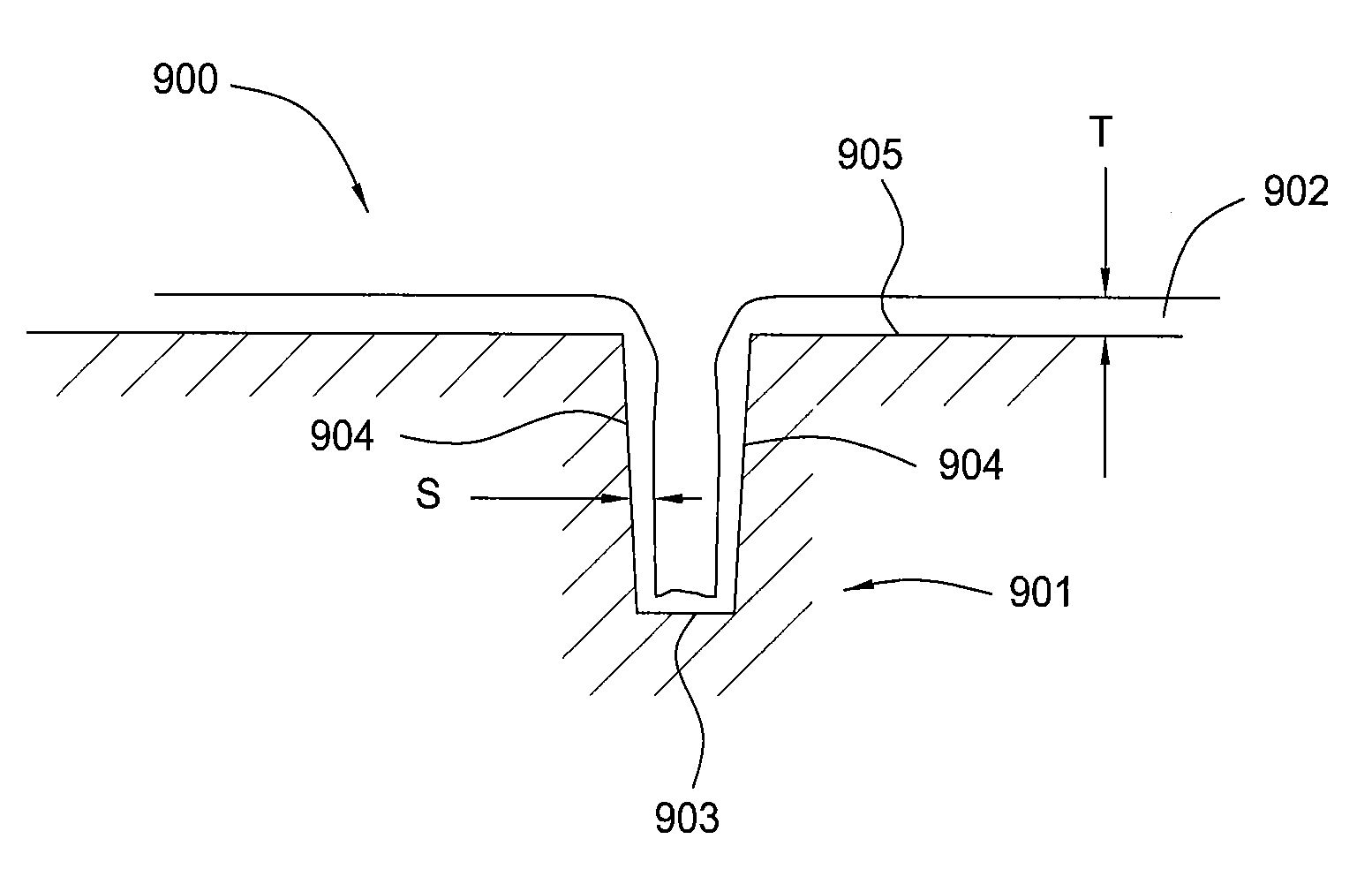

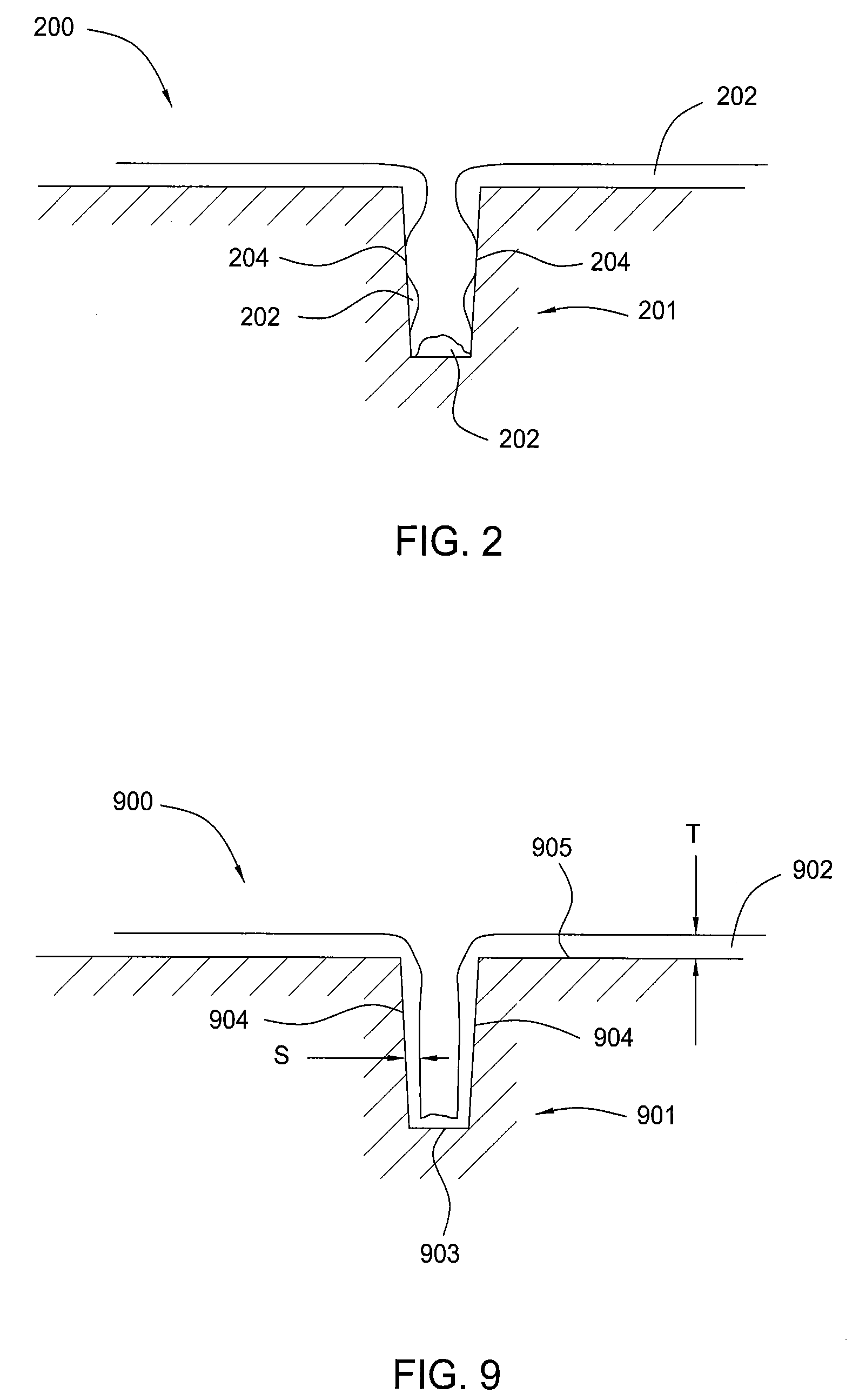

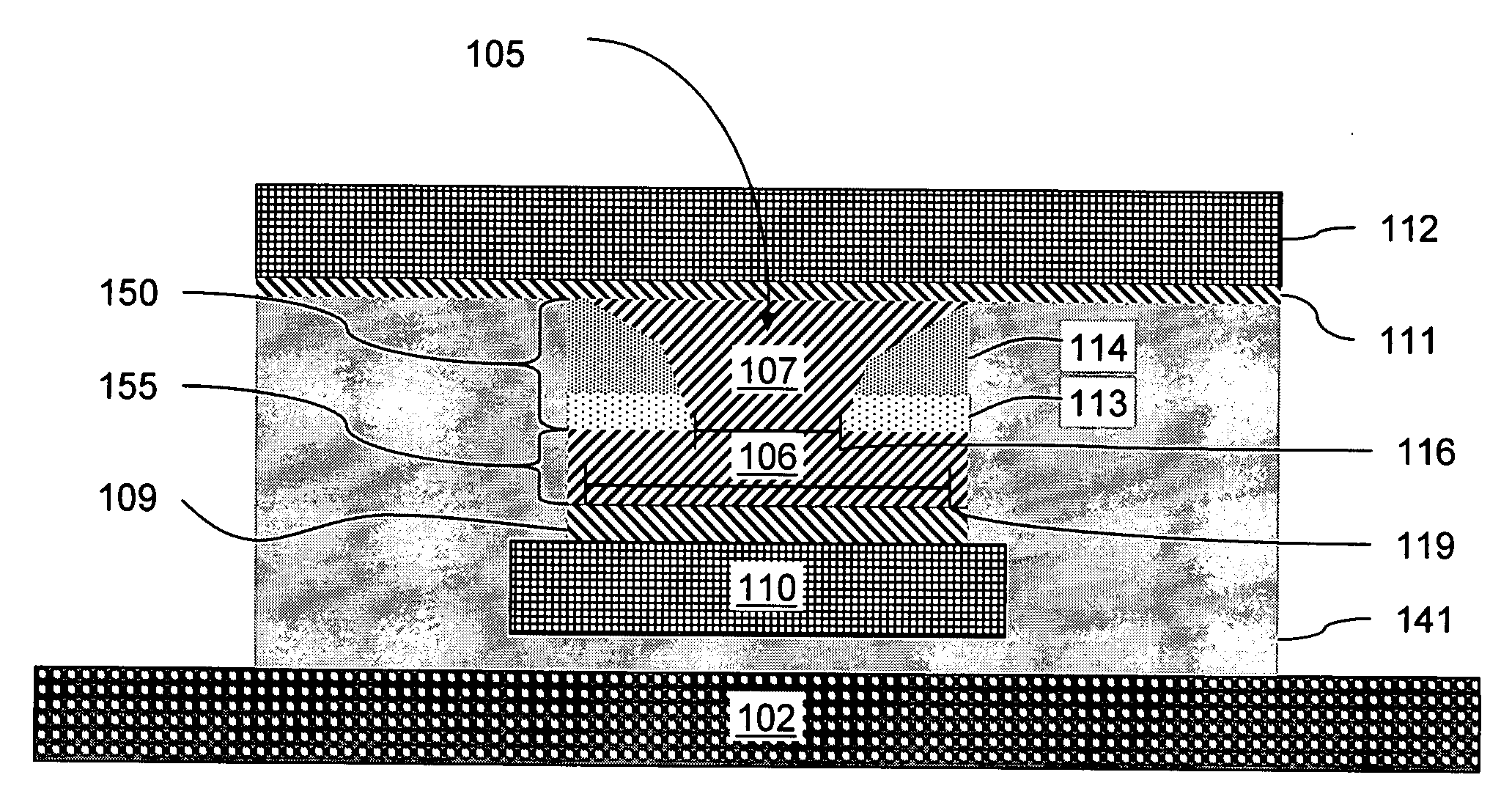

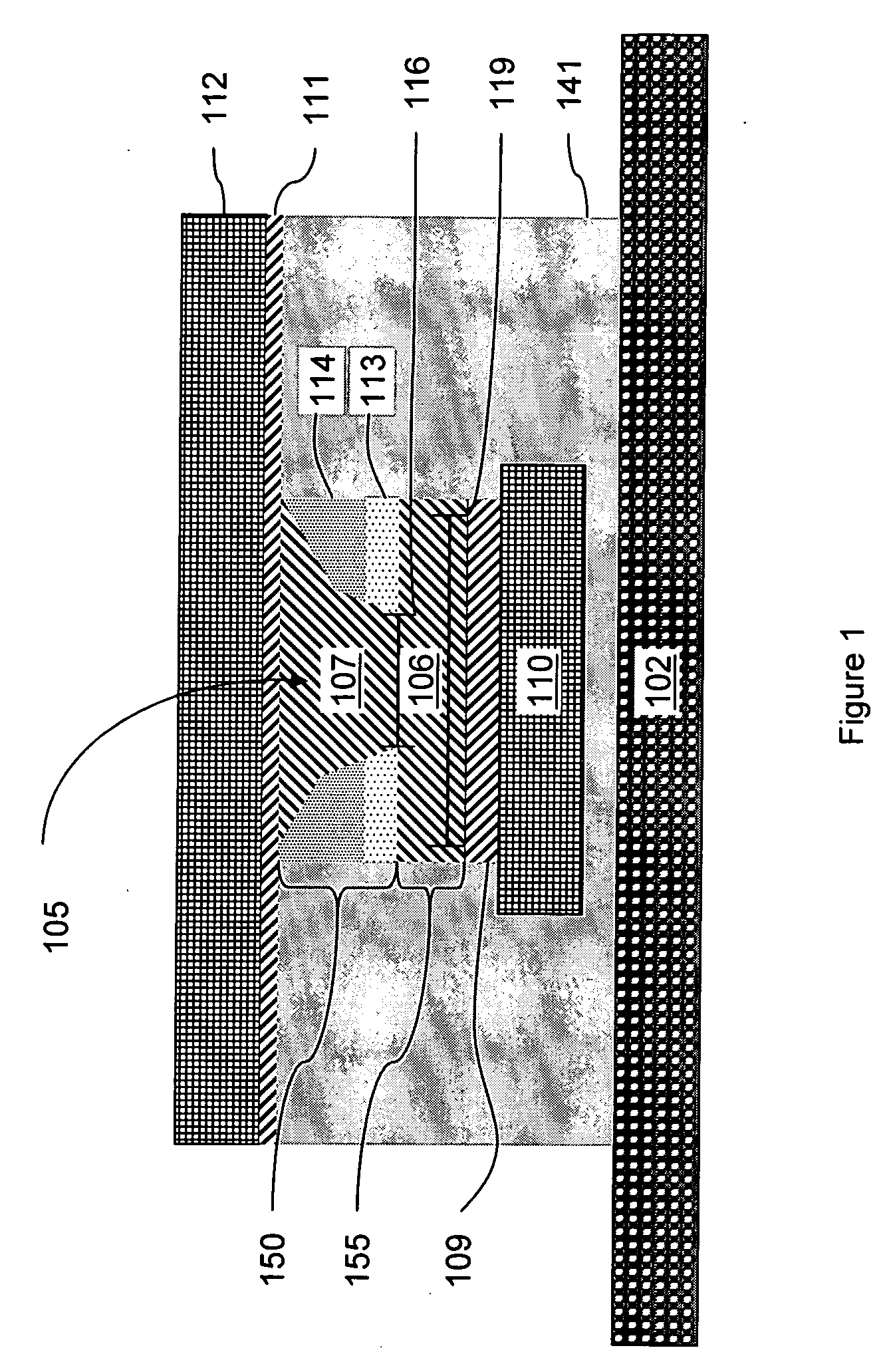

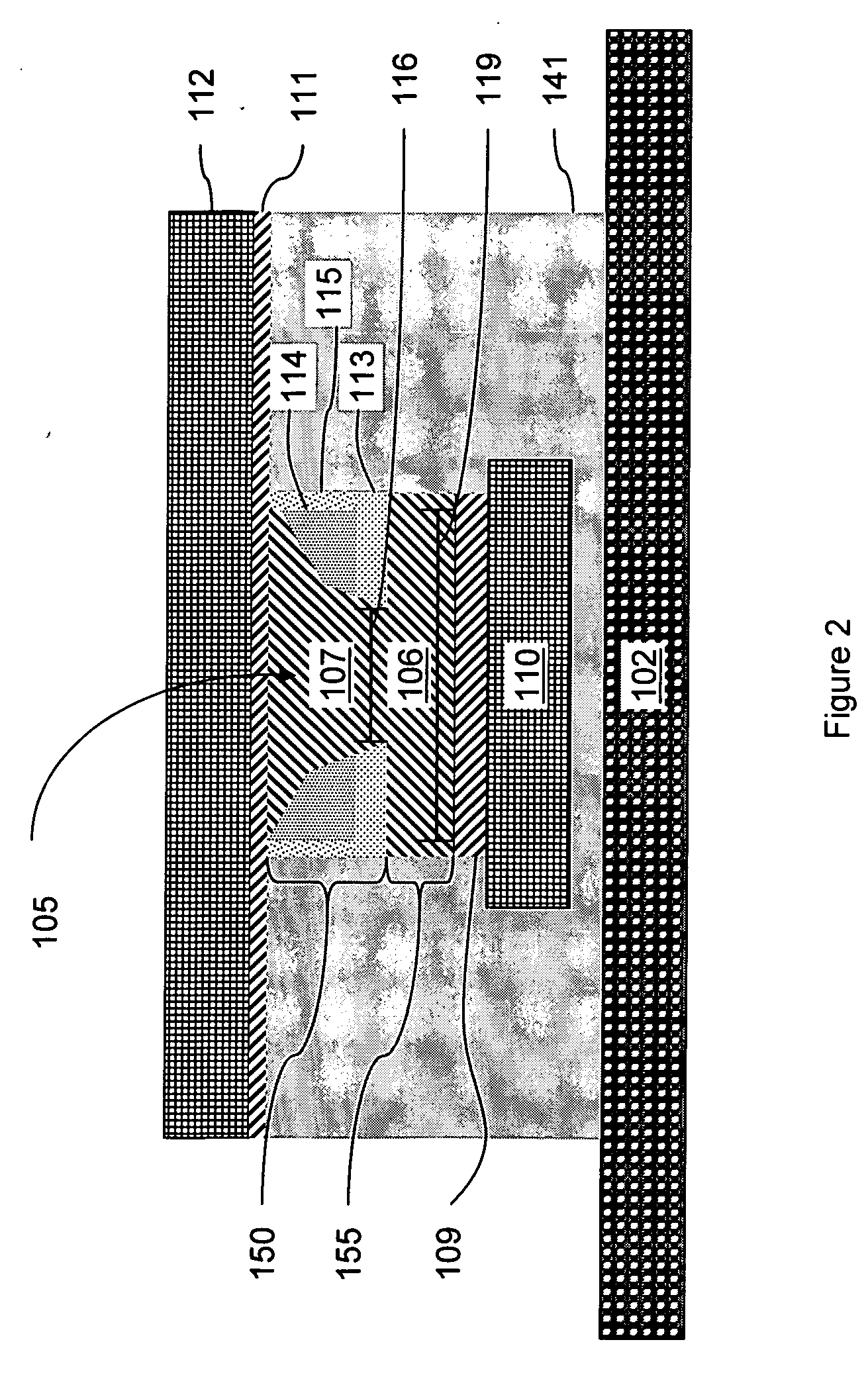

Structure for confining the switching current in phase memory (PCM) cells

InactiveUS20060226409A1Heat dissipation is limitedHigh densityBulk negative resistance effect devicesSemiconductor devicesPhase-change memorySwitched current

Disclosed are a phase change memory cell and a method of forming the memory cell. The memory cell comprises a main body of phase change material connected directly to a bottom contact and via a narrow channel of phase change material to a top contact. The channel is tapered from the top contact towards the main body. A minimum width of the channel has a less than minimum lithographic dimension and is narrower than a width of the main body. Therefore, the channel provides a confined region for the switching current path and restricts phase changing to within the channel. In addition an embodiment of the memory cell isolates the main body of phase change material by providing a space between the phase change material and the cell walls. The space allows the phase change material to expand and contract and also limits heat dissipation.

Owner:IBM CORP

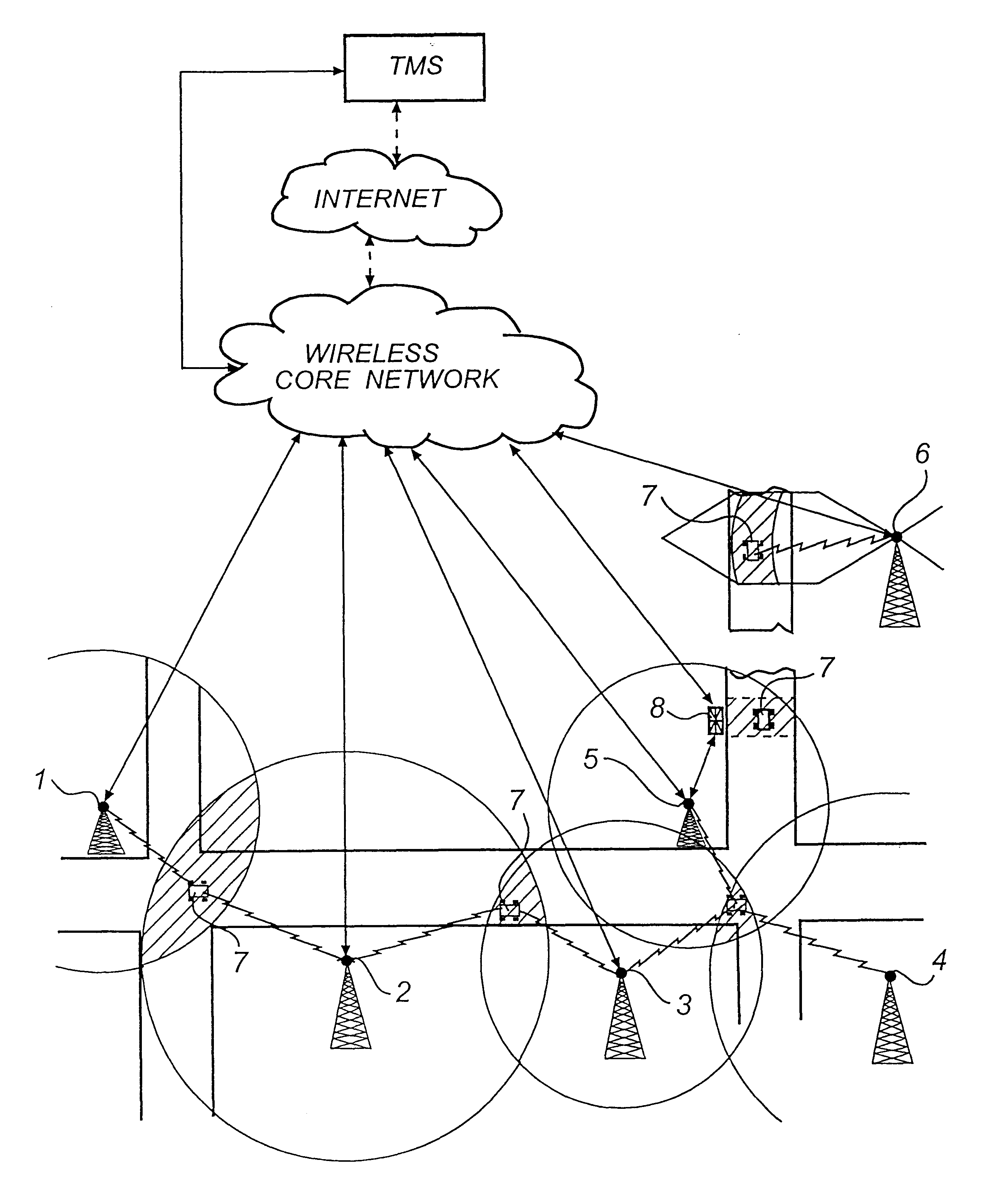

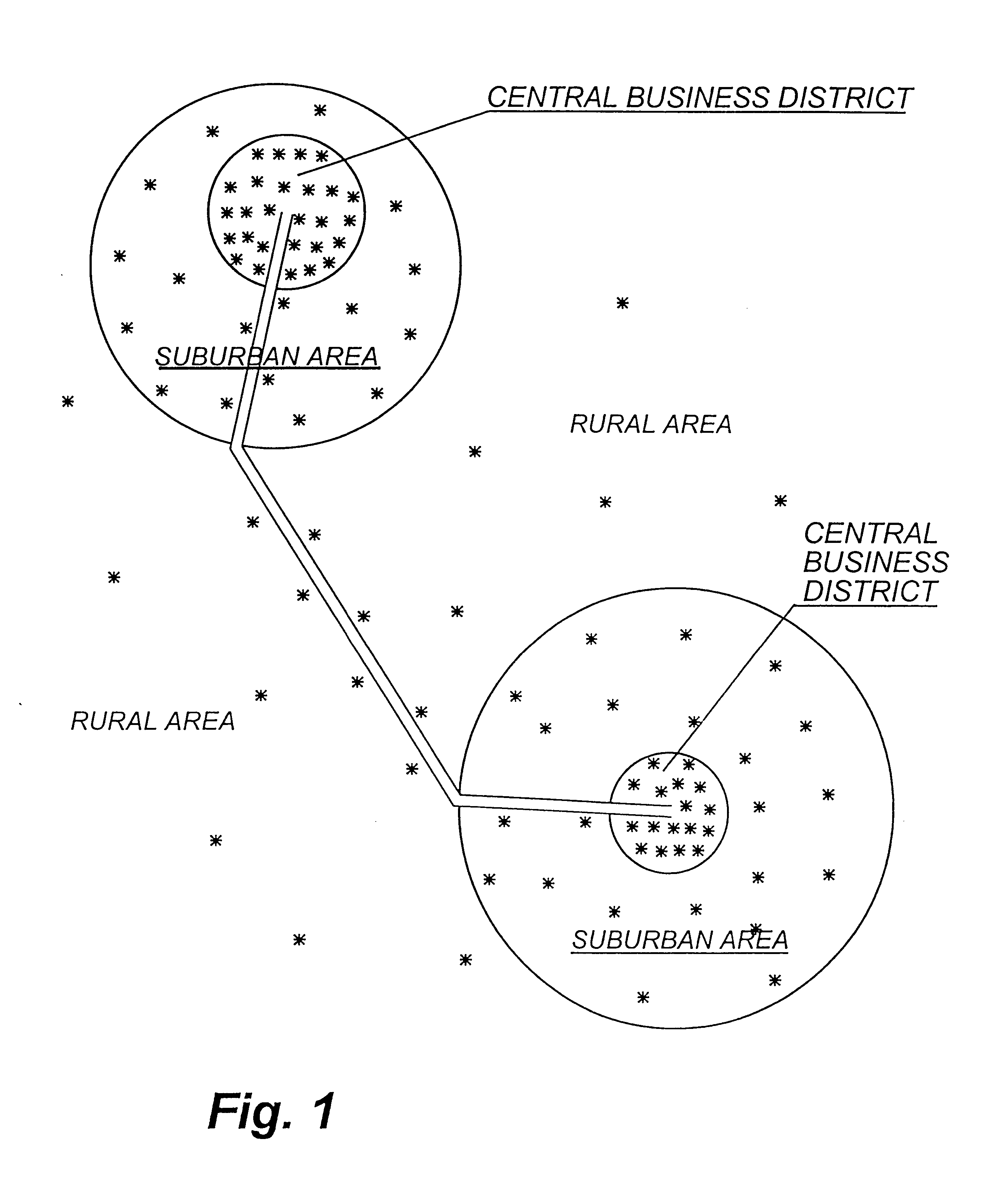

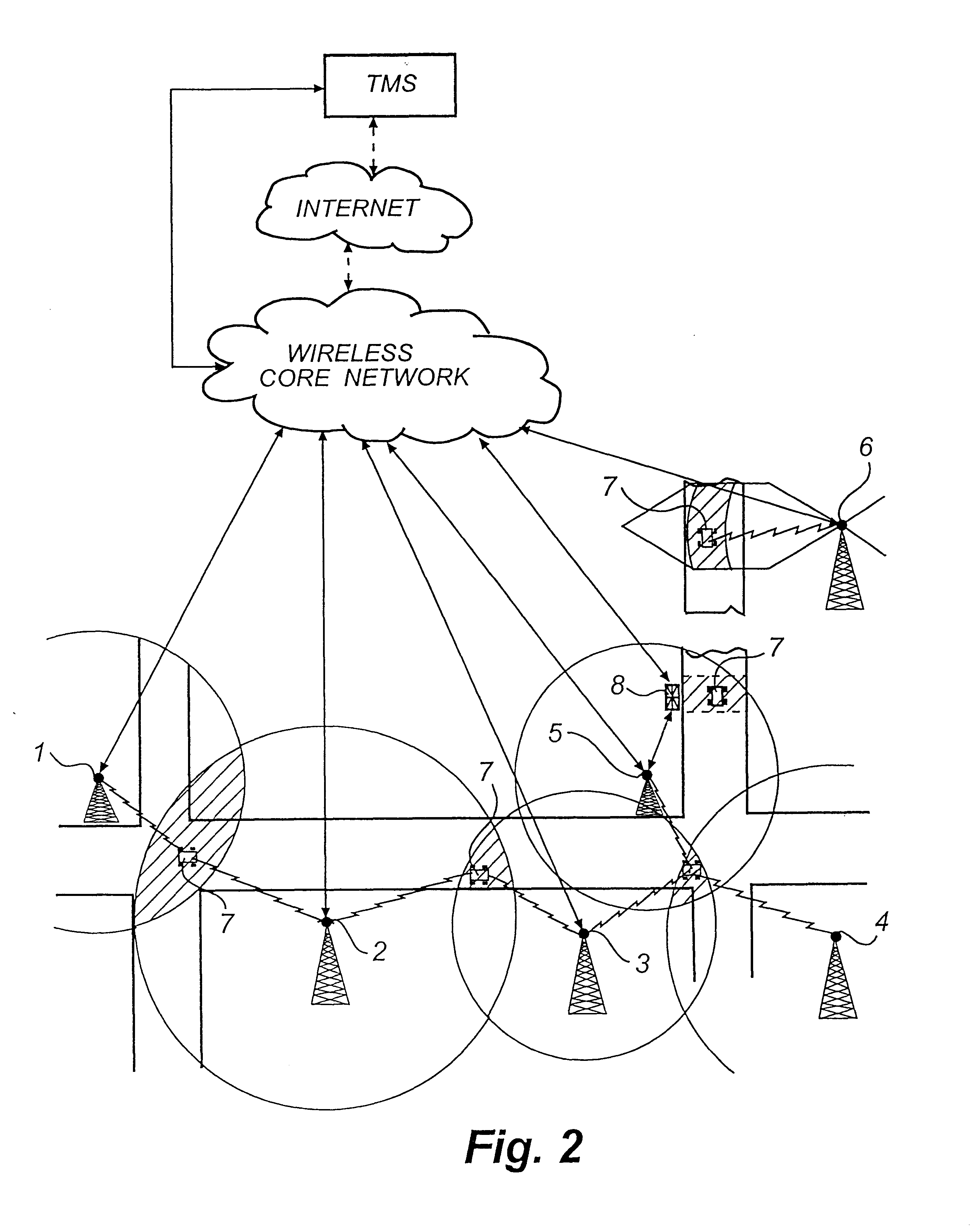

Traffic monitoring system and method

InactiveUS6505114B2High potential frequency reuseHigh densityAnalogue computers for vehiclesInstruments for road network navigationTraffic intensityTelecommunications network

A method and system for traffic monitoring and prediction of traffic intensity. The method comprises the steps of determining at least twice, within a specified time interval, geographical positions of a plurality of mobile devices in a mobile telecommunications network. This is done by means of measuring at least one property of signals transmitted between the mobile devices and base stations in the mobile telecommunications network. At least a subset of the geographical positions are compared with a route of a road provided in a route database in order to identify mobile devices having routes corresponding to at least a part of the road route. A velocity for the identified mobile devices based on the at least two positions, and the calculated velocity of at least one identified mobile device is compared with a reference velocity of the road in order to predict traffic intensity on the road. A system for short range monitoring is also provided.

Owner:STRATEGIC DESIGN FEDERATION W LLC

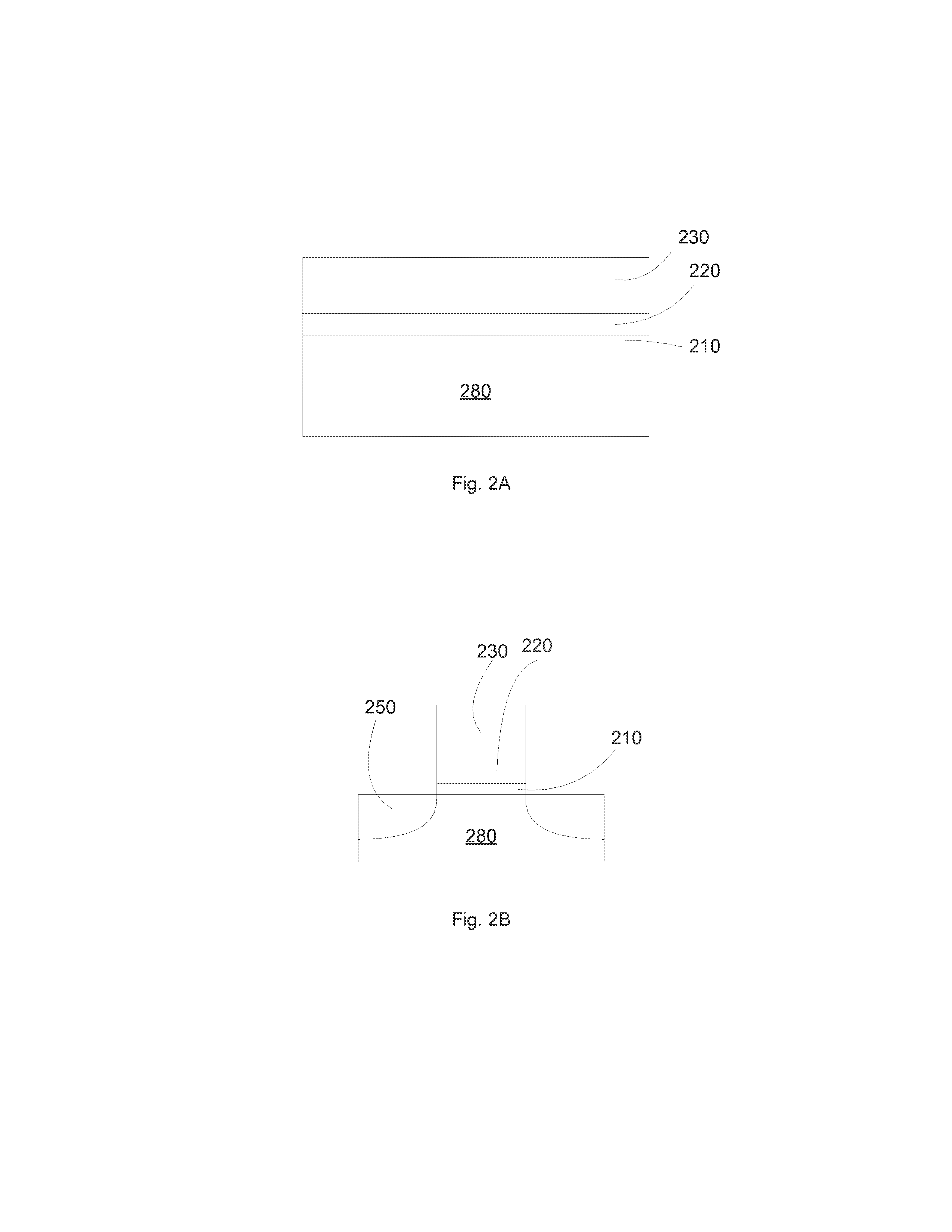

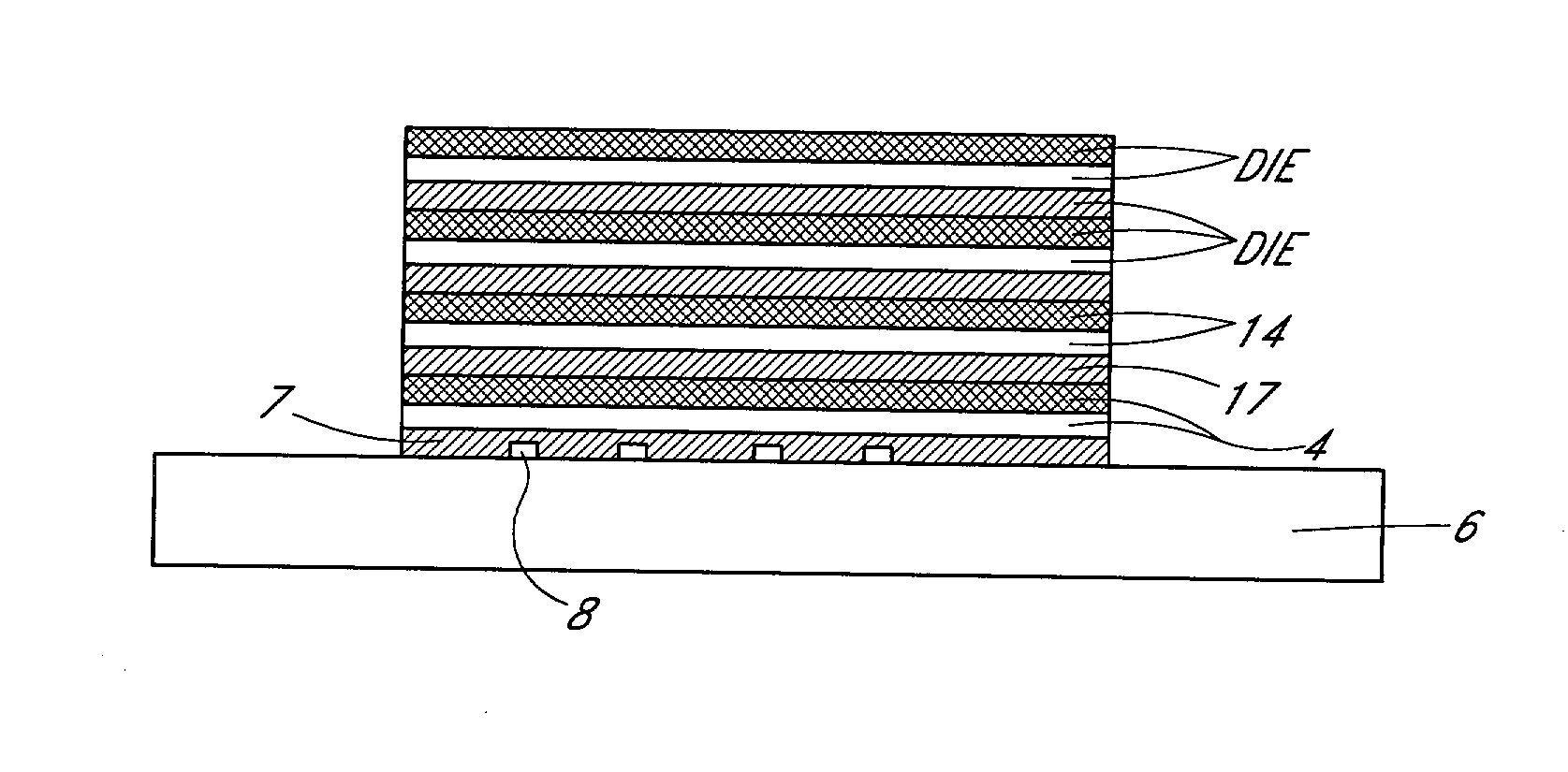

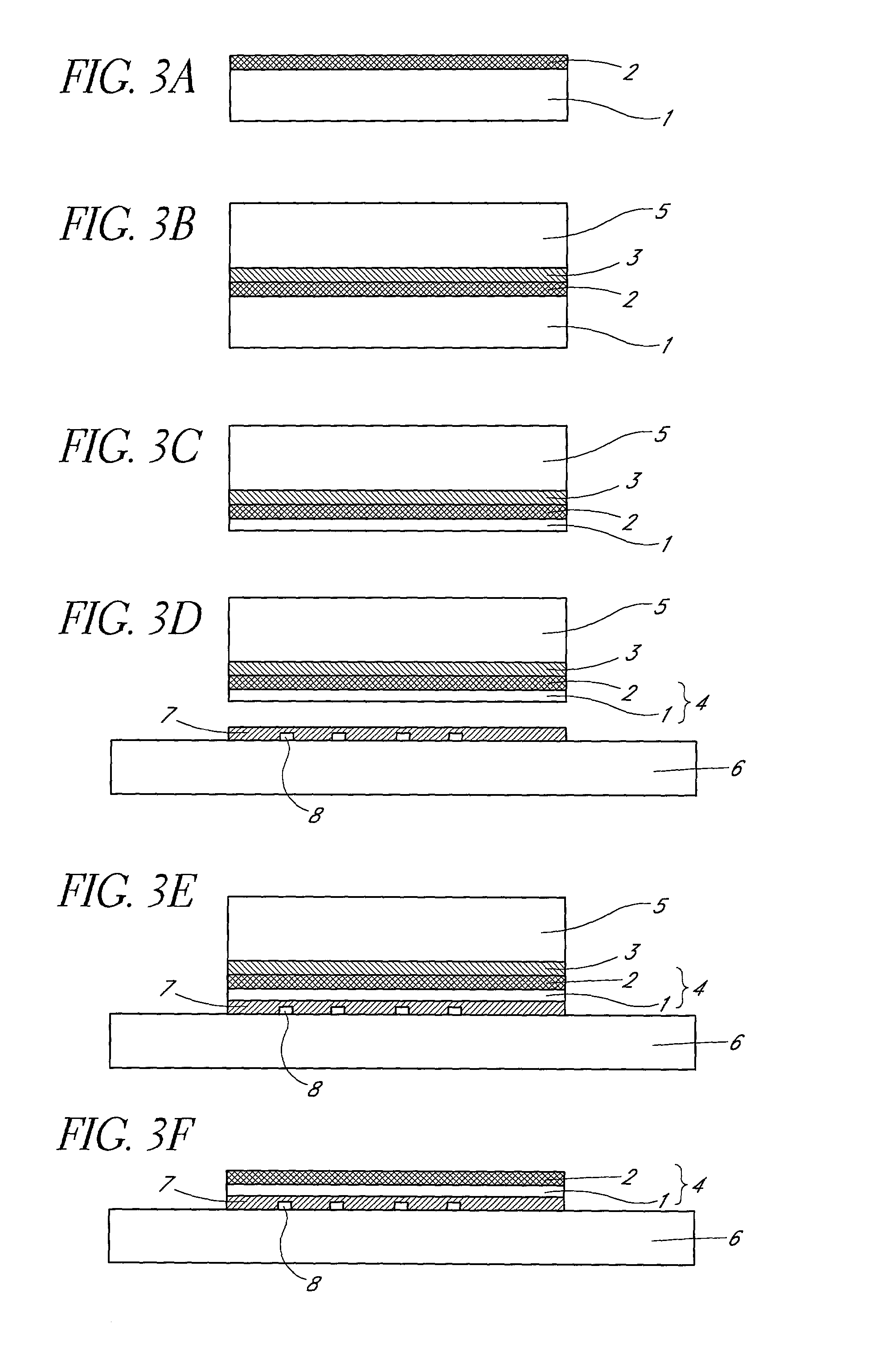

Method of transferring ultra-thin substrates and application of the method to the manufacture of a multi-layer thin film device

InactiveUS20030060034A1High densitySafe transferSemiconductor/solid-state device detailsSolid-state devicesPolymer adhesivePlanar substrate

The present invention provides a method of transfer of a first planar substrate with two major surfaces to a second substrate, comprising the steps of forming the first planar substrate, attaching one of the major surfaces of the first planar substrate to a carrier by means of a release layer attaching the other major surface of the first substrate to the second substrate with a curable polymer adhesive layer partly curing the polymer adhesive layer, disconnecting the release layer from the first substrate to separate the first substrate from the carrier, followed by curing the polymer adhesive layer. The method may be used to form a stack of dies (4, 14 . . . ) which are adhered together by cured polymeric layers (7, 17). Each die (4, 14 . . . ) may include a device layer and an ultra-thin substrate manufactured and assembled by the method described above.

Owner:INTERUNIVIR MICRO ELEKTRONICA CENTRYM VZW IMEC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com