Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

163549results about "Semiconductor/solid-state device details" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

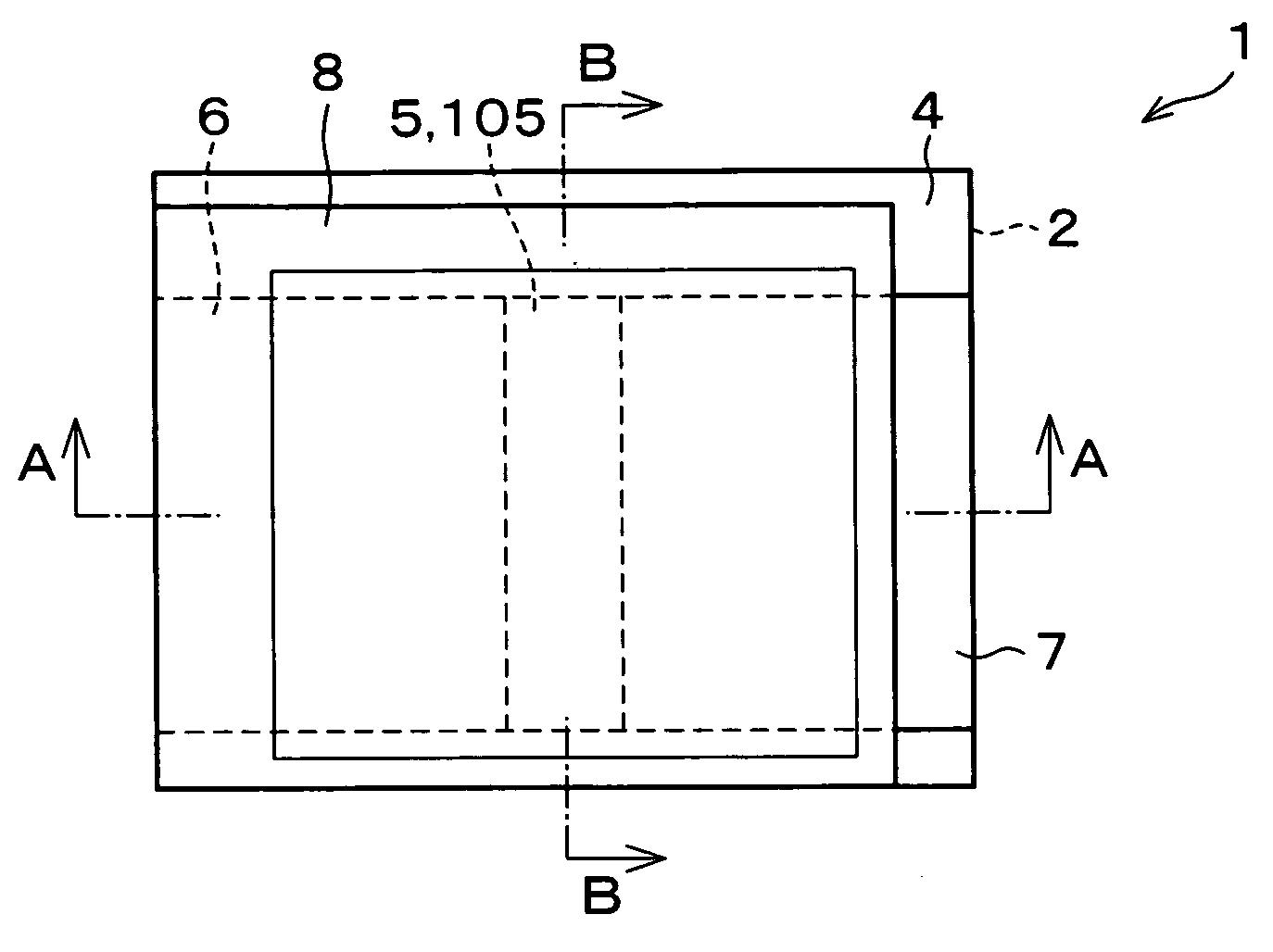

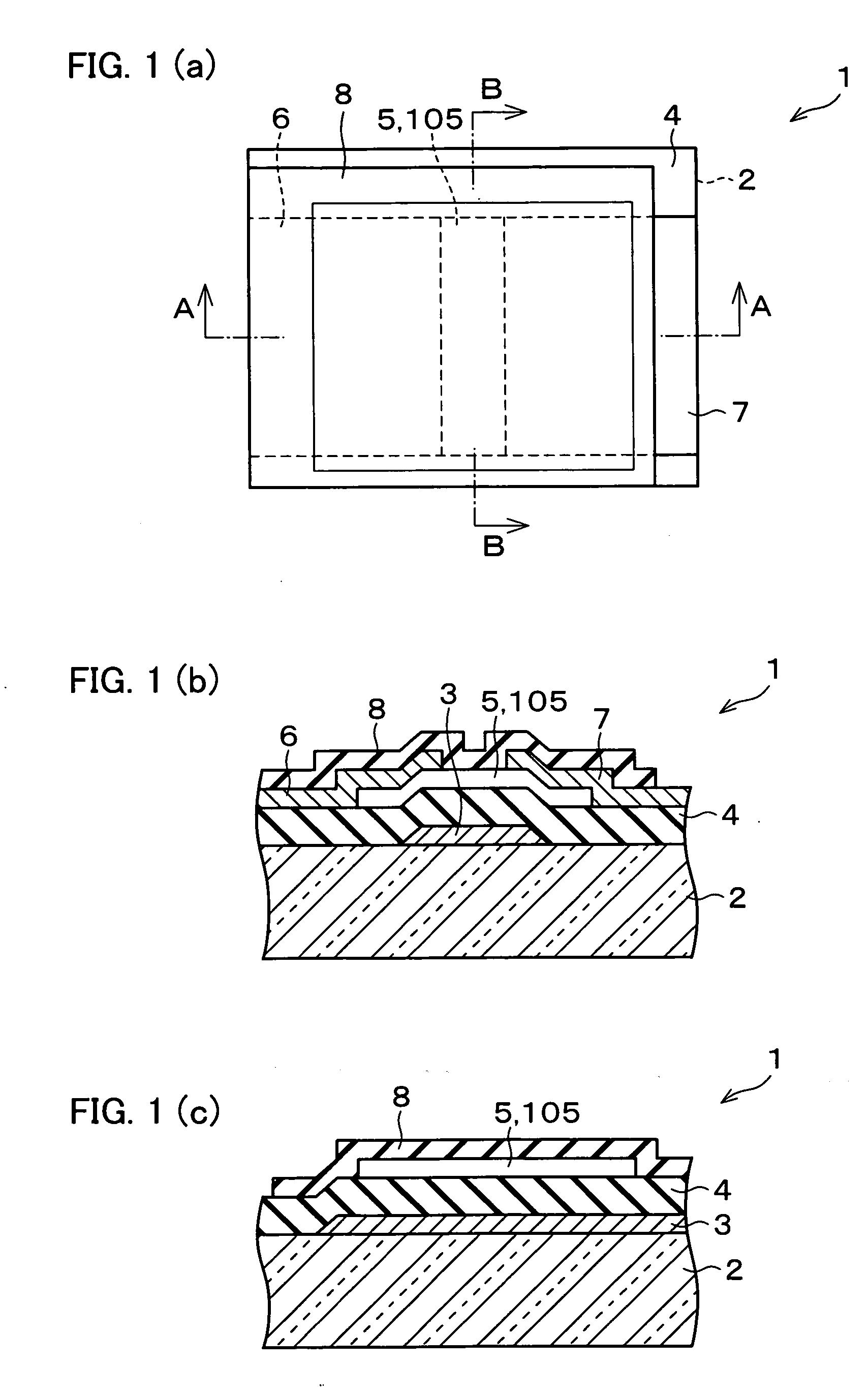

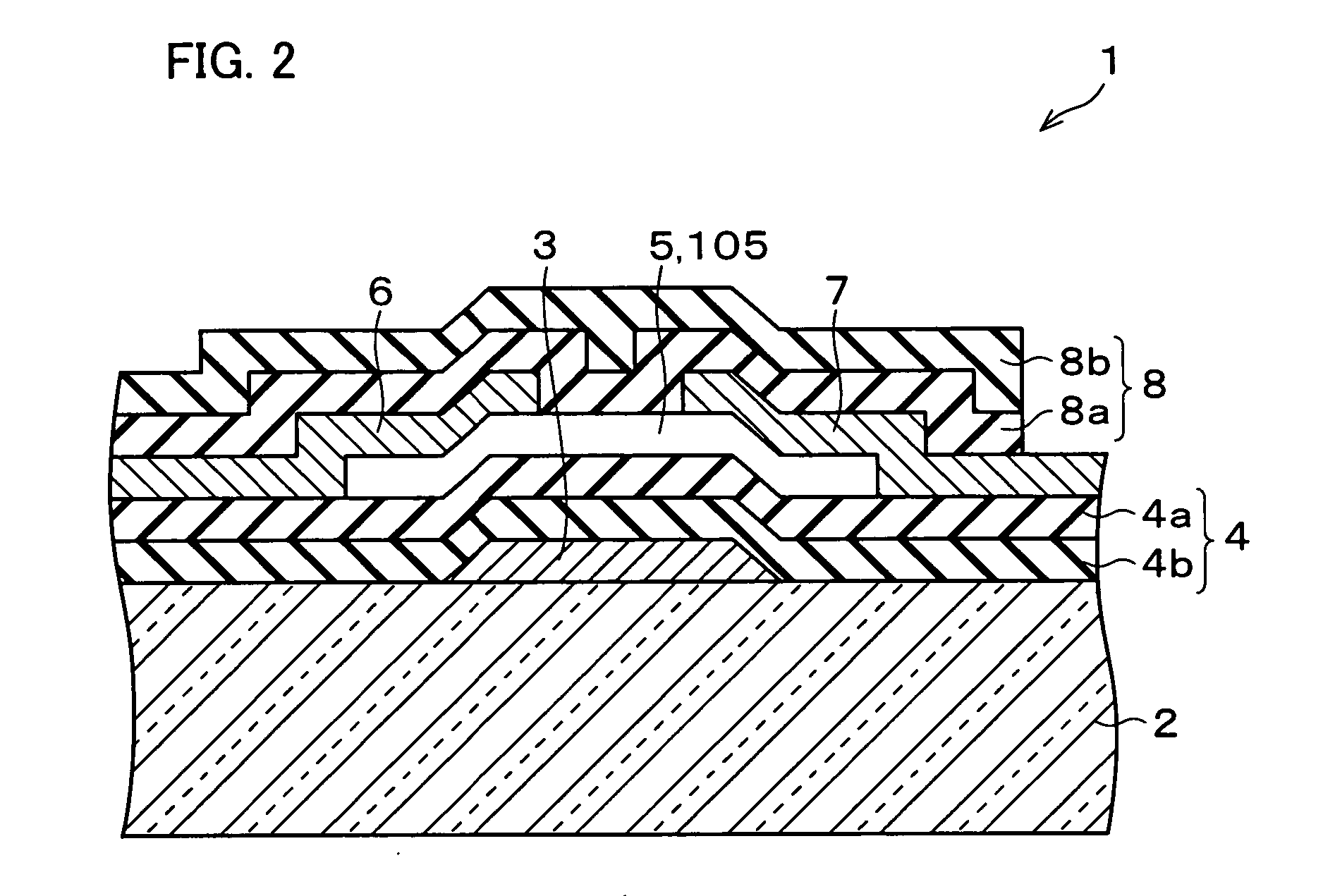

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

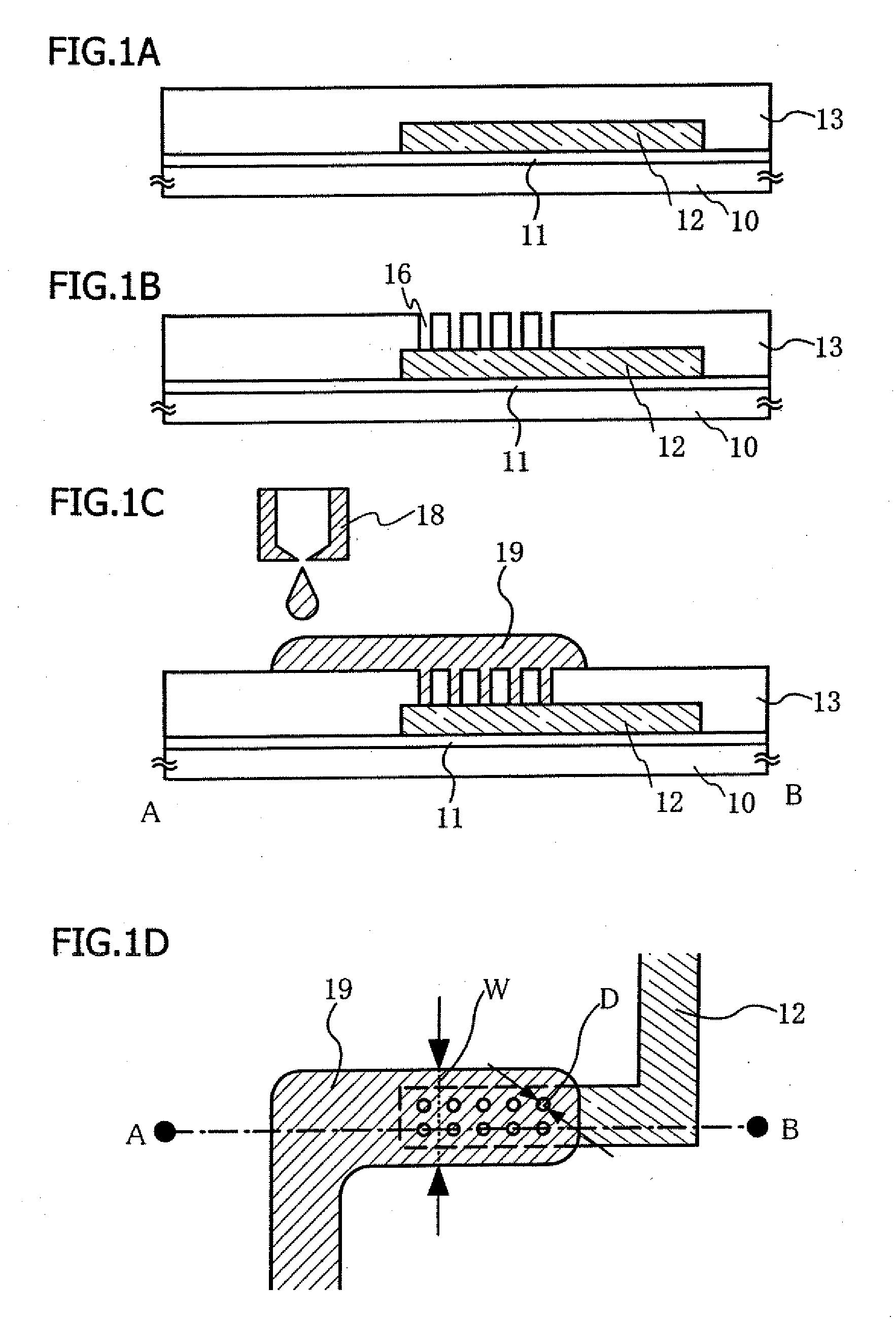

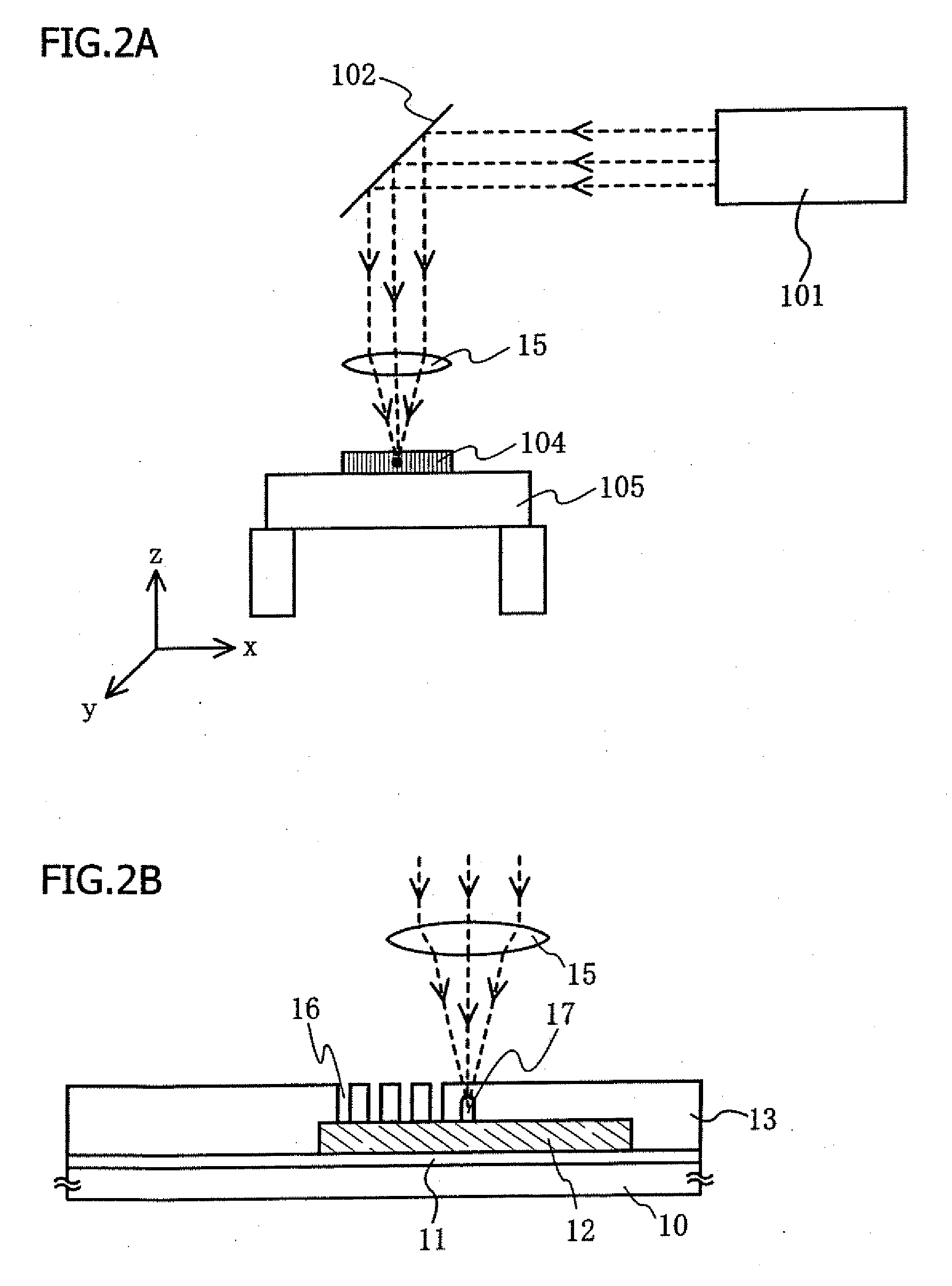

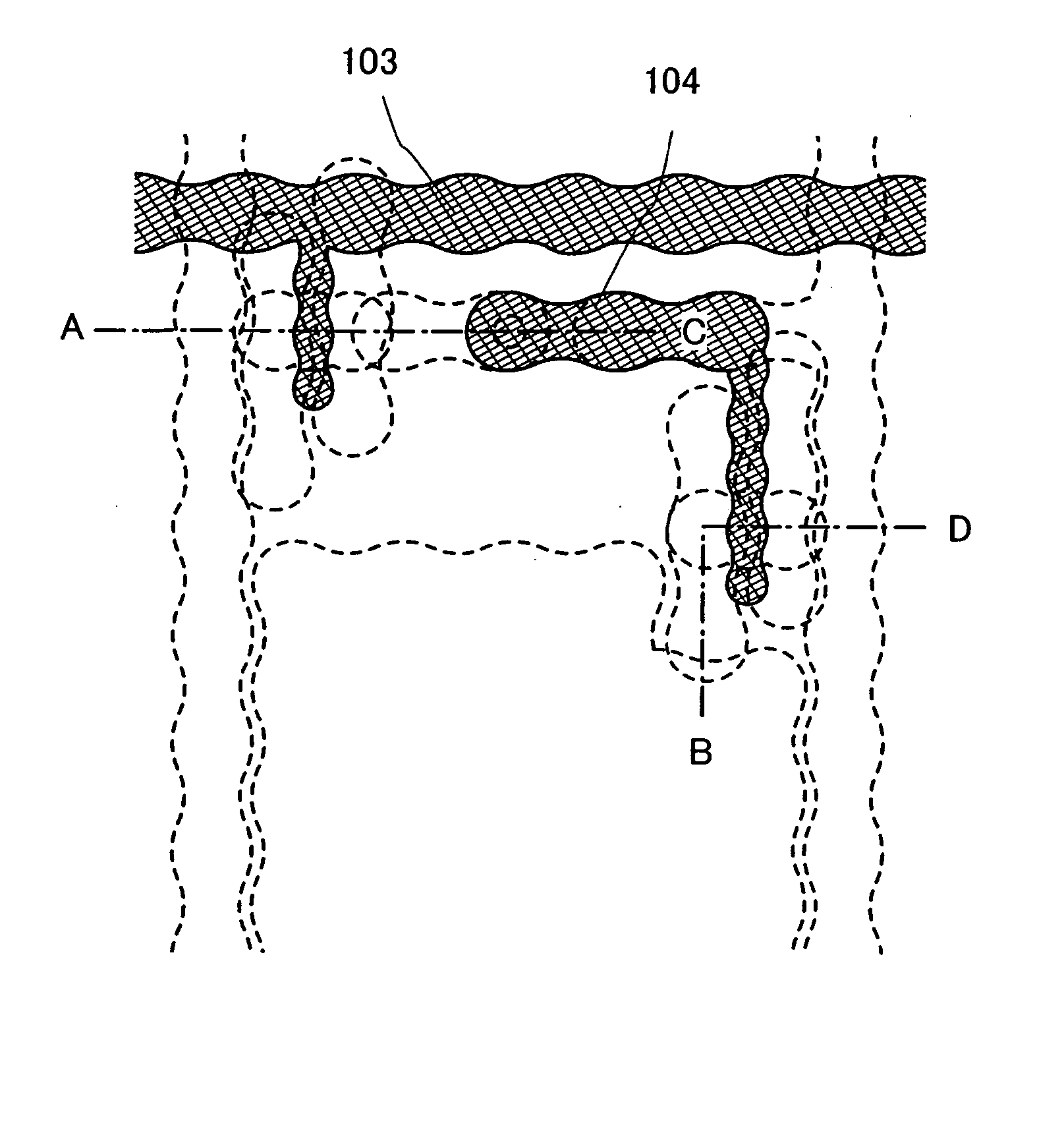

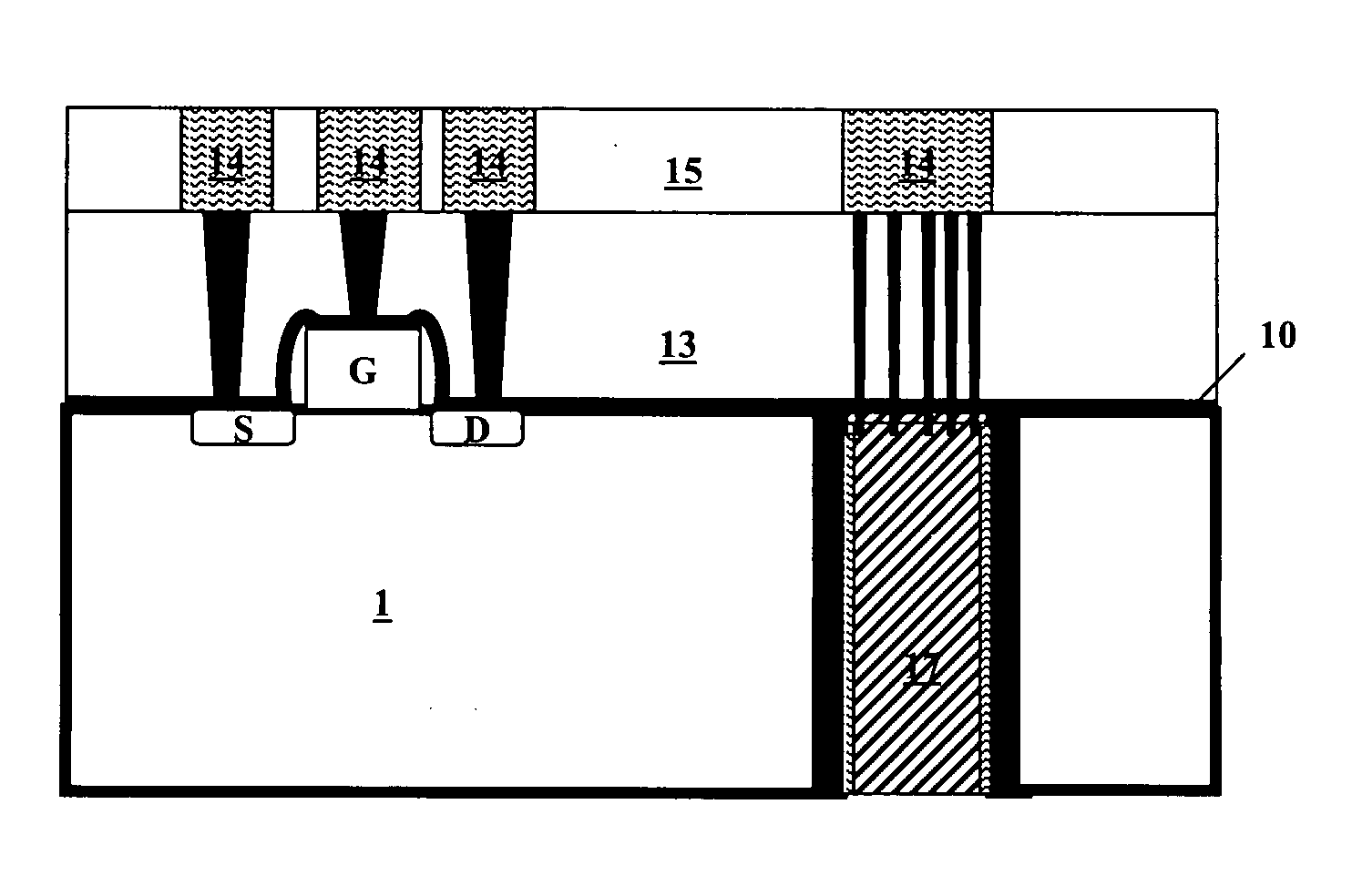

Semiconductor device and method for manufacturing the same, and electric device

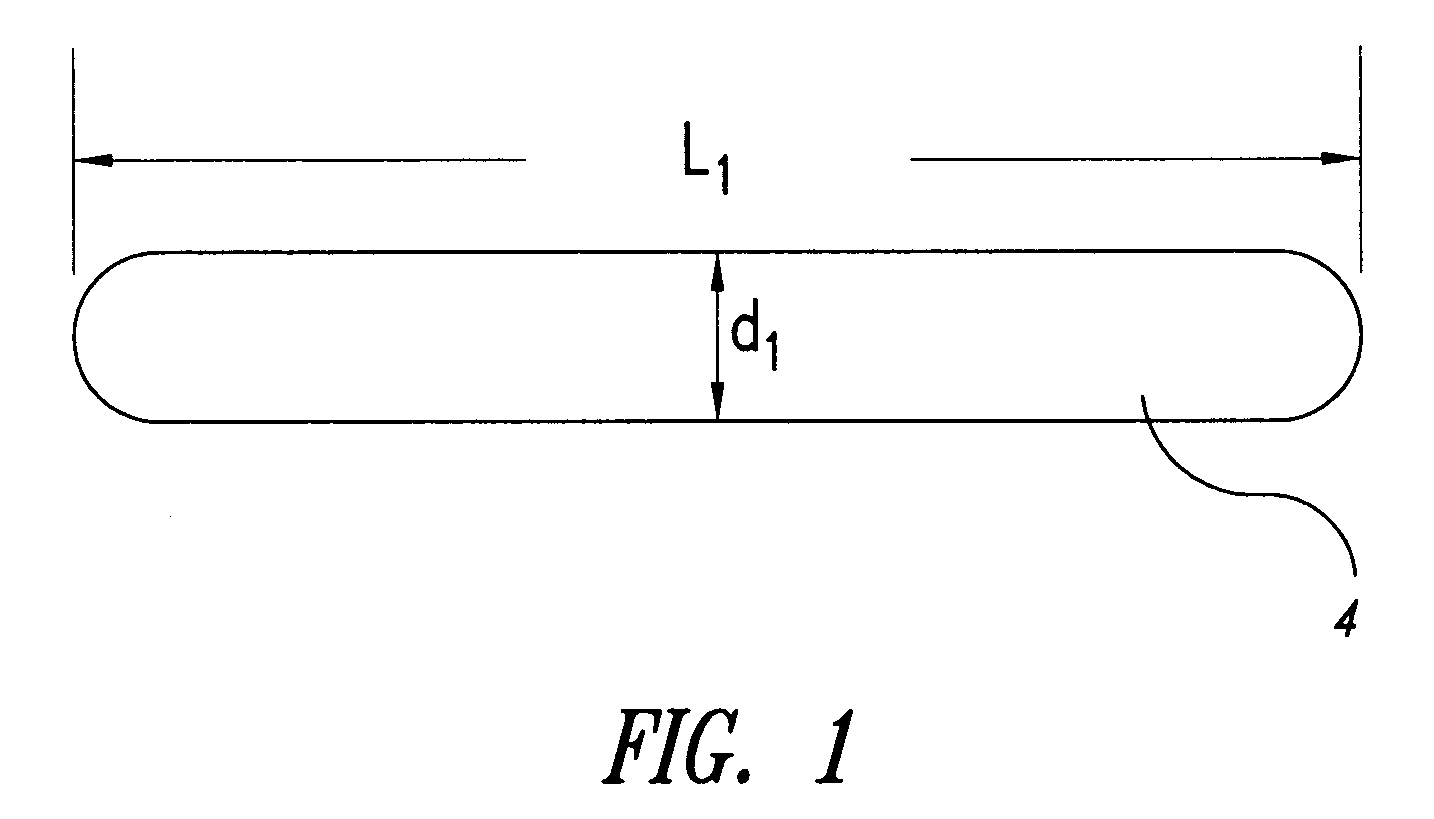

InactiveUS20090073325A1Simple stepsHighly integratedTransistorTelevision system detailsElectrical resistance and conductanceLongest Diameter

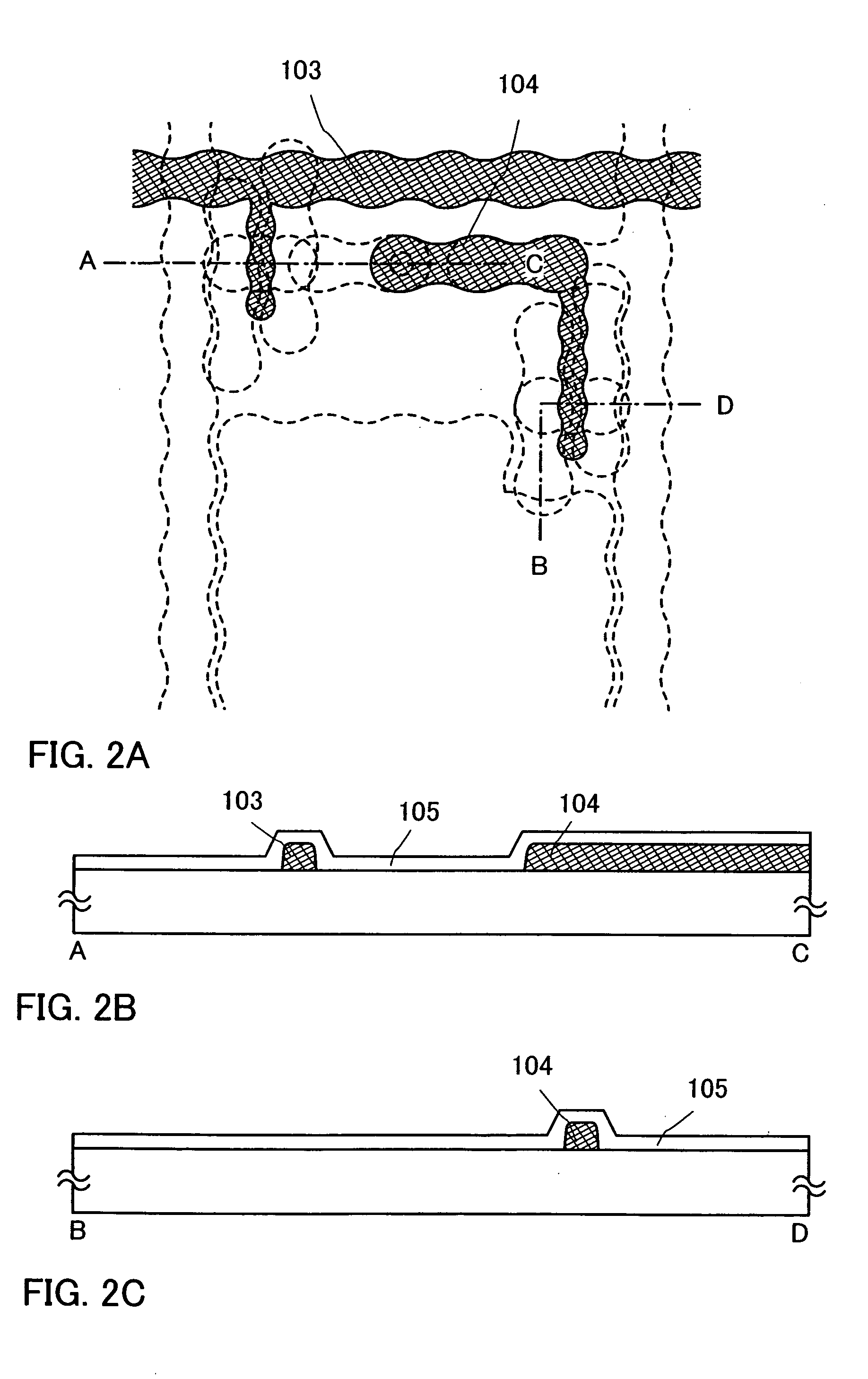

It is an object of the present invention to simplify steps needed to process a wiring in forming a multilayer wiring. In addition, when a droplet discharging technique or a nanoimprint technique is used to form a wiring in a contact hole having a comparatively long diameter, the wiring in accordance with the shape of the contact hole is formed, and the wiring portion of the contact hole is likely to have a depression compared with other portions. A penetrating opening is formed by irradiating a light-transmitting insulating film with laser light having high intensity and a pulse high in repetition frequency. A plurality of openings having a minute contact area is provided instead of forming one penetrating opening having a large contact area to have an even thickness of a wiring by reducing a partial depression and also to ensure contact resistance.

Owner:SEMICON ENERGY LAB CO LTD

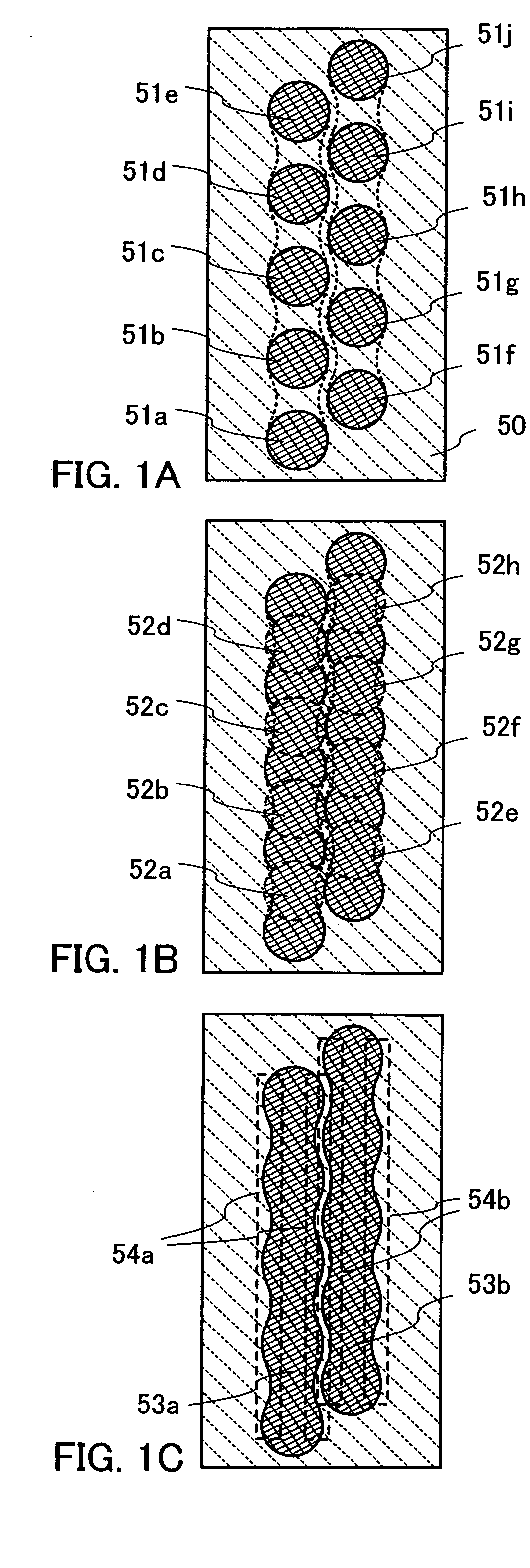

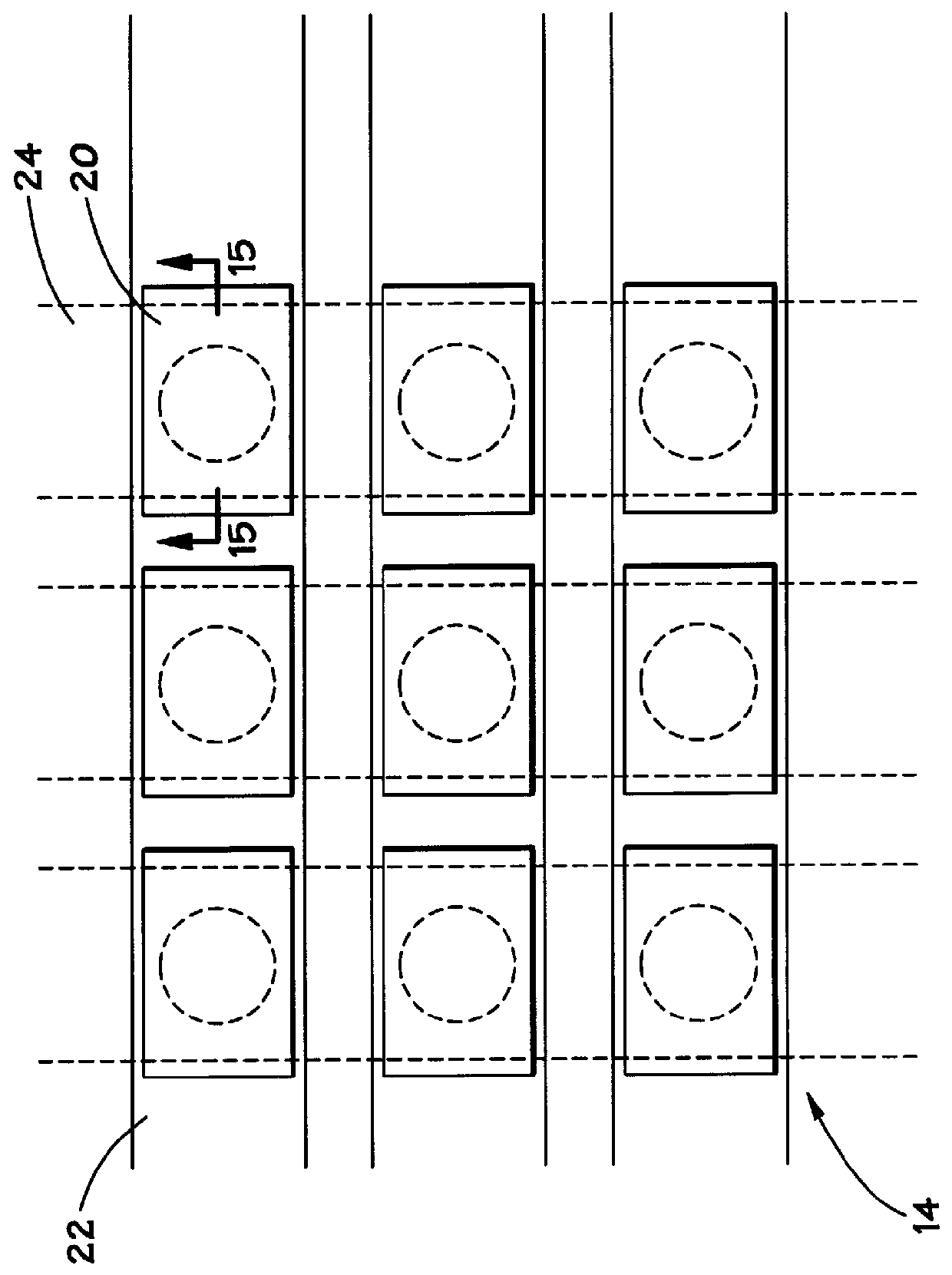

Semiconductor device, electronic device, and method of manufacturing semiconductor device

InactiveUS20060170111A1Stable formationImprove performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialShortest distance

Conductive layers having knots are adjacently formed with uniform distance therebetween. Droplets of the conductive layers are discharged to stagger centers of the droplets in a length direction of wirings so that the centers of the discharged droplets are not on the same line in a line width direction between the adjacent conductive layers. Since the centers of the droplets are staggered, parts of the conductive layers each having a widest line width (the widest width of knot) are not connected to each other, and the conductive layers can be formed adjacently with a shorter distance therebetween.

Owner:SEMICON ENERGY LAB CO LTD

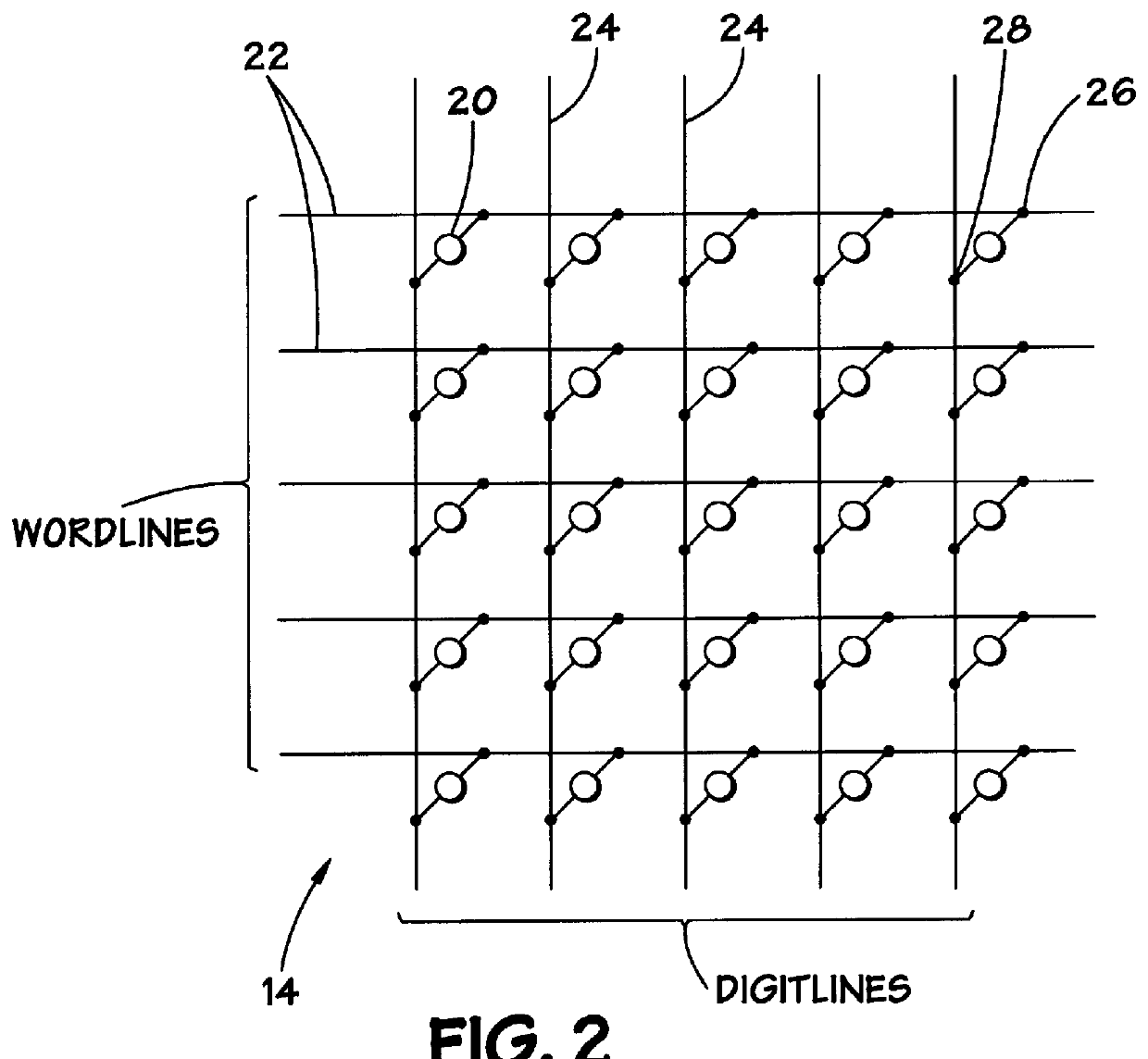

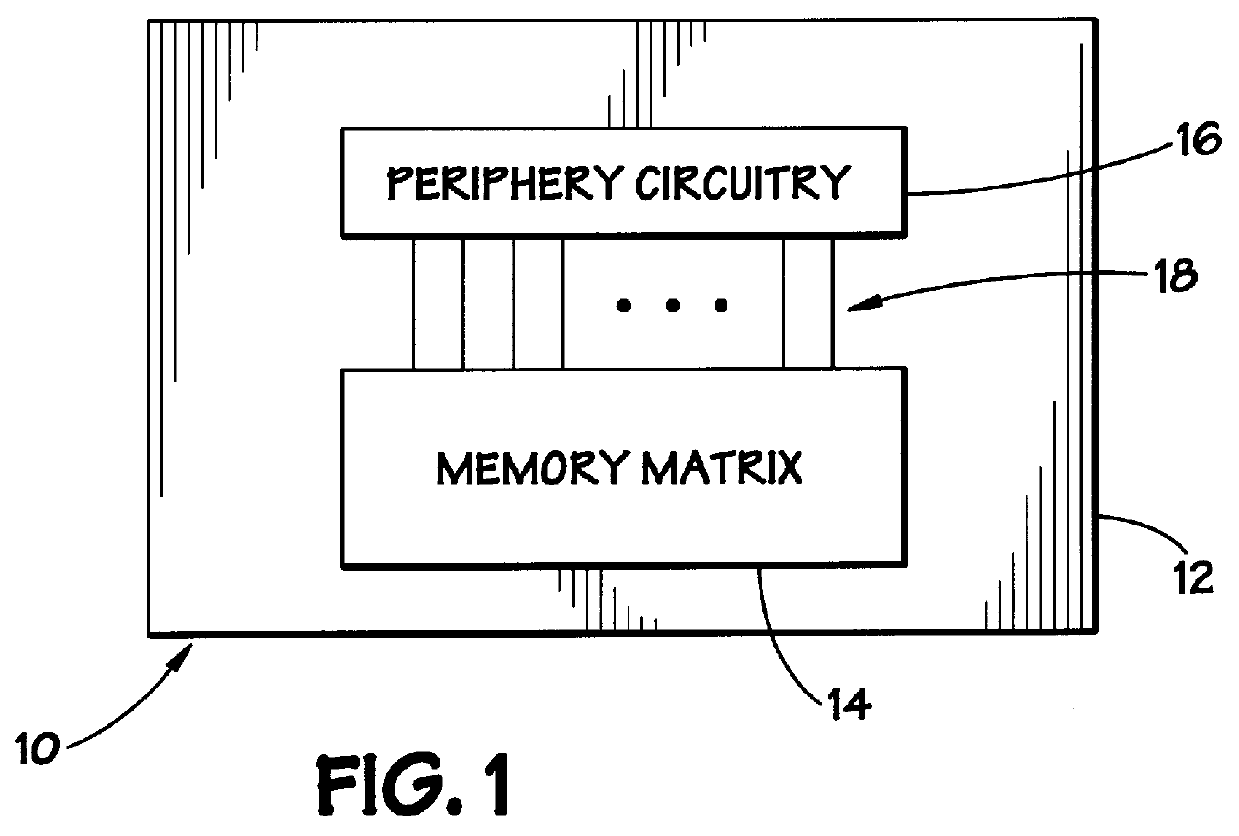

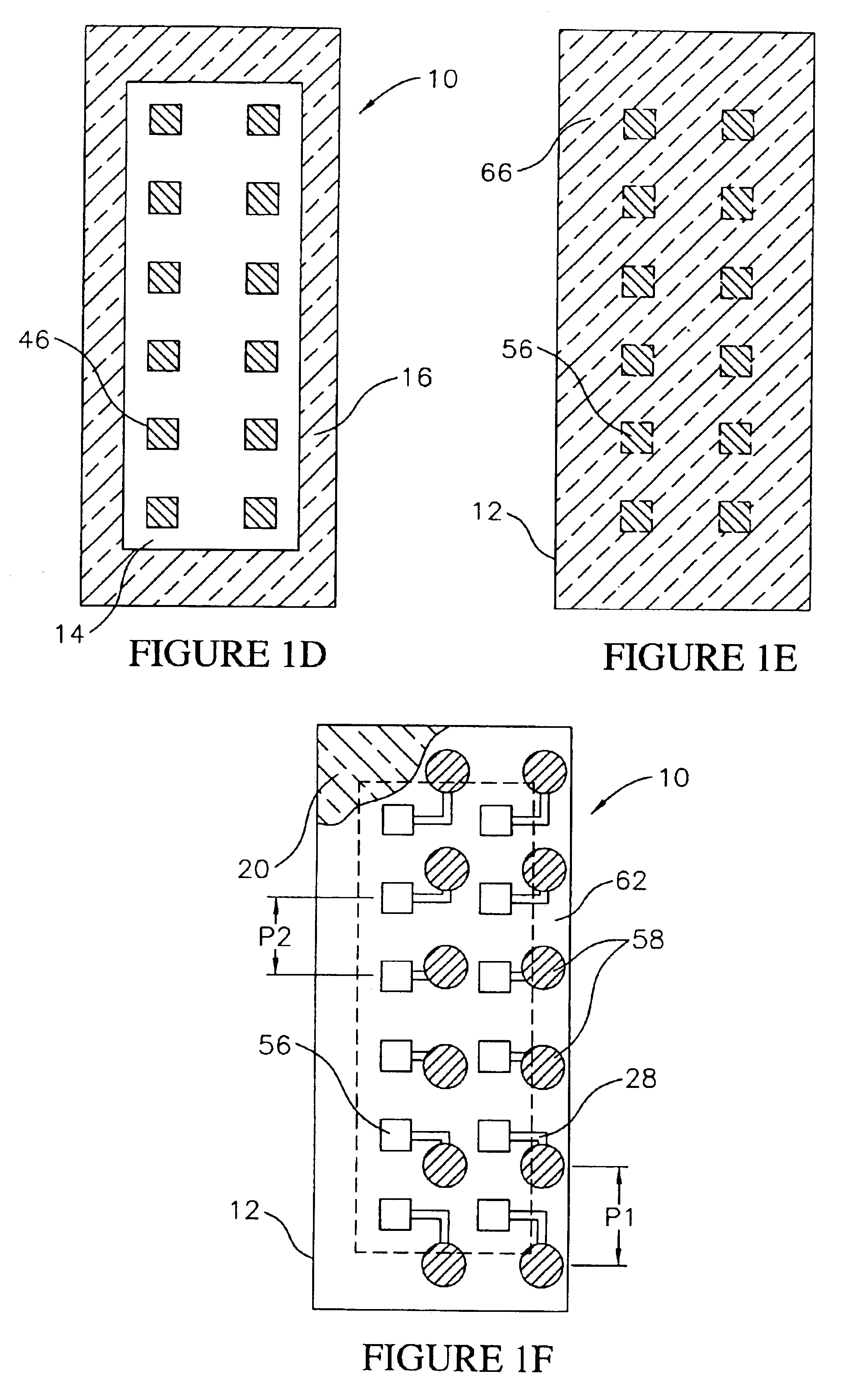

Contact structure and memory element incorporating the same

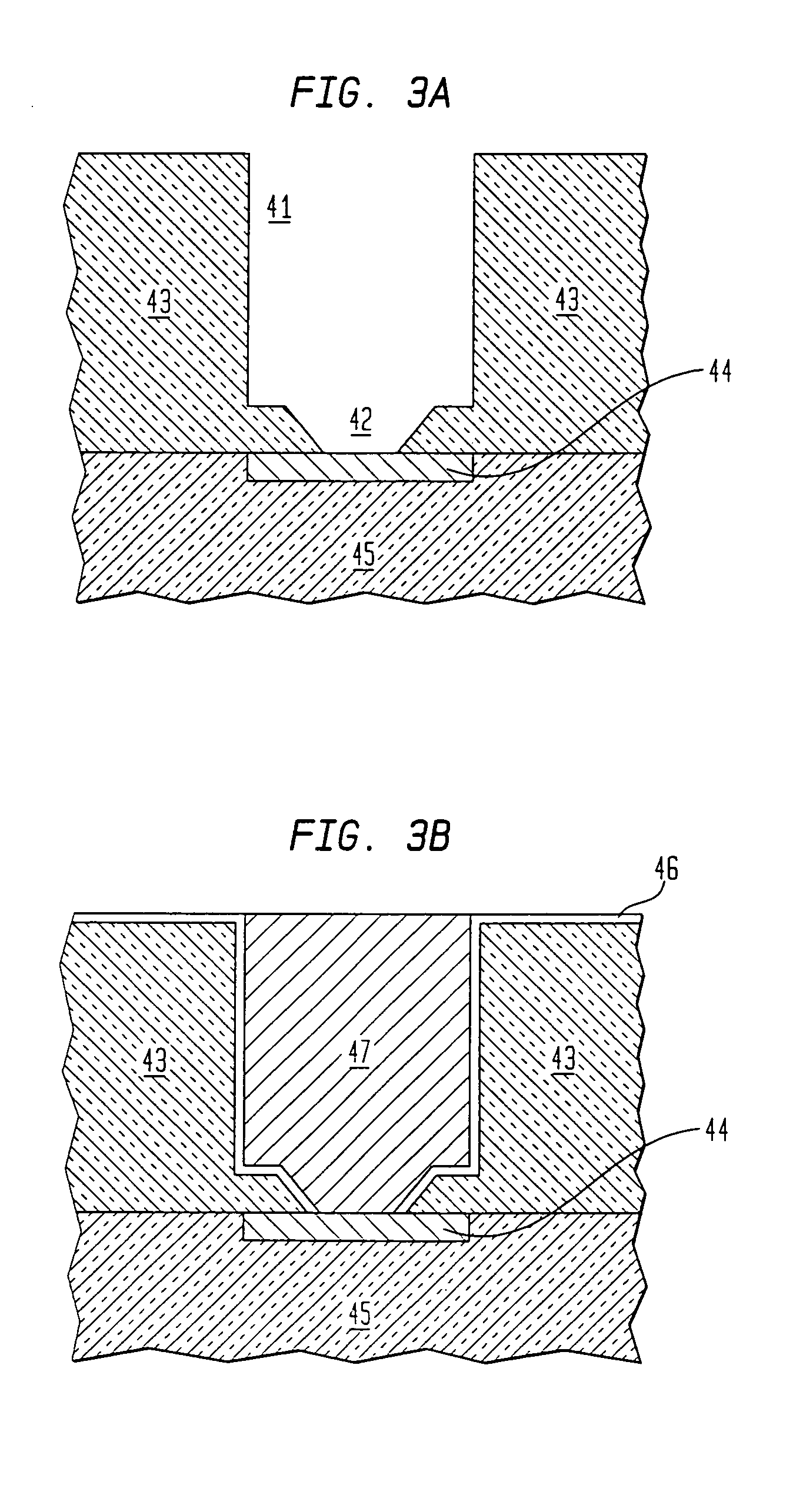

InactiveUS6031287ASemiconductor/solid-state device detailsSolid-state devicesChemical-mechanical planarizationEtching

Annular and linear contact structures are described which exhibit a greatly reduced susceptibility to process deviations caused by lithographic and deposition variations than does a conventional circular contact plug. In one embodiment, a standard conductive material such as carbon or titanium nitride is used to form the contact. In an alternative embodiment, a memory material itself is used to form the contact. These contact structures may be made by various processes, including chemical mechanical planarization and facet etching.

Owner:ROUND ROCK RES LLC

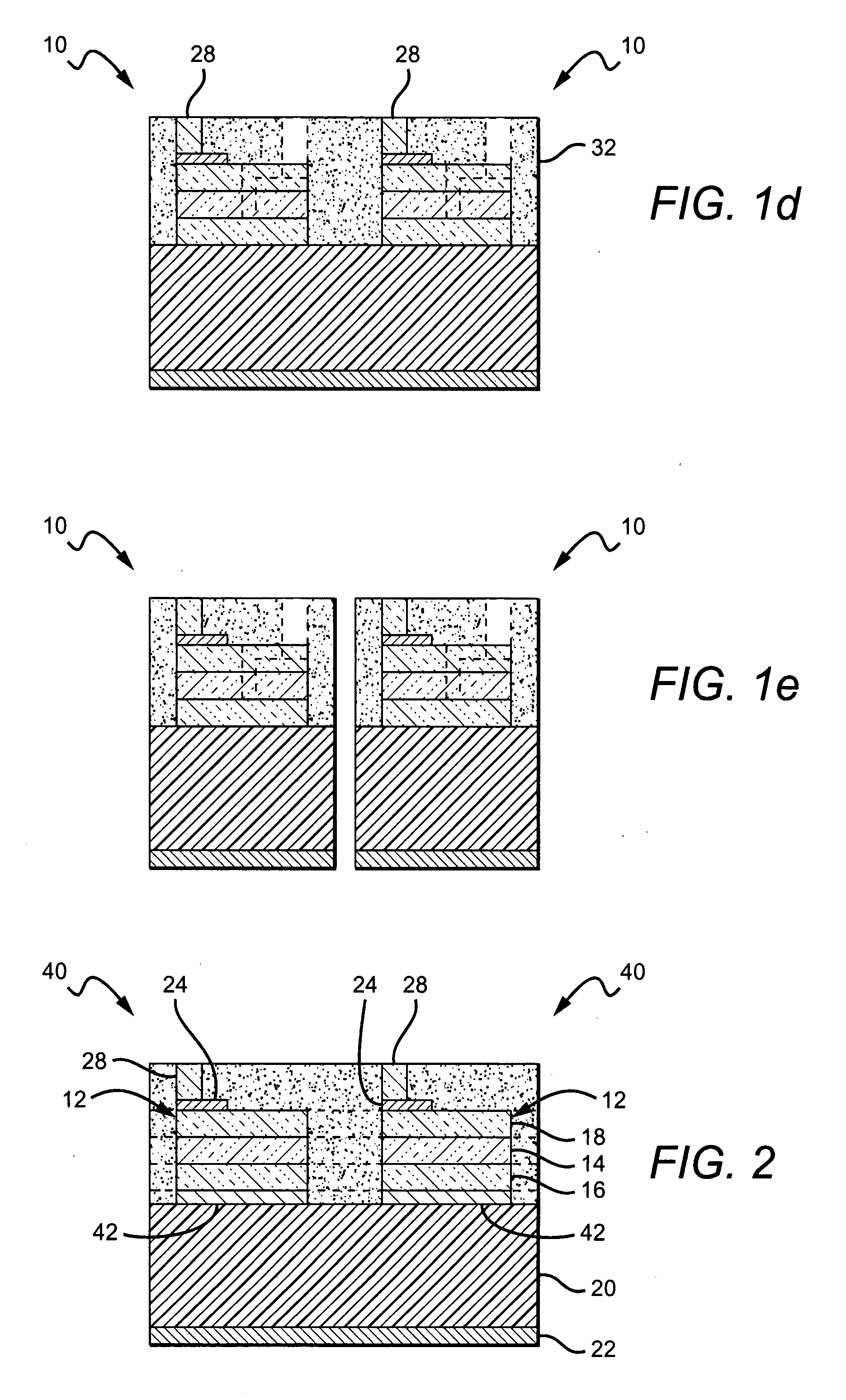

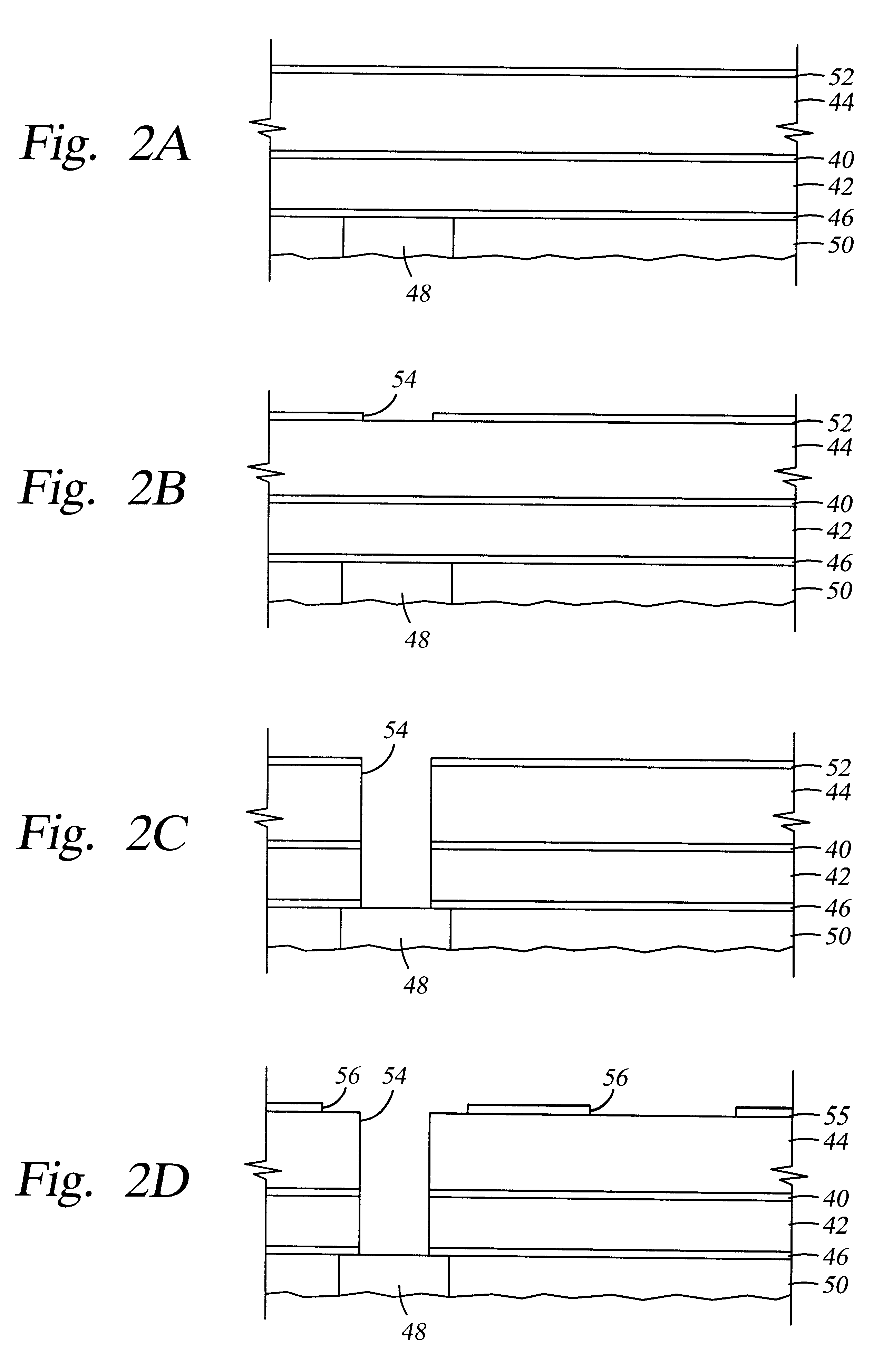

Wafer level phosphor coating method and devices fabricated utilizing method

ActiveUS20080173884A1Semiconductor/solid-state device detailsSolid-state devicesPhosphorLight-emitting diode

Methods for fabricating light emitting diode (LED) chips comprising providing a plurality of LEDs typically on a substrate. Pedestals are deposited on the LEDs with each of the pedestals in electrical contact with one of the LEDs. A coating is formed over the LEDs with the coating burying at least some of the pedestals. The coating is then planarized to expose at least some of the buried pedestals while leaving at least some of said coating on said LEDs. The exposed pedestals can then be contacted such as by wire bonds. The present invention discloses similar methods used for fabricating LED chips having LEDs that are flip-chip bonded on a carrier substrate and for fabricating other semiconductor devices. LED chip wafers and LED chips are also disclosed that are fabricated using the disclosed methods.

Owner:CREELED INC

Nanowires-based transparent conductors

ActiveUS20070074316A1Improve drawing legibilityMaterial nanotechnologyFrom normal temperature solutionsElectrical conductorNanowire

Owner:CHAMP GREAT INTL

High-density three-dimensional memory cell

InactiveUS6952030B2High densityReduce the overall heightTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

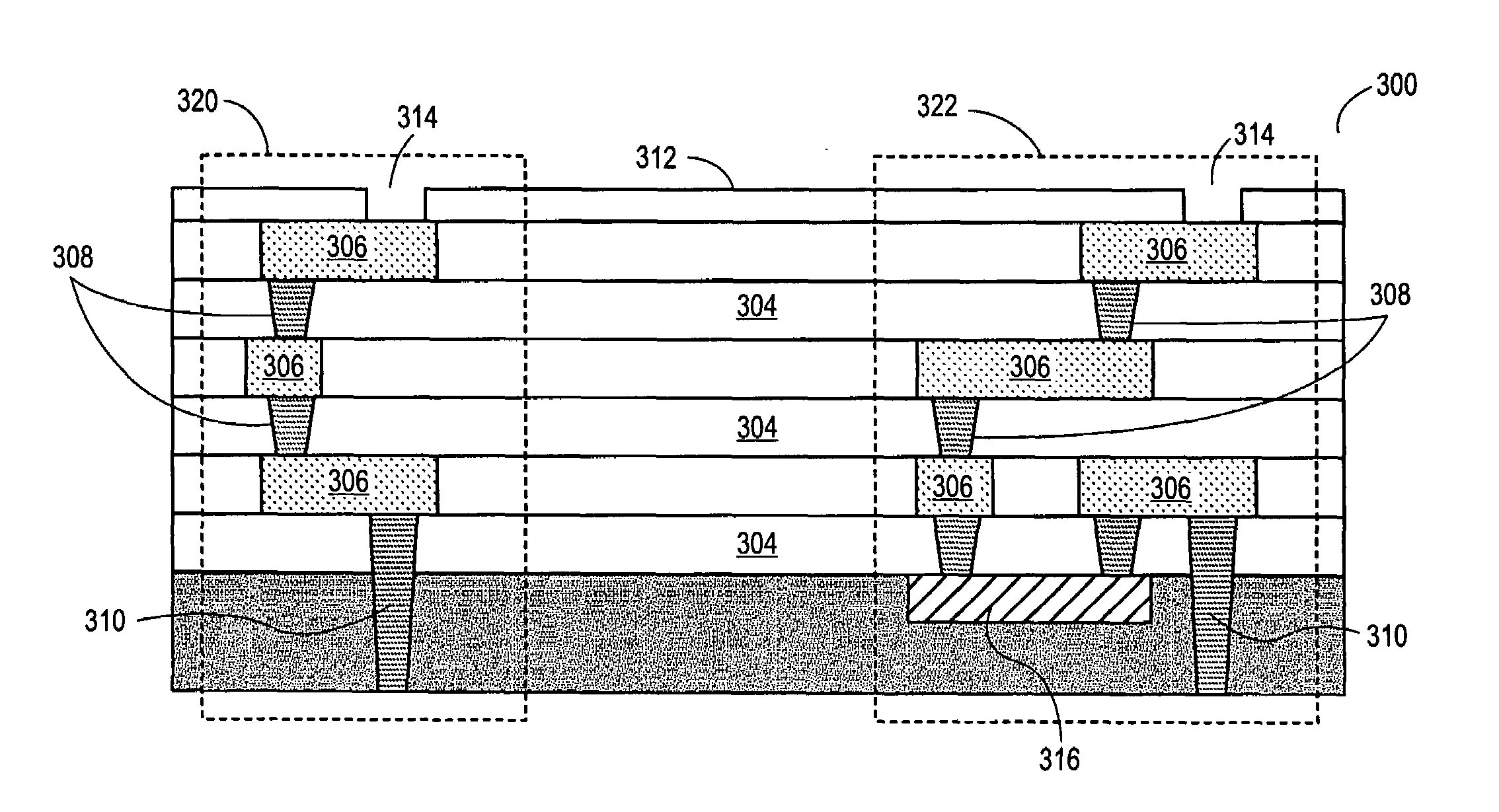

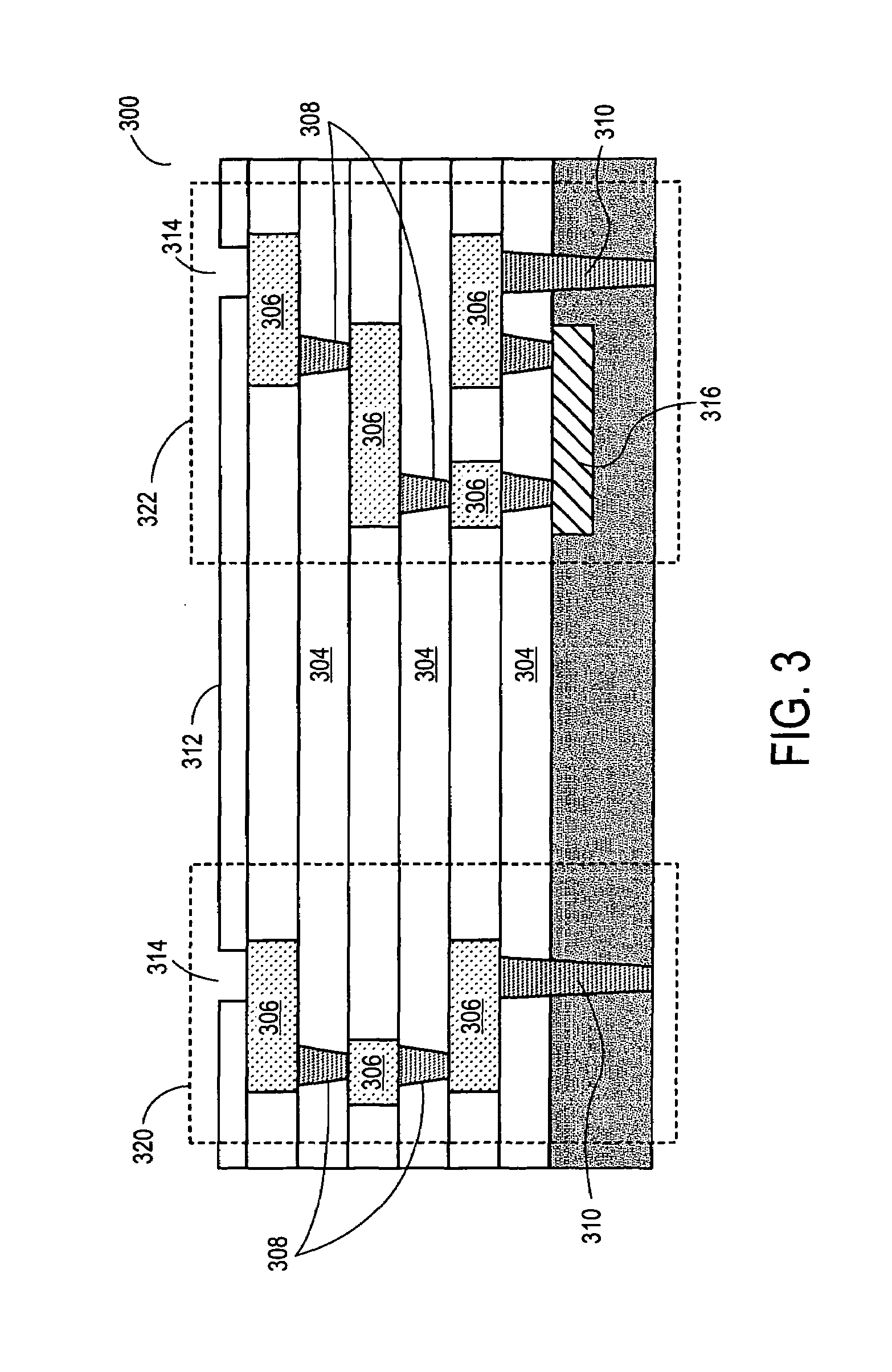

A three dimensional monolithic memory comprising a memory cell allowing for increased density is disclosed. In the memory cell of the present invention, a bottom conductor preferably comprising tungsten is formed. Above the bottom conductor a semiconductor element preferably comprises two diode portions and an antifuse. Above the semiconductor element are additional conductors and semiconductor elements in multiple stones of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

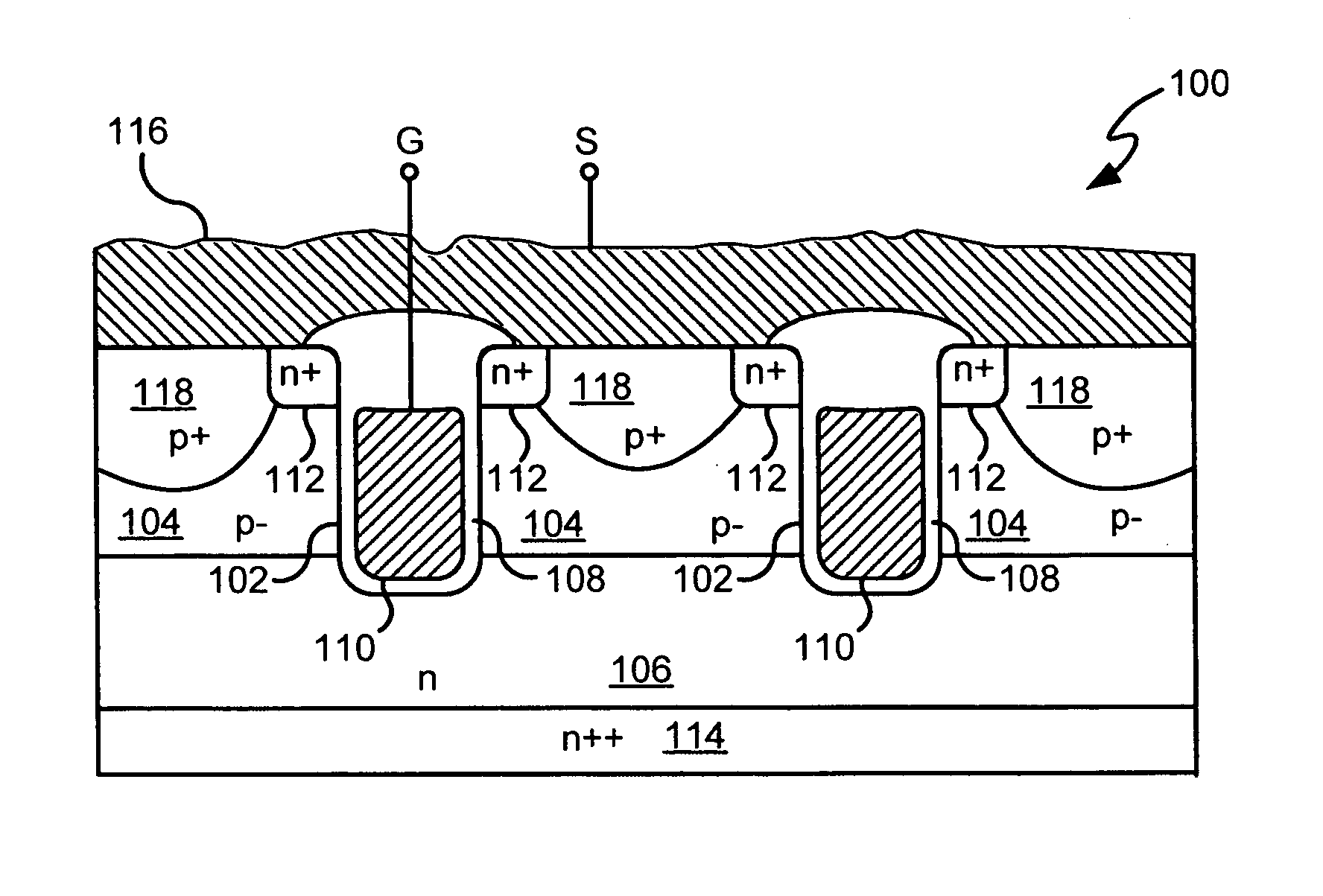

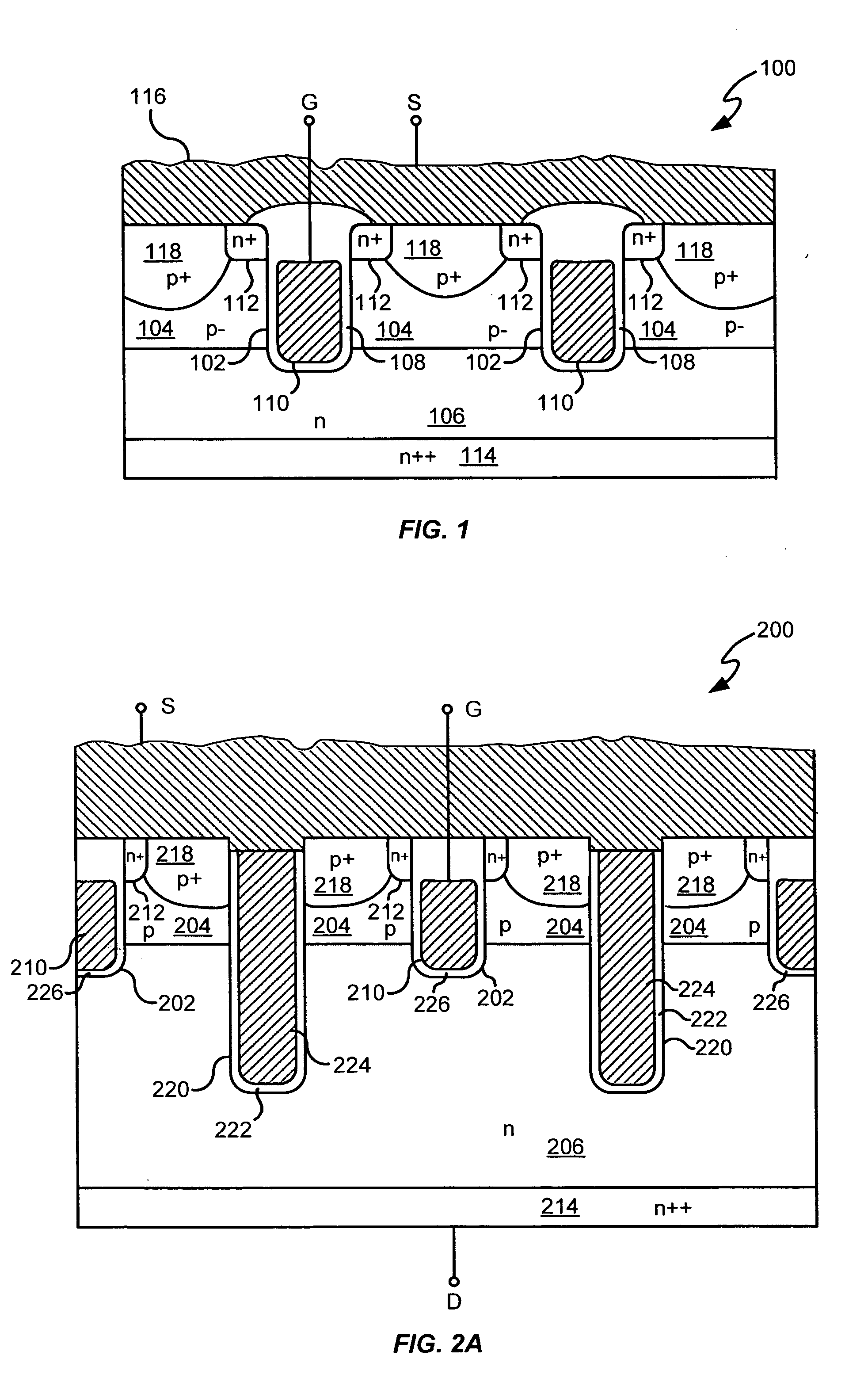

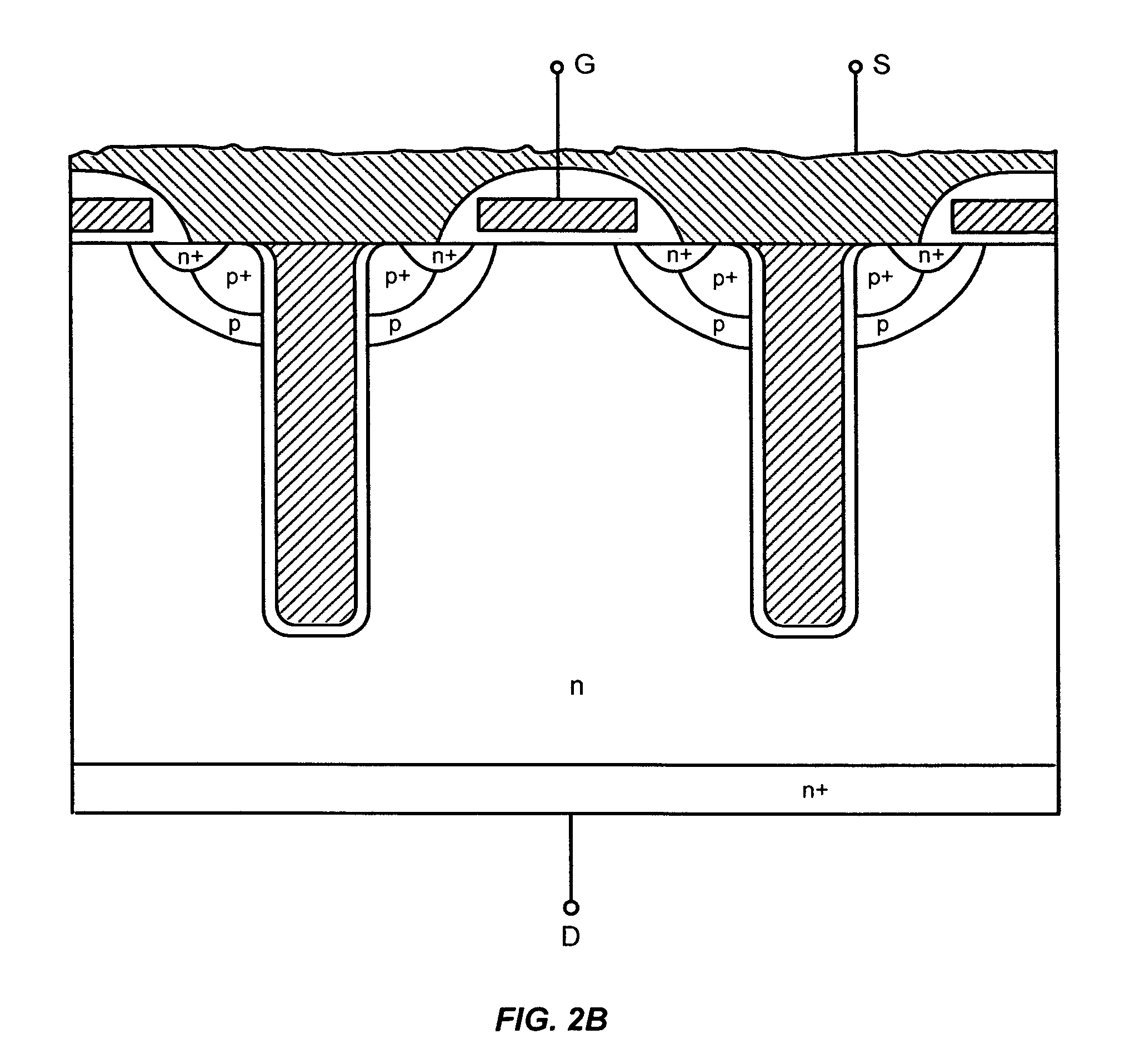

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

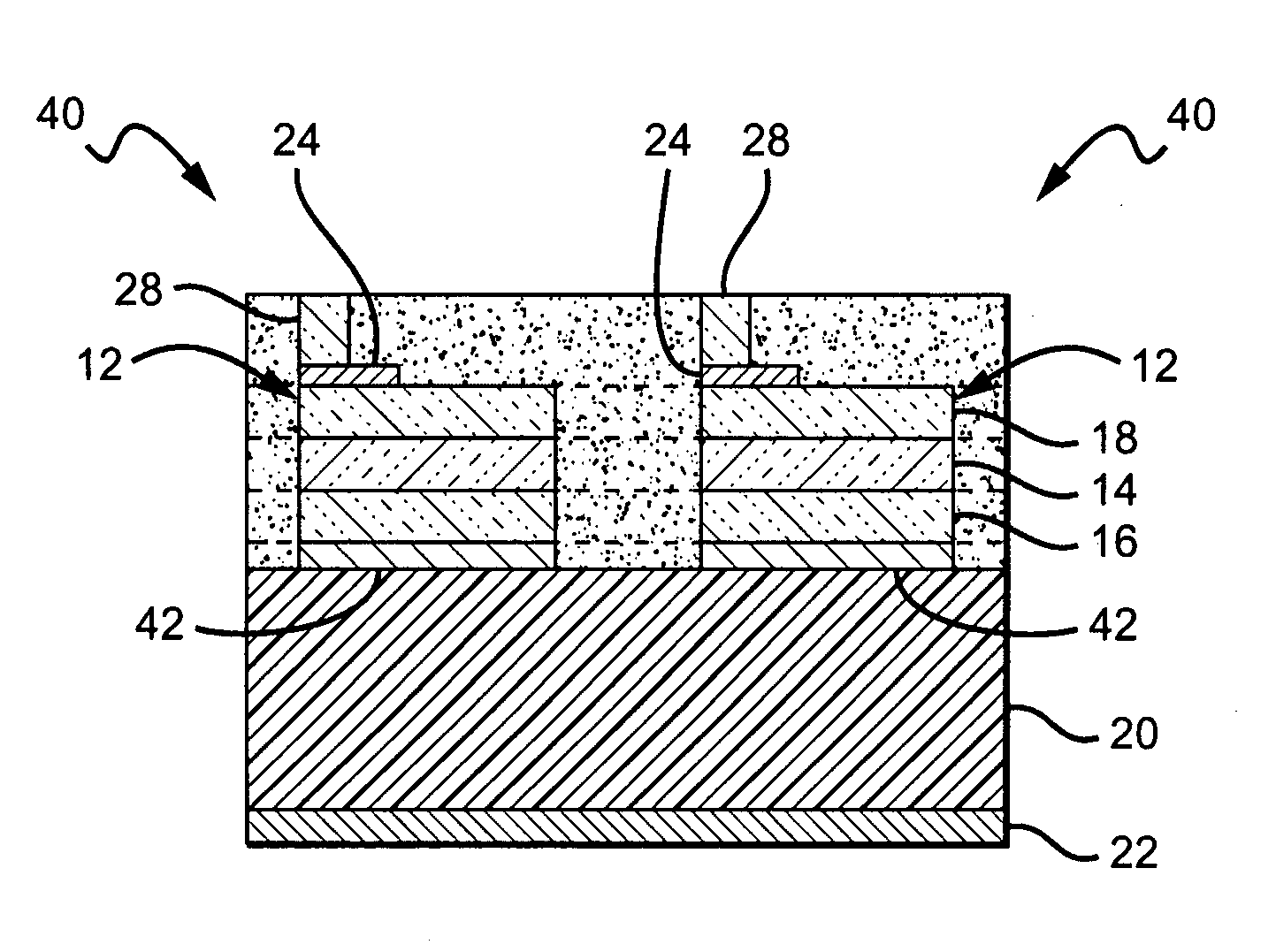

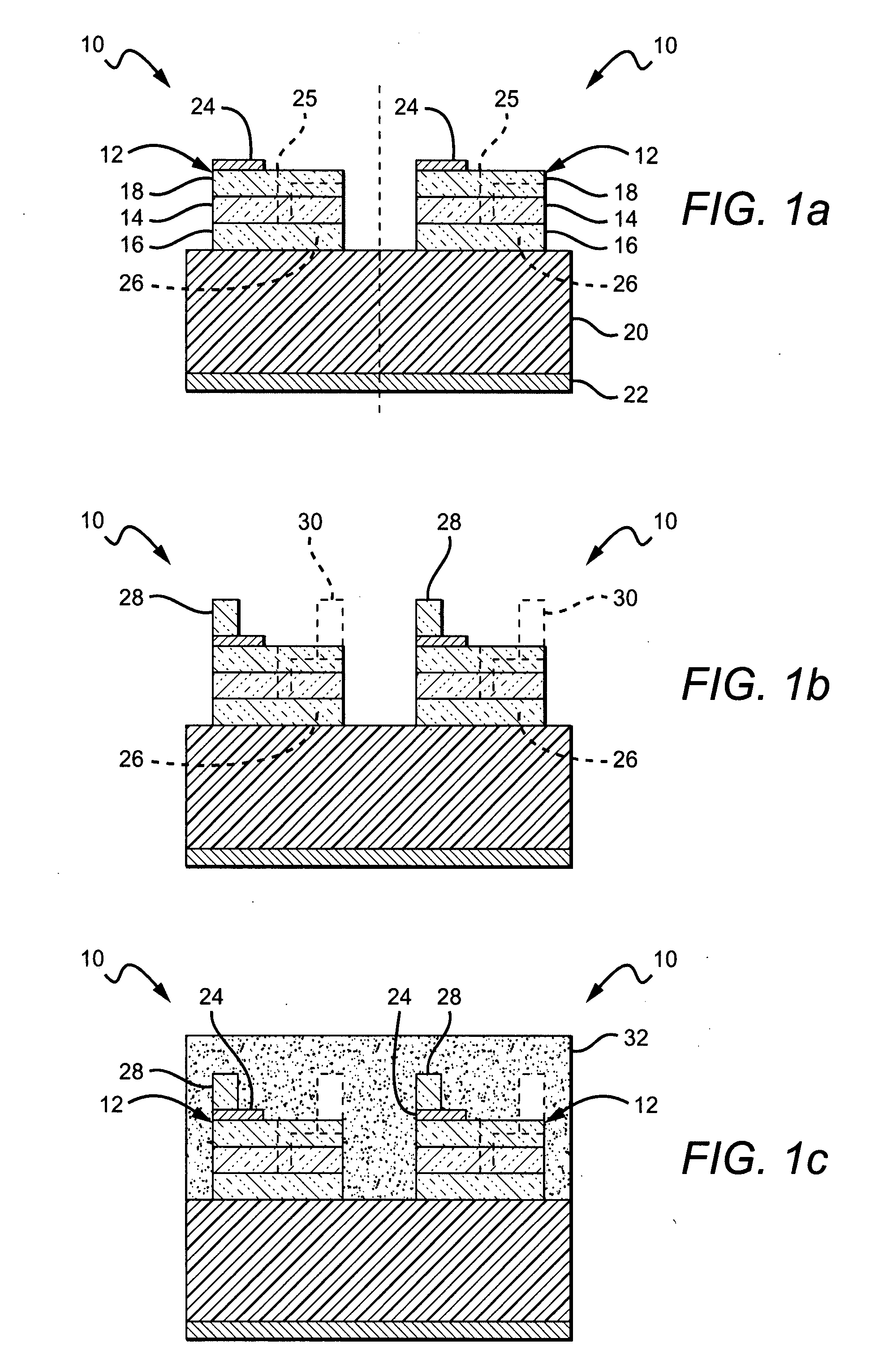

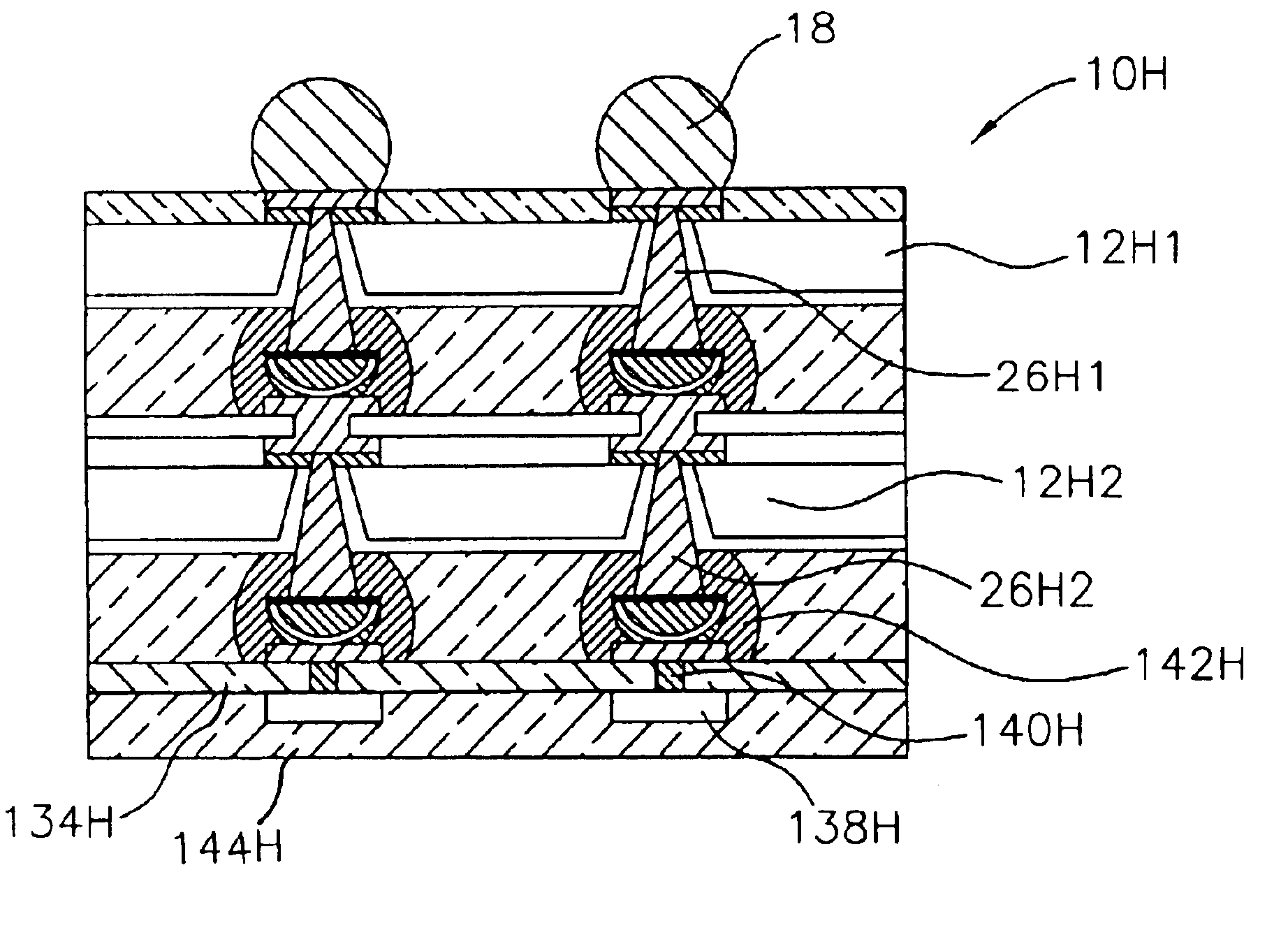

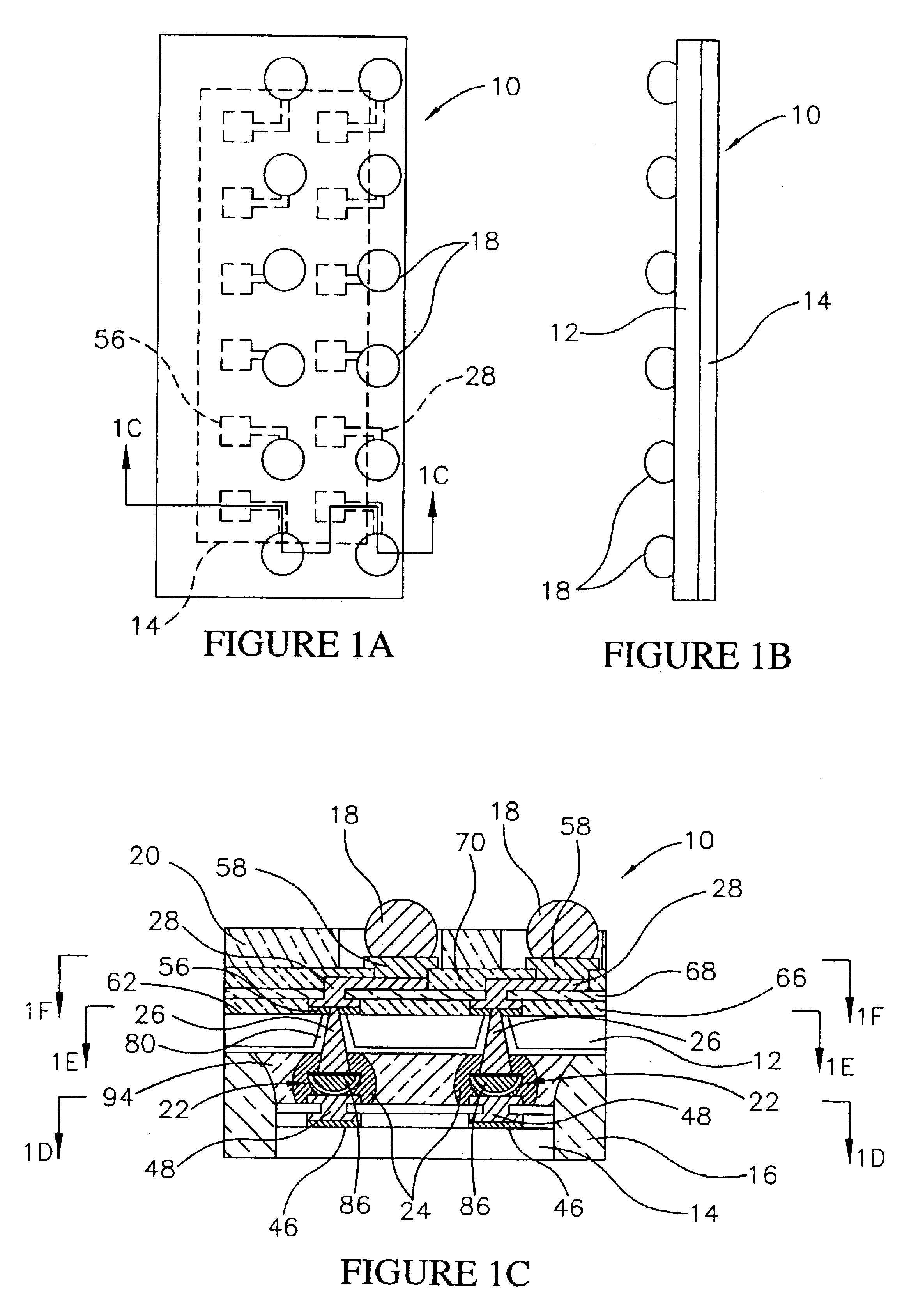

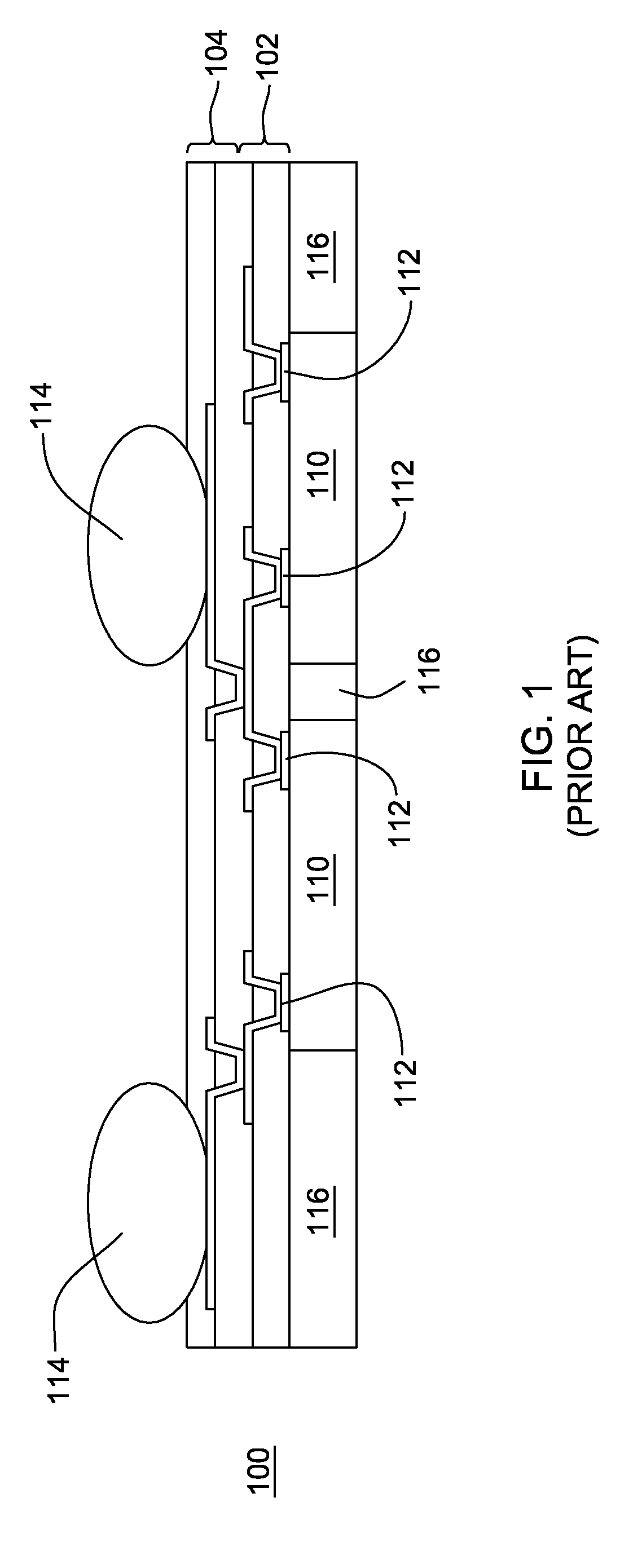

Multi-dice chip scale semiconductor components and wafer level methods of fabrication

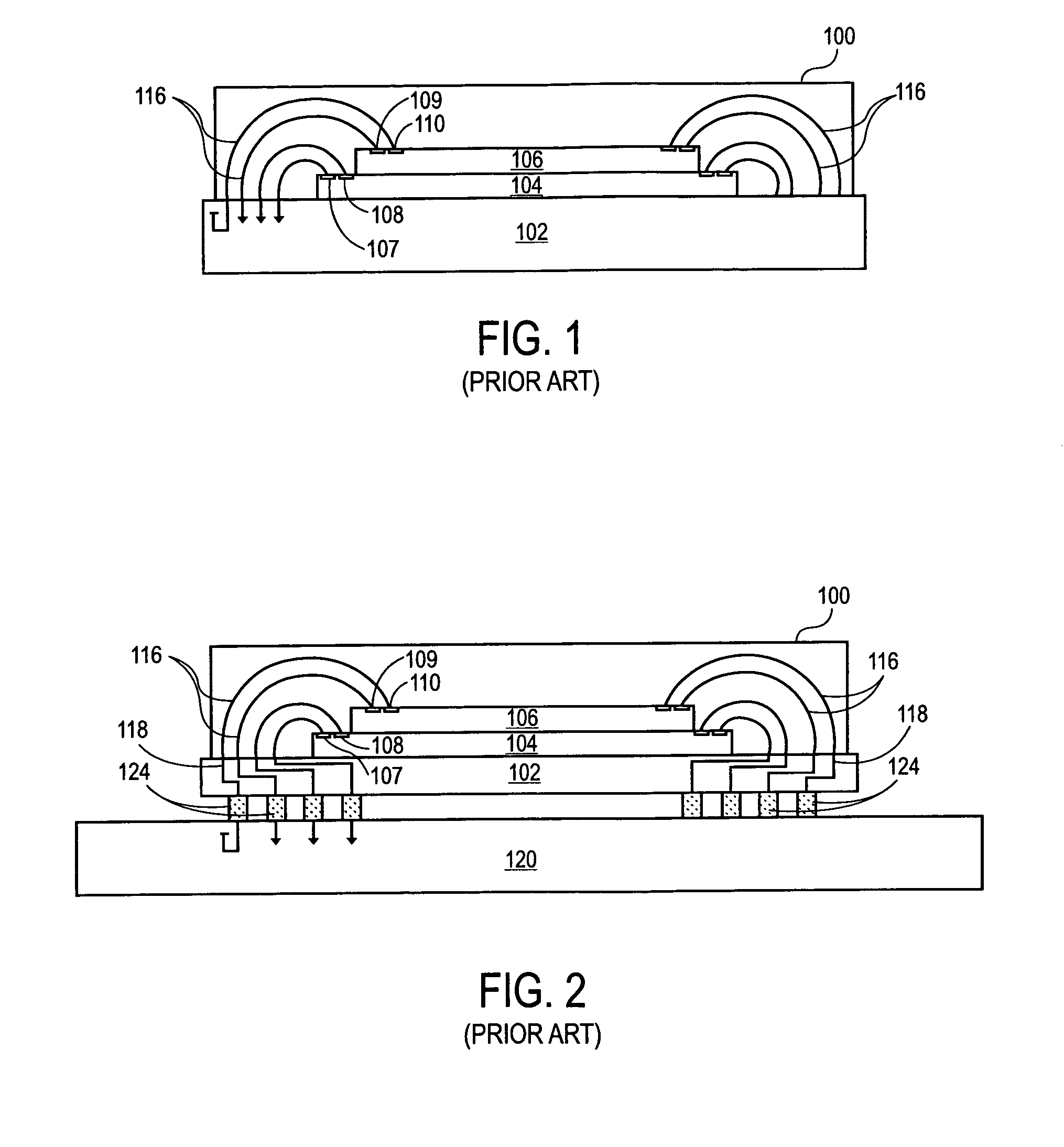

InactiveUS6841883B1Promote formationAdditive manufacturing apparatusSemiconductor/solid-state device detailsSealantPolymer

A semiconductor component includes a base die and a secondary die stacked on and bonded to the base die. The base die includes conductive vias which form an internal signal transmission system for the component, and allow the circuit side of the secondary die to be bonded to the back side of the base die. The component also includes an array of terminal contacts on the circuit side of the base die in electrical communication with the conductive vias. The component can also include an encapsulant on the back side of the base die, which substantially encapsulates the secondary die, and a polymer layer on the circuit side of the base die which functions as a protective layer, a rigidifying member and a stencil for forming the terminal contacts. A method for fabricating the component includes the step of bonding singulated secondary dice to base dice on a base wafer, or bonding a secondary wafer to the base wafer, or bonding singulated secondary dice to singulated base dice.

Owner:ROUND ROCK RES LLC

Precursor source mixtures

A precursor source mixture useful for CVD or ALD of a film comprising: at least one precursor composed of an element selected from the group consisting of Li, Na, K, Rb, Cs, Fr, Be, Mg, Ti, Zr, Hf, Sc, Y, La, V, Nb, Ta, Cr, Mo, W, Mn, Re, Fe, Ru, Os, Co, Rh, Ir, Ni, Pd, Pt, Cu, Ag, Au, Zn, Cd, Hg, B, Al, Ga, In, Tl, Si, Ge, Sn, Pb, As, P, Sb and Bi, to which is bound at least one ligand selected from the group consisting of hydride, alkyl, alkenyl, cycloalkenyl, aryl, alkyne, carbonyl, amido, imido, hydrazido, phosphido, nitrosyl, nitryl, nitrate, nitrile, halide, azide, alkoxy, siloxy, silyl, and halogenated, sulfonated or silyated derivatives thereof, which is dissolved, emulsified or suspended in an inert liquid selected from the group consisting of aliphatic hydrocarbons, aromatic hydrocarbons, alcohols, ethers, aldehydes, ketones, acids, phenols, esters, amines, alkylnitrile, halogenated hydrocarbons, silyated hydrocarbons, thioethers, amines, cyanates, isocyanates, thiocyanates, silicone oils, nitroalkyl, alkylnitrate, and mixtures thereof. The precursor source mixture may be a solution, emulsion or suspension and may consist of a mixture of solid, liquid and gas phases which are distributed throughout the mixture.

Owner:GLOBALFOUNDRIES INC

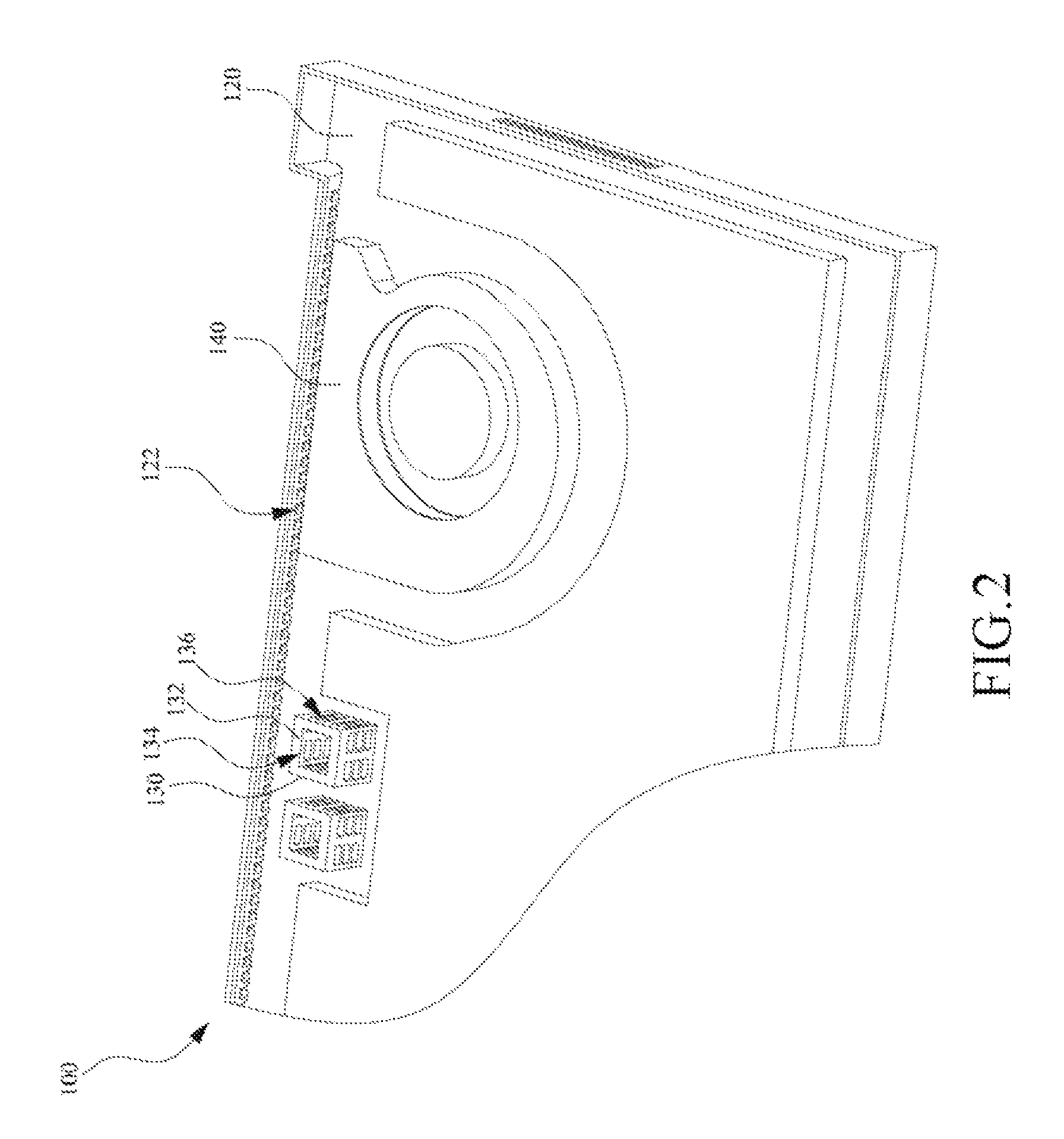

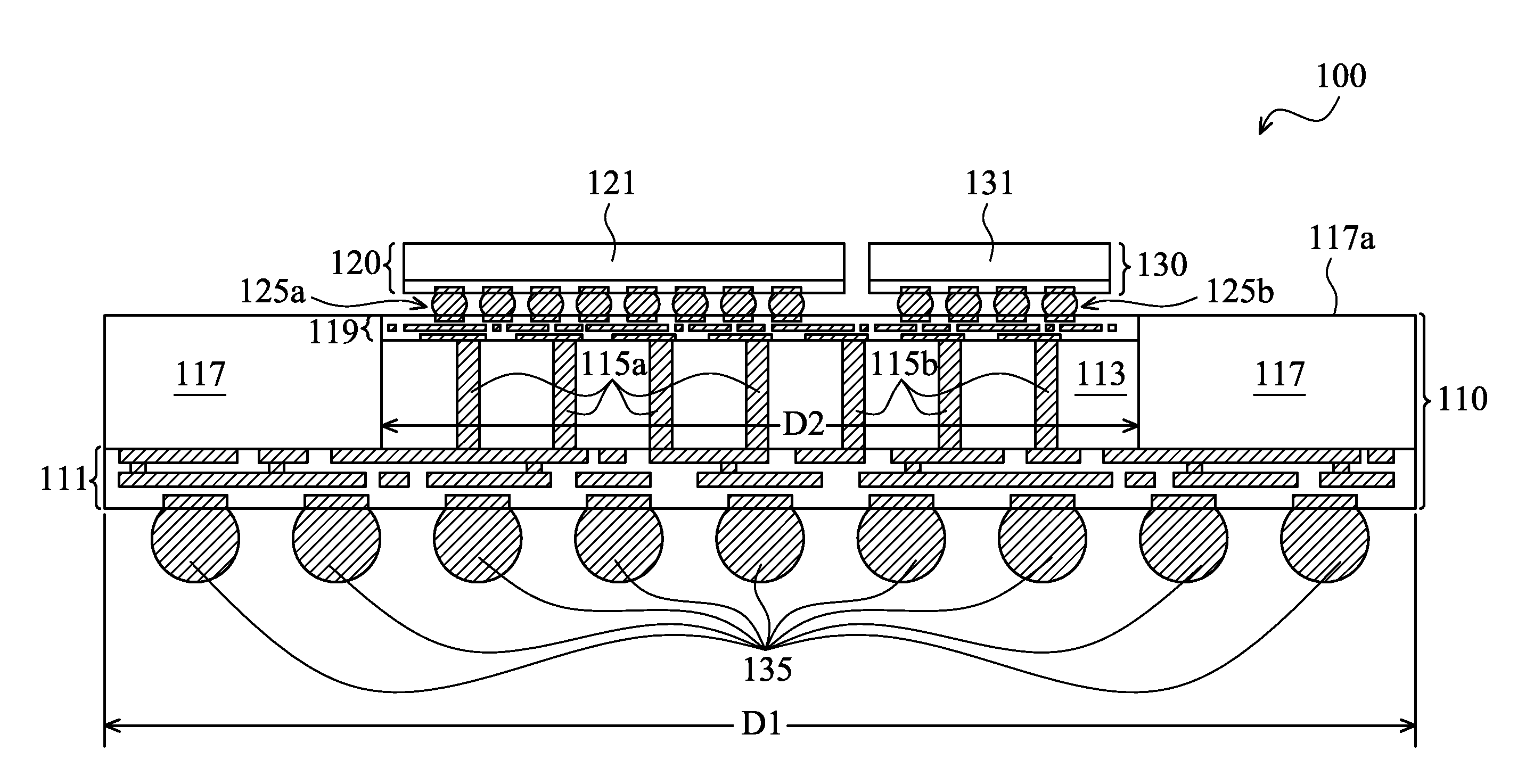

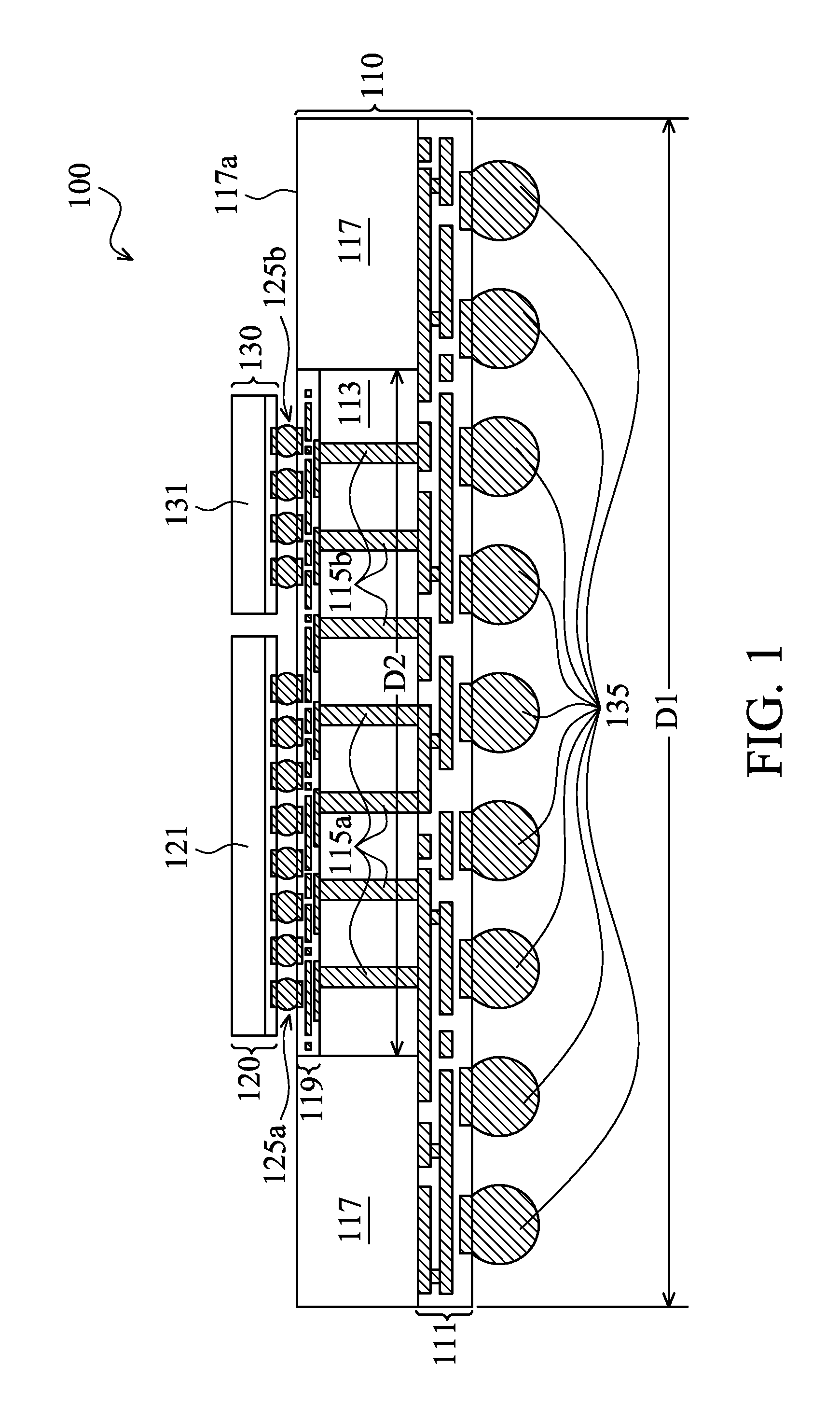

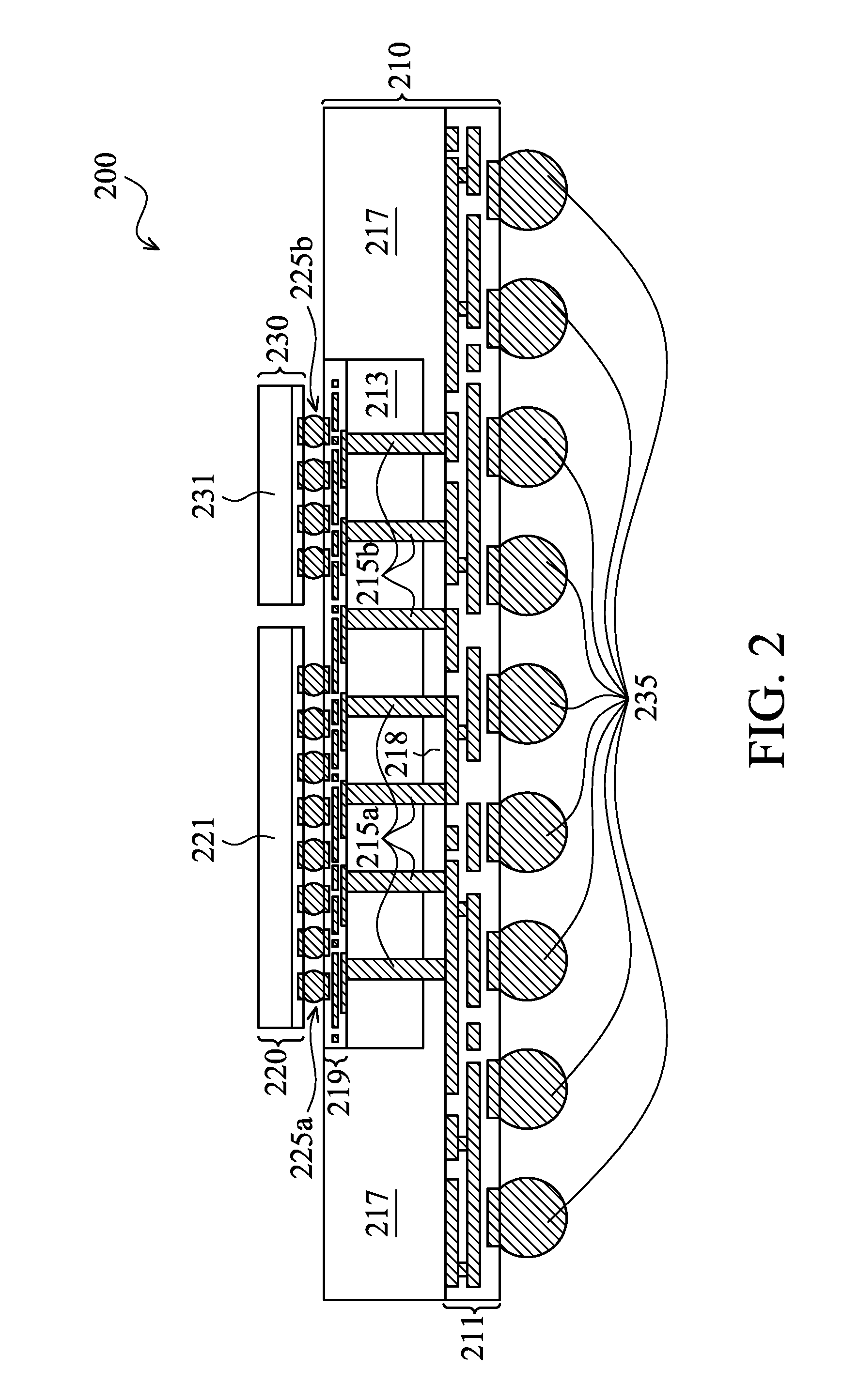

Package systems having interposers

A package system includes an integrated circuit disposed over an interposer. The interposer includes a first interconnect structure. A first substrate is disposed over the first interconnect structure. The first substrate includes at least one first through silicon via (TSV) structure therein. A molding compound material is disposed over the first interconnect structure and around the first substrate. The integrated circuit is electrically coupled with the at least one first TSV structure.

Owner:TAIWAN SEMICON MFG CO LTD

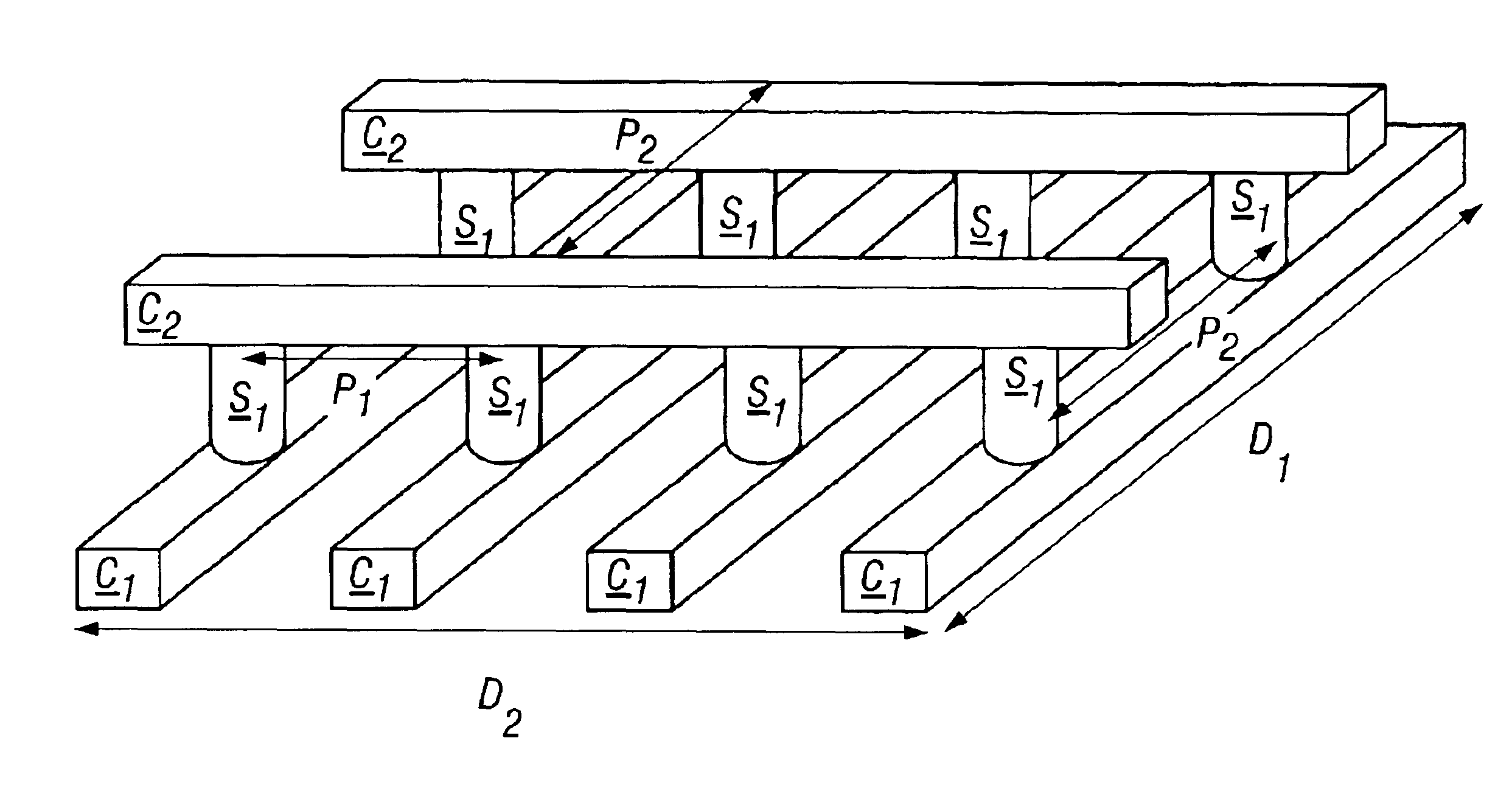

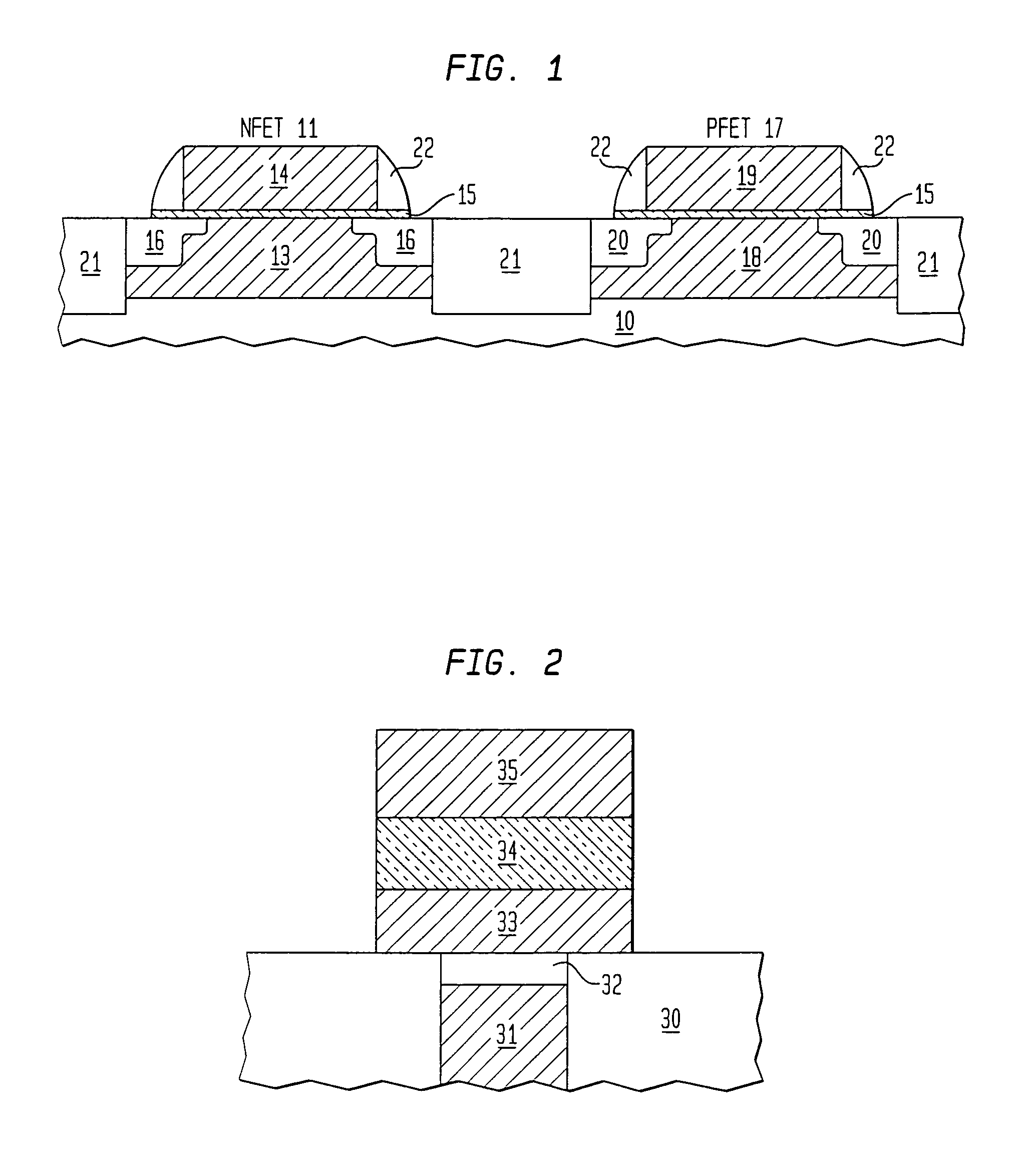

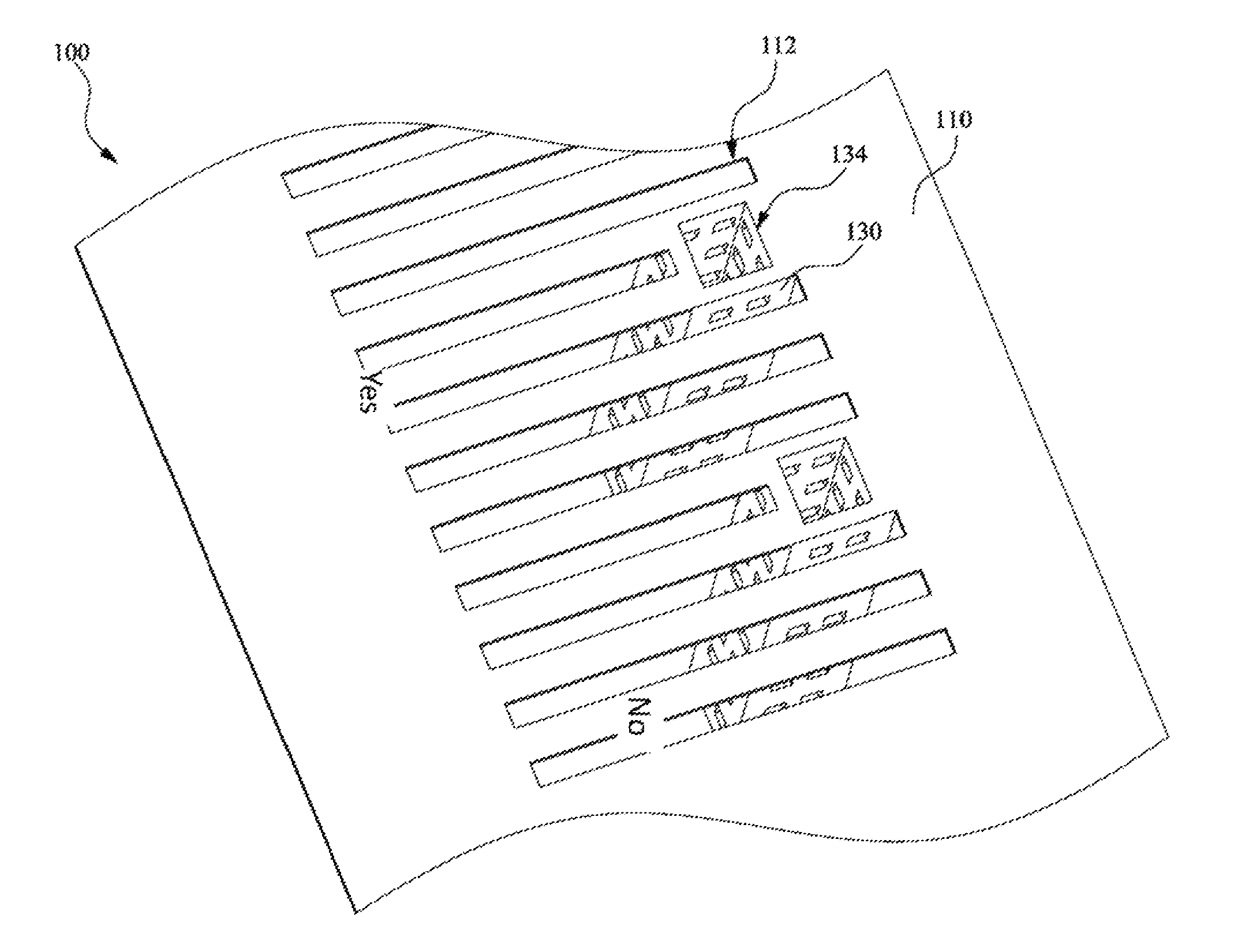

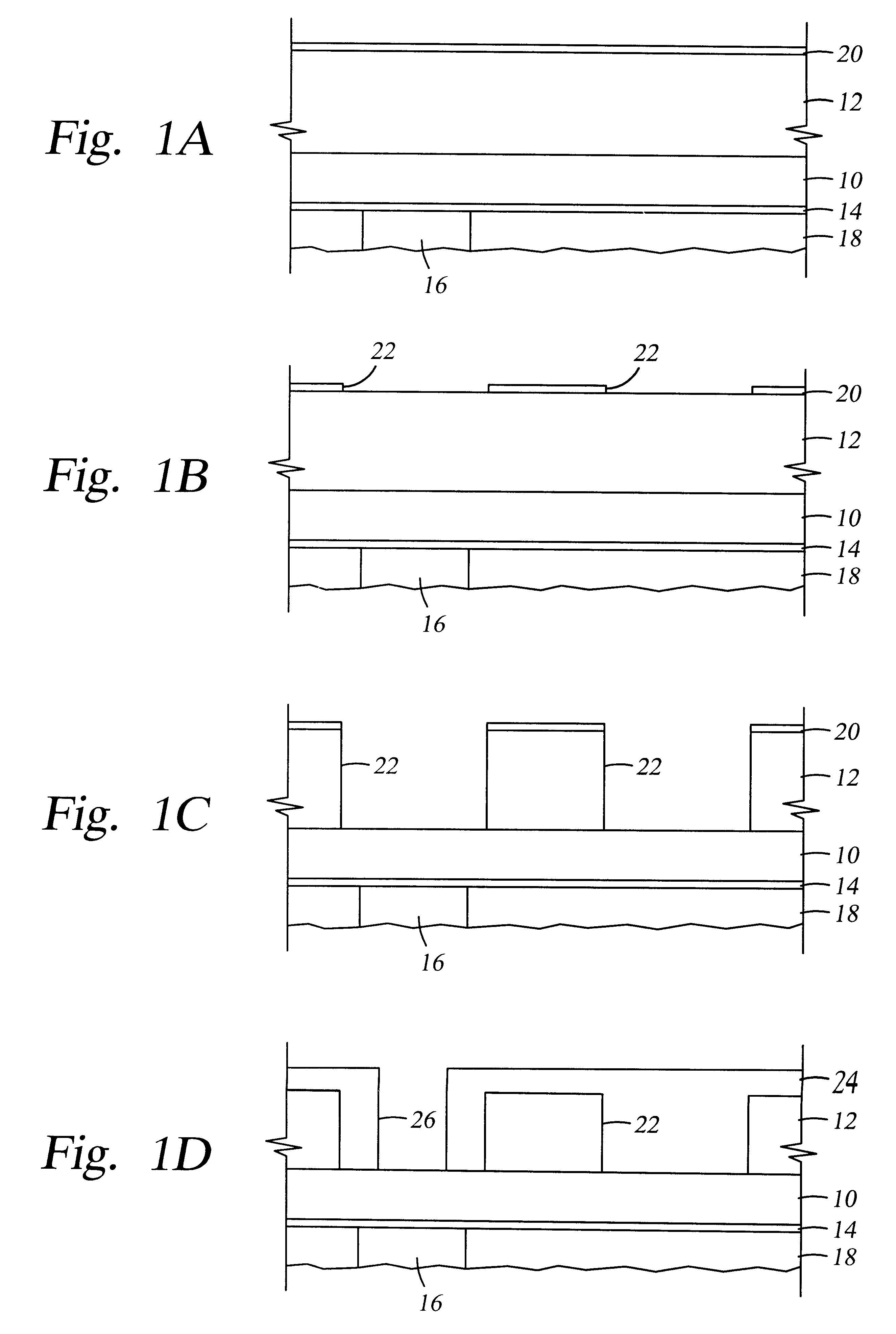

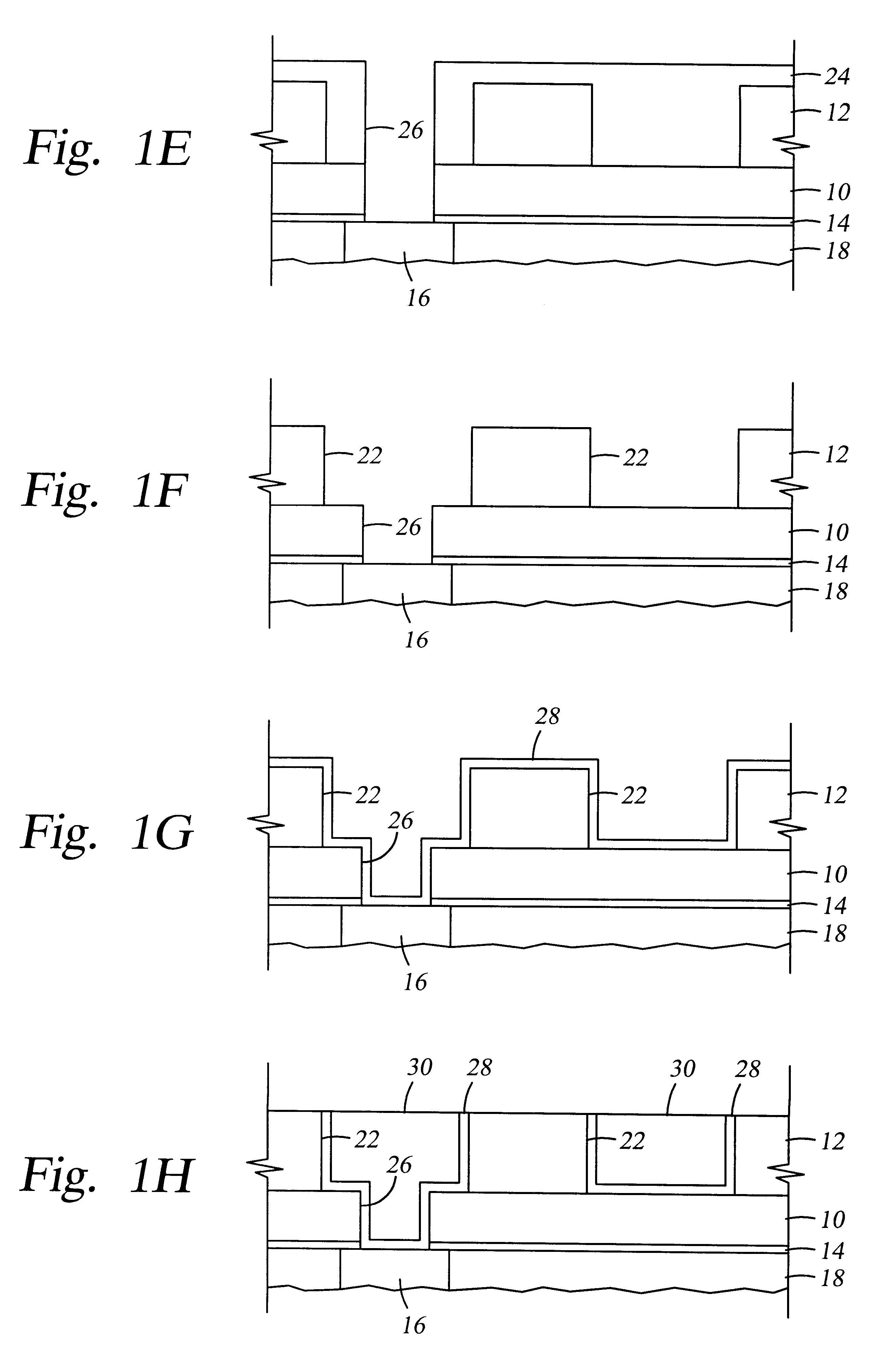

Single spacer process for multiplying pitch by a factor greater than two and related intermediate IC structures

Single spacer processes for multiplying pitch by a factor greater than two are provided. In one embodiment, n, where n≧2, tiers of stacked mandrels are formed over a substrate, each of the n tiers comprising a plurality of mandrels substantially parallel to one another. Mandrels at tier n are over and parallel to mandrels at tier n−1, and the distance between adjoining mandrels at tier n is greater than the distance between adjoining mandrels at tier n−1. Spacers are simultaneously formed on sidewalls of the mandrels. Exposed portions of the mandrels are etched away and a pattern of lines defined by the spacers is transferred to the substrate.

Owner:MICRON TECH INC

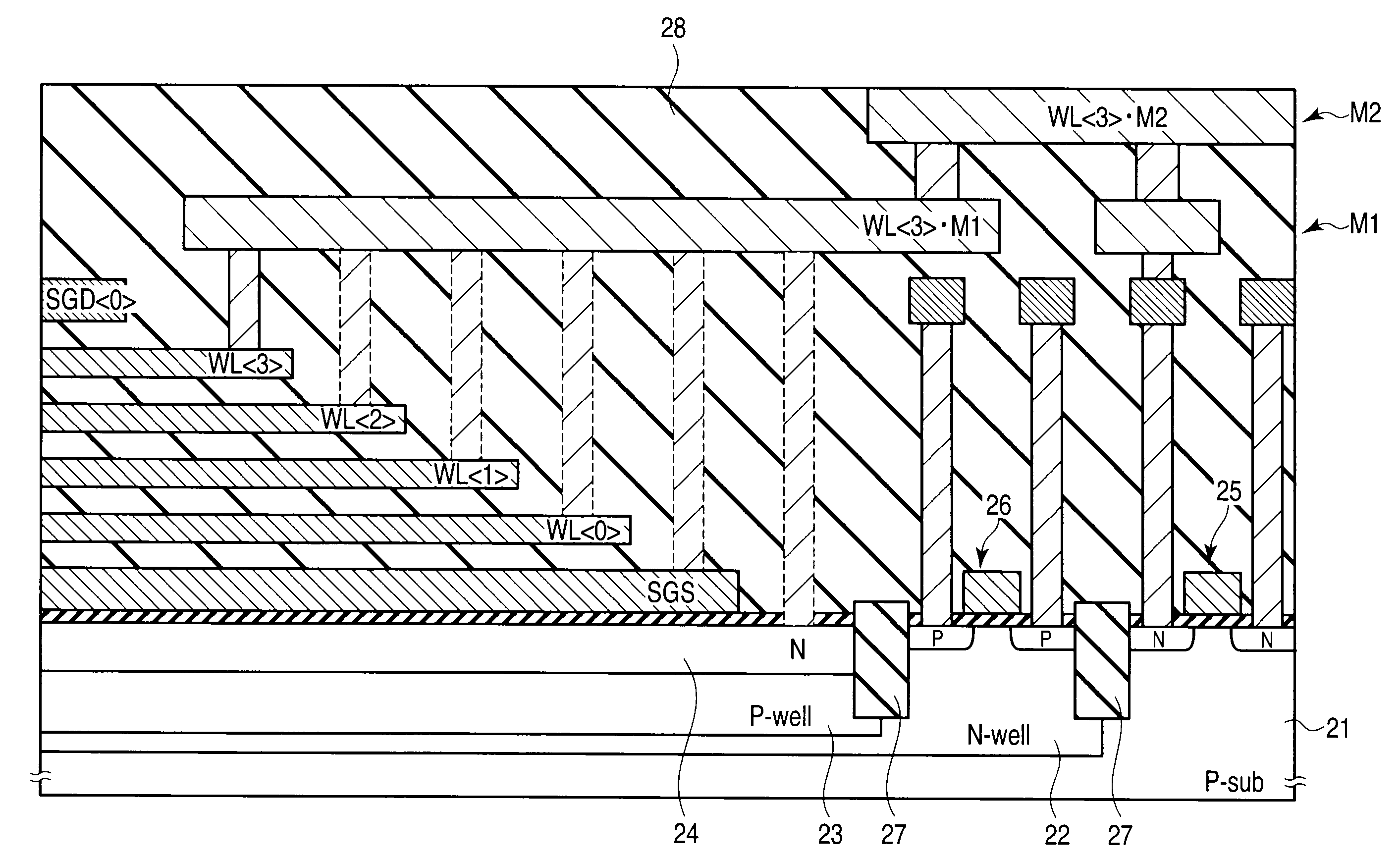

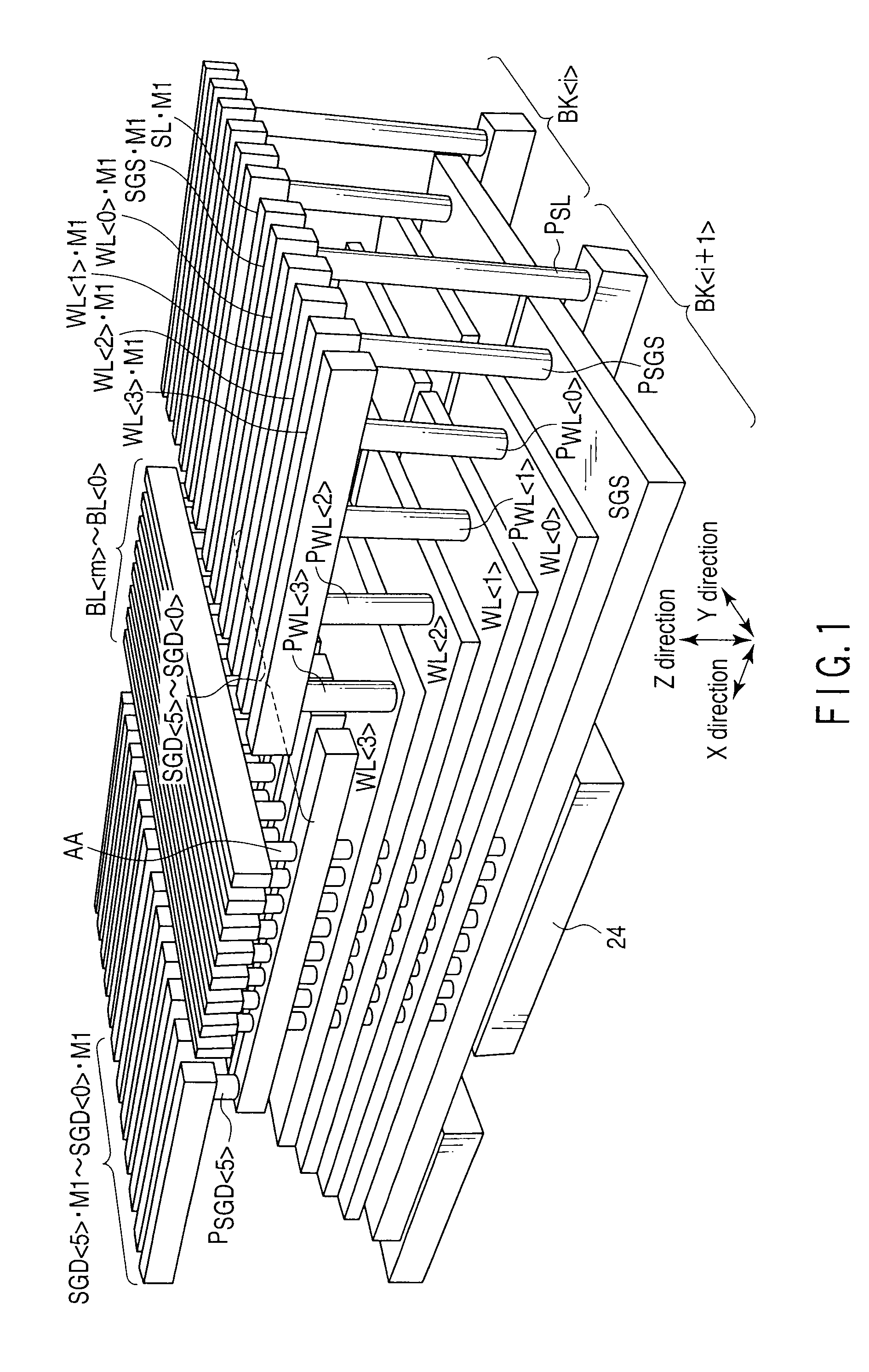

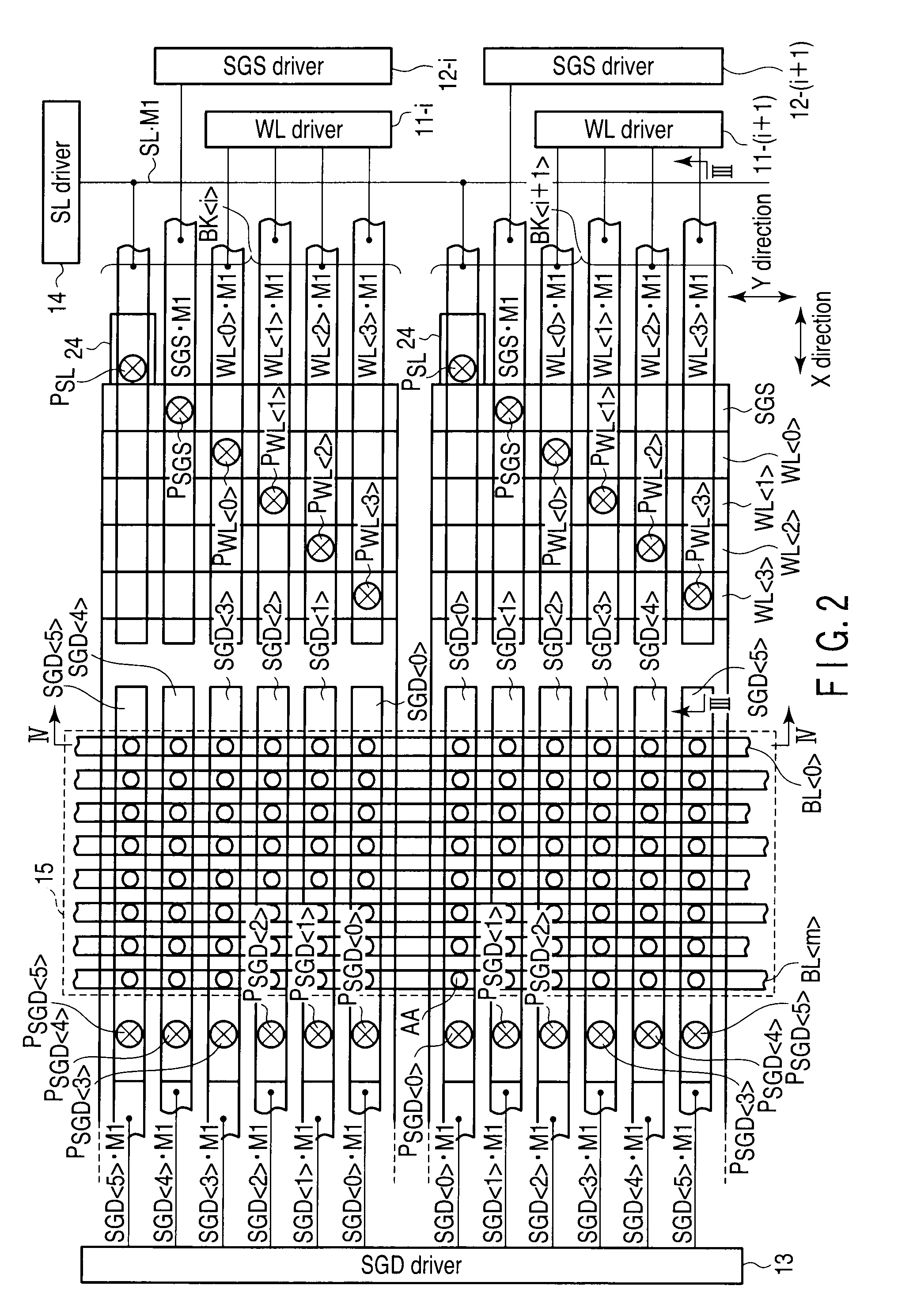

Three dimensional stacked nonvolatile semiconductor memory

A three dimensional stacked nonvolatile semiconductor memory according to an example of the present invention includes a memory cell array comprised of first and second blocks disposed side by side in a first direction, and a driver disposed on one end of the memory cell array in a second direction orthogonal to the first direction. A source diffusion layer, which is common to the first and second blocks, is disposed in a semiconductor substrate, and a contact plug, which has a lower end connected to the source diffusion layer and an upper end connected to a source line disposed above at least three conductive layers, is interposed between the first and second blocks.

Owner:KIOXIA CORP

Formation of deep via airgaps for three dimensional wafer to wafer interconnect

InactiveUS20060223301A1Semiconductor/solid-state device detailsSolid-state devicesConductive materialsSemiconductor

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Electronic device

ActiveUS9313915B2Improve cooling efficiencyPump componentsDigital data processing detailsHeat conductingElectron device

An electronic device includes an upper cover, a lower cover combined with the upper cover, and a heat conducting pillar. An accommodating space is formed by the upper cover and the lower cover. The heat conducting pillar is disposed in the accommodating space and physically connected with the upper cover and the lower cover to balance the temperature of the upper cover and the lower cover.

Owner:ASUSTEK COMPUTER INC

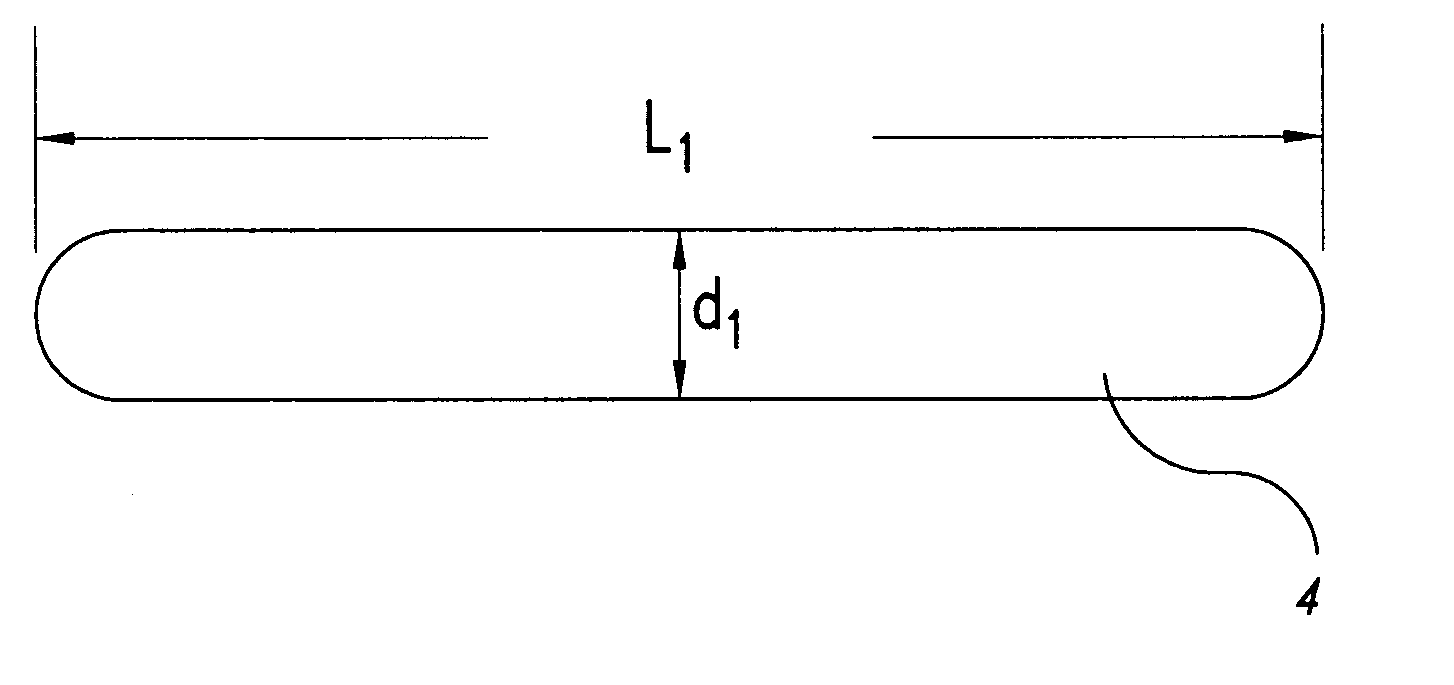

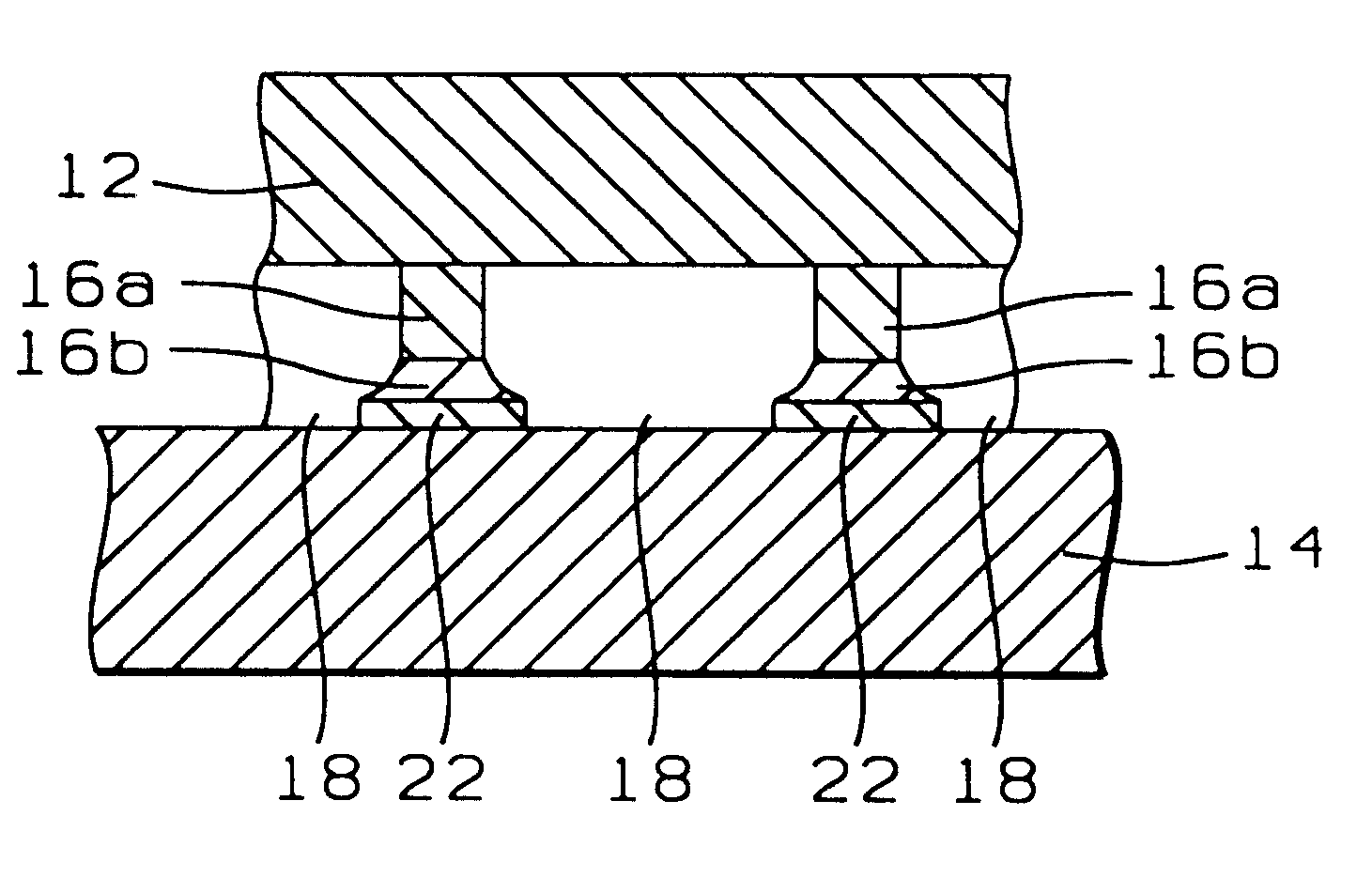

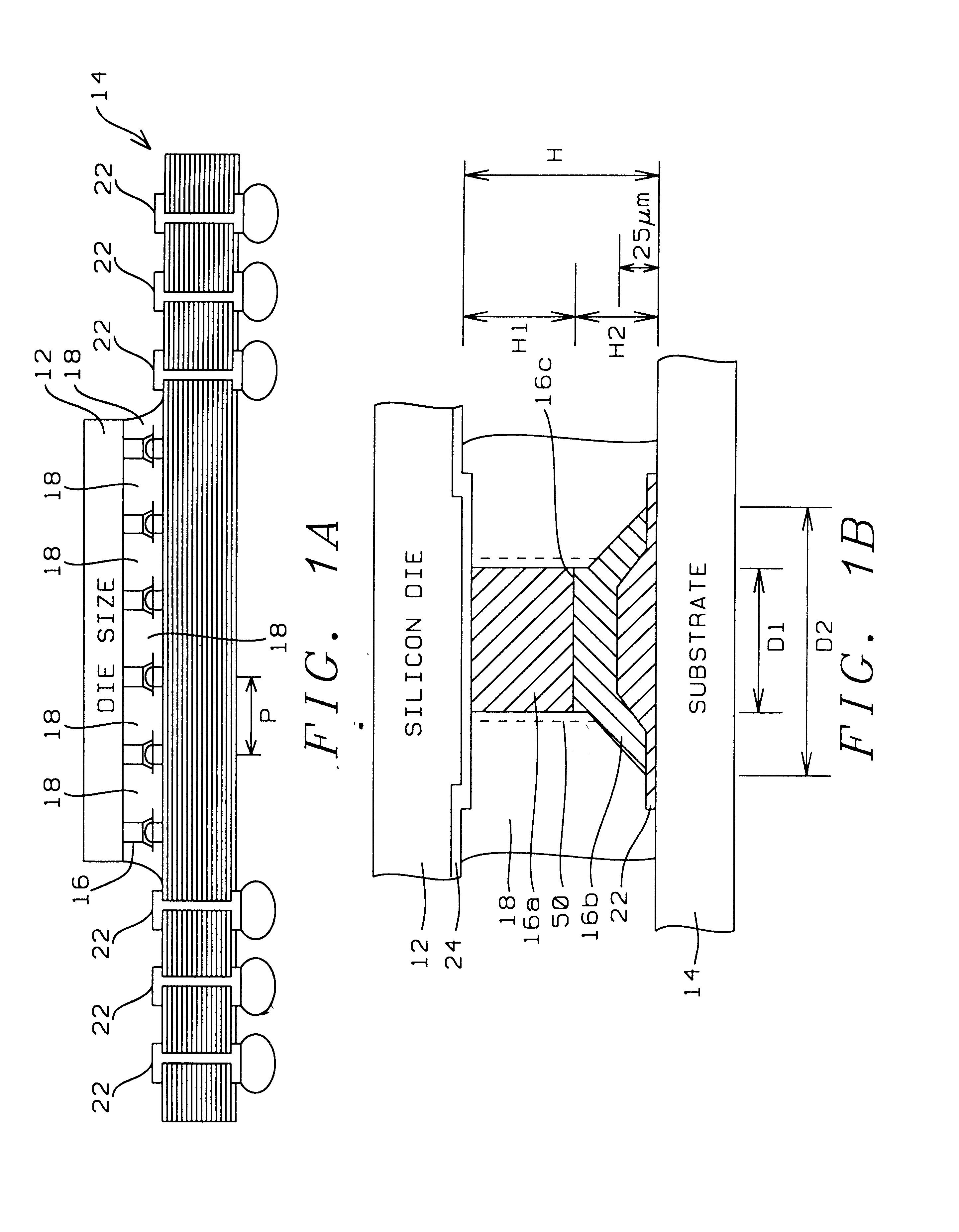

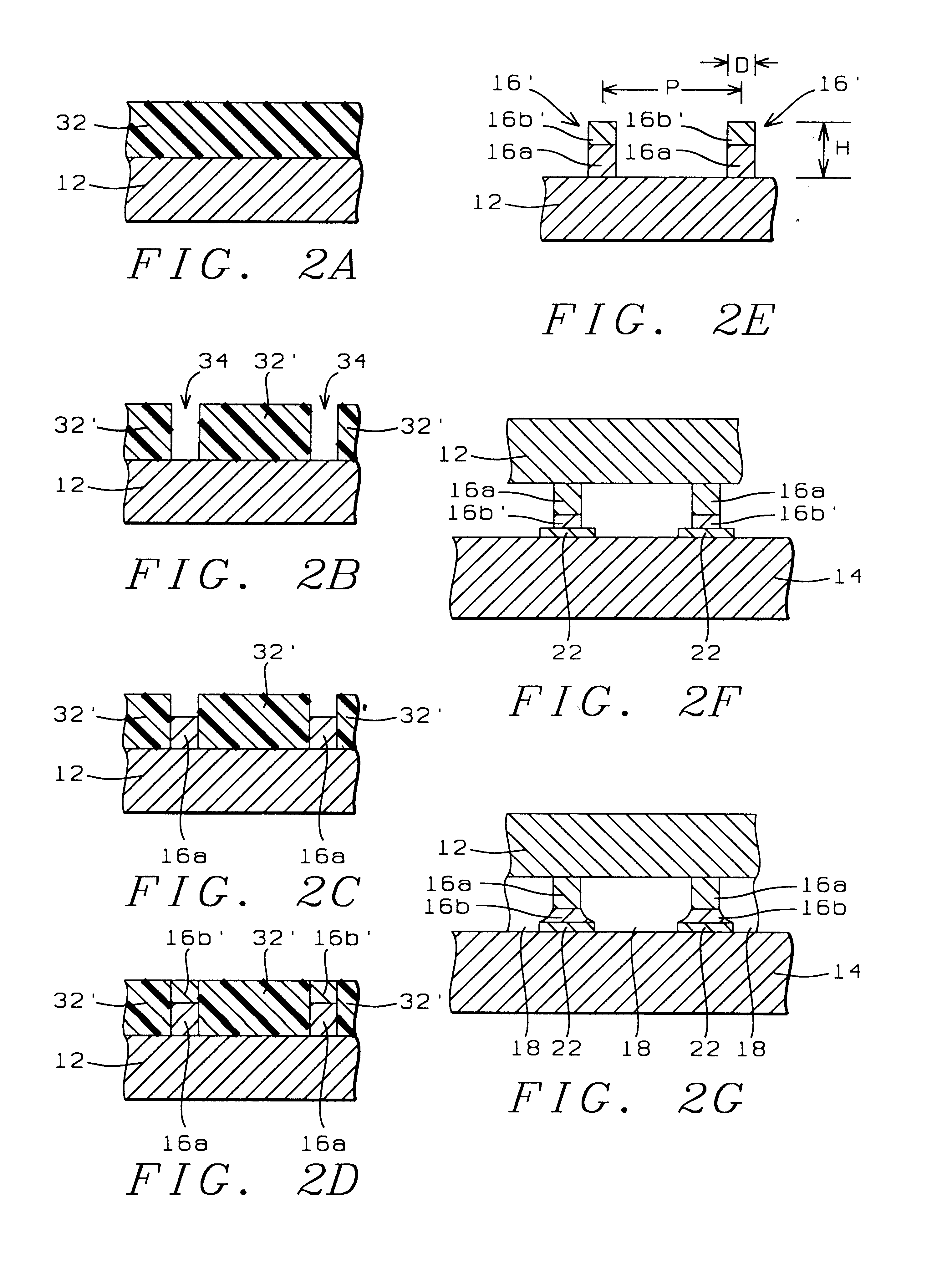

Pillar connections for semiconductor chips and method of manufacture

InactiveUS6578754B1Reduce chanceInduced in connectionSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor chip

A flip chip interconnect system comprises and elongated pillar comprising two elongated portions, one portion including copper and another portion including solder. The portion including copper is in contact with the semiconductor chip and has a length preferably of more than 55 microns to reduce the effect of .alpha. particles from the solder from affecting electronic devices on the chip. The total length of the pillar is preferably in the range of 80 to 120 microns.

Owner:ADVANPAK SOLUTIONS PTE

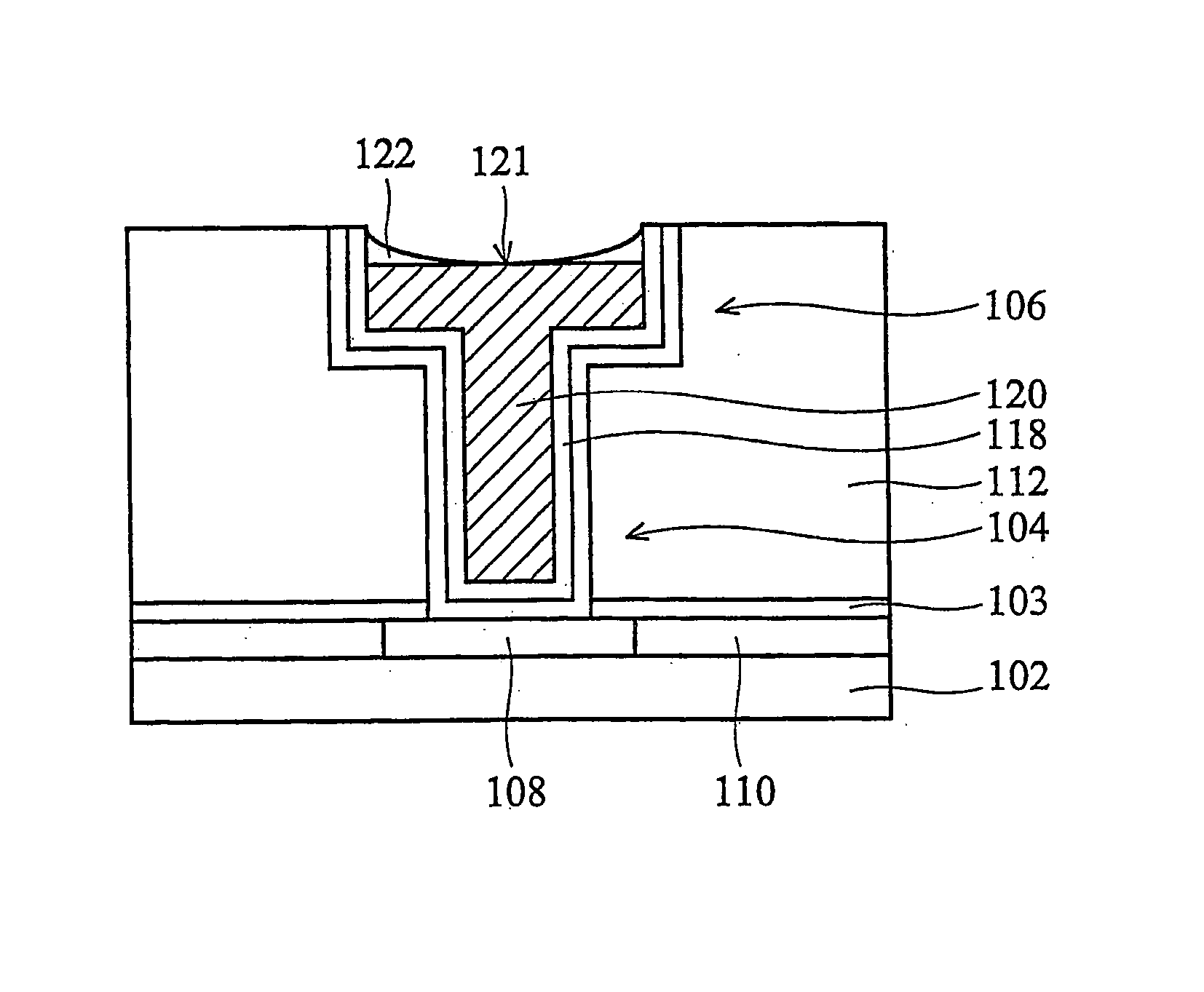

Barrier material and process for Cu interconnect

InactiveUS20060113675A1Improved electromigration performanceImprove performanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDiffusion barrier

A semiconductor diffusion barrier layer and its method of manufacture is described. The barrier layer includes of at least one layer of TaN, TiN, WN, TbN, VN, ZrN, CrN, WC, WN, WCN, NbN, AlN, and combinations thereof. The barrier layer may further include a metal rich surface. Embodiments preferably include a glue layer about 10 to 500 Angstroms thick, the glue layer consisting of Ru, Ta, Ti, W, Co, Ni, Al, Nb, AlCu, and a metal-rich nitride, and combinations thereof. The ratio of the glue layer thickness to the barrier layer thickness is preferably about 1 to 50. Other alternative preferred embodiments further include a conductor annealing step. The various layers may be deposited using PVD, CVD, PECVD, PEALD and / or ALD methods including nitridation and silicidation methods.

Owner:TAIWAN SEMICON MFG CO LTD

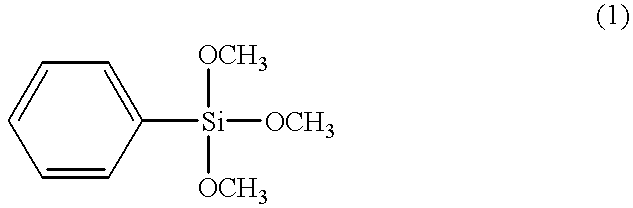

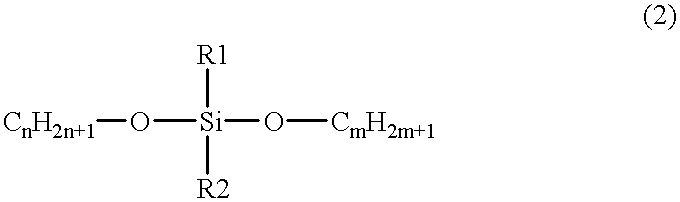

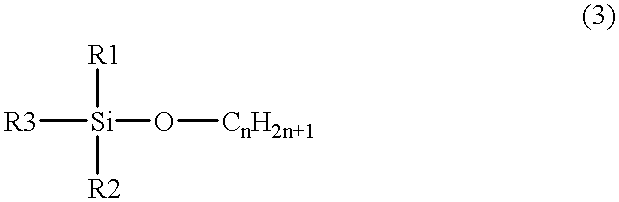

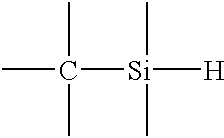

Silicone polymer insulation film on semiconductor substrate and method for forming the film

InactiveUS6352945B1Low dielectric constantImprove thermal stabilityLiquid surface applicatorsSemiconductor/solid-state device detailsPolymer scienceHigh humidity

A method for forming a silicone polymer insulation film having a low relative dielectric constant, high thermal stability and high humidity-resistance on a semiconductor substrate is applied to a plasma CVD apparatus. The first step is introducing a silicon-containing hydrocarbon compound expressed by the general formula SialphaObetaCxHy (alpha, beta, x, and y are integers) to the reaction chamber of the plasma CVD apparatus. The silicon-containing hydrocarbon compound has at most two O-CnH2n+1 bonds and at least two hydrocarbon radicals bonded to the silicon. The residence time of the material gas is lengthened by, for example, reducing the total flow of the reaction gas, in such a way as to form a silicone polymer film having a micropore porous structure with a low relative dielectric constant.

Owner:ASM JAPAN

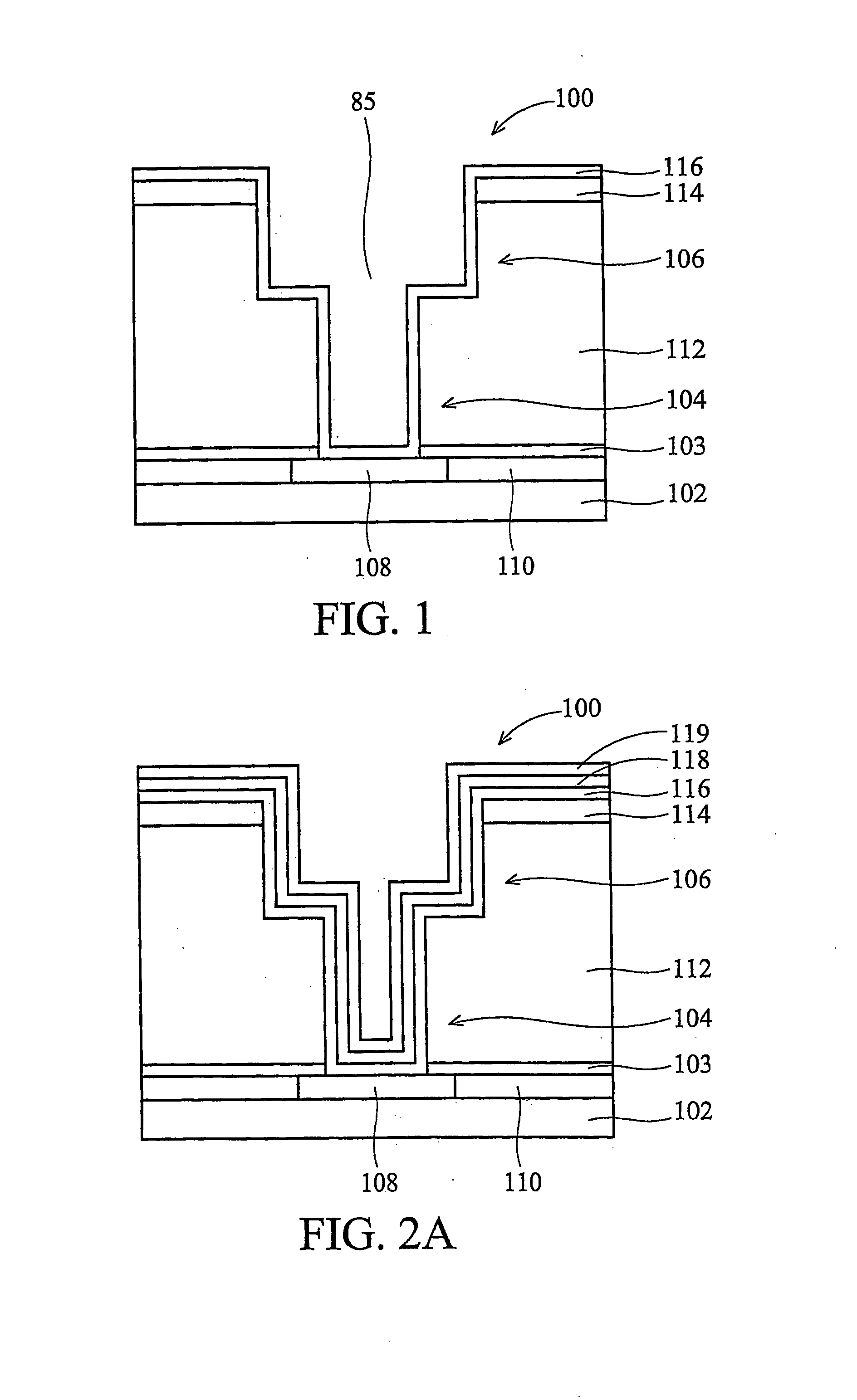

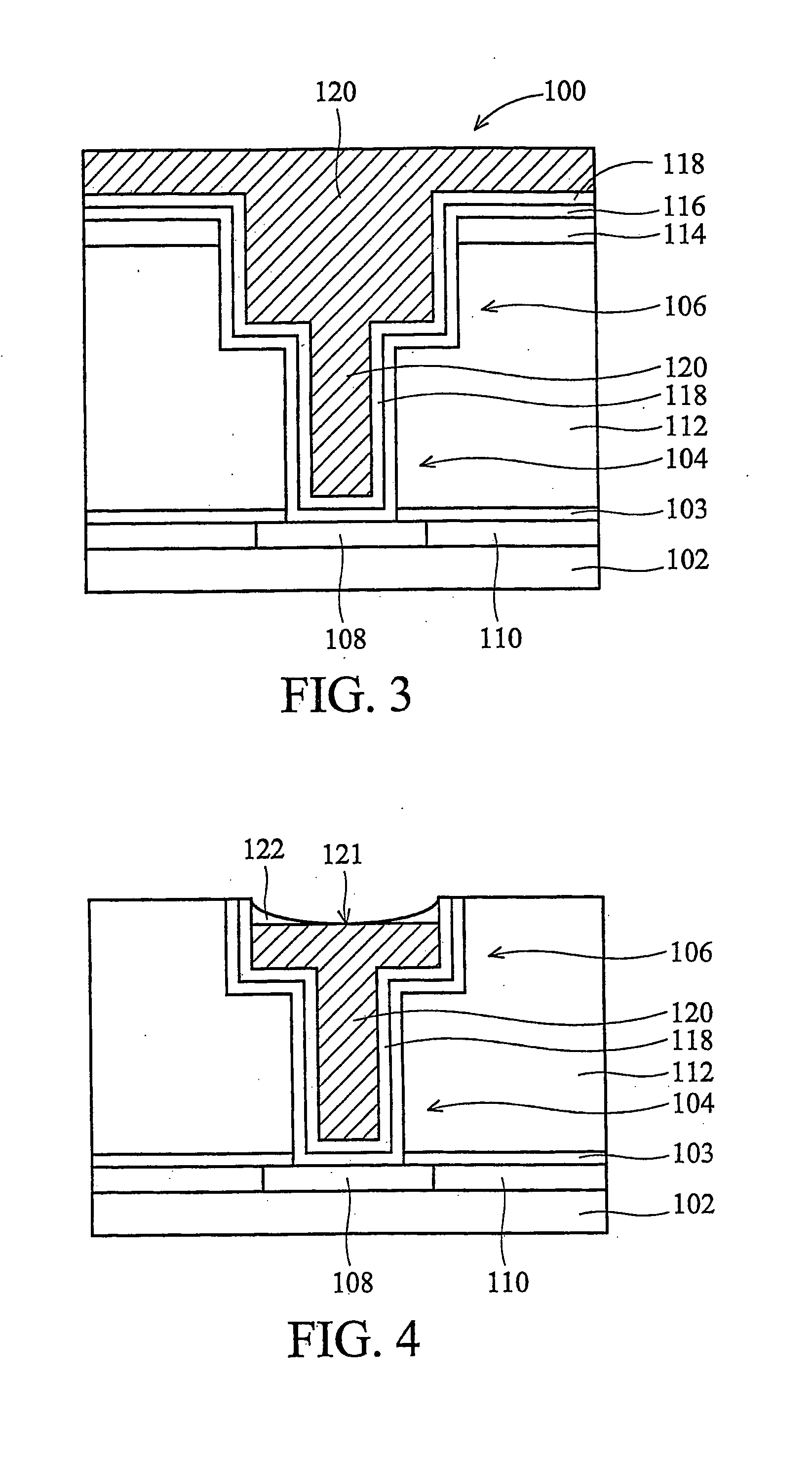

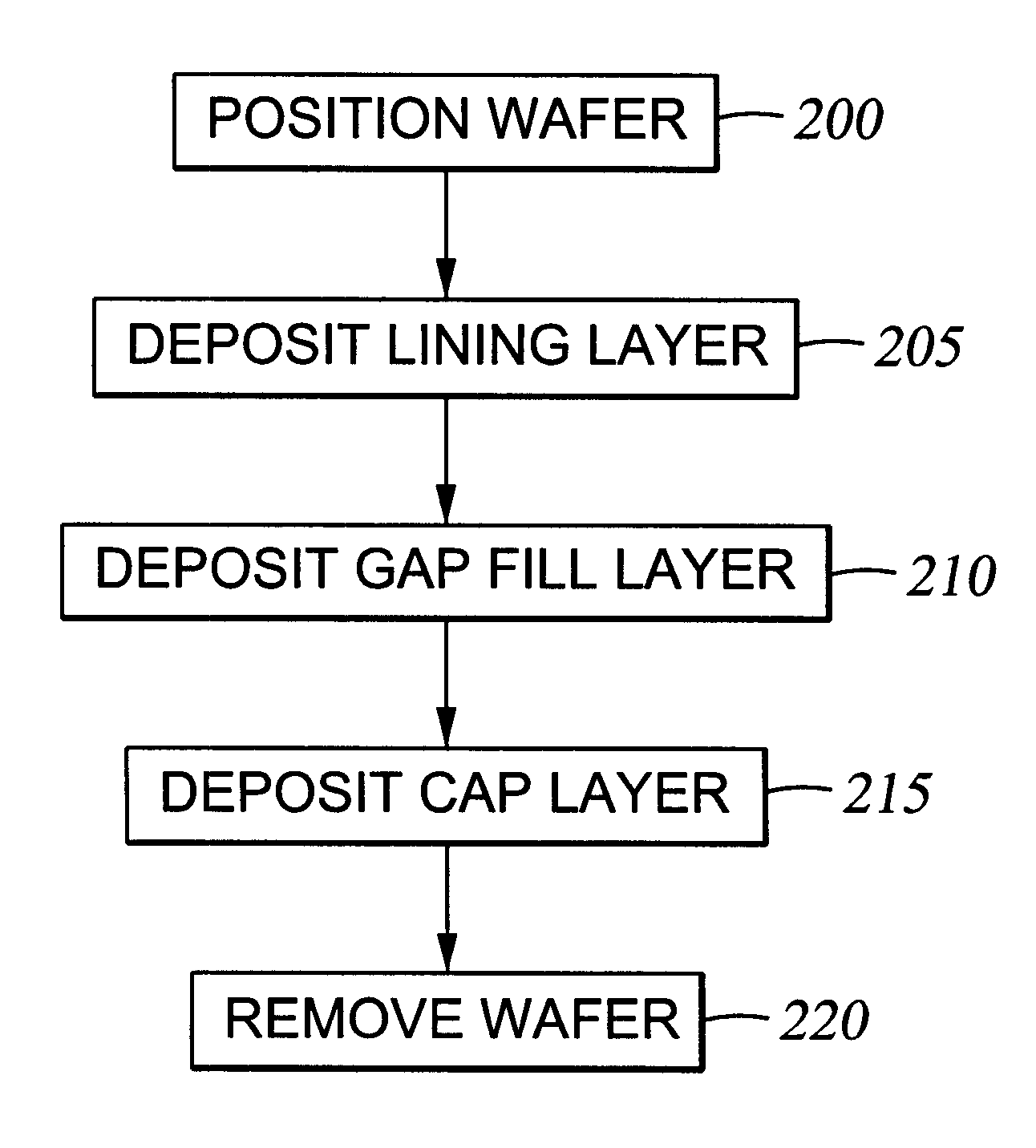

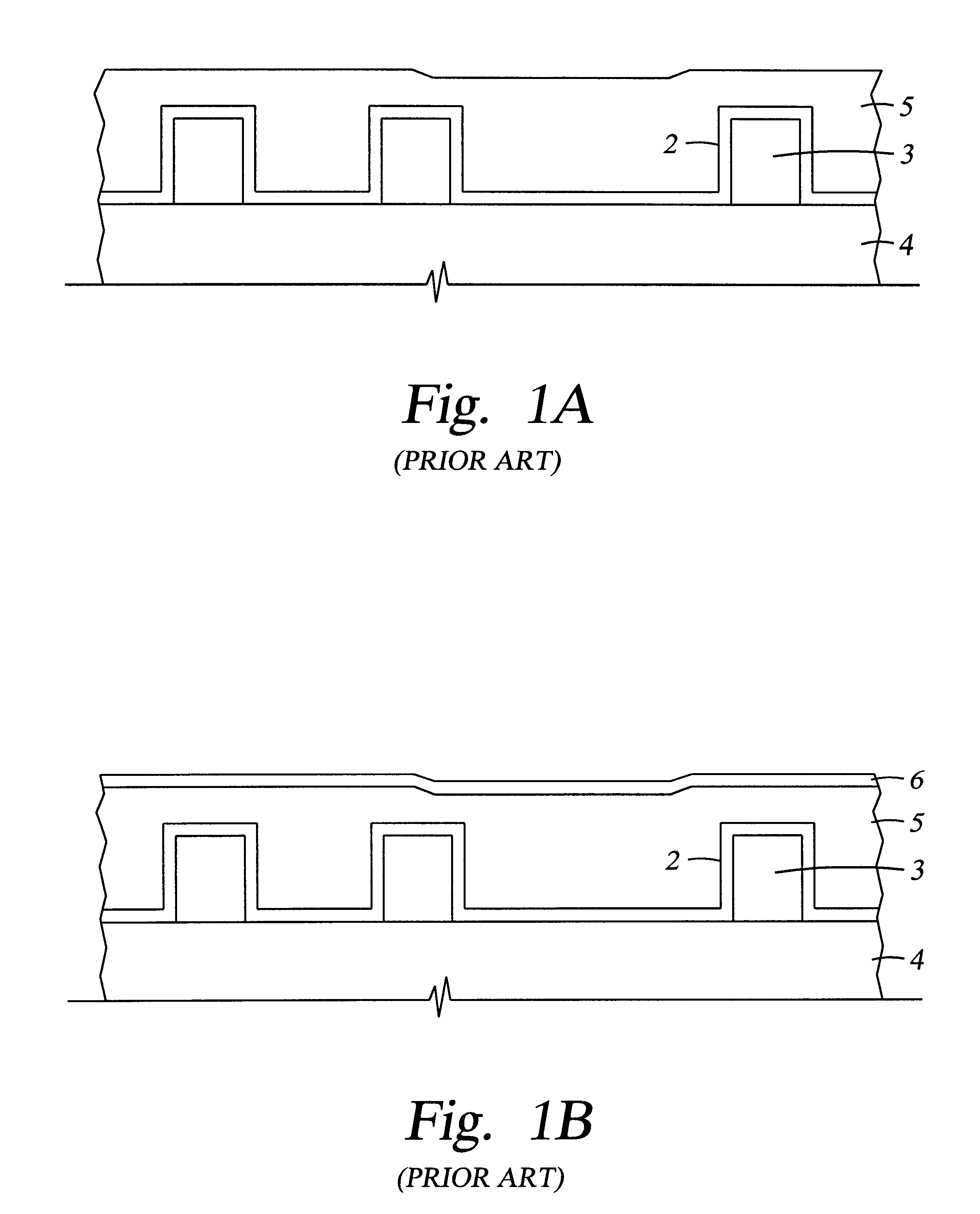

Formation of a liquid-like silica layer by reaction of an organosilicon compound and a hydroxyl forming compound

InactiveUS6413583B1Semiconductor/solid-state device detailsSolid-state devicesSilicon oxideSilicon dioxide

A method for depositing silicon oxide layers having a low dielectric constant by reaction of an organosilicon compound and a hydroxyl forming compound at a substrate temperature less than about 400° C. The low dielectric constant films contain residual carbon and are useful for gap fill layers, pre-metal dielectric layers, inter-metal dielectric layers, and shallow trench isolation dielectric layers in sub-micron devices. The hydroxyl compound can be prepared prior to deposition from water or an organic compound. The silicon oxide layers are preferably deposited at a substrate temperature less than about 40° C. onto a liner layer produced from the organosilicon compound to provide gap fill layers having a dielectric constant less than about 3.0.

Owner:APPLIED MATERIALS INC

Package systems having interposers

ActiveUS20110291288A1Semiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A package system includes an integrated circuit disposed over an interposer. The interposer includes a first interconnect structure. A first substrate is disposed over the first interconnect structure. The first substrate includes at least one first through silicon via (TSV) structure therein. A molding compound material is disposed over the first interconnect structure and around the first substrate. The integrated circuit is electrically coupled with the at least one first TSV structure.

Owner:TAIWAN SEMICON MFG CO LTD

Integrated low K dielectrics and etch stops

InactiveUS6340435B1Decorative surface effectsSemiconductor/solid-state device detailsHydrogenFluorocarbon

A method of depositing and etching dielectric layers having low dielectric constants and etch rates that vary by at least 3:1 for formation of horizontal interconnects. The amount of carbon or hydrogen in the dielectric layer is varied by changes in deposition conditions to provide low k dielectric layers that can replace etch stop layers or conventional dielectric layers in damascene applications. A dual damascene structure having two or more dielectric layers with dielectric constants lower than about 4 can be deposited in a single reactor and then etched to form vertical and horizontal interconnects by varying the concentration of a carbon:oxygen gas such as carbon monoxide. The etch gases for forming vertical interconnects preferably comprises CO and a fluorocarbon, and CO is preferably excluded from etch gases for forming horizontal interconnects.

Owner:APPLIED MATERIALS INC

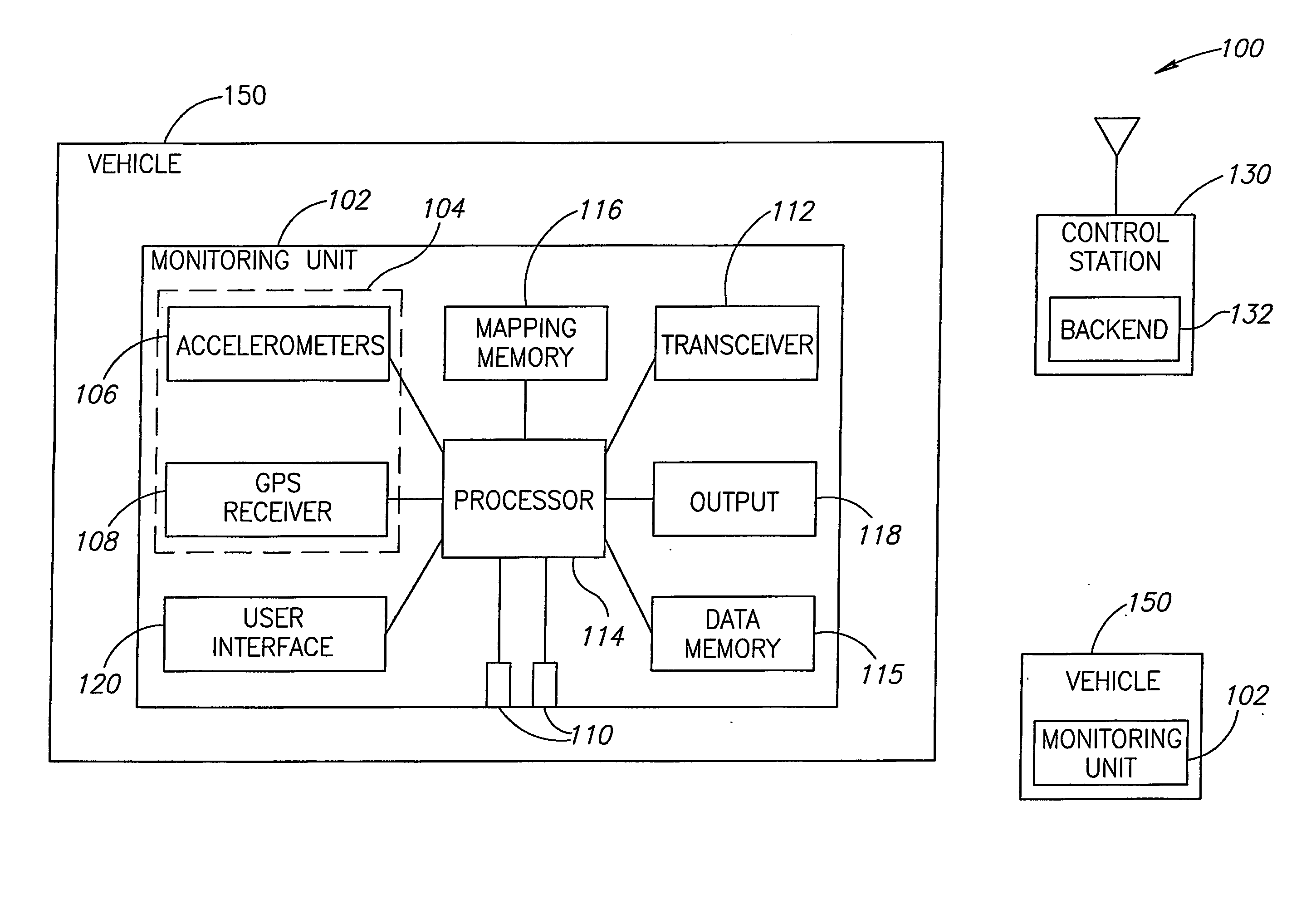

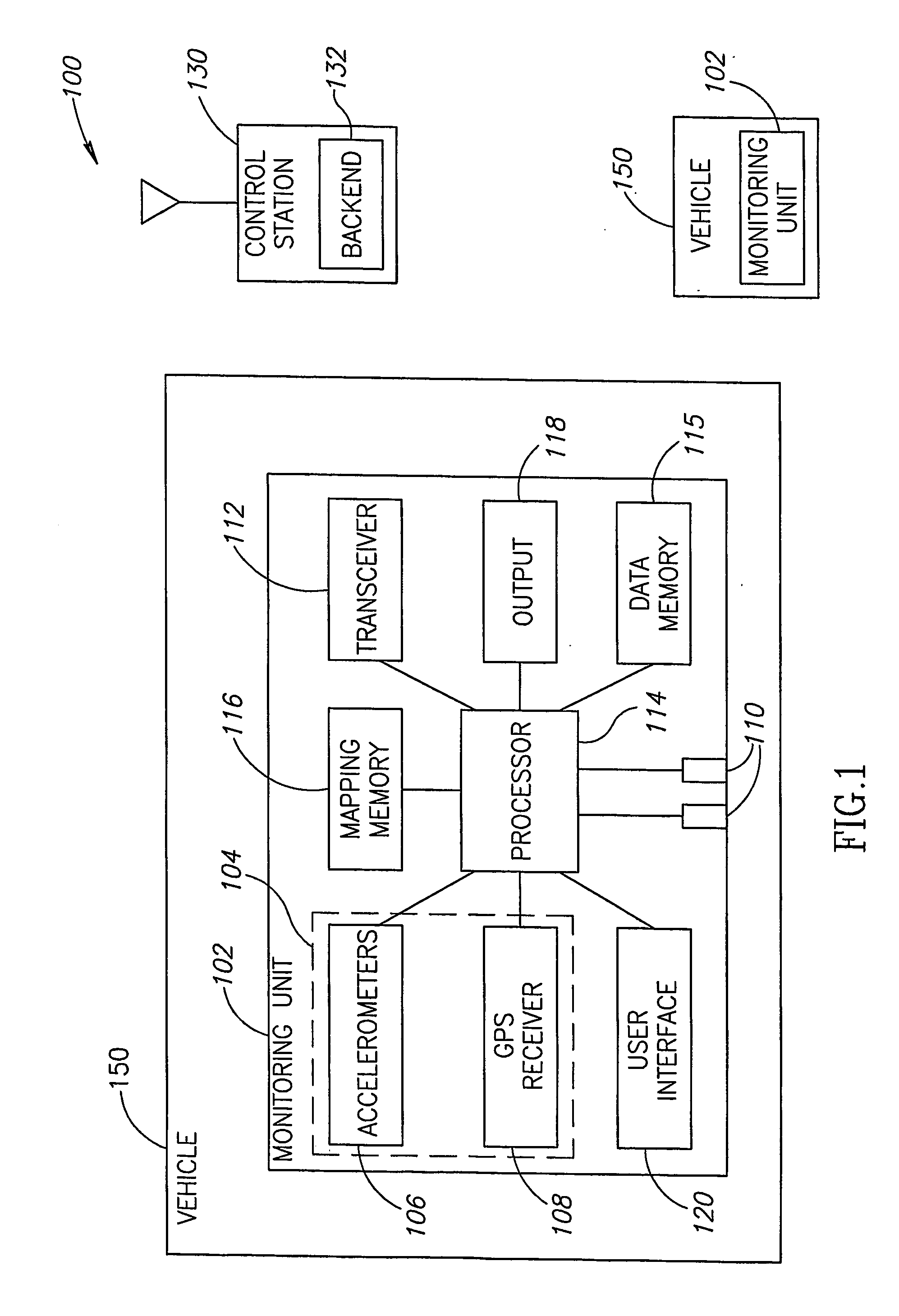

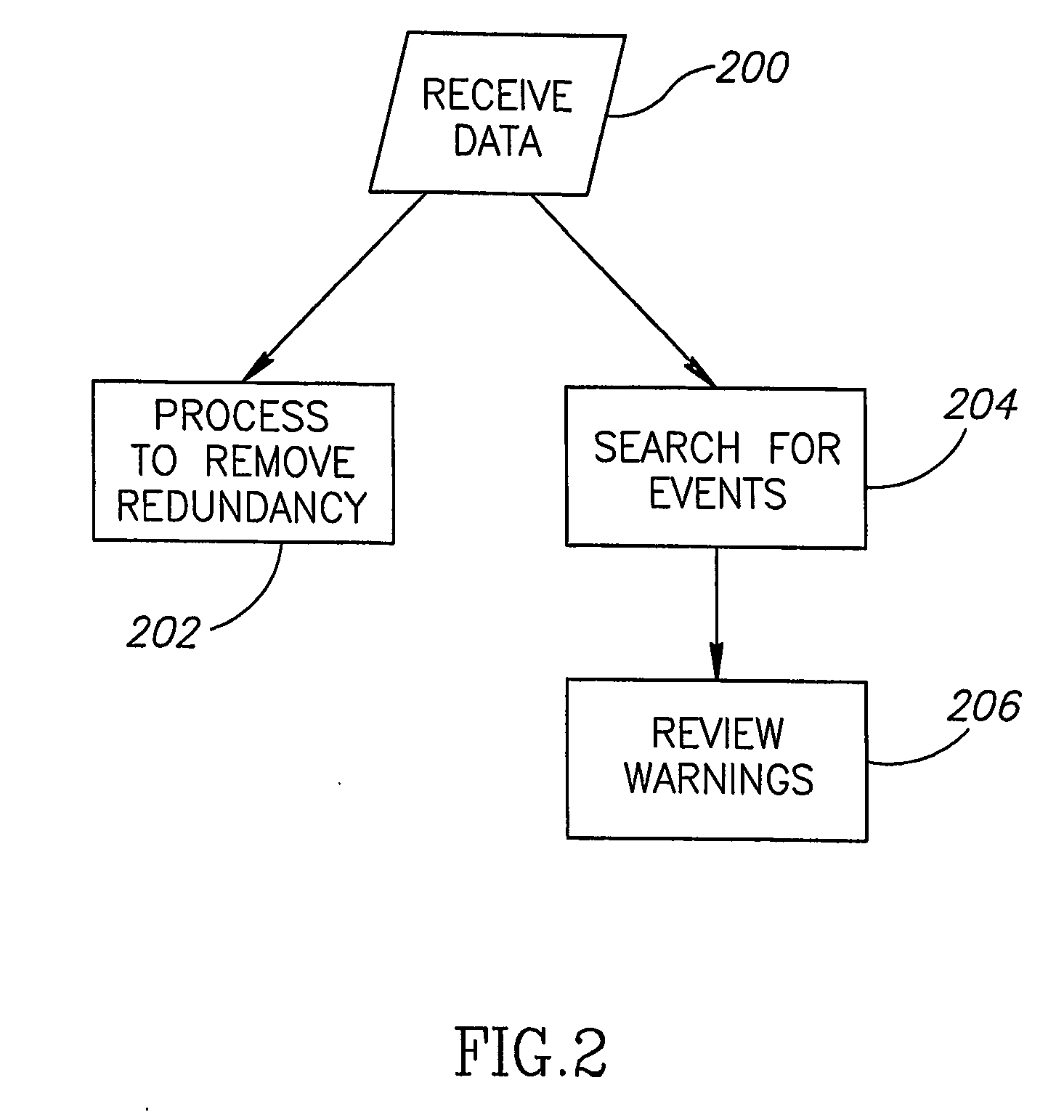

Traffic information system

ActiveUS20070027583A1Minimize the numberAccurate insurance rateAnalogue computers for vehiclesAnalogue computers for trafficEngineeringVehicle driving

Owner:INSURANCE SERVICES OFFICE INC

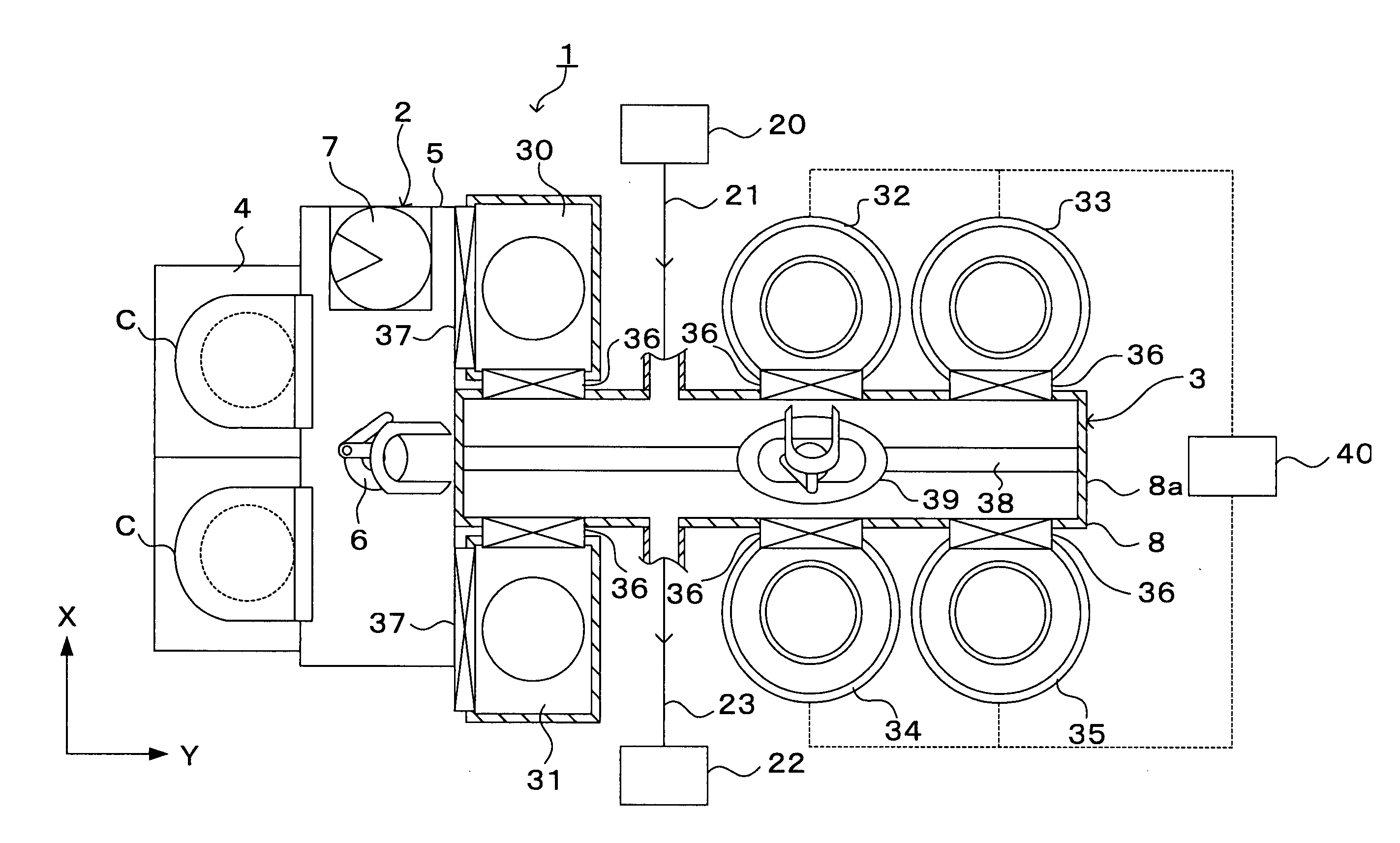

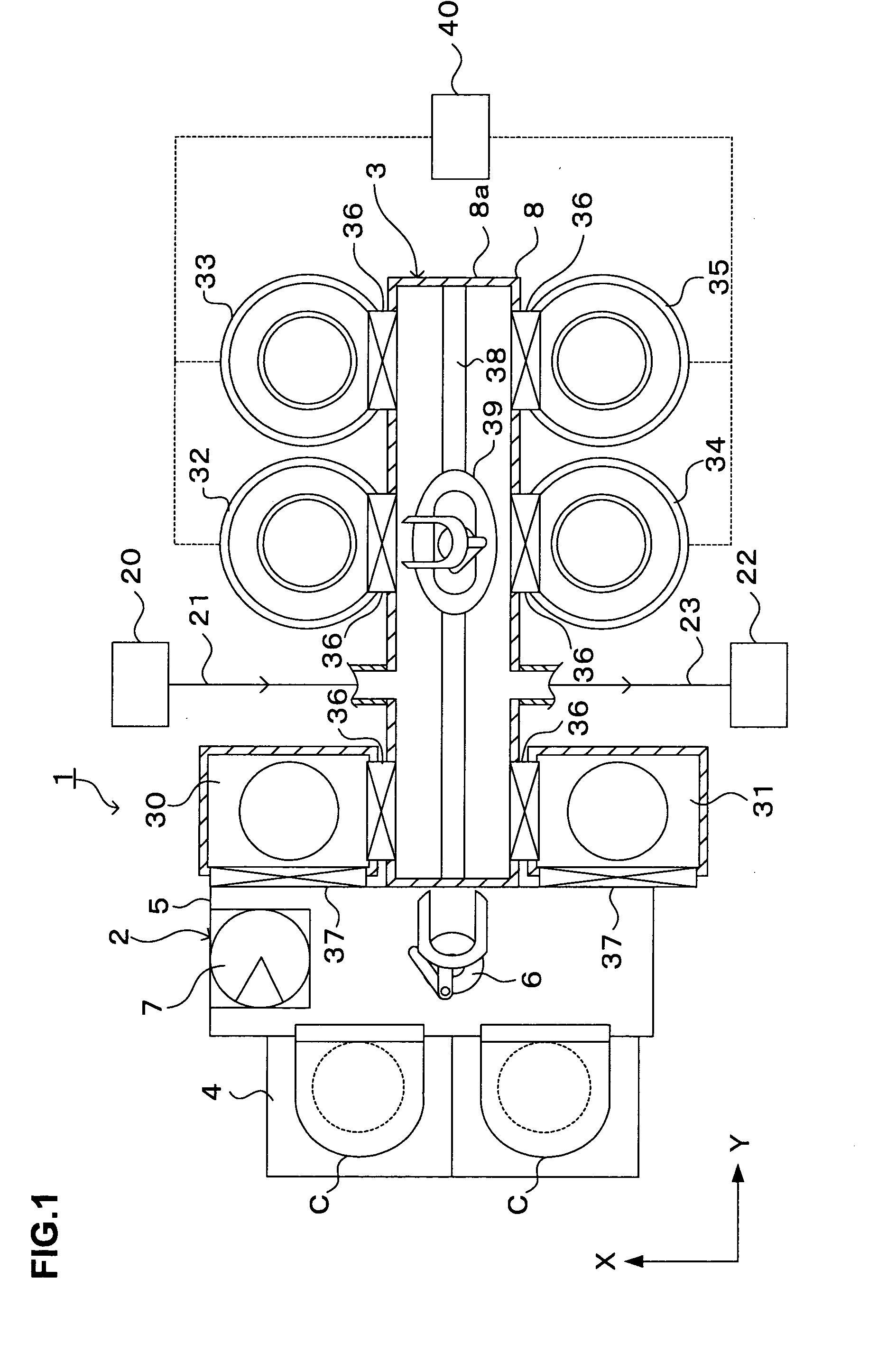

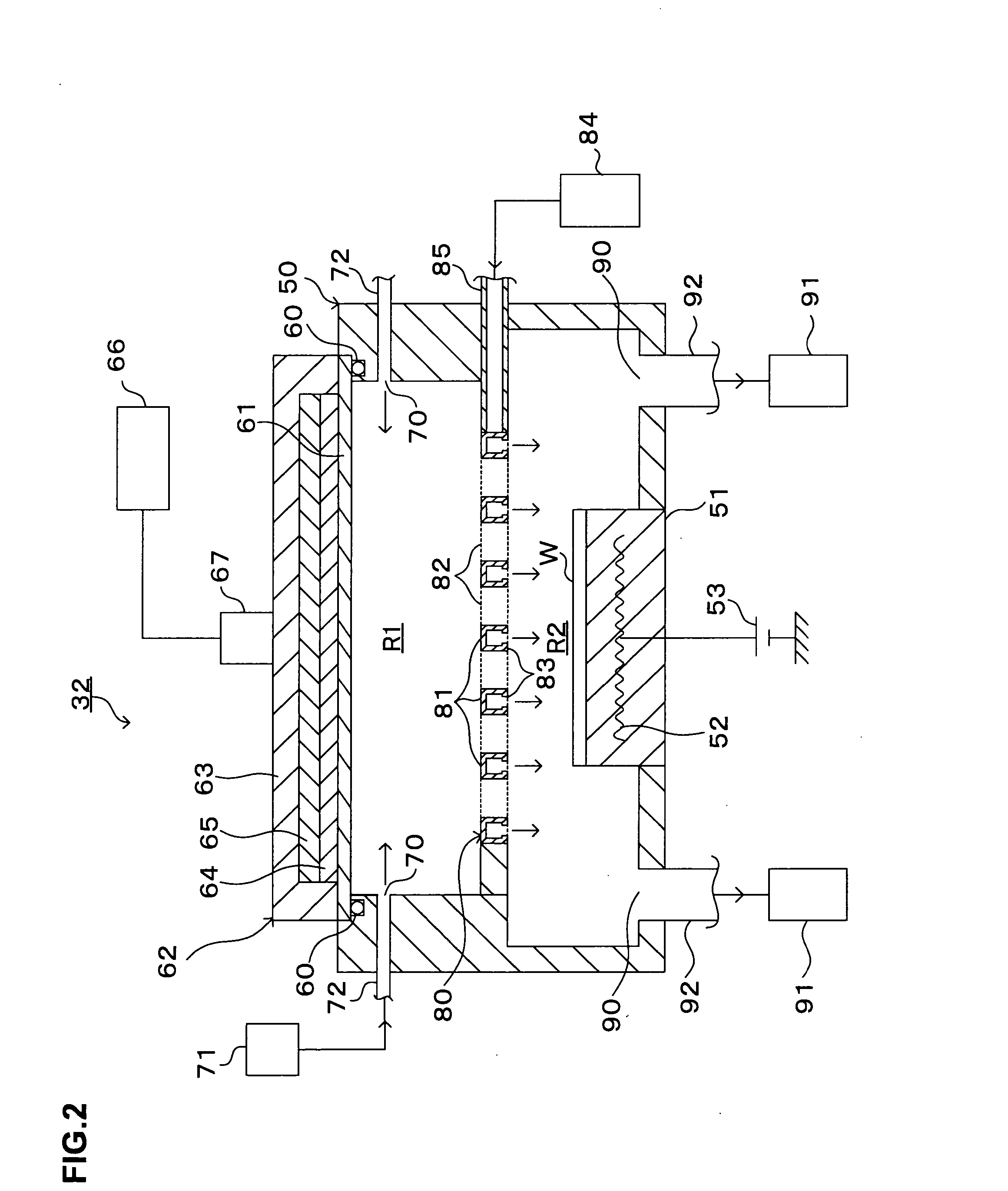

Substrate processing method, computer readable recording medium and substrate processing apparatus

InactiveUS20070062453A1Low dielectric constantImprove heat resistanceElectric discharge tubesSemiconductor/solid-state device detailsMicrowaveEngineering

In the present invention, Ar gas for plasma generation is supplied to a plasma generation region and butyne gas having a multiple bond is supplied to a film formation region at a substrate side as source gas, inside of a process vessel in an insulating film forming apparatus. A microwave is supplied inside of the process vessel from a radial line slot antenna under a state in which a bias voltage is not applied to a substrate W. A plasma is thereby generated in the plasma generation region, the butyne gas in the film formation region is activated by the plasma, and an insulating film of amorphous carbon is formed on the substrate.

Owner:TOKYO ELECTRON LTD

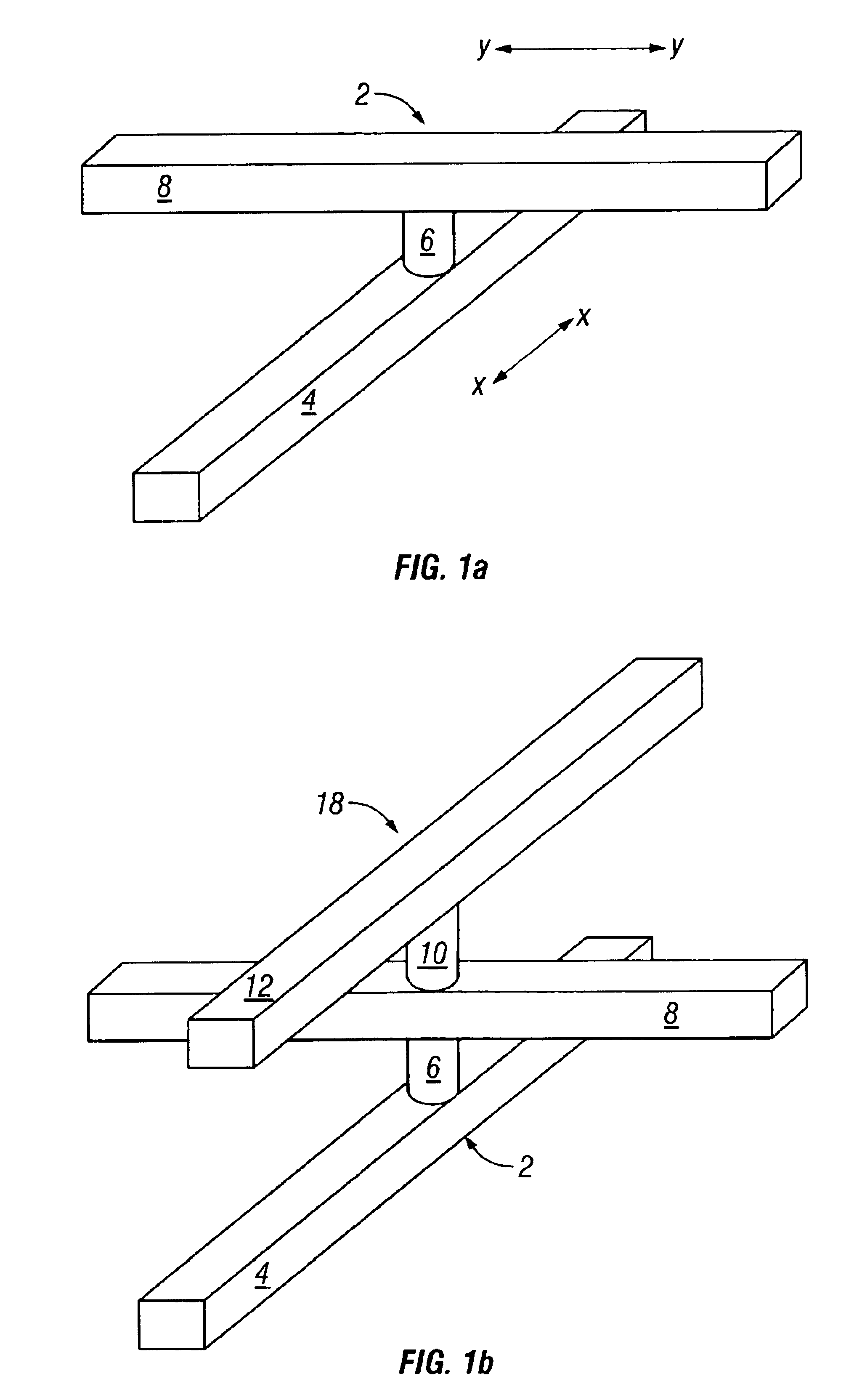

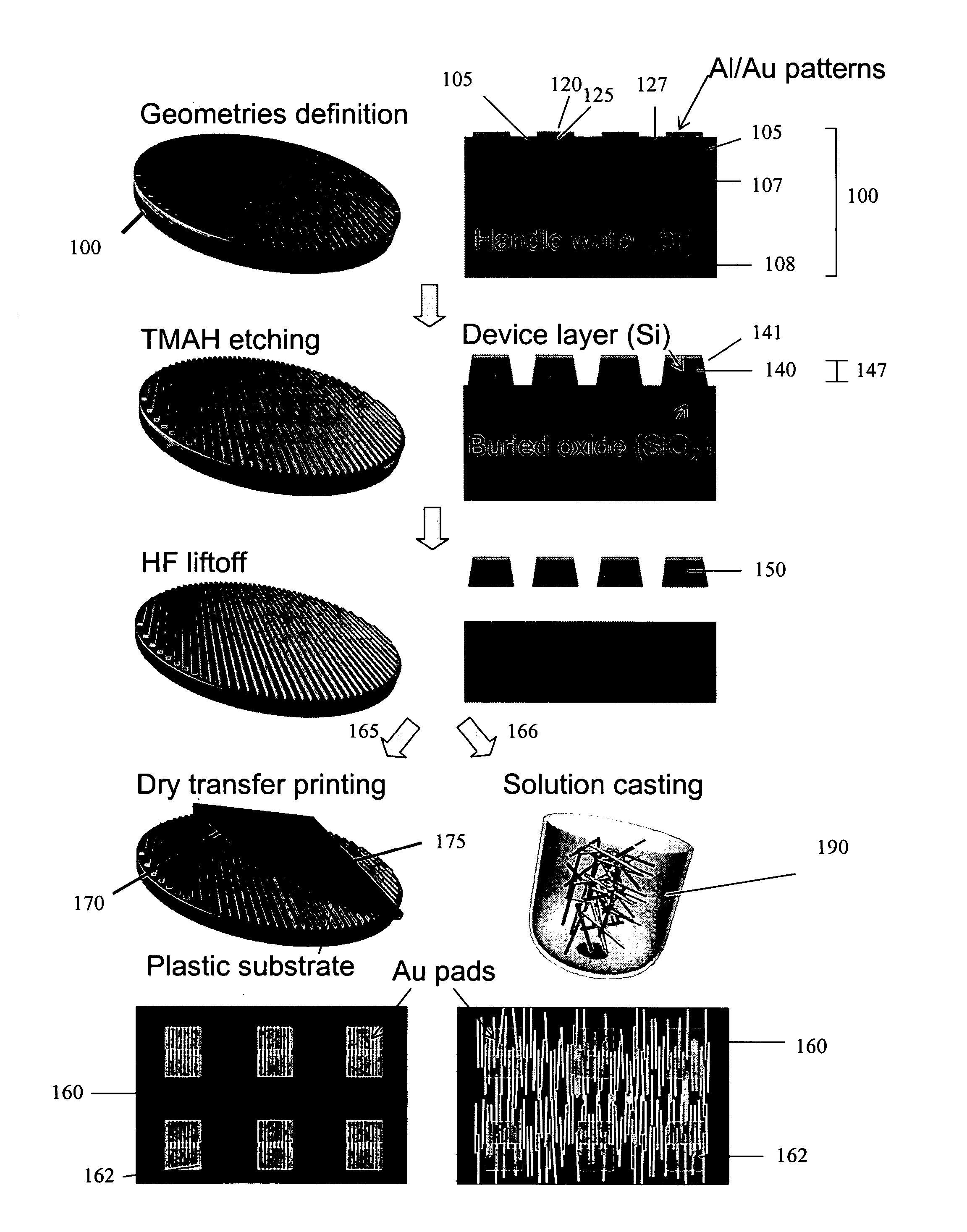

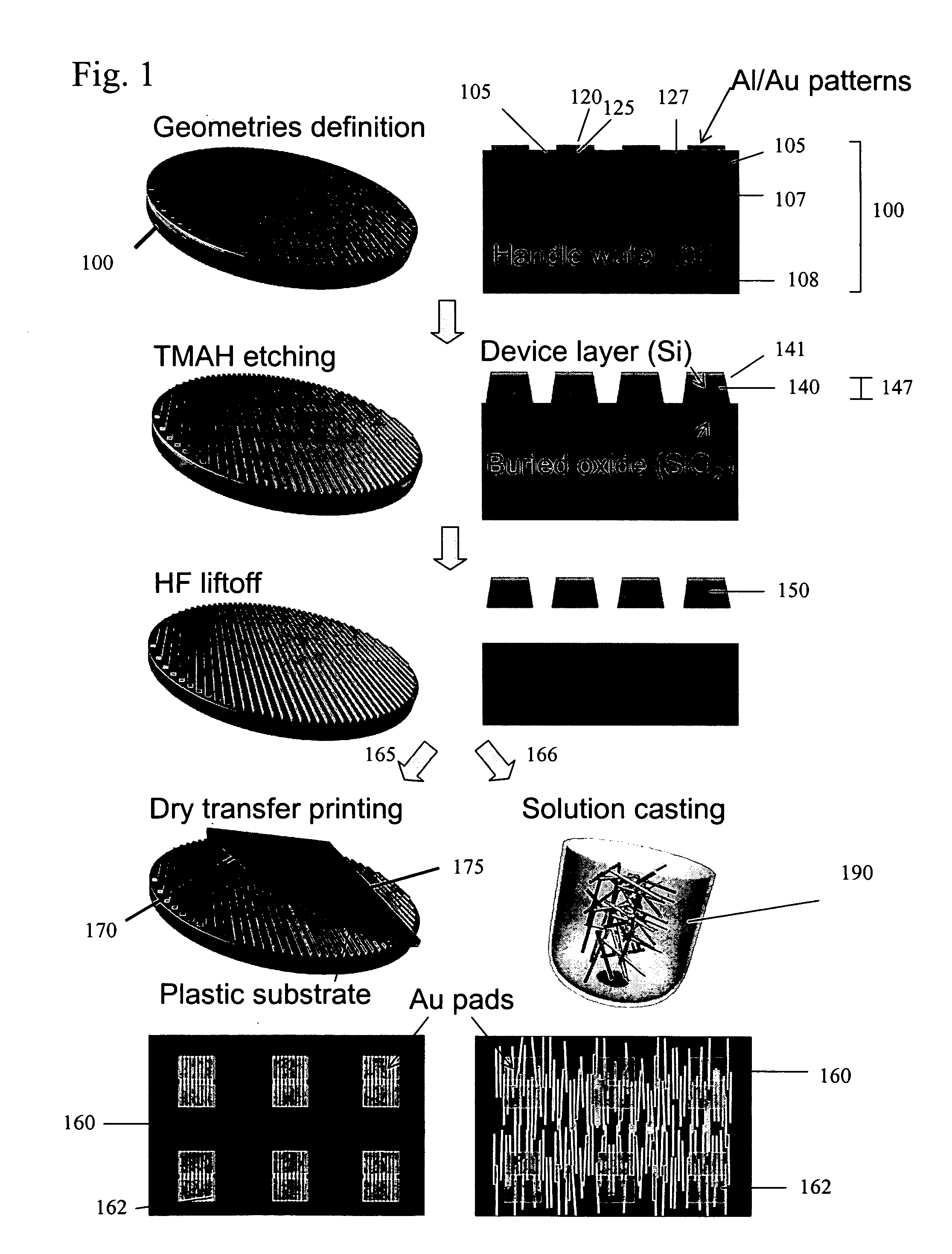

Stretchable semiconductor elements and stretchable electrical circuits

ActiveUS20060038182A1Complete release is preventedLow costTransistorDecorative surface effectsStretchable electronicsSemiconductor structure

The invention provides methods and devices for fabricating printable semiconductor elements and assembling printable semiconductor elements onto substrate surfaces. Methods, devices and device components of the present invention are capable of generating a wide range of flexible electronic and optoelectronic devices and arrays of devices on substrates comprising polymeric materials. The present invention also provides stretchable semiconductor structures and stretchable electronic devices capable of good performance in stretched configurations.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

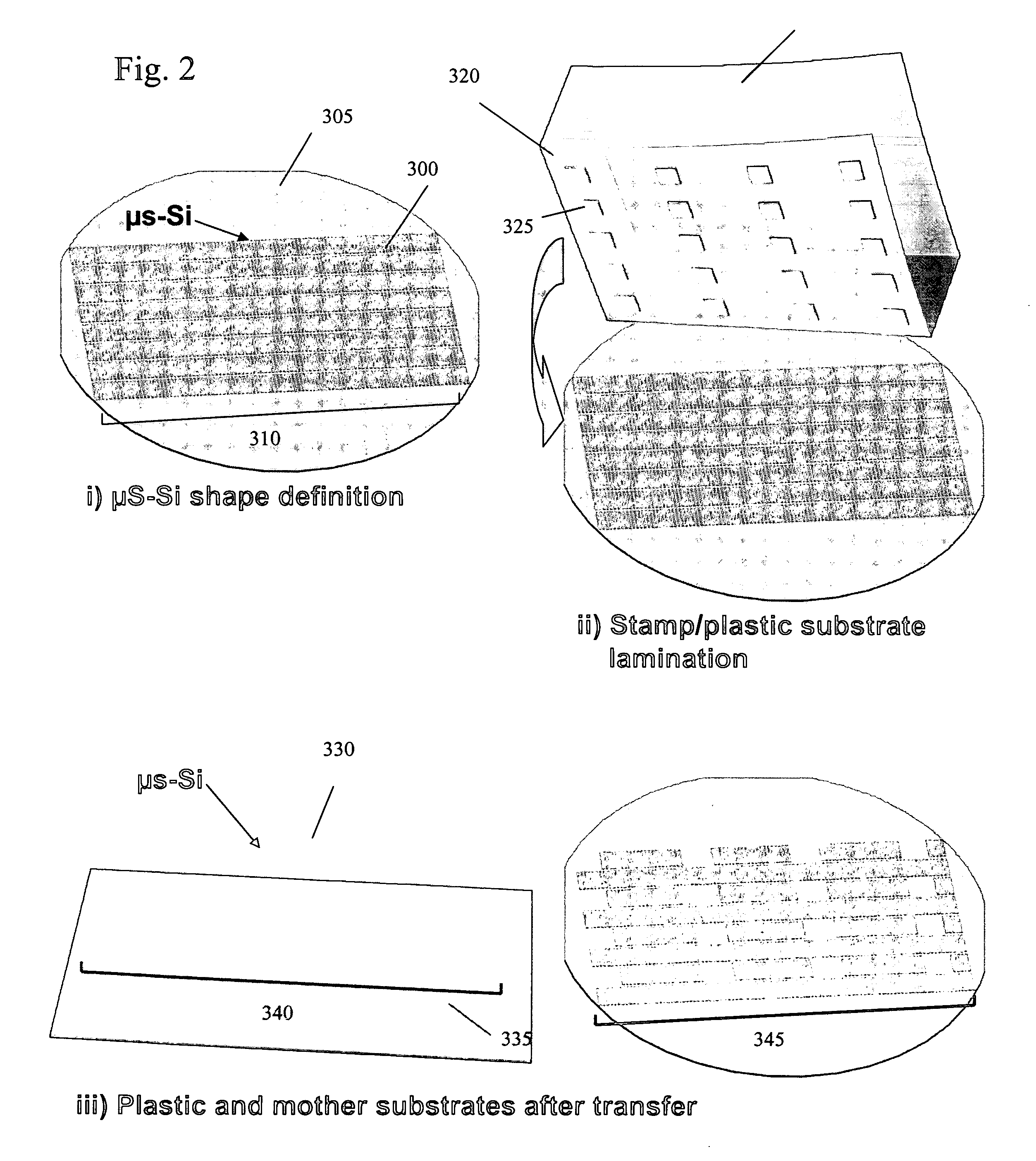

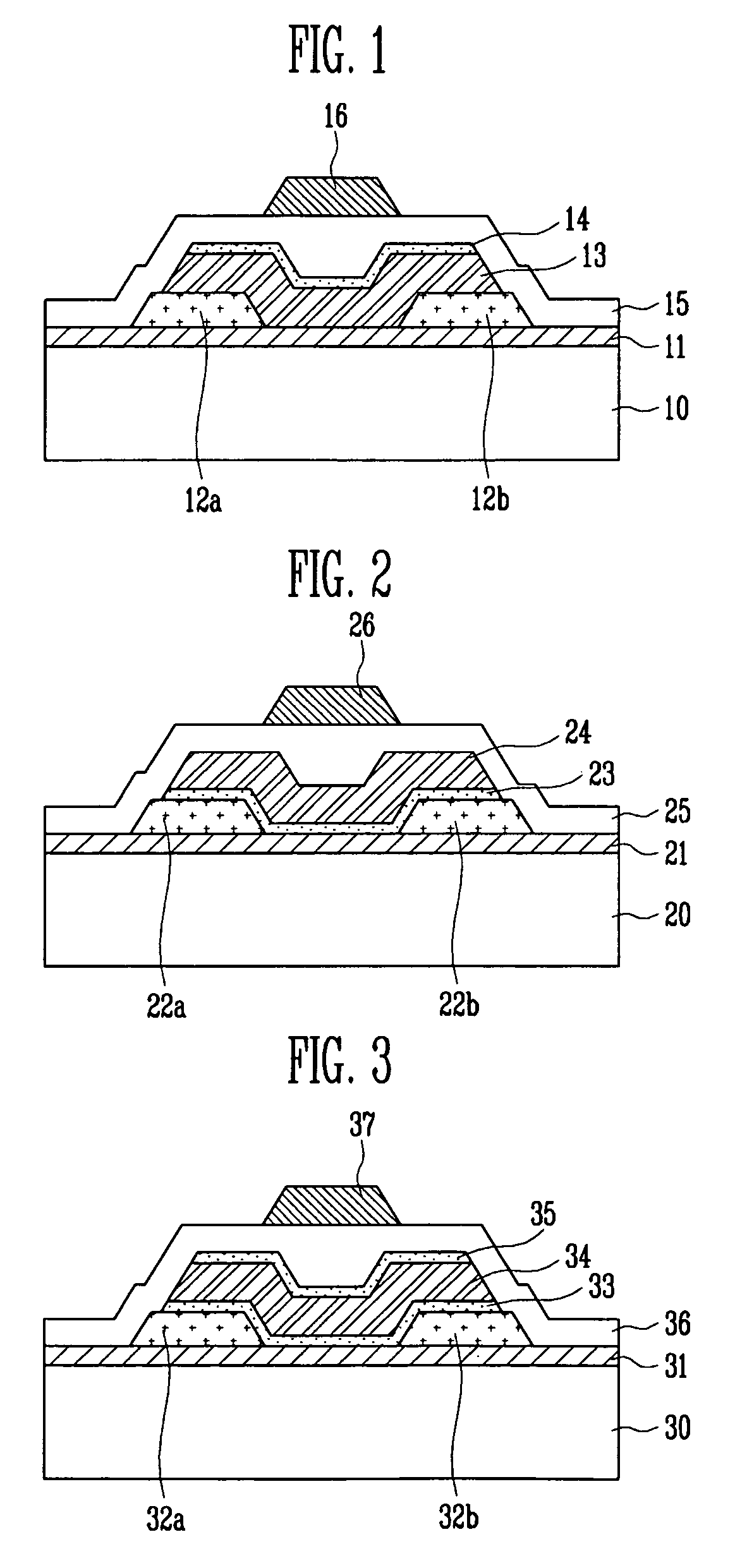

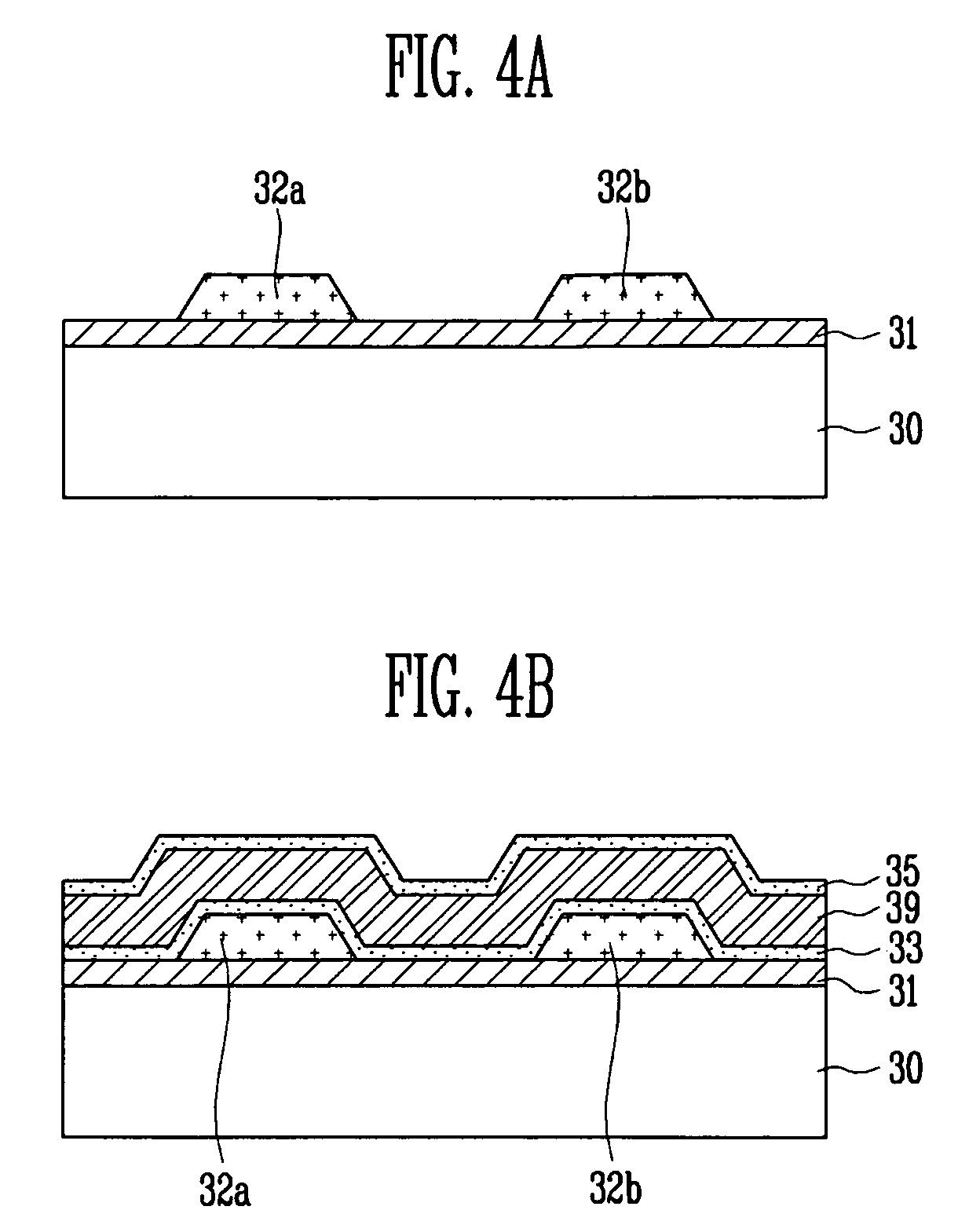

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS7994500B2Improve featuresAvoid chargingSemiconductor/solid-state device detailsSolid-state devicesTrappingOxide thin-film transistor

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

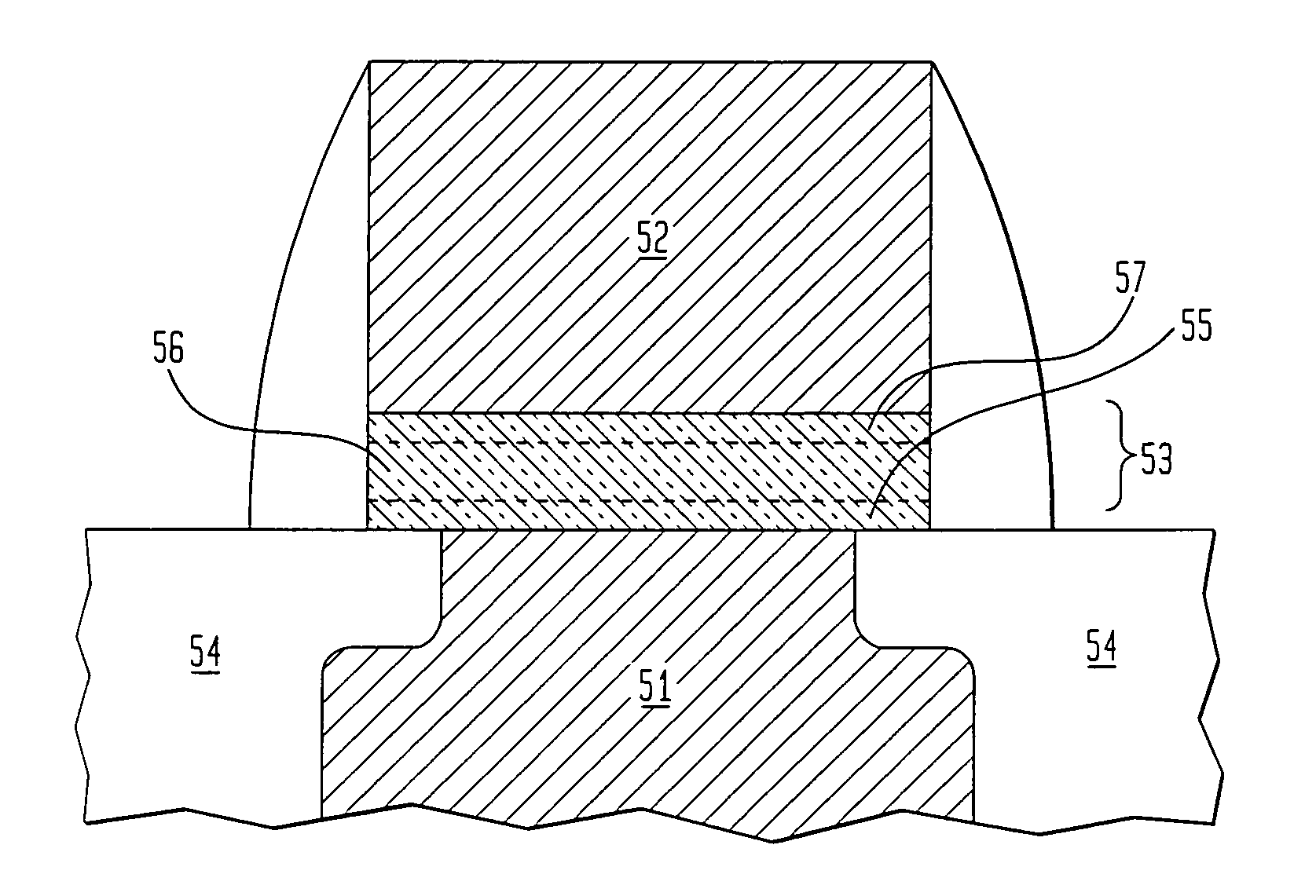

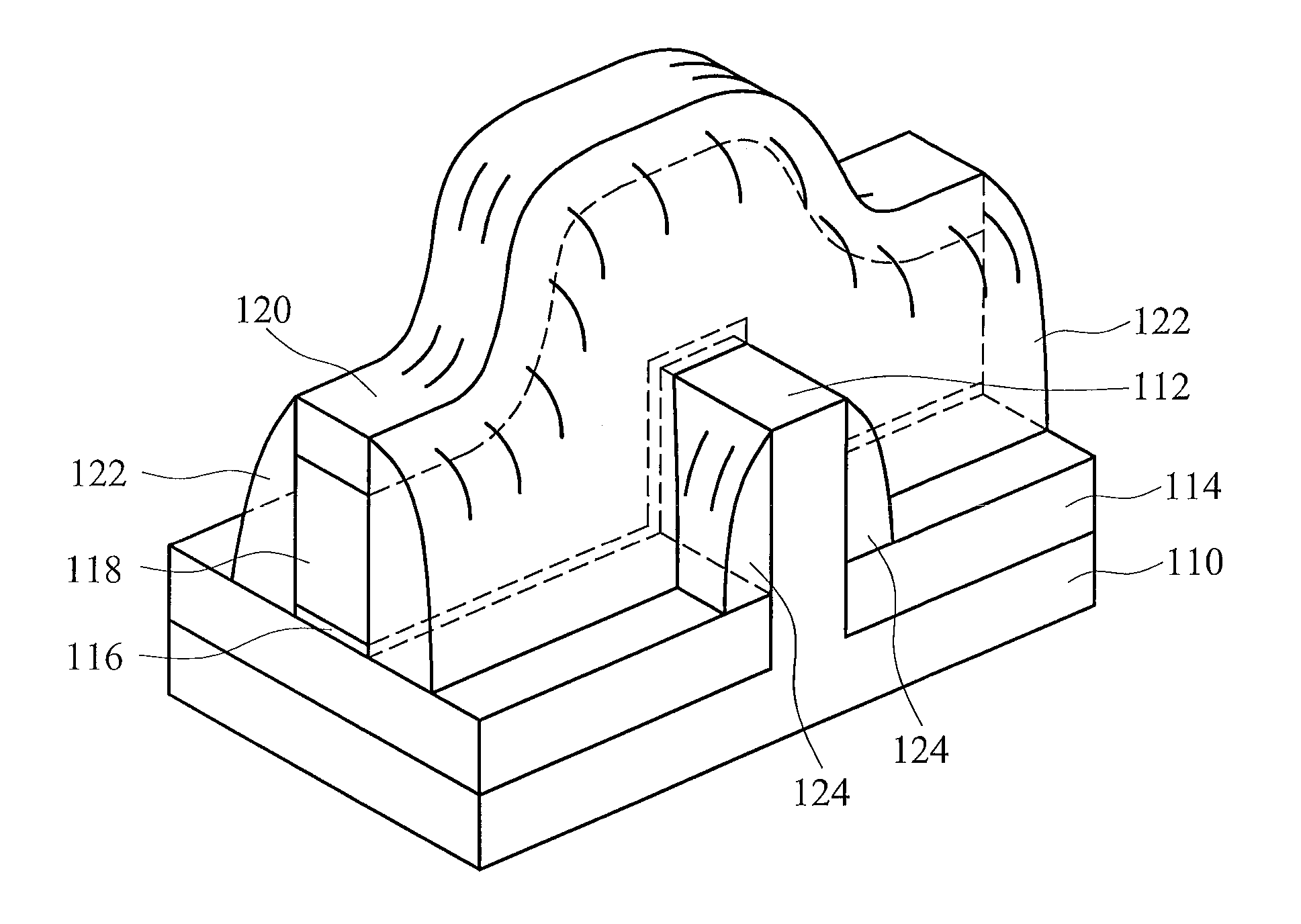

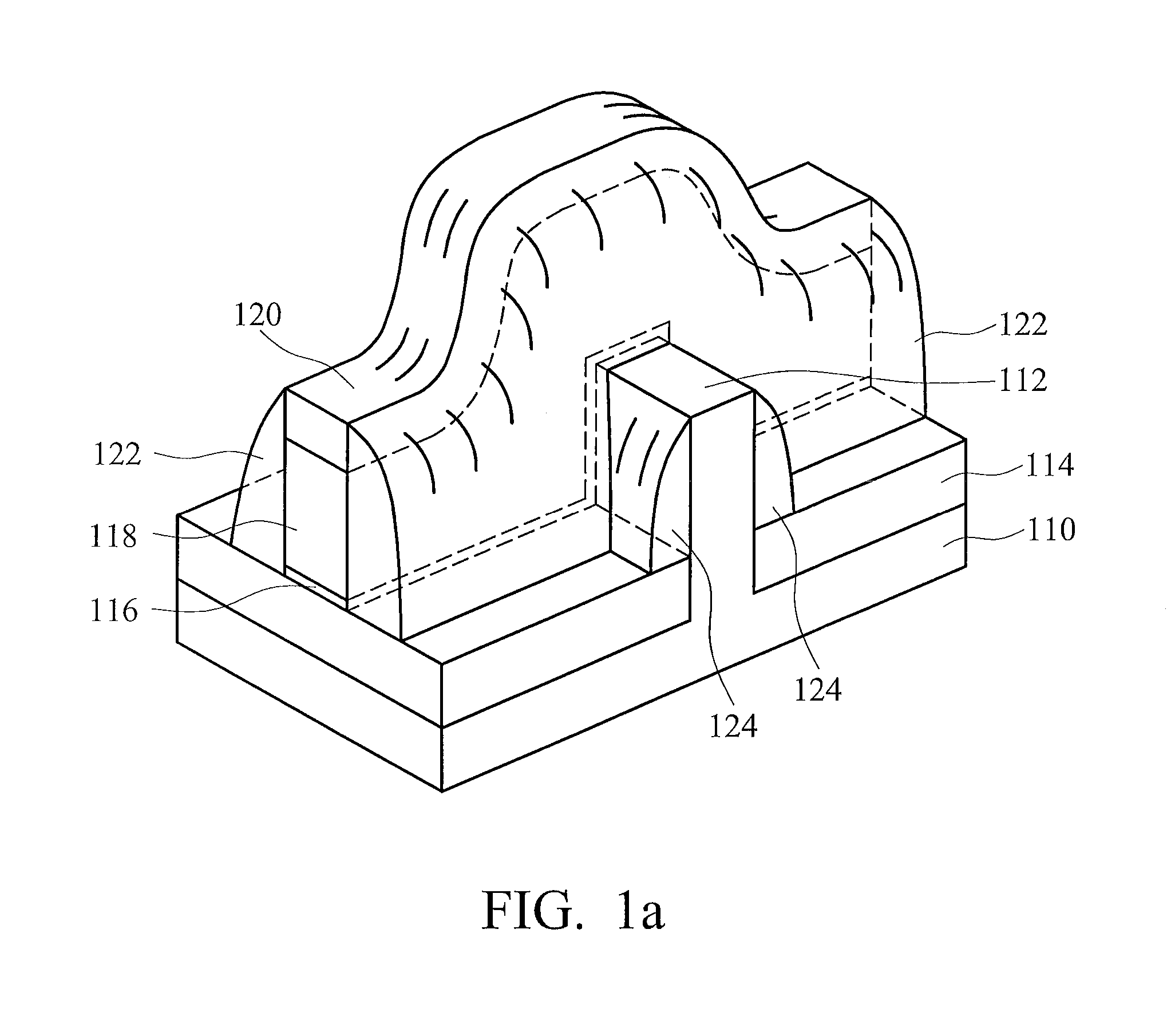

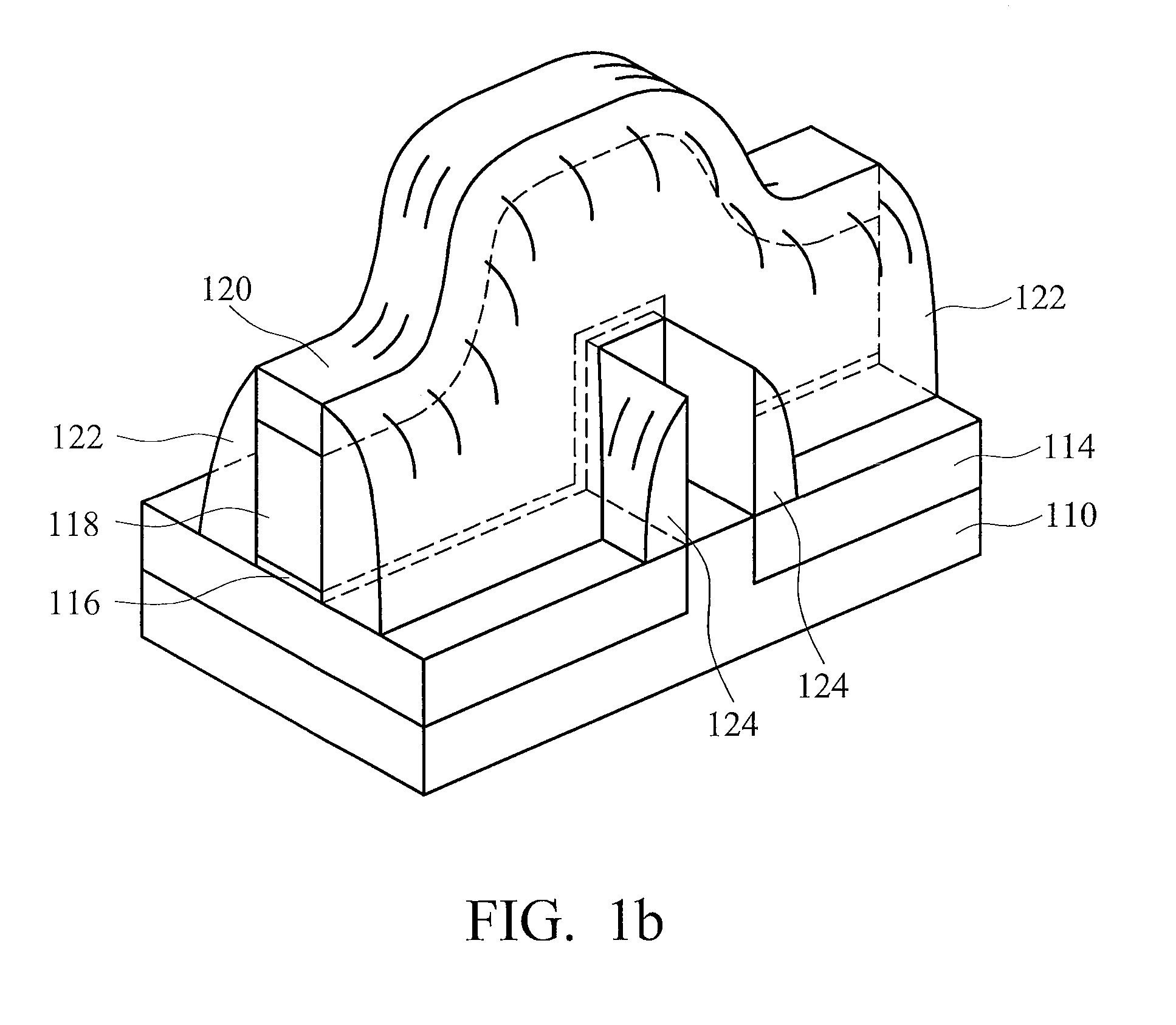

Fin field-effect transistors

InactiveUS7667271B2TransistorSemiconductor/solid-state device detailsEngineeringField-effect transistor

A fin field-effect transistor (finFET) with improved source / drain regions is provided. In an embodiment, the source / drain regions of the fin are removed while spacers adjacent to the fin remain. An angled implant is used to implant the source / drain regions near a gate electrode, thereby allowing for a more uniform lightly doped drain. The fin may be re-formed by either epitaxial growth or a metallization process. In another embodiment, the spacers adjacent the fin in the source / drain regions are removed and the fin is silicided along the sides and the top of the fin. In yet another embodiment, the fin and the spacers are removed in the source / drain regions. The fins are then re-formed via an epitaxial growth process or a metallization process. Combinations of these embodiments may also be used.

Owner:TAIWAN SEMICON MFG CO LTD

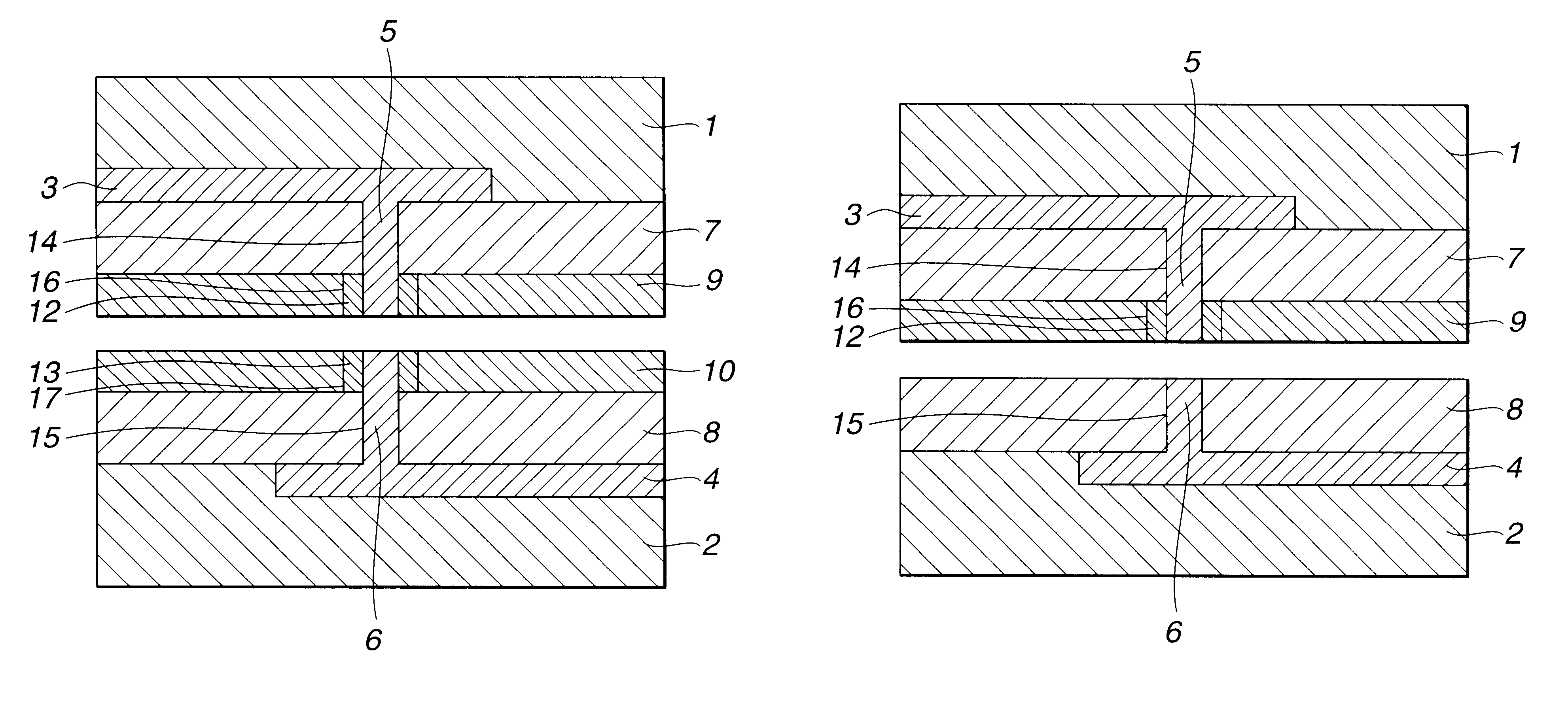

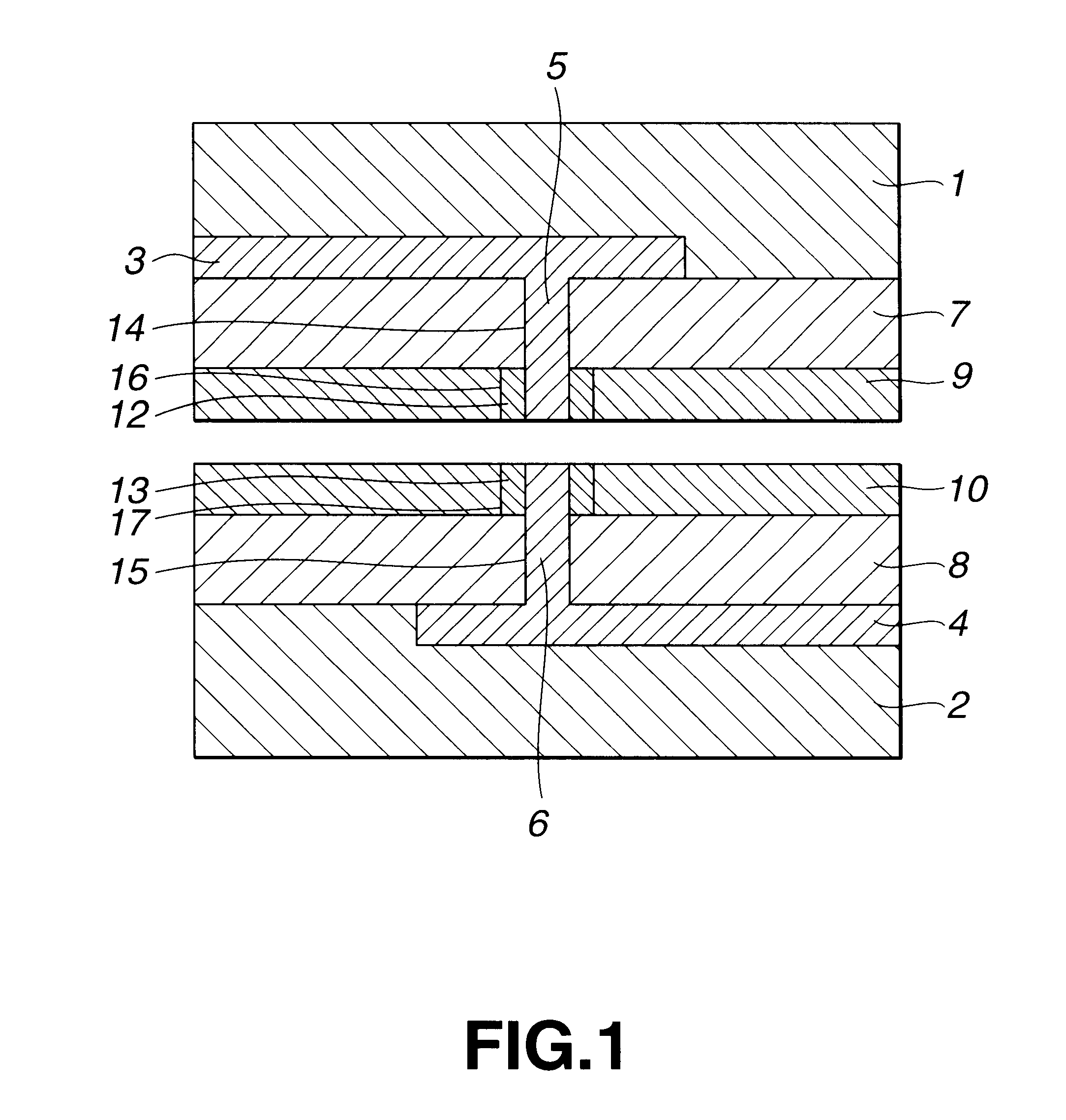

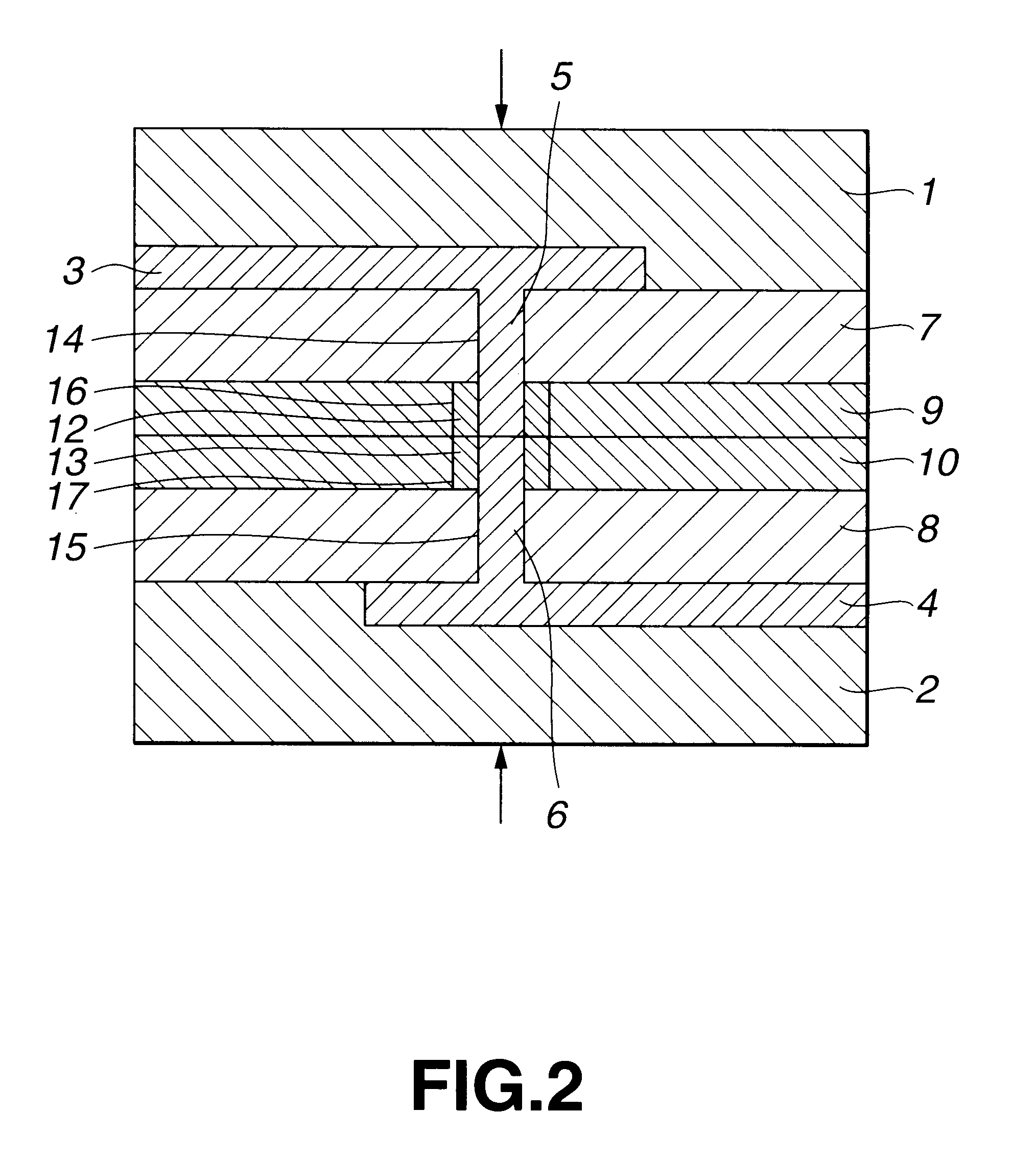

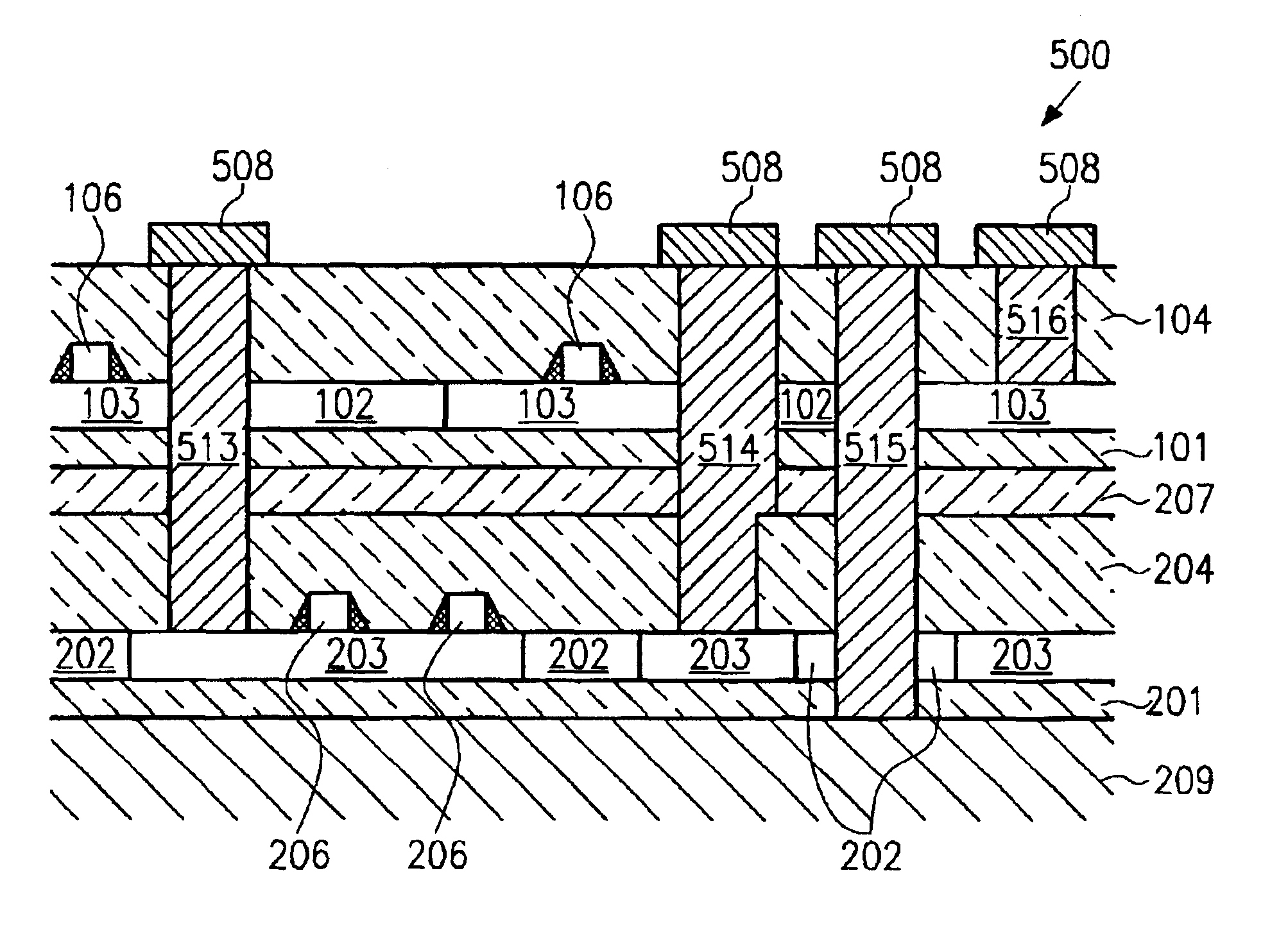

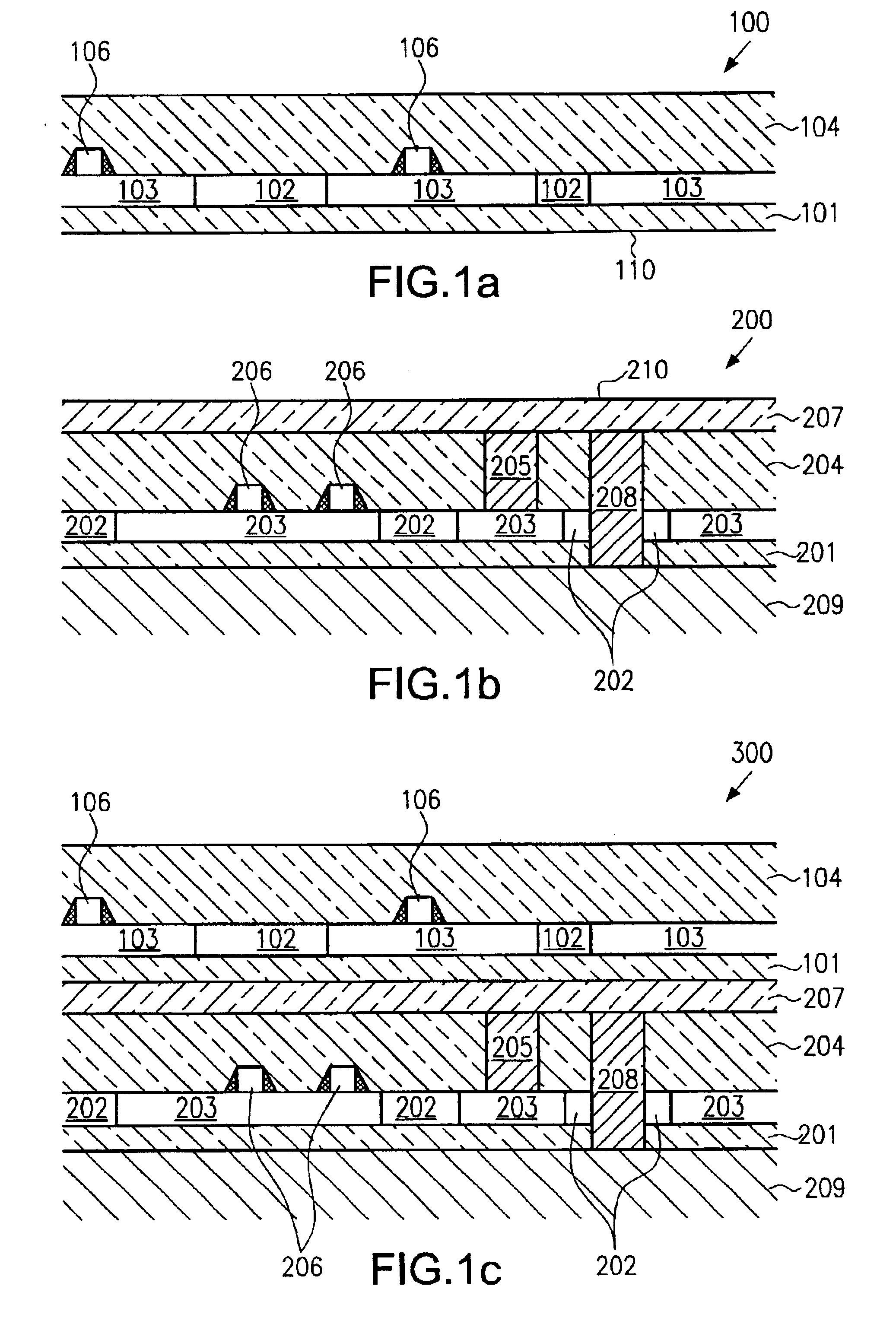

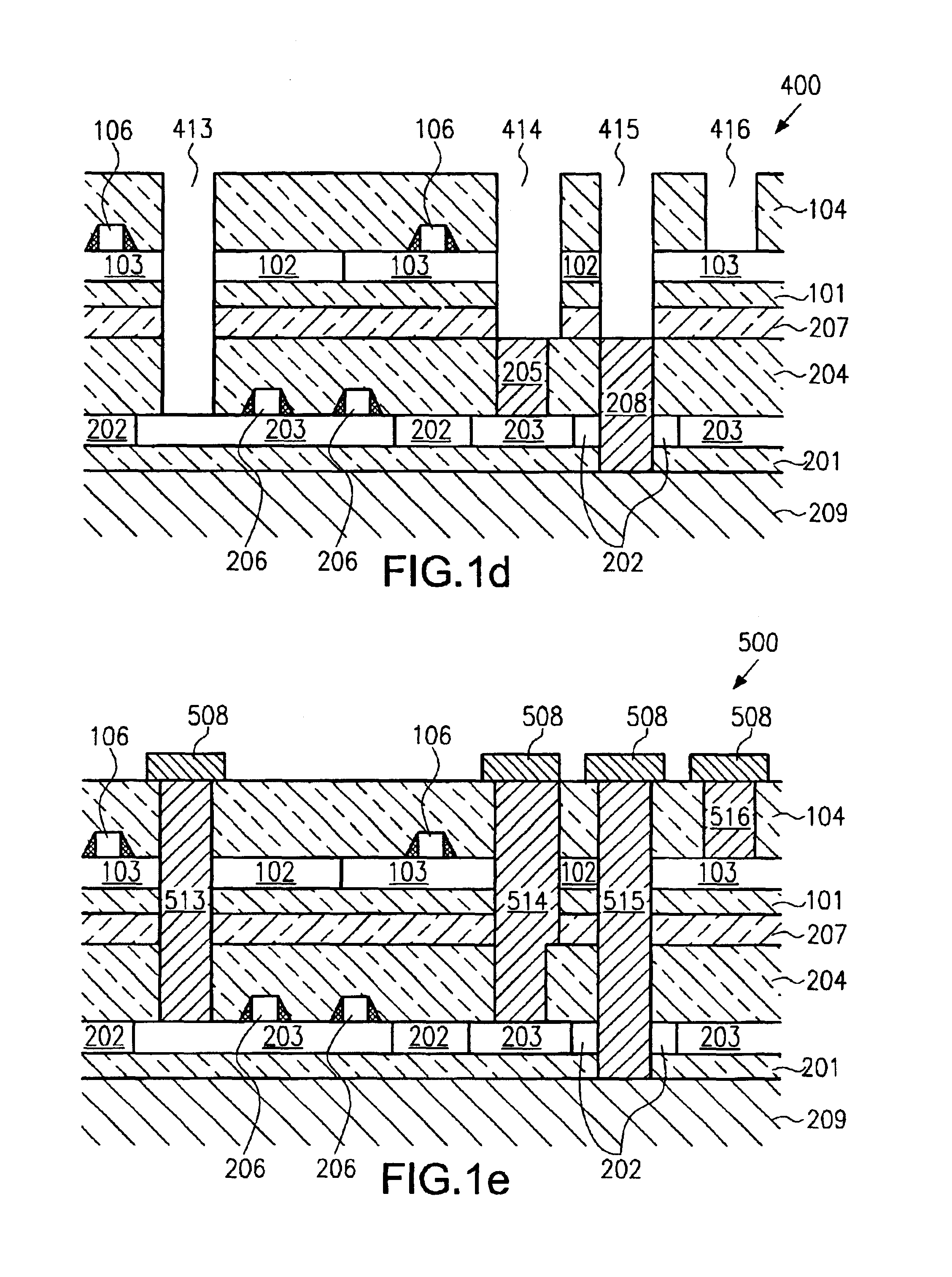

Interconnect structure for stacked semiconductor device

InactiveUS6465892B1Shorten the line lengthEasy to produceSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

In a multi-layer interconnection structure, the wiring length is to be reduced, and the interconnection is to be straightened, at the same time as measures need to be taken against radiation noise. To this end, there is disclosed a semiconductor device in which plural semiconductor substrates, each carrying semiconductor elements, are bonded together. On each semiconductor substrate is deposited an insulating layer through which is formed a connection wiring passed through the insulating layer so as to be connected to the interconnection layer of the semiconductor element. On a junction surface of at least one of the semiconductor substrates is formed an electrically conductive layer of an electrically conductive material in which an opening is bored in association with the connection wiring. The semiconductor substrates are bonded together by the solid state bonding technique to interconnect the connection wirings formed on each semiconductor substrate.

Owner:LAPIS SEMICON CO LTD +9

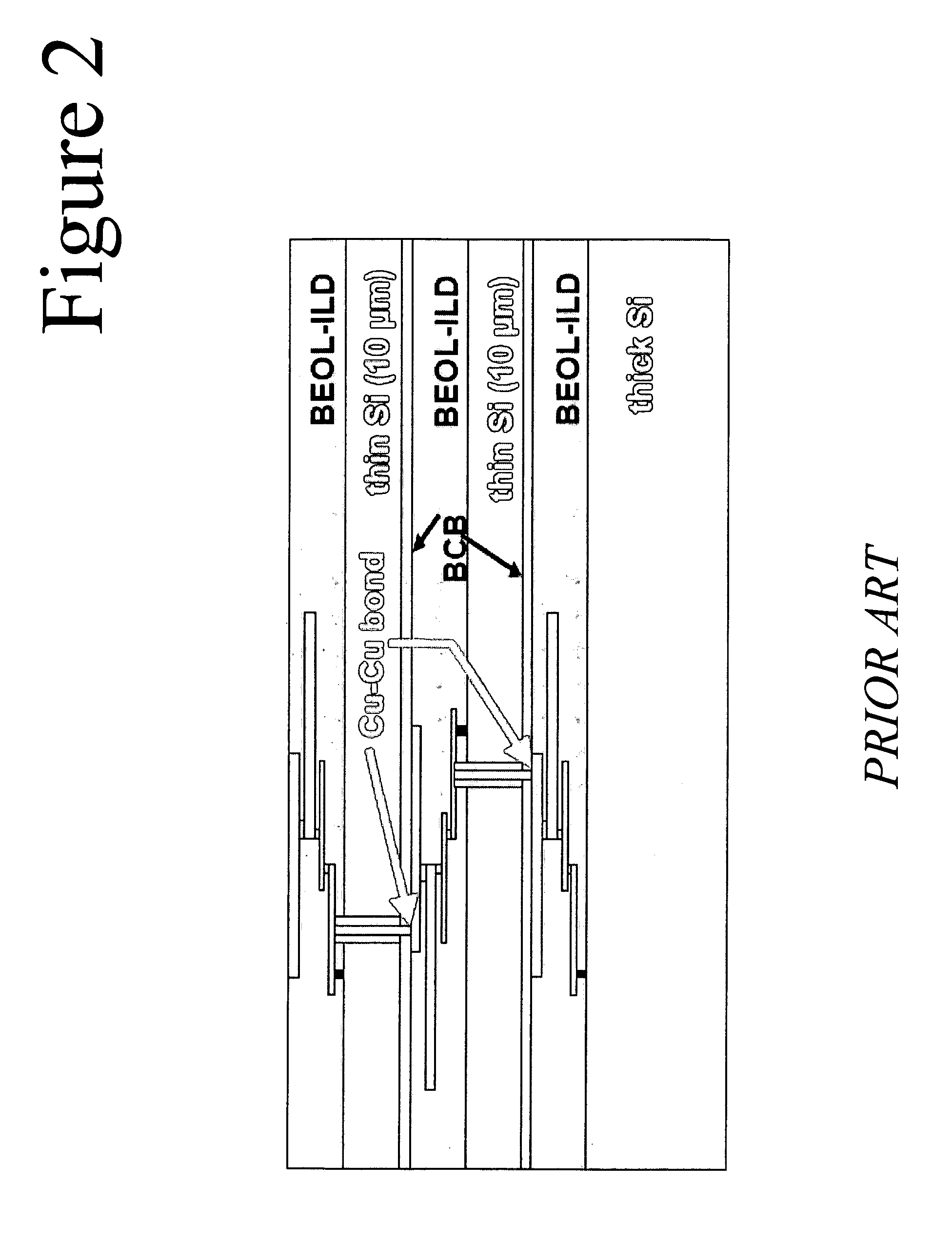

Three-dimensional integrated semiconductor devices

InactiveUS6943067B2Semiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

The present invention describes a process for three-dimensional integration of semiconductor devices and a resulting device. The process combines low temperature wafer bonding methods with backside / substrate contact processing methods, preferably with silicon on insulator devices. The present invention utilizes, in an inventive fashion, low temperature bonding processes used for bonded silicon on insulator (SOI) wafer technology. This low temperature bonding technology is adopted for stacking several silicon layers on top of each other and building active transistors and other circuit elements in each one. The back-side / substrate contact processing methods allow the interconnection of the bonded SOI layers.

Owner:ADVANCED MICRO DEVICES INC

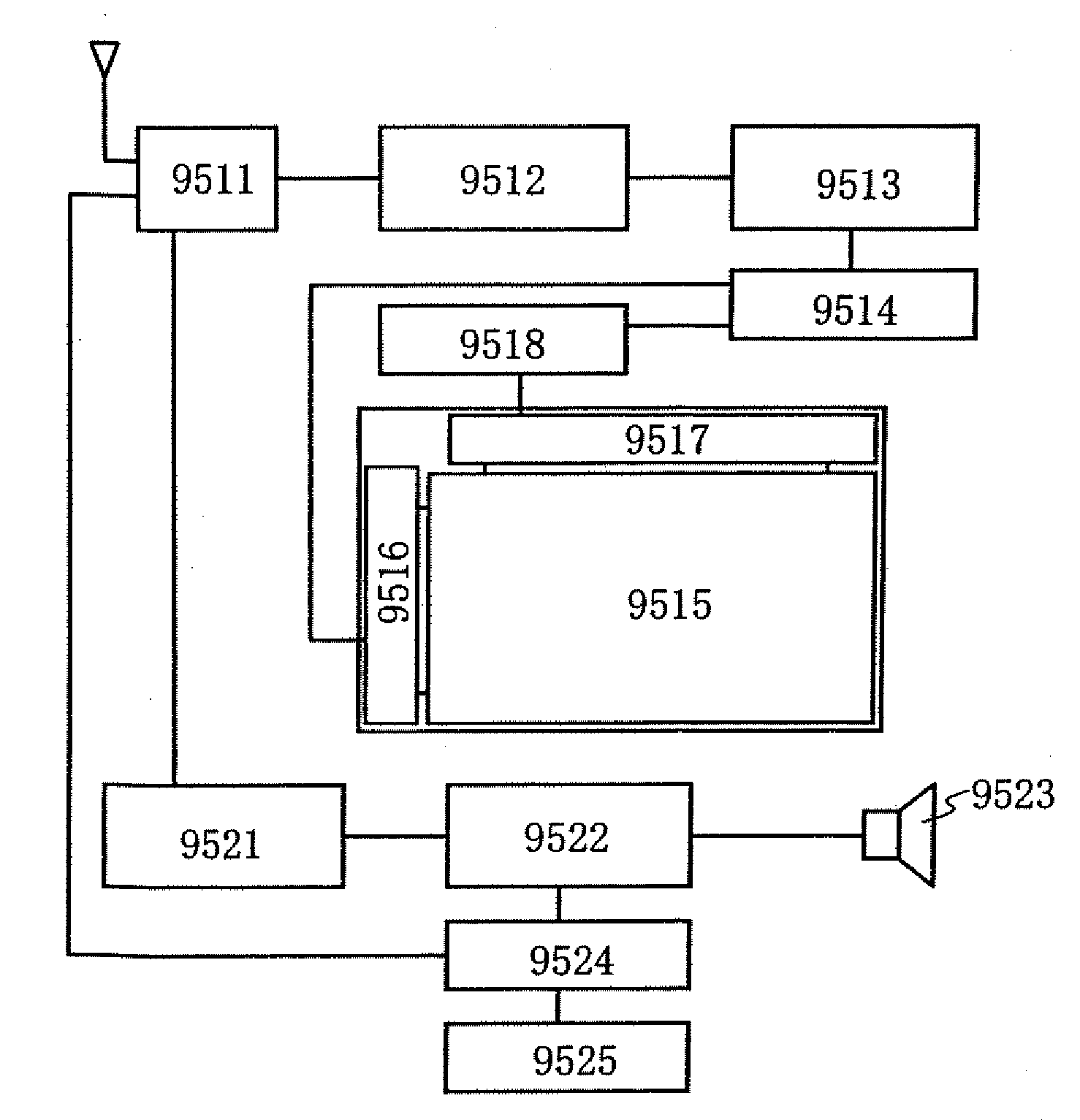

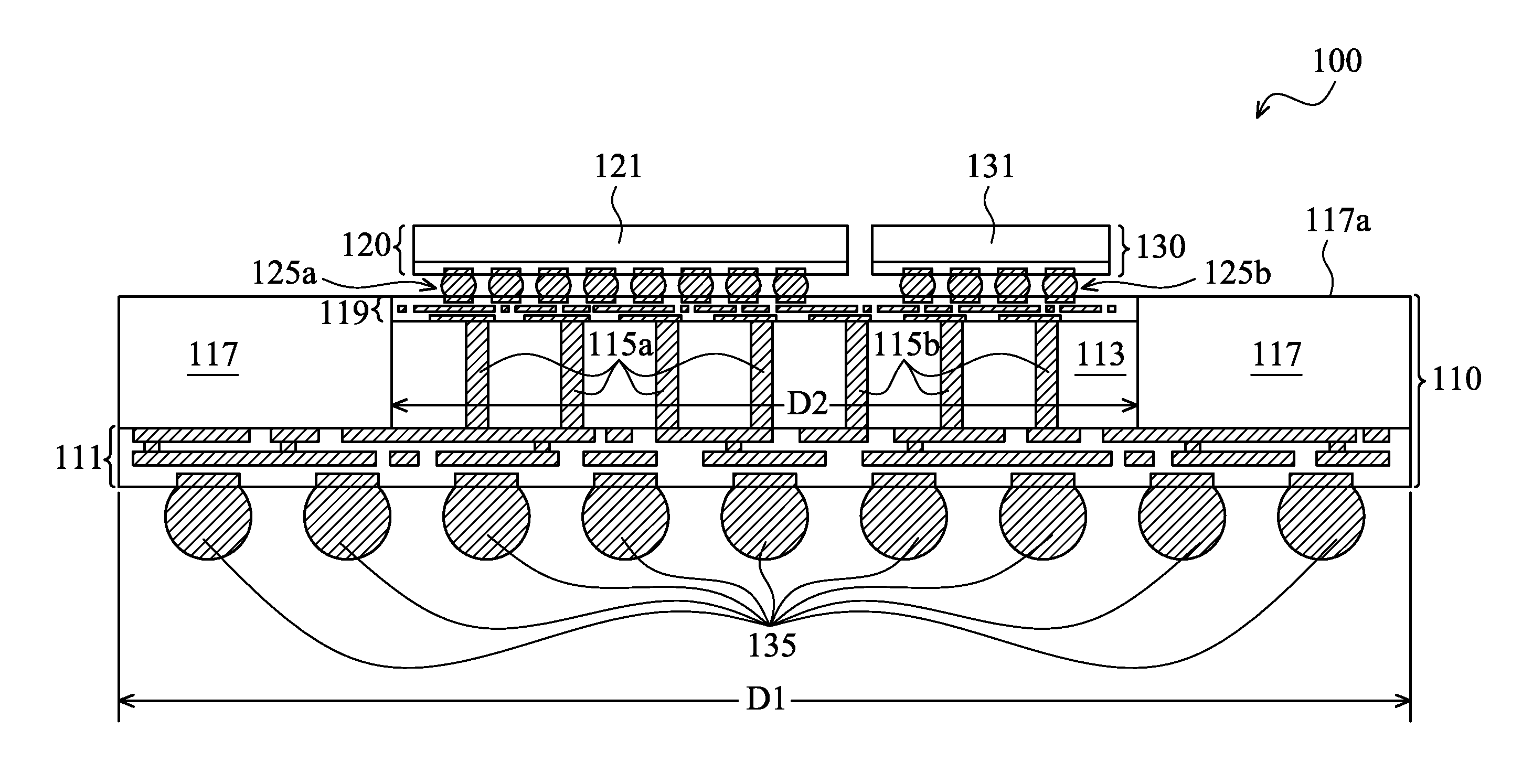

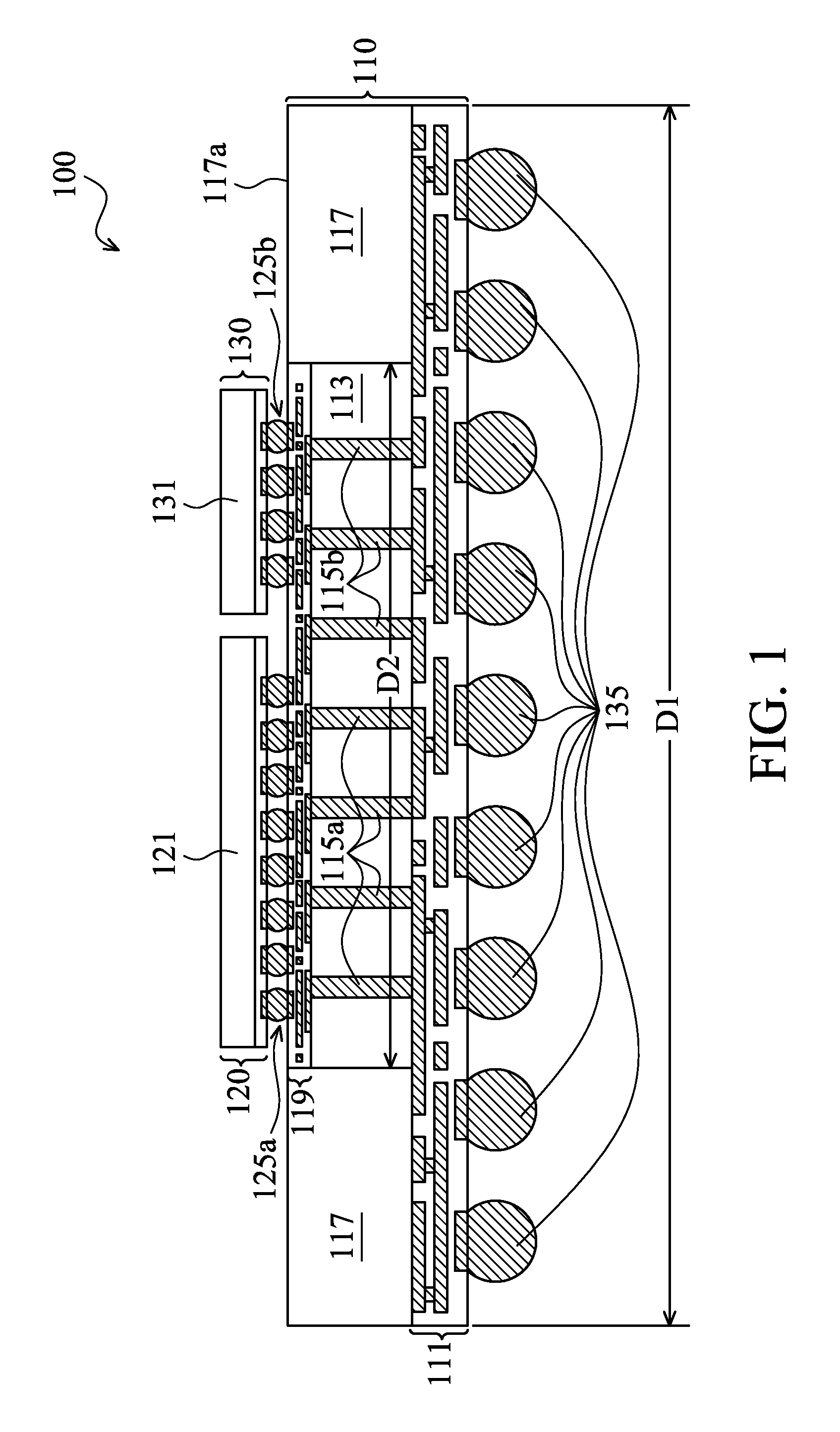

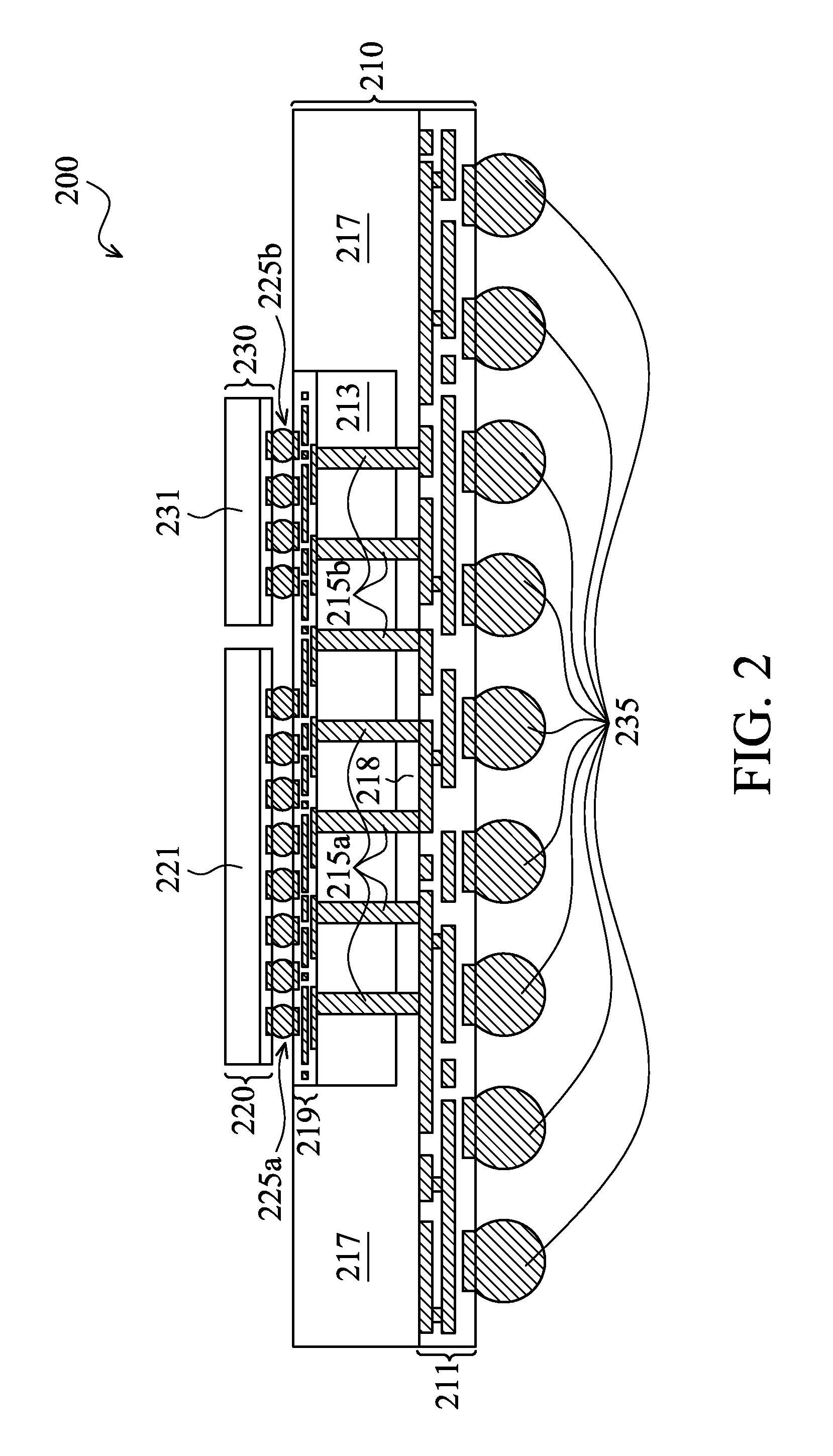

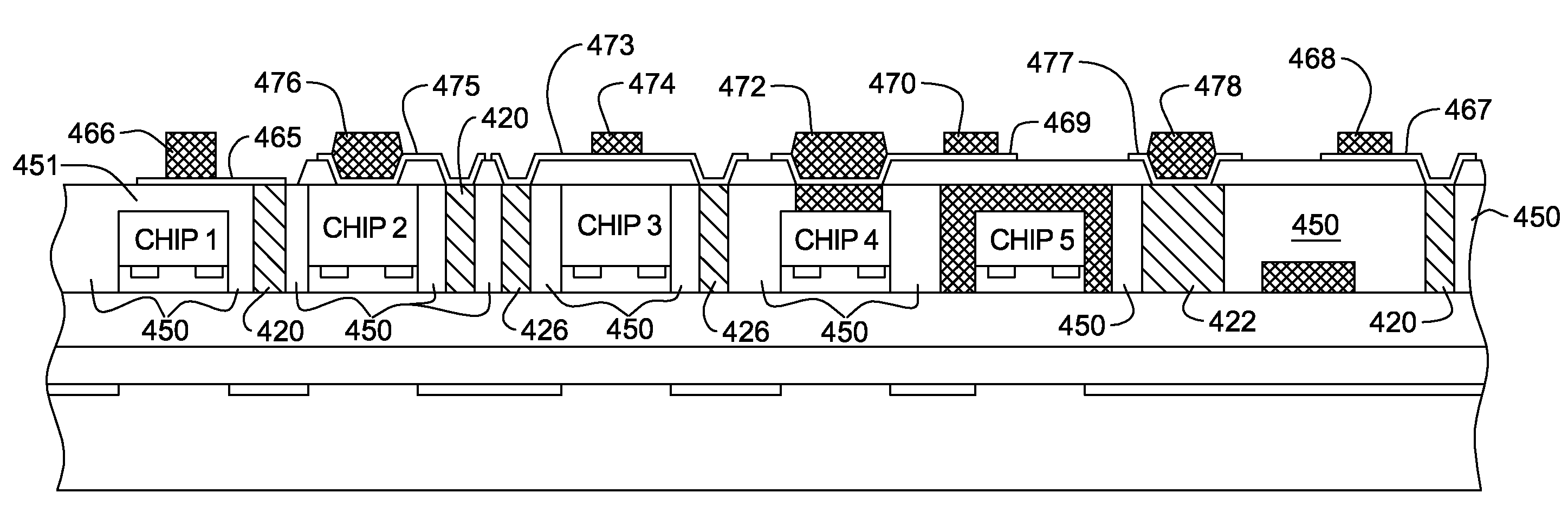

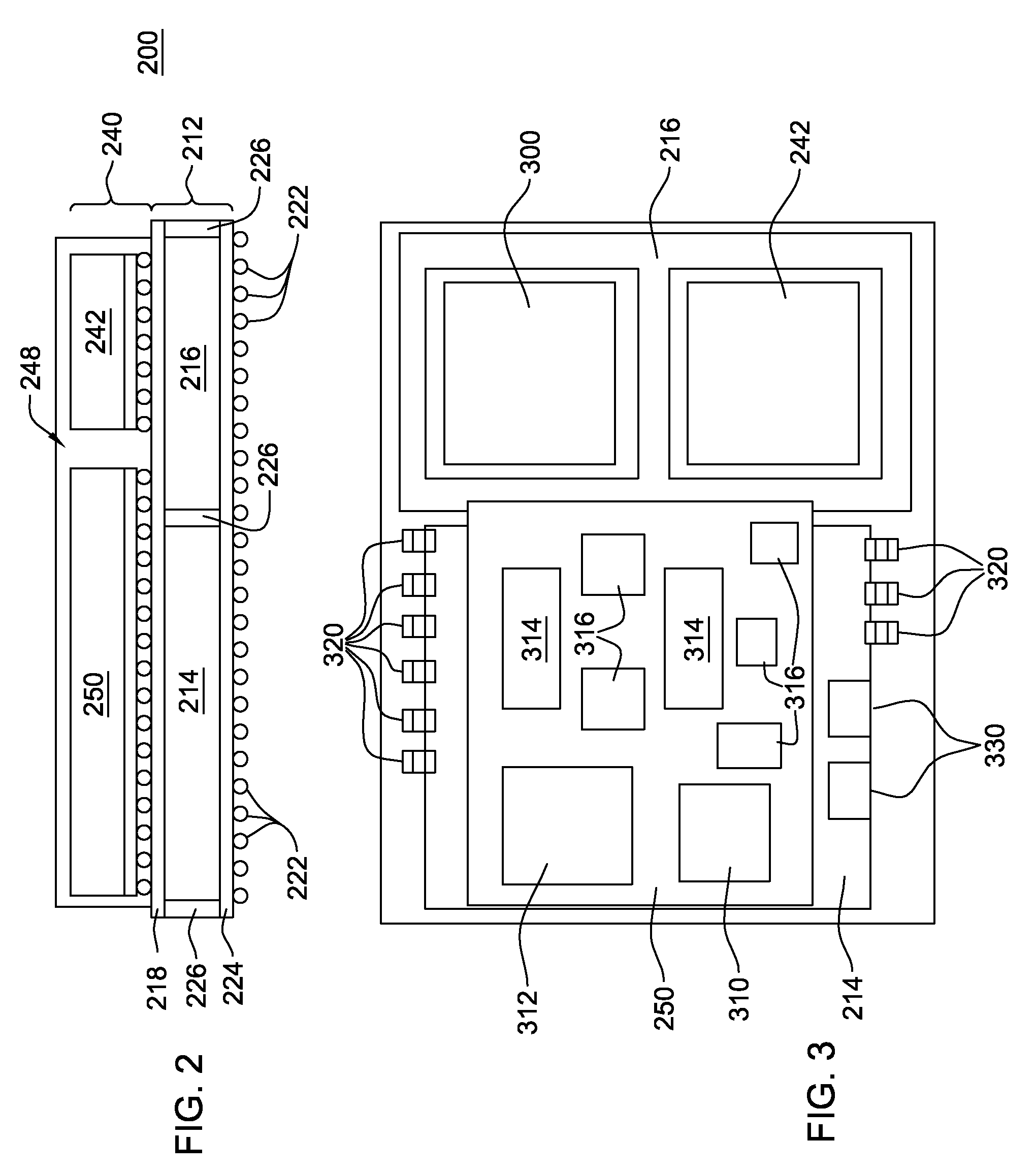

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS7619901B2Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com