Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5836 results about "Parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Parasitic capacitance, or stray capacitance is an unavoidable and usually unwanted capacitance that exists between the parts of an electronic component or circuit simply because of their proximity to each other. When two electrical conductors at different voltages are close together, the electric field between them causes electric charge to be stored on them; this effect is parasitic capacitance. All actual circuit elements such as inductors, diodes, and transistors have internal capacitance, which can cause their behavior to depart from that of 'ideal' circuit elements. Additionally, there is always non-zero capacitance between any two conductors; this can be significant at higher frequencies with closely spaced conductors, such as wires or printed circuit board traces. Parasitic capacitance is a significant problem in high frequency circuits and is often the factor limiting the operating frequency and bandwidth of electronic components and circuits.

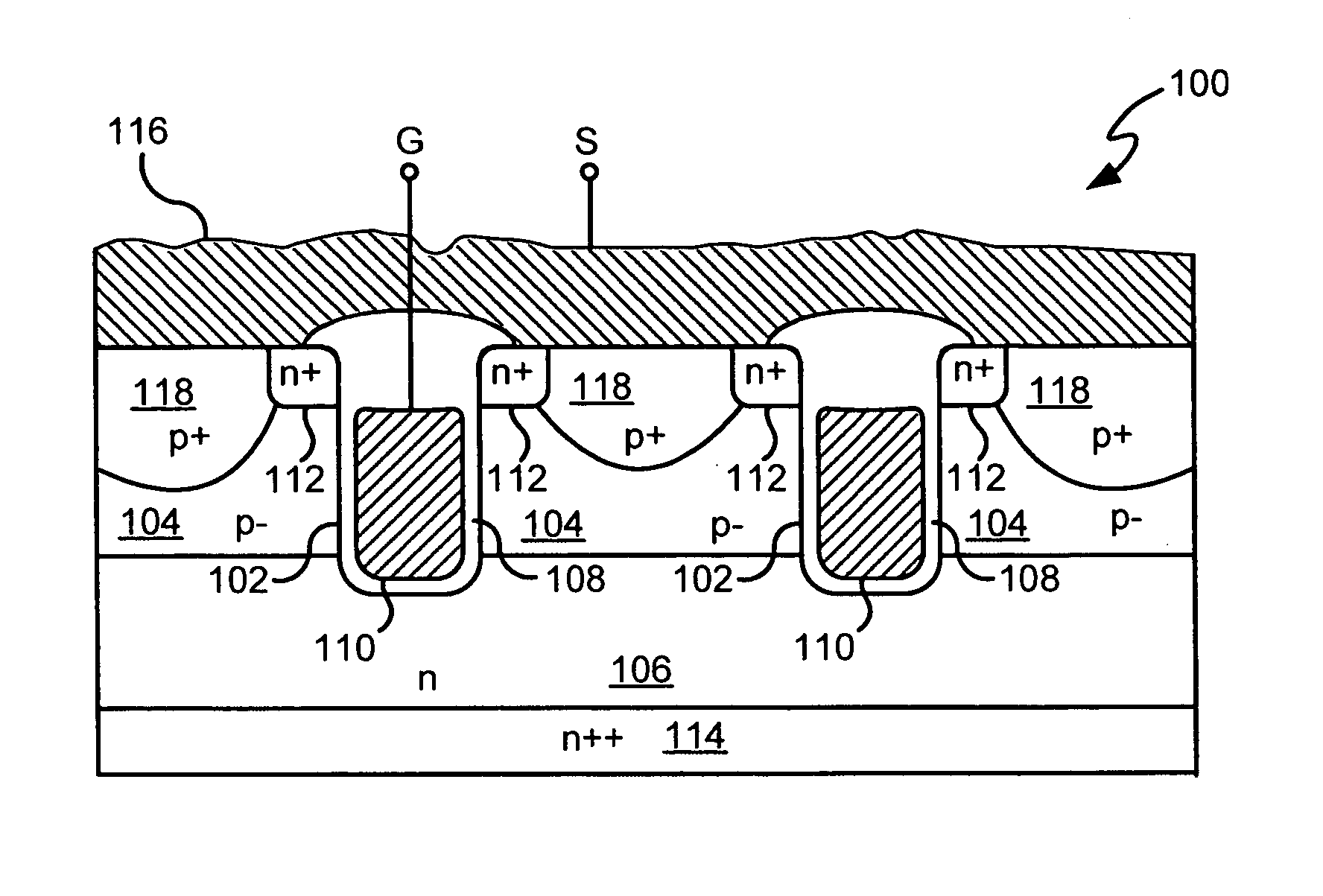

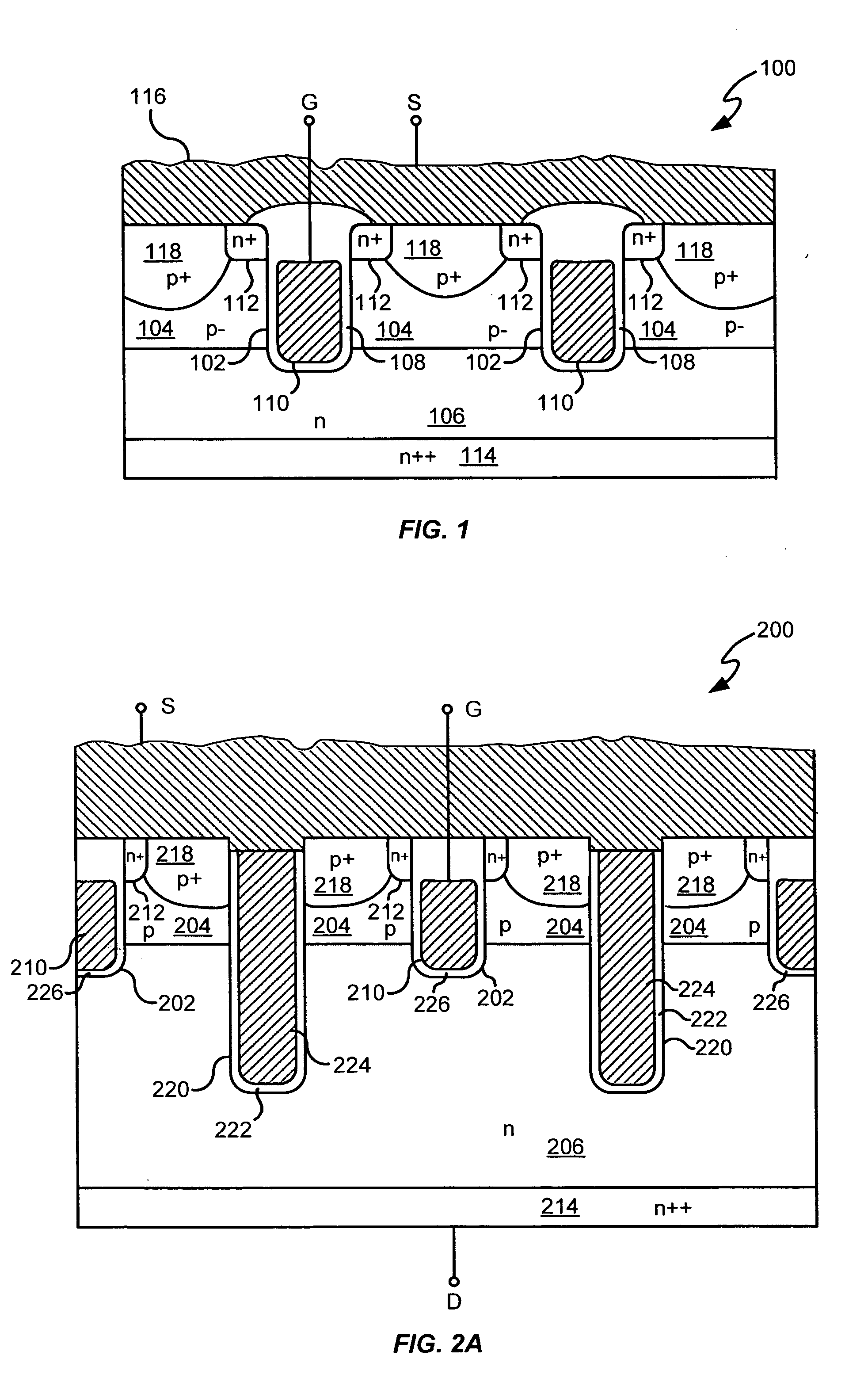

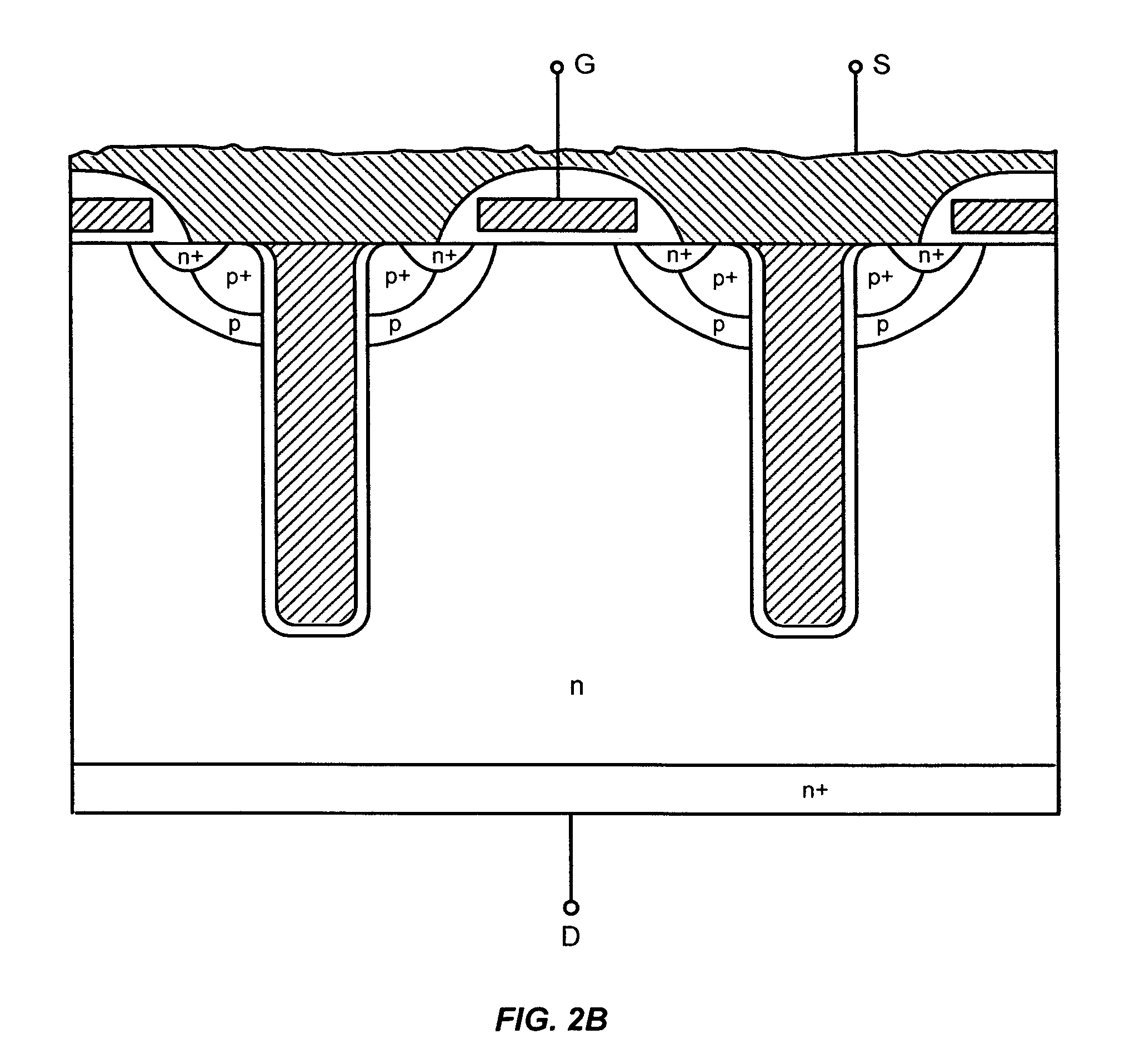

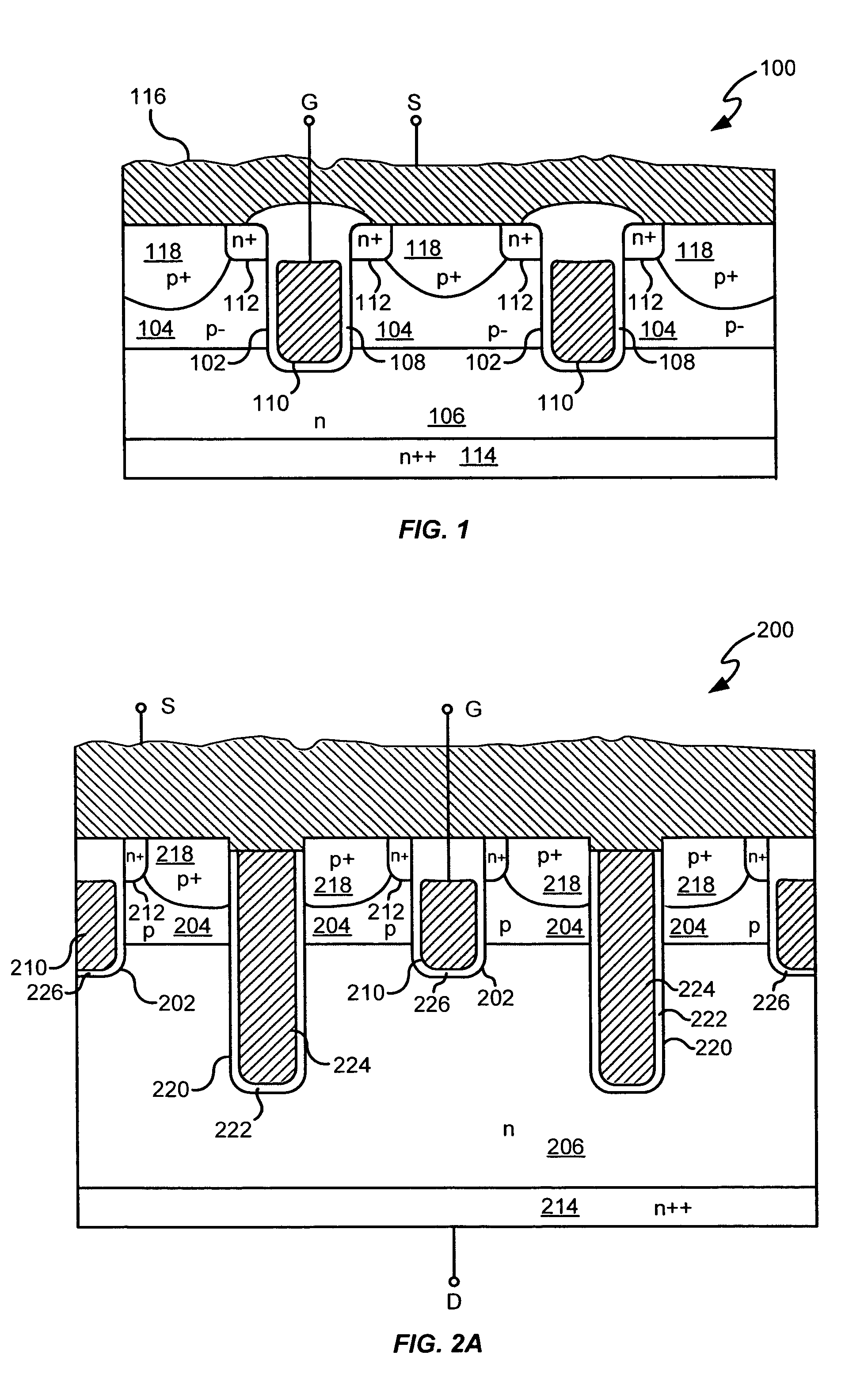

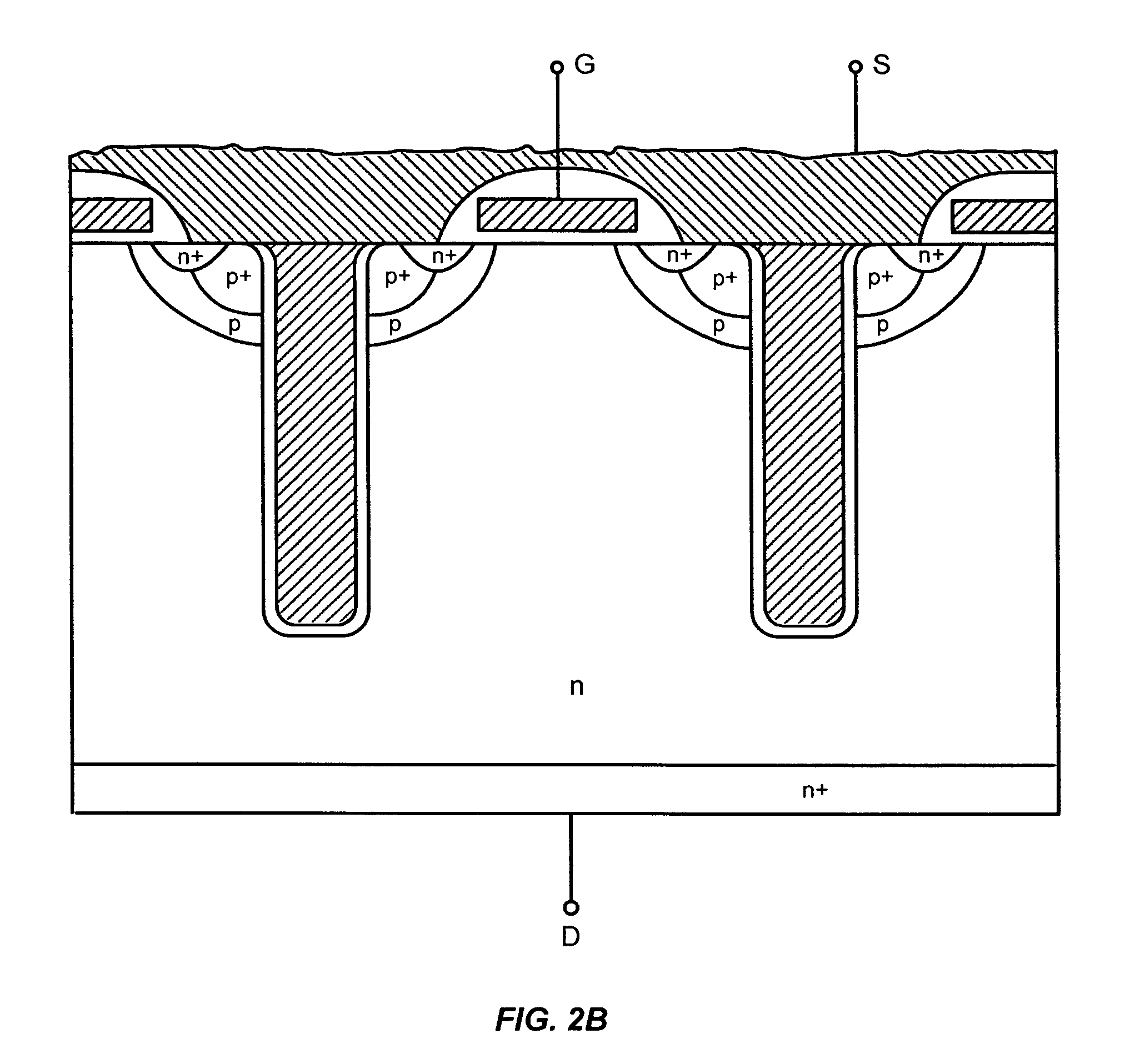

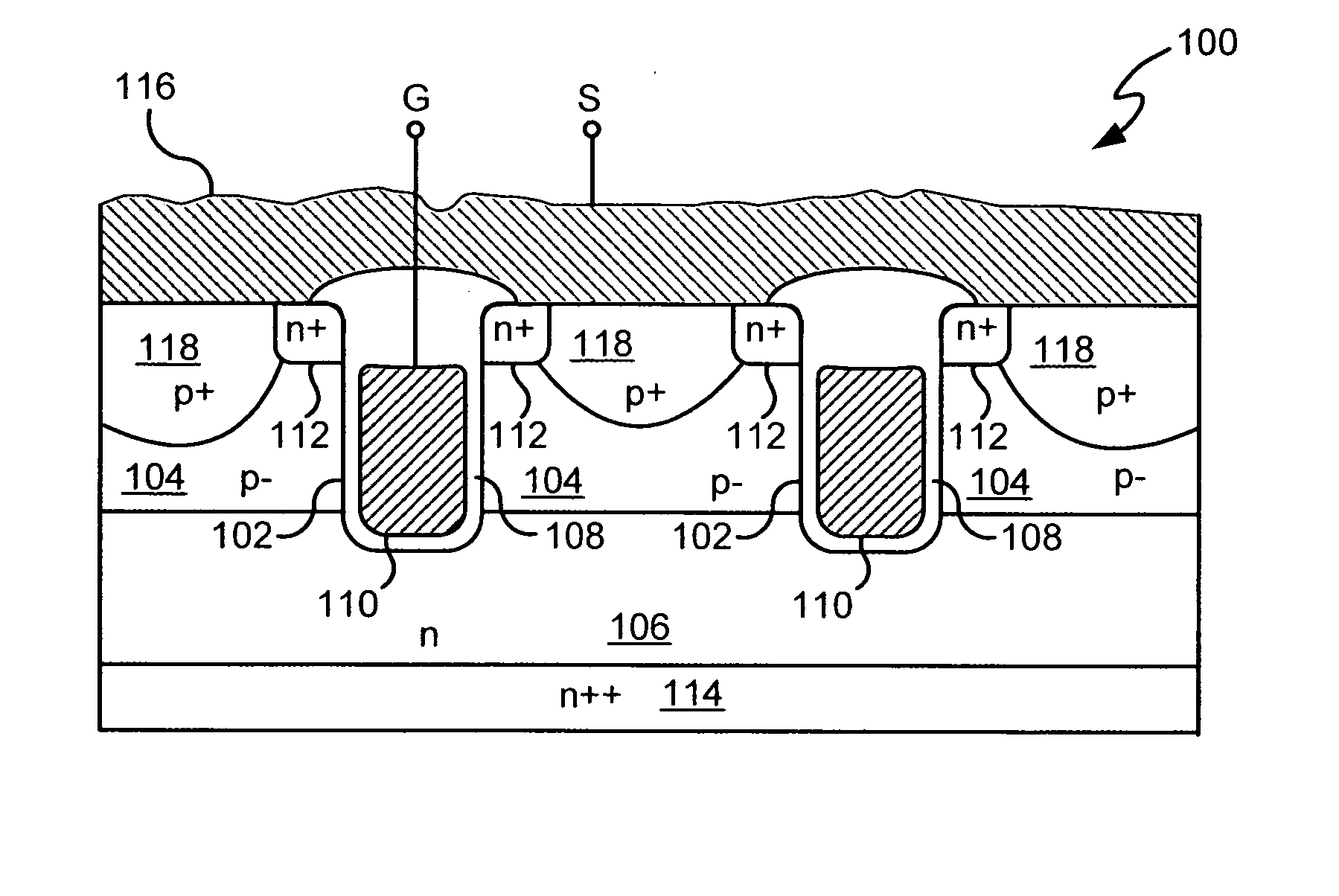

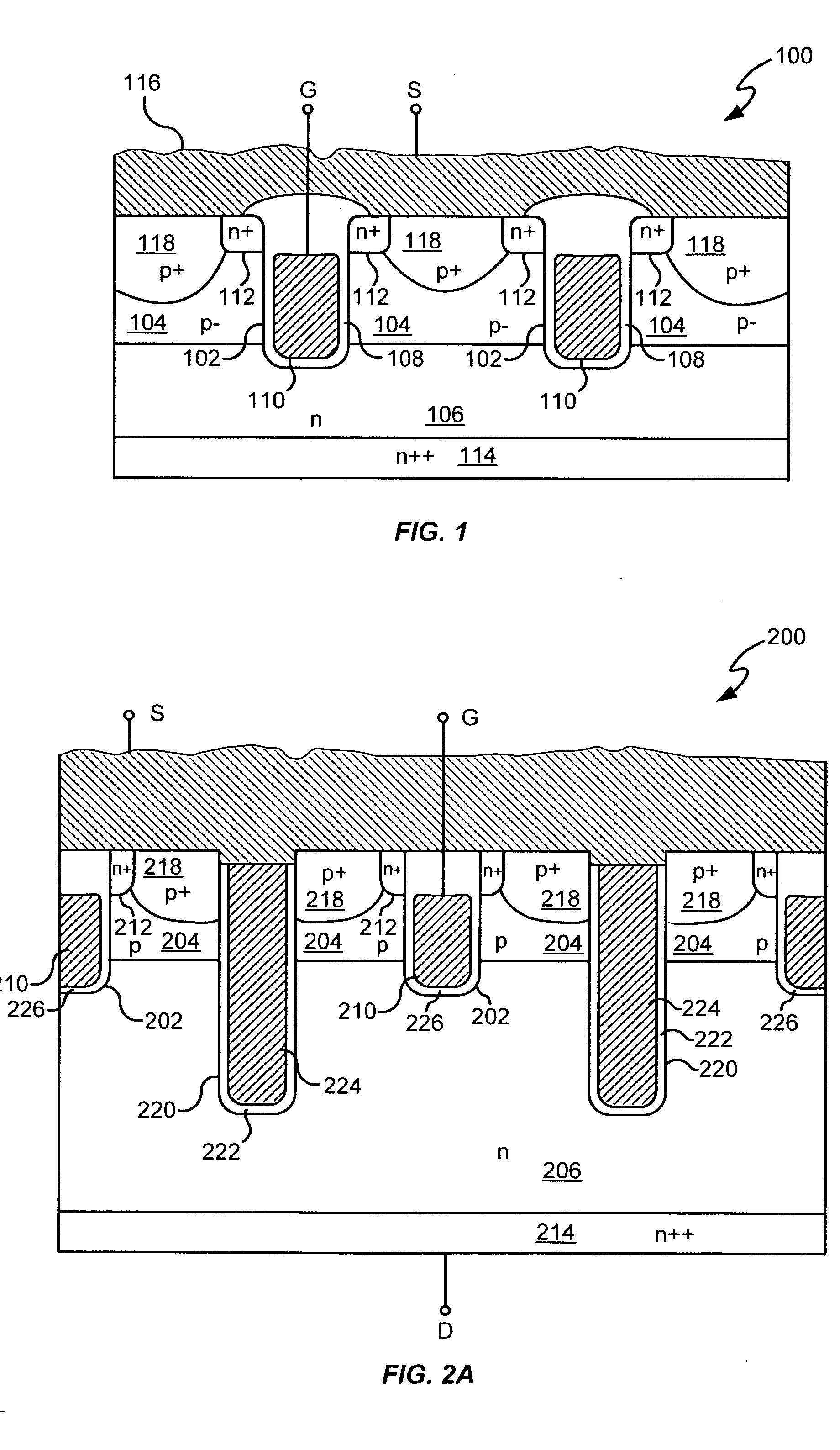

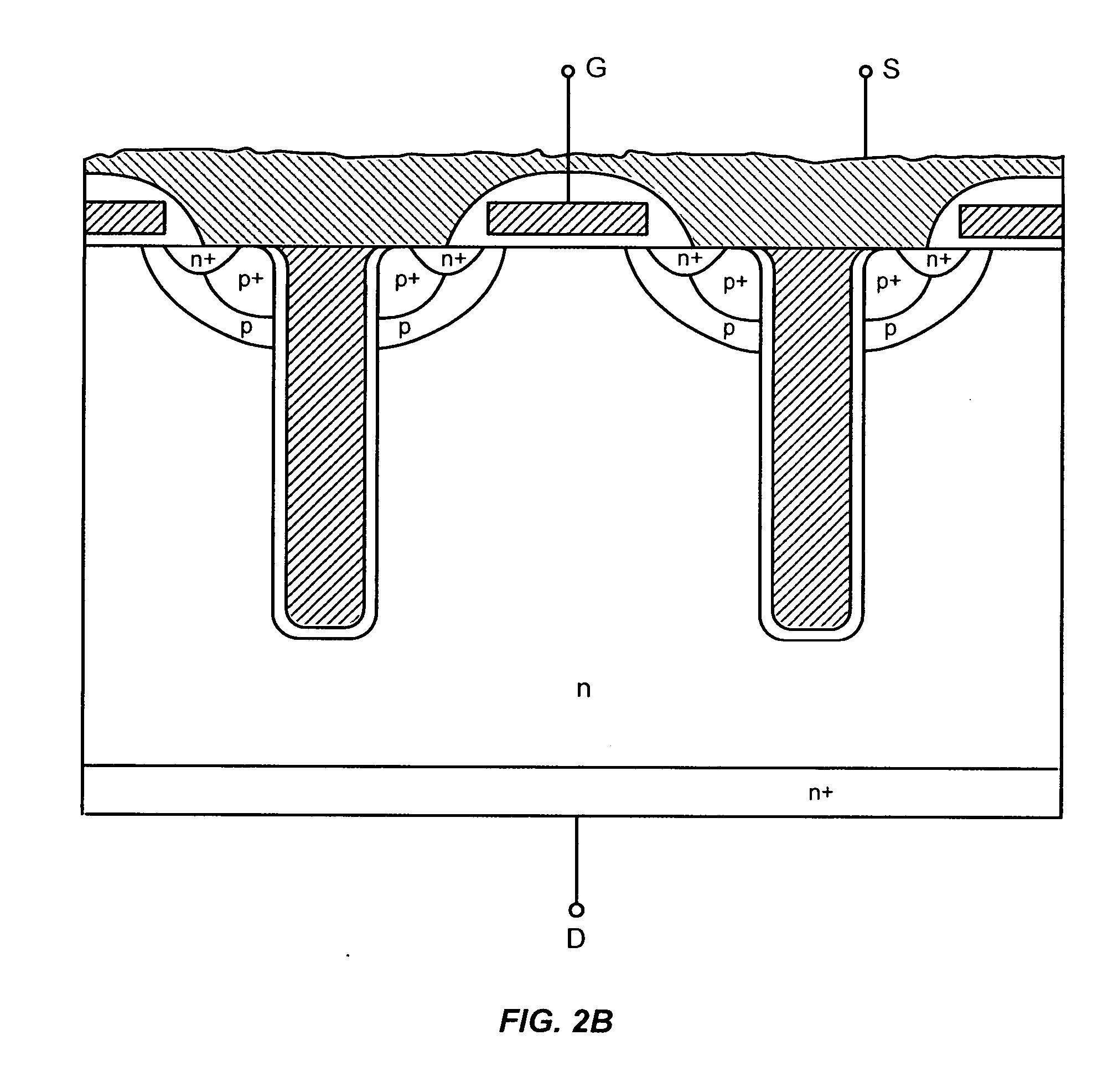

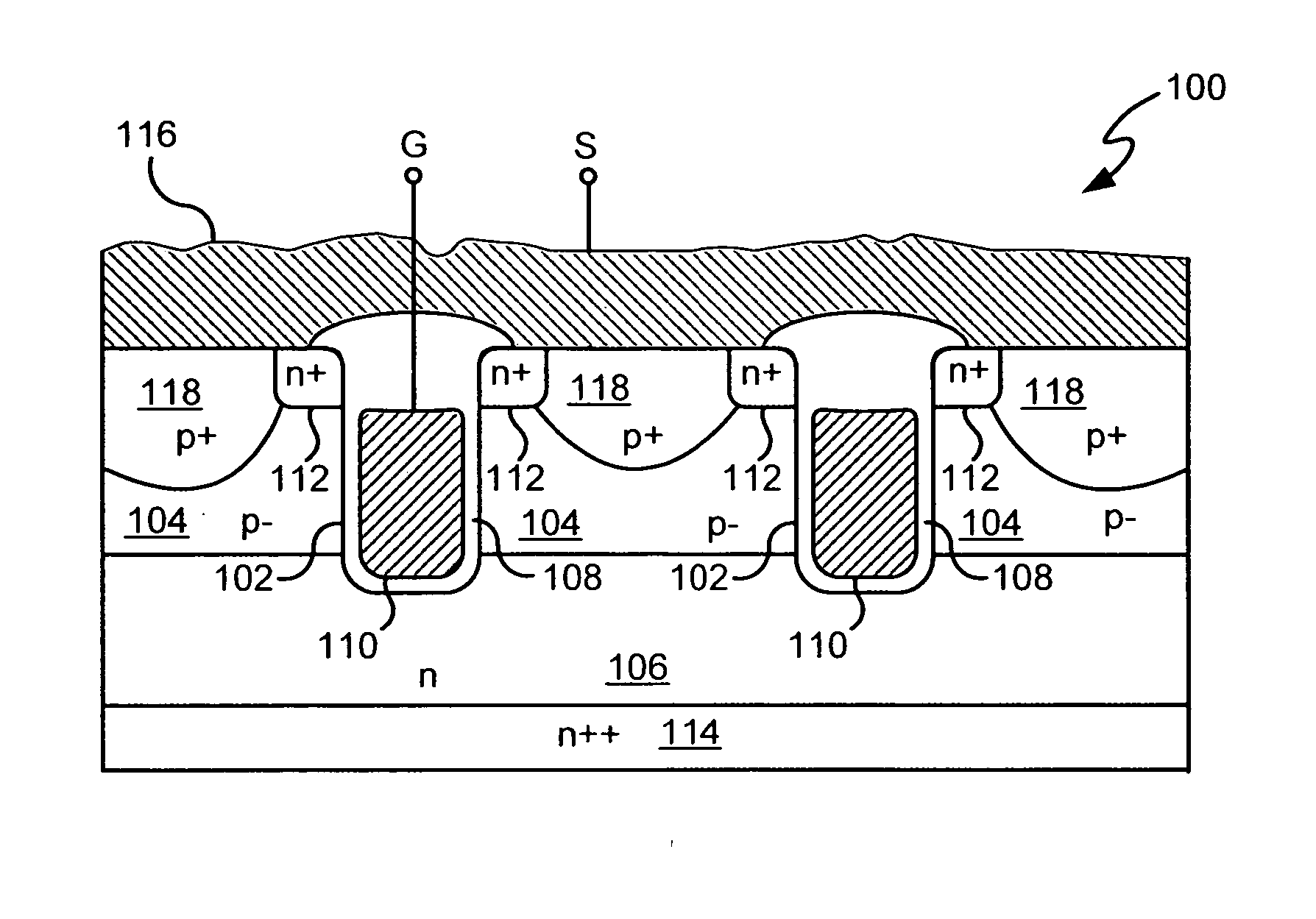

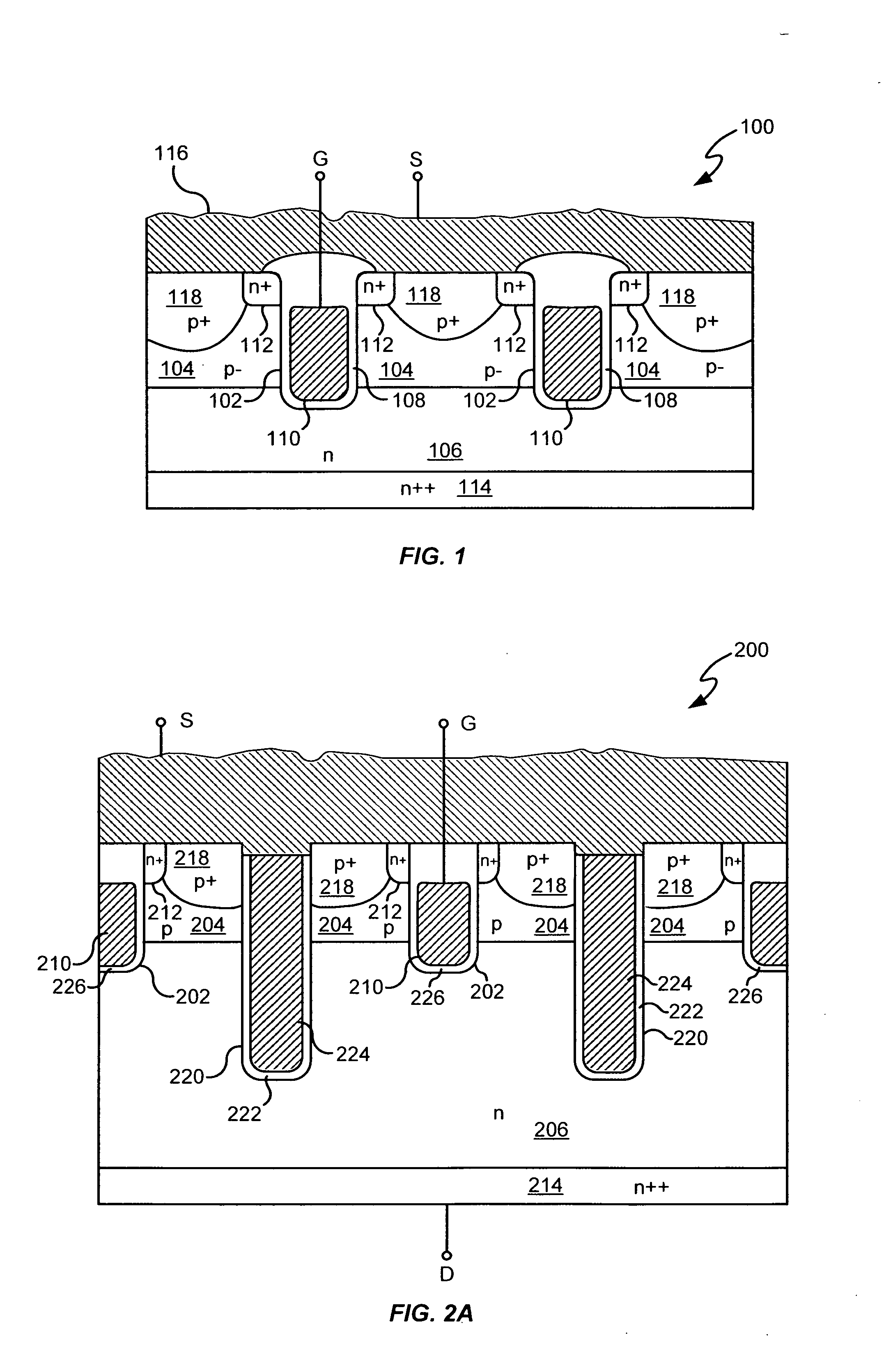

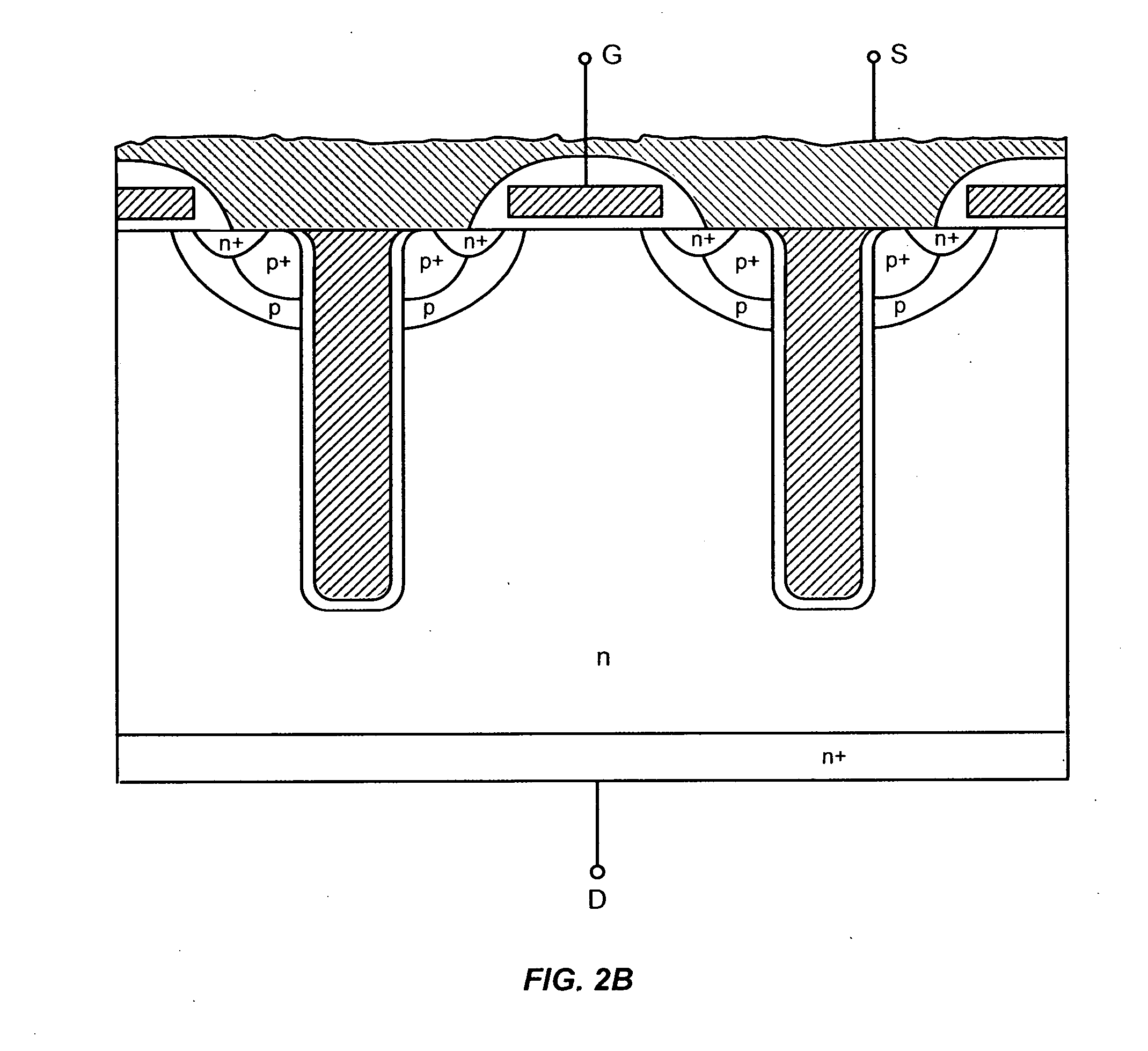

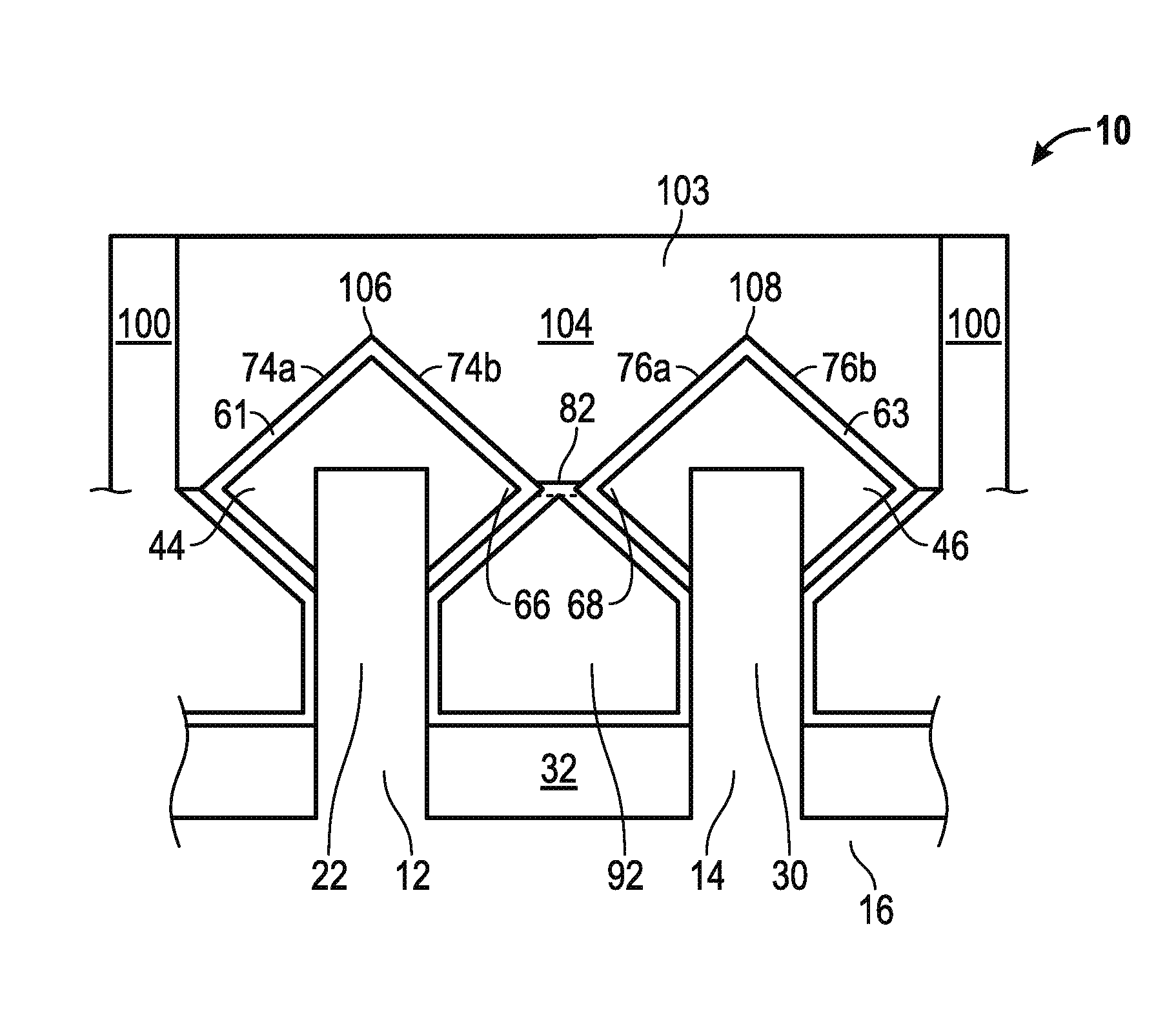

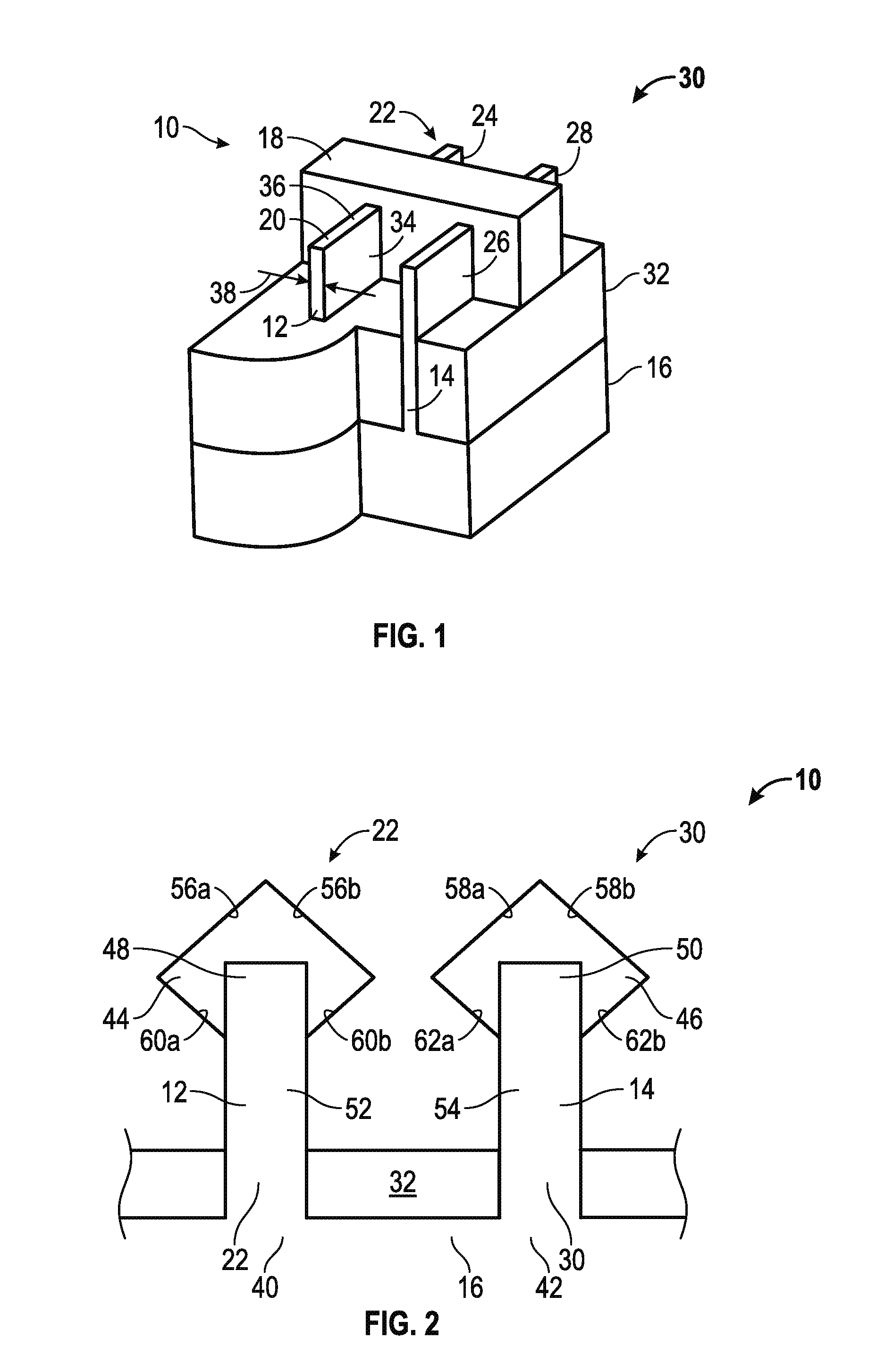

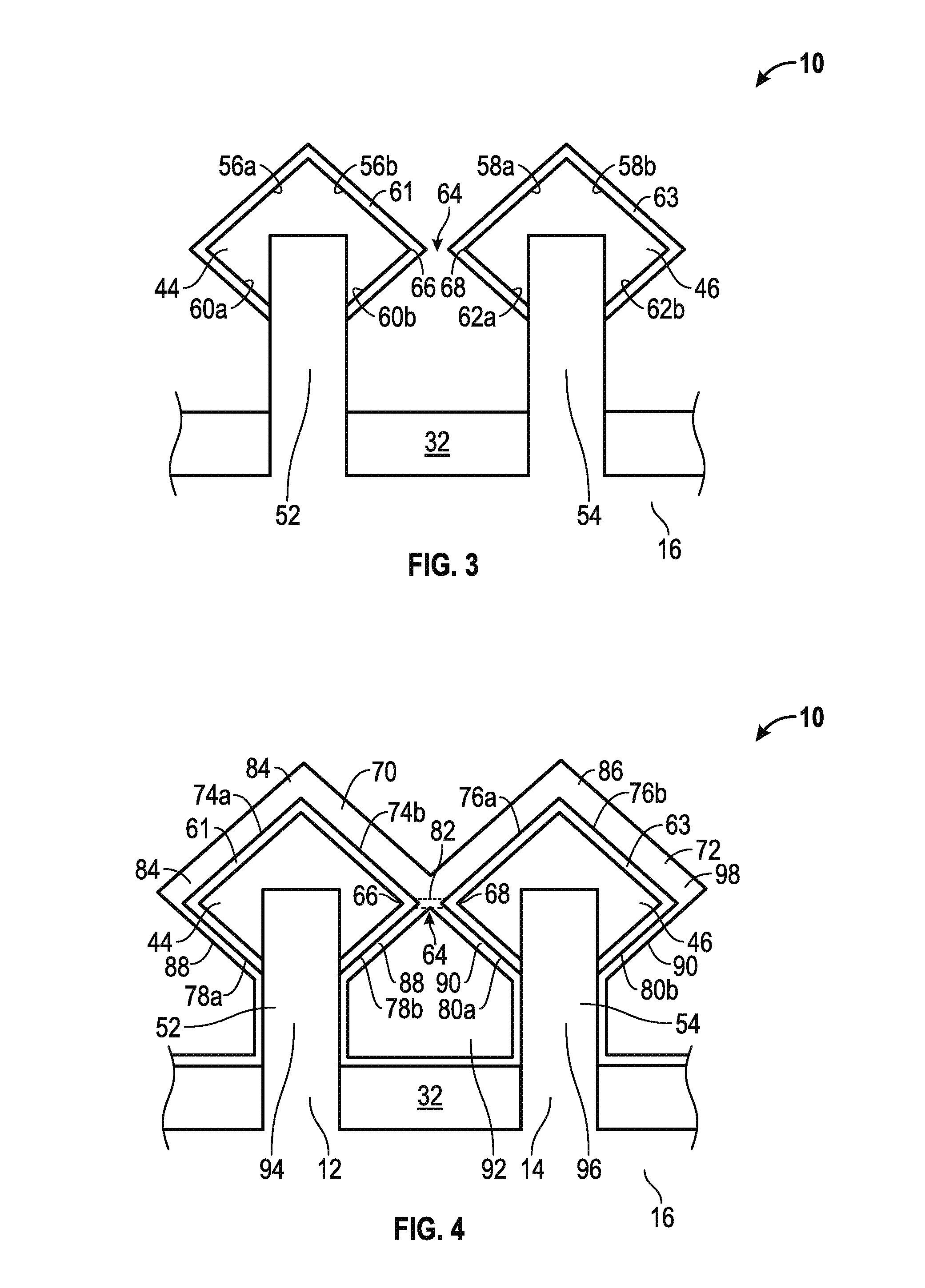

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

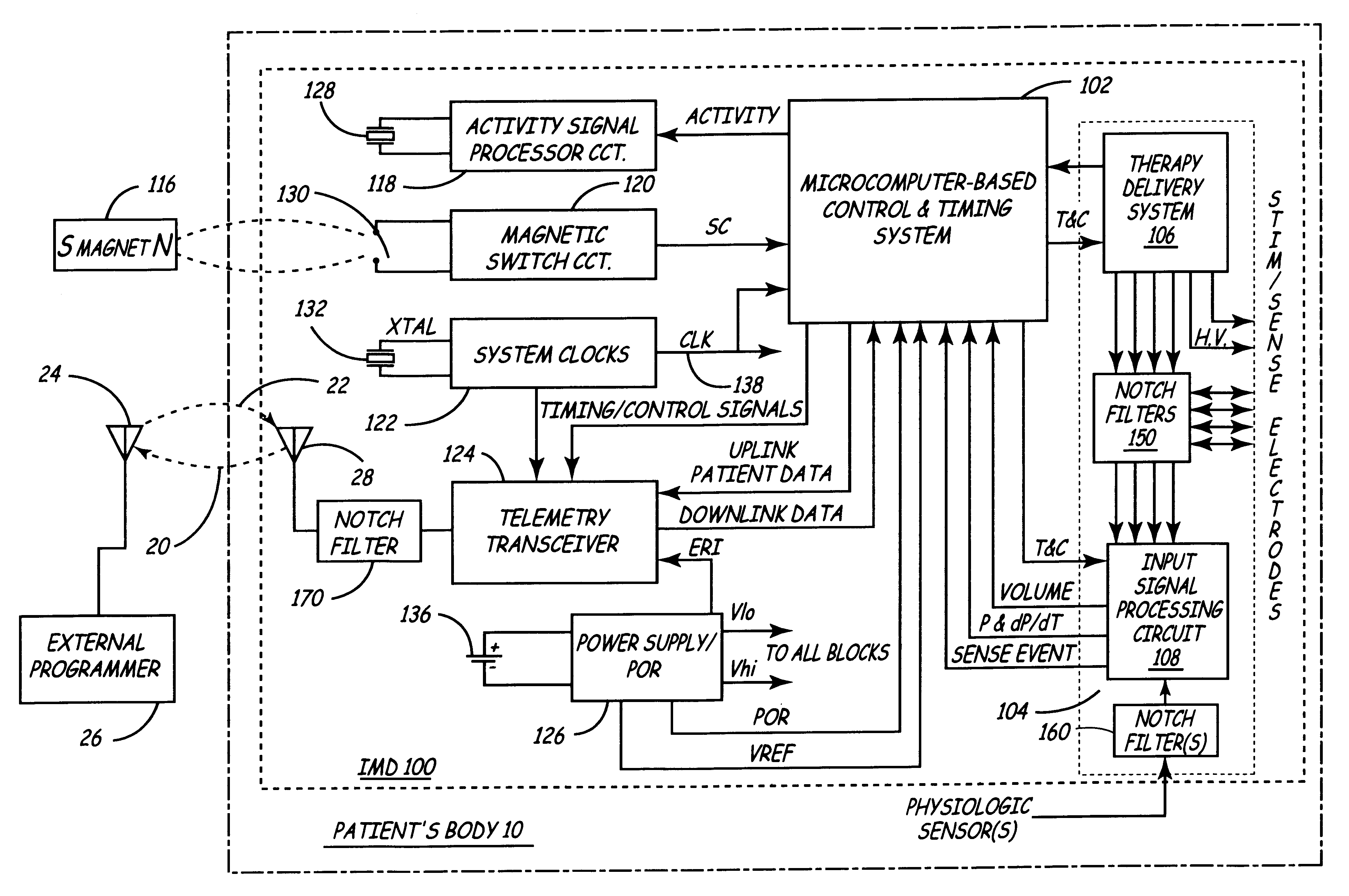

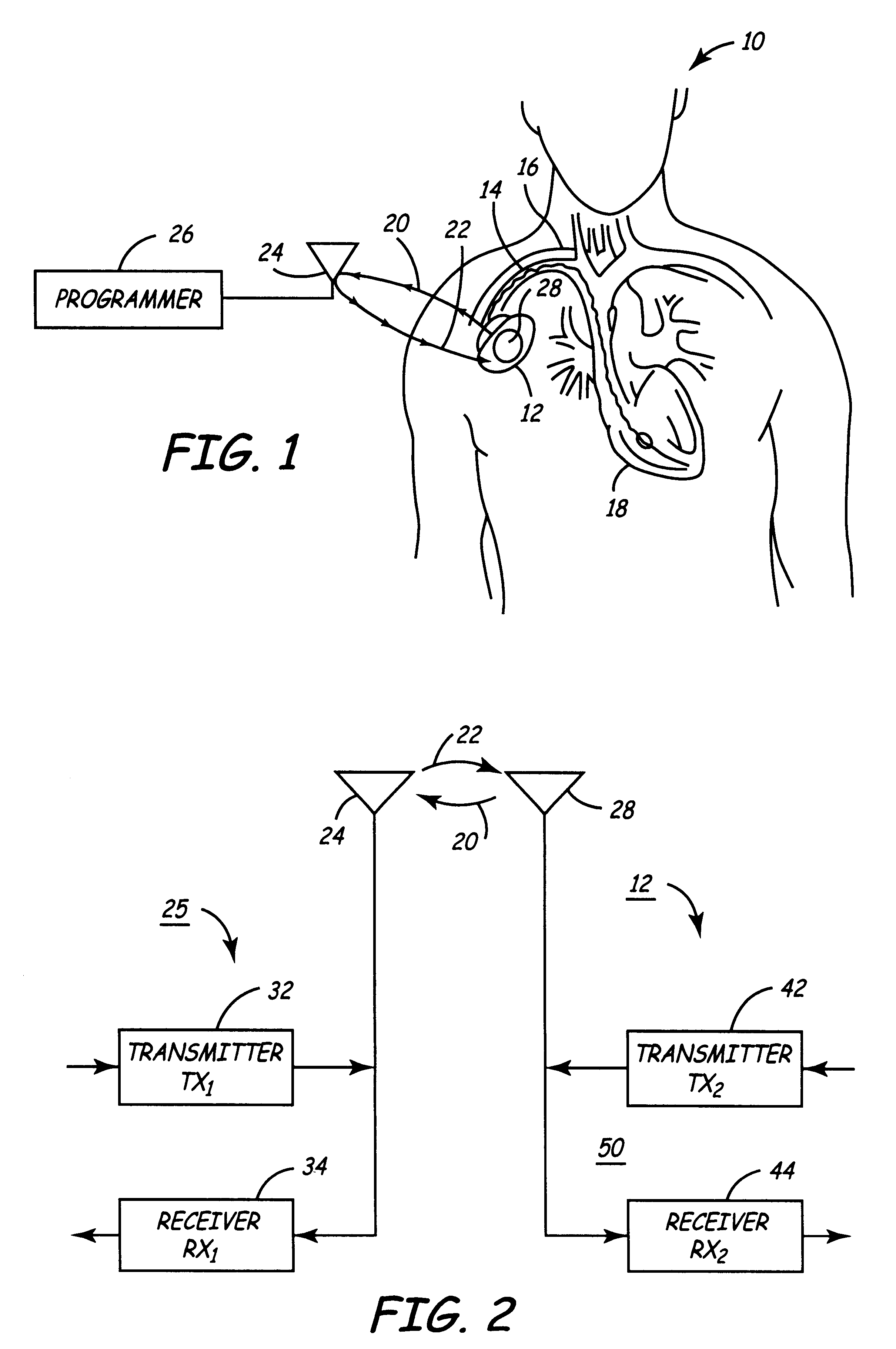

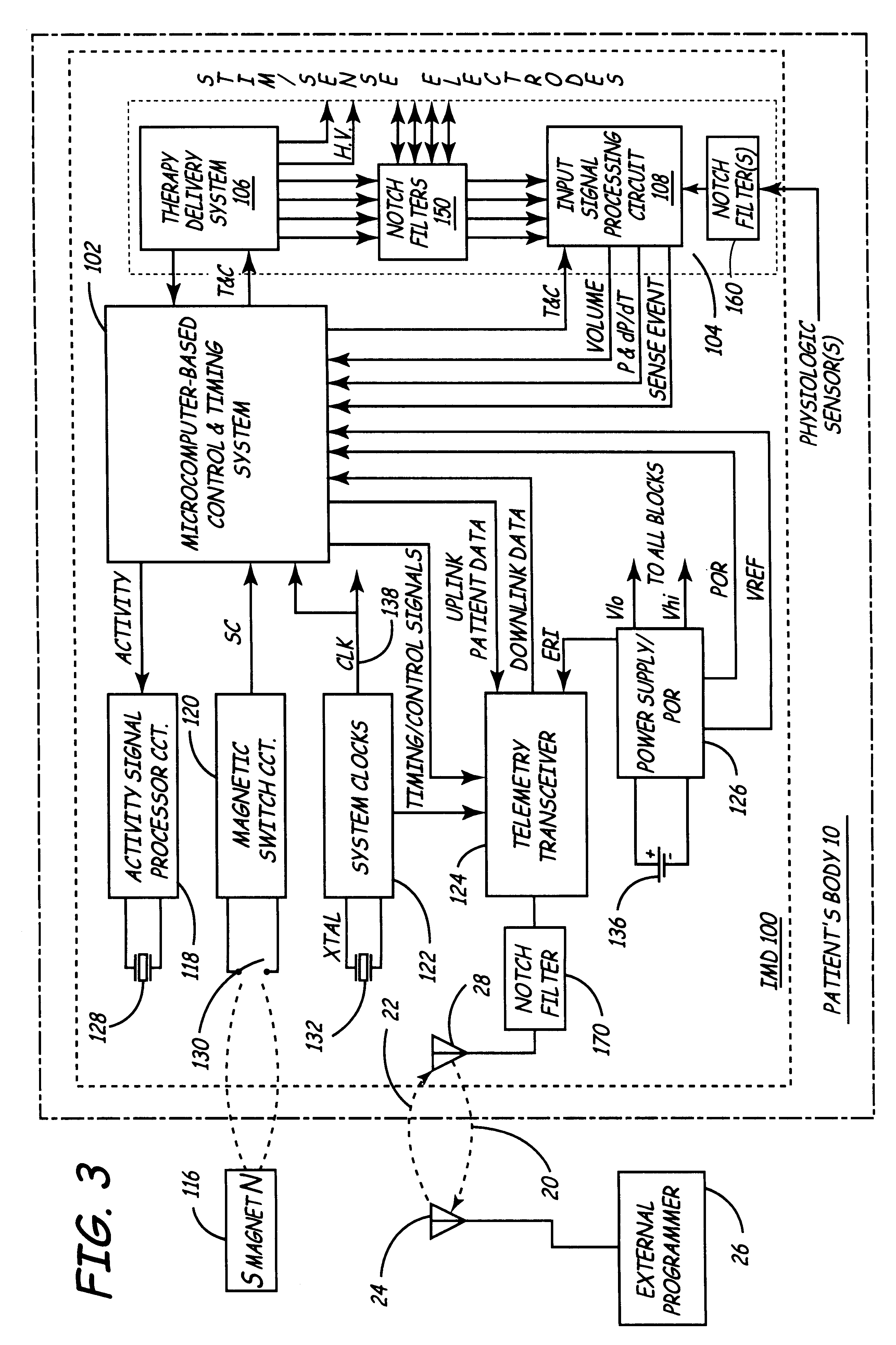

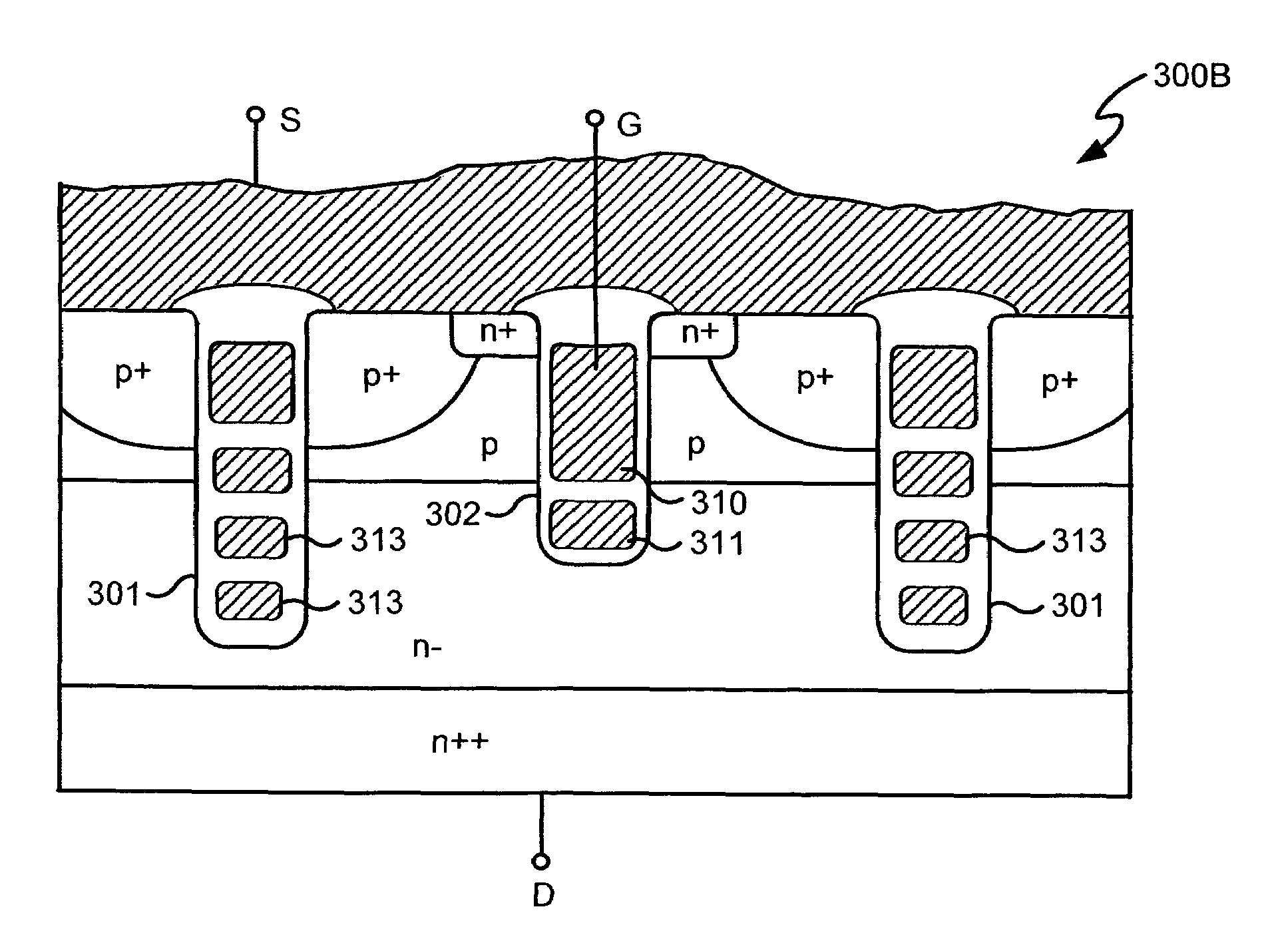

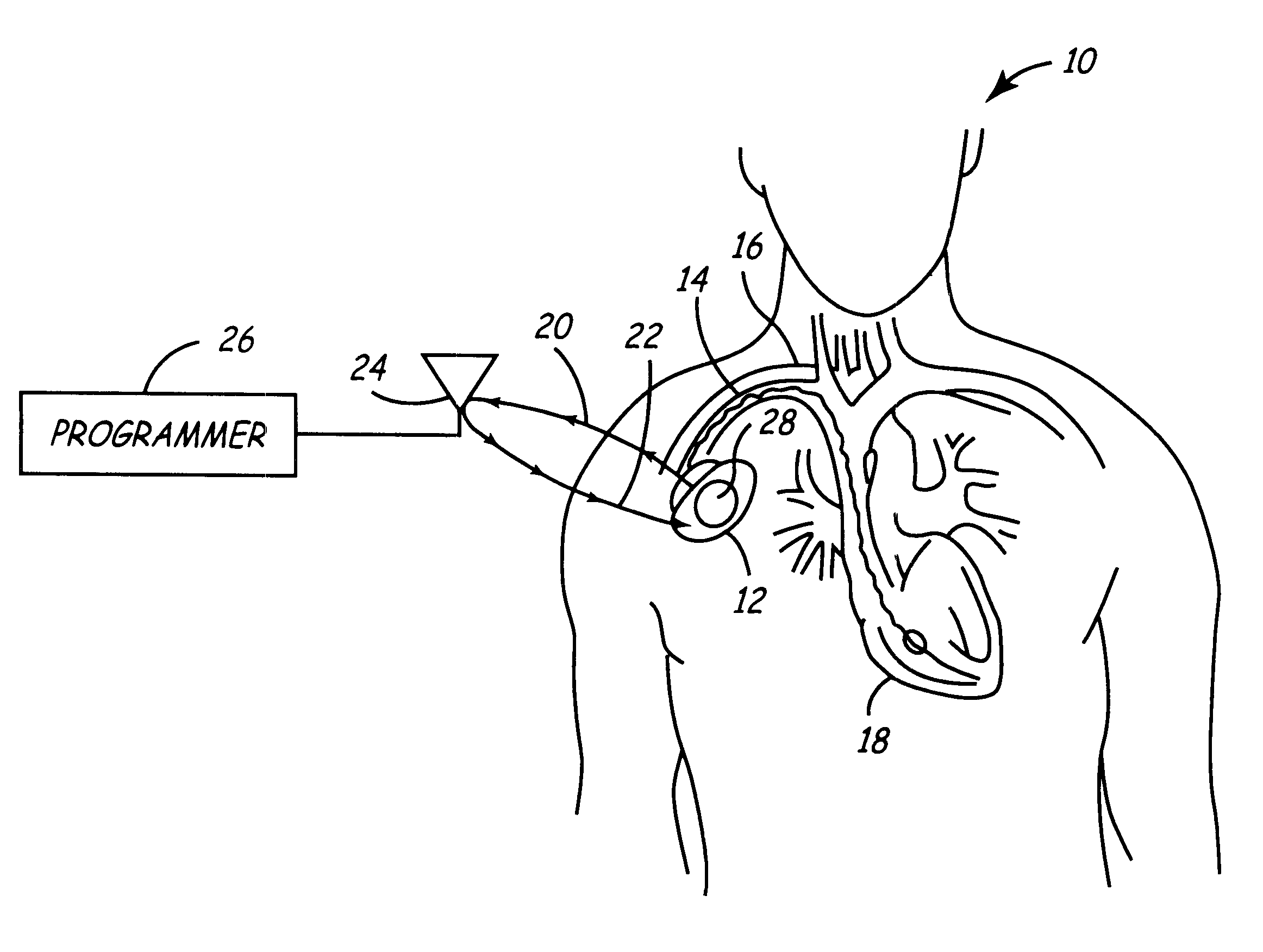

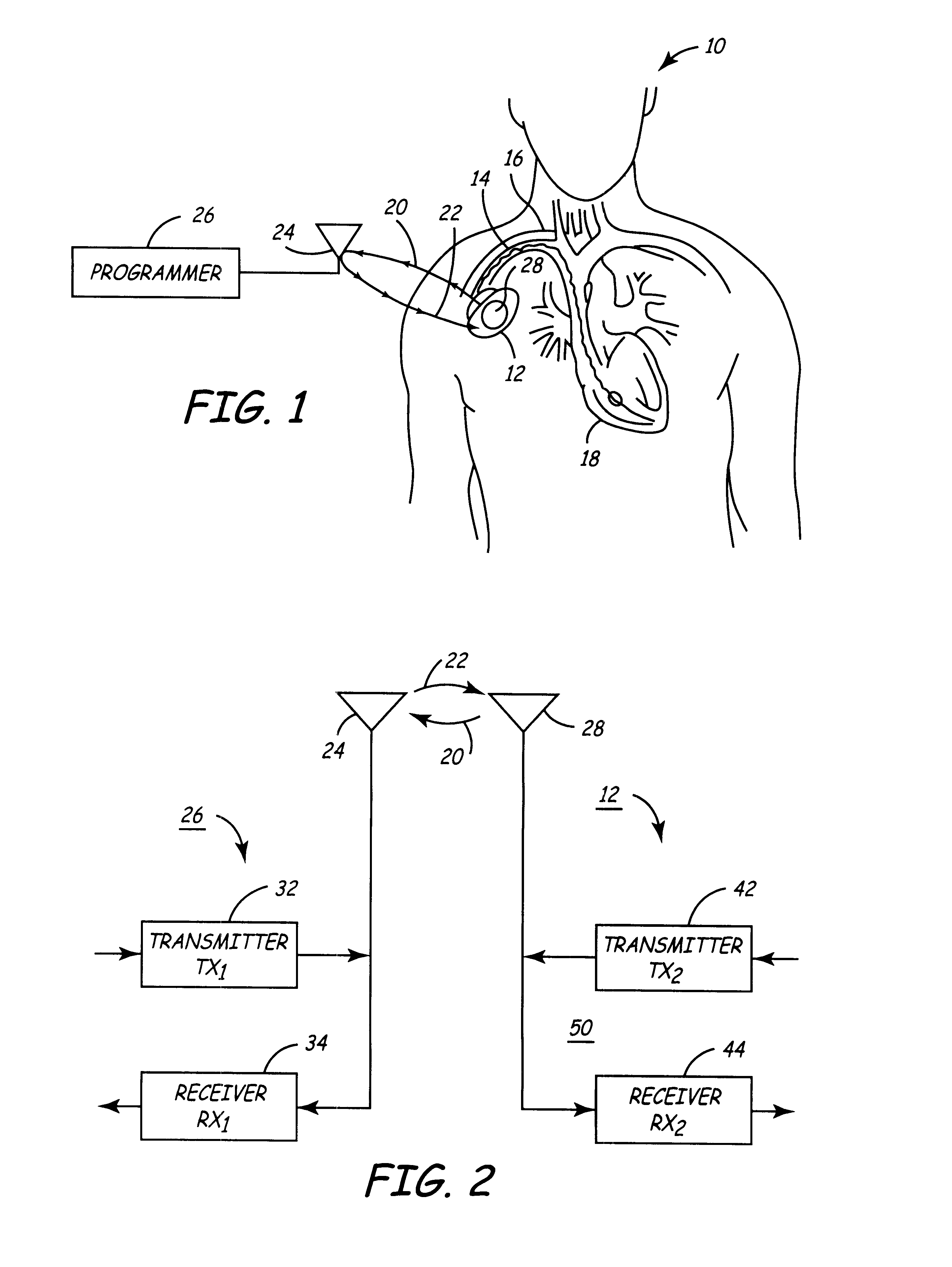

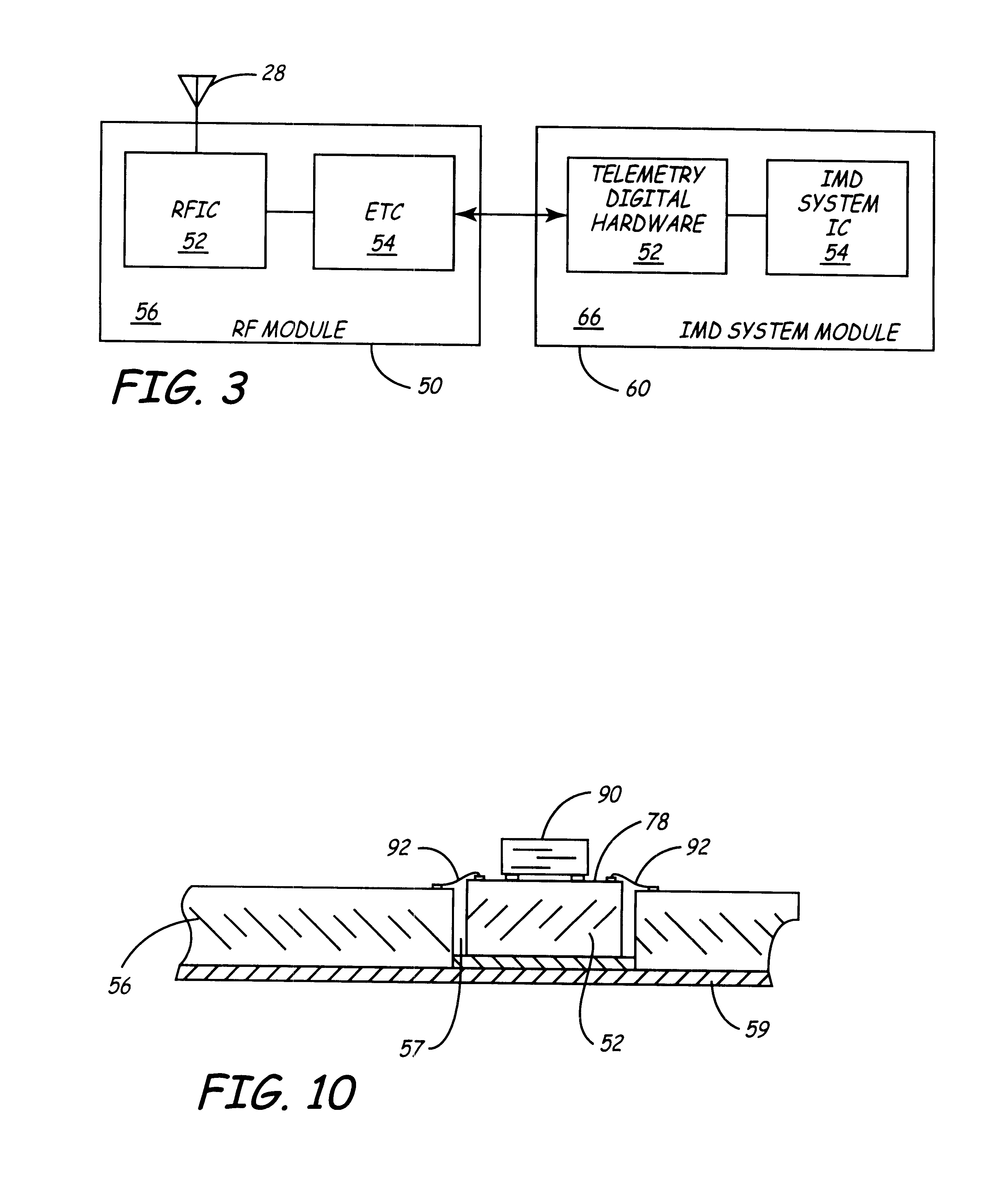

Implantable medical device incorporating integrated circuit notch filters

Implantable medical devices (IMDs) having sense amplifiers for sensing physiologic signals and parameters, RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming and interrogation commands to and from an external programmer or other medical device are disclosed. At least one IC chip and discrete components have a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include forming notch filters of MEMS structures or forming discrete circuit notch filters by one or more of: (1) IC fabricating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The IC fabricated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the IC chip substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

Power semiconductor devices and methods of manufacture

ActiveUS7345342B2Simple structureEasy to packEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

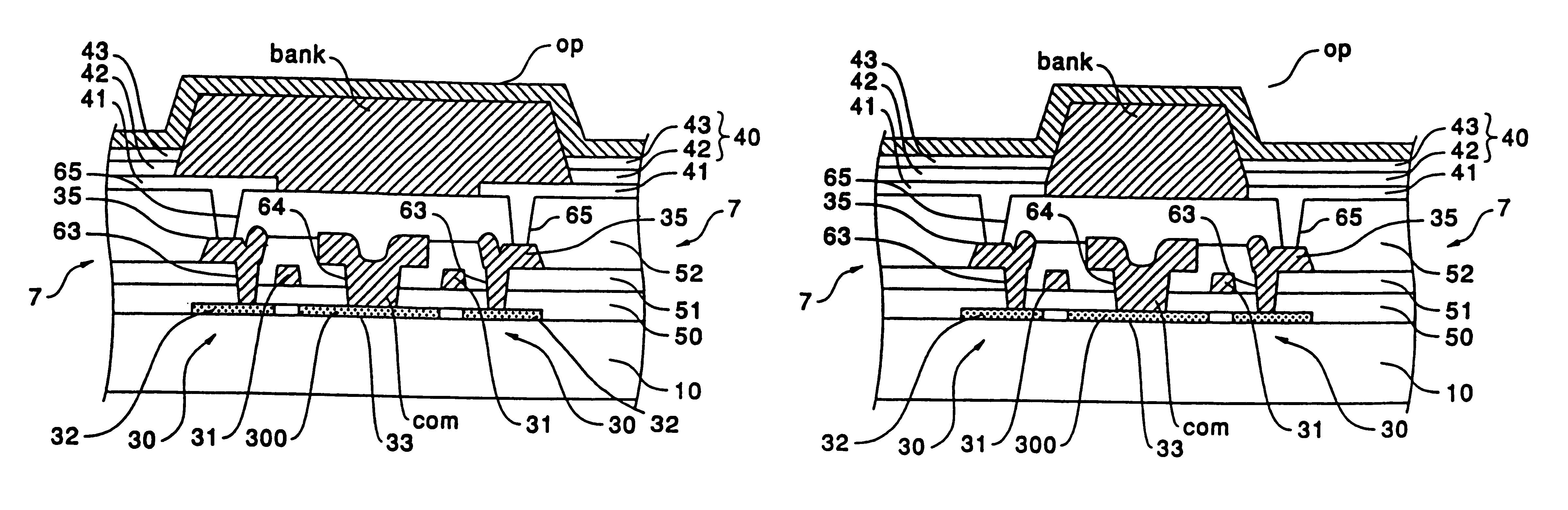

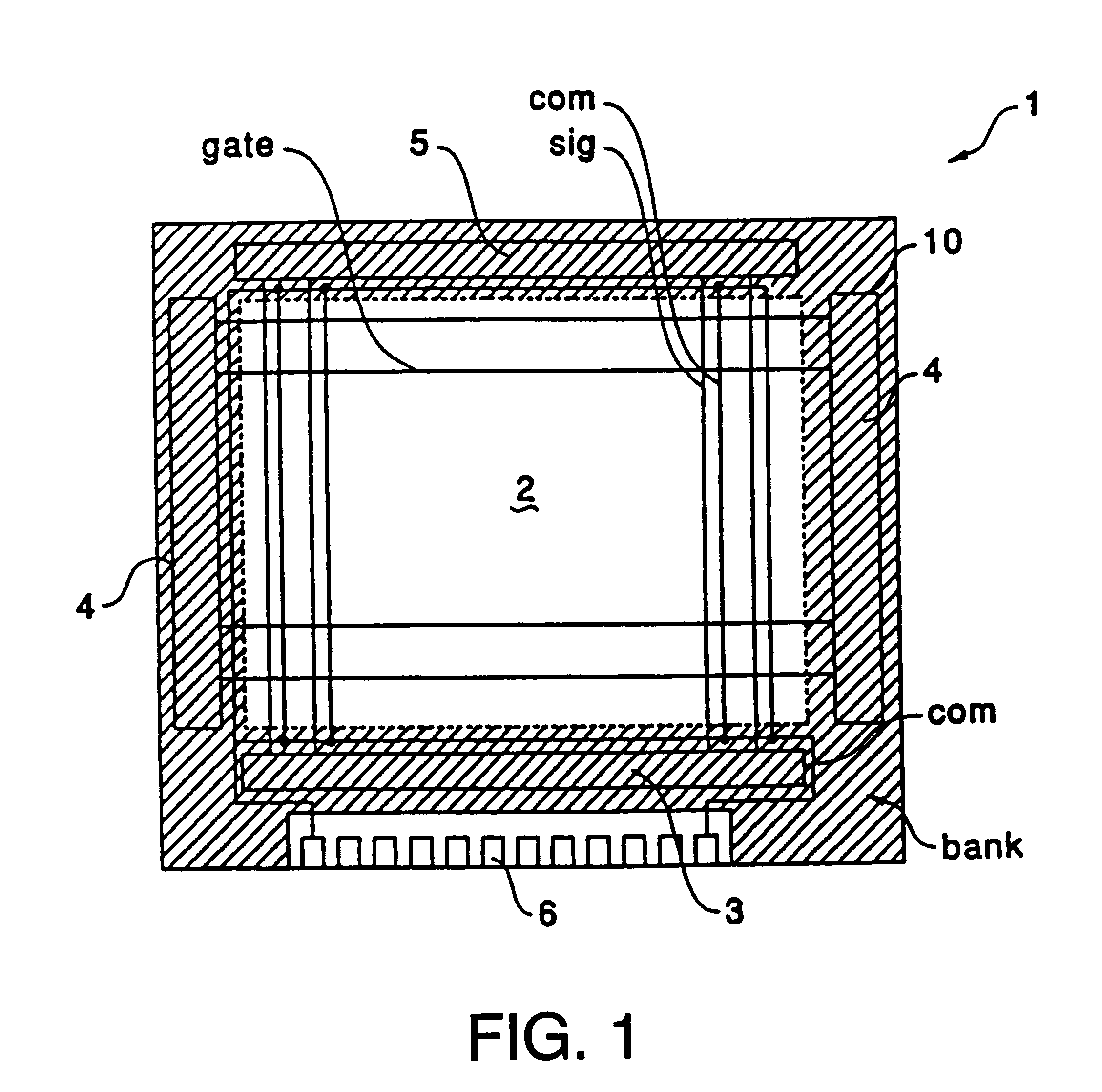

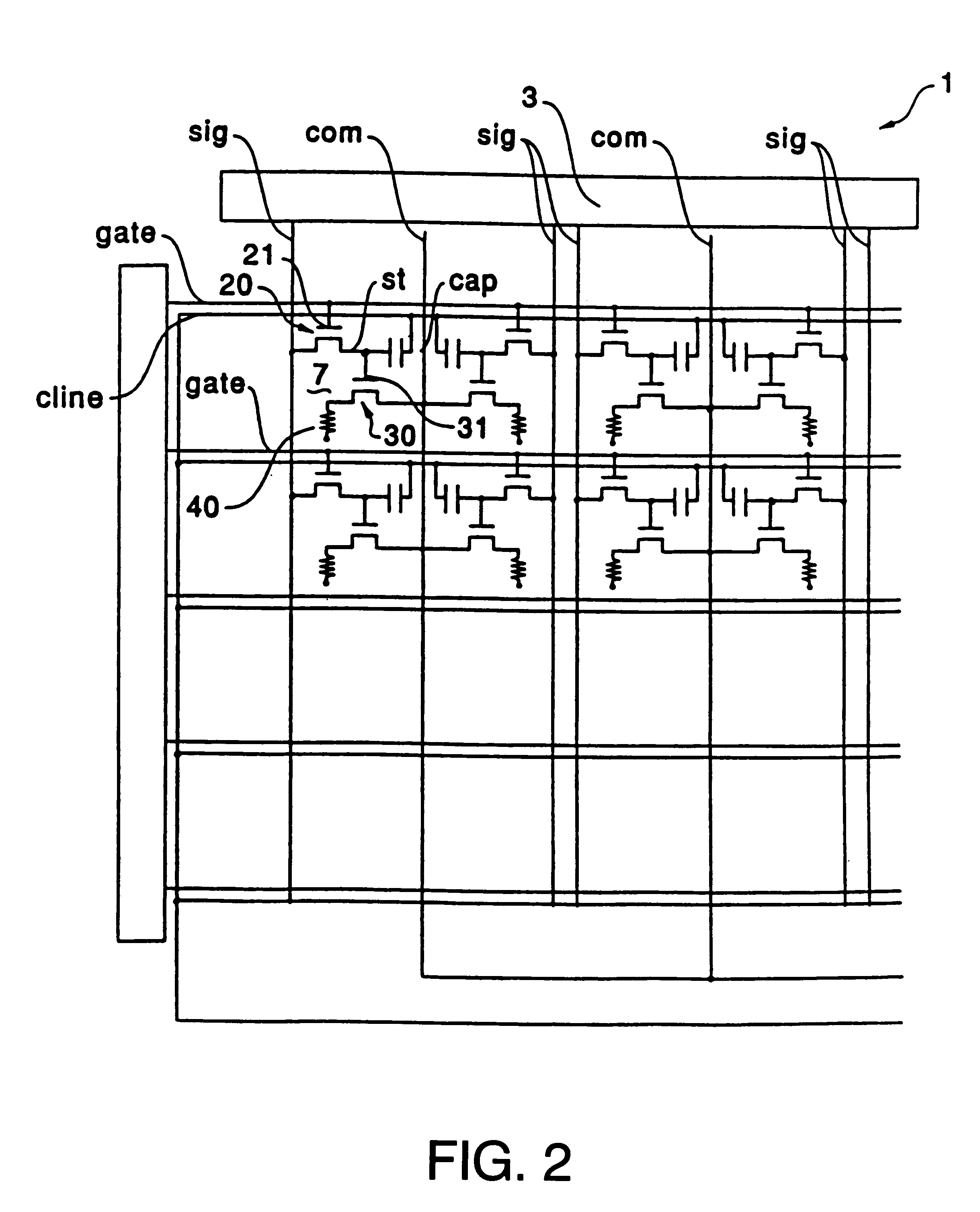

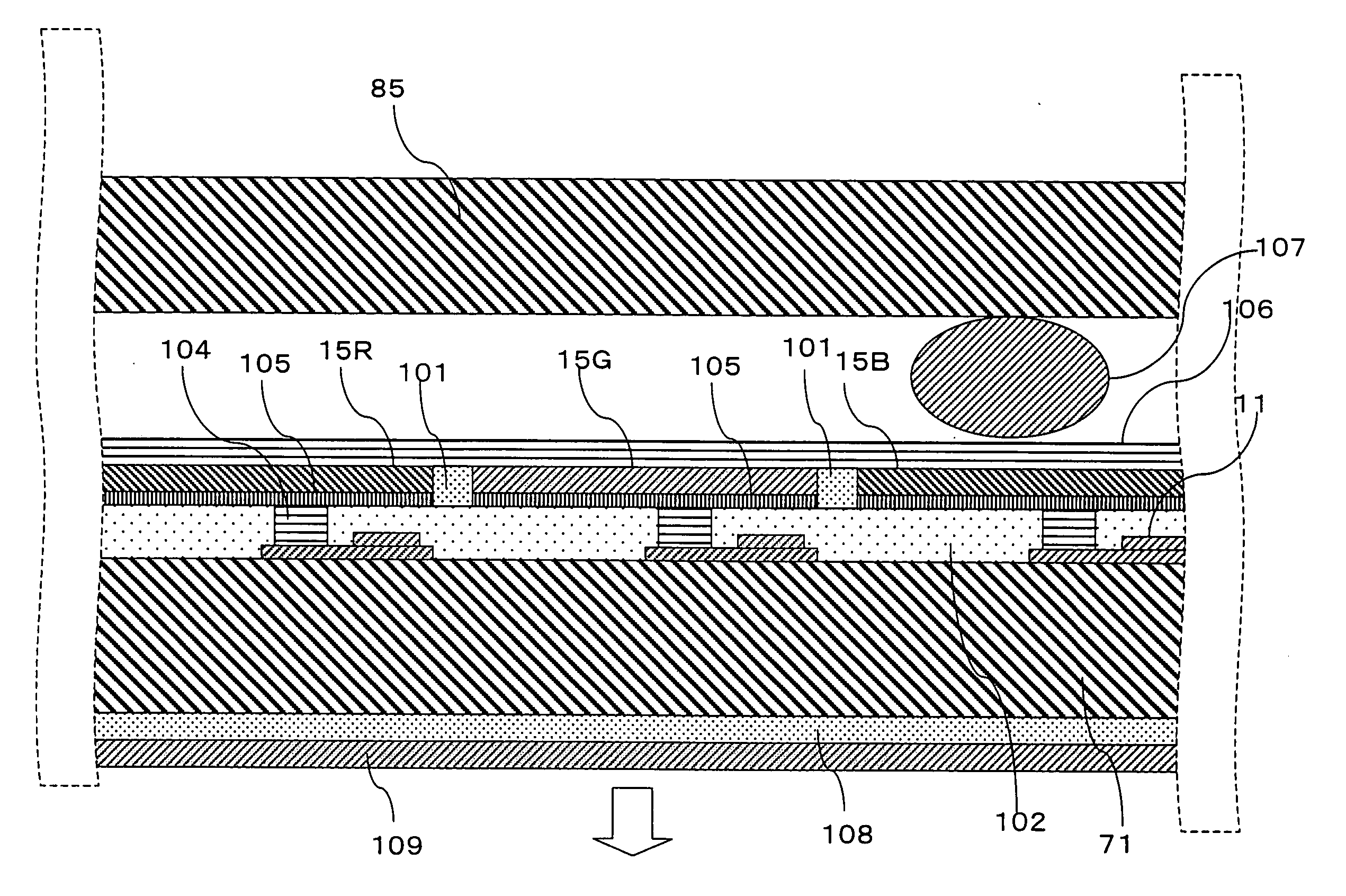

Display device

The invention provides a display device in which parasitic capacitance associated with data lines and driving circuits is prevented using a bank layer whose primary purpose is to define areas on a substrate in which an organic semiconductor film is formed. When the organic semiconductor film for forming a luminescent element such as an electroluminescent element or an LED is formed is formed in pixel regions (7), the organic semiconductor film is formed in the areas surrounded by the bank layer (bank) formed of a black resist. The bank layer (bank) is also formed between an opposite electrode (op) and data lines (sig) for supplying an image signal to first TFTs (20) and holding capacitors (cap) in the pixel regions (7) thereby preventing parasitic capacitance associated with the data lines (sig).

Owner:INTELLECTUAL KEYSTONE TECH LLC

SOI SiGe-Base Lateral Bipolar Junction Transistor

ActiveUS20120139009A1Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

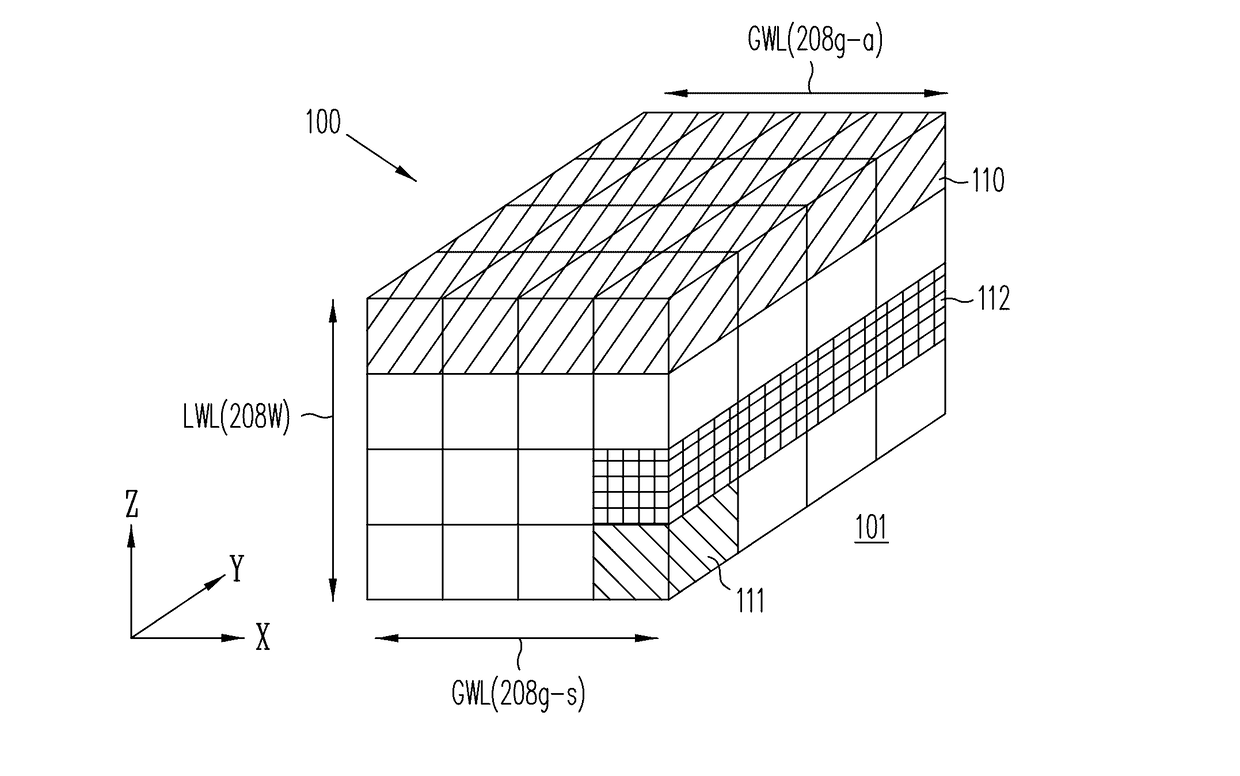

Capacitive-coupled non-volatile thin-film transistor strings in three dimensional arrays

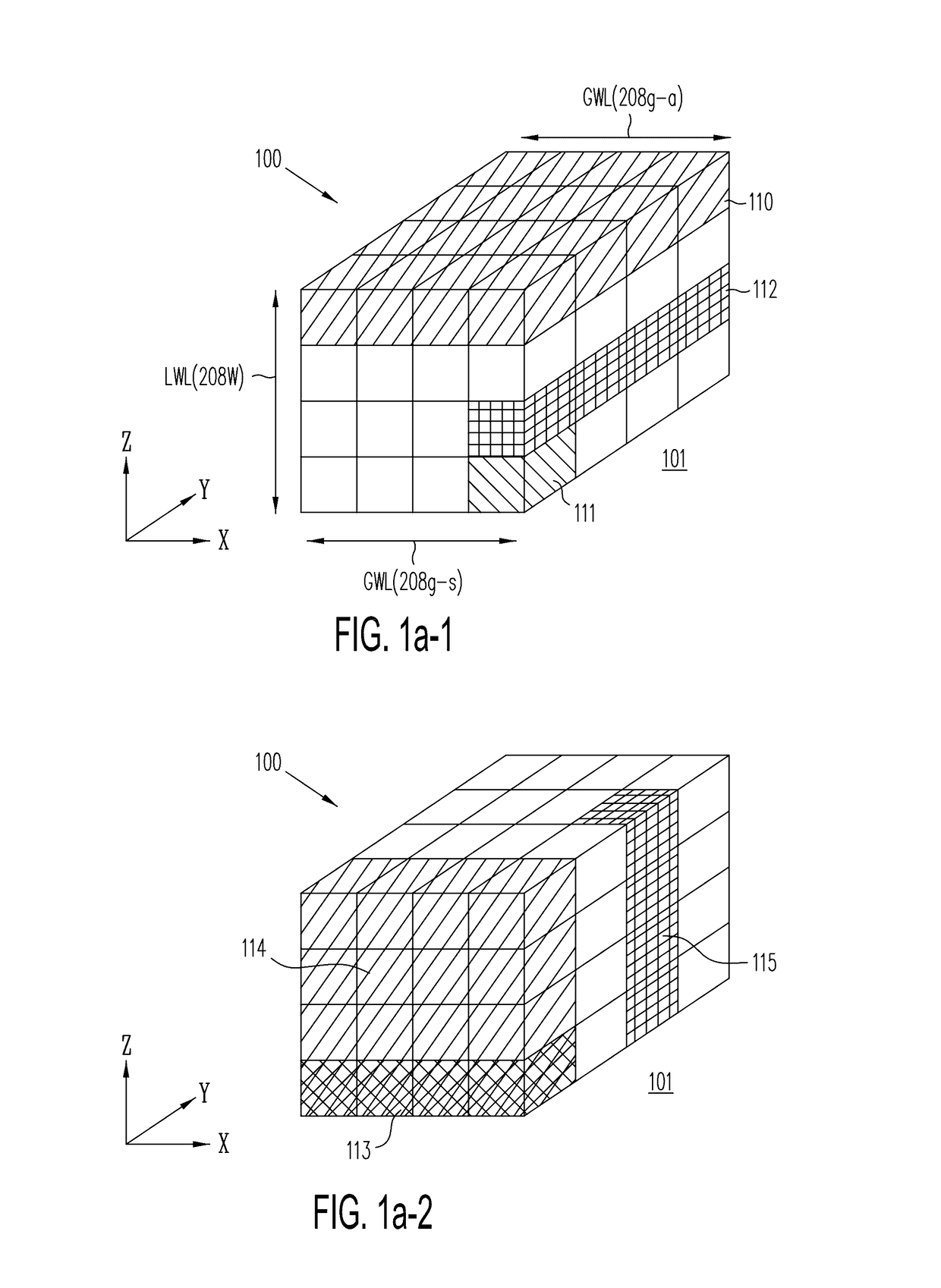

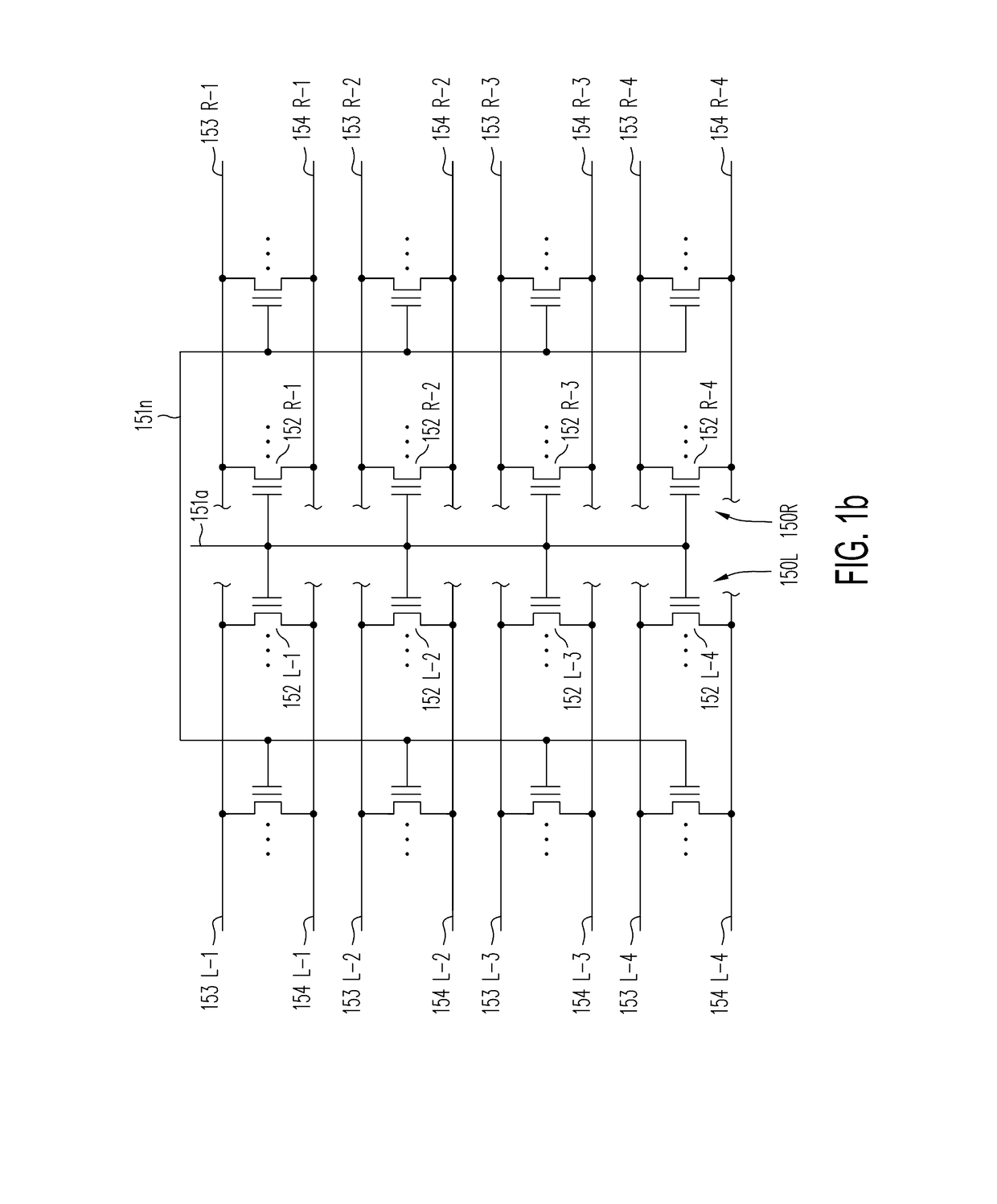

ActiveUS20170092371A1Improve storage densityLower read latencyTransistorSolid-state devicesCapacitive couplingParasitic capacitance

Multi-gate NOR flash thin-film transistor (TFT) string arrays are organized as three dimensional stacks of active strips. Each active strip includes a shared source sublayer and a shared drain sublayer that is connected to substrate circuits. Data storage in the active strip is provided by charge-storage elements between the active strip and a multiplicity of control gates provided by adjacent local word-lines. The parasitic capacitance of each active strip is used to eliminate hard-wire ground connection to the shared source making it a semi-floating, or virtual source. Pre-charge voltages temporarily supplied from the substrate through a single port per active strip provide the appropriate voltages on the source and drain required during read, program, program-inhibit and erase operations. TFTs on multiple active strips can be pre-charged separately and then read, programmed or erased together in a massively parallel operation.

Owner:SUNRISE MEMORY CORP

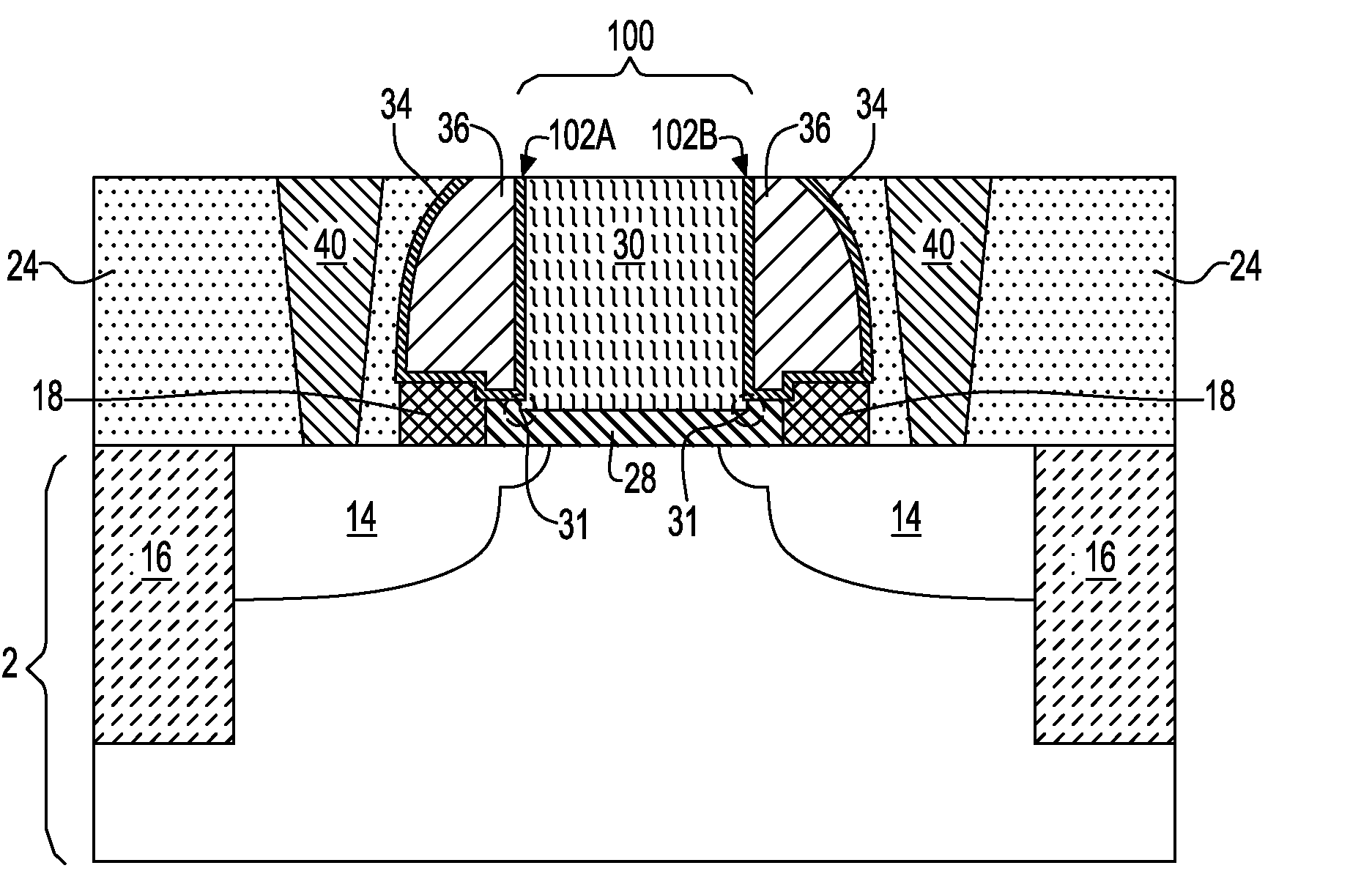

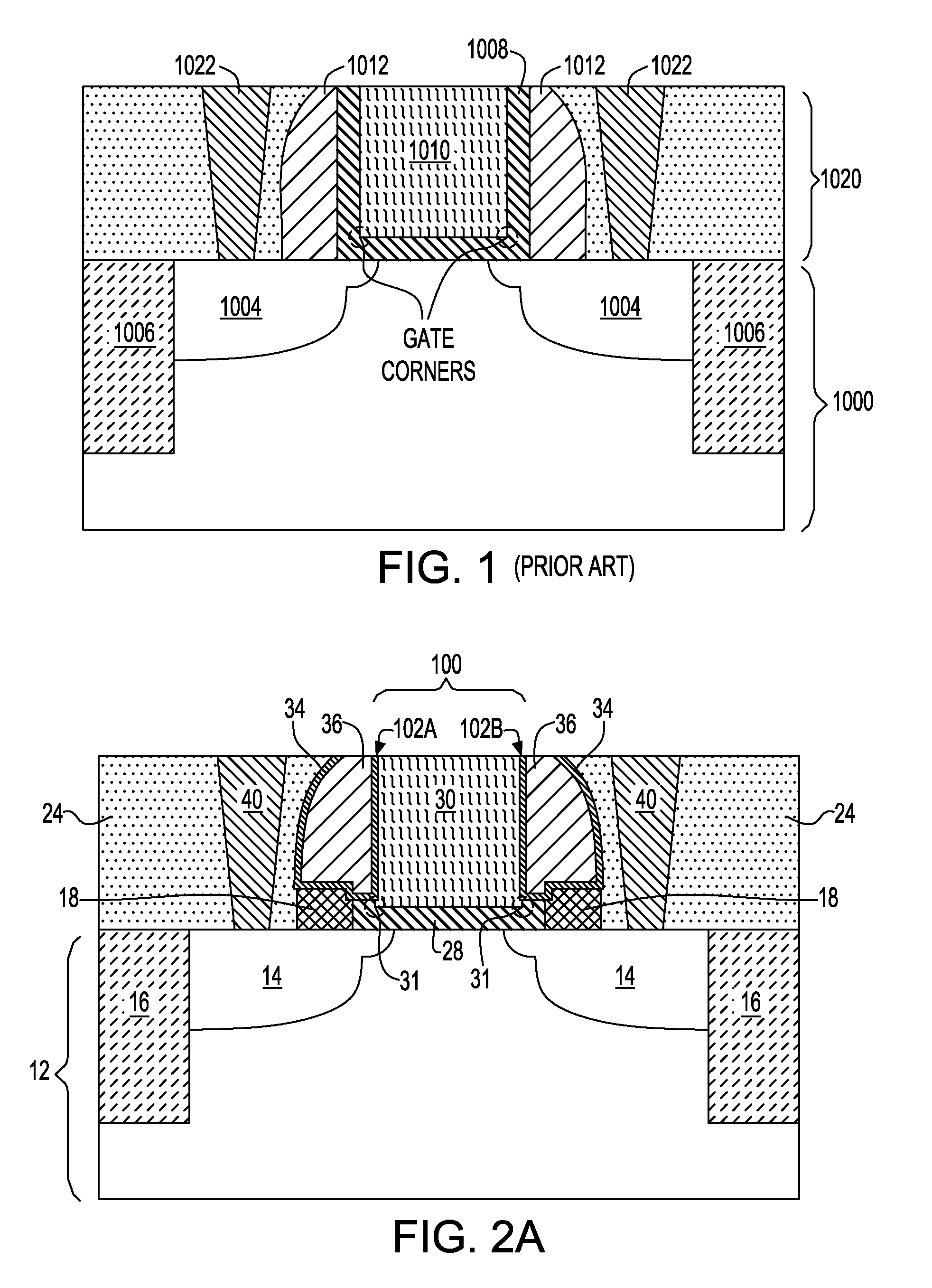

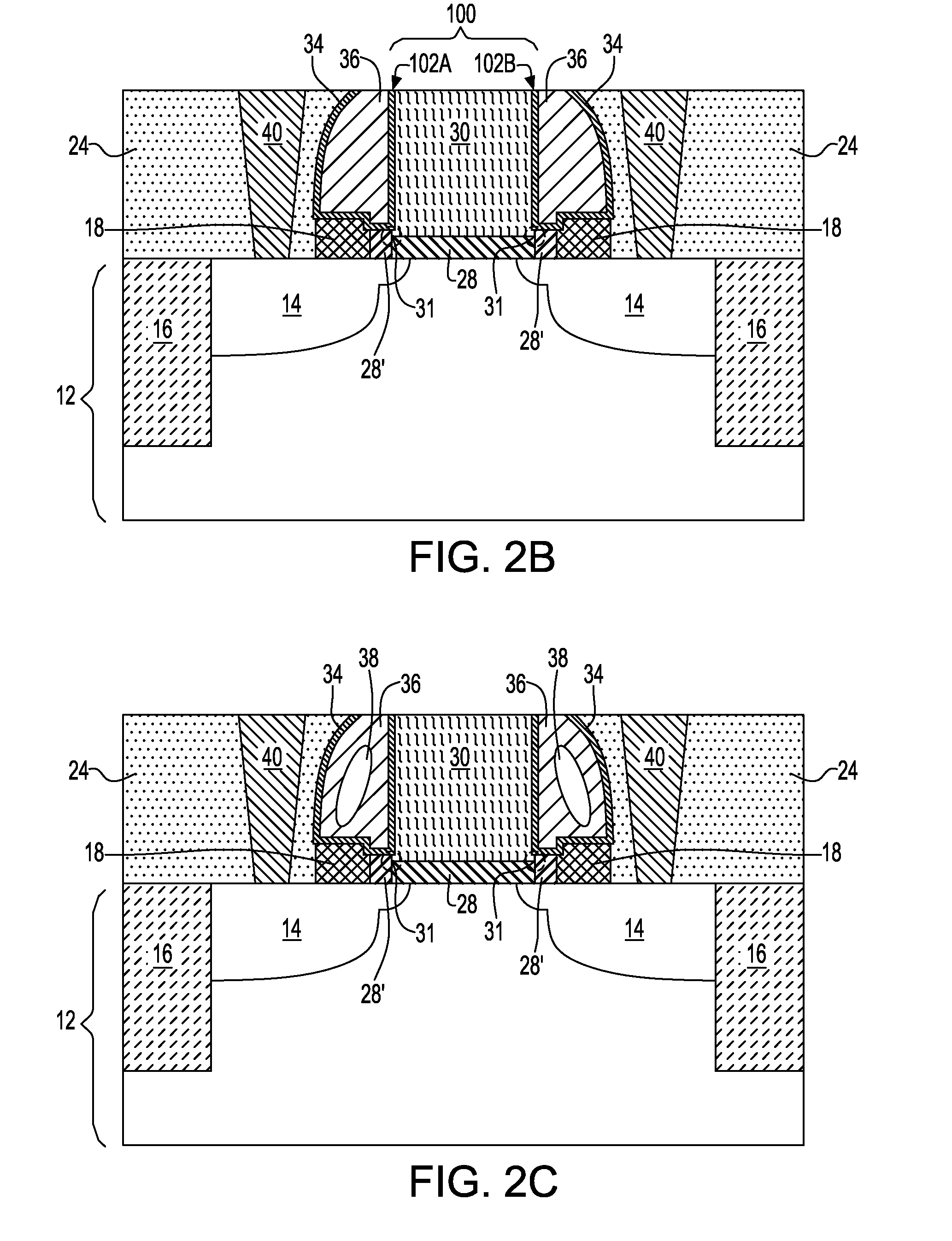

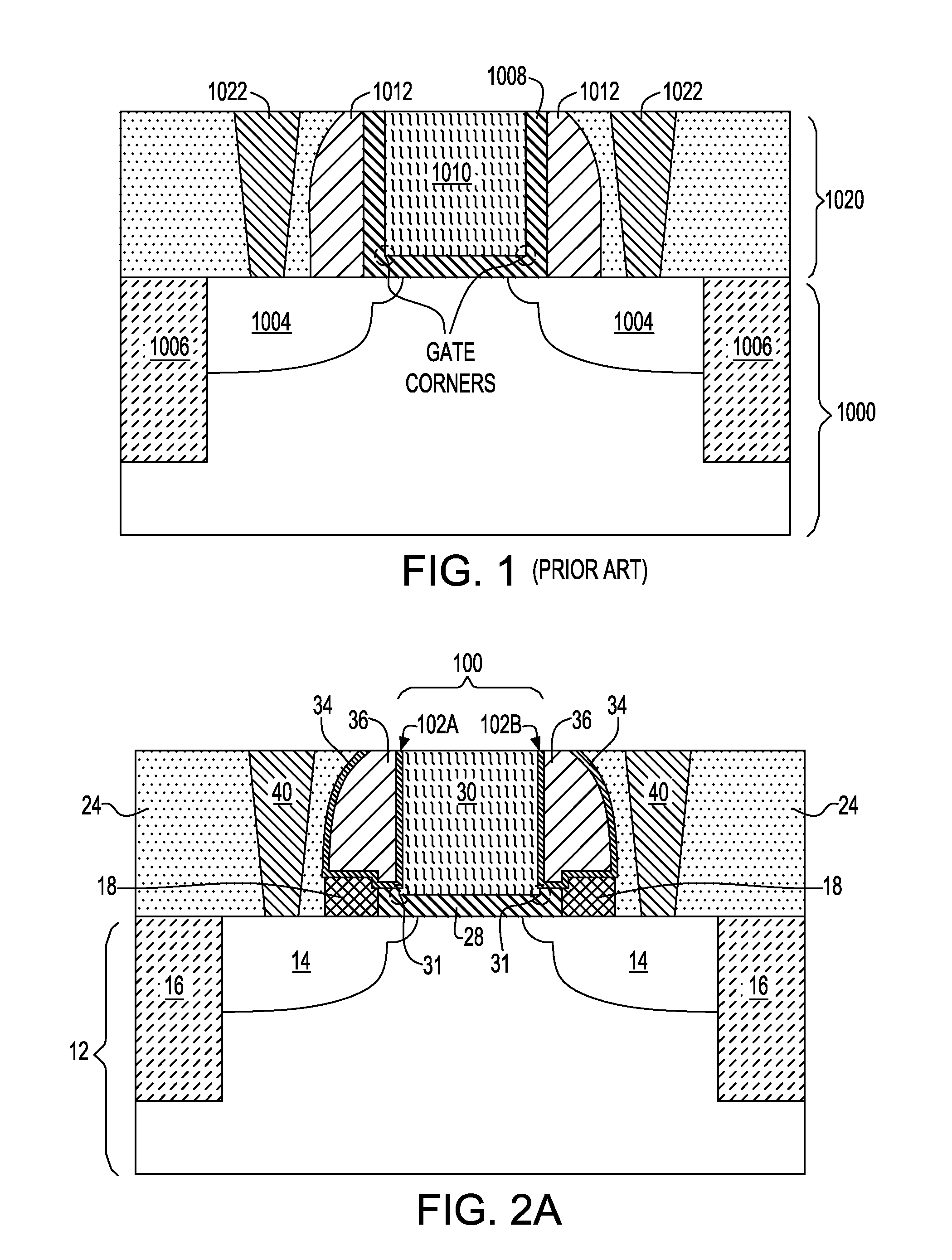

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

InactiveUS20090001480A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETElectrical conductor

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

Implantable medical device incorporating miniaturized circuit module

Implantable medical devices (IMDS) having RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming commands to and from an external programmer having an improved RF module configured to occupy small spaces within the IMD housing to further effect the miniaturization thereof. An RF module formed of an RF module substrate and at least one IC chip and discrete components has a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include: (1) integrating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The integrated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the RF module substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

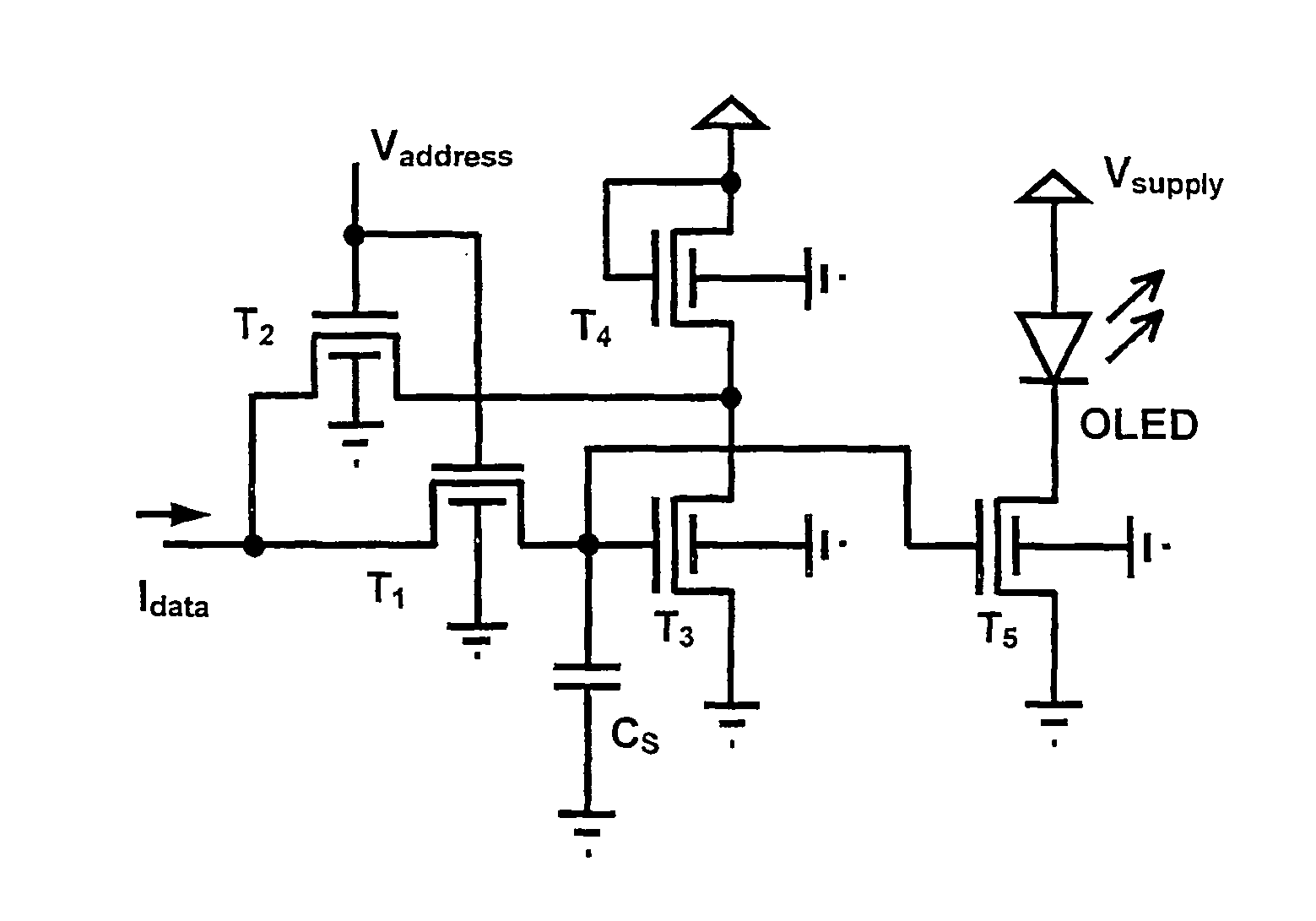

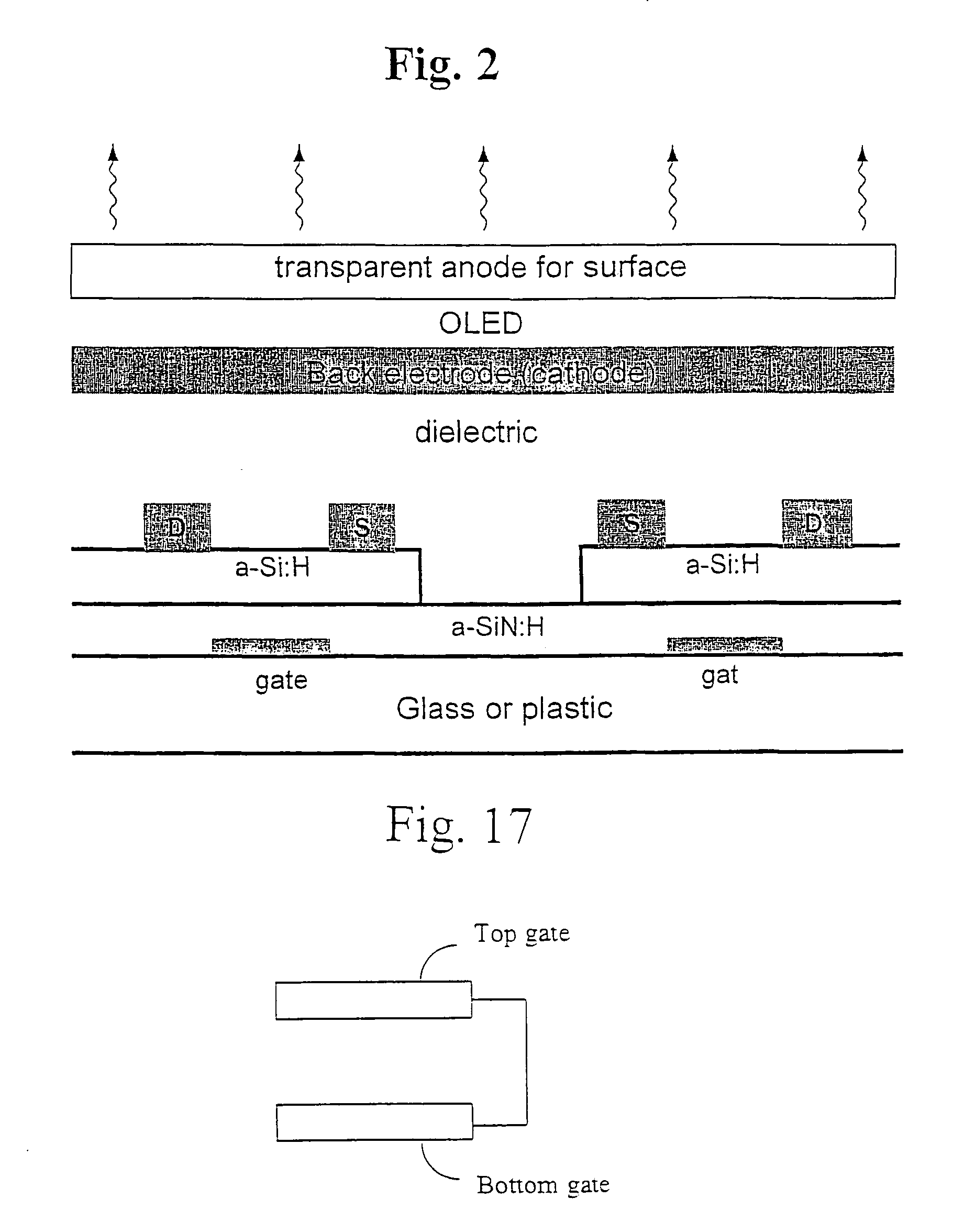

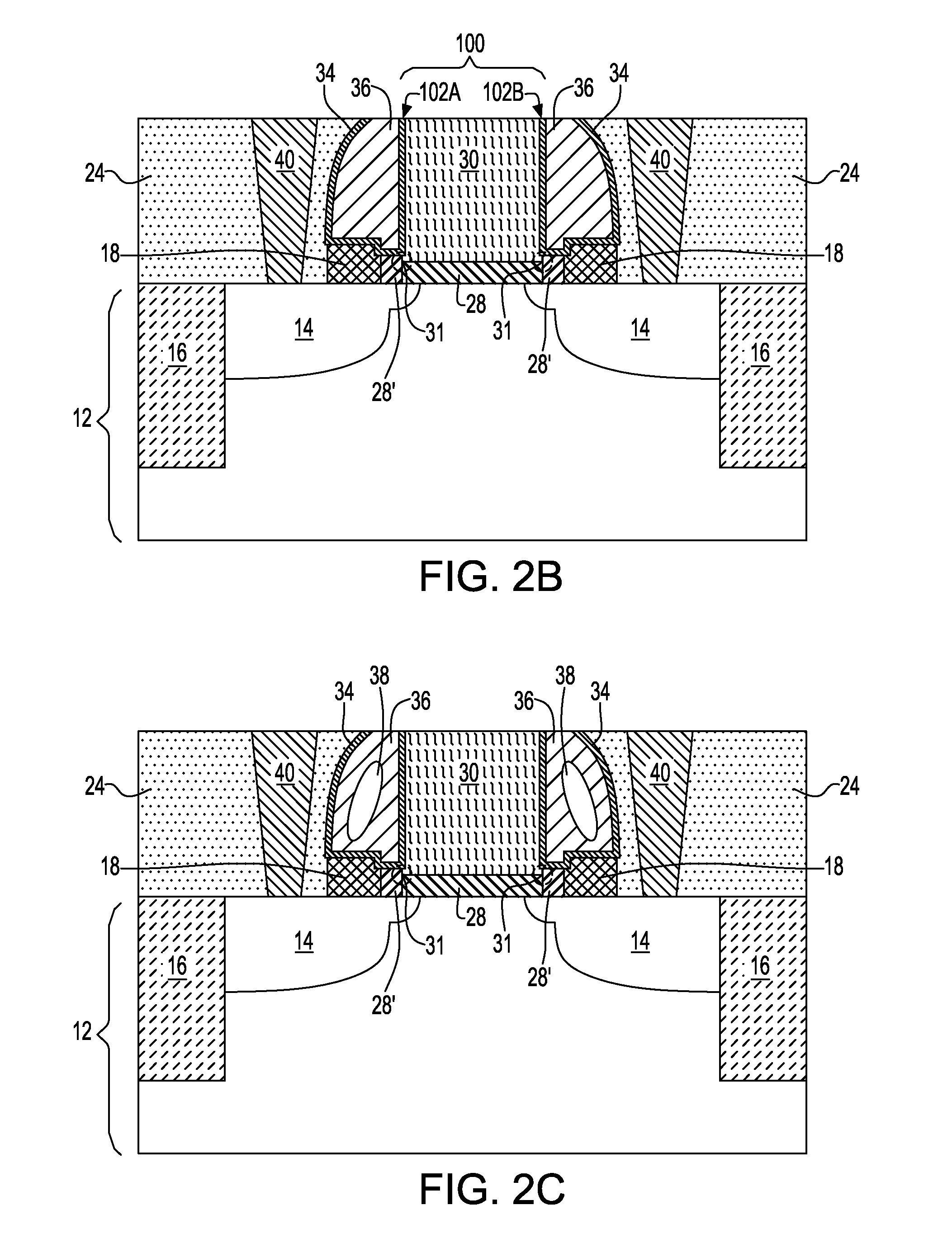

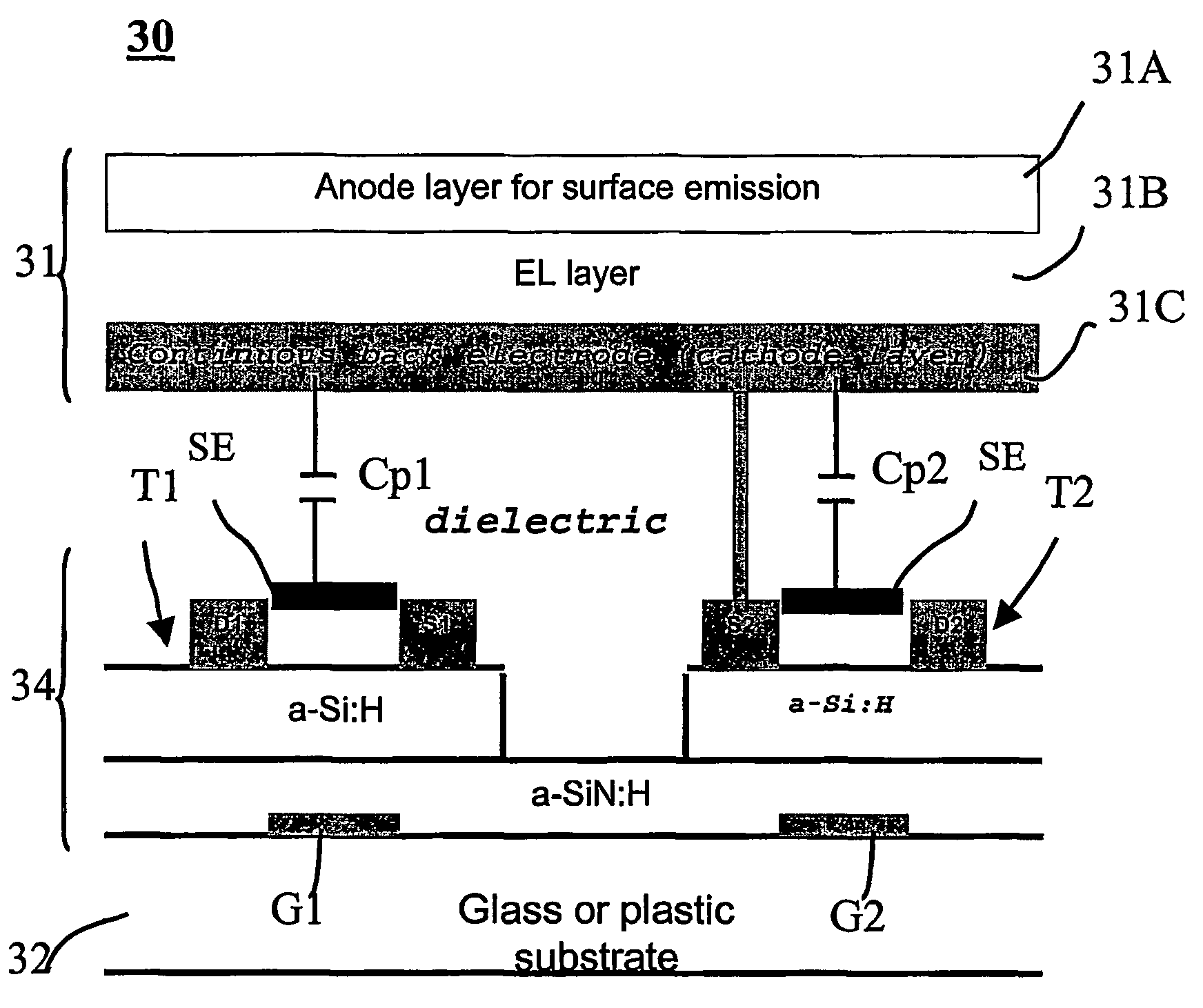

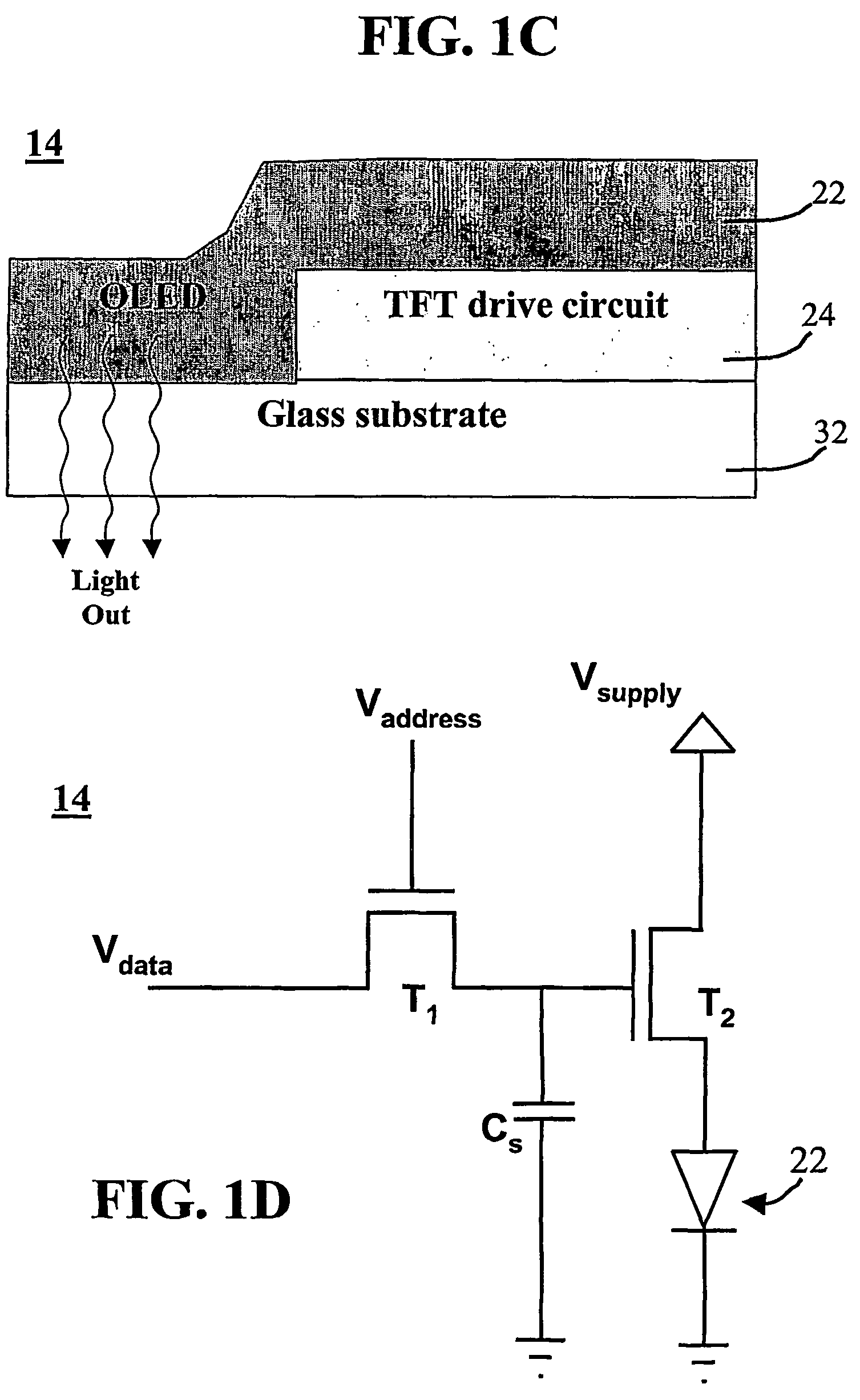

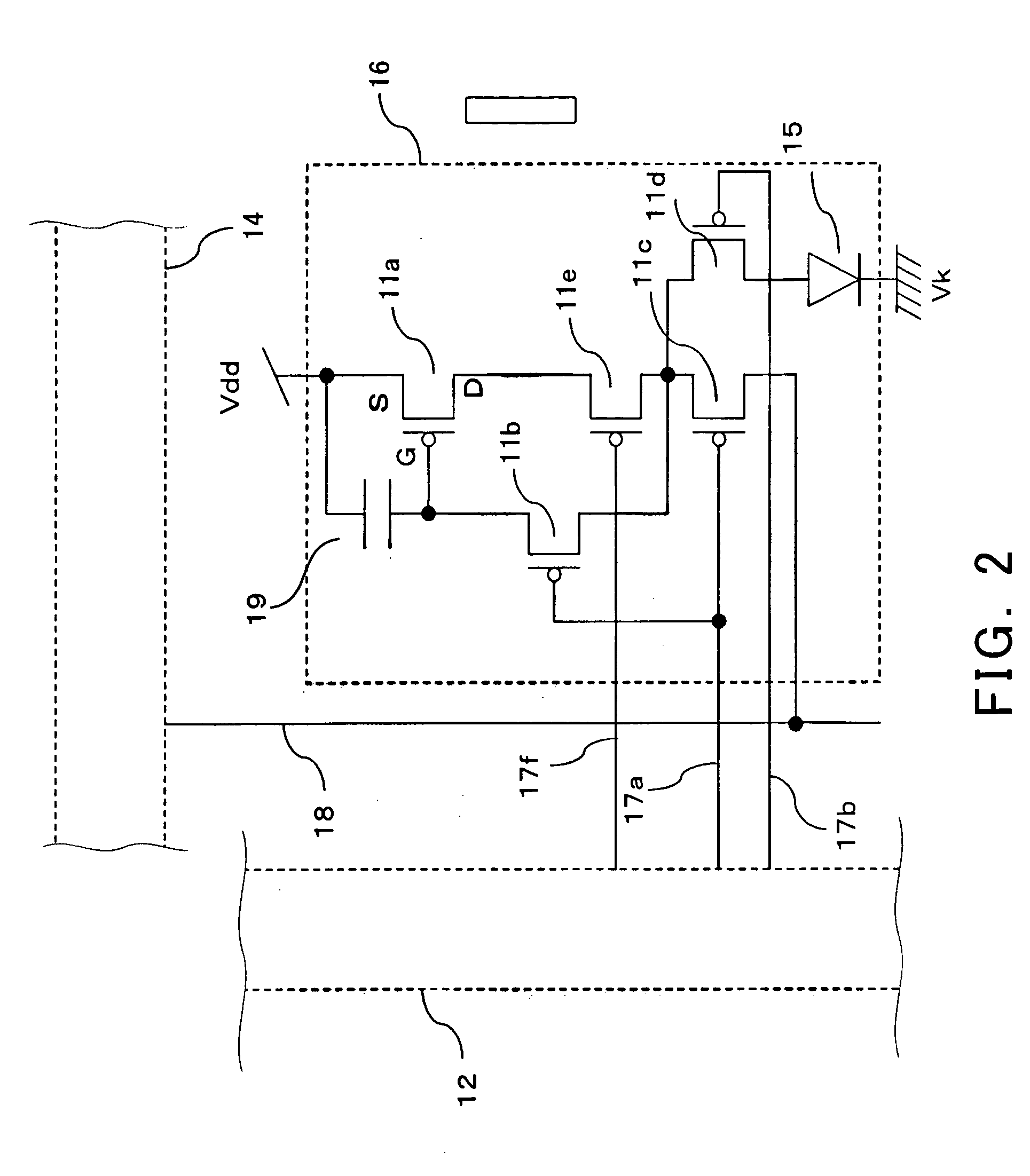

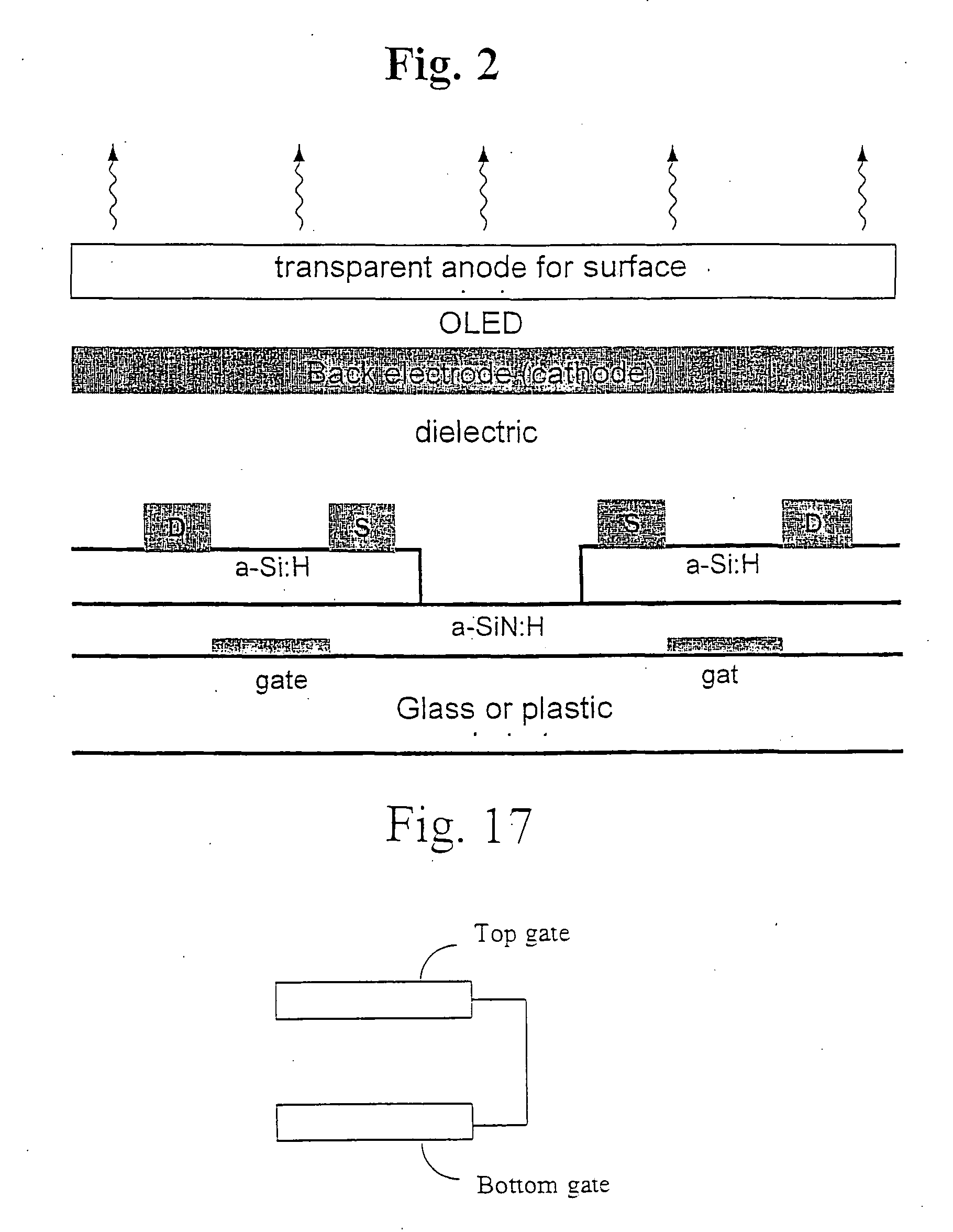

Pixel current driver for organic light emitting diode displays

InactiveUS7414600B2Minimizing parasitic couplingMinimizes parasitic capacitanceTransistorStatic indicating devicesBottom gateDisplay device

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

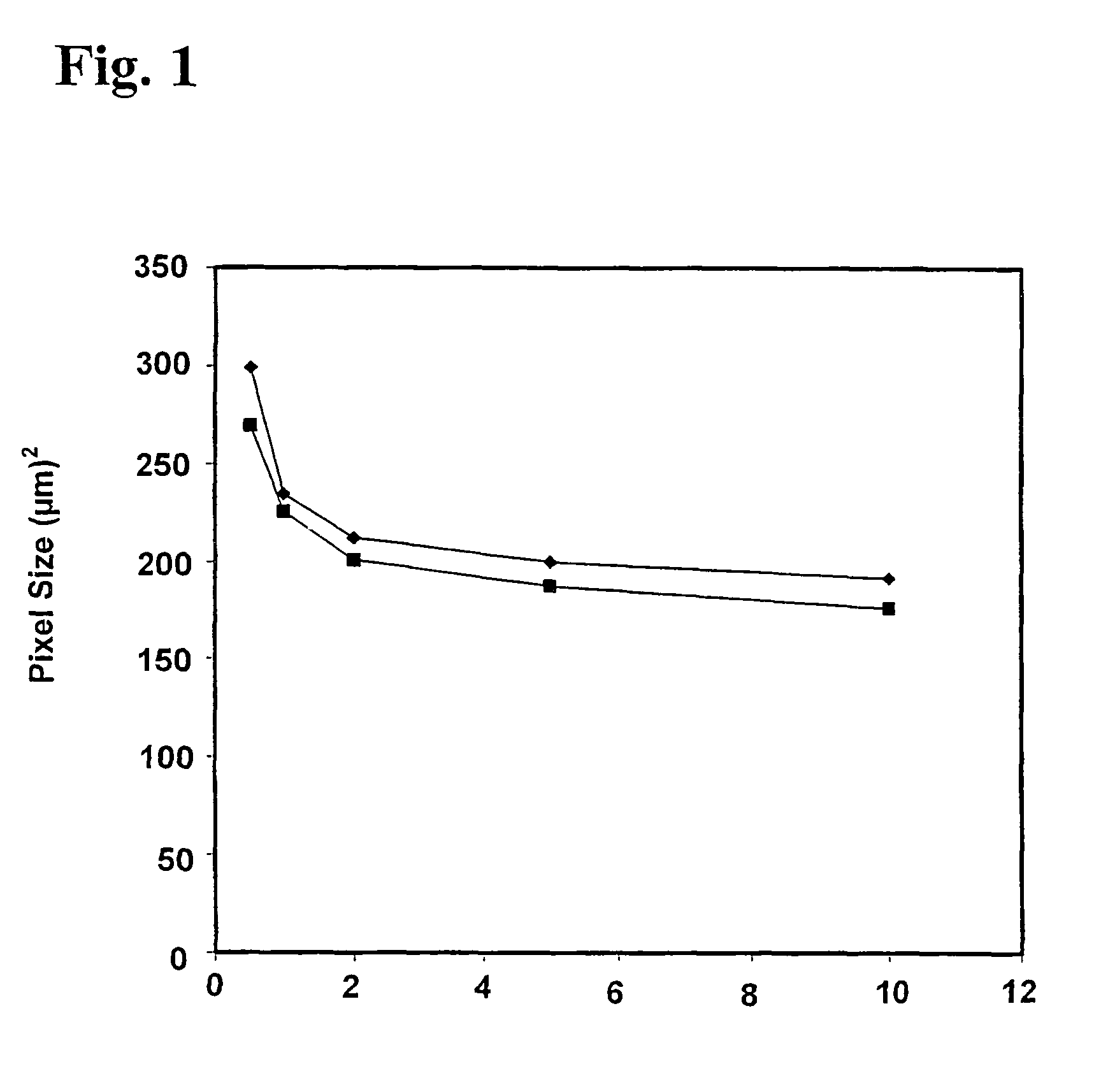

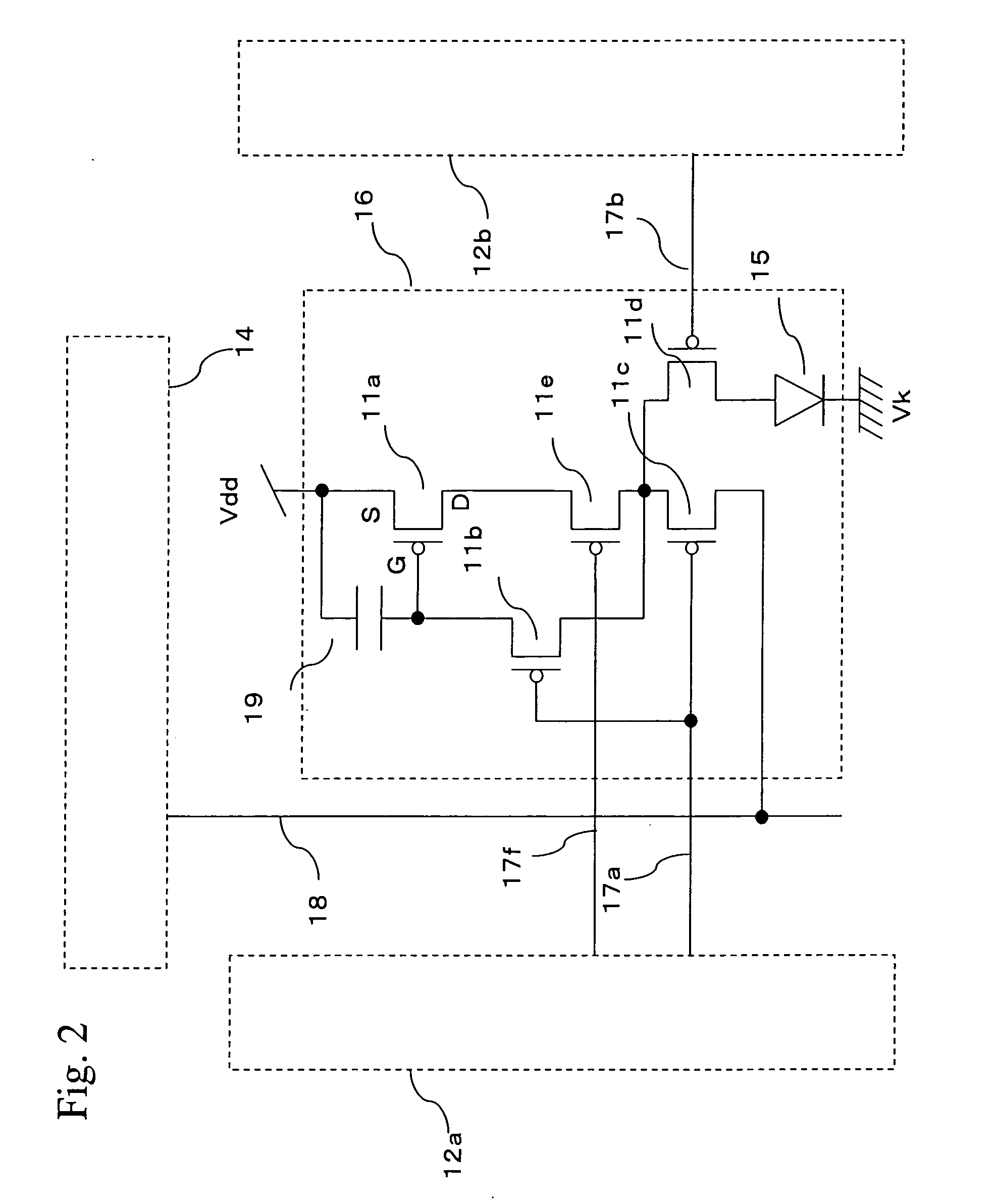

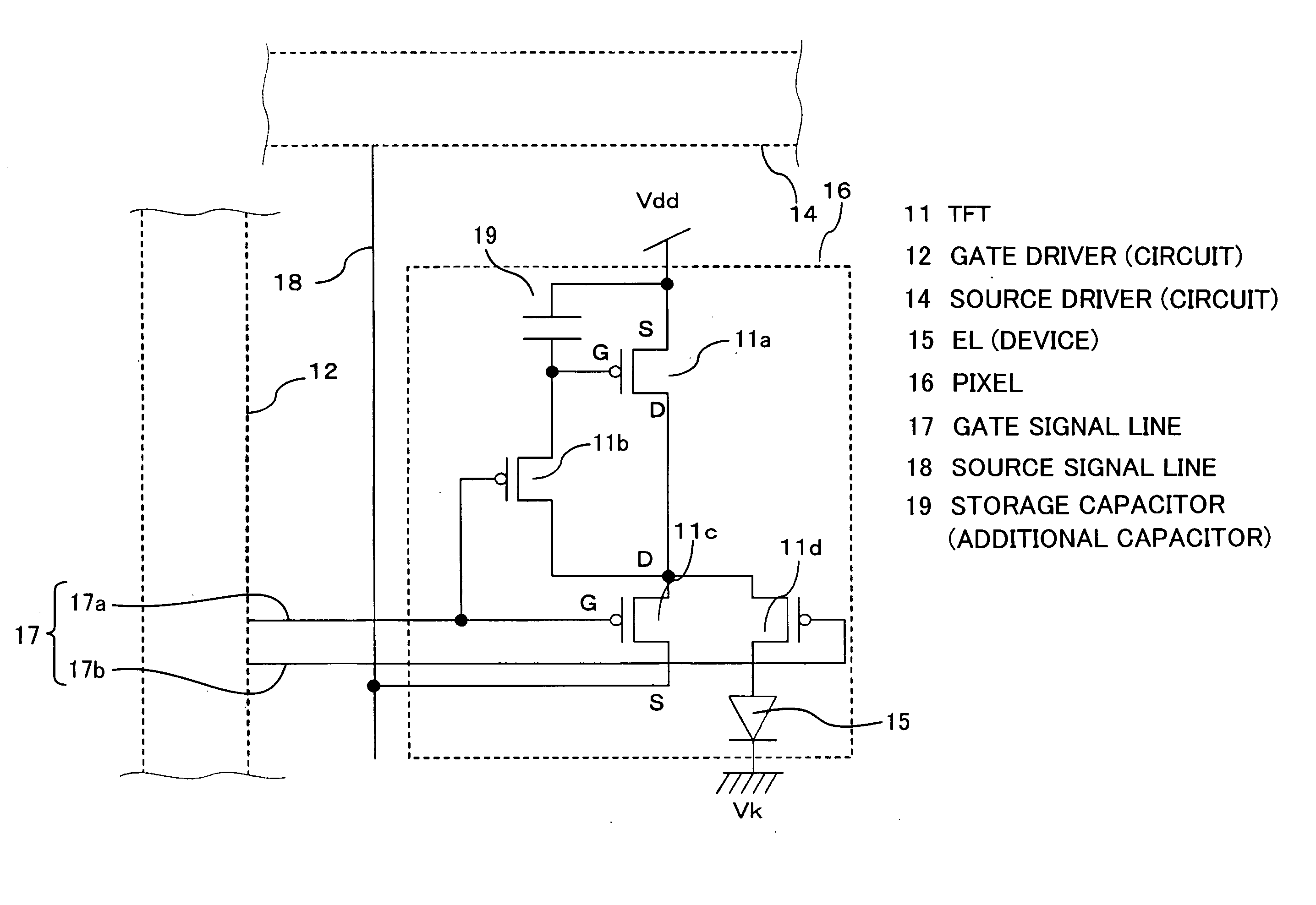

Drive method of el display panel

ActiveUS20050168491A1Show unityUniform screen displayElectroluminescent light sourcesSolid-state devicesDriver circuitParasitic capacitance

In order to charge and discharge parasitic capacitance of a source signal line sufficiently and program a predetermined current value into a pixel transistor, it is necessary to output a relatively large current from the source driver circuit. However, if such a large current is passed through the source signal line, the value of this current is programmed into the pixel, causing a larger than desired current to flow through an EL element 15. For example, if a 10 times larger current is used for programming, a 10 times larger current flows through the EL element 15, and thus the EL element 15 illuminates 10 times more brightly. To obtain predetermined emission brightness, the time during which the current flows through the EL element can be reduced to 1 / 10 of one frame (1 F). This way, the parasitic capacitance of the source signal line can be charged and discharged sufficiently and the predetermined emission brightness can be obtained.

Owner:JAPAN DISPLAY CENT INC

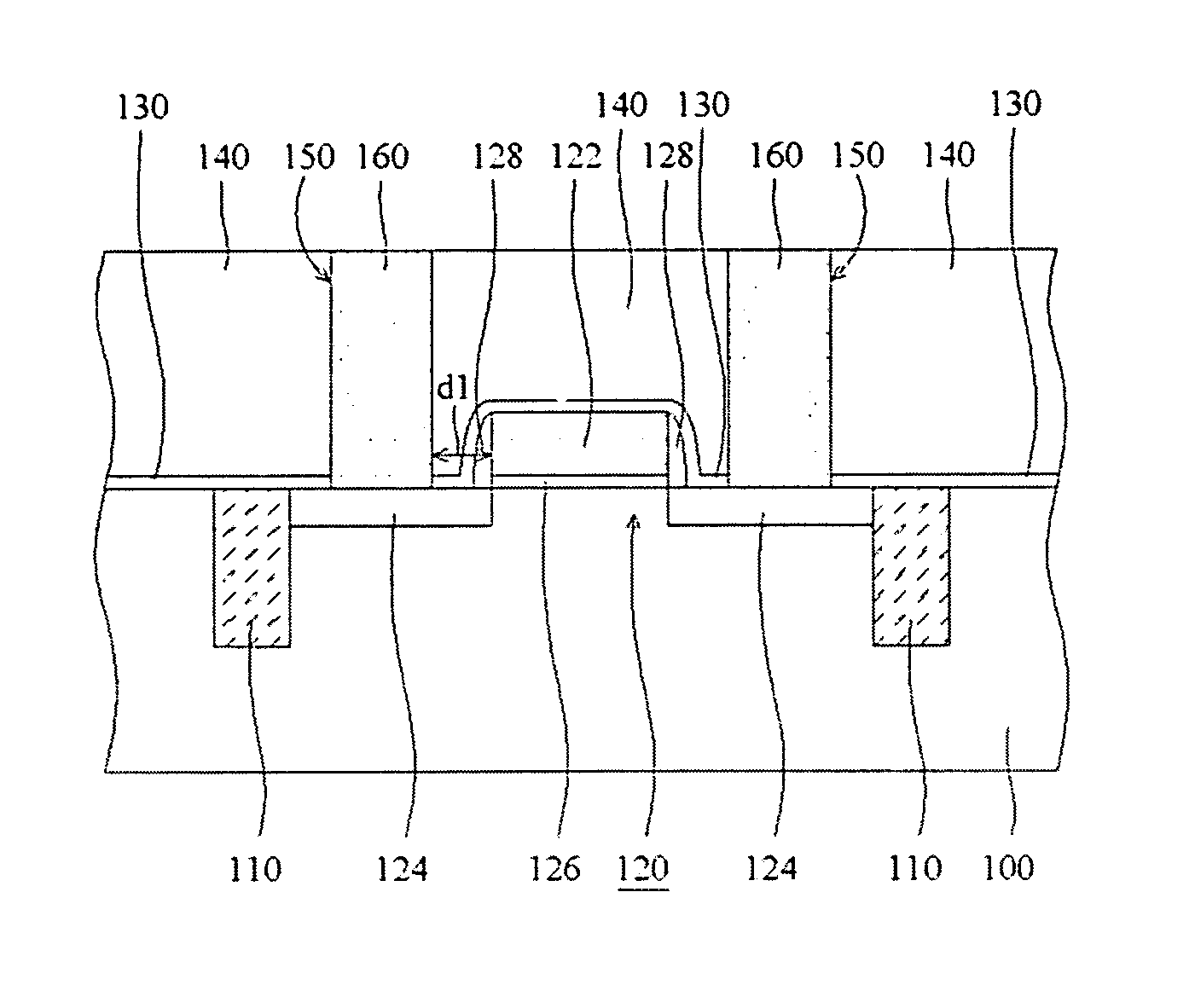

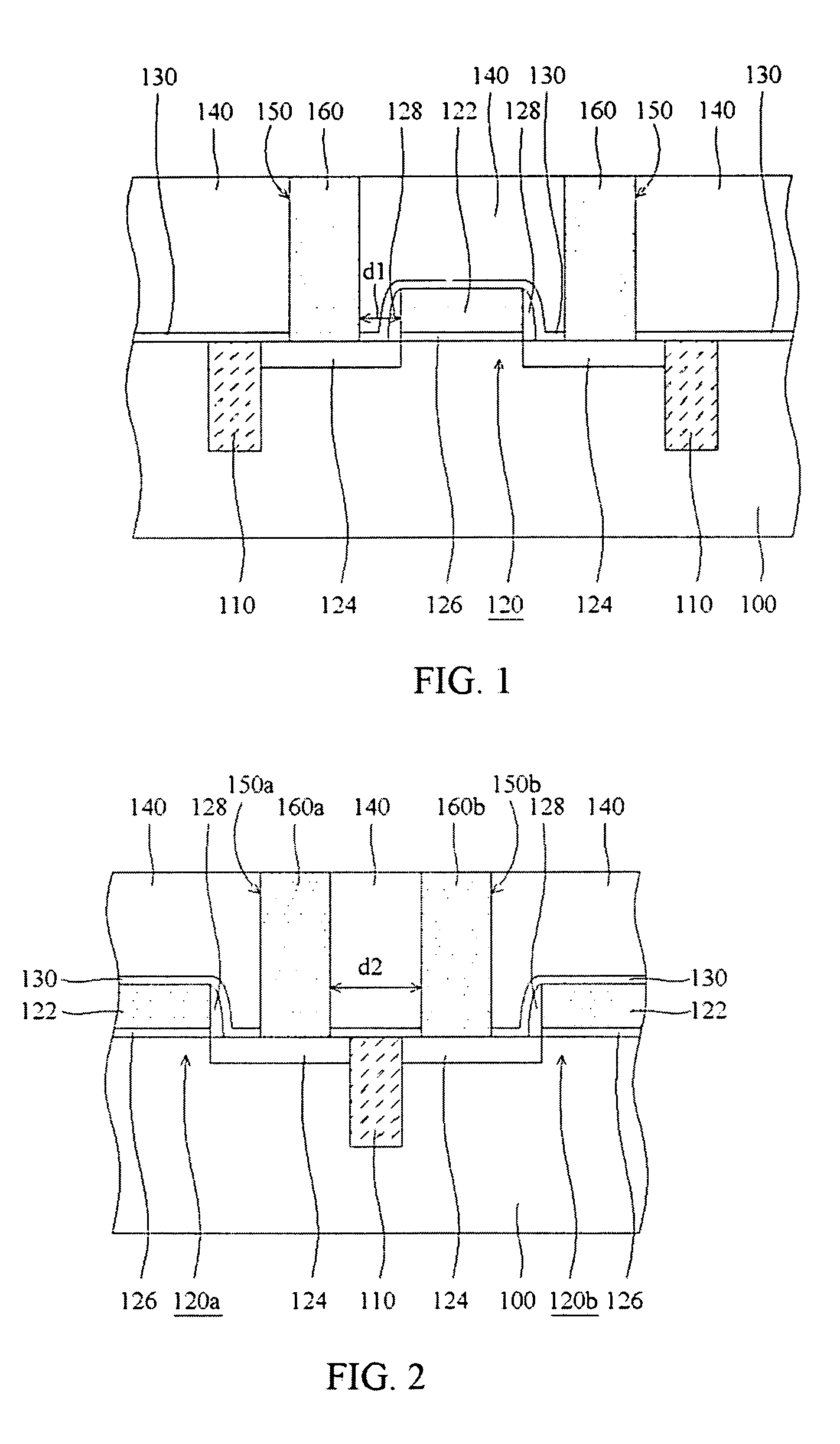

Device with low-k dielectric in close proximity thereto and its method of fabrication

InactiveUS20050035455A1Semiconductor/solid-state device detailsSolid-state devicesHigh densityDevice material

A semiconductor device with a low-k material in close proximity thereto and its fabrication method. The device includes a gate electrode overlying a substrate. An electrically conductive plug is provided immediately adjacent to the gate electrode and making electrical contact to the device. A low-k dielectric material is disposed in the space between the gate electrode and the electrically conductive plug whereby reducing the parasitic capacitance. Thus, higher density of devices can be formed without decreasing operating speed.

Owner:TAIWAN SEMICON MFG CO LTD

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

ActiveUS20090321853A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

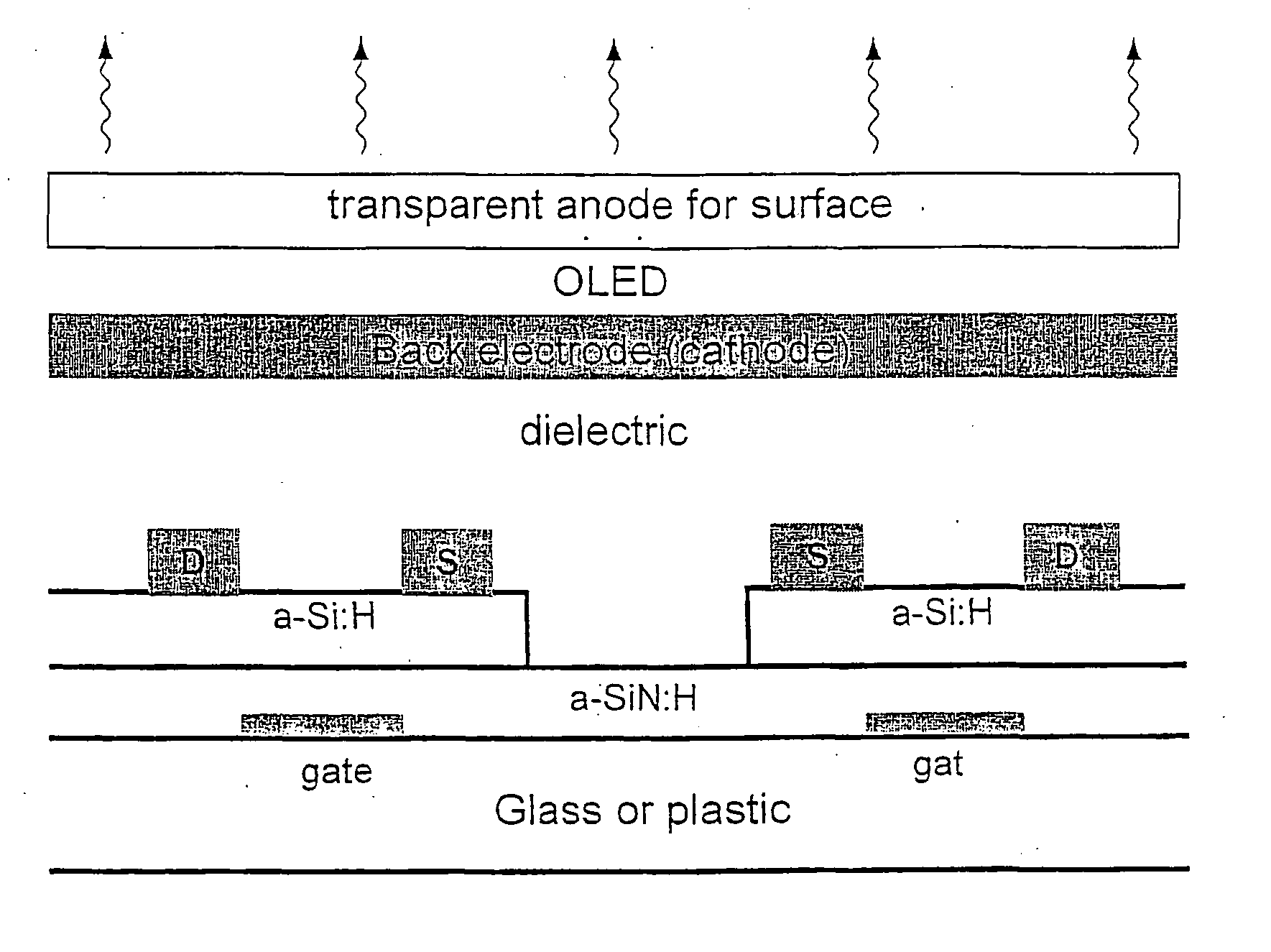

Organic light emitting diode display having shield electrodes

InactiveUS7248236B2Minimize parasitic capacitanceImprove performanceTransistorStatic indicating devicesDisplay deviceEngineering

An organic light emitting diode (OLED) display includes at least one shield electrode between a cathode layer and an OLED drive circuit. The OLED drive circuit has at least one thin-film transistor (TFT), and the shield electrode is disposed to correspond to the thin-film transistor and closer to the cathode layer, covering an entire region between the source and drain of the thin-film transistor. The shield electrode is either grounded or tied to the gate of the thin-film transistor, to thereby minimize parasitic capacitances in the pixels of the display to enhance the display performance. The presented architecture enables high density drive circuit integration in amorphous silicon or other technologies, yet preserving a high display aperture ratio.

Owner:IGNIS INNOVATION

Power semiconductor devices and methods of manufacture

InactiveUS20060214221A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

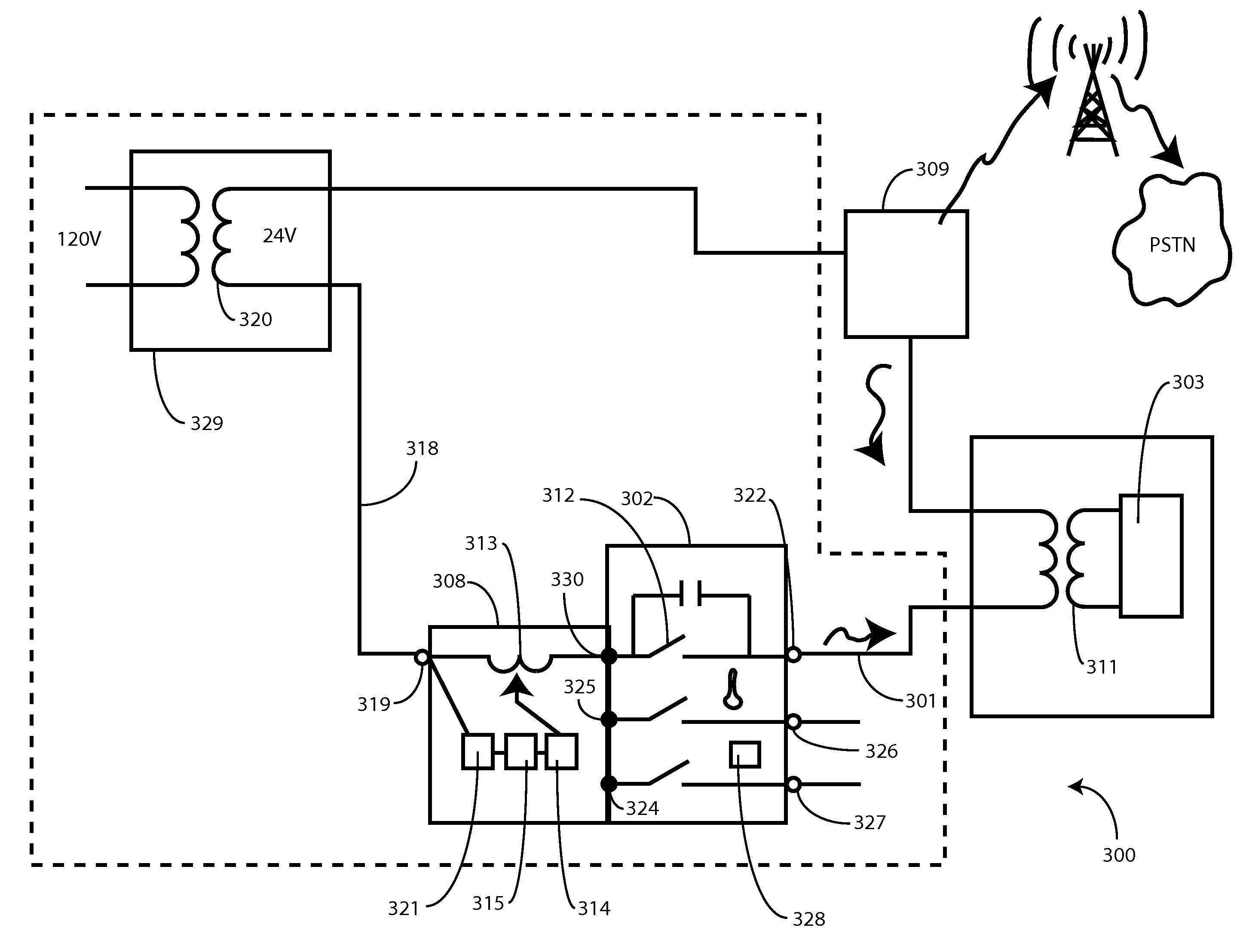

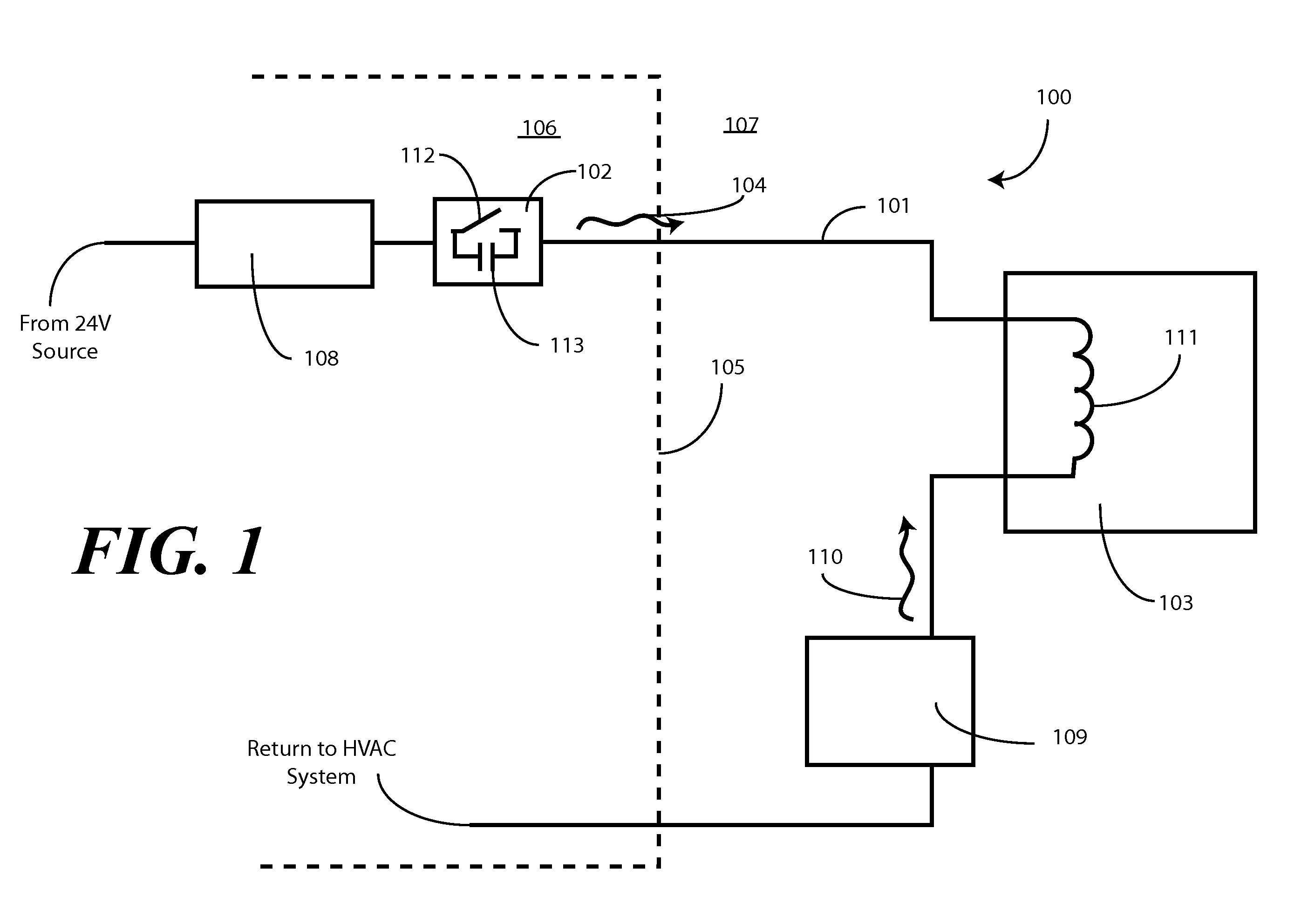

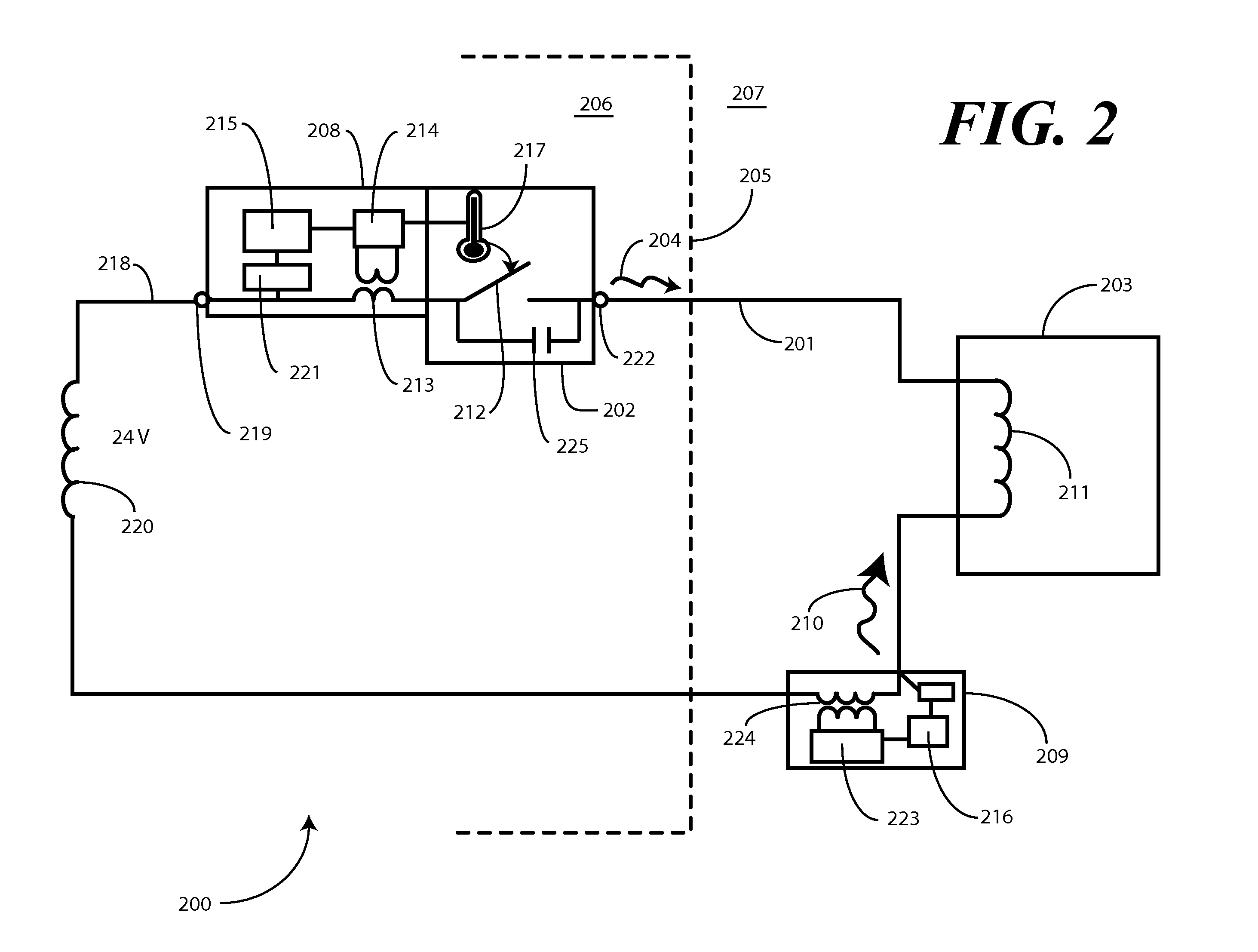

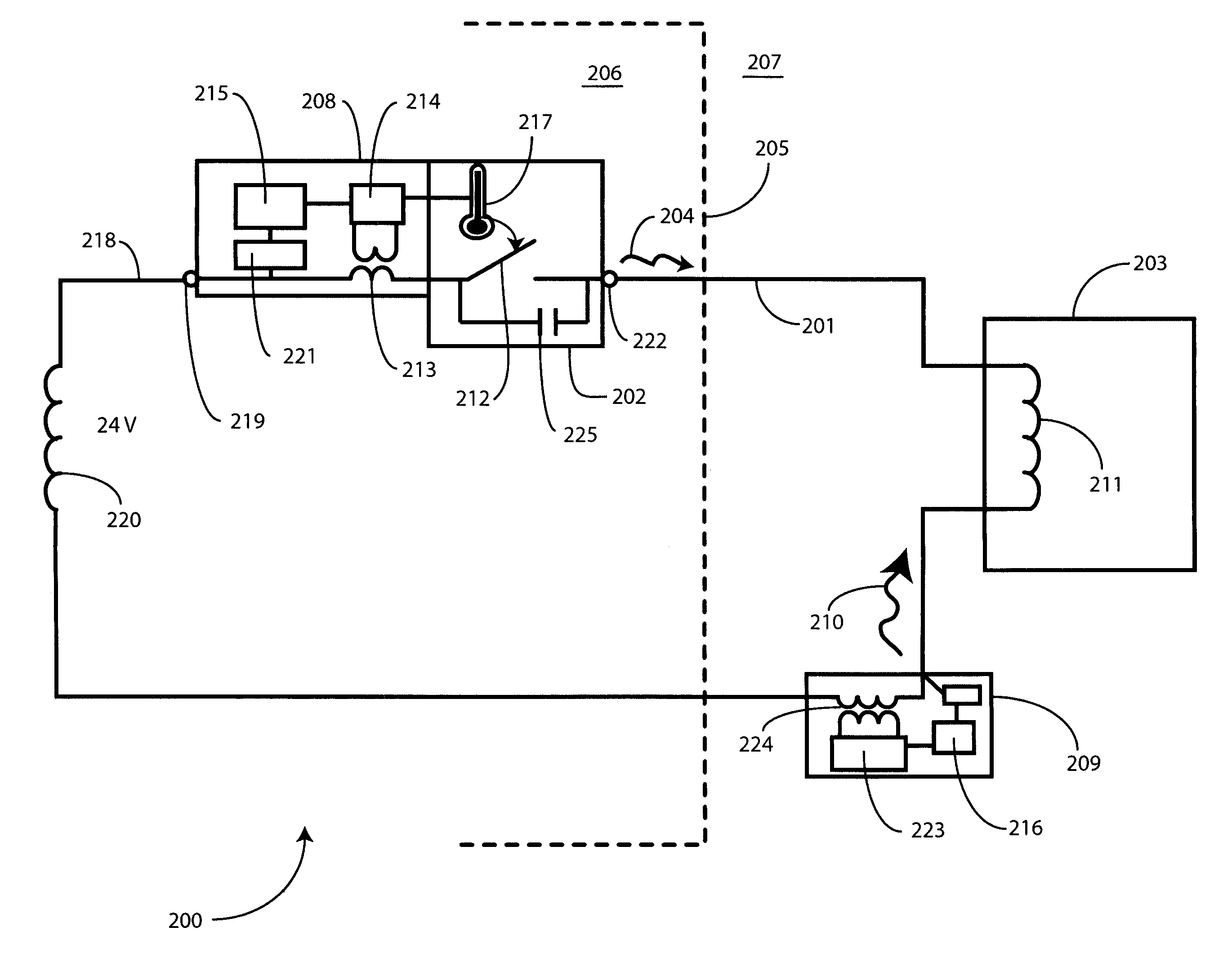

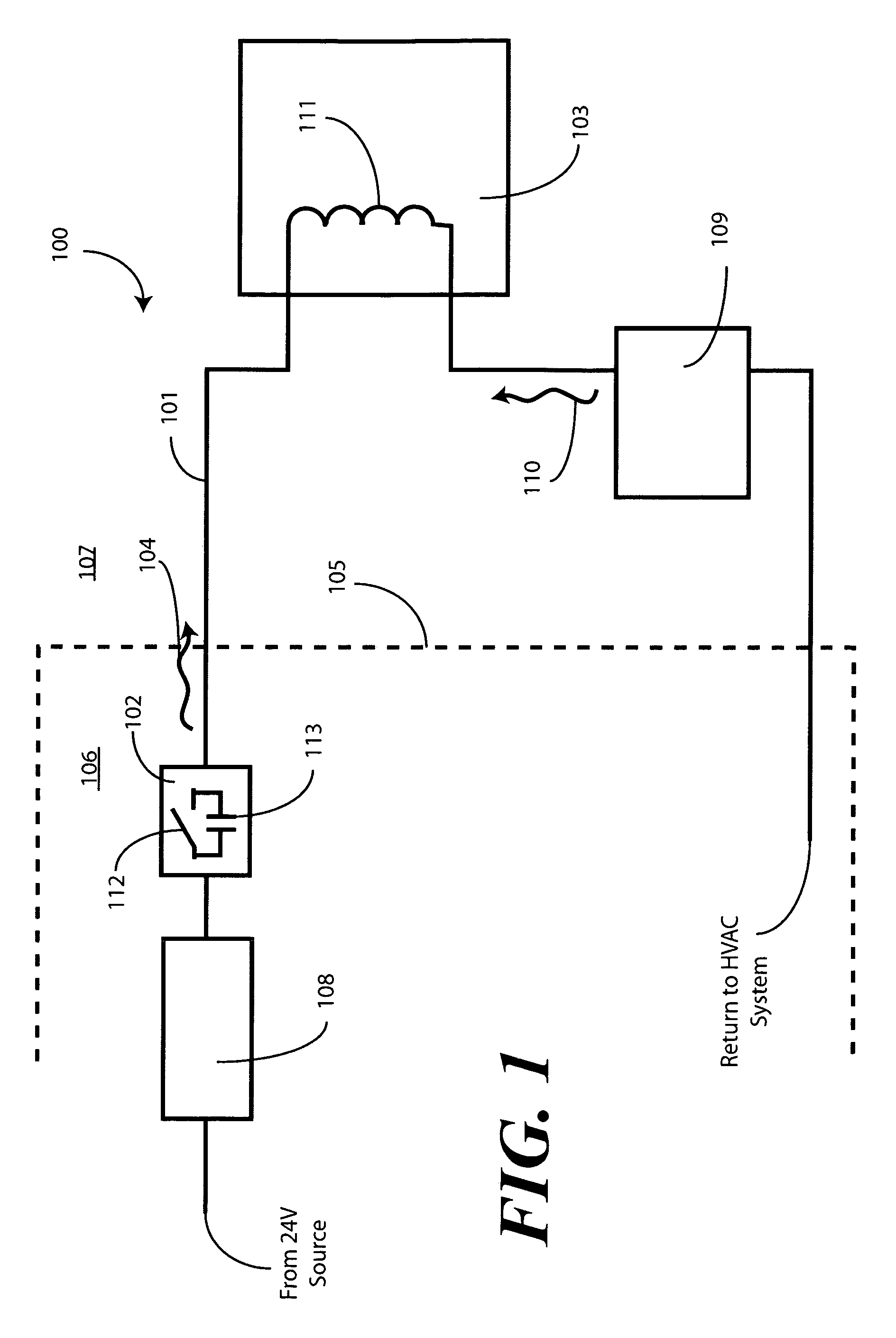

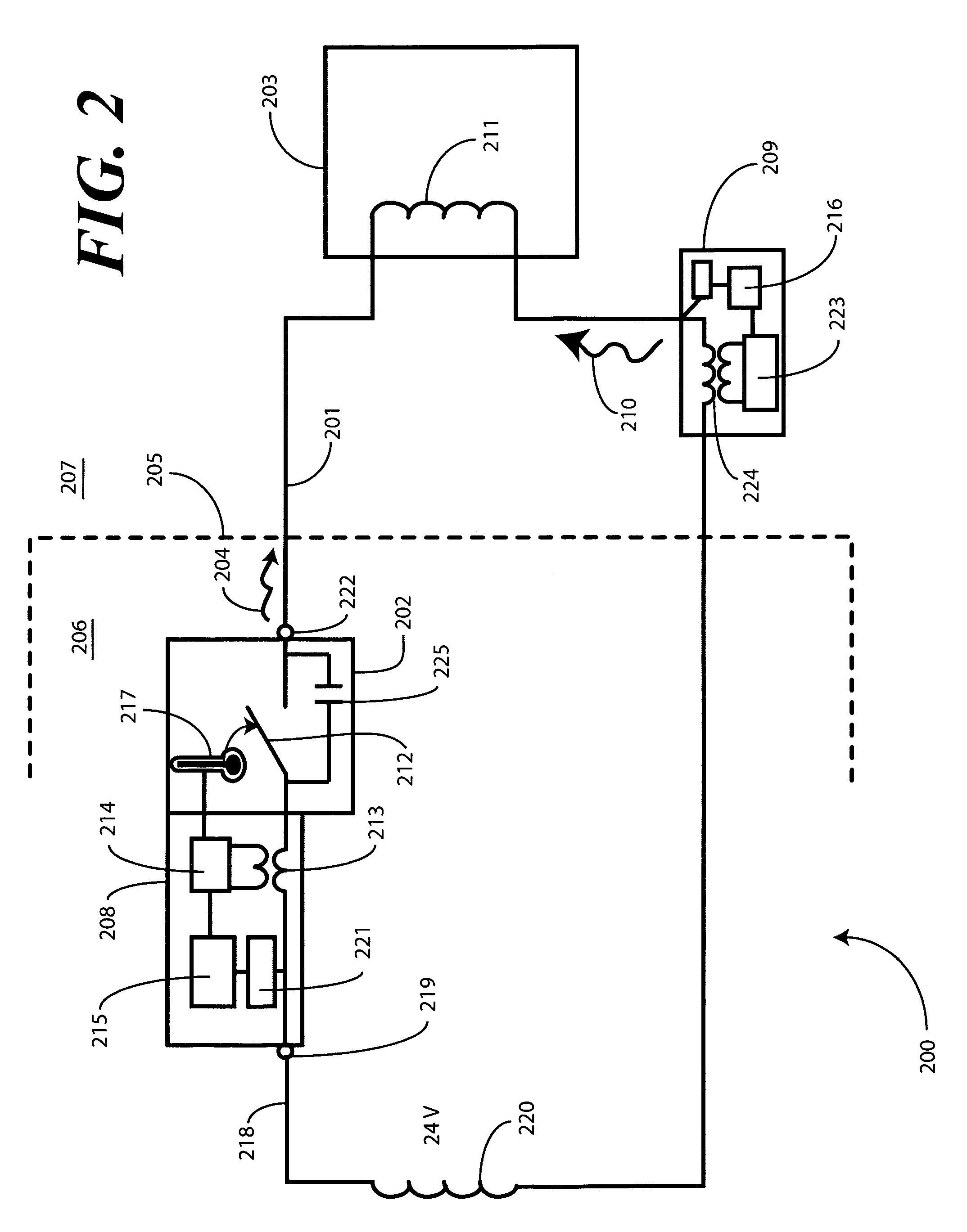

HVAC communication system

InactiveUS7510126B2Electric signal transmission systemsFrequency-division multiplex detailsTransceiverCommunications system

A system for communicating across conventional HVAC wiring is provided. The system includes a communication device having a communication module capable of inducing low power, high frequency current signals into a single control wire coupling, for example, a thermostat with a compressor. The communication module includes a power supply module that draws power sufficient to operate the communication module from the existing HVAC wiring, so as to eliminate any need for batteries or external power sources. A second communication module may be coupled to the single control wire. The second communication module operates as a transceiver sending communication signals to, and receiving communication signals from, the communication module. In one embodiment, the communication module is disposed within a building, for example coupled to an electronic thermostat, while the second communication module is disposed outside the building near the compressor. The communication signals are RF modulated signals between 5 and 50 MHz so as to take advantage of and pass across parasitic capacitances found inherent in transformers or other coils disposed within HVAC loads.

Owner:EMERSON ELECTRIC CO

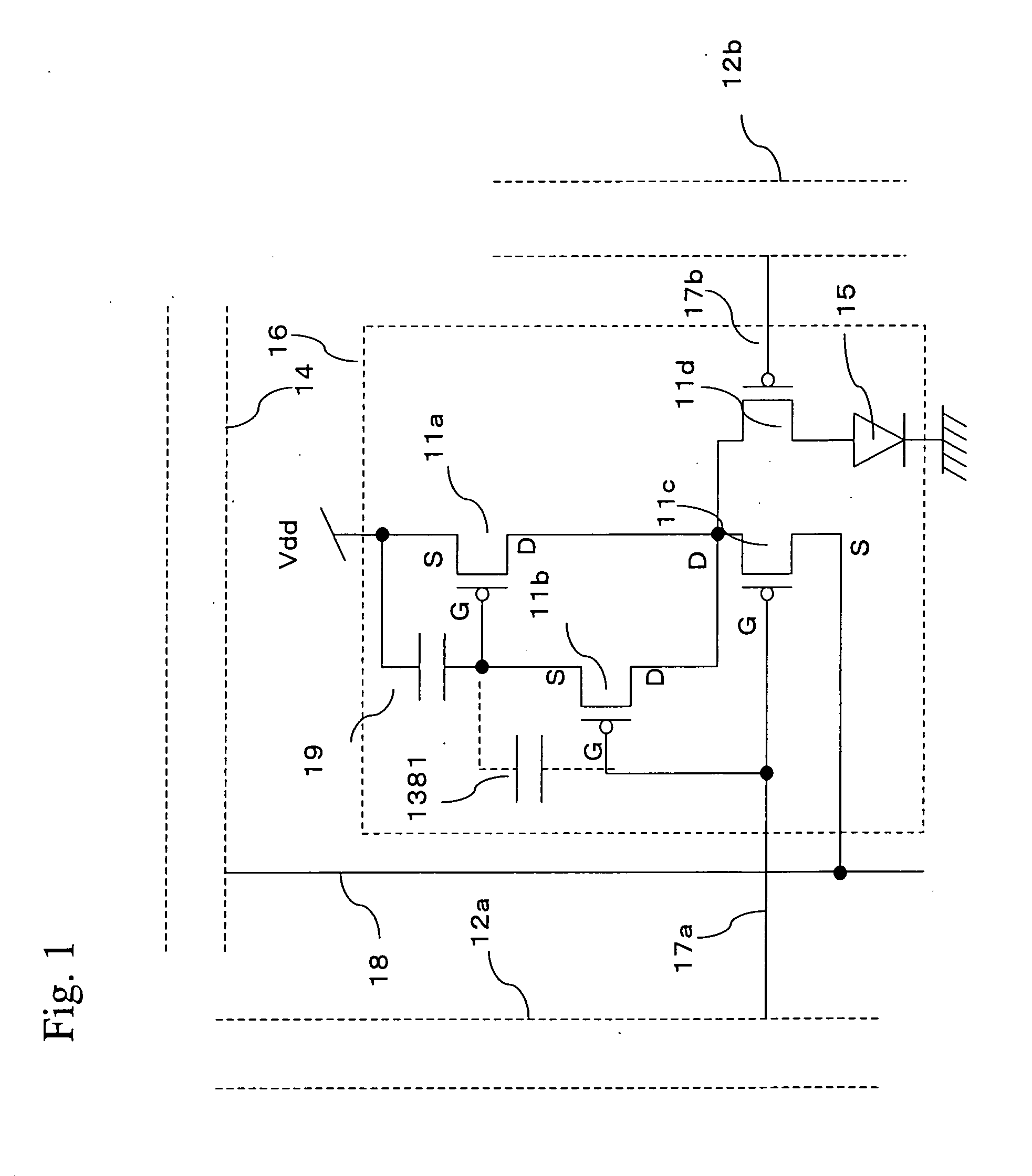

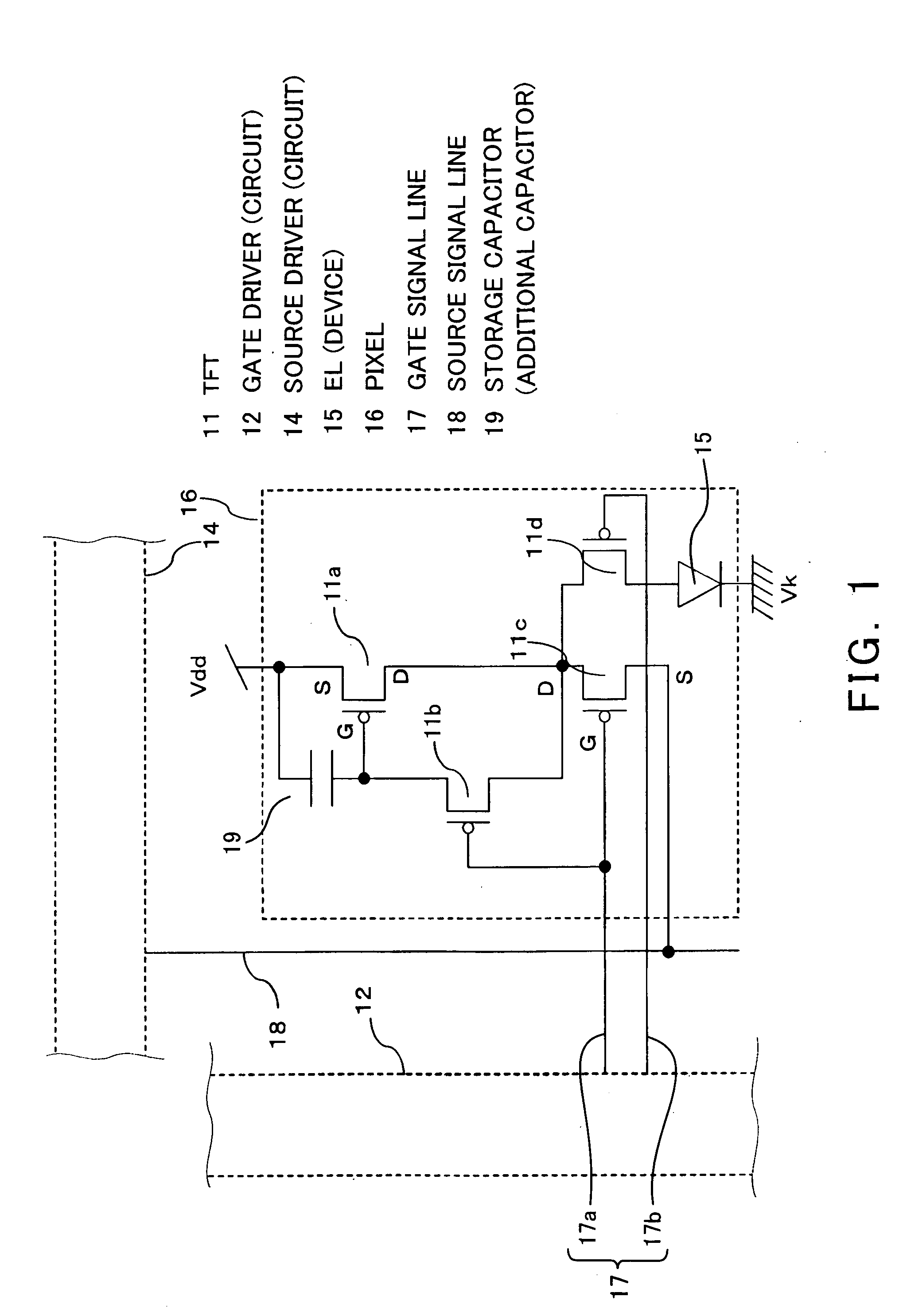

El display panel, its driving method, and el display apparatus

ActiveUS20050041002A1SatisfactoryLot of parasitic capacitanceSolid-state devicesCathode-ray tube indicatorsParasitic capacitanceEngineering

An EL display apparatus according to the present invention includes EL device (15) adapted to emit light at a luminance corresponding to a current fed thereto. A source driver (14) outputs a current higher than a current corresponding to an image signal to the EL device (16) through a source signal line (18). This operation charges / discharges a parasitic capacitance present in the source signal line (18). A transistor (11d) formed between the EL device (15) and the source driver (14) operates so that the EL device (15) is fed with the current for only a part of a one-frame period. As a result, the El device (15) emits light for only the part of the period.

Owner:JOLED INC

Pixel current driver for organic light emitting diode displays

InactiveUS20060027807A1Improve circuit performanceMinimize chargeTransistorStatic indicating devicesBottom gateDisplay device

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

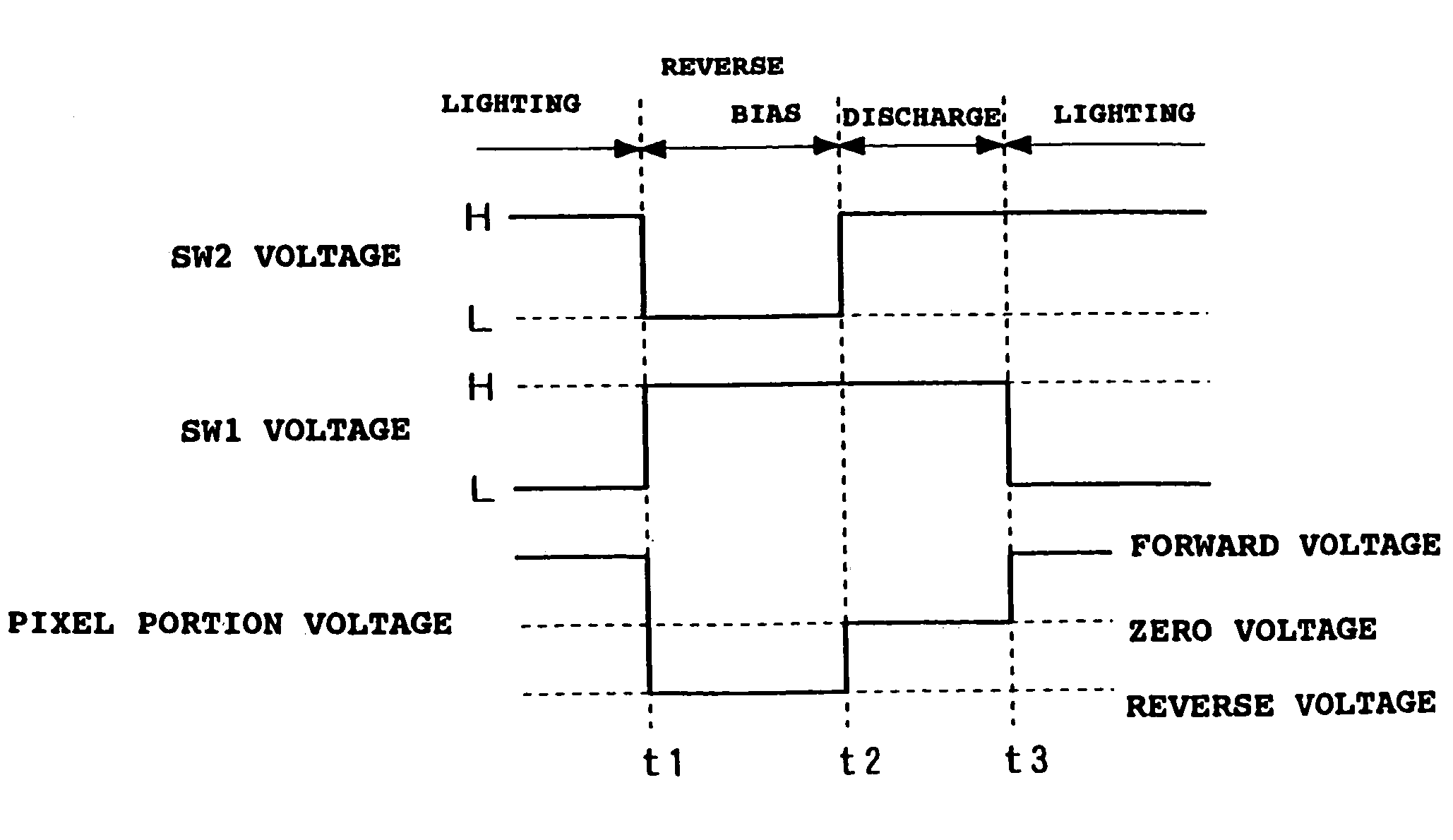

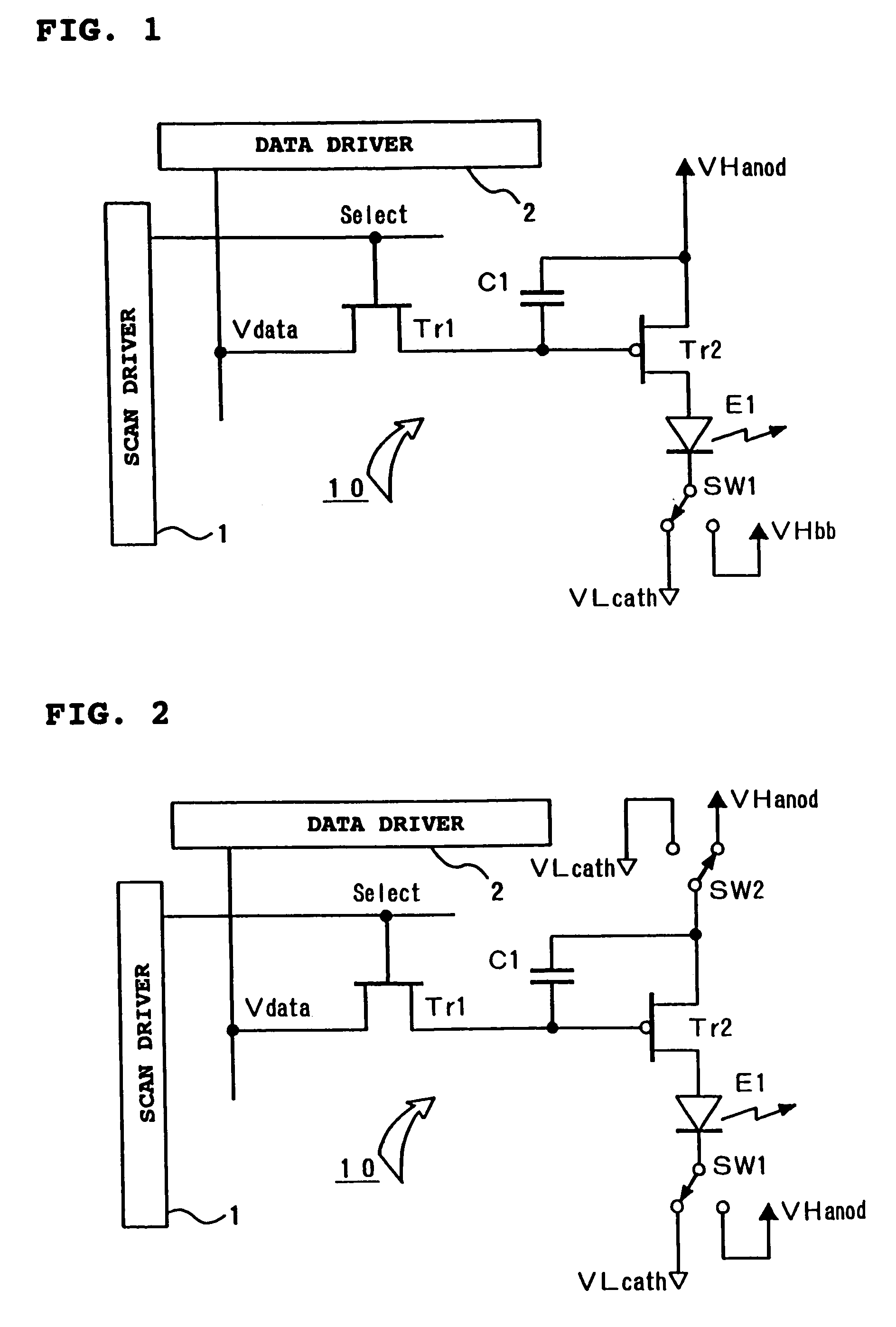

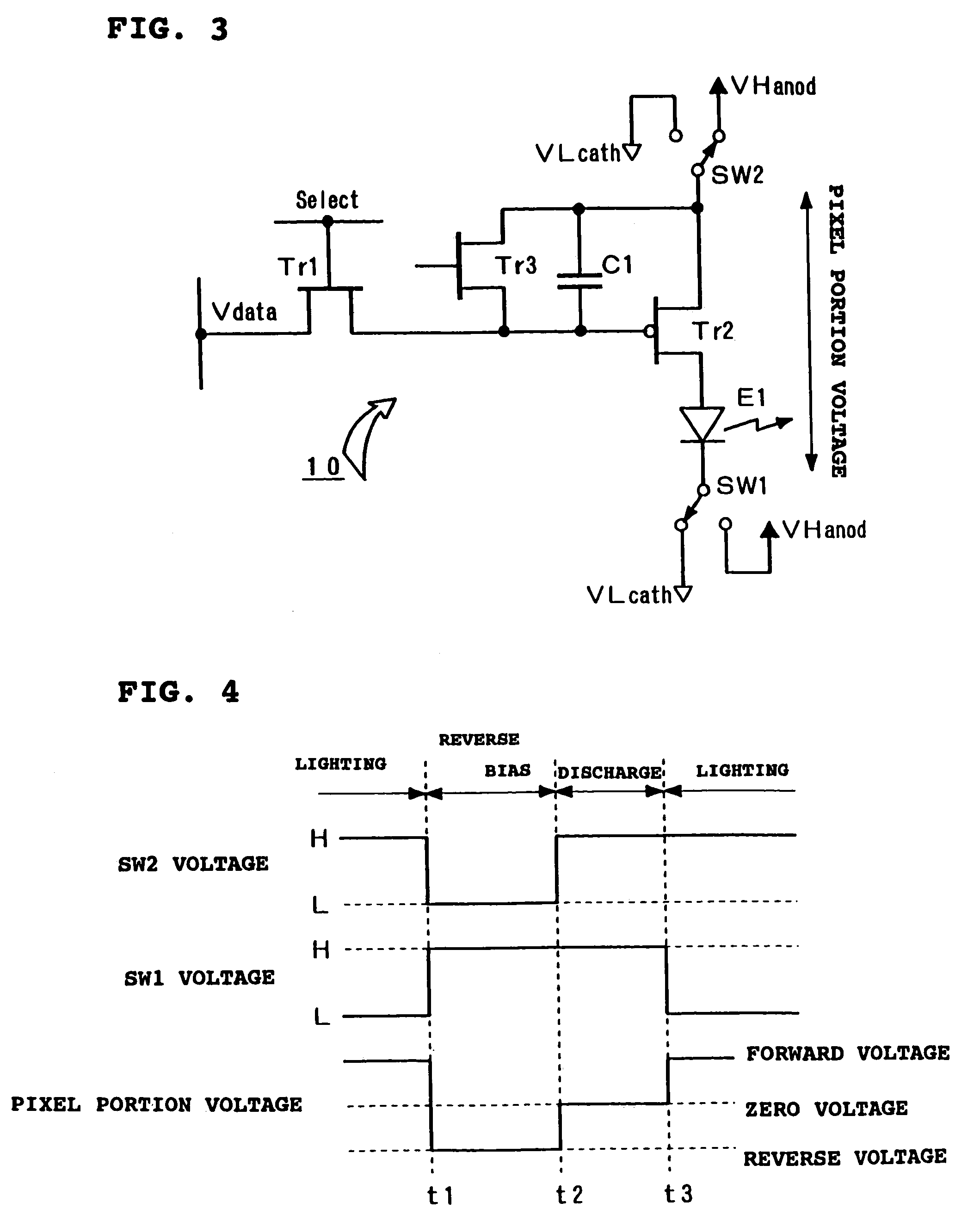

Drive methods and drive devices for active type light emitting display panel

InactiveUS7193589B2Static indicating devicesElectroluminescent light sourcesEffect lightParasitic capacitance

In a drive device for an active type light emitting display panel which can apply a reverse bias voltage to an EL element, in order to be able to compensate deterioration in light-emitting efficiency of the EL element accompanied by applying of the reverse bias voltage and the like, one pixel 10 is composed of a controlling TFT (Tr1), the driving TFT (Tr2), a capacitor C1, and the EL element E1. Switching switches SW1, SW2 mutually enables a supplying state of a forward current to the EL element E1 and an applying state of the reverse bias voltage to be selected. In one control form according to the present invention, when the applying state of the reverse bias voltage shifts to the supplying state of the forward current, by switching one switch first, the anode and cathode of the EL element E1 are made to the same electrical potential to allow electrical charges to be discharged. Thus, charge of the forward current for a parasitic capacitance of the EL element E1 can be performed rapidly, and rising of the lighting operation of the EL element can be advanced.

Owner:TOHOKU PIONEER CORP

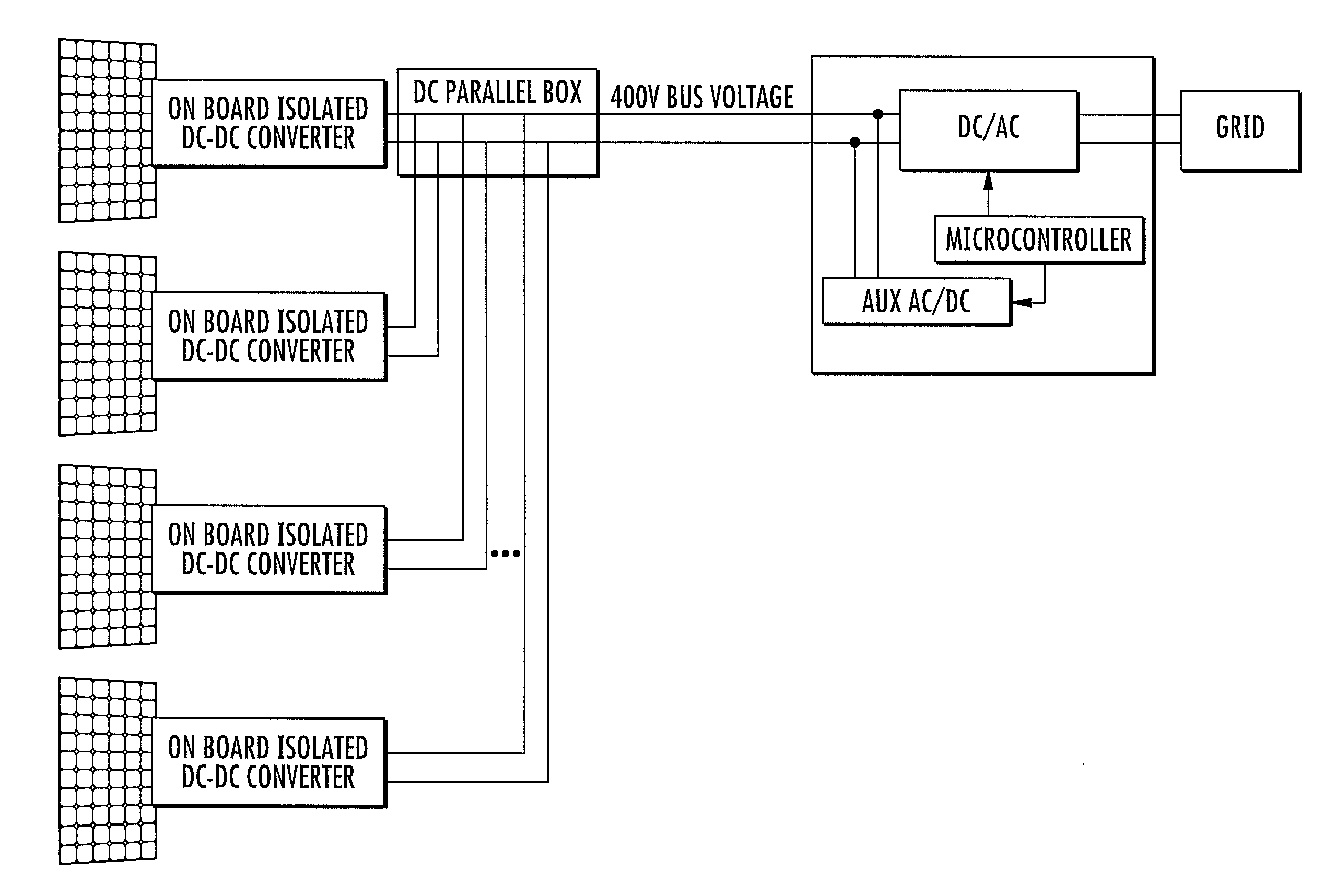

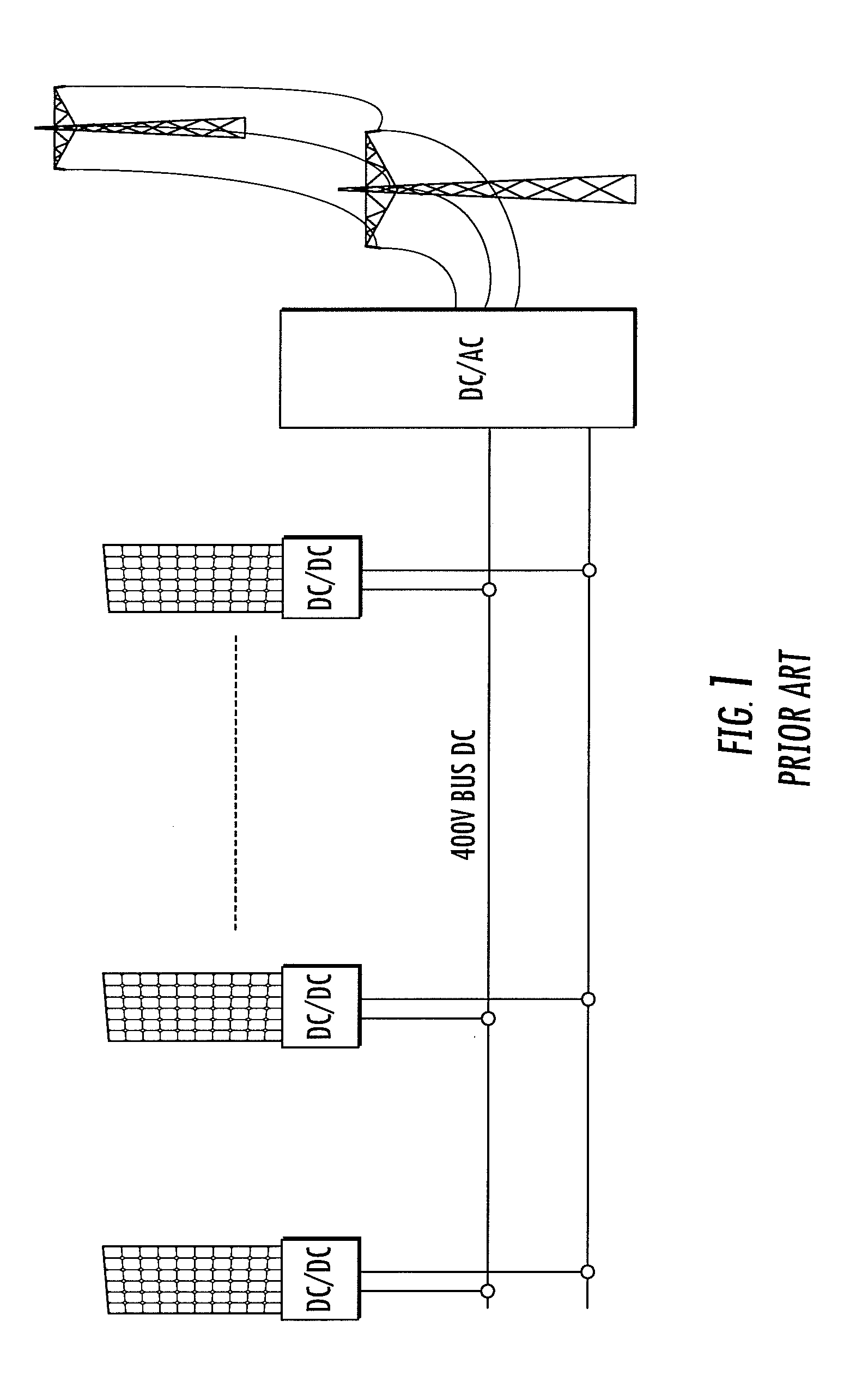

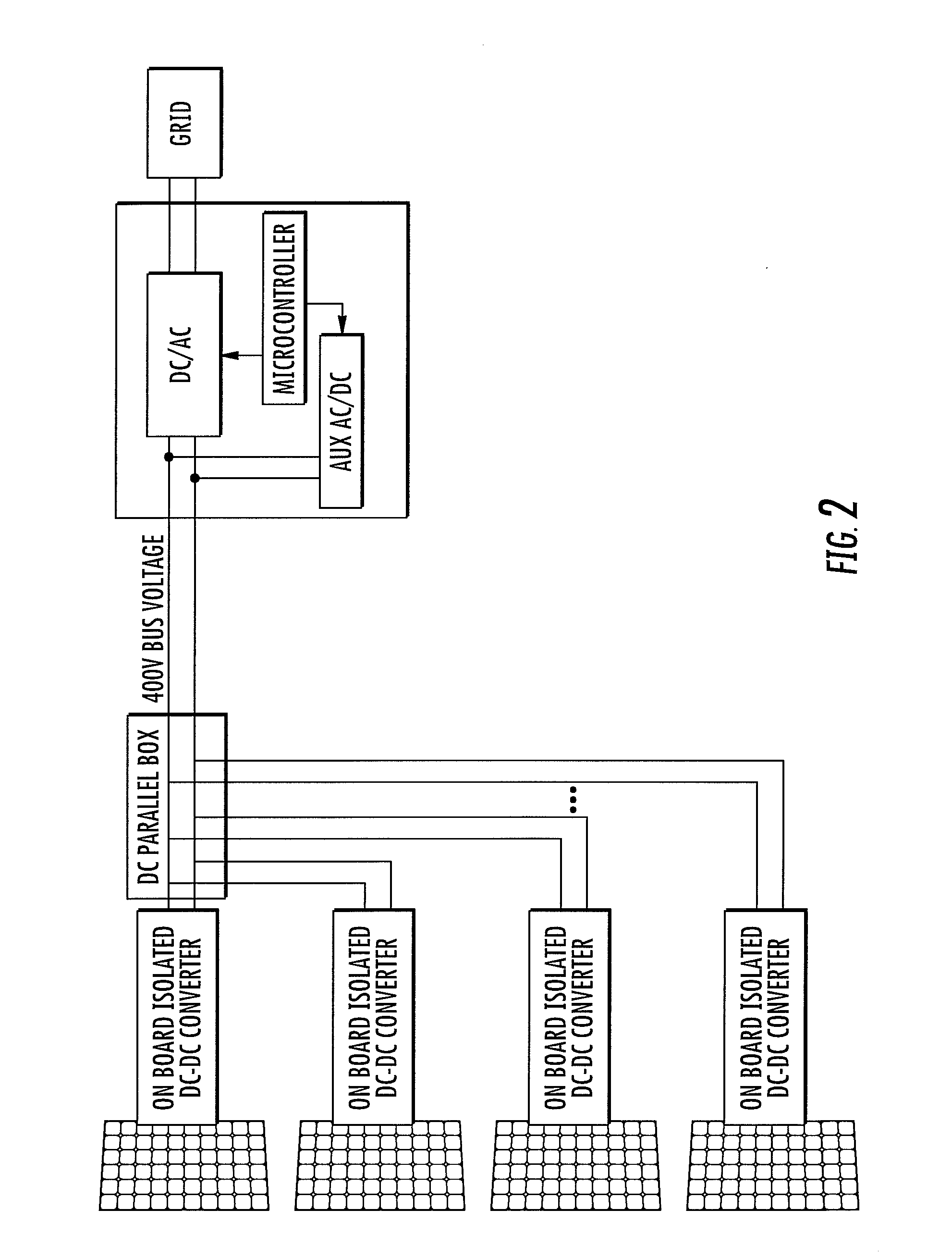

Automatic system for synchronous enablement-disablement of solar photovoltaic panels of an energy production plant with distributed dc/dc conversion

ActiveUS20120091810A1Low costEliminate riskDc network circuit arrangementsBatteries circuit arrangementsParasitic capacitanceDC-BUS

A solar energy plant may include a DC bus, photovoltaic panels coupled in parallel to the DC bus, each photovoltaic panel having a DC / DC converter, and a first controller controlling the DC / DC converter depending on whether a voltage on the DC bus is equal to or greater than a first threshold and lower than or equal to a second threshold. The solar energy plant may include a DC / AC inverter coupled to the DC bus and outputting an output AC voltage, an auxiliary start-up power supply charging a parasitic capacitance on the DC bus up to the first threshold, and a second controller turning on the auxiliary start-up power supply based upon a start command, and turning off the auxiliary start-up power supply and simultaneously turning on the DC / AC inverter.

Owner:STMICROELECTRONICS SRL

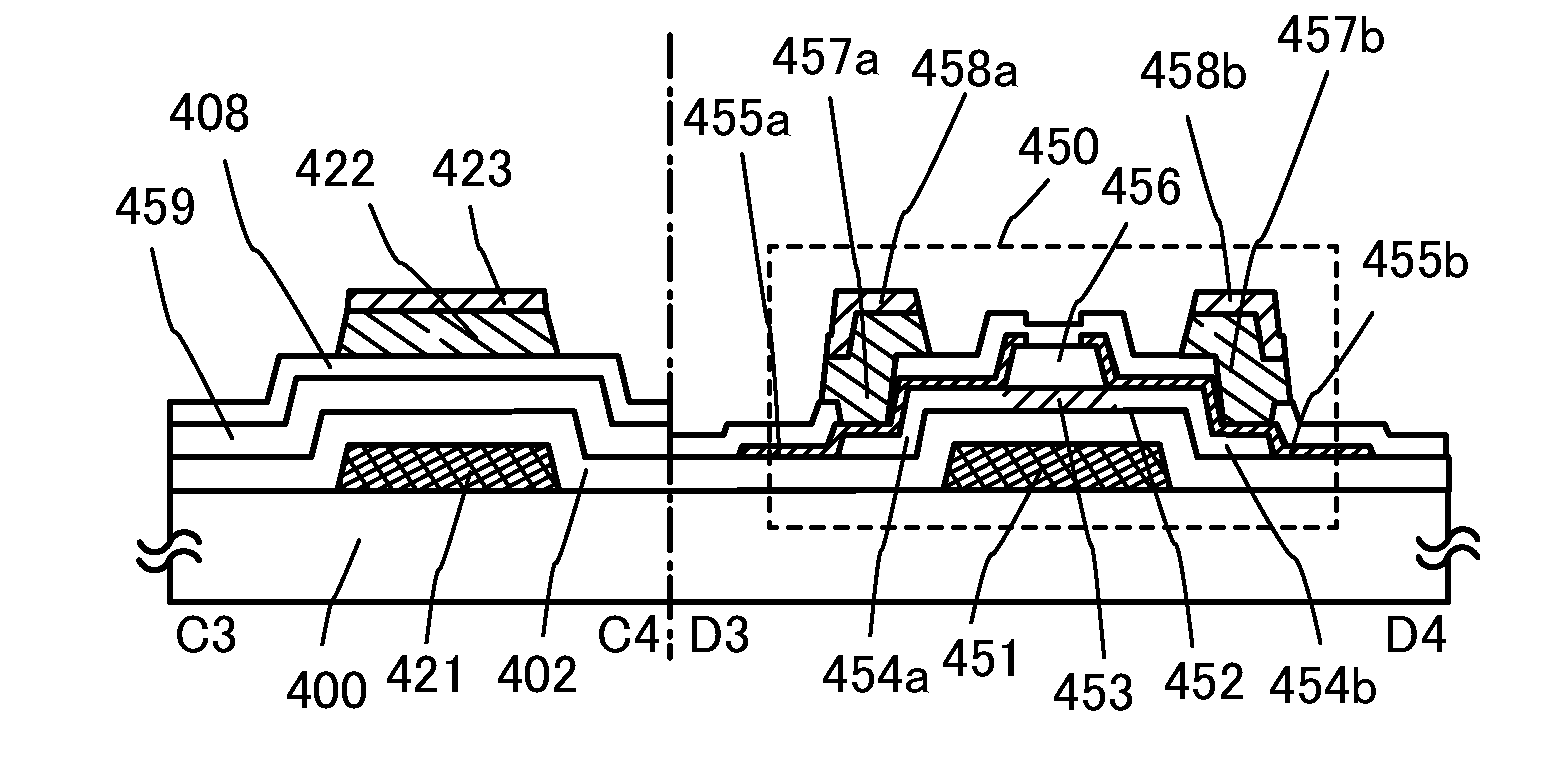

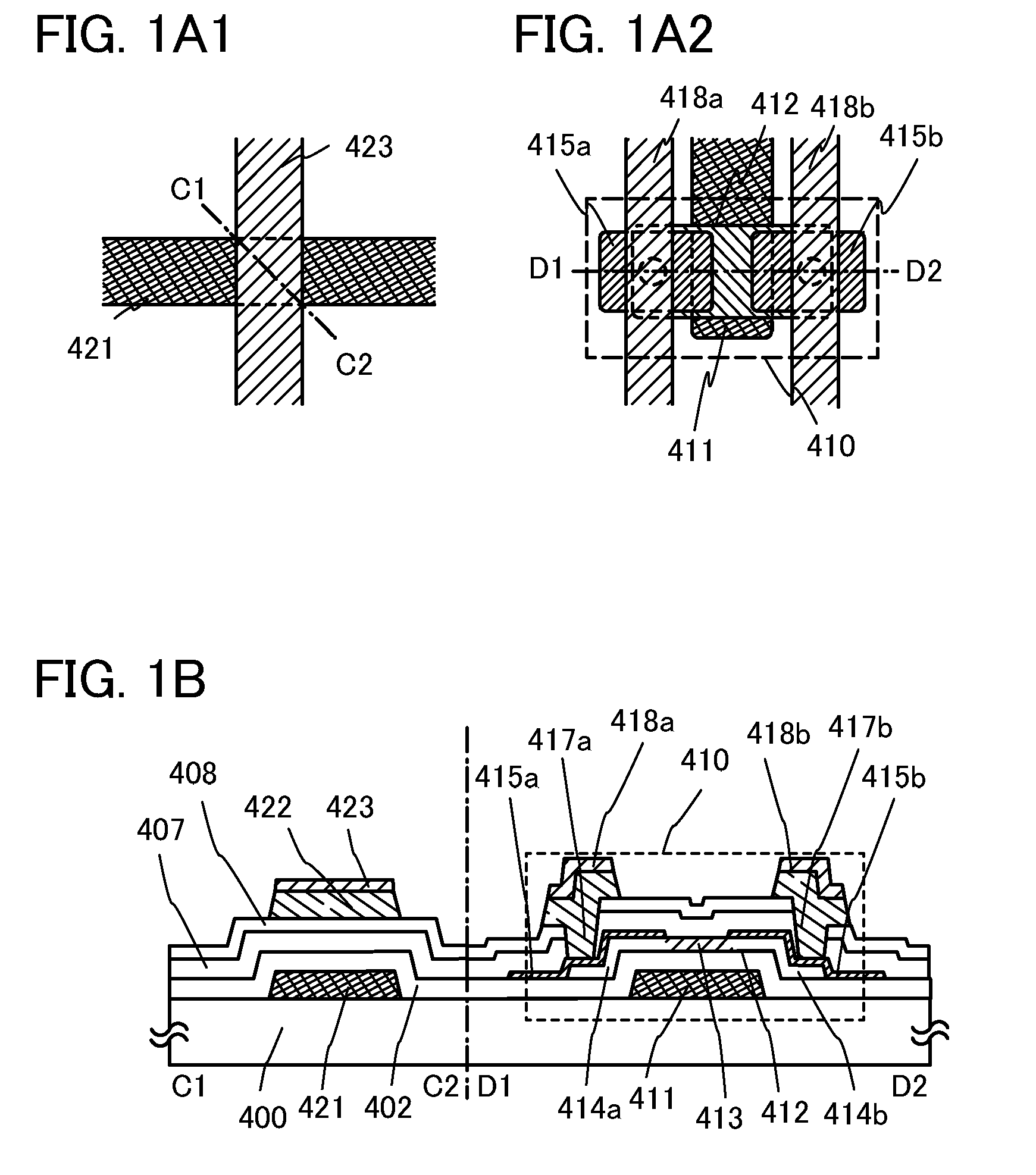

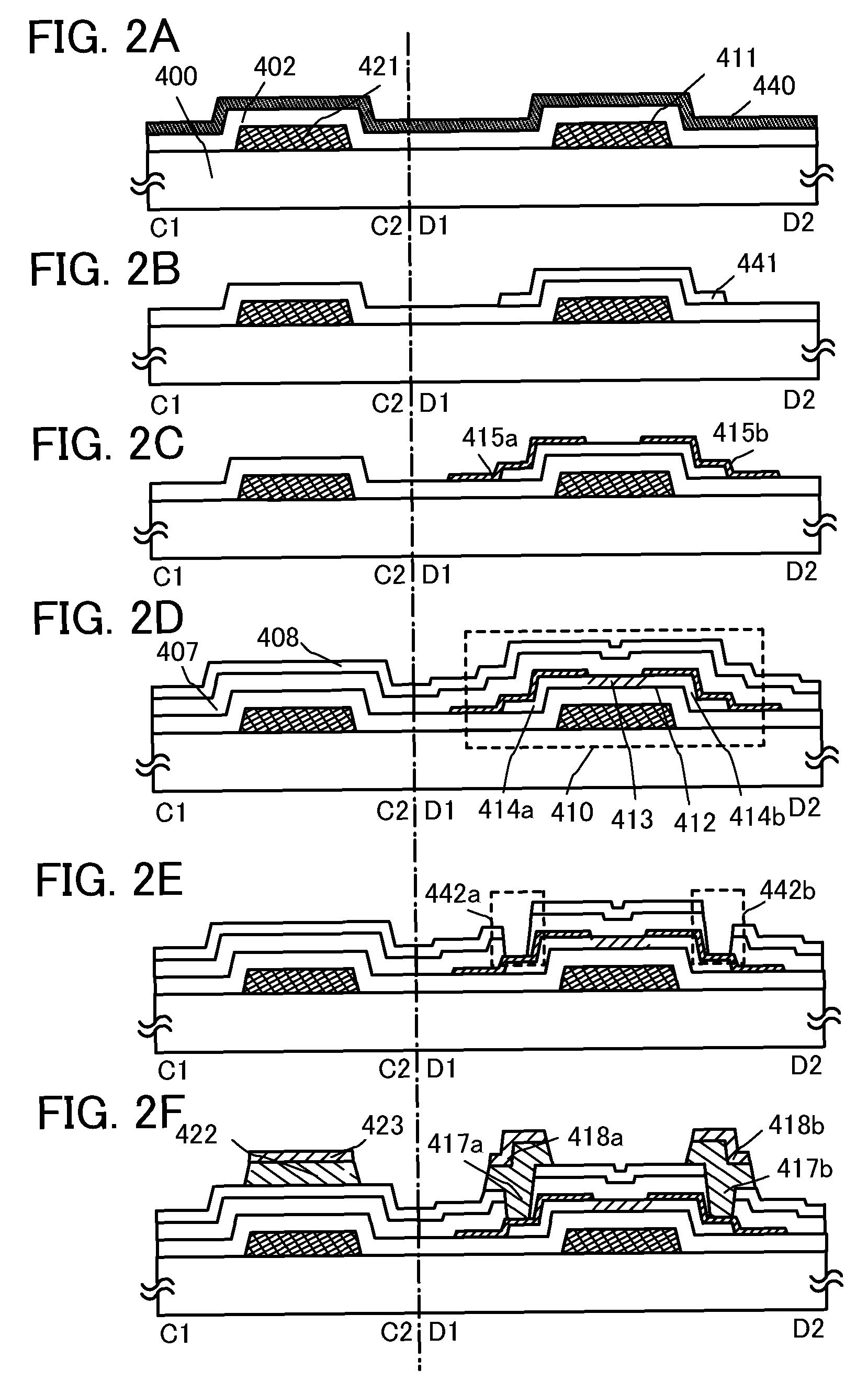

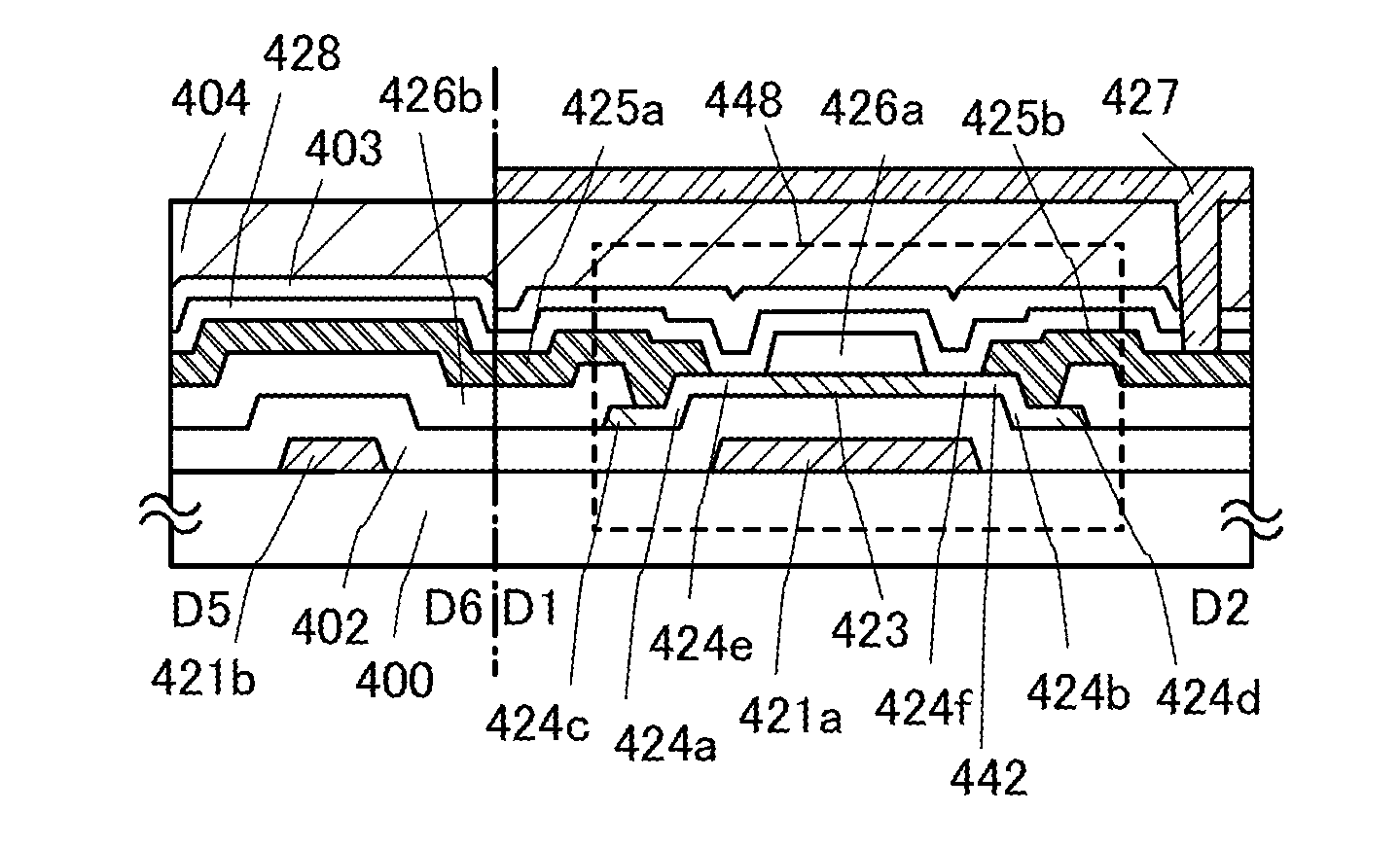

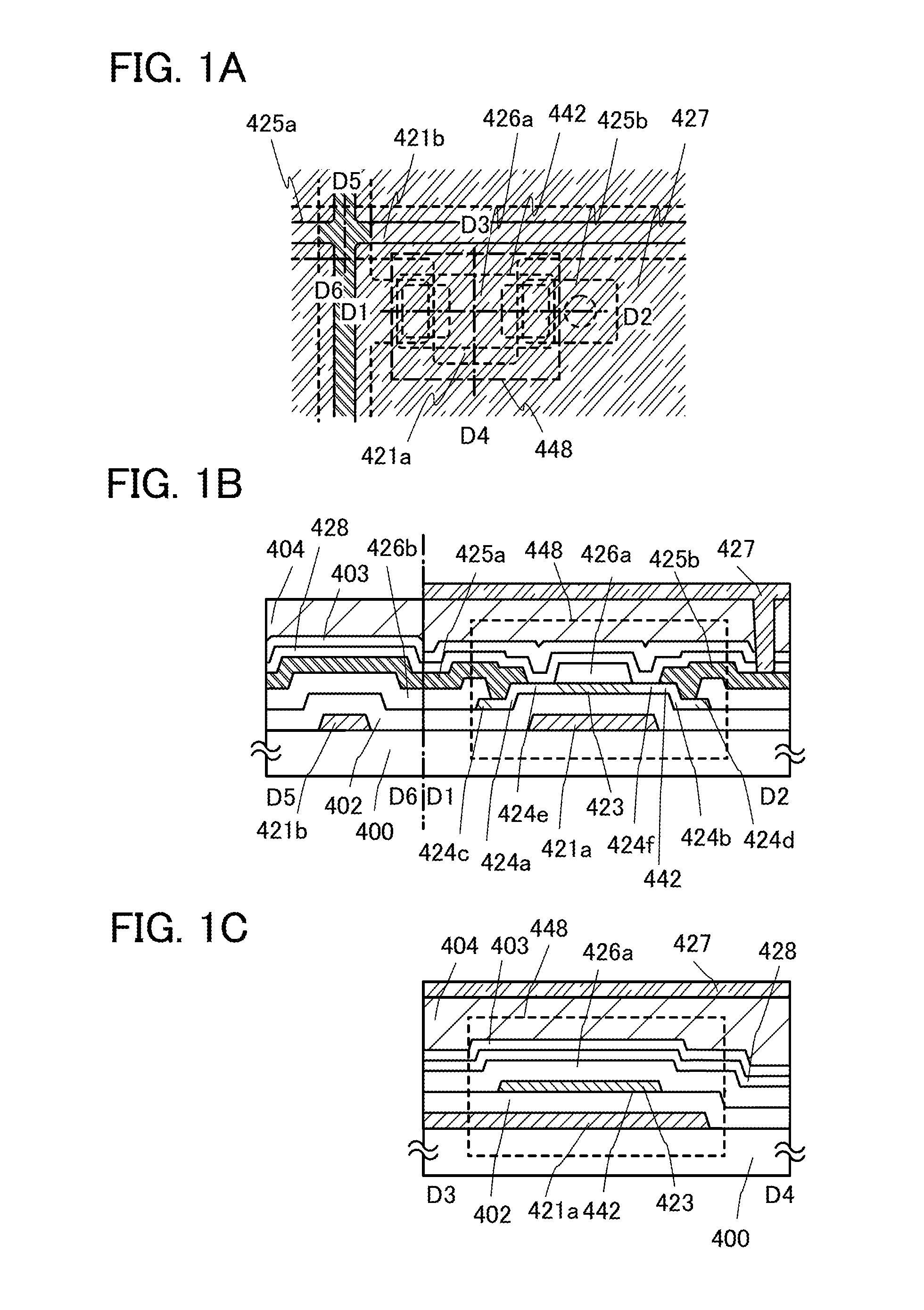

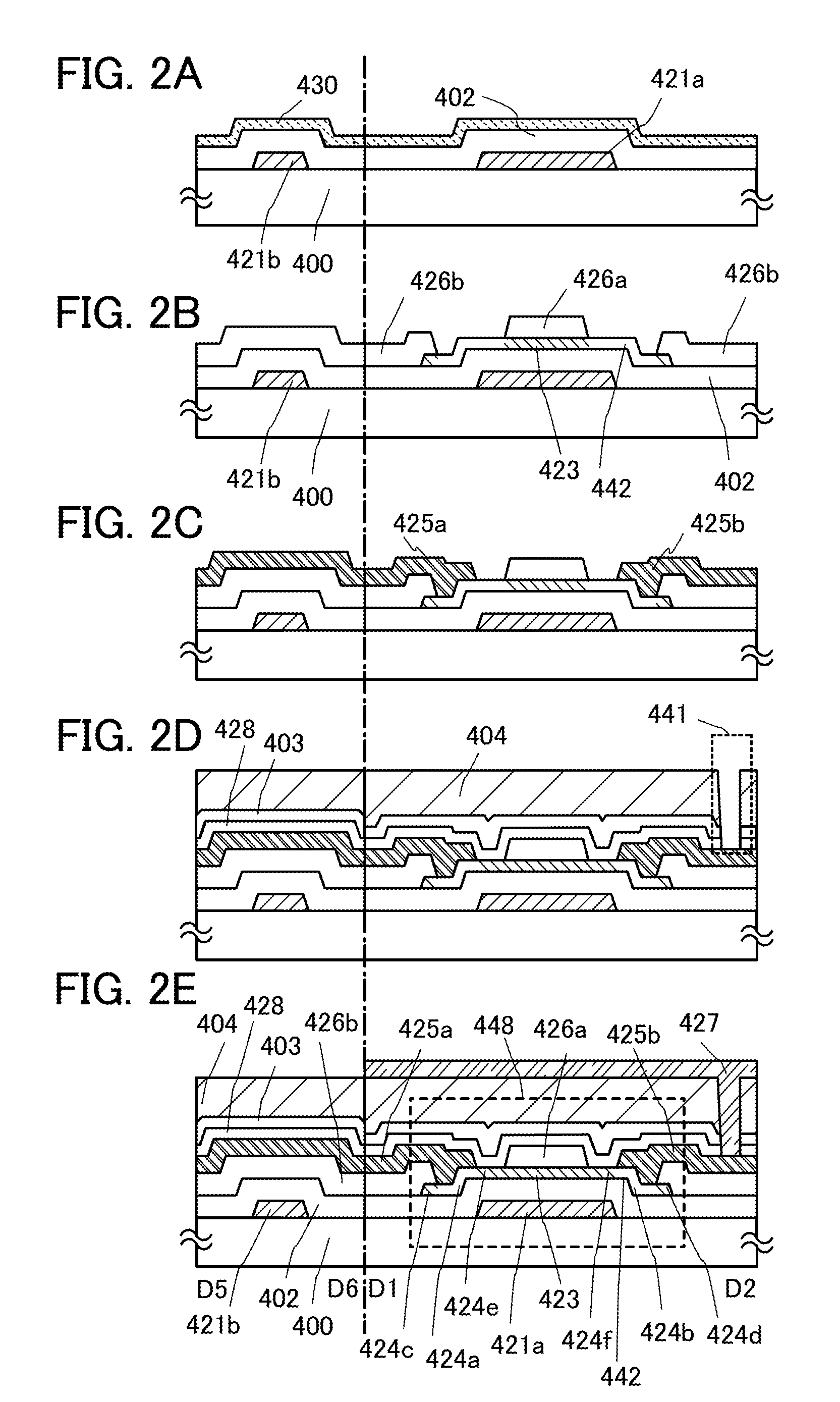

Semiconductor device and manufacturing method thereof

InactiveUS20110062433A1Less parasitic capacitanceReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingParasitic capacitanceSemiconductor

It is an object to provide a semiconductor device with less power consumption as a semiconductor device including a thin film transistor using an oxide semiconductor layer. It is an object to provide a semiconductor device with high reliability as a semiconductor device including a thin film transistor using an oxide semiconductor layer. In the semiconductor device, a gate electrode layer (a gate wiring layer) intersects with a wiring layer which is electrically connected to a source electrode layer or a drain electrode layer with an insulating layer which covers the oxide semiconductor layer of the thin film transistor and a gate insulating layer interposed therebetween. Accordingly, the parasitic capacitance formed by a stacked-layer structure of the gate electrode layer, the gate insulating layer, and the source or drain electrode layer can be reduced, so that low power consumption of the semiconductor device can be realized.

Owner:SEMICON ENERGY LAB CO LTD

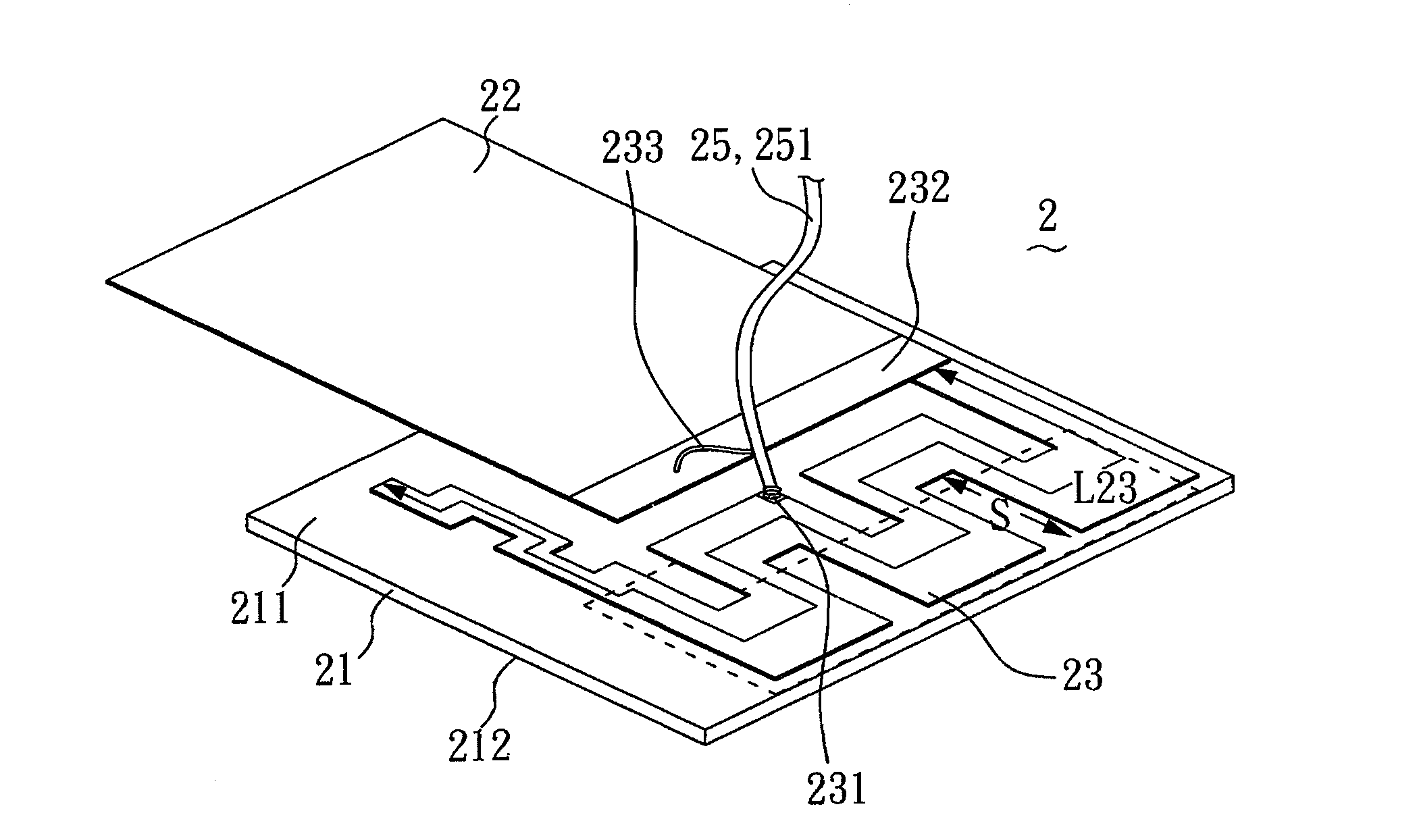

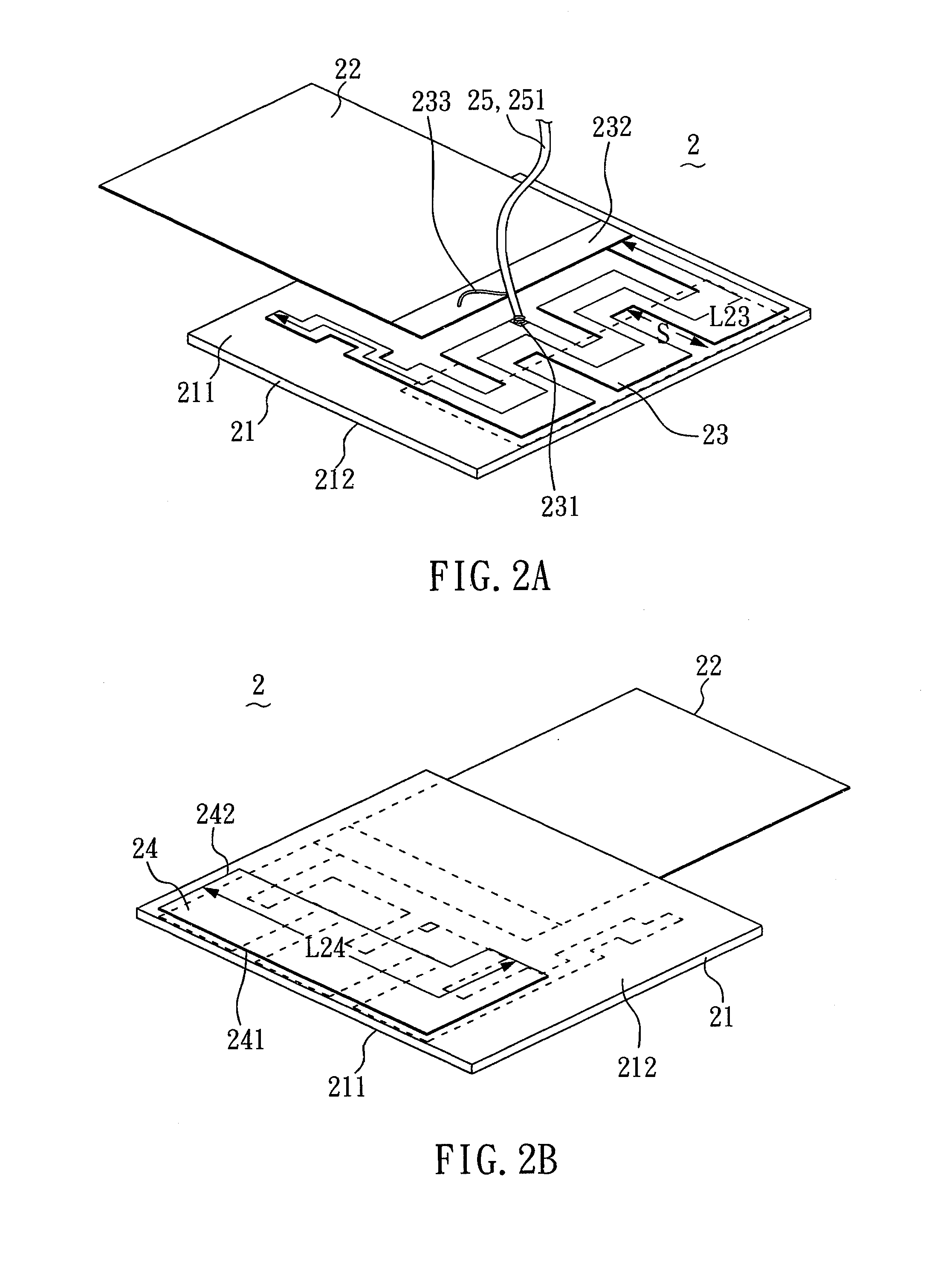

Three-band antenna device with resonance generation and portable electronic device having the same

InactiveUS20110199265A1Increasing antenna sizeIncrease in sizeSimultaneous aerial operationsRadiating elements structural formsResonanceParasitic capacitance

A three-band antenna device with resonance generation includes a dielectric layer having an upper surface and a lower surface, a grounding element, a first radiating element, and a second radiating element. The first radiating element is arranged on the upper surface for providing a first frequency band. The second radiating element is arranged on the lower surface and stacked below the first radiating element via the dielectric layer for providing a second frequency band, so as to generate a parasitic capacitance therebetween. A third frequency band is provided by the resonance of the parasitic capacitance and the parasitic inductance in the second radiating element.

Owner:FIRST INTERNATIONAL COMPUTER

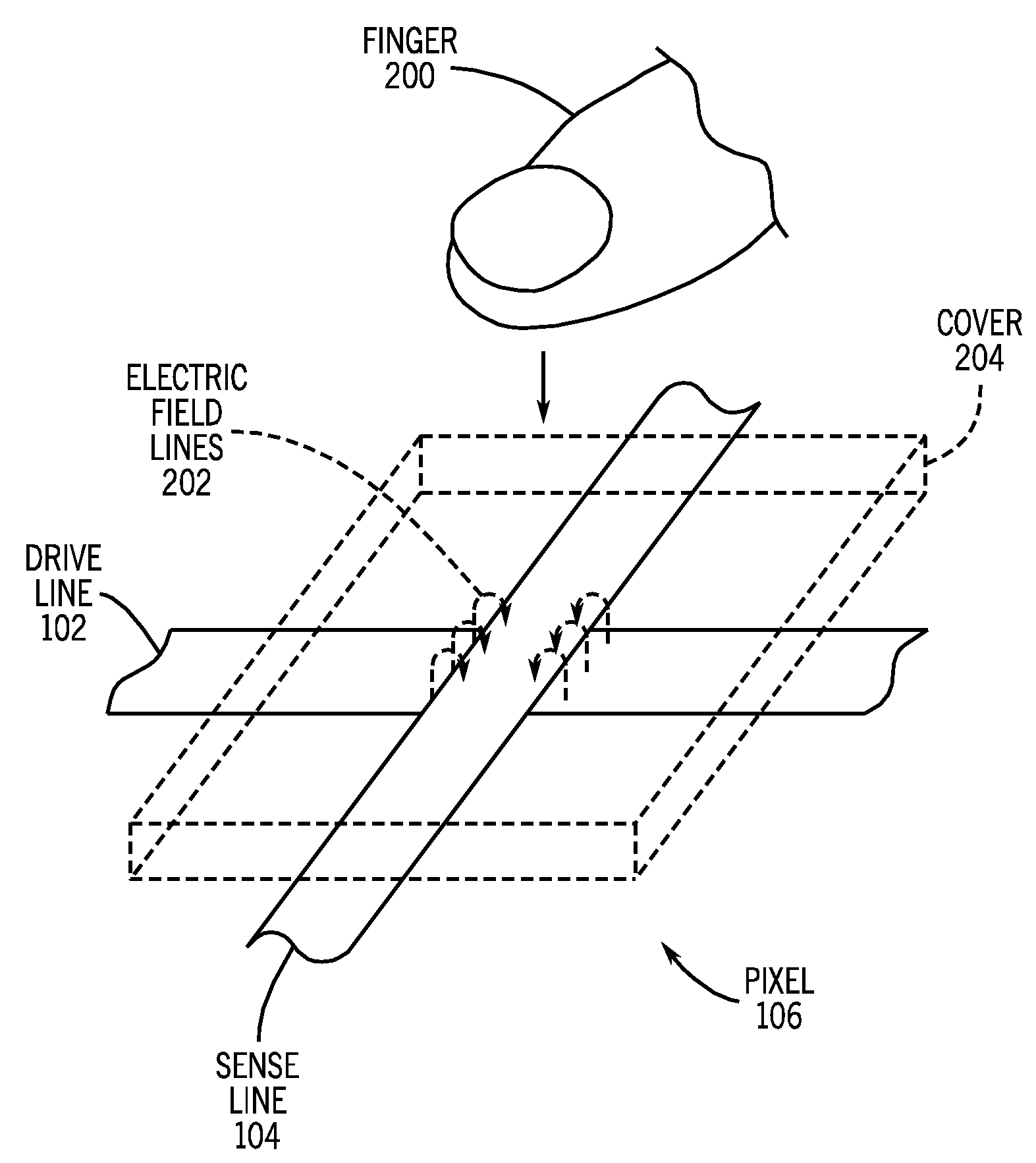

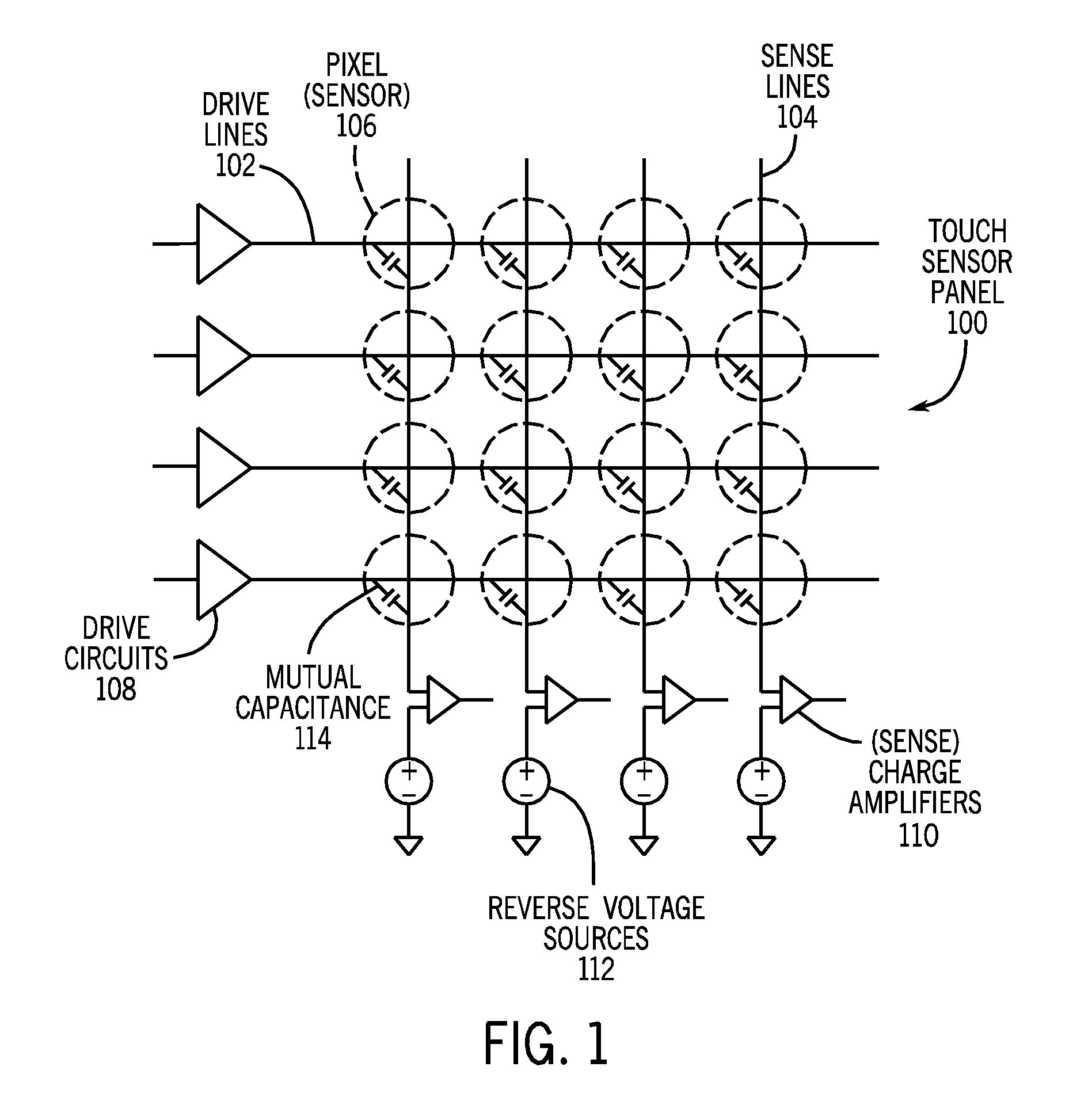

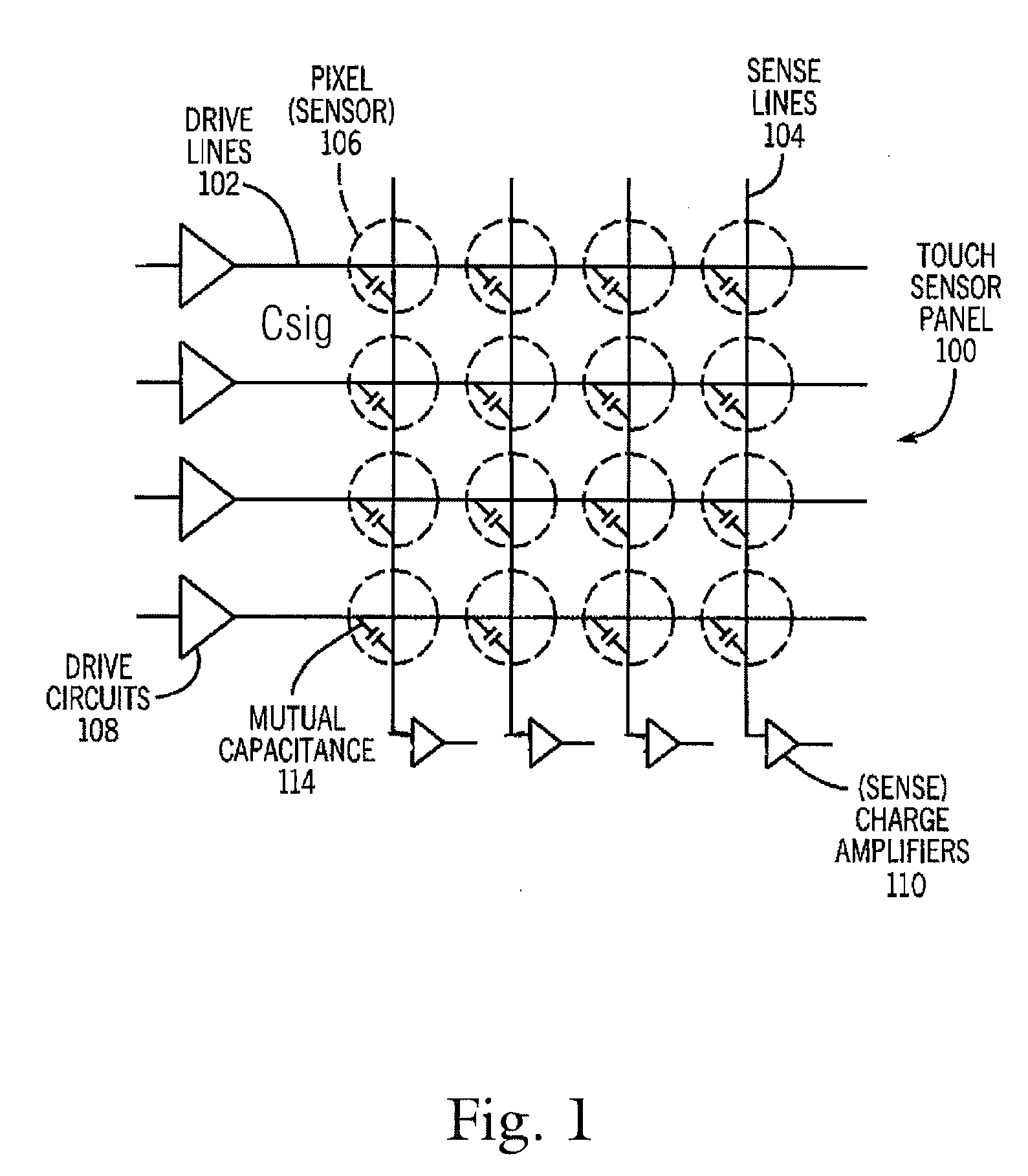

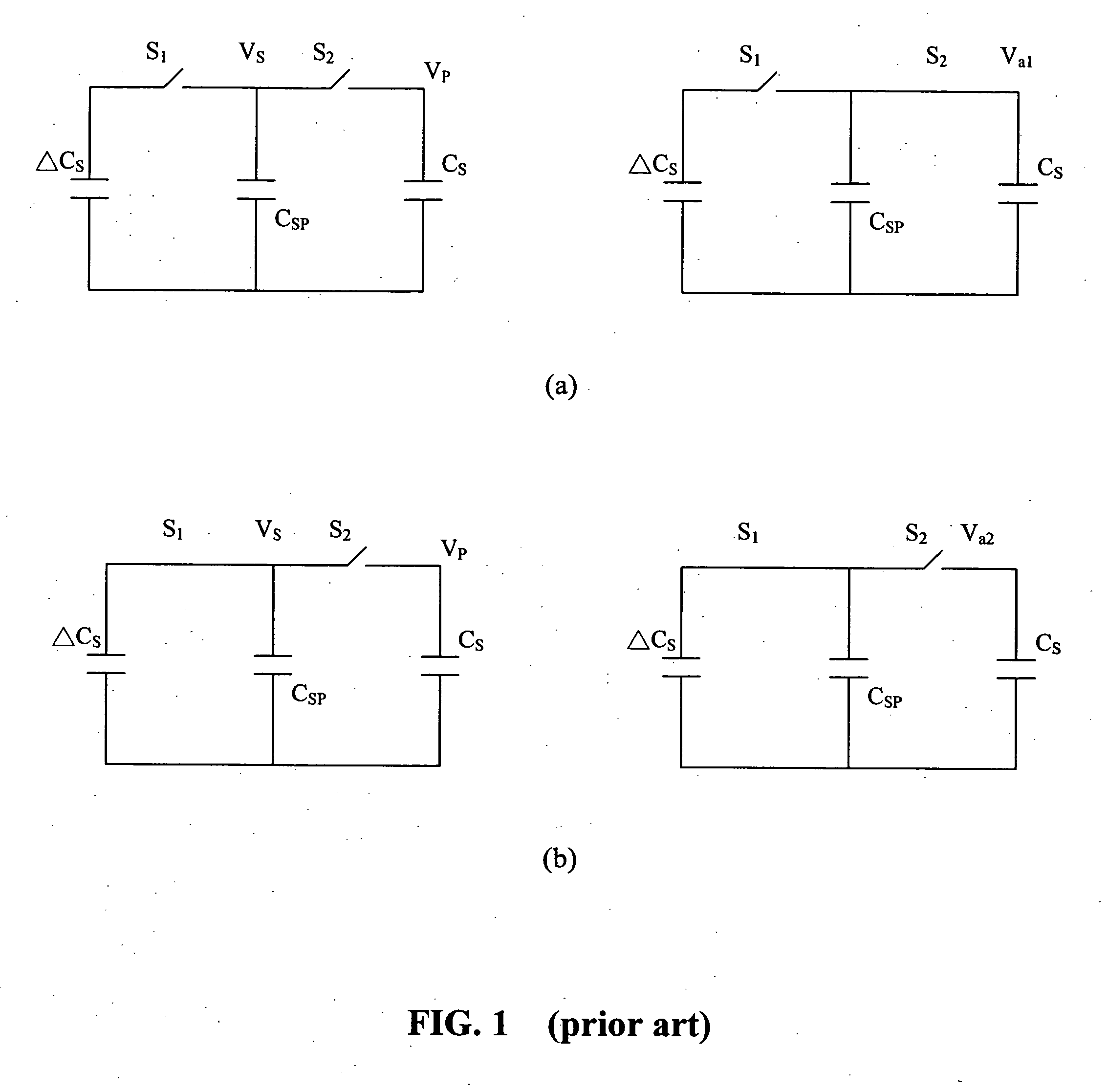

Correction of parasitic capacitance effect in touch sensor panels

ActiveUS20100060608A1Easy to calculateImprove accuracySubstation equipmentTransmissionParasitic capacitanceEngineering

Compensation of pixels included in a touch sensor panel that generate erroneous readings (so called “negative pixels”) due to a poor grounding condition of the object touching the touch sensor panel is disclosed herein. To compensate for the erroneous readings, sense lines of the touch sensor panel can include reverse driving circuits to facilitate calculation of an object-to-ground capacitance. If the calculated object-to-ground capacitance indicates the presence of a poor grounding condition, then the object-to-ground capacitance and detected pixel touch output values are used to estimate new pixel touch output values that are used instead of the detected pixel touch output values to determine touch event(s).

Owner:APPLE INC

Semiconductor device and manufacturing method thereof

ActiveUS20110031491A1Reduce parasitic capacitanceOff-current can be reducedTransistorStatic indicating devicesBottom gateParasitic capacitance

An object is to provide a semiconductor device having a structure in which parasitic capacitance between wirings can be efficiently reduced. In a bottom gate thin film transistor using an oxide semiconductor layer, an oxide insulating layer used as a channel protection layer is formed above and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer, and at the same time an oxide insulating layer covering a peripheral portion (including a side surface) of the stacked oxide semiconductor layer is formed. Further, a source electrode layer and a drain electrode layer are formed in a manner such that they do not overlap with the channel protection layer. Thus, a structure in which an insulating layer over the source electrode layer and the drain electrode layer is in contact with the oxide semiconductor layer is provided.

Owner:SEMICON ENERGY LAB CO LTD

HVAC communication system

InactiveUS7163158B2Electric signal transmission systemsFrequency-division multiplex detailsTransceiverElectrical battery

Owner:ITRON +1

Power semiconductor devices and methods of manufacture

ActiveUS20060214222A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

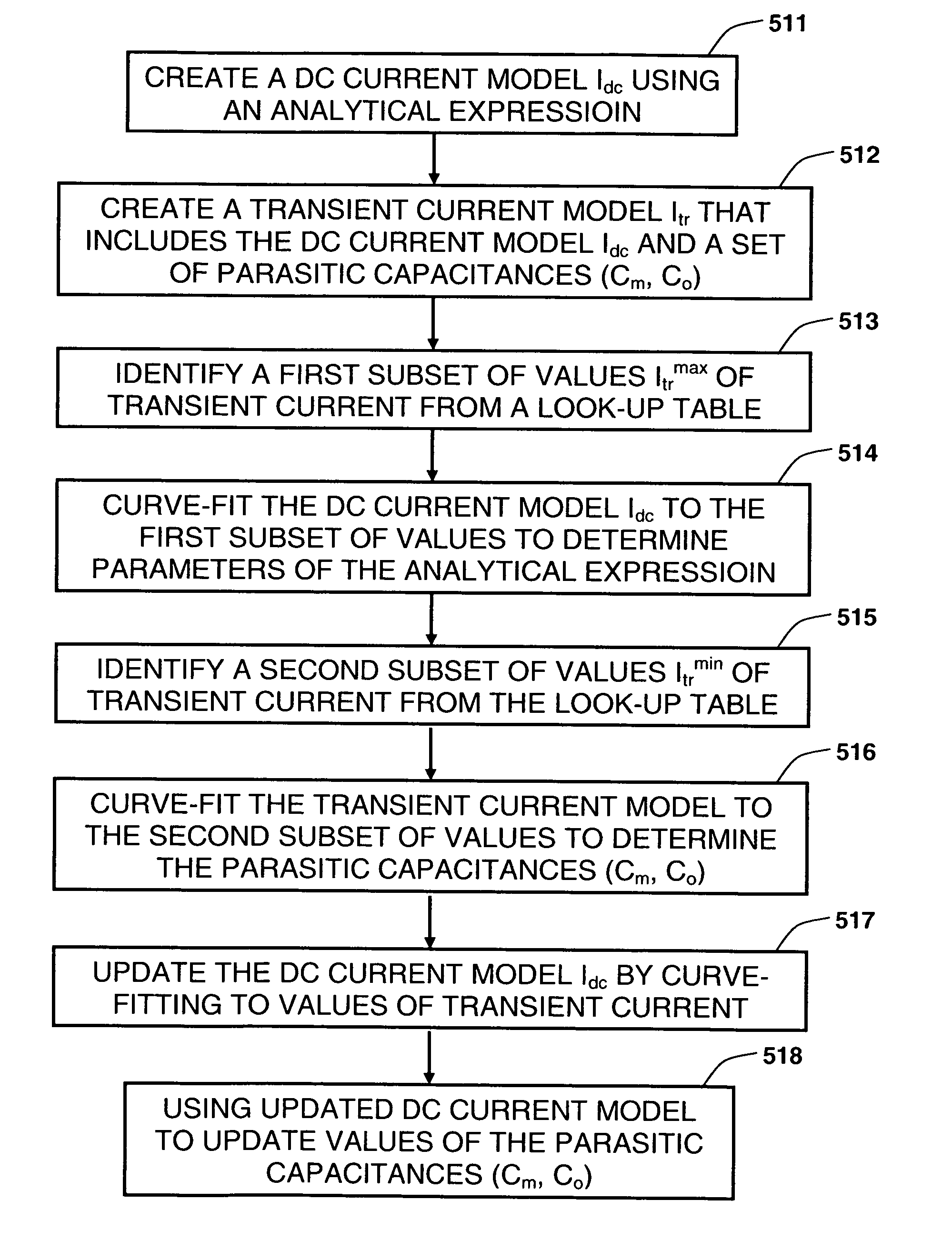

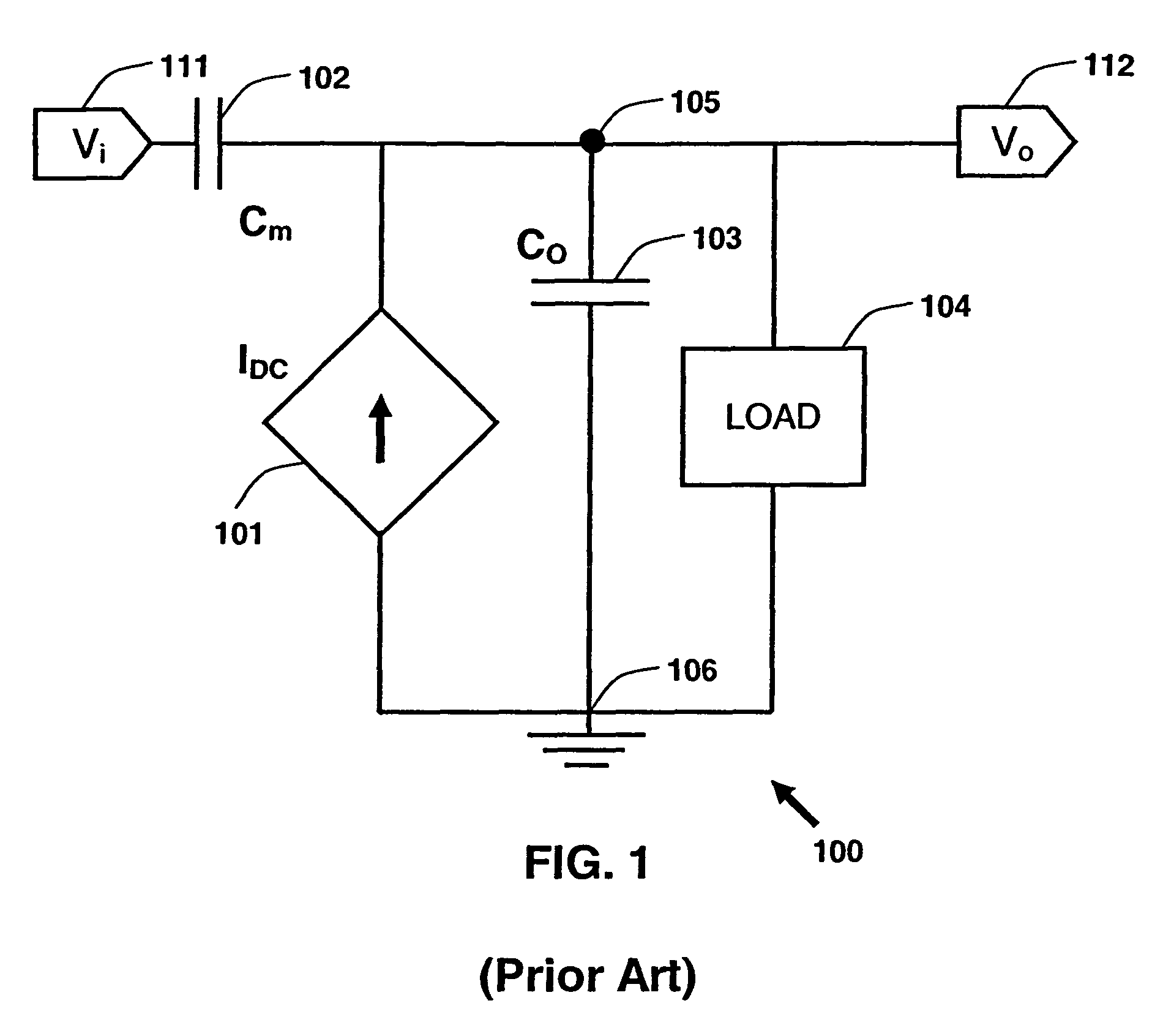

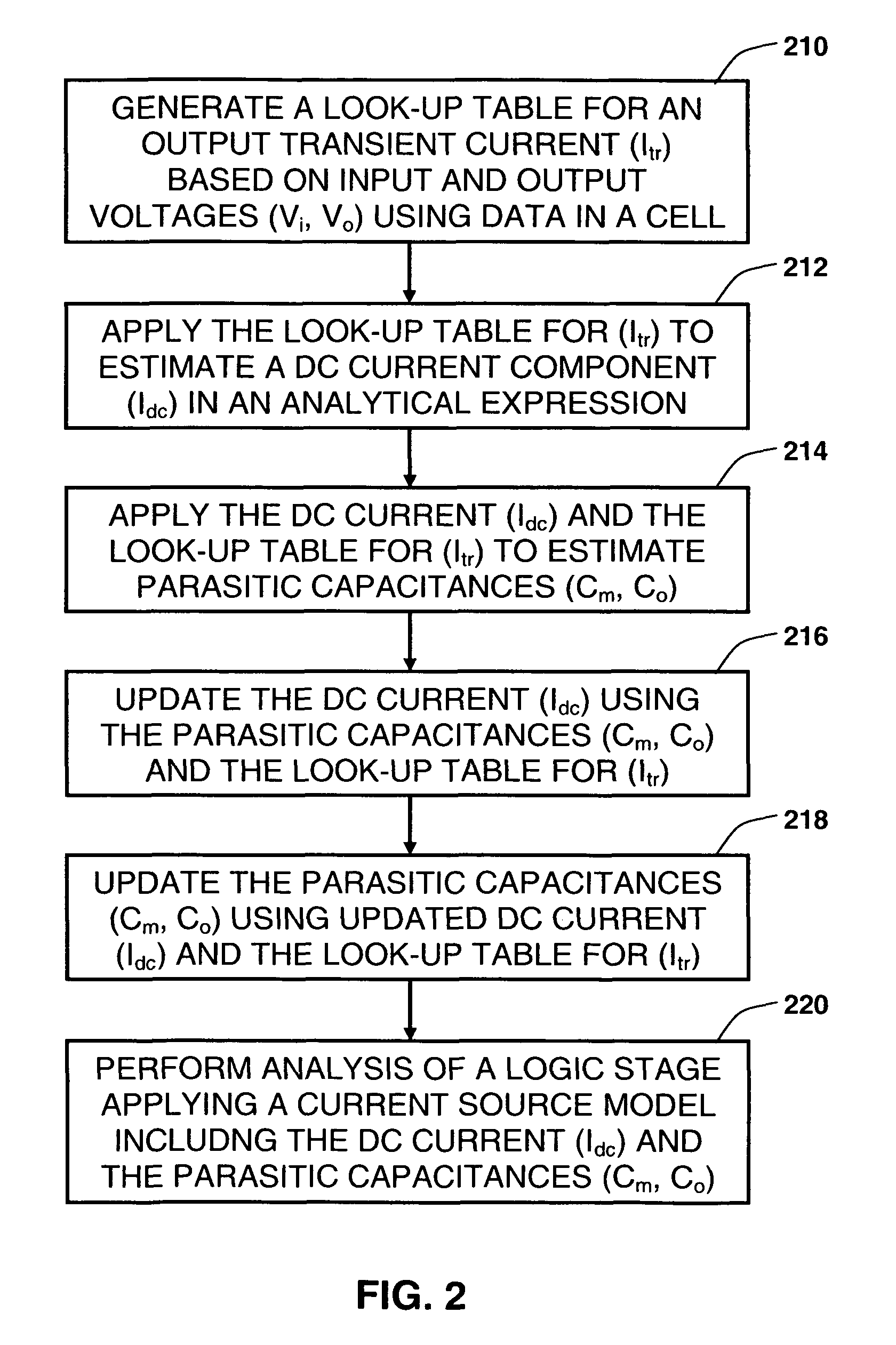

Synthesizing current source driver model for analysis of cell characteristics

InactiveUS7761275B2Analogue computers for electric apparatusCAD circuit designParasitic capacitanceEngineering

A method for performing an analysis of at least one logic stage in a netlist, which include one or more drivers, is provided. The method includes operations of generating at least one look-up table for an output transient current to be based on values of input and output voltages using data available from a cell library; synthesizing analytically at least one current source model, which includes a DC component and a plurality of parasitic capacitances, using the look-up table; simulating the logic stage using the current source model to model the drivers; and obtaining characteristics of the simulated logic stage. A system and a machine-readable medium for performing the method are also provided.

Owner:INT BUSINESS MASCH CORP

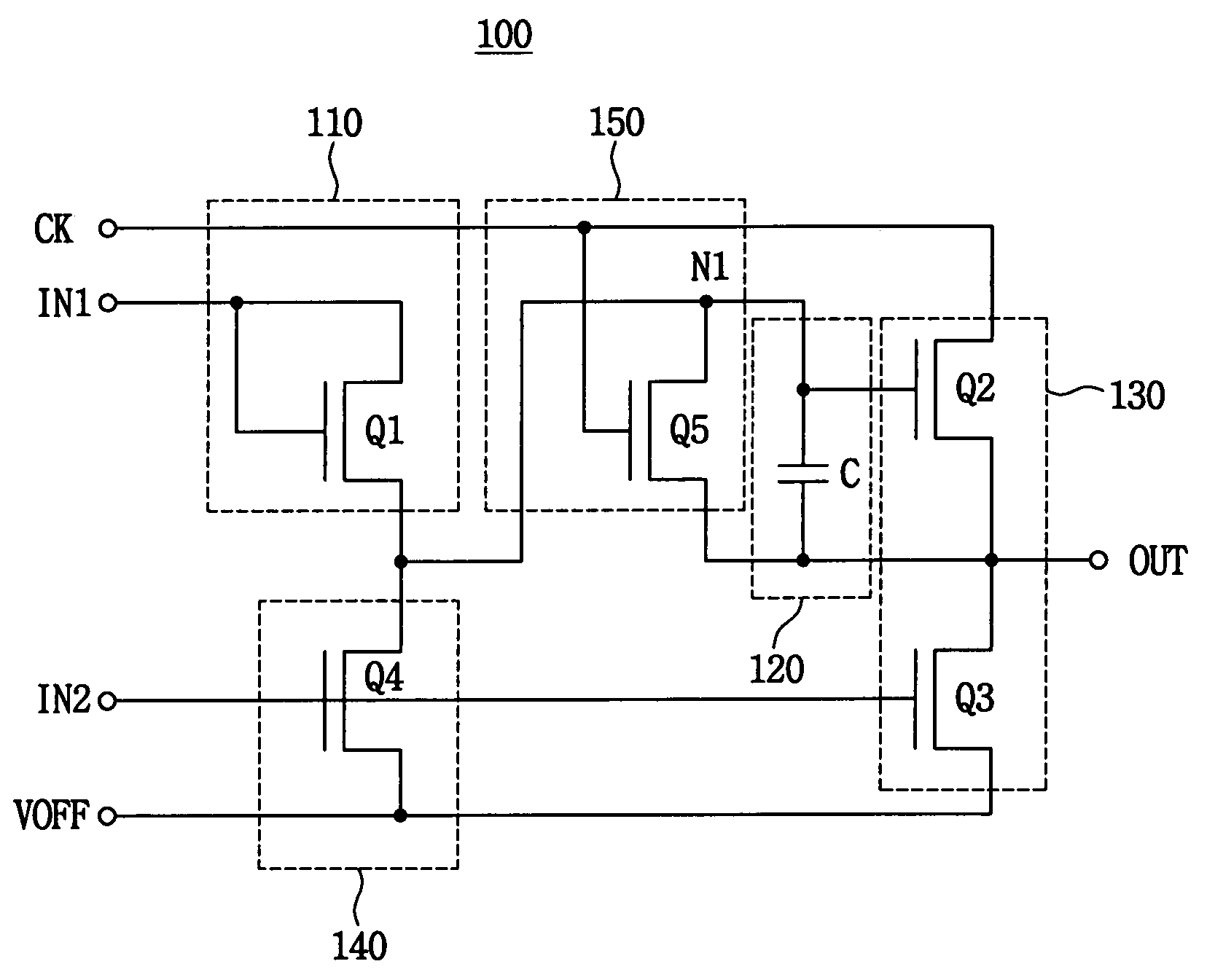

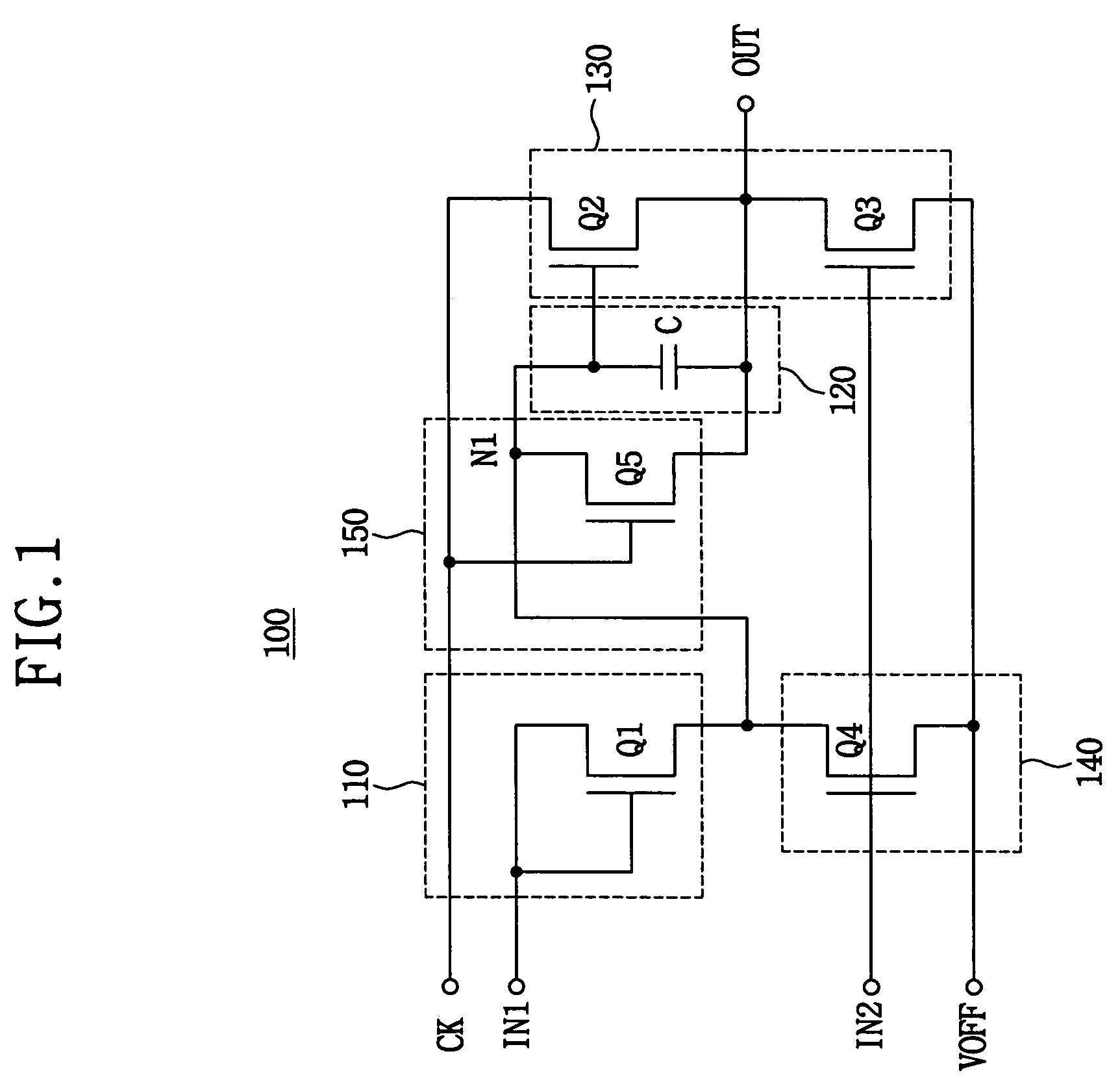

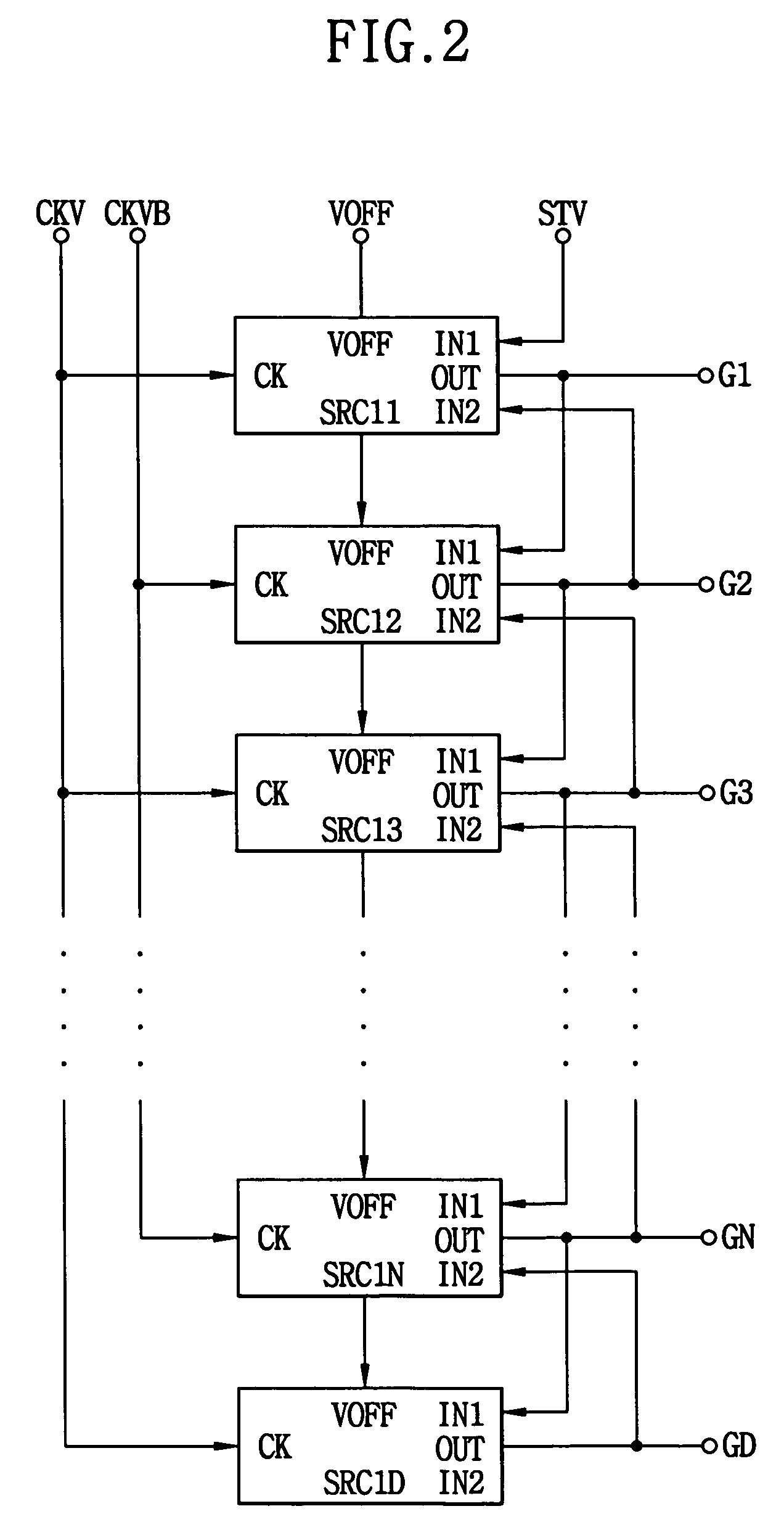

Shift register, scan driving circuit and display apparatus having the same

ActiveUS7486269B2Reduce parasitic capacitancePrevent floatingStatic indicating devicesDigital storageShift registerParasitic capacitance

A shift register includes a plurality of stages to generate a plurality of output signals, in sequence. Each of the stages includes a driving circuit, a charging circuit, a discharging circuit and a holding circuit. The driving circuit is configured to generate a first output signal in response to a first clock signal or a second clock signal having a phase different from the first clock signal. The charging circuit is configured to charge an electric charge in response to a scan start signal or a second output signal of an adjacent previous stage. The discharging circuit is configured to discharge the electric charge in response to a third output signal of an adjacent next stage. The holding circuit is configured to maintain the first output signal within a first voltage when the first output signal is in an inactive state. Therefore, a parasite capacitance is decreased to prevent a floating of a pull-up transistor.

Owner:SAMSUNG DISPLAY CO LTD

Correction of Parasitic Capacitance Effect in Touch Sensor Panels

ActiveUS20100073301A1Improve accuracyLow computing performanceInput/output processes for data processingParasitic capacitanceHuman–computer interaction

Embodiments of the invention relate to correction of erroneous touch data on a touch sensor panel. Erroneous touch data may occur when a user is touching locations on the touch sensor panel but fails to be in good contact with another part of the device including the touch sensor panel. These erroneous readings may be statistically compensated for. A capacitance value that combines various external capacitances that may cause erroneous results can be calculated. Then, if necessary, received touch data can be modified to take into account the external capacitance. Accordingly, improved accuracy is provided for determining touch event(s) on a touch sensor panel.

Owner:APPLE INC

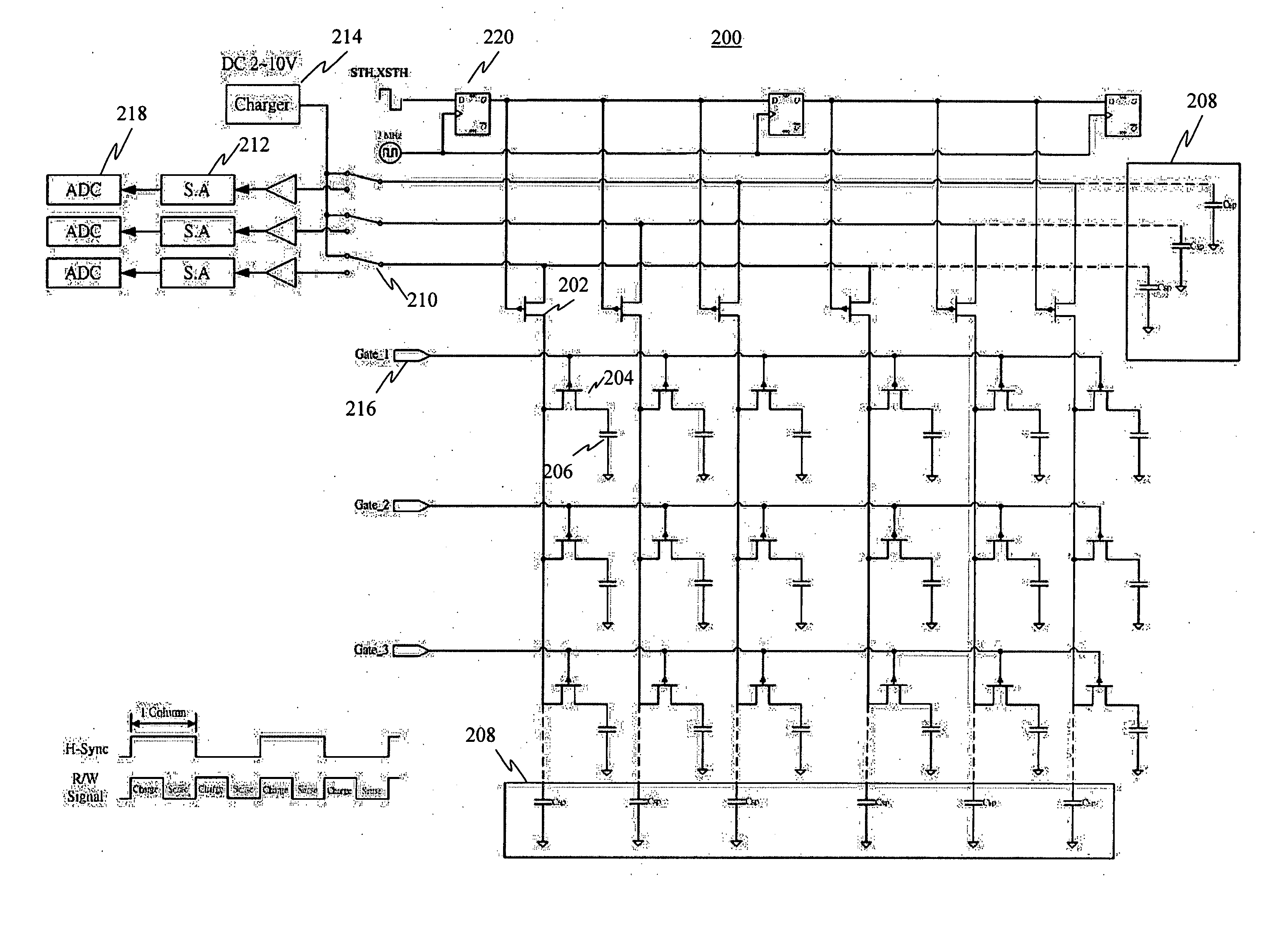

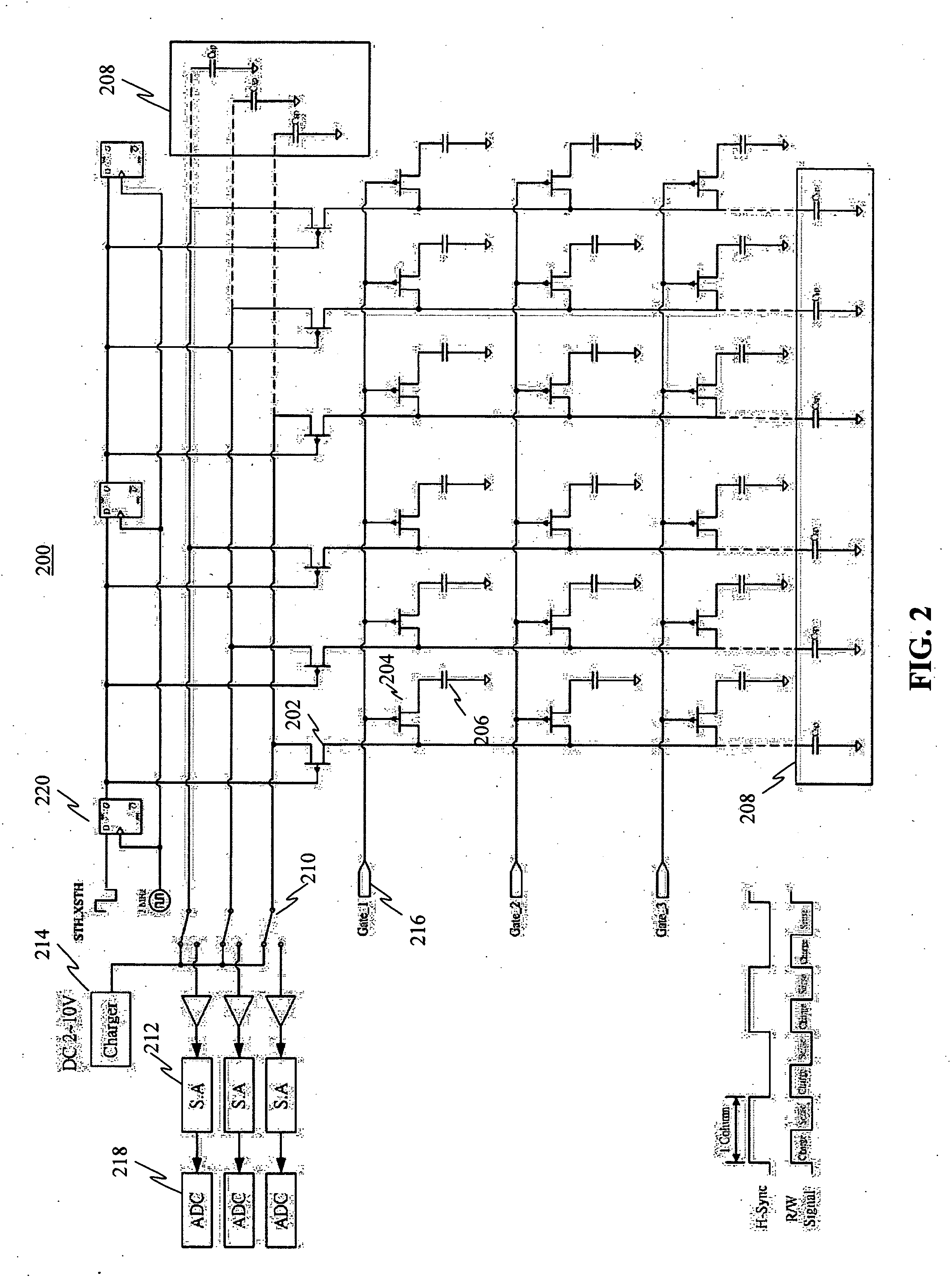

Testing apparatus and method for thin film transistor display array

InactiveUS20050024081A1Improve accuracyImprove reliabilityDigital circuit testingResistance/reactance/impedenceTransistor arrayHemt circuits

The present invention discloses a testing circuit and method for thin film transistor display array, for testing the yield of thin film transistor array. The testing circuit comprising: An array tester, a test panel (DUT), a sense amplifier array. The sense amplifier is composed by a plurality of trans- impedance amplifier unit and a plurality of parasitic capacitance discharge circuit unit. Every sense amplifier includes: a trans-impedance amplifier, which is implemented by an operational amplifier, two switches and an operation capacitance, the trans-impedance amplifier is used to form an integrated circuit, the output is transmitted to a sampling / hold circuit via a switch; a parasitic capacitance discharge circuit is used to form a discharge rout for the charge of the parasitic capacitance.

Owner:PRIMETECH INT CORP

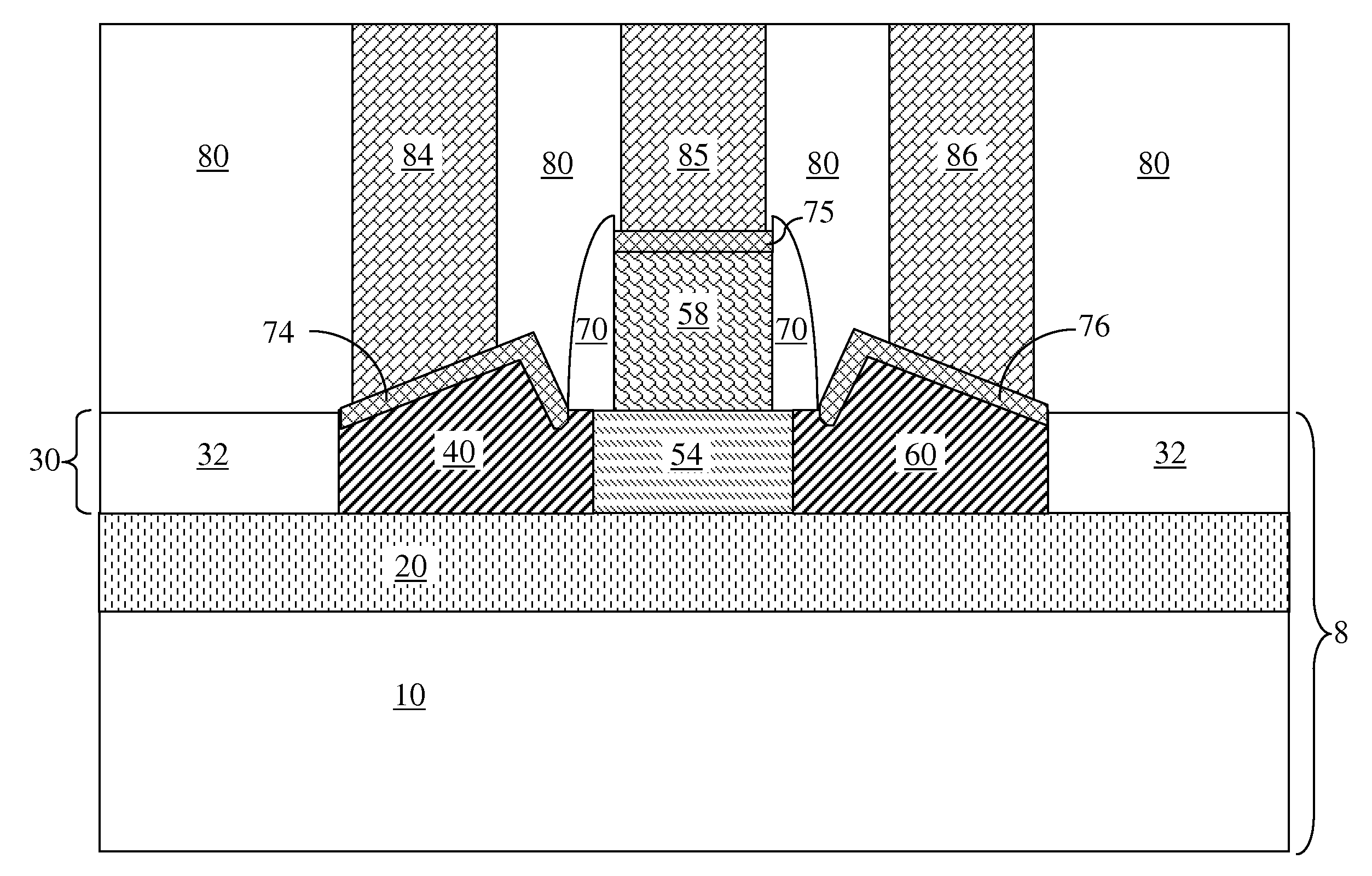

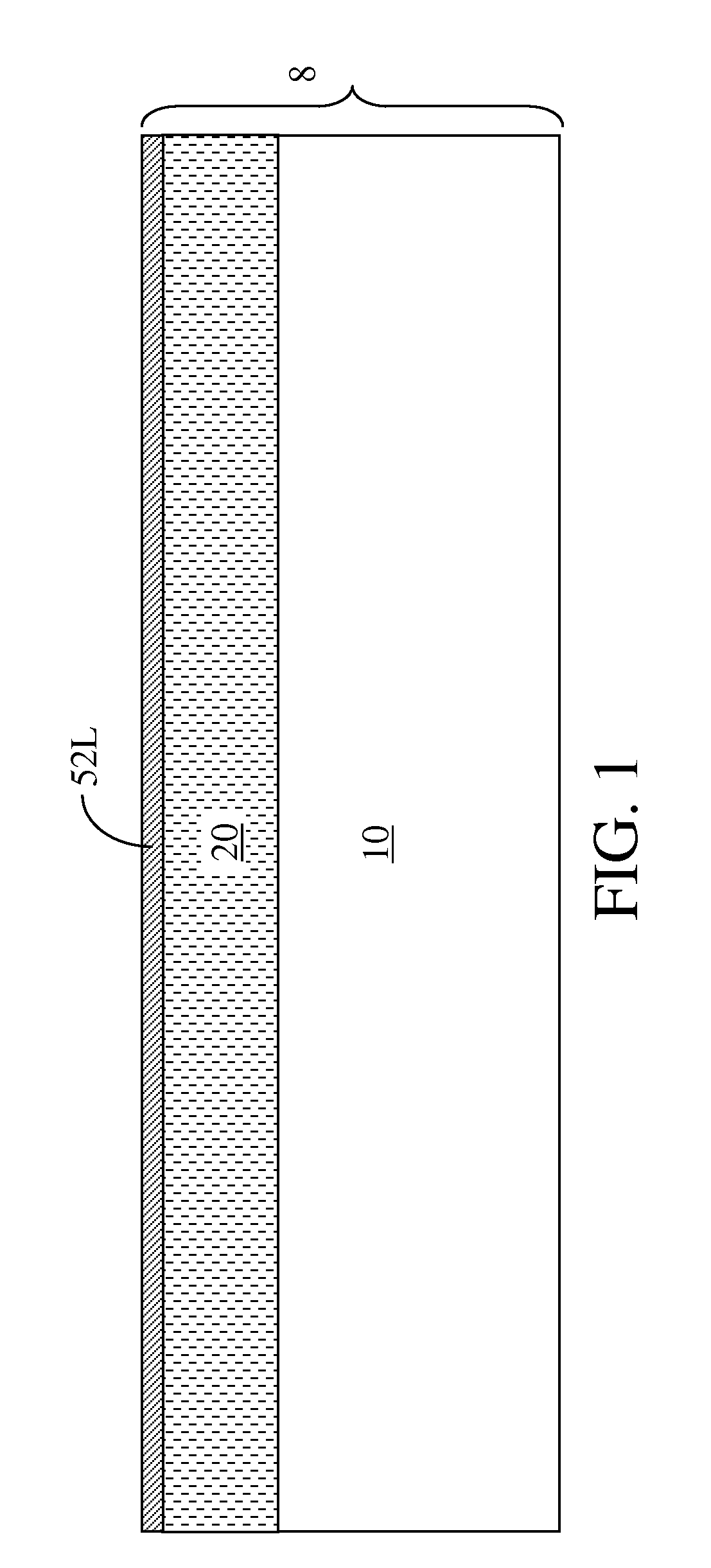

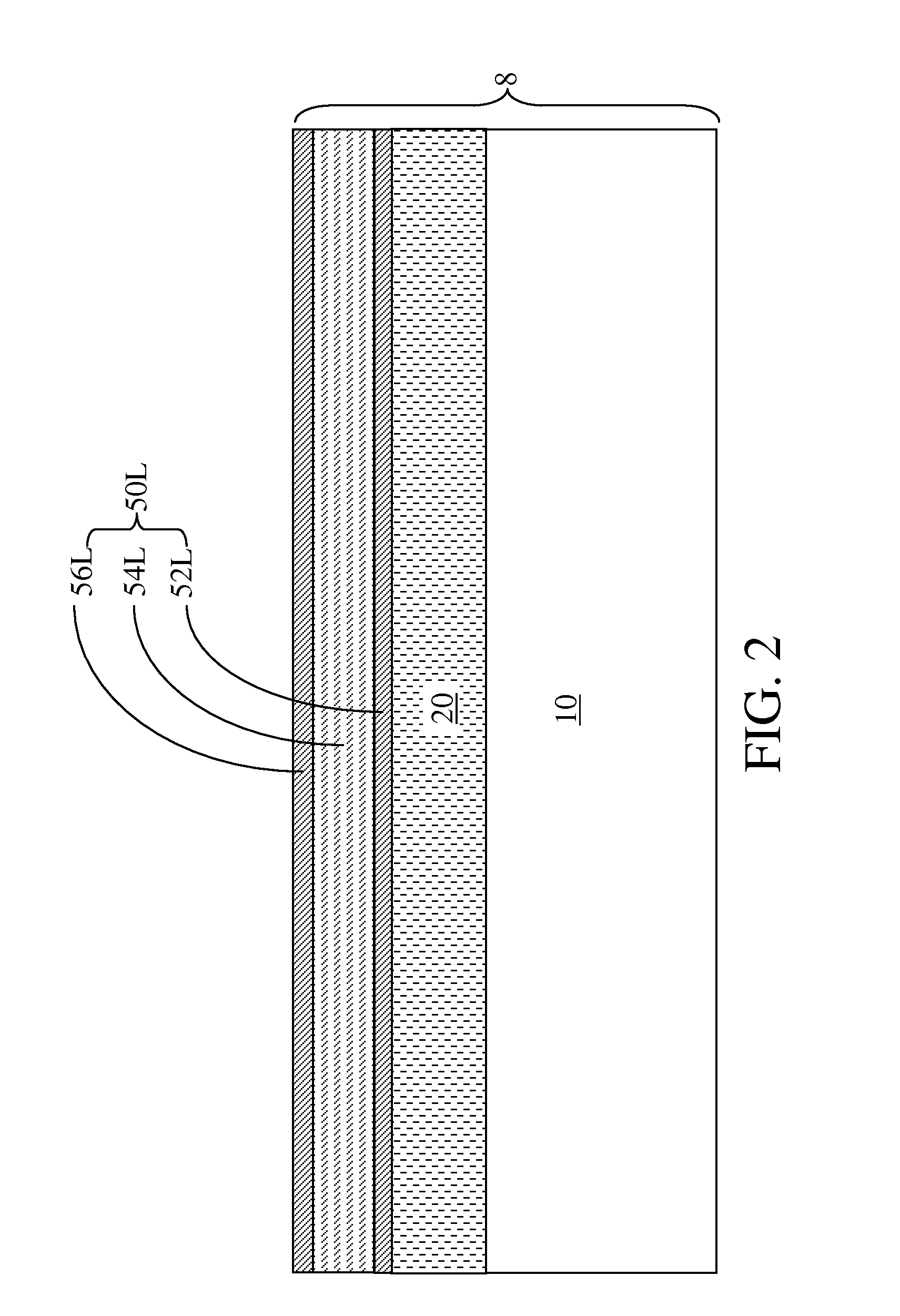

Integrated circuits including finfet devices with lower contact resistance and reduced parasitic capacitance and methods for fabricating the same

Integrated circuits and methods for fabricating integrated circuits are provided. In one example, an integrated circuit includes a semiconductor substrate. A first fin and a second fin are adjacent to each other extending from the semiconductor substrate. The first fin has a first upper section and the second fin has a second upper section. A first epi-portion overlies the first upper section and a second epi-portion overlies the second upper section. A first silicide layer overlies the first epi-portion and a second silicide layer overlies the second epi-portion. The first and second silicide layers are spaced apart from each other to define a lateral gap. A dielectric spacer is formed of a dielectric material and spans the lateral gap. A contact-forming material overlies the dielectric spacer and portions of the first and second silicide layers that are laterally above the dielectric spacer.

Owner:IBM CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com