Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3505results about How to "Reduce parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

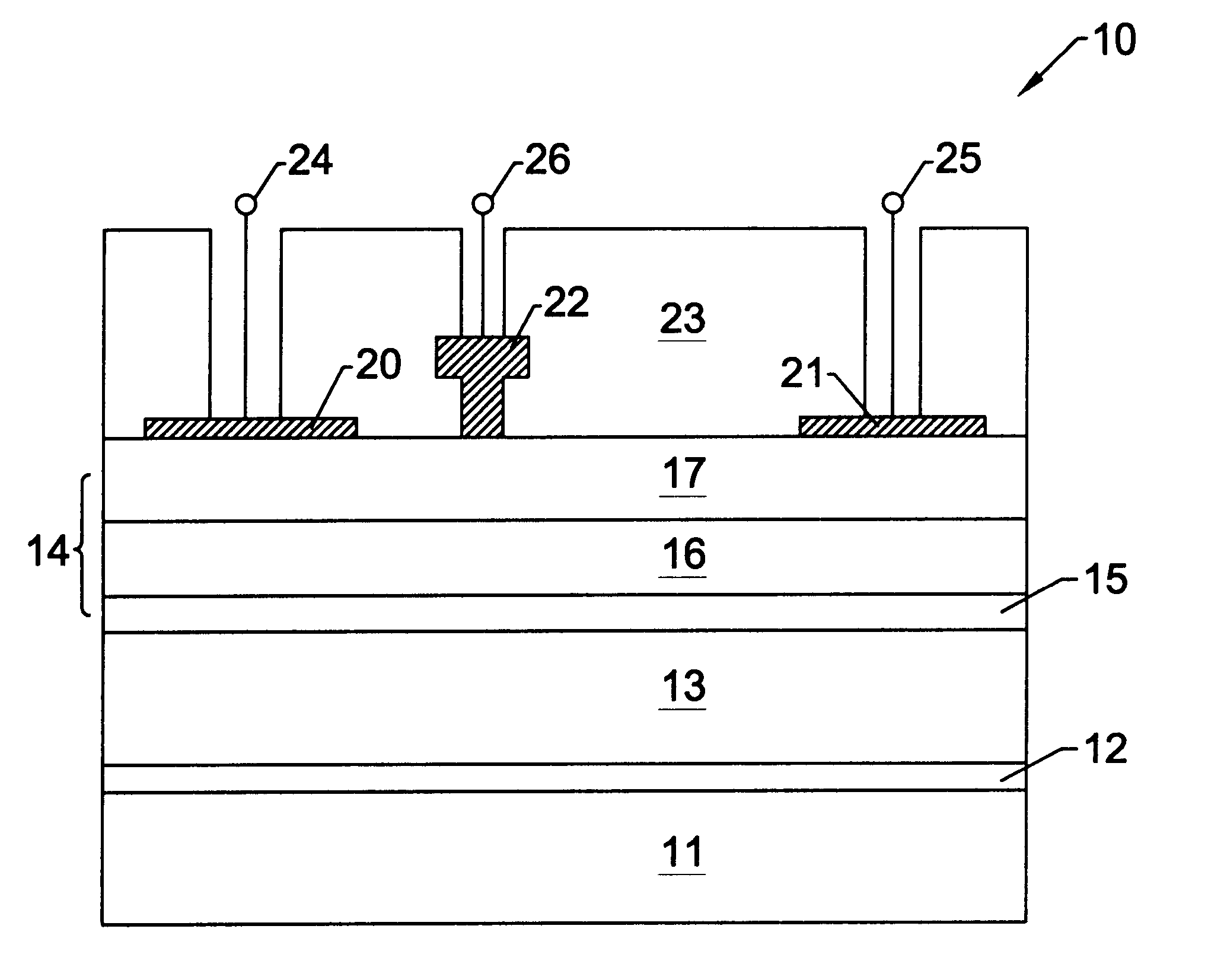

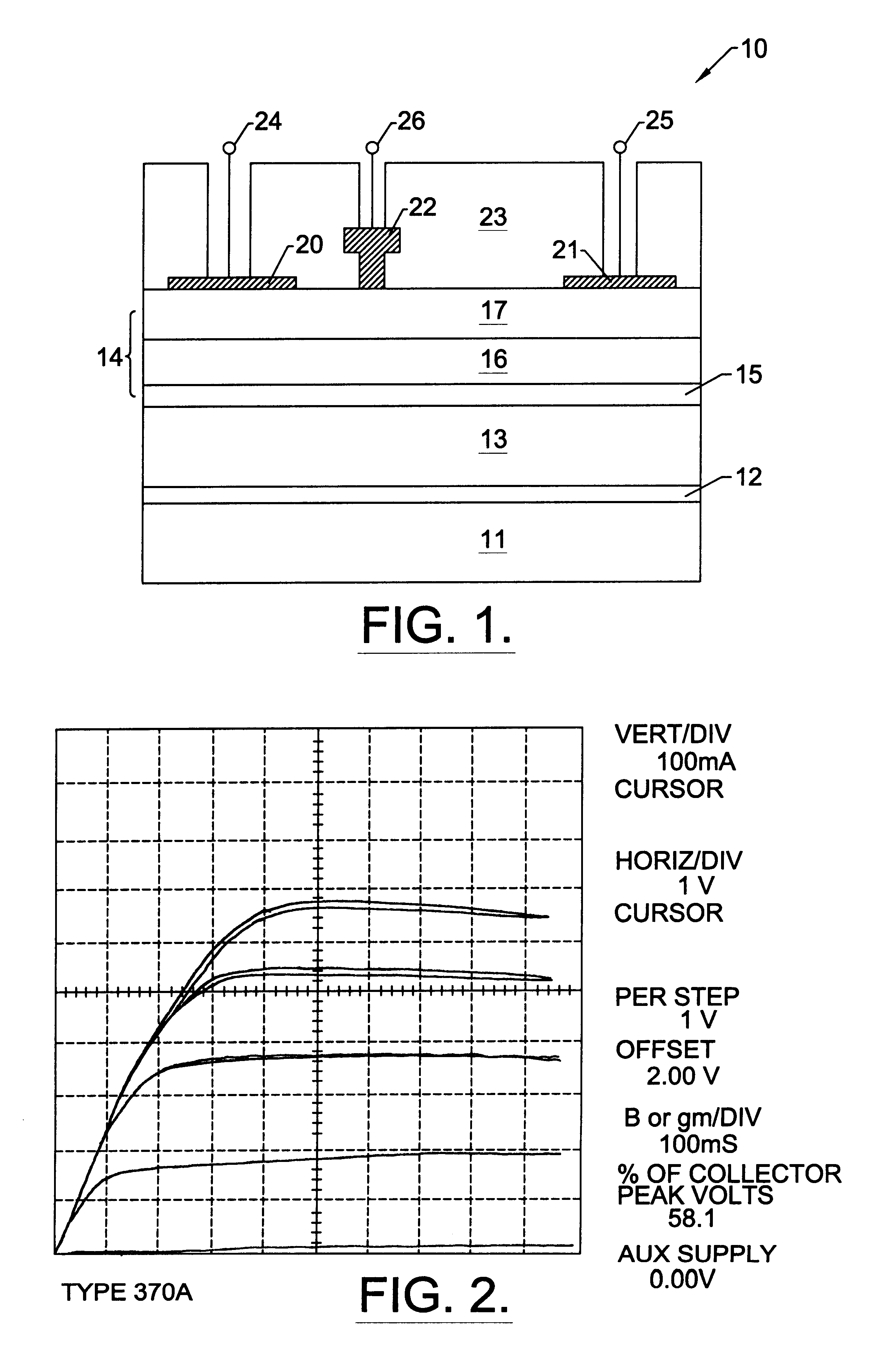

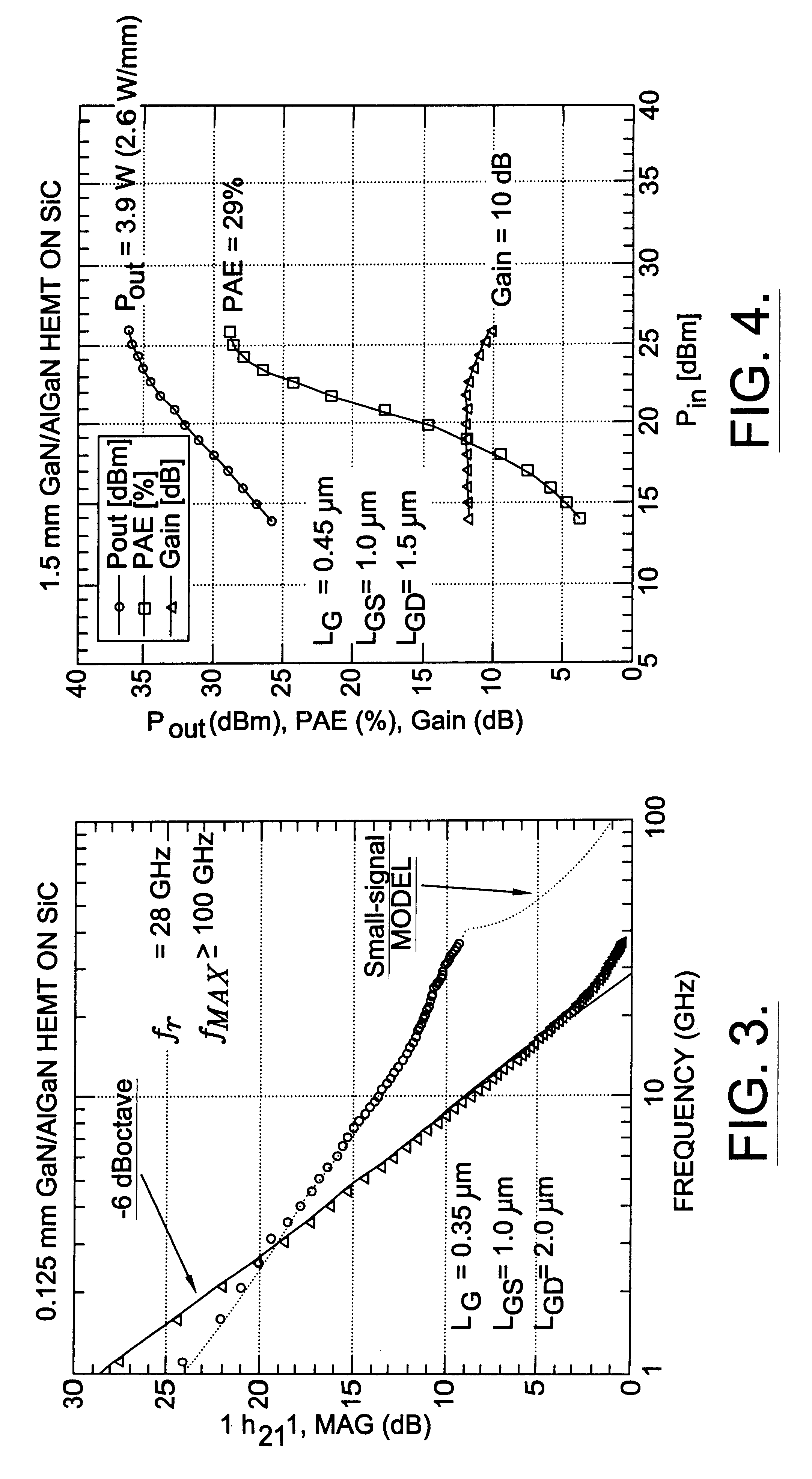

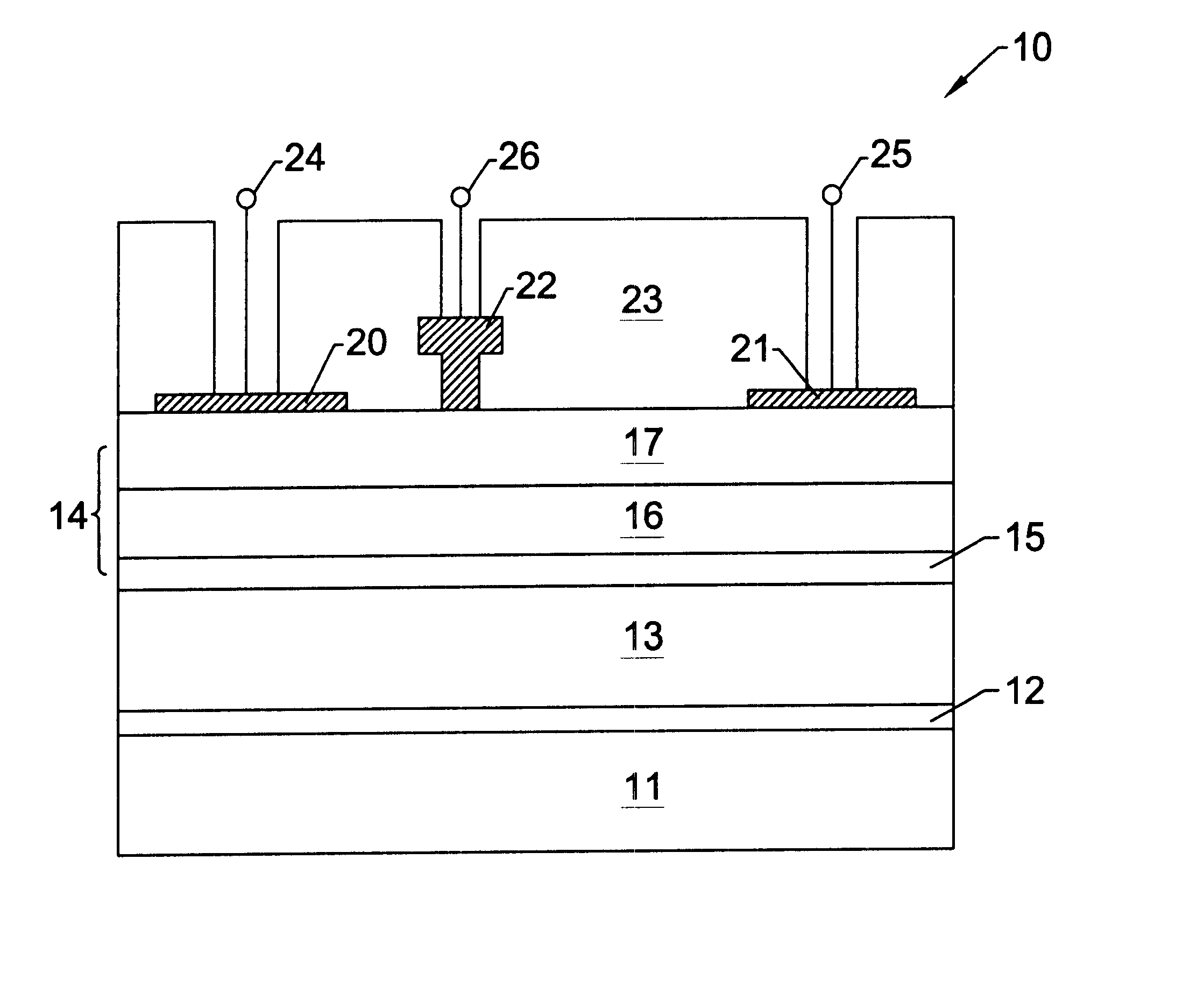

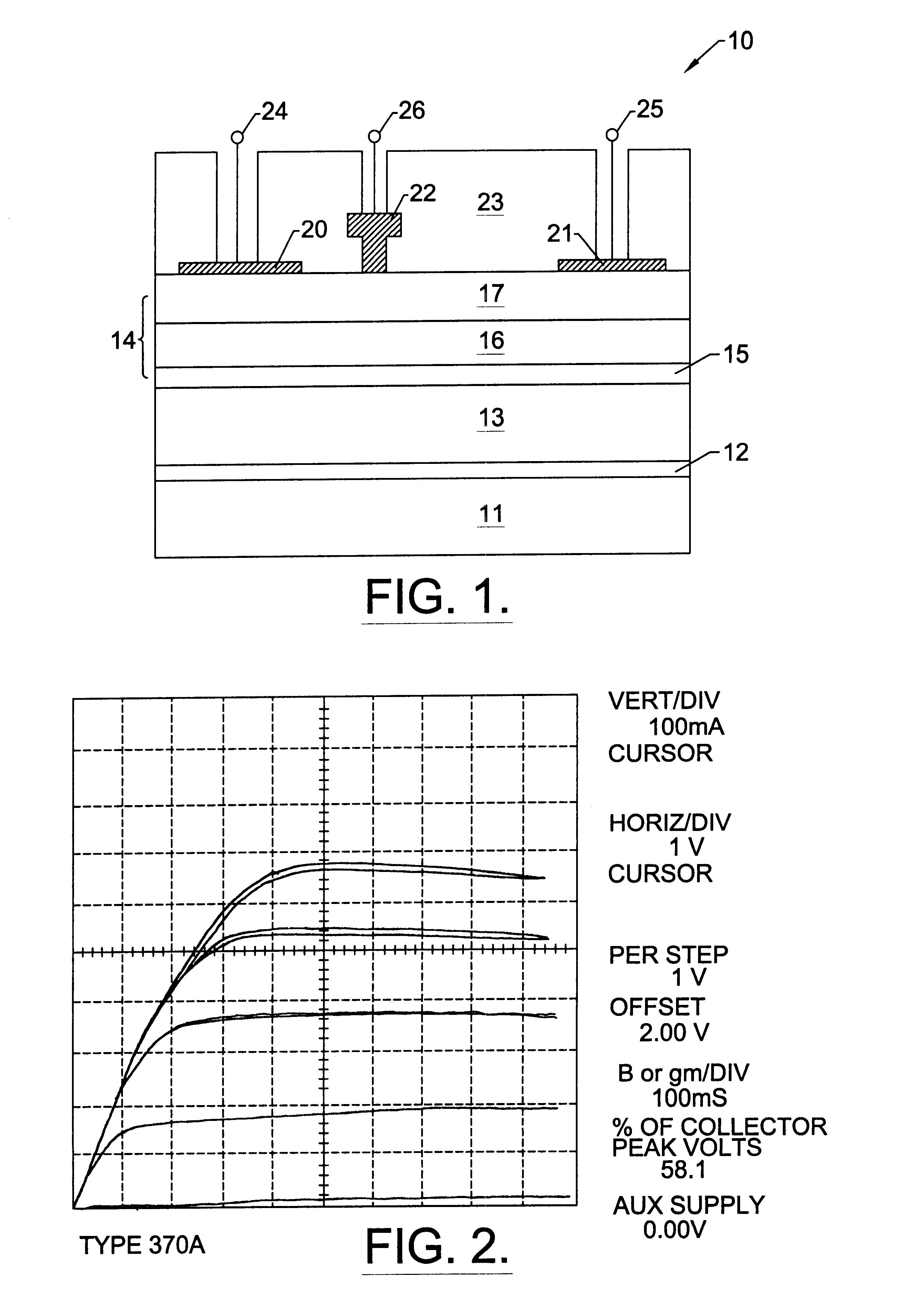

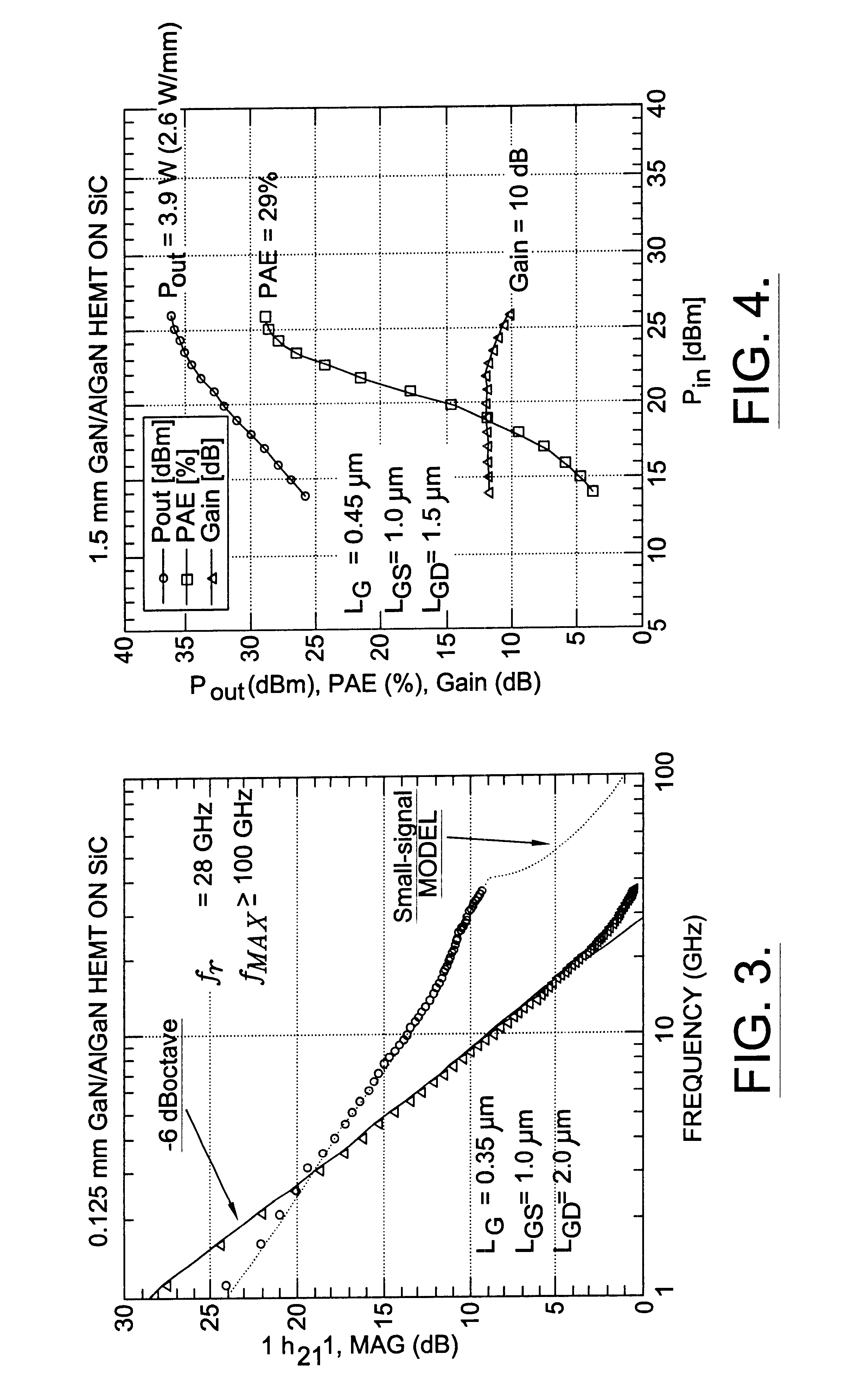

Nitride based transistors on semi-insulating silicon carbide substrates

InactiveUS6316793B1Quality improvementImprove thermal conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideMaterials science

A high electron mobility transistor (HEMT) is disclosed that includes a semi-insulating silicon carbide substrate, an aluminum nitride buffer layer on the substrate, an insulating gallium nitride layer on the buffer layer, an active structure of aluminum gallium nitride on the gallium nitride layer, a passivation layer on the aluminum gallium nitride active structure, and respective source, drain and gate contacts to the aluminum gallium nitride active structure.

Owner:WOLFSPEED INC

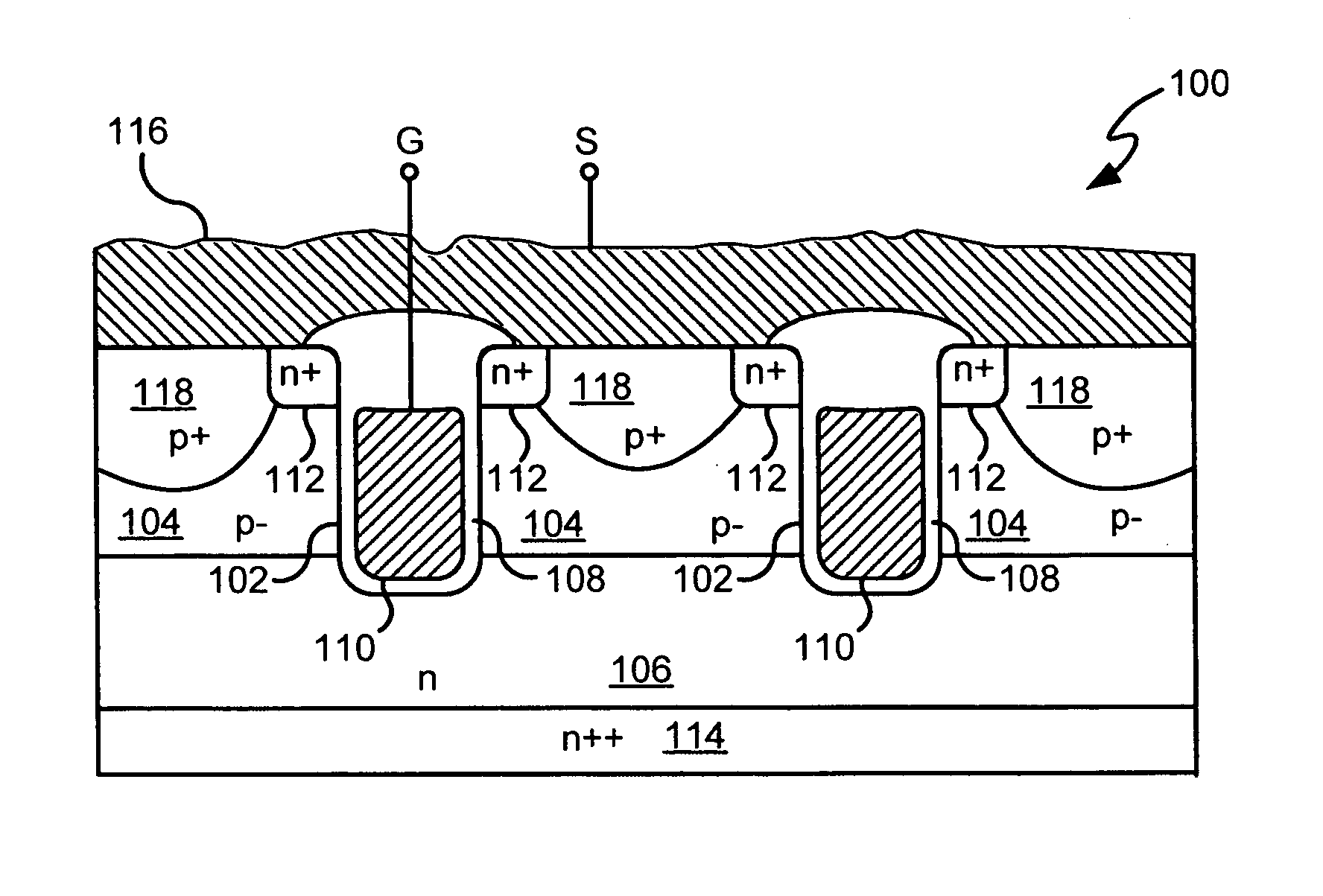

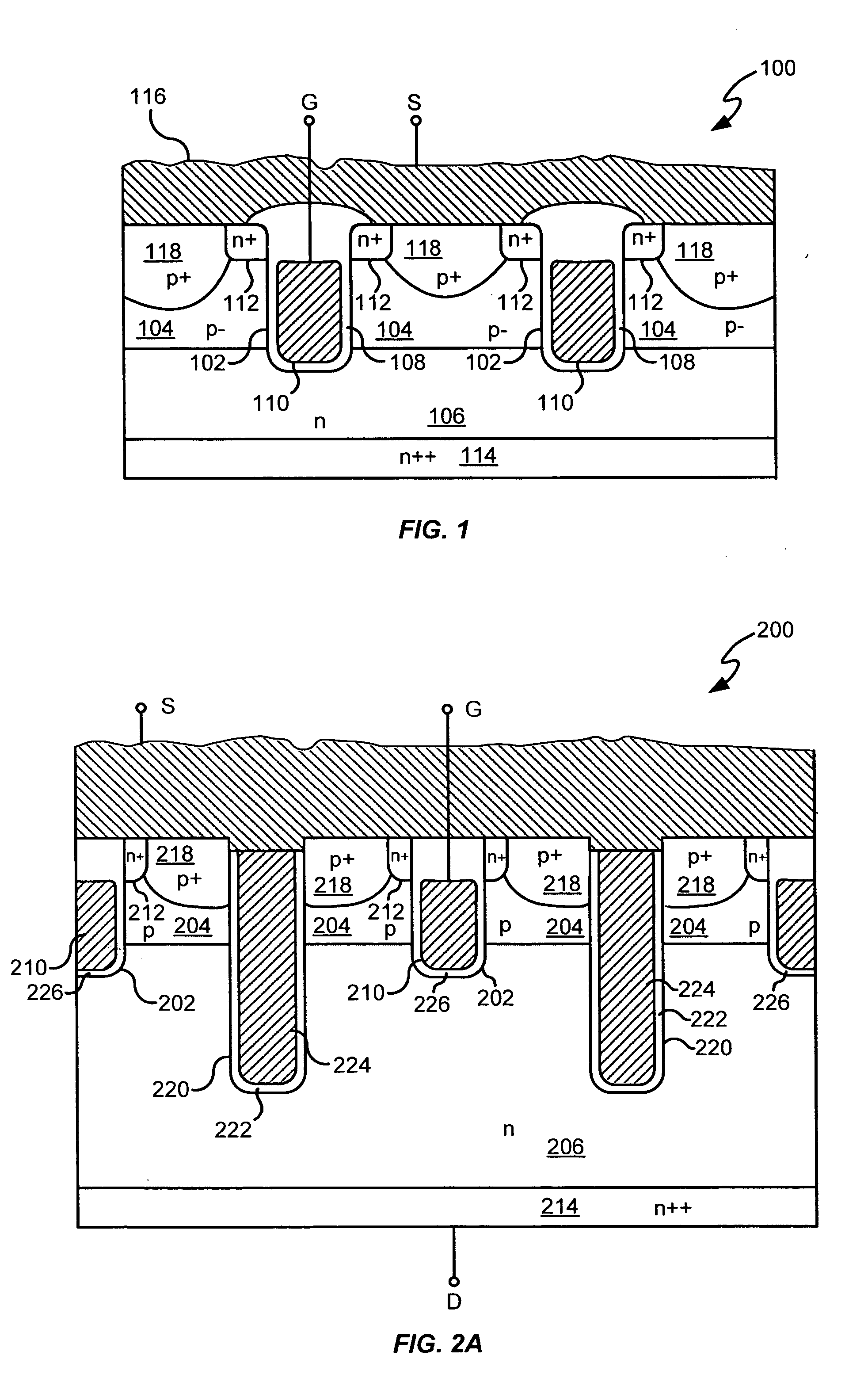

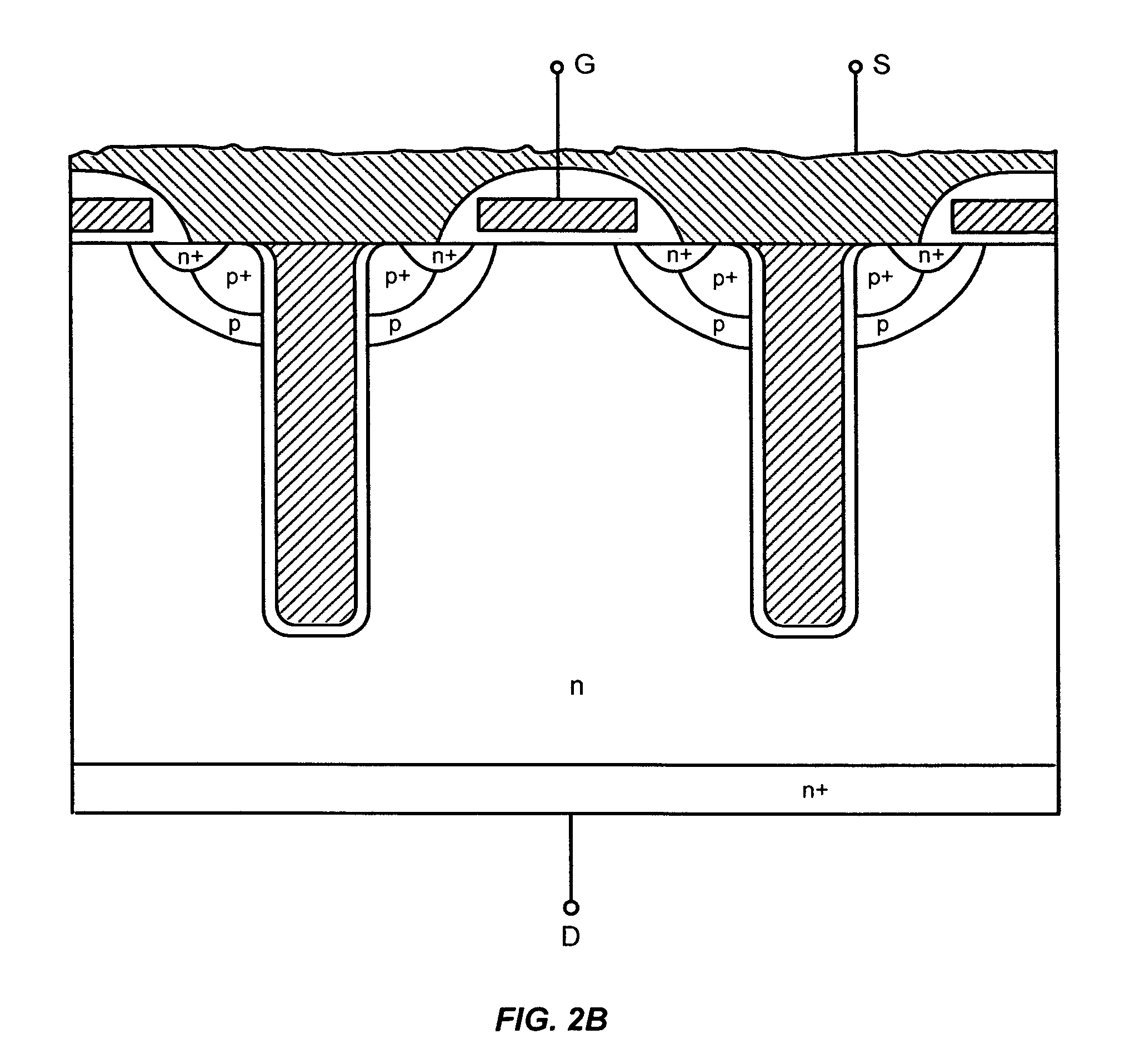

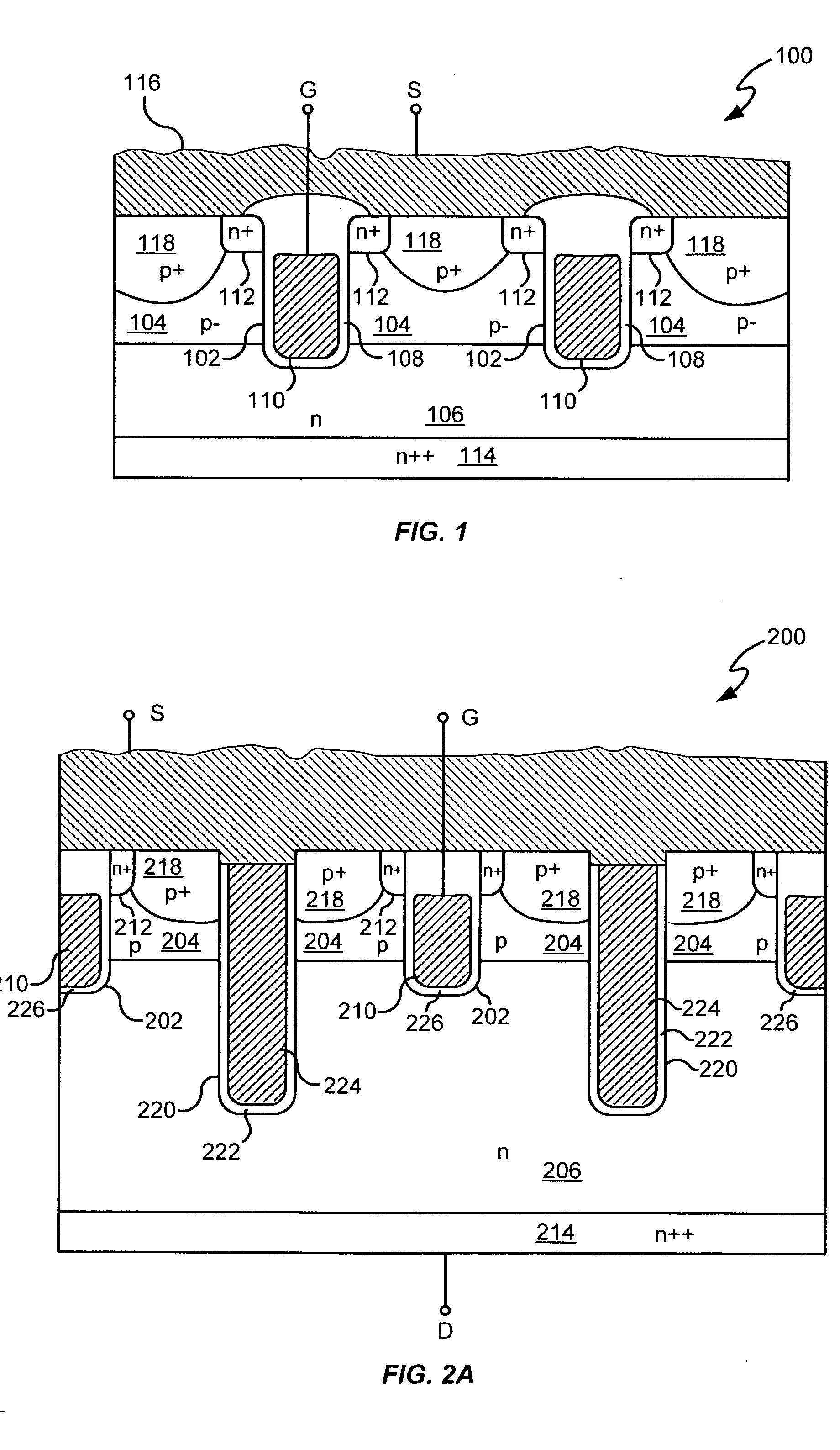

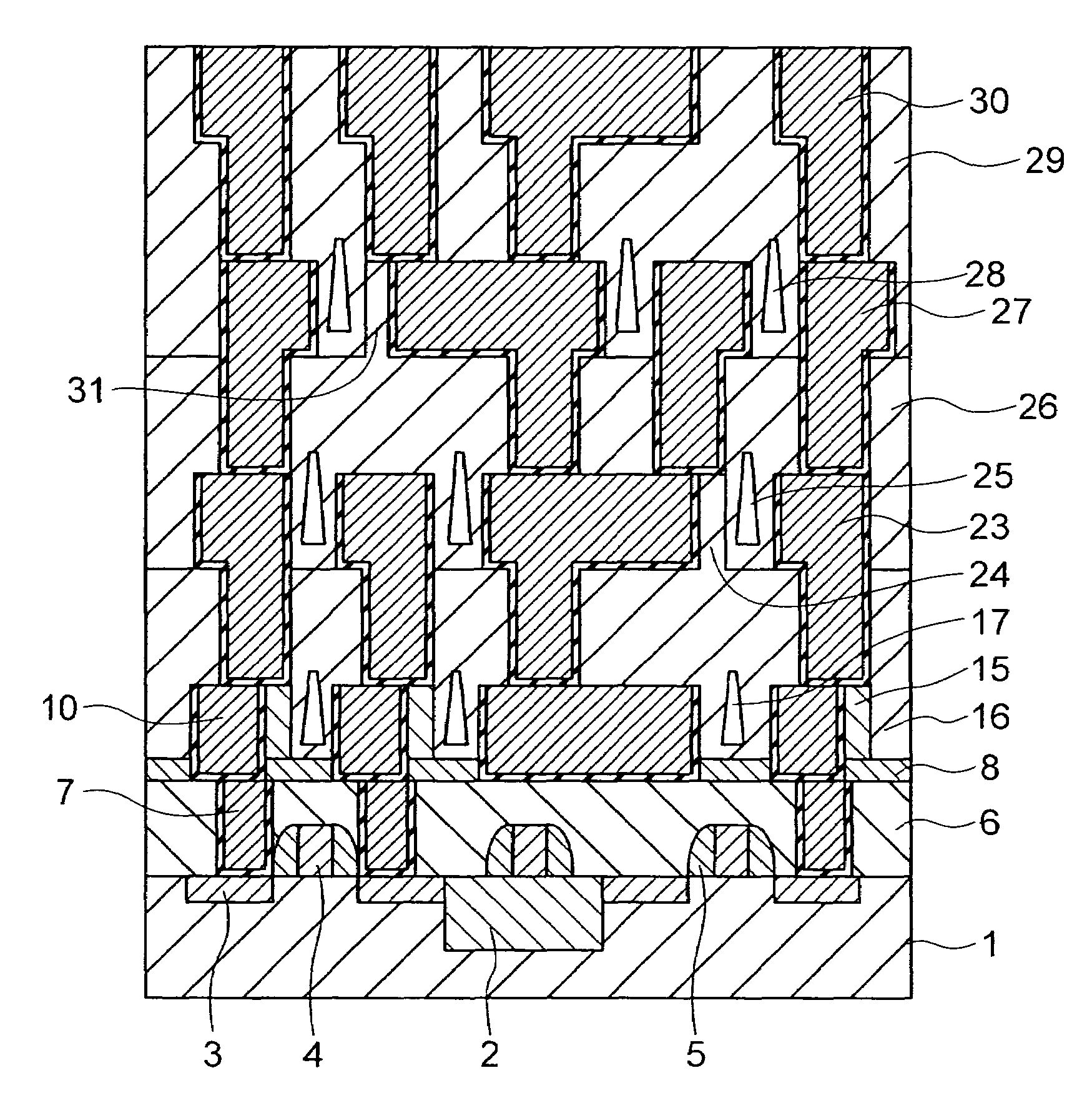

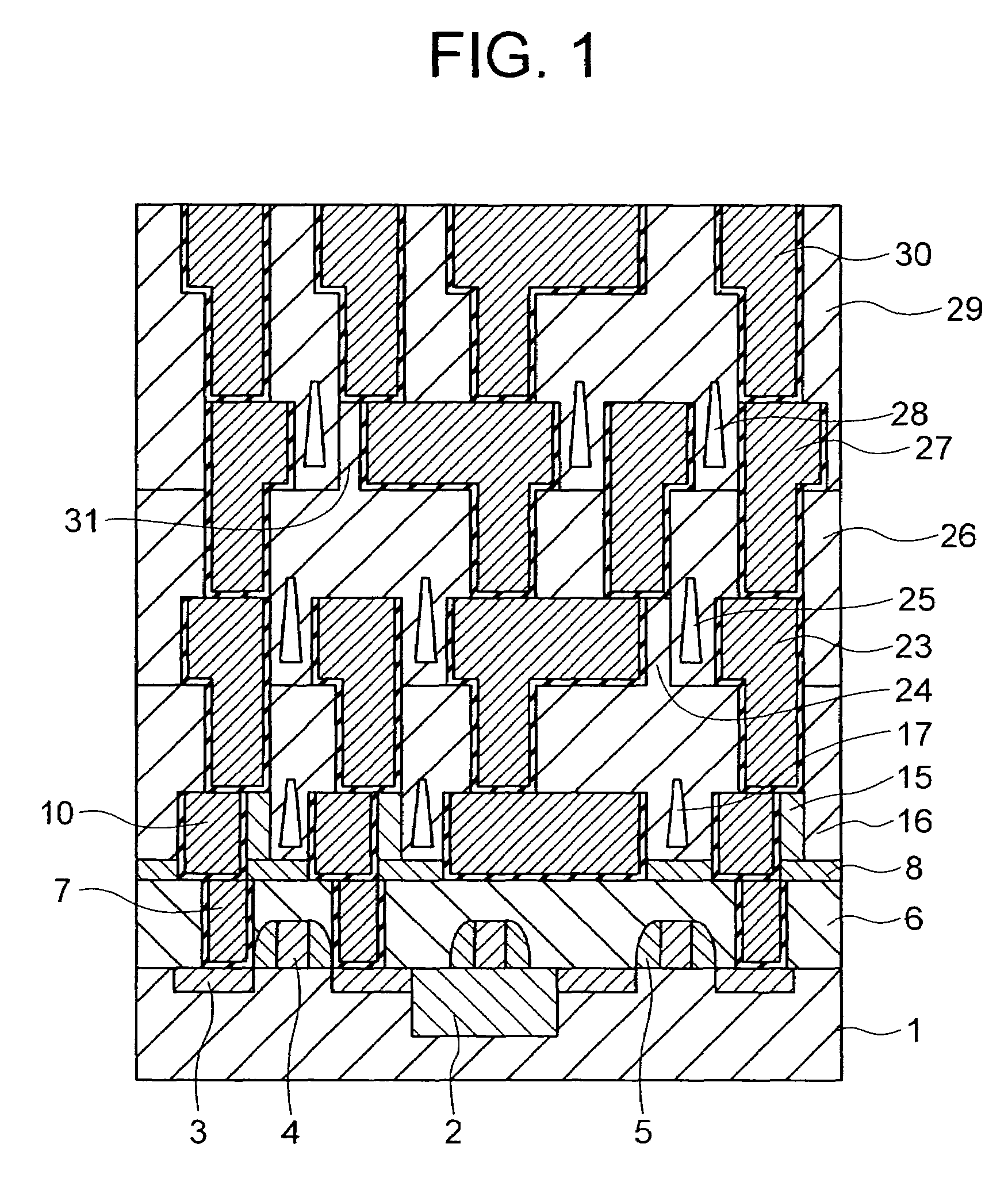

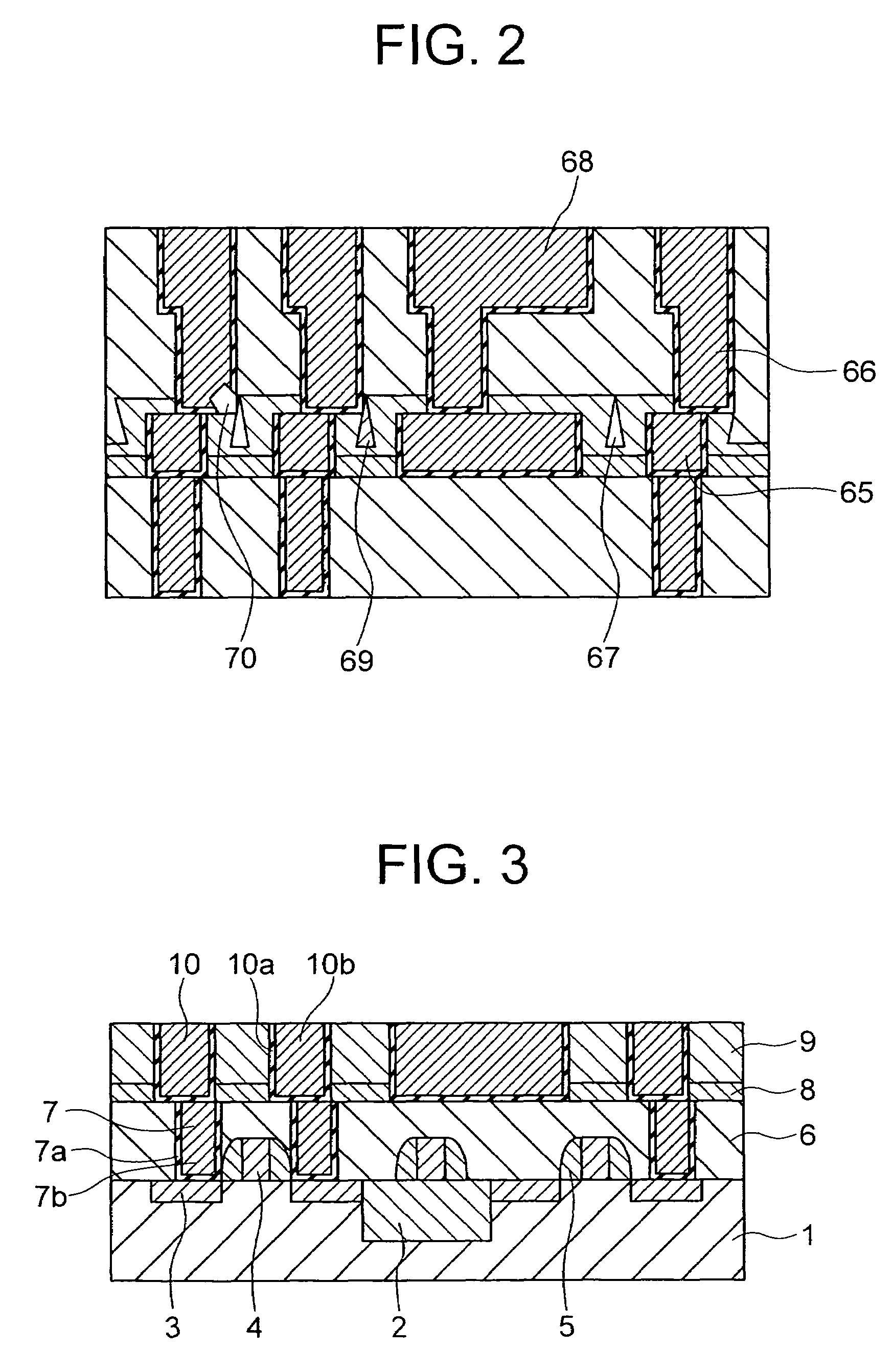

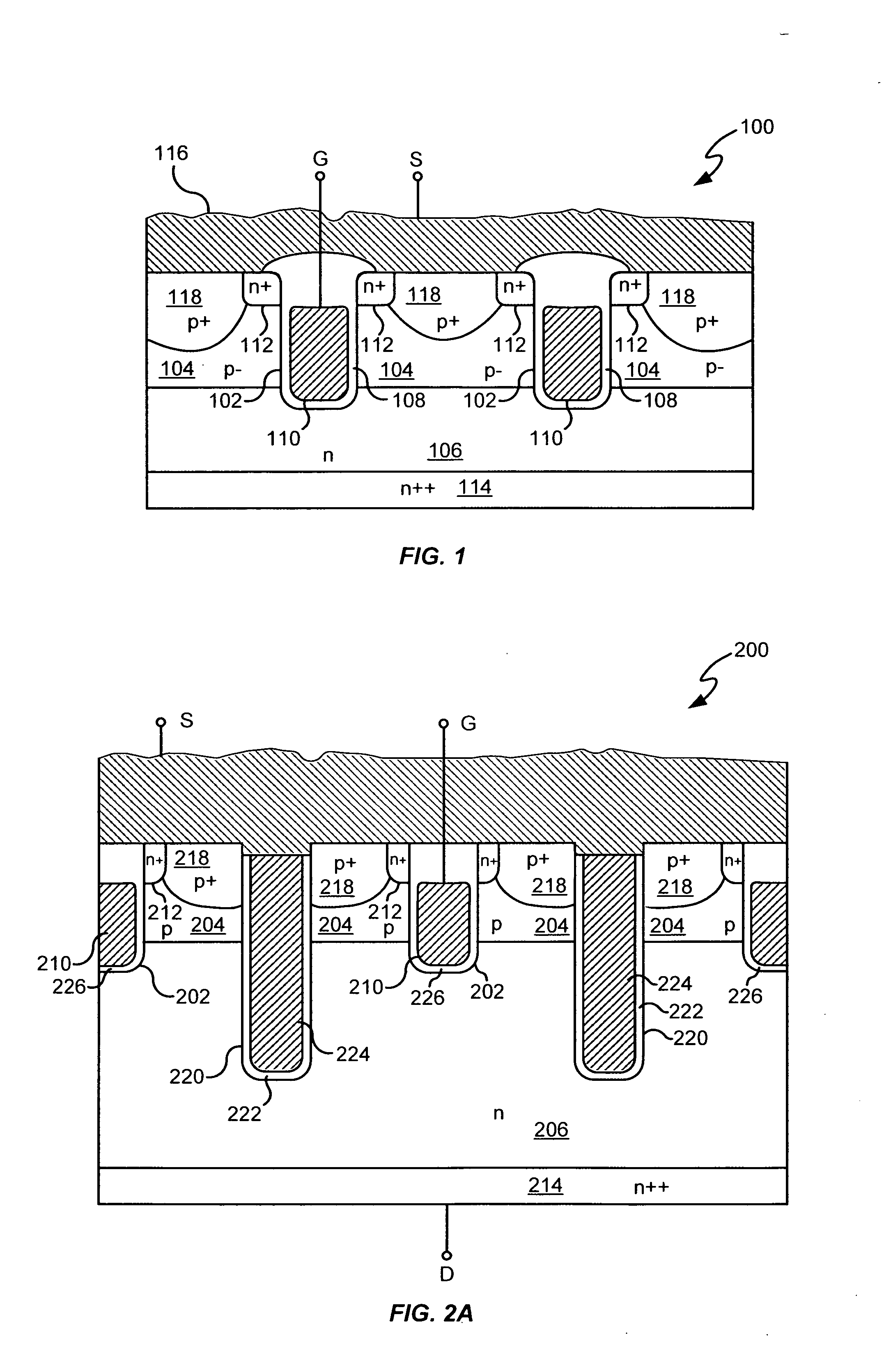

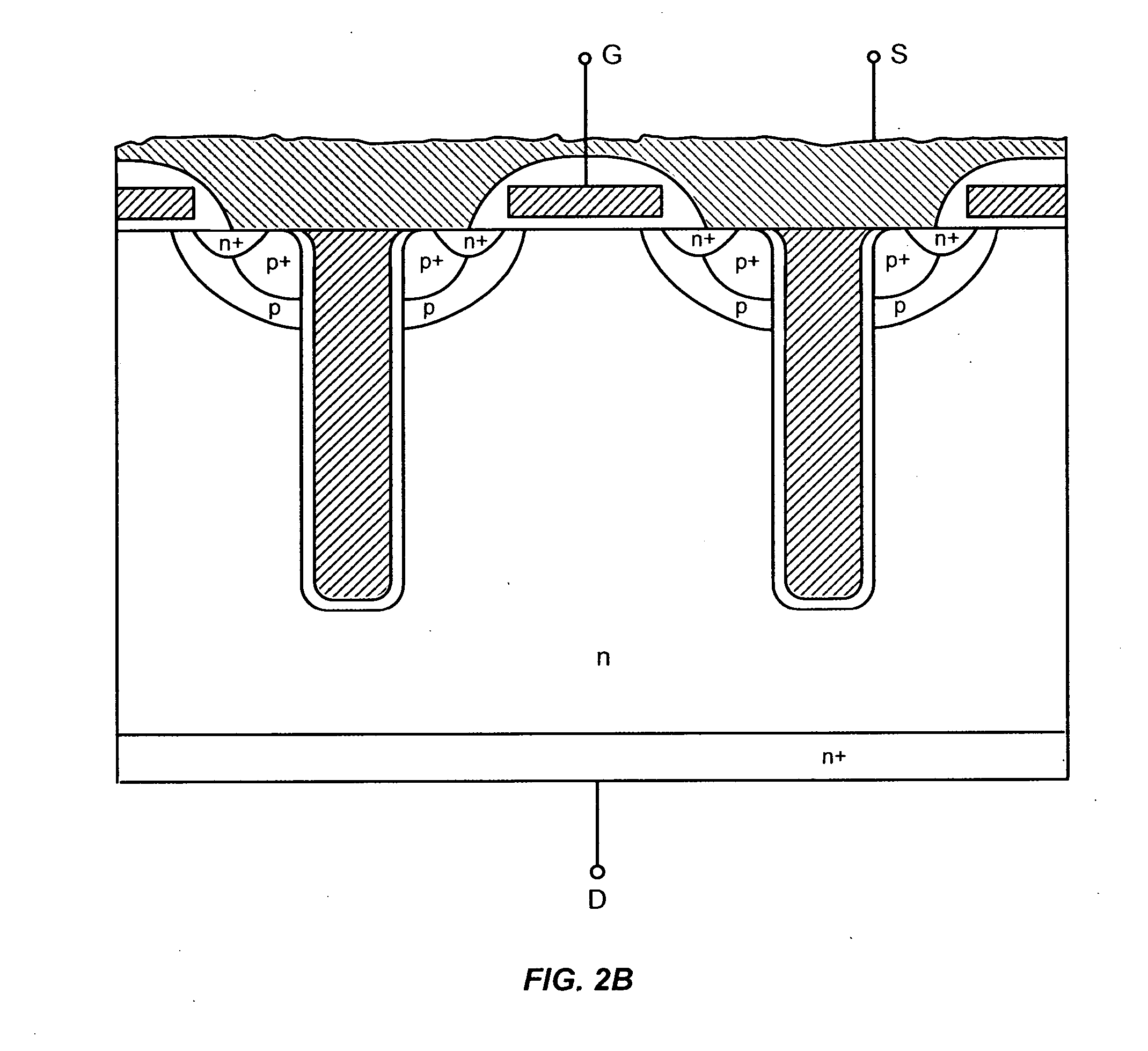

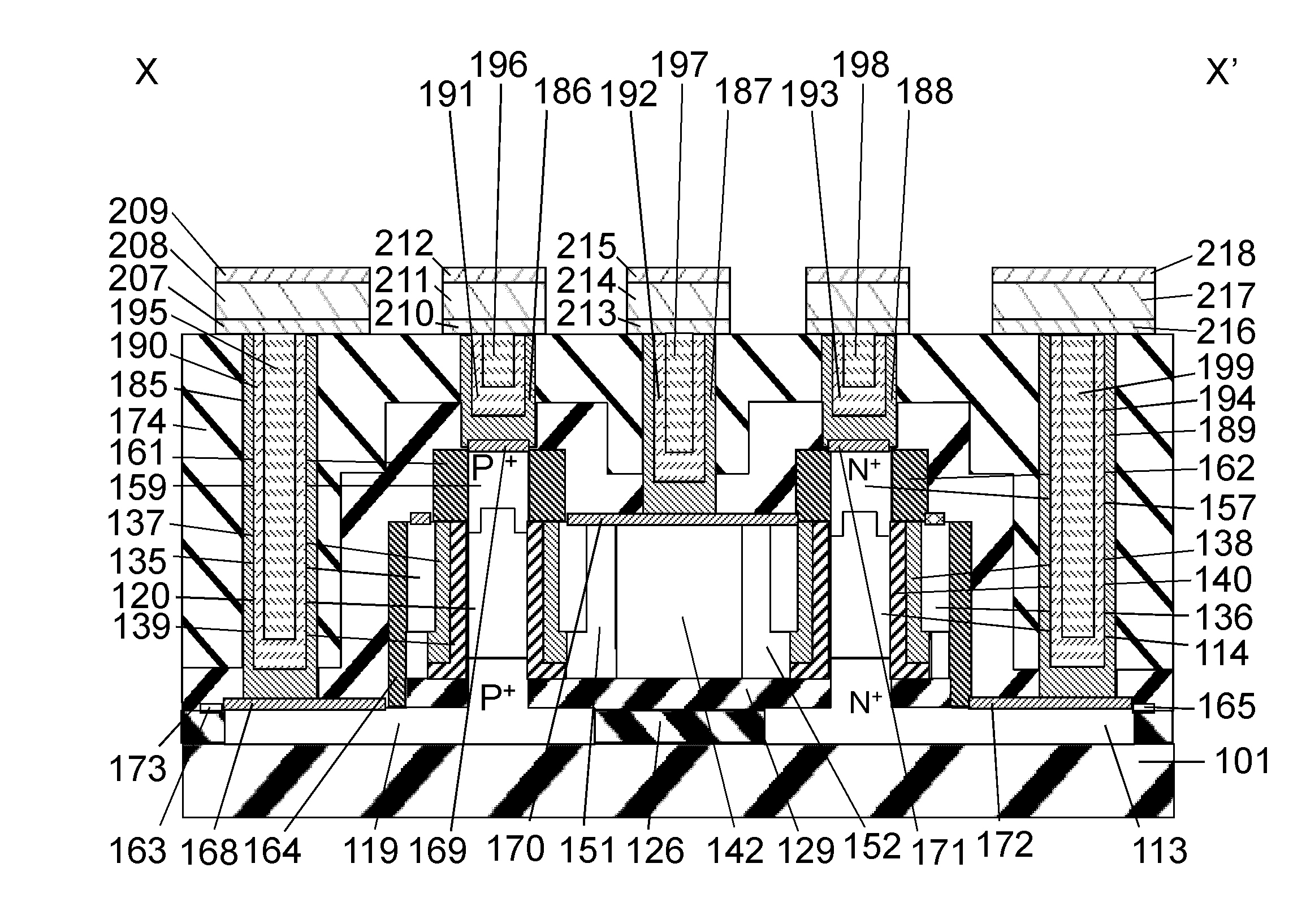

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

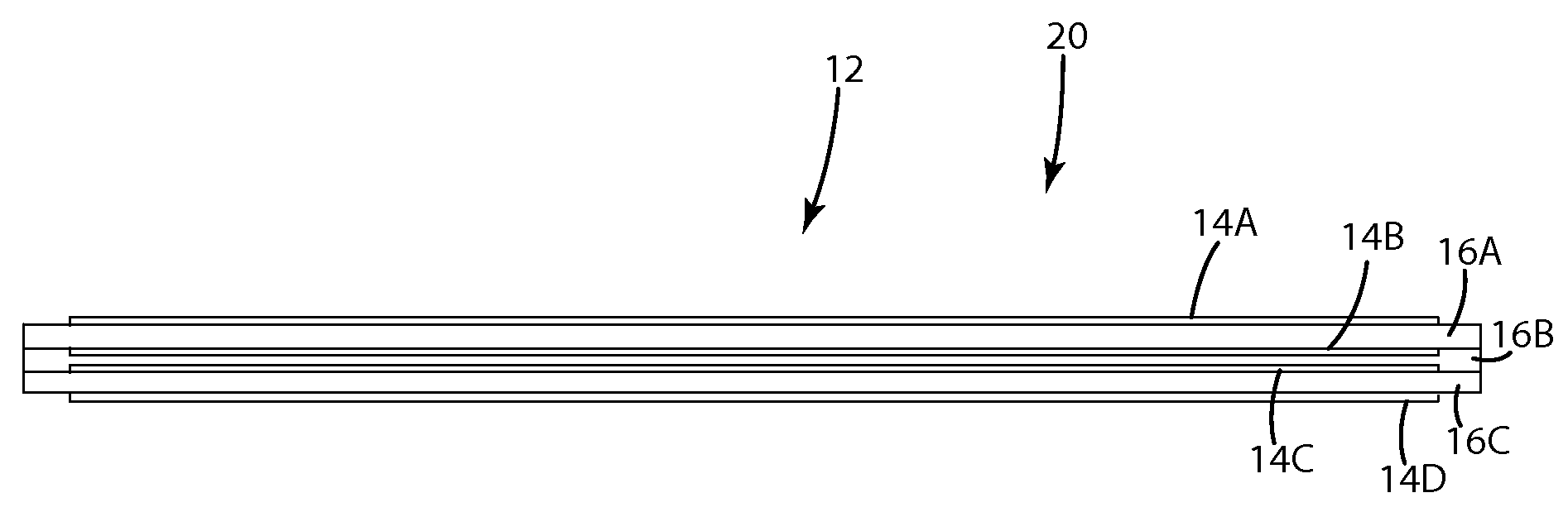

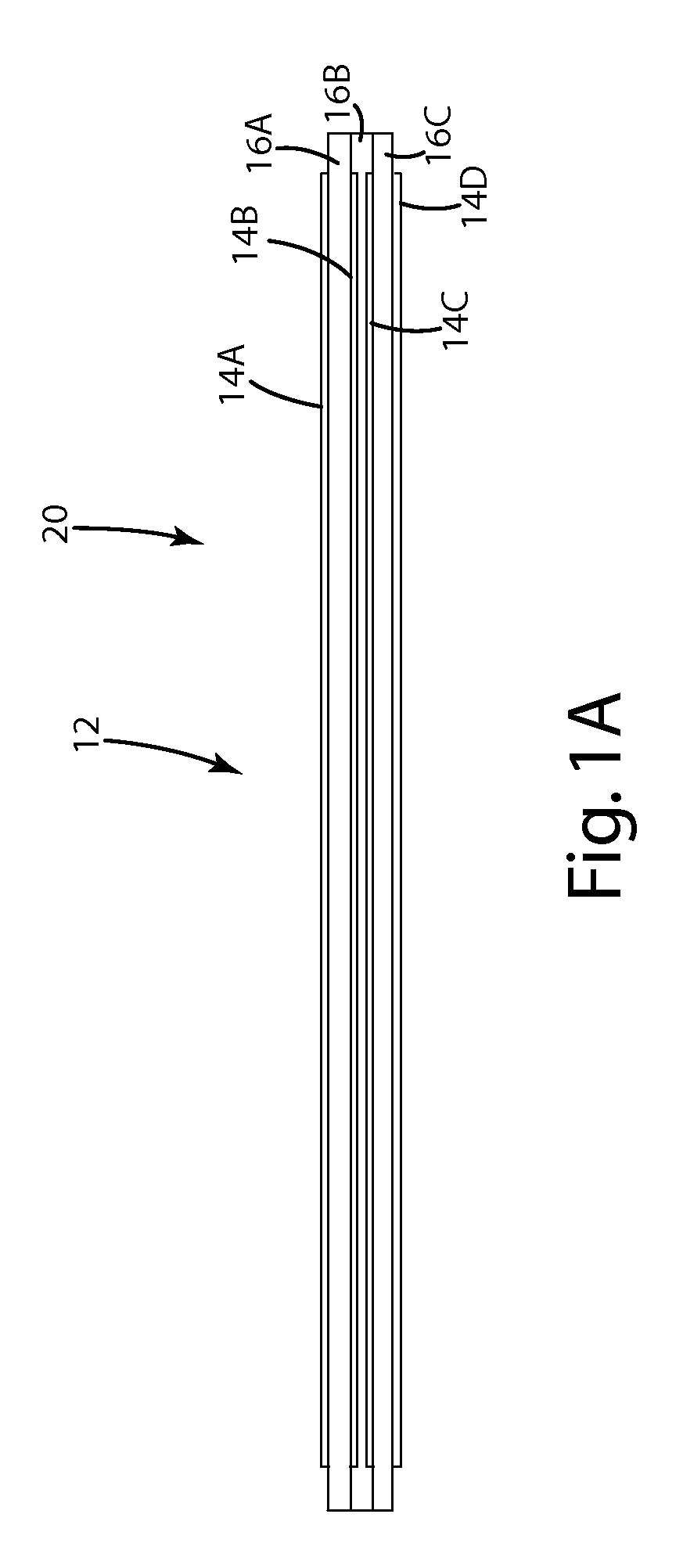

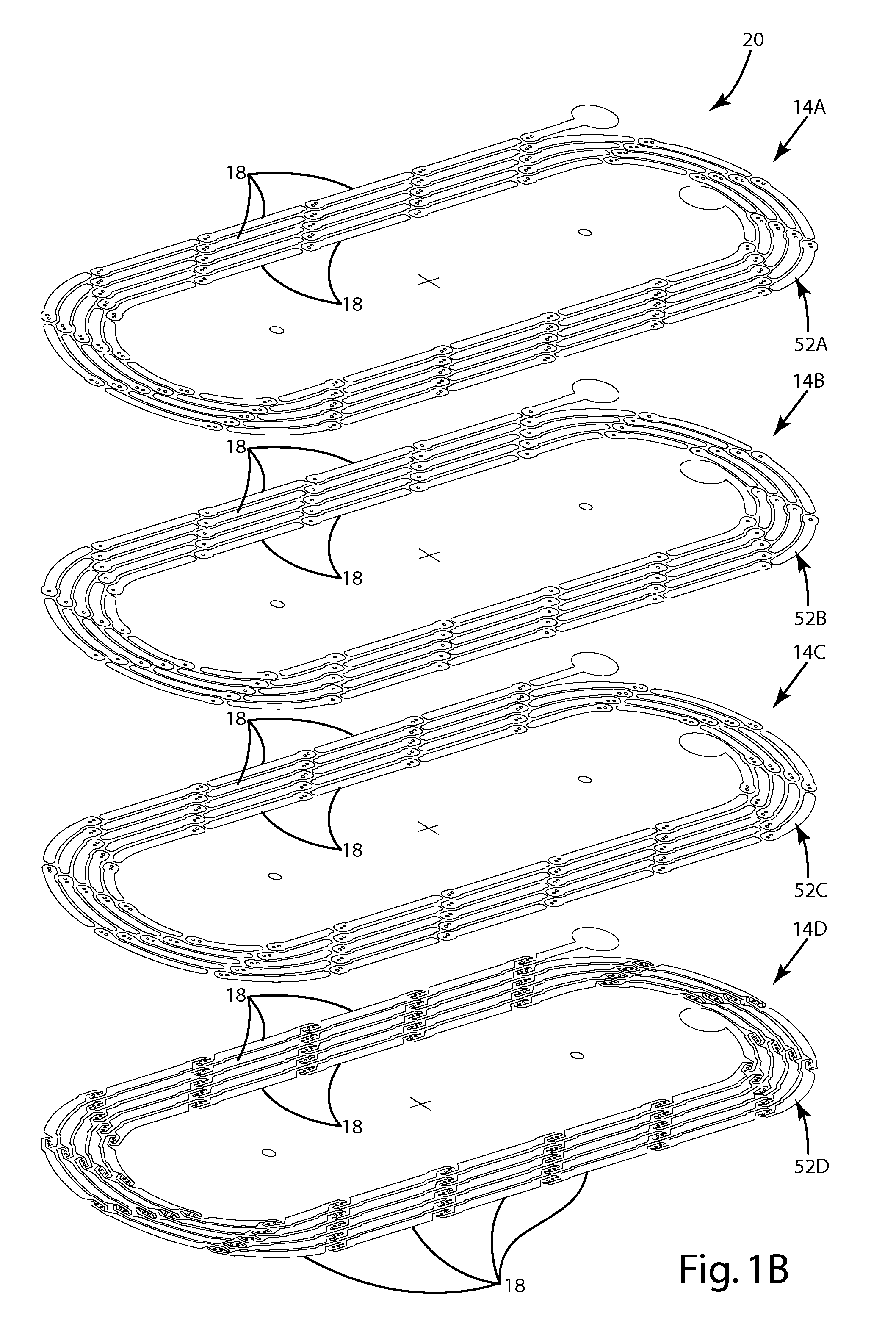

Printed circuit board coil

ActiveUS20090085706A1Reduce skin effectReduce lossTransformersTransformers/inductances coils/windings/connectionsElectrical conductorLitz wire

A multilayer printed circuit board (“PCB”) coil that simulates a coil formed from litz wire. The PCB includes a plurality of alternating conductor and insulating layers interconnected to cooperatively form the coil. Each conductor layer includes a trace that follows the desired coil shape and is divided into a plurality of discrete conductor segments. The segments are electrically connected across layers to provide a plurality of current flow paths (or filaments) that undulate between the layers in a regular, repeating pattern. The coil may be configured so that each filament spends a substantially equal amount of time in proximity to the paired coil and therefore contributes substantially equally to the self or mutual inductance of the coil. Each conductor layer may include a plurality of associated traces and intralayer connector that interconnected so that each filament undulates not only upwardly / downwardly, but also inwardly / outwardly in a regular, repeating pattern.

Owner:PHILIPS IP VENTURES BV

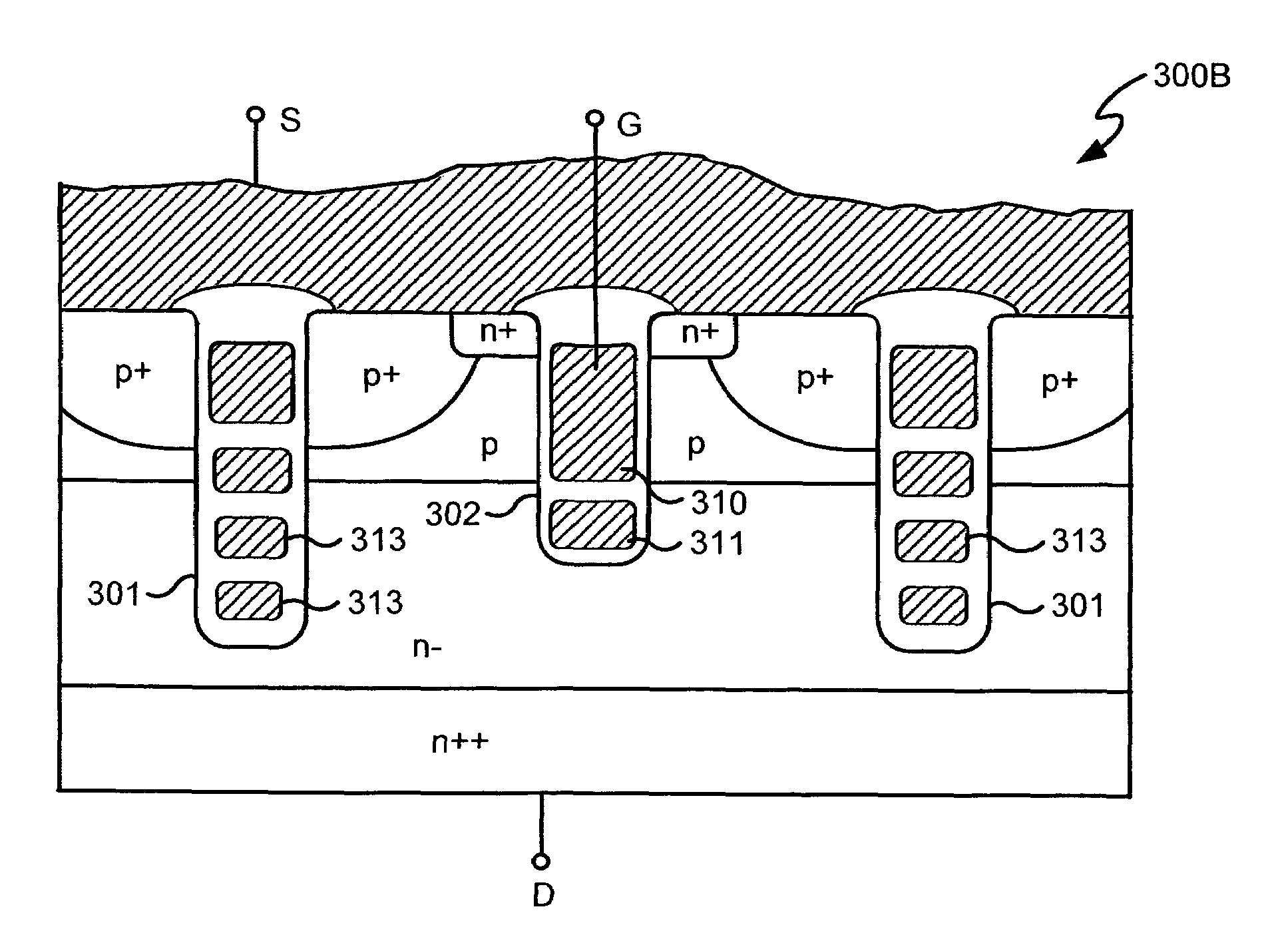

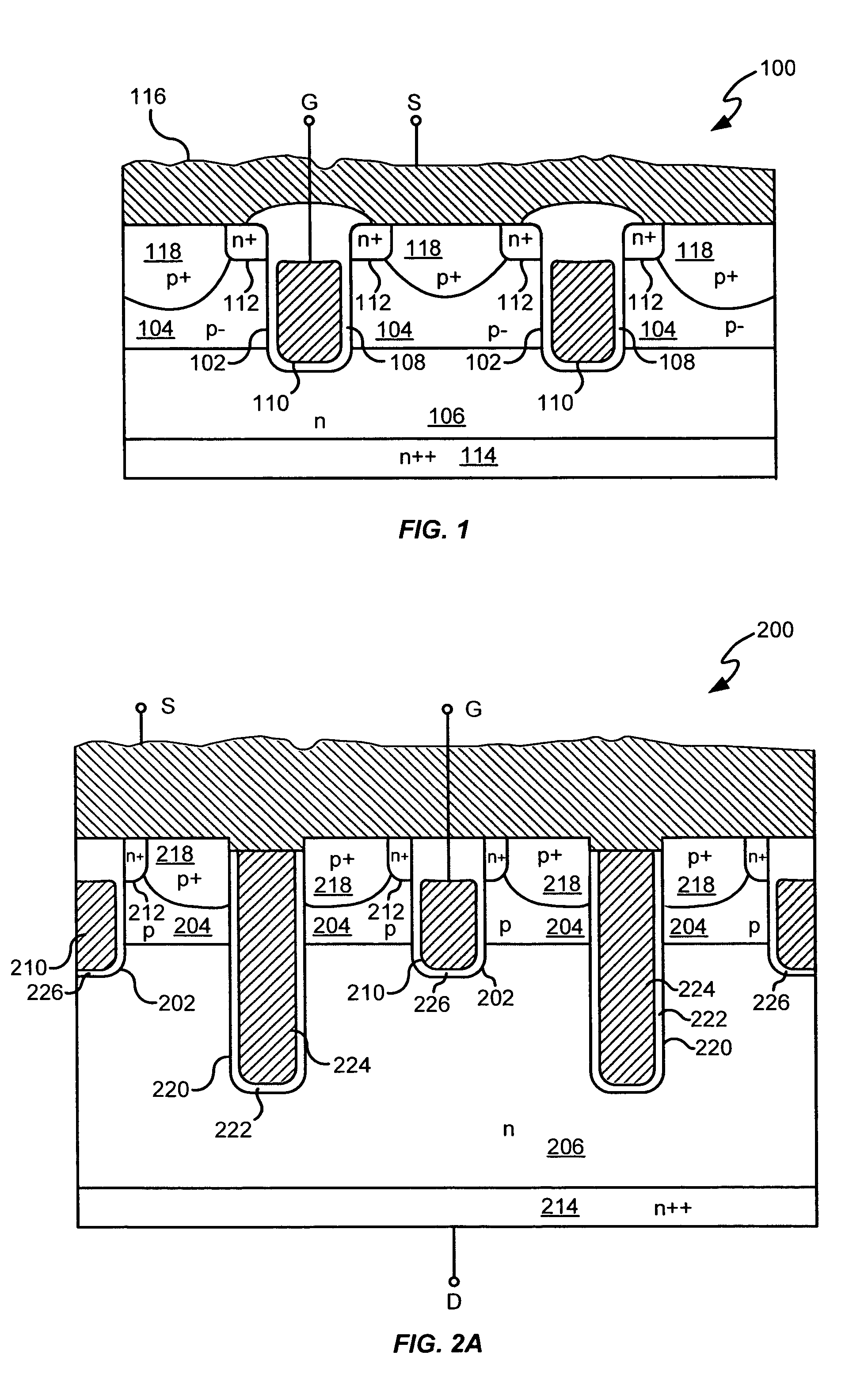

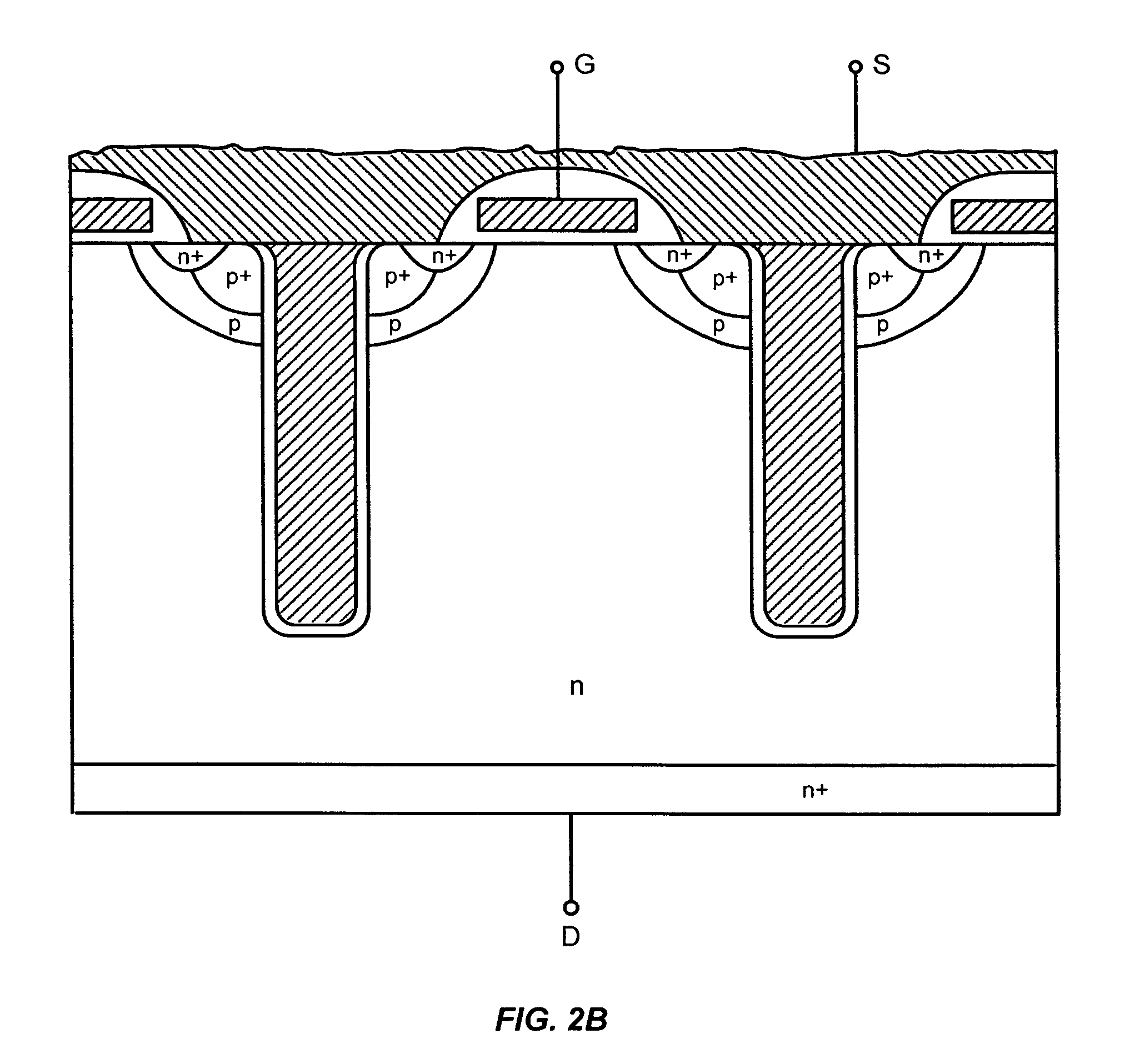

Power semiconductor devices and methods of manufacture

ActiveUS7345342B2Simple structureEasy to packEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

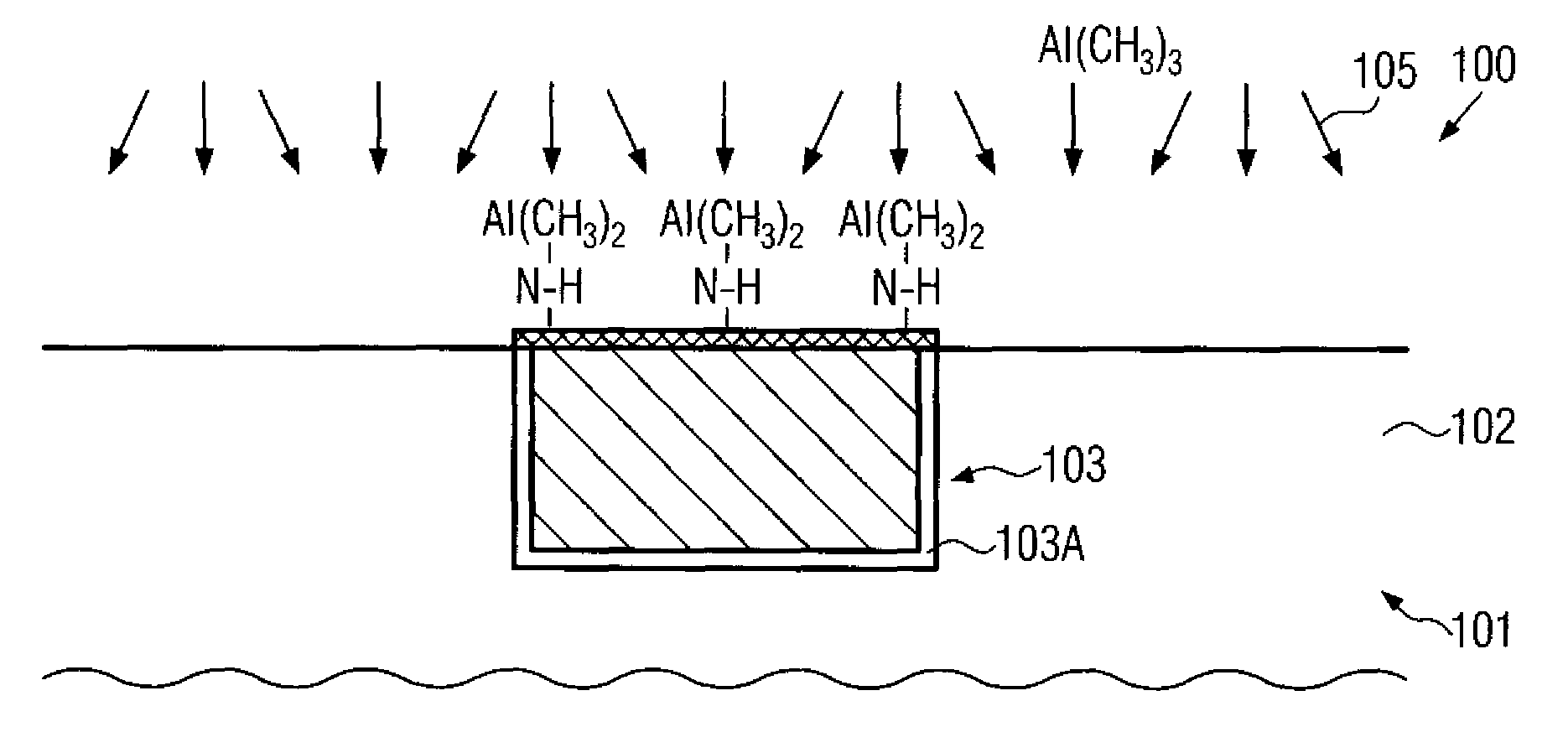

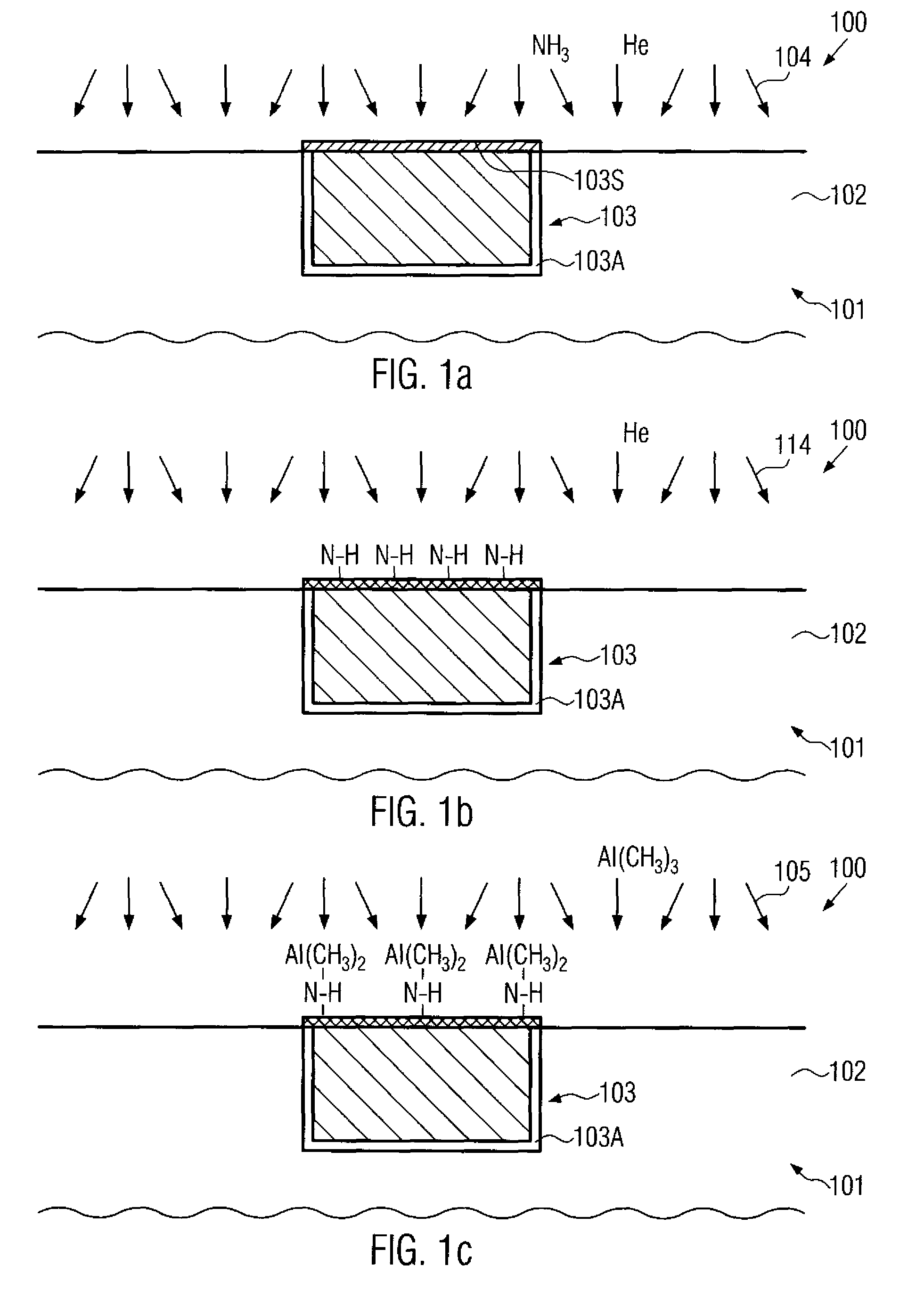

Method of manufracturing increasing reliability of copper-based metallization structures in a microstructure device by using aluminum nitride

ActiveUS7829460B2Reduce parasitic capacitanceEasy to controlSemiconductor/solid-state device detailsSolid-state devicesSelf limitingPermittivity

Owner:GLOBALFOUNDRIES U S INC

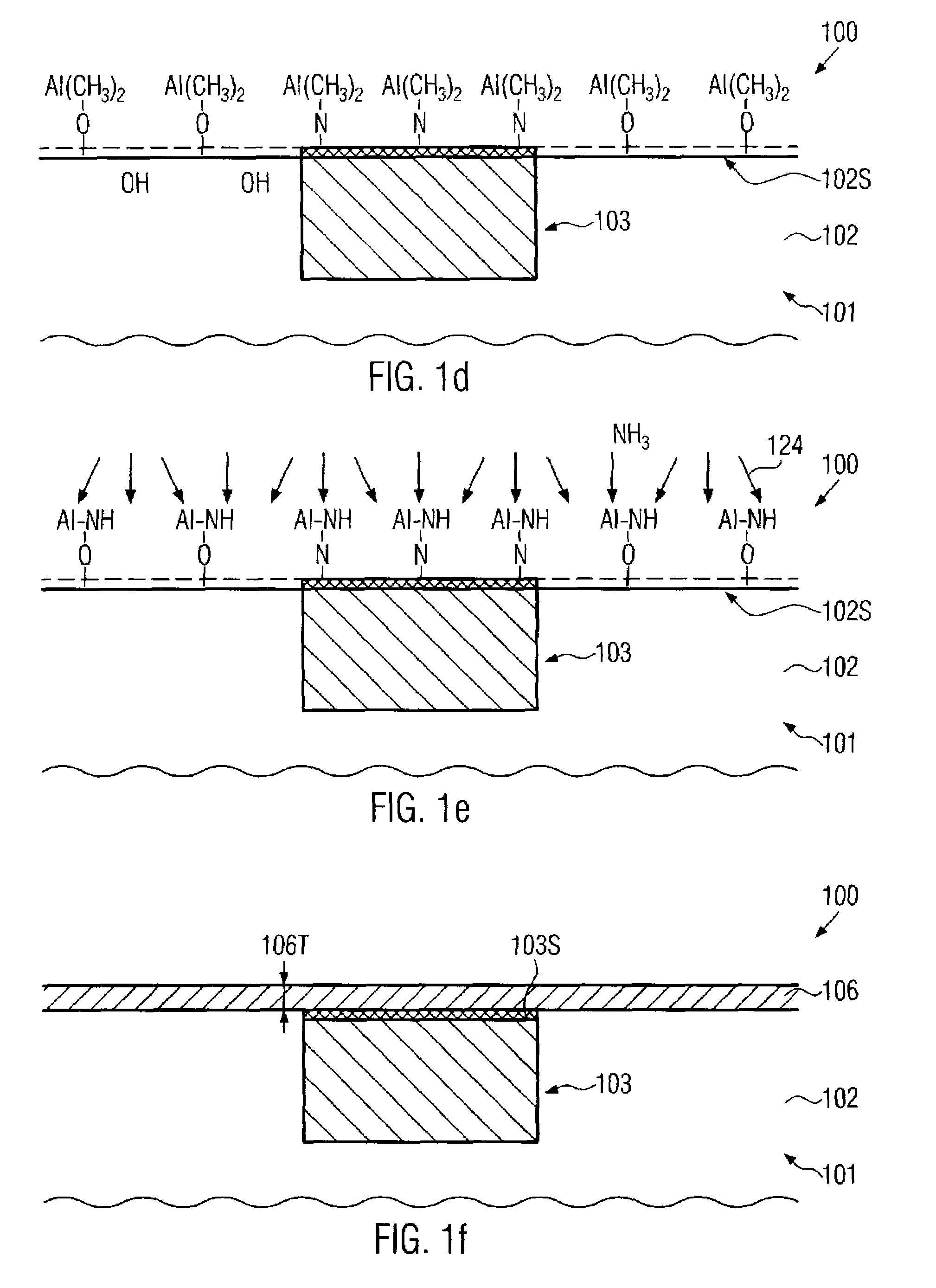

Semiconductor device and manufacturing method thereof

ActiveUS20120161126A1Reduce parasitic capacitanceIncrease speedTransistorSolid-state devicesDevice materialWurtzite crystal structure

A semiconductor device capable of high speed operation is provided. Further, a semiconductor device in which change in electric characteristics due to a short channel effect is hardly caused is provided. An oxide semiconductor having crystallinity is used for a semiconductor layer of a transistor. A channel formation region, a source region, and a drain region are formed in the semiconductor layer. The source region and the drain region are formed by self-aligned process in which one or more elements selected from Group 15 elements are added to the semiconductor layer with the use of a gate electrode as a mask. The source region and the drain region can have a wurtzite crystal structure.

Owner:SEMICON ENERGY LAB CO LTD

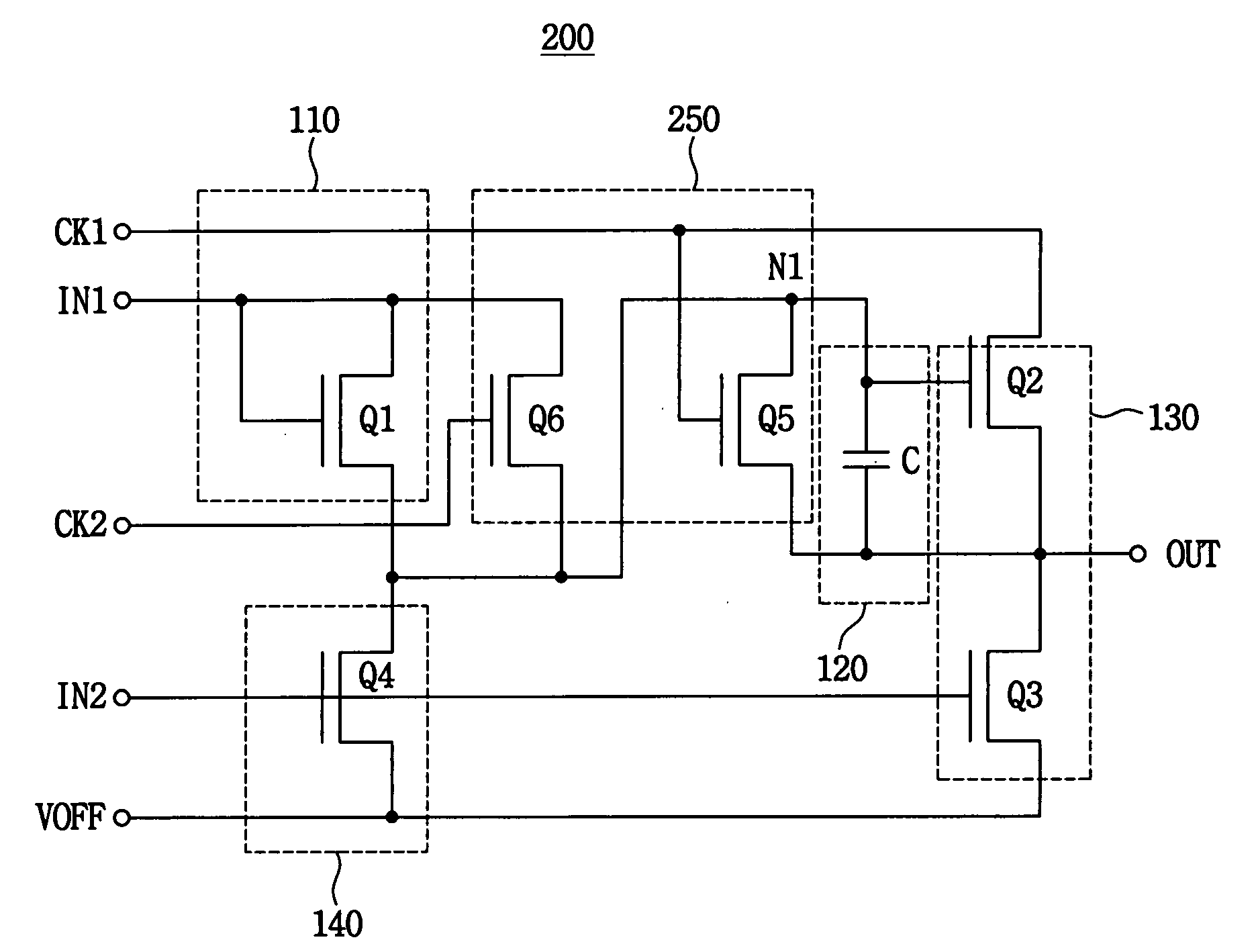

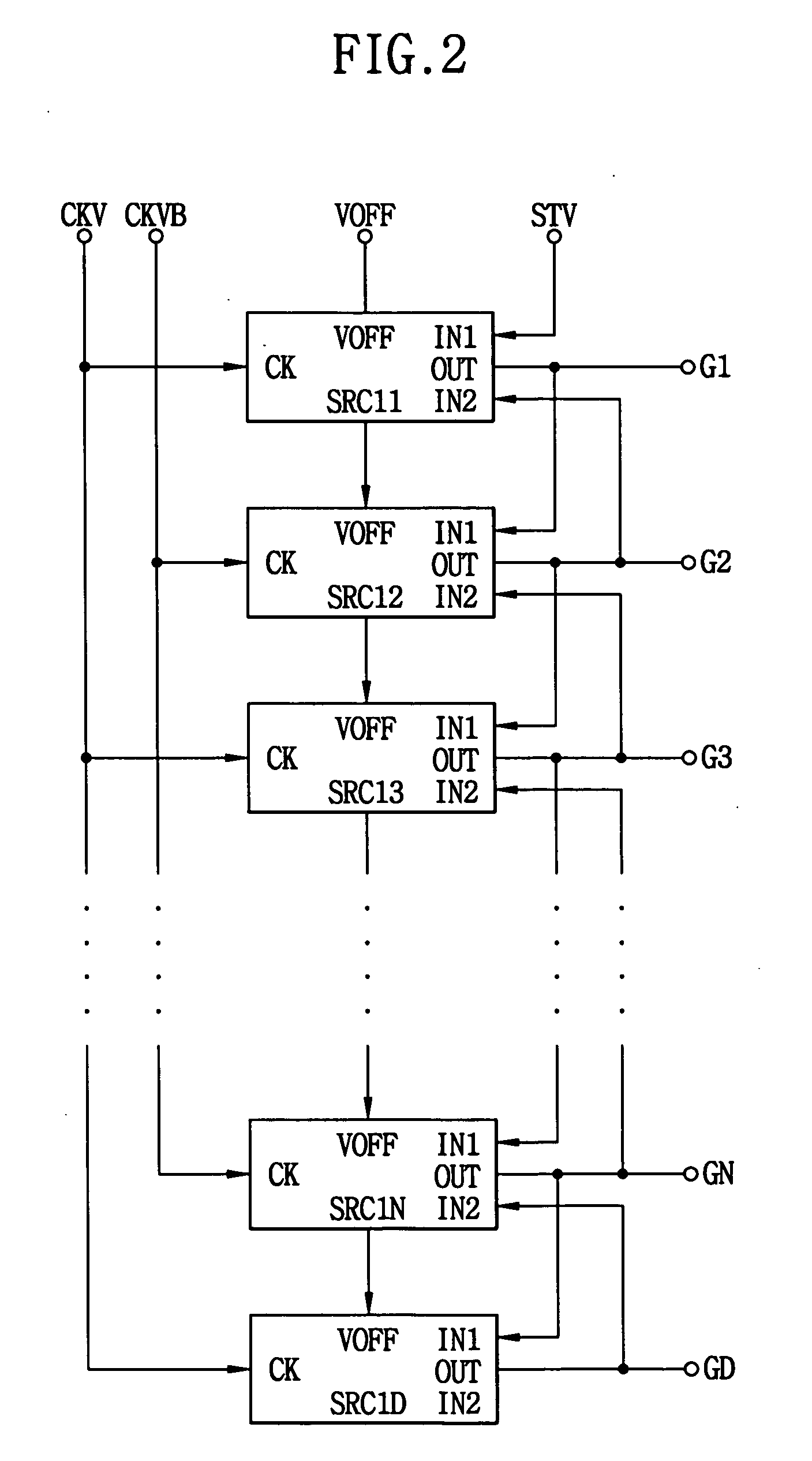

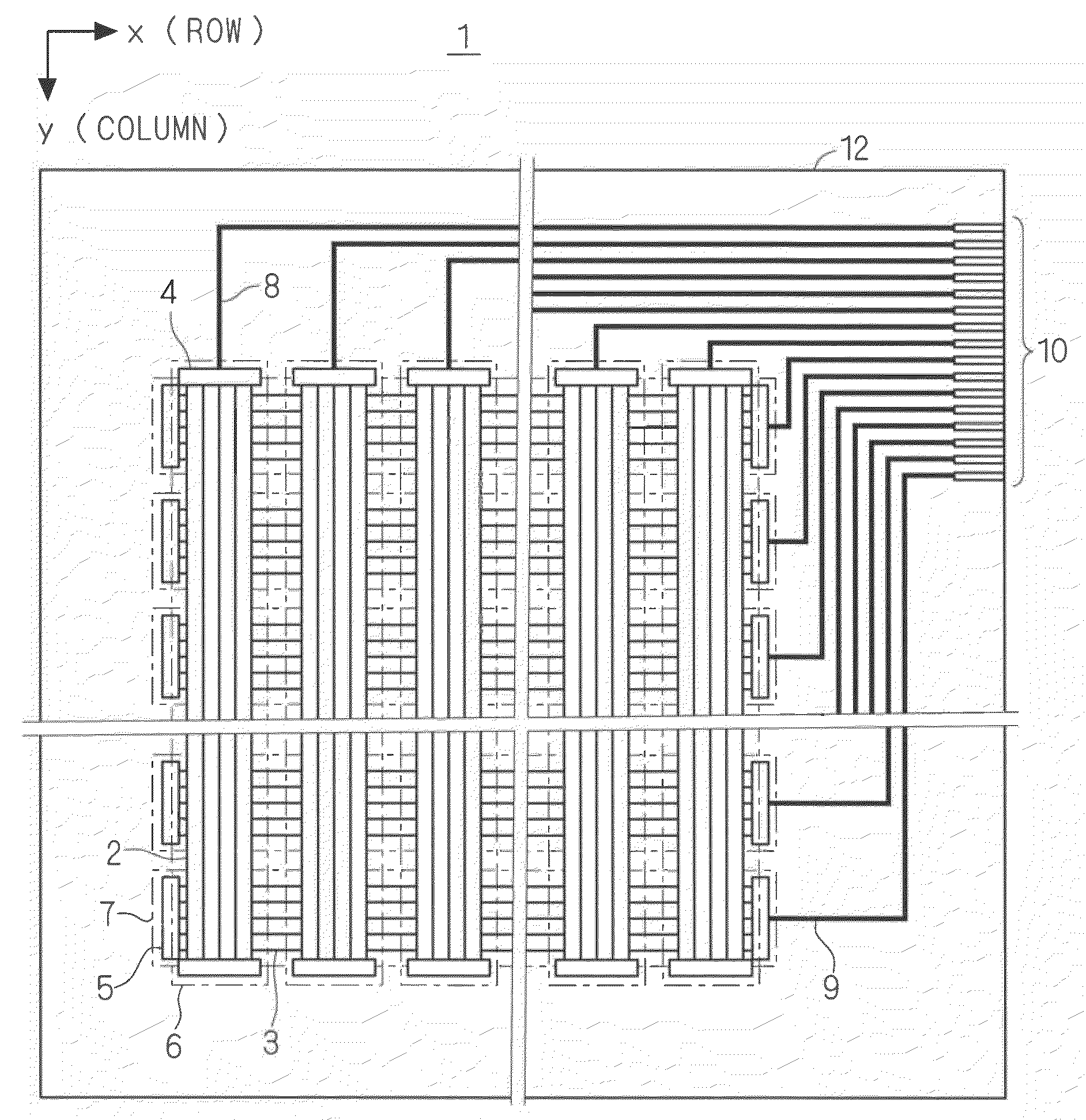

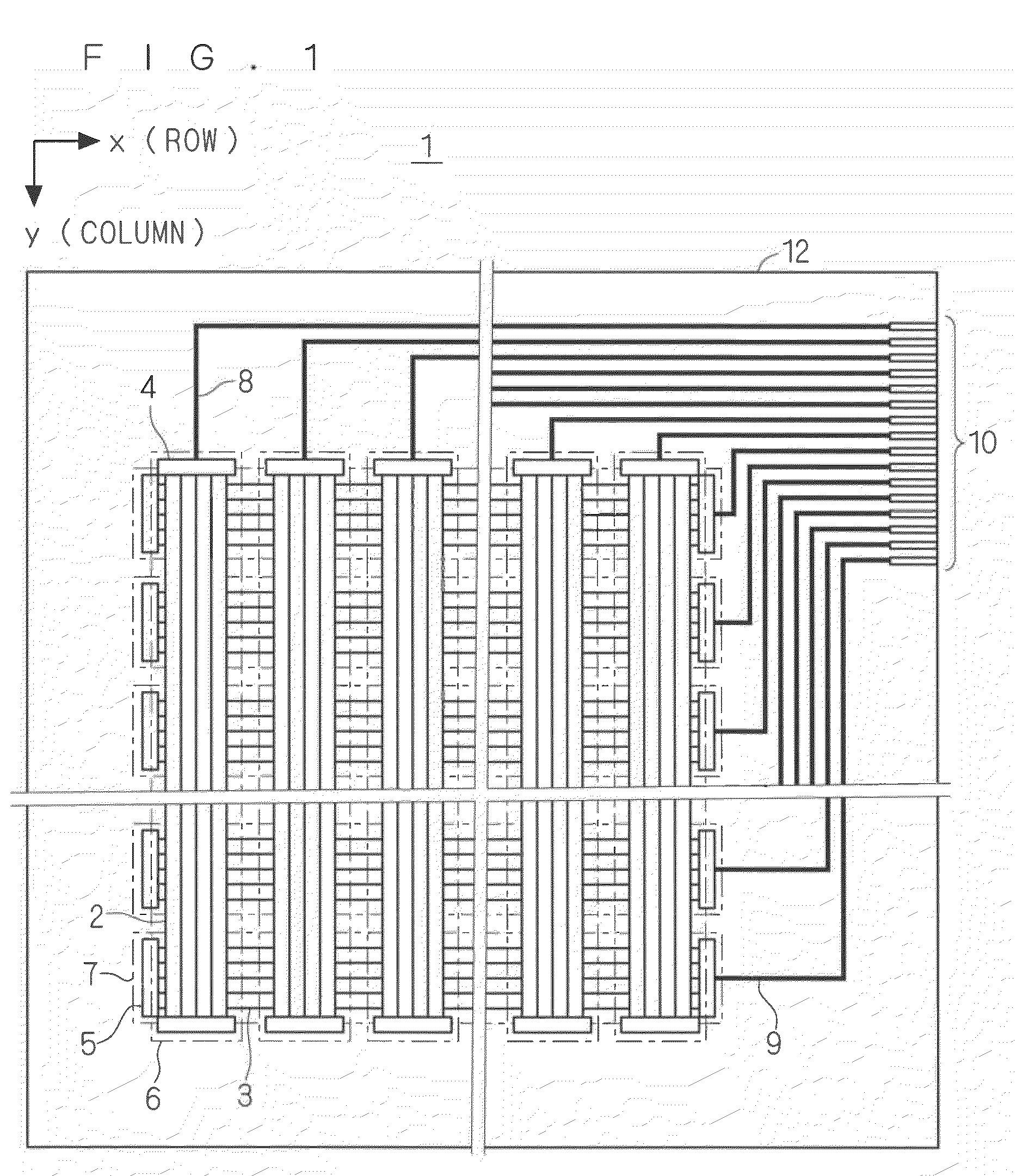

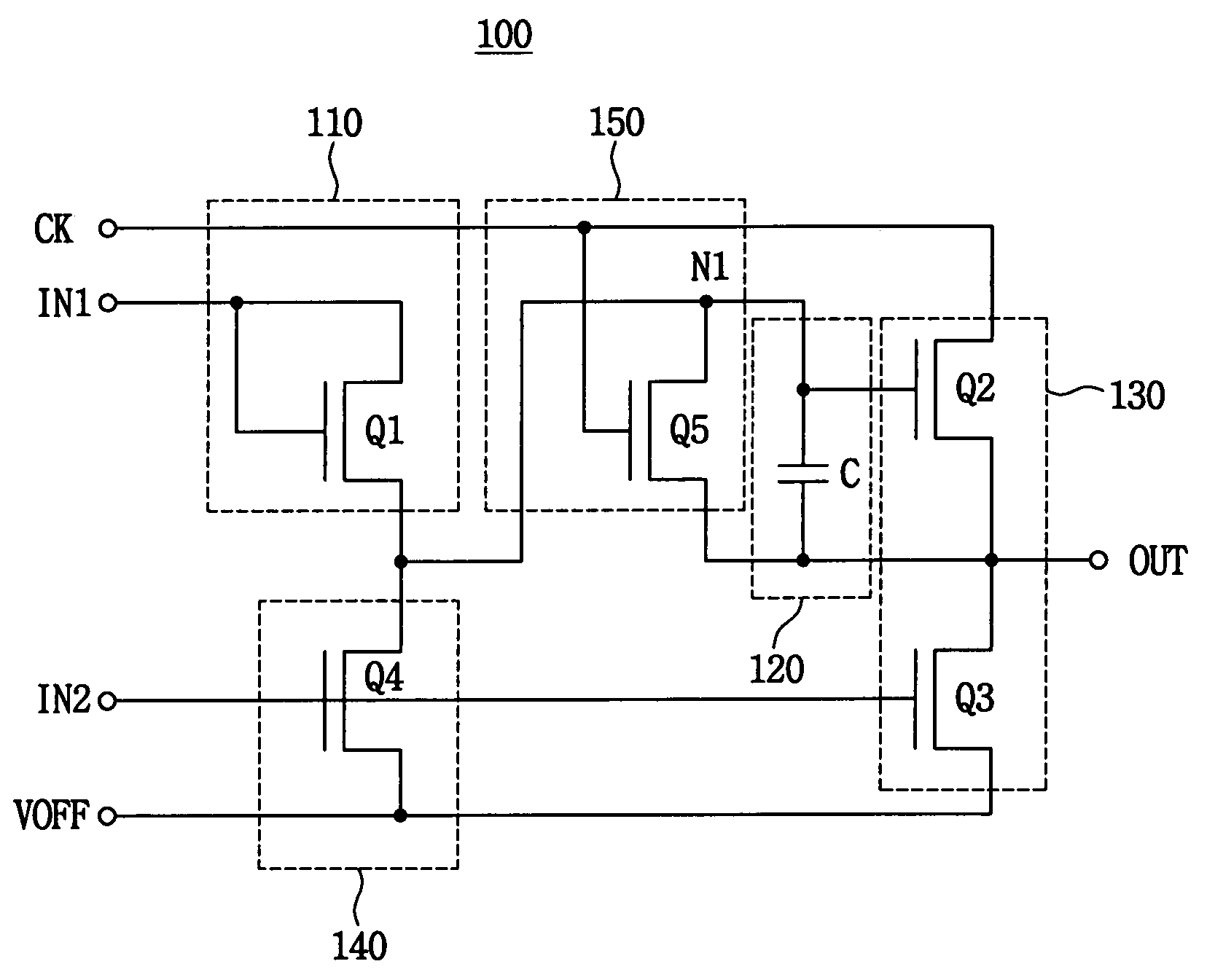

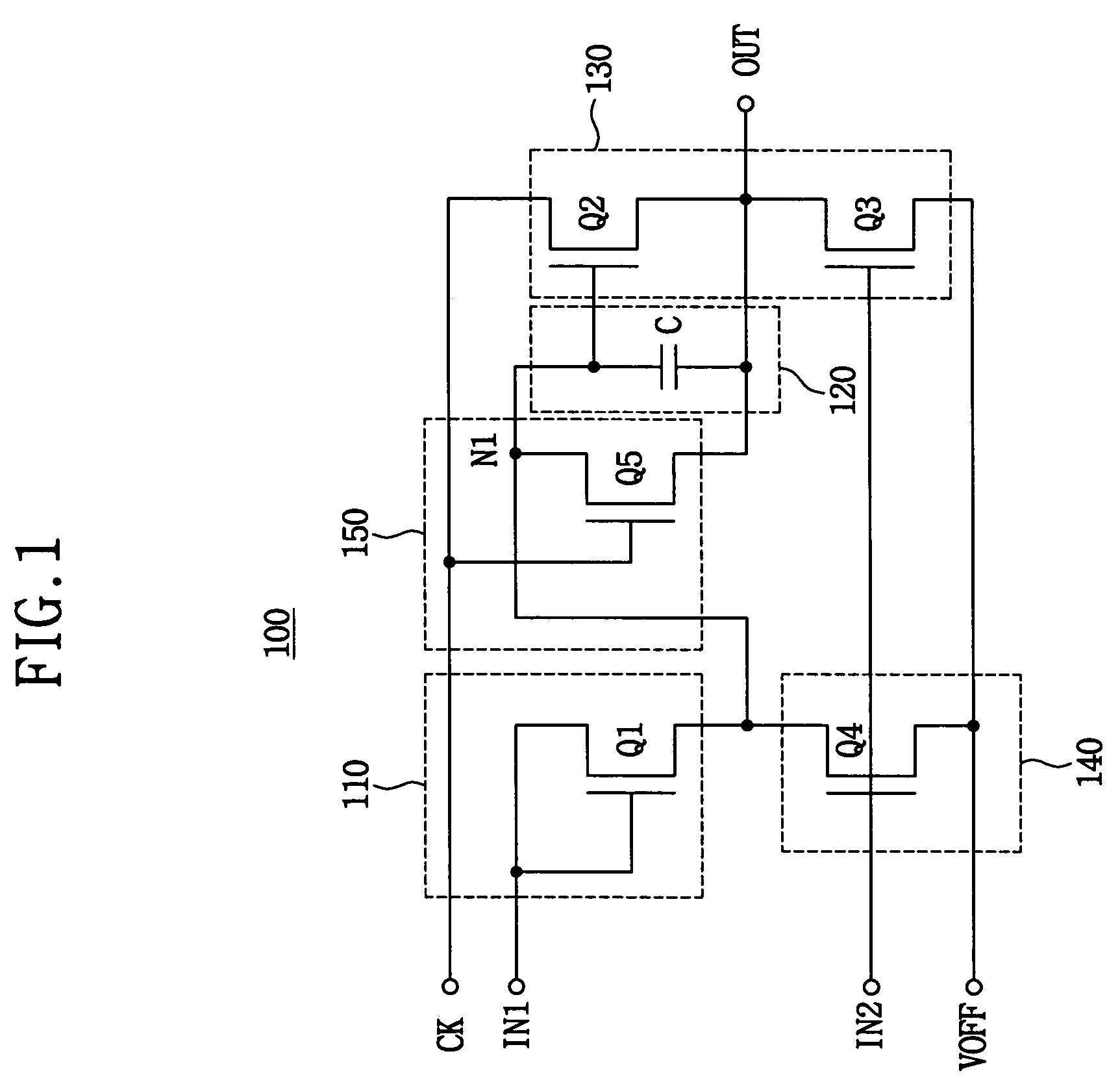

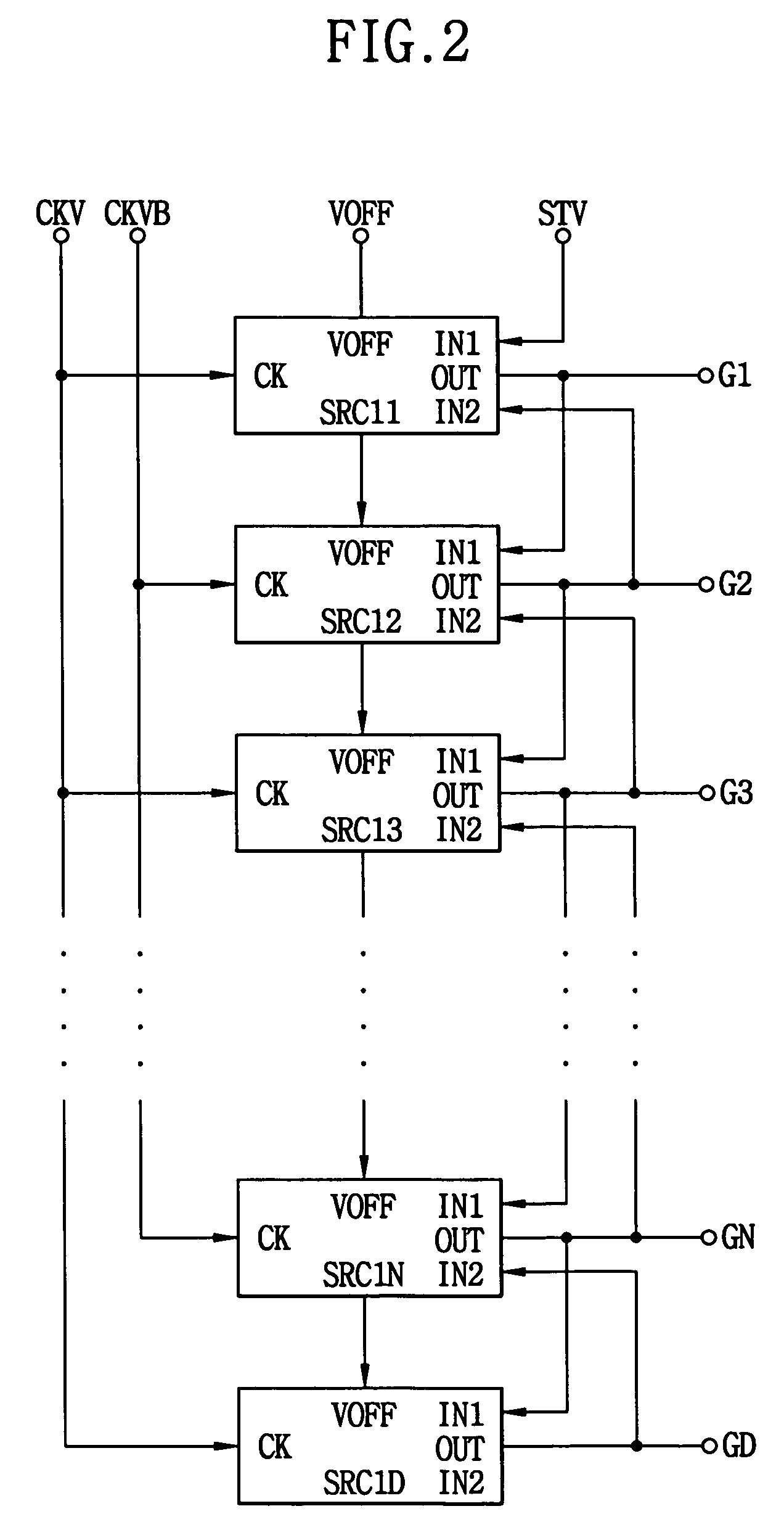

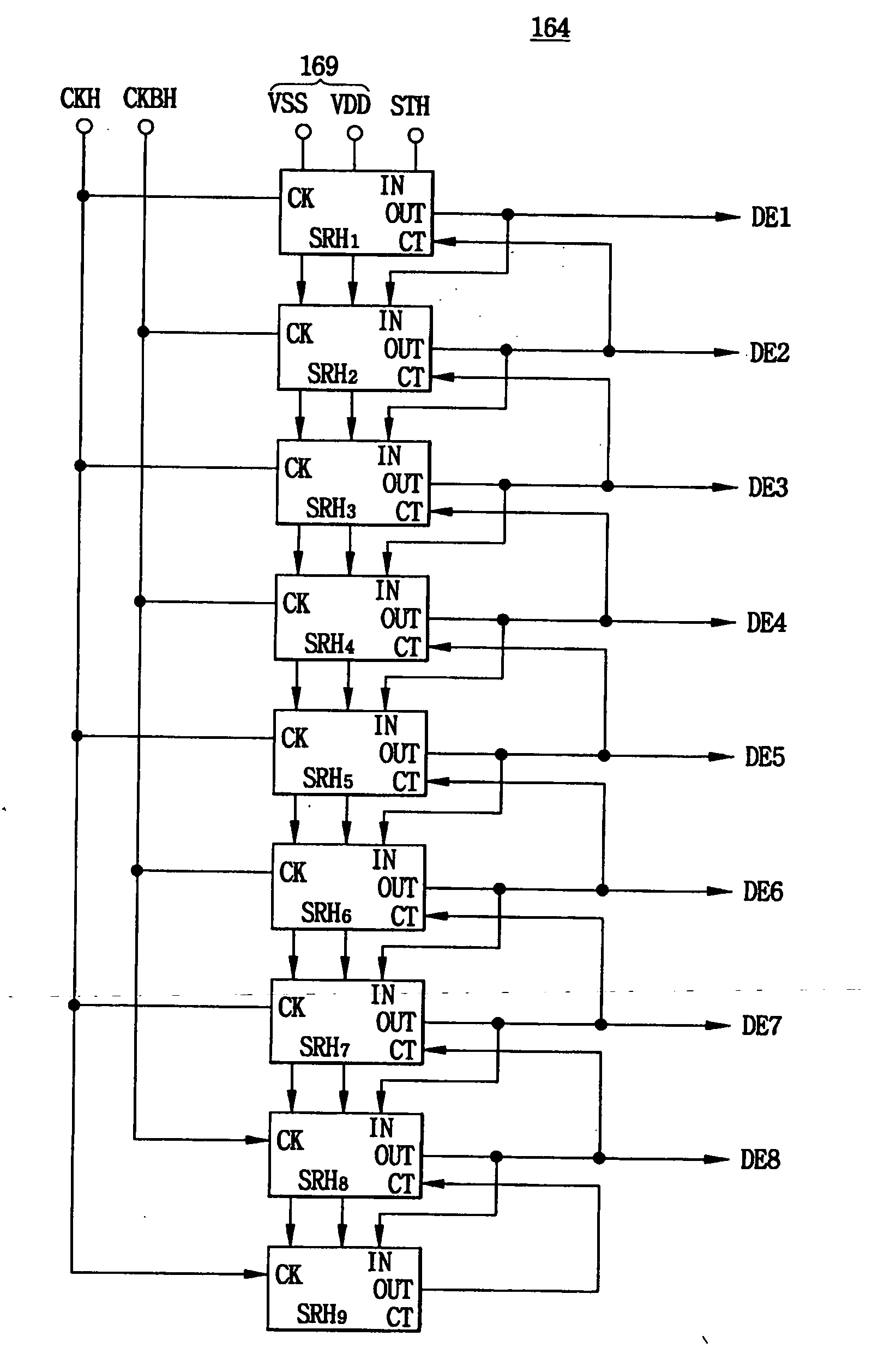

Shift register, scan driving circuit and display apparatus having the same

ActiveUS20050008114A1Reduce parasitic capacitancePrevent floatingStatic indicating devicesDigital storageStart signalEngineering

A shift register includes a plurality of stages to generate a plurality of output signals, in sequence. Each of the stages includes a driving circuit, a charging circuit, a discharging circuit and a holding circuit. The driving circuit is configured to generate a first output signal in response to a first clock signal or a second clock signal having a phase different from the first clock signal. The charging circuit is configured to charge an electric charge in response to a scan start signal or a second output signal of an adjacent previous stage. The discharging circuit is configured to discharge the electric charge in response to a third output signal of an adjacent next stage. The holding circuit is configured to maintain the first output signal within a first voltage when the first output signal is in an inactive state. Therefore, a parasite capacitance is decreased to prevent a floating of a pull-up transistor.

Owner:SAMSUNG DISPLAY CO LTD

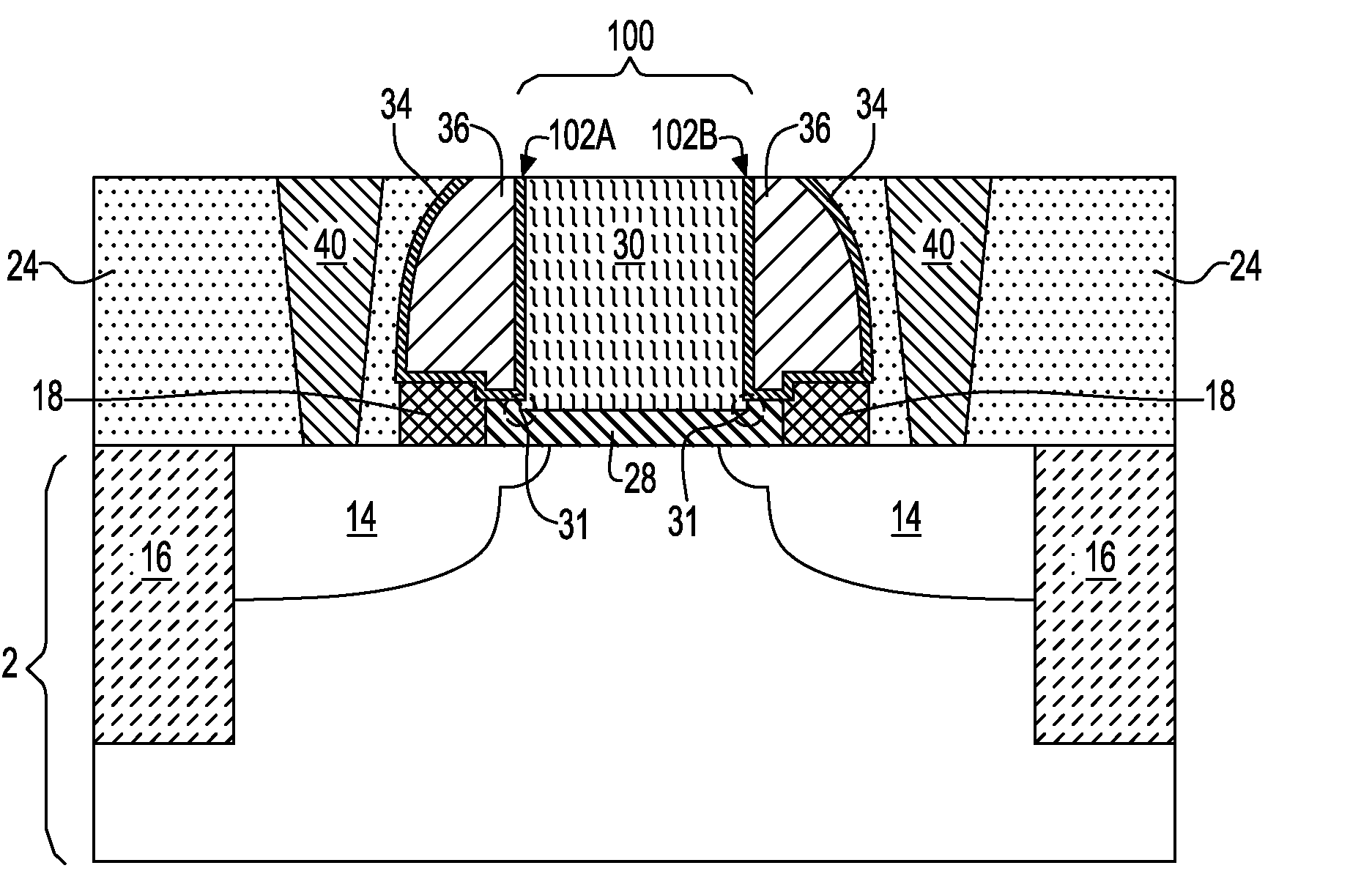

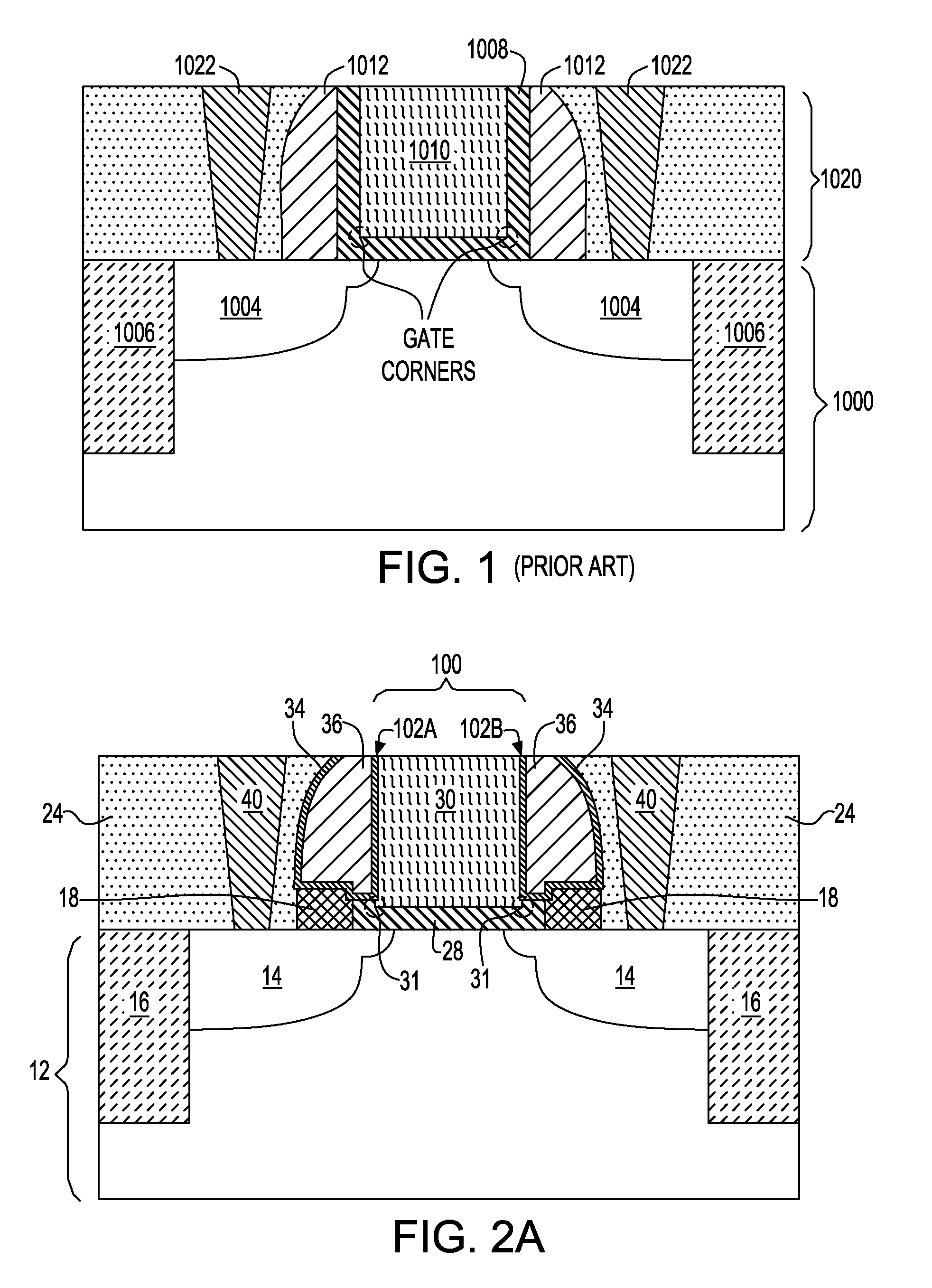

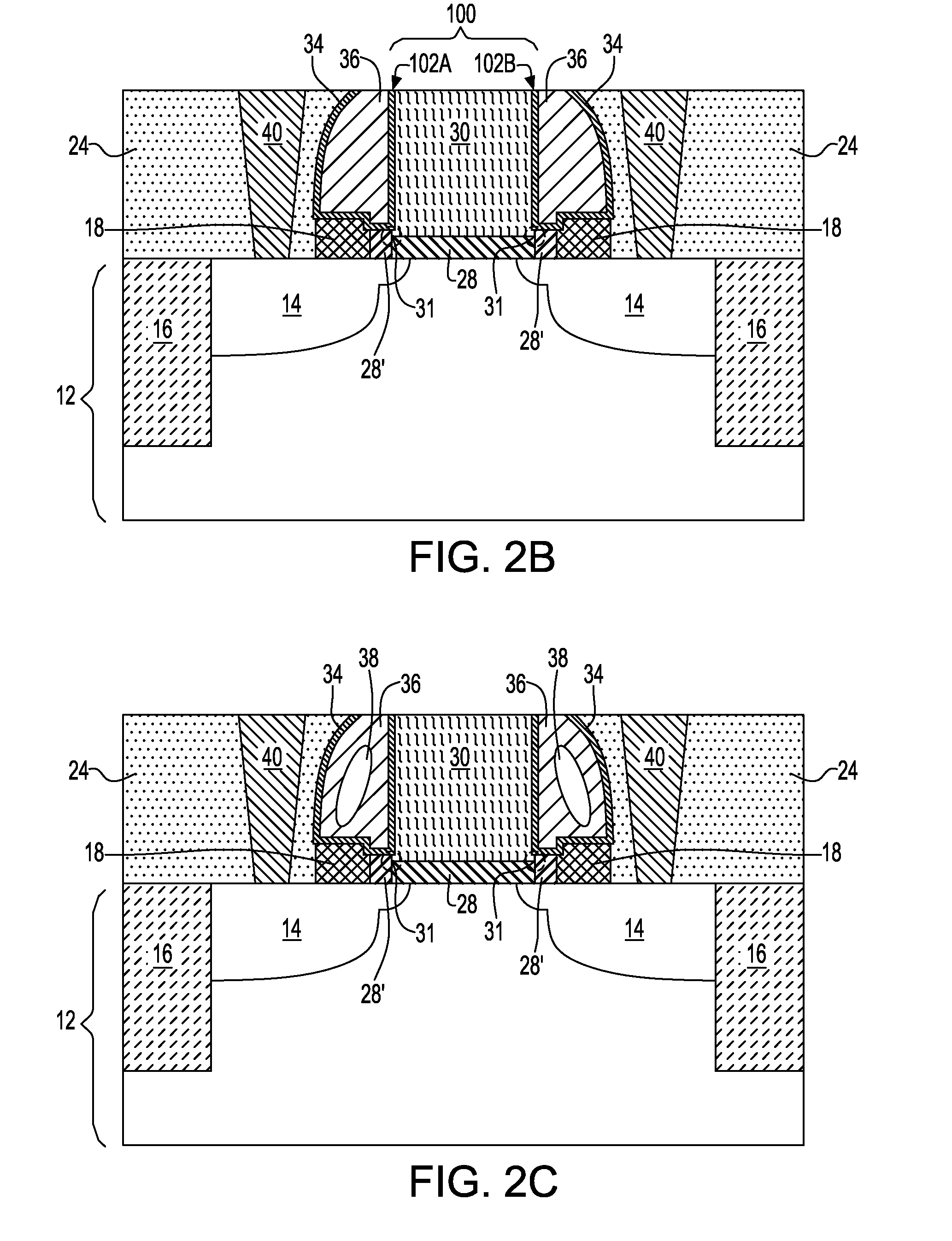

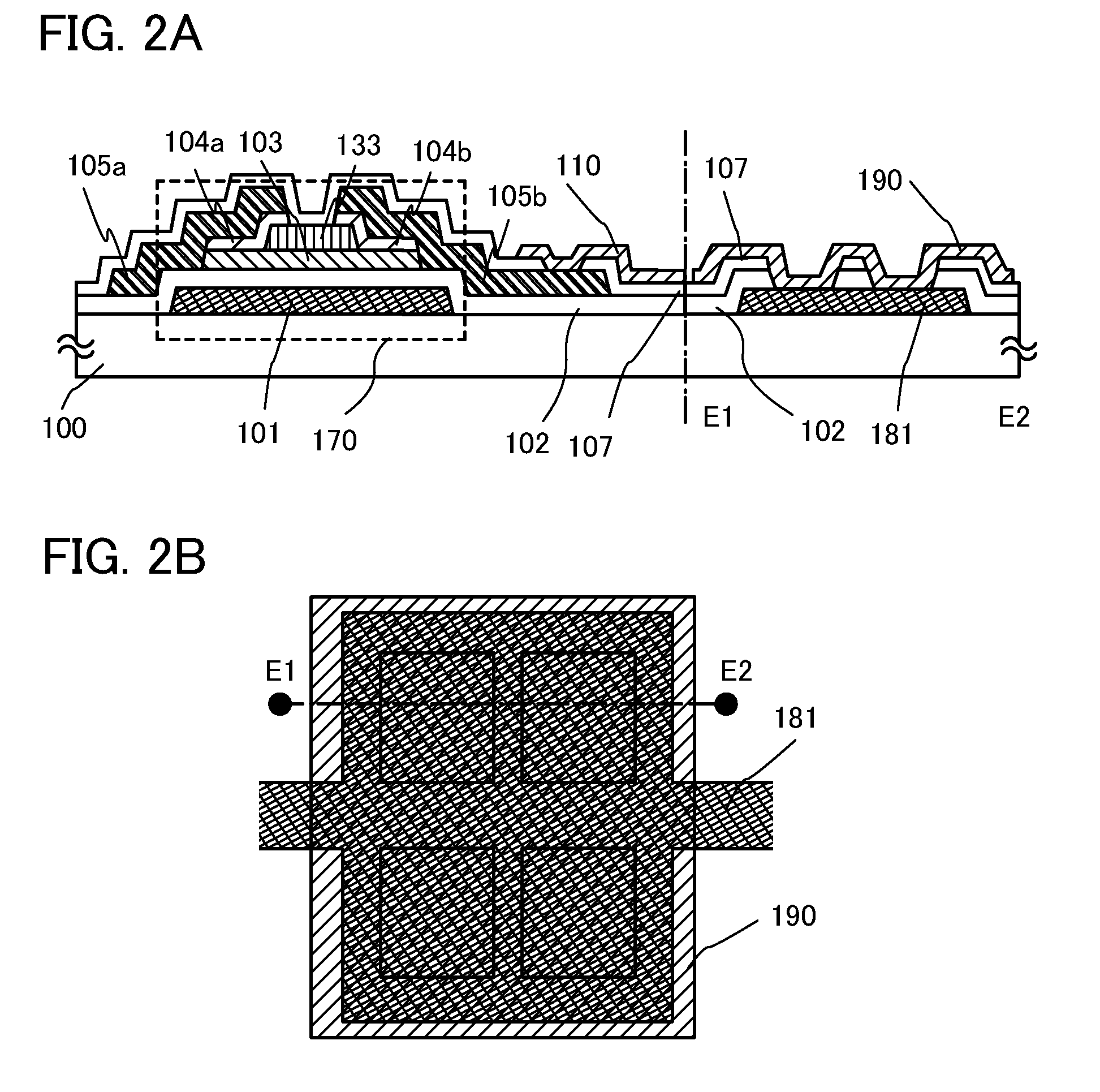

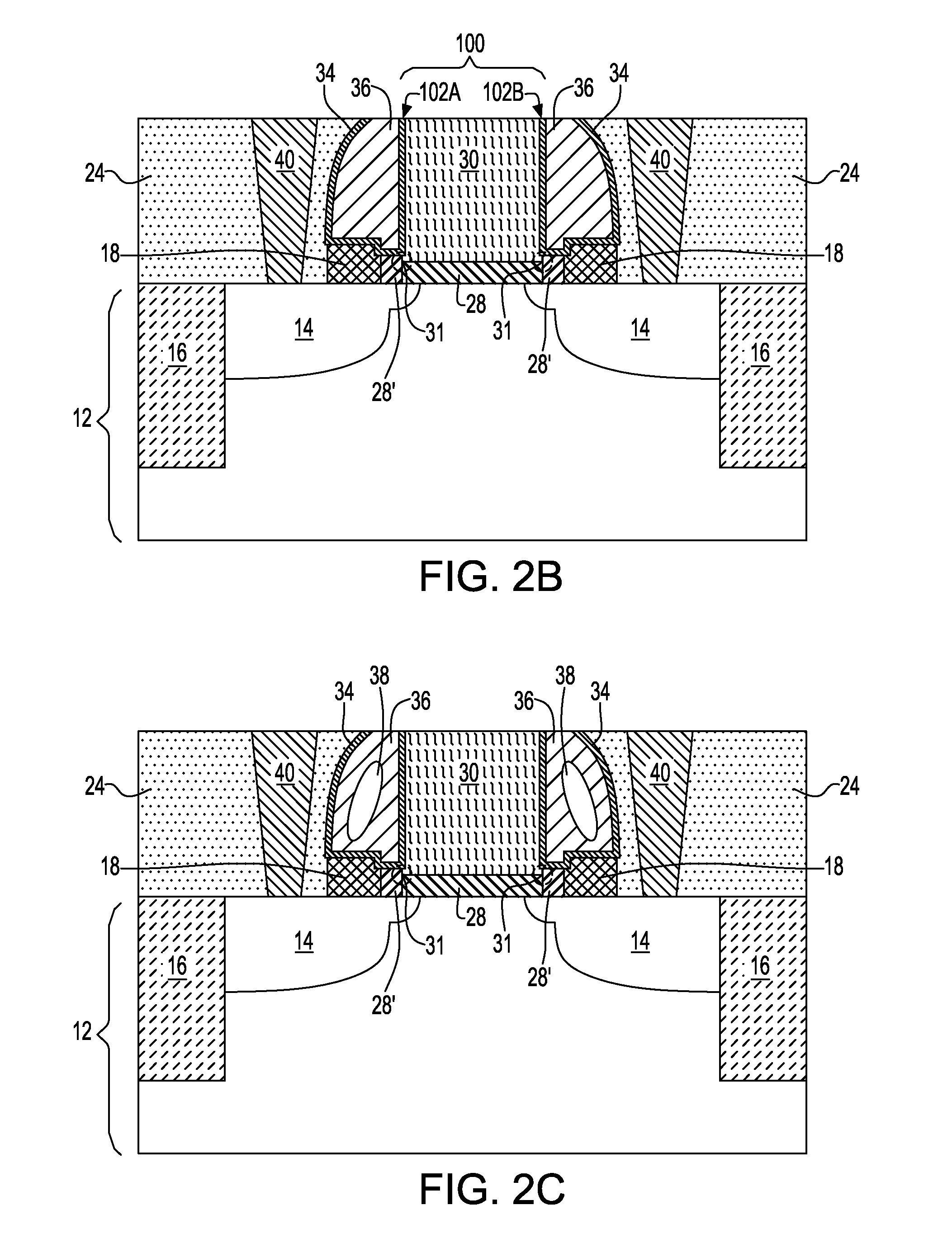

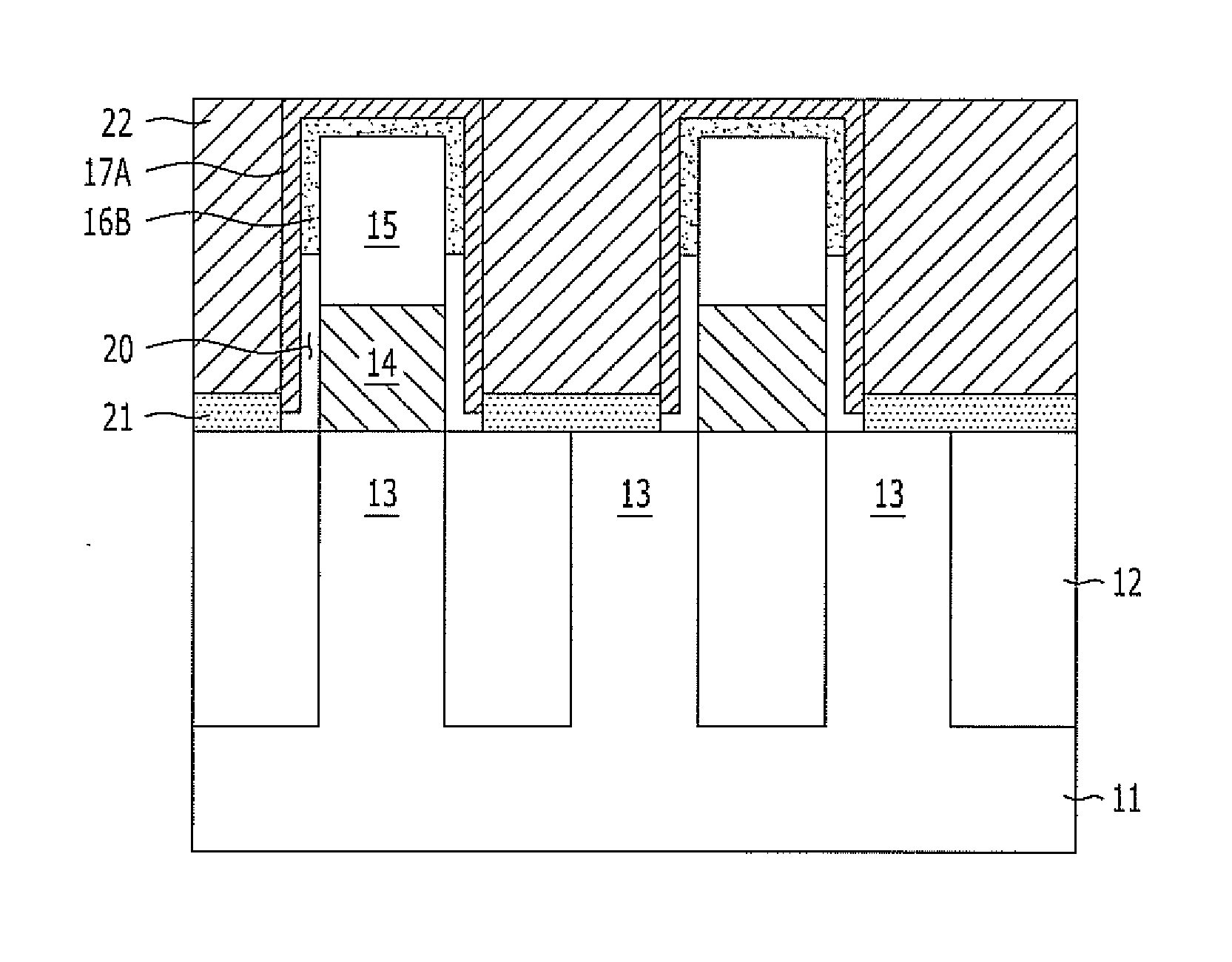

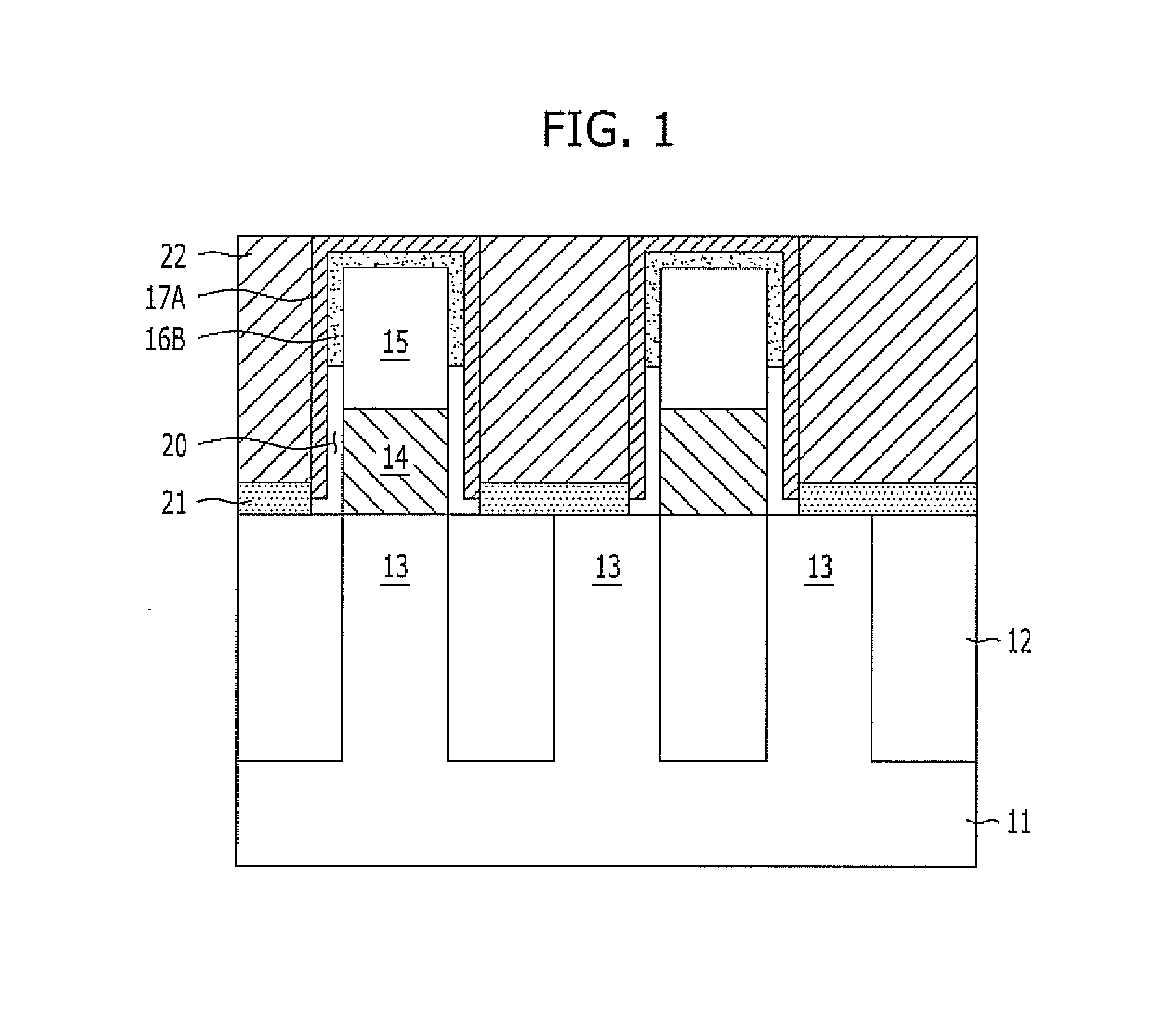

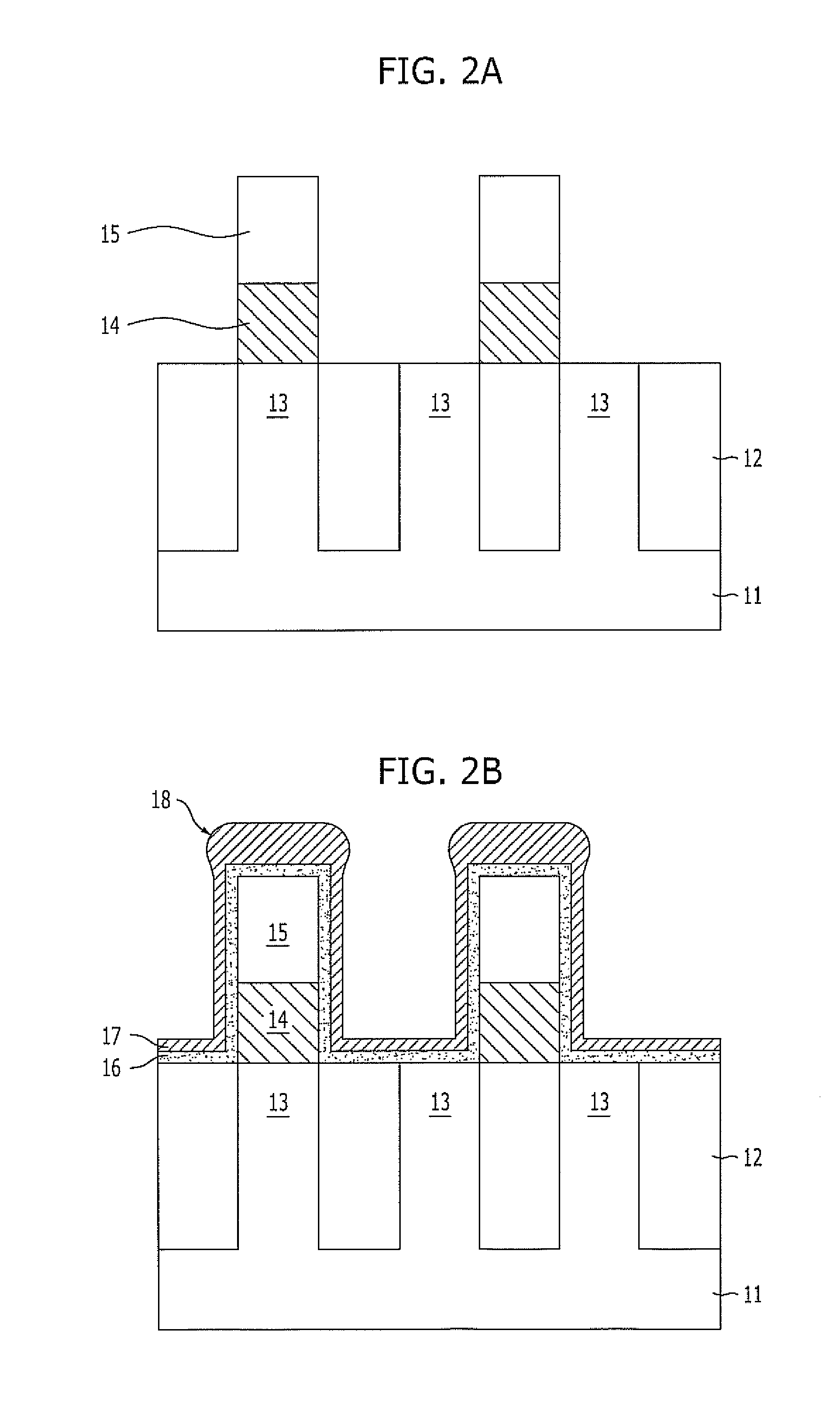

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

InactiveUS20090001480A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETElectrical conductor

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

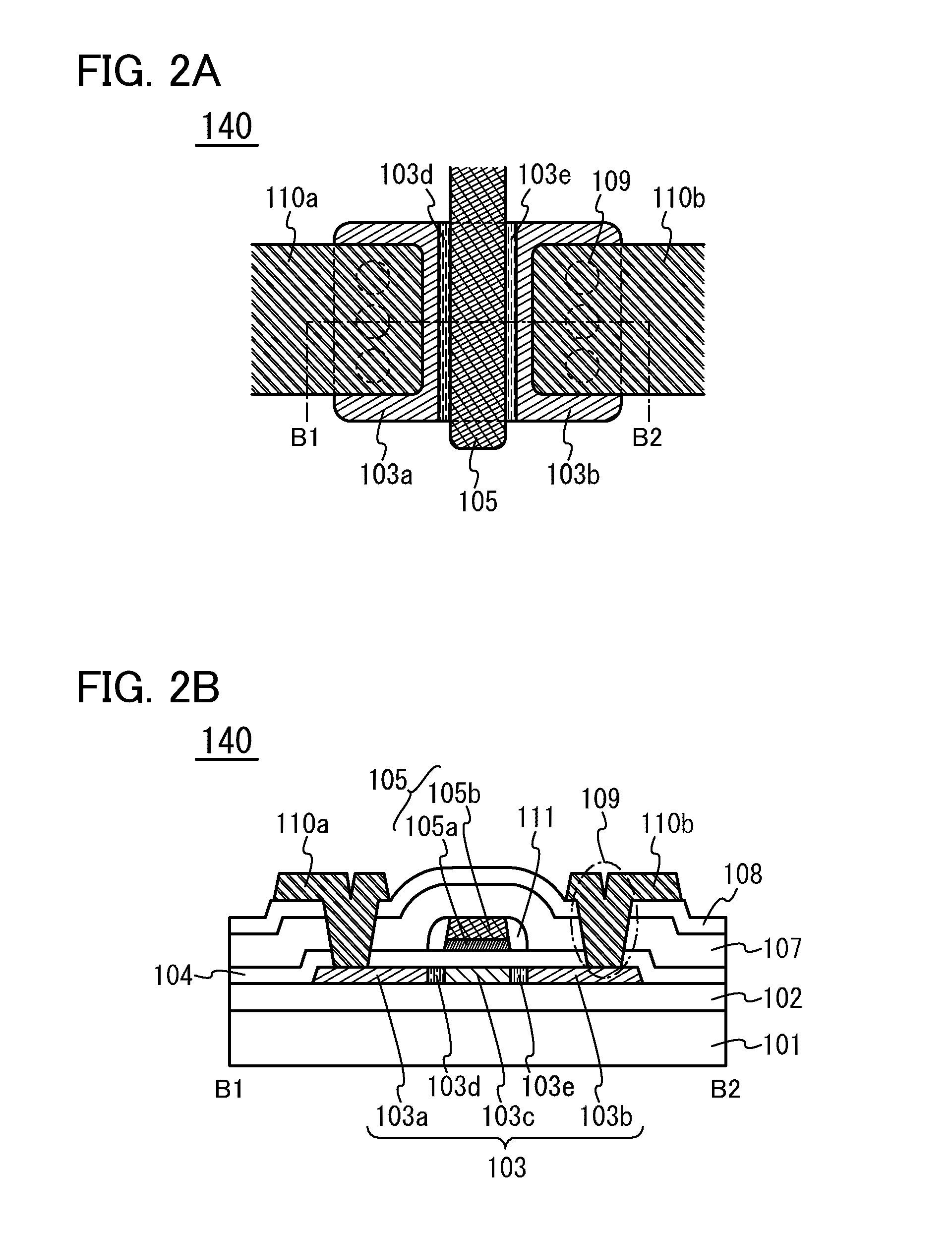

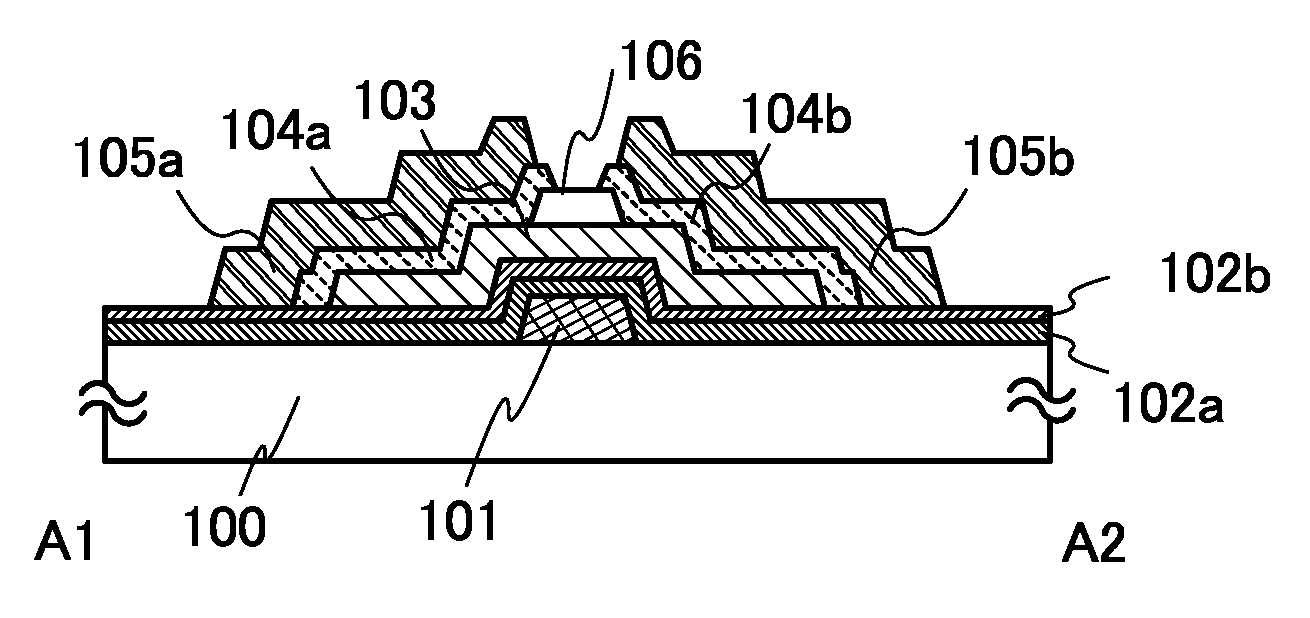

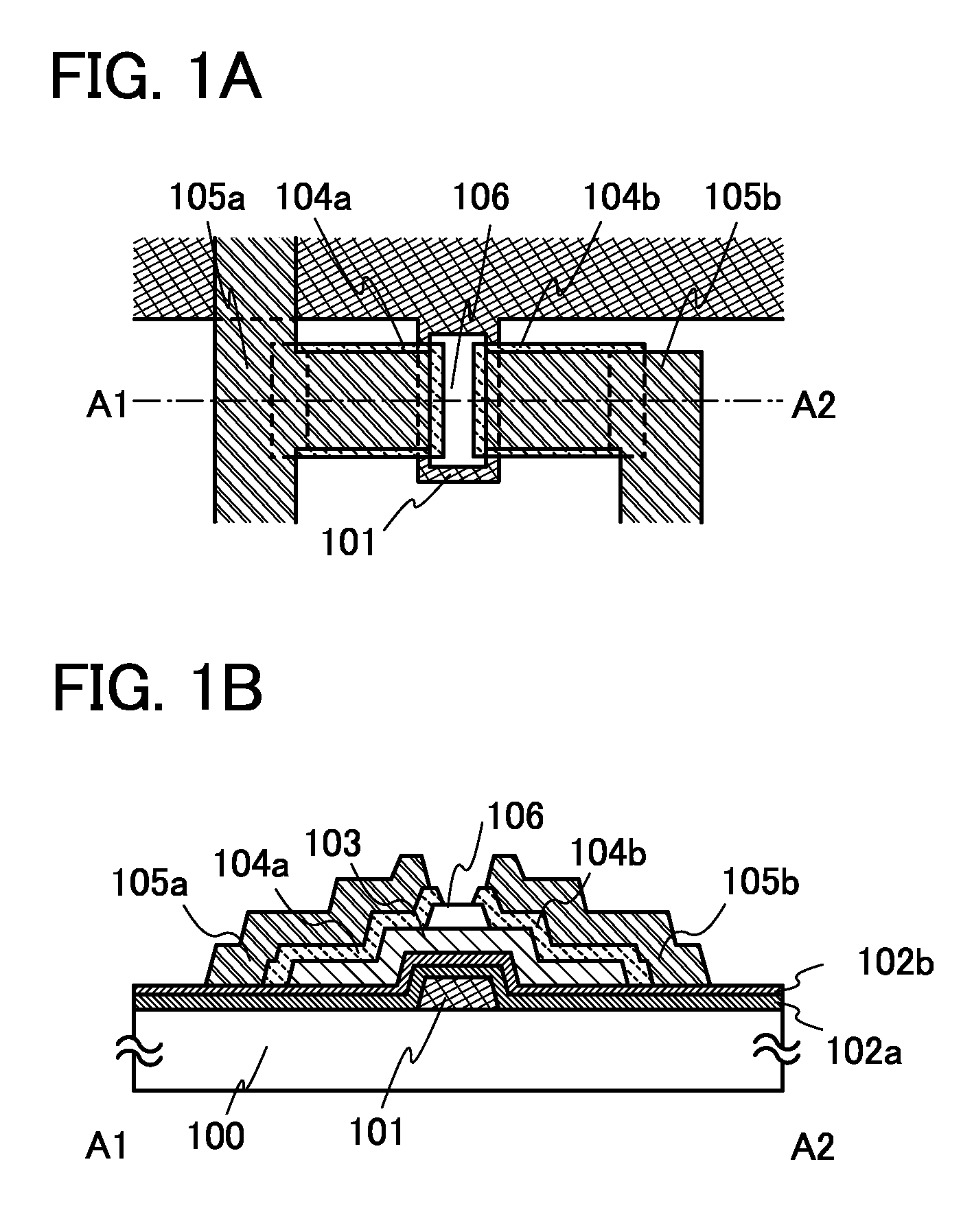

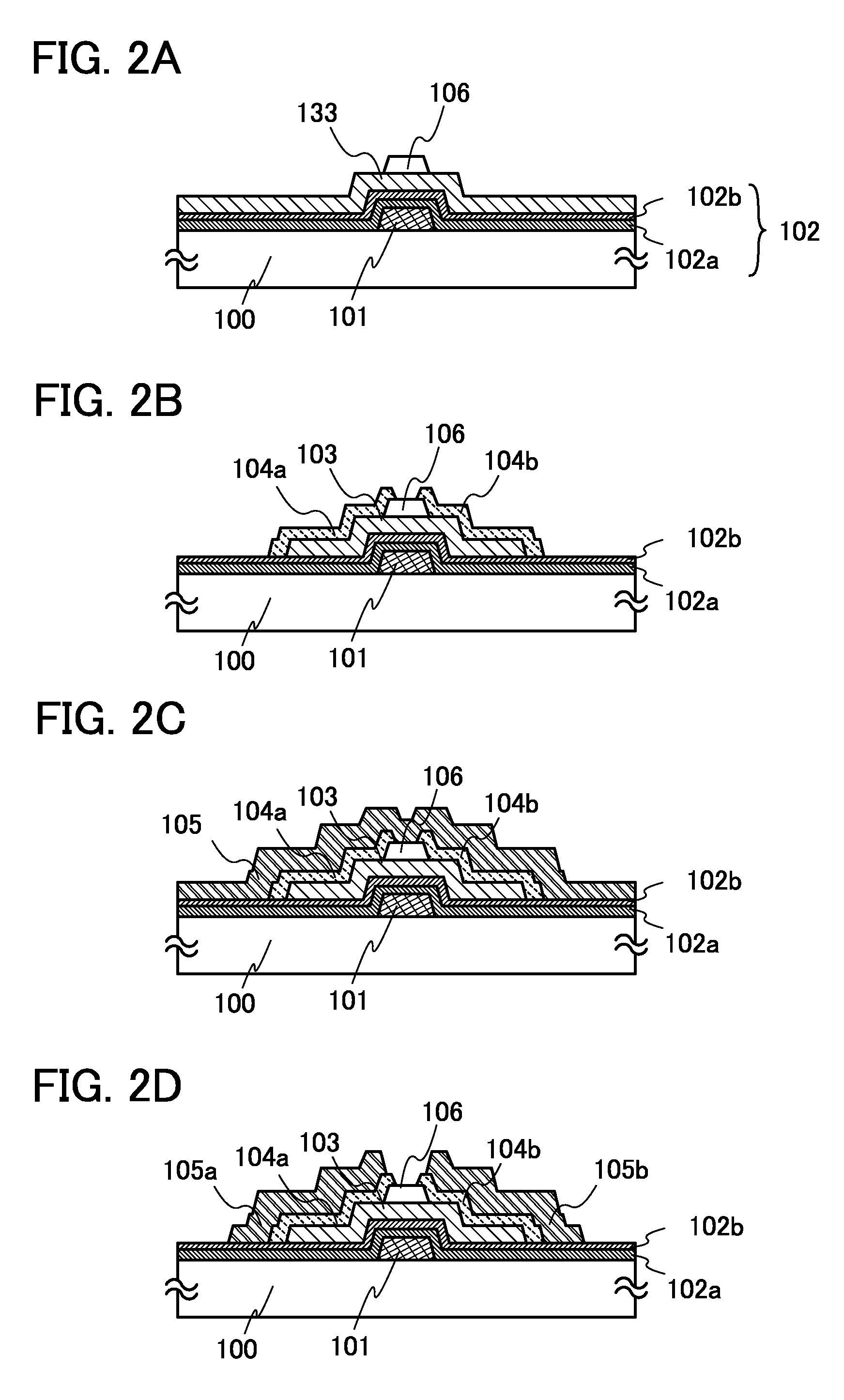

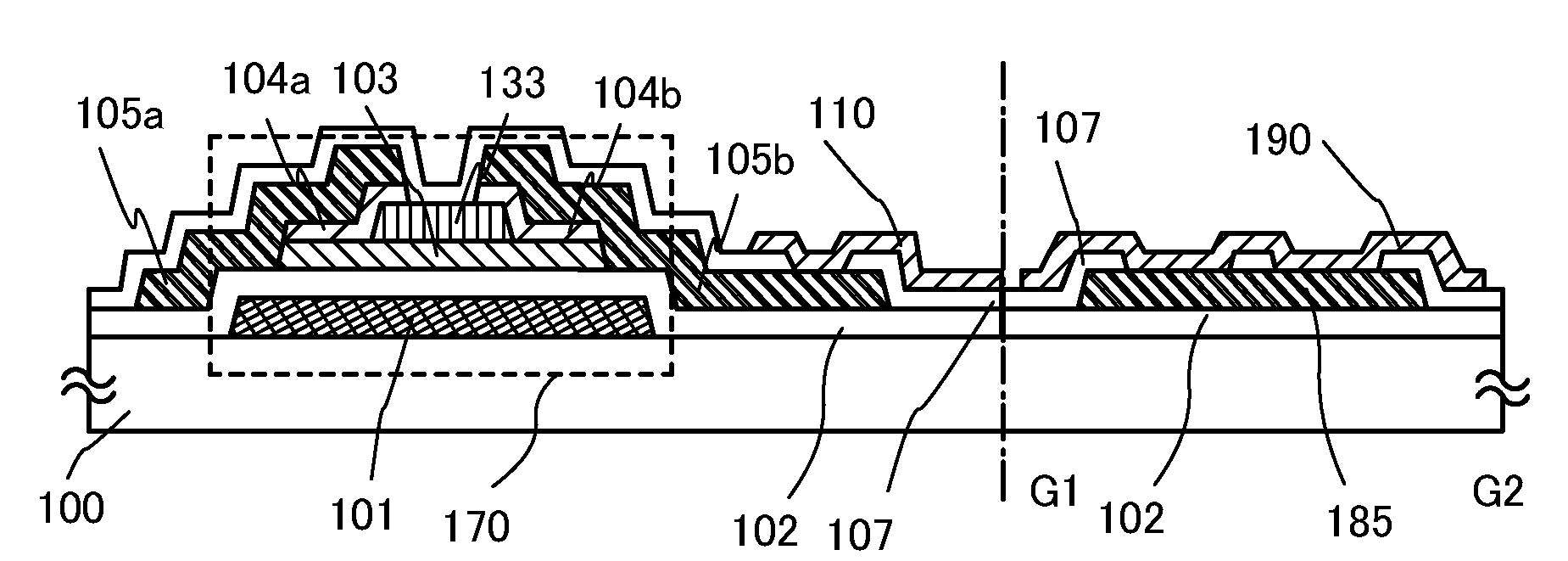

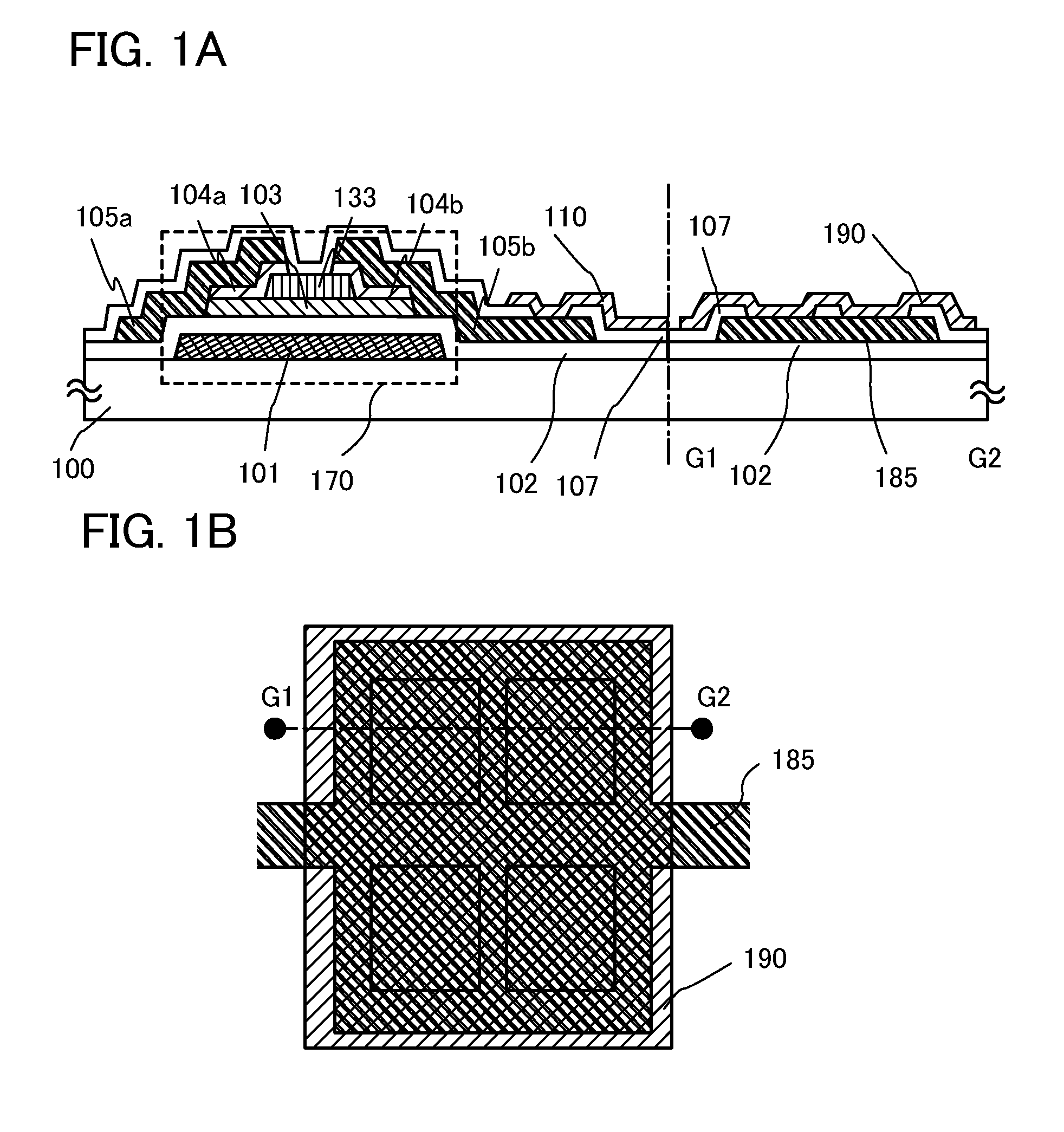

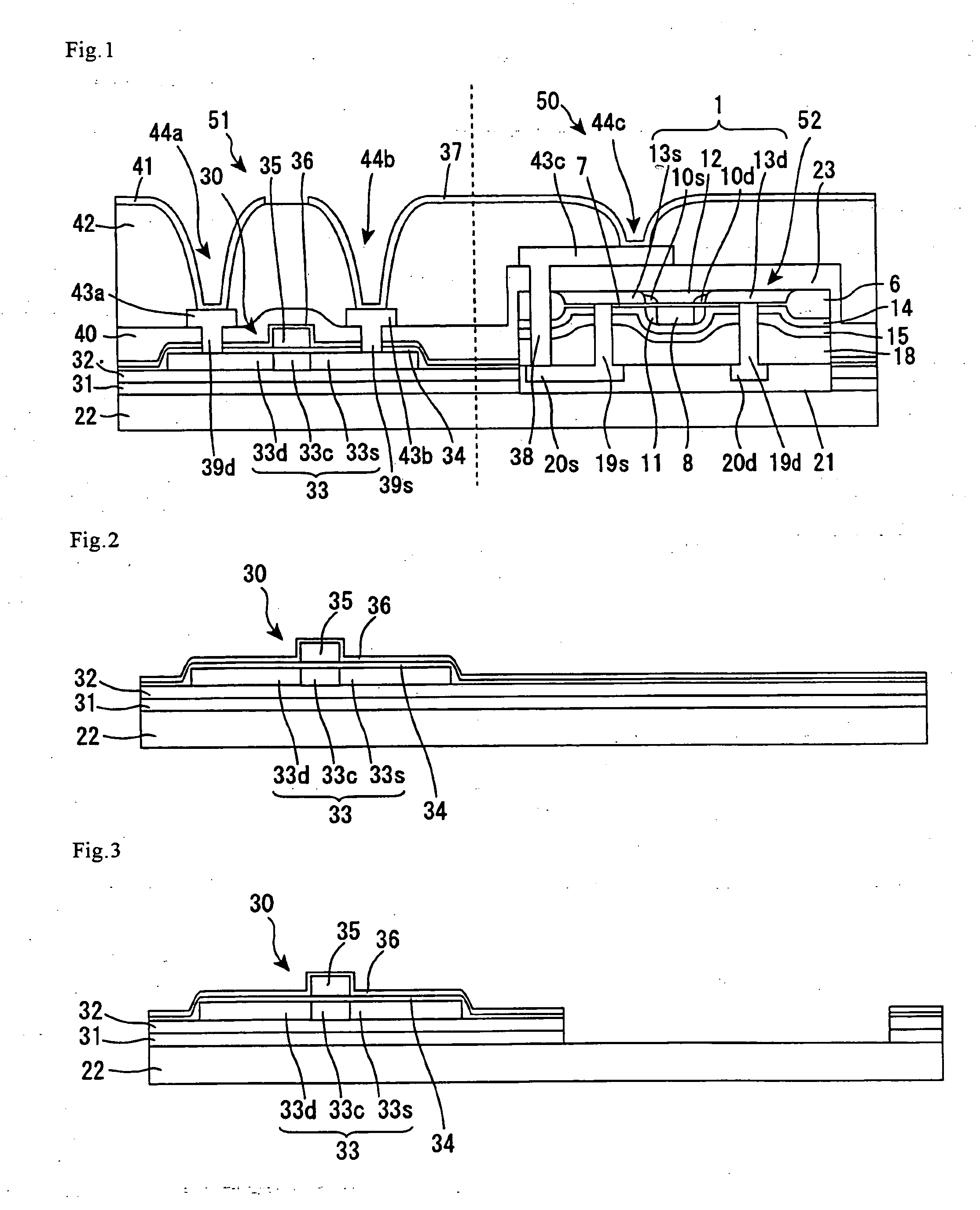

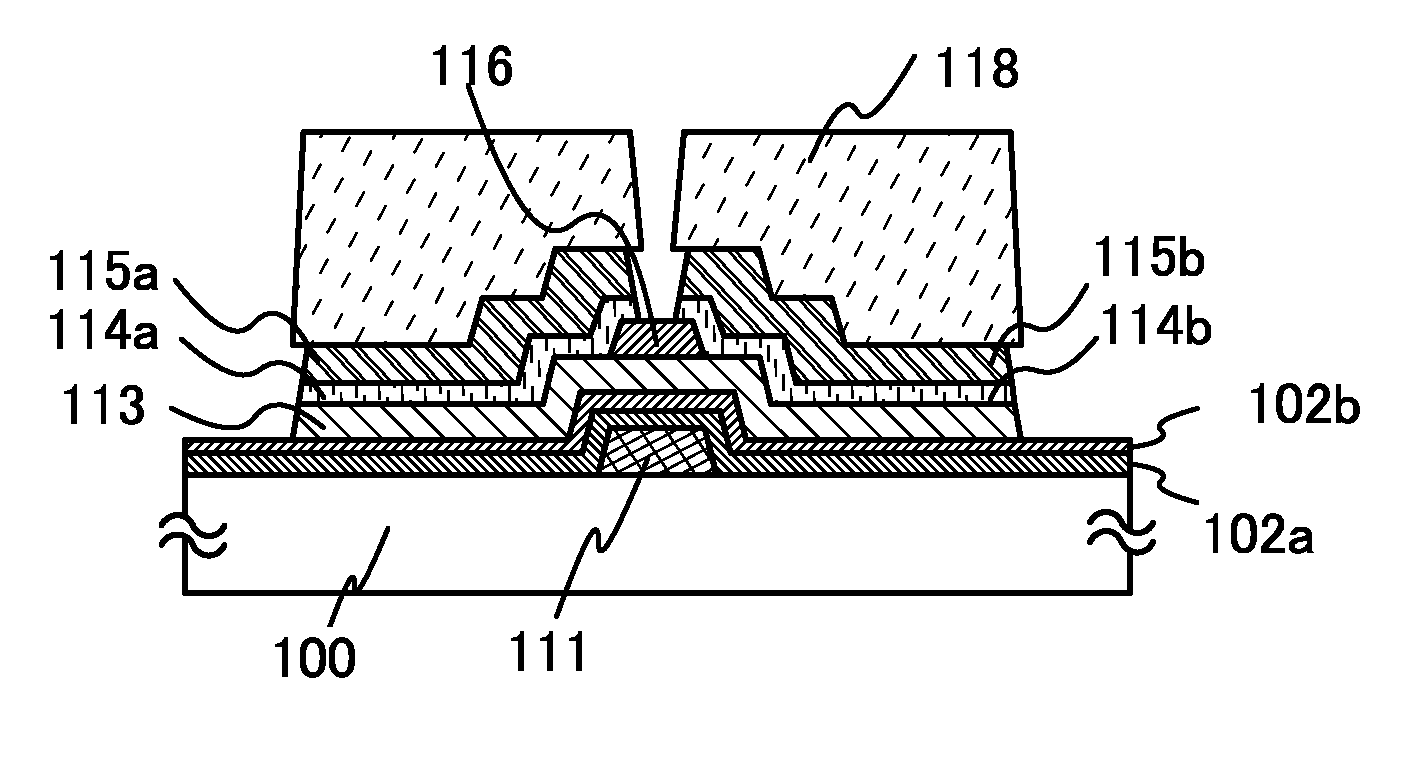

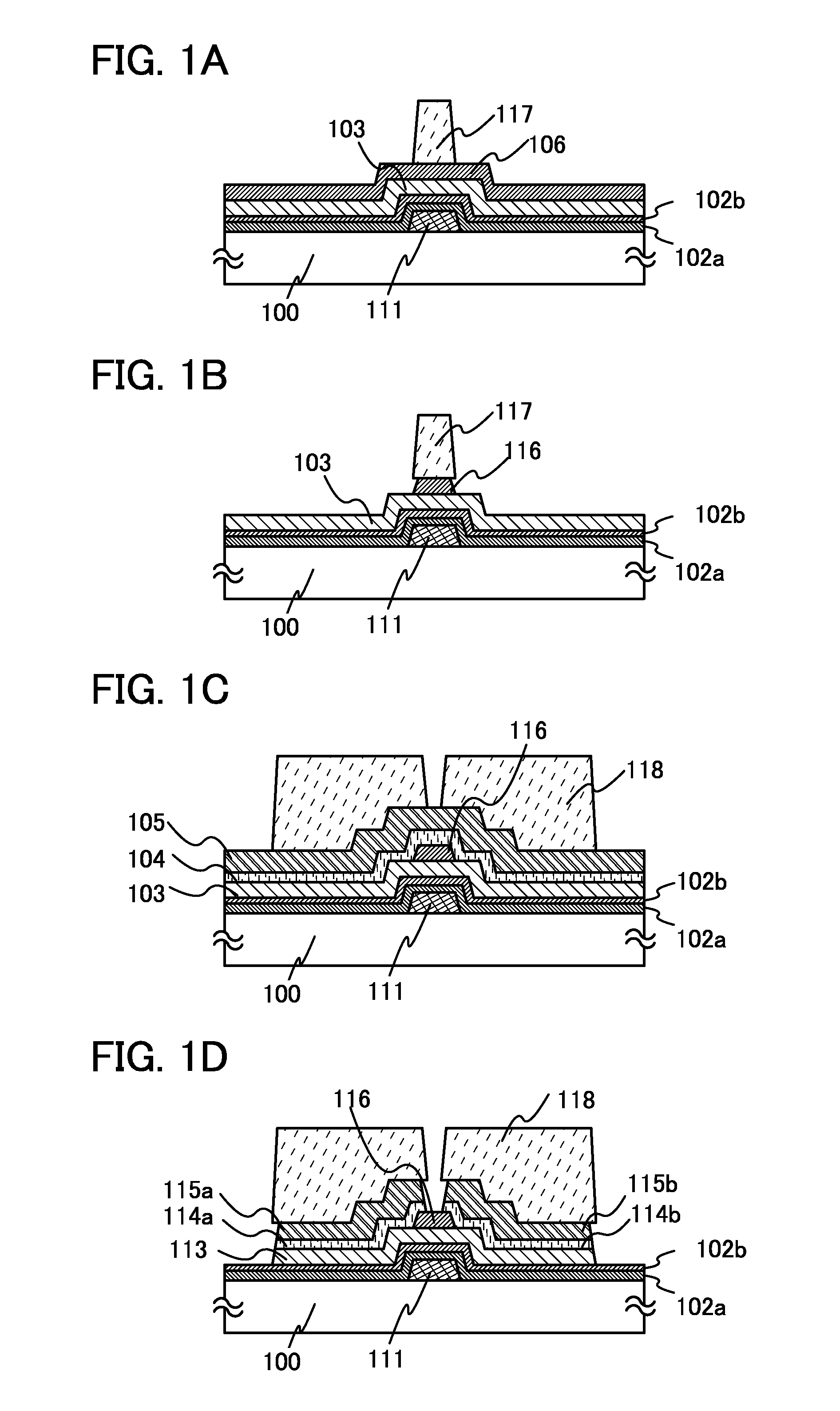

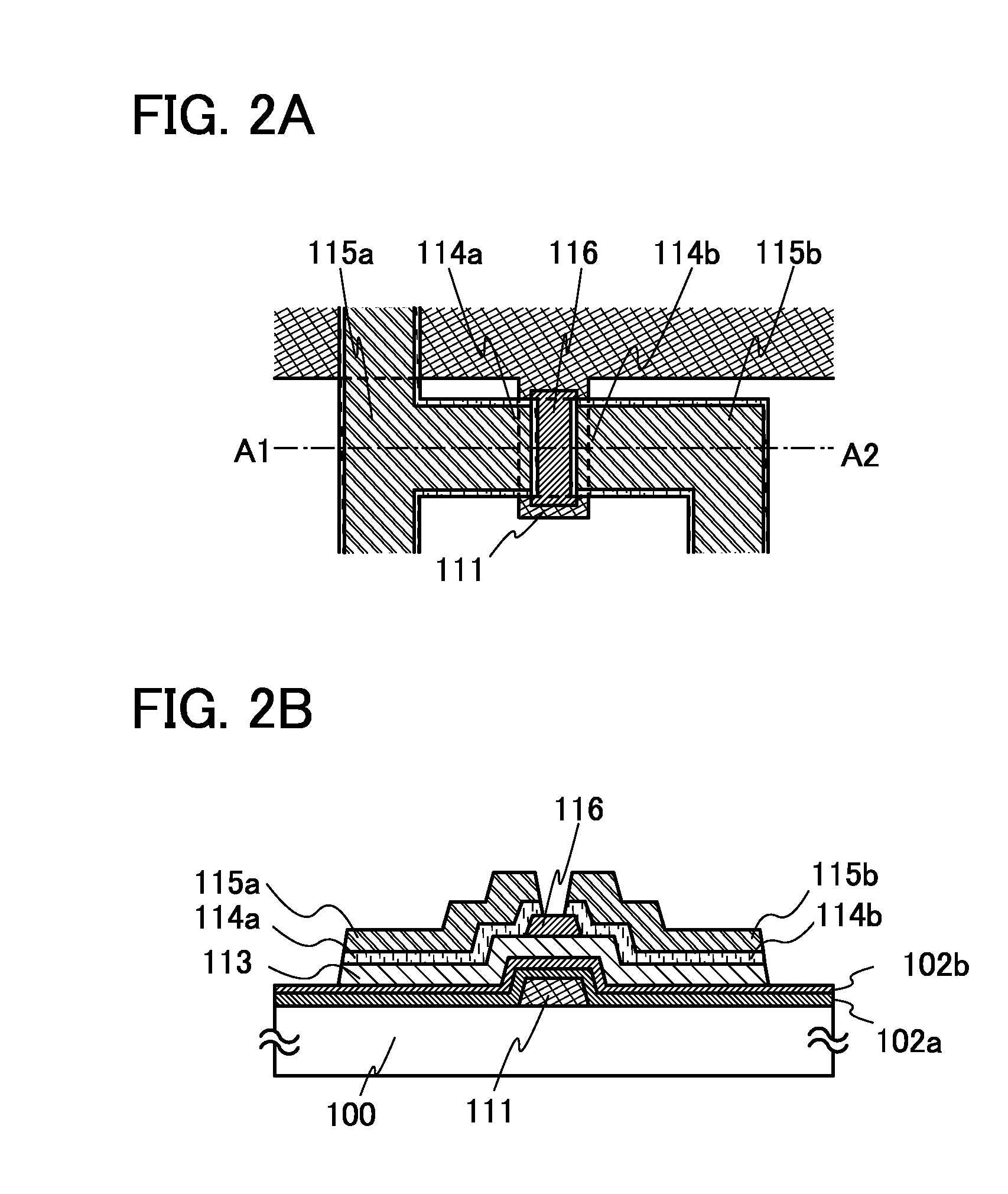

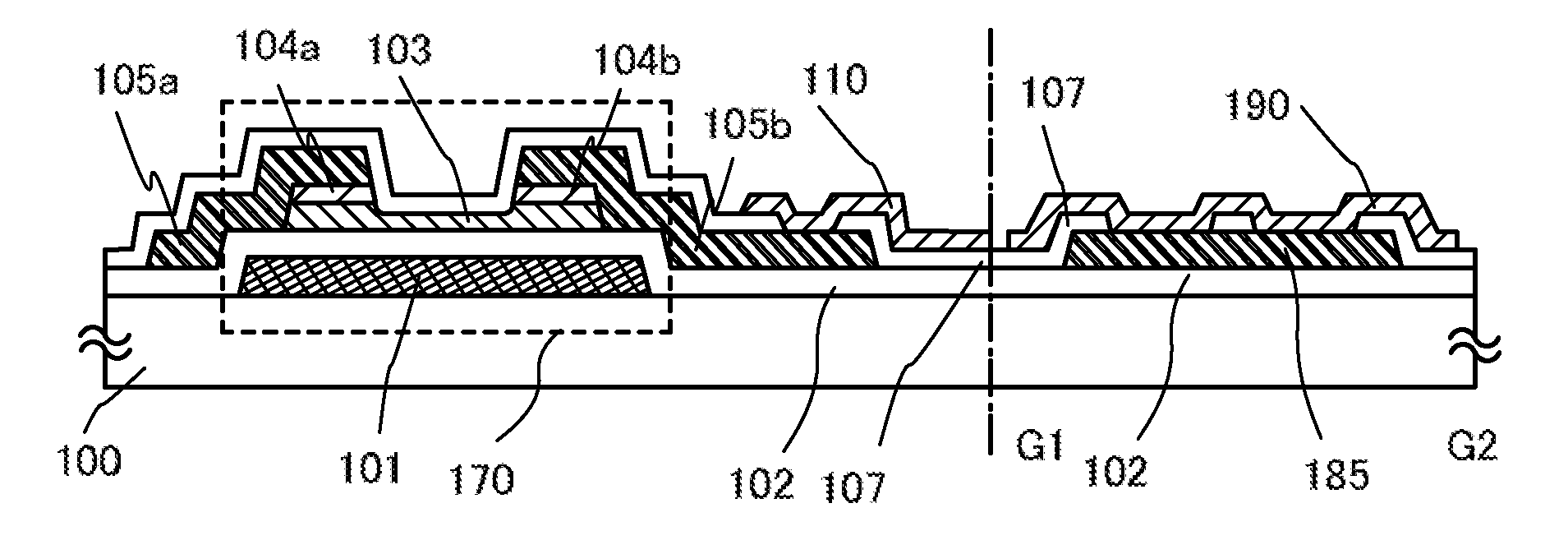

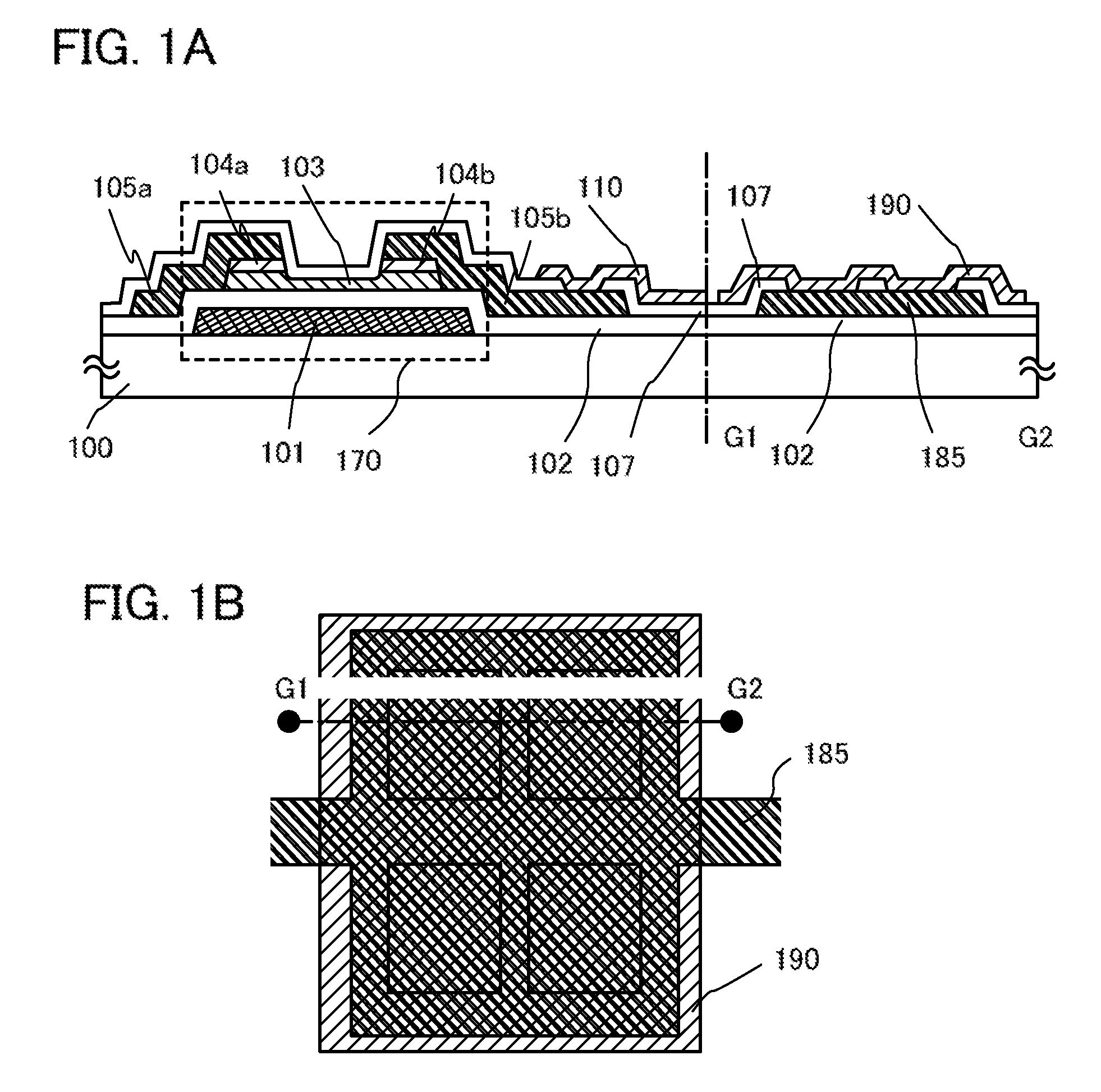

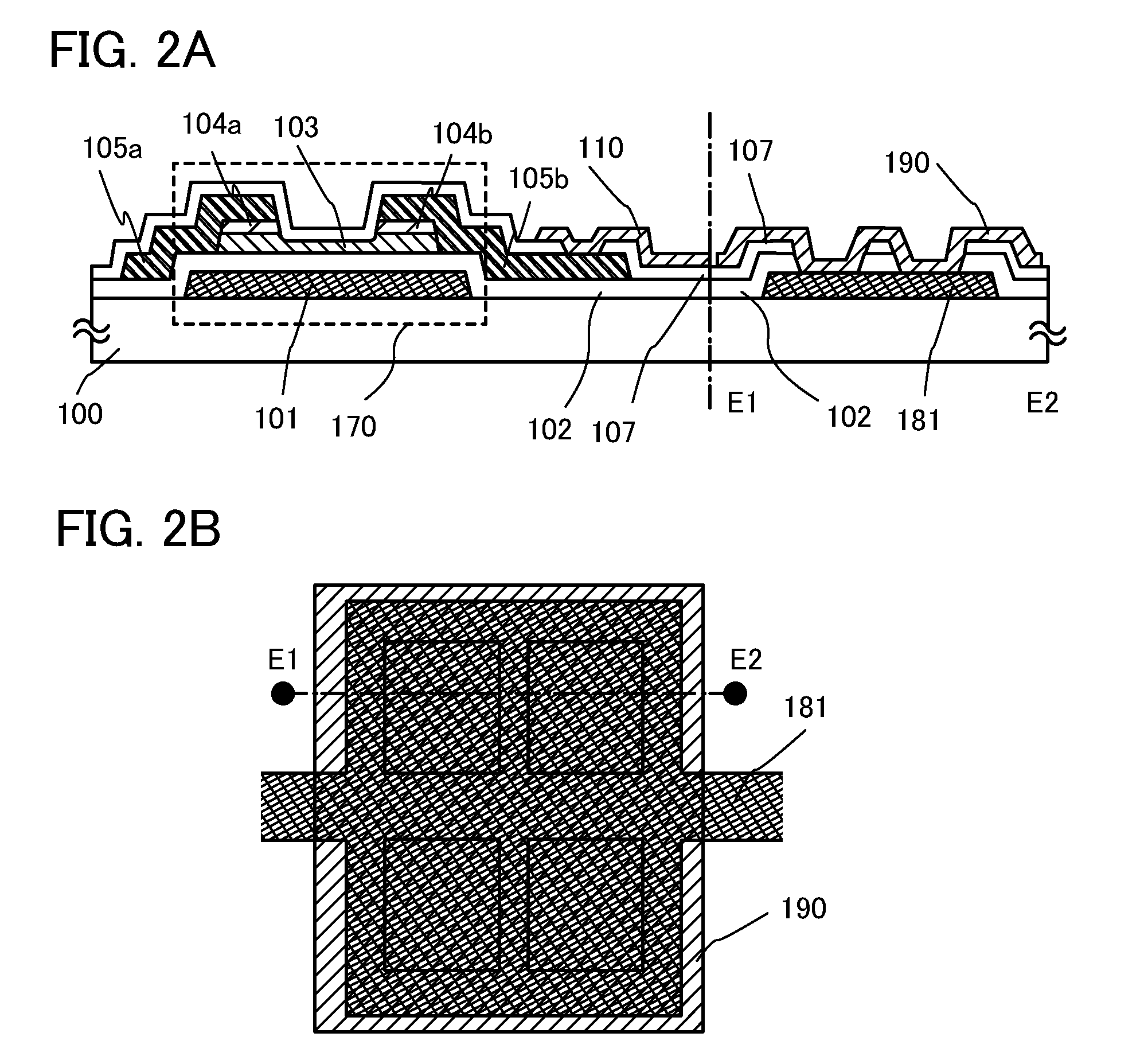

Semiconductor device and manufacturing method thereof

ActiveUS20100025677A1Small amount of photocurrentReduce parasitic capacitanceTransistorElectroluminescent light sourcesProduction rateCharge carrier

To provide a semiconductor device including a thin film transistor having excellent electric characteristics and high reliability and a manufacturing method of the semiconductor device with high mass productivity. The summary is that an inverted-staggered (bottom-gate) thin film transistor is included in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, a channel protective layer is provided in a region that overlaps a channel formation region of the semiconductor layer, and a buffer layer is provided between the semiconductor layer and source and drain electrodes. An ohmic contact is formed by intentionally providing the buffer layer having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

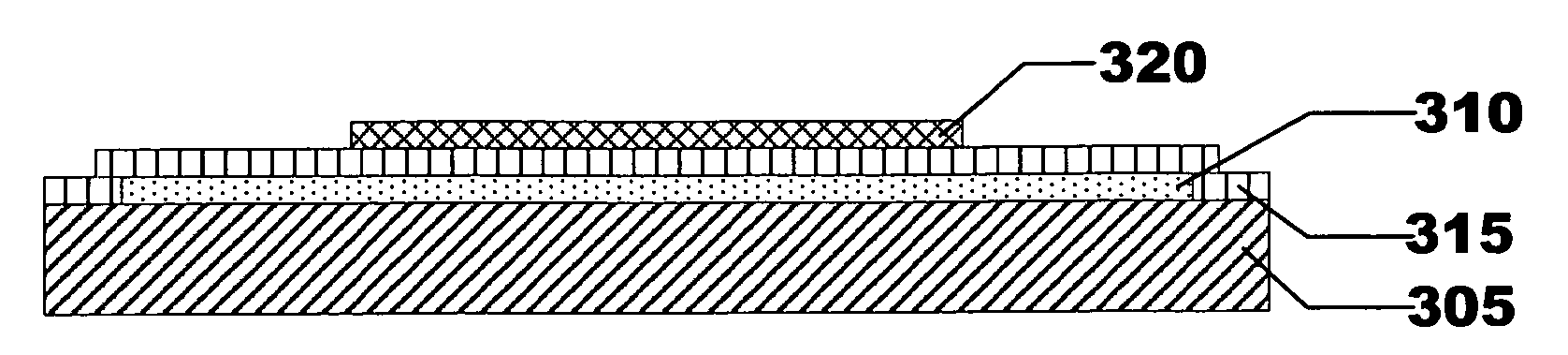

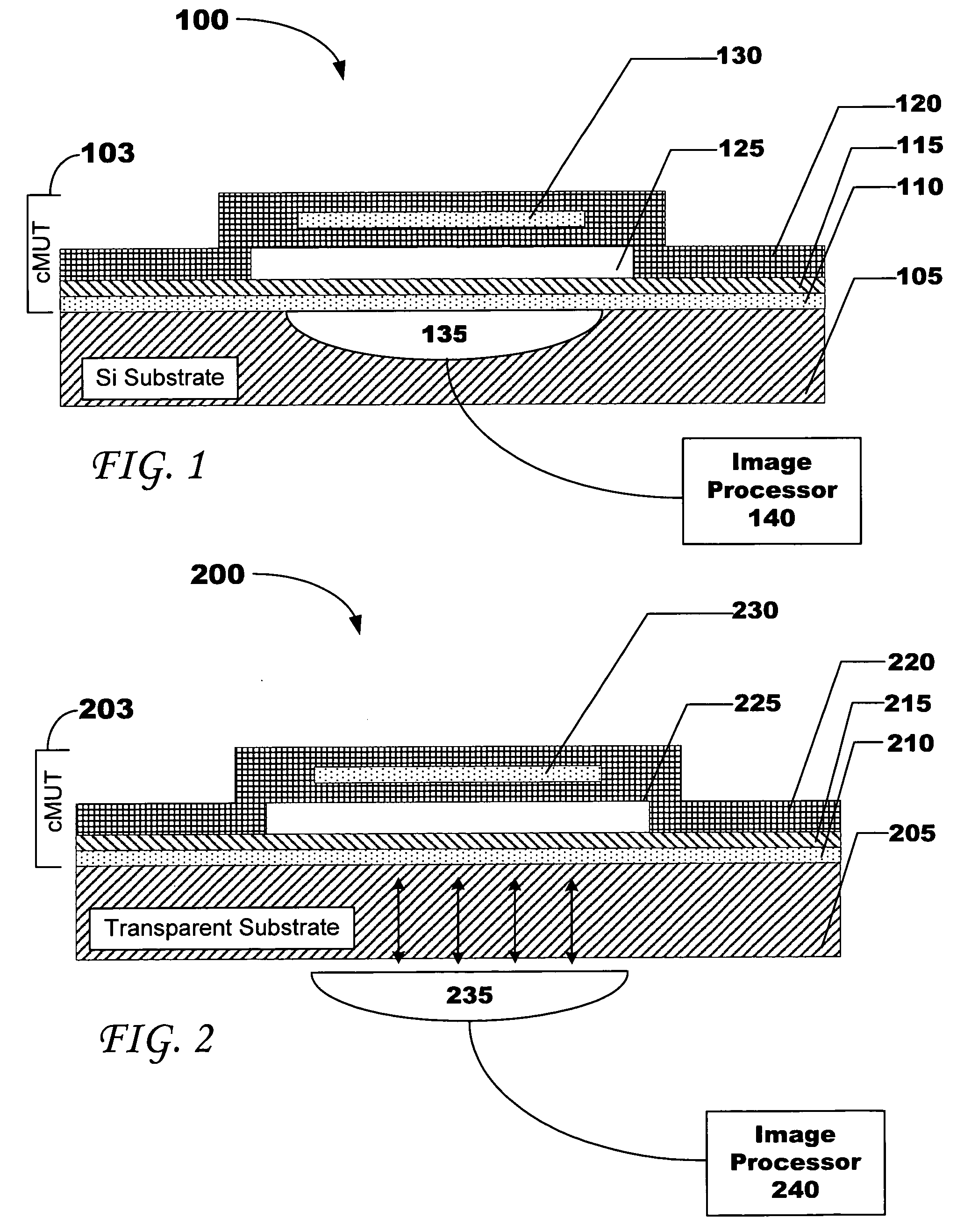

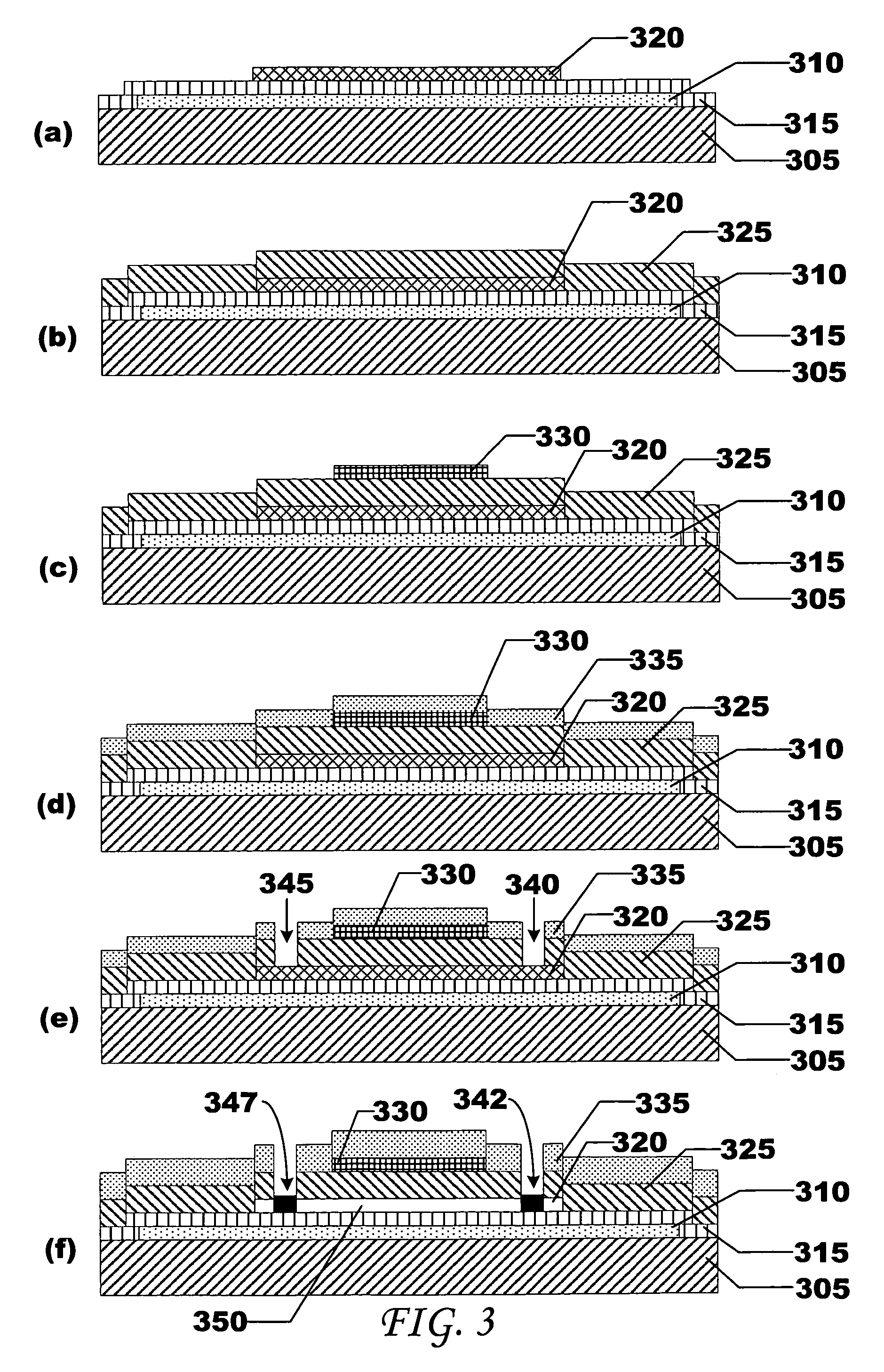

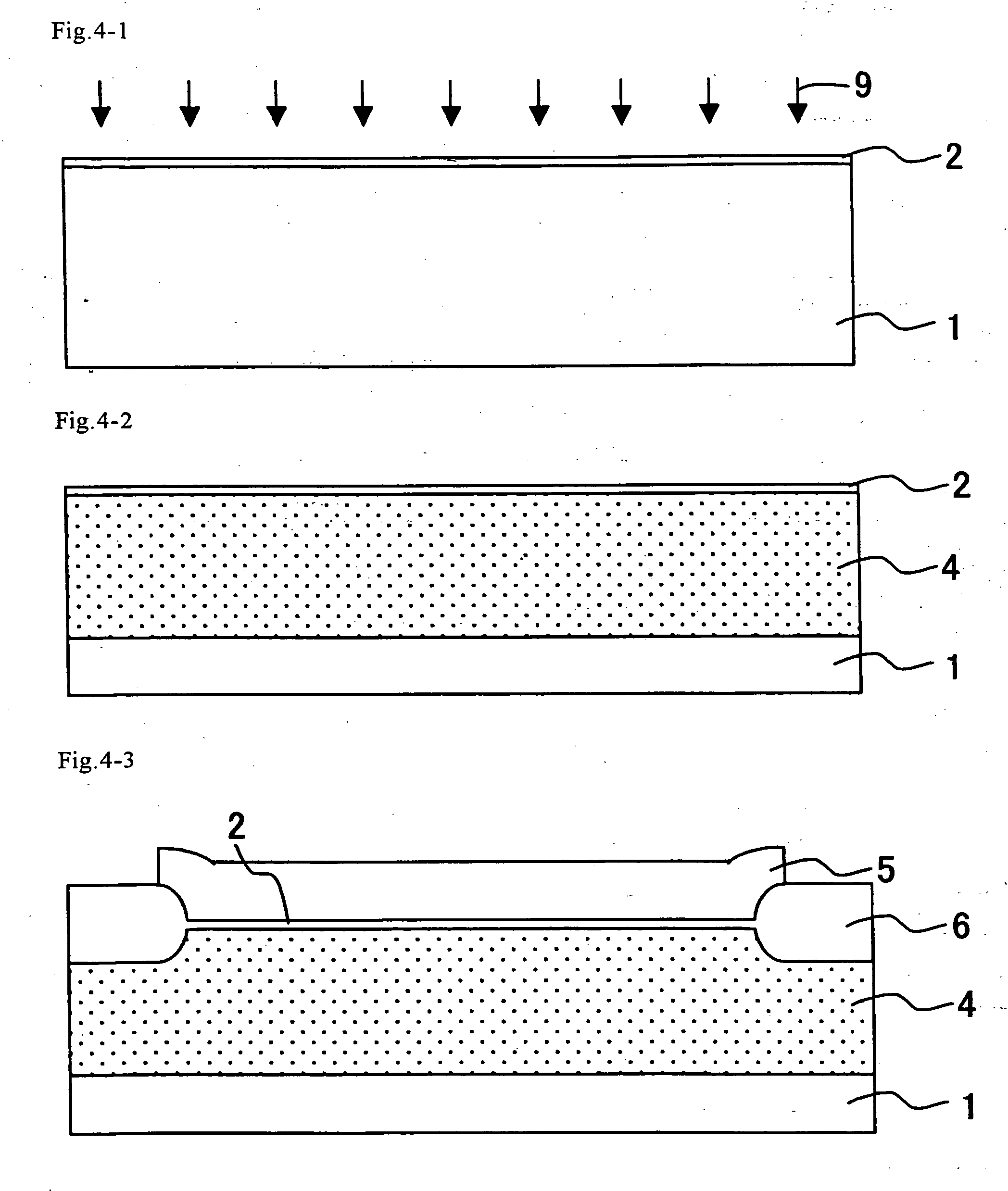

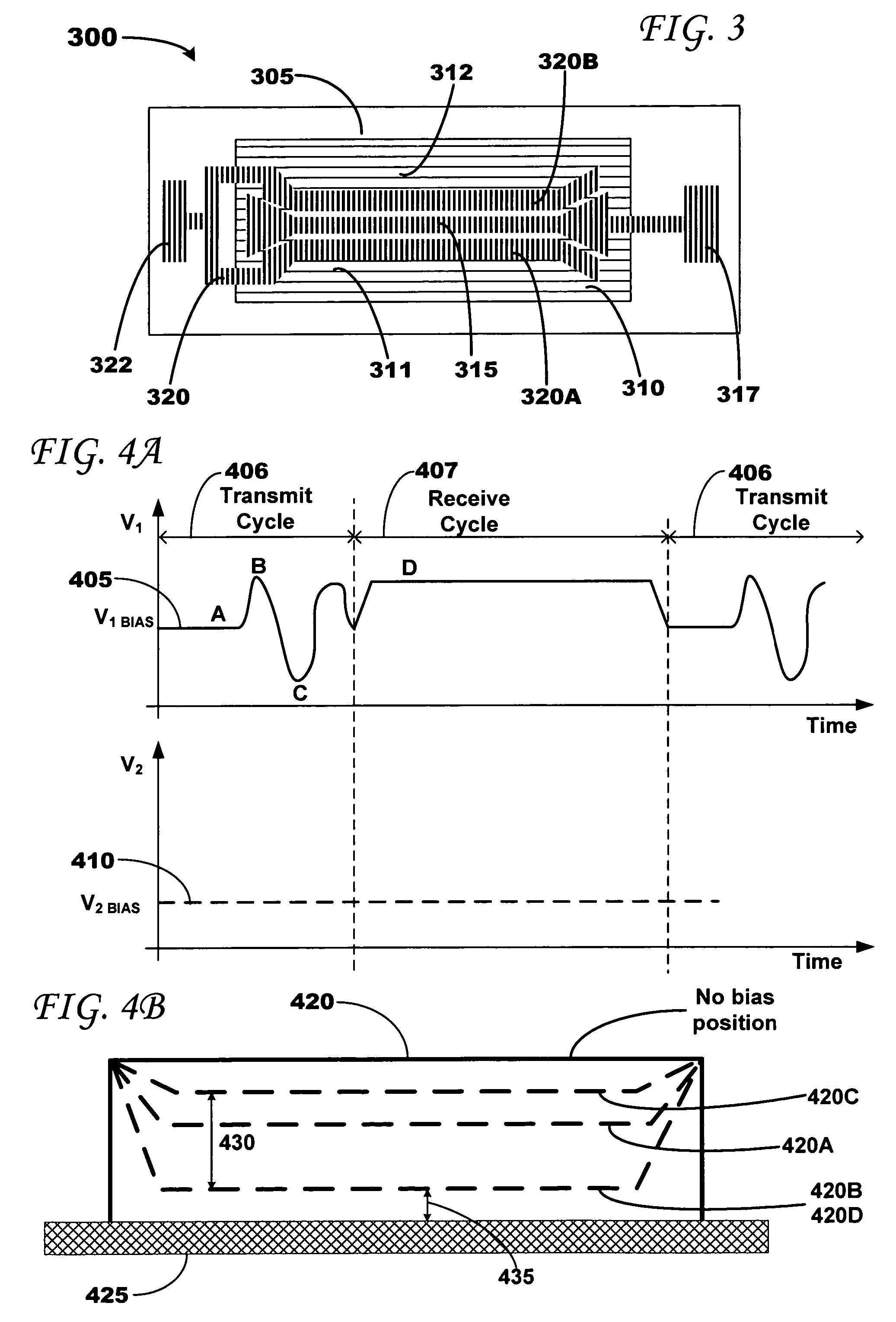

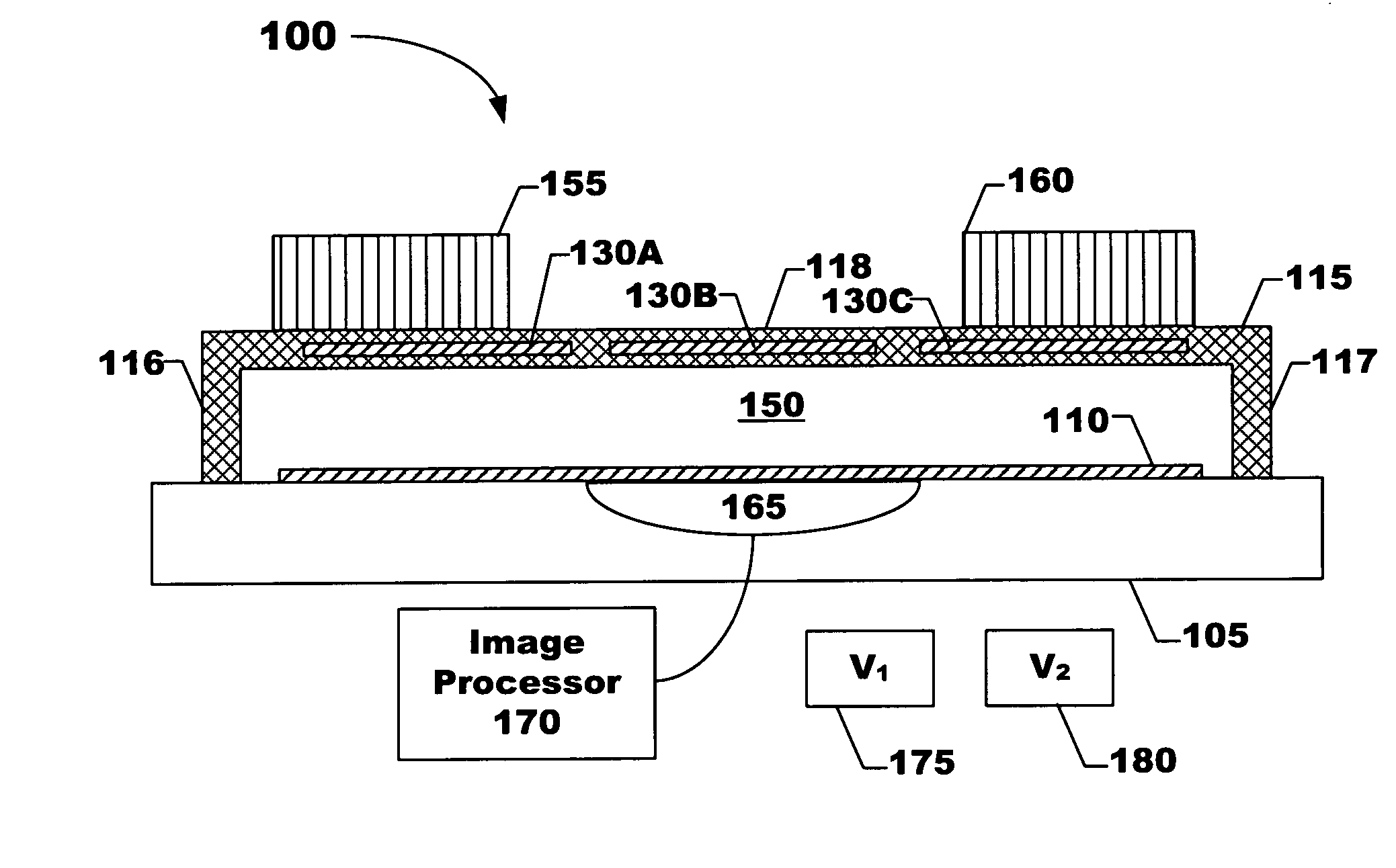

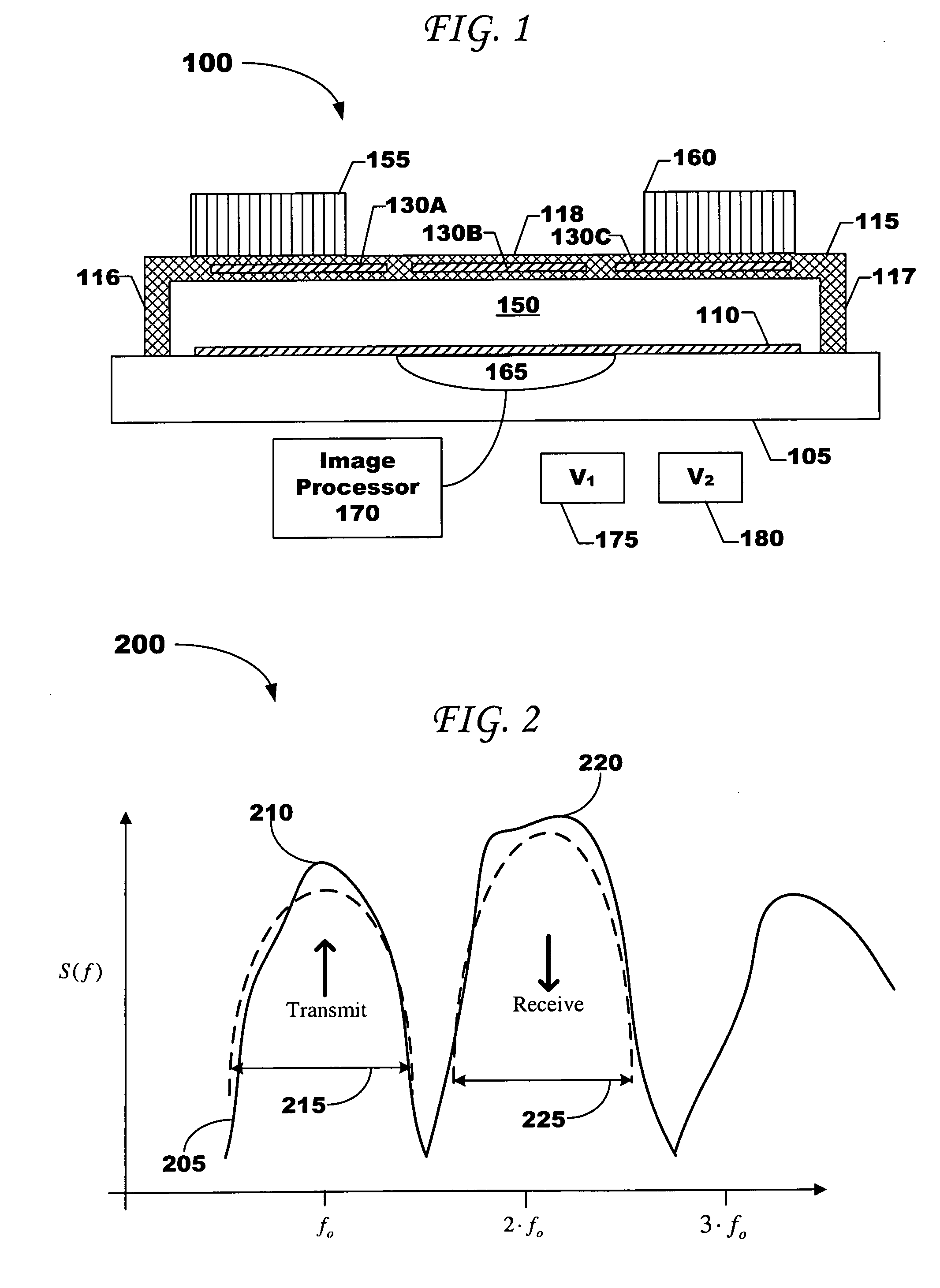

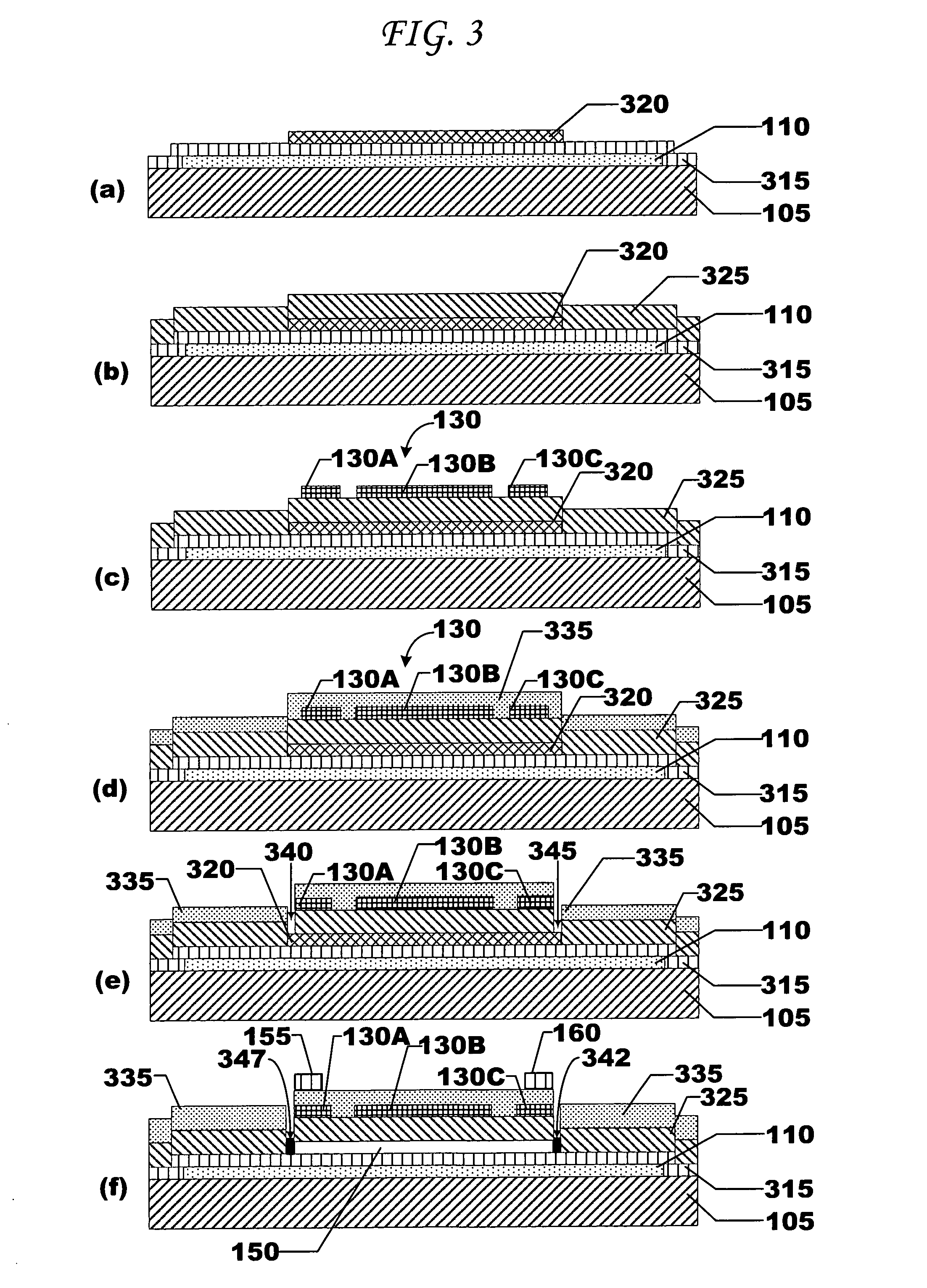

cMUT devices and fabrication methods

InactiveUS20050177045A1Reduce device parasitic capacitanceImprove electrical performanceMaterial analysis using sonic/ultrasonic/infrasonic wavesSurgeryCapacitanceCelsius Degree

Fabrication methods for capacitive-micromachined ultrasound transducers (“cMUT”) and cMUT imaging array systems are provided. cMUT devices fabricated from low process temperatures are also provided. In an exemplary embodiment, a process temperature can be less than approximately 300 degrees Celsius. A cMUT fabrication method generally comprises depositing and patterning materials on a substrate (400). The substrate (400) can be silicon, transparent, other materials. In an exemplary embodiment, multiple metal layers (405, 410, 415) can be deposited and patterned onto the substrate (400); several membrane layers (420, 435, 445) can be deposited over the multiple metal layers (405, 410, 415); and additional metal layers (425, 430) can be disposed within the several membrane layers (420, 435, 445). The second metal layer (410) is preferably resistant to etchants used to etch the third metal layer (415) when forming a cavity (447). Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

Semiconductor device

ActiveUS20100072467A1Increasing the thicknessAvoid separationTransistorElectroluminescent light sourcesDisplay deviceSemiconductor package

A display device includes a pixel portion in which a pixel is arranged in a matrix, the pixel including an inverted staggered thin film transistor having a combination of at least two kinds of oxide semiconductor layers with different amounts of oxygen and having a channel protective layer over a semiconductor layer to be a channel formation region overlapping a gate electrode layer and a pixel electrode layer electrically connected to the inverted staggered thin film transistor. In the periphery of the pixel portion in this display device, a pad portion including a conductive layer made of the same material as the pixel electrode layer is provided. In addition, the conductive layer is electrically connected to a common electrode layer formed on a counter substrate.

Owner:SEMICON ENERGY LAB CO LTD

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

ActiveUS20090321853A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

Power semiconductor devices and methods of manufacture

InactiveUS20060214221A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Process for producing semiconductor integrated circuit device

InactiveUS7553756B2High reliable via connectionReduce parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitorEngineering physics

Owner:HITACHI LTD

Semiconductor device, production method thereof, and display device

InactiveUS20090242893A1Reduce parasitic capacitanceReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The present invention provides a semiconductor device which can be produced by simple and cheap processes and effectively achieve improved performances and a reduced electric power consumption. Further, the present invention provides a production method thereof and a display device including the semiconductor device or a semiconductor device produced by the production method. The present invention is a semiconductor device including a pixel part and an integrated circuit part on a substrate, the pixel part including a switching element having a gate electrode formed on a semiconductor thin film, the integrated circuit part including a semiconductor layer on a gate electrode, wherein a passivation film is formed on the gate electrode in the pixel part.

Owner:SHARP KK

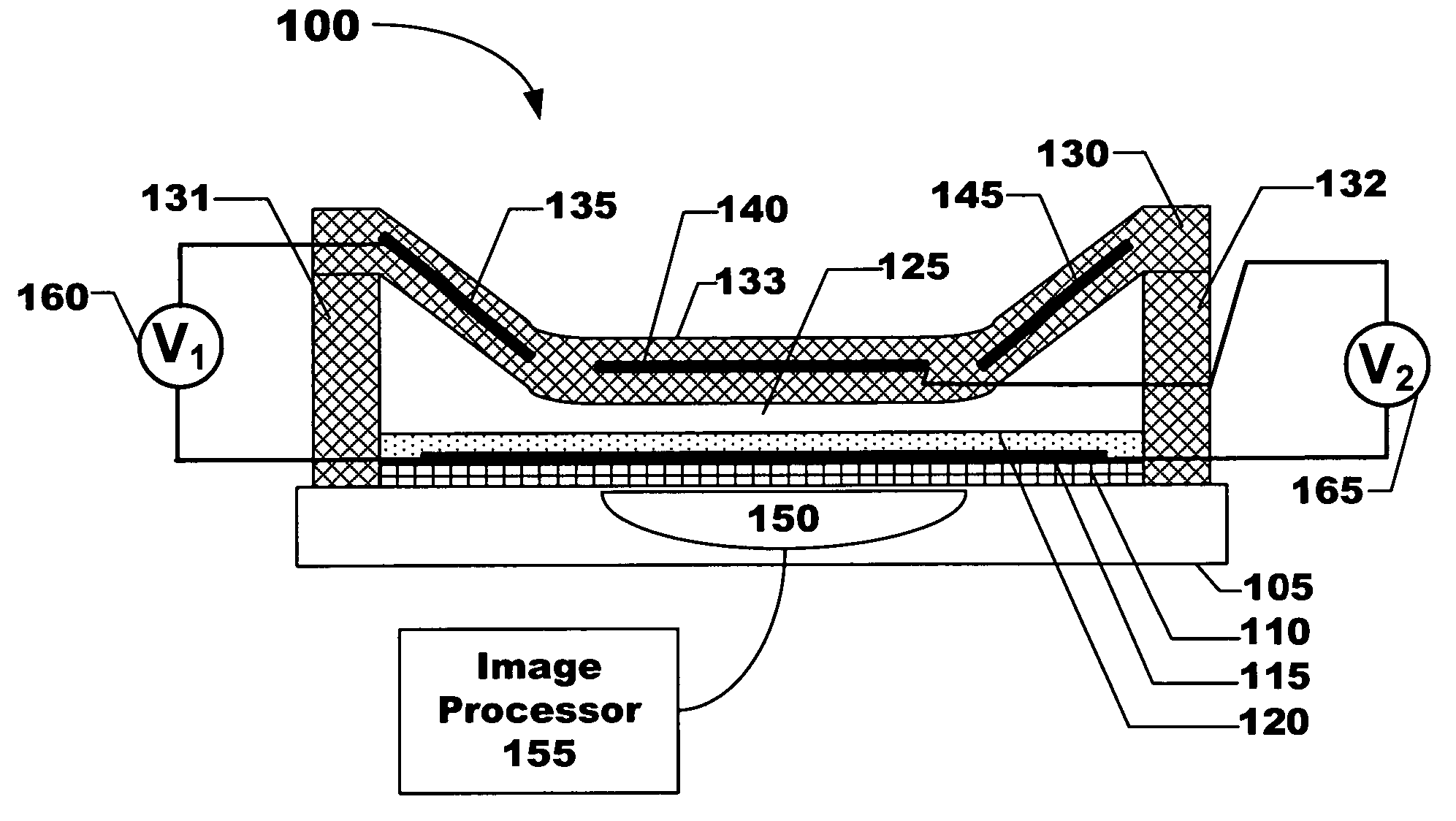

Multiple element electrode cMUT devices and fabrication methods

ActiveUS20050200241A1Optimizing receiptFacilitate transmissionMaterial analysis using sonic/ultrasonic/infrasonic wavesPiezoelectric/electrostriction/magnetostriction machinesCapacitive micromachined ultrasonic transducersBiomedical engineering

Multiple electrode element capacitive micromachined ultrasonic transducer (“cMUT”) devices and fabrication methods are provided. A cMUT device generally comprises a top electrode disposed within a membrane, a bottom electrode disposed on a substrate, and a cavity between the membrane and the bottom electrode. In a preferred embodiment of the present invention, at least one of the first electrode and the second electrode comprises a plurality of electrode elements. The electrode elements can be positioned and energized to shape the membrane and efficiently transmit and receive ultrasonic energy, such as ultrasonic waves. Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

Touch screen, touch panel and display device

ActiveUS20100060602A1Reduce decreaseHigh sensitivityInput/output processes for data processingDisplay deviceEngineering

Each detection column wiring is constituted by a set of a first metal wiring having a zigzag pattern and a second metal wiring having a structure axisymmetric with the first metal wiring about a column direction as an axis, wherein the first metal wiring is constituted by first sloped portions which are obliquely sloped by an inclination angle of 45 degrees with respect to the column direction, and first parallel portions which are parallel with the column direction and are continuous with the first sloped portions, such that the first sloped portions and the first parallel portions are repeatedly placed in a zigzag shape along the column direction. Each detection row wiring also has the same structure. A sloped portion out of the first sloped portions of the first metal wiring is always orthogonally and spatially intersected, at its middle point, with a sloped portion out of the second sloped portions of the third metal wiring at its middle point. There is also the same orthogonal relationship among the other portions.

Owner:MITSUBISHI ELECTRIC CORP

Power semiconductor devices and methods of manufacture

ActiveUS20060214222A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

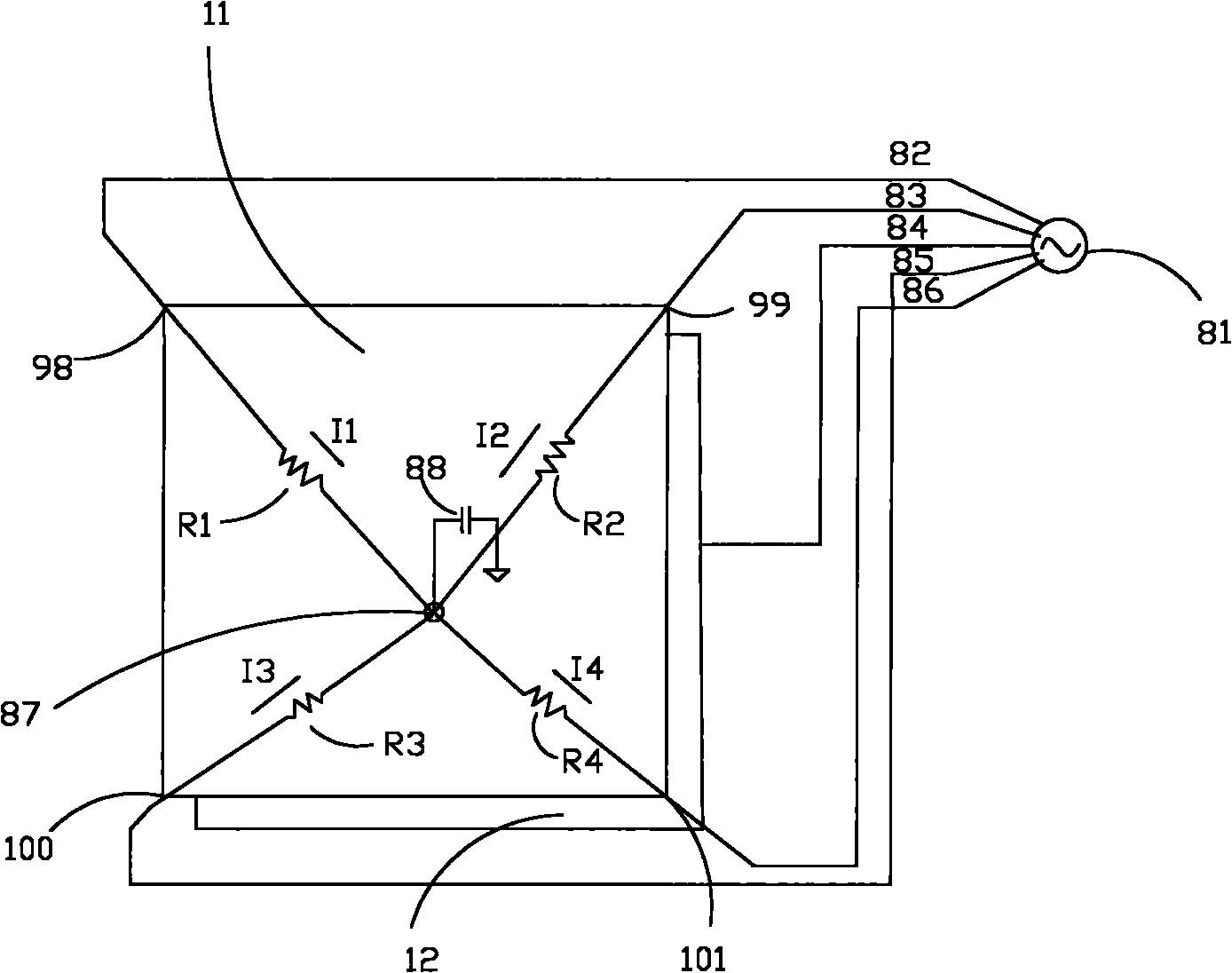

Shift register, scan driving circuit and display apparatus having the same

ActiveUS7486269B2Reduce parasitic capacitancePrevent floatingStatic indicating devicesDigital storageShift registerParasitic capacitance

A shift register includes a plurality of stages to generate a plurality of output signals, in sequence. Each of the stages includes a driving circuit, a charging circuit, a discharging circuit and a holding circuit. The driving circuit is configured to generate a first output signal in response to a first clock signal or a second clock signal having a phase different from the first clock signal. The charging circuit is configured to charge an electric charge in response to a scan start signal or a second output signal of an adjacent previous stage. The discharging circuit is configured to discharge the electric charge in response to a third output signal of an adjacent next stage. The holding circuit is configured to maintain the first output signal within a first voltage when the first output signal is in an inactive state. Therefore, a parasite capacitance is decreased to prevent a floating of a pull-up transistor.

Owner:SAMSUNG DISPLAY CO LTD

Method for manufacturing semiconductor device

ActiveUS20100035379A1Small photocurrentLow parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorResist

To provide a method by which a semiconductor device including a thin film transistor with excellent electric characteristics and high reliability is manufactured with a small number of steps. After a channel protective layer is formed over an oxide semiconductor film containing In, Ga, and Zn, a film having n-type conductivity and a conductive film are formed, and a resist mask is formed over the conductive film. The conductive film, the film having n-type conductivity, and the oxide semiconductor film containing In, Ga, and Zn are etched using the channel protective layer and gate insulating films as etching stoppers with the resist mask, so that source and drain electrode layers, a buffer layer, and a semiconductor layer are formed.

Owner:SEMICON ENERGY LAB CO LTD

Nitride based transistors on semi-insulating silicon carbide substrates

InactiveUS6486502B1Quality improvementImprove thermal conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideNitride

A high electron mobility transistor (HEMT) (10) is disclosed that includes a semi-insulating silicon carbide substrate (11), an aluminum nitride buffer layer (12) on the substrate, an insulating gallium nitride layer (13) on the buffer layer, an active structure of aluminum gallium nitride (14) on the gallium nitride layer, a passivation layer (23) on the aluminum gallium nitride active structure, and respective source, drain and gate contacts (21, 22, 23) to the aluminum gallium nitride active structure.

Owner:WOLFSPEED INC

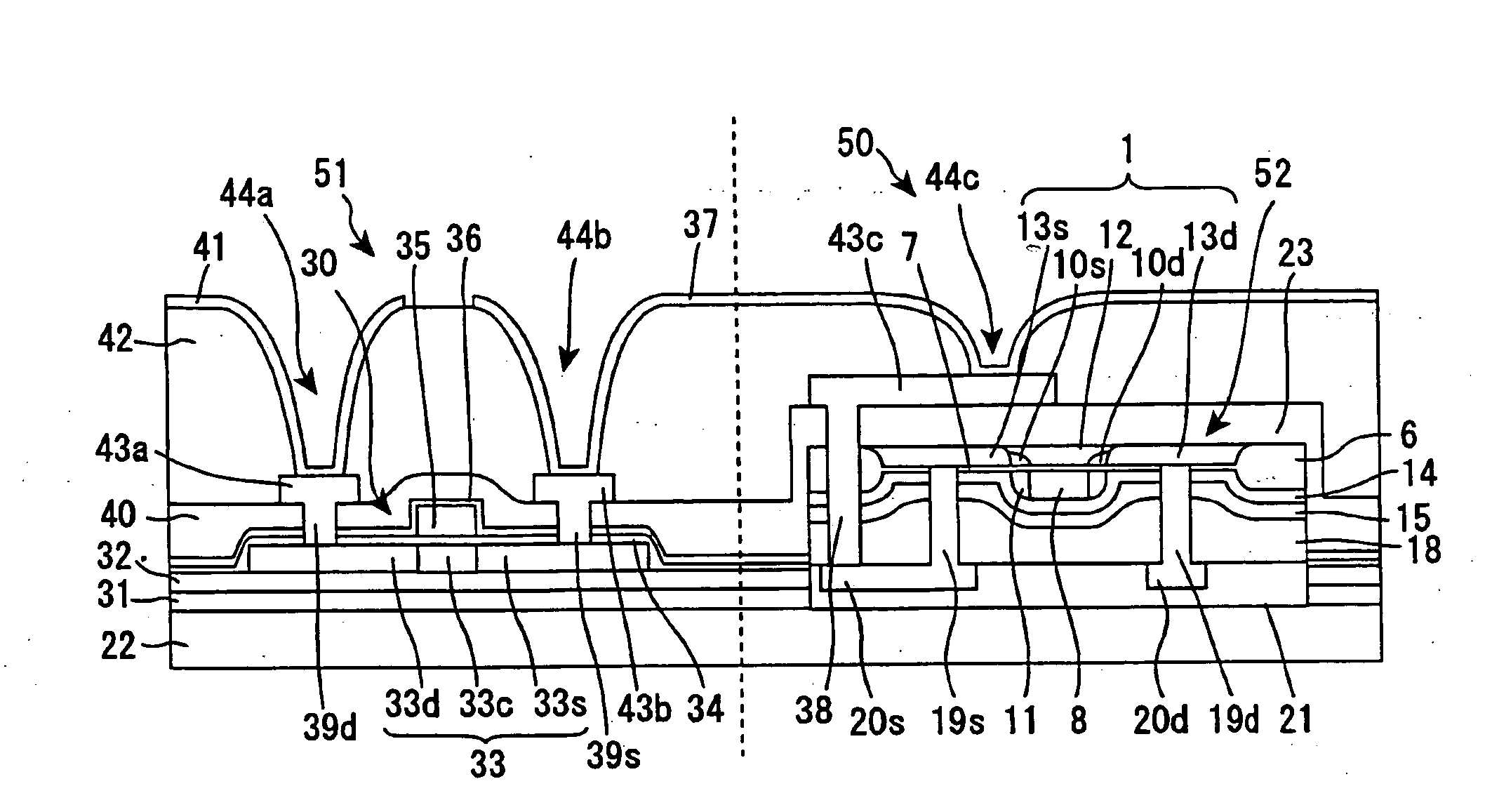

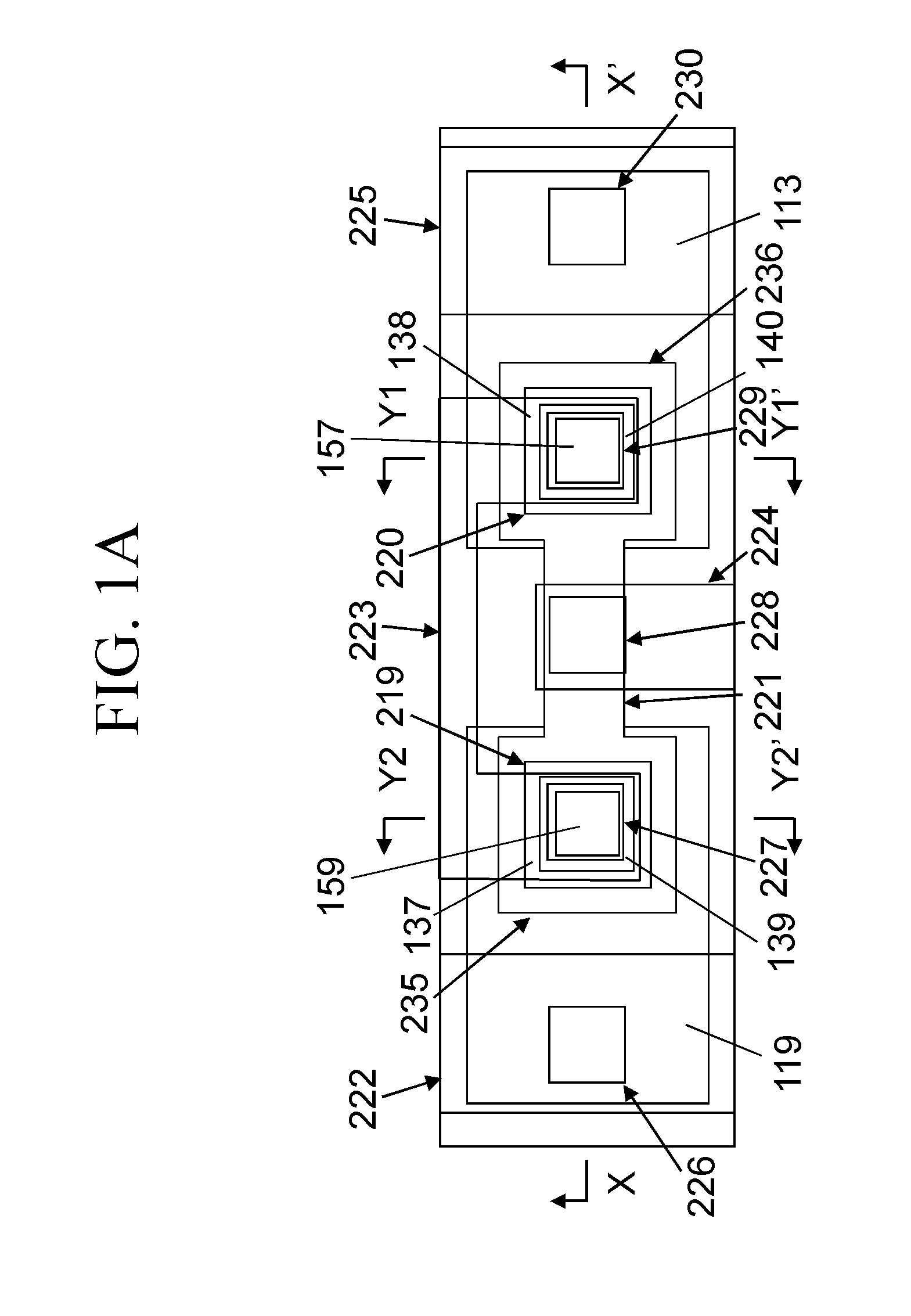

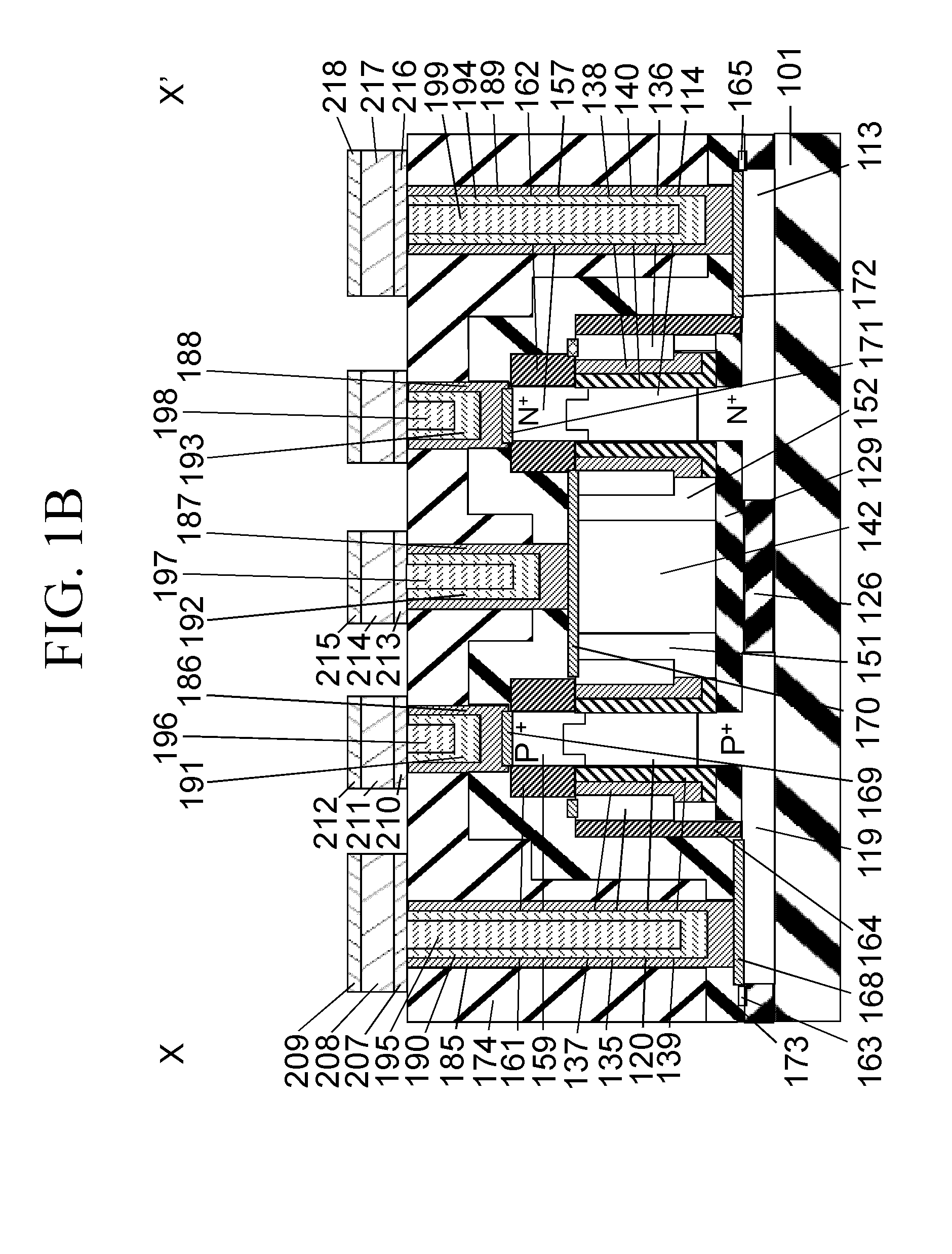

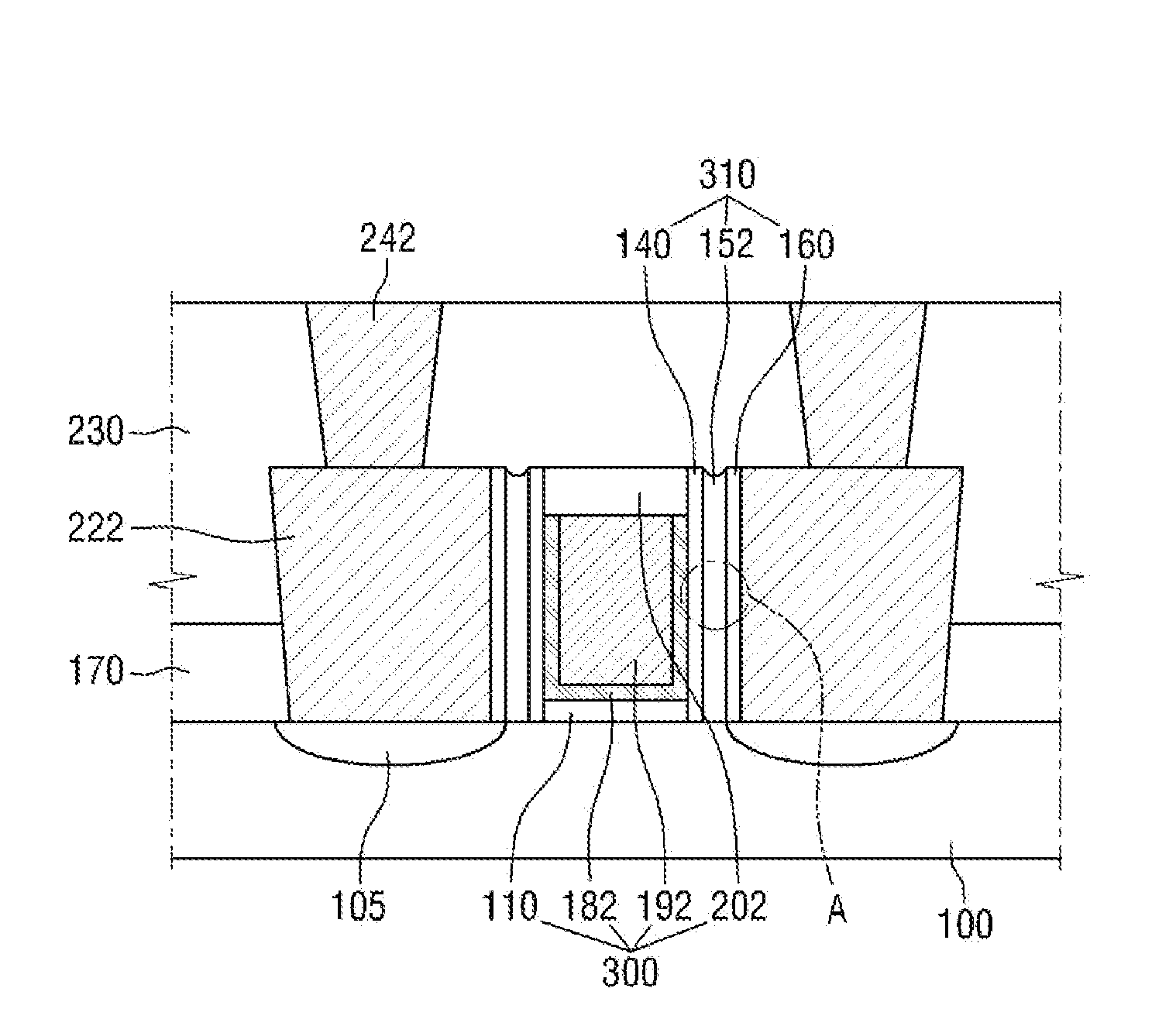

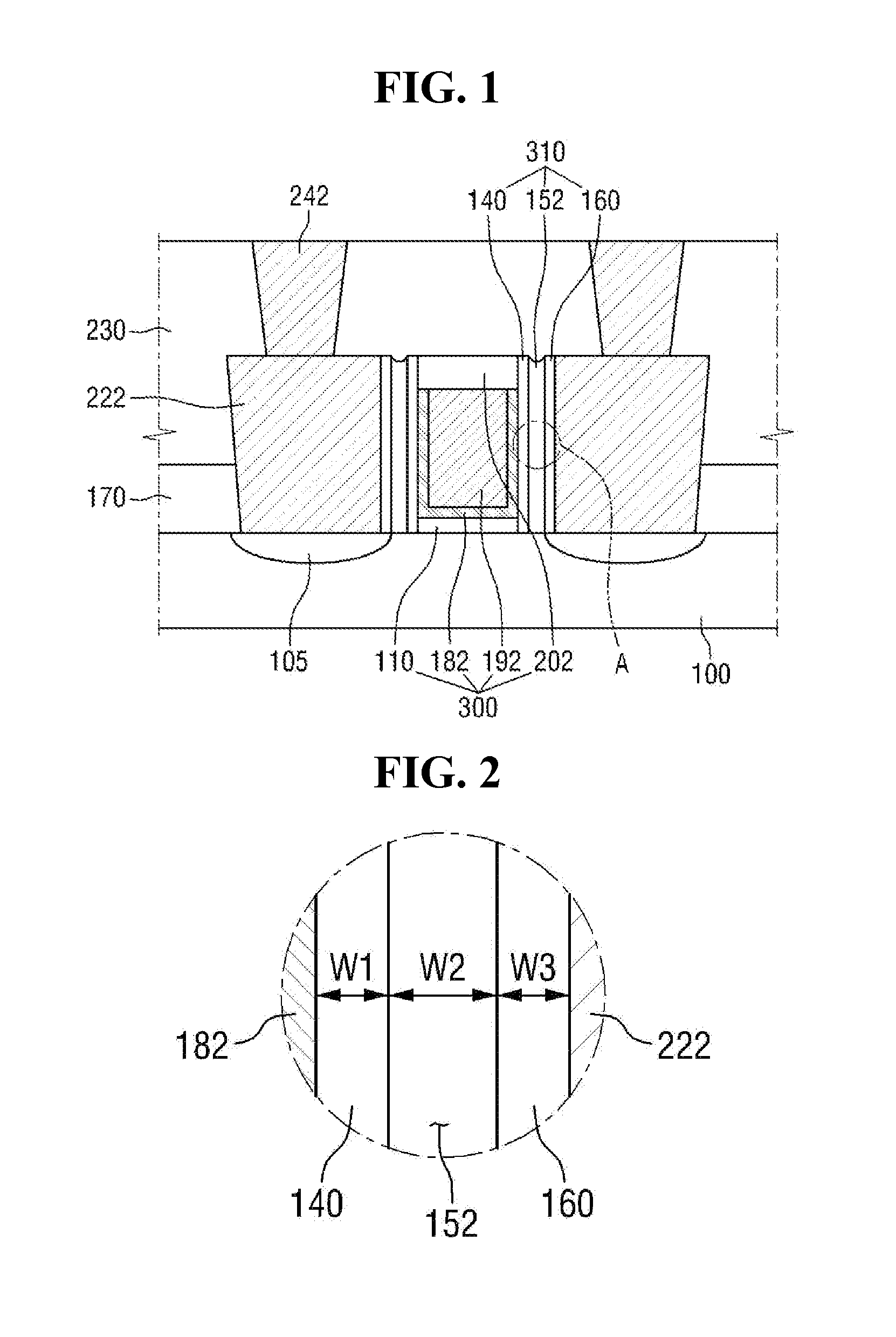

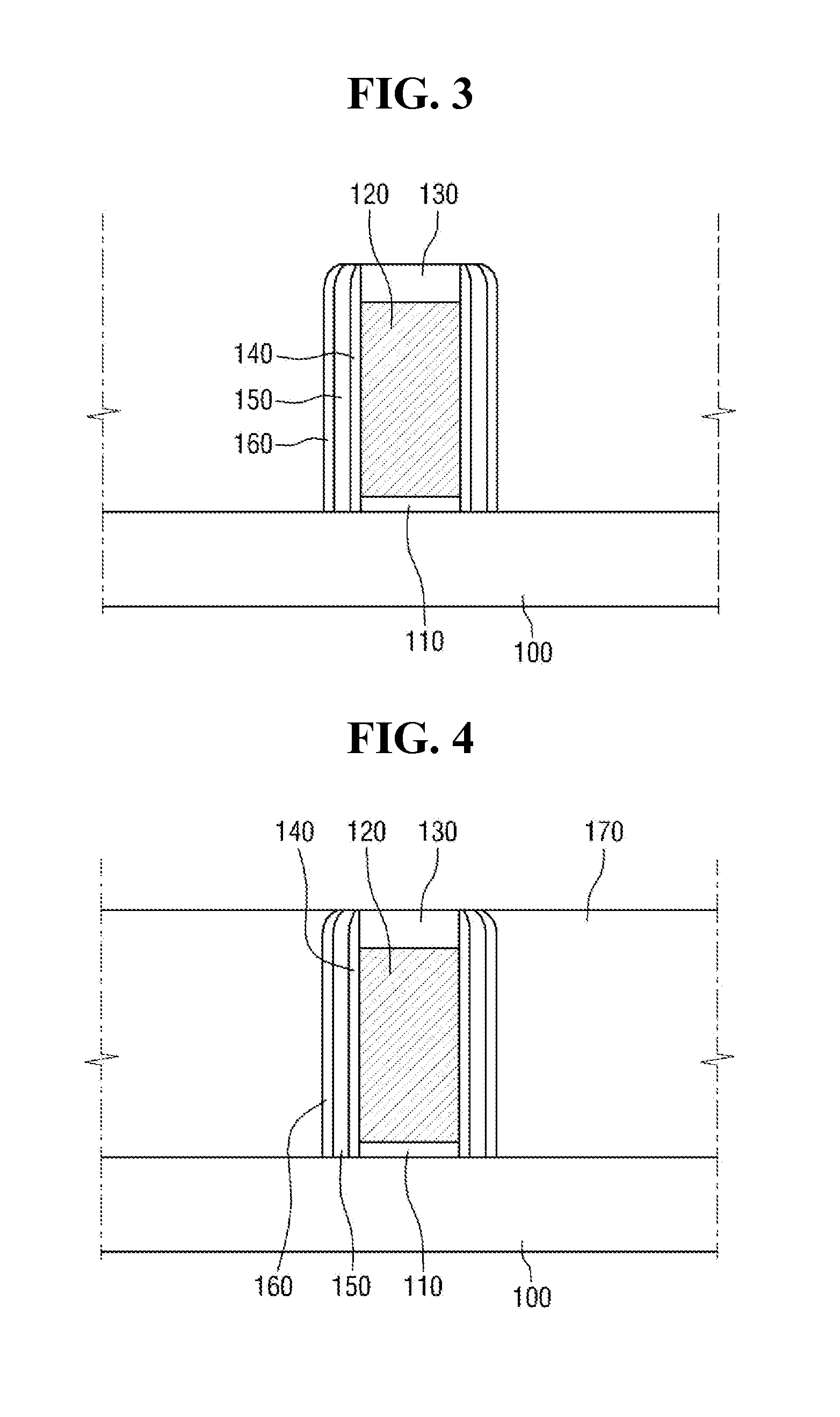

Semiconductor device and production method

ActiveUS20110303973A1Limitation on gate lengthReduce metal pollutionTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceSilicon

The semiconductor device according to the present invention is an nMOS SGT and is composed of a first n+ type silicon layer, a first gate electrode containing metal and a second n+ type silicon layer arranged on the surface of a first columnar silicon layer positioned vertically on a first planar silicon layer. Furthermore, a first insulating film is positioned between the first gate electrode and the first planar silicon layer, and a second insulating film is positioned on the top surface of the first gate electrode. In addition, the first gate electrode containing metal is surrounded by the first n+ type silicon layer, the second n+ type silicon layer, the first insulating film and the second insulating film.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

Semiconductor devices and method of manufacturing the same

ActiveUS20130248950A1Improve business performanceReduce parasitic capacitanceTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Semiconductor devices, and a method of manufacturing the same, include a gate insulating film pattern over a semiconductor substrate. A gate electrode is formed over the gate insulating film pattern. A spacer structure is formed on at least one side of the gate electrode and the gate insulating film pattern. The spacer structure includes a first insulating film spacer contacting the gate insulating film pattern, and a second insulating film spacer on an outer side of the first insulating film spacer. The semiconductor device has an air gap between the first insulating film spacer and the second insulating film spacer.

Owner:SAMSUNG ELECTRONICS CO LTD

Shift register, liquid crystal display device having the shift register and method of driving scan lines using the same

ActiveUS20060256066A1Reduce power consumptionReduce layout areaStatic indicating devicesDigital storageShift registerLiquid-crystal display

In a bi-directional shift register and a liquid crystal display device having the bi-directional shift register, the shift register further includes a dummy stage for resetting a last stage. The dummy stage is reset by a control signal of the last stage or by the output signal of the dummy stage. Therefore, power consumption and layout area may be reduced. The shift register includes a plurality of stages and two dummy stages, and two selection signals for selecting shift direction is applied to each of the stages.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Display device

ActiveUS20100072468A1Increasing the thicknessAvoid separationTransistorStatic indicating devicesDisplay deviceSemiconductor

A display device includes a pixel portion in which a pixel electrode layer is arranged in a matrix, and an inverted staggered thin film transistor having a combination of at least two kinds of oxide semiconductor layers with different amounts of oxygen is provided corresponding to the pixel electrode layer. In the periphery of the pixel portion in this display device, a pad portion is provided to be electrically connected to a common electrode layer formed on a counter substrate through a conductive layer made of the same material as the pixel electrode layer. One objection of our invention to prevent a defect due to separation of a thin film in various kinds of display devices is realized, by providing a structure suitable for a pad portion provided in a display panel.

Owner:SEMICON ENERGY LAB CO LTD

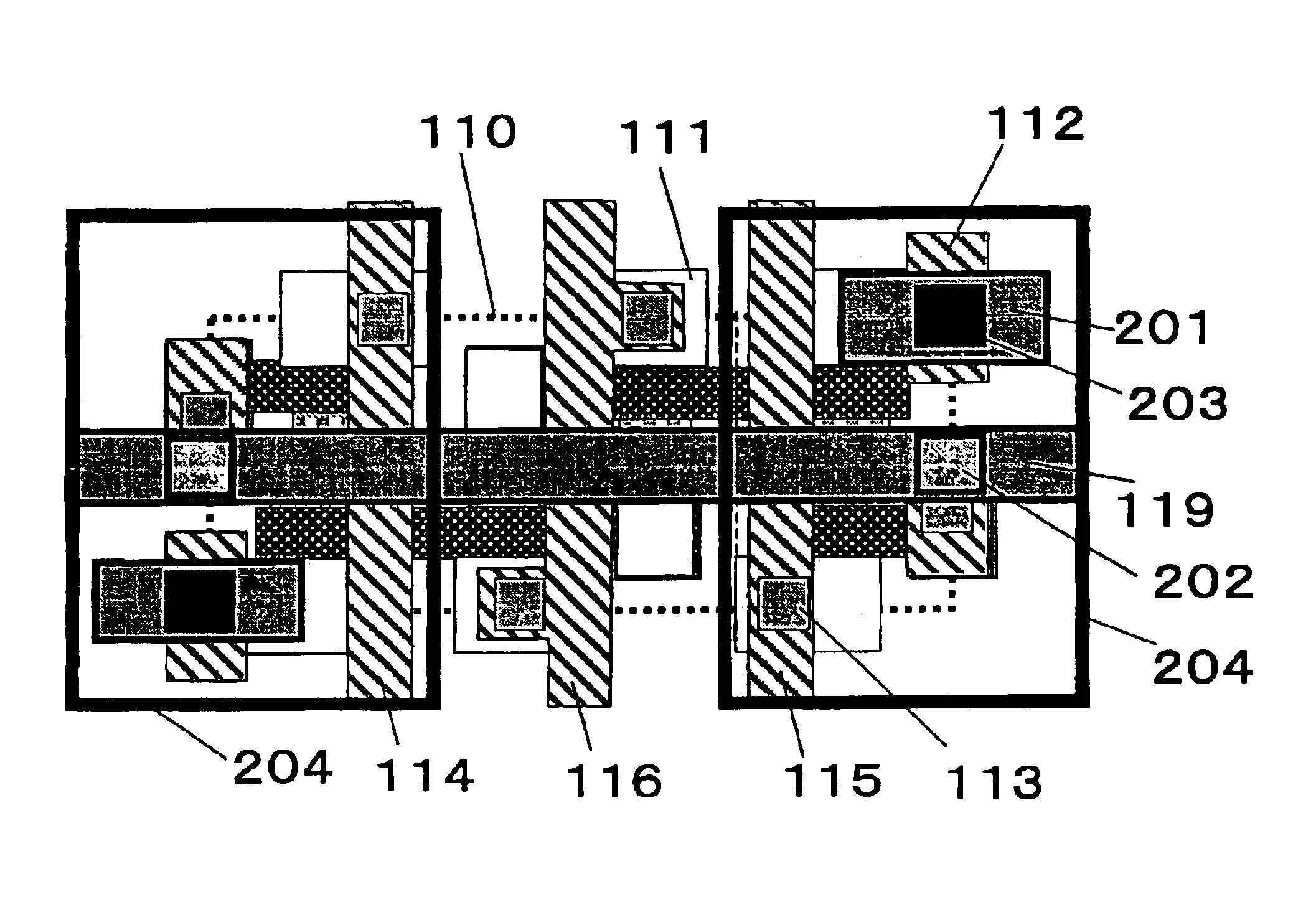

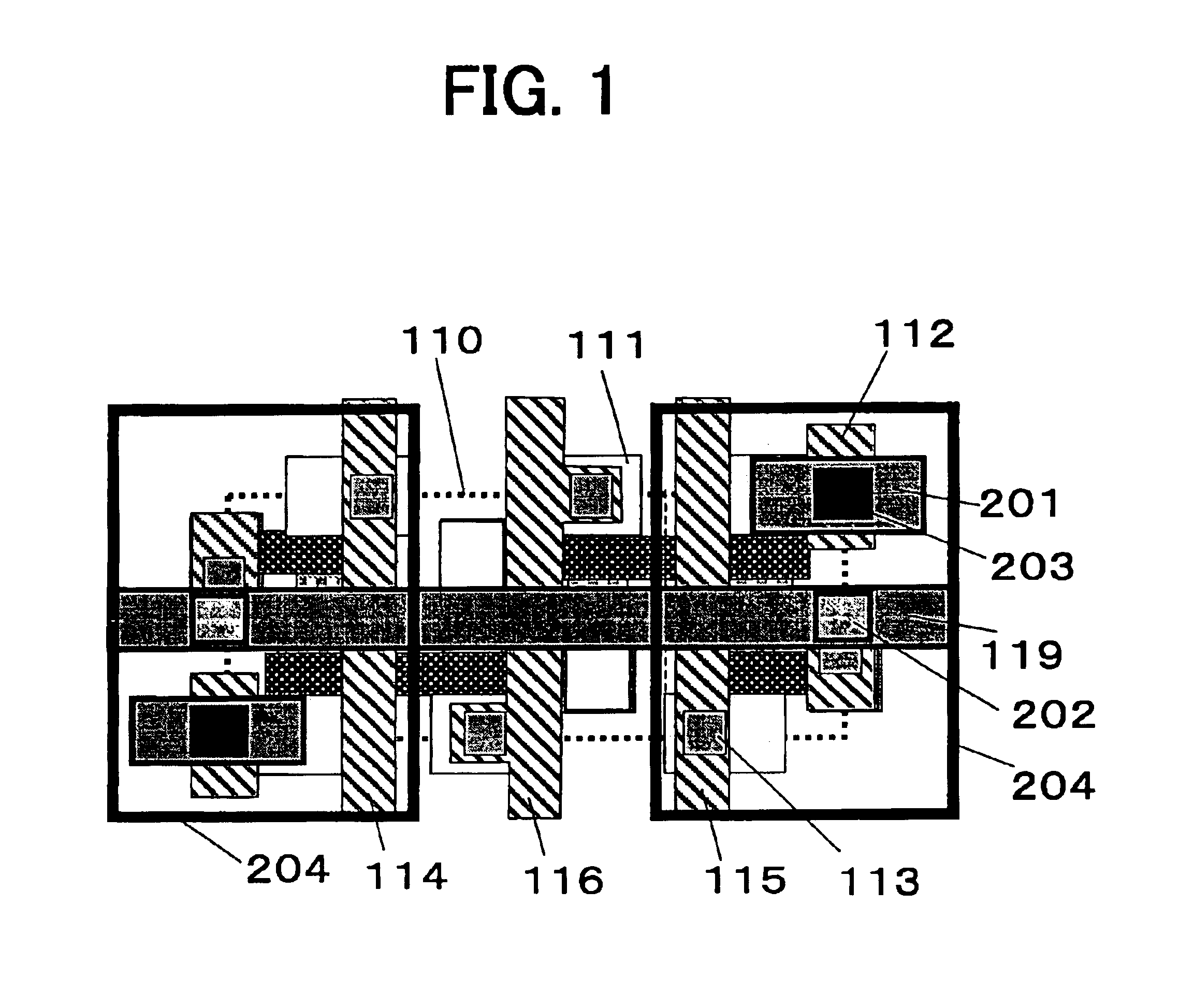

Semiconductor memory device

ActiveUS6922354B2Increase areaHigh performanceTransistorSolid-state devicesEngineeringSemiconductor memory

Positive / negative bit lines are arranged on a second-layer interconnection the VDD power supply interconnection is arranged between the positive / negative bit lines, the word line is arranged on a third-layer interconnection, and the VSS power supply interconnection is arranged on a fourth-layer interconnection. Alternatively, the word line is arranged on the second-layer interconnection, the positive / negative bit lines are arranged on the third-layer interconnection, the VDD power supply interconnection is arranged between the positive / negative bit lines, and the VSS power supply interconnection is arranged on the fourth-layer interconnection. Alternatively, the VDD power supply interconnection is arranged on the second-layer interconnection, the positive / negative bit lines are arranged on the third-layer interconnection, the word line is arranged on the fourth-layer interconnection, and the VSS power supply interconnection is arranged on the fifth-layer interconnection.

Owner:SOCIONEXT INC

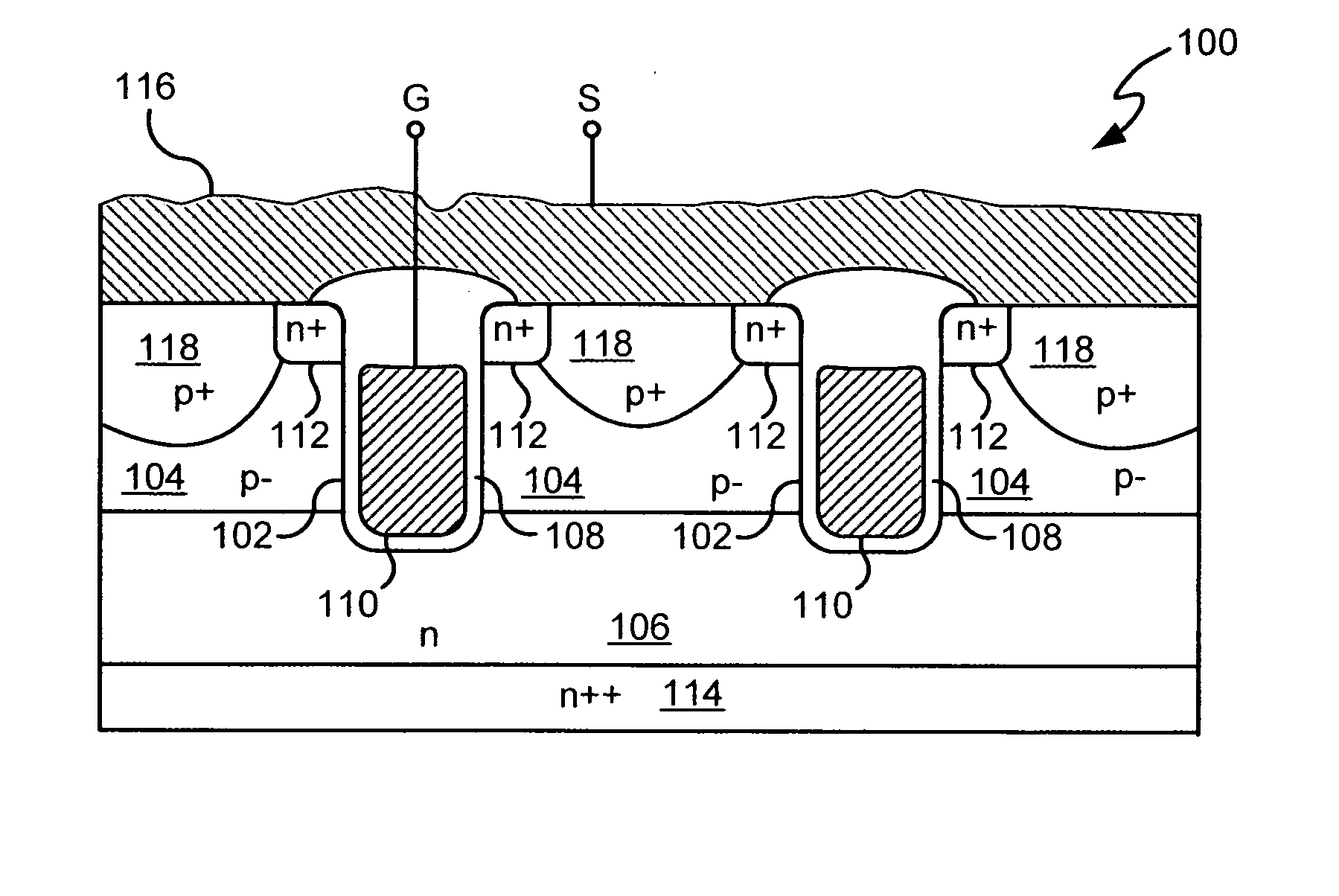

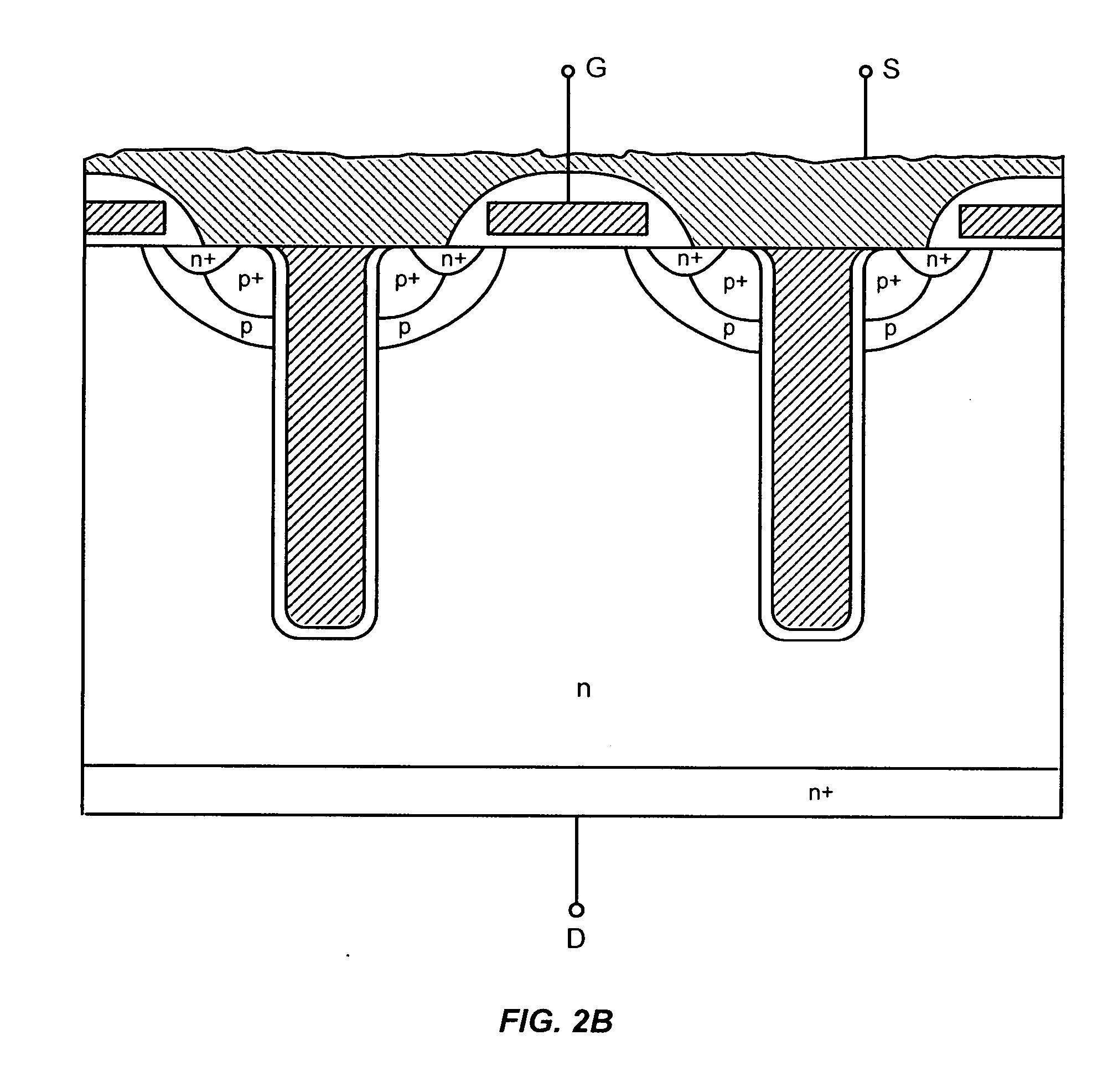

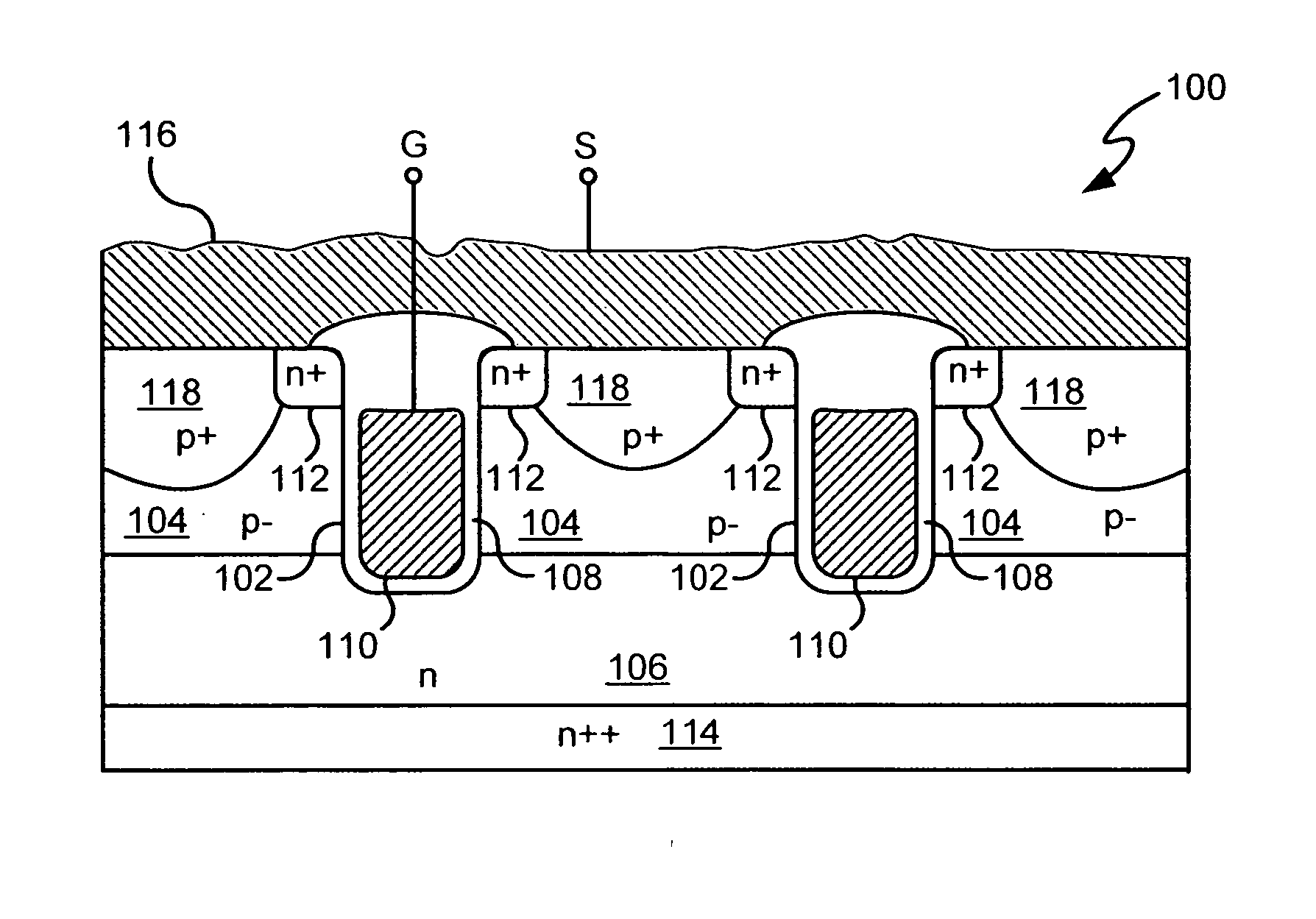

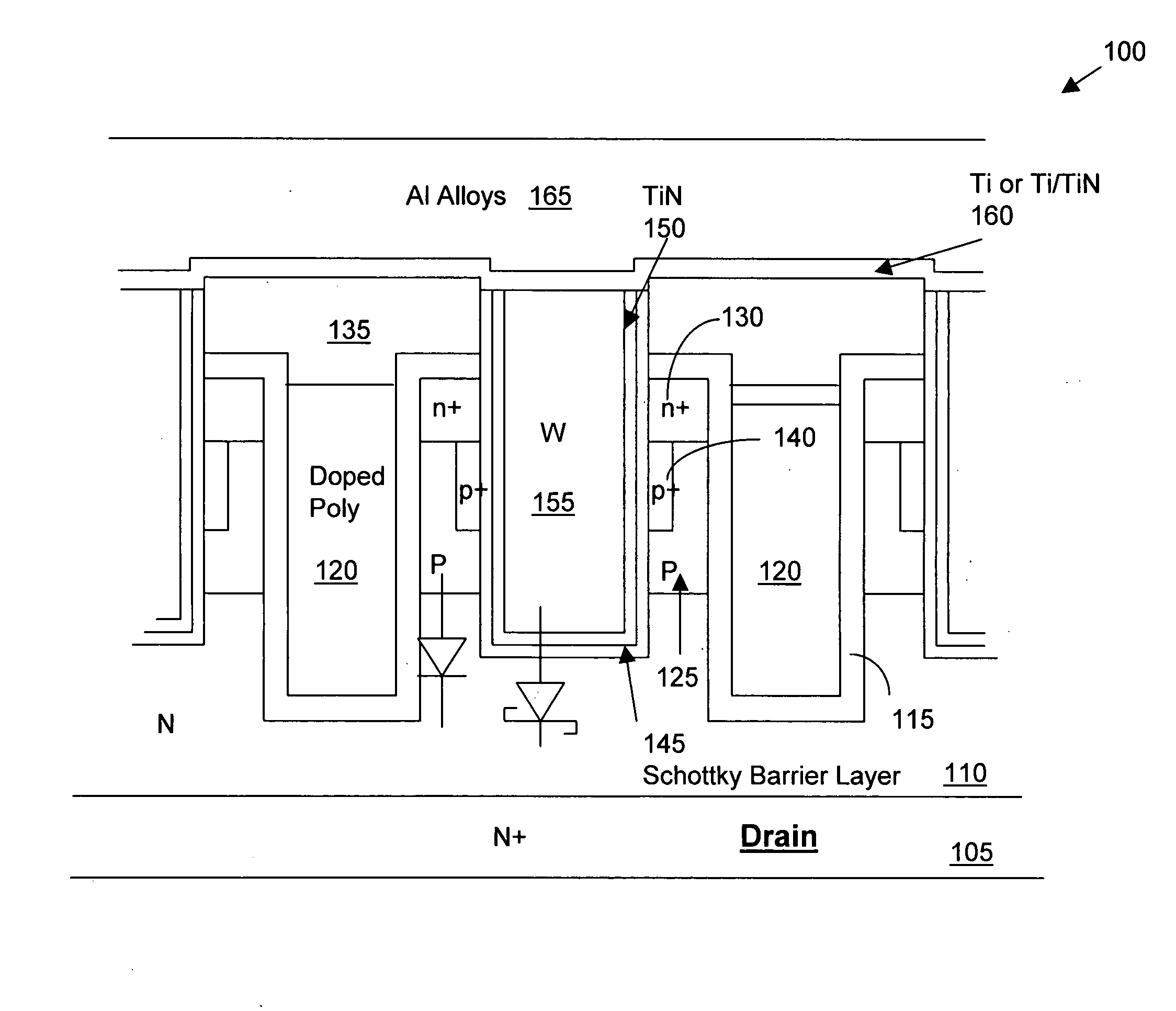

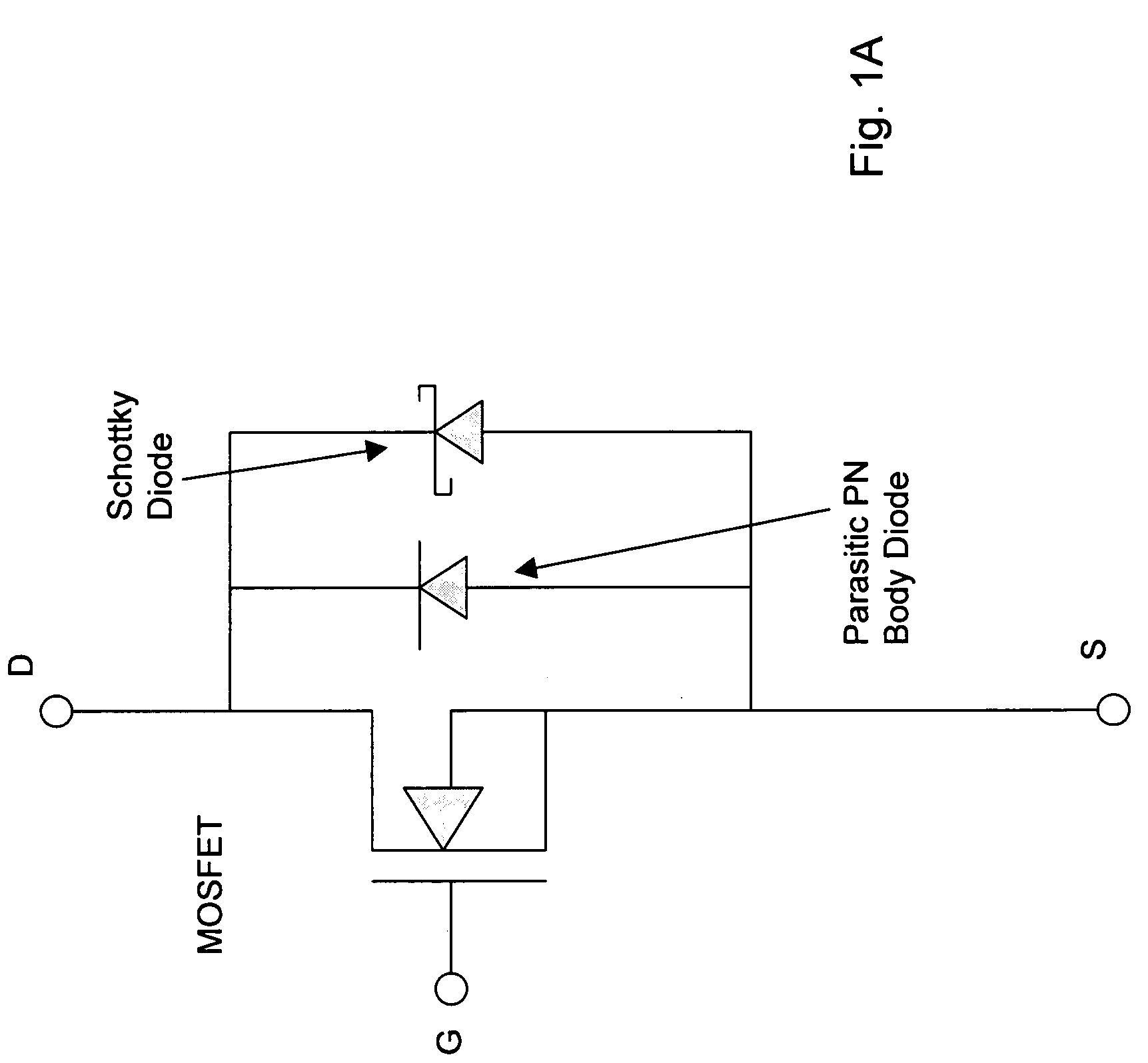

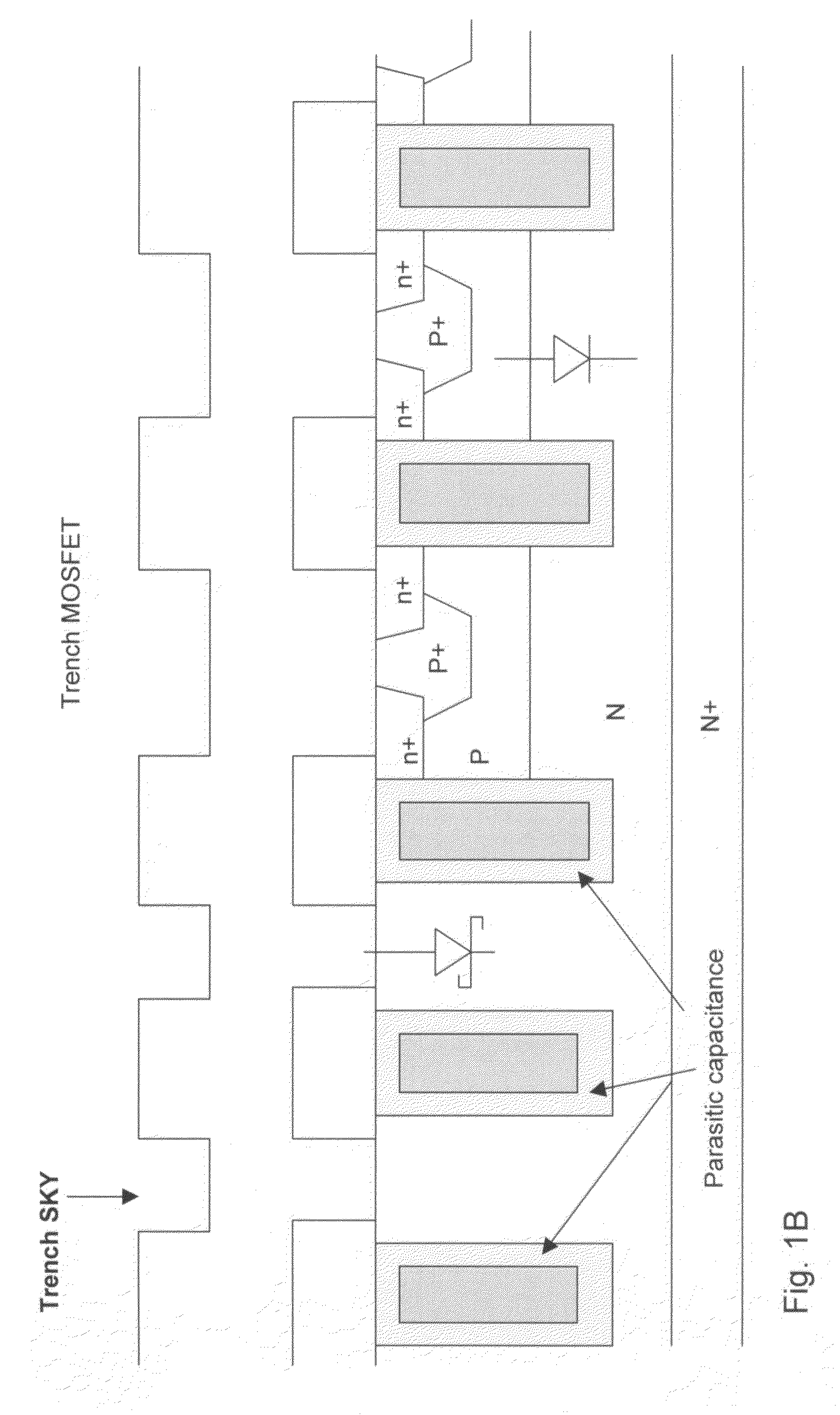

Trenched mosfets with embedded schottky in the same cell

InactiveUS20080246082A1Overcome limitationsReduce parasitic capacitanceSemiconductor/solid-state device manufacturingDiodeMOSFETSchottky barrier

A semiconductor power device includes trenched semiconductor power device comprising a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The semiconductor power device further includes an insulation layer covering the trenched semiconductor power device with a source-body contact trench opened therethrough the source and body regions and extending into an epitaxial layer below the body regions and filled with contact metal plug therein. The semiconductor power device further includes an embedded Schottky diode disposed near a bottom of the source-body contact trench below the contact metal plug wherein the Schottky diode further includes a Schottky barrier layer having a barrier height for reducing a leakage current through the embedded Schottky diode during a reverse bias between the drain and the source.

Owner:FORCE MOS TECH CO LTD

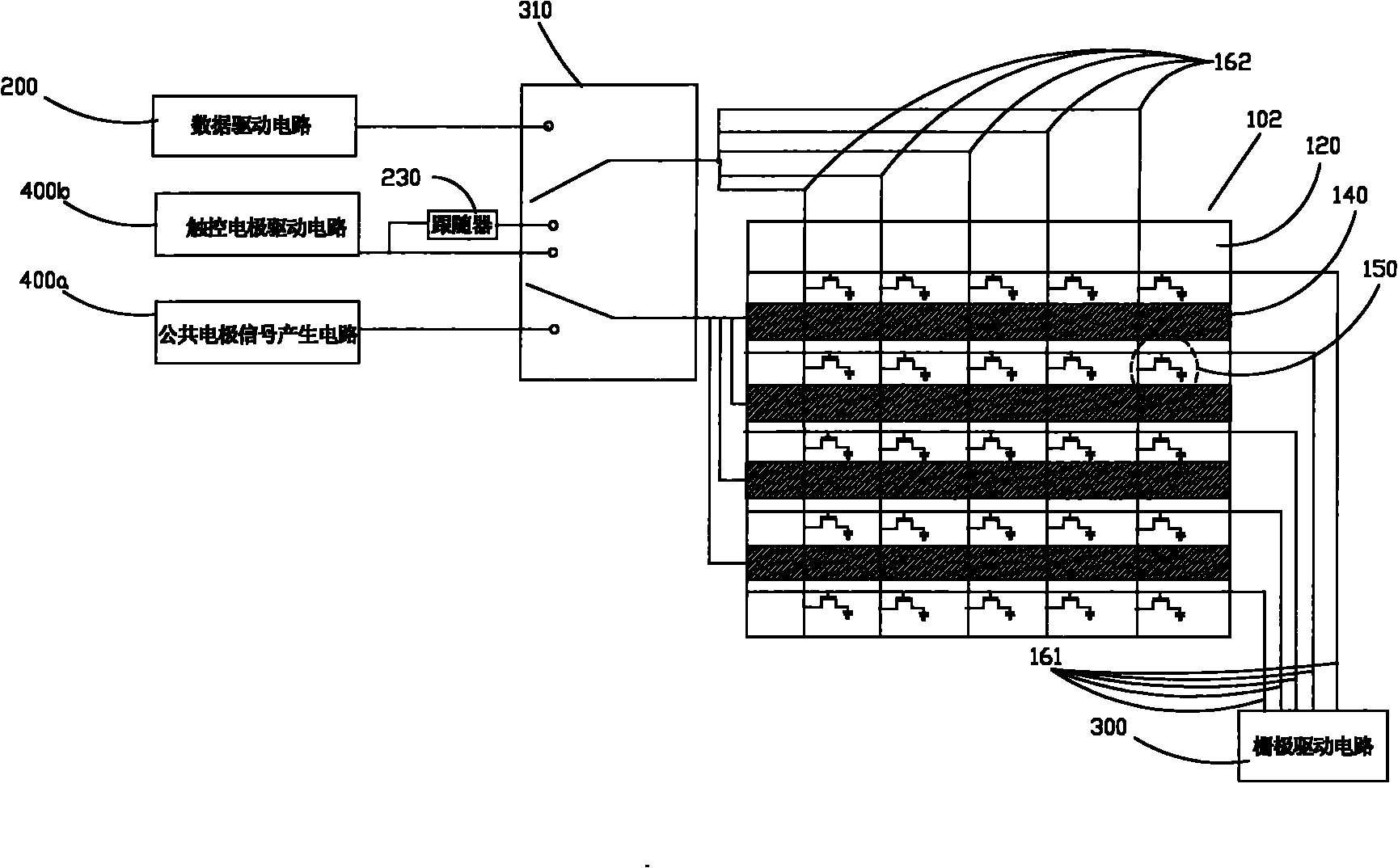

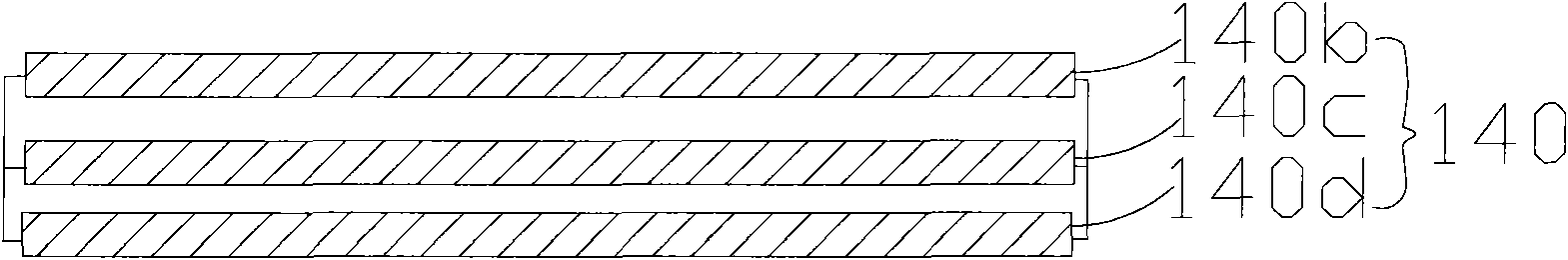

Touch screen, liquid crystal display device and driving method of touch screen

ActiveCN101866228AImprove accuracyReduce parasitic capacitanceStatic indicating devicesInput/output processes for data processingLiquid-crystal displayData lines

The invention discloses a touch screen, a liquid crystal display device and a driving method of the touch screen. The touch screen comprises a display panel, wherein the display panel comprises a first baseplate and a second baseplate, wherein the first baseplate and the second baseplate are oppositely placed, and the second baseplate is provided with a plurality of groups of public electrode wires; a data driving circuit is connected with a data wire and used for supplying a display data driving signal for the data wire in a display mode; a grid driving circuit is connected with a grid wire and used for supplying a display grid driving signal for the grid wire in the display mode and supplying a touch grid driving signal for the grid wire in a touch mode; a public electrode signal generating circuit is connected with the public electrode wire and used for supplying a display public electrode signal for the public electrode wire in the display mode; and a touch driving circuit is connected with the data wire and the public electrode wire and used for supplying the same touch driving signal for the data wire and the public electrode wire in the touch mode, thereby improving the detection accuracy on the touch point position on the touch screen.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Semiconductor device with air gap and method for fabricating the same

ActiveUS20130320550A1Reduce parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceSemiconductor

A method for fabricating a semiconductor device includes forming a plurality of bit line structures over a substrate, forming multiple layers of spacer layers with a capping layer interposed therebetween over the bit line structures, exposing a surface of the substrate by selectively etching the spacer layers, forming air gaps and capping spacers for covering upper portions of the air gaps by selectively etching the capping layer, and forming storage node contact plugs between the bit line structures.

Owner:SK HYNIX INC

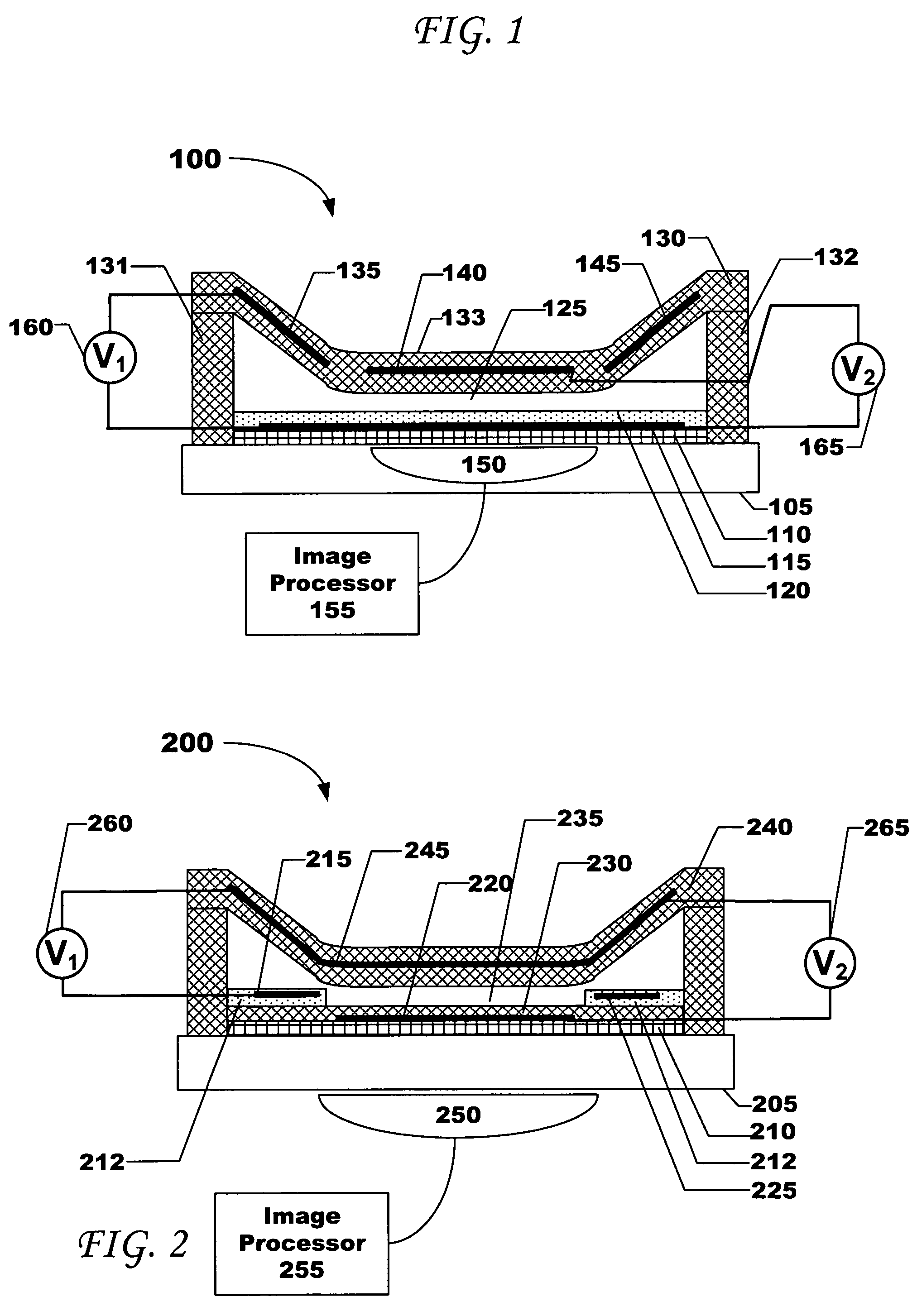

Asymetric membrane cMUT devices and fabrication methods

ActiveUS20050203397A1Reduce parasitic capacitanceImprove electrical performanceUltrasonic/sonic/infrasonic diagnosticsSurgeryCapacitanceCapacitive micromachined ultrasonic transducers

Asymmetric membrane capacitive micromachined ultrasonic transducer (“cMUT”) devices and fabrication methods are provided. In a preferred embodiment, a cMUT device according to the present invention generally comprises a membrane having asymmetric properties. The membrane can have a varied width across its length so that its ends have different widths. The asymmetric membrane can have varied flex characteristics due to its varied width dimensions. In another preferred embodiment, a cMUT device according to the present invention generally comprises an electrode element having asymmetric properties. The electrode element can have a varied width across its length so that its ends have different widths. The asymmetric electrode element can have different reception and transmission characteristics due to its varied width dimensions. In another preferred embodiment, a mass load positioned along the membrane can alter the mass distribution of the membrane. Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com