Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2811 results about "High electron" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

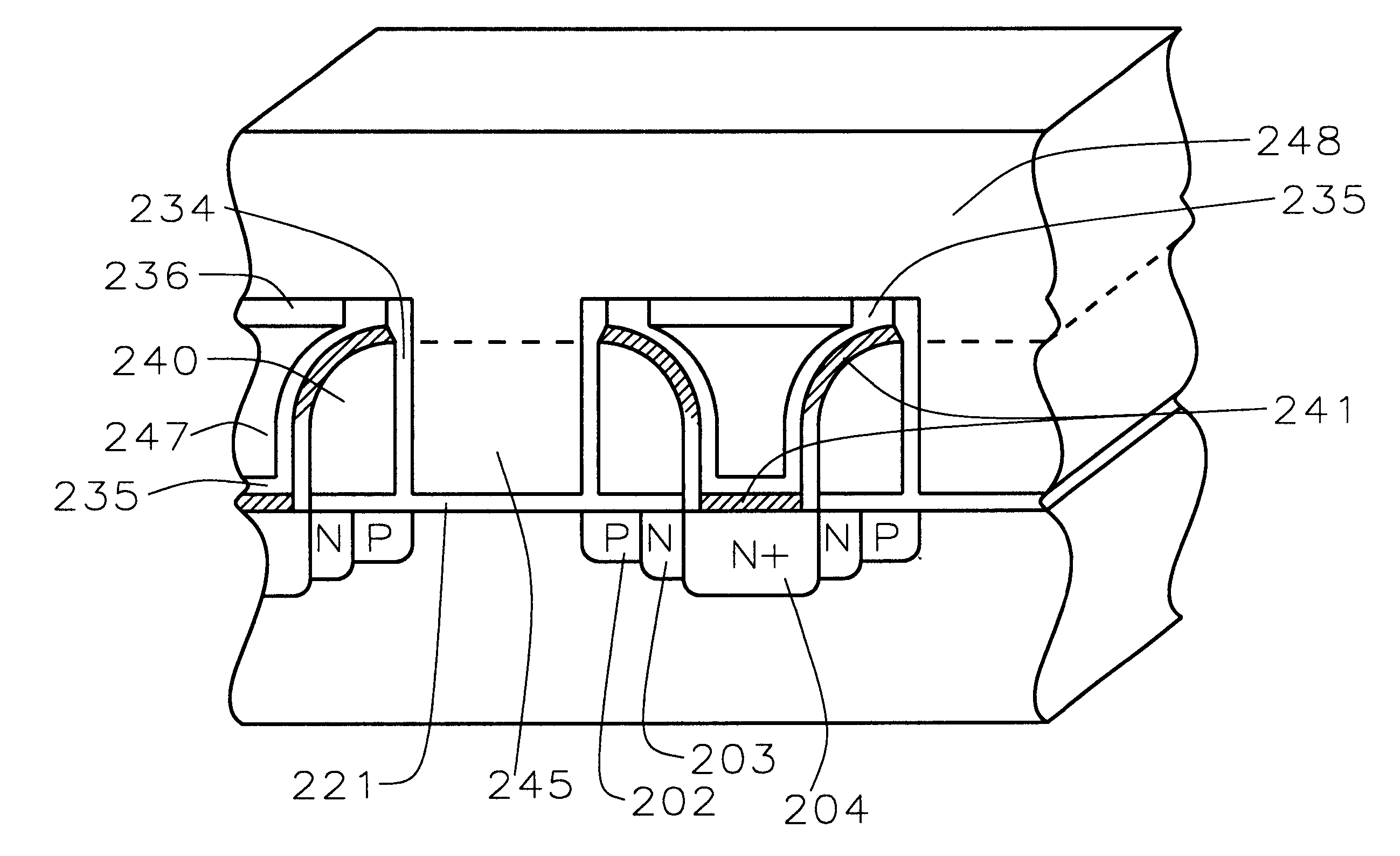

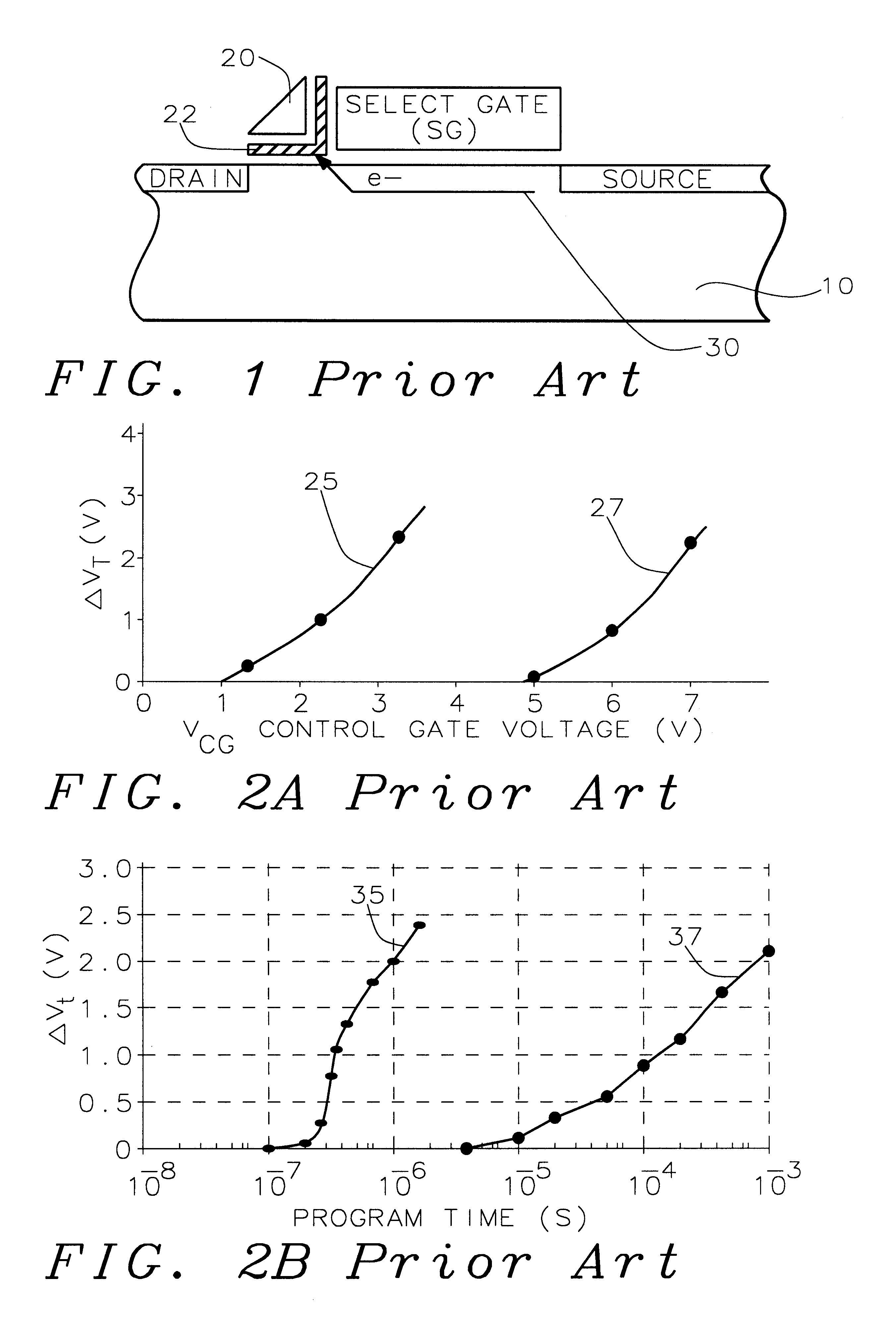

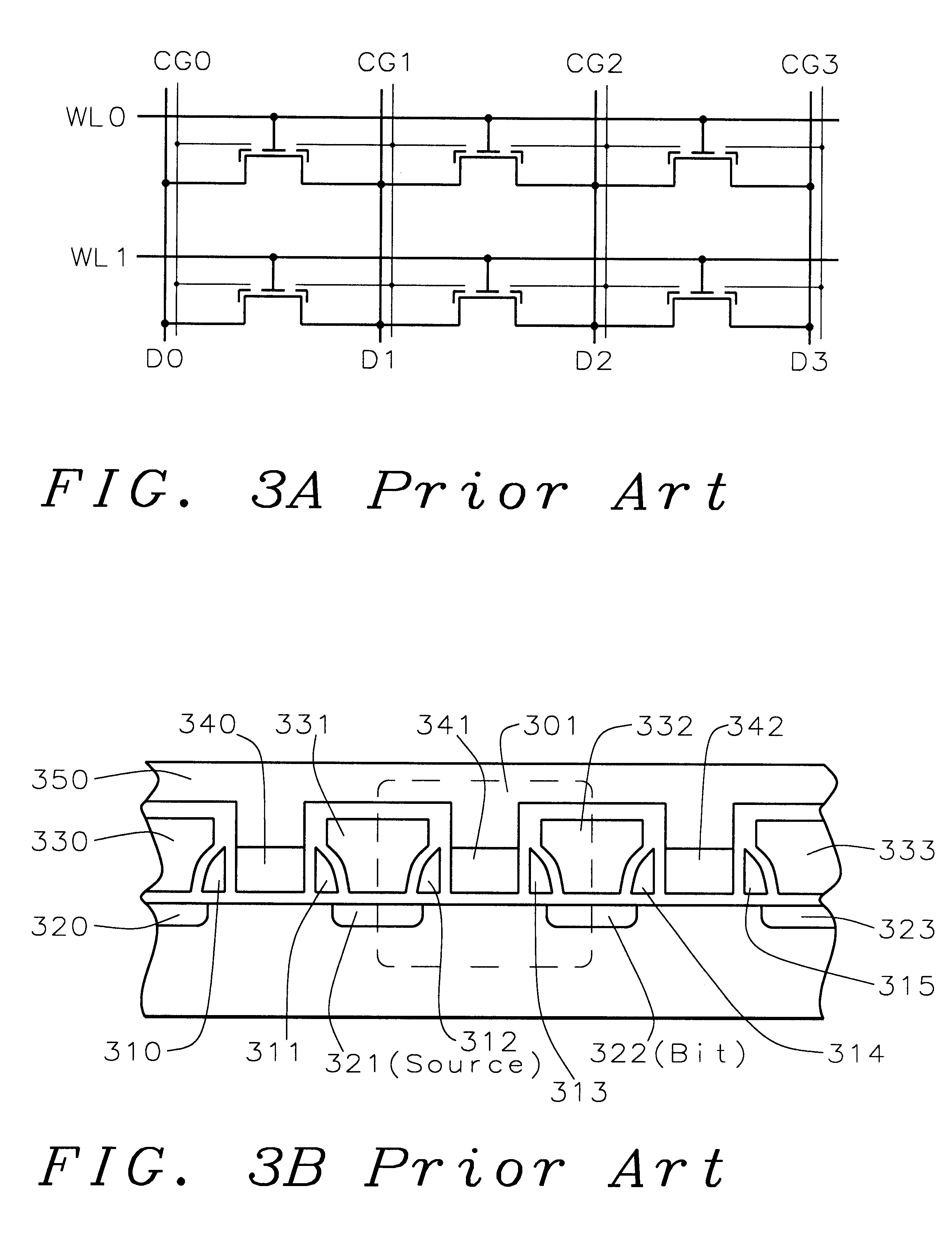

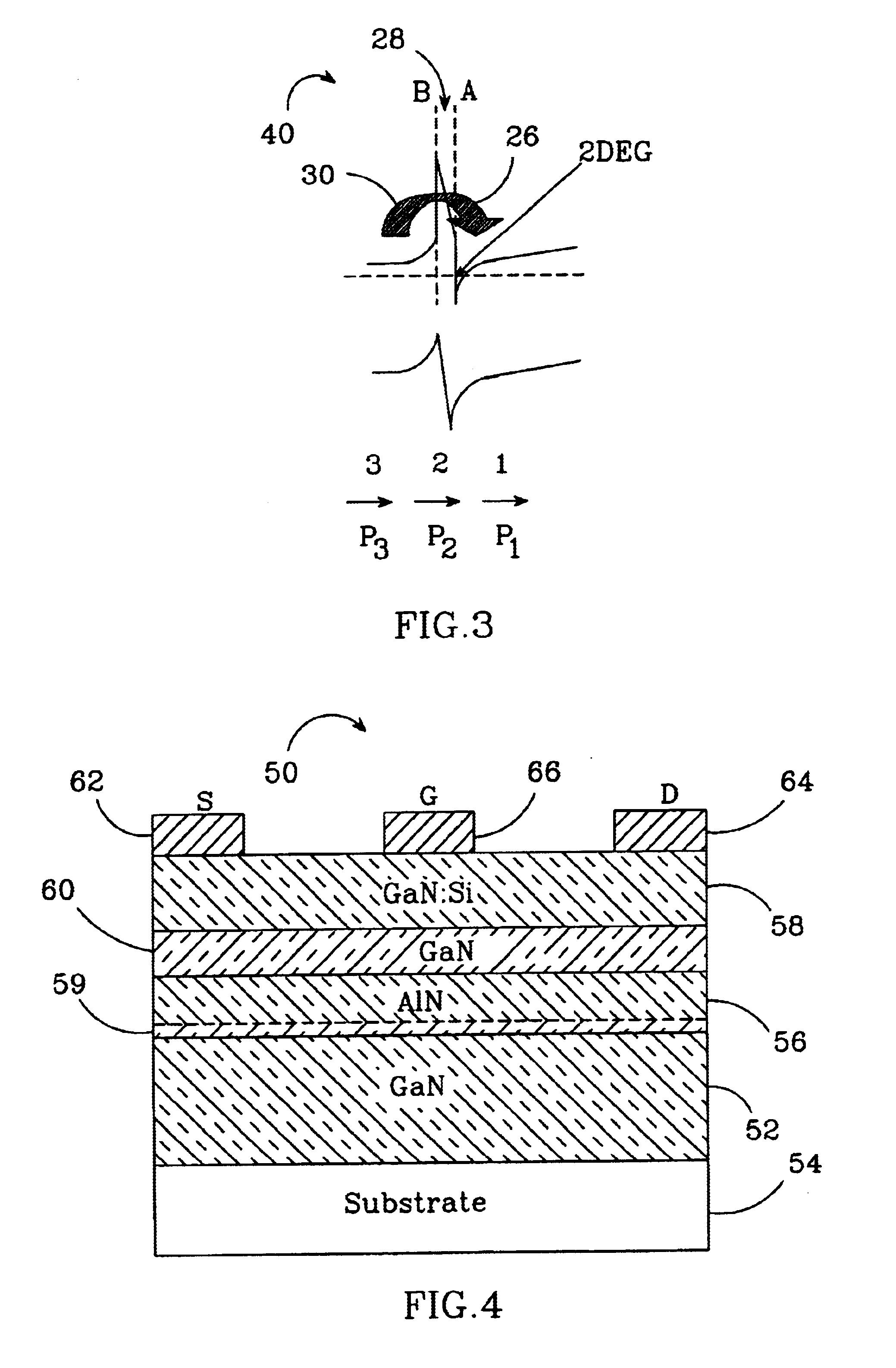

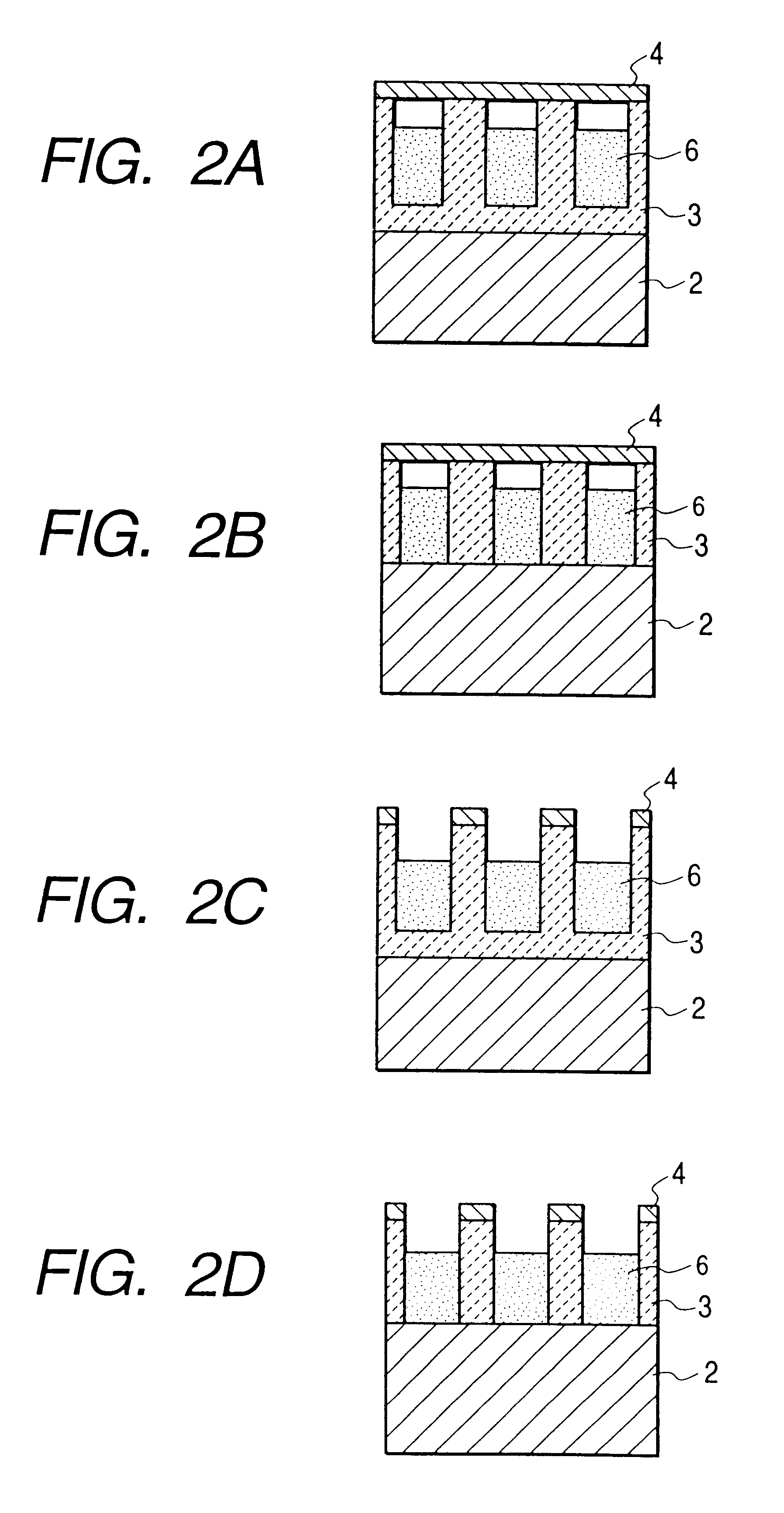

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

Method for achieving improved epitaxy quality (surface texture and defect density) on free-standing (aluminum, indium, gallium) nitride ((al,in,ga)n) substrates for opto-electronic and electronic devices

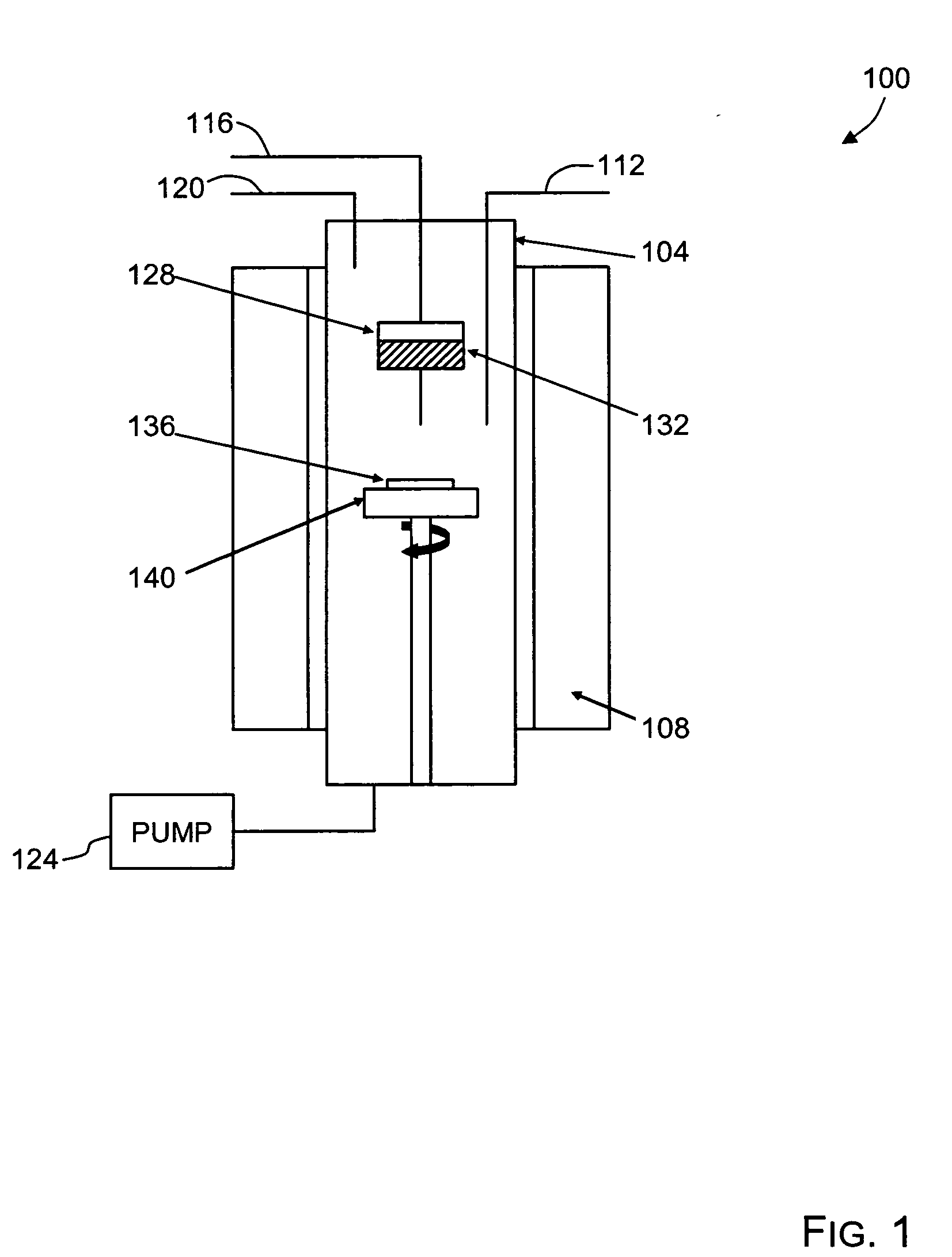

A III-V nitride homoepitaxial microelectronic device structure comprising a III-V nitride homoepitaxial epi layer on a III-V nitride material substrate, e.g., of freestanding character. Various processing techniques are described, including a method of forming a III-V nitride homoepitaxial layer on a corresponding III-V nitride material substrate, by depositing the III-V nitride homoepitaxial layer by a VPE process using Group III source material and nitrogen source material under process conditions including V / III ratio in a range of from about 1 to about 105, nitrogen source material partial pressure in a range of from about 1 to about 103 torr, growth temperature in a range of from about 500 to about 1250 degrees Celsius, and growth rate in a range of from about 0.1 to about 500 microns per hour. The III-V nitride homoepitaxial microelectronic device structures are usefully employed in device applications such as UV LEDs, high electron mobility transistors, and the like.

Owner:WOLFSPEED INC

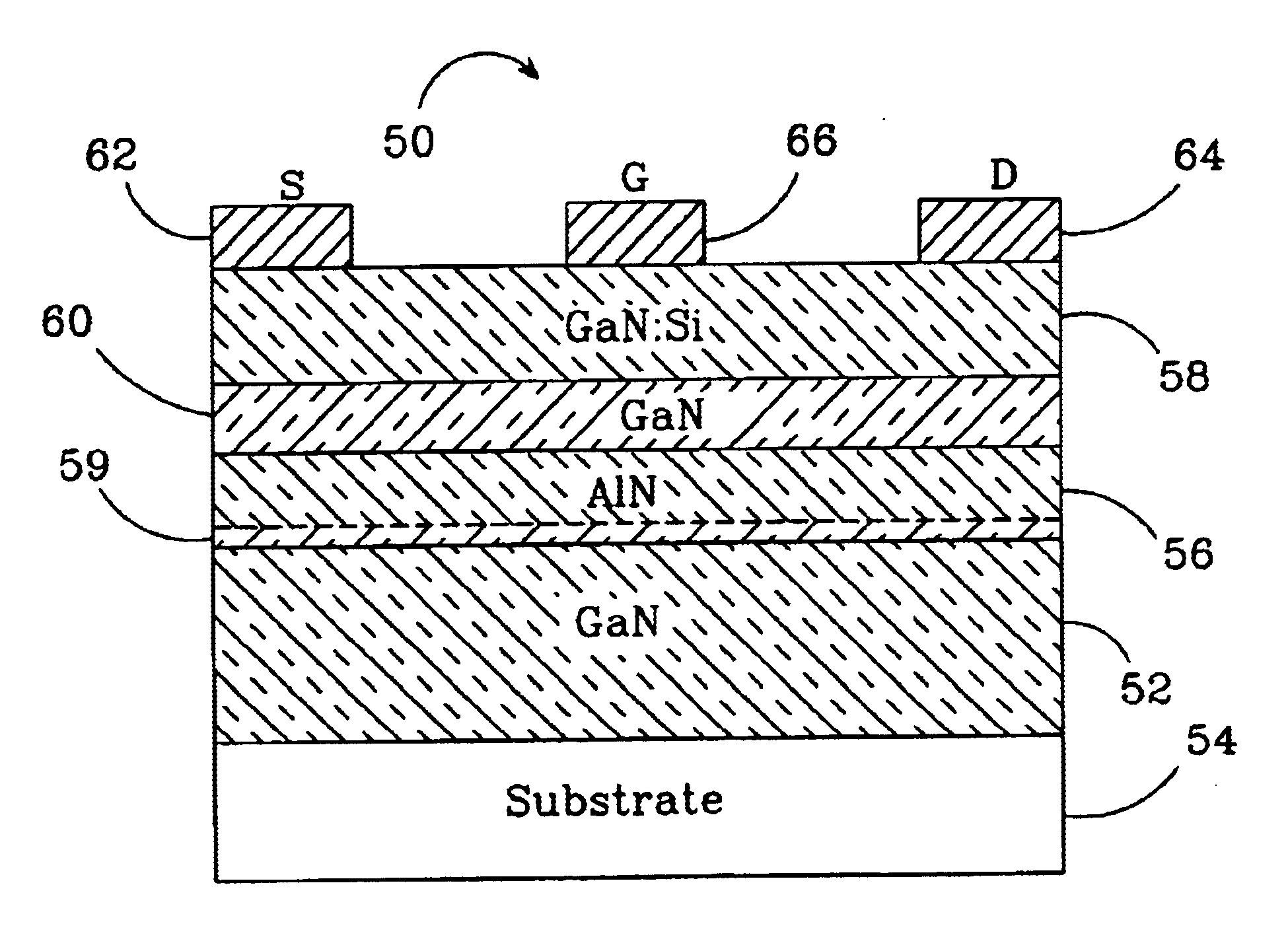

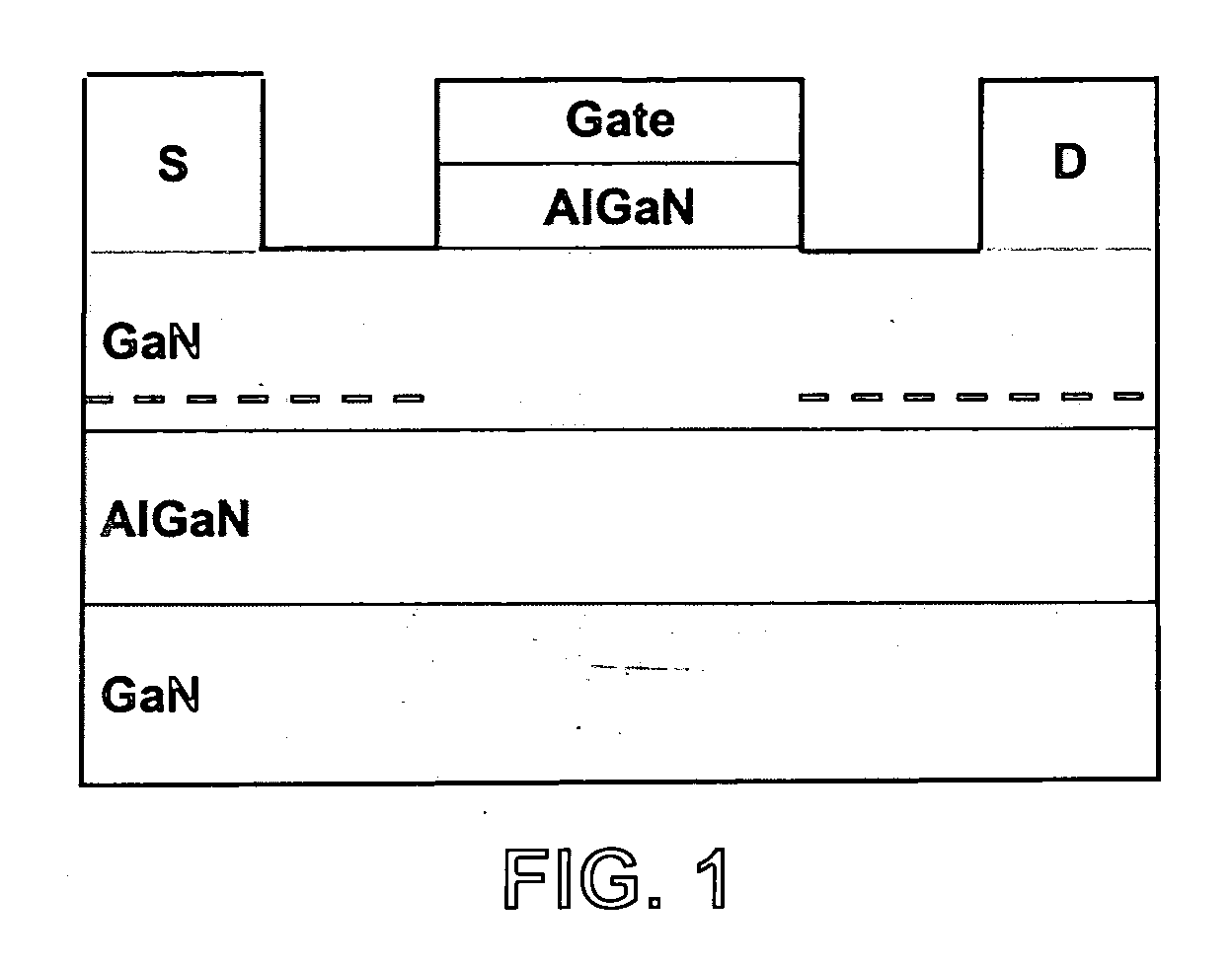

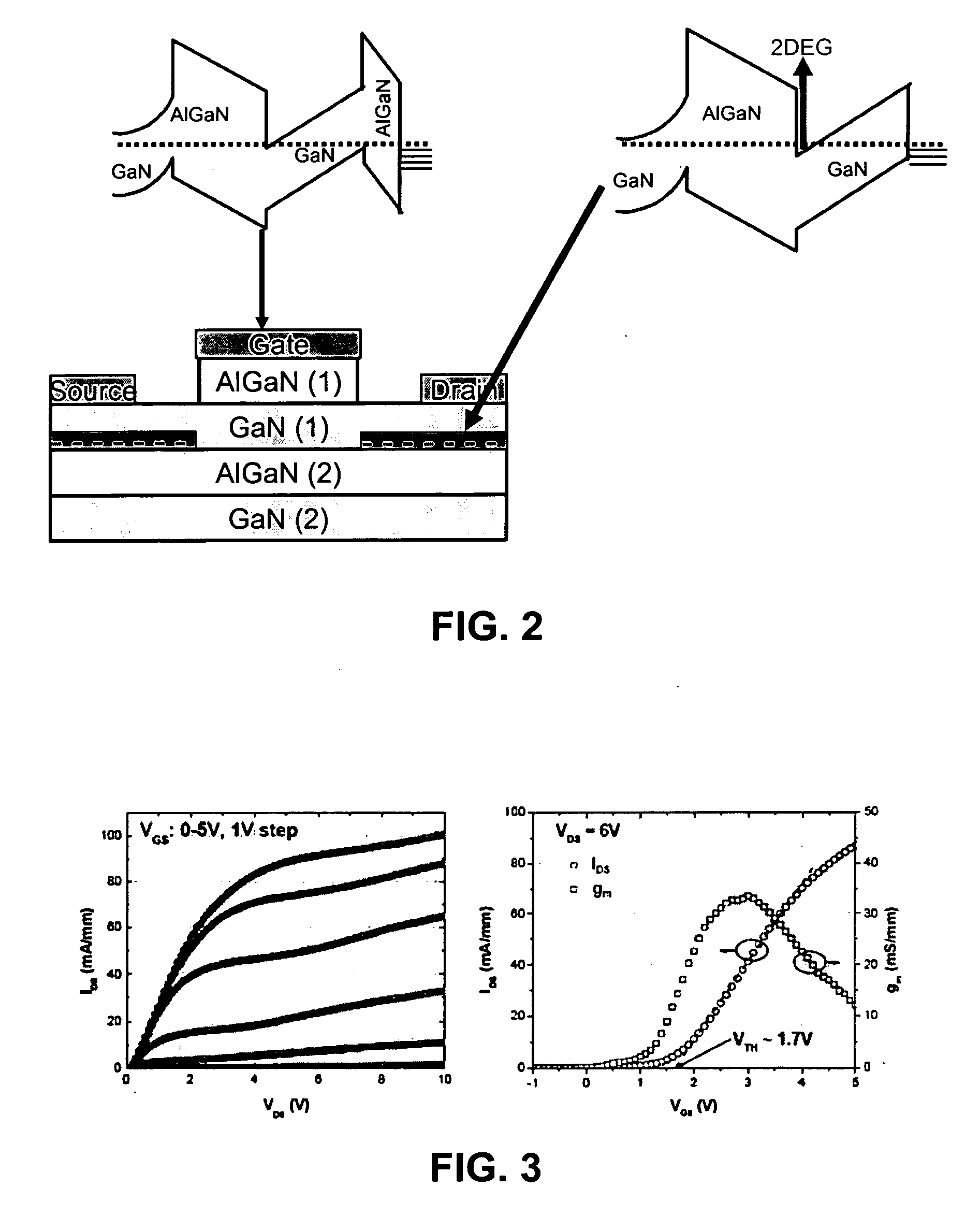

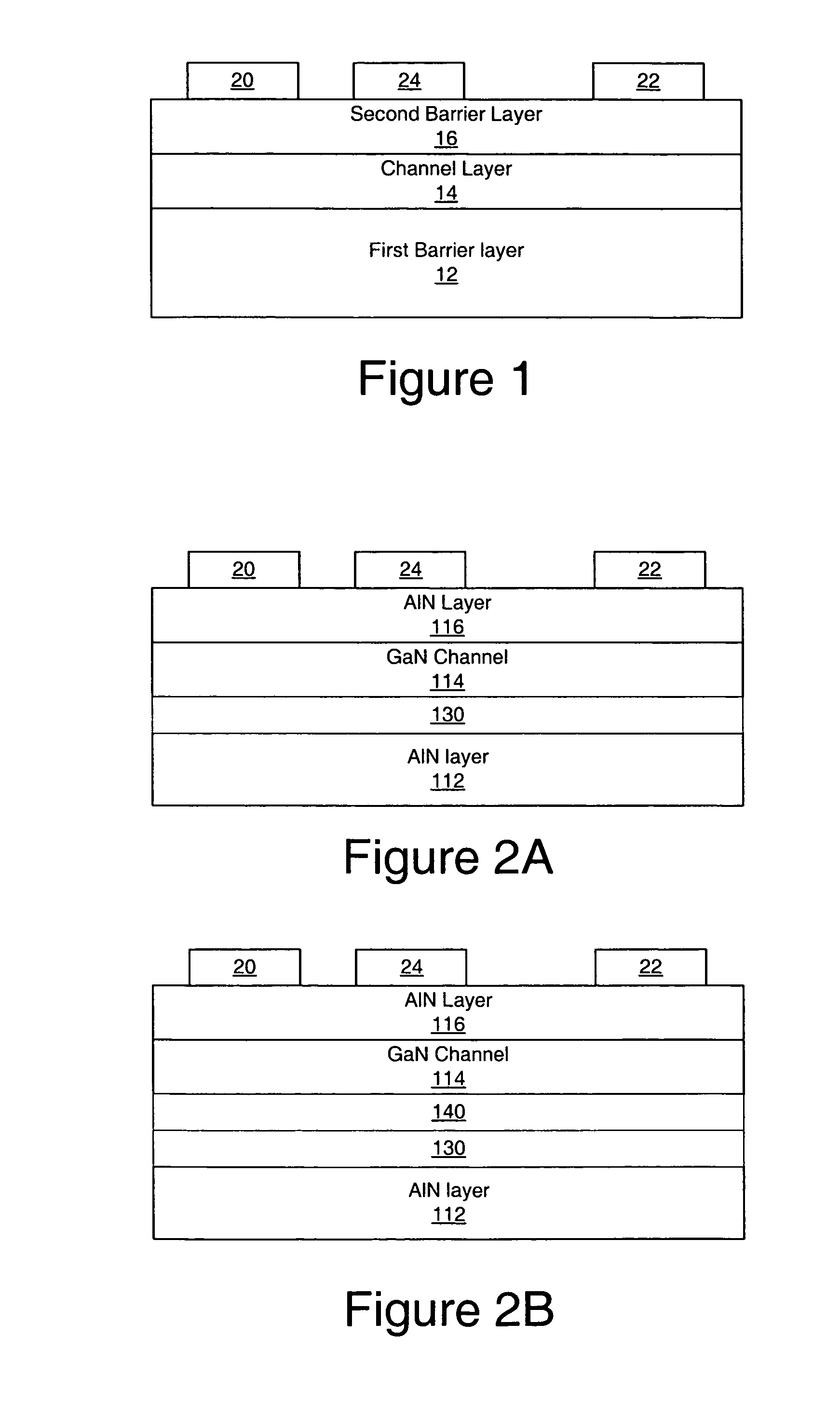

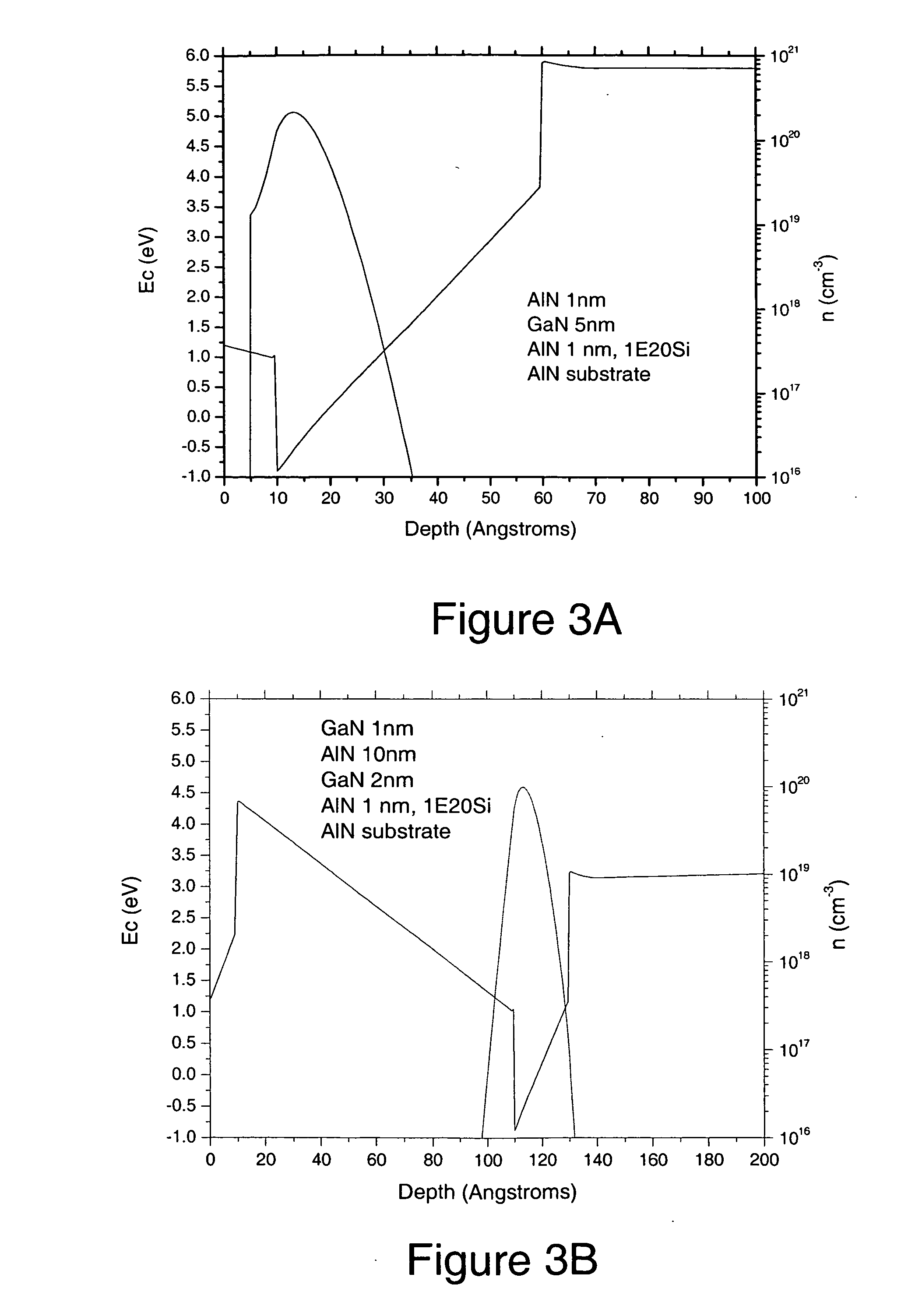

Group-III nitride based high electron mobility transistor (HEMT) with barrier/spacer layer

InactiveUS6849882B2High piezoelectric chargeReduction in piezoelectric scatteringSemiconductor/solid-state device manufacturingSemiconductor devicesHigh electronNucleation

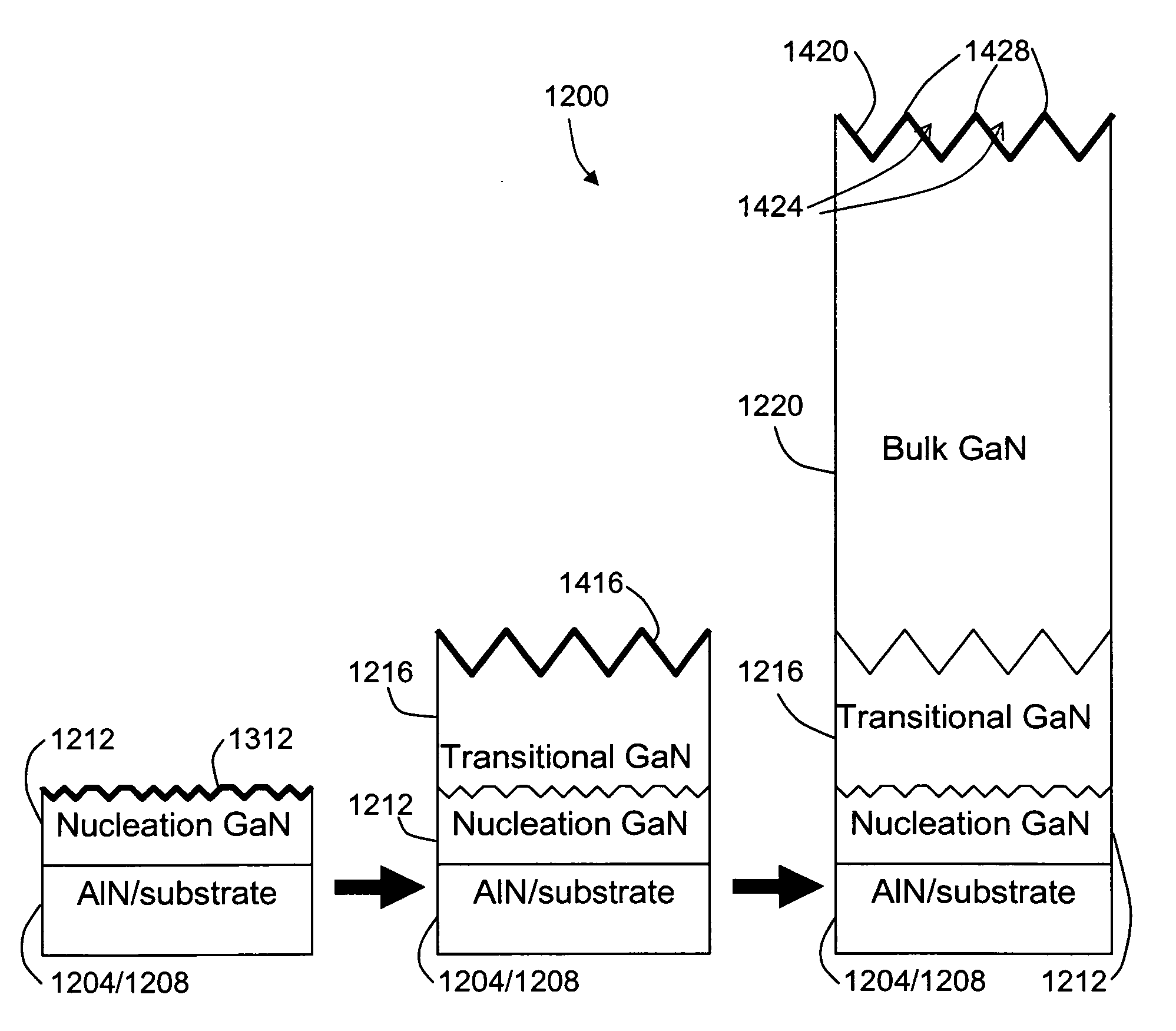

A Group III nitride based high electron mobility transistors (HEMT) is disclosed that provides improved high frequency performance. One embodiment of the HEMT comprises a GaN buffer layer, with an AlyGa1−yN (y=1 or y 1) layer on the GaN buffer layer. An AlxGa1−xN (0≦x≦0.5) barrier layer on to the AlyGa1−yN layer, opposite the GaN buffer layer, AlyGa1−yN layer having a higher Al concentration than that of the AlxGa1−xN barrier layer. A preferred AlyGa1−yN layer has y=1 or y˜1 and a preferred AlxGa1−xN barrier layer has 0≦x≦0.5. A 2DEG forms at the interface between the GaN buffer layer and the AlyGa1−yN layer. Respective source, drain and gate contacts are formed on the AlxGa1−xN barrier layer. The HEMT can also comprising a substrate adjacent to the buffer layer, opposite the AlyGa1−yN layer and a nucleation layer between the AlxGa1−xN buffer layer and the substrate.

Owner:CREE INC +1

Group III Nitride Articles and Methods for Making Same

ActiveUS20100044718A1Promote formationEasy to fillPolycrystalline material growthSemiconductor/solid-state device manufacturingPhotovoltaic detectorsPhotodetector

Owner:KYMA TECH

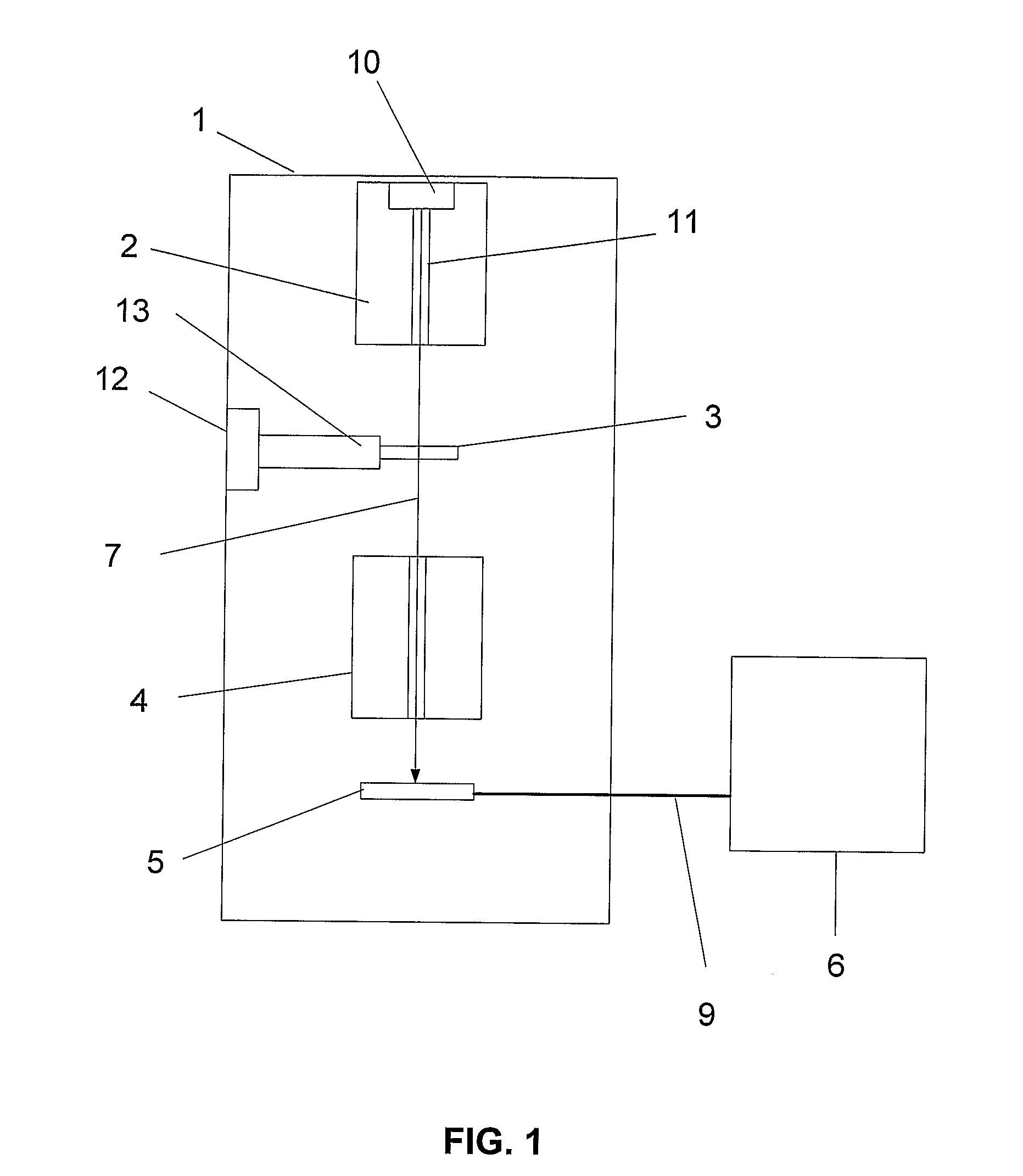

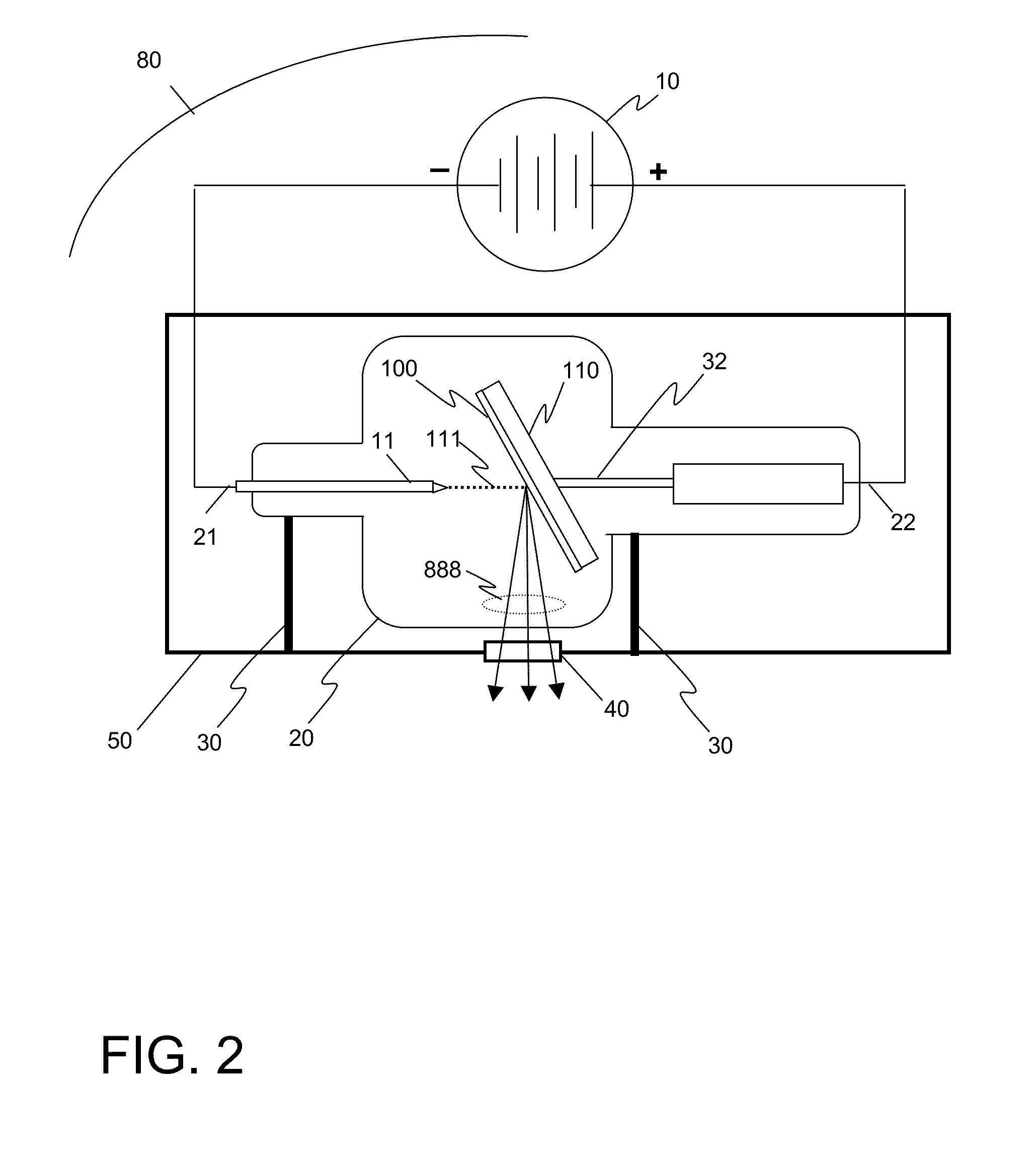

Plasma processing apparatus and method for plasma-processing semiconductor substrate

InactiveUS20100279512A1Reduce harmEnhance plasma processingElectric discharge tubesSemiconductor/solid-state device manufacturingElectron temperatureStops device

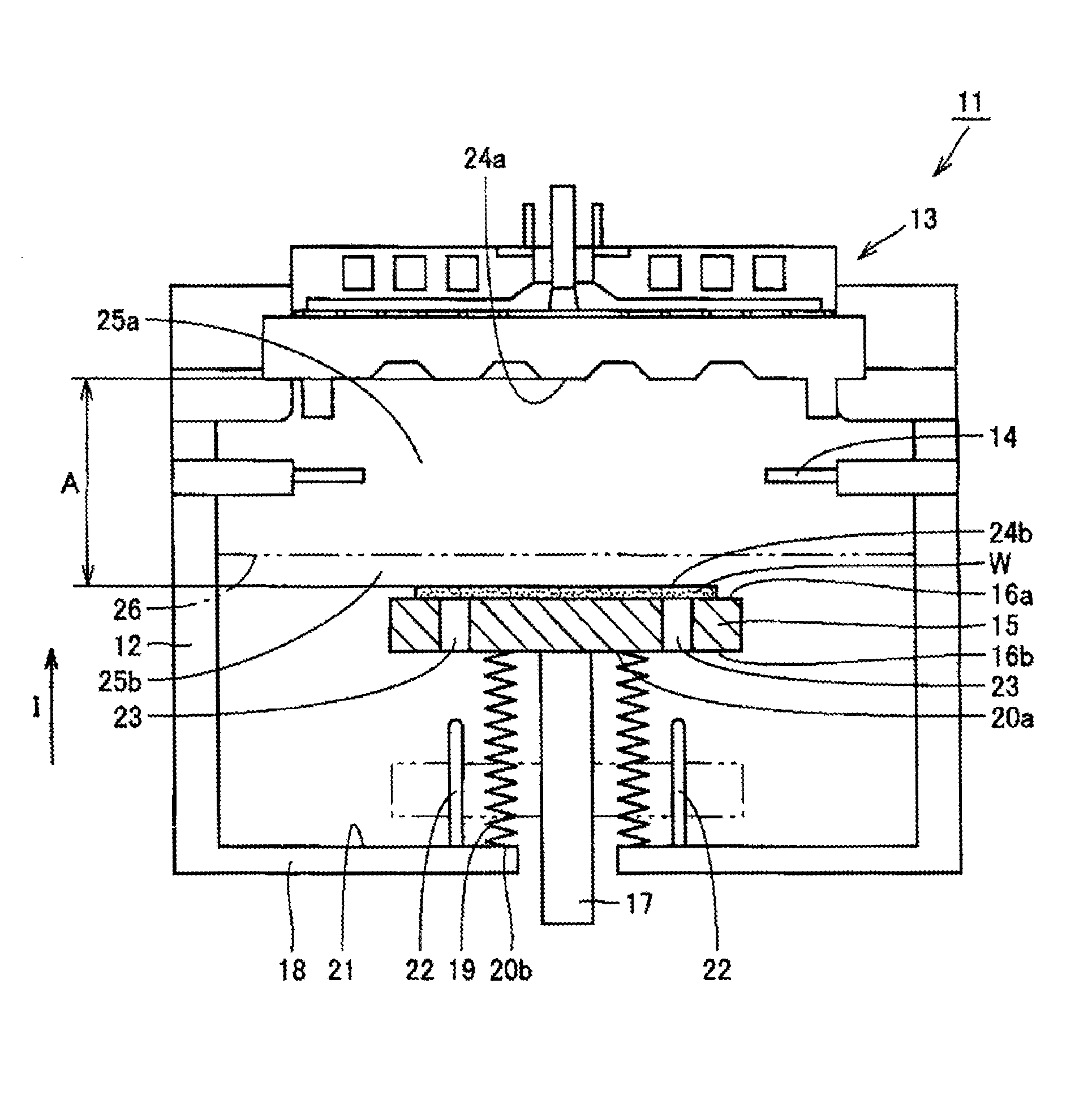

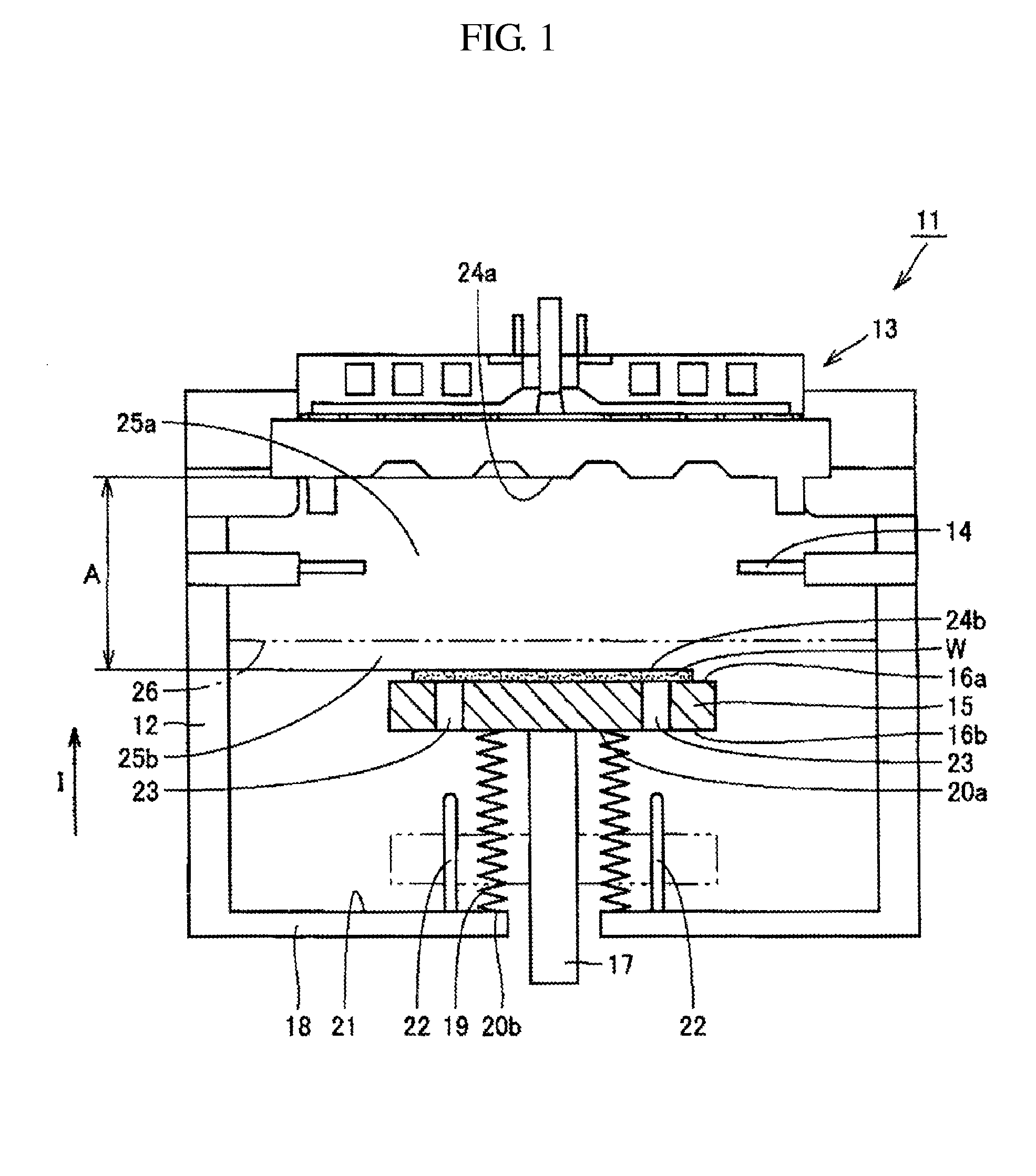

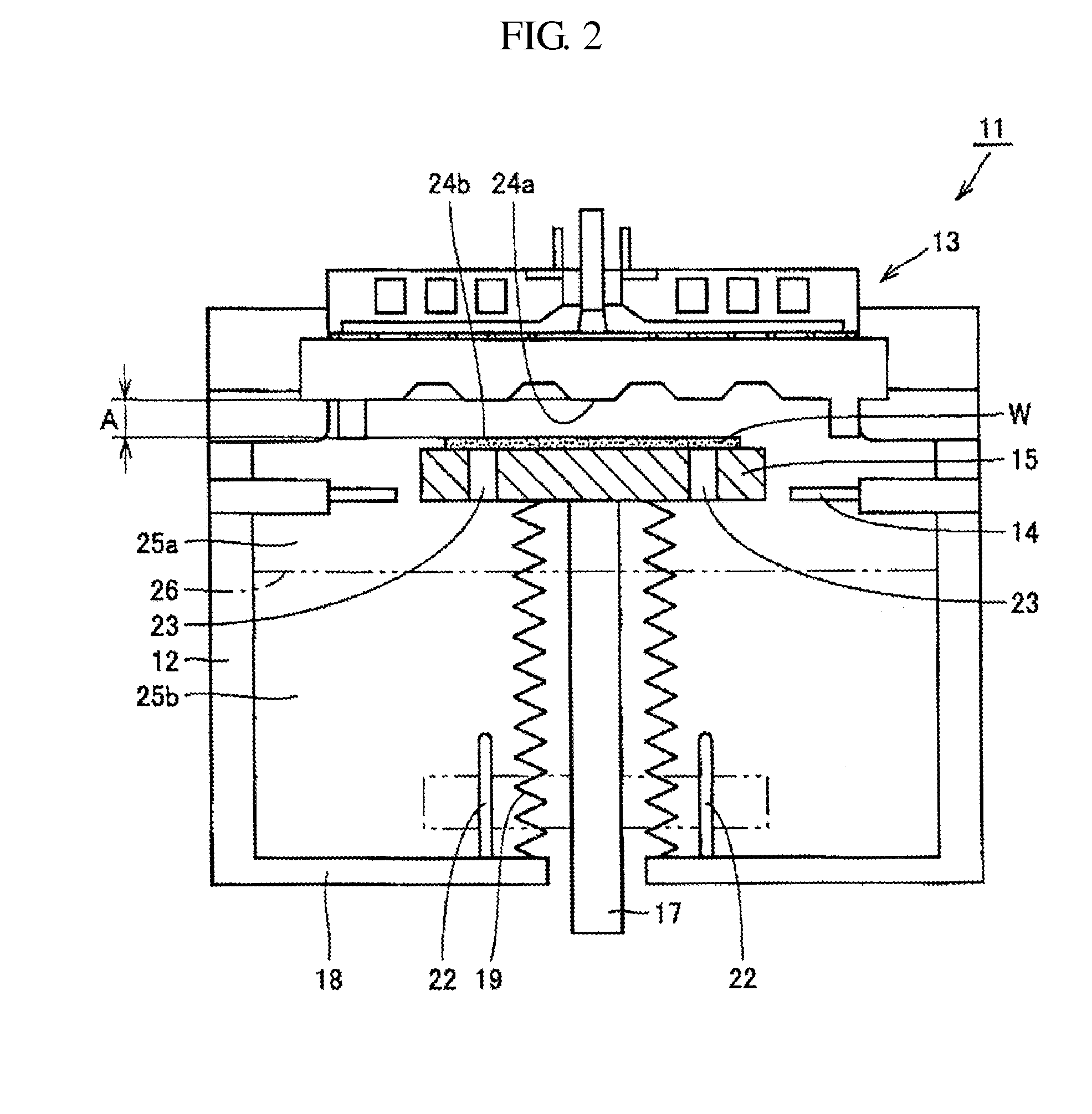

A plasma processing apparatus includes an antenna unit for generating plasma by using microwaves as a plasma source in such a way that a first region having a relatively high electron temperature of plasma, and a second region having a lower electron temperature of plasma than the first region are formed in a chamber, a first arranging means for arranging a semiconductor substrate W in the first region, a second arranging means for arranging the semiconductor substrate in the second region, and a plasma generation stopping means for stopping the generation of plasma of a plasma generating means, while the semiconductor substrate is arranged in the second region.

Owner:TOKYO ELECTRON LTD

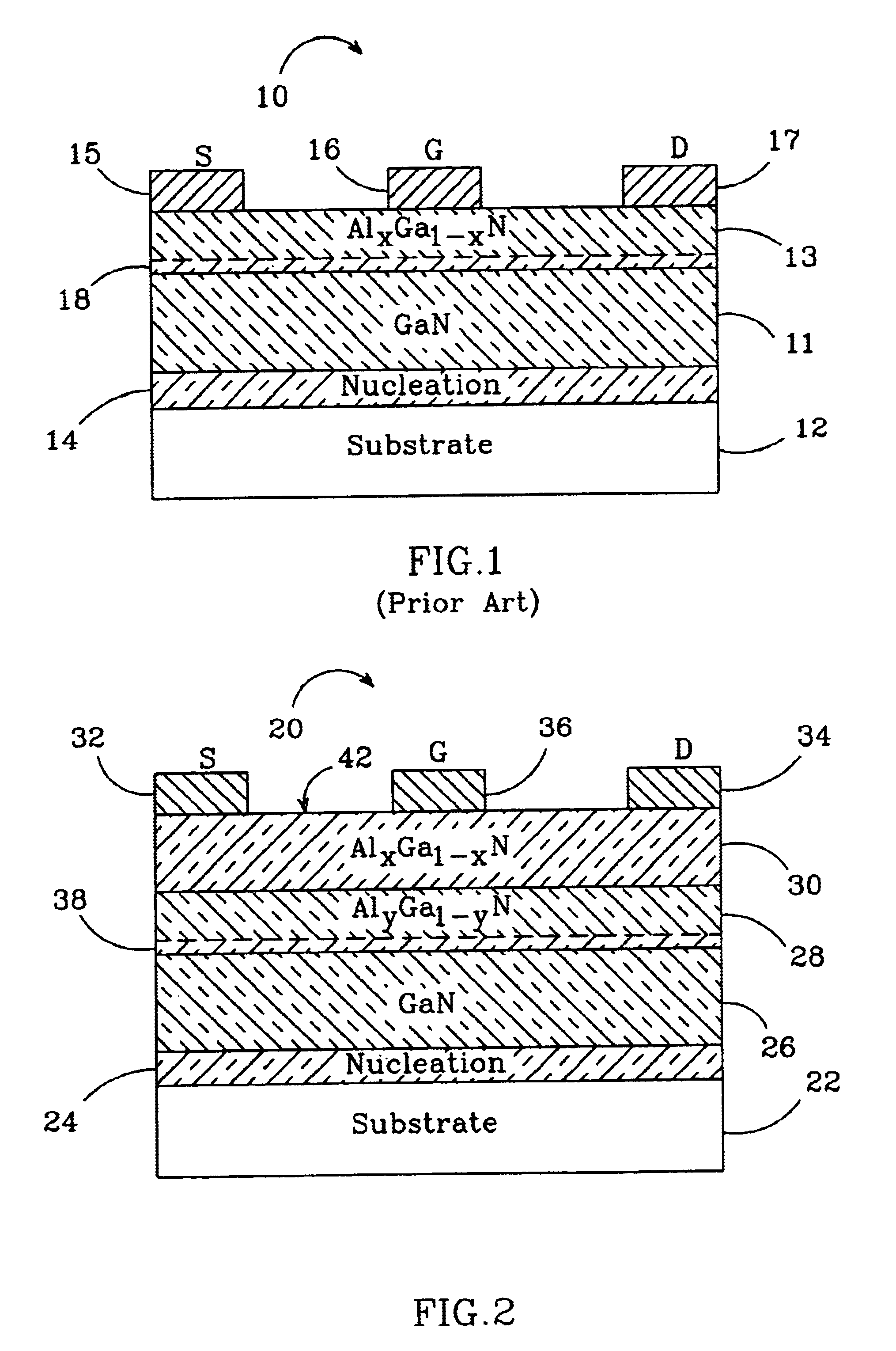

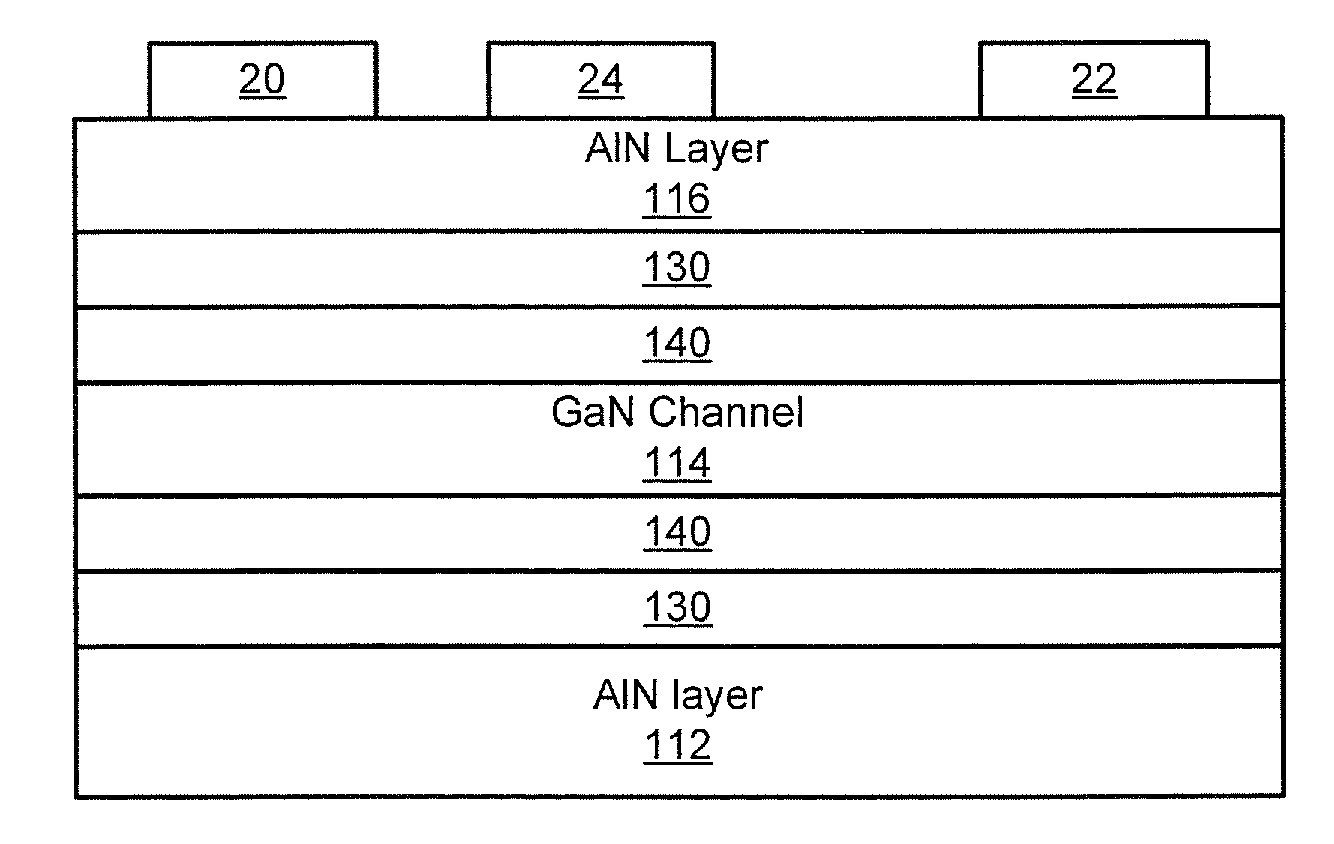

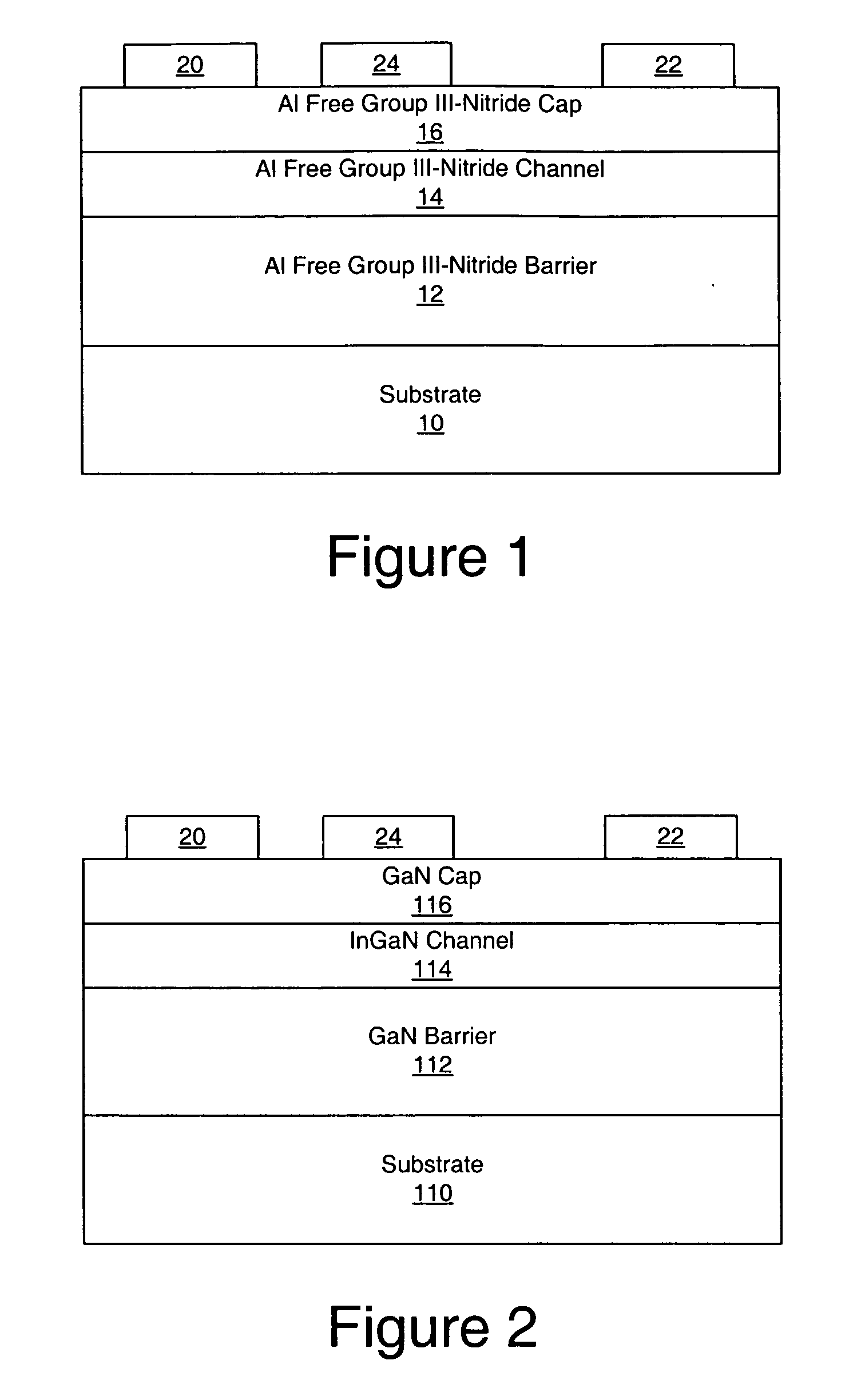

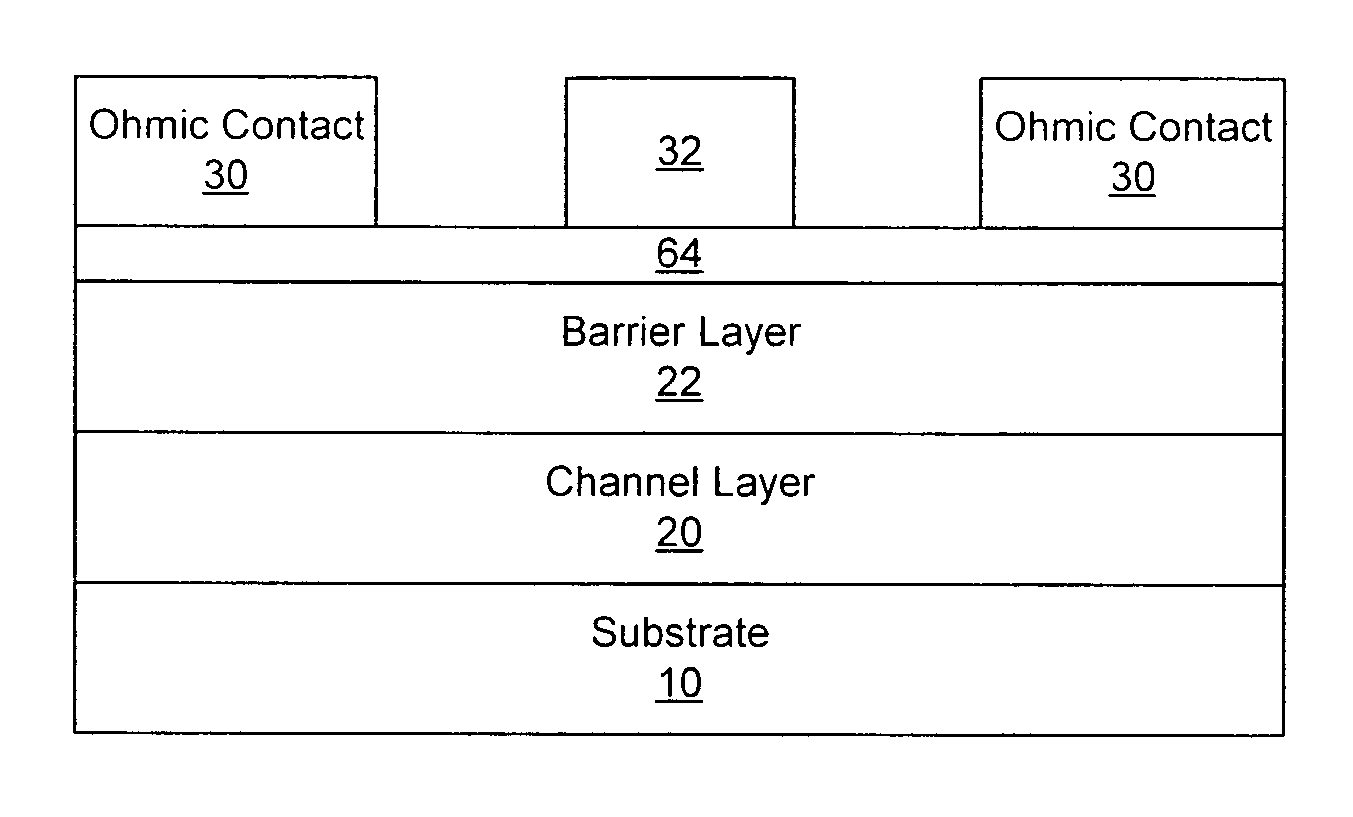

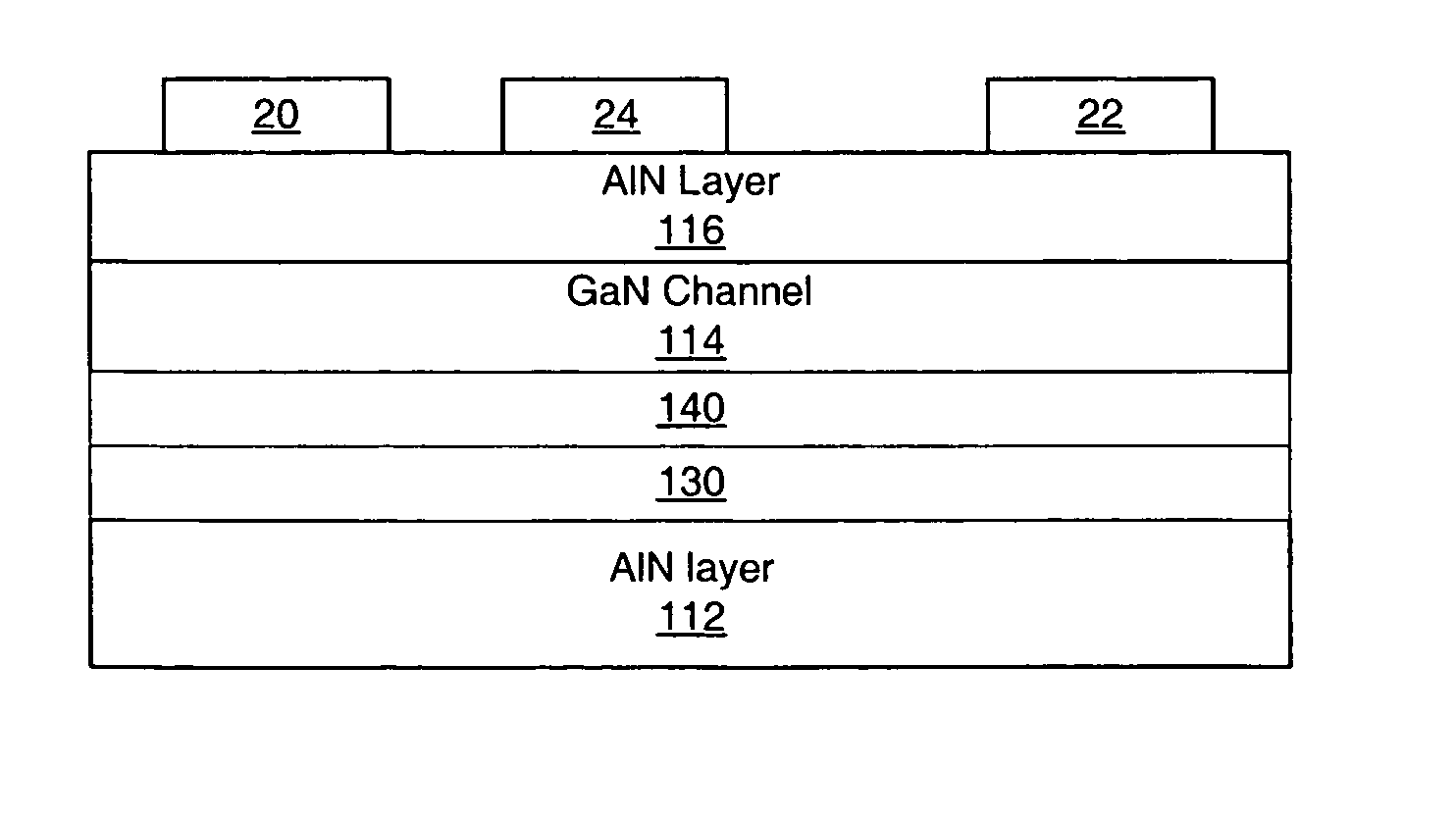

Binary group III-nitride based high electron mobility transistors

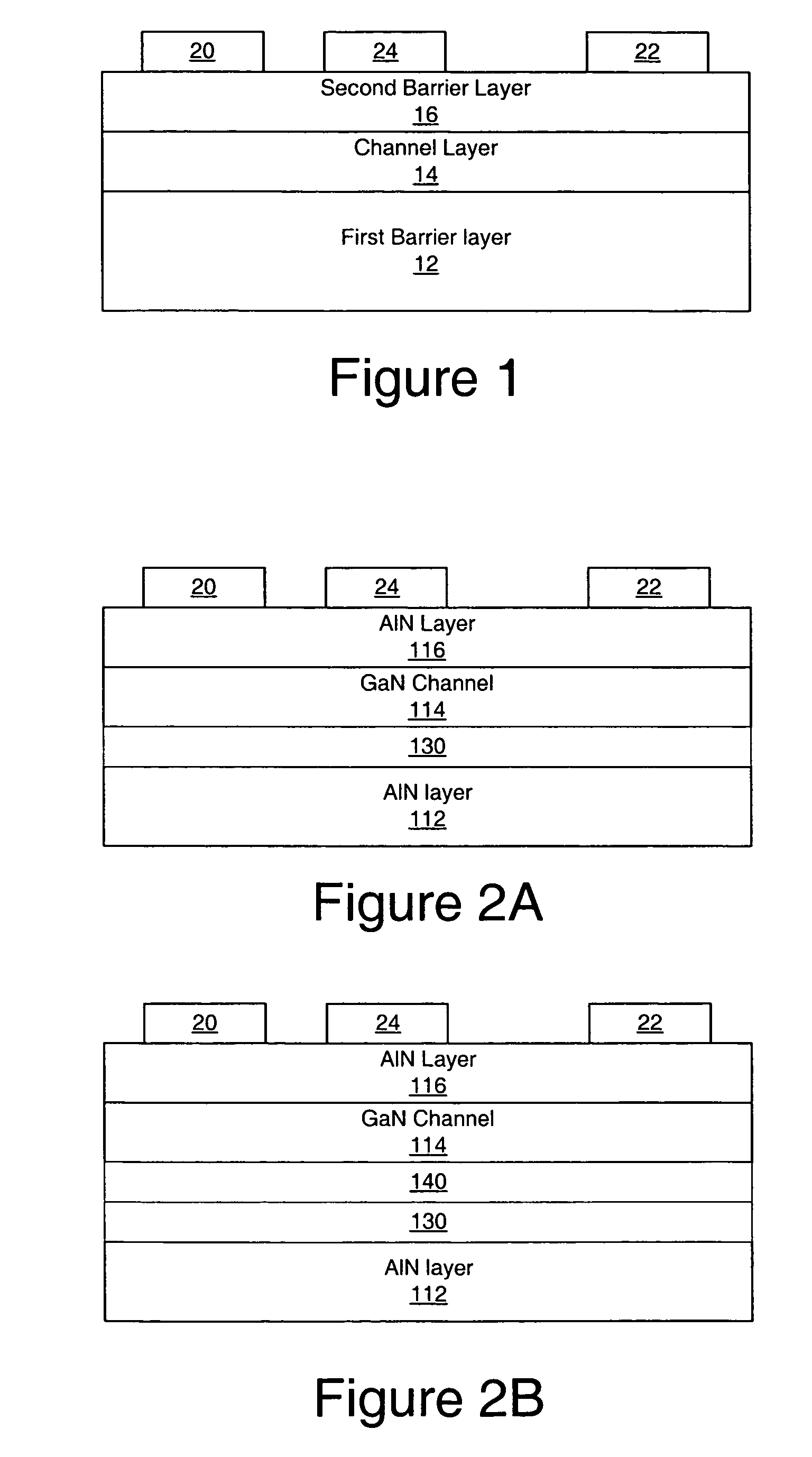

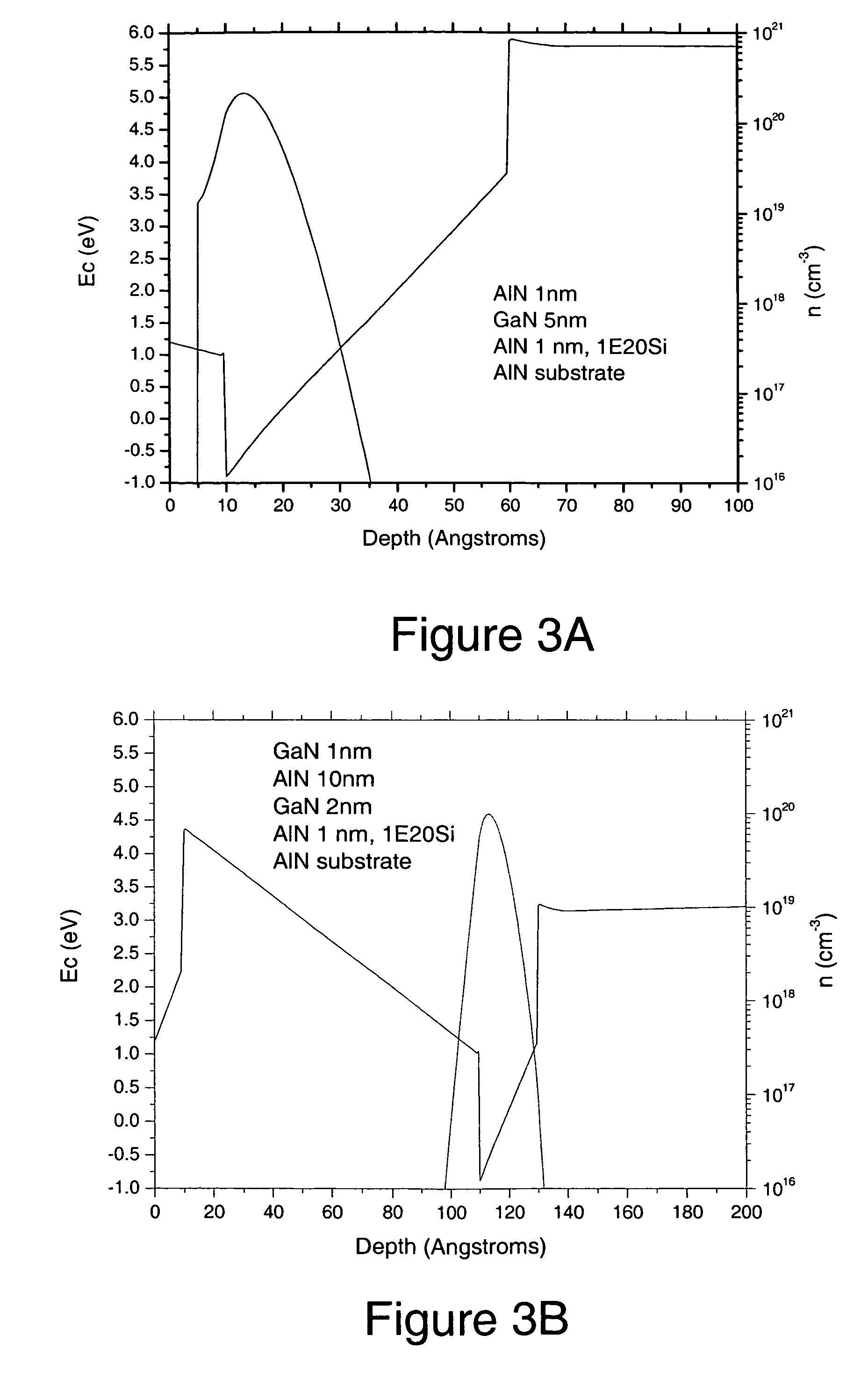

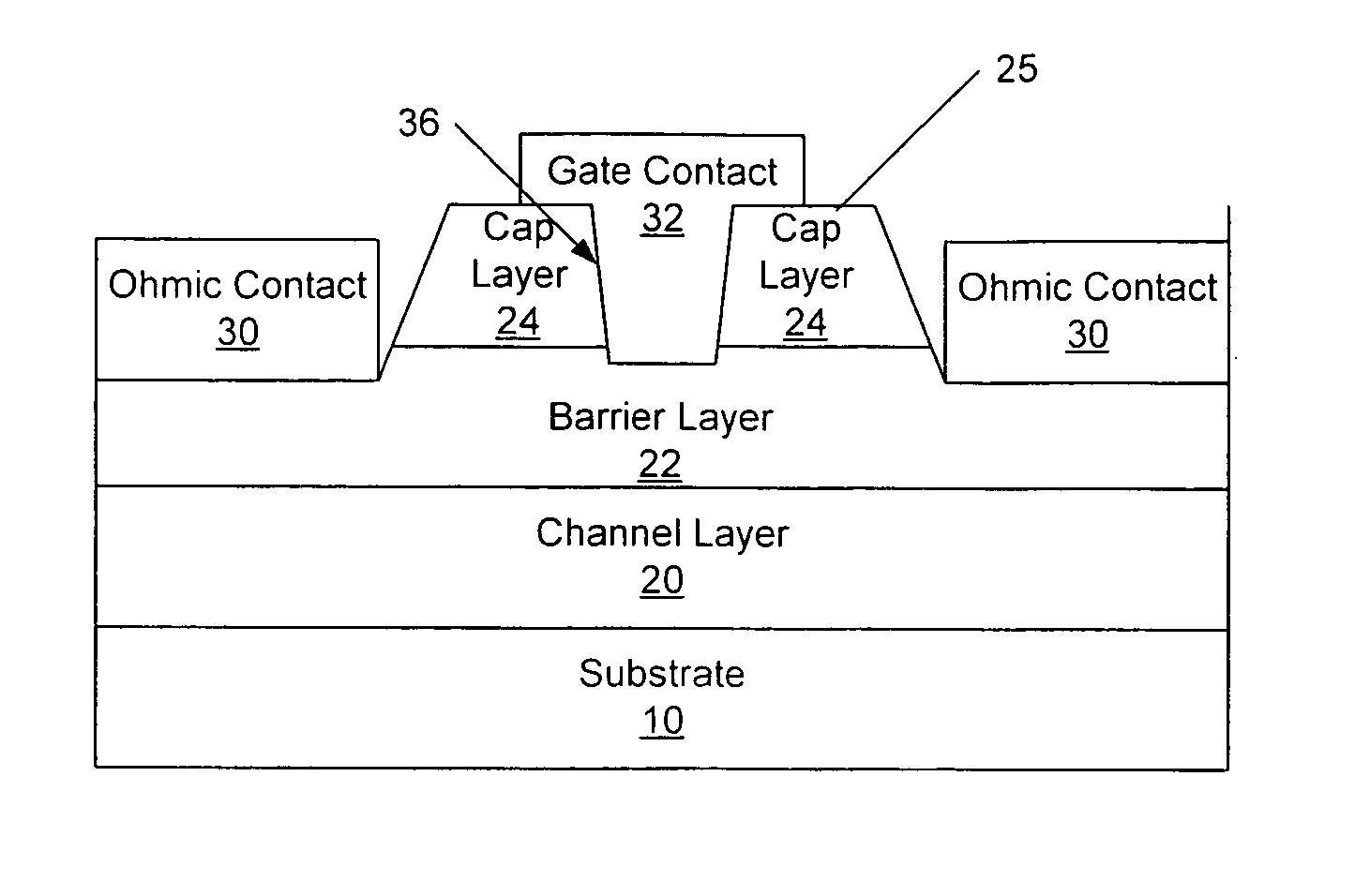

Binary Group III-nitride high electron mobility transistors (HEMTs) and methods of fabricating binary Group III-nitride HEMTs are provided. In some embodiments, the binary Group III-nitride HEMTs include a first binary Group III-nitride barrier layer, a binary Group III-nitride channel layer on the first barrier layer; and a second binary Group III-nitride barrier layer on the channel layer. In some embodiments, the binary Group III-nitride HEMTs include a first AIN barrier layer, a GaN channel layer and a second AIN barrier layer.

Owner:CREE INC

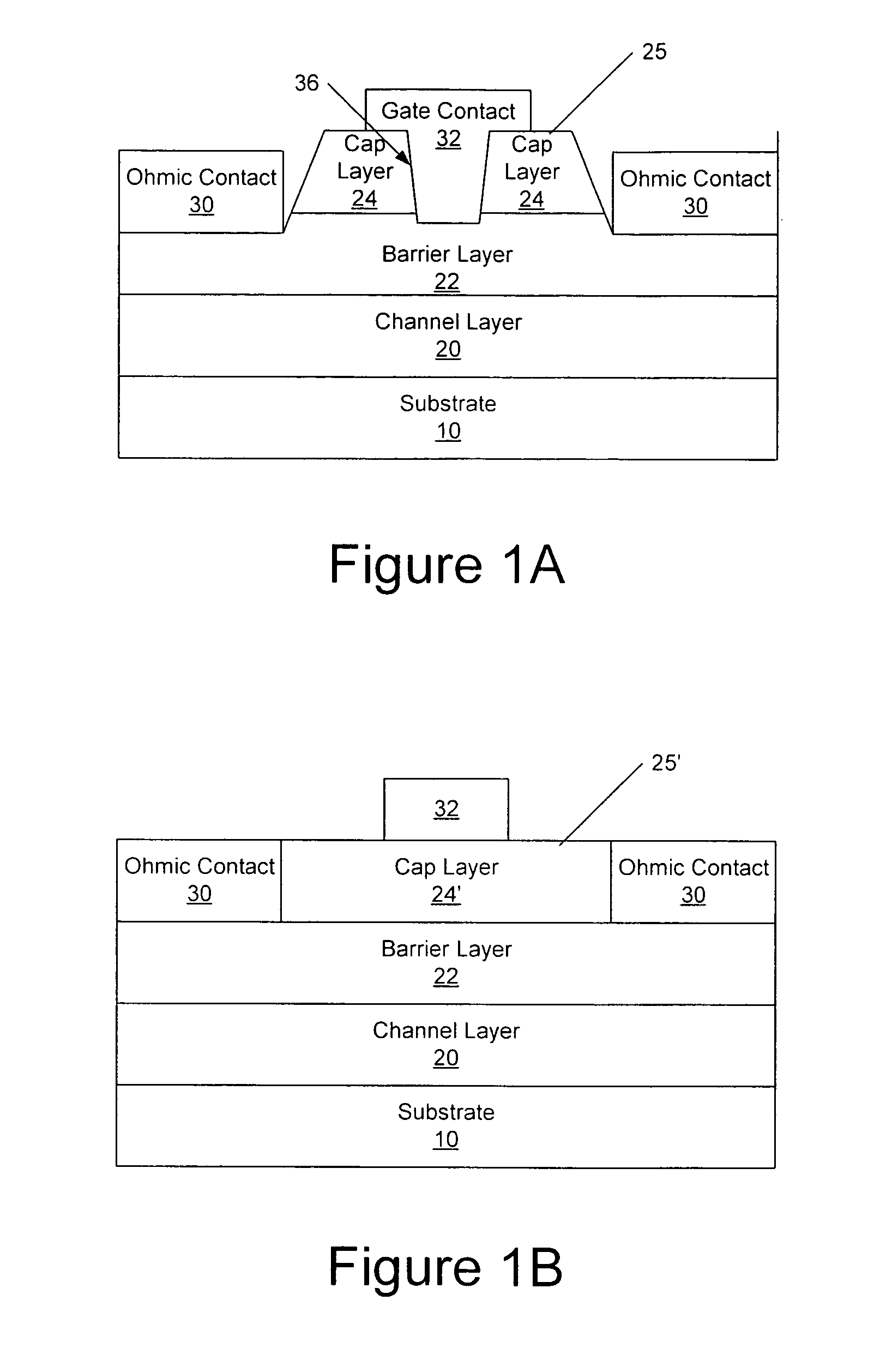

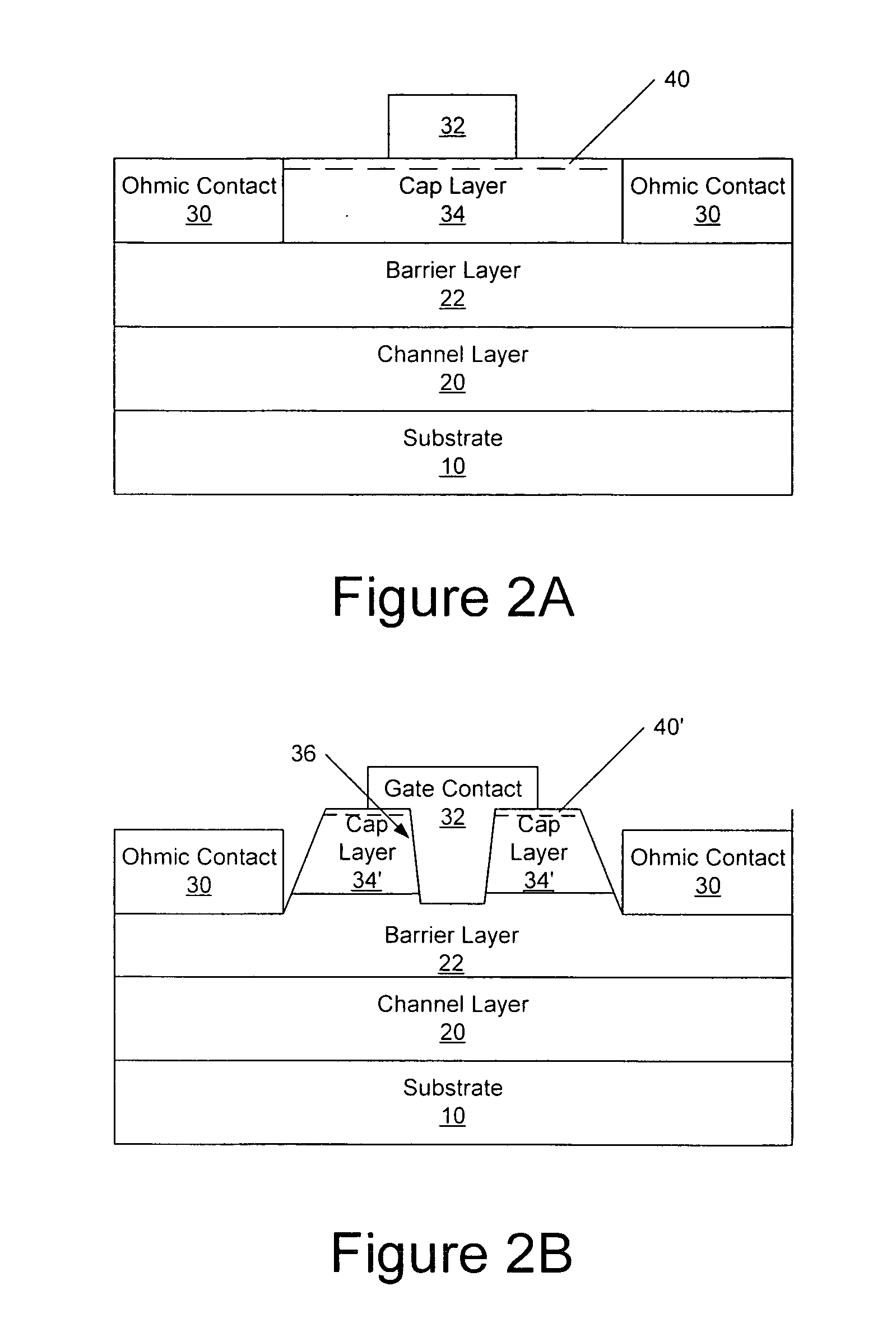

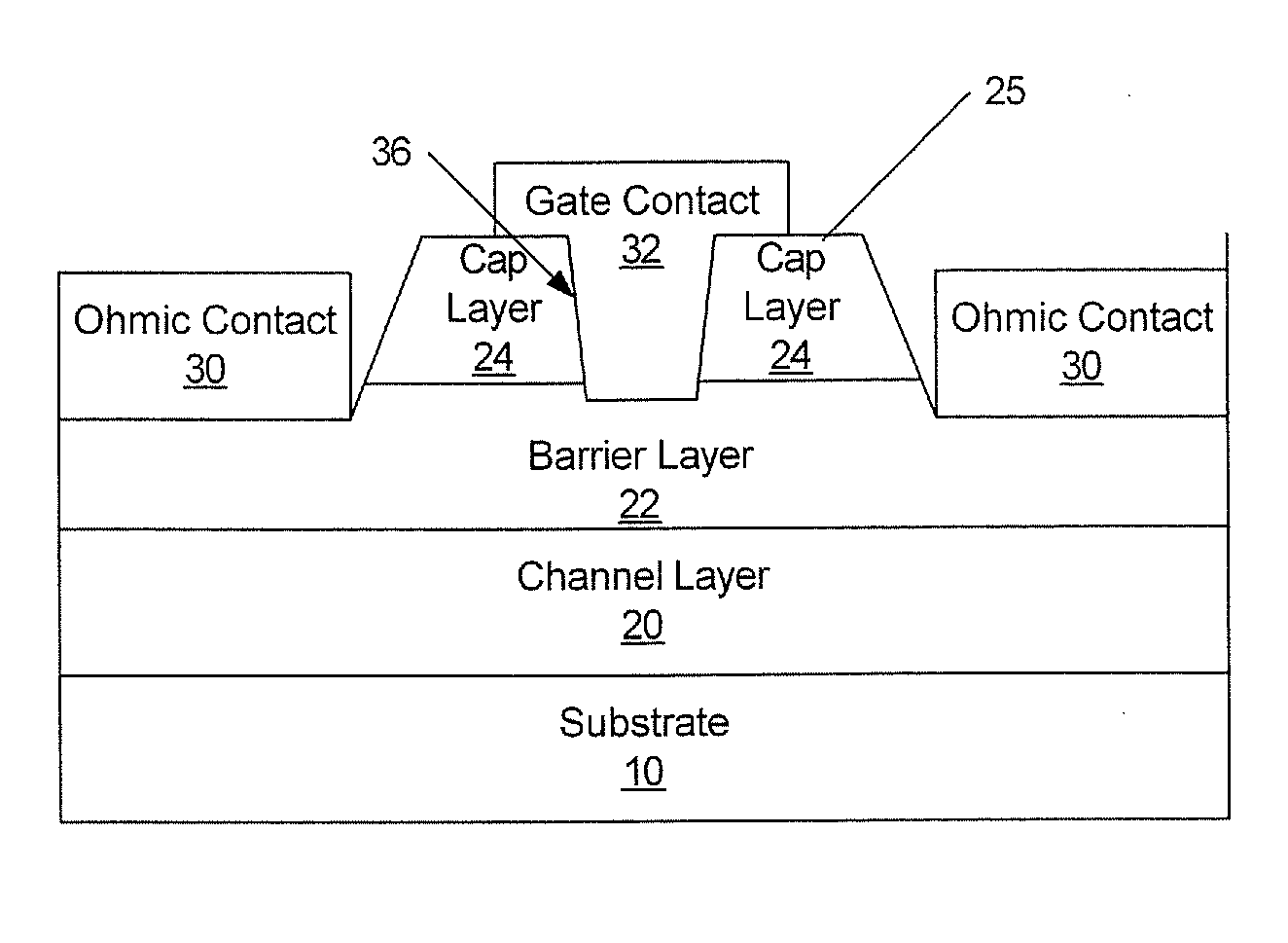

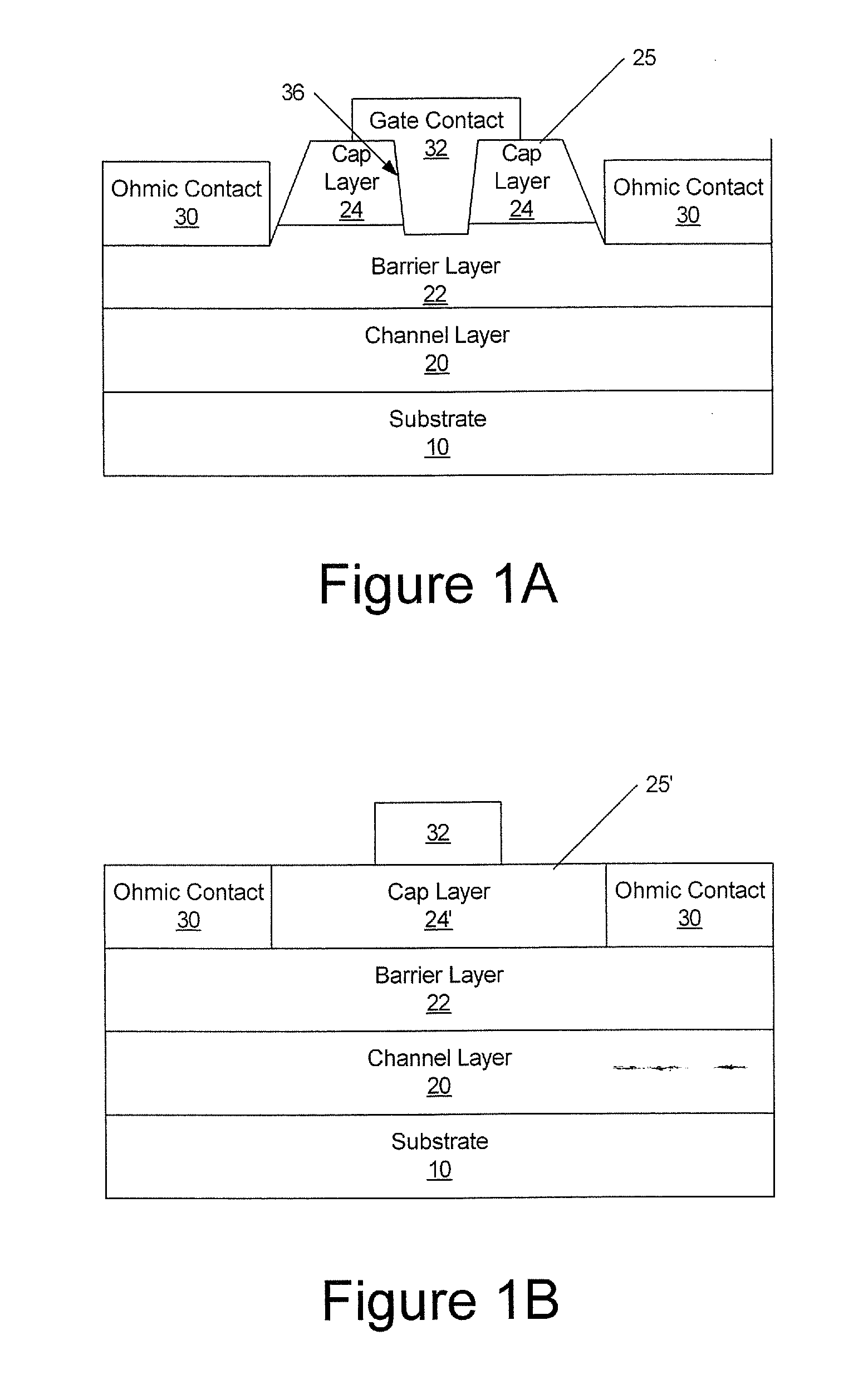

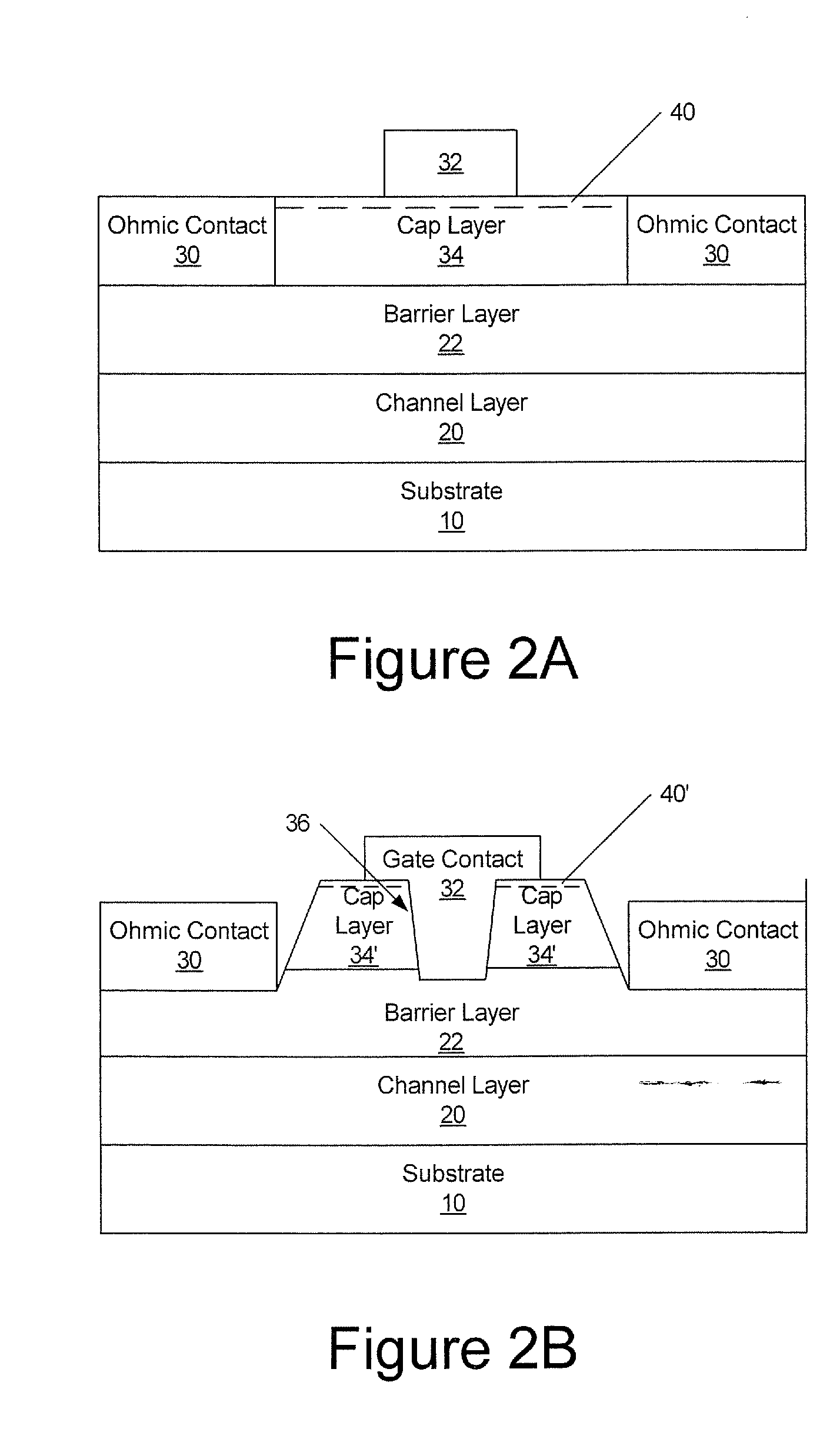

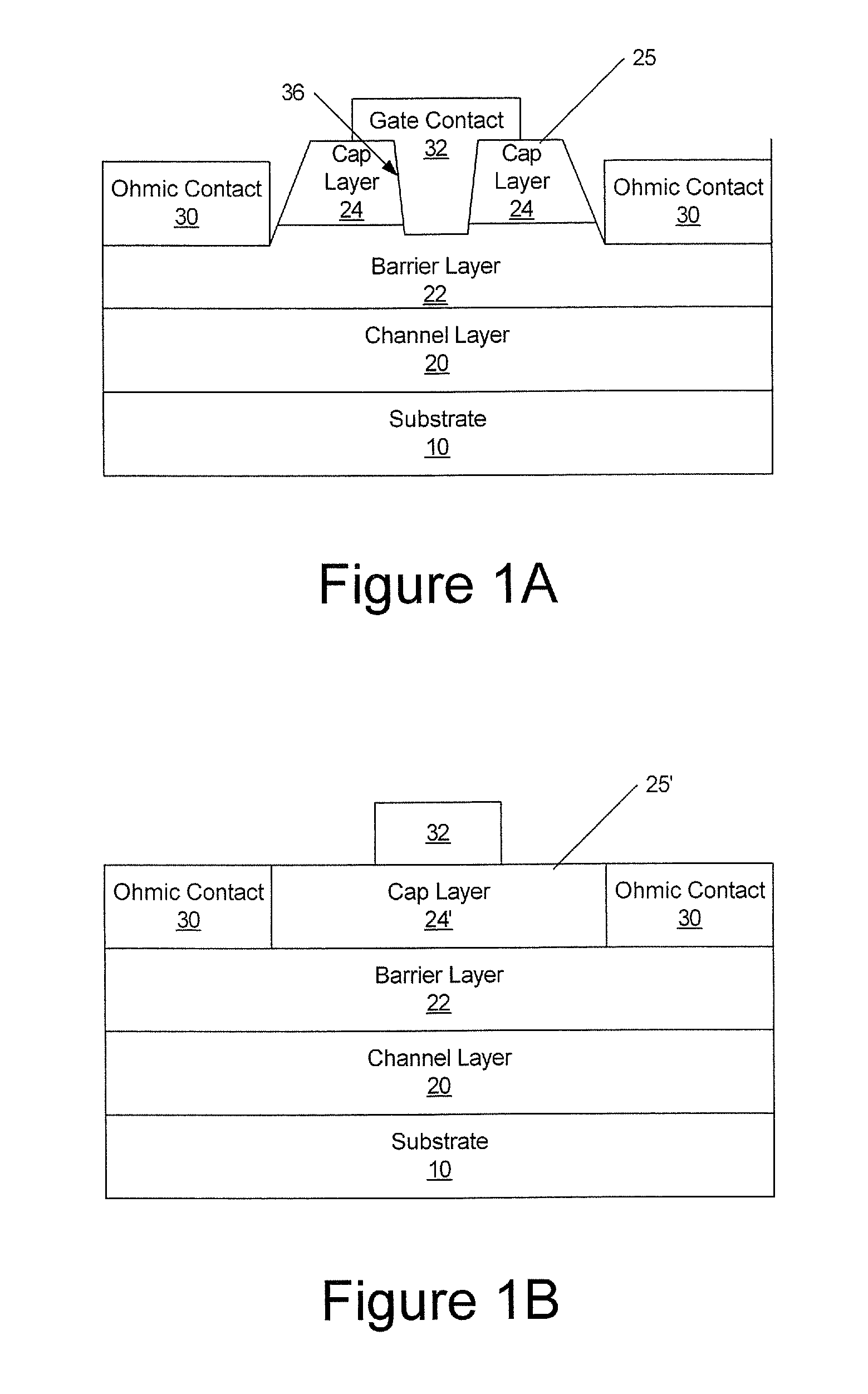

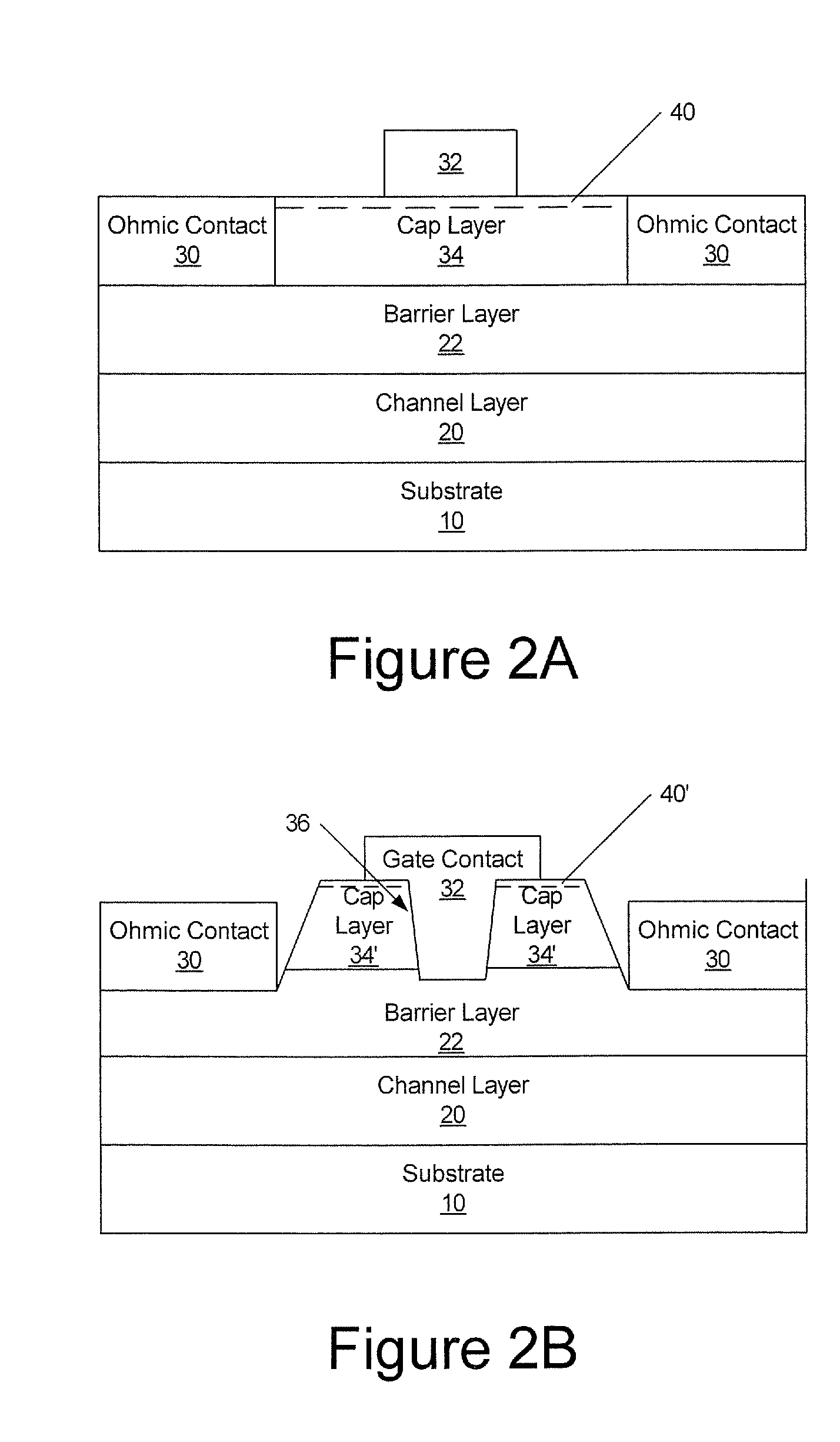

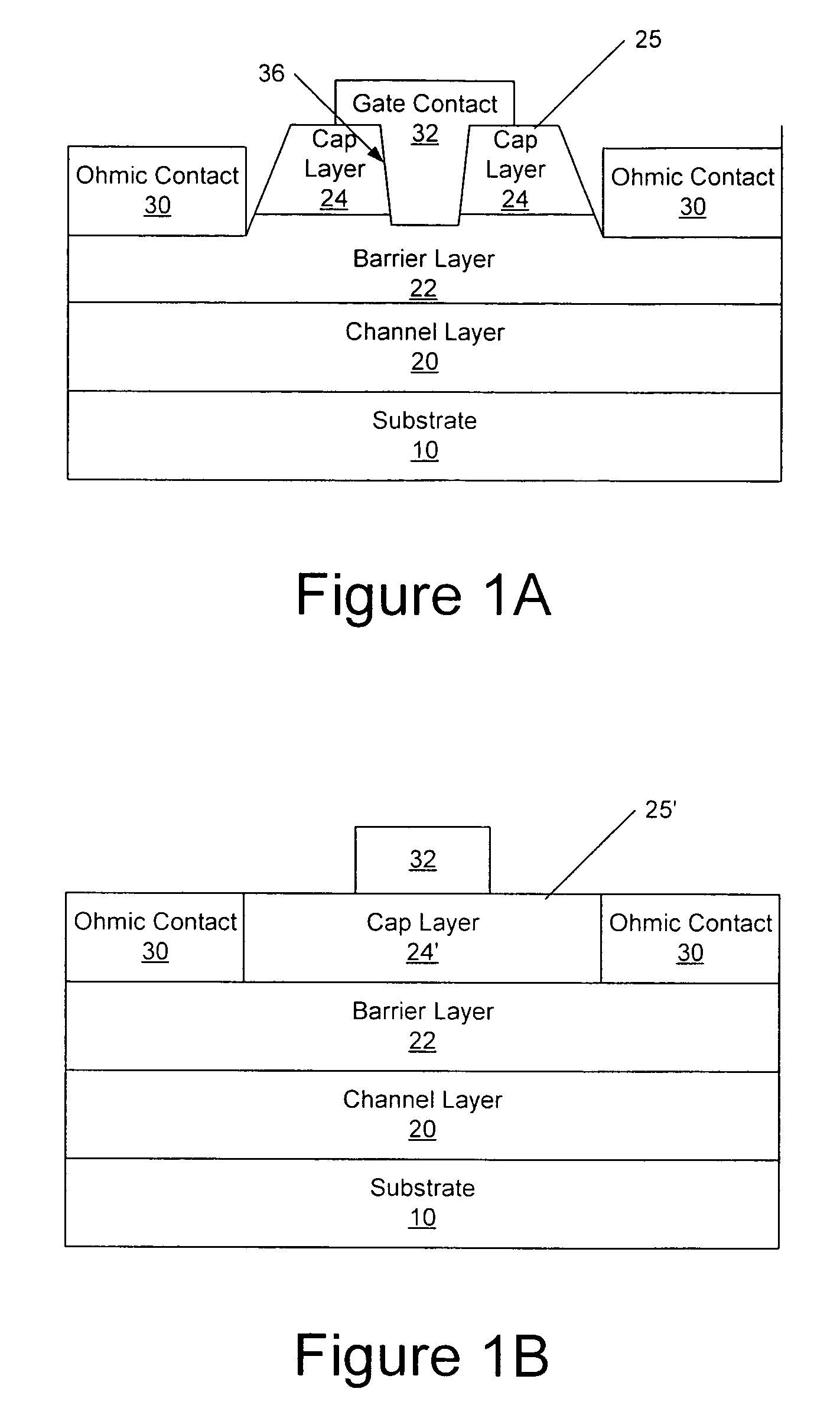

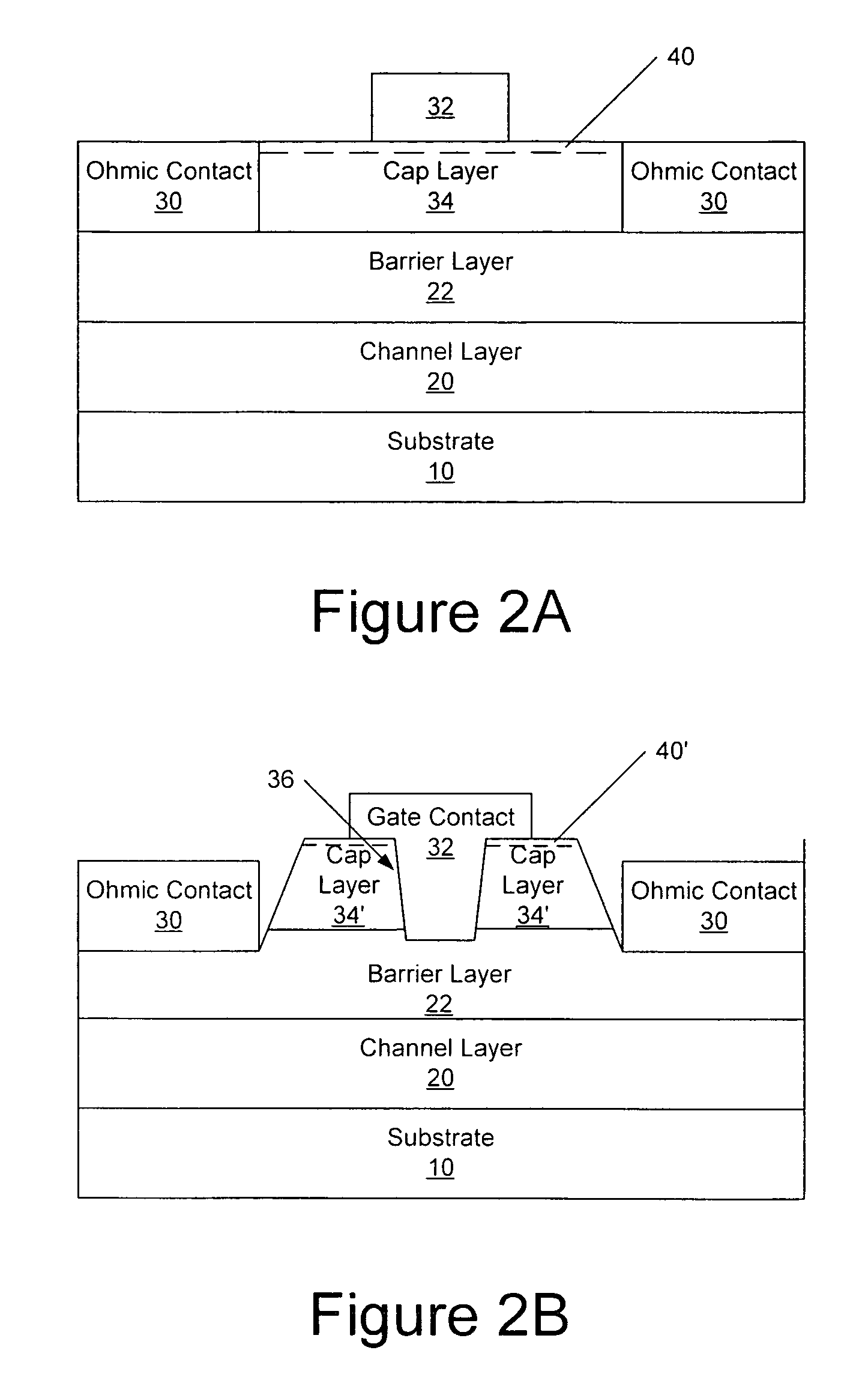

Cap layers and/or passivation layers for nitride-based transistors, transistor structures and methods of fabricating same

ActiveUS20060108606A1Increase concentrationSemiconductor/solid-state device detailsSolid-state devicesOhmic contactHigh electron

High electron mobility transistors are provided that include a non-uniform aluminum concentration AlGaN based cap layer having a high aluminum concentration adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. High electron mobility transistors are provided that include a cap layer having a doped region adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. Graphitic BN passivation structures for wide bandgap semiconductor devices are provided. SiC passivation structures for Group III-nitride semiconductor devices are provided. Oxygen anneals of passivation structures are also provided. Ohmic contacts without a recess are also provided.

Owner:CREE INC

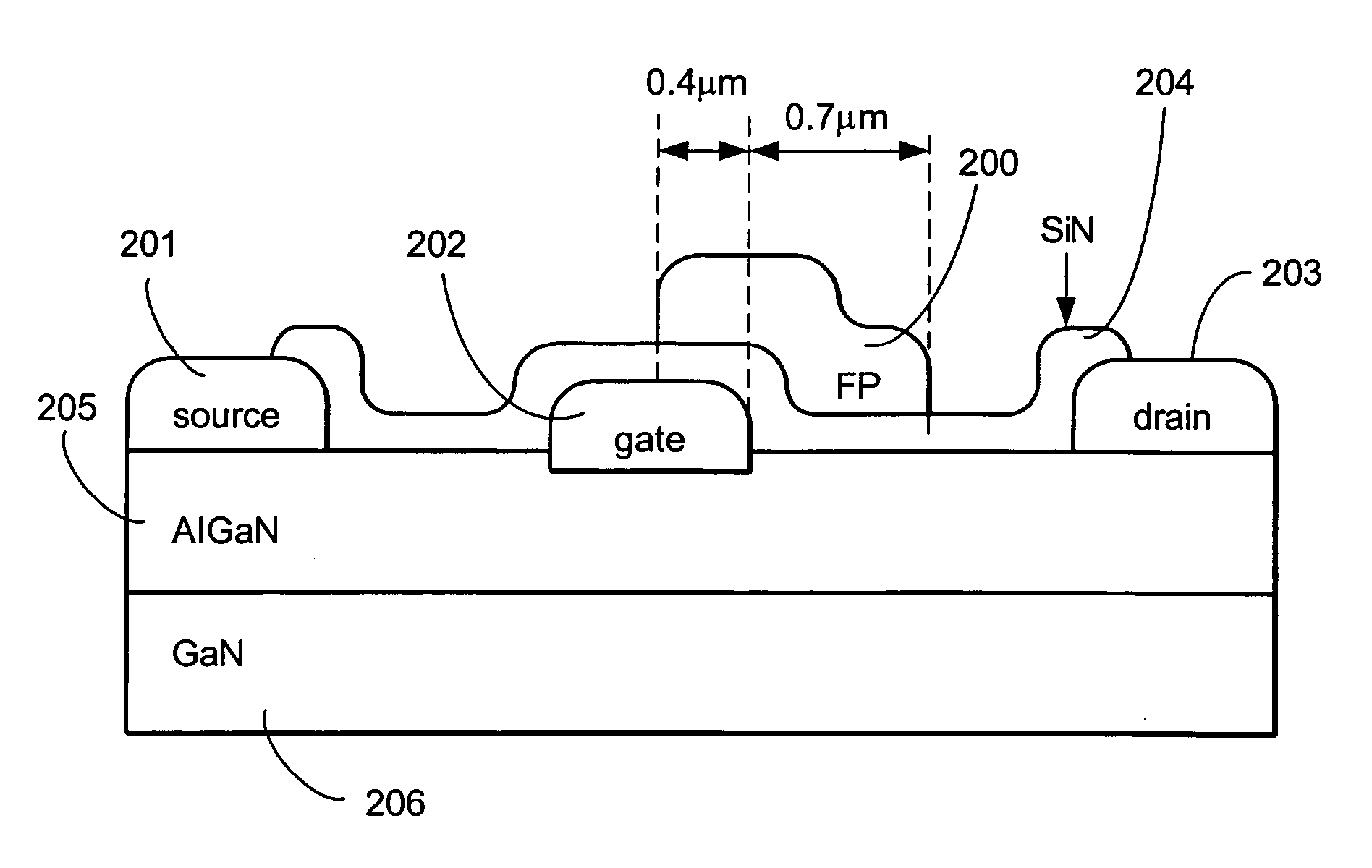

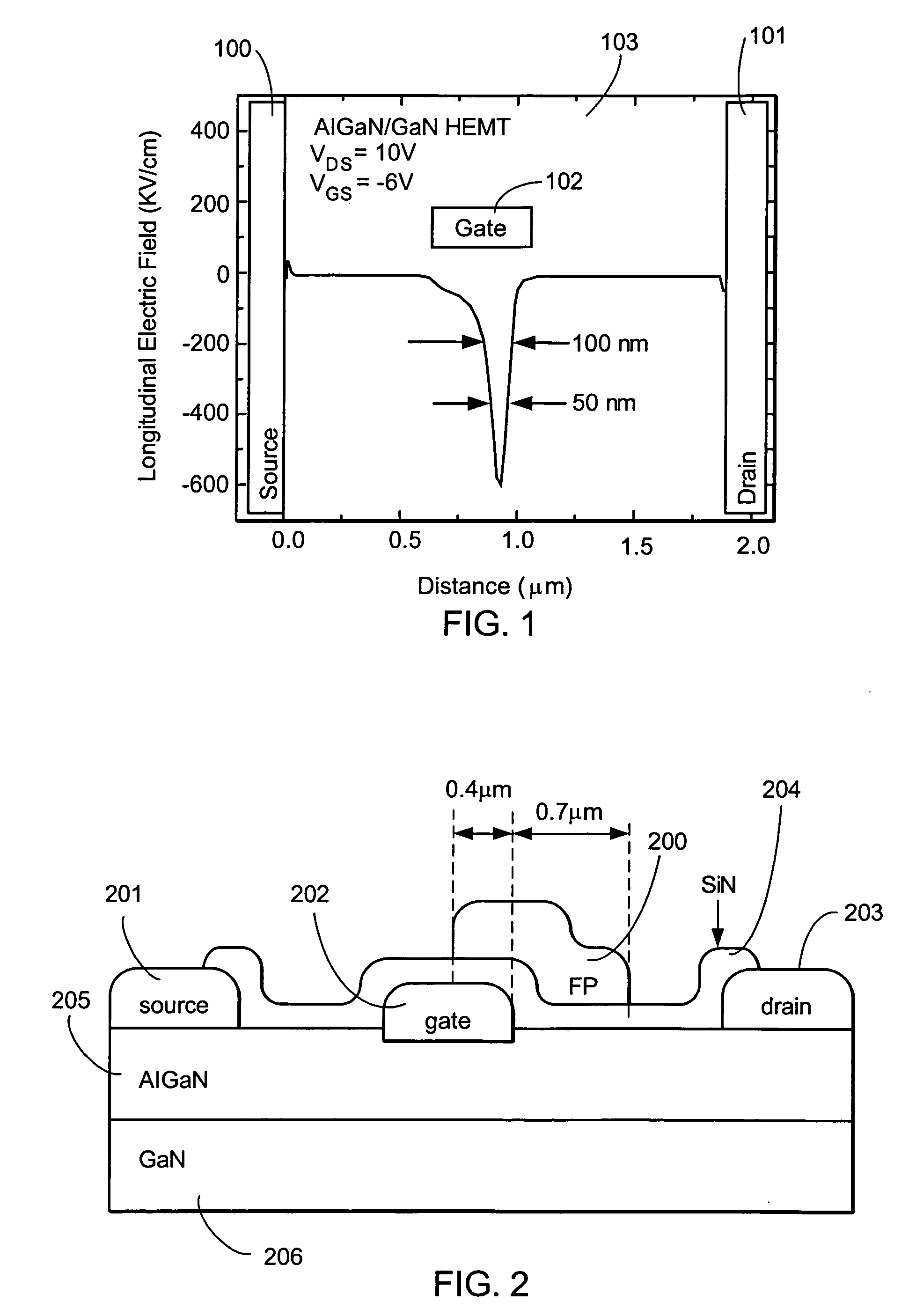

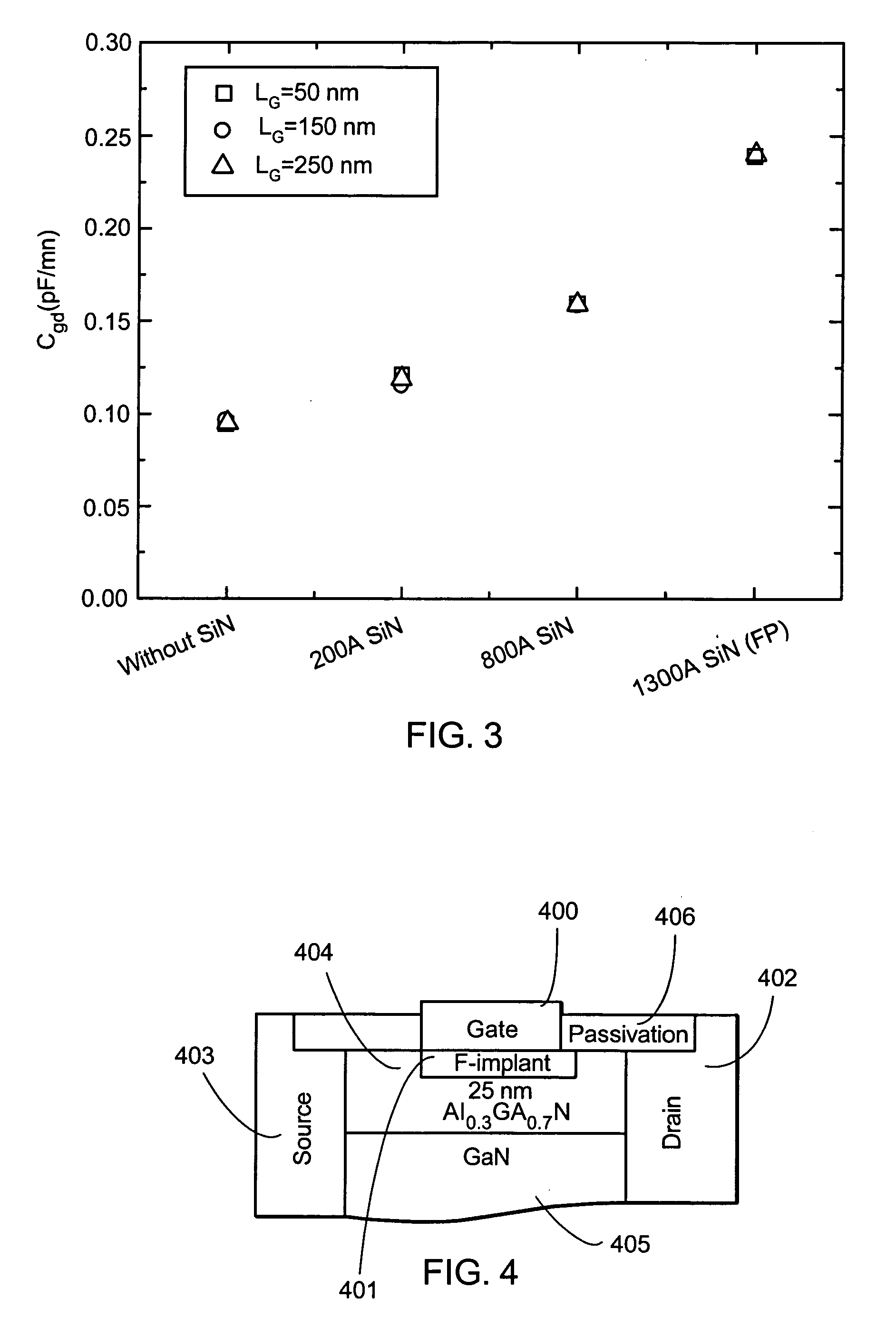

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

ActiveUS20070224710A1Increase output powerReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueDislocation

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

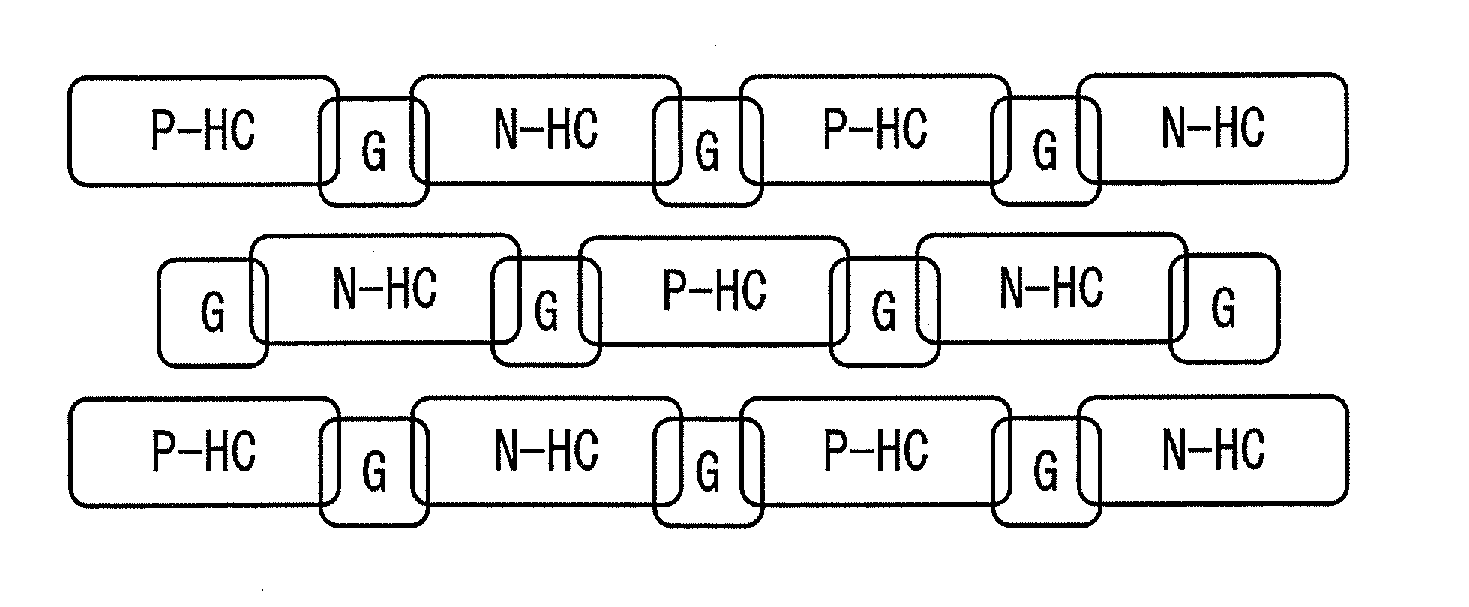

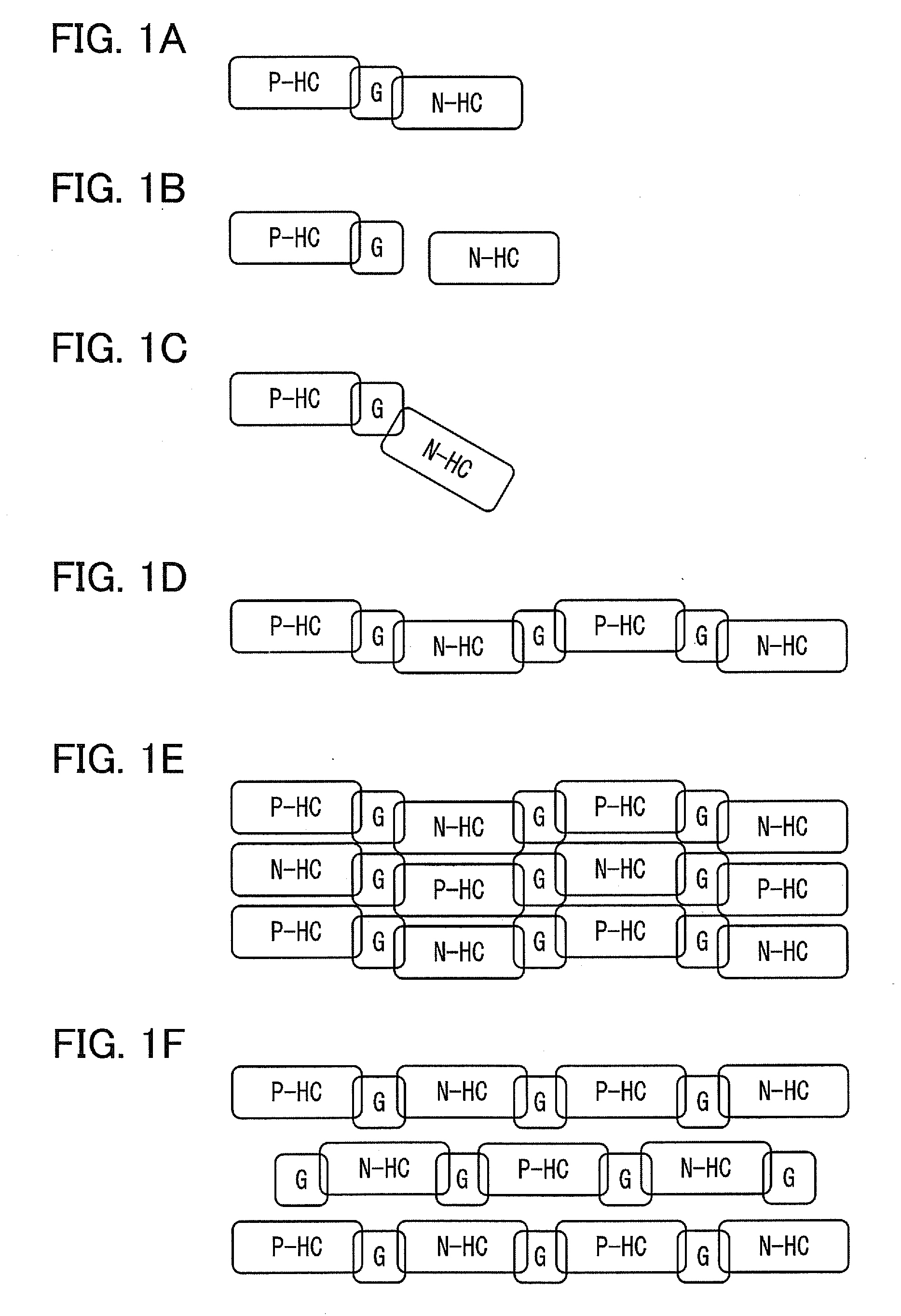

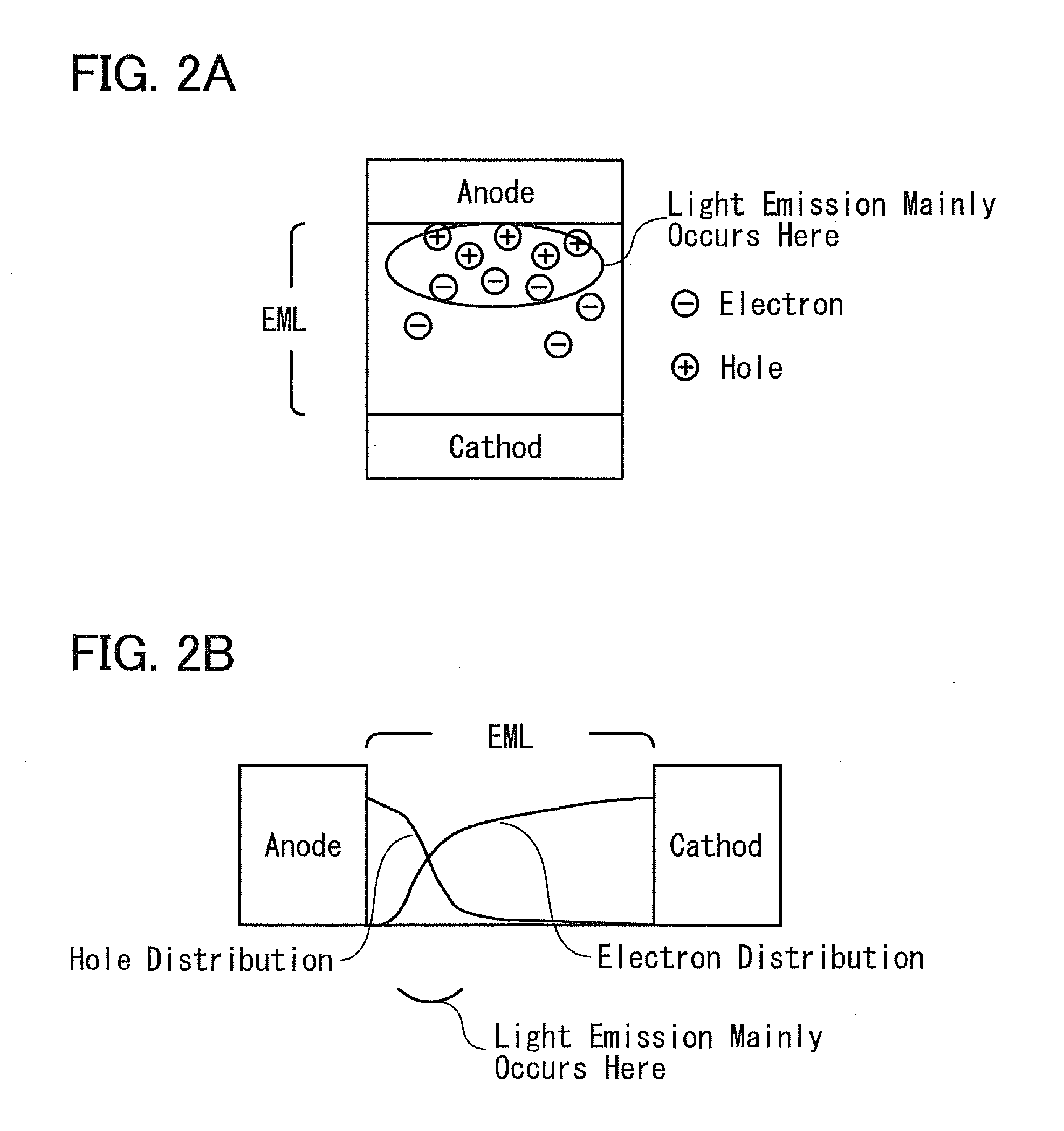

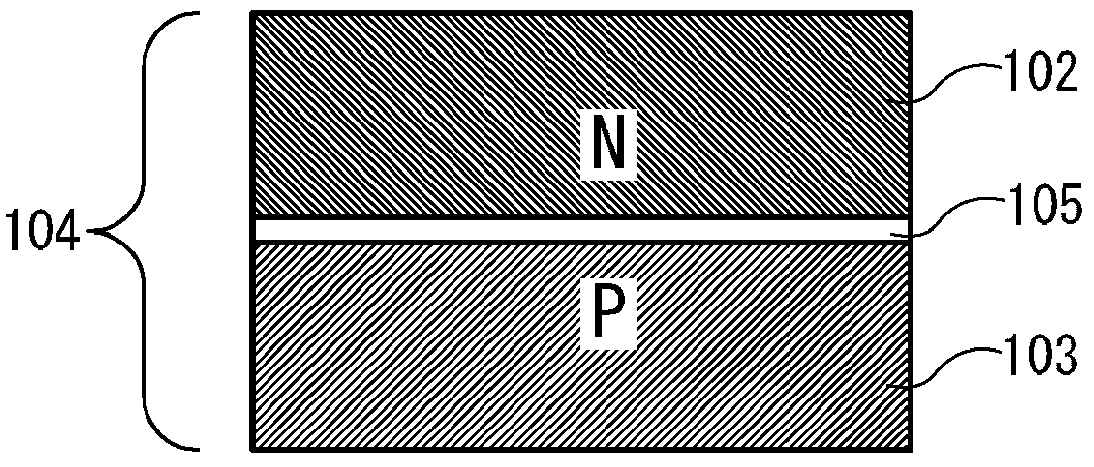

Light-emitting body, light-emitting layer, and light-emitting device

ActiveUS20120205687A1Improve propertiesPoor propertySolid-state devicesSemiconductor/solid-state device manufacturingElectron holeHigh electron

An organic light-emitting element having high efficiency and long lifetime is provided. An organic light-emitting body is provided which includes a host having a high electron-transport property (n-type host), a host having a high hole-transport property (p-type host), and a guest such as an iridium complex and in which the n-type host and the p-type host are located so as to be adjacent to each other. When an electron and a hole are injected to such a light-emitting body, the electron is trapped by the n-type host and the hole is trapped by the p-type host. Then, both the electron and the hole are injected to the guest, and thus the guest is brought into an excited state. In this process, less thermal deactivation occurs and the working rate of the guest is high; thus, highly efficient light emission can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

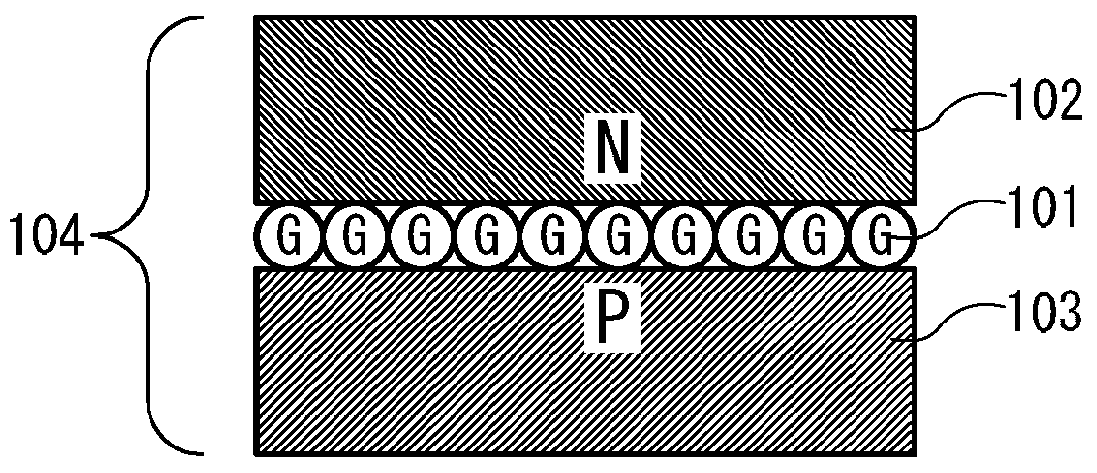

Light-emitting layer and light-emitting element

ActiveUS20120217486A1Increase energy levelInhibition transitionSolid-state devicesSemiconductor/solid-state device manufacturingIridiumExcited state

To provide a highly efficient organic light-emitting element. An extremely thin layer (a monomolecular film or the like) containing an organic light-emitting material such as an iridium complex is provided between a layer of an n-type organic material (an organic material having a high electron-transport property) and a layer of a p-type organic material (an organic material having a high hole-transport property). In a structure described above, in a layer of the organic light-emitting material, electrons are injected from the LUMO of the n-type organic material to the LUMO of the organic light-emitting material, and holes are injected from the HOMO of the p-type organic material to the HOMO of the organic light-emitting material, whereby the organic light-emitting material is brought into an excited state and emits light.

Owner:SEMICON ENERGY LAB CO LTD

Cap Layers Including Aluminum Nitride for Nitride-Based Transistors and Methods of Fabricating Same

ActiveUS20070164315A1Increase concentrationSemiconductor/solid-state device detailsSolid-state devicesOhmic contactGraphite

High electron mobility transistors are provided that include a non-uniform aluminum concentration AlGaN based cap layer having a high aluminum concentration adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. High electron mobility transistors are provided that include a cap layer having a doped region adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. Graphitic BN passivation structures for wide bandgap semiconductor devices are provided. SiC passivation structures for Group III-nitride semiconductor devices are provided. Oxygen anneals of passivation structures are also provided. Ohmic contacts without a recess are also provided.

Owner:CREE INC

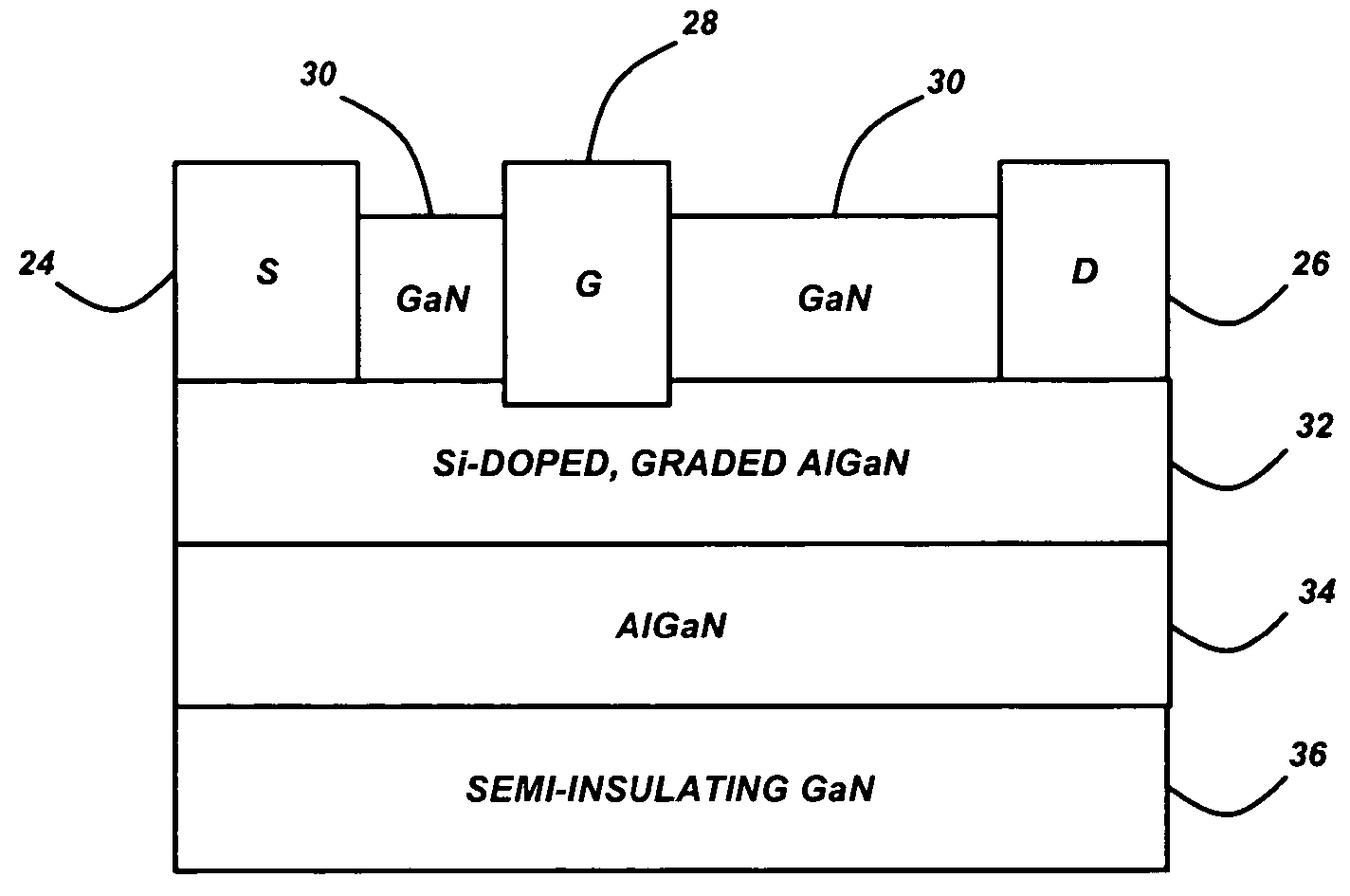

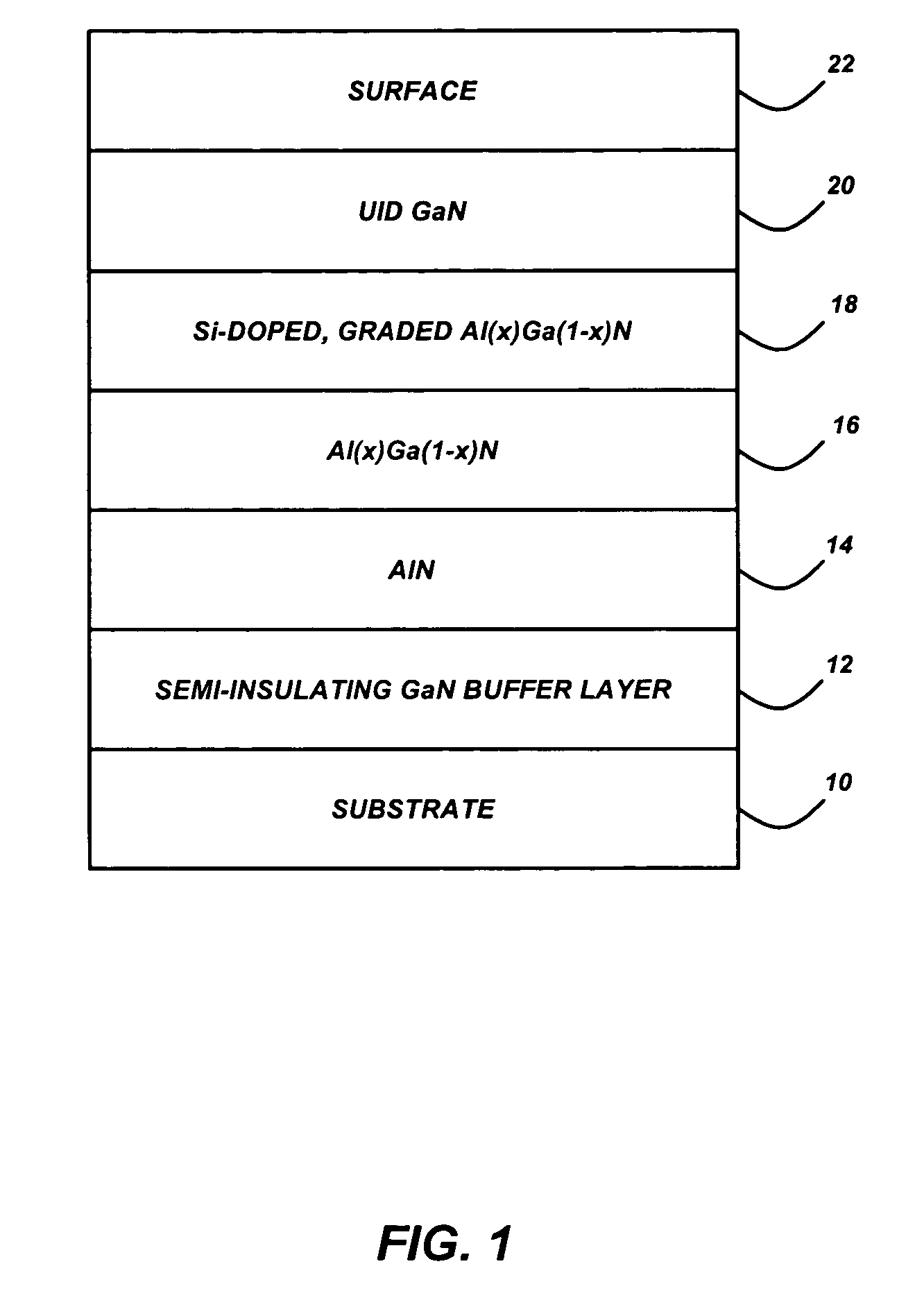

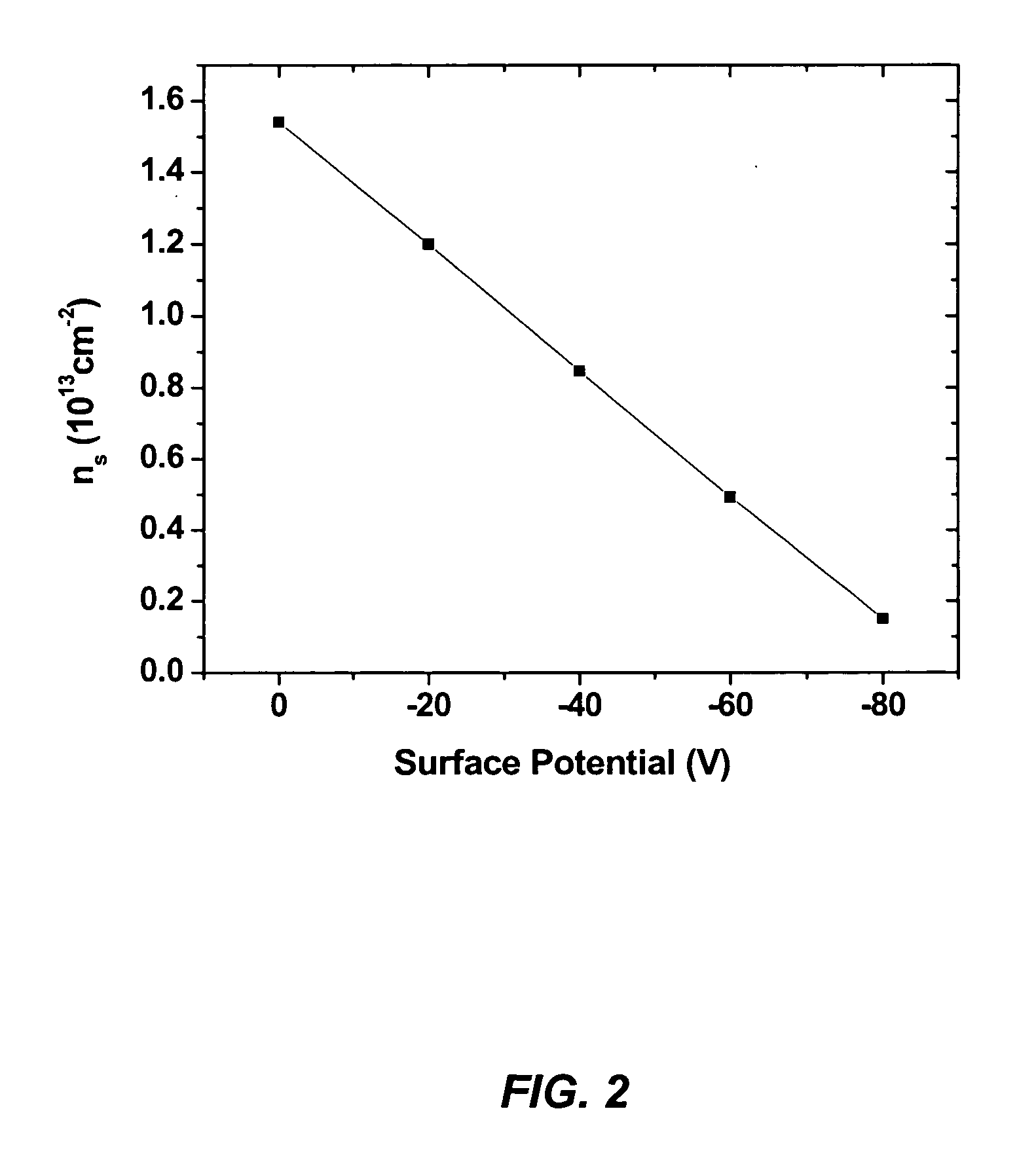

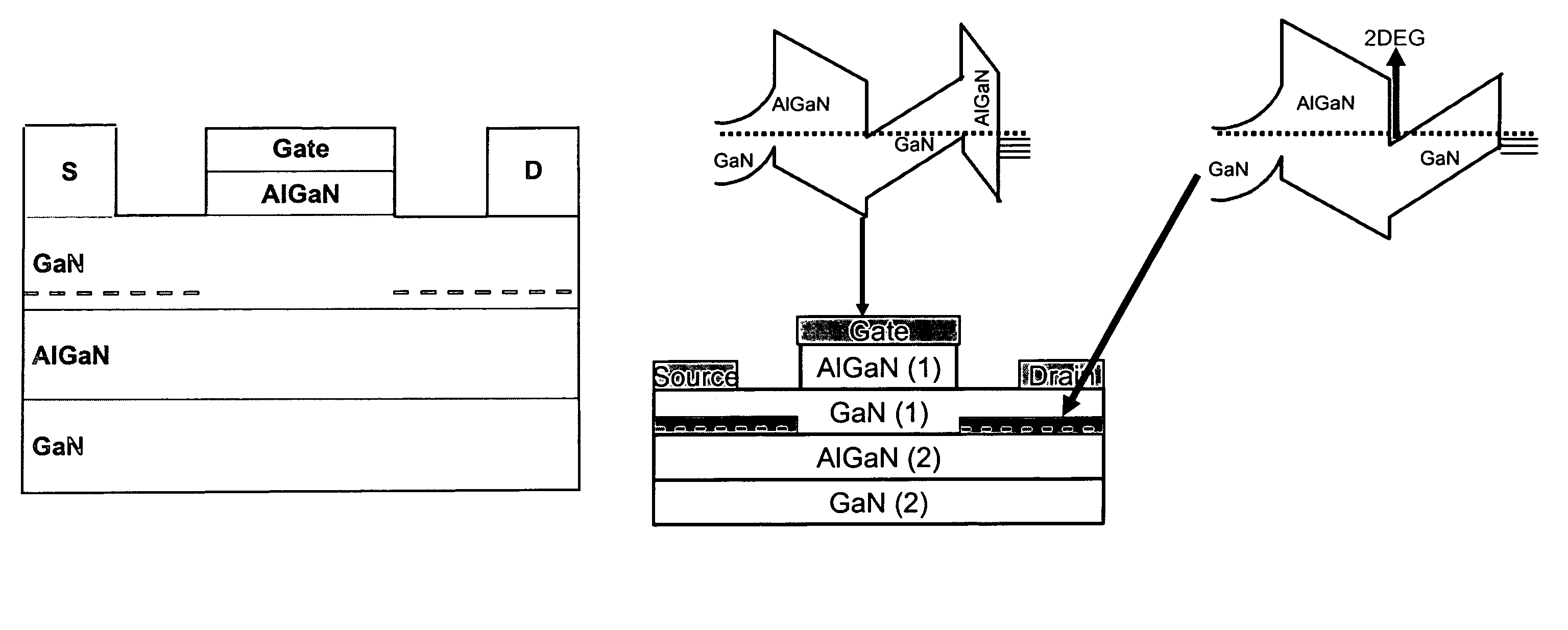

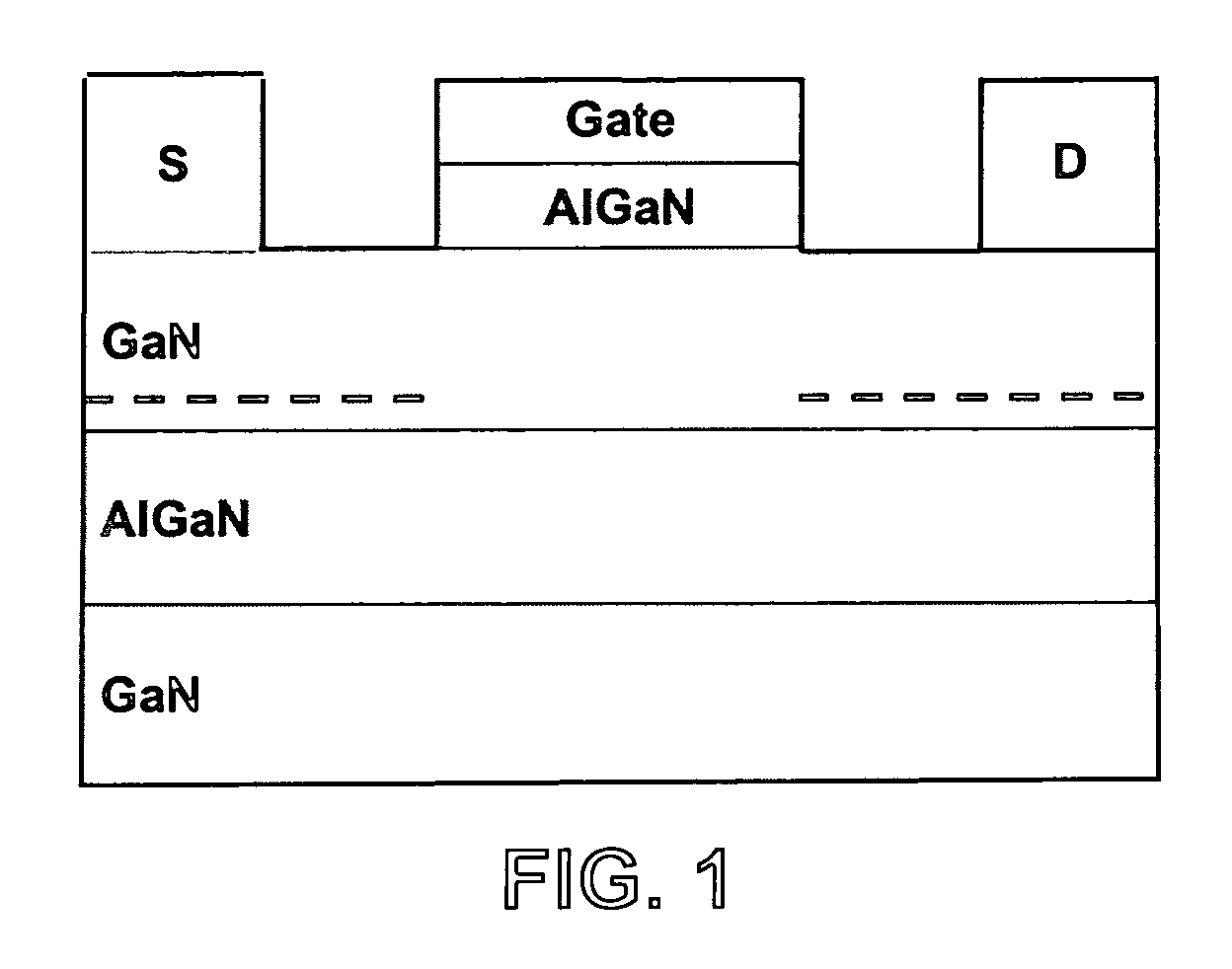

GaN/AIGaN/GaN dispersion-free high electron mobility transistors

InactiveUS20050077541A1High electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh electronGallium nitride

A dispersion-free high electron mobility transistor (HEMT), comprised of a substrate; a semi-insulating buffer layer, comprised of gallium nitride (GaN) or aluminum gallium nitride (AlGaN), deposited on the substrate, an AlGaN barrier layer, with an aluminum (Al) mole fraction larger than that of the semi-insulating buffer layer, deposited on the semi-insulating buffer layer, an n-type doped graded AlGaN layer deposited on the AlGaN barrier layer, wherein an Al mole fraction is decreased from a bottom of the n-type doped graded AlGaN layer to a top of the n-type doped graded AlGaN layer, and a cap layer, comprised of GaN or AlGaN with an Al mole fraction smaller than that of the AlGaN barrier layer, deposited on the n-type doped graded AlGaN layer.

Owner:RGT UNIV OF CALIFORNIA

III-V Nitride homoepitaxial material of improved MOVPE epitaxial quality (surface texture and defect density) formed on free-standing (Al,In,Ga)N substrates, and opto-electronic and electronic devices comprising same

InactiveUS20030213964A1Improve material qualityReduce dislocation densityPolycrystalline material growthAfter-treatment detailsCelsius DegreeSource material

A III-V nitride homoepitaxial microelectronic device structure comprising a III-V nitride homoepitaxial epi layer of improved epitaxial quality deposited on a III-V nitride material substrate, e.g., of freestanding character. Various processing techniques are described, including a method of forming a III-V nitride homoepitaxial layer on a corresponding III-V nitride material substrate, by depositing the III-V nitride homoepitaxial layer by a VPE process using Group III source material and nitrogen source material under process conditions including V / III ratio in a range of from about 1 to about 10<5>, nitrogen source material partial pressure in a range of from about 1 to about 10<3 >torr, growth temperature in a range of from about 500 to about 1250 degrees Celsius, and growth rate in a range of from about 0.1 to about 10<2 >microns per hour. The III-V nitride homoepitaxial microelectronic device structures are usefully employed in device applications such as UV LEDs, high electron mobility transistors, and the like.

Owner:WOLFSPEED INC

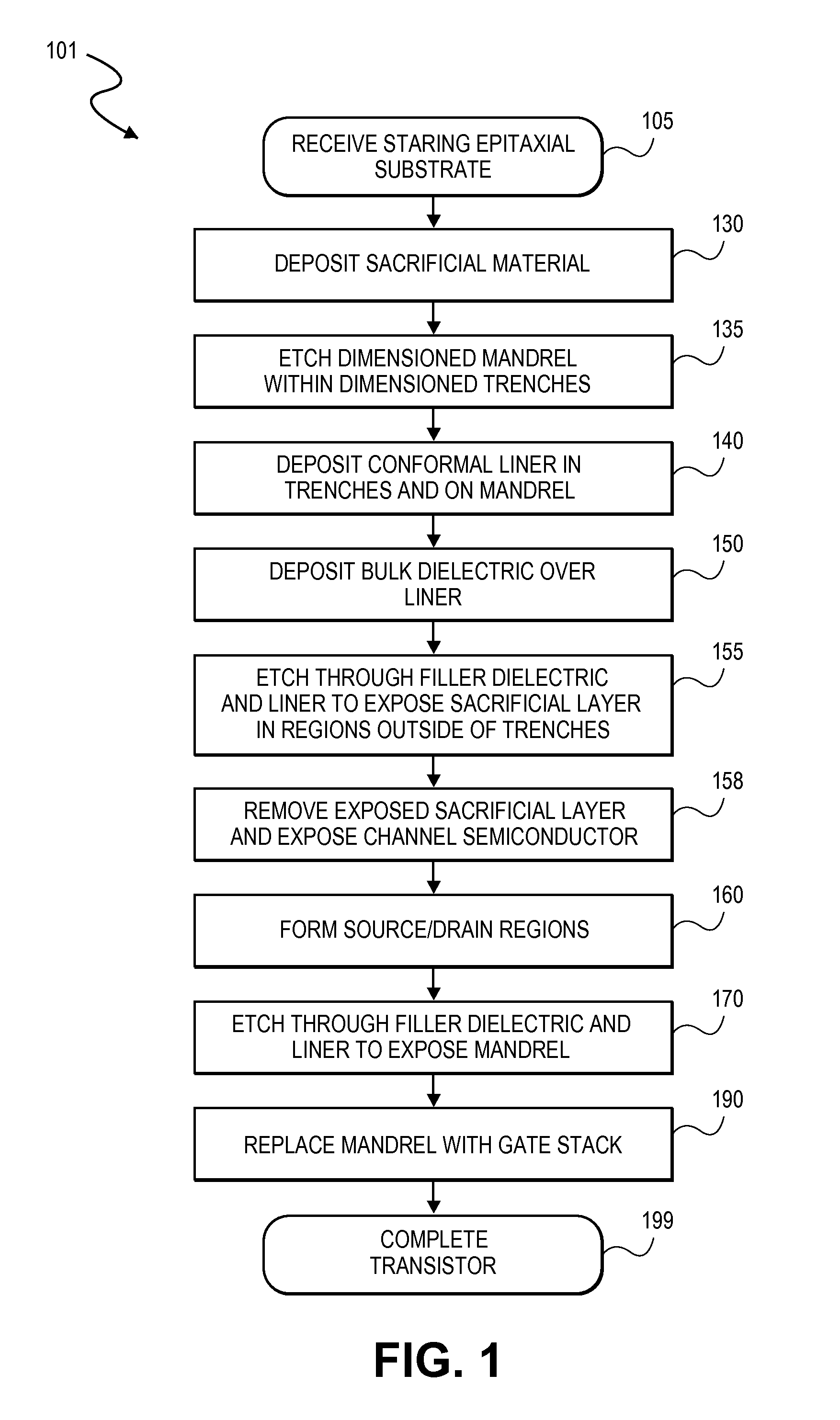

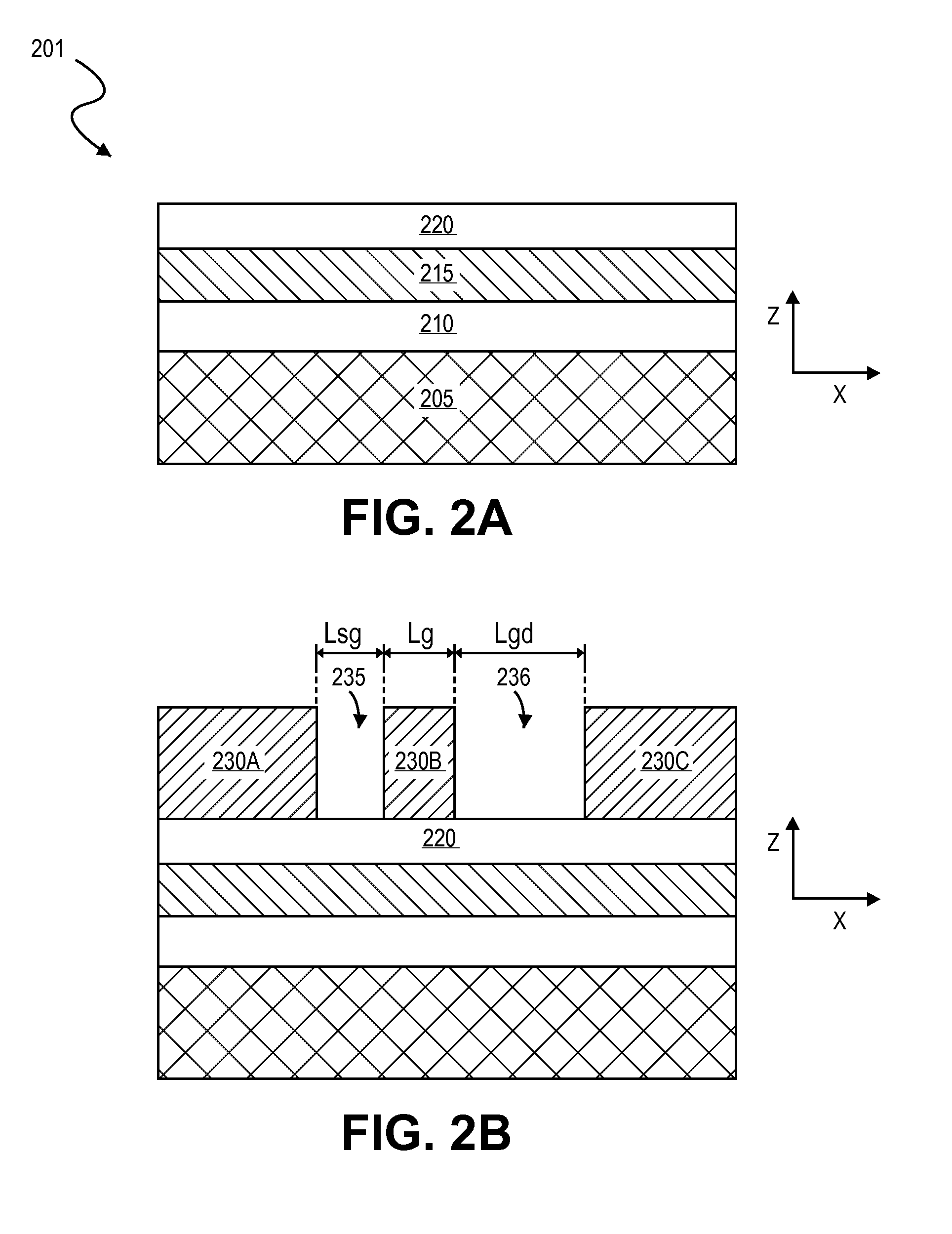

Self-aligned structures and methods for asymmetric GAN transistors & enhancement mode operation

ActiveUS20140091308A1Semiconductor/solid-state device manufacturingSemiconductor devicesNon symmetricEngineering

Embodiments include high electron mobility transistors (HEMT). In embodiments, a gate electrode is spaced apart by different distances from a source and drain semiconductor region to provide high breakdown voltage and low on-state resistance. In embodiments, self-alignment techniques are applied to form a dielectric liner in trenches and over an intervening mandrel to independently define a gate length, gate-source length, and gate-drain length with a single masking operation. In embodiments, III-N HEMTs include fluorine doped semiconductor barrier layers for threshold voltage tuning and / or enhancement mode operation.

Owner:INTEL CORP

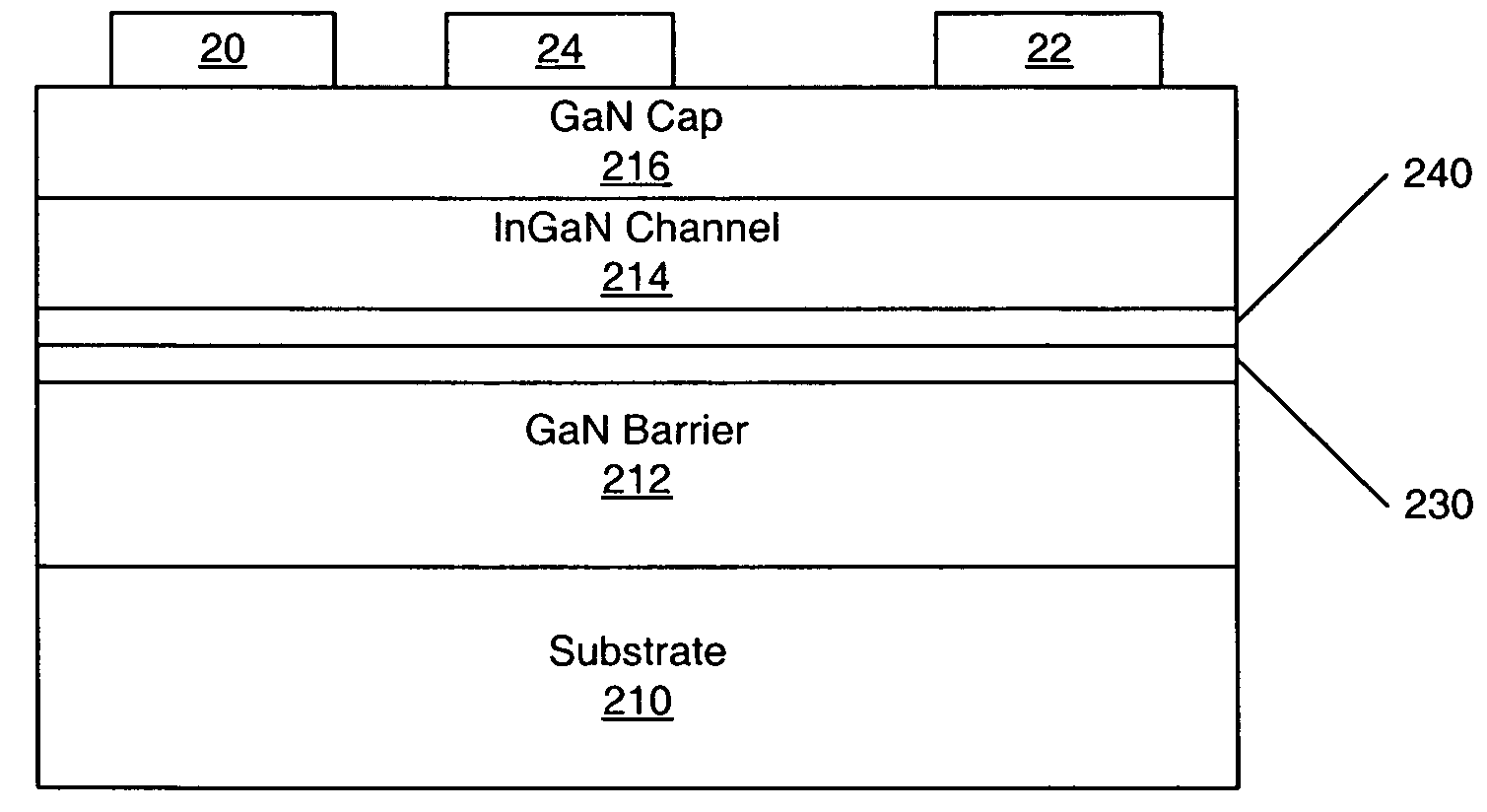

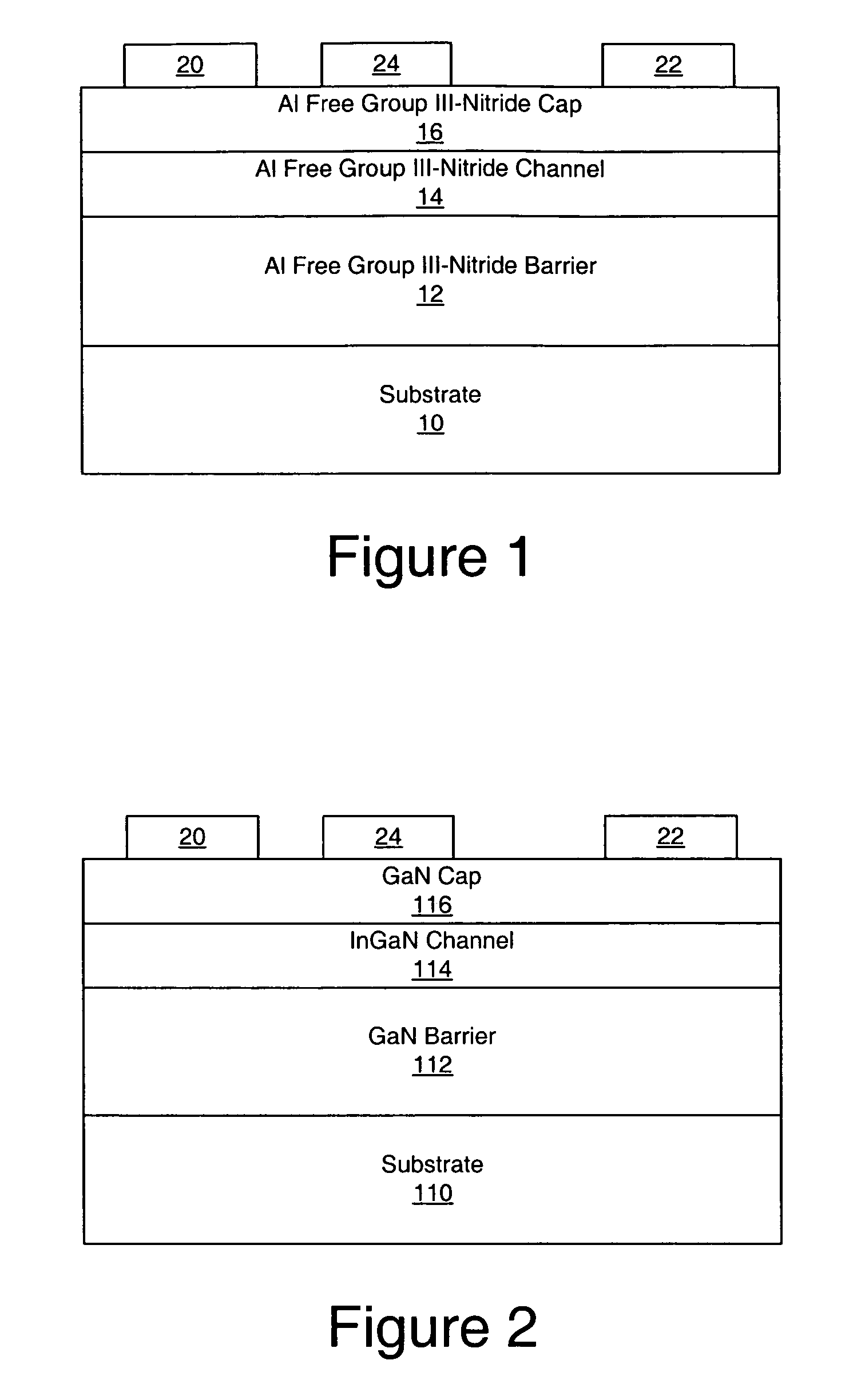

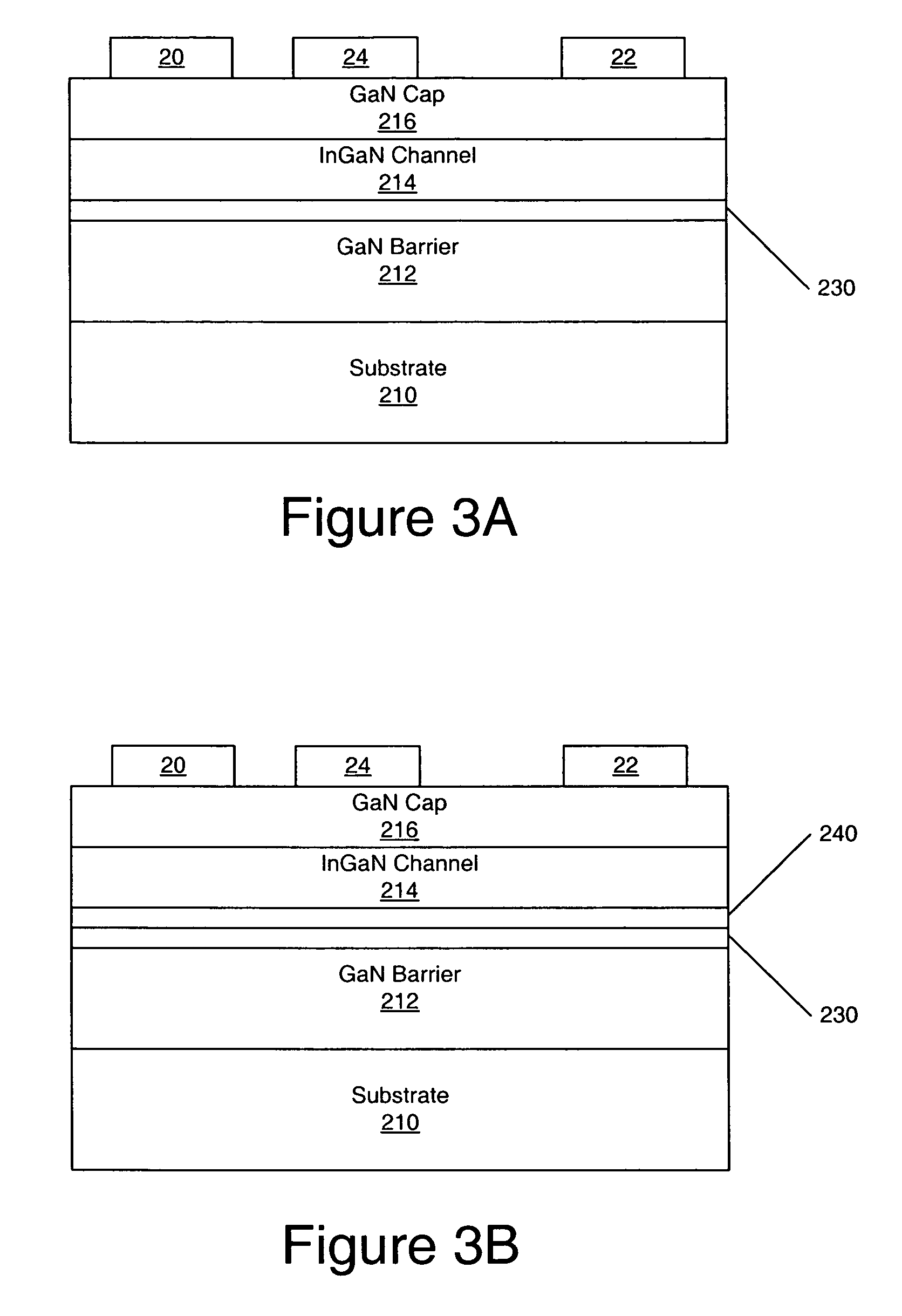

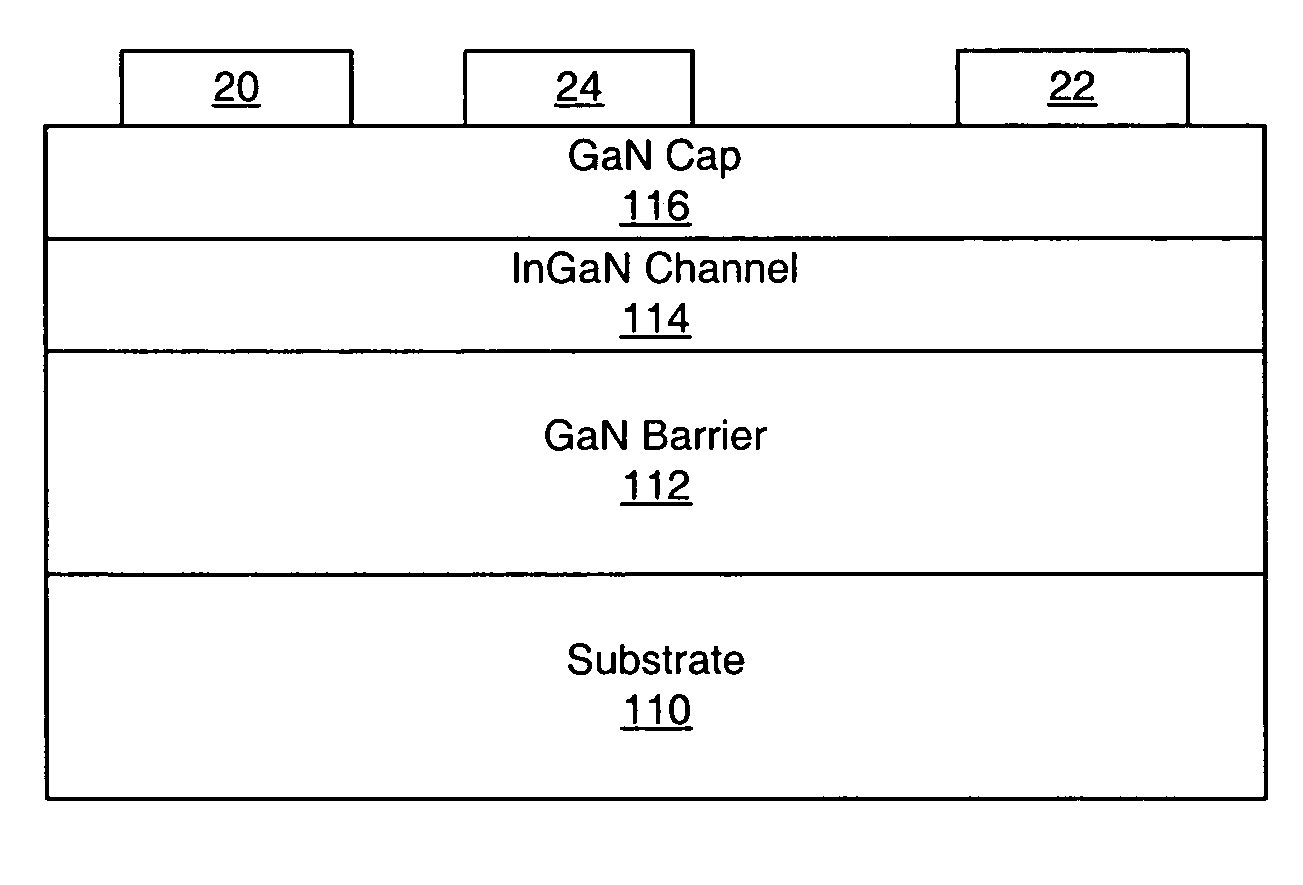

Aluminum free group III-nitride based high electron mobility transistors

Aluminum free high electron mobility transistors (HEMTs) and methods of fabricating aluminum free HEMTs are provided. In some embodiments, the aluminum free HEMTs include an aluminum free Group III-nitride barrier layer, an aluminum free Group III-nitride channel layer on the barrier layer and an aluminum free Group III-nitride cap layer on the channel layer.

Owner:WOLFSPEED INC

Cap layers including aluminum nitride for nitride-based transistors

ActiveUS7709859B2Semiconductor/solid-state device detailsSolid-state devicesOhmic contactHigh electron

High electron mobility transistors are provided that include a non-uniform aluminum concentration AlGaN based cap layer having a high aluminum concentration adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. High electron mobility transistors are provided that include a cap layer having a doped region adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. Graphitic BN passivation structures for wide bandgap semiconductor devices are provided. SiC passivation structures for Group III-nitride semiconductor devices are provided. Oxygen anneals of passivation structures are also provided. Ohmic contacts without a recess are also provided.

Owner:CREE INC

Method for preparing graphene-doped anode material for lithium-ion batteries

ActiveCN101800310AImprove conductivitySimple processing technologyCell electrodesLithium iron phosphateElectrical battery

The invention discloses a method for preparing a graphene-doped anode material for lithium-ion batteries. The main component of the anode material is lithium iron phosphate nanoparticles. The method comprises the following steps of: firstly preparing the graphene, graphene oxide, and intercalation graphene respectively; secondly, doping the mixture of the graphene, the graphene oxide and the intercalation graphene in the synthetic material of the lithium iron phosphate nanoparticles or directly mixing the lithium iron phosphate nanoparticles and the intercalation graphene, the graphene oxide,or chemically reduced graphene after the preparation of lithium iron phosphate nanoparticles; and finally, synthesizing the graphene or graphene oxide bridged or lithium iron phosphate nanoparticle-clad material after the treatment of drying, filtering, eluting, re-drying, and annealing. The lithium iron phosphate nanoparticles prepared by the method of the invention are characterized by the capability of greatly improving electron conductivity and providing the lithium-ion batteries anode material having the advantages of simple processing technique, low cost, high capacity and safety for lithium-ion batteries.

Owner:苏州格瑞丰纳米科技有限公司

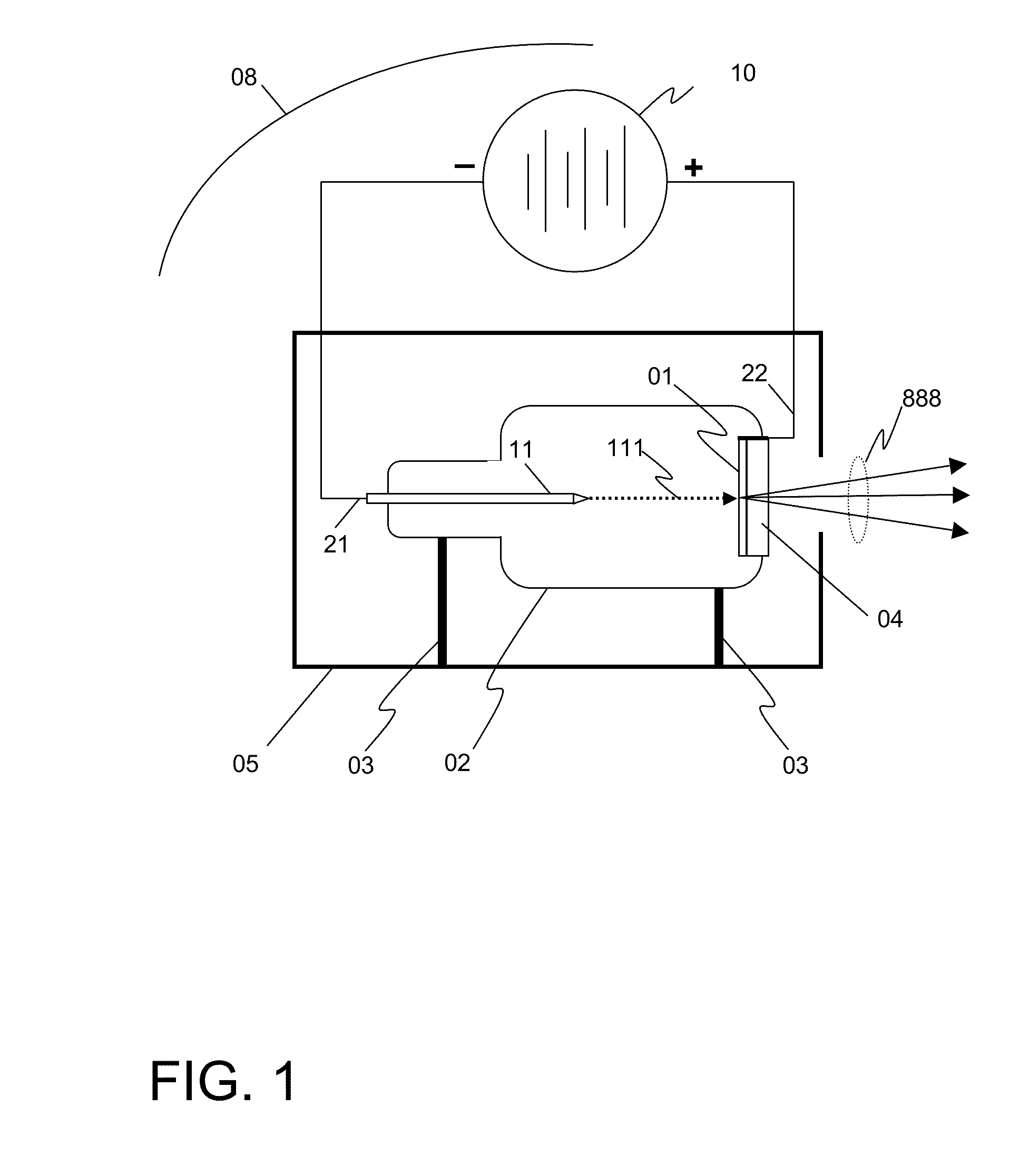

Electron-emitting device provided with pores that have carbon deposited therein

An electron-emitting device disclosed has stable electron emission characteristics with little variation, in high electron emission efficiency, in high definition, and at low driving voltage. The electron-emitting device disclosed is constructed in such structure that on a substrate there are a lower electrode, an insulating layer having pores, and an upper electrode stacked in this order, the insulating layer is an anodic oxide layer, and a carbon deposit is formed in the pores.

Owner:CANON KK

Aluminum free group III-nitride based high electron mobility transistors and methods of fabricating same

Aluminum free high electron mobility transistors (HEMTs) and methods of fabricating aluminum free HEMTs are provided. In some embodiments, the aluminum free HEMTs include an aluminum free Group III-nitride barrier layer, an aluminum free Group III-nitride channel layer on the barrier layer and an aluminum free Group III-nitride cap layer on the channel layer.

Owner:WOLFSPEED INC

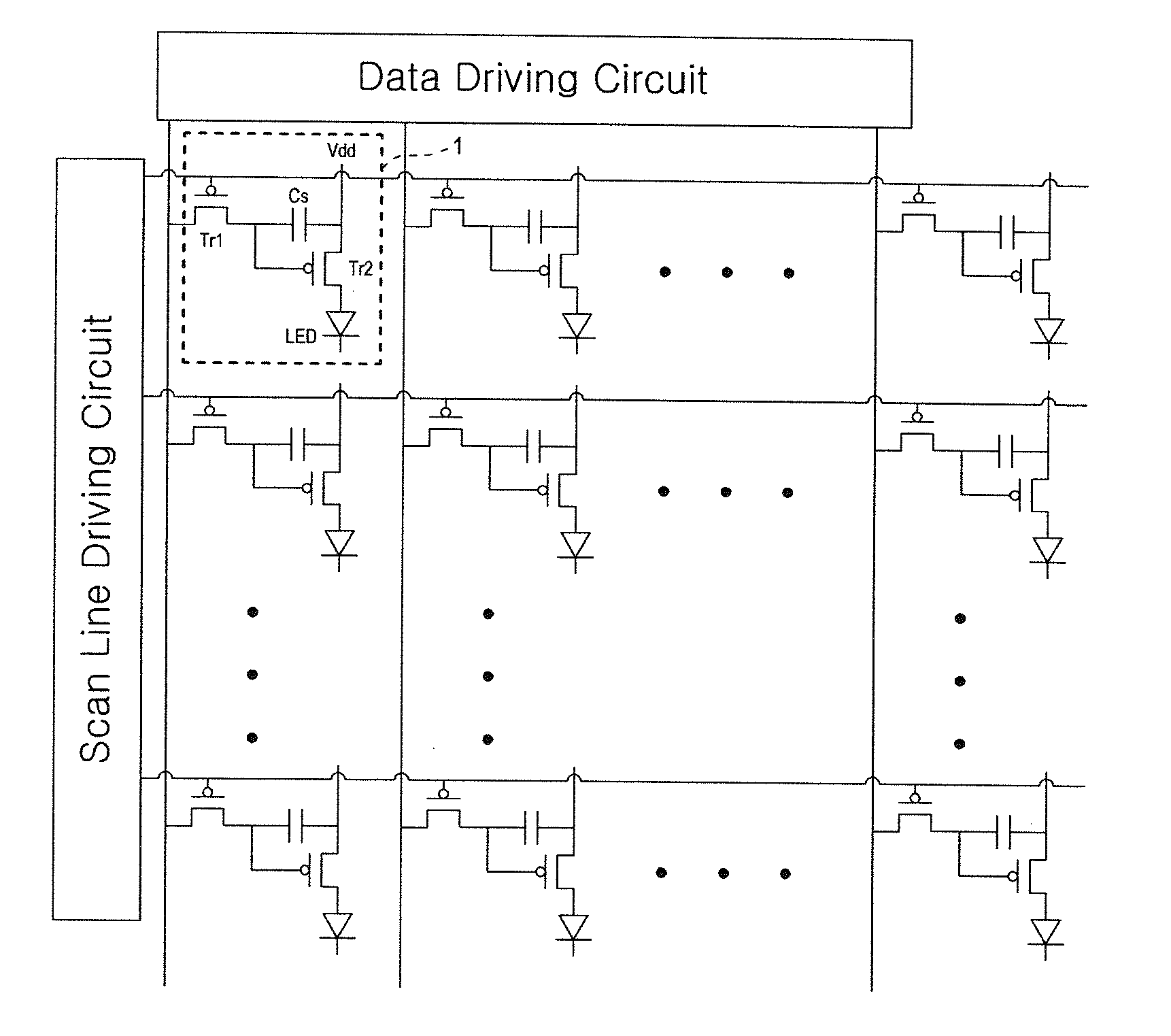

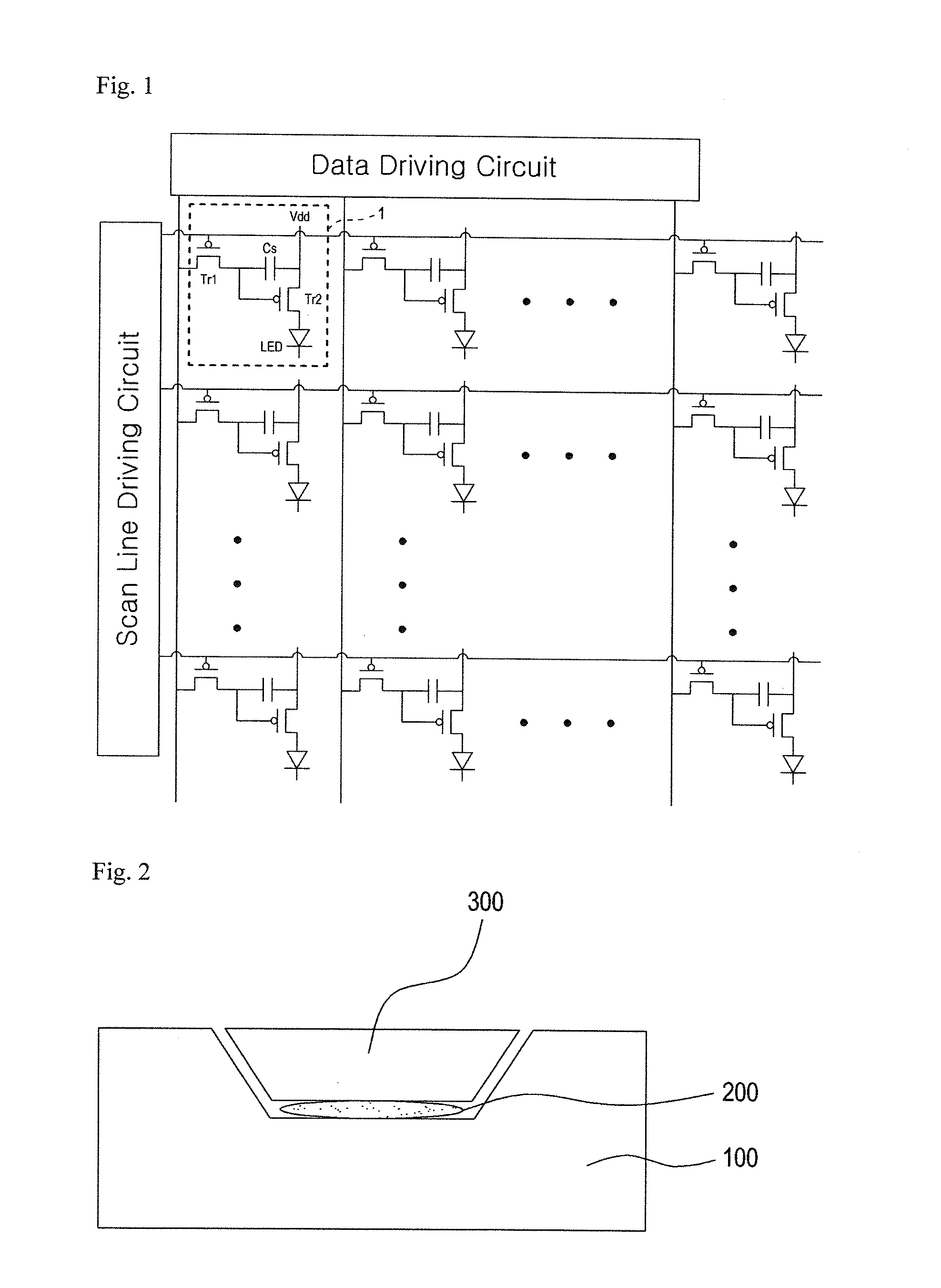

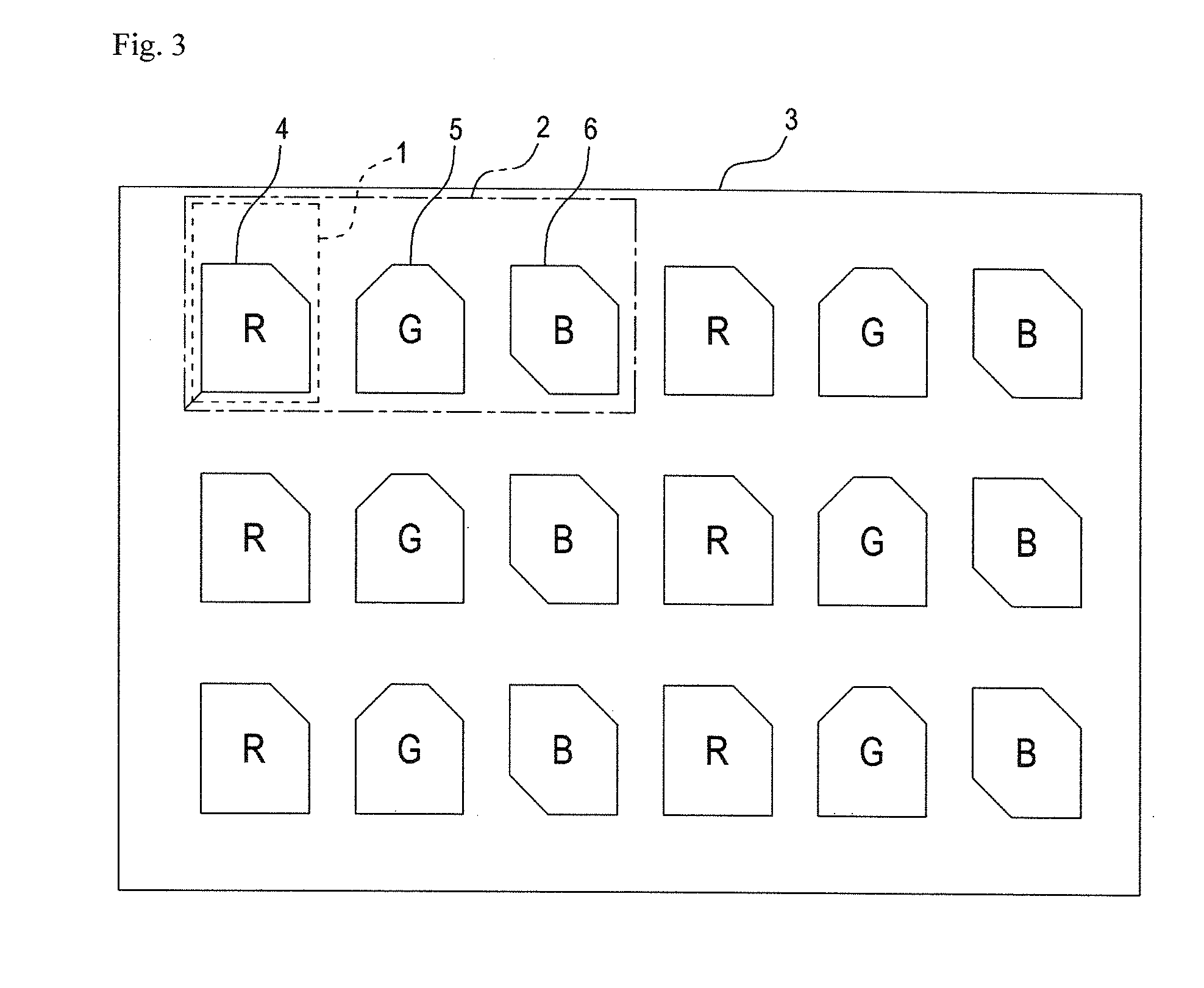

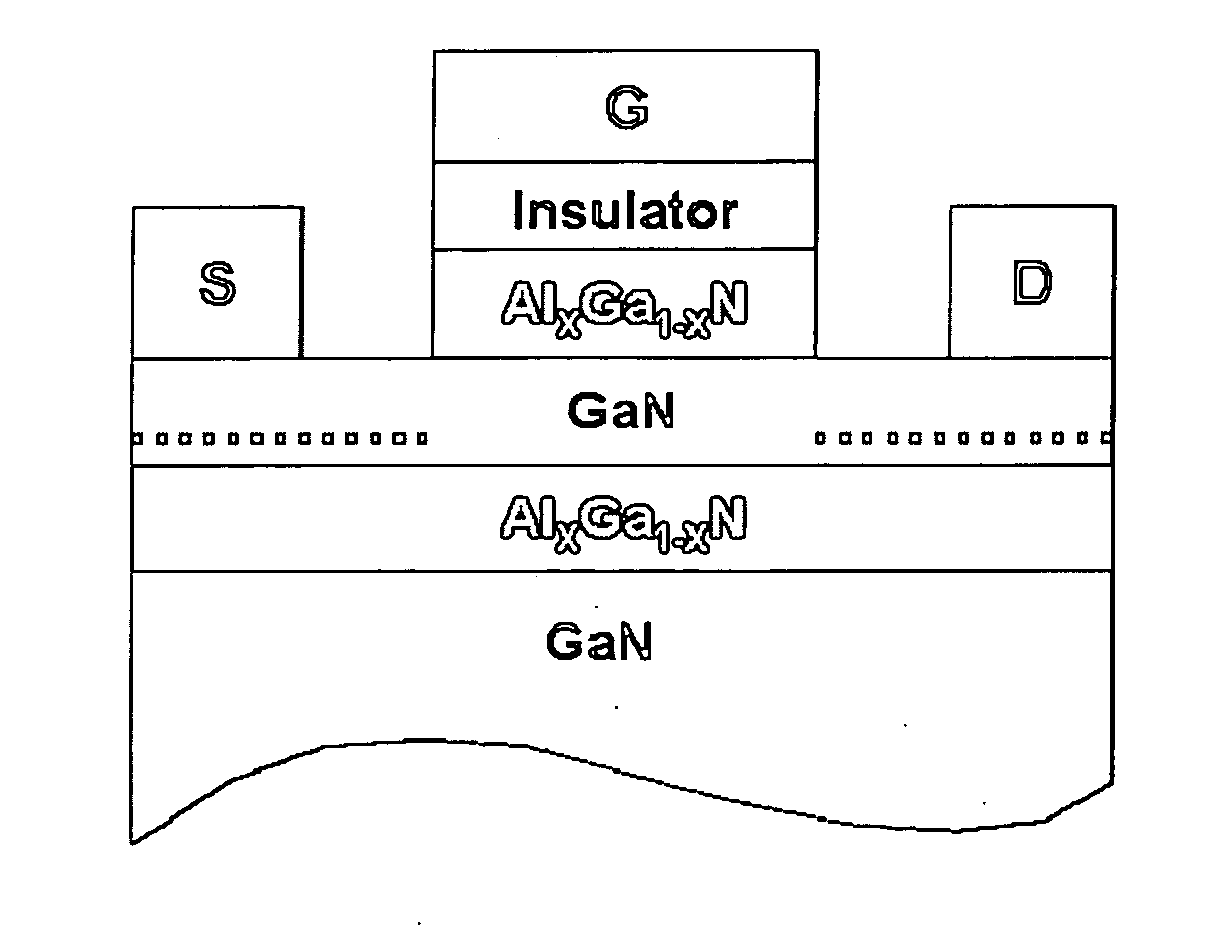

LED display apparatus having active devices and fabrication method thereof

ActiveUS20110273410A1Increase brightnessReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingOptical propertyLED display

An active matrix LED display apparatus and a fabrication method thereof are provided. The active matrix LED display apparatus enables to miniaturize pixel by a formation of wiring on bottom layer and an assembly of each block through each eutectic layer into each transistor block receptor and / or each LED block receptor formed according to each color element unit, and to be embodied with high luminance, low power consumption, high reliability and superior optical property by assembling a transistor block having high electron mobility. And the fabricating method of the present invention enables to make efficiently an AM-LED display apparatus at room temperature in a short time by using different shapes of receptor and block depending on the function of a transistor and / or on the color of an LED.

Owner:SEOUL NAT UNIV R&DB FOUND

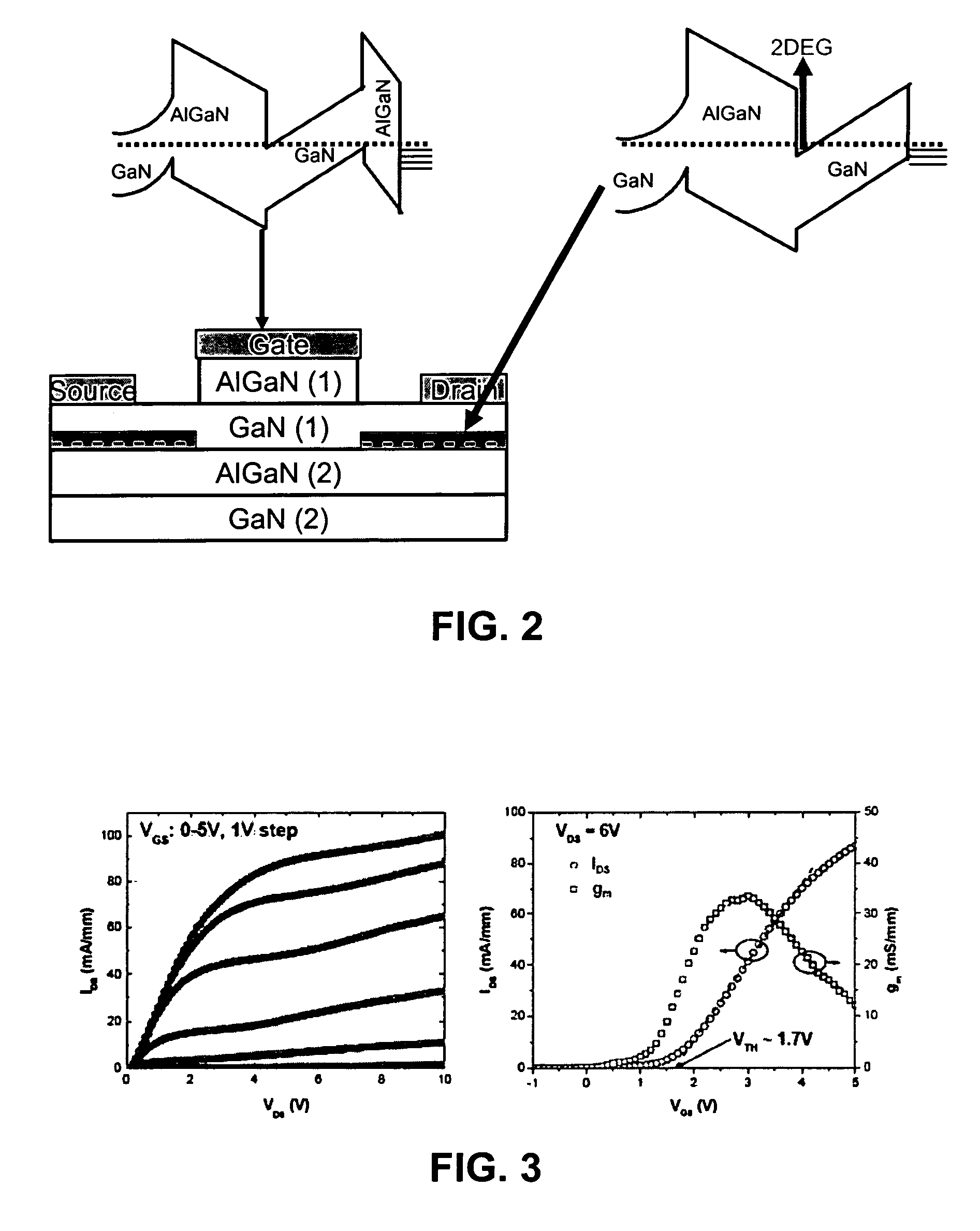

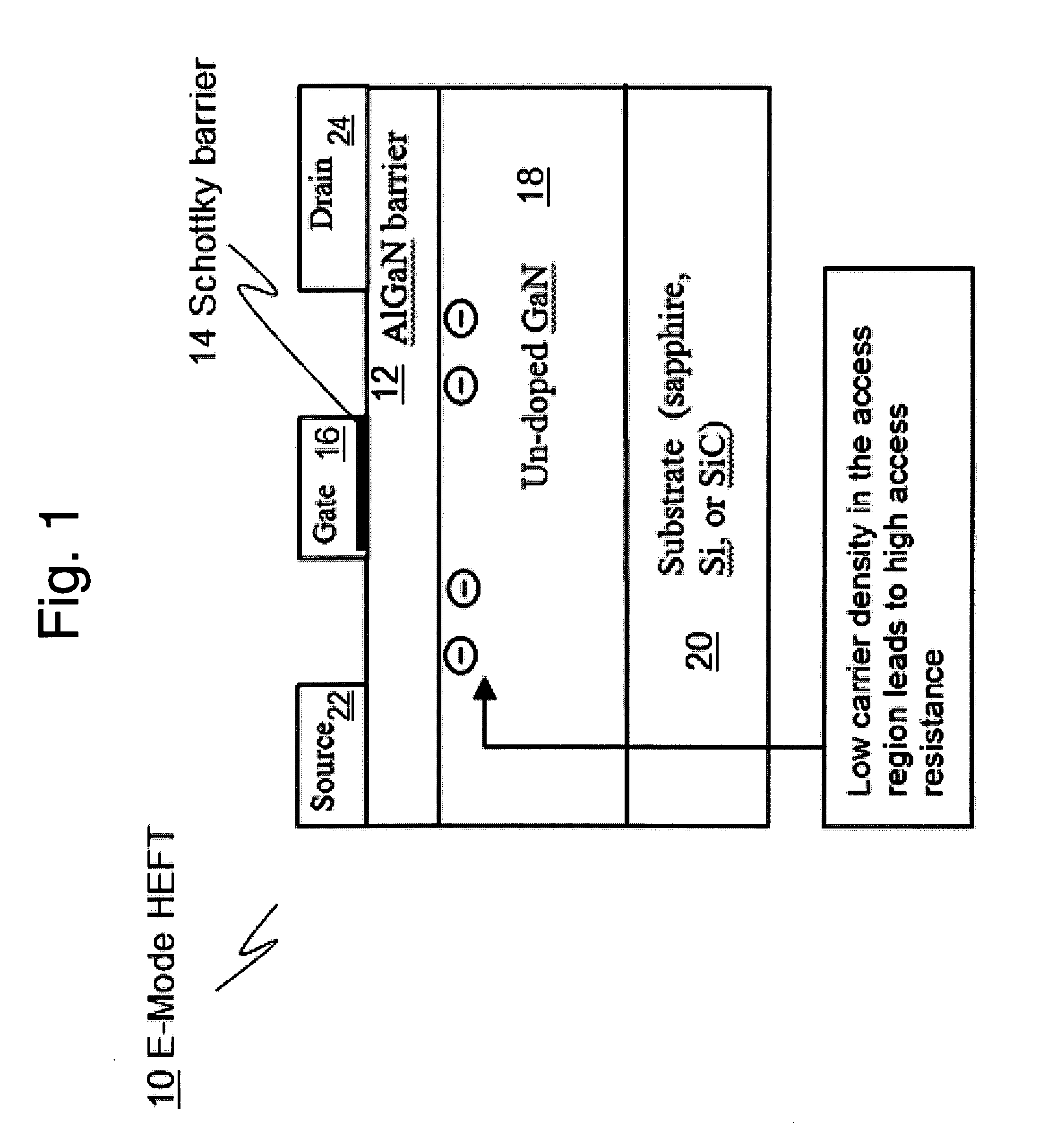

N-polar aluminum gallium nitride/gallium nitride enhancement-mode field effect transistor

ActiveUS20100264461A1High electron mobilityGood dispersionSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical polarityField effect

A novel enhancement mode field effect transistor (FET), such as a High Electron Mobility Transistors (HEMT), has an N-polar surface uses polarization fields to reduce the electron population under the gate in the N-polar orientation, has improved dispersion suppression, and low gate leakage.

Owner:RGT UNIV OF CALIFORNIA

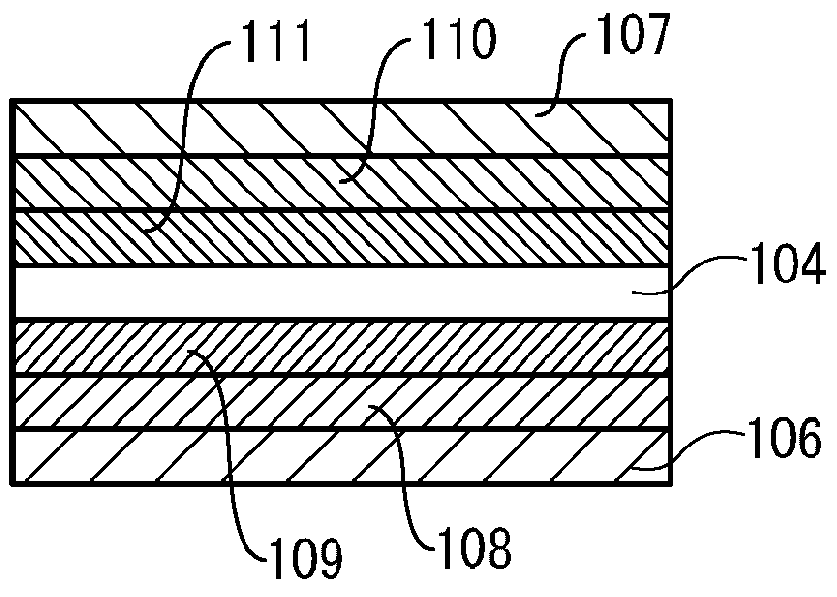

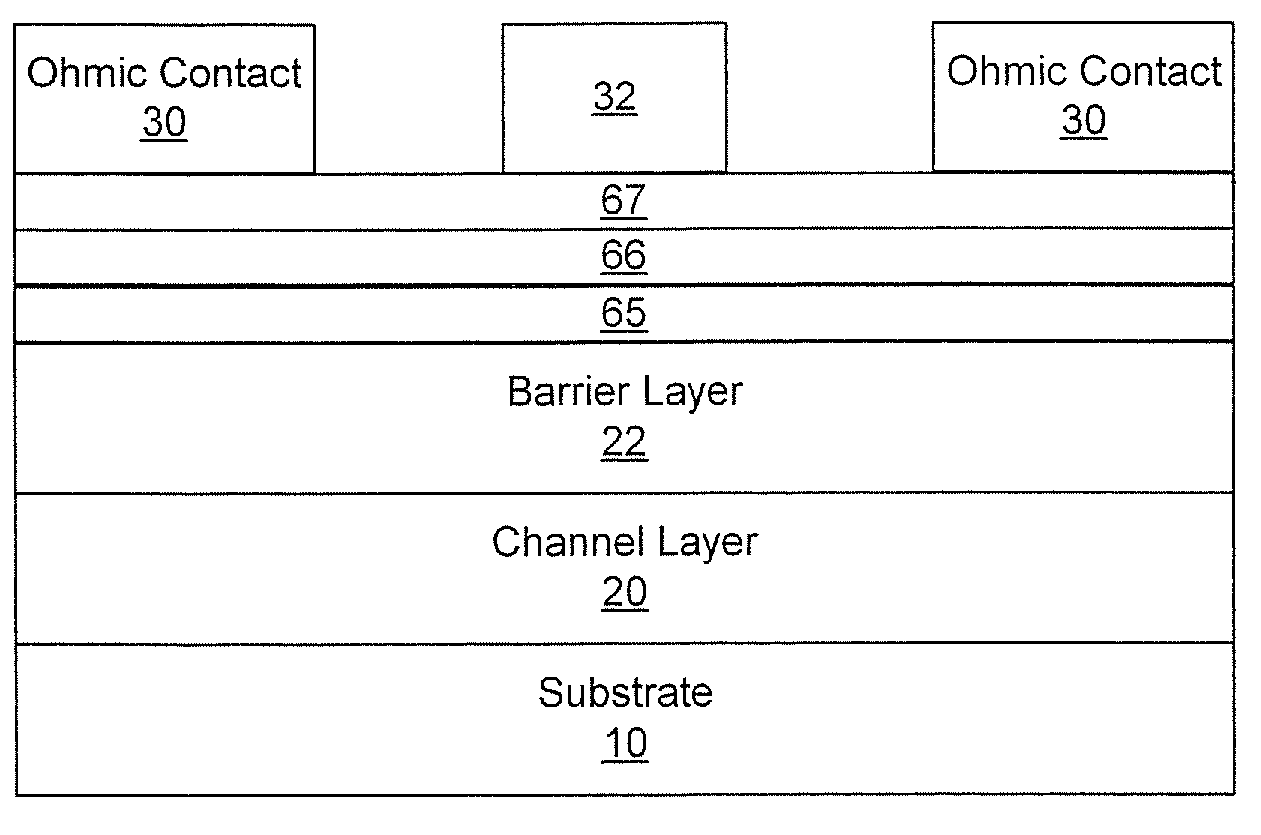

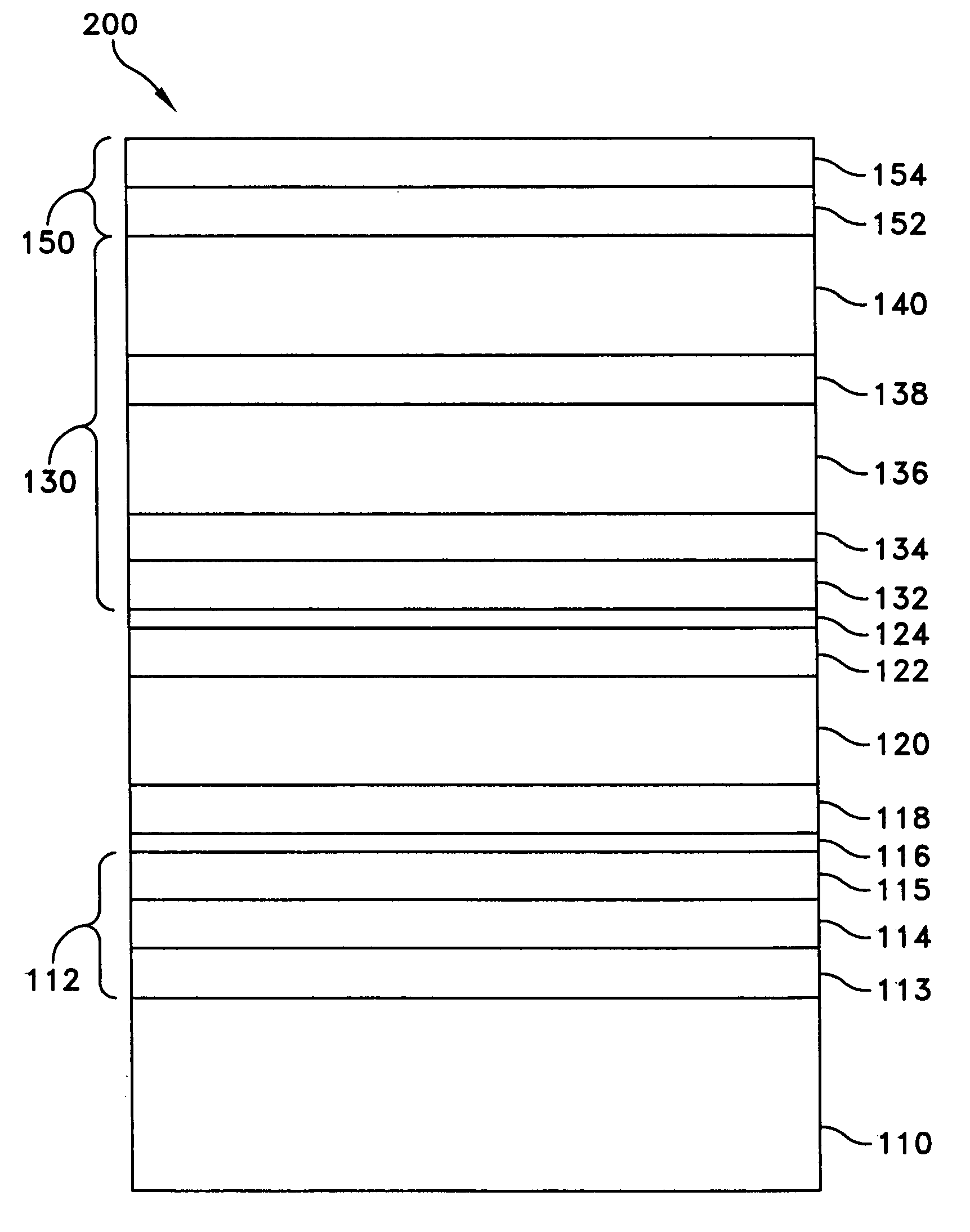

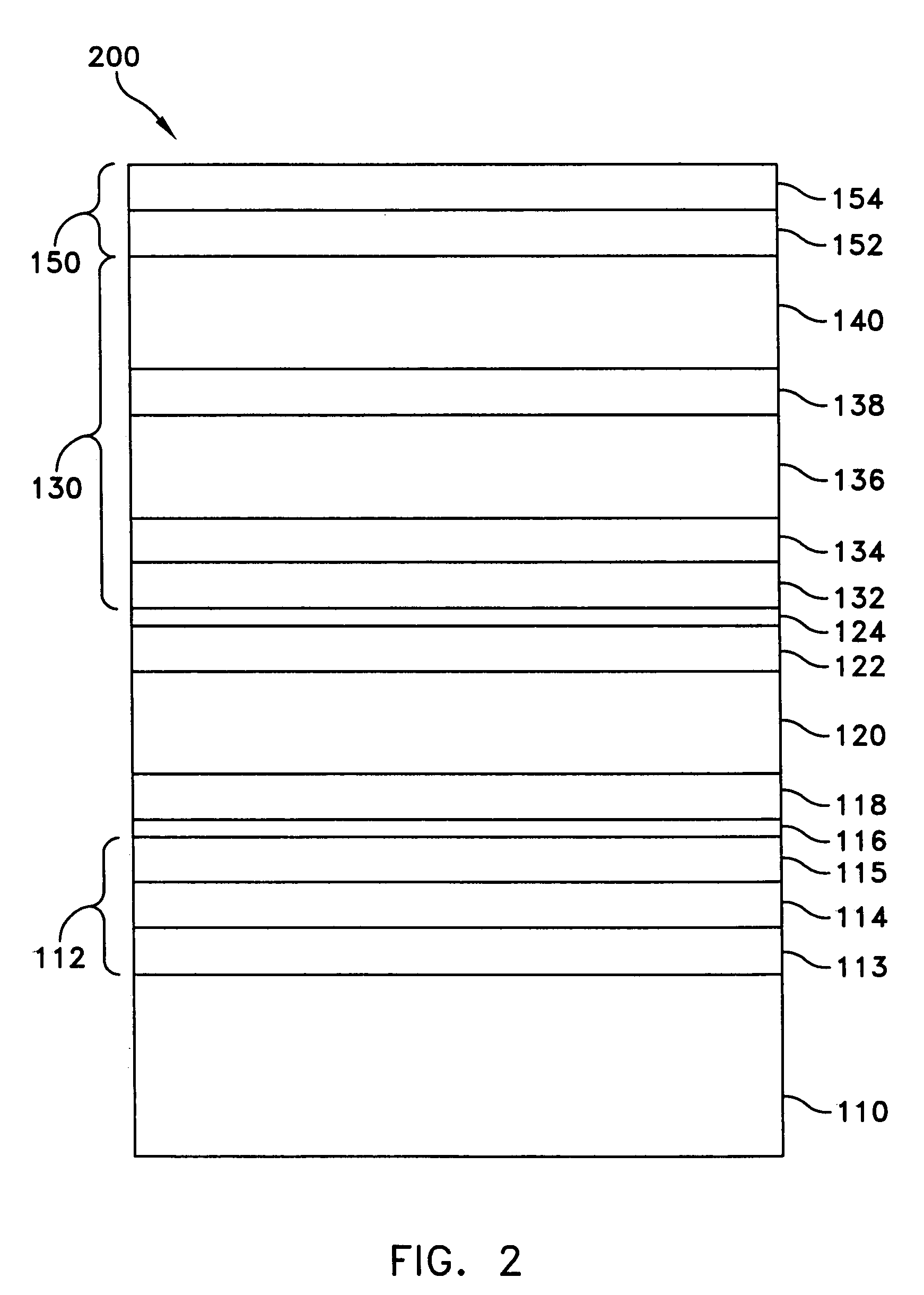

Multi-layer structure for use in the fabrication of integrated circuit devices and methods for fabrication of same

InactiveUS7321132B2Semiconductor/solid-state device manufacturingSemiconductor devicesHigh electronContact layer

A multi-layer structure for use in the fabrication of integrated circuit devices is adapted for the formation of enhancement mode high electron mobility transistors, depletion mode high electron mobility transistors, and power high electron mobility transistors. The structure has, on a substrate, a channel layer, spacer layer on the channel layer, a first Schottky layer, a second Schottky layer on the first Schottky layer, and a third Schottky layer on the second Schottky layer, and a contact layer on the third Schottky layer. Etch stops are defined intermediate the first and second Schottky layers, intermediate the second and third Schottky layers, and intermediate the third Schottky layer and the contact layer.

Owner:LOCKHEED MARTIN CORP +1

N-polar aluminum gallium nitride/gallium nitride enhancement-mode field effect transistor

ActiveUS7948011B2High electron mobilityGood dispersionSemiconductor/solid-state device manufacturingSemiconductor devicesField effectHigh electron

A novel enhancement mode field effect transistor (FET), such as a High Electron Mobility Transistors (HEMT), has an N-polar surface uses polarization fields to reduce the electron population under the gate in the N-polar orientation, has improved dispersion suppression, and low gate leakage.

Owner:RGT UNIV OF CALIFORNIA

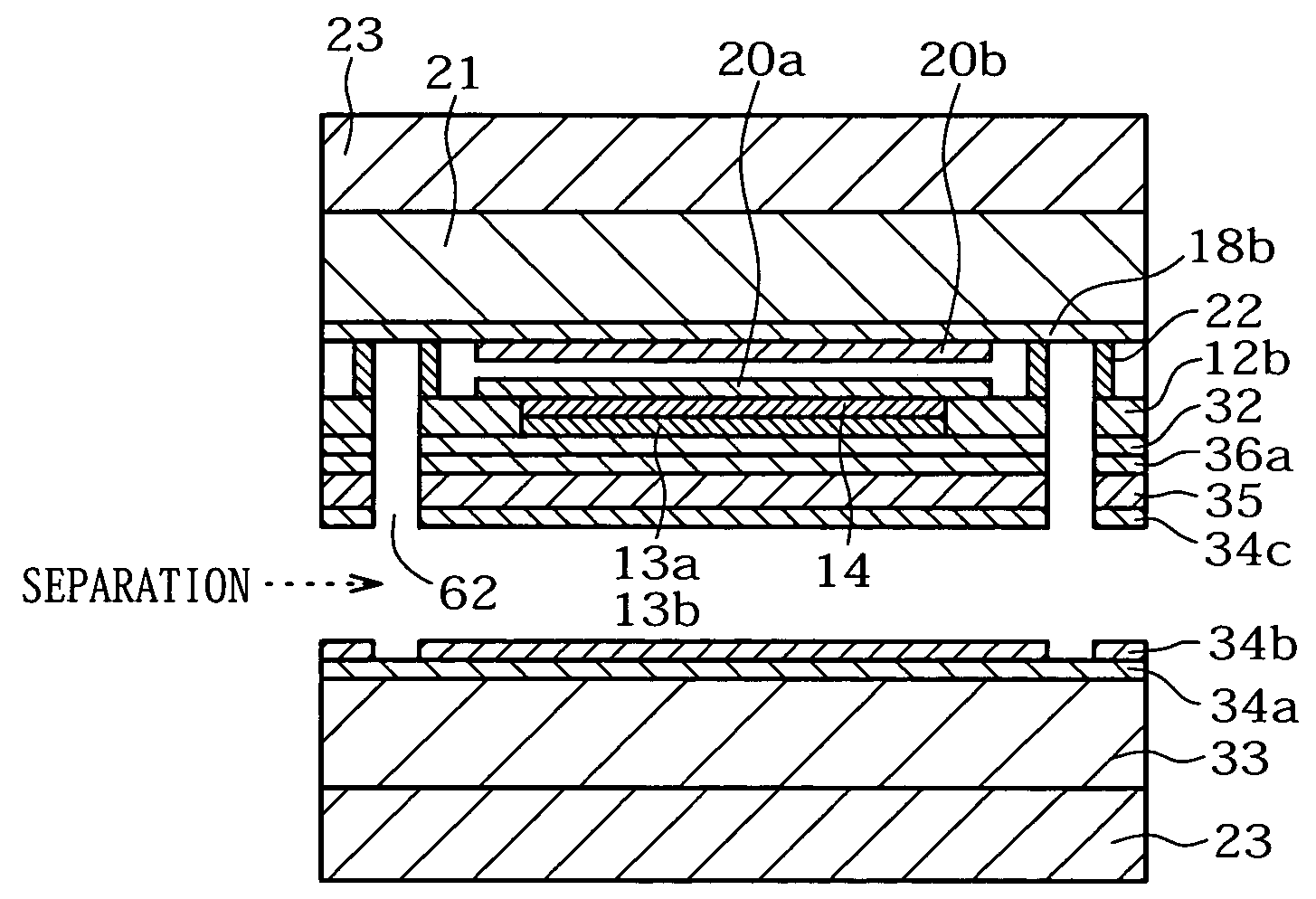

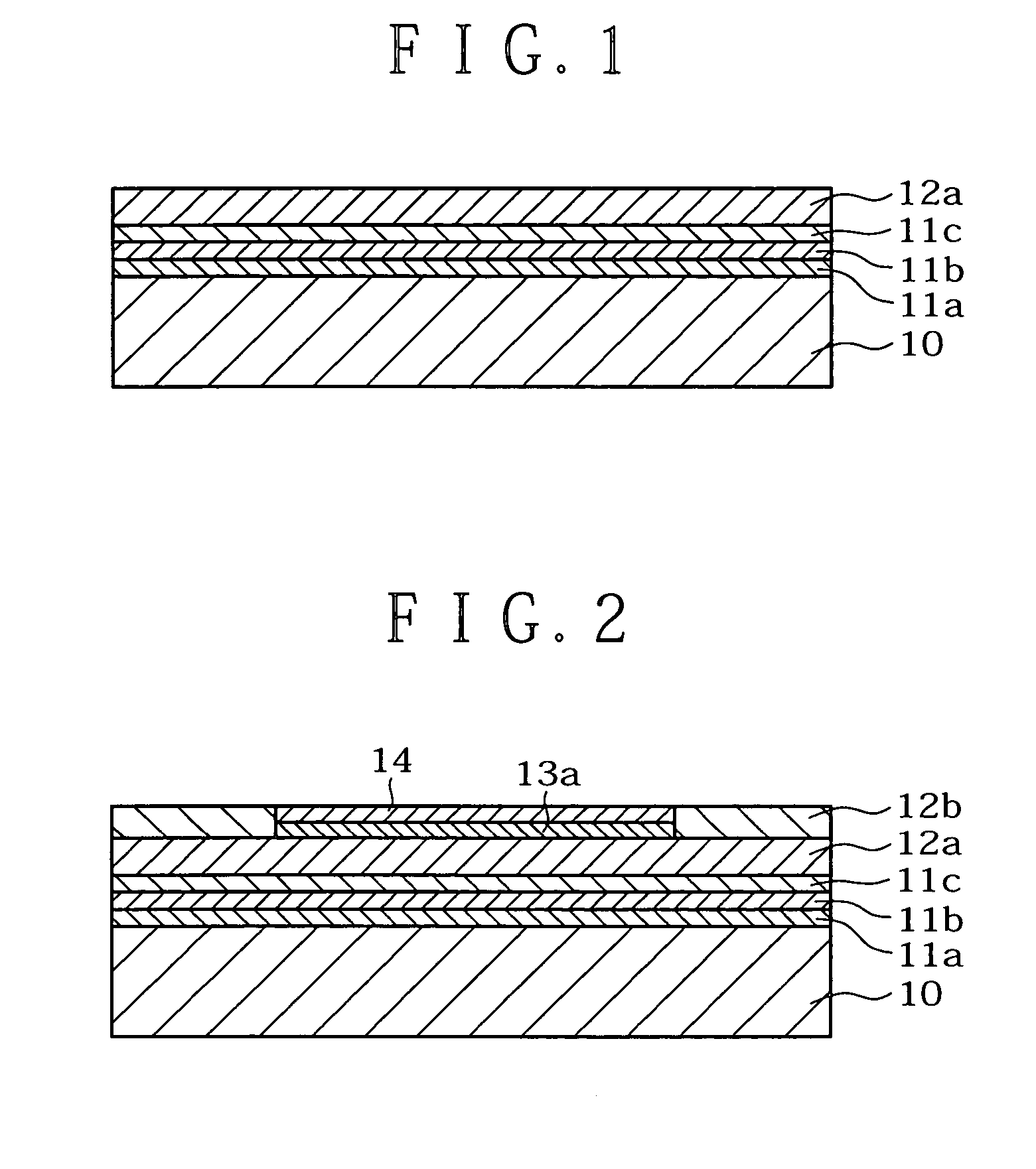

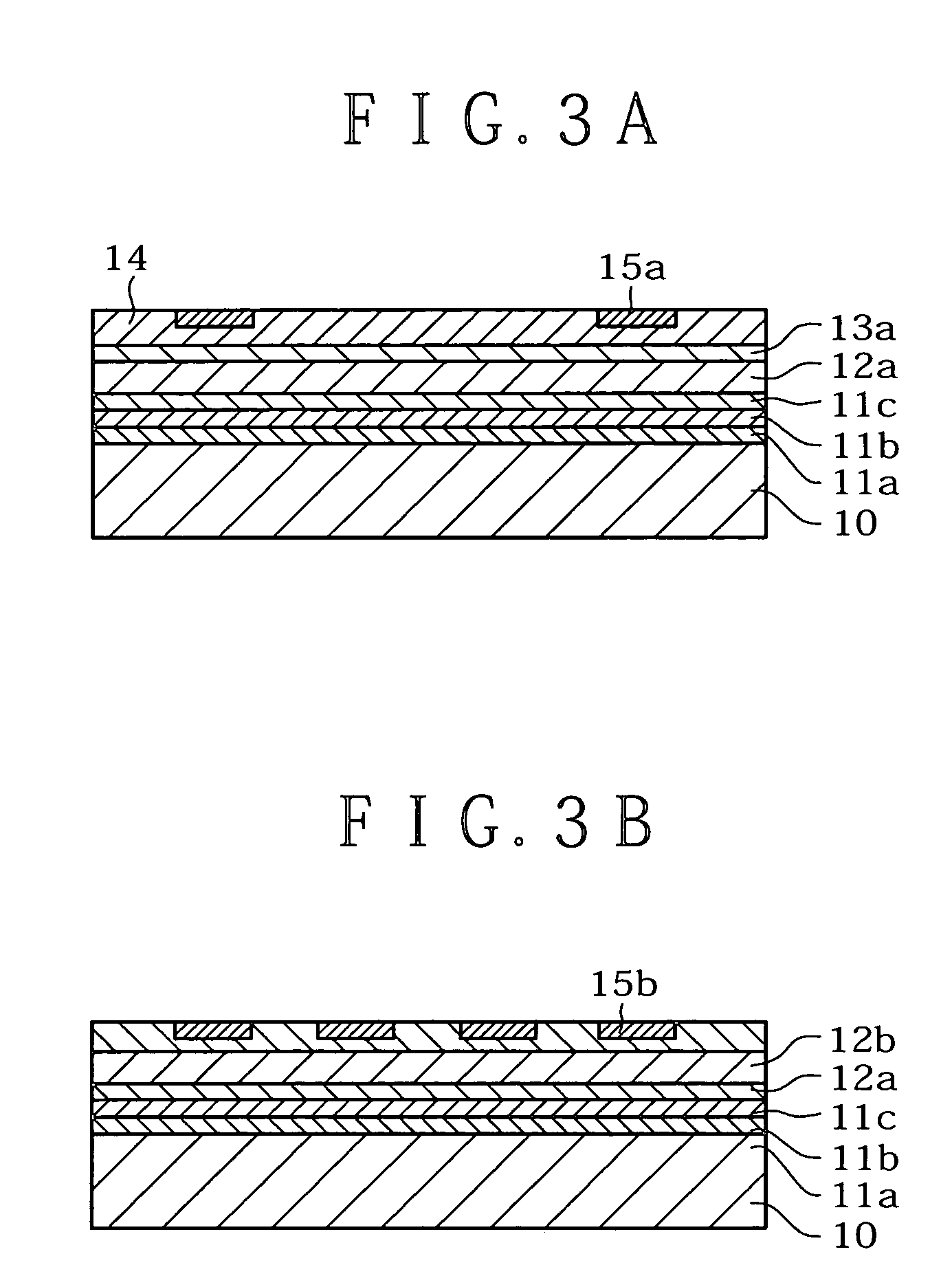

Manufacturing process for ultra slim electrooptic display device unit

To obtain a high intensity, high definition and sophisticated electrooptic display device unit such as transmissive type LCD, a semi-transmissive type LCD, a reflective type LCD, a surface emitter type organic EL, or an underside emitter type organic EL, etc. which has high electron and positive hole mobility and low leak electric current qualities.A porous semiconductor layer (low porous Si layer 11a / high porous Si layer 11b / low porous Si layer 11c), a monocrystalline Si layer12a, and the Si O2 layer 13a are formed on a monocrystalline Si substrate 10. The Si O2 layer 13a of the peripheral circuit area is removed, leaving the Si O2 layer 13a in the display area. The poly Si layer 14a is formed in the display area by semiconductor epitaxial growth, and a monocrystalline Si layer 12b is formed in the peripheral circuit area. Then, the display element section is formed in the poly Si layer 14 of the display area and the peripheral circuitry section is formed in the monocrystalline Si layer 12b of the peripheral circuit area. The assembly is divided into each ultra slim electrooptic display device unit after separation from the backing, and after the process of separating the Si substrate 10 from the porous Si layer 11b and by attaching the backing to the ultra slim electrooptic display element substrate after its separation. Each ultra slim electrooptic display device unit is divided after attaching the backing.

Owner:SONY CORP

Transistors having buried n-type and p-type regions beneath the source region

High electron mobility transistors are provided that include a non-uniform aluminum concentration AlGaN based cap layer having a high aluminum concentration adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. High electron mobility transistors are provided that include a cap layer having a doped region adjacent a surface of the cap layer that is remote from the barrier layer on which the cap layer is provided. Graphitic BN passivation structures for wide bandgap semiconductor devices are provided. SiC passivation structures for Group III-nitride semiconductor devices are provided. Oxygen anneals of passivation structures are also provided. Ohmic contacts without a recess are also provided.

Owner:CREE INC

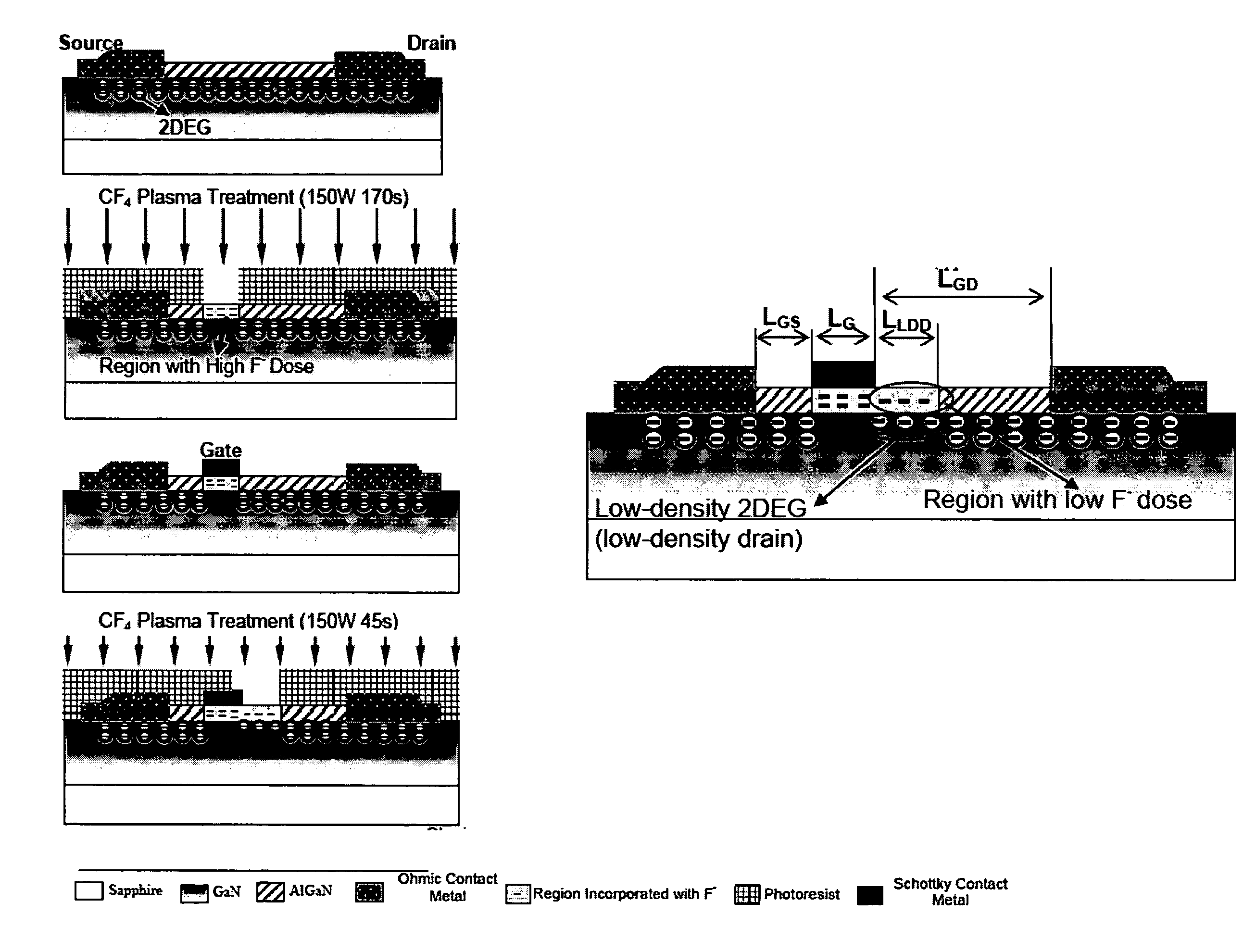

Low Density Drain HEMTs

ActiveUS20070295993A1Simple circuit configurationFavorable operating condition for device safetySemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationBreakdown voltage

Methods and devices for fabricating AlGaN / GaN normally-off high electron mobility transistors (HEMTs). A fluorine-based (electronegative ions-based) plasma treatment or low-energy ion implantation is used to modify the drain-side surface field distribution without the use of a field plate electrode. The off-state breakdown voltage can be improved and current collapse can be completely suppressed in LDD-HEMTs with no significant degradation in gains and cutoff frequencies.

Owner:THE HONG KONG UNIV OF SCI & TECH

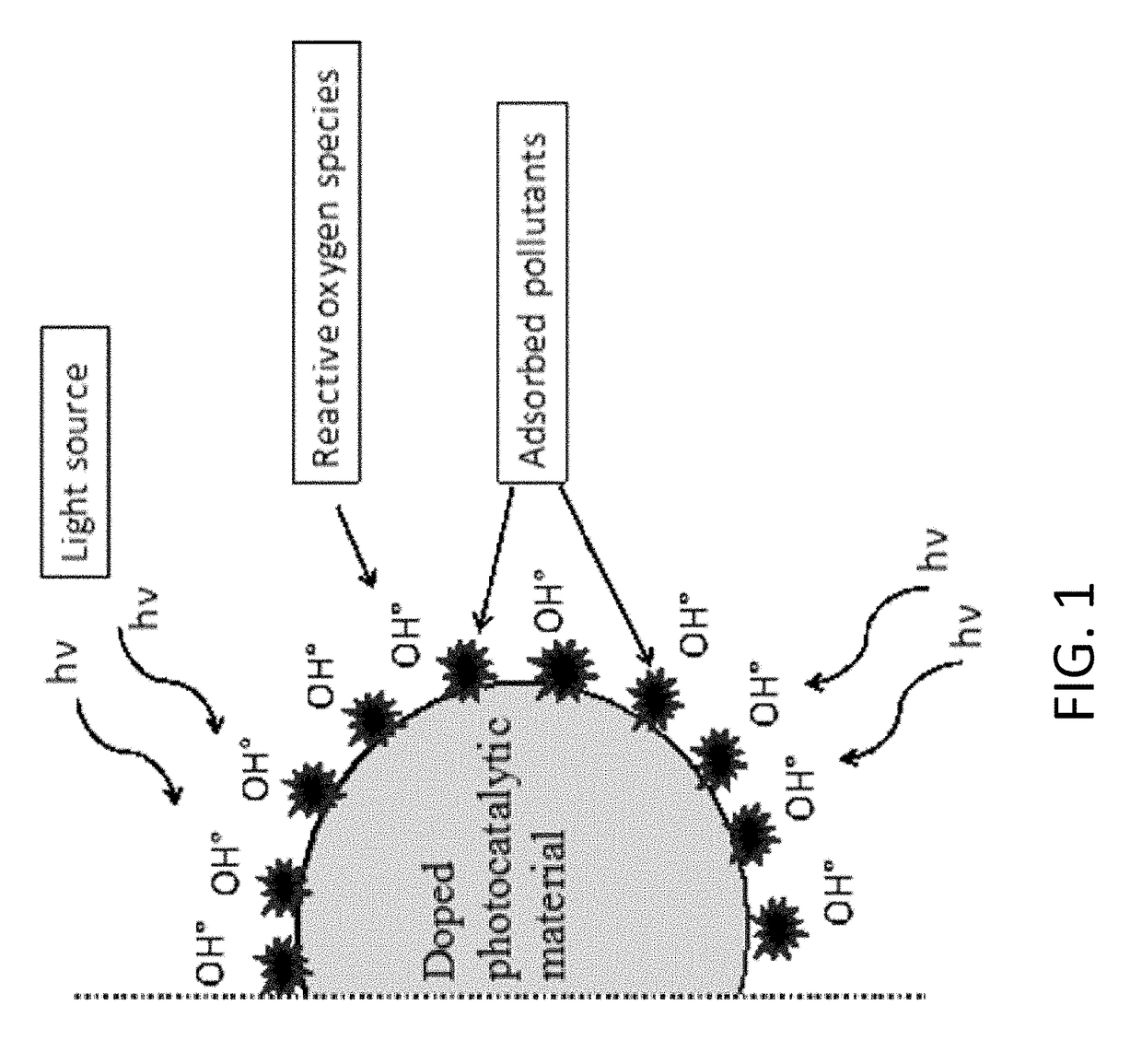

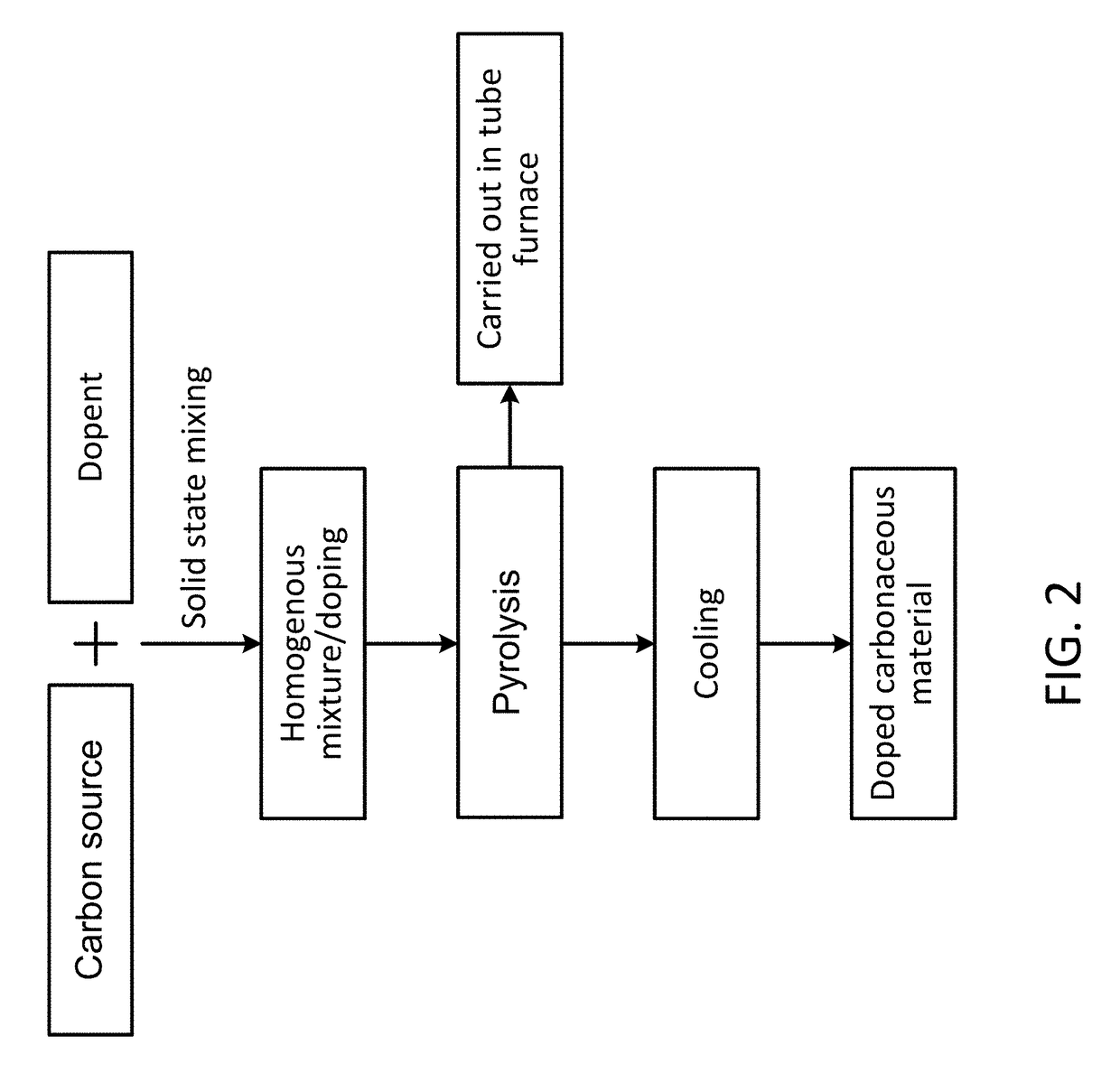

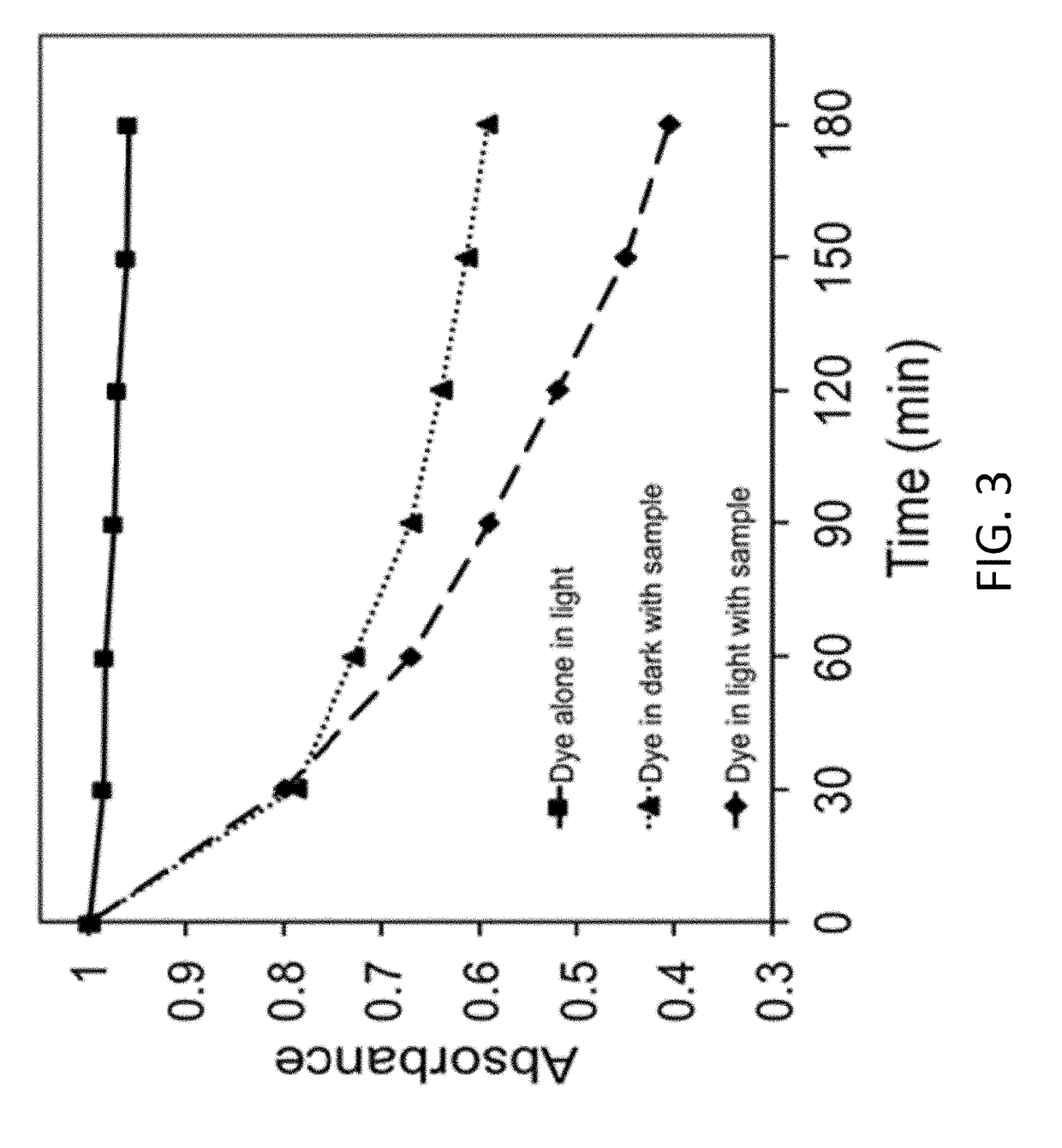

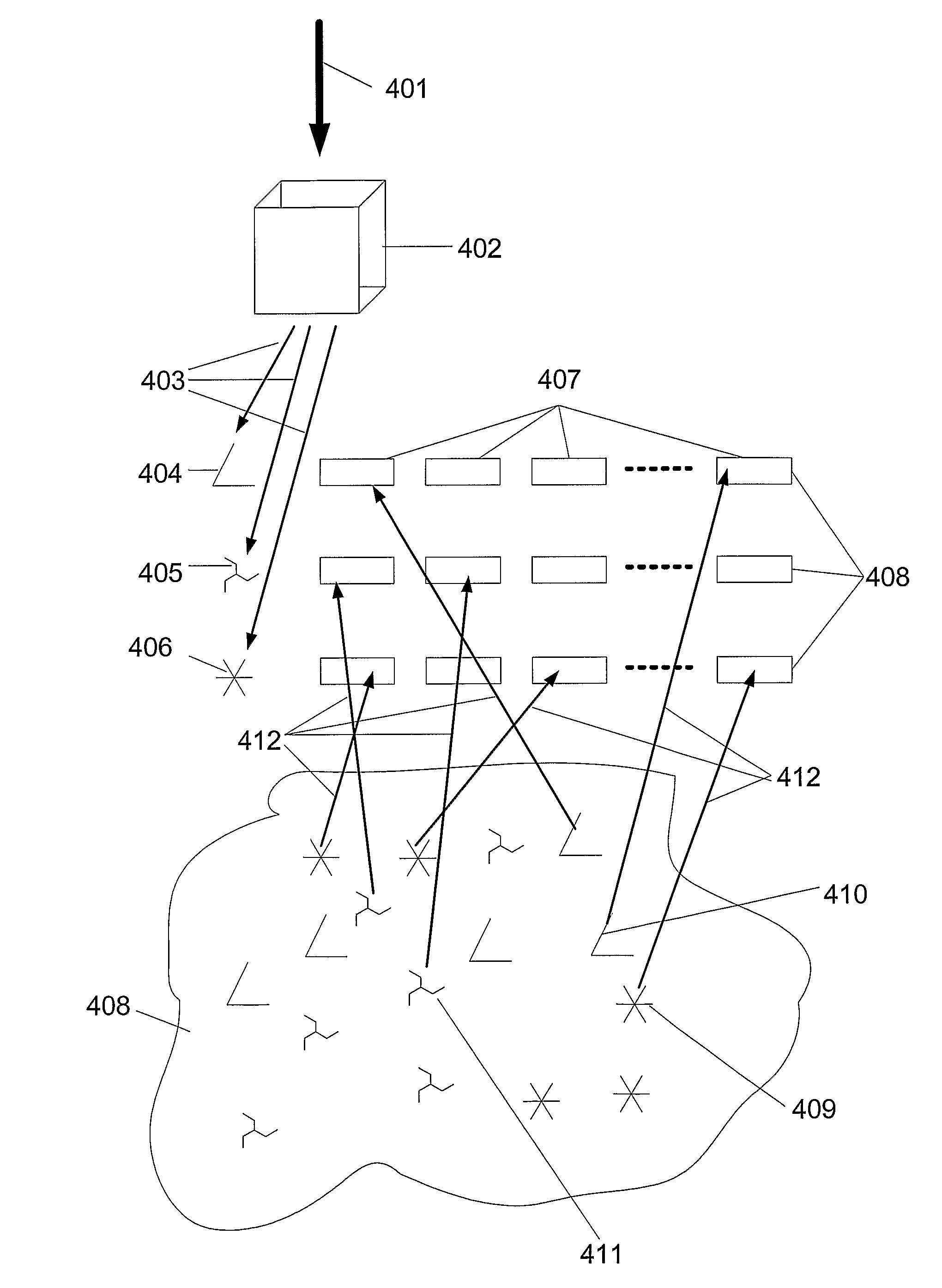

Doped carbonaceous materials for photocatalytic removal of pollutants under visible light, making methods and applications of same

ActiveUS20190015818A1Efficient removalWater/sewage treatment by irradiationWater treatment compoundsSuperoxide radicalSinglet oxygen

A method of synthesizing a doped carbonaceous material includes mixing a carbon precursor material with at least one dopant to form a homogeneous / heterogeneous mixture; and subjecting the mixture to pyrolysis in an inert atmosphere to obtain the doped carbonaceous material. A method of purifying water includes providing an amount of the doped carbonaceous material in the water as a photocatalyst; and illuminating the water containing the doped carbonaceous material with visible light such that under visible light illumination, the doped carbonaceous material generates excitons (electron-hole pairs) and has high electron affinity, which react with oxygen and water adsorbed on its surface forming reactive oxygen species (ROS), such as hydroxyl radicals and superoxide radicals, singlet oxygen, hydrogen peroxide, that, in turn, decompose pollutants and micropollutants.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS

Extended electron tomography

ActiveUS20090283676A1High resolutionMicroscopic object acquisitionMaterial analysis by transmitting radiationData setImage resolution

A method for improving image resolution of a three dimensional structure of at least one molecule conformation includes: determining a three dimensional structure of at least one conformation of a molecule in a sample from a first data set obtained from a series of 2D measurements of different geometrical projections of the molecule at a low electron beam dose in an electron microscope; producing a second data set including calculated two dimensional projections of the determined three dimensional structure of the at least one conformation of the same molecule; correlating data from a third data set obtained from at least one measurement of the same molecule using a higher electron beam dose with the second data set; and using the correlated data to improve the resolution of the three dimensional structure of the at least one conformation of the molecule by increasing the first data set with the correlated data and re-determining a three dimensional structure.

Owner:OKINAWA INST OF SCI & TECH PROMOTION CORP

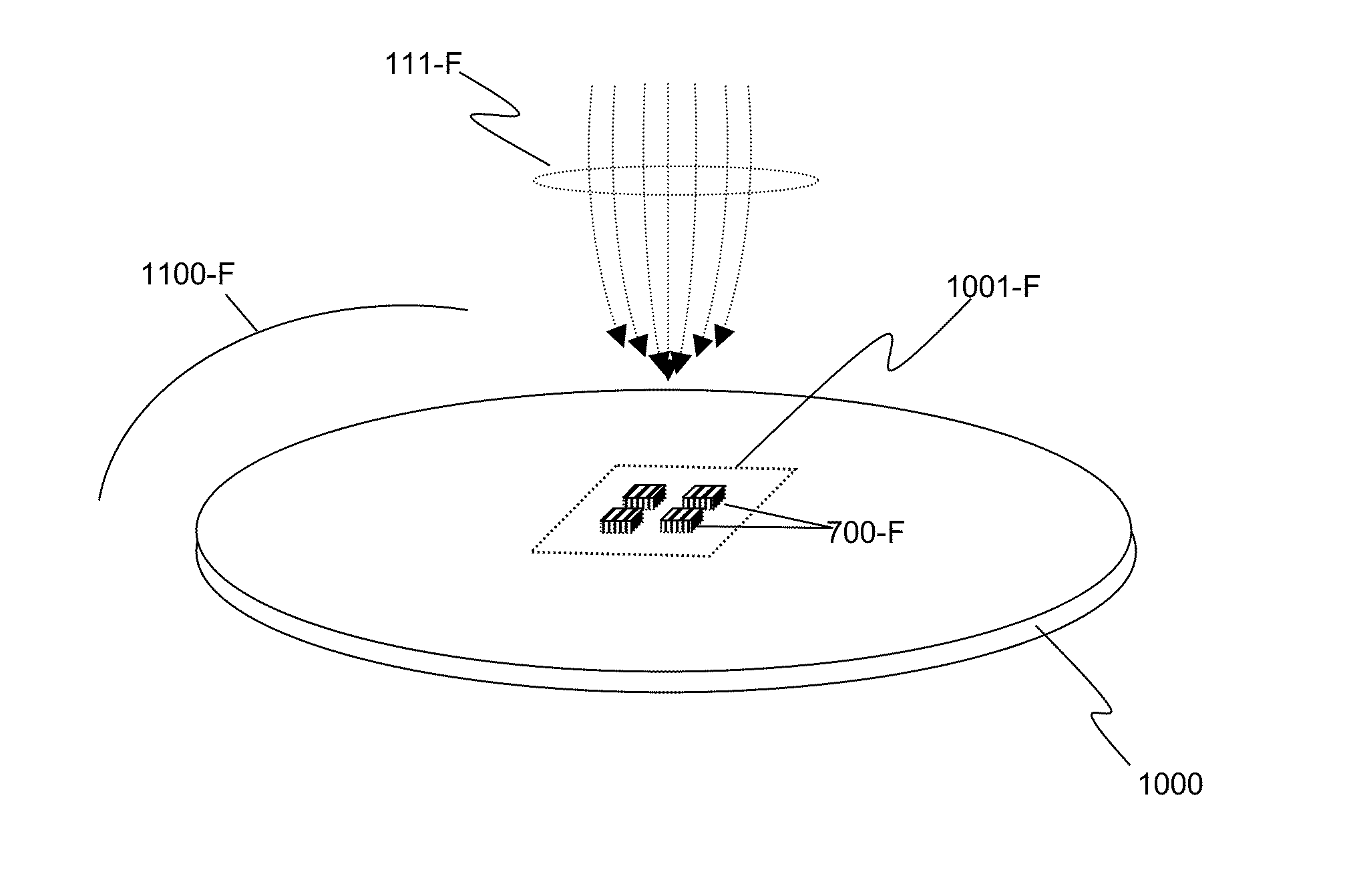

Structured targets for x-ray generation

InactiveUS20150092924A1Improve cooling effectHeat generationX-ray tube laminated targetsX-ray tube anode coolingMicron scaleHigh energy

We disclose targets for generating x-rays using electron beams, along with their method of fabrication. The targets comprise a number of microstructures fabricated from an x-ray target material arranged in close thermal contact with a substrate such that the heat is more efficiently drawn out of the x-ray target material. This in turn allows irradiation of the x-ray generating substance with higher electron density or higher energy electrons, which leads to greater x-ray brightness, without inducing damage or melting.The microstructures may comprise conventional x-ray target materials (such as tungsten) that are patterned at micron-scale dimensions on a thermally conducting substrate, such as diamond. The microstructures may have any number of geometric shapes to best generate x-rays of high brightness and efficiently disperse heat.In some embodiments, the target comprising microstructures may be incorporated into a rotating anode geometry, to enhance x-ray generation in such systems.

Owner:SIGRAY INC

Binary group III-nitride based high electron mobility transistors and methods of fabricating same

Binary Group III-nitride high electron mobility transistors (HEMTs) and methods of fabricating binary Group III-nitride HEMTs are provided. In some embodiments, the binary Group III-nitride HEMTs include a first binary Group III-nitride barrier layer, a binary Group III-nitride channel layer on the first barrier layer; and a second binary Group III-nitride barrier layer on the channel layer. In some embodiments, the binary Group III-nitride HEMTs include a first AIN barrier layer, a GaN channel layer and a second AlN barrier layer.

Owner:CREE INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com