Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4060 results about "Field effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In physics, the field effect refers to the modulation of the electrical conductivity of a material by the application of an external electric field. In a metal, the electron density that responds to applied fields is so large that an external electric field can penetrate only a very short distance into the material. However, in a semiconductor the lower density of electrons (and possibly holes) that can respond to an applied field is sufficiently small that the field can penetrate quite far into the material. This field penetration alters the conductivity of the semiconductor near its surface, and is called the field effect. The field effect underlies the operation of the Schottky diode and of field-effect transistors, notably the MOSFET, the JFET and the MESFET.

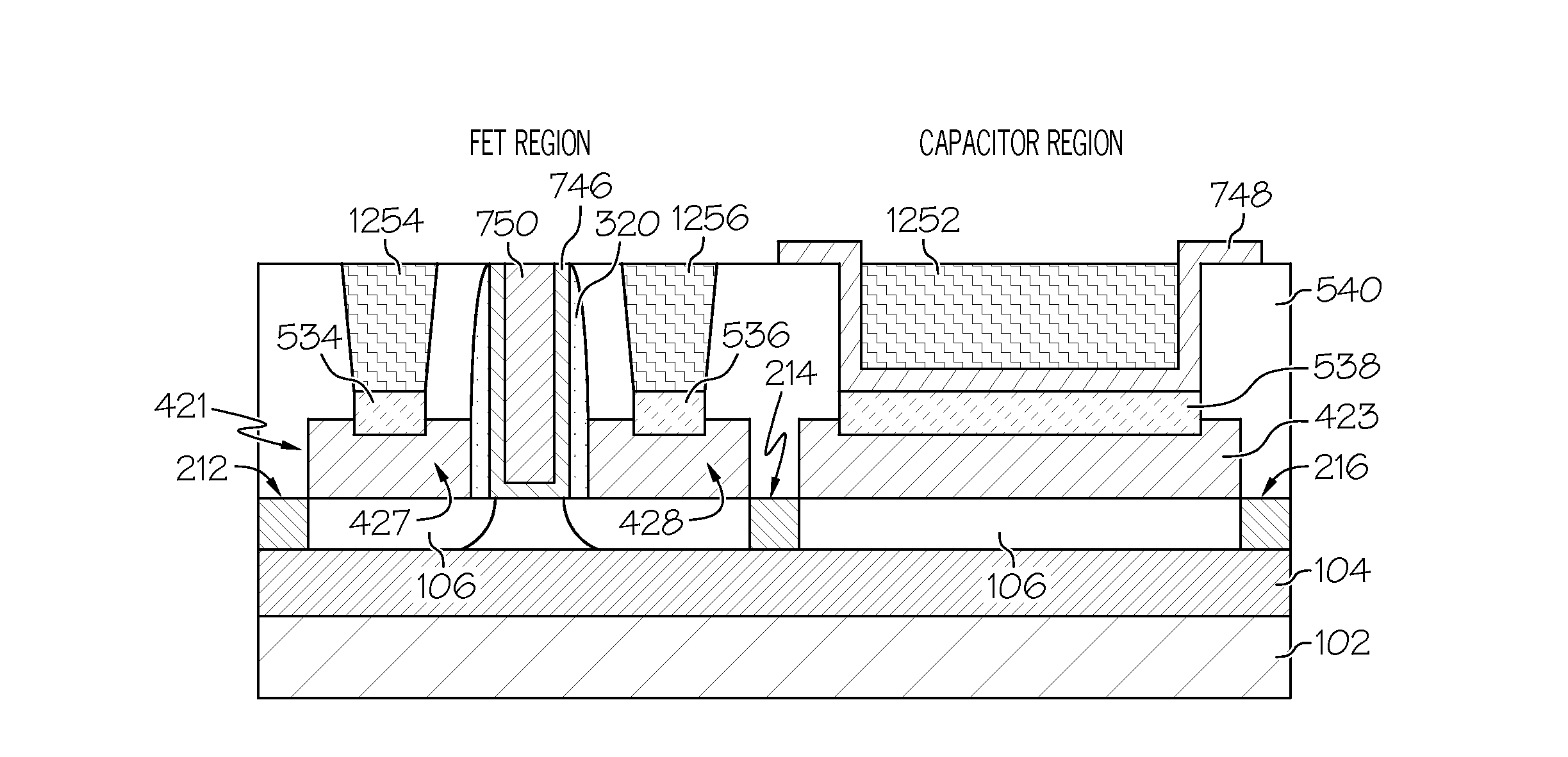

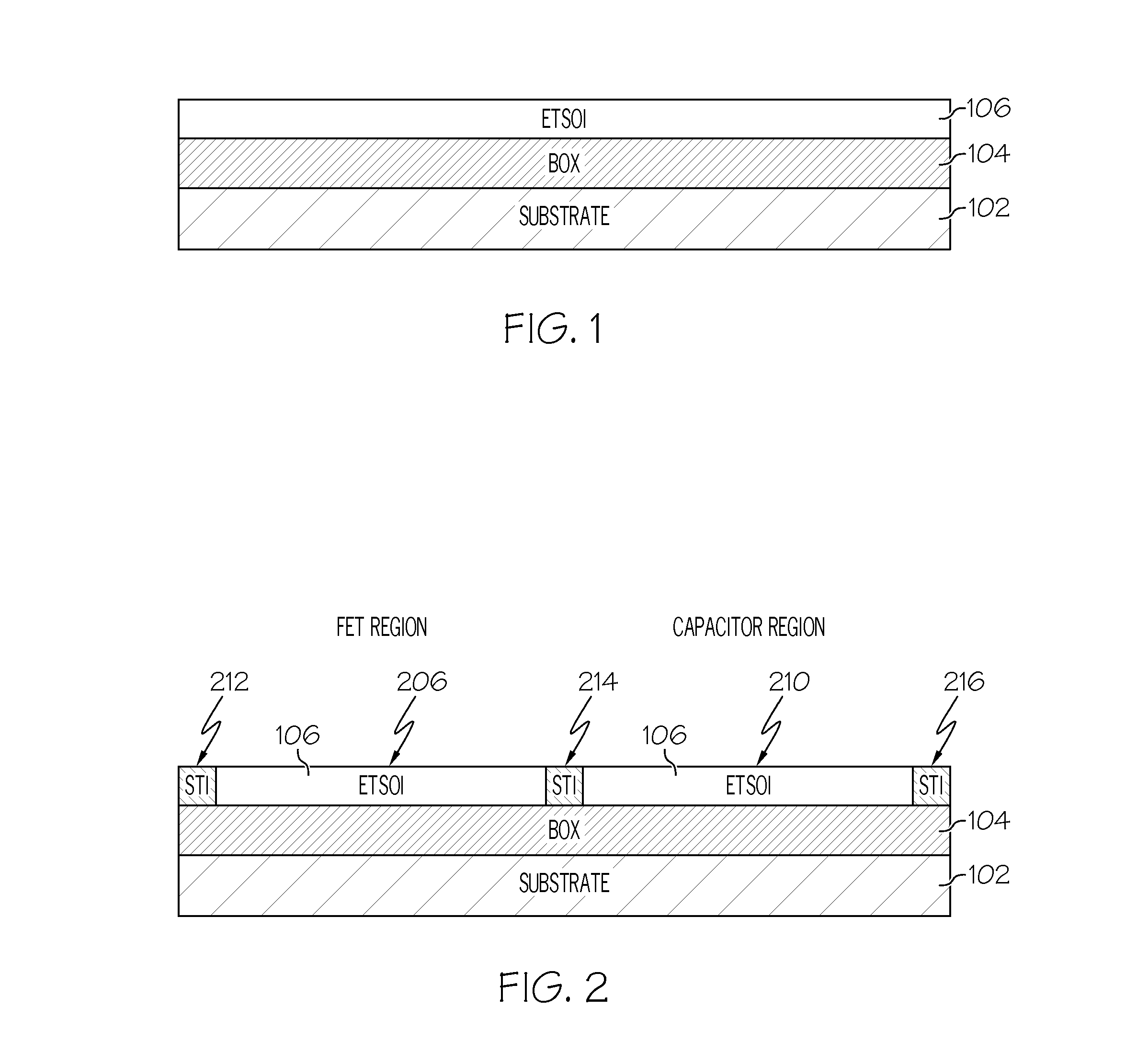

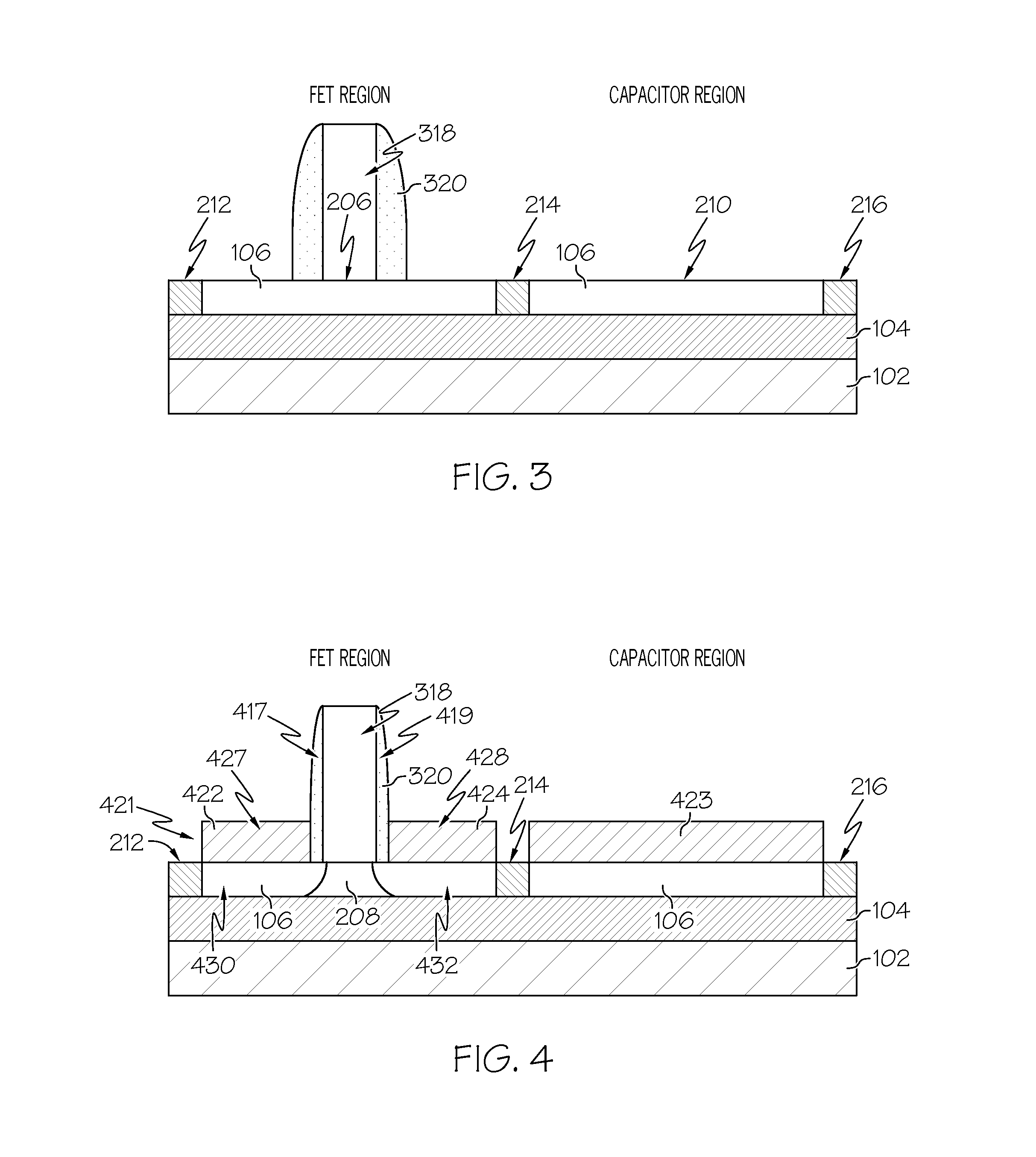

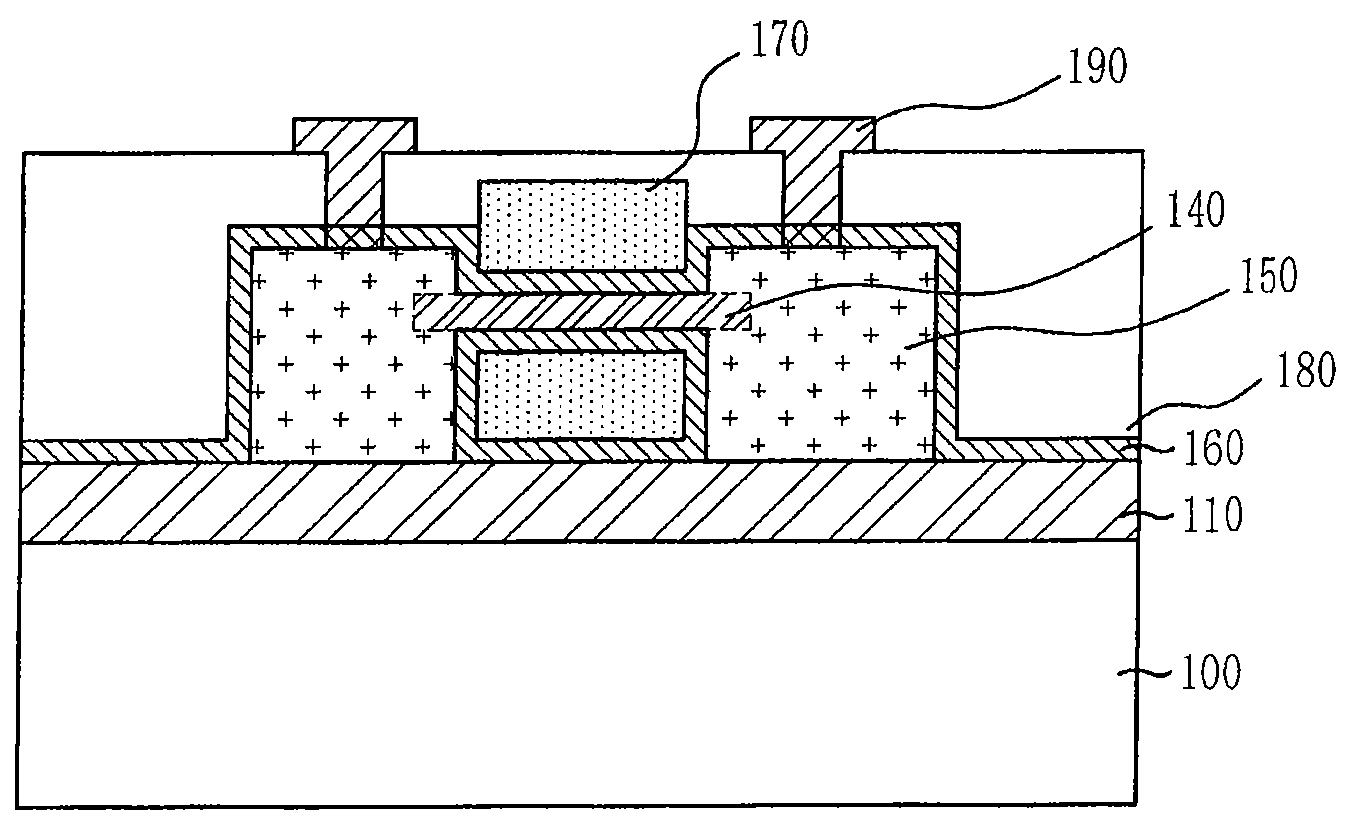

Integrated circuit with a thin body field effect transistor and capacitor

An integrated circuit includes a transistor and a capacitor. The transistor includes a first semiconductor layer and a gate stack located on the first semiconductor layer. The gate stack includes a metal layer and a first high-k dielectric layer. A gate spacer is located on sidewalls of the gate stack. The first high-k dielectric layer is located between the first semiconductor layer and the metal layer and between the gate spacer and sidewalls of the metal layer. A first silicide region is located on a first source / drain region. A second silicide region is located on a second source / drain region. The capacitor includes a first terminal that comprises a third silicide region located on a portion of the second semiconductor. A second high-k dielectric layer is located on the silicide region. A second terminal comprises a metal layer that is located on the second high-k dielectric layer.

Owner:GLOBALFOUNDRIES US INC

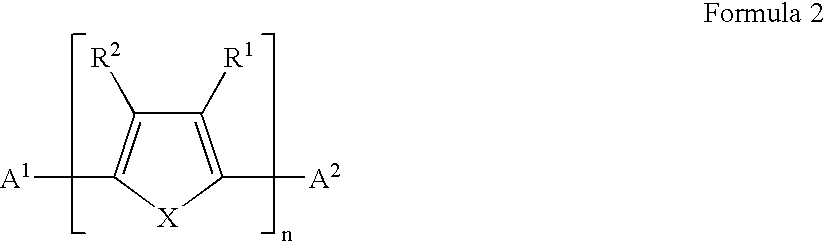

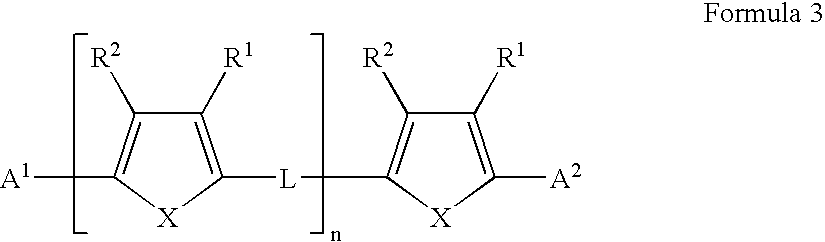

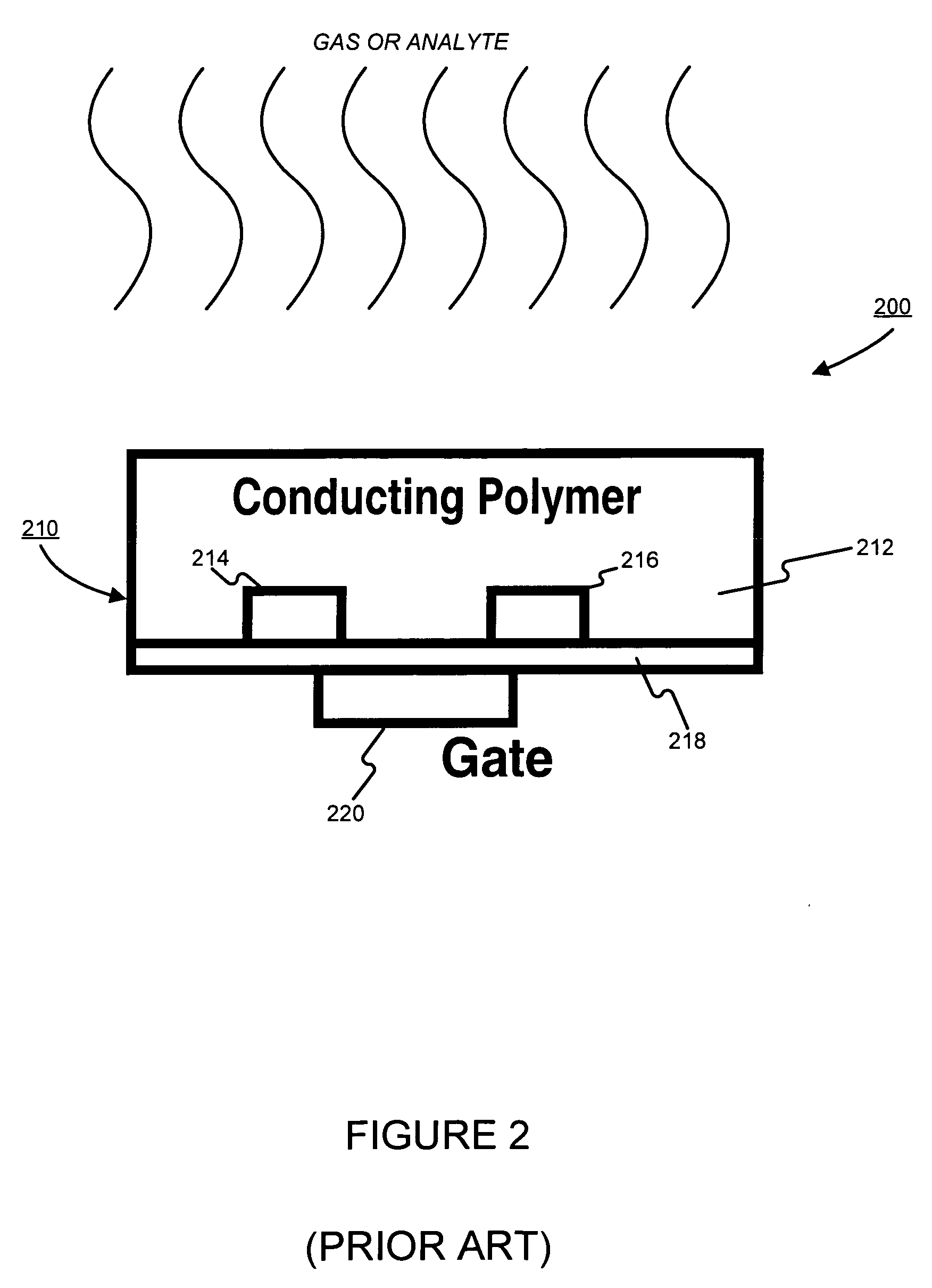

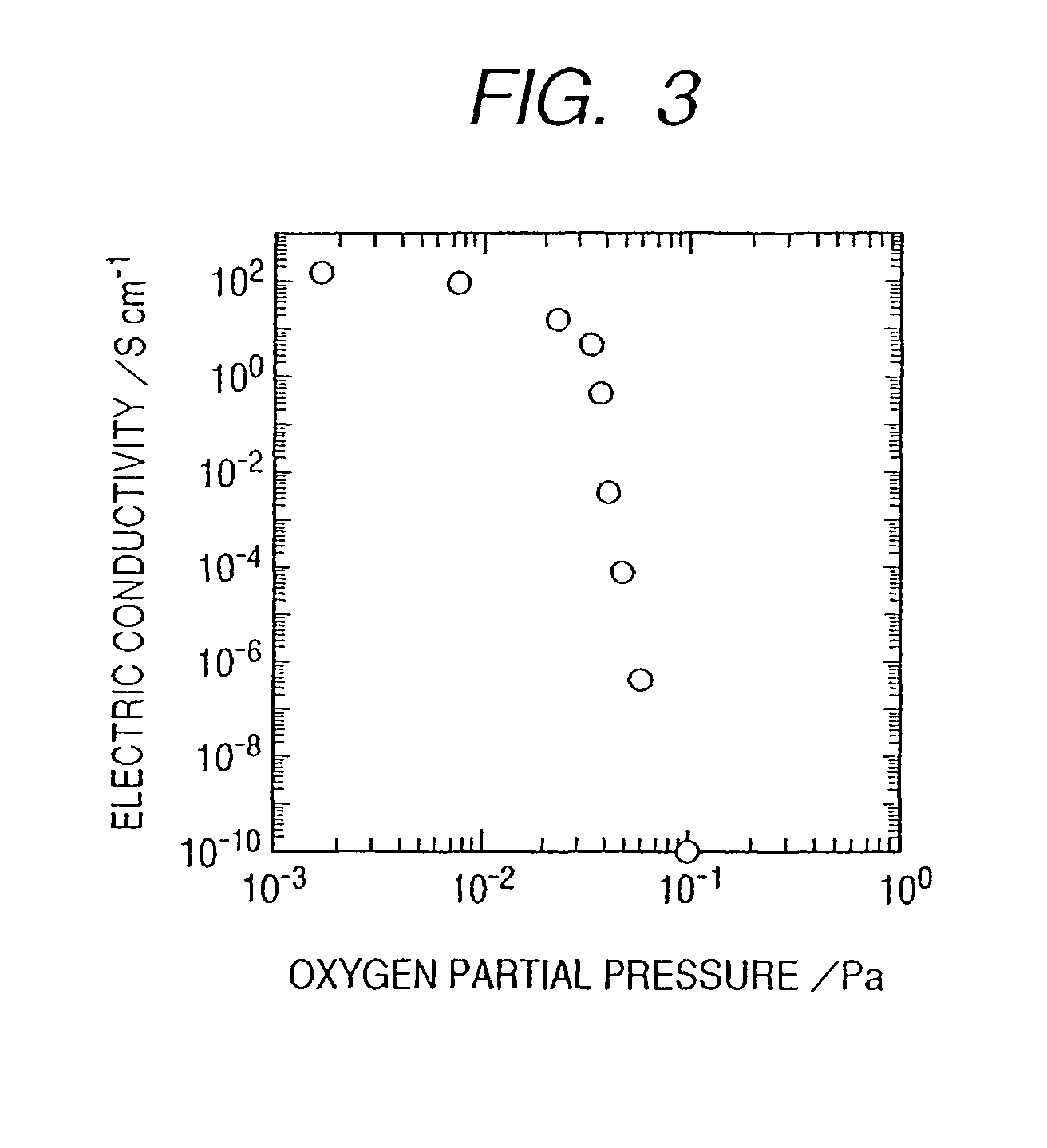

Field effect transistors and materials and methods for their manufacture

A field effect transistor in which a continuous semiconductor layer comprises:a) an organic semiconductor; and,b) an organic binder which has an inherent conductivity of less than 10−6Scm−1 and a permittivity at 1,000 Hz of less than 3.3and a process for its production comprising:coating a substrate with a liquid layer which comprises the organic semiconductor and a material capable of reacting to form the binder; and,converting the liquid layer to a solid layer comprising the semiconductor and the binder by reacting the material to form the binder.

Owner:MERCK PATENT GMBH

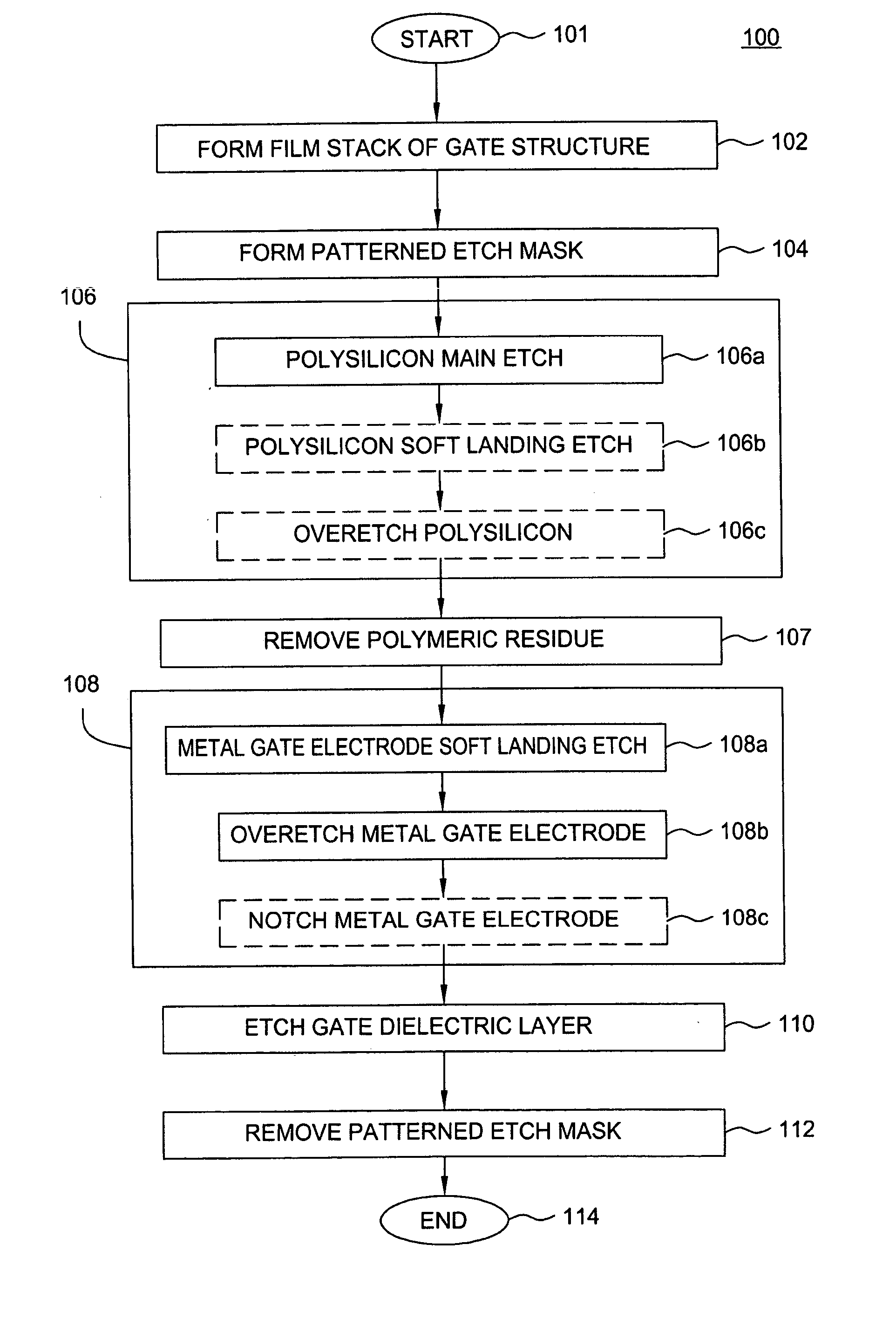

Method of fabricating a gate structure of a field effect transistor having a metal-containing gate electrode

InactiveUS20050009358A1High selectivitySemiconductor/solid-state device detailsSolid-state devicesBromineTitanium nitride

A method of etching metals and / or metal-containing compounds using a plasma comprising a bromine-containing gas. In one embodiment, the method is used during fabrication of a gate structure of a field effect transistor having a titanium nitride gate electrode, an ultra-thin (about 10 to 20 Angstroms) silicon dioxide gate dielectric, and a polysilicon upper contact. In a further embodiment, the gate electrode is selectively notched to a pre-determined width.

Owner:APPLIED MATERIALS INC

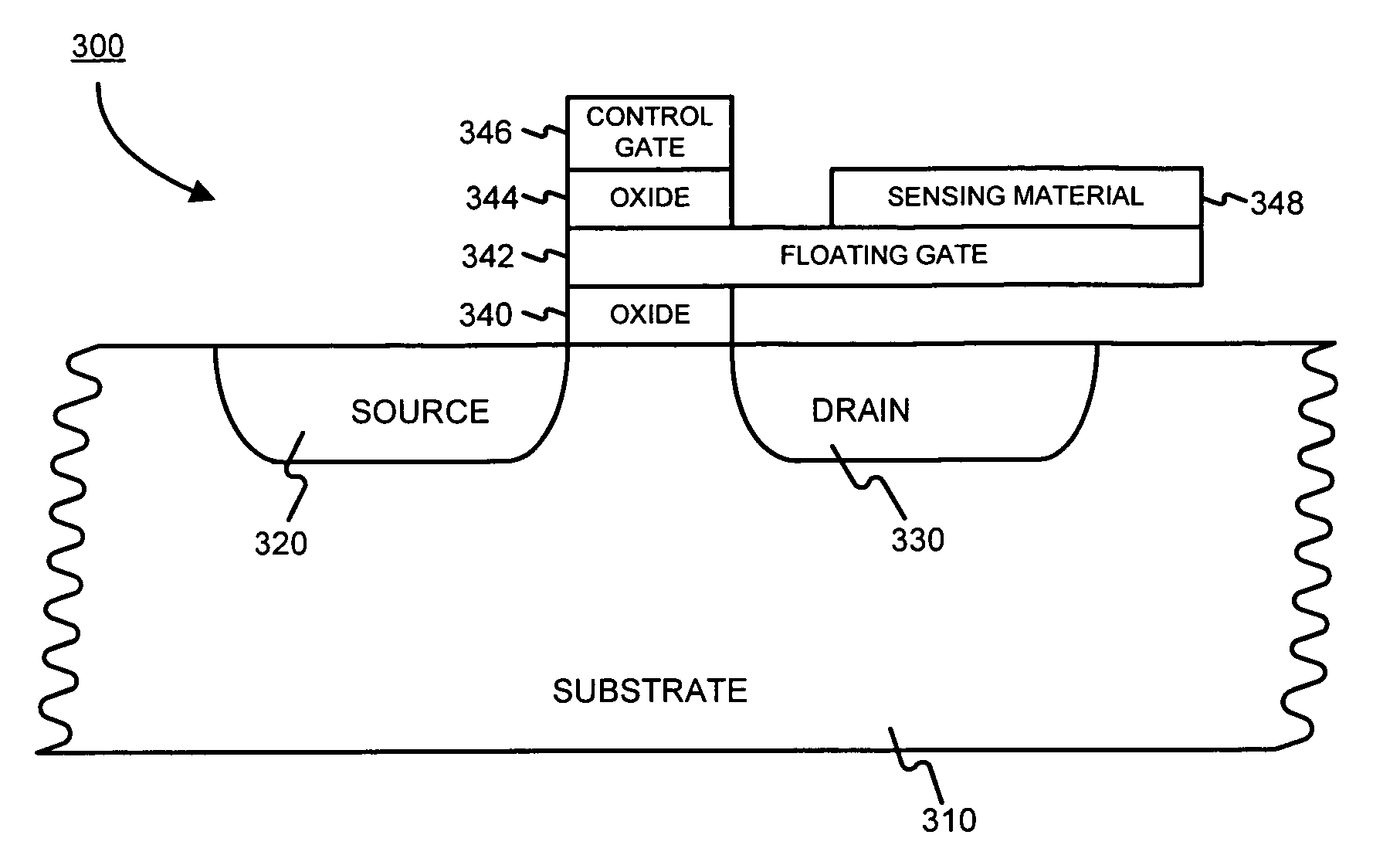

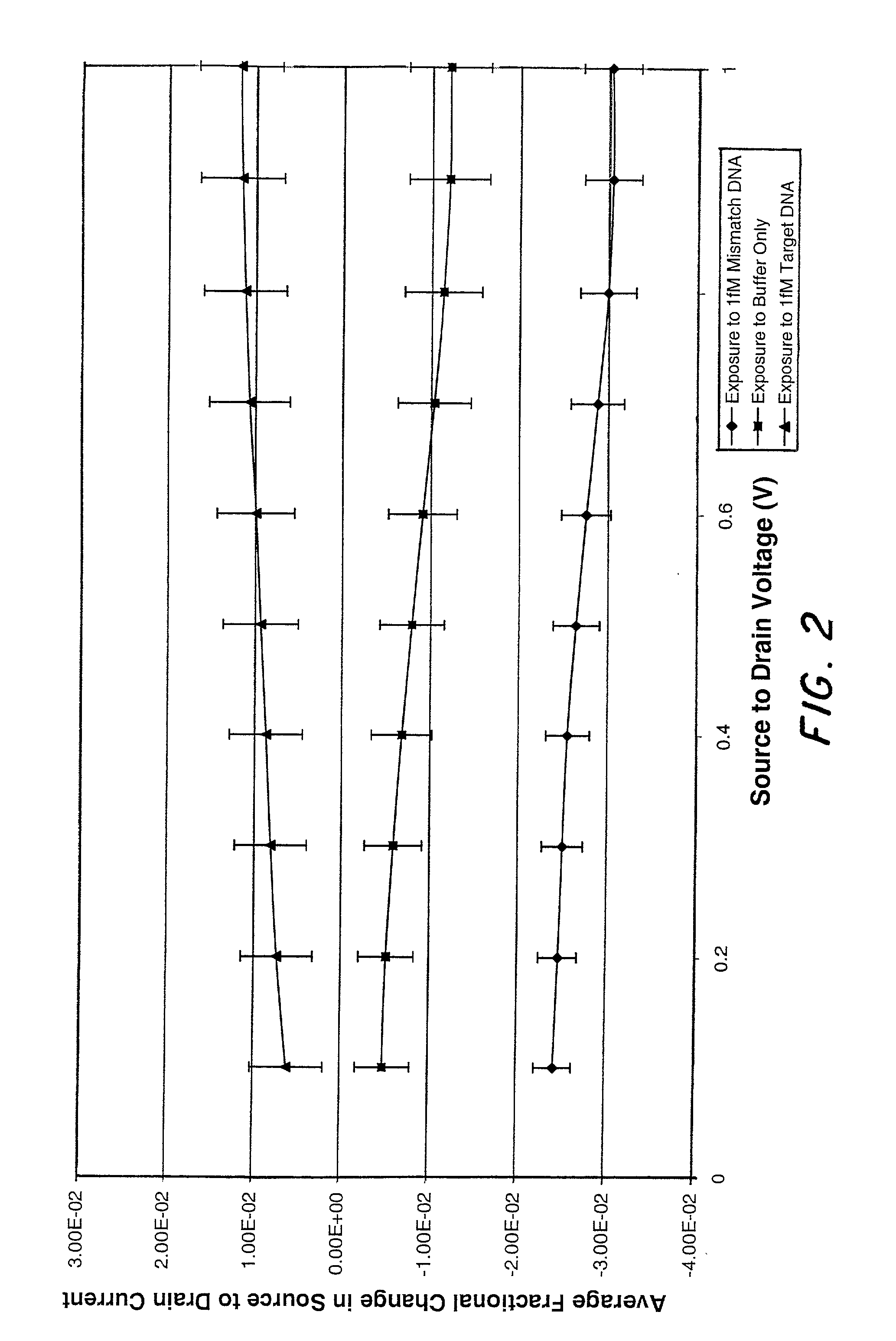

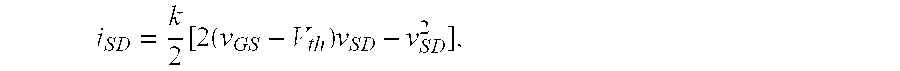

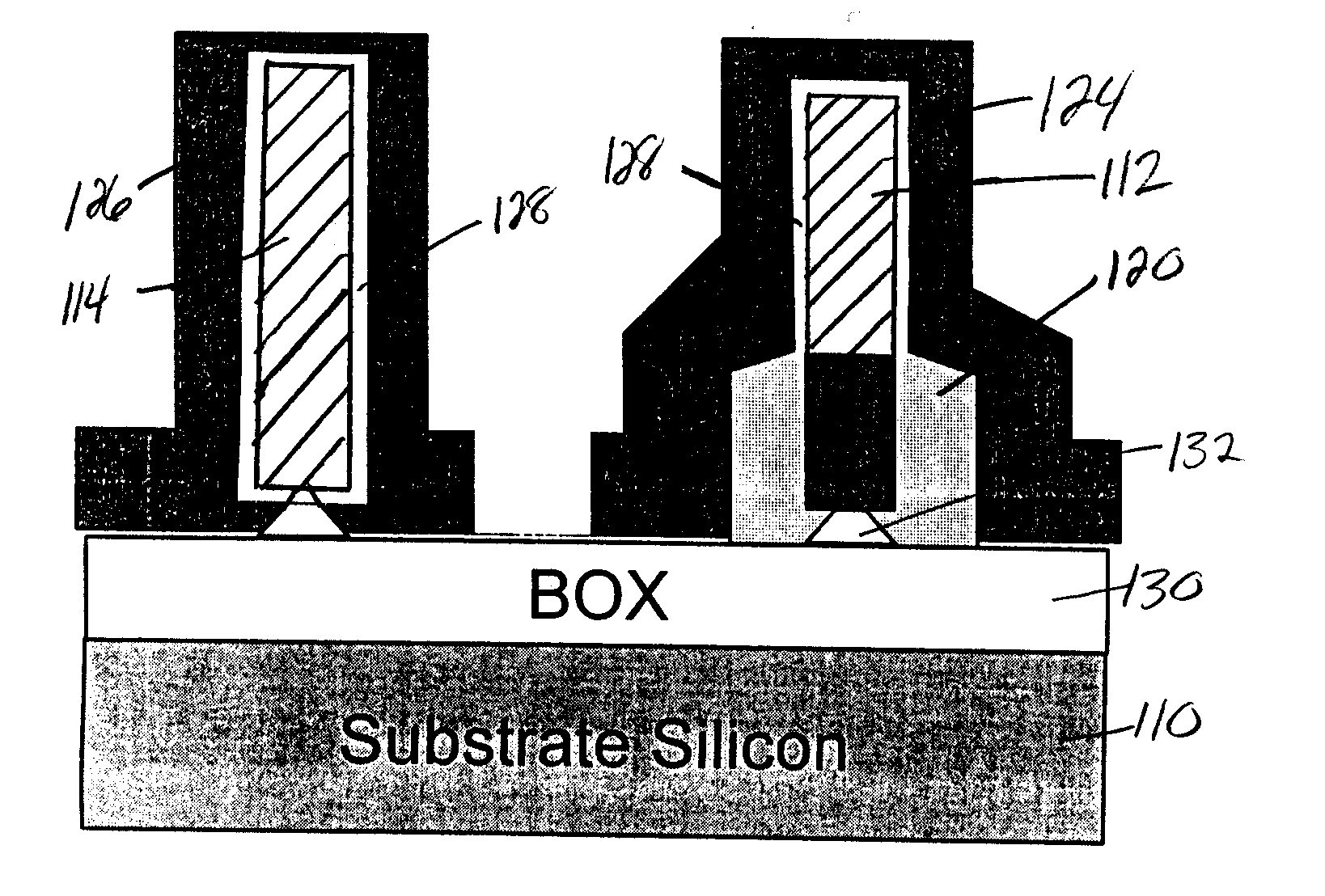

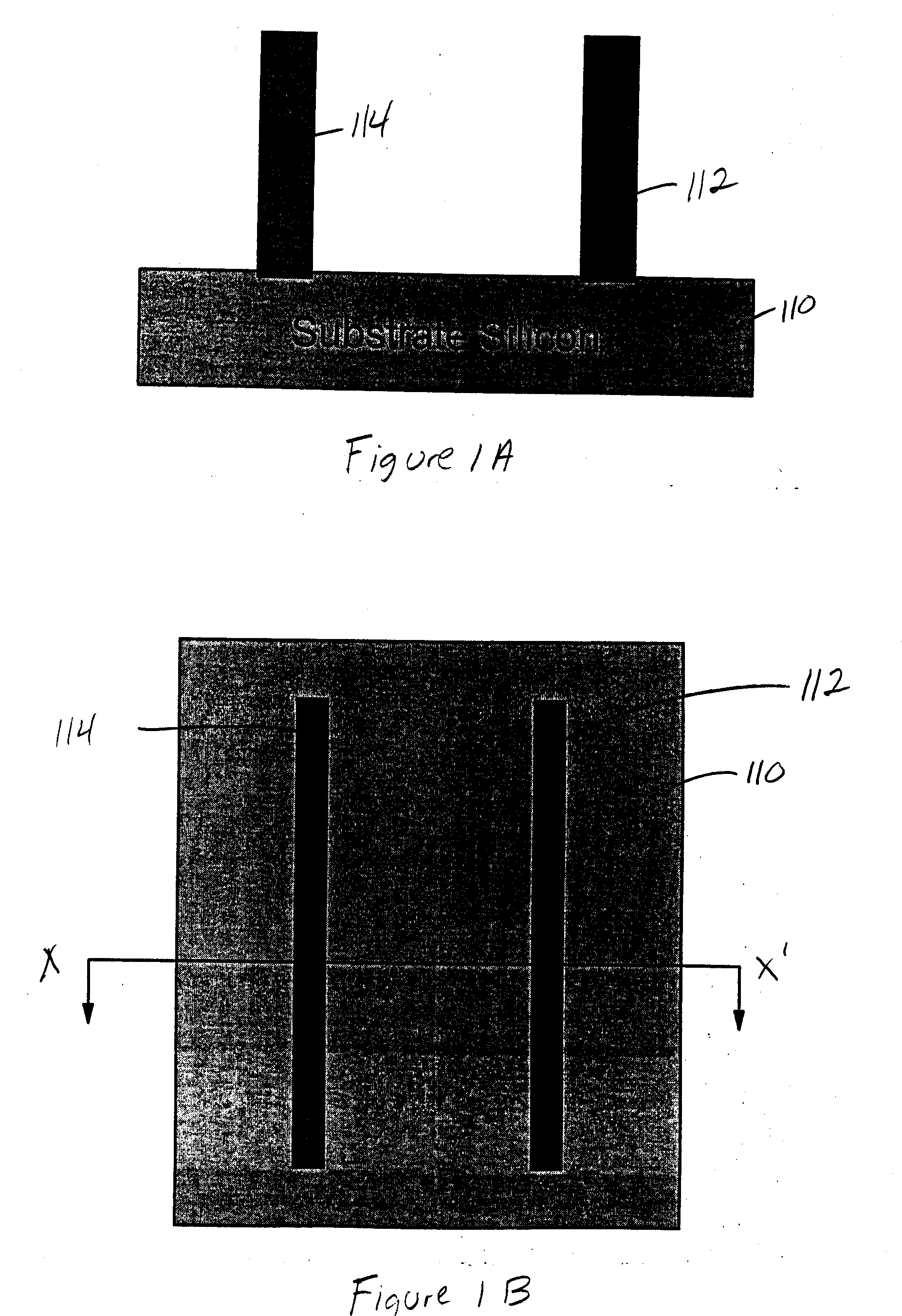

Floating gate field effect transistors for chemical and/or biological sensing

ActiveUS20050230271A1Weather/light/corrosion resistanceVolume/mass flow measurementChemical physicsEngineering

Specific ionic interactions with a sensing material that is electrically coupled with the floating gate of a floating gate-based ion sensitive field effect transistor (FGISFET) may be used to sense a target material. For example, an FGISFET can use (e.g., previously demonstrated) ionic interaction-based sensing techniques with the floating gate of floating gate field effect transistors. The floating gate can serves as a probe and an interface to convert chemical and / or biological signals to electrical signals, which can be measured by monitoring the change in the device's threshold voltage, VT.

Owner:POLYTECHNIC INSTITUTE OF NEW YORK UNIVERSITY

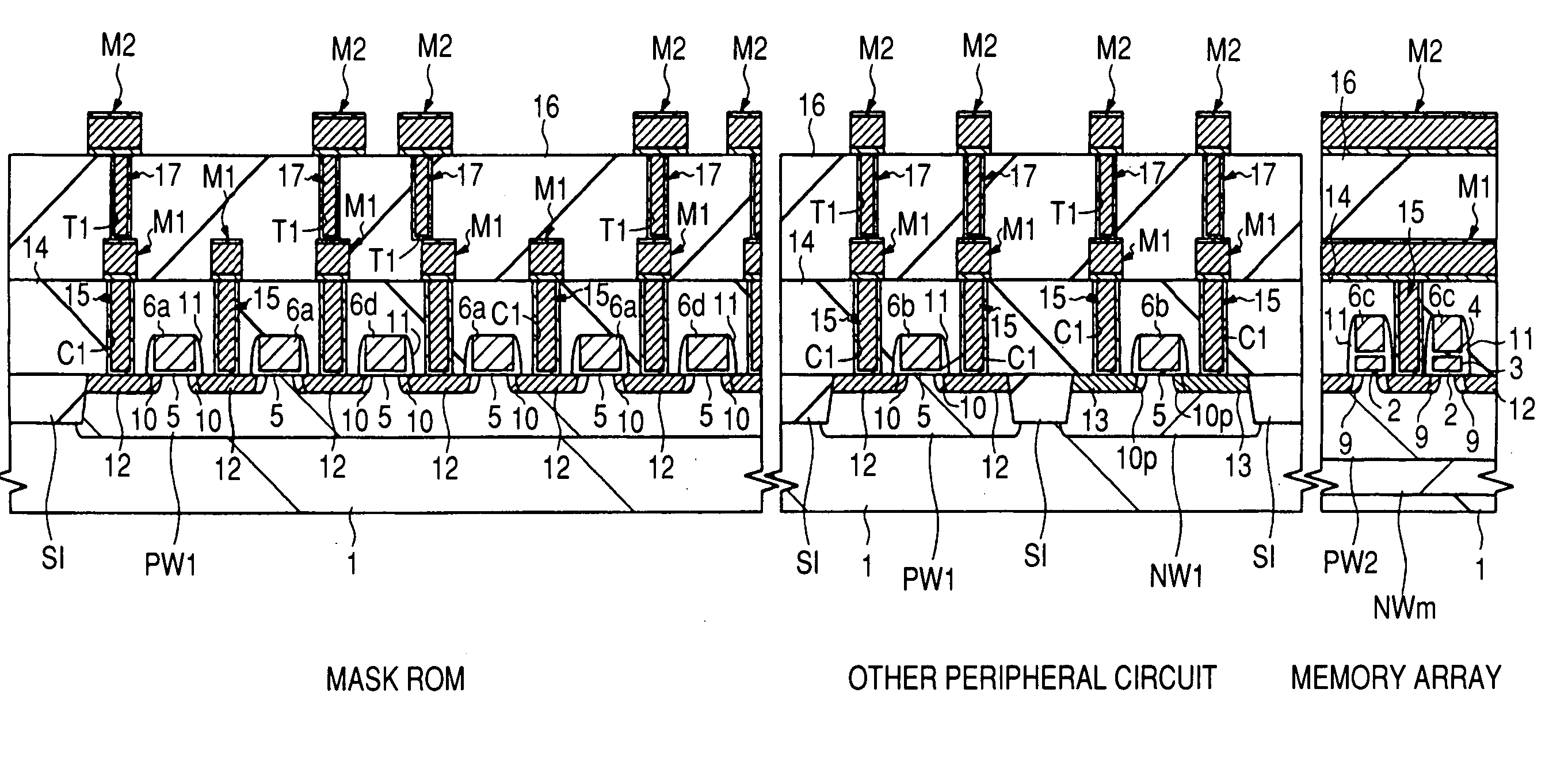

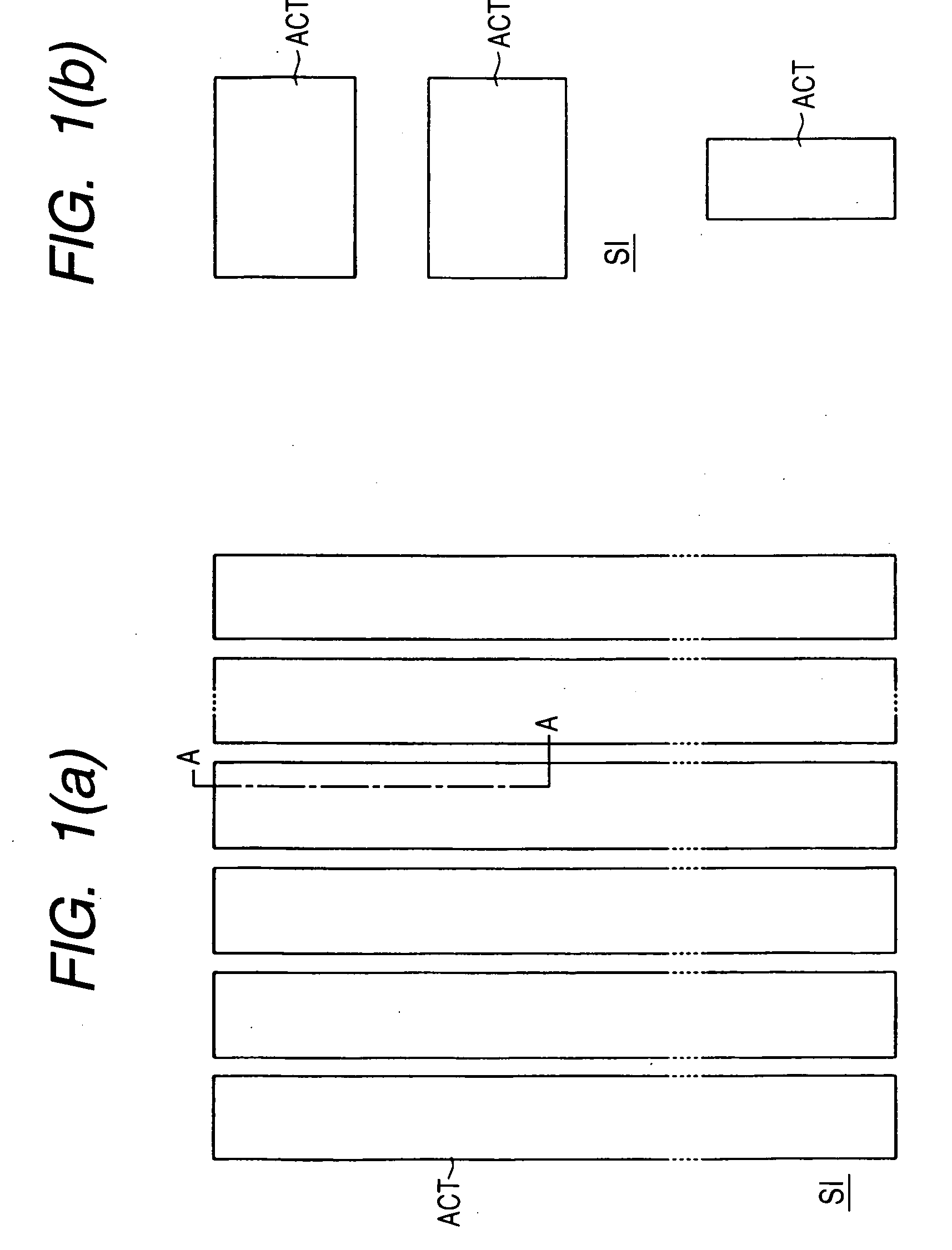

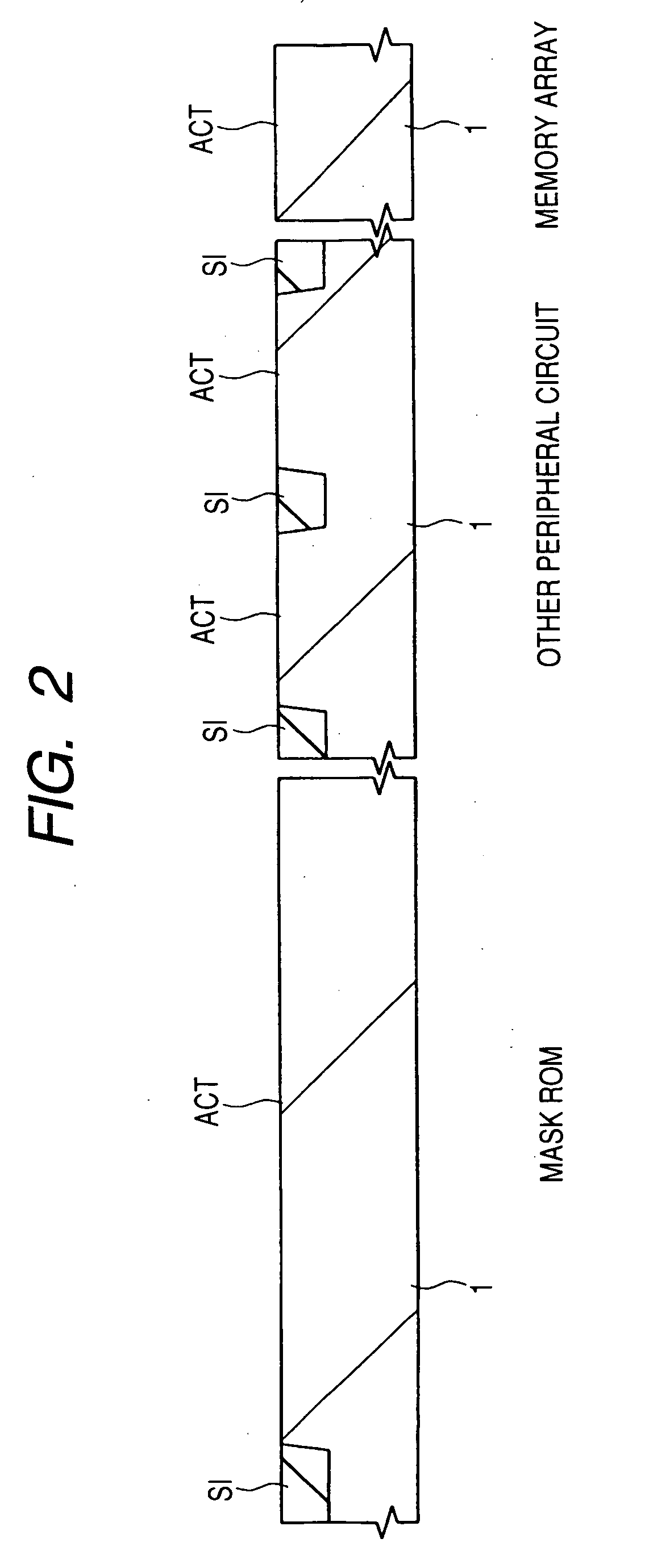

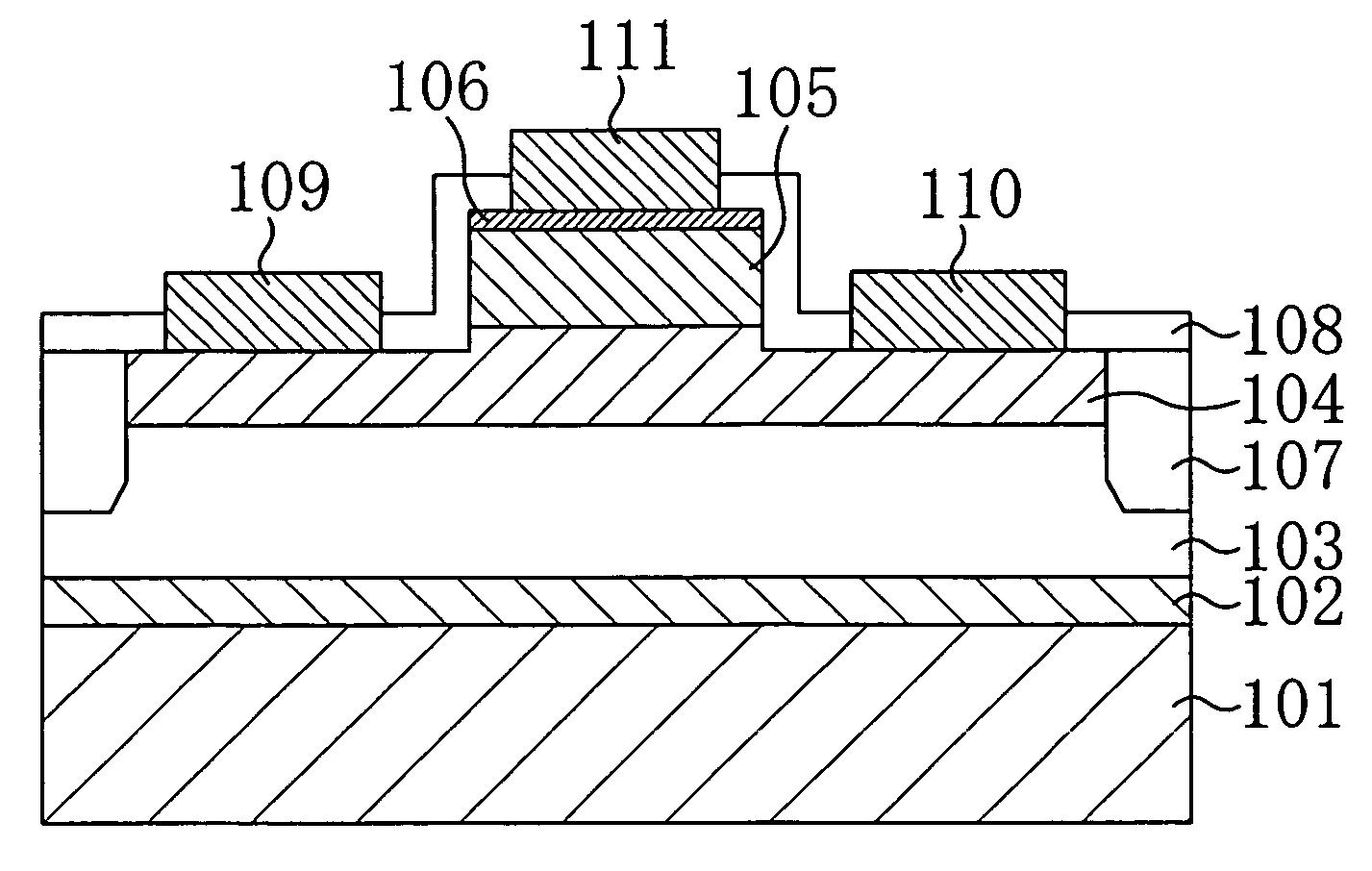

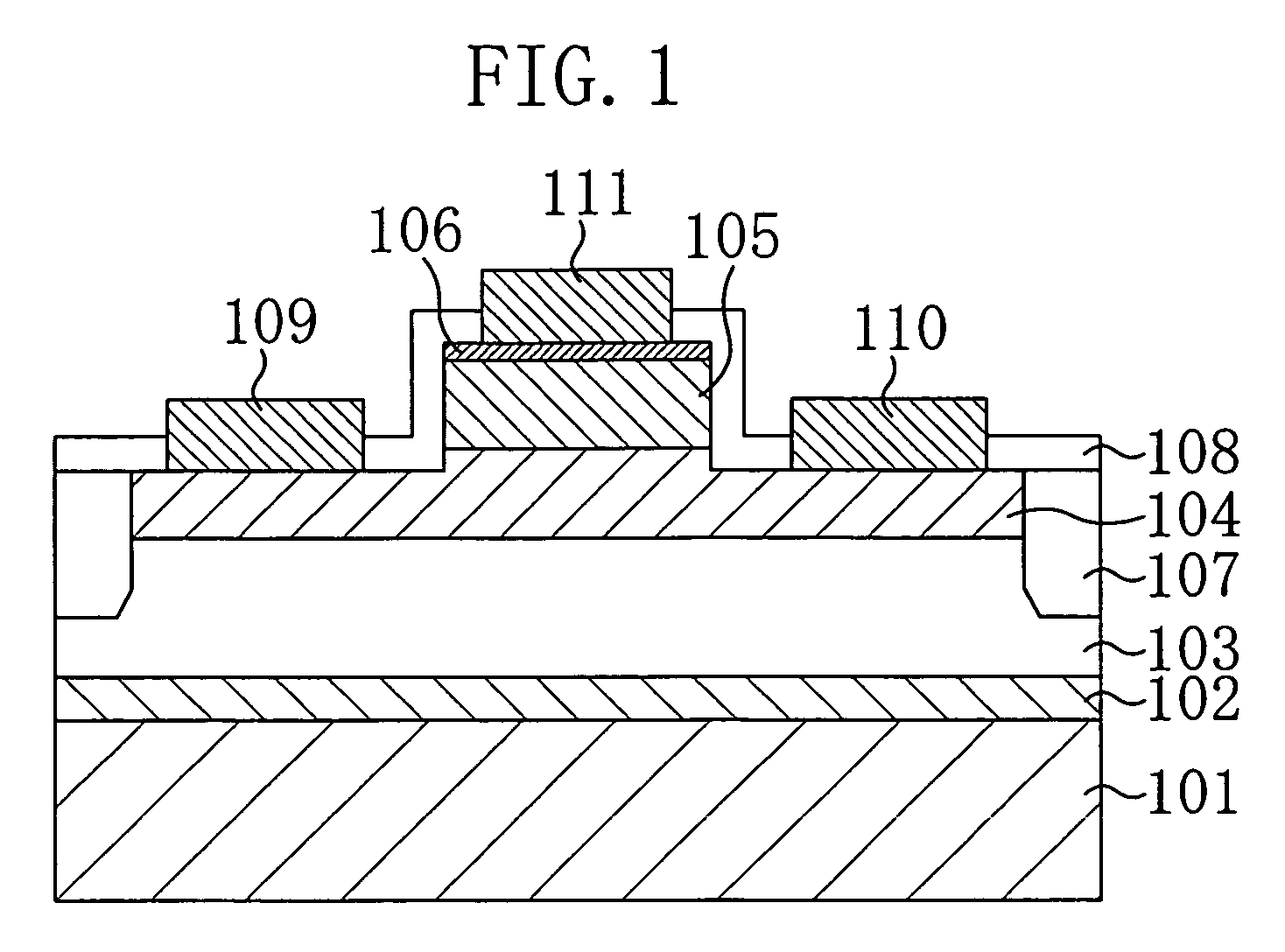

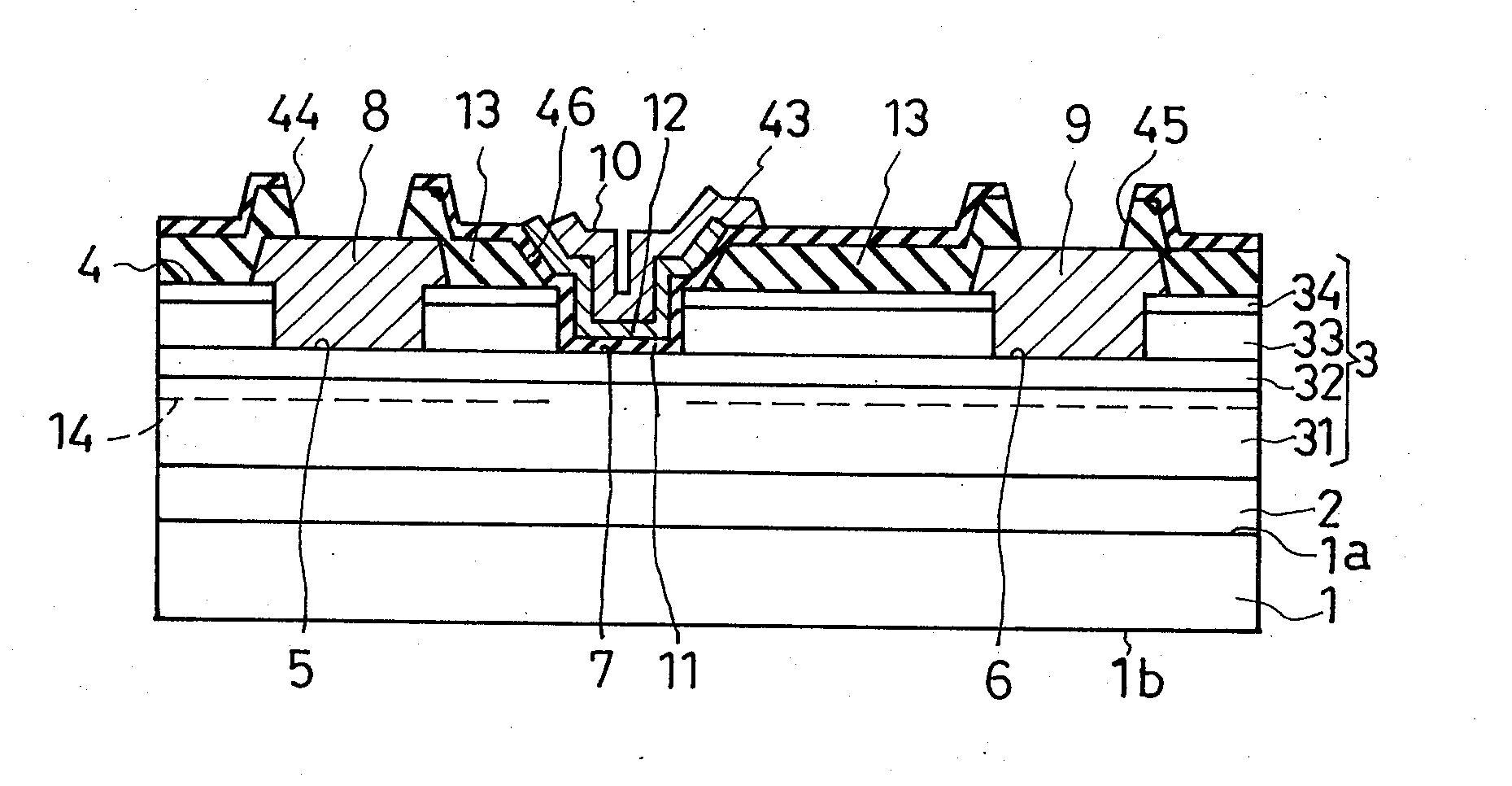

Semiconductor device and a method of manufacturing the same

InactiveUS20060125024A1Improve reliabilityGood effectSolid-state devicesSemiconductor/solid-state device manufacturingMask ROMDevice material

To improve reliability of FETs having element isolation regions for electrically isolating field effect transistors adjacent to each other in the gate length direction in a mask ROM region, the isolation regions are each constructed by field plate isolation formed simultaneously with gate electrodes of the field effect transistors. This relatively lessens a stress generated in an active region ACT sandwiched by the element isolation regions even if the isolation width of each element isolation region is made relatively small, specifically, less than 0.3 μm. It is therefore possible to relax or prevent the generation of crystal defects resulting from the stress, thereby reducing occurrence of an undesired leak current between the source and drain of each field effect transistor.

Owner:RENESAS TECH CORP

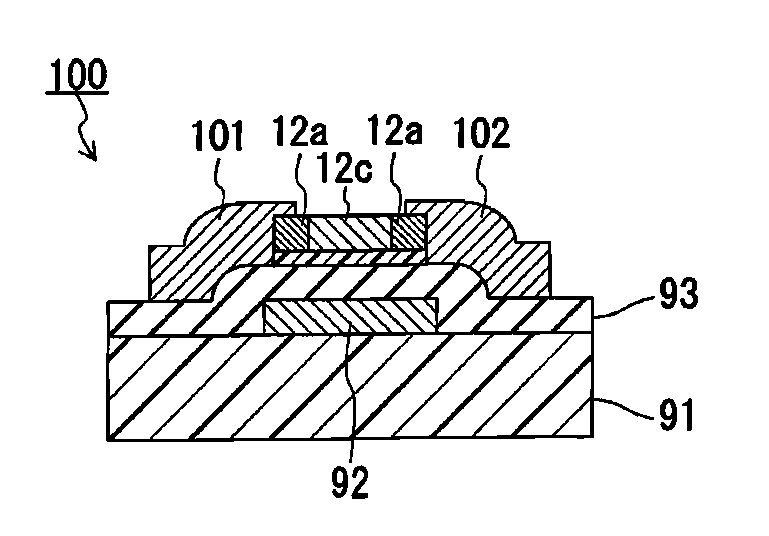

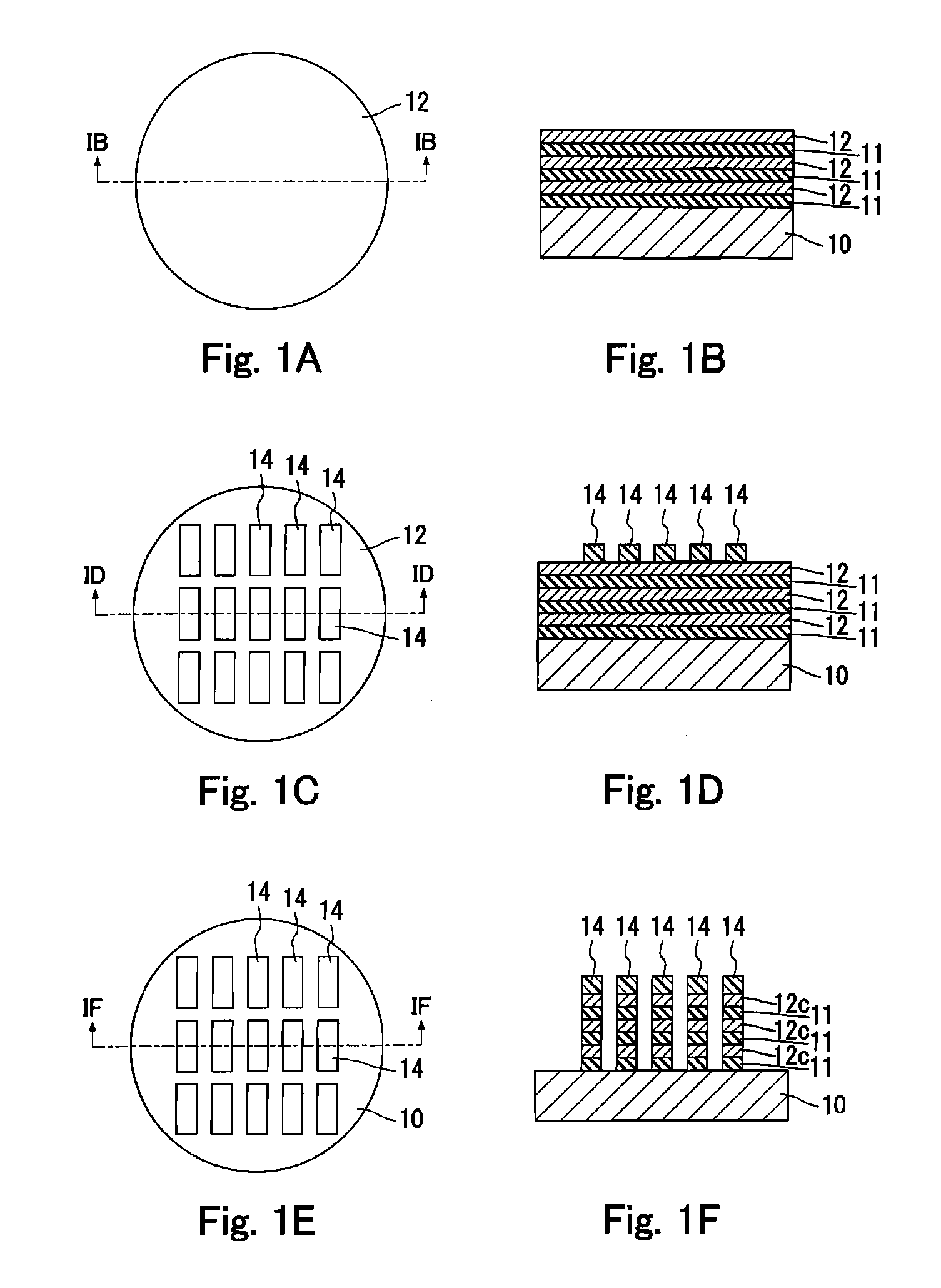

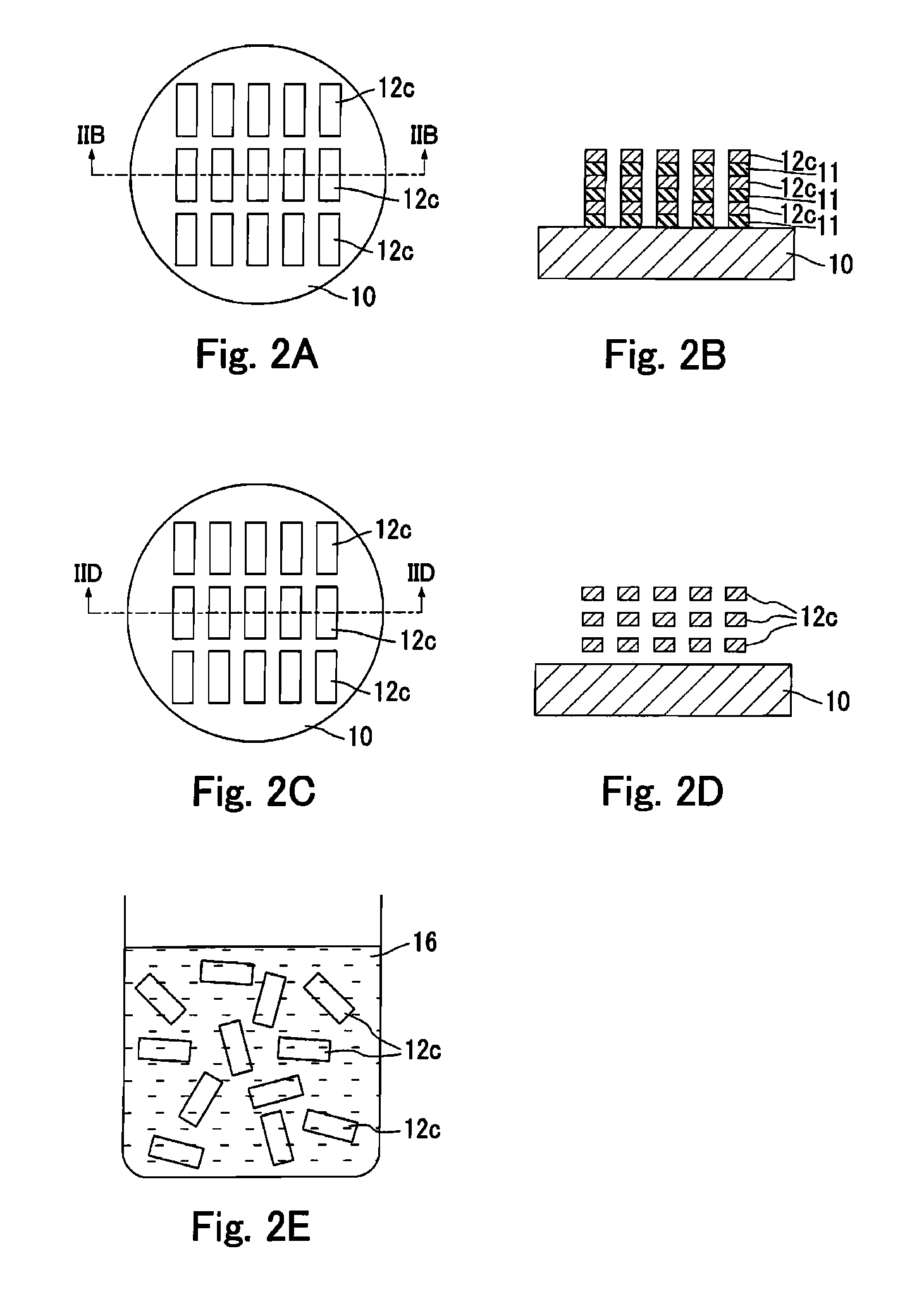

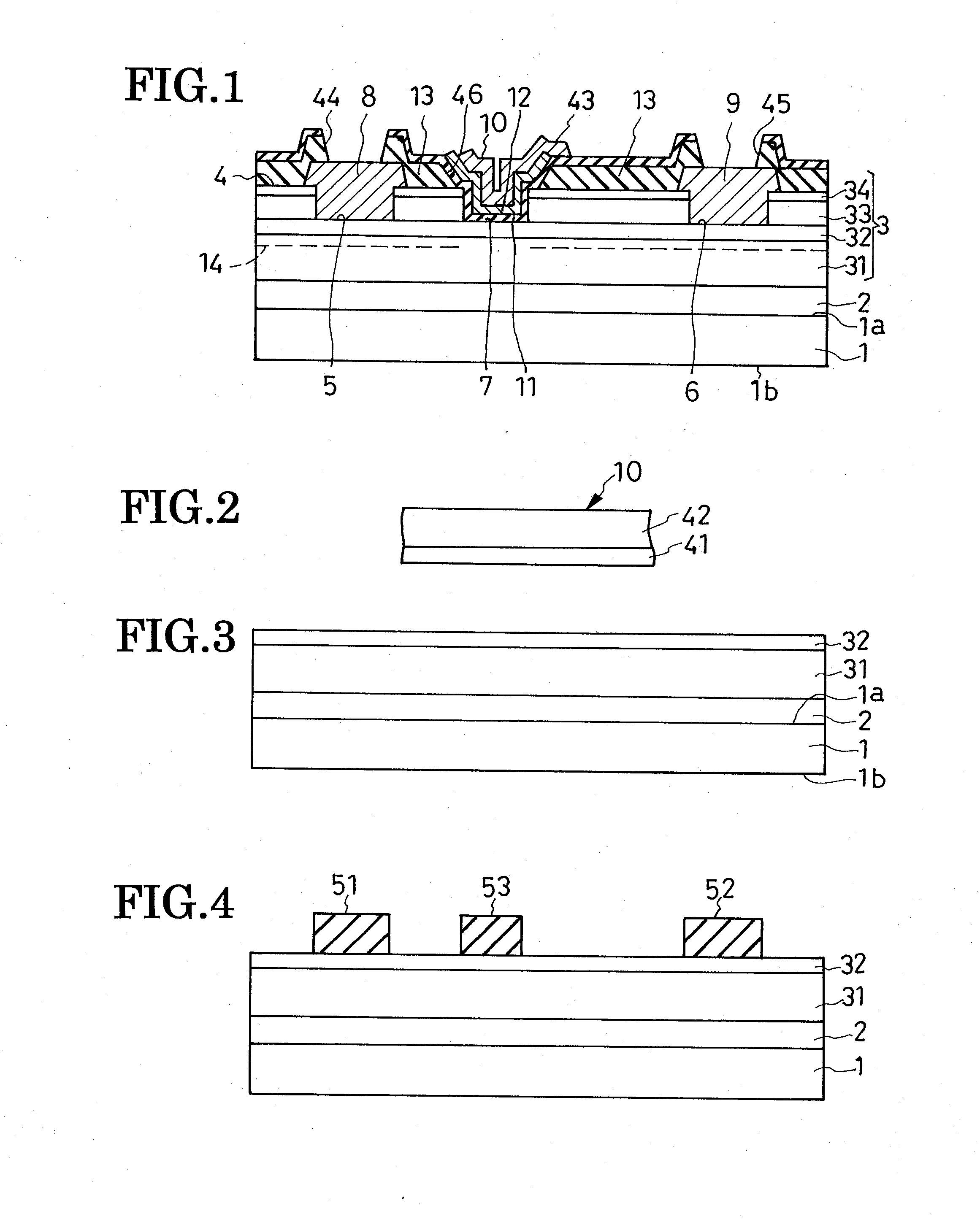

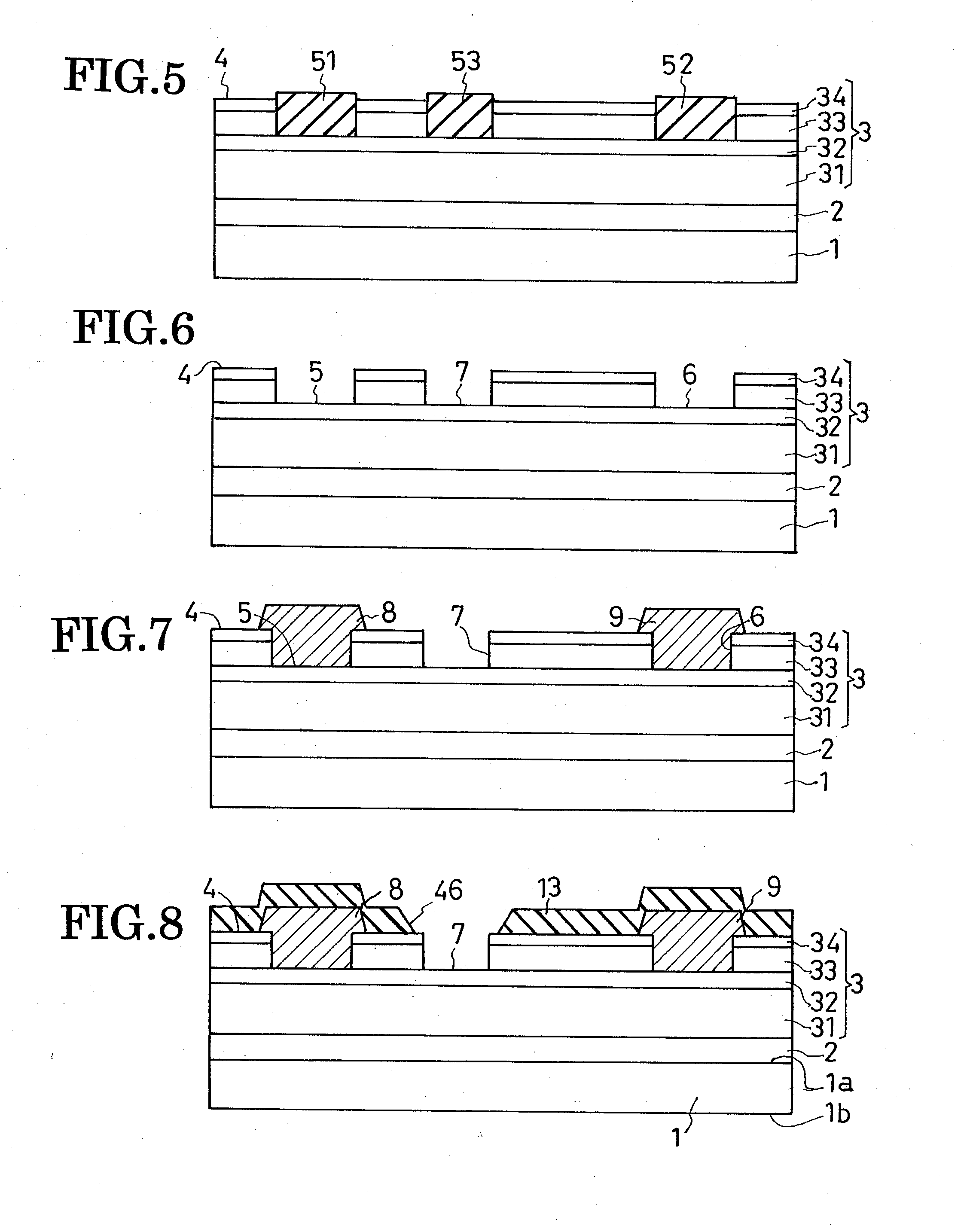

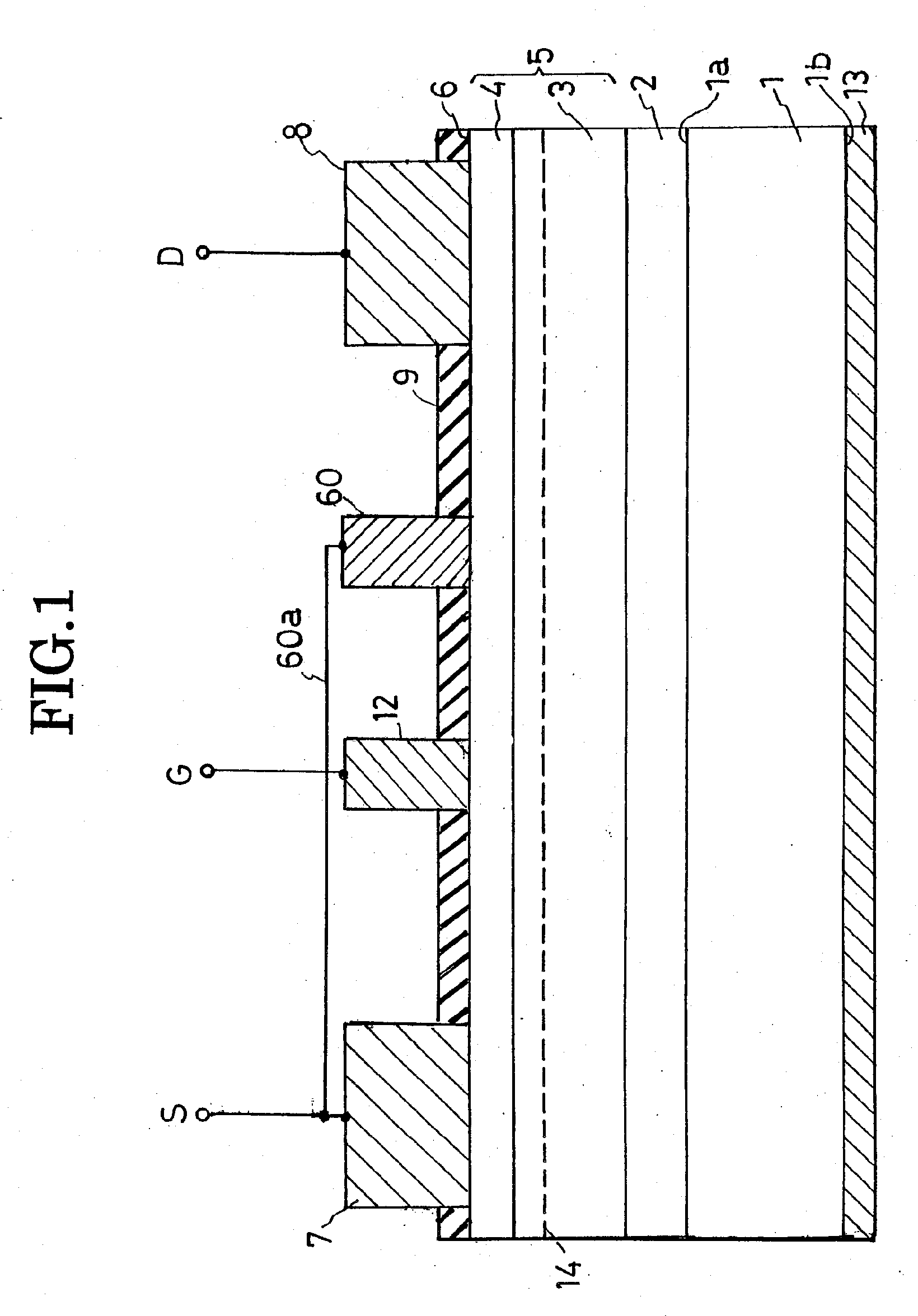

Method for producing semiconductor chip, and field effect transistor and method for manufacturing same

InactiveUS20100224915A1Low costEasy to changeSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor chipEngineering

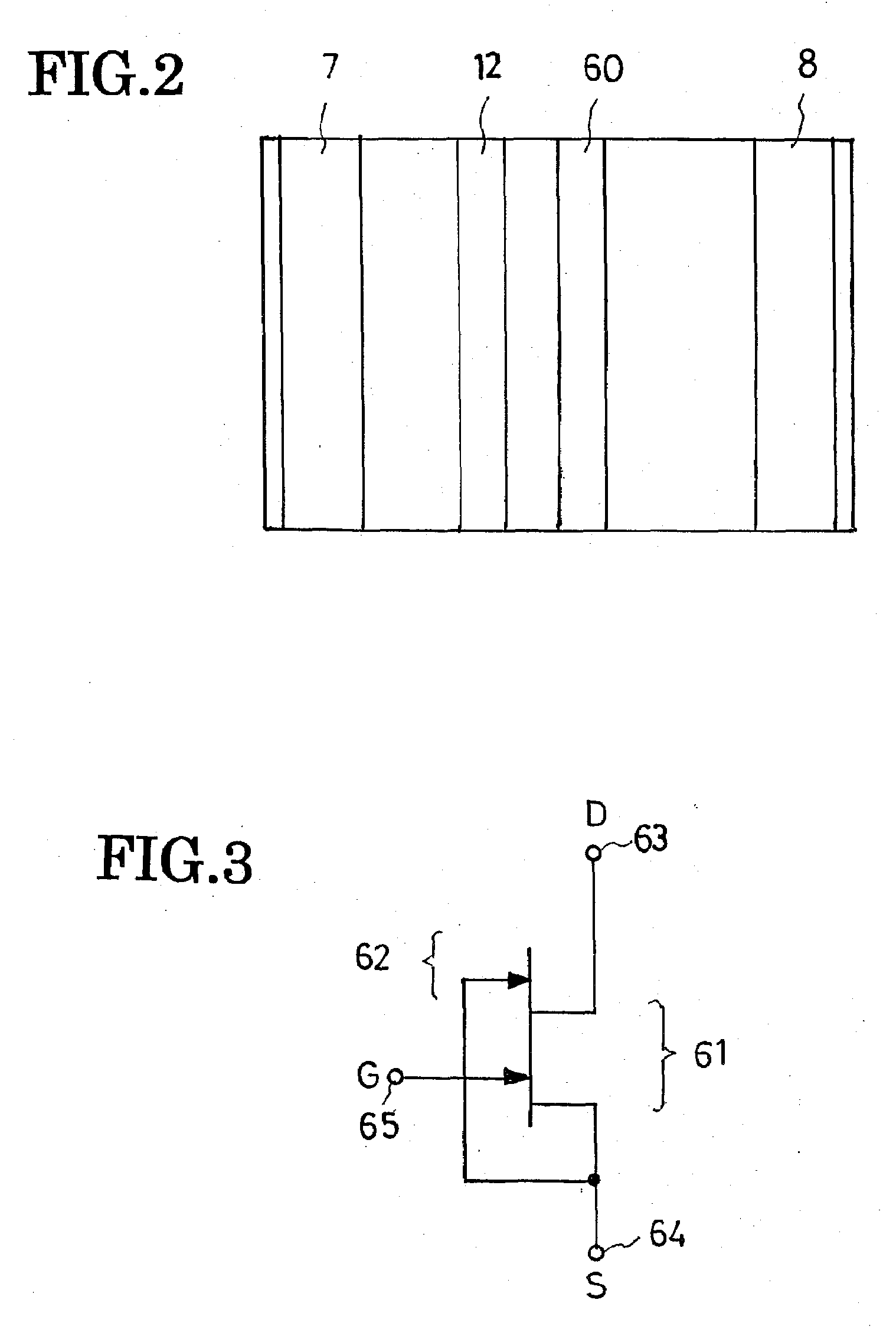

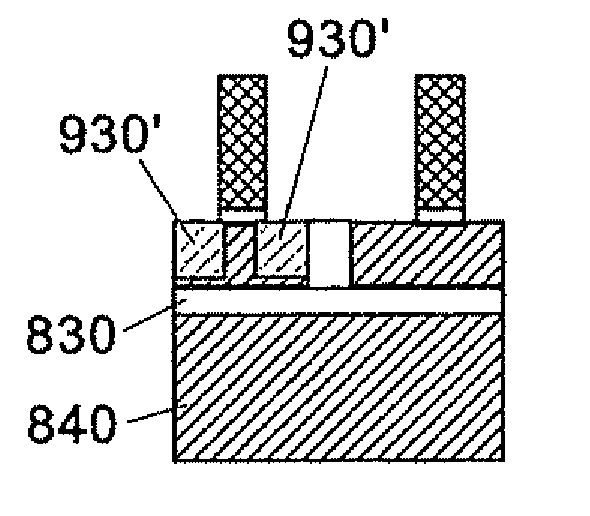

According to a method of the present invention for manufacturing a semiconductor piece, at least two semiconductor layers (12) are first formed on a substrate (10) by stacking a sacrificial layer (11) and the semiconductor layer (12) on the substrate (10) in this order and repeating this stacking. Next, the semiconductor layers (12) are divided into pieces by etching part of the sacrificial layers (11) and part of the semiconductor layers (12). Then, the pieces are separated from the substrate by removing the sacrificial layers (11).

Owner:JOLED INC

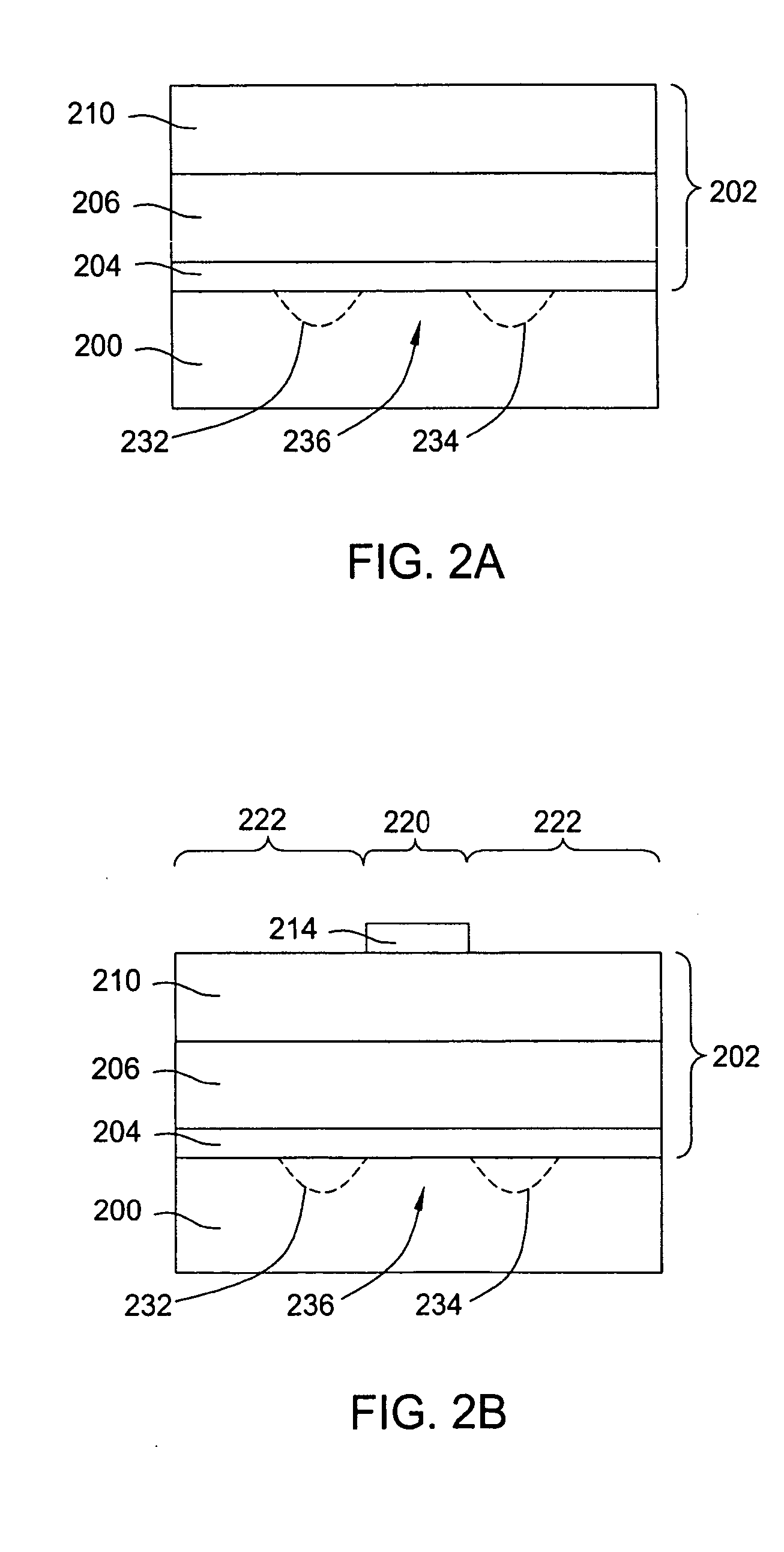

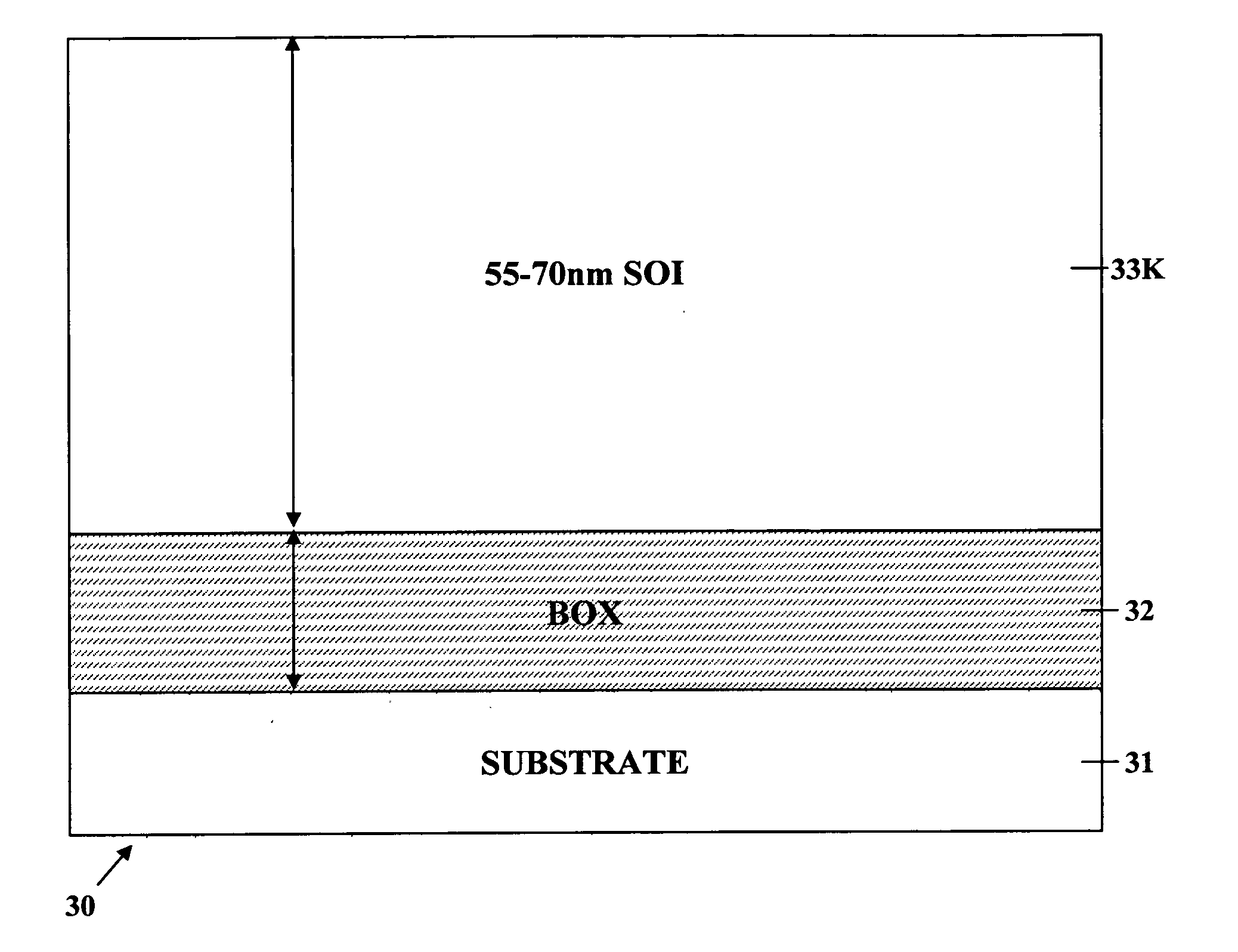

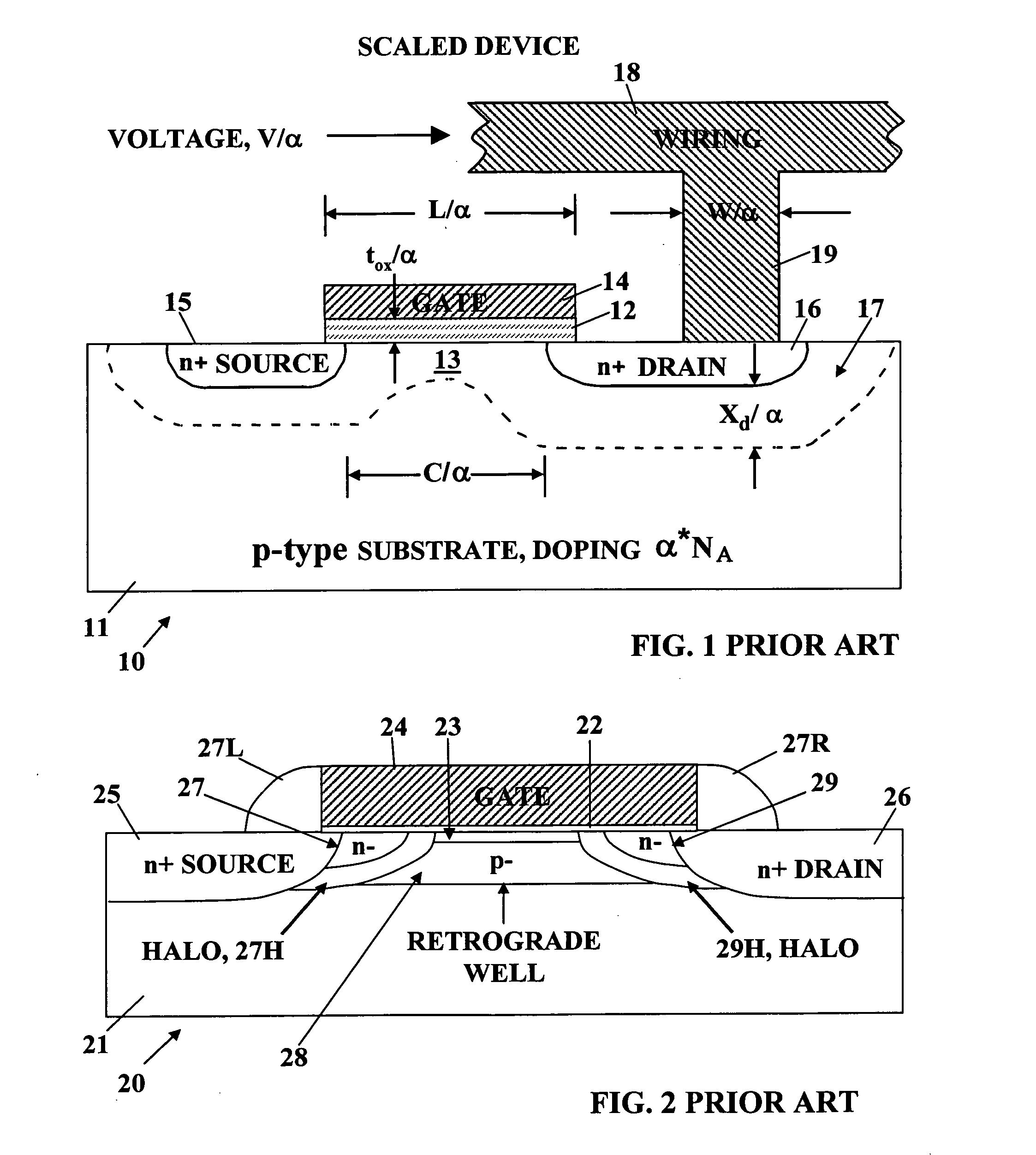

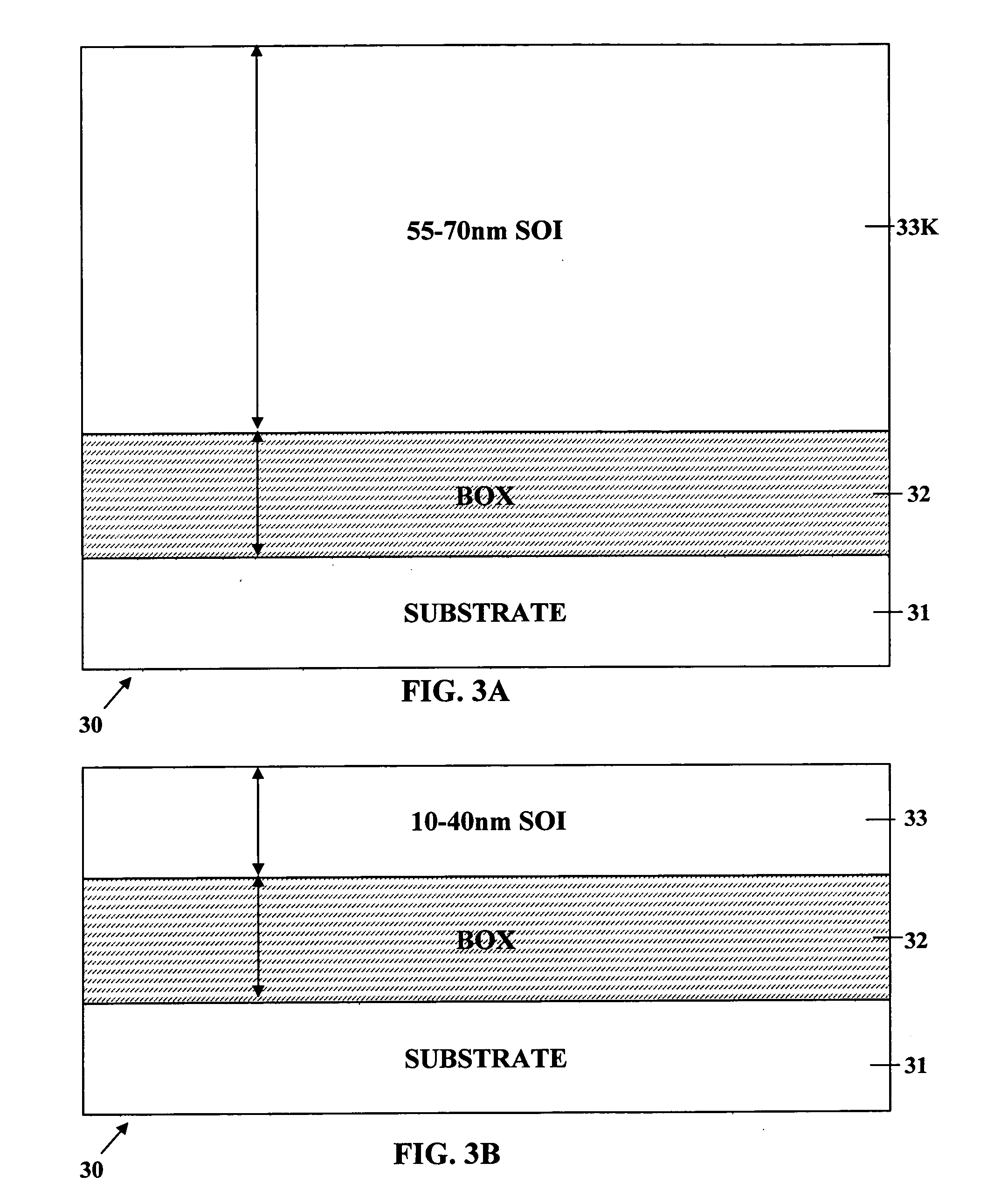

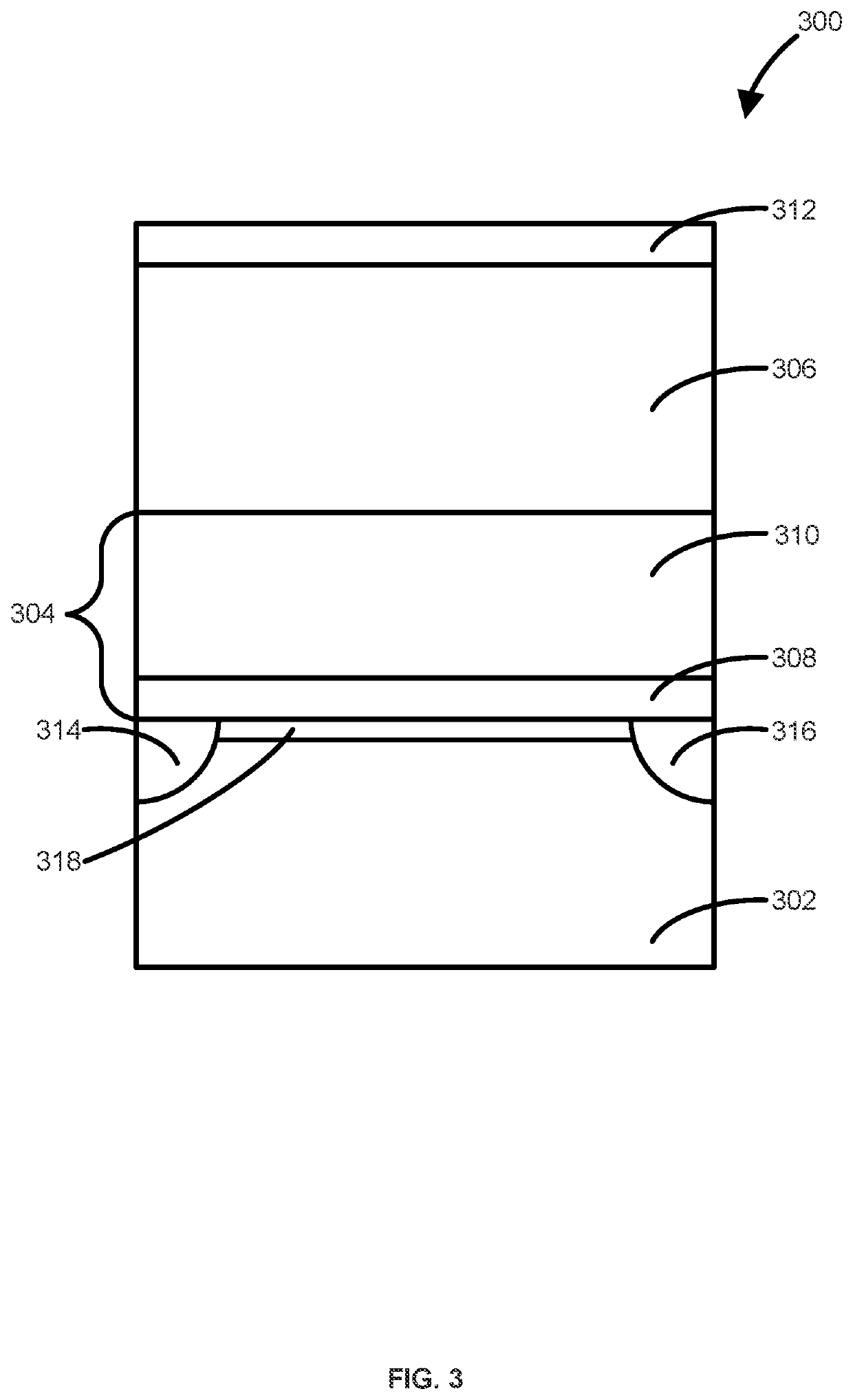

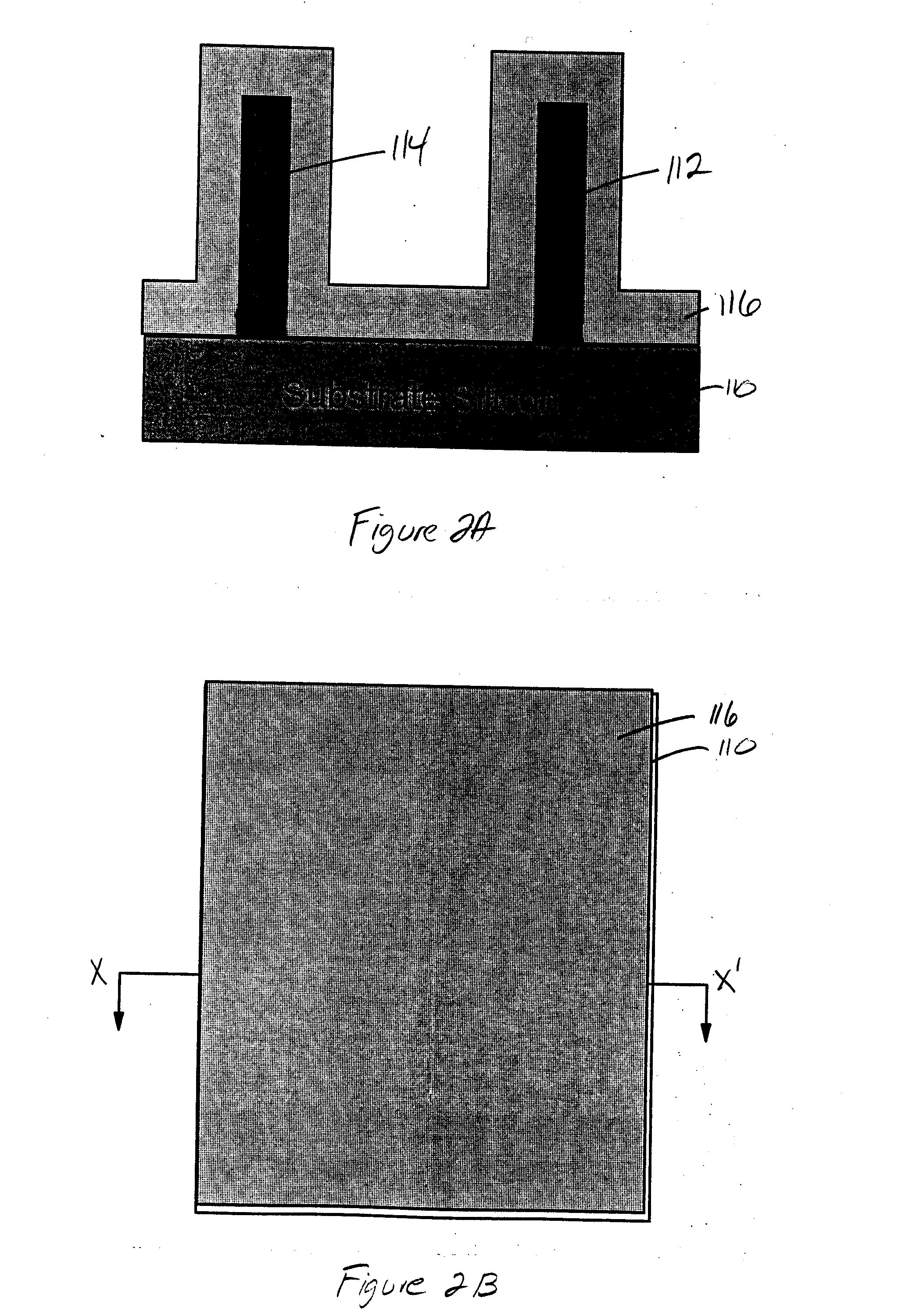

Ultra-thin body super-steep retrograde well (SSRW) FET devices

ActiveUS20060022270A1Minimize space-charge related fluctuationReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

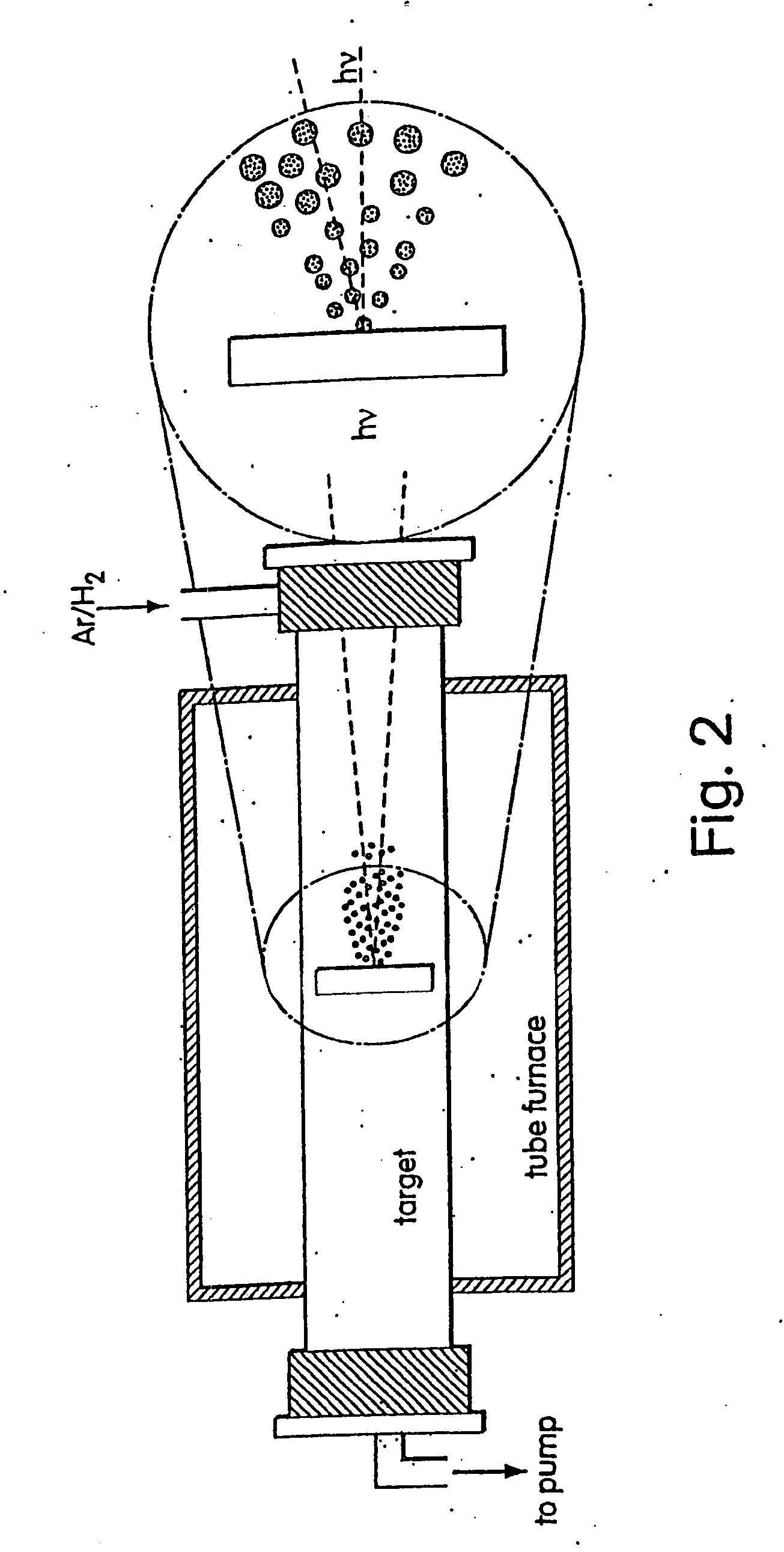

Nanoscale wires and related devices

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Field-effect transistor and method for fabricating the same

ActiveUS20060273347A1Small gateHigh currentSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactOptoelectronics

An AlN buffer layer, an undoped GaN layer, an undoped AlGaN layer, a p-type GaN layer and a heavily doped p-type GaN layer are formed in this order. A gate electrode forms an Ohmic contact with the heavily doped p-type GaN layer. A source electrode and a drain electrode are provided on the undoped AlGaN layer. A pn junction is formed in a gate region by a two dimensional electron gas generated at an interface between the undoped AlGaN layer and the undoped GaN layer and the p-type GaN layer, so that a gate voltage can be increased.

Owner:PANASONIC CORP

Method for forming self-aligned contact in semiconductor device

ActiveUS20050239282A1Prevent short-circuitingRule out the possibilitySemiconductor/solid-state device manufacturingDevice materialEngineering

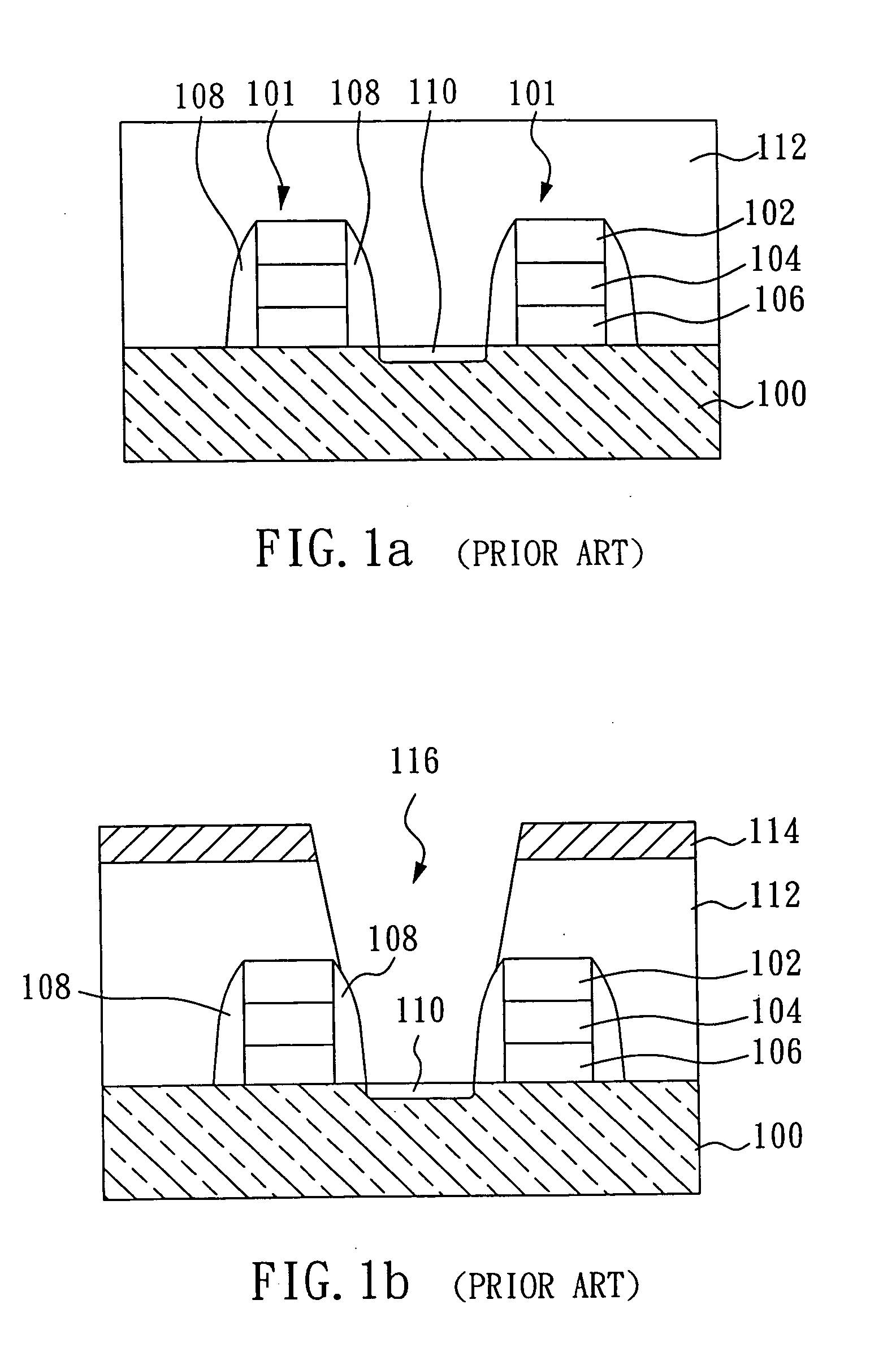

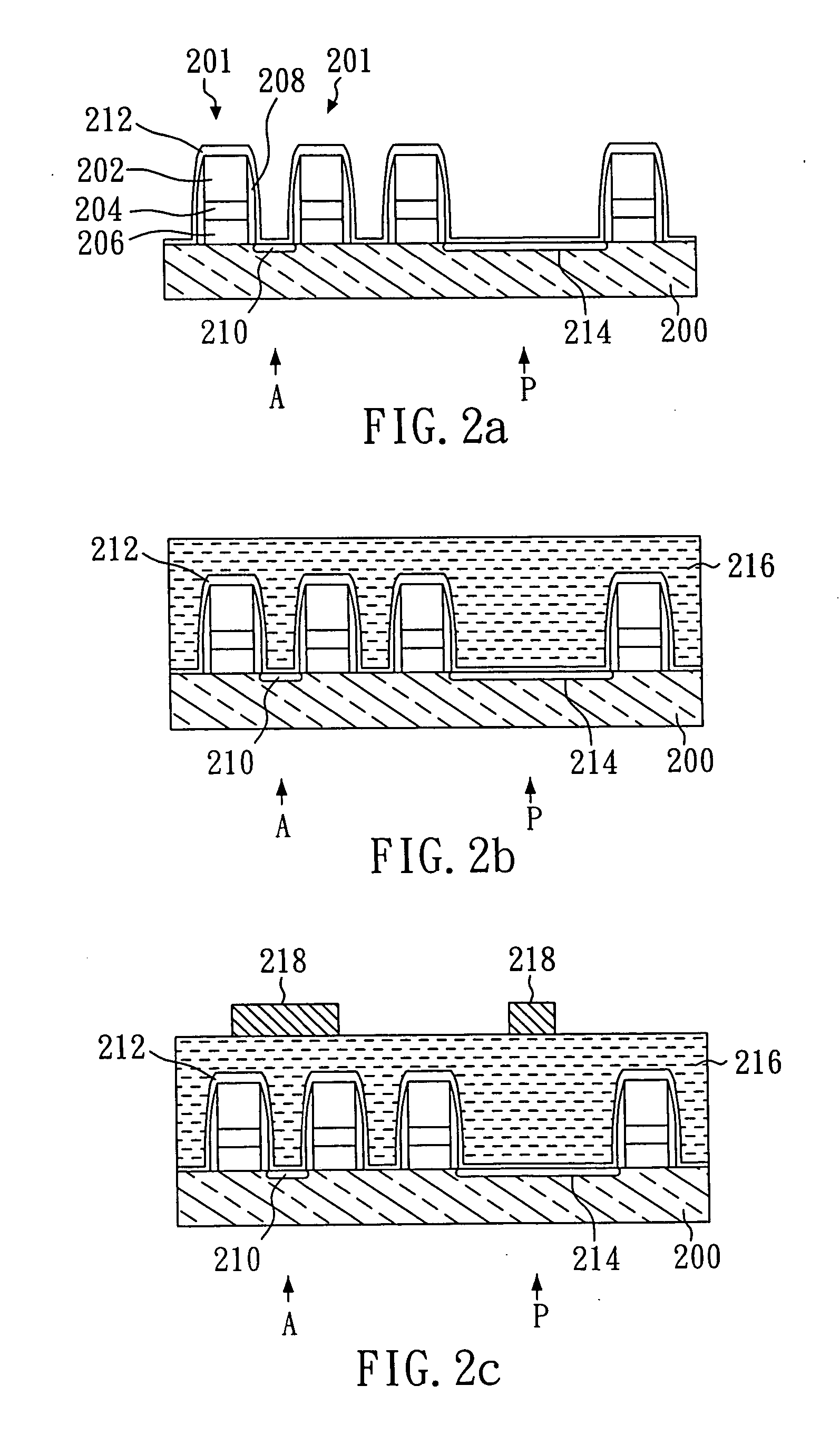

A method for forming a self-aligned contact on a semiconductor substrate provided with a plurality of field-effect transistors. The method comprises the steps of forming a first insulating layer comprising a nitride along a profile of a gate structure and a junction region, forming a temporary layer comprising a doped oxide on the first insulating layer, removing a portion of the temporary layer by performing a selective etch of the oxide with a mask while leaving a plug portion of the temporary layer over the junction region, forming a second insulating layer comprising an undoped oxide in a region where the portion of the temporary layer is removed, removing the plug portion by performing a selective etch of the undoped oxide to form a contact hole, removing a portion of the first insulating layer at a bottom of the contact hole, and forming a conductive contact in the contact hole.

Owner:NAN YA TECH

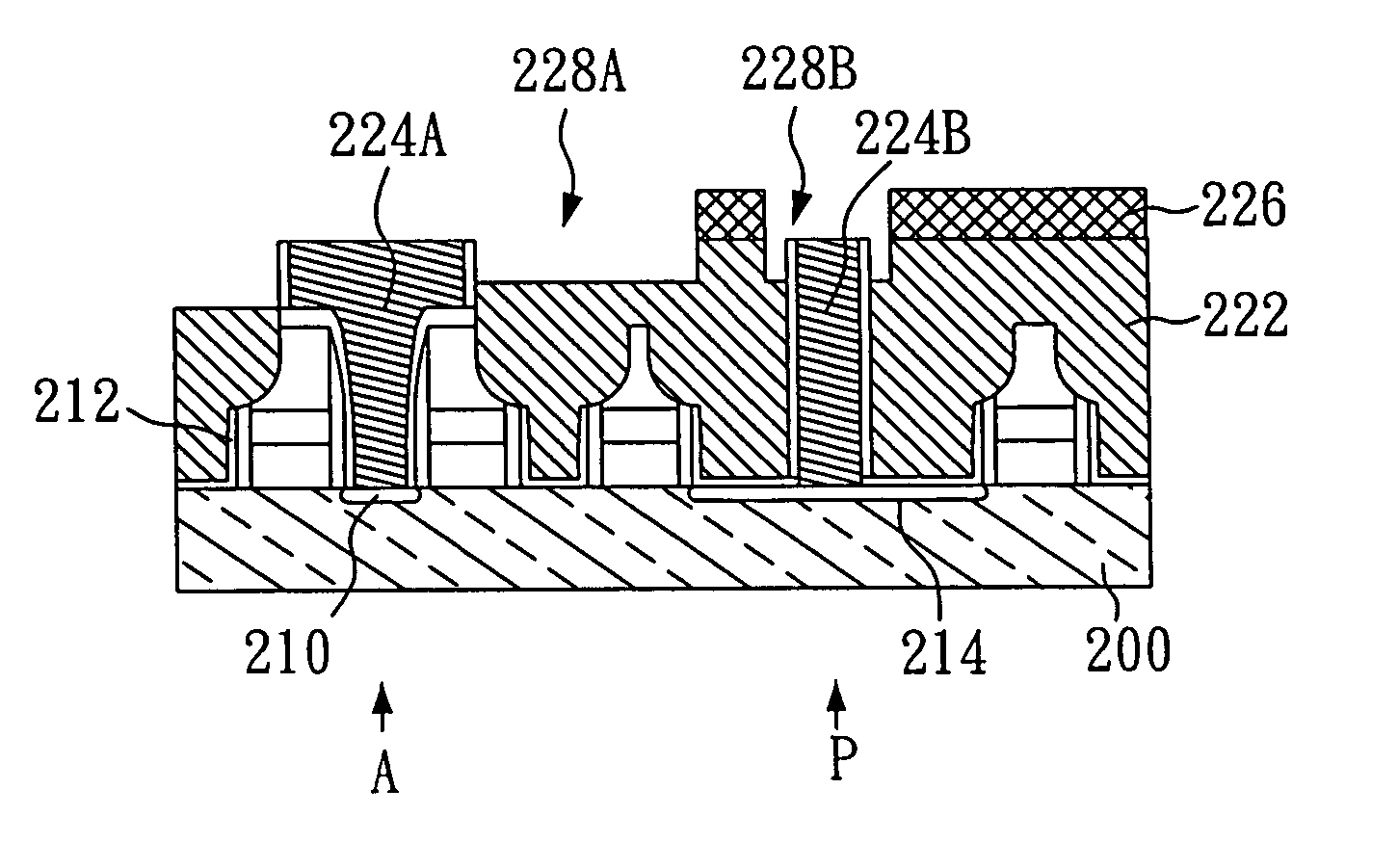

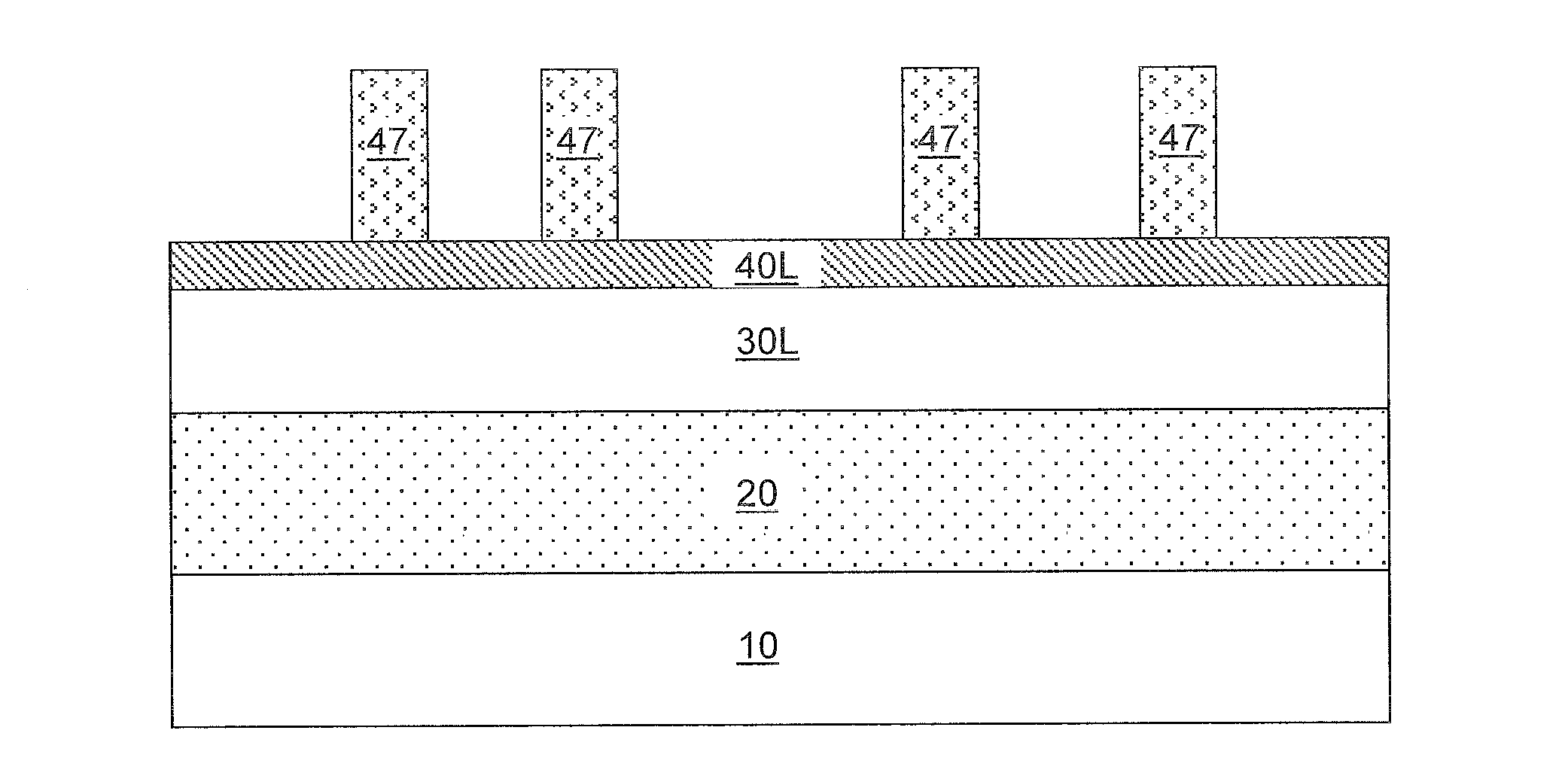

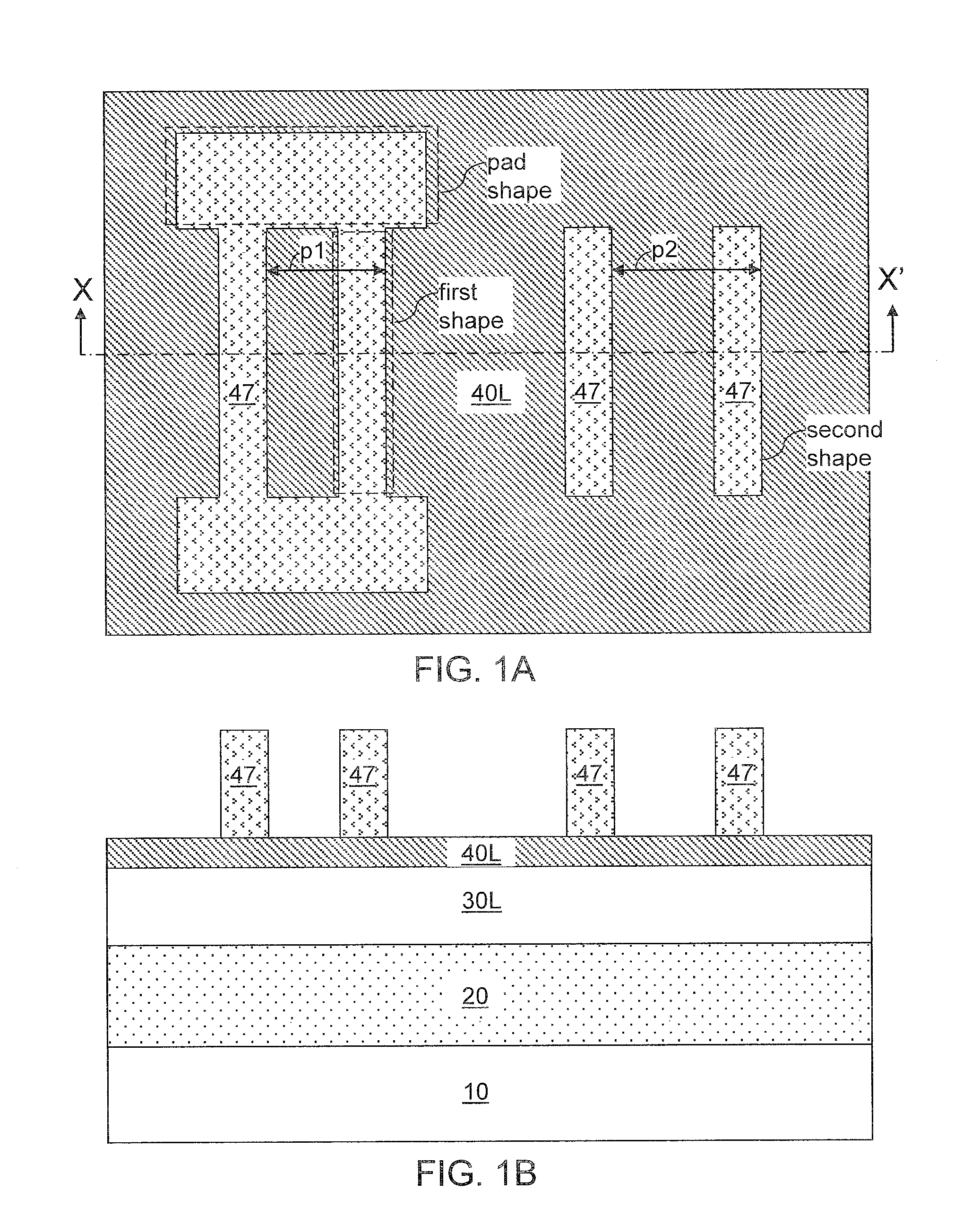

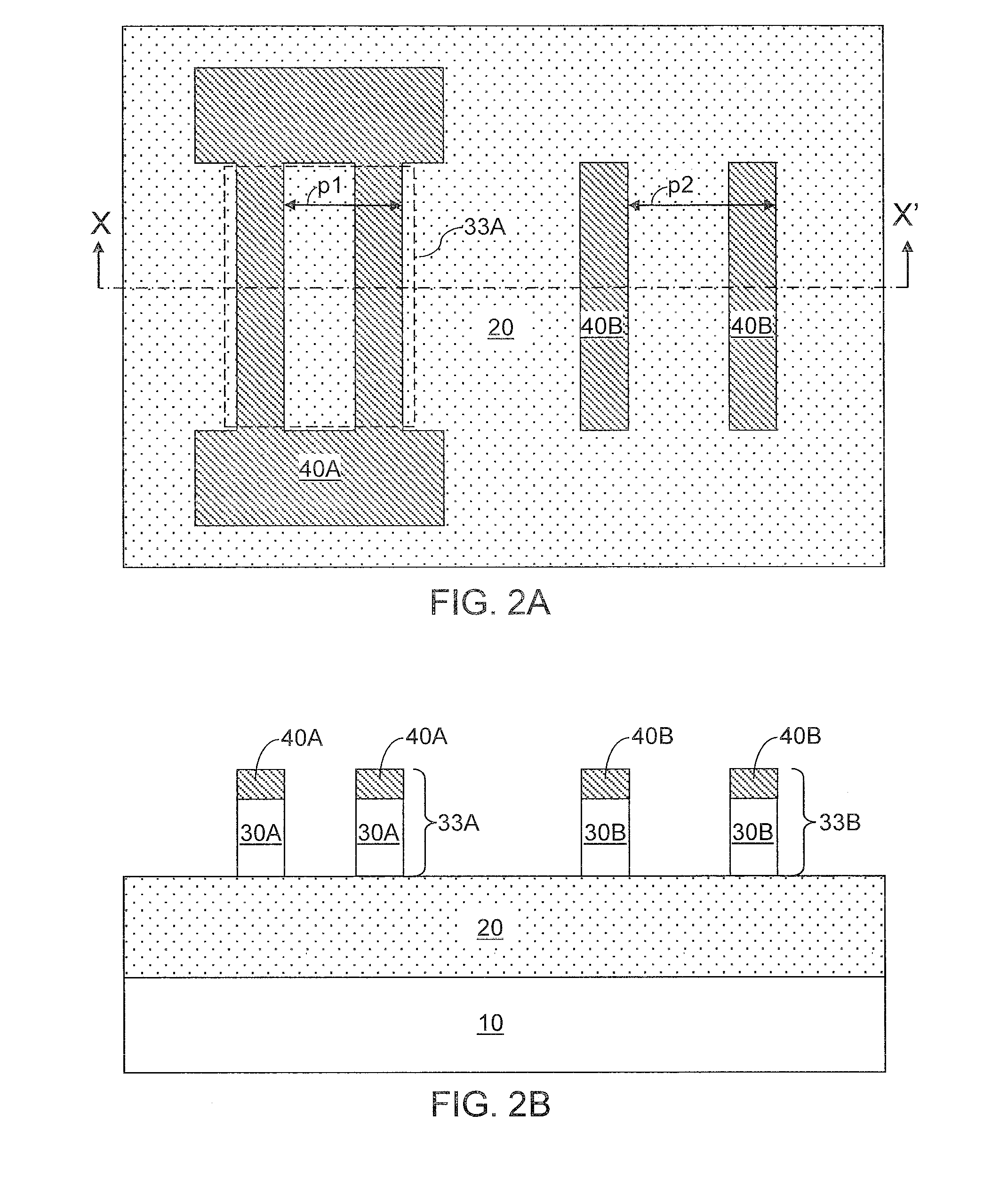

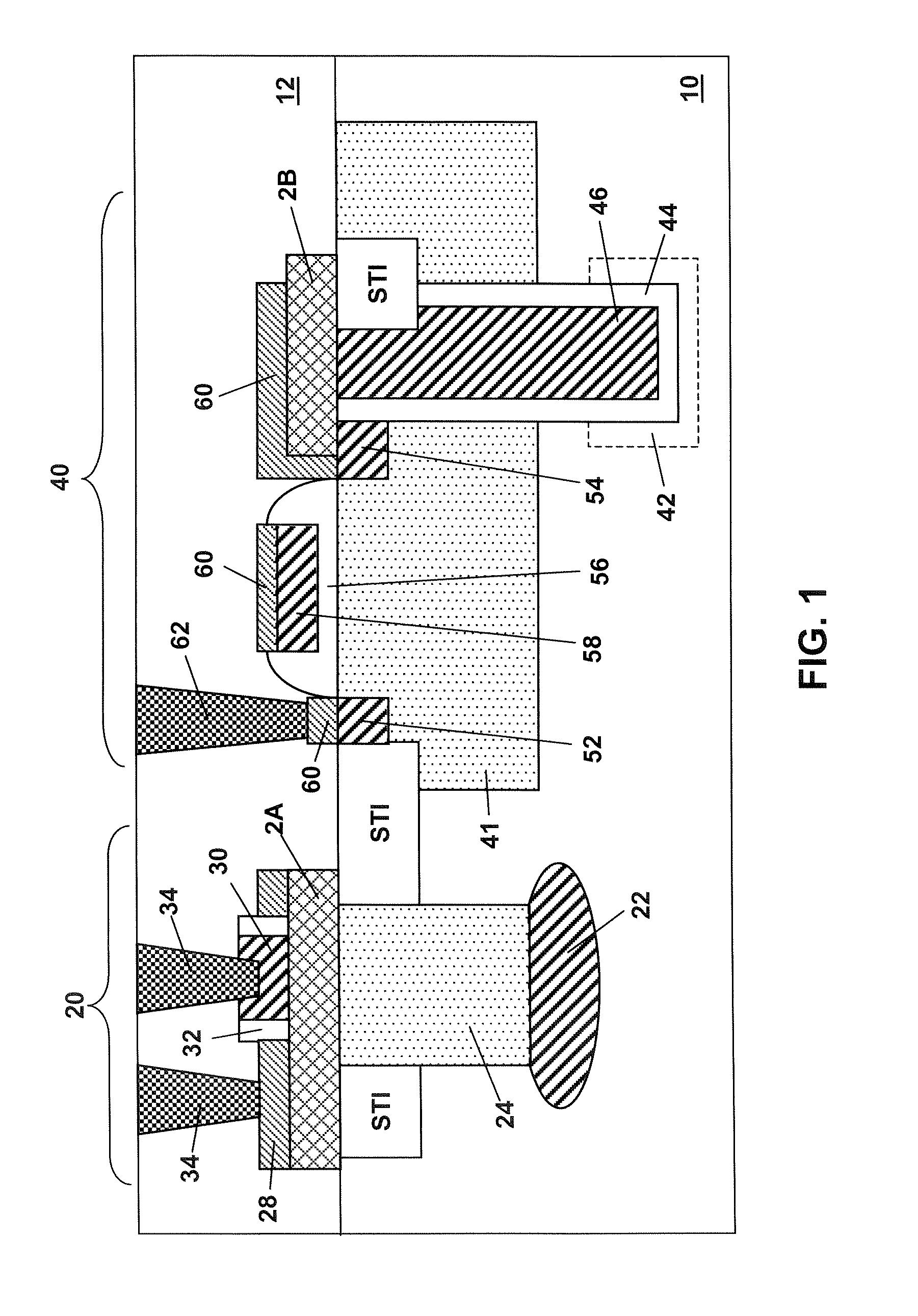

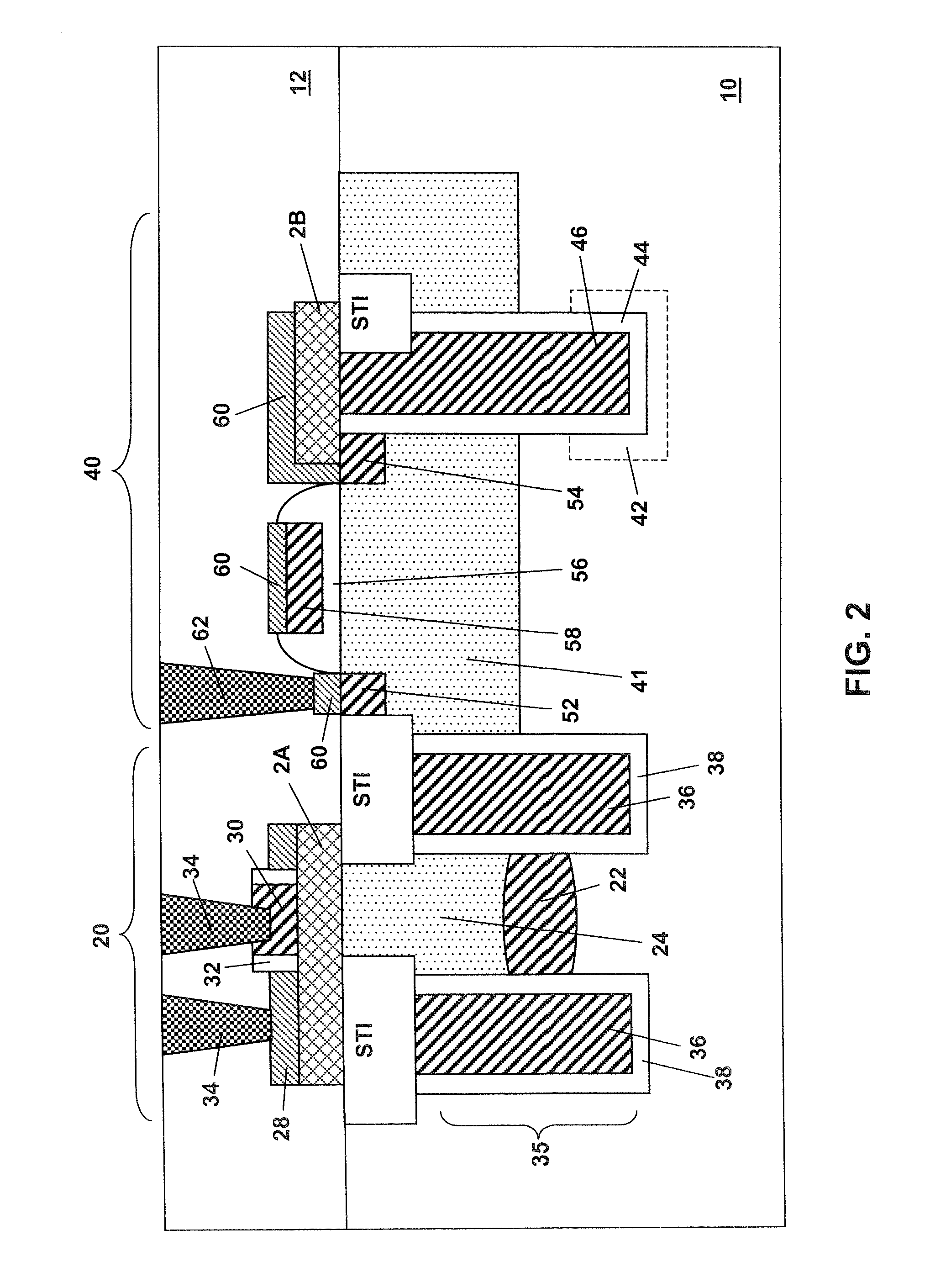

Finfet-compatible metal-insulator-metal capacitor

At least one semiconductor fin for a capacitor is formed concurrently with other semiconductor fins for field effect transistors. A lower conductive layer is deposited and lithographically patterned to form a lower conductive plate located on the at least one semiconductor fin. A dielectric layer and at least one upper conductive layer are formed and lithographically patterned to form a node dielectric and an upper conductive plate over the lower conductive plate as well as a gate dielectric and a gate conductor over the other semiconductor fins. The lower conductive plate, the node dielectric, and the upper conductive plate collectively form a capacitor. The finFETs may be dual gate finFETs or trigate finFETs. A buried insulator layer may be optionally recessed to increase the capacitance. Alternately, the lower conductive plate may be formed on a planar surface of the buried insulator layer.

Owner:GLOBALFOUNDRIES US INC

Schottky barrier nanowire field effect transistor and method for fabricating the same

InactiveUS20080128760A1Easy to makeEnsure thermal stabilityNanoinformaticsSolid-state devicesSalicideInsulation layer

Provided is a Schottky barrier nanowire field effect transistor, which has source / drain electrodes formed of metal silicide and a channel formed of a nanowire, and a method for fabricating the same. The Schottky barrier nanowire field effect transistor includes: a channel suspended over a substrate and including a nanowire; metal silicide source / drain electrodes electrically connected to both ends of the channel over the substrate; a gate electrode disposed to surround the channel; and a gate insulation layer disposed between the channel and the gate electrode.

Owner:ELECTRONICS & TELECOMM RES INST

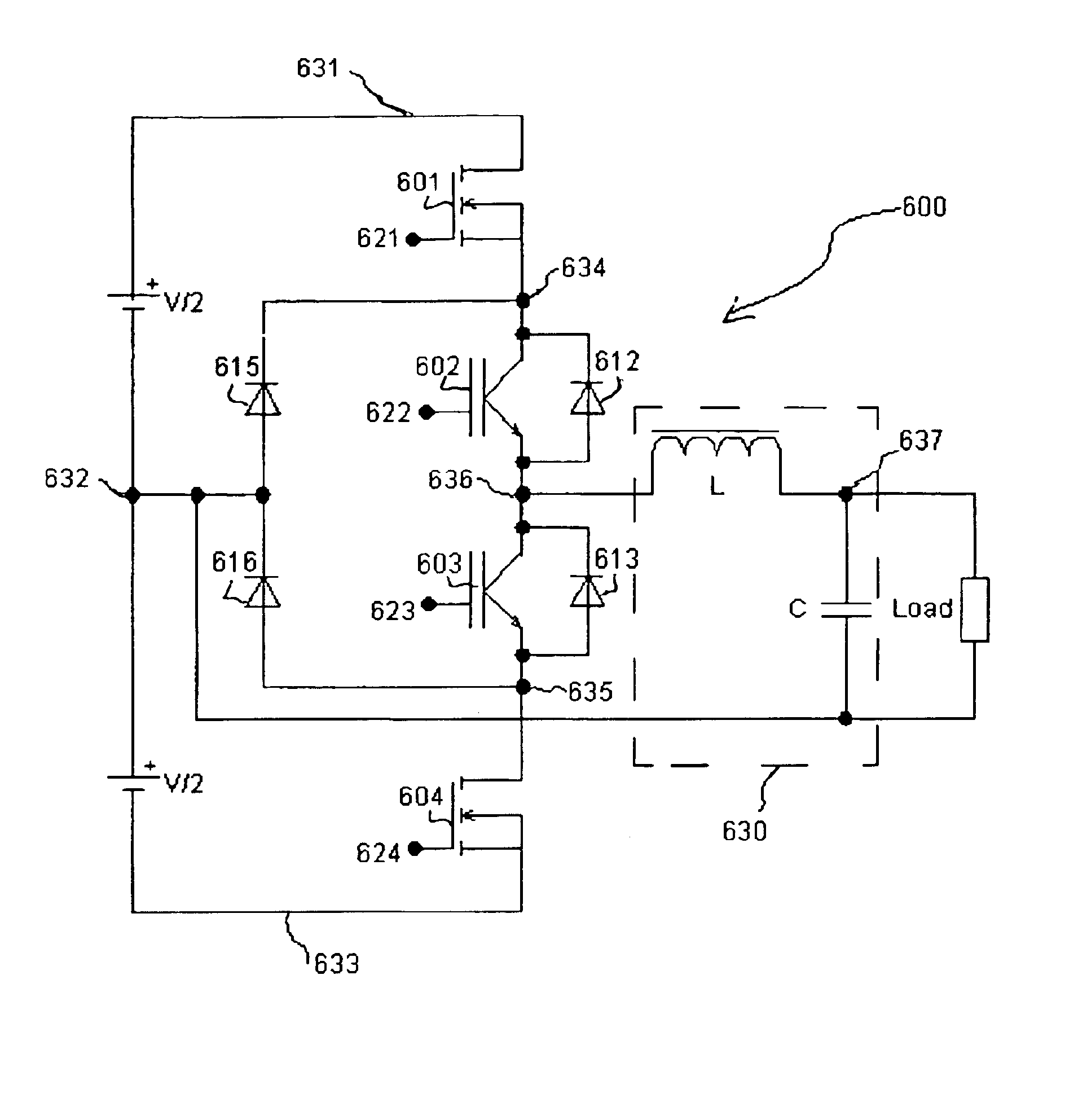

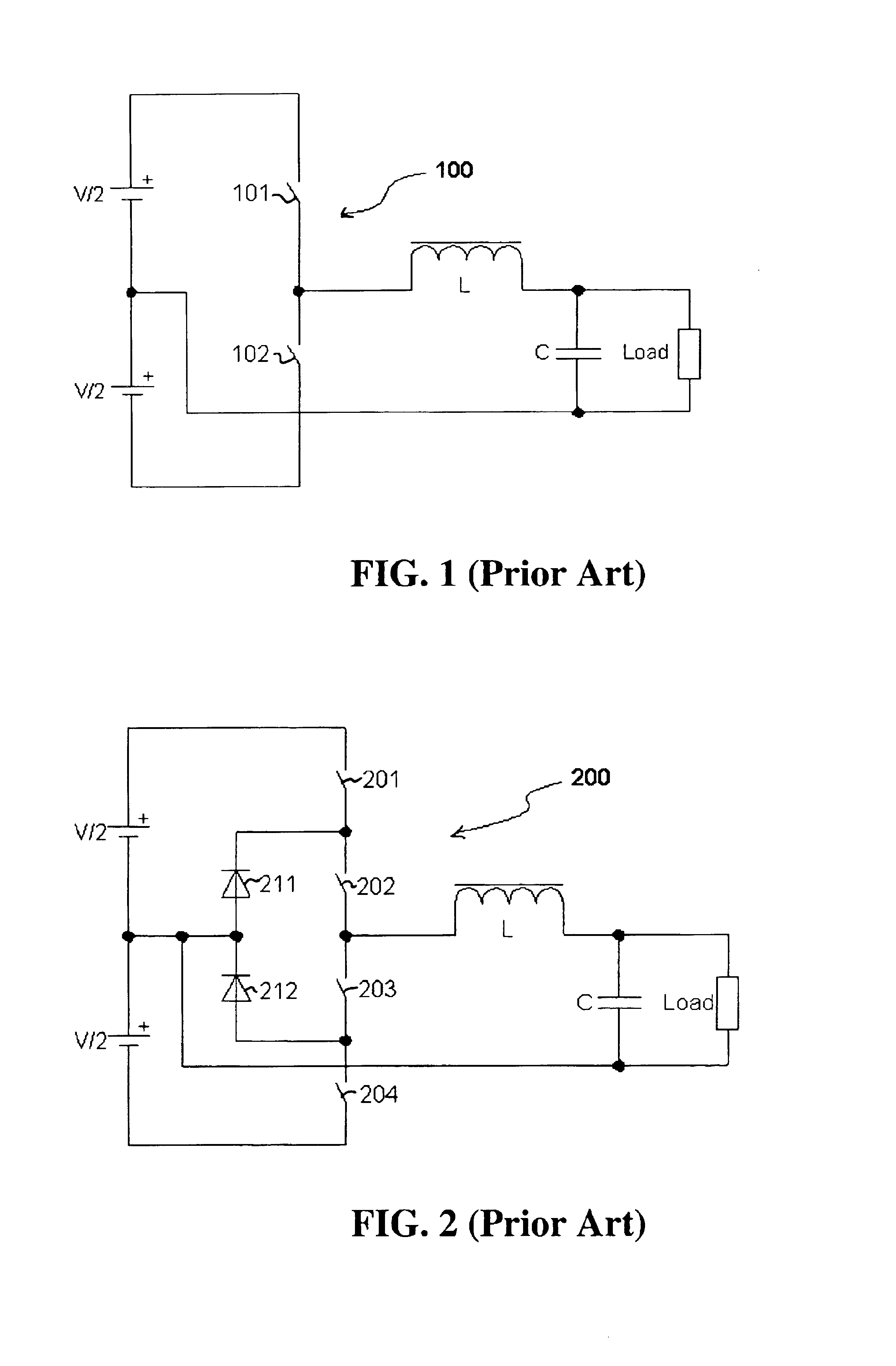

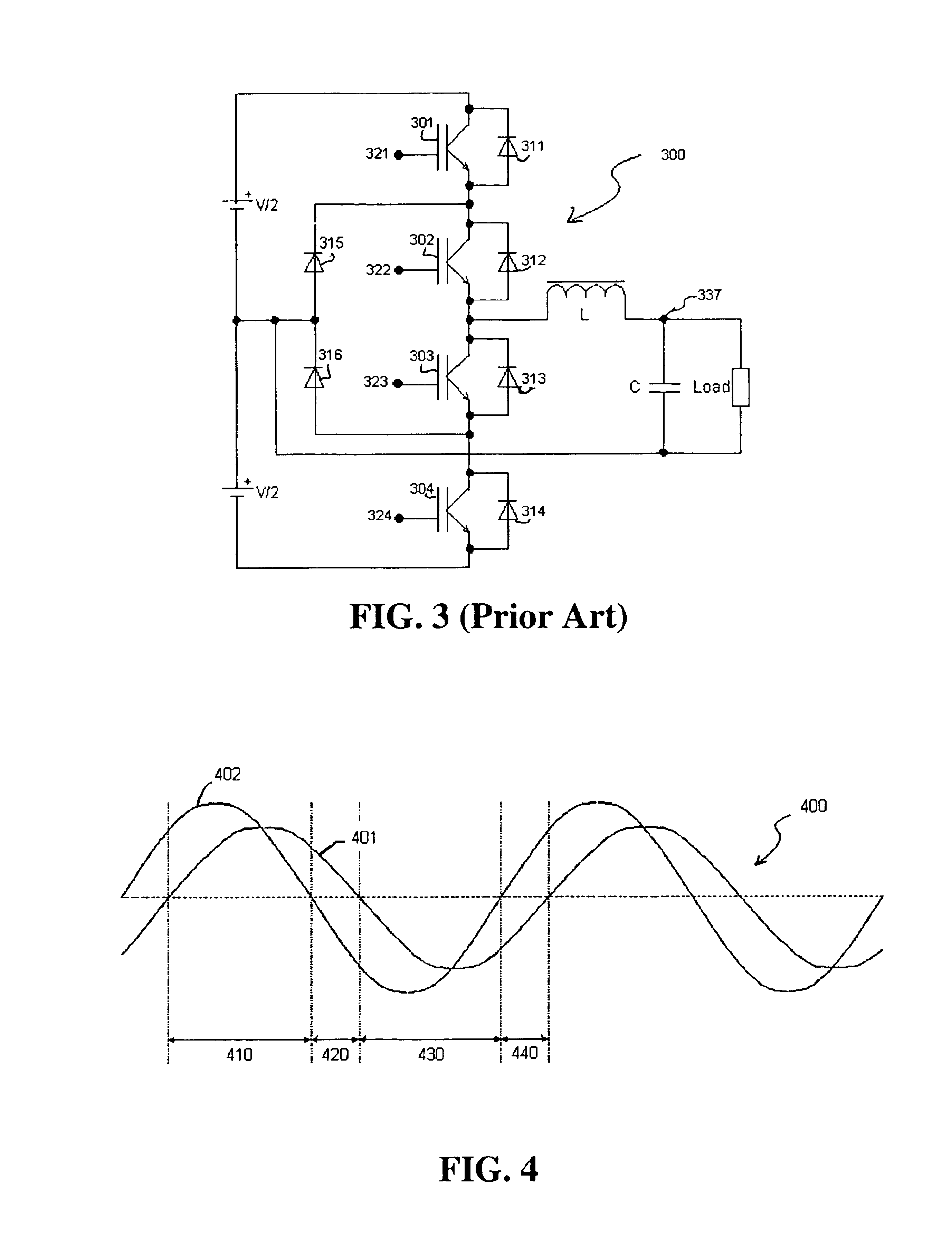

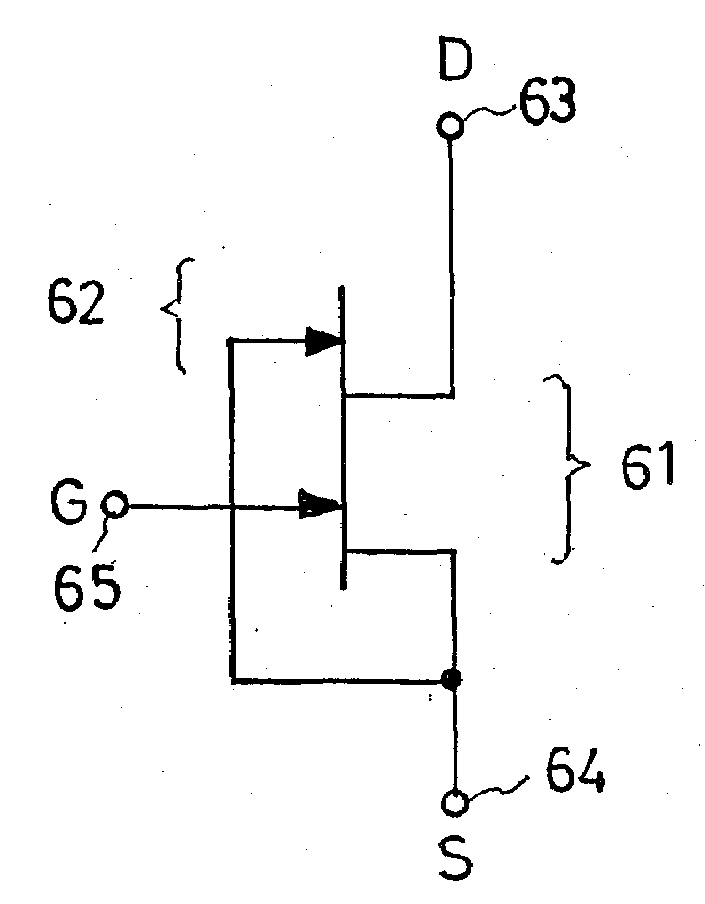

Three level inverter

ActiveUS6838925B1Delays determinationConversion with intermediate conversion to dcDc-dc conversionEngineeringField-effect transistor

The present invention relates to a high efficiency three-level inverter apparatus containing both bipolar and field effect transistors. An embodiment of a modified control scheme is also presented whereby transistors are modulated differently for each quadrant of output voltage-current phase. This embodiment of a modified control scheme allows efficient switching of field effect transistors without additional freewheeling and series diodes.

Owner:AMERICA POWER CONVERSION CORP

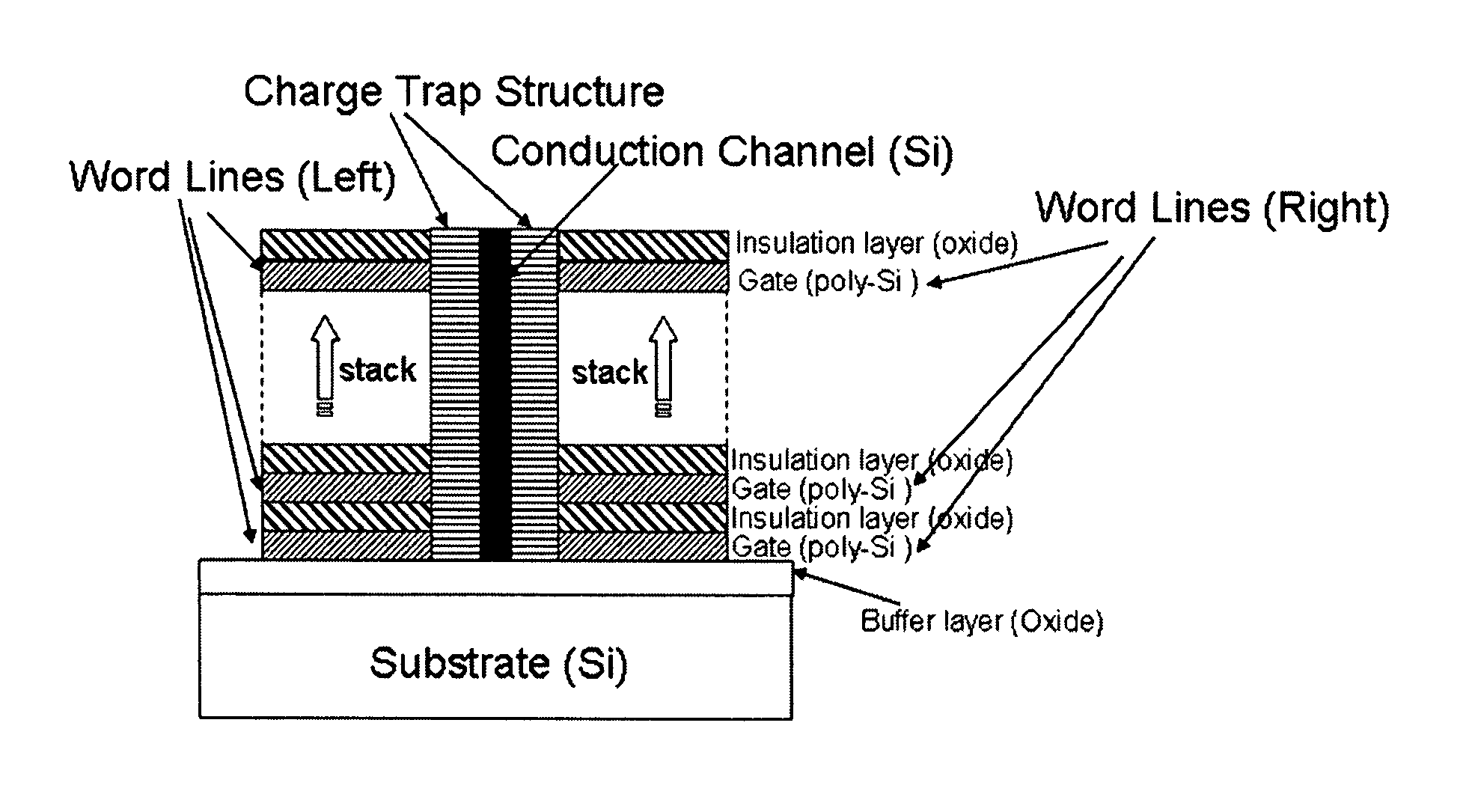

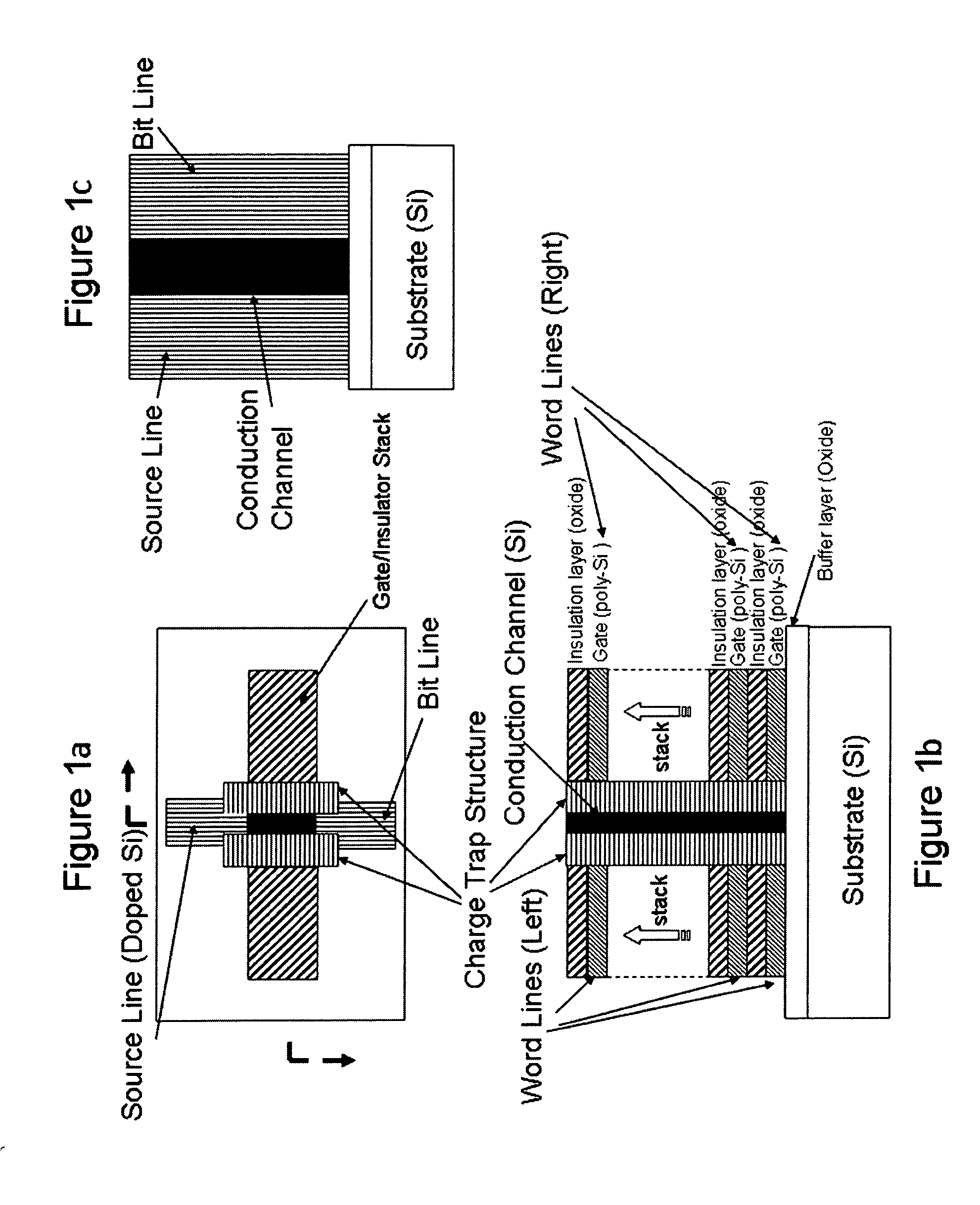

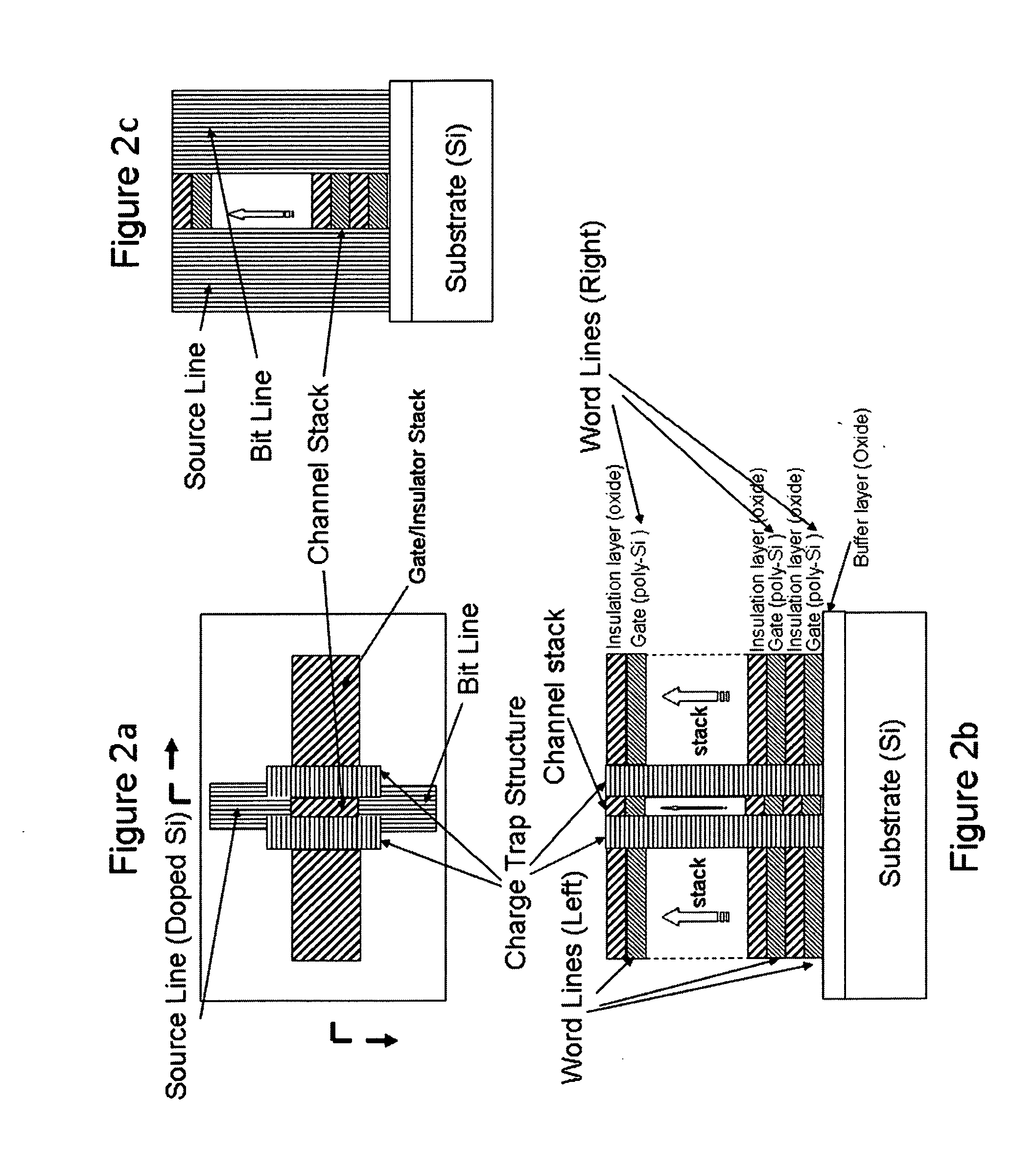

Three-dimensional non-volatile nor-type flash memory

ActiveUS20160086970A1High storage densitySolid-state devicesSemiconductor devicesElectricityEngineering

The present invention provides a design of three-dimensional non-volatile NOR flash memory devices consisting of arrays of basic NOR memory group in which individual memory cells (field-effect-transistors) are stacked along a direction (or directions) either out of or parallel to the plane of the substrate and electrically connected in parallel to achieve high storage densities approaching 1 TB with lower manufacturing cost. Offering full random access to every individual memory cells and also capability of parallel programming / erasing in blocks of memory cells, such three-dimensional non-volatile NOR flash memory can be widely used for both executable-code storage and mass data storage applications.

Owner:PENG HAIBING

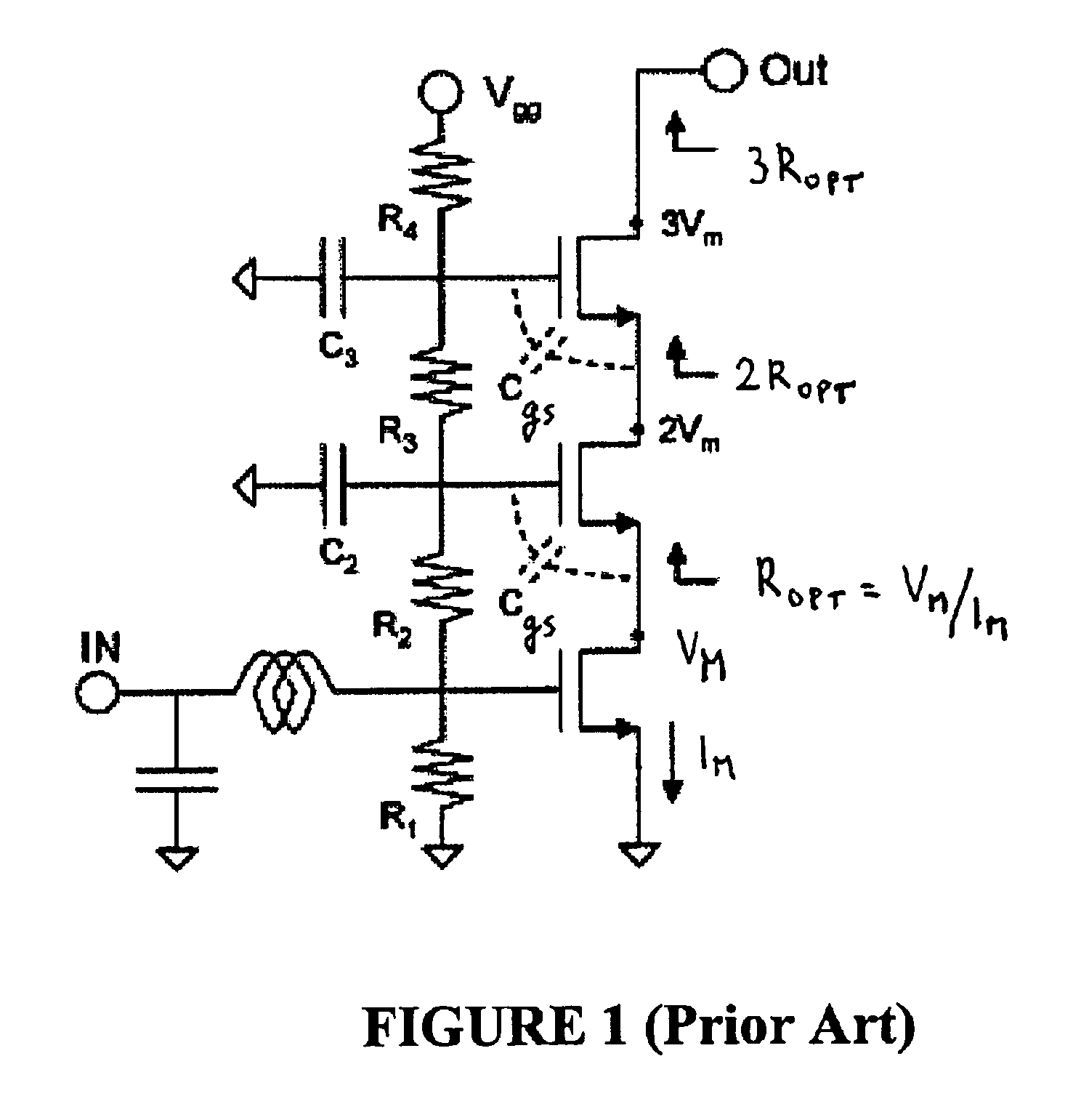

Stacked linear power amplifier with capacitor feedback and resistor isolation

ActiveUS8487706B2MinimizationMaximizeAmplifier combinationsAmplififers with field-effect devicesCapacitanceLinear power amplifier

A power amplifier with stacked, serially connected, field effect transistors is described. DC control voltage inputs are fed to the gates of each transistor. Capacitors are coupled to the transistors. The inputs and the capacitors are controlled to minimize generation of non-linearities of each field effect transistor and / or to maximize cancellation of distortions between the field effect transistors of the power amplifier in order to improve linearity of the power amplifier output.

Owner:PSEMI CORP

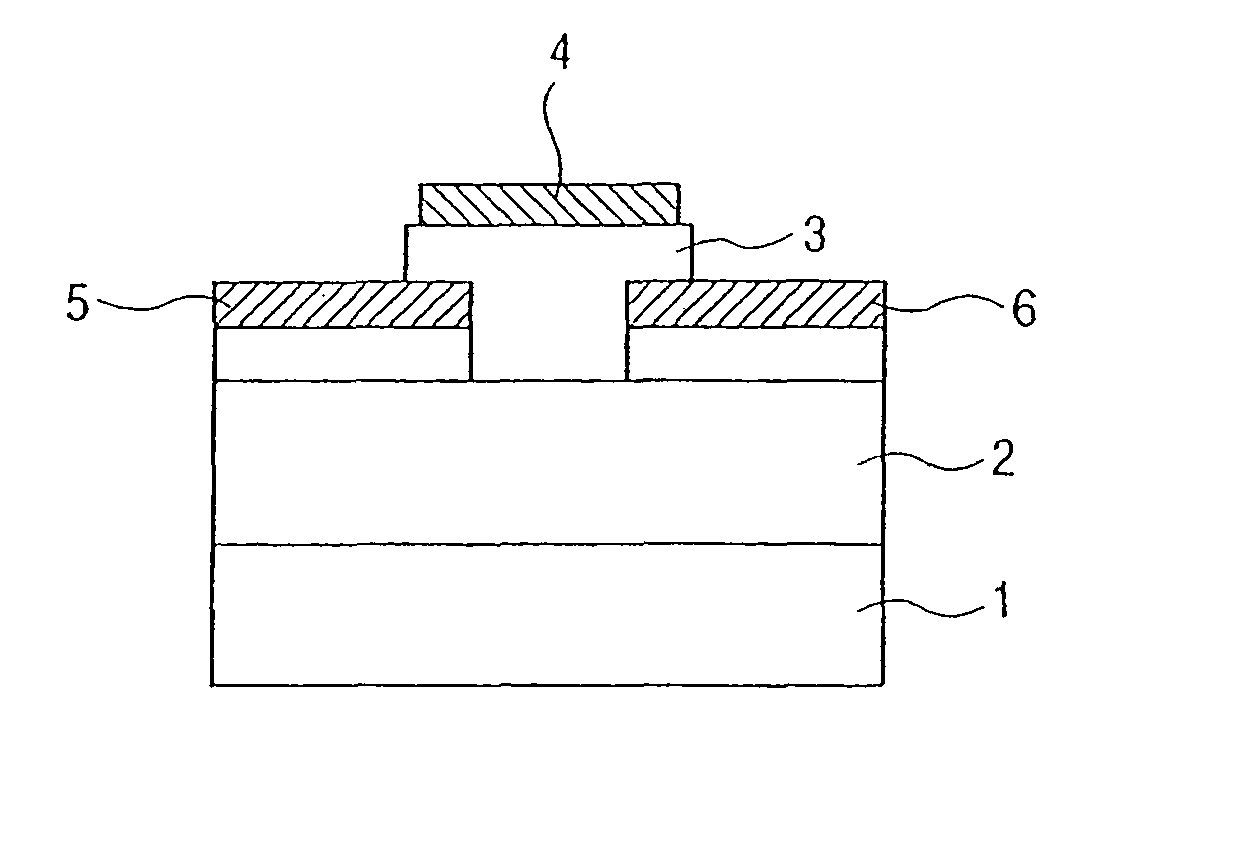

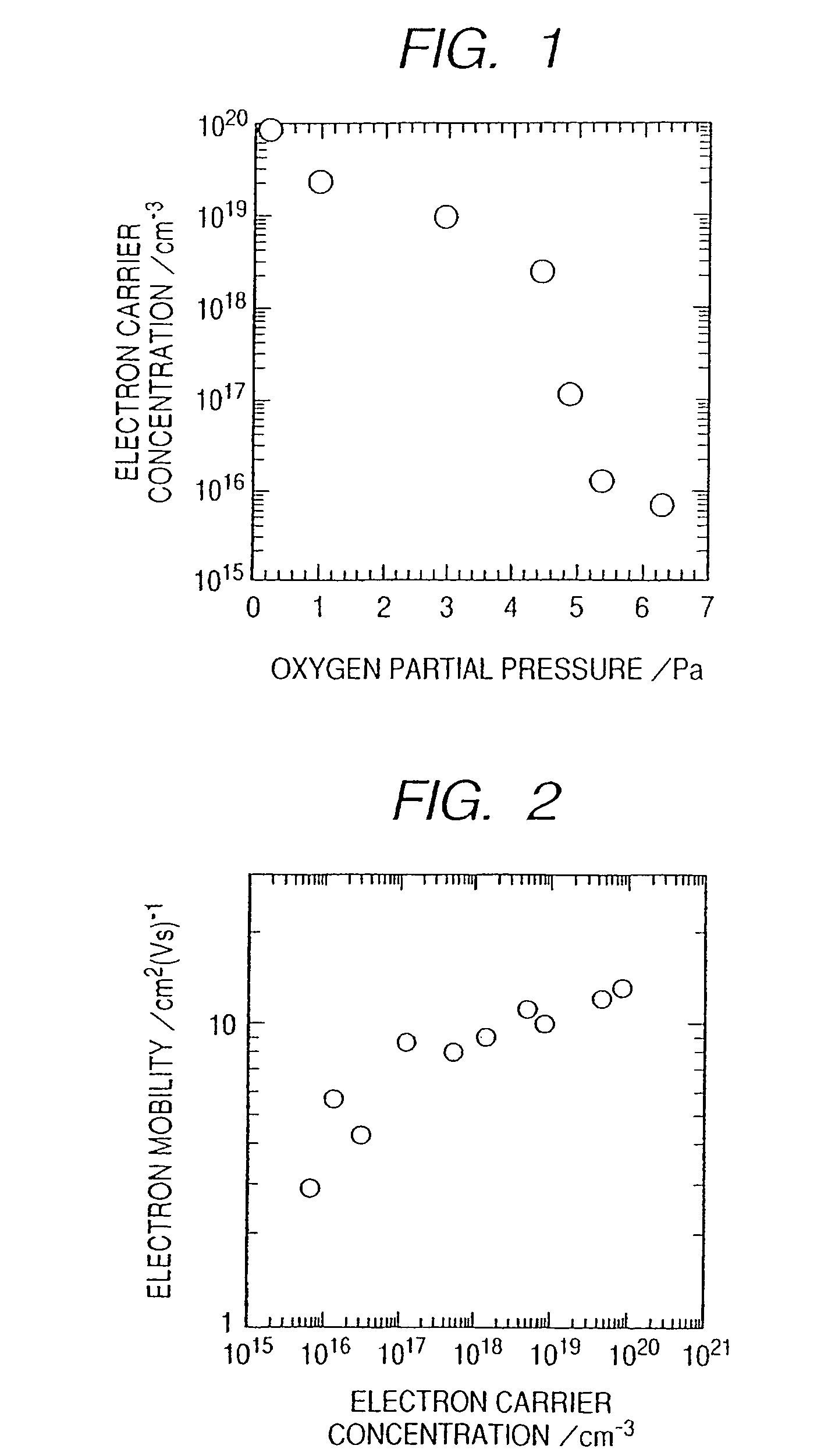

Field effect transistor

ActiveUS7868326B2Inhibit currentMaintain good propertiesSolid-state devicesSemiconductor/solid-state device manufacturingField-effect transistorElectron

A novel field-effect transistor is provided which employs an amorphous oxide. In an embodiment of the present invention, the transistor comprises an amorphous oxide layer containing electron carrier at a concentration less than 1×10−18 / cm3, and the gate-insulating layer is comprised of a first layer being in contact with the amorphous oxide and a second layer different from the first layer.

Owner:CANON KK +2

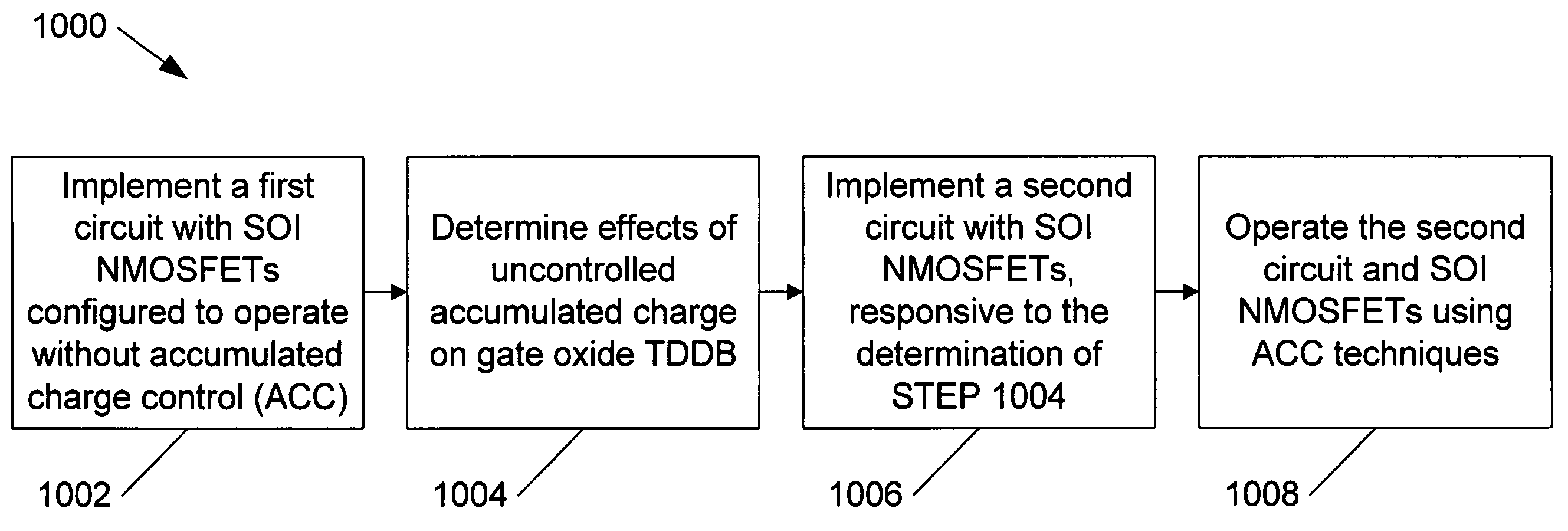

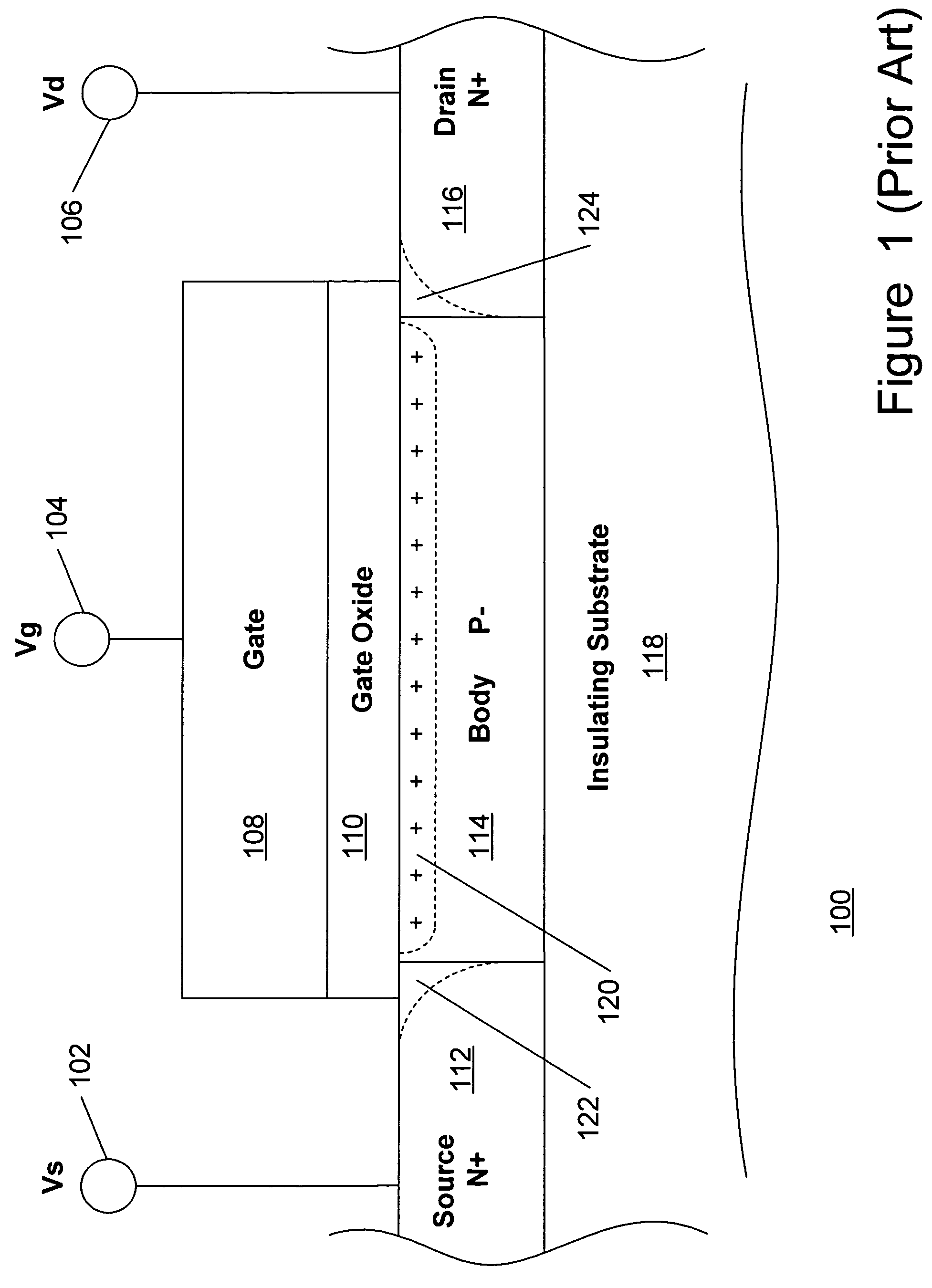

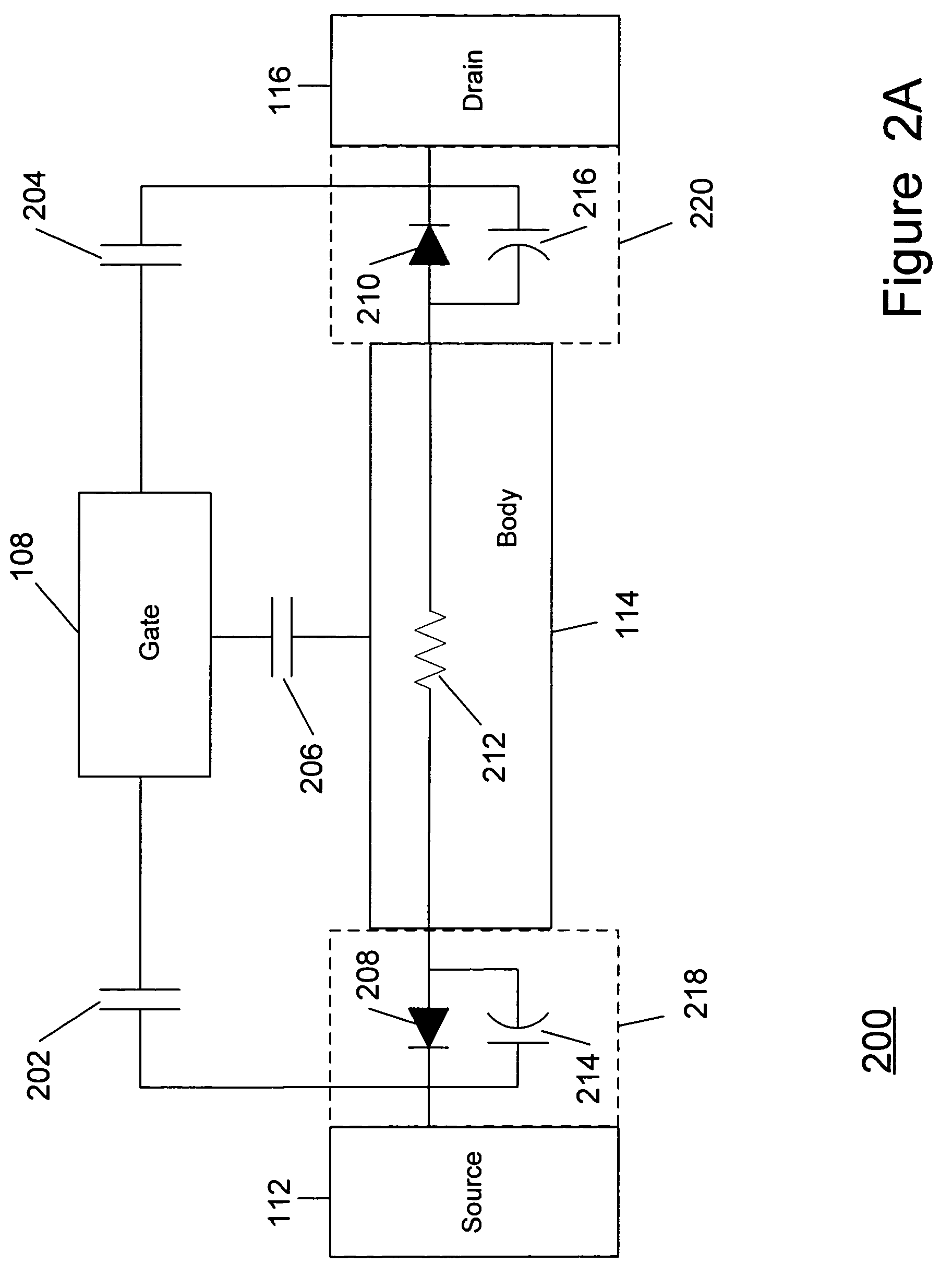

Method and apparatus improving gate oxide reliability by controlling accumulated charge

ActiveUS7890891B2Improving nonlinear responses and harmonic and intermodulaton distortion effectsReduce non-linearitySolid-state devicesElectronic switchingMOSFETDielectric

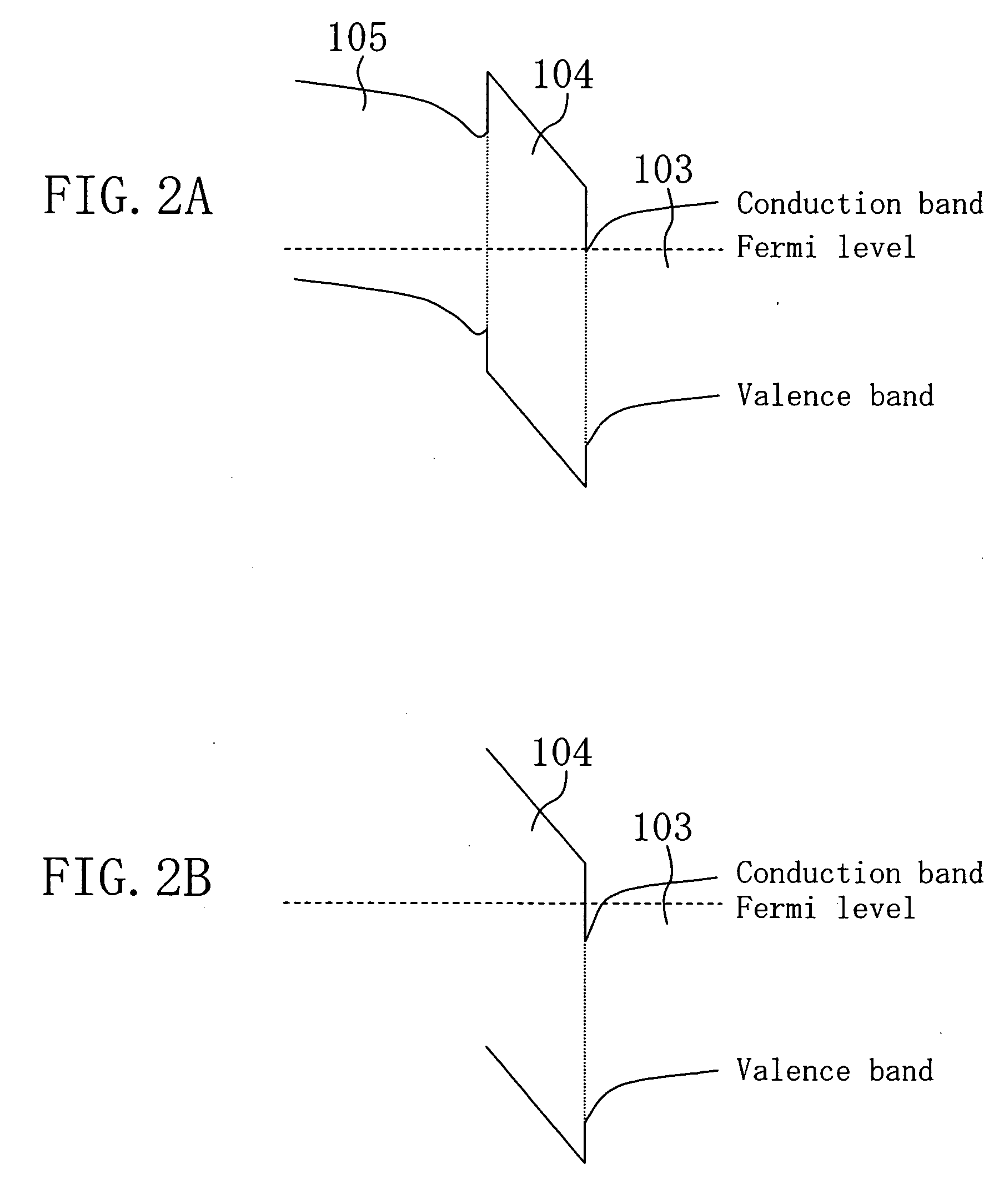

A method and apparatus are disclosed for use in improving the gate oxide reliability of semiconductor-on-insulator (SOI) metal-oxide-silicon field effect transistor (MOSFET) devices using accumulated charge control (ACC) techniques. The method and apparatus are adapted to remove, reduce, or otherwise control accumulated charge in SOI MOSFETs, thereby yielding improvements in FET performance characteristics. In one embodiment, a circuit comprises a MOSFET, operating in an accumulated charge regime, and means for controlling the accumulated charge, operatively coupled to the SOI MOSFET. A first determination is made of the effects of an uncontrolled accumulated charge on time dependent dielectric breakdown (TDDB) of the gate oxide of the SOI MOSFET. A second determination is made of the effects of a controlled accumulated charge on TDDB of the gate oxide of the SOI MOSFET. The SOI MOSFET is adapted to have a selected average time-to-breakdown, responsive to the first and second determinations, and the circuit is operated using techniques for accumulated charge control operatively coupled to the SOI MOSFET. In one embodiment, the accumulated charge control techniques include using an accumulated charge sink operatively coupled to the SOI MOSFET body.

Owner:PSEMI CORP

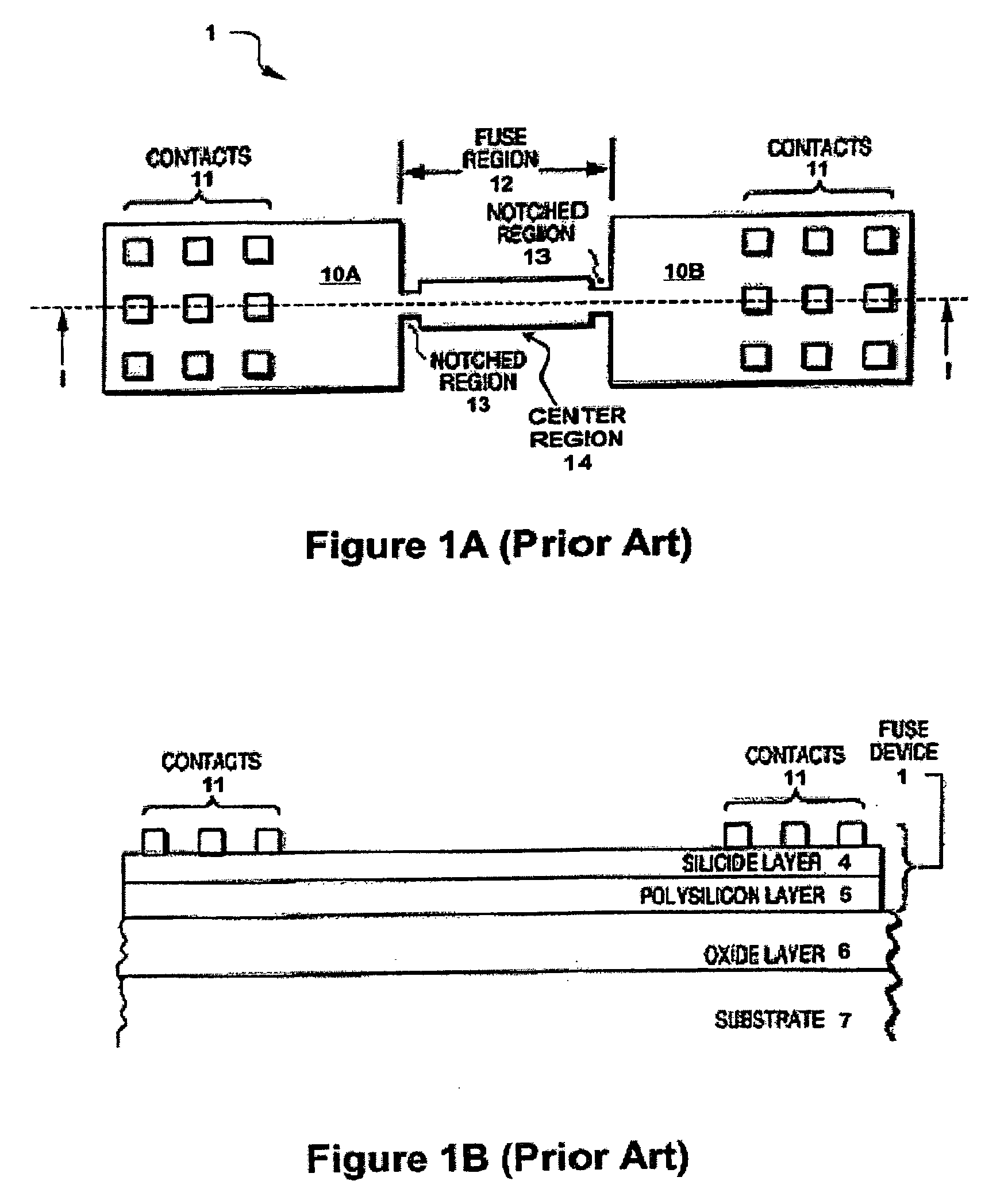

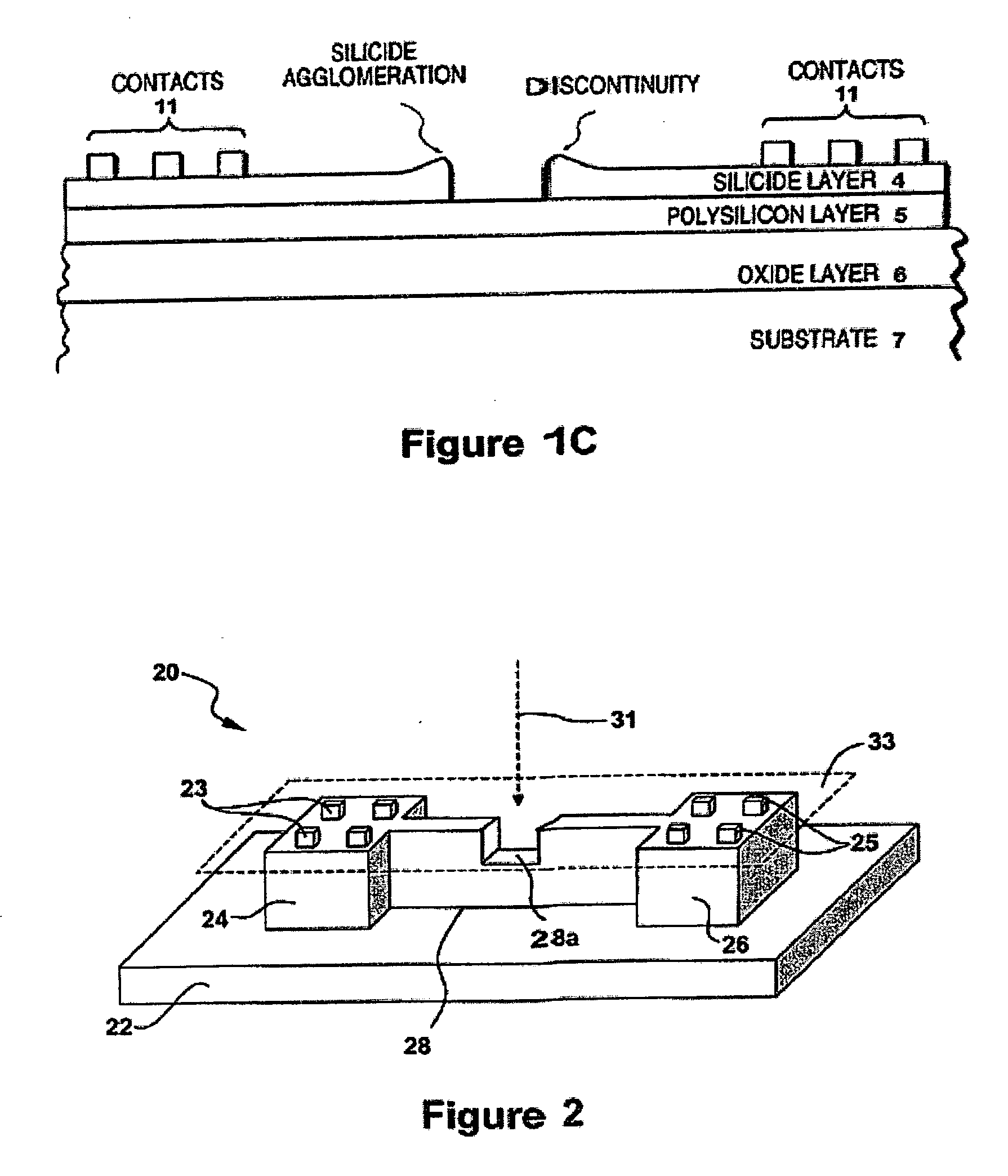

Programmable semiconductor device containing a vertically notched fusible link region and methods of making and using same

InactiveUS20070029576A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present invention relates to a programmable semiconductor device, preferably a FinFET or tri-gate structure, that contains a first contact element, a second contact element, and at least one fin-shaped fusible link region coupled between the first and second contact elements. The second contact element is laterally spaced apart from the first contact element, and the fin-shaped fusible link region has a vertically notched section. A programming current flowing through the fin-shaped fusible link region causes either significant resistance increase or formation of an electric discontinuity in the vertically notched section. Alternatively, the vertically notched section may contain a dielectric material, and application of a programming voltage between a gate electrode overlaying the vertically notched section and one of the contact elements breaks down the dielectric material and allows current flow between the gate electrode and the fin-shaped fusible link region.

Owner:IBM CORP

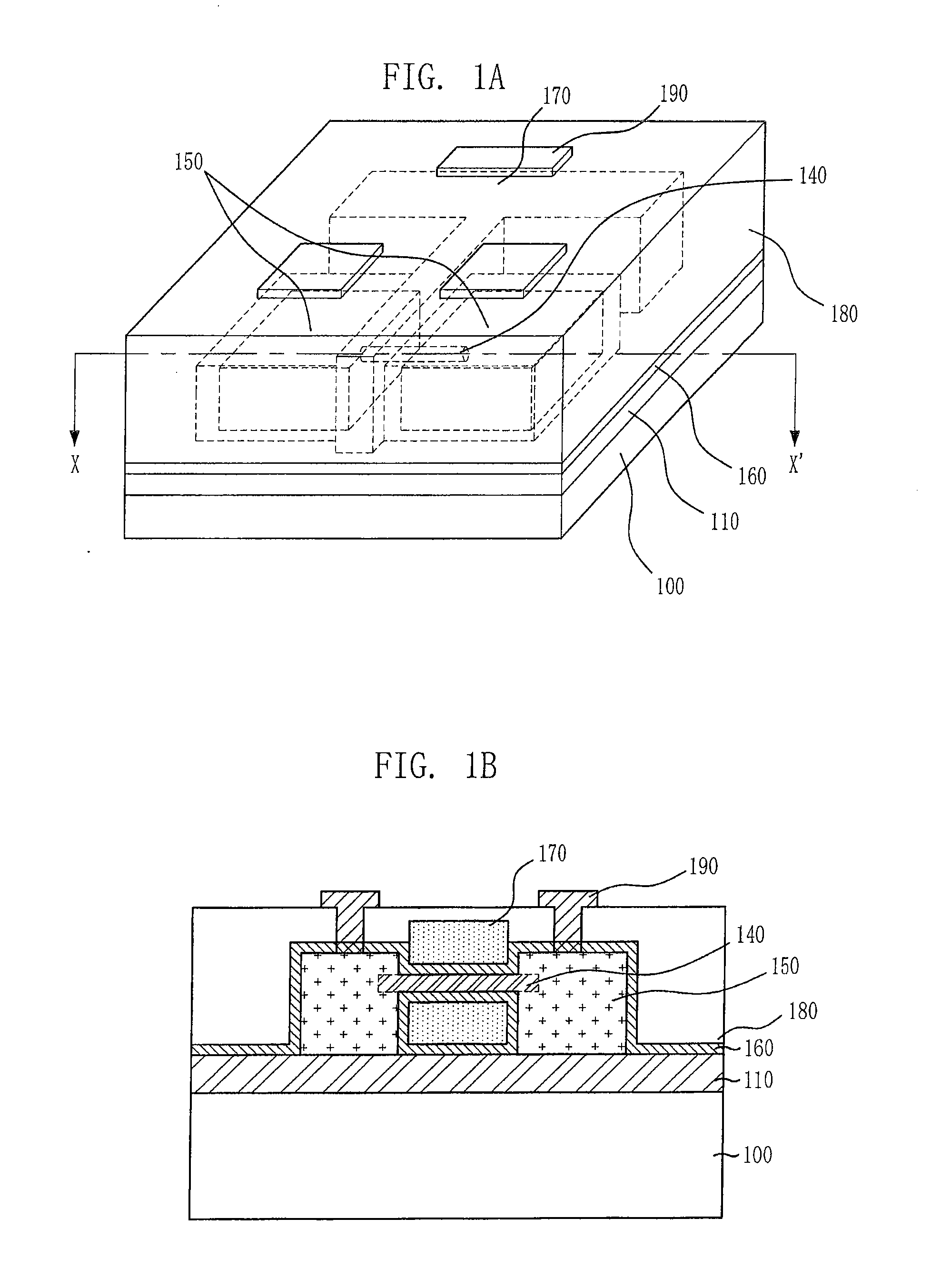

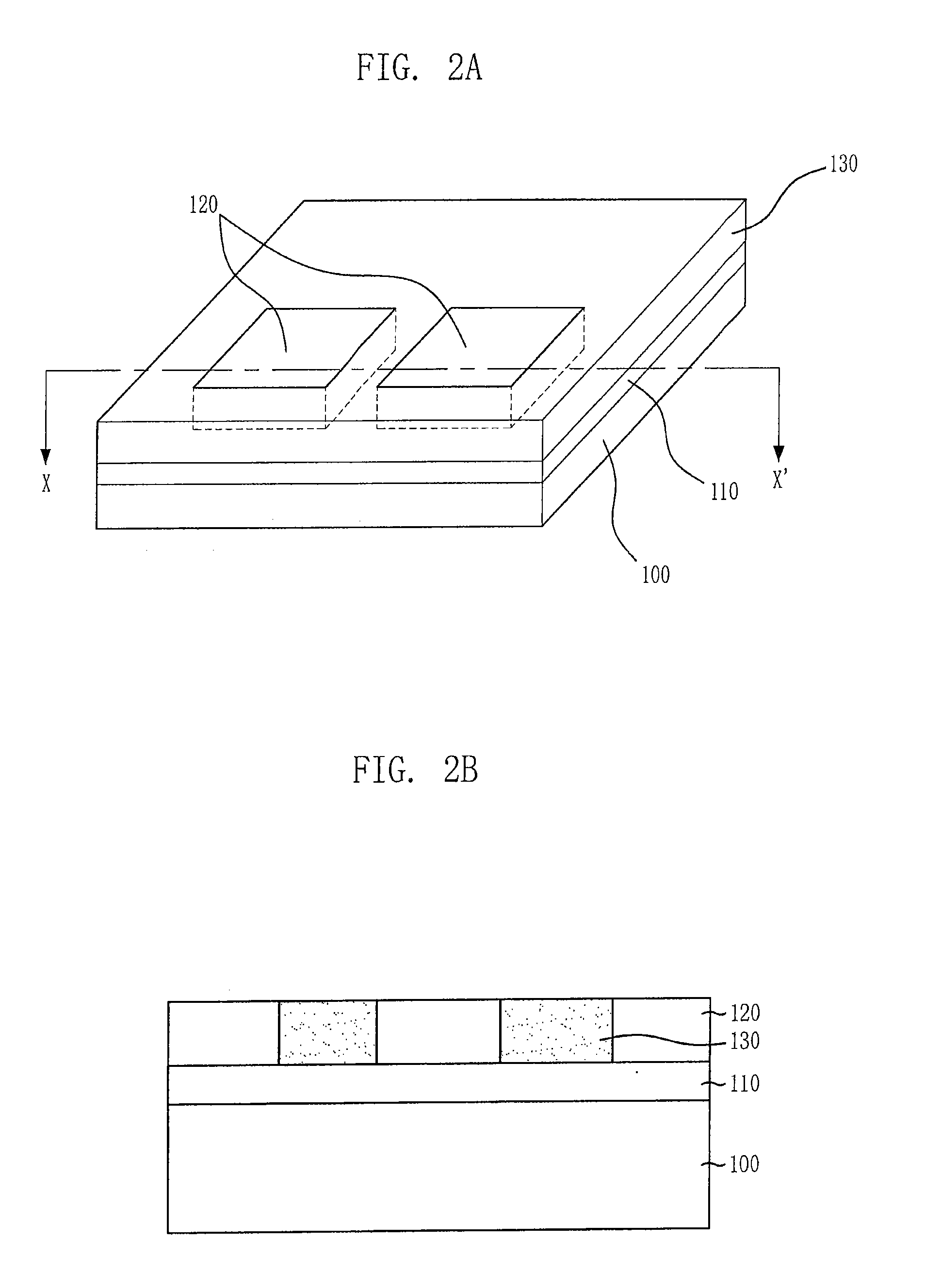

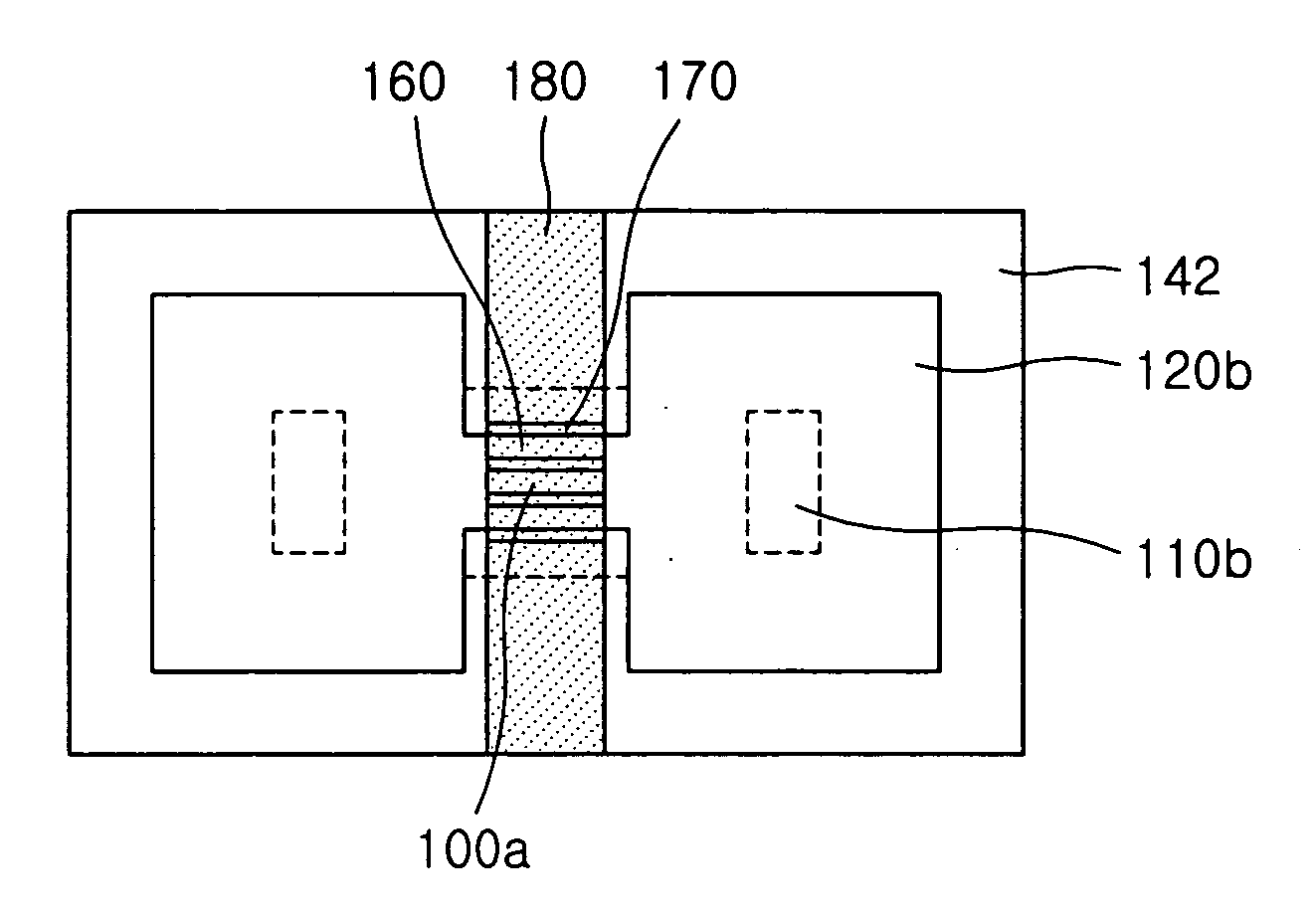

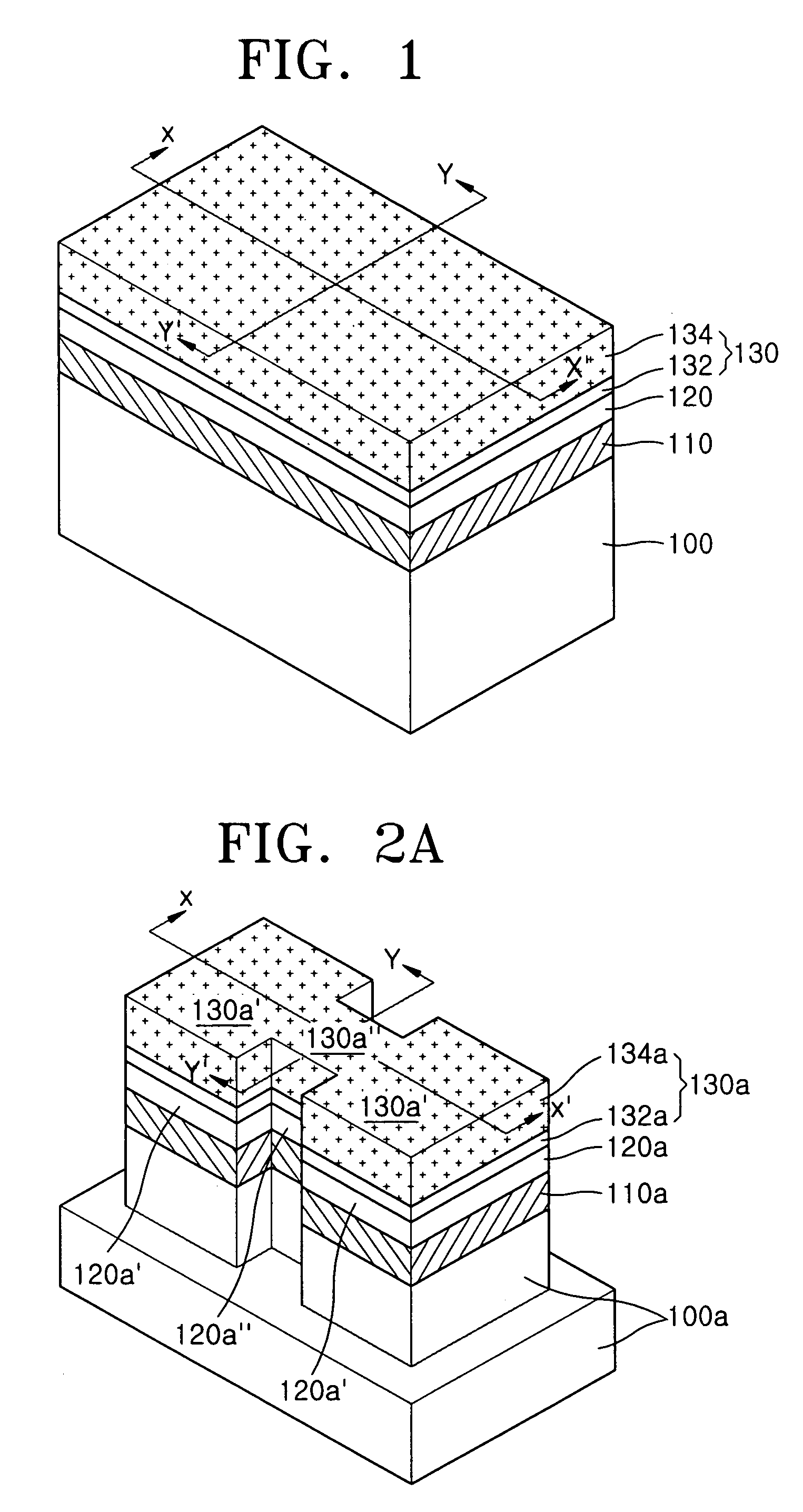

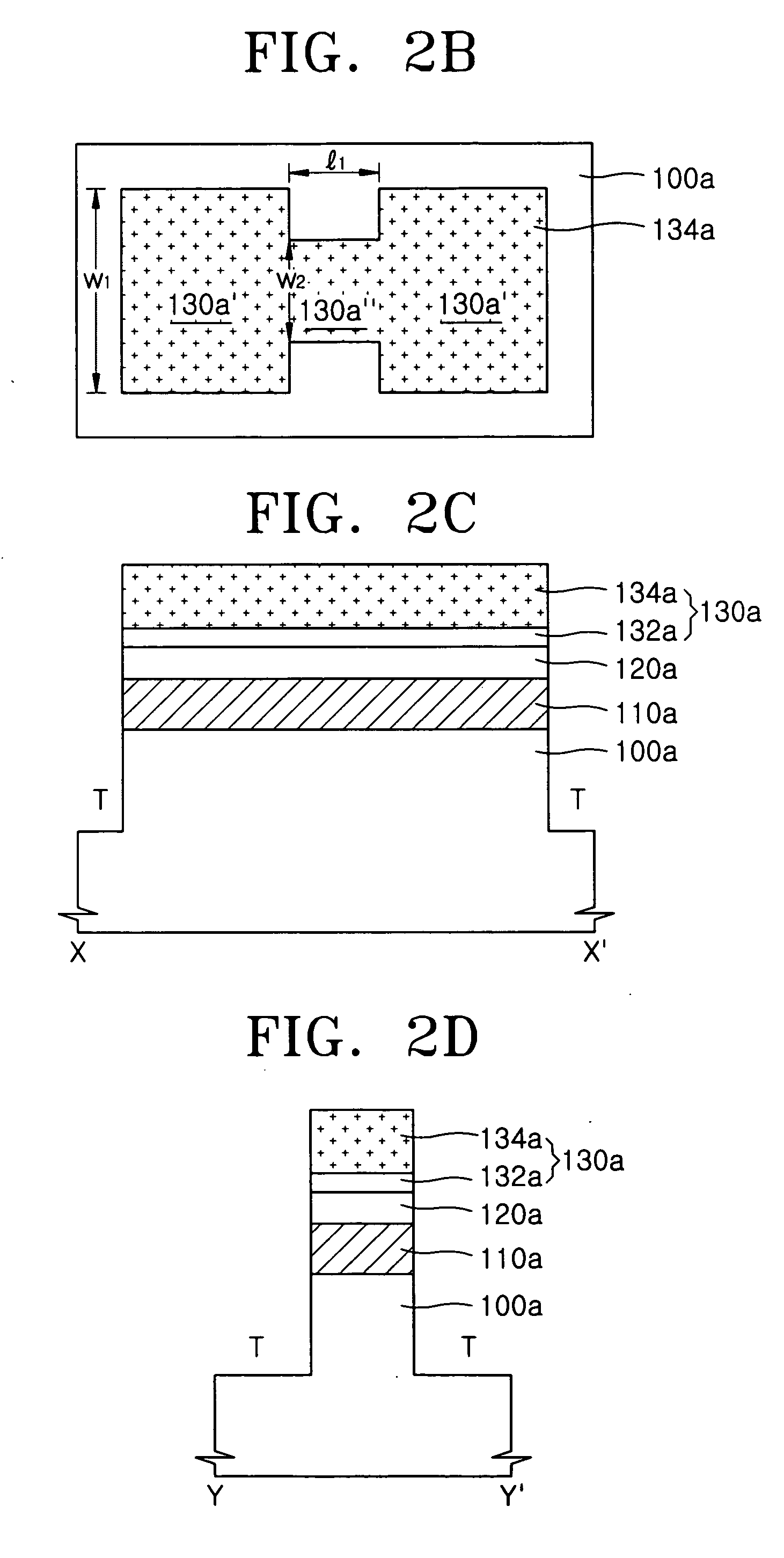

Multi bridge channel field effect transistors with nano-wire channels and methods of manufacturing the same

A field effect transistor (FET) includes spaced apart source and drain regions disposed on a substrate and at least one pair of elongate channel regions disposed on the substrate and extending in parallel between the source and drain regions. A gate insulating region surrounds the at least one pair of elongate channel regions, and a gate electrode surrounds the gate insulating region and the at least one pair of elongate channel regions. Support patterns may be interposed between the semiconductor substrate and the source and drain regions. The elongate channel regions may have sufficiently small cross-section to enable complete depletion thereof. For example, a width and a thickness of the elongate channel regions may be in a range from about 10 nanometers to about 20 nanometers. The elongate channel regions may have rounded cross-sections, e.g., each of the elongate channel regions may have an elliptical cross-section. The at least one pair of elongate channel regions may include a plurality of stacked pairs of elongate channel regions.

Owner:SAMSUNG ELECTRONICS CO LTD

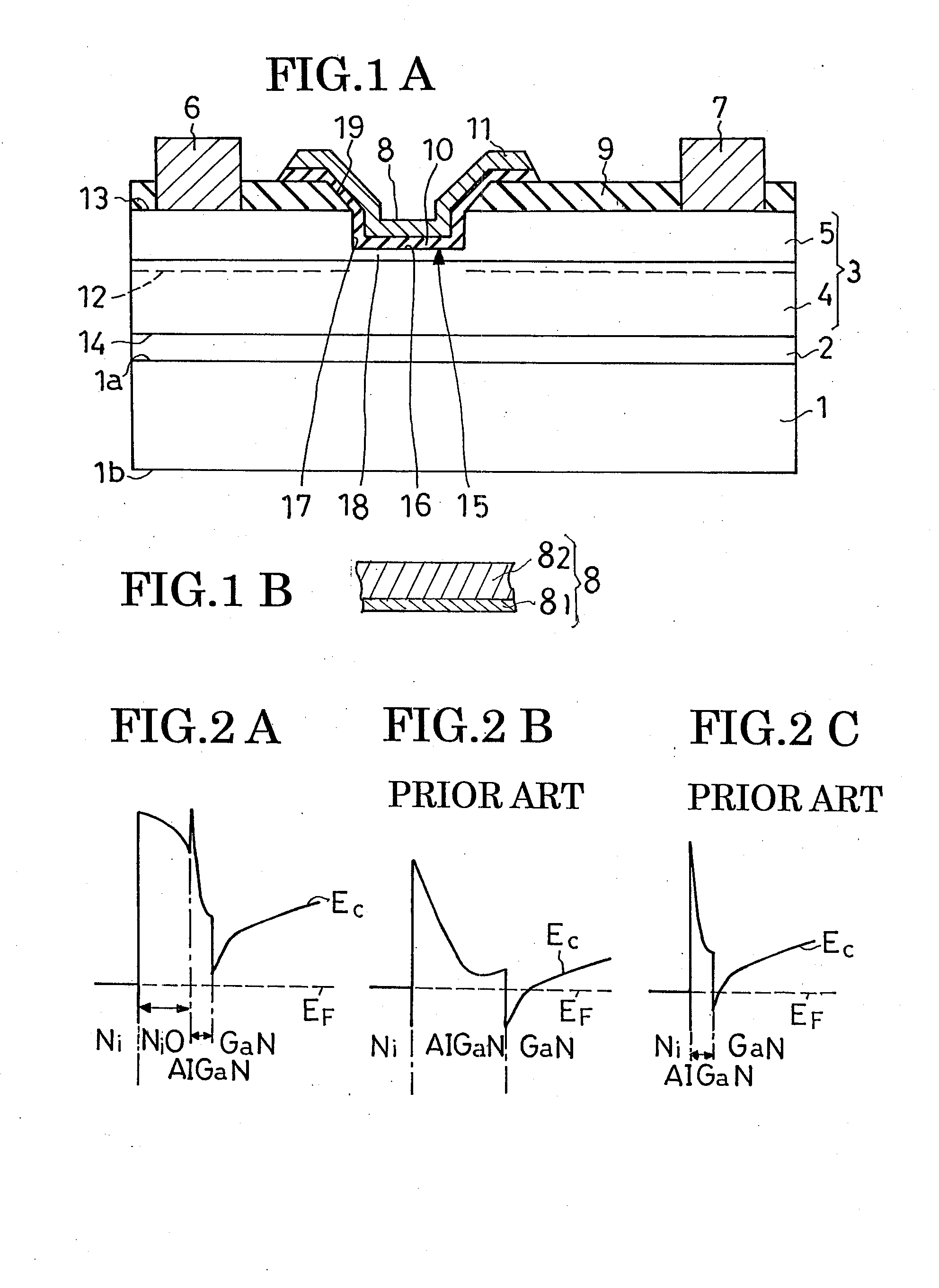

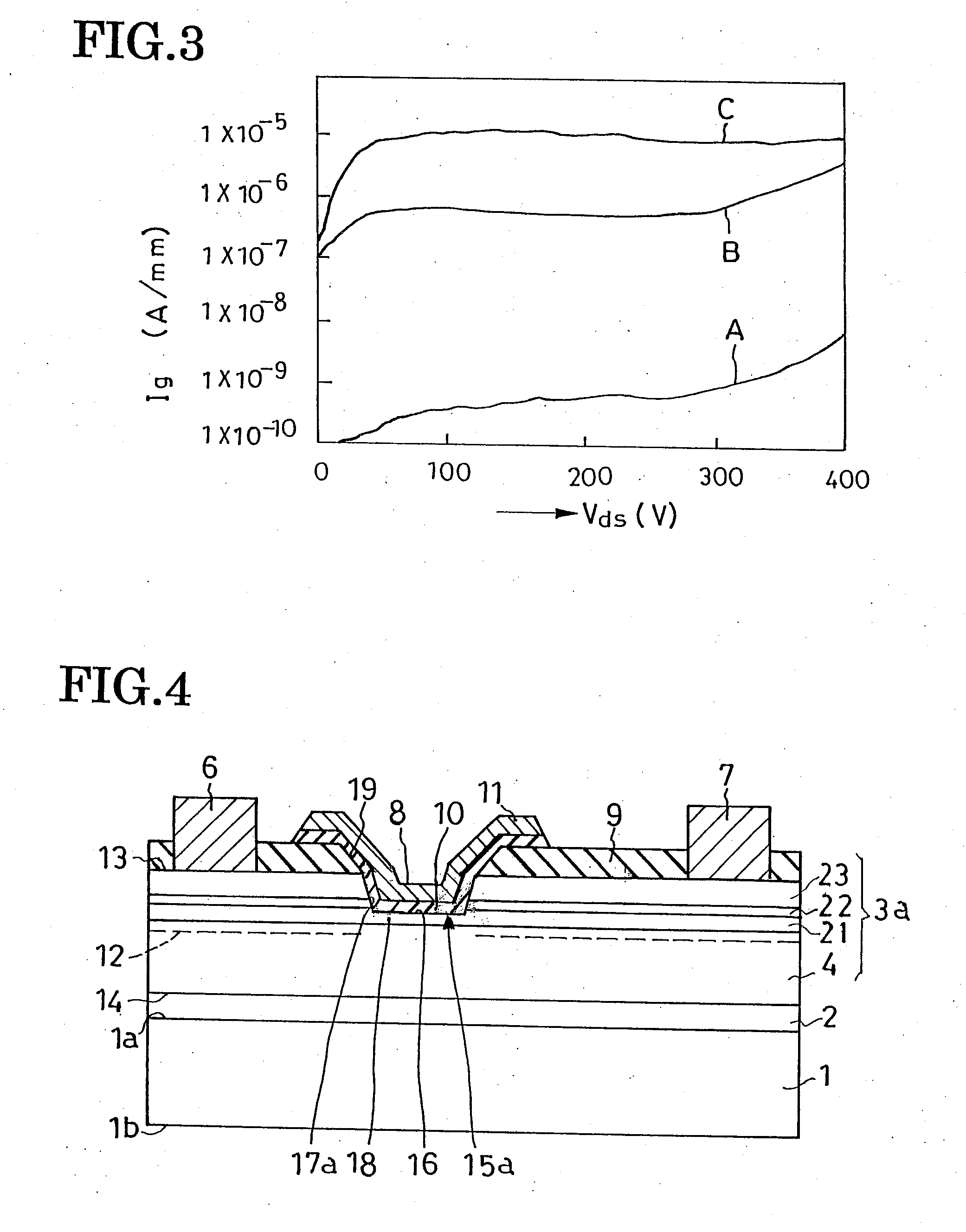

Field-Effect Semiconductor Device, and Method of Fabrication

ActiveUS20090057720A1Reduce leakage currentPreventing current collapseSemiconductor/solid-state device detailsSolid-state devicesHeterojunctionField effect

A HEMT-type field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film whereby a depletion zone is normally created in the electron gas layer, with a minimum of turn-on resistance and gate leak current.

Owner:SANKEN ELECTRIC CO LTD

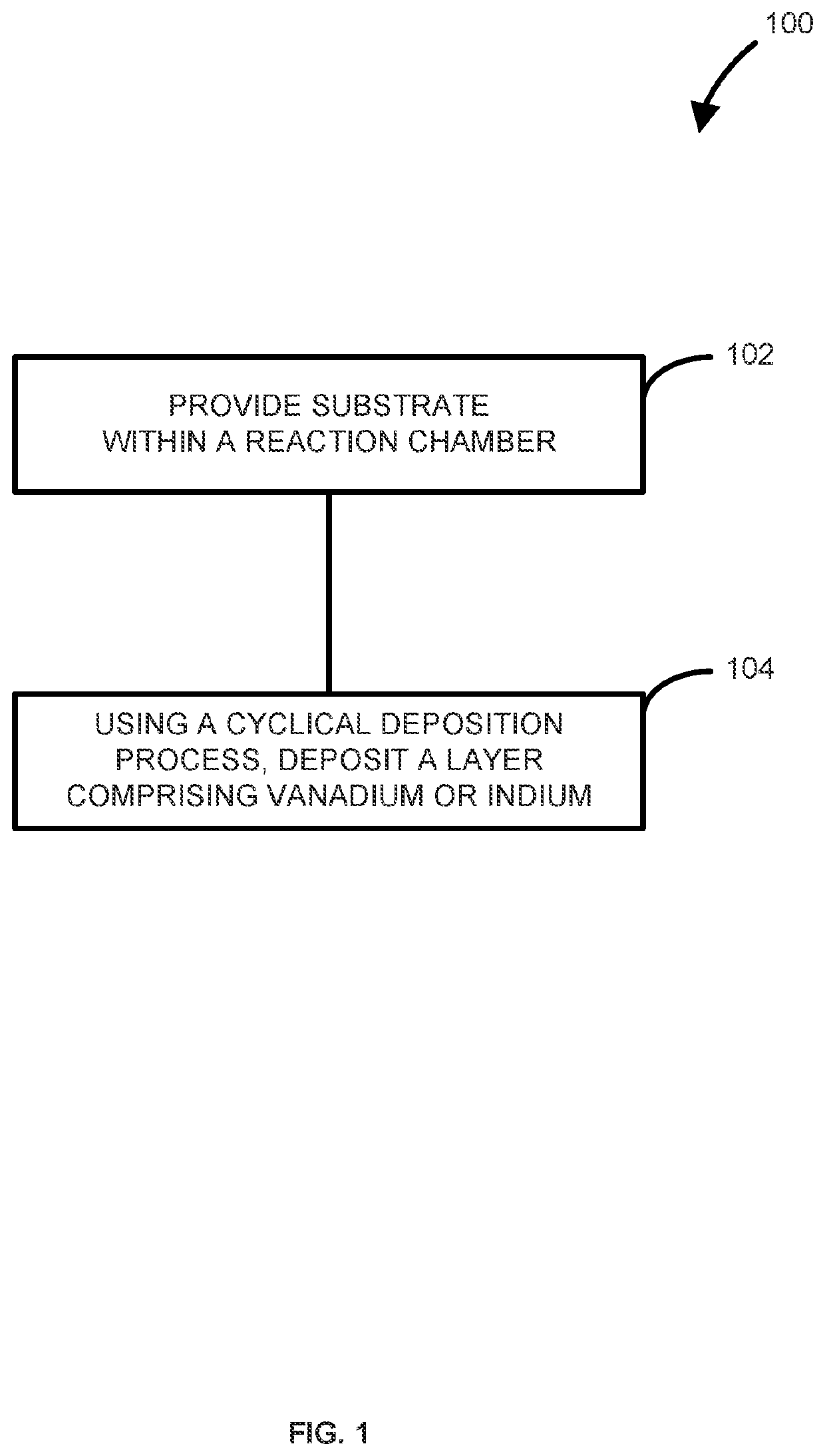

Method of forming structures including a vanadium or indium layer

ActiveUS20210242011A1Readily apparentTransistorSemiconductor/solid-state device manufacturingIndiumChemical physics

Methods and systems for depositing vanadium and / or indium layers onto a surface of a substrate and structures and devices formed using the methods are disclosed. An exemplary method includes using a cyclical deposition process, depositing a vanadium and / or indium layer onto the surface of the substrate. The cyclical deposition process can include providing a vanadium and / or indium precursor to the reaction chamber and separately providing a reactant to the reaction chamber. The cyclical deposition process may desirably be a thermal cyclical deposition process. Exemplary structures can include field effect transistor structures, such as gate all around structures. The vanadium and / or indium layers can be used, for example, as barrier layers or liners, as work function layers, as dipole shifter layers, or the like.

Owner:ASM IP HLDG BV

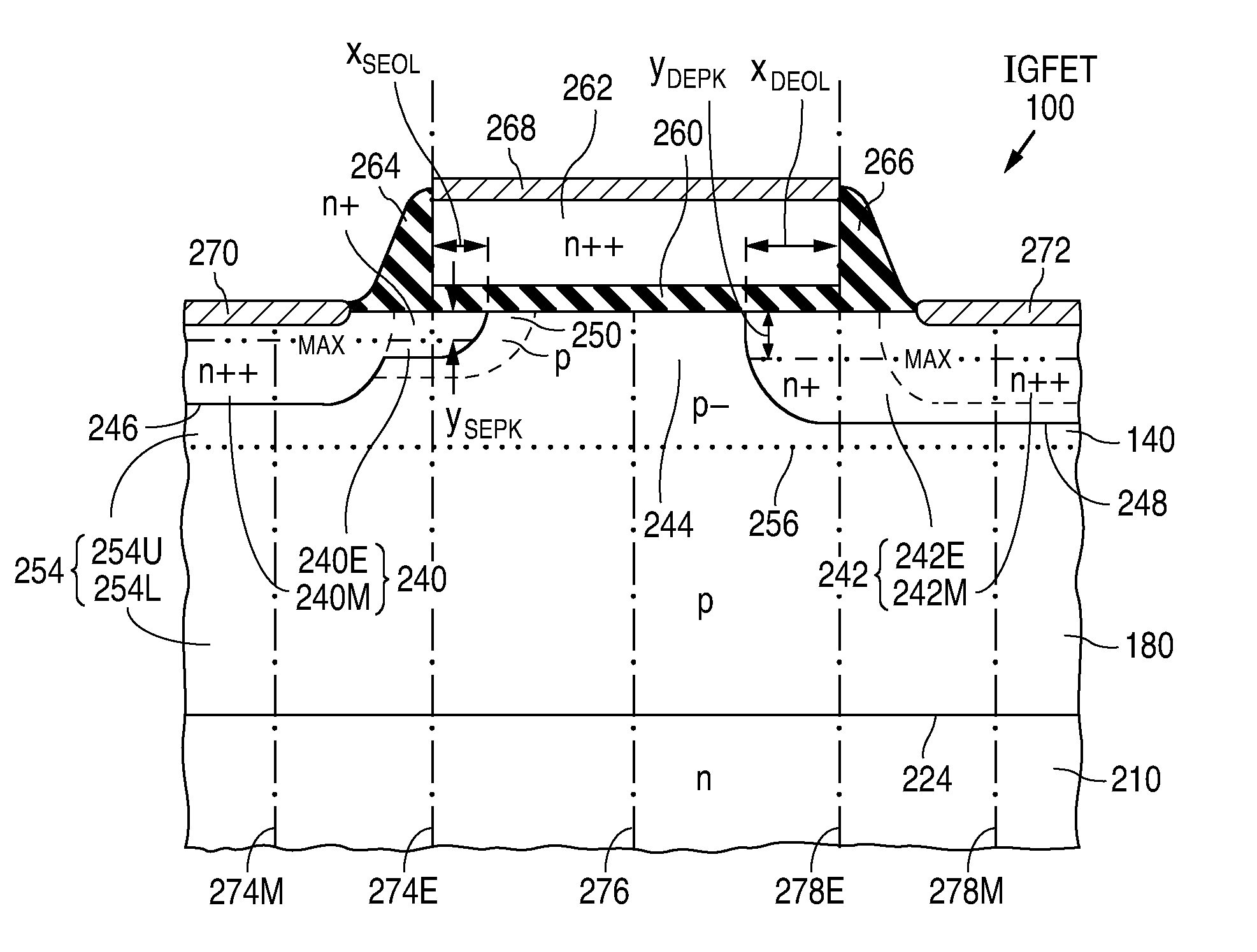

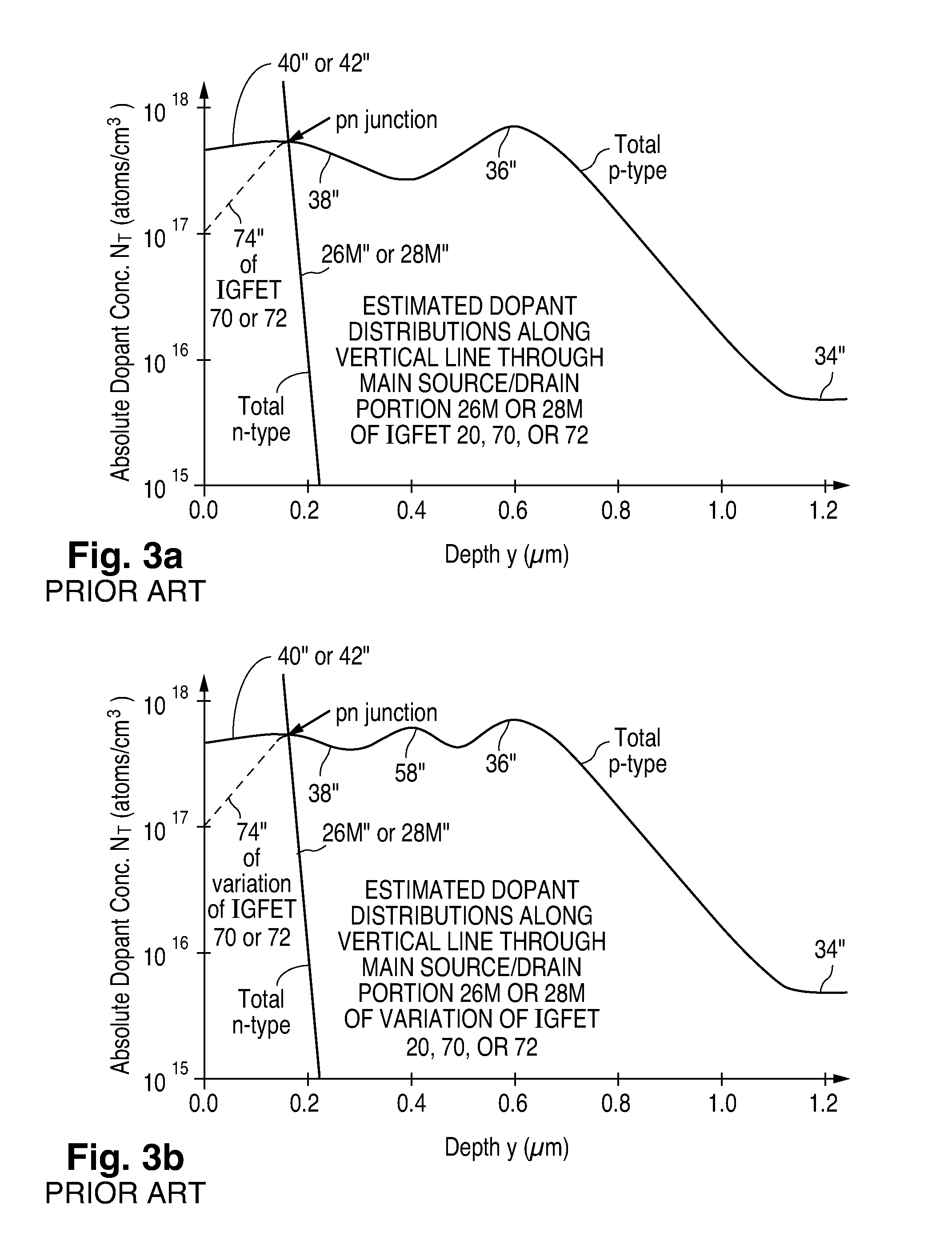

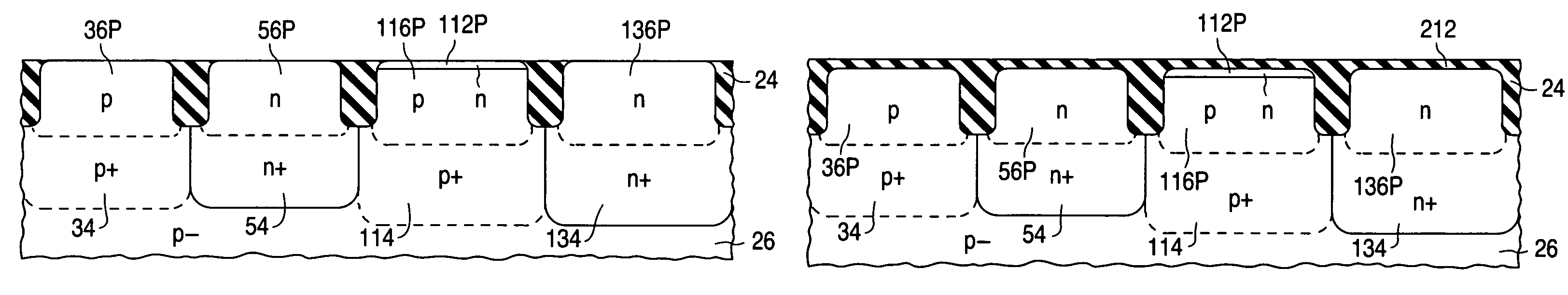

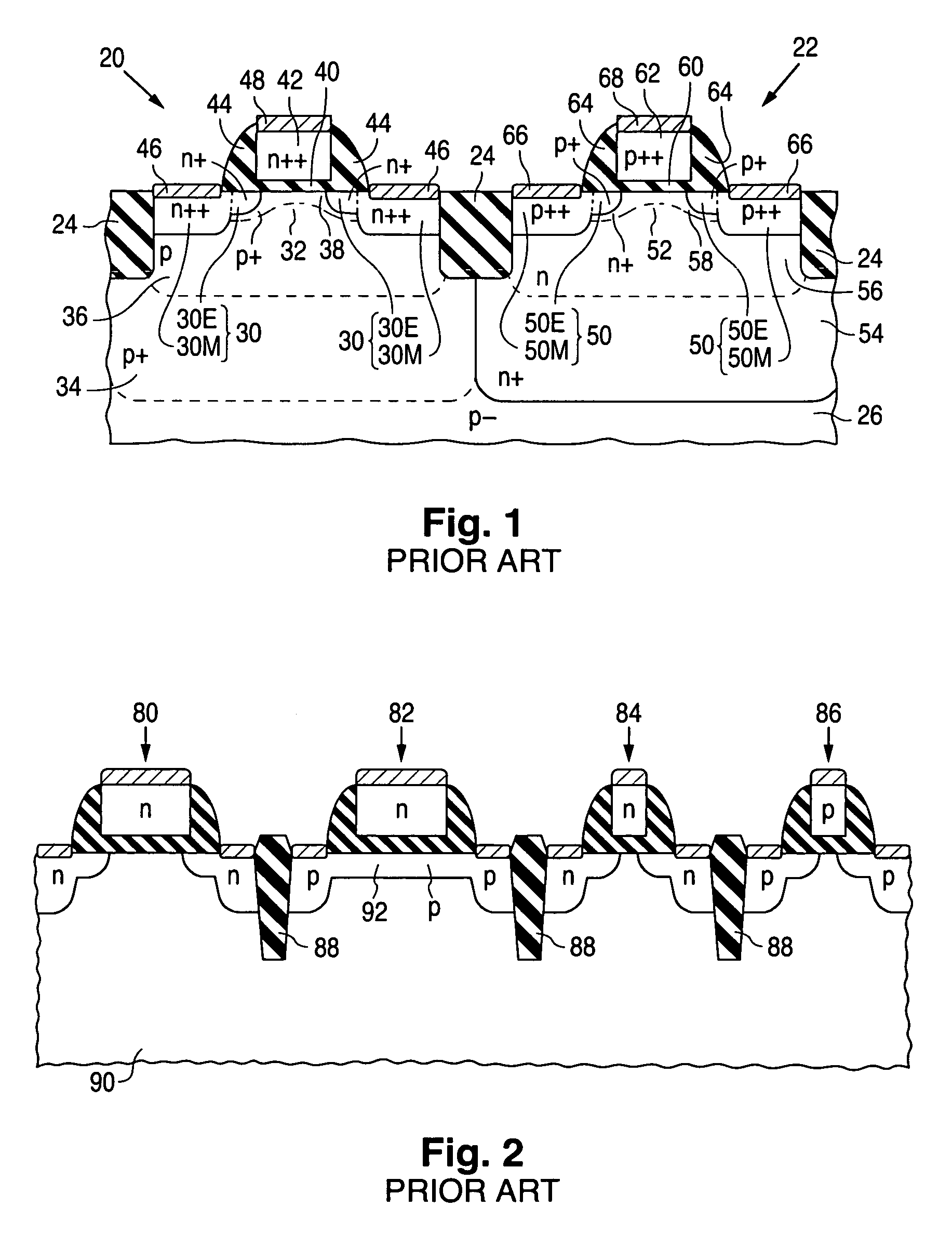

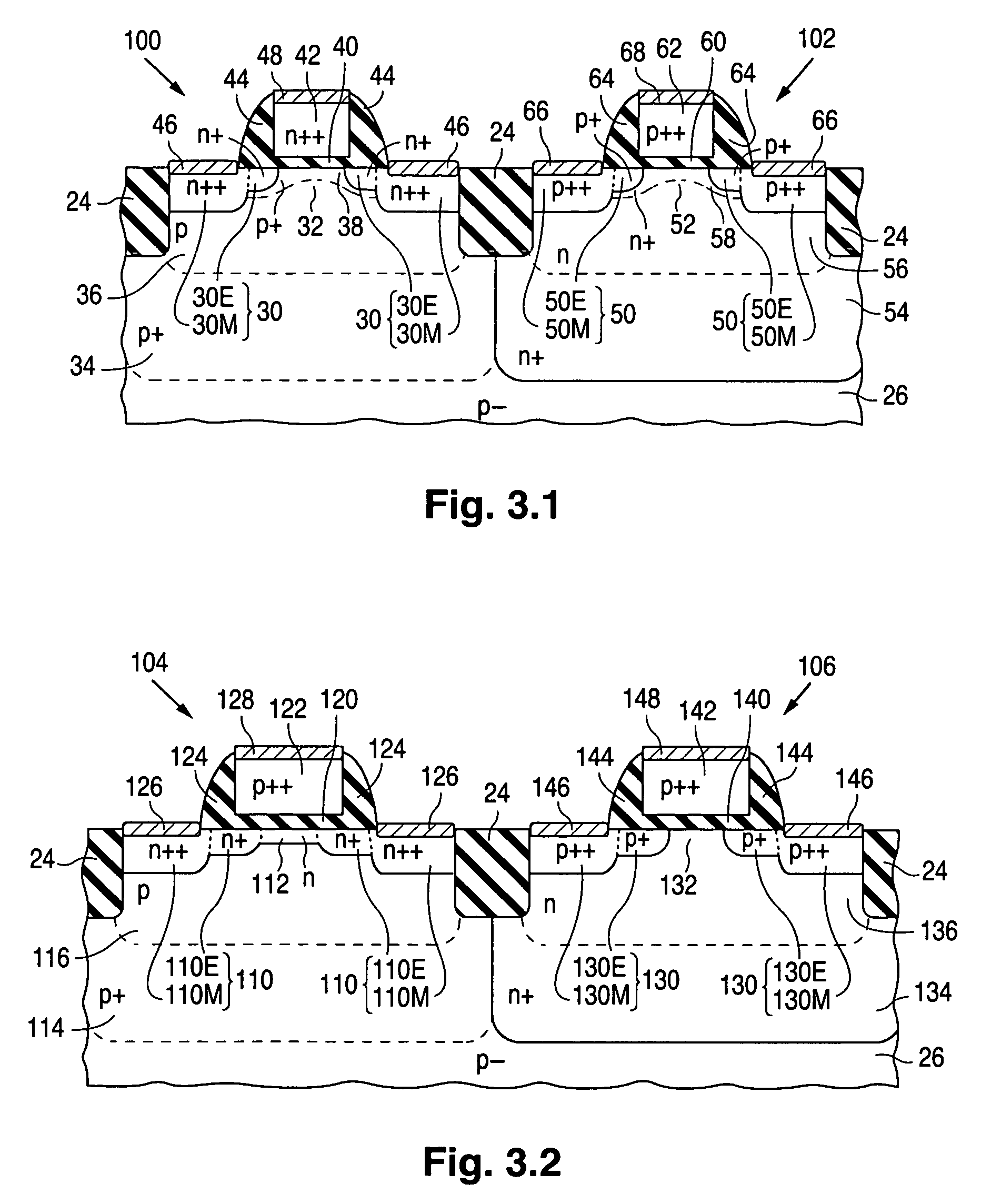

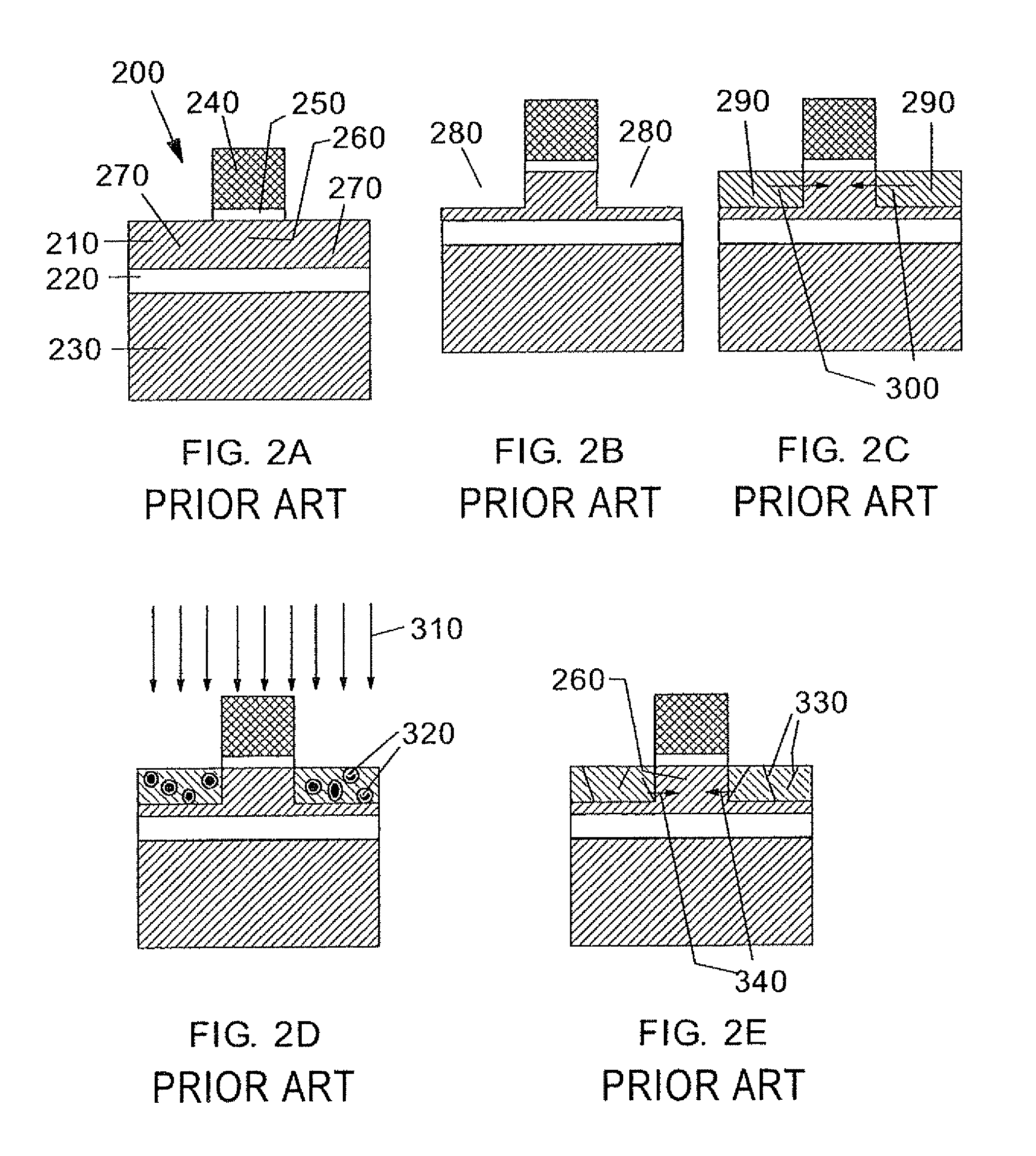

Fabrication of semiconductor structure having asymmetric field-effect transistor with tailored pocket portion along source/drain zone

ActiveUS8163619B2Good analog characteristicReduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingDopantGate dielectric

An asymmetric insulated-gate field effect transistor (100U or 102U) is provided along an upper surface of a semiconductor body so as to have first and second source / drain zones (240 and 242 or 280 and 282) laterally separated by a channel zone (244 or 284) of the transistor's body material. A gate electrode (262 or 302) overlies a gate dielectric layer (260 or 300) above the channel zone. A pocket portion (250 or 290) of the body material more heavily doped than laterally adjacent material of the body material extends along largely only the first of the S / D zones and into the channel zone. The vertical dopant profile of the pocket portion is tailored to reach a plurality of local maxima at respective locations (PH-1-PH-3-NH-3) spaced apart from one another. This typically enables the transistor to have reduced current leakage.

Owner:NAT SEMICON CORP

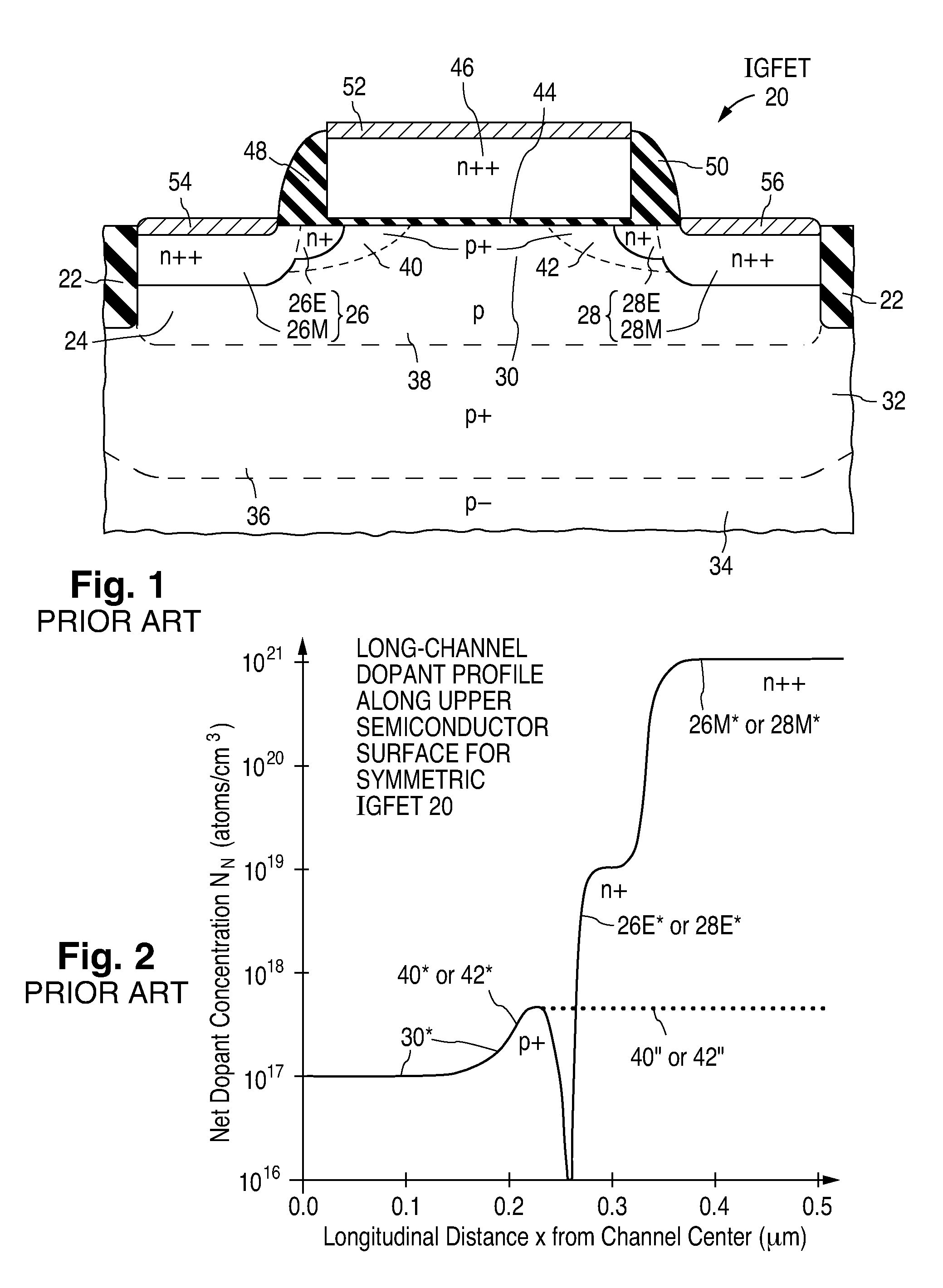

Fabrication of semiconductor structure having N-channel channel-junction field-effect transistor

ActiveUS7595243B1Performance characteristicHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

A semiconductor technology combines a normally off n-channel channel-junction insulated-gate field-effect transistor (“IGFET”) (104) and an n-channel surface-channel IGFET (100 or 160) to reduce low-frequency 1 / f noise. The channel-junction IGFET is normally fabricated to be of materially greater gate dielectric thickness than the surface-channel IGFET so as to operate across a greater voltage range than the surface-channel IGFET. A p-channel surface-channel IGFET (102 or 162), which is typically fabricated to be of approximately the same gate-dielectric thickness as the n-channel surface-channel IGFET, is preferably combined with the two n-channel IGFETs to produce a complementary-IGFET structure. A further p-channel IGFET (106, 180, 184, or 192), which is typically fabricated to be of approximately the same gate dielectric thickness as the n-channel channel-junction IGFET, is also preferably included. The further p-channel IGFET can be a surface-channel or channel-junction device.

Owner:NAT SEMICON CORP

Field-effect semiconductor device, and method of fabrication

ActiveUS20100155720A1Leakage currentLittle and no physical impairmentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionField effect

A heterojunction field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region and electrically coupled to the 2DEG layer. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film and insulating film, whereby a depletion zone is normally created in the 2DEG layer, making the device normally off. The p-type metal oxide semiconductor film of high hole concentration serves for the normally-off performance of the device with low gate leak current, and the insulating film for further reduction of gate leak current.

Owner:SANKEN ELECTRIC CO LTD

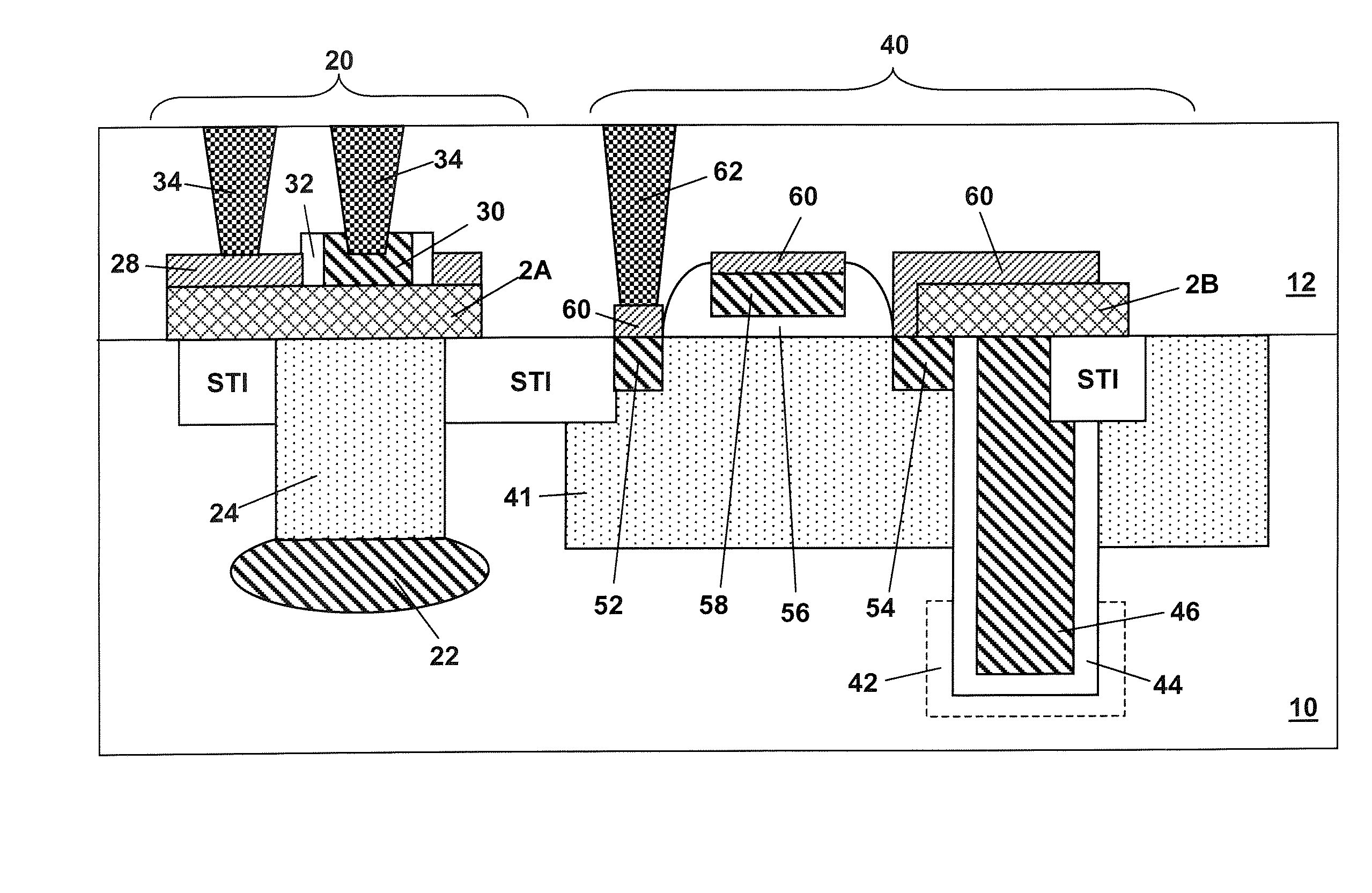

INTEGRATION OF A SiGe- OR SiGeC-BASED HBT WITH A SiGe- OR SiGeC-STRAPPED SEMICONDUCTOR DEVICE

ActiveUS20080111154A1TransistorSolid-state devicesHeterojunction bipolar transistorField-effect transistor

The present invention provides an integrated semiconductor device that includes a semiconductor substrate, a first device containing a heterojunction bipolar transistor (HBT) located in a first region of the semiconductor substrate, wherein the HBT includes a base region containing a first portion of a SiGe or SiGeC layer, and a second device located in a second region of the semiconductor substrate, wherein the second device includes an interconnect containing a second portion of the SiGe or SiGeC layer. In a specific embodiment of the present invention, the second device is a memory device including a trench capacitor and a field effect transistor (FET) that are electrically connected together by the second portion of the SiGe or SiGeC layer. Alternatively, the second device is a trench-biased PNPN silicon controlled rectifier (SCR). The present invention also provides a novel reversibly programmable device or a novel memory device formed by a novel trench-biased SCR device.

Owner:GLOBALFOUNDRIES US INC

Monolithic integrated circuit of a field-effect semiconductor device and a diode

InactiveUS20070228477A1Flow assuranceEasy to FeedbackTransistorSolid-state devicesMESFETField effect

A field-effect semiconductor device such as a HEMT or MESFET is monolithically integrated with a Schottky diode for feedback, regeneration, or protection purposes. The field-effect semiconductor device includes a main semiconductor region having formed thereon a source, a drain, and a gate between the source and the drain. Also formed on the main semiconductor region, preferably between gate and drain, is a Schottky electrode electrically coupled to the source. The Schottky electrode provides a Schottky diode in combination with the main semiconductor region. A current flow is assured from Schottky electrode to drain without interruption by a depletion region expanding from the gate.

Owner:SANKEN ELECTRIC CO LTD

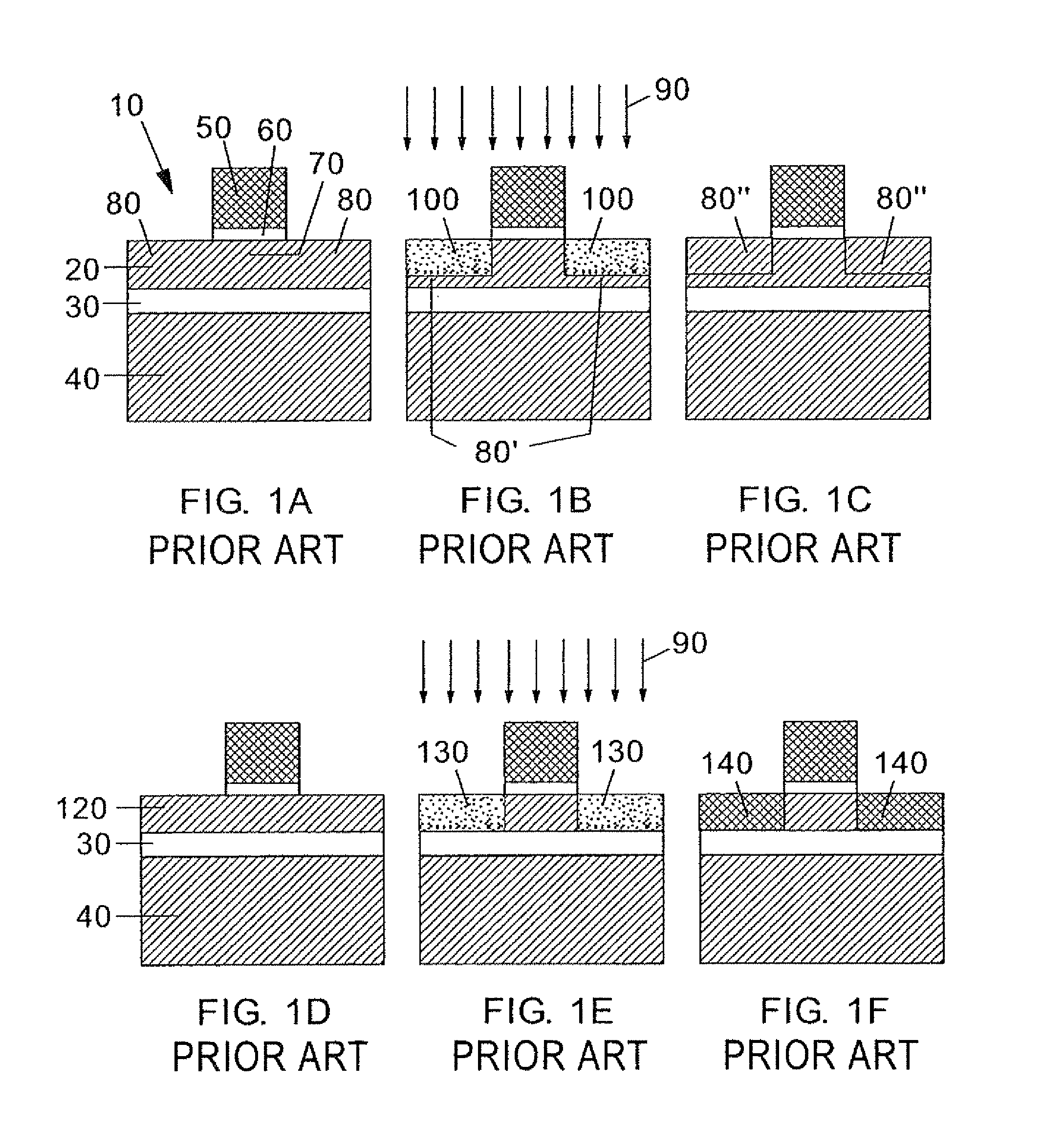

Ion implantation combined with in situ or ex situ heat treatment for improved field effect transistors

InactiveUS7968459B2Reduce and avoidReduce harmSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringField effect

This invention teaches methods of combining ion implantation steps with in situ or ex situ heat treatments to avoid and / or minimize implant-induced amorphization (a potential problem for source / drain (S / D) regions in FETs in ultrathin silicon on insulator layers) and implant-induced plastic relaxation of strained S / D regions (a potential problem for strained channel FETs in which the channel strain is provided by embedded S / D regions lattice mismatched with an underlying substrate layer). In a first embodiment, ion implantation is combined with in situ heat treatment by performing the ion implantation at elevated temperature. In a second embodiment, ion implantation is combined with ex situ heat treatments in a “divided-dose-anneal-in-between” (DDAB) scheme that avoids the need for tooling capable of performing hot implants.

Owner:GLOBALFOUNDRIES INC

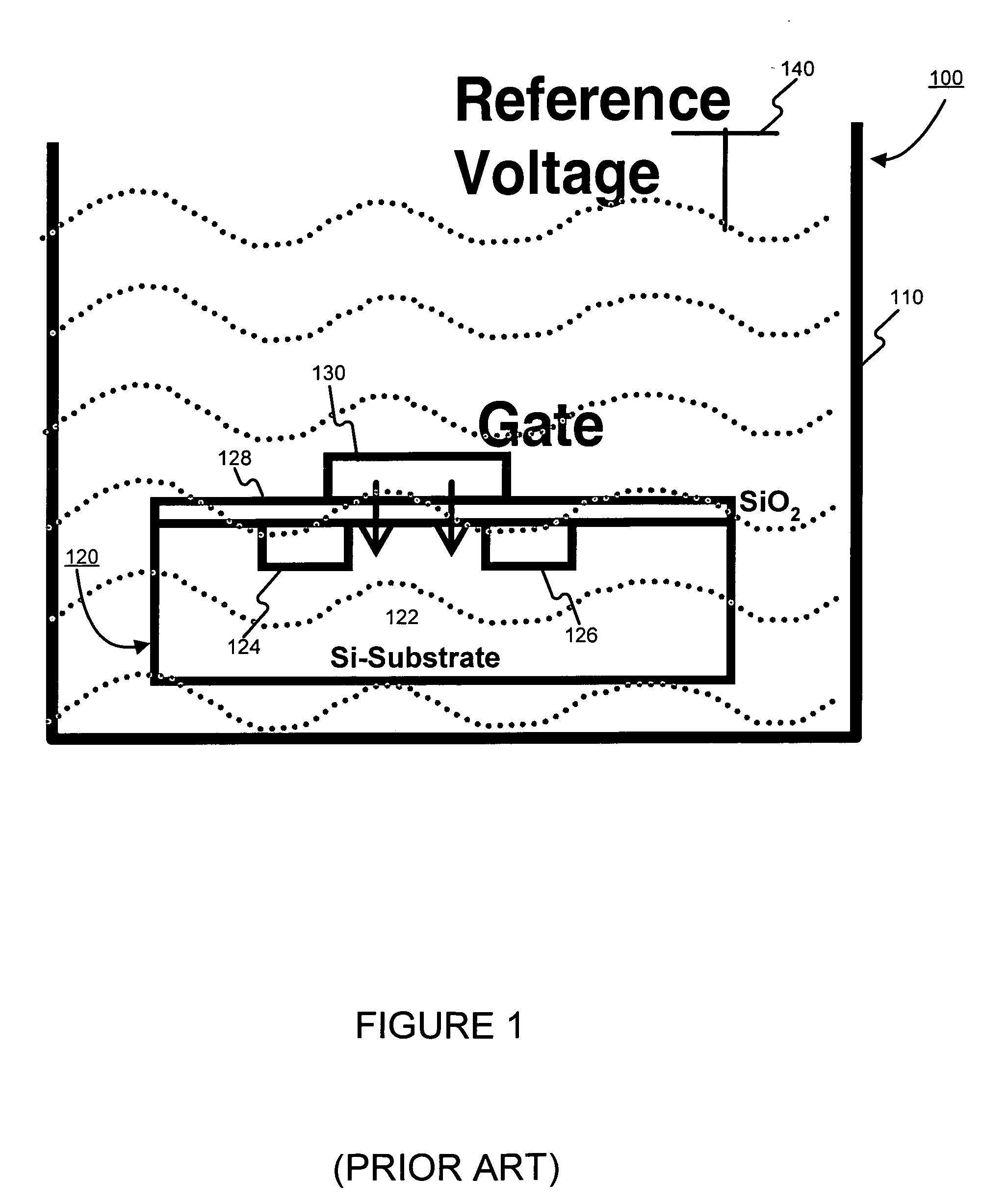

Microelectronic device and method for label-free detection and quantification of biological and chemical molecules

InactiveUS20020012937A1Wide scope of practicalWide scope of worthwhile utilizationBioreactor/fermenter combinationsBiological substance pretreatmentsCapacitanceField-effect transistor

Molecular recognition-based electronic sensor, which is gateless, depletion mode field effect transistor consisting of source and drain diffusions, a depletion-mode implant, and insulating layer chemically modified by immobilized molecular receptors that enables miniaturized label-free molecular detection amenable to high-density array formats. The conductivity of the active channel modulates current flow through the active channel when a voltage is applied between the source and drain diffusions. The conductivity of the active channel is determined by the potential of the sample solution in which the device is immersed and the device-solution interfacial capacitance. The conductivity of the active channel modulates current flow through the active channel when a voltage is applied between the source and drain diffusions. The interfacial capacitance is determined by the extent of occupancy of the immobilized receptor molecules by target molecules. Target molecules can be either charged or uncharged. Change in interfacial capacitance upon target molecule binding results in modulation of an externally supplied current through the channel.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Method and structure to create multiple device widths in finfet technology in both bulk and soi

ActiveUS20050161739A1Remove/reduce unwanted spacersSmall activity areaTransistorSolid-state devicesEngineeringField-effect transistor

Disclosed is a structure and method for producing a fin-type field effect transistor (FinFET) that has a buried oxide layer over a substrate, at least one first fin structure and at least one second fin structure positioned on the buried oxide layer. First spacers are adjacent the first fin structure and second spacers are adjacent the second fin structure. The first spacers cover a larger portion of the first fin structure when compared to the portion of the second fin structure covered by the second spacers. Those fins that have larger spacers will receive a smaller area of semiconductor doping and those fins that have smaller spacers will receive a larger area of semiconductor doping. Therefore, there is a difference in doping between the first fins and the second fins that is caused by the differently sized spacers. The difference in doping between the first fins and the second fins changes an effective width of the second fins when compared to the first fins.

Owner:GLOBALFOUNDRIES US INC

Active matrix oled voltage drive pixel circuit

InactiveUS20030107565A1Cathode-ray tube indicatorsInput/output processes for data processingSignal onSignal lines

There is provided a circuit for driving a current mode light modulating device. The circuit includes (a) a capacitor for storing a data voltage, (b) a field effect transistor (FET) controlled by a signal on a scan line, for coupling the data voltage from a signal line to the capacitor, and (c) a current source, controlled by the stored data voltage, for driving the device with current provided from a power line. The power line is in a plane that is geometrically parallel to a plane within which the scan line is located.

Owner:INNOLUX CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com