Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

179 results about "Mask ROM" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Mask ROM (MROM) is a type of read-only memory (ROM) whose contents are programmed by the integrated circuit manufacturer (rather than by the user). The terminology mask comes from integrated circuit fabrication, where regions of the chip are masked off during the process of photolithography.

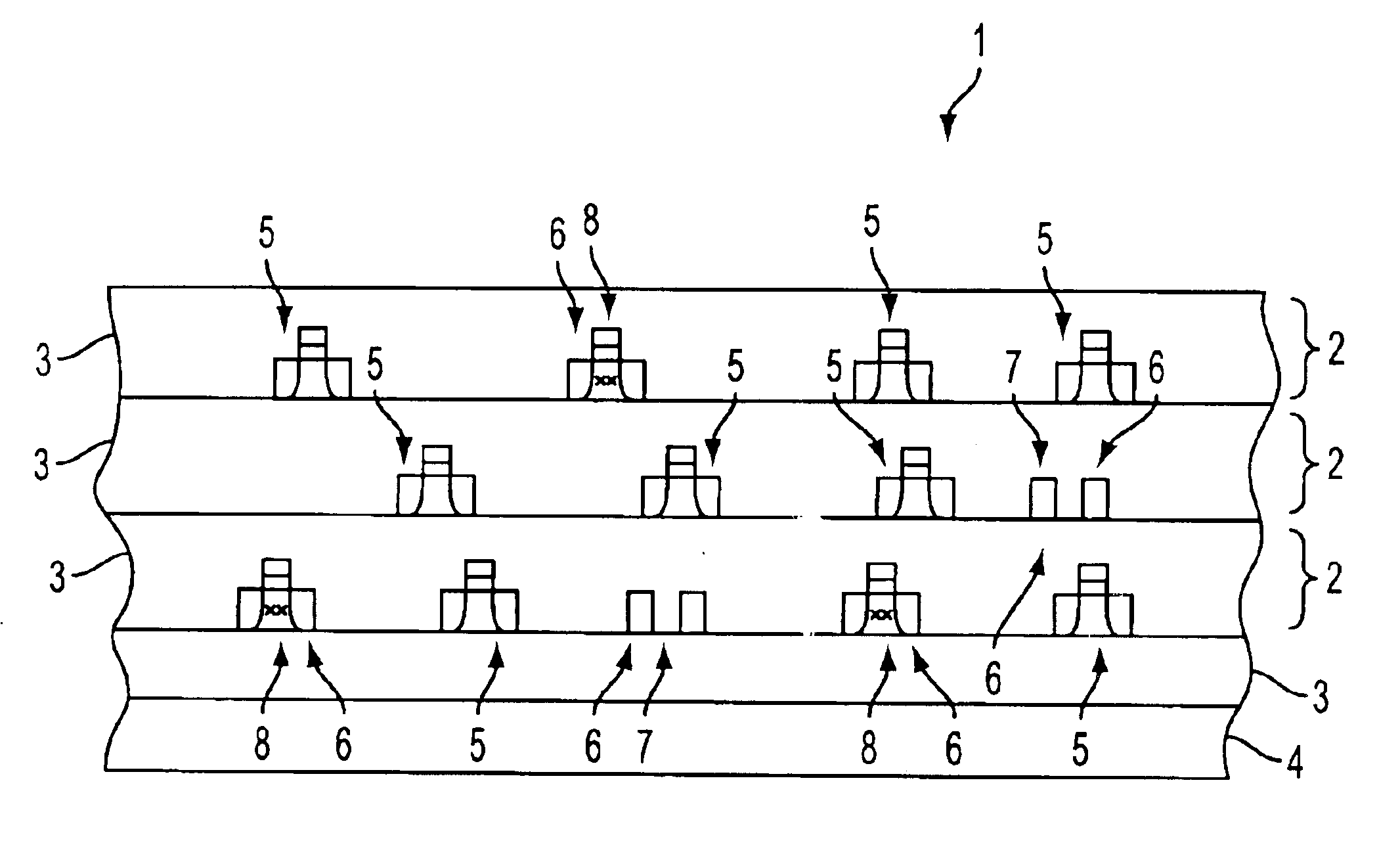

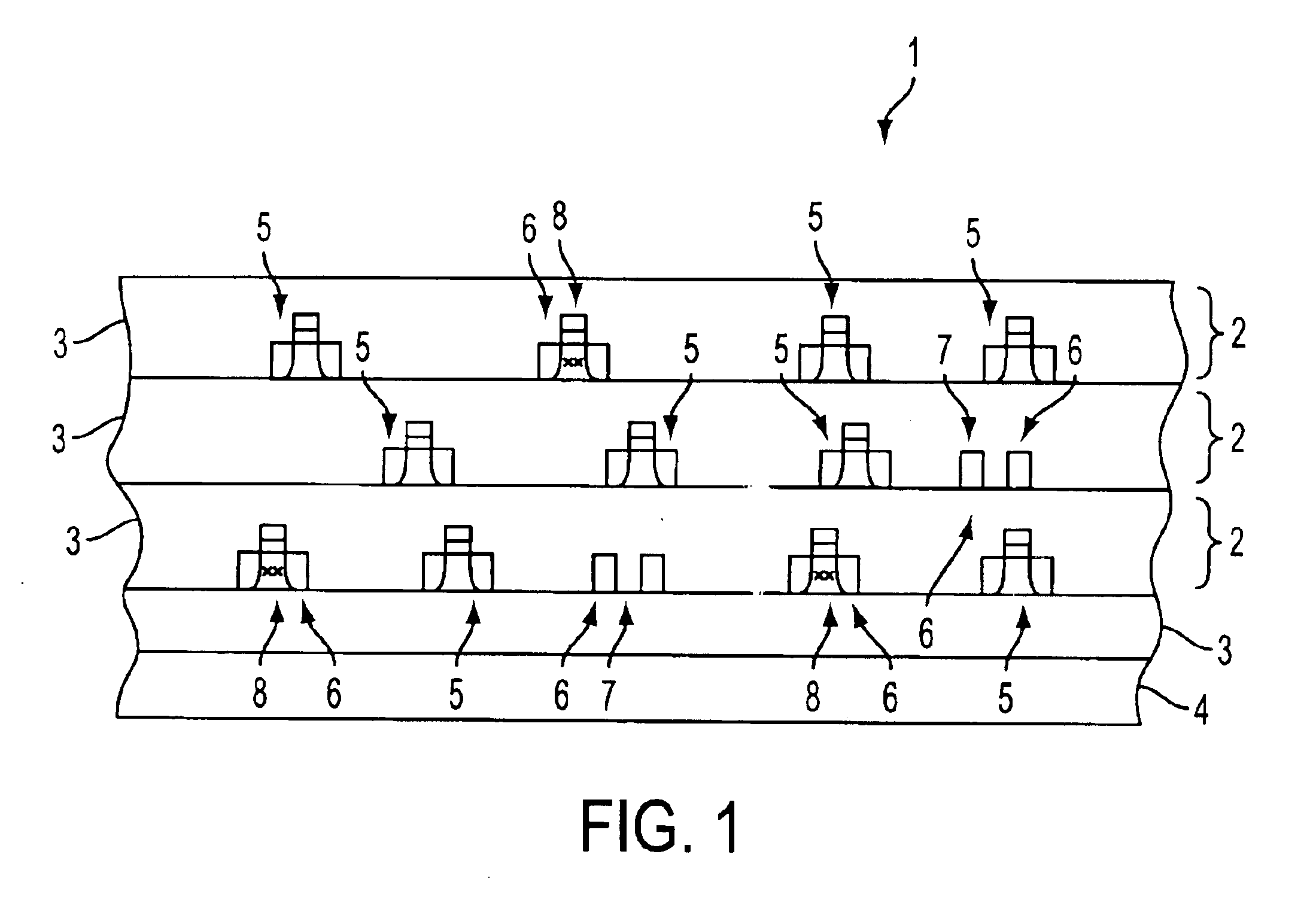

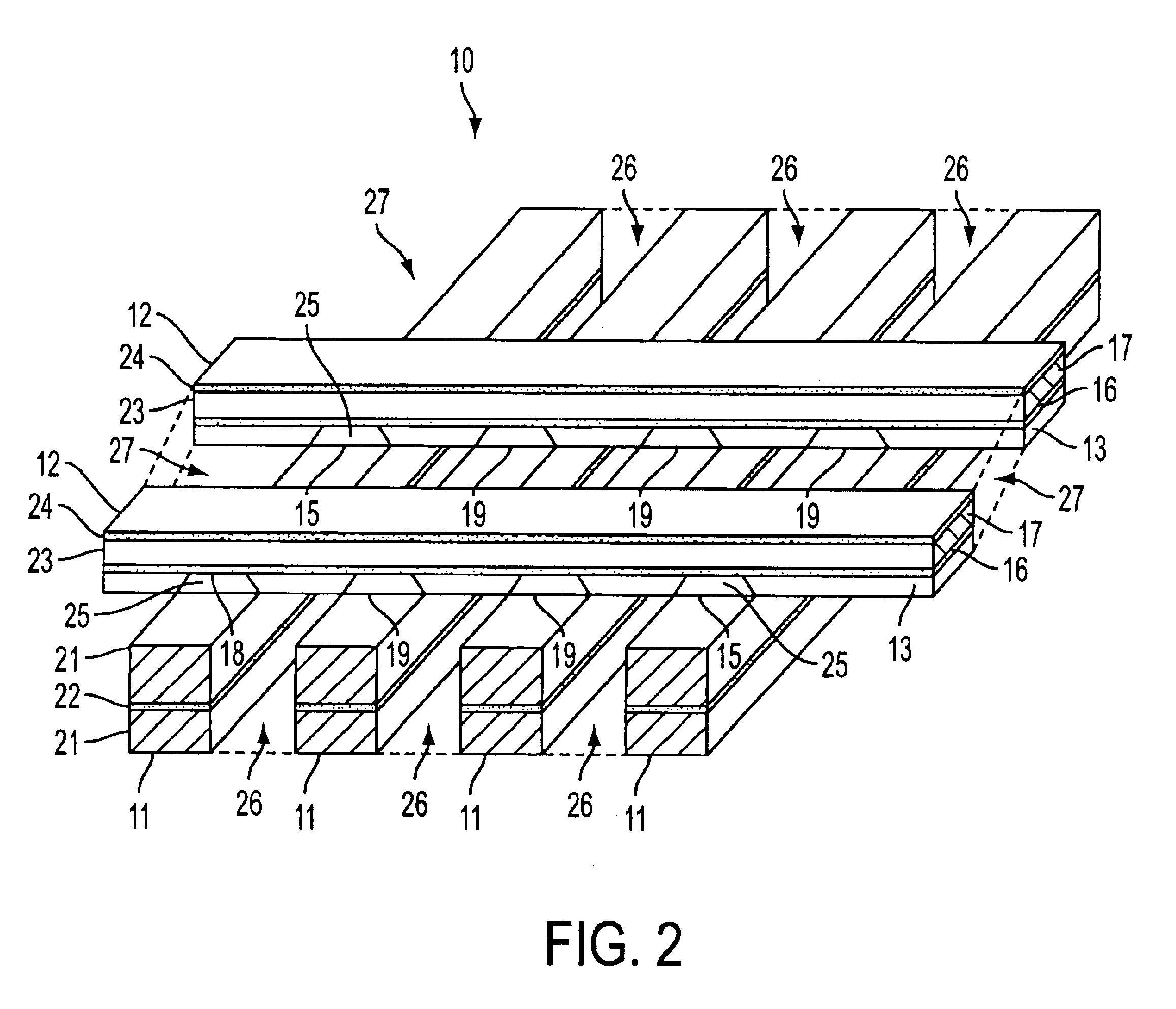

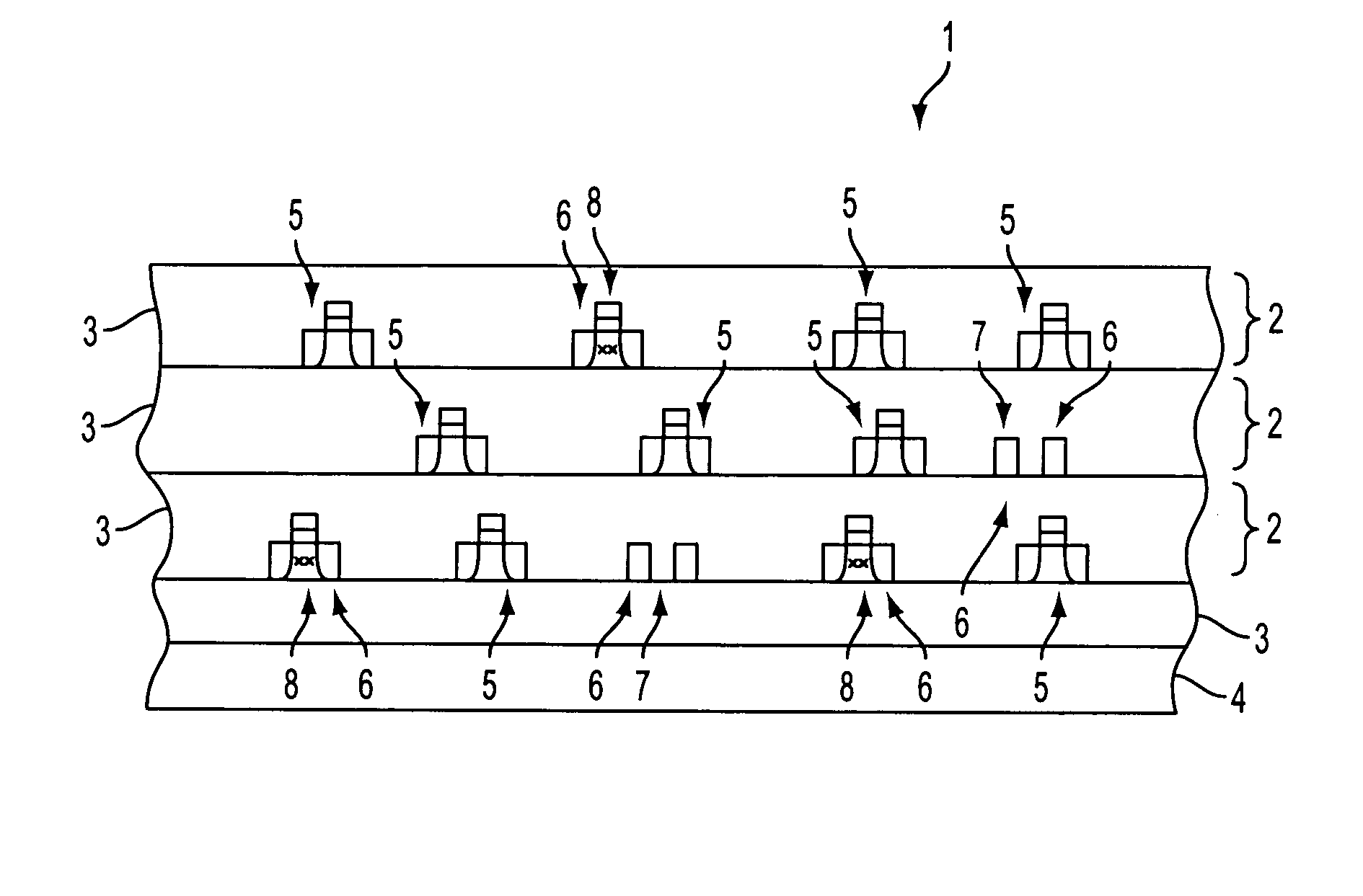

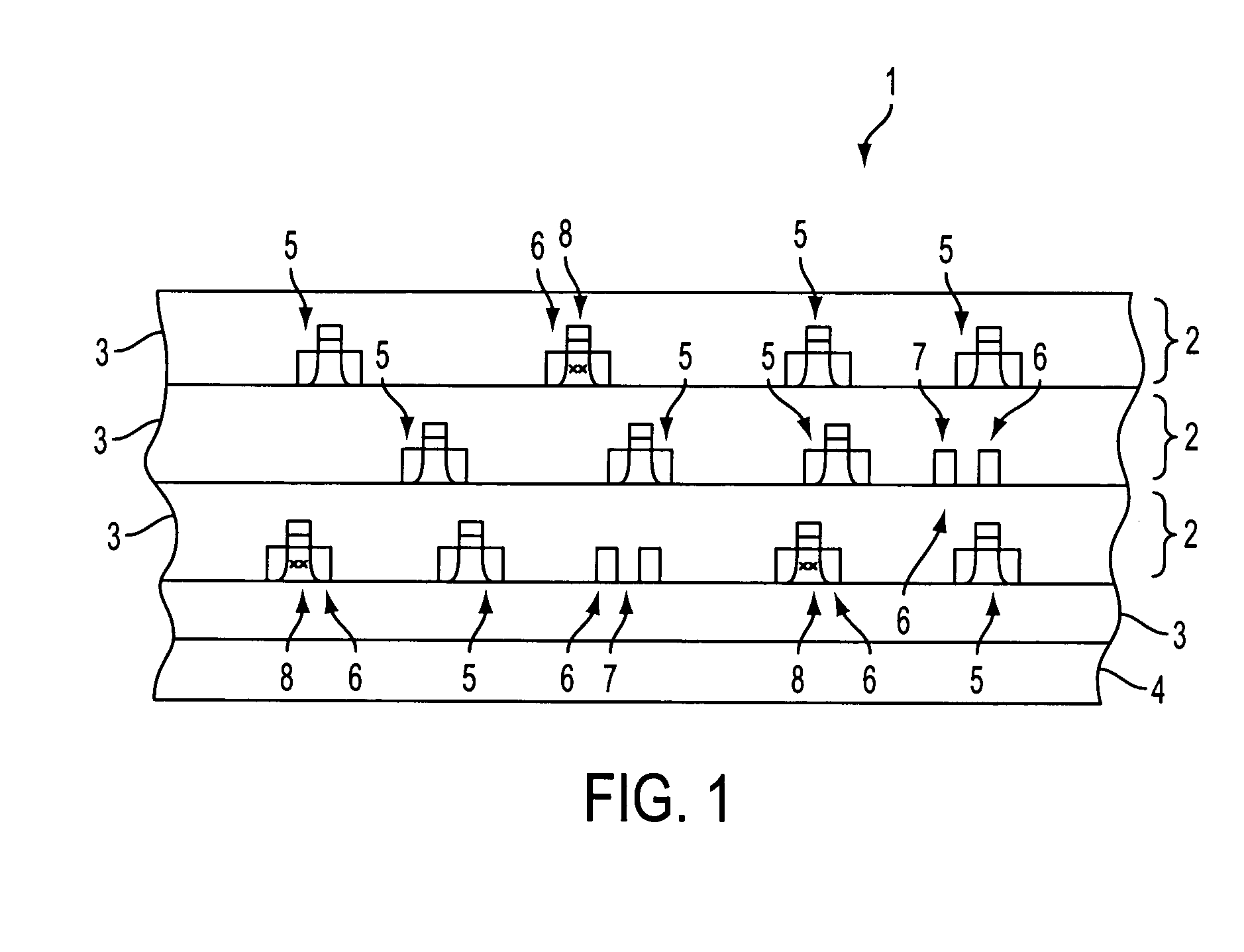

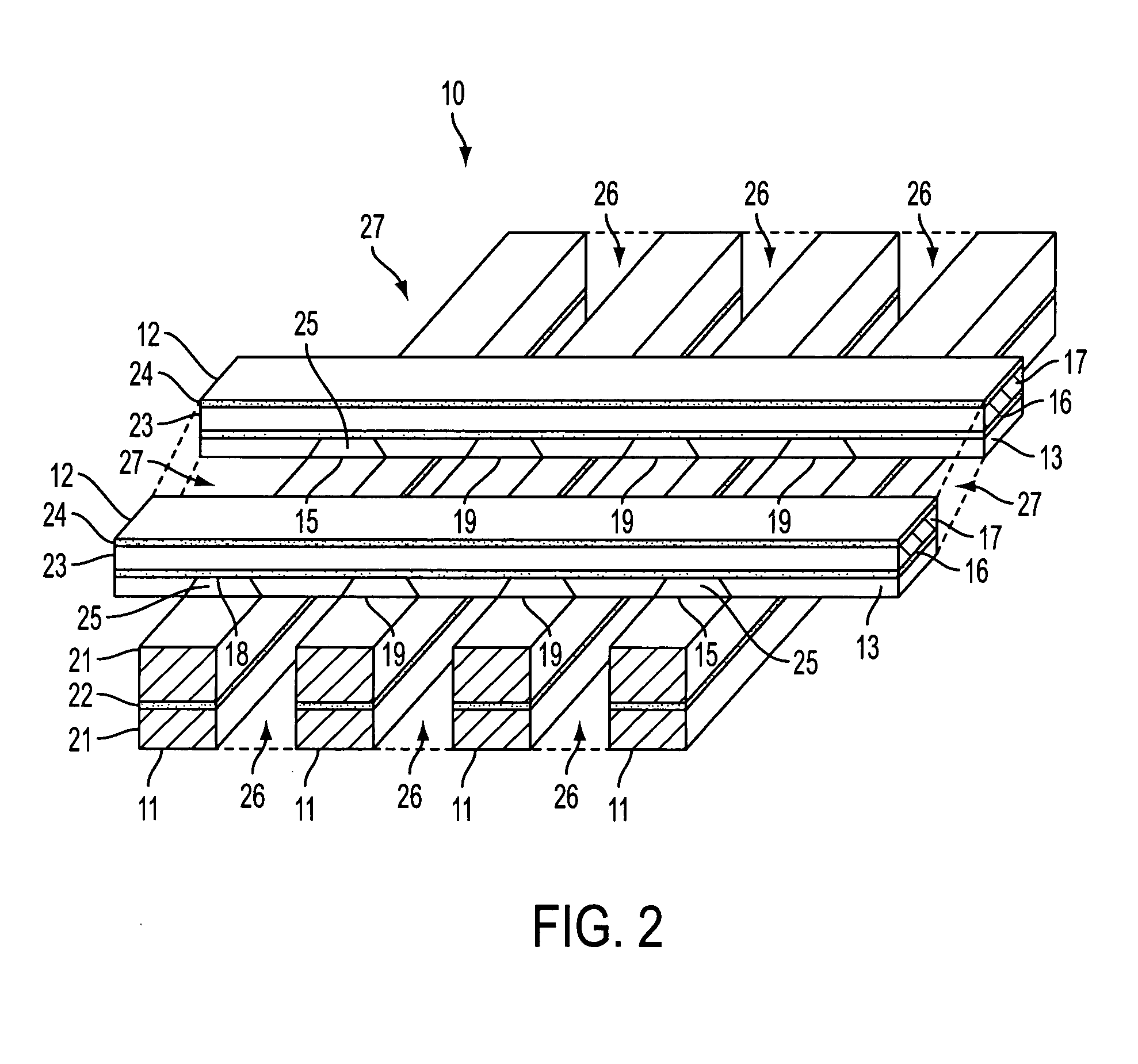

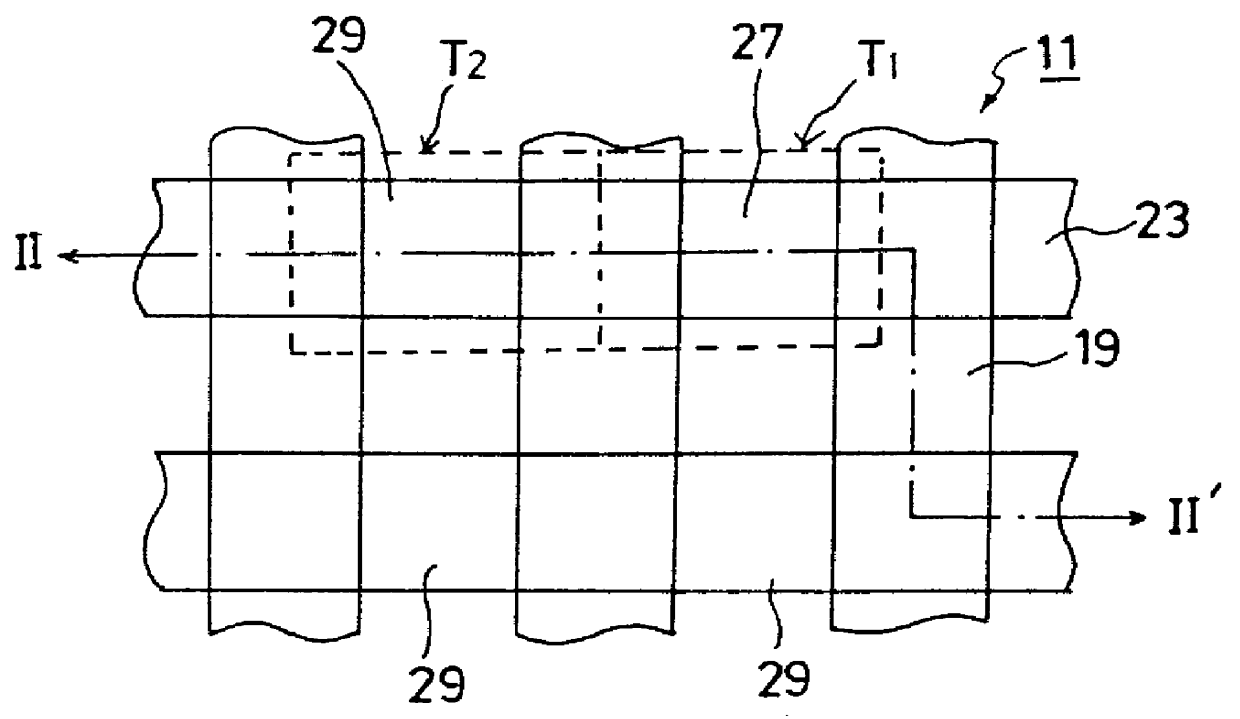

TFT mask ROM and method for making same

There is provided a monolithic three dimensional TFT mask ROM array. The array includes a plurality of device levels. Each of the plurality of device levels contains a first set of enabled TFTs and a second set of partially or totally disabled TFTs.

Owner:WODEN TECH INC

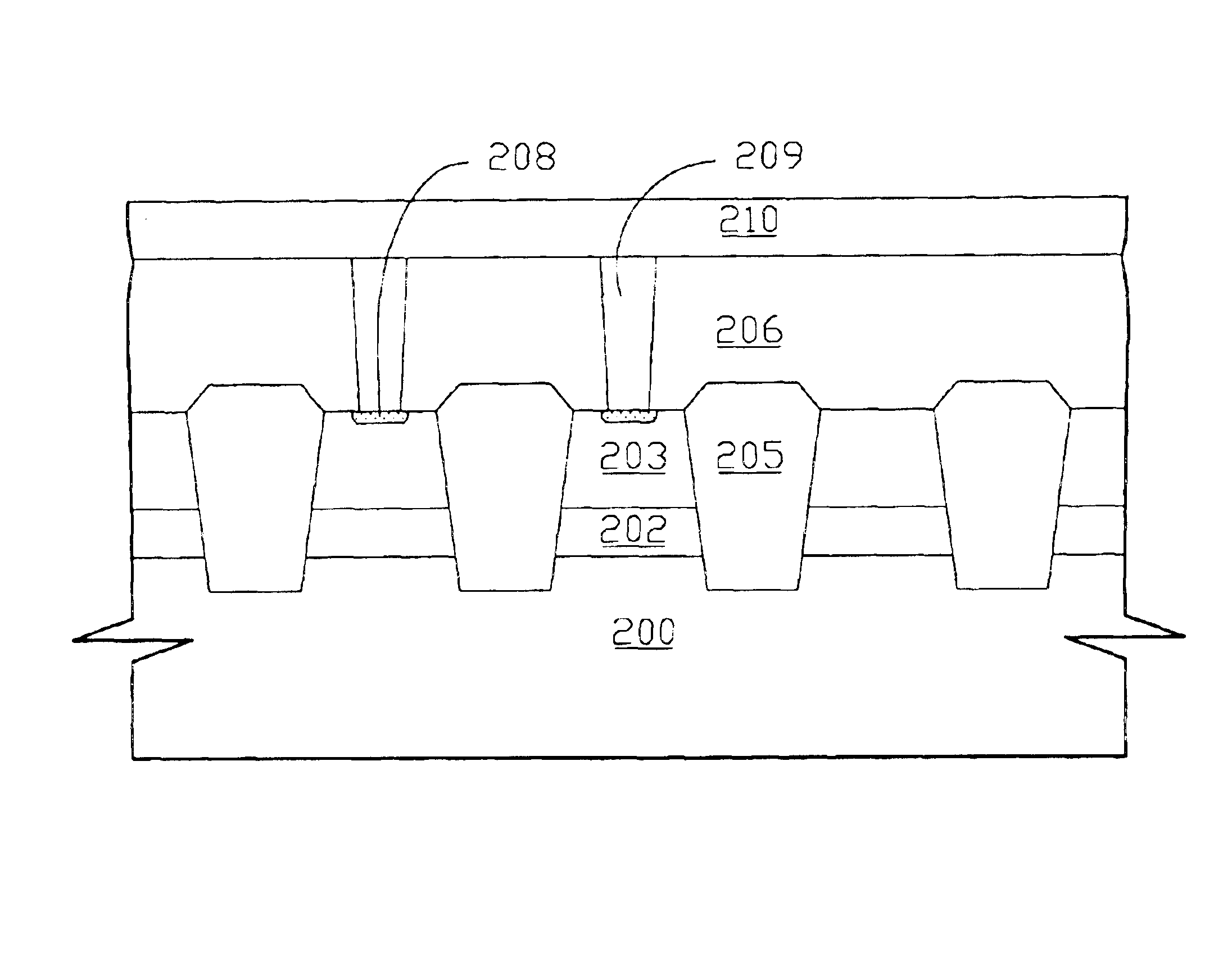

Semiconductor device and a method of manufacturing the same

InactiveUS20060125024A1Improve reliabilityGood effectSolid-state devicesSemiconductor/solid-state device manufacturingMask ROMDevice material

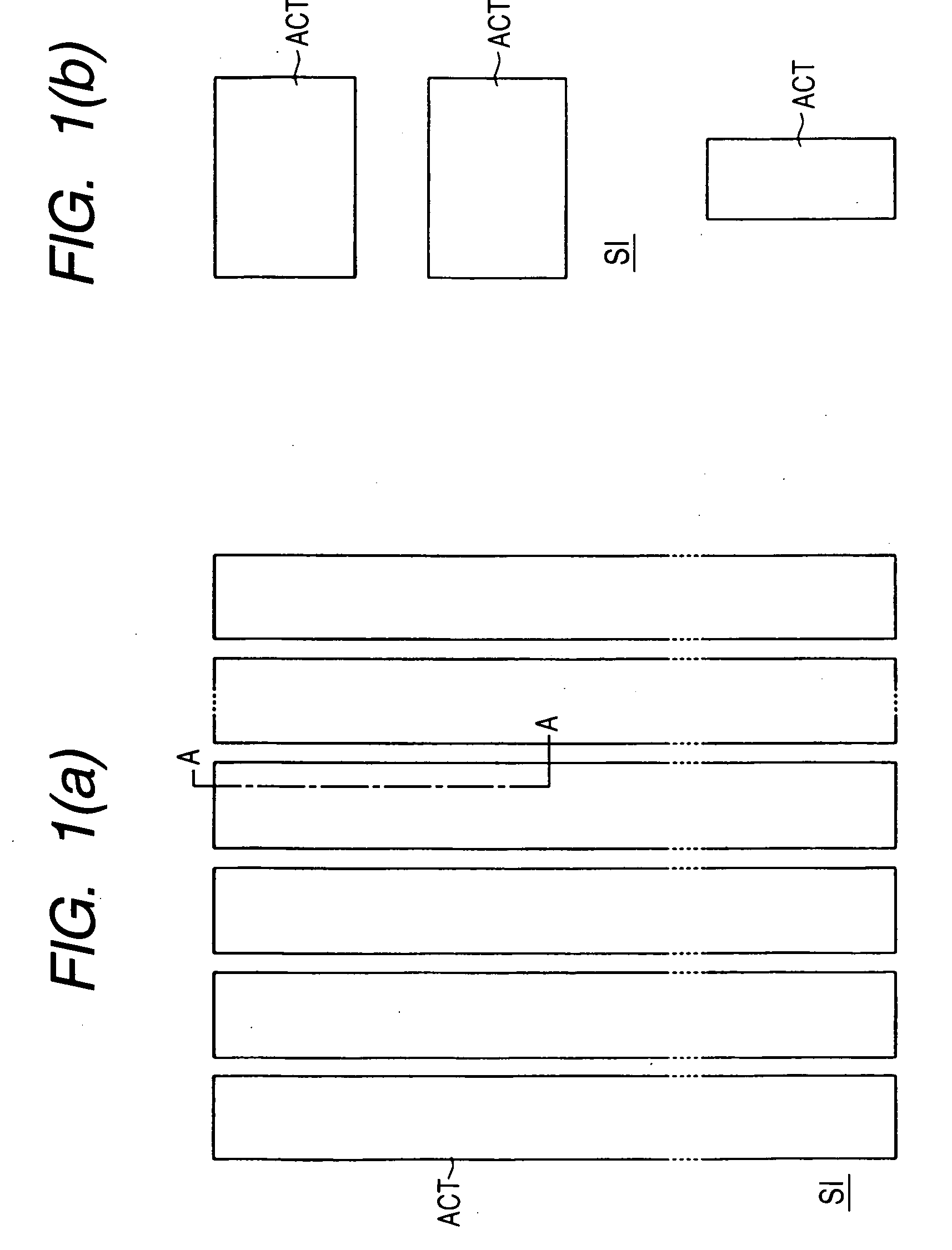

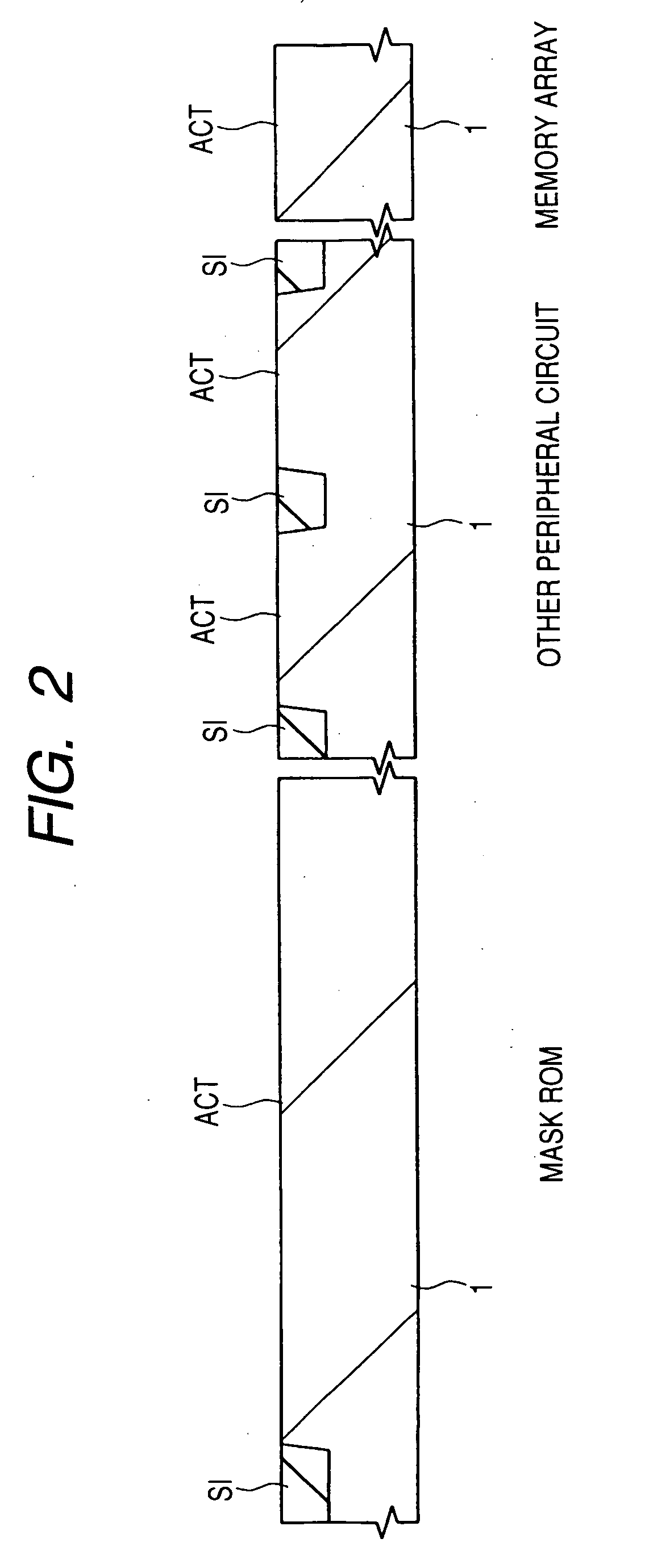

To improve reliability of FETs having element isolation regions for electrically isolating field effect transistors adjacent to each other in the gate length direction in a mask ROM region, the isolation regions are each constructed by field plate isolation formed simultaneously with gate electrodes of the field effect transistors. This relatively lessens a stress generated in an active region ACT sandwiched by the element isolation regions even if the isolation width of each element isolation region is made relatively small, specifically, less than 0.3 μm. It is therefore possible to relax or prevent the generation of crystal defects resulting from the stress, thereby reducing occurrence of an undesired leak current between the source and drain of each field effect transistor.

Owner:RENESAS TECH CORP

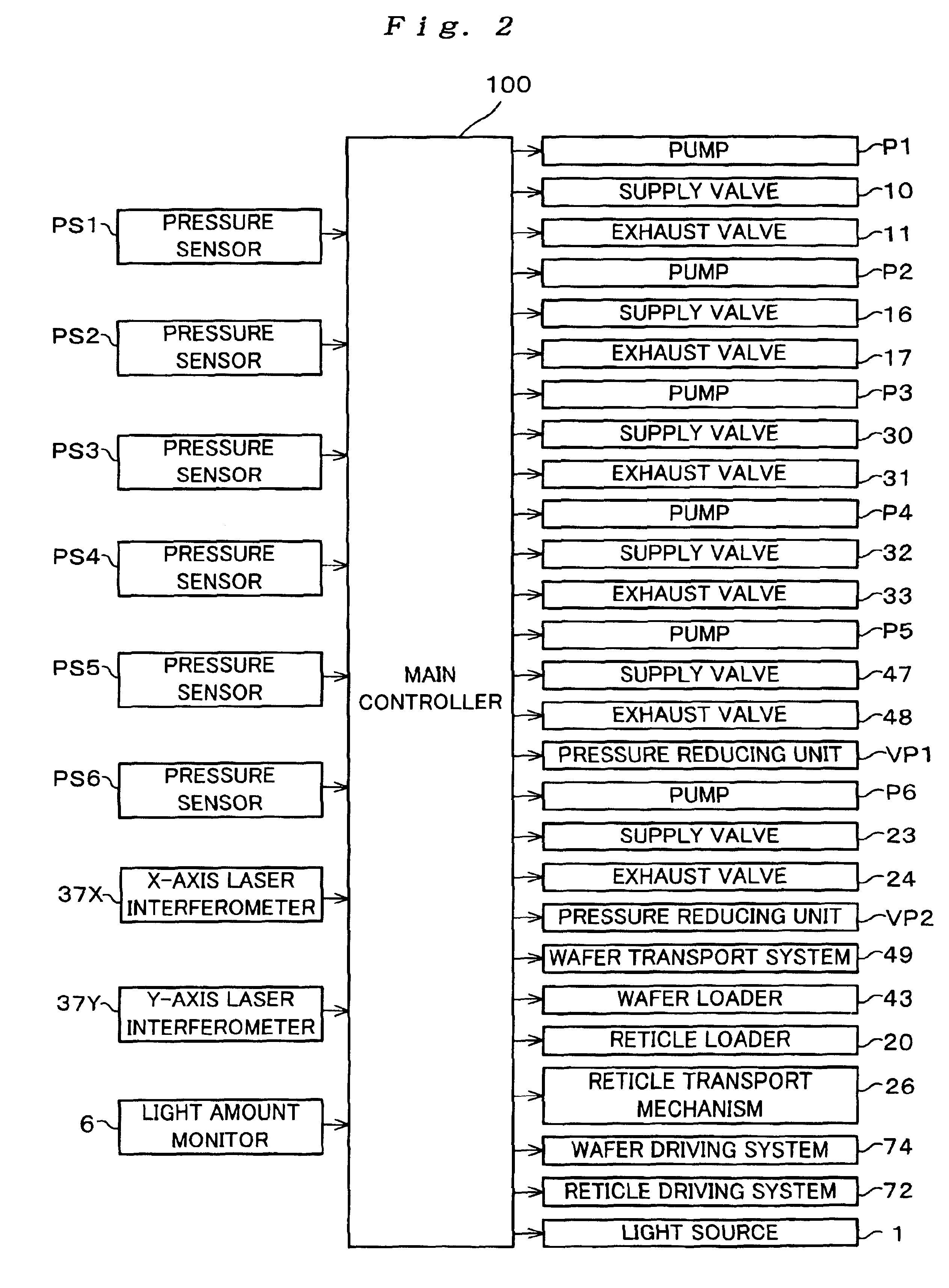

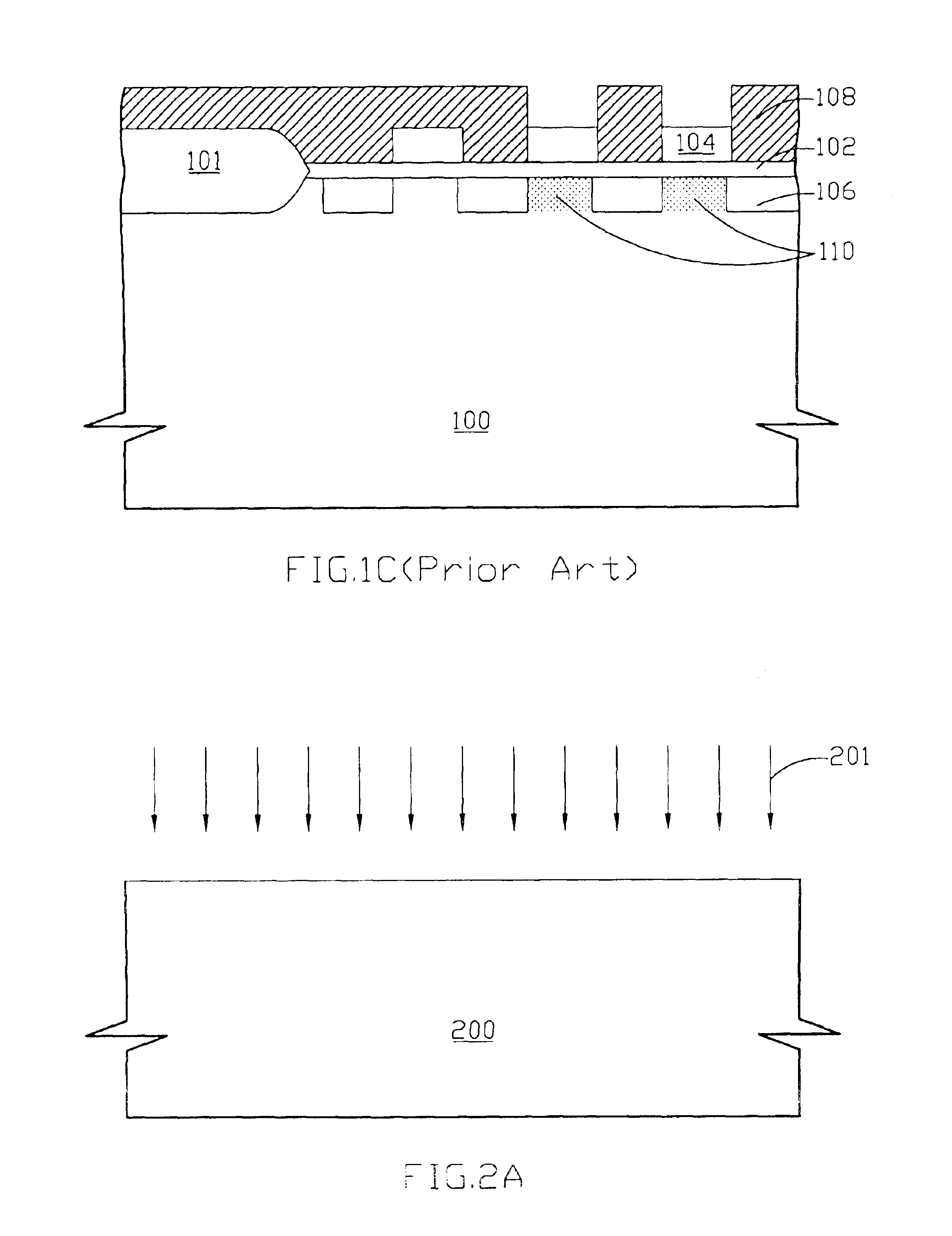

Exposure apparatus and exposure method, and device manufacturing method

InactiveUS6842221B1Stable exposure intensityForming accuratelyPhotomechanical exposure apparatusMicrolithography exposure apparatusMask ROMEngineering

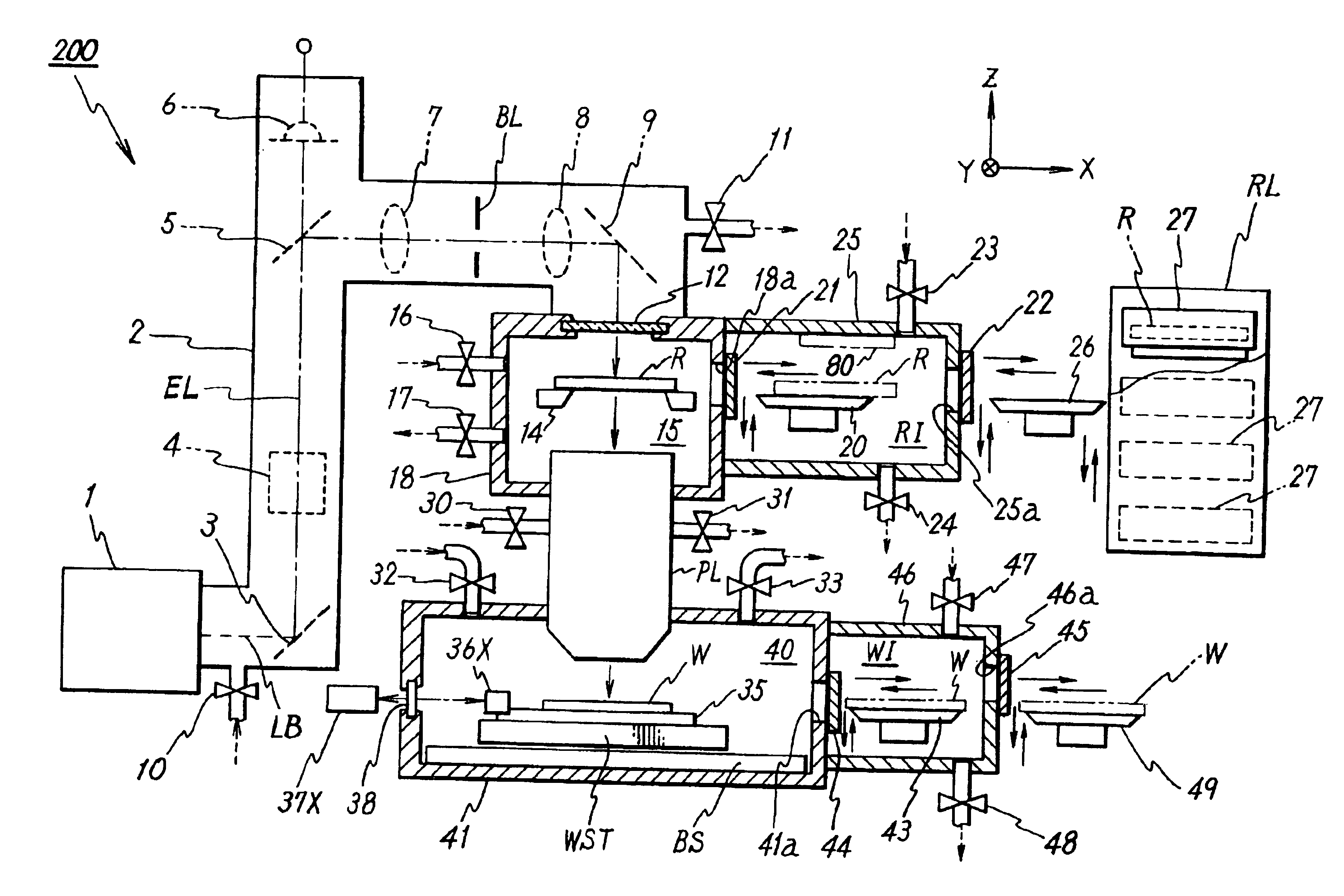

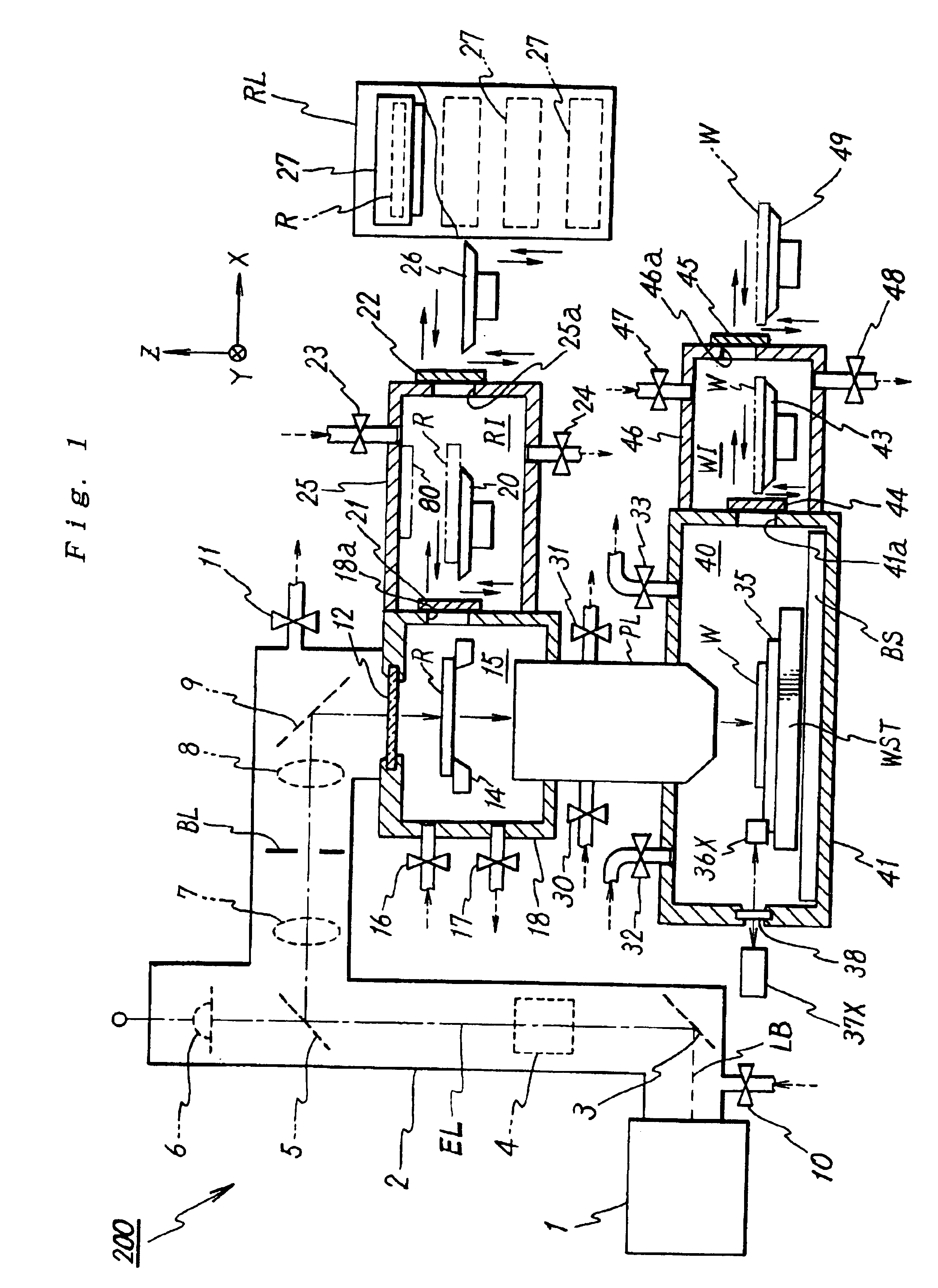

After a mask is carried into a reserve room for temporarily storing before carrying into a mask room filled with specific gas that has an impurity concentration lower than a first concentration (e.g. 1 ppb) and that has a characteristic of absorbing little exposure light, gas-replacement mechanisms replace gas in the reserve room with specific gas having an oxygen concentration not lower than the first concentration. Therefore, when subsequently carrying the mask into the mask room, impurities from the outside (including absorbent gas) can be substantially prevented from getting into the optical path inside the mask room. When replacing a wafer, gas in a reserve room is also replaced in the same way as the above.

Owner:NIKON CORP

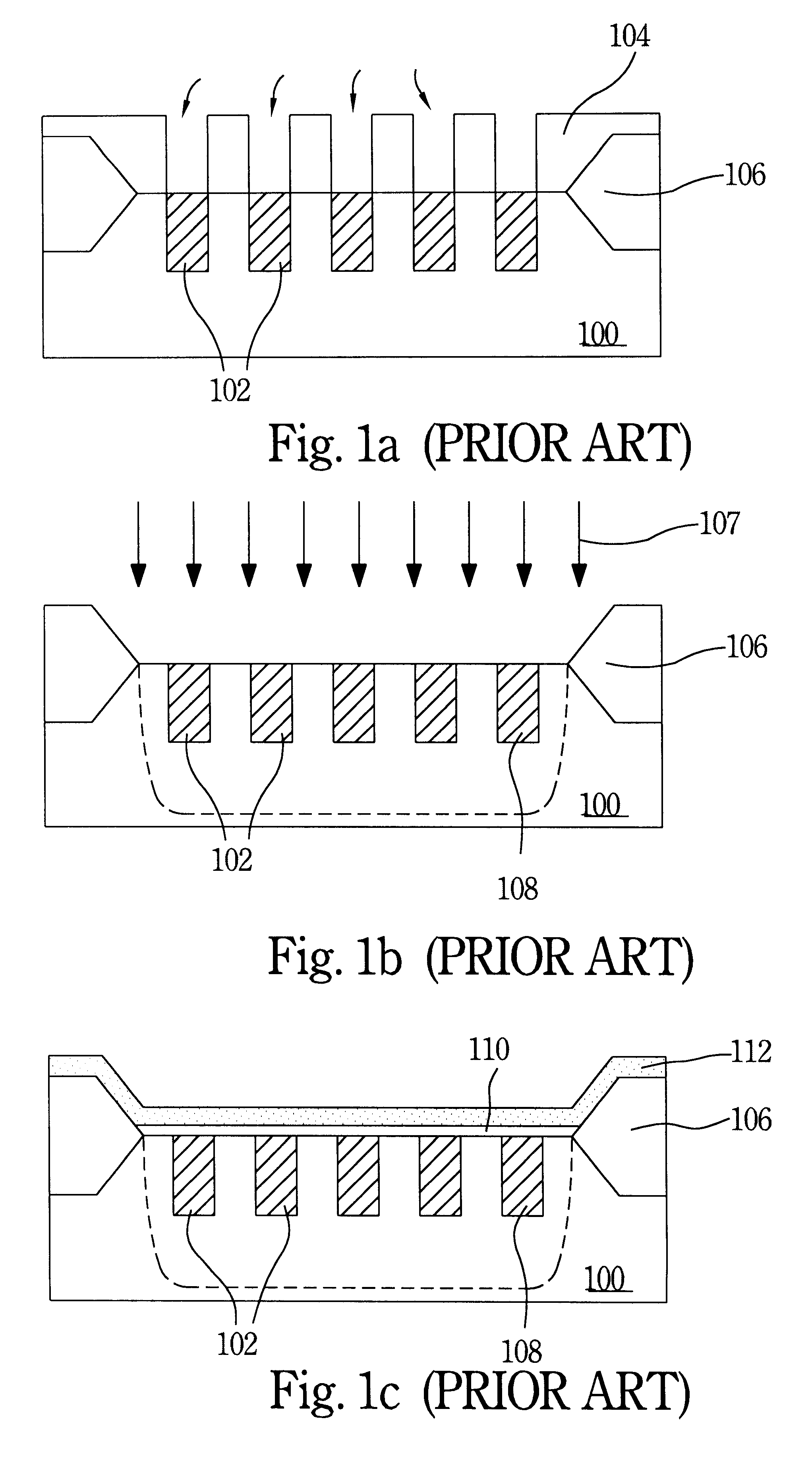

Method for fabricating a type of trench mask ROM cell

A method for fabricating a type of Trench Mask ROM cell comprises steps including: providing a substrate doped lightly with p-type dopant, sequentially forming a pad oxide layer and a nitride layer on the substrate; etching back the pad oxide layer, the nitride layer and the substrate to form plural trenches; a gate oxide layer being formed on surfaces of each trench; then, implanting n+-type ions into the substrate beneath the pad oxide layer and between each two adjacent trenches; and, forming a polysilicon layer on the gate oxide and pad oxide; finally, implanting n+-type ions into the substrate beneath the gate oxide layer on bottoms of selected trenches. And, it is appreciated that the sequence of the formation of plural trenches and implanting n+-type ions into substrate between each trench can be reversed in the embodiment without affecting subsequent steps.

Owner:PROMOS TECH INC

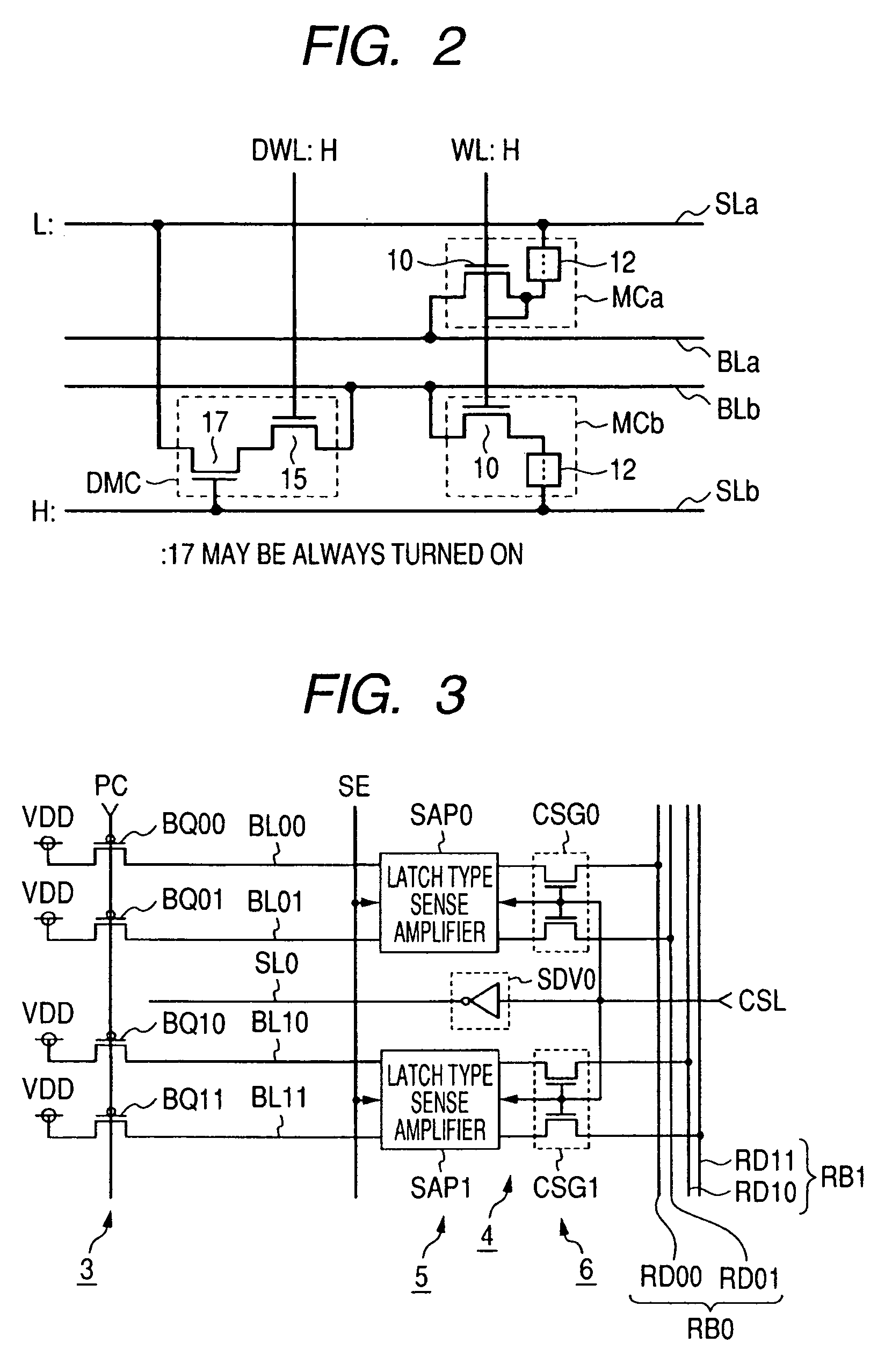

Mask ROM with light bit line architecture

InactiveUS7715246B1Configuring memory is more flexibleReduce in quantityTransistorSolid-state devicesCapacitanceBit line

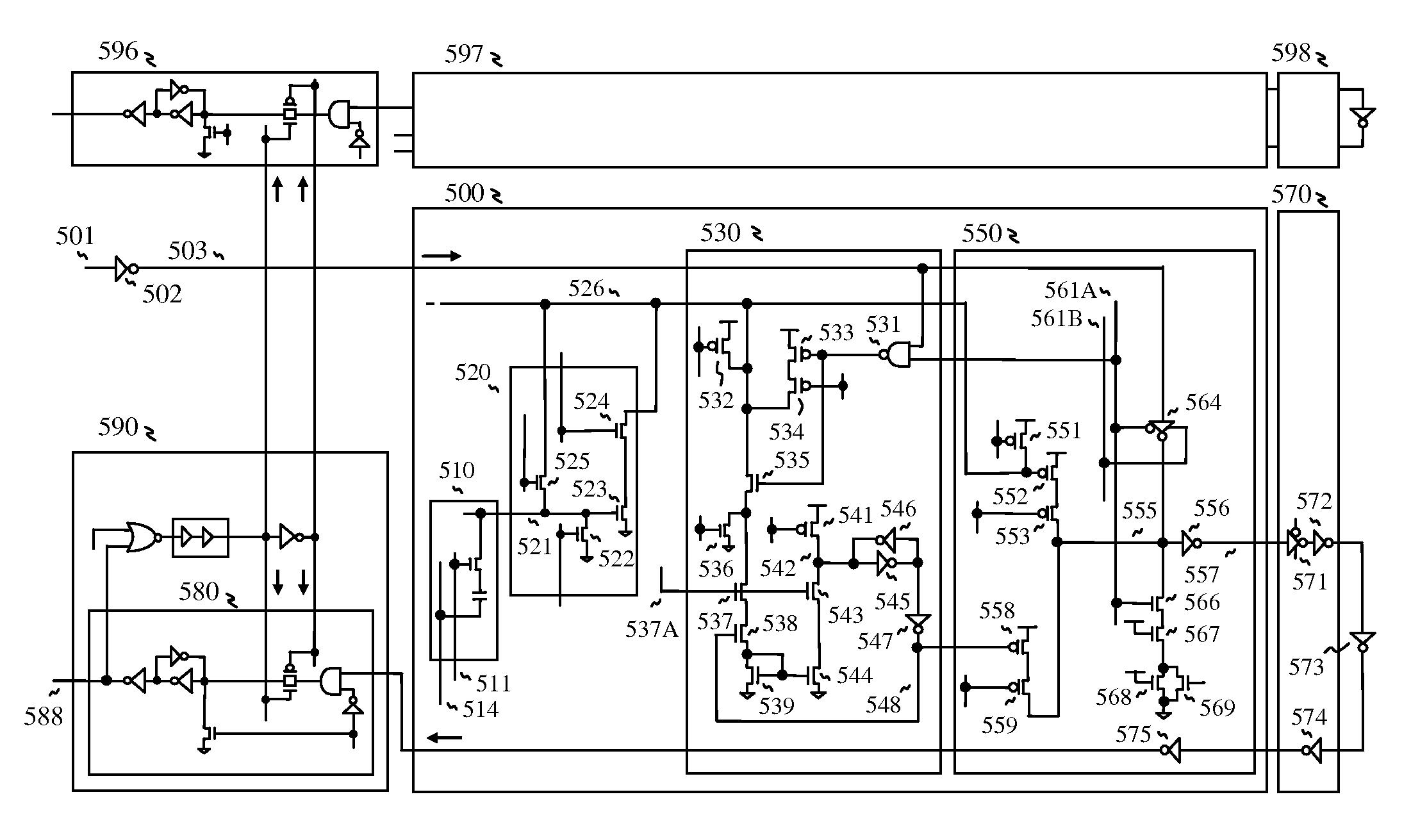

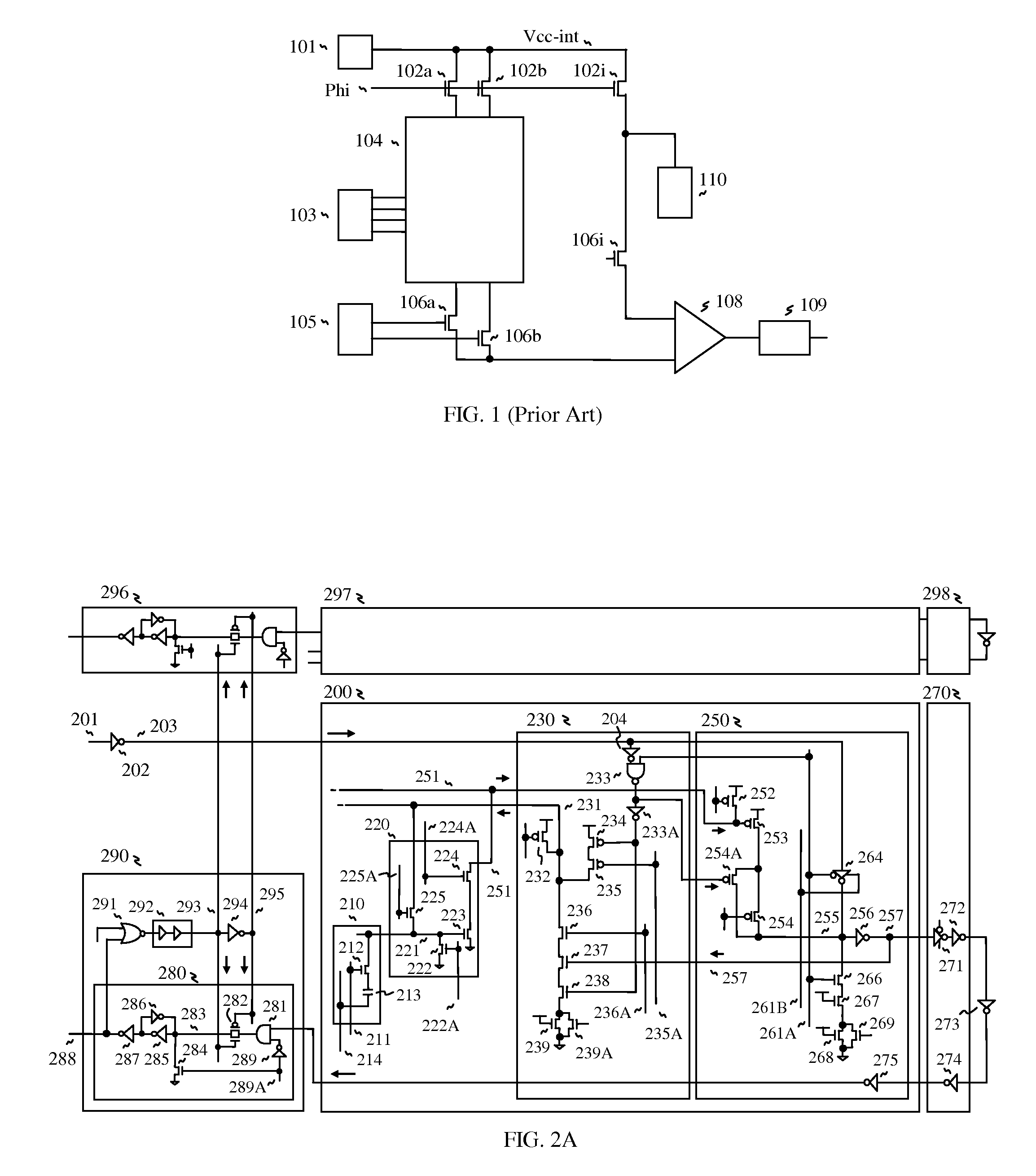

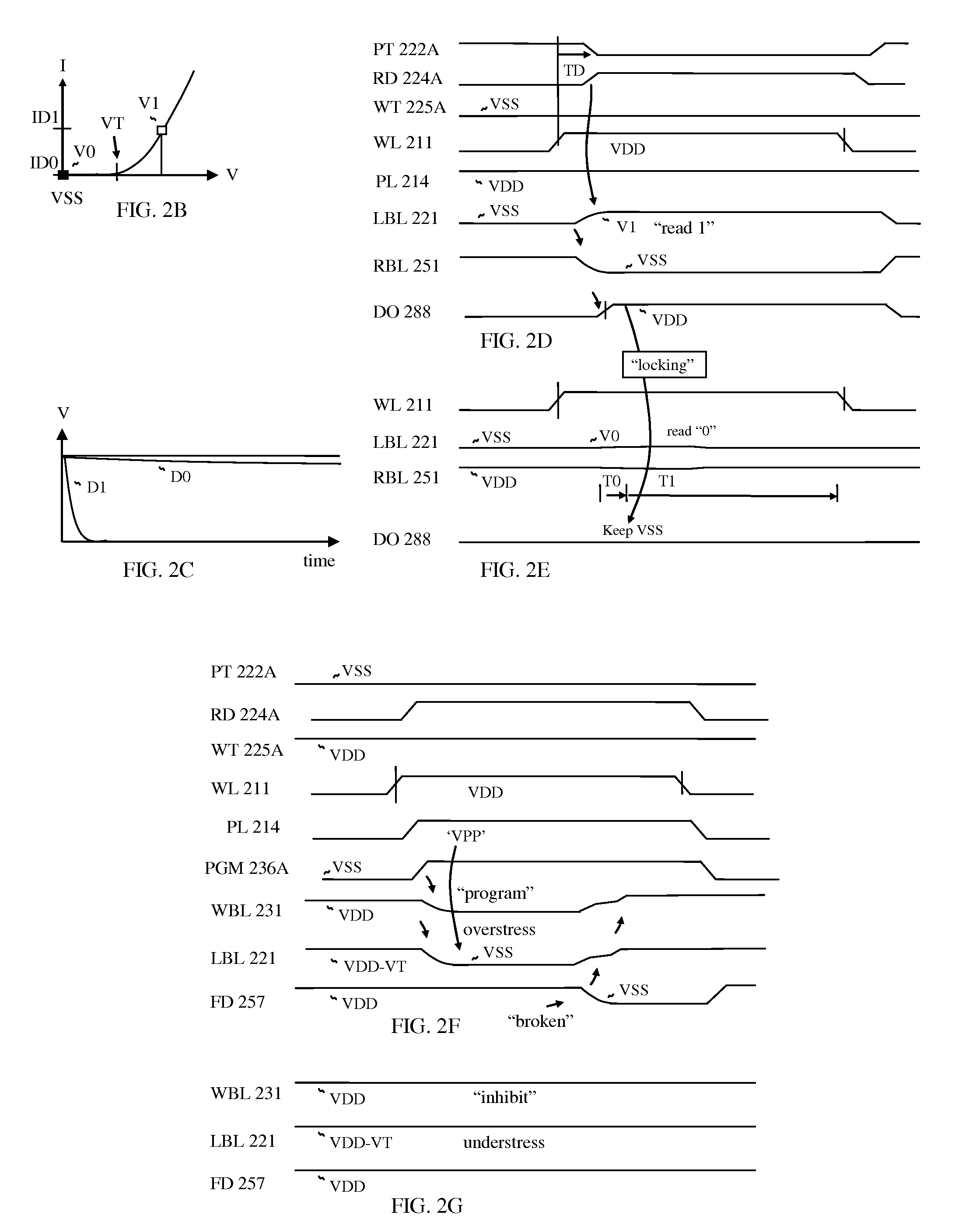

For improving performance of mask ROM, bit line is multi-divided for reducing capacitance, so that multi-stage sense amps are used for reading, wherein a local sense amp receives an output from a memory cell through the bit line, and a global sense amp receives the local sense amp output. By the sense amps, a voltage difference in the bit line is converted to a time difference for differentiating data “1” and data “0”. For example, data “1” is quickly transferred to an output latch circuit through the sense amps with high gain, but data “0” is rejected by a locking signal based on data “1” as a reference signal. Furthermore, a buffered data path is used for transferring data wherein the buffered data path includes a forwarding write line and a returning read line. Additionally, alternative circuits and memory cell structures for implementing the mask ROM are described.

Owner:KIM JUHAN

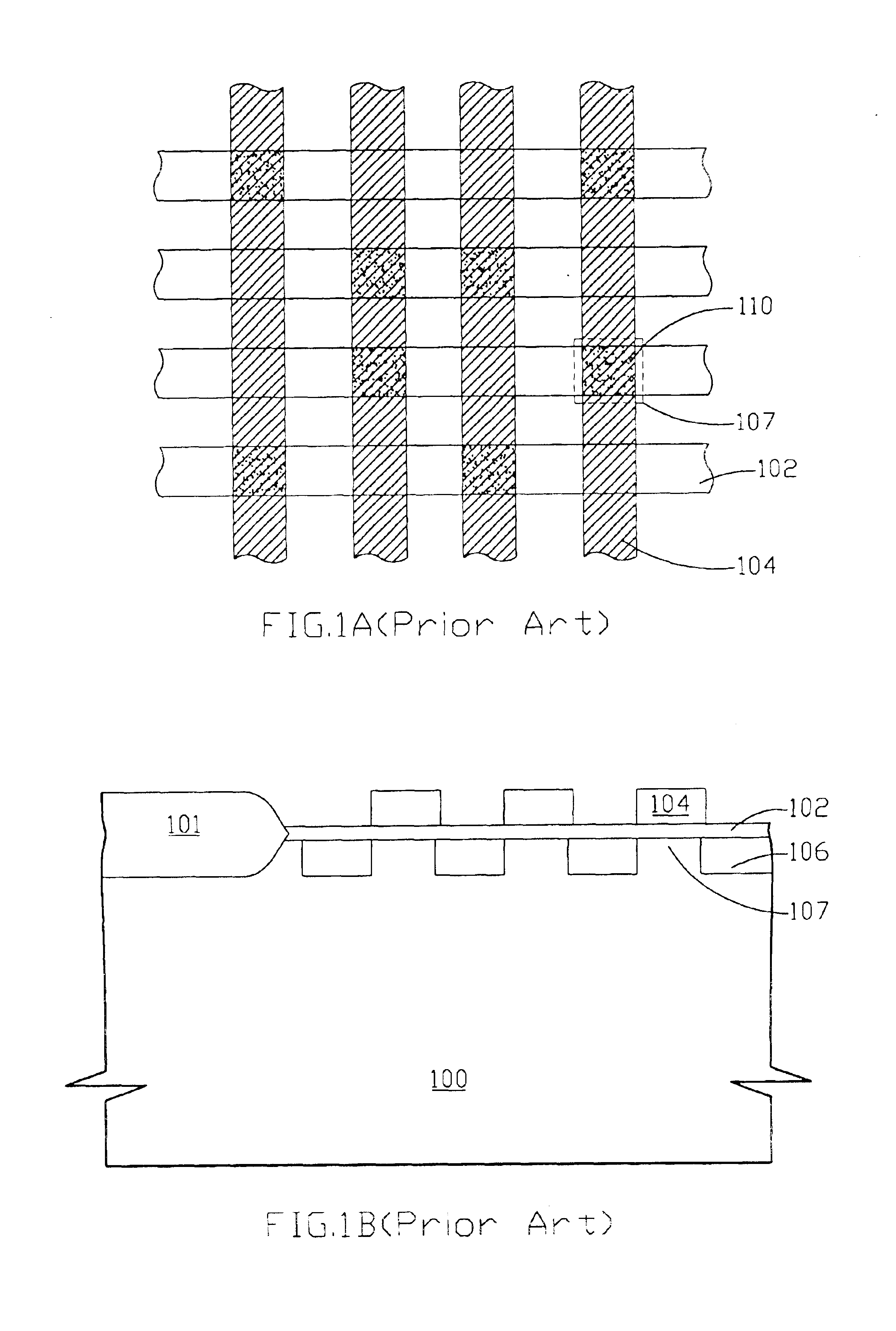

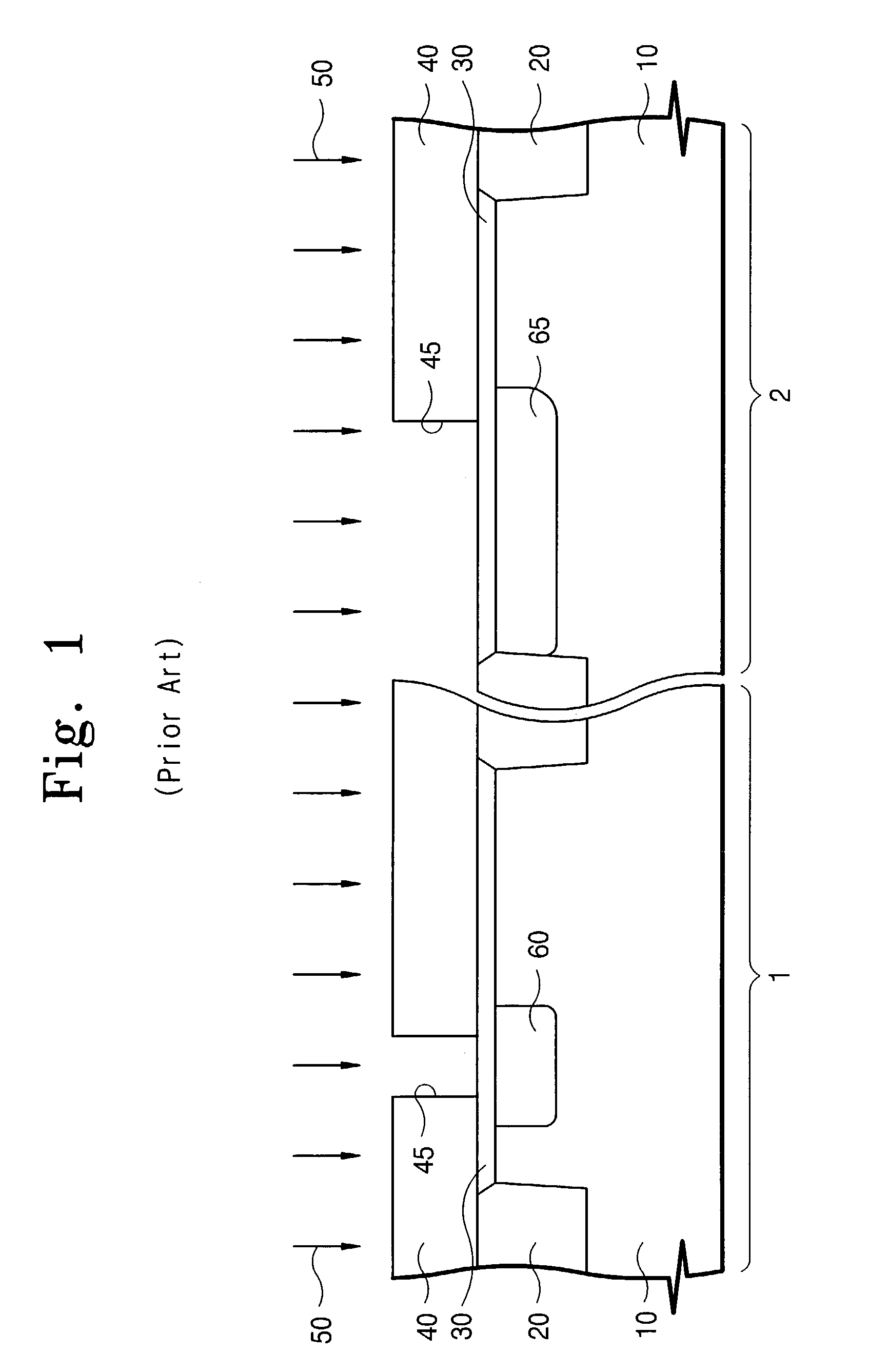

Short turn around time mask ROM process

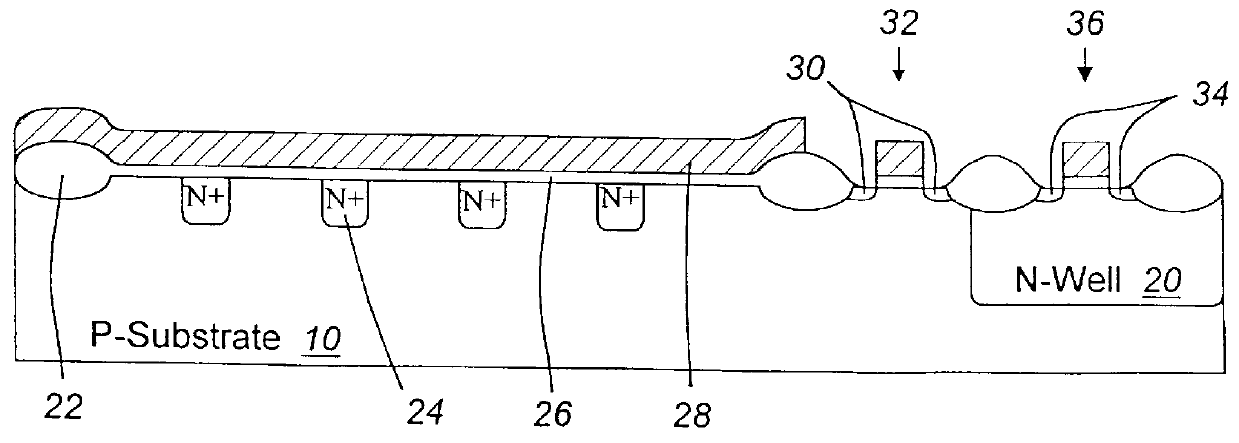

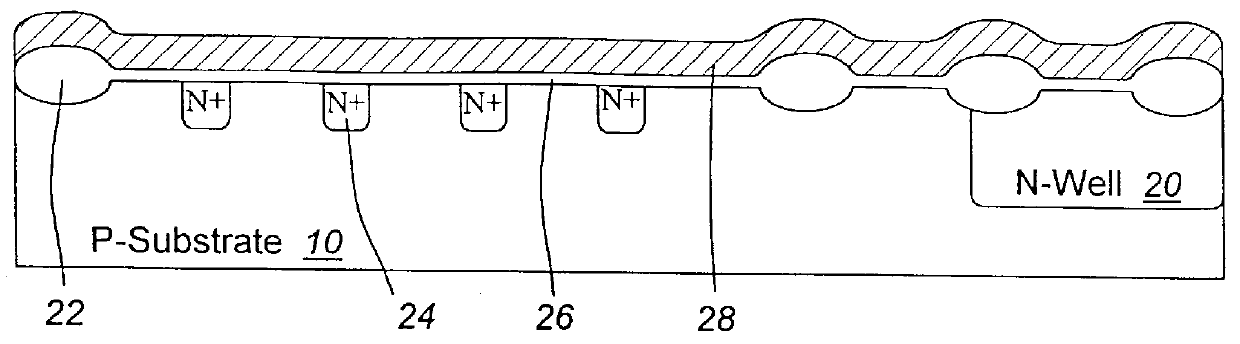

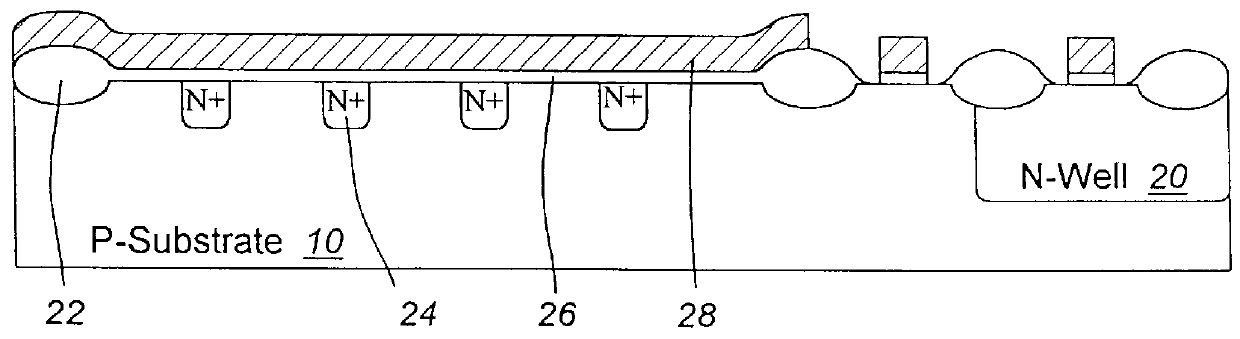

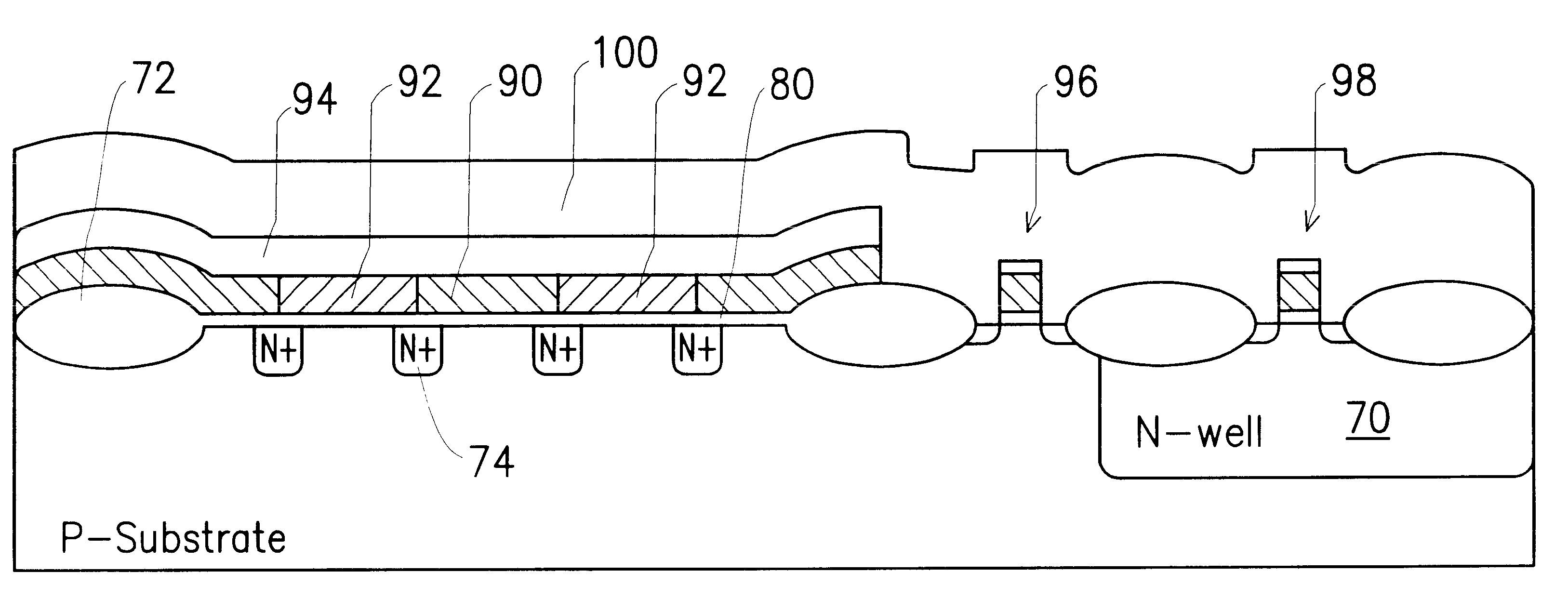

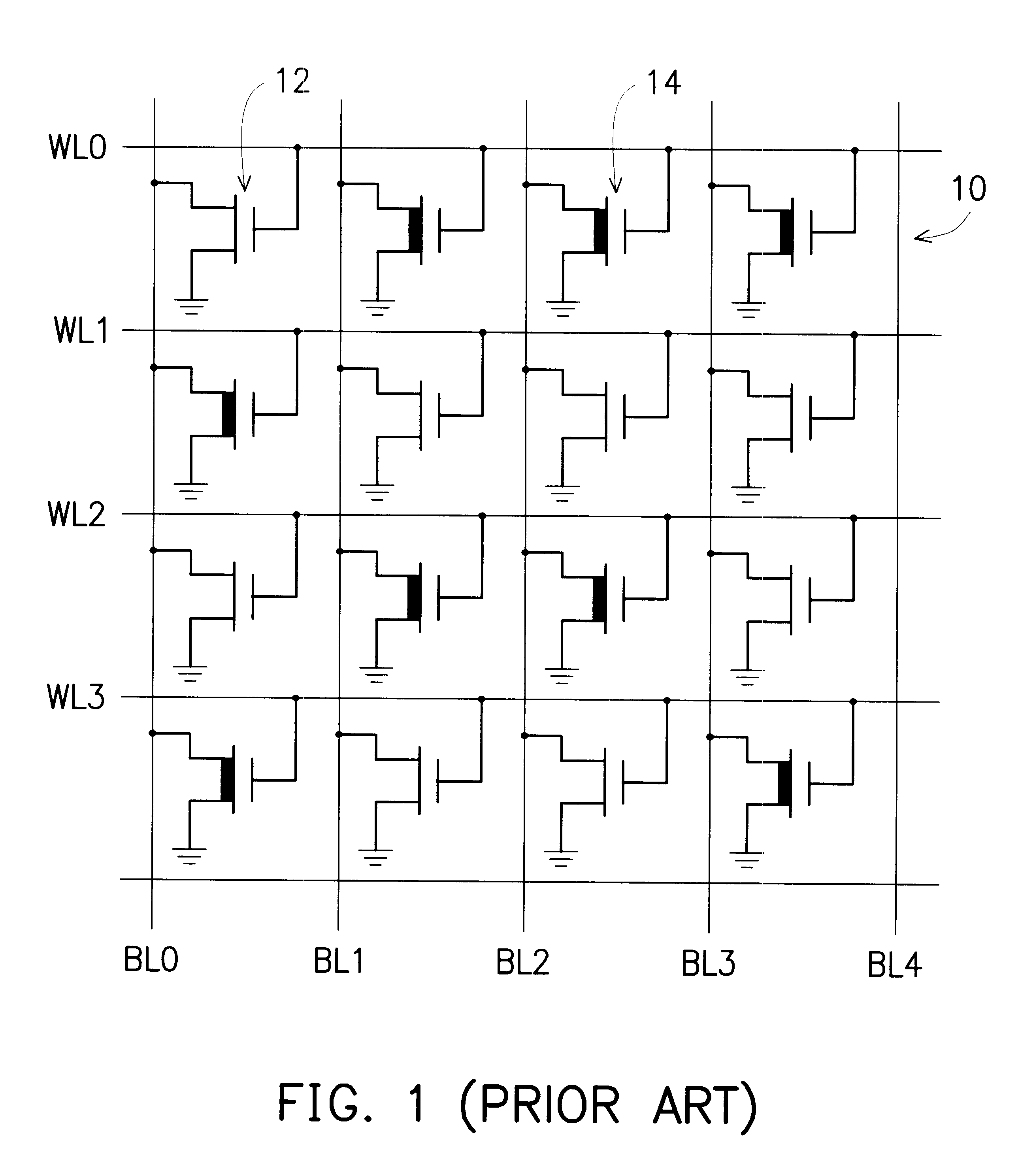

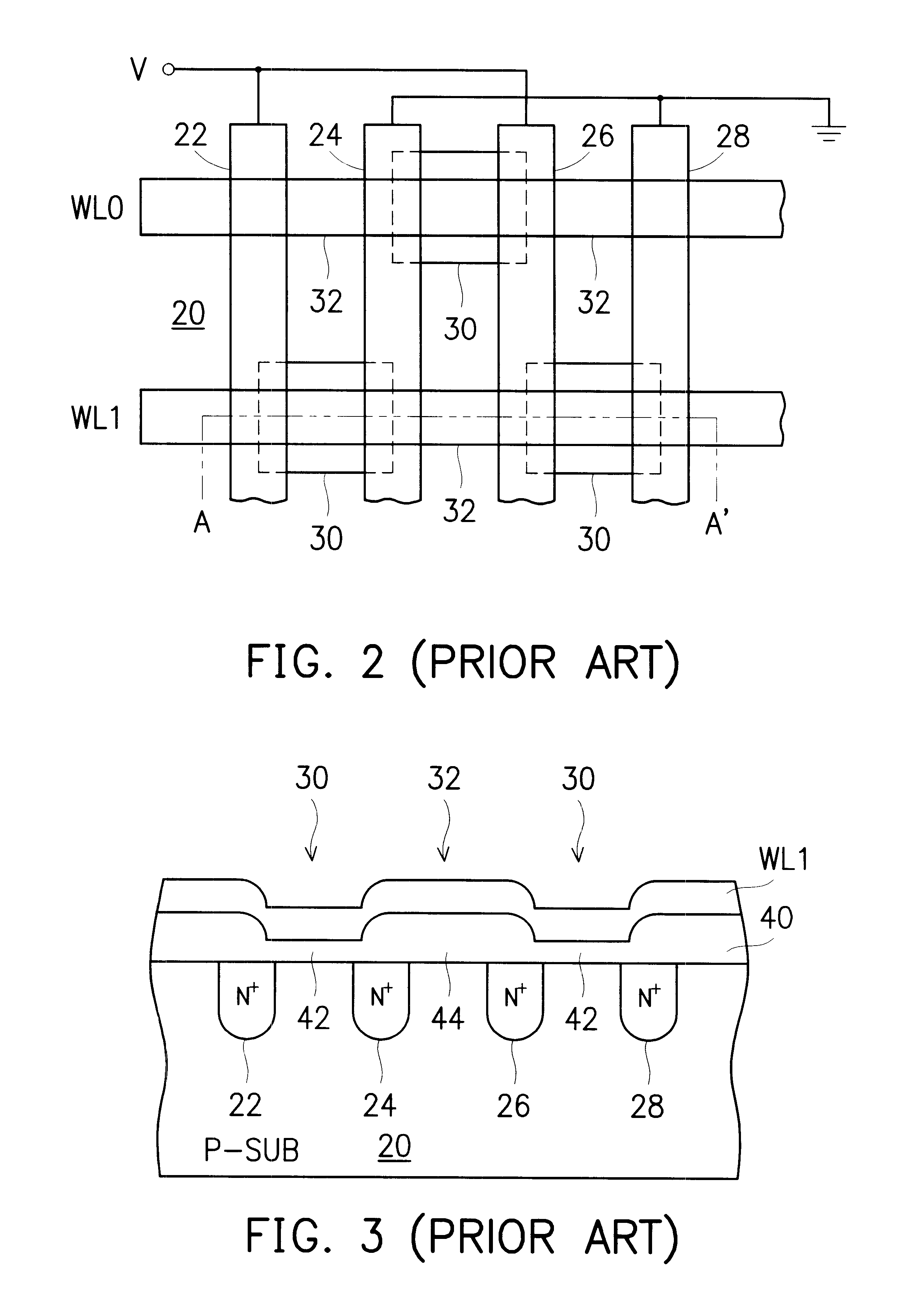

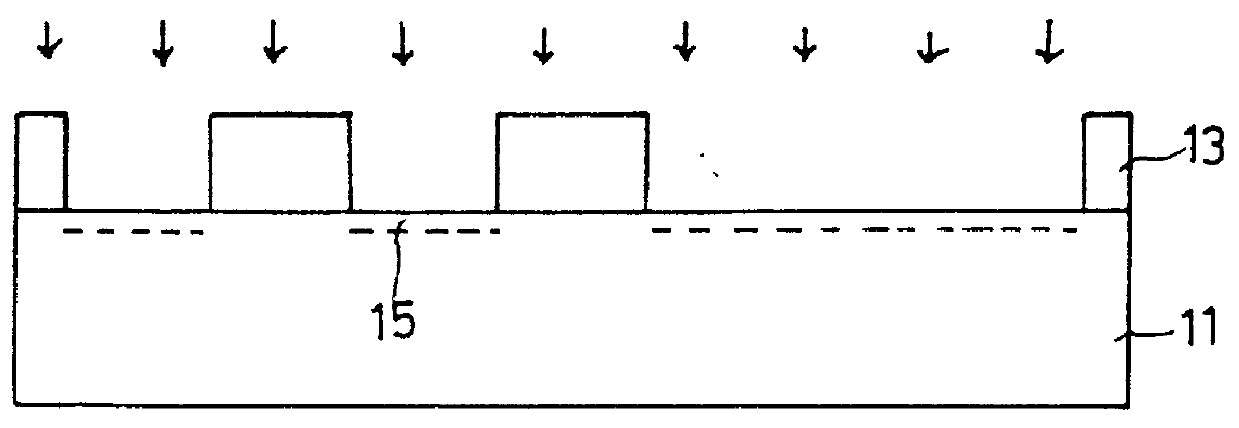

A mask ROM stores information by selecting the work function of the gates of each FET in an array of FETs at a late stage in the manufacture of the ROM. The polysilicon gates of some of the FETs are doped N-type and the gates of the other FETs are doped P-type to form gates having different work functions, thereby forming FETs having different threshold voltages. The ROM consists of a parallel array of buried N+ bit lines formed in the substrate, a gate oxide layer deposited over the bit lines and a layer of polysilicon deposited on the gate oxide. The polysilicon is blanket doped N-type, gate electrodes are defined by photolithography, and then self-aligned silicide layers are formed on the gate electrodes. An insulating layer is then formed over the gate electrodes. Programming of the ROM is accomplished by forming a mask on the insulating layer and then implanting ions through openings in the mask, through the insulating layer and the silicide layer, and into the polysilicon layer. The implantation converts individual gate electrodes from N-type to P-type to alter the threshold voltage of the selected transistors. Relatively few additional processing steps are needed after the programming to complete the ROM.

Owner:UNITED MICROELECTRONICS CORP

Methods of code programming a mask ROM device

ActiveUS7132334B2Fast and clean and controlled and simple in constructionReduce complexityTransistorSolid-state devicesAnti-reflective coatingMask ROM

A method of code programming a mask read only memory (ROM) is disclosed. A method of the present invention includes forming a layer of developable anti-reflective coating over a plurality of code openings located on a substrate of a ROM device. The plurality of code openings are typically elements of a first code, or pre-code, pattern, and a portion of the developable anti-reflective coating layer is removed or processed to define a second code, or real-code, pattern of the device. The method may be practiced by applying and patterning a layer of photoresist material over the developable anti-reflective coating to form a second code pattern, and then removing portions of the developable anti-reflective coating that remain exposed beneath the patterned photoresist material.

Owner:MACRONIX INT CO LTD

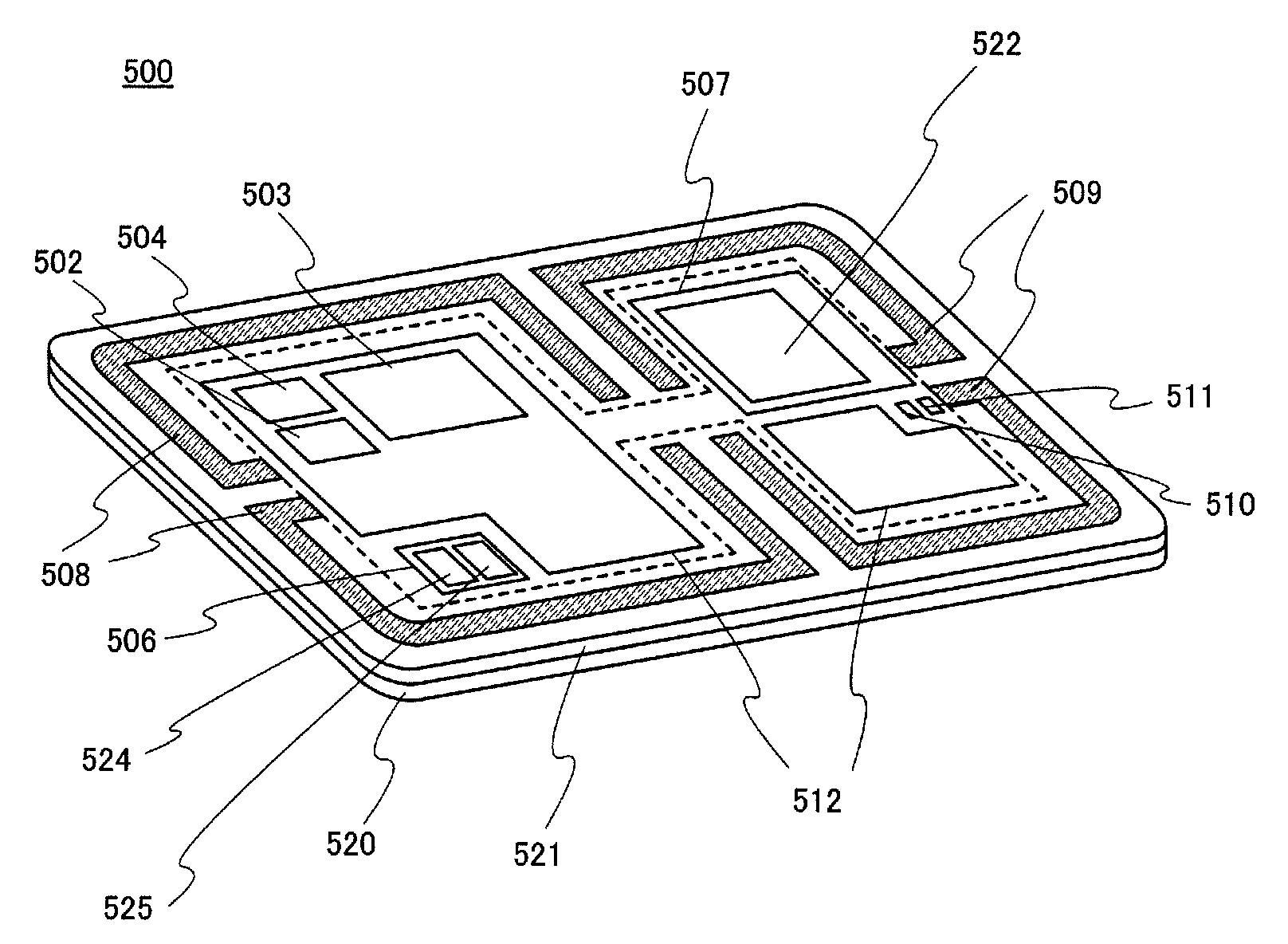

TFT mask ROM and method for making same

There is provided a monolithic three dimensional TFT mask ROM array. The array includes a plurality of device levels. Each of the plurality of device levels contains a first set of enabled TFTs and a second set of partially or totally disabled TFTs.

Owner:WODEN TECH INC

Variable work function transistor high density mask ROM

InactiveUS6417548B1Solid-state devicesSemiconductor/solid-state device manufacturingBit lineMask ROM

A mask ROM stores information by selecting the work function of the gates of each FET in an array of FETs. The polysilicon gates of some of the FETs are doped N-type and the gates of the other FETs are doped P-type to form gates having different work functions, thereby forming FETs having different threshold voltages. The ROM consists of a parallel array of buried N+ bit lines formed in the substrate, a gate oxide layer deposited over the bit lines and a layer of polysilicon deposited on the gate oxide. The polysilicon is blanket doped P-type and then an encoding mask is formed, with openings in the encoding mask exposing regions of the polysilicon to be formed into gates of FETs with low threshold voltages. Either arsenic or phosphorus is doped into the polysilicon through the mask openings. The mask is removed, a layer of conductive material such as tungsten silicide is deposited and the polysilicon and the conductive material are formed into word lines for the ROM. The word lines of the ROM serve as gates for the FETs and the bit lines serve as sources and drains for the FETs.

Owner:UNITED MICROELECTRONICS CORP

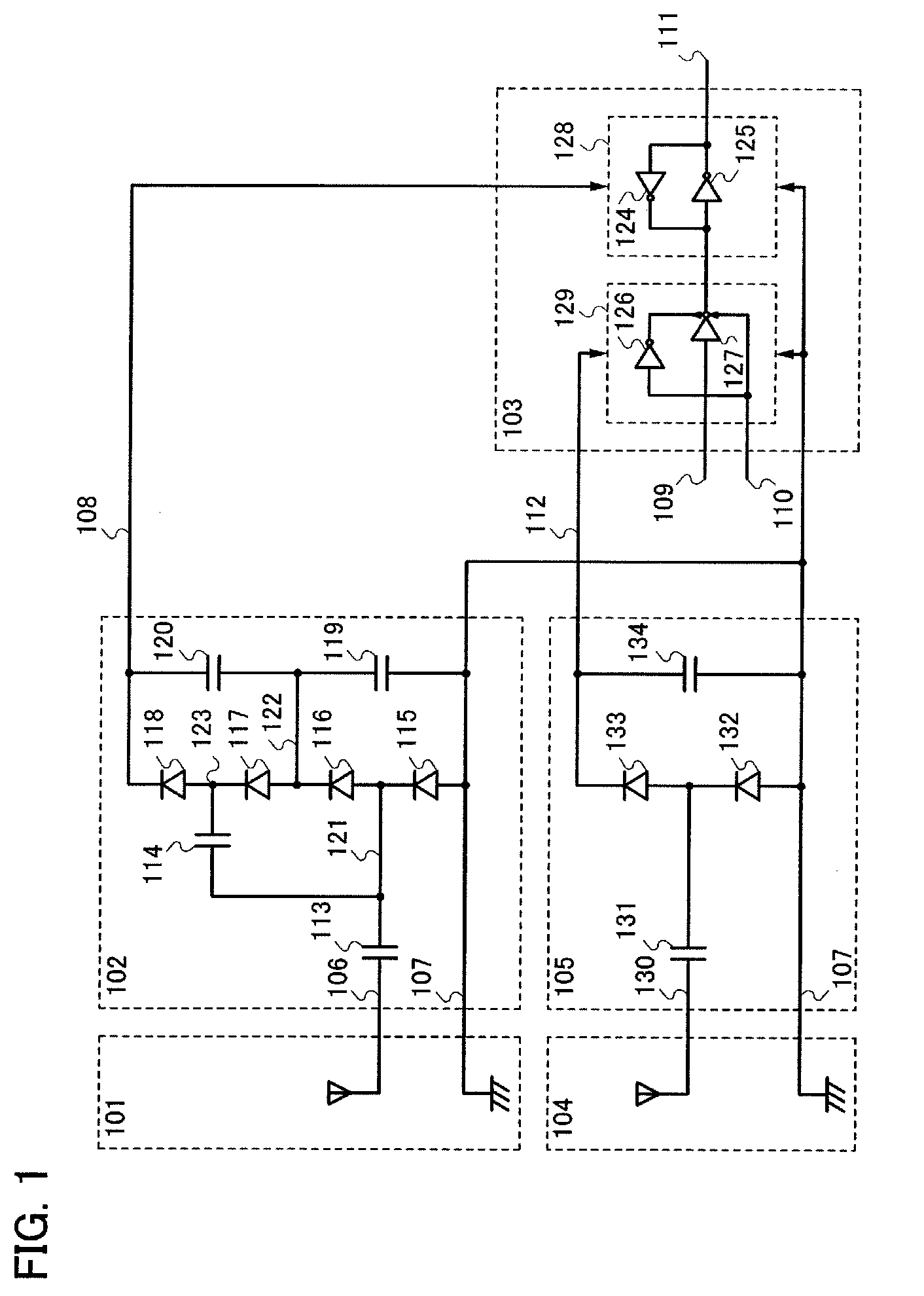

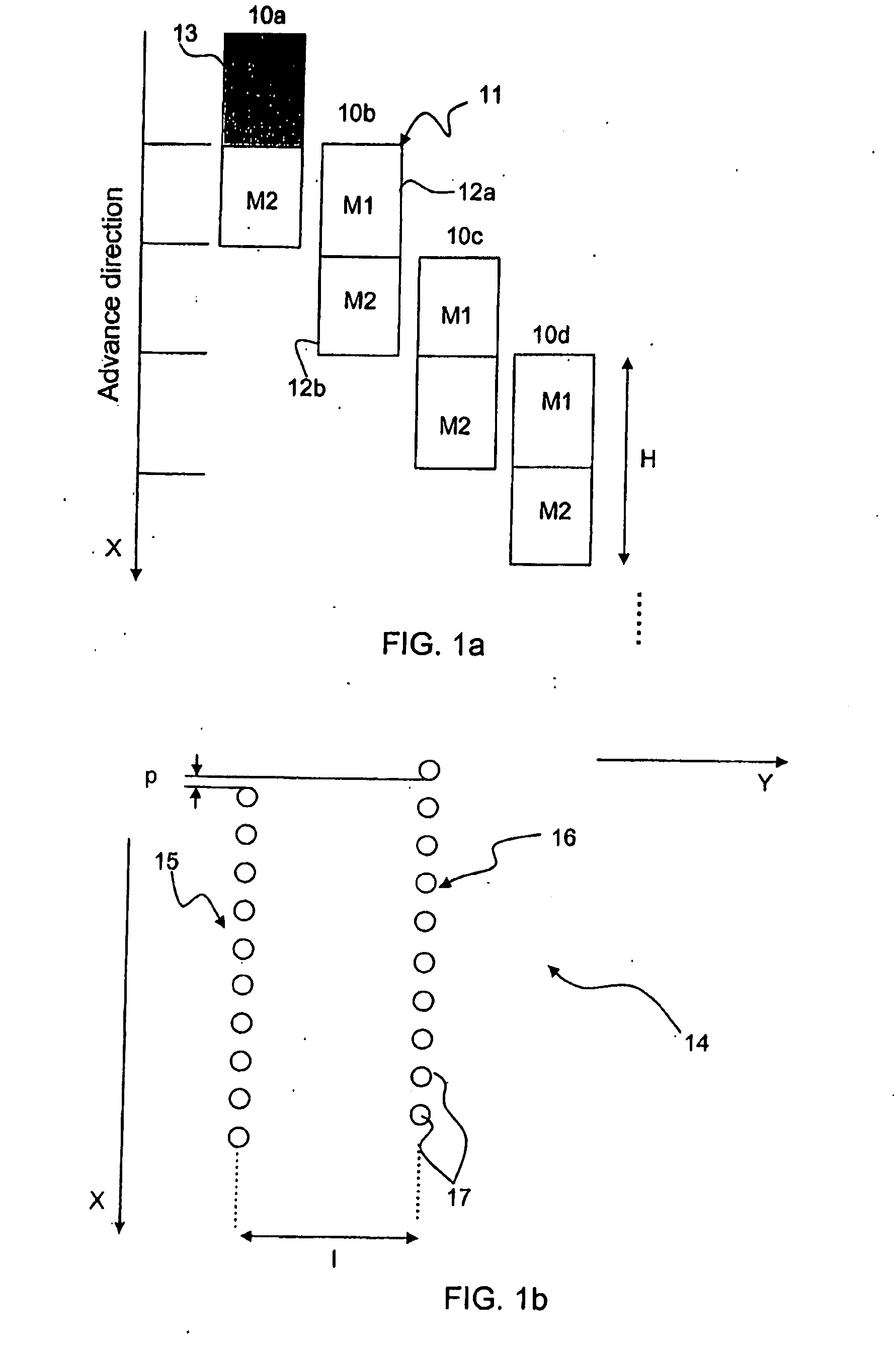

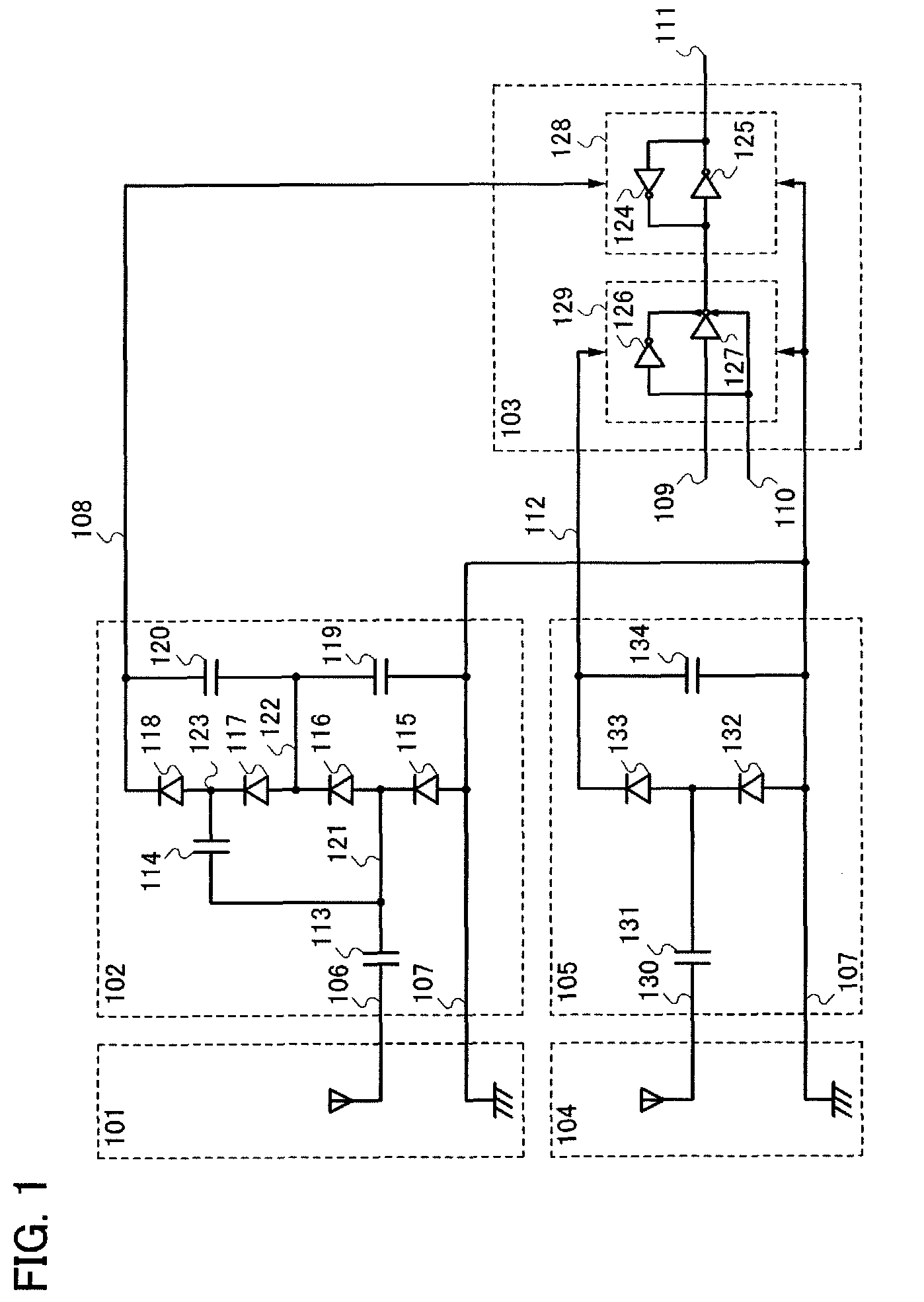

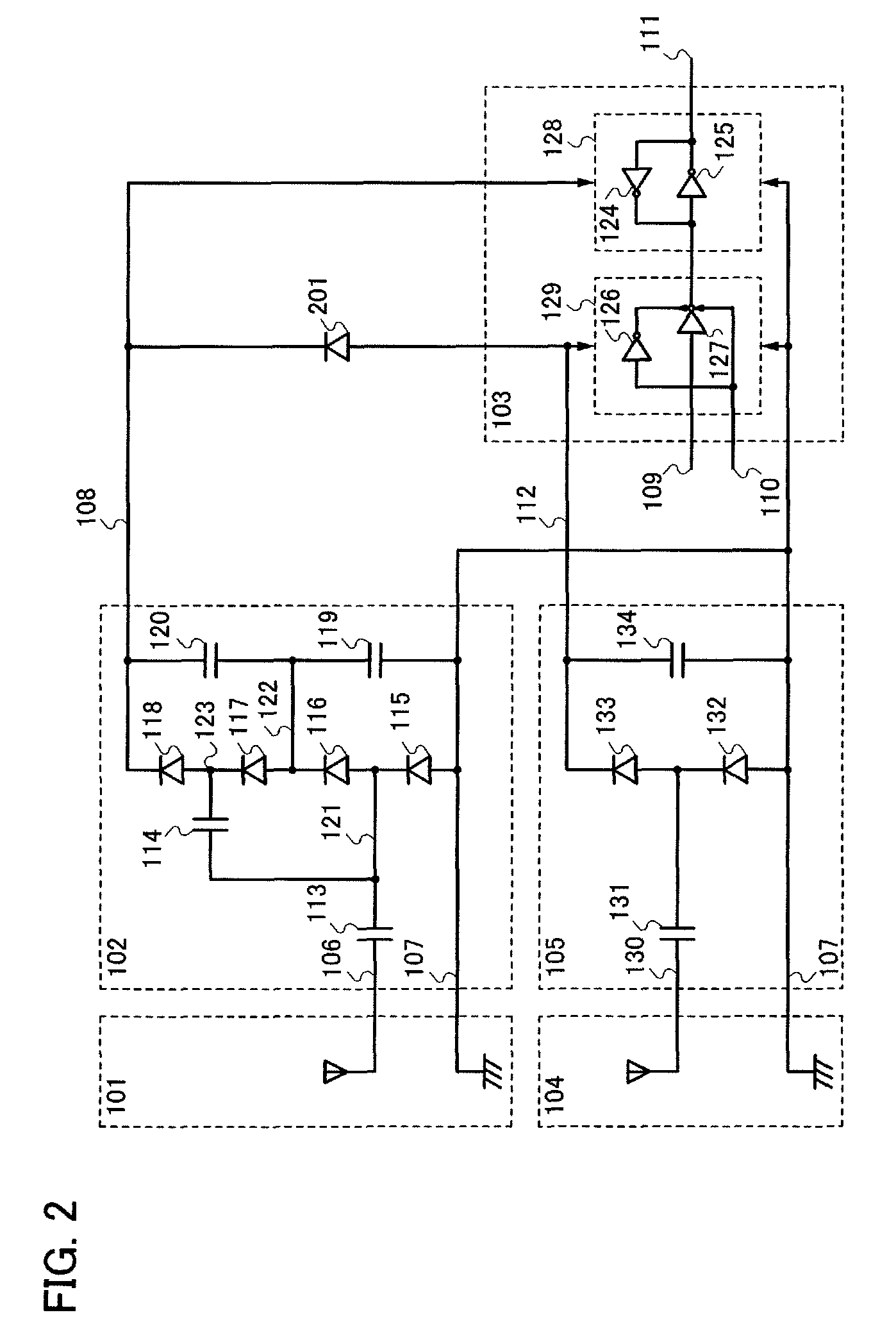

Semiconductor device

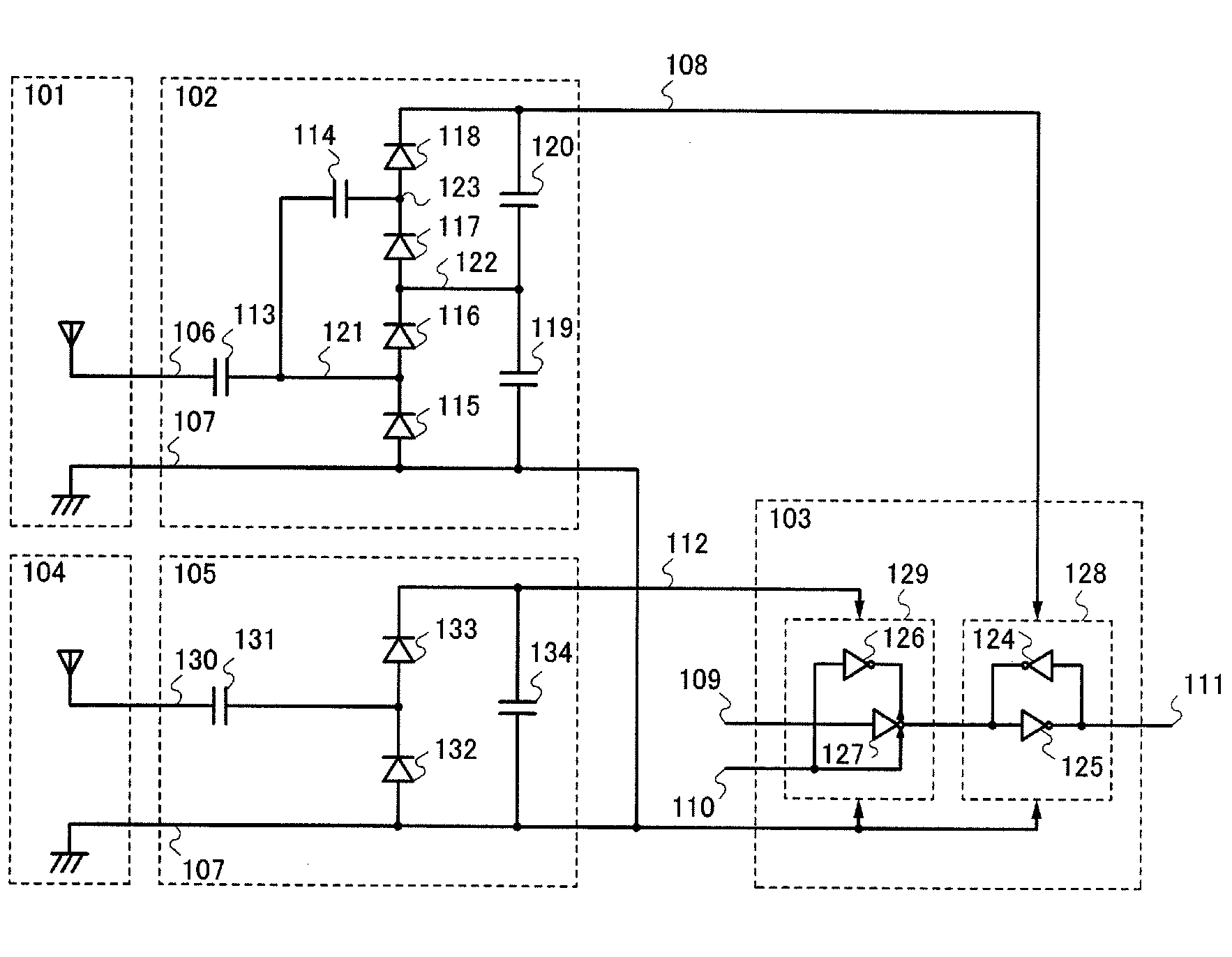

InactiveUS20080214132A1Low priceConvenience is lostResonant long antennasElectromagnetic wave systemMask ROMData storing

In an RF tag, a mask ROM or a flash memory is used for storing data such as an ID number. Although the mask ROM can be realized at a low price, rewriting is not possible. In addition, in the flash memory, although electric rewriting is possible, production cost increases. Accordingly, it is difficult to provide an RF tag by which data rewriting is possible at a low price. An RF tag is provided with a power supply circuit having a function to generate a power supply voltage from a weak radio signal and a memory which can hold data stored in a data holding portion by the power supply voltage. With the above structure, a high-performance RF tag capable of rewriting data such as an ID number after production can be provided at a low price.

Owner:SEMICON ENERGY LAB CO LTD

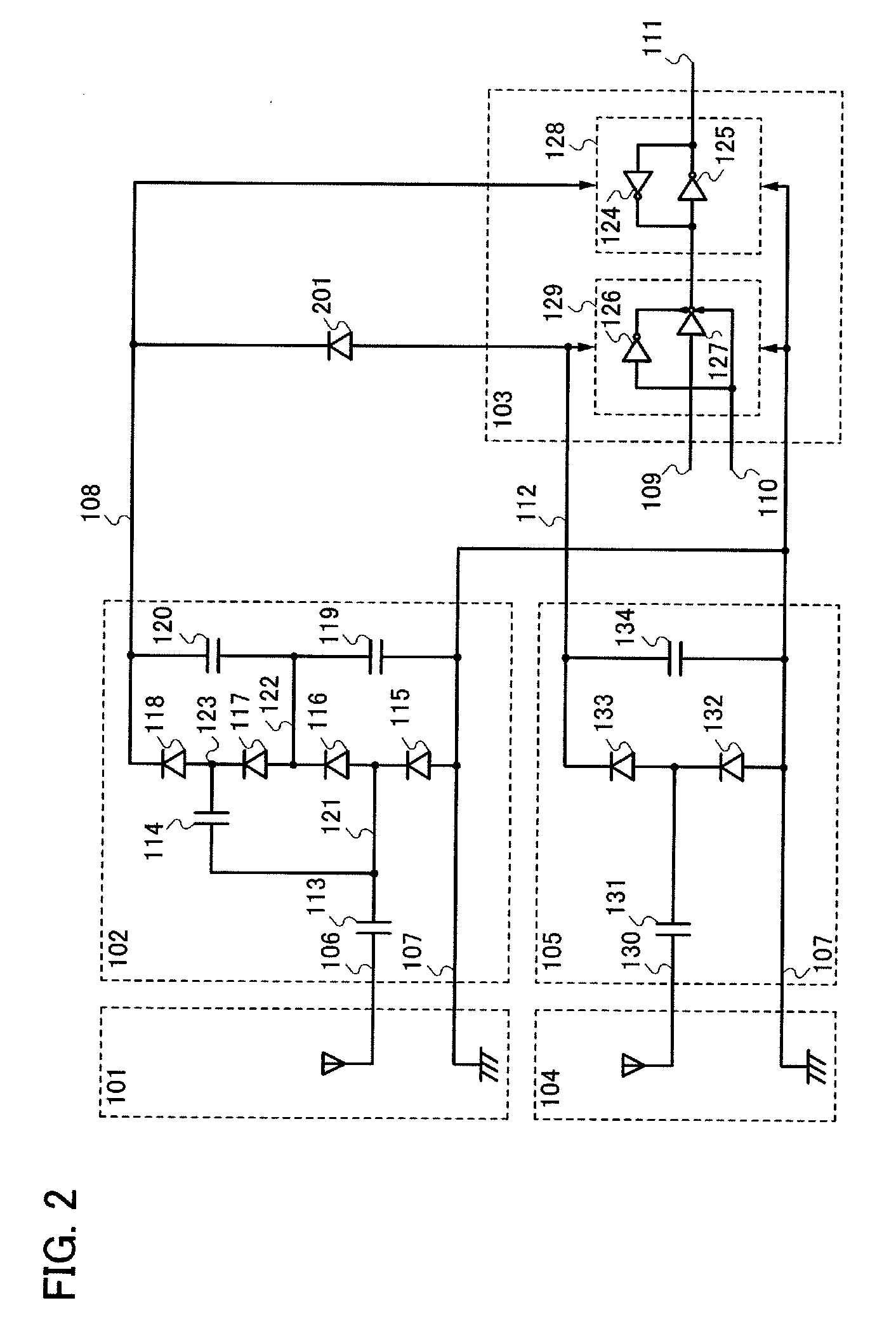

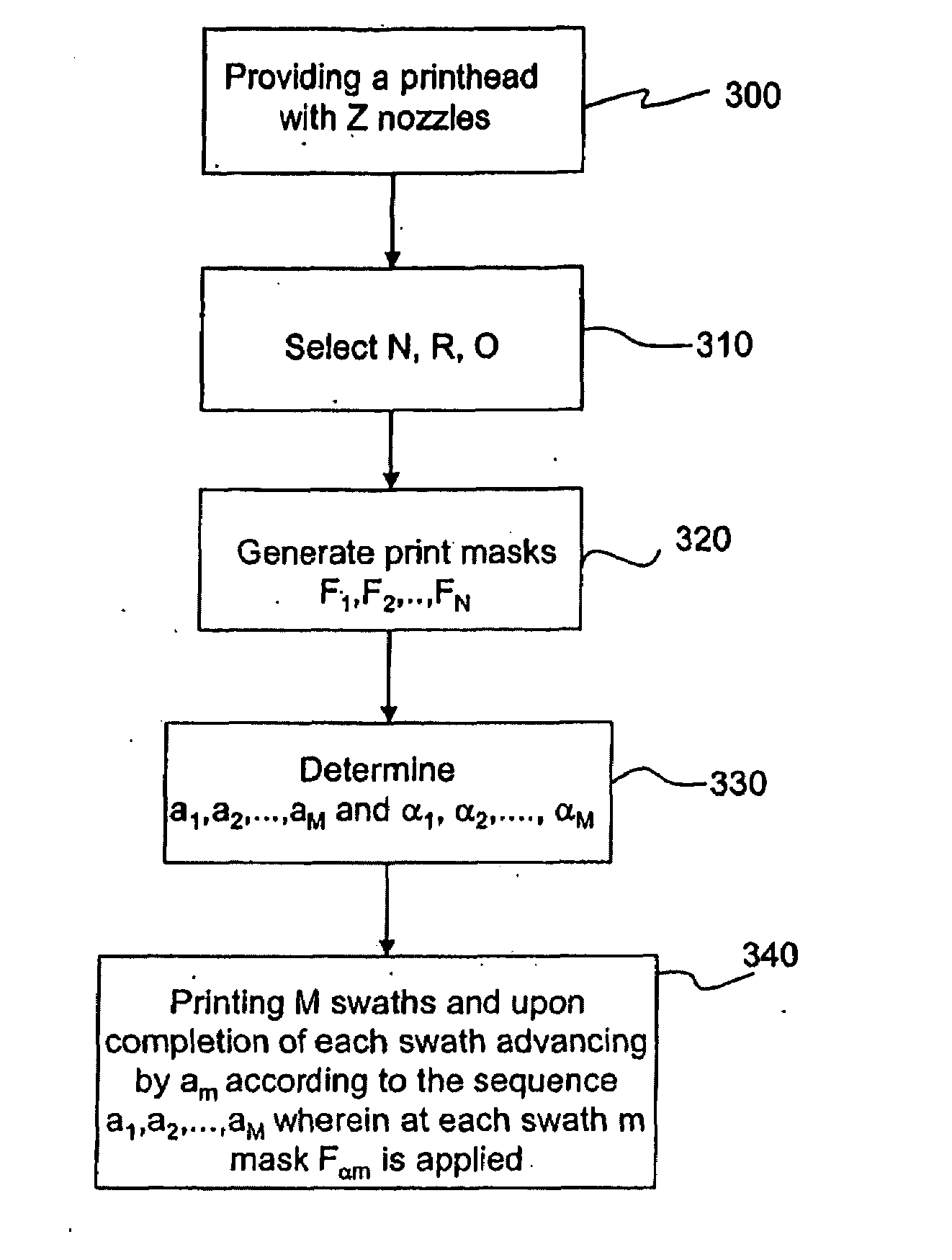

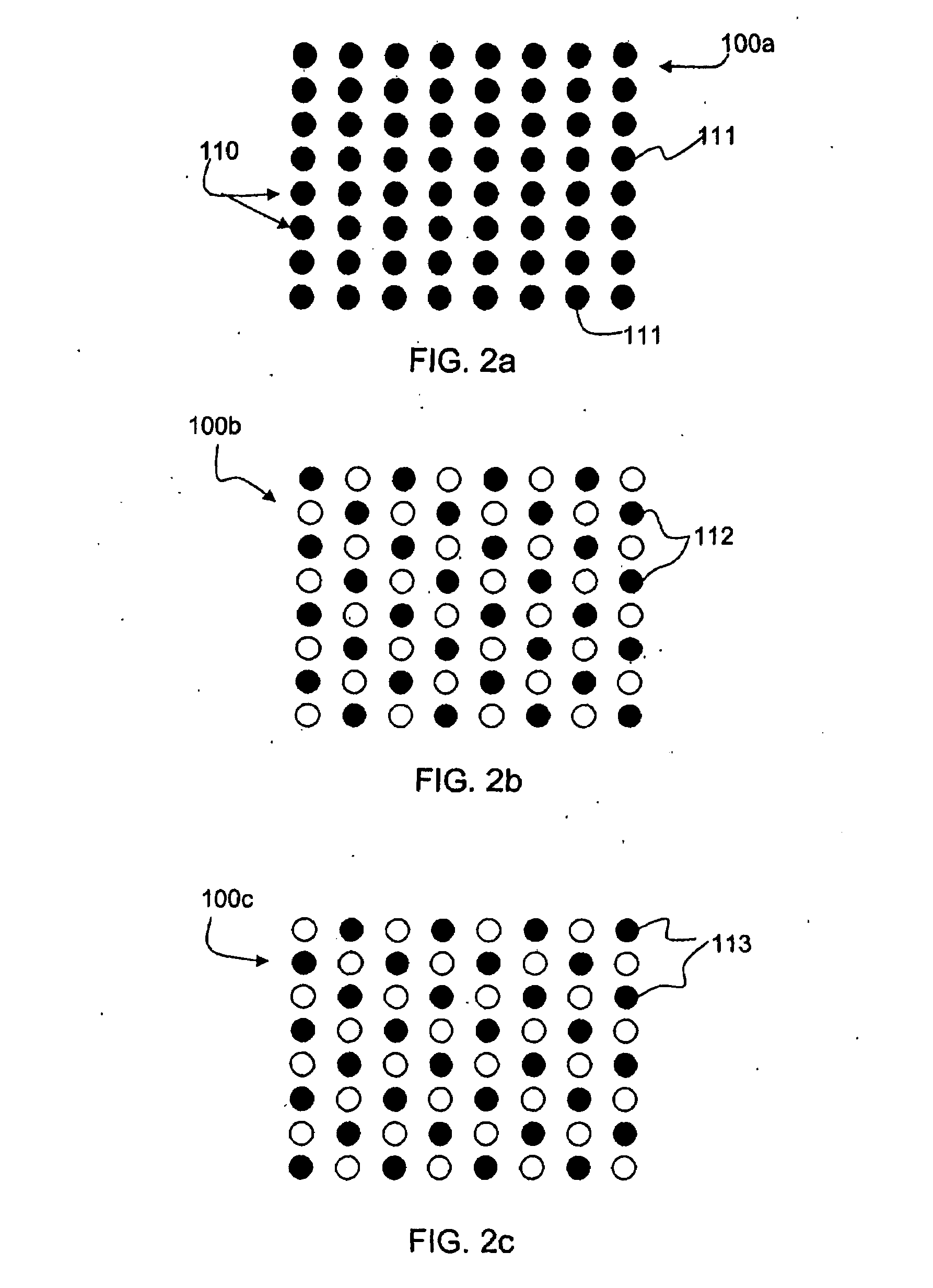

Method and system for high speed multi-pass inkjet printing

A method of printing from a printhead includes virtually dividing a nozzle array of the printhead into first and second nozzle sections. N print masks associated with the first and second nozzle sections govern the deposition of ink drops on a print medium. The N print masks are associated with one swath and are defined as a mask grid. The mask grid is arranged as a series of vertically extending adjacent mask columns and a series of horizontally extending mask rows. The vertically extending mask columns comprise enabling mask columns comprising first mask elements and disabling mask columns consisting essentially of second mask elements. The N print masks are associated with the first and second nozzle sections for printing an input image. Each print mask is defined as a mask grid arranged in an N series of vertically extending adjacent mask columns and a series of Z horizontally extending mask rows. The series of mask rows are divided in first and second adjacent mask sections corresponding to the first and second nozzle sections, respectively. The mask rows of the second mask section are arranged spaced from one another by N−1 adjacent second mask elements and the mask rows of the first nozzle section are arranged spaced from one another by 2N−1 adjacent second mask elements within the same mask row

Owner:TELECOM ITALIA SPA +1

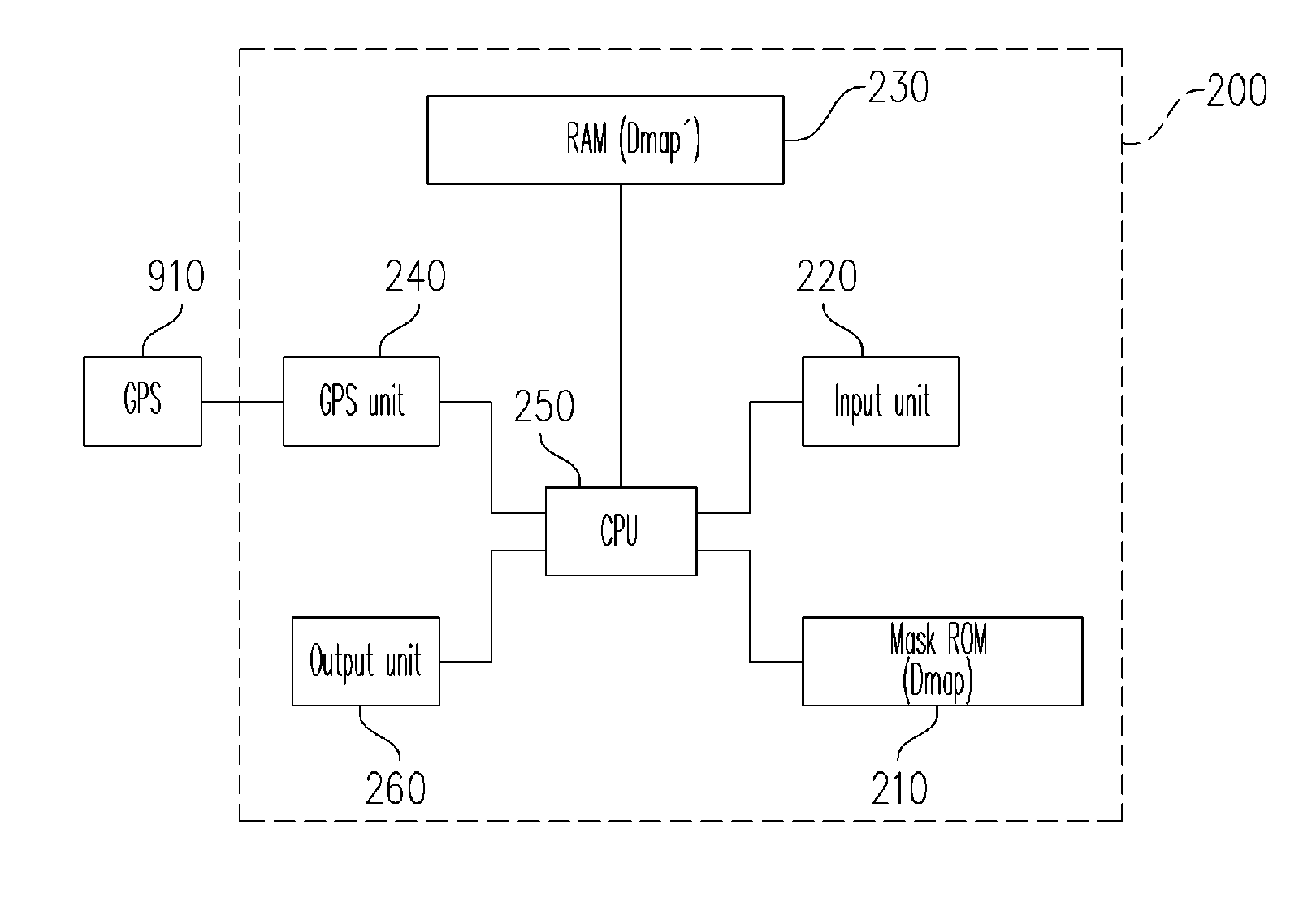

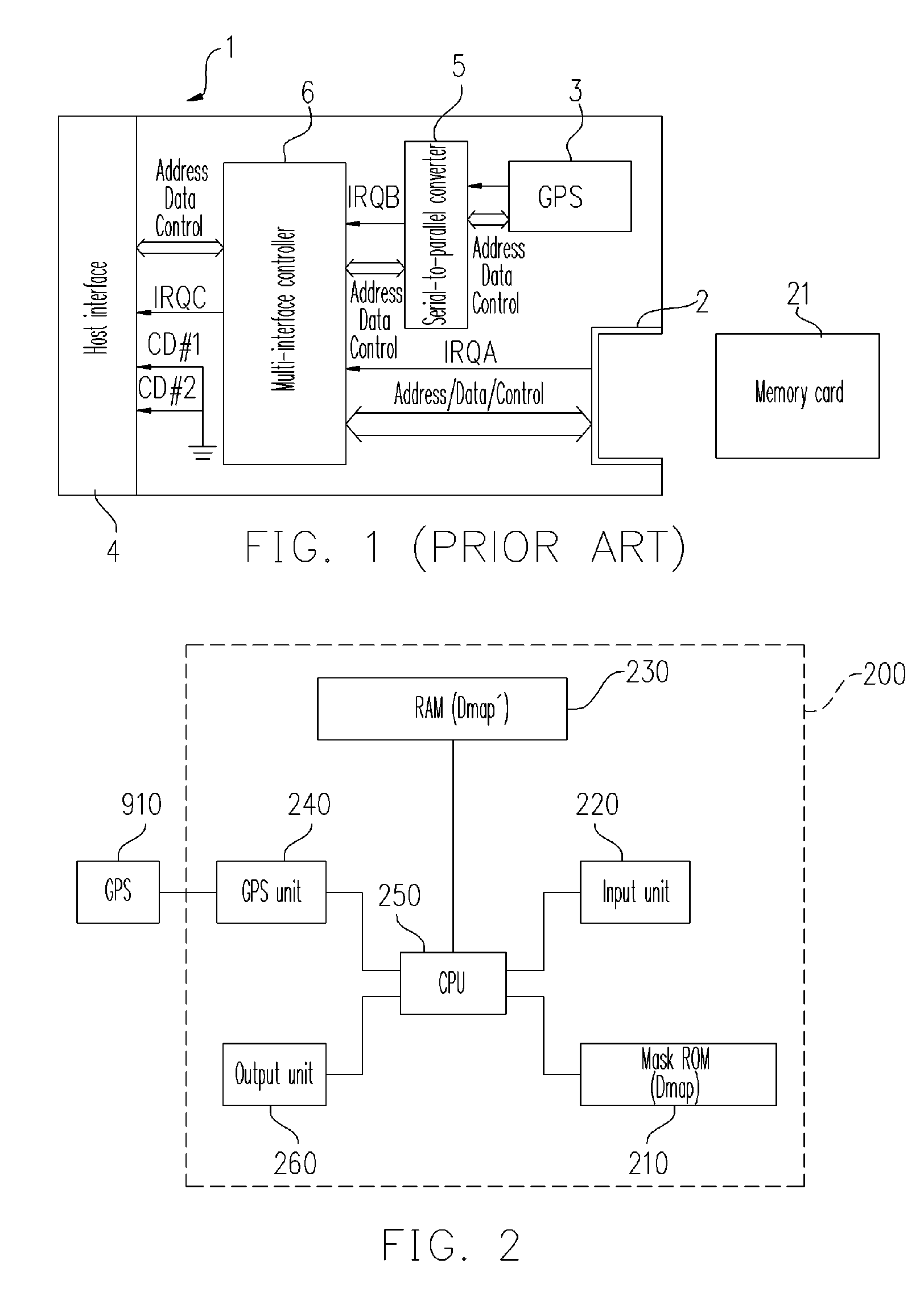

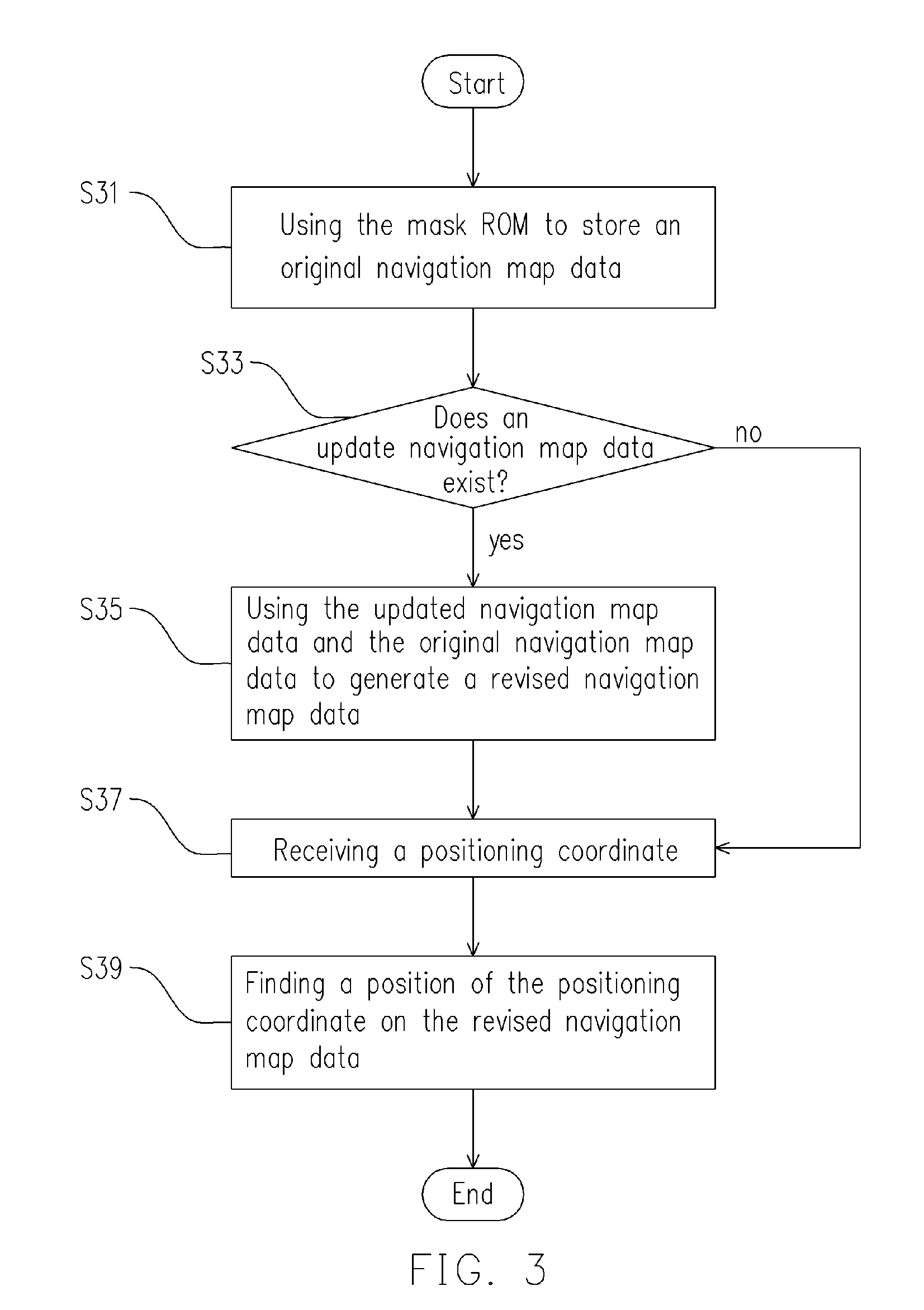

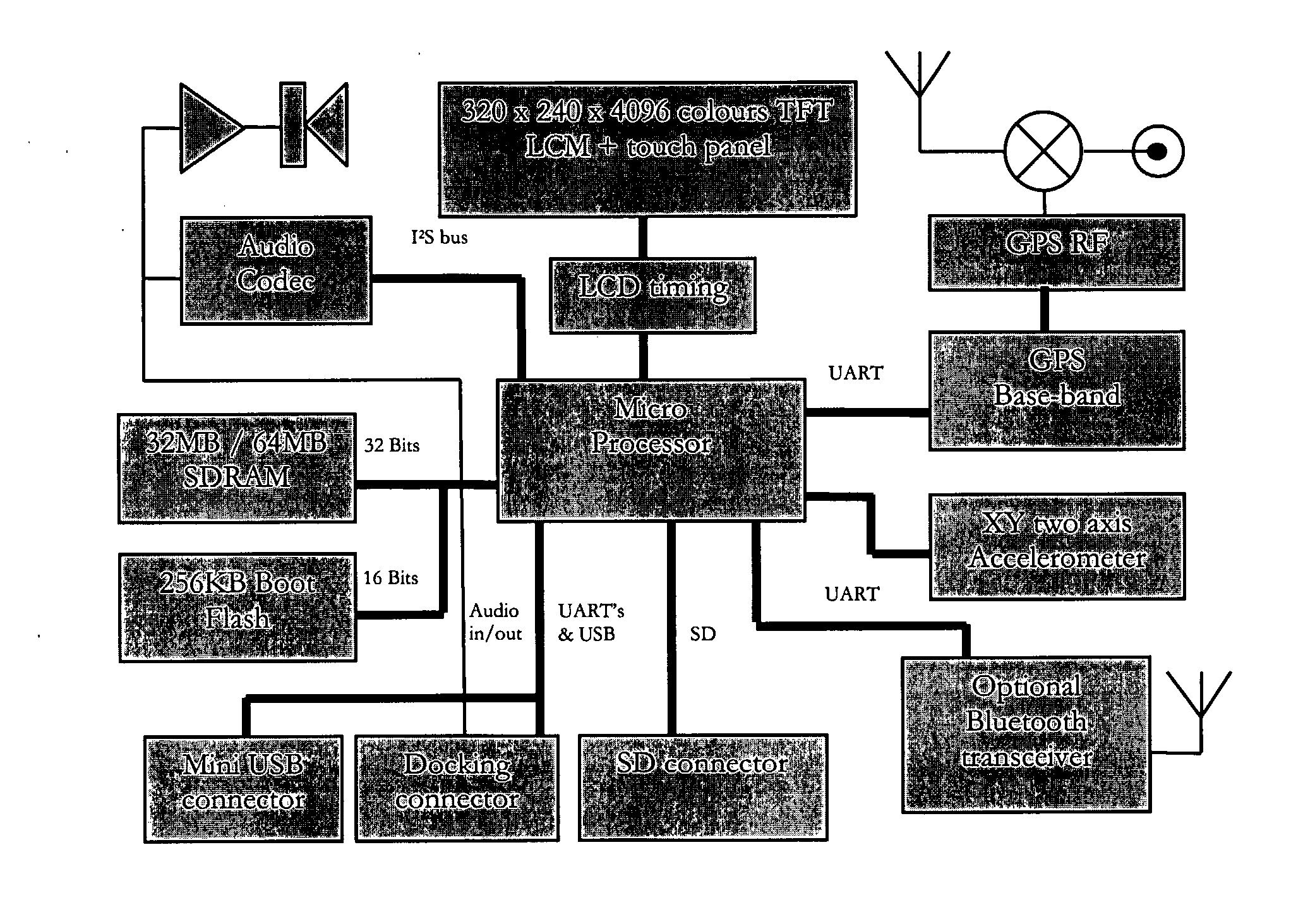

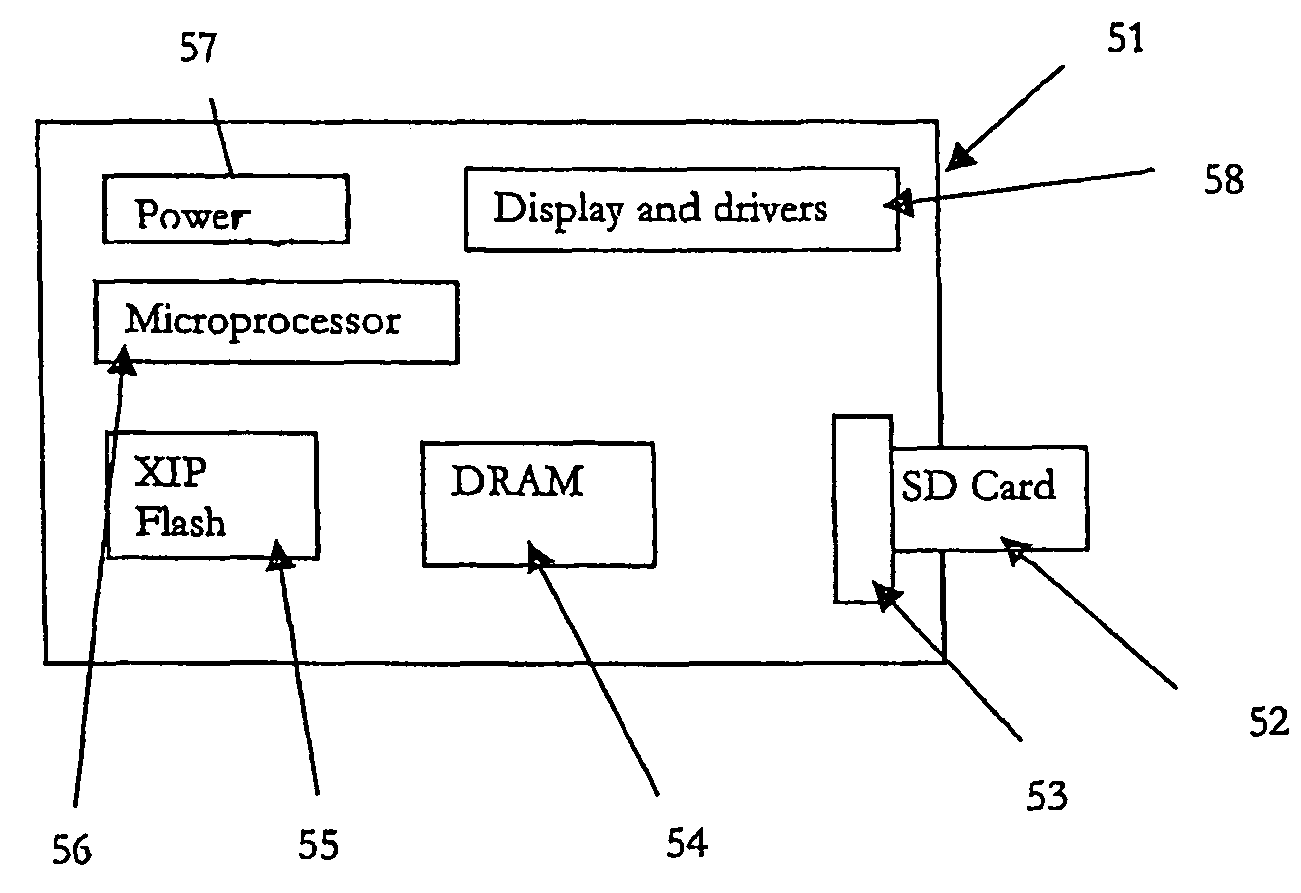

Portable device and method for providing navigation data

InactiveUS20070143016A1Low costImprove reading speedInstruments for road network navigationPosition fixationMask ROMRandom access memory

A portable device capable for providing navigation data and the method thereof. The portable device includes a mask ROM (Read Only Memory), an input unit, a RAM (Random Access Memory), a GPS (Global Positioning System) unit, a CPU (Central Processing Unit), and an output unit. First, an updated navigation map data is provided into the input unit of the portable device and stored in the RAM. Then, the CPU compares the updated navigation map data with an original navigation map data stored in the mask ROM to generate a revised navigation map data. Afterwards, the CPU calculates the position of the user on the revised navigation map data according to a positioning coordinate from the GPS unit.

Owner:COMPAL ELECTRONICS INC

Semiconductor device

InactiveUS7881693B2Low priceConvenience is lostResonant long antennasElectromagnetic wave systemMask ROMData storing

In an RF tag, a mask ROM or a flash memory is used for storing data such as an ID number. Although the mask ROM can be realized at a low price, rewriting is not possible. In addition, in the flash memory, although electric rewriting is possible, production cost increases. Accordingly, it is difficult to provide an RF tag by which data rewriting is possible at a low price. An RF tag is provided with a power supply circuit having a function to generate a power supply voltage from a weak radio signal and a memory which can hold data stored in a data holding portion by the power supply voltage. With the above structure, a high-performance RF tag capable of rewriting data such as an ID number after production can be provided at a low price.

Owner:SEMICON ENERGY LAB CO LTD

Navigation device displaying travel information

ActiveUS20070185648A1Only be usedInexpensively formedInstruments for road network navigationRoad vehicles traffic controlOperational systemMask ROM

A navigation device, programmable with map data and a navigation application that enables a route to be planned between two user-defined places; the device is operable to read a removable memory card storing the device operating system, the navigation application, and the map data. It does not need to store the operating system in mask ROM; hence, customisation for a specific country requires only that the appropriate memory card be inserted at the time of use.

Owner:TOMTOM INT BV

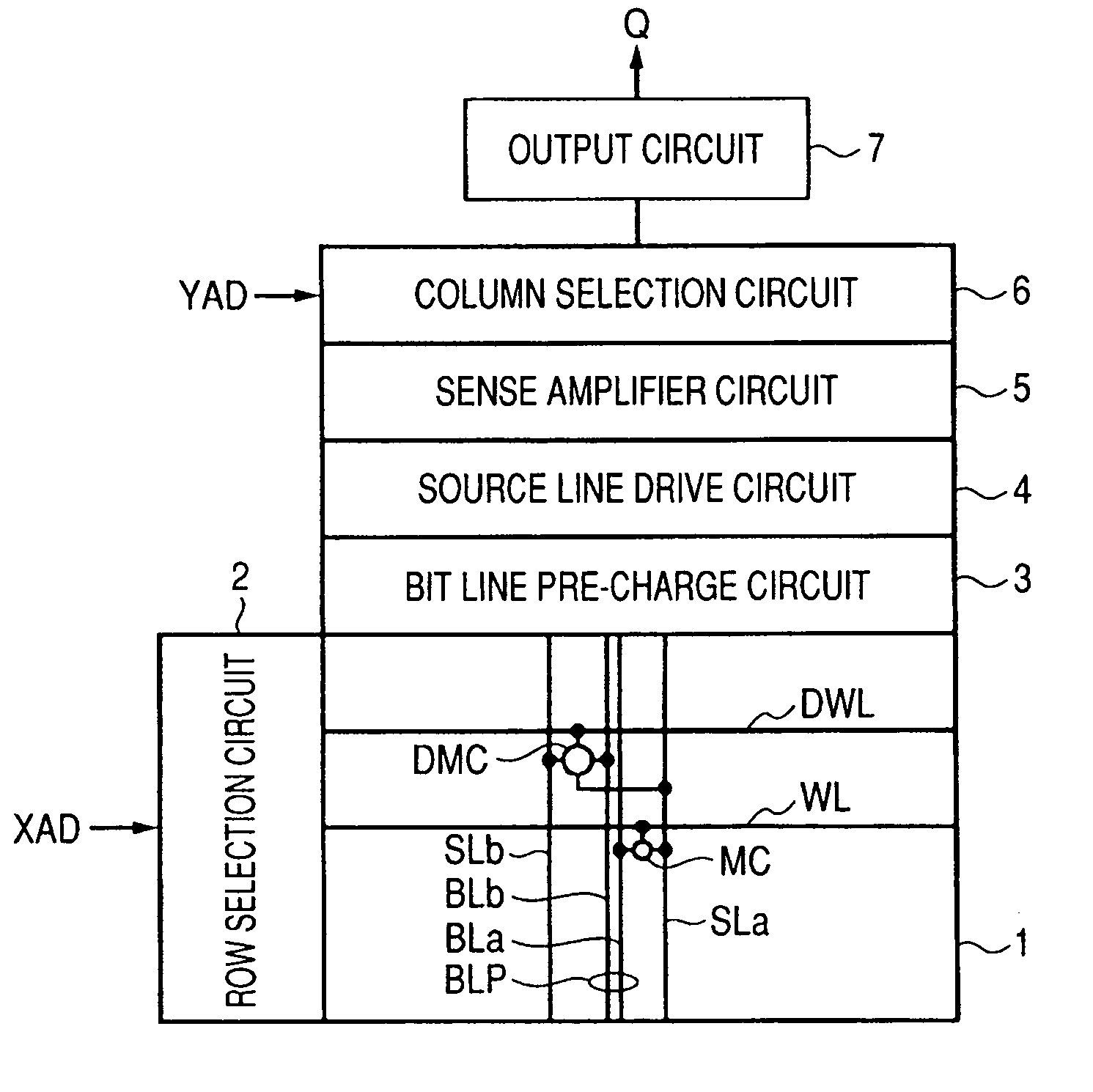

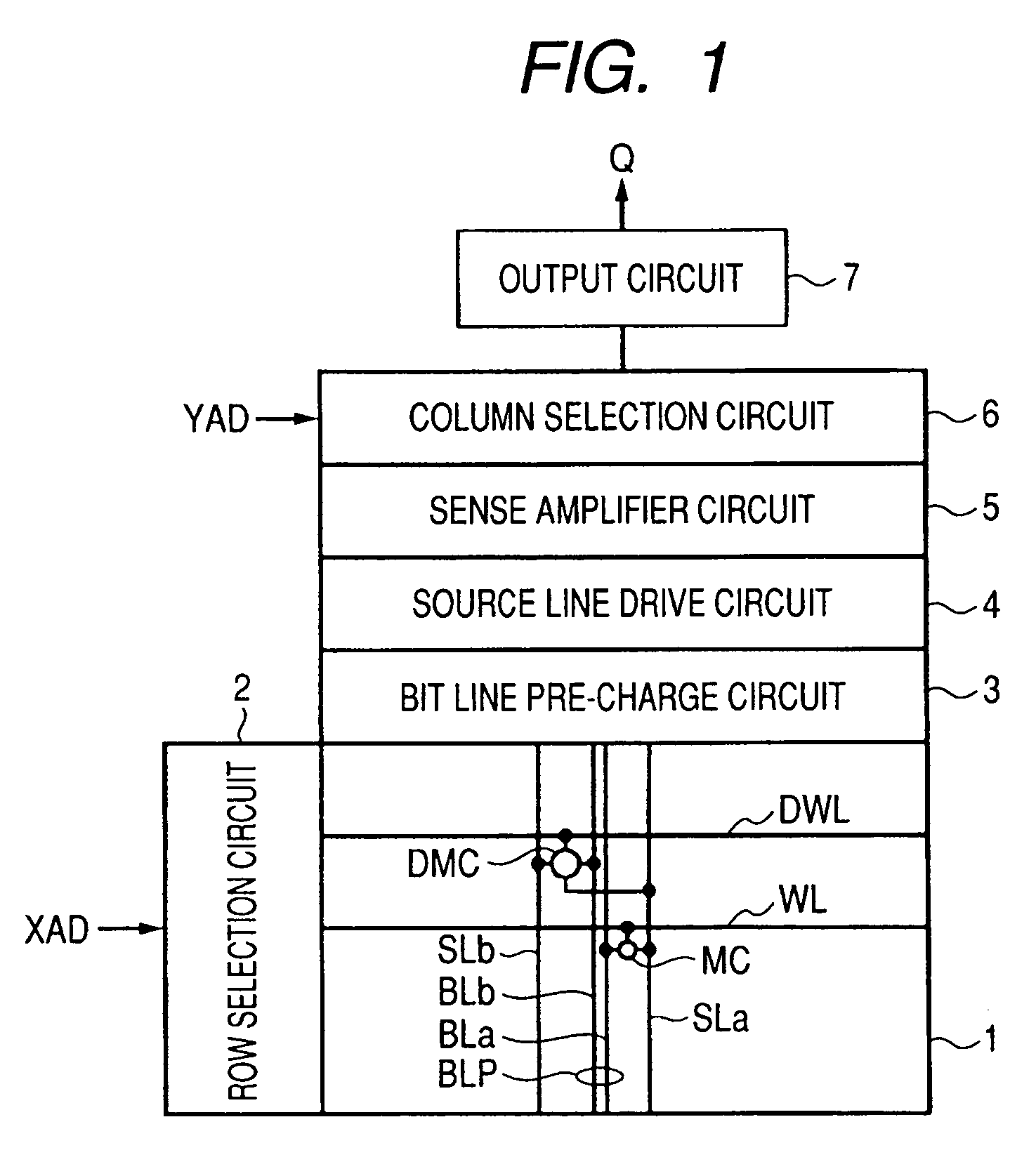

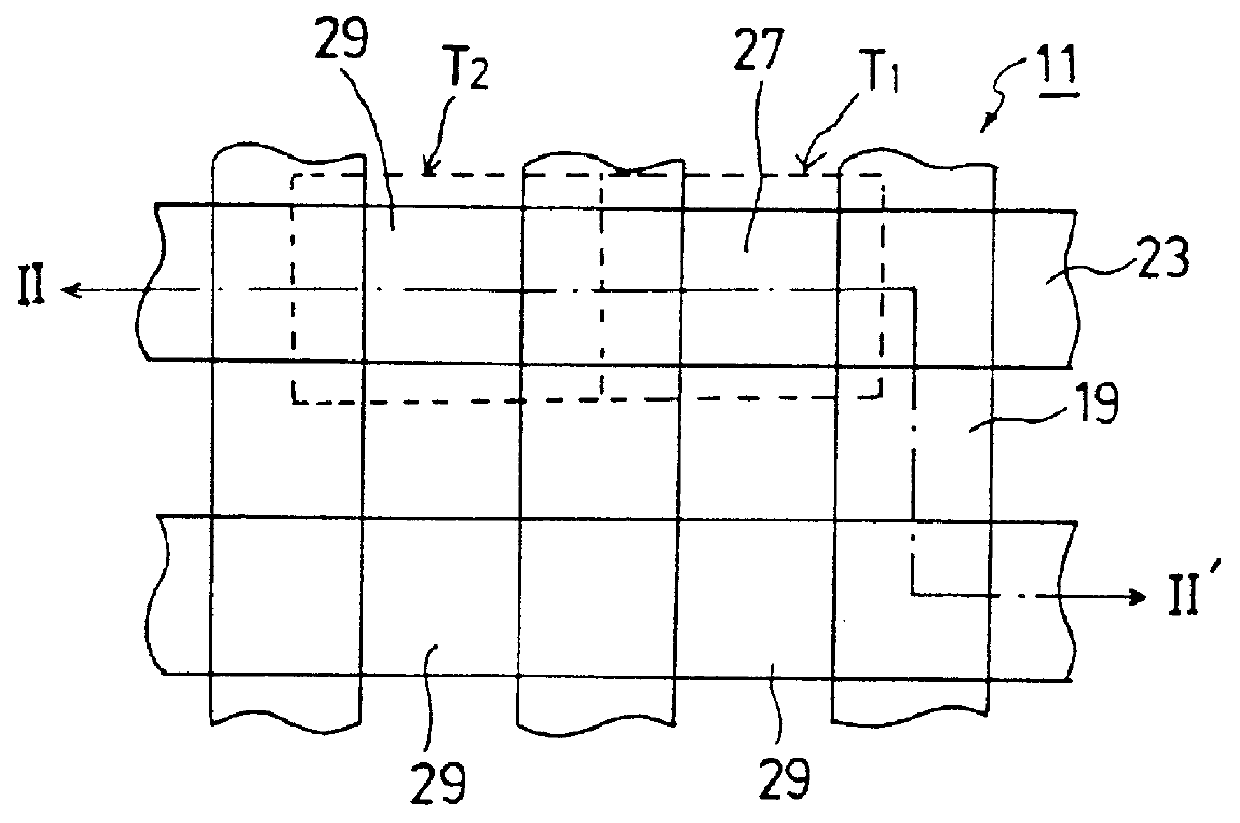

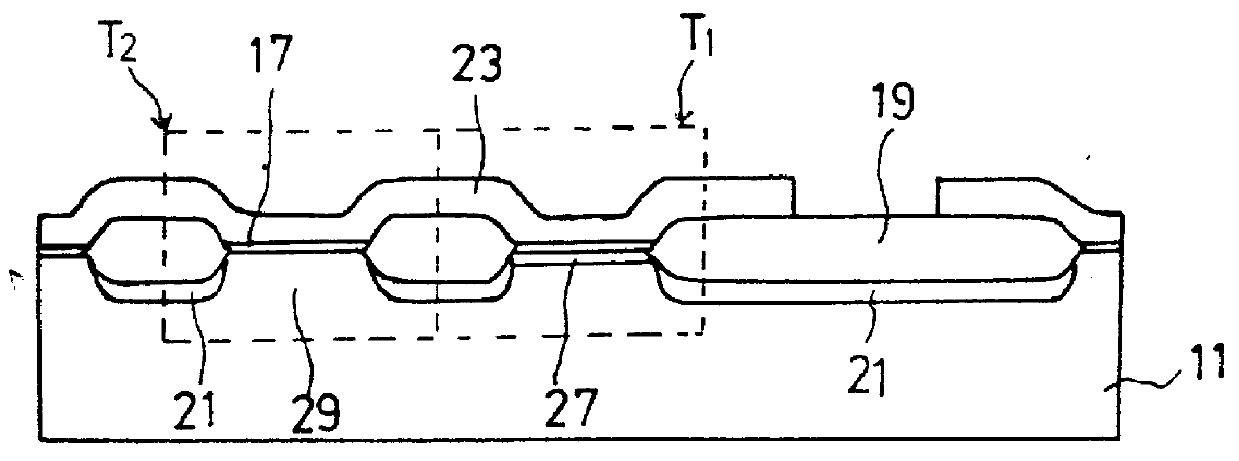

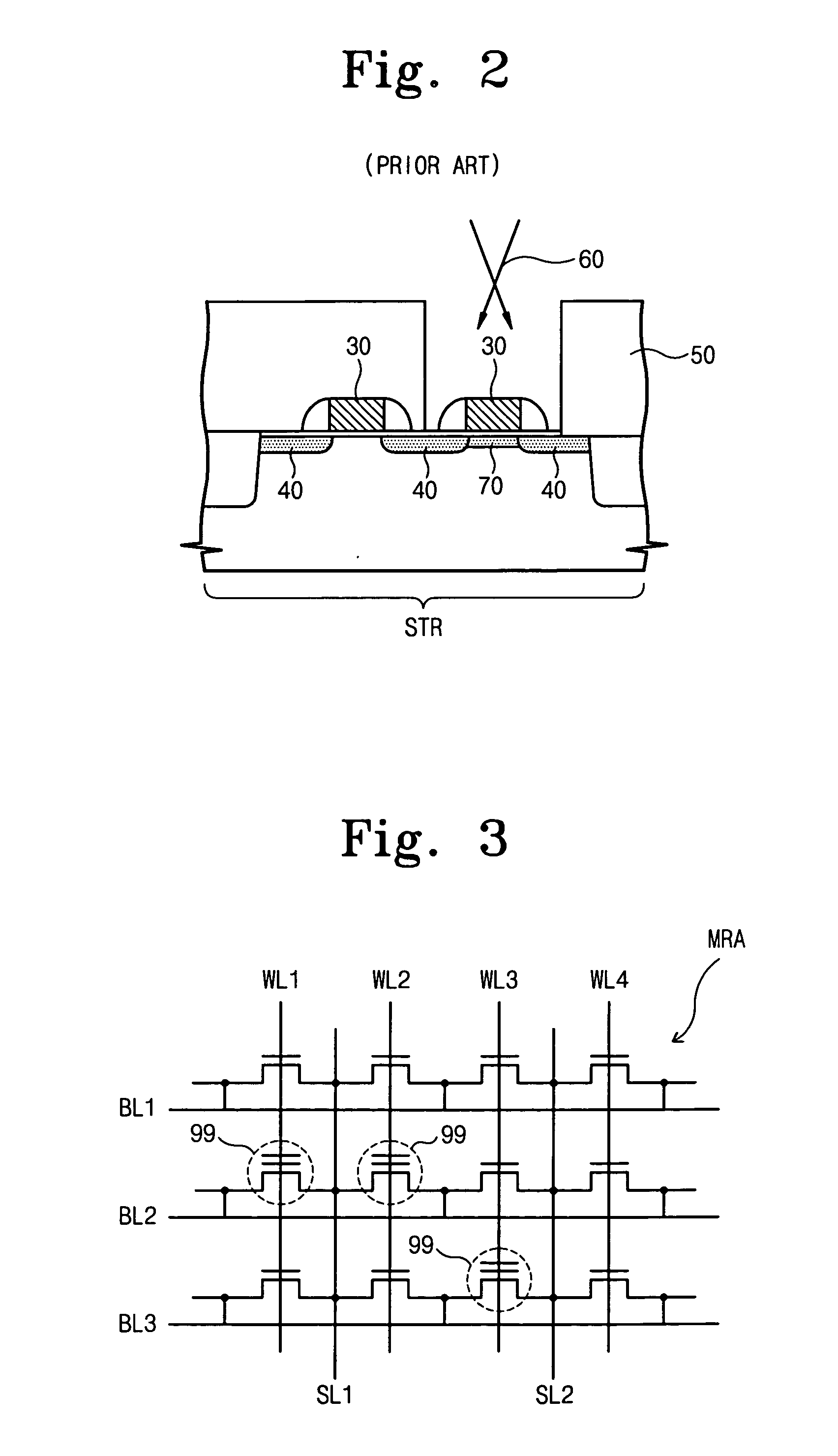

Nonvolatile semiconductor memory

InactiveUS20070127302A1Fast readoutRead data quicklyRead-only memoriesDigital storageBit lineMask ROM

There is provided a high-density mask ROM operable at a high speed. With the mask ROM, respective source lines are disposed so as to be shared by memory cells in respective columns adjacent to each other, and bit lines are disposed so as to correspond to the respective columns of the memory cells. Further, the dummy cells are disposed for the respective columns of the memory cells. The dummy cells are each made up of a series-circuit including a first switching transistor that is turned into the conducting state in response to a signal potential on a dummy word line (DWL), and a second switching transistor 17 for coupling an adjacent source line to the bit line corresponding thereto in response to a potential of the source line in a column corresponding thereto. The memory cells each are made up of one unit of a transistor and a data storage formed by mask wiring. At the time of reading data, a potential of the source line in a select column is caused to undergo a change, whereupon there occurs a potential difference between a pair made up of the bit line as selected to which the memory cells as selected are coupled, and a reference bit line with the dummy cells coupled thereto, so that it is possible to execute readout of data by detecting the potential difference.

Owner:RENESAS ELECTRONICS CORP

Method for fabricating a mask read-only-memory with diode cells

InactiveUS6821841B1Solid-state devicesSemiconductor/solid-state device manufacturingBit lineMask ROM

A method for fabricating a mask read-only-memory with diode cells is provided. A doped conductive layer with a first conductivity is formed on bit lines. Then, a photoresist layer with a mask ROM pattern is formed on an interlayer dielectric layer on the doped conductive layer for serving as an etching mask, thereby forming openings in the interlayer dielectric layer unto the exposed regions of the doped conductive layer. Performing ion implantation to form a diffusion region with a second conductivity opposite to the first conductivity in each exposed region of the doped conductive layer, so that the doped conductive layer and the diffusion regions formed therein constitute diode cells that are served as memory cells. A contact plug is formed in each opening unto the diode cell and a conductive layer is formed on the contact plug for serving as word lines.

Owner:MACRONIX INT CO LTD

Method of forming mask ROM

A method of fabricating a mask ROM includes forming a trench on a first conductivity type semiconductor substrate, implanting a second conductivity type impurity ion in at least a surface portion of the semiconductor substrate where the trench is formed, forming an insulating oxide layer on a surface of the semiconductor substrate, including a surface of the trench, forming gate oxide layers of both sides of the trench, forming first and second gates on the gate oxide layers and forming a first conductivity type channel by implanting a first conductivity type impurity ion in one side of the trench. As such, the resulting mask ROM includes two transistors on either side of a trench having channels along the side walls of the trench. The resulting mask ROM has a reduced surface width, enhancing integration.

Owner:LG SEMICON CO LTD

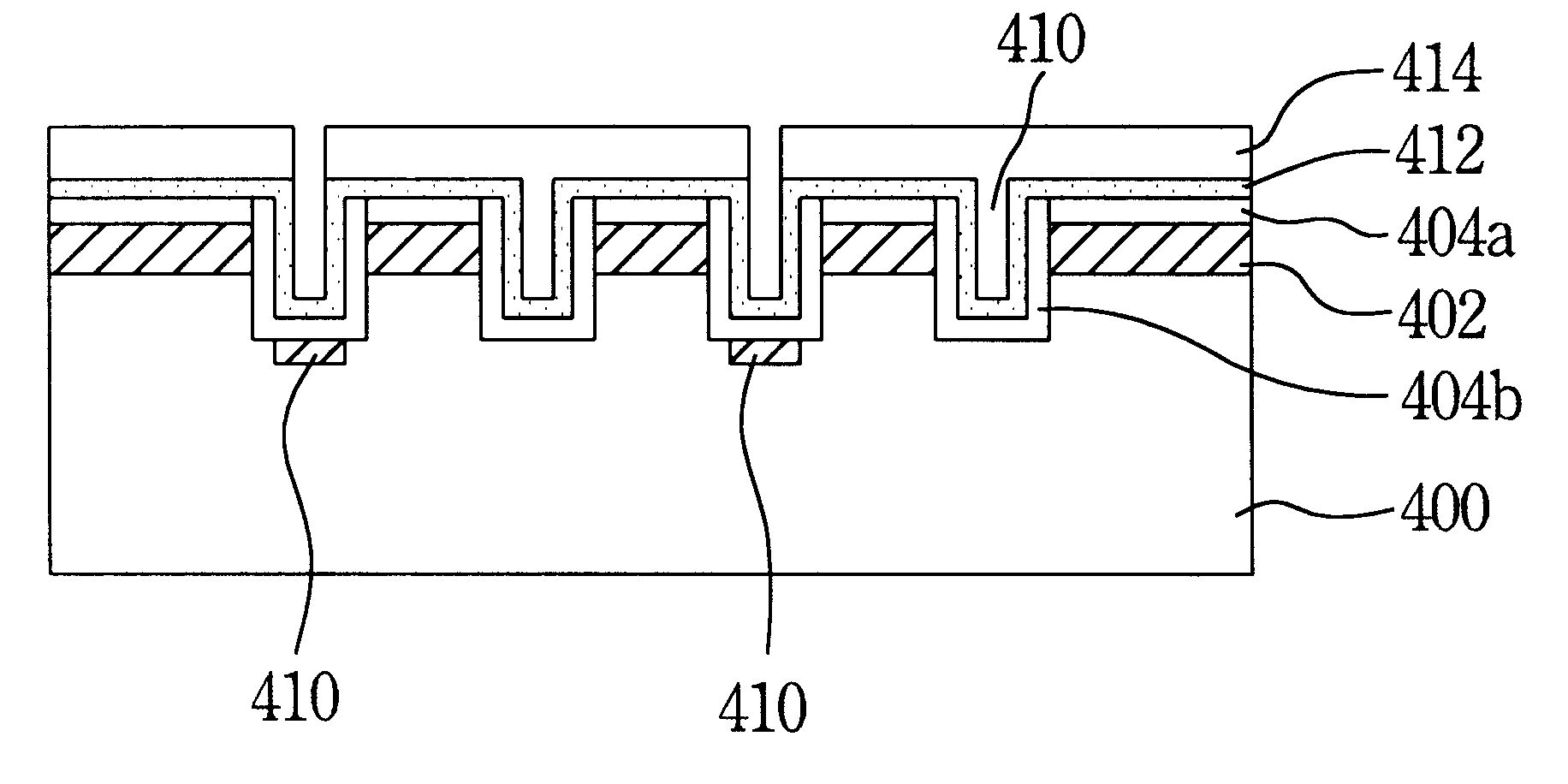

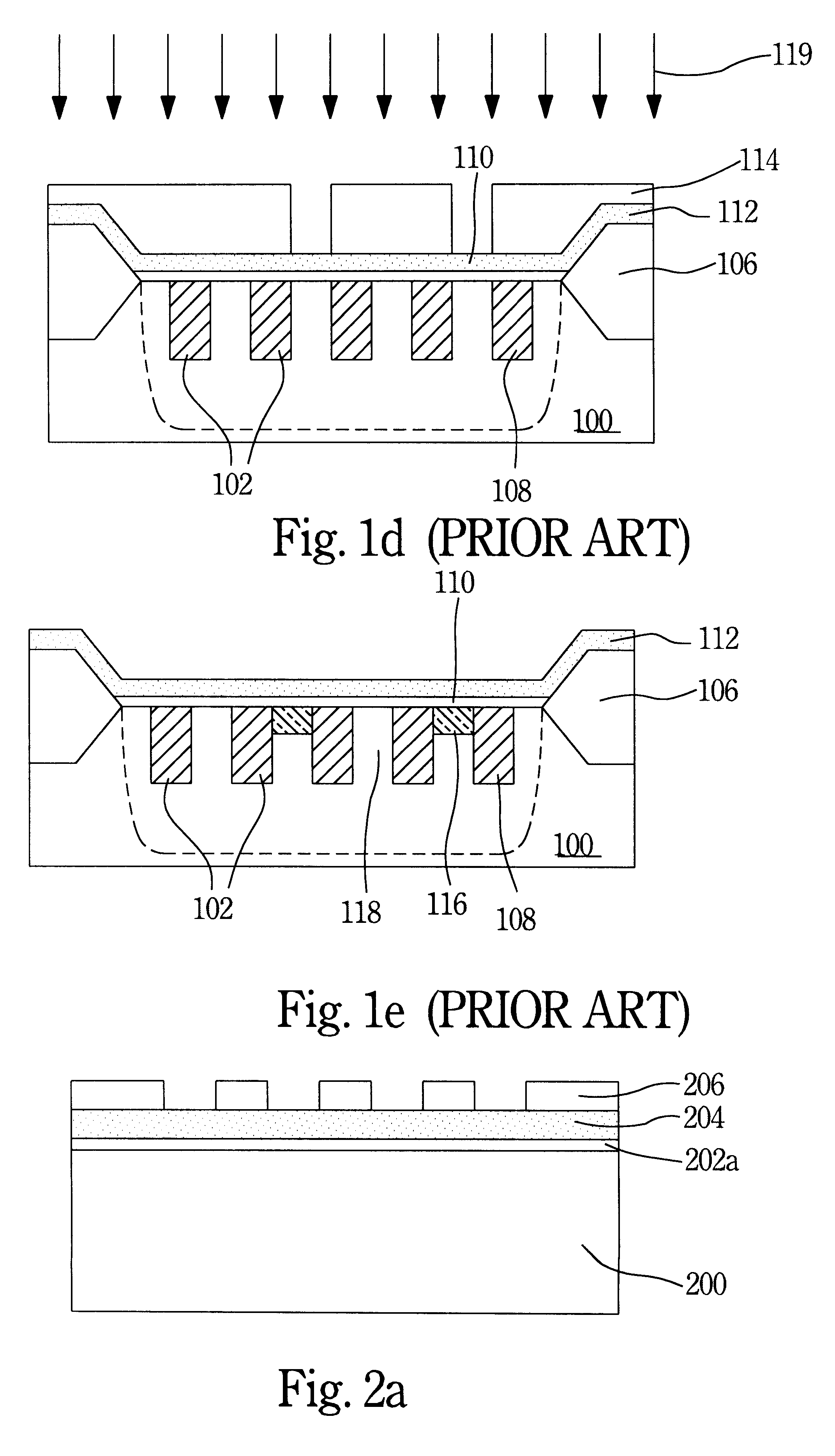

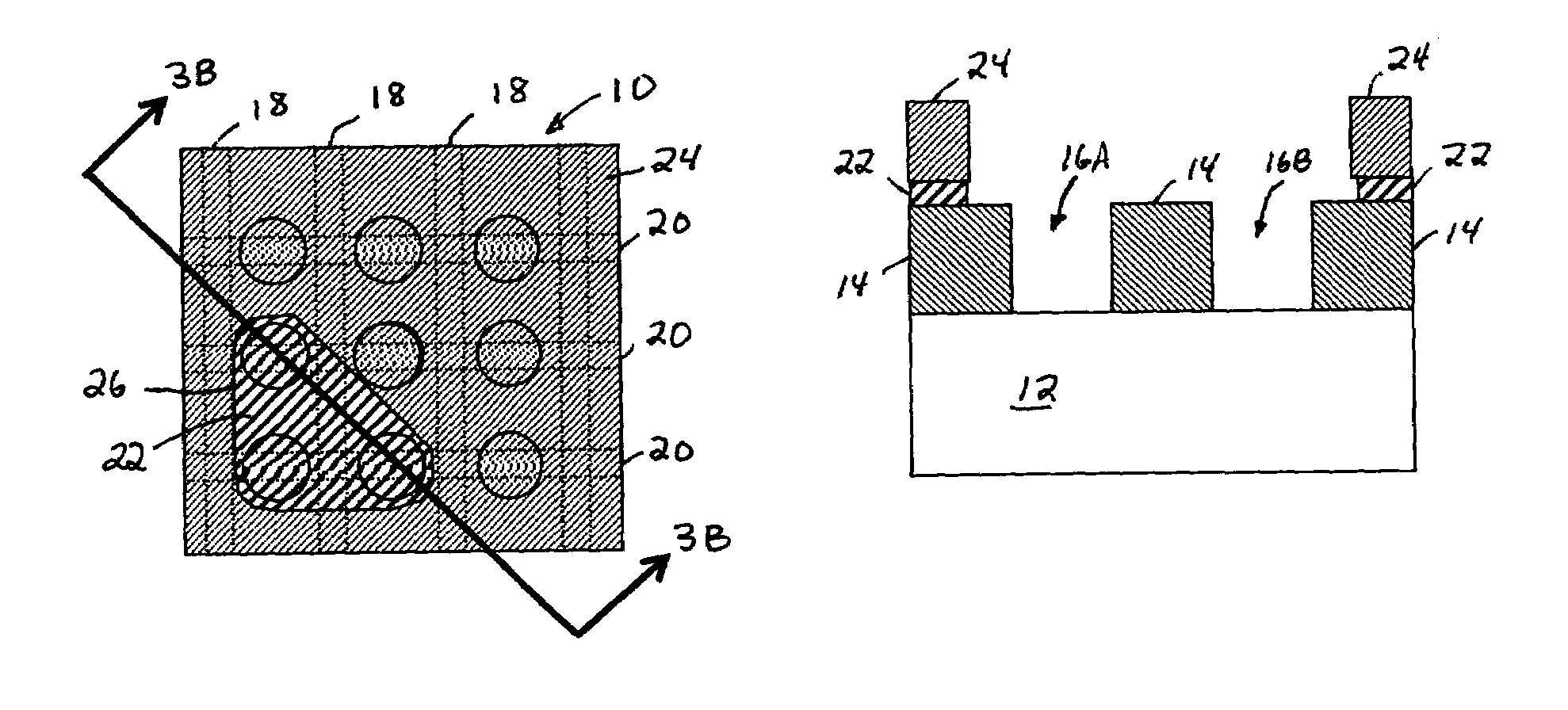

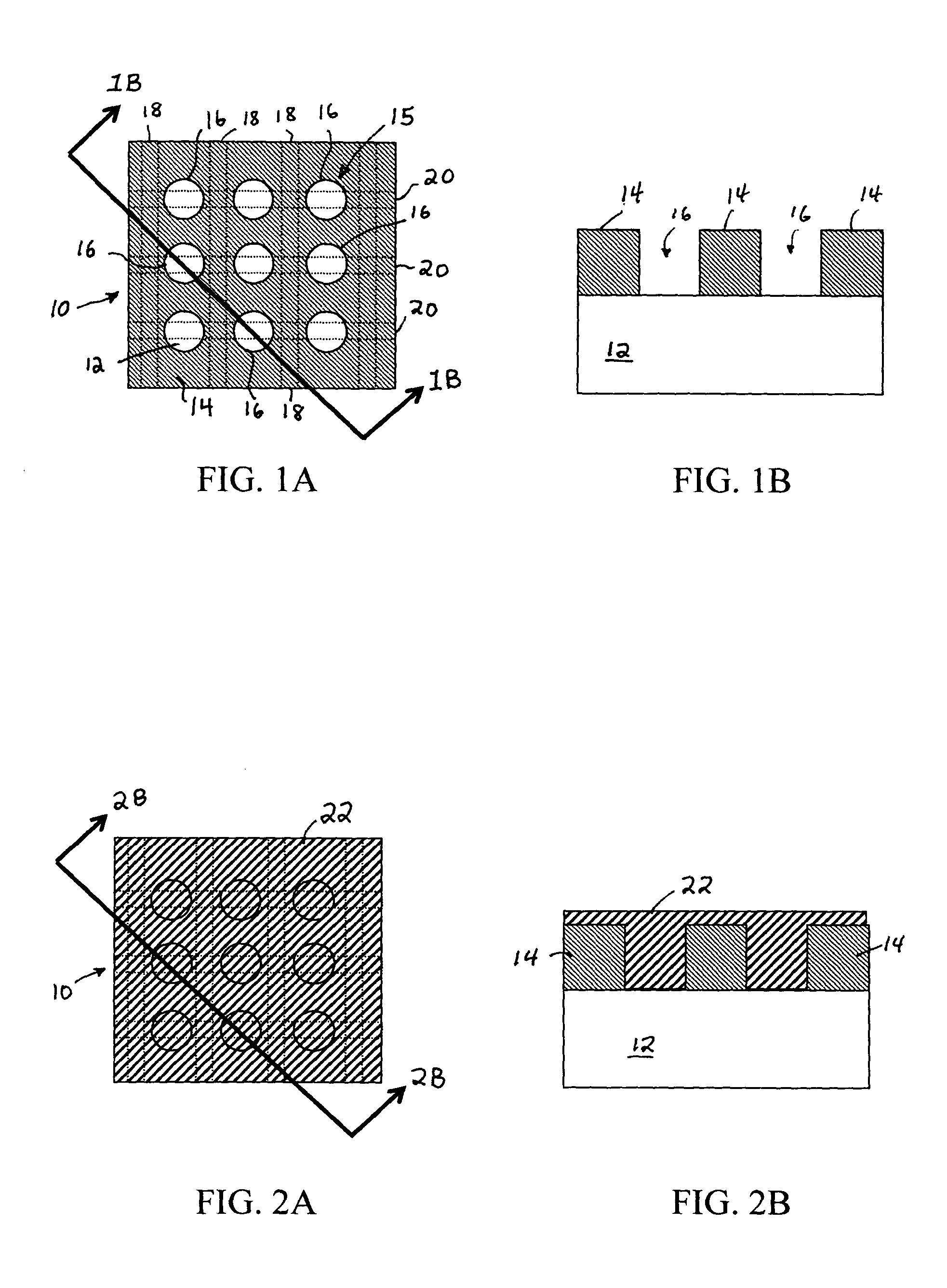

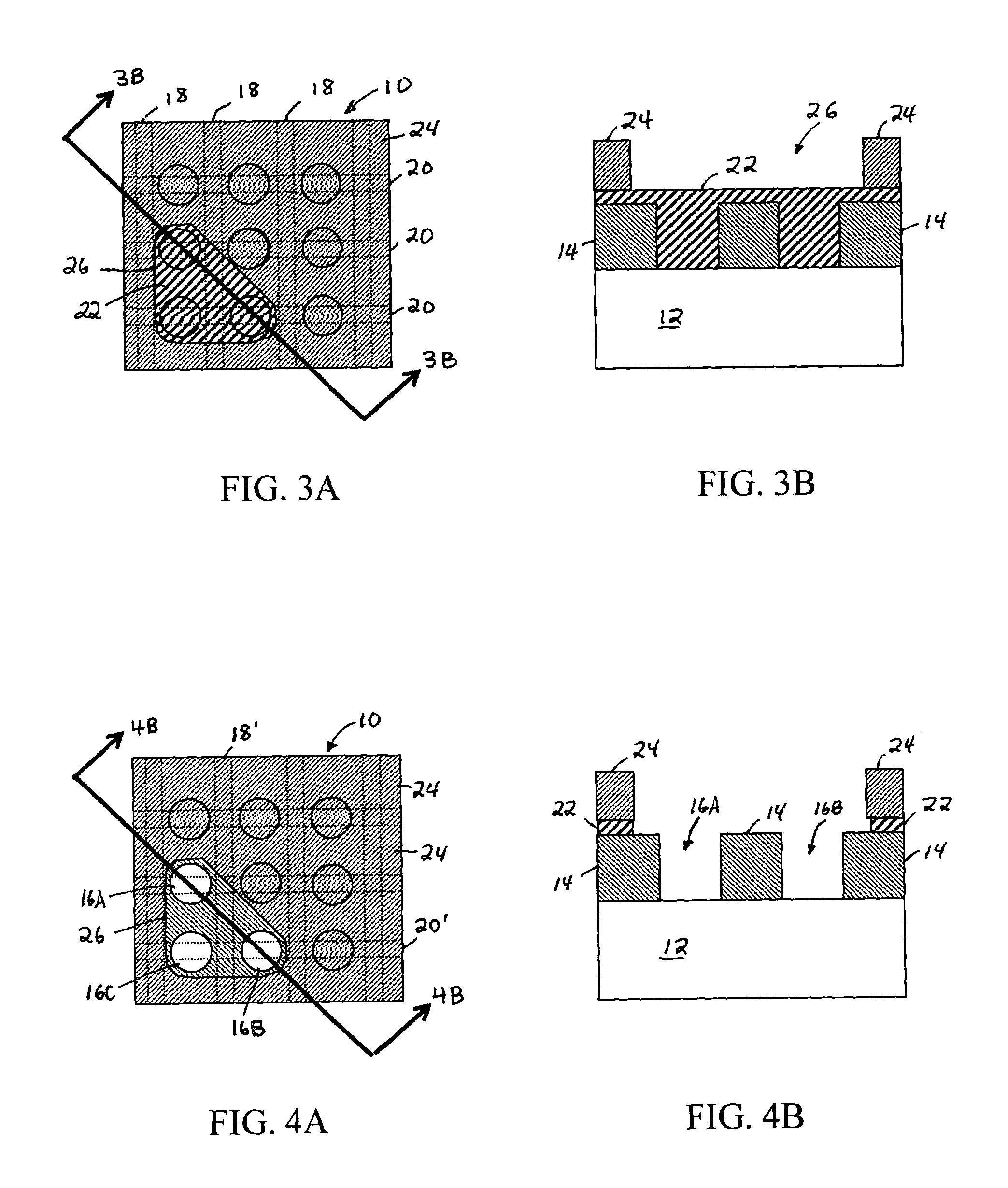

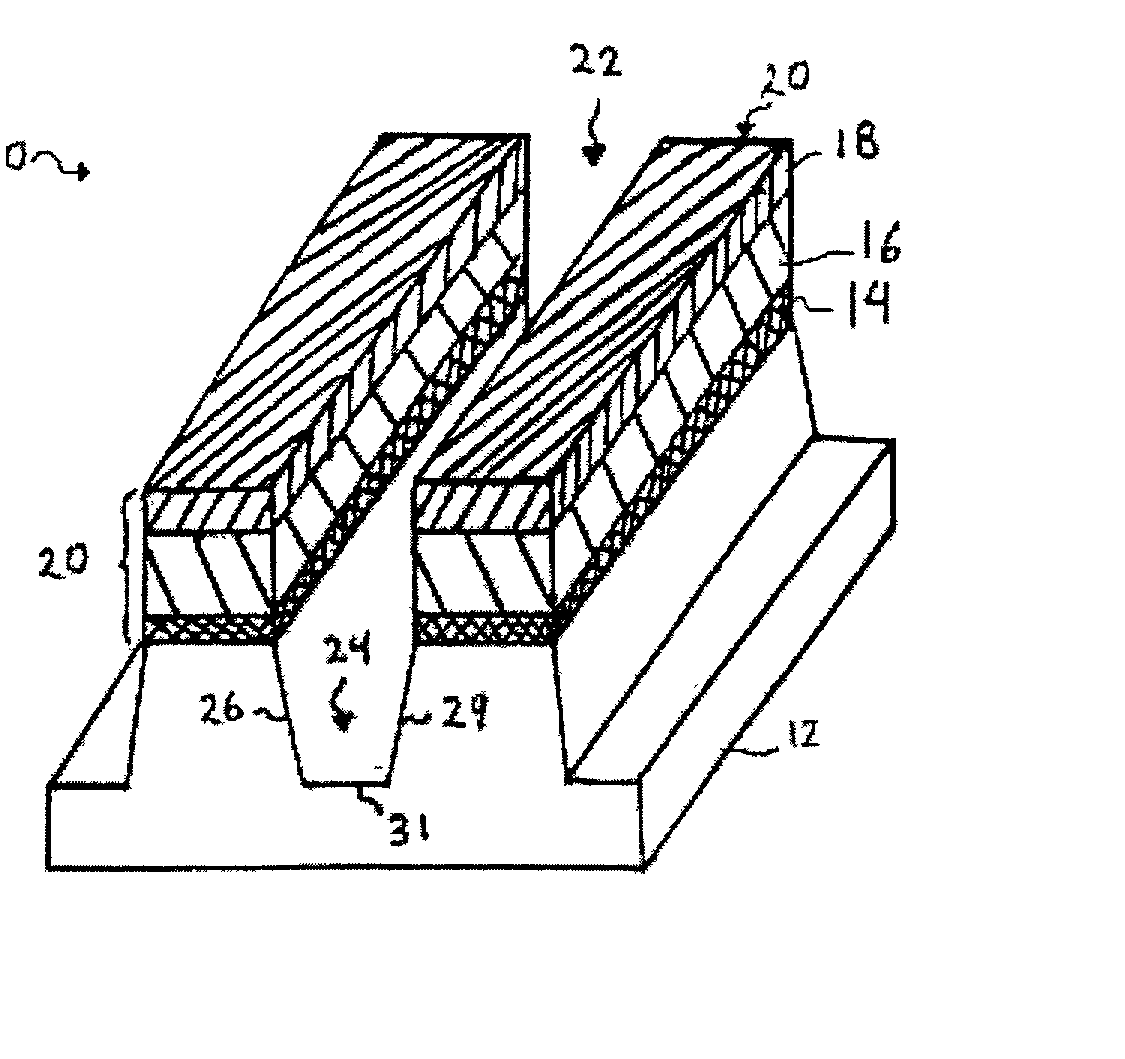

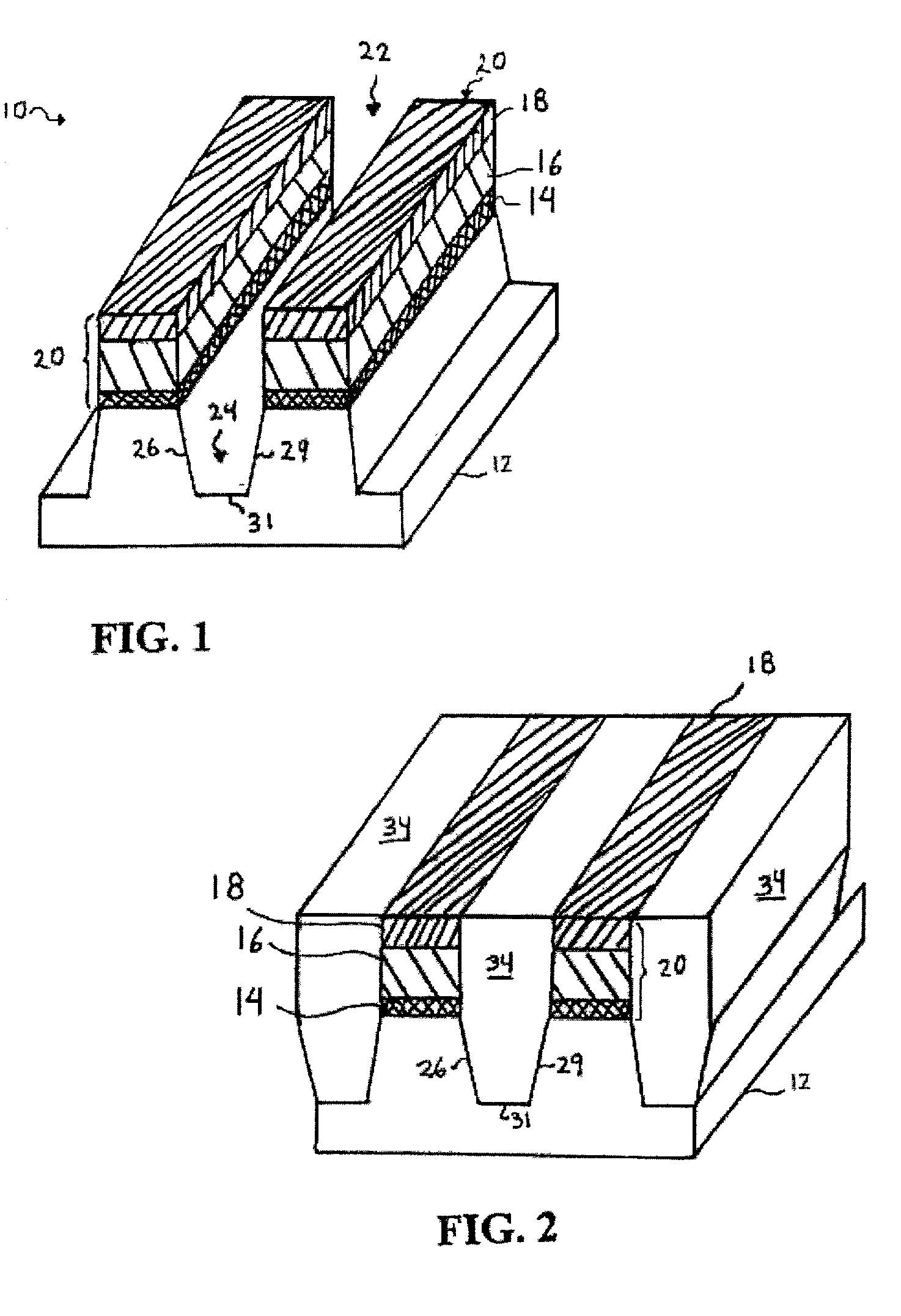

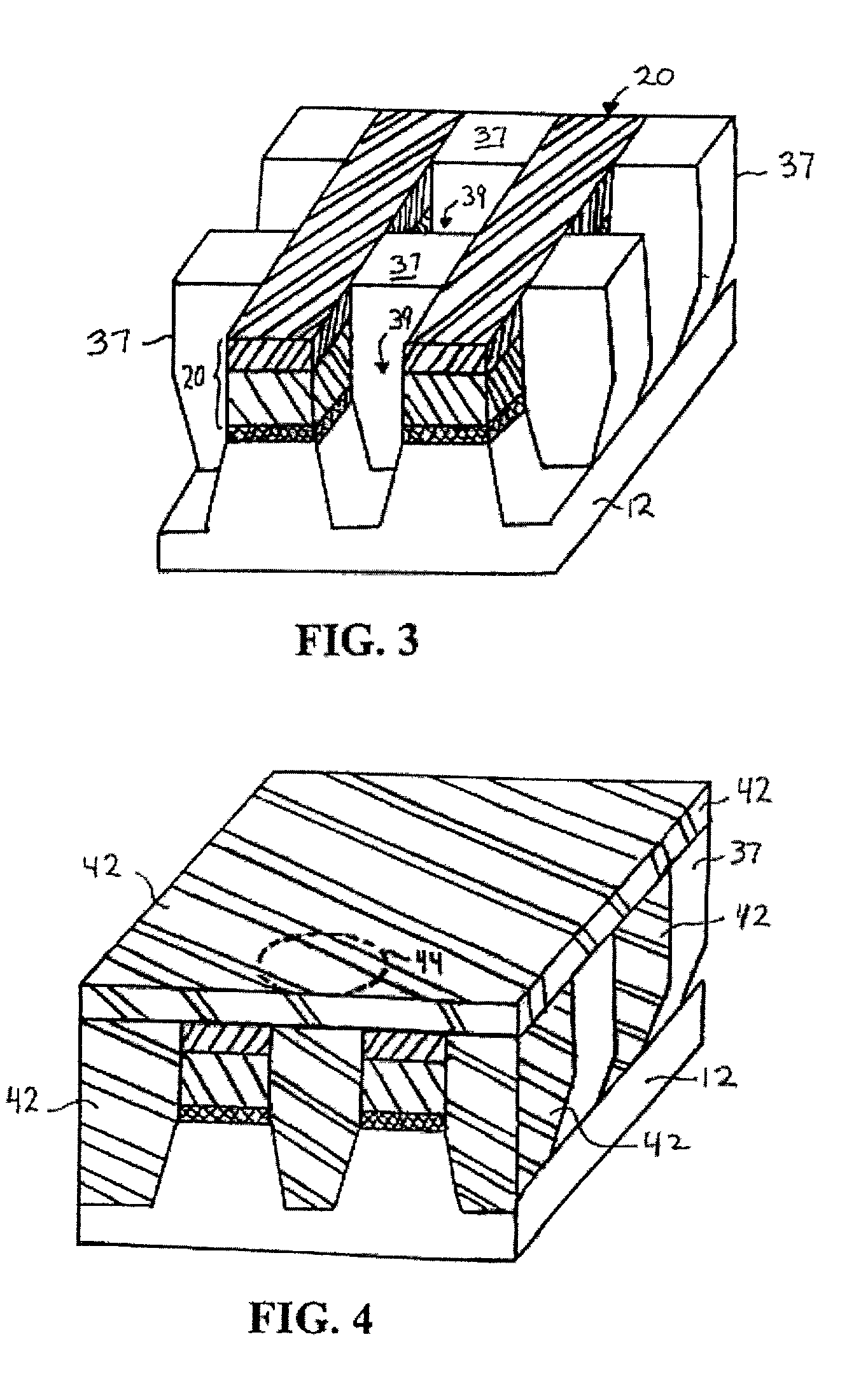

Methods of fabricating high density mask ROM cells

InactiveUS20030211695A1Easy to controlGood removal effectSolid-state devicesSemiconductor/solid-state device manufacturingHigh densityMask ROM

Methods for making integrated circuit devices, such as high density memory devices and memory devices exhibiting dual bits per cell, include forming multiple oxide fences on a semiconductor substrate between multiple polybars. The oxide fences create a hole pre-code pattern that facilitates ion implantation into trenches disposed between the polybars. The holes, or voids, formed by the oxide fences provide greater control of the critical dimension of ion implantation, for example, the critical dimension of the trench sidewalls. Semiconductor devices used in the manufacture of memory devices include the oxide fences during the manufacturing process.

Owner:MACRONIX INT CO LTD

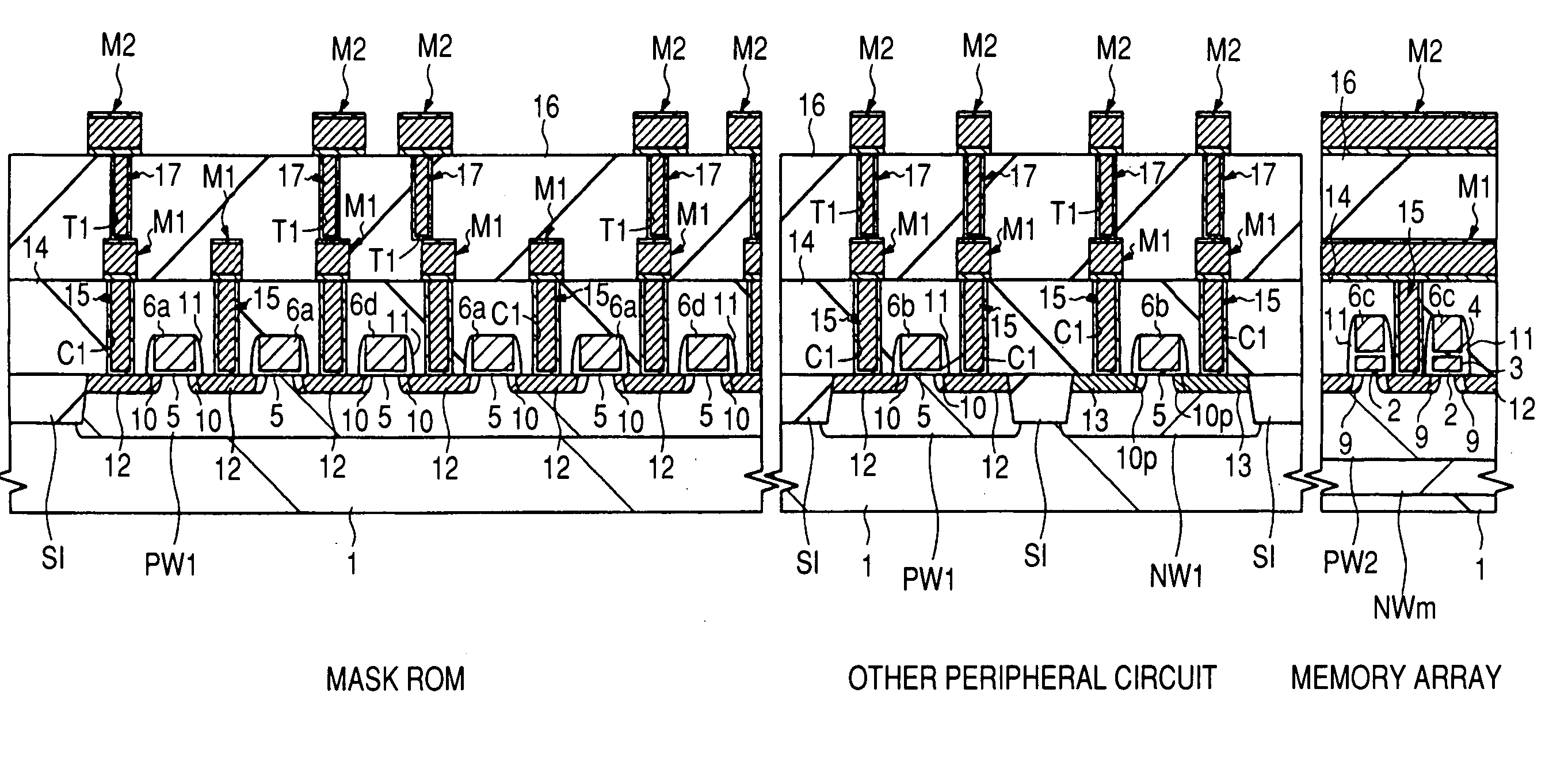

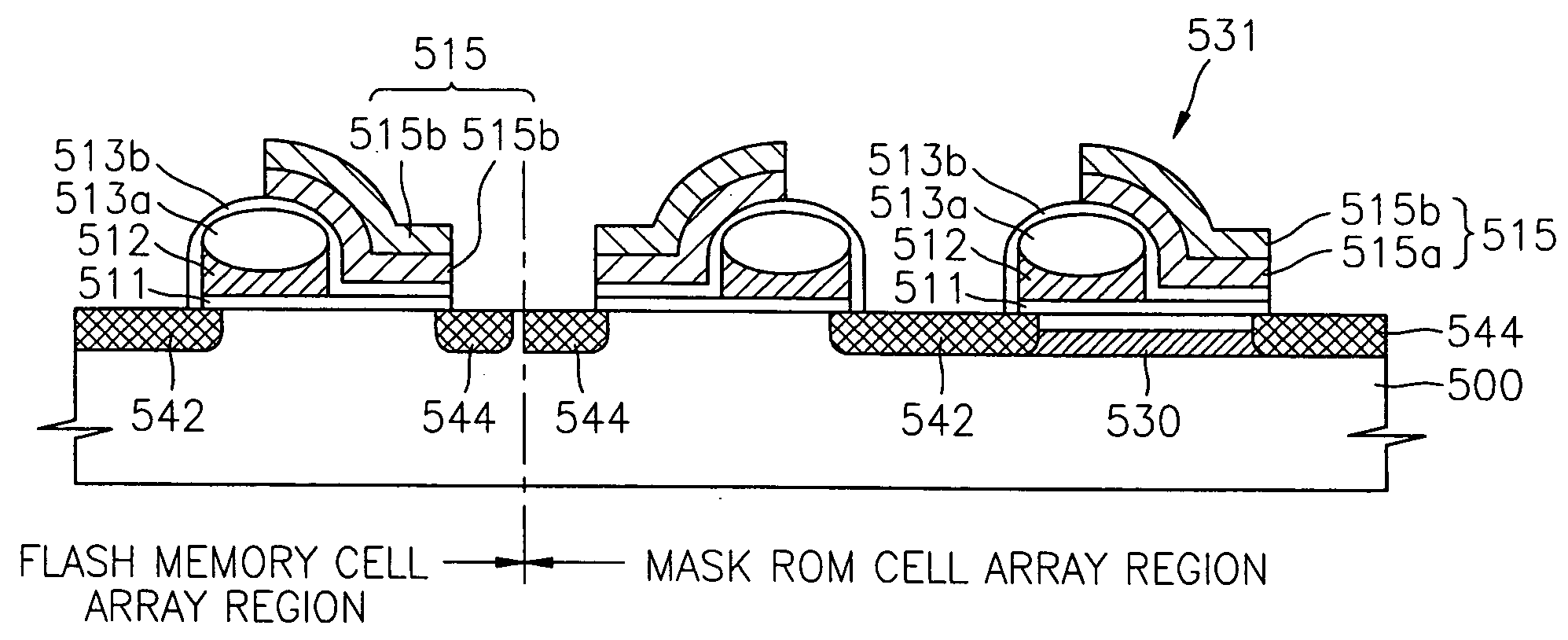

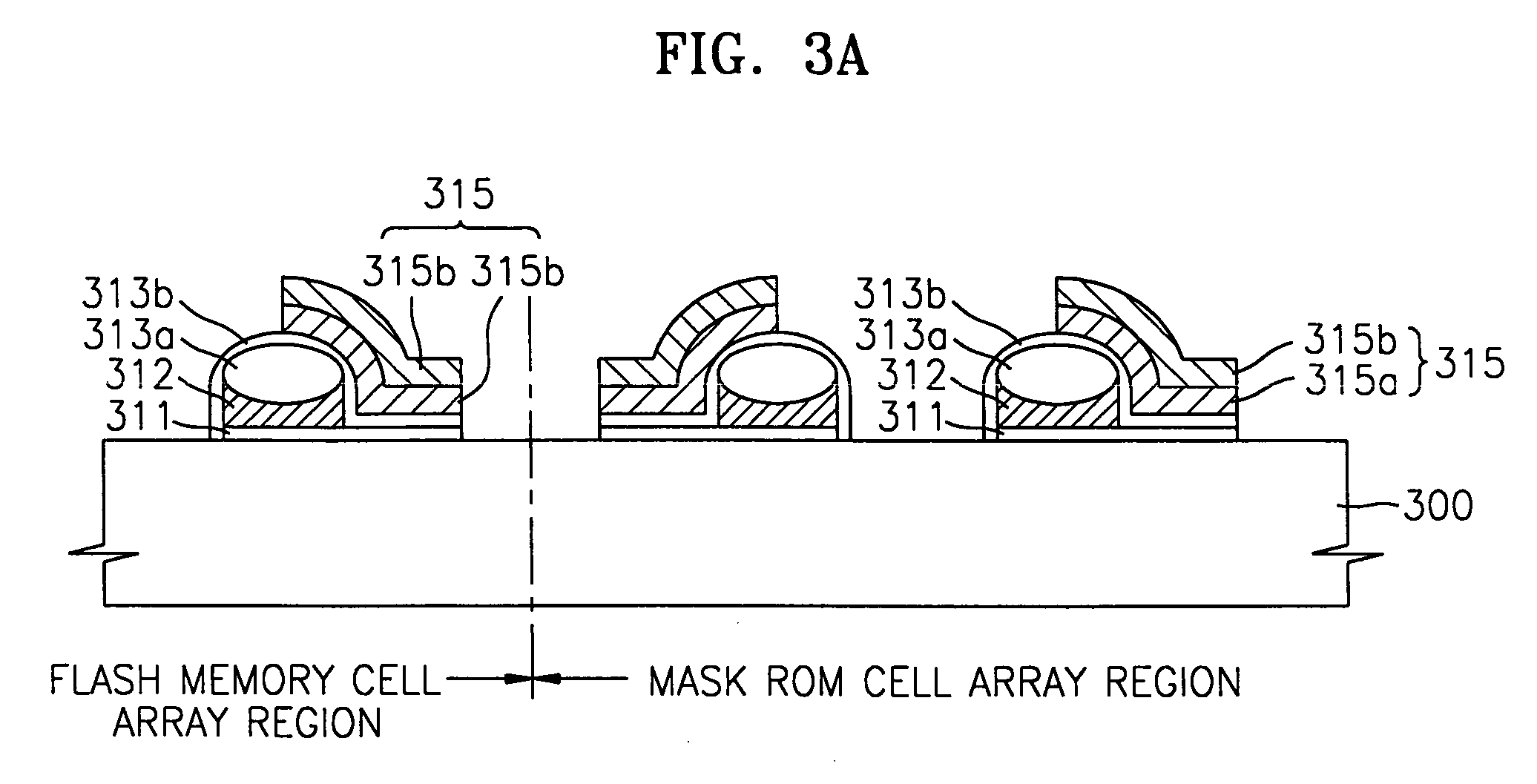

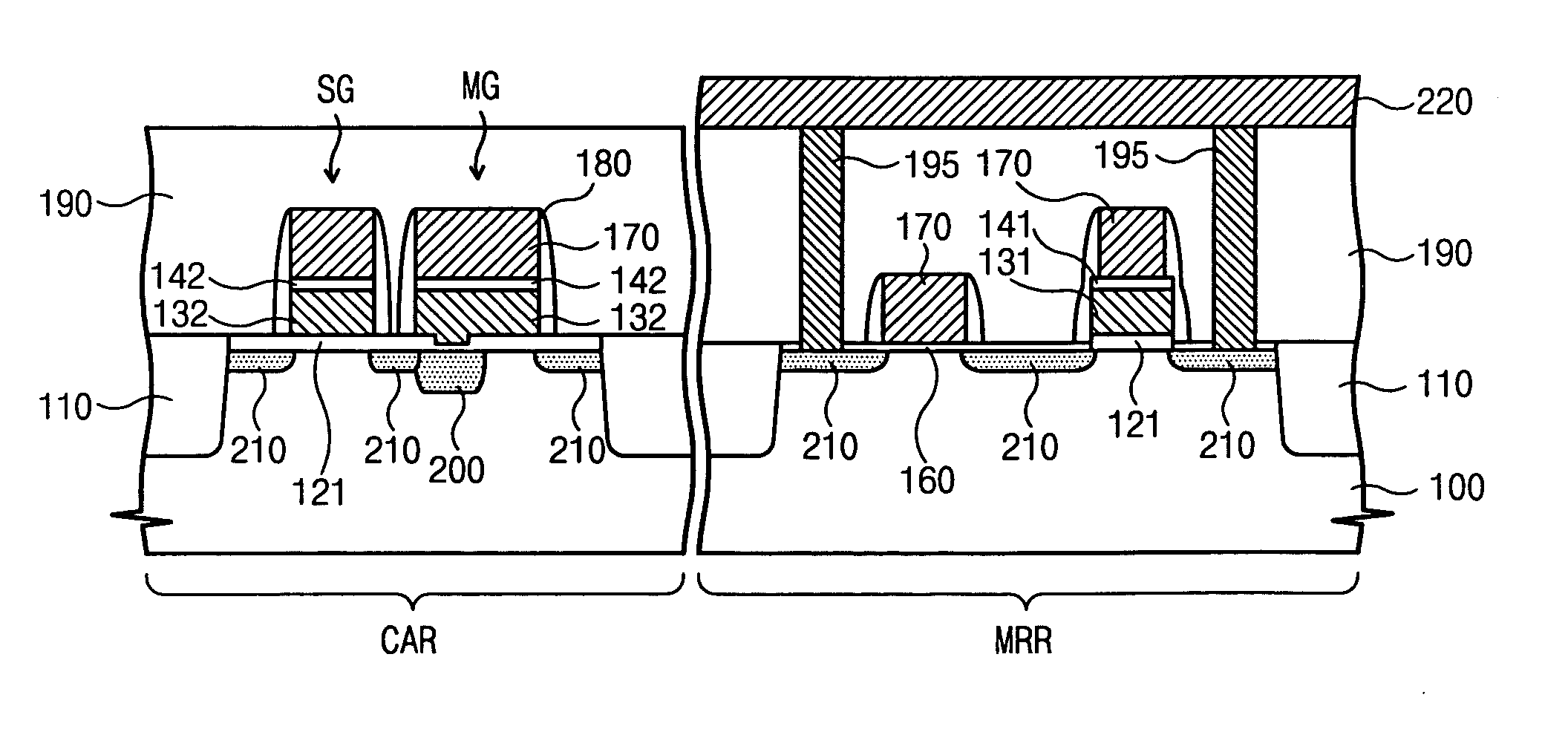

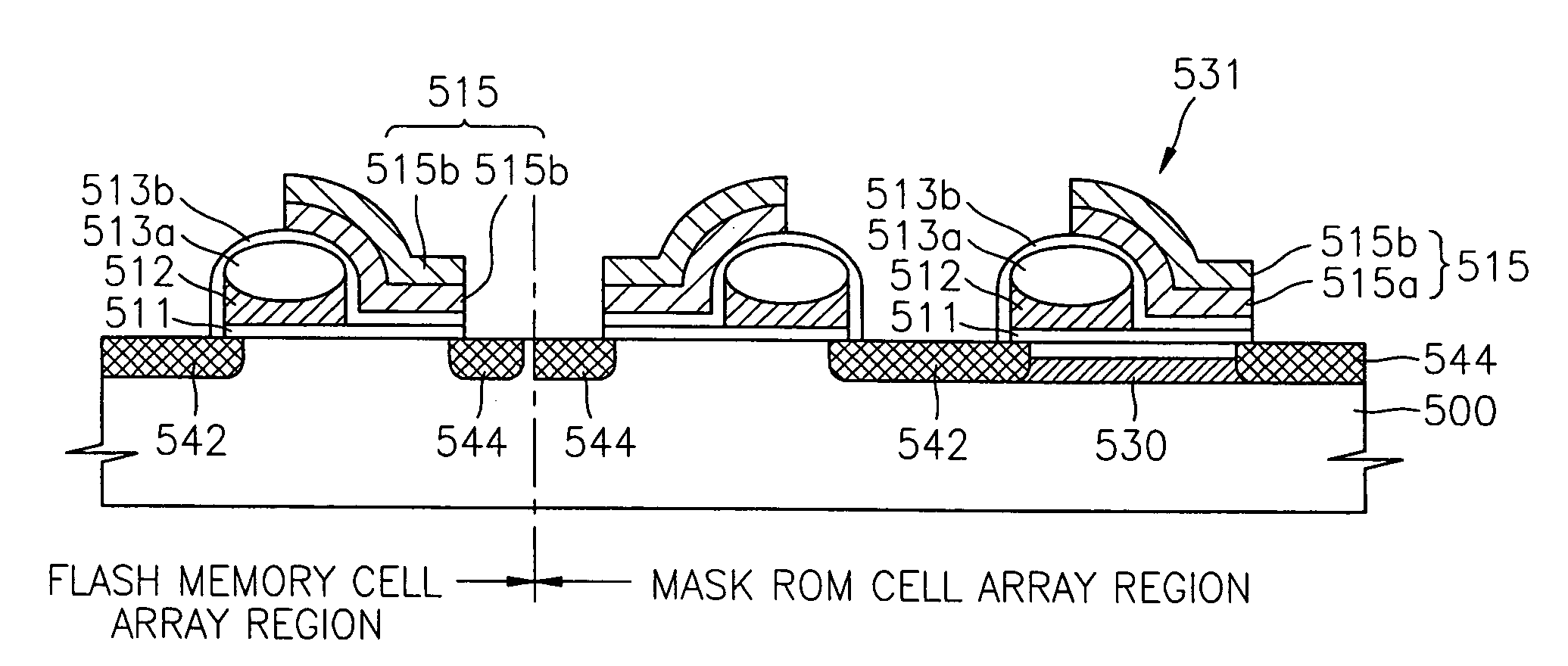

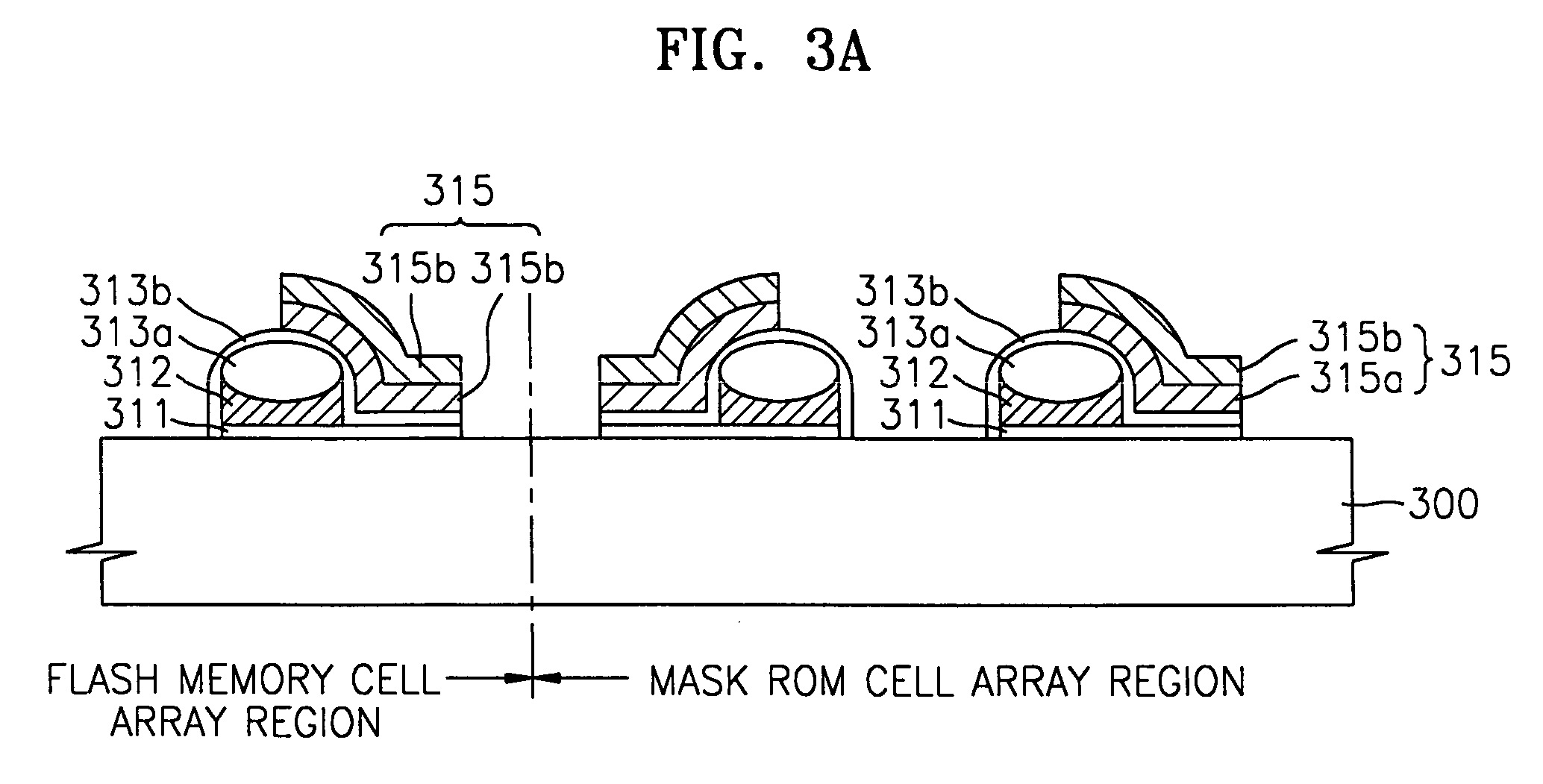

Semiconductor memory device including a flash memory cell array and a mask read-only memory cell array

InactiveUS20050003614A1Highly integratedShorten the timeSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideIon

A semiconductor memory device included in a system-on-chip (SOC) or a microcomputer chip. The semiconductor memory device may include a flash memory cell array unit and a mask read-only memory (ROM) cell array unit which are formed in a single memory block without an isolation layer for separating the two units. Transistors included in the flash memory unit and the mask ROM unit are the same type and may have two threshold voltages. The transistor in each memory cell unit may be a split gate transistor, a metal-oxide-nitride-oxide-silicon, or silicon-oxide-nitride-oxide-silicon transistor. Further, the transistor included in the mask ROM unit in the semiconductor memory device may include enhancement transistors or depletion transistors in which a dopant ion-implanted region is formed at channel portions.

Owner:SAMSUNG ELECTRONICS CO LTD

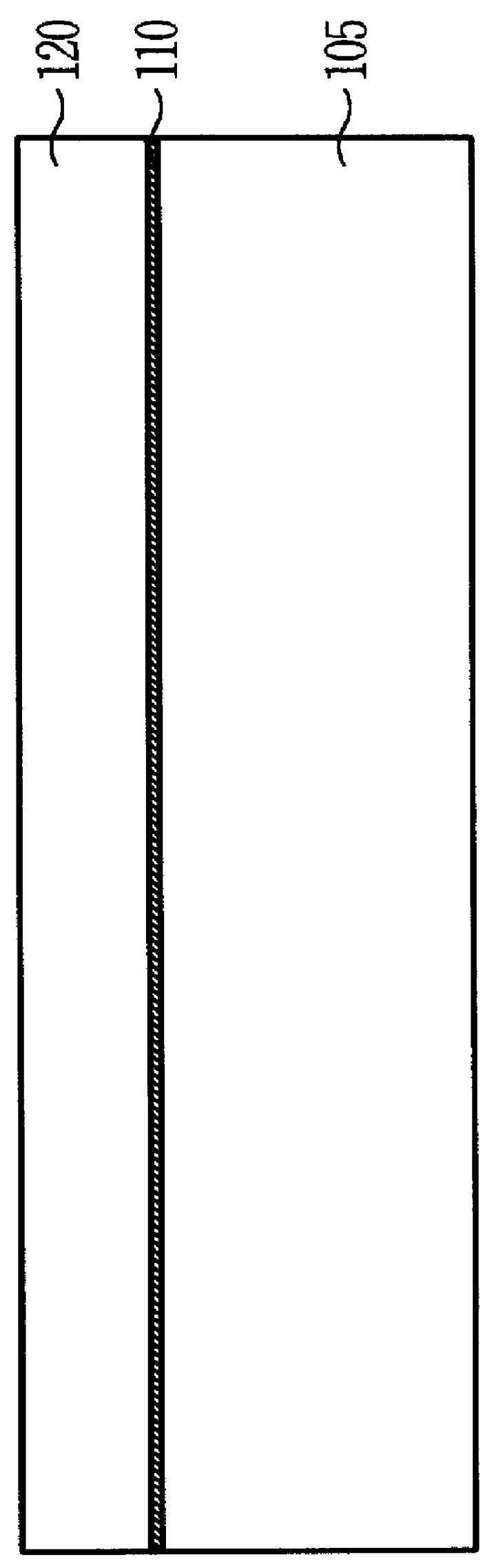

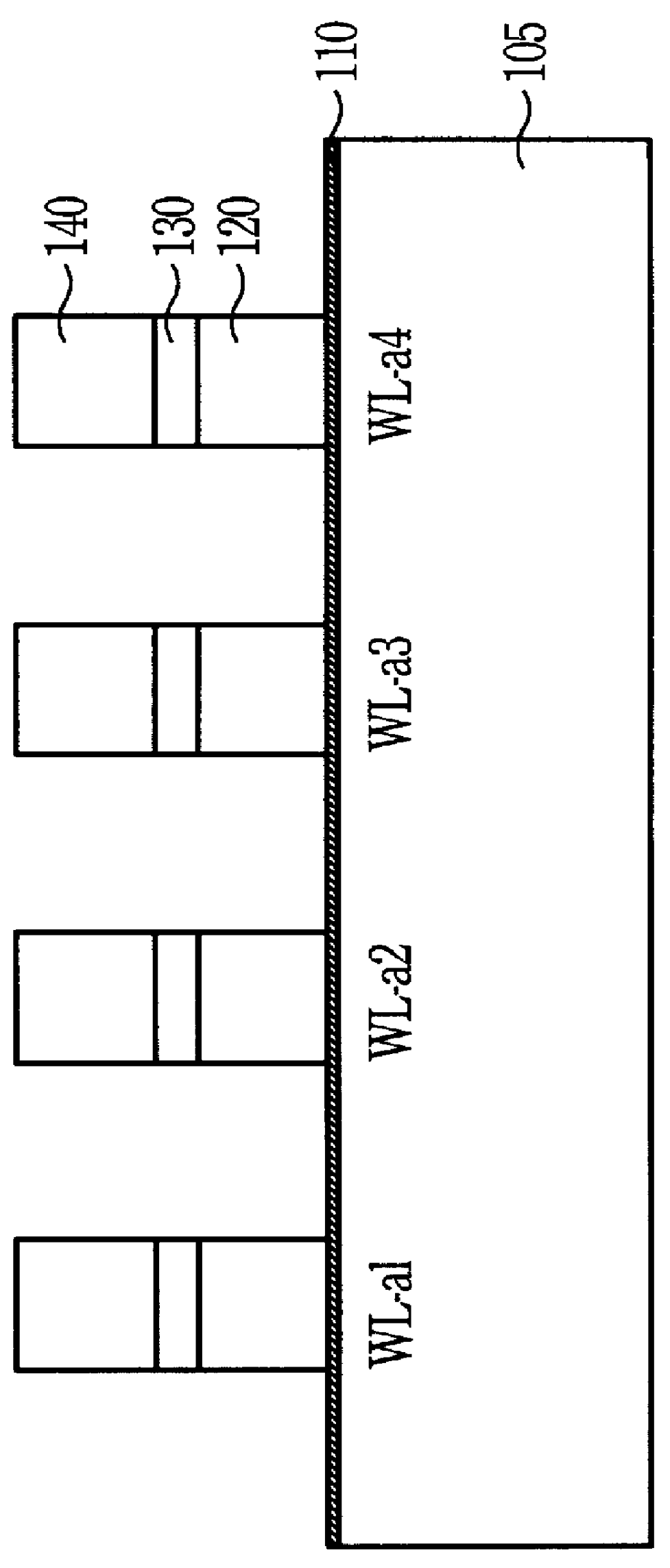

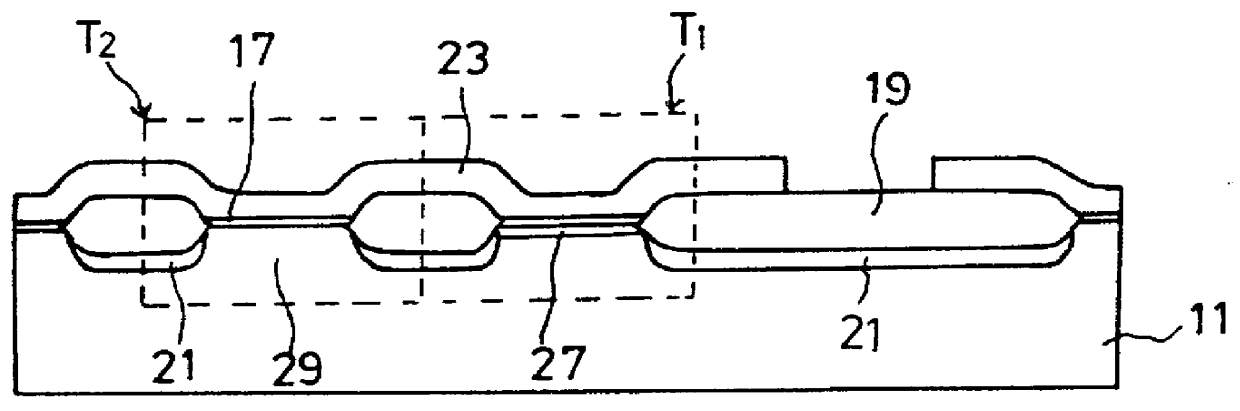

Double poly-gate high density multi-state flat mask ROM cells

InactiveUS6091119ASolid-state devicesSemiconductor/solid-state device manufacturingMask ROMHigh density

The mask ROM cell structure is described as follows: a plurality of first polysilicon gates is formed on the semiconductor substrate, being separated to keep a space. Each of first polysilicon gates comprises first nitride layer / a n+ polysilicon layer / a first pad oxide layer, and two spacers that formed over the remnant portion of the pad oxide layer, and formed, respectively, on two sidewalls of the first nitride layer 130, and the first n+ polysilicon layer. A plurality of second polysilicon gates is formed on the semiconductor substrate 105. Each of the second polysilicon gates comprises second n+doped polysilicon gate / second pad oxide layer, wherein the pad oxide layer is formed on the semiconductor substrate, and the n+doped polysilicon gate is formed on the second pad oxide layer. The first polysilicon gates separate the second polysilicon gates each.

Owner:ACER SEMICON MFG +1

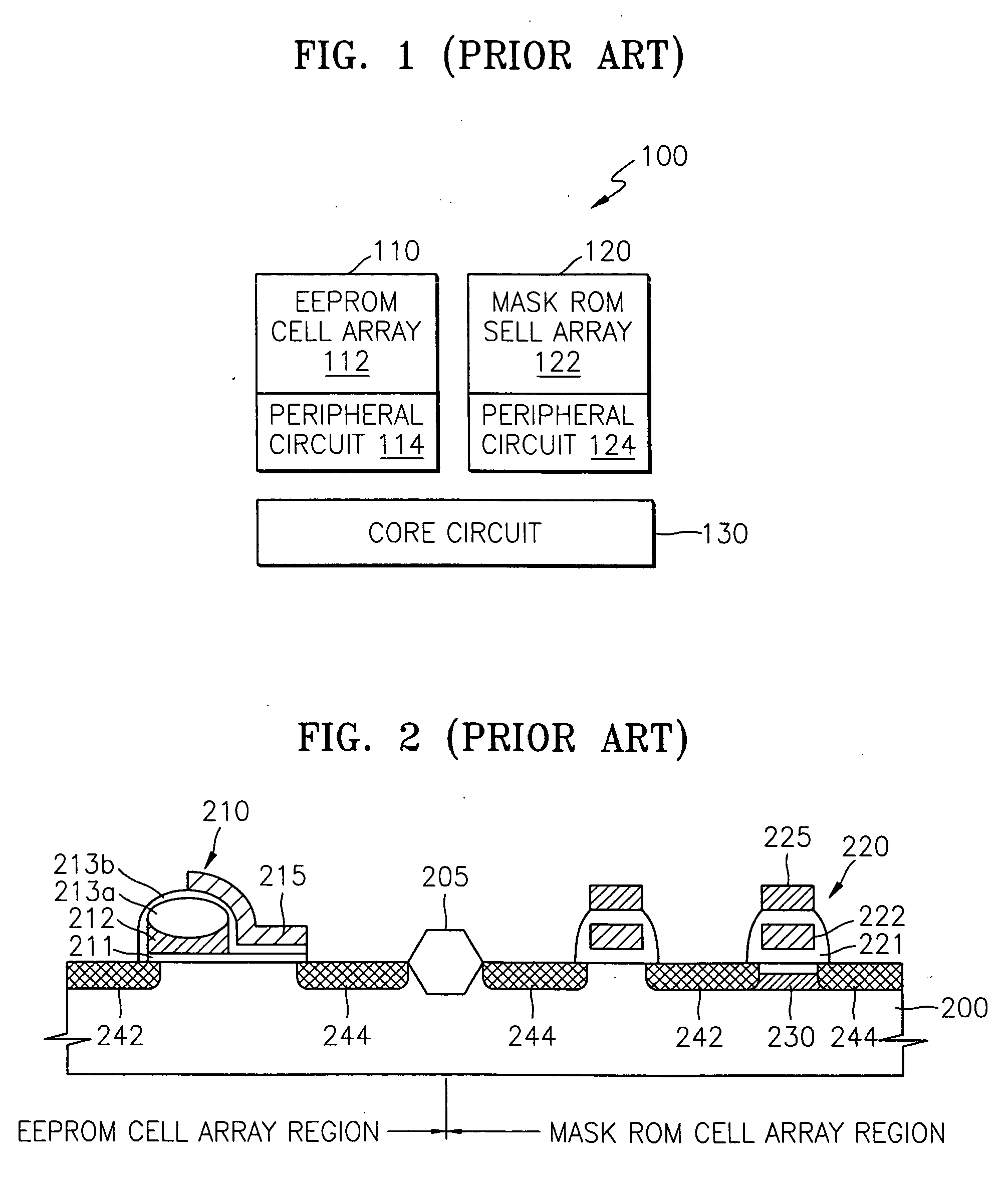

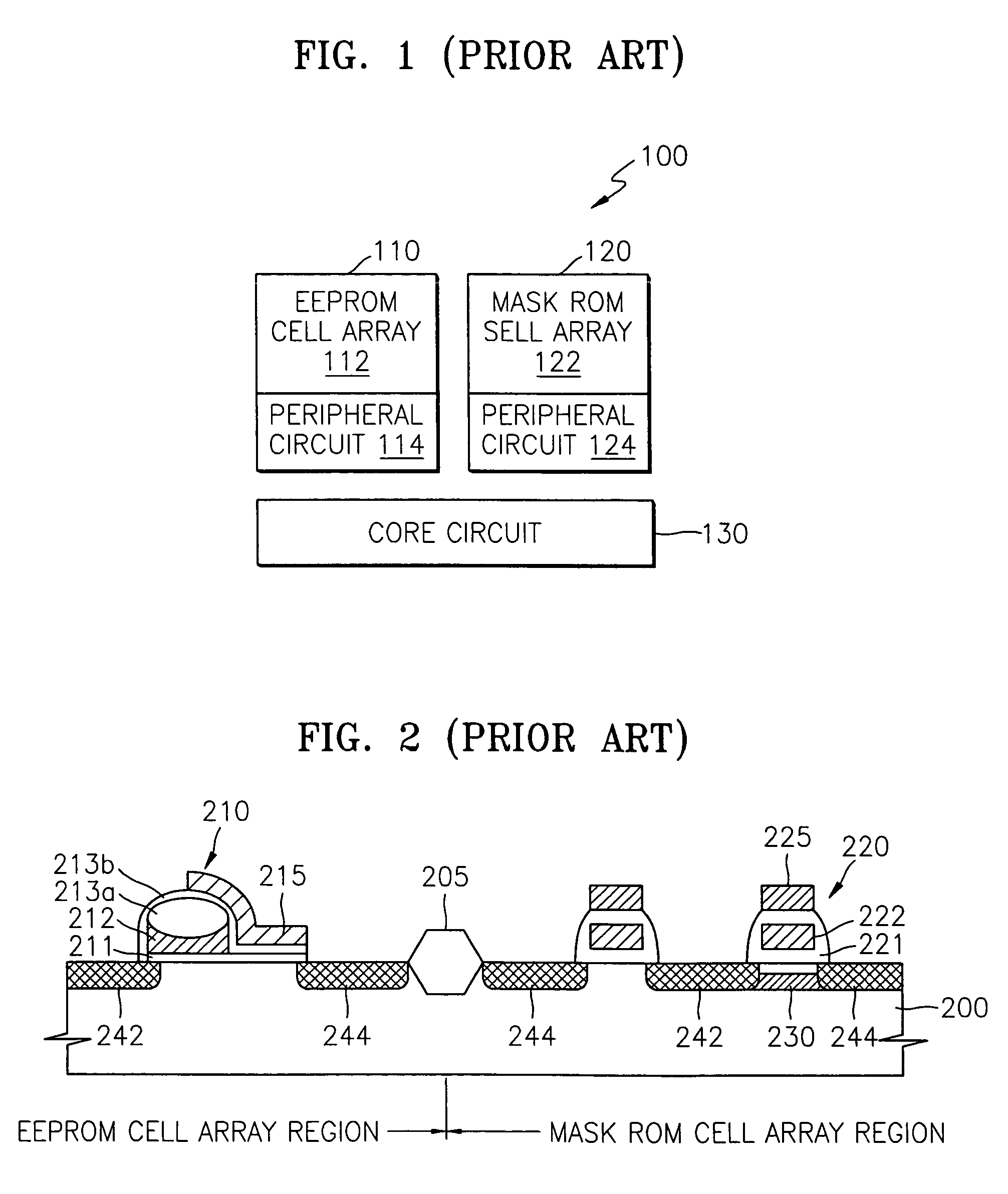

Semiconductor device having electrically erasable programmable read-only memory (EEPROM) and mask-ROM and method of fabricating the same

Owner:SAMSUNG ELECTRONICS CO LTD

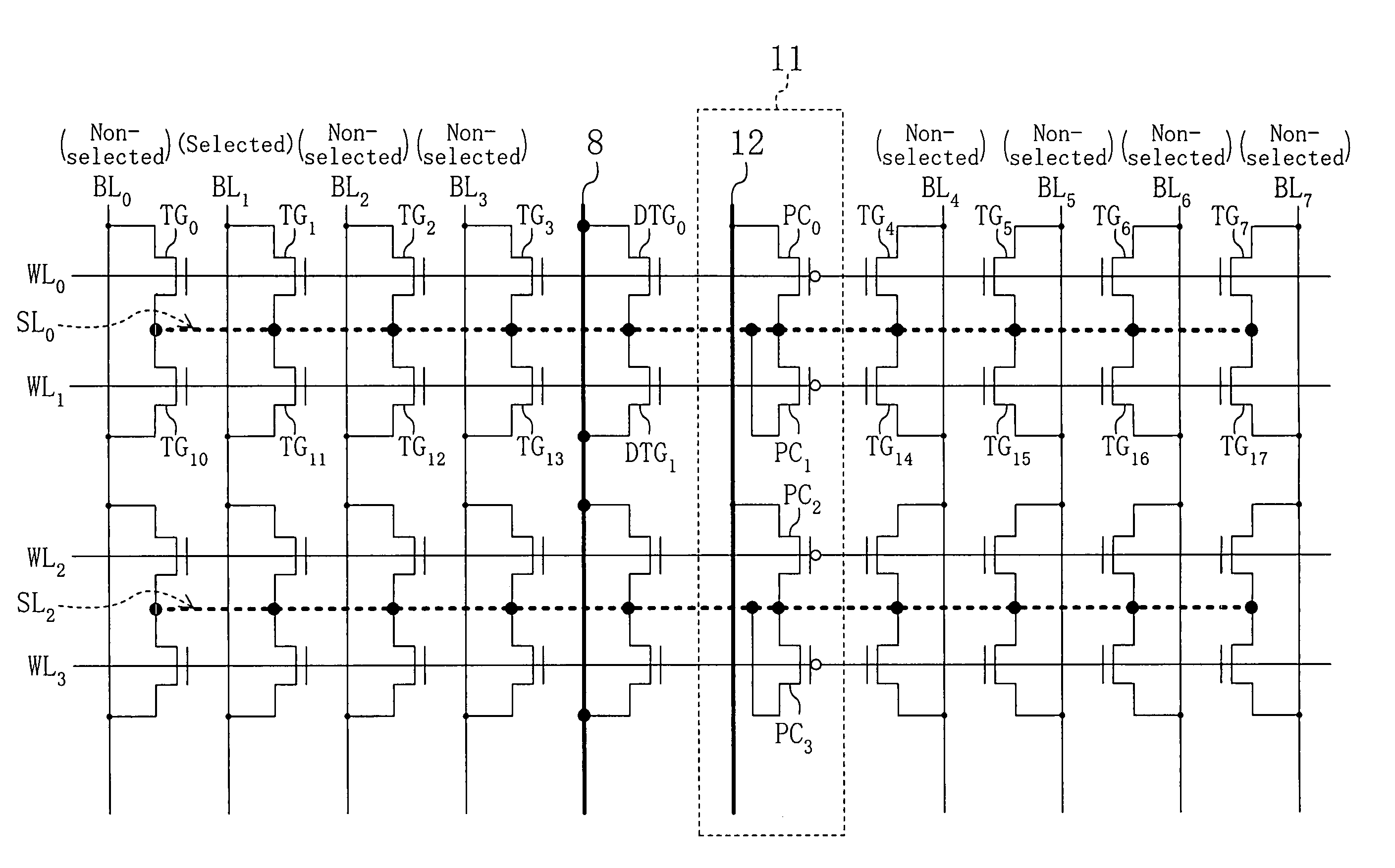

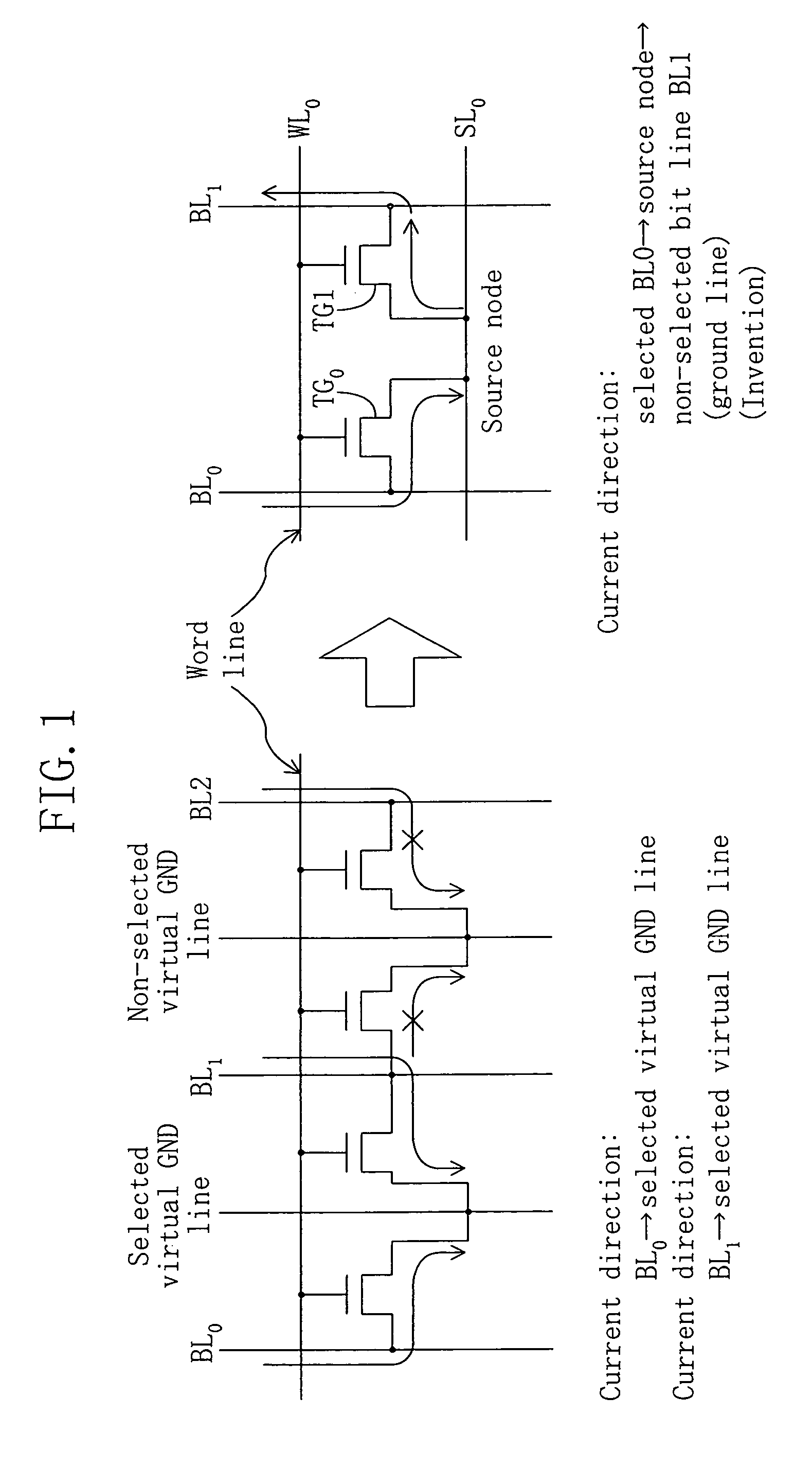

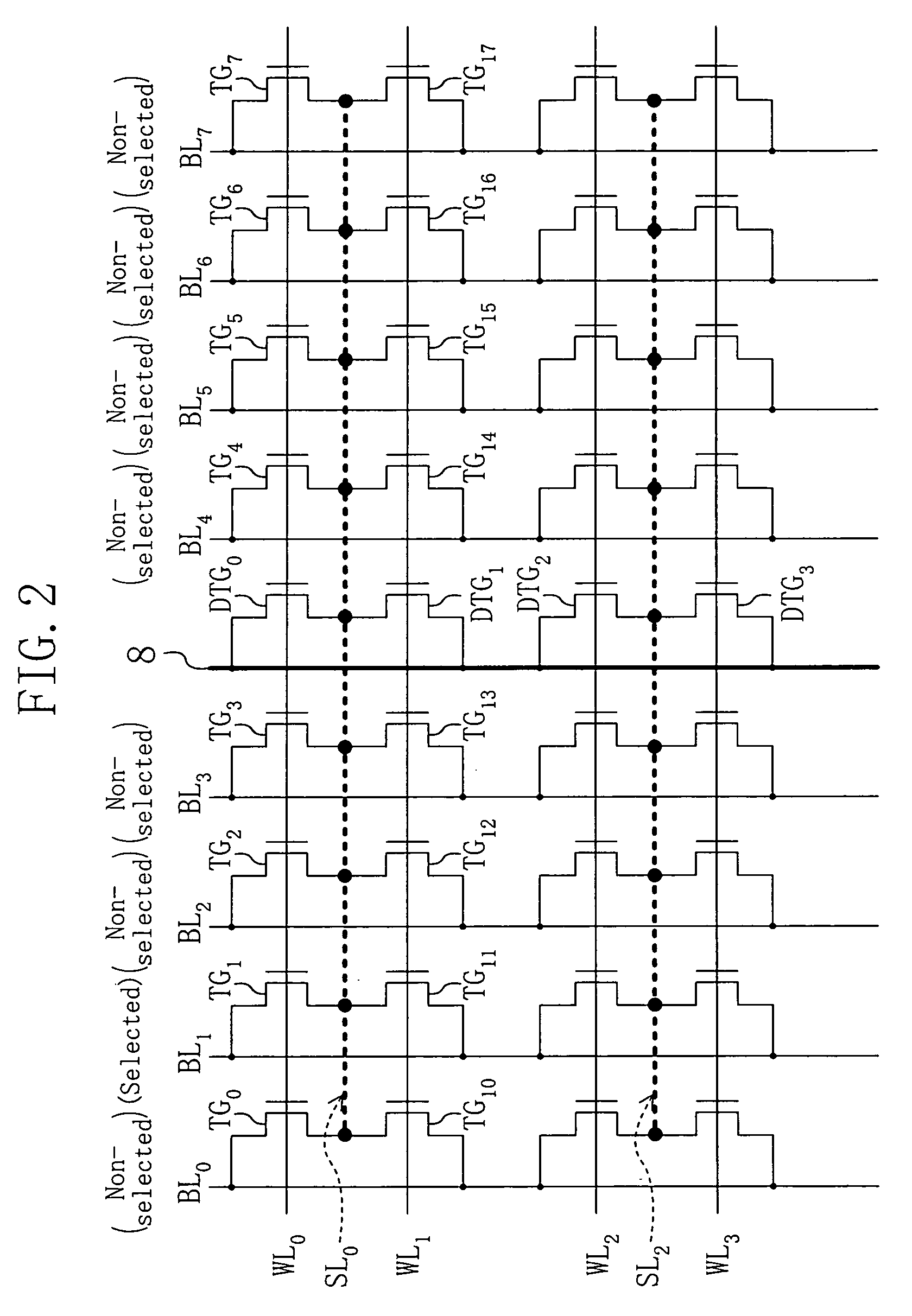

Mask ROM

InactiveUS7218544B2Extension of timeIncreased power consumptionSolid-state devicesRead-only memoriesBit lineMask ROM

A mask ROM includes bit lines, word lines intersecting with the bit lines and bit cells provided along the word lines, each of the bit lines being formed of a cell transistor having a gate connected to an associated one of the word lines. In the mask ROM, further provided is a source node commonly connected to respective sources of ones of the cell transistors having a gate connected to one of adjacent two word lines. A current flows from a selected bit line to a non-selected bit line via a cell transistor selected in reading out data and the source node.

Owner:SOCIONEXT INC

Navigation device displaying travel information

ActiveUS7835857B2Late configurabilityInexpensively formedInstruments for road network navigationRoad vehicles traffic controlOperational systemMask ROM

A navigation device, programmable with map data and a navigation application that enables a route to be planned between two user-defined places; the device is operable to read a removable memory card storing the device operating system, the navigation application, and the map data. It does not need to store the operating system in mask ROM; hence, customization for a specific country requires only that the appropriate memory card be inserted at the time of use.

Owner:TOMTOM INT BV

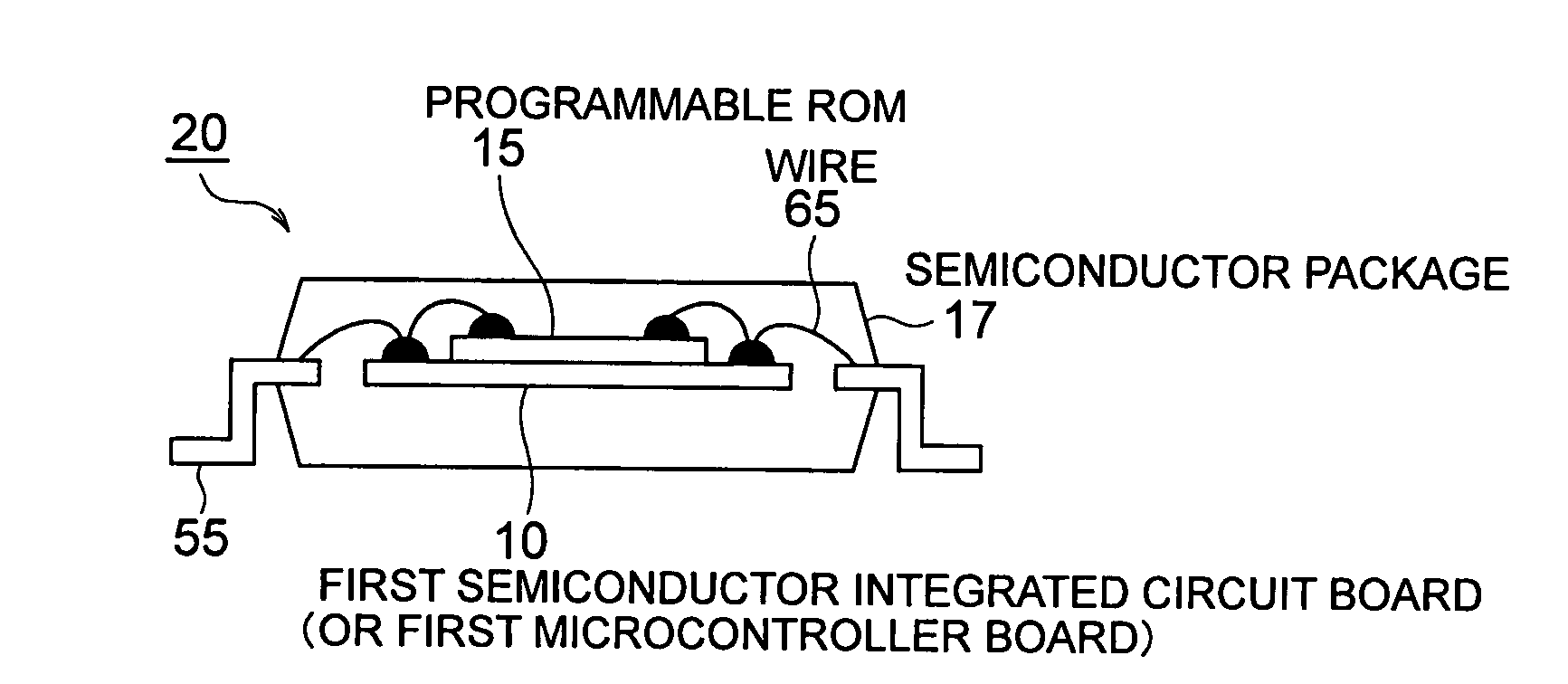

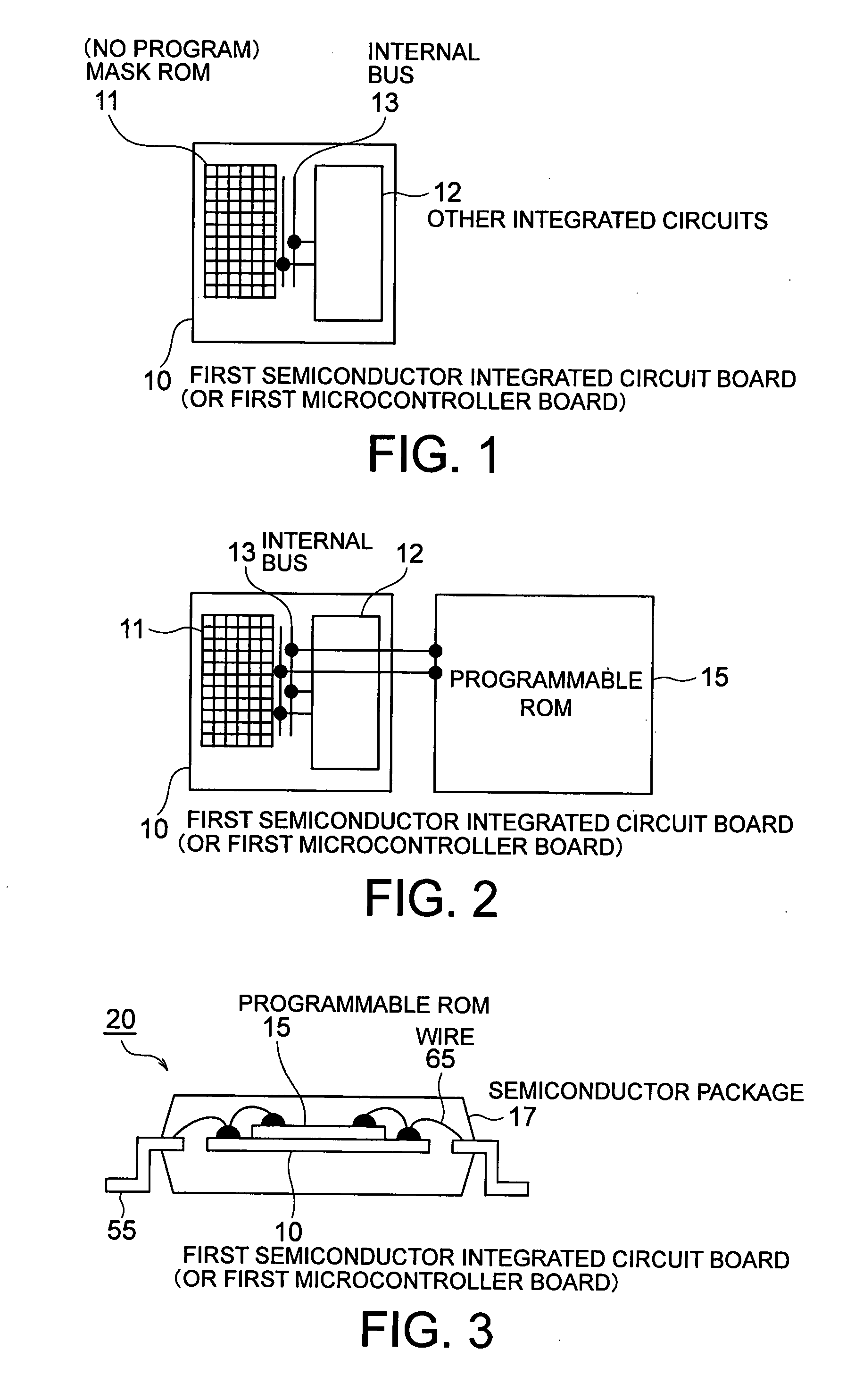

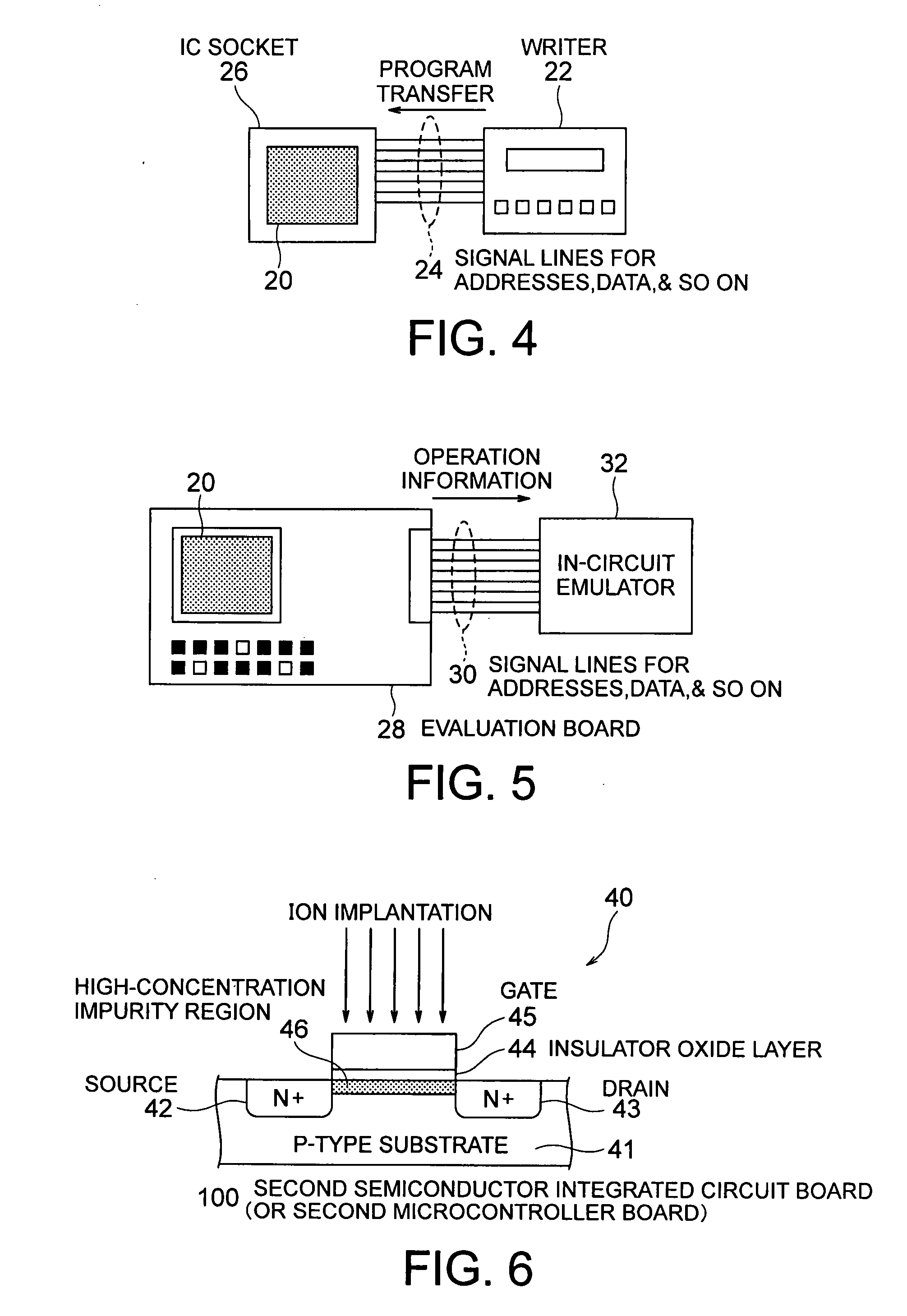

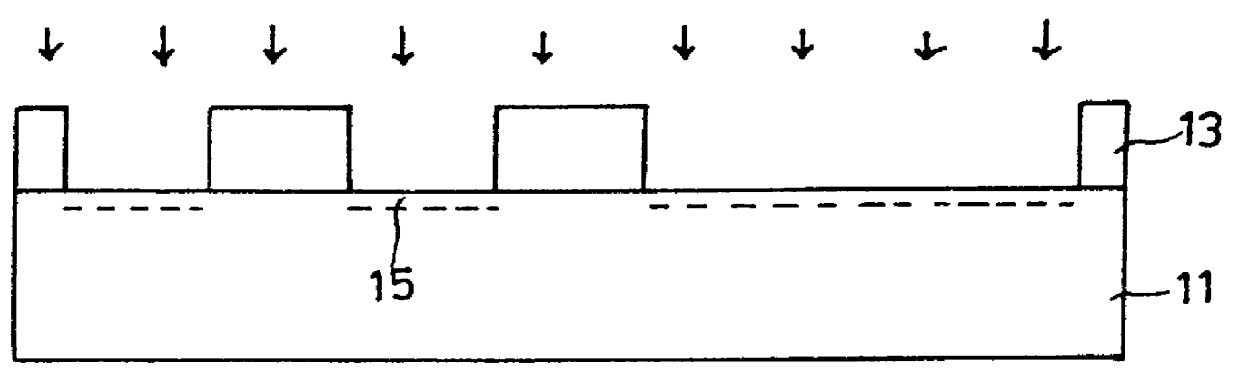

Method of manufacturing a single chip semiconductor integrated circuit device including a mask ROM in a short time

InactiveUS20080050862A1Short timeSemiconductor/solid-state device detailsSolid-state devicesMask ROMEngineering

In a state of a first semiconductor integrated circuit device on which a first semiconductor integrated circuit board including a first mask ROM and a programmable ROM are mounted, an ultimate program determined by using the programmable ROM is stored in a second ROM of a second semiconductor integrated circuit board which is substantially similar in structure to the first semiconductor integrated circuit board, thereby manufacturing a second semiconductor integrated circuit device as an ultimate product.

Owner:MITSUMI ELECTRIC CO LTD

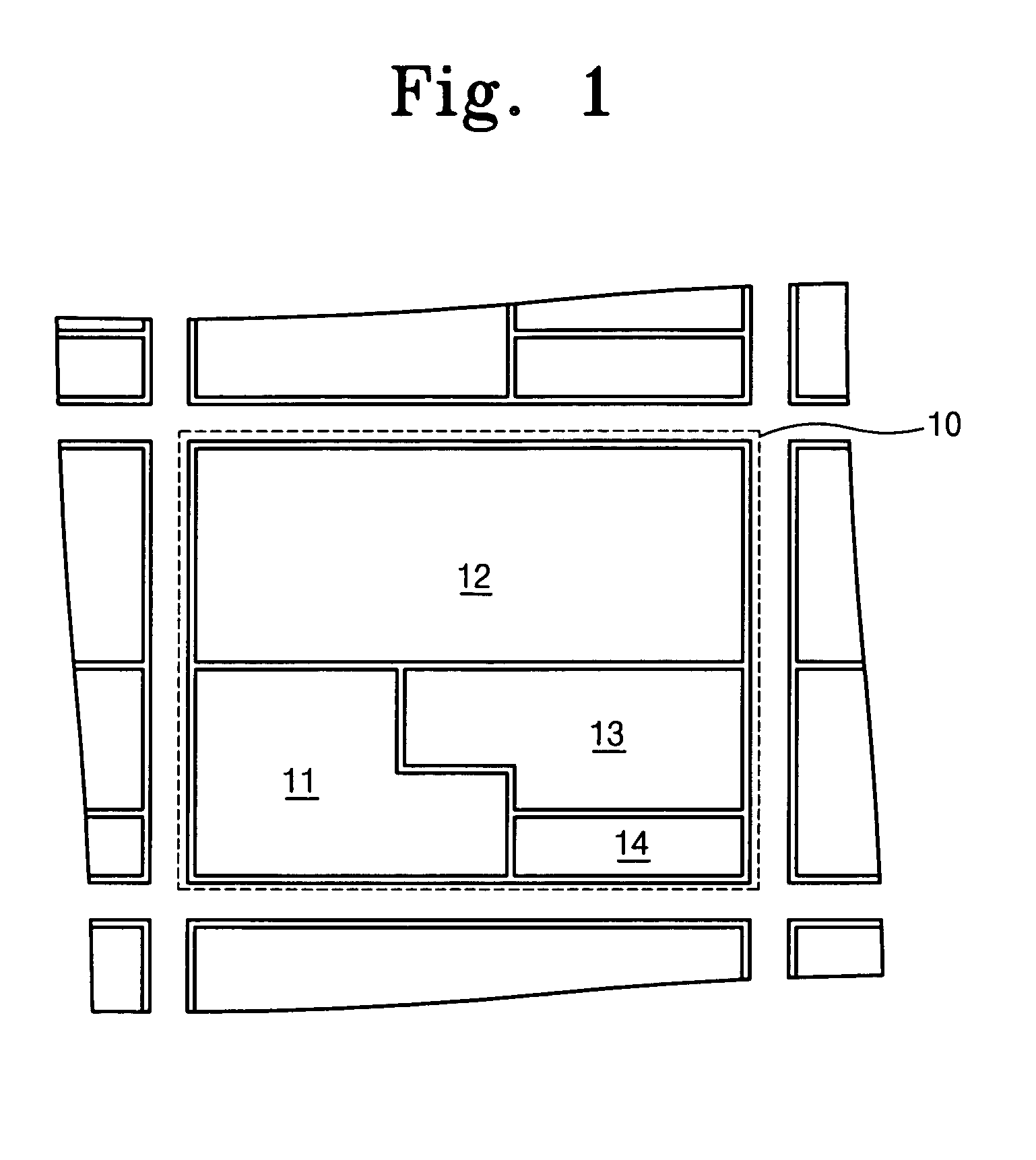

Sequential access memory

InactiveUS20070165482A1High data reliabilityRead-only memoriesUnauthorized memory use protectionSequential access memoryMask ROM

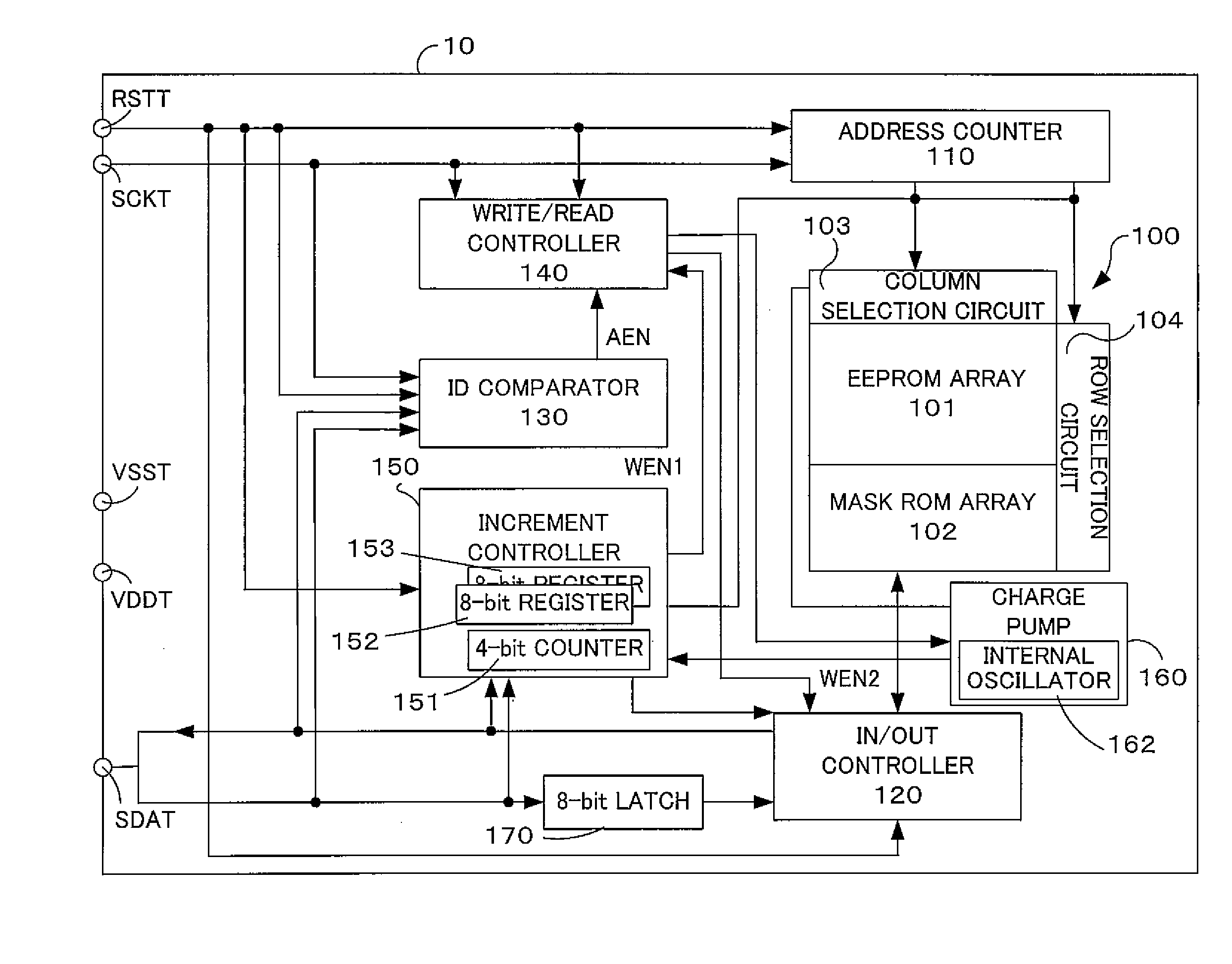

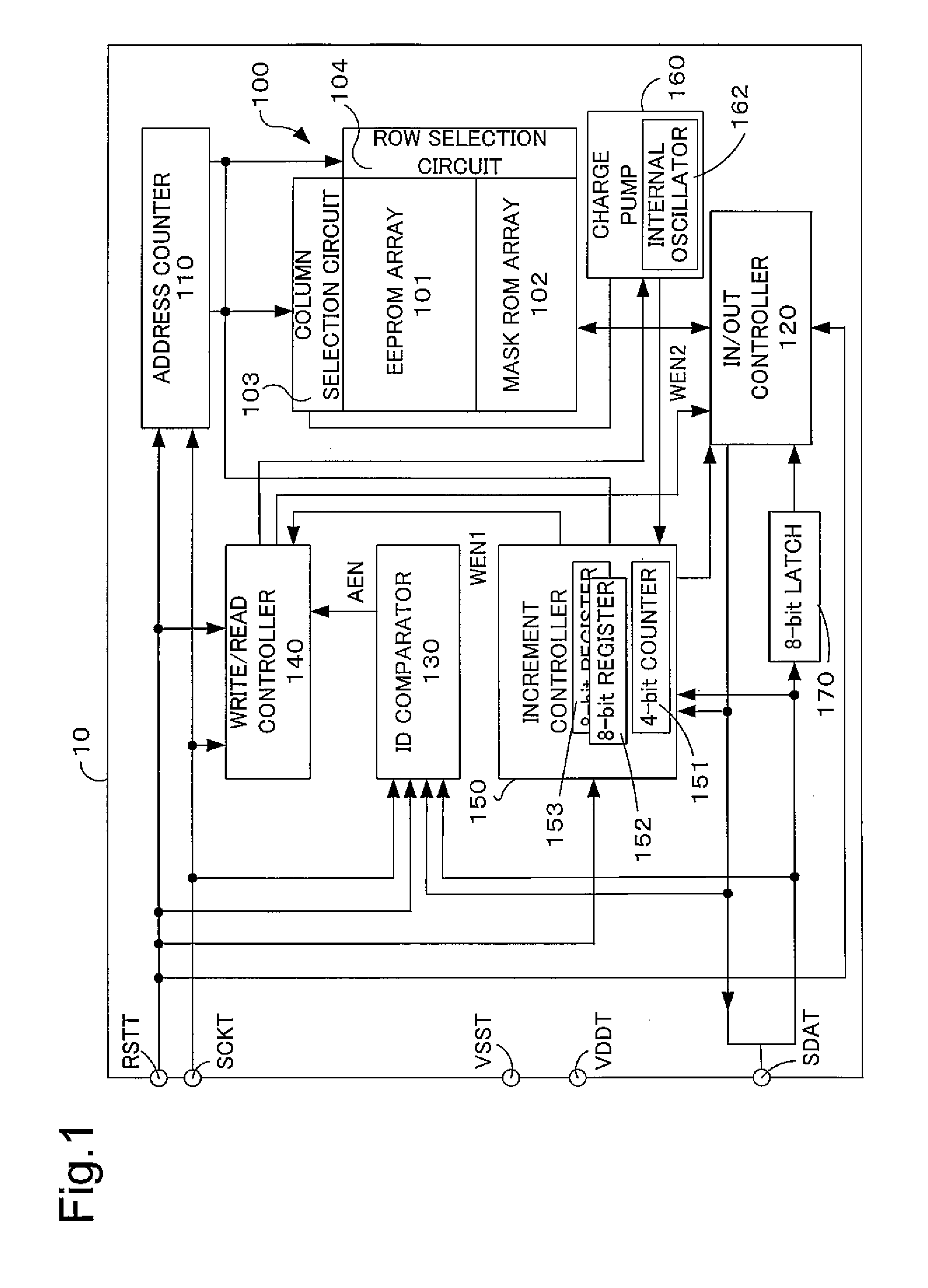

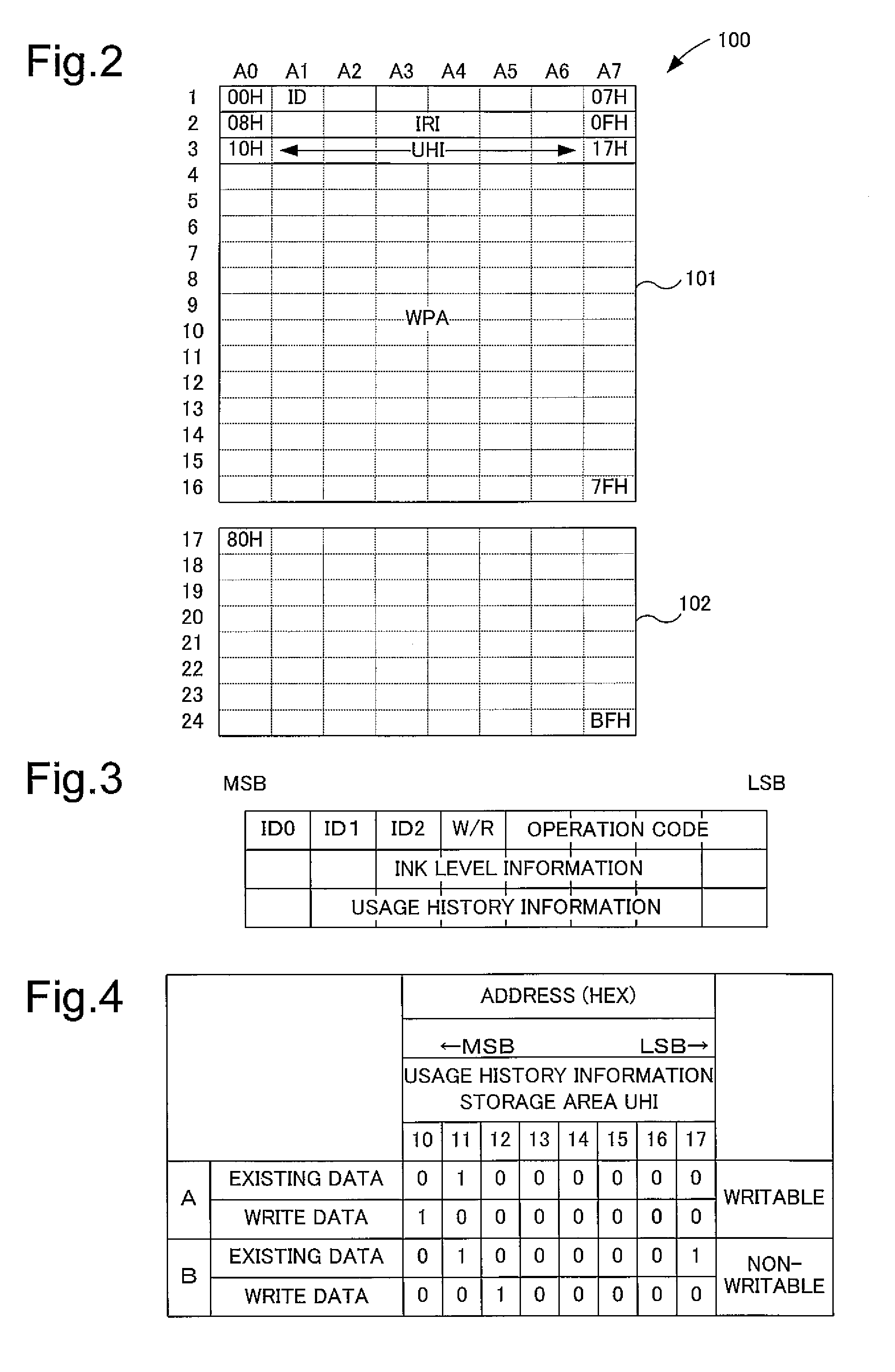

Semiconductor memory devices 10 are each furnished with a memory array 100 having an EEPROM array 101 and a mask ROM array 102. Identifying information for identifying each semiconductor memory device 10 is stored at the beginning three addresses of the EEPROM array 101. 8-bit data relating to ink level is stored at the ninth address to sixteenth address of the EEPROM array 101. The seventeenth address to the twenty-fourth address of the EEPROM array 101 is provided with a usage history information storage area for storing 8-bit usage history information that is rewriteable under certain conditions.

Owner:SEIKO EPSON CORP

Highly integrated mask ROM for coding data

A method of fabricating a mask ROM includes forming a trench on a first conductivity type semiconductor substrate, implanting a second conductivity type impurity ion in at least a surface portion of the semiconductor substrate where the trench is formed, forming an insulating oxide layer on a surface of the semiconductor substrate, including a surface of the trench, forming gate oxide layers of both sides of the trench, forming first and second gates on the gate, oxide layers and forming a first conductivity type channel by implanting a first conductivity type impurity ion in one side of the trench. As such, the resulting mask ROM includes two transistors on either side of a trench having channels along the side walls of the trench. The resulting mask ROM has a reduced surface width, enhancing integration.

Owner:HYUNDAI ELECTRONICS IND CO LTD

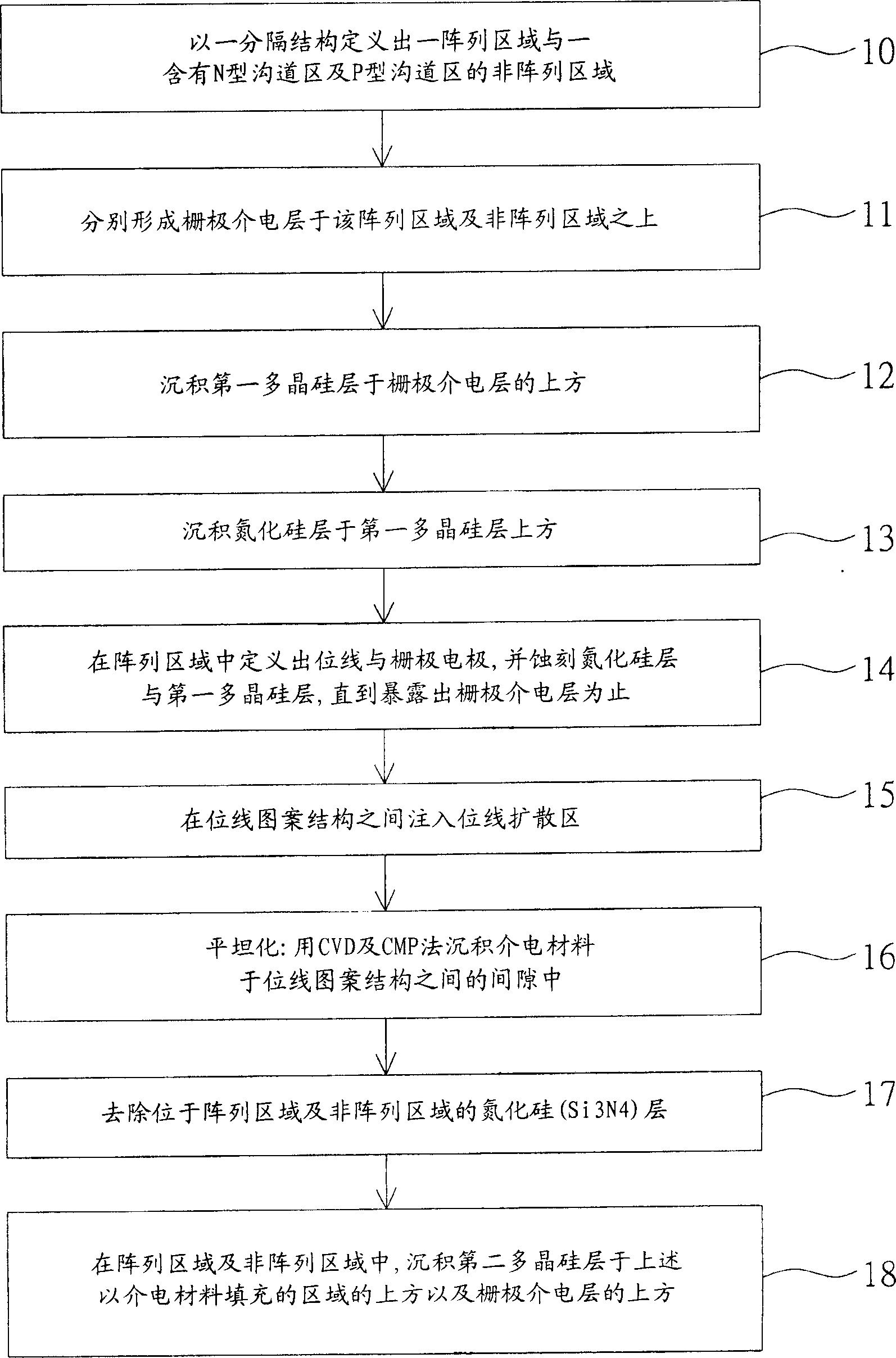

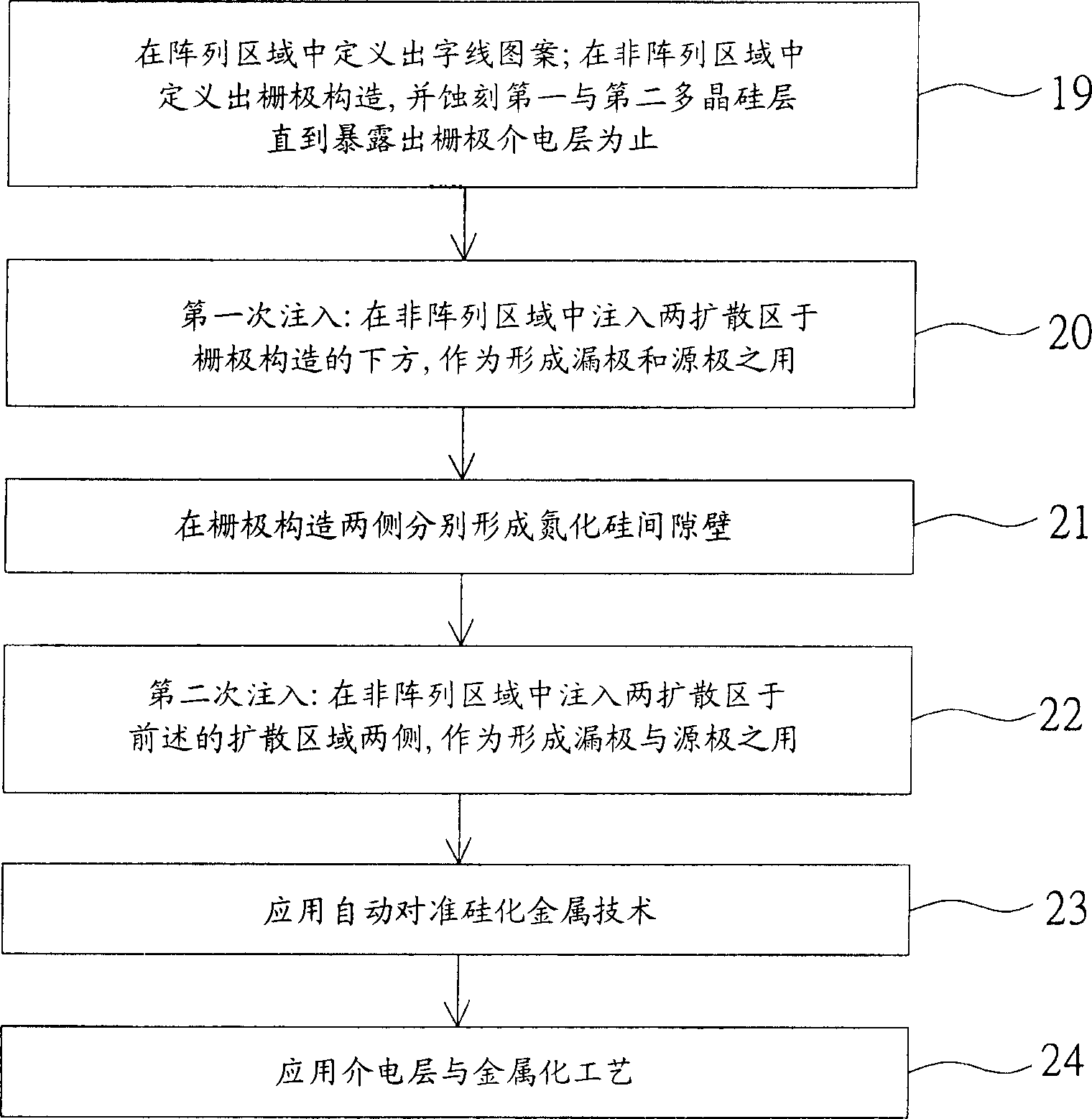

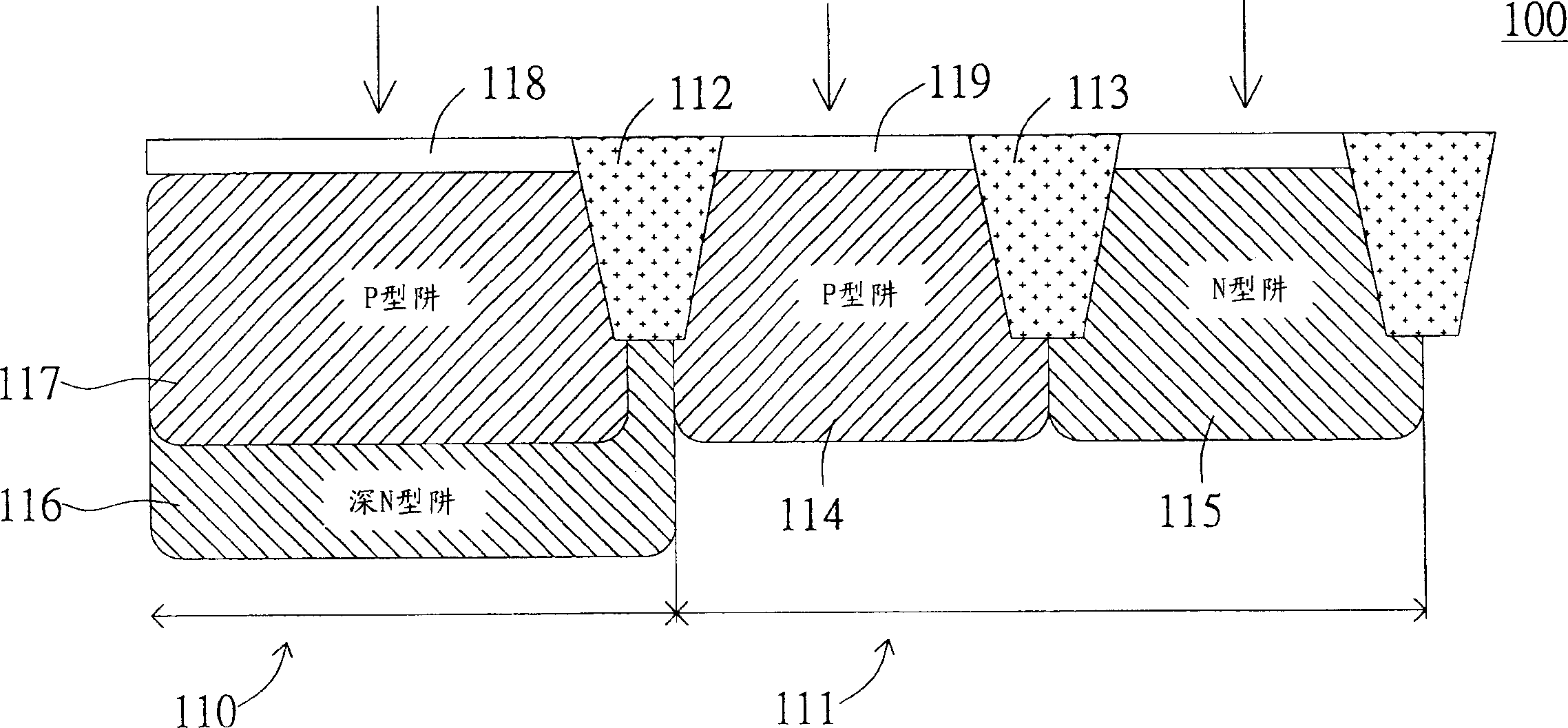

Process for manufacturing integrated circuit on a substrate

InactiveCN1521831AAvoid the phenomenon of soft electric collapseHigh selectivitySolid-state devicesSemiconductor/solid-state device manufacturingBit lineGate dielectric

A process uses two layers of polysilicon for fabricating high-density nonvolatile memory, such as mask ROM or SONOS memory, integrated with advanced peripheral logic on a single chip. The method includes covering a gate dielectric layer with a first layer of polysilicon in the array portion and in the non-array portion; covering the first layer of polysilicon with a layer of silicon nitride; using two masks for gate electrode formation in a first layer of polysilicon and bit line implant processes; depositing a dielectric material among the gate electrode structures to fill gaps among the gate structures; planarizing the deposited oxide; removing said layer of silicon nitride and applying a second layer of polysilicon material; patterning wordlines in the array portion over said gate electrode structures, and transistor gate structures in said non-array portion, and applying LDD, silicide and other logic circuit processes.

Owner:MACRONIX INT CO LTD

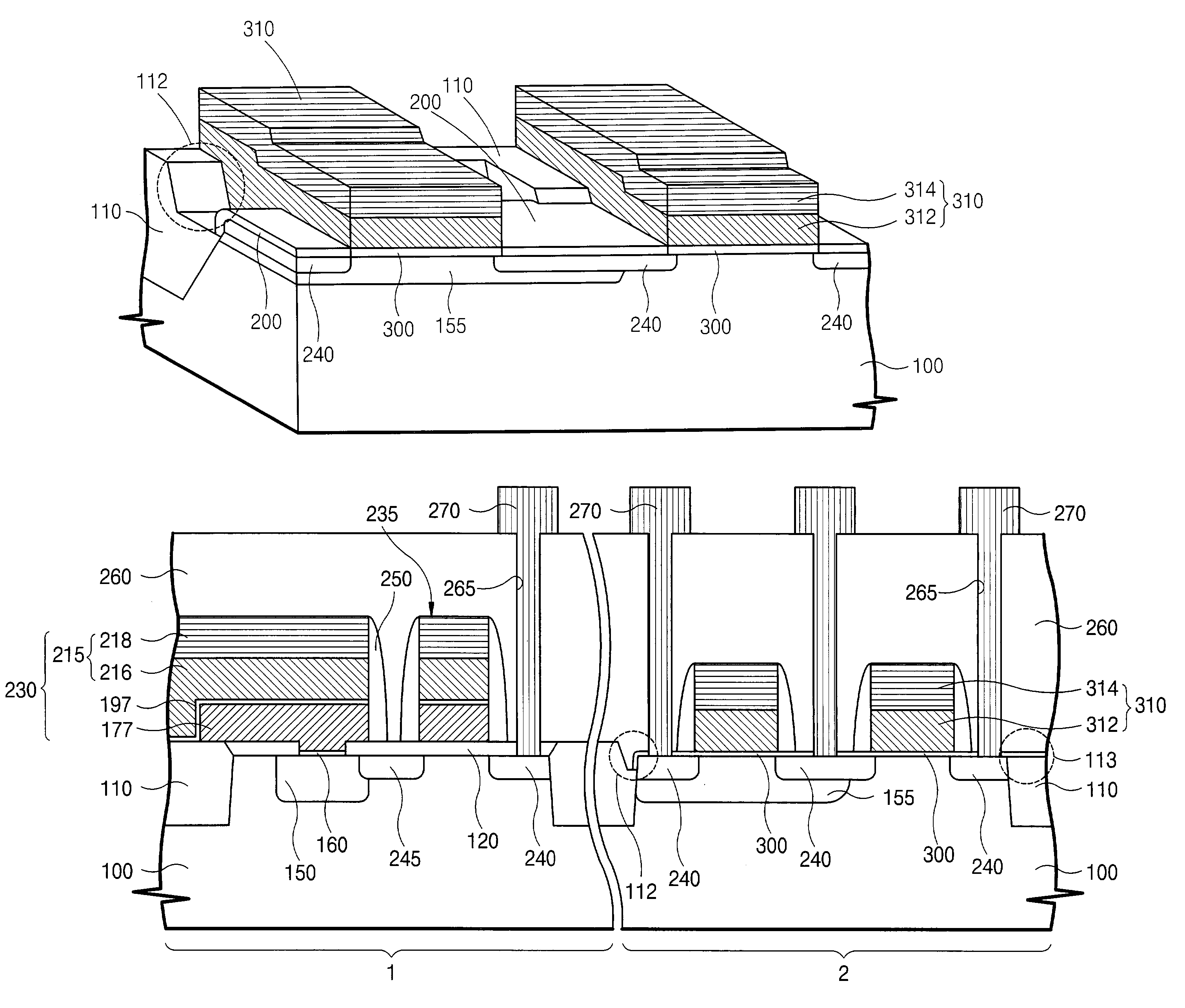

Semiconductor device with mask read-only memory and method of fabricating the same

InactiveUS20070158737A1Low costReducing change of threshold voltageTransistorSolid-state devicesMask ROMGate dielectric

A mask read only memory (ROM) device includes a plurality of isolation patterns disposed at predetermined regions of a semiconductor substrate to define a plurality of active regions. The semiconductor substrate includes a mask ROM region where a plurality of on cells and a plurality of off-cells are disposed. The mask ROM further includes a plurality of gate lines disposed over the active regions, and which cross over the isolation patterns, a plurality of gate insulating layers interposed between the gate lines and the active regions and a floating conductive pattern and a inter-gate dielectric pattern located between the gate line and the gate insulating layer of the off-cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device including a flash memory cell array and a mask read-only memory cell array

InactiveUS7230305B2Highly integratedShorten the timeSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideIon

A semiconductor memory device included in a system-on-chip (SOC) or a microcomputer chip. The semiconductor memory device may include a flash memory cell array unit and a mask read-only memory (ROM) cell array unit which are formed in a single memory block without an isolation layer for separating the two units. Transistors included in the flash memory unit and the mask ROM unit are the same type and may have two threshold voltages. The transistor in each memory cell unit may be a split gate transistor, a metal-oxide-nitride-oxide-silicon, or silicon-oxide-nitride-oxide-silicon transistor. Further, the transistor included in the mask ROM unit in the semiconductor memory device may include enhancement transistors or depletion transistors in which a dopant ion-implanted region is formed at channel portions.

Owner:SAMSUNG ELECTRONICS CO LTD

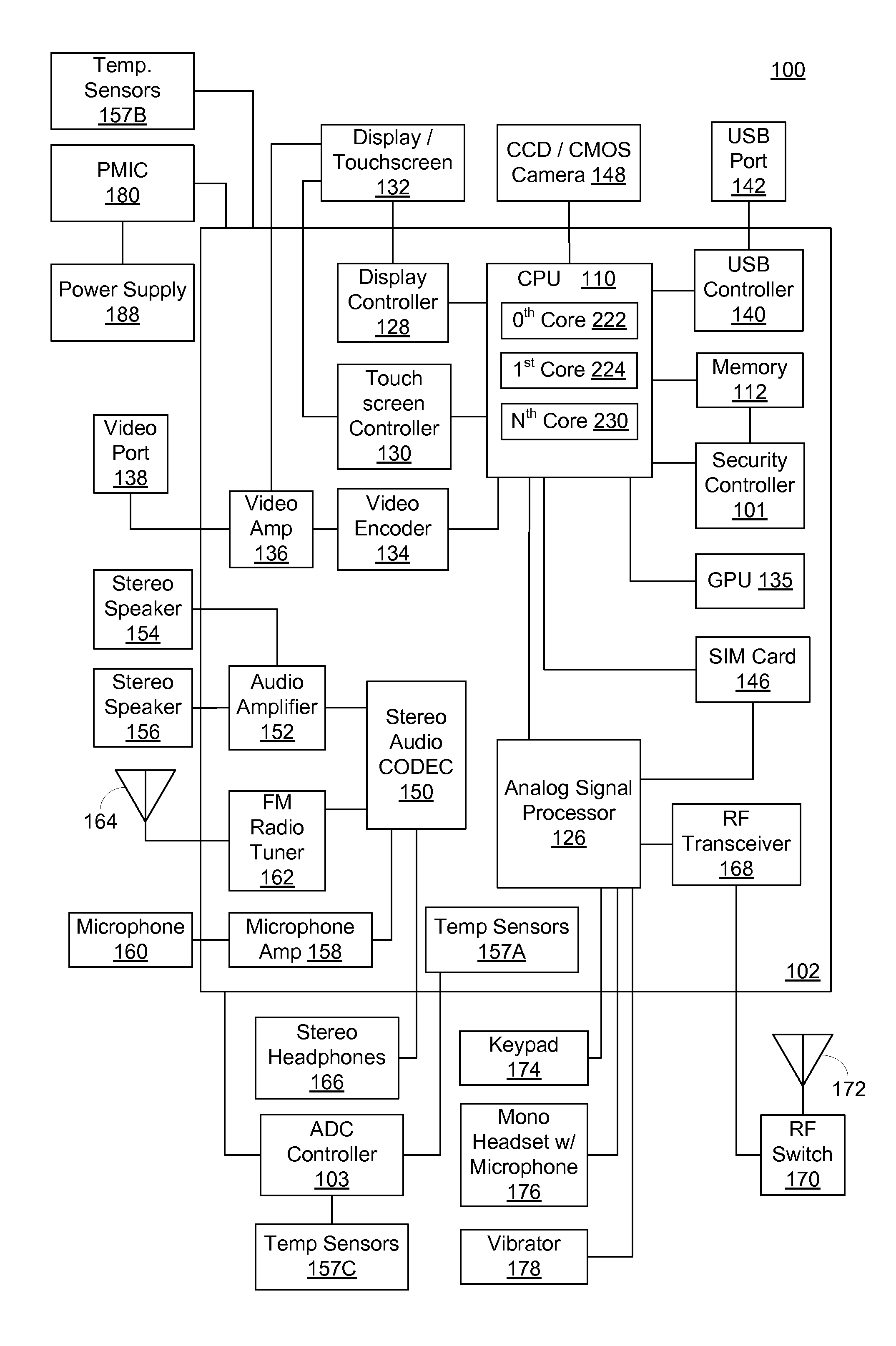

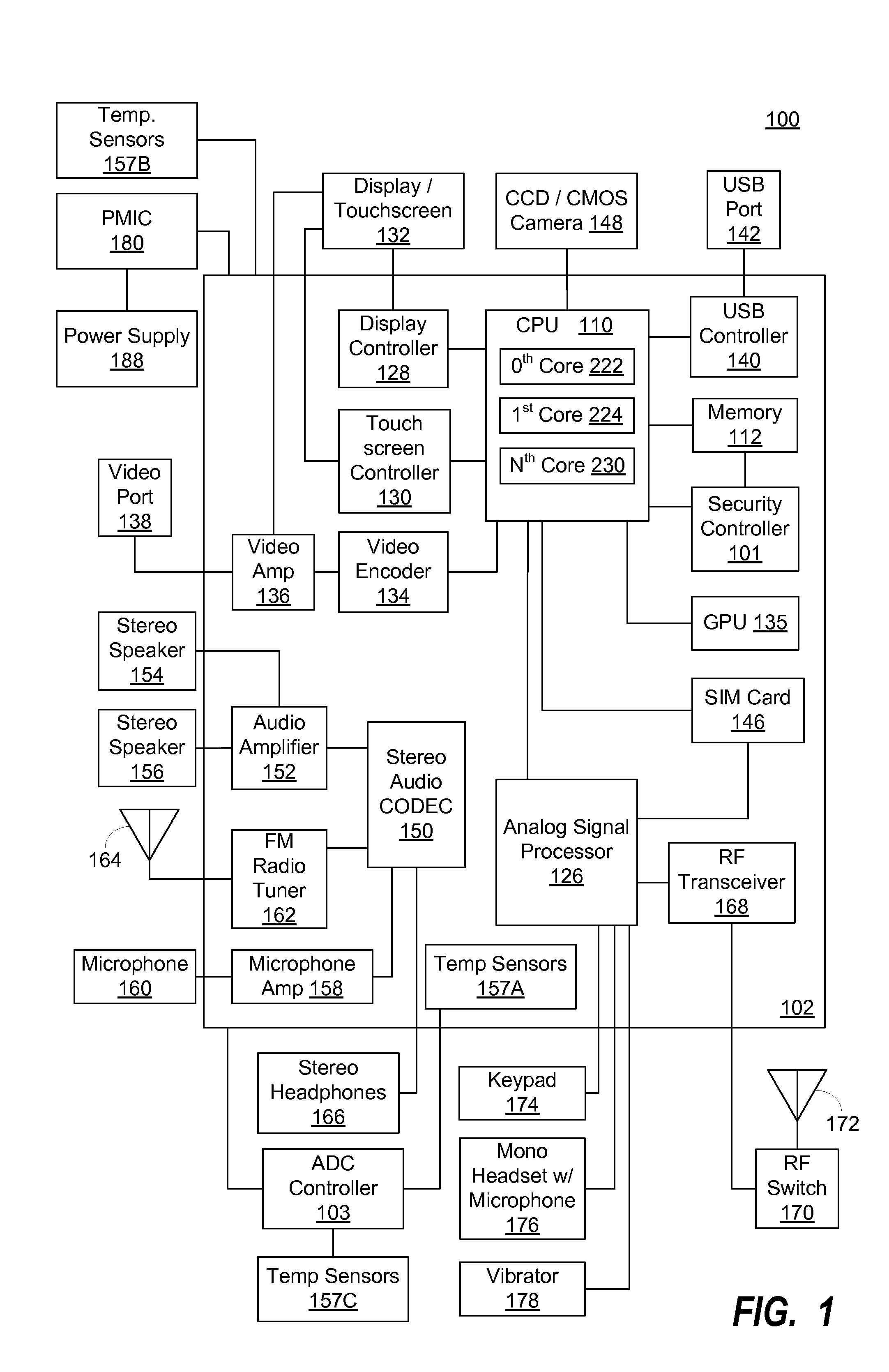

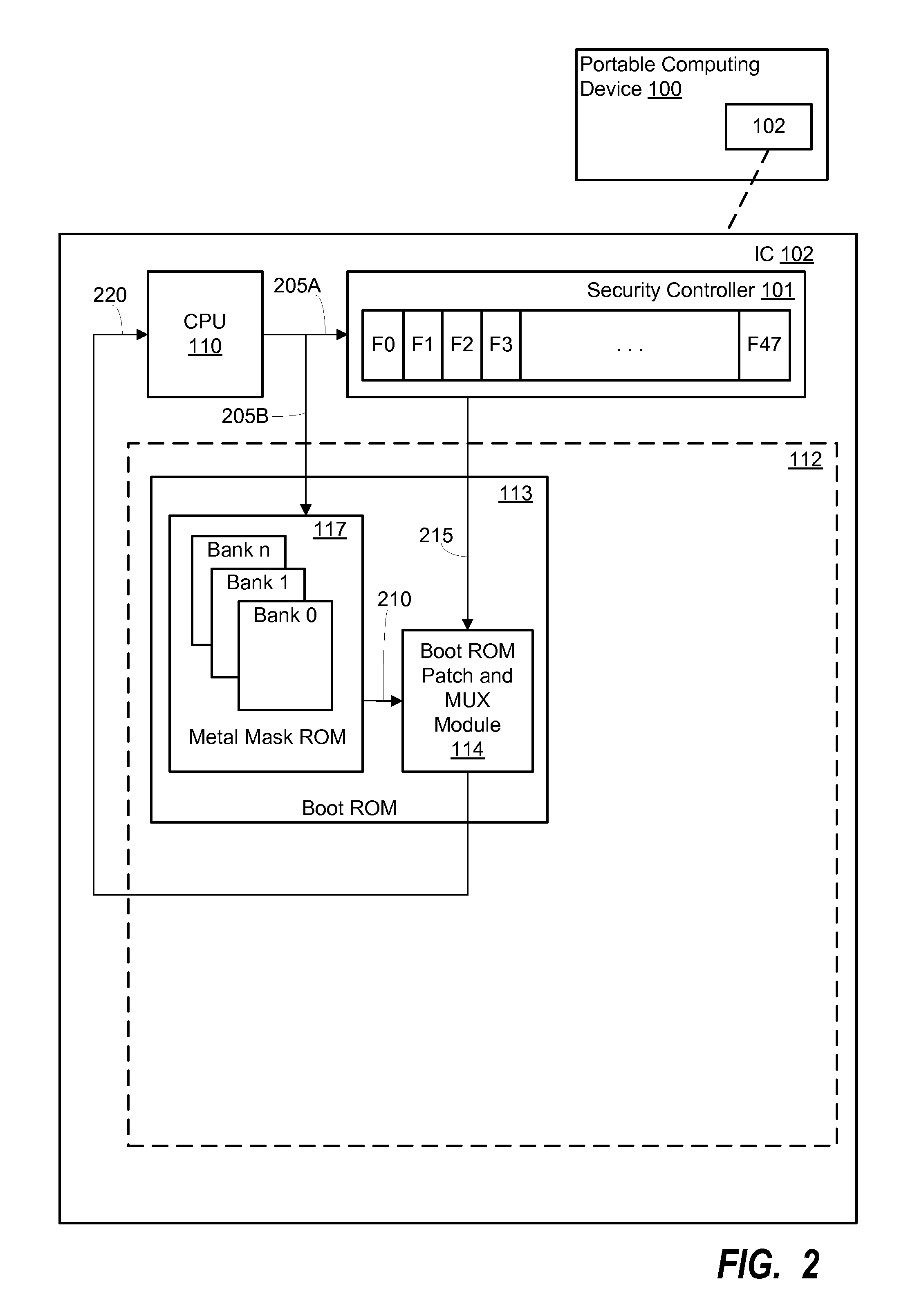

System and method for modification of coded instructions in read-only memory using one-time programmable memory

InactiveUS20150242213A1Reduce in quantitySave spaceDigital computer detailsConcurrent instruction executionMask ROMController (computing)

Various embodiments of methods and systems for flexible read only memory (“ROM”) storage of coded instructions in a portable computing device (“PCD”) are disclosed. Because certain instructions and / or data associated with a primary boot loader (“PBL”) may be defective or in need of modification after manufacture of a mask ROM component, embodiments of flexible ROM storage (“FRS”) systems and methods use a closely coupled one-time programmable (“OTP”) memory component to store modified instructions and / or data. Advantageously, because the OTP memory component may be manufactured “blank” and programmed at a later time, modifications to code and / or data stored in an unchangeable mask ROM may be accomplished via pointers in fuses of a security controller that branch the request to the OTP and bypass the mask ROM.

Owner:QUALCOMM INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com