Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

21451 results about "Photoresist" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A photoresist is a light-sensitive material used in several processes, such as photolithography and photoengraving, to form a patterned coating on a surface. This process is crucial in the electronic industry.

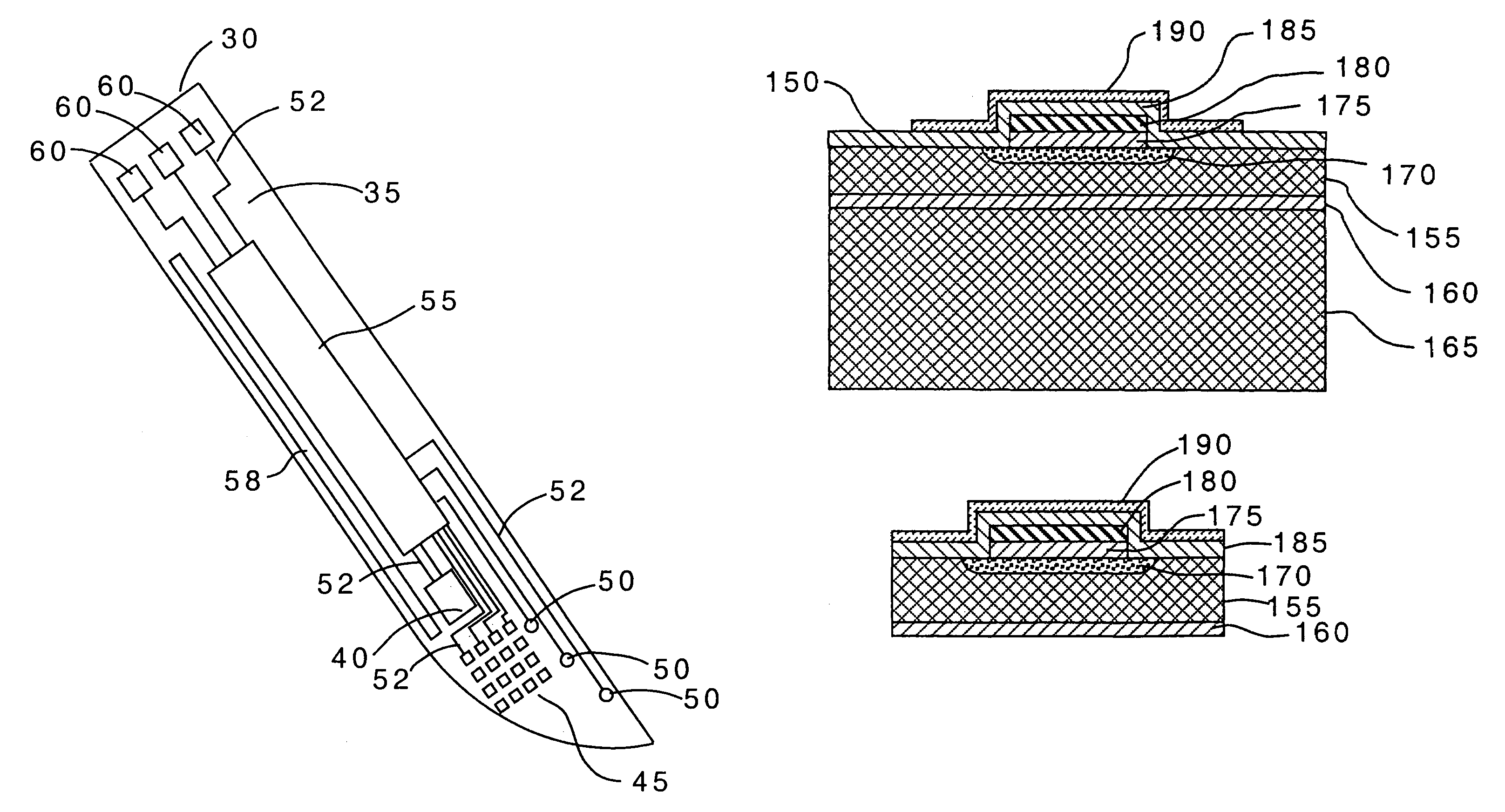

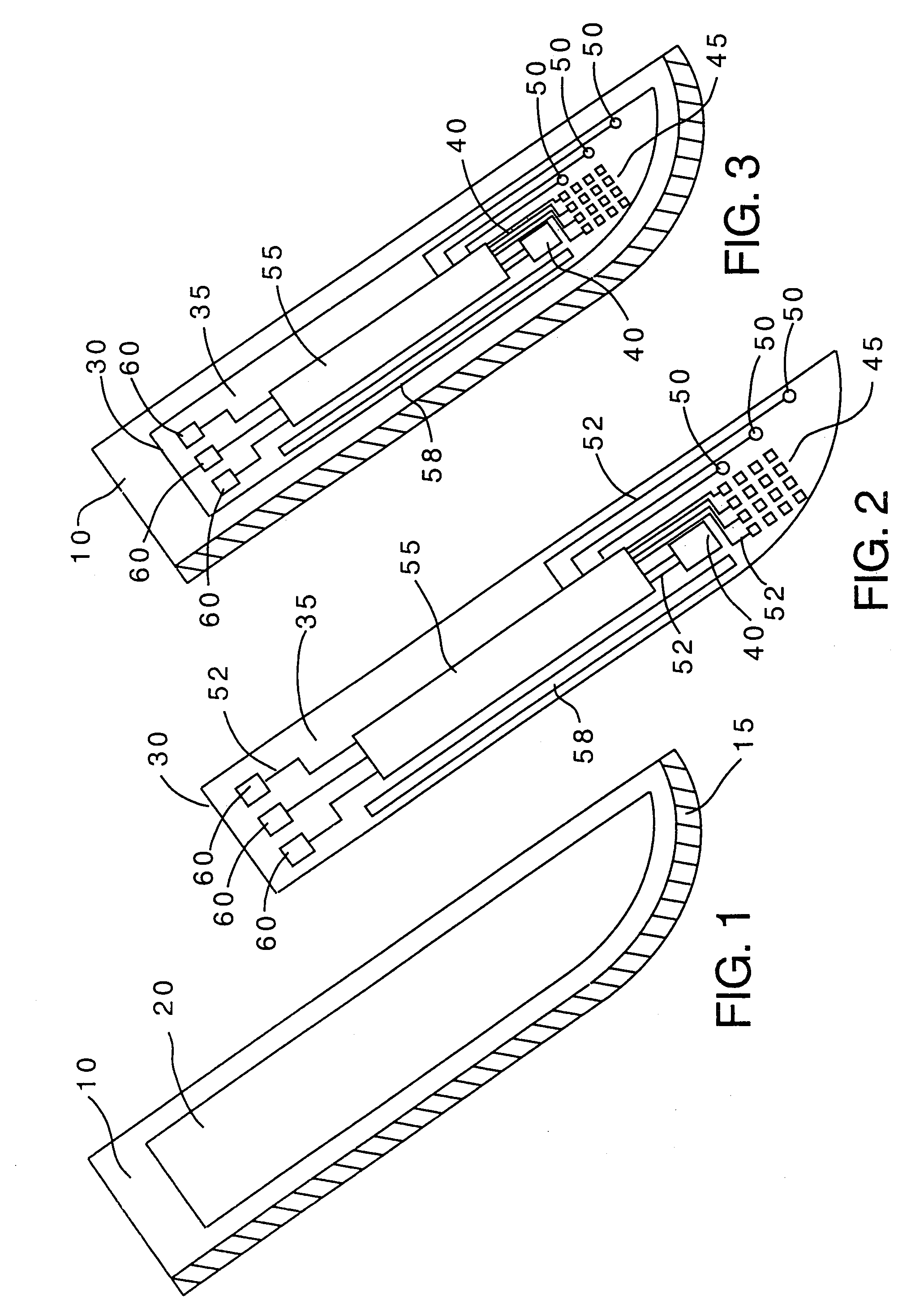

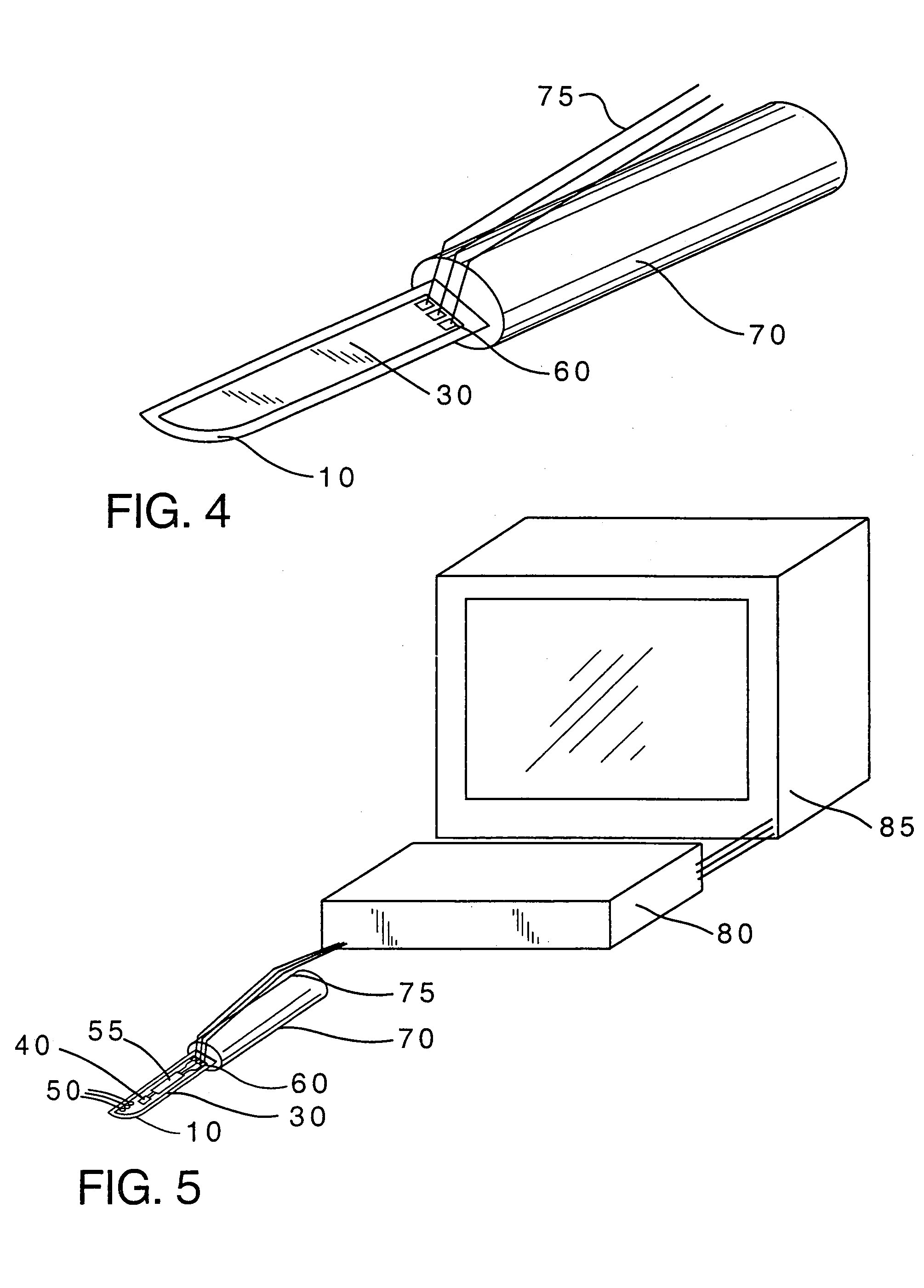

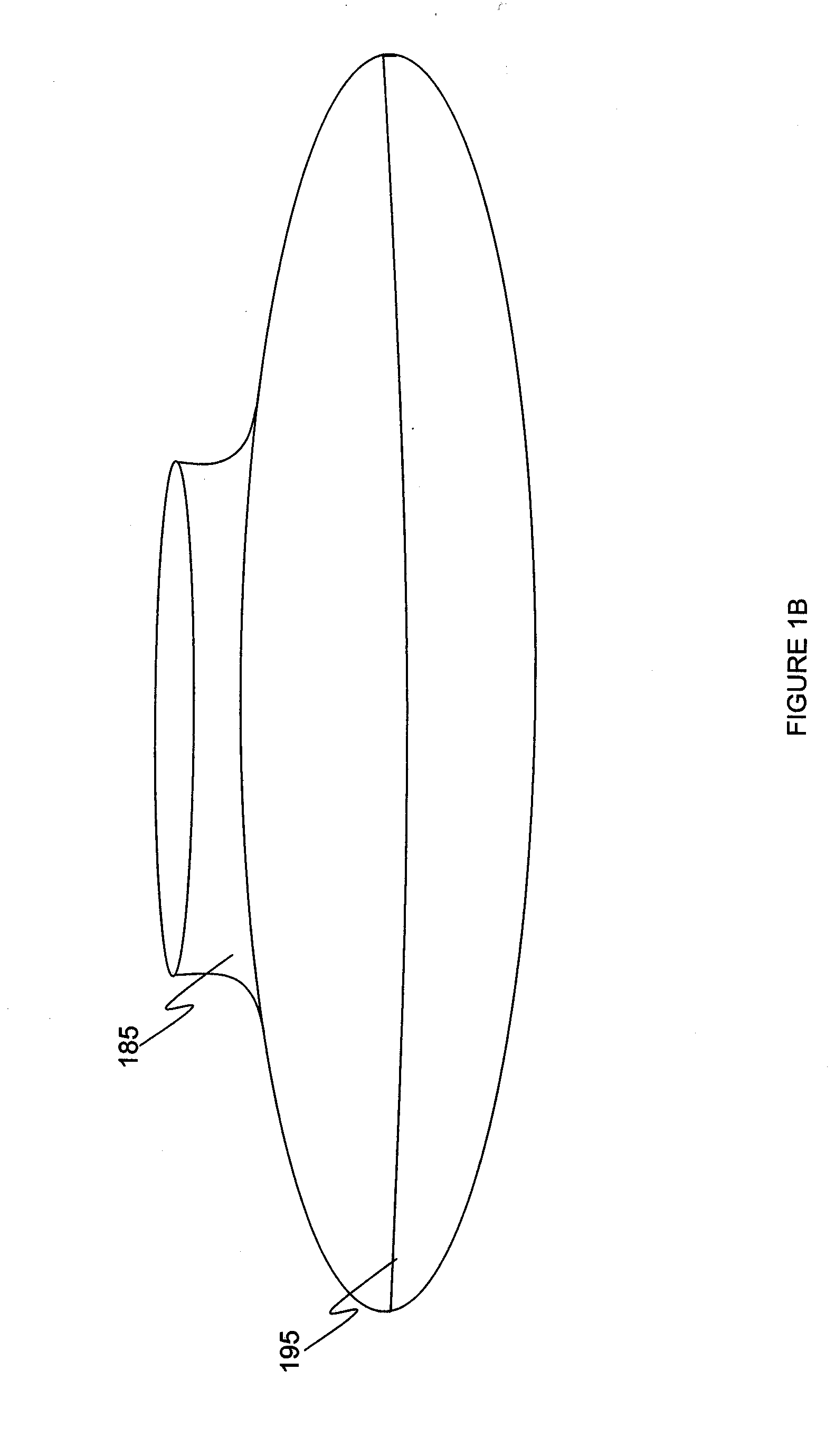

Method of making a cutting instrument having integrated sensors

A cutting instrument including a metal blade has a recess formed therein and a semiconductor substrate affixed to the blade in the recess. The semiconductor substrate includes at least one sensor formed thereon. The sensor formed on the semiconductor substrate may comprise at least one or an array of a strain sensors, pressure sensors, nerve sensors, temperature sensors, density sensors, accelerometers, and gyroscopes. The cutting instrument may also further include a handle wherein the blade is affixed to the handle and the semiconductor substrate is electrically coupled to the handle. The handle may then be coupled, either physically or by wireless transmission, to a computer that is adapted to display information to a person using the cutting instrument based on signals generated by one or more of the sensors formed on the semiconductor substrate. The computer or handle may also be adapted to store data based on the signals generated by one or more of the sensors. A method of making said cutting instrument includes the steps of at least one sensor being formed on a semiconductor wafer and a layer of photoresist being applied on a top side of the semiconductor wafer according to a pattern that matches the defined shape of the semiconductor substrate. The portion of the semiconductor wafer not covered by the photoresist is removed and thereafter the photoresist is removed from the semiconductor wafer, thereby leaving the semiconductor substrate having a defined shape and at least one sensor formed thereon. The semiconductor substrate having a defined shape and at least one sensor formed thereon is then affixed to a metal blade in a recess formed in said blade.

Owner:VERIMETRA

Immersion fluid for immersion Lithography, and method of performing immersion lithography

ActiveUS20050036183A1Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSemiconductor structureOptical surface

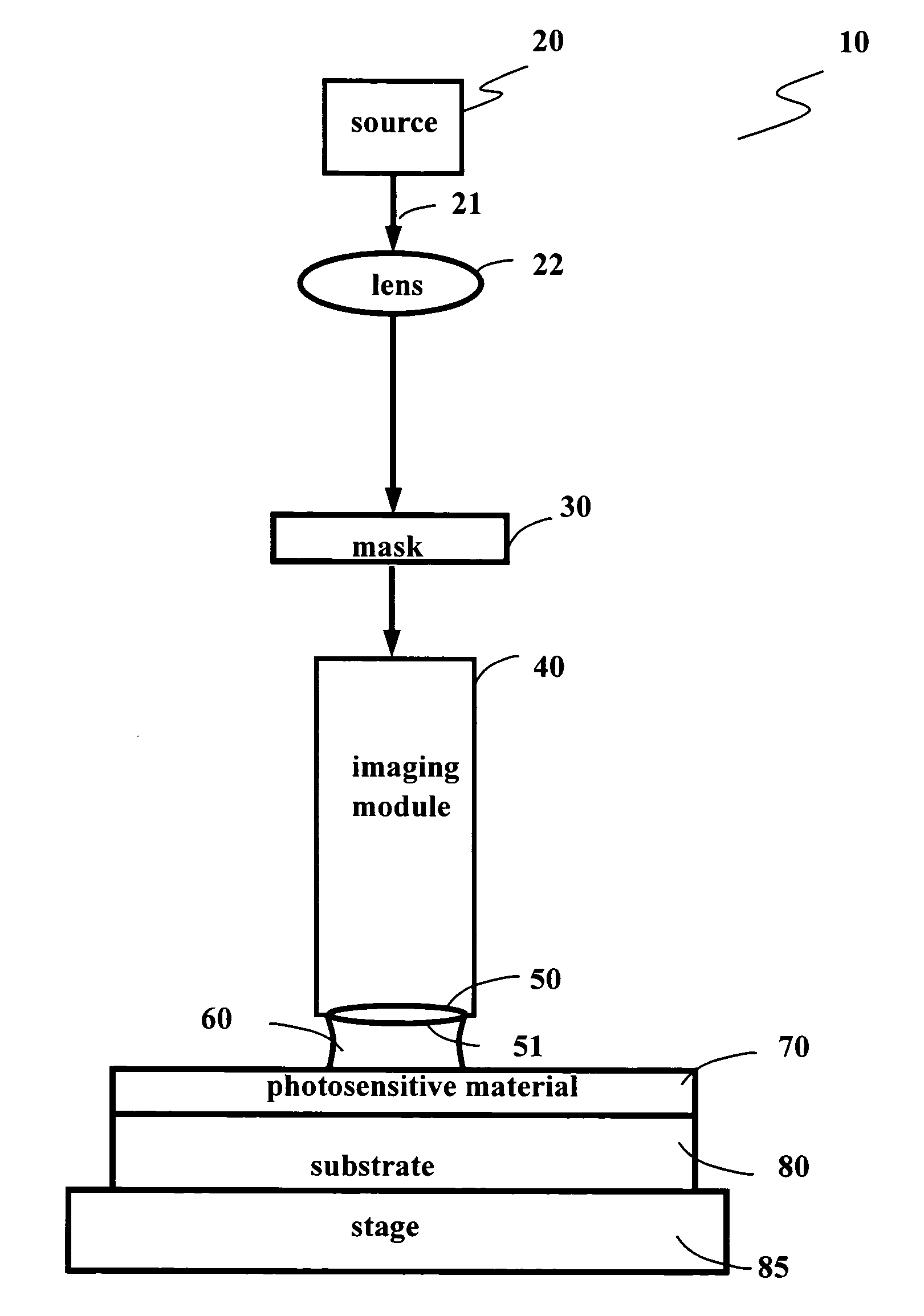

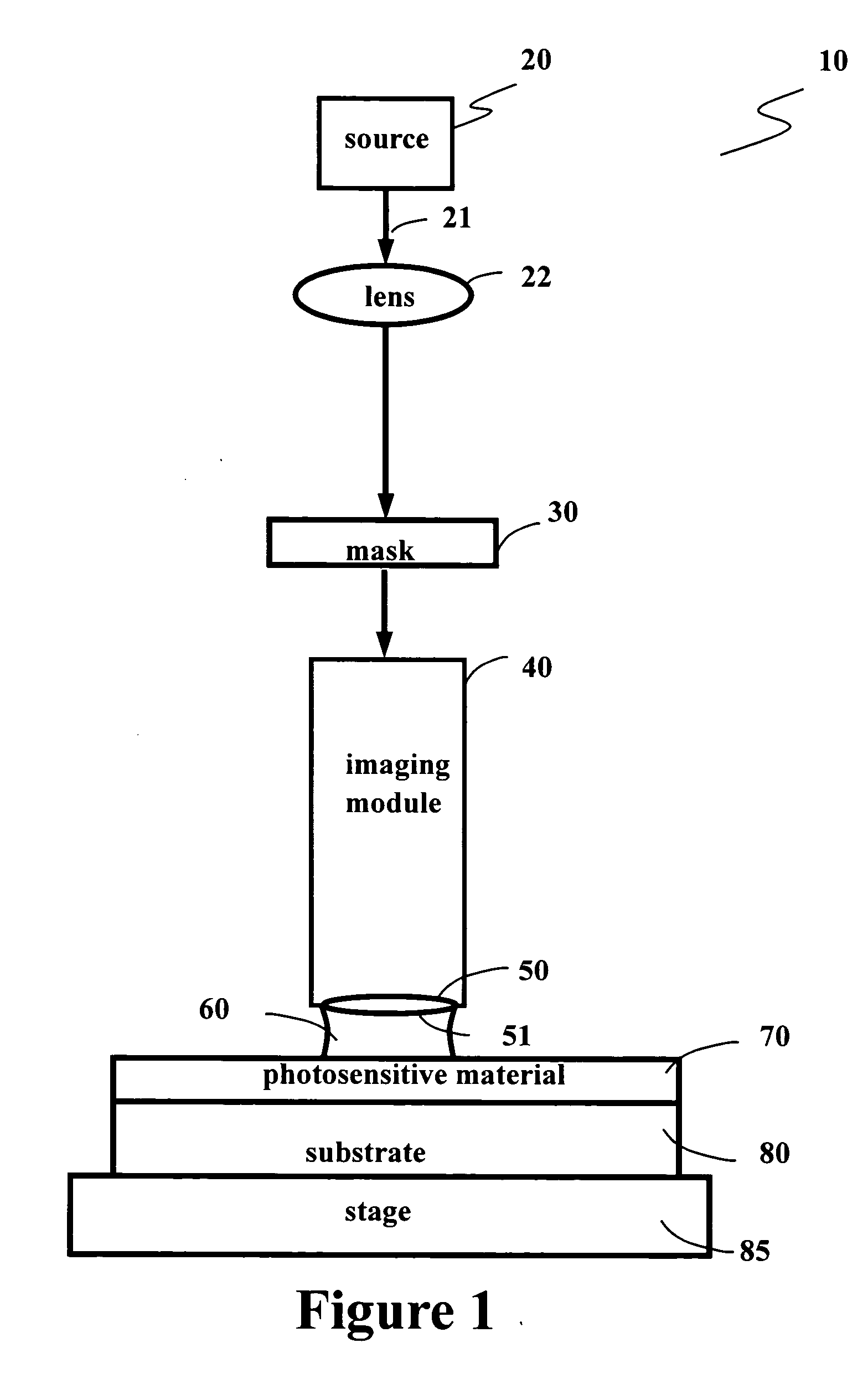

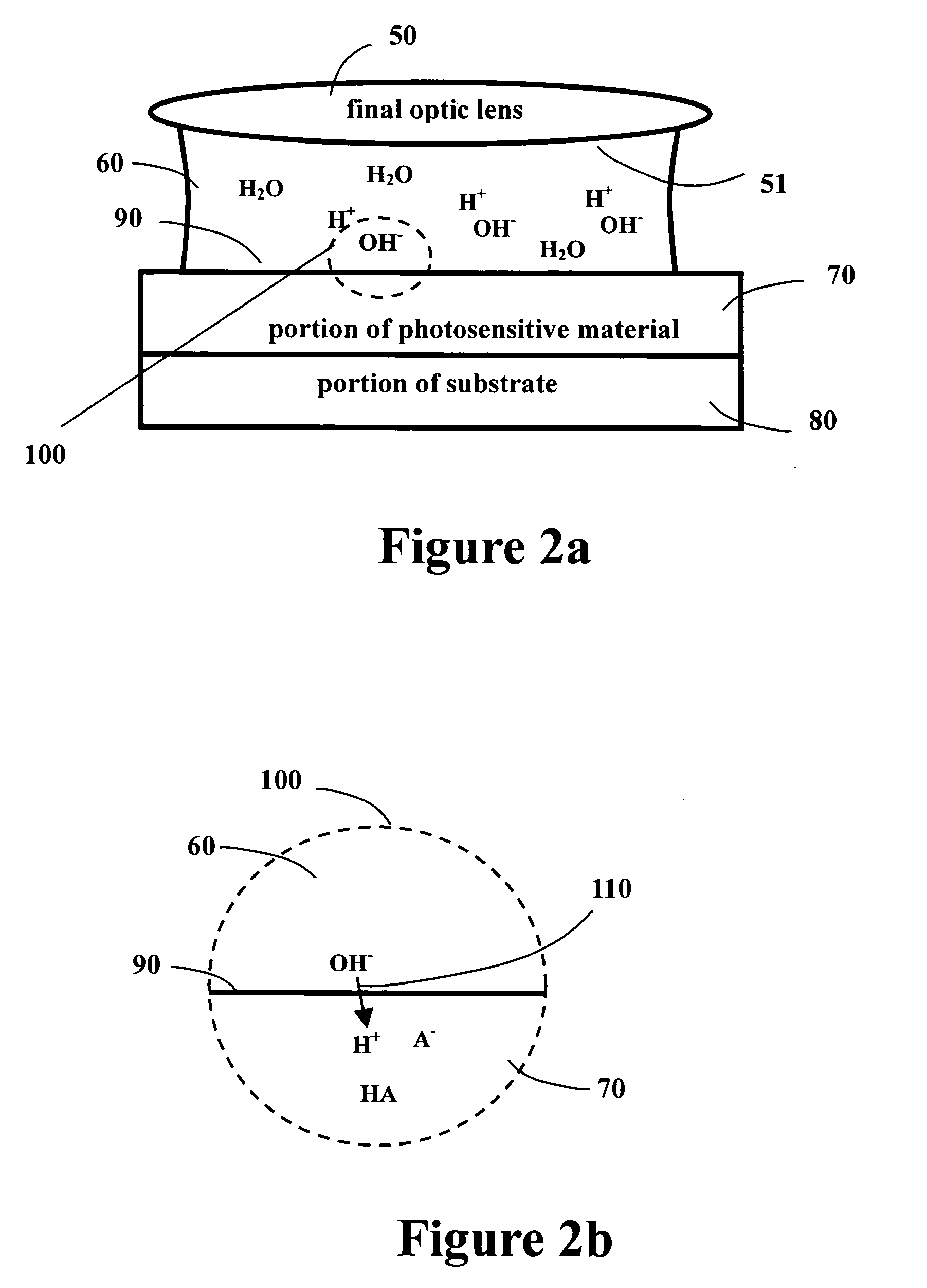

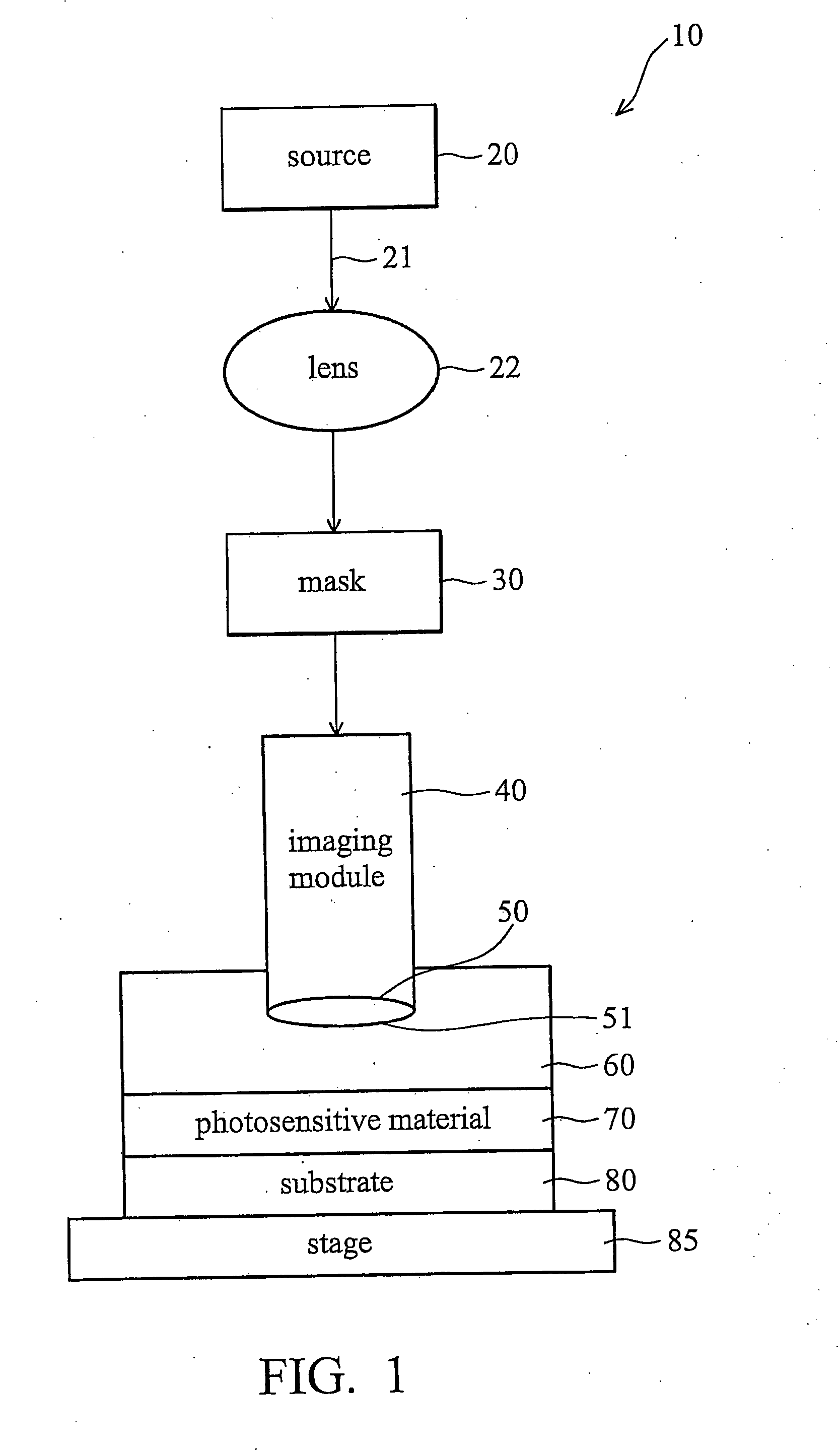

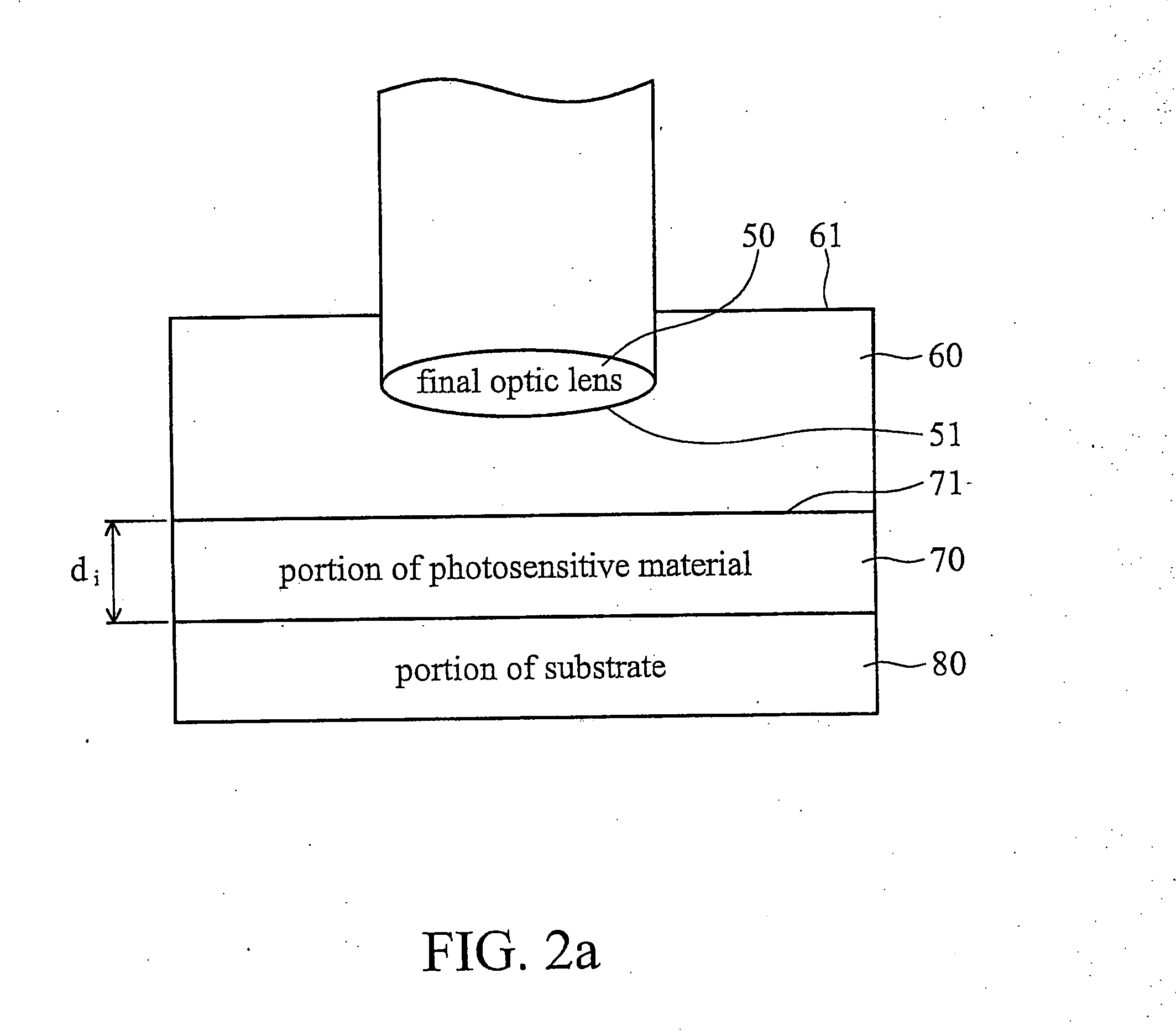

An immersion lithographic system 10 comprises an optical surface 51, an immersion fluid 60 with a pH less than 7 contacting at least a portion of the optical surface, and a semiconductor structure 80 having a topmost photoresist layer 70 wherein a portion of the photoresist is in contact with the immersion fluid. Further, a method for illuminating a semiconductor structure 80 having a topmost photoresist layer 70 comprising the steps of: introducing an immersion fluid 60 into a space between an optical surface 51 and the photoresist layer wherein the immersion fluid has a pH of less than 7, and directing light preferably with a wavelength of less than 450 nm through the immersion fluid and onto the photoresist.

Owner:TAIWAN SEMICON MFG CO LTD

Lithography apparatus for manufacture of integrated circuits

ActiveUS20050036184A1Limit amount of swellingSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusLithographic artistSemiconductor structure

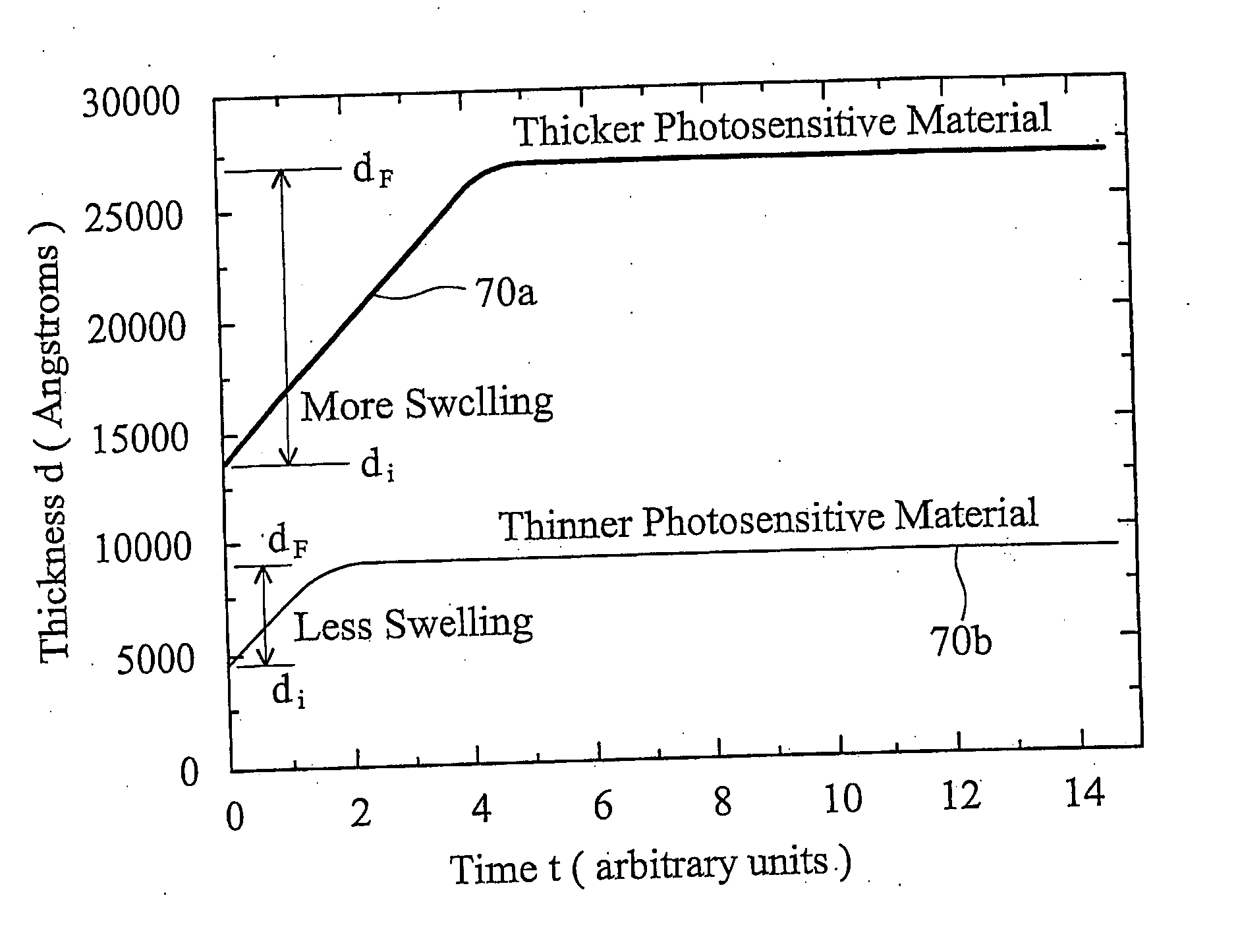

An immersion lithographic system 10 comprises an optical surface 51, an immersion fluid 60 contacting at least a portion of the optical surface, and a semiconductor structure 80 having a topmost photoresist layer 70 having a thickness of less than about 5000 angstroms, wherein a portion of the photoresist is in contact with the immersion fluid. Further, a method for illuminating a semiconductor structure 80 having a topmost photoresist layer 70 with a thickness of less than about 5000 angstroms, comprising introducing an immersion fluid 60 into a space between an optical surface 51 and the photoresist layer, and directing light preferably with a wavelength of less than about 450 nm through the immersion fluid and onto the photoresist.

Owner:TAIWAN SEMICON MFG CO LTD

Processes for the production of electrophoretic displays

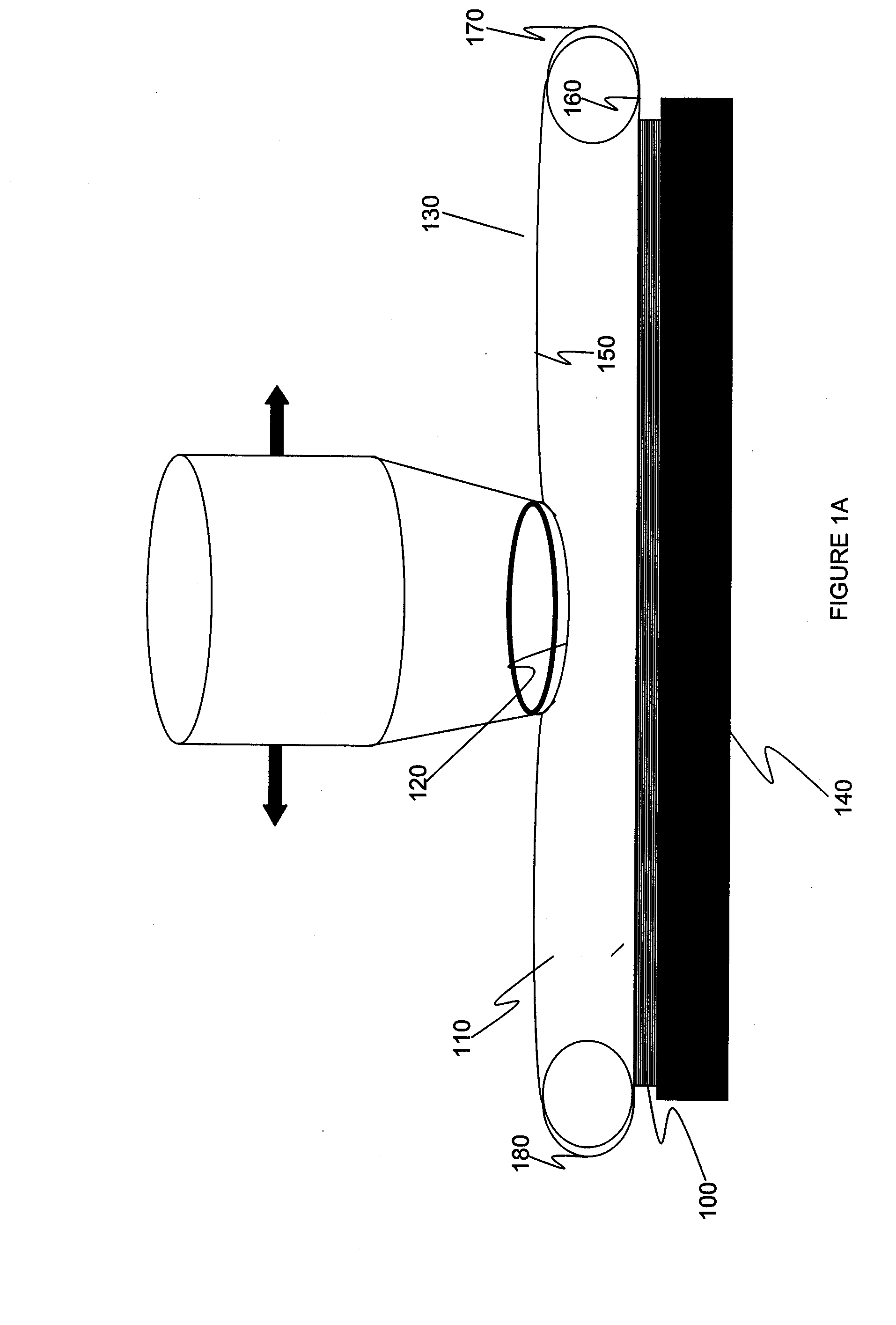

ActiveUS7339715B2Electric shock equipmentsElectrophoretic coatingsElectrophoresisPotential difference

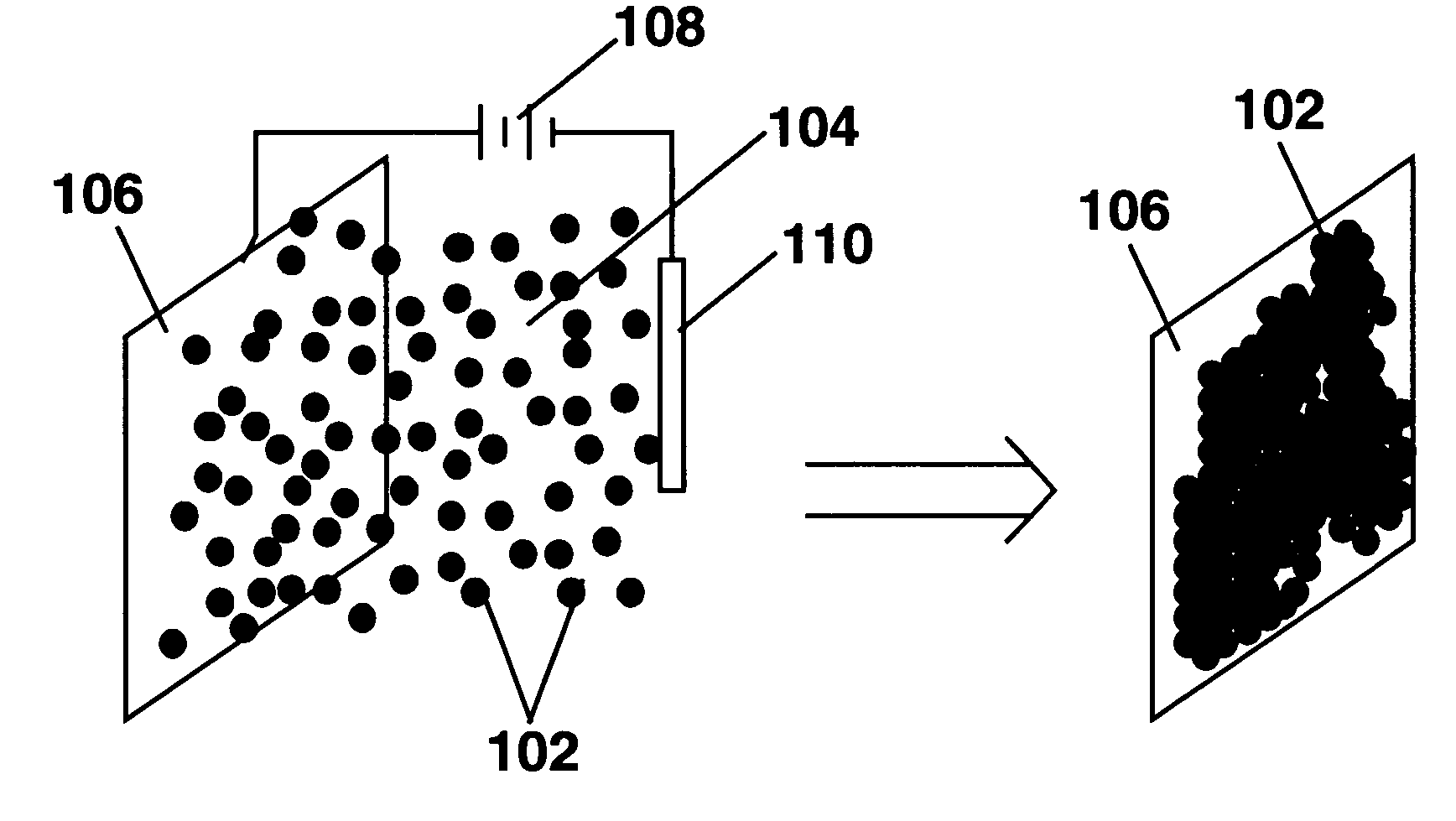

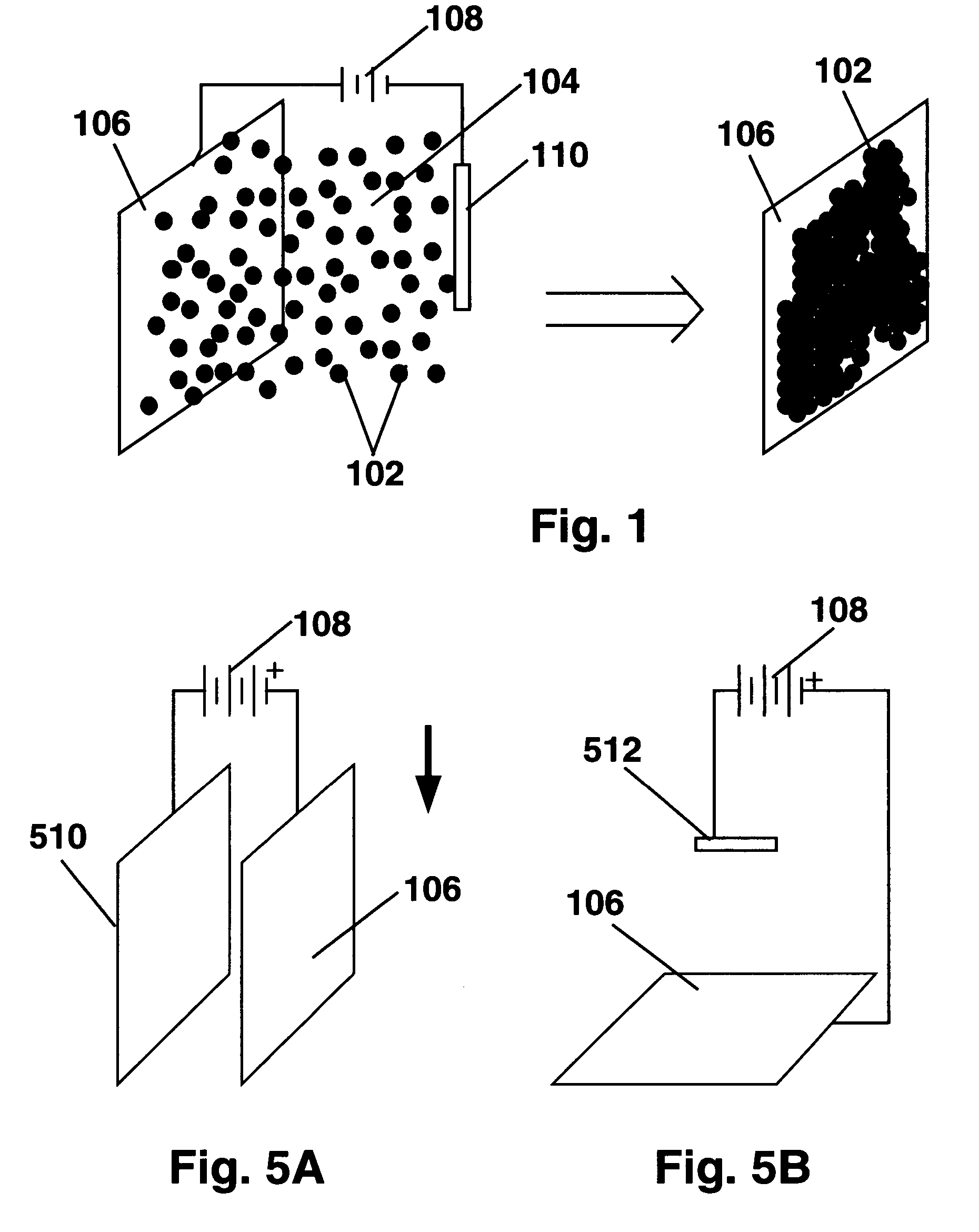

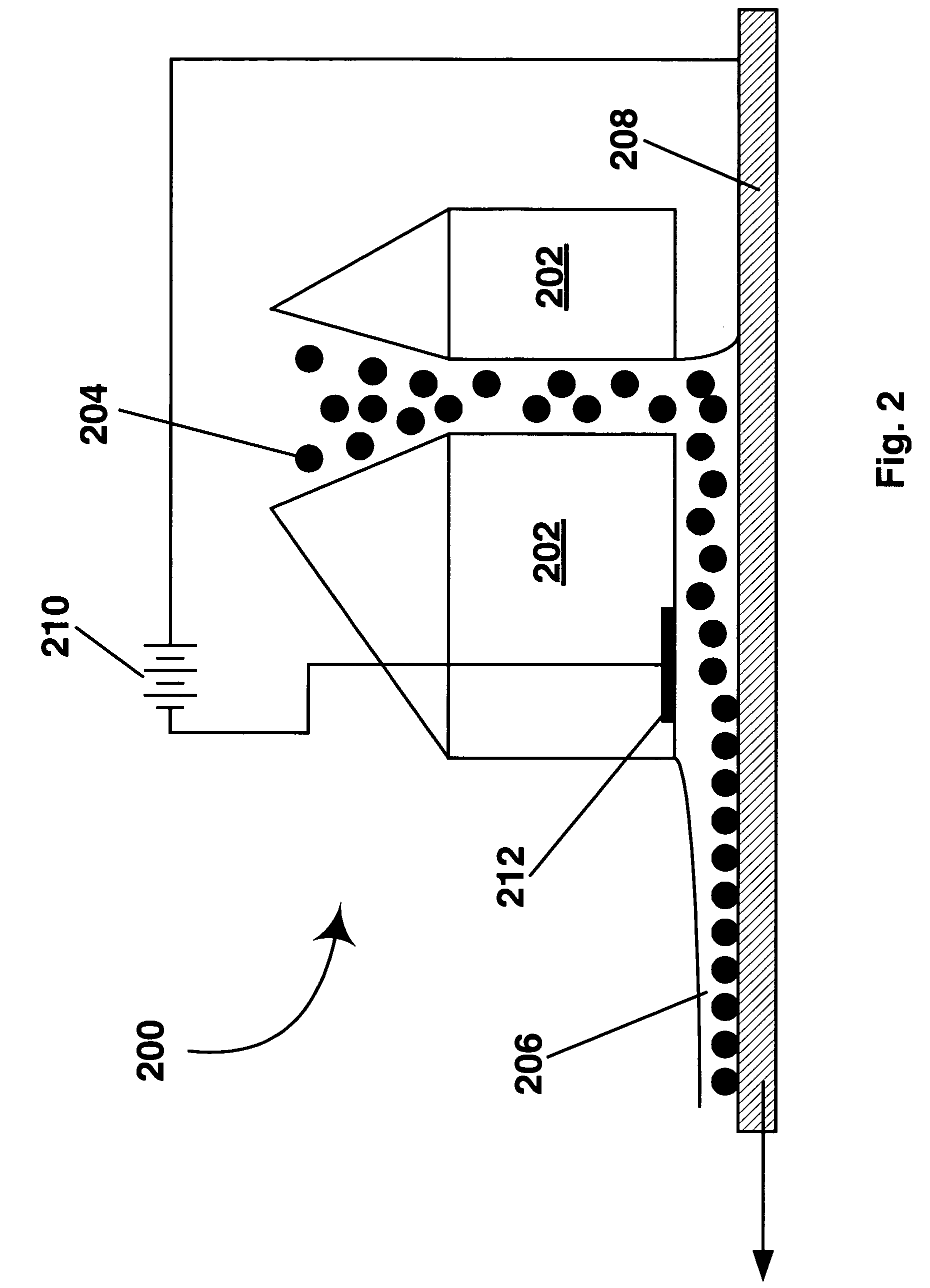

A coating of an encapsulated electrophoretic medium is formed on a substrate (106) by dispersing in a fluid (104) a plurality of electrophoretic capsules (102), contacting at least a portion of a substrate (106) with the fluid (104); and applying a potential difference between at least a part of the portion of the substrate (106) contacting the fluid (104) and a counter-electrode (110) in electrical contact with the fluid (104), thereby causing capsules (102) to be deposited upon at least part of the portion of the substrate (106) contacting the fluid (102). Patterned coatings of capsules containing different colors may be deposited in registration with electrodes using multiple capsule deposition steps. Alternatively, a patterned coating may be deposited upon a substrate containing a conductive layer by varying the conductivity of the conductive layer by radiation exposure or by coating portions of the conductive layer with an insulating layer, typically a photoresist.

Owner:E INK CORPORATION

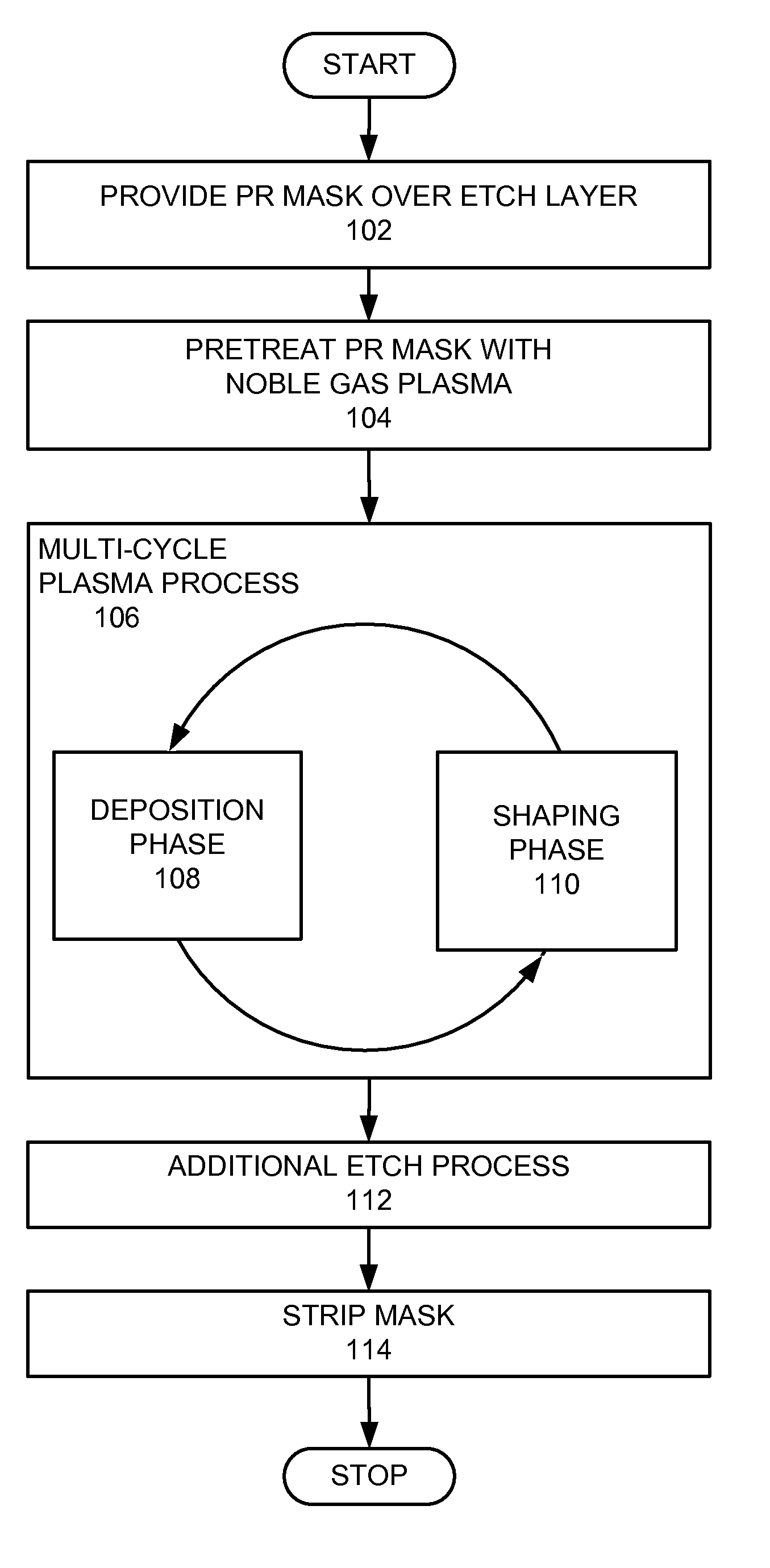

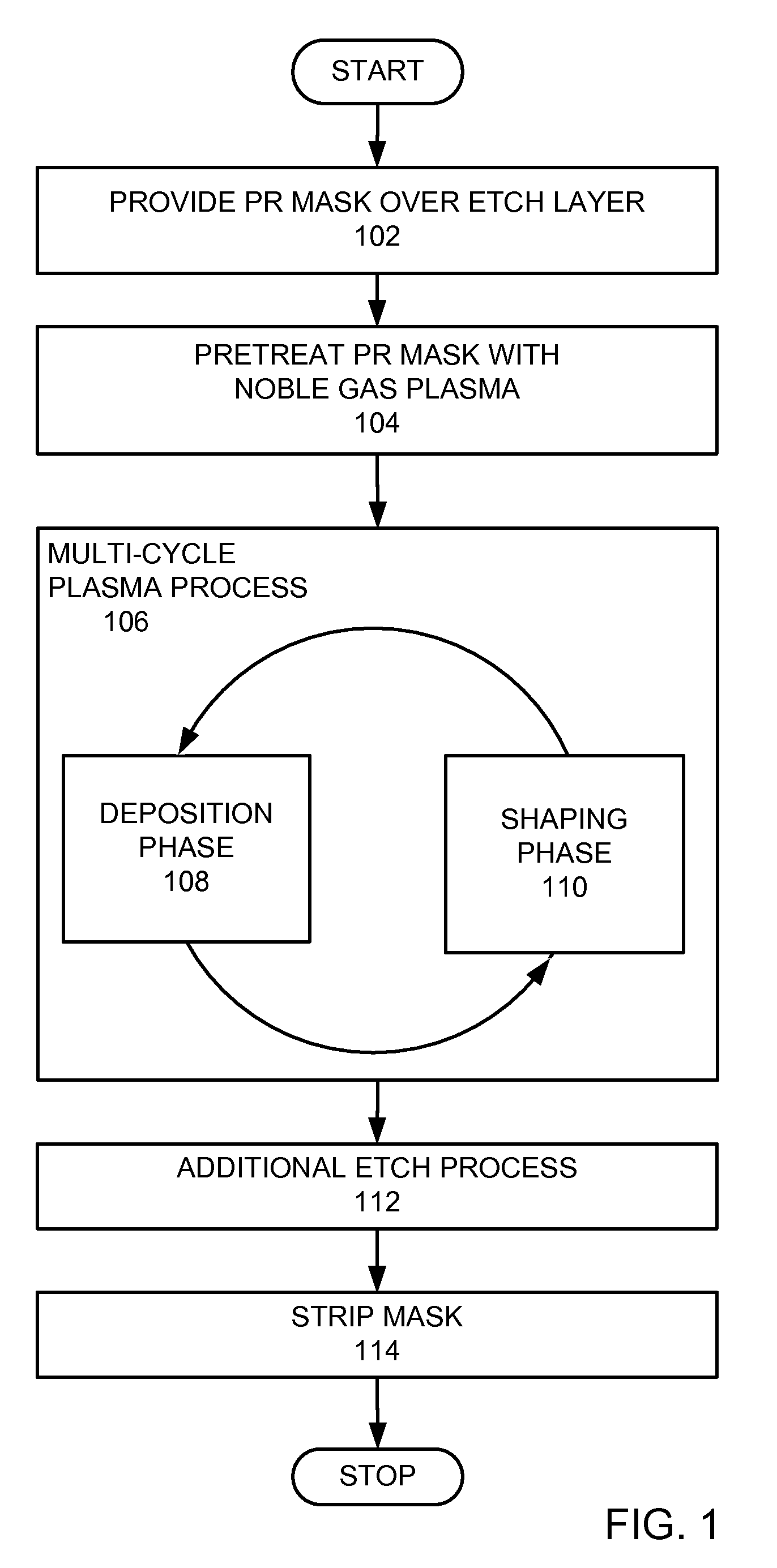

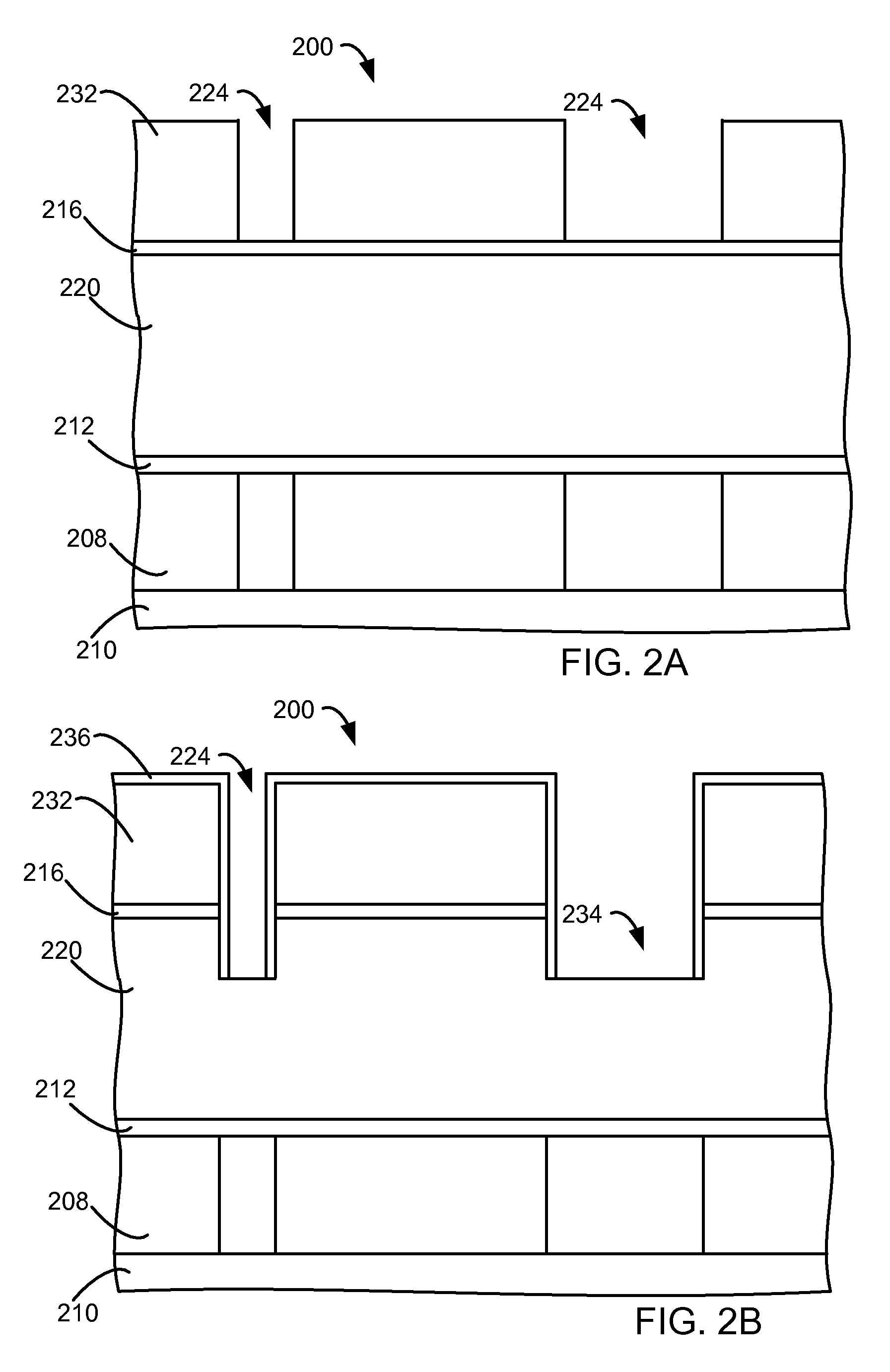

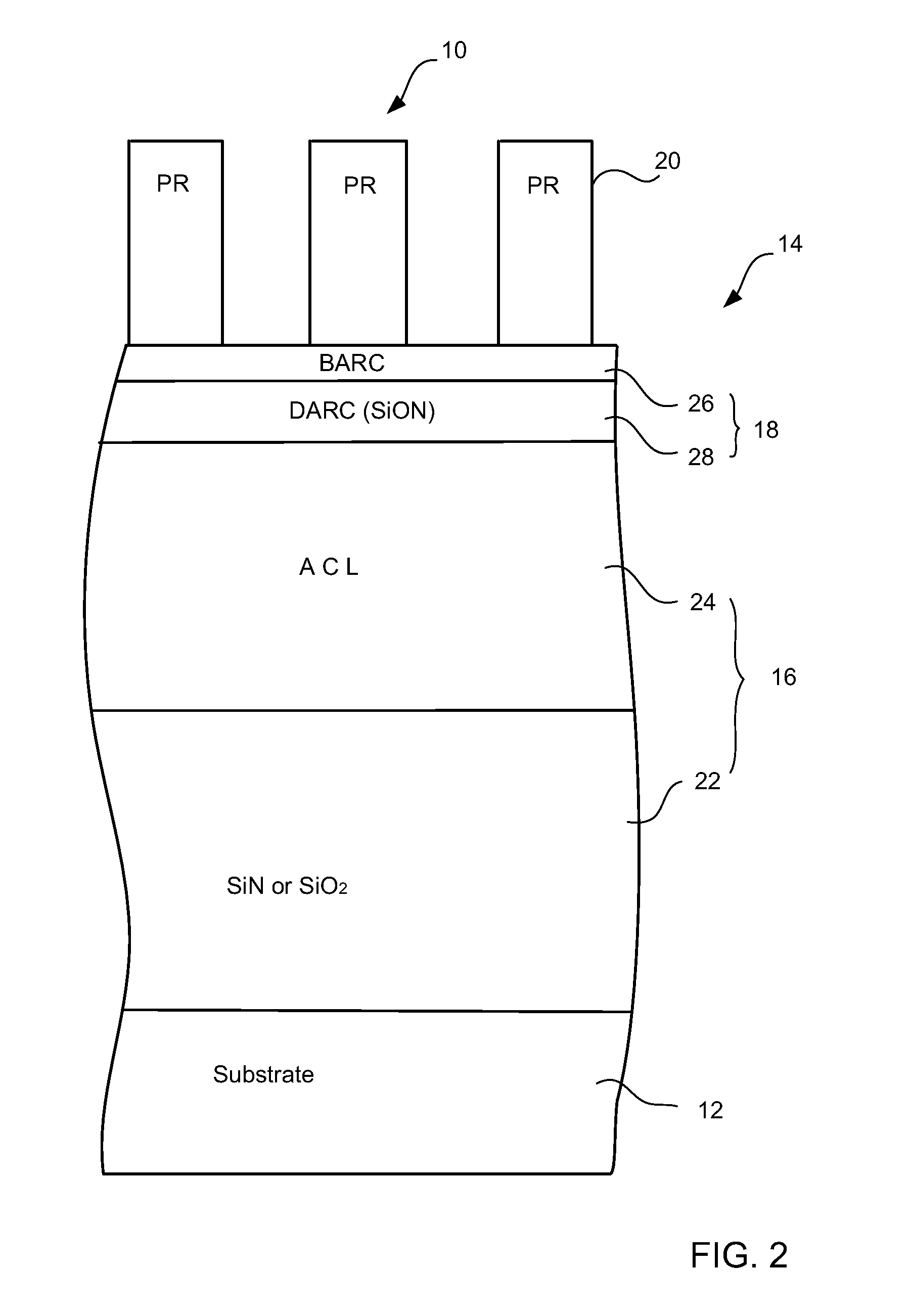

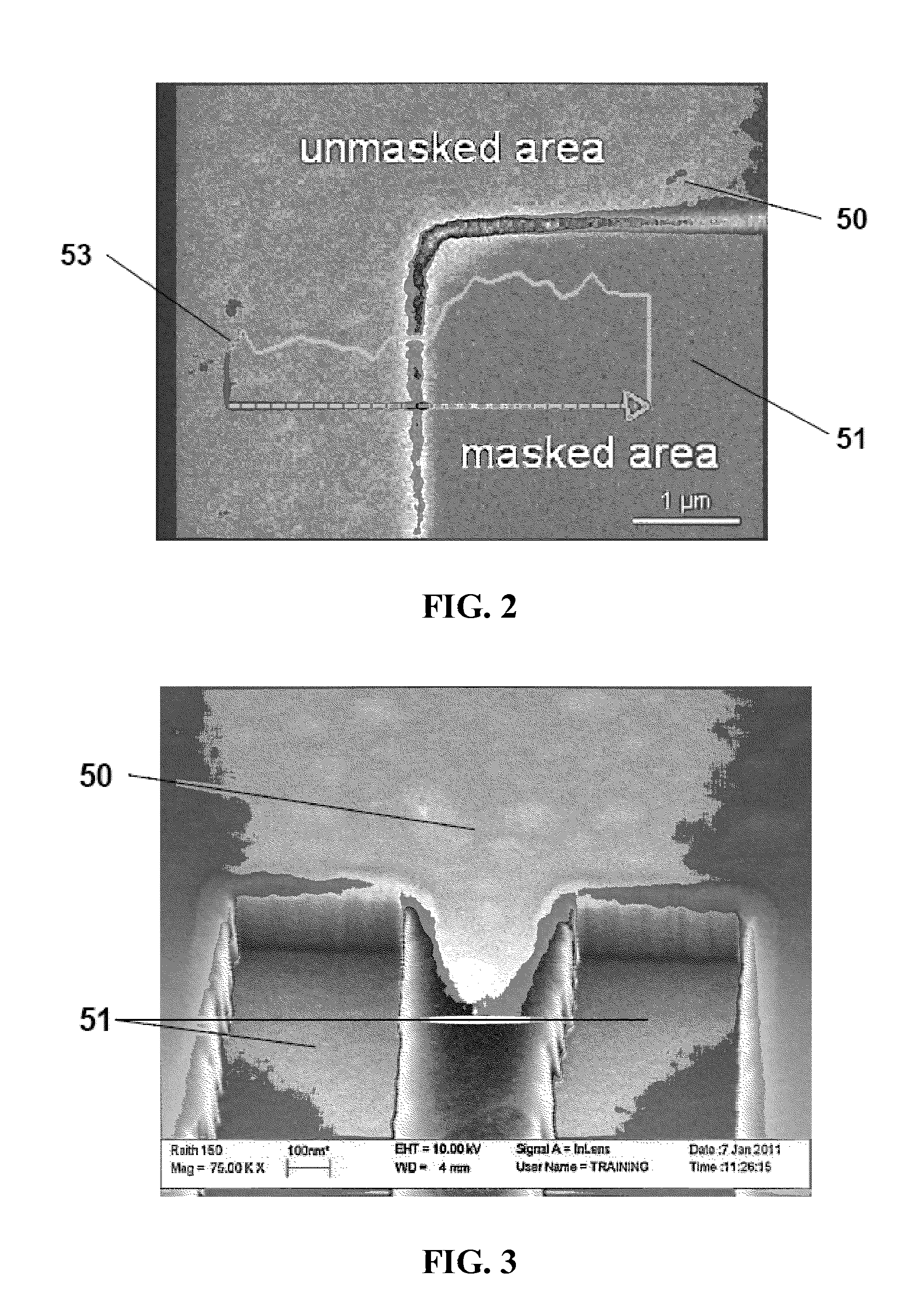

Plasma process with photoresist mask pretreatment

InactiveUS20090286400A1Decorative surface effectsSemiconductor/solid-state device manufacturingNoble gasLaser light

A method for etching features in a dielectric layer through a photoresist (PR) mask is provided. The PR mask is patterned using laser light having a wavelength not more than 193 nm. The PR mask is pre-treated with a noble gas plasma, and then a plurality of cycles of a plasma process is provided. Each cycle includes a deposition phase that deposits a deposition layer over the PR mask, the deposition layer covering a top and sidewalls of mask features of the PR mask, and a shaping phase that shapes the deposition layer deposited over the PR mask.

Owner:LAM RES CORP

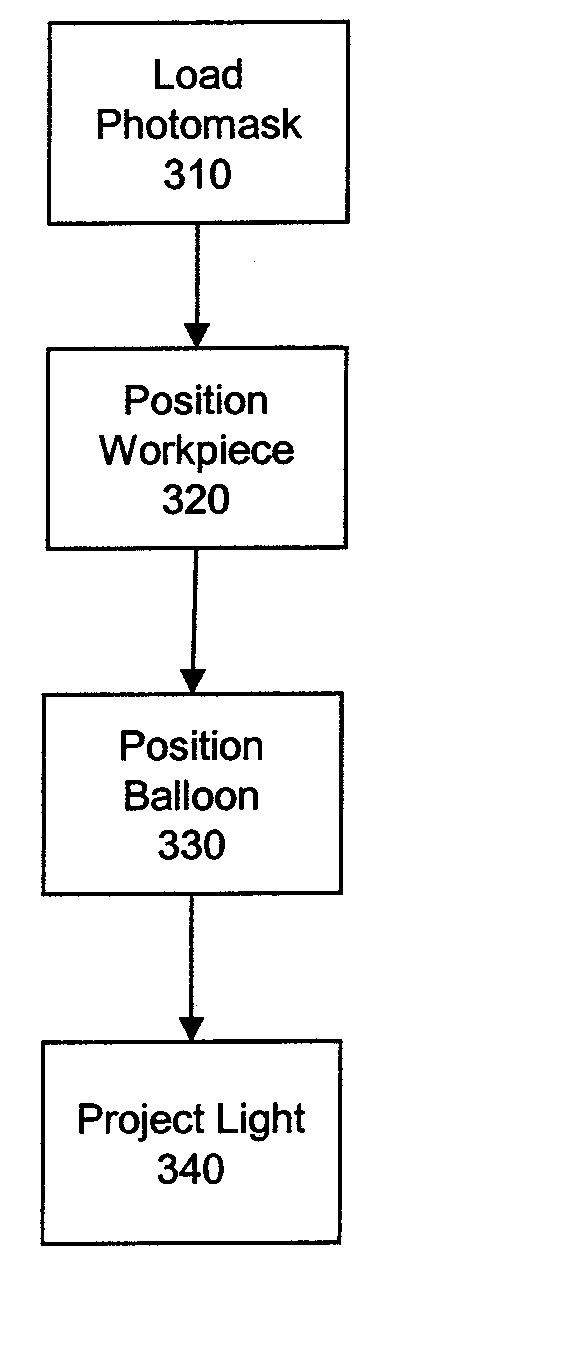

Liquid-filled balloons for immersion lithography

ActiveUS20050158673A1Suitable optical propertyPhotoprinting processesSemiconductor/solid-state device manufacturingOptical propertySemiconductor structure

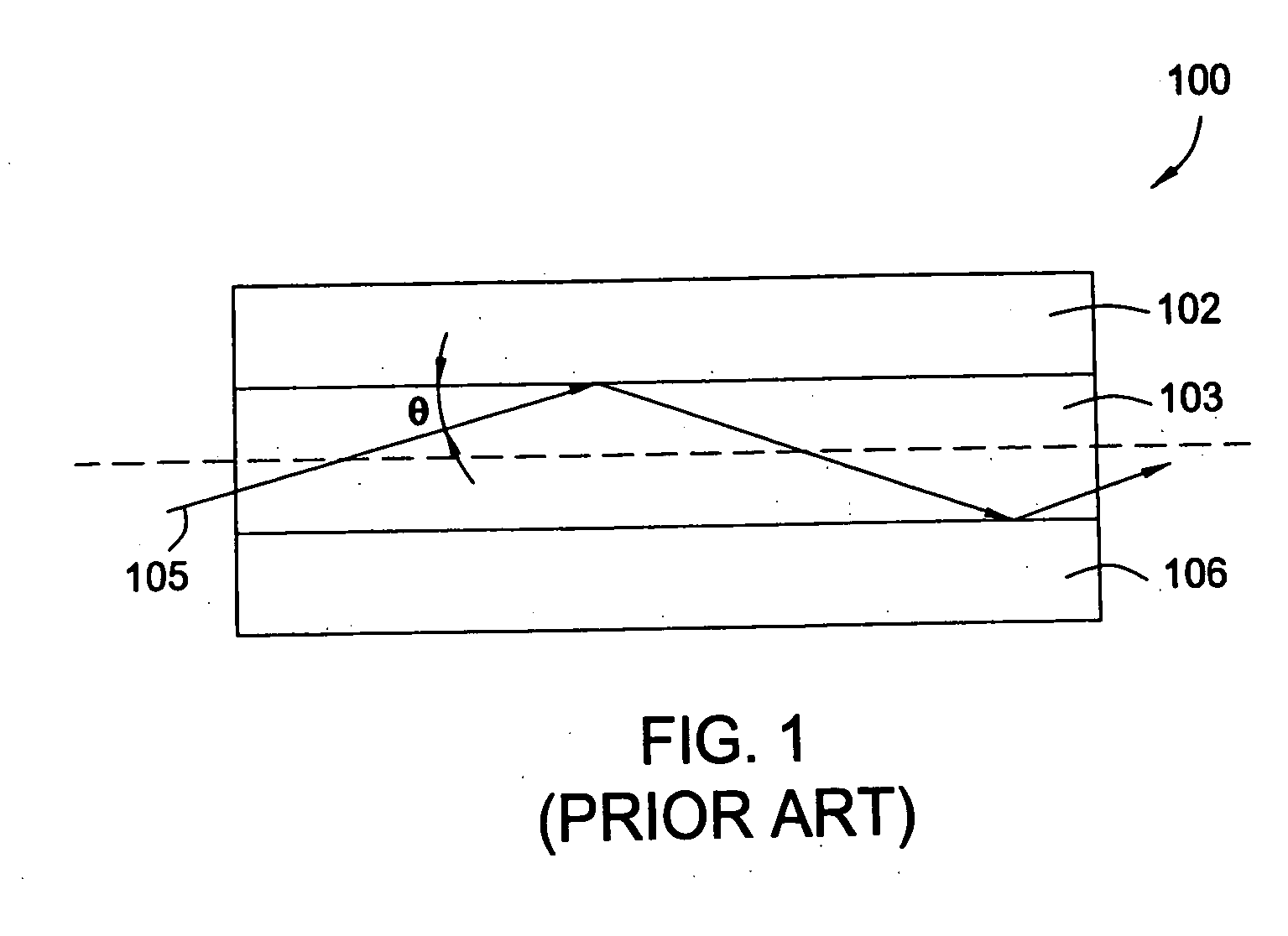

A liquid-filled balloon may be positioned between a workpiece, such as a semiconductor structure covered with a photoresist, and a lithography light source. The balloon includes a thin membrane that exhibits good optical and physical properties. Liquid contained in the balloon also exhibits good optical properties, including a refractive index higher than that of air. Light from the lithography light source passes through a mask, through a top layer of the balloon membrane, through the contained liquid, through a bottom layer of the balloon membrane, and onto the workpiece where it alters portions of the photoresist. As the liquid has a low absorption and a higher refractive index than air, the liquid-filled balloon system enhances resolution. Thus, the balloon provides optical benefits of liquid immersion without the complications of maintaining a liquid between (and in contact with) a lithographic light source mechanism and workpiece.

Owner:TWITTER INC

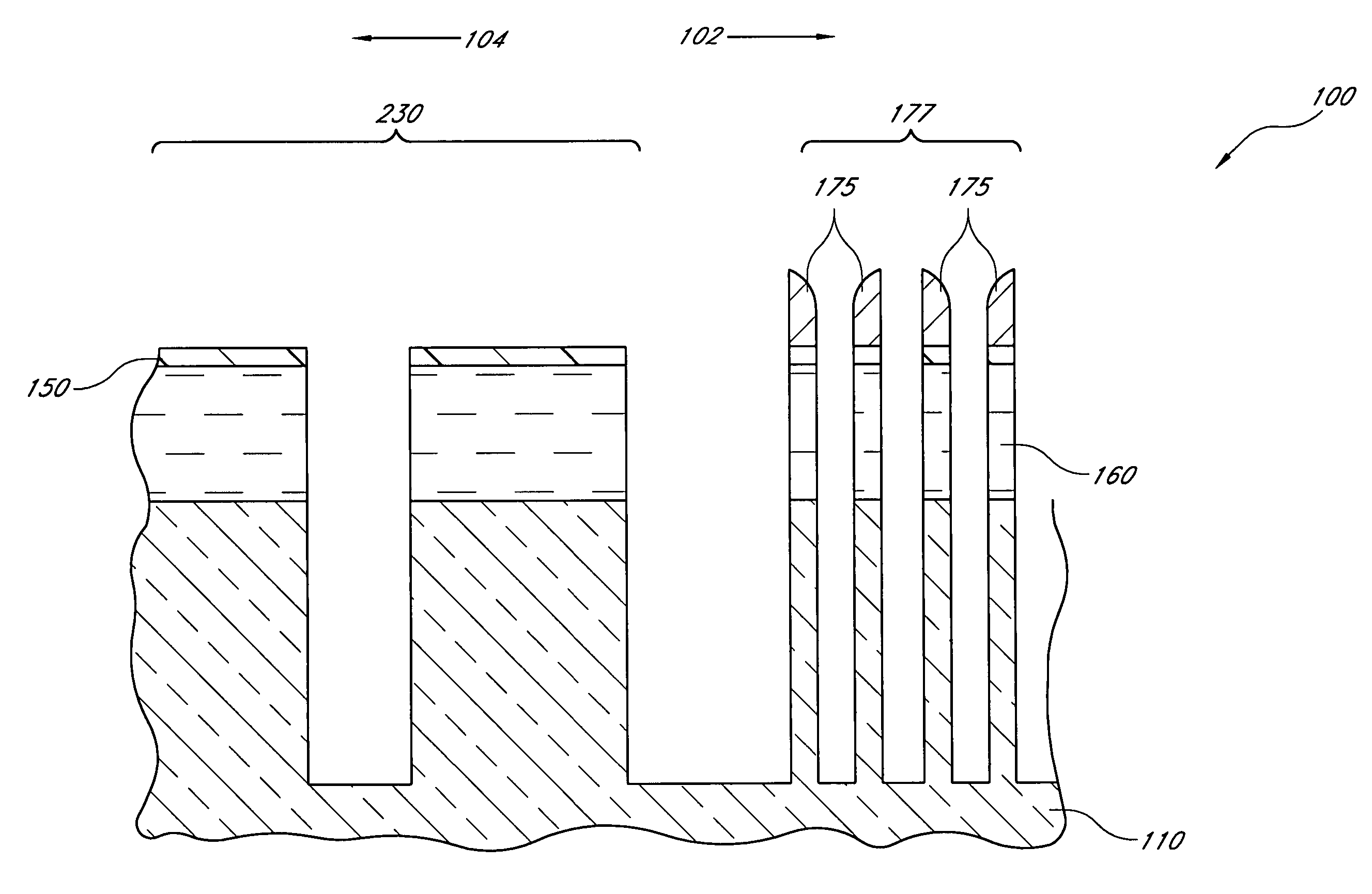

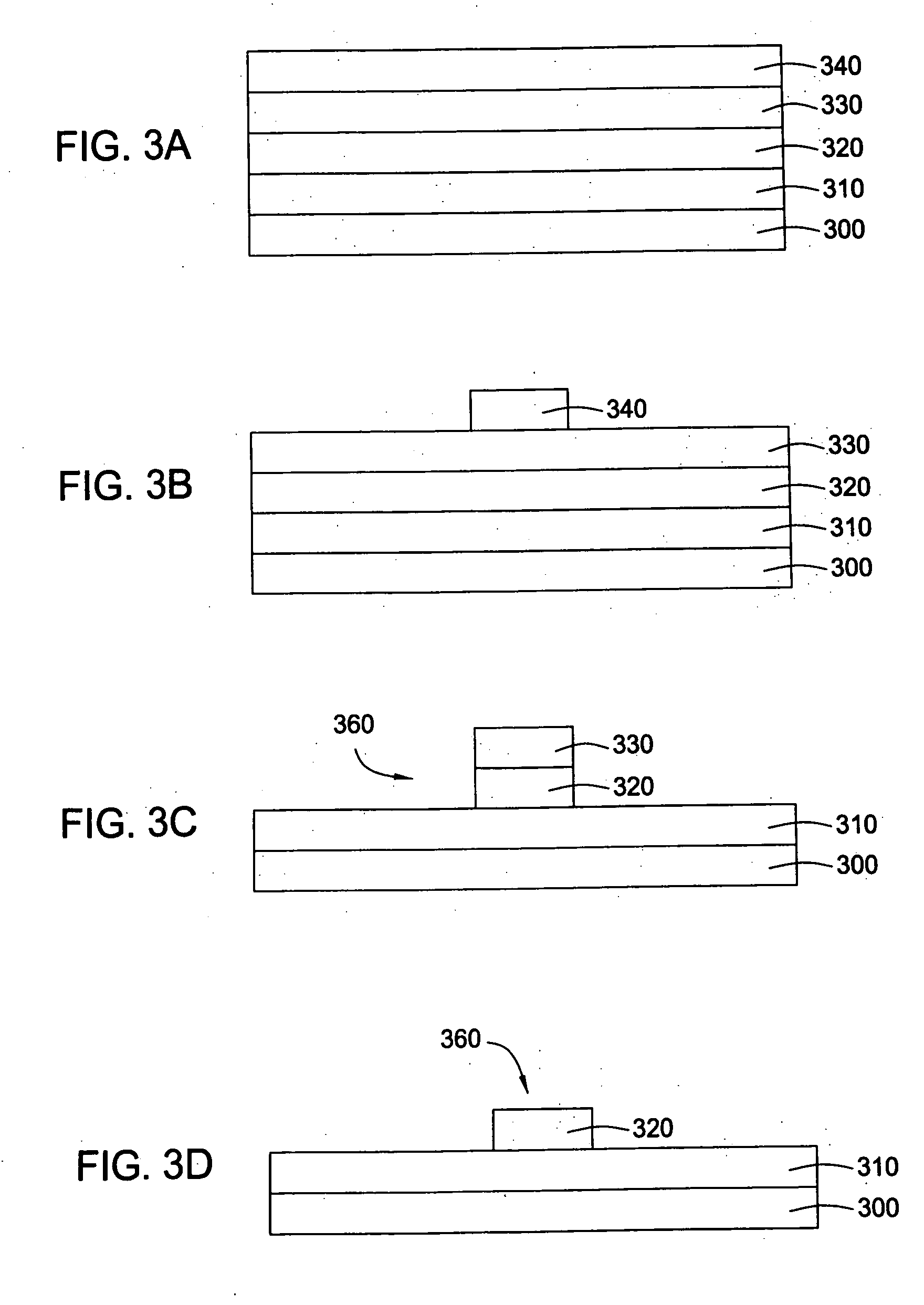

Method for integrated circuit fabrication using pitch multiplication

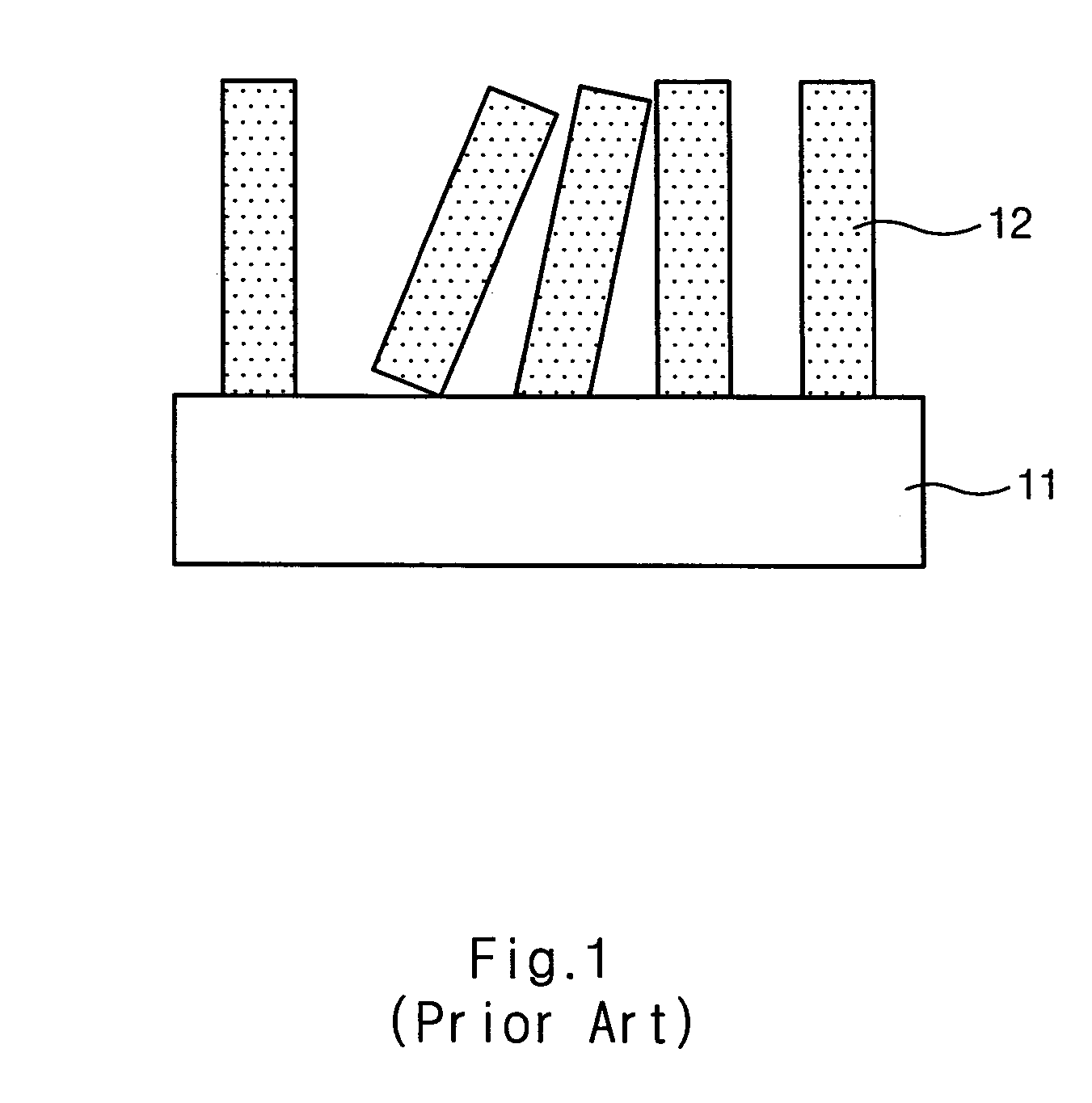

InactiveUS7115525B2Electric discharge tubesSemiconductor/solid-state device manufacturingResistEngineering

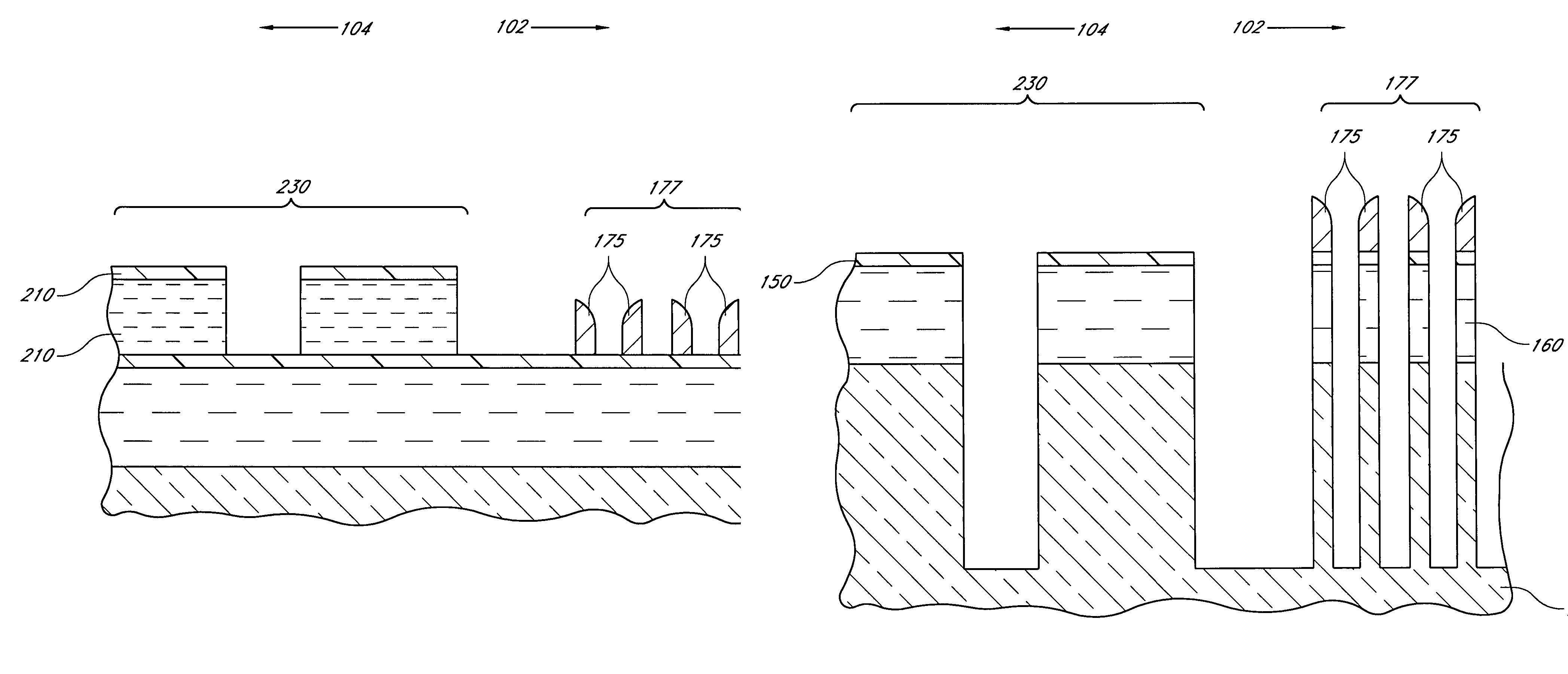

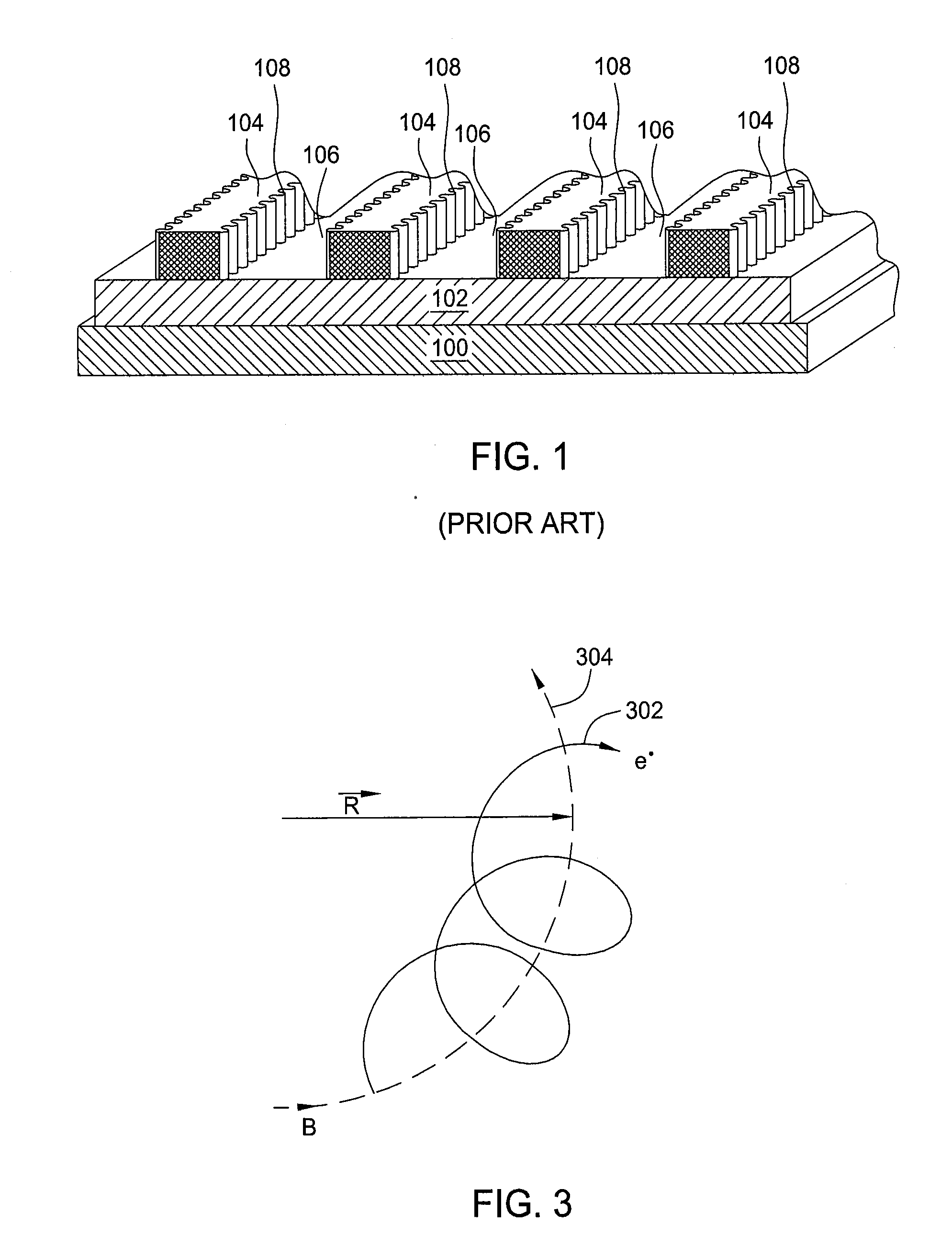

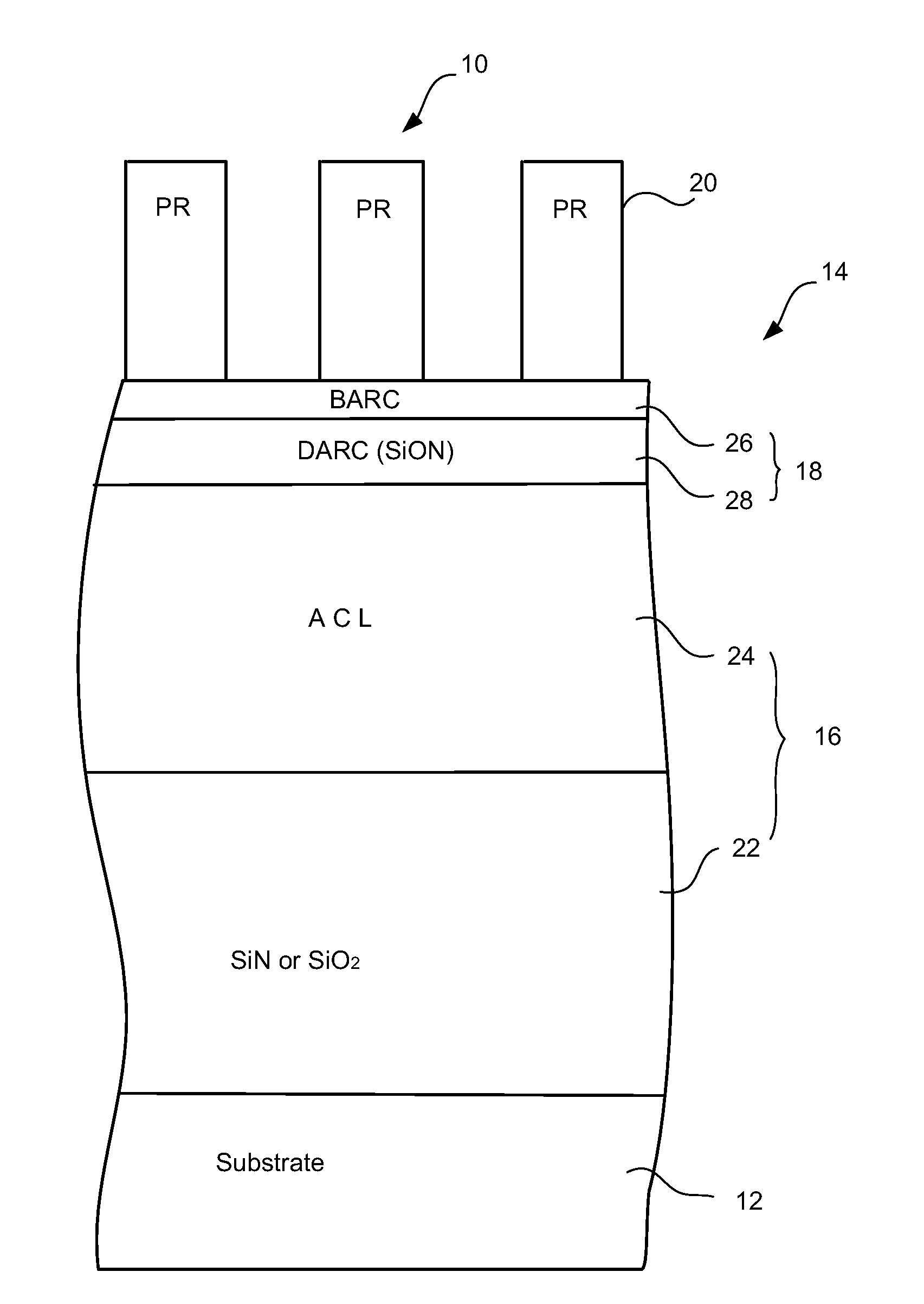

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

Method for integrated circuit fabrication using pitch multiplication

InactiveUS20060046484A1Electric discharge tubesSemiconductor/solid-state device manufacturingImage resolutionDifferences size

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

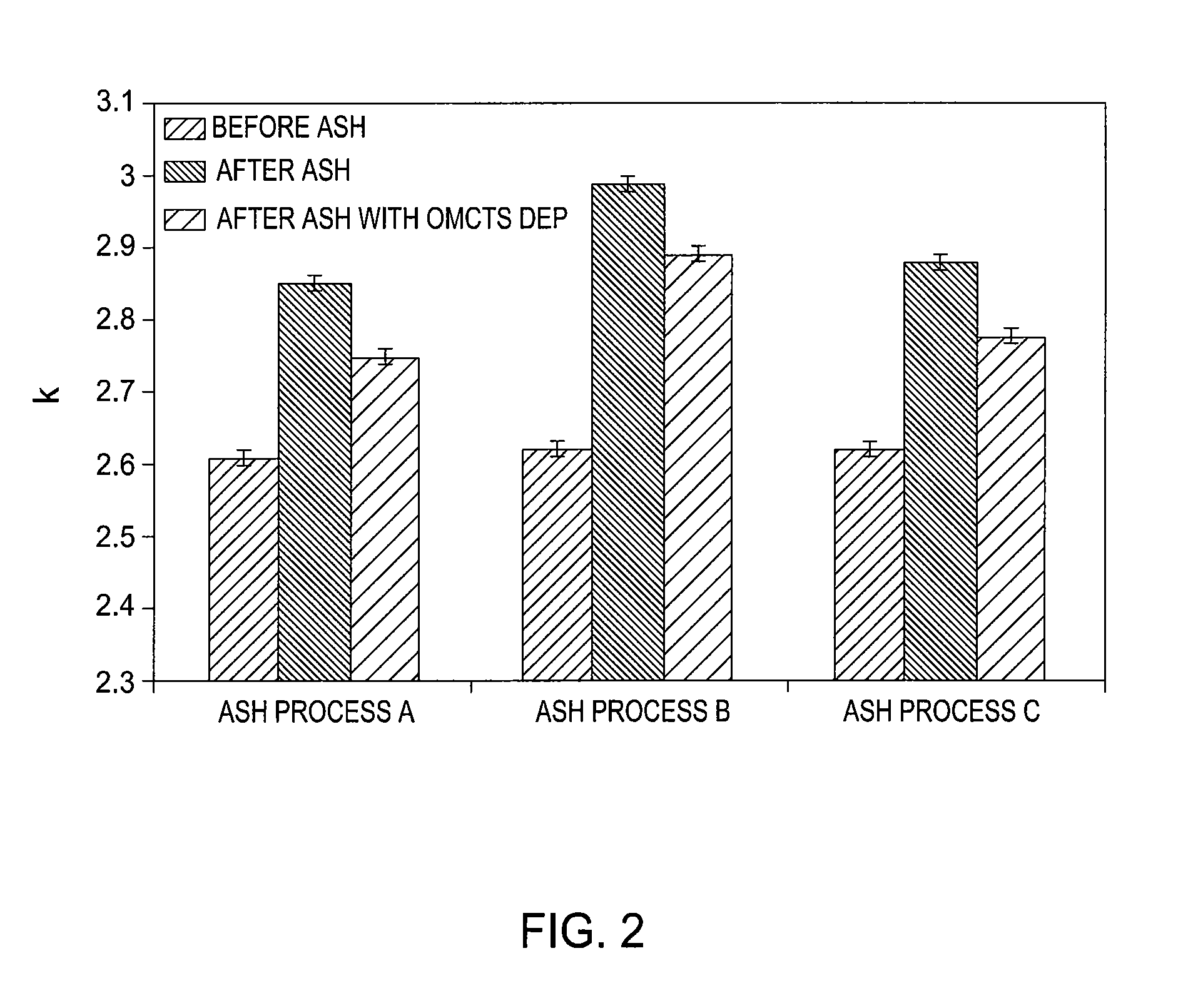

Method to minimize wet etch undercuts and provide pore sealing of extreme low k (k<2.5) dielectrics

ActiveUS8445075B2Constant ratePrevents undercuts and CD lossVacuum evaporation coatingPretreated surfacesNitrogenThin layer

Methods of processing films on substrates are provided. In one aspect, the methods comprise treating a patterned low dielectric constant film after a photoresist is removed from the film by depositing a thin layer comprising silicon, carbon, and optionally oxygen and / or nitrogen on the film. The thin layer provides a carbon-rich, hydrophobic surface for the patterned low dielectric constant film. The thin layer also protects the low dielectric constant film from subsequent wet cleaning processes and penetration by precursors for layers that are subsequently deposited on the low dielectric constant film.

Owner:APPLIED MATERIALS INC

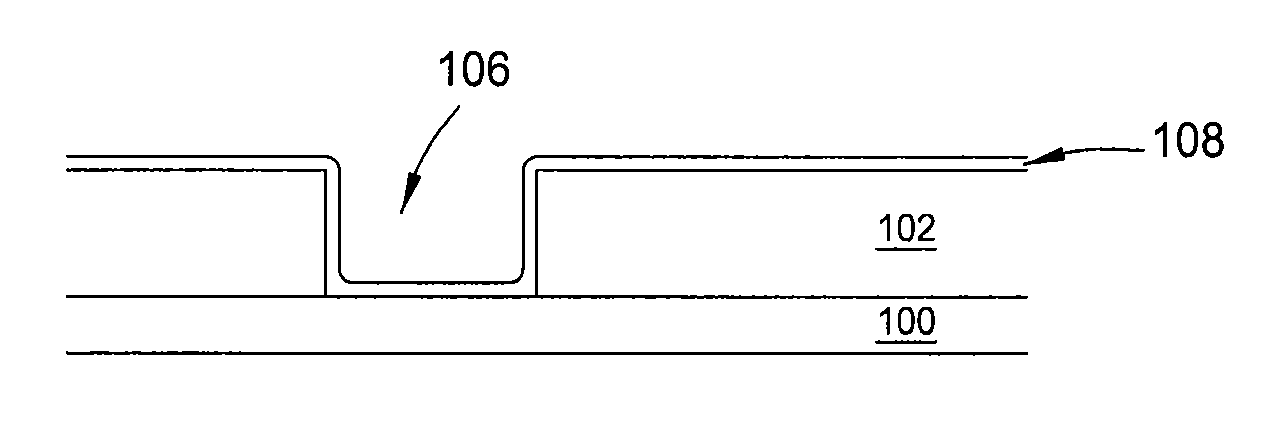

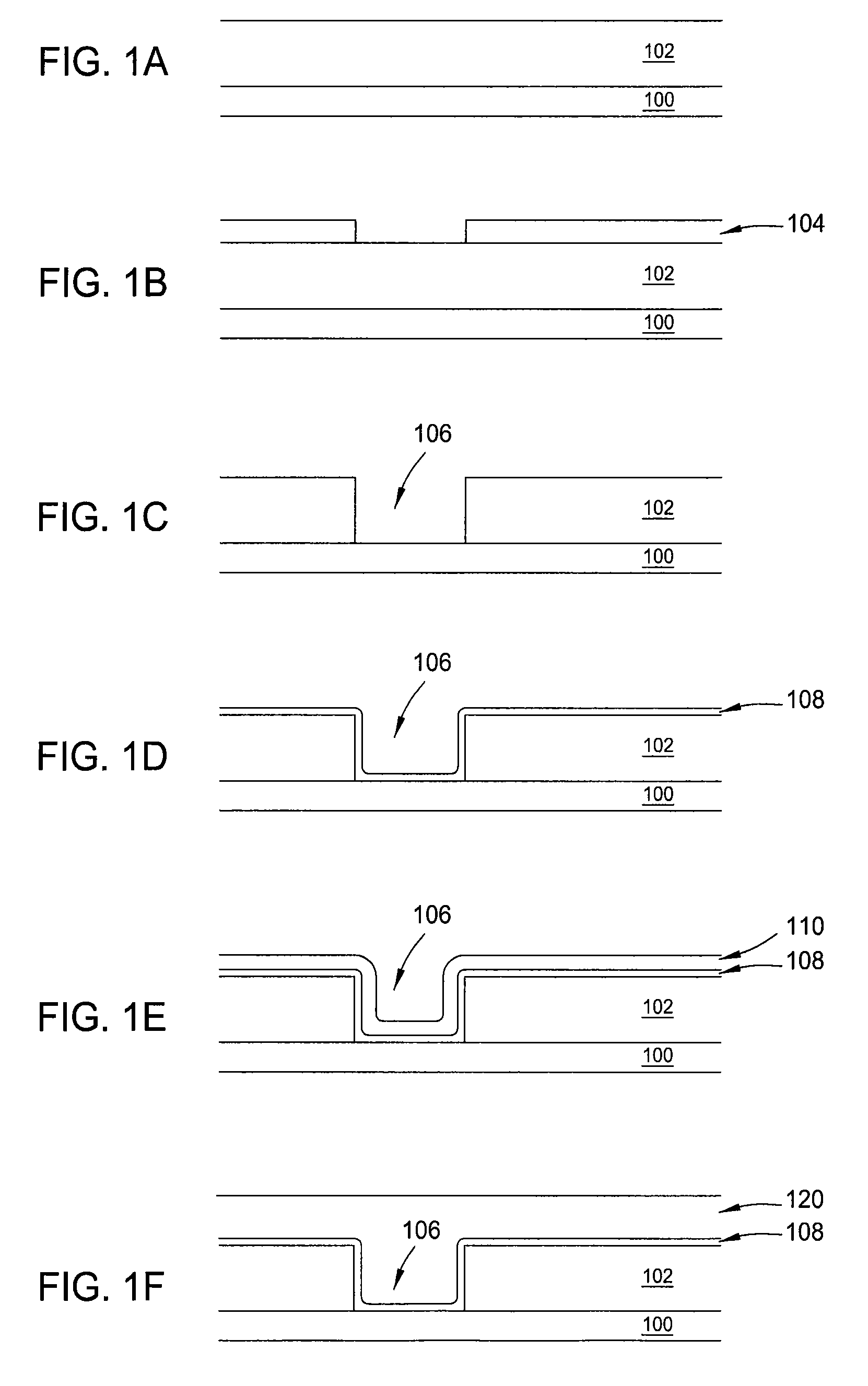

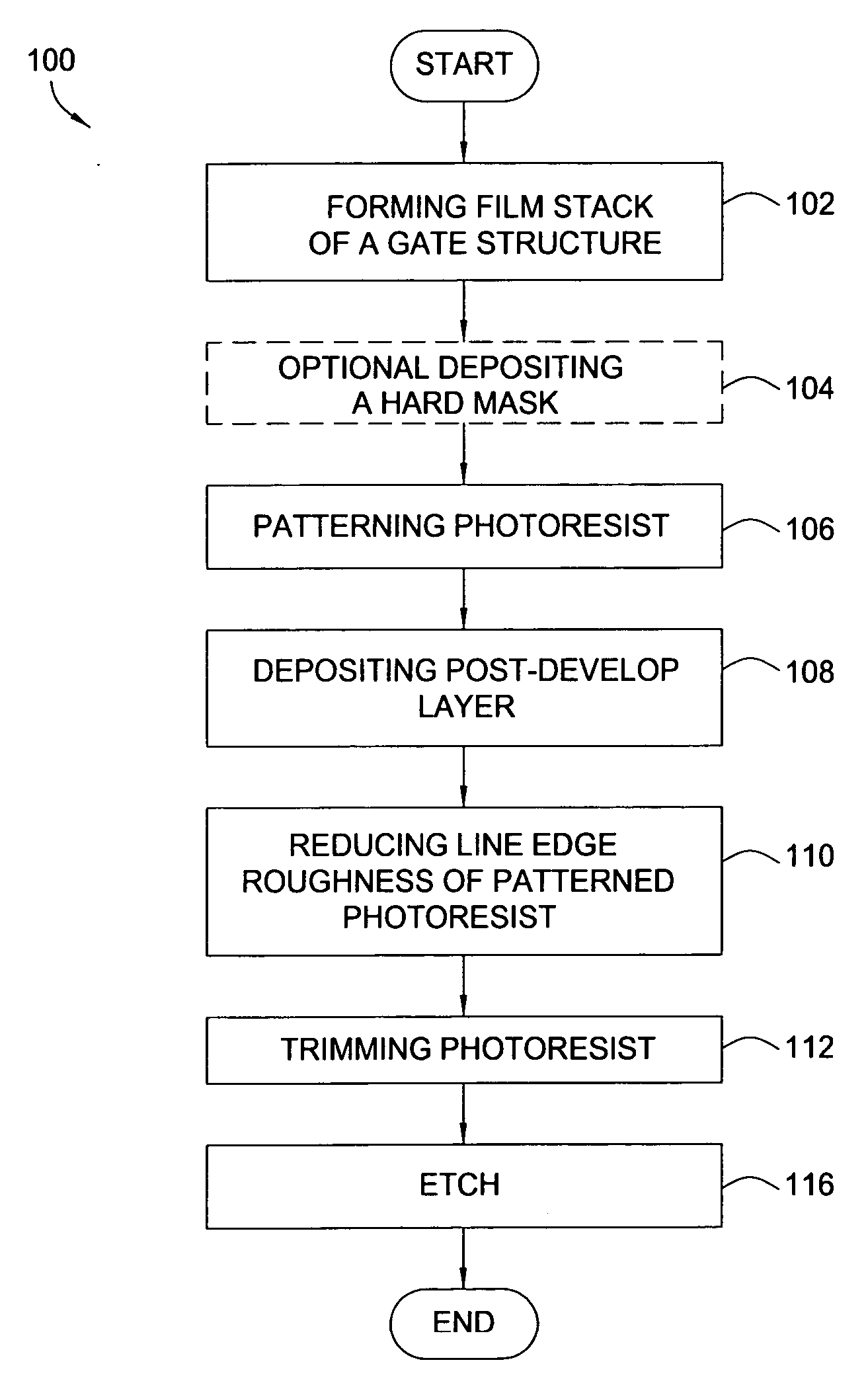

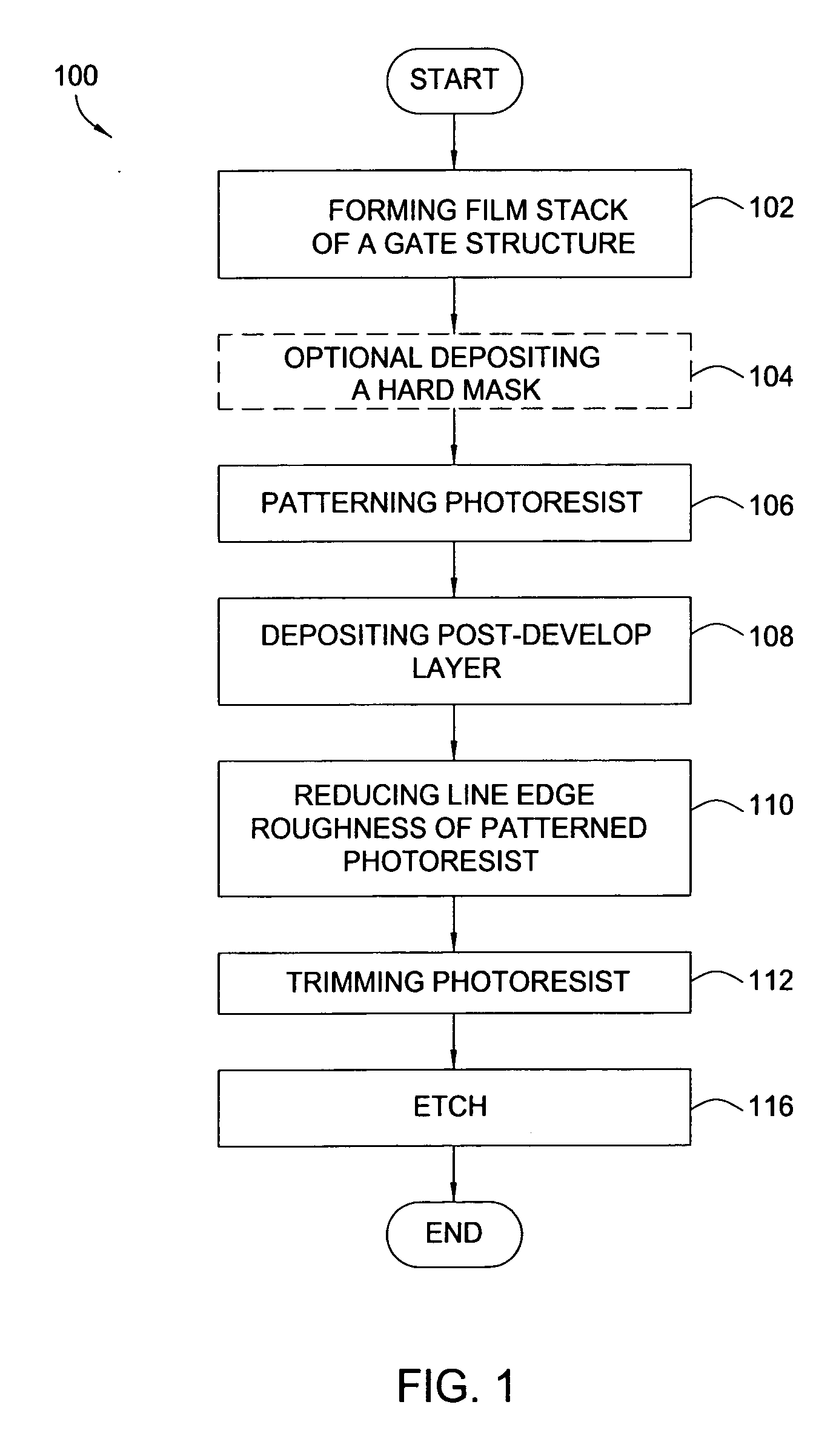

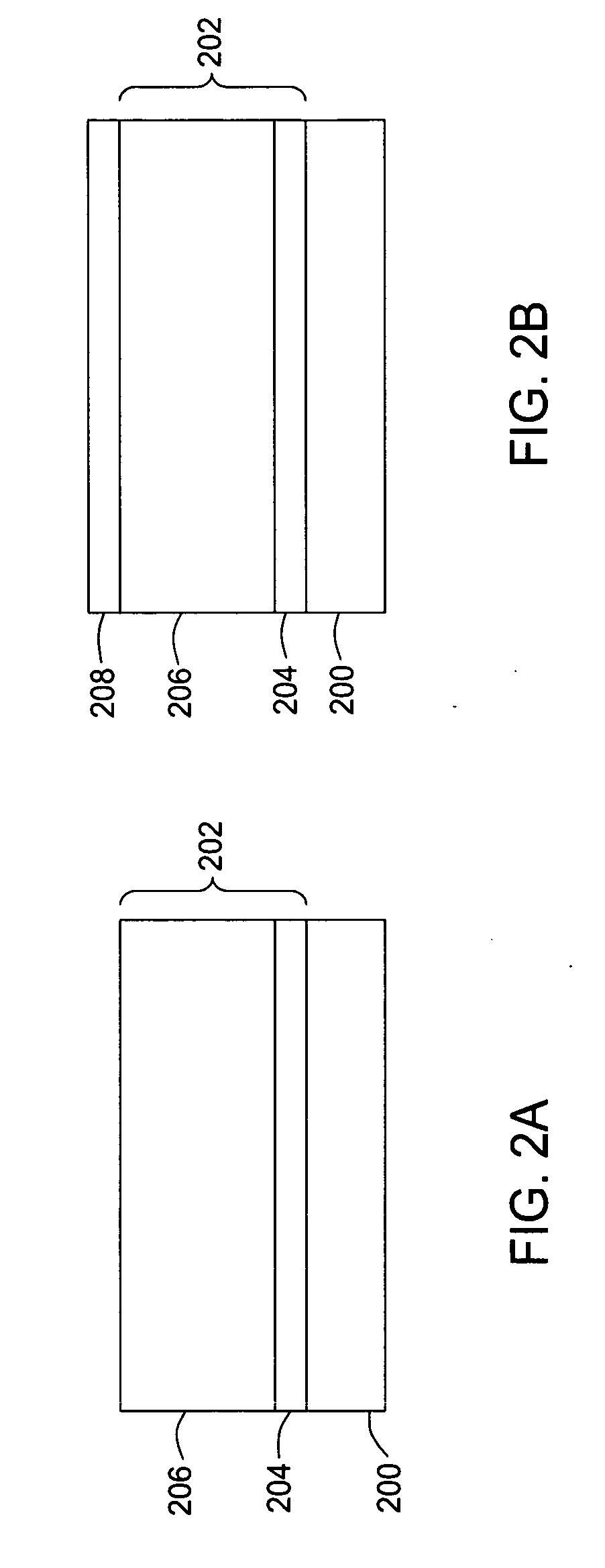

Line edge roughness reduction compatible with trimming

InactiveUS20060205223A1Semiconductor/solid-state device manufacturingPhotosensitive material processingEngineeringPhotoresist

A method and apparatus for reducing line edge roughness, comprising patterning a photoresist to define lines for etching an underlying layer, depositing a post development material between the lines, curing and removing the post development material to reduce line edge roughness, trimming the lines in the underlying layer, and then etching the underlying layer.

Owner:APPLIED MATERIALS INC

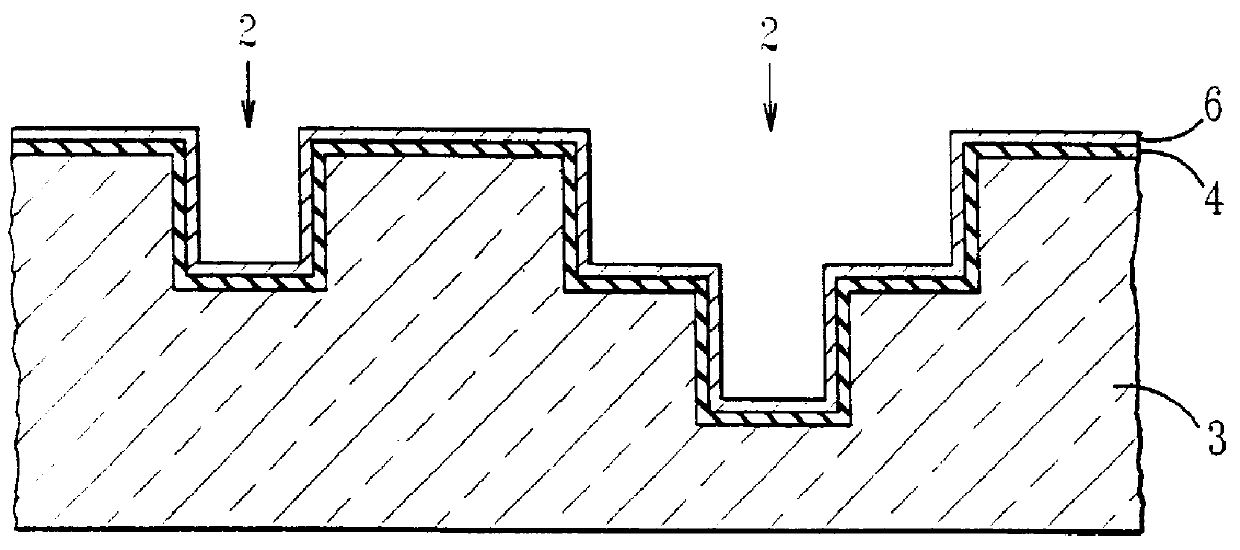

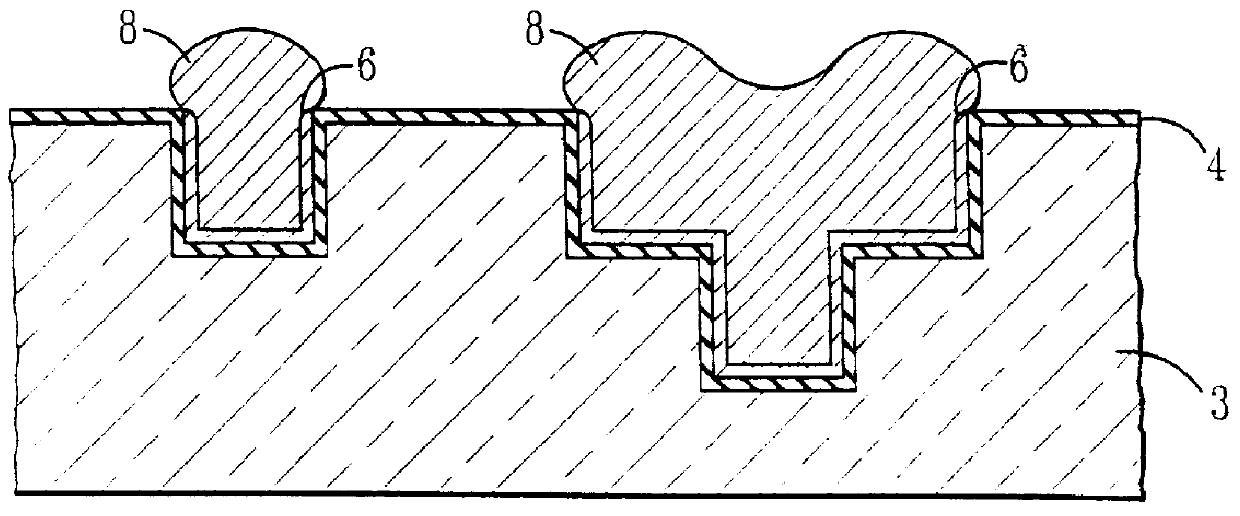

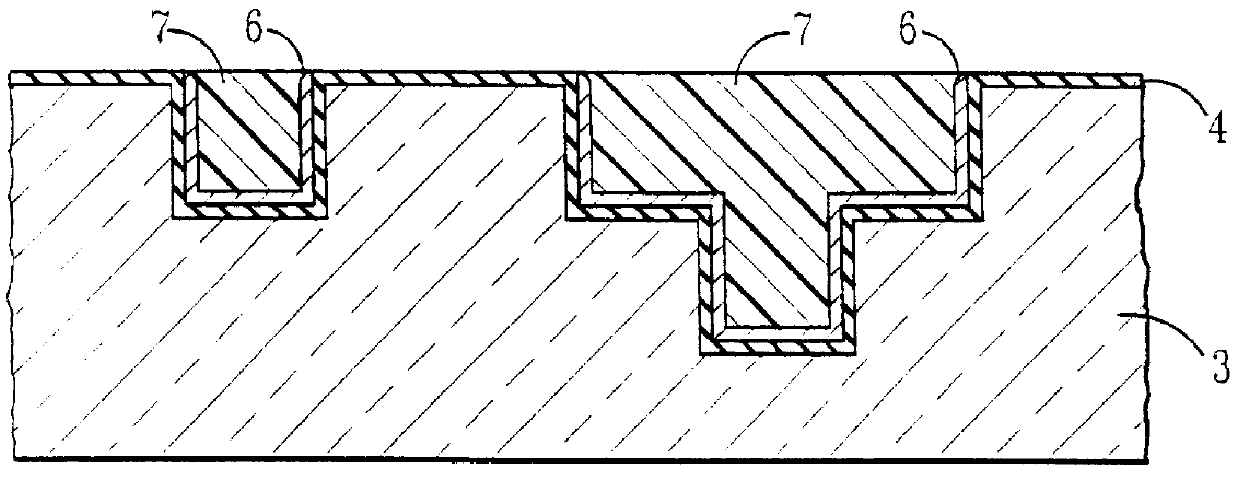

Method to selectively fill recesses with conductive metal

InactiveUS6140234AShorten the timeIncrease productionSolid-state devicesSemiconductor/solid-state device manufacturingResistSemiconductor structure

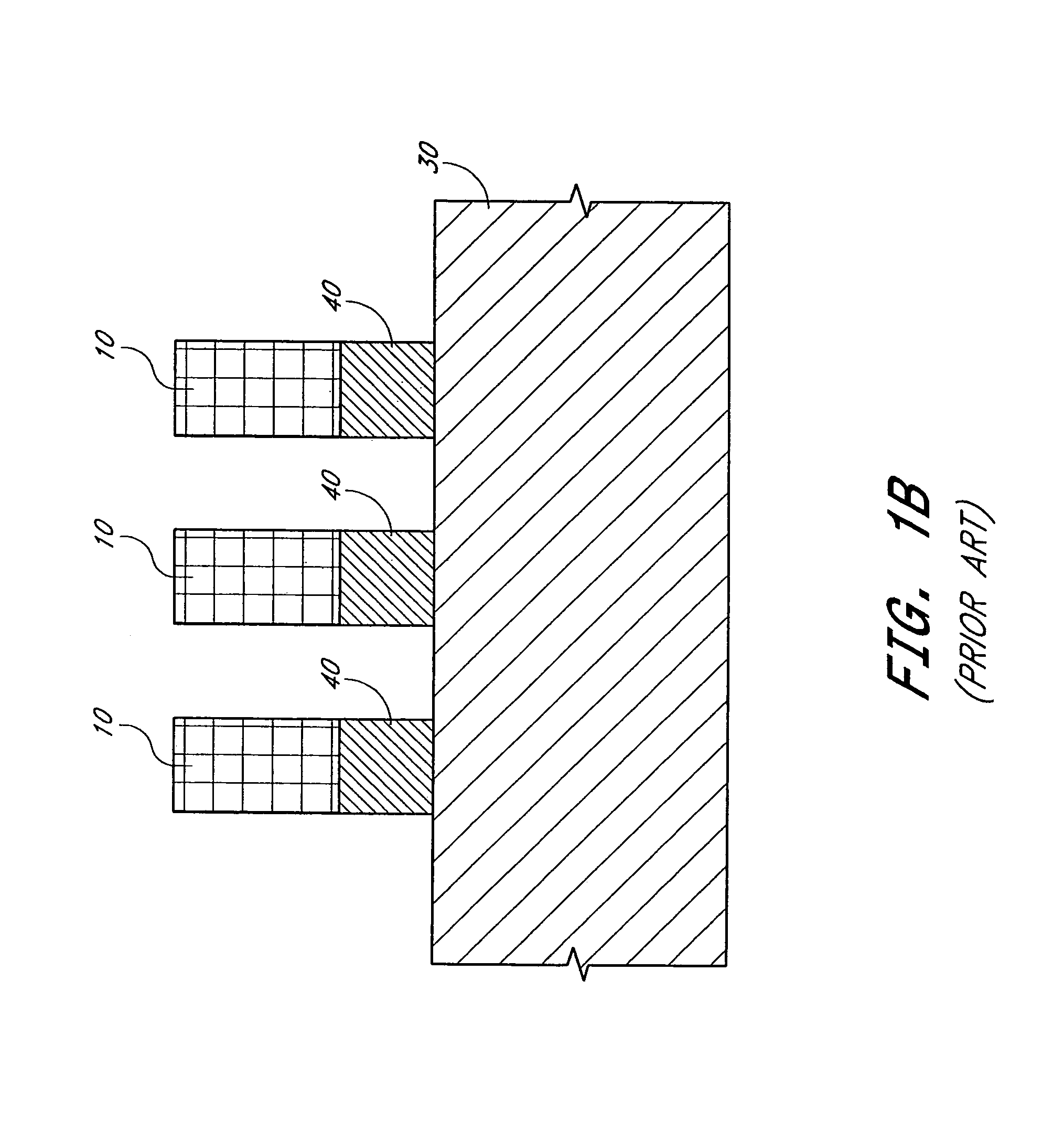

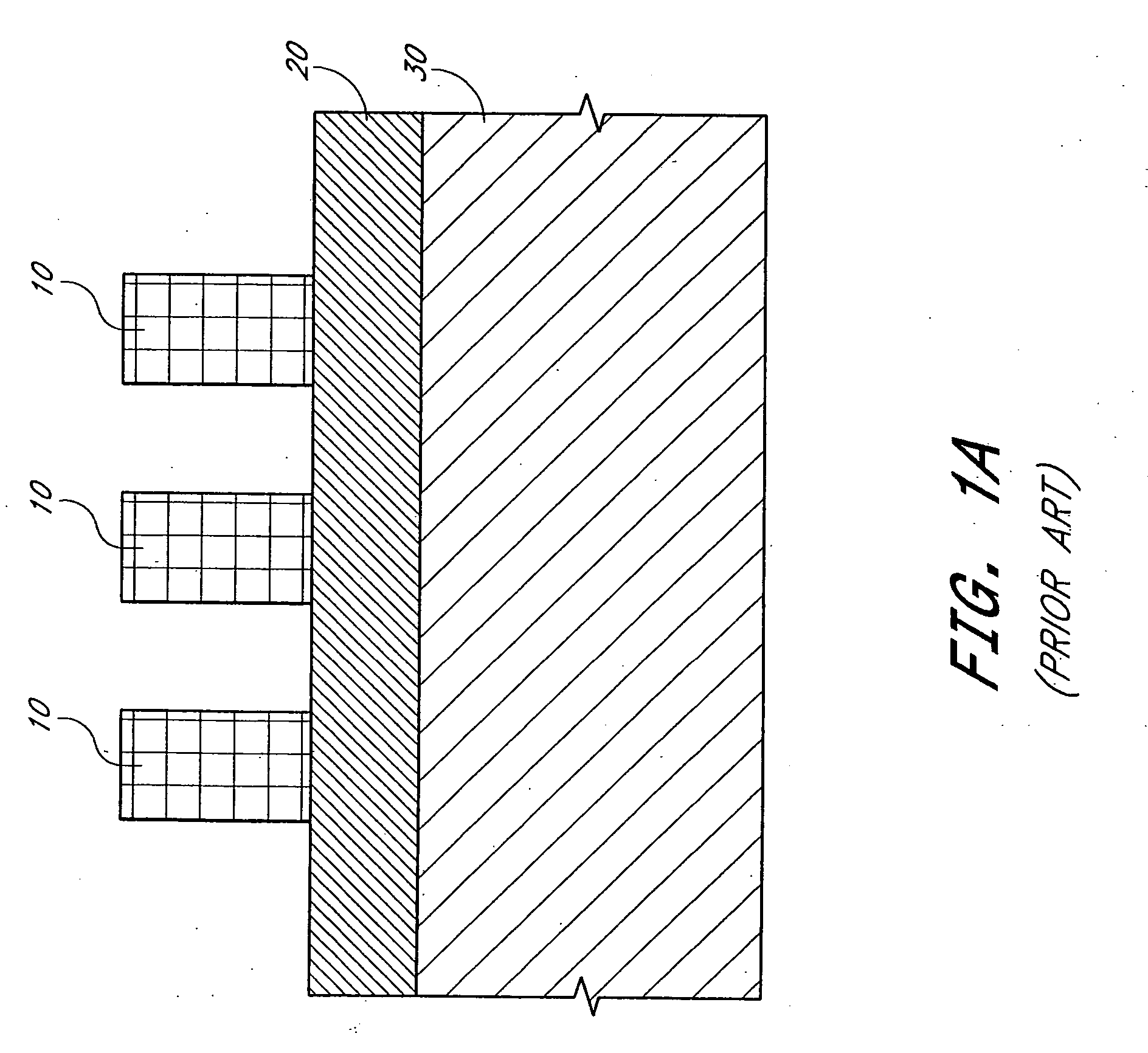

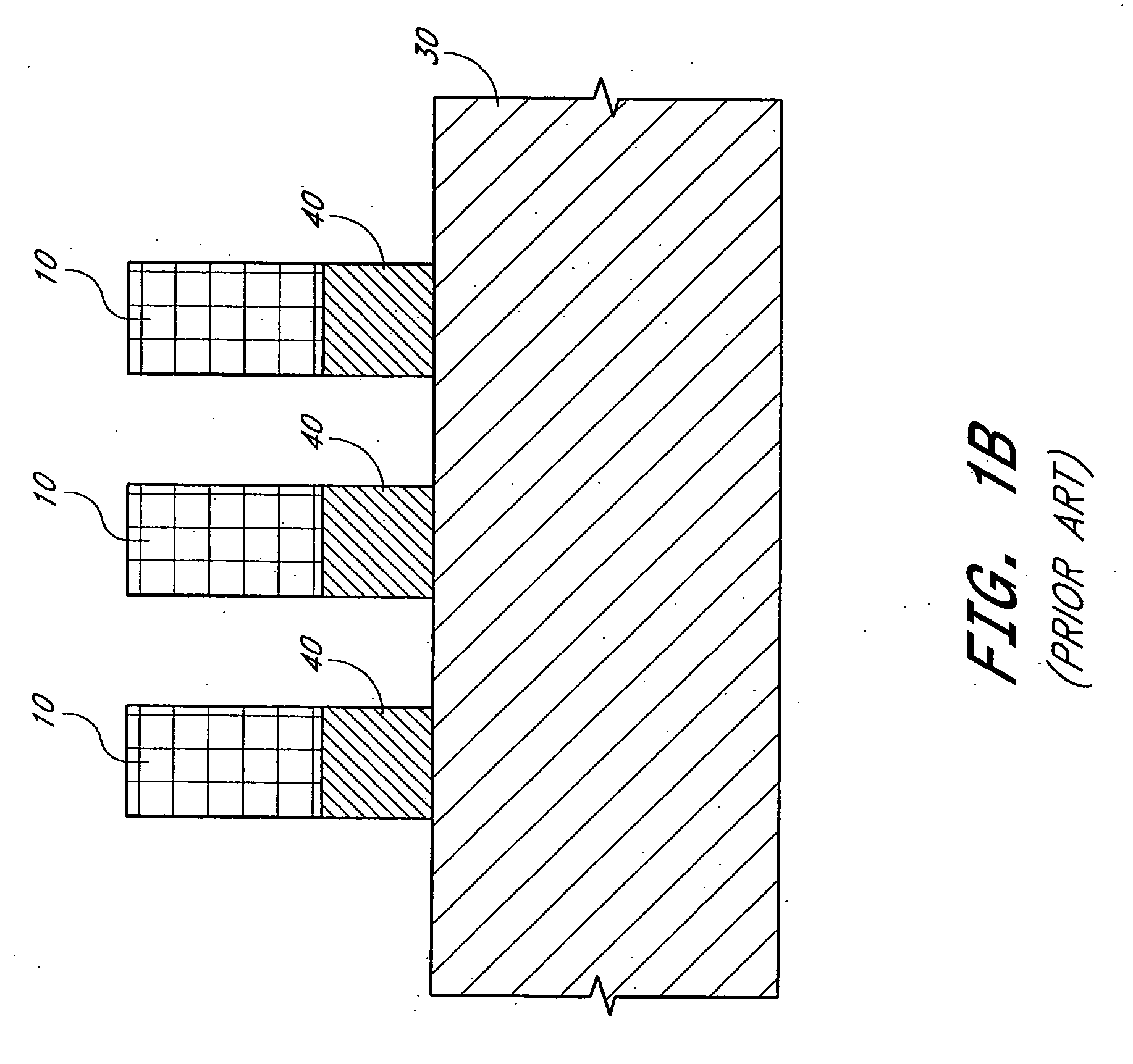

Recesses in a semiconductor structure are selectively plated by providing electrical insulating layer over the semiconductor substrate and in the recesses followed by forming a conductive barrier over the insulating layer; providing a plating seed layer over the barrier layer; depositing and patterning a photoresist layer over the plating seed layer; planarizing the insulated horizontal portions by removing the horizontal portions of the seed layer between the recesses; removing the photoresist remaining in the recesses; and then electroplating the patterned seed layer with a conductive metal using the barrier layer to carry the current during the electroplating to thereby only plate on the seed layer. In an alternative process, a barrier film is deposited over recesses in an insulator. Then, relatively thick resists are lithographically defined on the field regions, on top of the barrier film over the recesses. A plating base or seedlayer is deposited, so as to be continuous on the horizontal regions of the recesses in the insulator, but discontinuous on their surround wall. The recesses are then plated using the barrier film without seedlayers at the periphery of the substrate wafers for electrical contact. After electroplating, the resist is removed by lift-off process and exposed barrier film is etched by RIE method or by CMP. Also provided is a semiconductor structure obtained by the above processes.

Owner:GLOBALFOUNDRIES INC

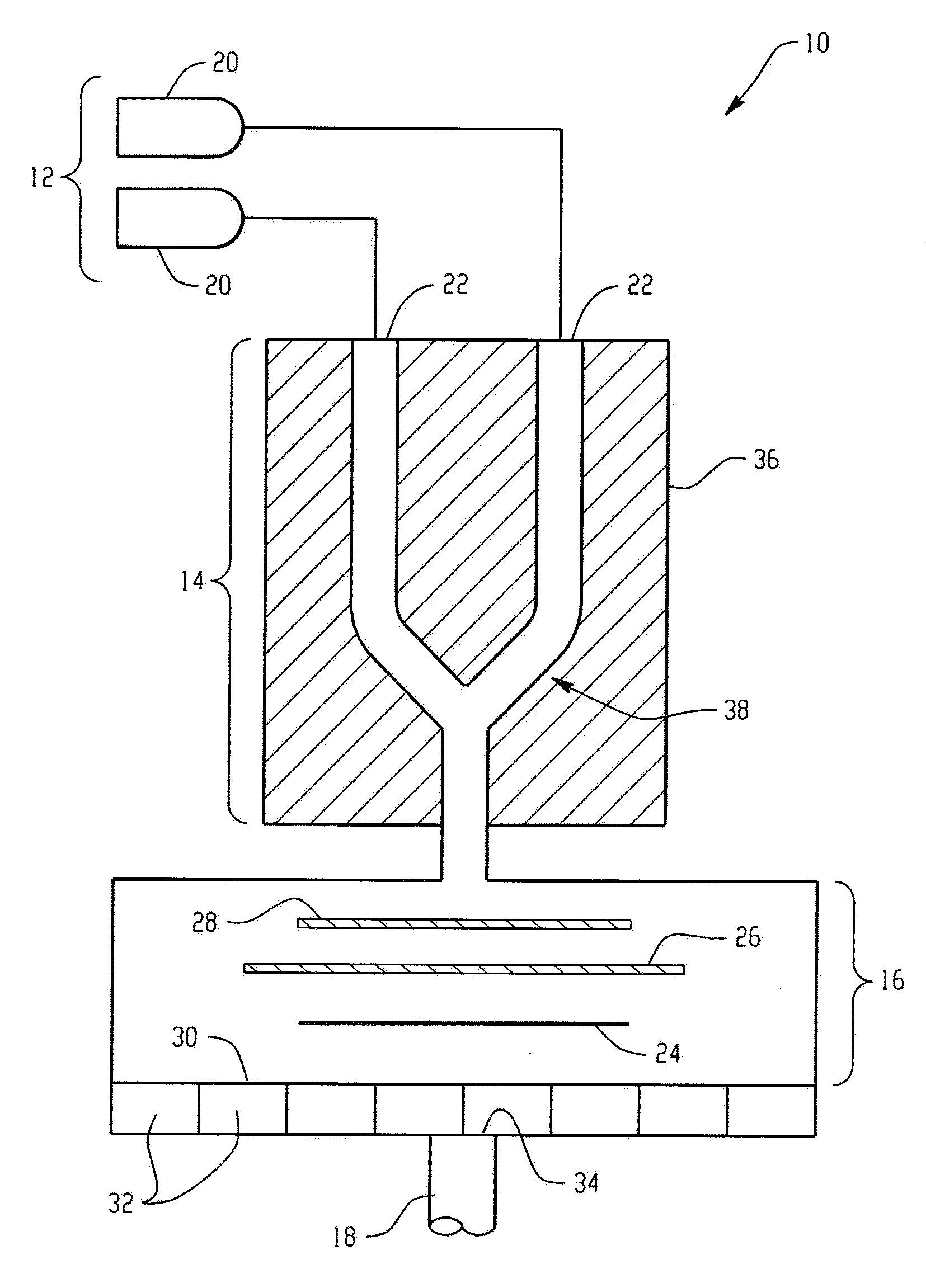

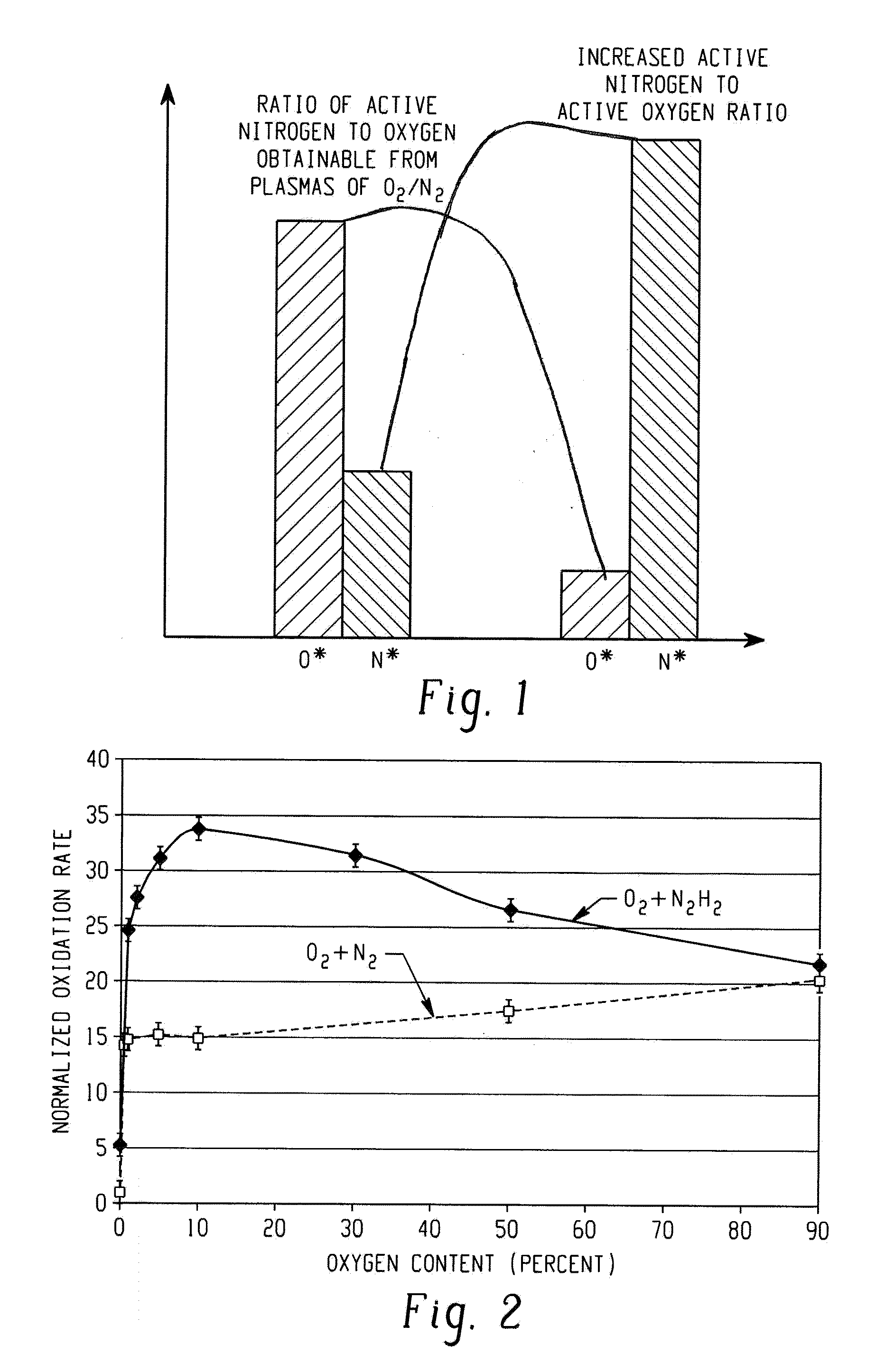

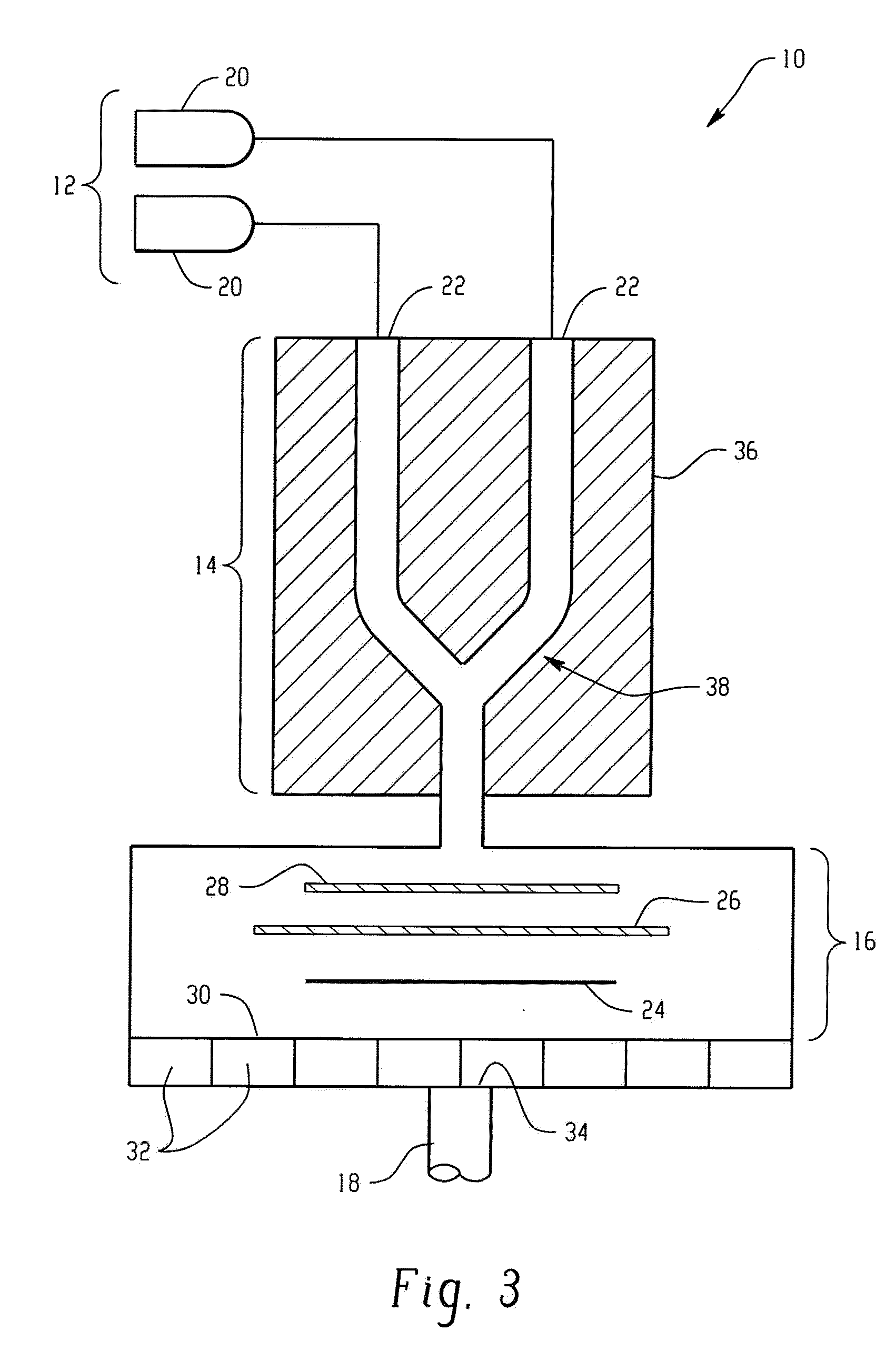

Front end of line plasma mediated ashing processes and apparatus

InactiveUS20100130017A1Increased formationElectric discharge tubesSemiconductor/solid-state device manufacturingResistFront end of line

Front end of line (FEOL) plasma mediated ashing processes for removing organic material from a substrate generally includes exposing the substrate to the plasma to selectively remove photoresist, implanted photoresist, polymers and / or residues from the substrate, wherein the plasma contains a ratio of active nitrogen and active oxygen that is larger than a ratio of active nitrogen and active oxygen obtainable from plasmas of gas mixtures comprising oxygen gas and nitrogen gas. The plasma exhibits high throughput while minimizing and / or preventing substrate oxidation and dopant bleaching. Plasma apparatuses are also described.

Owner:LAM RES CORP

Method of trimming technology

ActiveUS7354847B2Easy to controlAvoid insufficient thicknessSolid-state devicesSemiconductor/solid-state device manufacturingResistMOSFET

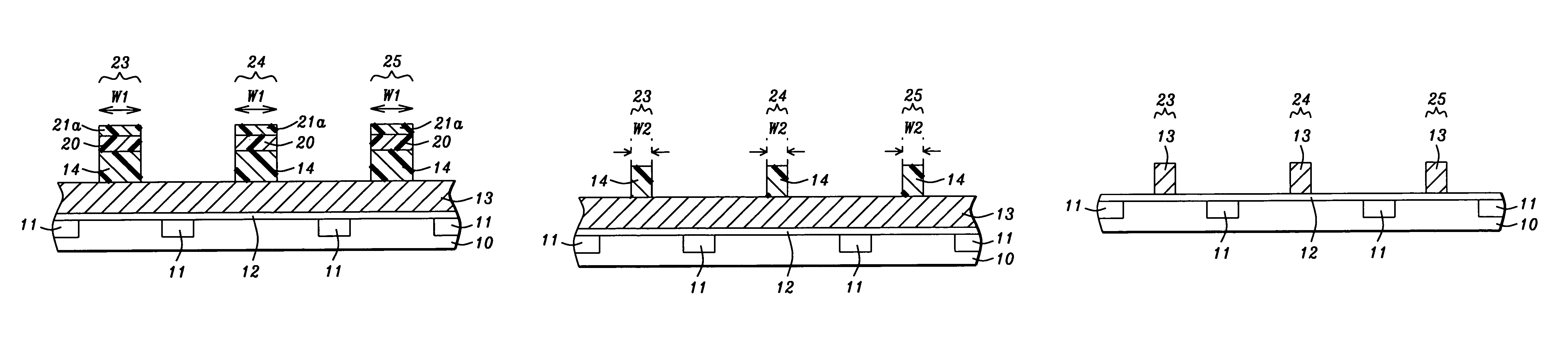

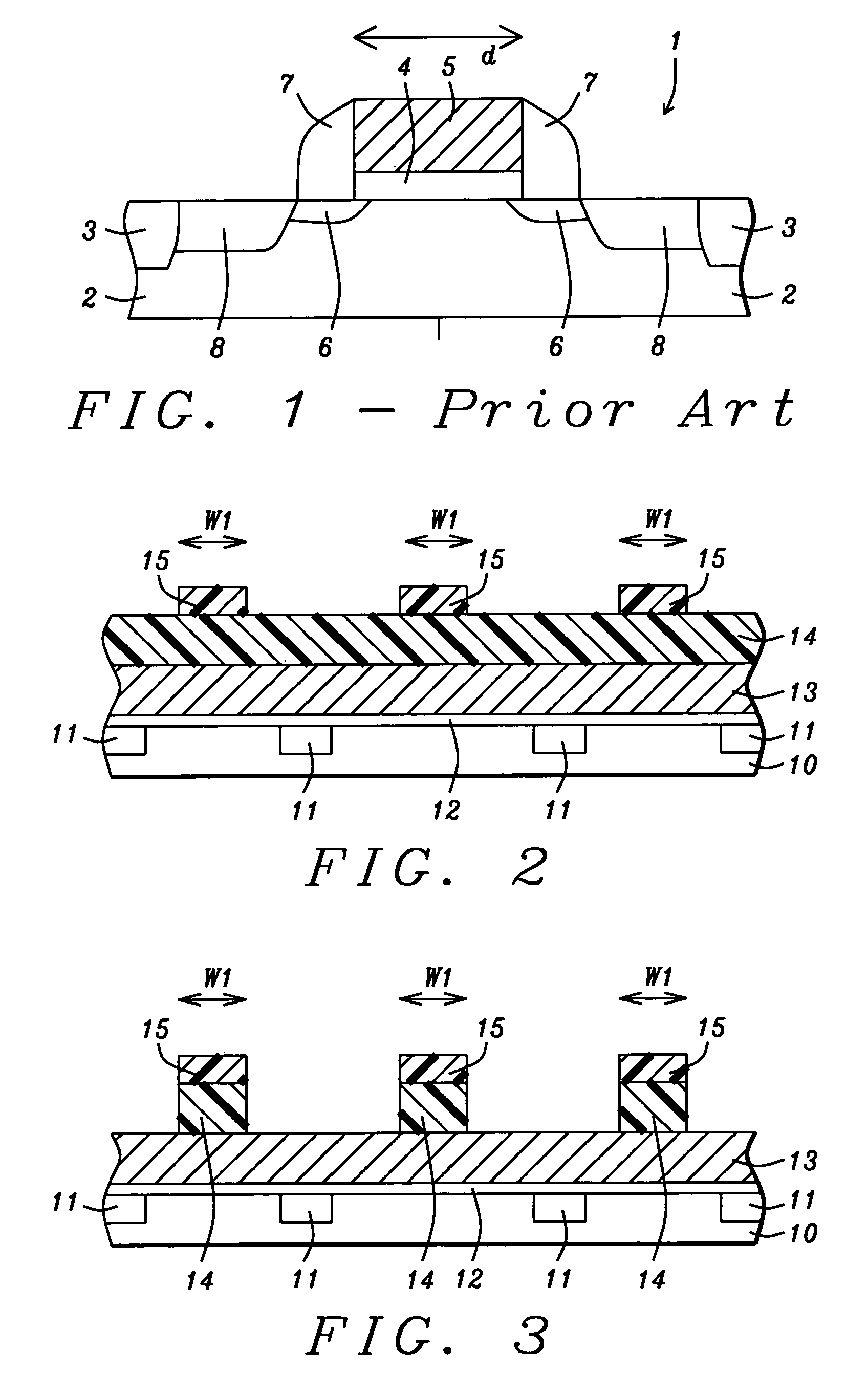

A process for trimming a photoresist layer during the fabrication of a gate electrode in a MOSFET is described. A bilayer stack with a top photoresist layer on a thicker organic underlayer is patternwise exposed with 193 nm or 157 nm radiation to form a feature having a width w1 in the top layer. A pattern transfer through the underlayer is performed with an anisotropic etch based on H2 / N2 and SO2 chemistry. The feature formed in the bilayer stack is trimmed by 10 nm or more to a width w2 by a HBr / O2 / Cl2 plasma etch. The pattern transfer through an underlying gate layer is performed with a third etch based on HBr / O2 / Cl2 chemistry. The underlayer is stripped by an O2 ashing with no damage to the gate electrode. Excellent profile control of the gate electrode is achieved and a larger (w1−w2) is possible than in prior art methods.

Owner:TAIWAN SEMICON MFG CO LTD

Use of amorphous carbon film as a hardmask in the fabrication of optical waveguides

Methods are provided for forming optical devices, such as waveguides, with minimal defect formation. In one aspect, the invention provides a method for forming a waveguide structure on a substrate surface including forming a cladding layer on the substrate surface, forming a core layer on the cladding layer, depositing an amorphous carbon hardmask on the core layer, forming a patterned photoresist layer on the amorphous carbon hardmask, etching the amorphous carbon hardmask, and etching the core material.

Owner:APPLIED MATERIALS INC

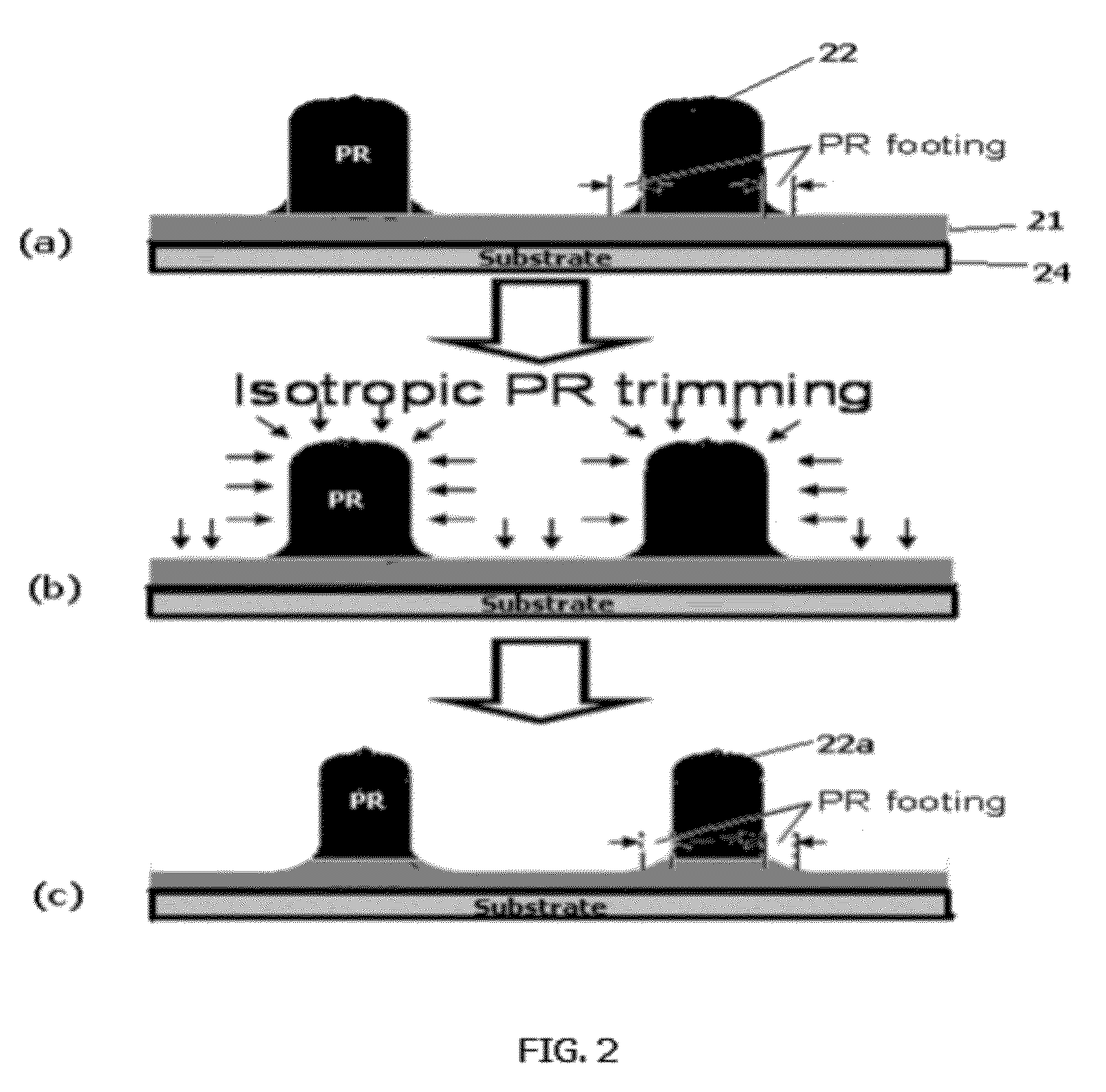

Footing reduction using etch-selective layer

ActiveUS8298951B1Reduce etch rateReducing a widened footing of the photoresistDecorative surface effectsSemiconductor/solid-state device manufacturingEngineeringOxygen

A method of forming side spacers upwardly extending from a substrate, includes: providing a template constituted by a photoresist formed on and in contact with an etch-selective layer laminated on a substrate; anisotropically etching the template in a thickness direction with an oxygen-containing plasma to remove a footing of the photoresist and an exposed portion of the underlying layer; depositing a spacer film on the template by atomic layer deposition (ALD); and forming side spacers using the spacer film by etching. The etch-selective layer has a substantially lower etch rate than that of the photoresist.

Owner:ASM JAPAN

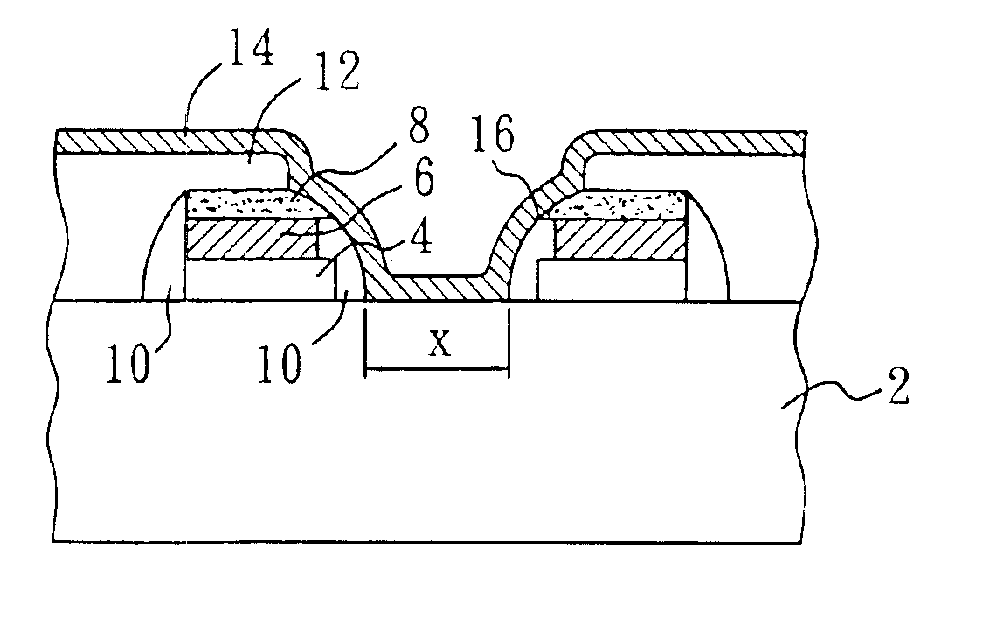

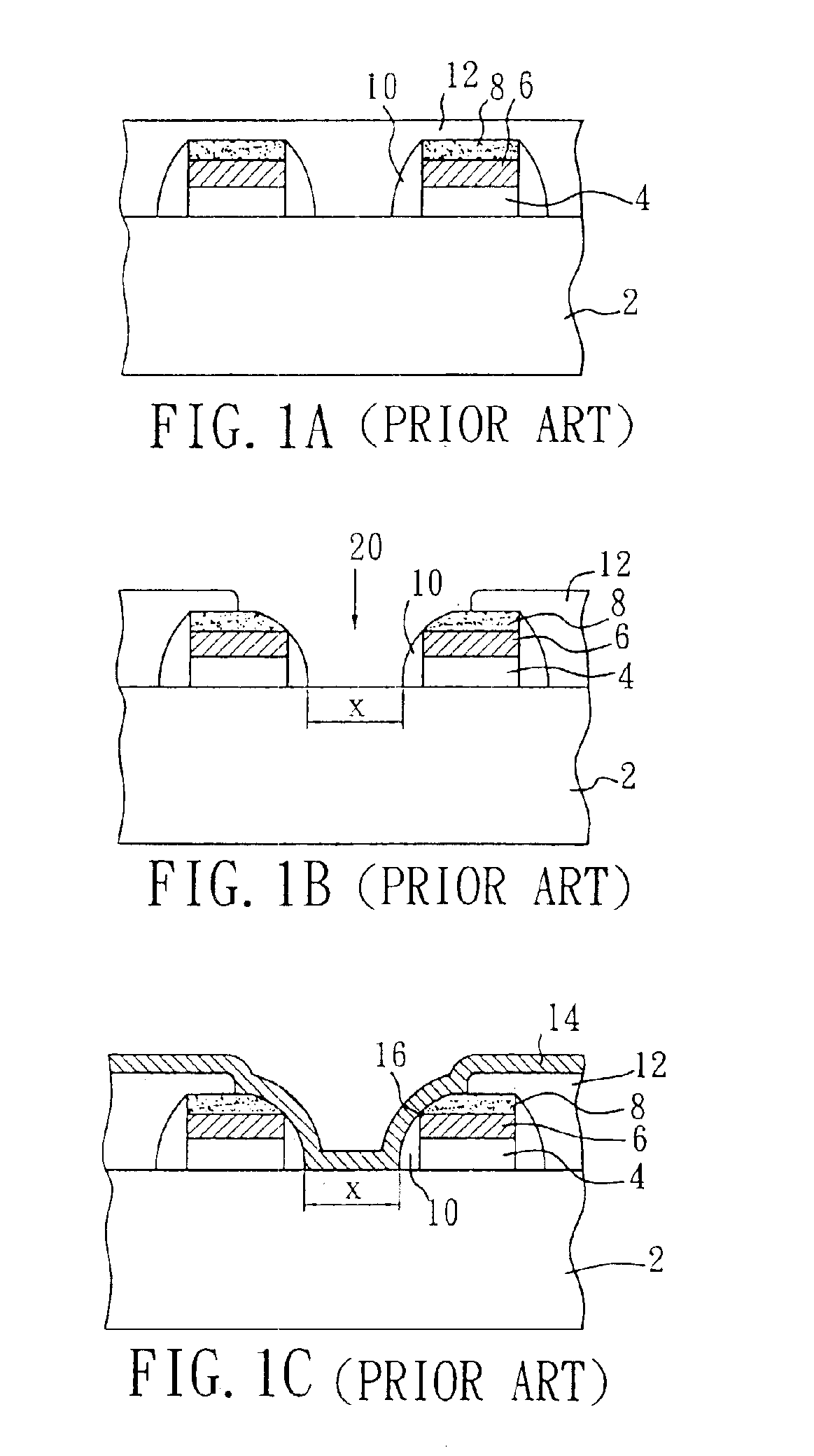

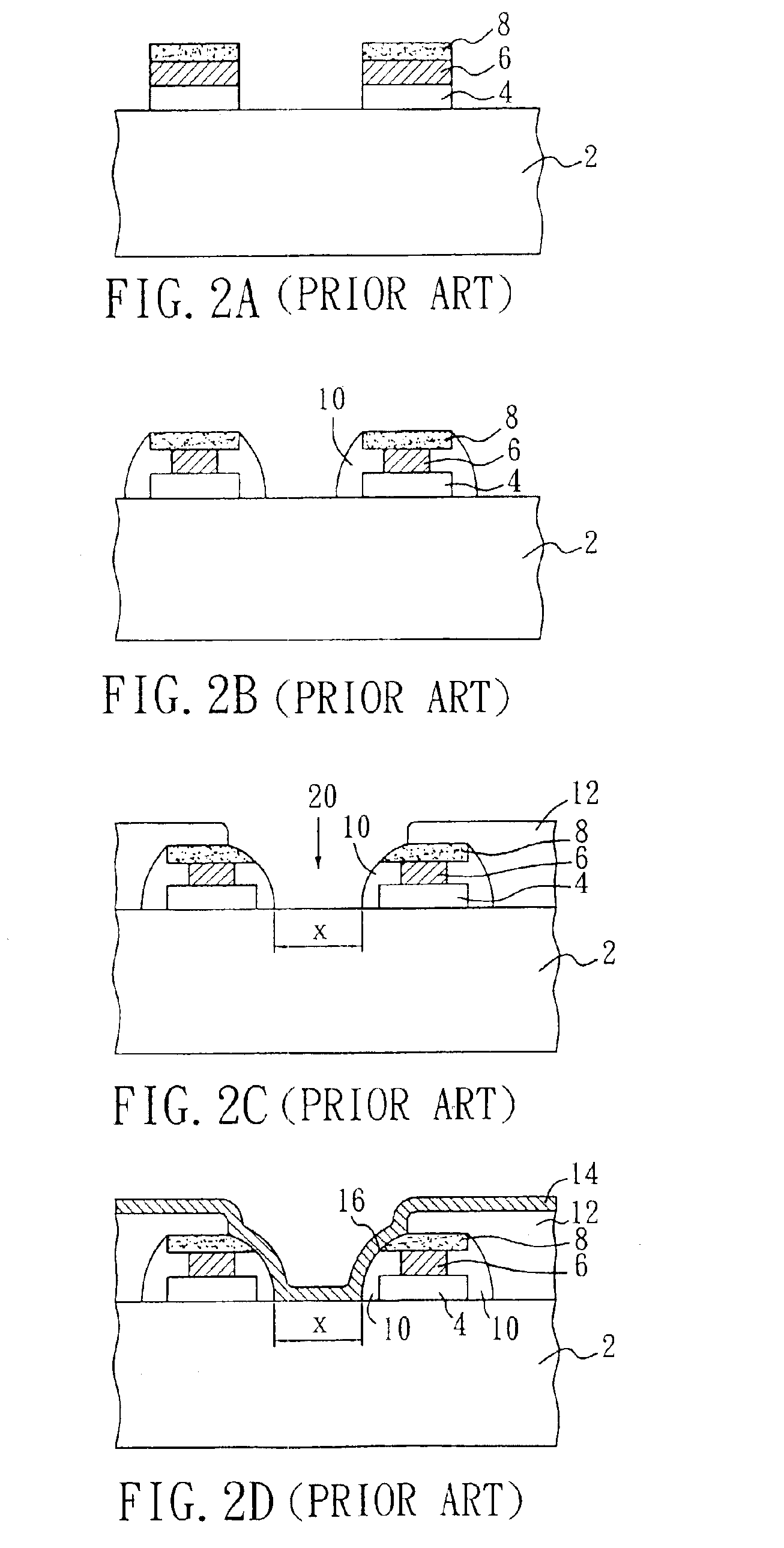

Method of forming self-aligned contact structure with locally etched gate conductive layer

InactiveUS6855610B2Reduce resistanceLarge processing windowSemiconductor/solid-state device detailsSolid-state devicesBit lineDielectric layer

A method of forming a self-aligned contact structure with a locally etched conductive layer comprises the steps of: preparing a substrate formed with gate structures comprising a first conductive layer, a second conductive layer, and an insulating layer; depositing a photoresist material layer on the substrate; performing a lithographic step with a bit-line contact node photomask or a bit-line contact photomask to expose a portion of the surface of the substrate; etching the exposed second conductive layer with an etchant; removing the remaining photoresist material layer; forming a sidewall spacer on the sidewalls of each gate structure; forming a dielectric layer to cover the substrate; and performing lithographic and etching steps to remove the dielectric layer and to form self-aligned contact structure.

Owner:PROMOS TECH INC

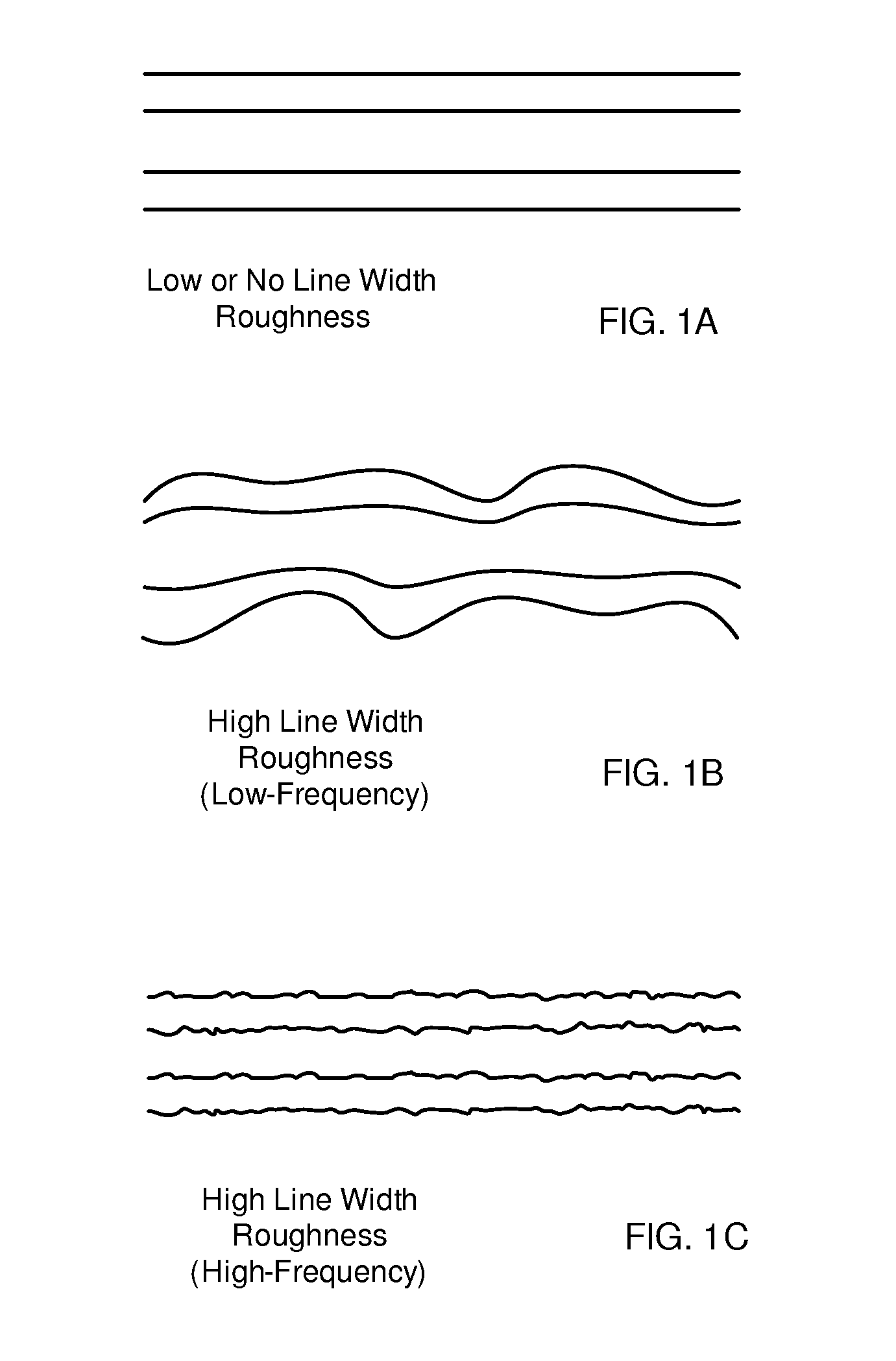

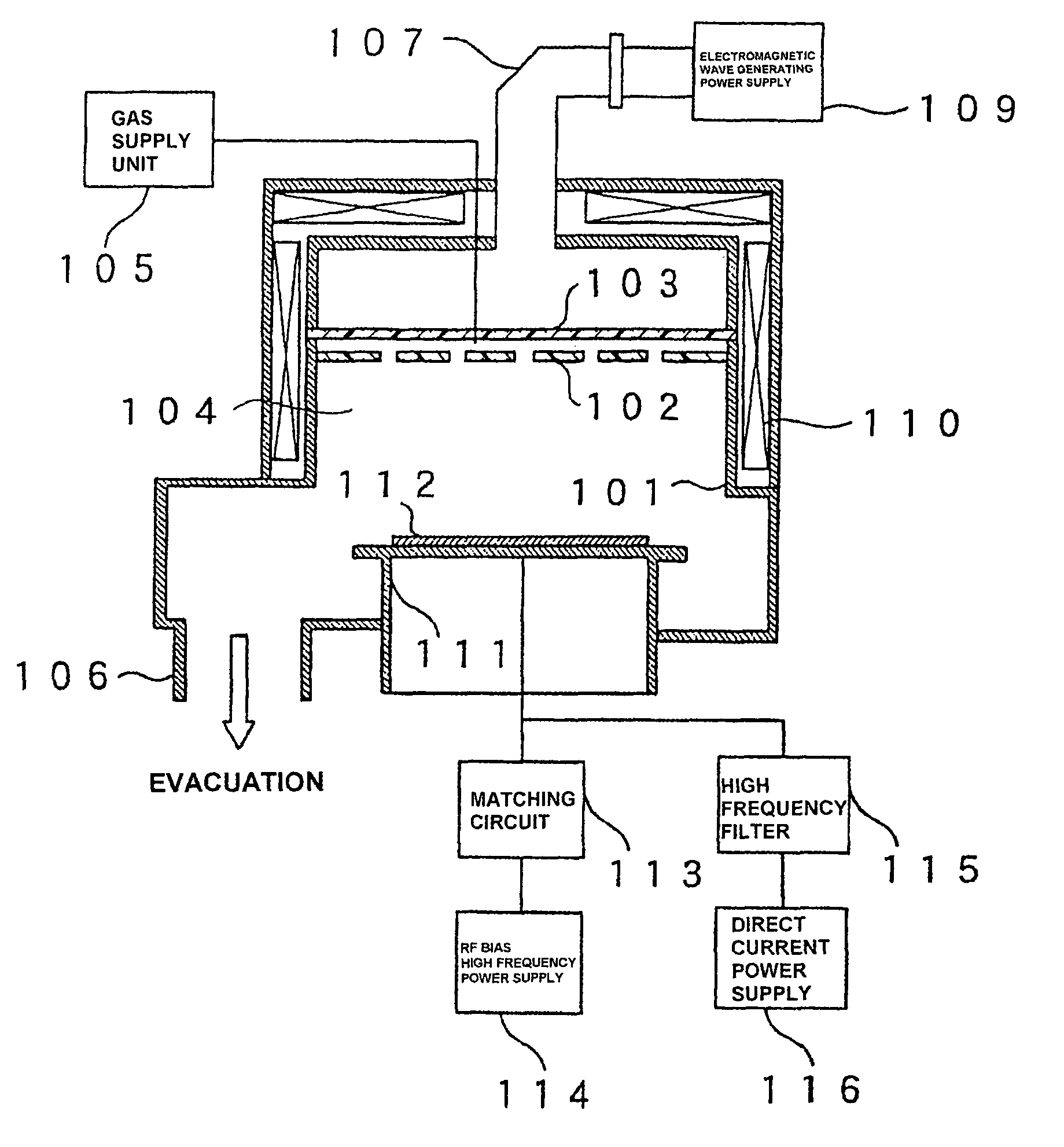

Methods and apparatus for controlling photoresist line width roughness

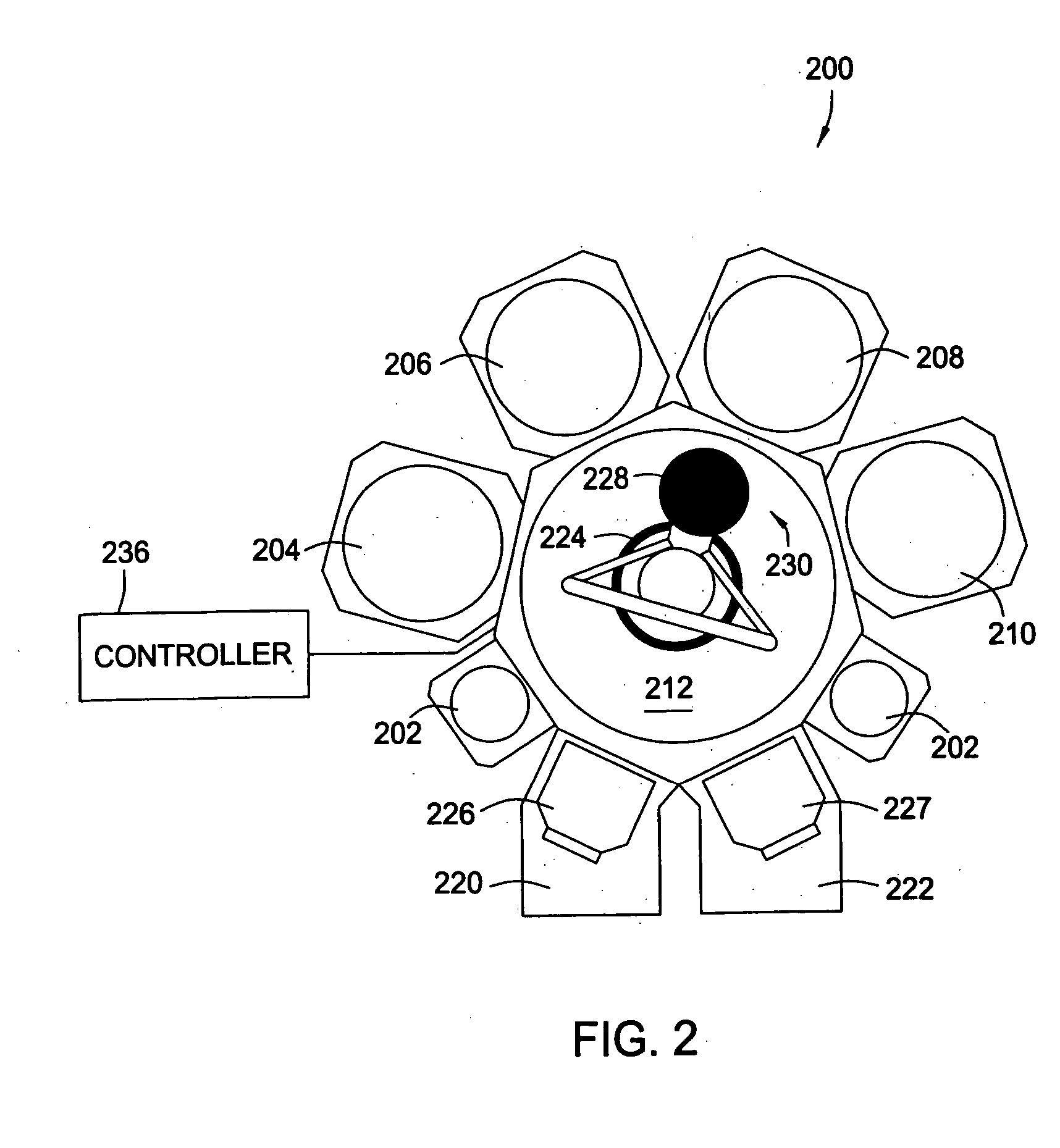

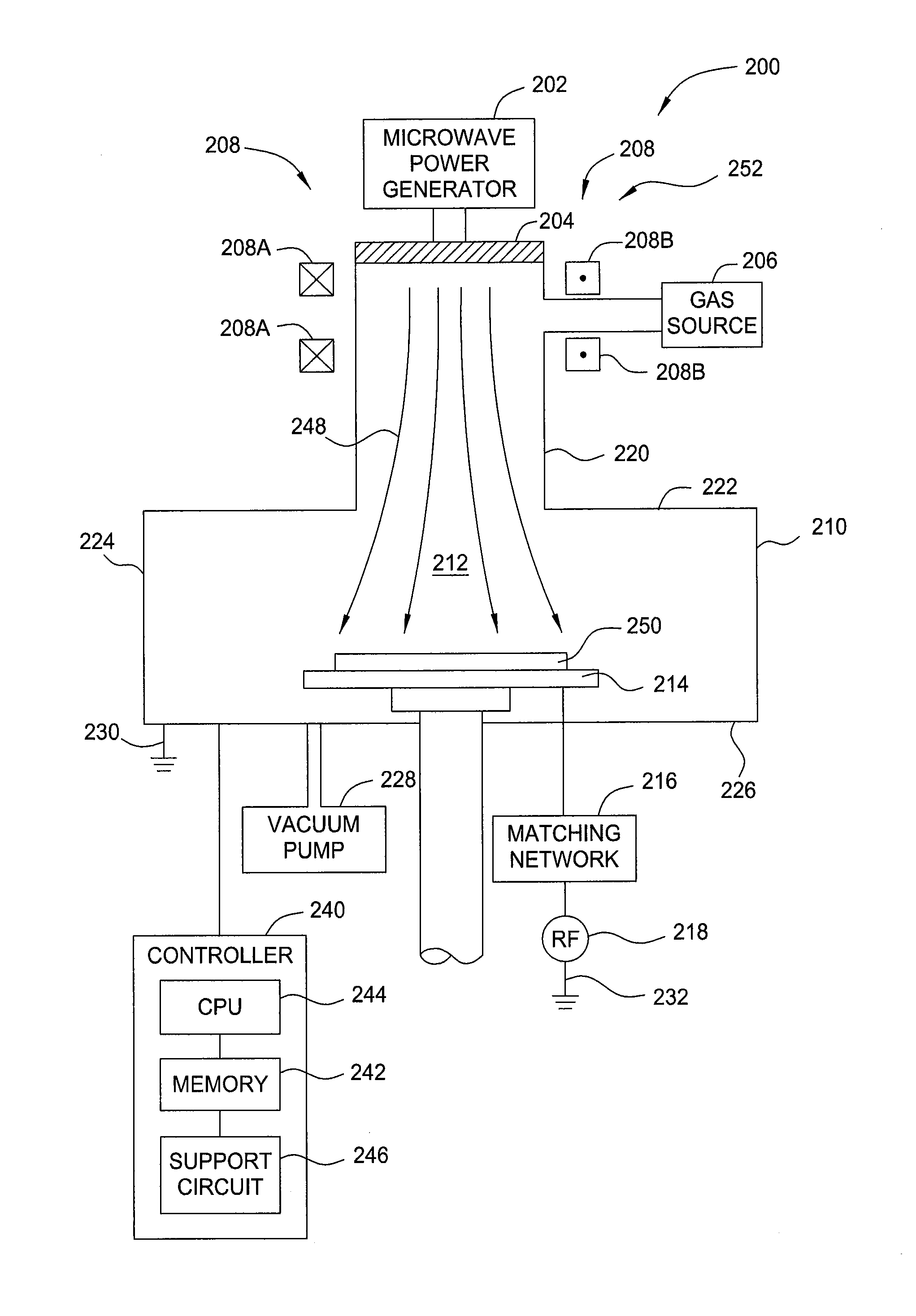

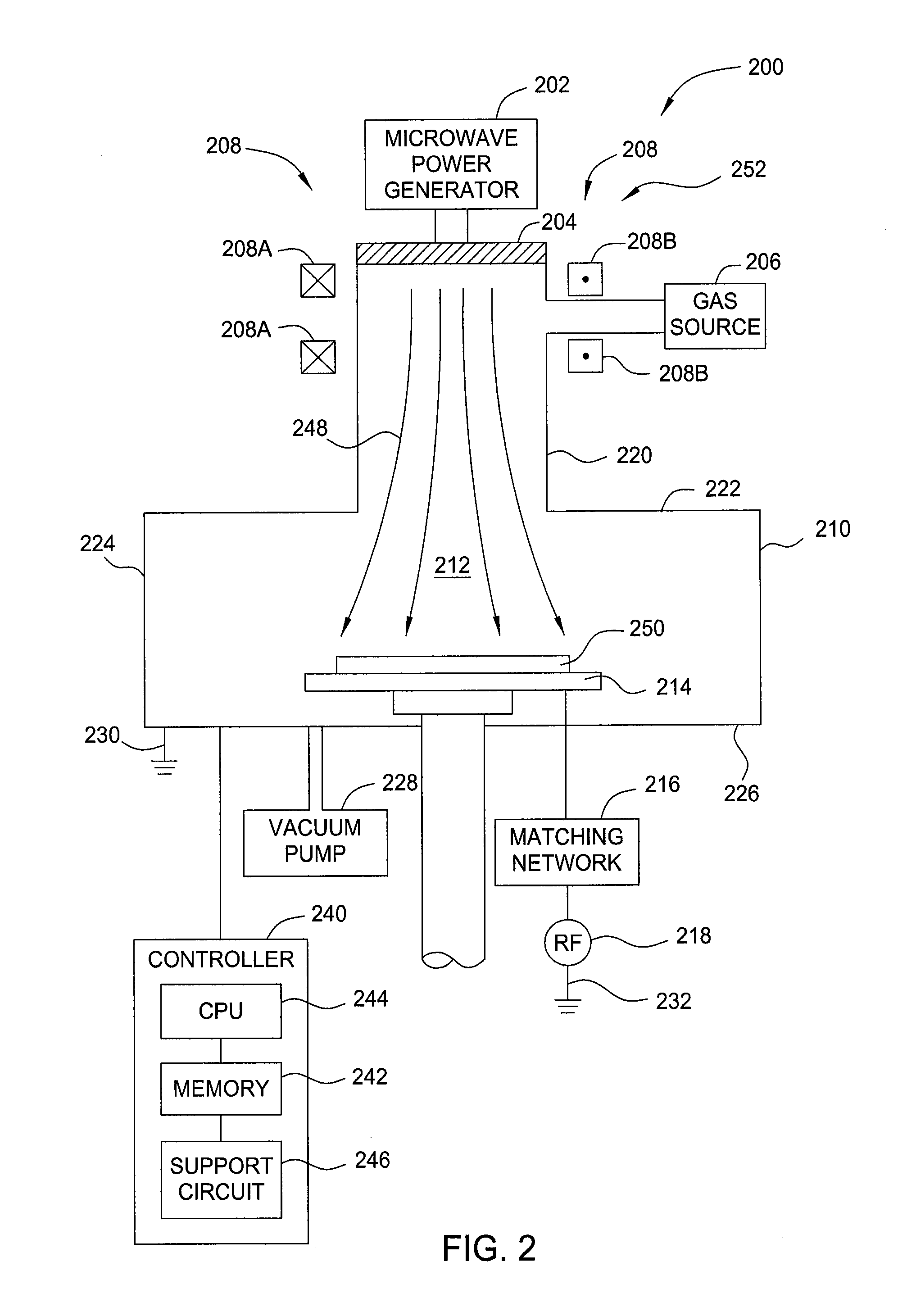

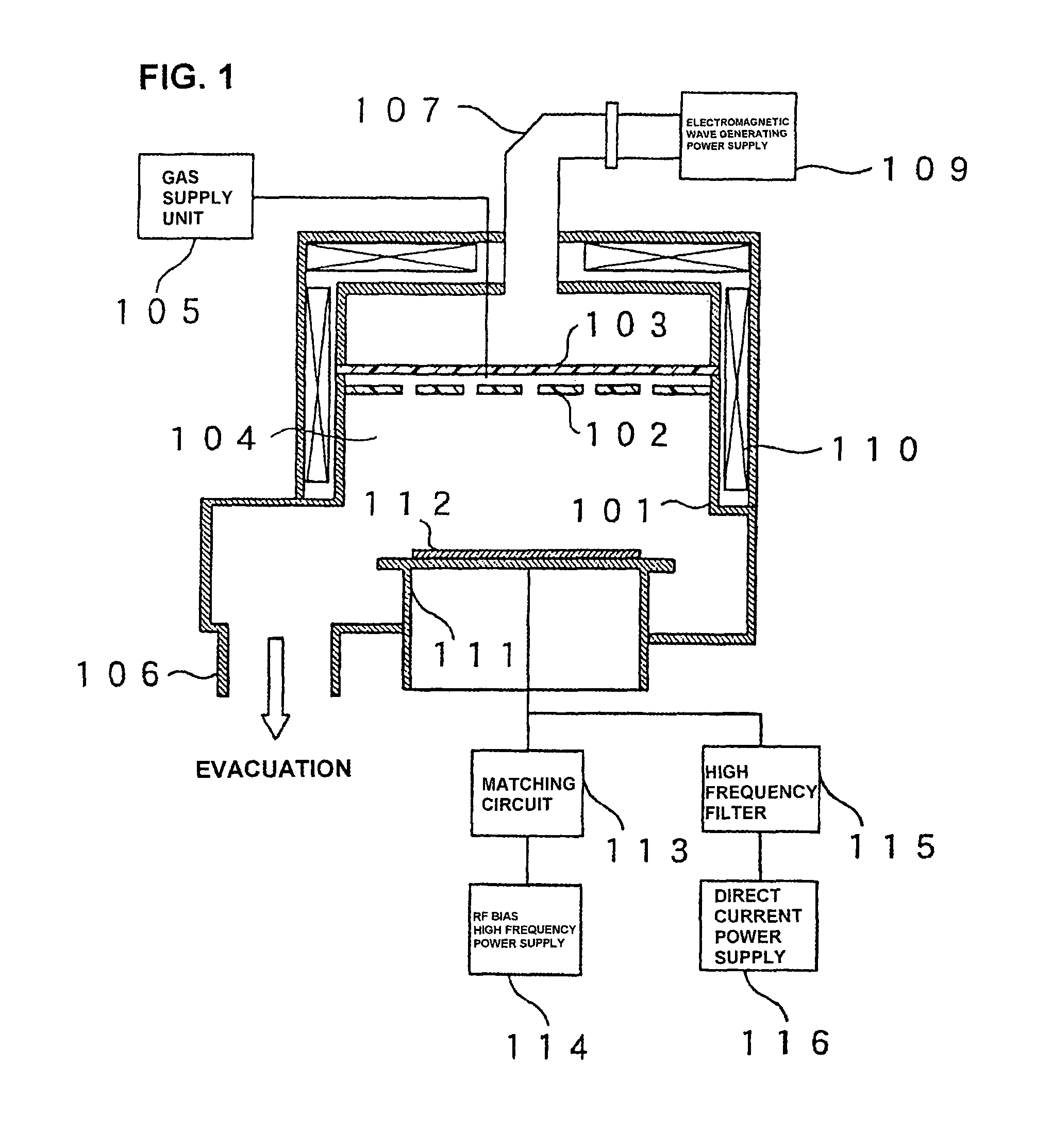

The present invention provides methods and an apparatus for controlling and modifying line width roughness (LWR) of a photoresist layer. In one embodiment, an apparatus for controlling a line width roughness of a photoresist layer disposed on a substrate includes a chamber body having a top wall, side wall and a bottom wall defining an interior processing region, a microwave power generator coupled to the to the chamber body through a waveguild, and one or more coils or magnets disposed around an outer circumference of the chamber body adjacent to the waveguide, and a gas source coupled to the waveguide through a gas delivery passageway.

Owner:APPLIED MATERIALS INC

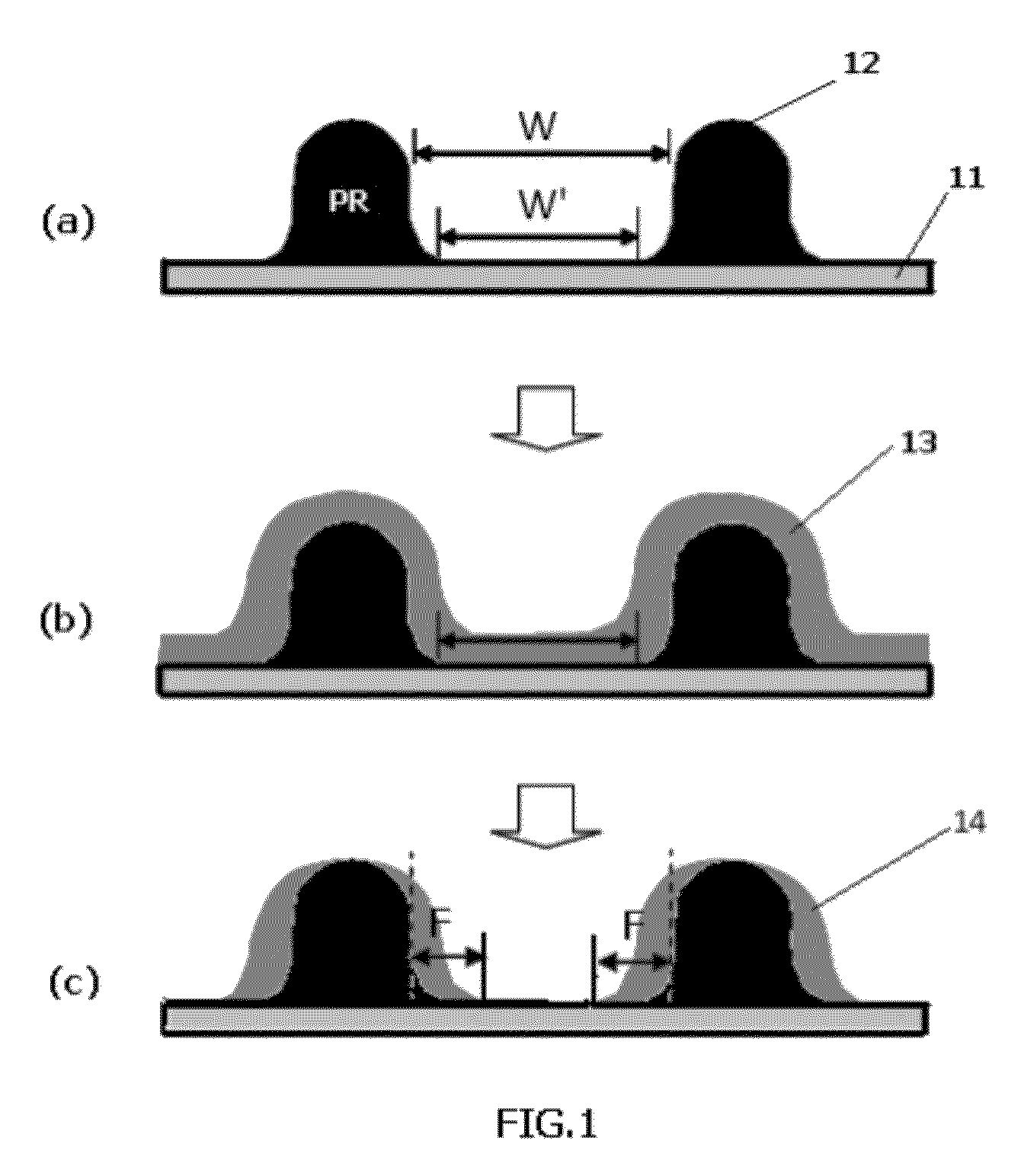

Method for reducing line width roughness with plasma pre-etch treatment on photoresist

InactiveUS20110117749A1Reduce line width roughnessElectric discharge tubesDecorative surface effectsEtchingLine width

A method for reducing line width roughness (LWR) of a feature in an etch layer below a patterned photoresist mask having mask features is provided. The method includes (a) non-etching plasma pre-etch treatment of the photoresist mask, and (b) etching of a feature in the etch layer through the pre-treated photoresist mask using an etching gas. The non-etching plasma pre-etch treatment includes (a1) providing a treatment gas containing H2 and COS, (a2) forming a plasma from the treatment gas, and (a3) stopping the treatment gas.

Owner:LAM RES CORP

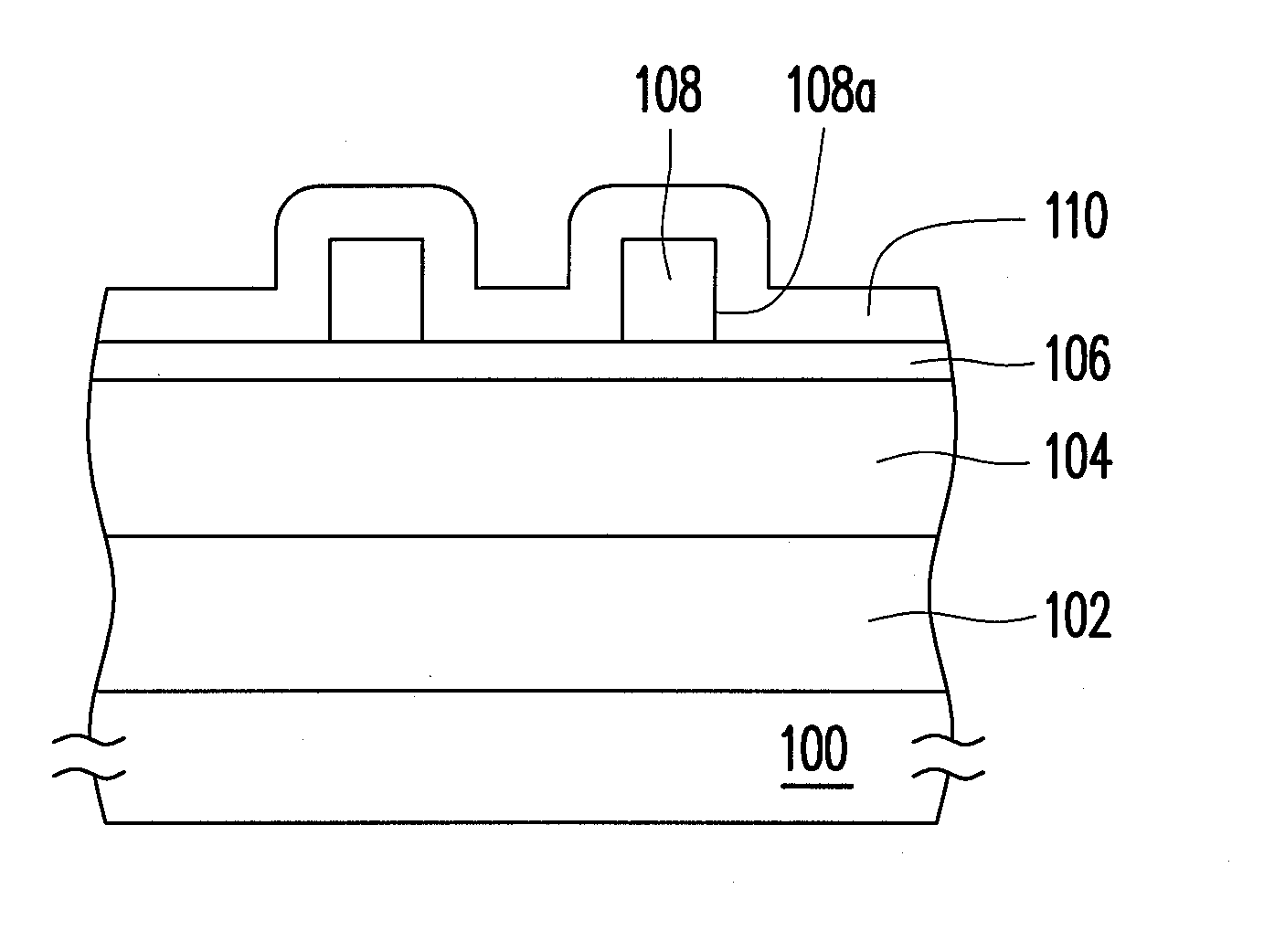

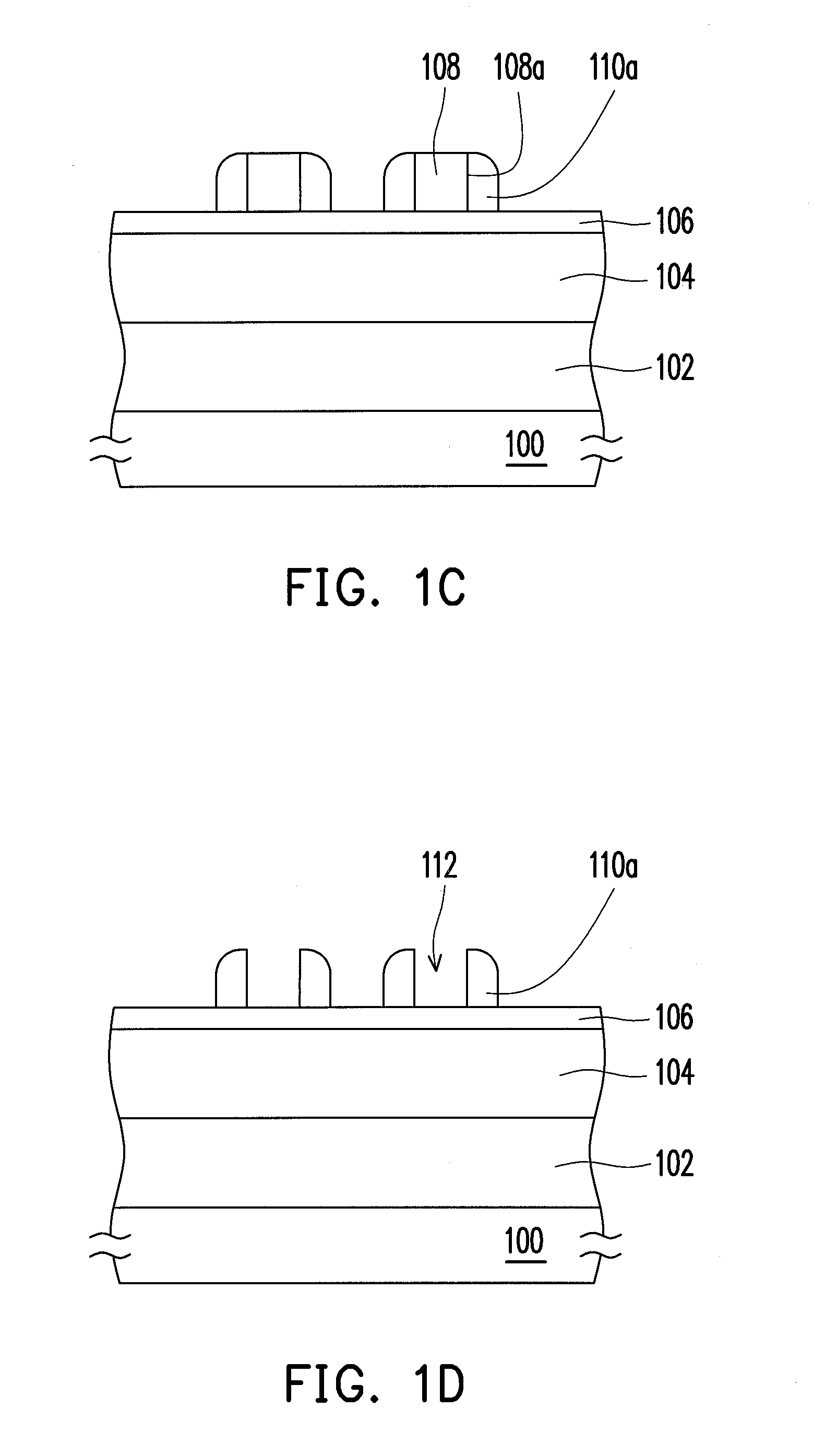

Patterning method

InactiveUS20110294075A1Reduce line widthLow costSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusPhotoresistMask layer

A patterning method of the present invention is described as follows. A mask layer and a patterned photoresist layer are formed on a target layer in sequence, wherein an etching rate of the mask layer is different from an etching rate of the target layer. A plurality of spacers is formed on sidewalls of the patterned photoresist layer respectively, wherein an etching rate of the spacers is different from the etching rate of the mask layer. The patterned photoresist layer is removed to form an opening between any two adjacent spacers. A portion of the mask layer is removed by using the spacers as a mask so as to form a patterned mask layer. A portion of the target layer is removed by using the patterned mask layer as a mask.

Owner:UNITED MICROELECTRONICS CORP

Sequential Infiltration Synthesis for Enhancing Multiple-Patterning Lithography

ActiveUS20130256265A1Reduce in quantityImprove throughputDecorative surface effectsPhotomechanical apparatusPhotoresistMultiple patterning lithography

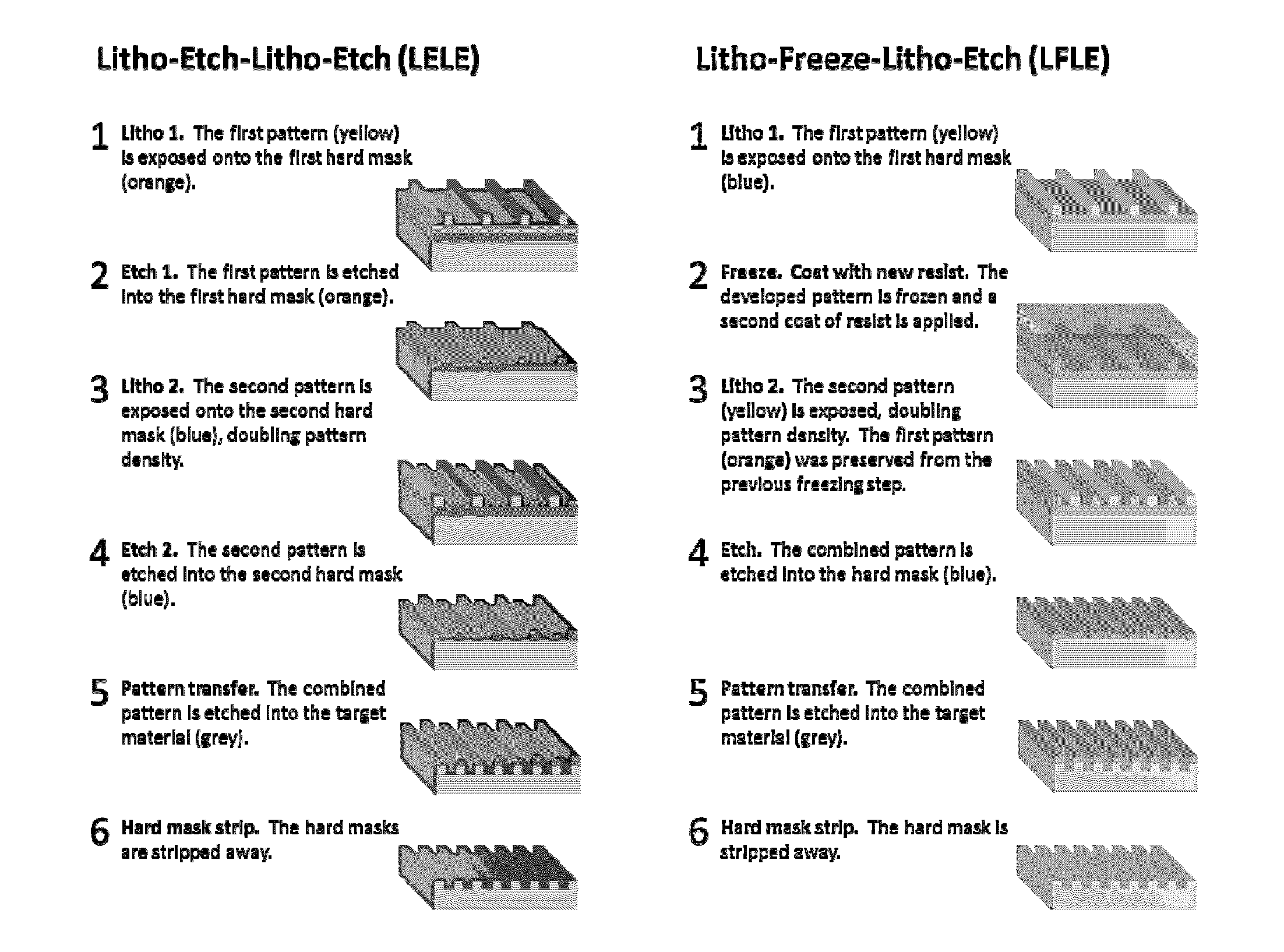

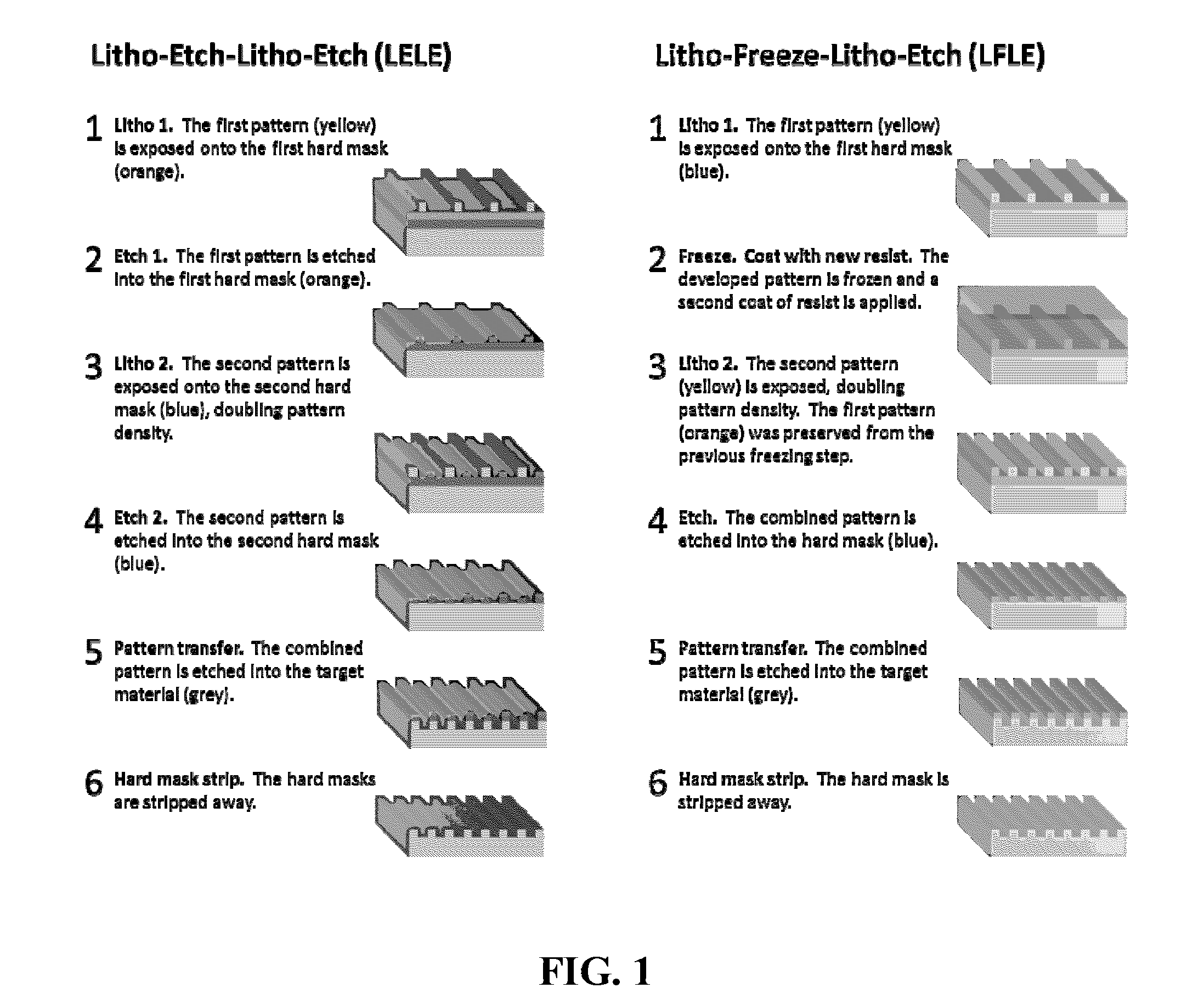

Simplified methods of multiple-patterning photolithography using sequential infiltration synthesis to modify the photoresist such that it withstands plasma etching better than unmodified resist and replaces one or more hard masks and / or a freezing step in MPL processes including litho-etch-litho-etch photolithography or litho-freeze-litho-etch photolithography.

Owner:UCHICAGO ARGONNE LLC

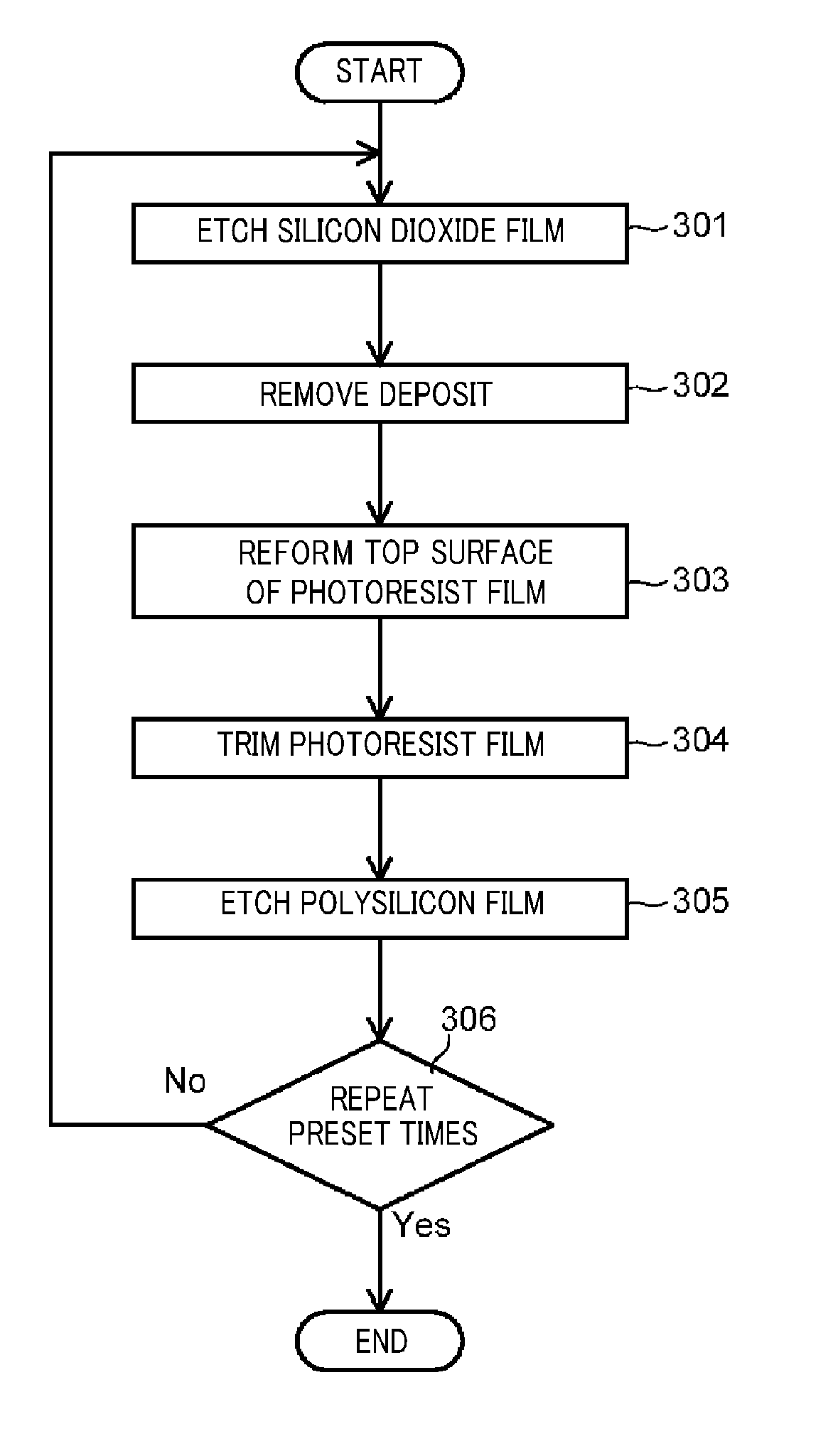

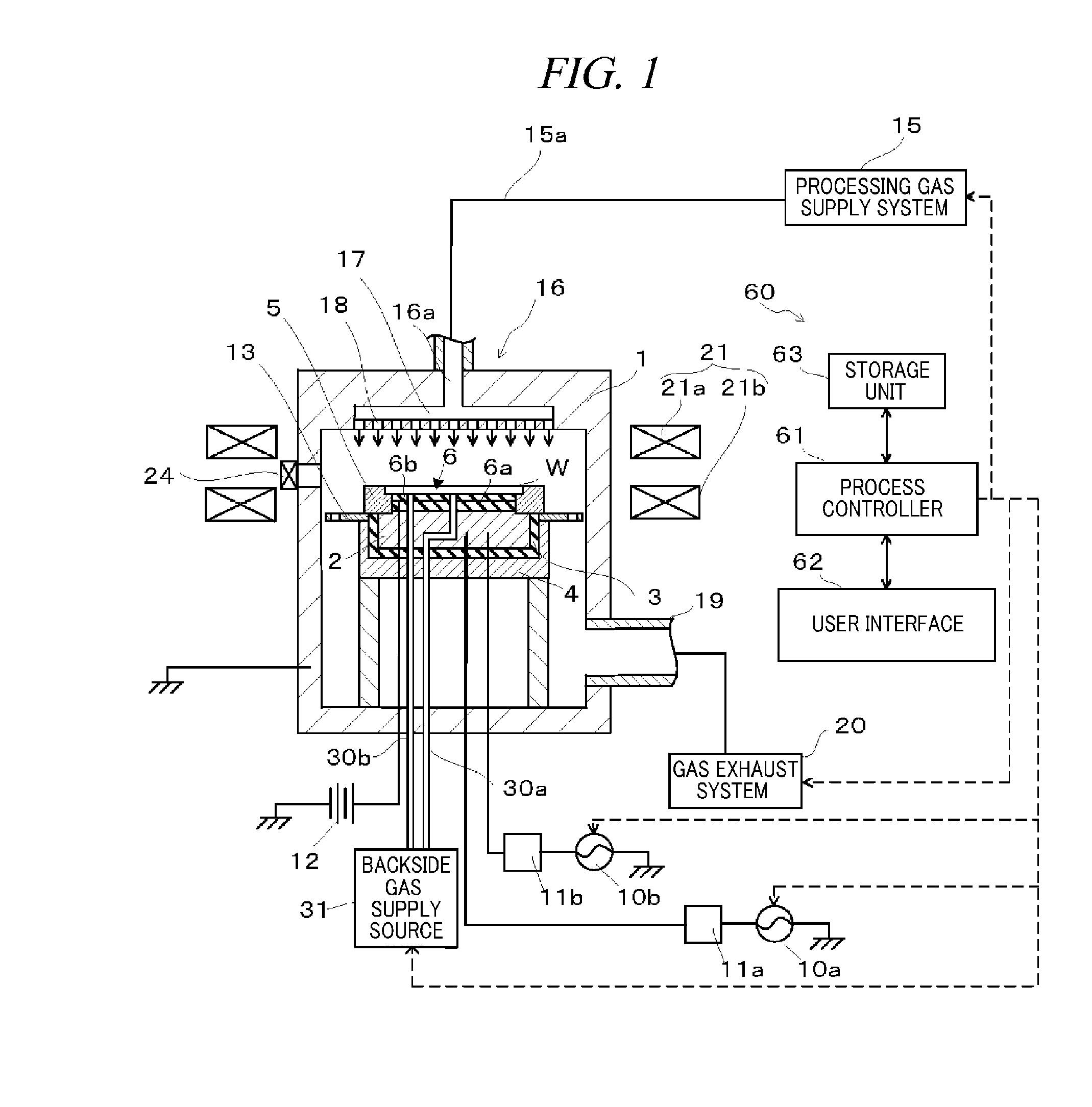

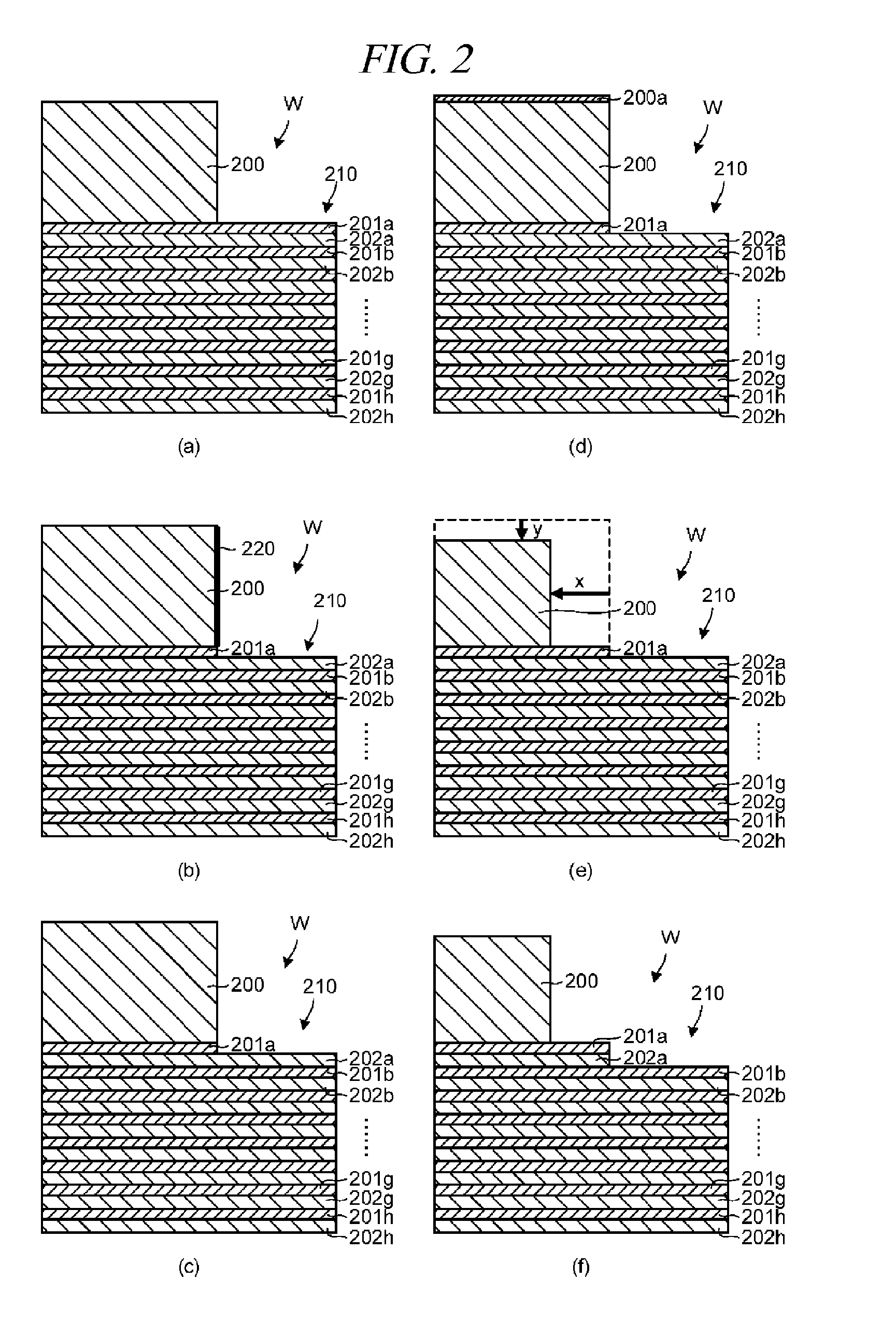

Semiconductor device manufacturing method and computer-readable storage medium

ActiveUS20120225561A1Efficiently formedLiquid surface applicatorsElectric discharge tubesResistHydrogen

There is provided a semiconductor device manufacturing method for forming a step-shaped structure in a substrate by etching the substrate having thereon a multilayer film and a photoresist film on the multilayer film and serving as an etching mask. The multilayer film is formed by alternately layering a first film having a first permittivity and a second film having a second permittivity different from the first permittivity. The method includes a first process for plasma-etching the first film by using the photoresist film as a mask; a second process for exposing the photoresist film to hydrogen-containing plasma; a third process for trimming the photoresist film; and a fourth process for etching the second film by using the trimmed photoresist film and the plasma-etched first film as a mask. The step-shaped structure is formed in the multilayer film by repeatedly performing the first process to the fourth process in this sequence.

Owner:TOKYO ELECTRON LTD

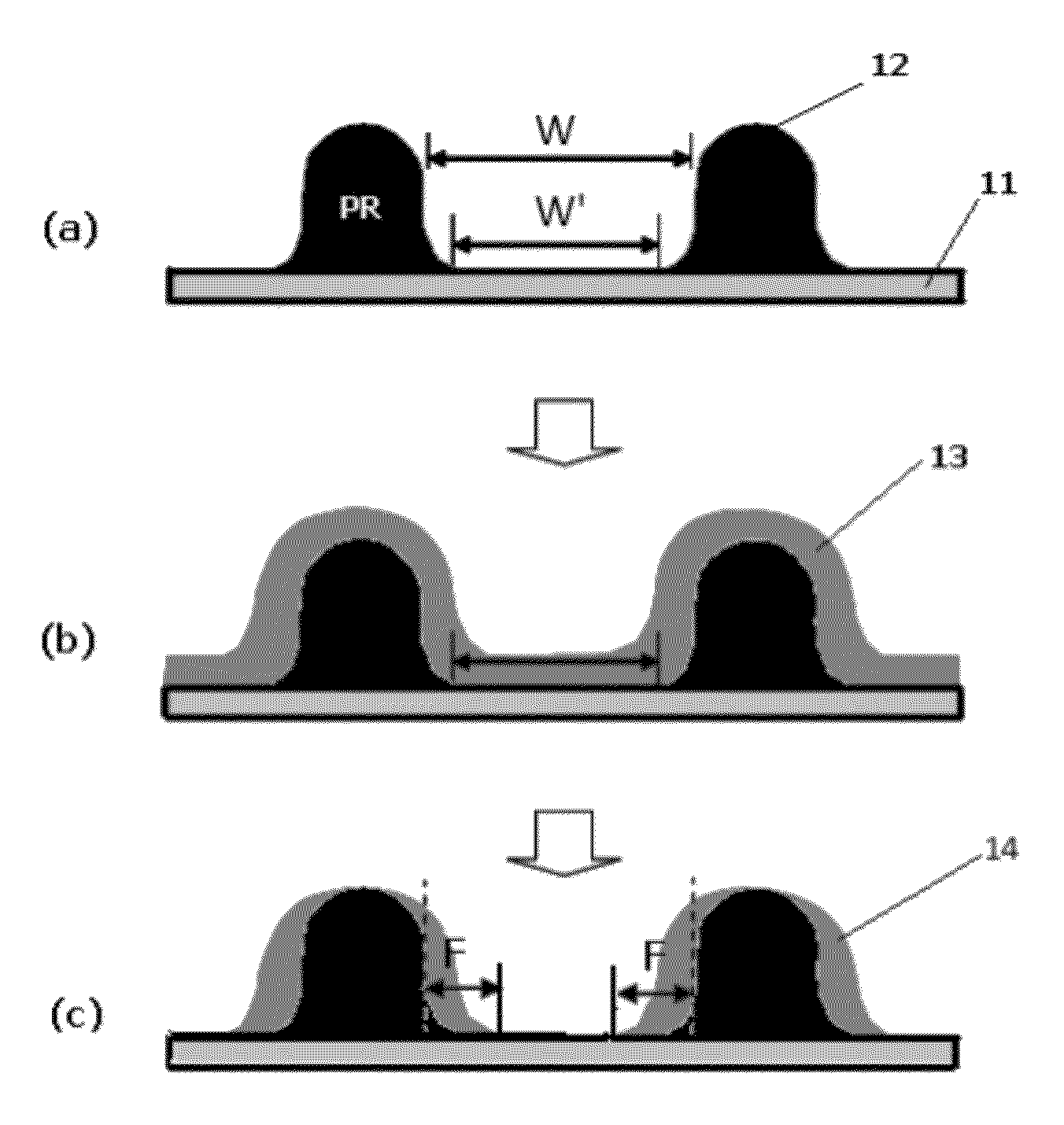

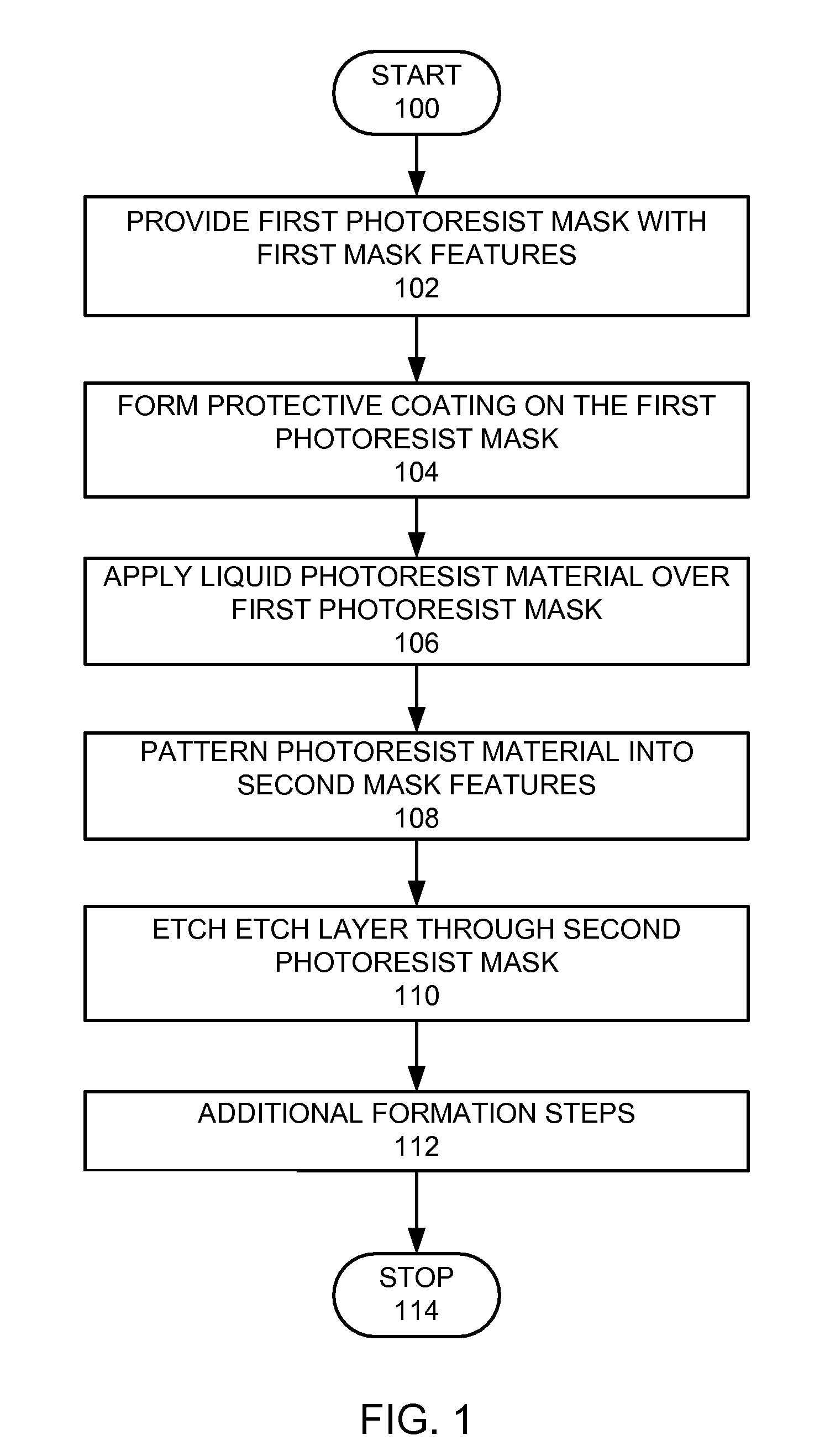

Photoresist double patterning

A method for etching an etch layer formed on a substrate is provided. A first photoresist (PR) mask with first mask features is provided on the etch layer. A protective coating is provided on the first PR mask by a process including at least one cycle. Each cycle includes (a) a deposition phase for depositing a deposition layer over the surface of the first mask features using a deposition gas, and (b) a profile shaping phase for shaping the profile of the deposition layer using a profile shaping gas. A liquid PR material is applied over the first PR mask having the protective coating. The PR material is patterned into a second mask features, where the first and second mask features form a second PR mask. The etch layer is etched though the second PR mask.

Owner:LAM RES CORP

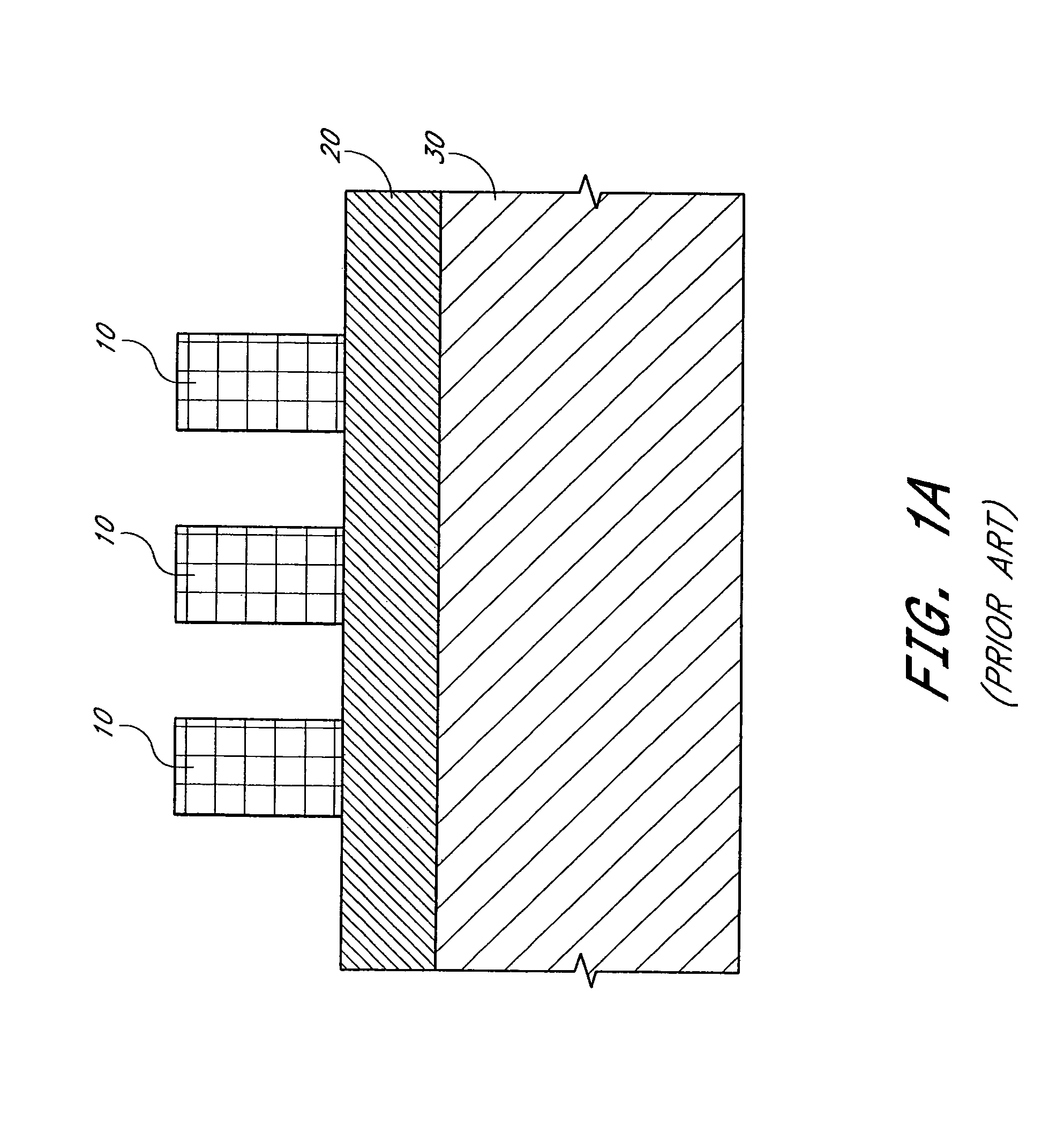

Method of electroless plating copper on nitride barrier

InactiveUS6436816B1Insulating substrate metal adhesion improvementSolid-state devicesCopper platingElectroless deposition

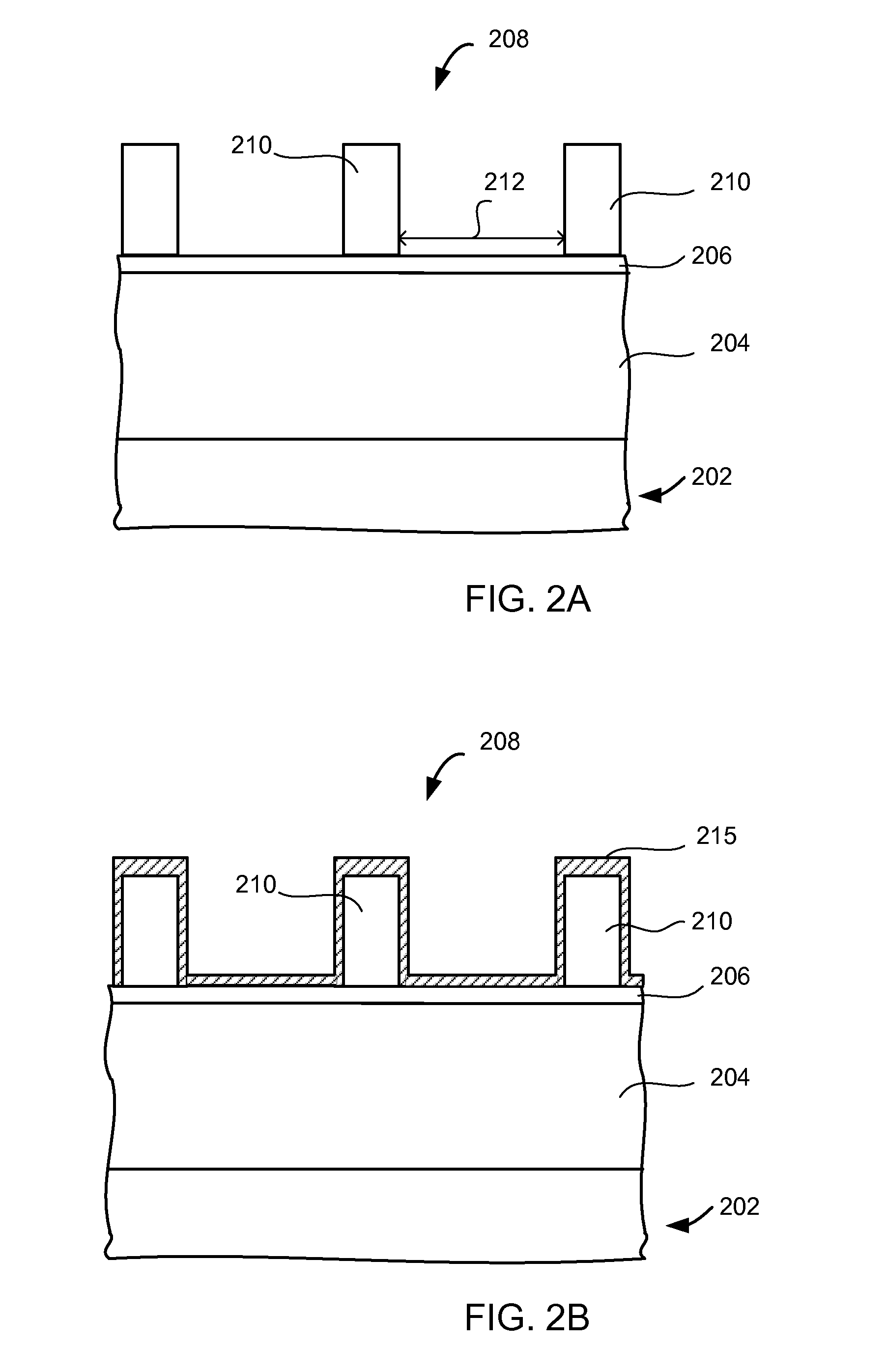

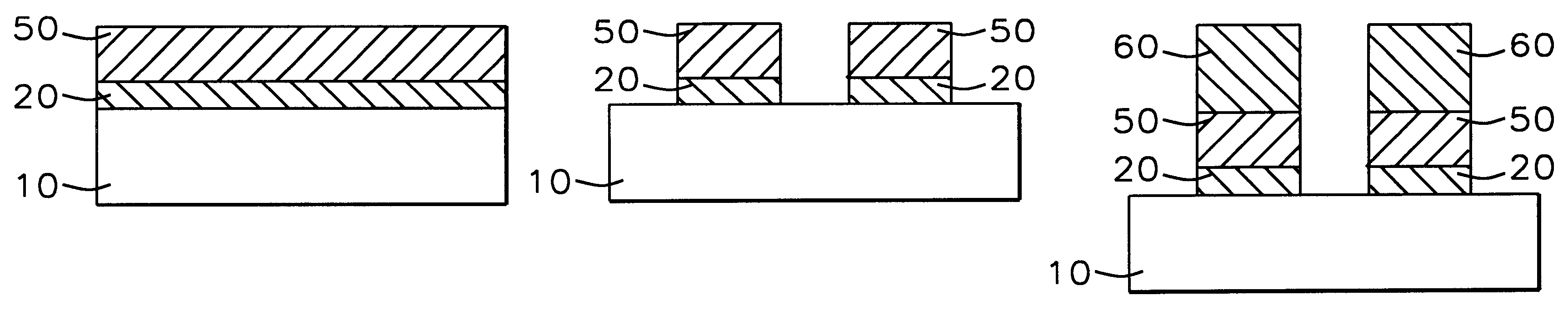

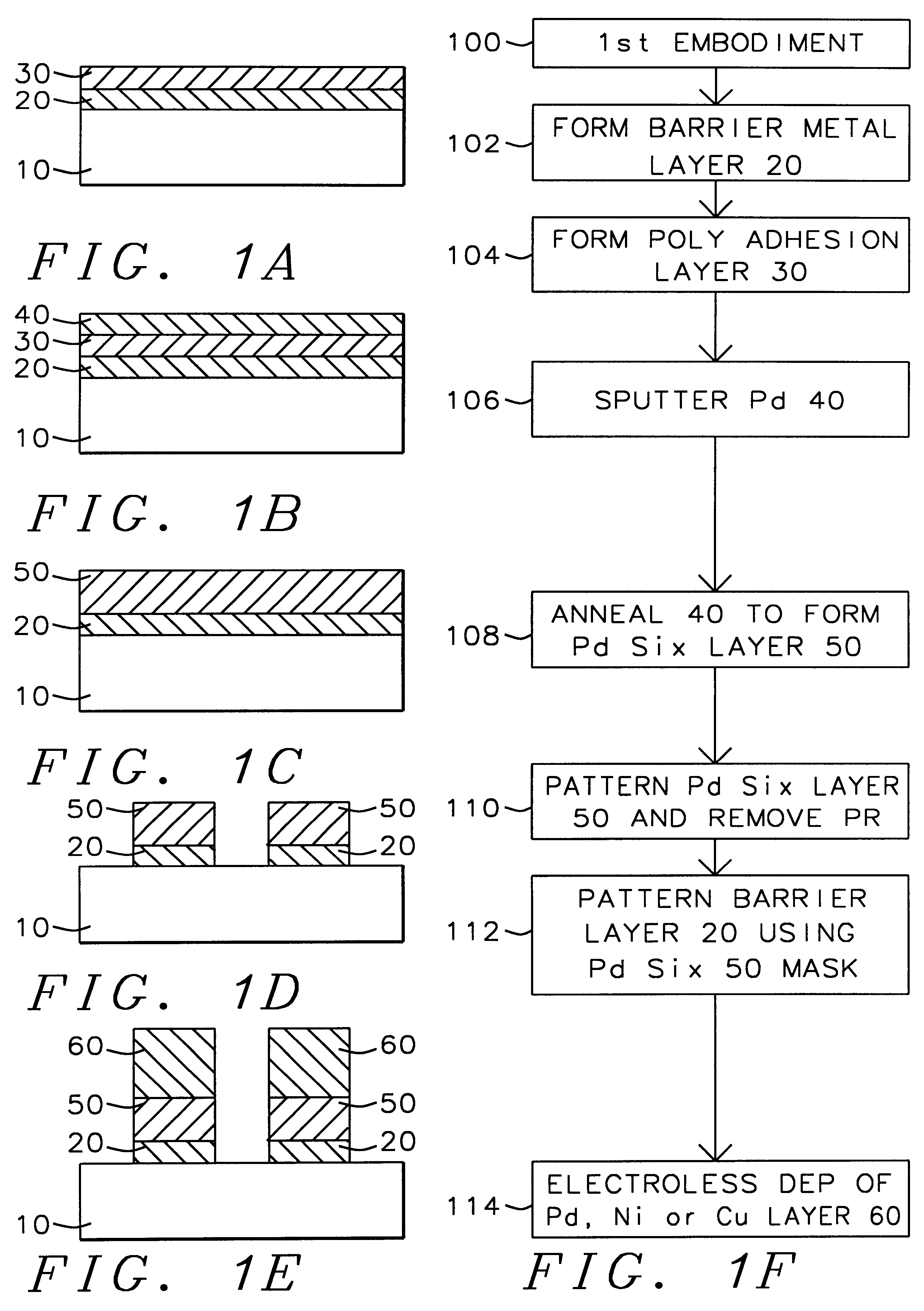

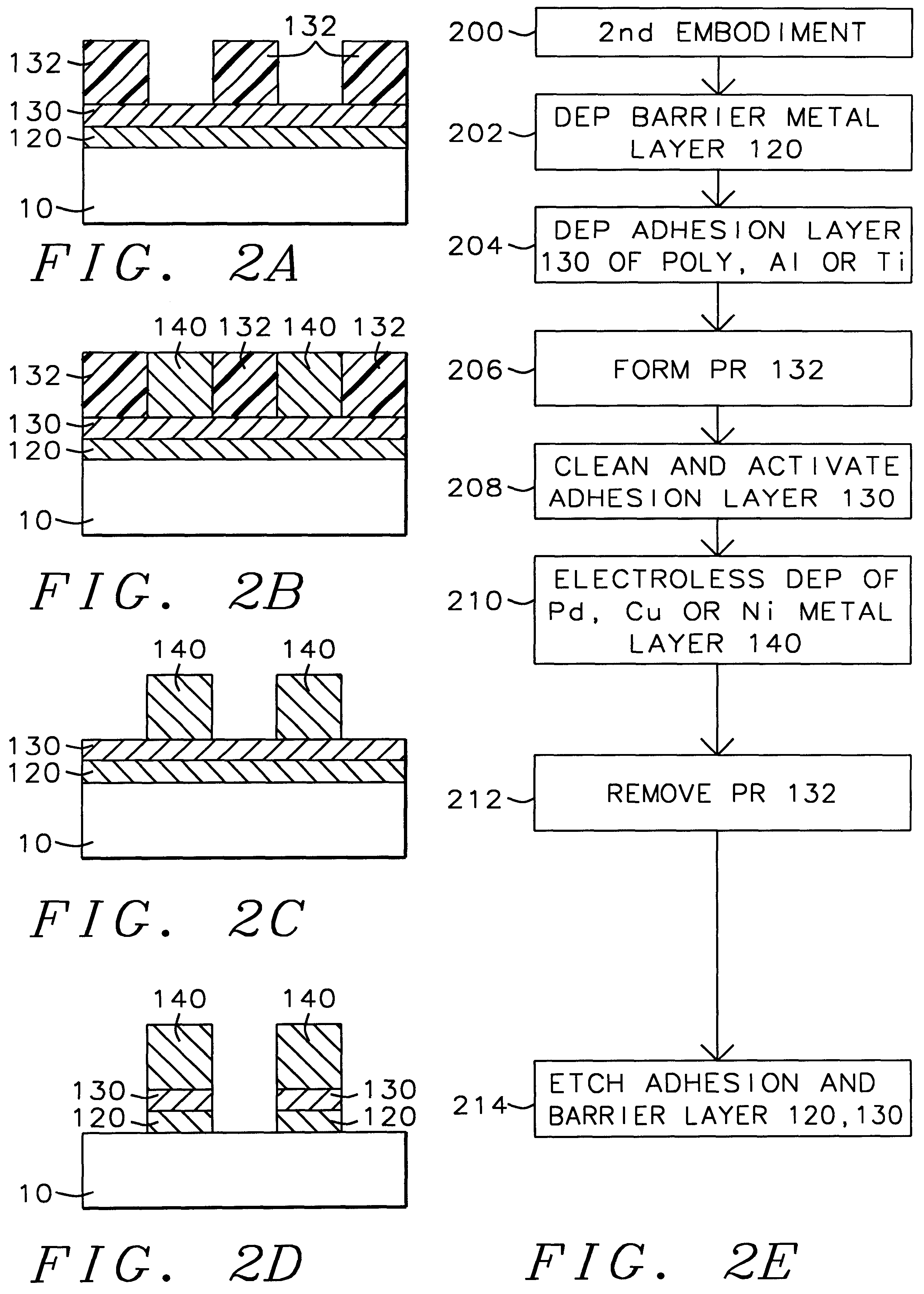

A method with three embodiments of manufacturing metal lines and solder bumps using electroless deposition techniques. The first embodiment uses a PdSix seed layer 50 for electroless deposition. The PdSix layer 50 does not require activation. A metal line is formed on a barrier layer 20 and an adhesion layer 30. A Palladium silicide seed layer 50 is then formed and patterned. Ni, Pd or Cu is electroless deposited over the Palladium silicide layer 50 to form a metal line. The second embodiment selectively electrolessly deposits metal 140 over an Adhesion layer 130 composed of Poly Si, Al, or Ti. A photoresist pattern 132 is formed over the adhesion layer. A metal layer 140 of Cu or Ni is electrolessly deposited over the adhesion layer. The photoresist layer 132 is removed and the exposed portion of the adhesion layer 130 and the underlying barrier metal layer 120 are etched thereby forming a metal line. The third embodiment electroless deposits metal over a metal barrier layer that is roughen by chemical mechanical polishing. A solder bump is formed using an electroless deposition of Cu or Ni by: depositing an Al layer 220 and a barrier metal layer 230 over a substrate 10. The barrier layer 230 is polished and activated. Next, the aluminum layer 220 and the barrier metal layer 230 are patterned. A metal layer 240 is electroless deposited. Next a solder bump 250 is formed over the electroless metal layer 240.

Owner:TAIWAN SEMICON MFG CO LTD

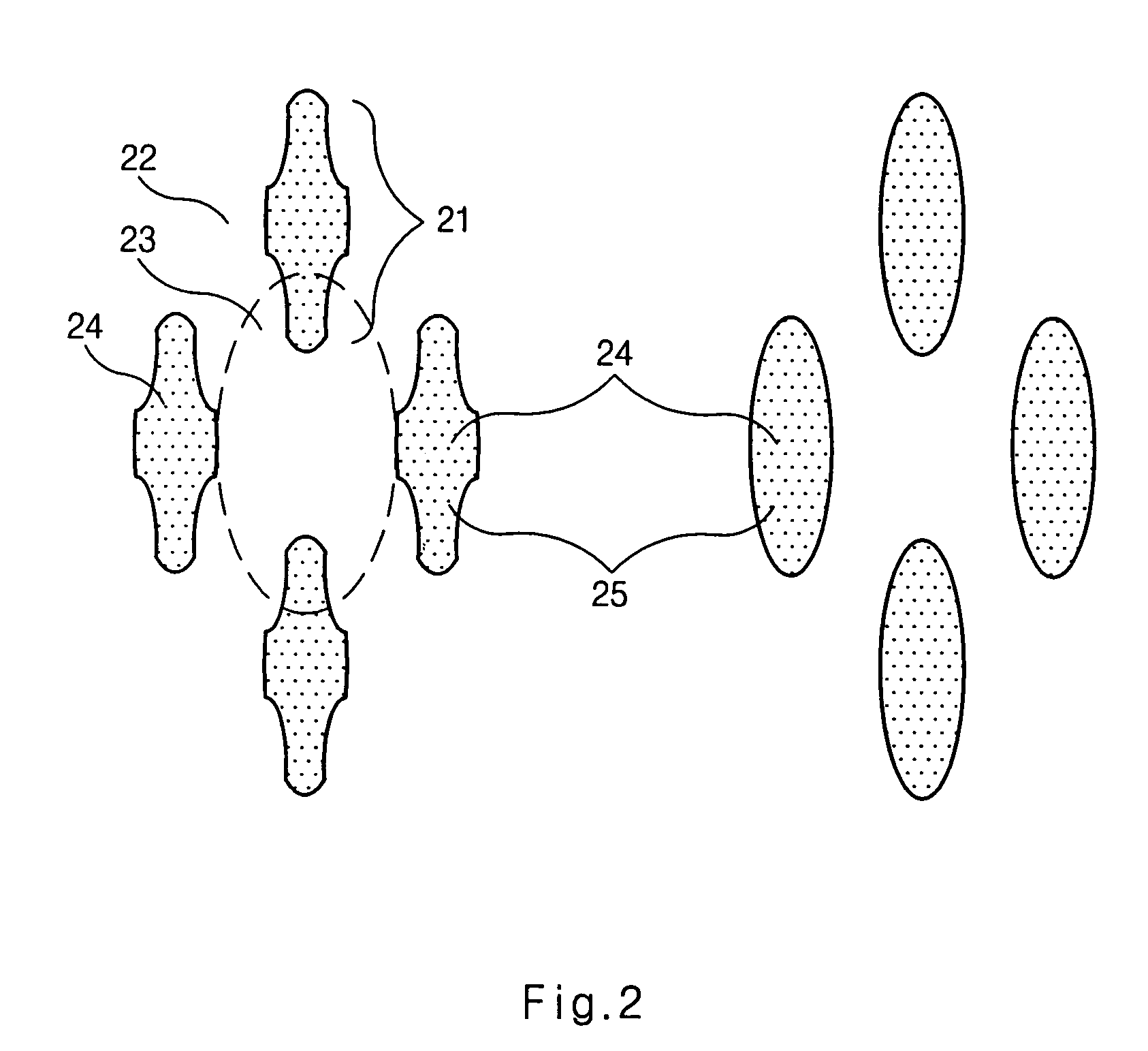

Cleaning solution for photoresist and method for forming pattern using the same

ActiveUS7238653B2Use cleanOrganic detergent compounding agentsTransportation and packagingResistAlcohol

Cleaning solutions for photoresist are disclosed which are useful for cleaning a semiconductor substrate in the last step of development when photoresist patterns are formed. Also, methods for forming photoresist patterns using the same are disclosed. The disclosed cleaning solution comprises H2O as a solution, a surfactant which is phosphate-alcoholamine salt represented by Formula 1, and an alcohol compound. The disclosed cleaning solution has lower surface tension than that of distilled water which has been used for conventional cleaning solutions, thereby improving resistance to photoresist pattern collapse and stabilizing the photoresist pattern formation.wherein R, x, y, z, a and b are as defined in the specification.

Owner:SK HYNIX INC

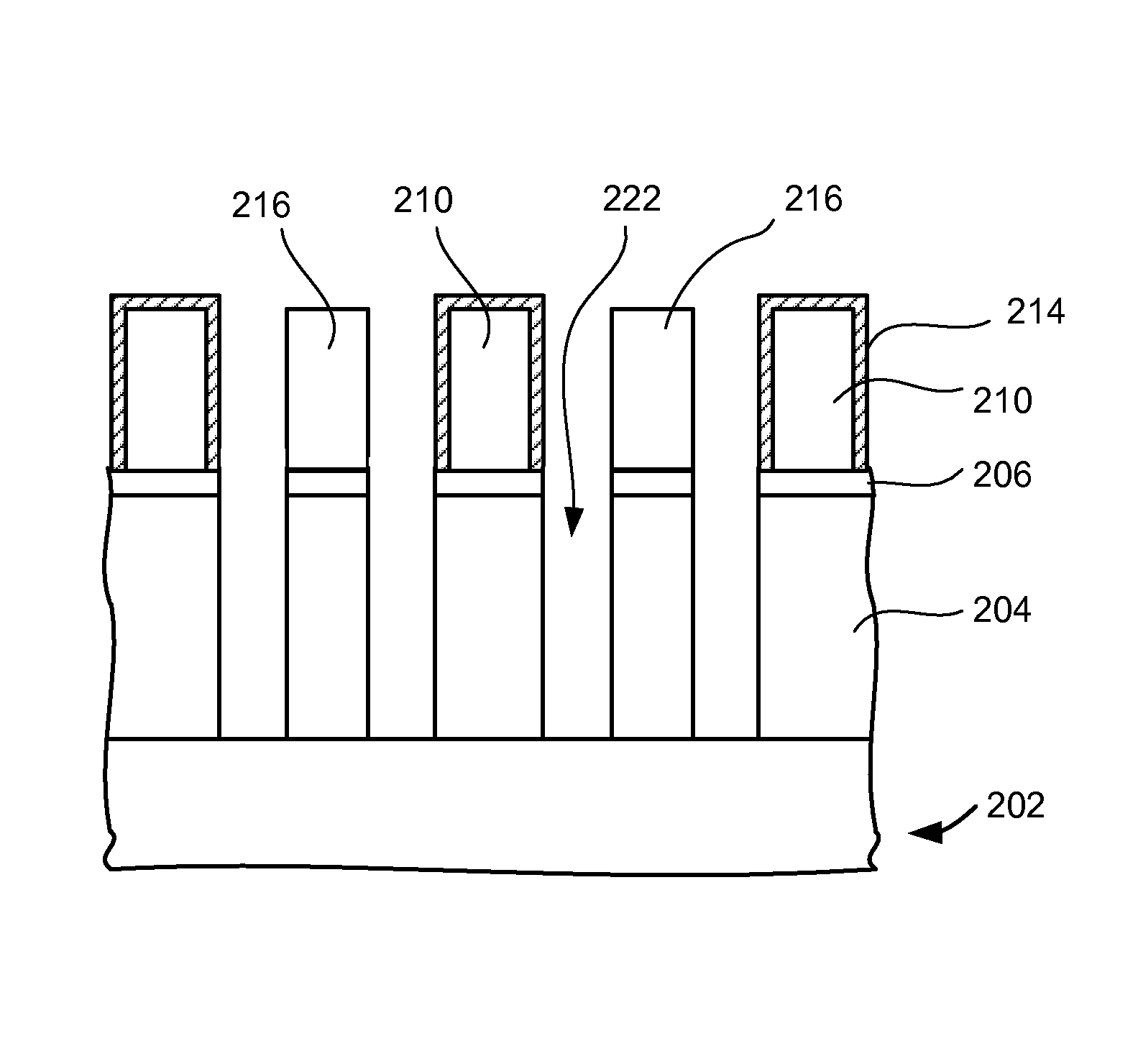

Plasma processing method

ActiveUS8497213B2Preventing deterioration of semiconductor device performanceReduce roughnessDecorative surface effectsSemiconductor/solid-state device manufacturingResistNitrogen gas

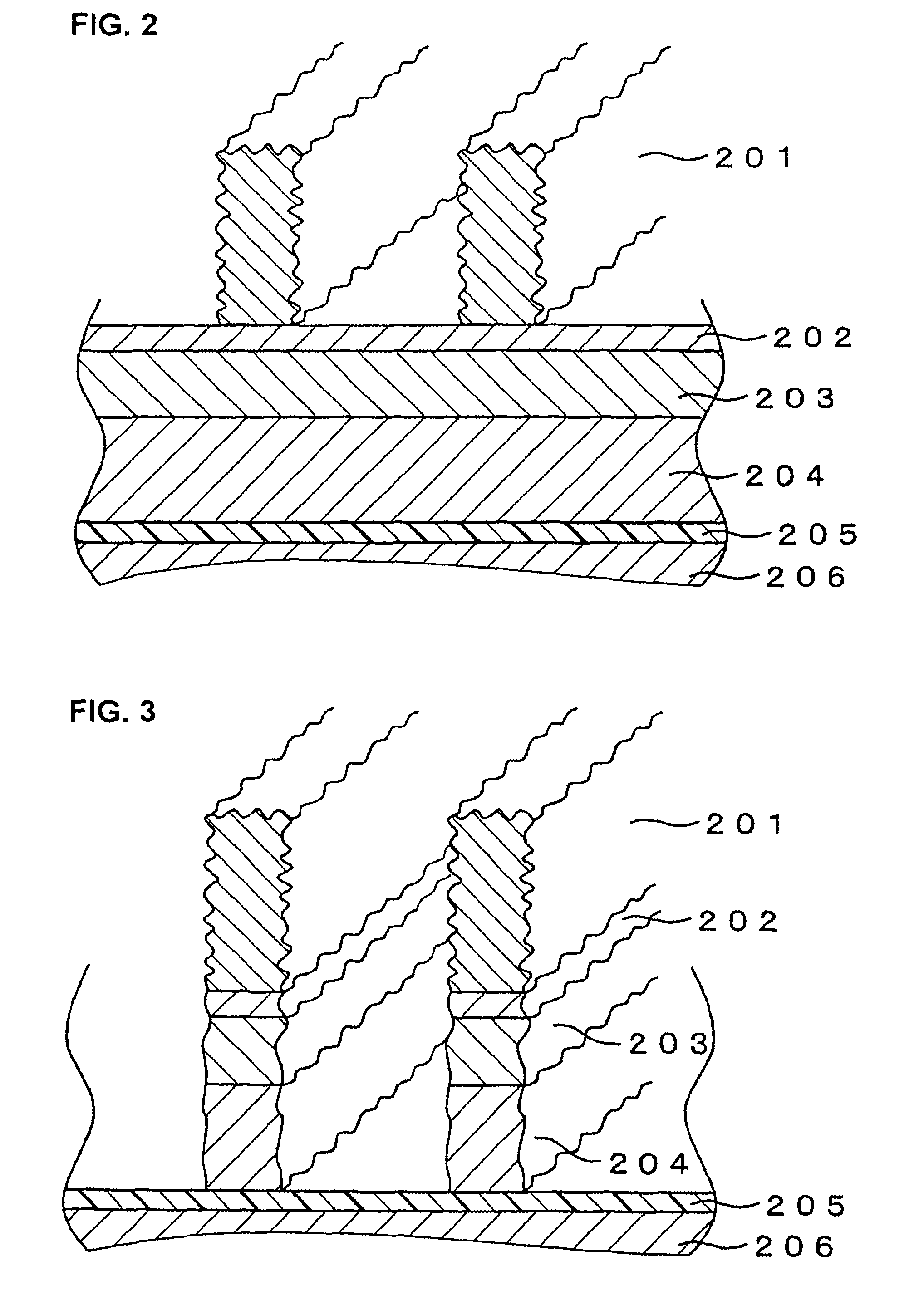

The invention provides a method for subjecting laminated thin films disposed below a photoresist mask pattern to plasma processing, wherein the roughness on the side walls of the formed pattern is reduced, and the LER and LWR are reduced. When etching a material to be processed to form a gate electrode including thin films such as a gate insulating film 205, a conducting layer 204, a mask layer 203 and an antireflection film 202 laminated on a semiconductor substrate 206 and a photoresist mask pattern 201 disposed on the antireflection film, prior to etching the mask pattern 201, plasma is generated from nitrogen gas or a mixed gas including nitrogen gas and deposition gas to subject the mask pattern 201 to a plasma curing process so as to reduce the roughness on the surface and side walls of the mask pattern 201, and then the laminated thin films 202, 203 and 204 disposed below the mask pattern 201 are subjected to a plasma etching process.

Owner:HITACHI HIGH-TECH CORP

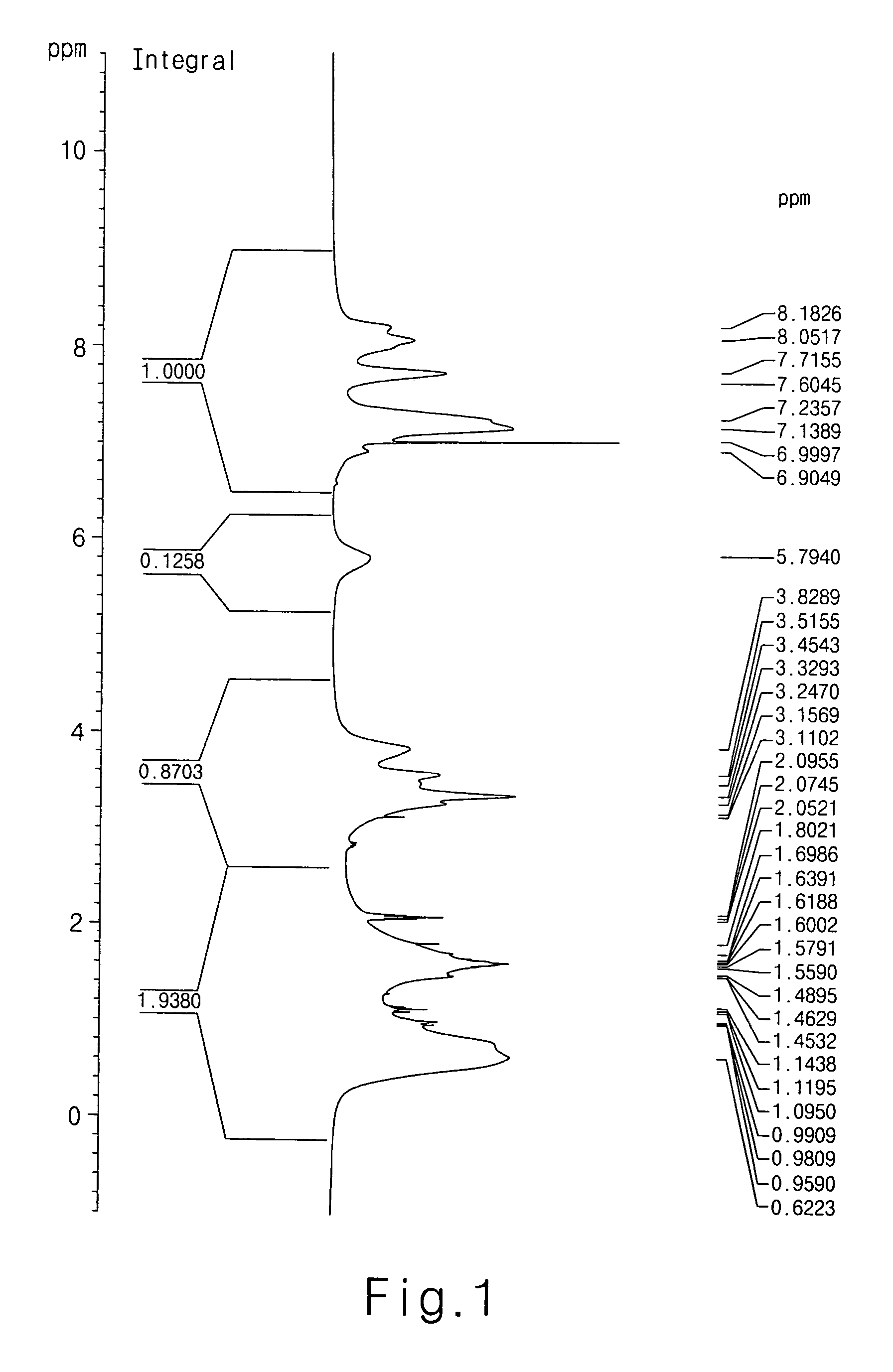

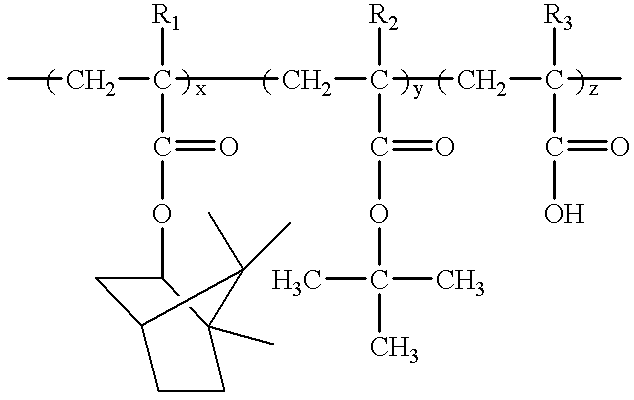

Photoresist polymer and photoresist composition containing the same

InactiveUS7361447B2Semiconductor/solid-state device manufacturingPhotosensitive material auxillary/base layersResistPolymer science

Photoresist polymers and photoresist compositions containing the same. Photoresist patterns of less than 50 nm are achieved with EUV (Extreme Ultraviolet) as an exposure light source with photoresist compositions comprising (i) a photoresist polymer comprising a polymerization repeating unit of Formula 2 or (ii) a photoresist polymer comprising a polymerization repeating unit of Formula 3 with polyvinylphenol. As a result, excellent etching resistance can be secured although the photoresist patterns have a very small thickness.wherein R1, R2, R3, R4, R5, R6, R7, R8, R9, R10, R11, R12, a, b, c, d, e, f and g are as defined in the specification.

Owner:SK HYNIX INC

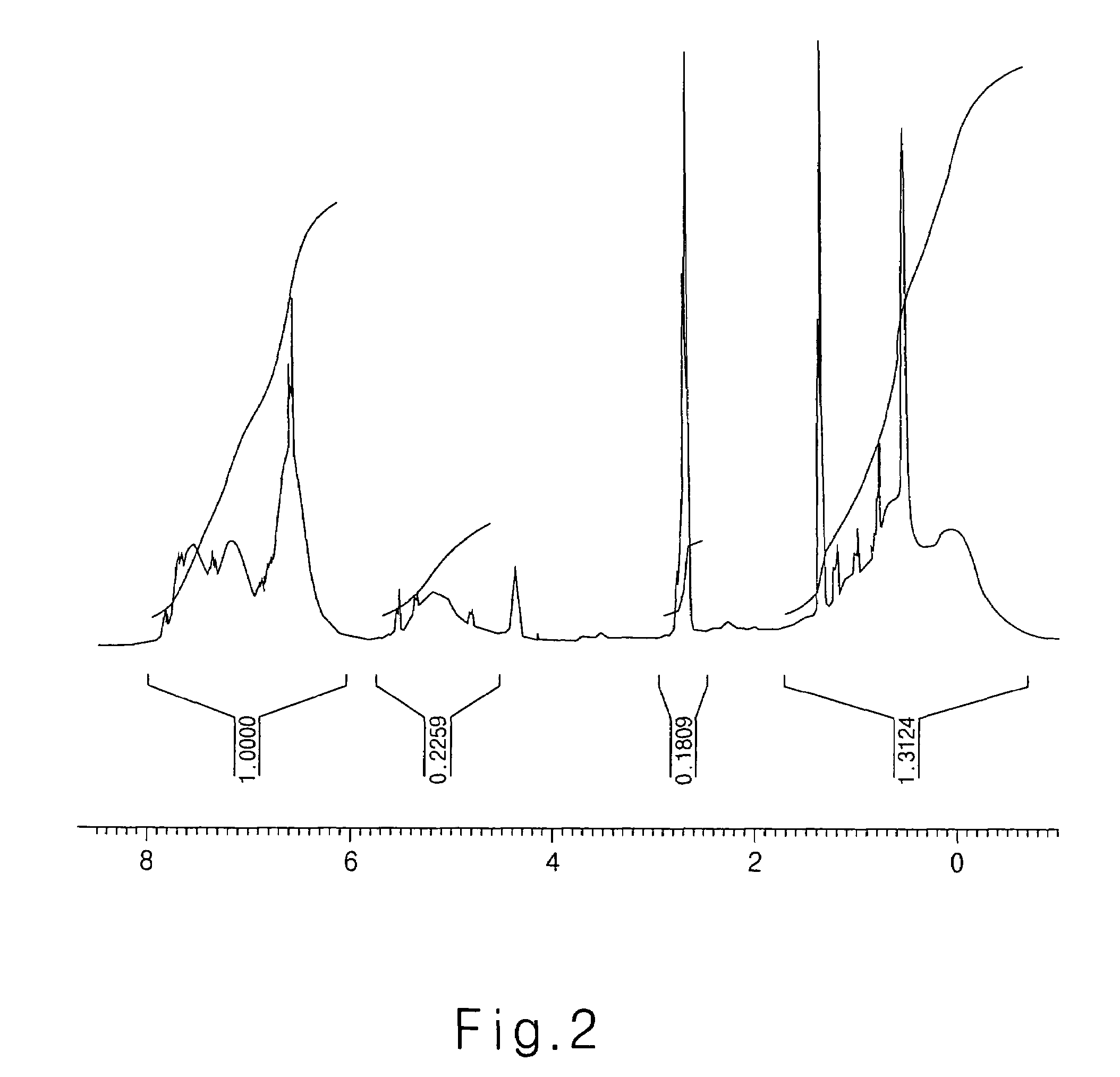

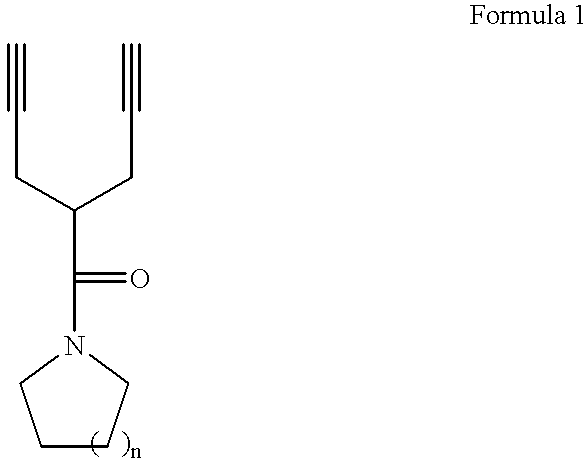

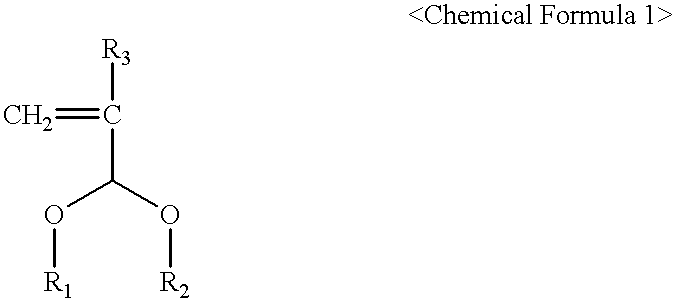

Photoresist monomers, polymers thereof, and photoresist compositions containing the same

Dipropargyl acetamide derivatives of following Formula 1 which are photoresist monomers, polymers thereof, and photoresist compositions containing the same. The photoresist polymer has high etching resistance, adhesiveness and post-exposure delay stability. As a result, the photoresist composition is suitable to form a fine pattern in a deep ultraviolet region.wherein, n is an integer from 0 to 5.

Owner:SK HYNIX INC

Photoresist monomers, polymers and photoresist compositions for preventing acid diffusion

Photoresist monomers, polymers thereof, photoresist compositions containing the same for preventing acid generated in the exposed area during the course of a photolithography process from being diffused to the unexposed area. The line edge roughness and slope pattern are improved when an ultrafine photoresist pattern is formed using photoresist copolymer having a multi-oxygen-containing compound as a repeating unit such as an ethyleneoxy moiety represented by Formula 1 with at least one polymerizable carbon-carbon double bond. In addition, the shape of pattern is improved by eliminating top loss and the adhesion of pattern to the substrate is improved. wherein n is an integer ranging from 1 to 5.

Owner:SK HYNIX INC +1

Photoresist polymer and photoresist composition containing the same

InactiveUS7279256B2Enhance the imageImprove the immunityPhotosensitive materialsRadiation applicationsResistEnergy variation

Photoresist polymers and photoresist compositions are disclosed. A photoresist polymer comprising a polymerization repeating unit represented by Formula I is less sensitive to change in the amount of energy due to its higher active energy than that of a conventional photoresist polymer. As a result, a phenomenon where the portion of the pattern for the storage electrode contact region that receives relatively large amount of light becomes too thin is avoided when the device isolation film pattern is formed, and wherein pattern collapse caused by a high aspect ratio due to high etching resistance is prevented or avoided.whereinR1–R10, a, b, c and d are as defined in the description.

Owner:SK HYNIX INC

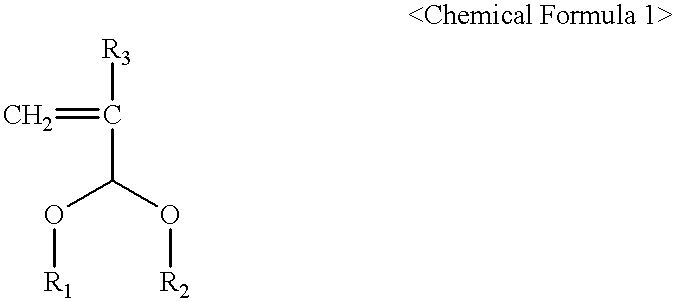

Photoresist cross-linker and photoresist composition comprising the same

InactiveUS6368773B1Enhance the imageAdequate resultOrganic chemistryPhotosensitive materialsCarboxylic acidKetone

The present invention relates to a cross-linker for photoresist compositions which is suitable for a photolithography process using KrF (248 mn), ArF (193 mn), E-beam, ion beam or EUV light sources. Preferred cross-linkers, according to the present invention, comprise a copolymer of (i) a compound represented by following Chemical Formula 1 and / or (ii) one or more compound(s) selected from the group consisting of acrylic acid, methacrylic acid and maleic anhydride. ##STR1## wherein, R.sub.1 and R.sub.2 individually represent straight or branched C.sub.1-10 alkyl, straight or branched C.sub.1-10 ester, straight or branched C.sub.1-10 ketone, straight or branched C.sub.1-10 carboxylic acid, straight or branched C.sub.1-10 acetal, straight or branched C.sub.1-10 alkyl including at least one hydroxyl group, straight or branched C.sub.1-10 ester including at least one hydroxyl group, straight or branched C.sub.1-10 ketone including at least one hydroxyl group, straight or branched C.sub.1-10 carboxylic acid including at least one hydroxyl group, and straight or branched C.sub.1-10 acetal including at least one hydroxyl group; and R.sub.3 represents hydrogen or methyl.

Owner:HYUNDAI ELECTRONICS IND CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com