Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5779 results about "Photomask" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A photomask is an opaque plate with holes or transparencies that allow light to shine through in a defined pattern. They are commonly used in photolithography.

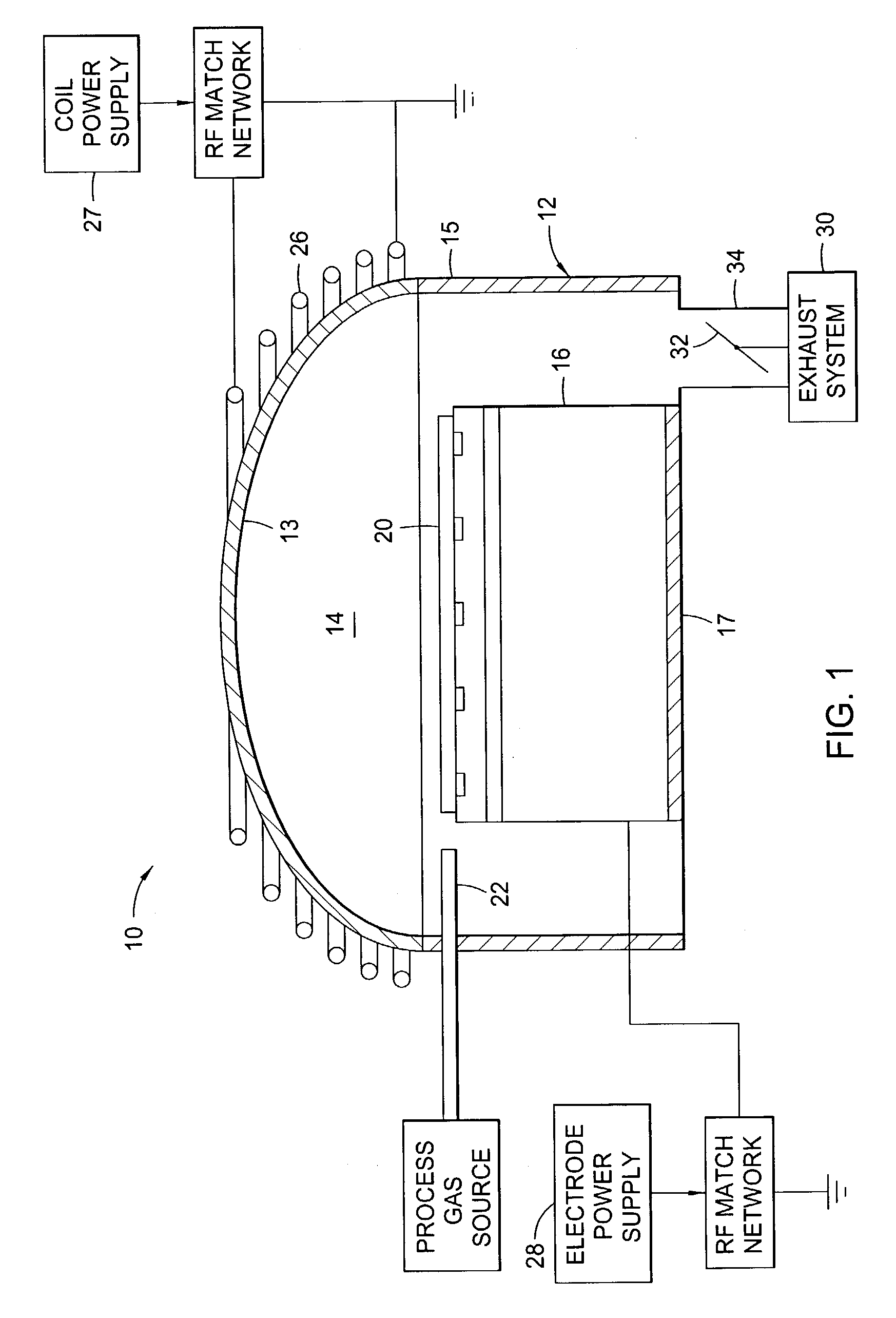

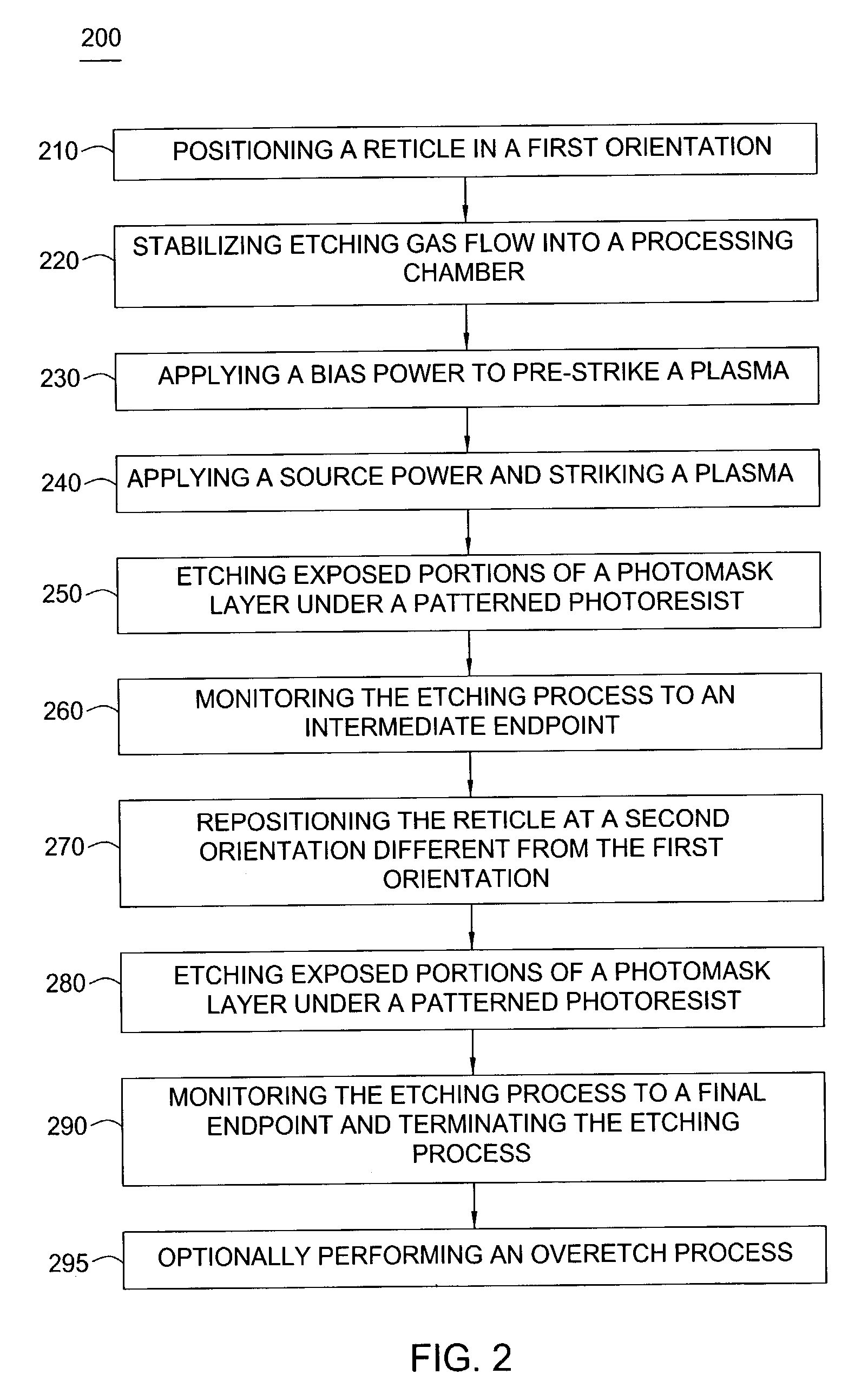

Etching of nano-imprint templates using an etch reactor

Owner:APPLIED MATERIALS INC

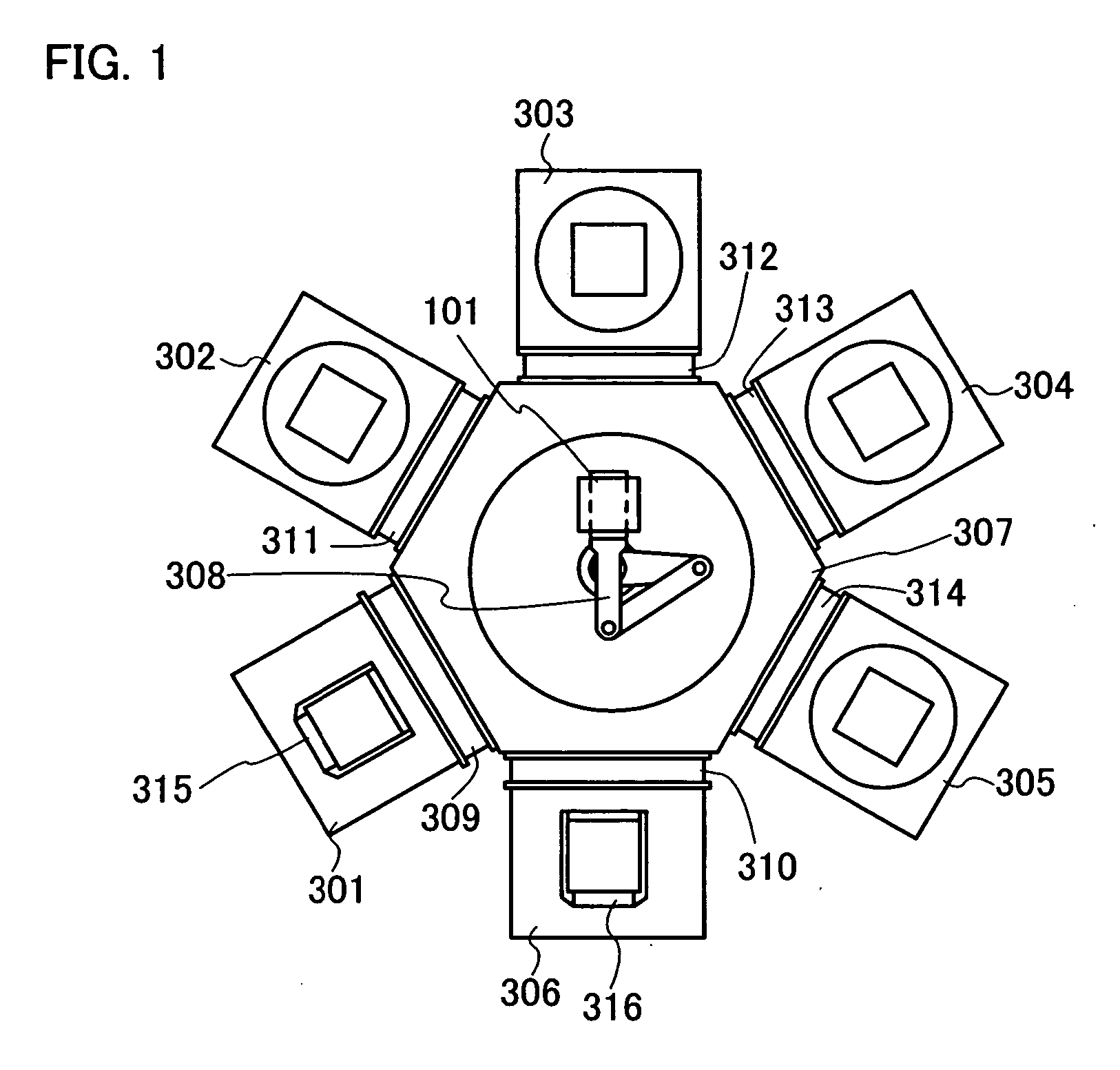

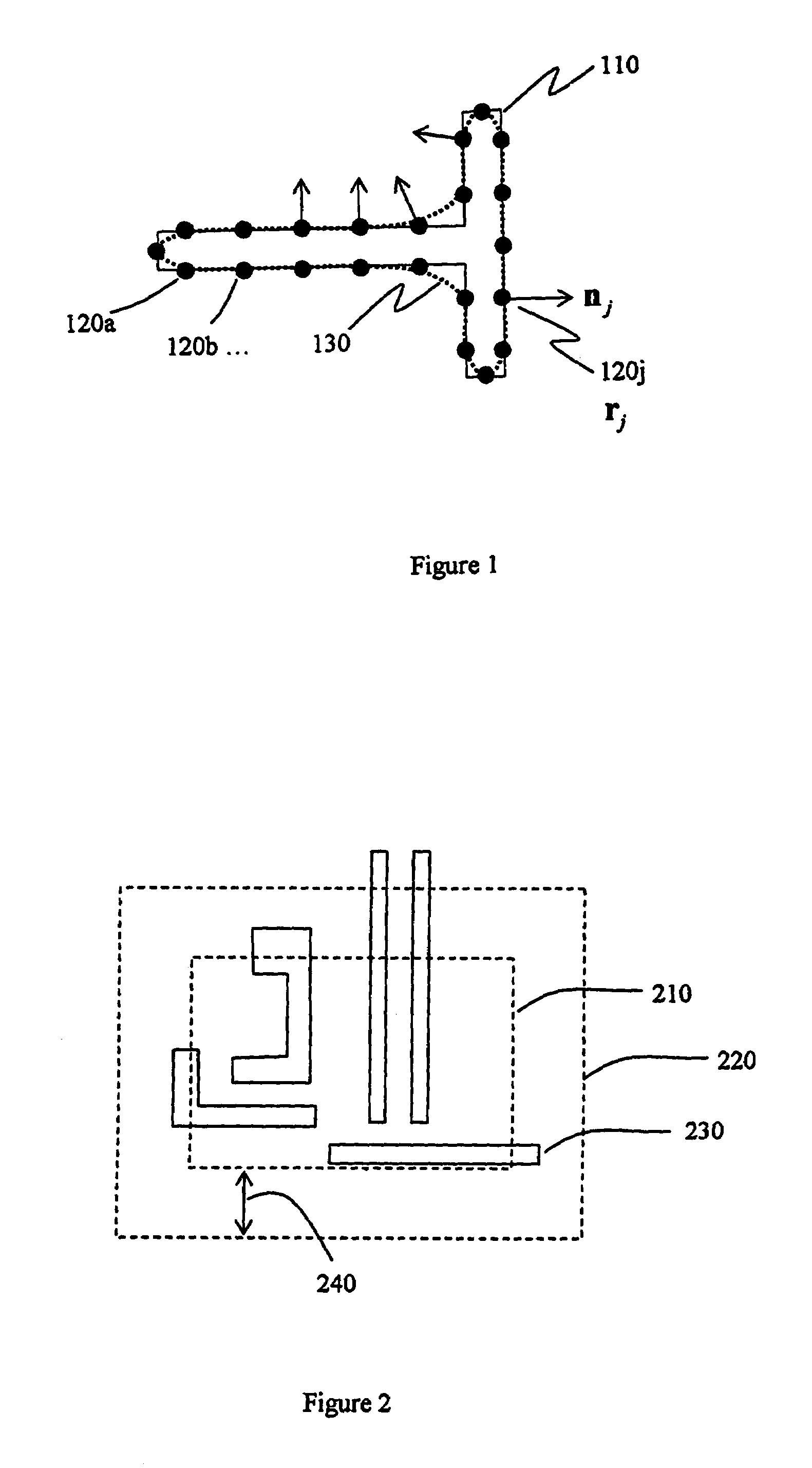

Methods for substrate orientation

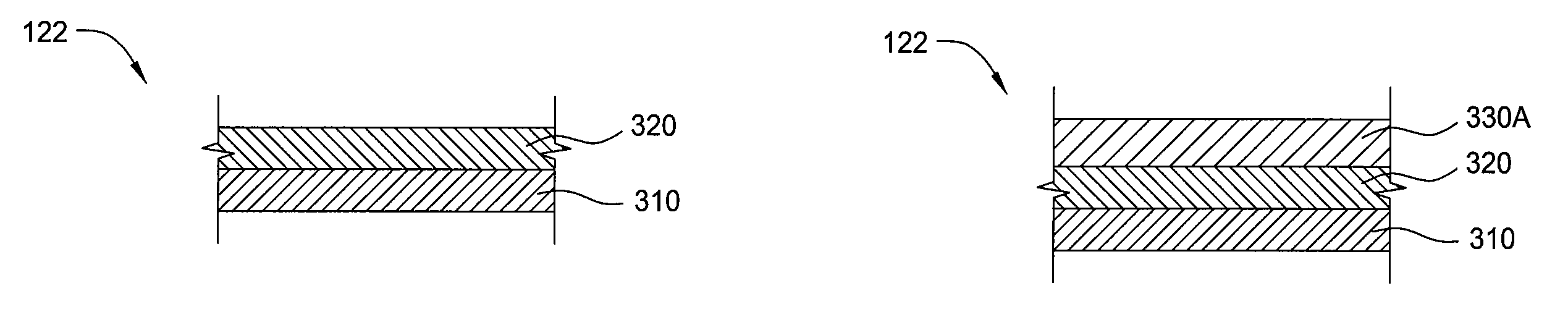

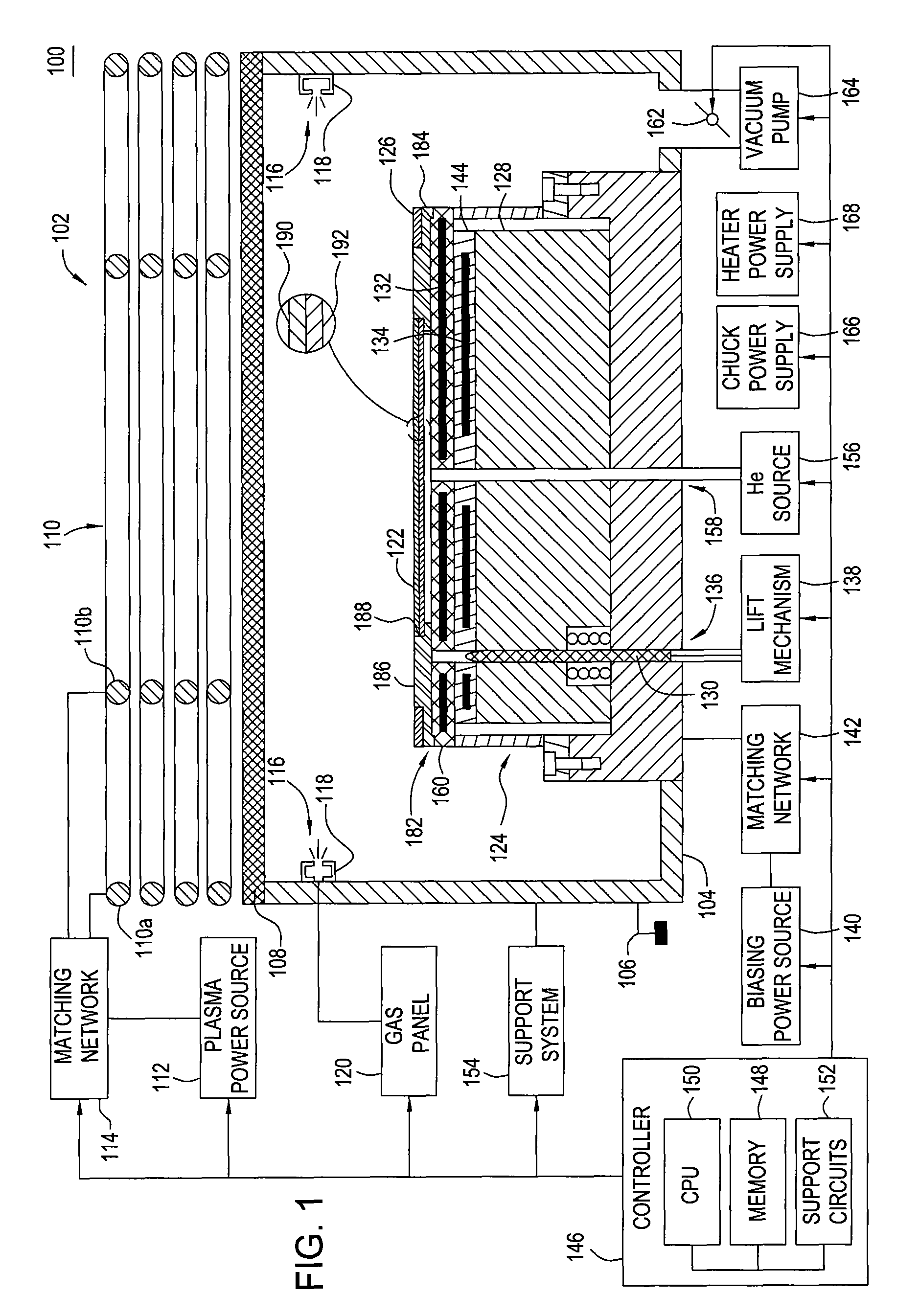

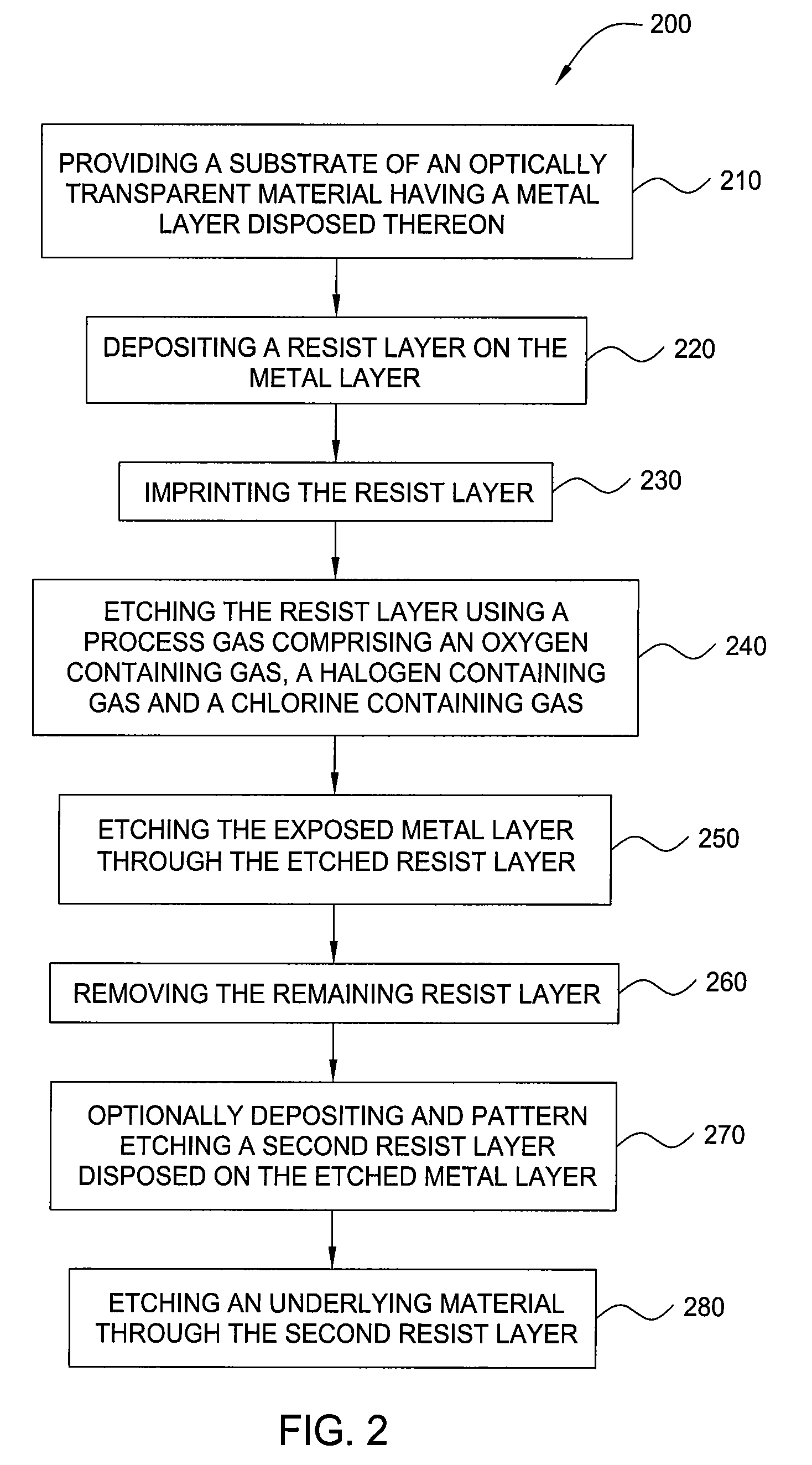

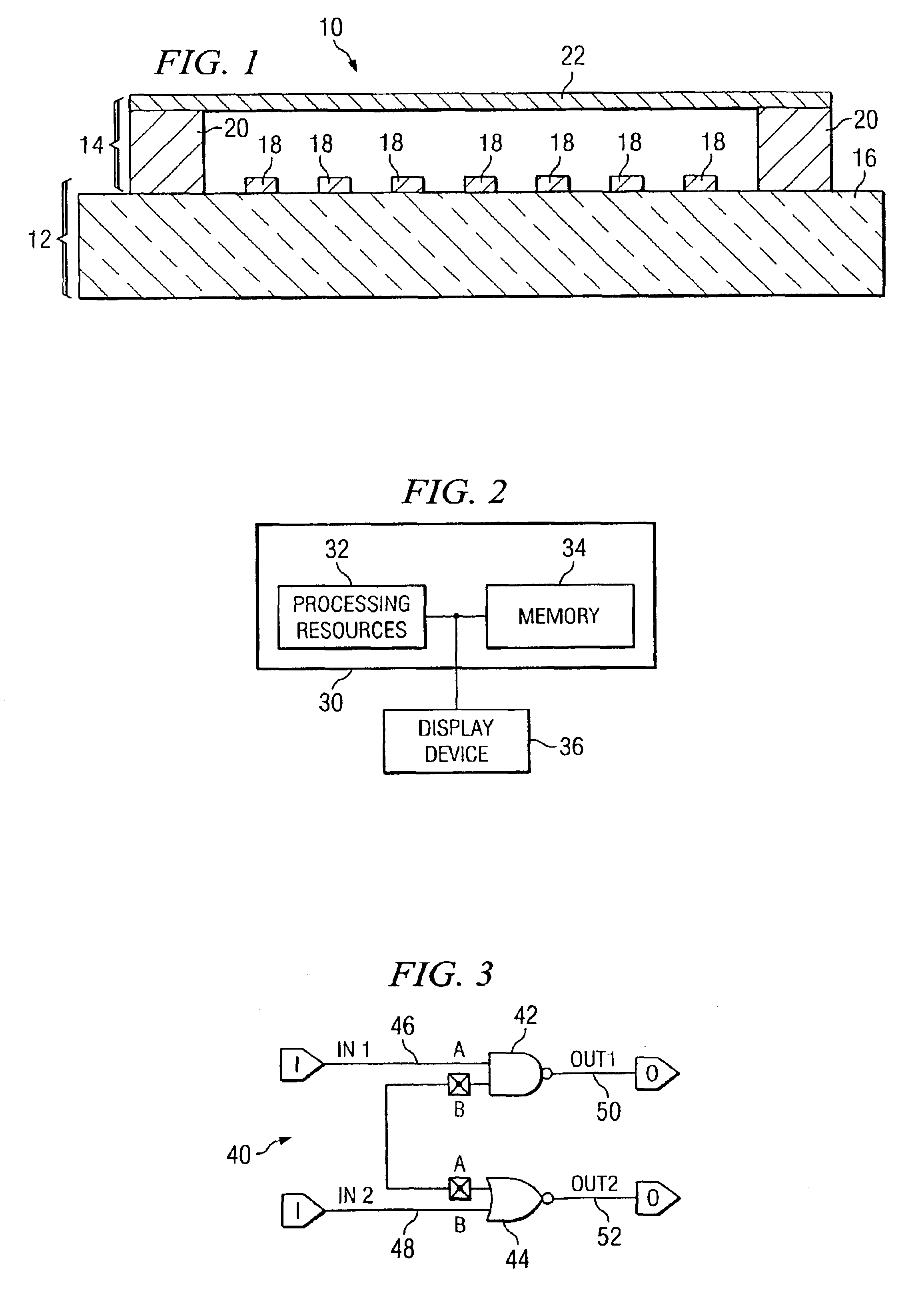

Method and apparatus for etching a metal layer disposed on a substrate, such as a photolithographic reticle, are provided. In one aspect, a method is provided for processing a photolithographic reticle including positioning the reticle in a first orientation on a reticle support in a processing chamber, wherein the reticle comprises a metal photomask layer formed on an optically transparent substrate, and a patterned resist material deposited on the metal photomask layer, etching the metal photomask layer in the first orientation, positioning the reticle in at least a second orientation, and etching the metal photomask layer in the at least second orientation.

Owner:APPLIED MATERIALS INC

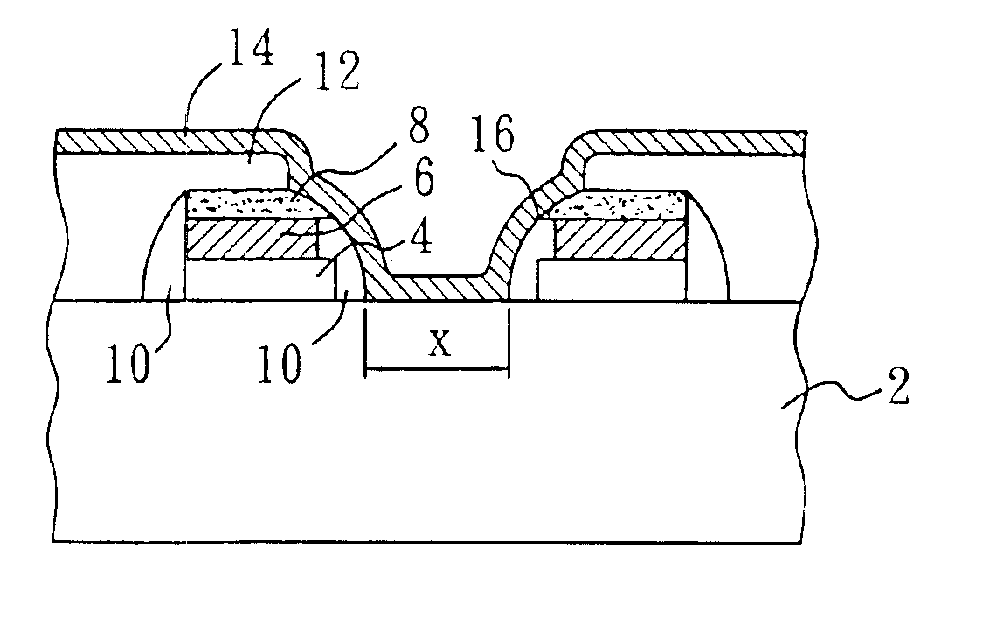

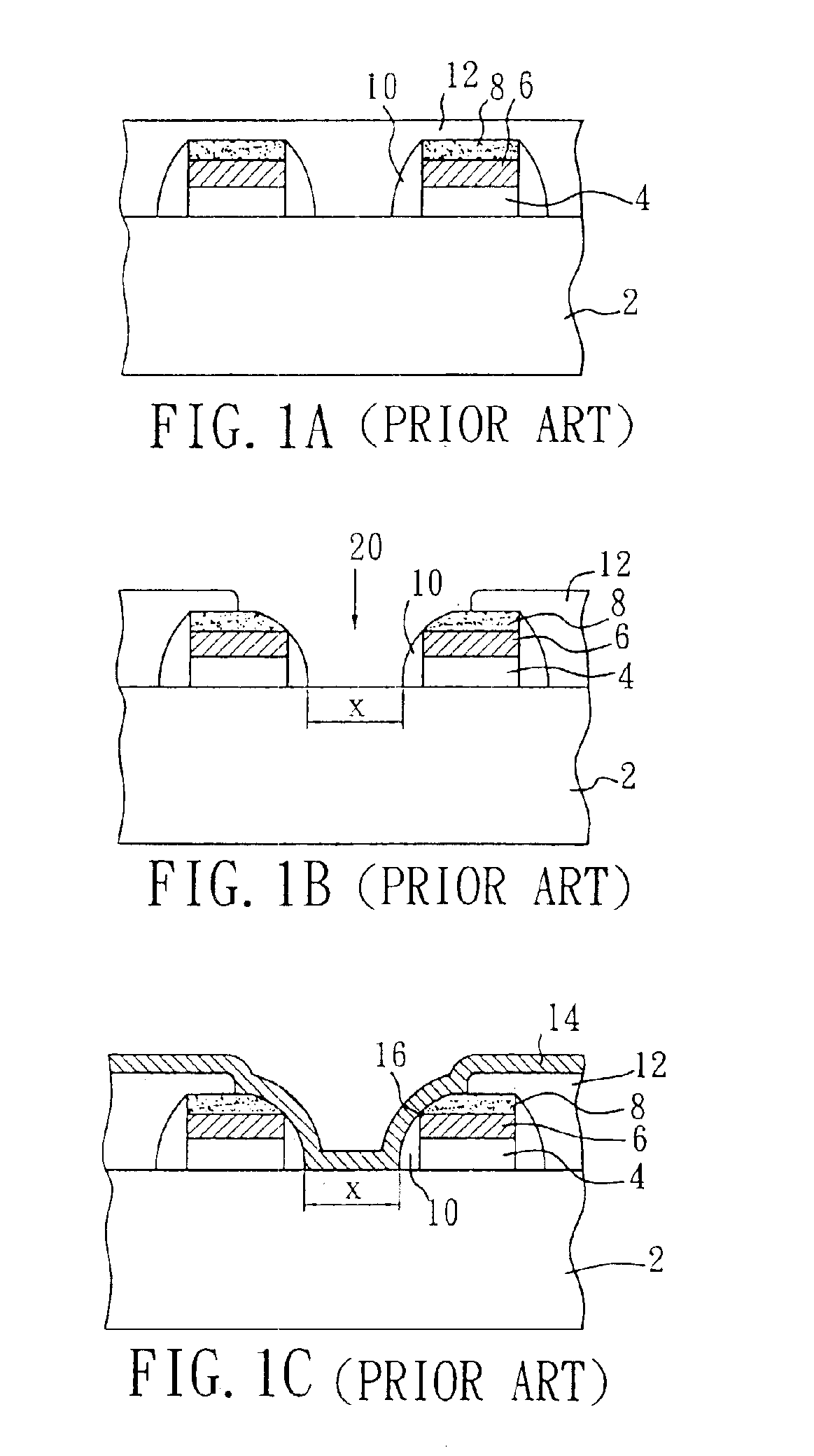

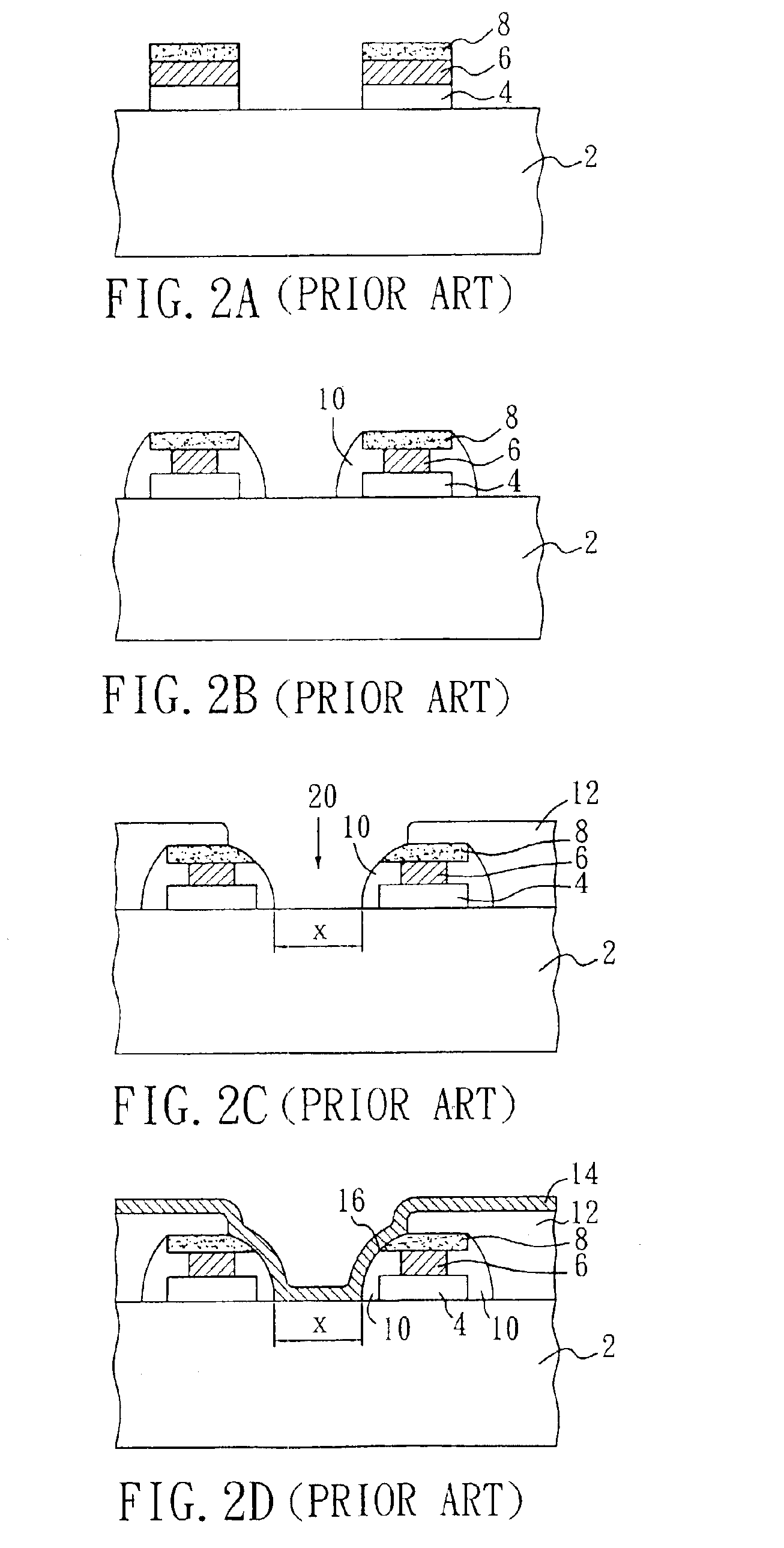

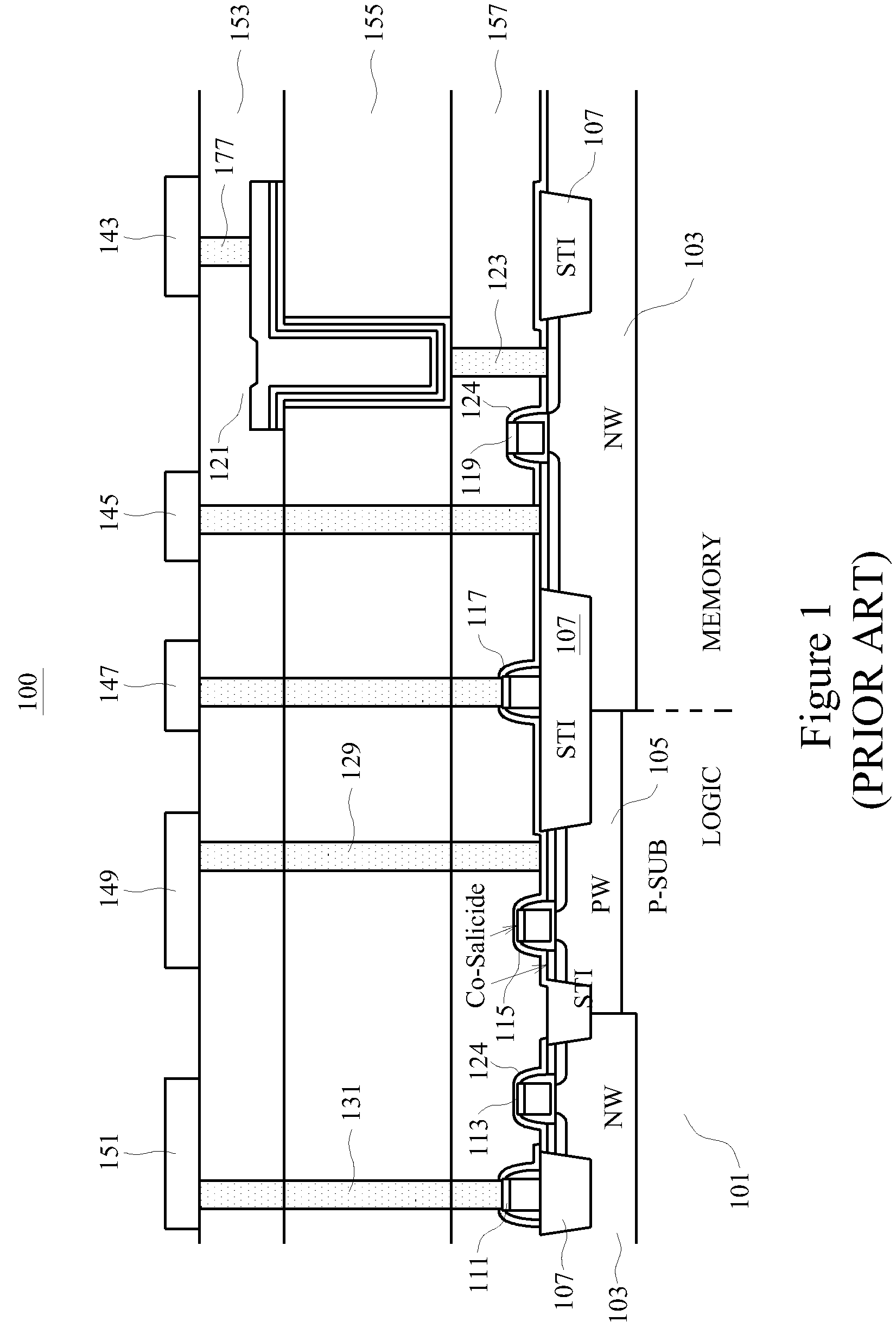

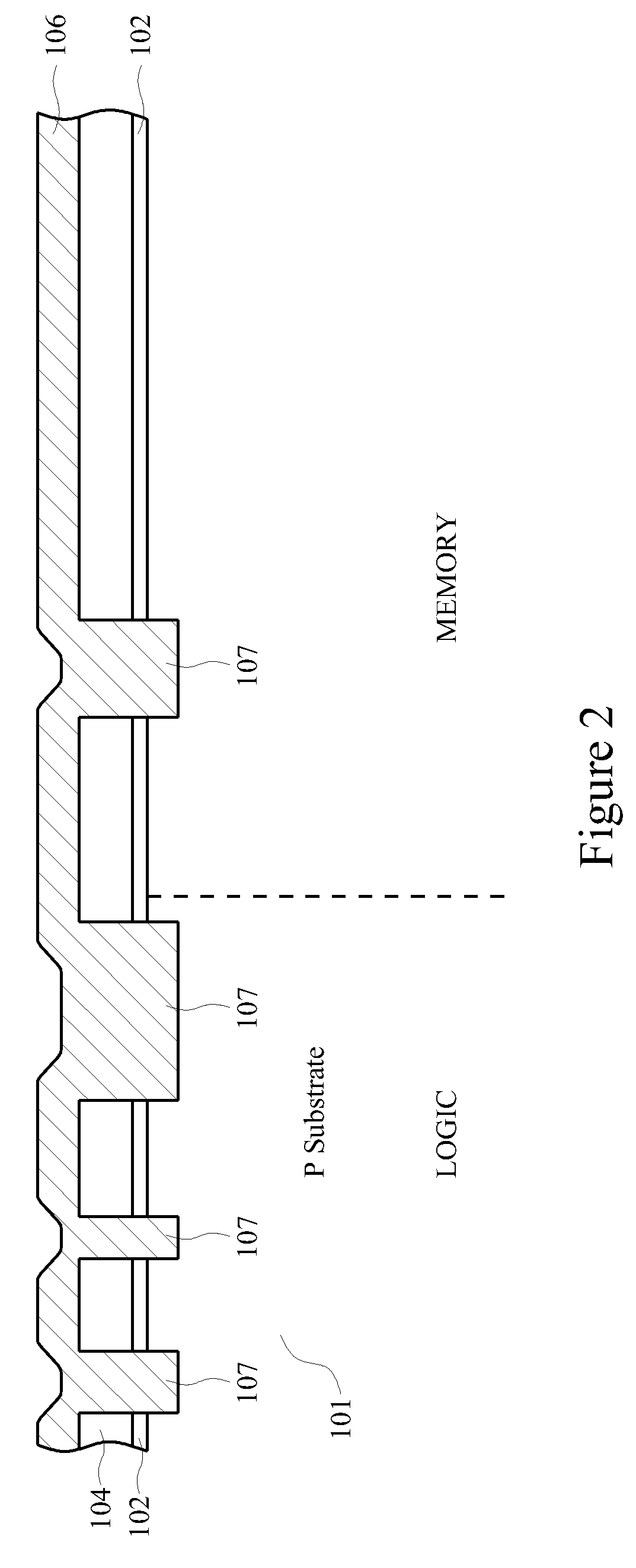

Method of forming self-aligned contact structure with locally etched gate conductive layer

InactiveUS6855610B2Reduce resistanceLarge processing windowSemiconductor/solid-state device detailsSolid-state devicesBit lineDielectric layer

A method of forming a self-aligned contact structure with a locally etched conductive layer comprises the steps of: preparing a substrate formed with gate structures comprising a first conductive layer, a second conductive layer, and an insulating layer; depositing a photoresist material layer on the substrate; performing a lithographic step with a bit-line contact node photomask or a bit-line contact photomask to expose a portion of the surface of the substrate; etching the exposed second conductive layer with an etchant; removing the remaining photoresist material layer; forming a sidewall spacer on the sidewalls of each gate structure; forming a dielectric layer to cover the substrate; and performing lithographic and etching steps to remove the dielectric layer and to form self-aligned contact structure.

Owner:PROMOS TECH INC

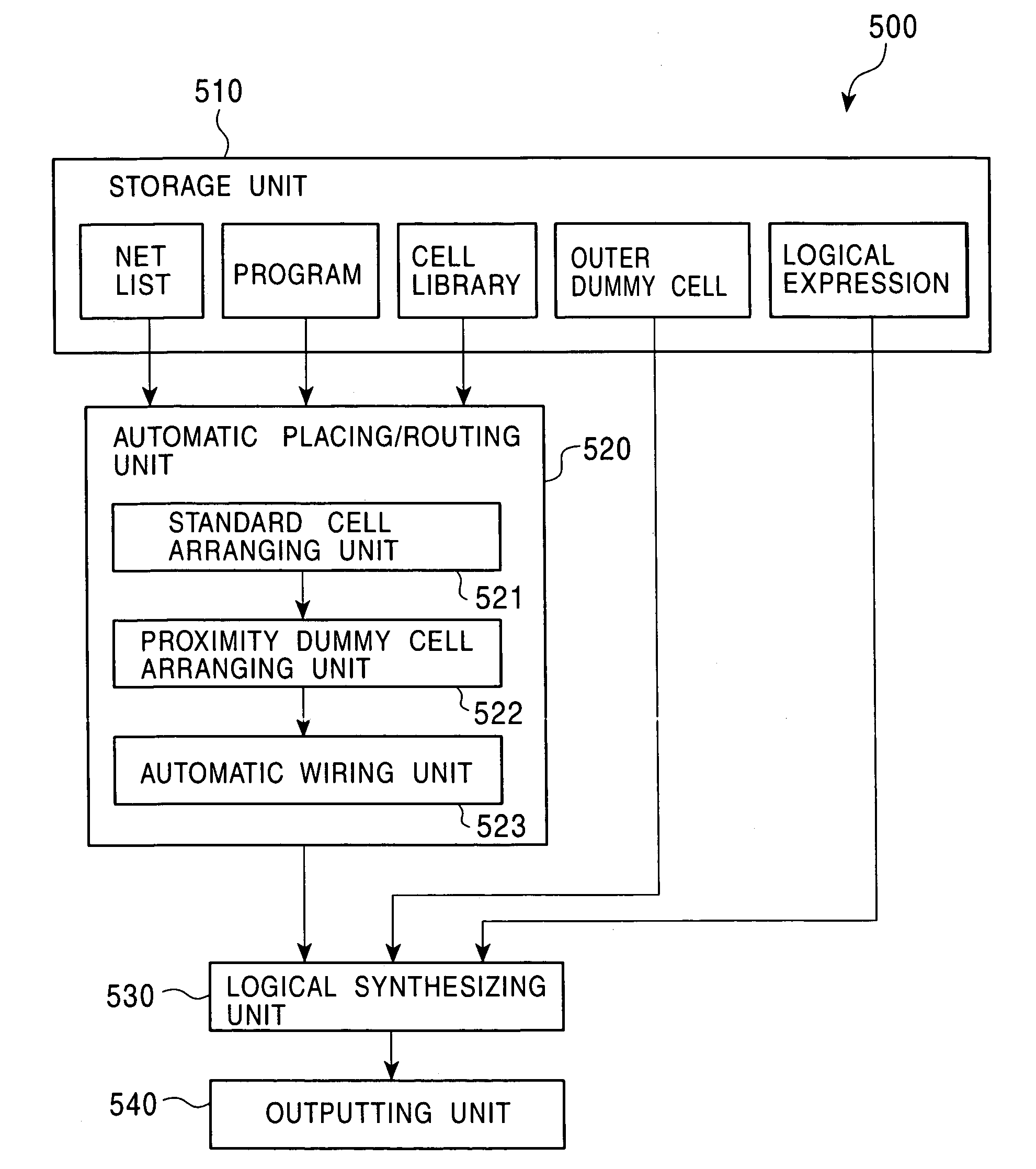

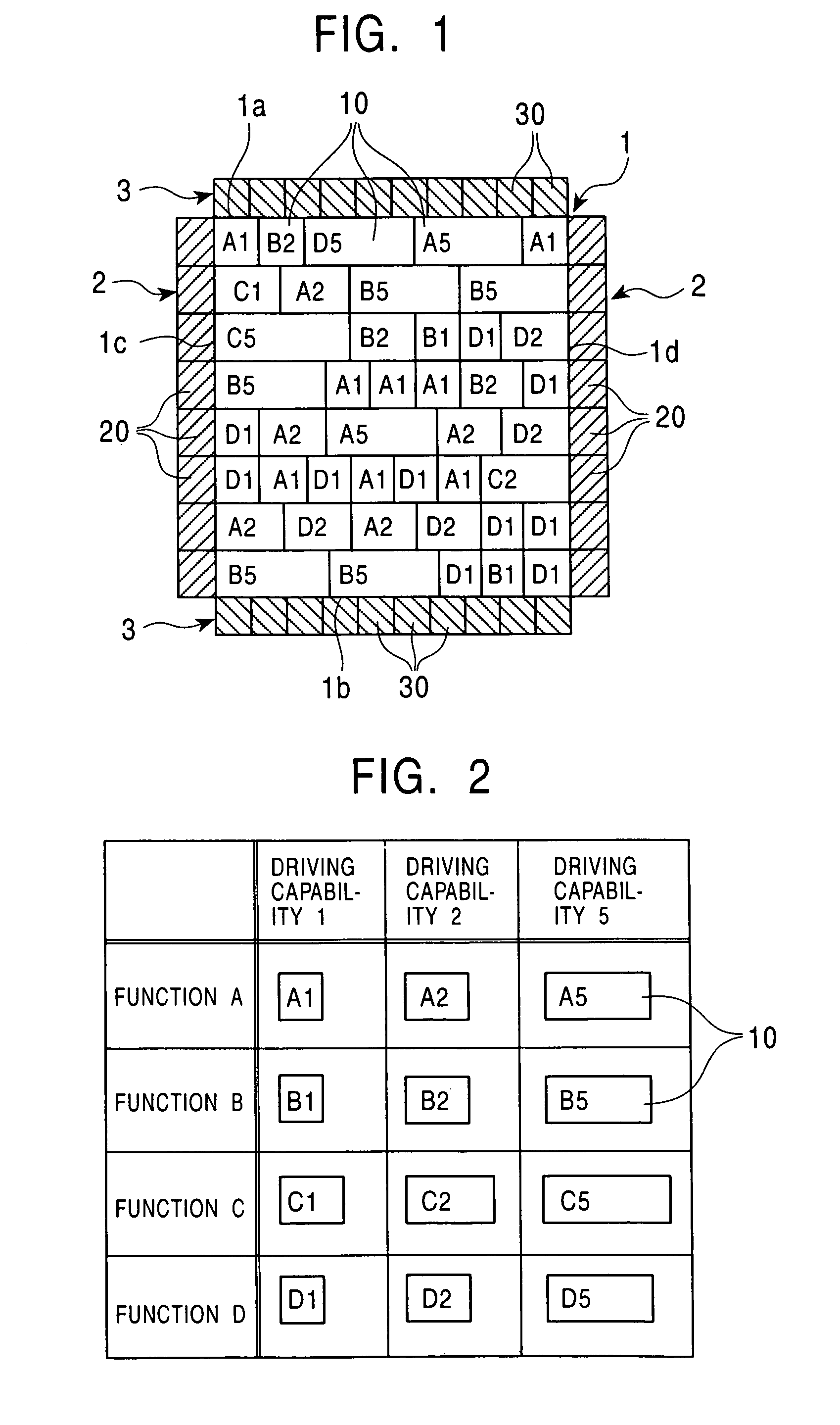

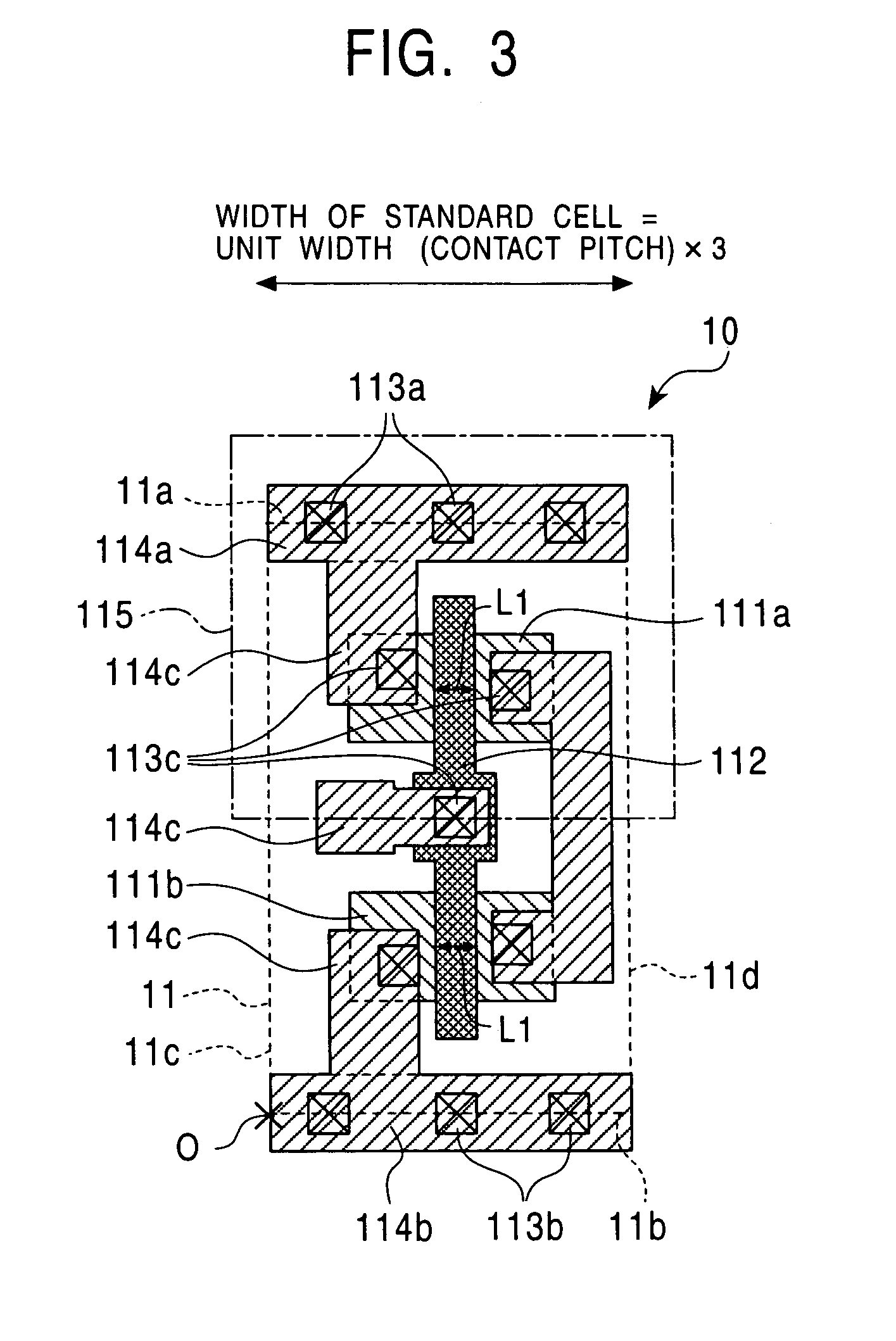

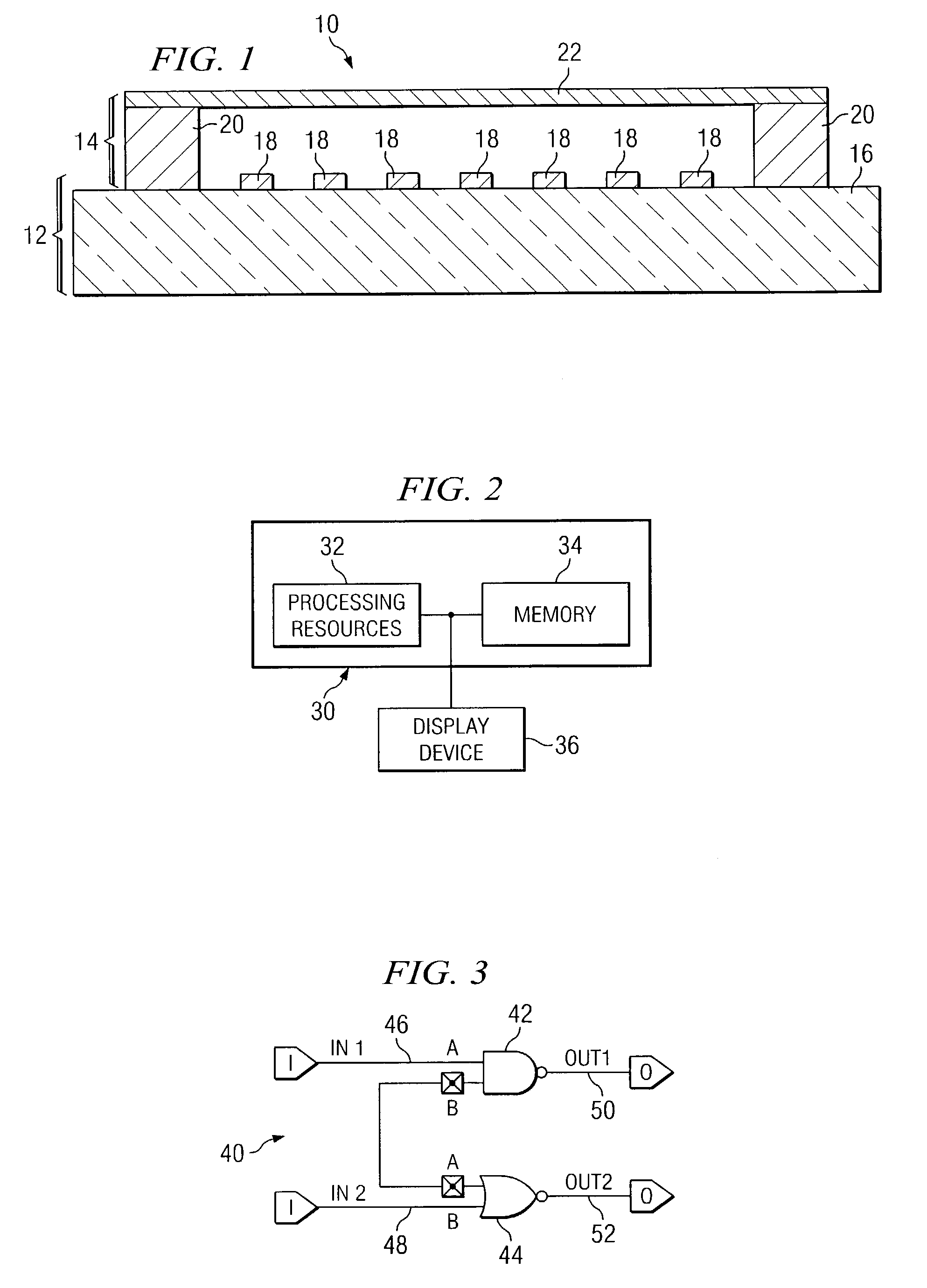

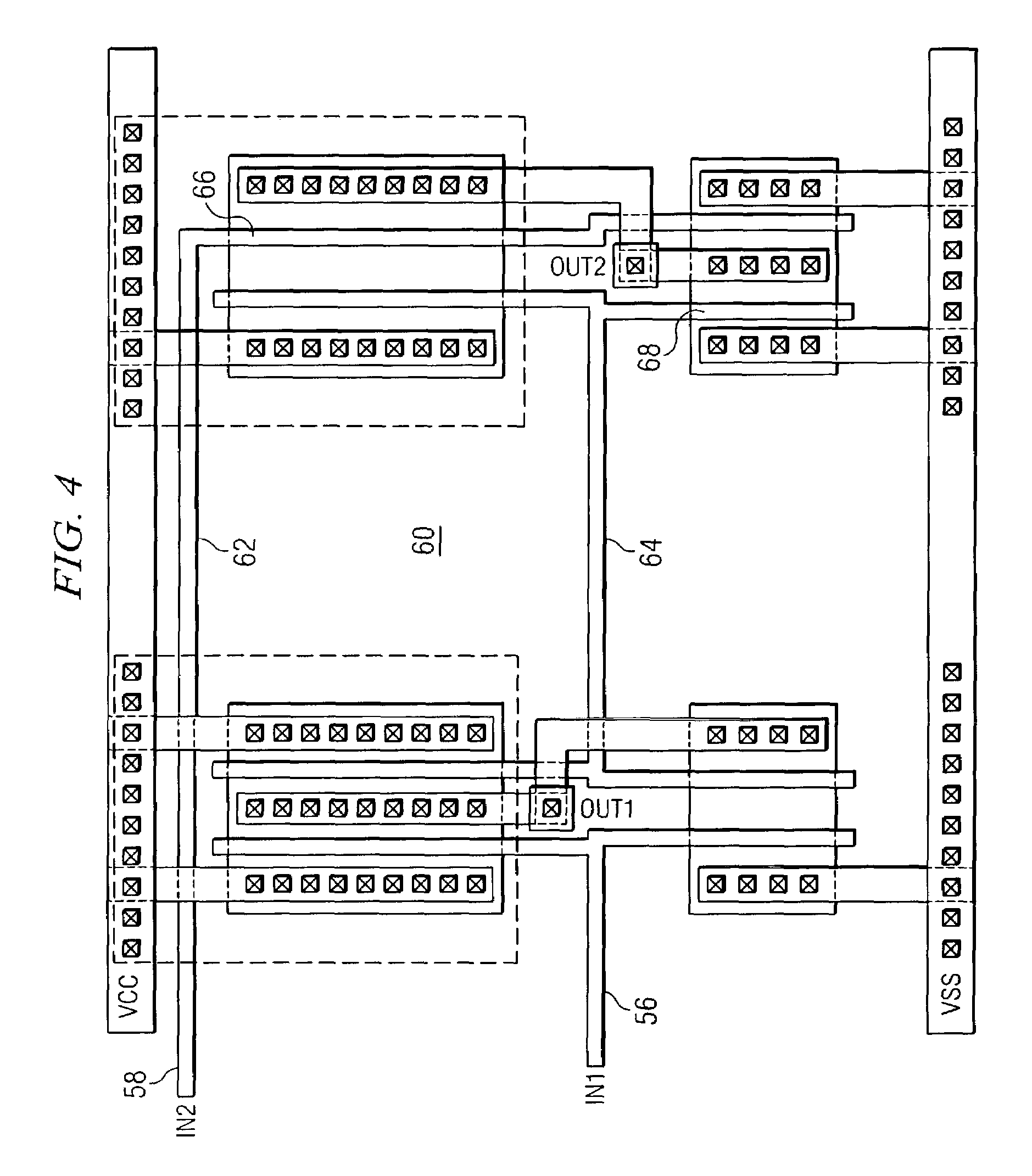

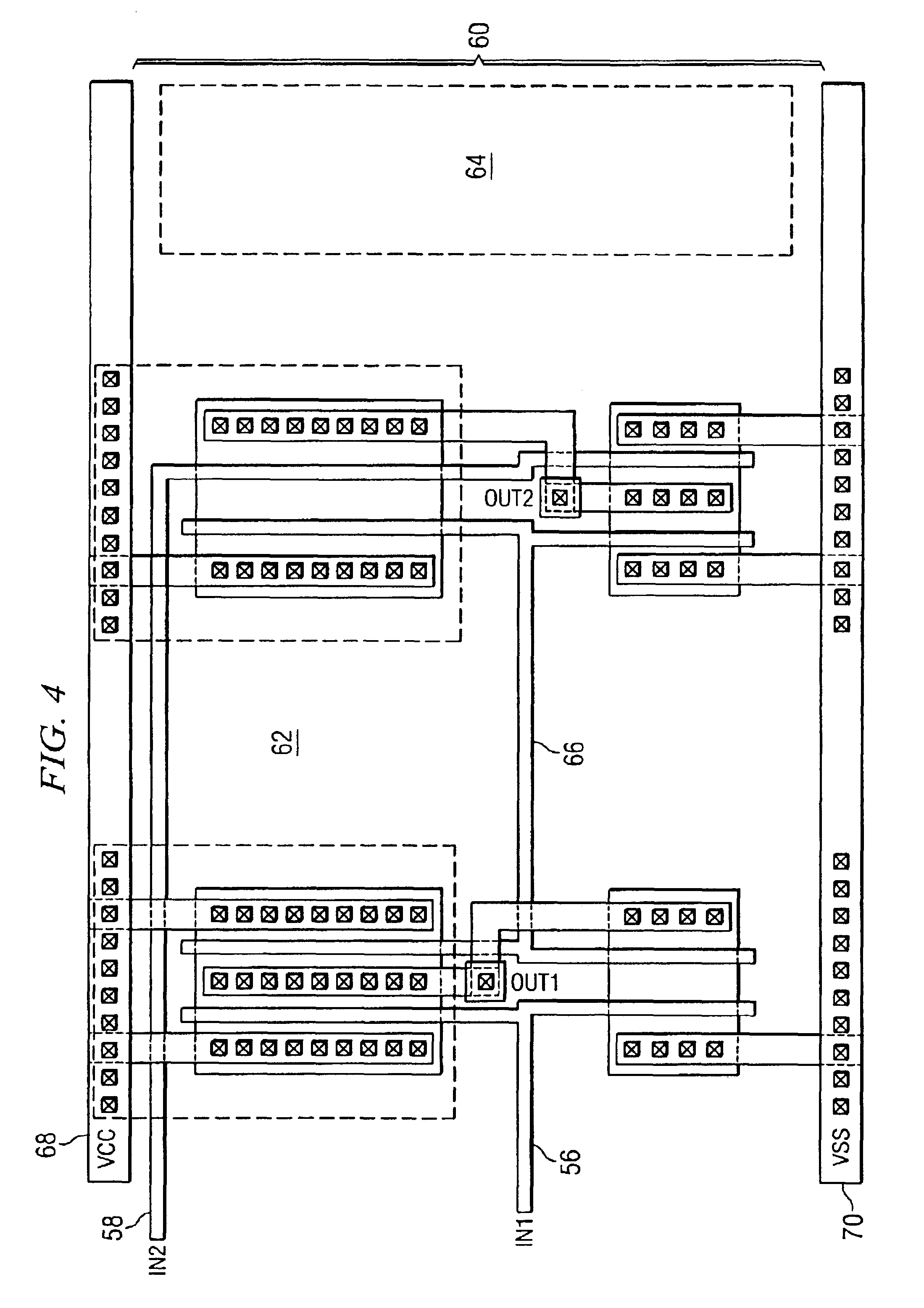

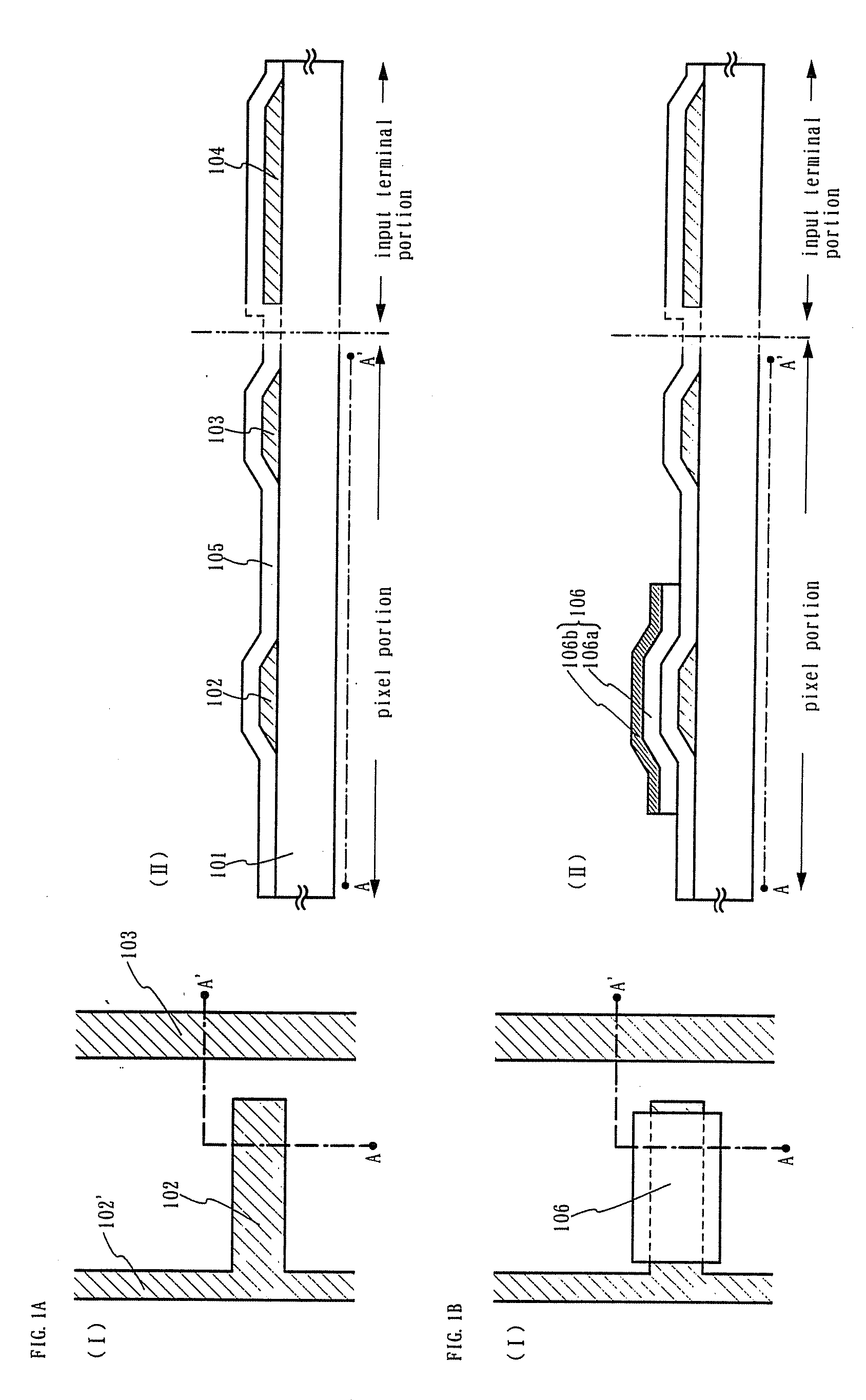

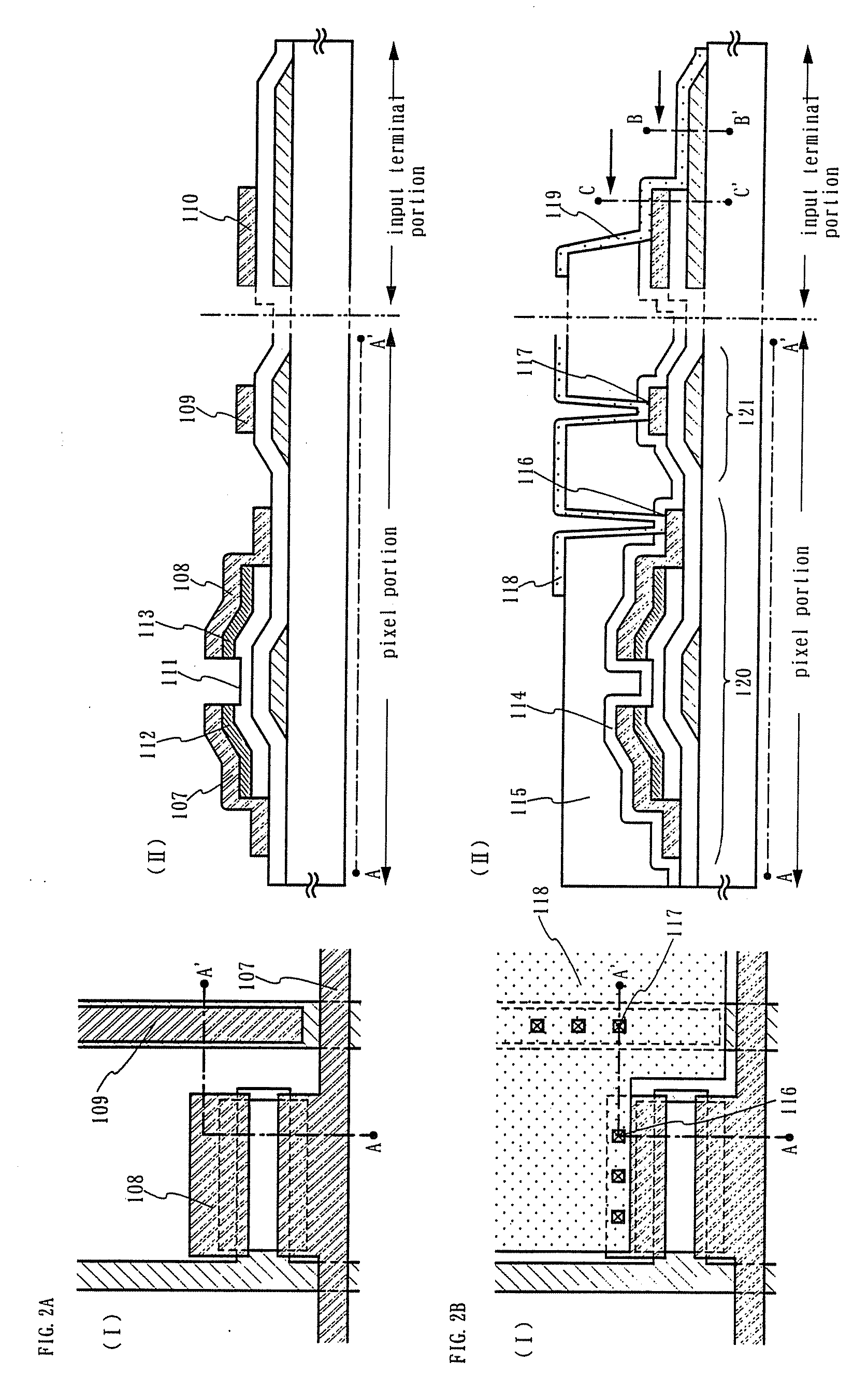

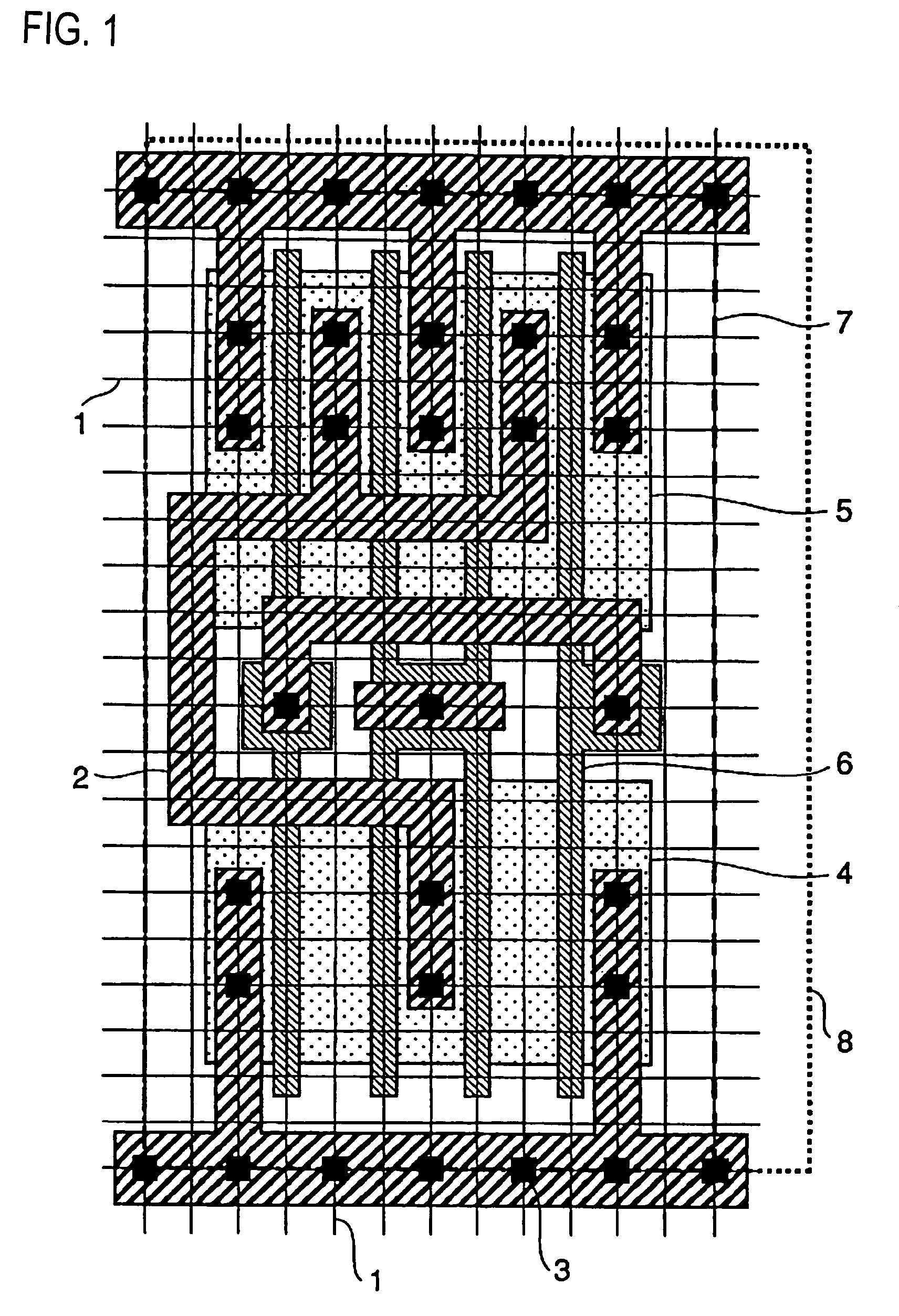

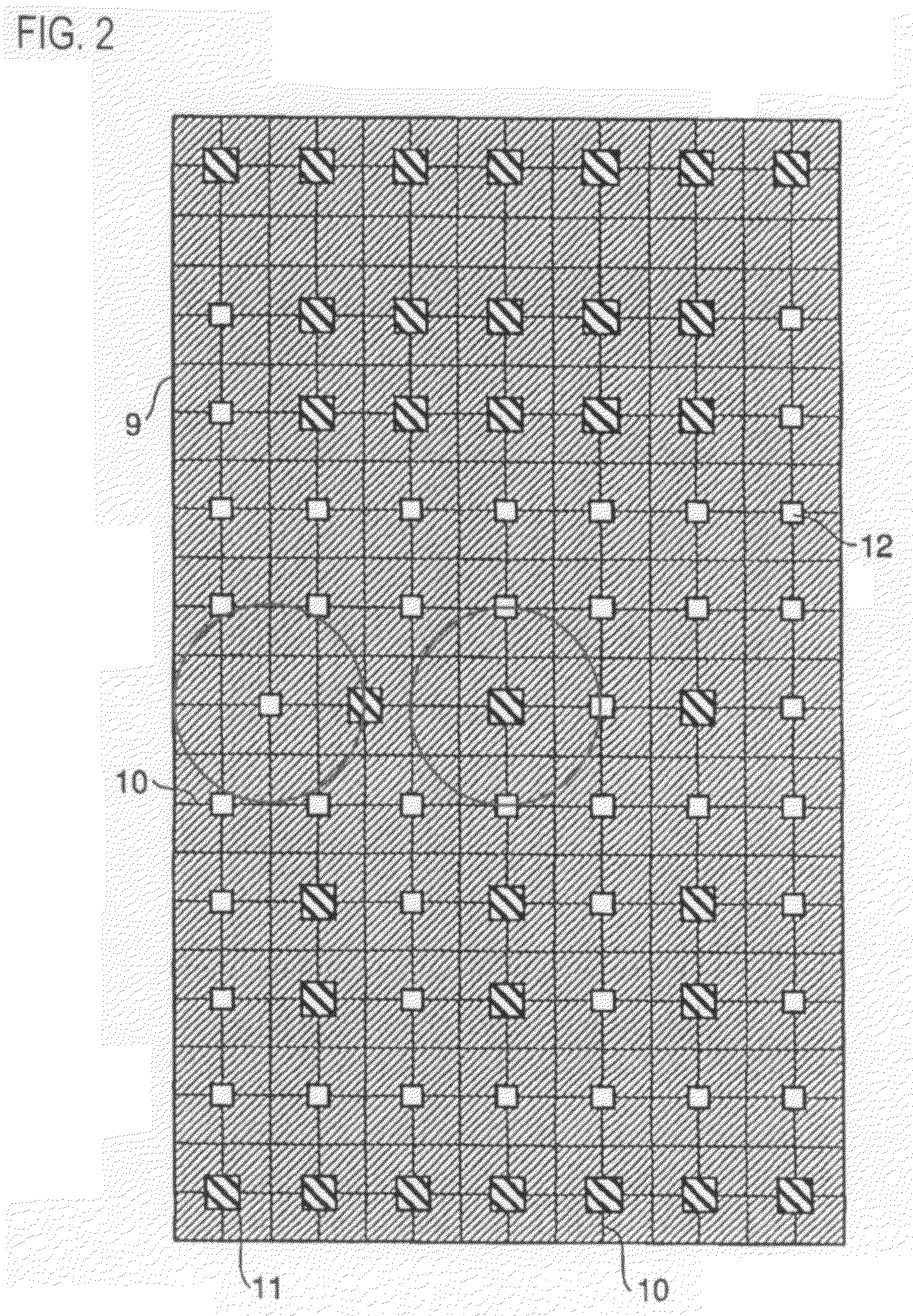

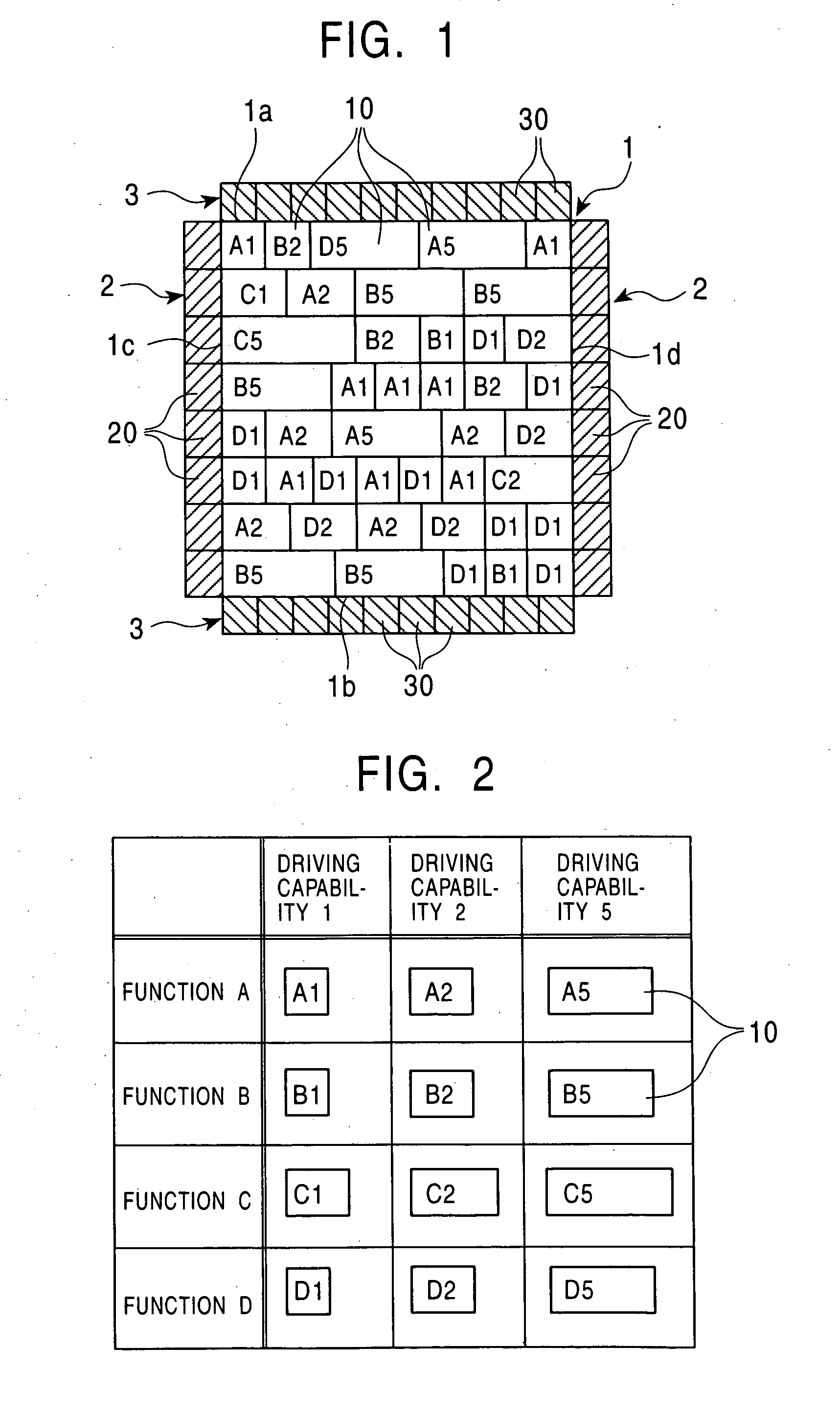

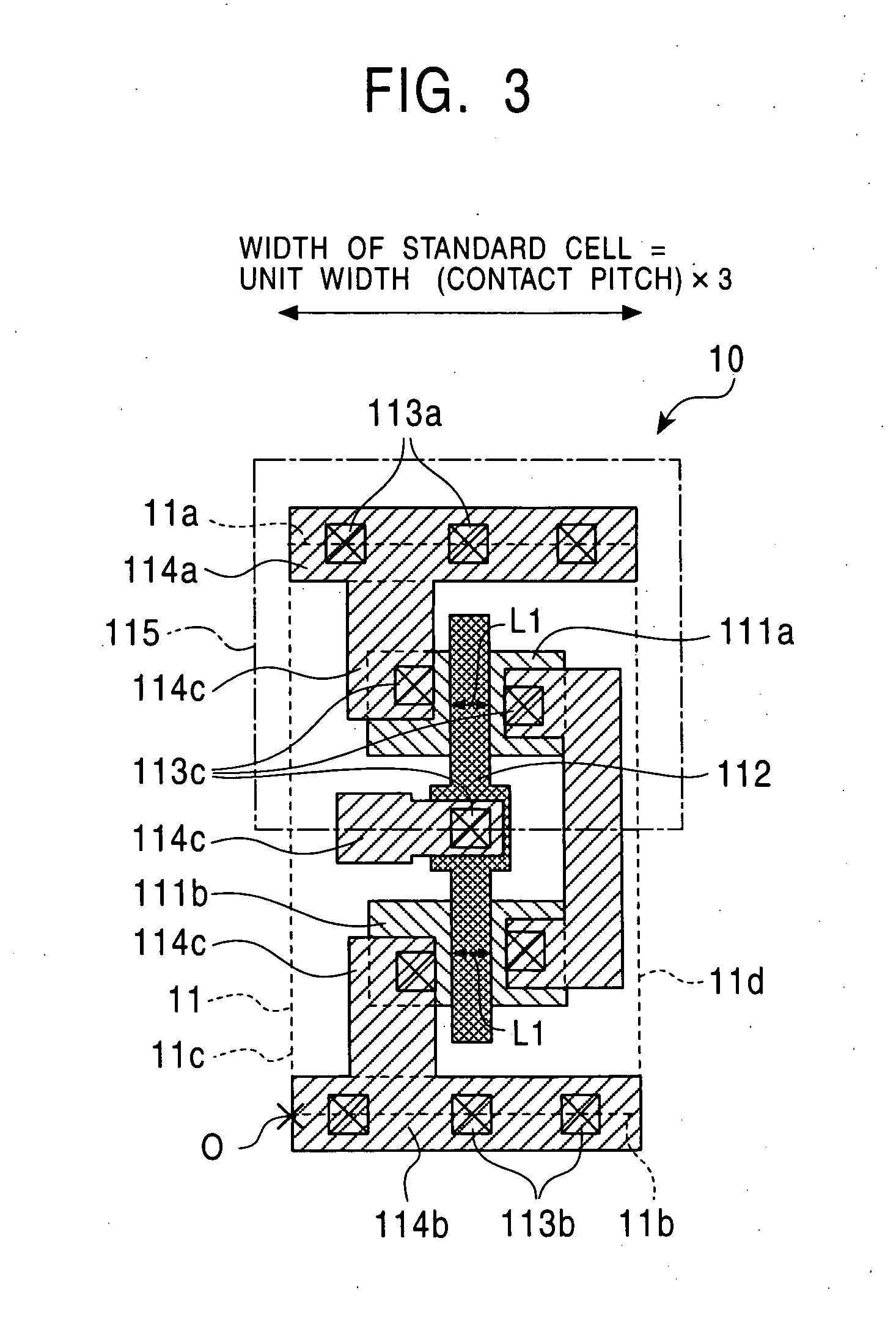

Layout method of semiconductor integrated circuit, layout structure thereof, and photomask for forming the layout structure

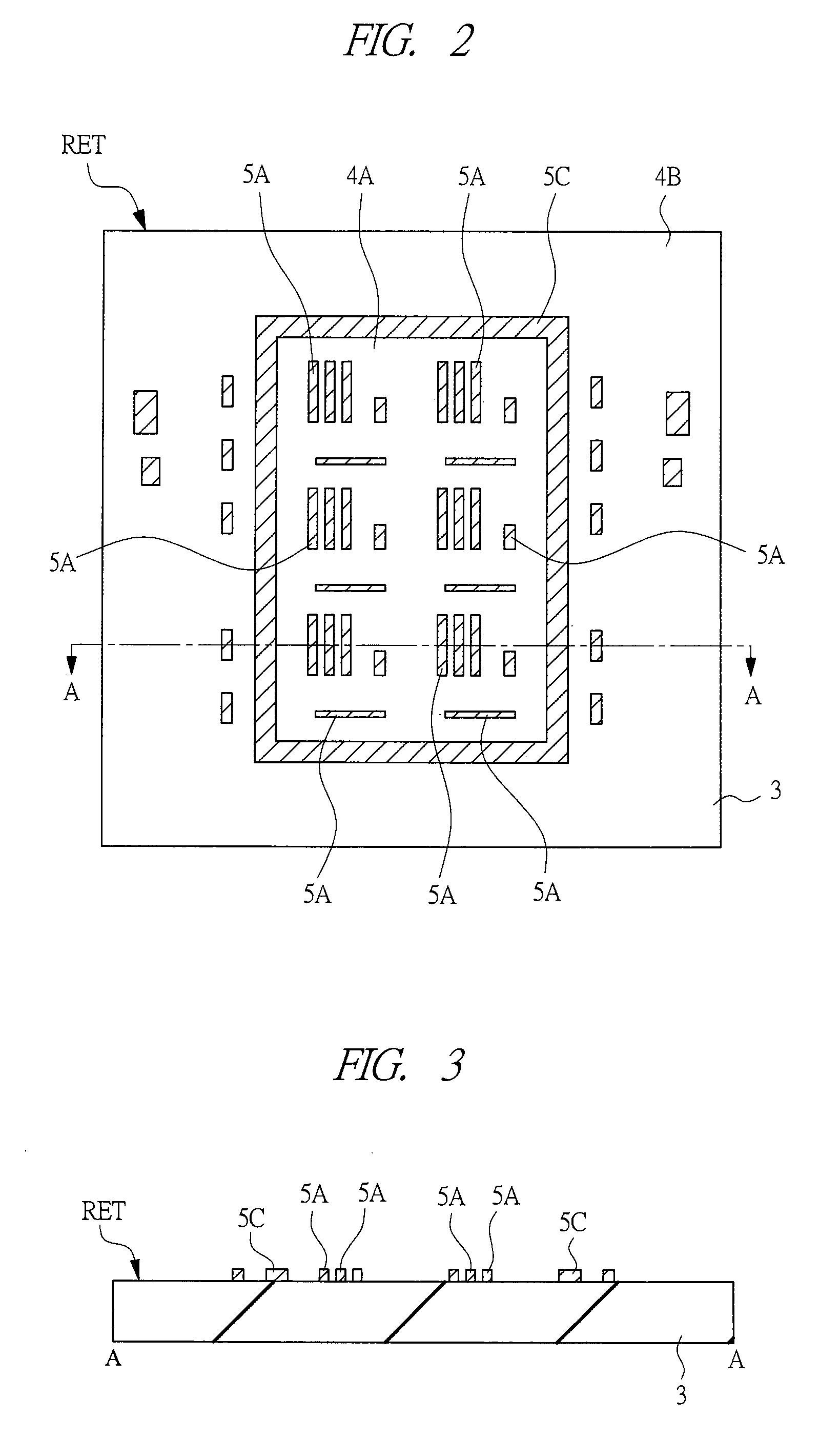

ActiveUS7137092B2Eliminate biasHigh dimensionalSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorPhotomask

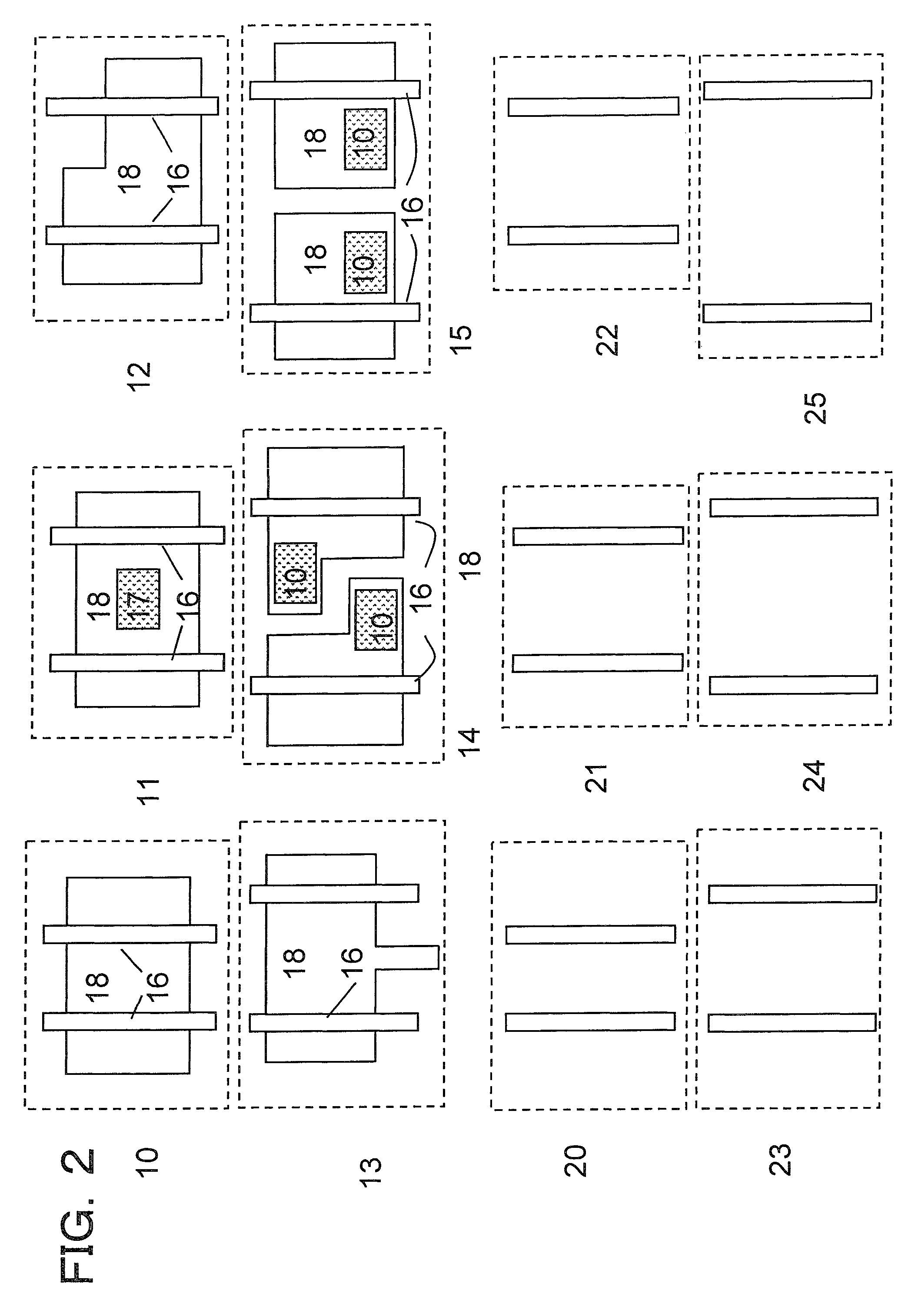

A plurality of standard cells 10 are arranged to form a channel-less standard cell array 1, which has vertical and horizontal sides. A plurality of first proximity dummy cells 20 are arranged along each of the vertical sides of the standard cell array to form a first proximity dummy bands 20 such that the upper and lower sides of the first proximity dummy cells are in contact with each other and such that the left or right side of each of the first proximity dummy cells is in contact with the vertical side of the standard cell array 1. Furthermore, a plurality of second proximity dummy bands are arranged along each of the horizontal sides of the standard cell array to form a second proximity dummy bands such that the upper or lower side of each of the second proximity dummy cells is in contact with the horizontal side of the standard cell 1.

Owner:KAWASAKI MICROELECTRONICS

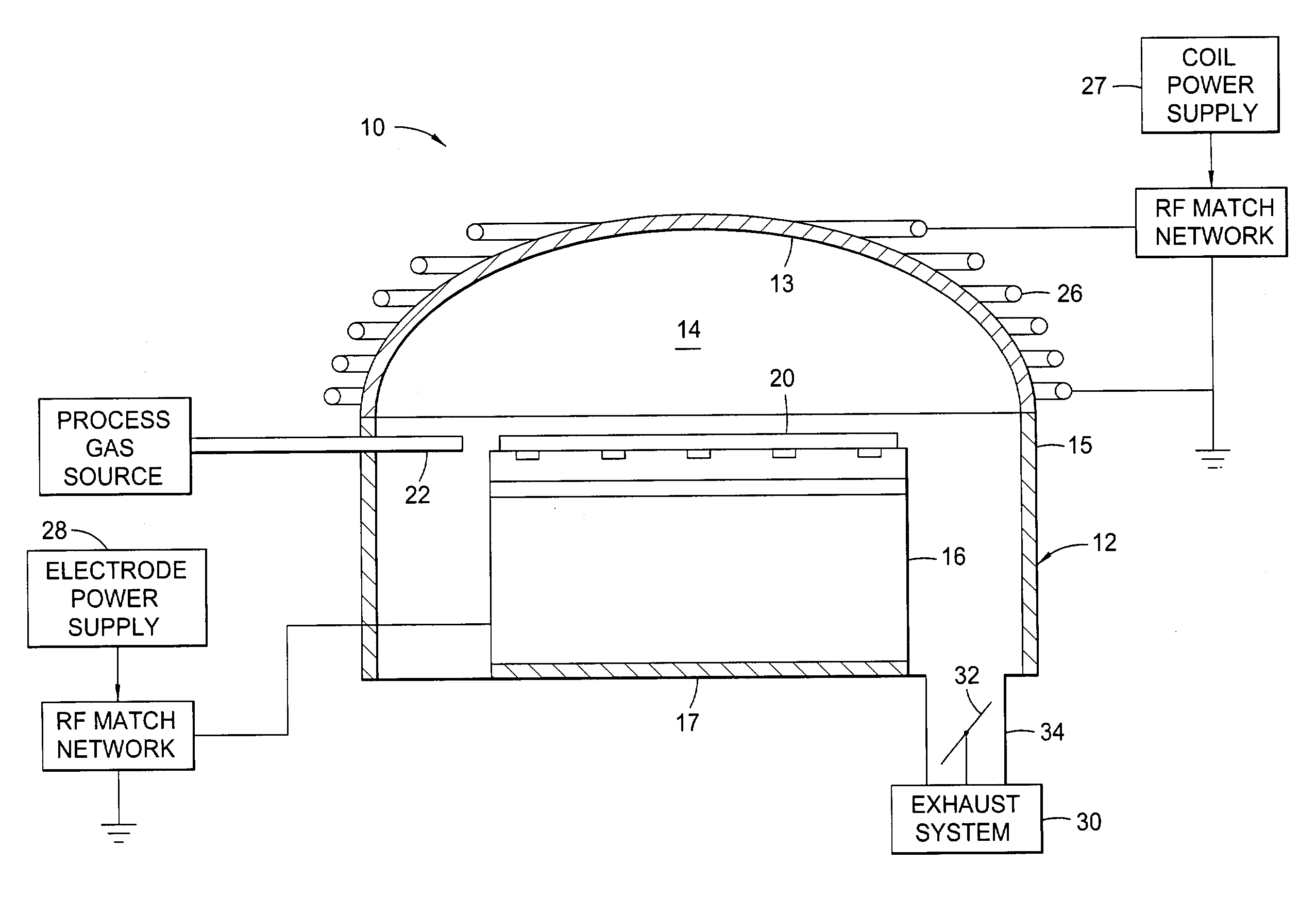

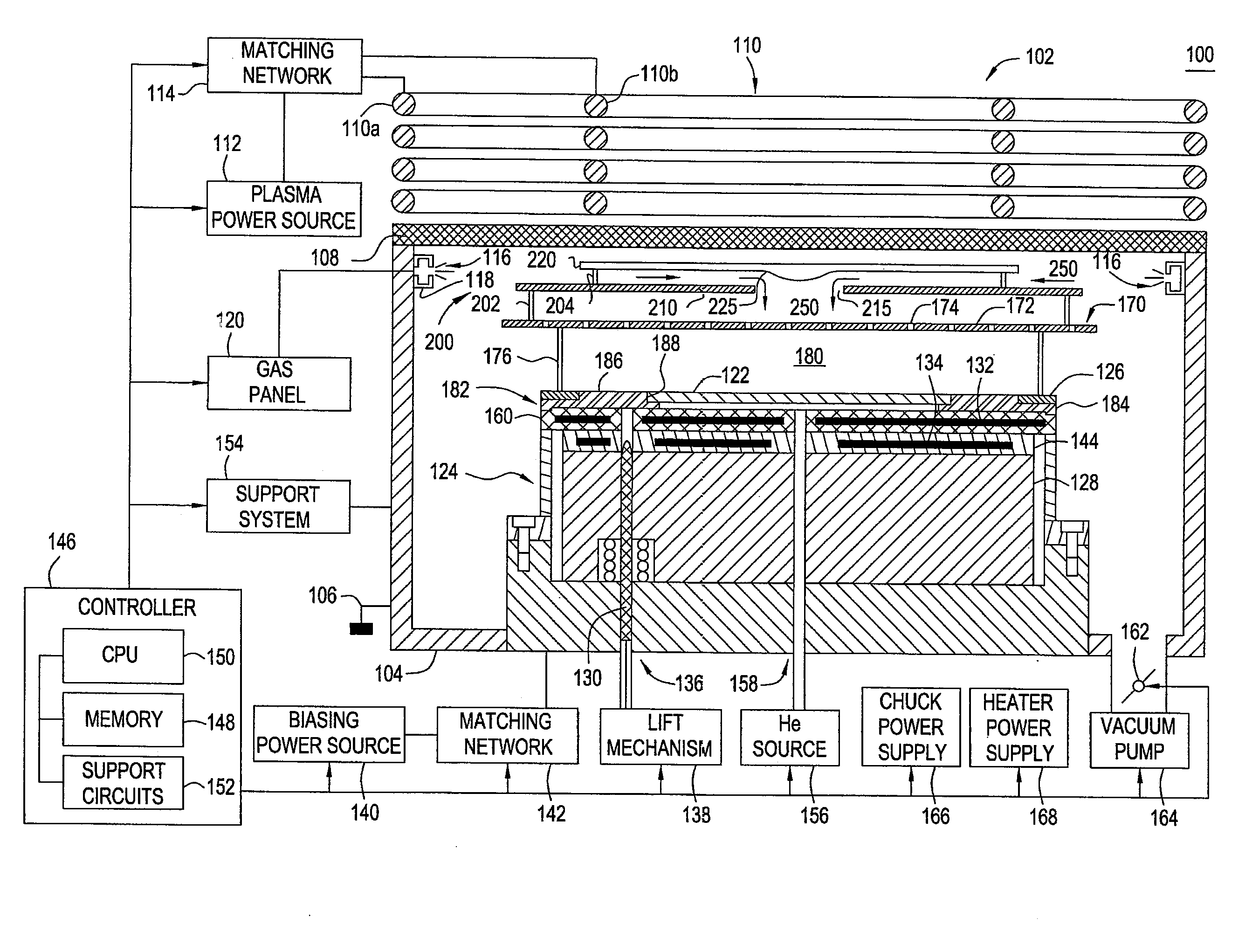

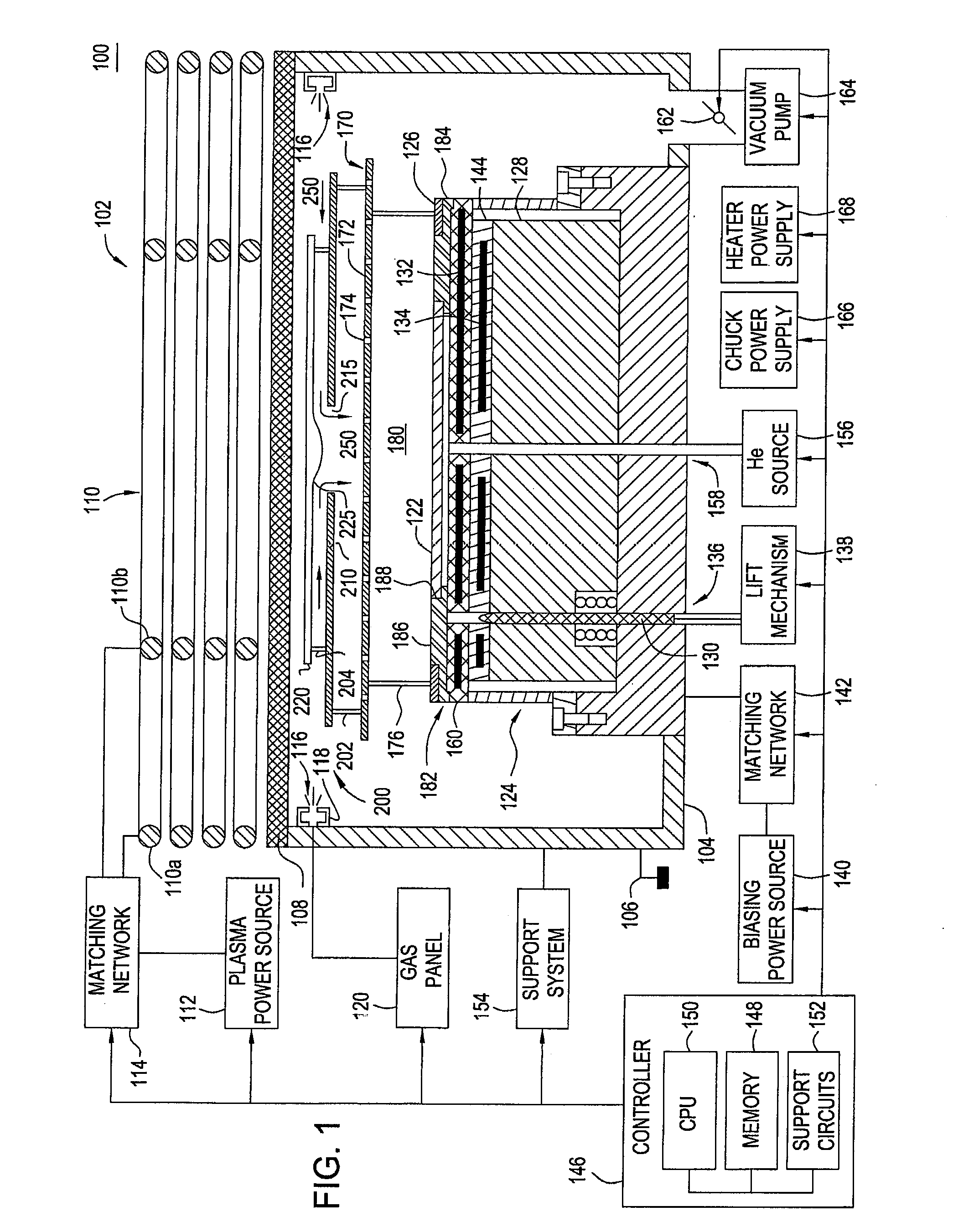

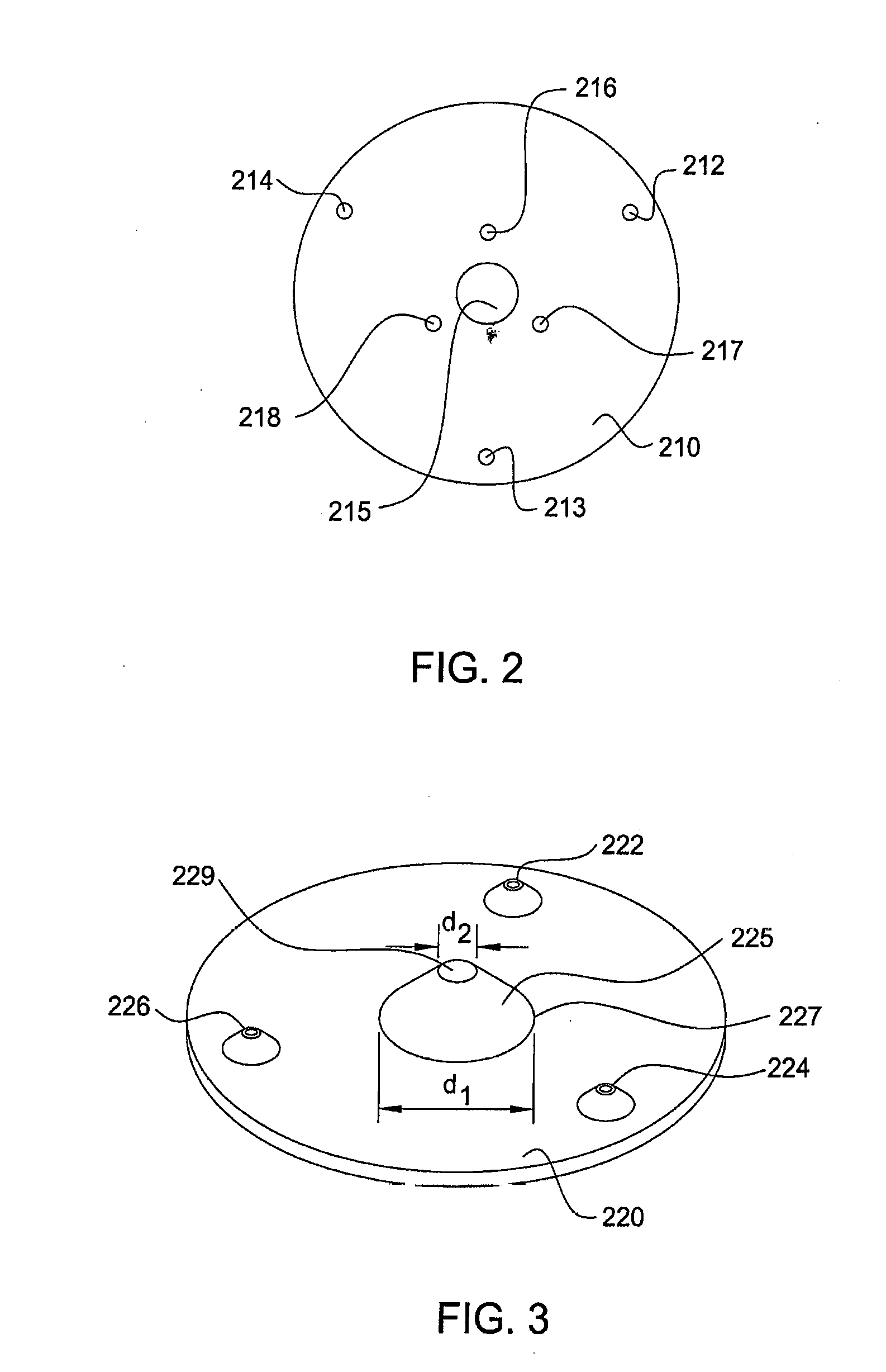

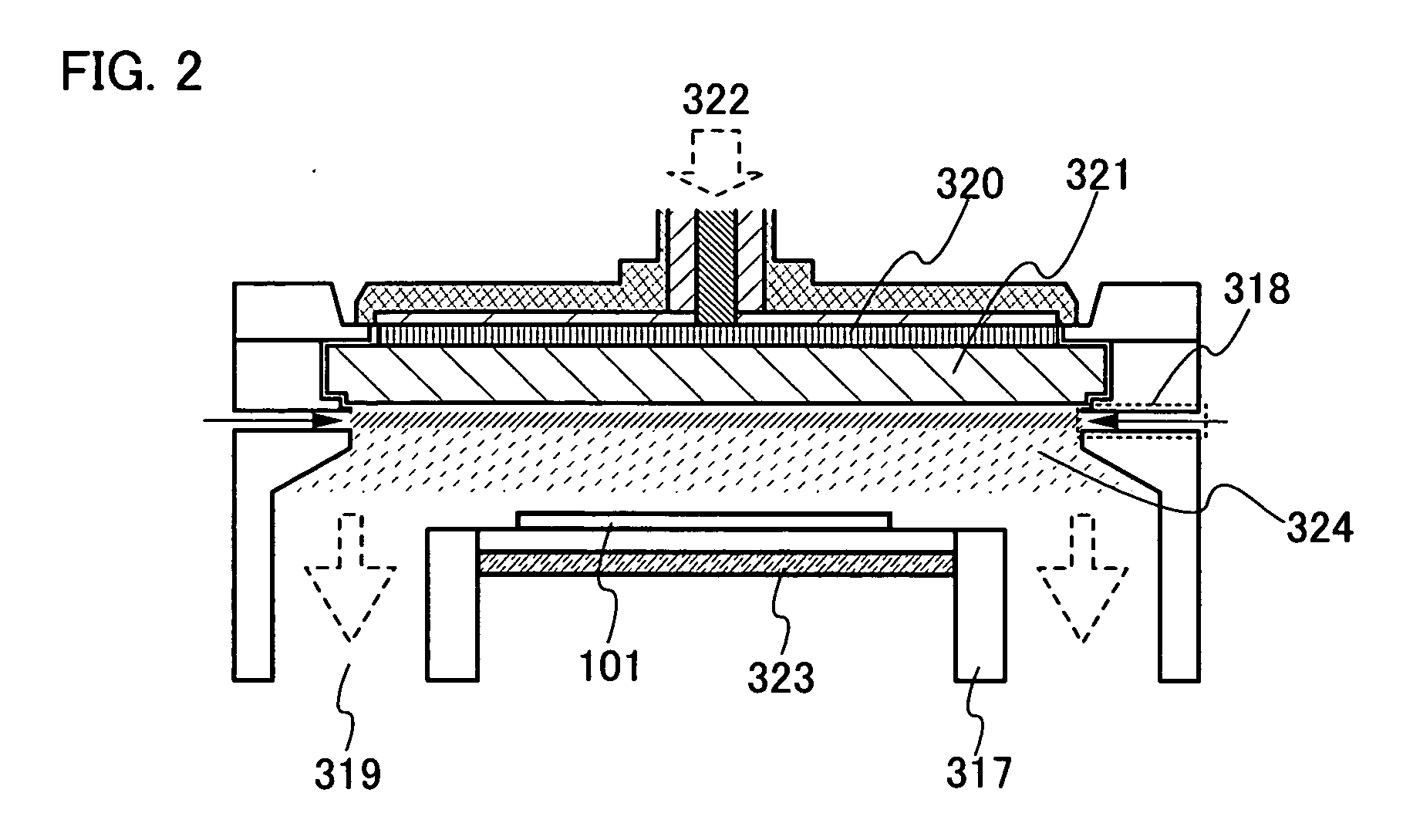

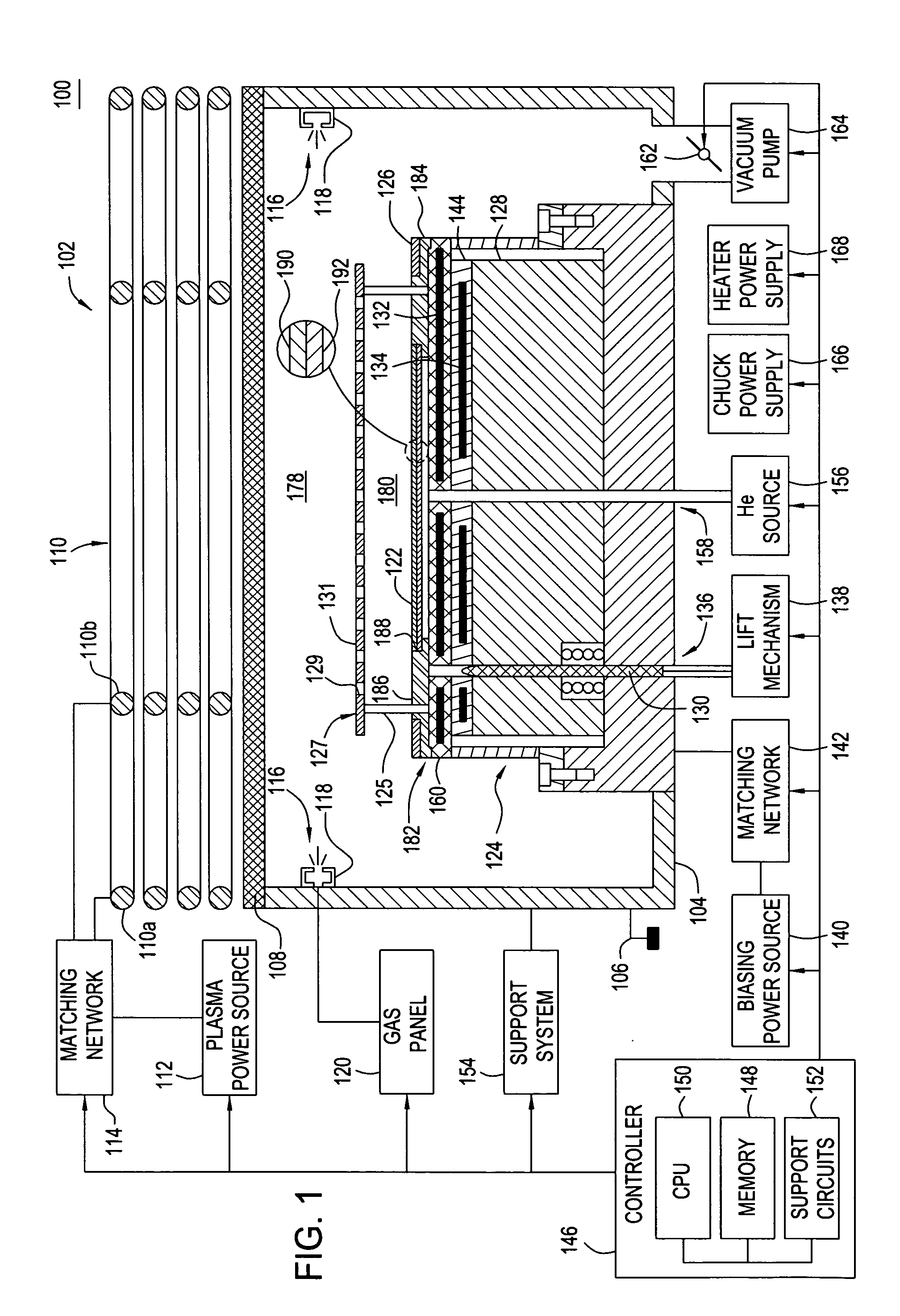

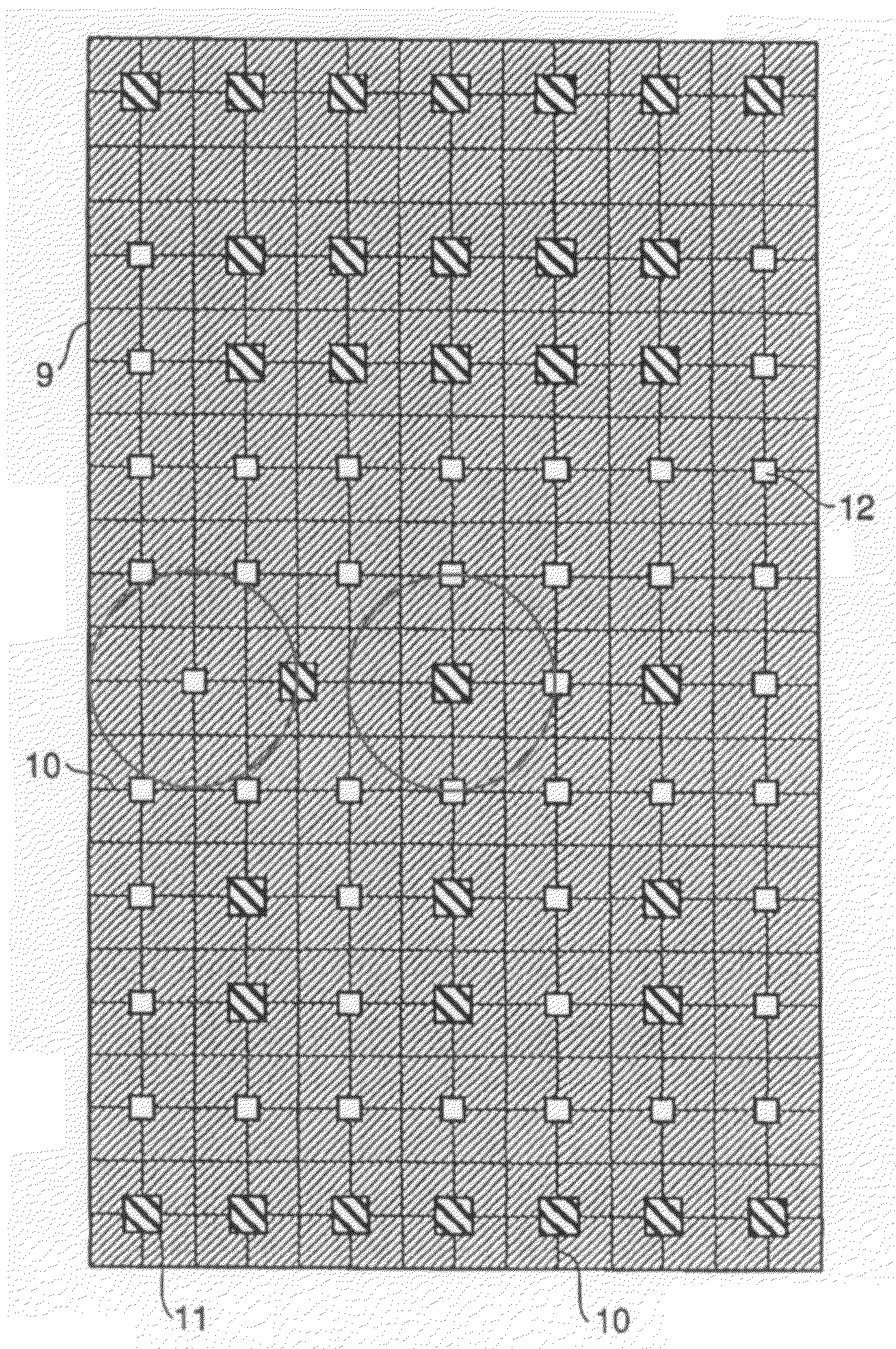

Method and apparatus for photomask plasma etching

A method and apparatus for etching photomasks is provided herein. In one embodiment, the apparatus comprises a process chamber having a support pedestal adapted for receiving a photomask. An ion-neutral shield is disposed above the pedestal and a deflector plate assembly is provided above the ion-neutral shield. The deflector plate assembly defines a gas flow direction for process gases towards the ion-neutral shield, while the ion-neutral shield is used to establish a desired distribution of ion and neutral species in a plasma for etching the photomask.

Owner:APPLIED MATERIALS INC

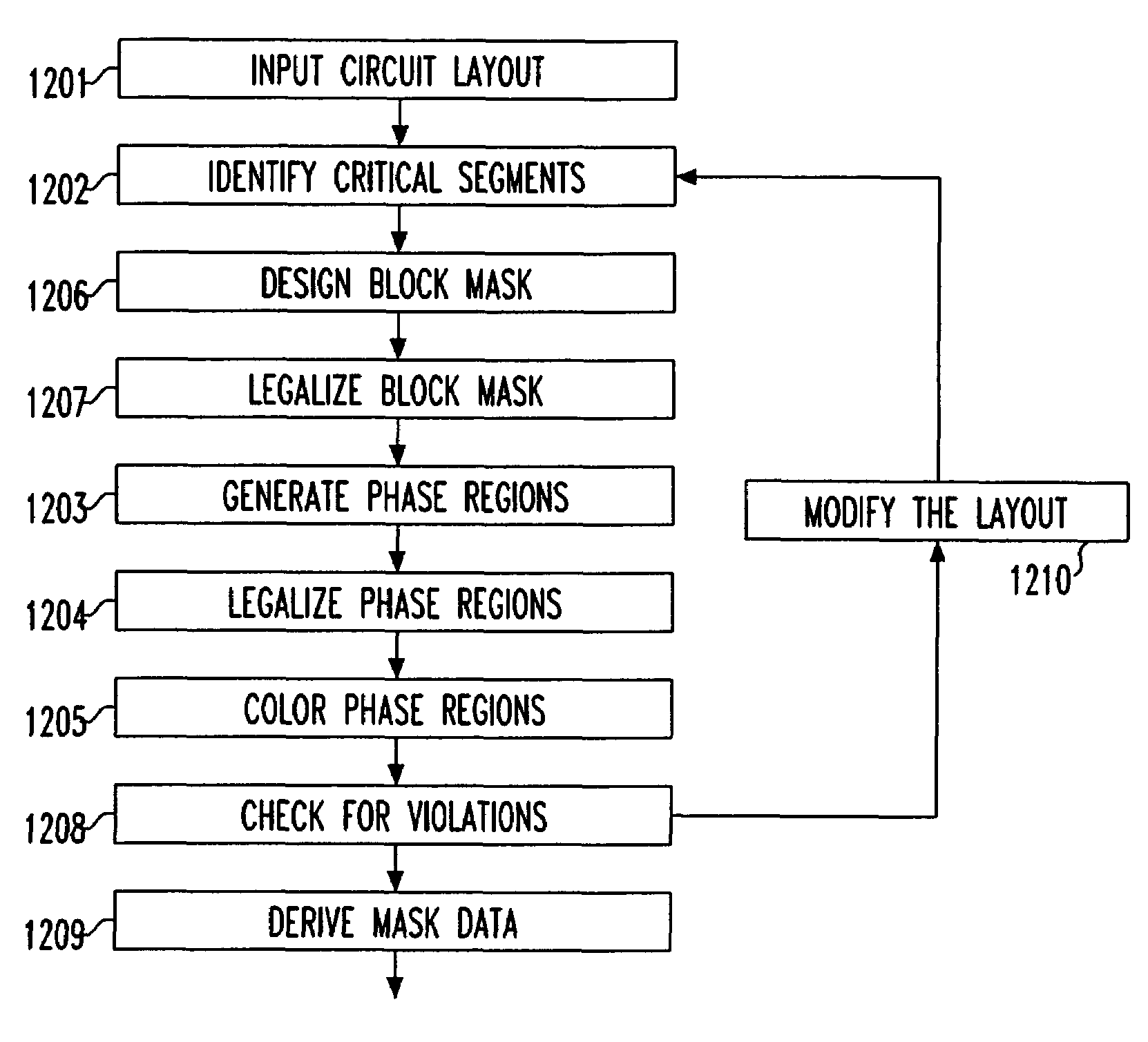

Generating mask patterns for alternating phase-shift mask lithography

InactiveUS6993741B2Photosensitive materialsSemiconductor/solid-state device manufacturingResistEngineering

A method of generating patterns of a pair of photomasks from a data set defining a circuit layout to be provided on a substrate includes identifying critical segments of the circuit layout to be provided on the substrate. Block mask patterns are generated and then legalized based on the identified critical segments. Thereafter, phase mask patterns are generated, legalized and colored. The legalized block mask patterns and the legalized phase mask patterns that have been colored define features of a block mask and an alternating phase shift mask, respectively, for use in a dual exposure method for patterning features in a resist layer of a substrate.

Owner:GLOBALFOUNDRIES INC

Semiconductor device and manufacturing method thereof

InactiveUS20060275710A1Reduce light intensityImprove routing densitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialContinuous wave laser beam

To provide a semiconductor device having a circuit with high operating performance and high reliability, and improve the reliability of the semiconductor device, thereby improving the reliability of an electronic device having the same. The aforementioned object is achieved by combining a step of crystallizing a semiconductor layer by irradiation with continuous wave laser beams or pulsed laser beams with a repetition rate of 10 MHz or more, while scanning in one direction; a step of photolithography with the use of a photomask or a leticle including an auxiliary pattern which is formed of a diffraction grating pattern or a semi-transmissive film having a function of reducing the light intensity; and a step of performing oxidation, nitridation, or surface-modification to the surface of the semiconductor film, an insulating film, or a conductive film, with high-density plasma with a low electron temperature.

Owner:SEMICON ENERGY LAB CO LTD

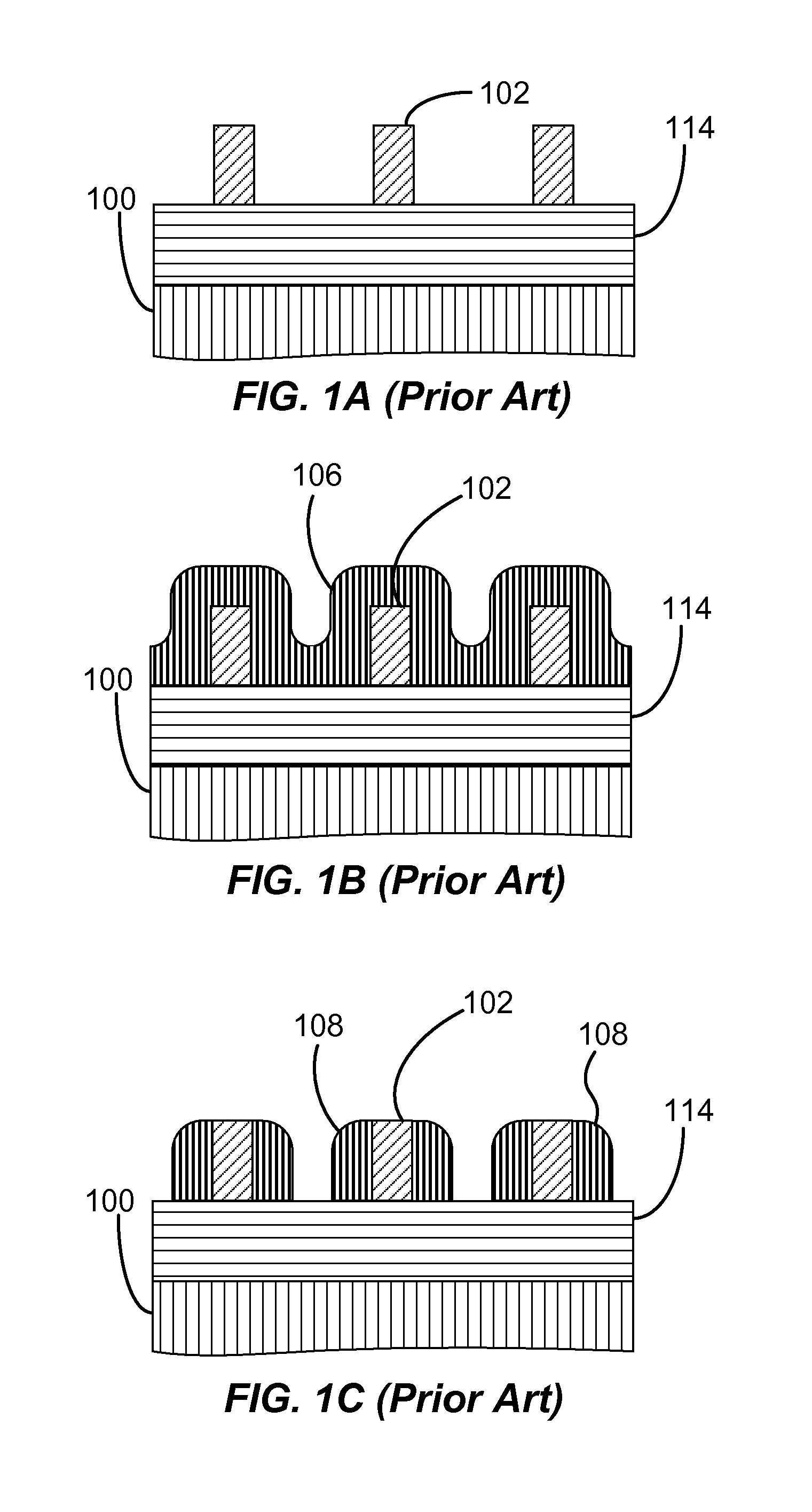

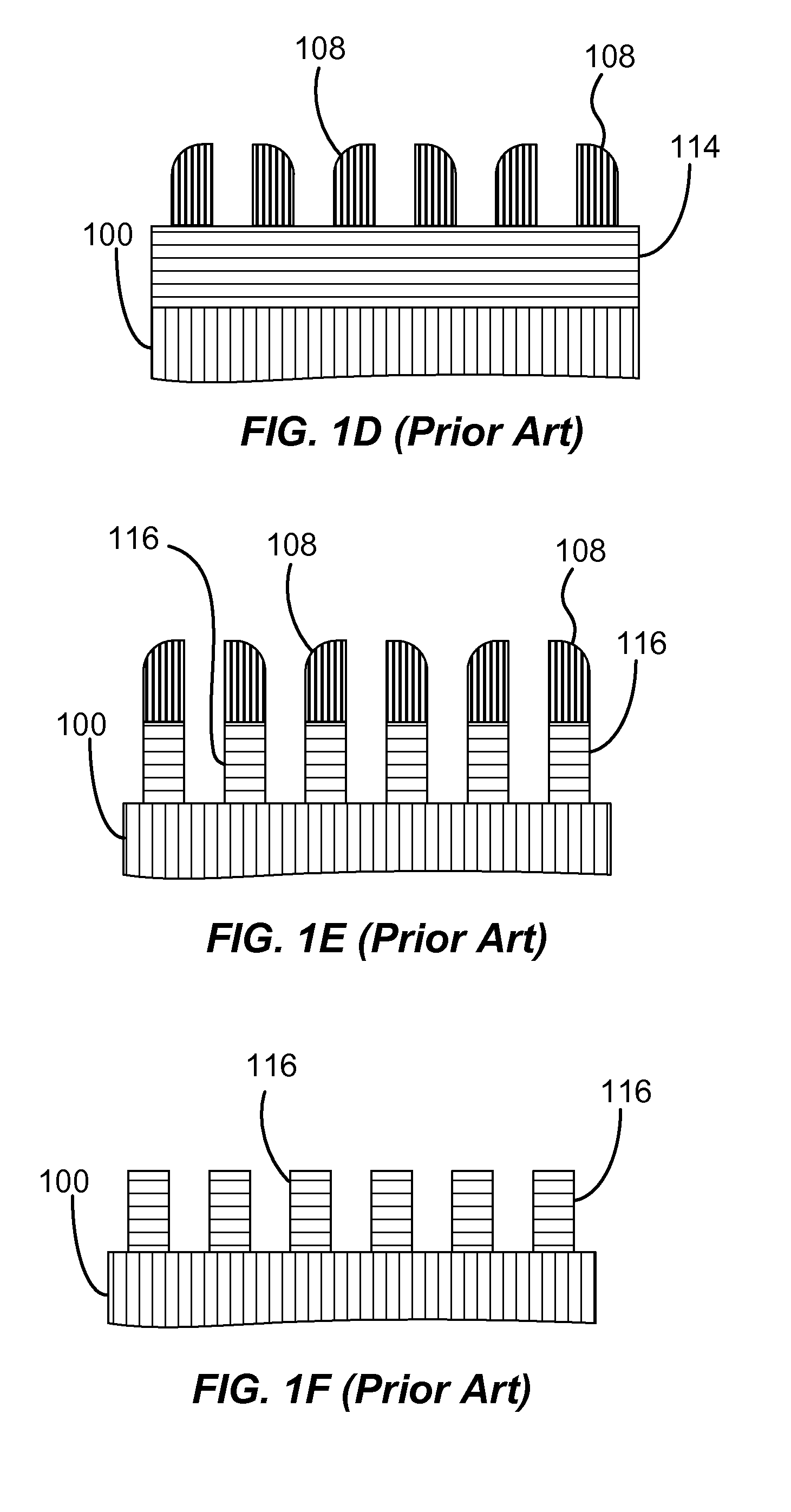

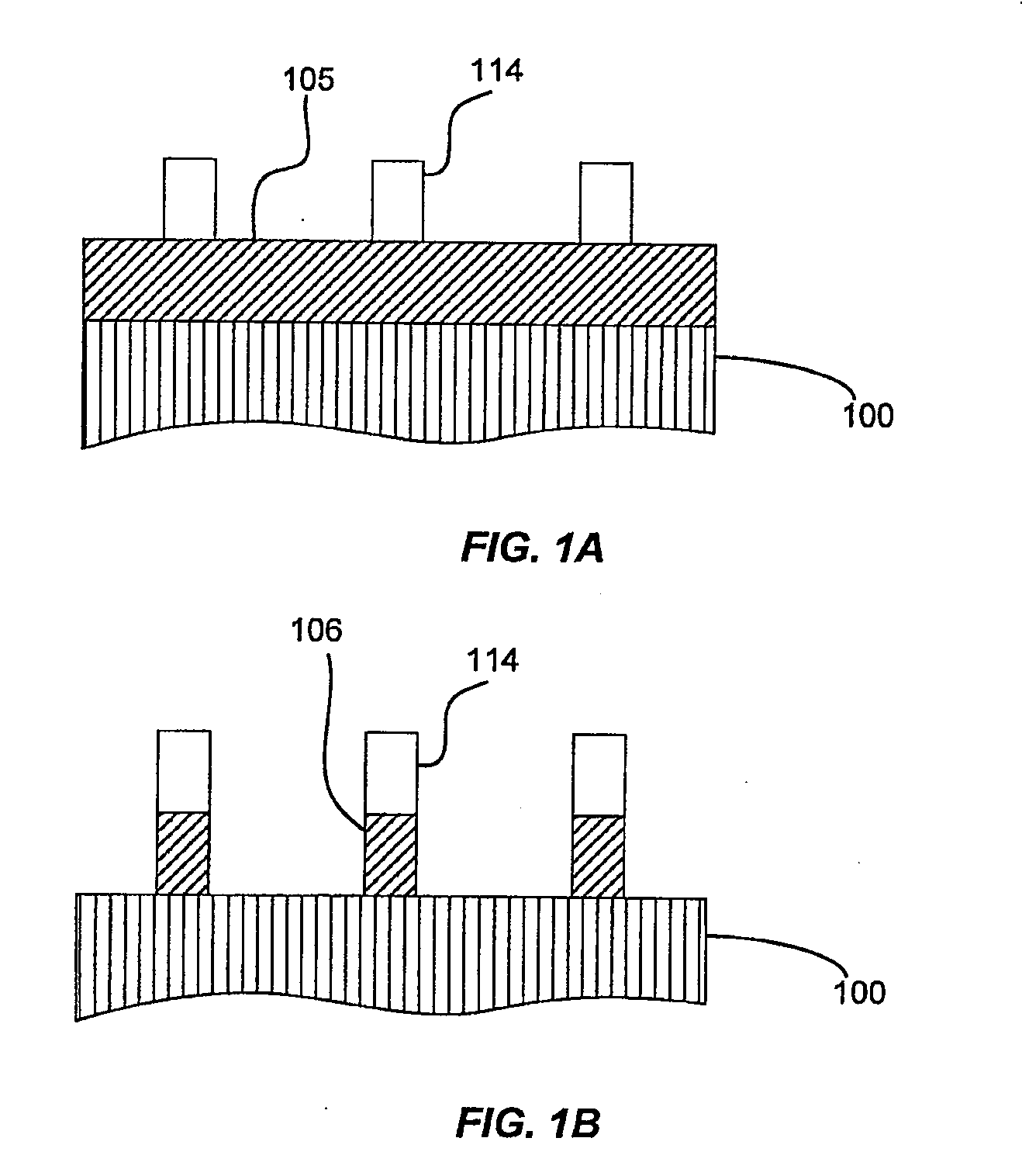

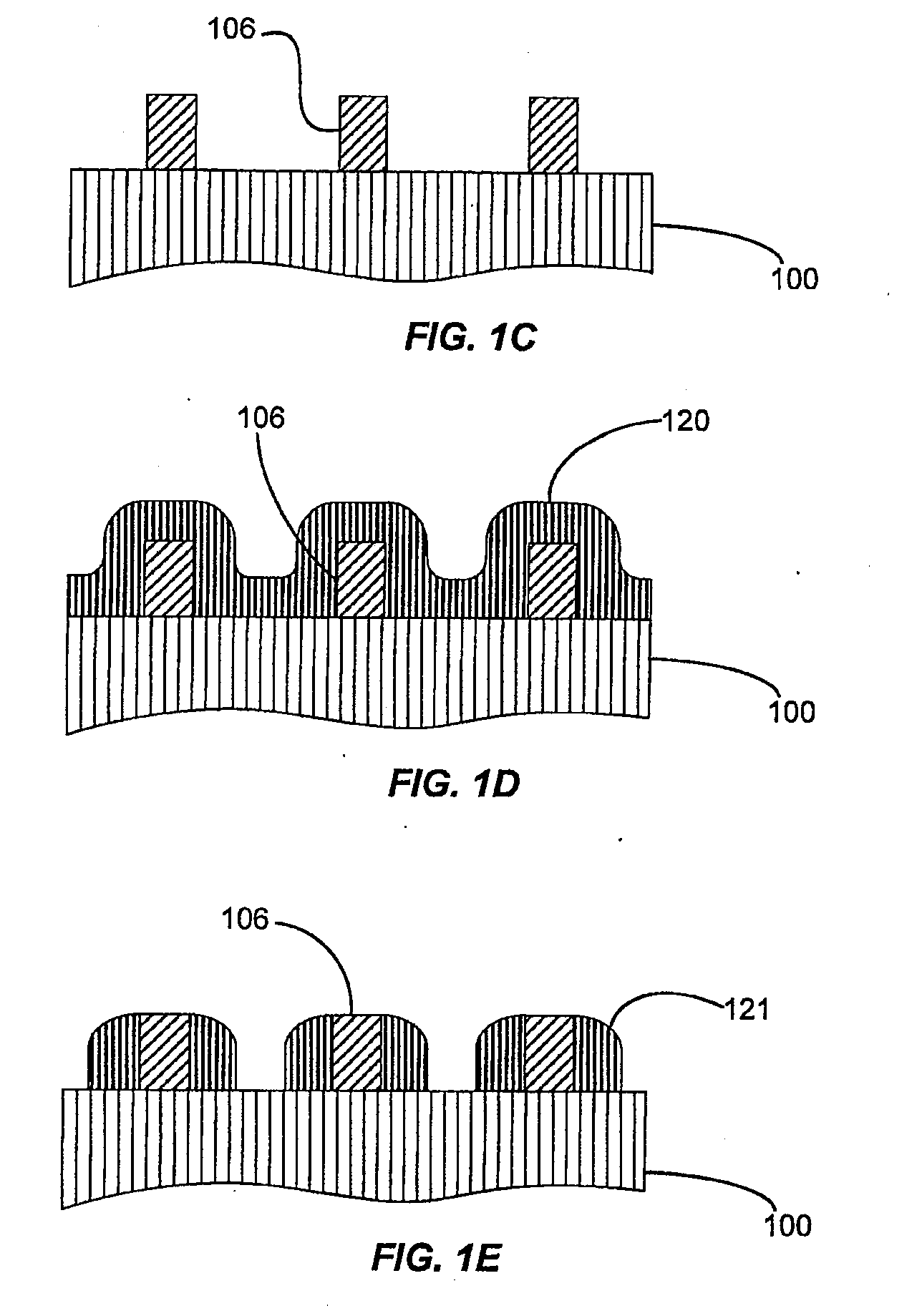

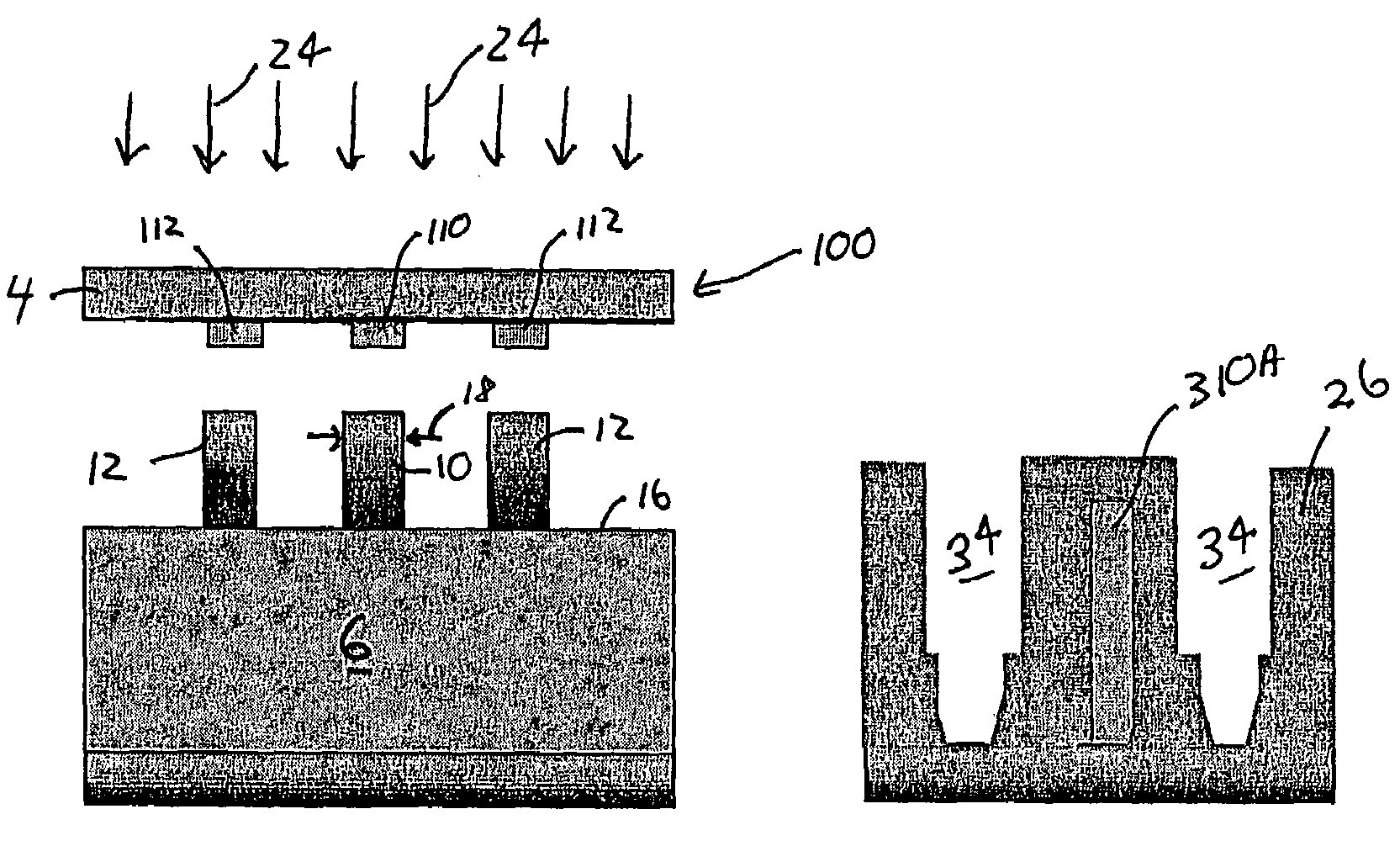

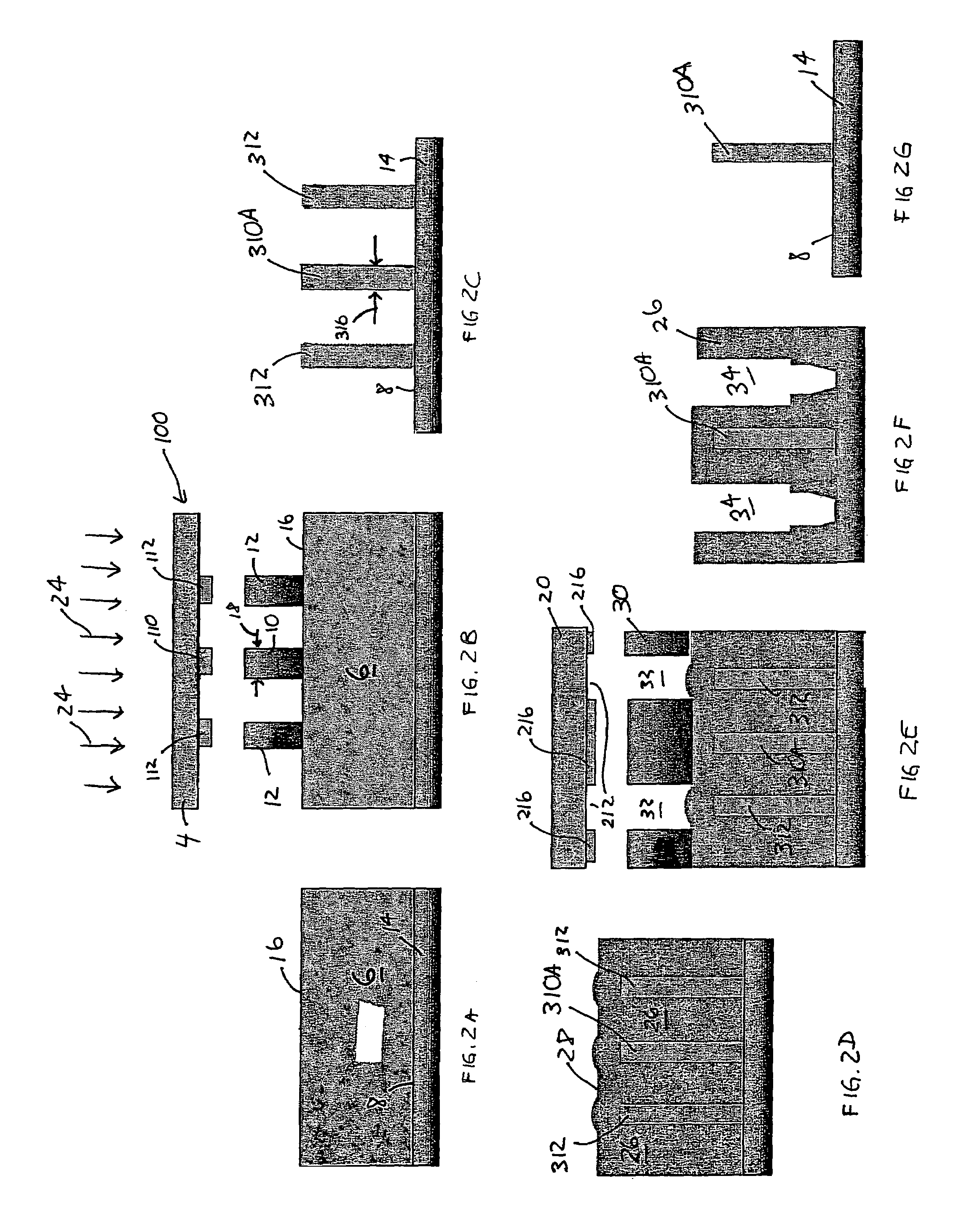

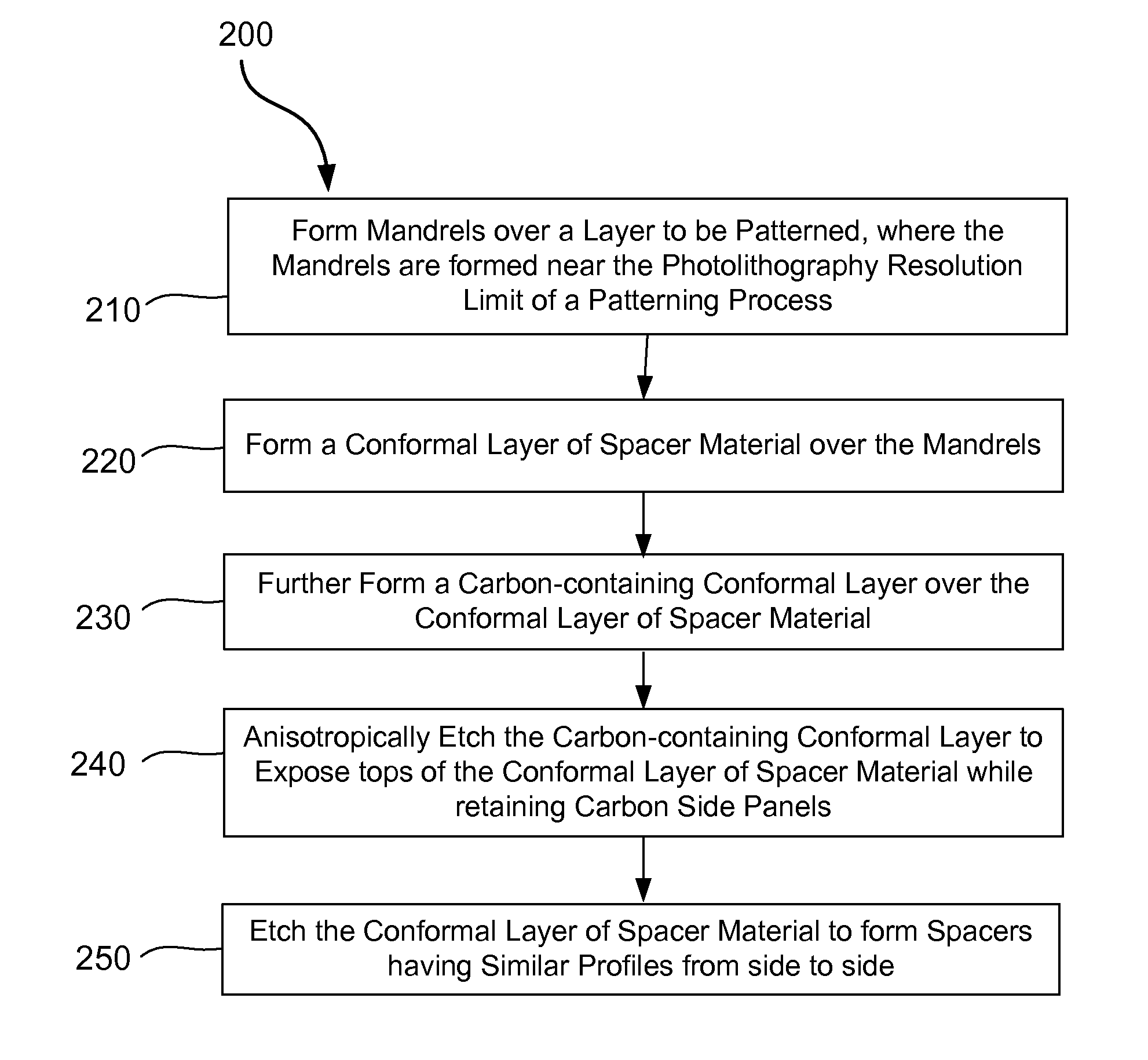

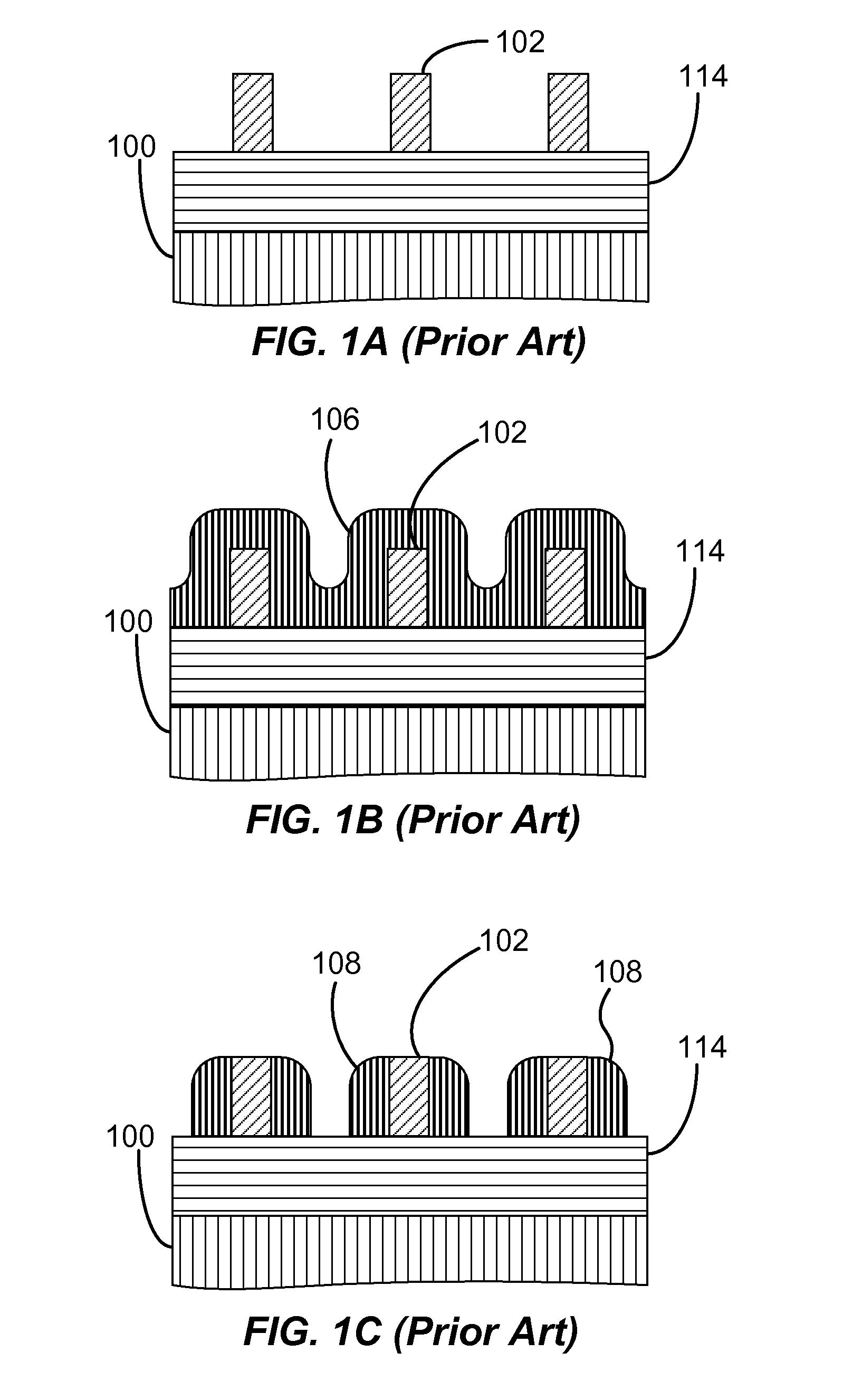

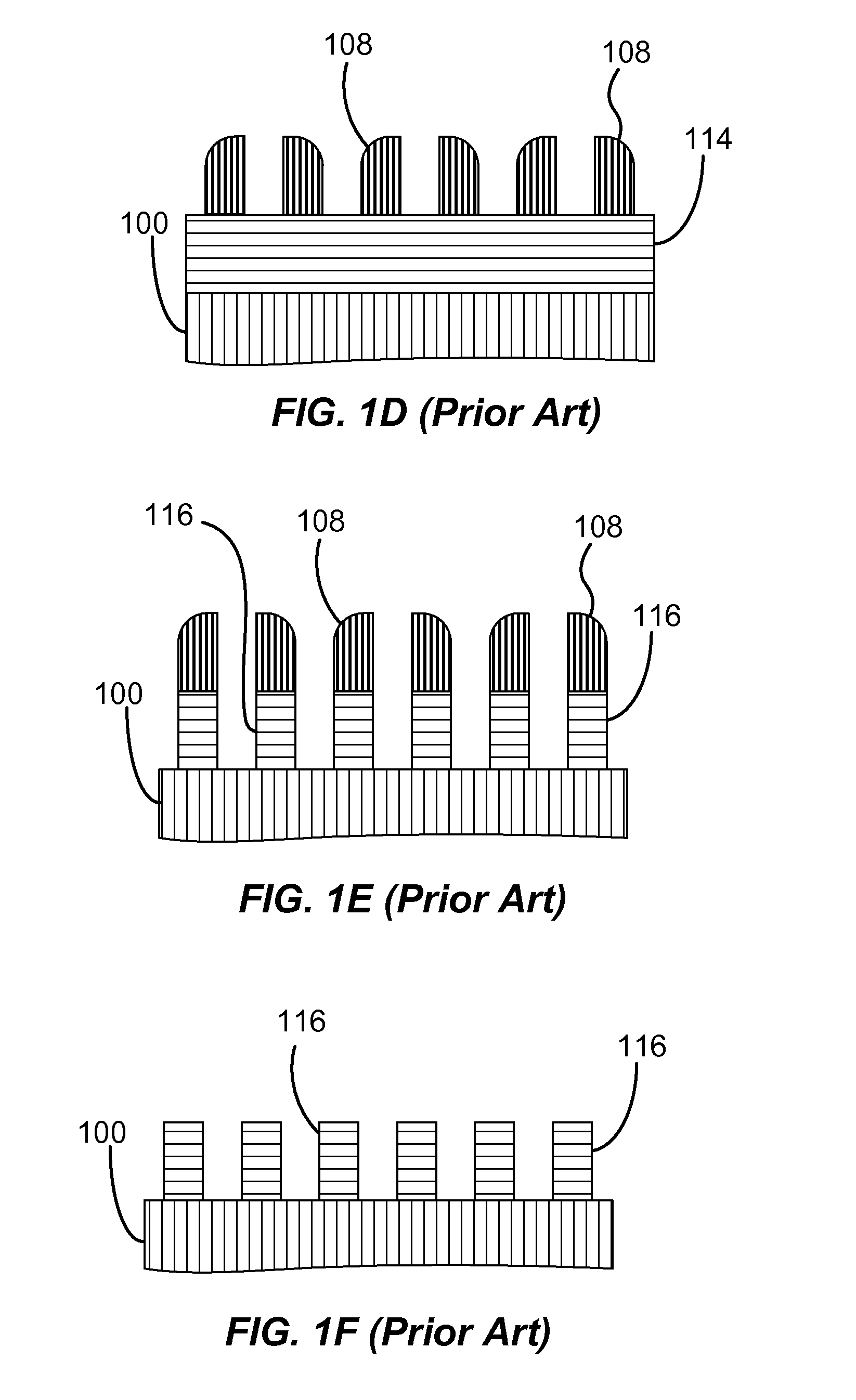

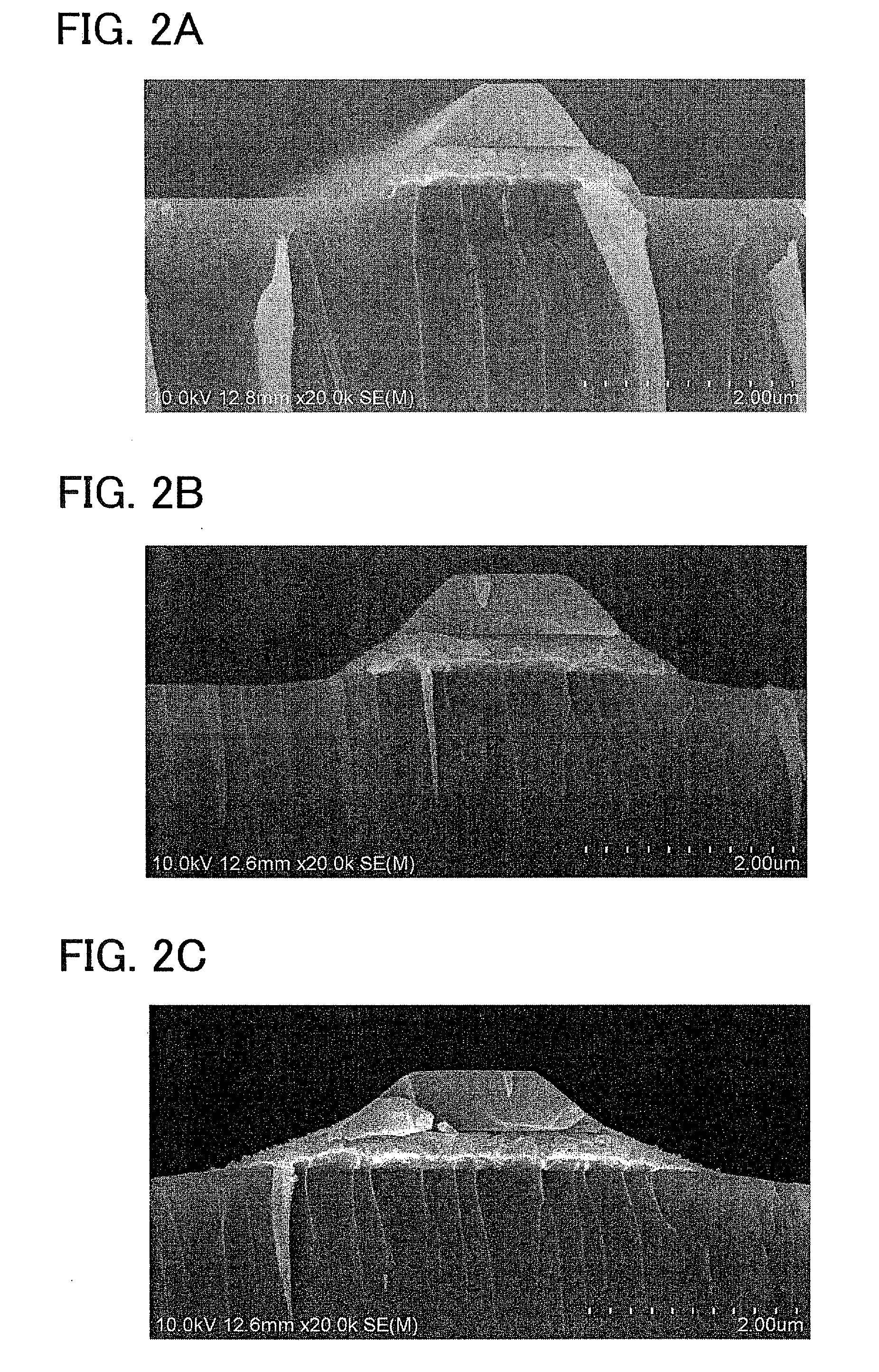

Spacer formation

ActiveUS20150287612A1Semiconductor/solid-state device manufacturingImage resolutionOptical resolution

Embodiments of the present invention pertain to methods of forming more symmetric spacers which may be used for self-aligned multi-patterning processes. A conformal spacer layer of spacer material is formed over mandrels patterned near the optical resolution of a photolithography system using a high-resolution photomask. A carbon-containing layer is further formed over the conformal spacer layer. The carbon-containing layer is anisotropically etched to expose the high points of the conformal spacer layer while retaining carbon side panels. The conformal spacer layer may then be etched to form spacers without the traditional skewing of the profile towards one side or the other.

Owner:APPLIED MATERIALS INC

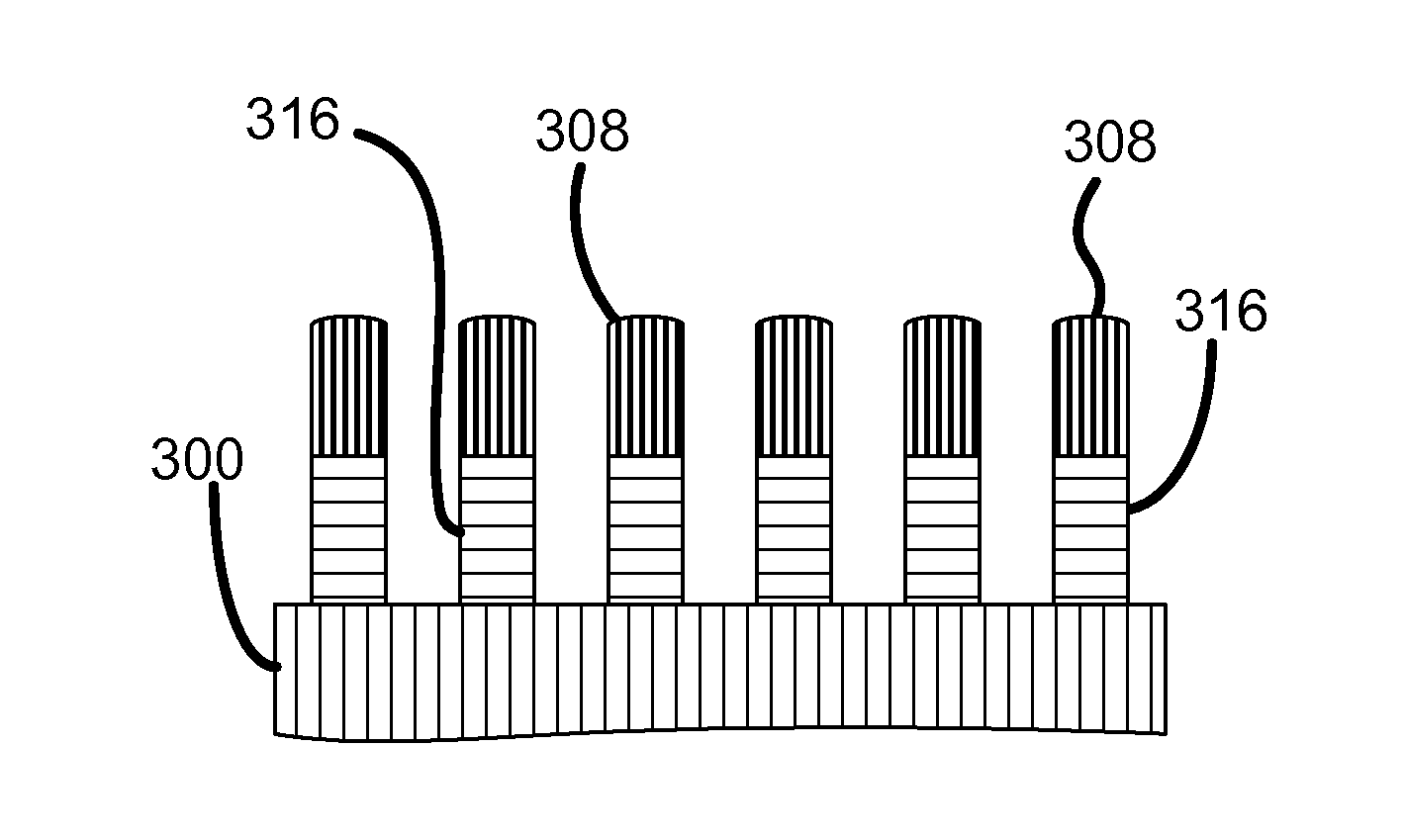

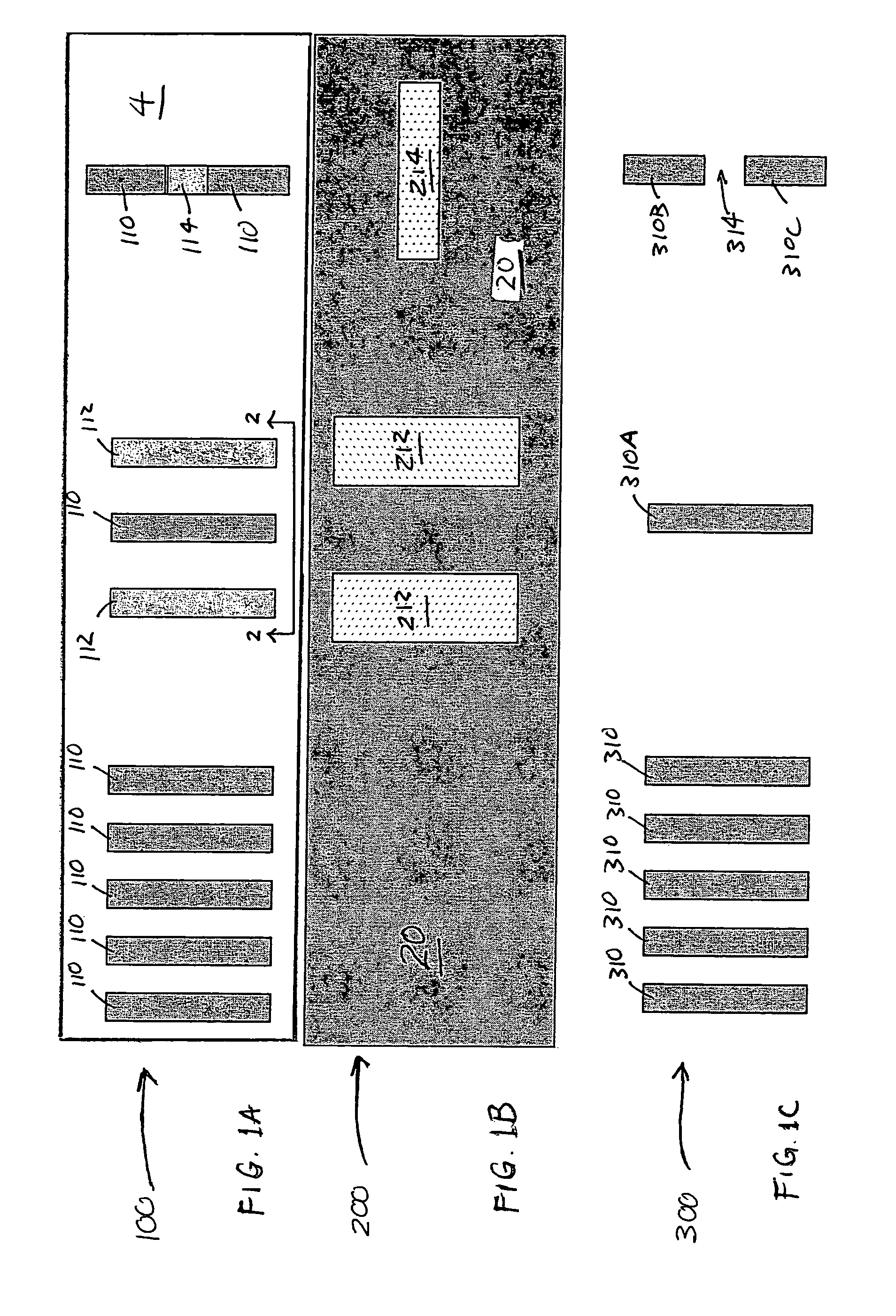

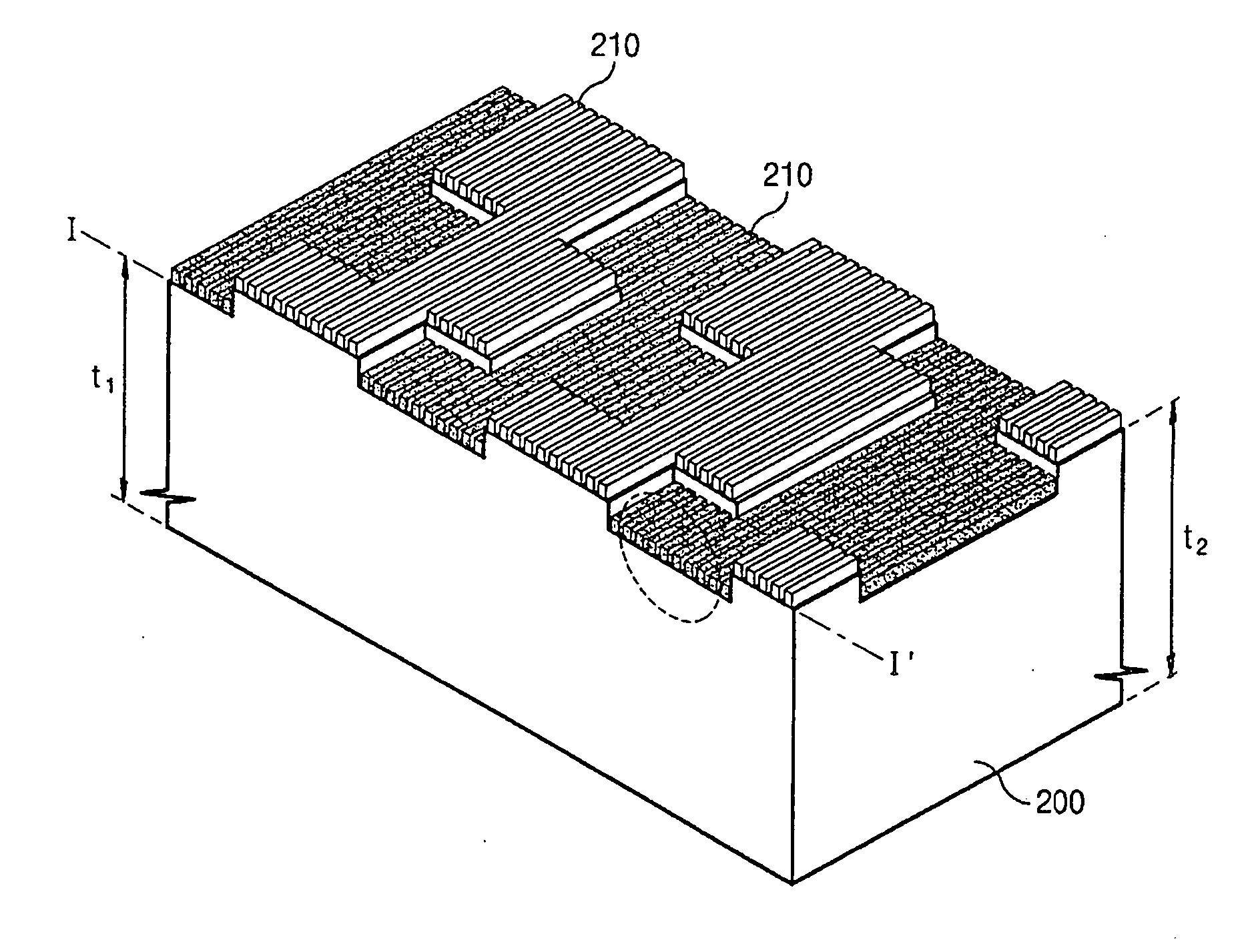

Integral patterning of large features along with array using spacer mask patterning process flow

InactiveUS20100075503A1Reduce spacingHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotolithography

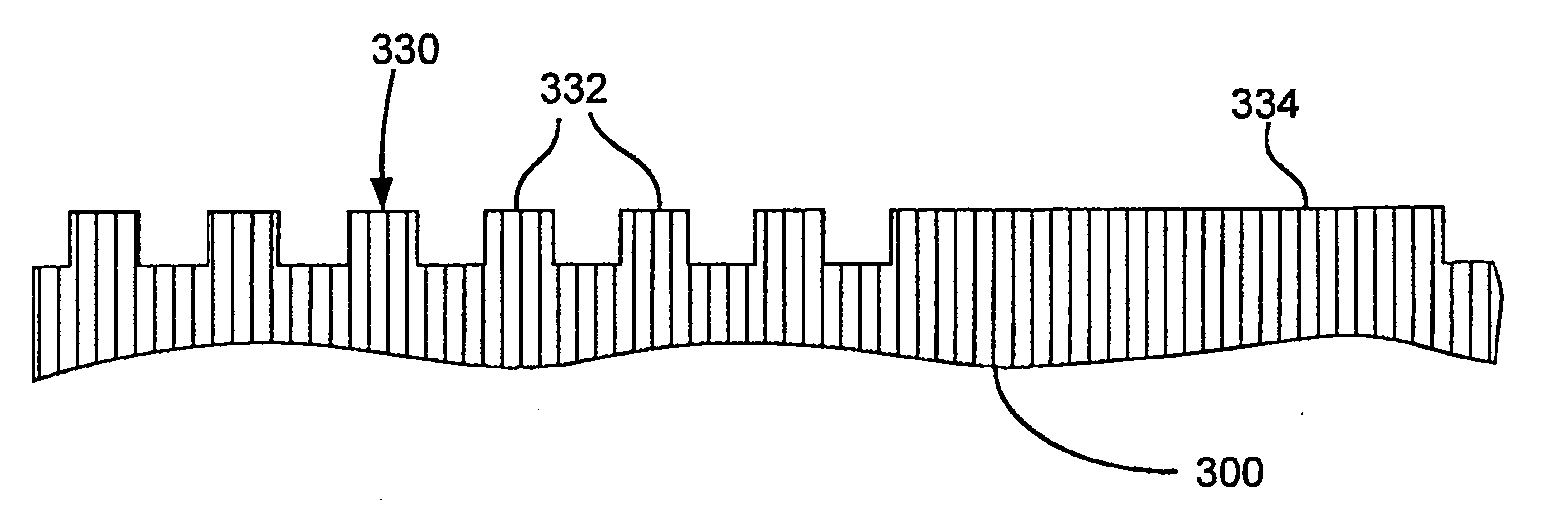

Embodiments of the present invention pertain to methods of forming patterned features on a substrate having an increased density (i.e. reduced pitch) as compared to what is possible using standard photolithography processing techniques using a single high-resolution photomask while also allowing both the width of the patterned features and spacing (trench width) between the patterned features to vary within an integrated circuit.

Owner:APPLIED MATERIALS INC

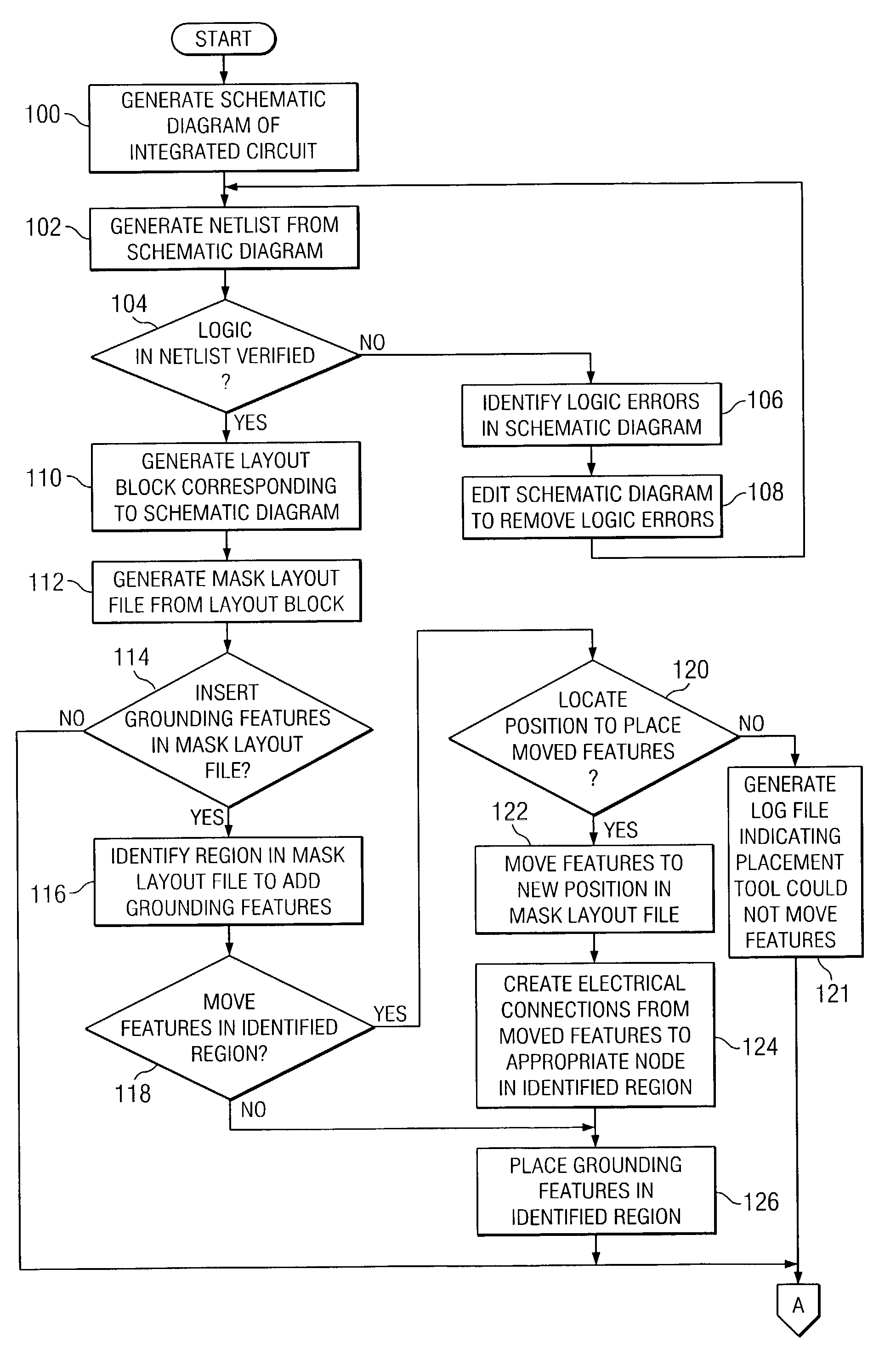

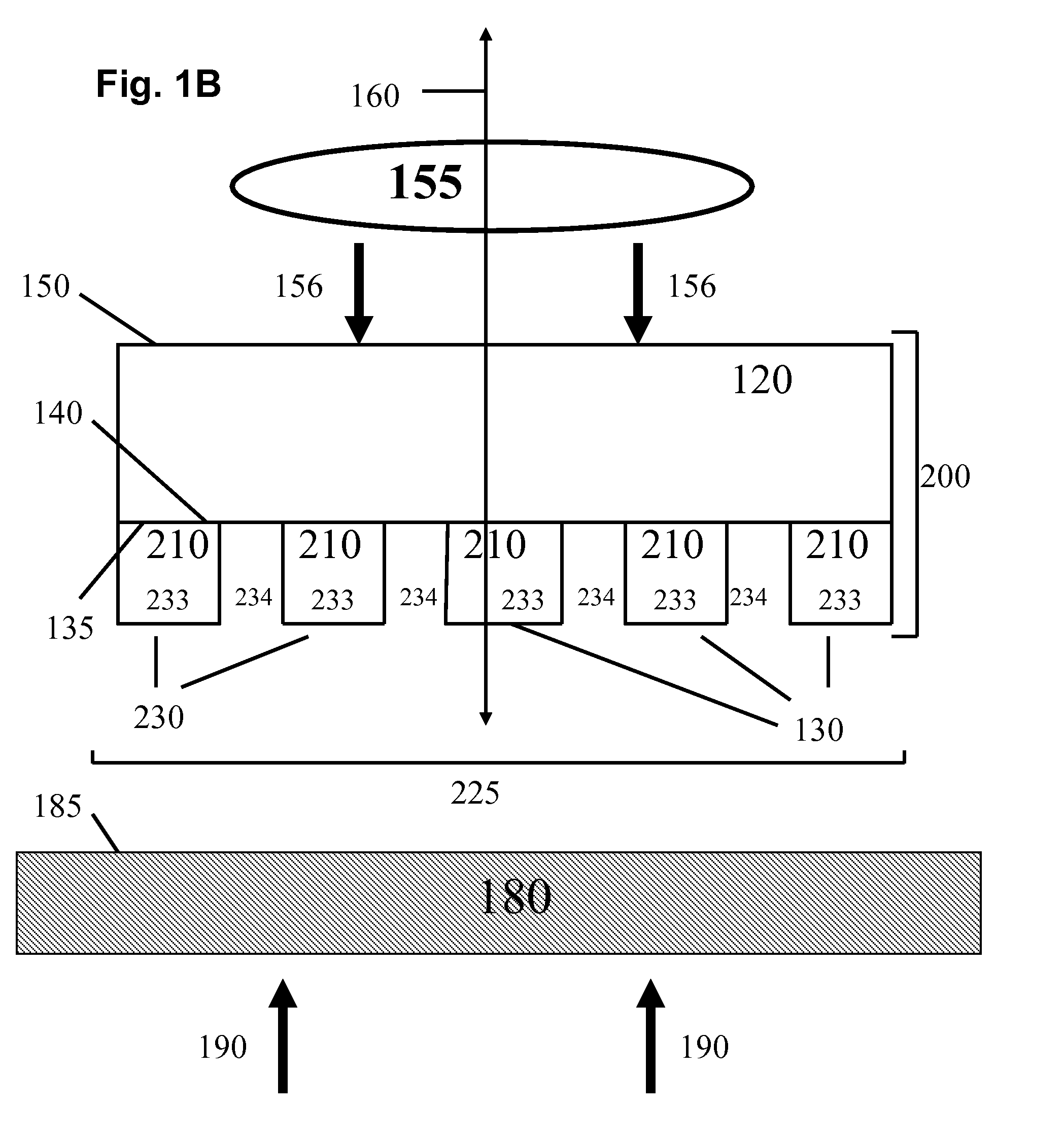

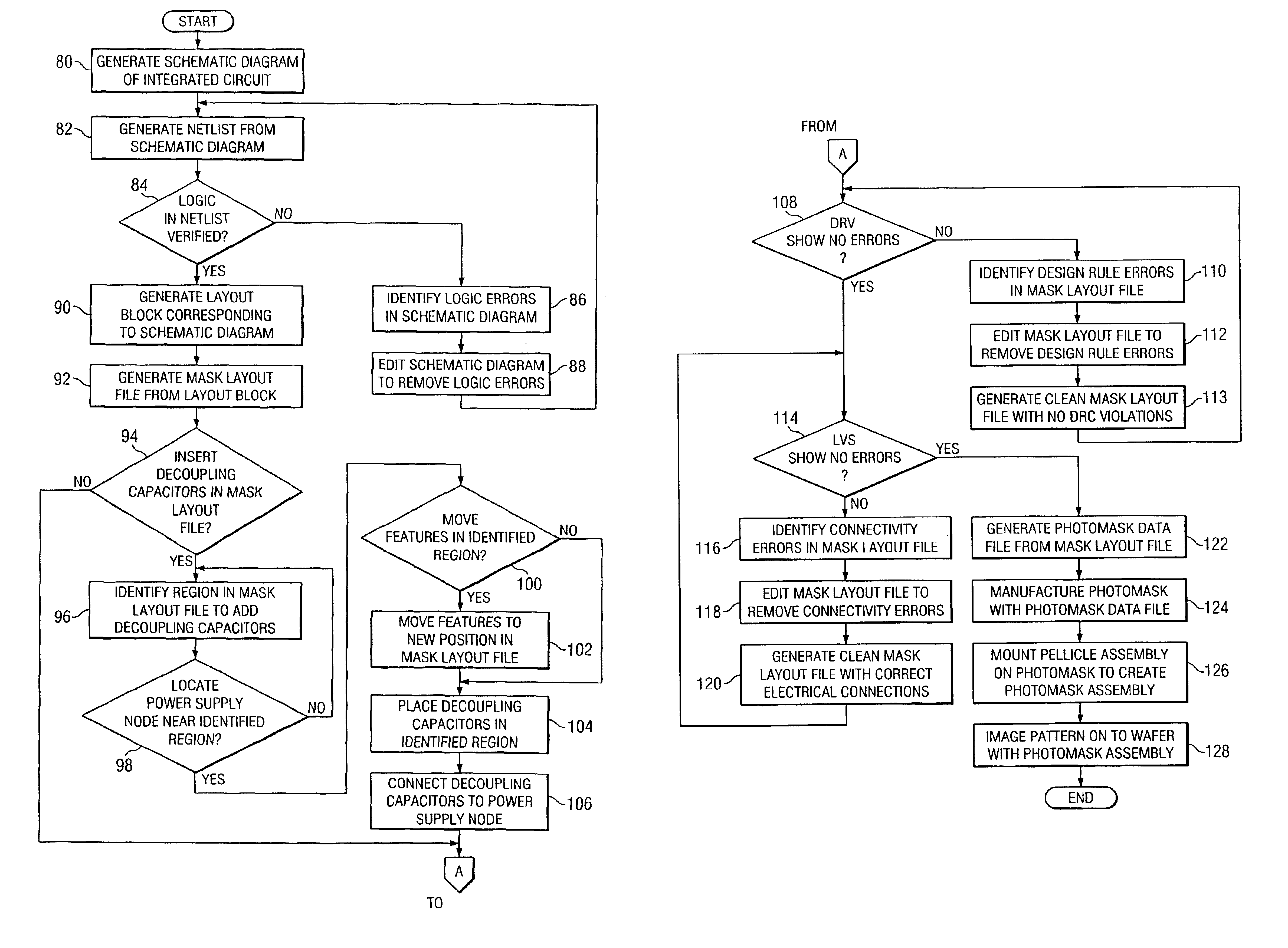

Photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufacture with same

InactiveUS6978437B1Increase antenna ratioRaise the ratioSemiconductor/solid-state device detailsSolid-state devicesAntenna effectEngineering

A photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufactured with the photomask are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region including an antenna ratio less than a first design rule. A feature located in the identified region is moved based on a second design rule from a first position to a second position in the mask layout file to create a space in the identified region. A grounding feature is placed in the space and automatically connected to a gate feature in the mask layout file such that the antenna ratio is increased to greater than or approximately equal to the first design rule.

Owner:CELERICS TECH

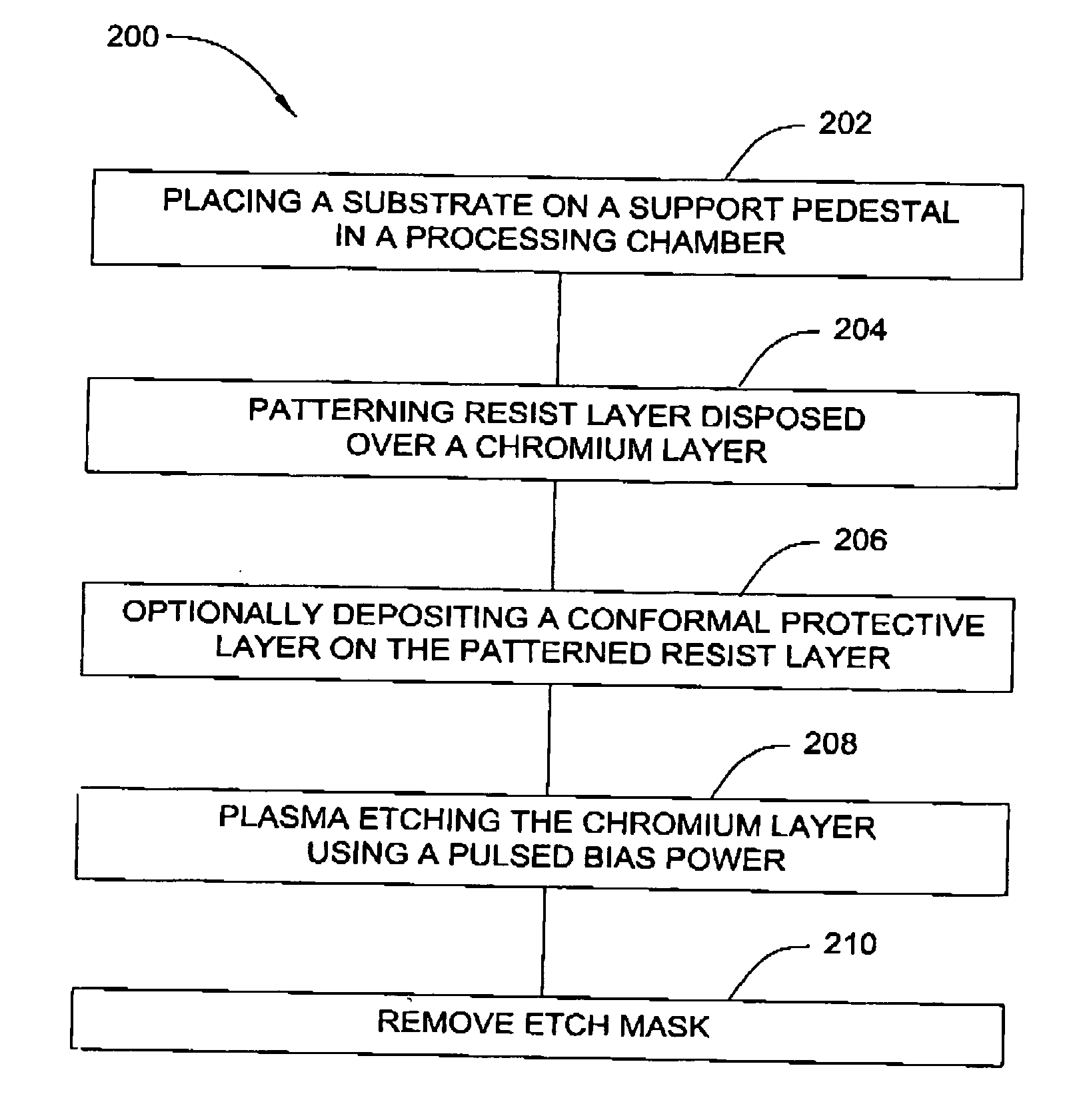

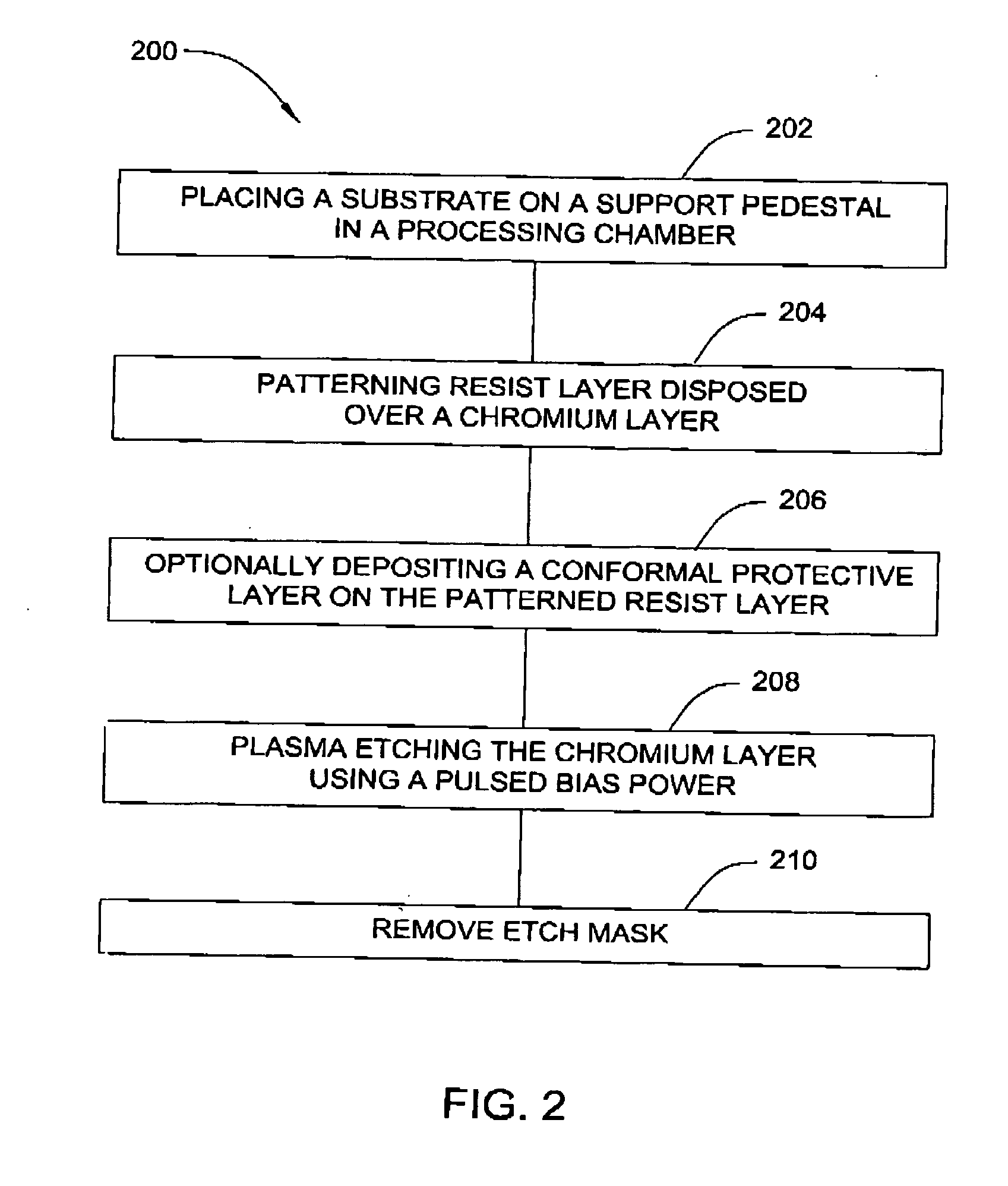

Method for plasma etching a chromium layer suitable for photomask fabrication

A method for etching a chromium layer is provided herein. In one embodiment, a method for etching a chromium layer includes providing a filmstack in an etching chamber, the filmstack having a chromium layer partially exposed through a patterned layer, providing at least one halogen containing process gas to a processing chamber, biasing the layer disposed on a substrate support in the processing chamber with a plurality of power pulses less than 600 Watts, and etching the chromium layer through a patterned mask. The method for plasma etching a chromium layer described herein is particularly suitable for fabricating photomasks.

Owner:APPLIED MATERIALS INC

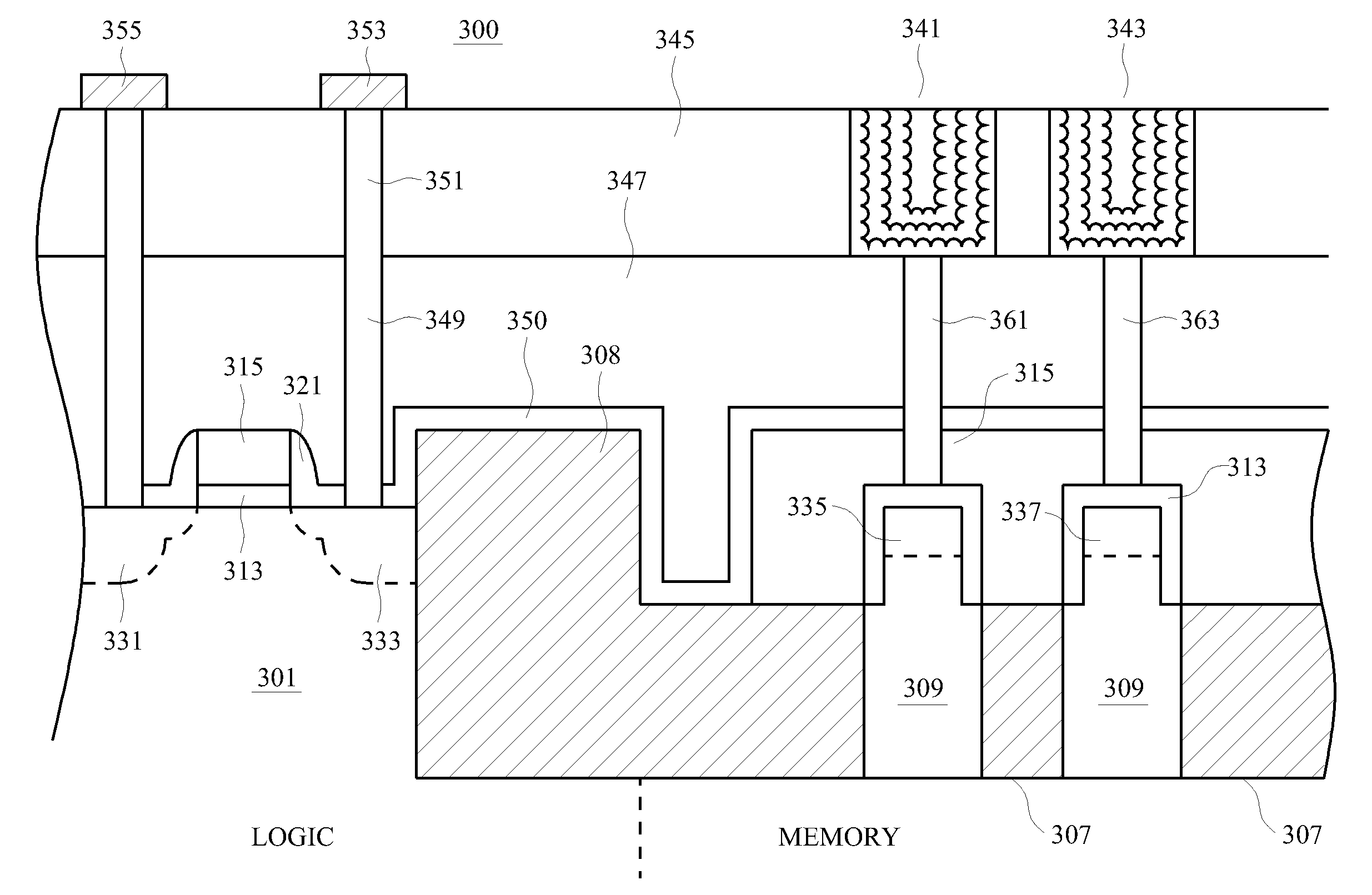

Method and structure for a 1T-RAM bit cell and macro

InactiveUS7425740B2Increase capacitanceTransistorSolid-state devicesMetal-insulator-metalCapacitance

A one transistor (1T-RAM) bit cell and method for manufacture are provided. A metal-insulator-metal (MIM) capacitor structure and method of manufacturing it in an integrated process that includes a finFET transistor for the 1T-RAM bit cell is provided. In some embodiments, the finFET transistor and MIM capacitor are formed in a memory region and an asymmetric processing method is disclosed, which allows planar MOSFET transistors to be formed in another region of a single device. In some embodiments, the 1T-RAM cell and additional transistors may be combined to form a macro cell, multiple macro cells may form an integrated circuit. The MIM capacitors may include nanoparticles or nanostructures to increase the effective capacitance. The finFET transistors may be formed over an insulator. The MIM capacitors may be formed in interlevel insulator layers above the substrate. The process provided to manufacture the structure may advantageously use conventional photomasks.

Owner:TAIWAN SEMICON MFG CO LTD

Method of manufacturing photomask

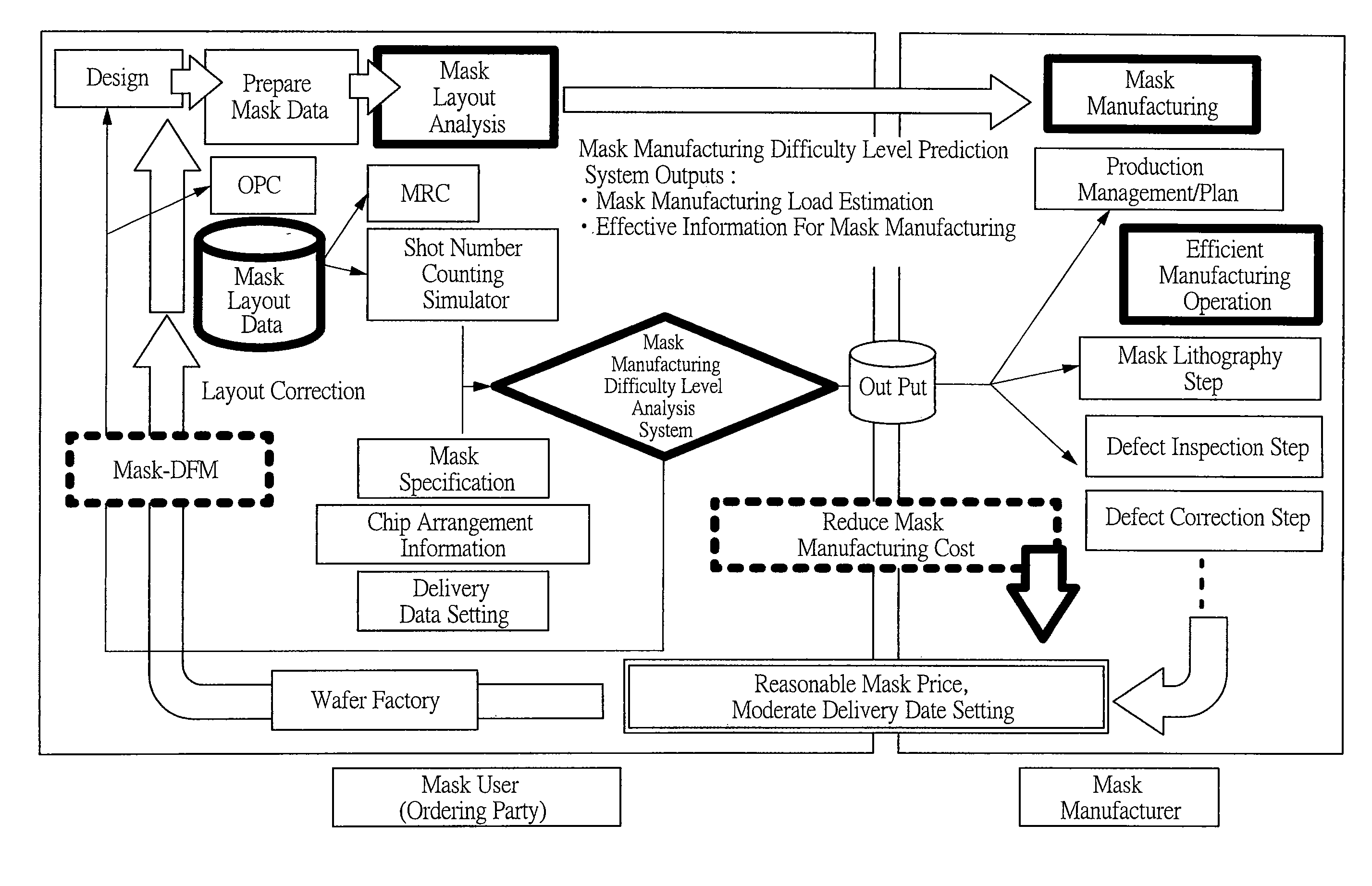

InactiveUS20090077524A1Efficient preparationImprove efficiencyOriginals for photomechanical treatmentSpecial data processing applicationsPrediction systemPhotomask

A technique for quantitatively expressing a manufacturing difficulty level of a photomask and for efficiently manufacturing the photomask is provided. A mask manufacturing difficulty level different for each mask layout, product, and mask layer is relatively recognized with a mask manufacturing load index calculated by a mask manufacturing load prediction system, and when layout correction is possible, the final layout is corrected to a layout with a low difficulty level, and a mask ordering party provides a mask manufacturer with information regarding the mask manufacturing difficulty level in an early stage. The mask manufacturing load index is expressed with a defect guarantee load index and a lithography load index.

Owner:DAI NIPPON PRINTING CO LTD +1

Method utilizing compensation features in semiconductor processing

InactiveUS7202148B2Increased process windowReduce depthRadiation applicationsSemiconductor/solid-state device manufacturingEngineeringFlare

A photolithography and etch process sequence includes a photomask having a pattern with compensation features that alleviate patterning variations due to the proximity effect and depth of focus concerns during photolithography. The compensation features may be disposed near isolated or outermost lines of a device pattern. A photoresist pattern is formed to include the compensation features and the pattern etched to form a corresponding etched pattern including the compensation features. After etching, a protection material is formed over the layer and a trim mask is used to form a further photoresist pattern over the protection material. A subsequent etching pattern etches the protection material and removes the compensation features and results in the device lines being formed unaffected by proximity effects. Flare dummies may additionally be added to the mask pattern to increase pattern density and assist in endpoint detection. Flare dummies, like the compensation features, are subsequently removed by a photolithography and etching process sequence.

Owner:TAIWAN SEMICON MFG CO LTD

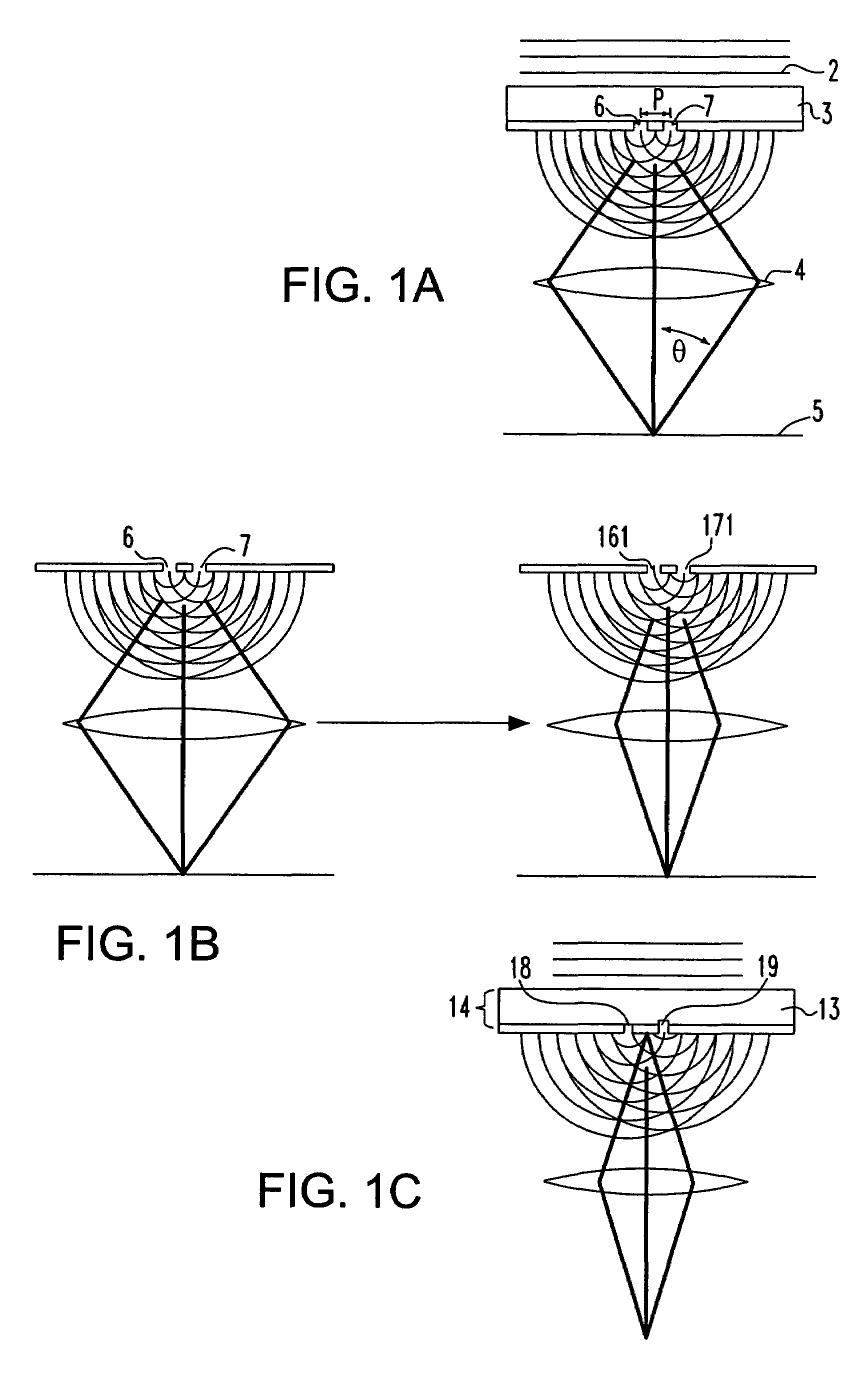

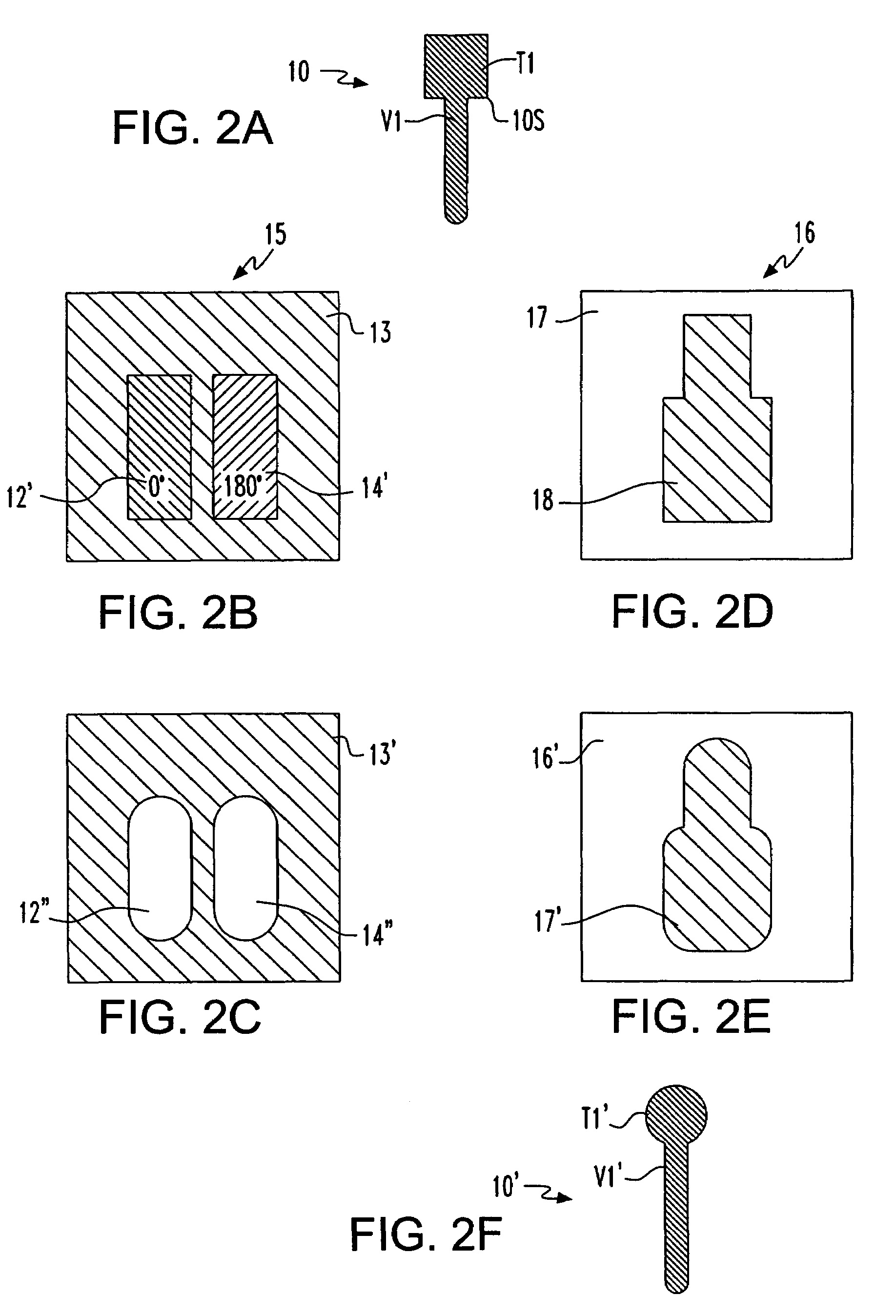

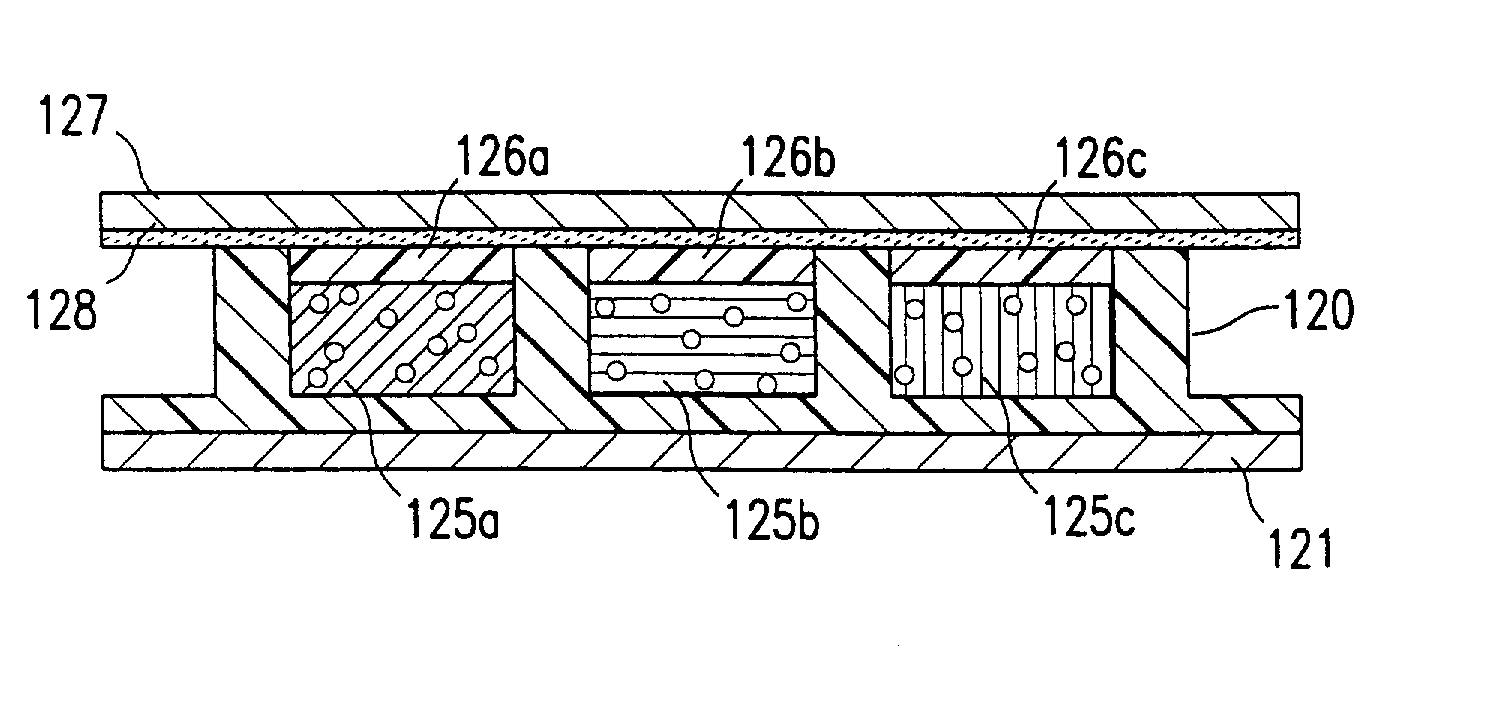

Process for roll-to-roll manufacture of a display by synchronized photolithographic exposure on a substrate web

InactiveUS20020182544A1High aspect ratioWell-defined shapePhoto-taking processesPhotomechanical apparatusDisplay deviceRefractive index

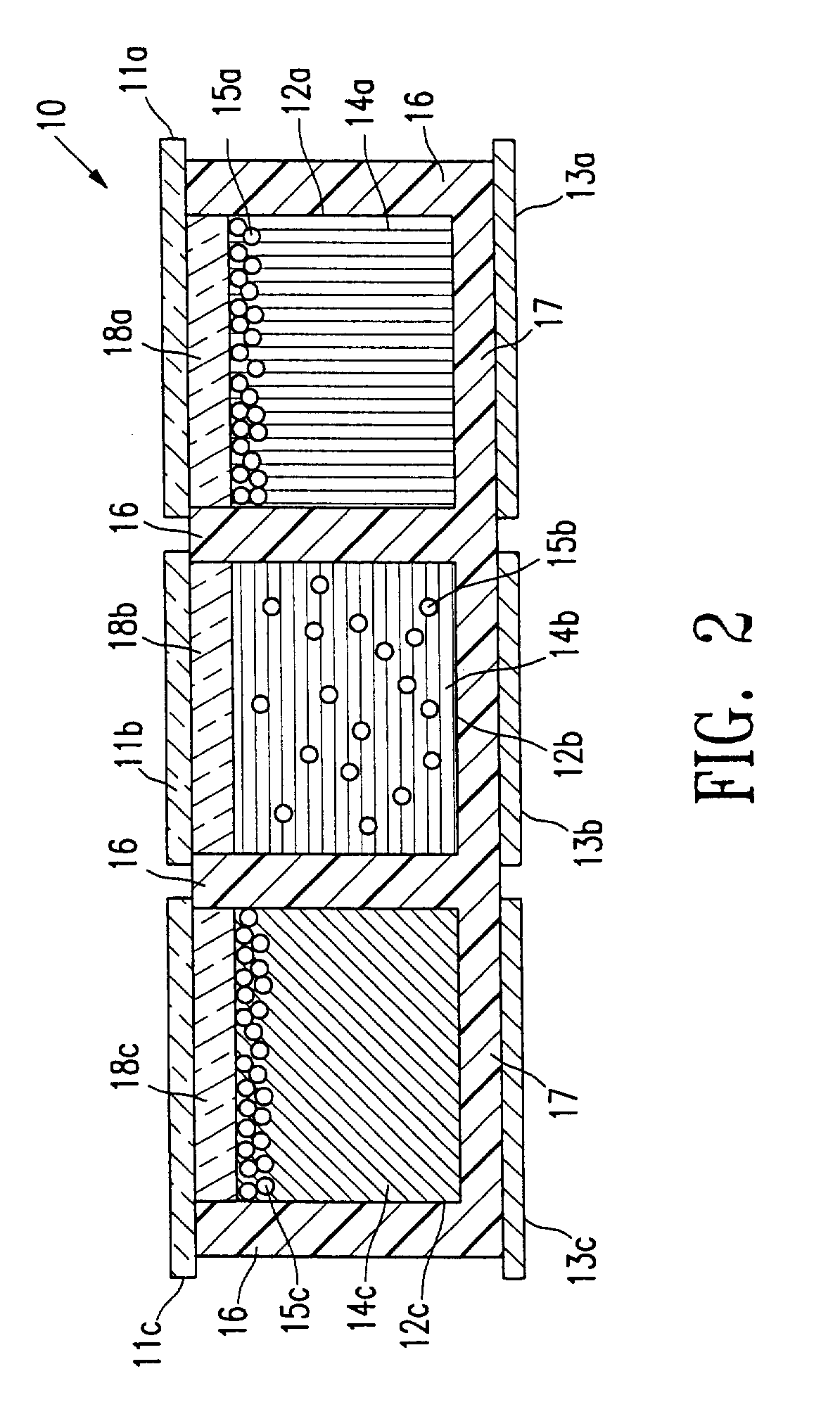

<heading lvl="0">Abstract of Disclosure< / heading> This invention relates to an electrophoretic display or a liquid crystal display and novel processes for its manufacture. The electrophoretic display (EPD) of the present invention comprises microcups of well-defined shape, size and aspect ratio and the microcups are filled with charged pigment particles dispersed in an optically contrasting dielectric solvent. The liquid crystal display (LCD) of this invention comprises well-defined microcups filled with at least a liquid crystal composition having its ordinary refractive index matched to that of the isotropic cup material. A novel roll-to-roll process and apparatus of the invention permits the display manufacture to be carried out continuously by a synchronized photo-lithographic process. The synchronized roll-to-roll process and apparatus permits a pre-patterned photomask, formed as a continuous loop, to be rolled in a synchronized motion in close parallel alignment to a web which has been pre-coated with a radiation sensitive material, so as to maintain image alignment during exposure to a radiation source. The radiation sensitive material may be a radiation curable material, in which the exposed and cured portions form the microcup structure. In an additional process step, the radiation sensitive material may be a positively working photoresist which temporarily seals the microcups. Exposure of a selected subset of the microcups via the photomask image permits selective re-opening, filling and sealing of the microcup subset. Repetition with additional colors permits the continuous assembly of a multicolor EPD or LCD display.

Owner:E INK CALIFORNIA

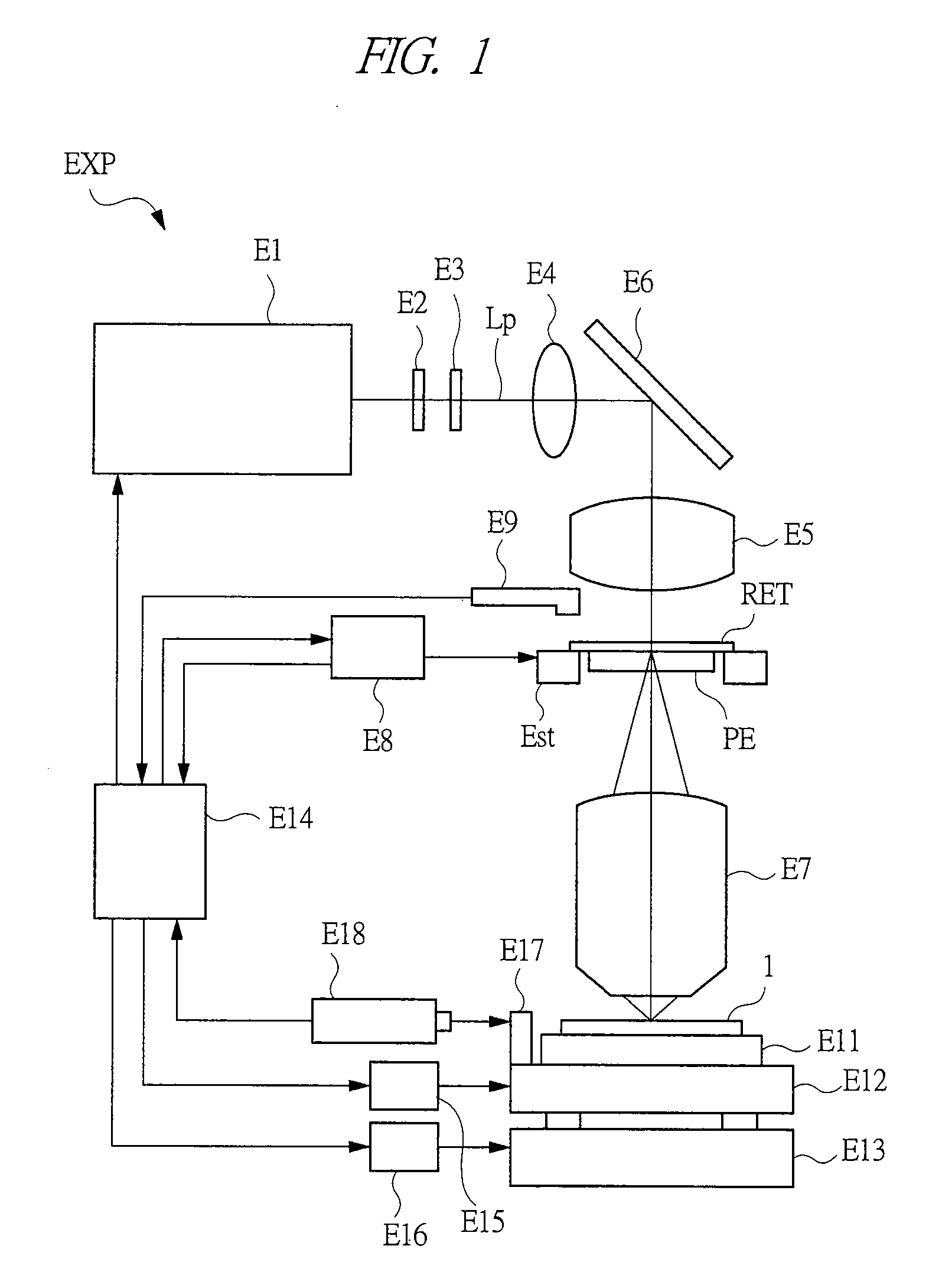

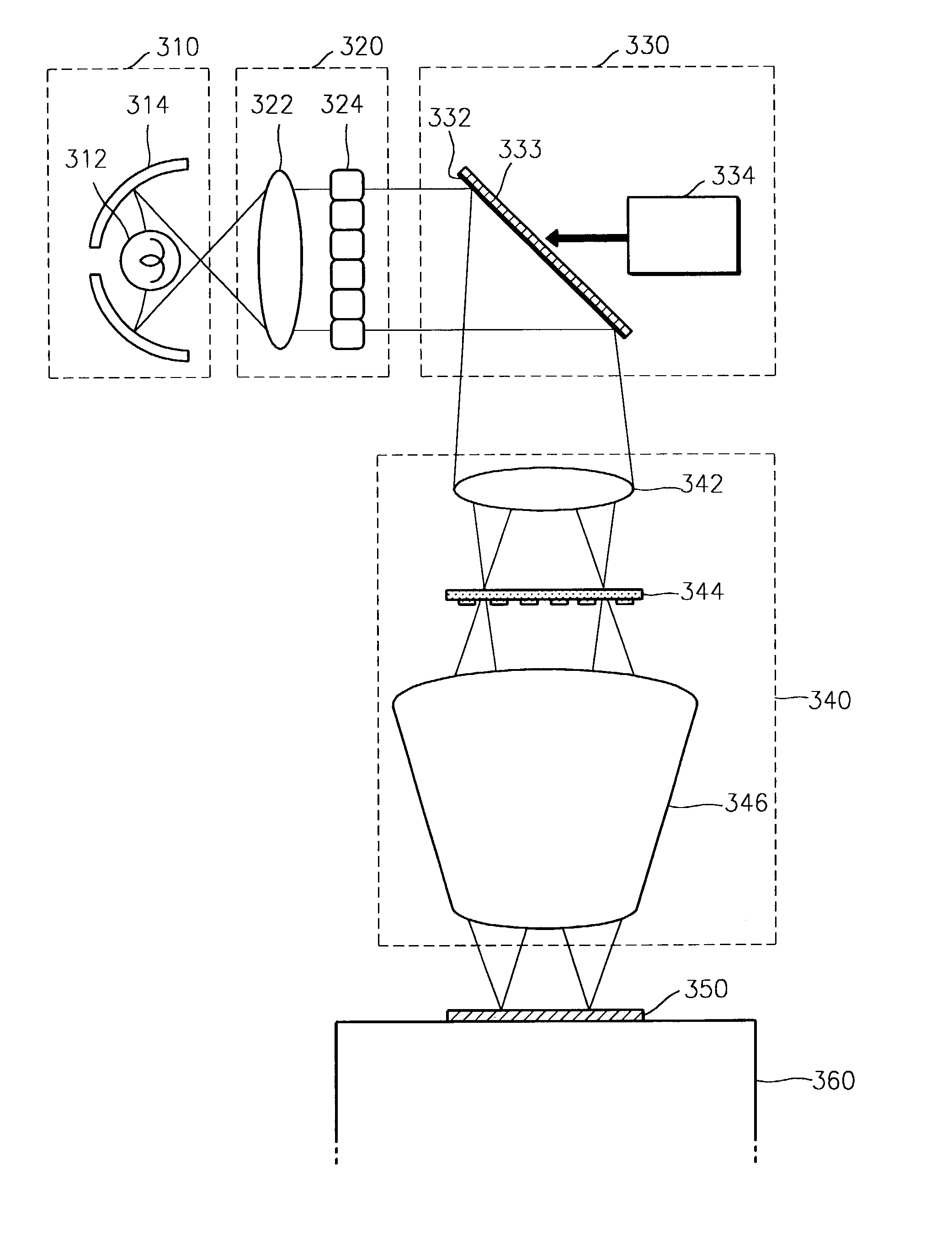

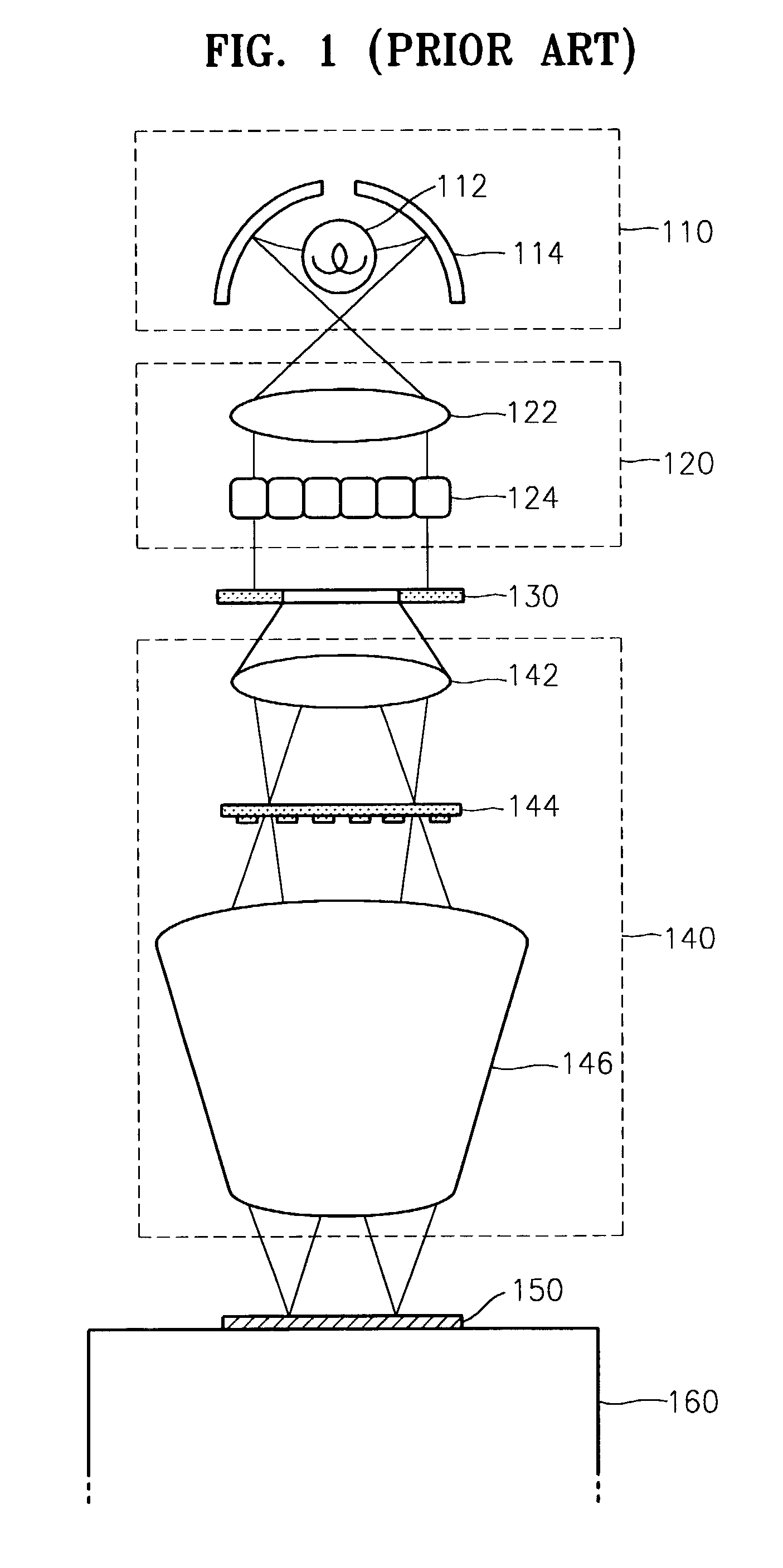

Exposure apparatus including micro mirror array and exposure method using the same

InactiveUS7061582B2High resolutionShort amount of timeSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusResistImage resolution

An exposure method and apparatus for use in exposing a photoresist on a semiconductor wafer do not employ an aperture for shaping the exposure light. The exposure apparatus includes a light source unit, a reflecting mirror unit having a micro mirror array (MMA) and a control unit that controls the MMA, and a pattern transfer unit that transfers the pattern of a photomask onto the photoresist. The angles of inclination of the respective mirrors of the MMA are adjusted to reflect incident light in a manner that shapes the incident light. Accordingly, it is possible to form a pattern having the highest degree of resolution and optimum depth of focus (DOF) in the shortest amount of processing time.

Owner:SAMSUNG ELECTRONICS CO LTD

Devices and methods for pattern generation by ink lithography

InactiveUS20080055581A1Improve fidelityIncrease resistanceNanostructure manufactureNanoinformaticsElastomerLithographic artist

The present invention provides methods, devices and device components for fabricating patterns on substrate surfaces, particularly patterns comprising structures having microsized and / or nanosized features of selected lengths in one, two or three dimensions and including relief and recess features with variable height, depth or height and depth. Composite patterning devices comprising a plurality of polymer layers each having selected mechanical and thermal properties and physical dimensions provide high resolution patterning on a variety of substrate surfaces and surface morphologies. Gray-scale ink lithography photomasks for gray-scale pattern generation or molds for generating embossed relief features on a substrate surface are provided. The particular shape of the fabricated patterned can be manipulated by varying the three-dimensional recess pattern on an elastomeric patterning device which is brought into conformal contact with a substrate to localize patterning agent to the recess portion of the pattern.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

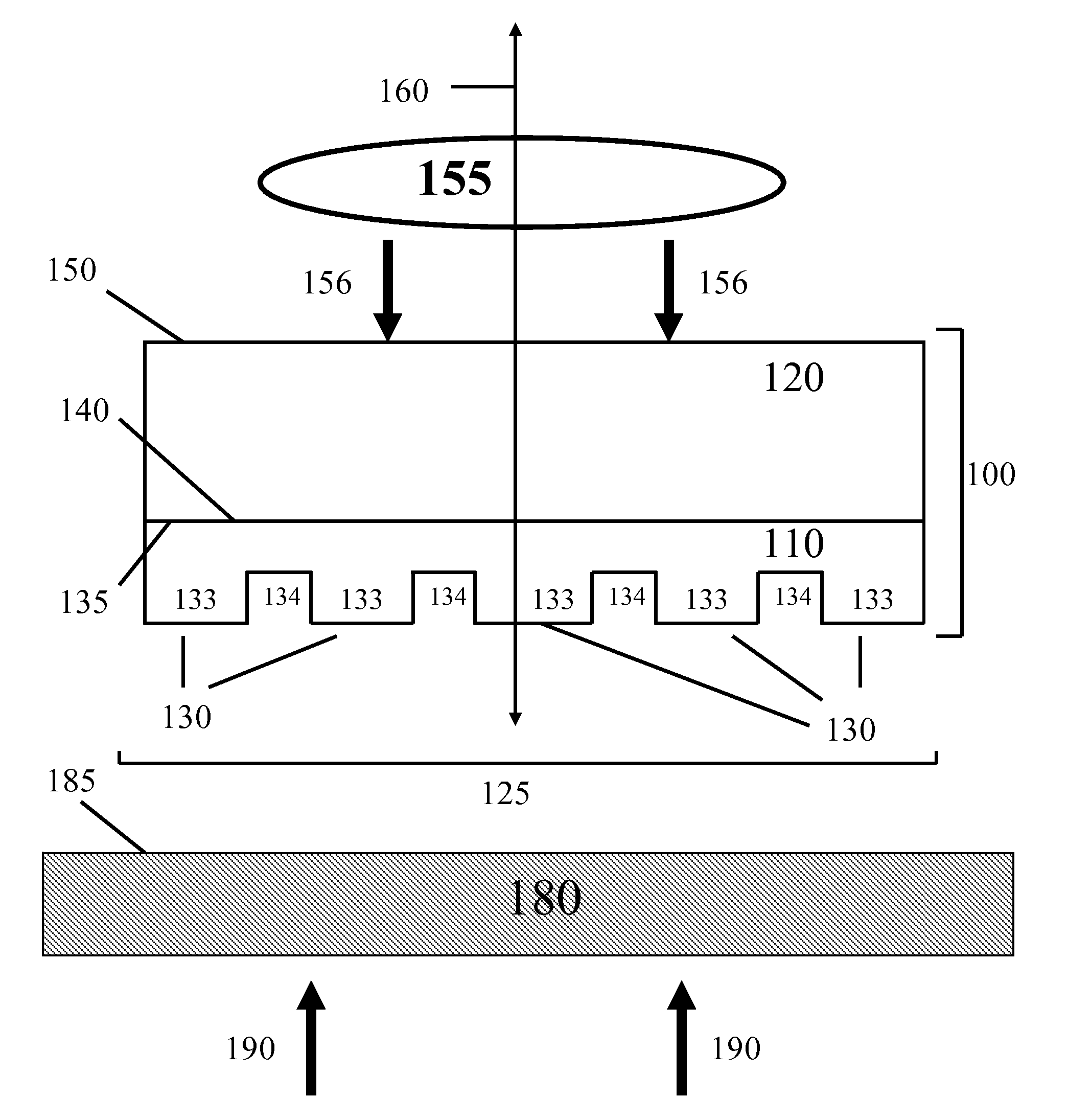

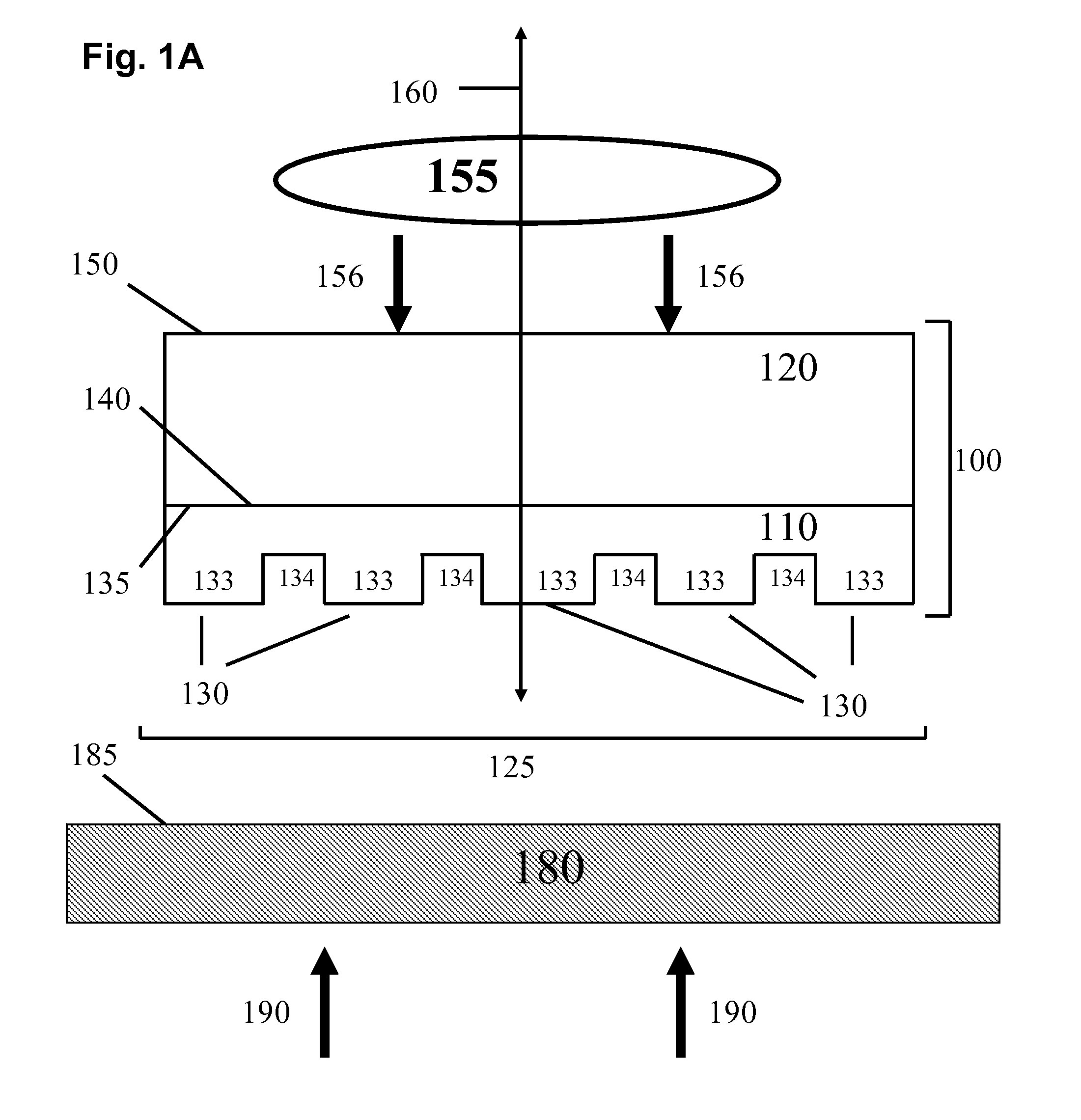

Photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured with the same

InactiveUS6904582B1Shorten the timeShorten cycle timeSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit layoutDecoupling capacitor

A photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured by the same are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region in the pattern to add one or more decoupling capacitors. Once the region is identified, a feature located in the identified region is moved based on a design rule from a first position to a second position in the mask layout file to create a space in the identified region. The decoupling capacitors are placed in the space in the identified region.

Owner:CELERICS TECH

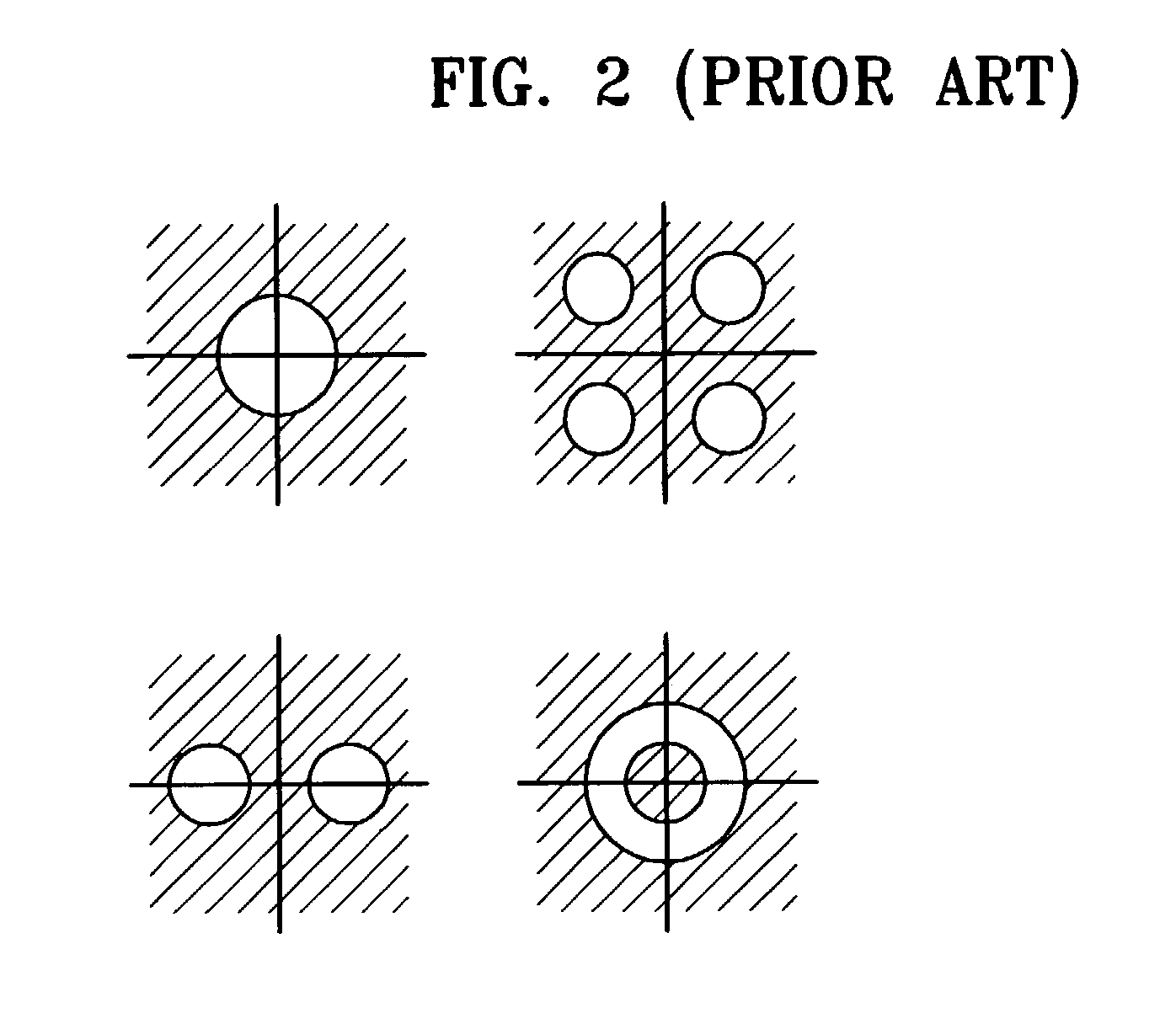

Apparatus for exposing a substrate, photomask and modified illuminating system of the apparatus, and method of forming a pattern on a substrate using the apparatus

InactiveUS20060083996A1Easy to shapeRaise transfer toPolarising elementsSemiconductor/solid-state device manufacturingSingle exposureEngineering

An exposure apparatus and photo-mask of the exposure apparatus can form a perpendicular line / space circuit pattern through only a single exposure process. The photo-mask includes a first line / space pattern oriented in a first direction, a second line / space pattern oriented in a second direction and lattice patterns, operating as polarizers, occupying the spaces of the line / space patterns. The exposure apparatus also includes a modified illuminating system. The modified illuminate system may be a composite polarization illuminating system having a shielding region, and a plurality of light transmission regions defined within the field of the shielding region. The light transmission regions are implemented as polarizers that polarize the light incident thereon in the first and second directions, respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

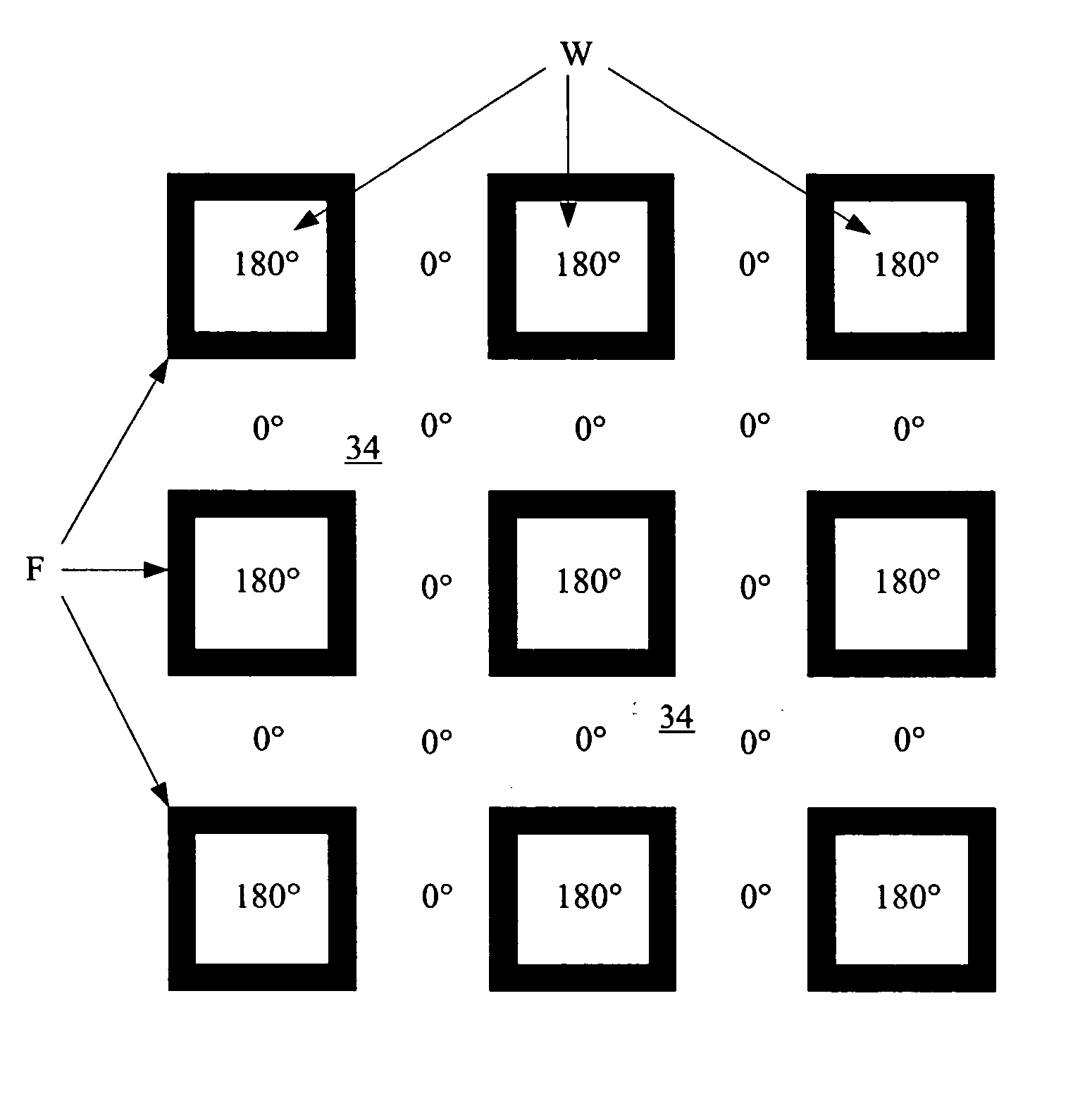

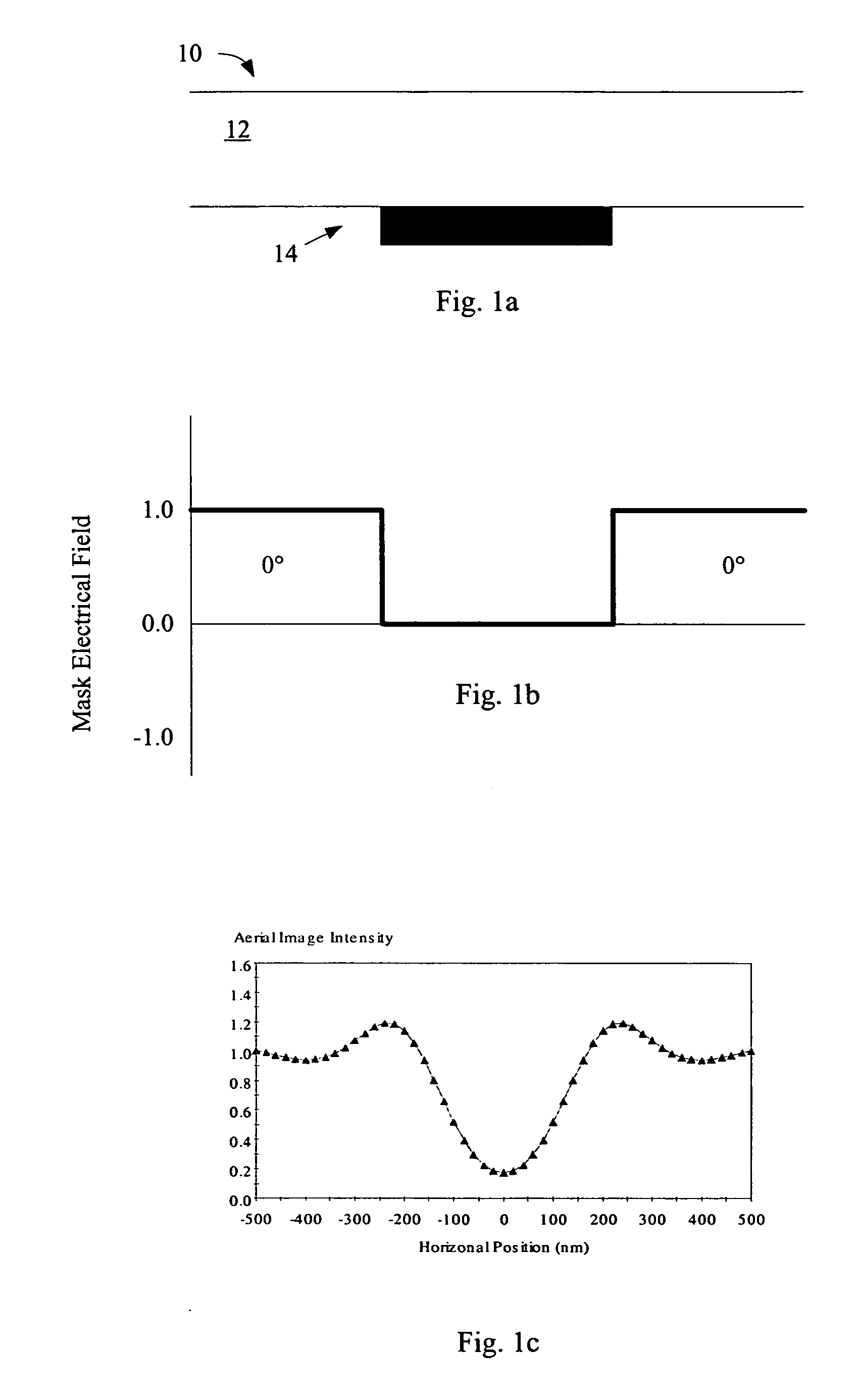

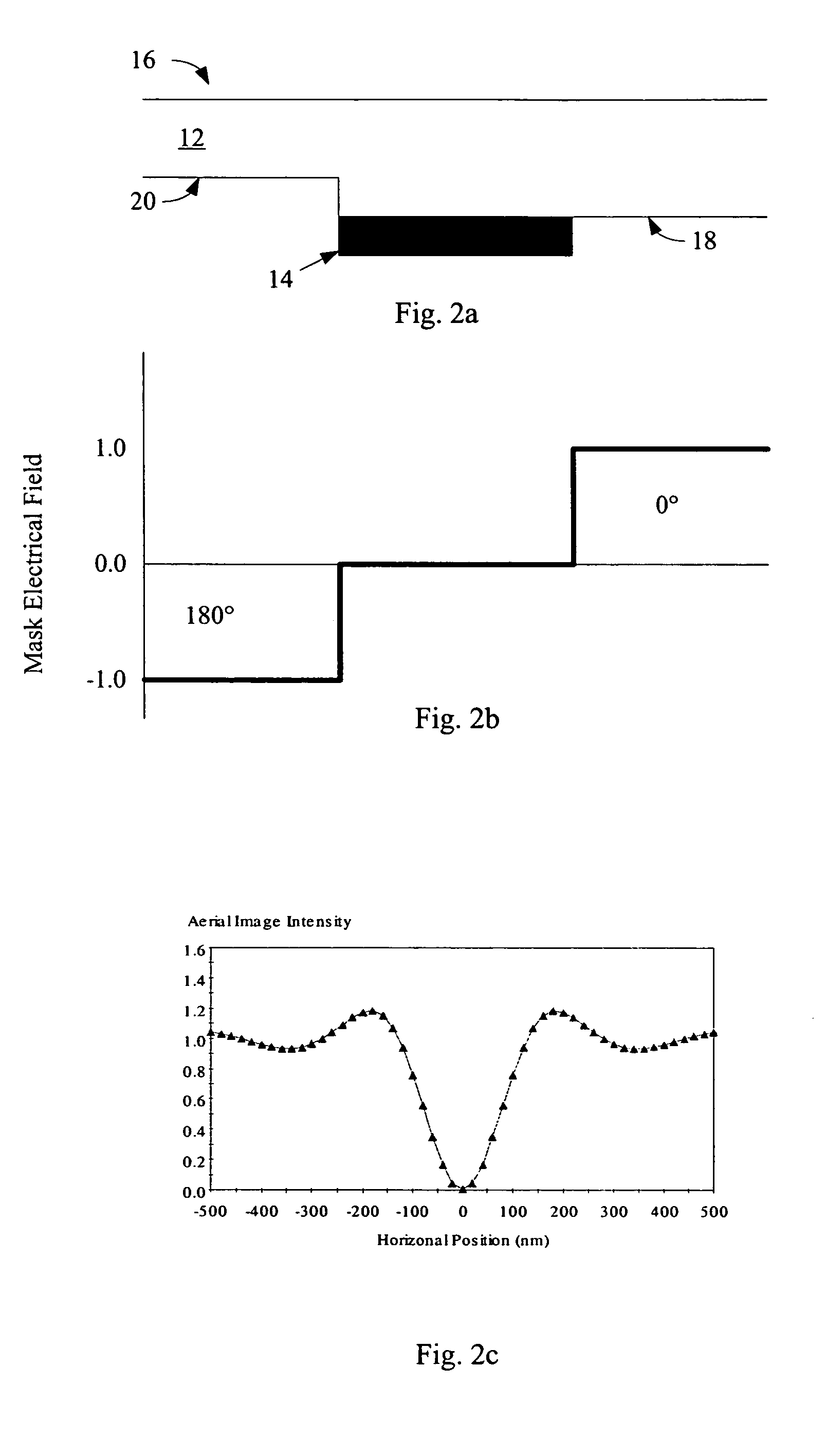

Photomask features with chromeless nonprinting phase shifting window

InactiveUS20050221200A1Originals for photomechanical treatmentSpecial data processing applicationsPhase cancellationPhotoresist

Aspects of the present invention provide for a novel photomask for patterning features for an integrated circuit, the photomask including a first area transmitting light in a first phase surrounded by second area, the second area transmitting light in a second phase, the second phase opposite the first phase. No blocking material separates the first area from the second area. After development of photoresist, the transition between the first and second area causes formation of a residual photoresist feature on the photoresist surface due to phase canceling of light. If the first area is small enough, it is nonprinting, ie., the opposite sides of the residual photoresist feature formed at its perimeter merge, forming a contiguous photoresist feature, and thus a corresponding patterned feature after etch.

Owner:SANDISK TECH LLC

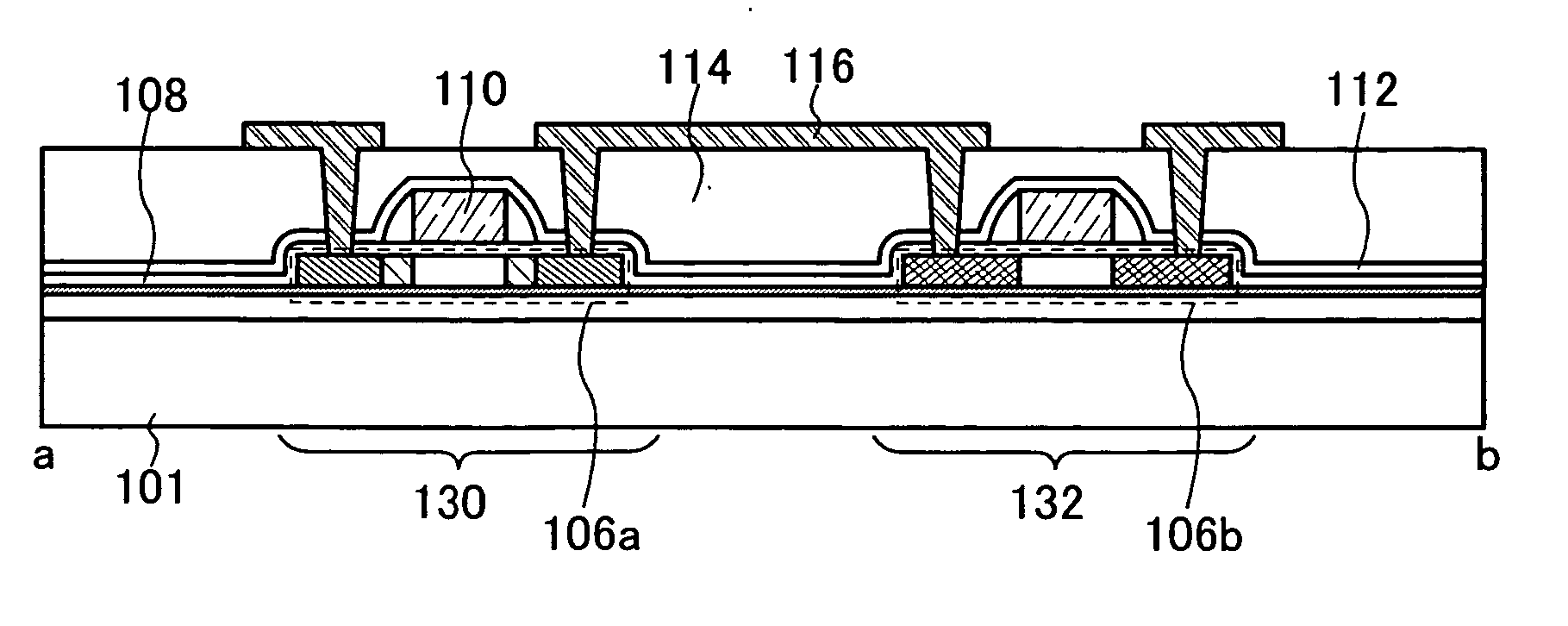

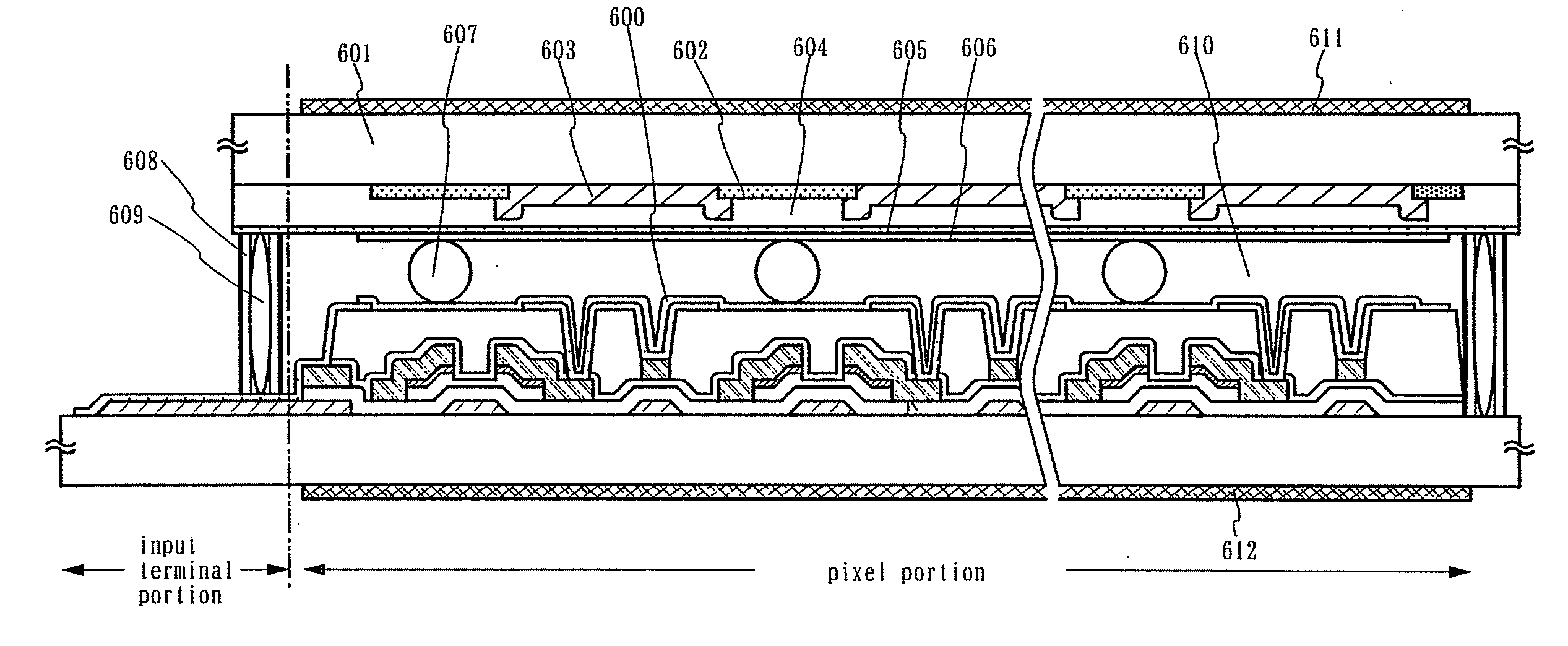

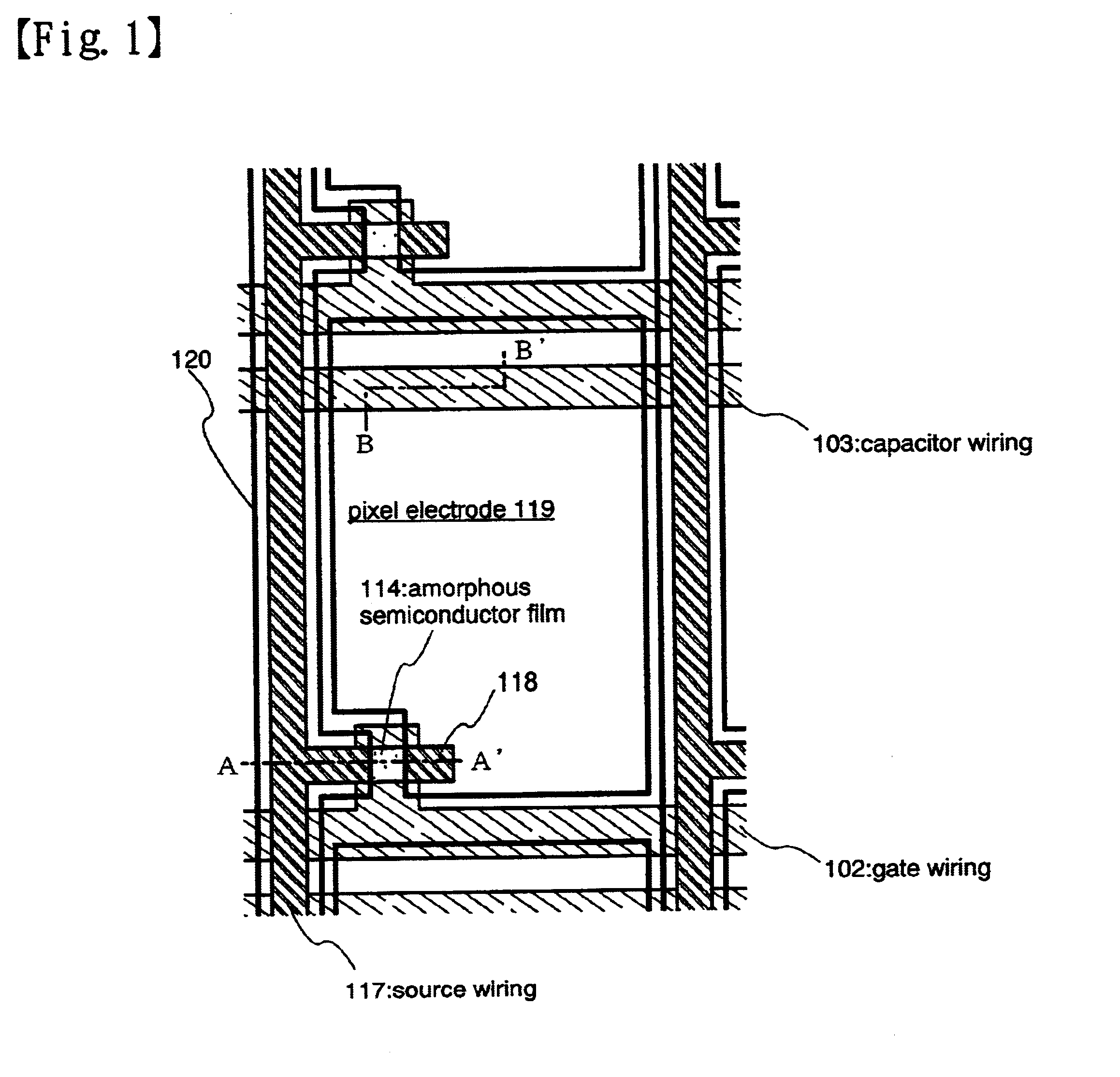

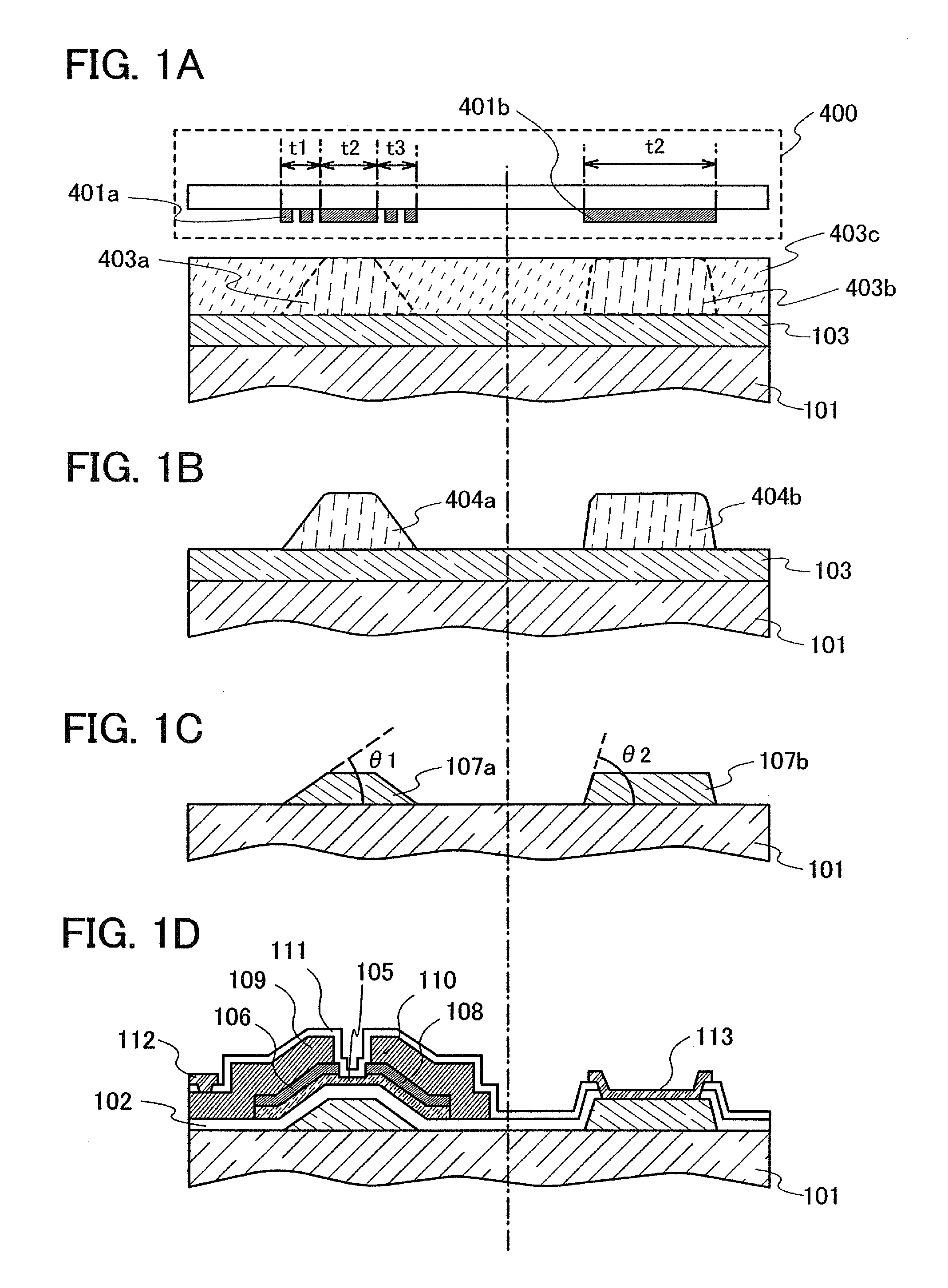

Semiconductor Device and Method of Manufacturing the Semiconductor Device

InactiveUS20090033818A1Reduce manufacturing costIncrease productionTransistorSolid-state devicesInorganic materialsPhotolithography

In a semiconductor device, a first interlayer insulating layer made of an inorganic material and formed on inverse stagger type TFTs, a second interlayer insulating layer made of an organic material and formed on the first interlayer insulating layer, and a pixel electrode formed in contact with the second interlayer insulating layer are disposed on a substrate, and an input terminal portion that is electrically connected to a wiring of another substrate is provided on an end portion of the substrate. The input terminal portion includes a first layer made of the same material as that of the gate electrode and a second layer made of the same material as that of the pixel electrode. With this structure, the number of photomasks used in the photolithography method can be reduced to 5.

Owner:SEMICON ENERGY LAB CO LTD

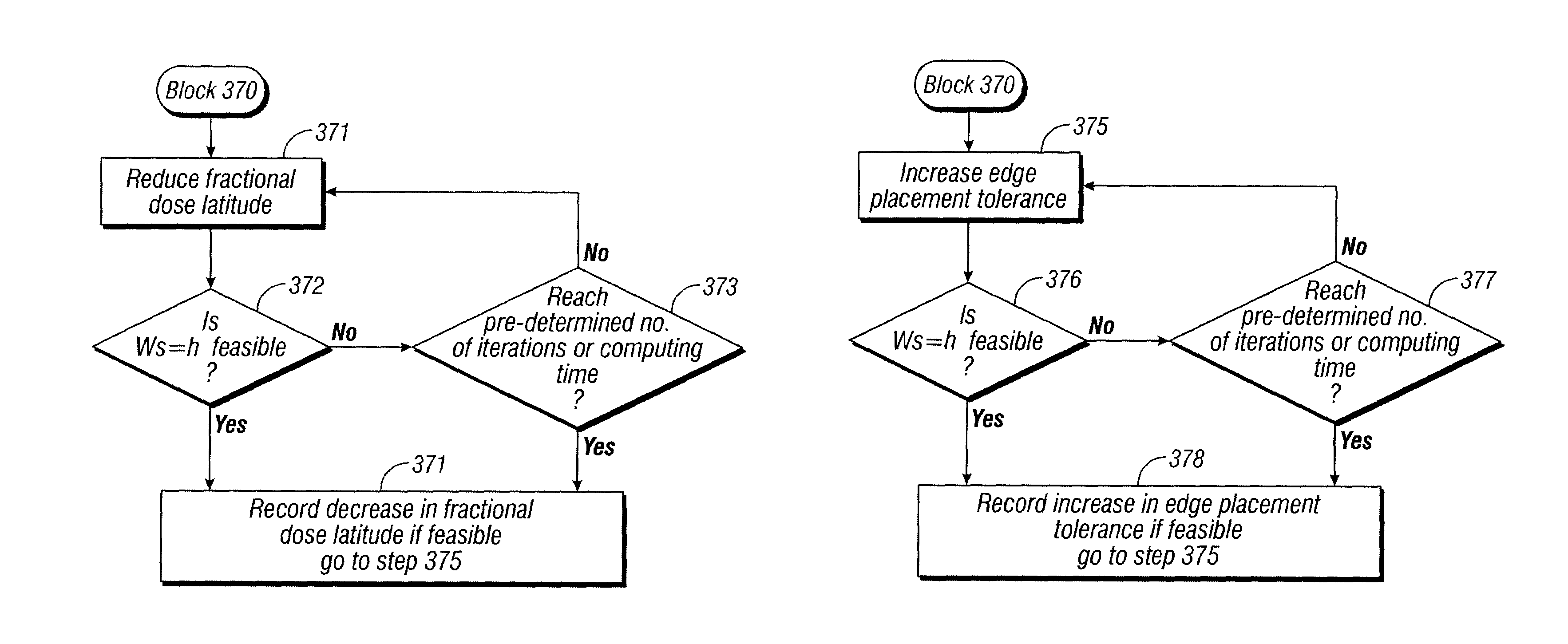

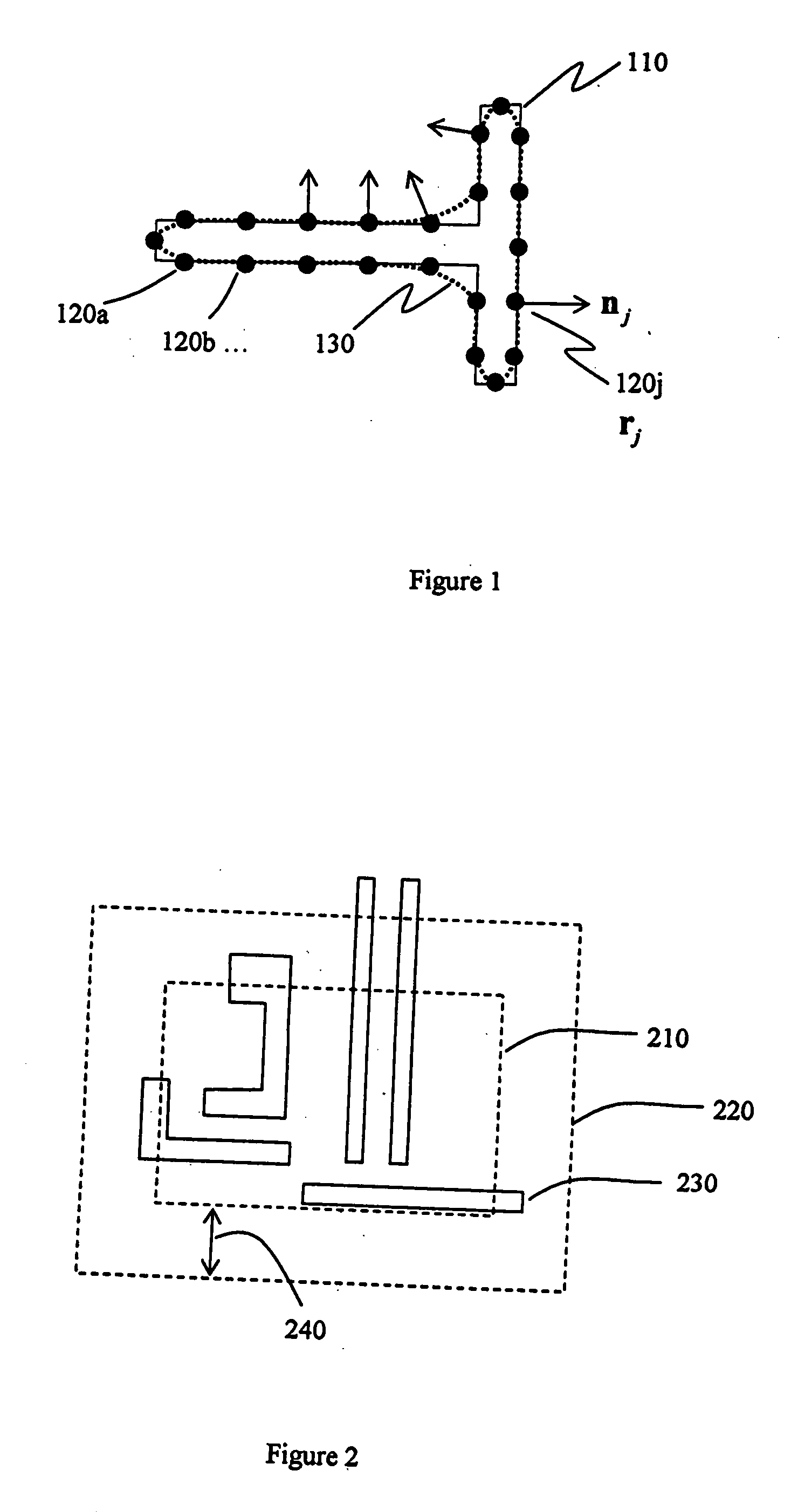

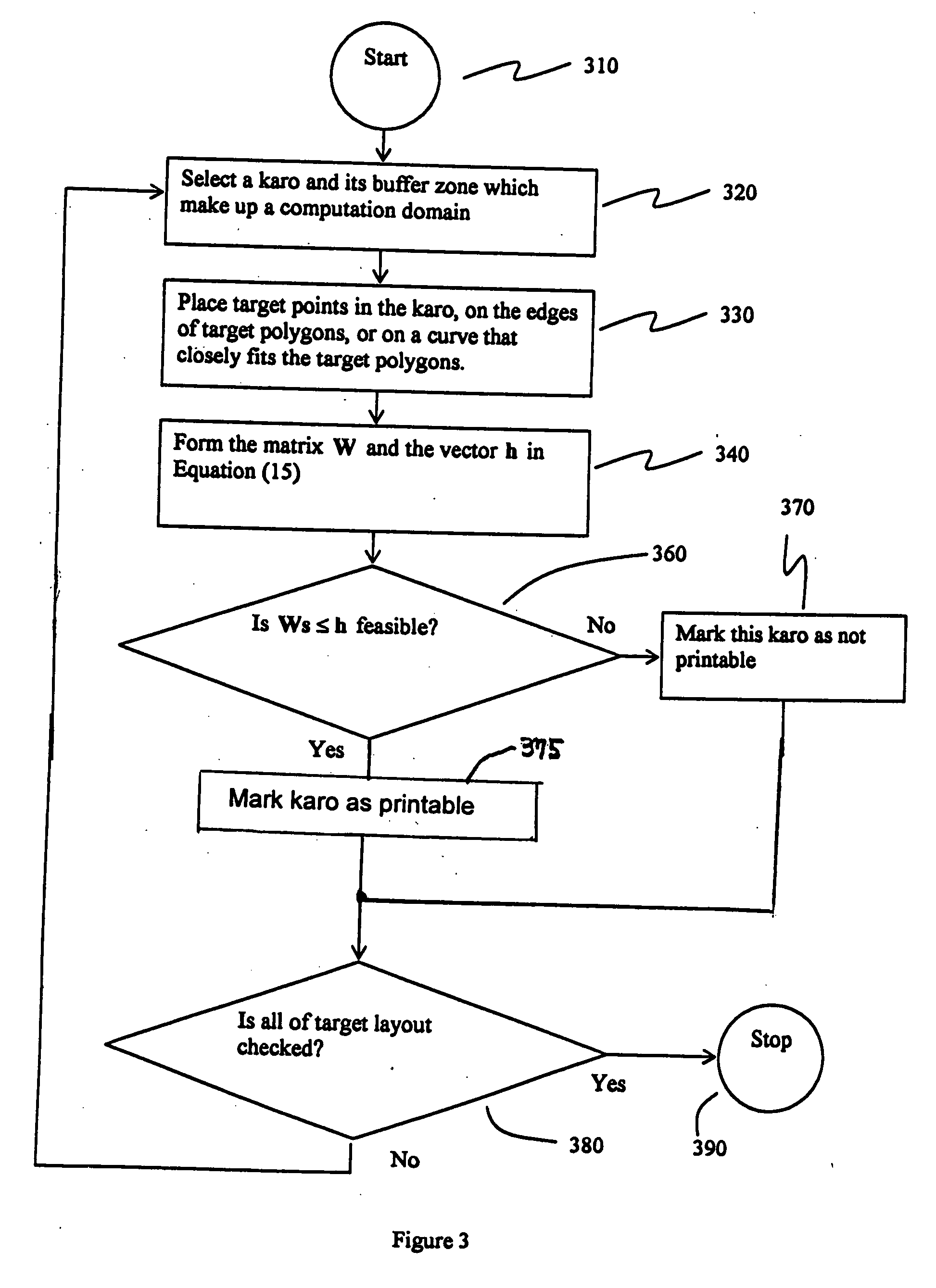

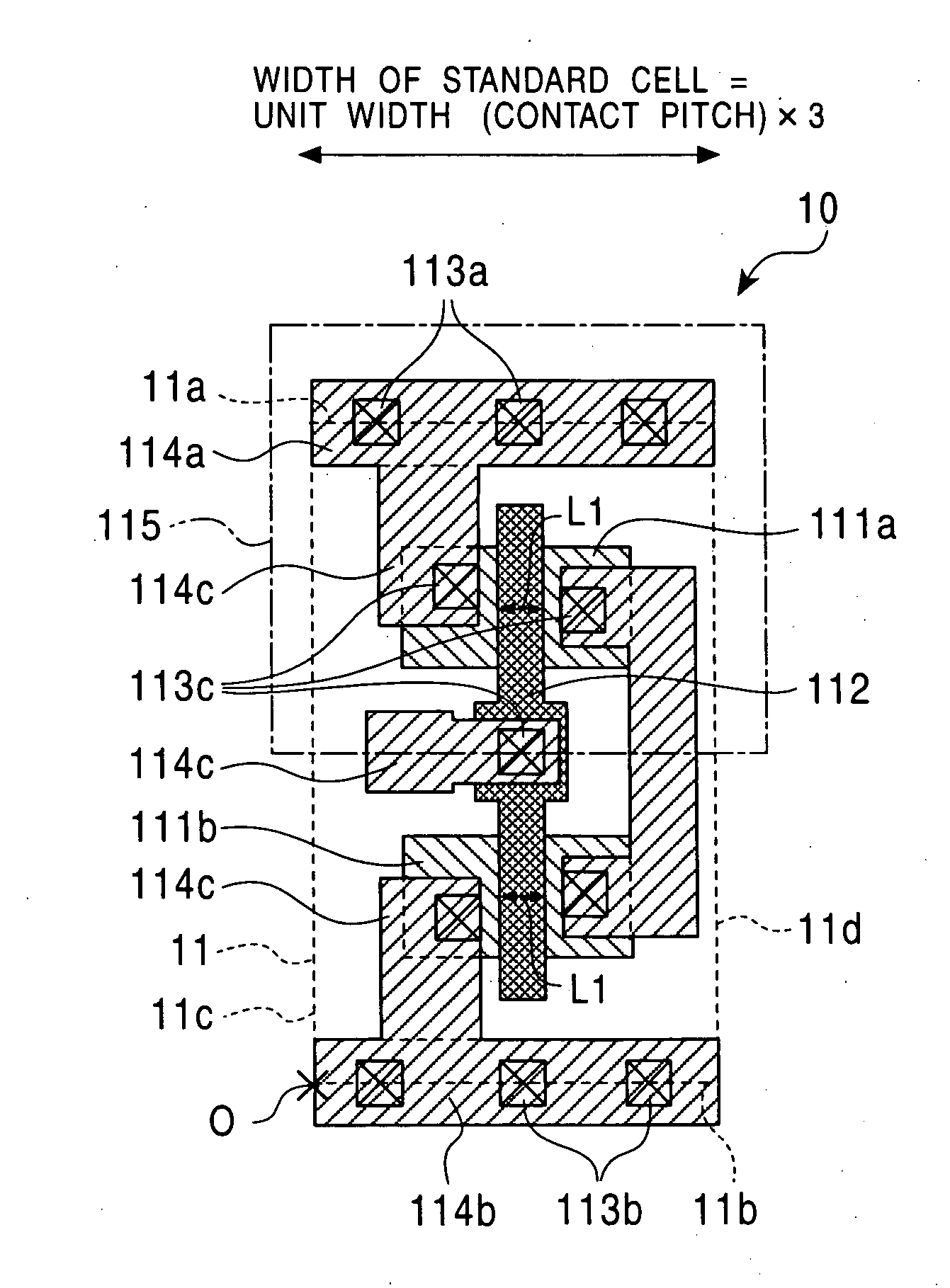

Method for checking printability of a lithography target

InactiveUS7568174B2Detecting faulty computer hardwarePhotomechanical apparatusOptical radiationLithographic artist

A technique for determining, without having to perform optical proximity correction, when the result of optical proximity correction will fail to meet the design requirements for printability. A disclosed embodiment has application to a process for producing a photomask for use in the printing of a pattern on a wafer by exposure with optical radiation to optically image the photomask on the wafer. A method is set forth for checking the printability of a target layout proposed for defining the photomask, including the following steps: deriving a system of inequalities that expresses a set of design requirements with respect to the target layout; and checking the printability of the target layout by determining whether the system of inequalities is feasible.

Owner:CADENCE DESIGN SYST INC

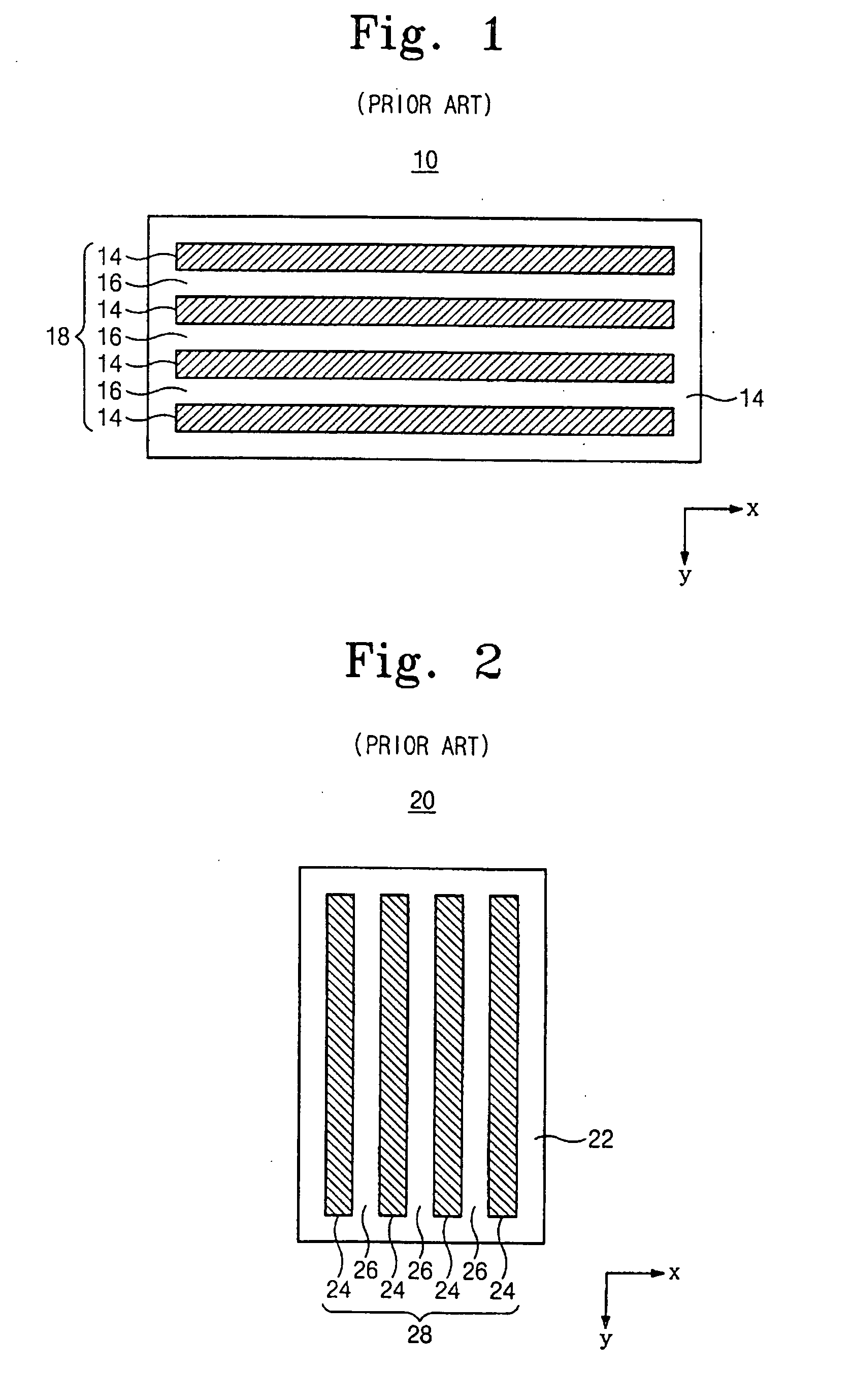

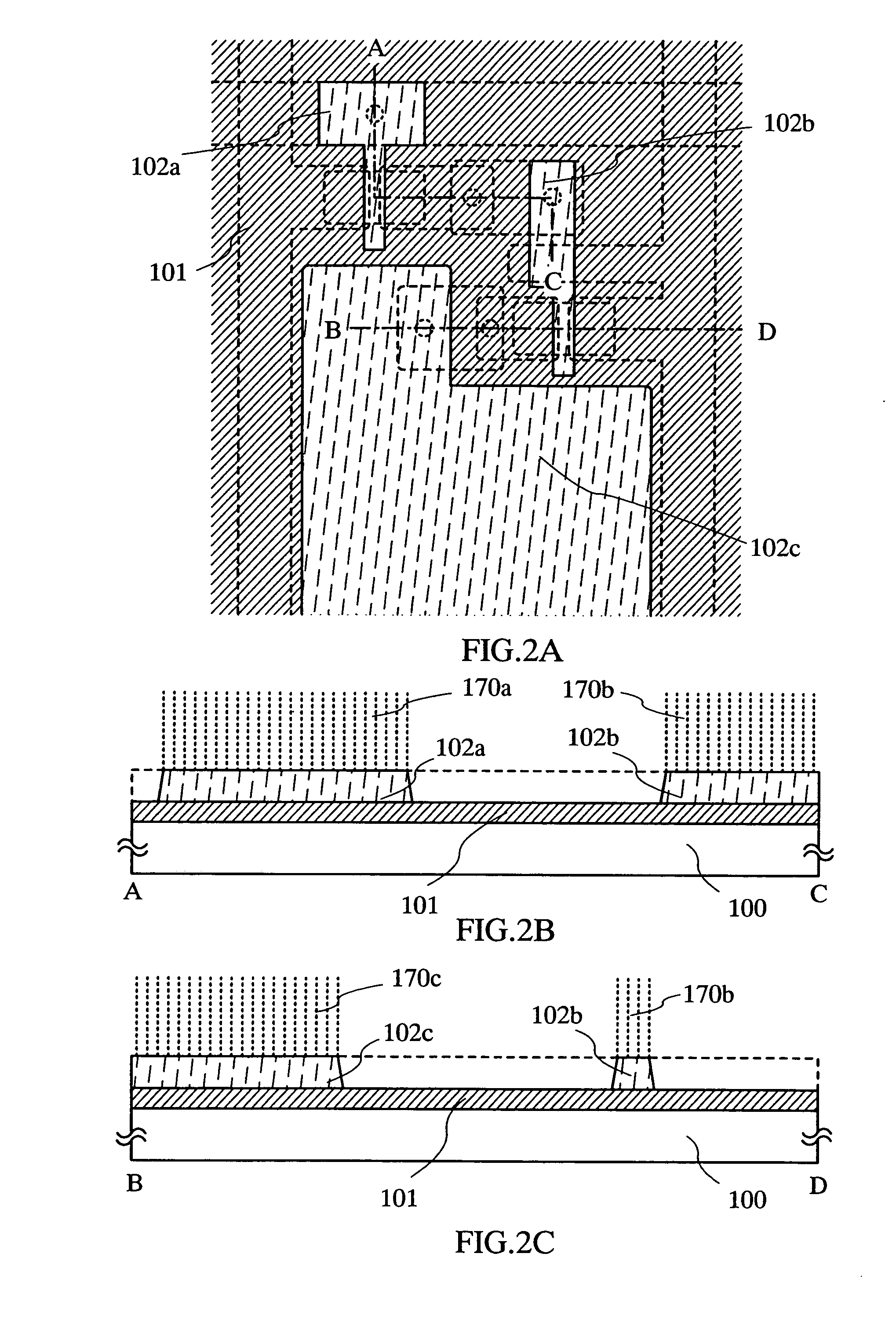

Method for providing layout design and photo mask

A method for providing the layout design of semiconductor integrated circuit that is capable of promoting the reduction of the circuit pattern area is provided. A hole pattern is disposed at the mesh point which is an intersecting point of mutually orthogonal virtual grid lines and another hole pattern is not disposed at the adjacent mesh point that is the closed mesh point having the hole pattern thereon.

Owner:RENESAS ELECTRONICS CORP

Method for checking printability of a lithography target

InactiveUS20070094634A1Detecting faulty computer hardwarePhotomechanical apparatusOptical radiationLithographic artist

A technique for determining, without having to perform optical proximity correction, when the result of optical proximity correction will fail to meet the design requirements for printability. A disclosed embodiment has application to a process for producing a photomask for use in the printing of a pattern on a wafer by exposure with optical radiation to optically image the photomask on the wafer. A method is set forth for checking the printability of a target layout proposed for defining the photomask, including the following steps: deriving a system of inequalities that expresses a set of design requirements with respect to the target layout; and checking the printability of the target layout by determining whether the system of inequalities is feasible.

Owner:CADENCE DESIGN SYST INC

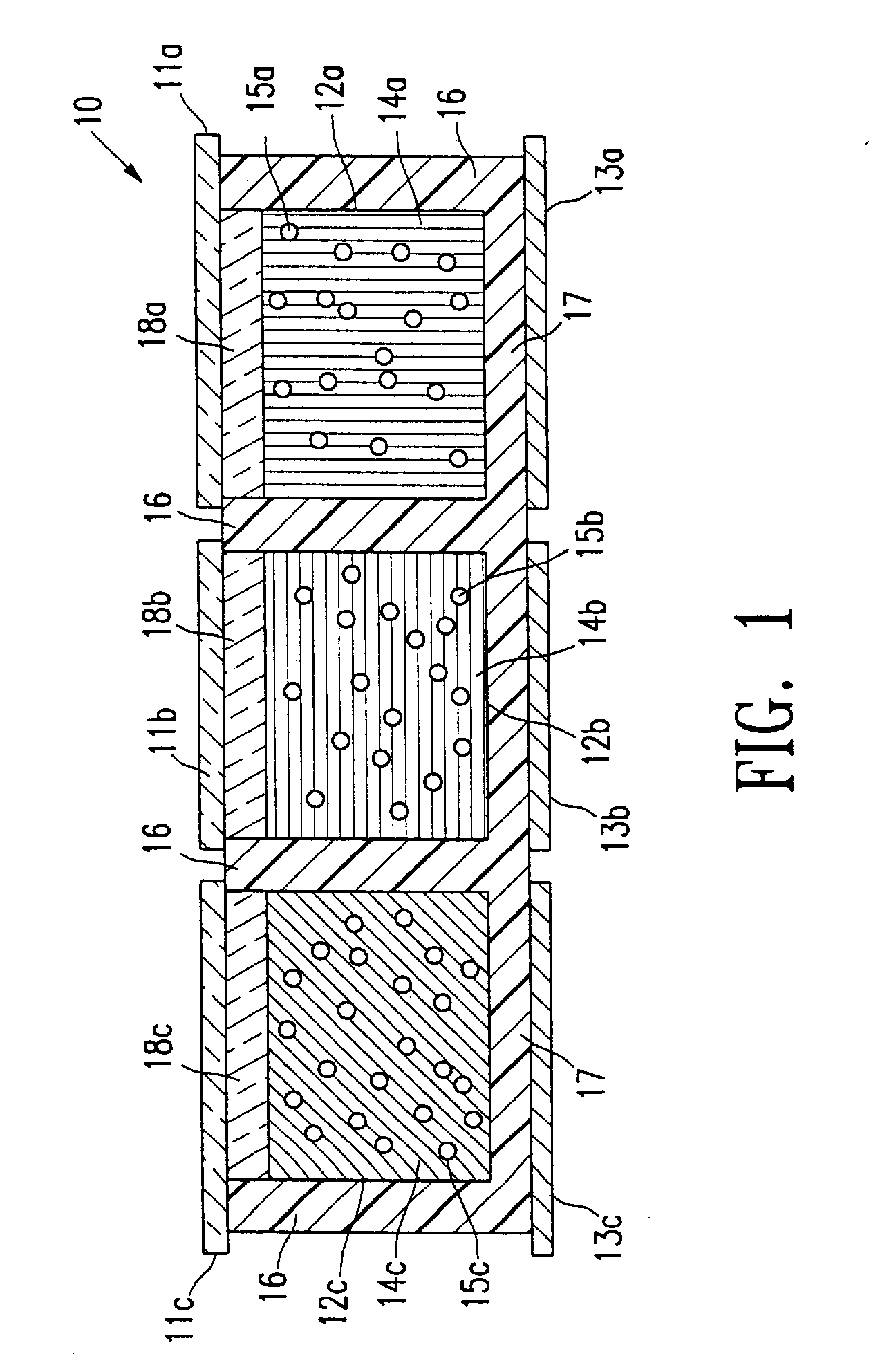

Layout method of semiconductor integrated circuit, layout structure thereof, and photomask for forming the layout structure

ActiveUS20050044522A1Reduces dimensional deviationHigh dimensional accuracySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A plurality of standard cells 10 are arranged to form a channel-less standard cell array 1, which has vertical and horizontal sides. A plurality of first proximity dummy cells 20 are arranged along each of the vertical sides of the standard cell array to form a first proximity dummy bands 20 such that the upper and lower sides of the first proximity dummy cells are in contact with each other and such that the left or right side of each of the first proximity dummy cells is in contact with the vertical side of the standard cell array 1. Furthermore, a plurality of second proximity dummy bands are arranged along each of the horizontal sides of the standard cell array to form a second proximity dummy bands such that the upper or lower side of each of the second proximity dummy cells is in contact with the horizontal side of the standard cell 1.

Owner:KAWASAKI MICROELECTRONICS

Spacer formation

Embodiments of the present invention pertain to methods of forming more symmetric spacers which may be used for self-aligned multi-patterning processes. A conformal spacer layer of spacer material is formed over mandrels patterned near the optical resolution of a photolithography system using a high-resolution photomask. A carbon-containing layer is further formed over the conformal spacer layer. The carbon-containing layer is anisotropically etched to expose the high points of the conformal spacer layer while retaining carbon side panels. The conformal spacer layer may then be etched to form spacers without the traditional skewing of the profile towards one side or the other.

Owner:APPLIED MATERIALS INC

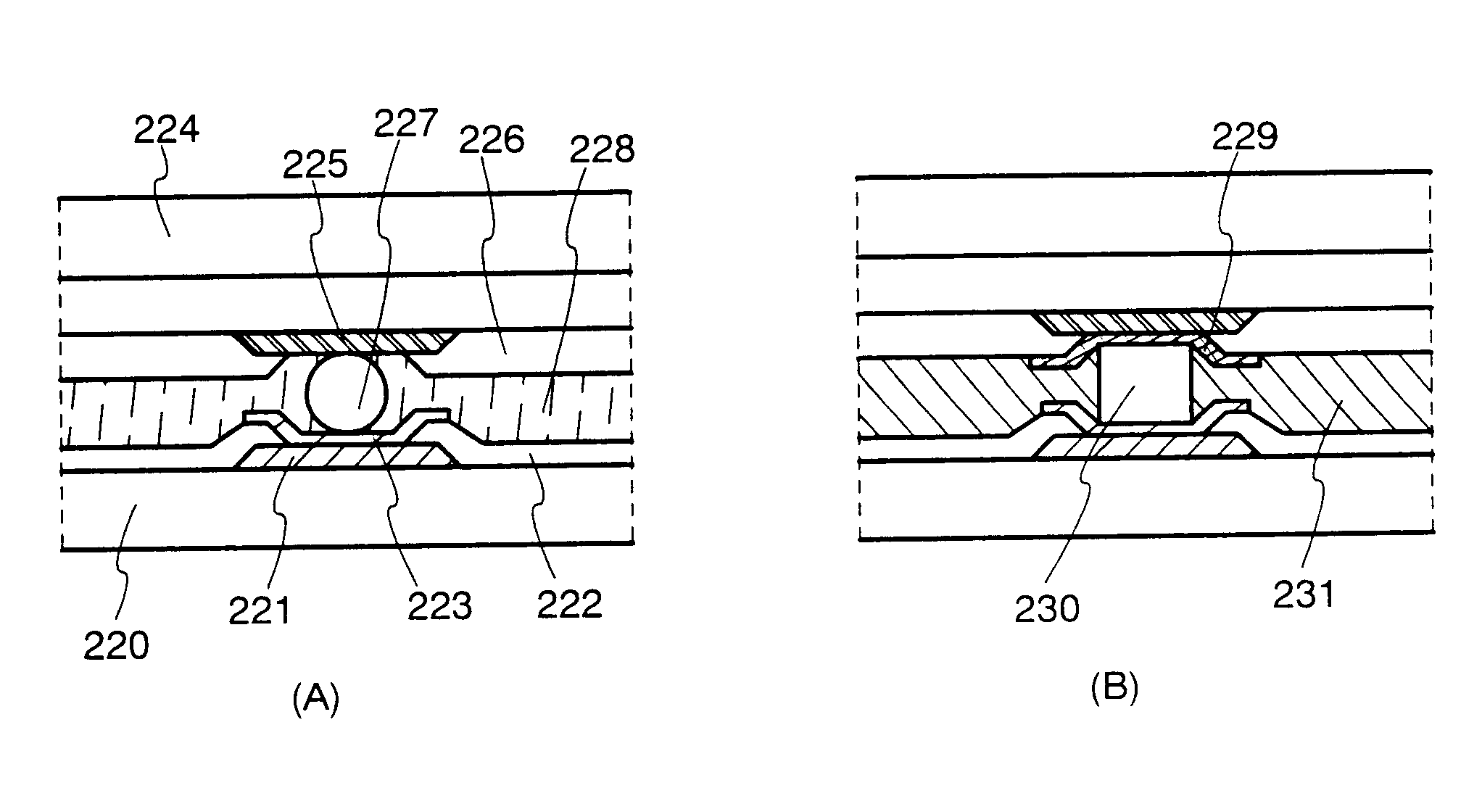

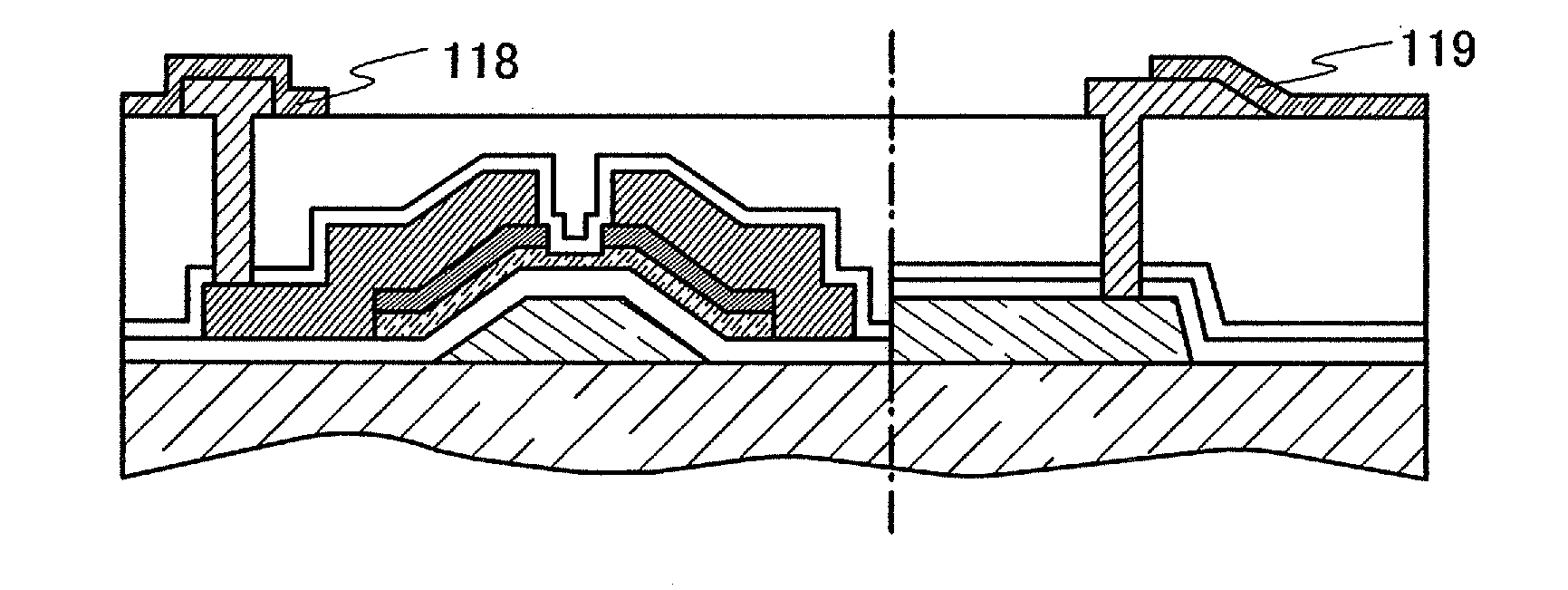

Semiconductor device having stick drivers and a method of manufacturing the same

A pixel TFT formed in a pixel region is formed on a first substrate by a channel etch type reverse stagger type TFT, and patterning of a source region and a drain region, and patterning of a pixel electrode are performed by the same photomask. A driver circuit formed by using TFTs having a crystalline semiconductor layer, and an input-output terminal dependent on the driver circuit, are taken as one unit. A plurality of units are formed on a third substrate, and afterward the third substrate is partitioned into individual units, and the obtained stick drivers are mounted on the first substrate.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and manufacturing method thereof

InactiveUS20090140438A1Reduce stepsMade preciselySemiconductor/solid-state device detailsSolid-state devicesEngineeringPhotoresist

Wirings each having a side face with a different angle, which is made accurately, in a desired portion over one mother glass substrate are provided without increasing the steps. With the use of a multi-tone mask, a photoresist layer is formed, which has a tapered shape in which the area of a cross section is reduced gradually in a direction away from one mother glass substrate. At the time of forming one wiring, one photomask is used and a metal film is selectively etched, whereby one wiring having a side face, the shape (specifically, an angle with respect to a principal plane of a substrate) of which is different depending on a place, is obtained.

Owner:SEMICON ENERGY LAB CO LTD

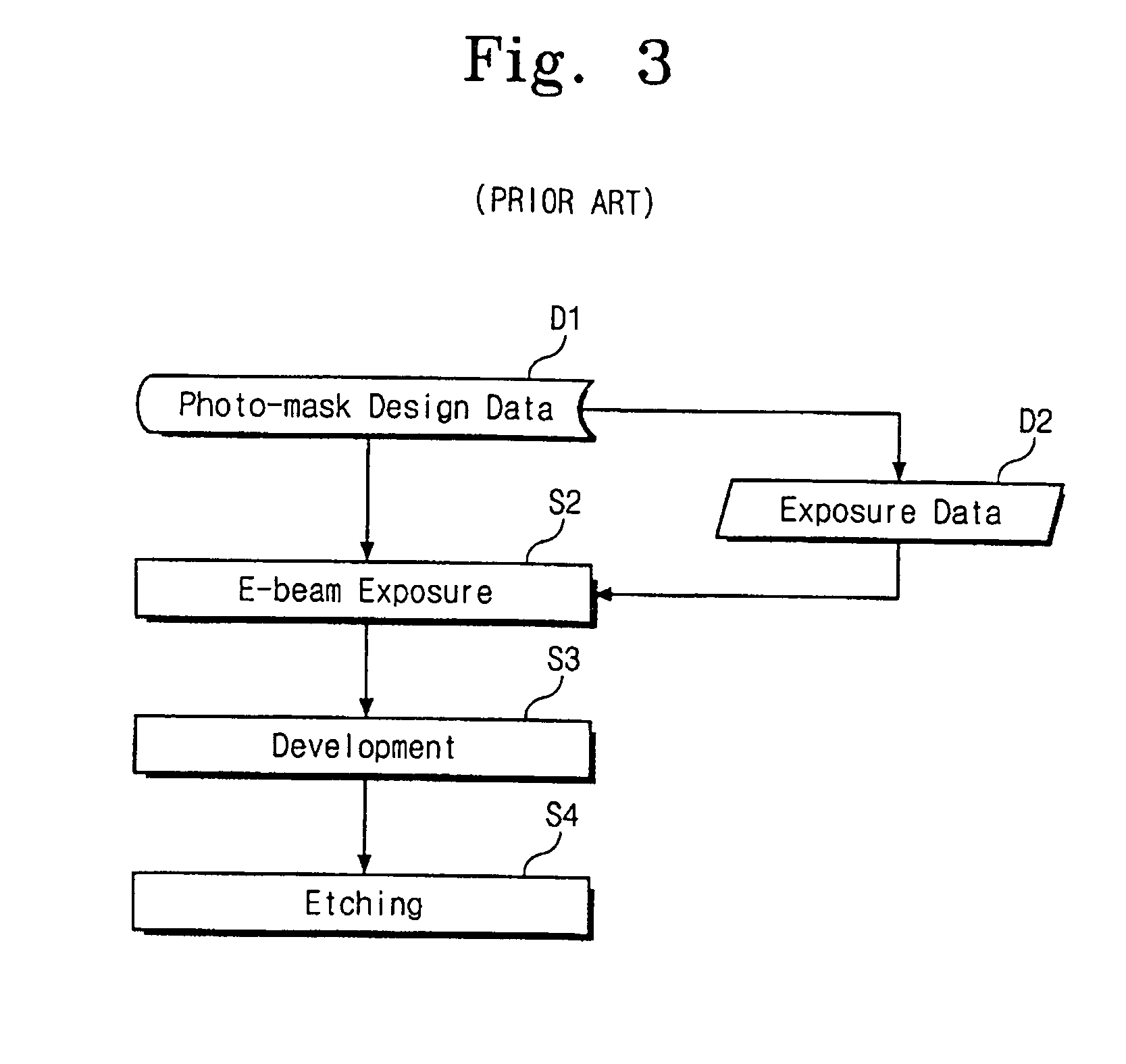

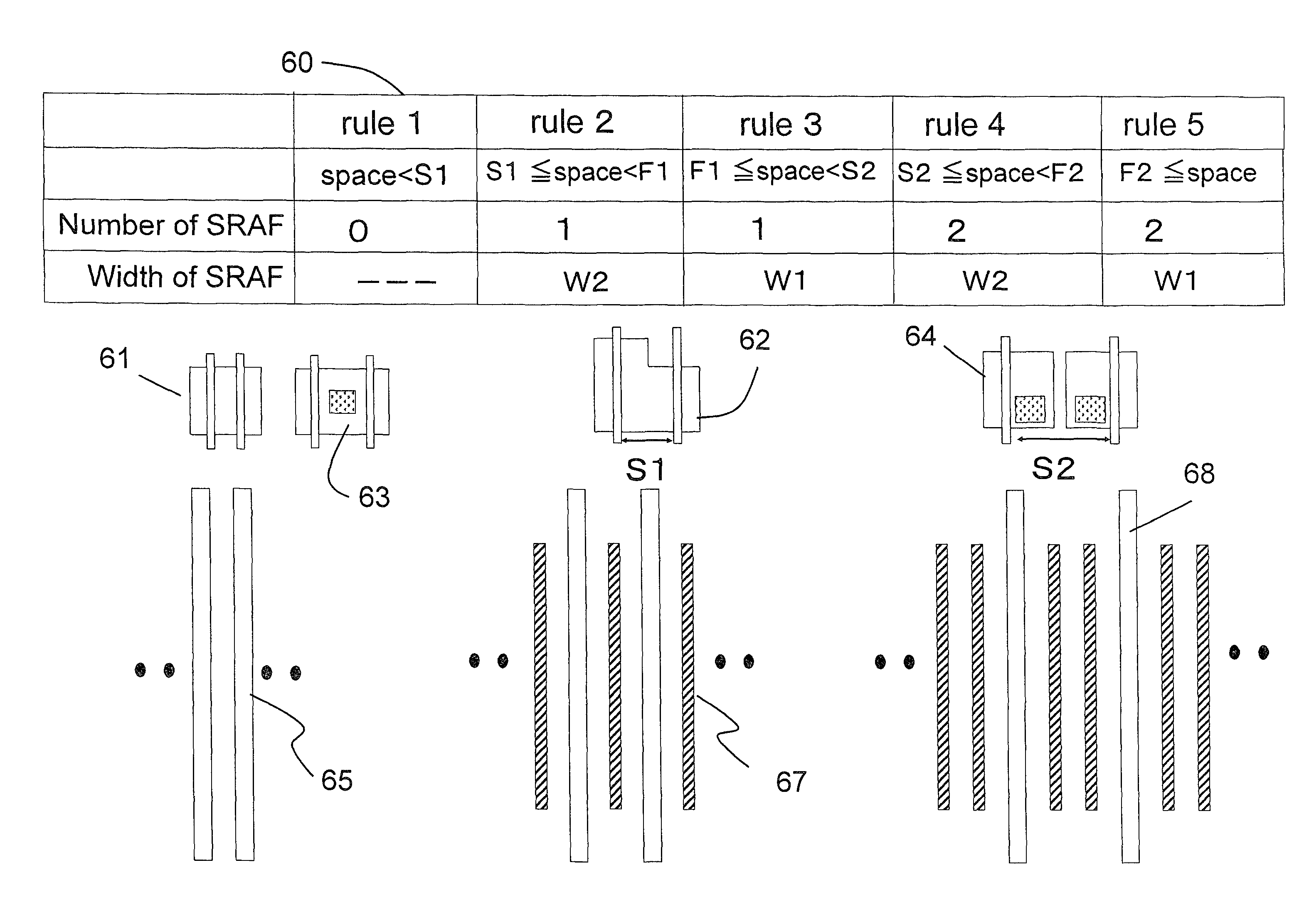

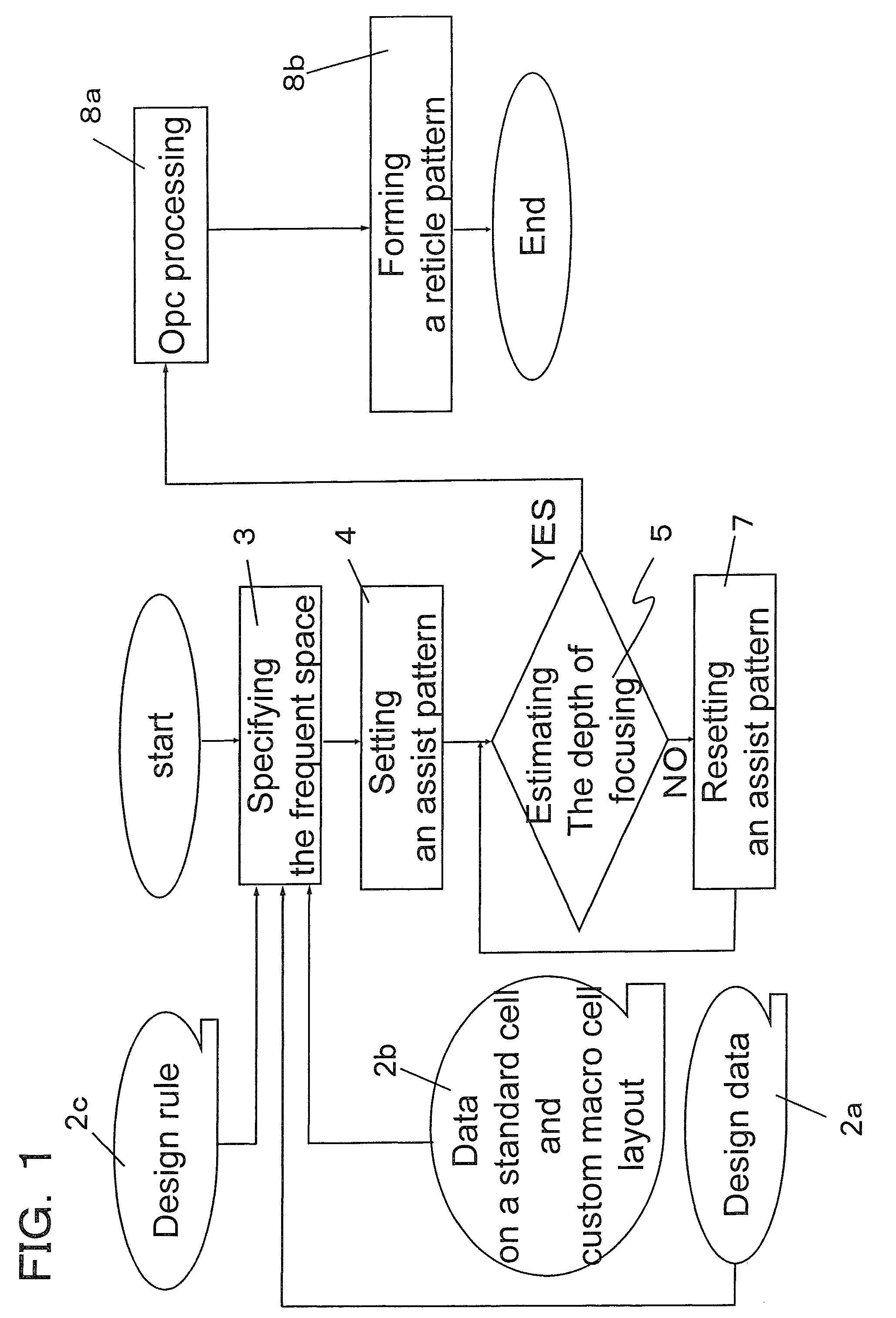

Creating method of photomask pattern data, photomask created by using the photomask pattern data, and manufacturing method of semiconductor apparatus using the photomask

A method for creating a pattern on a photomask includes steps of recognizing a space between main patterns by using pattern data which indicate the main patterns to be adjacently transferred onto a wafer, determining a 1st rule about arrangement of an assist pattern on the photomask, the assist pattern being adjacent to the main patterns and not being transferred onto the wafer, estimating a depth of focus in the presence of the assist pattern among the main patterns, determining a 2nd rule about arrangement of the assist pattern on the photomask to improve the depth of focus in the presence of the 1st assist pattern among the main patterns in a group having one or more number of appearance times of the space between main patterns, and correcting the assist pattern on the photomask using the assist pattern data on the basis of the 2nd rule.

Owner:FUJITSU SEMICON LTD

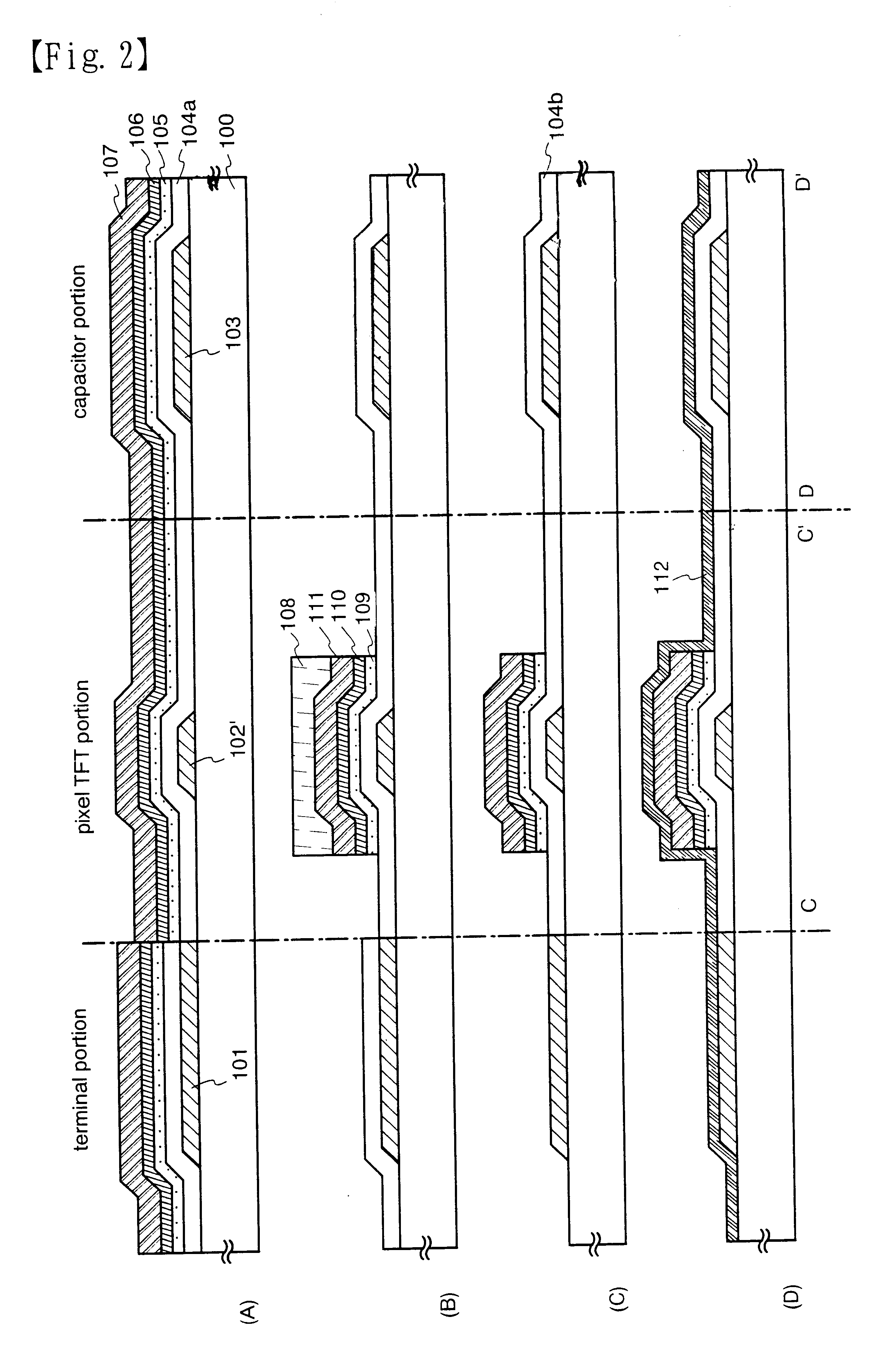

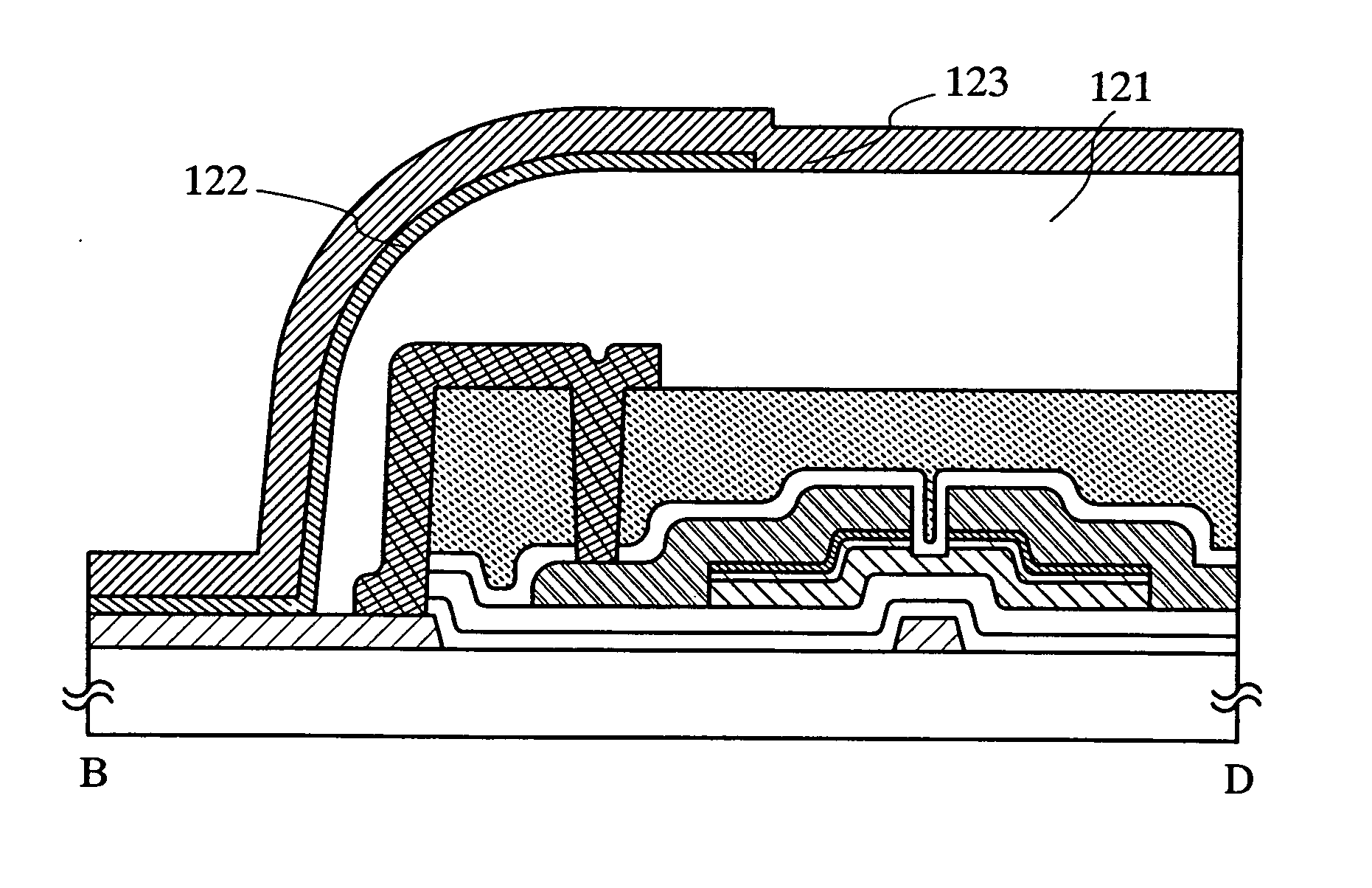

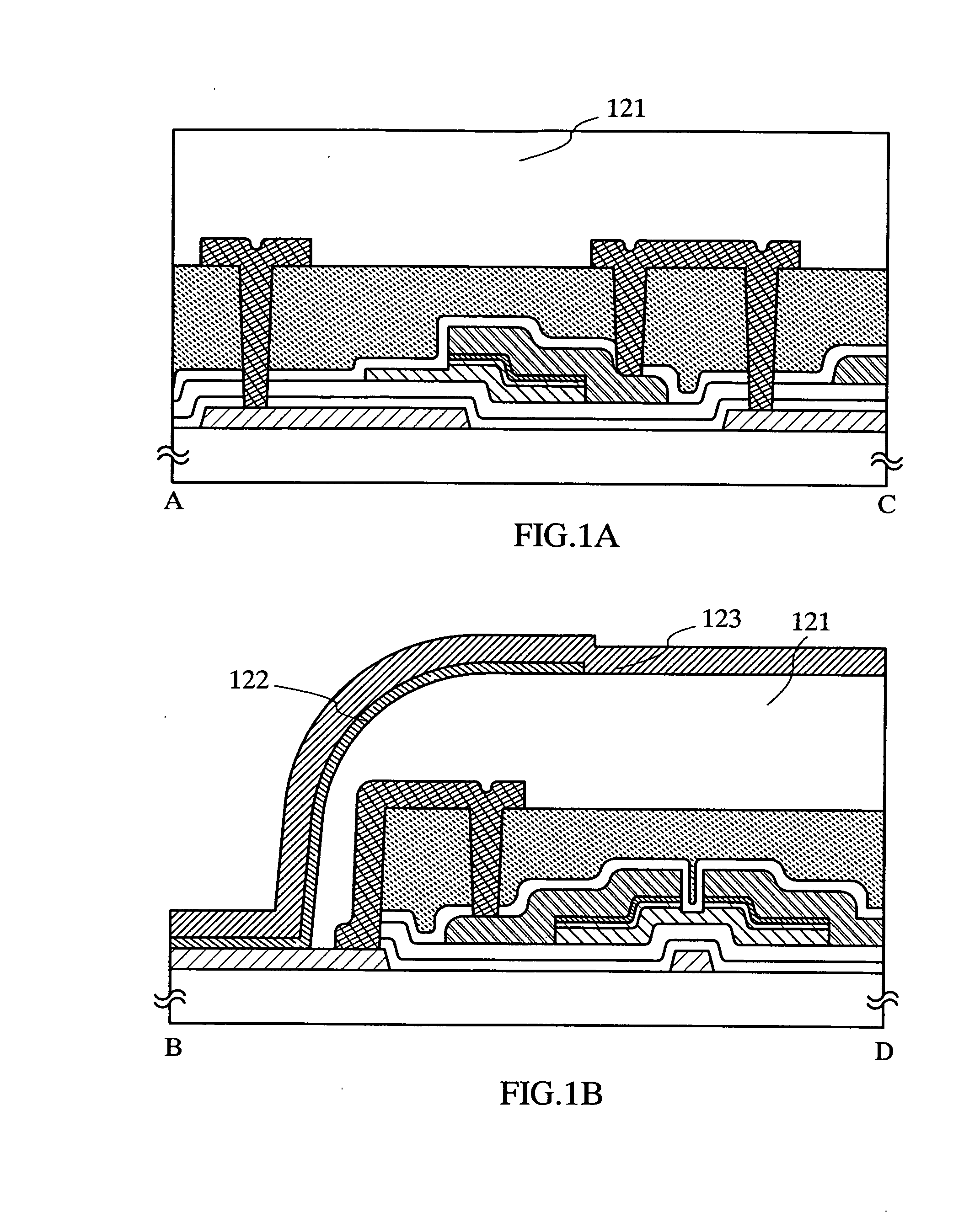

Display device, manufacturing method thereof, and television set

InactiveUS20060027804A1Improve mobilityLow resistivitySolid-state devicesSemiconductor/solid-state device manufacturingContact formationDisplay device

A manufacturing method of a display device having TFTs capable of high-speed operation with few variations of threshold voltage is provided, in which materials are used with high efficiency and a small number of photomasks is required. The display device of the invention comprises a gate electrode layer and a pixel electrode layer formed over an insulating surface, a gate insulating layer formed over the gate electrode layer, a crystalline semiconductor layer formed over the gate insulating layer, a semiconductor layer having one conductivity type formed in contact with the crystalline semiconductor layer, a source electrode layer and a drain electrode layer formed in contact with the semiconductor layer having one conductivity type, an insulating later formed over the source electrode layer, the drain electrode layer, and the pixel electrode layer, a first opening formed in the insulating layer to reach the source electrode layer or the drain electrode layer, a second opening formed in the gate insulating layer and the insulating layer to reach the pixel electrode layer, and a wiring layer formed in the first opening and the second opening to electrically connect the source electrode layer or the drain electrode layer to the pixel electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com