Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1125 results about "Standard cell" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

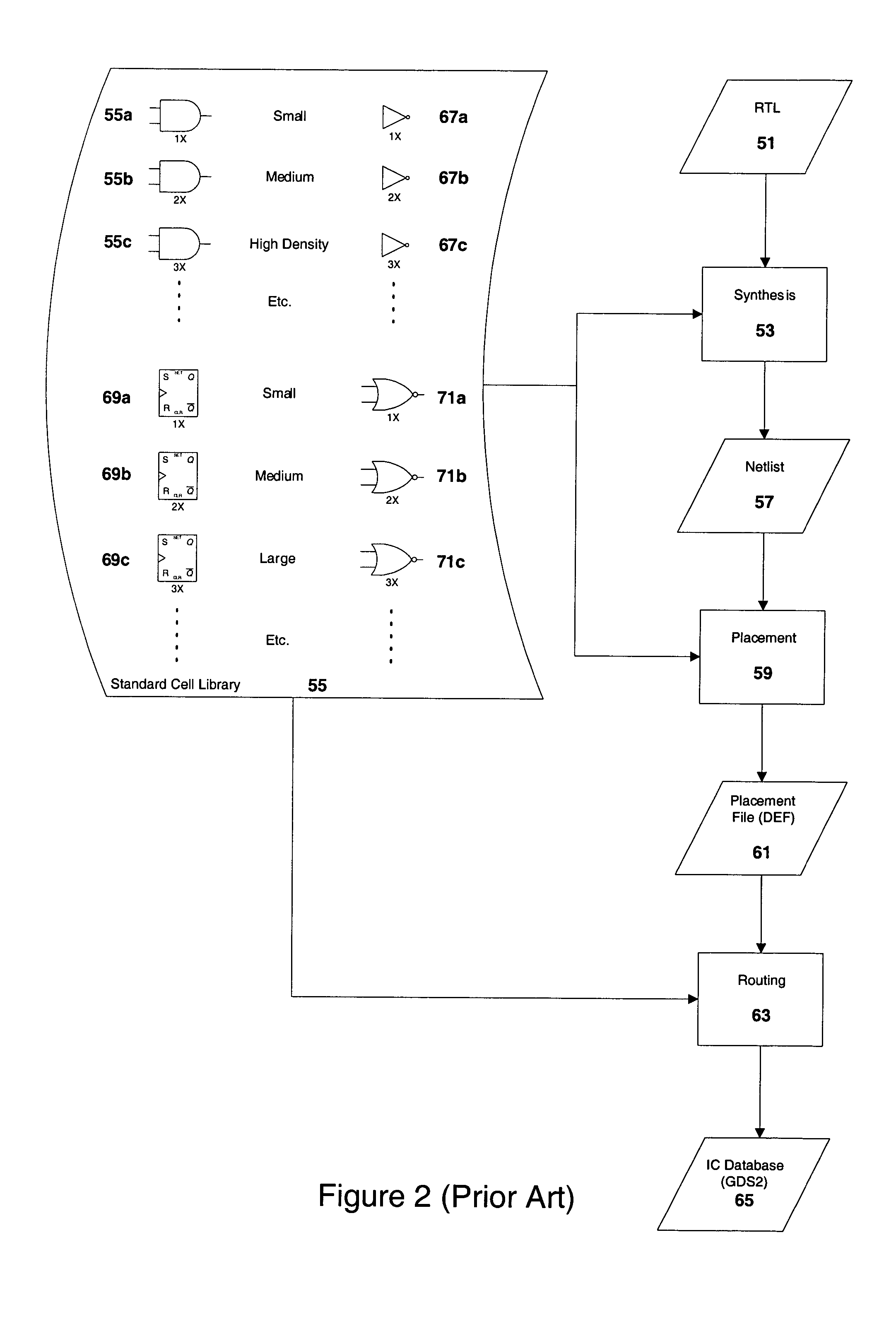

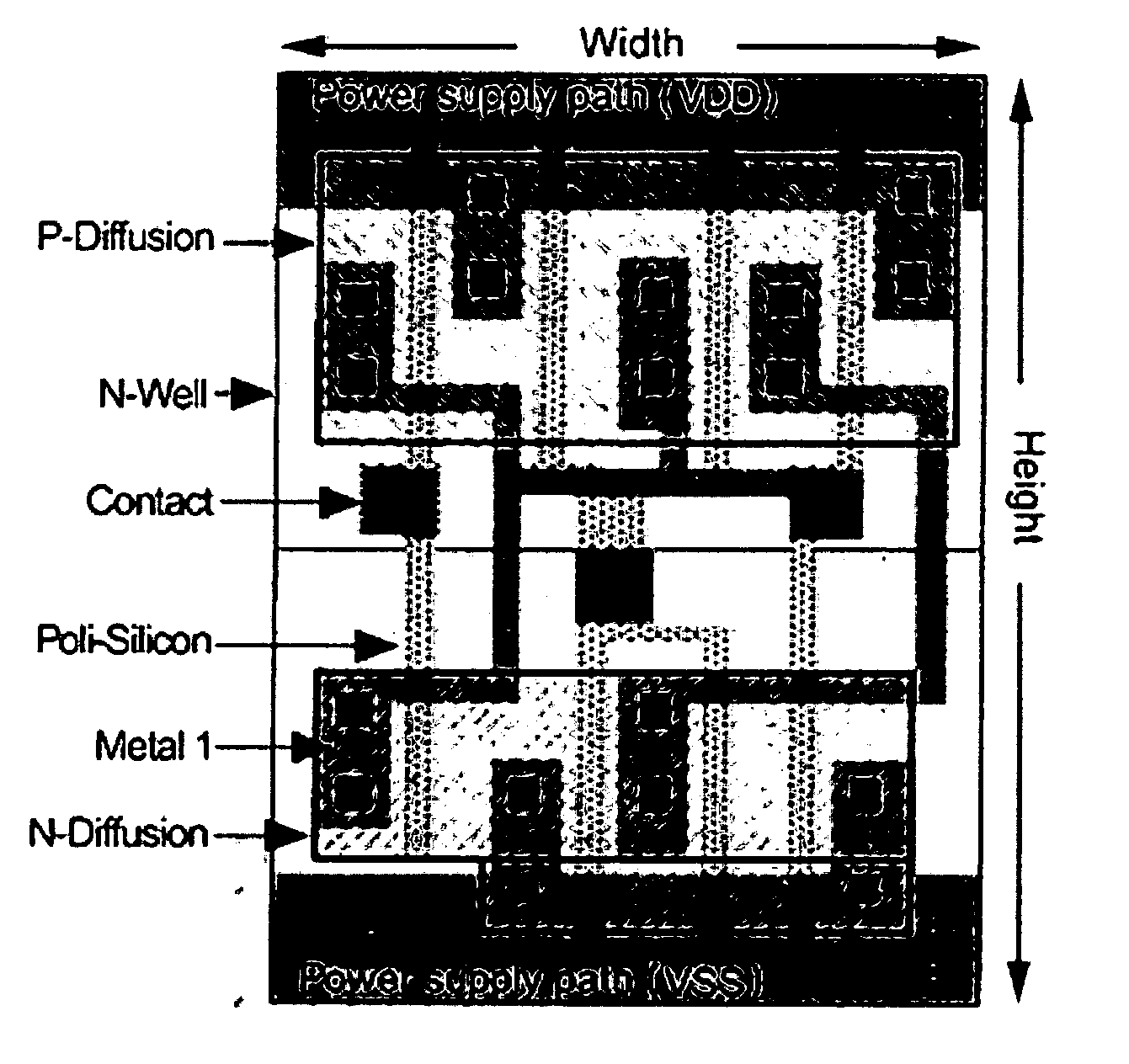

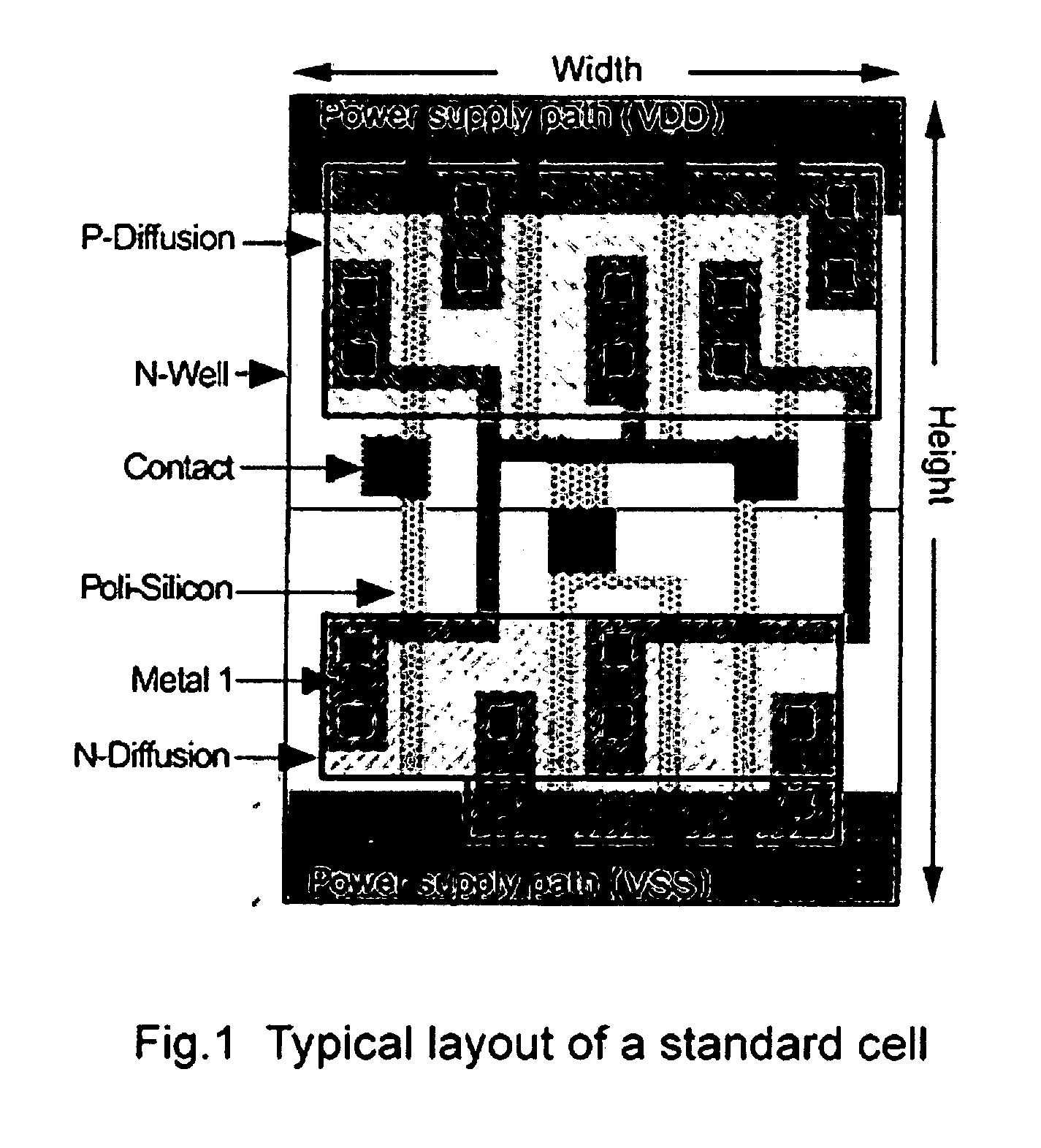

In semiconductor design, standard cell methodology is a method of designing application-specific integrated circuits (ASICs) with mostly digital-logic features. Standard cell methodology is an example of design abstraction, whereby a low-level very-large-scale integration (VLSI) layout is encapsulated into an abstract logic representation (such as a NAND gate). Cell-based methodology — the general class to which standard cells belong — makes it possible for one designer to focus on the high-level (logical function) aspect of digital design, while another designer focuses on the implementation (physical) aspect. Along with semiconductor manufacturing advances, standard cell methodology has helped designers scale ASICs from comparatively simple single-function ICs (of several thousand gates), to complex multi-million gate system-on-a-chip (SoC) devices.

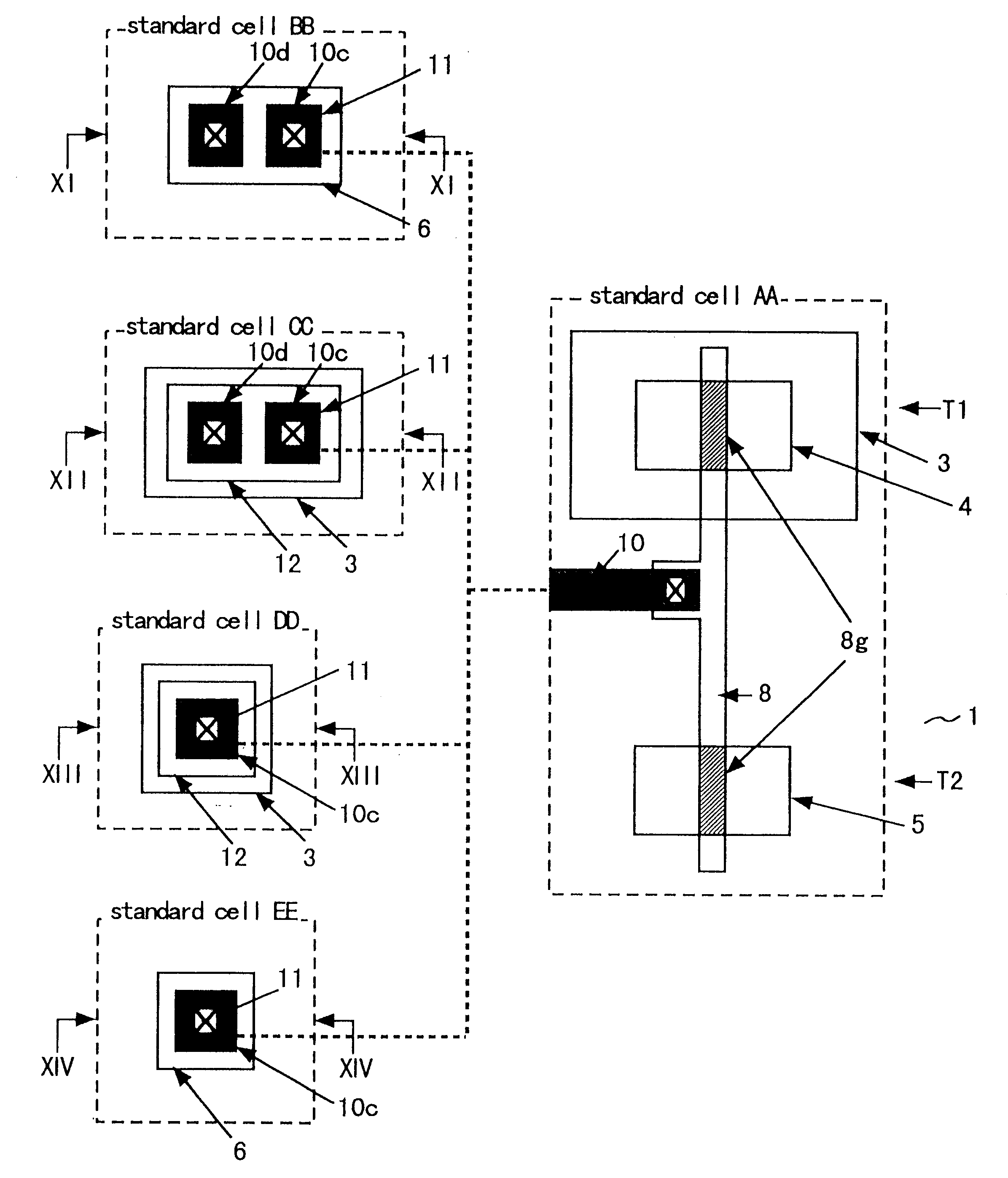

Layout method of semiconductor integrated circuit, layout structure thereof, and photomask for forming the layout structure

ActiveUS7137092B2Eliminate biasHigh dimensionalSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorPhotomask

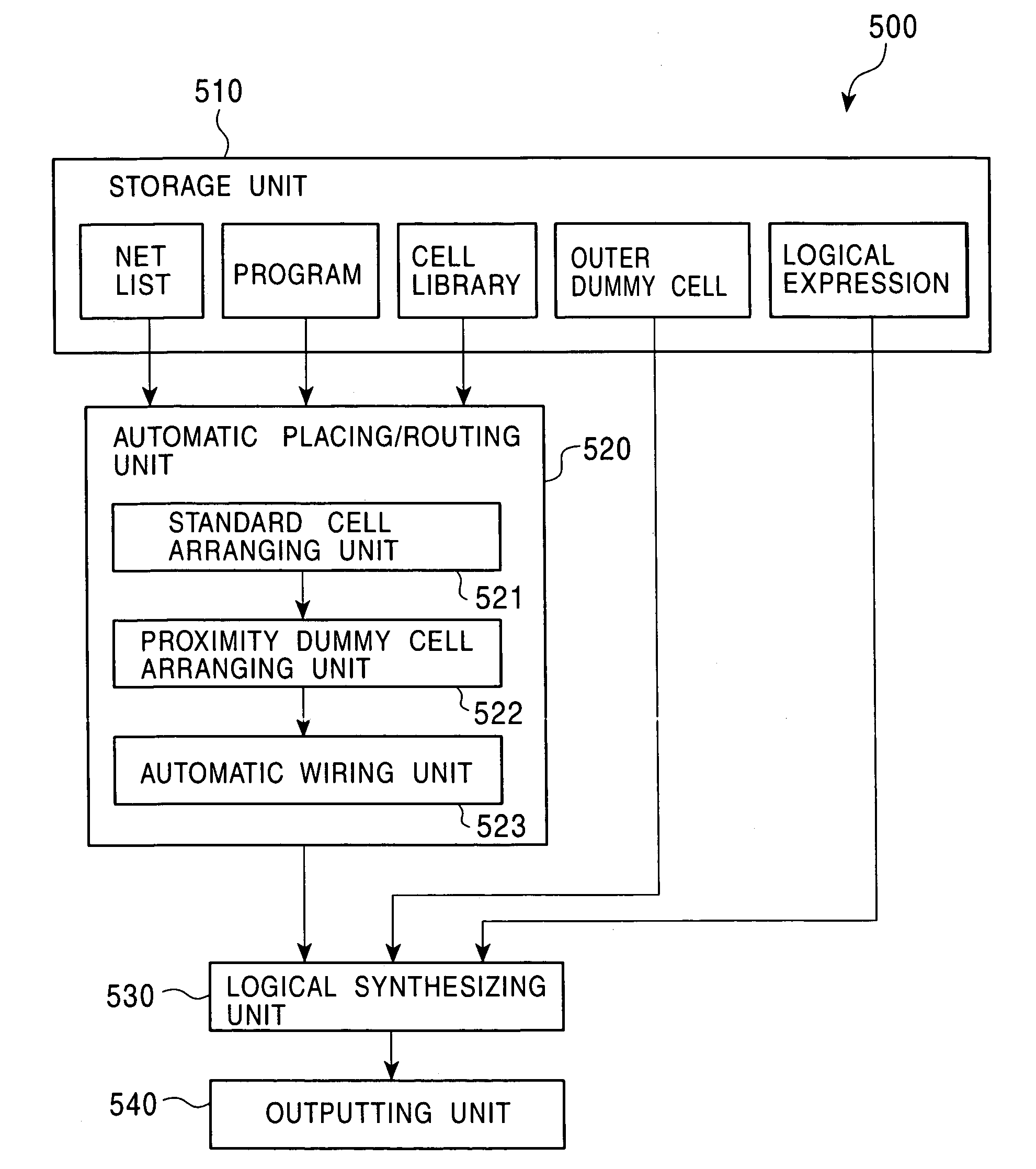

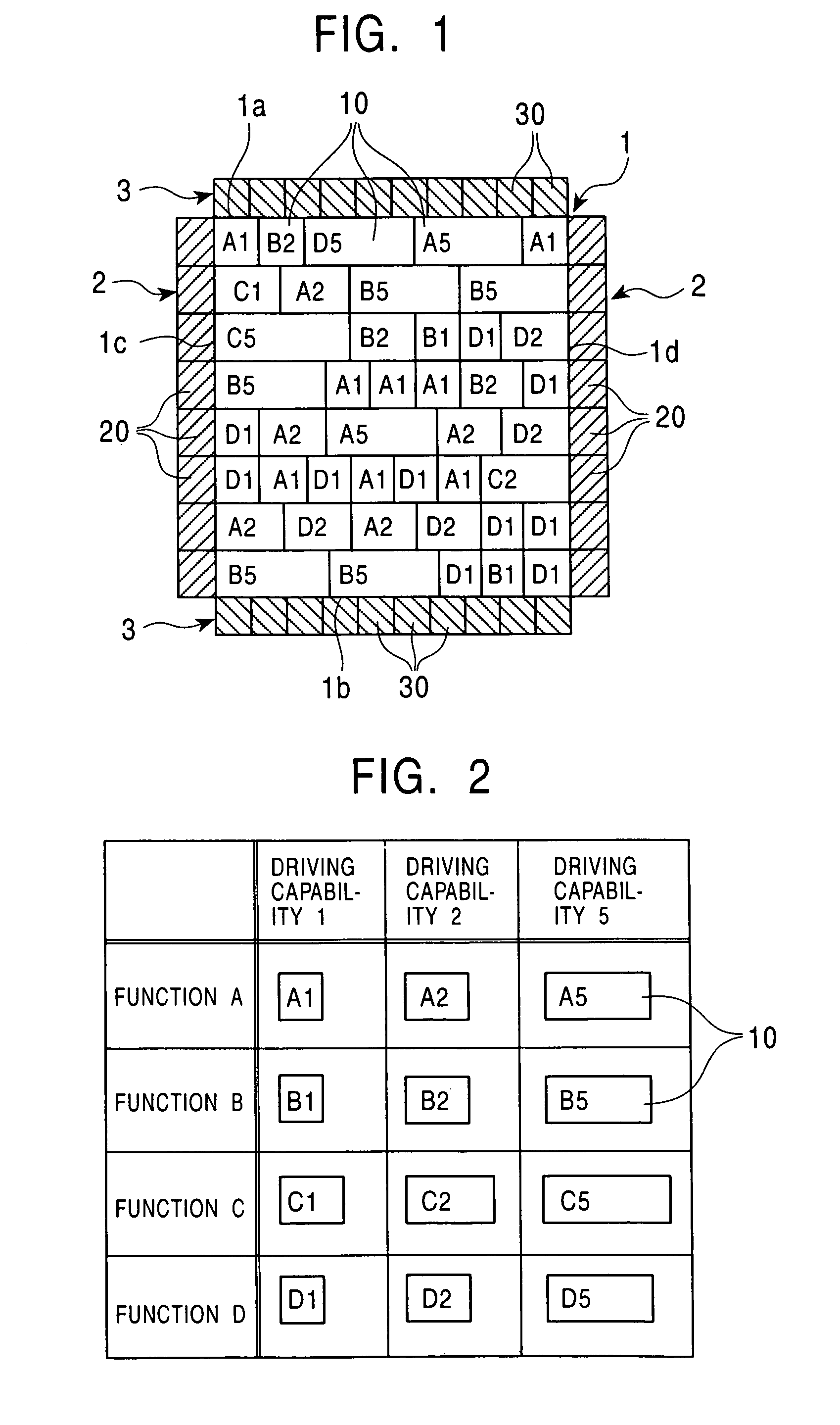

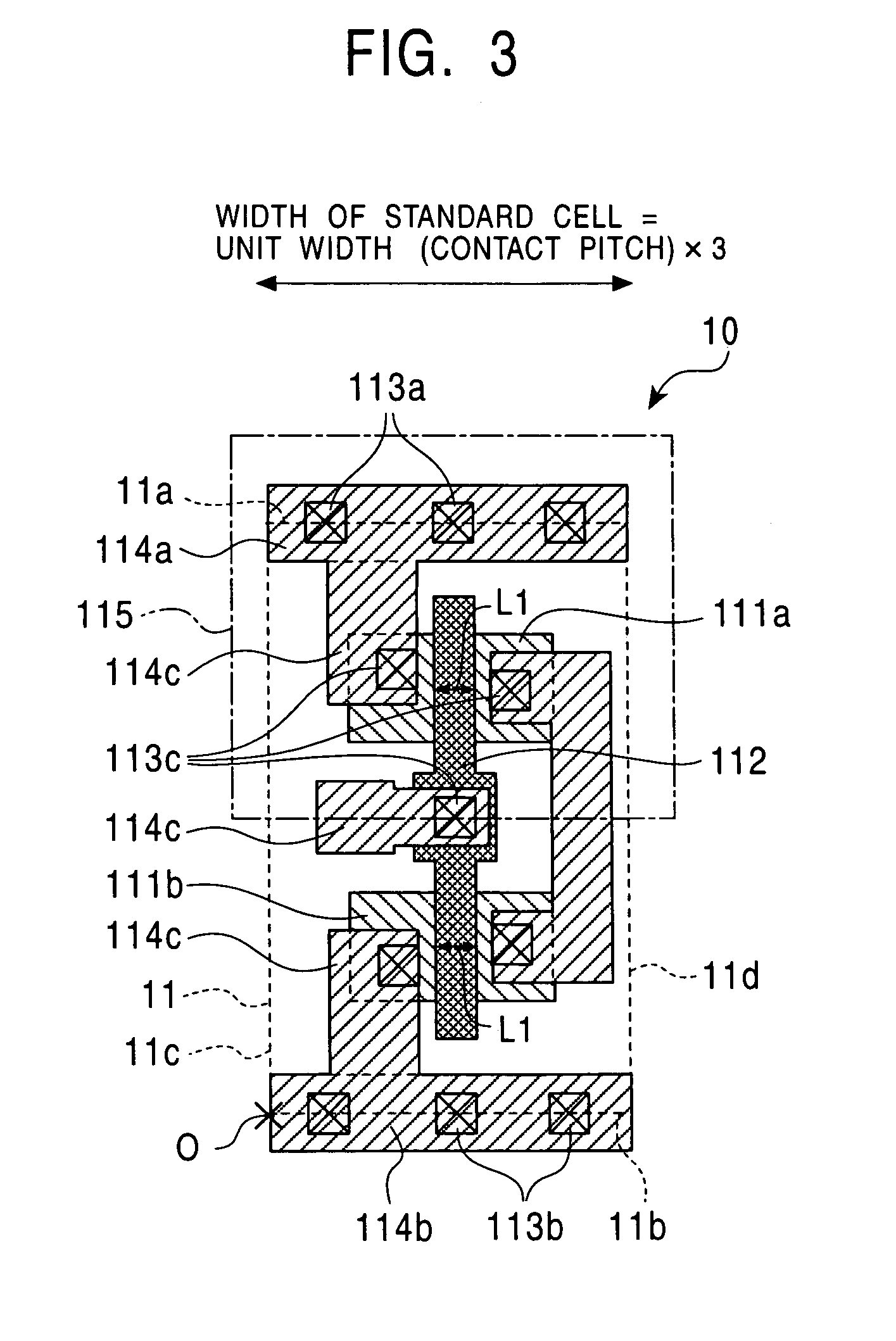

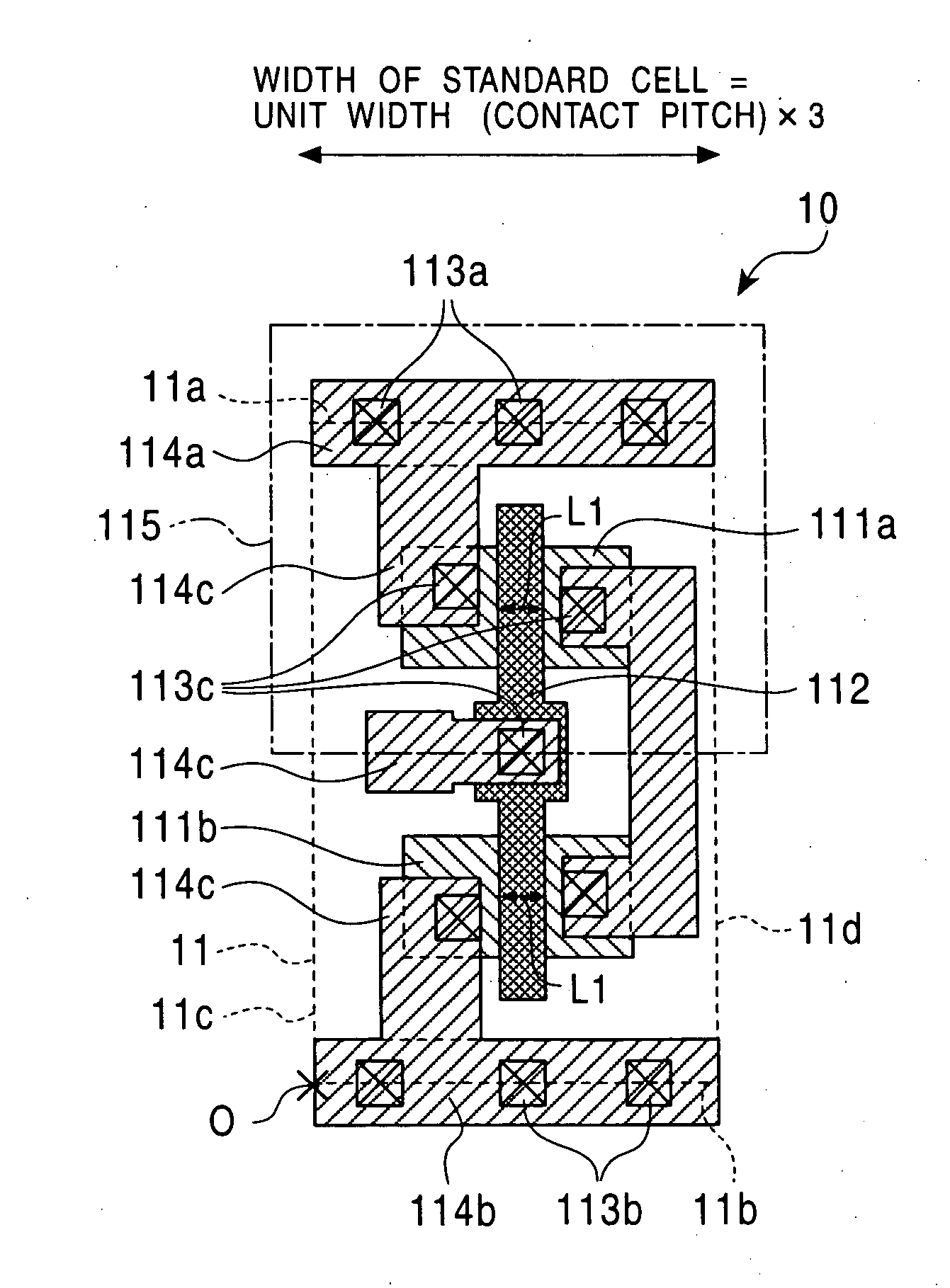

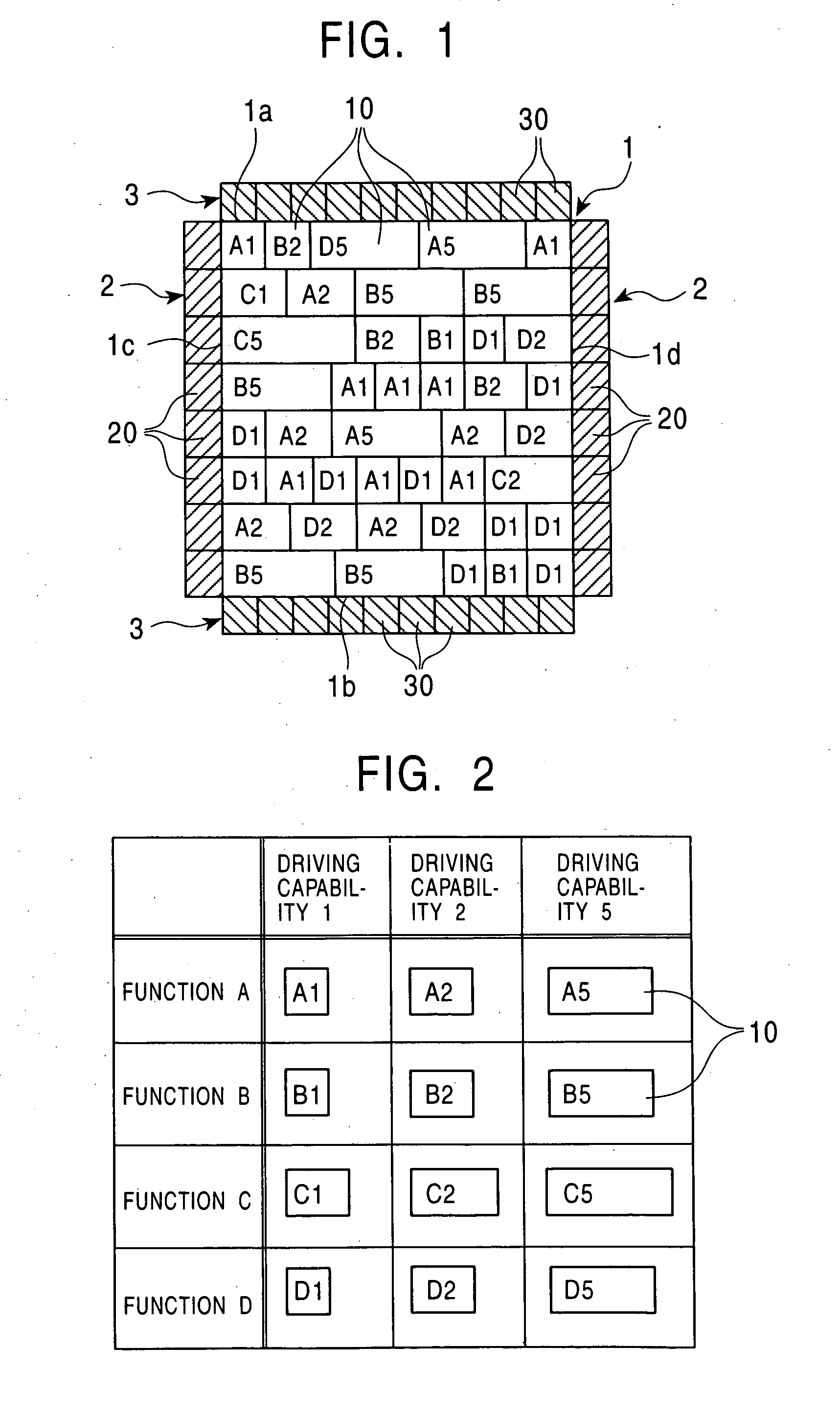

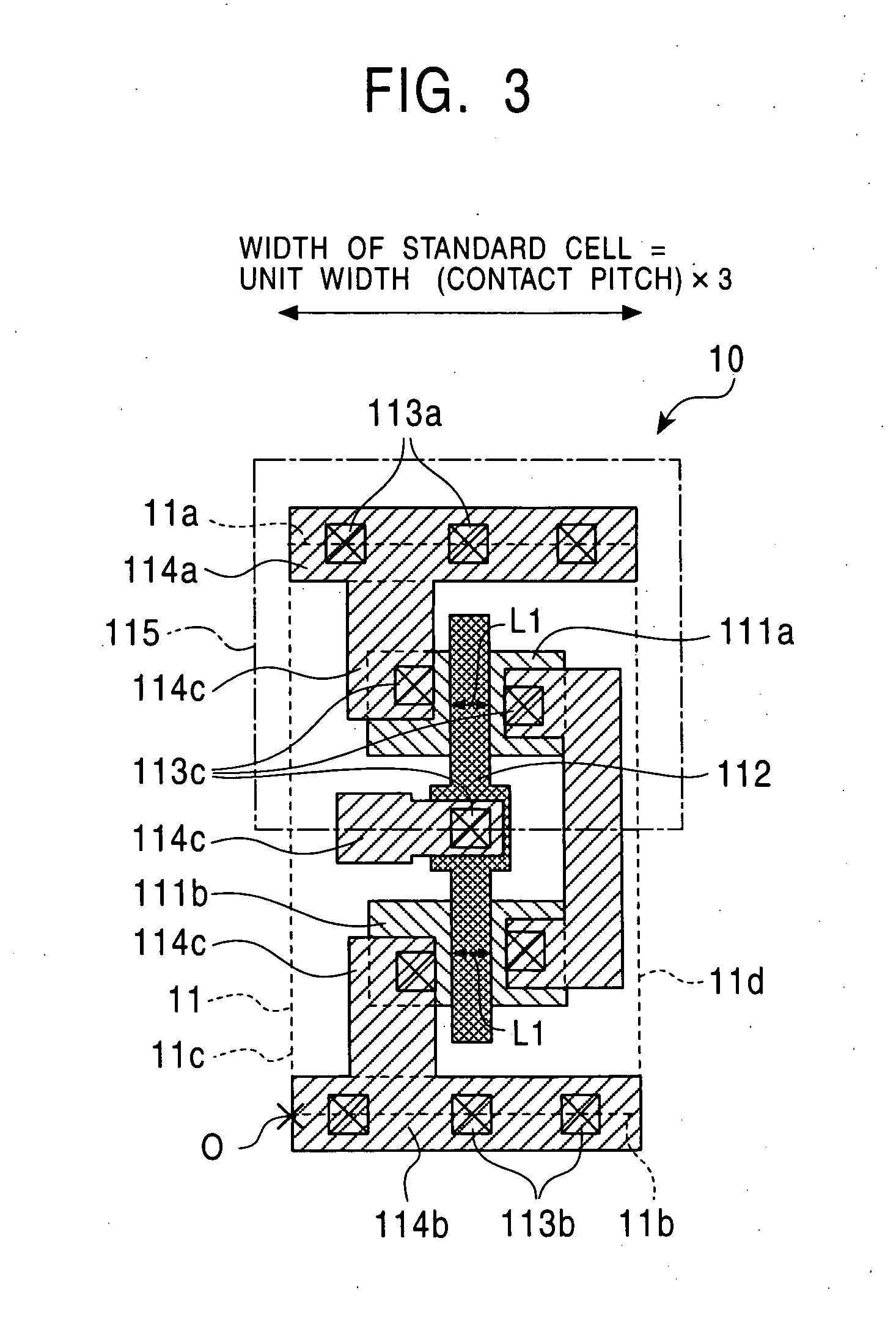

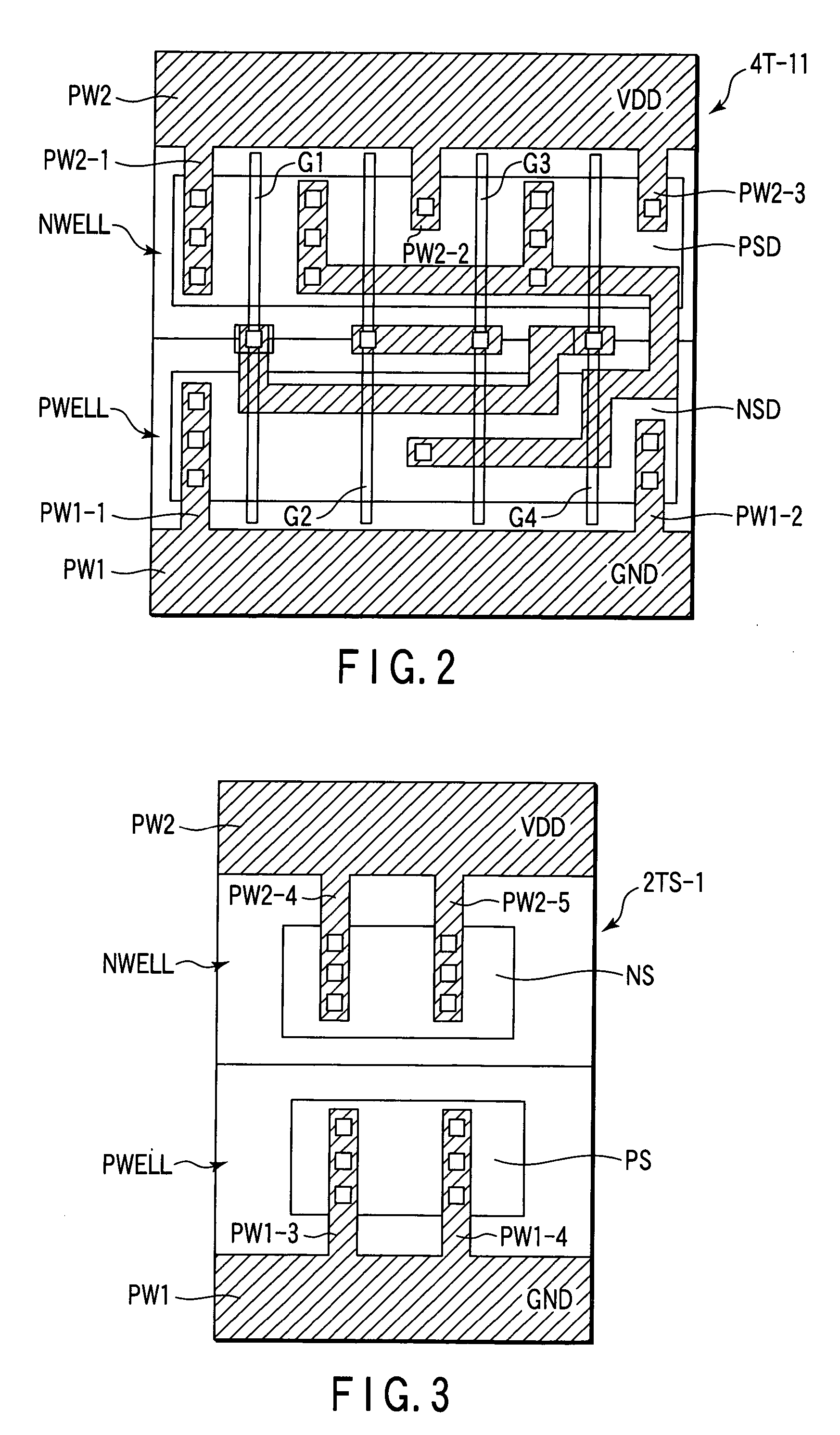

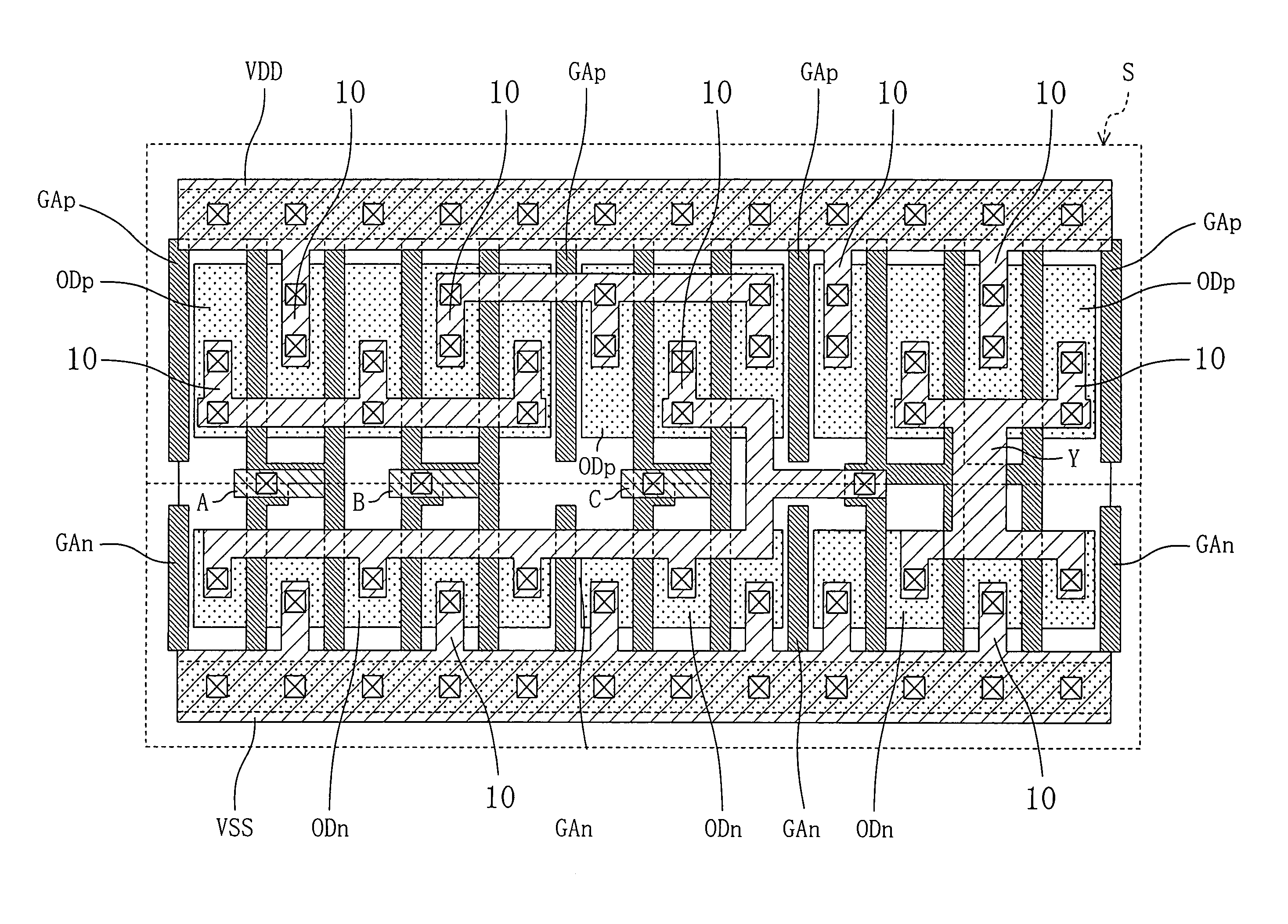

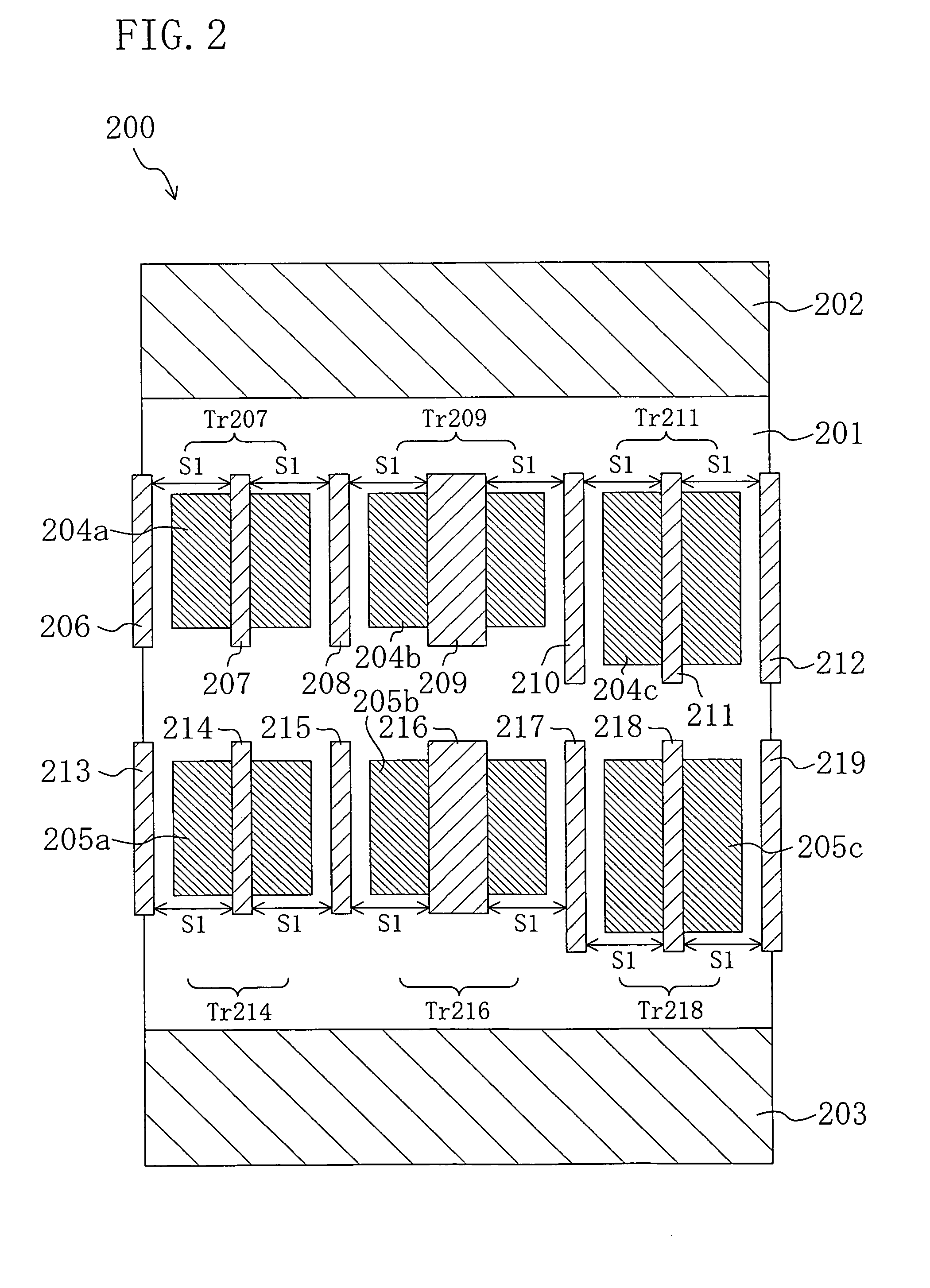

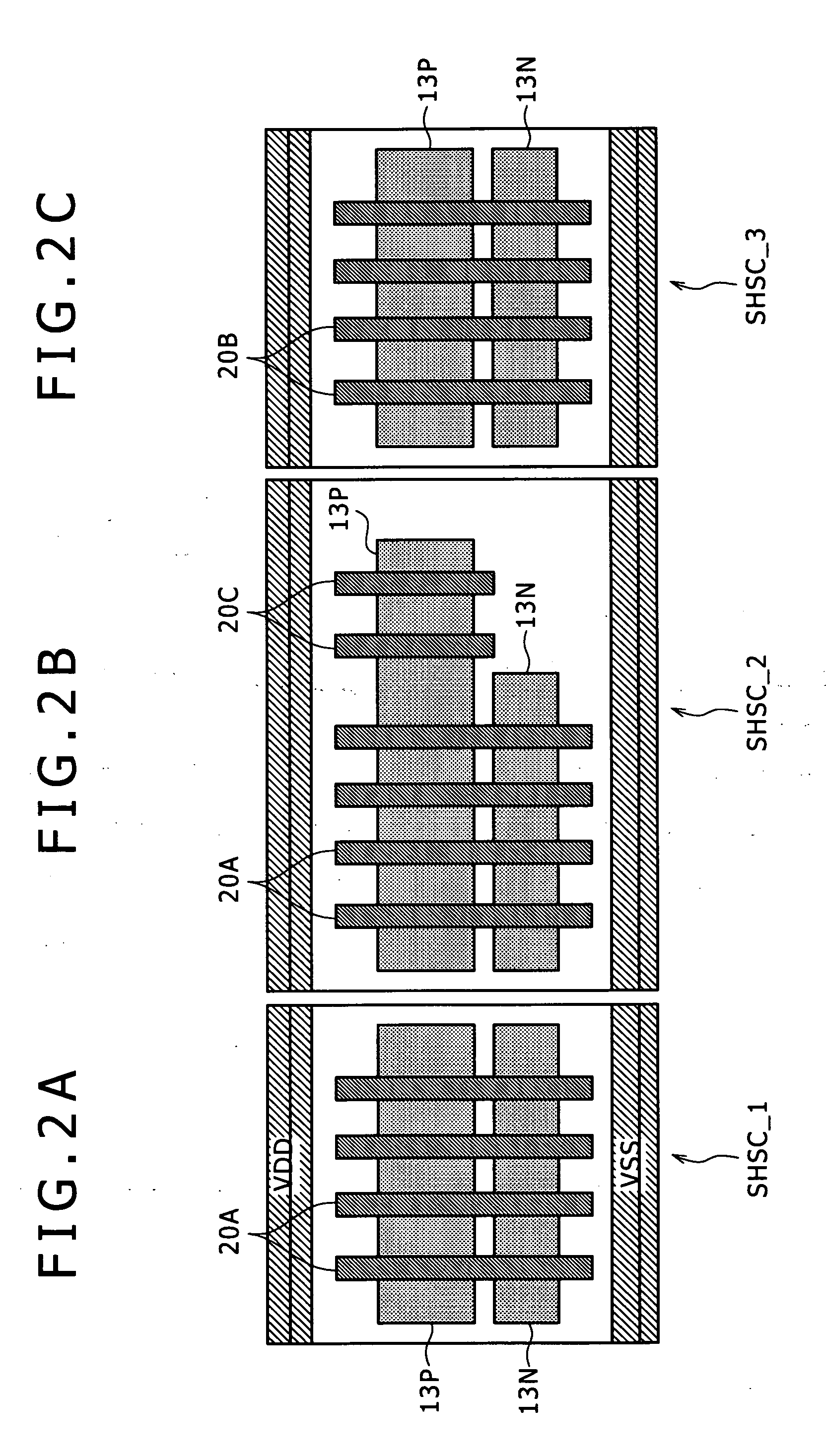

A plurality of standard cells 10 are arranged to form a channel-less standard cell array 1, which has vertical and horizontal sides. A plurality of first proximity dummy cells 20 are arranged along each of the vertical sides of the standard cell array to form a first proximity dummy bands 20 such that the upper and lower sides of the first proximity dummy cells are in contact with each other and such that the left or right side of each of the first proximity dummy cells is in contact with the vertical side of the standard cell array 1. Furthermore, a plurality of second proximity dummy bands are arranged along each of the horizontal sides of the standard cell array to form a second proximity dummy bands such that the upper or lower side of each of the second proximity dummy cells is in contact with the horizontal side of the standard cell 1.

Owner:KAWASAKI MICROELECTRONICS

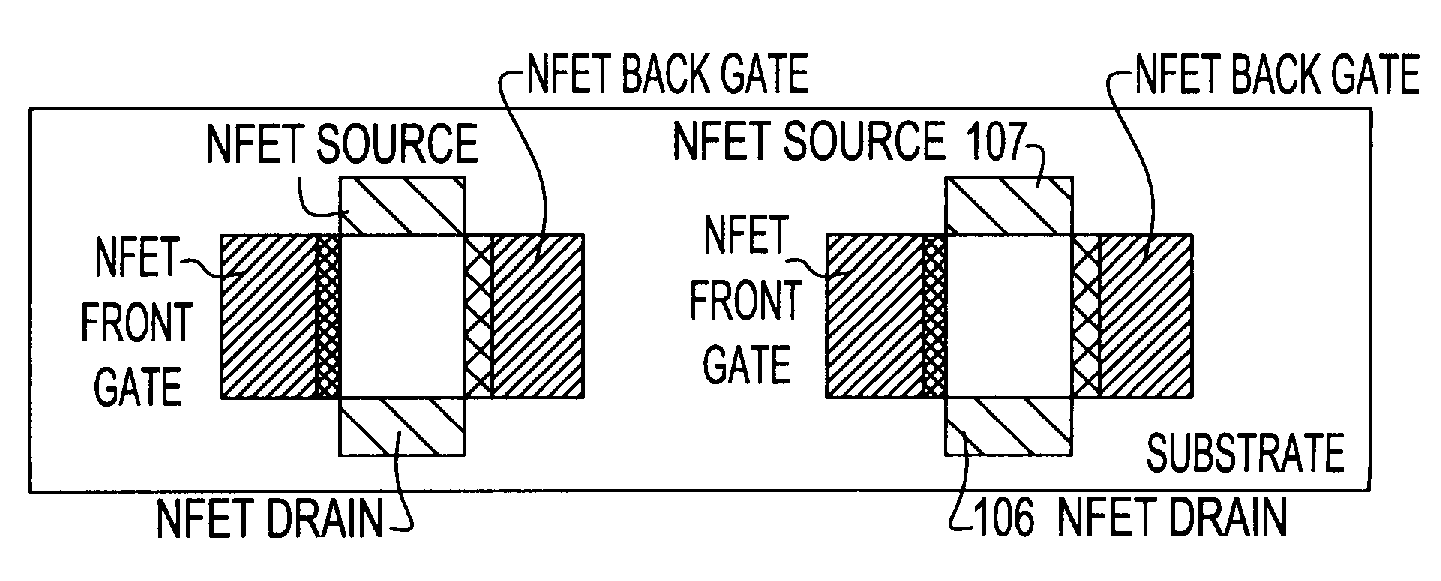

Dual gate fet structures for flexible gate array design methodologies

InactiveUS20090101940A1Easy to operateSolid-state devicesSemiconductor/solid-state device manufacturingGate arrayStandard cell

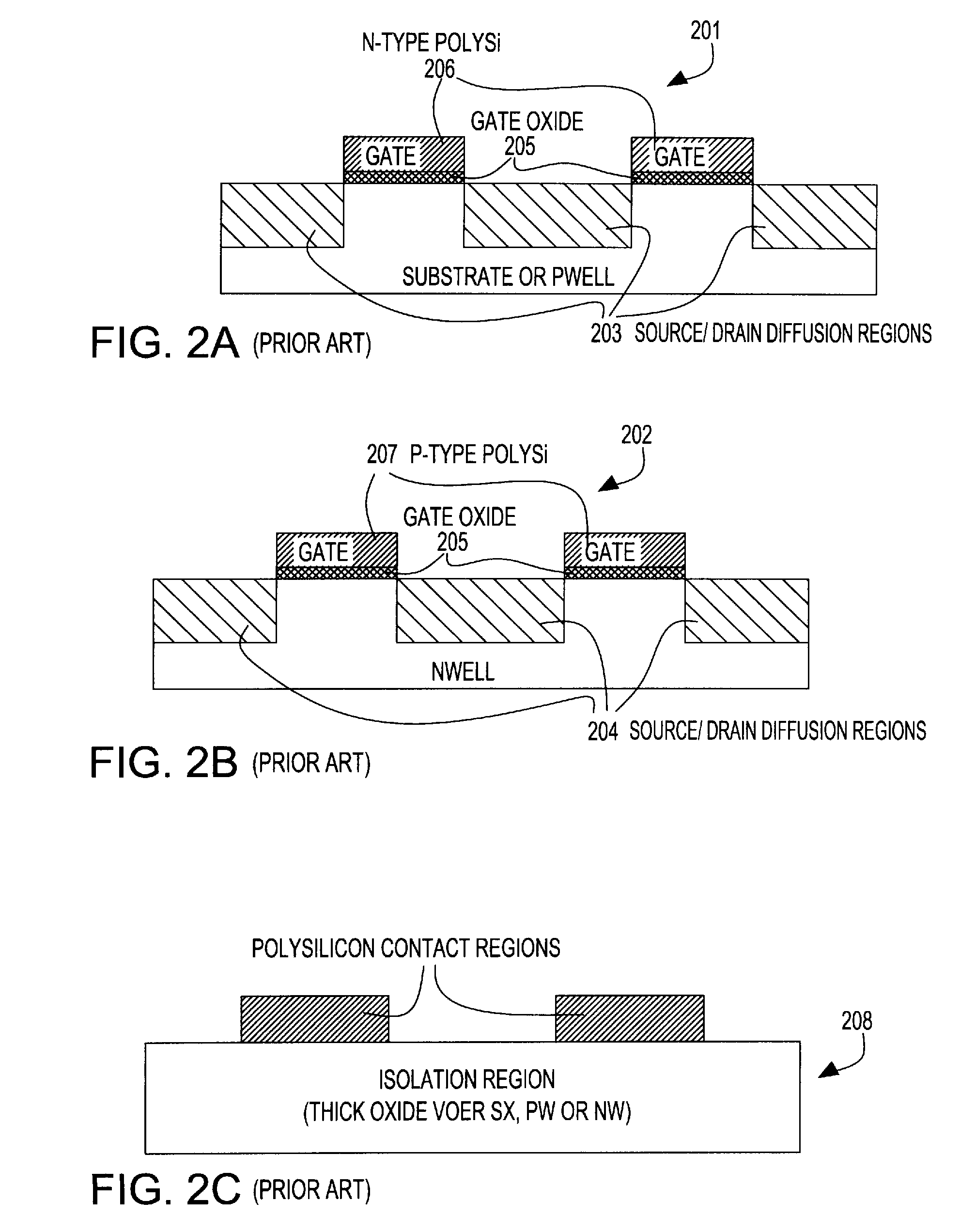

A gate array cell adapted for standard cell design methodology or programmable gate array that incorporates a dual gate FET device to offer a range of performance options within the same unit cell area. The conductivity and drive strength of the dual gate device may be selectively tuned through independent processing of manufacturing parameters to provide an asymmetric circuit response for the device or a symmetric response as dictated by the circuit application.

Owner:GLOBALFOUNDRIES INC

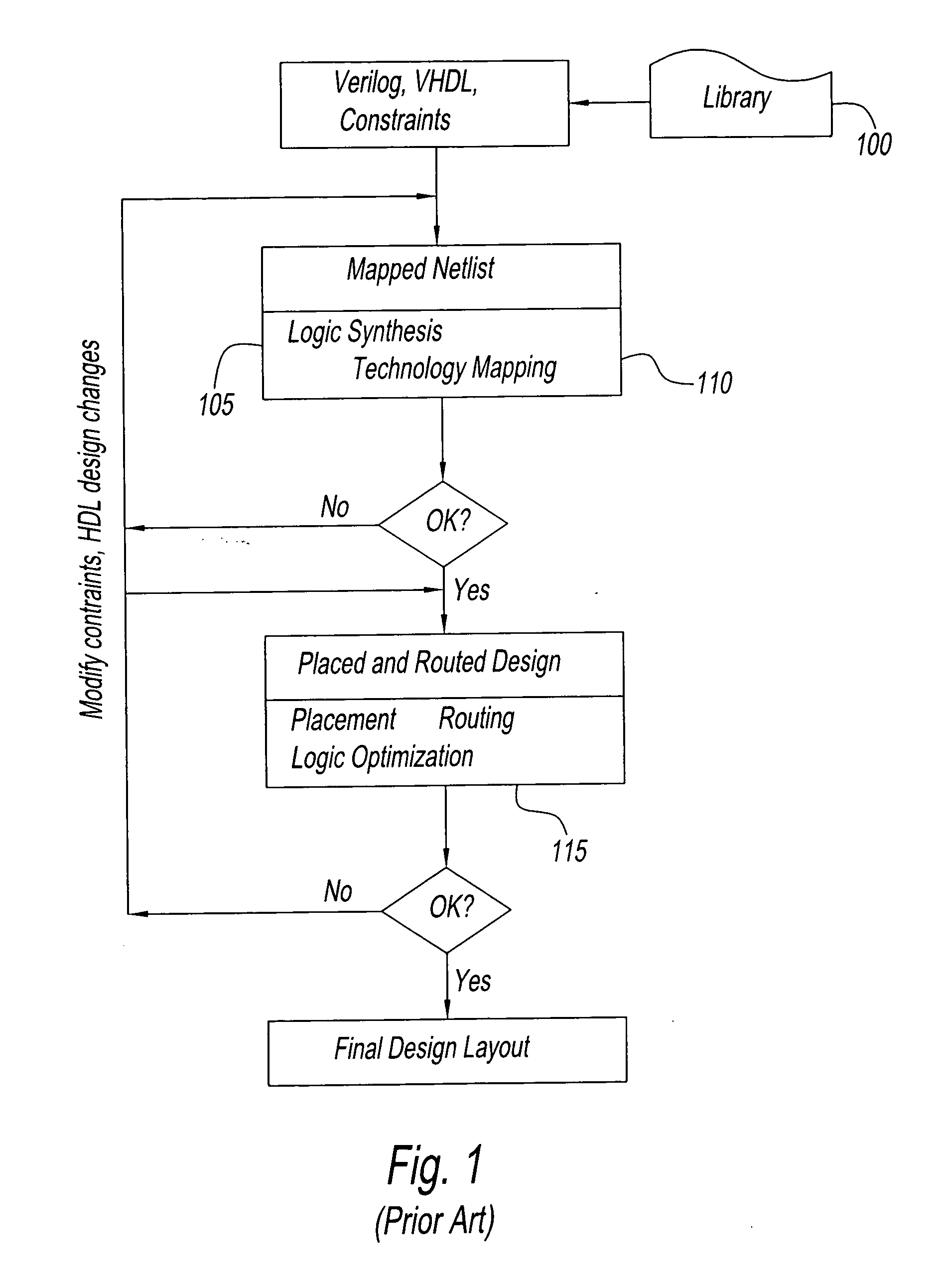

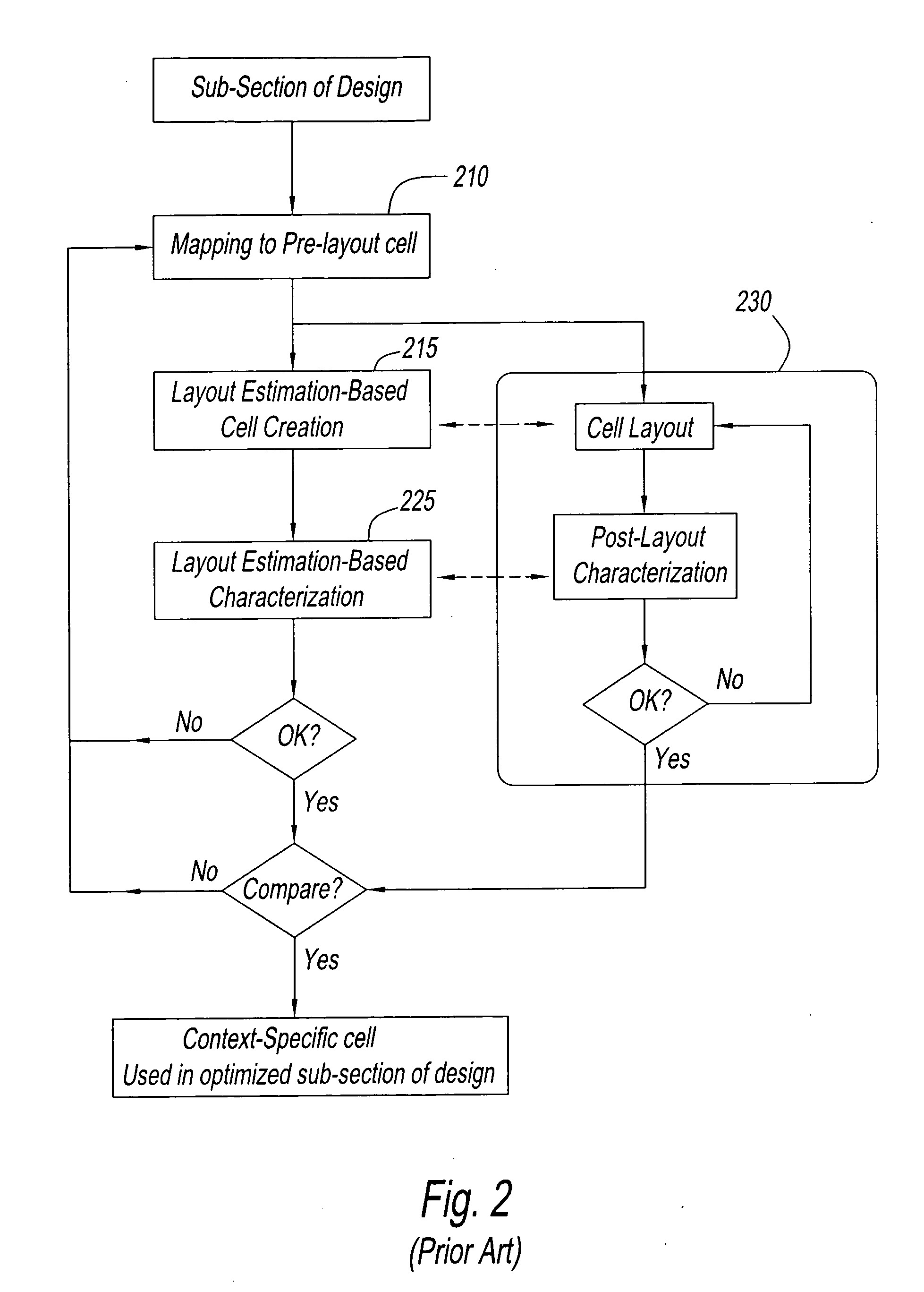

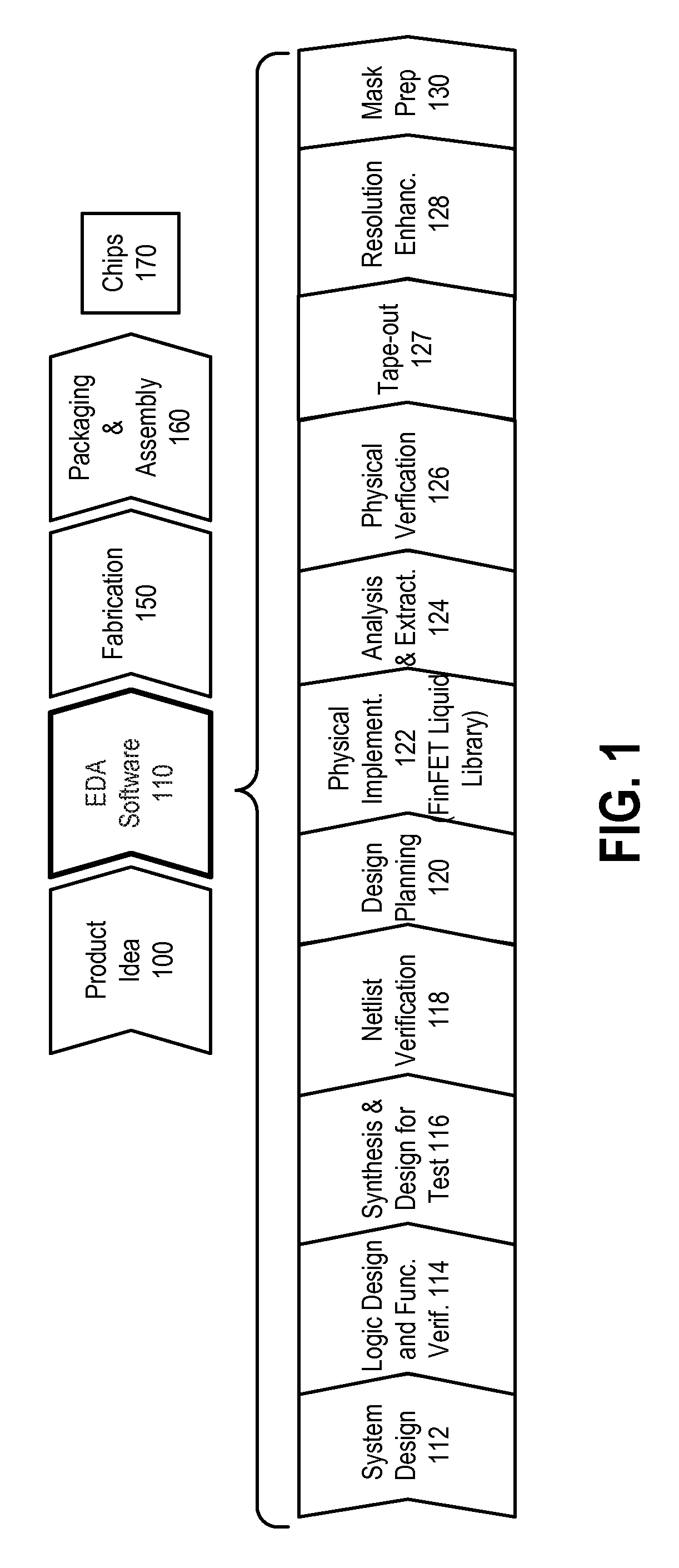

Method for automated design of integrated circuits with targeted quality objectives using dynamically generated building blocks

InactiveUS7225423B2Improve propertiesMinimize the numberCAD circuit designSoftware simulation/interpretation/emulationTarget analysisComputer architecture

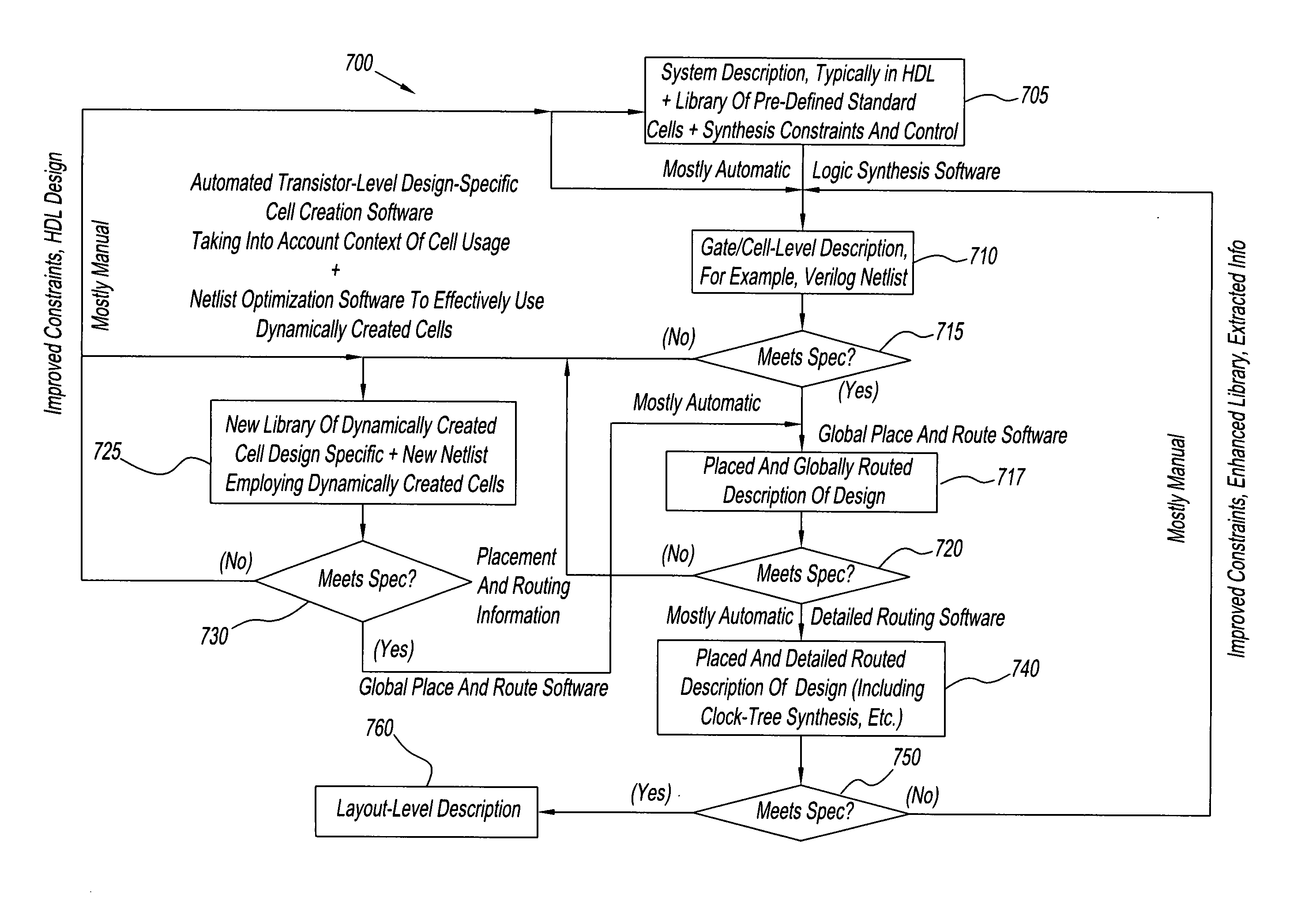

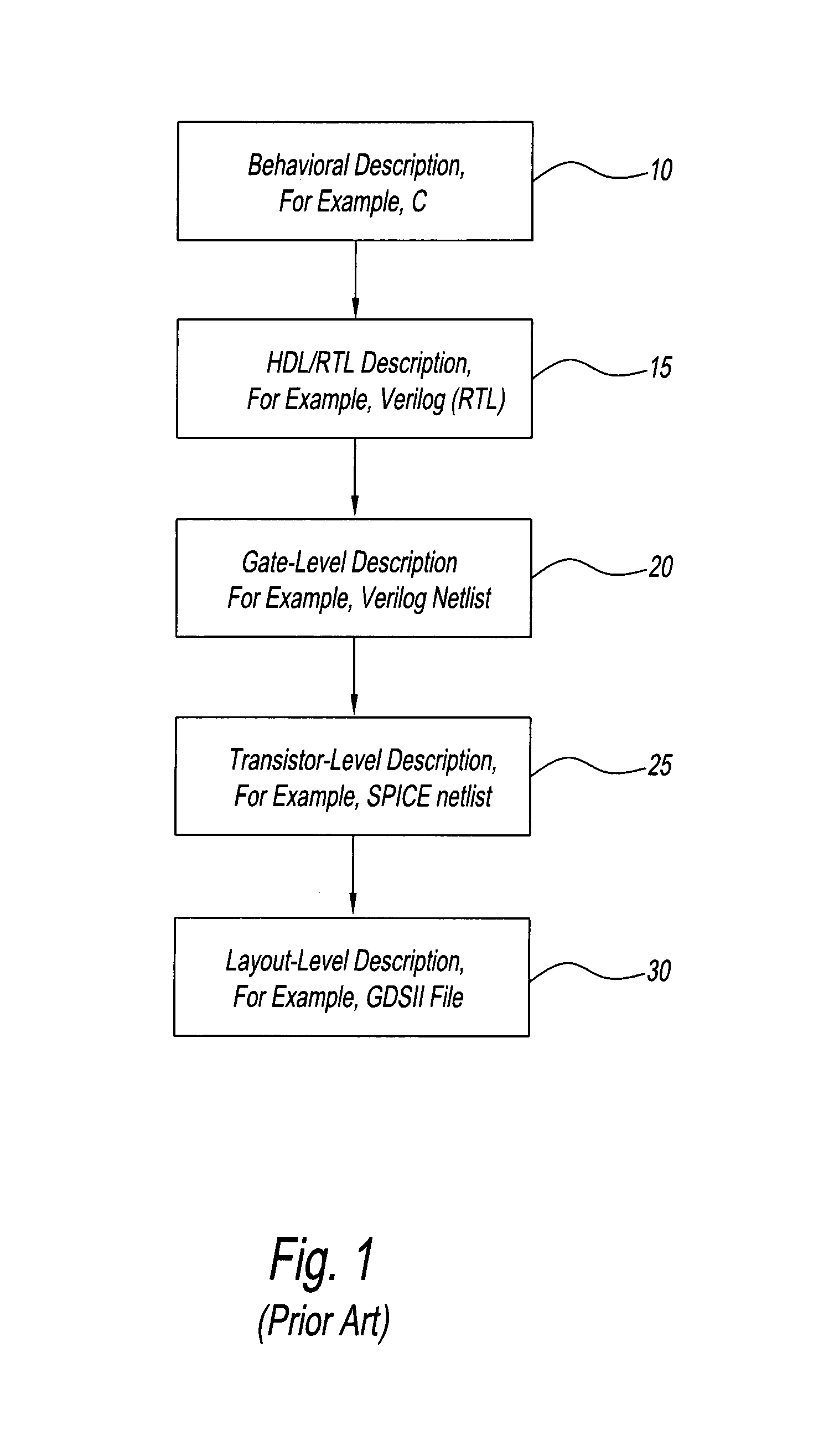

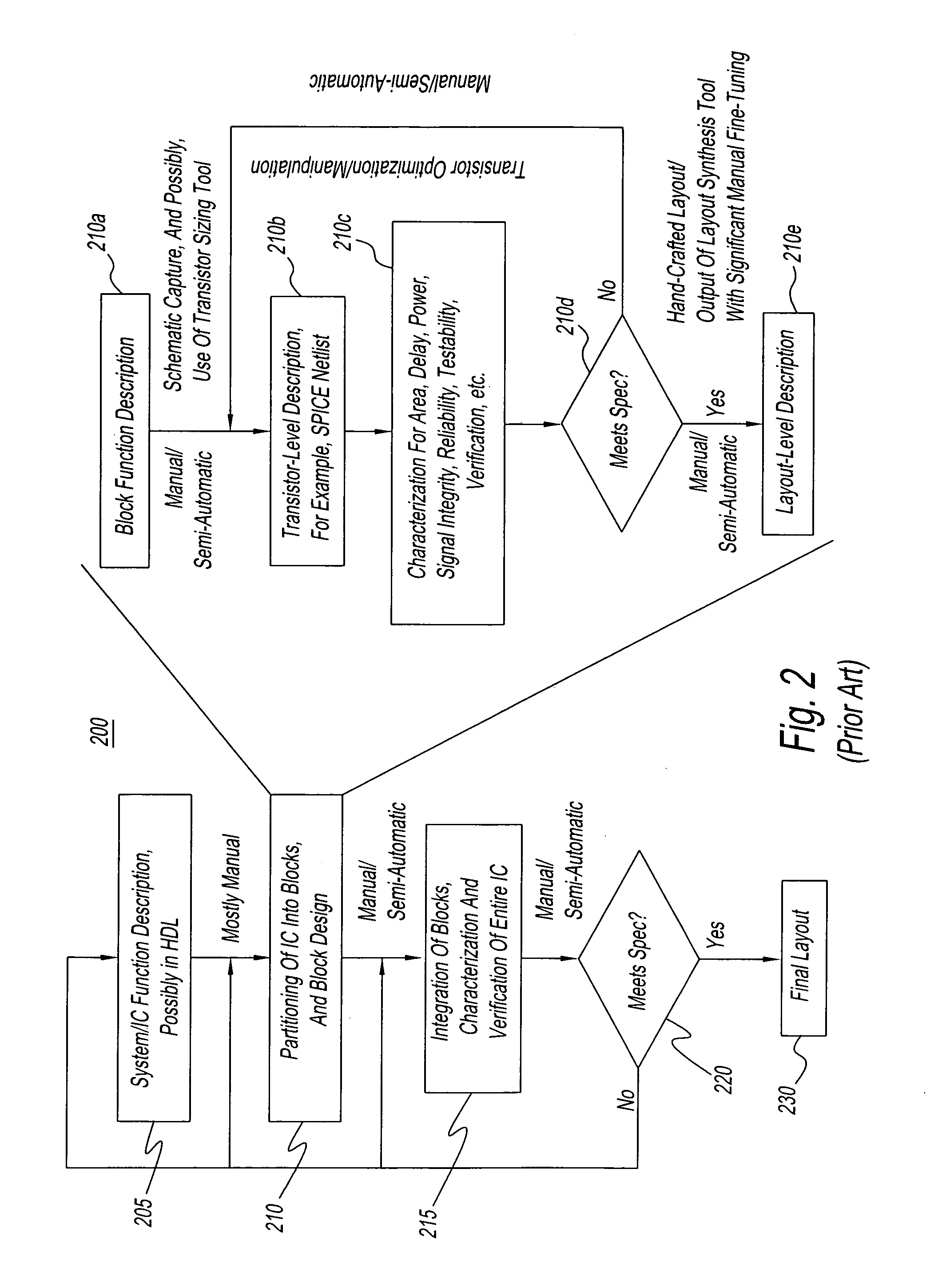

A system and method for designing ICs, including the steps of: analyzing and optimizing a target IC design based on design-specific objectives; partitioning the optimized target IC design into pre-defined standard-cells from one or more libraries and creating design-specific cells specifically having unique functionality and characteristics not found amongst the standard-cells; identifying and determining a minimal subset of the standard-cells and design-specific cells, the interconnection of which represents the target IC design; generating the necessary views, including layout and characterizing of the design-specific cells included in a unique, minimal subset, wherein the IC design is subject to objectives and constraints of the target IC.

Owner:OPEN-SILICON

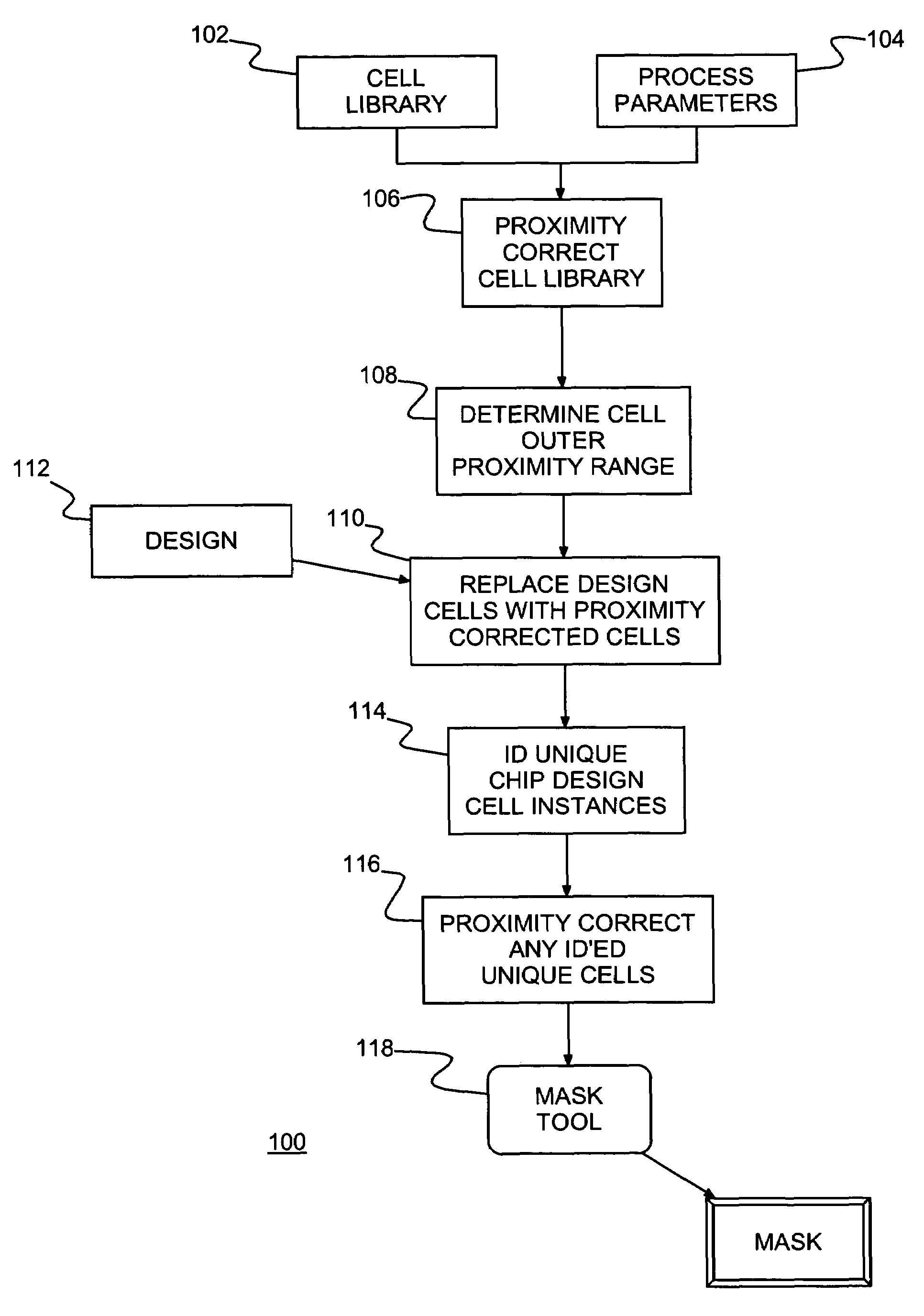

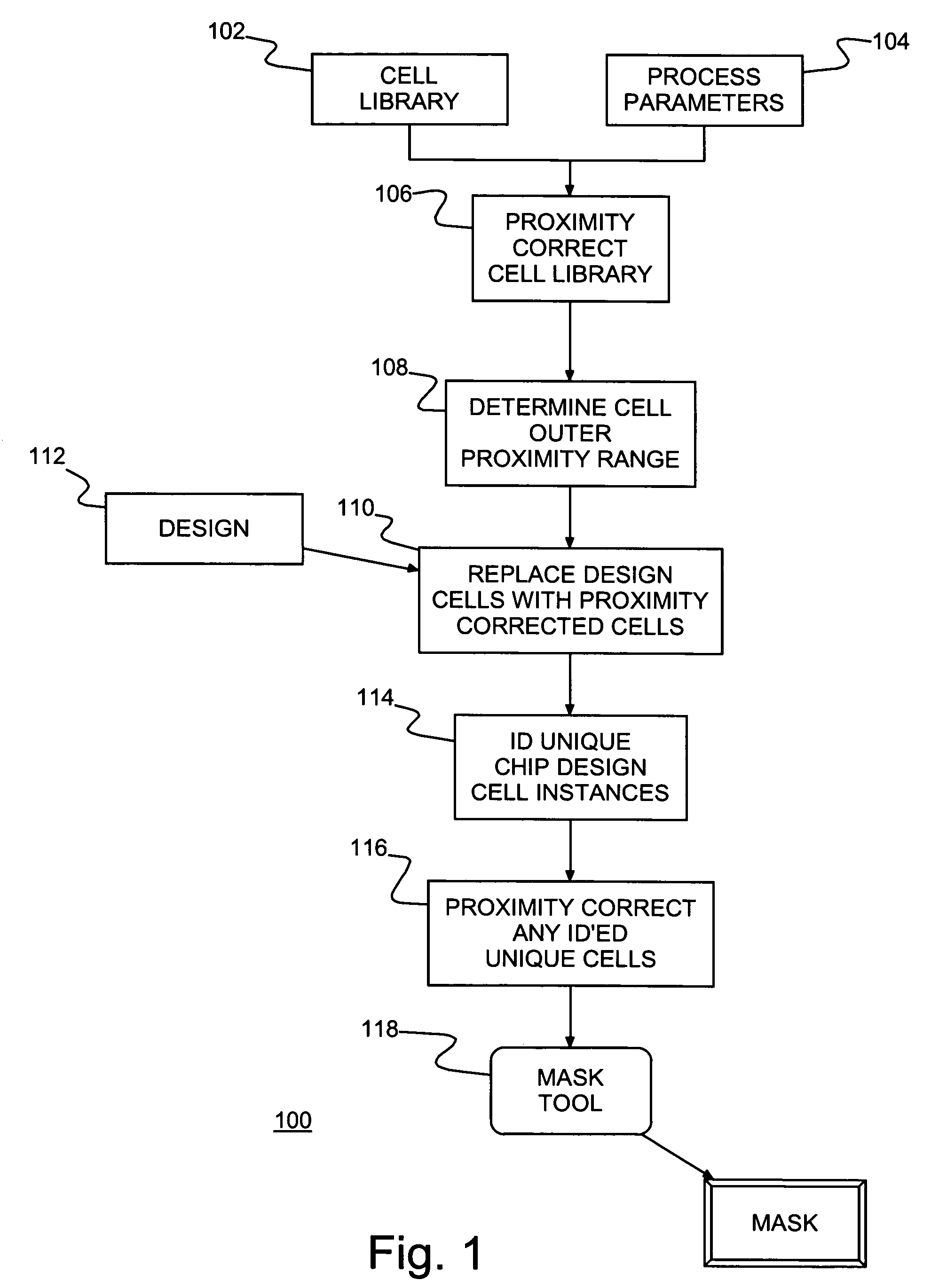

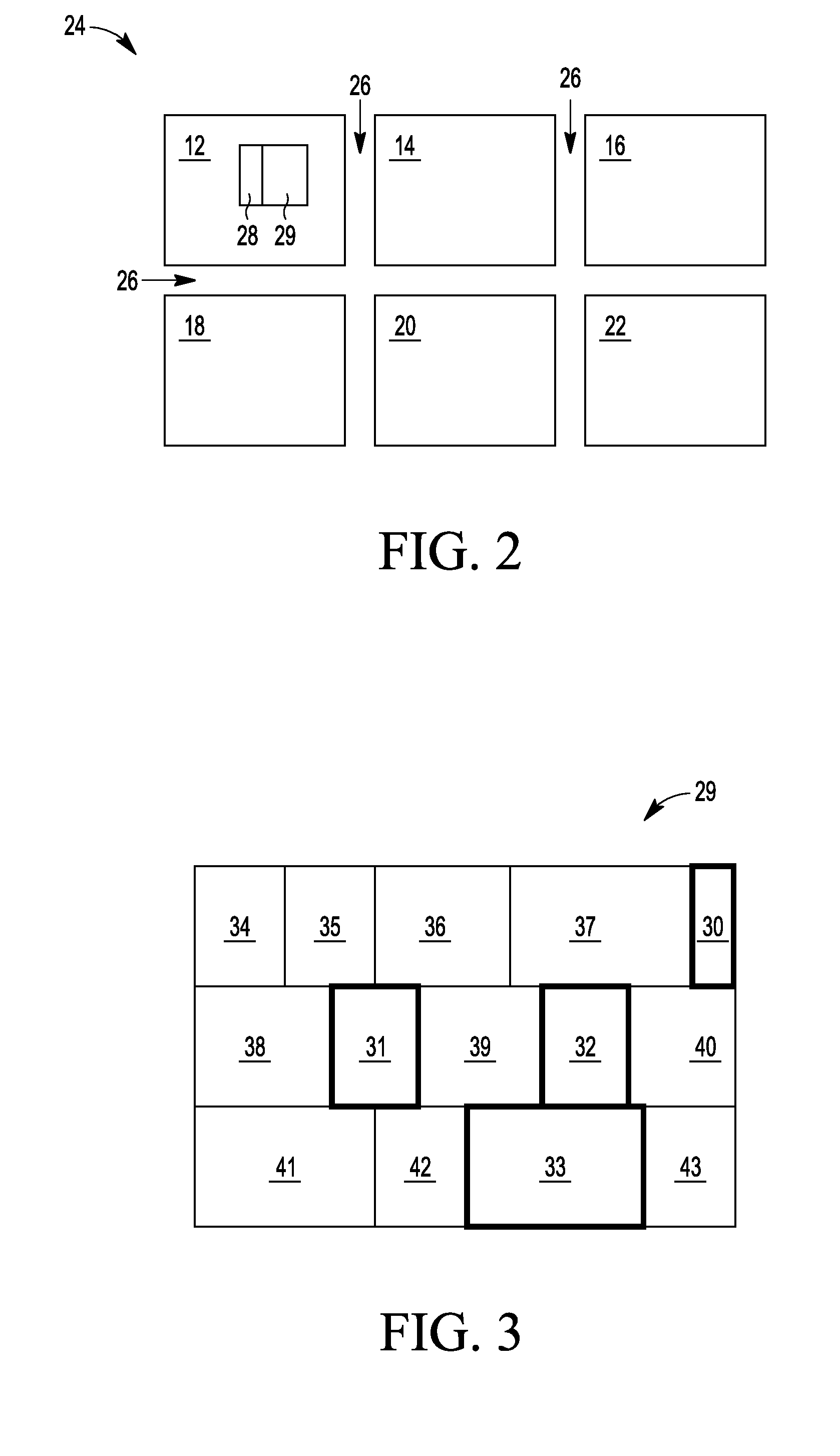

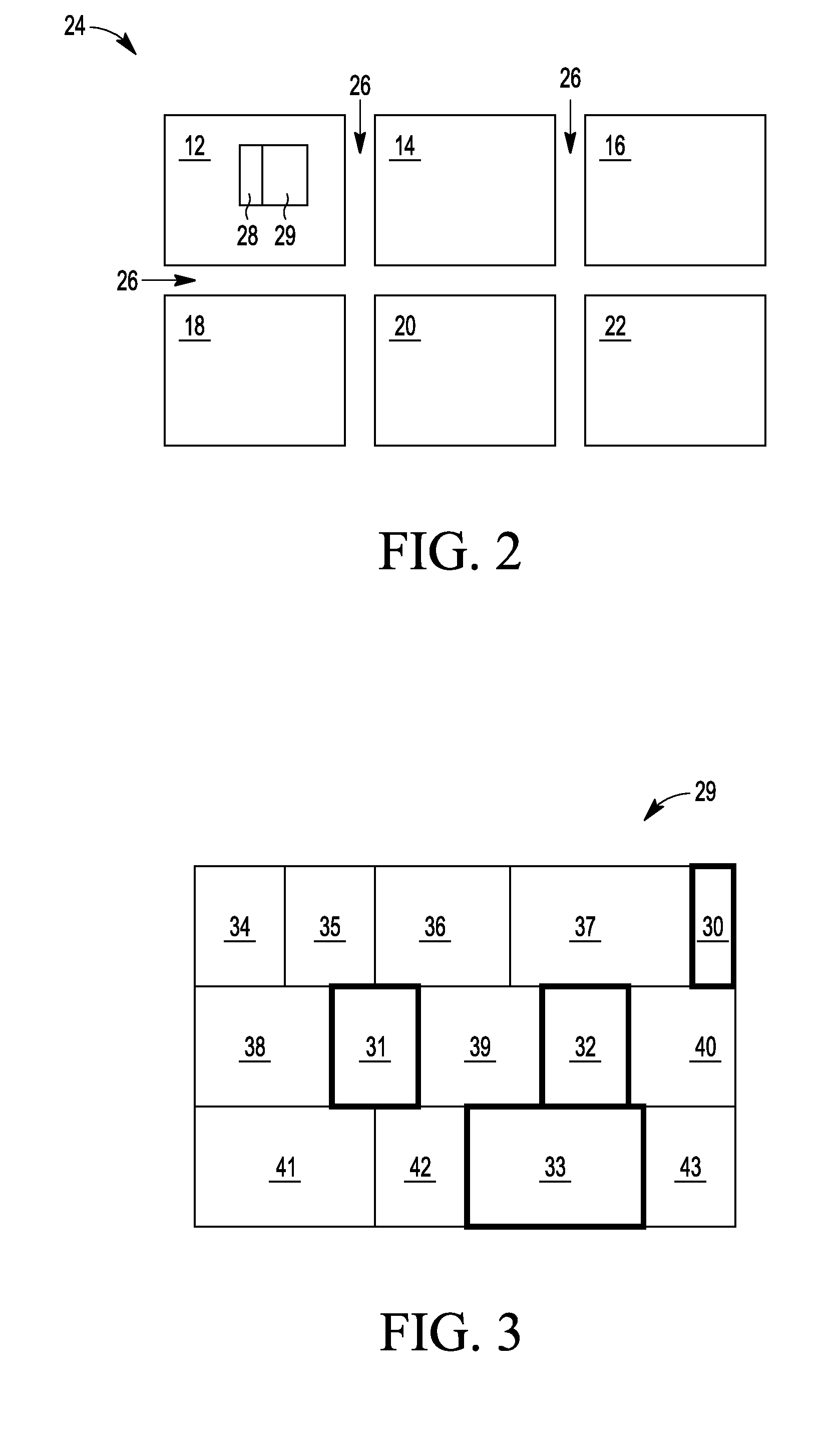

Method of IC fabrication, IC mask fabrication and program product therefor

InactiveUS7353492B2Reduce designReduce resource consumptionPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringBoundary cell

A method of forming integrated circuit (IC) chip shapes and a method and computer program product for converting an IC design to a mask, e.g., for standard cell design. Individual book / macro physical designs (layouts) are proximity corrected before unnesting and an outer proximity range is determined for each proximity corrected physical design. Shapes with a unique design (e.g., in boundary cells and unique instances of books) are tagged and the design is unnested. Only the unique shapes are proximity corrected in the unnested design, which may be used to make a mask for fabricating IC chips / wafers.

Owner:GOOGLE LLC

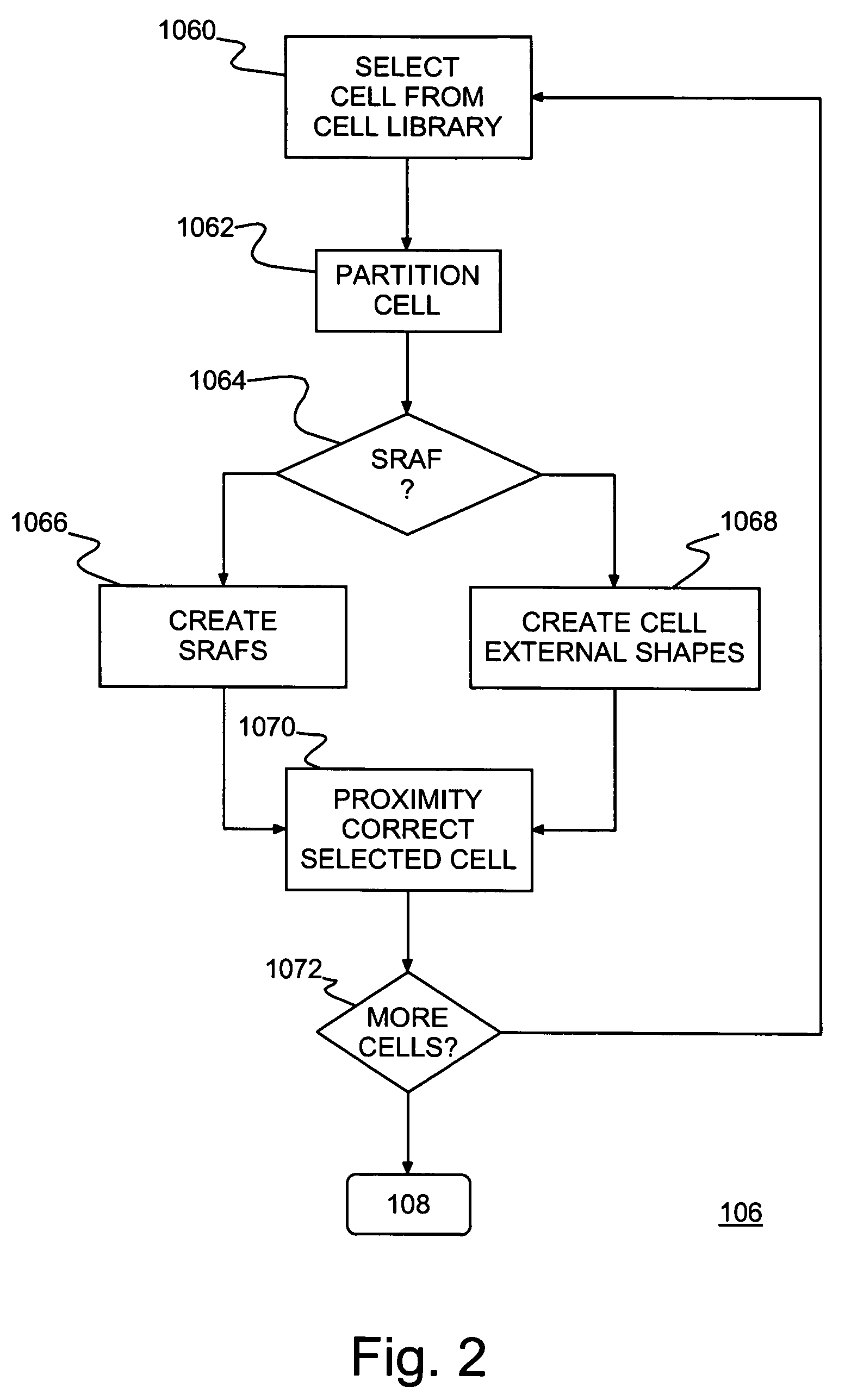

Yield maximization in the manufacture of integrated circuits

InactiveUS6957402B2Increase productionHigh yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingComputer-aidedEngineering

A method and apparatus for improving the manufacturability of Integrated Circuits (ICs) formed on semiconductor dies is described. A plurality of different designs for some or all of the standard cells are made available to the circuit designer. Each different design may address a different problem associated with different manufacturing processes or a different design related yield limiter. Each of the design variants is characterized indicating its relative ease of manufacture, or it's yield sensitivity to certain IC design factors. The designer, typically with assistance from computer aided tools, can then select the standard cell variant for each of the cell used in the IC design that best addresses his or her design constraints. In other embodiments, variant versions of I / O cells and memory cells could also be created and made available to the designer in a similar fashion.

Owner:ARM INC

Standard cell, standard cell library, and semiconductor integrated circuit

ActiveUS20050280031A1Variation in characteristicTransistorSolid-state devicesEngineeringSemiconductor

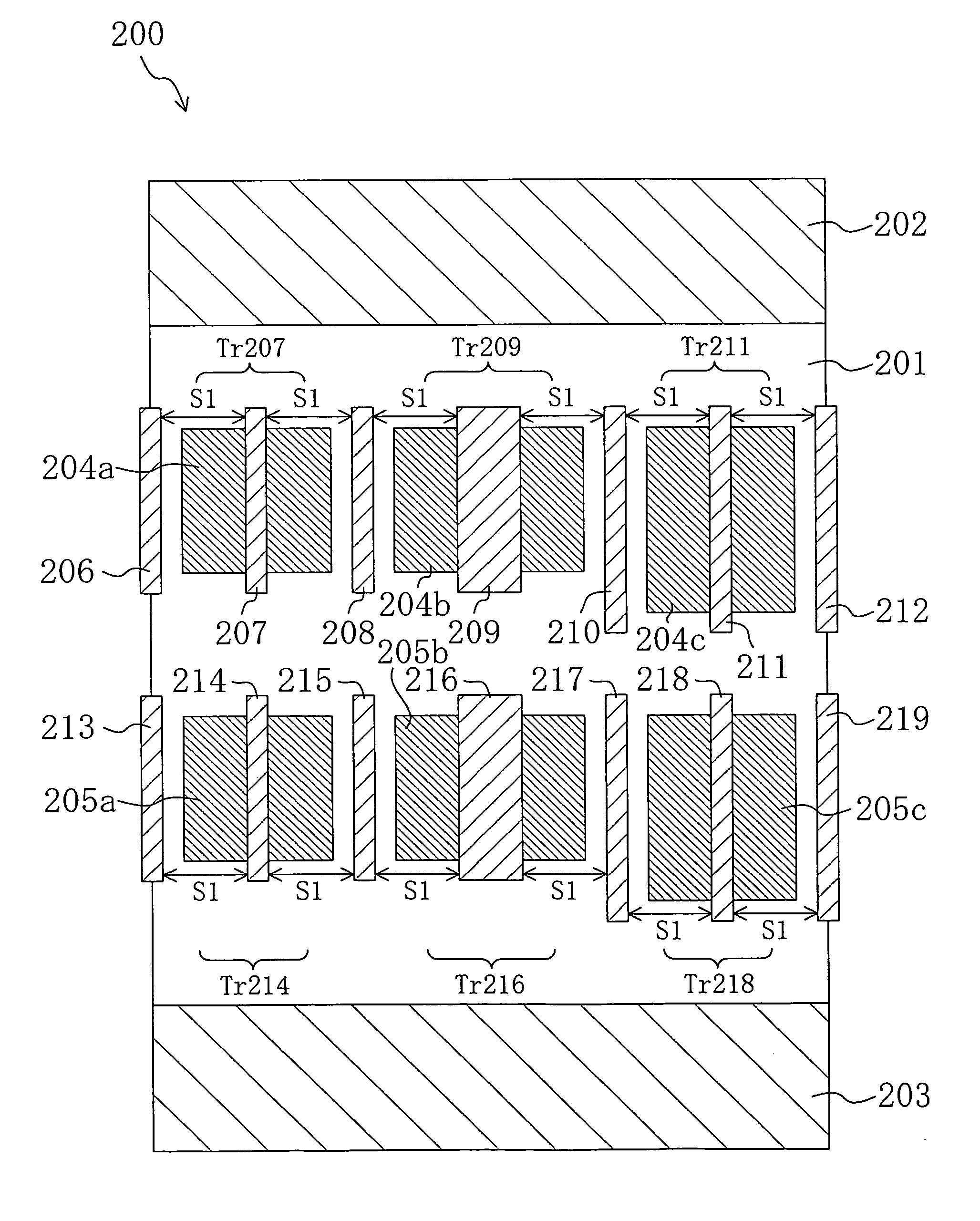

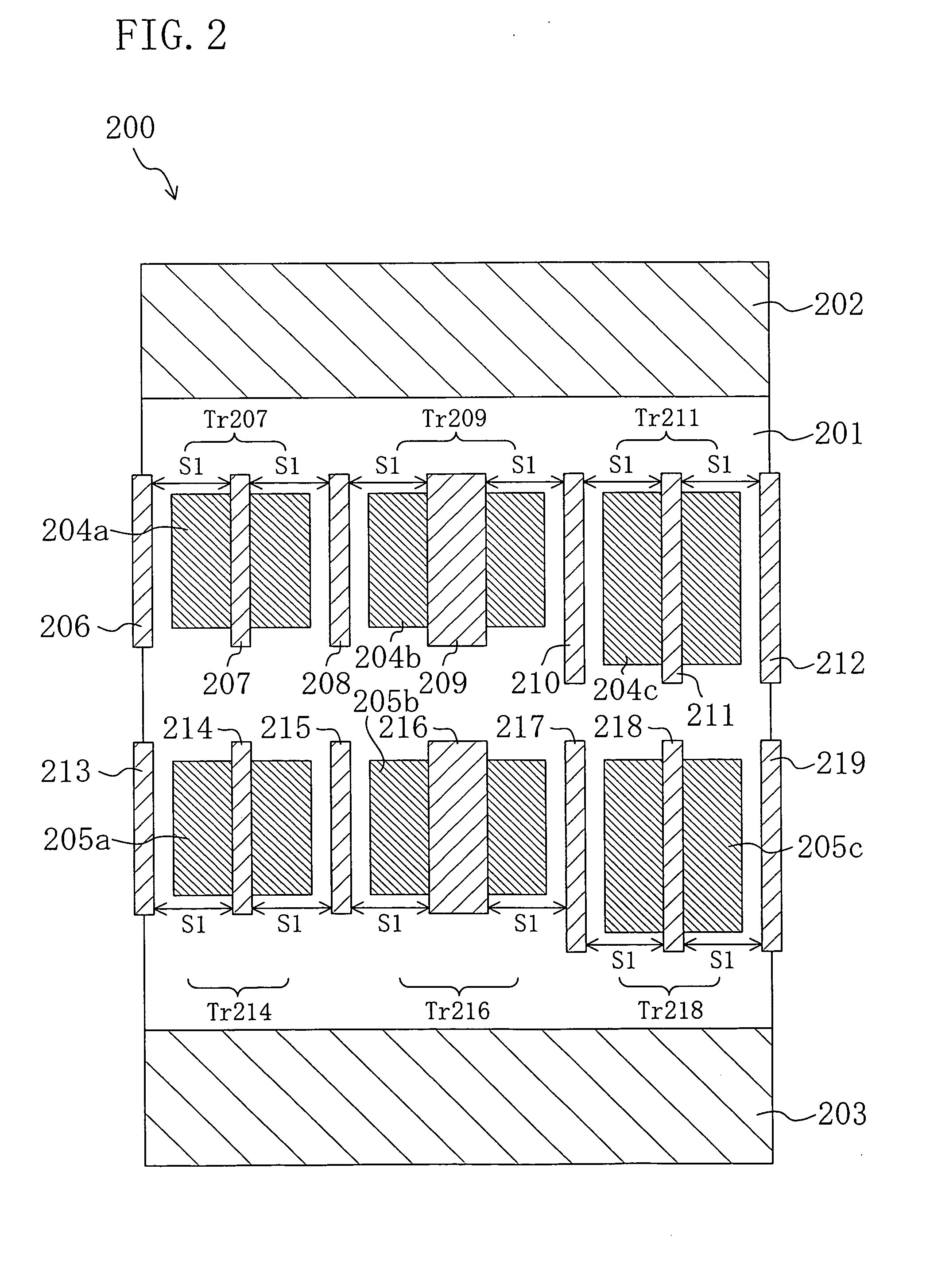

In a standard cell, at least one of transistors on either side of a transistor having gate length different from that of the other transistors are set to be always in the OFF state. This prevents influence to the operation of the standard cell even with variation in final gate dimension, suppressing variation in characteristics of the standard cell.

Owner:SOCIONEXT INC

Layout method of semiconductor integrated circuit, layout structure thereof, and photomask for forming the layout structure

ActiveUS20050044522A1Reduces dimensional deviationHigh dimensional accuracySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A plurality of standard cells 10 are arranged to form a channel-less standard cell array 1, which has vertical and horizontal sides. A plurality of first proximity dummy cells 20 are arranged along each of the vertical sides of the standard cell array to form a first proximity dummy bands 20 such that the upper and lower sides of the first proximity dummy cells are in contact with each other and such that the left or right side of each of the first proximity dummy cells is in contact with the vertical side of the standard cell array 1. Furthermore, a plurality of second proximity dummy bands are arranged along each of the horizontal sides of the standard cell array to form a second proximity dummy bands such that the upper or lower side of each of the second proximity dummy cells is in contact with the horizontal side of the standard cell 1.

Owner:KAWASAKI MICROELECTRONICS

Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit

ActiveUS20060136848A1Reducing cell area areaReduce chip areaSolid-state devicesProgram controlEngineeringSemiconductor

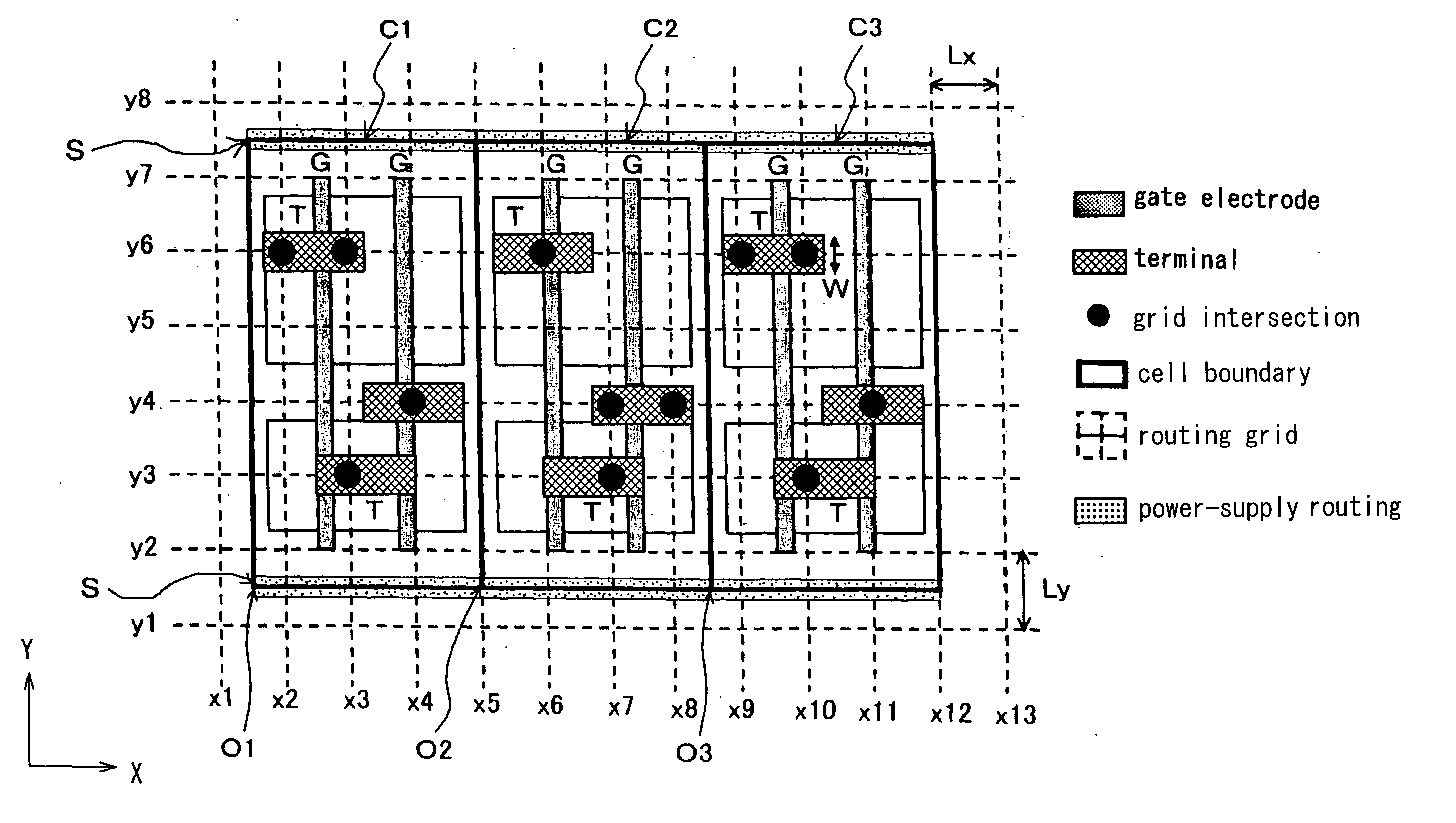

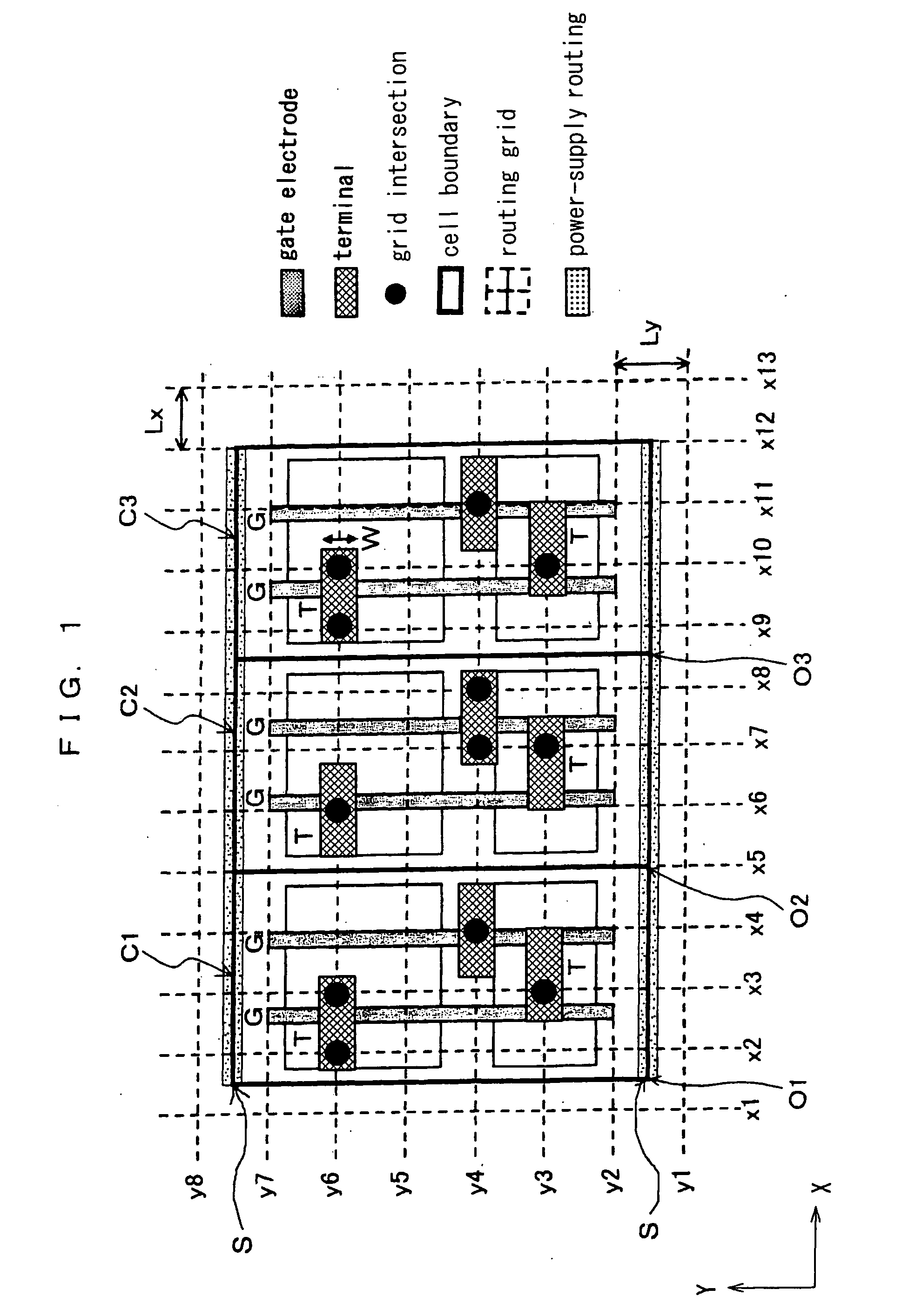

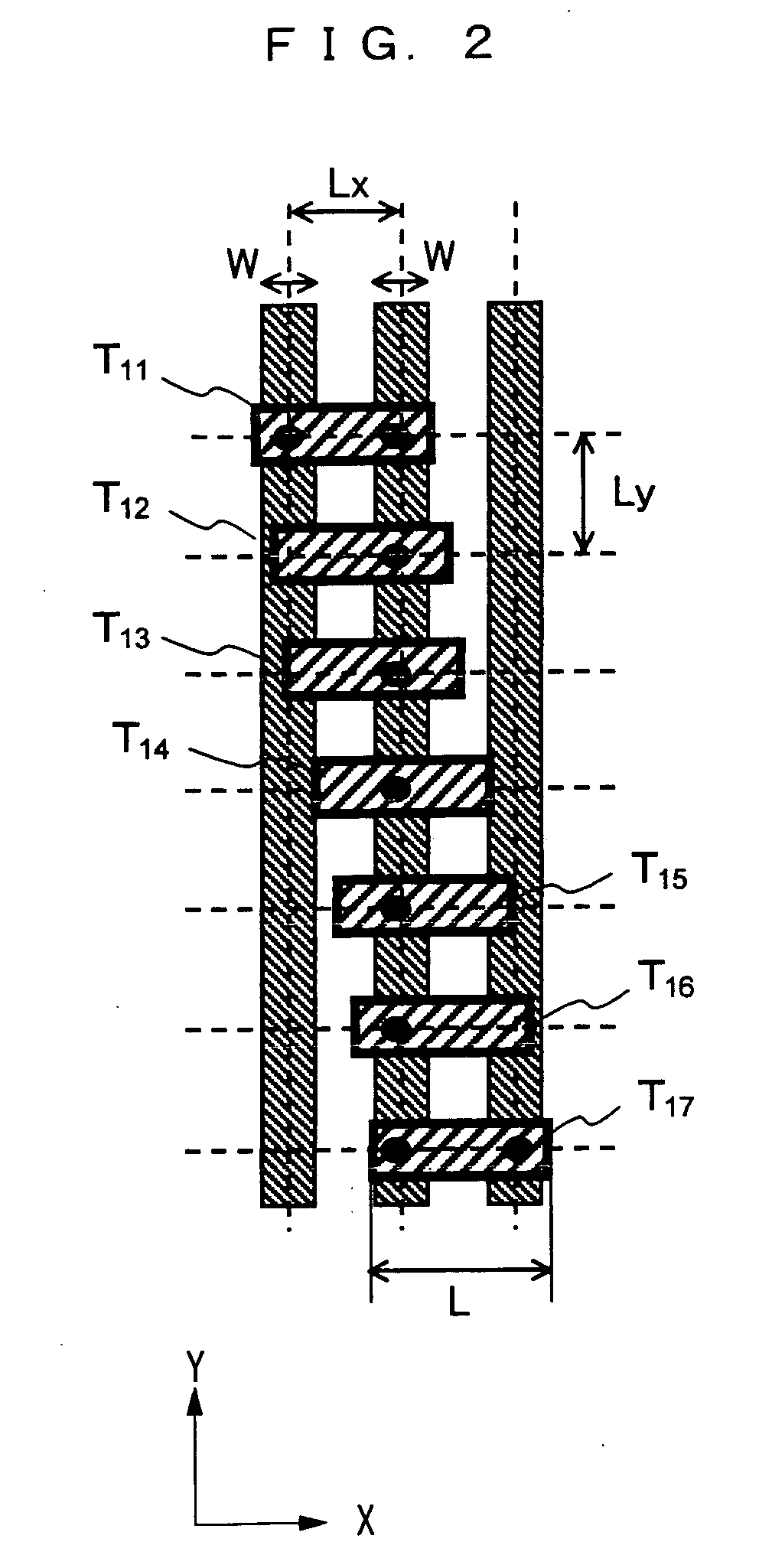

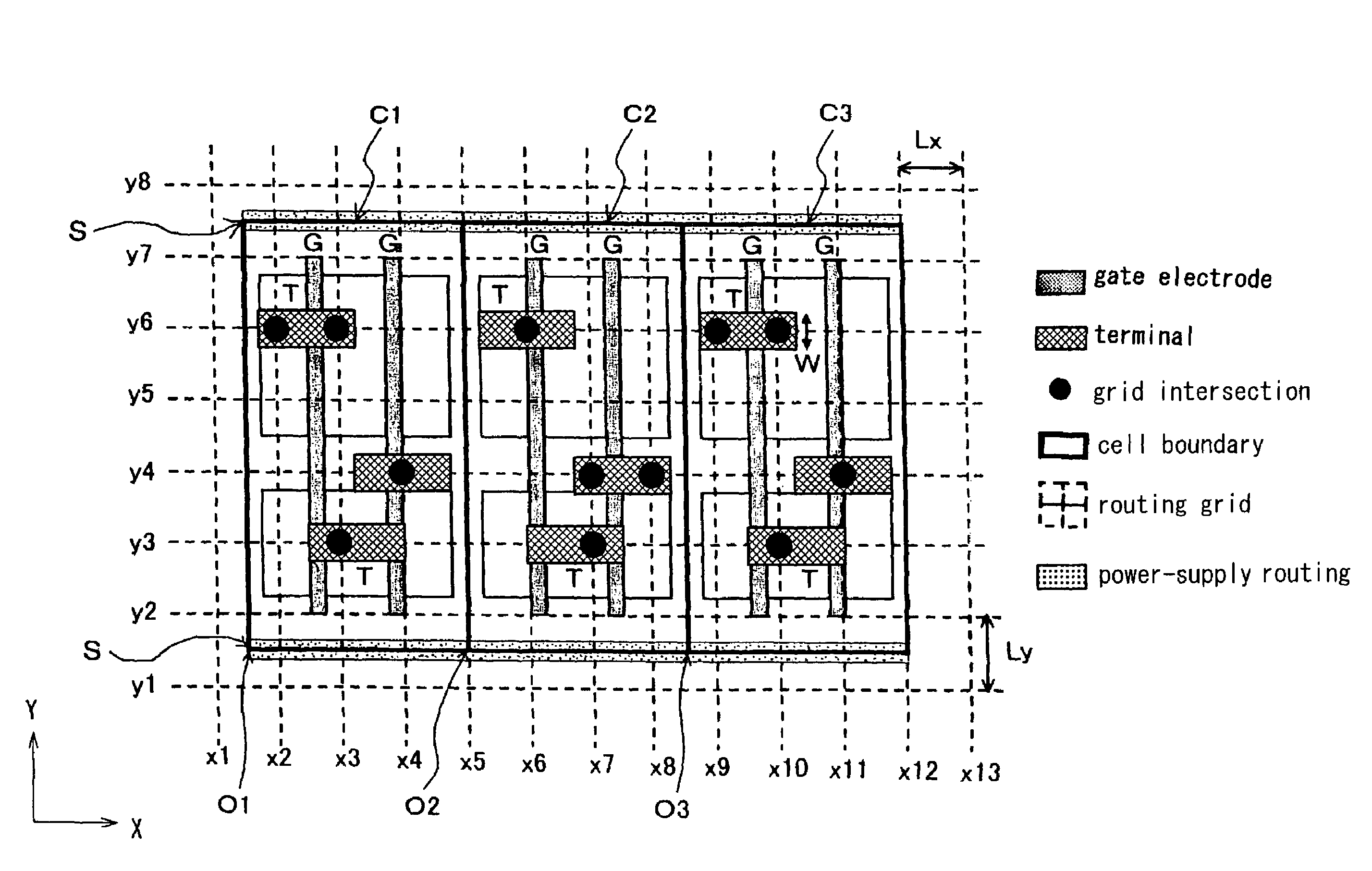

A cell according to the present invention comprises a plurality of terminals capable of transmitting an input signal or an output signal and serving as a minimum unit in designing a semiconductor integrated circuit, wherein the plurality of terminals is located on routing grids lined in a Y direction which is a direction vertical to a power-supply wiring of the cell used in automatic placement & routing and has a shape extended in an X direction which is a direction in parallel with the power-supply wiring, more specifically such a shape that, for example, a longer-side dimension of the terminal is equal to “a routing grid interval in the X direction+a wiring width. According to the constitution, a cell area is reduced, which advantageously leads to the reduction of a chip area.

Owner:SOCIONEXT INC

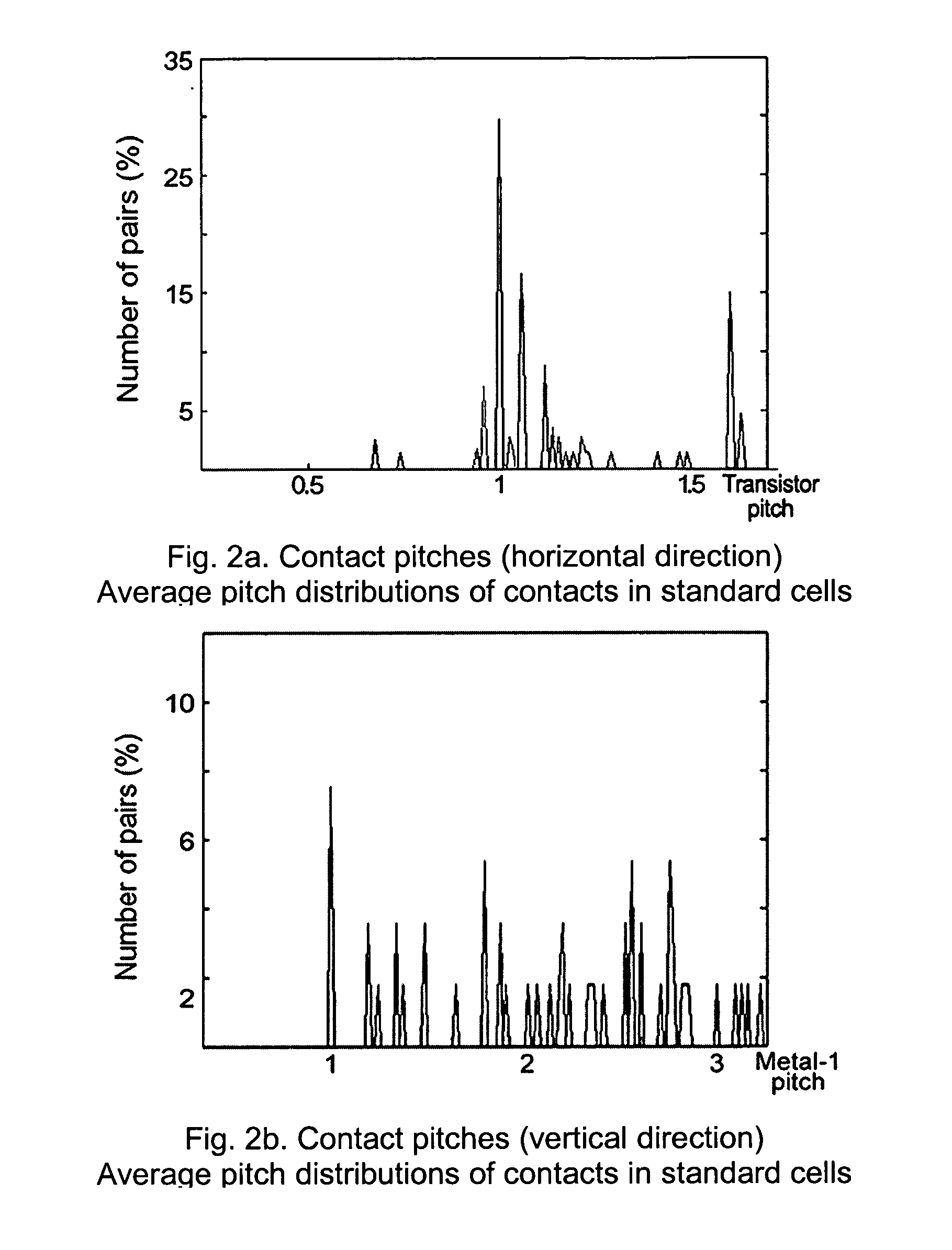

Rectangular contact lithography for circuit performance improvement and manufacture cost reduction

ActiveUS20050196685A1Reduce manufacturing costLot of restrictionPhoto-taking processesSemiconductor/solid-state device manufacturingManufacturing cost reductionEngineering

An optical lithography method is disclosed that uses double exposure of a reusable template mask and a trim mask to fabricate regularly-placed rectangular contacts in standard cells of application-specific integrated circuits (ASICs). A first exposure of the reusable template mask with periodic patterns forms periodic dark lines on a wafer and a second exposure of an application-specific trim mask remove the unwanted part of the dark lines and the small cuts of the dark lines left form the rectangular regularly-placed contacts. All contacts are placed regularly in one direction while unrestrictedly in the perpendicular direction. The regular placement of patterns on the template mask enable more effective use of resolution enhancement technologies, which in turn allows a decrease in manufacturing cost and the minimum contact size and pitch. Since there is no extra application-specific mask needed comparing with the conventional lithography method for unrestrictedly-placed contacts, the extra cost is kept to the lowest. The method of the invention can be used in the fabrication of standard cells in application-specific integrated circuits (ASICs) to improve circuit performance and decrease circuit area and manufacturing cost.

Owner:THE UNIVERSITY OF HONG KONG

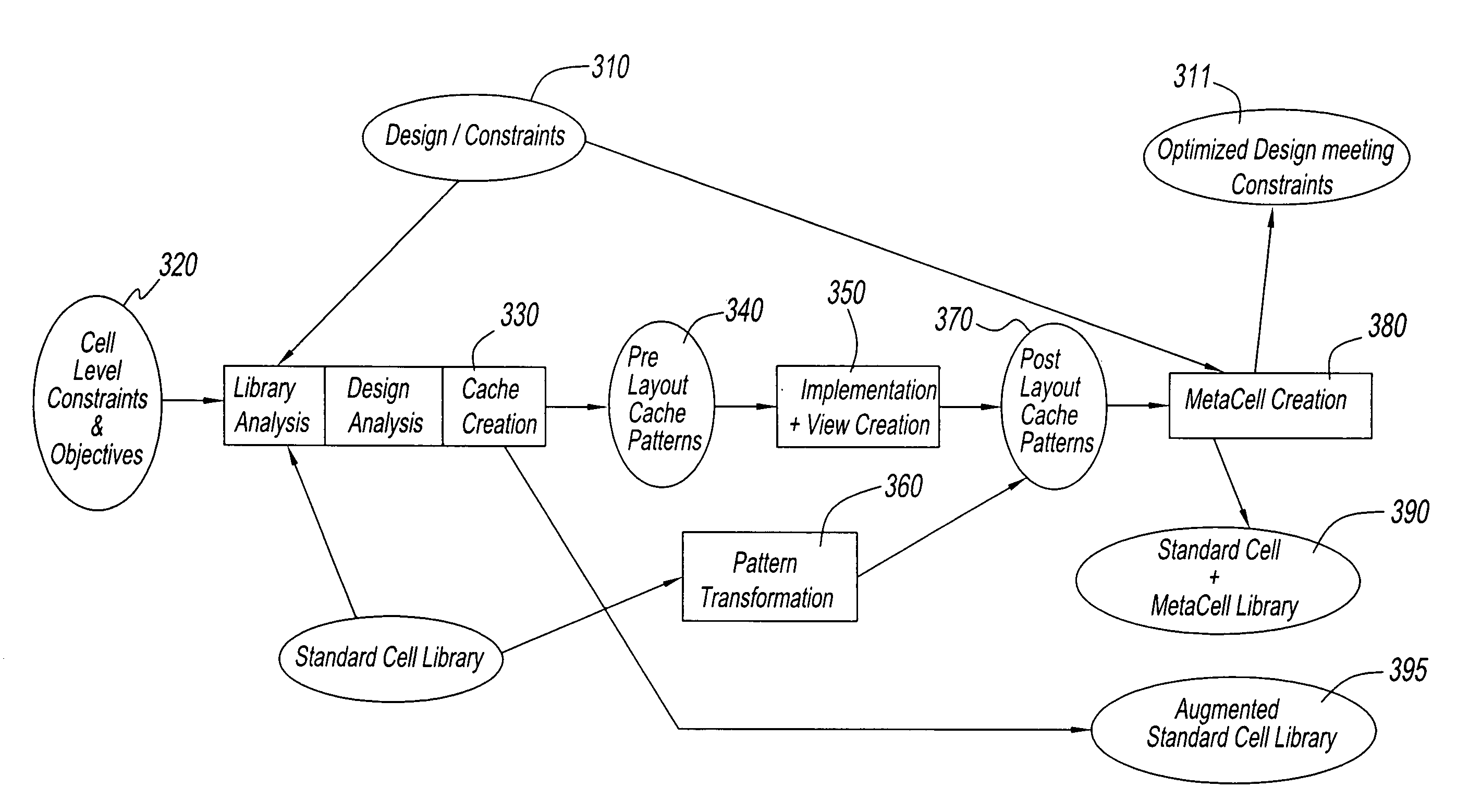

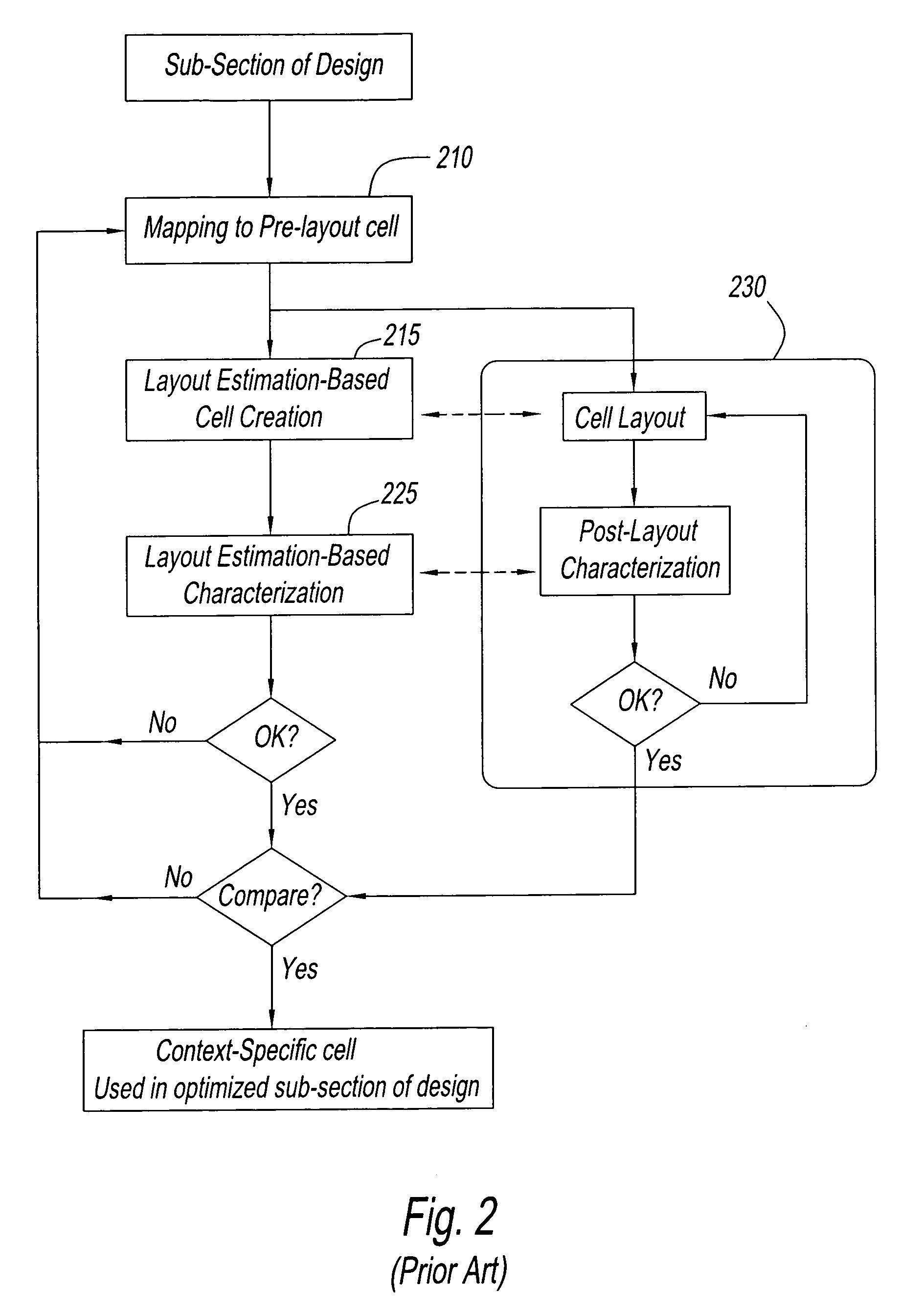

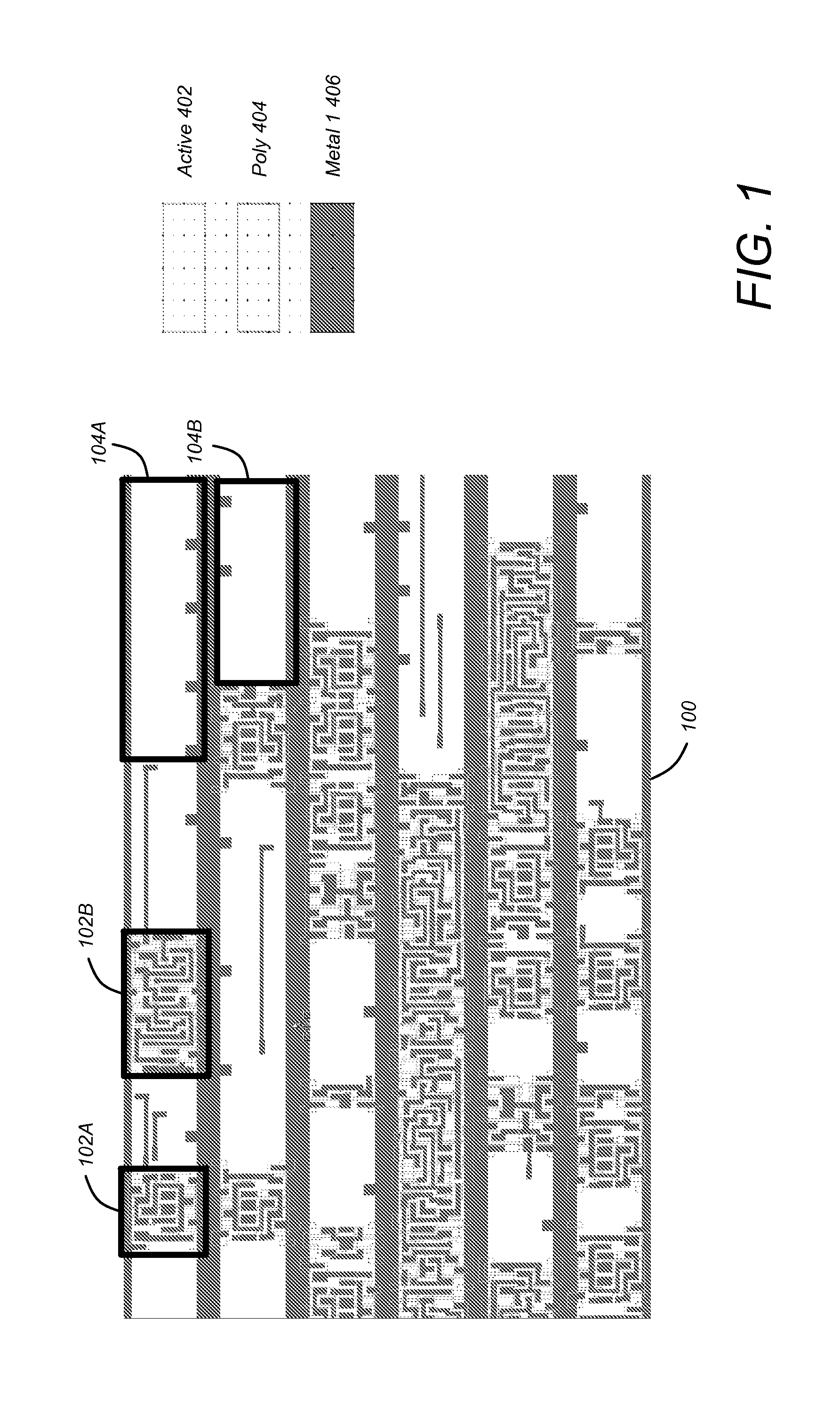

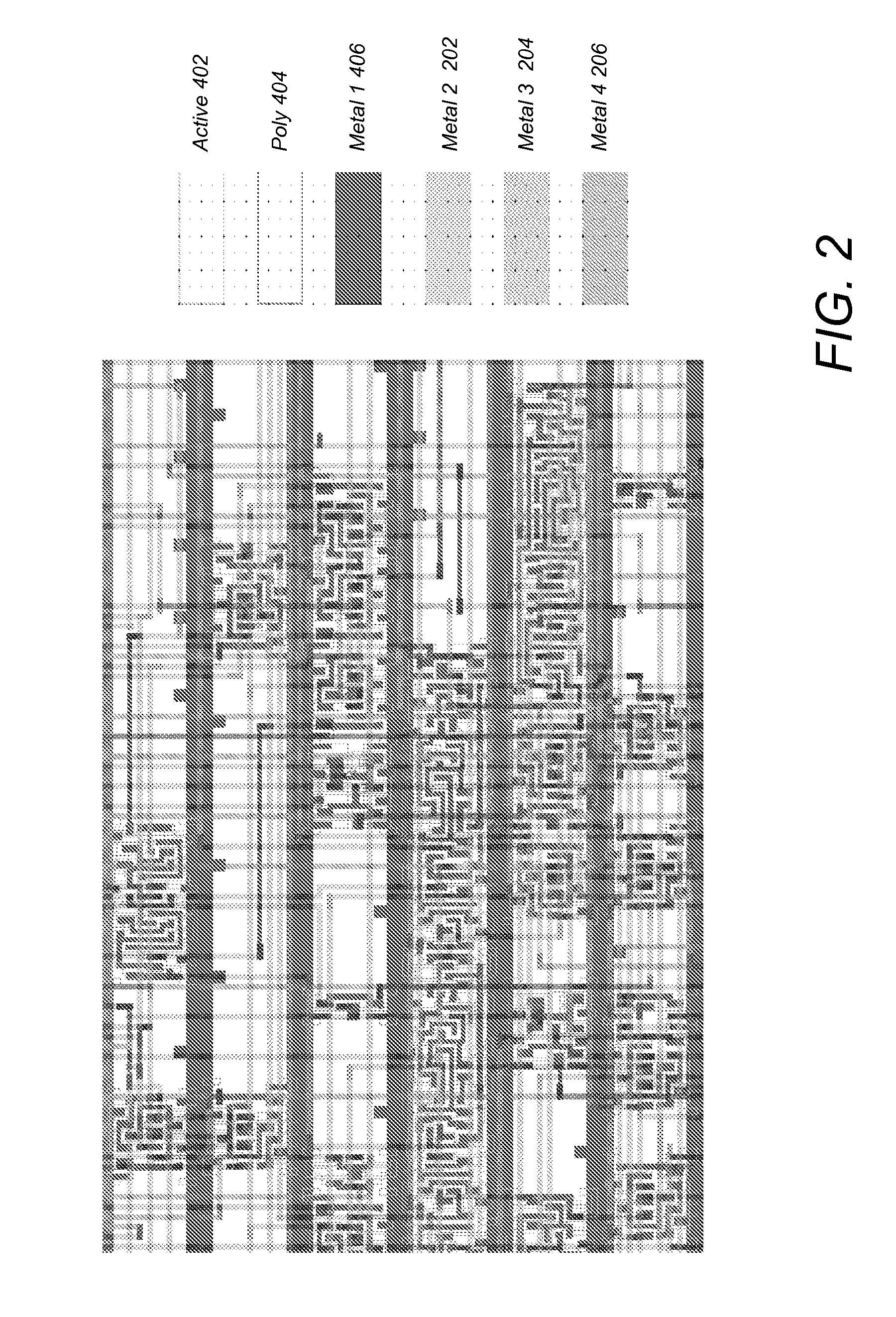

Method of IC design optimization via creation of design-specific cells from post-layout patterns

ActiveUS20080127000A1Increase diversityQuality improvementComputer aided designSoftware simulation/interpretation/emulationClosed loopEngineering

A closed-loop IC design optimization process by automatically or manually creating design-specific cells with desired characteristics (e.g., performance, area, power, noise, etc.), which will be then implemented as a standard cell (also known hereafter as metacell), from a set of post-layout patterns. A post-layout pattern represents a part or whole of a standard cell and contains information regarding the pattern including, but not limited to, layout, timing, area, power and noise. As the metacells are created from post-layout patterns, the inaccuracies of prior dynamic library techniques are easily avoided. Such metacells, being design-specific, are optimized to satisfy the constraints imposed by the design context, thus bringing the powerful design-specific customization to standard cell-based design methodology.

Owner:ALPHAWAVE SEMI INC

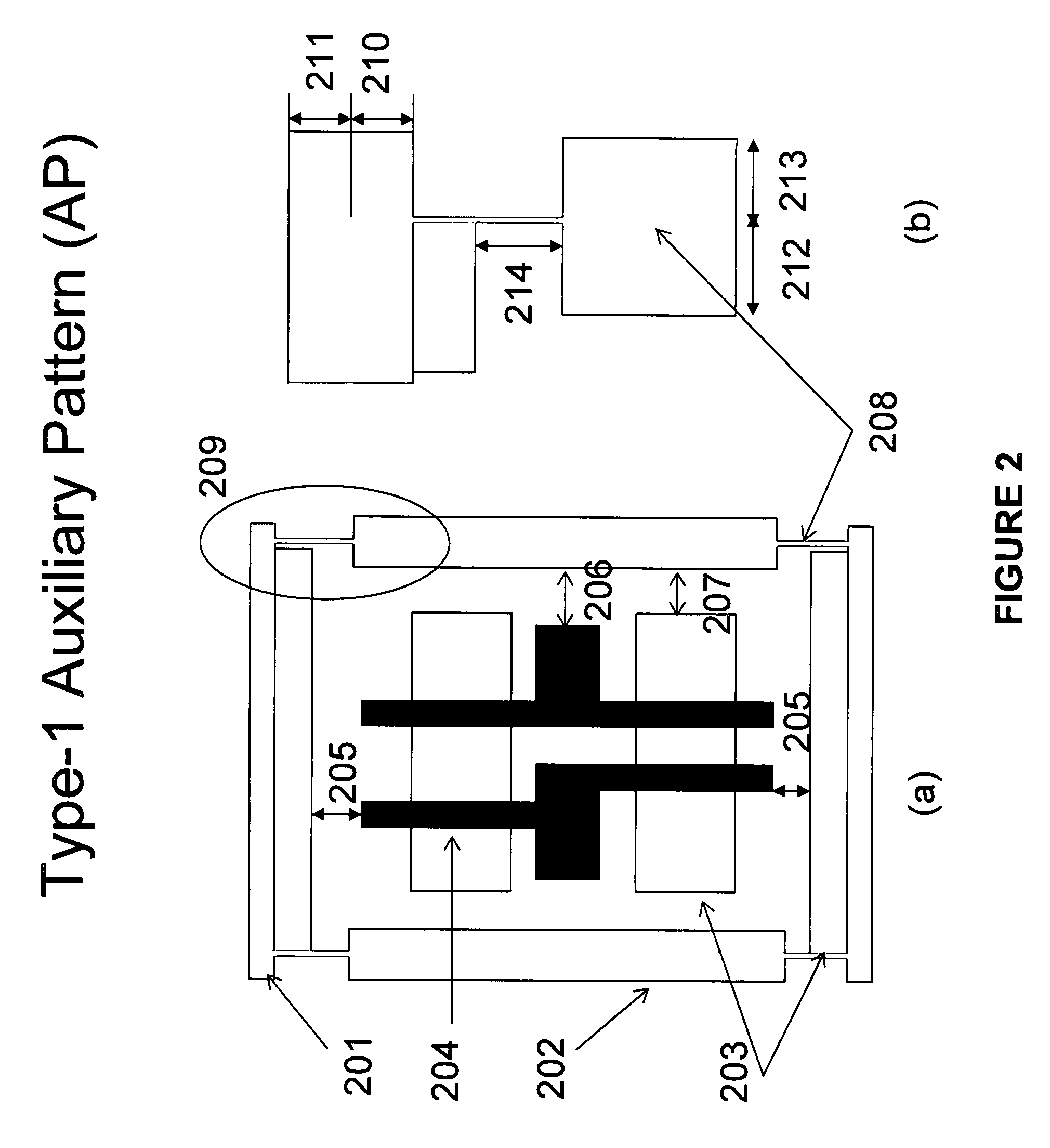

Method, apparatus and system for designing an integrated circuit including generating at least one auxiliary pattern for cell-based optical proximity correction

InactiveUS7873929B2Reduce running timeSemiconductor/solid-state device detailsSolid-state devicesCell basedObject function

Method and apparatus for designing an integrated circuit. A new layout is generated for at least one standard cell that incorporates an auxiliary pattern on a gate layer to facilitate cell-based optical proximity correction. An original placement solution is modified for a plurality of standard cells to permit incorporation of cells containing auxiliary patterns while improving an objective function of a resulting placement solution for the plurality of standard cells.

Owner:RGT UNIV OF CALIFORNIA

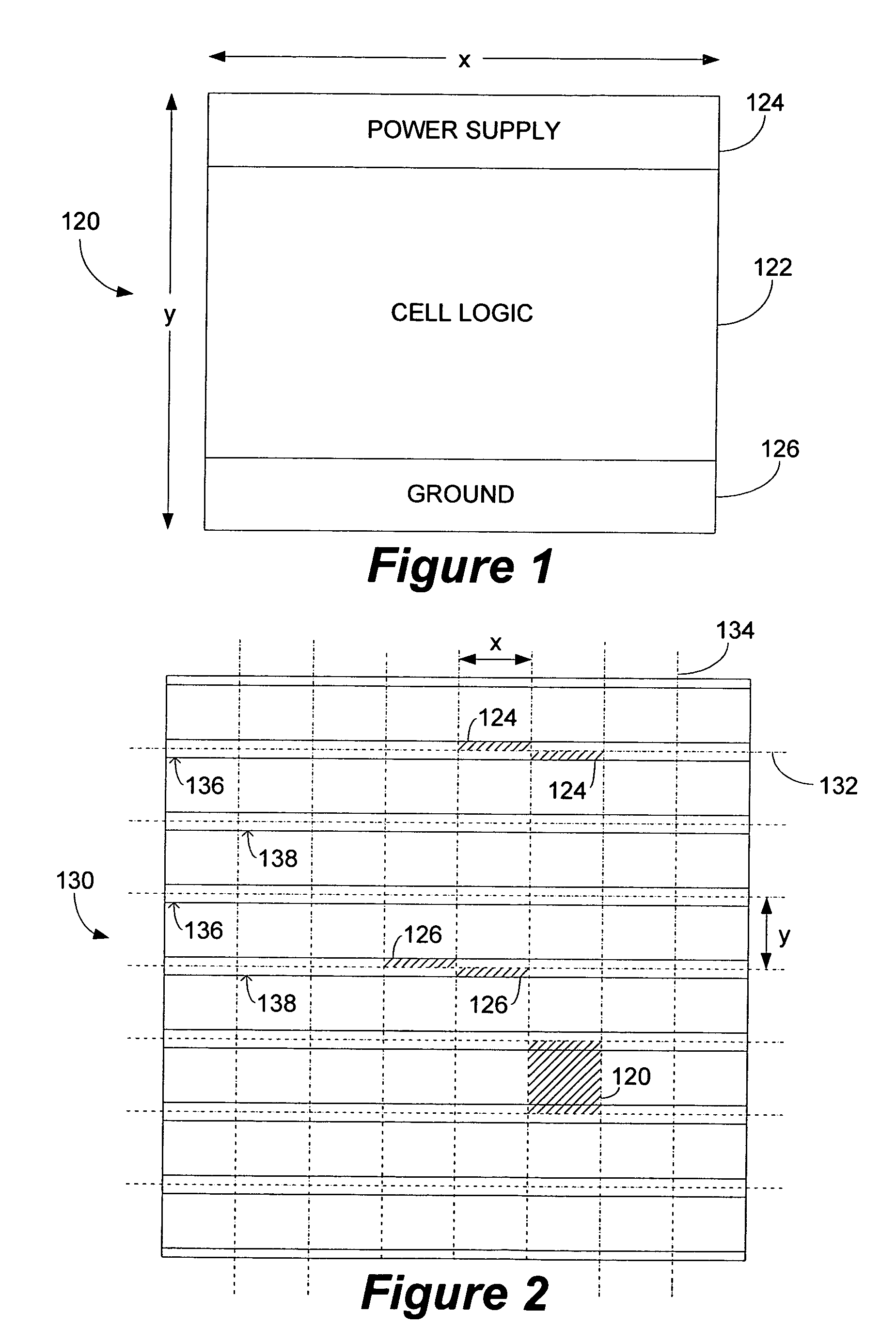

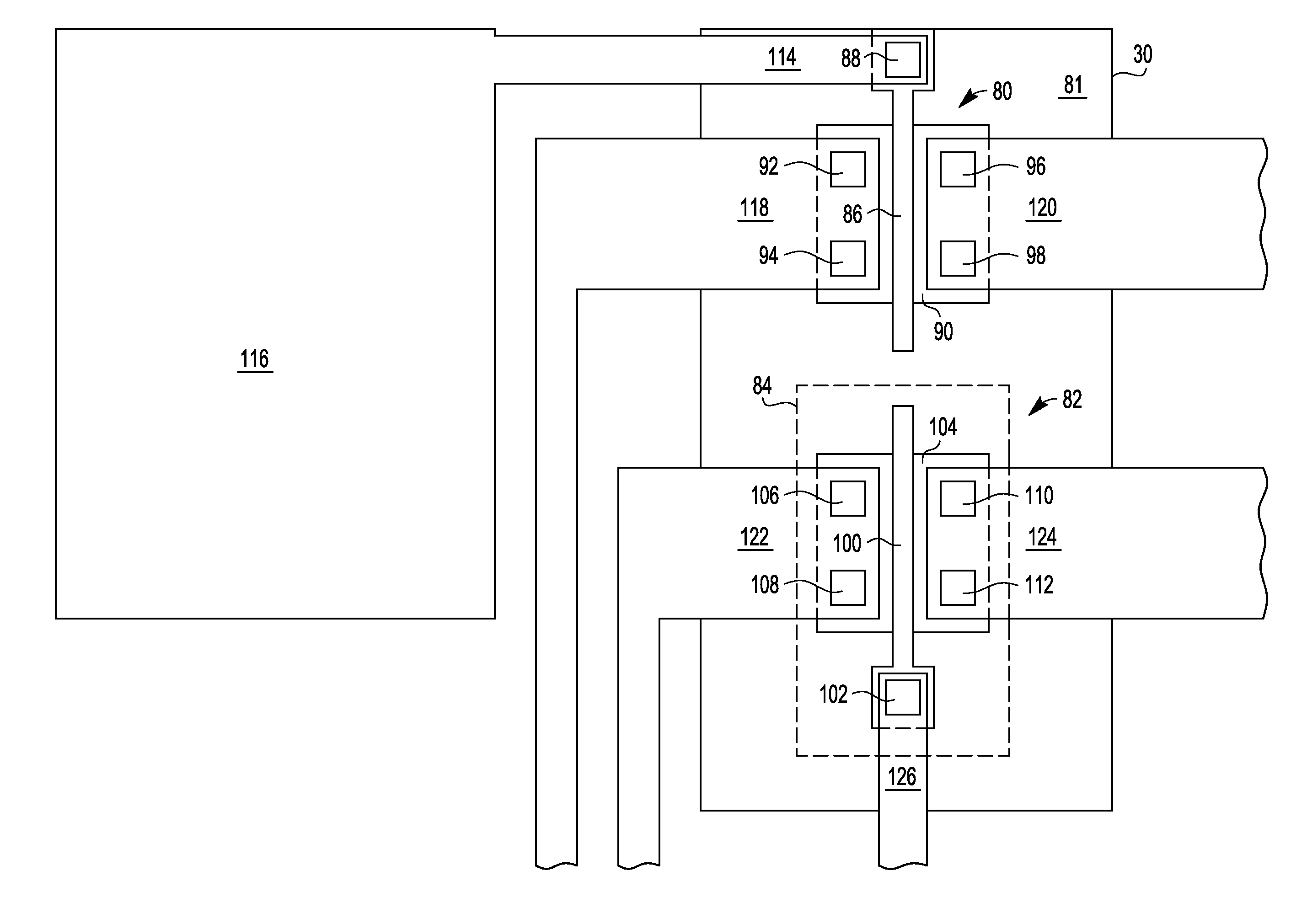

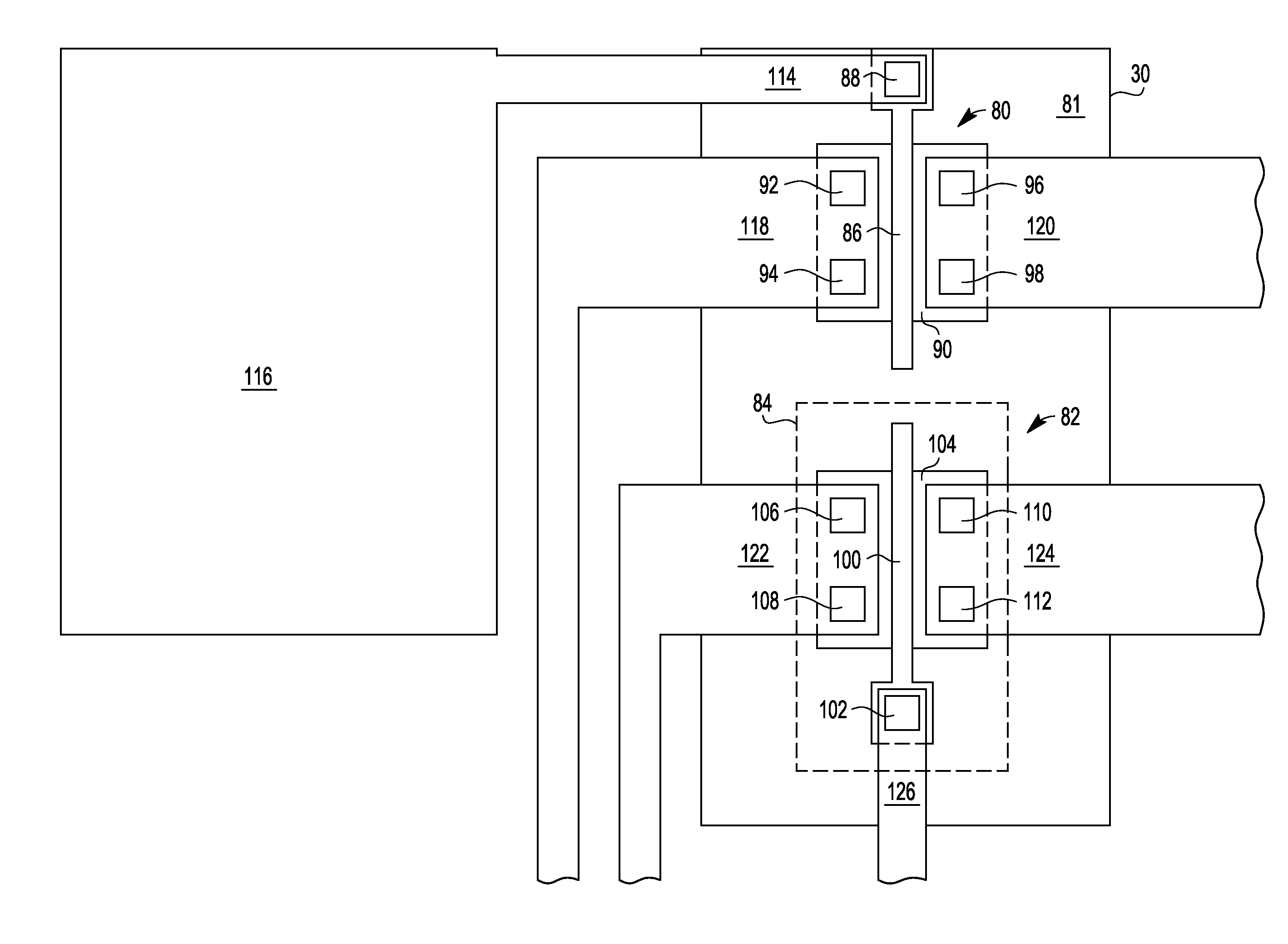

Method and apparatus for power routing in an integrated circuit

A system and method for routing power between circuit blocks in an integrated circuit, such as macros and standard cells. A macro is wrapped in a relatively narrow power interface ring and placed in the integrated circuit such that the lower metal layers of the power interface ring are aligned and in direct contact with the power rails of a standard cell block. A power grid is formed above the macro and the upper metal layers of the power interface ring are coupled to the power grid. The upper power grid is tied either to an outer power bus or directly to power pins in the surrounding I / O ring. Data signals may be routed in the I / O ring space.

Owner:SYNAPTICS INC

Semiconductor integrated circuit device formed by automatic layout wiring by use of standard cells and design method of fixing its well potential

InactiveUS20060131609A1Semiconductor/solid-state device detailsSolid-state devicesDevice formEngineering

A standard cell is read from a library and automatic layout wiring is performed, thereby configuring a circuit. Next, each cell column in the configured circuit is searched for an empty region. In the empty region in the cell column searched for, a spacer cell or a filler cell is placed. At this time, using the spacer cell or filler cell, the well potential of the standard cells in the cell column is fixed.

Owner:KK TOSHIBA

Method for variability constraints in design of integrated circuits especially digital circuits which includes timing closure upon placement and routing of digital circuit or network

InactiveUS20050205894A1Delay variationSmall differenceSolid-state devicesSemiconductor/solid-state device manufacturingStandard cellIntegrated circuit

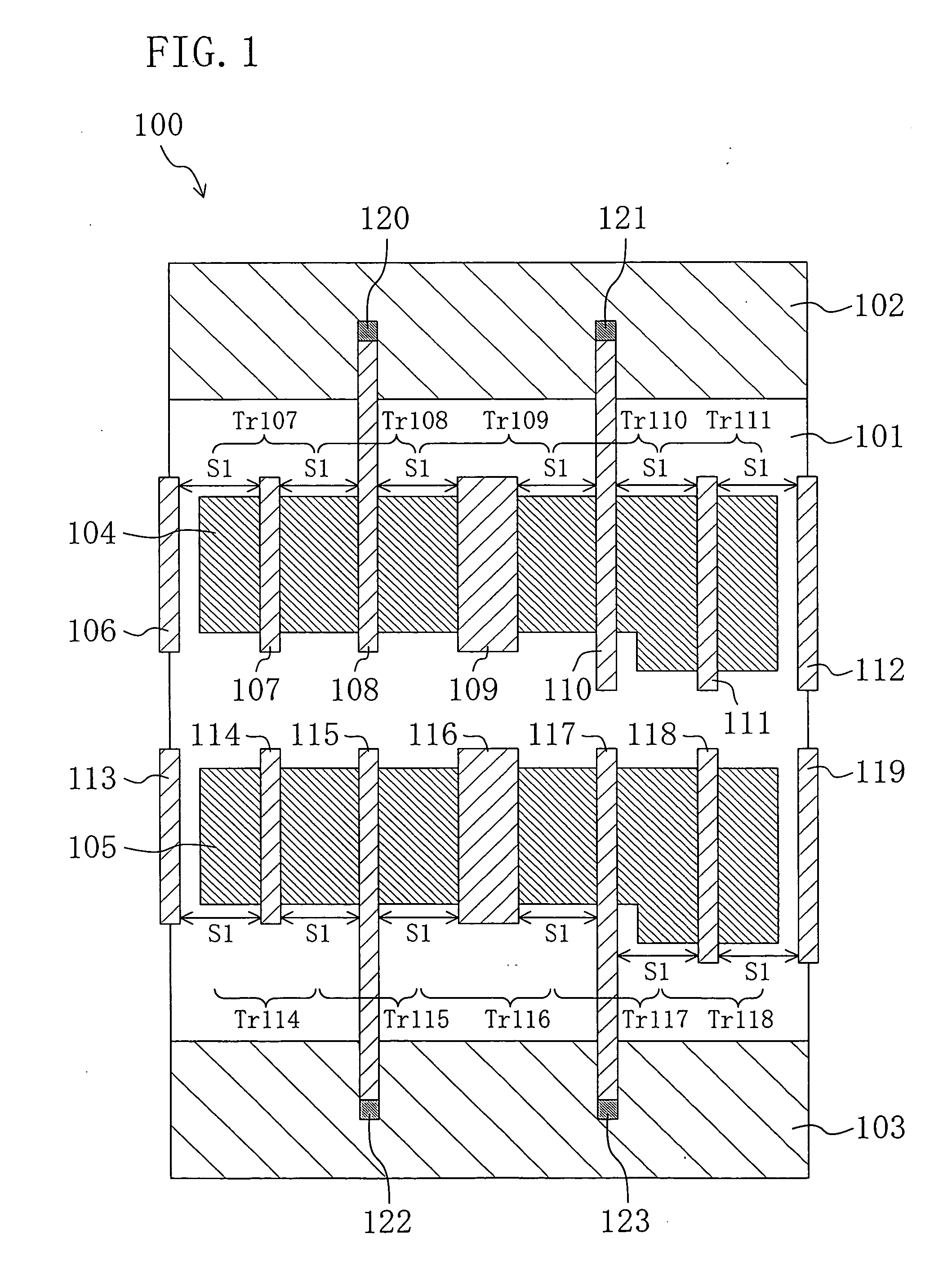

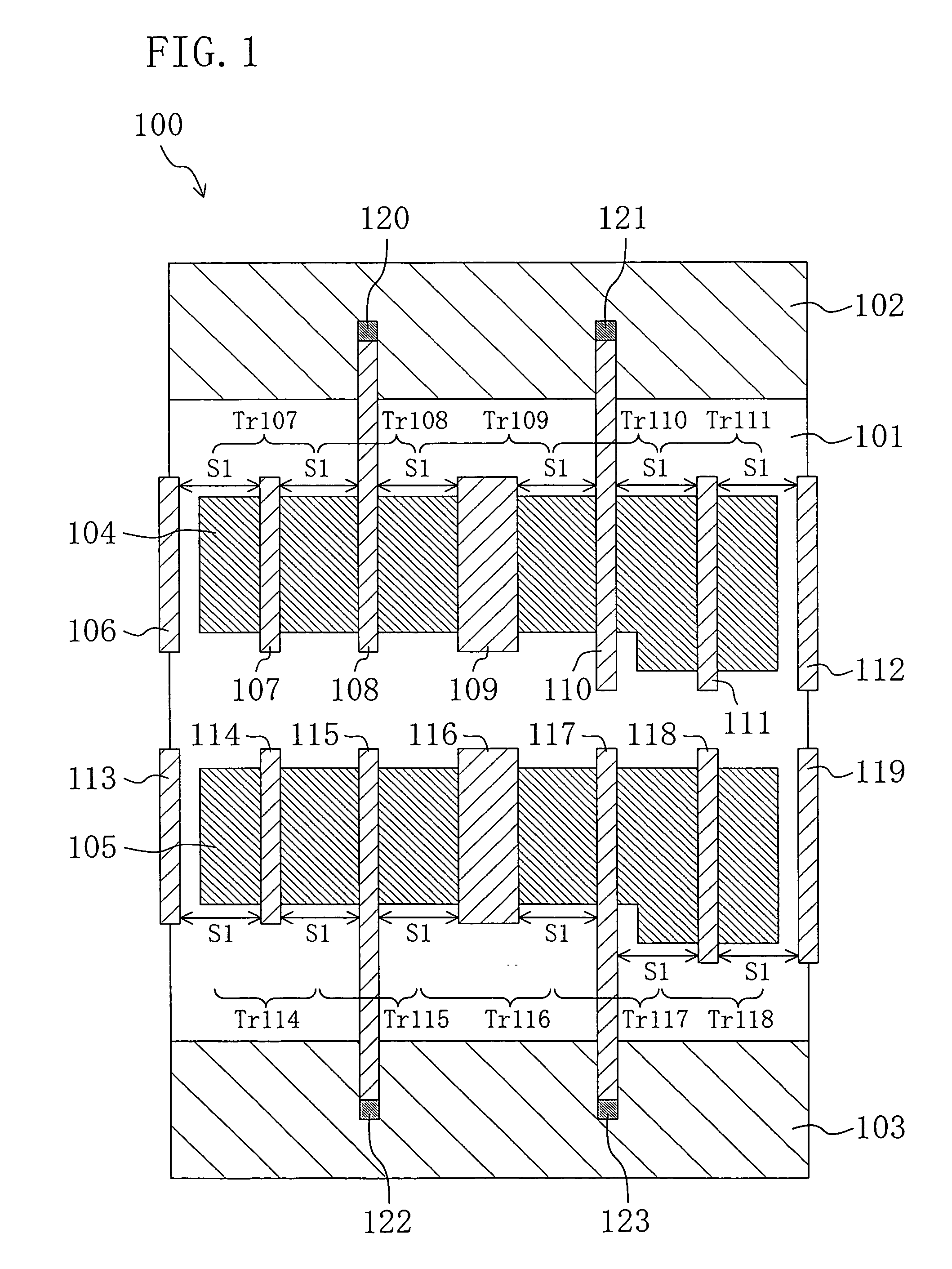

In a standard cell, dummy transistors have p-type and n-type dummy gate electrodes. The dummy transistors are in an OFF state all the time. The gate length of each of the dummy gate electrodes is extended over an end portion of a diffusion region toward the inside of the standard cell. Thus, the total surface area and the total perimeter of respective gate electrodes of all transistors provided in the standard cell are increased. As a result, for example, even though shapes of gate electrodes of transistors vary between the standard cell and each of other standard cells, transistor characteristics are substantially equal among the standard cells. Therefore, variations in delays of signals generated between the standard cells can be suppressed.

Owner:PANASONIC CORP

Standard cell, standard cell library, and semiconductor integrated circuit with suppressed variation in characteristics

In a standard cell, at least one of transistors on either side of a transistor having gate length different from that of the other transistors are set to be always in the OFF state. This prevents influence to the operation of the standard cell even with variation in final gate dimension, suppressing variation in characteristics of the standard cell.

Owner:SOCIONEXT INC

Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit

ActiveUS7503026B2Reducing cell area and chip areaHigh precisionSolid-state devicesComputer aided designElectrical batteryEngineering

A cell according to the present invention comprises a plurality of terminals capable of transmitting an input signal or an output signal and serving as a minimum unit in designing a semiconductor integrated circuit, wherein the plurality of terminals is located on routing grids lined in a Y direction which is a direction vertical to a power-supply wiring of the cell used in automatic placement & routing and has a shape extended in an X direction which is a direction in parallel with the power-supply wiring, more specifically such a shape that, for example, a longer-side dimension of the terminal is equal to “a routing grid interval in the X direction+a wiring width. According to the constitution, a cell area is reduced, which advantageously leads to the reduction of a chip area.

Owner:SOCIONEXT INC

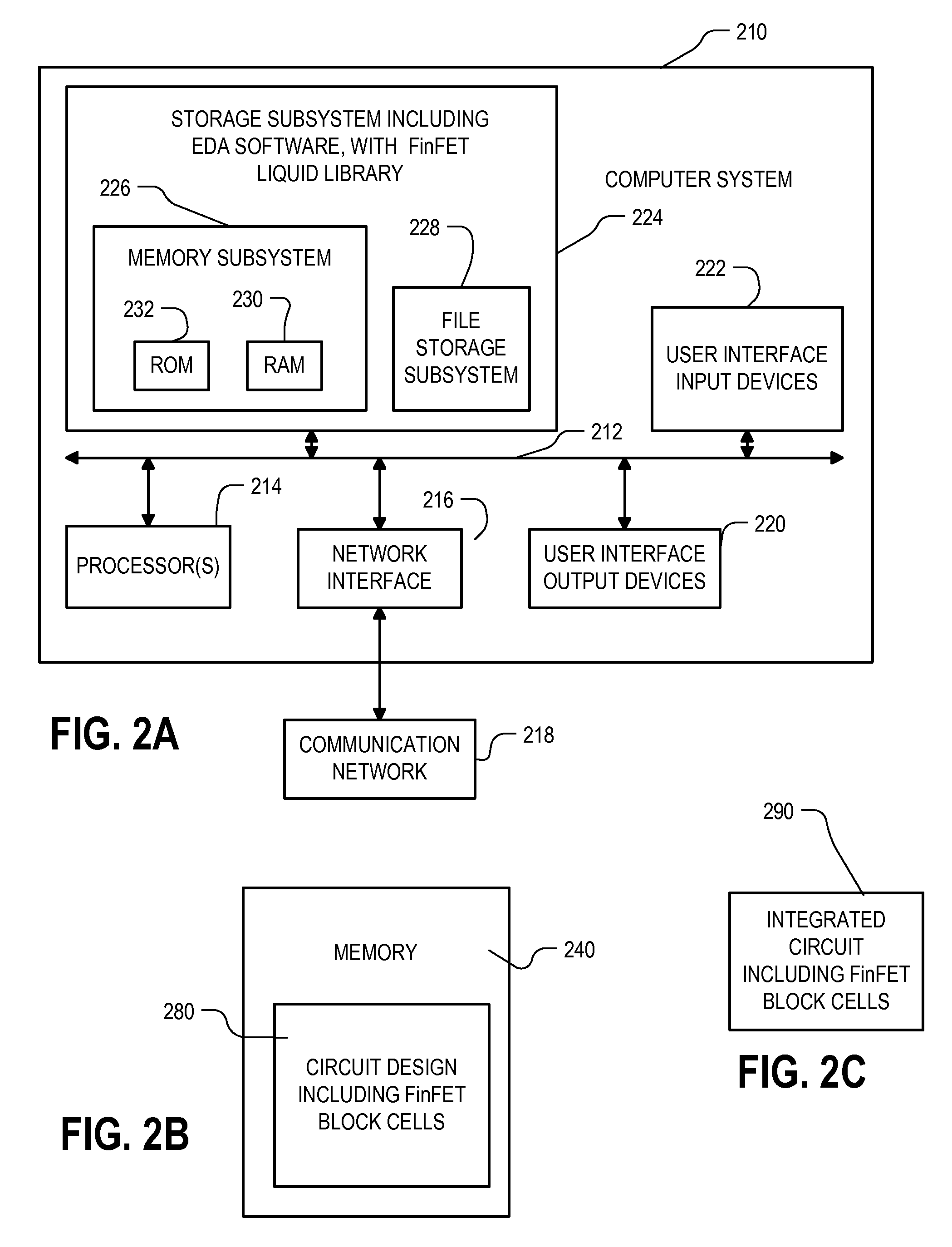

N-channel and p-channel finfet cell architecture

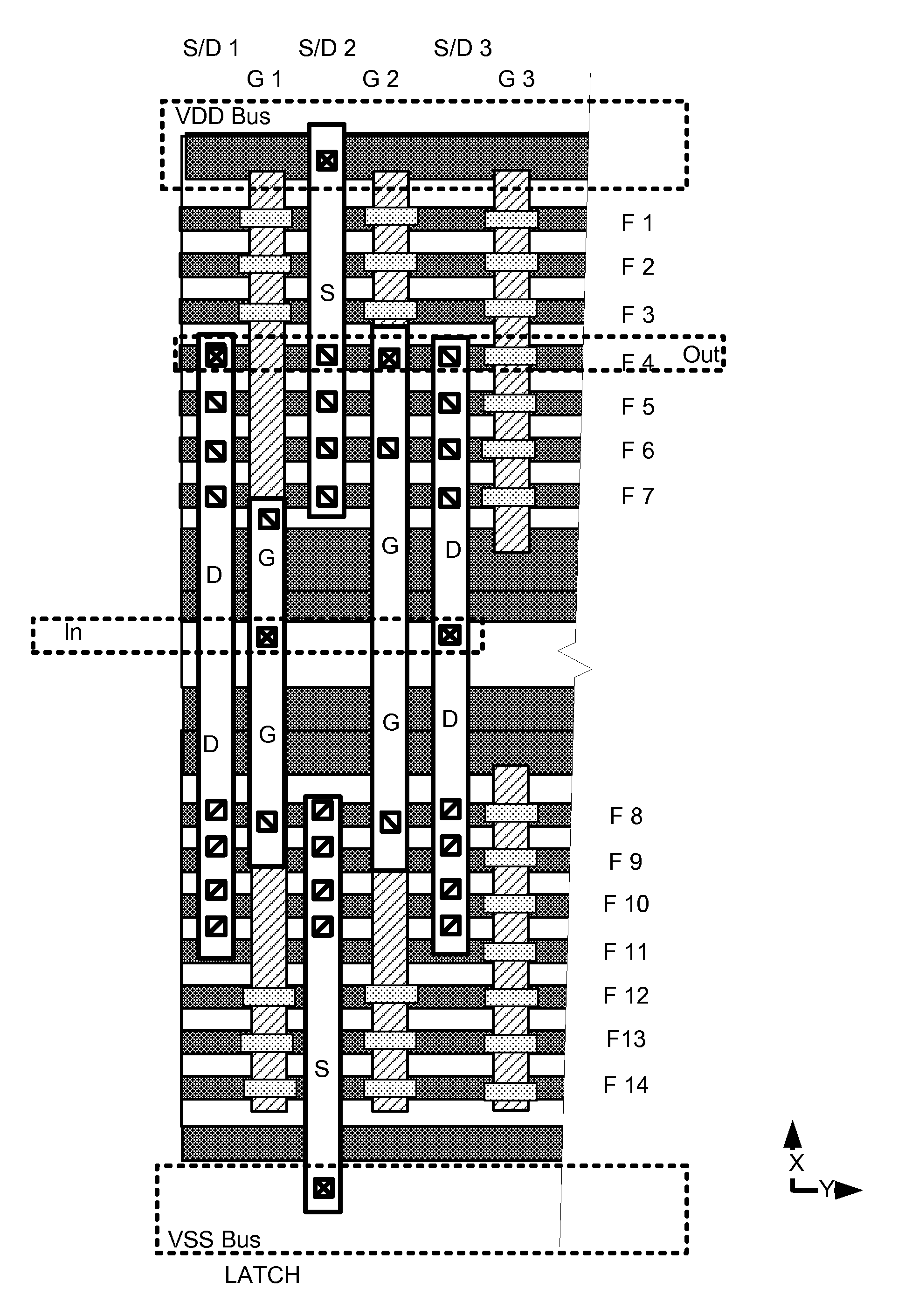

ActiveUS20130026572A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorP channel

A finFET block architecture suitable for use of a standard cell library, is based on an arrangement including a first set of semiconductor fins in a first region of the substrate having a first conductivity type, and a second set of semiconductor fins in a second region of the substrate, the second region having a second conductivity type. A patterned gate conductor layer including gate traces in the first and second regions, arranged over channel regions of the first and second sets of semiconductor fins is used for transistor gates. Patterned conductor layers over the gate conductor layer are arranged in orthogonal layout patterns, and can include a plurality of floating power buses over the fins in the first and second regions.

Owner:SYNOPSYS INC

Semiconductor device having a library of standard cells and method of designing the same

InactiveUS6504186B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

In a semiconductor device provided with a plurality of standard cells each comprising an input terminal and MOS transistors, a diffused region having a substantially negligibly small resistance is formed in a semiconductor substrate, and the input terminal of the standard cell and gates of the MOS transistors are connected through the diffused region. Also, a diffused region is formed under the input terminal in the substrate, and the input terminal is connected to the diffused region. In a modification, another standard cell is formed by forming a diffused region and a metal layer connected to the diffused region on the substrate, and the another standard cell is connected to the input terminal.

Owner:RENESAS ELECTRONICS CORP

Method of IC design optimization via creation of design-specific cells from post-layout patterns

ActiveUS7941776B2Increase diversityQuality improvementComputer aided designSoftware simulation/interpretation/emulationClosed loopComputer module

A closed-loop IC design optimization process by automatically or manually creating design-specific cells with desired characteristics (e.g., performance, area, power, noise, etc.), which will be then implemented as a standard cell (also known hereafter as metacell), from a set of post-layout patterns. A post-layout pattern represents a part or whole of a standard cell and contains information regarding the pattern including, but not limited to, layout, timing, area, power and noise. As the metacells are created from post-layout patterns, the inaccuracies of prior dynamic library techniques are easily avoided. Such metacells, being design-specific, are optimized to satisfy the constraints imposed by the design context, thus bringing the powerful design-specific customization to standard cell-based design methodology.

Owner:ALPHAWAVE SEMI INC

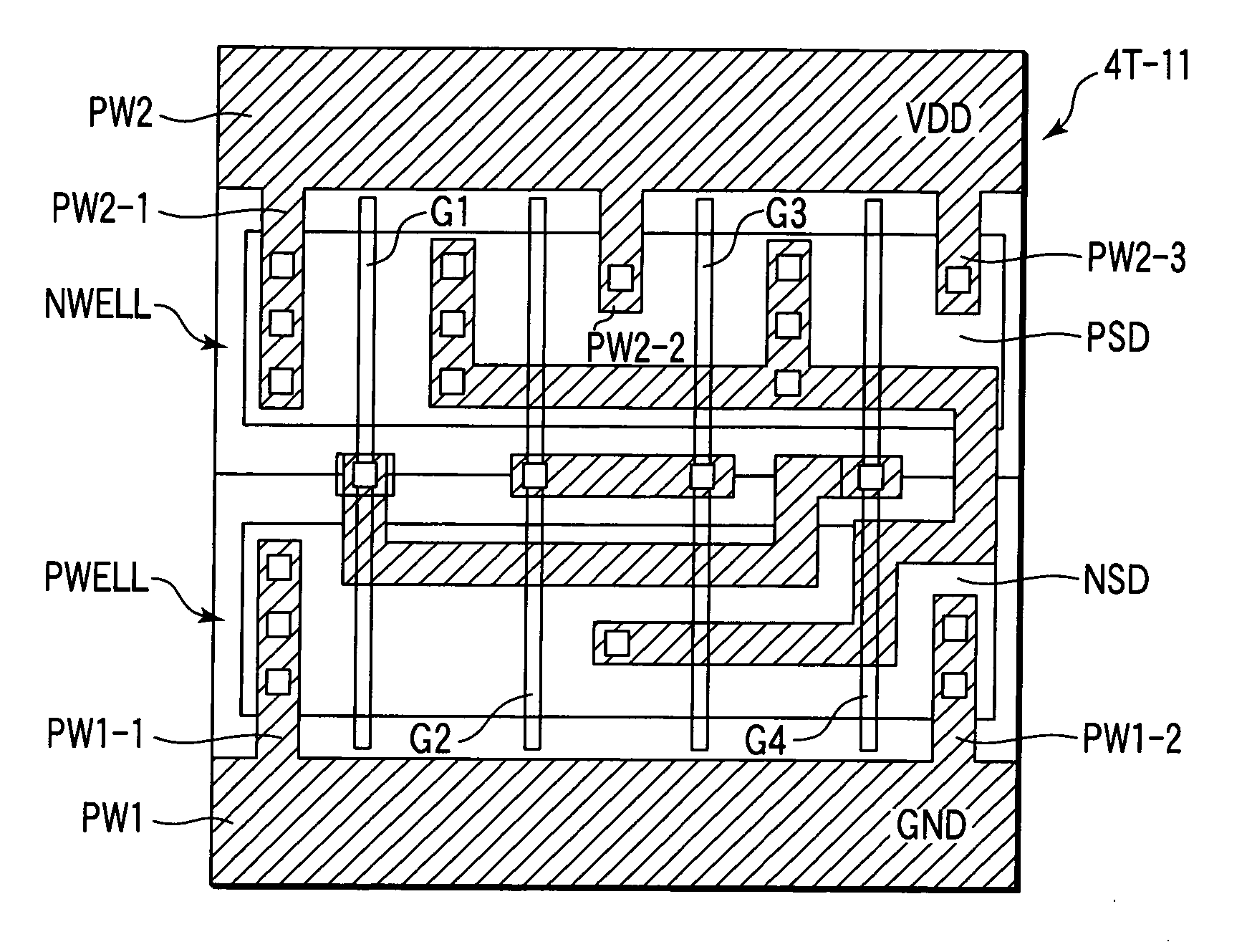

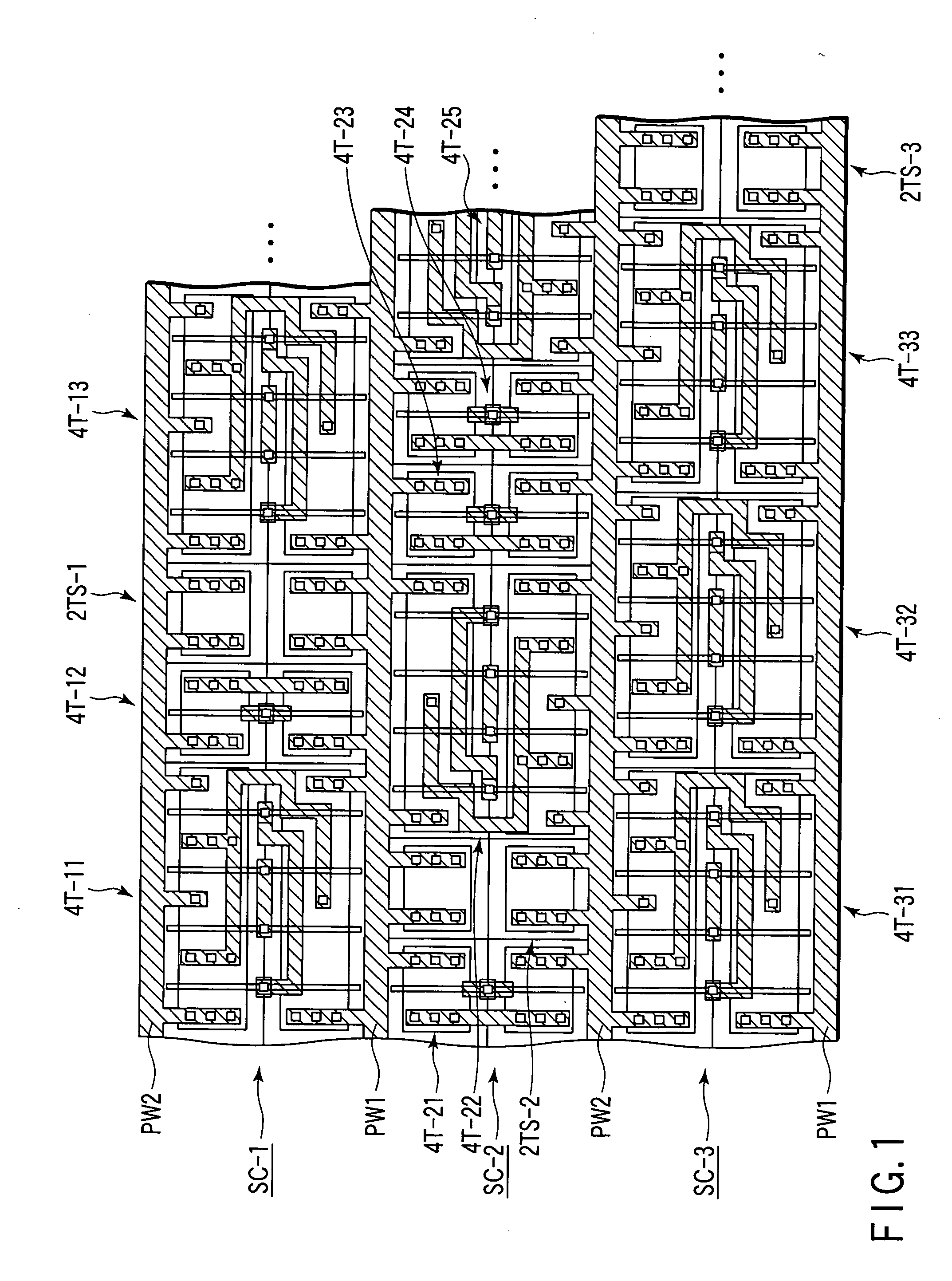

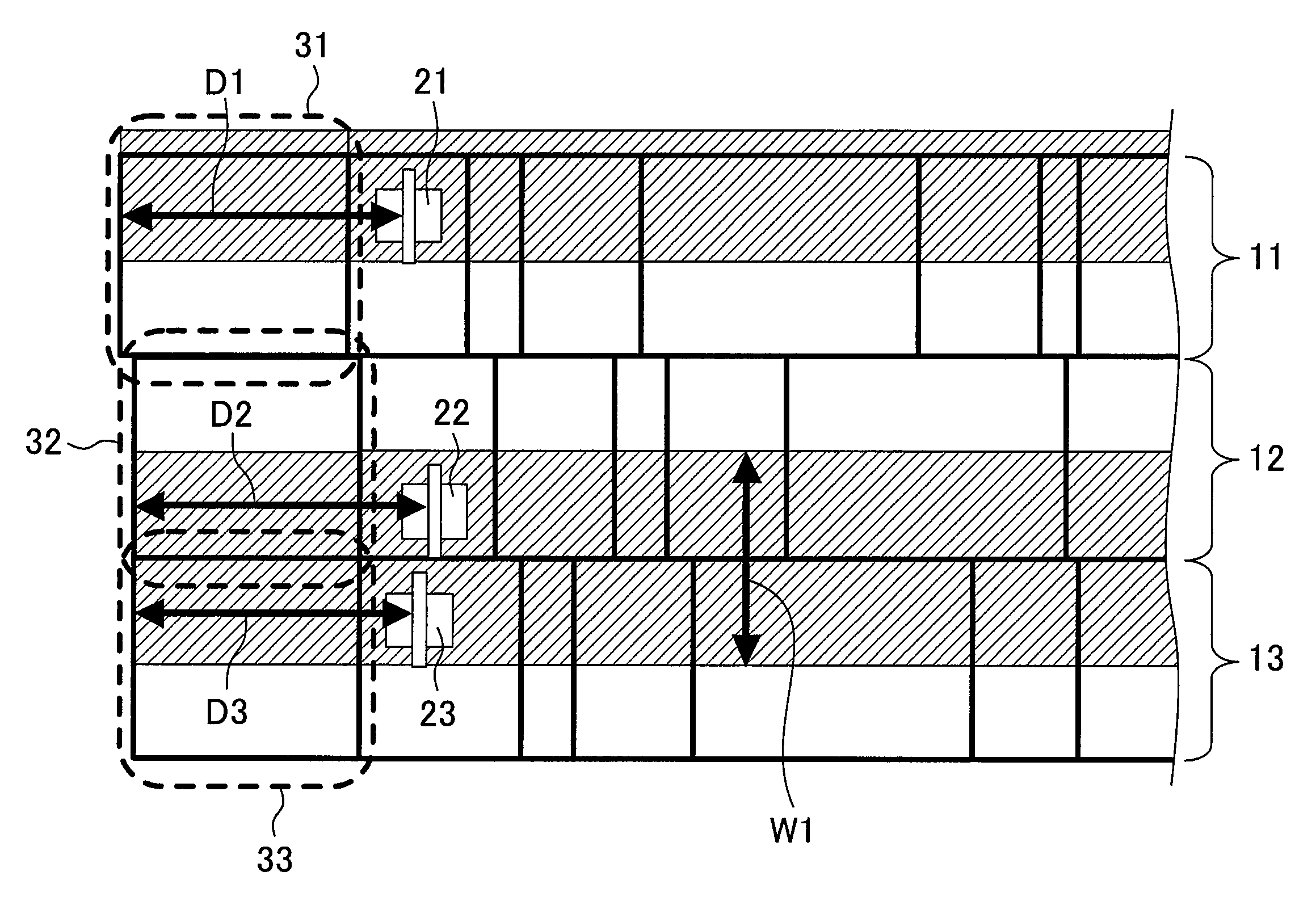

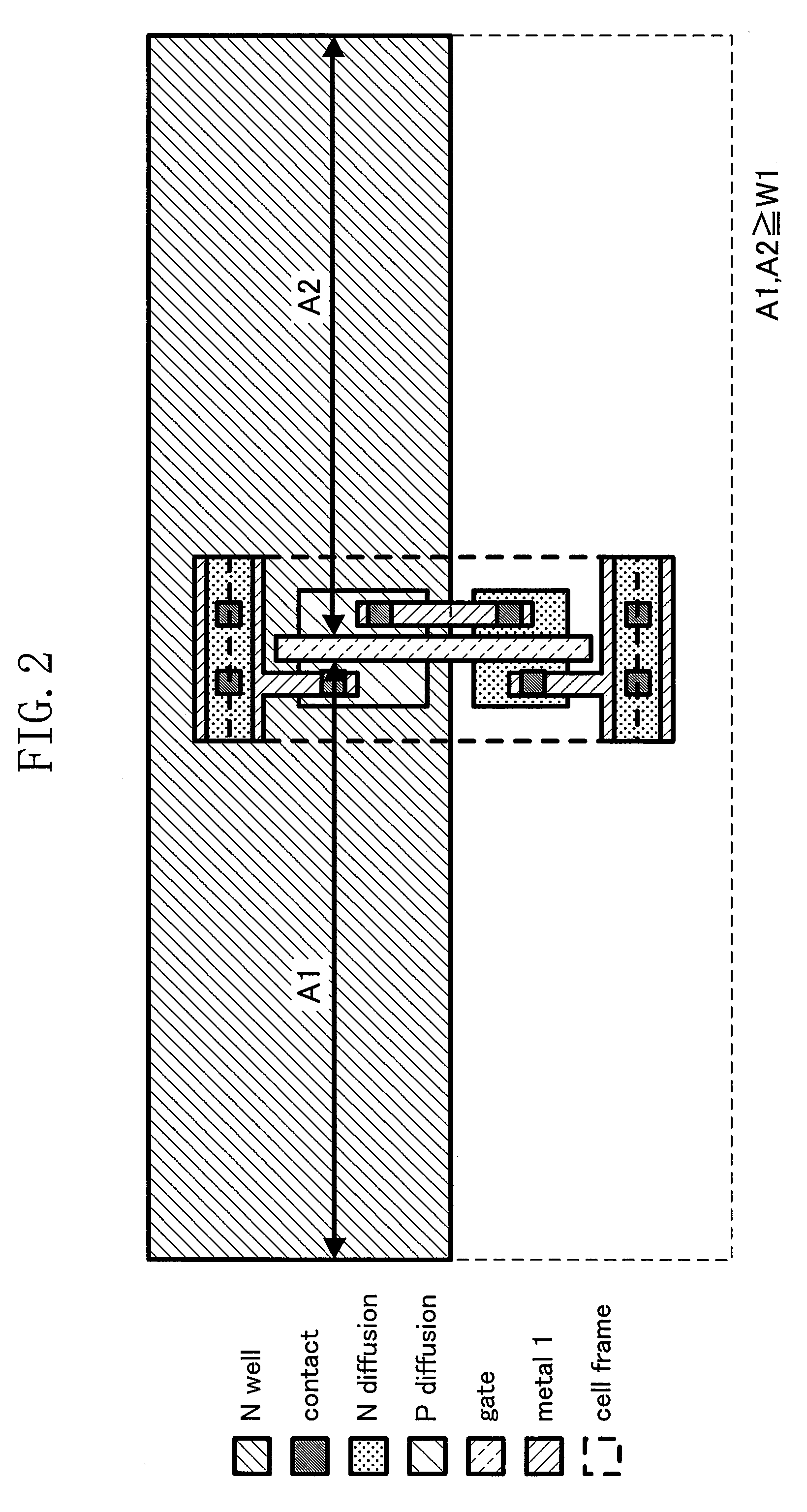

Semiconductor integrated circuit device

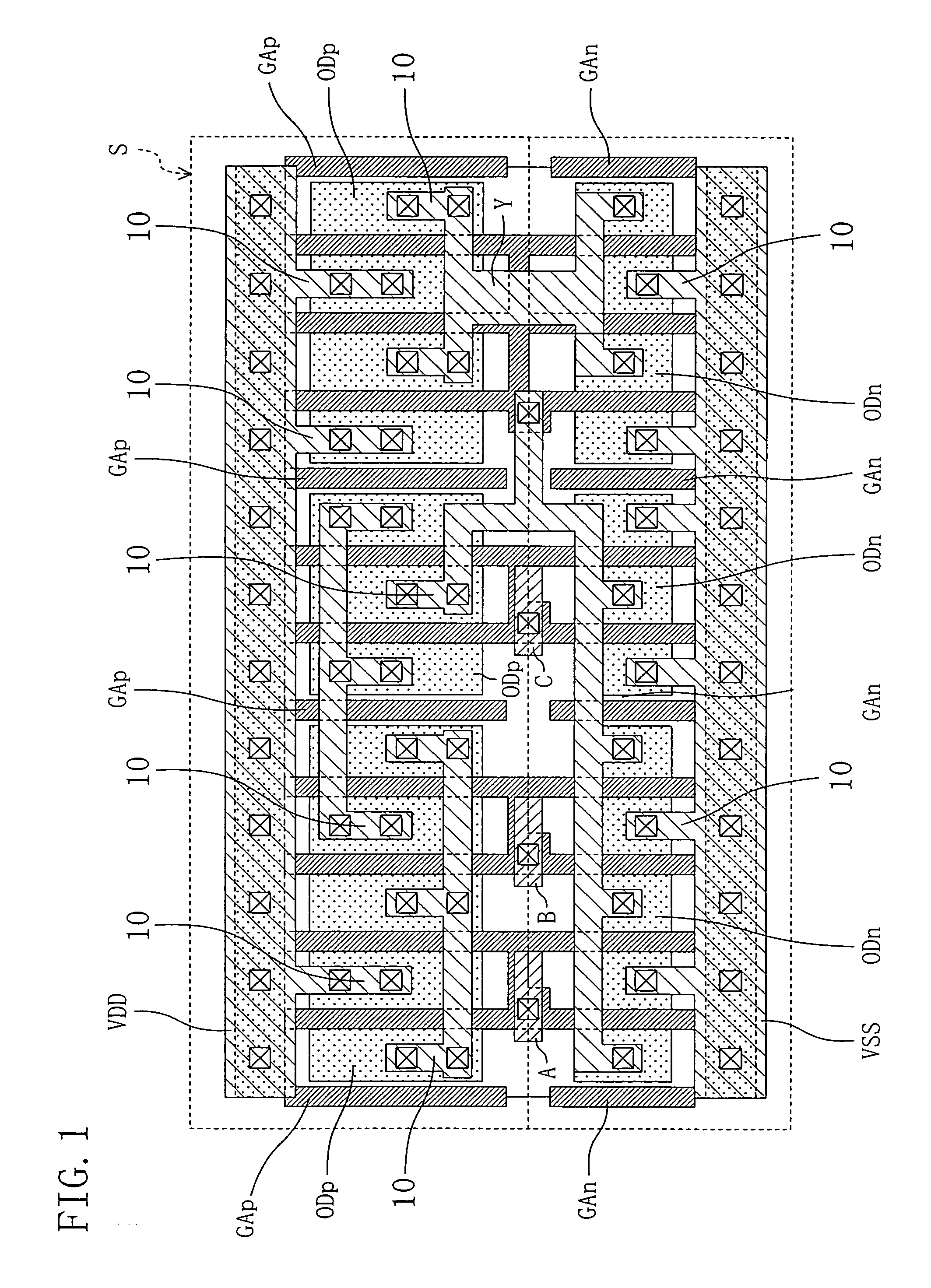

A semiconductor integrated circuit device capable of suppressing variations in transistor characteristics due to the well proximity effect is provided. Standard cell rows are arranged in a vertical direction, each standard cell row including standard cells arranged in a horizontal direction. In the standard cell rows, positions of the N well and the P region in the vertical direction are switched every other row. Adjacent standard cell rows share the P region or the N well. A distance from a PMOS transistor located at an end of a standard cell row to an end of an N well is greater than or equal to a width of an N well shared by standard cell rows.

Owner:SOCIONEXT INC

Integrated circuit having a filler standard cell

InactiveUS20100258798A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsFunctional testingEngineering

An integrated circuit includes a functional block having a plurality of standard cells. The plurality of standard cells includes a plurality of functional standard cells and a filler standard cell. Each functional standard cell of the plurality of functional standard cells has a rectangular boundary. The filler standard cell has a rectangular boundary adjacent to at least one of the functional standard cells. The filler standard cell is selectable between a first state and a second state. The filler standard cell is non-functional in the first state. The filler standard cell has functional test structures coupled to a first metal layer in the second state. This allows for test structures helpful in analyzing functionality of circuit features such as transistors without requiring additional space on the integrated circuit.

Owner:NXP USA INC

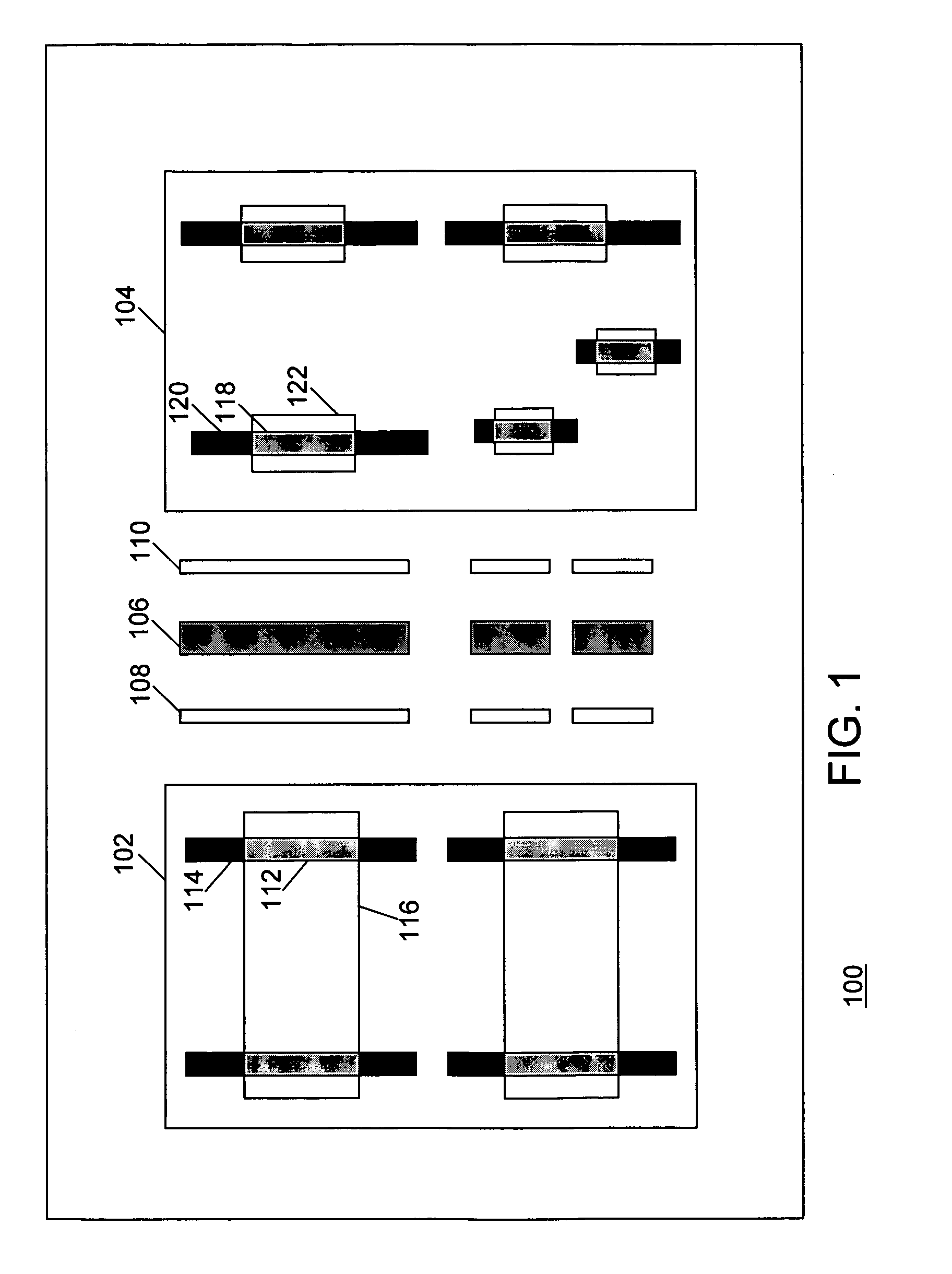

Method for optimising transistor performance in integrated circuits

ActiveUS7266787B2Solid-state devicesSemiconductor/solid-state device manufacturingDiffusionEngineering

A method (300) for optimising transistor performance in semiconductor integrated circuits built from standard cells (12), or custom transistor level layout, is disclosed. An active area of NMOS diffusion is extended with a joining area (102) between two adjacent cells (112) having the same net on diffusion at the adjacent edges of each cell. The diffusion area is extended to limit the occurrence of active and nonactive interface to minimise lattice strain effects and improve transistor performance.

Owner:ICERA INC

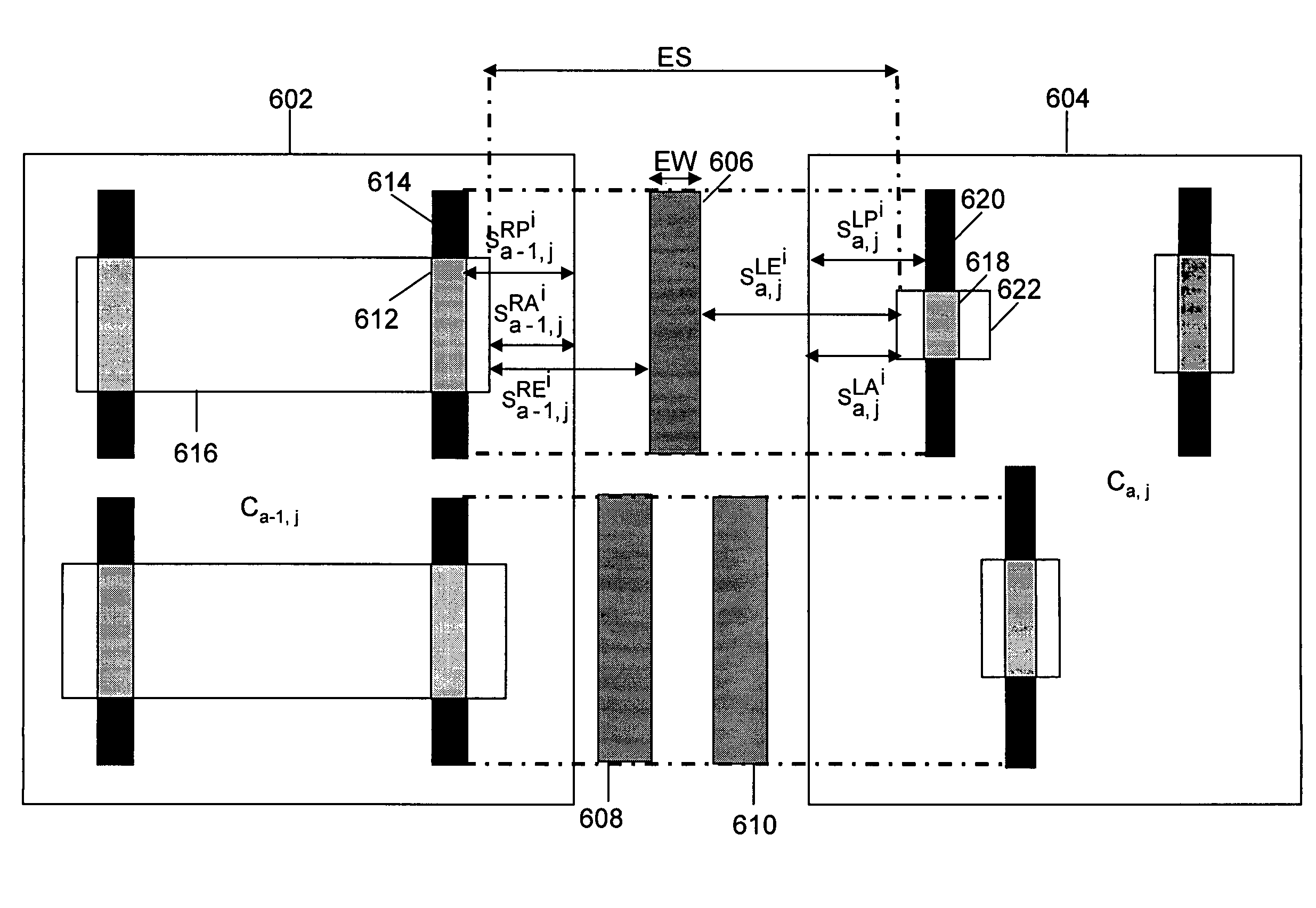

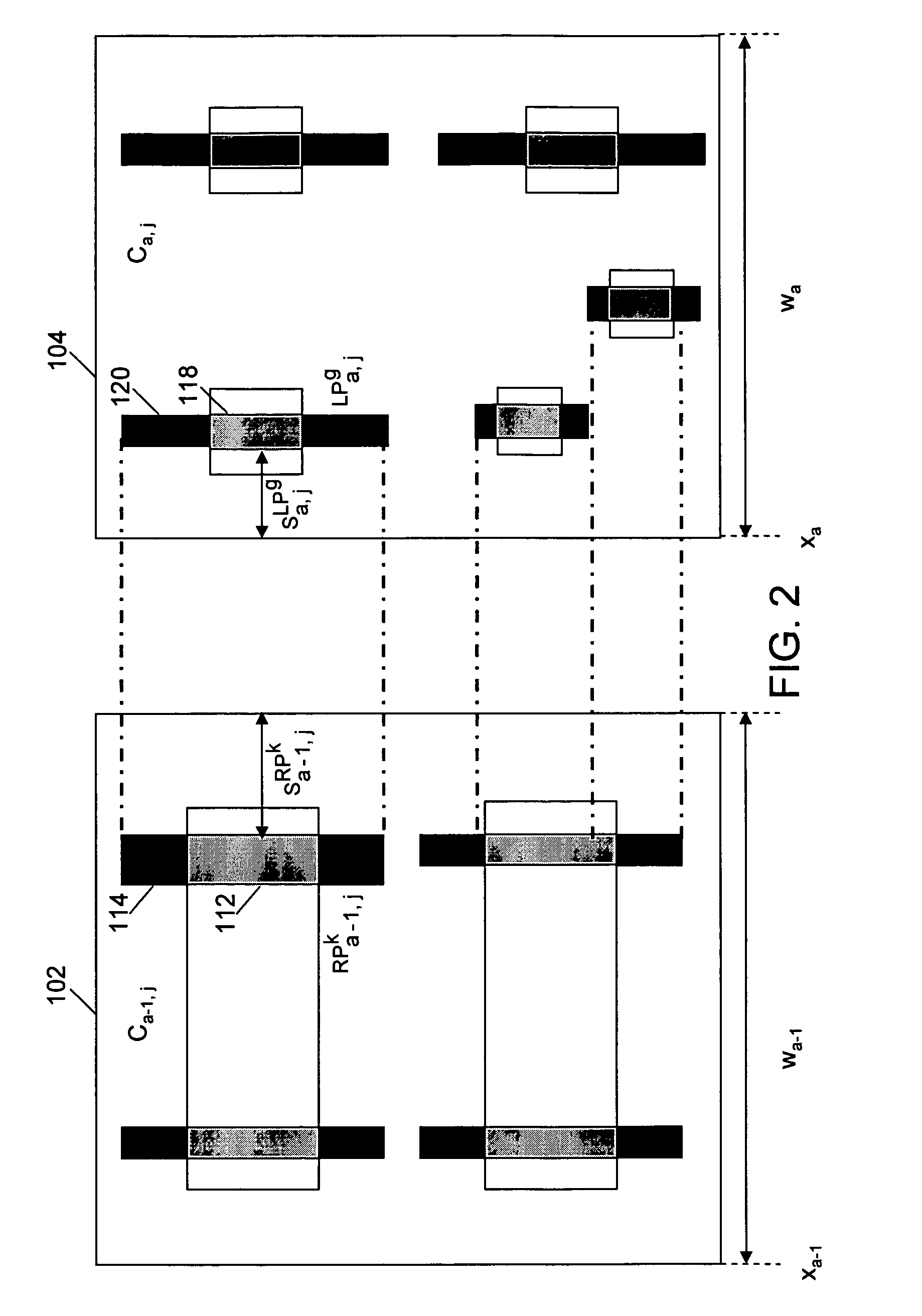

Method and system for placing layout objects in a standard-cell layout

InactiveUS7640522B2Reduce forbidden pitchesReduce CD skewCAD circuit designOriginals for photomechanical treatmentComputer architectureCritical dimension

A method and system for detailed placement of layout objects in a standard-cell layout design are disclosed. Layout objects comprise cells and etch dummies. The method includes a programming based technique to calculate layout object perturbation distances for the layout objects. The method includes adjusting the layout objects with their corresponding layout object perturbation distances. This leads to improved photolithographic characteristics such as reduced Critical Dimension (CD) errors and forbidden pitches in the standard-cell layout.

Owner:RPX CORP

Semiconductor integrated circuit device and method of designing the same

A method of designing a semiconductor integrated circuit device includes: arranging standard cells constituting a MISFET; analyzing an operation timing and / or power consumption of the arranged standard cells; identifying one of the standard cells that is desired to have improved properties as a cell of interest based on the obtained analysis result; optimizing an arrangement and a shape of blank areas around the cell of interest taking into account an influence of a well proximity effect; and replacing the blank area and / or the cell of interest with a WPE-reduced or WPE-enhancing cell.

Owner:KK TOSHIBA

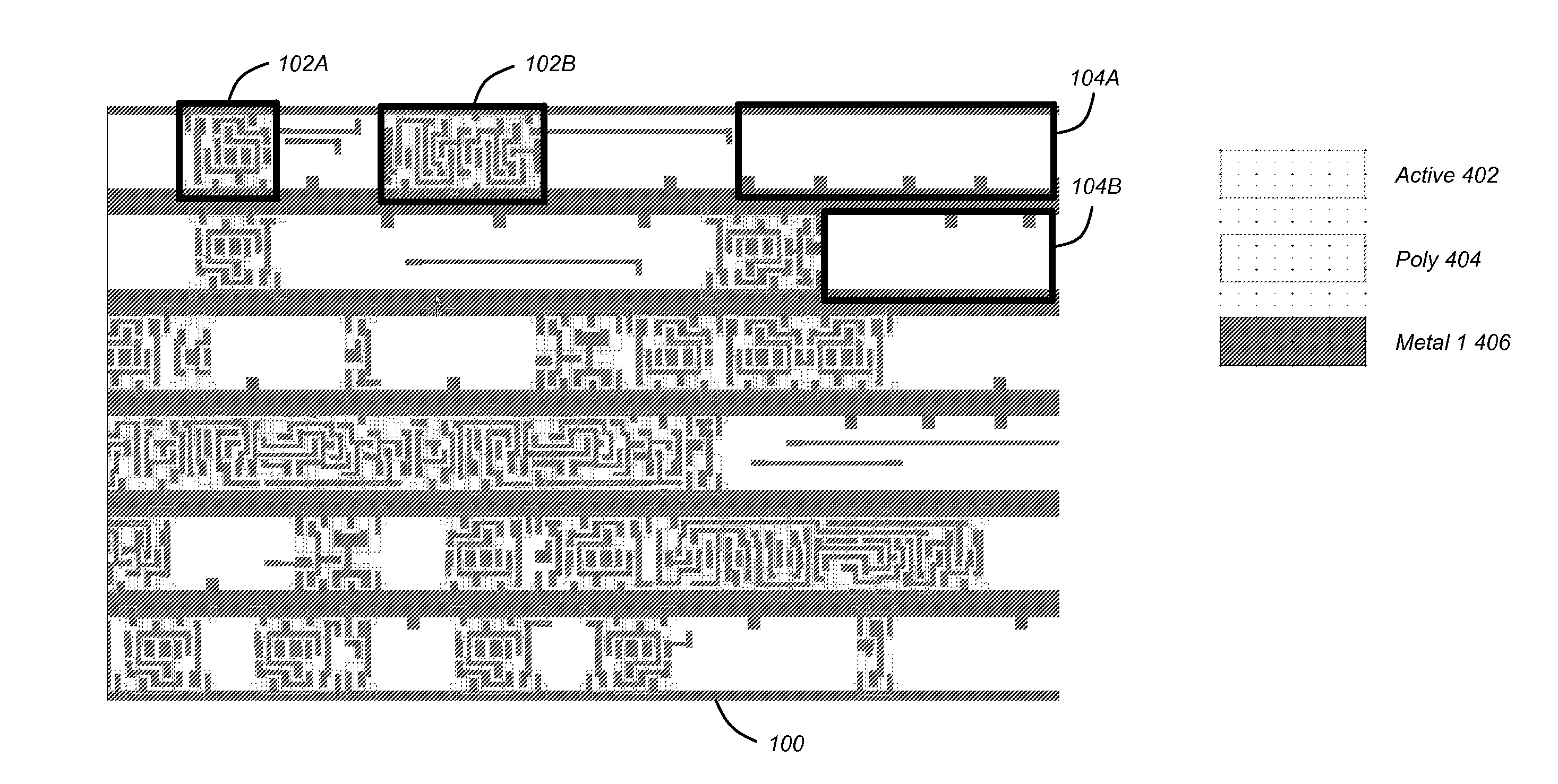

Method and apparatus for camouflaging a standard cell based integrated circuit with micro circuits and post processing

ActiveUS20120139582A1Solid-state devicesCAD circuit designComputer architectureIntegrated circuit layout

A method and apparatus for camouflaging an application specific integrated circuit (ASIC), wherein the ASIC comprises a plurality of interconnected functional logic is disclosed. The method adds functionally inert elements to the logical description or provides alternative definitions of standard logical cells to make it difficult for reverse engineering programs to be used to discover the circuit's function. Additionally, post processing may be performed on GDS layers to provide a realistic fill of the empty space so as to resemble structural elements found in a functional circuit.

Owner:RAMBUS INC

Integrated circuit having a filler standard cell

InactiveUS8063402B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringNon functional

An integrated circuit includes a functional block having a plurality of standard cells. The plurality of standard cells includes a plurality of functional standard cells and a filler standard cell. Each functional standard cell of the plurality of functional standard cells has a rectangular boundary. The filler standard cell has a rectangular boundary adjacent to at least one of the functional standard cells. The filler standard cell is selectable between a first state and a second state. The filler standard cell is non-functional in the first state. The filler standard cell has functional test structures coupled to a first metal layer in the second state. This allows for test structures helpful in analyzing functionality of circuit features such as transistors without requiring additional space on the integrated circuit.

Owner:NXP USA INC

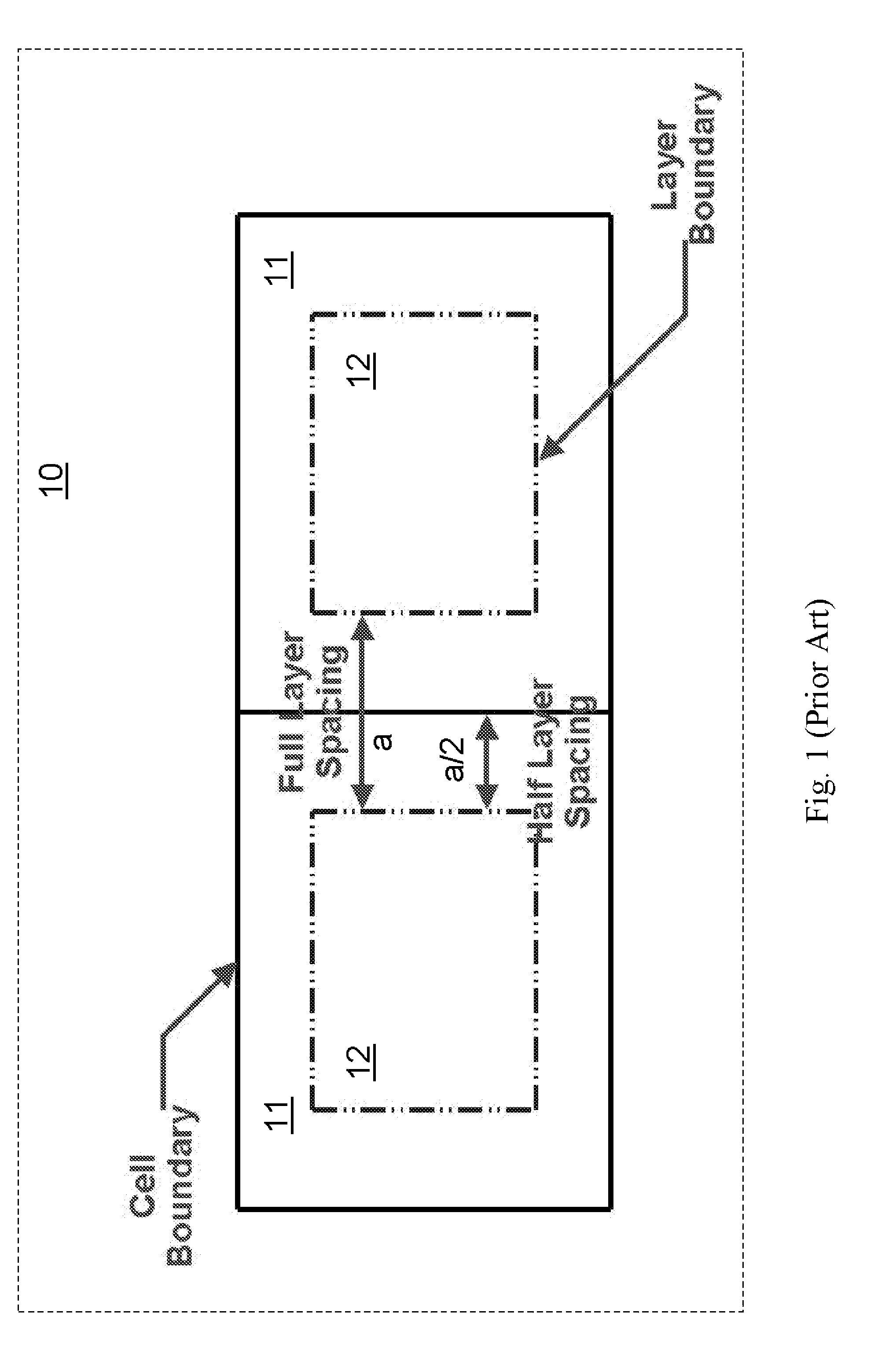

Standard Cell Architecture and Methods with Variable Design Rules

InactiveUS20100155783A1Easy to useSemiconductor/solid-state device detailsSolid-state devicesEngineeringStandard cell

Structures and methods for standard cell layouts having variable rules for spacing of layers to cell boundaries are disclosed. In one embodiment, a first standard cell layout is provided with a conductive layer having at least two portions spaced apart by a minimum spacing distance, the conductive layer having at least one portion spaced from a cell boundary by a first spacing distance of less than half of the minimum spacing distance; a second standard cell disposed adjacent the first standard cell with at least one second portion of the conductive layer in the second cell disposed adjacent the first portion in the first standard cell and spaced apart from a common cell boundary by a second spacing greater than half of the minimum; wherein the sum of the first and second spacings is at least as great as the minimum spacing. A method for forming standard is disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

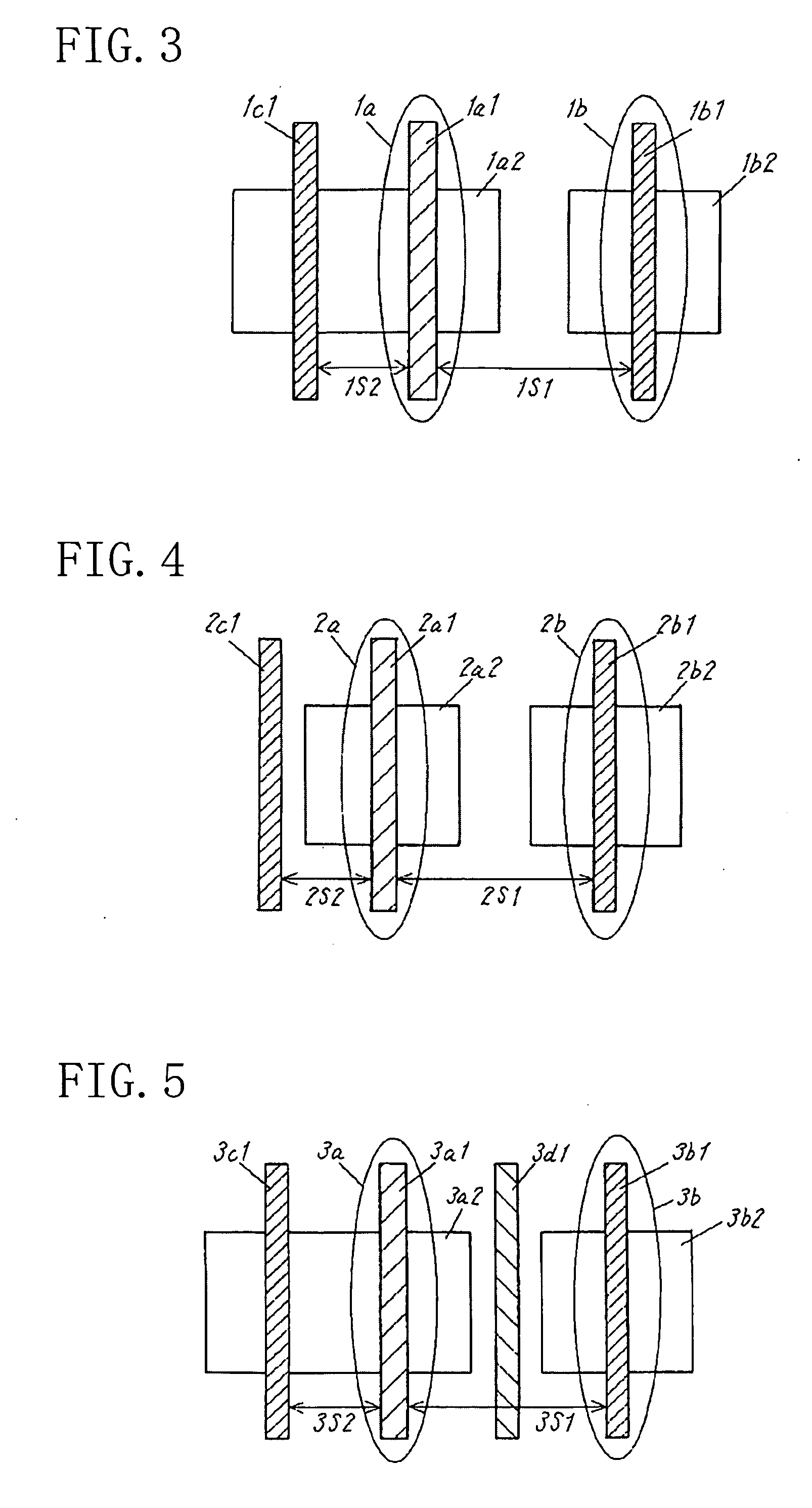

Semiconductor integrated circuit, standard cell, standard cell library, semiconductor integrated circuit designing method, and semiconductor integrated circuit designing equipment

ActiveUS20070004147A1Dispersion suppressionEnsure flexibilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorCircuit design

A semiconductor integrated circuit includes a first transistor which is formed of a first gate extending in a first direction and a first diffusion region and which is capable of being active, a second transistor which is formed of a second gate extending in the first direction and a second diffusion region and which is arranged adjacent to the first transistor in a second direction intersected at a right angle with the first direction, and a third gate which extends in the first direction and which is arranged adjacent in the second direction to the first transistor on an opposite side to the second transistor. A space between the first gate and the second gate is larger than a space between the first gate and the third gate.

Owner:PANASONIC CORP

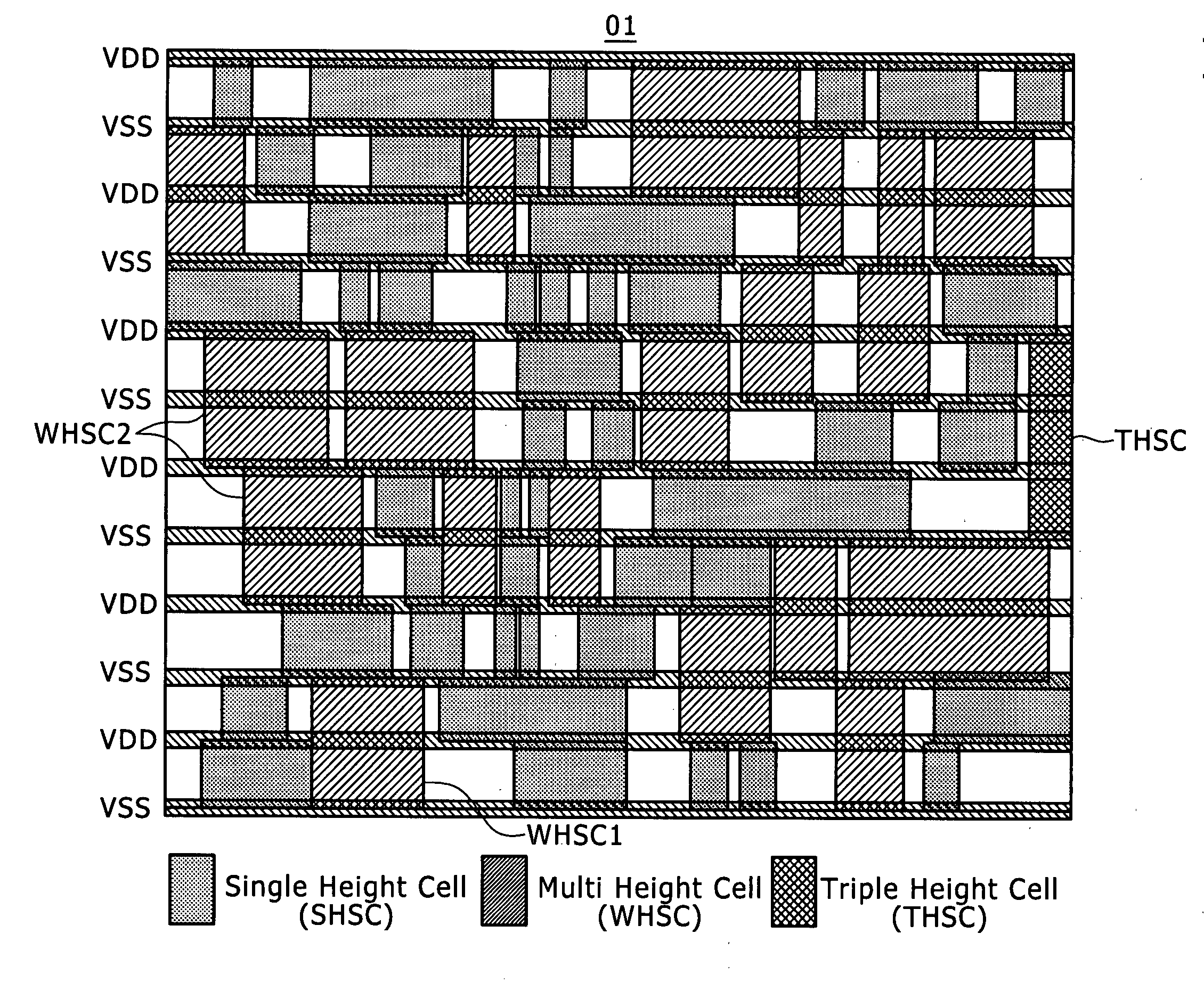

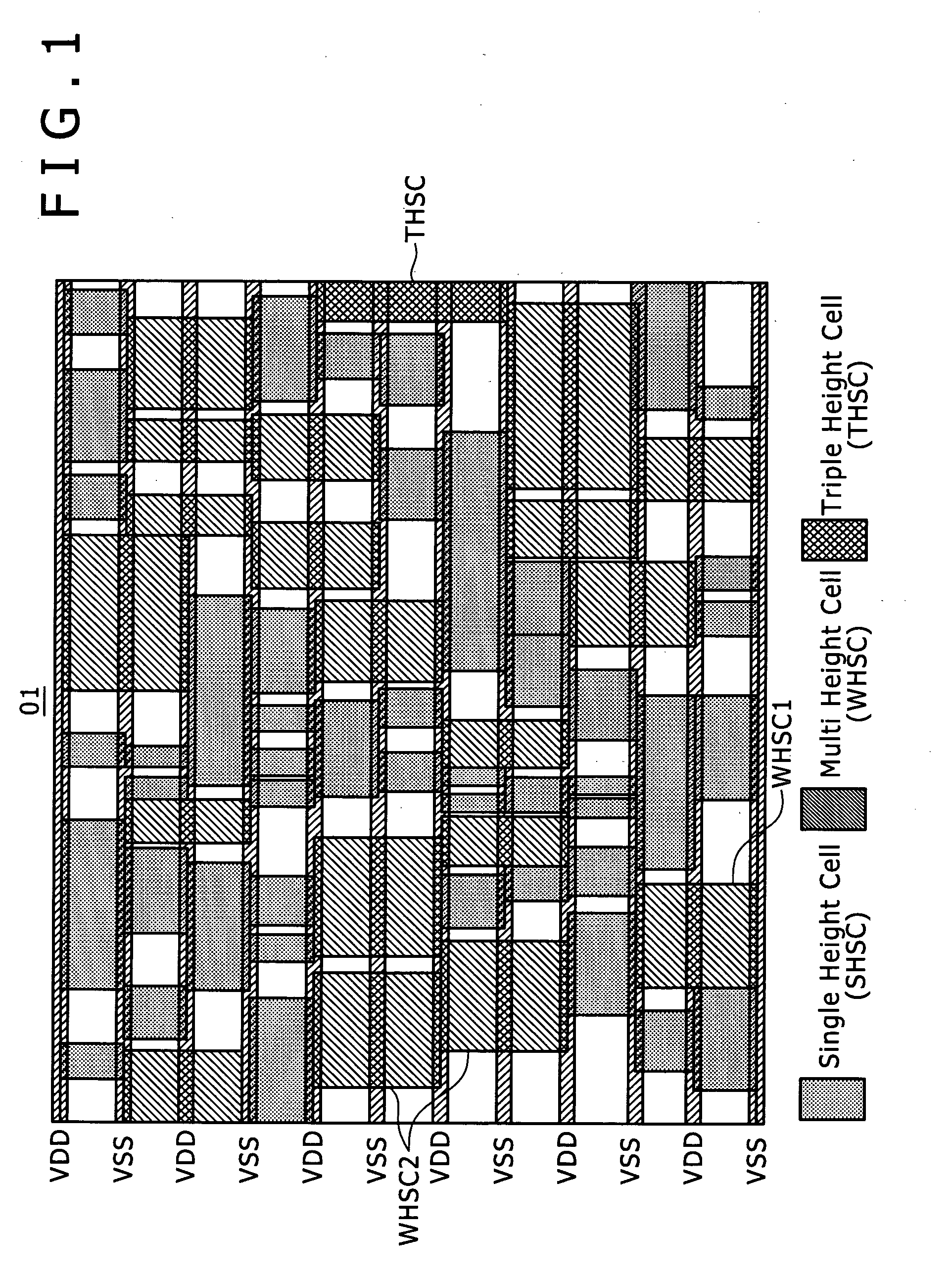

Semiconductor integrated circuit

ActiveUS20110049575A1Eliminating wasted spaceReduce in quantitySolid-state devicesLogic circuitsEngineeringSemiconductor

Disclosed herein is a semiconductor integrated circuit, wherein a desired circuit is formed by combining and laying out a plurality of standard cells and connecting the cells together, of which the cell length, i.e., the gap between a pair of opposed sides, is standardized, the plurality of standard cells forming the desired circuit include complementary in-phase driven standard cells, each of which includes a plurality of complementary transistor pairs that are complementary in conductivity type to each other and have their gate electrodes connected together, and N (≧2) pairs of all the complementary transistor pairs are driven in phase, and the size of the standardized cell length of the complementary in-phase driven standard cell is defined as an M-fold cell length which is M (N≧M≧2) times the basic cell length which is appropriate to the single complementary transistor pair.

Owner:SONY CORP

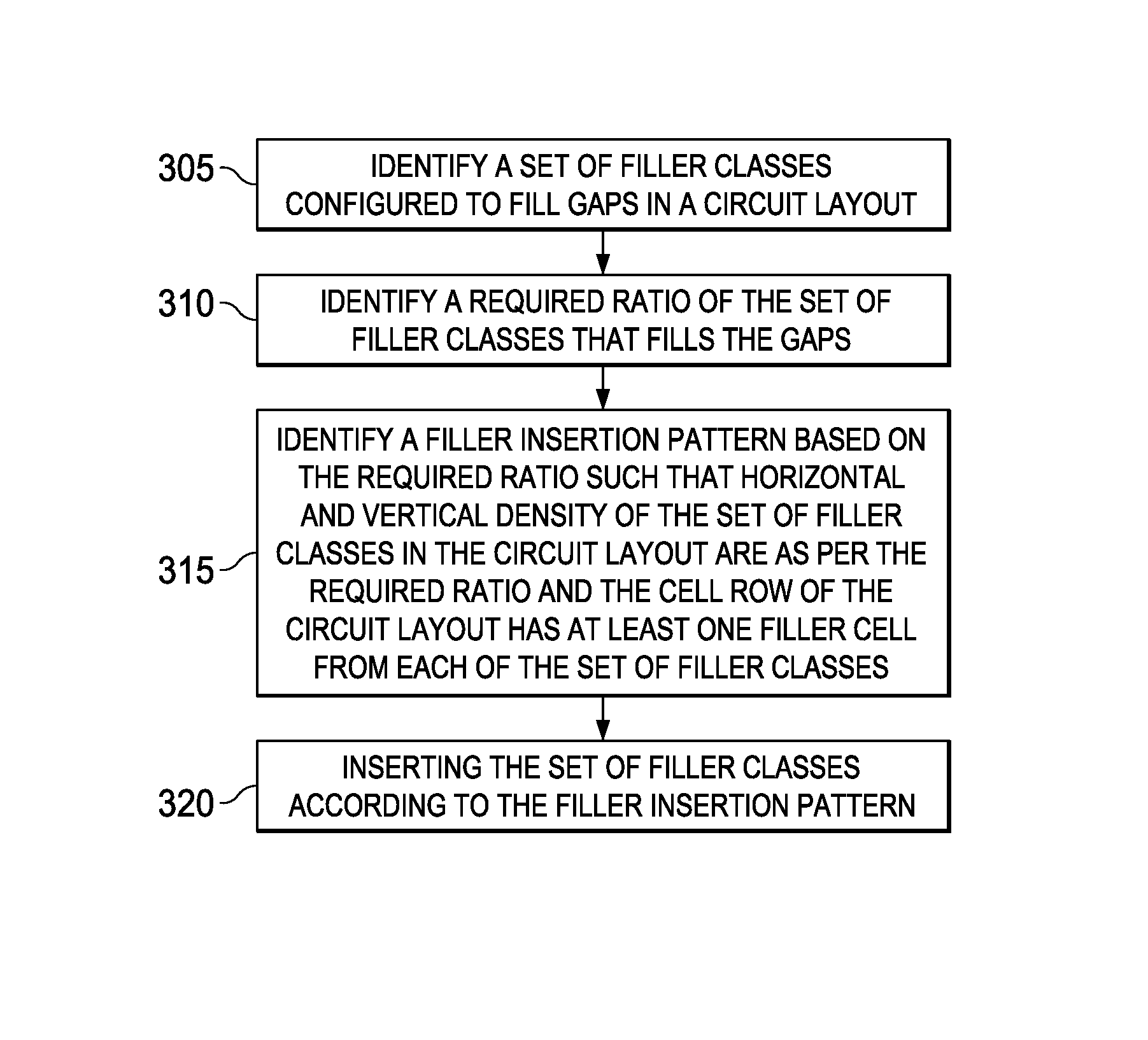

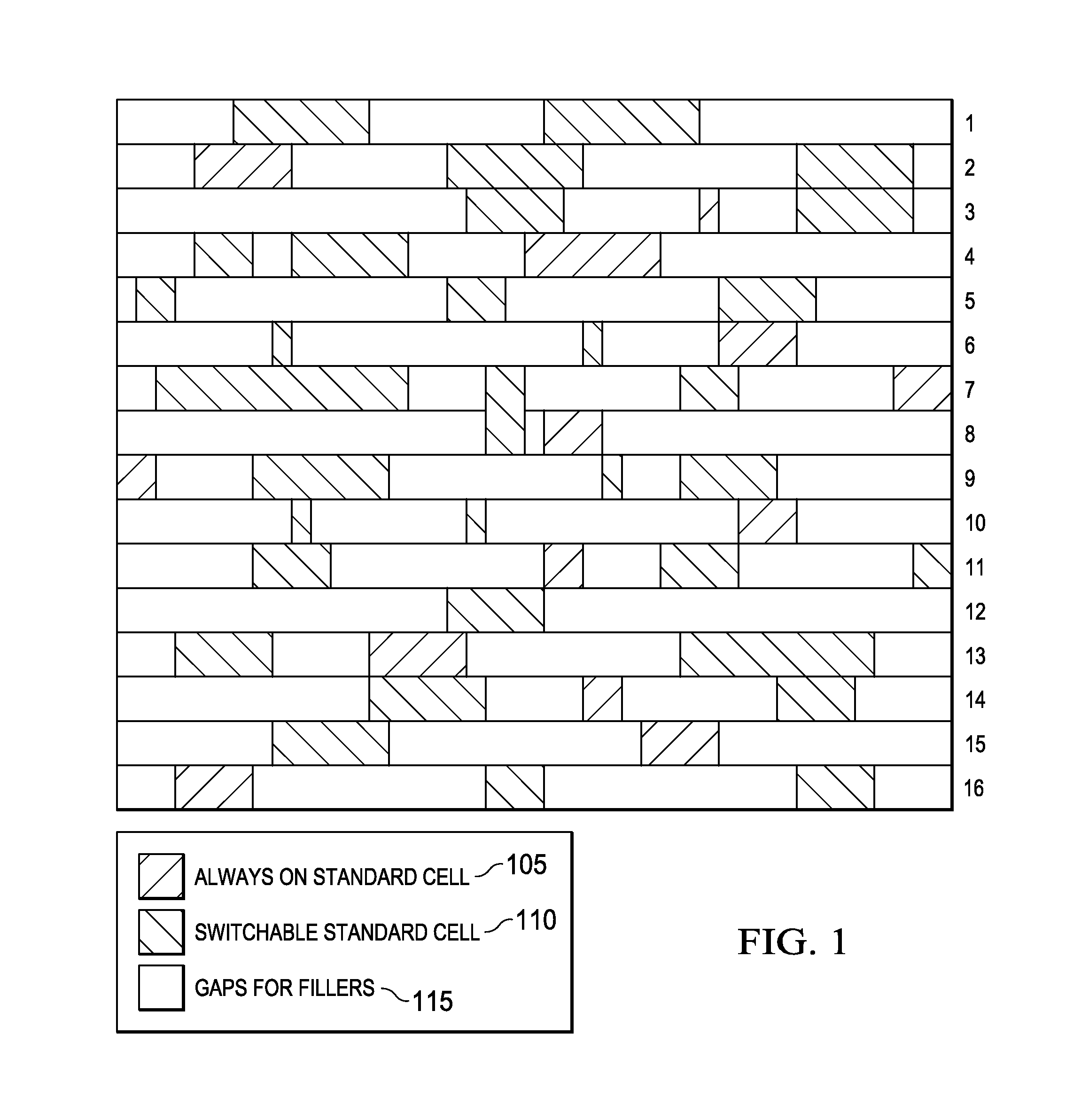

Filler insertion in circuit layout

ActiveUS9542521B2Computer aided designSpecial data processing applicationsEngineeringHorizontal and vertical

A method for filler insertions in a circuit layout having a cell row of standard cells and gaps between the standard cells is disclosed. First, a set of filler classes, each filler class having a set of filler cells, is classified that are configured to fill the gaps depending on a design requirement. Then, a filler insertion pattern based on a required ratio is identified such that horizontal and vertical density of the set of filler classes in the circuit layout are as per the required ratio and the cell row of the circuit layout has at least one filler cell from each of the set of filler classes.

Owner:TEXAS INSTR INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com