Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

111 results about "Lattice strain" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

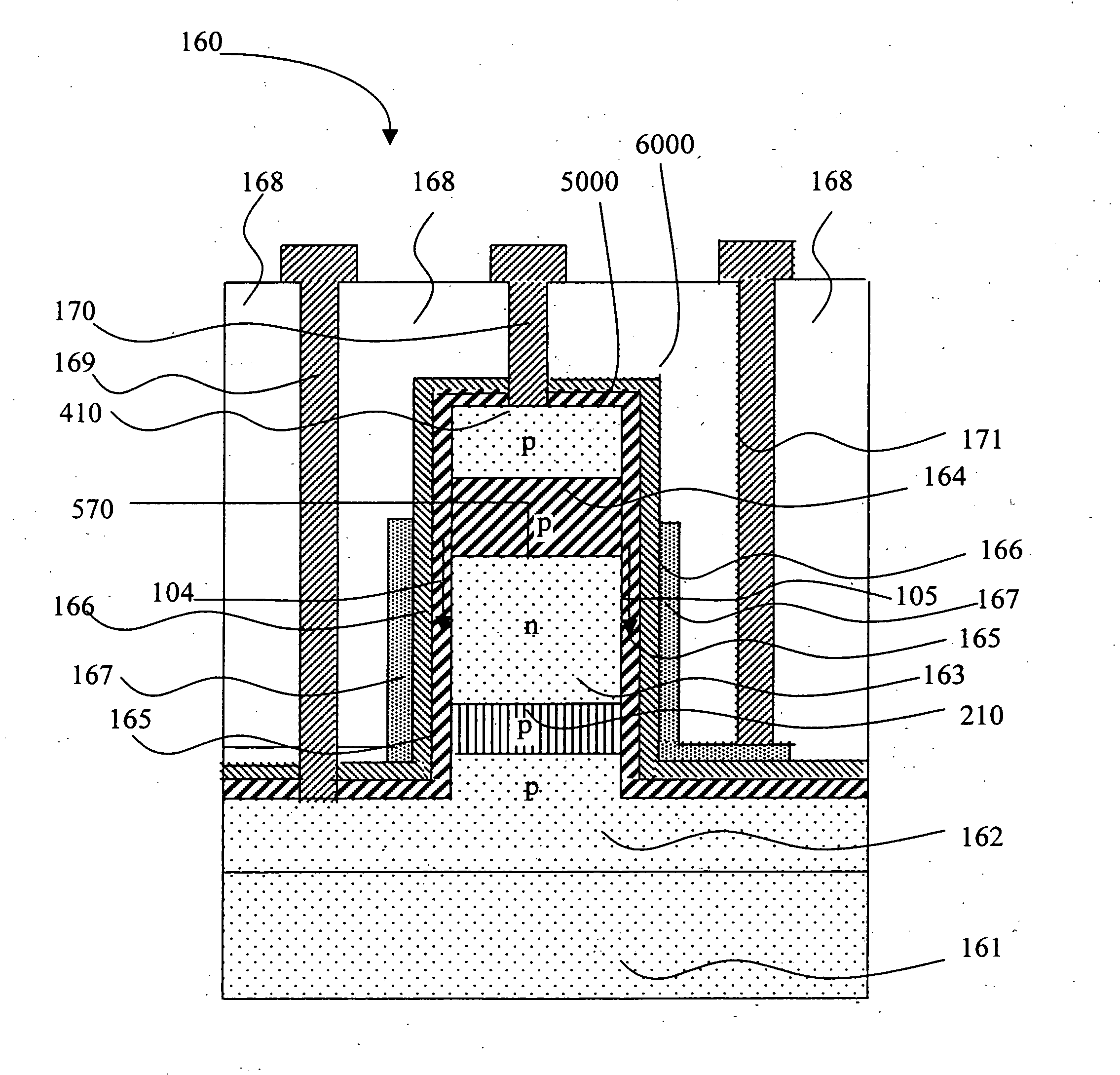

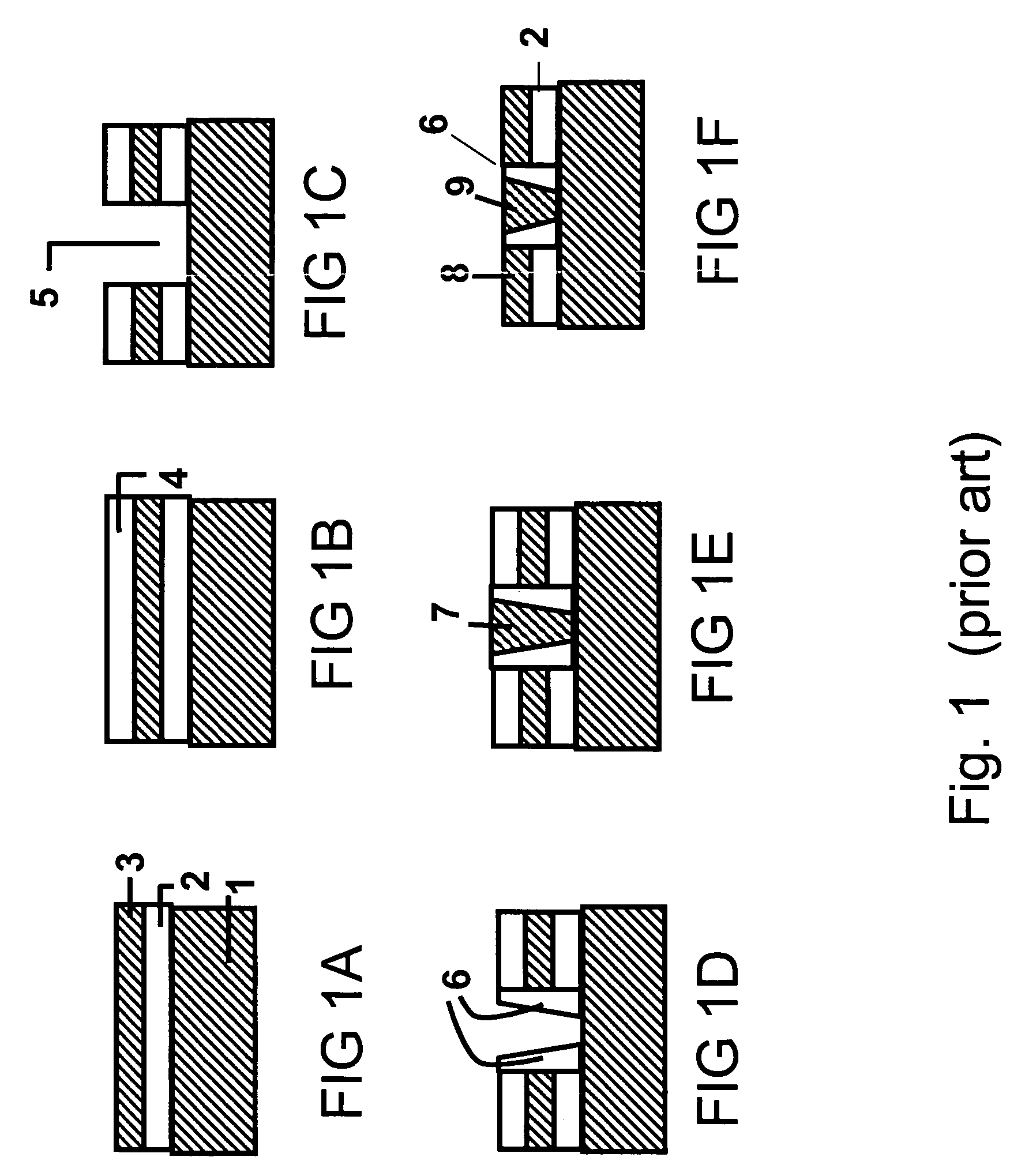

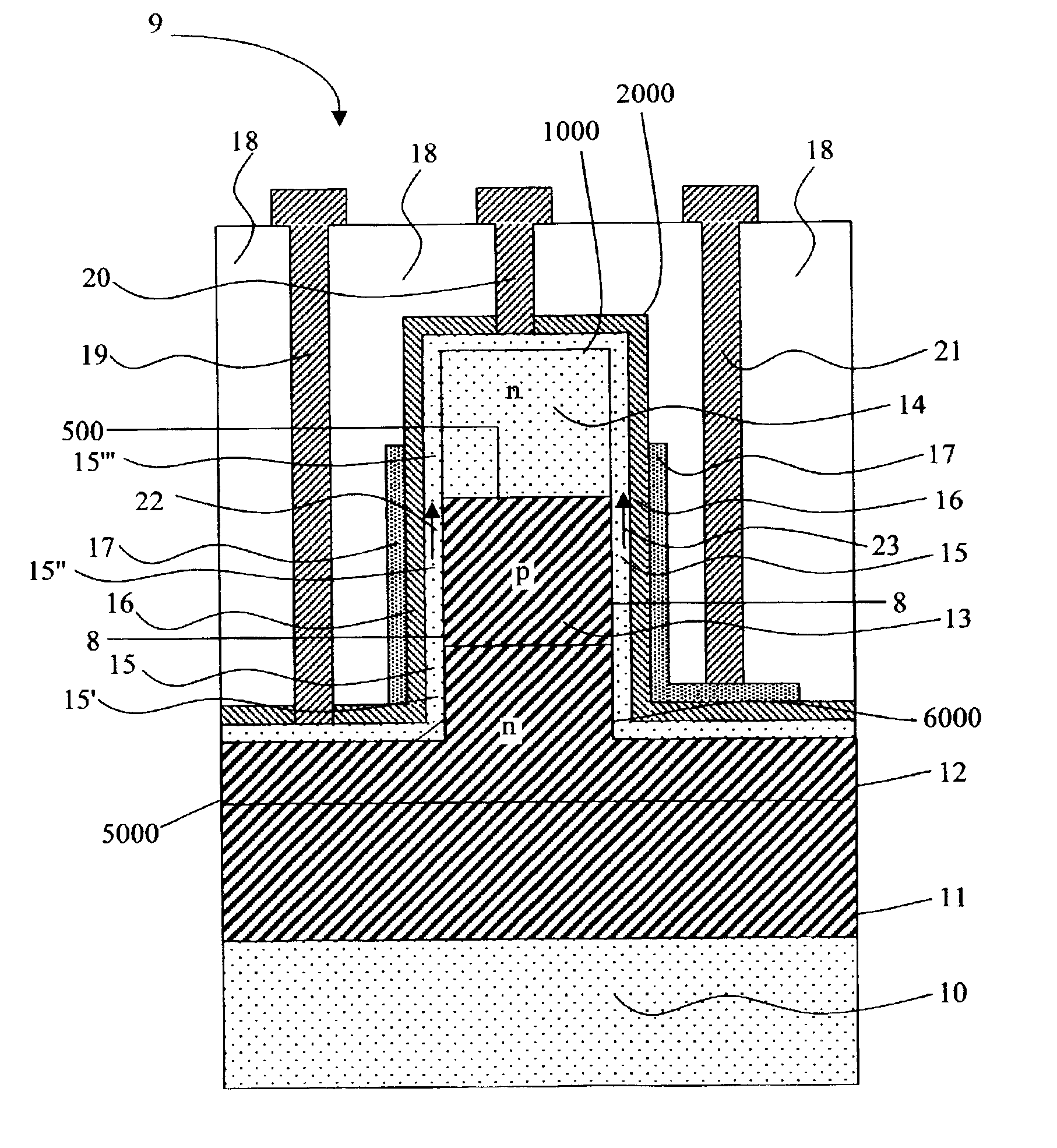

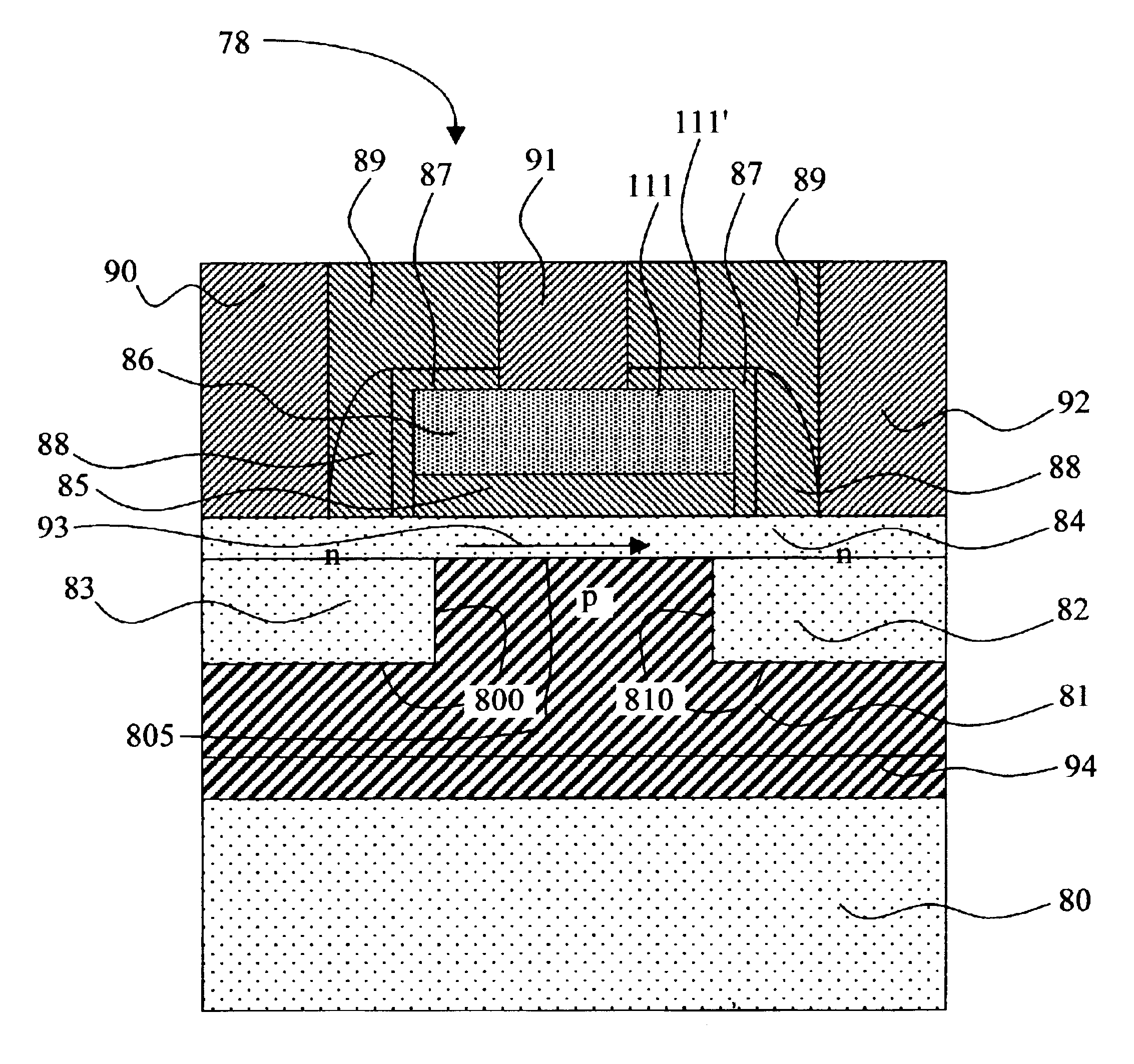

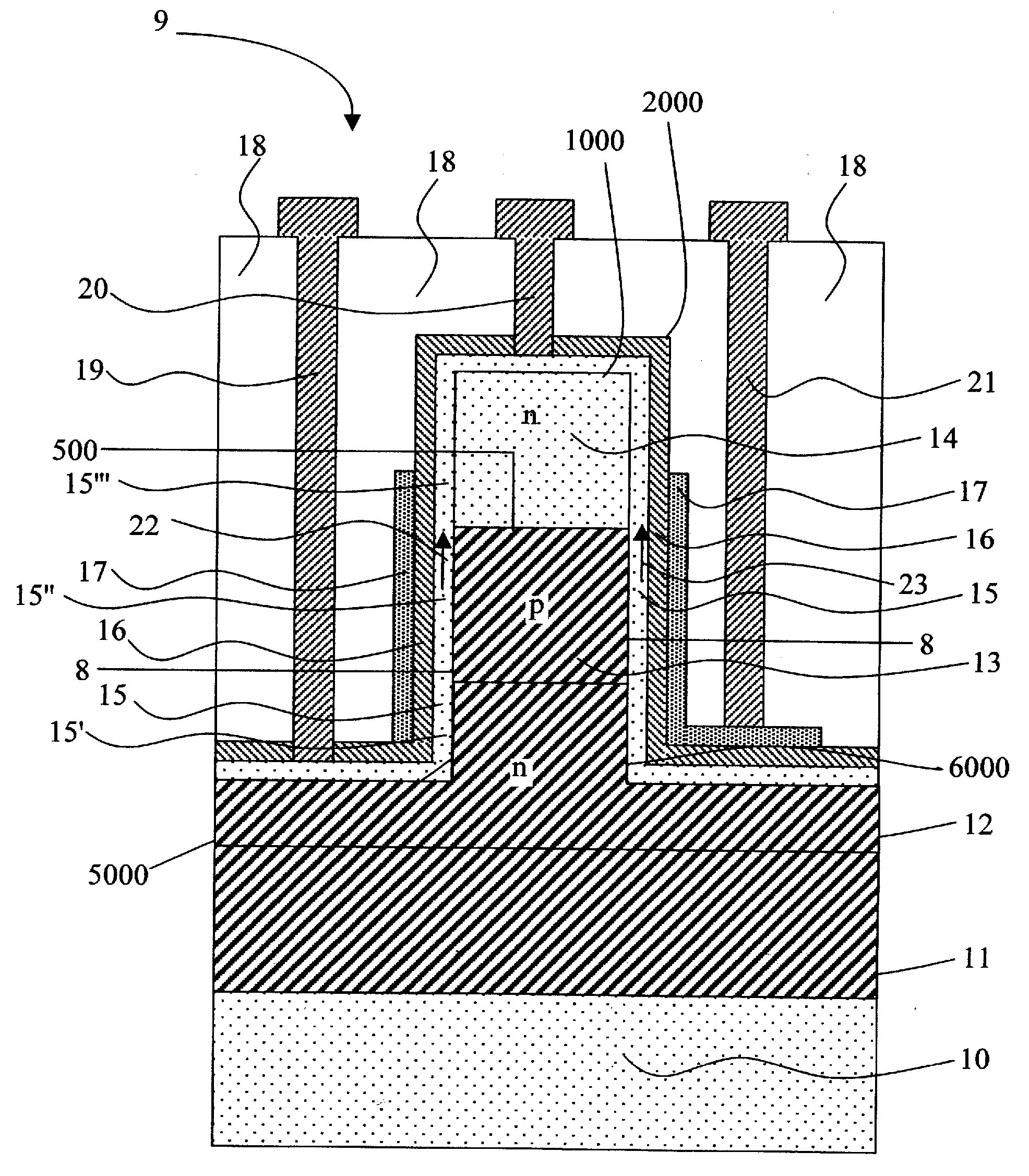

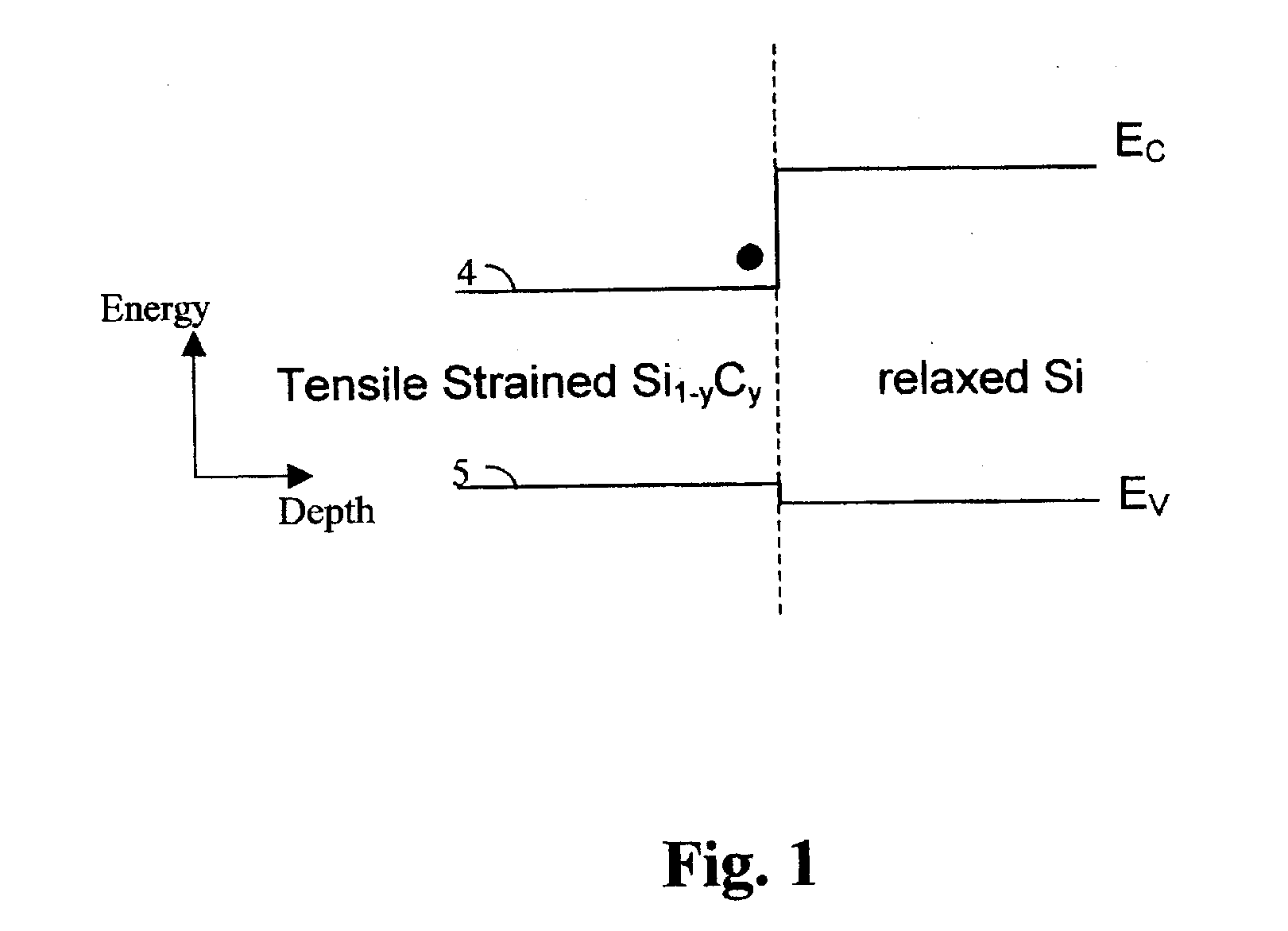

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

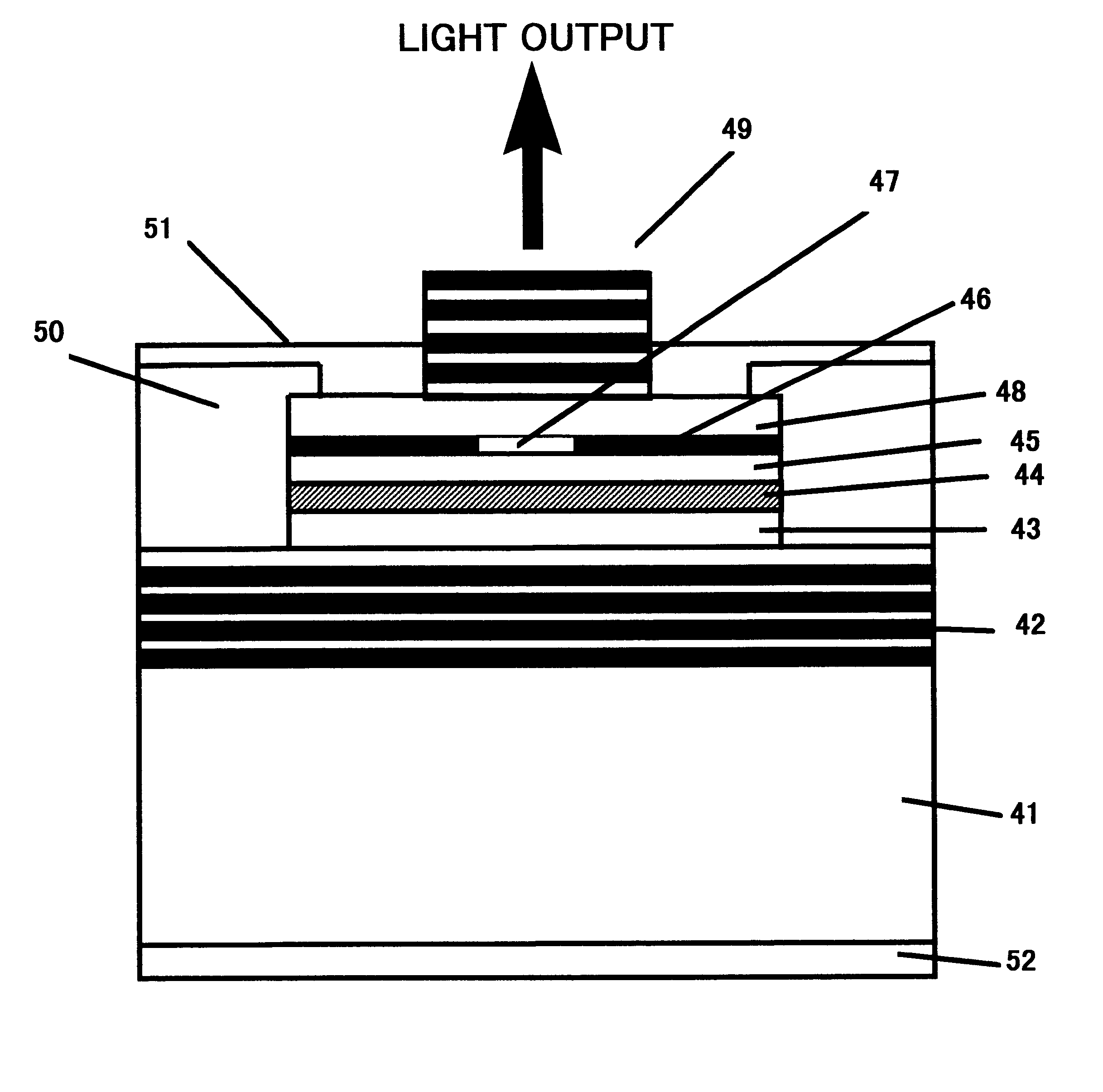

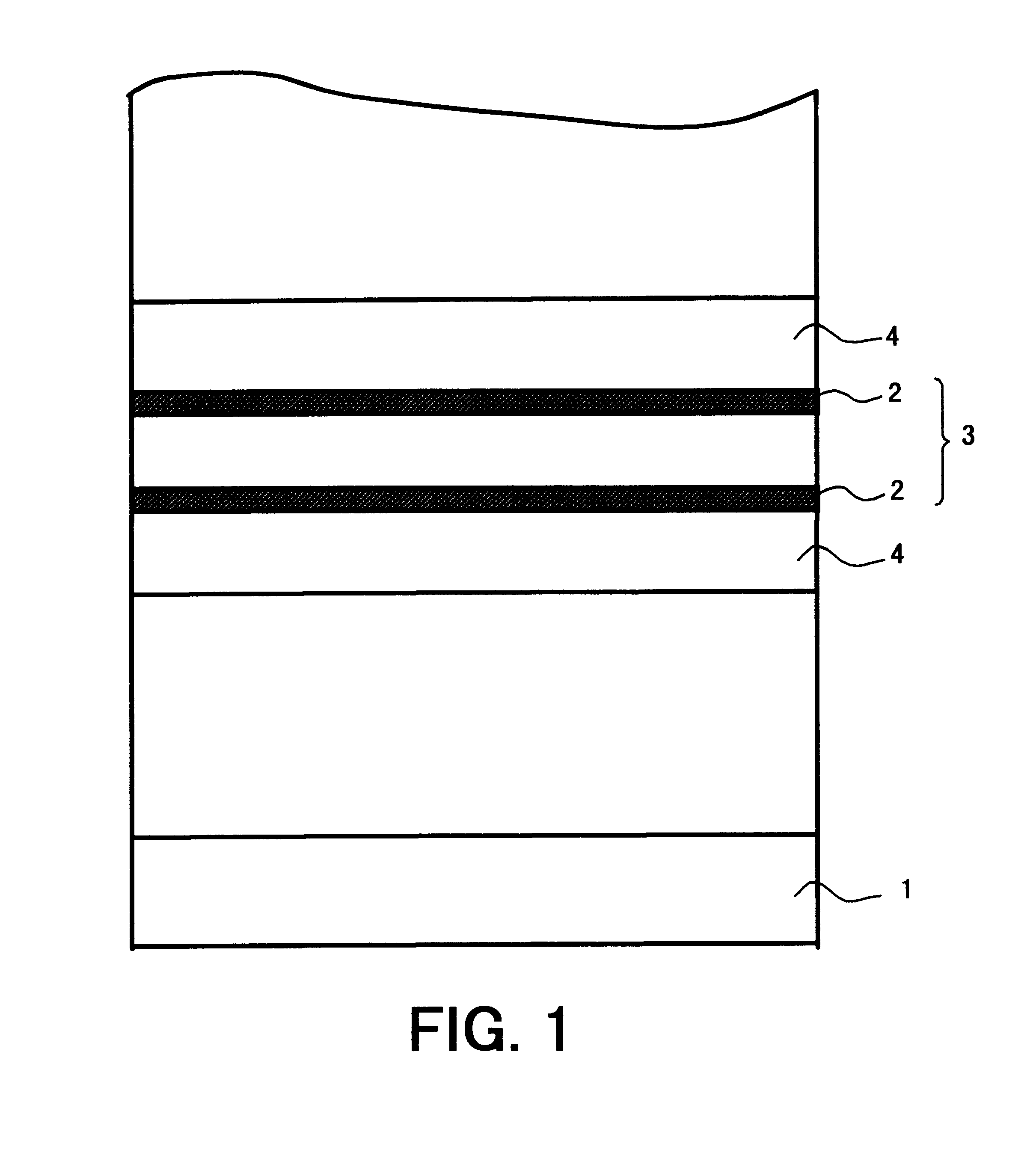

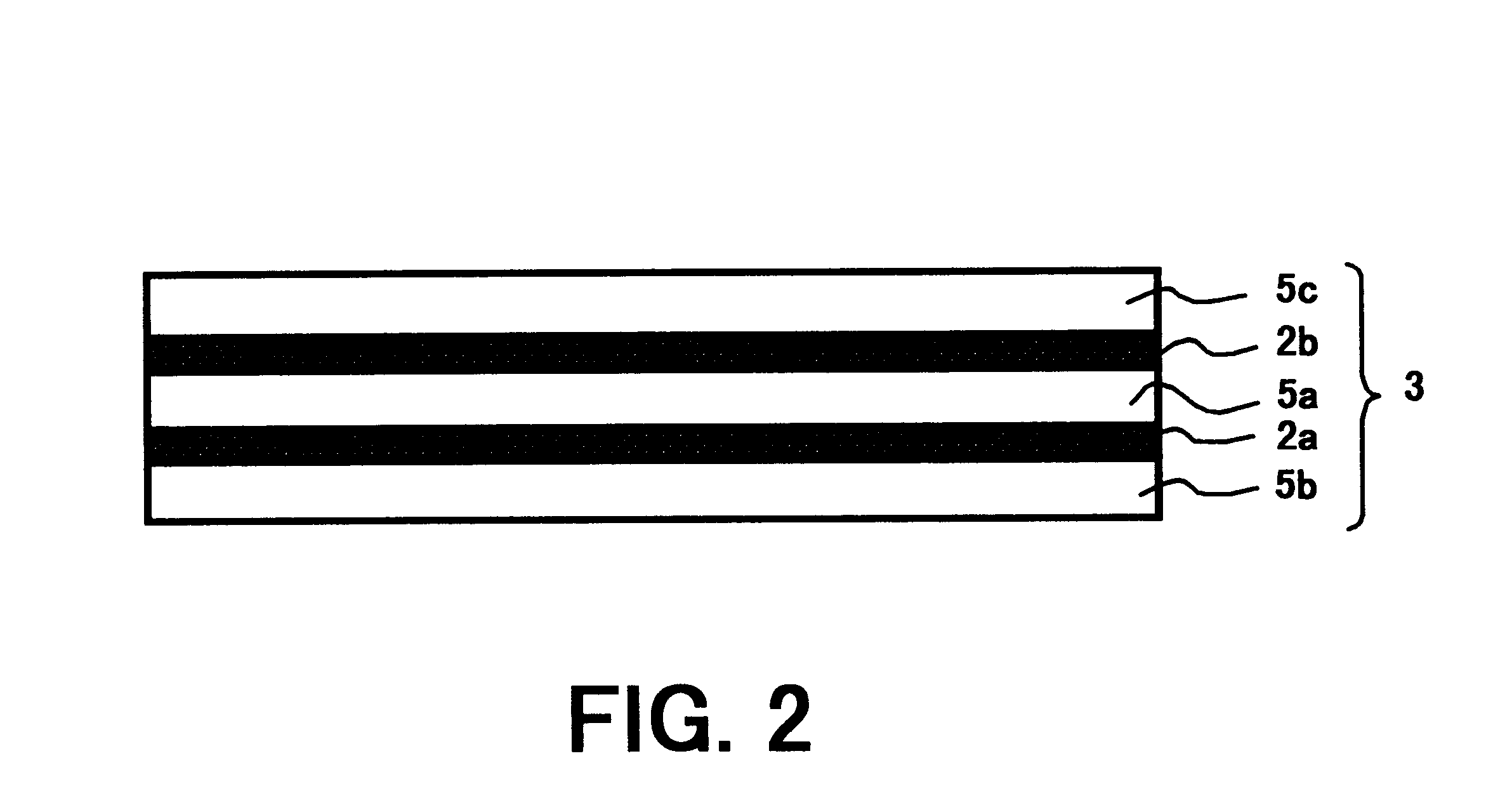

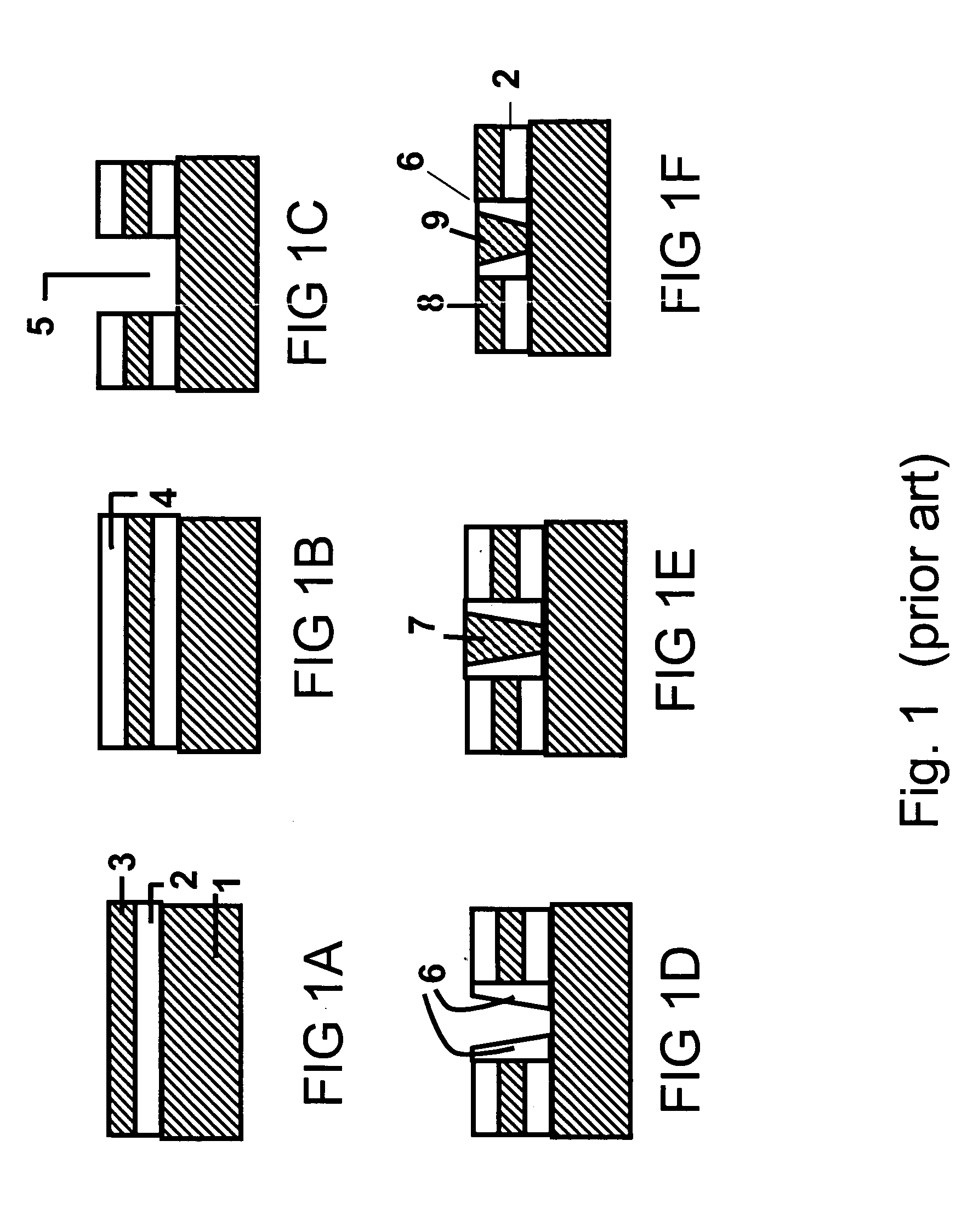

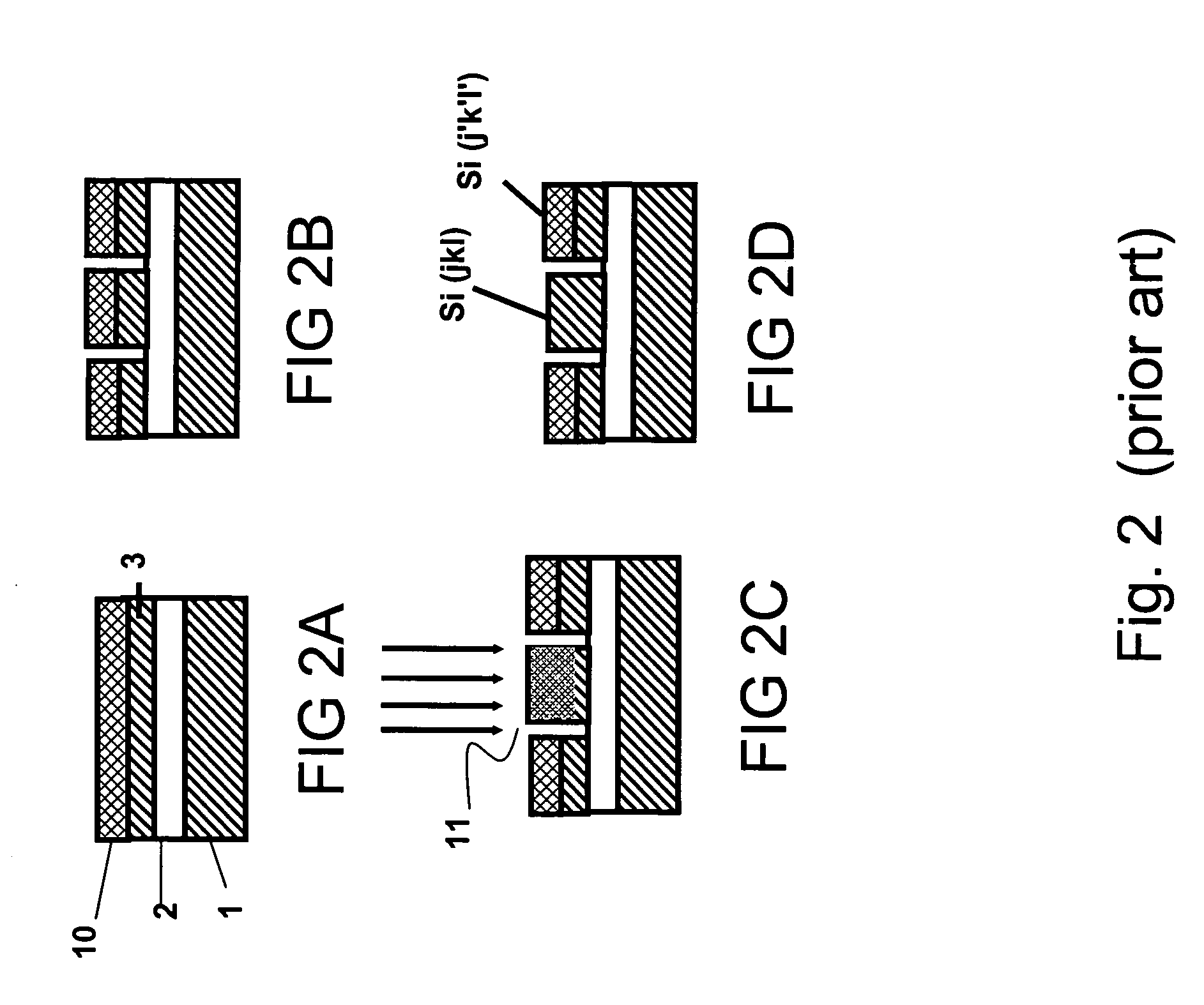

Light emitting devices with layered III-V semiconductor structures

InactiveUS6207973B1Improve crystal qualityFacilitates layerLaser detailsLaser active region structureCharge carrierSemiconductor structure

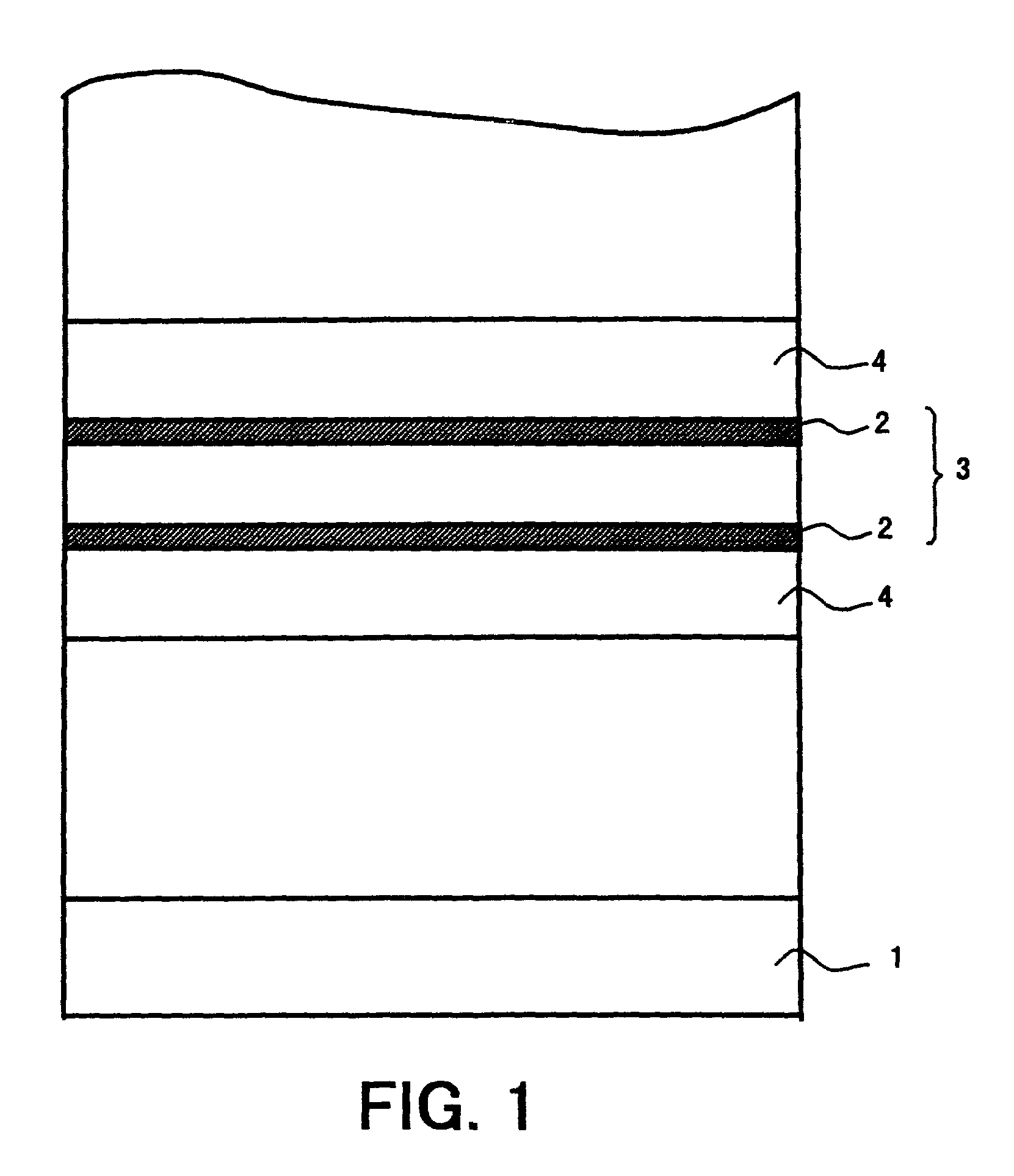

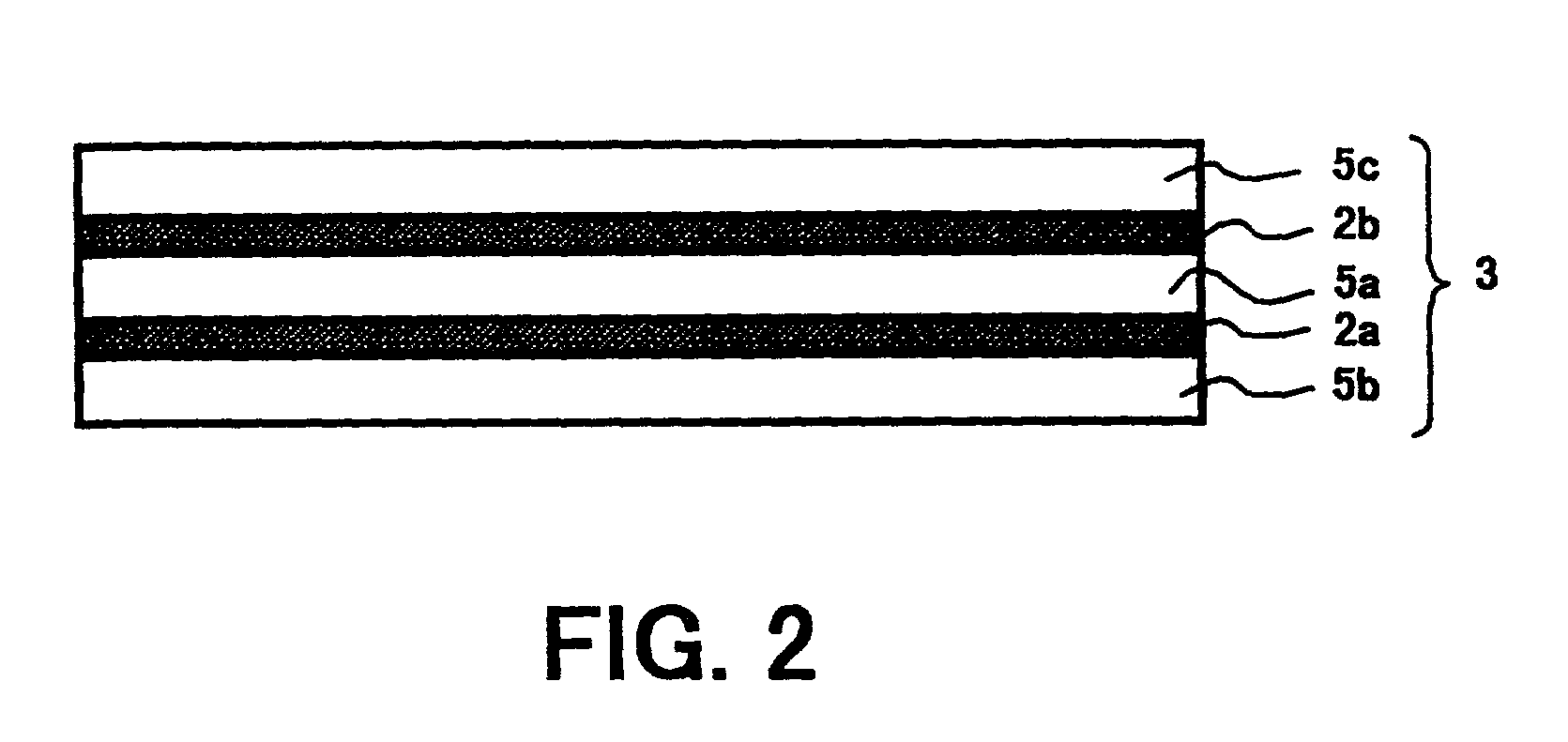

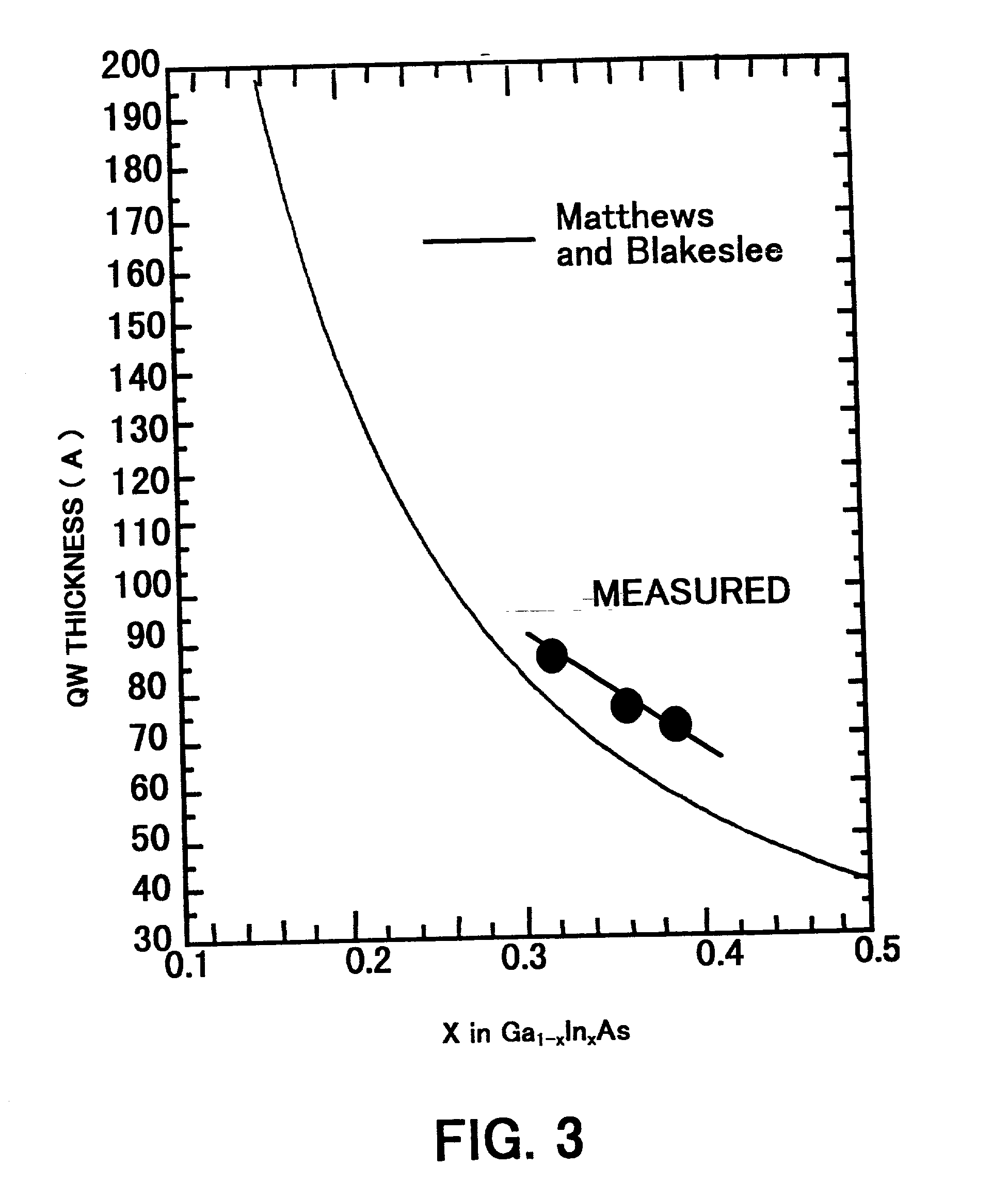

A semiconductor light emitting device is disclosed, including a semiconductor substrate, an active region comprising a strained quantum well layer, and a cladding layer for confining carriers and light emissions, wherein the amount of lattice strains in the quantum well layer is in excess of 2% against either the semiconductor substrate or cladding layer and, alternately, the thickness of the quantum well layer is in excess of the critical thickness calculated after Matthews and Blakeslee.

Owner:RICOH KK

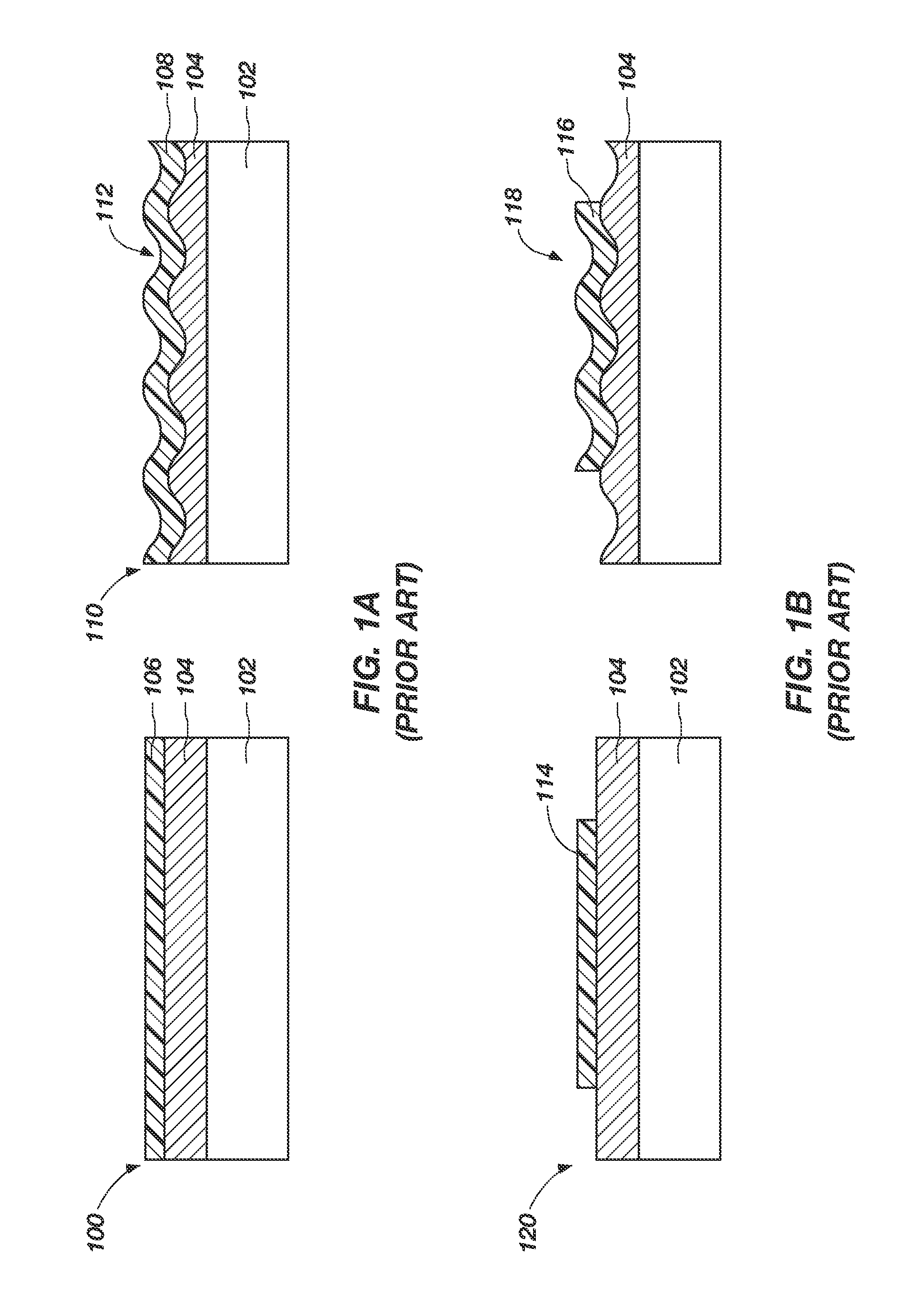

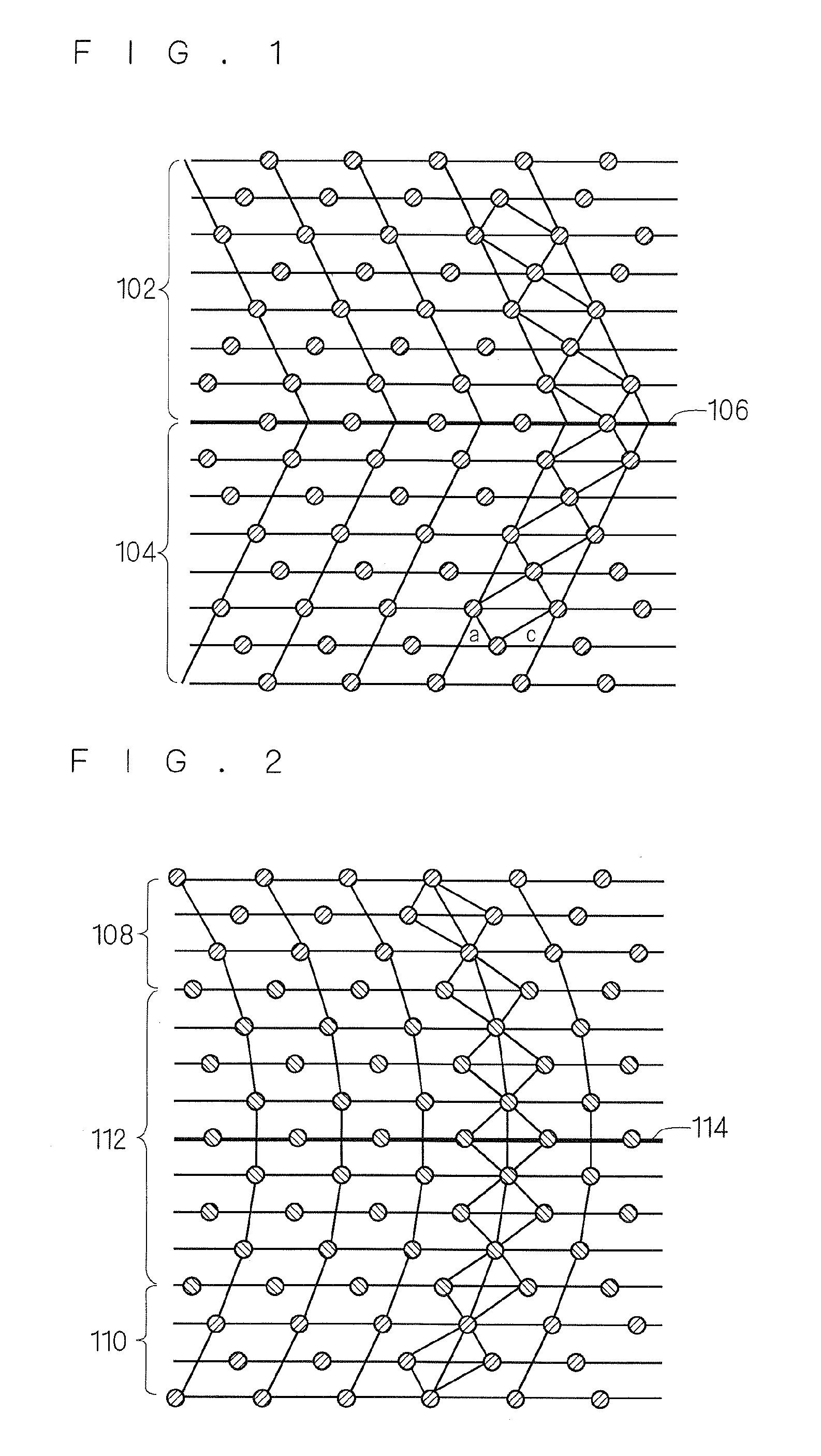

Method for optimising transistor performance in integrated circuits

ActiveUS7266787B2Solid-state devicesSemiconductor/solid-state device manufacturingDiffusionEngineering

A method (300) for optimising transistor performance in semiconductor integrated circuits built from standard cells (12), or custom transistor level layout, is disclosed. An active area of NMOS diffusion is extended with a joining area (102) between two adjacent cells (112) having the same net on diffusion at the adjacent edges of each cell. The diffusion area is extended to limit the occurrence of active and nonactive interface to minimise lattice strain effects and improve transistor performance.

Owner:ICERA INC

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS20070148939A1Superb performanceSuperb scalabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

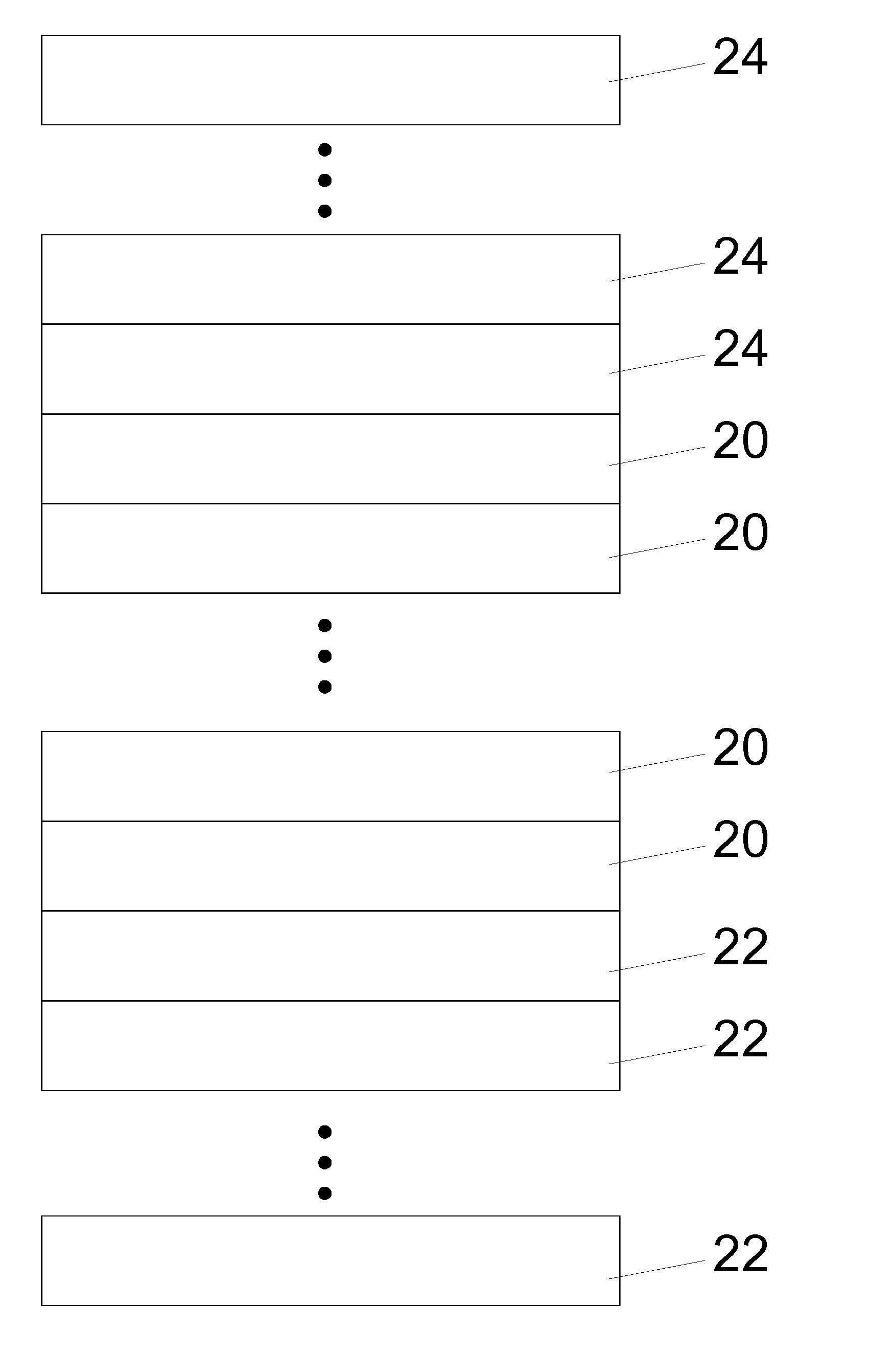

Methods of forming layers of semiconductor material having reduced lattice strain, semiconductor structures, devices and engineered substrates including same

ActiveUS20100109126A1Low viscositySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSemiconductor structure

Methods of fabricating semiconductor devices or structures include forming structures of a semiconductor material overlying a layer of a compliant material, subsequently changing the viscosity of the compliant material to relax the semiconductor material structures, and utilizing the relaxed semiconductor material structures as a seed layer in forming a continuous layer of relaxed semiconductor material. In some embodiments, the layer of semiconductor material may comprise a III-V type semiconductor material, such as, for example, indium gallium nitride. Novel intermediate structures are formed during such methods. Engineered substrates include a continuous layer of semiconductor material having a relaxed lattice structure.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Mixed orientation and mixed material semiconductor-on-insulator wafer

The present disclosure relates, generally, to a semiconductor substrate with a planarized surface comprising mixed single-crystal orientation regions and / or mixed single-crystal semiconductor material regions, where each region is electrically isolated. In accordance with one embodiment of the disclosure CMOS devices on SOI regions are manufactured on semiconductors having different orientations. According to another embodiment, an SOI device is contemplated as having a plurality of semiconductor regions having at least one of a different semiconductor material, crystalline lattice constant or lattice strain. Methods and processes for fabricating the different embodiments of the invention is also disclosed.

Owner:GLOBALFOUNDRIES INC

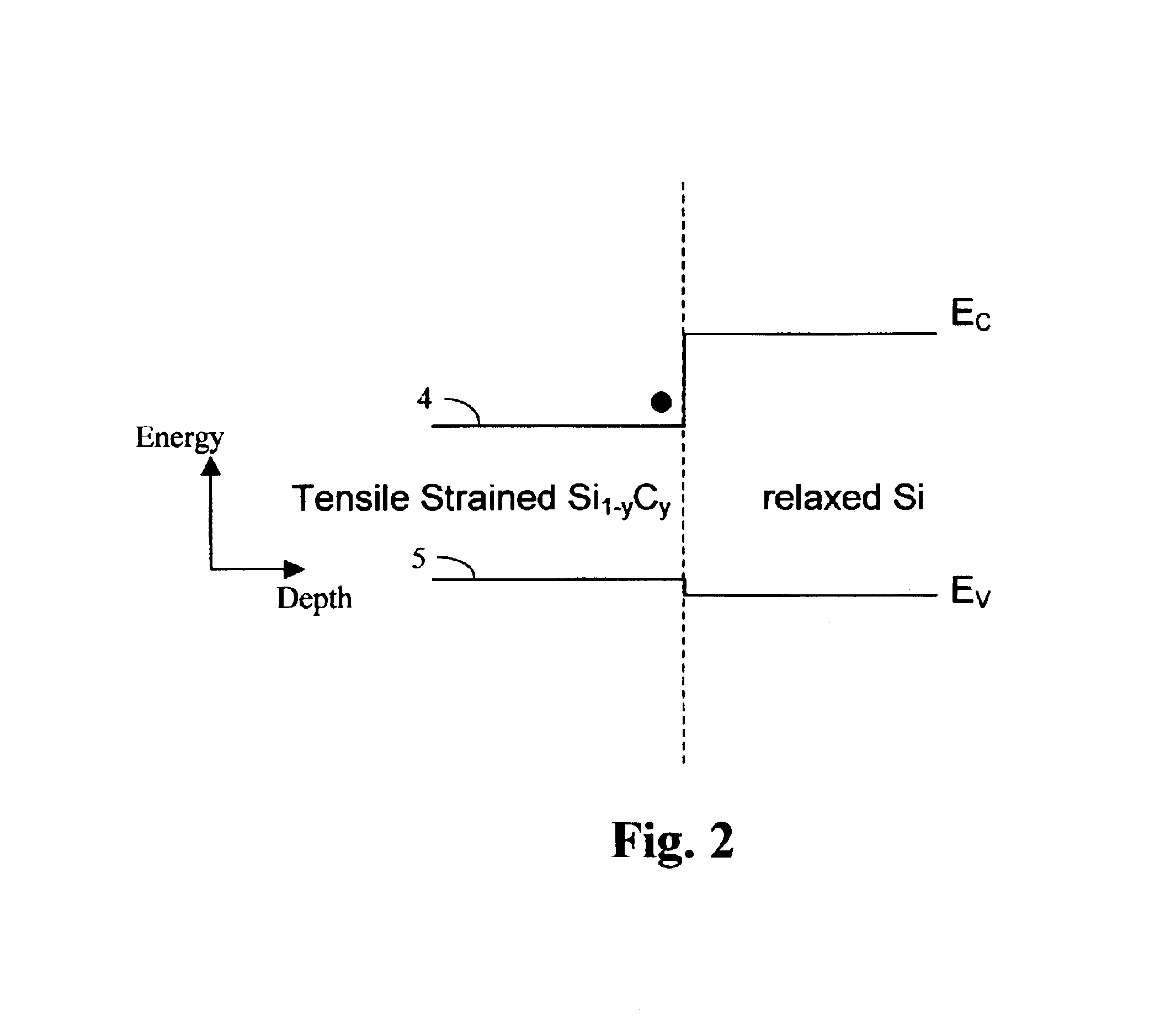

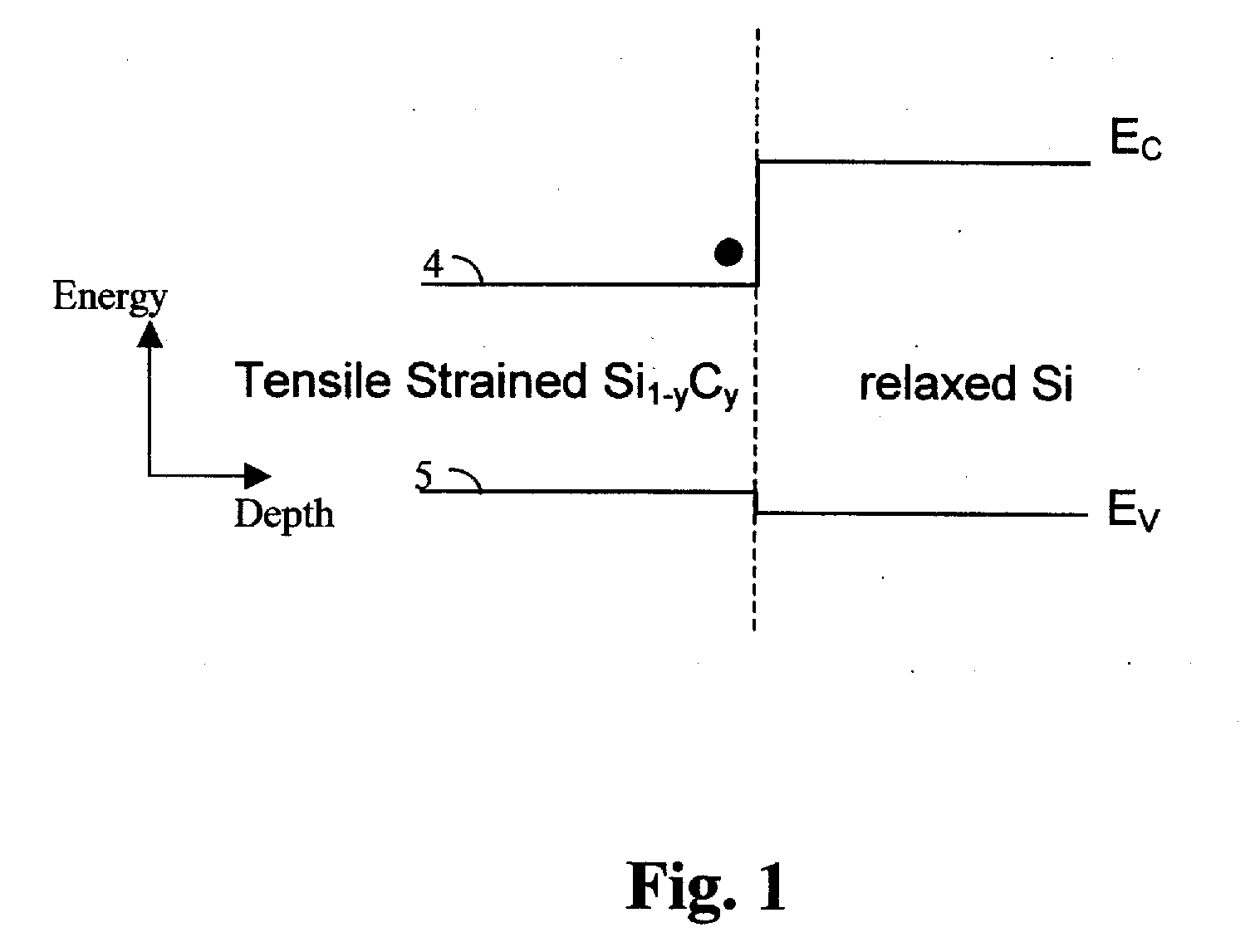

Ultra scalable high speed heterojunction vertical n-channel MISFETs and methods thereof

ActiveUS7205604B2Superb performanceSuperb scalabilityTransistorDiagnosticsHeterojunctionSemiconductor materials

A method for forming and the structure of a strained vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a heterojunction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect to the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (boron) into the body. The invention reduces the problem of leakage current from the source region via the heterojunction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials.

Owner:GLOBALFOUNDRIES US INC

Mixed orientation and mixed material semiconductor-on-insulator wafer

InactiveUS20050277260A1Enable formationFrom solid stateSolid-state devicesCMOSSemiconductor materials

The present disclosure relates, generally, to a semiconductor substrate with a planarized surface comprising mixed single-crystal orientation regions and / or mixed single-crystal semiconductor material regions, where each region is electrically isolated. In accordance with one embodiment of the disclosure CMOS devices on SOI regions are manufactured on semiconductors having different orientations. According to another embodiment, an SOI device is contemplated as having a plurality of semiconductor regions having at least one of a different semiconductor material, crystalline lattice constant or lattice strain. Methods and processes for fabricating the different embodiments of the invention is also disclosed.

Owner:GLOBALFOUNDRIES INC

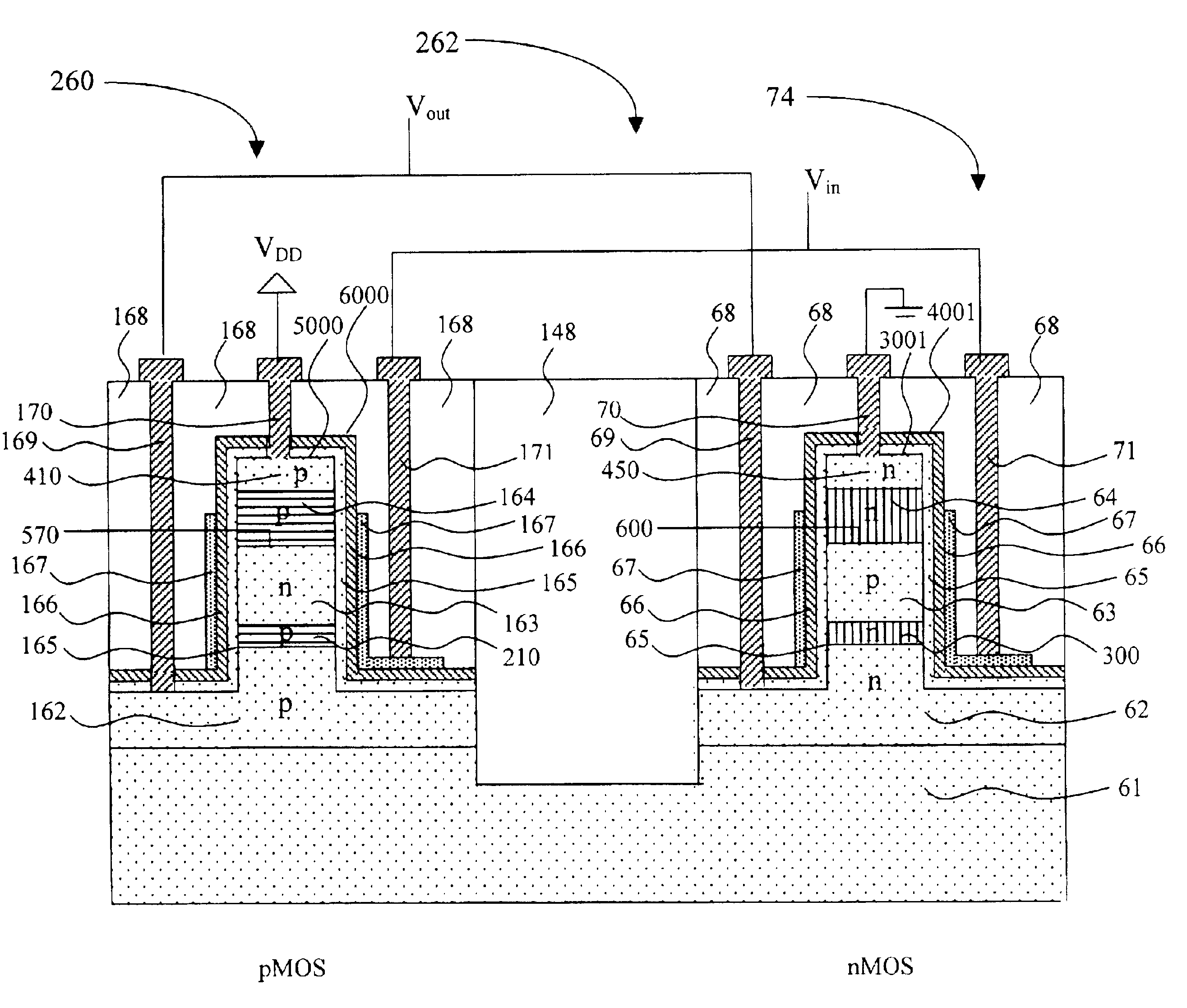

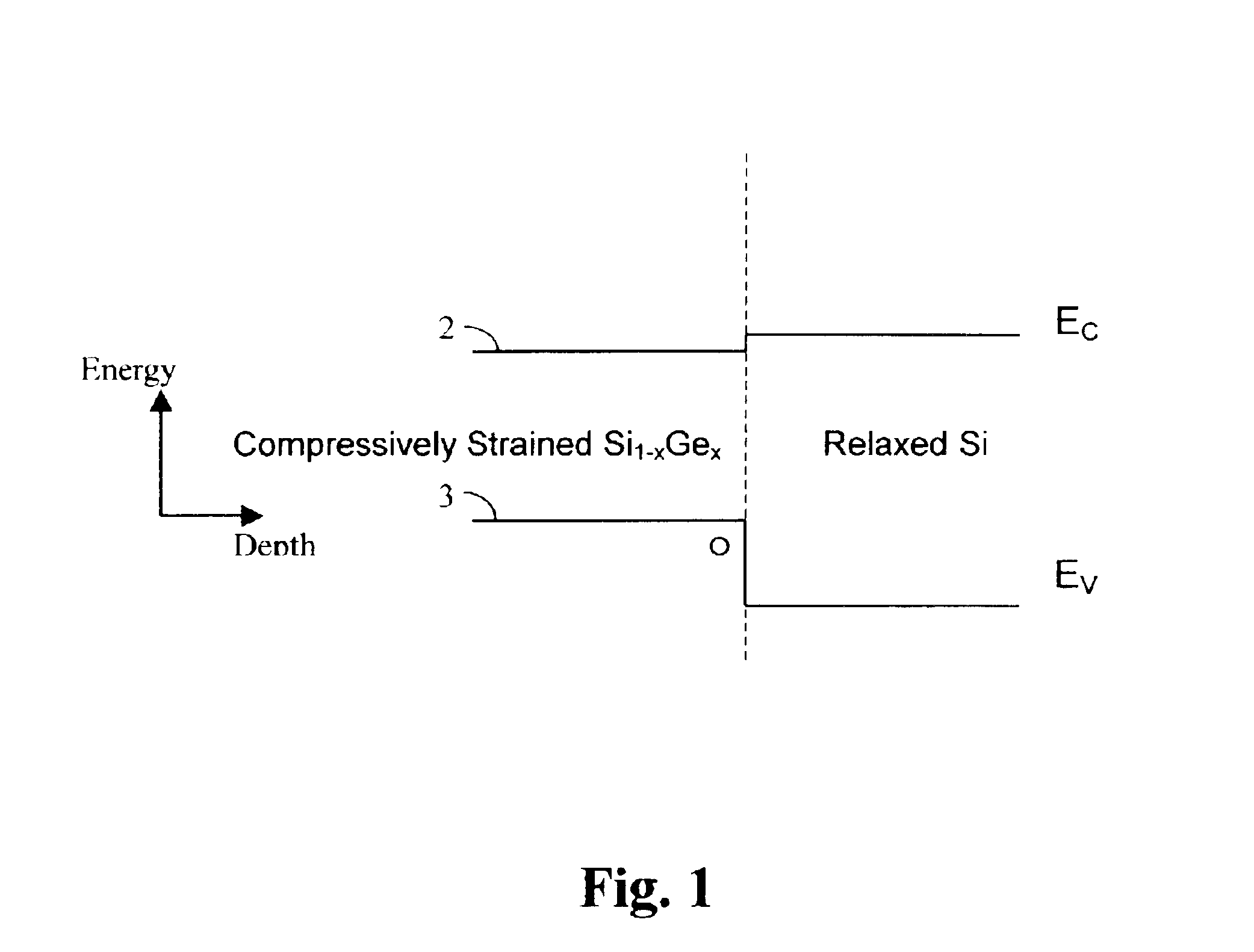

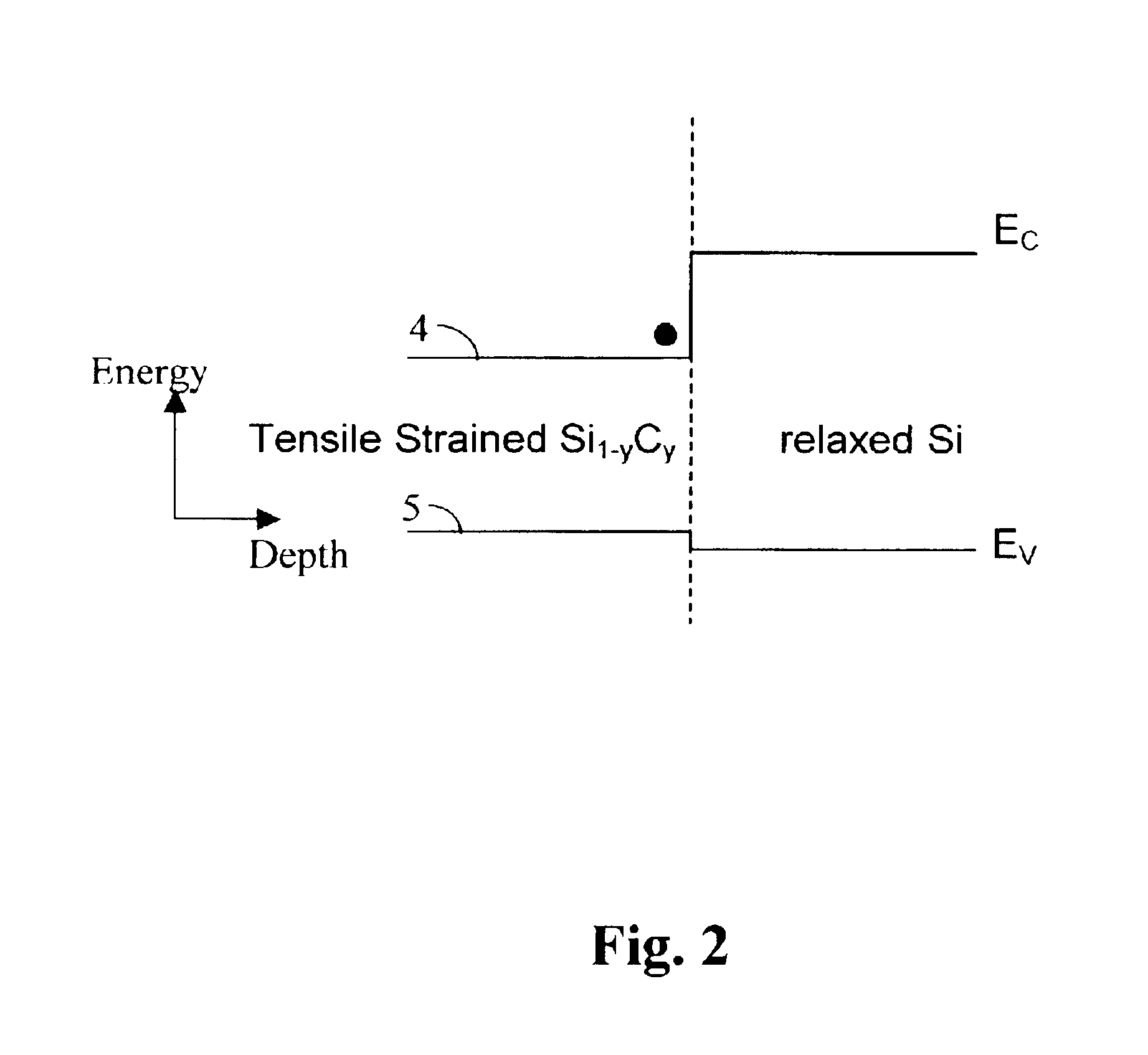

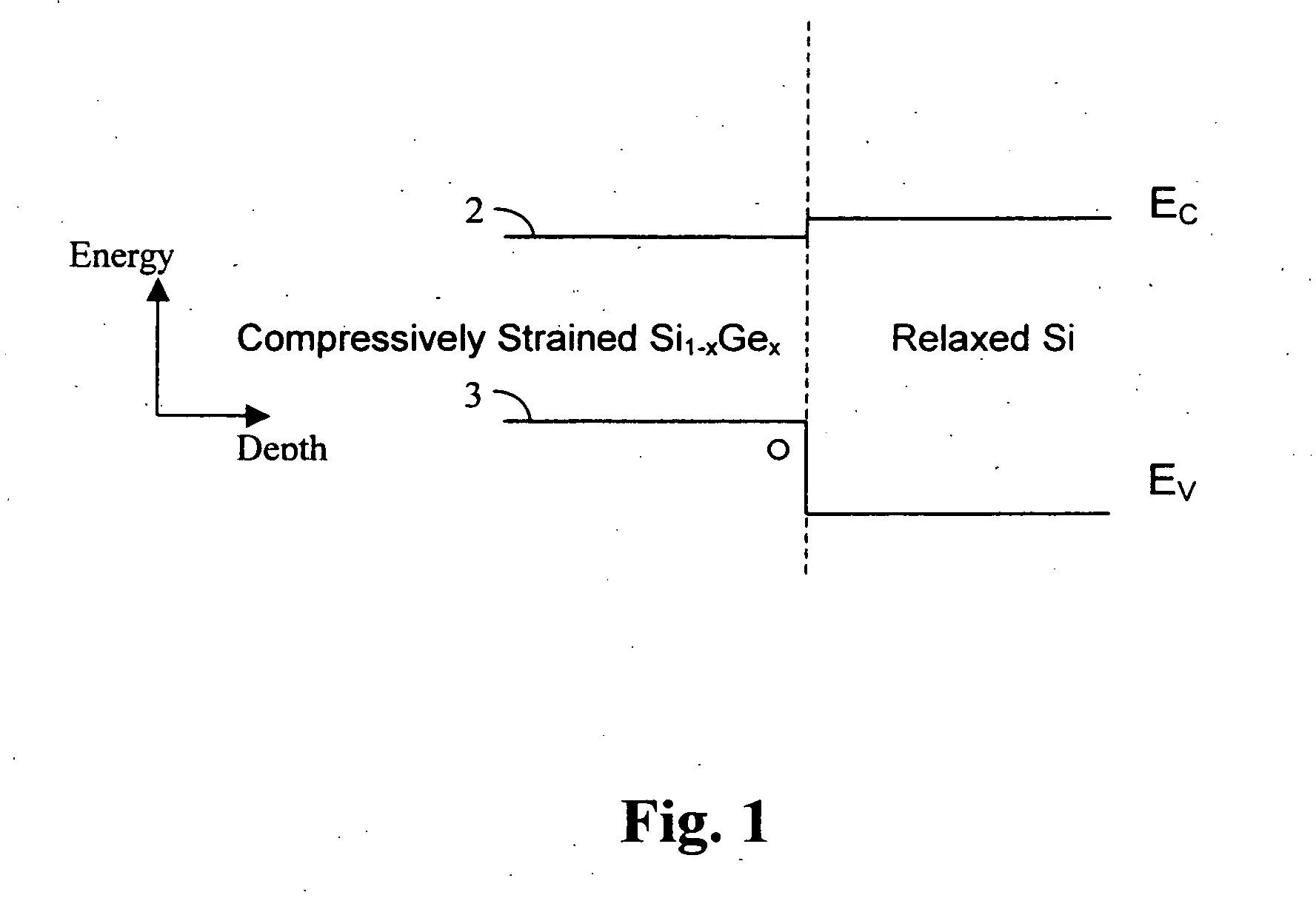

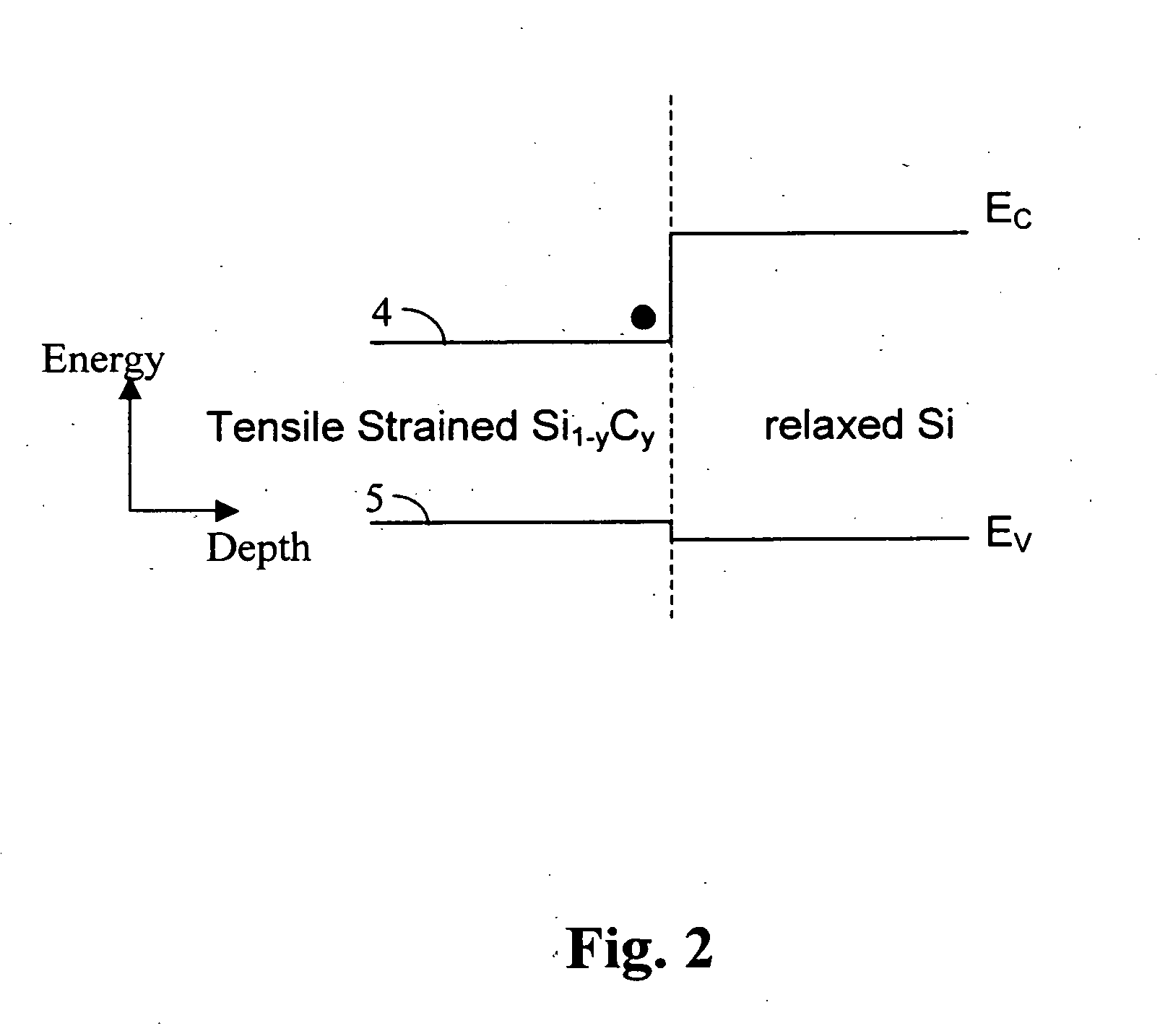

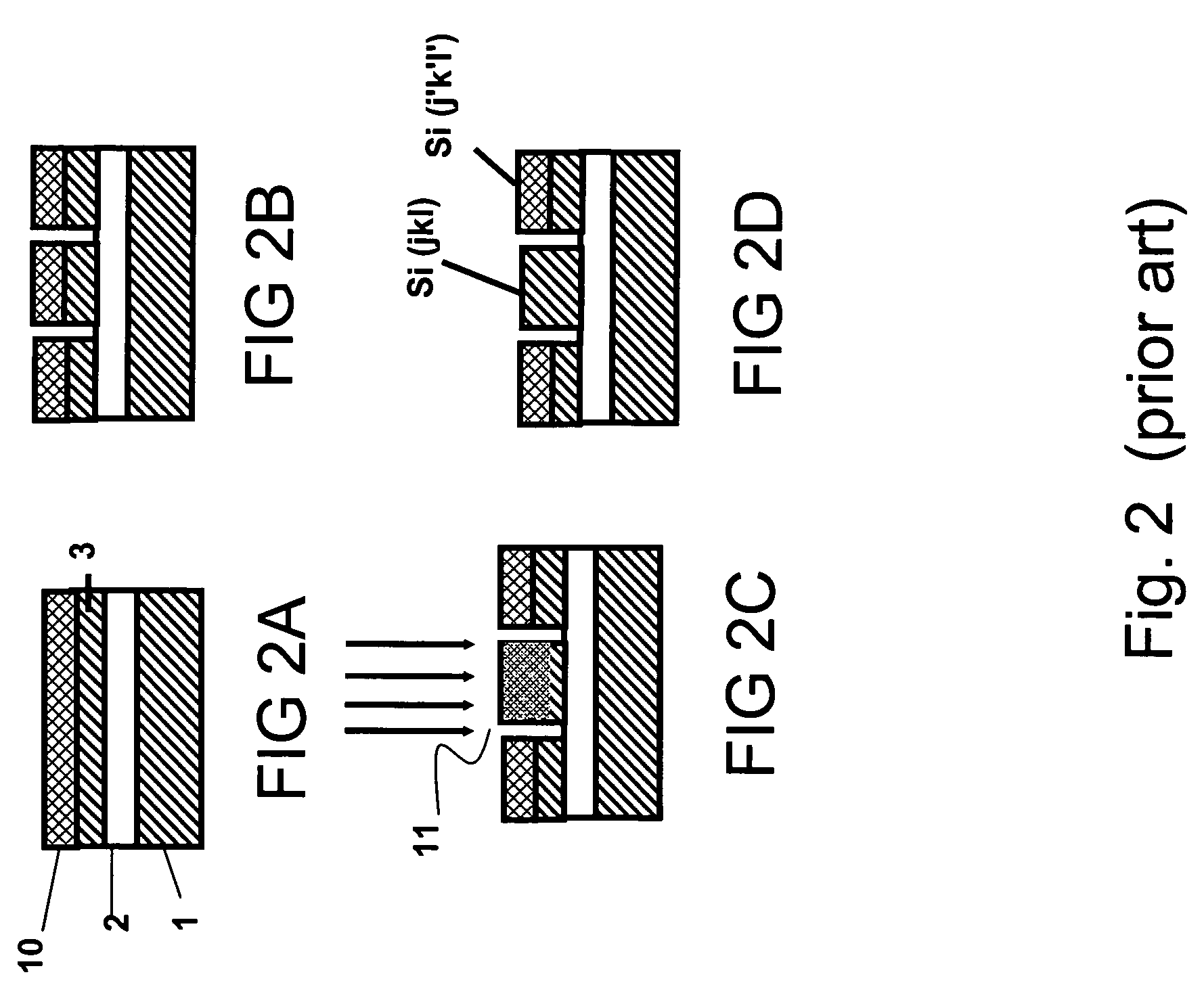

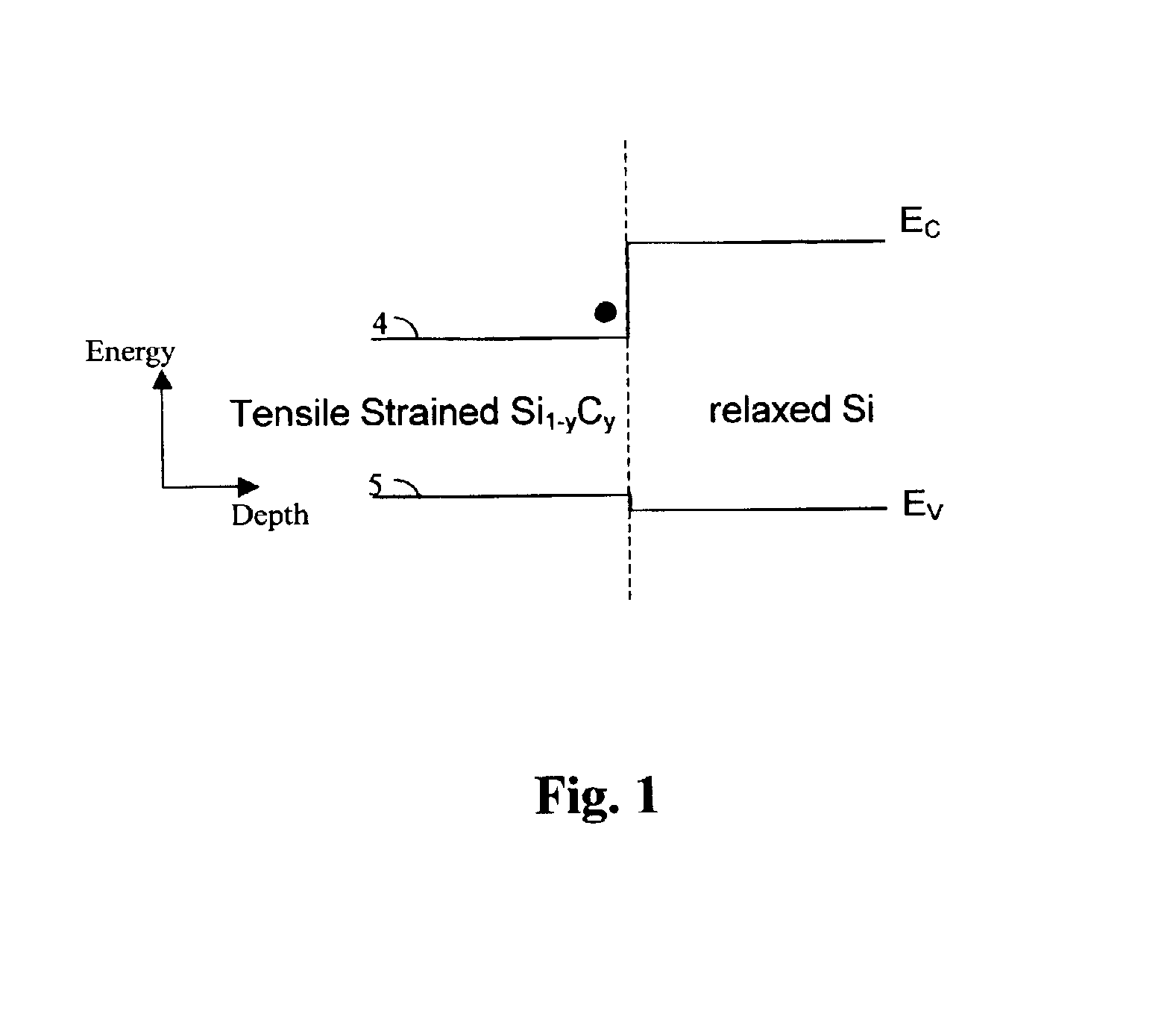

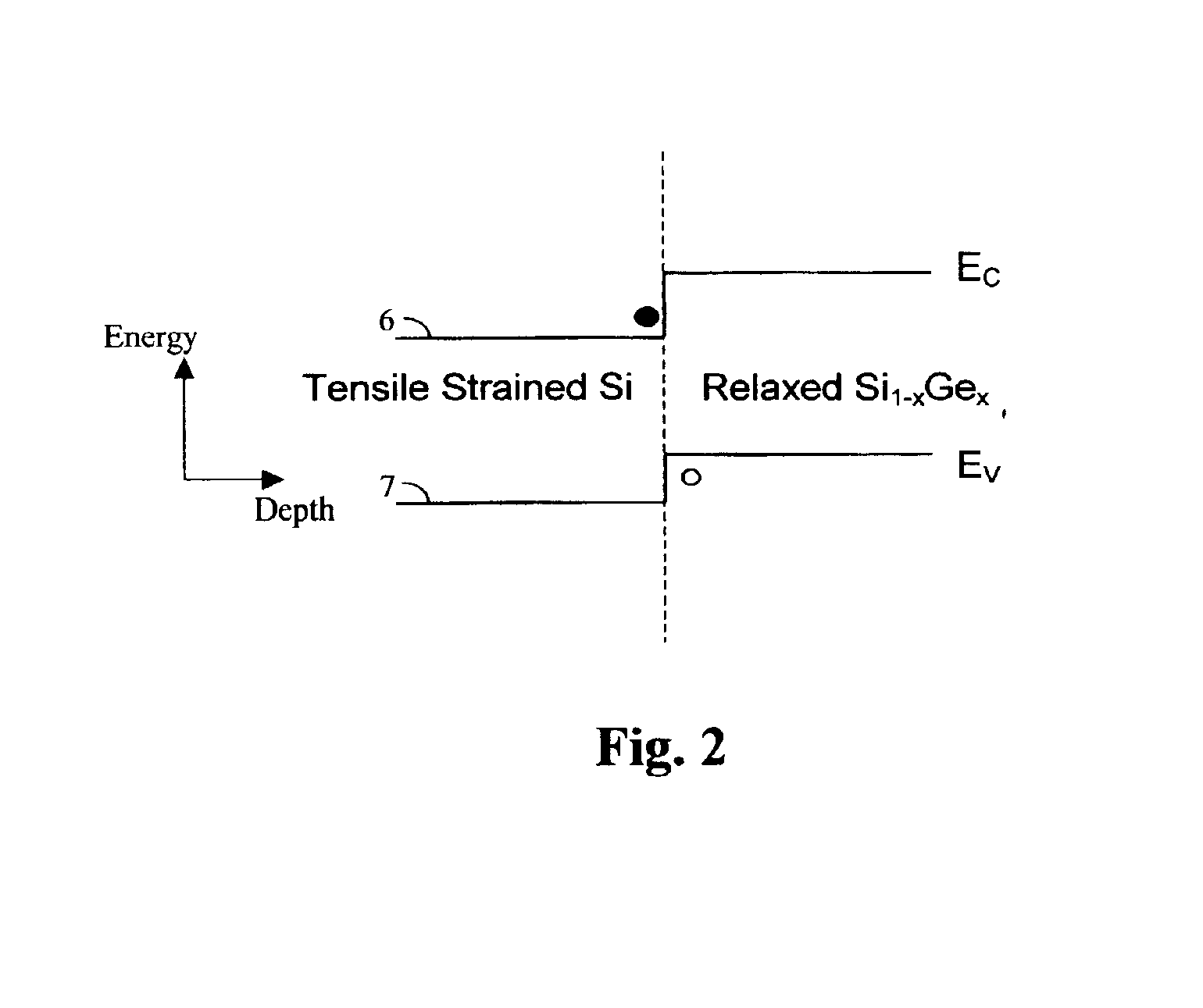

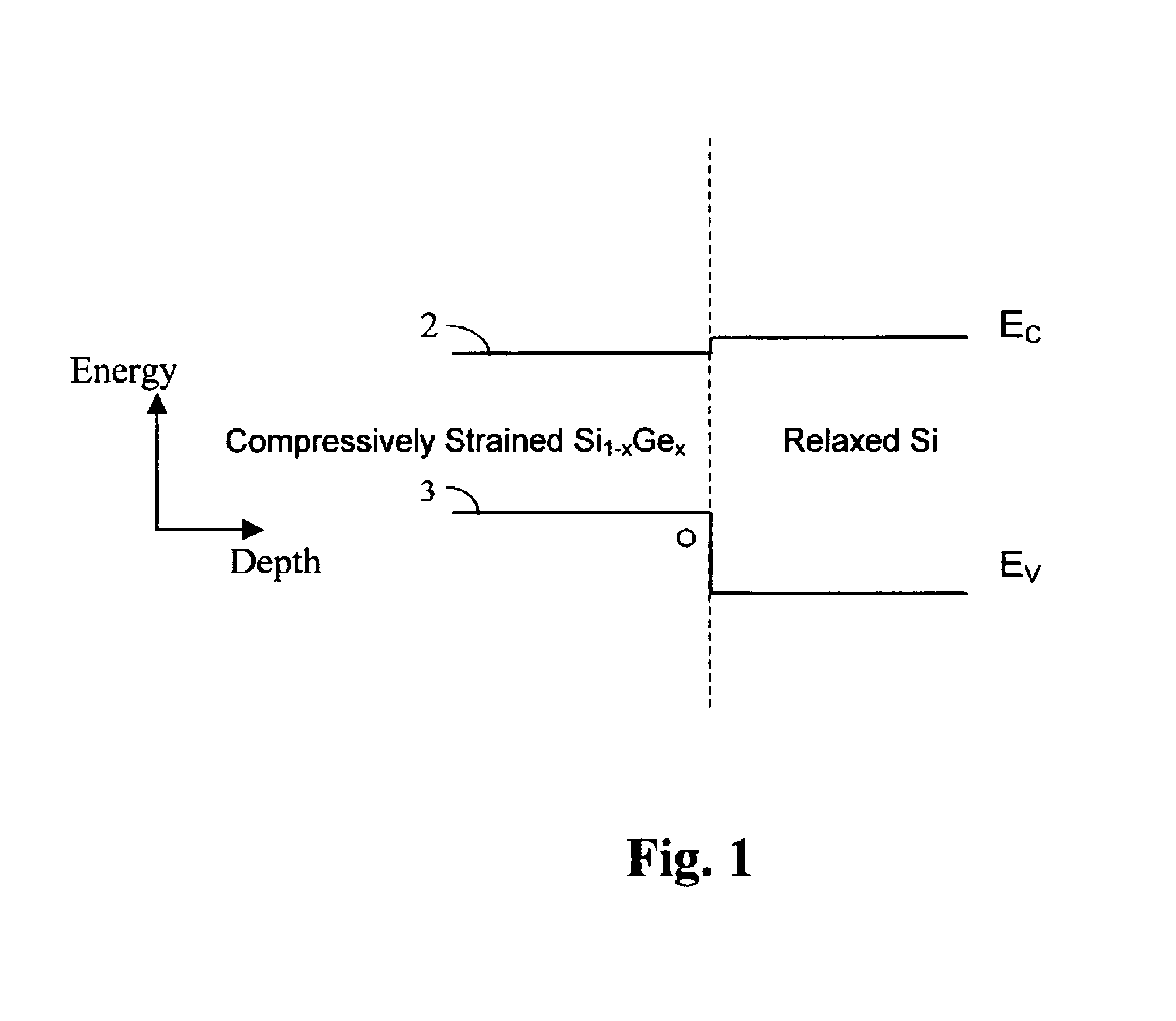

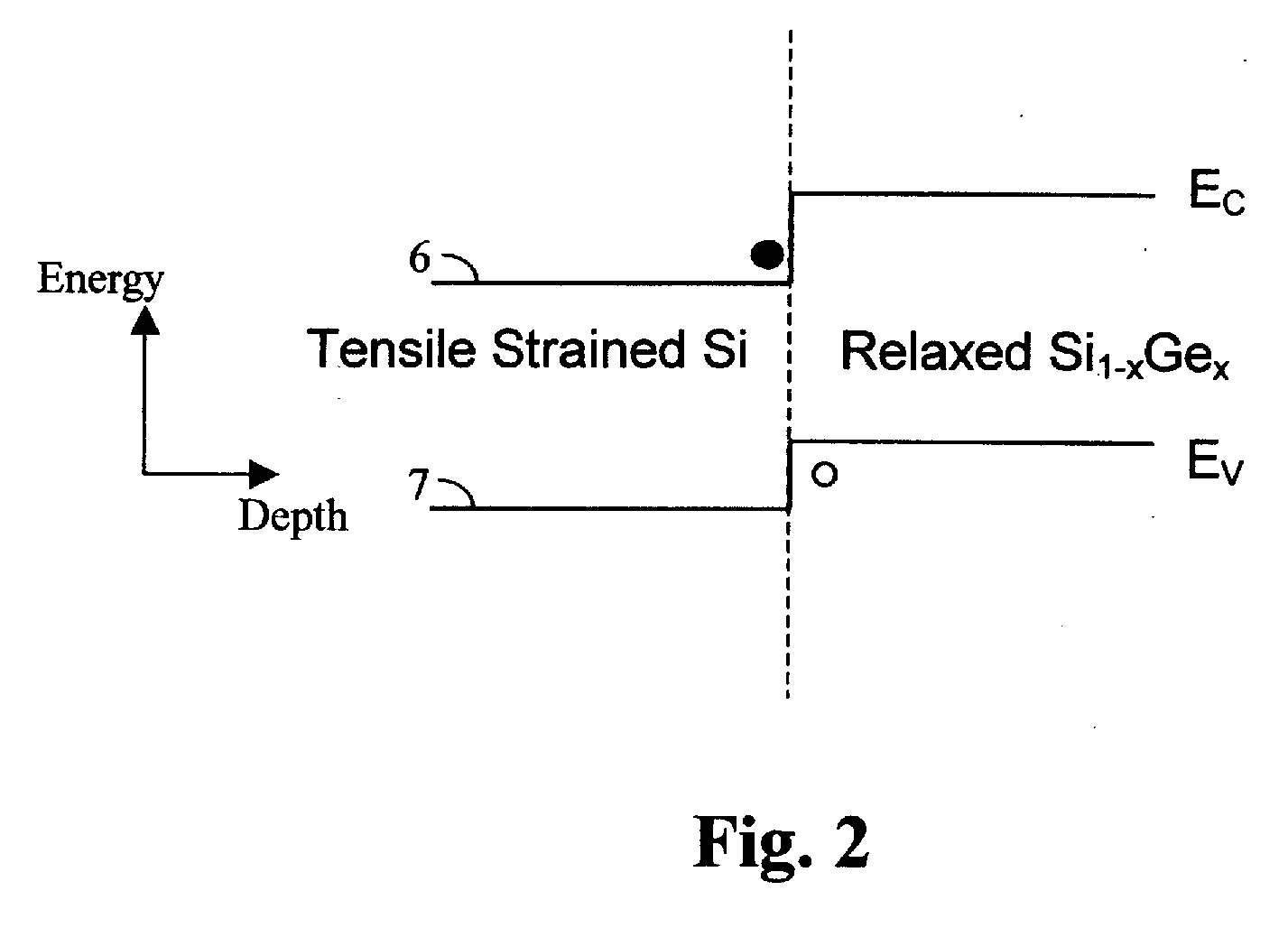

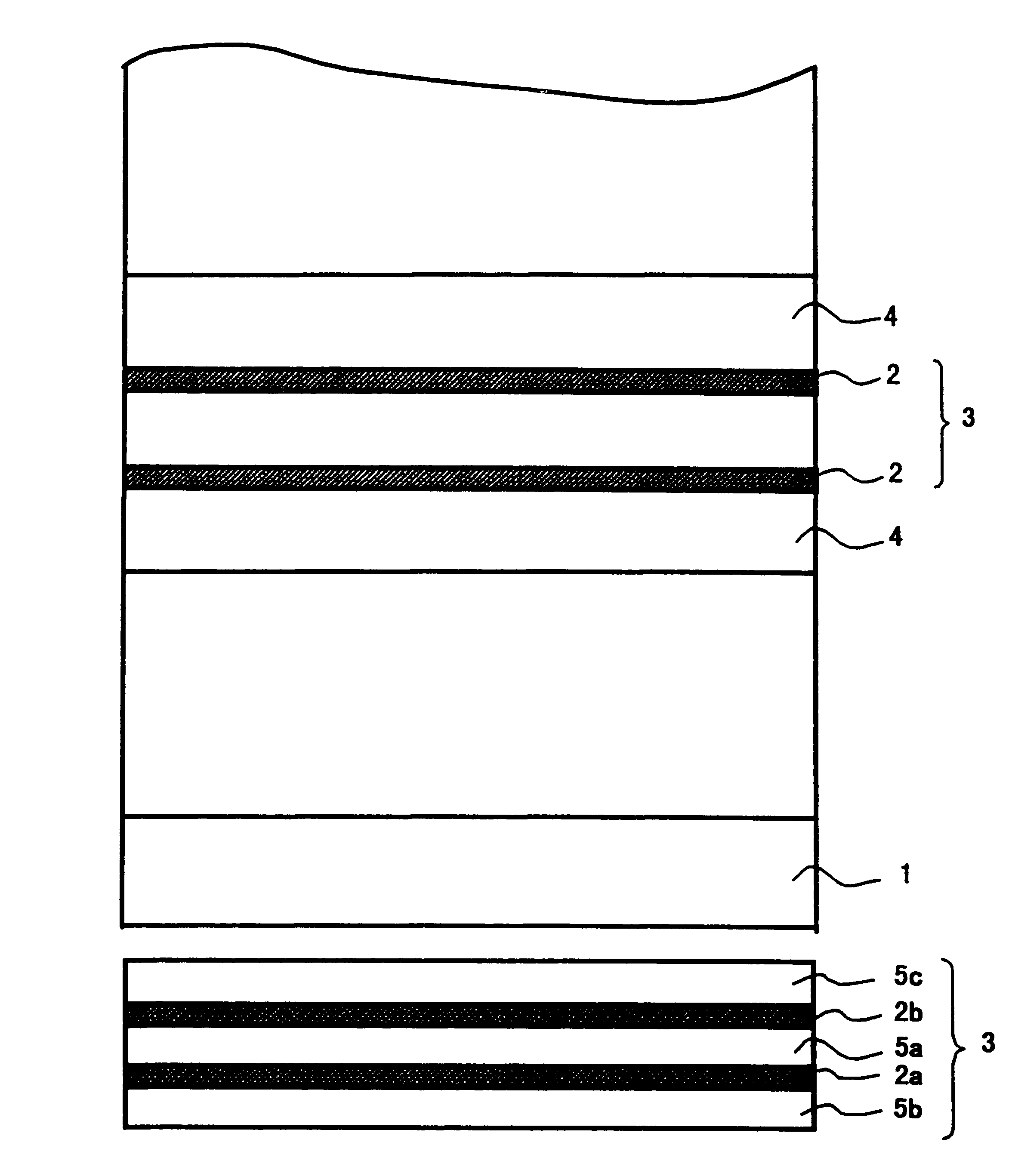

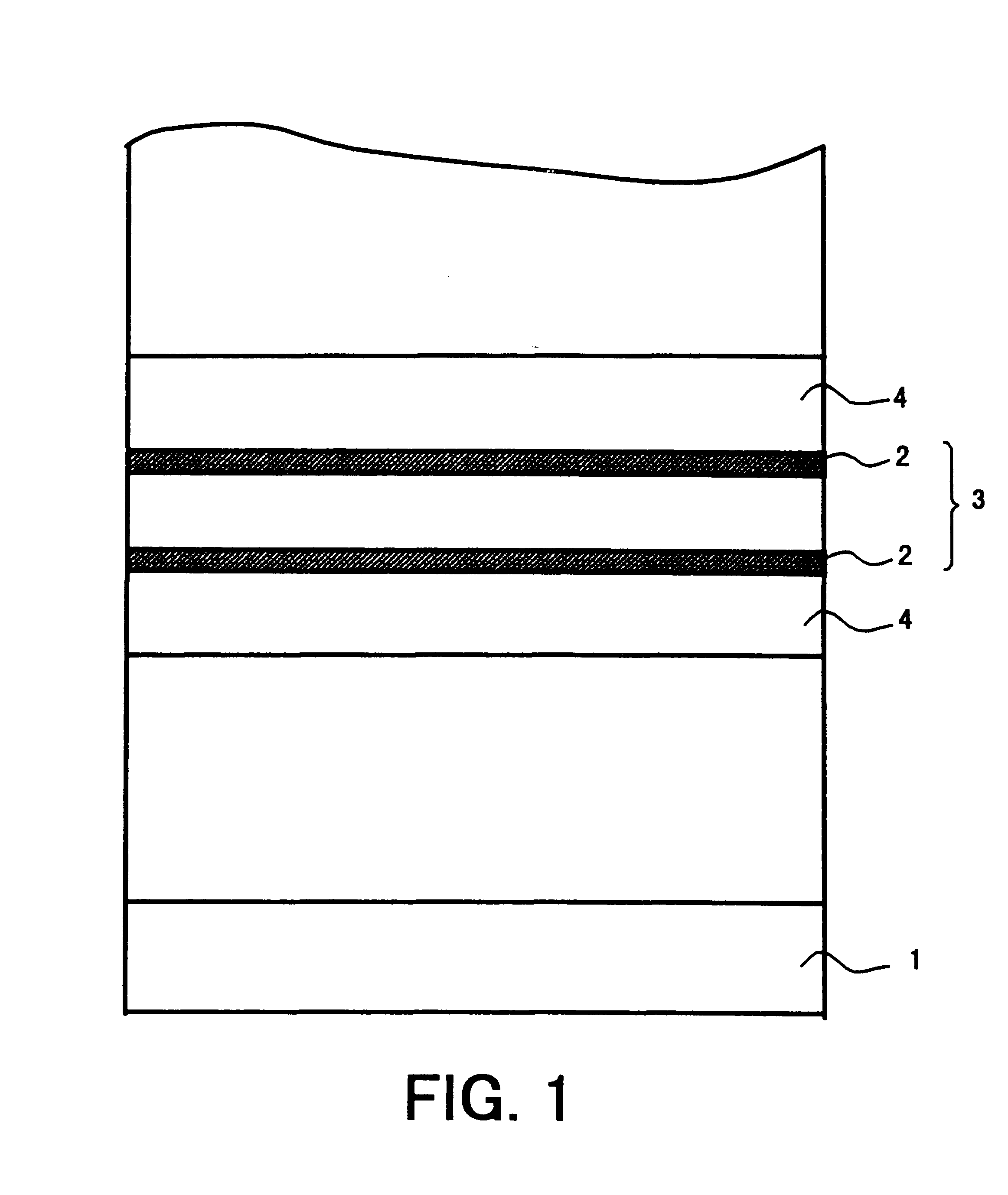

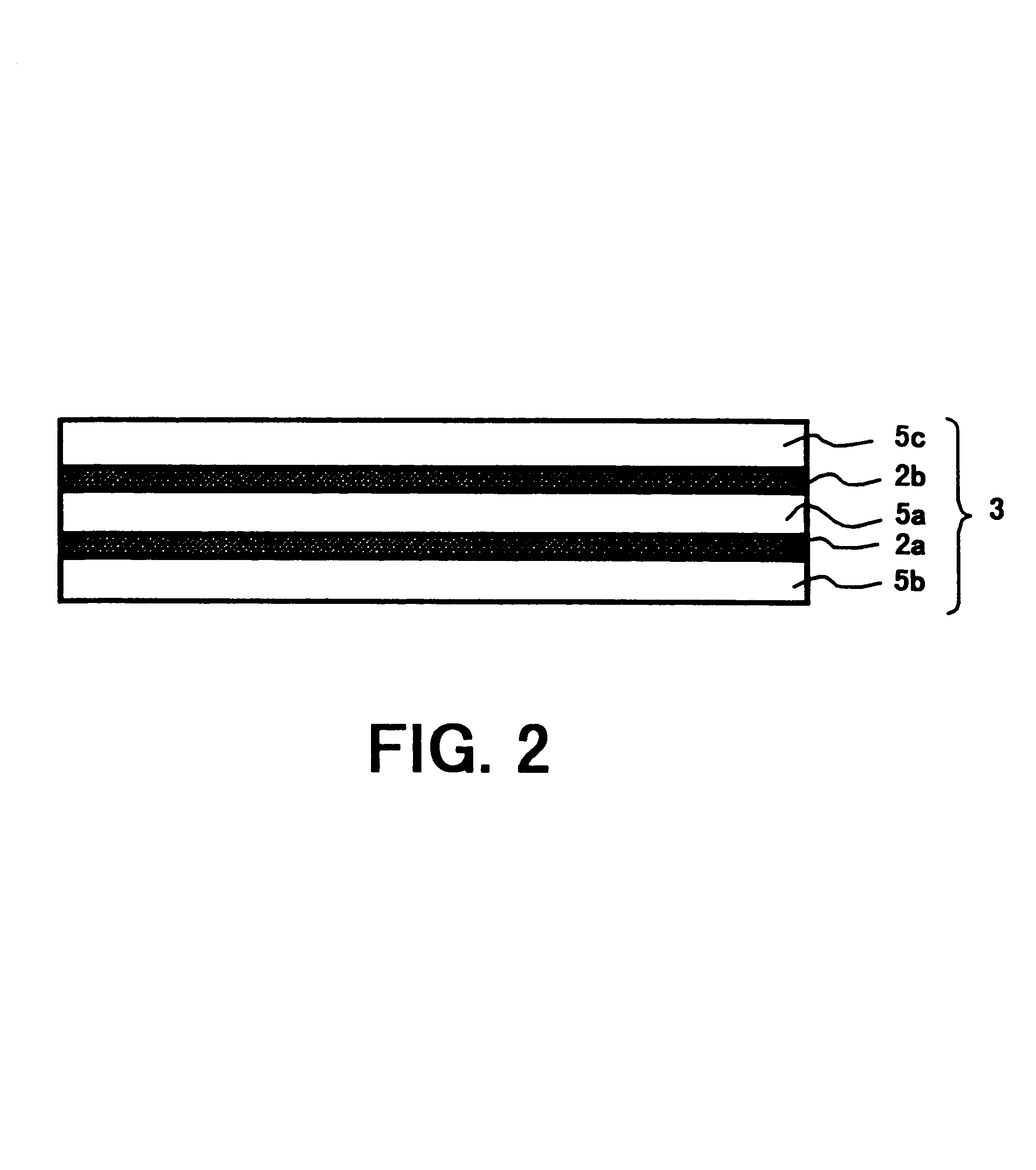

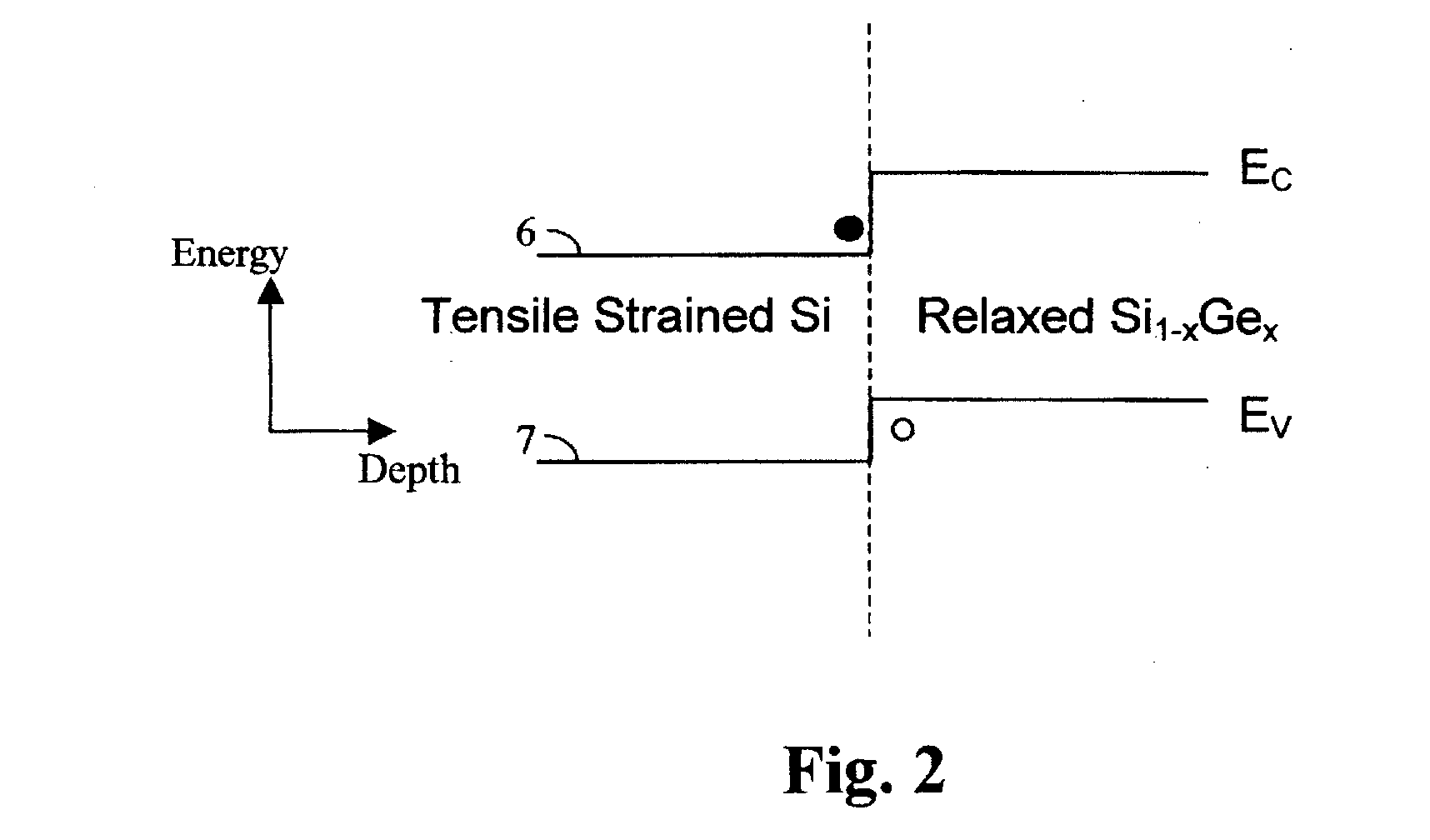

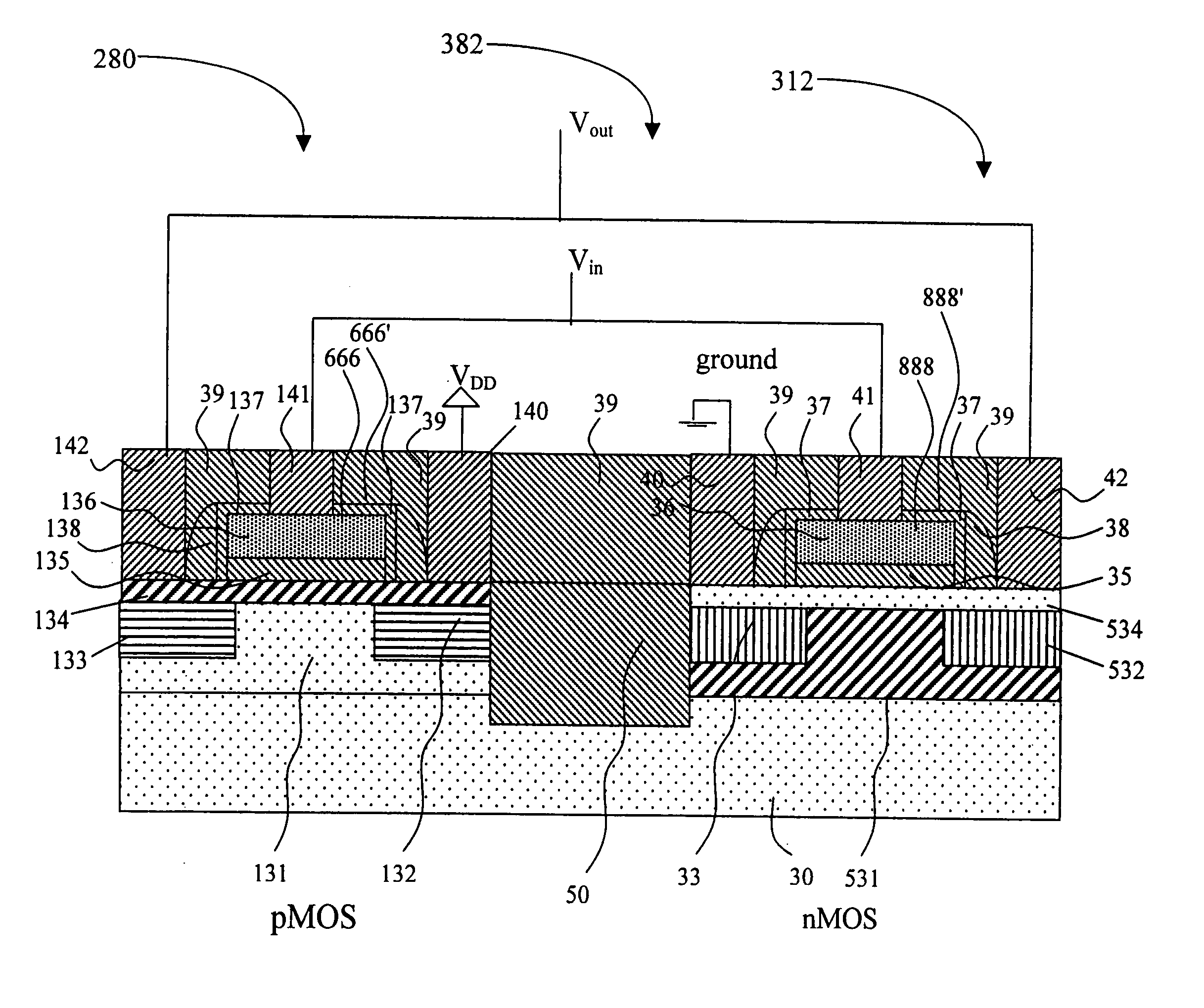

High speed lateral heterojunction MISFETs realized by 2-dimensional bandgap engineering and methods thereof

InactiveUS6927414B2Superb performanceSuperb scalabilityTransistorSemiconductor/solid-state device manufacturingHeterojunctionCMOS

A method for forming and the structure of a strained lateral channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a single crystal semiconductor substrate wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region. The invention reduces the problem of leakage current from the source region via the hetero-junction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials and alloy composition.

Owner:GLOBALFOUNDRIES US INC

Ultra Scalable High Speed Heterojunction Vertical n-Channel Misfets and Methods Thereof

InactiveUS20070241367A1Superb performanceSuperb scalabilityTransistorSolid-state devicesHeterojunctionSemiconductor materials

A method for forming and the structure of a strained vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect to the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (boron) into the body. The invention reduces the problem of leakage current from the source region via the hetero-junction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials.

Owner:GLOBALFOUNDRIES INC

Method for optimising transistor performance in integrated circuits

ActiveUS20060186478A1Optimising transistor performanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringPhotonic integrated circuit

A method (300) for optimising transistor performance in semiconductor integrated circuits built from standard cells (12), or custom transistor level layout, is disclosed. An active area of NMOS diffusion is extended with a joining area (102) between two adjacent cells (112) having the same net on diffusion at the adjacent edges of each cell. The diffusion area is extended to limit the occurrence of active and nonactive interface to minimise lattice strain effects and improve transistor performance.

Owner:ICERA INC

Mixed orientation and mixed material semiconductor-on-insulator wafer

The present disclosure relates, generally, to a semiconductor substrate with a planarized surface comprising mixed single-crystal orientation regions and / or mixed single-crystal semiconductor material regions, where each region is electrically isolated. In accordance with one embodiment of the disclosure CMOS devices on SOI regions are manufactured on semiconductors having different orientations. According to another embodiment, an SOI device is contemplated as having a plurality of semiconductor regions having at least one of a different semiconductor material, crystalline lattice constant or lattice strain. Methods and processes for fabricating the different embodiments of the invention is also disclosed.

Owner:GLOBALFOUNDRIES INC

Light emitting devices with layered III-V semiconductor structures, and modules and systems for computer, network and optical communication, using such device

InactiveUS6657233B2Improve crystal qualityFacilitates layerLaser detailsLaser active region structureQuantum wellCharge carrier

A semiconductor light emitting device is disclosed, including a semiconductor substrate, an active region comprising a strained quantum well layer, and a cladding layer for confining carriers and light emissions, wherein the amount of lattice strains in the quantum well layer is in excess of 2% against either the semiconductor substrate or cladding layer and, alternately, the thickness of the quantum well layer is in excess of the critical thickness calculated after Matthews and Blakeslee.

Owner:RICOH KK

Light emitting devices with layered III-V semiconductor structures, and modules and systems for computer, network and optical communication, using such device

InactiveUS20010030319A1Improve crystal qualityGood temperature characteristicsLaser detailsLaser active region structureSemiconductor structureQuantum well

A semiconductor light emitting device is disclosed, including a semiconductor substrate, an active region comprising a strained quantum well layer, and a cladding layer for confining carriers and light emissions, wherein the amount of lattice strains in the quantum well layer is in excess of 2% against either the semiconductor substrate or cladding layer and, alternately, the thickness of the quantum well layer is in excess of the critical thickness calculated after Matthews and Blakeslee.

Owner:RICOH KK

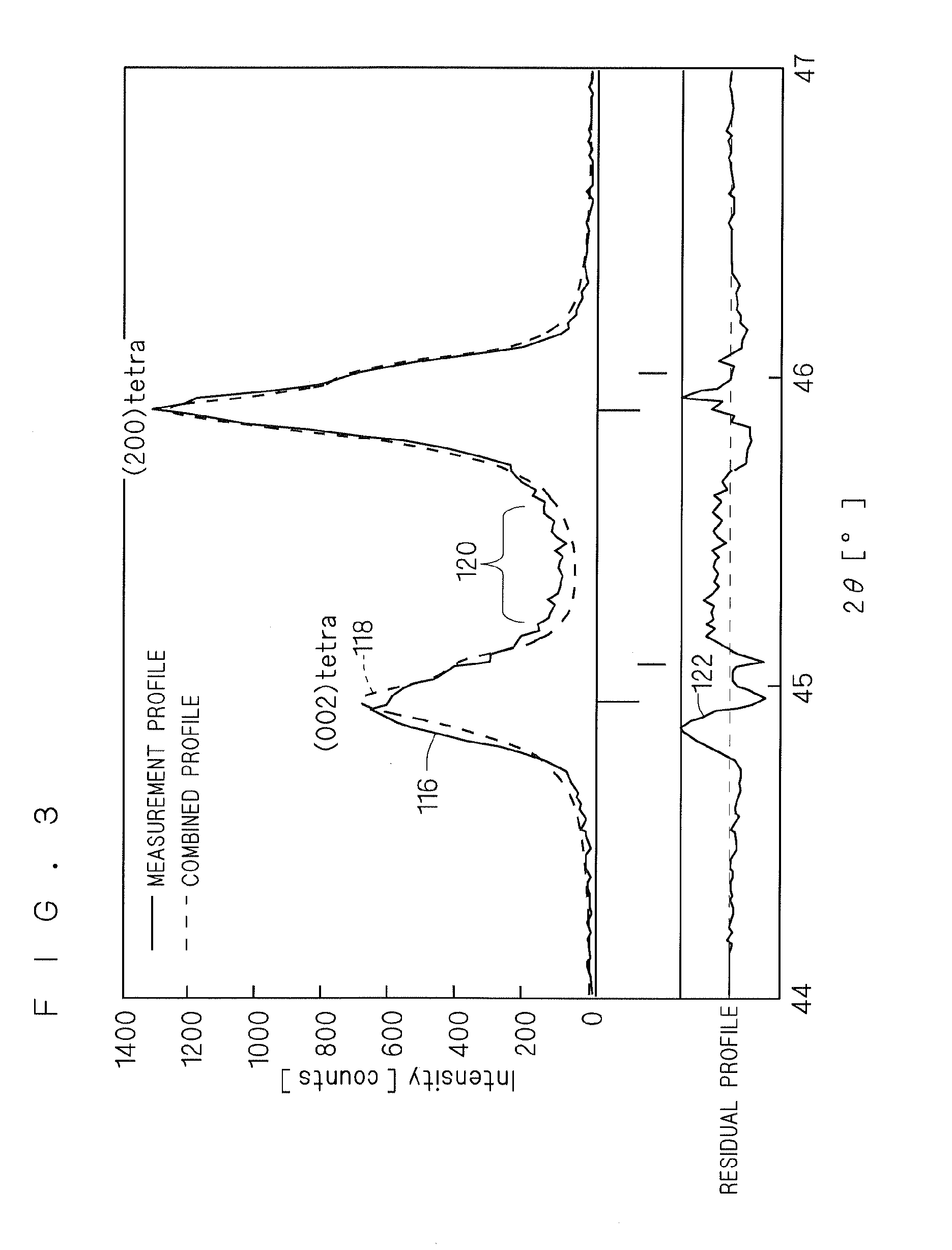

Piezoelectric/electrostrictive ceramics sintered body and method of calculating diffuse scattering intensity ratio

InactiveUS20100019624A1Easy accessPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesSymmetry reductionLattice plane

An alkali niobate-based piezoelectric / electrostrictive ceramics sintered body including, as a main crystal phase, a perovskite type oxide containing at least one type of element selected from the group consisting of Li, Na and K as A site constituent elements and at least one type of element selected from the group consisting of Nb and Ta as B site constituent elements. The number of lattice-strained layers of the piezoelectric / electrostrictive ceramics sintered body is preferably small. A diffuse scattering intensity ratio, which is a ratio of an intensity of diffuse scattering by a lattice-strained layer present near a domain wall to a sum of an X-ray diffraction intensity of a first lattice plane and that of a second lattice plane different in interplanar spacing from the first lattice plane due to crystallographic symmetry reduction is preferably 0.5 or lower.

Owner:NGK INSULATORS LTD

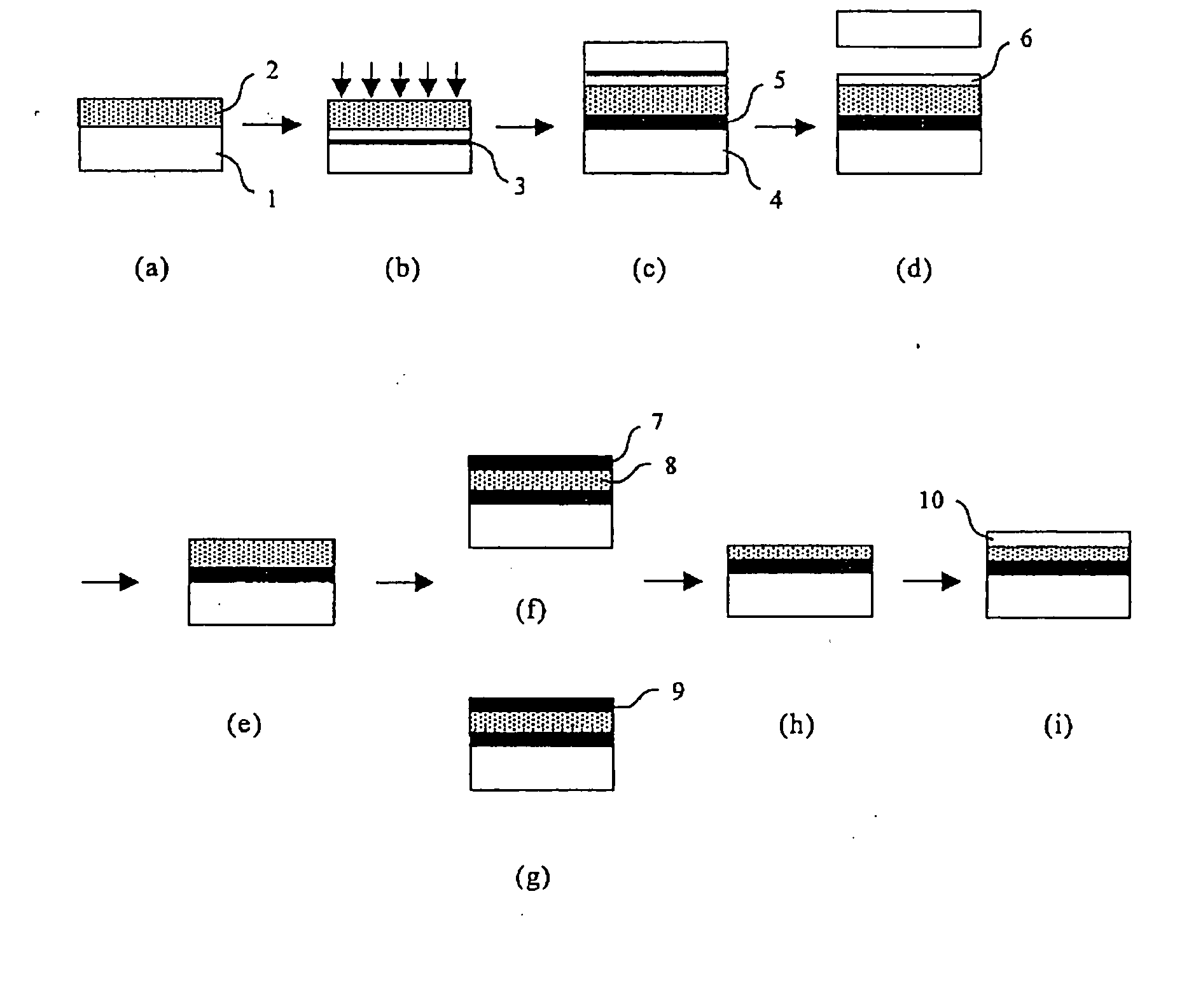

Method For Producing Semiconductor Wafer

InactiveUS20070287269A1Suppress surface roughnessHigh crystallinitySolid-state devicesSemiconductor/solid-state device manufacturingNoble gasWafering

The present invention is a method for producing a semiconductor wafer, comprising at least steps of: epitaxially growing a SiGe layer on a surface of a silicon single crystal wafer that is to be a bond wafer; implanting at least one kind of hydrogen ion and rare gas ion through the SiGe layer, so that an ion implanted layer is formed inside the bond wafer; closely contacting and bonding a surface of the SiGe layer and a surface of a base wafer through an insulator film; then performing delamination at the ion implanted layer, removing a Si layer in a delaminated layer transferred to a side of the base wafer by the delamination, so that the SiGe layer is exposed; and then subjecting the exposed SiGe layer to a heat treatment for enriching Ge under an oxidizing atmosphere and / or a heat treatment for relaxing lattice strain under a non-oxidizing atmosphere. Thereby, a method for producing a semiconductor wafer having a SiGe layer in which lattice relaxation is sufficiently performed and of which surface roughness is suppressed and of which crystallinity is good is provided.

Owner:SHIN-ETSU HANDOTAI CO LTD

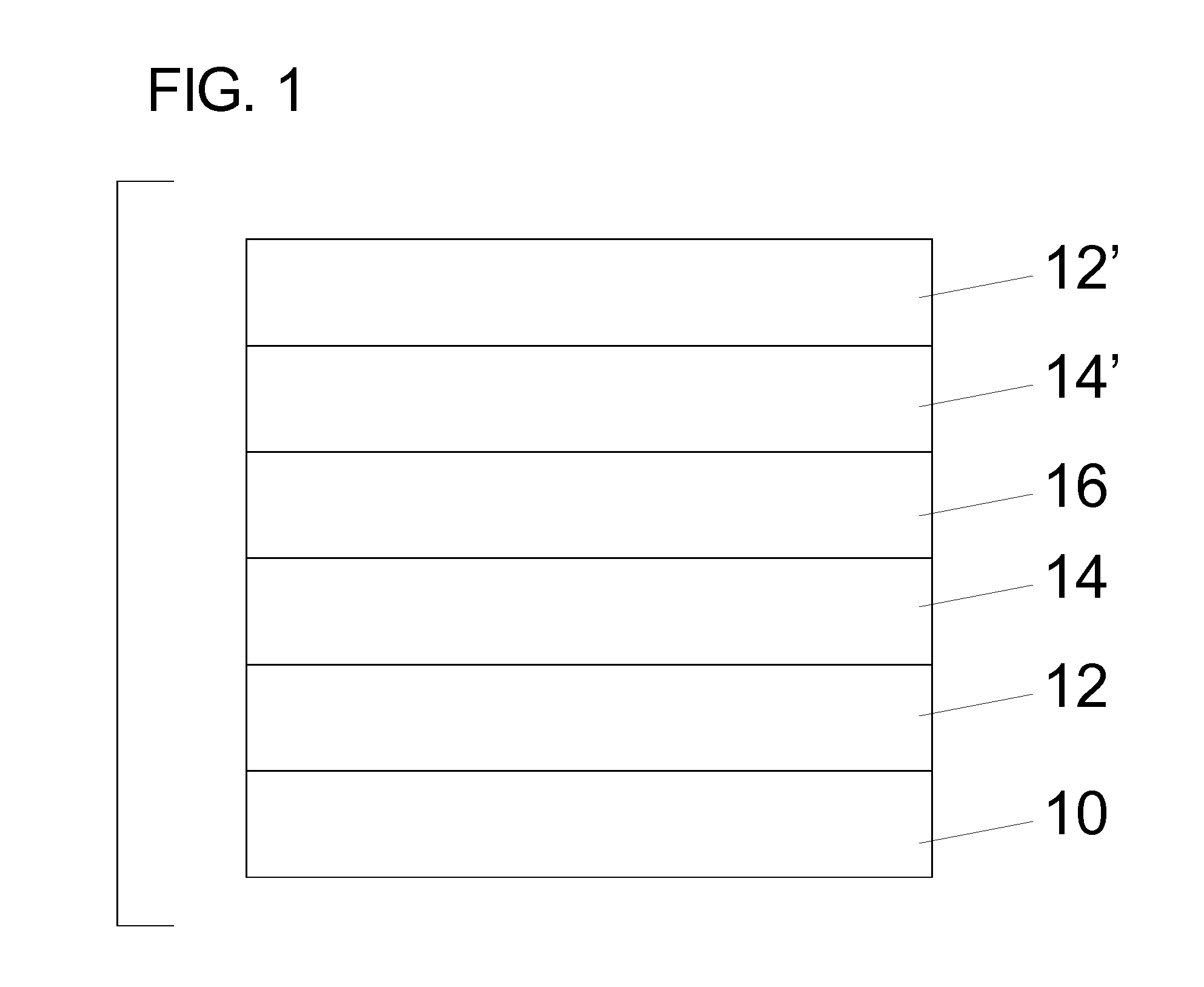

Method of semiconductor device fabrication

InactiveUS6927138B2High electric reliabilityImprove reliabilitySemiconductor/solid-state device manufacturingSilicon dioxideSemiconductor

Provided is a method of semiconductor device fabrication capable of rounding the sharp edge portions of trenches so as to form device isolation regions having high electrical reliability. A semiconductor substrate comprising a lattice-strain relaxed silicon germanium layer, a silicon germanium layer, and a lattice strained silicon layer formed in this order of mention onto a silicon substrate is used, while trenches are formed in the portions for device isolation regions of the semiconductor substrate by etching. Then, a silicon film is deposited on the entirety of the exposed surface, and the deposited silicon film is dry-oxidized so as to form a silicon dioxide film. As a result, the edge portions of the trenches are rounded.

Owner:SHARP KK

Semiconductor device having compressively strained channel region and method of making same

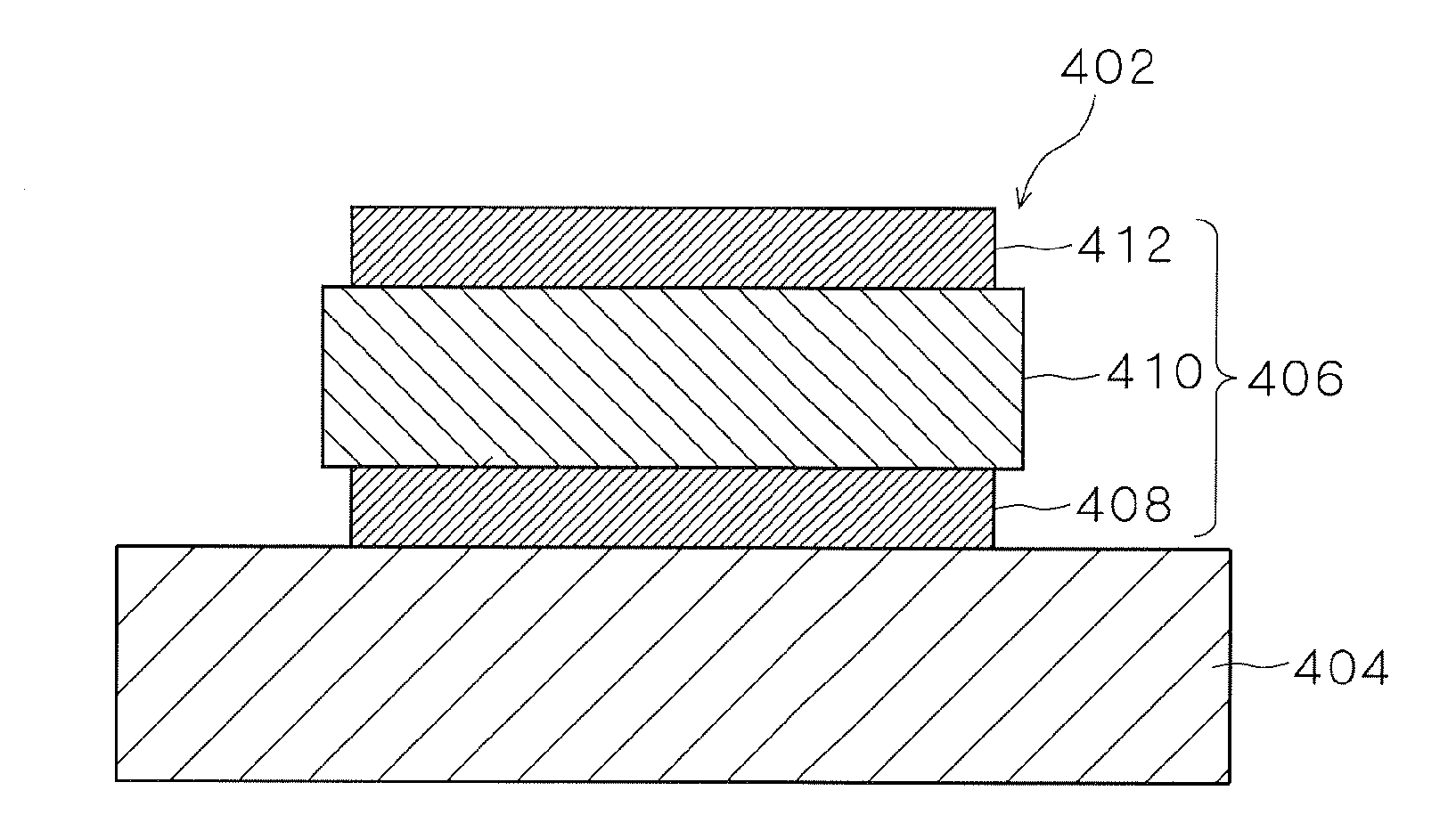

ActiveUS20140239399A1Solid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor materials

A semiconductor device and method making it utilize a three-dimensional channel region comprising a core of a first semiconductor material and an epitaxial covering of a second semiconductor material. The first and second semiconductor materials have respectively different lattice constants, thereby to create a strain in the epitaxial covering. The devices are formed by a gate-last process, so that the second semiconductor material is deposited only after the high temperature processes have been performed. Consequently, the lattice strain is not substantially relaxed, and the improved performance benefits of the lattice strained channel region are not compromised.

Owner:RENESAS ELECTRONICS CORP

ULTRA SCALABLE HIGH SPEED HETEROJUNCTION VERTICAL n-CHANNEL MISFETS AND METHODS THEREOF

InactiveUS20080237637A1Superb performanceSuperb scalabilityTransistorSolid-state devicesHeterojunctionSemiconductor materials

A method for forming and the structure of a strained vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect to the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (boron) into the body. The invention reduces the problem of leakage current from the source region via the hetero-junction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials.

Owner:GLOBALFOUNDRIES INC

Long Wavelength Infrared Superlattice

InactiveUS20130043458A1Quality lossOvercome lossSemiconductor/solid-state device manufacturingNanoopticsGallium antimonideIndium arsenide

An embodiment of the present invention improves the fabrication and operational characteristics of a type-II superlattice material. Layers of indium arsenide and gallium antimonide comprise the bulk of the superlattice structure. One or more layers of indium antimonide are added to unit cells of the superlattice to provide a further degree of freedom in the design for adjusting the effective bandgap energy of the superlattice. One or more layers of gallium arsenide antimonide are added to unit cells of the superlattice to counterbalance the crystal lattice strain forces introduced by the aforementioned indium antimonide layers.

Owner:SVT ASSOCS

High speed lateral heterojunction MISFETS realized by 2-dimensional bandgap engineering and methods thereof

ActiveUS20050239241A1Superb performanceSuperb scalabilityTransistorSemiconductor/solid-state device manufacturingHeterojunctionCMOS

A method for forming and the structure of a strained lateral channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a single crystal semiconductor substrate wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region. The invention reduces the problem of leakage current from the source region via the hetero-junction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials and alloy composition.

Owner:GLOBALFOUNDRIES U S INC

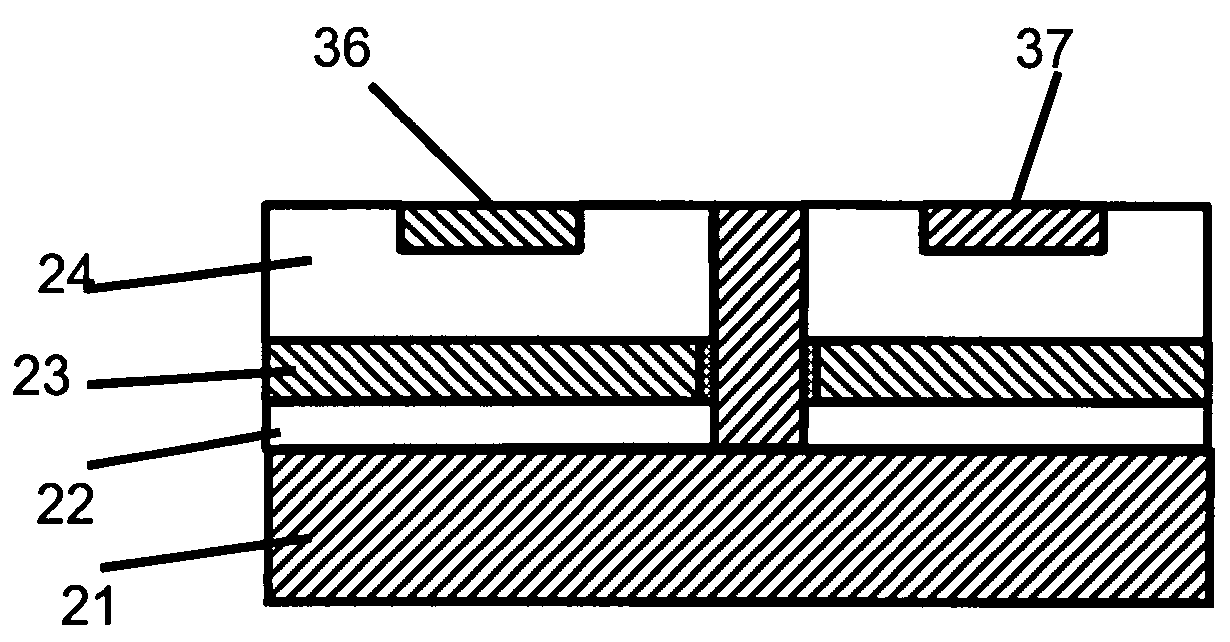

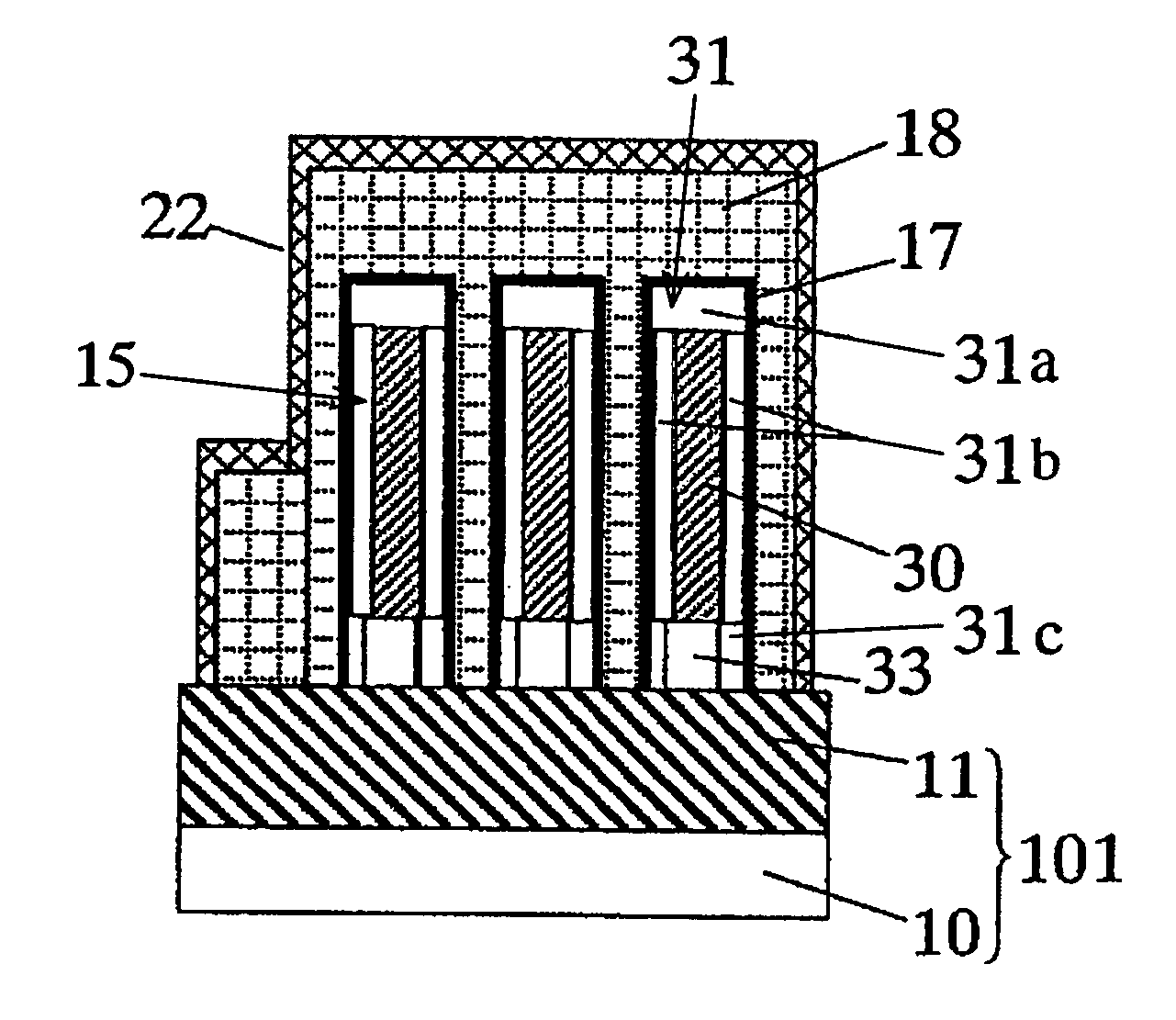

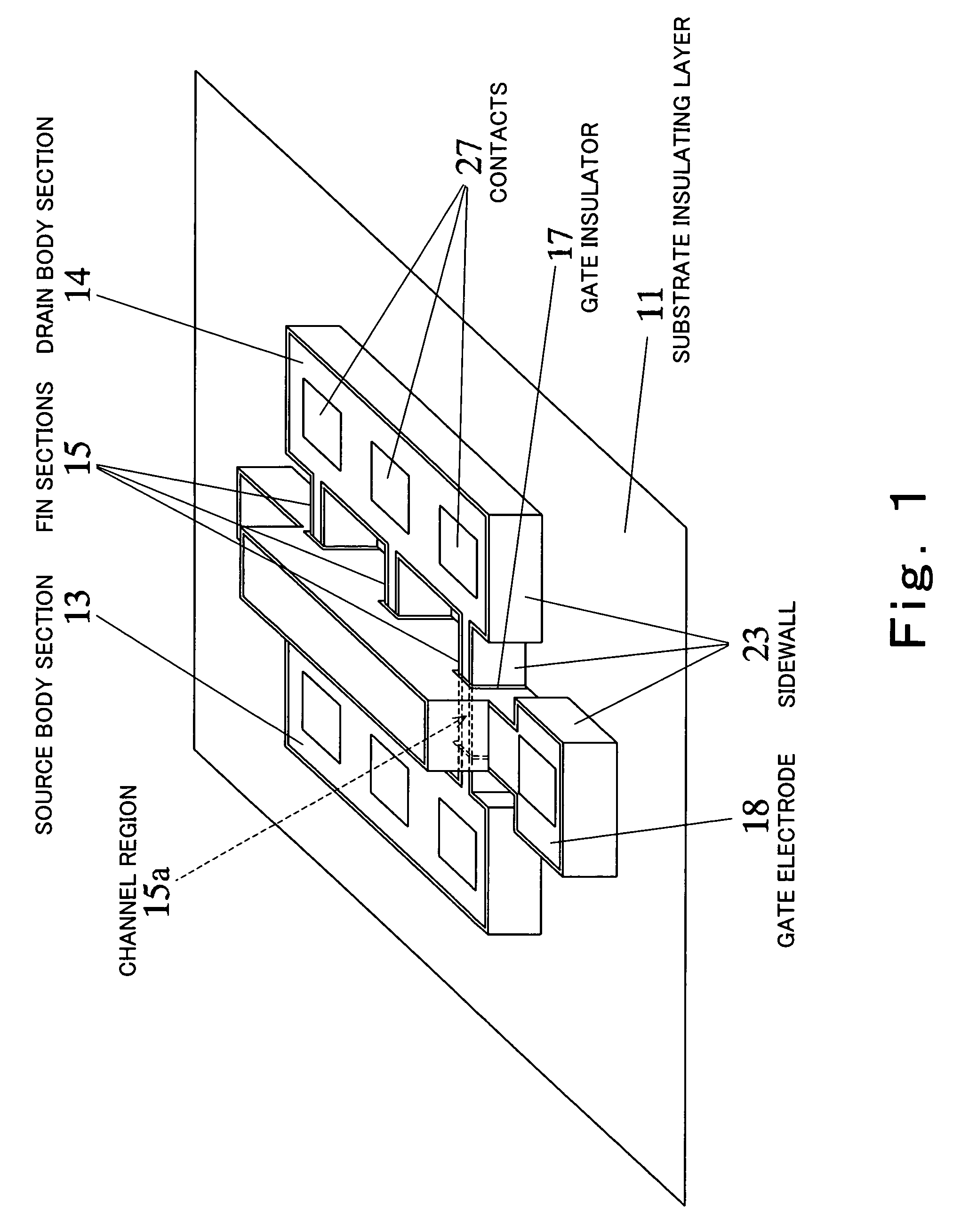

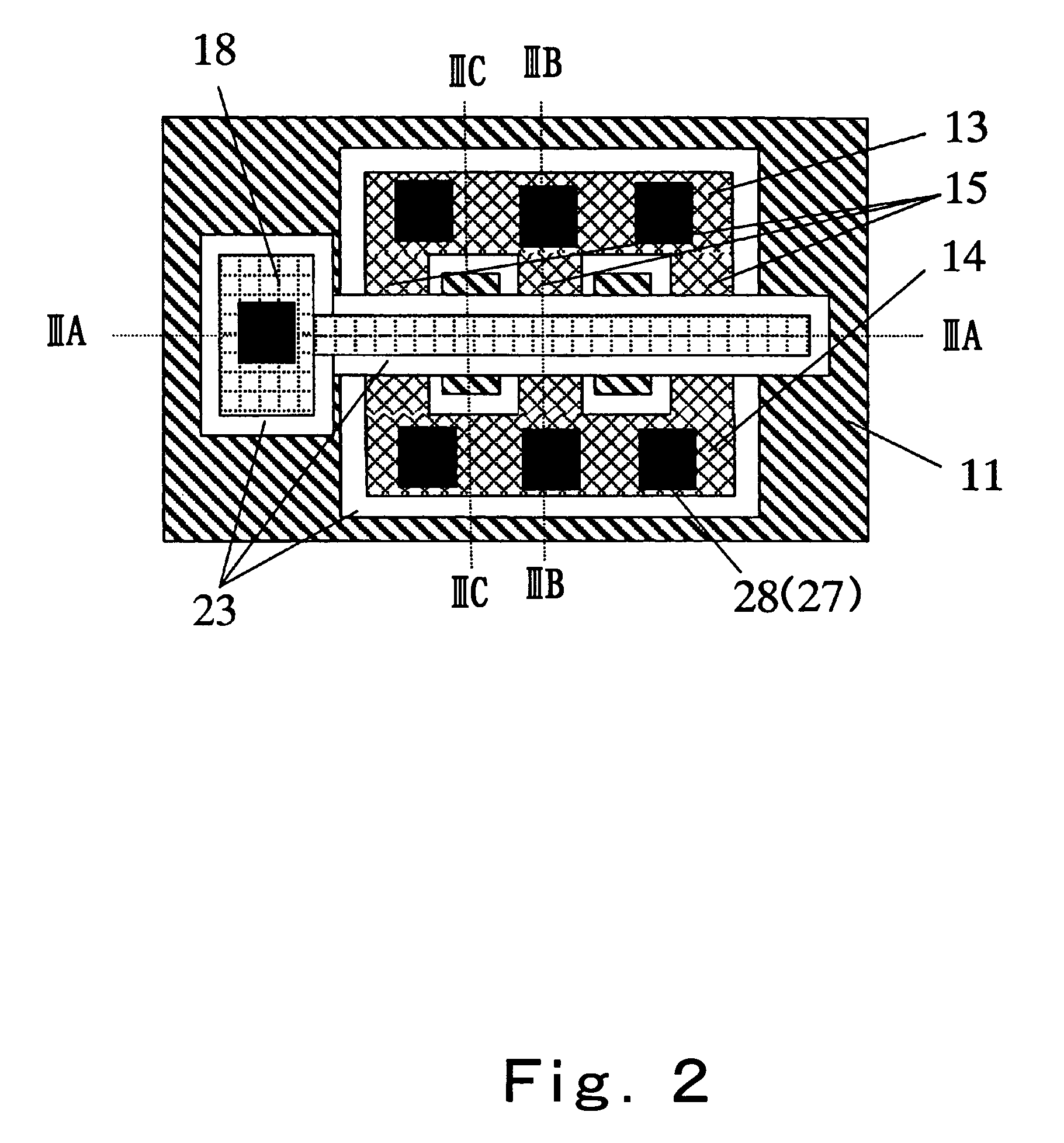

Strained channel finFET device

InactiveUS7473967B2High carrier mobilityImprove current drive capabilityTransistorSolid-state devicesSemiconductorLattice strain

A semiconductor device according to this invention includes: a first insulating layer (11); a first body section (13) including an island-shaped semiconductor formed on the first insulating layer; a second body section (14) including an island-shaped semiconductor formed on the first insulating layer; a ridge-shaped connecting section (15) formed on the first insulating layer to interconnect the first body section and the second body section; a channel region (15a) formed by at least a part of the connecting section in lengthwise direction of the connecting section; a gate electrode (18) formed to cover a periphery of the channel region, with a second insulating layer intervening therebetween; a source region formed to extend over the first body section and a portion of the connecting section between the first body section and the channel region; and a drain region formed to extend over the second body section and a portion of the connecting section between the second body section and the channel region, wherein a semiconductor forming the channel region has a lattice strain.

Owner:PANASONIC CORP

Long Wavelength Infrared Superlattice

InactiveUS20130043459A1Extend the cutoff wavelengthQuality lossSemiconductor/solid-state device manufacturingNanoopticsGallium antimonideIndium arsenide

An embodiment of the present invention improves the fabrication and operational characteristics of a type-II superlattice material. Layers of indium arsenide and gallium antimonide comprise the bulk of the superlattice structure. One or more layers of indium antimonide are added to unit cells of the superlattice to provide a further degree of freedom in the design for adjusting the effective bandgap energy of the superlattice. One or more layers of gallium arsenide antimonide are added to unit cells of the superlattice to counterbalance the crystal lattice strain forces introduced by the aforementioned indium antimonide layers.

Owner:SVT ASSOCS

Thermal barrier coating and process therefor

InactiveUS7087266B2Reduce conductivityLow densityMolten spray coatingBlade accessoriesStrain energyVolumetric Mass Density

Owner:GENERAL ELECTRIC CO

Blue-light-emitting phosphor and light-emitting device equipped with the blue-light-emitting phosphor

InactiveUS20130200777A1High strengthImprove stabilityDischarge tube luminescnet screensElectroluminescent light sourcesLe Bail methodX-ray

Owner:UBE IND LTD

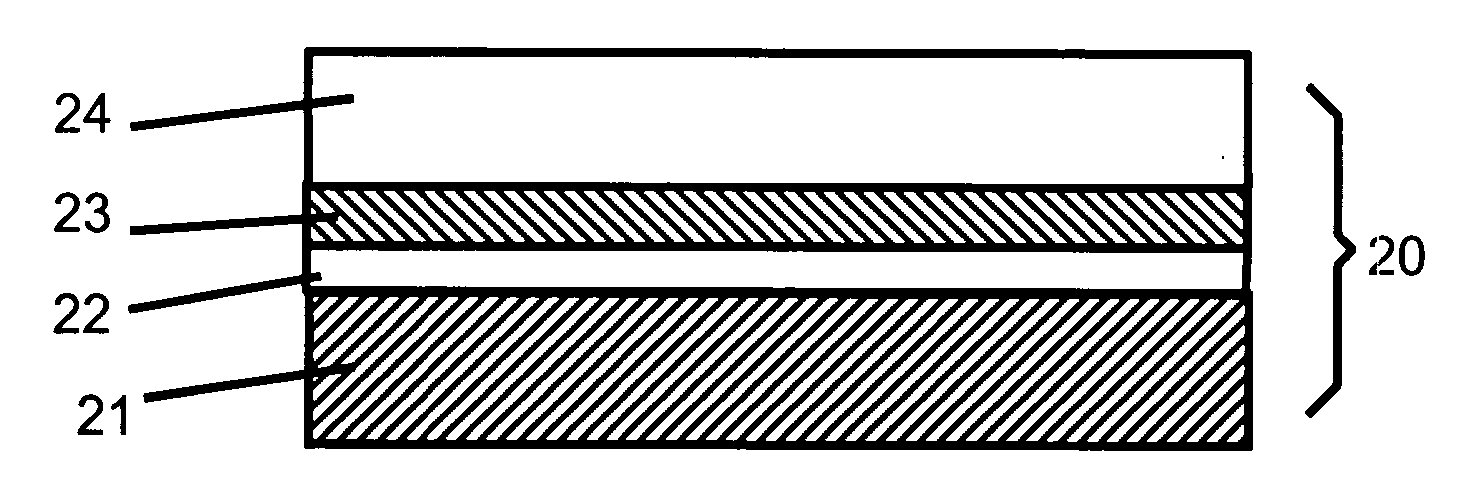

Thin-film dielectric and thin-film capacitor element

ActiveUS20160027587A1High dielectric constantFixed capacitor dielectricStacked capacitorsDielectricSingle crystal

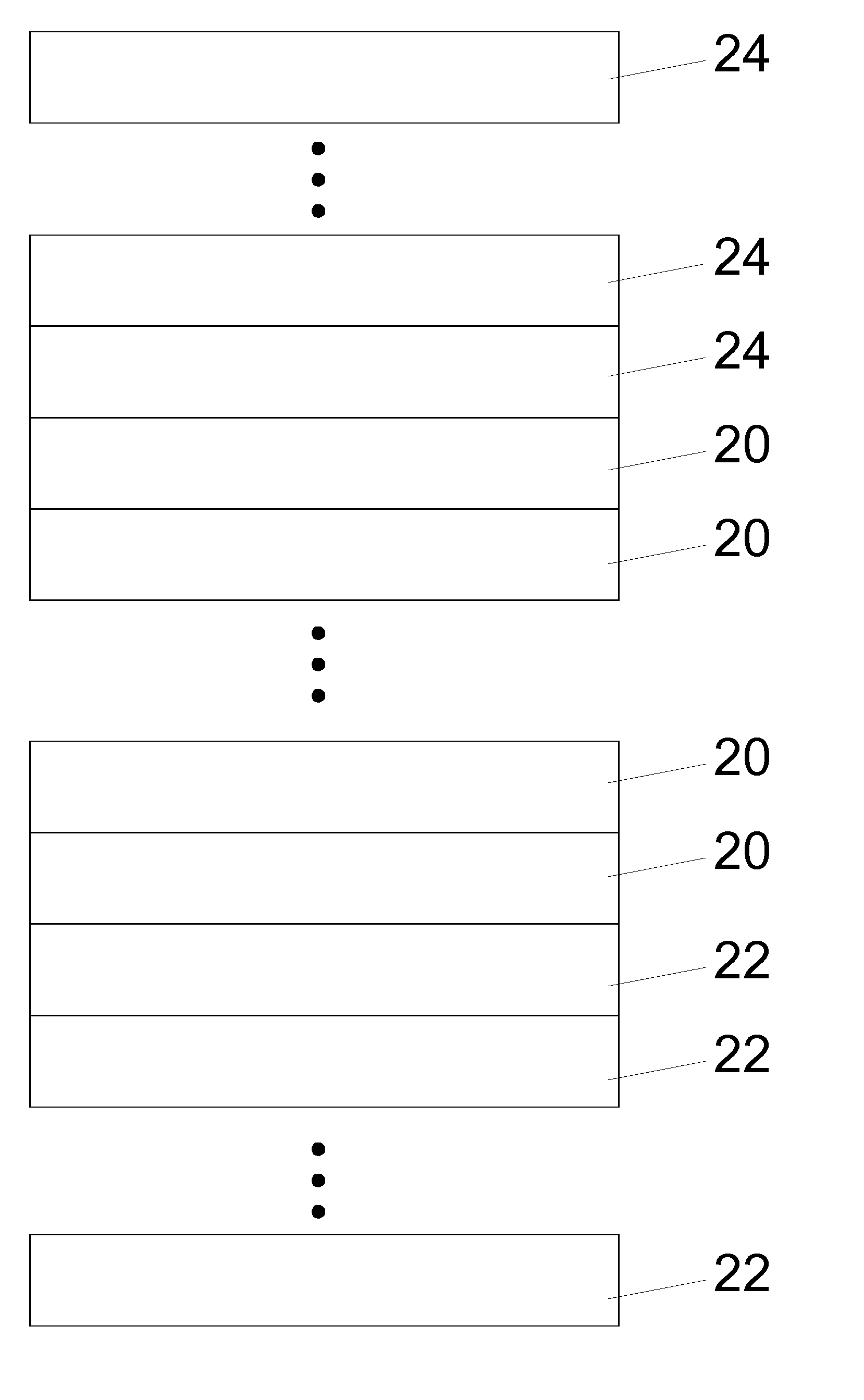

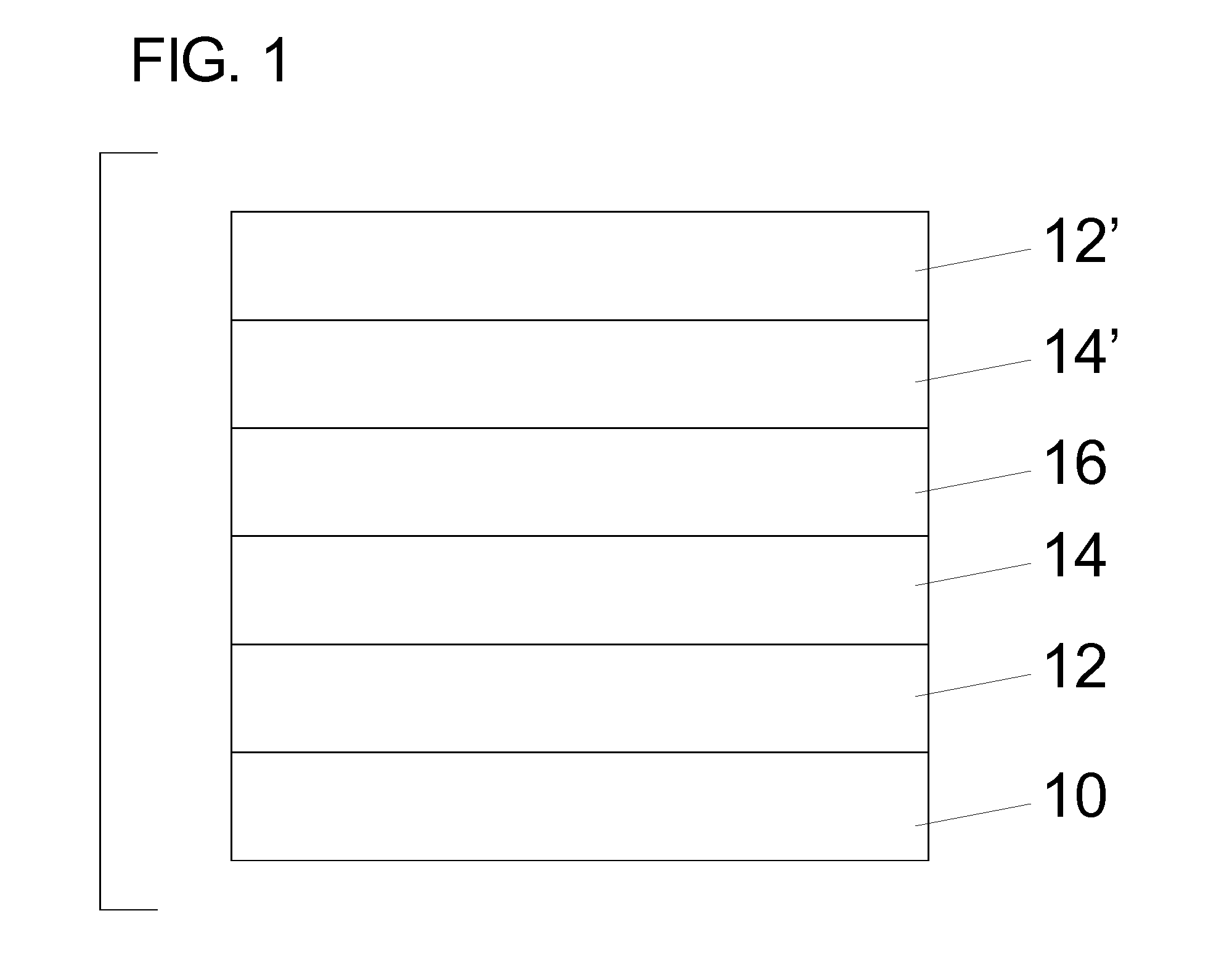

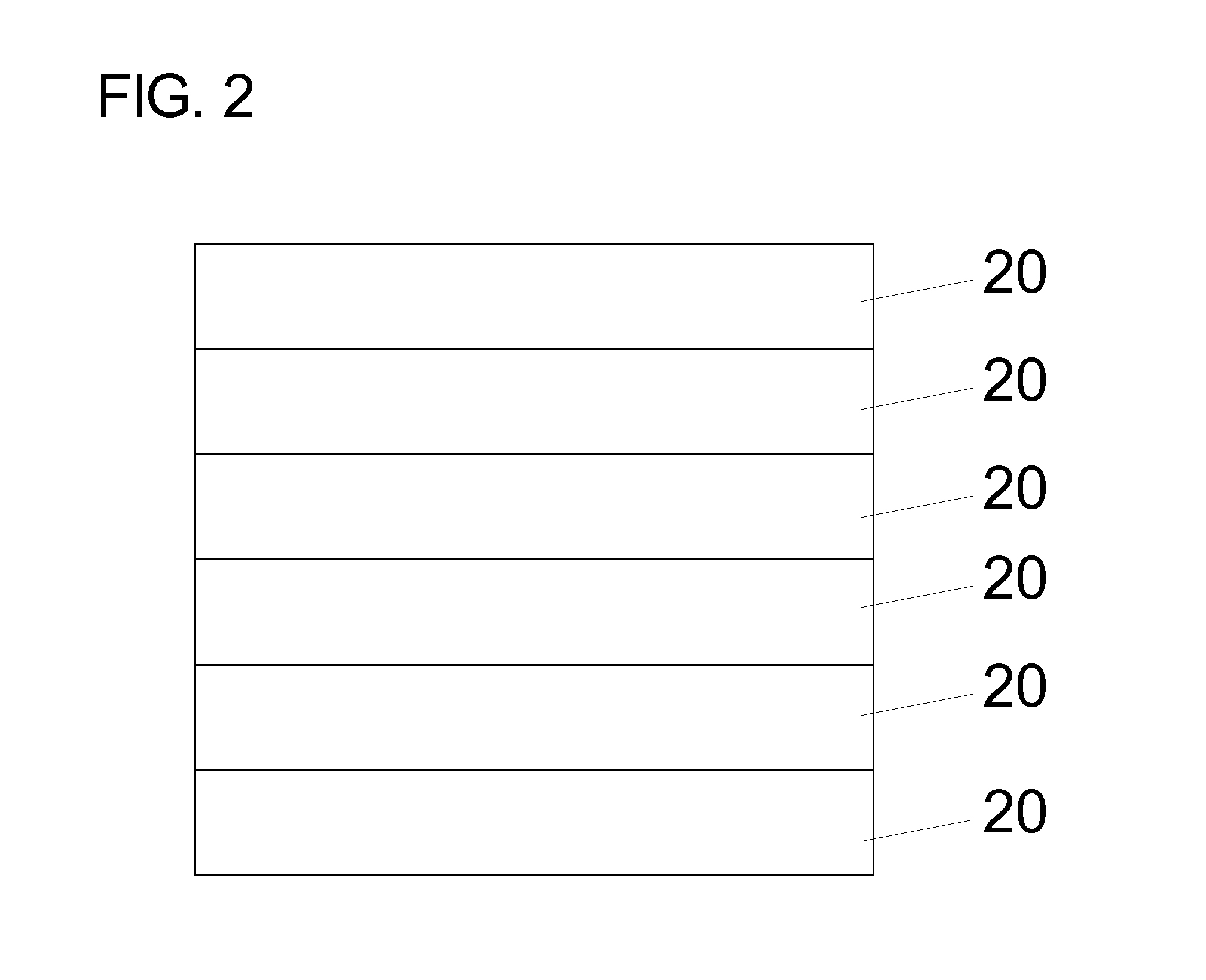

The present invention provides a thin-film dielectric having a higher dielectric constant than usual ones and not requiring a special single crystal substrate, and also provides a large-capacity thin-film capacitor element using the thin-film dielectric.A BaTiO3-based perovskite solid solution and a KNbO3-based perovskite solid solution are alternately formed to form a crystal structure gradient region where a lattice constant continuously changes at the interface, and thus crystal lattice strain occurs, thereby permitting the production of a thin-film dielectric having a high dielectric constant. Also, a large-capacity thin-film capacitor element can be produced by using the thin-film dielectric of the present invention.

Owner:TDK CORPARATION

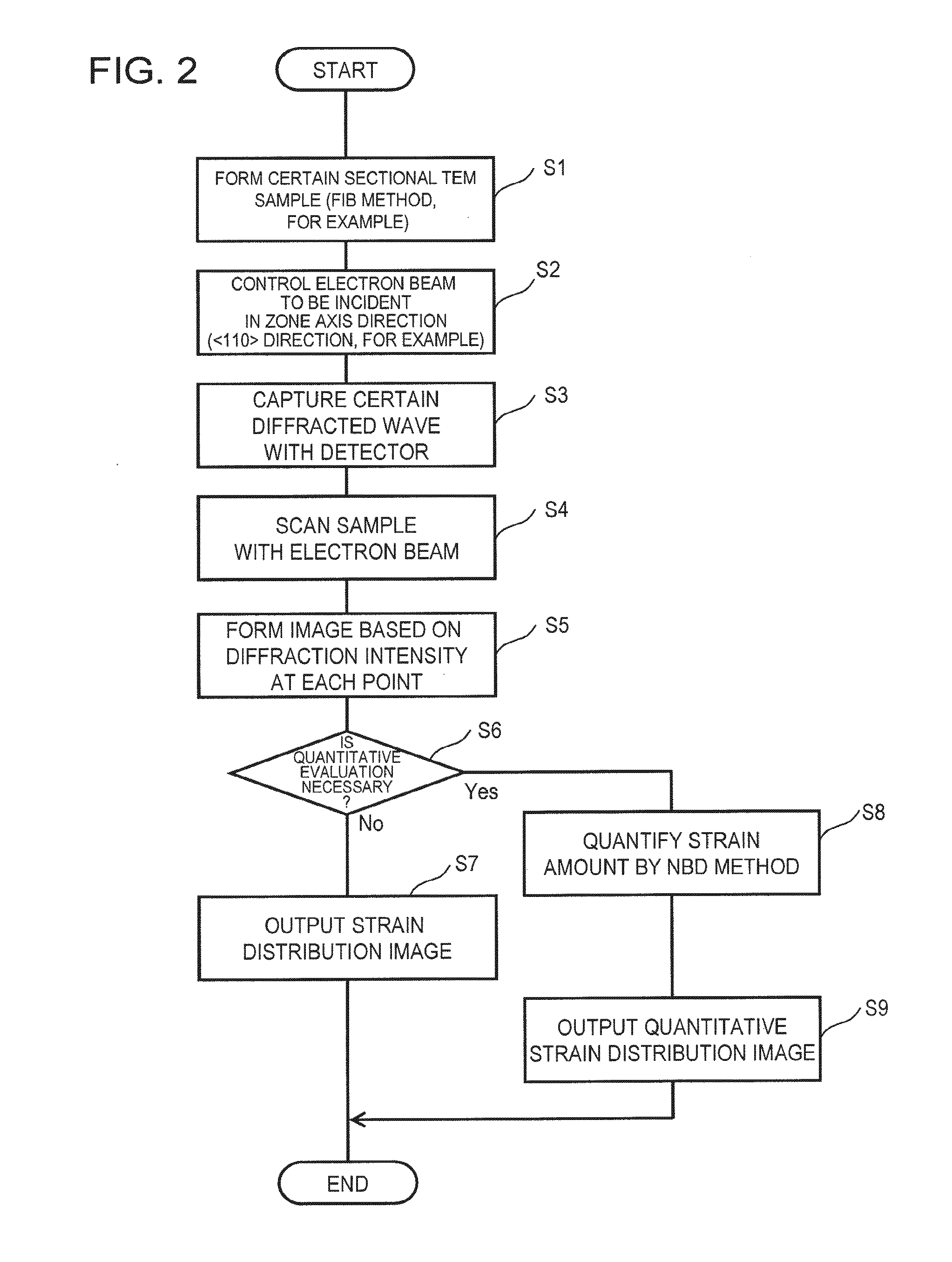

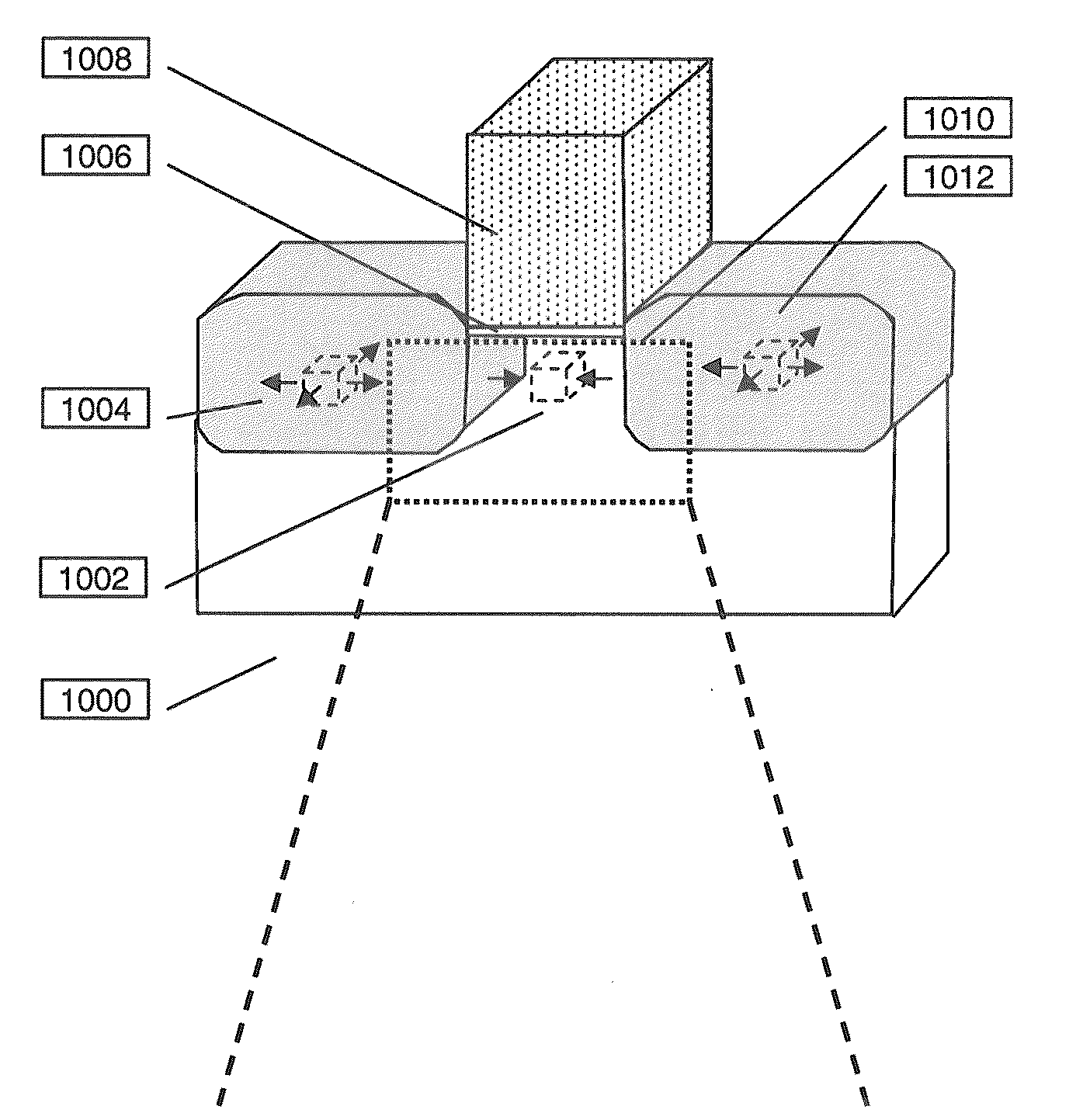

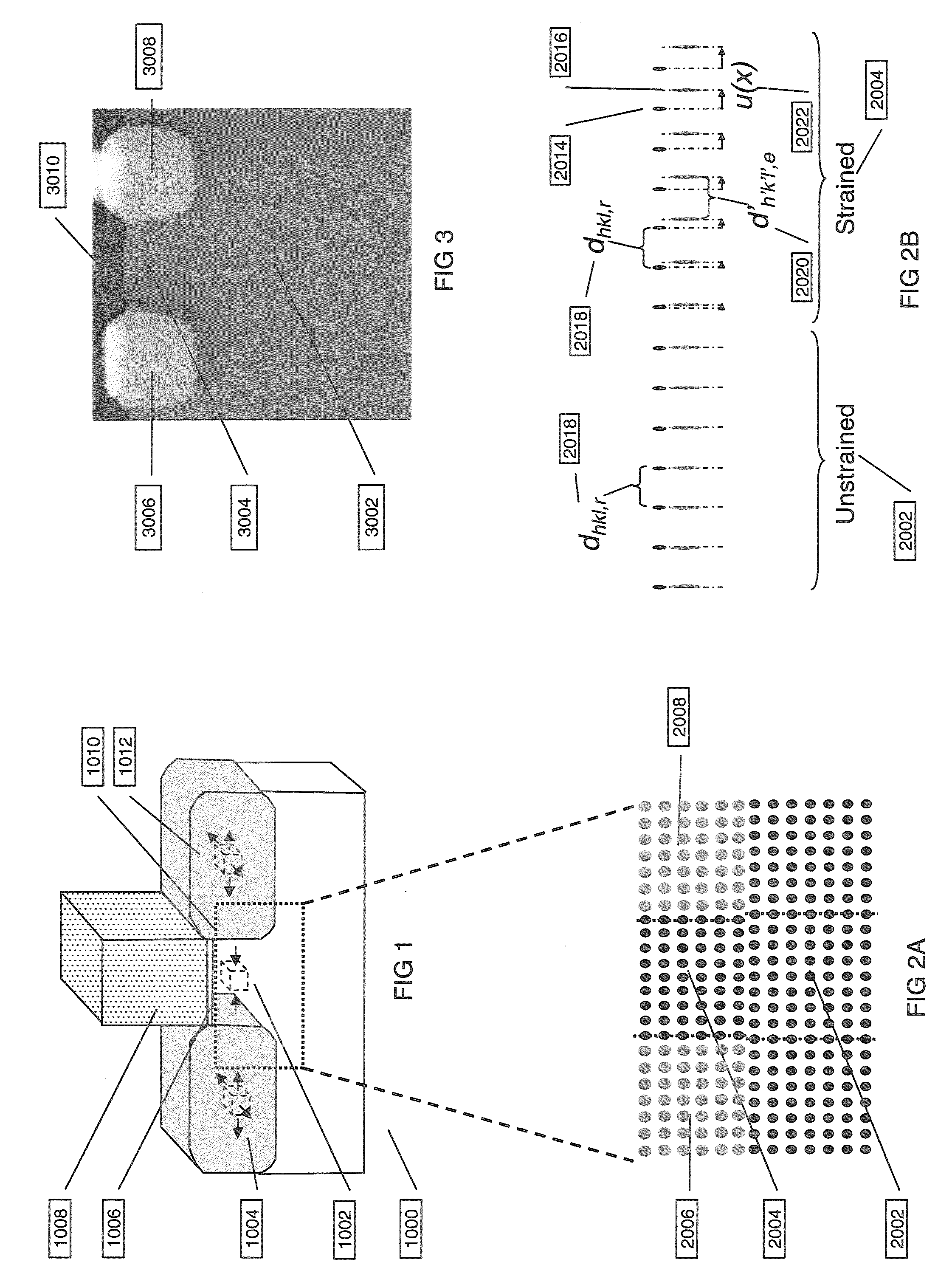

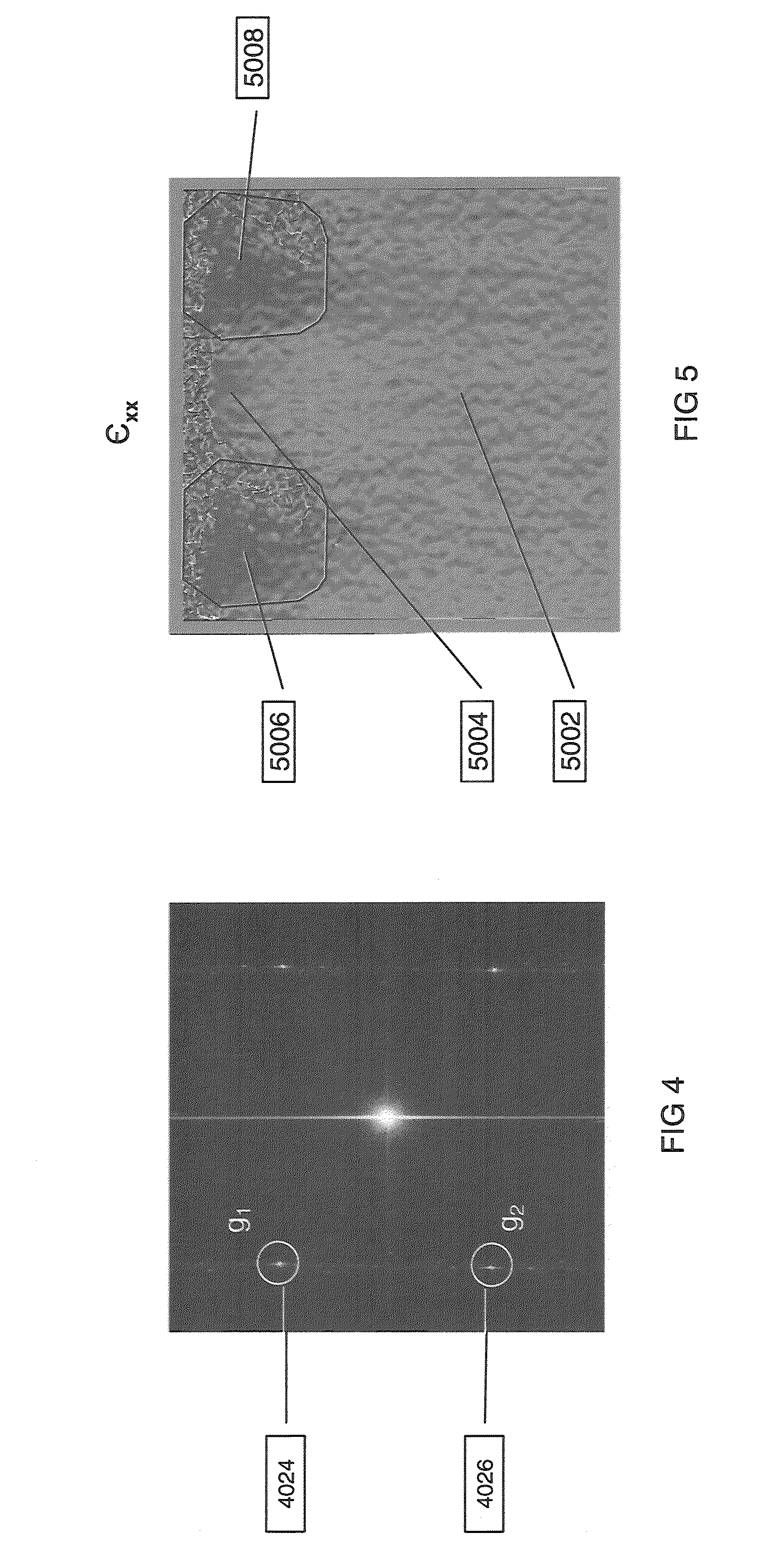

Method and system of evaluating distribution of lattice strain on crystal material

InactiveUS20120292504A1Not effectiveMaterial analysis using wave/particle radiationElectric discharge tubesCrystal structureCondensed matter physics

A crystal material lattice strain evaluation method includes illuminating a sample having a crystal structure with an electron beam in a zone axis direction, and selectively detecting a certain diffracted wave diffracted in a certain direction among a plurality of diffracted waves diffracted by the sample. The method further includes repeating the illuminating step and the selectively detecting step while scanning the sample, and obtaining a strain distribution image in a direction corresponding to the certain diffracted wave from diffraction intensity at each point of the sample.

Owner:LONGITUDE SEMICON S A R L

Reproducible lattice strain measurement method

InactiveUS20110084209A1Material analysis using wave/particle radiationGamma-ray/x-ray microscopesScan lineLight beam

Lattice strain is reproducibly measured using geometric phase analysis (GPA) of a high angle annular dark field mode scanning transmission electron microscope (HAADF-STEM). Errors caused by beam shift (also known as fly-back error) between scan lines are eliminated.

Owner:TEXAS INSTR INC

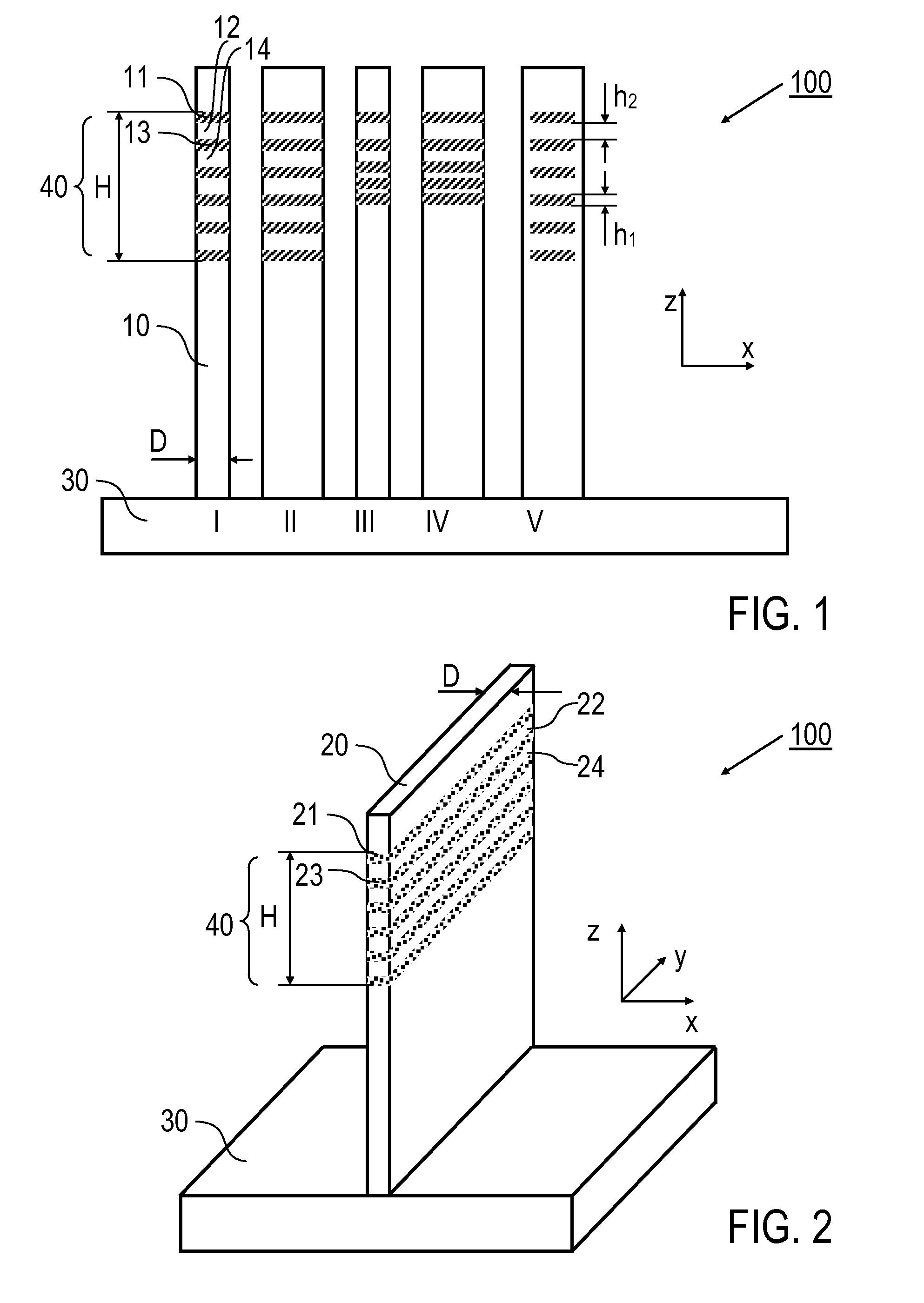

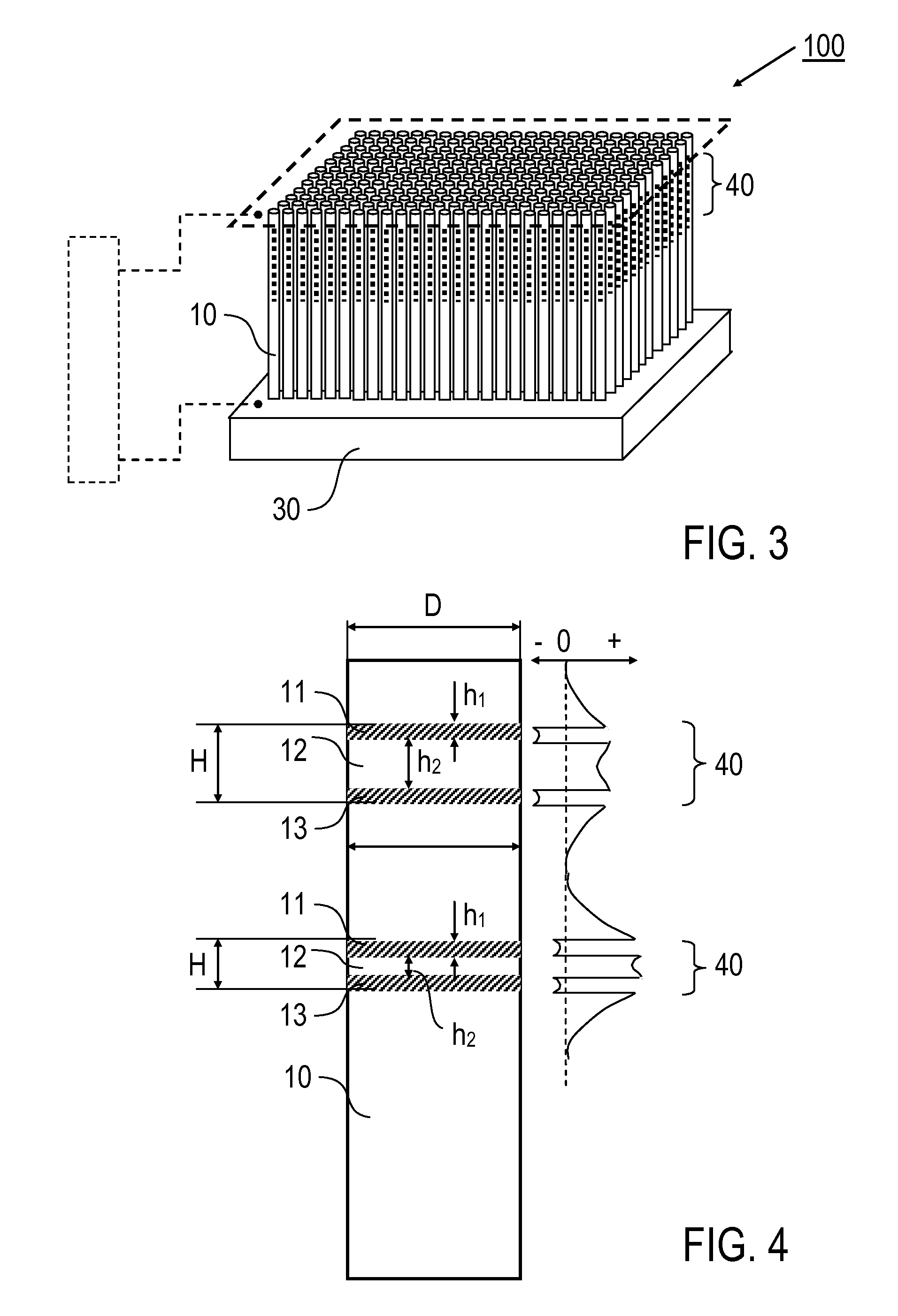

Production of a semiconductor device having at least one column-shaped or wall-shaped semiconductor element

ActiveUS9184235B2Simple procedureImprove accuracySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLattice constant

Described is a method for producing a semiconductor device (100), in which at least one column-shaped or wall-shaped semiconductor device (10, 20) extending in a main direction (z) is formed on a substrate (30), wherein at least two sections (11, 13, 21, 23) of a first crystal type and one section (12, 22) of a second crystal type therebetween are formed in an active region (40), each section with a respective predetermined height (h1, h2), wherein the first and second crystal types have different lattice constants and each of the sections of the first crystal type has a lattice strain which depends on the lattice constants in the section of the second crystal type. According to the invention, at least a height (h2) of the section (12, 22) of the second crystal type and a lateral thickness (D) of the active region (40) is formed perpendicular to the main direction, in such a manner that the lattice strain in one of the sections (11) of the first crystal type also depends on the lattice constants in the other section (13) of the first crystal type. A semiconductor device (100) is also described, having at least one column-shaped or wall-shaped semiconductor element (10, 20) on a substrate (30), which can be produced in particular by means of the stated method.

Owner:FORSCHUNGSVERBUND BERLIN EV

High speed lateral heterojunction MISFETS realized by 2-dimensional bandgap engineering and methods thereof

ActiveUS7569442B2Superb performanceSuperb scalabilityTransistorSemiconductor/solid-state device manufacturingCMOSHeterojunction

A method for forming and the structure of a strained lateral channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a single crystal semiconductor substrate wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region. The invention reduces the problem of leakage current from the source region via the hetero-junction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials and alloy composition.

Owner:GLOBALFOUNDRIES U S INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com