Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

76594 results about "Alloy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An alloy is a combination of metals or a combination of one or more metals with non-metallic elements. For example, combining the metallic elements gold and copper produces red gold, gold and silver becomes white gold, and silver combined with copper produces sterling silver. Elemental iron, combined with non-metallic carbon or silicon, produces alloys called steel or silicon steel. The resulting mixture forms a substance with properties that often differ from those of the pure metals, such as increased strength or hardness. Unlike other substances that may contain metallic bases but do not behave as metals, such as aluminium oxide (sapphire), beryllium aluminium silicate (emerald) or sodium chloride (salt), an alloy will retain all the properties of a metal in the resulting material, such as electrical conductivity, ductility, opaqueness, and luster. Alloys are used in a wide variety of applications, from the steel alloys, used in everything from buildings to automobiles to surgical tools, to exotic titanium-alloys used in the aerospace industry, to beryllium-copper alloys for non-sparking tools. In some cases, a combination of metals may reduce the overall cost of the material while preserving important properties. In other cases, the combination of metals imparts synergistic properties to the constituent metal elements such as corrosion resistance or mechanical strength. Examples of alloys are steel, solder, brass, pewter, duralumin, bronze and amalgams.

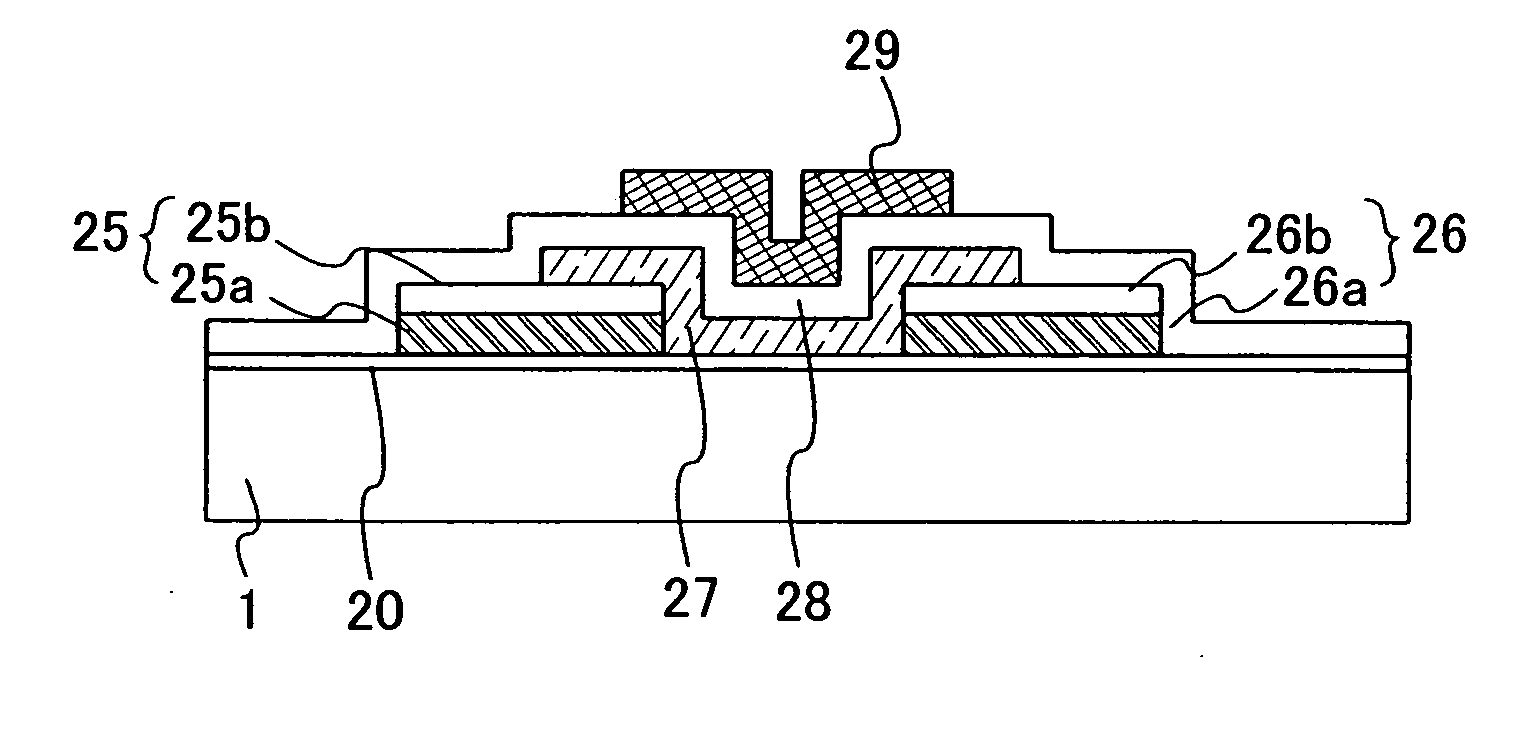

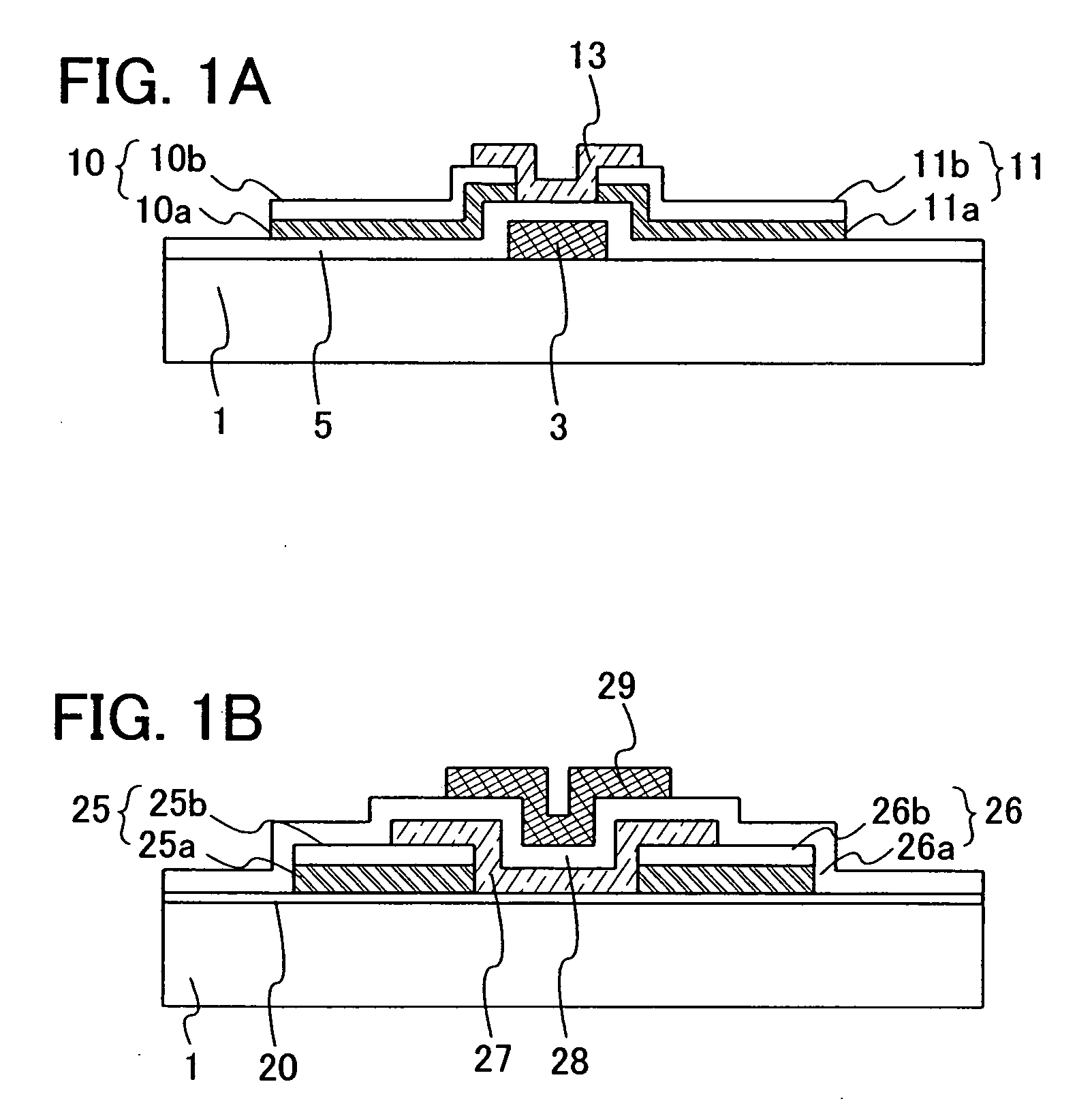

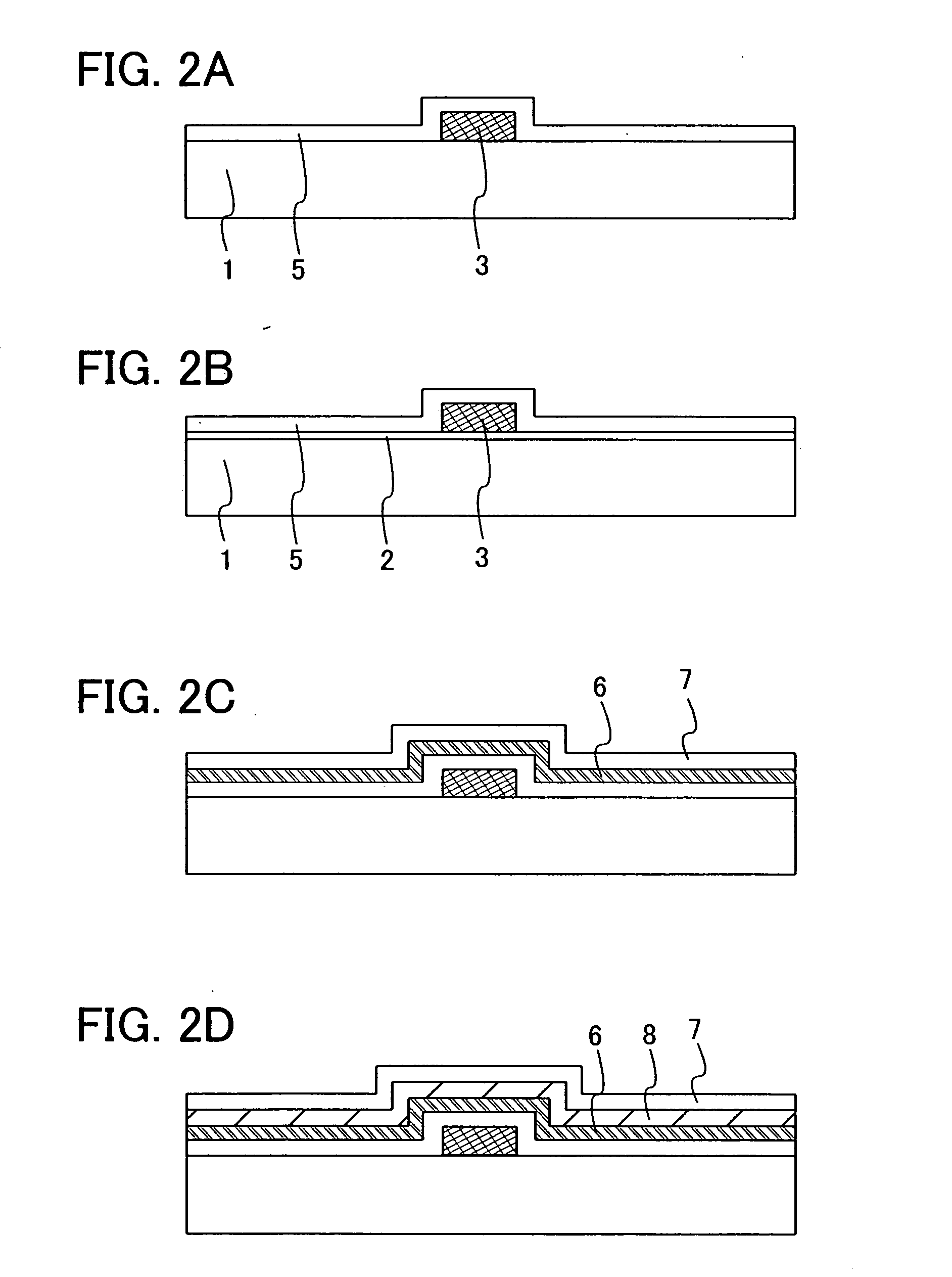

Semiconductor device and manufacturing method thereof

ActiveUS20070108446A1Low resistance of wireLower resistanceTransistorElectroluminescent light sourcesAlloySilicon oxide

To provide a semiconductor device in which a defect or fault is not generated and a manufacturing method thereof even if a ZnO semiconductor film is used and a ZnO film to which an n-type or p-type impurity is added is used for a source electrode and a drain electrode. The semiconductor device includes a gate insulating film formed by using a silicon oxide film or a silicon oxynitride film over a gate electrode, an Al film or an Al alloy film over the gate insulating film, a ZnO film to which an n-type or p-type impurity is added over the Al film or the Al alloy film, and a ZnO semiconductor film over the ZnO film to which an n-type or p-type impurity is added and the gate insulating film.

Owner:SEMICON ENERGY LAB CO LTD

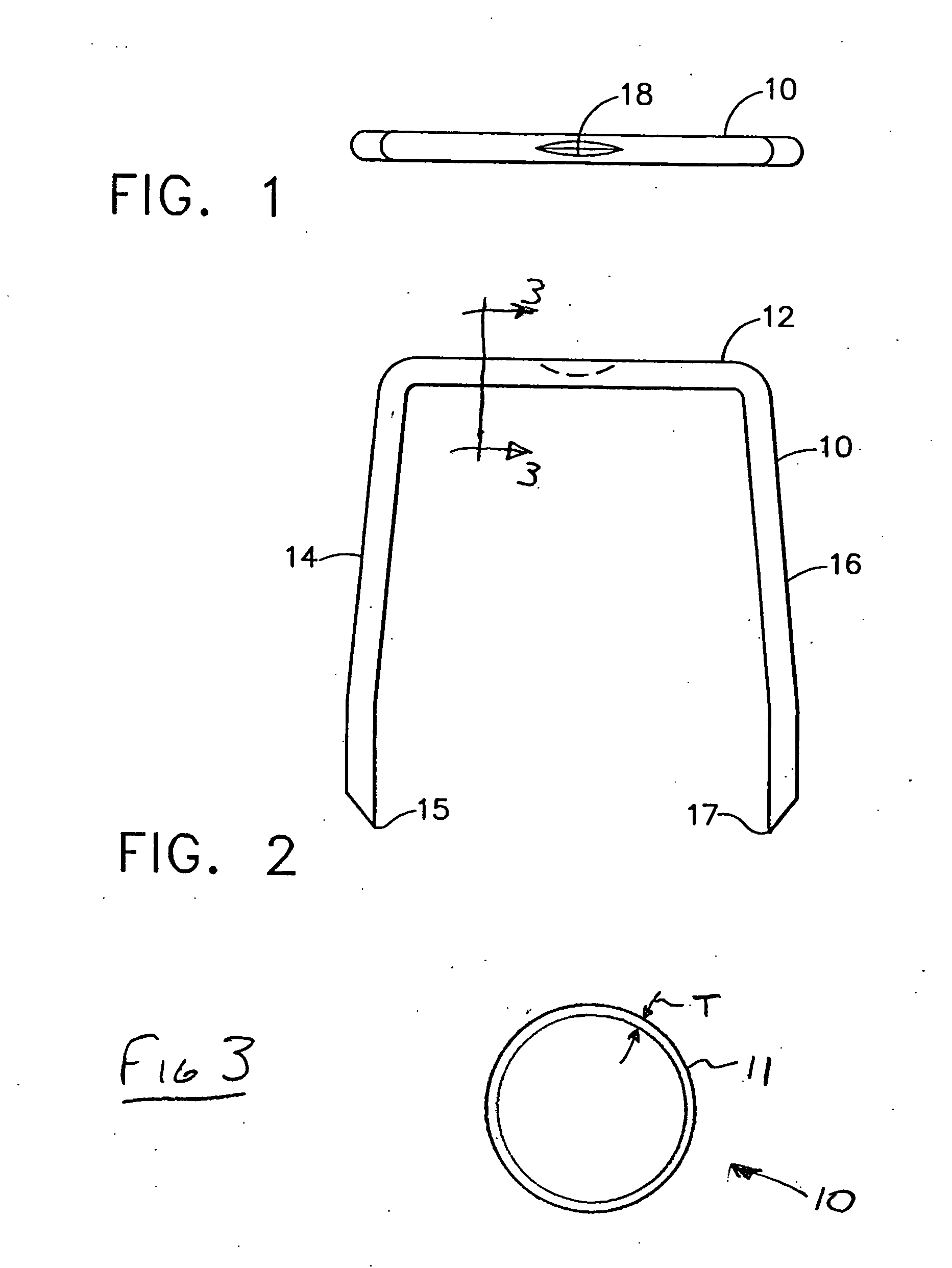

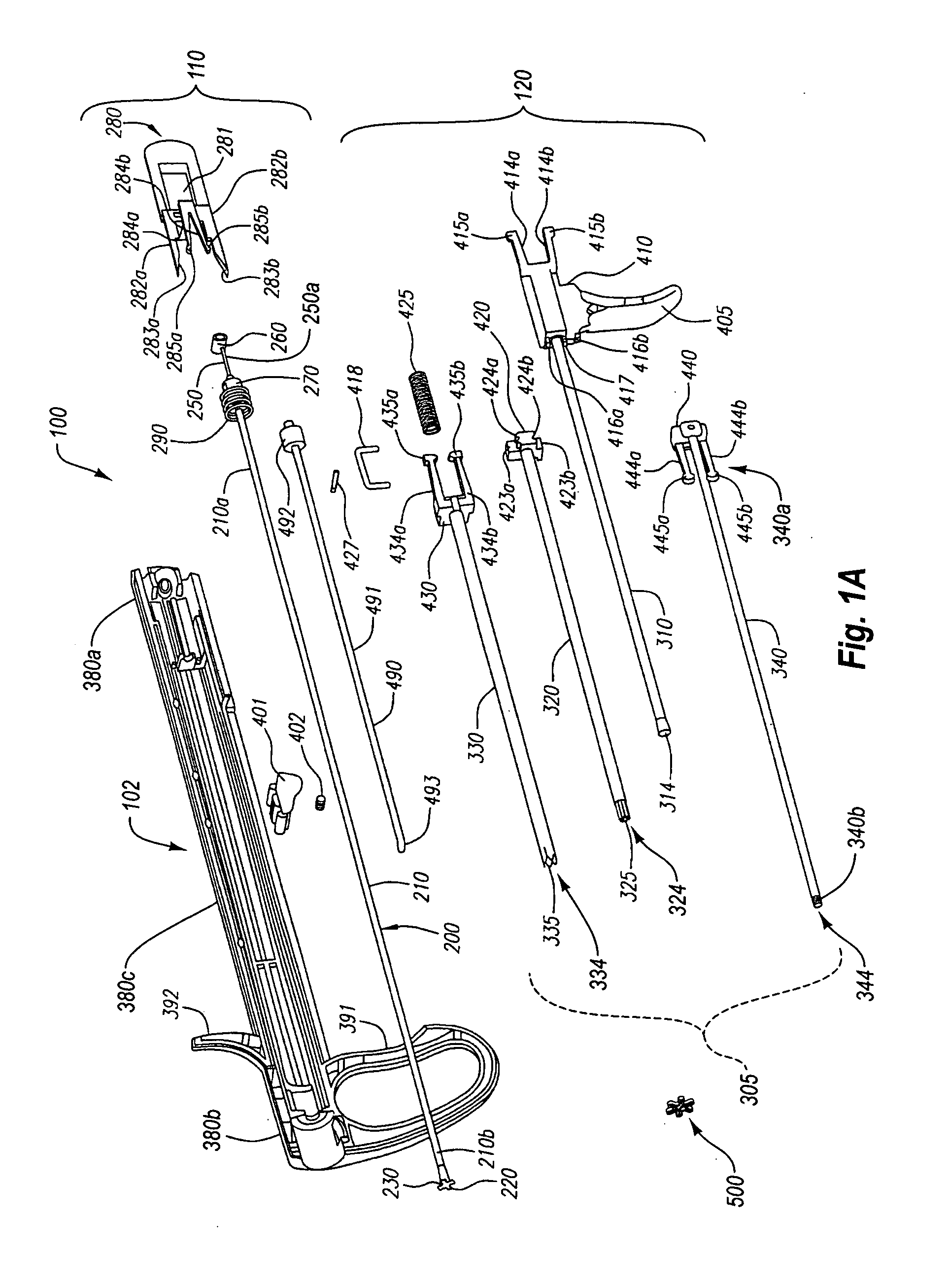

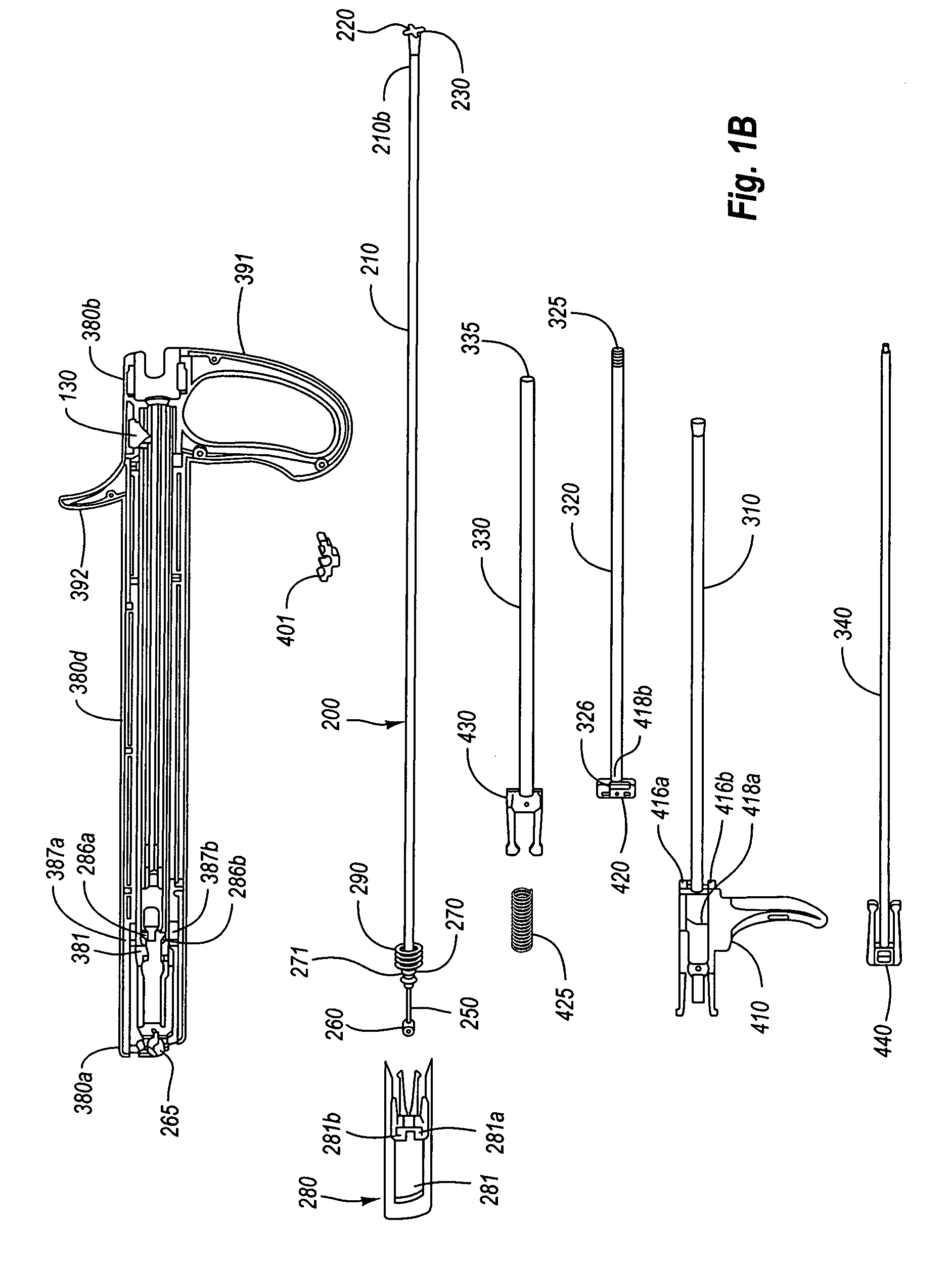

Surgical implant alloy

InactiveUS20060052825A1Reduce the possibilityReduce or minimize sparking or electrical activityStaplesNailsSurface layerAlloy

The present invention provides a surgical implant which can be made of a metal that corrodes while implanted in the tissue of a patient. The surgical implant can include a electrical insulator for reducing the conductivity of the implant. The surgical implant can be in the form of a staple, and insulator can be in the form of an anodized surface layer.

Owner:ETHICON ENDO SURGERY INC

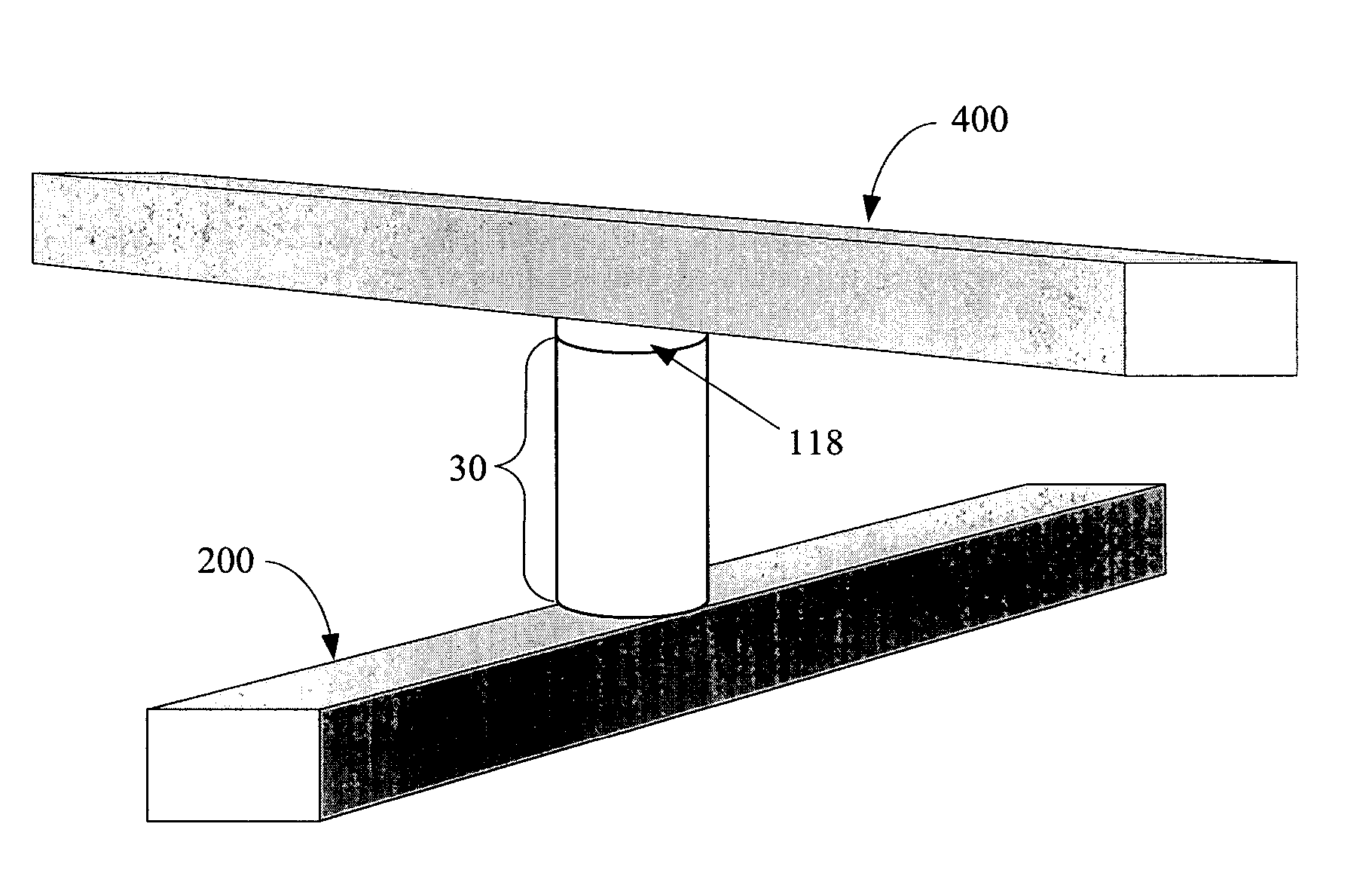

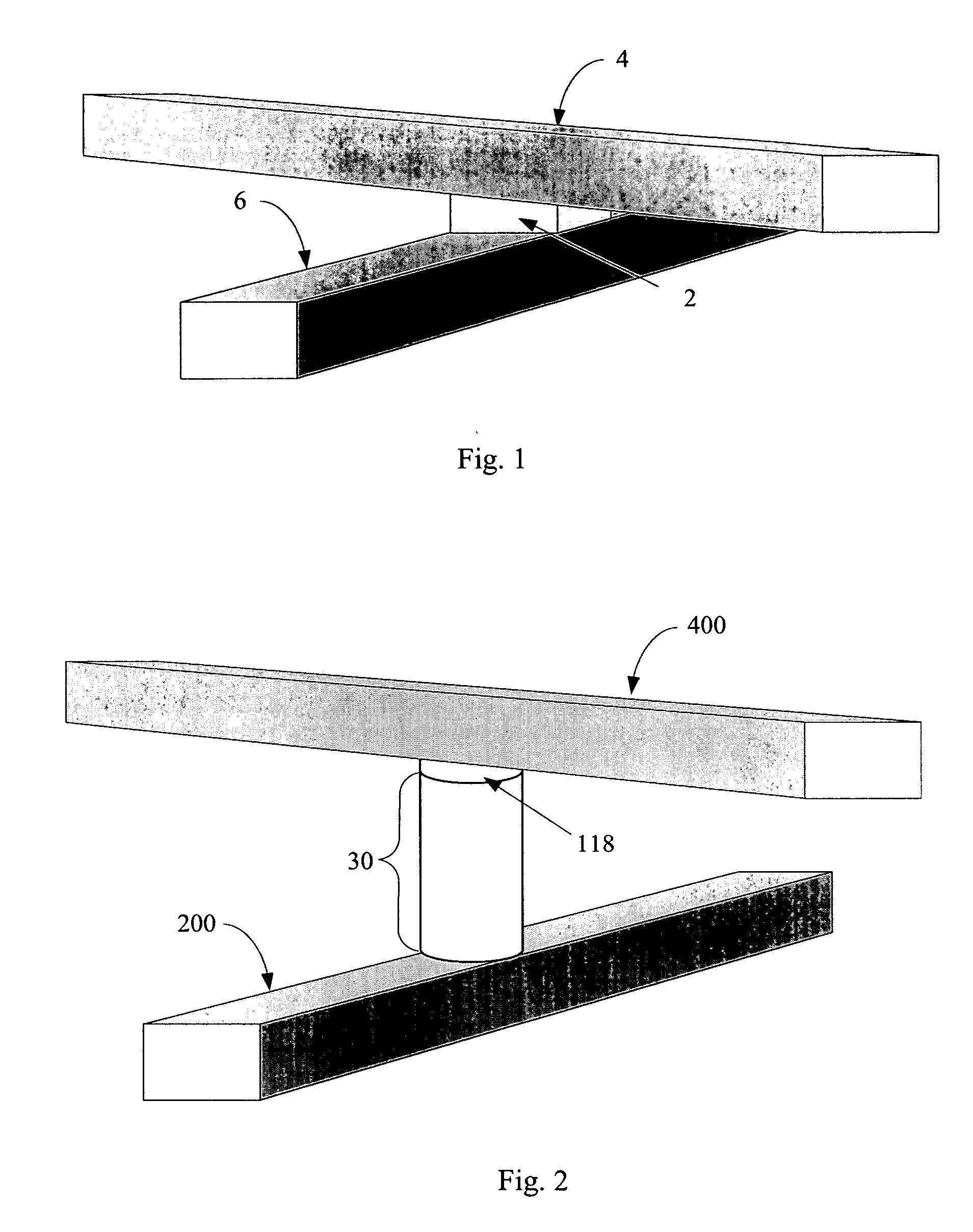

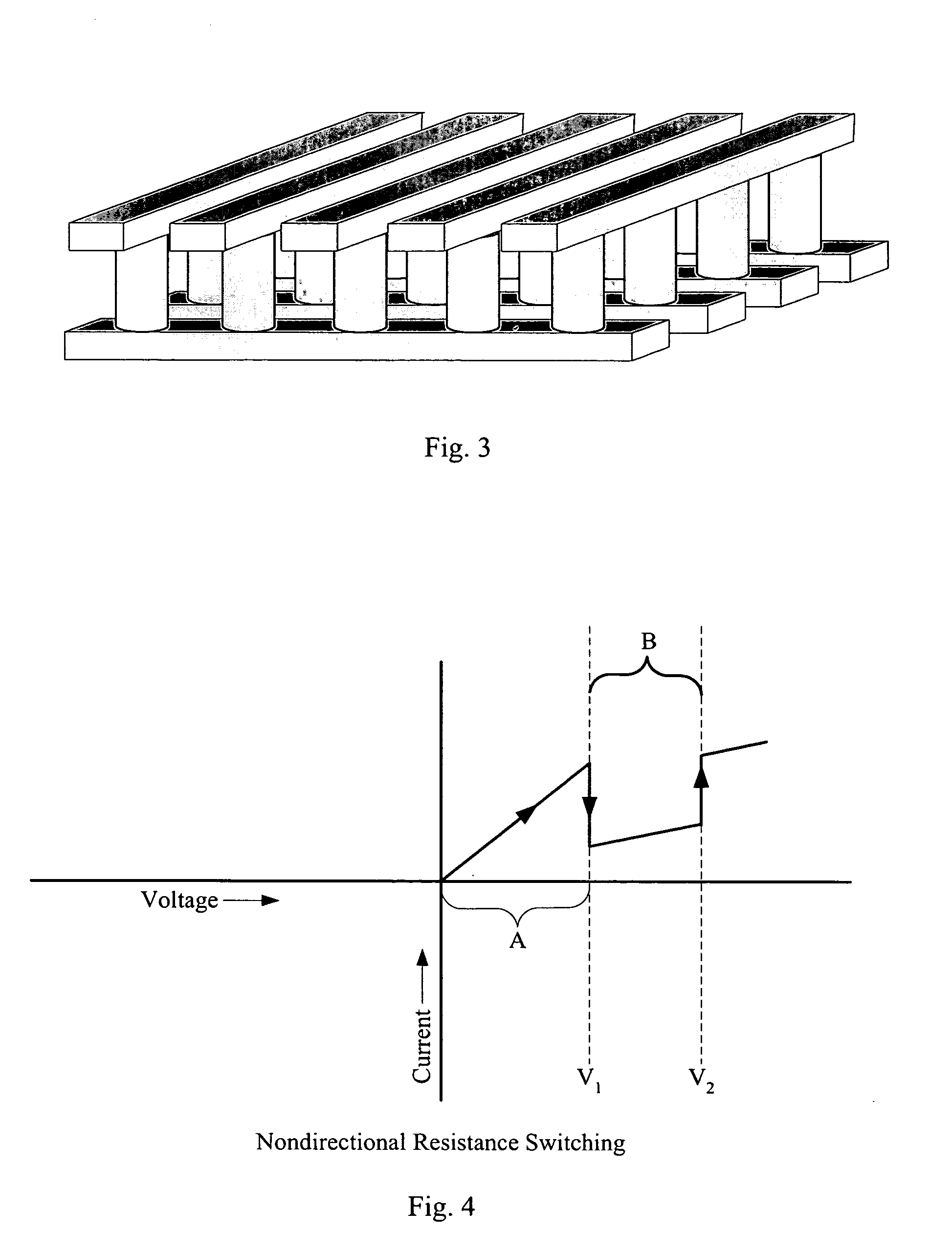

Rewriteable memory cell comprising a diode and a resistance-switching material

In a novel rewriteable nonvolatile memory cell formed above a substrate, a diode is paired with a reversible resistance-switching material, preferably a metal oxide or nitride such as, for example, NiO, Nb2O5, TiO2, HfO2, Al2O3, MgOx, CrO2, VO, BN, and AlN. In preferred embodiments, the diode is formed as a vertical pillar disposed between conductors. Multiple memory levels can be stacked to form a monolithic three dimensional memory array. In some embodiments, the diode comprises germanium or a germanium alloy, which can be deposited and crystallized at relatively low temperatures, allowing use of aluminum or copper in the conductors.

Owner:SANDISK TECH LLC

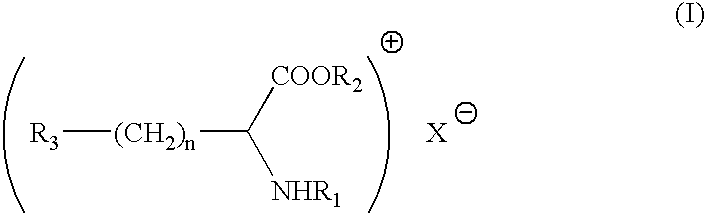

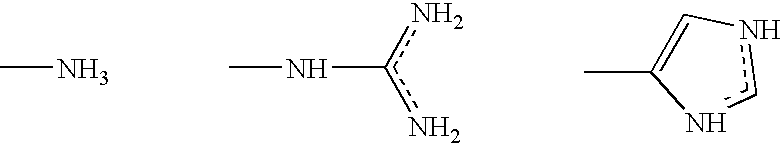

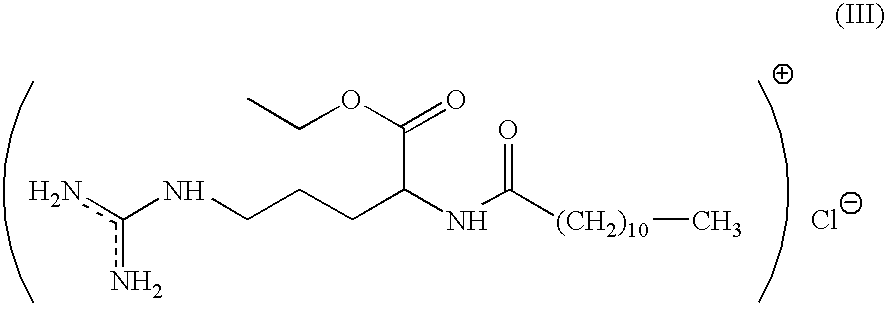

Antimicrobial composition

An antimicrobial composition comprising (a) a cationic surfactant derived from the condensation of fatty acids and esterified dibasic amino acids, such as lauric arginate, and (b) an antimicrobial metal, such as elemental silver or alloys thereof or silver compounds. The composition may be used as a stand alone antimicrobial formulation, or in combination with medical articles or medical devices.

Owner:ETHICON INC

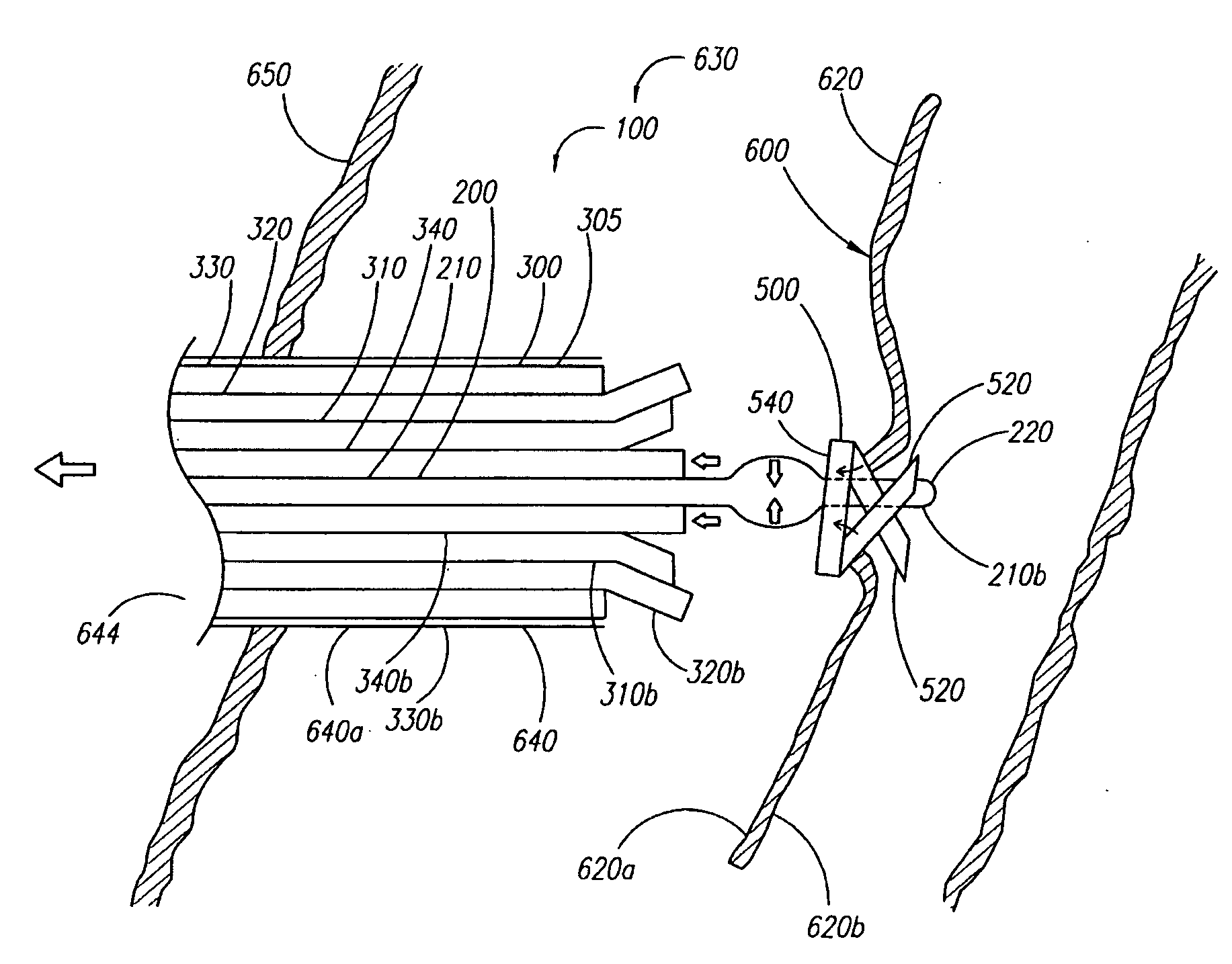

Antimicrobial closure element and closure element applier

A closure element is disclosed. The closure element includes a body. The body includes a plurality of tissue engaging portions extending from the body. The body is movable from a compressed state to a deployed state. The body includes a material. Silver or alloys thereof are included as a component of a coating over and / or a mixture with the material of at least a portion of the body.

Owner:ABBOTT LAB INC

Device and method employing shape memory alloy

InactiveUS6916159B2Low costSmall size and weightTesting/calibration apparatusVolume/mass flow measurementShape-memory alloyEngineering

Owner:THERASENSE

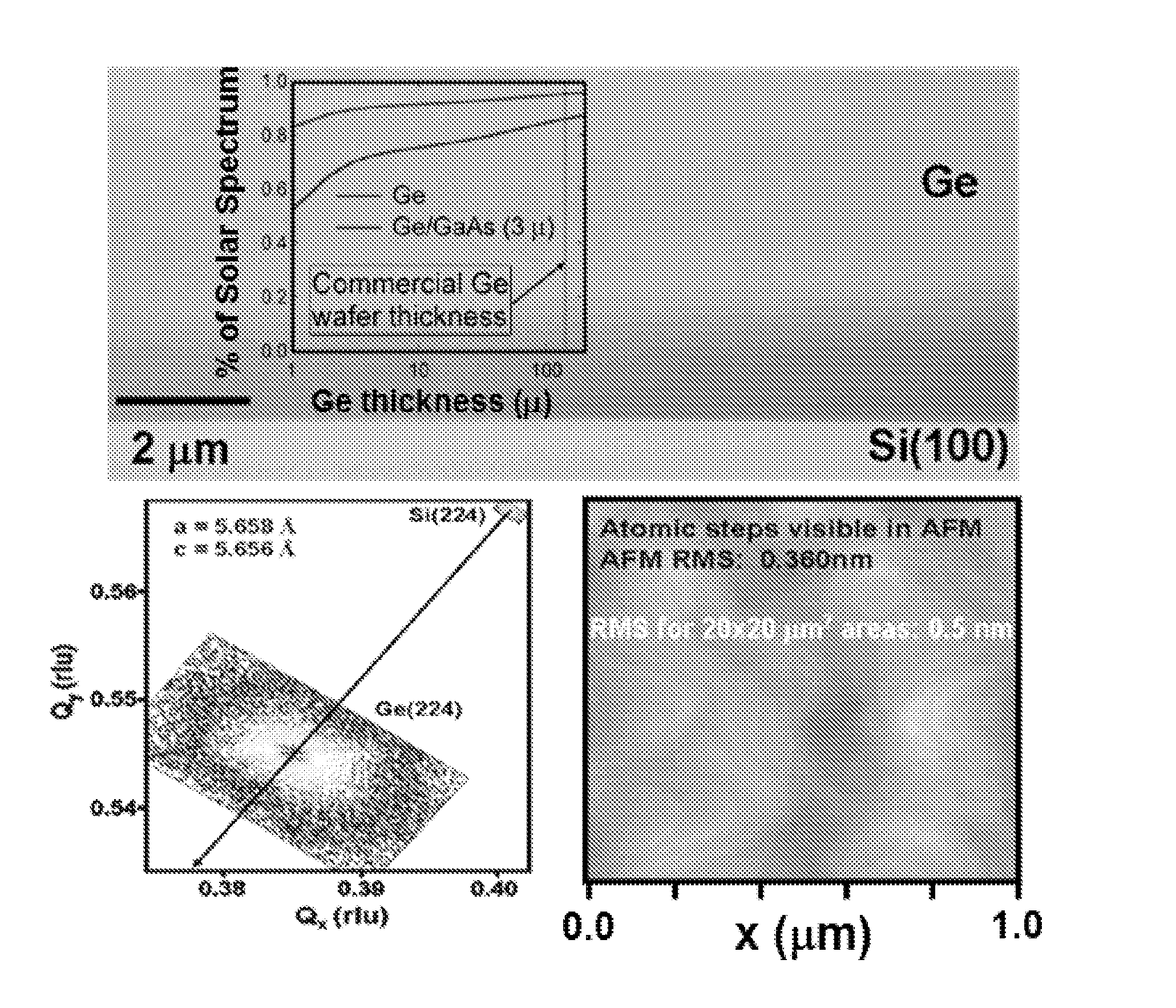

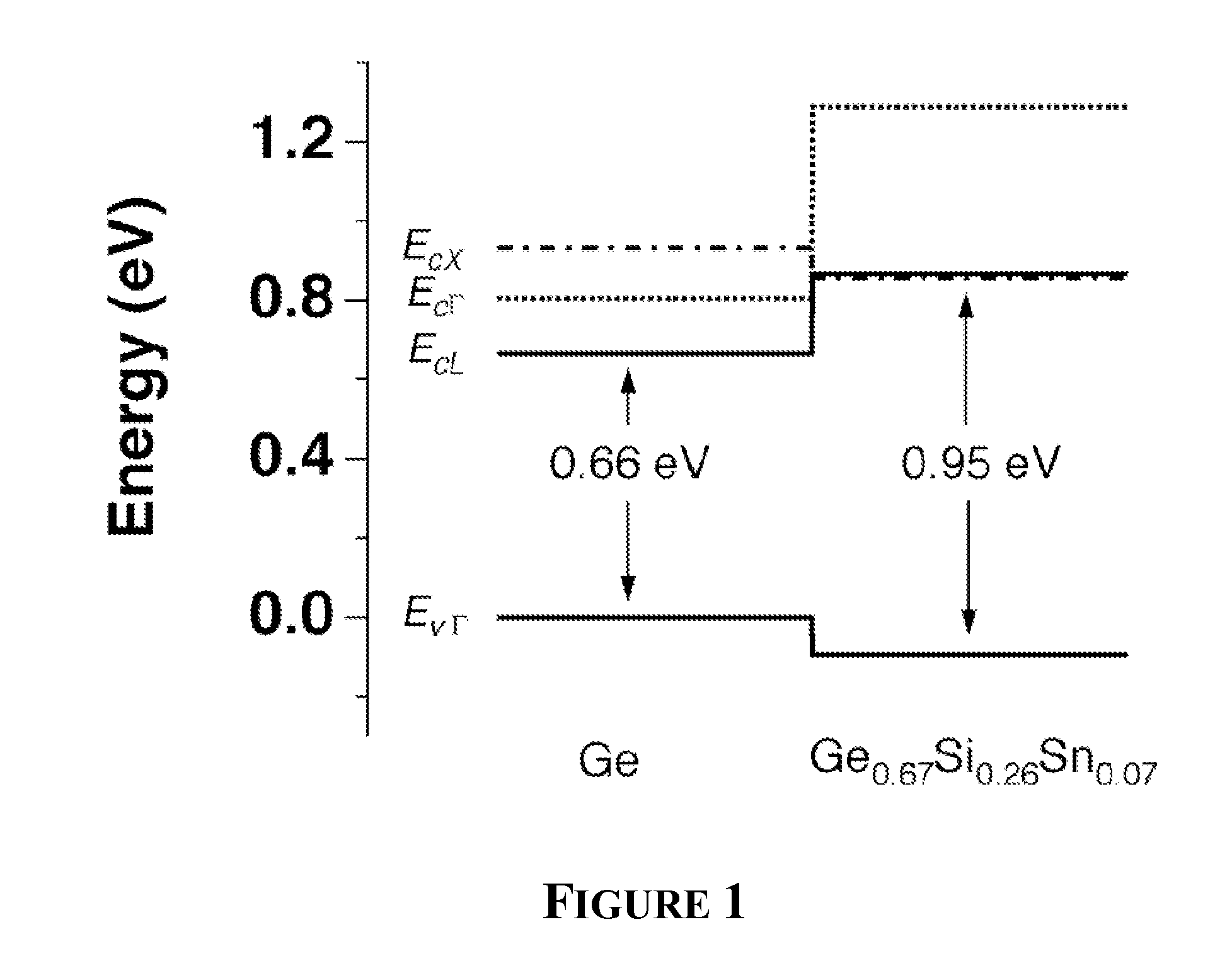

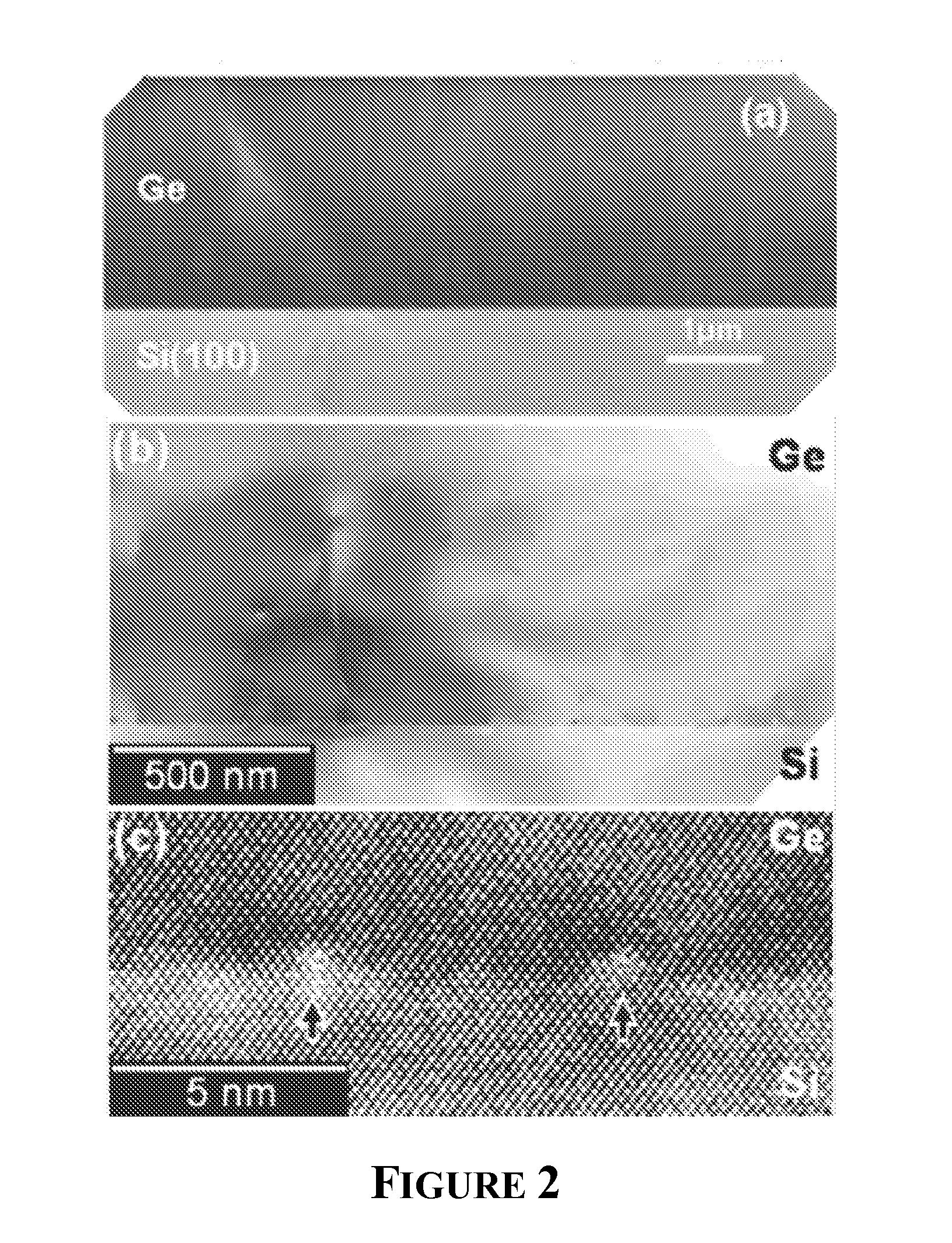

Hybrid Group IV/III-V Semiconductor Structures

InactiveUS20110254052A1Low costImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor structureAlloy

Described herein are semiconductor structures comprising (i) a Si substrate; (ii) a buffer region formed directly over the Si substrate, wherein the buffer region comprises (a) a Ge layer having a threading dislocation density below about 105 cm−2; or (b) a Ge1-xSnx layer formed directly over the Si substrate and a Ge1-x-ySixSny layer formed over the Ge1-xSnx layer; and (iii) a plurality of III-V active blocks formed over the buffer region, wherein the first III-V active block formed over the buffer region is lattice matched or pseudomorphically strained to the buffer region. Further, methods for forming the semiconductor structures are provided and novel Ge1-x-ySixSny, alloys are provided that are lattice matched or pseudomorphically strained to Ge and have tunable band gaps ranging from about 0.80 eV to about 1.4O eV.

Owner:ARIZONA STATE UNIVERSITY

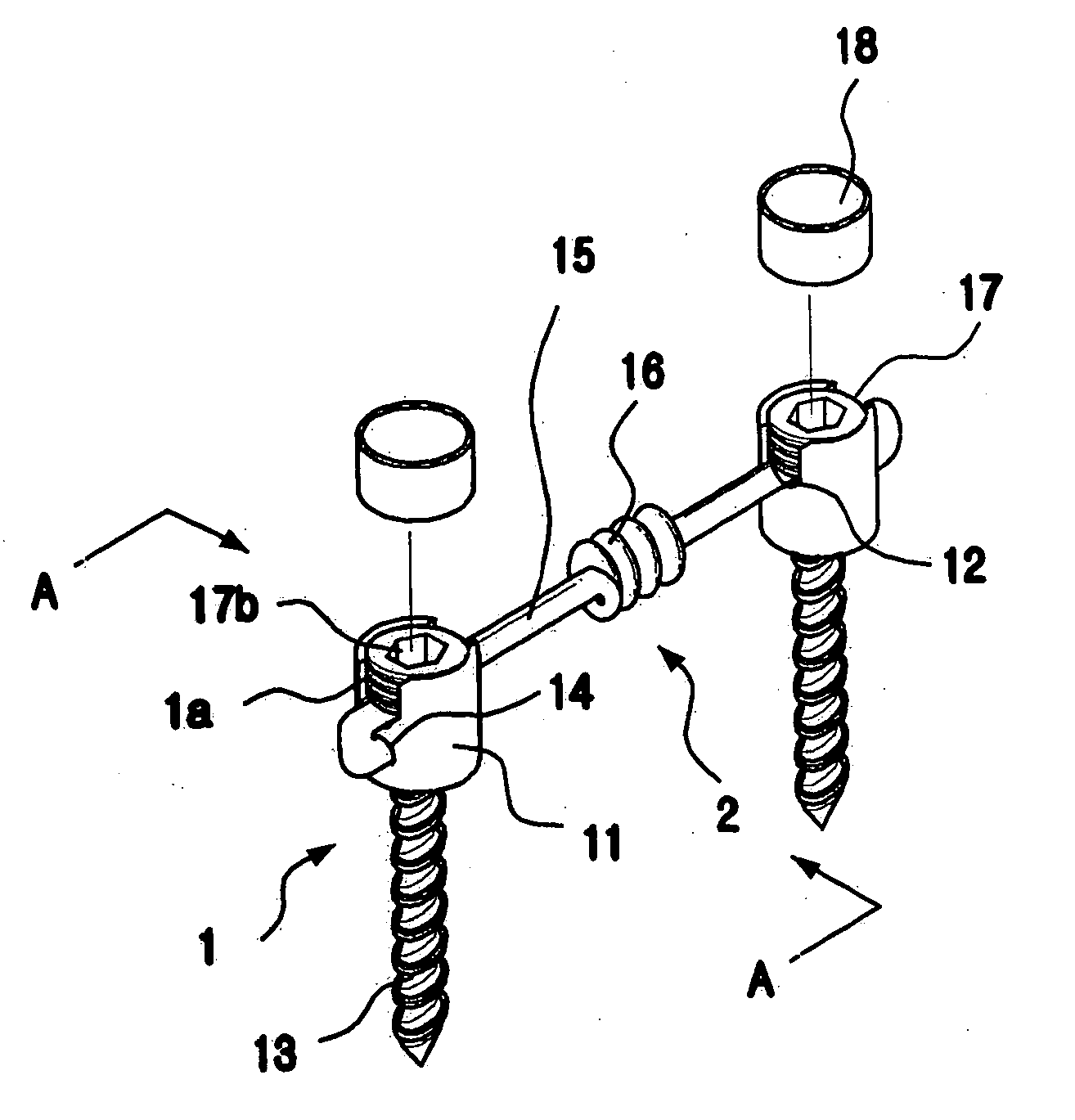

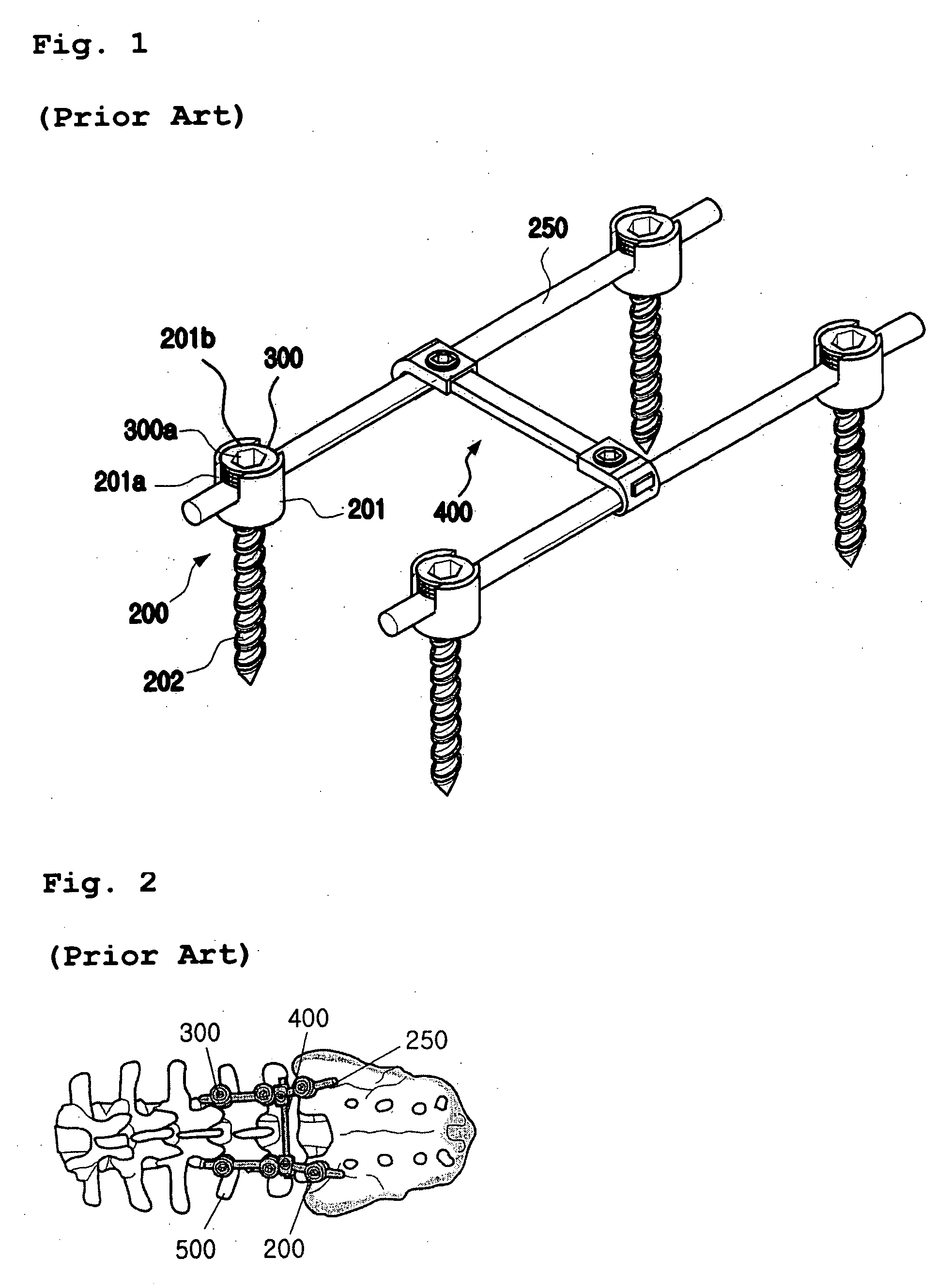

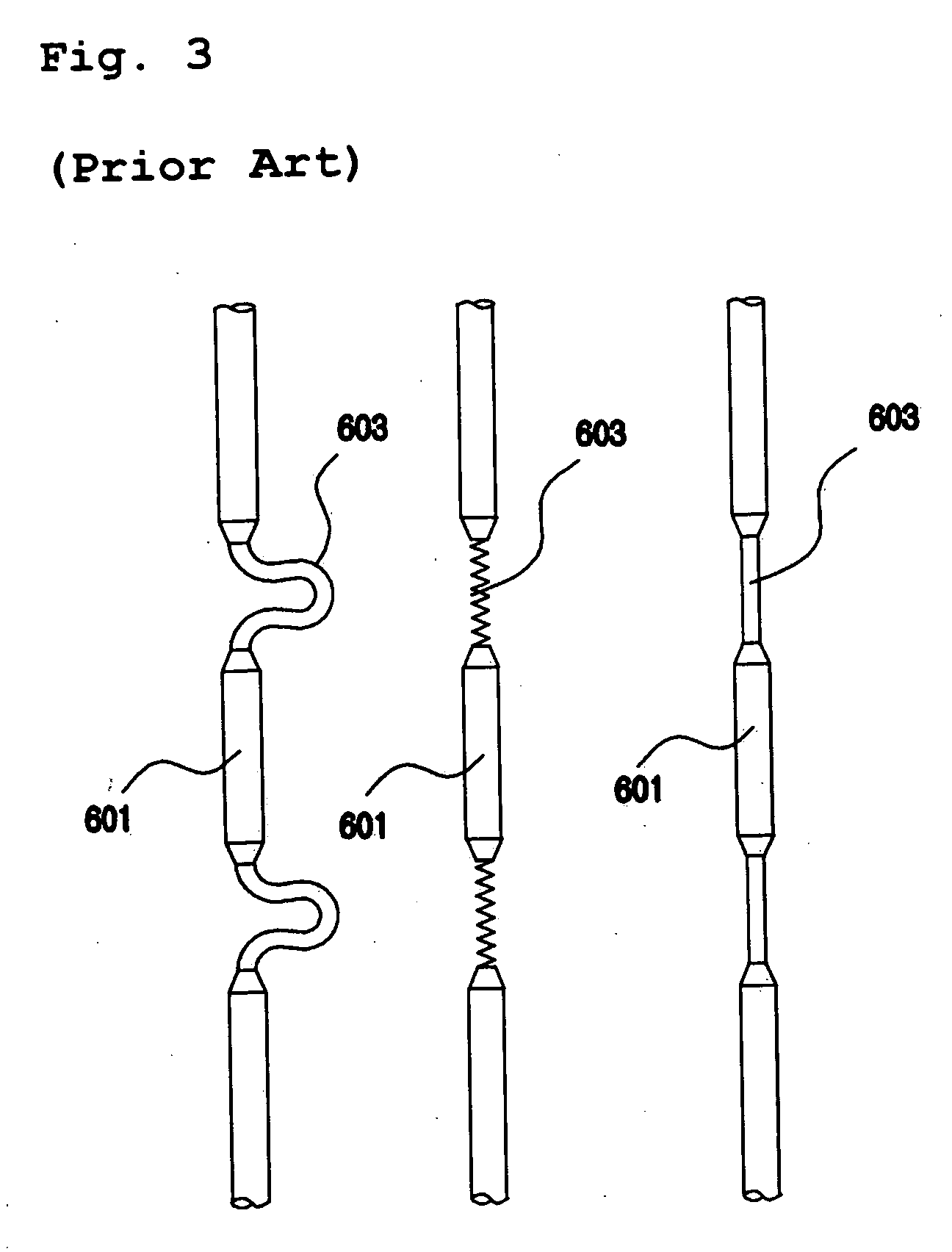

Bio-flexible spinal fixation apparatus with shape memory alloy

ActiveUS20060064090A1Easily simply achieveAccurate operationInternal osteosythesisJoint implantsShape-memory alloyEngineering

The present invention relates to a spinal fixation apparatus having a segment flexible rod for connecting pedicle screws and a transverse link for spacing out the rods, which are made from a shape memory alloy, thereby easily and simply connecting the rods and the pedicle screws. According to the present invention, it can easily and simply fit the rods to the misaligned pedicle screw, even if it may be a failure of alignment of the pedicle screws in surgery. Also, it can easily set up the transverse link on a pair of the longitudinal rods, even if the longitudinal rods are declined or are not in parallel.

Owner:PARK KYUNG WOO

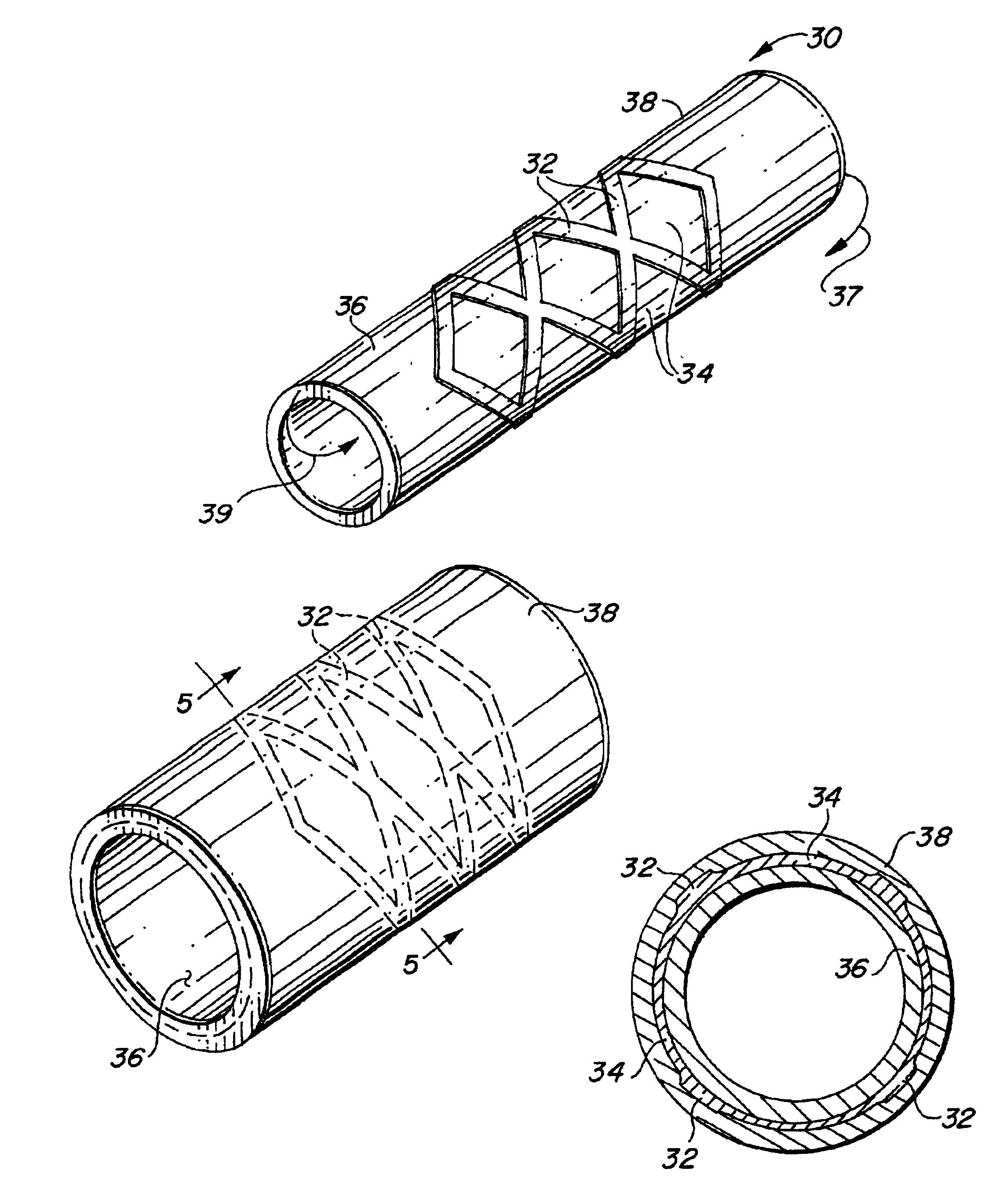

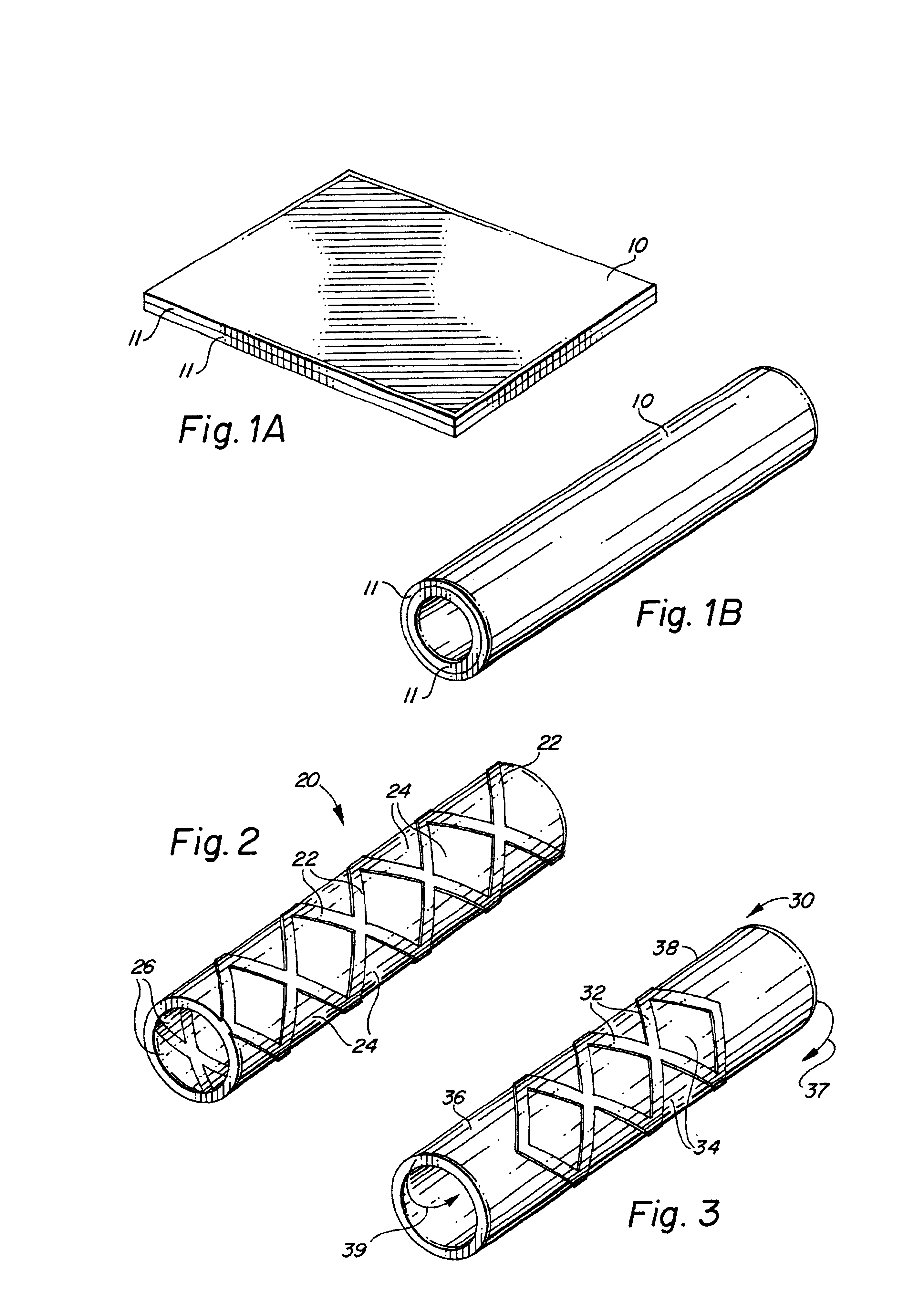

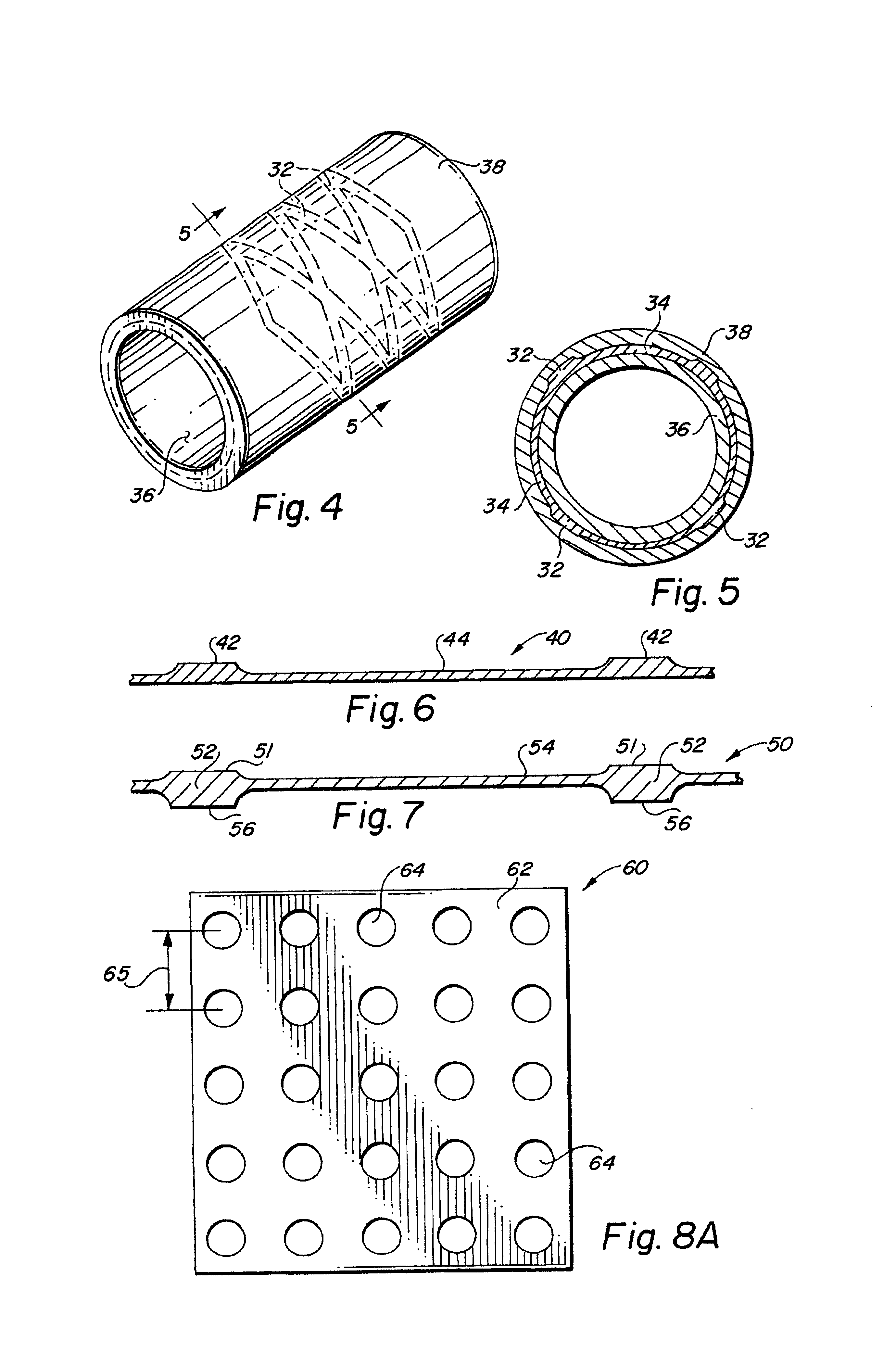

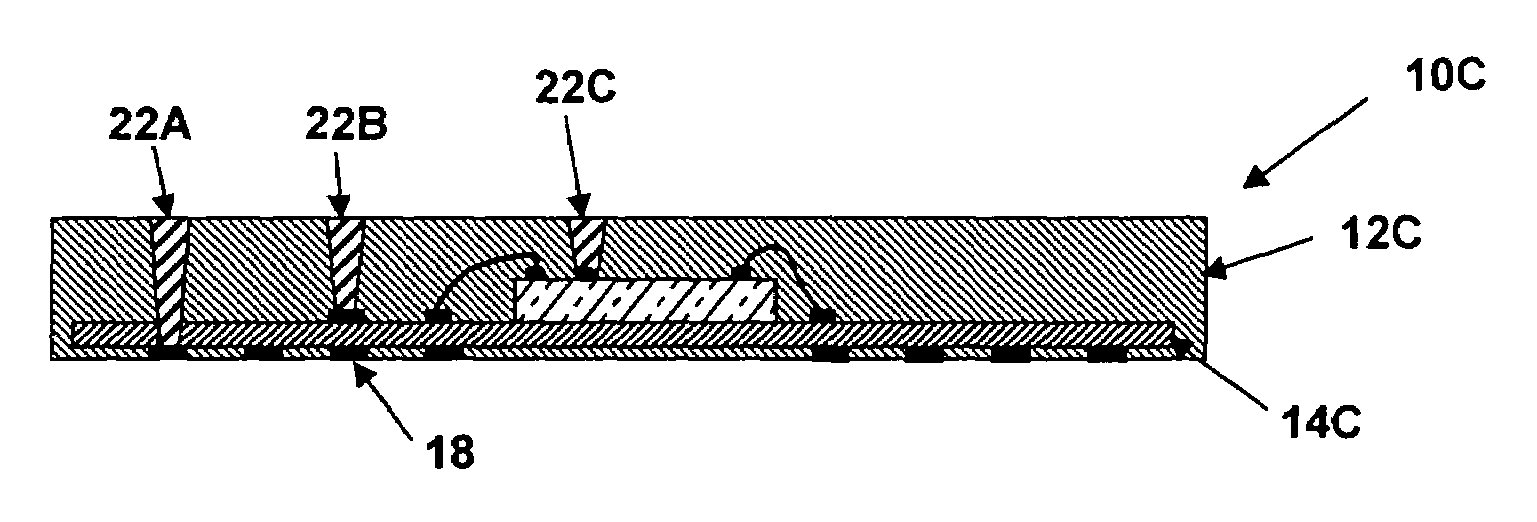

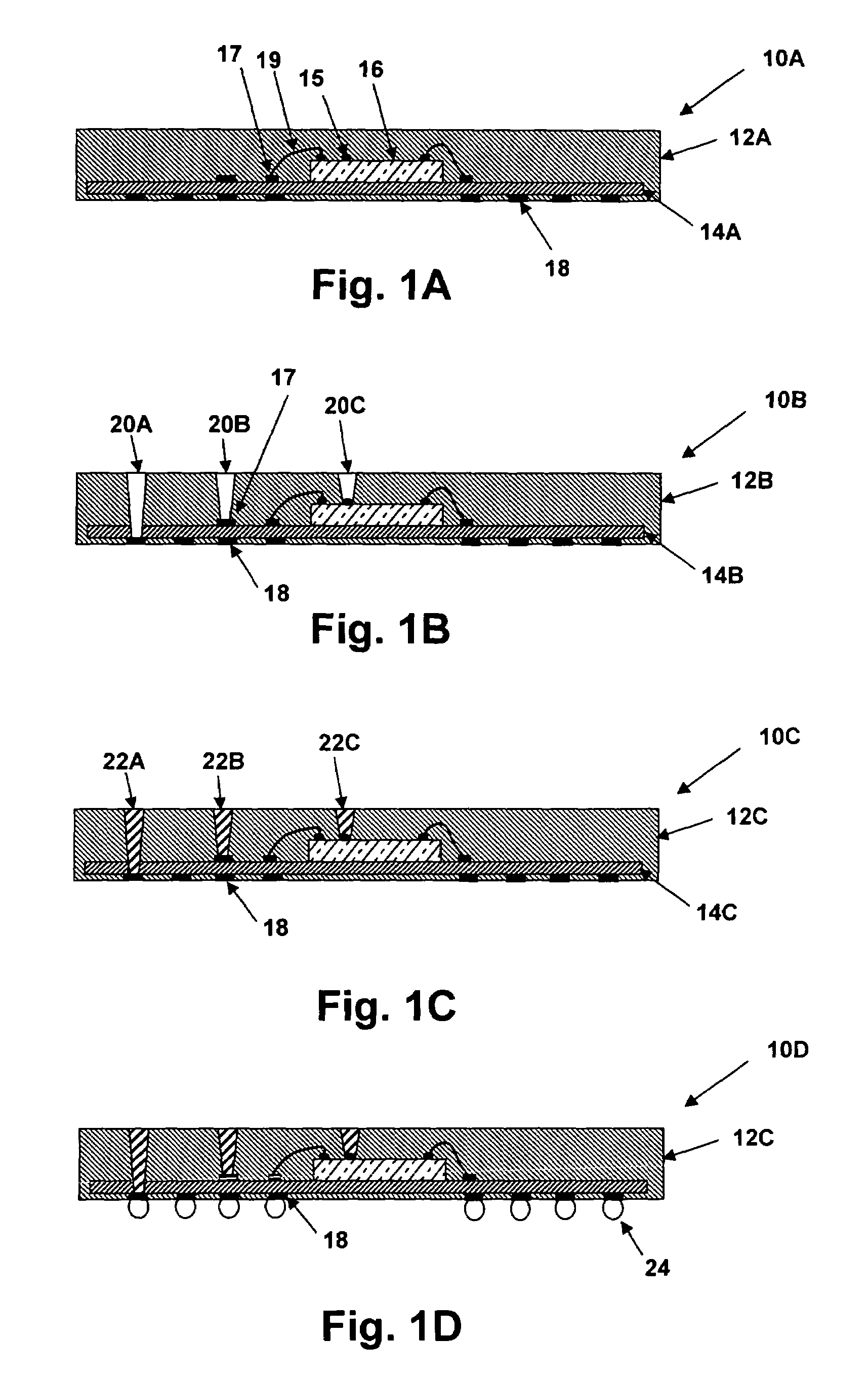

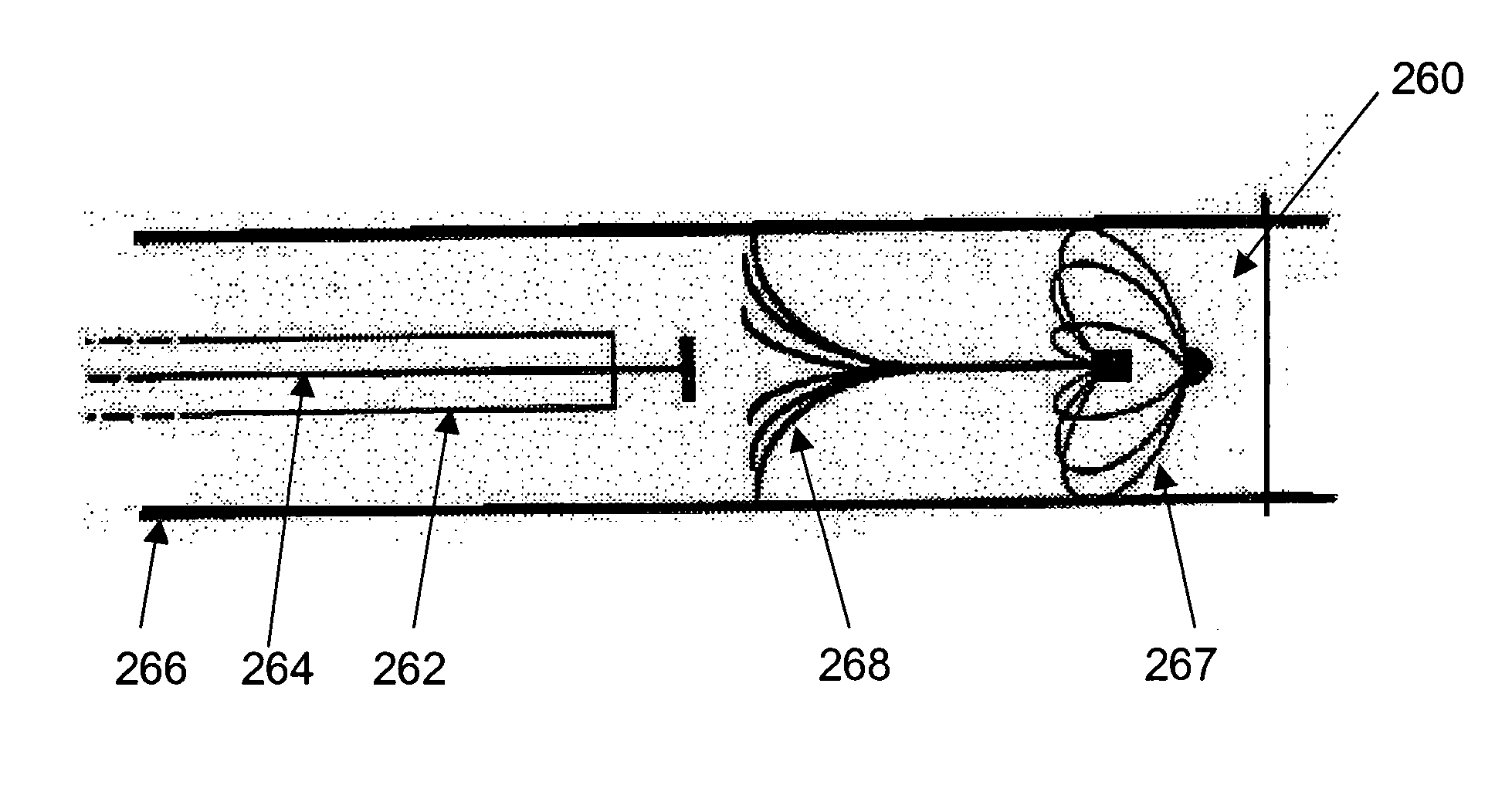

Self-supporting laminated films, structural materials and medical devices manufactured therefrom and methods of making same

Metal foils, wires, and seamless tubes with increased mechanical strength are provided. As opposed to wrought materials that are made of a single metal or alloy, these materials are made of two or more layers forming a laminate structure. Laminate structures are known to increase mechanical strength of sheet materials such as wood and paper products and are used in the area of thin films to increase film hardness, as well as toughness. Laminate metal foils have not been used or developed because the standard metal forming technologies, such as rolling and extrusion, for example, do not lend themselves to the production of laminate structures. Vacuum deposition technologies can be developed to yield laminate metal structures with improved mechanical properties. In addition, laminate structures can be designed to provide special qualities by including layers that have special properties such as superelasticity, shape memory, radio-opacity, corrosion resistance etc. Examples of articles which may be made by the inventive laminate structures include implantable medical devices that are fabricated from the laminated deposited films and which present a blood or body fluid and tissue contact surface that has controlled heterogeneities in material constitution. An endoluminal stent-graft and web-stent that is made of a laminated film material deposited and etched into regions of structural members and web regions subtending interstitial regions between the structural members. An endoluminal graft is also provided which is made of a biocompatible metal or metal-like material. The endoluminal stent-graft is characterized by having controlled heterogeneities in the stent material along the blood flow surface of the stent and the method of fabricating the stent using vacuum deposition methods.

Owner:VACTRONIX SCI LLC

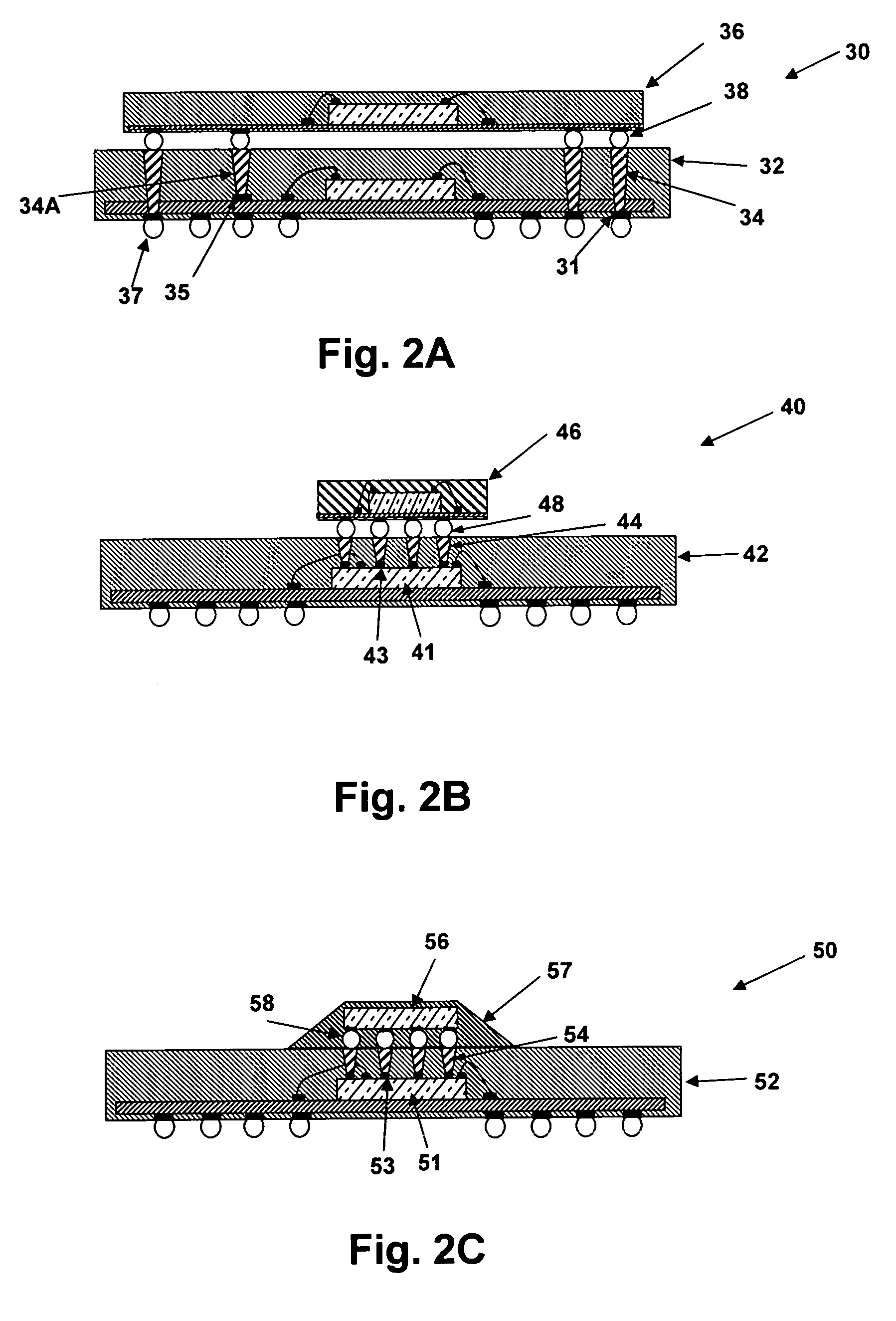

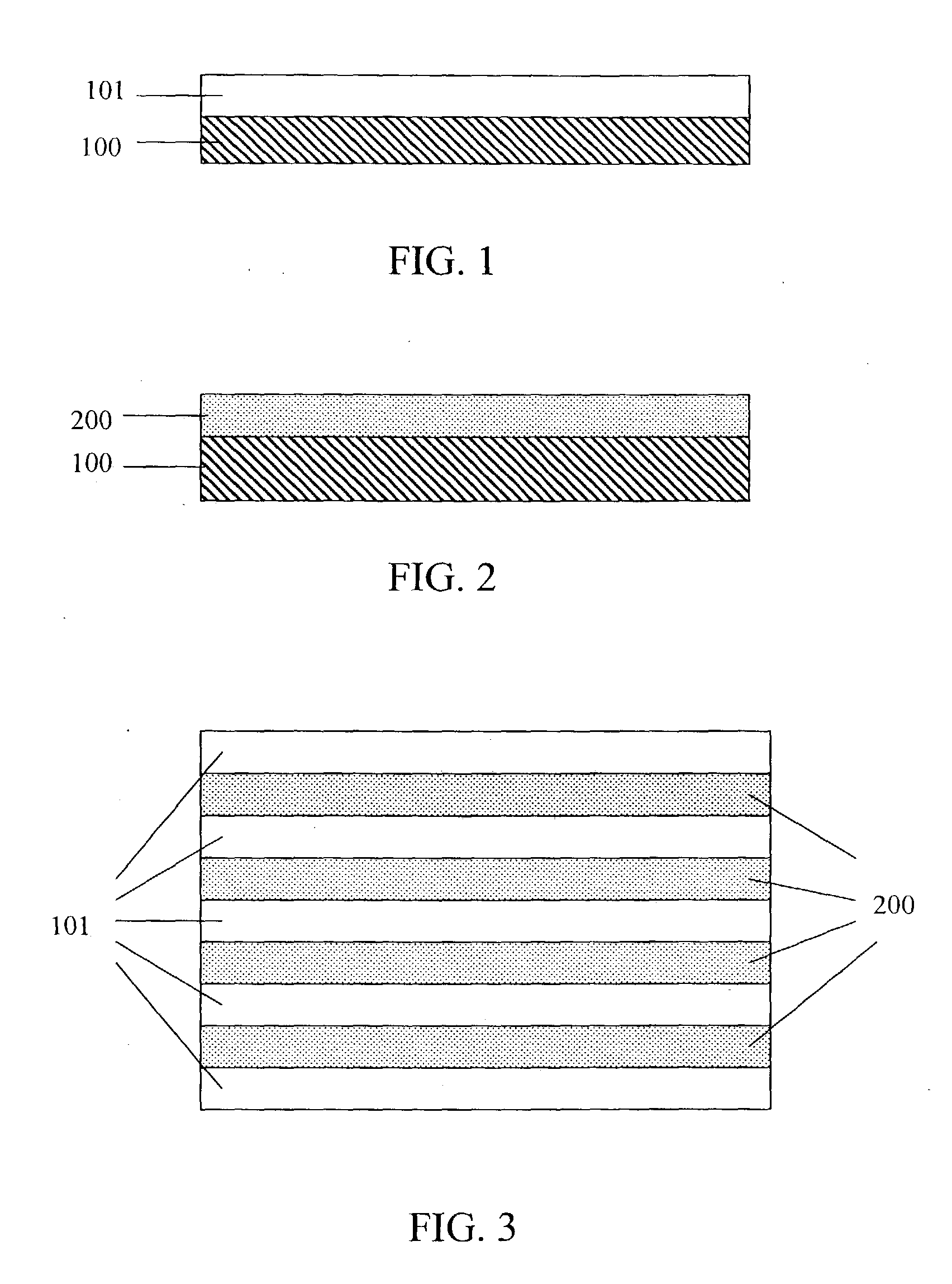

Method of manufacturing a semiconductor package

InactiveUS7185426B1Printed circuit assemblingSemiconductor/solid-state device detailsElectrical conductorSemiconductor package

A semiconductor package including top-surface terminals for mounting another semiconductor package provides a three-dimensional circuit configuration that can provide removable connection of existing grid-array packages having a standard design. A semiconductor die is mounted on an electrically connected to a circuit substrate having terminals disposed on a bottom side for connection to an external system. The die and substrate are encapsulated and vias are laser-ablated or otherwise formed through the encapsulation to terminals on the top surface of the substrate that provide a grid array mounting lands to which another grid array semiconductor package may be mounted. The bottom side of the vias may terminate and electrically connect to terminals on the substrate, terminals on the bottom of the semiconductor package (through terminals) or terminals on the top of the semiconductor die. The vias may be plated, paste-filled, filled with a low melting point alloy and may have a conical profile for improved plating performance.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

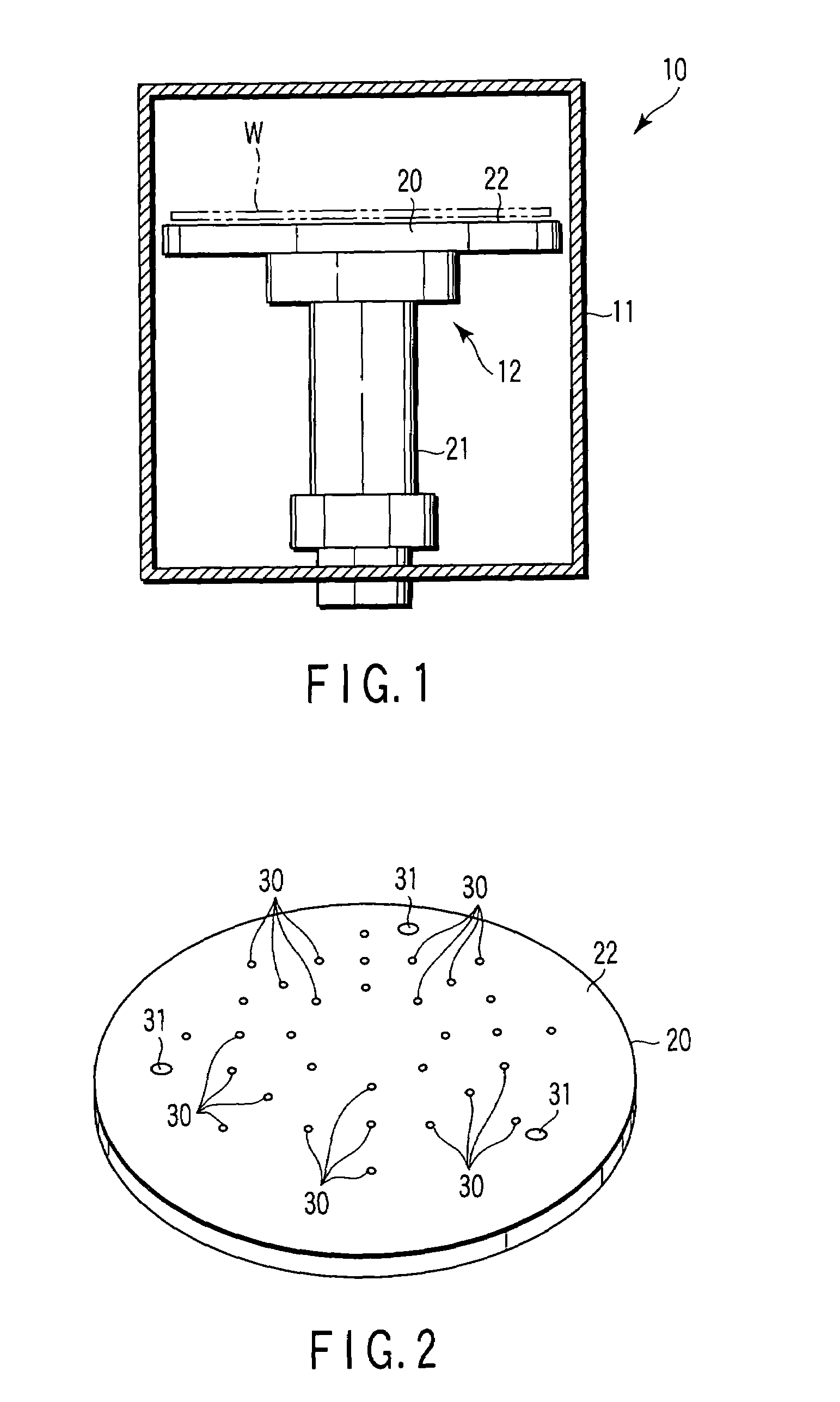

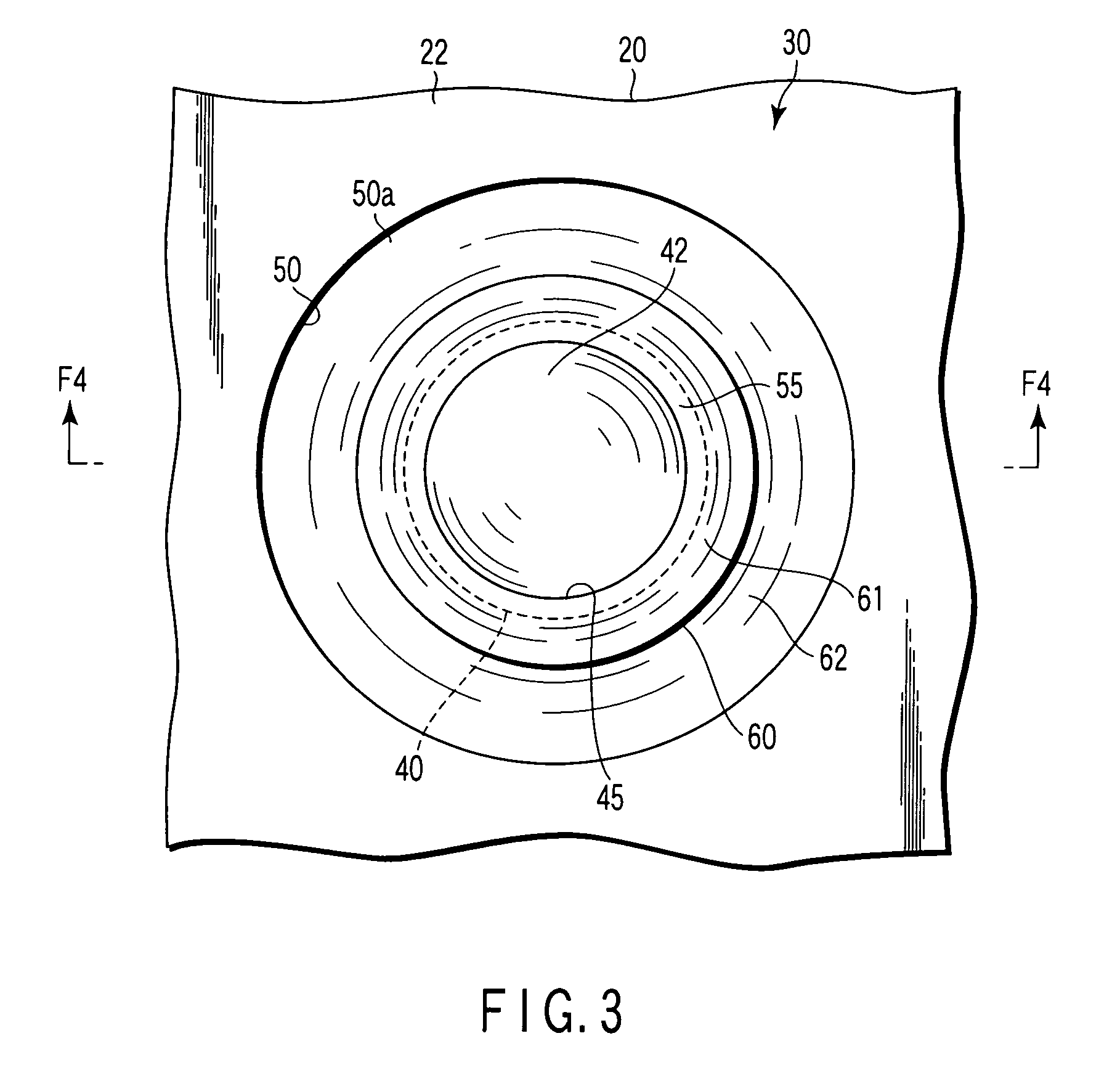

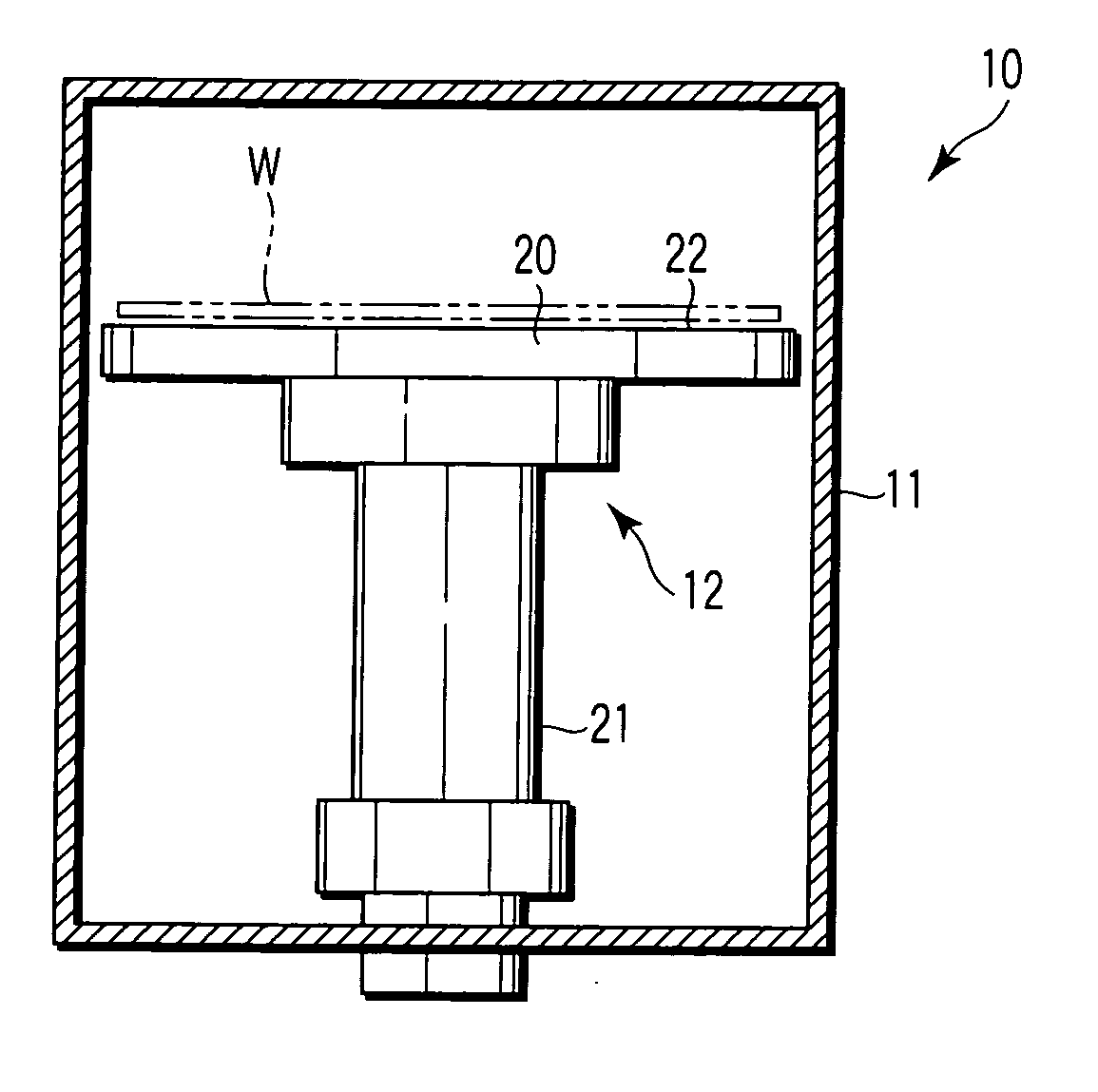

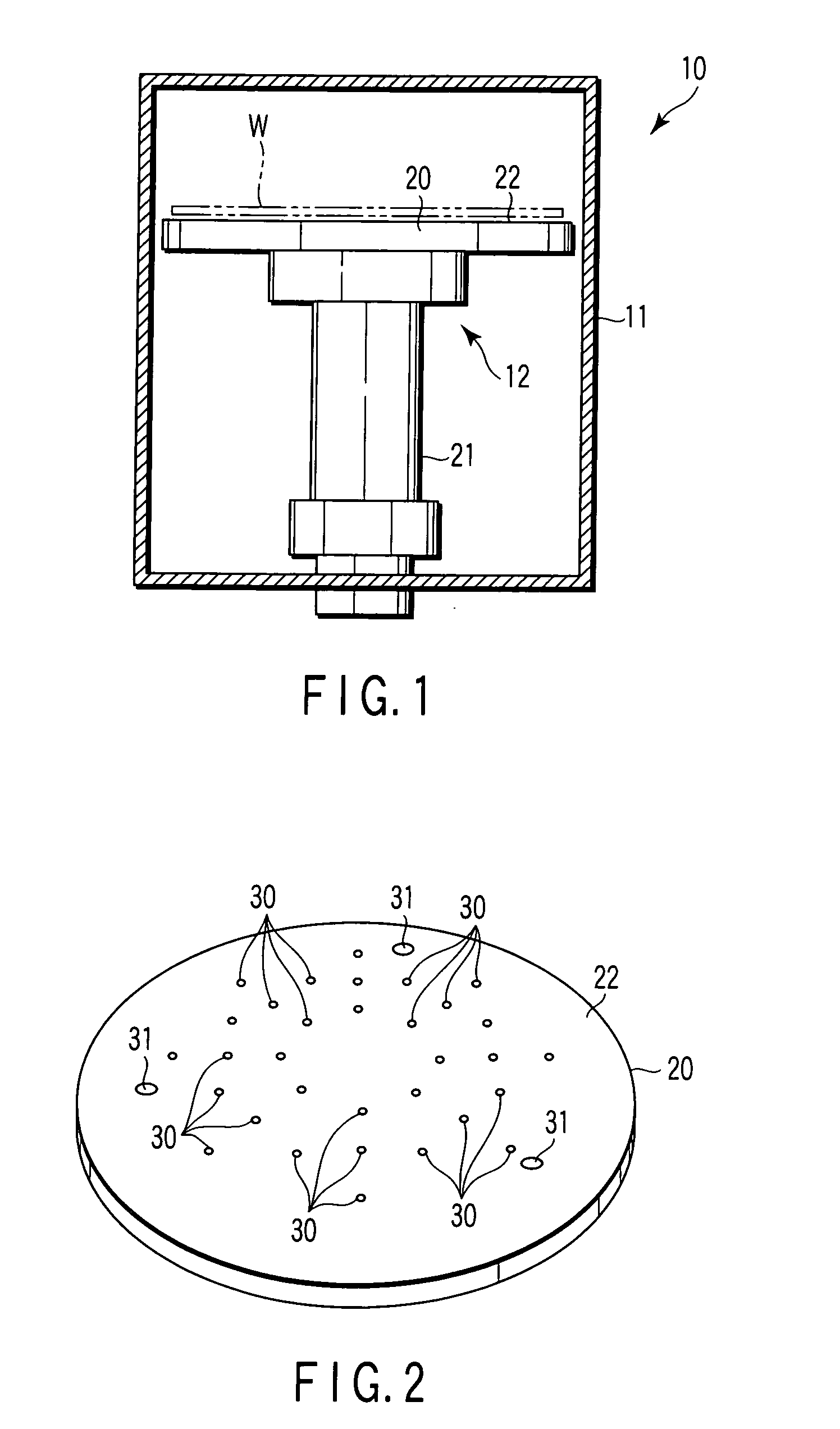

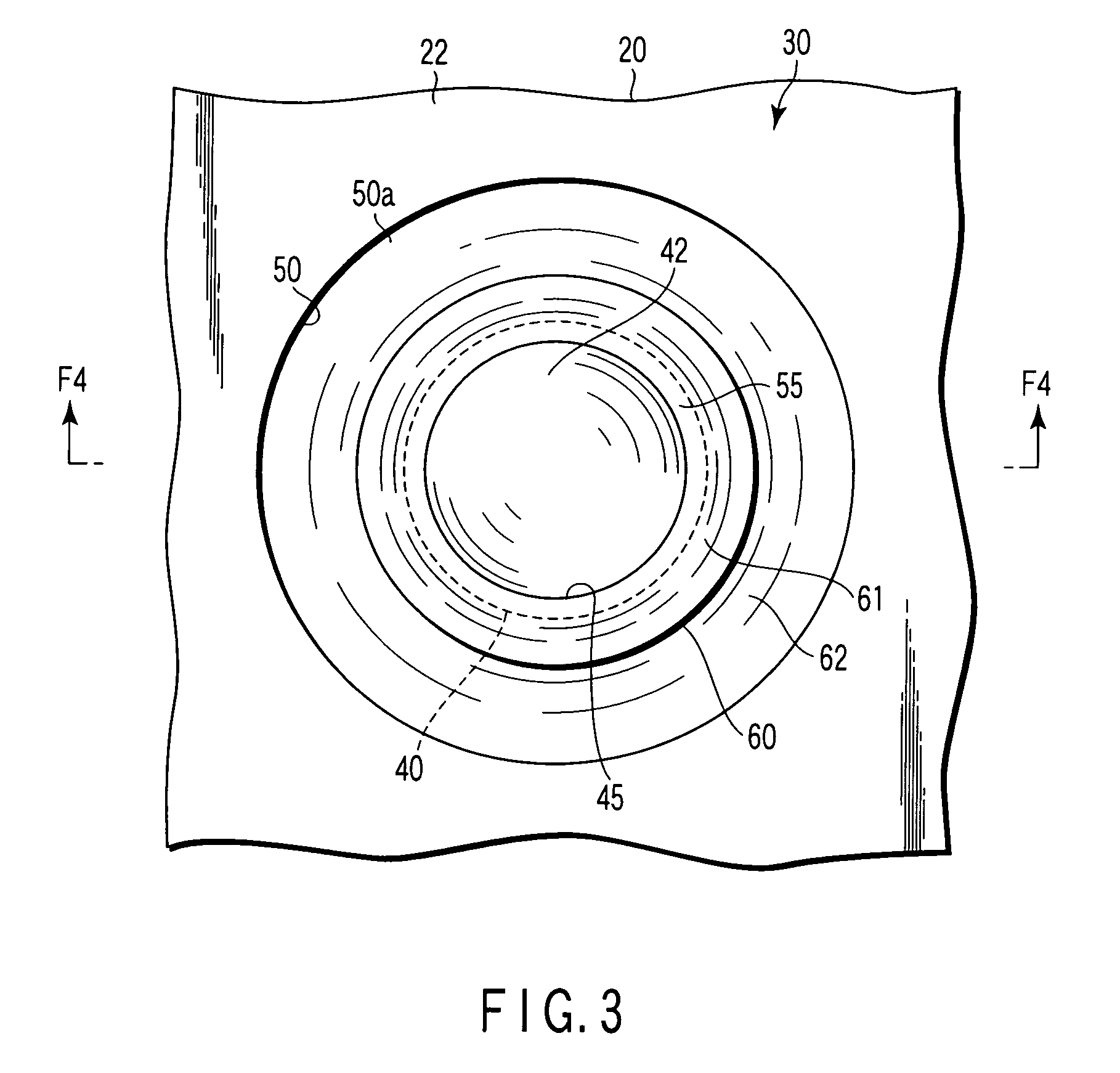

Substrate supporting apparatus

ActiveUS7503980B2Preventing slipping-off and breakageInhibit transferLiquid surface applicatorsLinear bearingsAlloyEngineering

A substrate supporting apparatus includes a plate member of an aluminum alloy having a flat upper surface, bottomed pits formed in the plate member, and spacer members held in the pits, individually. The spacer members are sapphire spheres. The diameter of each spacer member is a little smaller than that of each pit. The upper end of each spacer member projects from the upper surface of the plate member. A spot facing is formed in a region that includes the open edge portion of the pit. A bending portion which is obtained by plastically deforming the open edge portion of the pit toward the spacer member is formed on a bottom surface of the spot facing. A V-shaped groove is formed behind the bending portion.

Owner:NHK SPRING CO LTD

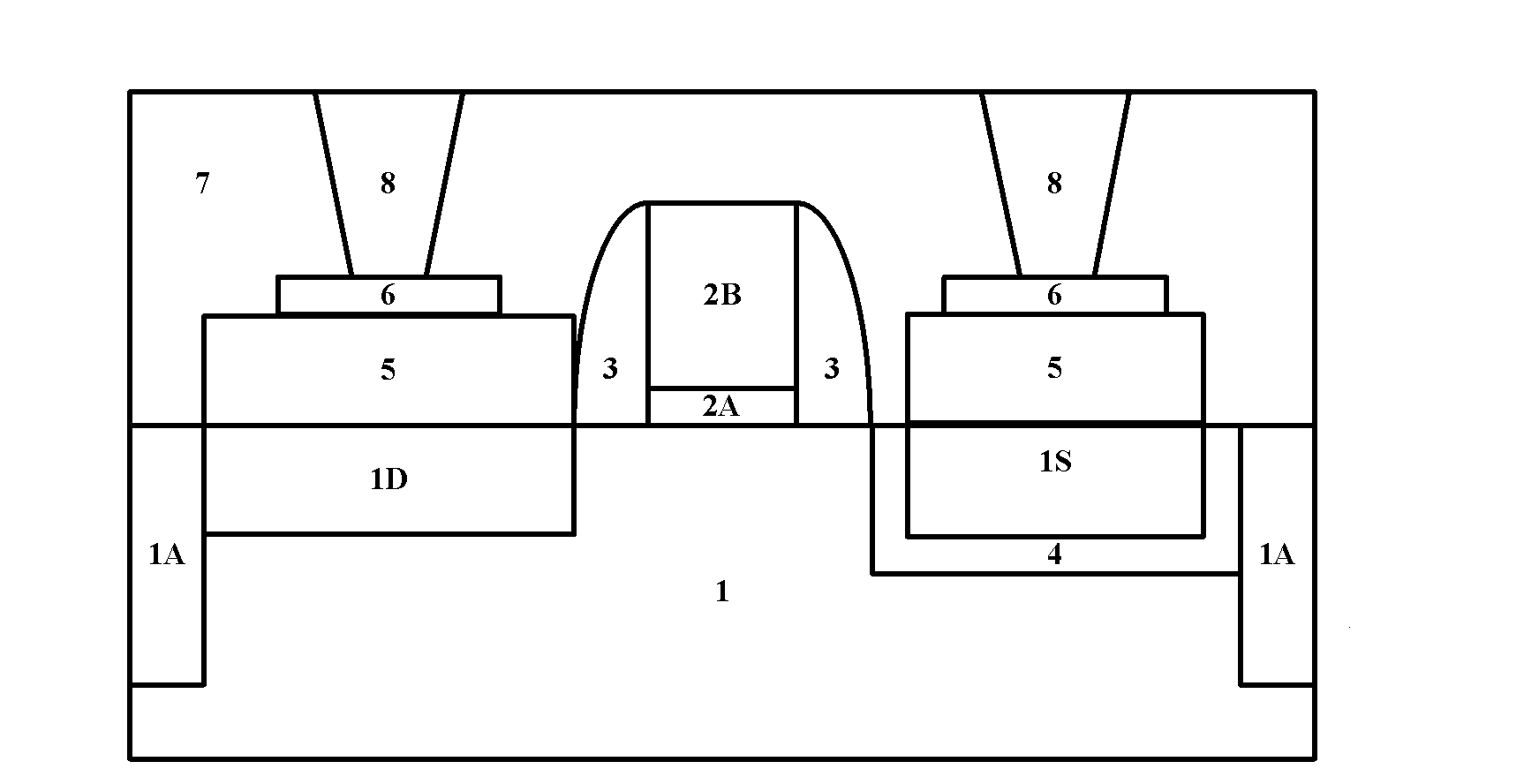

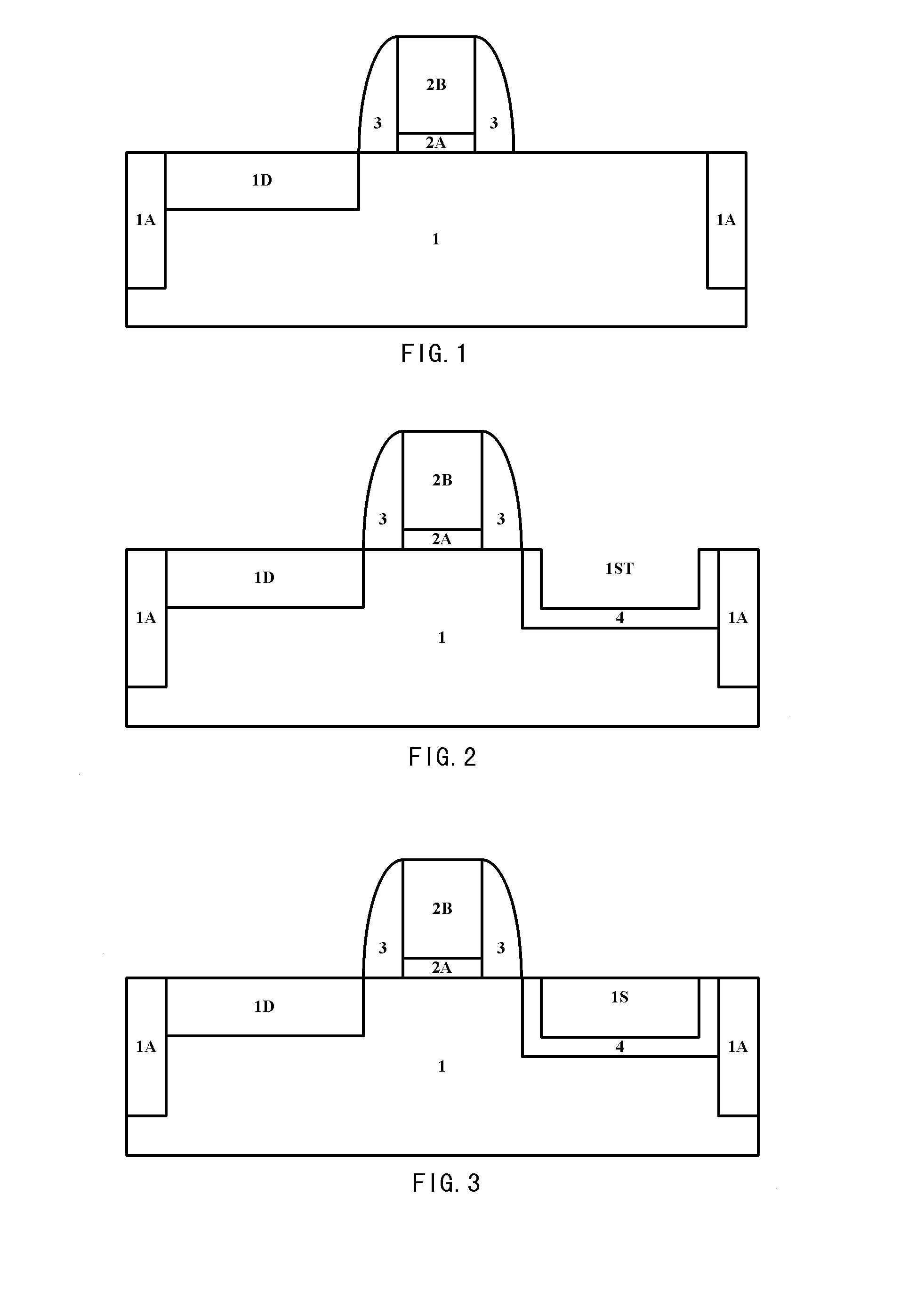

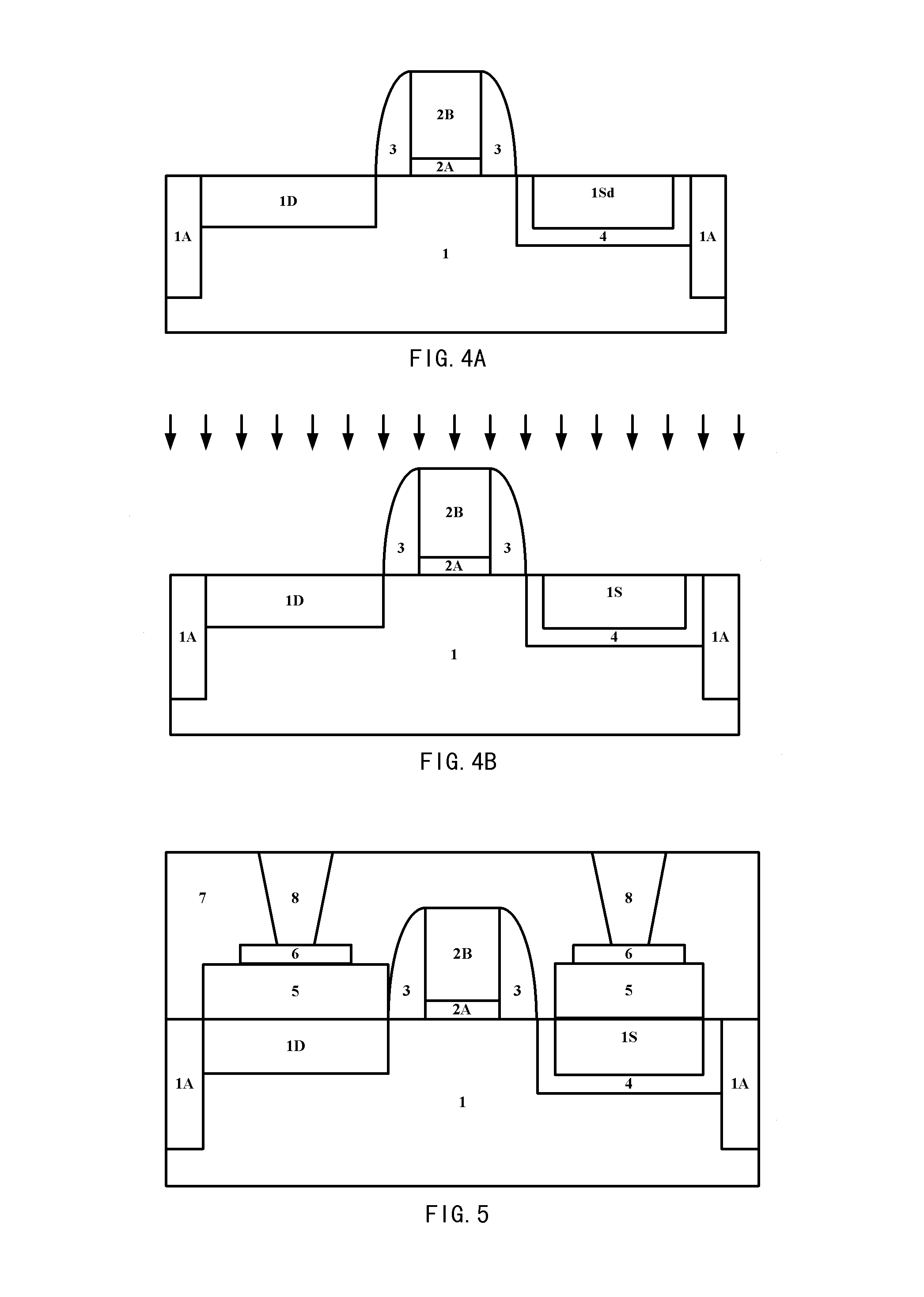

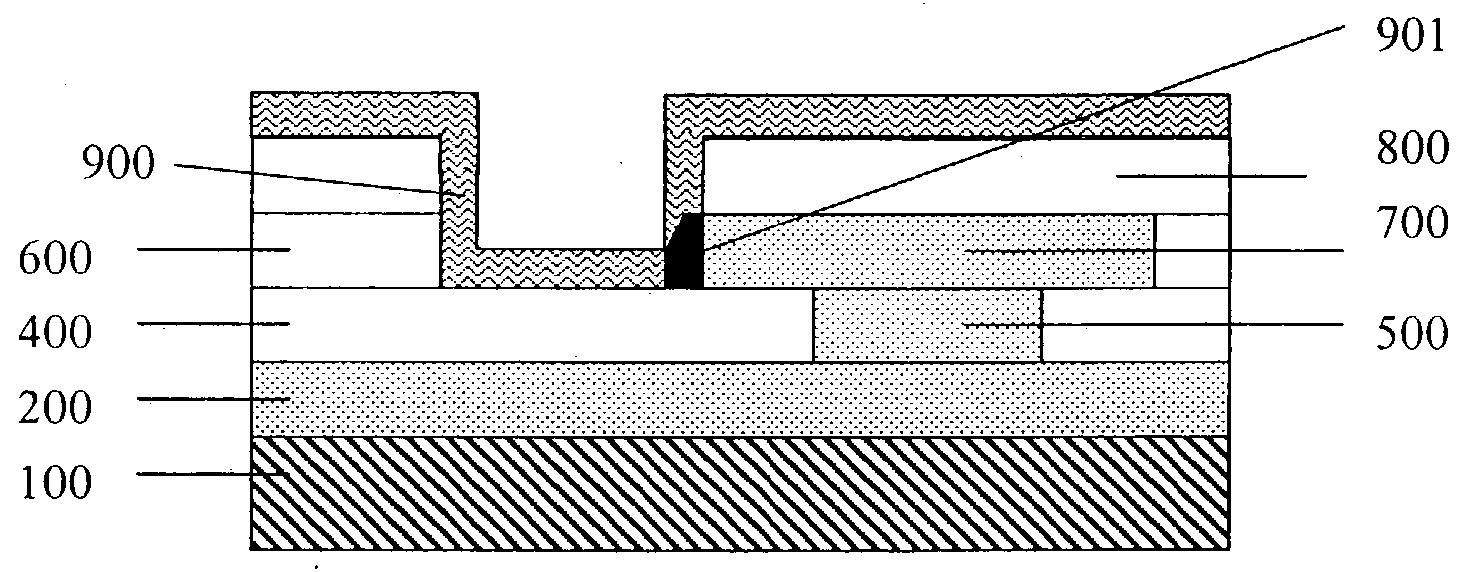

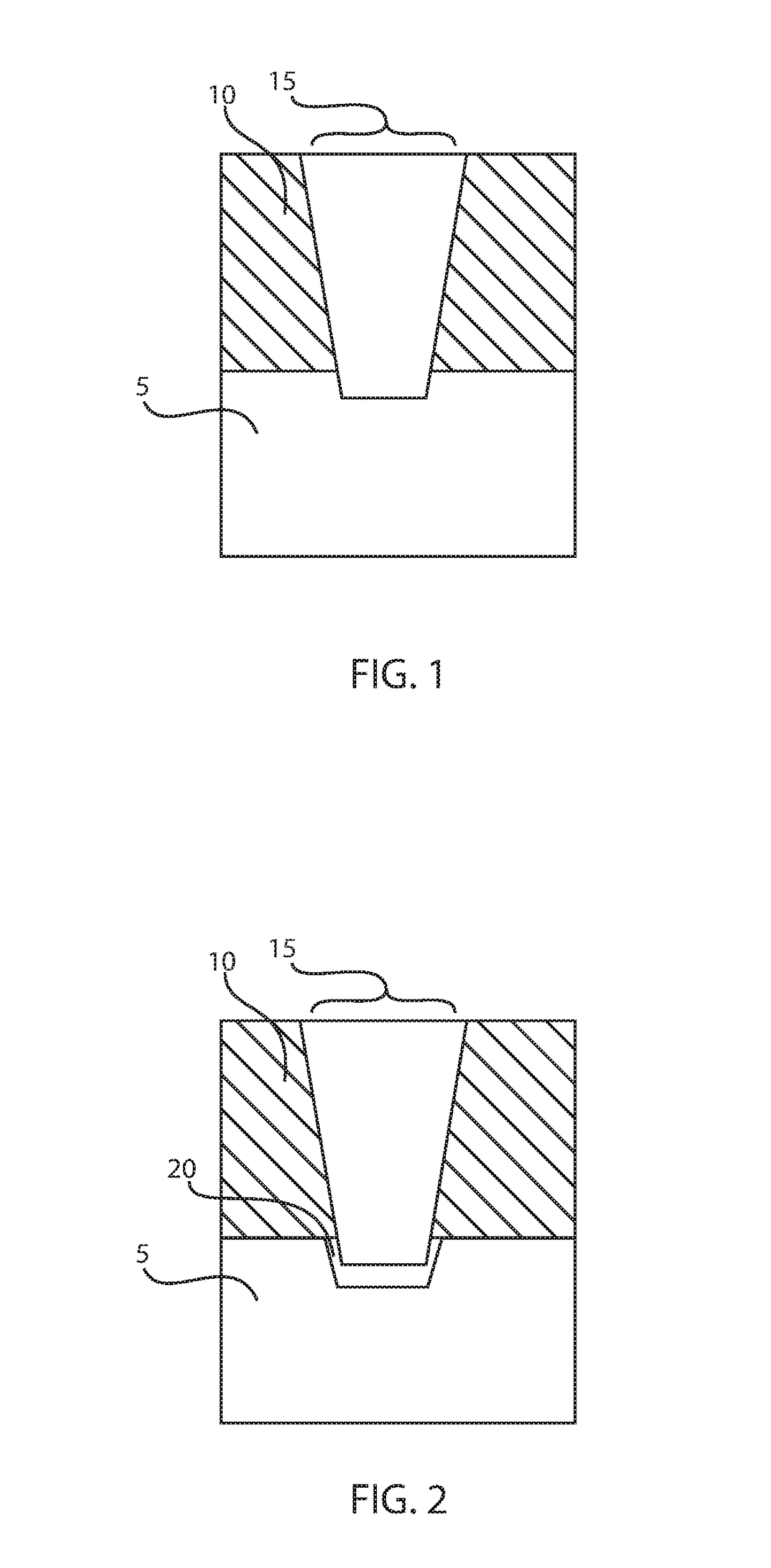

Semiconductor device and method for manufacturing the same

ActiveUS20140048765A1Increase currentReduce power consumptionSemiconductor/solid-state device manufacturingDiodeAlloyGate stack

The present invention discloses a semiconductor device, comprising: a substrate, a gate stack structure on the substrate, source and drain regions in the substrate on both sides of the gate stack structure, and a channel region between the source and drain regions in the substrate, characterized in that the source region in the source and drain regions comprises GeSn alloy, and a tunnel dielectric layer is optionally comprised between the GeSn alloy of the source region and the channel region. In accordance with the semiconductor device and method for manufacturing the same of the present invention, GeSn alloy having a narrow band gap is formed by implanting precursors and performing a laser rapid annealing, the on-state current of TFET is effectively enhanced, accordingly it has an important application prospect in a high performance low power consumption application.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

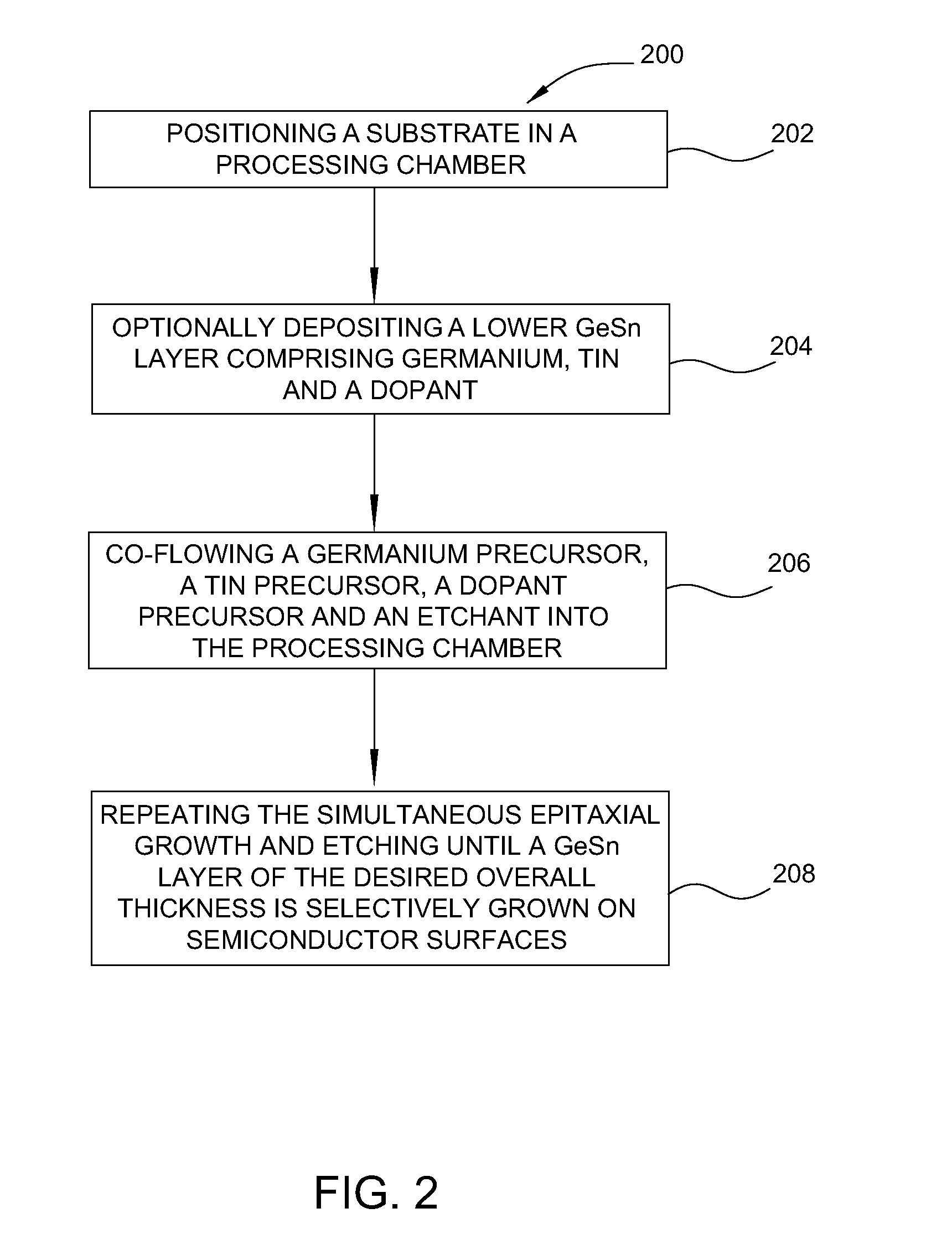

Method of epitaxial doped germanium tin alloy formation

ActiveUS20130256838A1Reduce lossesSemiconductor/solid-state device manufacturingSemiconductor devicesDopantAlloy

A method for forming germanium tin layers and the resulting embodiments are described. A germanium precursor and a tin precursor are provided to a chamber, and an epitaxial layer of germanium tin is formed on the substrate. The germanium tin layer is selectively deposited on the semiconductor regions of the substrate and can include thickness regions of varying tin and dopant concentrations. The germanium tin layer can be selectively deposited by either alternating or concurrent flow of a halide gas to etch the surface of the substrate.

Owner:APPLIED MATERIALS INC

Degradable Compositions, Apparatus Comprising Same, and Method of Use

InactiveUS20070181224A1Improve responseSafe handlingDrilling compositionSealing/packingElemental compositionSubject matter

Compositions, apparatus incorporating a composition, and methods of use are described, one composition embodiment consisting essentially of one or more reactive metals in major proportion, and one or more alloying elements in minor proportion, with the provisos that the composition is high-strength, controllably reactive, and degradable under defined conditions. Compositions of the invention may exist in a variety of morphologies, including a reactive metal or degradable alloy processed into an alloy of crystalline, amorphous or mixed structure that may constitute the matrix of other composition, for instance a composite. Methods of using apparatus comprising a composition, particularly in oilfield operations are also described (e.g. flow and displacement control, sensors, actuators). This abstract allows a searcher or other reader to quickly ascertain the subject matter of the disclosure. It will not be used to interpret or limit the scope or meaning of the claims. 37 CFR 1.72(b).

Owner:SCHLUMBERGER TECH CORP

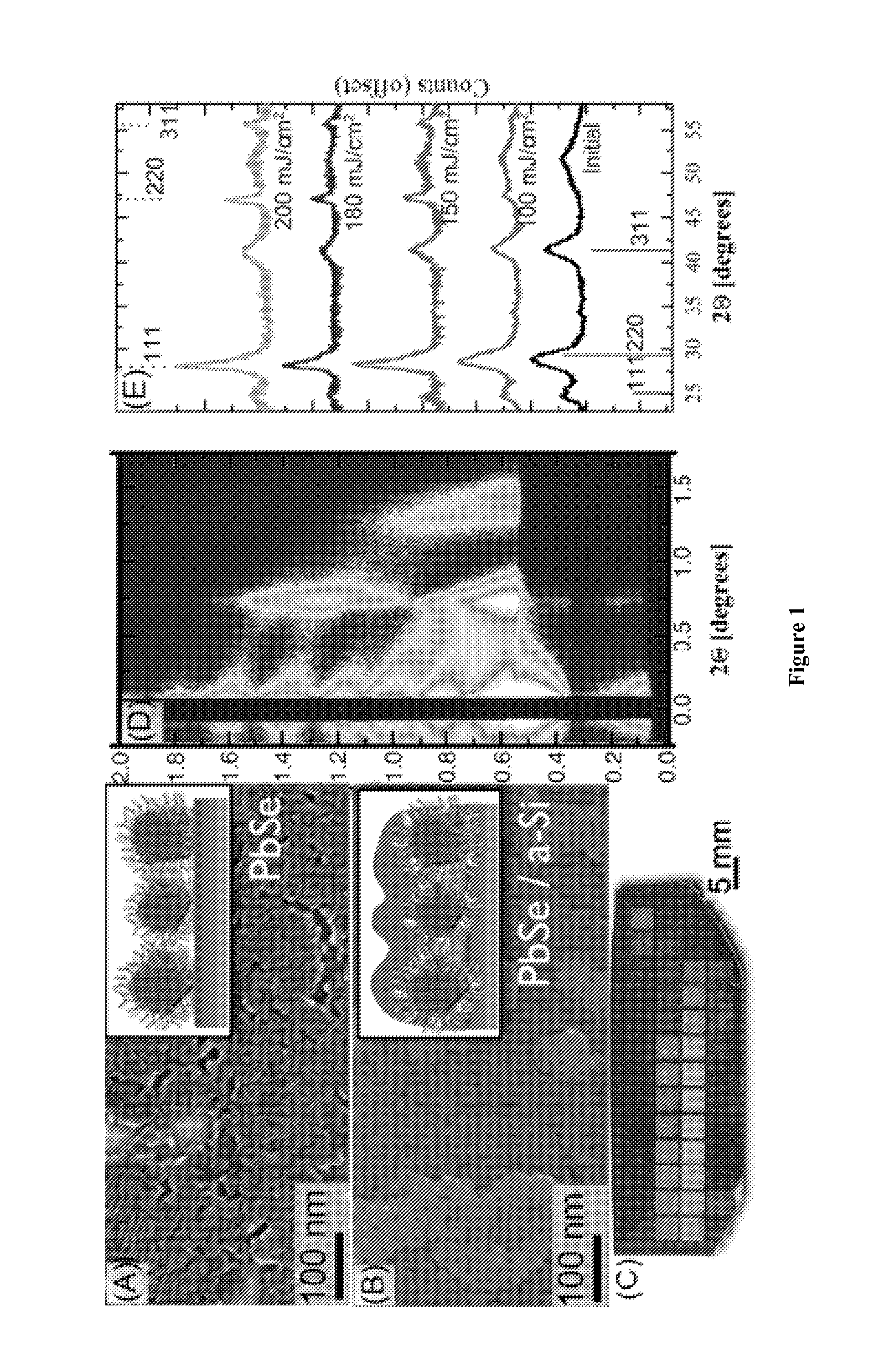

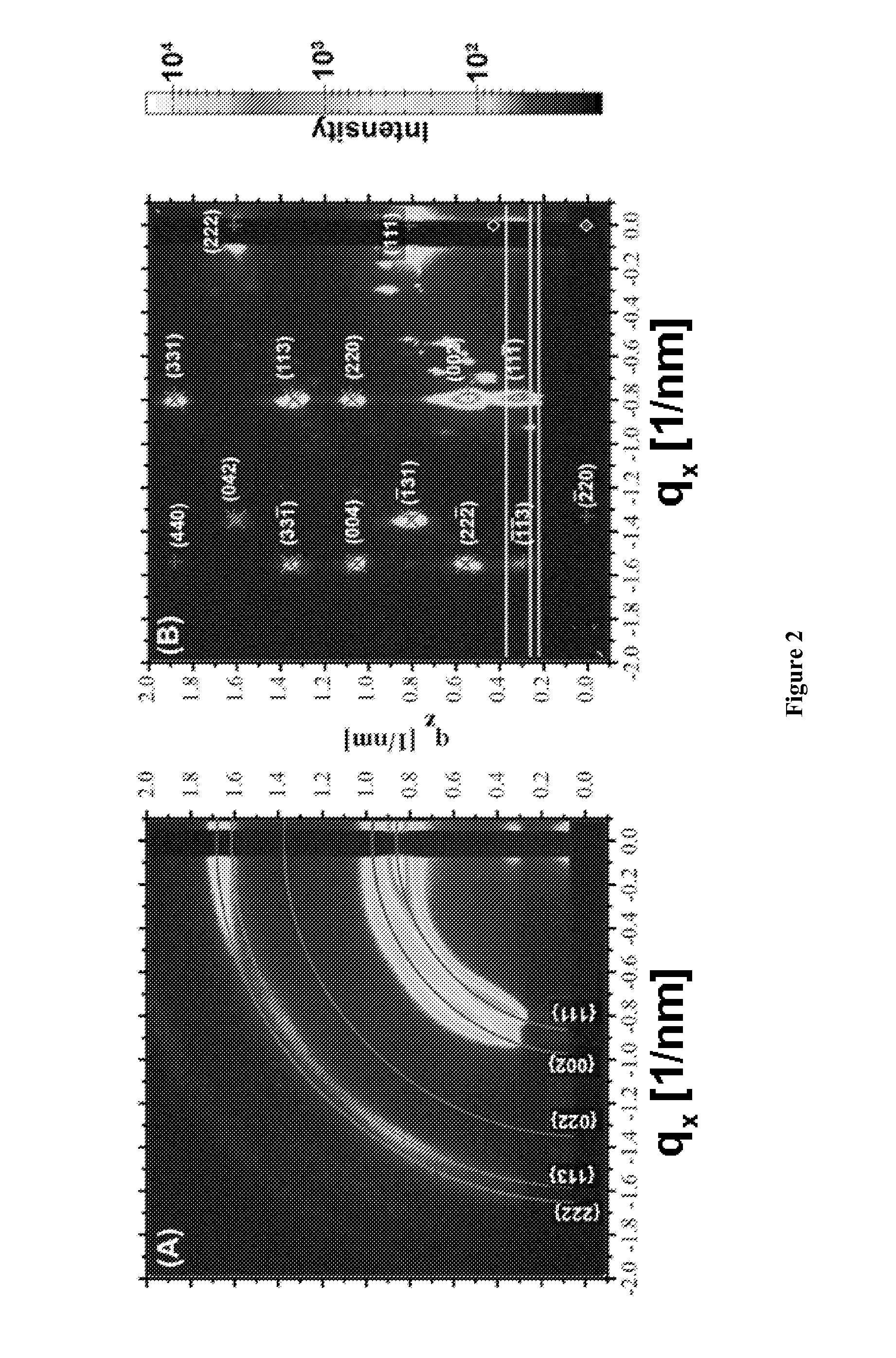

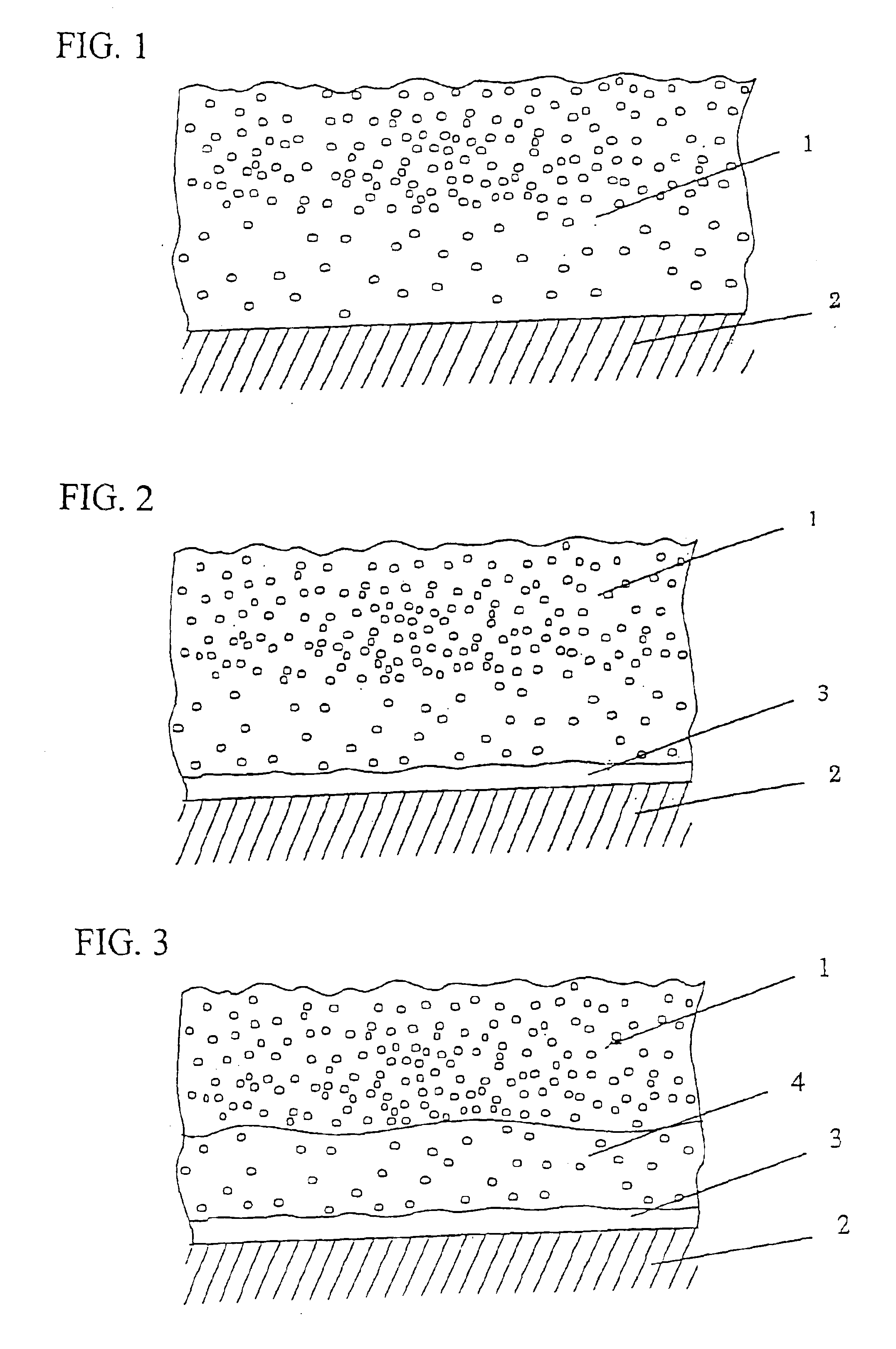

Inorganic Bulk Multijunction Materials and Processes for Preparing the Same

InactiveUS20110220874A1Material nanotechnologyFinal product manufactureAlloySemiconductor nanocrystals

A nanostructured composite material comprising semiconductor nanocrystals in a crystalline semiconductor matrix. Suitable nanocrystals include silicon, germanium, and silicon-germanium alloys, and lead salts such as PbS, PbSe, and PbTe. Suitable crystalline semiconductor matrix materials include Si and silicon-germanium alloys. A process for making the nanostructured composite materials. Devices comprising nanostructured composite materials.

Owner:CORNELL UNIVERSITY

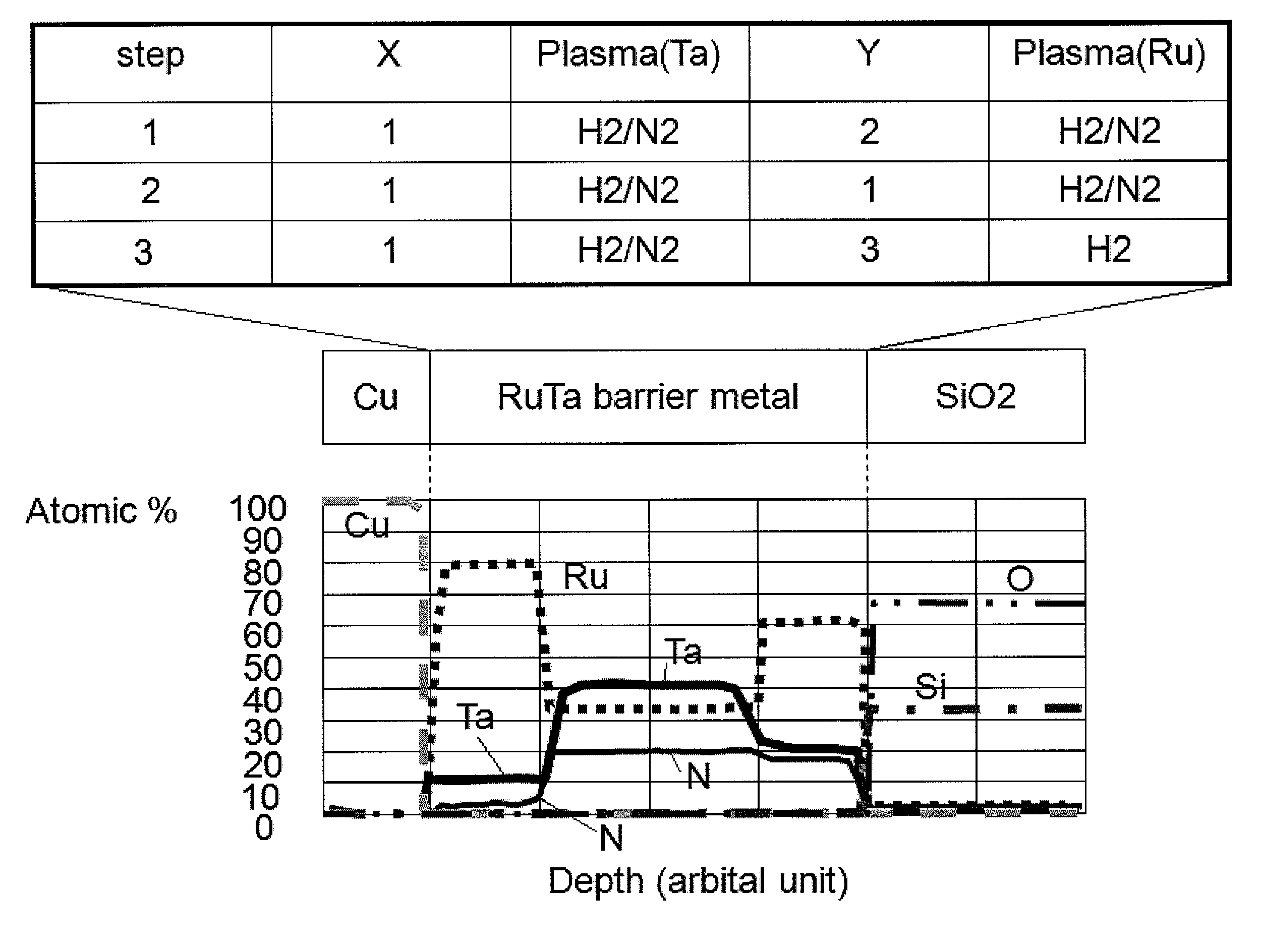

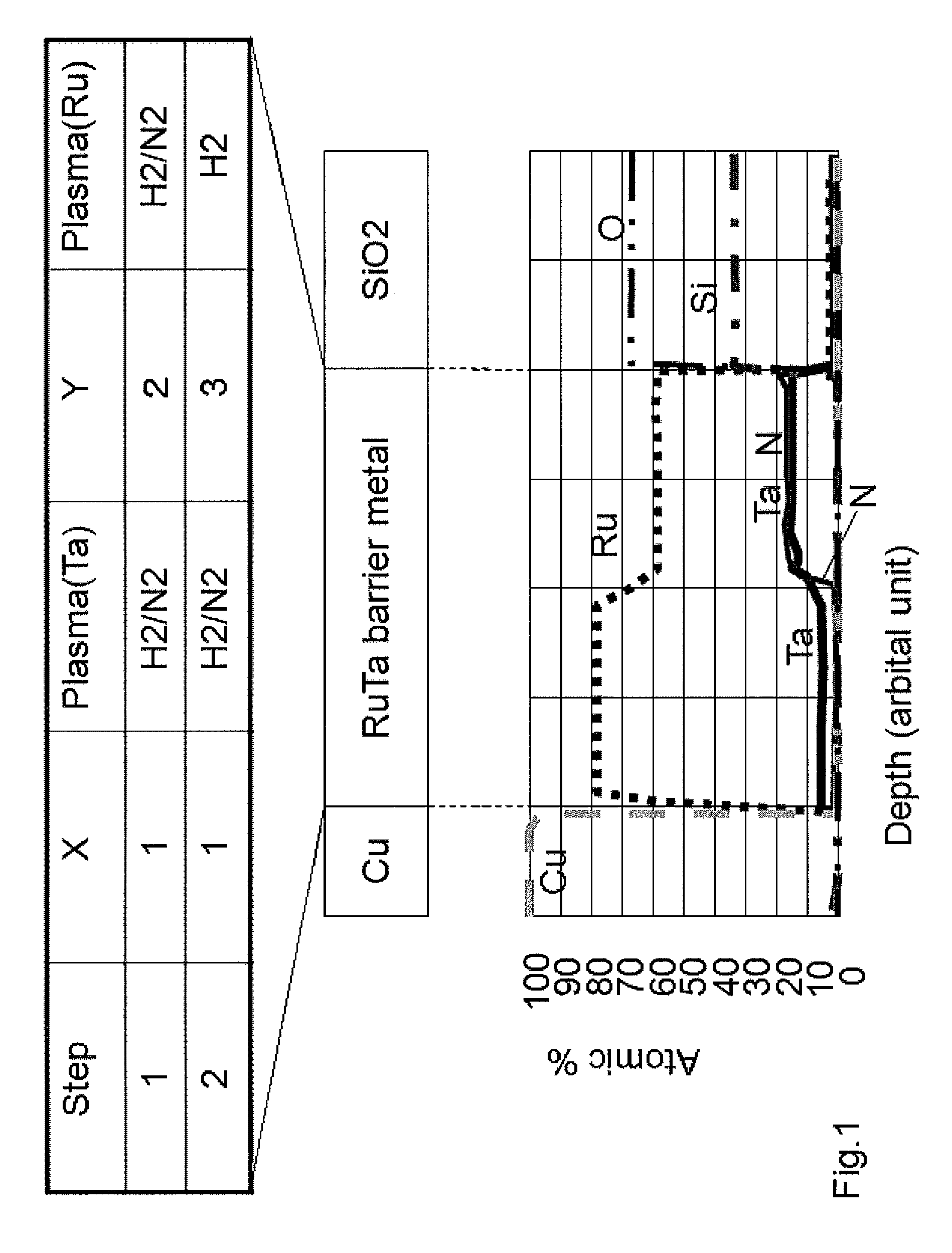

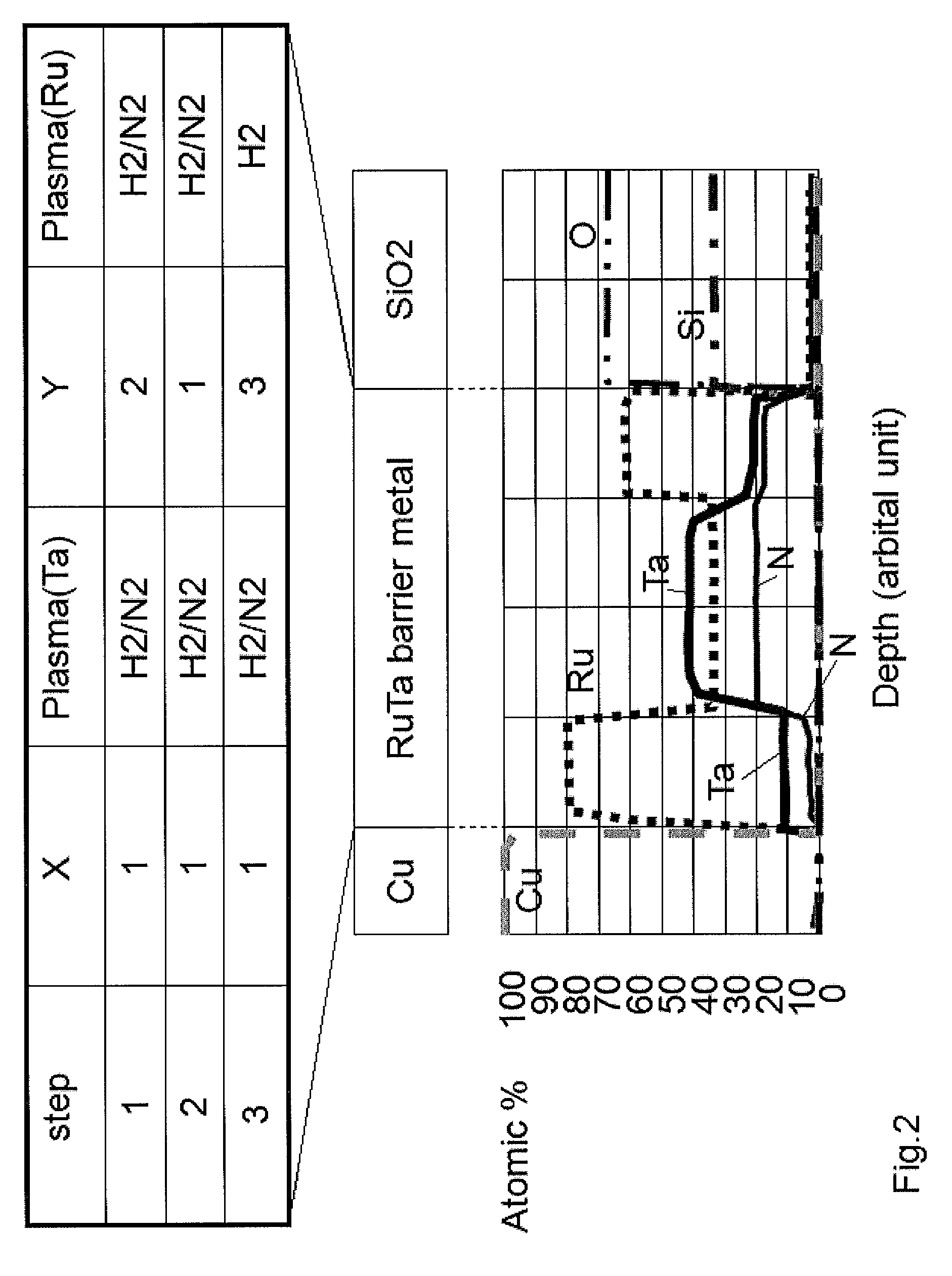

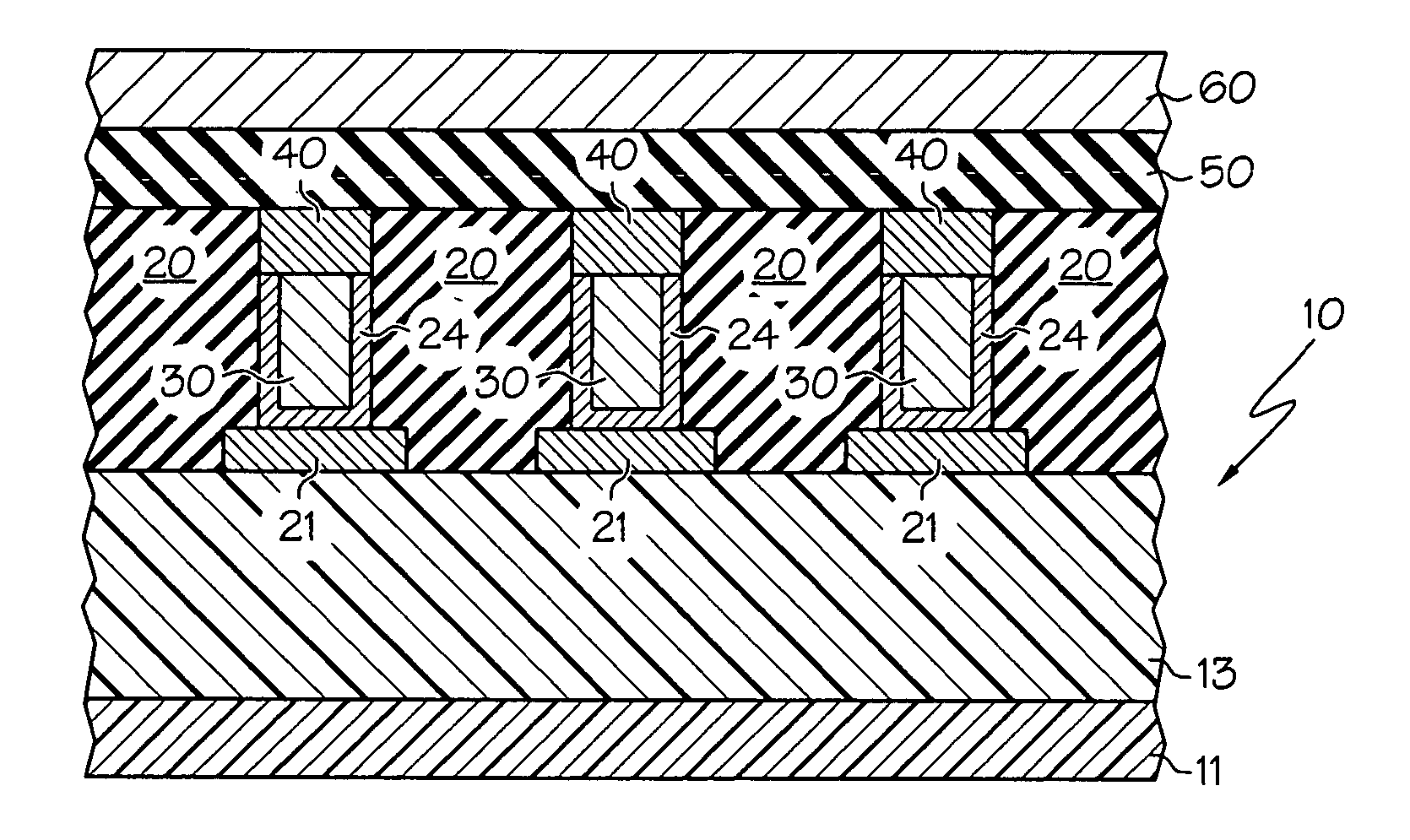

Atomic composition controlled ruthenium alloy film formed by plasma-enhanced atomic layer deposition

ActiveUS8084104B2Reduce resistanceLow densitySemiconductor/solid-state device detailsSynthetic resin layered productsRutheniumAlloy

A metal film composed of multiple atomic layers continuously formed by atomic layer deposition of Ru and Ta or Ti includes at least a top section and a bottom section, wherein an atomic composition of Ru, Ta or Ti, and N varies in a thickness direction of the metal film. The atomic composition of Ru, Ta or Ti, and N in the top section is represented as Ru(x1)Ta / Ti(y1)N(z1) wherein an atomic ratio of Ru(x1) / (Ta / Ti(y1)) is no less than 15, and z1 is 0.05 or less. The atomic composition of Ru, Ta or Ti, and N in the bottom section is represented as Ru(x2)Ta / Ti(y2)N(z2) wherein an atomic ratio of Ru(x2) / (Ta / Ti(y2)) is more than zero but less than 15, and z2 is 0.10 or greater.

Owner:ASM JAPAN

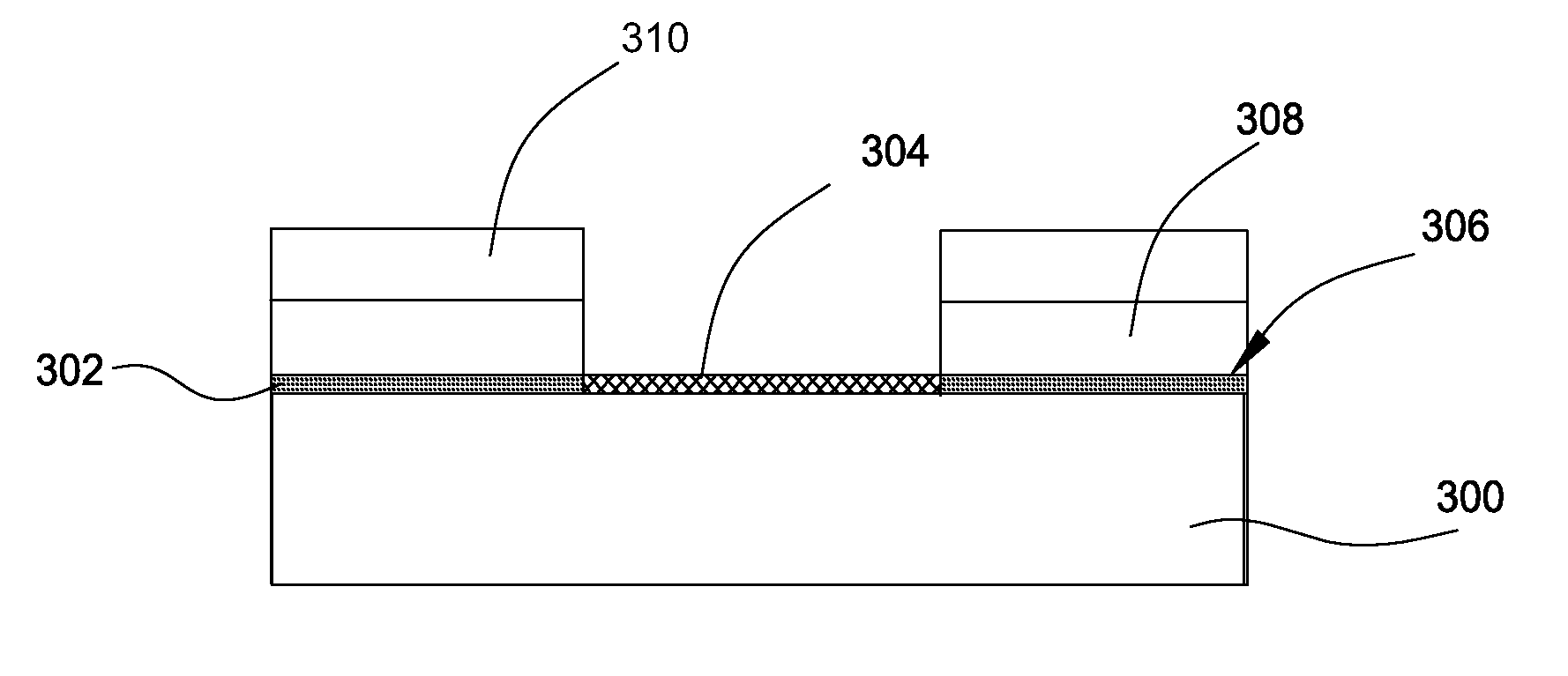

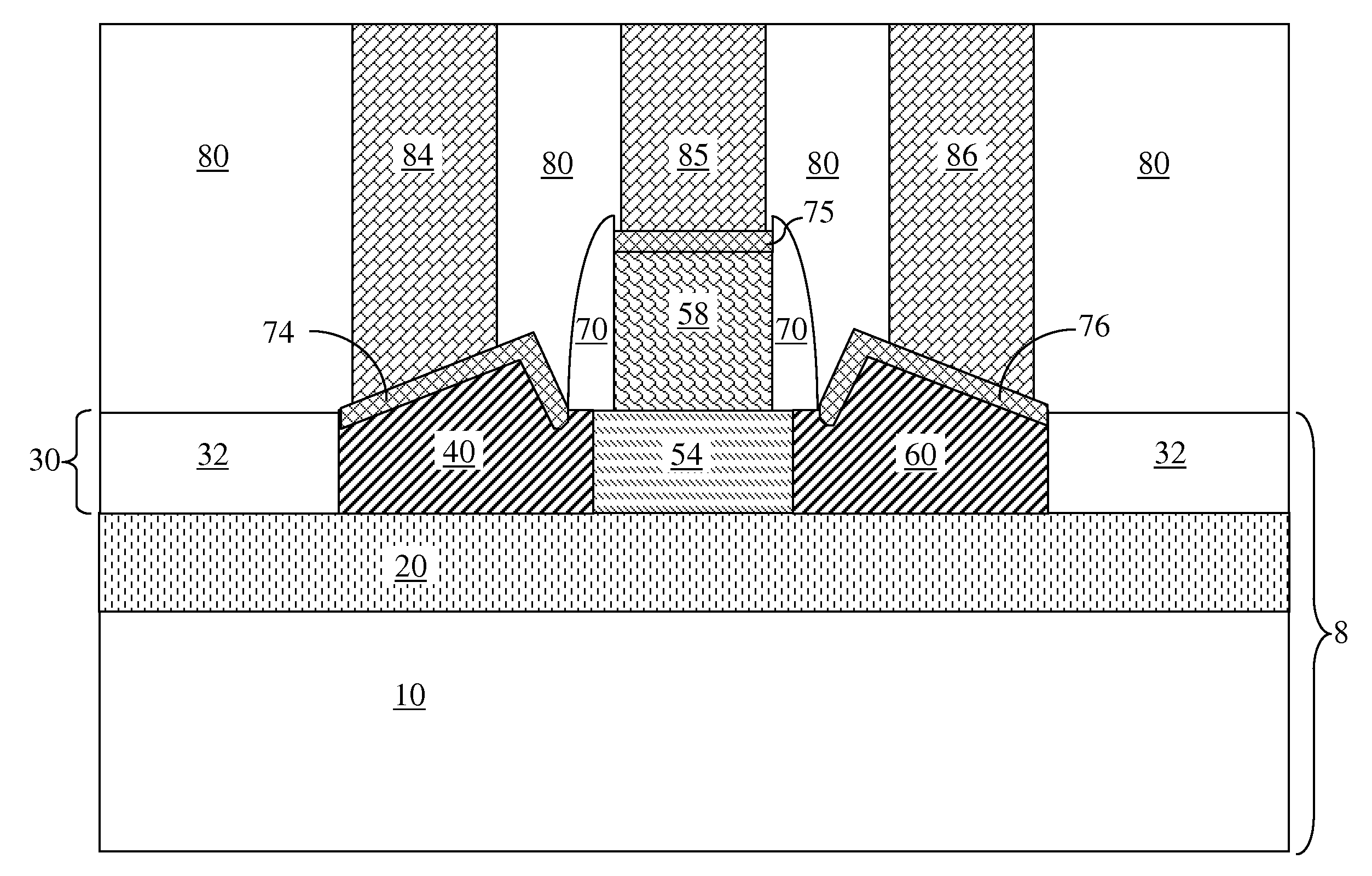

SOI SiGe-Base Lateral Bipolar Junction Transistor

ActiveUS20120139009A1Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

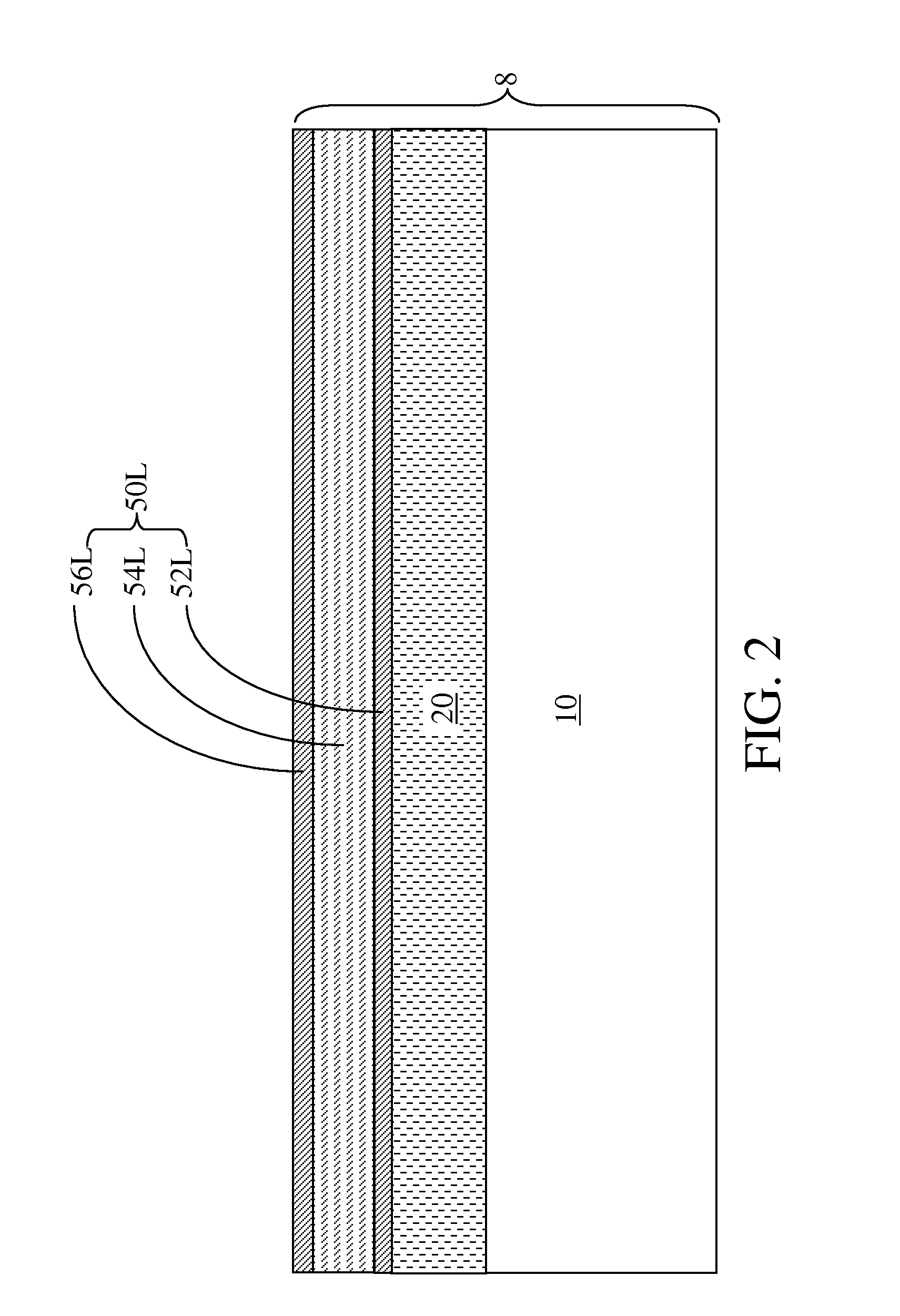

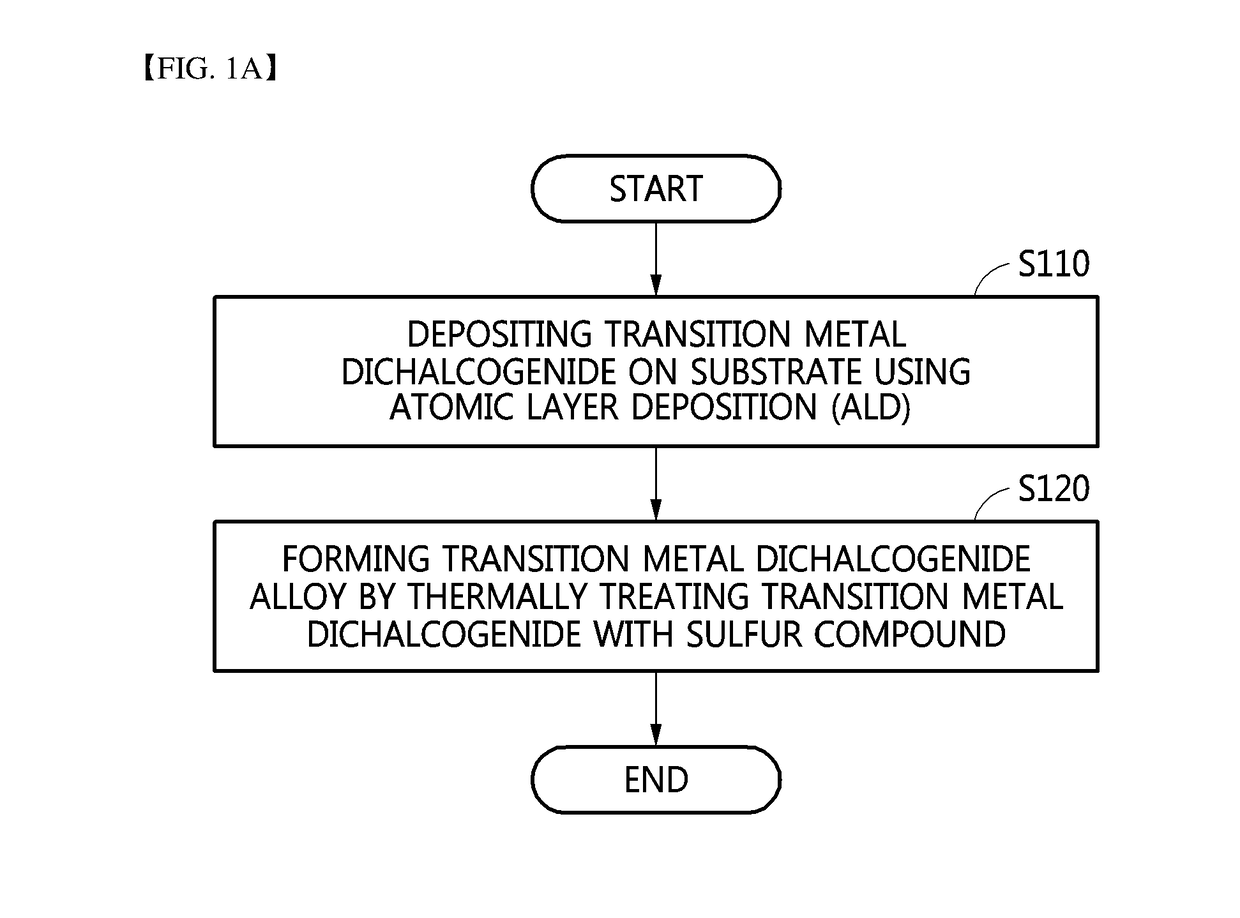

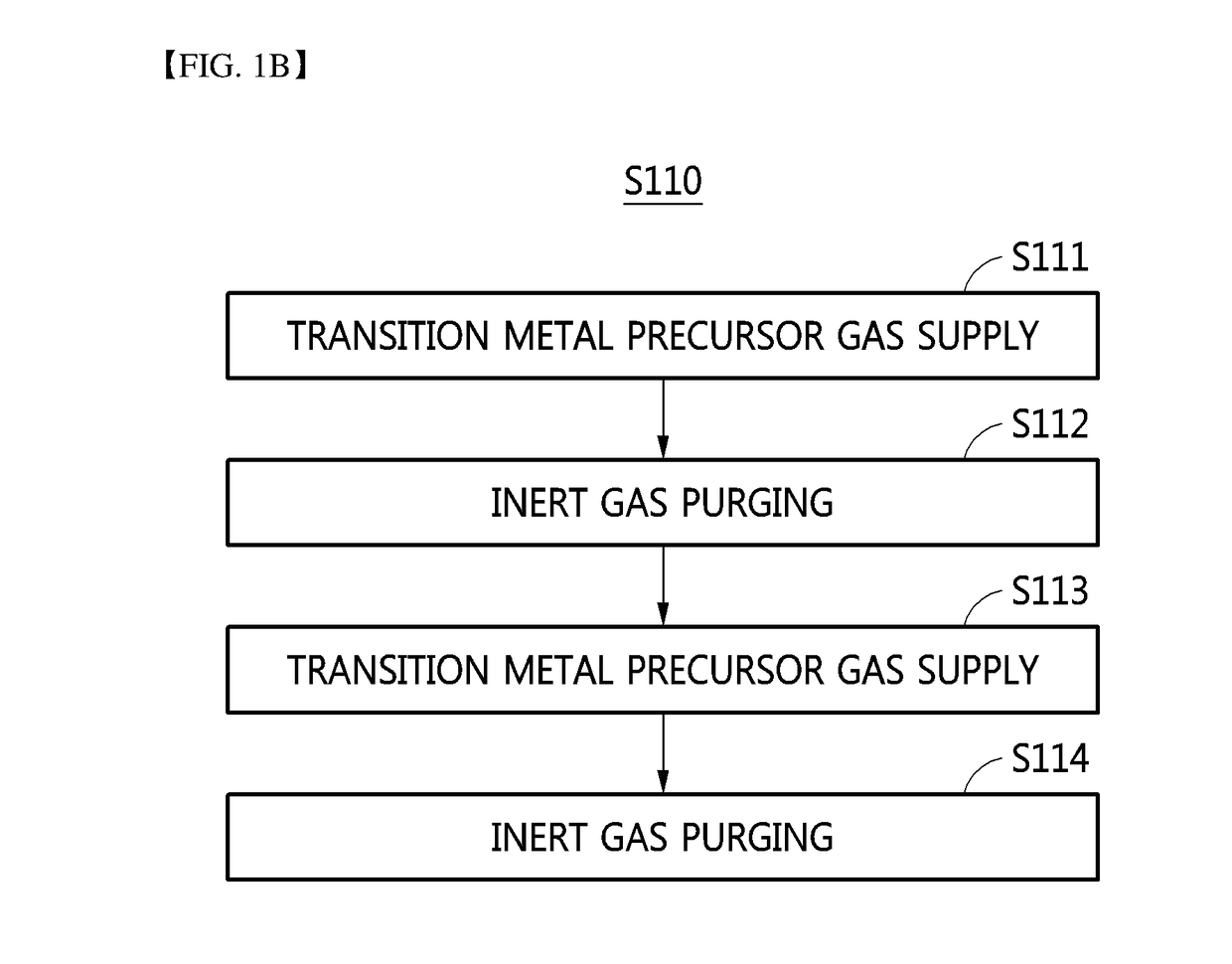

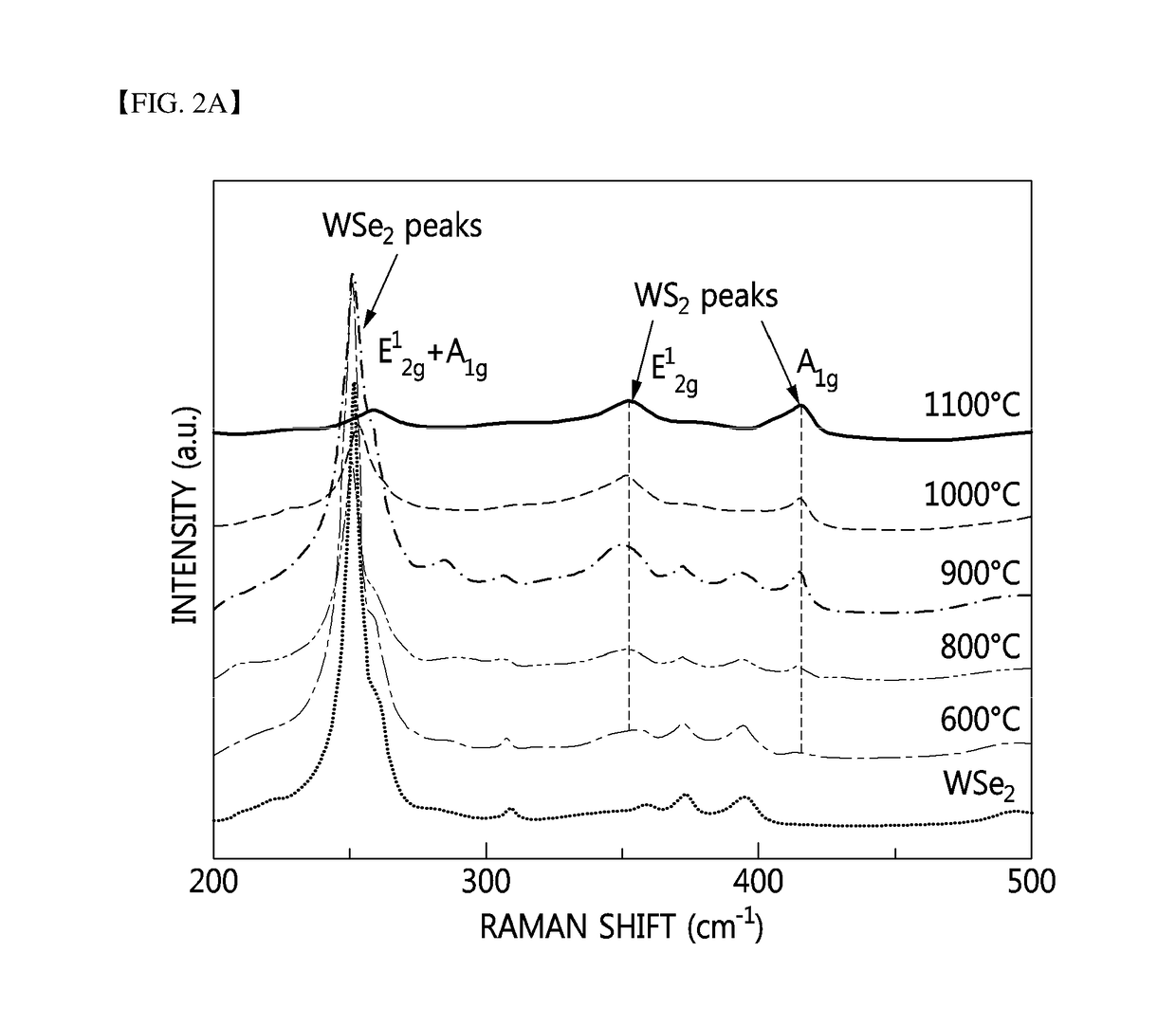

Transition metal dichalcogenide alloy and method of manufacturing the same

ActiveUS20170267527A1Semiconductor/solid-state device manufacturingSelenium/tellurium compounds with other elementsSulfurAlloy

Disclosed are a transition metal dichalcogenide alloy and a method of manufacturing the same. A method of manufacturing a transition metal dichalcogenide alloy according to an embodiment of the present disclosure includes a step of depositing transition metal dichalcogenide on a substrate using atomic layer deposition (ALD); and a step of forming a transition metal dichalcogenide alloy by thermally treating the transition metal dichalcogenide with a sulfur compound.

Owner:IND ACADEMIC CORP FOUND YONSEI UNIV

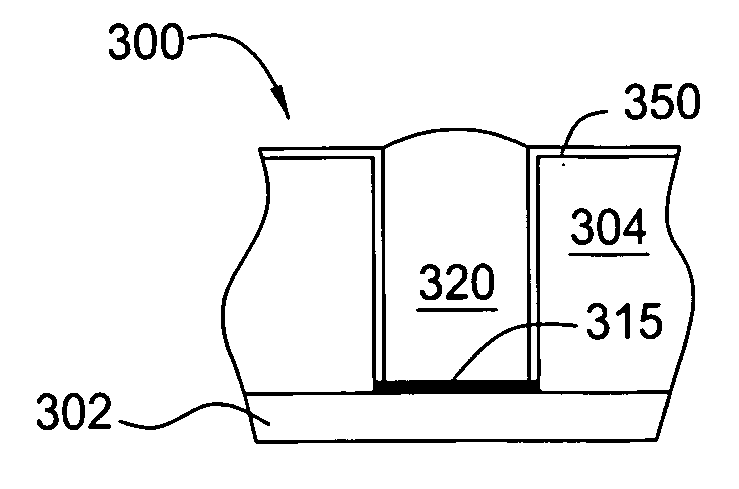

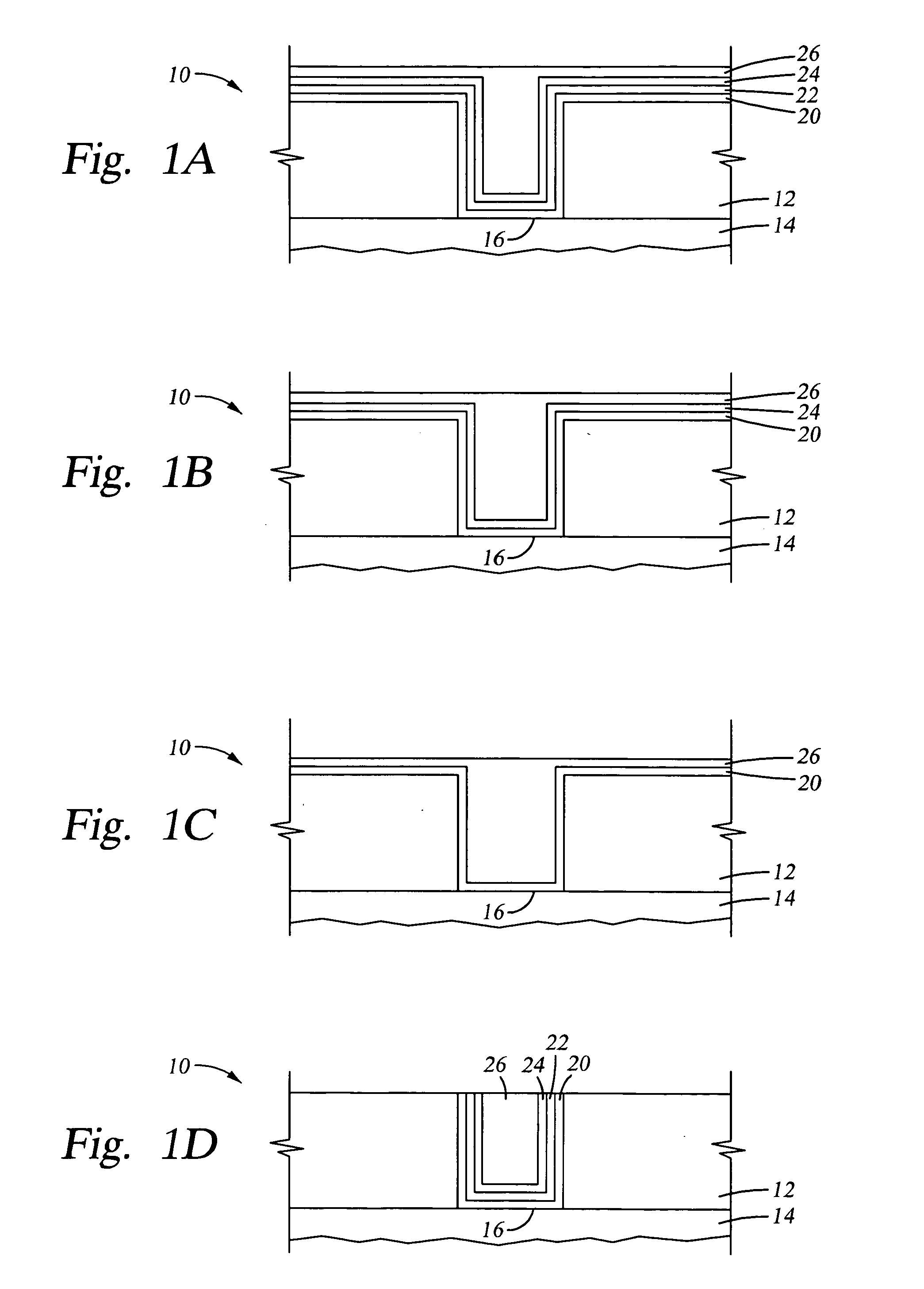

Electroless deposition process on a silicon contact

ActiveUS20060264043A1Material nanotechnologySemiconductor/solid-state device manufacturingSalicideAlloy

Embodiments as described herein provide methods for depositing a material on a substrate during electroless deposition processes, as well as compositions of the electroless deposition solutions. In one embodiment, the substrate contains a contact aperture having an exposed silicon contact surface. In another embodiment, the substrate contains a contact aperture having an exposed silicide contact surface. The apertures are filled with a metal contact material by exposing the substrate to an electroless deposition process. The metal contact material may contain a cobalt material, a nickel material, or alloys thereof. Prior to filling the apertures, the substrate may be exposed to a variety of pretreatment processes, such as preclean processes and activations processes. A preclean process may remove organic residues, native oxides, and other contaminants during a wet clean process or a plasma etch process. Embodiments of the process also provide the deposition of additional layers, such as a capping layer.

Owner:APPLIED MATERIALS INC

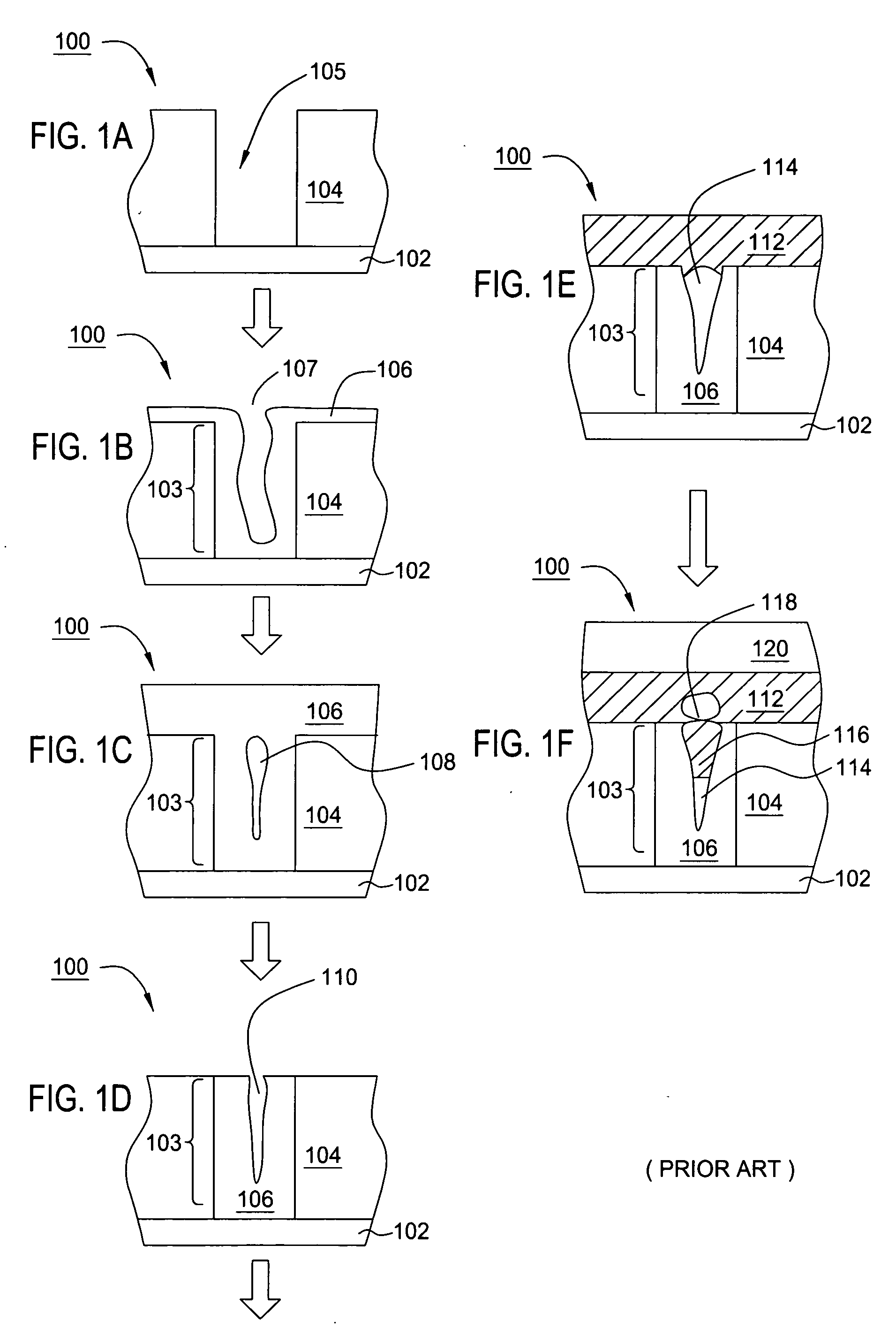

Electroless plating of metal caps for chalcogenide-based memory devices

InactiveUS20060094236A1Good electrical contactSemiconductor/solid-state device manufacturingPlatinumSulfur

A method of forming a metal cap over a conductive interconnect in a chalcogenide-based memory device is provided and includes, forming a layer of a first conductive material over a substrate, depositing an insulating layer over the first conductive material and the substrate, forming an opening in the insulating layer to expose at least a portion of the first conductive material, depositing a second conductive material over the insulating layer and within the opening, removing portions of the second conductive material to form a conductive area within the opening, recessing the conductive area within the opening to a level below an upper surface of the insulating layer, forming a cap of a third conductive material over the recessed conductive area within the opening, the third conductive material selected from the group consisting of cobalt, silver, gold, copper, nickel, palladium, platinum, and alloys thereof, depositing a stack of a chalcogenide based memory cell material over the cap, and depositing a conductive material over the chalcogenide stack.

Owner:MICRON TECH INC

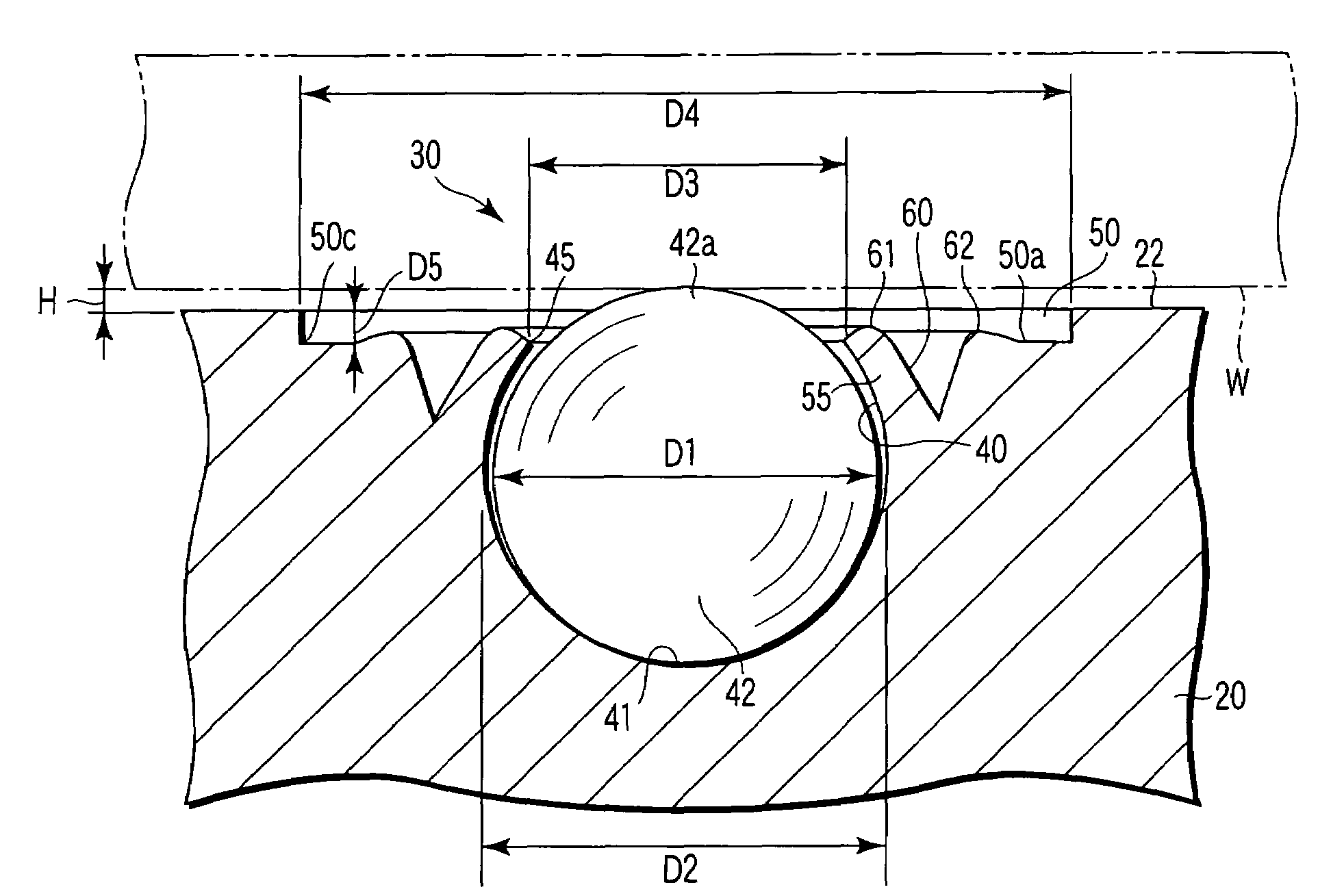

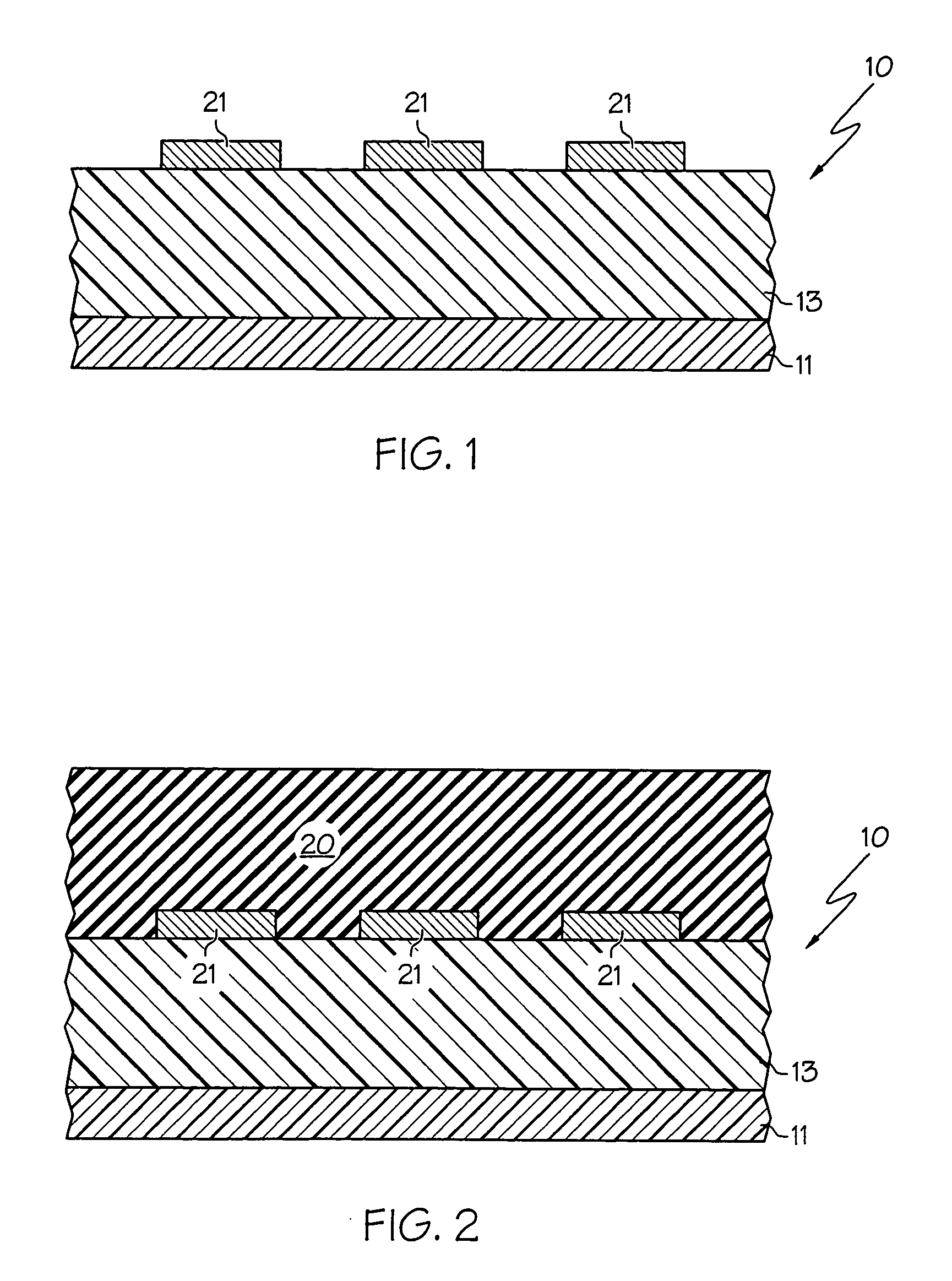

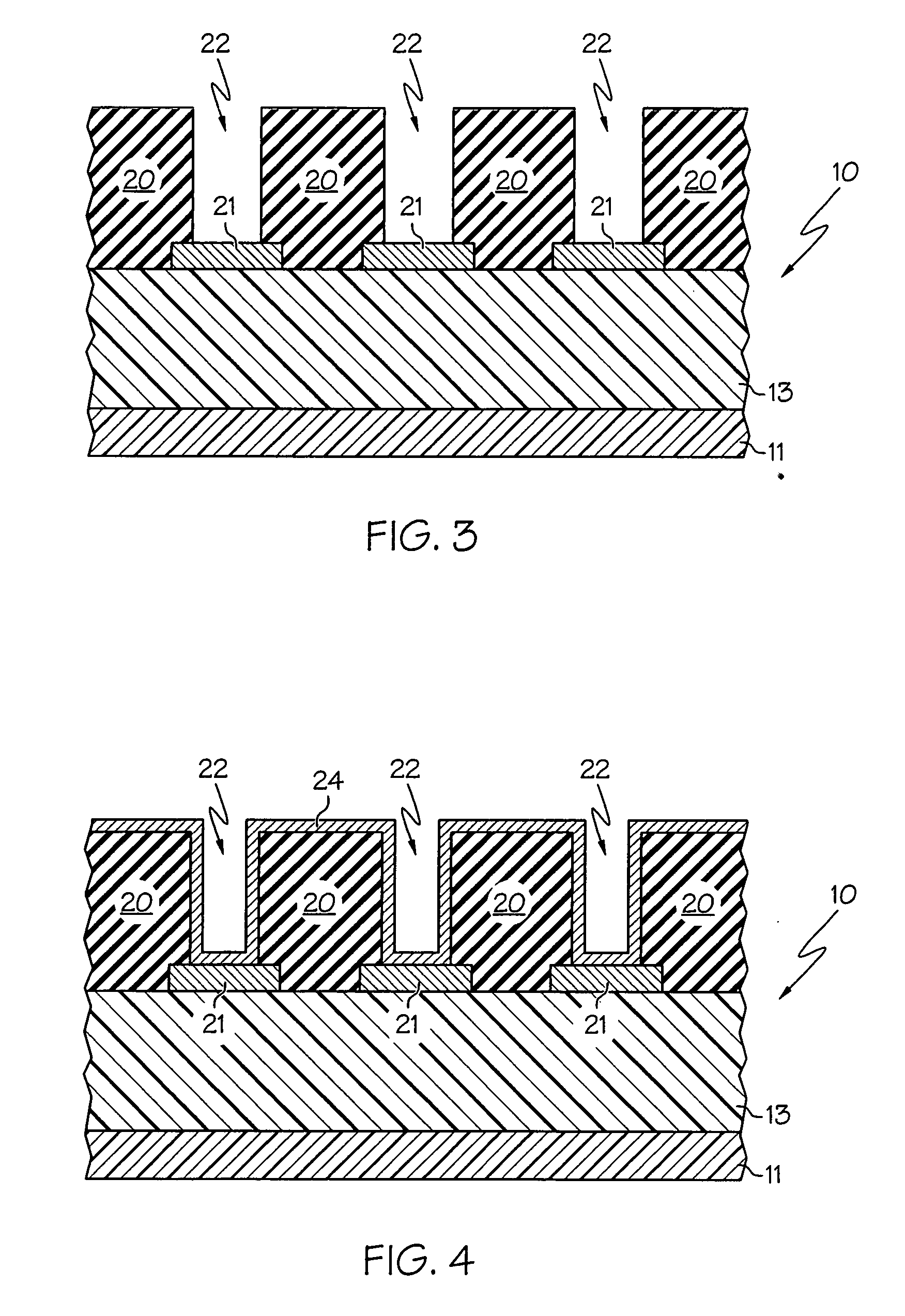

Substrate supporting apparatus and manufacturing method therefor

ActiveUS20070157466A1Preventing slipping-offAvoid breakingLiquid surface applicatorsLinear bearingsEngineeringAlloy

A substrate supporting apparatus includes a plate member of an aluminum alloy having a flat upper surface, bottomed pits formed in the plate member, and spacer members held in the pits, individually. The spacer members are sapphire spheres. The diameter of each spacer member is a little smaller than that of each pit. The upper end of each spacer member projects from the upper surface of the plate member. A spot facing is formed in a region that includes the open edge portion of the pit. A bending portion which is obtained by plastically deforming the open edge portion of the pit toward the spacer member is formed on a bottom surface of the spot facing. A V-shaped groove is formed behind the bending portion.

Owner:NHK SPRING CO LTD

Printable electrical conductors

An electrical conductor formed from one or more metallic inks. The electrical conductor comprises a network of interconnected metallic nodes. Each node comprises a metallic composition, e.g., one or more metals or alloys. The network defines a plurality of pores having an average pore volume of less than about 10,000,000 nm3. The electrical conductors advantageously have a high degree of conductivity, e.g., a resistivity of not greater than about 10× the resistivity of the (bulk) metallic composition, which forms the individual nodes.

Owner:CABOT CORP

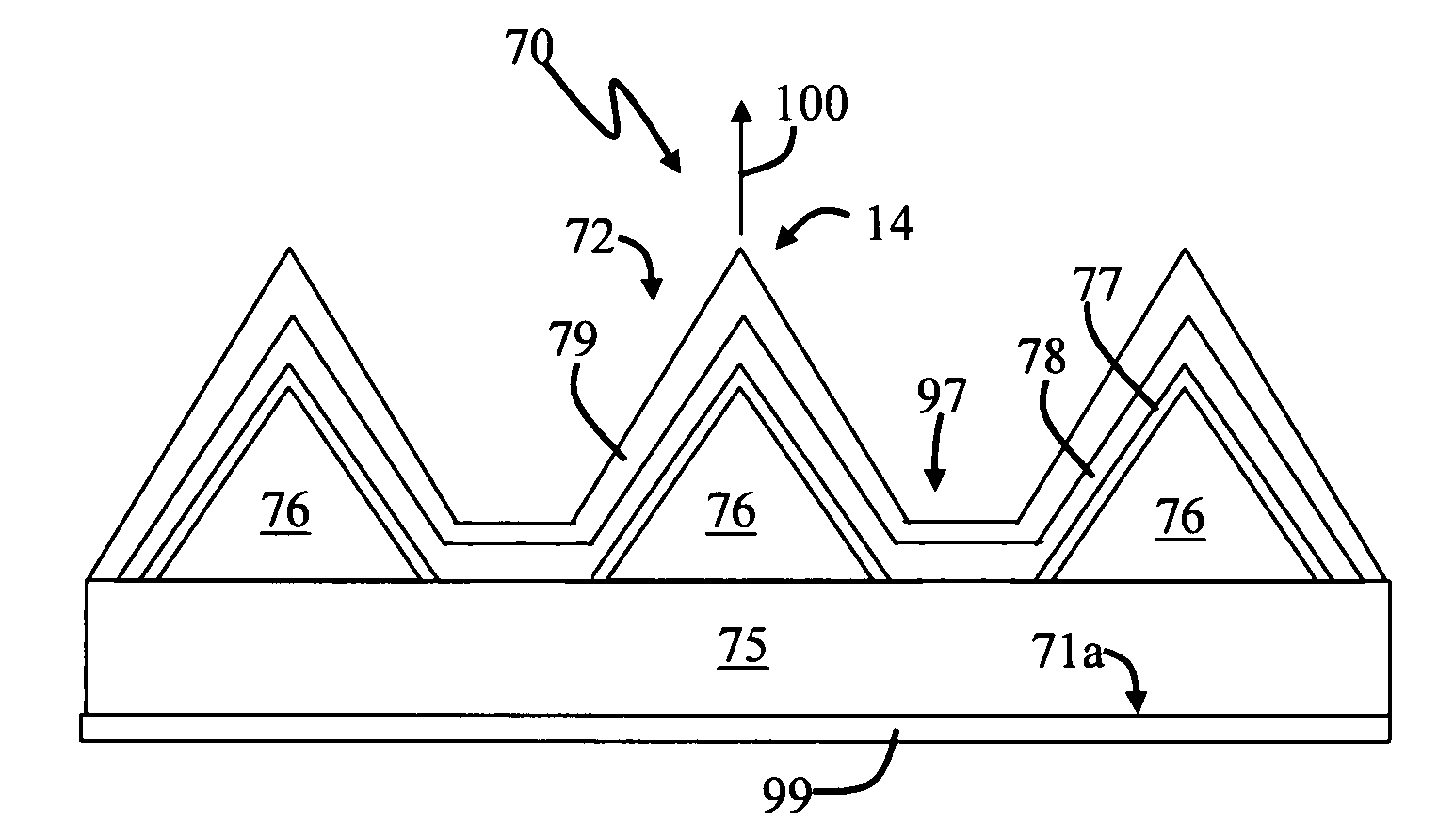

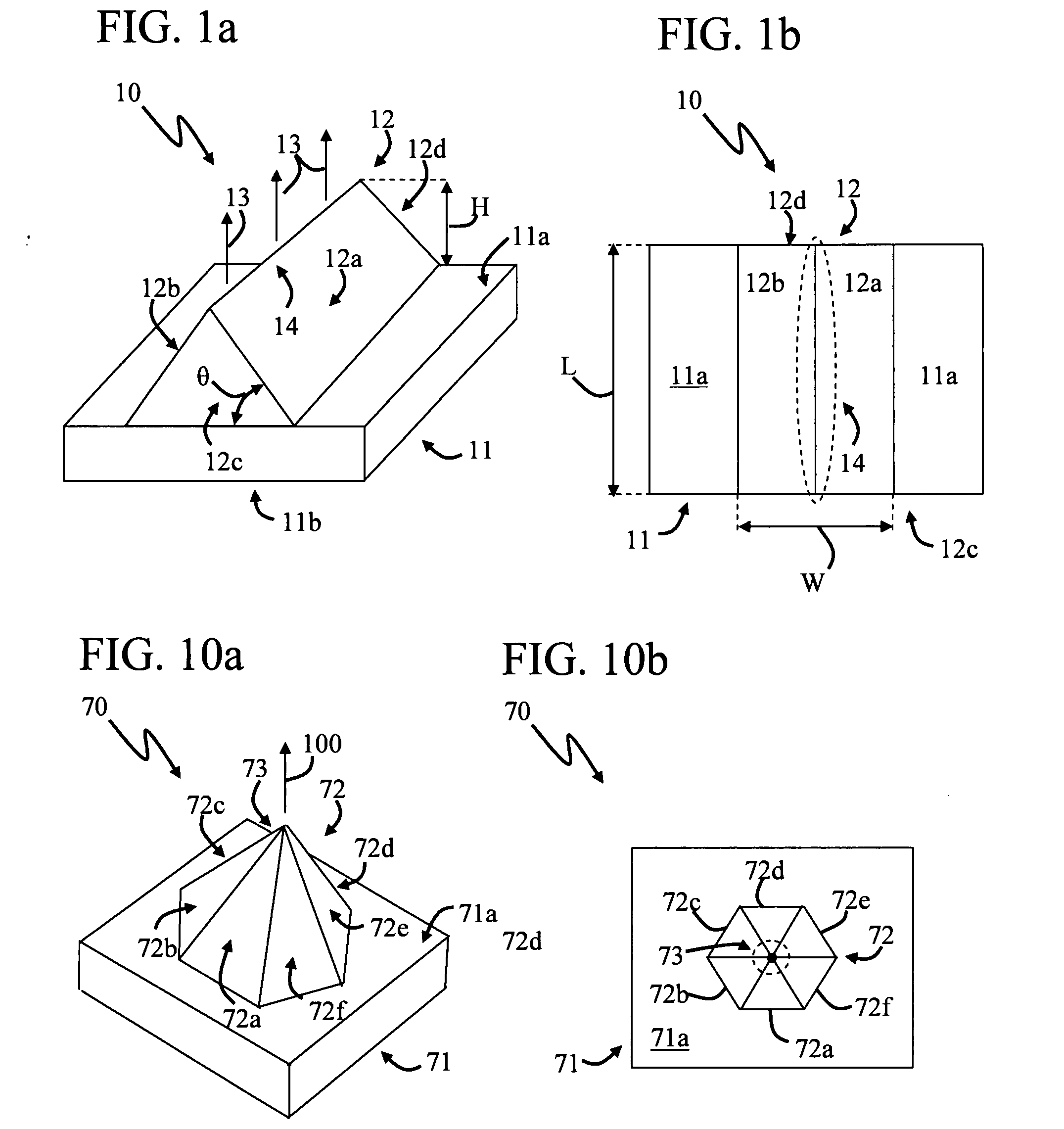

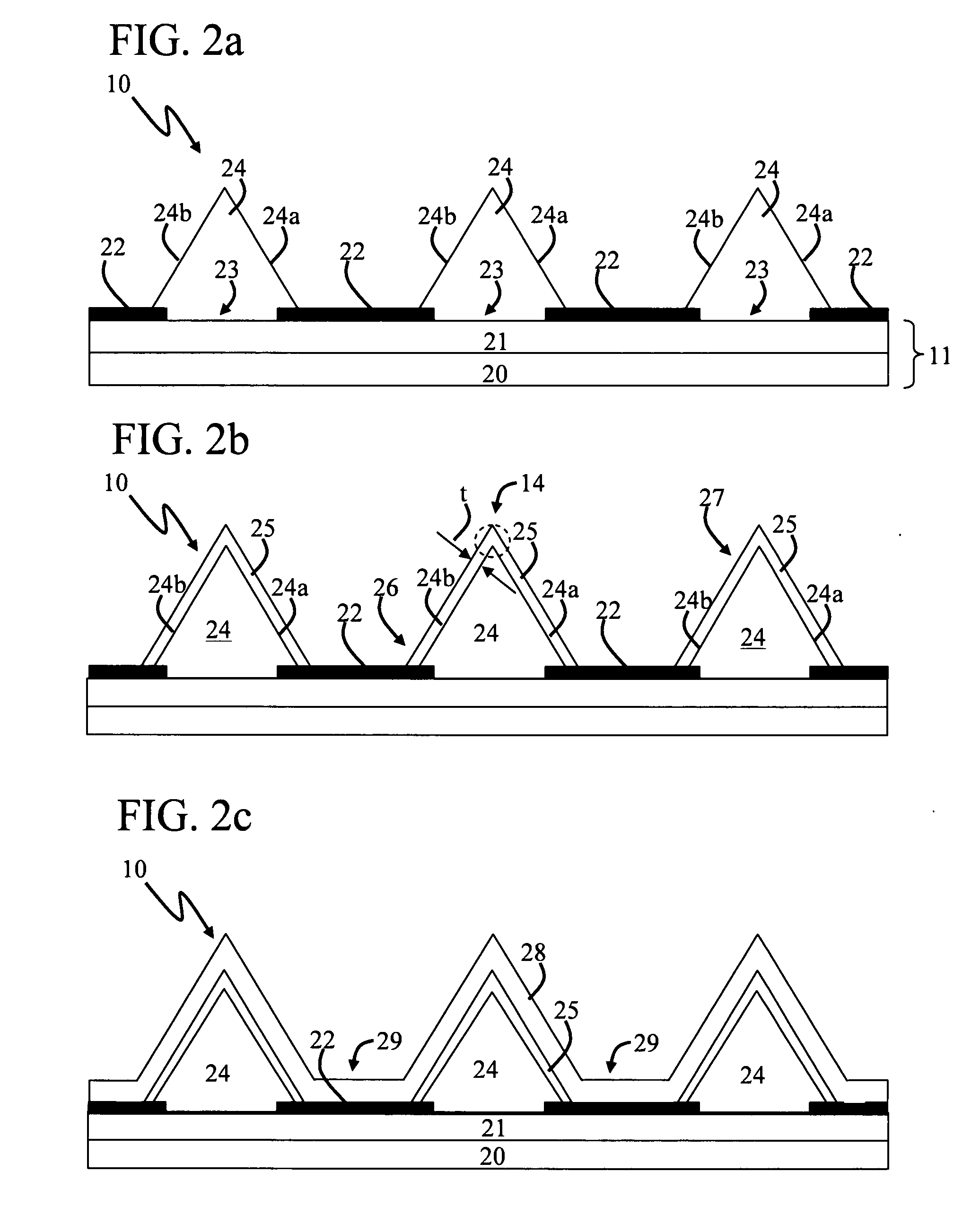

Solid State Light Emitting Device

InactiveUS20090159869A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureAlloy

A semiconductor structure (10, 10′, 70, 80) includes a light emitter (12, 72) carried by a support structure (11). The light emitter (12, 72) includes a base region (24, 76) with a sloped sidewall (12a, 12b) and a light emitting region (25, 77) positioned thereon. The light emitting (25, 77) region includes a nitride semiconductor alloy having a composition that is different in a first region (26, 95) near the support structure (11) compared to a second region (27, 96) away from the support structure (11).

Owner:PONCE FERNANDO A +2

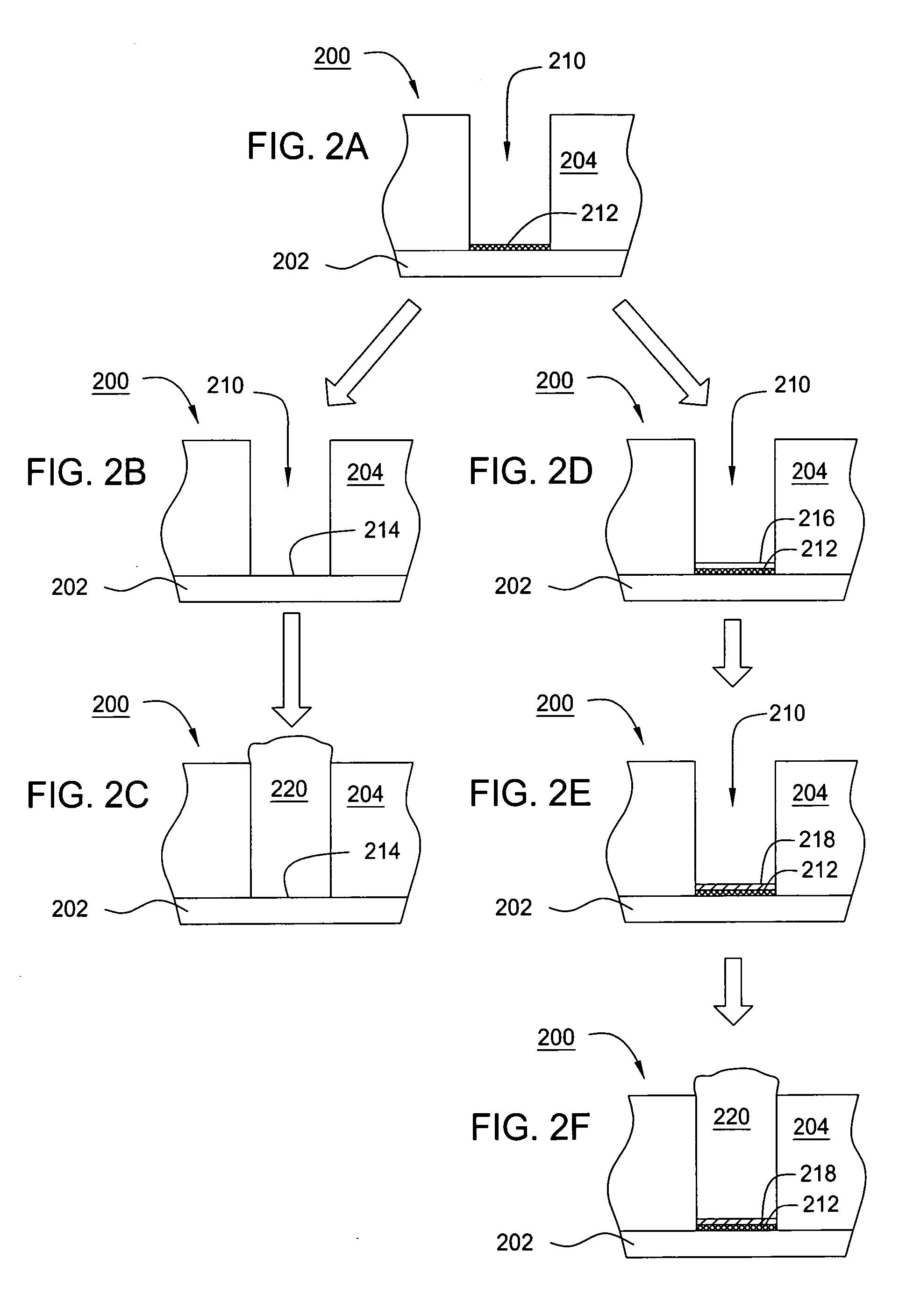

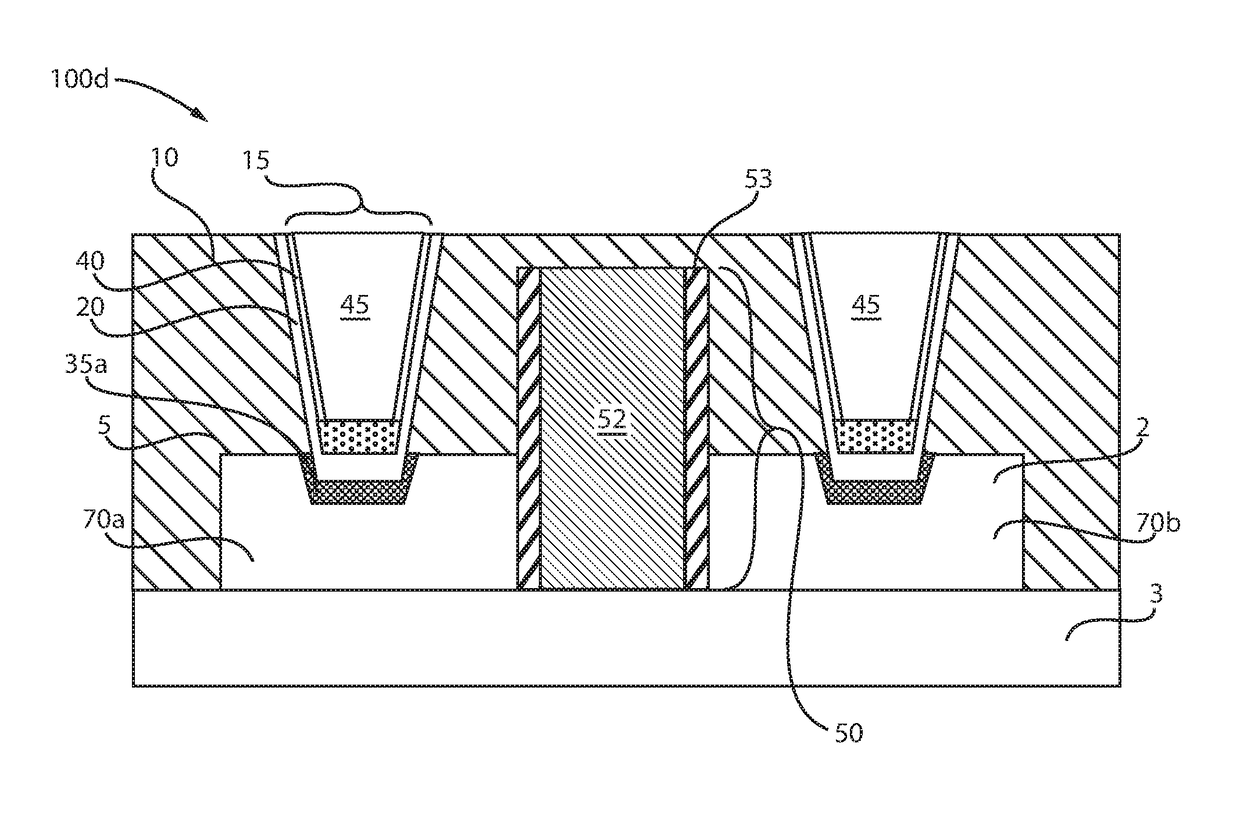

High density chalcogenide memory cells

ActiveUS20040248339A1Tight and repeatable controlImprove electrical isolationSolid-state devicesSemiconductor/solid-state device manufacturingHigh densityAlloy

A non-volatile memory cell is constructed from a chalcogenide alloy structure and an associated electrode side wall. The electrode is manufactured with a predetermined thickness and juxtaposed against a side wall of the chalcogenide alloy structure, wherein at least one of the side walls is substantially perpendicular to a planar surface of the substrate. The thickness of the electrode is used to control the size of the active region created within the chalcogenide alloy structure. Additional memory cells can be created along rows and columns to form a memory matrix. The individual memory cells are accessed through address lines and address circuitry created during the formation of the memory cells. A computer can thus read and write data to particular non-volatile memory cells within the memory matrix.

Owner:MACRONIX INT CO LTD

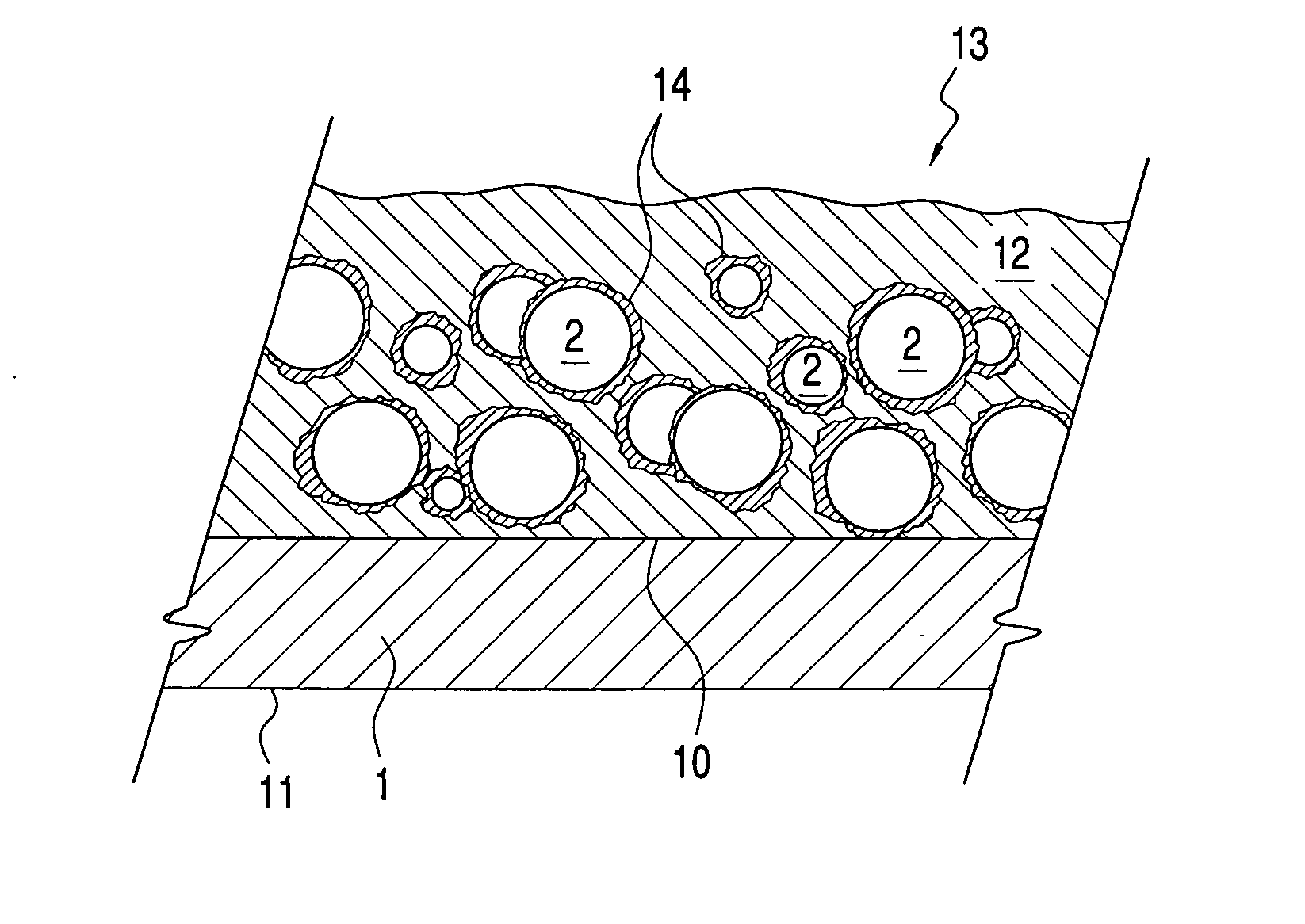

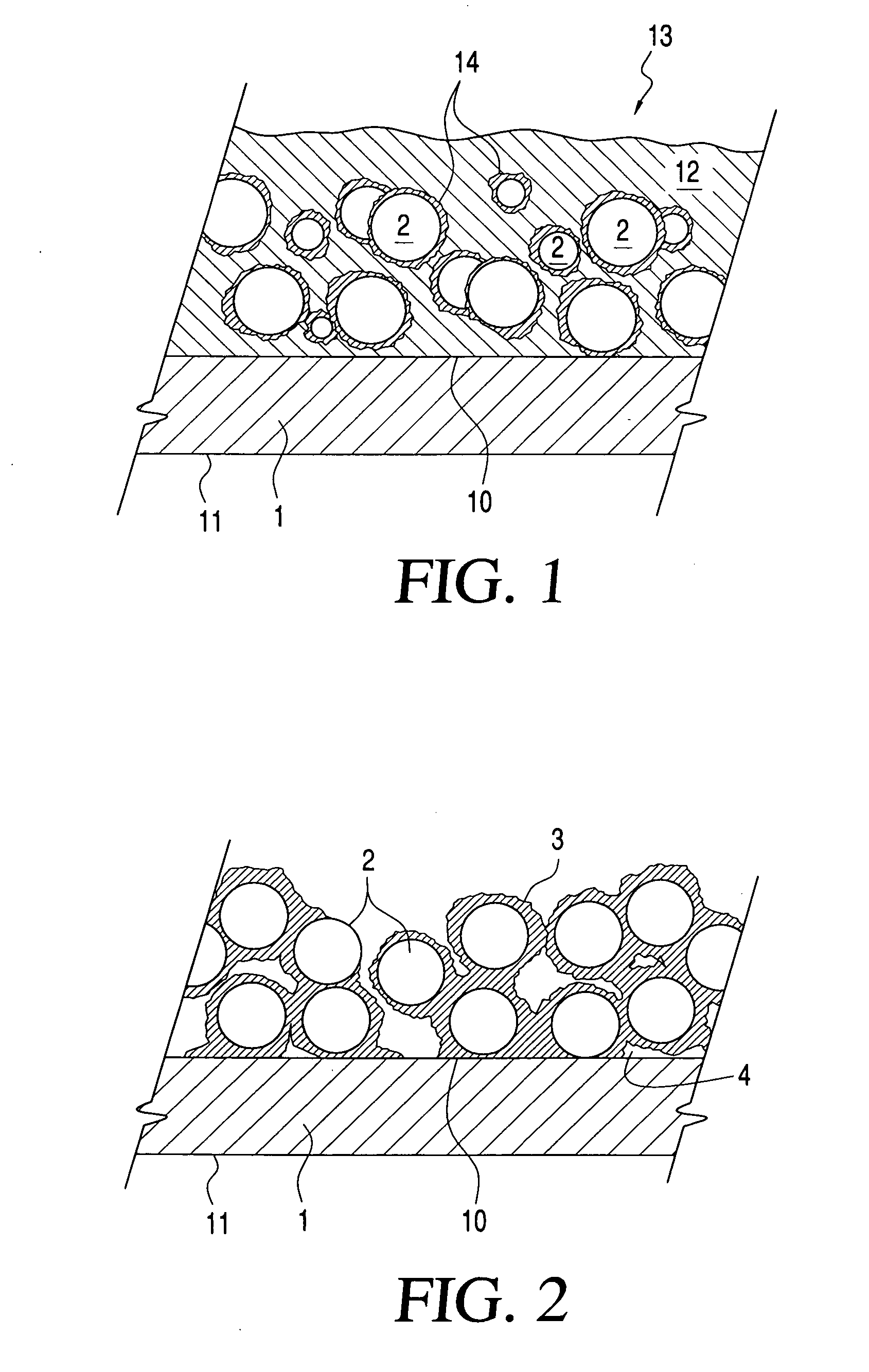

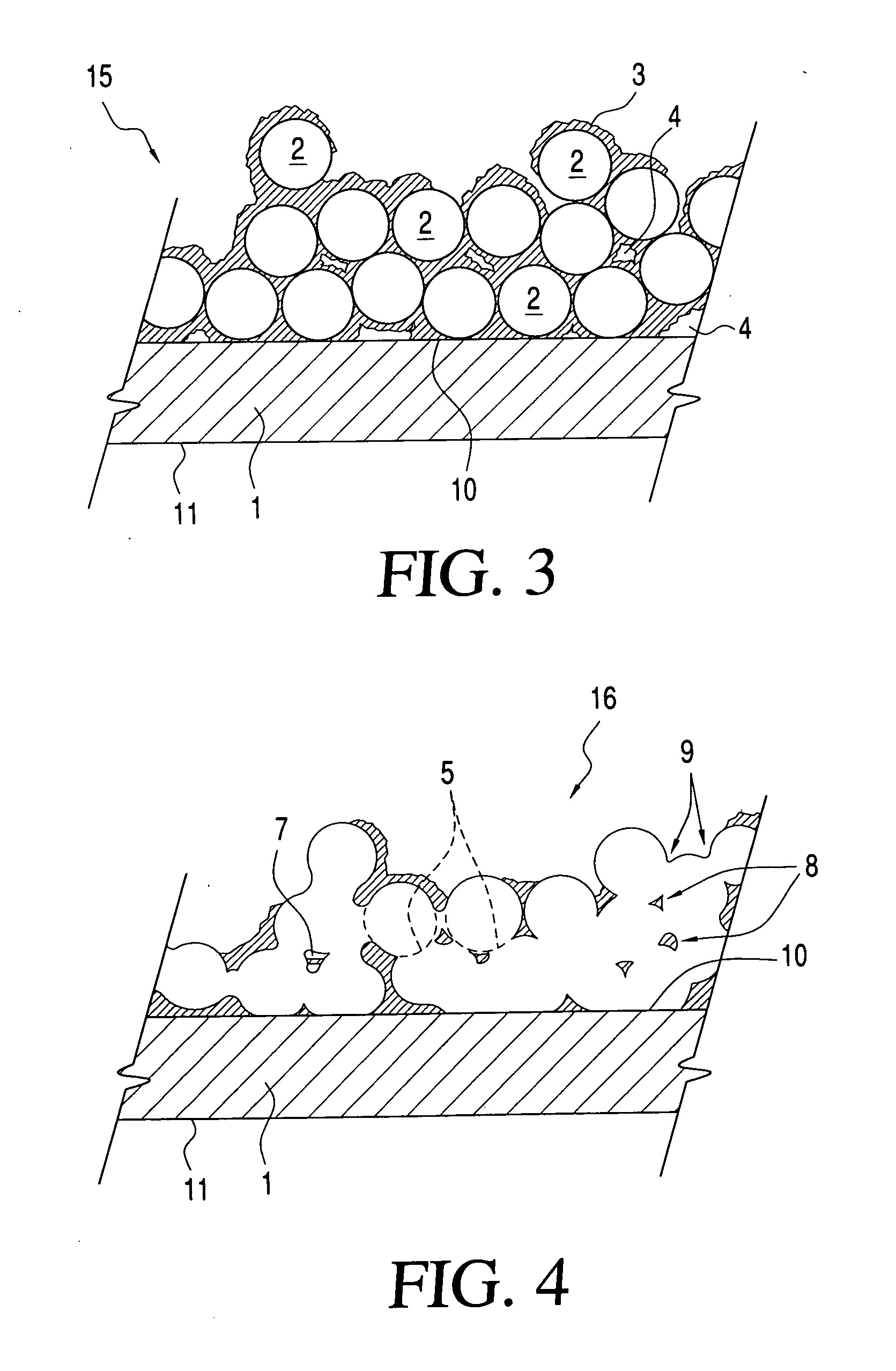

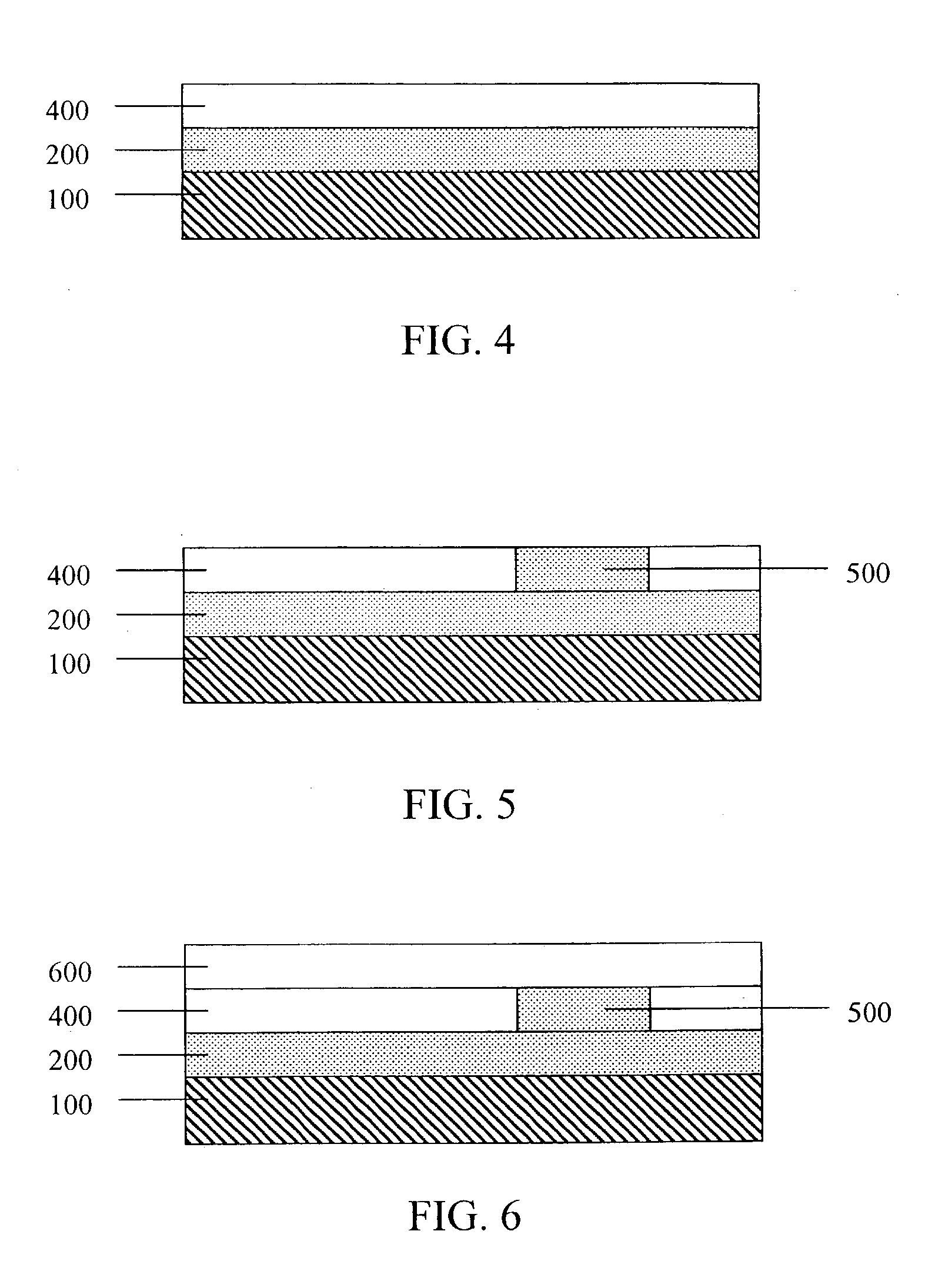

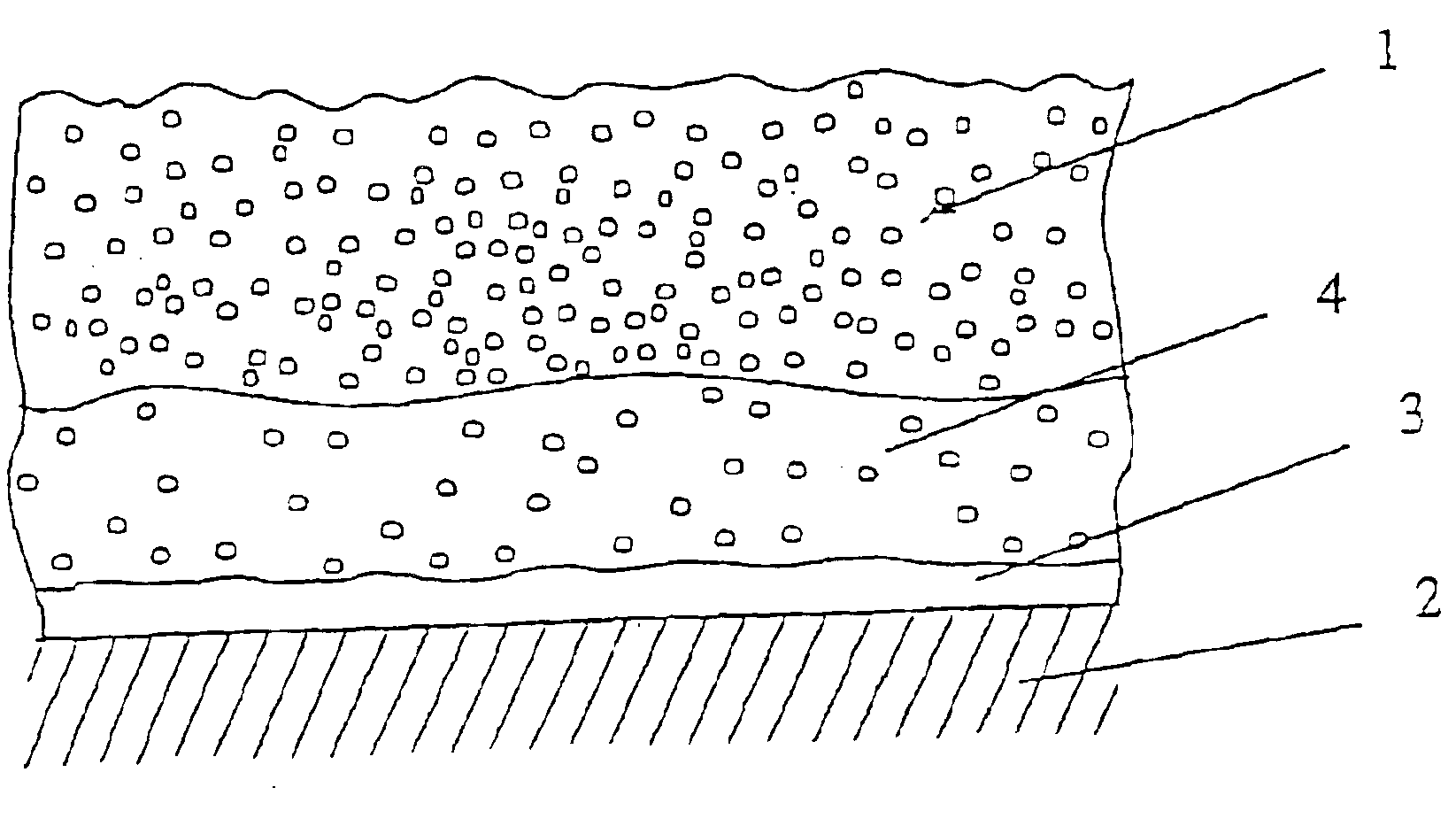

Method for coating internal surface of plasma processing chamber

InactiveUS6875477B2Improve the immunityMinimize thermal expansionLiquid surface applicatorsMolten spray coatingThermal expansionAlloy

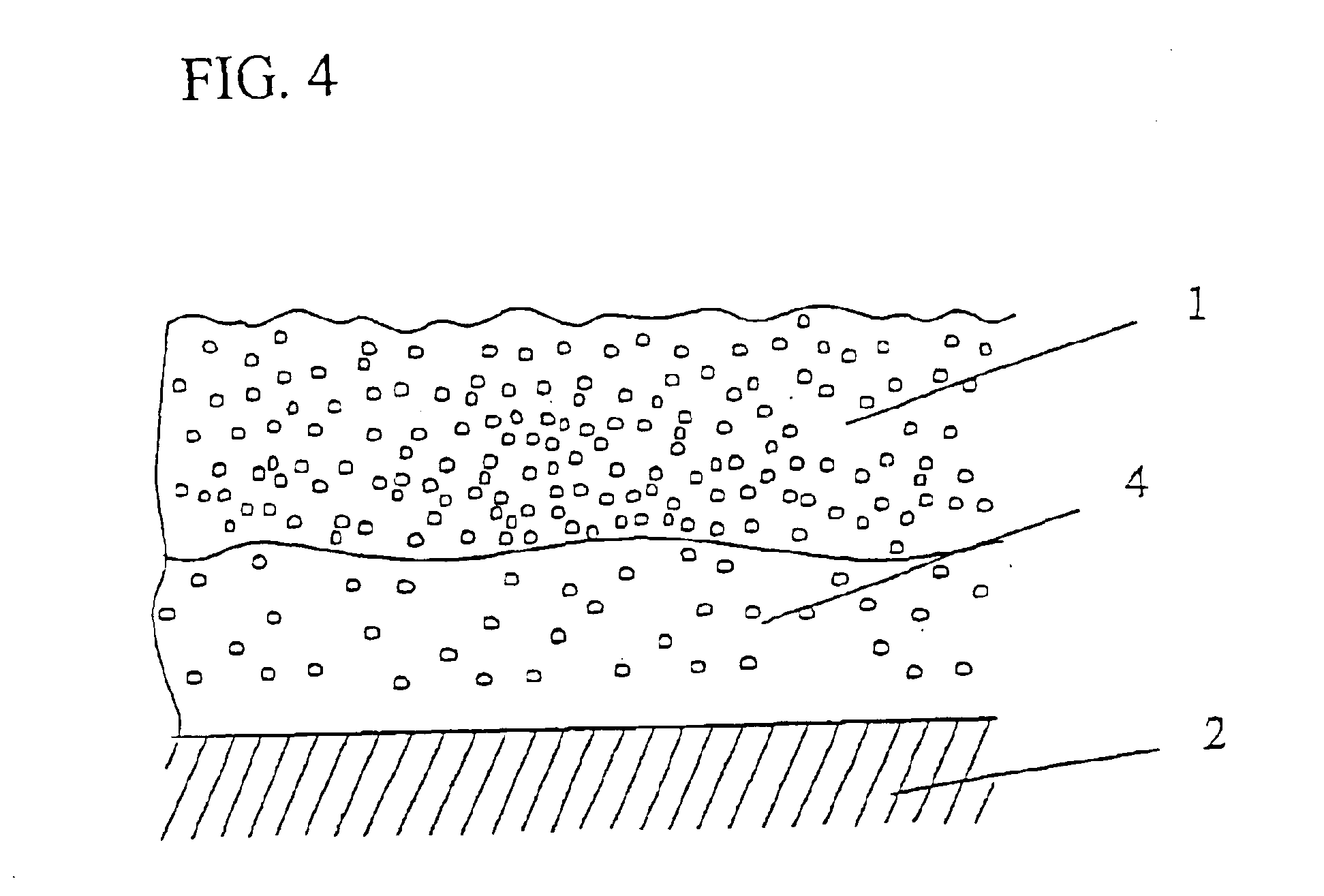

The present invention comprises an aluminum base material 2 constituting the plasma processing chamber of the plasma processing apparatus, a bonding layer 3 deposited on the base material consisting of a transition metal or transition metal alloy that modifies the difference in thermal expansion coefficient of the base material and the material constituting a plasma contact surface, and the plasma contact surface 1 formed of a material selected from a group consisting of La2O3, LaAlO3, MgLaAl11O19, and a mixture of La2O3 and Al2O3 being a metal oxide including at least La and O deposited on the bonding layer 3 via a thermal spray process.

Owner:HITACHI HIGH-TECH CORP

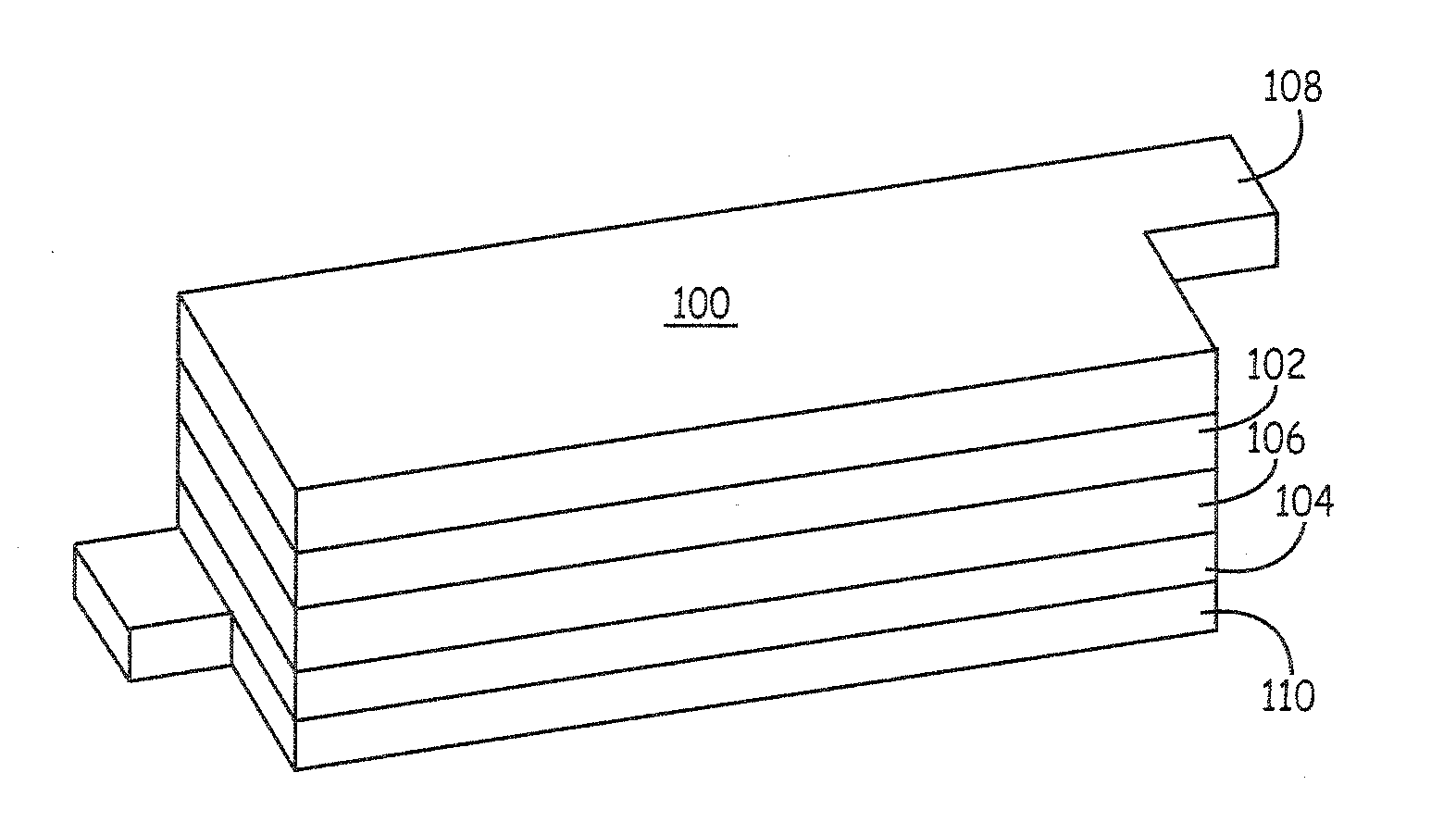

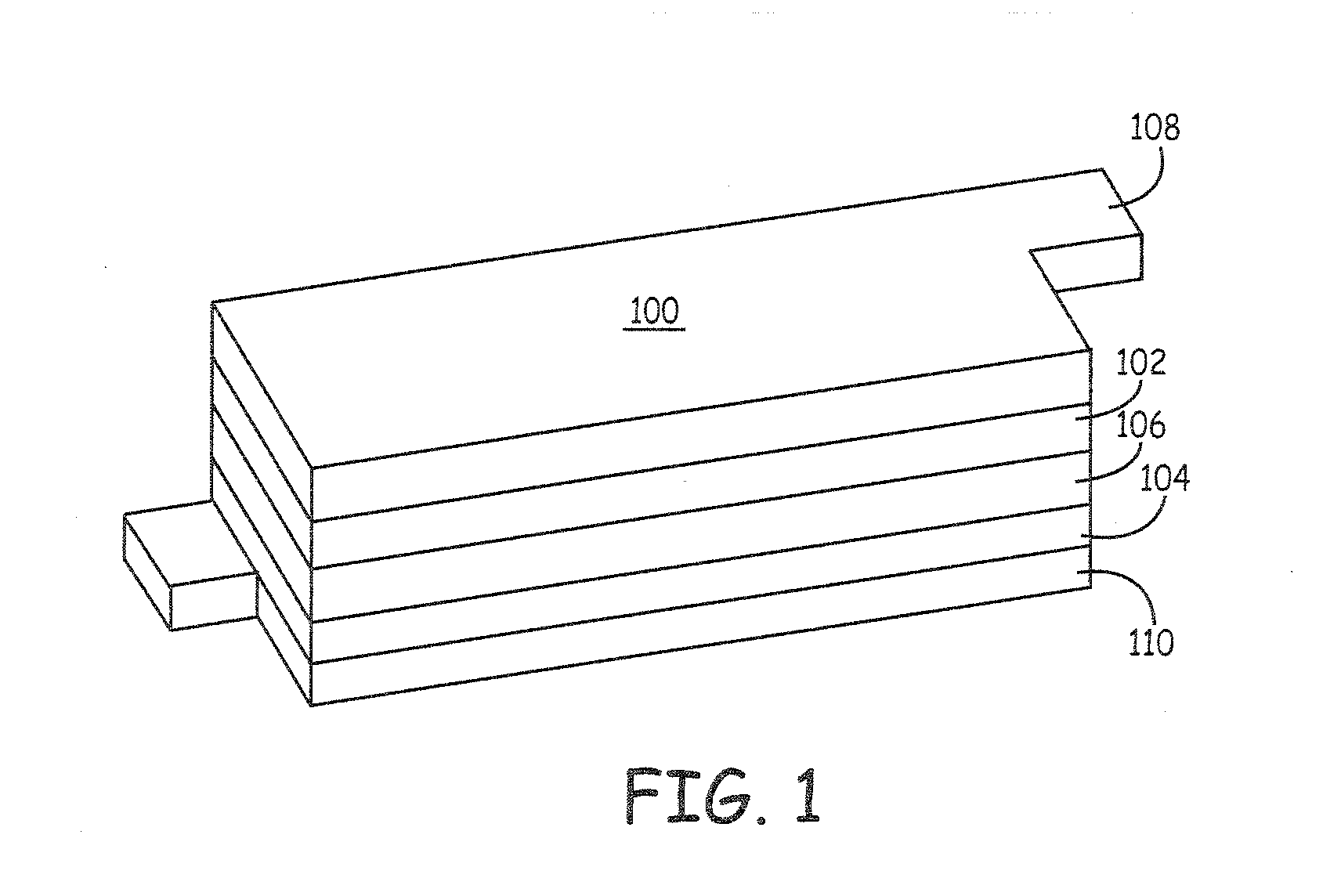

Electrode material for lithium secondary battery and electrode structure having the electrode material

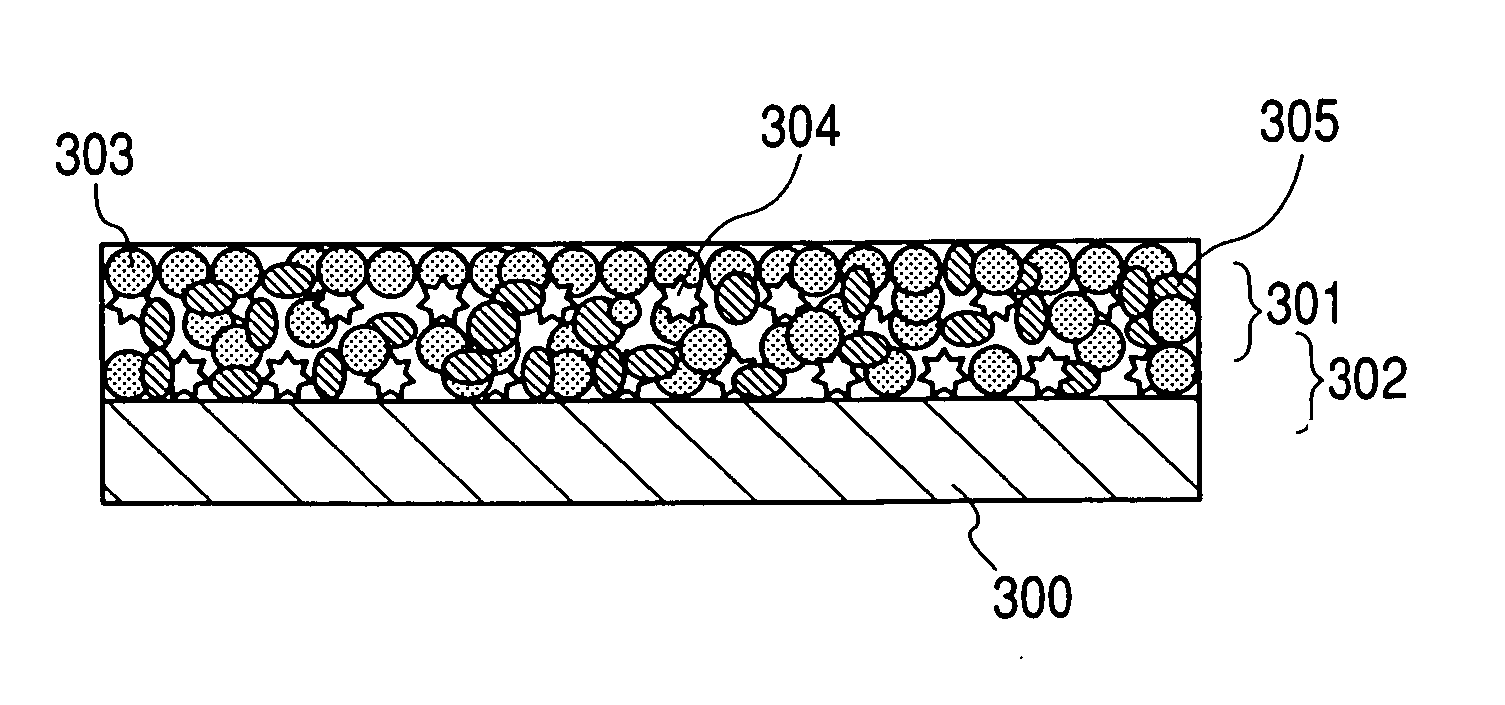

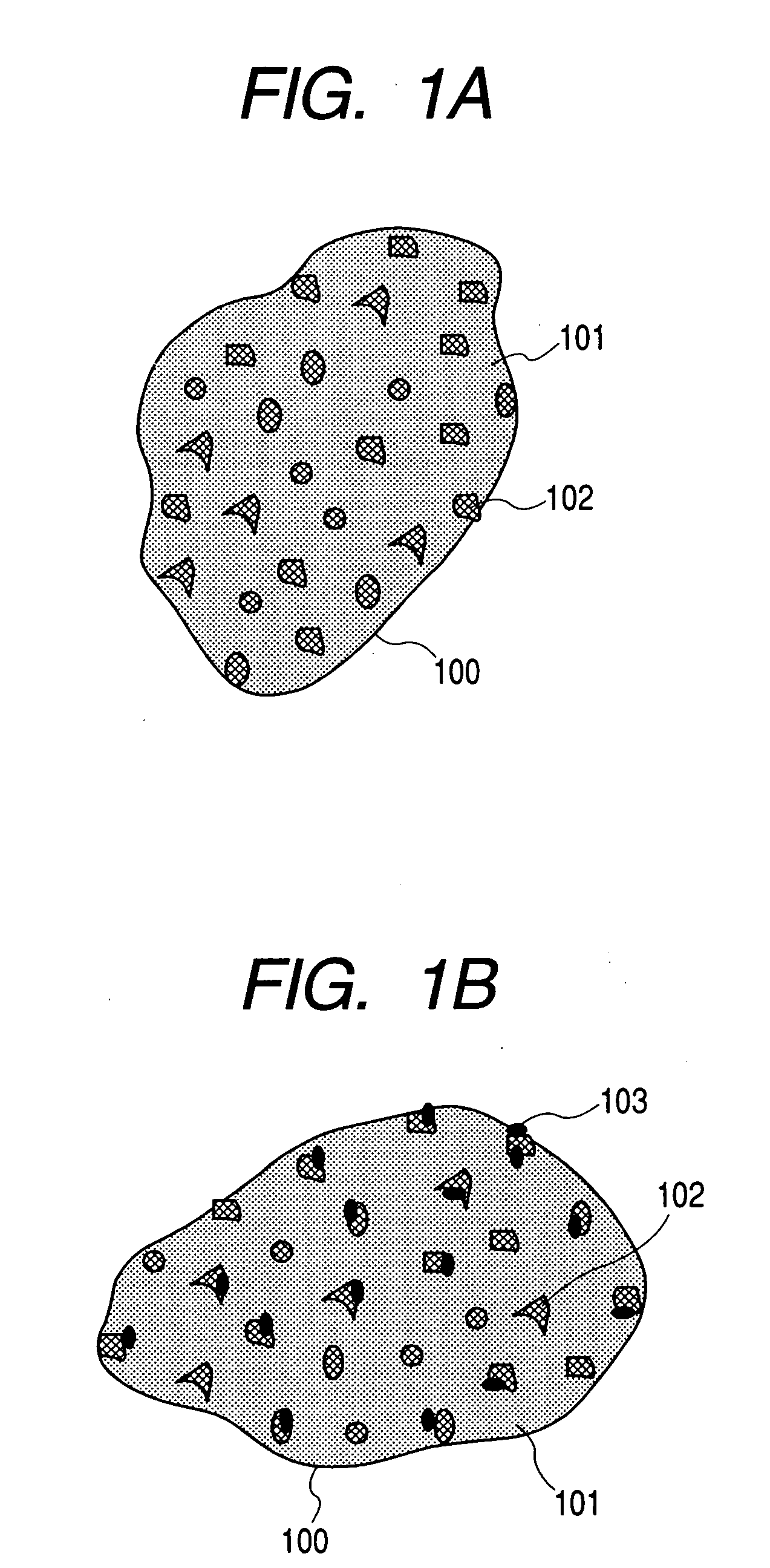

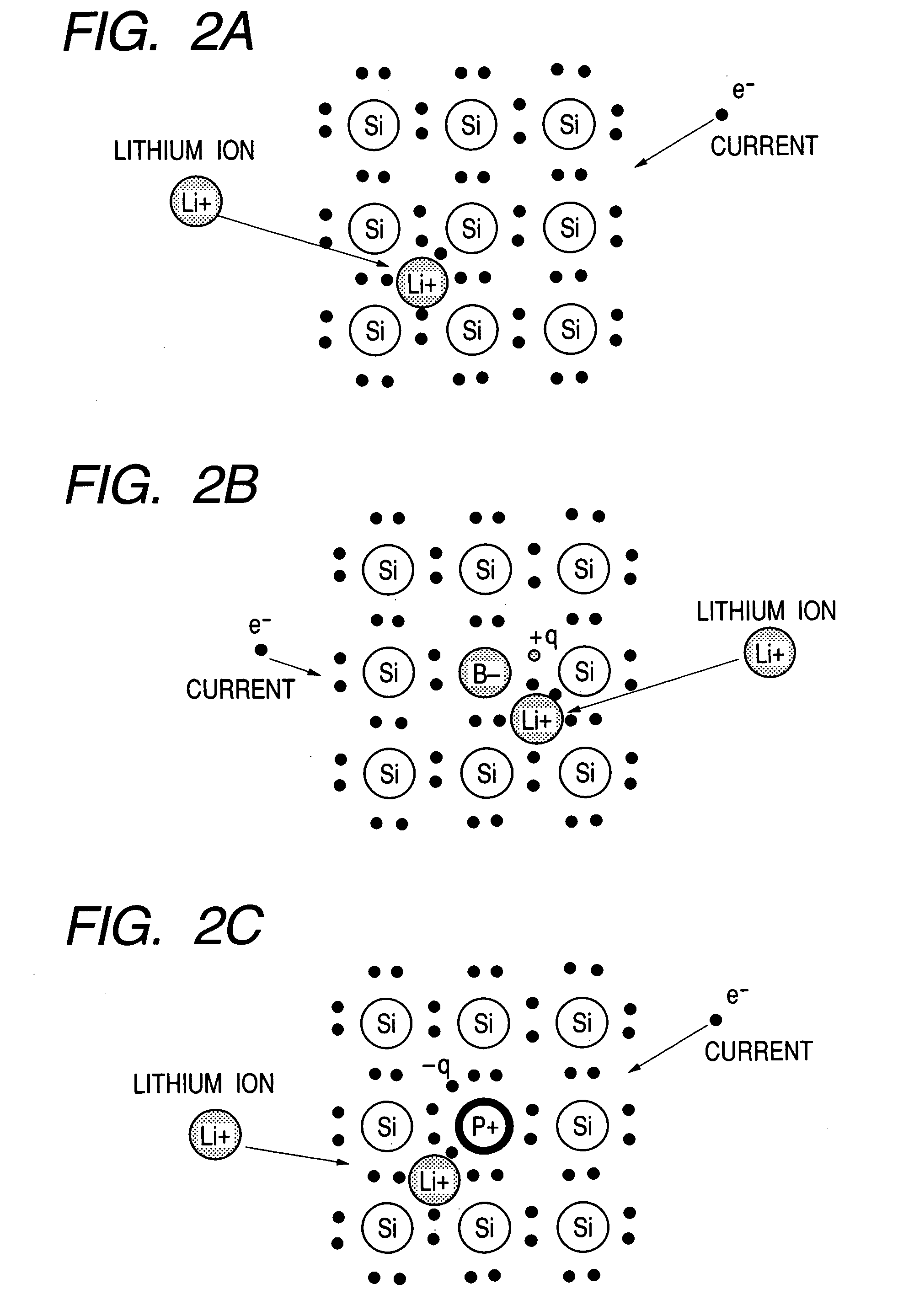

InactiveUS20060040182A1Reduce conductivityImprove conductivityLi-accumulatorsNon-aqueous electrolyte accumulator electrodesLithiumLiquid state

The electrode material for a lithium secondary battery according to the present invention includes particles of a solid state alloy having silicon as a main component, wherein the particles of the solid state alloy have a microcrystal or amorphous material including an element other than silicon, dispersed in microcrystalline silicon or amorphized silicon. The solid state alloy preferably contains a pure metal or a solid solution. The composition of the alloy preferably has an element composition in which the alloy is completely mixed in a melted liquid state, whereby the alloy has a single phase in a melted liquid state without presence of two or more phases. The element composition can be determined by the kind of elements constituting the alloy and an atomic ratio of the elements.

Owner:CANON KK

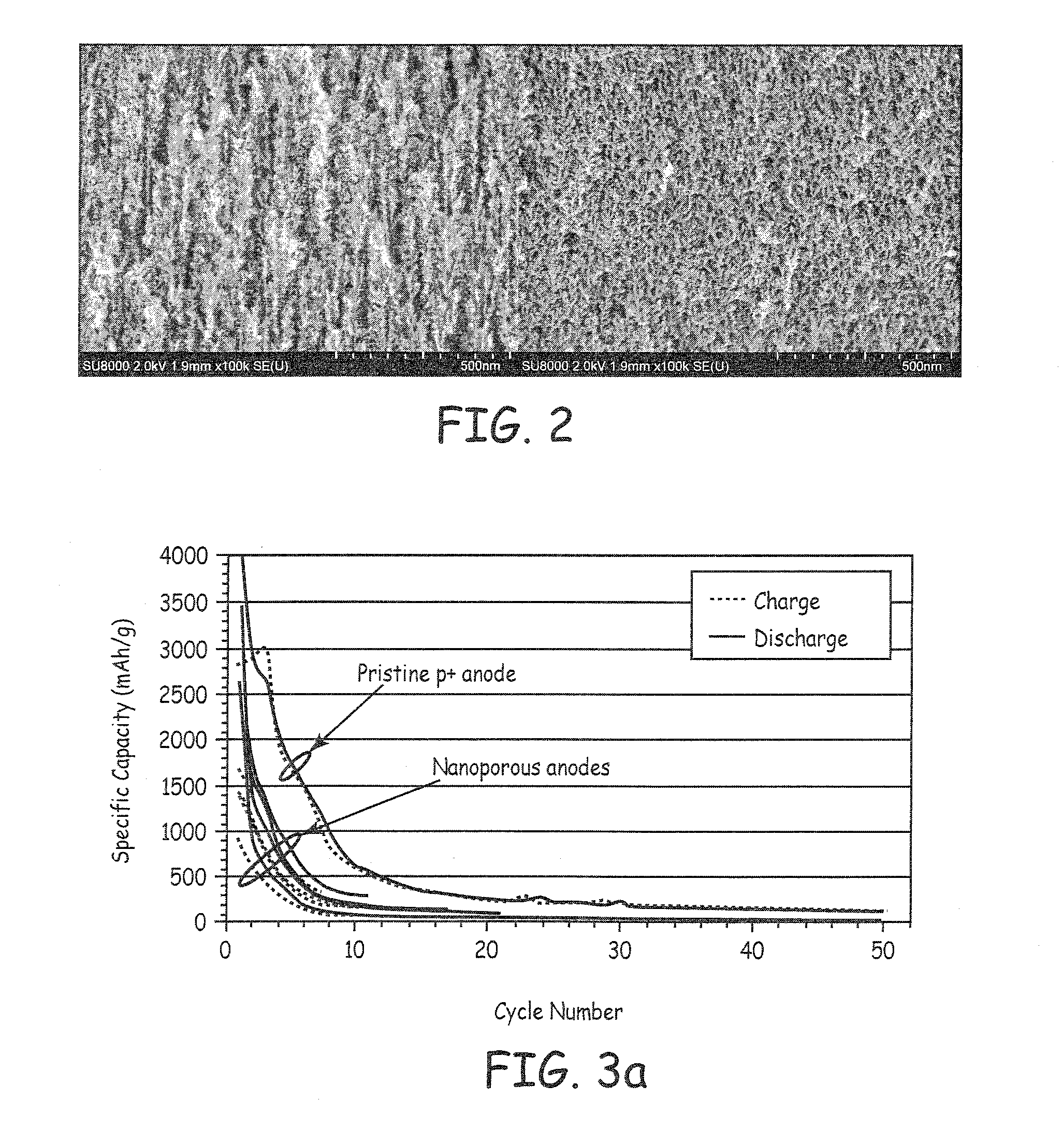

High Capacity Anode Materials for Lithium Ion Batteries

High capacity silicon based anode active materials are described for lithium ion batteries. These materials are shown to be effective in combination with high capacity lithium rich cathode active materials. Supplemental lithium is shown to improve the cycling performance and reduce irreversible capacity loss for at least certain silicon based active materials. In particular silicon based active materials can be formed in composites with electrically conductive coatings, such as pyrolytic carbon coatings or metal coatings, and composites can also be formed with other electrically conductive carbon components, such as carbon nanofibers and carbon nanoparticles. Additional alloys with silicon are explored.

Owner:IONBLOX INC

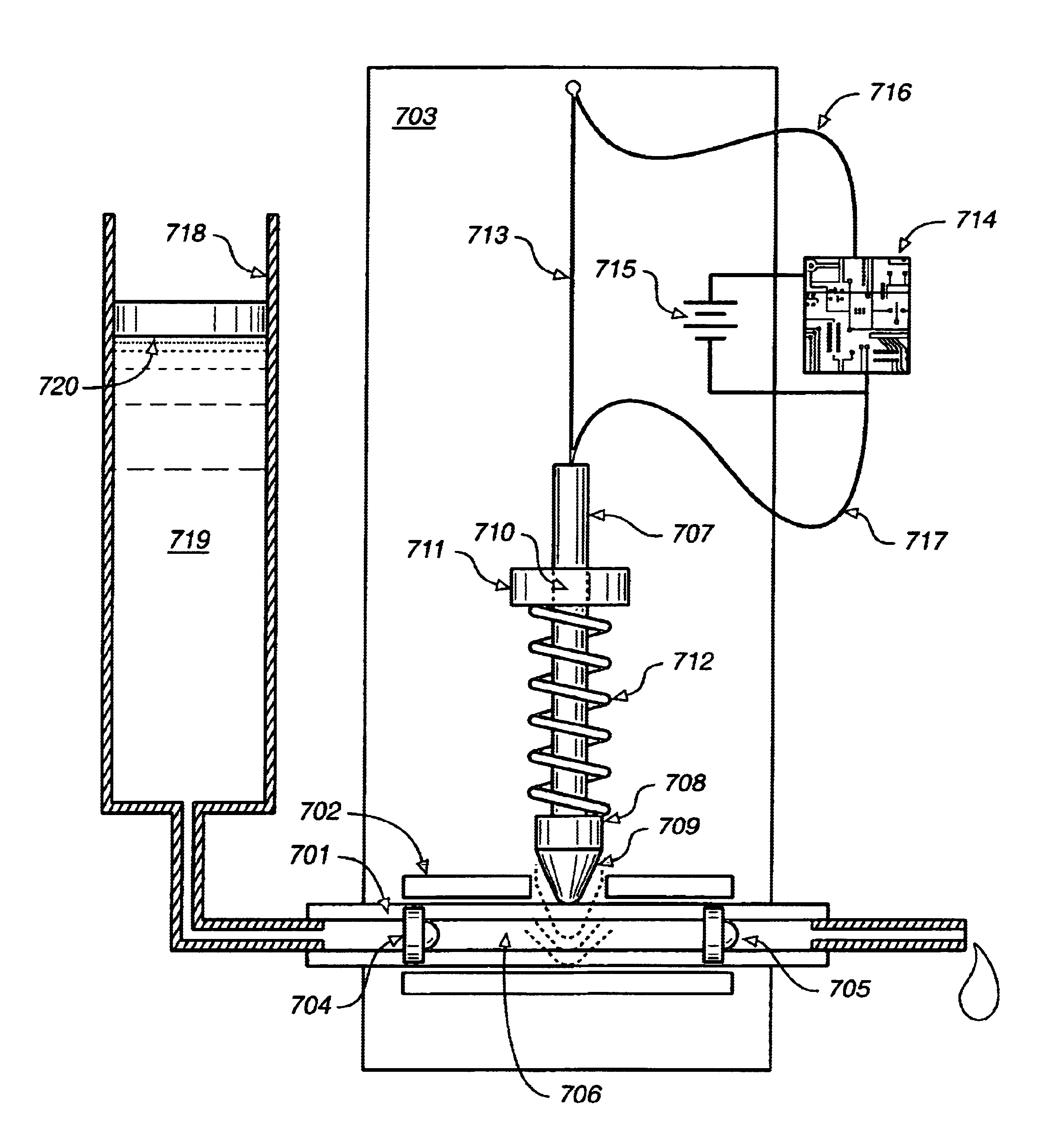

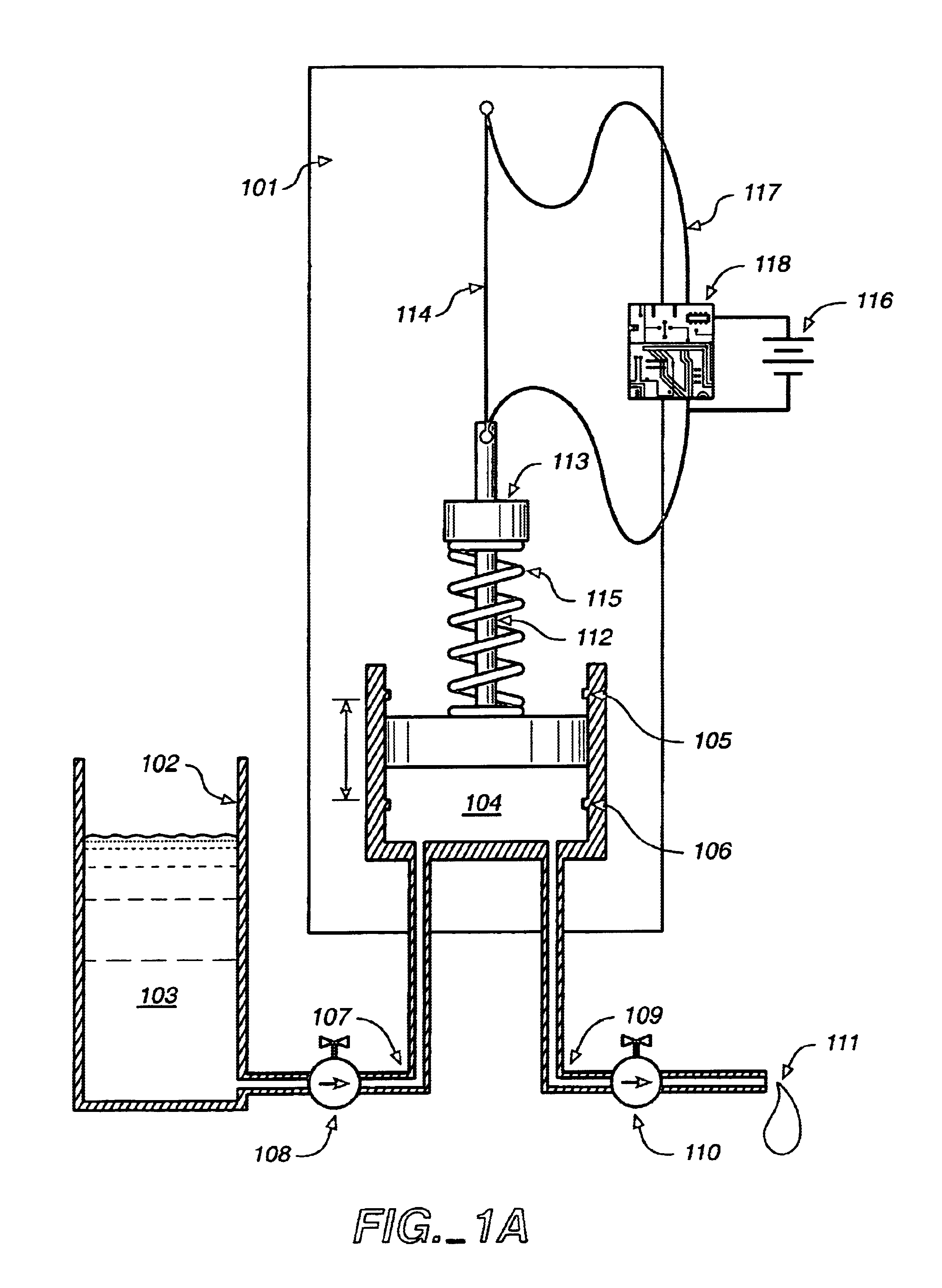

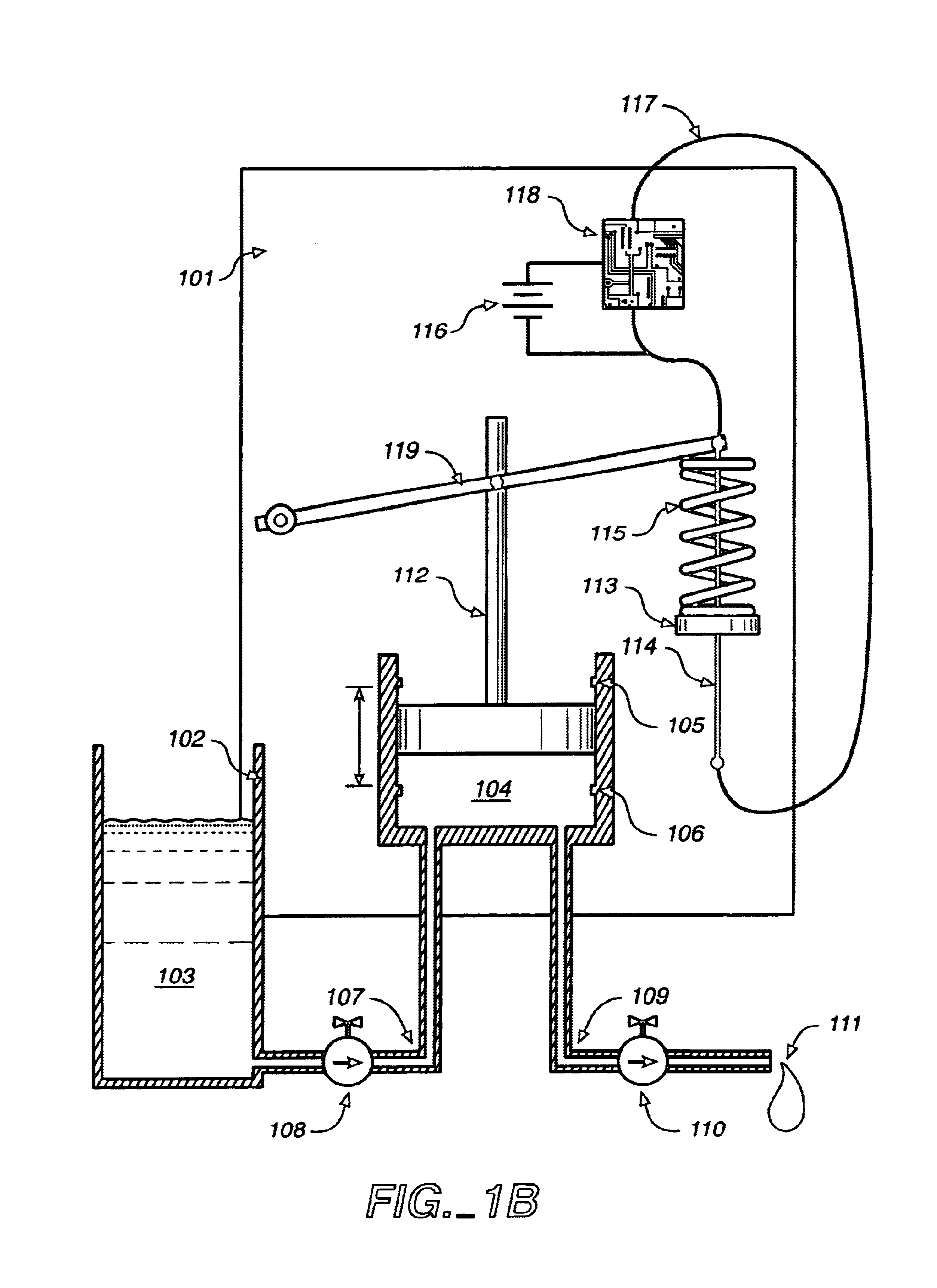

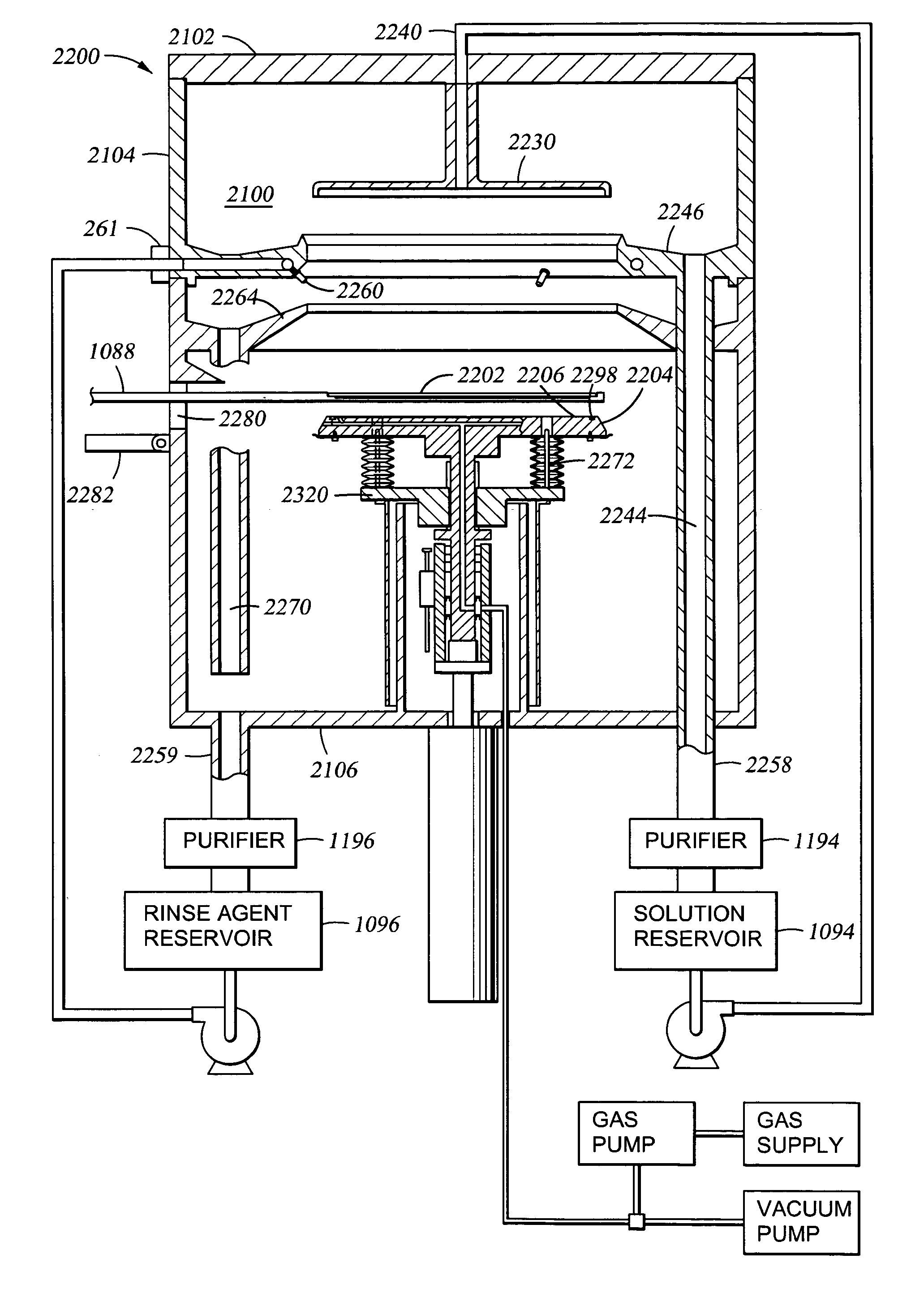

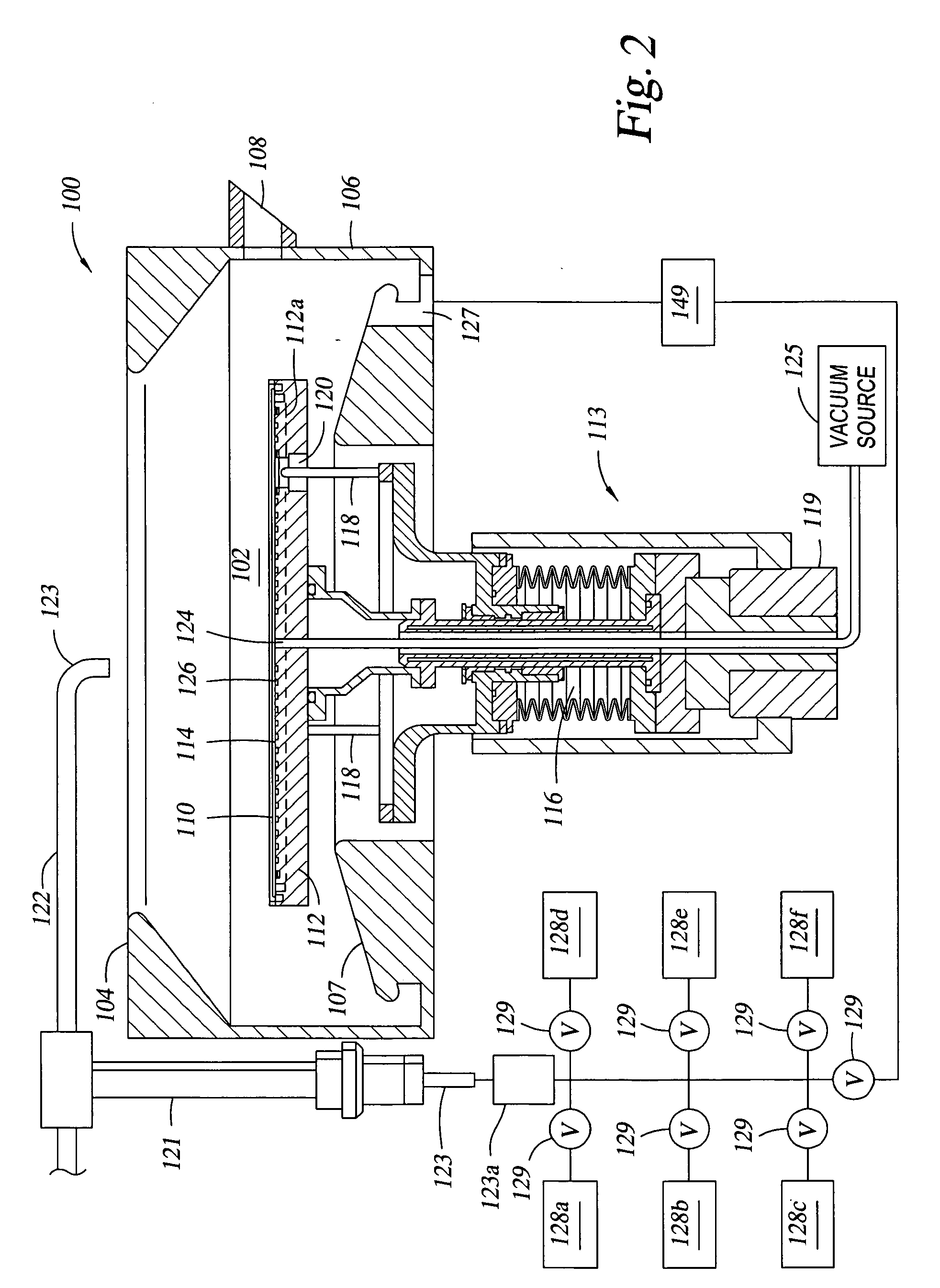

Electroless deposition apparatus

An apparatus and a method of depositing a catalytic layer comprising at least one metal selected from the group consisting of noble metals, semi-noble metals, alloys thereof, and combinations thereof in sub-micron features formed on a substrate. Examples of noble metals include palladium and platinum. Examples of semi-noble metals include cobalt, nickel, and tungsten. The catalytic layer may be deposited by electroless deposition, electroplating, or chemical vapor deposition. In one embodiment, the catalytic layer may be deposited in the feature to act as a barrier layer to a subsequently deposited conductive material. In another embodiment, the catalytic layer may be deposited over a barrier layer. In yet another embodiment, the catalytic layer may be deposited over a seed layer deposited over the barrier layer to act as a “patch” of any discontinuities in the seed layer. Once the catalytic layer has been deposited, a conductive material, such as copper, may be deposited over the catalytic layer. In one embodiment, the conductive material is deposited over the catalytic layer by electroless deposition. In another embodiment, the conductive material is deposited over the catalytic layer by electroless deposition followed by electroplating or followed by chemical vapor deposition. In still another embodiment, the conductive material is deposited over the catalytic layer by electroplating or by chemical vapor deposition.

Owner:APPLIED MATERIALS INC

Low resistance contacts including intermetallic alloy of nickel, platinum, titanium, aluminum and type iv semiconductor elements

ActiveUS20180068950A1Semiconductor/solid-state device detailsSolid-state devicesPlatinumSemiconductor materials

A method of forming a contact to a semiconductor device is provided that forms an alloy composed of nickel (Ni), platinum (Pt), aluminum (Al), titanium (Ti) and a semiconductor material. The methods may include forming a nickel and platinum semiconductor alloy at a base of a via. A titanium layer having an angstrom scale thickness is deposited in the via in contact with the nickel platinum semiconductor alloy. An aluminum containing fill is deposited atop the titanium layer. A forming gas anneal including an oxygen containing atmosphere is applied to the structure to provide a contact alloy comprising nickel, platinum, aluminum, titanium and a semiconductor element from the contact surface of the semiconductor device.

Owner:IBM CORP

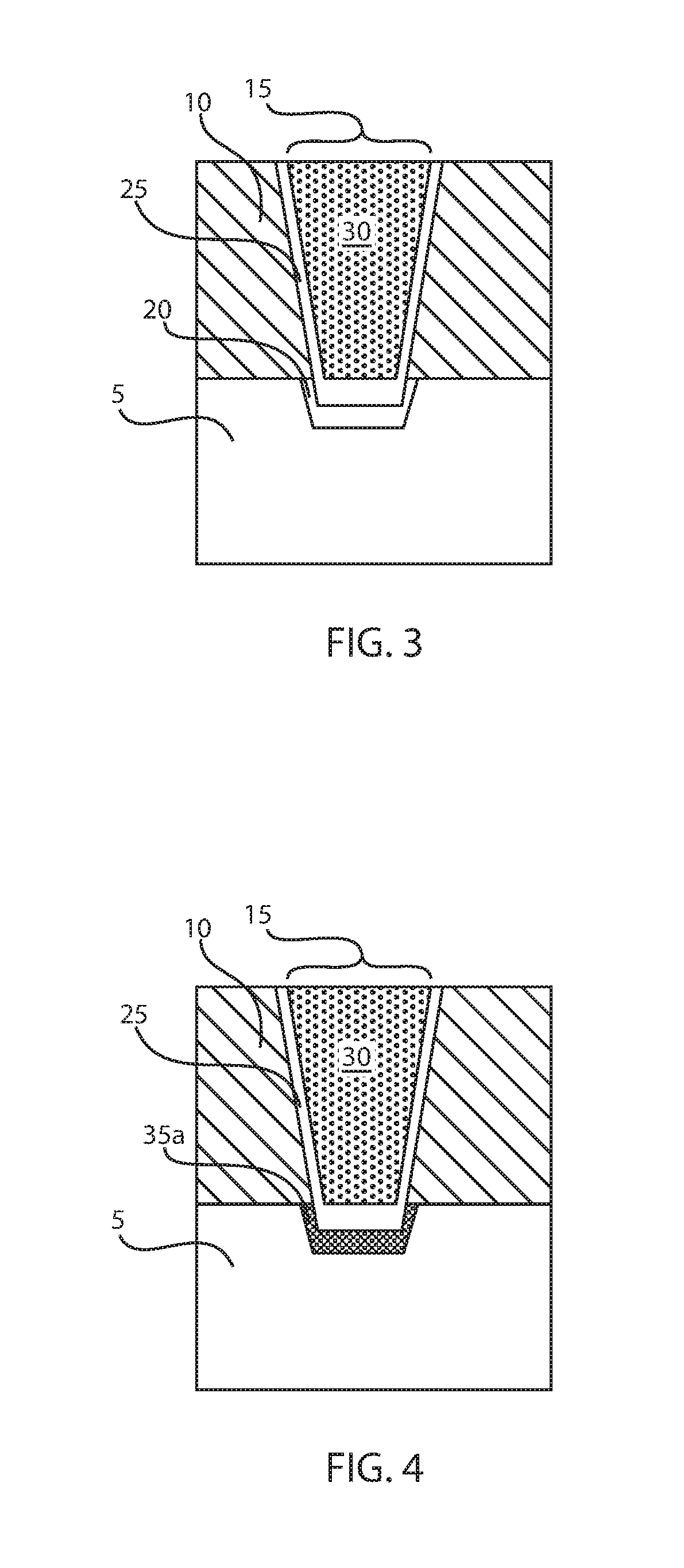

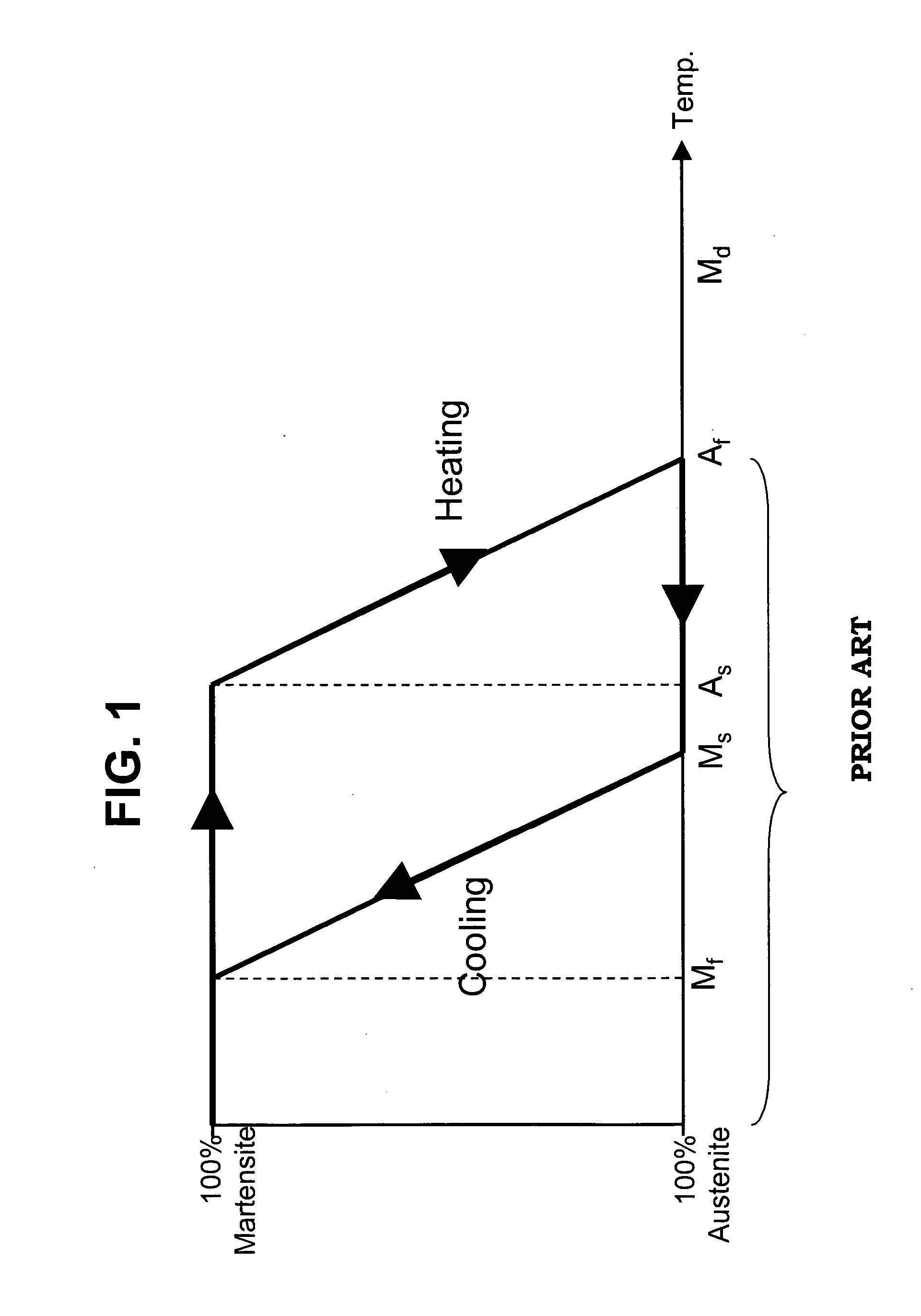

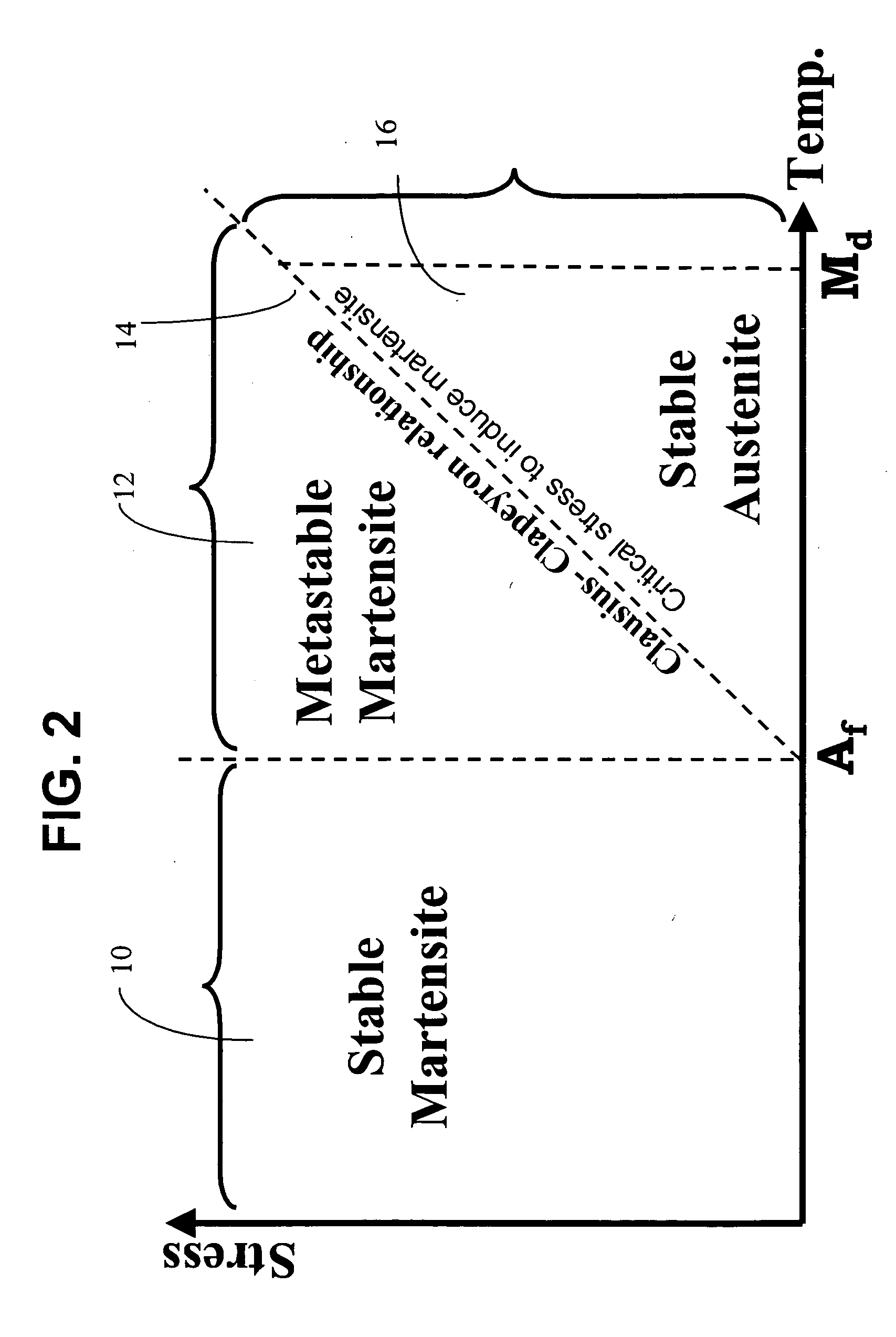

Medical devices formed from shape memory alloys displaying a stress-retained martensitic state and method for use thereof

InactiveUS20050043757A1Good body shapePromote recoverySuture equipmentsDental implantsManufactured formShape-memory alloy

A method is disclosed for utilizing a deformable article of manufacture formed at least partly of a shape memory alloy. The method includes the steps of deforming the article from a first predetermined configuration to a second predetermined configuration while the shape memory alloy is, at least partially, in its stable martensitic state and at a first temperature. A resisting force is applied to the deformed article of manufacture using a restraining means and the article is heated from the first temperature to a second temperature in the presence of the resisting force. The stable martensitic state is transformed to a metastable stress-retained martensitic state. The resisting force is then removed allowing the alloy to transform to its austenitic state and the shape of the article to be restored substantially to its first configuration. Devices primarily medical devices operative by employing this method are also disclosed.

Owner:NITI SURGICAL SOLUTIONS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com