Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2408 results about "Silicide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A silicide is a compound that has silicon with (usually) more electropositive elements. Silicon is more electropositive than carbon. Silicides are structurally closer to borides than to carbides. Similar to borides and carbides, the composition of silicides cannot be easily specified as covalent molecules. The chemical bonds in silicides range from conductive metal-like structures to covalent or ionic. Silicides of all non-transition metals, with exception of beryllium, have been described.

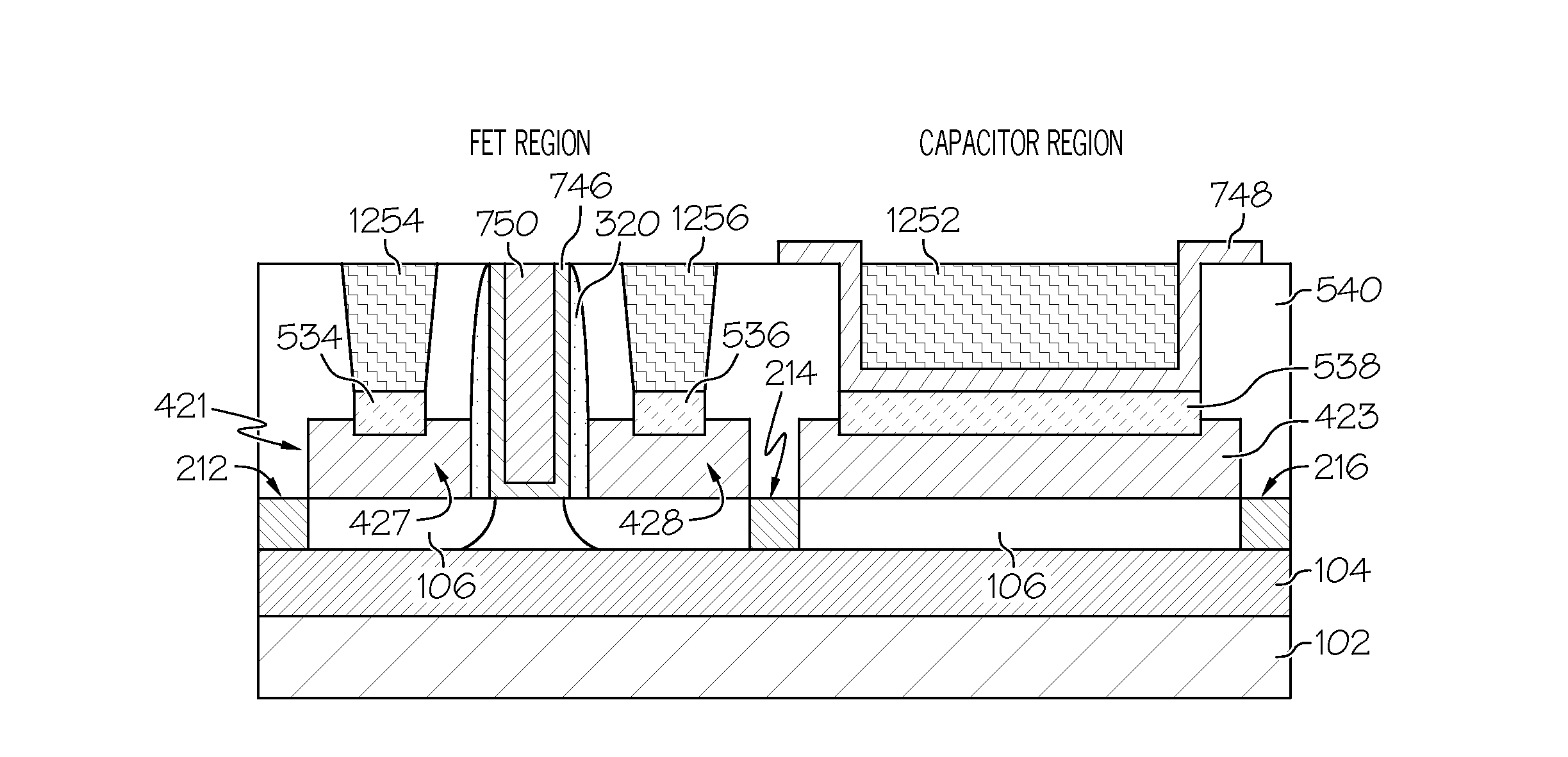

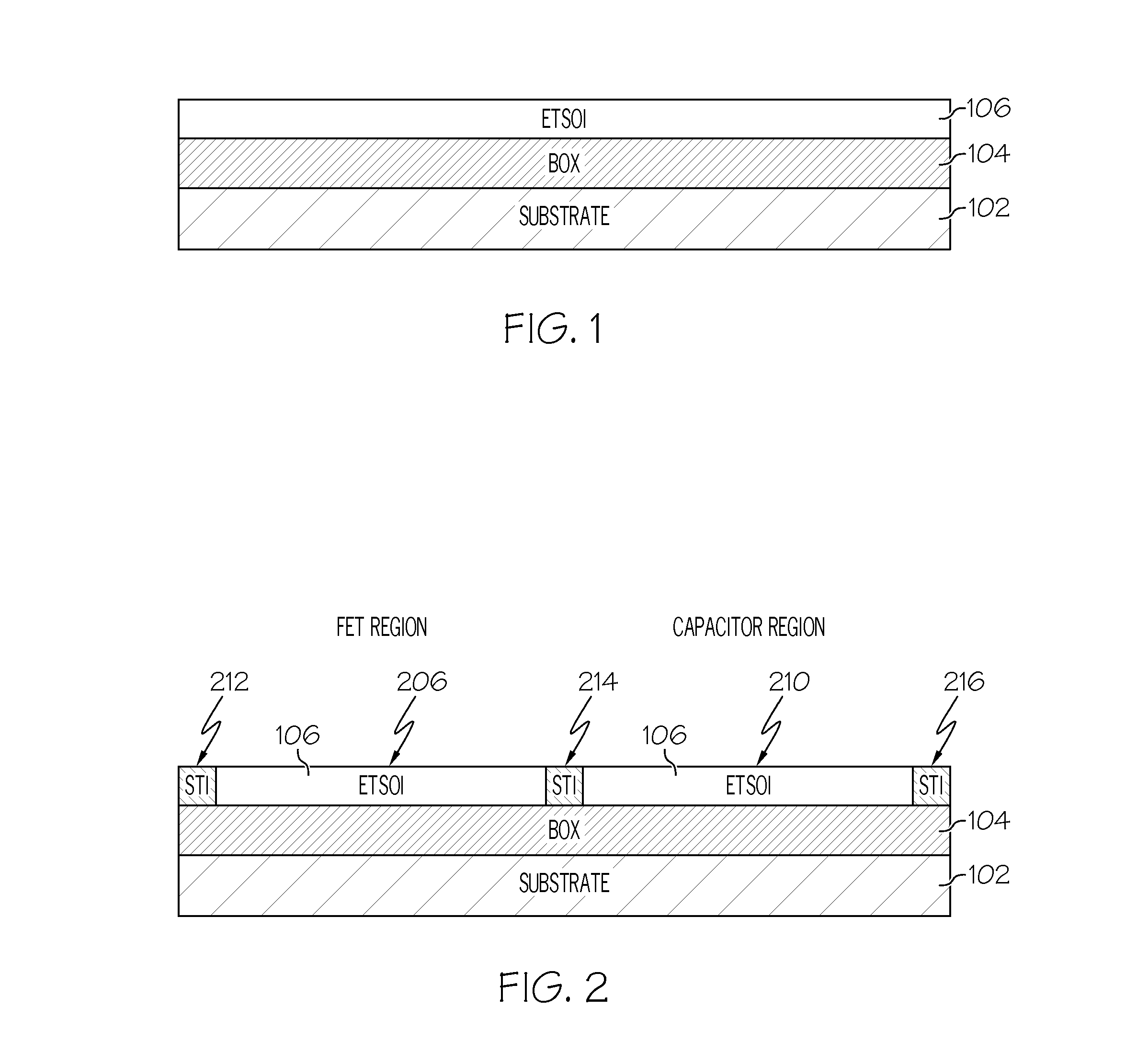

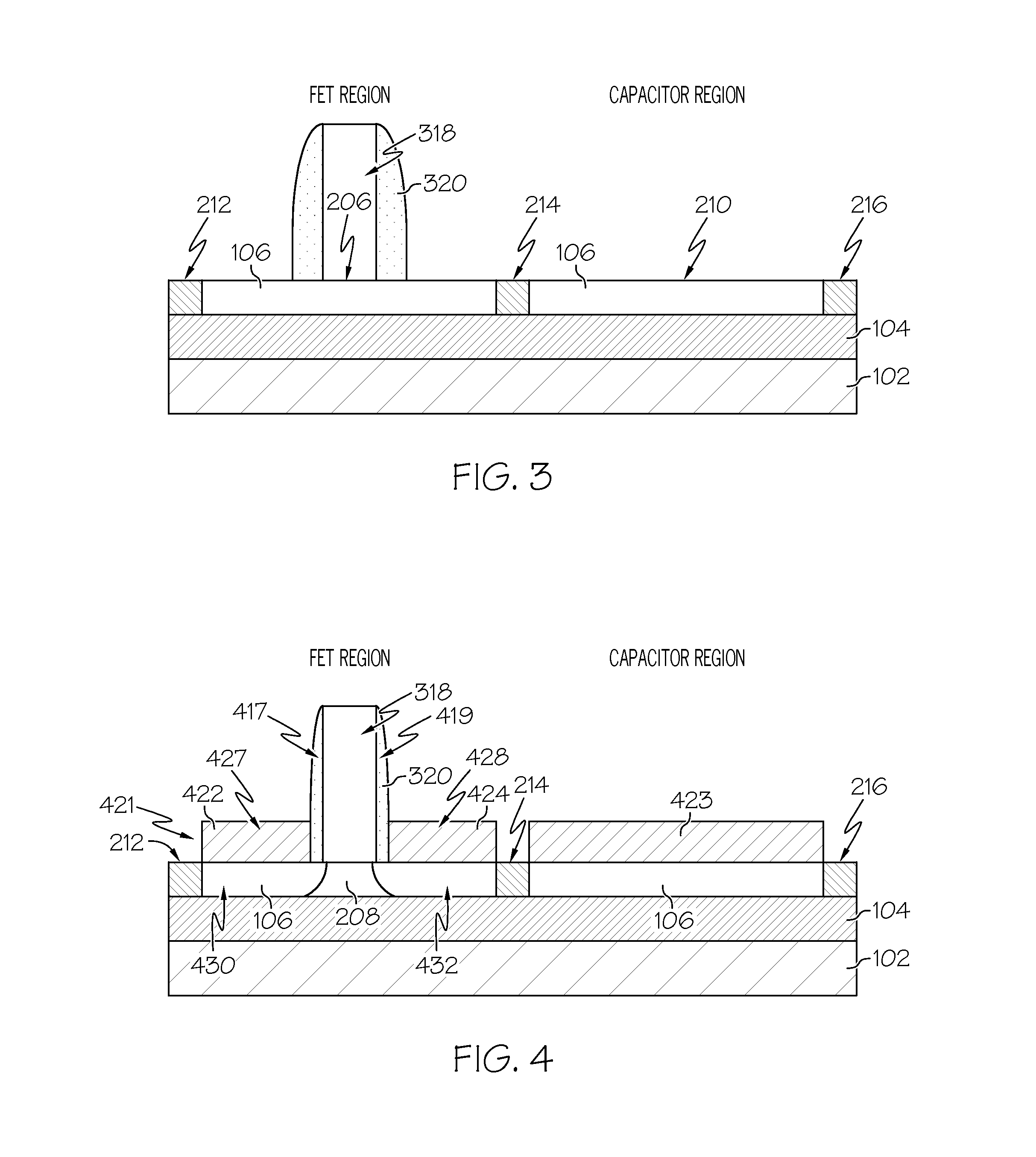

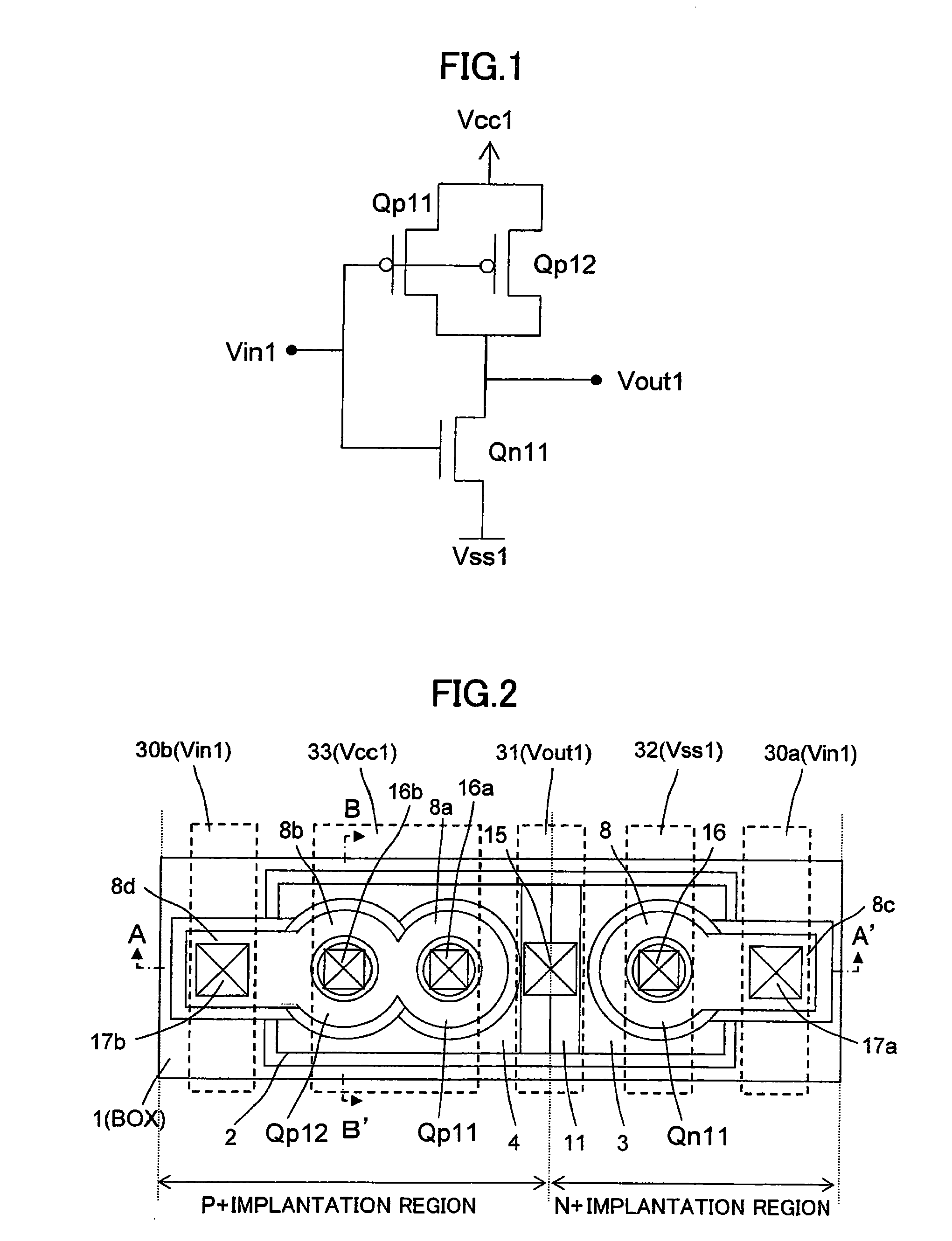

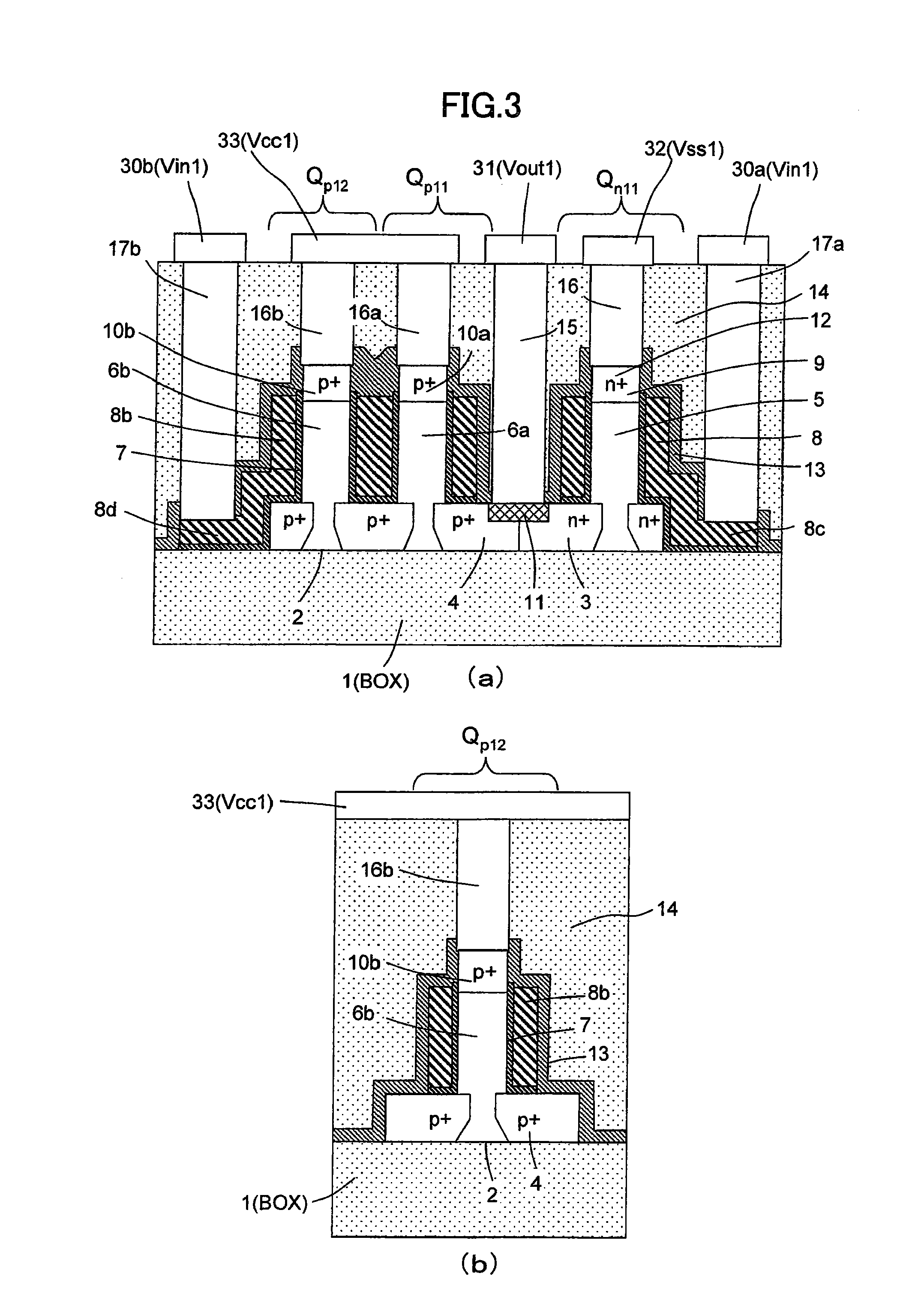

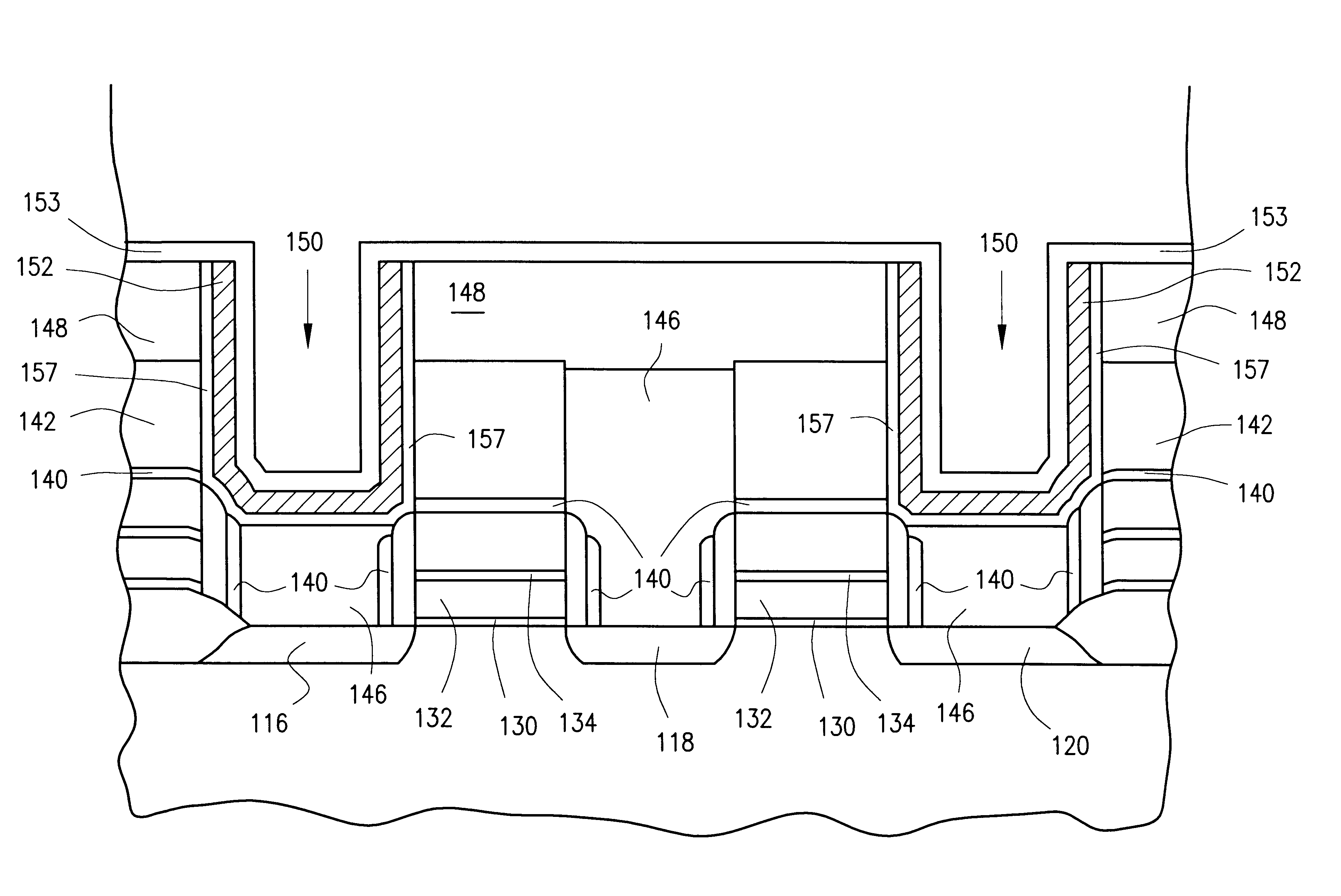

Integrated circuit with a thin body field effect transistor and capacitor

An integrated circuit includes a transistor and a capacitor. The transistor includes a first semiconductor layer and a gate stack located on the first semiconductor layer. The gate stack includes a metal layer and a first high-k dielectric layer. A gate spacer is located on sidewalls of the gate stack. The first high-k dielectric layer is located between the first semiconductor layer and the metal layer and between the gate spacer and sidewalls of the metal layer. A first silicide region is located on a first source / drain region. A second silicide region is located on a second source / drain region. The capacitor includes a first terminal that comprises a third silicide region located on a portion of the second semiconductor. A second high-k dielectric layer is located on the silicide region. A second terminal comprises a metal layer that is located on the second high-k dielectric layer.

Owner:GLOBALFOUNDRIES US INC

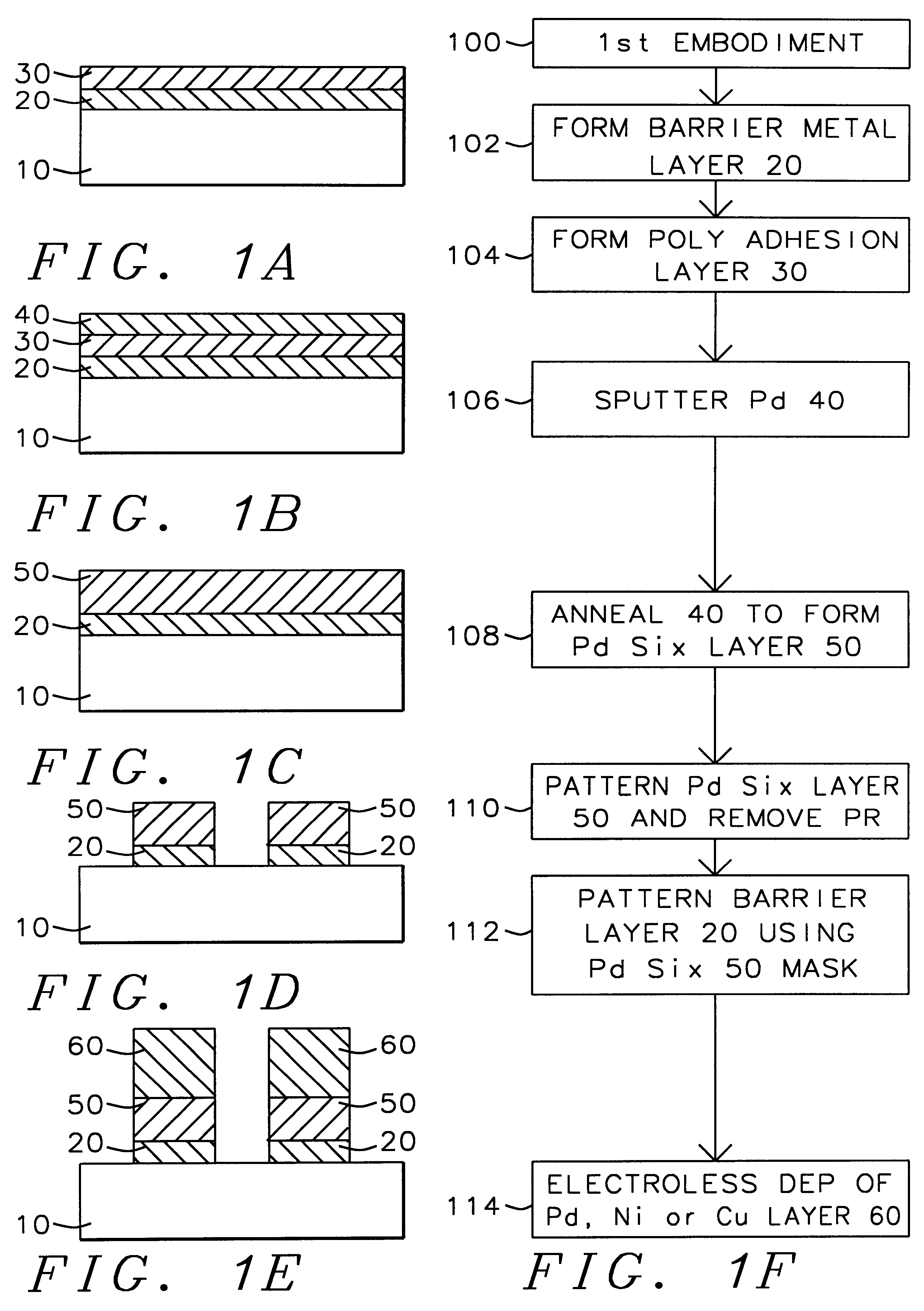

Method of electroless plating copper on nitride barrier

InactiveUS6436816B1Insulating substrate metal adhesion improvementSolid-state devicesCopper platingElectroless deposition

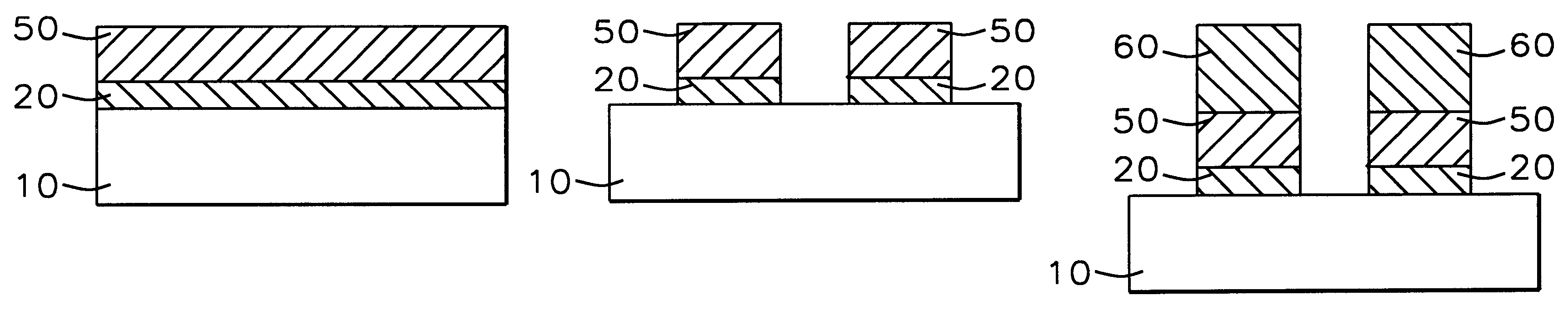

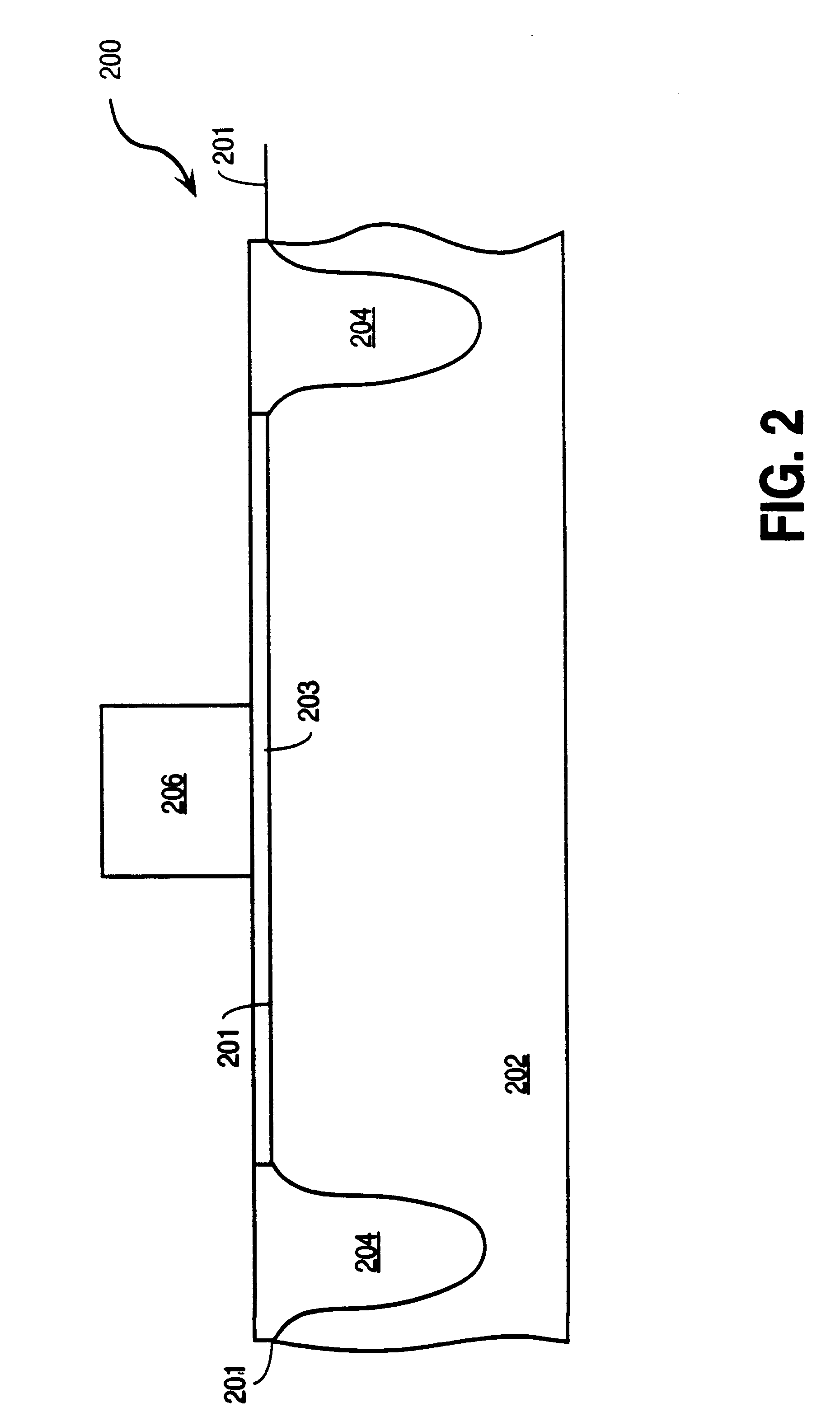

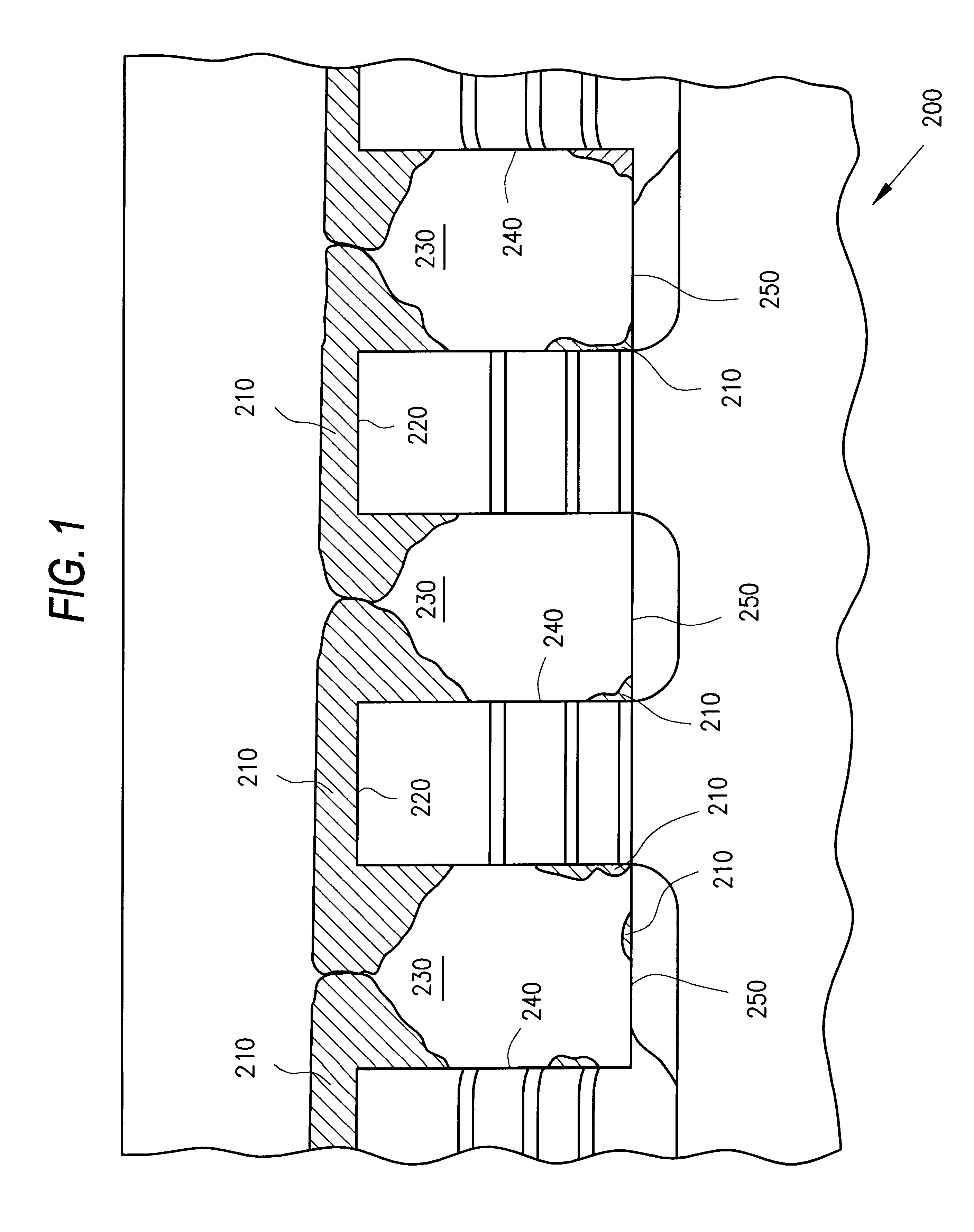

A method with three embodiments of manufacturing metal lines and solder bumps using electroless deposition techniques. The first embodiment uses a PdSix seed layer 50 for electroless deposition. The PdSix layer 50 does not require activation. A metal line is formed on a barrier layer 20 and an adhesion layer 30. A Palladium silicide seed layer 50 is then formed and patterned. Ni, Pd or Cu is electroless deposited over the Palladium silicide layer 50 to form a metal line. The second embodiment selectively electrolessly deposits metal 140 over an Adhesion layer 130 composed of Poly Si, Al, or Ti. A photoresist pattern 132 is formed over the adhesion layer. A metal layer 140 of Cu or Ni is electrolessly deposited over the adhesion layer. The photoresist layer 132 is removed and the exposed portion of the adhesion layer 130 and the underlying barrier metal layer 120 are etched thereby forming a metal line. The third embodiment electroless deposits metal over a metal barrier layer that is roughen by chemical mechanical polishing. A solder bump is formed using an electroless deposition of Cu or Ni by: depositing an Al layer 220 and a barrier metal layer 230 over a substrate 10. The barrier layer 230 is polished and activated. Next, the aluminum layer 220 and the barrier metal layer 230 are patterned. A metal layer 240 is electroless deposited. Next a solder bump 250 is formed over the electroless metal layer 240.

Owner:TAIWAN SEMICON MFG CO LTD

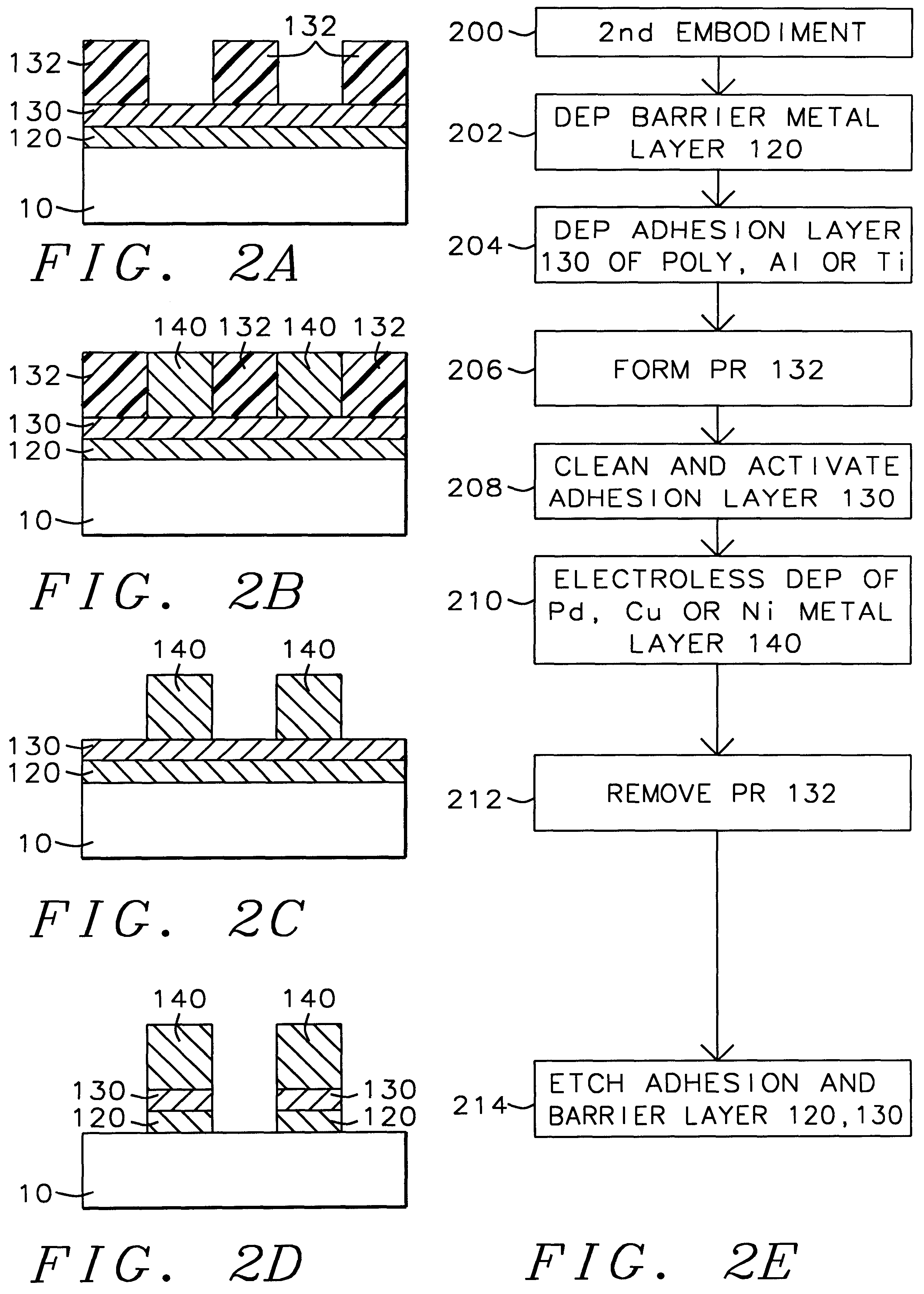

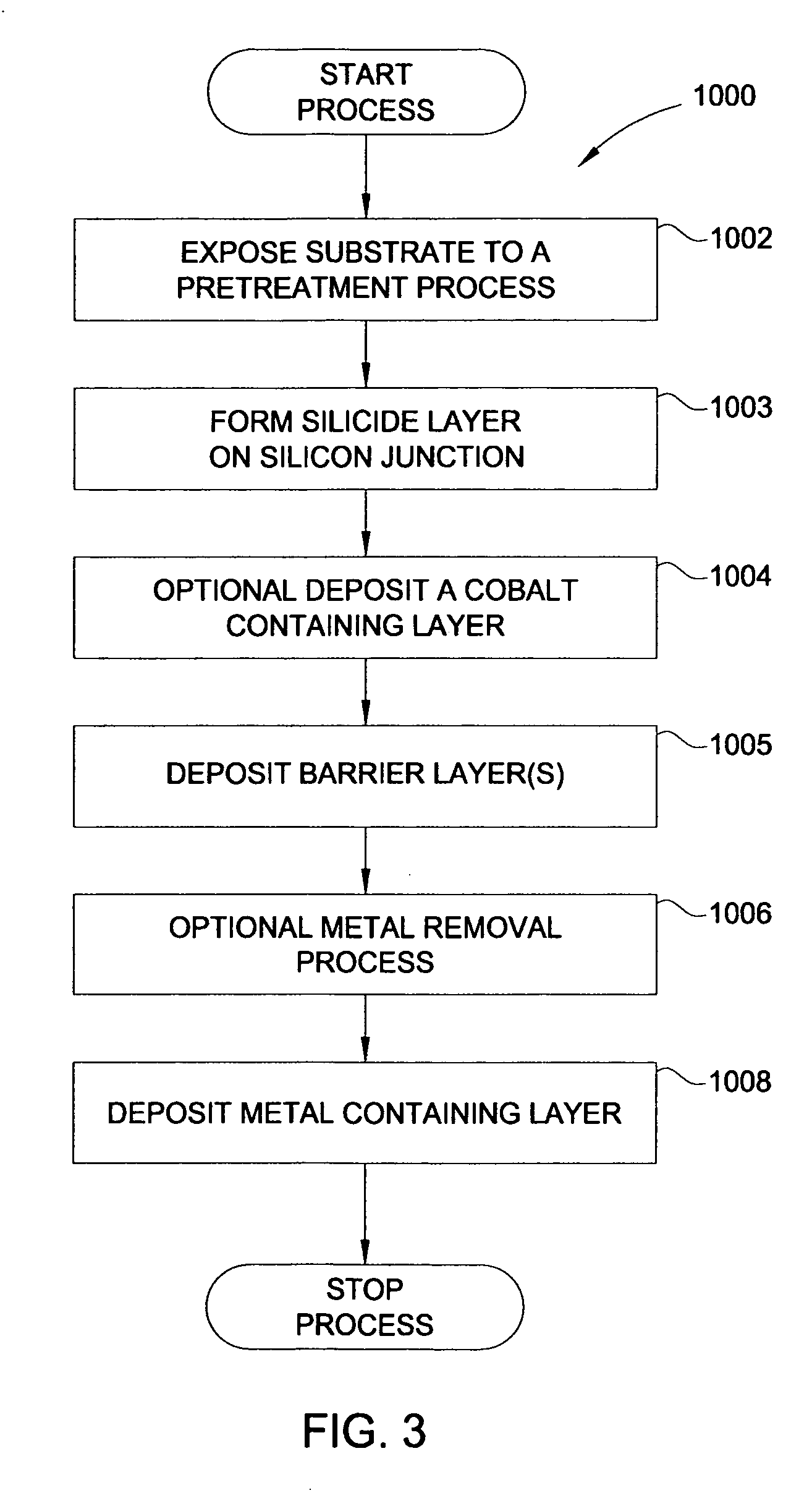

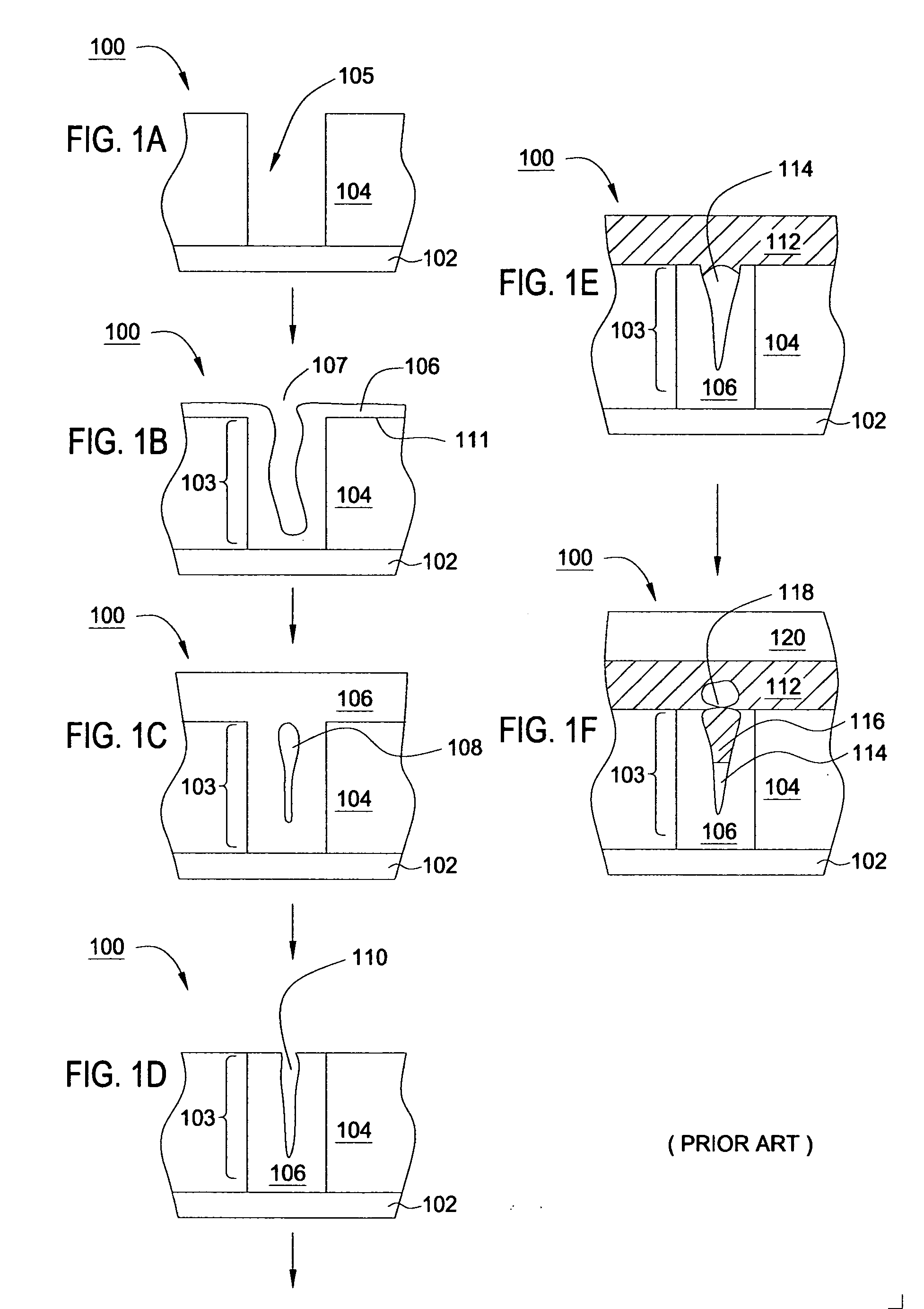

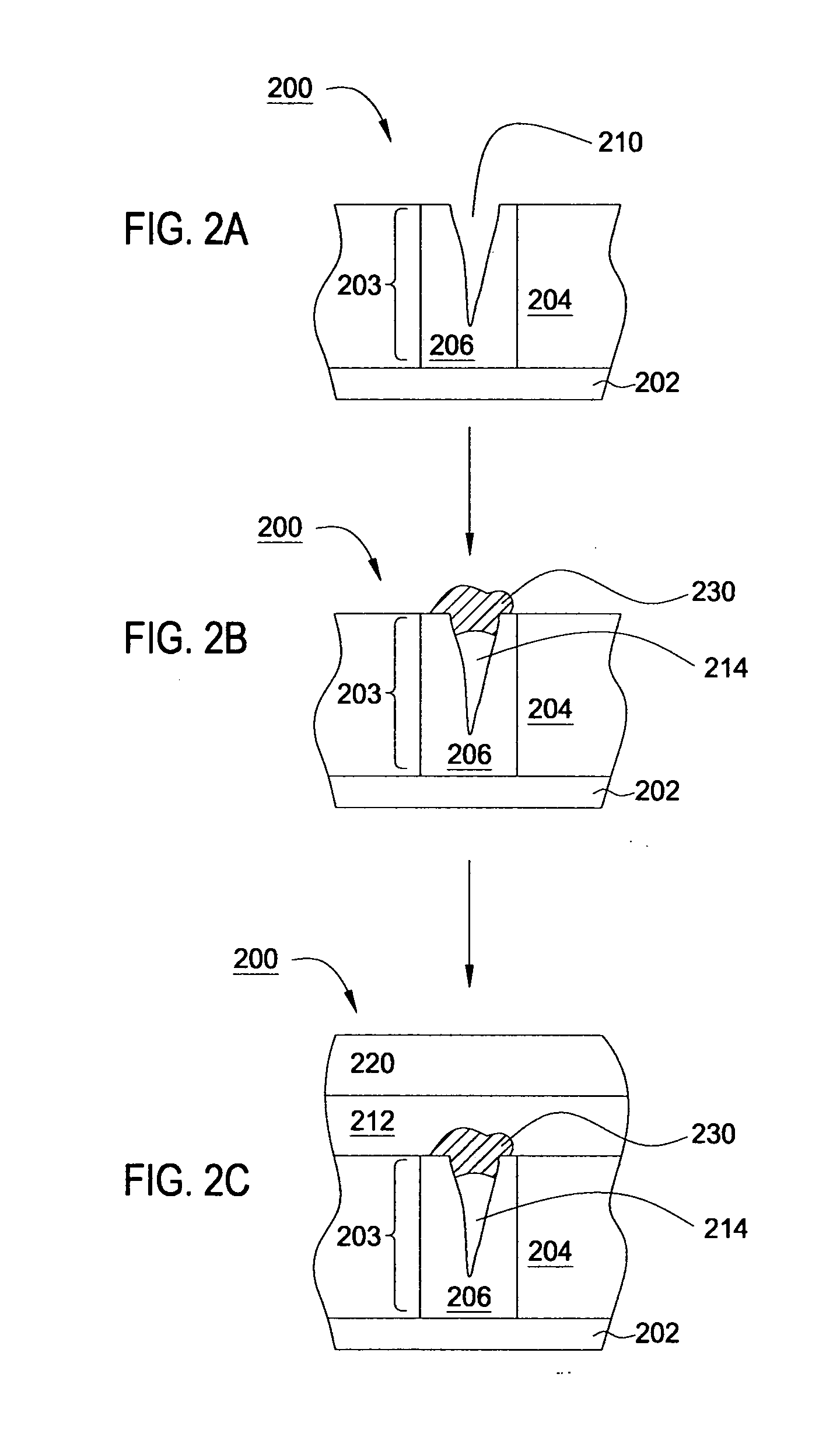

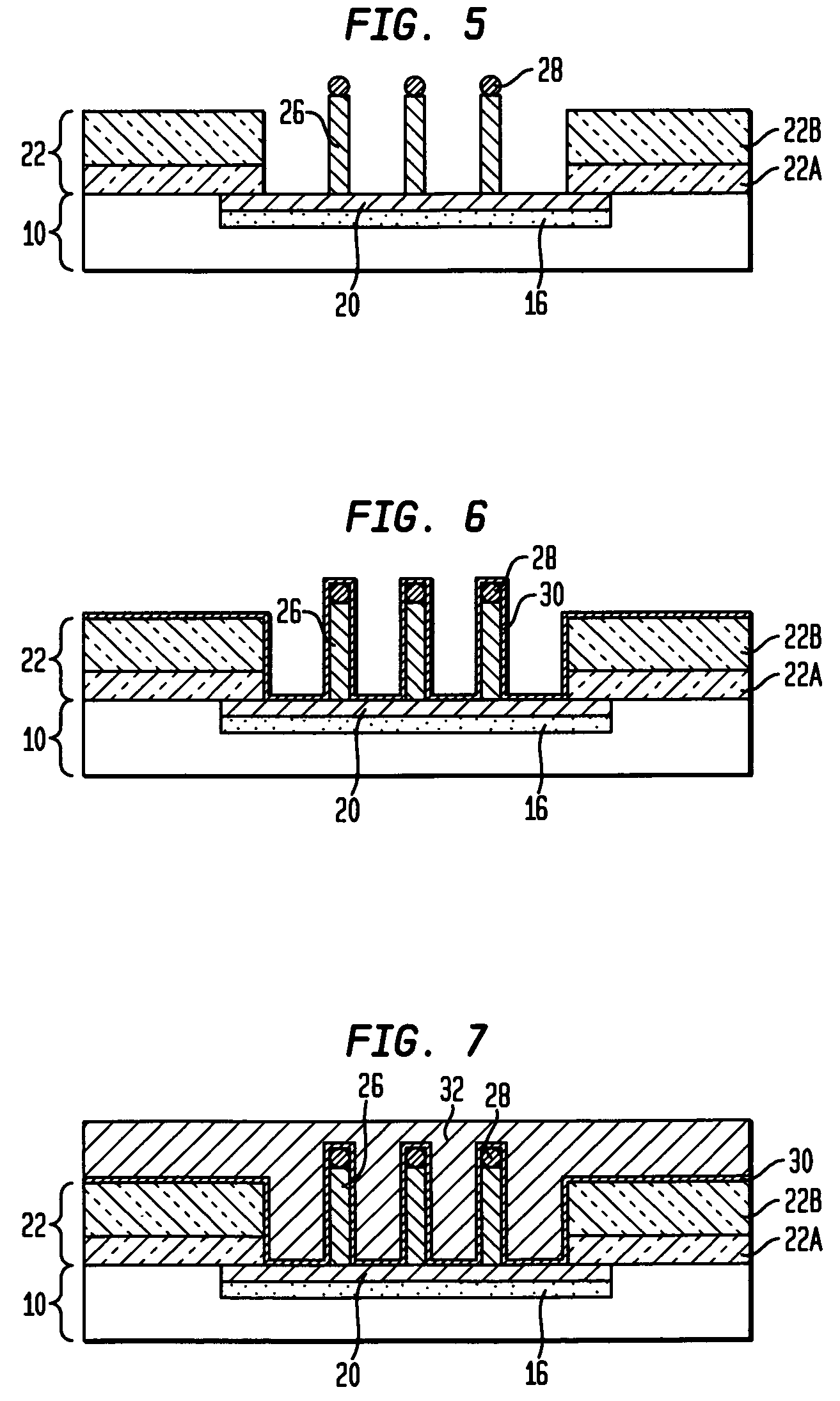

Contact metallization scheme using a barrier layer over a silicide layer

ActiveUS20060251800A1Material nanotechnologySemiconductor/solid-state device detailsDevice materialElectroless deposition

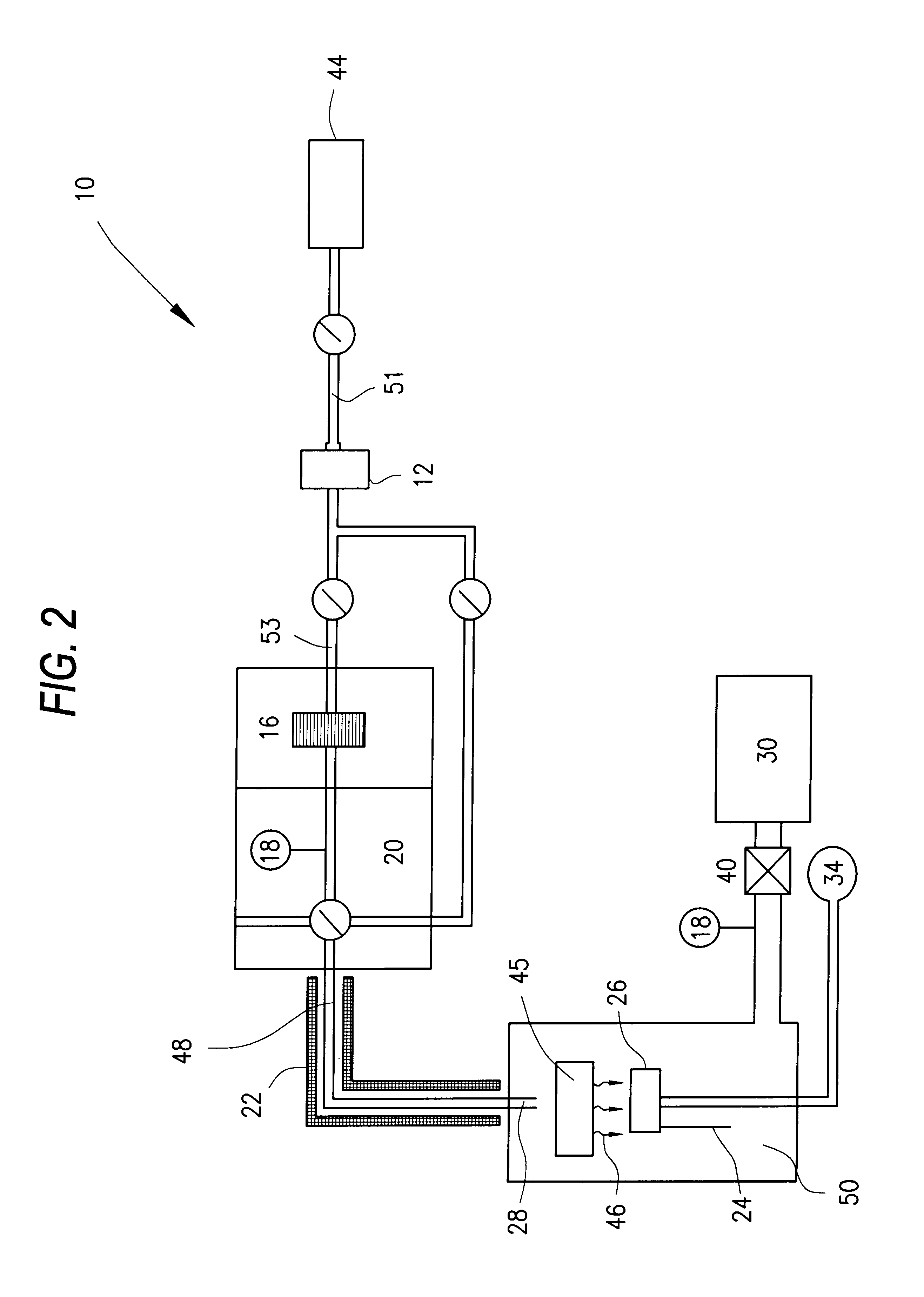

Embodiments of the invention generally provide methods of filling contact level features formed in a semiconductor device by depositing a barrier layer over the contact feature and then filing the layer using an PVD, CVD, ALD, electrochemical plating process (ECP) and / or electroless deposition processes. In one embodiment, the barrier layer has a catalytically active surface that will allow the electroless deposition of a metal on the barrier layer. In one aspect, the electrolessly deposited metal is copper or a copper alloy. In one aspect, the contact level feature is filled with a copper alloy by use of an electroless deposition process. In another aspect, a copper alloy is used to from a thin conductive copper layer that is used to subsequently fill features with a copper containing material by use of an ECP, PVD, CVD, and / or ALD deposition process. In one embodiment, a portion of the barrier layer is purposely allowed to react with traces of residual oxide at the silicon junction of the contact level feature to form a low resistance connection.

Owner:APPLIED MATERIALS INC

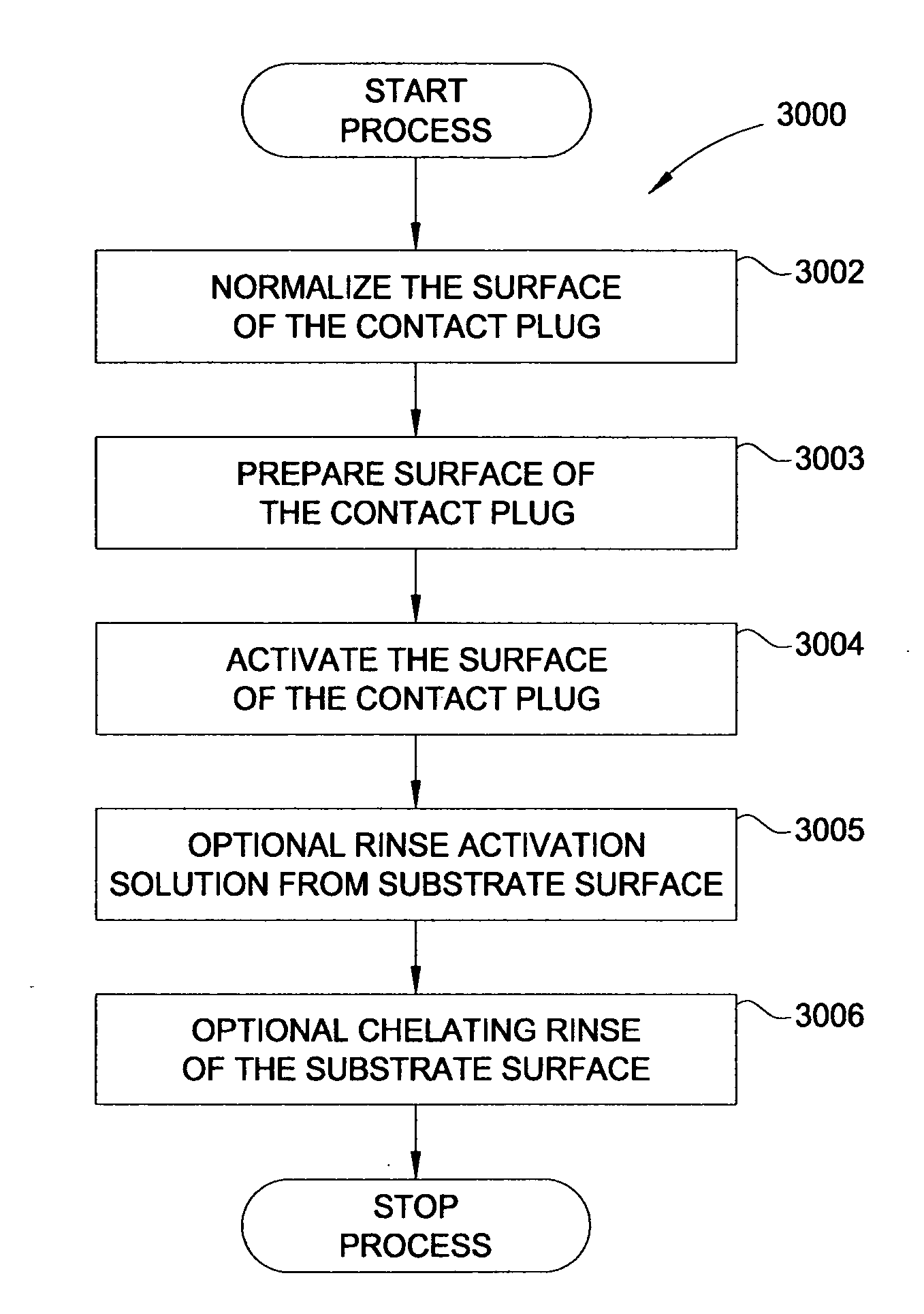

Electroless deposition processes and compositions for forming interconnects

InactiveUS20060252252A1Material nanotechnologySemiconductor/solid-state device detailsHydrogen fluorideTungstate

In one embodiment, a method for depositing a material on a substrate is provided which includes positioning a substrate containing a contact within a process chamber, exposing the substrate to at least one pretreatment step and depositing a fill the contact vias by an electroless deposition process. The pretreatment step contains multiple processes for exposing the substrate to a wet-clean solution, a hydrogen fluoride solution, a tungstate solution, a palladium activation solution, an acidic rinse solution, a complexing agent solution or combinations thereof. Generally, the HARC via contains a tungsten oxide surface and the shallow contact via may contain a tungsten silicide surface. In some example, the substrate is pretreated such that both vias are filled at substantially the same time by a nickel-containing material through an electroless deposition process.

Owner:APPLIED MATERIALS INC

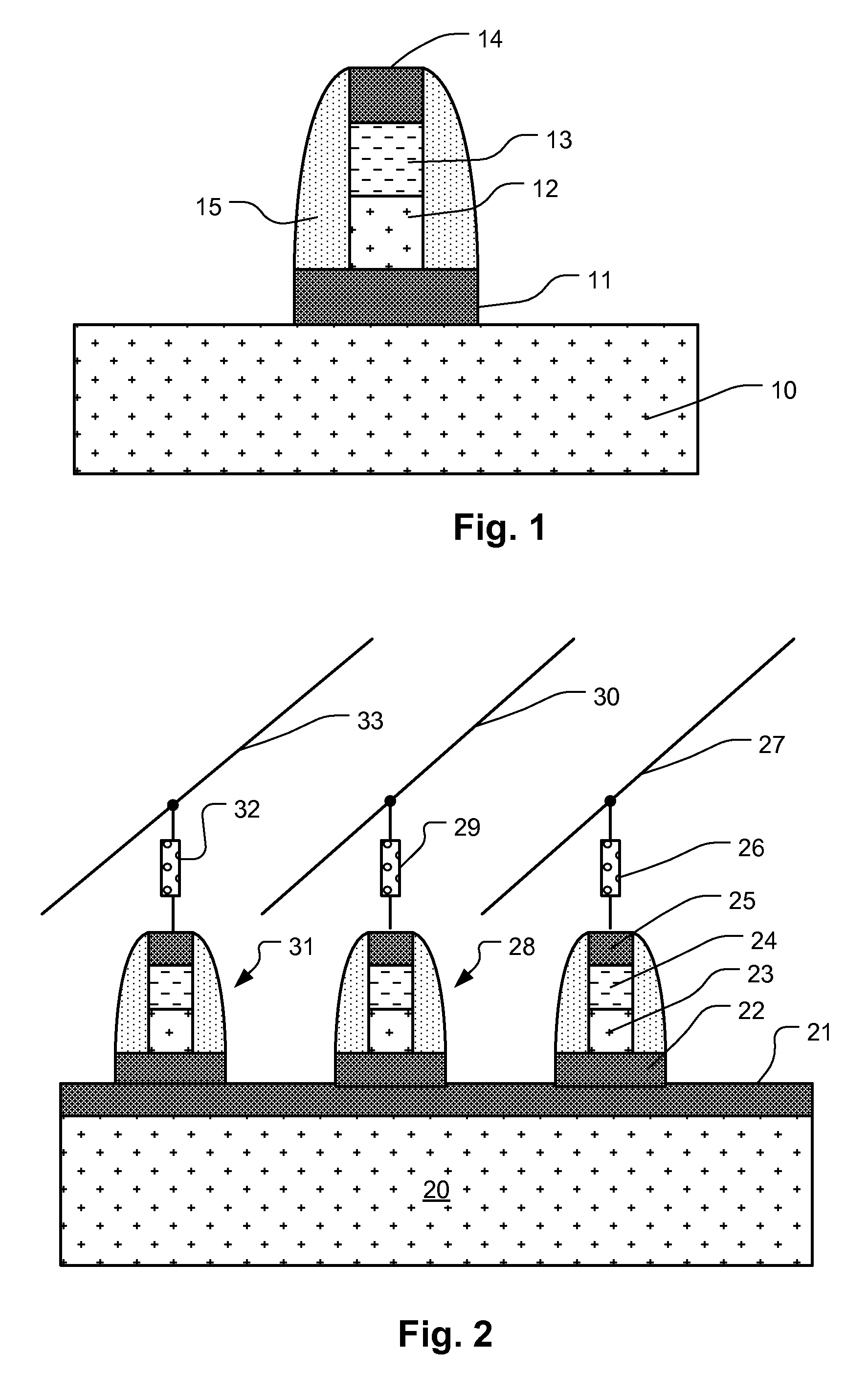

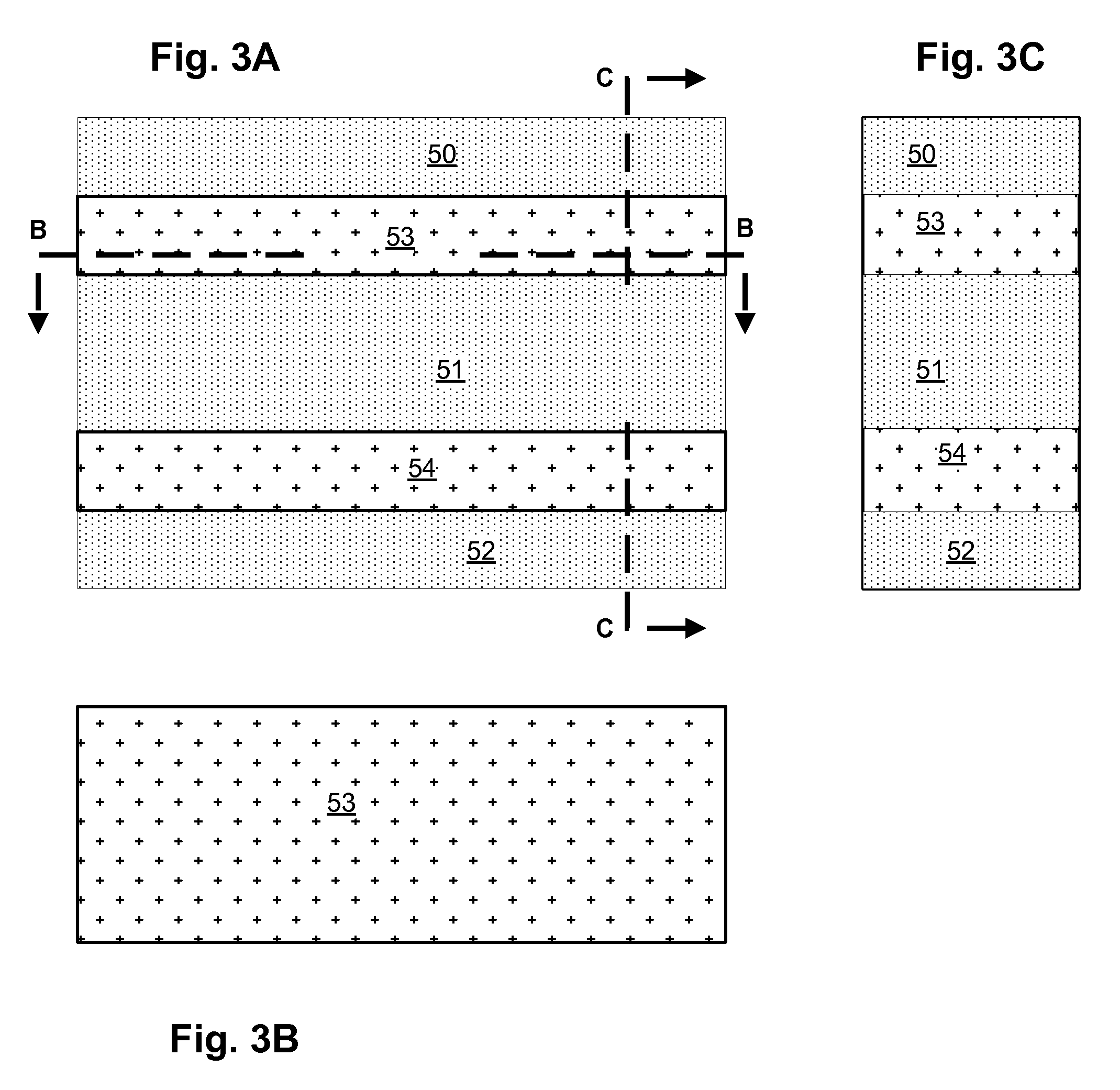

Method to form upward pointing p-i-n diodes having large and uniform current

A method is disclosed to form an upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

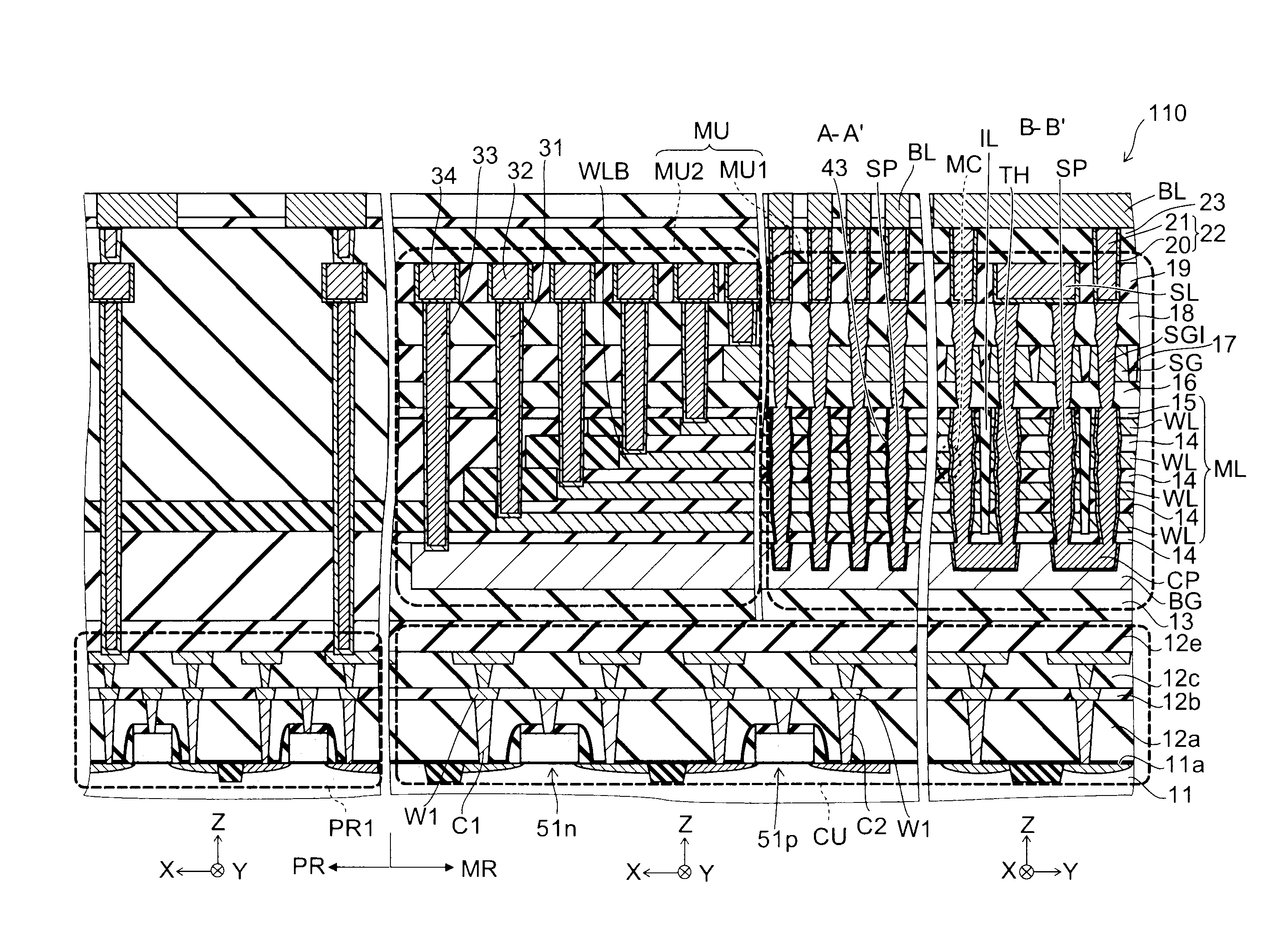

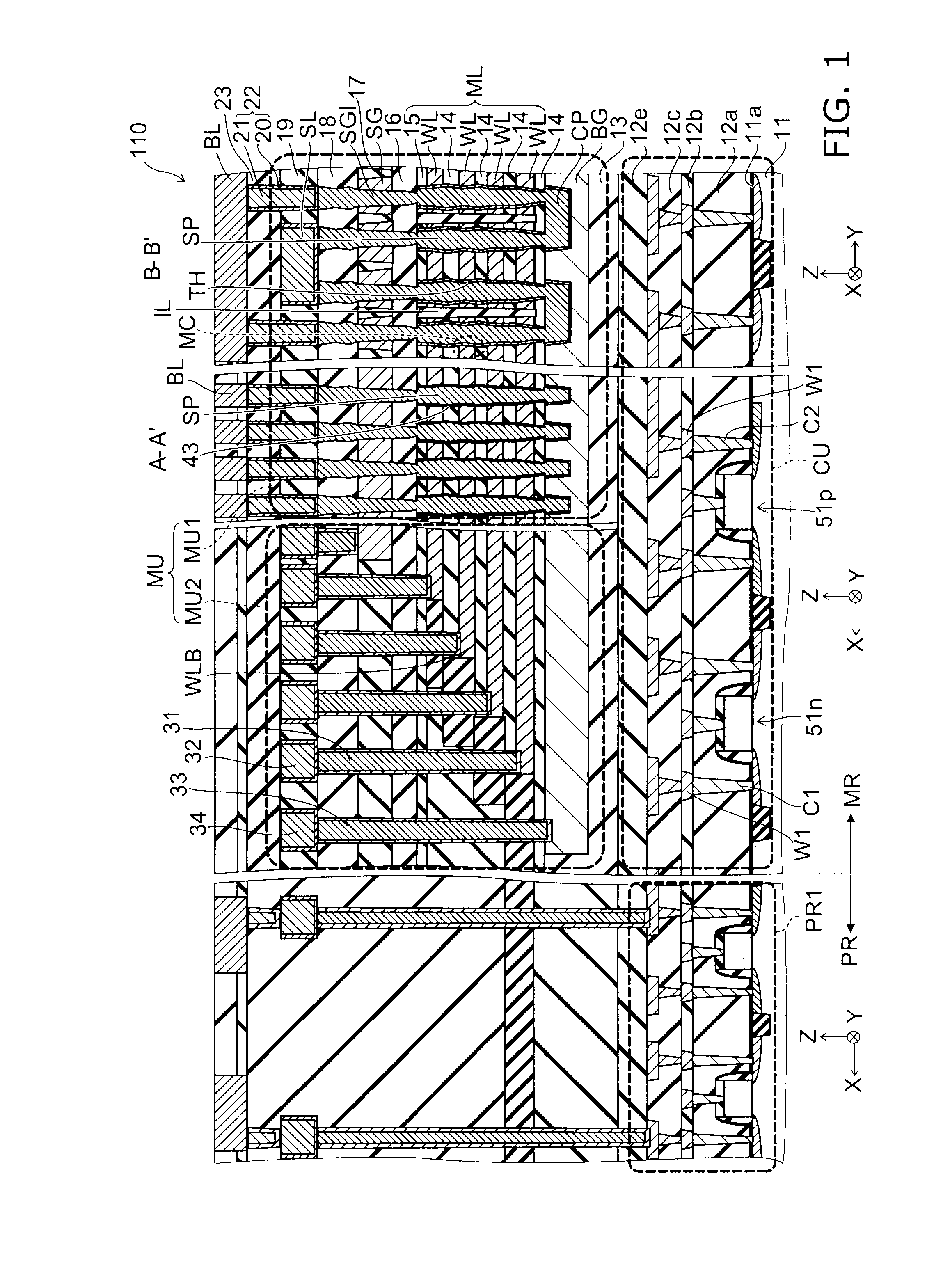

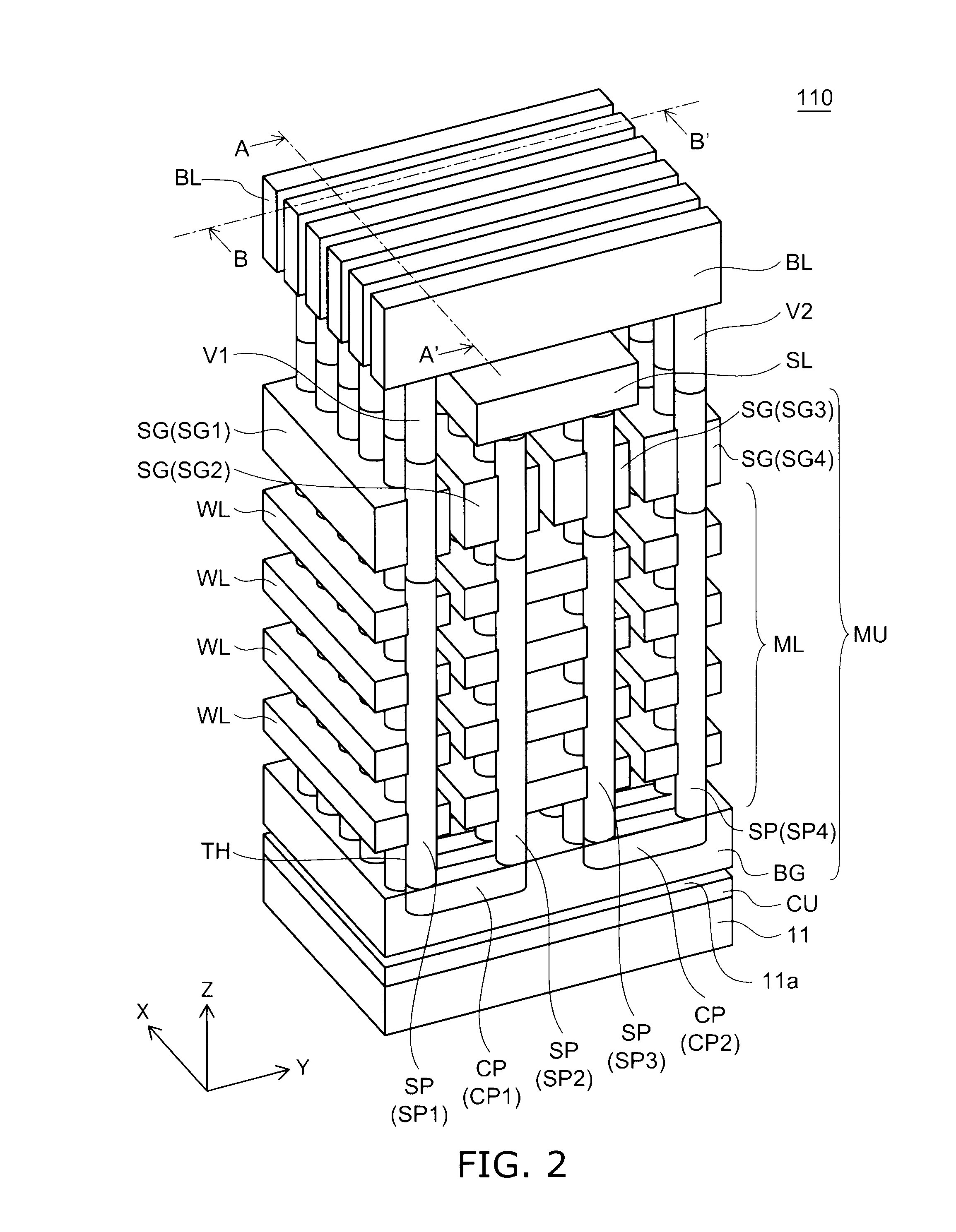

Nonvolatile semiconductor memory device and method for manufacturing same

InactiveUS20100320526A1Semiconductor/solid-state device detailsSolid-state devicesStructural unitSemiconductor

A nonvolatile semiconductor memory device includes: a semiconductor substrate; a memory unit; and a circuit unit provided between the semiconductor substrate and the memory unit. The memory unit includes: a stacked structural unit having electrode films alternately stacked with inter-electrode-film insulating films; a semiconductor pillar piercing the stacked structural unit; and a storage unit provided corresponding to an intersection between the electrode films and the semiconductor pillar. The circuit unit includes first and second transistors having different conductivity type, a first interconnect, and first and second contact plugs. The first interconnect includes silicide provided on a side of the first and second transistors opposite to the semiconductor substrate. The first contact plug made of polysilicon of the first conductivity type connects the first interconnect to the first transistor. The second contact plug made of polysilicon of the second conductivity type connects the first interconnect to the second transistor.

Owner:KK TOSHIBA

Cobalt salicidation method on a silicon germanium film

A method of forming a cobalt germanosilicide film is described. According to the present invention a silicon germanium alloy is formed on a substrate. A cobalt film is then formed on the silicon germanium alloy. The substrate is then heated to a temperature of greater than 850° C. for a period of time less than 20 seconds to form a cobalt germanium silicide film.

Owner:INTEL CORP

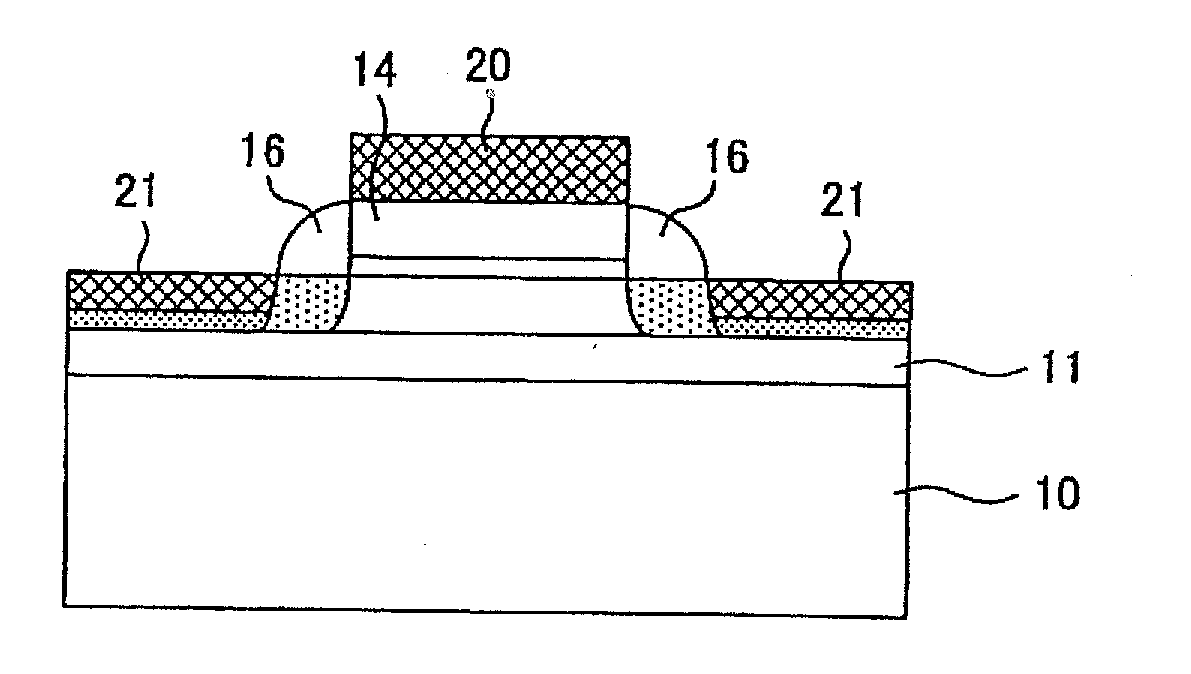

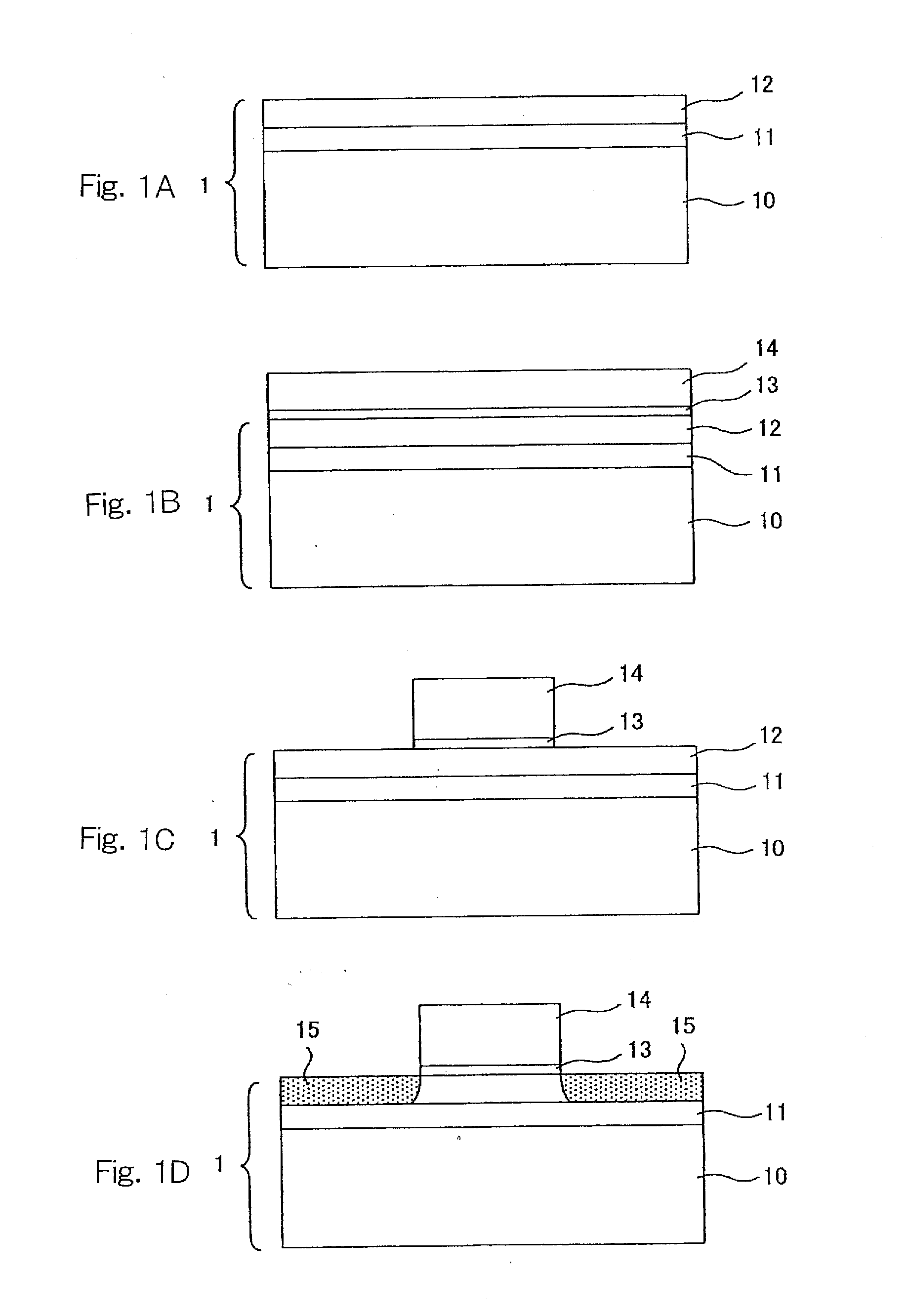

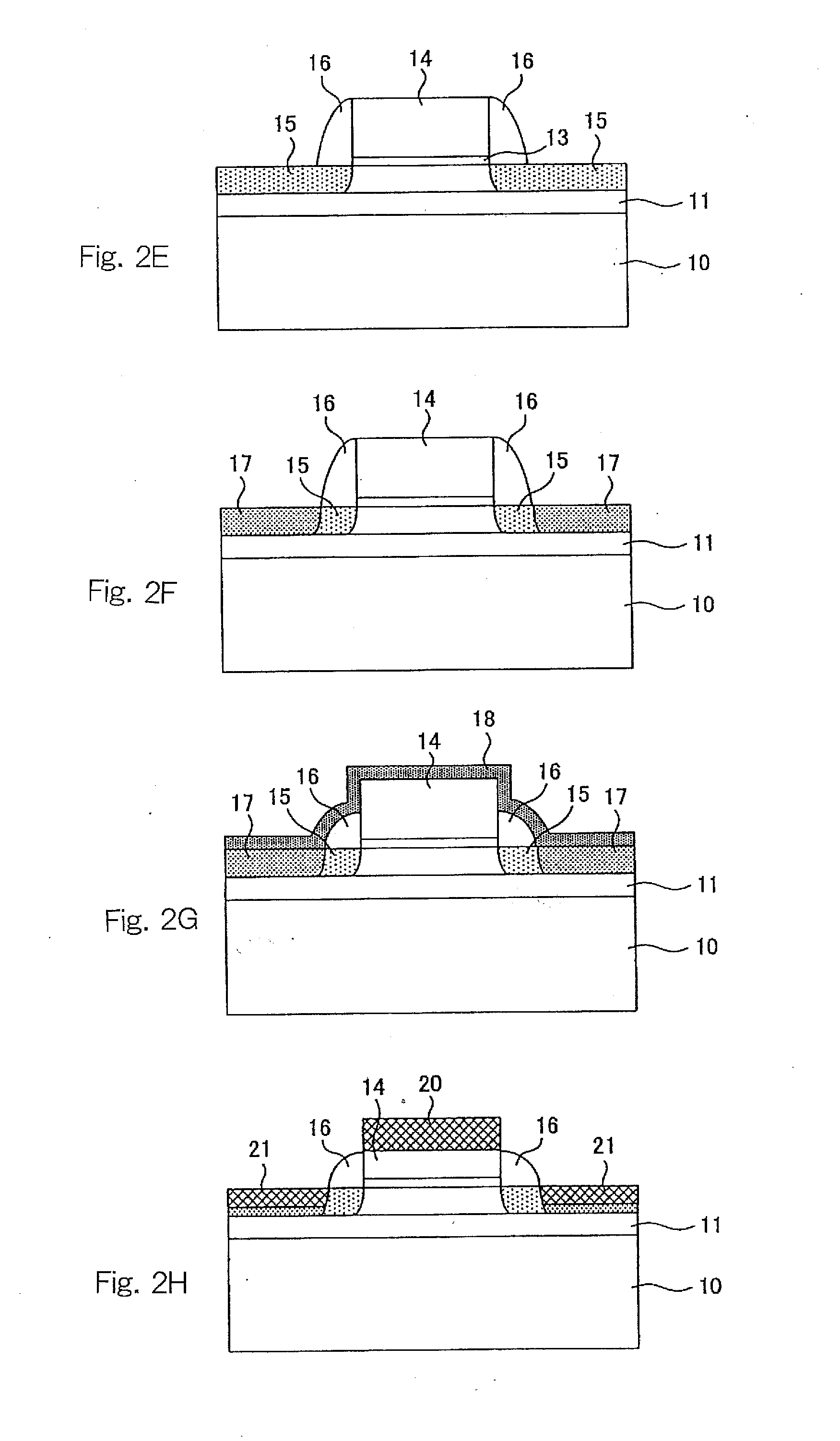

Method of manufacturing semiconductor device

InactiveUS20090317950A1Reduce parasitic resistanceImprove leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageSoi substrate

A semiconductor device manufacturing method which sequentially forms a gate oxide film and gate electrode material over a semiconductor layer of an SOI substrate and patterns the material into gate electrodes. The method further comprises the steps of forming sidewalls made of an insulator to cover side surfaces of the gate electrode; ion-implanting into the semiconductor layer on both sides of the gate electrode to form drain / source regions; partially etching the sidewalls to expose upper parts of the side surfaces of the gate electrode; depositing a metal film to cover the tops of the drain / source regions and of the gate electrode and the exposed upper parts of the side surfaces of the gate electrode; and performing heat treatment on the SOI substrate to form silicide layers respectively in the surfaces of the gate electrode and of the drain / source regions.

Owner:LAPIS SEMICON CO LTD

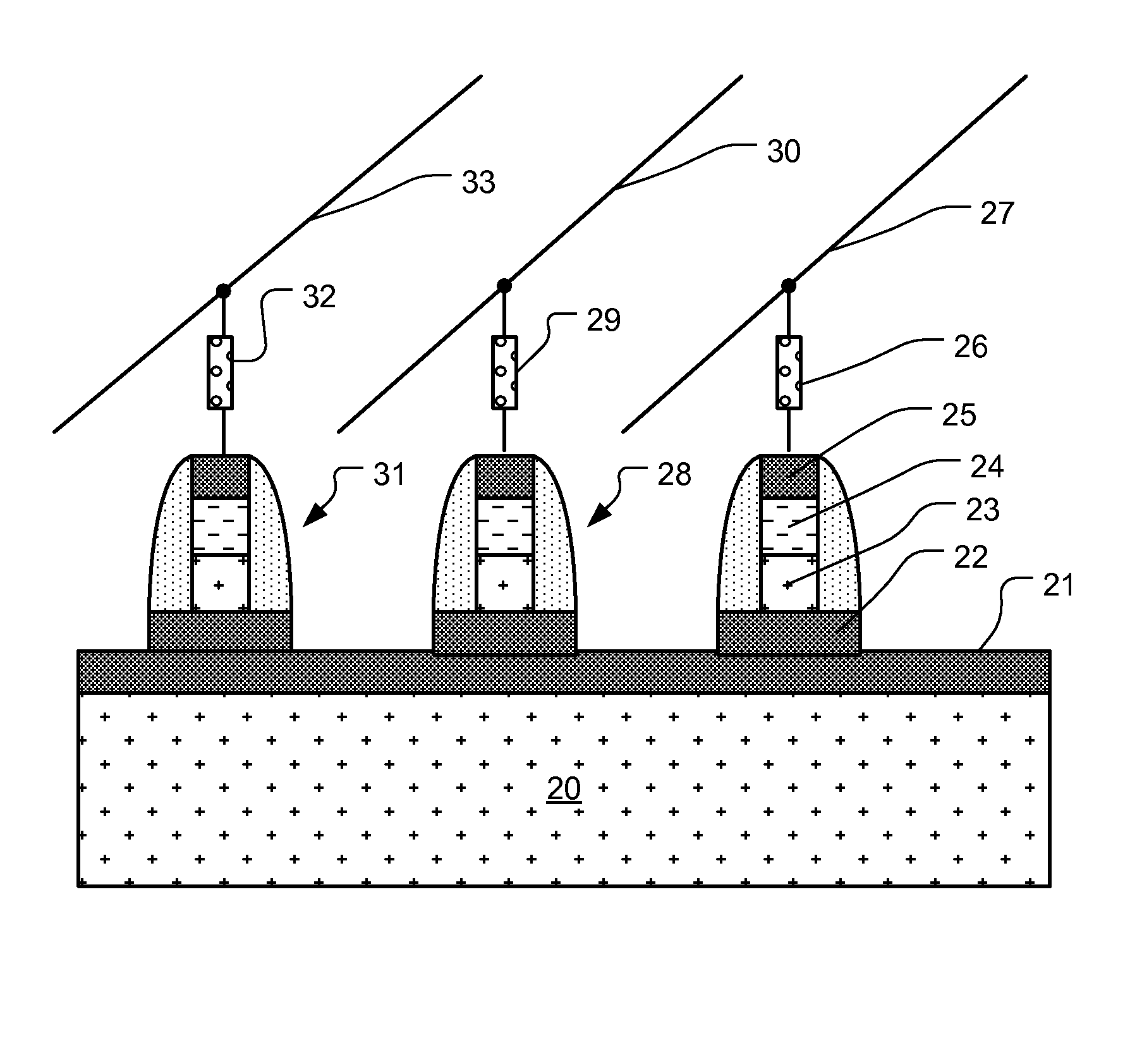

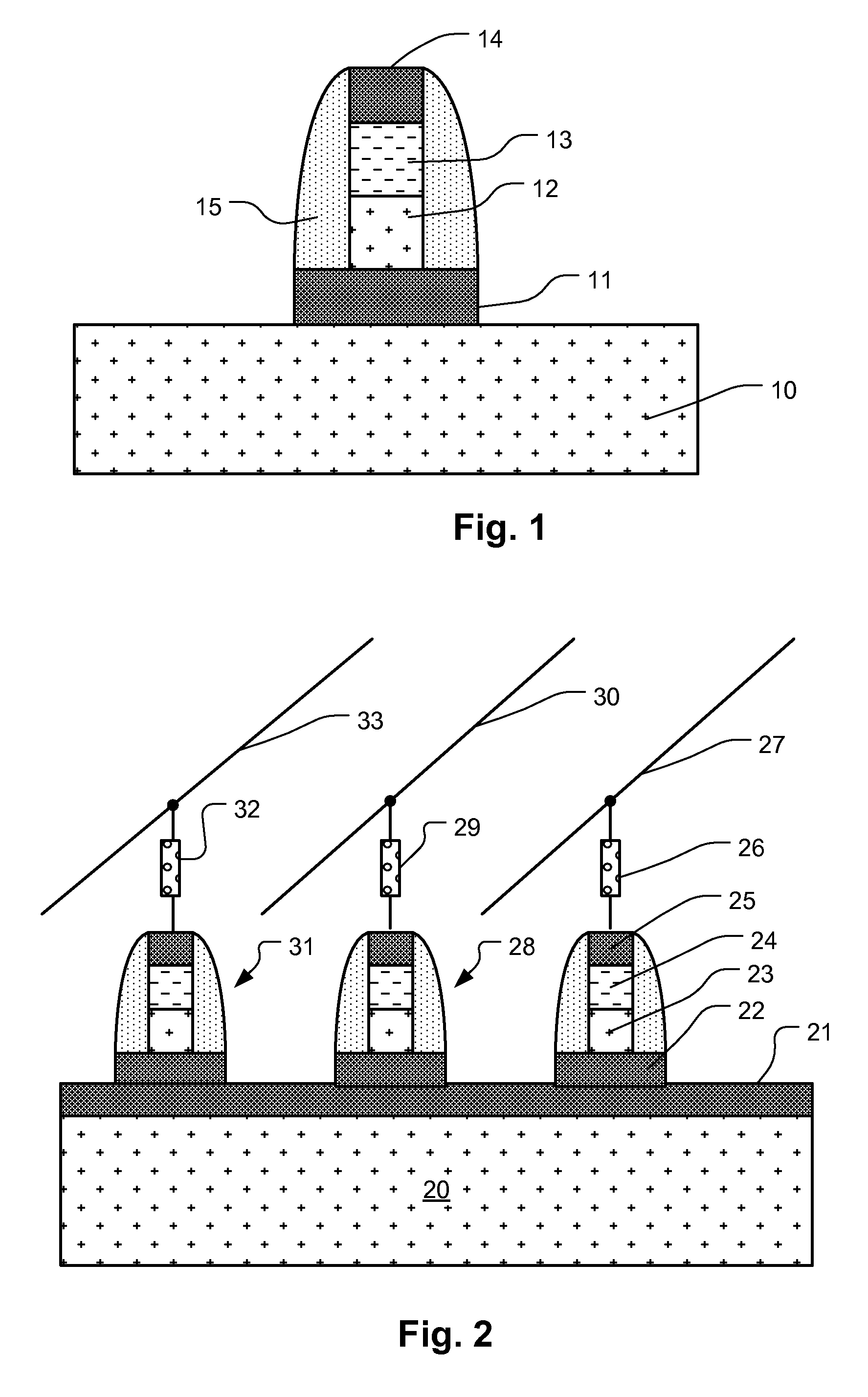

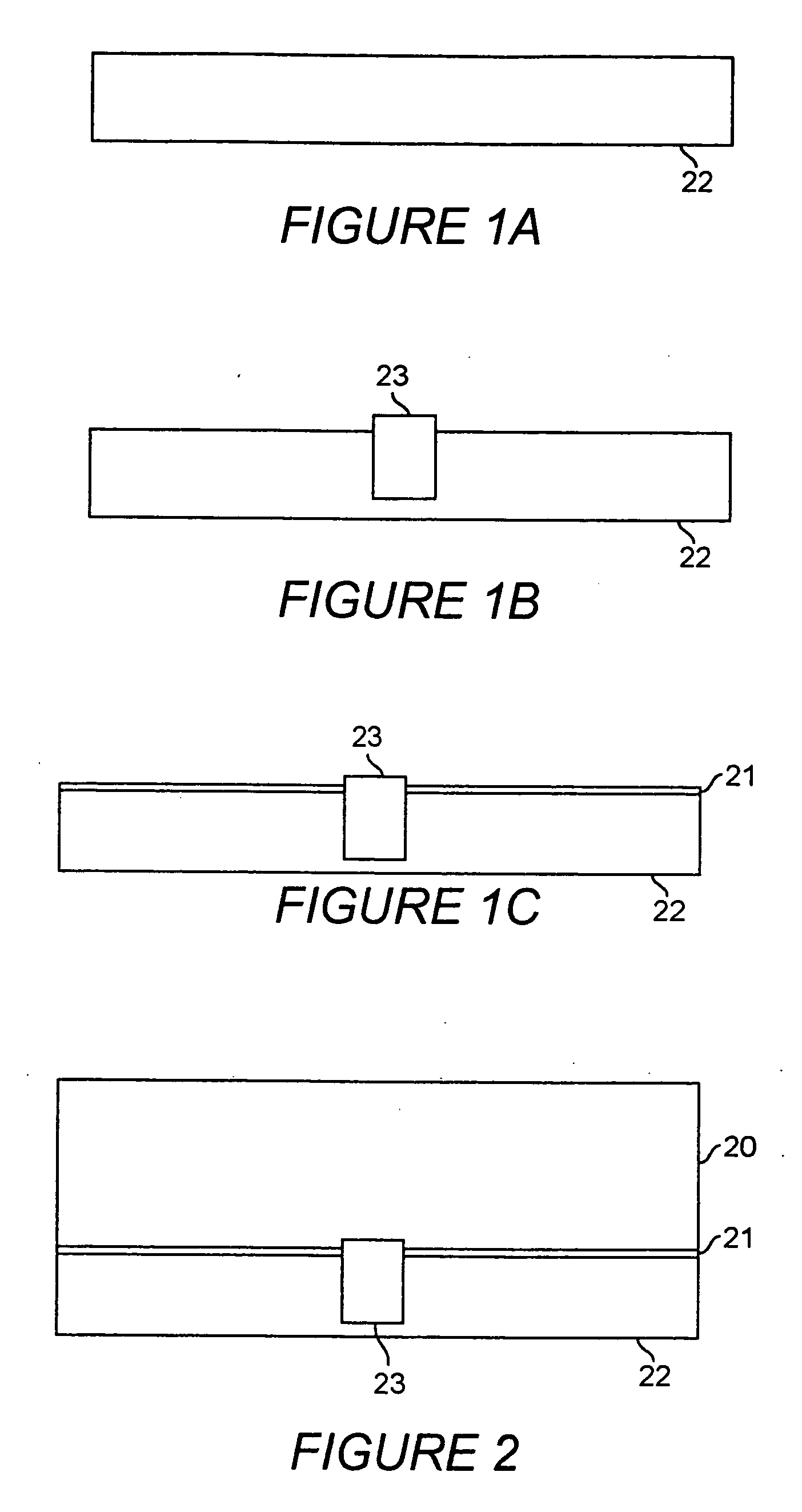

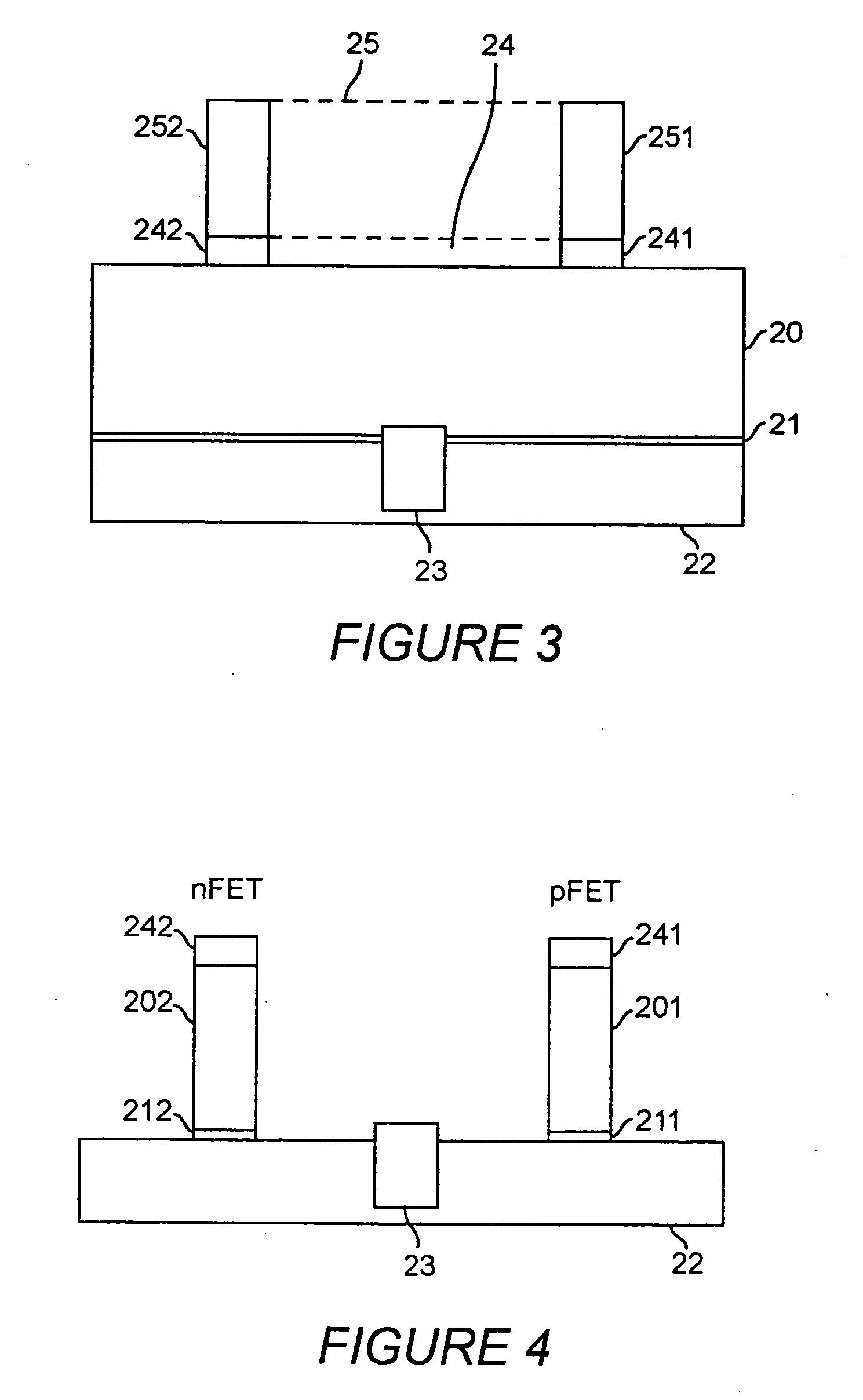

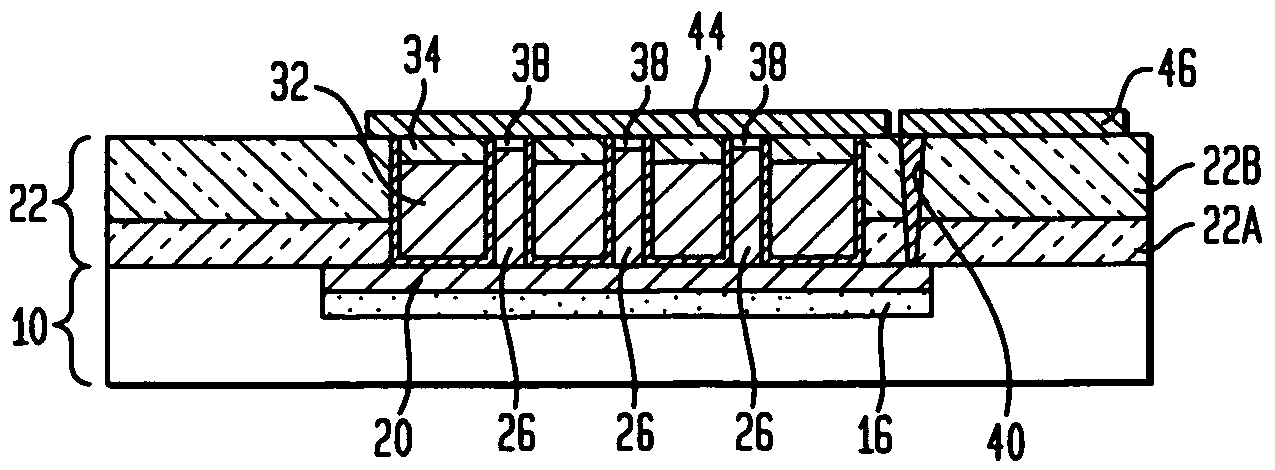

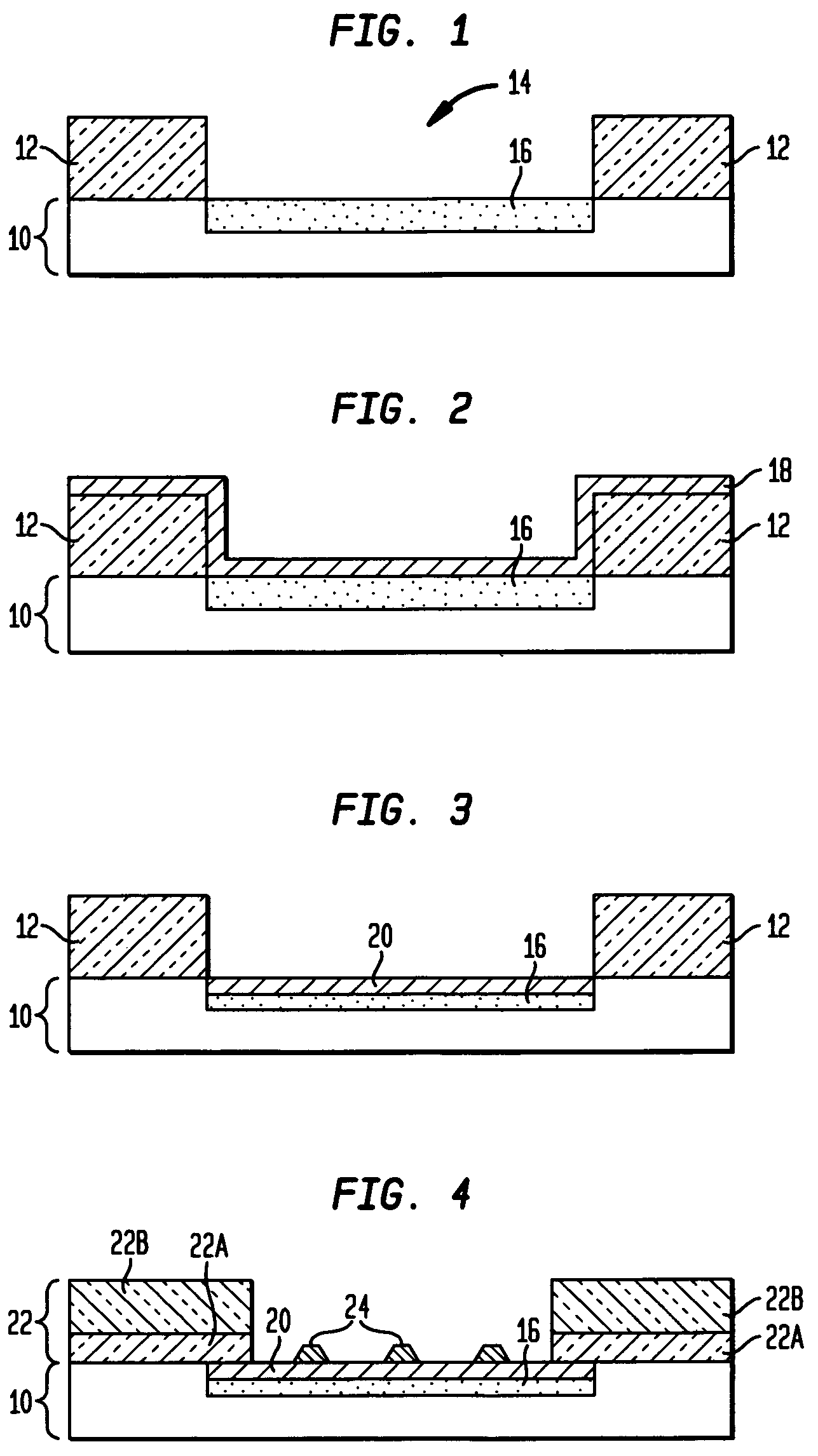

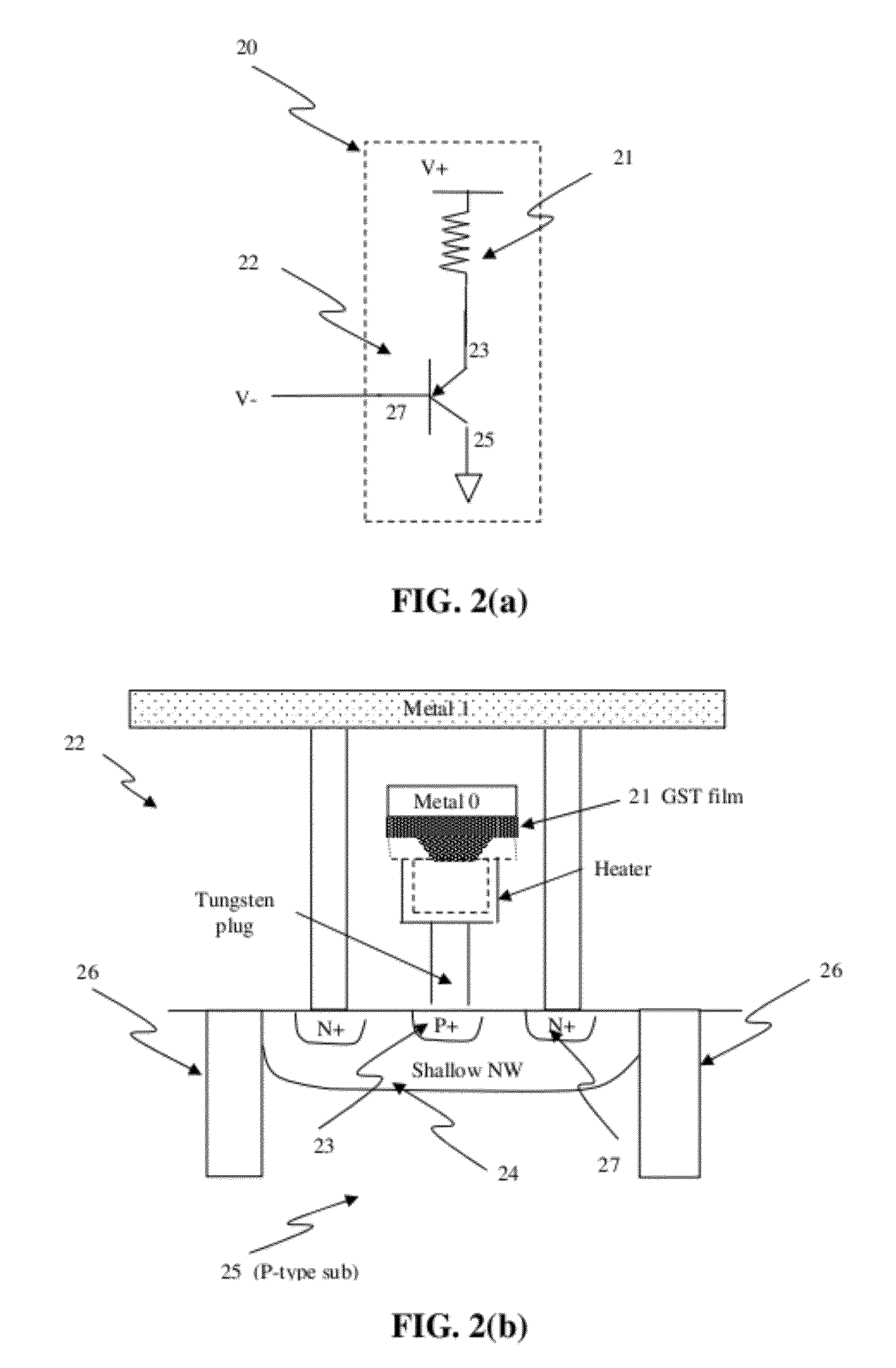

Integrated circuit memory with single crystal silicon on silicide driver and manufacturing method

ActiveUS20100171086A1Excellent ElectricalExcellent structural characteristicSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitMonocrystalline silicon

A memory device includes a diode driver and a data storage element, such as an element comprising phase change memory material, and in which the diode driver comprises a silicide element on a silicon substrate with a single crystal silicon node on the silicide element. The silicide element separates the single crystal silicon node from the underlying silicon substrate, preventing the flow of carriers from the single crystal silicon node into the substrate, and is capable of acting as a conductive element for interconnecting devices on the device. The single crystal silicon node acts as one terminal of a diode, and a second semiconductor node is formed on top of it, acting as the other terminal of the diode.

Owner:MACRONIX INT CO LTD

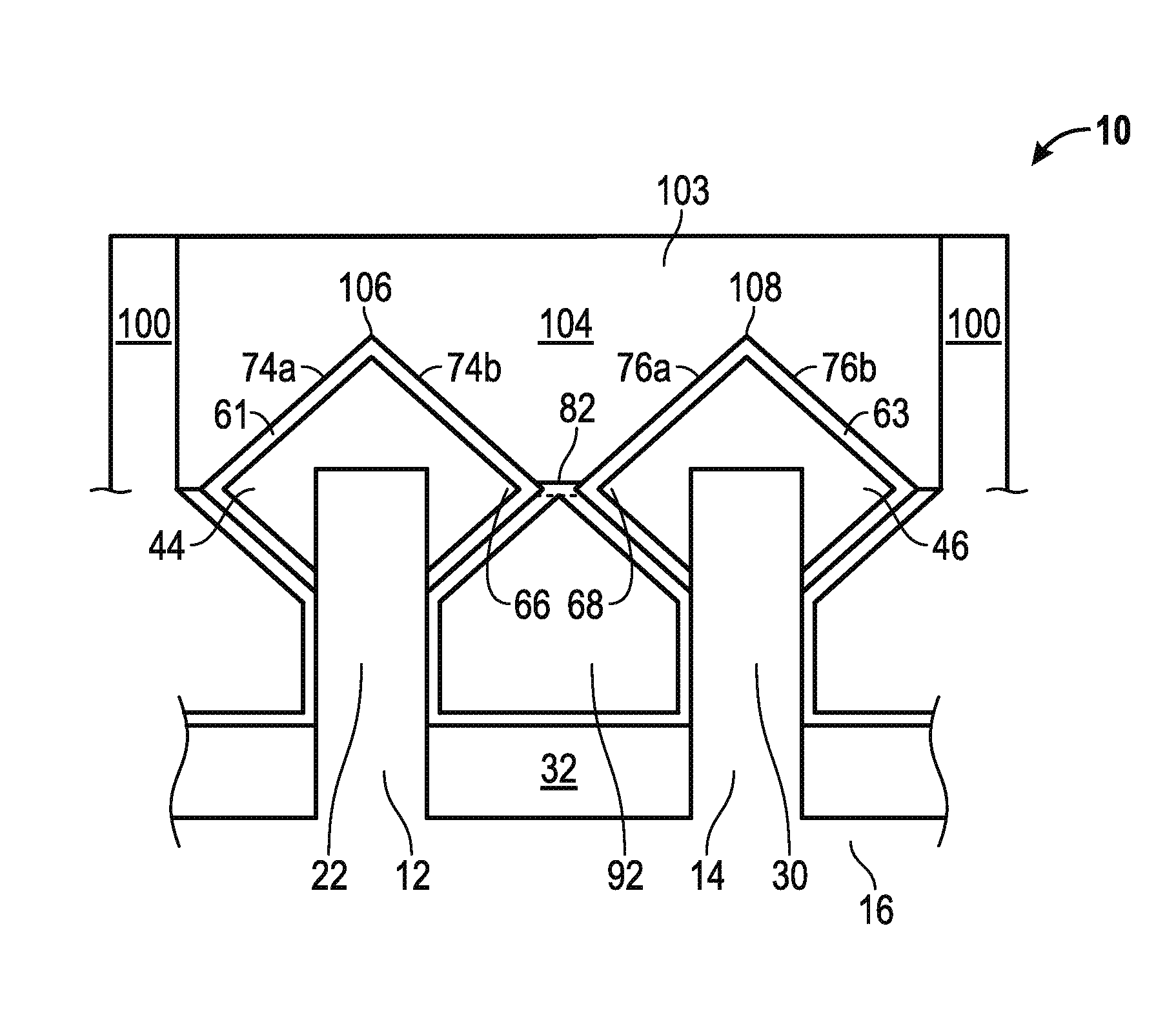

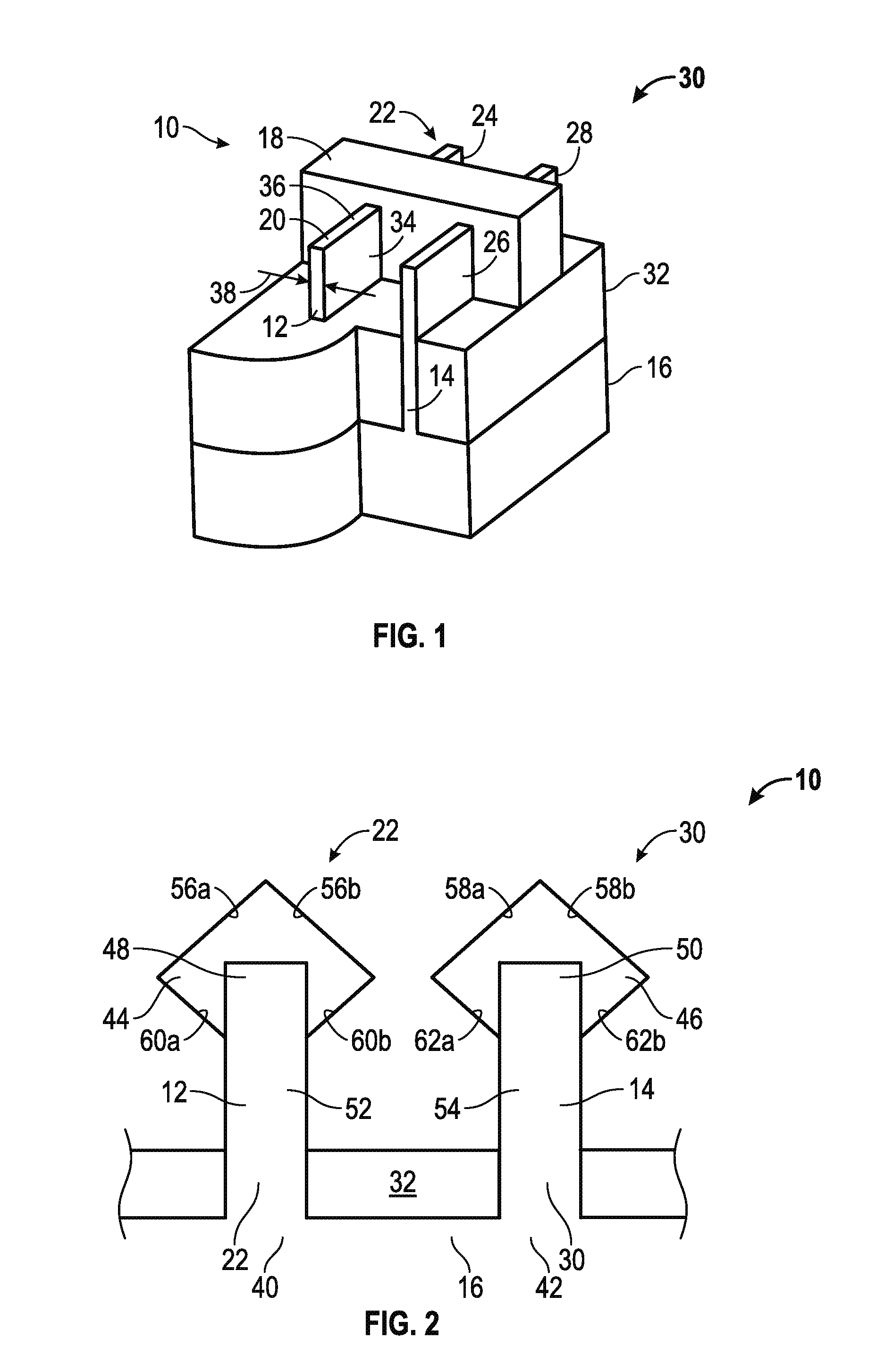

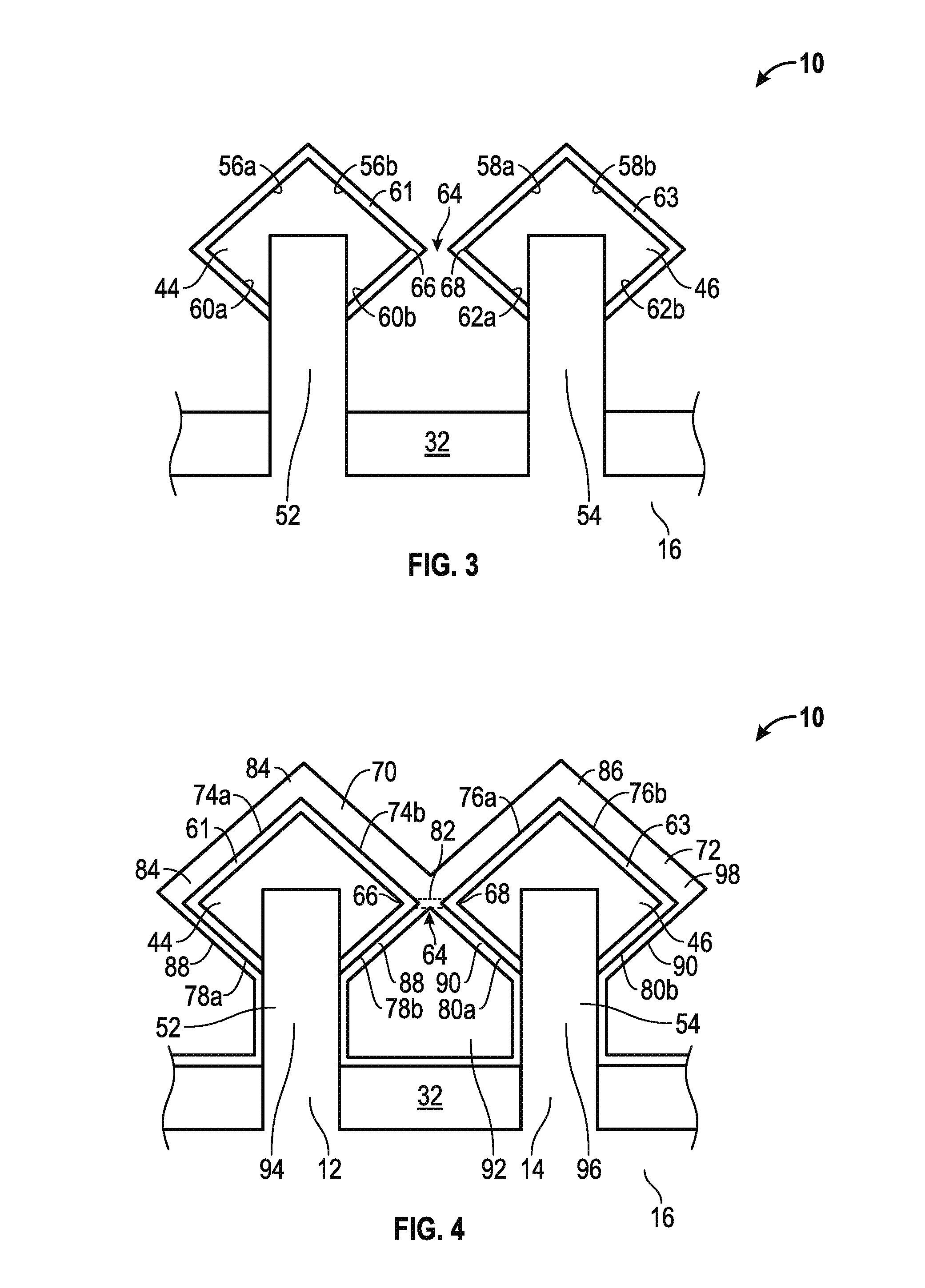

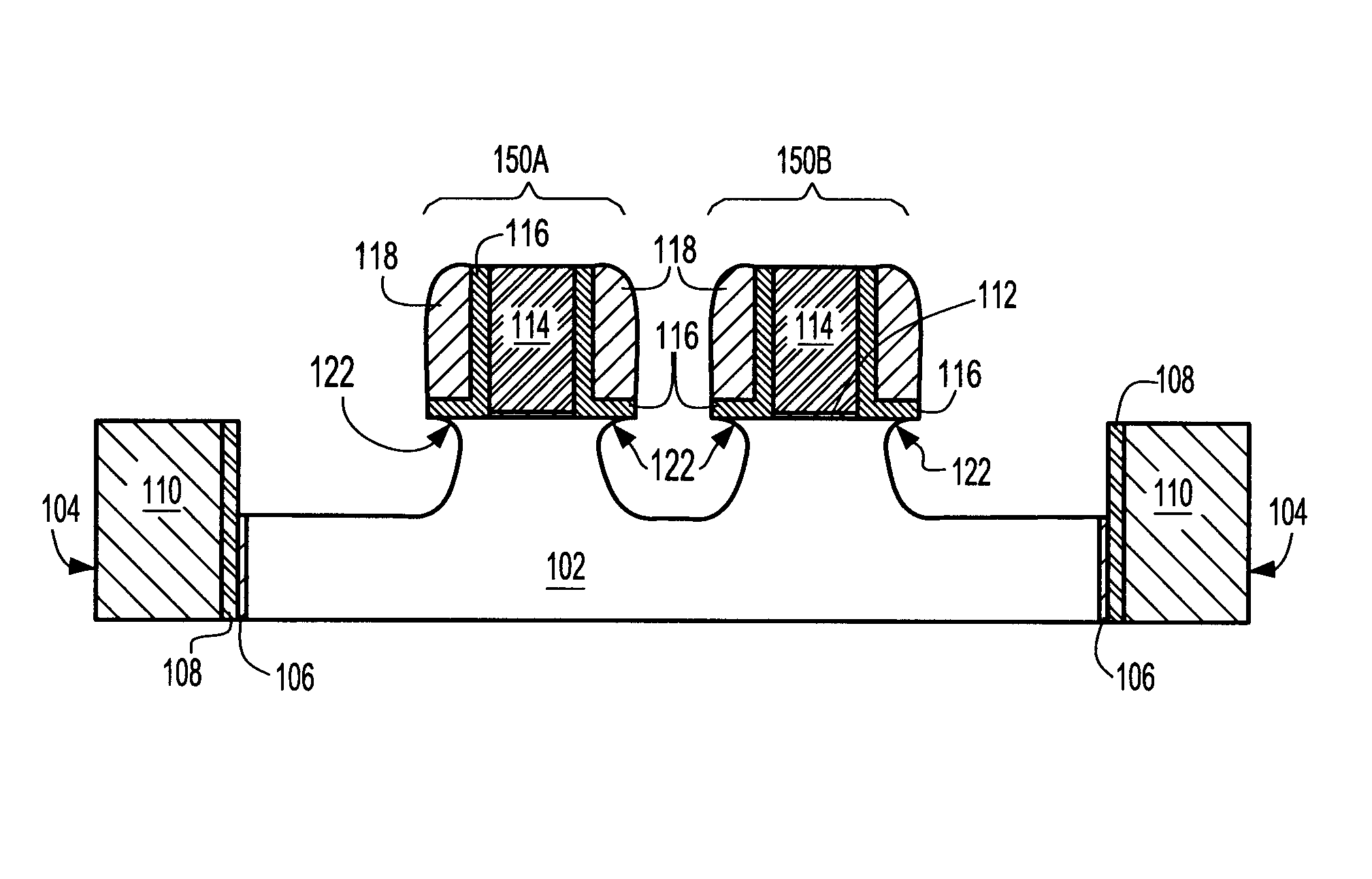

Integrated circuits including finfet devices with lower contact resistance and reduced parasitic capacitance and methods for fabricating the same

Integrated circuits and methods for fabricating integrated circuits are provided. In one example, an integrated circuit includes a semiconductor substrate. A first fin and a second fin are adjacent to each other extending from the semiconductor substrate. The first fin has a first upper section and the second fin has a second upper section. A first epi-portion overlies the first upper section and a second epi-portion overlies the second upper section. A first silicide layer overlies the first epi-portion and a second silicide layer overlies the second epi-portion. The first and second silicide layers are spaced apart from each other to define a lateral gap. A dielectric spacer is formed of a dielectric material and spans the lateral gap. A contact-forming material overlies the dielectric spacer and portions of the first and second silicide layers that are laterally above the dielectric spacer.

Owner:IBM CORP +1

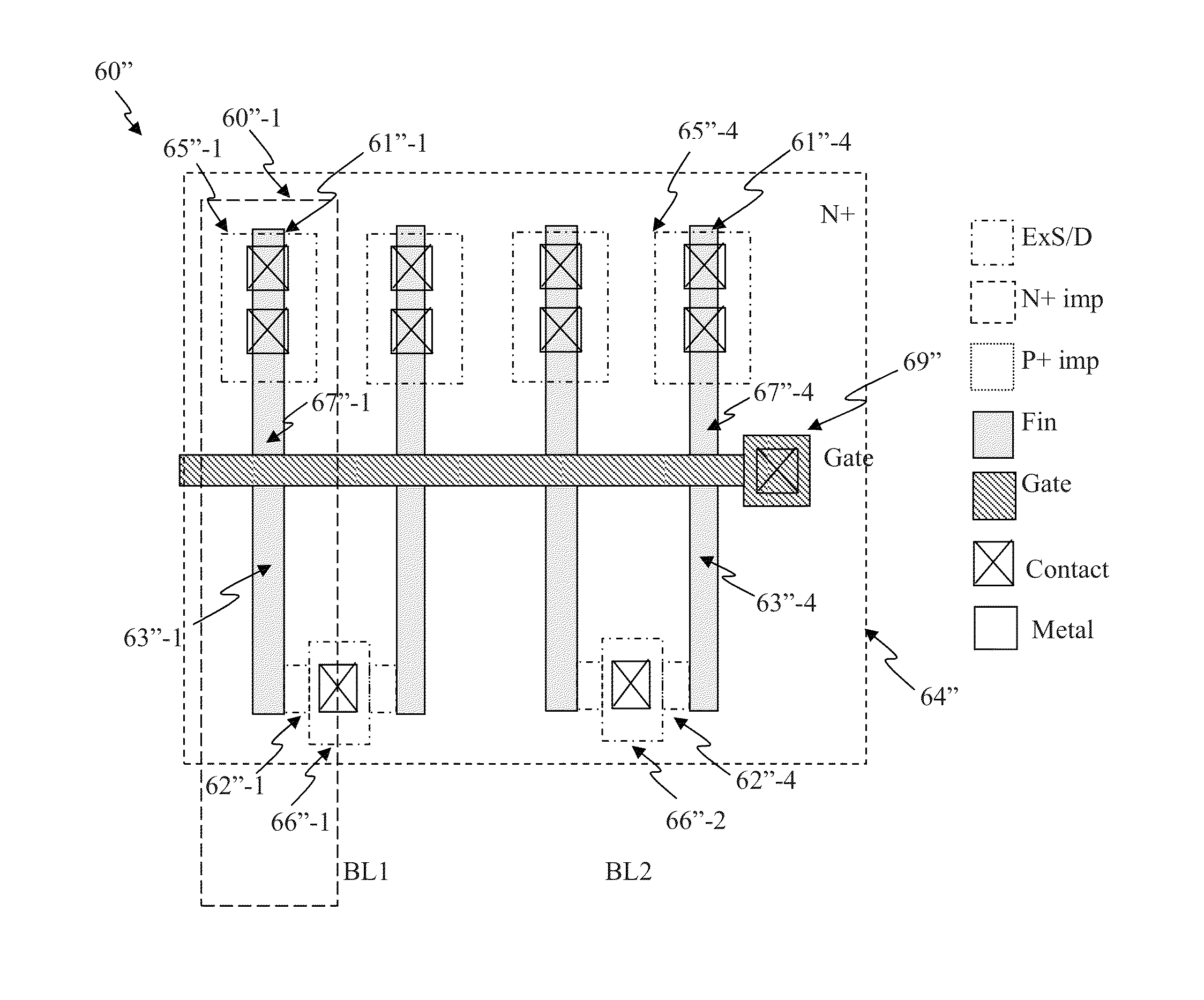

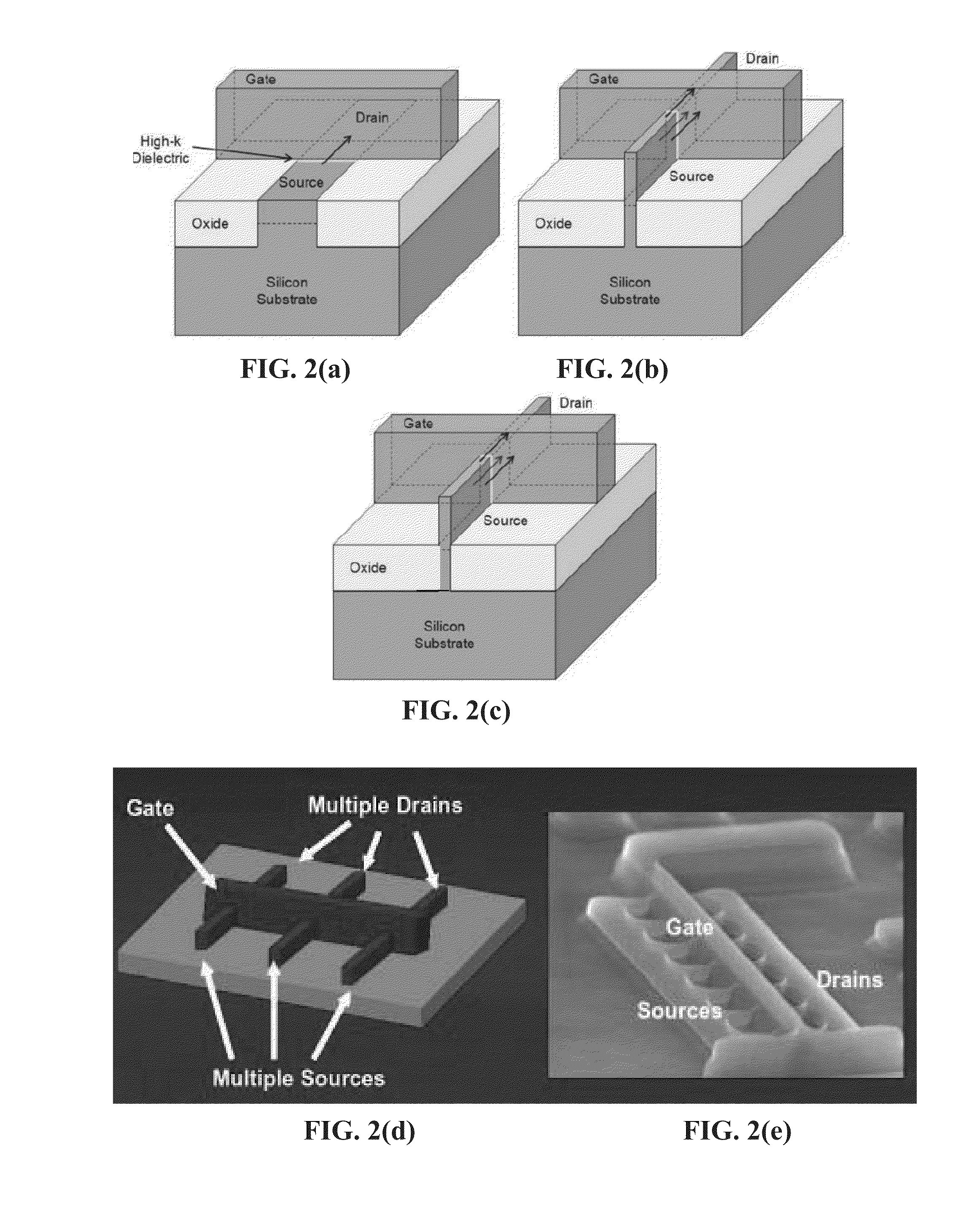

Circuit and system of using finfet for building programmable resistive devices

ActiveUS20130148409A1Small cell sizeLow costSolid-state devicesRead-only memoriesHemt circuitsEngineering

Junction diodes or MOS devices fabricated in standard FinFET technologies can be used as program selectors or One-Time Programmable (OTP) element in a programmable resistive device, such as interconnect fuse, contact / via fuse, anti-fuse, or emerging nonvolatile memory such as MRAM, PCRAM, CBRAM, or RRAM. The MOS or diode can be built on at least one fin structure or at least one active region that has at least one first active region and a second active region. The first and the second active regions can be isolated by a dummy MOS gate or silicide block layer (SBL) to construct a diode.

Owner:ATTOPSEMI TECH CO LTD

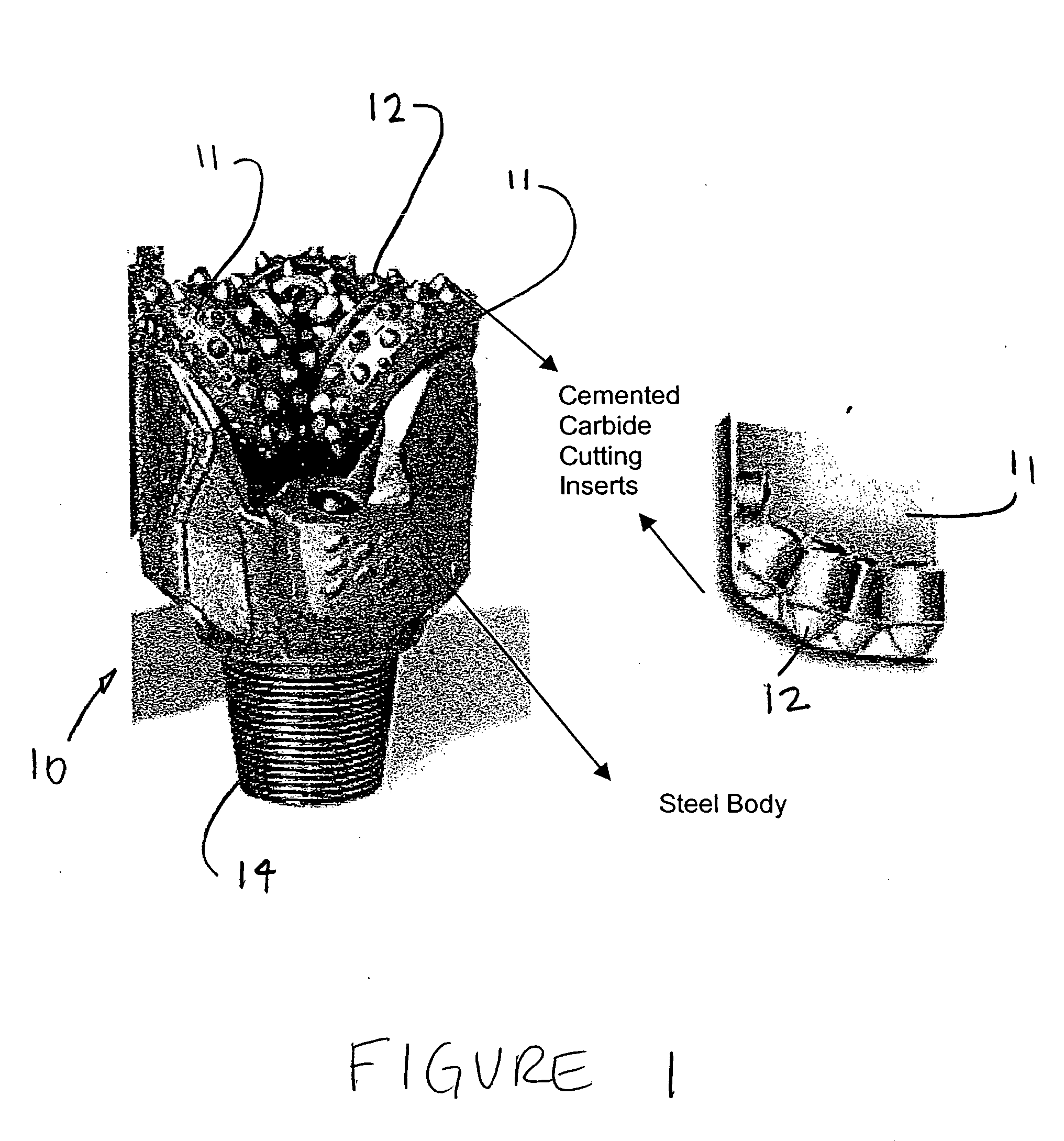

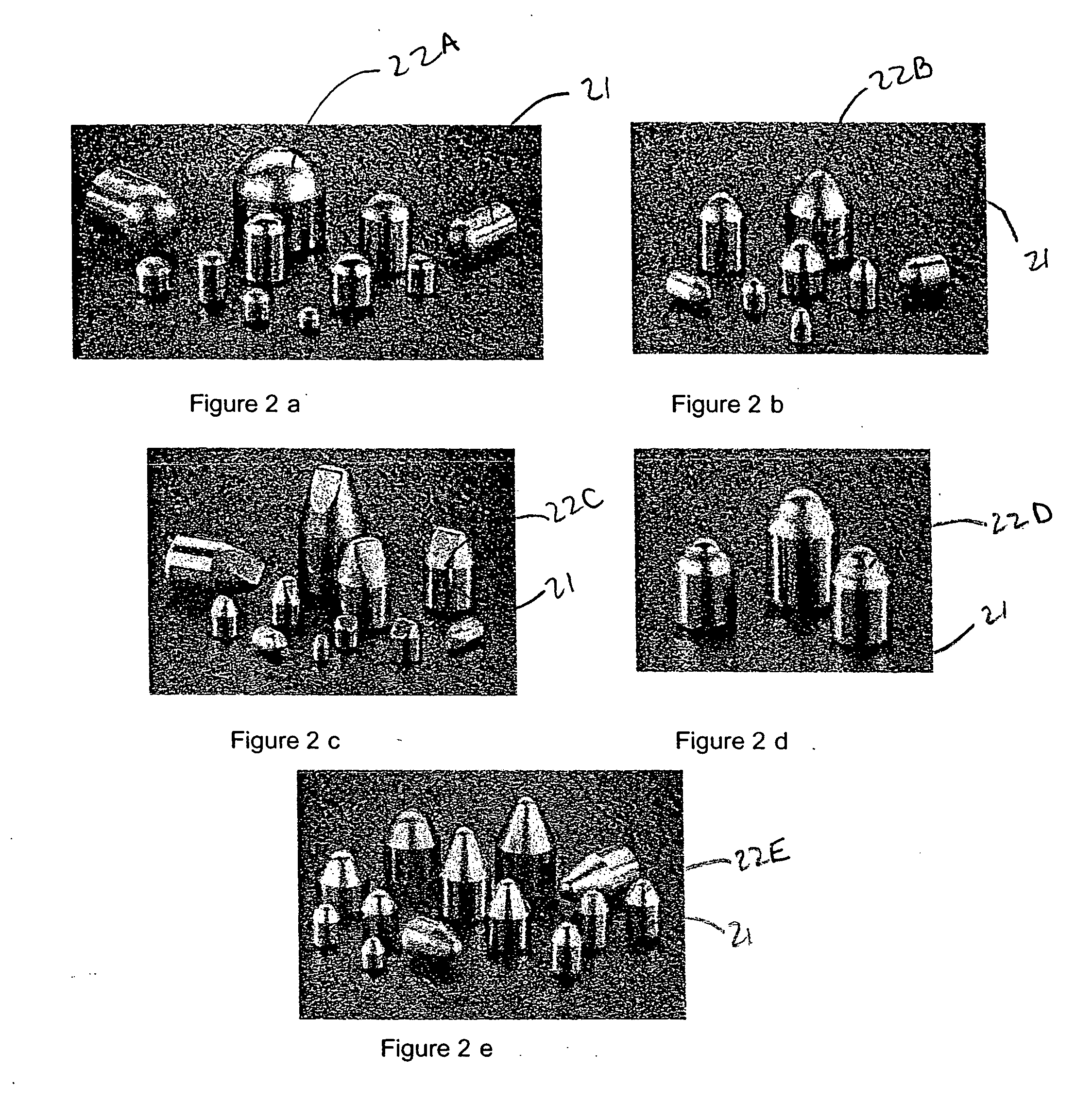

Cemented carbide inserts for earth-boring bits

This invention relates to cutting inserts for earth boring bits comprising a cutting zone, wherein the cutting zone comprises first cemented hard particles and a body zone, wherein the body zone comprises second cemented hard particles. The first cemented hard particles may differ in at least one property from the second cemented hard particles. As used herein, the cemented hard particles means a material comprising hard particles in a binder. The hard particles may be at least one of a carbide, a nitride, a boride, a silicide, an oxide, and solid solutions thereof and the binder may be at least one metal selected from cobalt, nickel, iron and alloys of cobalt, nickel or iron.

Owner:KENNAMETAL INC

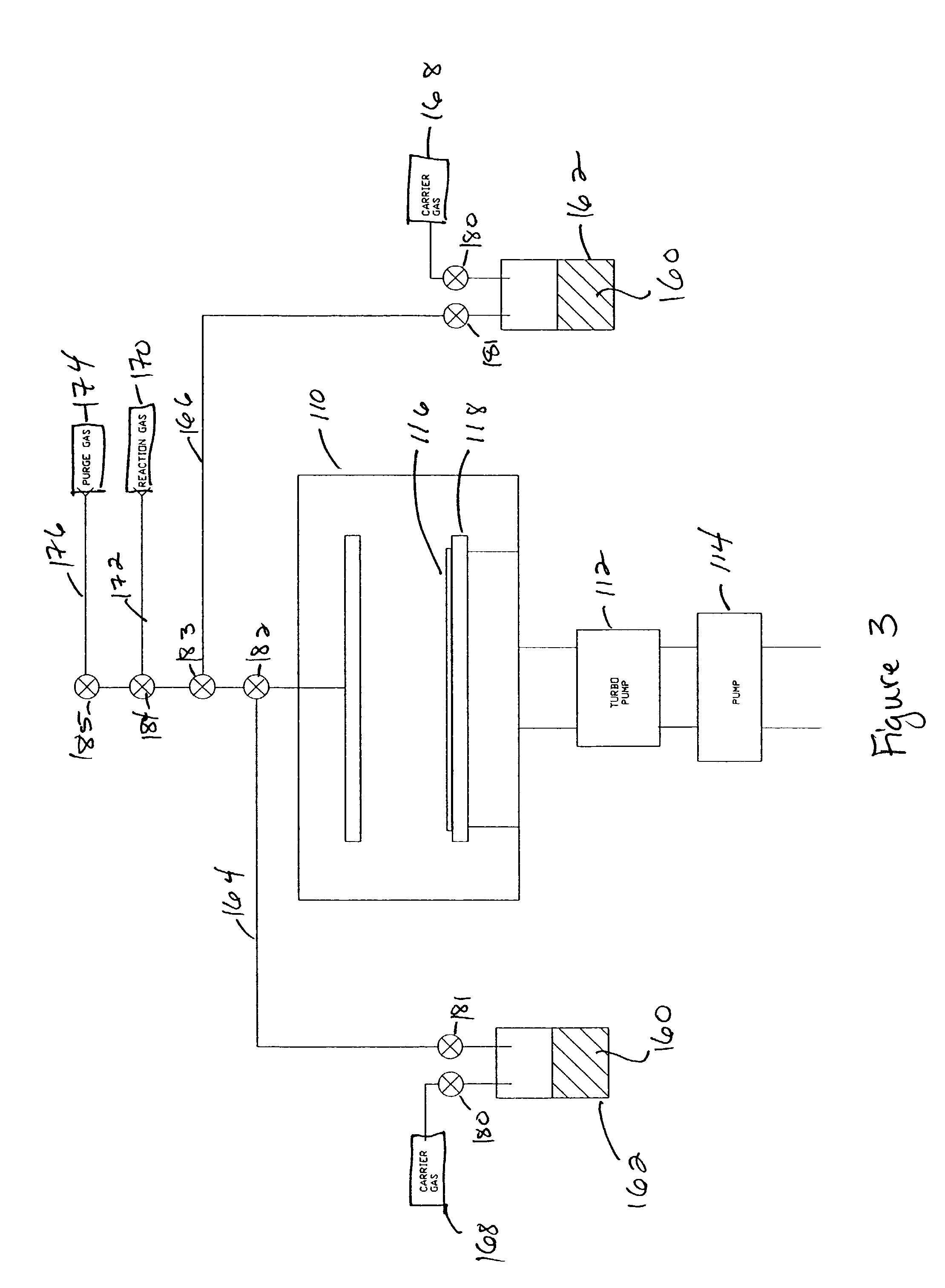

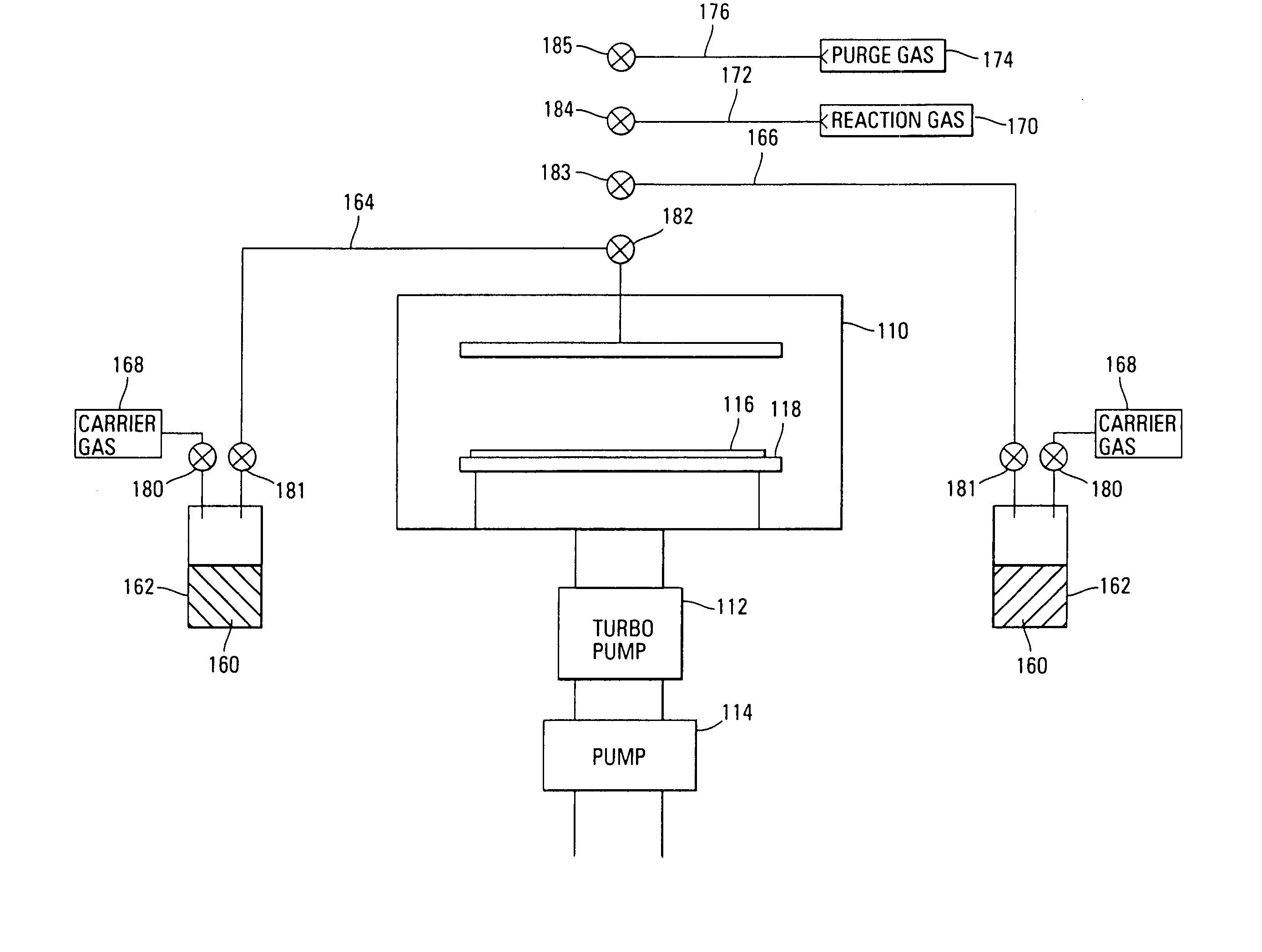

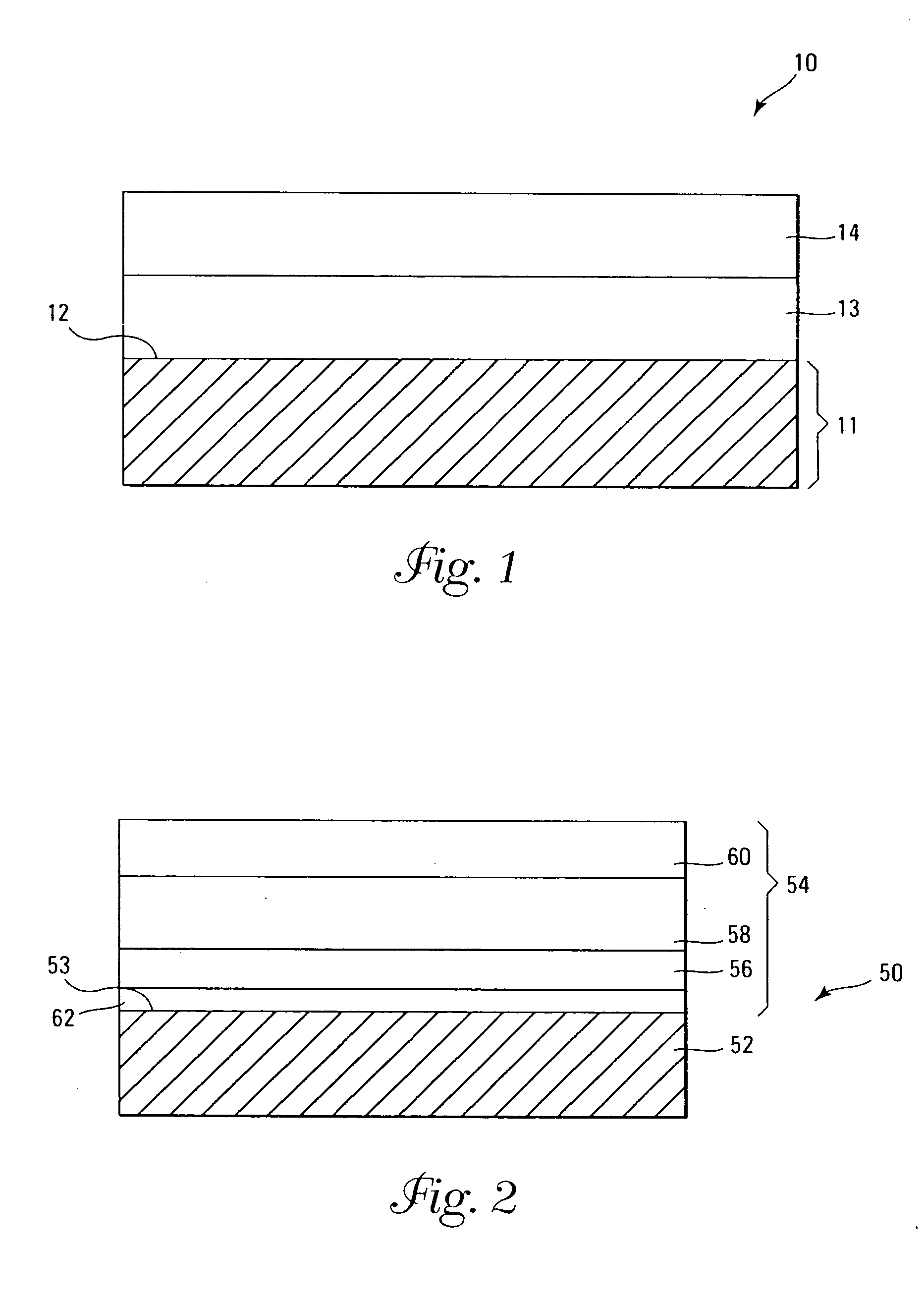

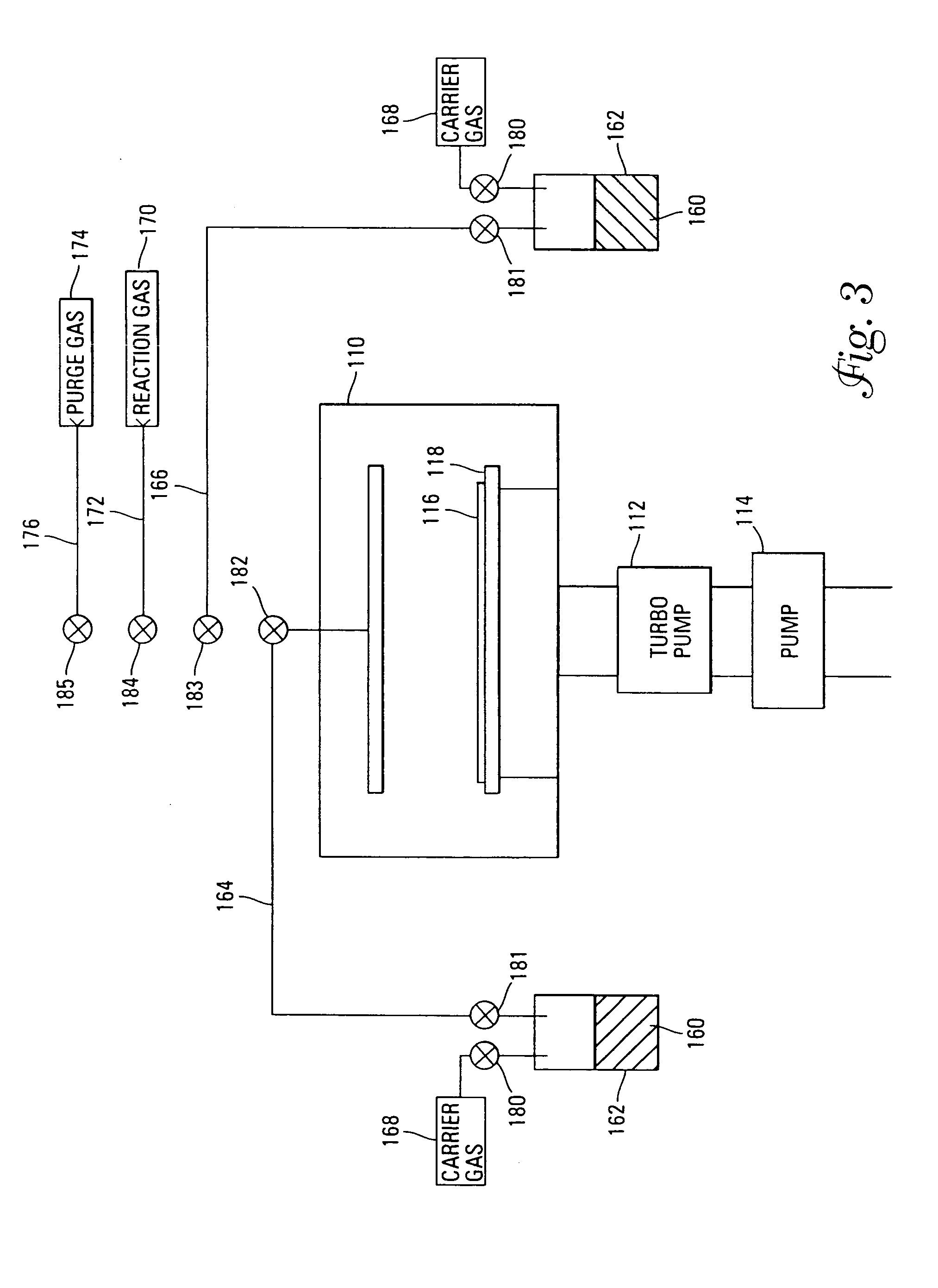

Systems and methods for forming tantalum silicide layers

InactiveUS6995081B2Easy to controlMinimizing detrimental gas phase reactionSemiconductor/solid-state device manufacturingCapacitorsGas phaseNitrogen

A method of forming (and apparatus for forming) tantalum suicide layers (including tantalum silicon nitride layers), which are typically useful as diffusion barrier layers, on a substrate by using a vapor deposition process with a tantalum halide precursor compound, a silicon precursor compound, and an optional nitrogen precursor compound.

Owner:MICRON TECH INC

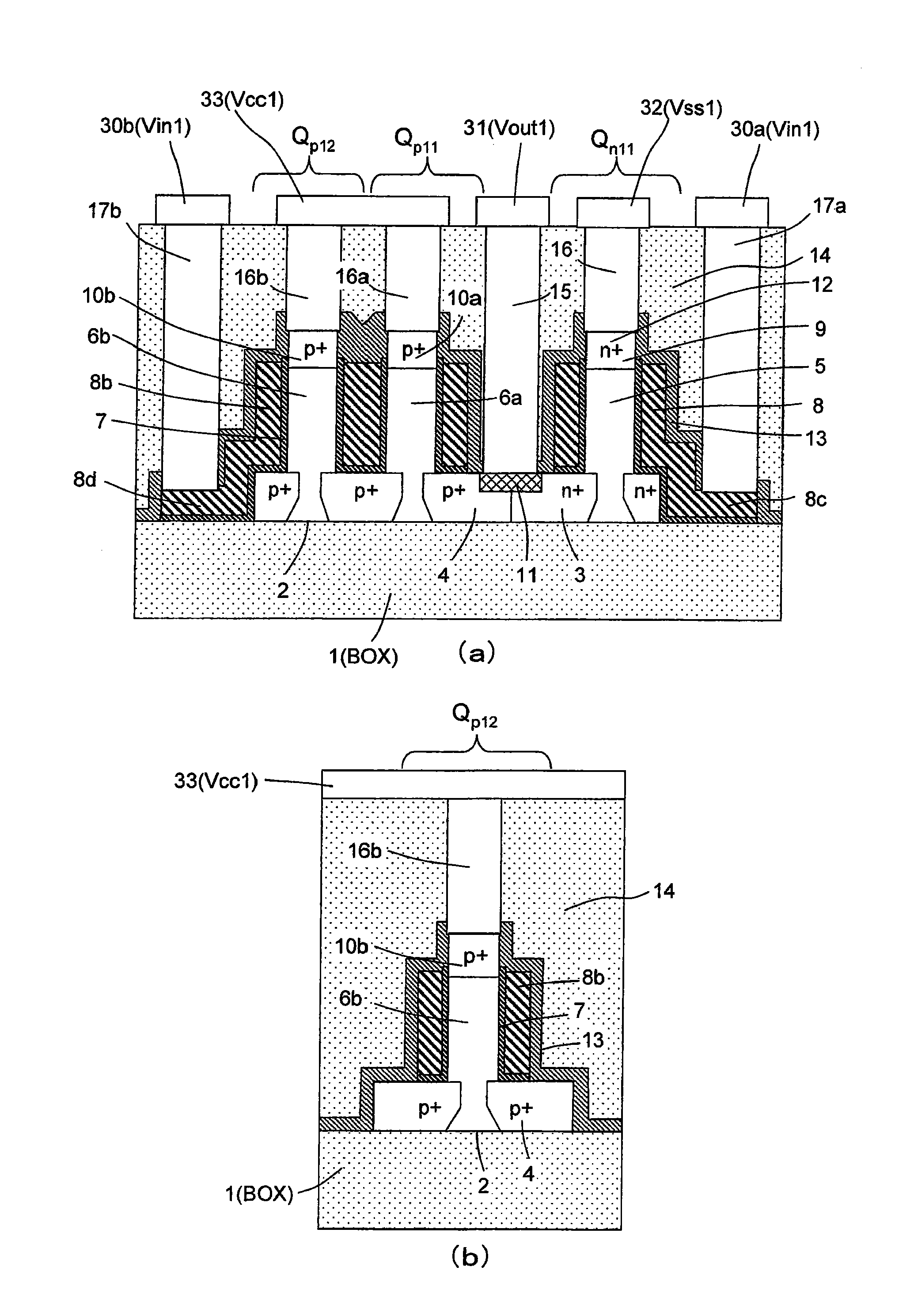

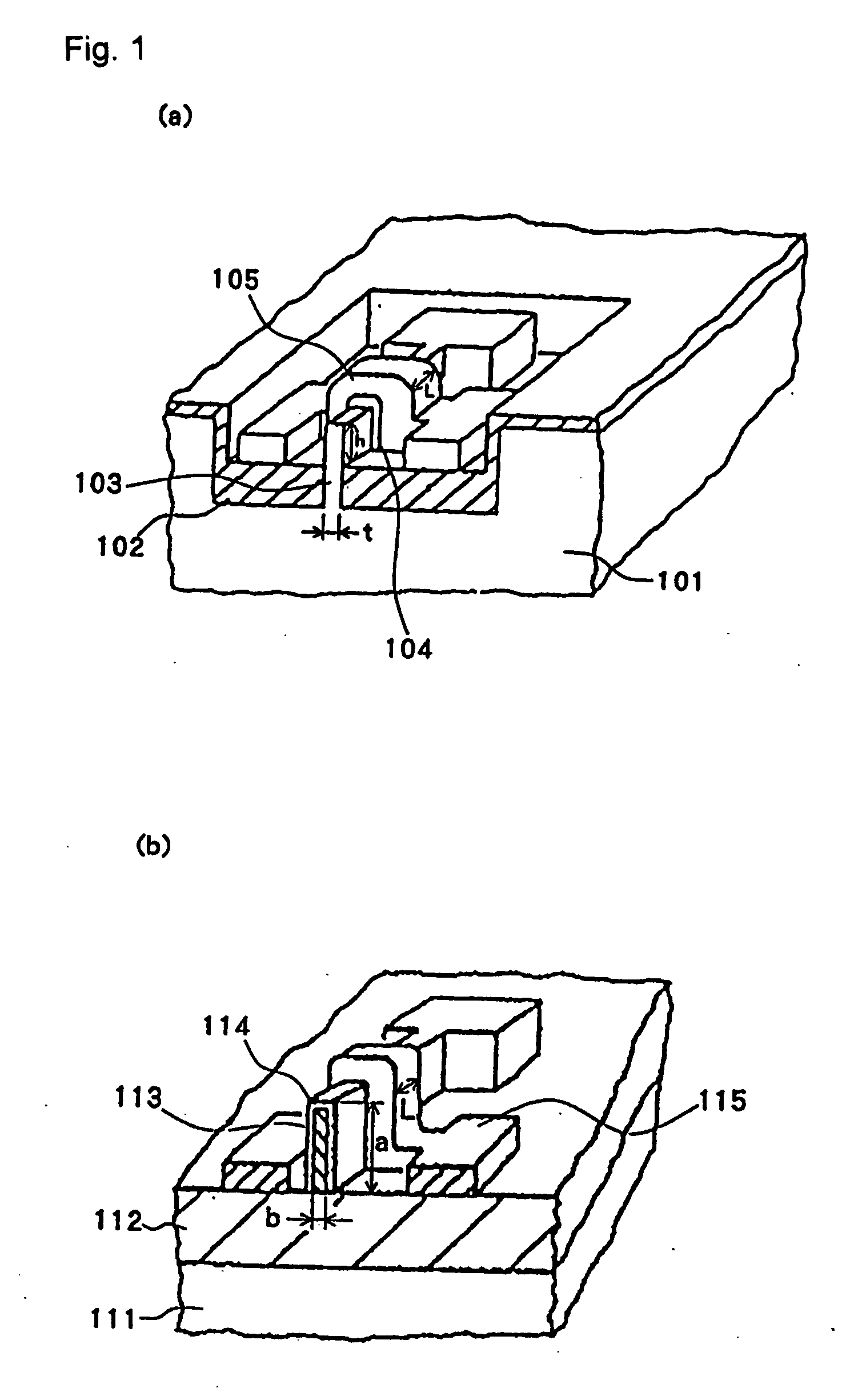

Semiconductor device and production method therefor

ActiveUS20100207201A1Reduce widthImprove area efficiencyTransistorSolid-state devicesDielectricEngineering

It is intended to provide a semiconductor device comprising a circuit which has a connection between one of a drain region and a source region of a first MOS transistor and one of a drain region and a source region of a second MOS transistor. The semiconductor device comprises: a substrate; a dielectric film on the substrate; and a planar semiconductor layer formed on the on-substrate dielectric film, wherein: the first MOS transistor includes a first drain or source region formed in the planar semiconductor layer, a first pillar-shaped semiconductor layer formed on the planar semiconductor layer, a second source or drain region formed in an upper portion of the first pillar-shaped semiconductor layer, and a first gate electrode formed in such a manner that the first gate electrode surrounds a sidewall of the first pillar-shaped semiconductor layer through a first dielectric film; and the second MOS transistor includes a third drain or source region formed in the planar semiconductor layer, a second pillar-shaped semiconductor layer formed on the planar semiconductor layer, a fourth source or drain region formed in an upper portion of the second pillar-shaped semiconductor layer, and a second gate electrode formed in such a manner that the second gate electrode surrounds a sidewall of the second pillar-shaped semiconductor layer through a second dielectric film, and wherein a first silicide layer is formed to connect at least a part of a surface of the first drain or source region and at least a part of a surface of the third drain or source region, wherein the first silicide layer is formed in an area other than an area in which a contact for at least the first drain or source region and the third drain or source region is formed.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

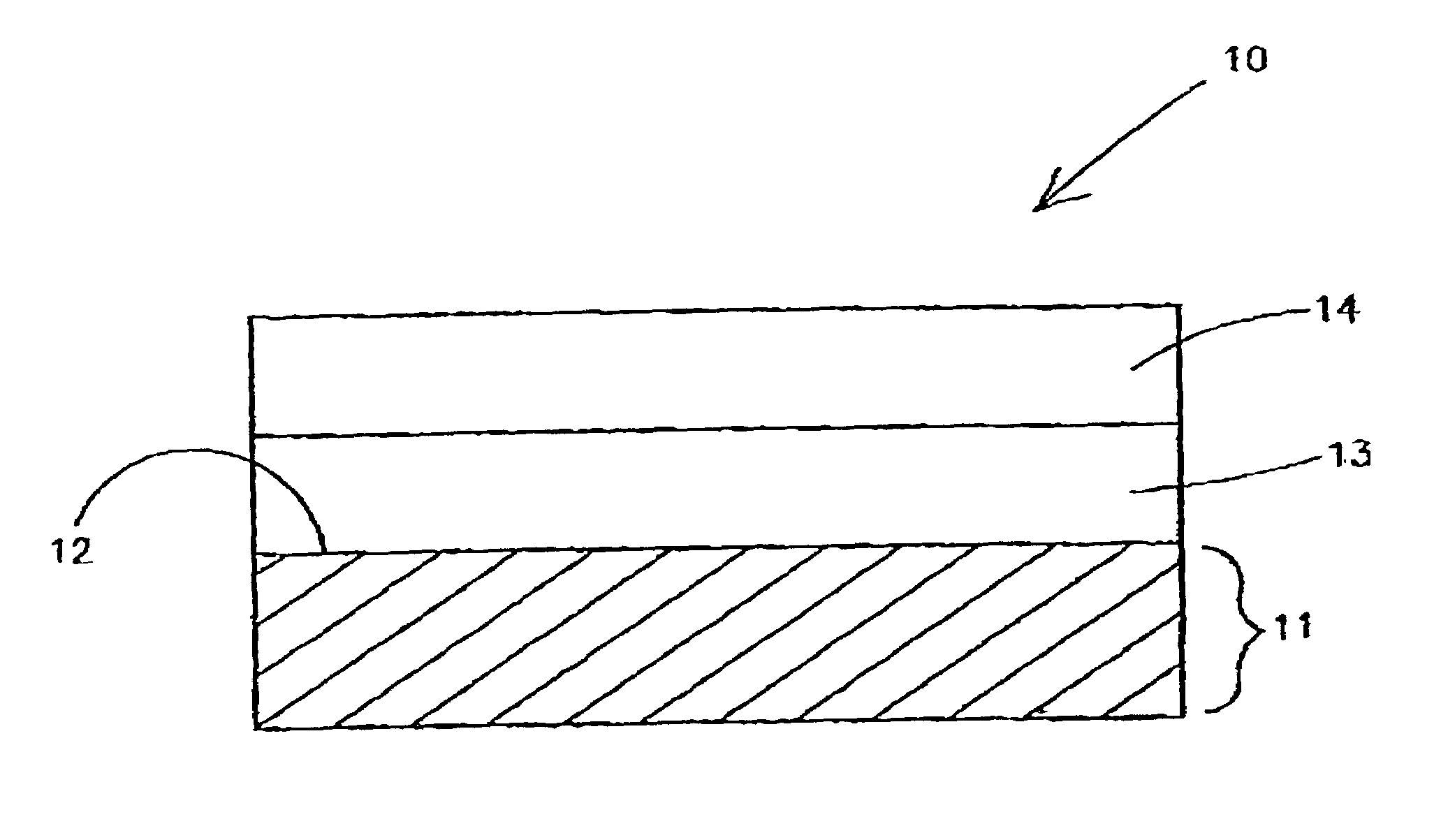

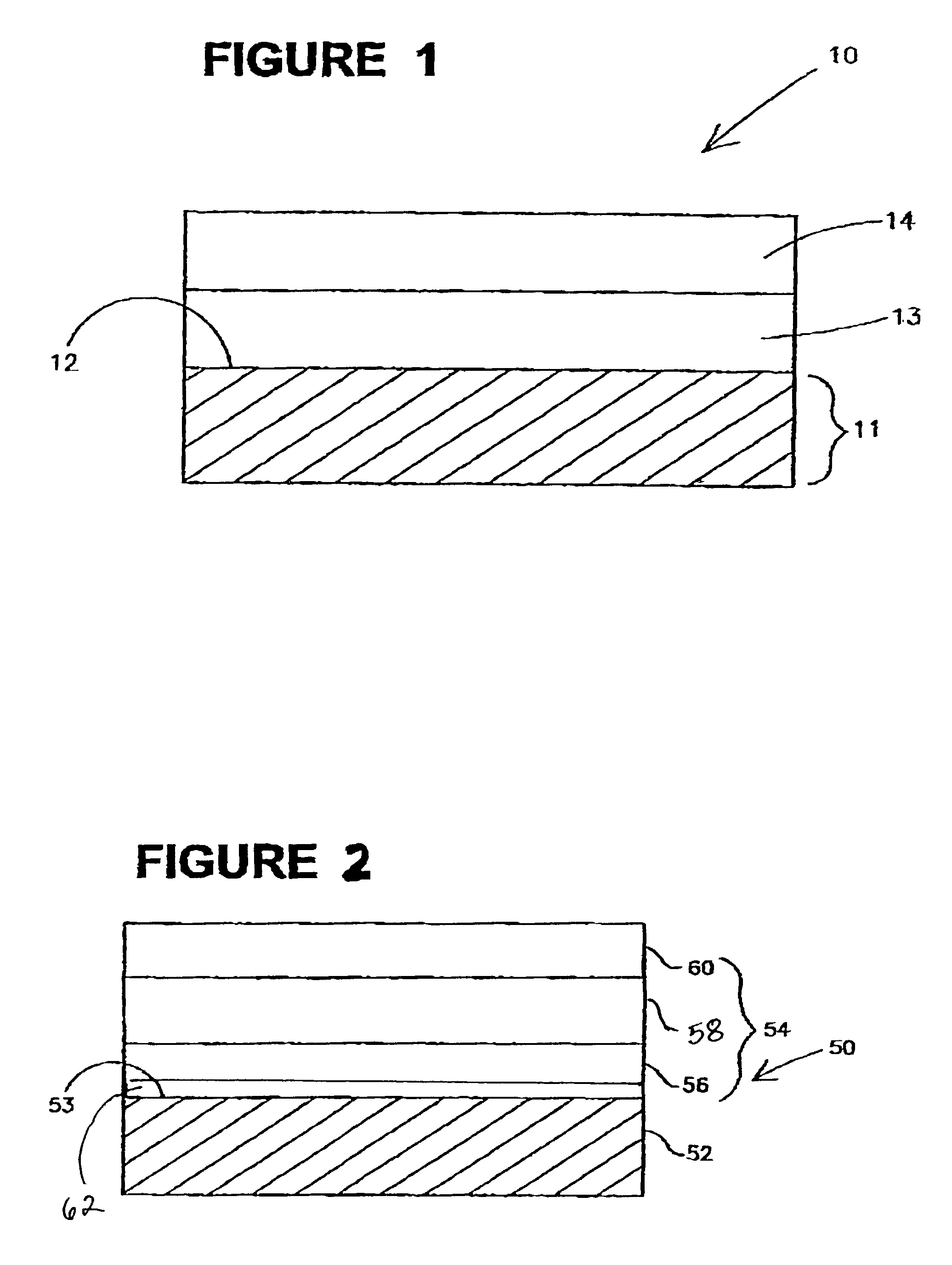

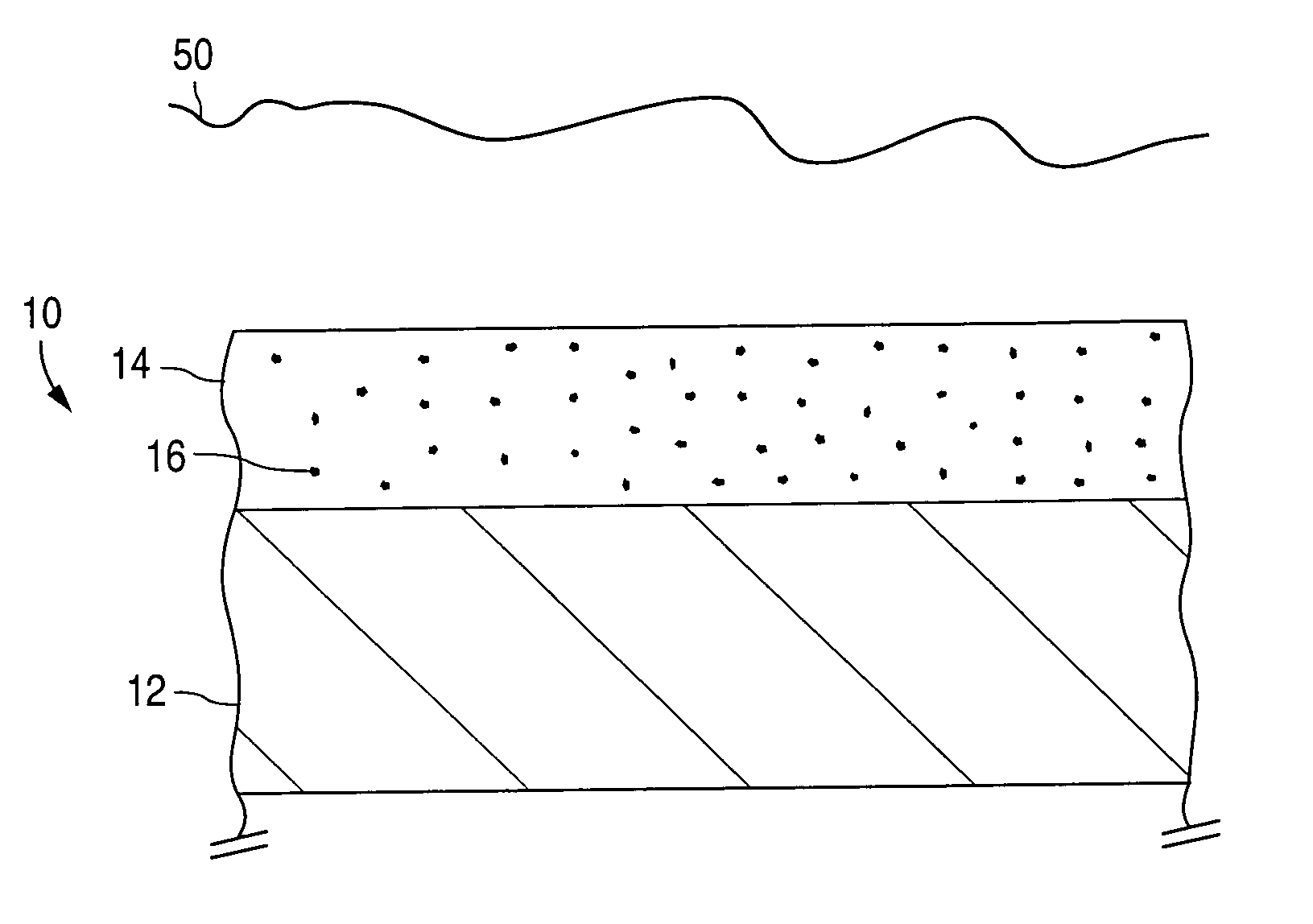

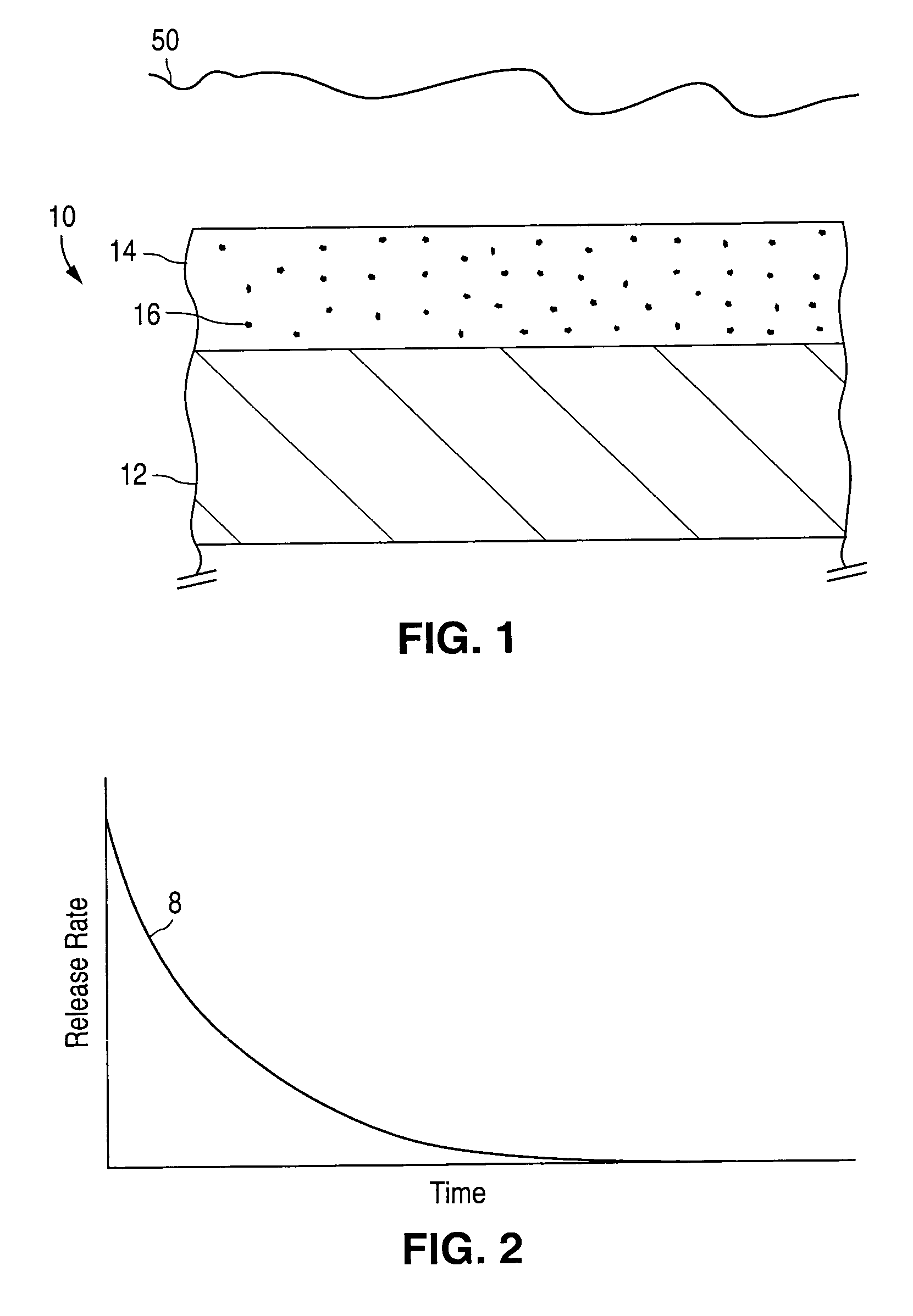

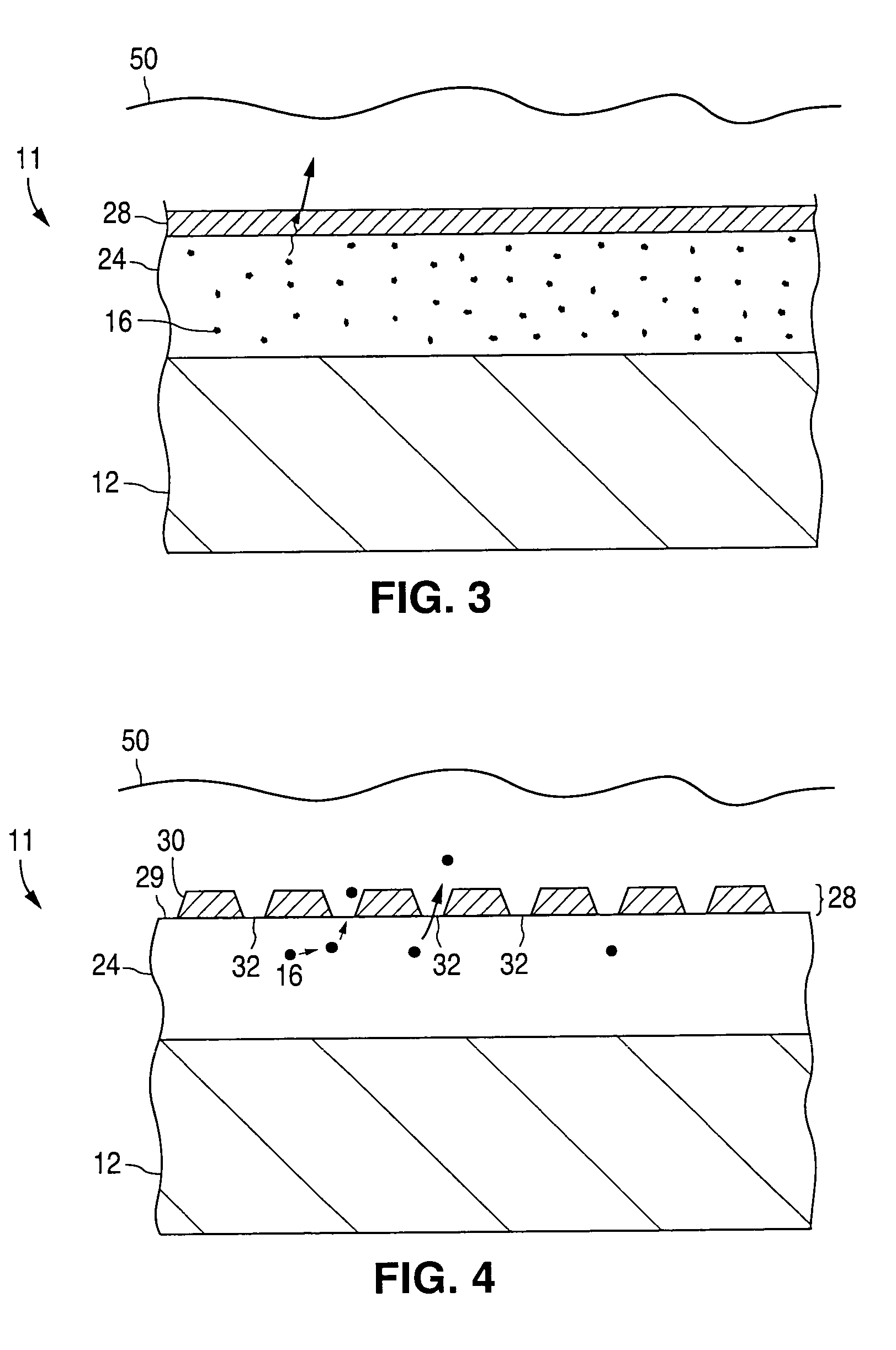

Barriers for polymer-coated implantable medical devices and methods for making the same

InactiveUS6953560B1Reduce and prevent and inflammationReduce and prevent proliferationStentsSurgeryHafniumPt element

An implantable medical device and methods for making the implantable medical device are disclosed. The implantable medical device includes a substrate. At least a portion of the substrate is coated with a first layer including a polymer containing a drug. A barrier overlies the first layer. The barrier significantly reduces the rate of release of the drug from the polymer, thereby sustaining release of the drug from the medical device for a longer time.The barrier may be a homogeneous layer overlying the first layer, or a number of discrete deposits over the first layer. Alternatively, the barrier may be intermixed with an outer portion of the first layer. The barrier material is biocompatible, and typically has a thickness ranging from about 50 angstroms to about 20,000 microns. Suitable materials for the barrier include, but are not limited to, inorganic compounds, such as inorganic silicides, oxides, nitrides, carbides, as well as pure metals such as aluminum, chromium, gold, hafnium, iridium, niobium, palladium, platinum, tantalum, titanium, tungsten, zirconium, and alloys of these metals. The barriers disclosed may be applied to the first layer by several techniques, depending on the material being applied. Exemplary deposition techniques include physical vapor deposition, alkoxide hydrolysis, and electroless plating.The implantable device may be a stent or a graft, among other possibilities.

Owner:ABBOTT CARDIOVASCULAR

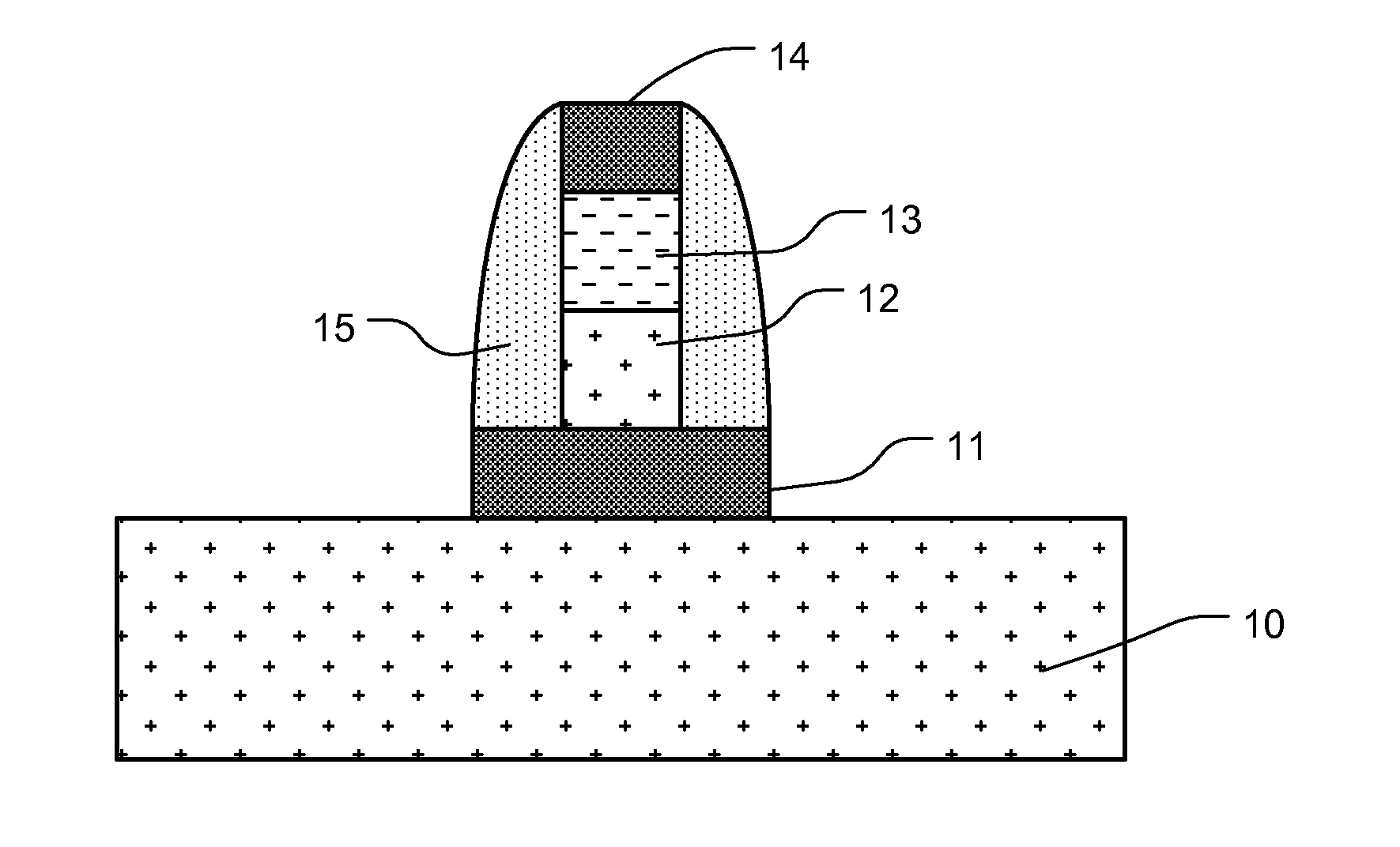

Integrated circuit memory with single crystal silicon on silicide driver and manufacturing method

ActiveUS8089137B2Excellent electrical and structural characteristicSemiconductor/solid-state device detailsSolid-state devicesPhase-change memoryEngineering

A memory device includes a diode driver and a data storage element, such as an element comprising phase change memory material, and in which the diode driver comprises a silicide element on a silicon substrate with a single crystal silicon node on the silicide element. The silicide element separates the single crystal silicon node from the underlying silicon substrate, preventing the flow of carriers from the single crystal silicon node into the substrate, and is capable of acting as a conductive element for interconnecting devices on the device. The single crystal silicon node acts as one terminal of a diode, and a second semiconductor node is formed on top of it, acting as the other terminal of the diode.

Owner:MACRONIX INT CO LTD

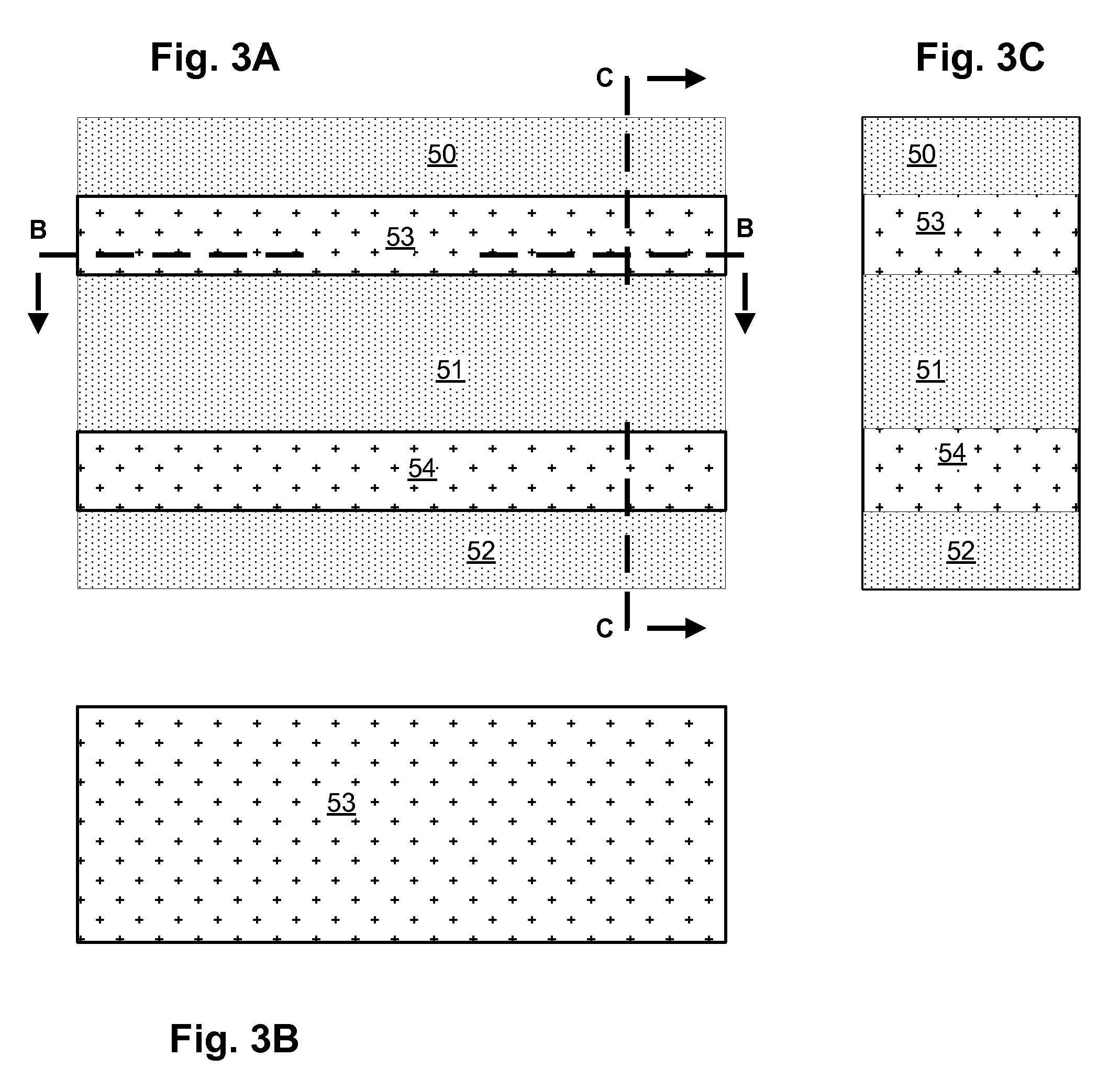

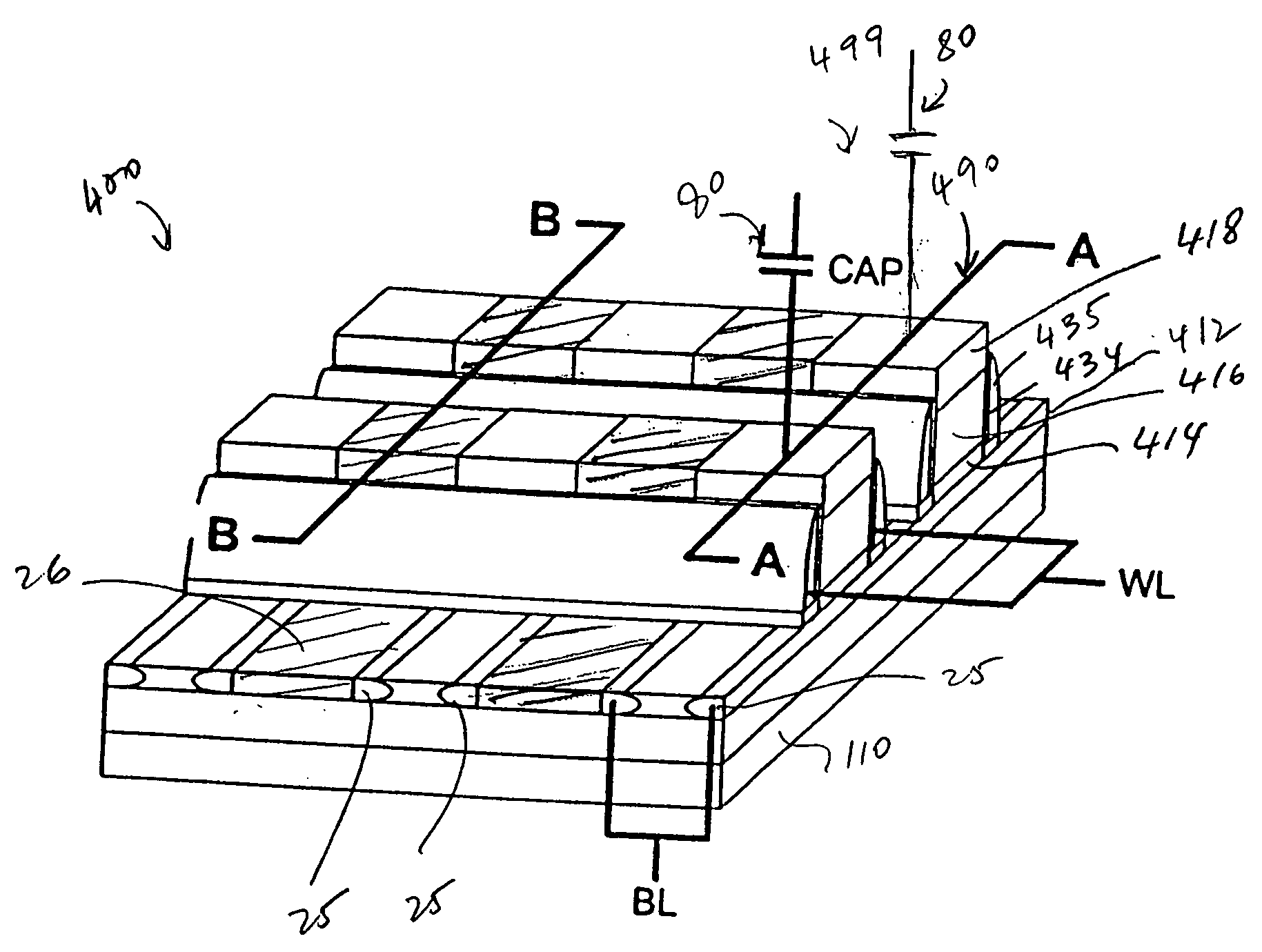

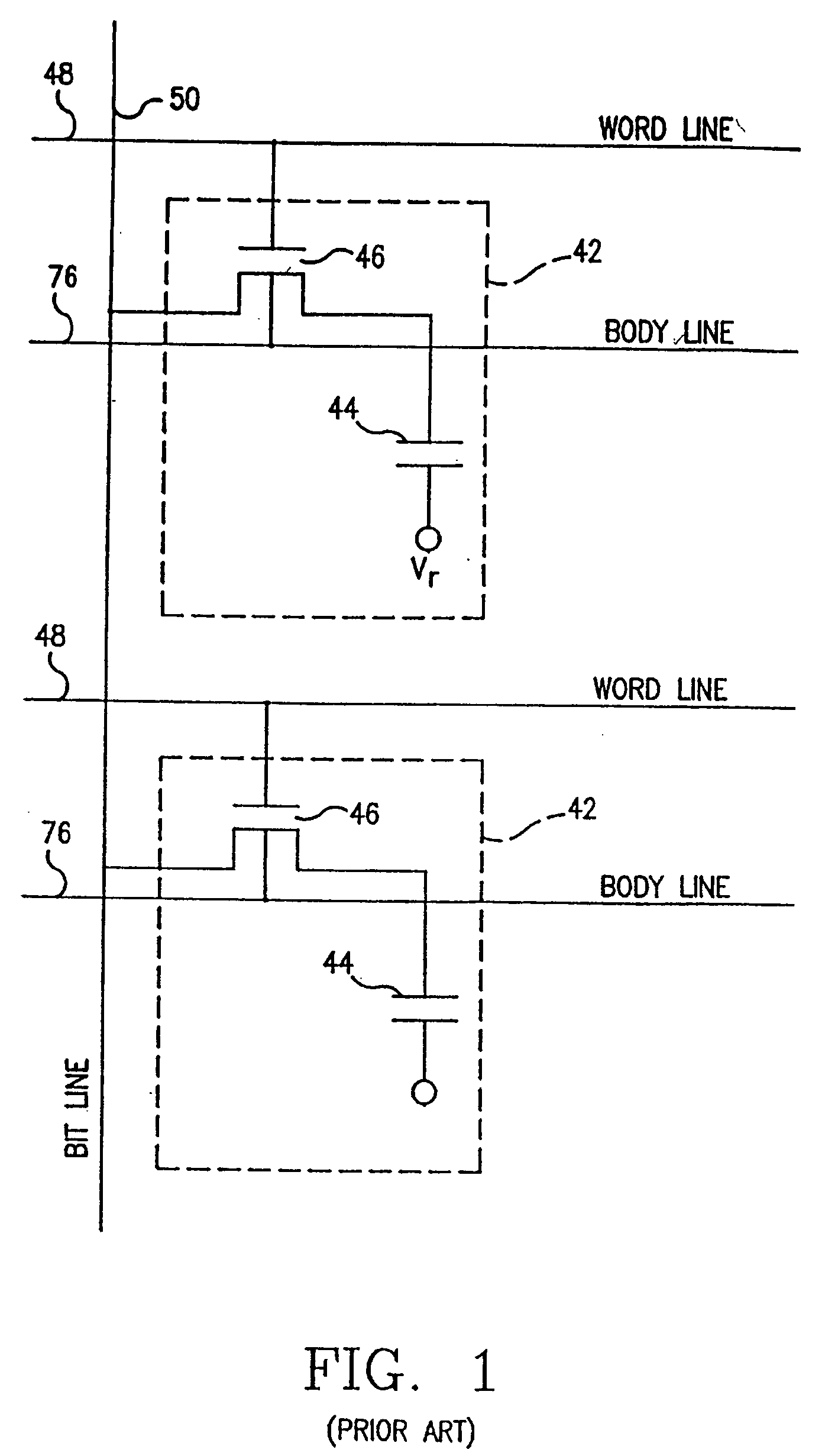

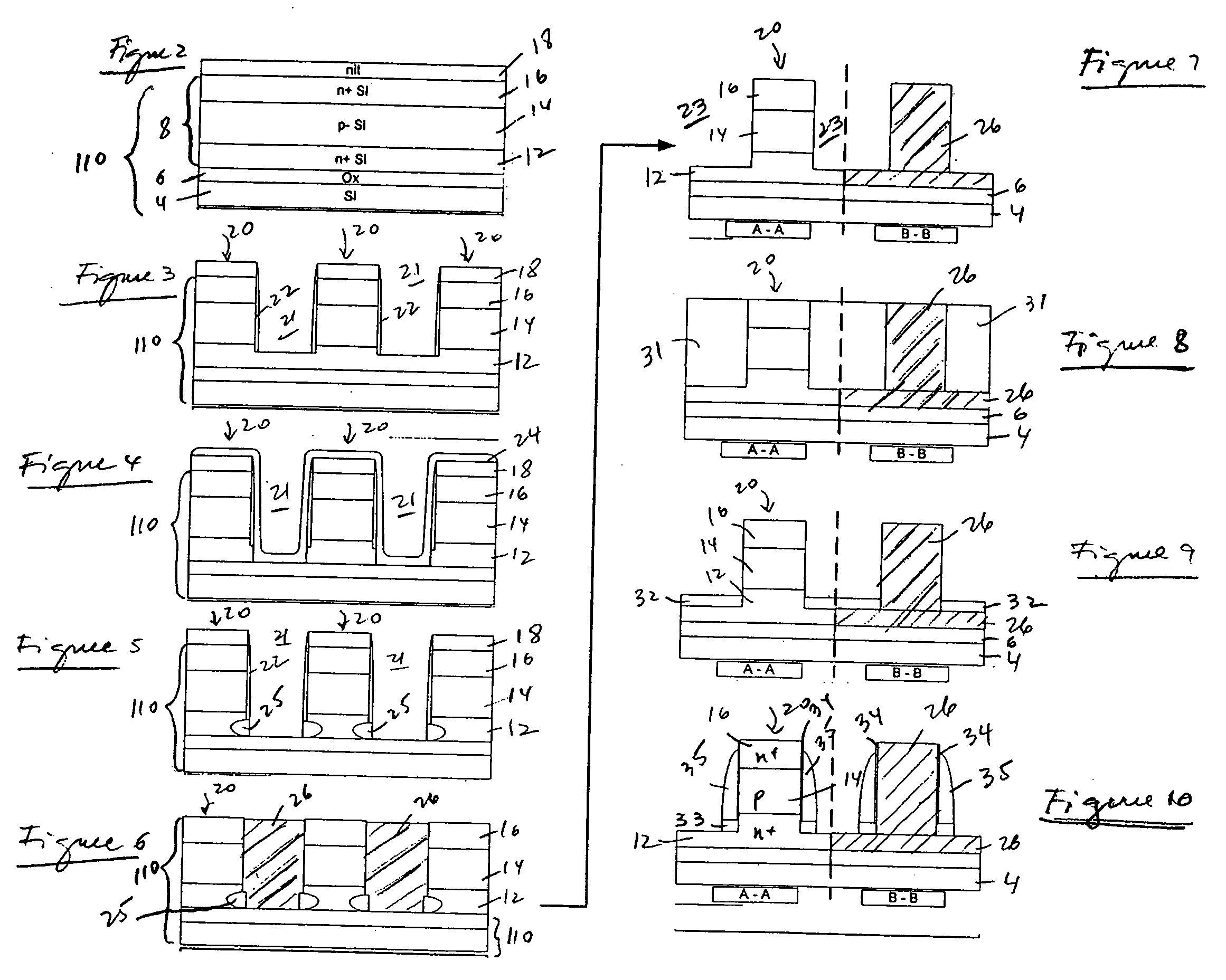

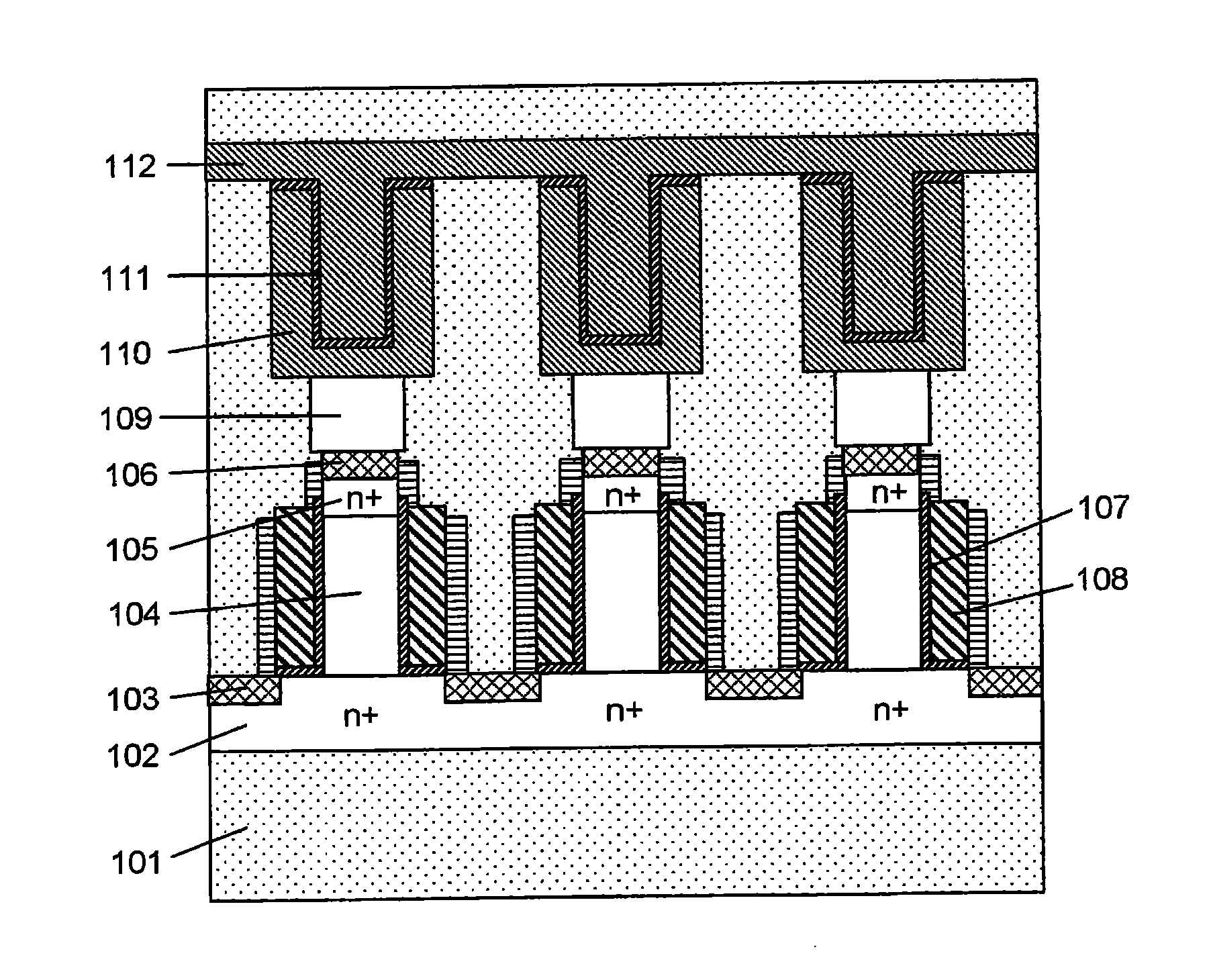

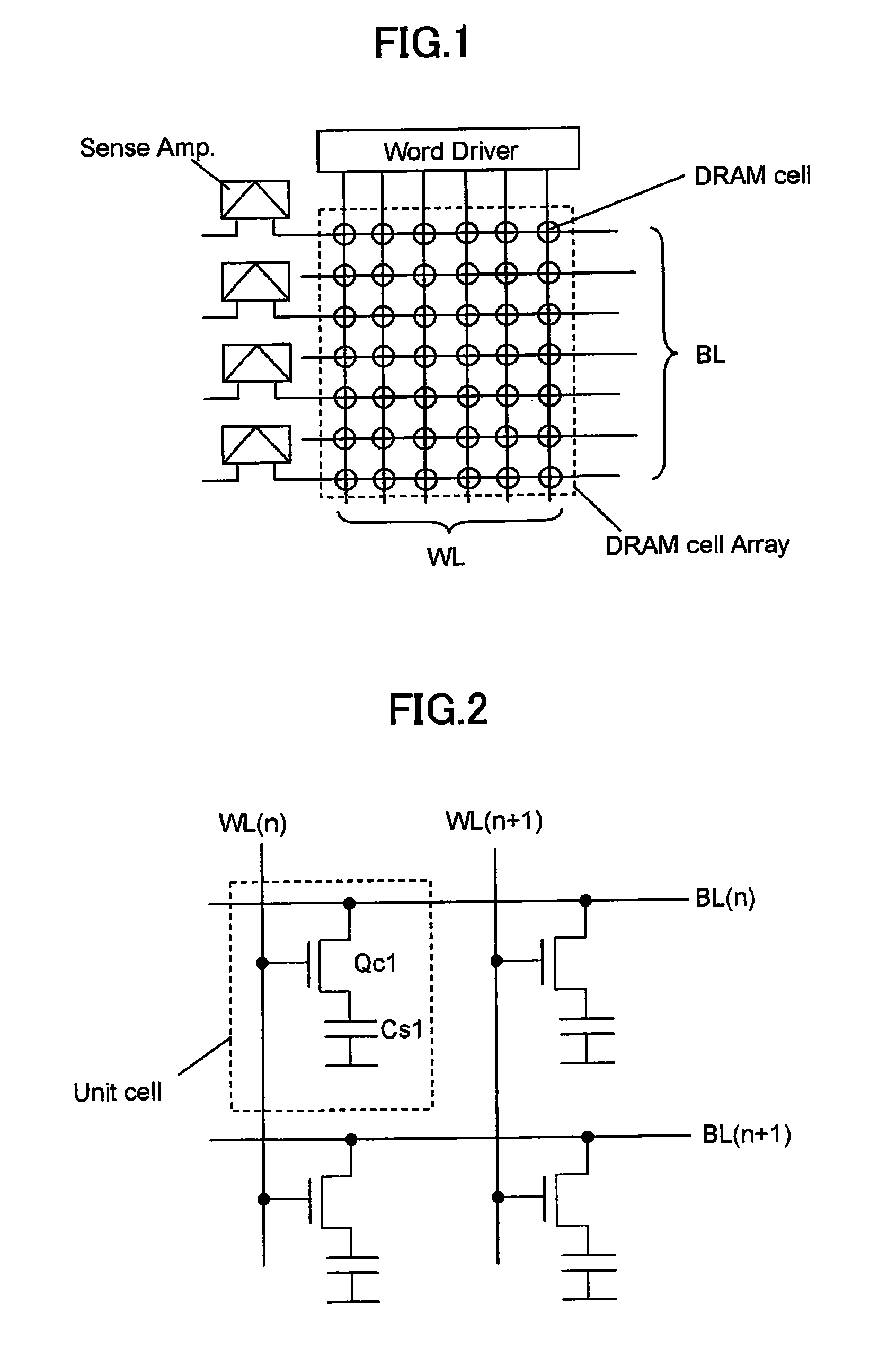

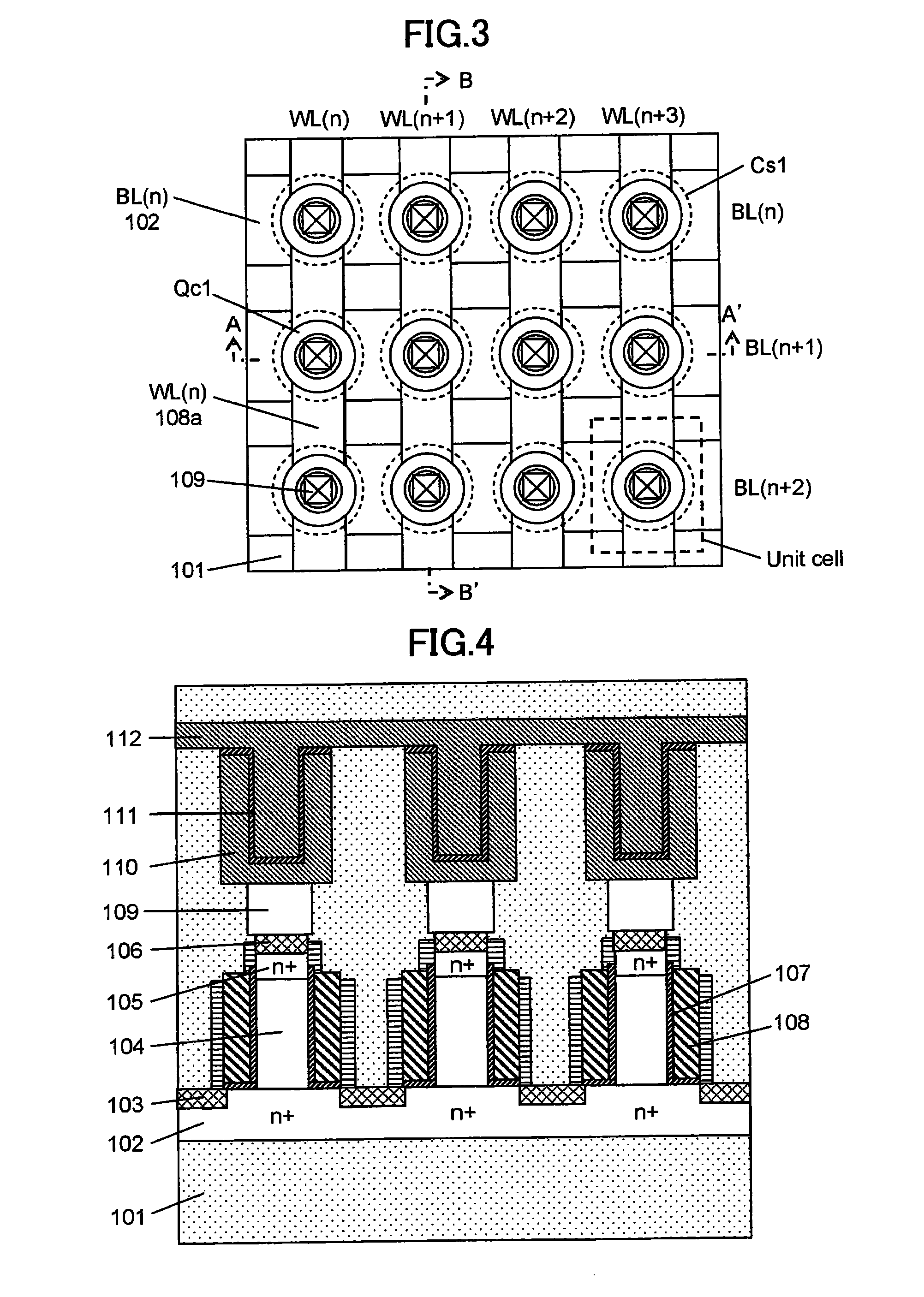

DRAM layout with vertical FETS and method of formation

DRAM cell arrays having a cell area of about 4F2 comprise an array of vertical transistors with buried bit lines and vertical double gate electrodes. The buried bit lines comprise a silicide material and are provided below a surface of the substrate. The word lines are optionally formed of a silicide material and form the gate electrode of the vertical transistors. The vertical transistor may comprise sequentially formed doped polysilicon layers or doped epitaxial layers. At least one of the buried bit lines is orthogonal to at least one of the vertical gate electrodes of the vertical transistors.

Owner:MICRON TECH INC

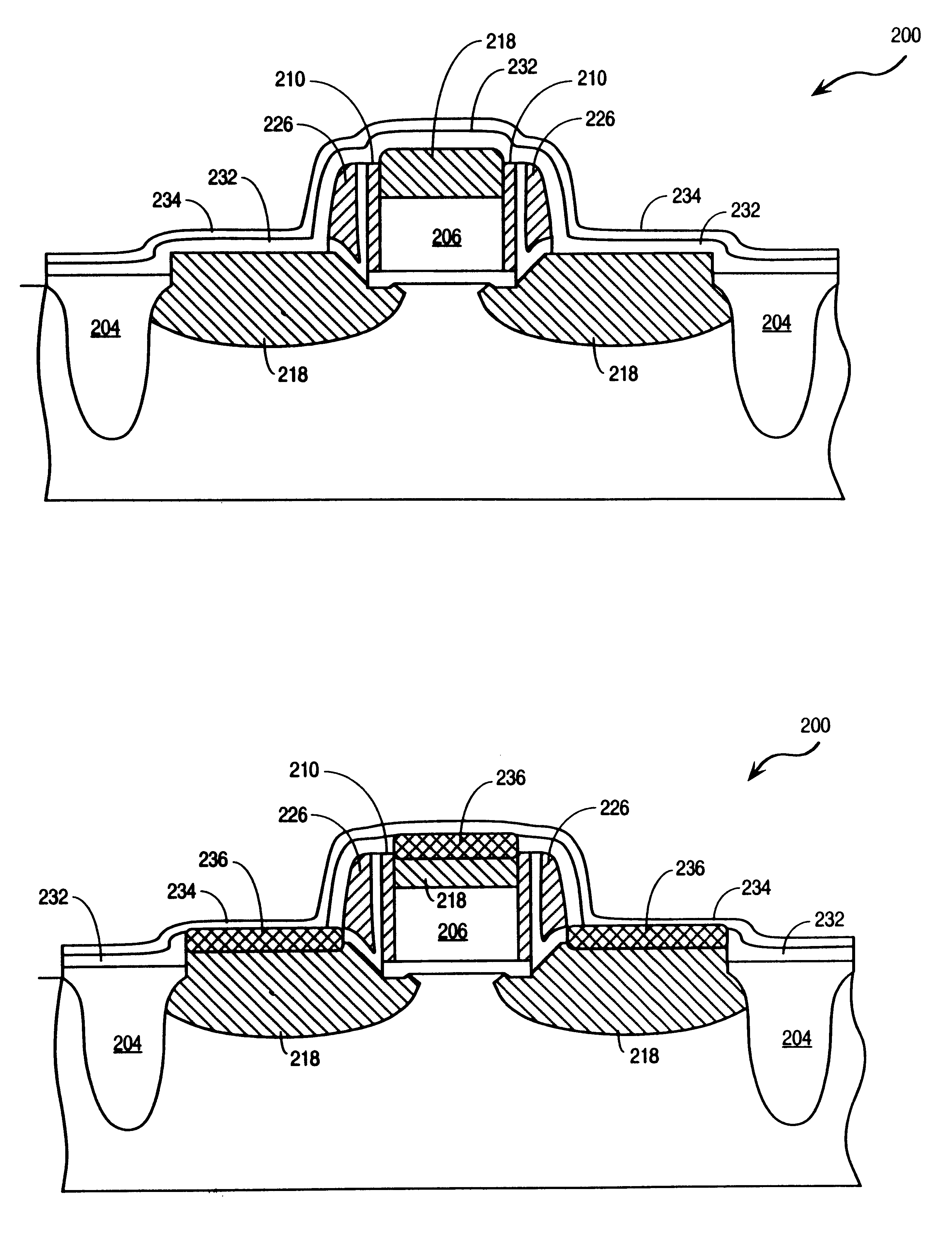

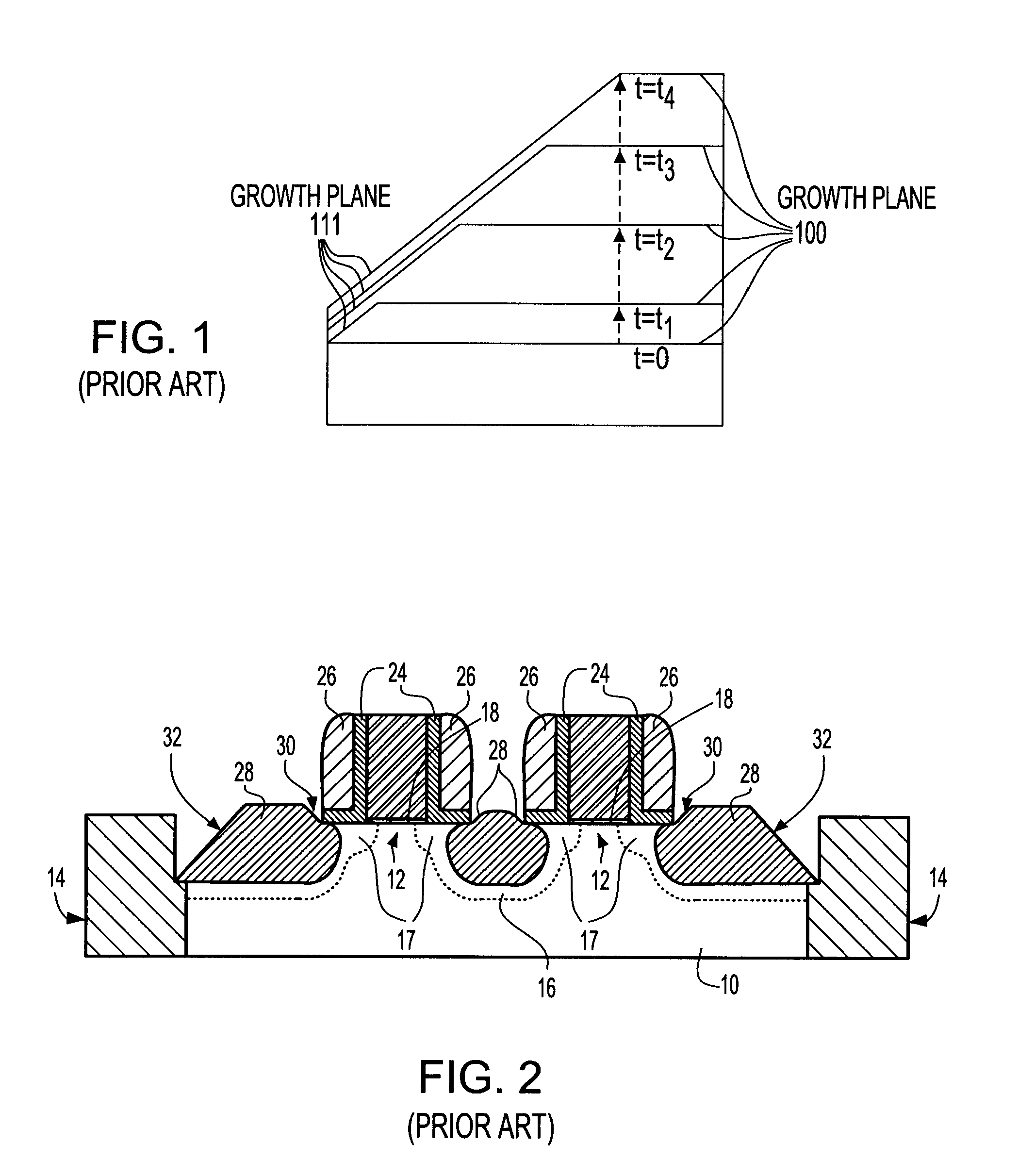

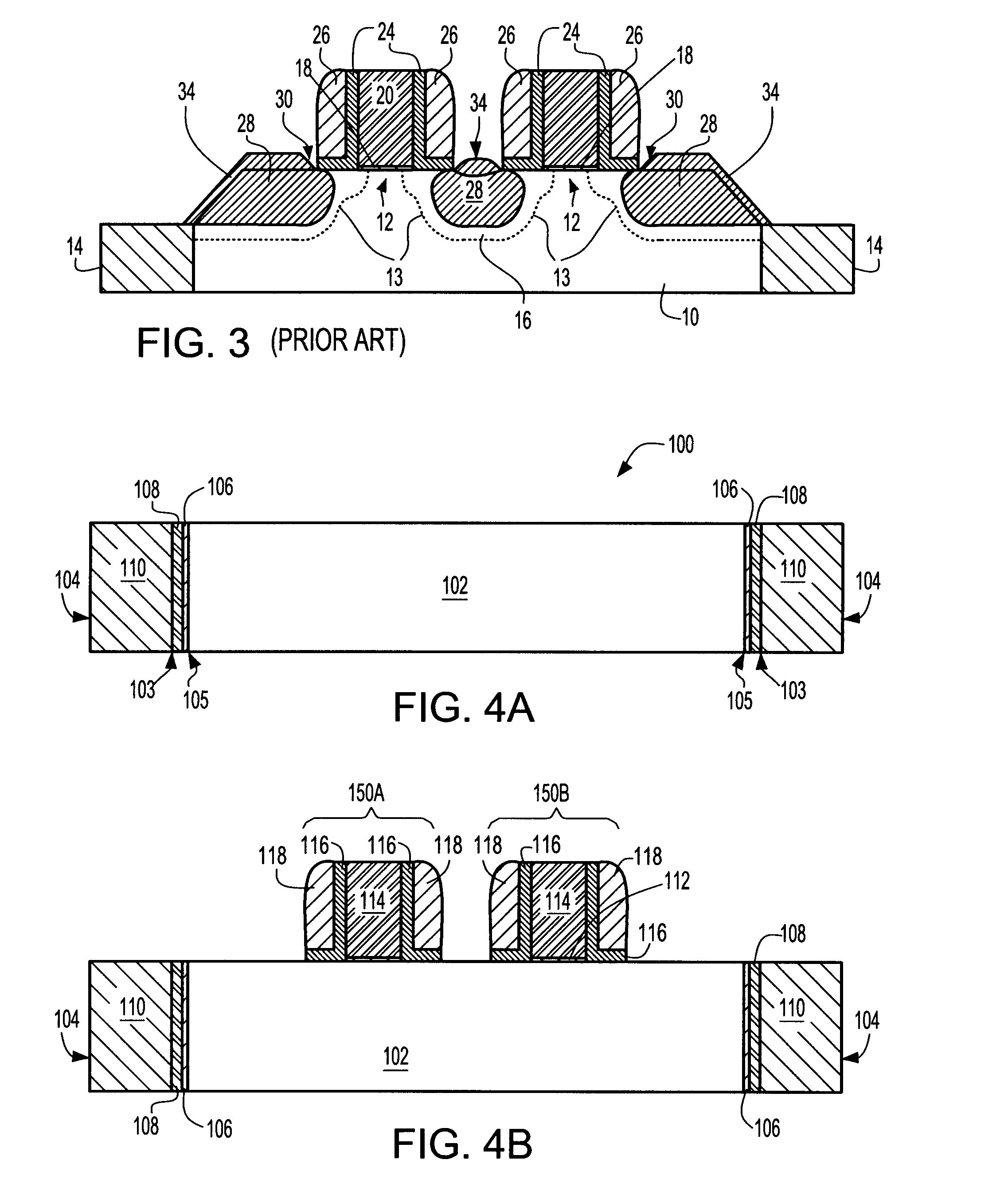

STRUCTURE AND METHOD FOR IMPROVED STRESS AND YIELD IN pFETS WITH EMBEDDED SiGe SOURCE/DRAIN REGIONS

ActiveUS20070018205A1High uniaxial stressAvoid problemsSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCMOS

The present invention provides a technique for forming a CMOS structure including at least one pFET that has a stressed channel which avoids the problems mentioned in the prior art. Specifically, the present invention provides a method for avoiding formation of deep canyons at the interface between the active area and the trench isolation region, without requiring a trench isolation pulldown, thereby eliminating the problems of silicide to source / drain shorts and contact issues. At the same time, the method of the present invention provides a structure that allows for a facet to form at the spacer edge, retaining the Miller capacitance benefit that such a structure provides. The inventive structure also results in higher uniaxial stress in the MOSFET channel compared to one which allows for a facet to grow at the trench isolation edge.

Owner:GLOBALFOUNDRIES US INC

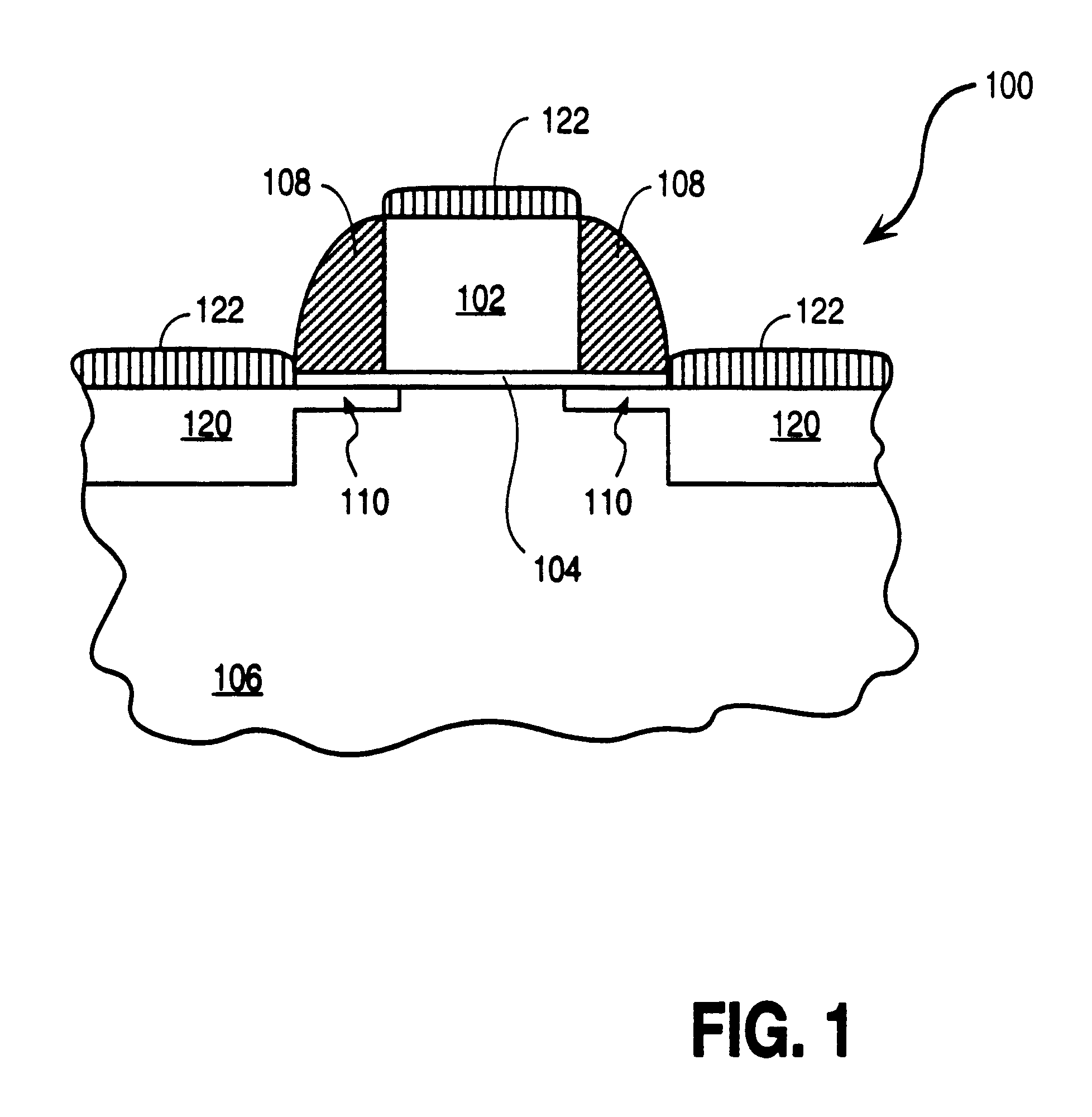

Structure and method to improve channel mobility by gate electrode stress modification

InactiveUS20050245017A1Easily and repeatably formedImprove production yieldTransistorSolid-state devicesCMOSCharge carrier mobility

Owner:GLOBALFOUNDRIES INC

Nucleation and deposition of PT films using ultraviolet irradiation

InactiveUS6204178B1Semiconductor/solid-state device manufacturingPretreated surfacesPlatinumReactive gas

A method of depositing a platinum based metal film by CVD deposition includes bubbling a non-reactive gas through an organic platinum based metal precursor to facilitate transport of precursor vapor to the chamber. The platinum based film is deposited onto a non-silicon bearing substrate in a CVD deposition chamber in the presence of ultraviolet light at a predetermined temperature and under a predetermined pressure. The film is then annealed in an oxygen atmosphere at a sufficiently low temperature to avoid oxidation of substrate. The resulting film is free of silicide and consistently smooth and has good step coverage.

Owner:MICRON TECH INC

Systems and methods of forming tantalum silicide layers

InactiveUS20060048711A1Reduce diffuseReduce layeringSemiconductor/solid-state device manufacturingCapacitorsGas phaseNitrogen

A method of forming (and apparatus for forming) tantalum silicide layers (including tantalum silicon nitride layers), which are typically useful as diffusion barrier layers, on a substrate by using a vapor deposition process with a tantalum halide precursor compound, a silicon precursor compound, and an optional nitrogen precursor compound.

Owner:MICRON TECH INC

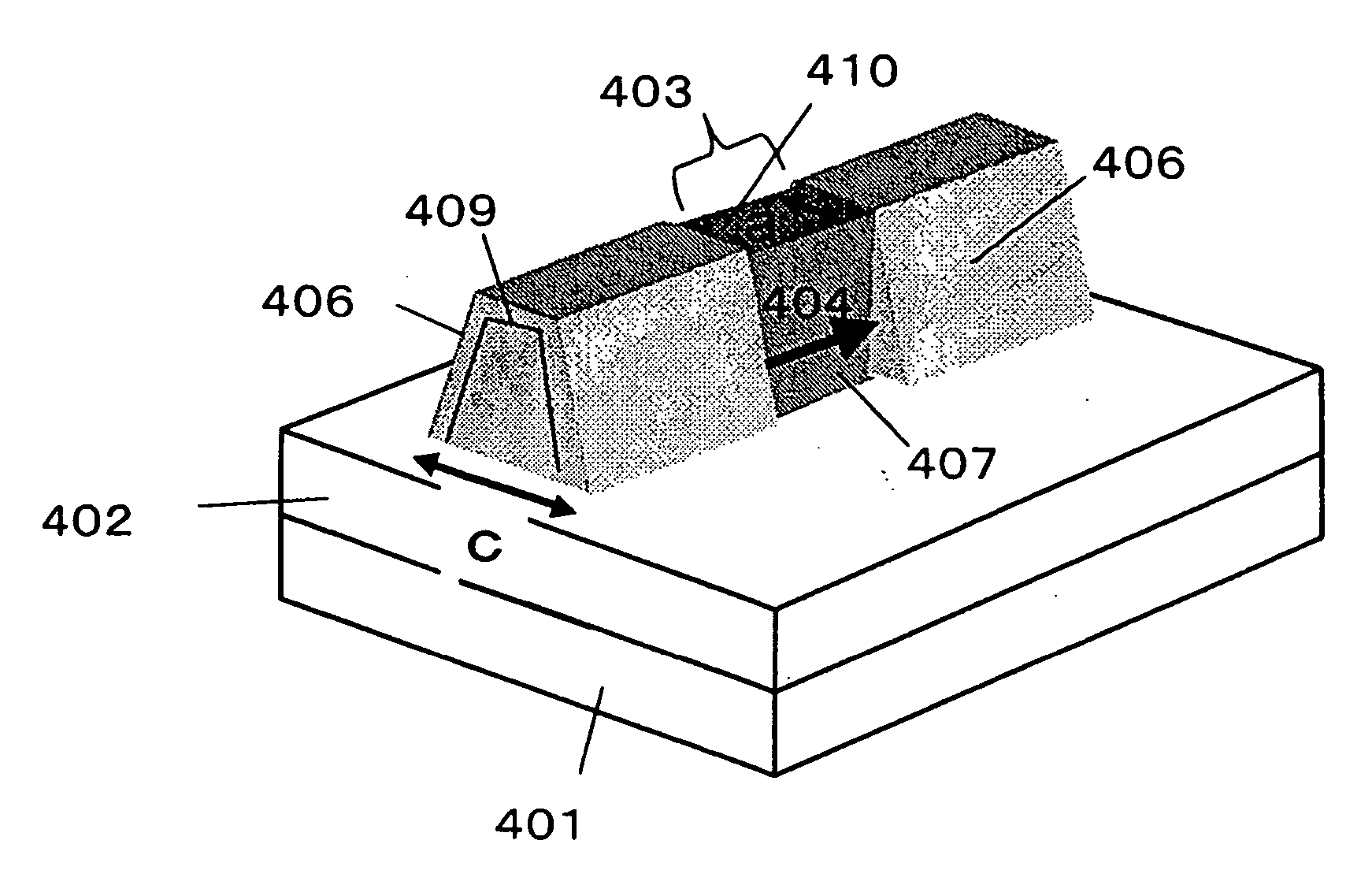

Vertical FET with nanowire channels and a silicided bottom contact

ActiveUS7230286B2Reduce resistanceGood short channel characteristicsTransistorNanoinformaticsCapacitanceNanowire

A vertical FET structure with nanowire forming the FET channels is disclosed. The nanowires are formed over a conductive silicide layer. The nanowires are gated by a surrounding gate. Top and bottom insulator plugs function as gate spacers and reduce the gate-source and gate-drain capacitance.

Owner:GLOBALFOUNDRIES U S INC

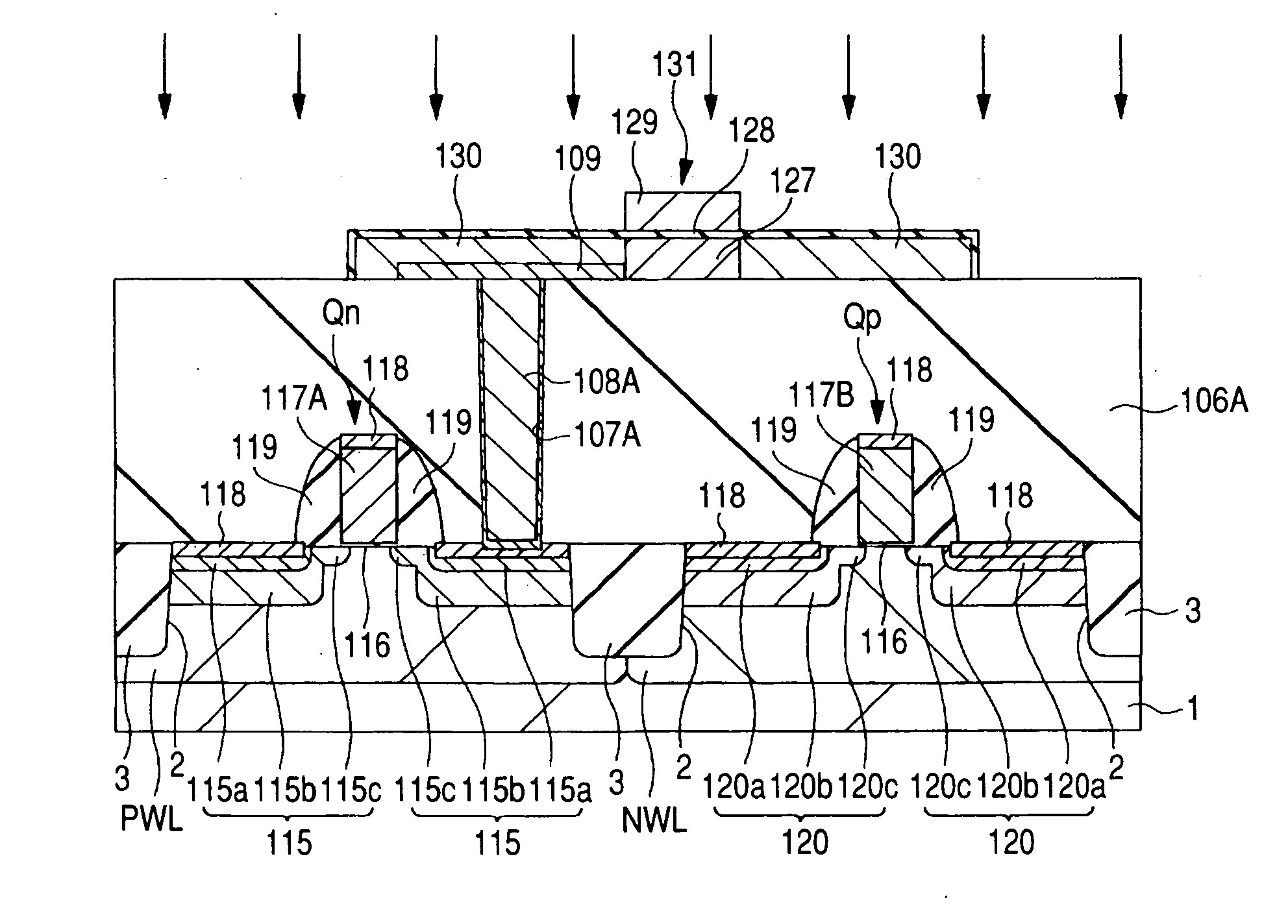

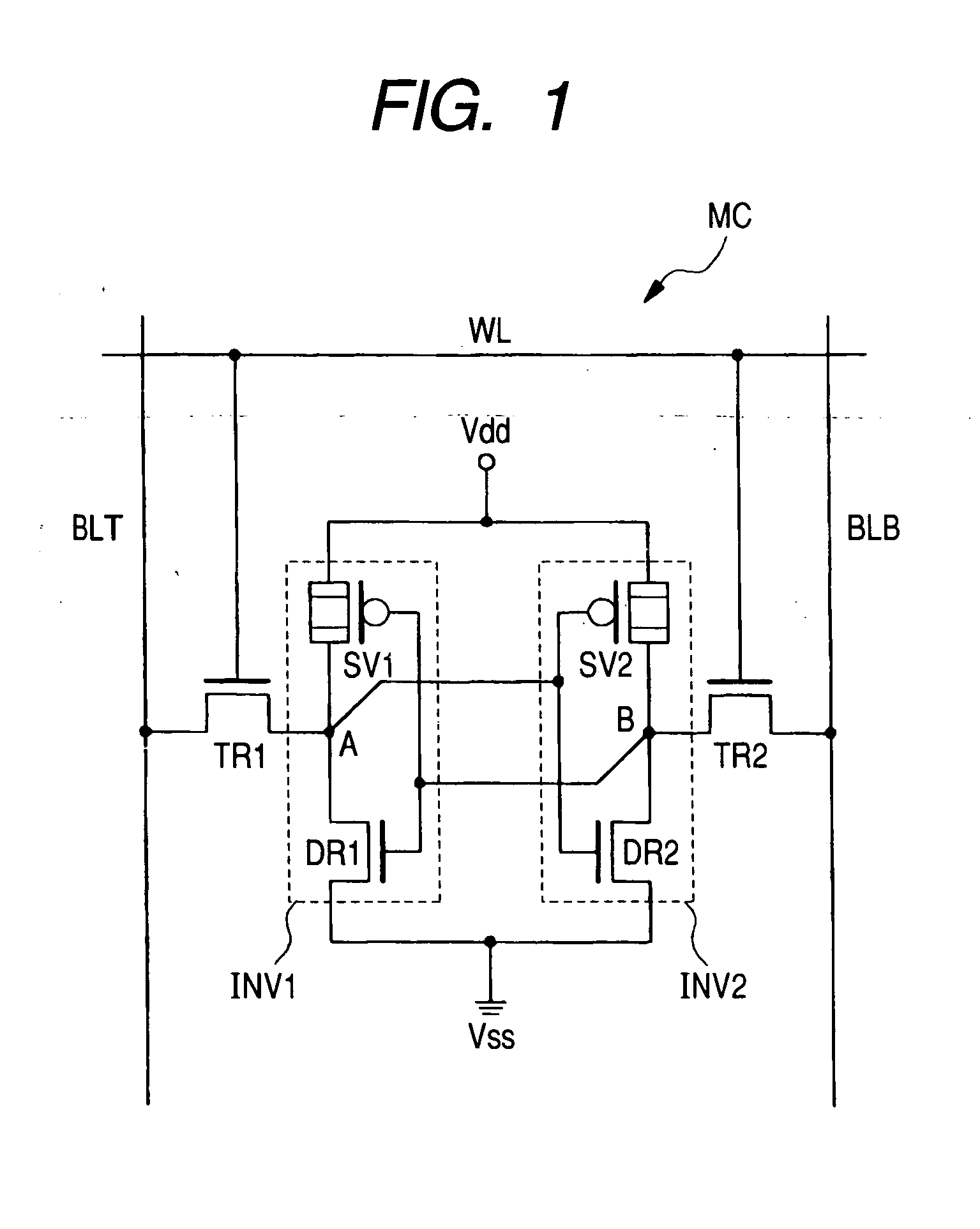

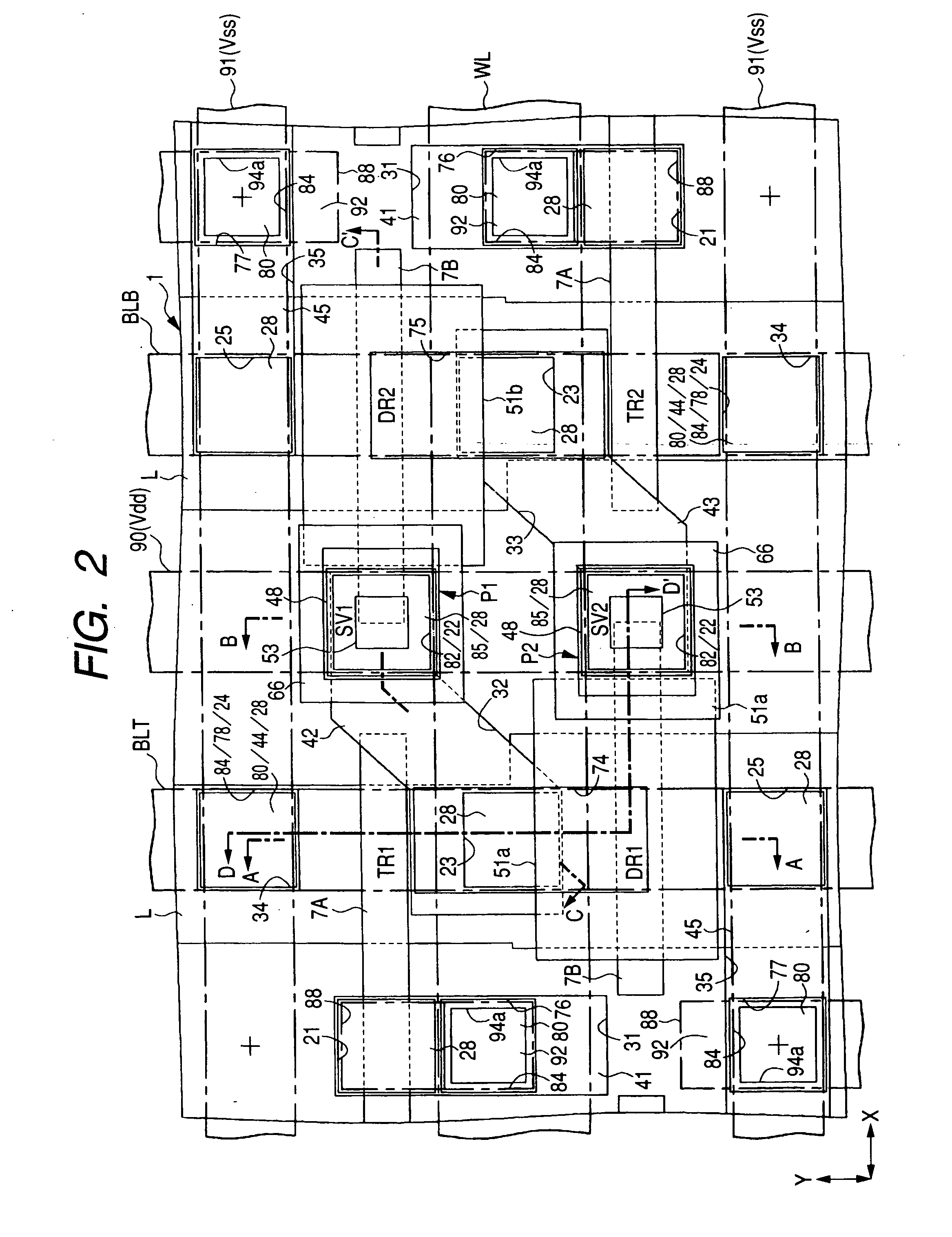

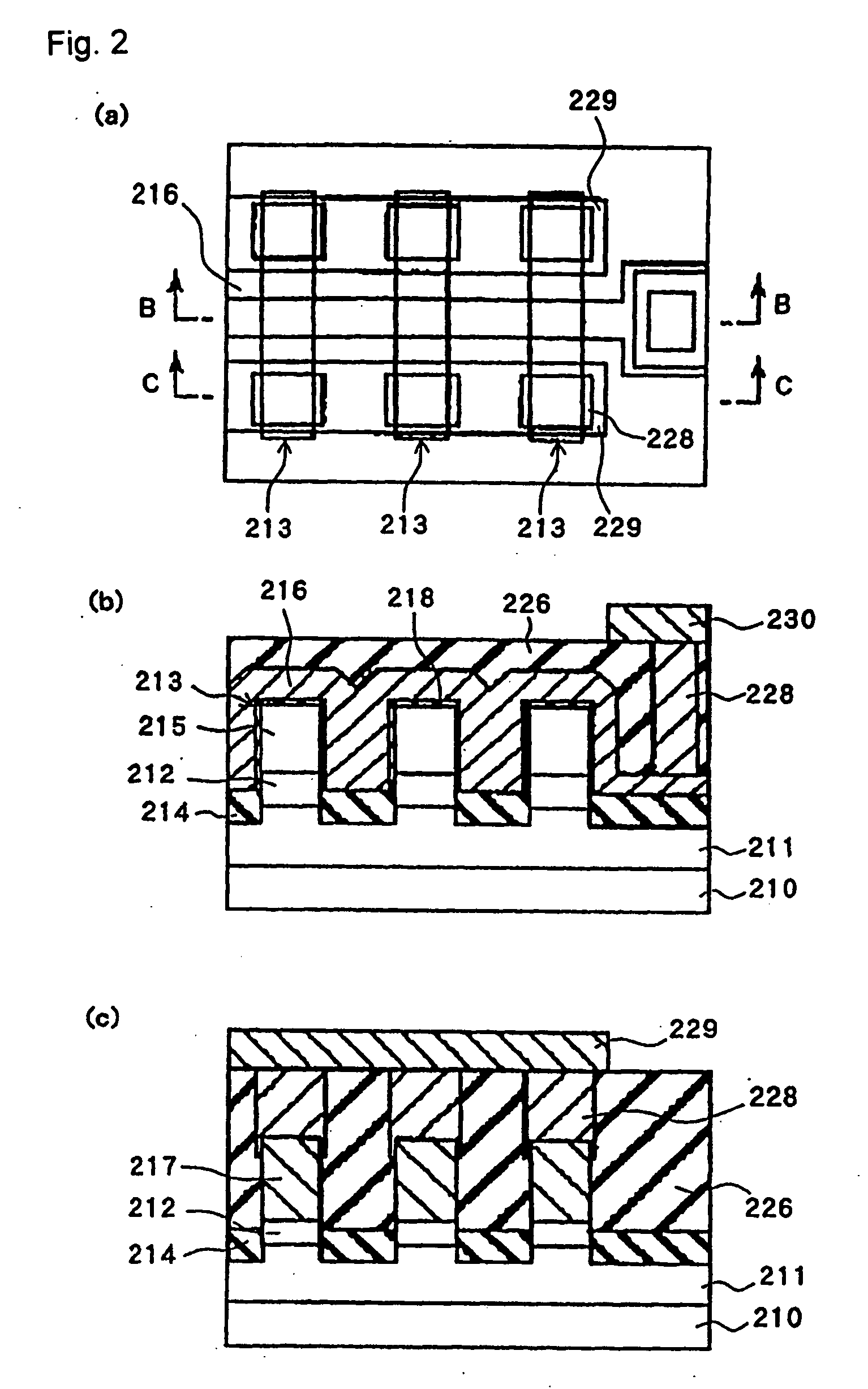

Semiconductor storage device and methods of producing it

ActiveUS20100213525A1Small footprintReduced footprintTransistorSolid-state devicesSemiconductor storage devicesEngineering

The present invention provides a semiconductor storage device having a memory cell section and a peripheral circuit section each formed using one or more MOS transistors, comprising: a substrate; a dielectric film on the substrate; and a planar semiconductor layer formed on the on-substrate dielectric layer, wherein: the at least one MOS transistor in the memory cell section comprises a selection transistor, the at least one MOS transistor in the peripheral circuit section comprises a first MOS transistor and a second MOS transistor which are different in conductivity type from each other, the first MOS transistor includes a first lower drain or source region formed in the planar semiconductor layer, a first pillar-shaped semiconductor layer formed on the planar semiconductor layer, a first upper source or drain region formed in an upper portion of the first pillar-shaped semiconductor layer, and a first gate electrode formed such that the first gate electrode surrounds a sidewall of the first pillar-shaped semiconductor layer through a first dielectric film, the second MOS transistor includes a second lower drain or source region formed in the planar semiconductor layer, a second pillar-shaped semiconductor layer formed on the planar semiconductor layer, a second upper source or drain region formed in an upper portion of the second pillar-shaped semiconductor layer, and a second gate electrode formed such that the second gate electrode surrounds a sidewall of the second pillar-shaped semiconductor layer through a second dielectric film; and the selection transistor includes a third lower drain or source region formed in the planar semiconductor layer, a third pillar-shaped semiconductor layer formed on the planar semiconductor layer, a third lower source or drain region formed in an upper portion of the third pillar-shaped semiconductor layer, and a third gate electrode formed such that the third gate electrode surrounds a sidewall of the third pillar-shaped semiconductor layer through a third dielectric film, and wherein the semiconductor storage device has a first silicide layer formed thereon to connect at least a part of a surface of the first lower drain or source region of the first MOS transistor and at least a part of a surface of the second lower drain or source region of the second MOS transistor, and a second silicide layer formed on at least a part of a surface of the third lower drain or source region of the selection transistor.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

Semiconductor device and a method of manufacturing the same

InactiveUS20050059236A1Improve featuresEasy to understandTransistorSemiconductor/solid-state device detailsElectrical conductorMetal interconnect

In a semiconductor device, the ohmic contact at the junction between the metal interconnection and the semiconductor layer is lowered by depositing a first conductor layer comprised of, for example, tungsten nitride and a second conductor layer comprised of, for example, tungsten silicide successively from the lower layer so as to cover the upper surface of intermediate conductive layers comprised of a metal, for example, tungsten as a main interconnection material, subsequently introducing an impurity, for example, boron (b) to the second conductor layer, then patterning the first and the second conductor layers thereby forming a conductor layer, and then forming a lower semiconductor layer comprised of, for example, polycrystal silicon for forming a semiconductor region for source and drain of load MISFET of SRAM so as to be in contact with the conductor layer.

Owner:RENESAS TECH CORP

Semiconductor device and manufacturing process therefor

InactiveUS20070075372A1Easy alignmentReduce contact resistanceTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

There is provided a semiconductor device wherein at least the largest width of a source / drain region is larger than the width of a semiconductor region and the source / drain region has a slope having a width continuously increasing from the uppermost side to the substrate side, and a silicide film is formed in the surface of the slope.

Owner:NEC CORP

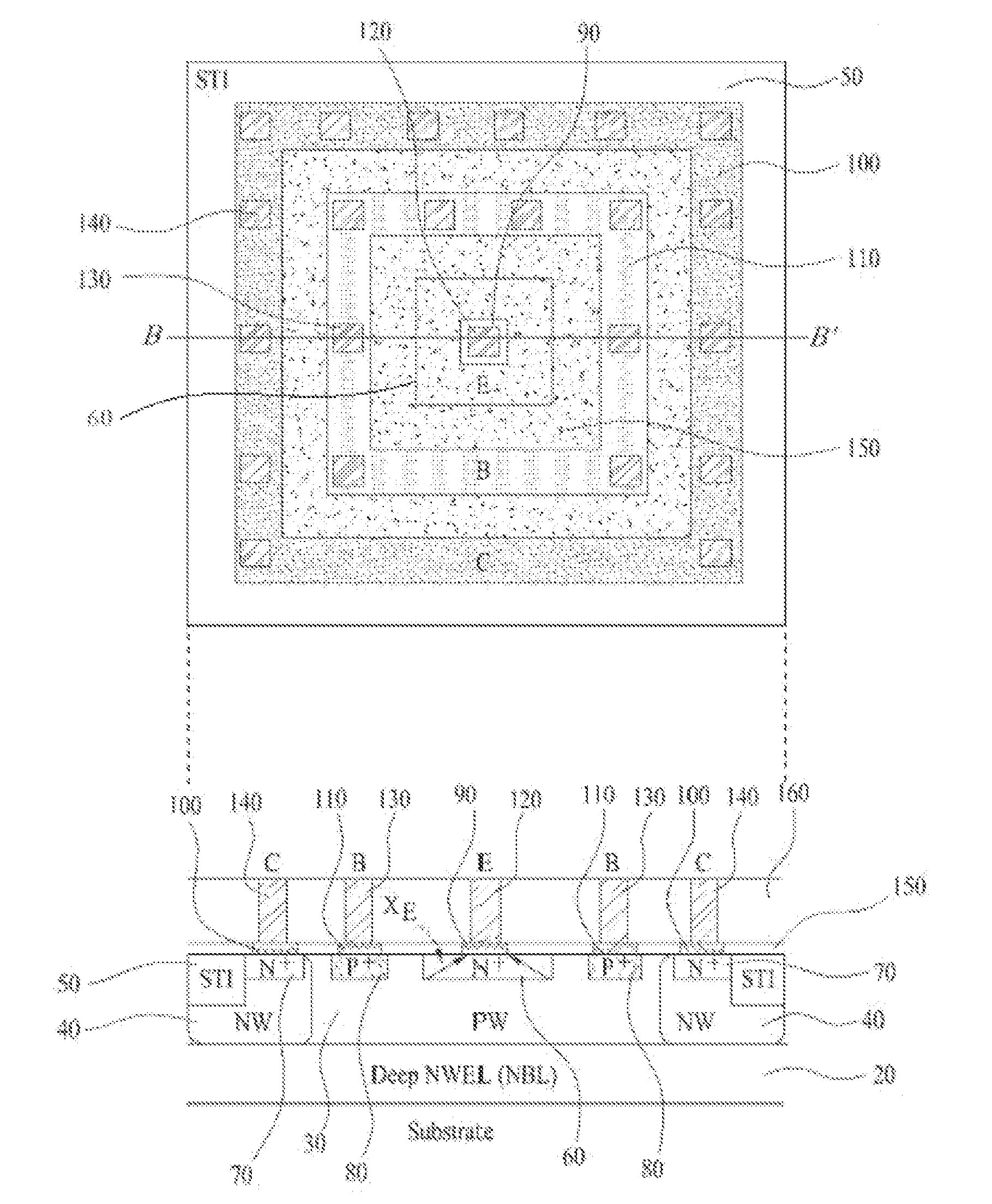

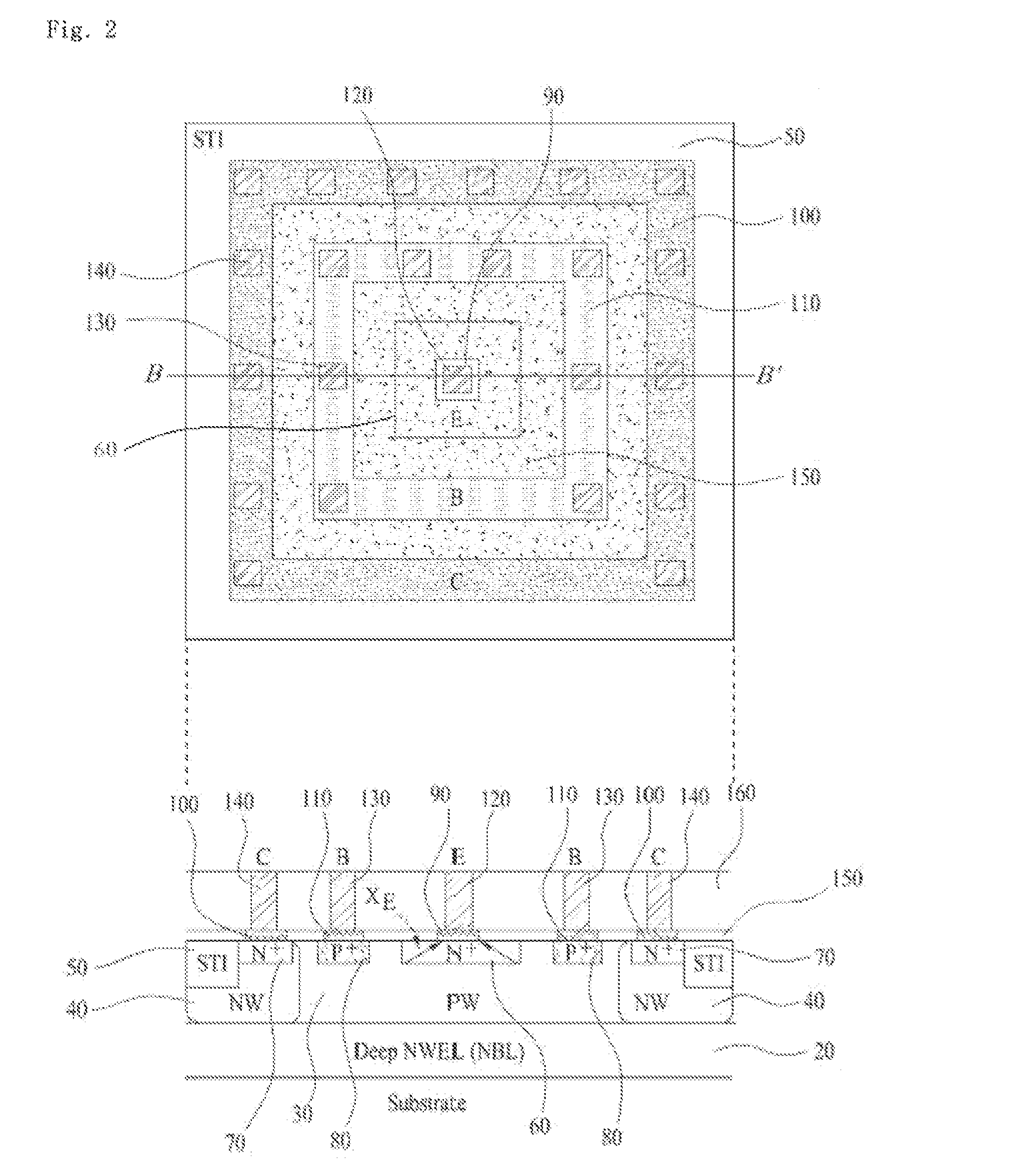

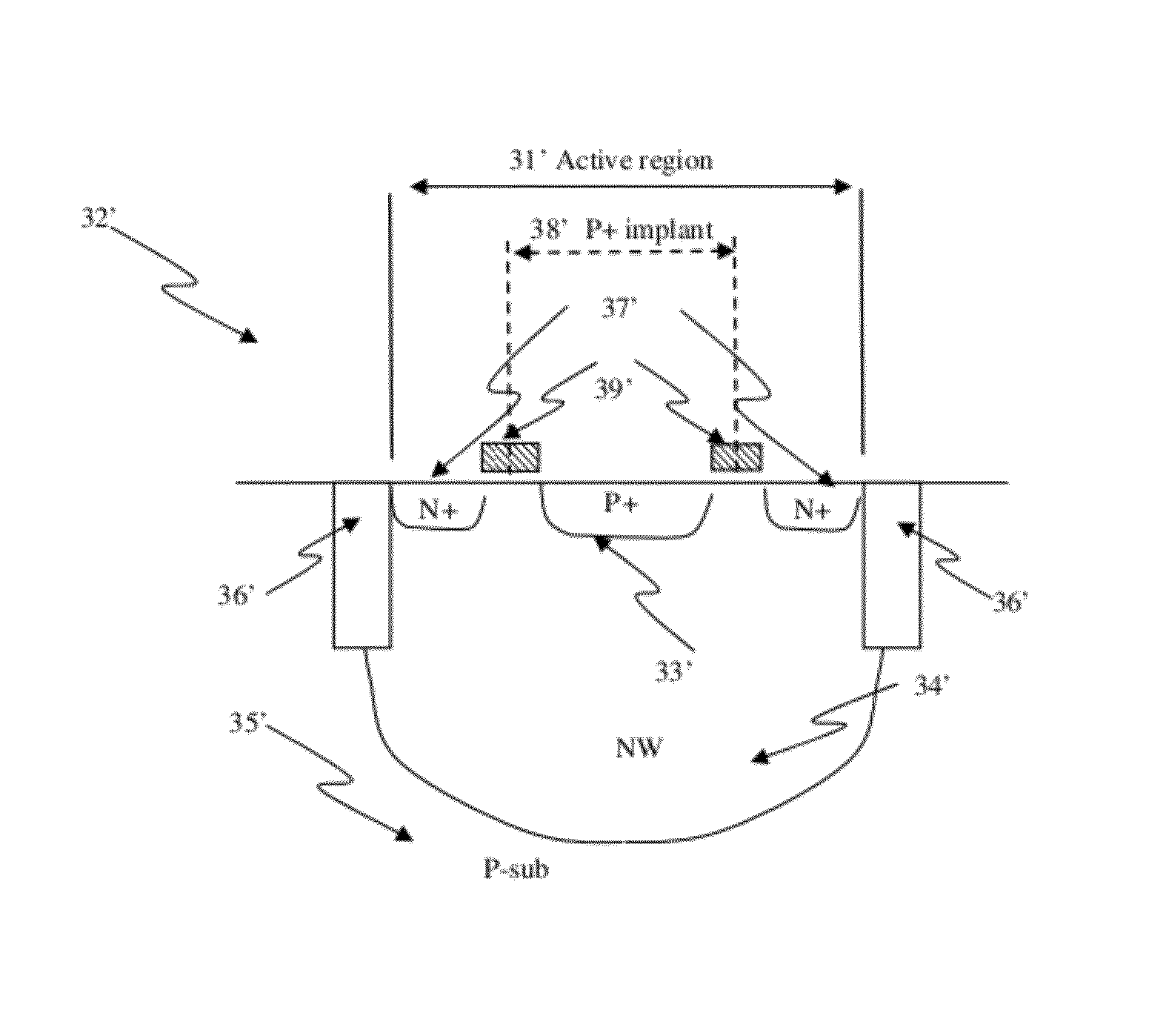

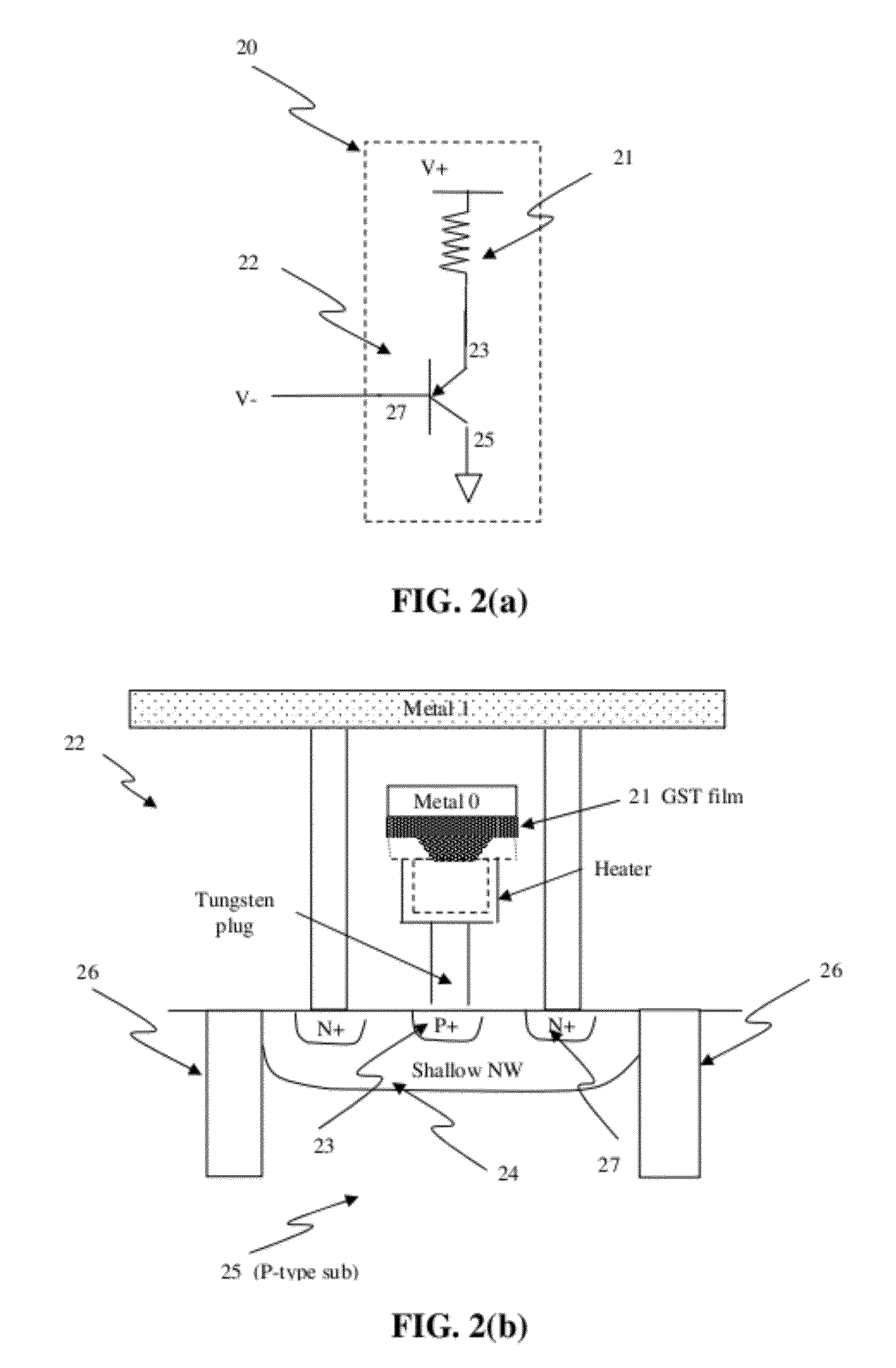

Bipolar Junction Transistor Based on CMOS Technology

InactiveUS20120032303A1Increase currentHigh base resistanceTransistorSemiconductor/solid-state device manufacturingCMOSEngineering

The present invention relates to semiconductor technologies, and more particularly to a bipolar junction transistor (BJT) in a CMOS base technology and methods of forming the same. The BJT includes a semiconductor substrate having an emitter region, a base having a first contact, and a collector having a second contact and a well plug; a first silicide film on the first contact; a second silicide film on the second contact; a first silicide blocking layer on or over the semiconductor substrate between the first and second silicide films, and a second silicide blocking layer on the semiconductor substrate between the first silicide film and the emitter region.

Owner:DONGBU HITEK CO LTD

In-line voltage contrast detection of PFET silicide encroachment

InactiveUS8039837B2TransistorSemiconductor/solid-state device testing/measurementBody contactEngineering

Owner:INT BUSINESS MASCH CORP

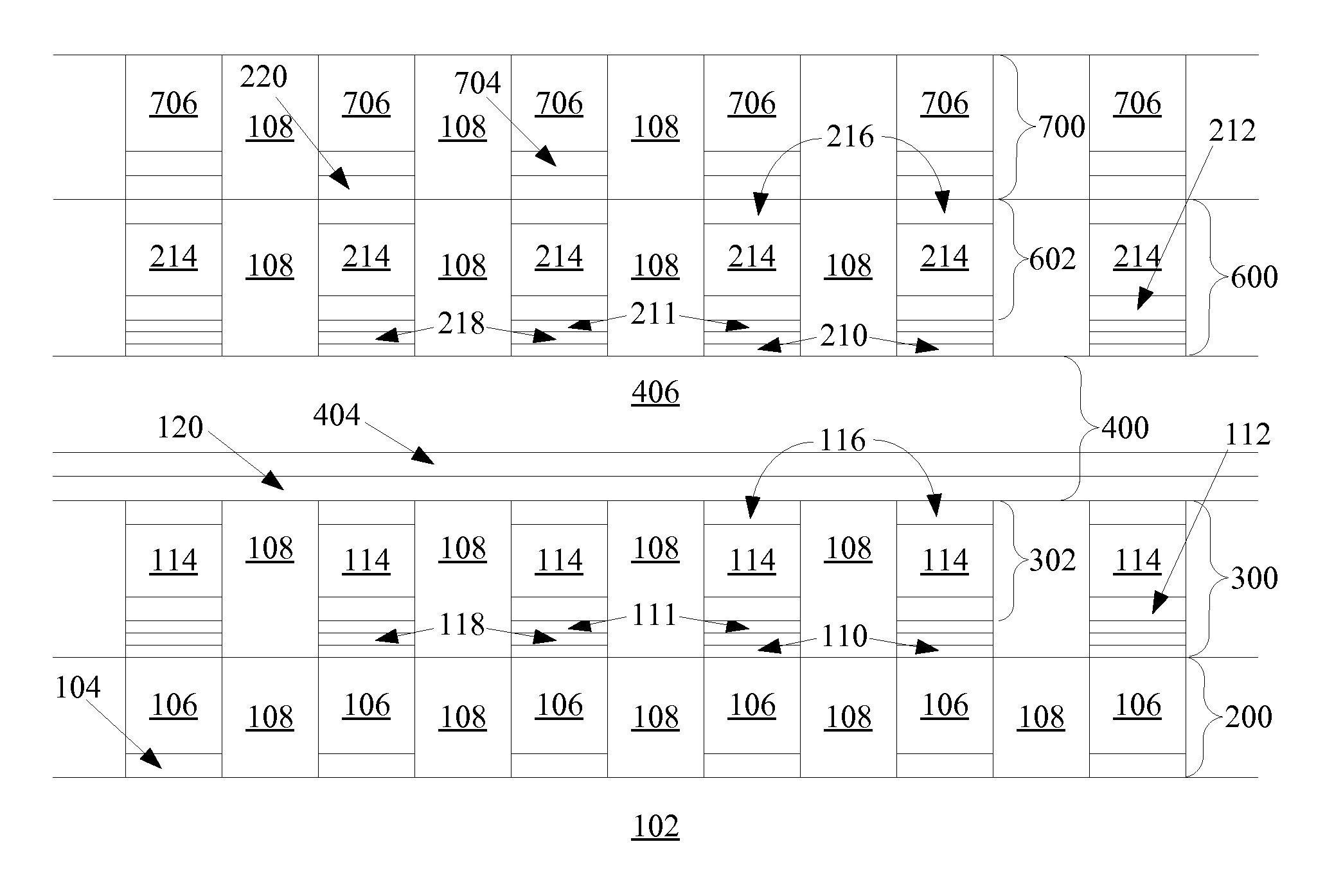

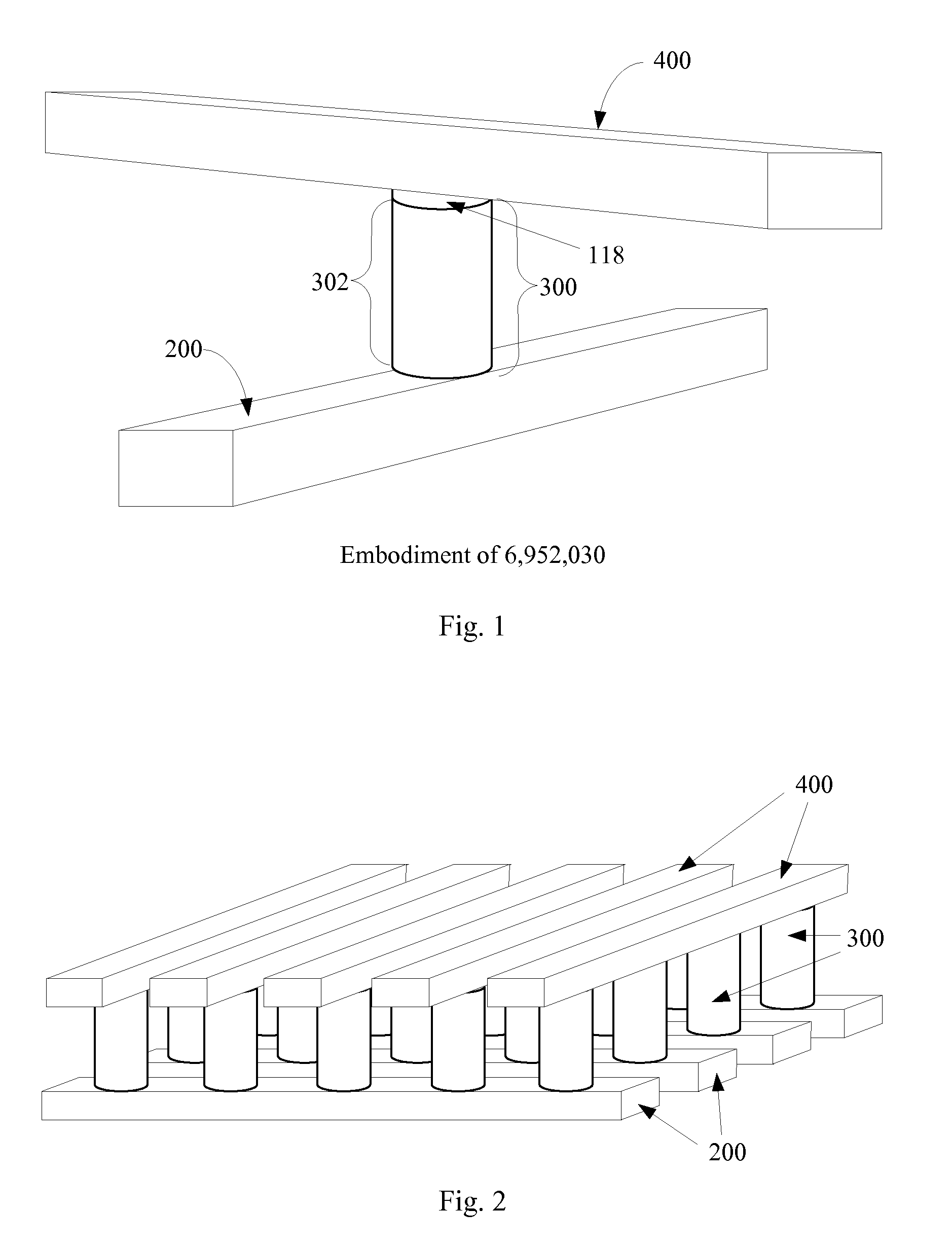

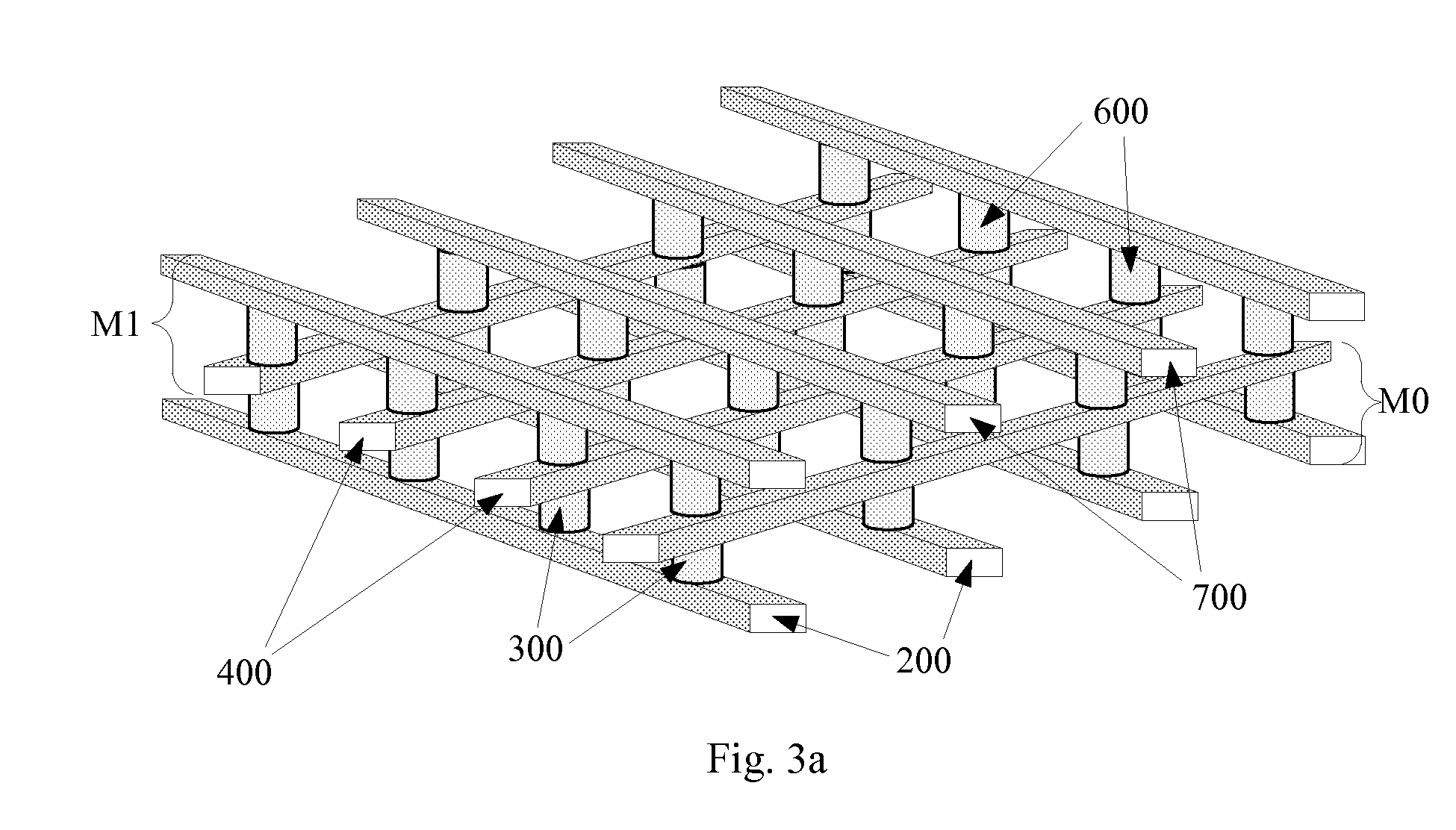

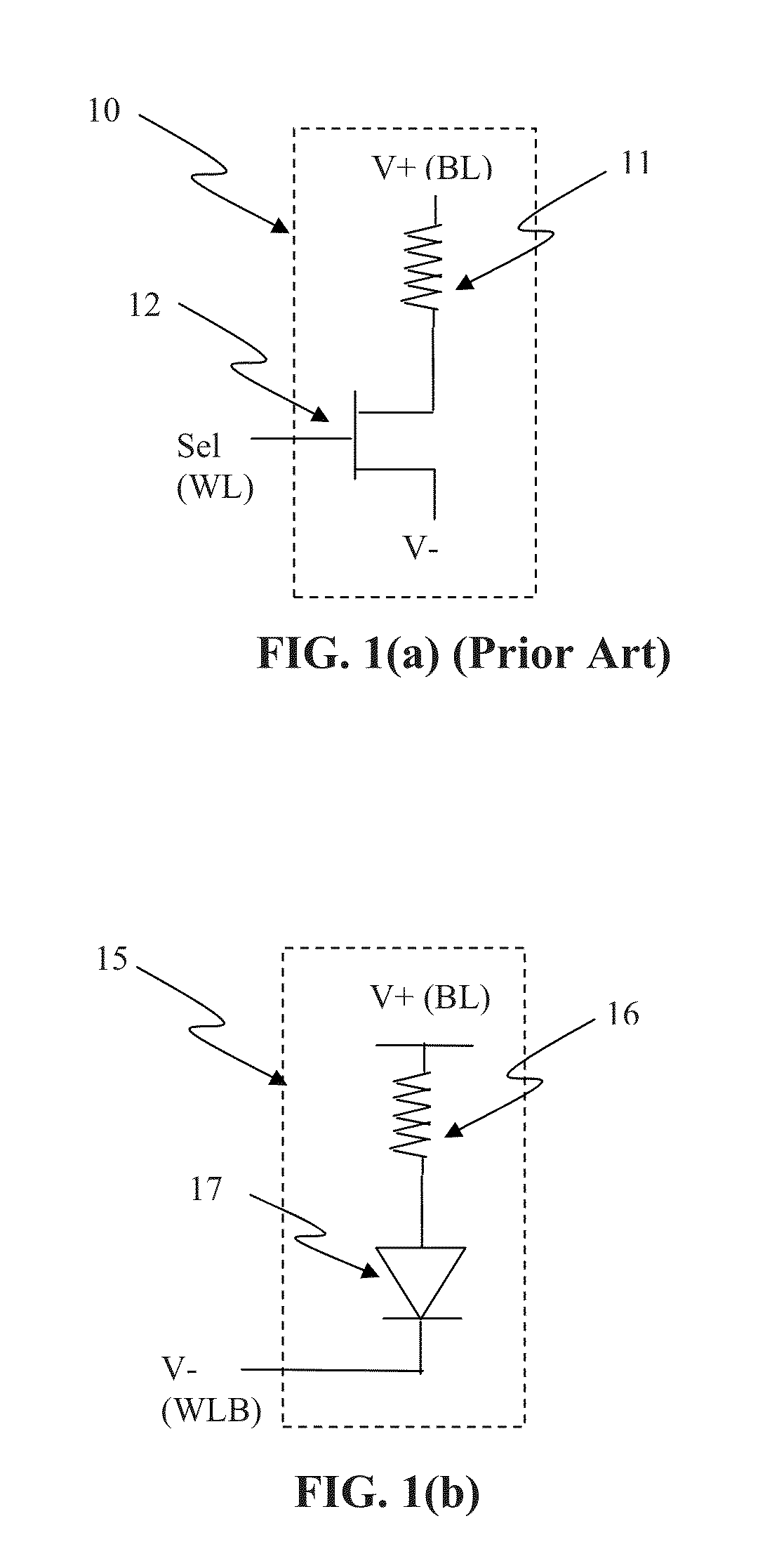

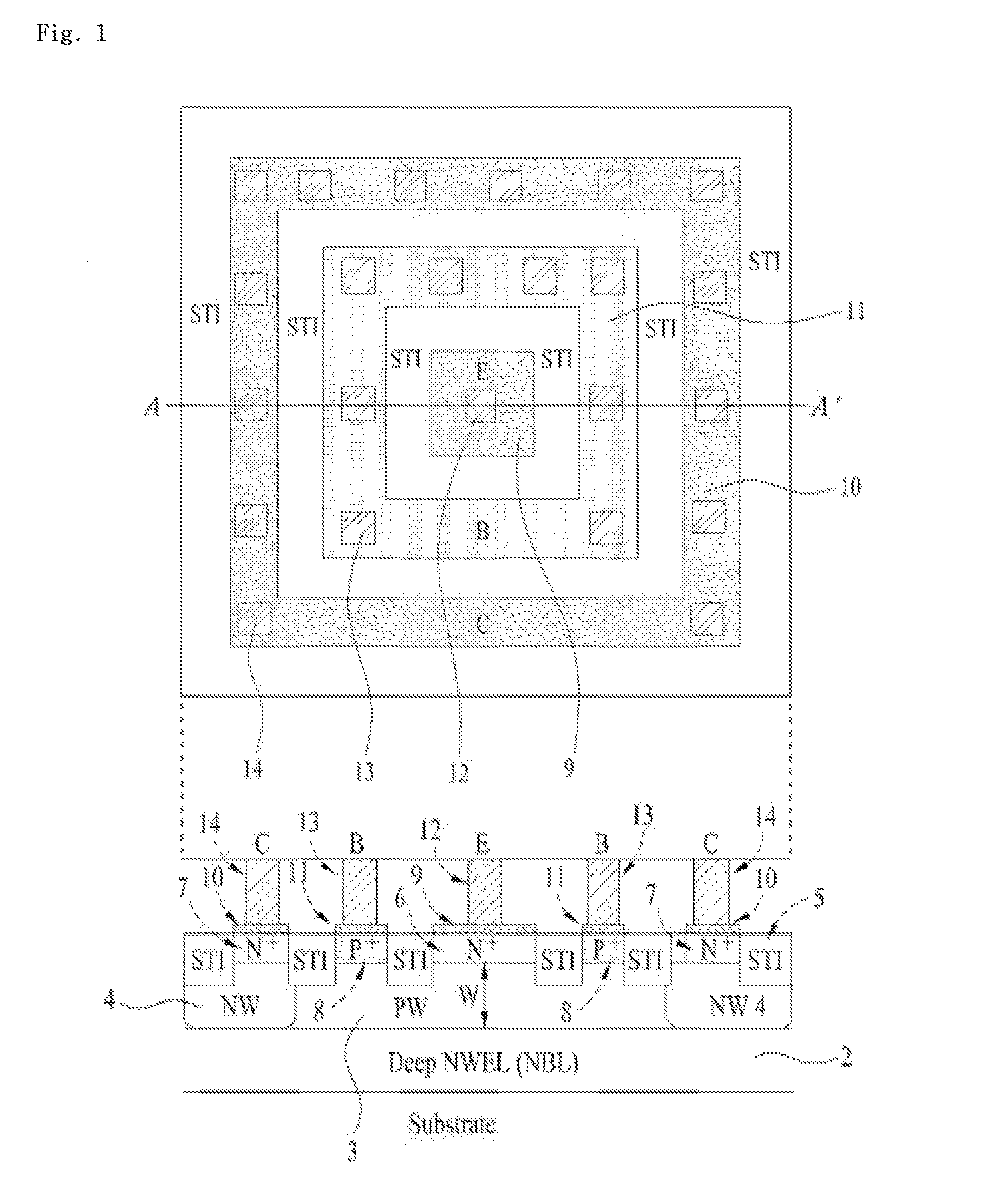

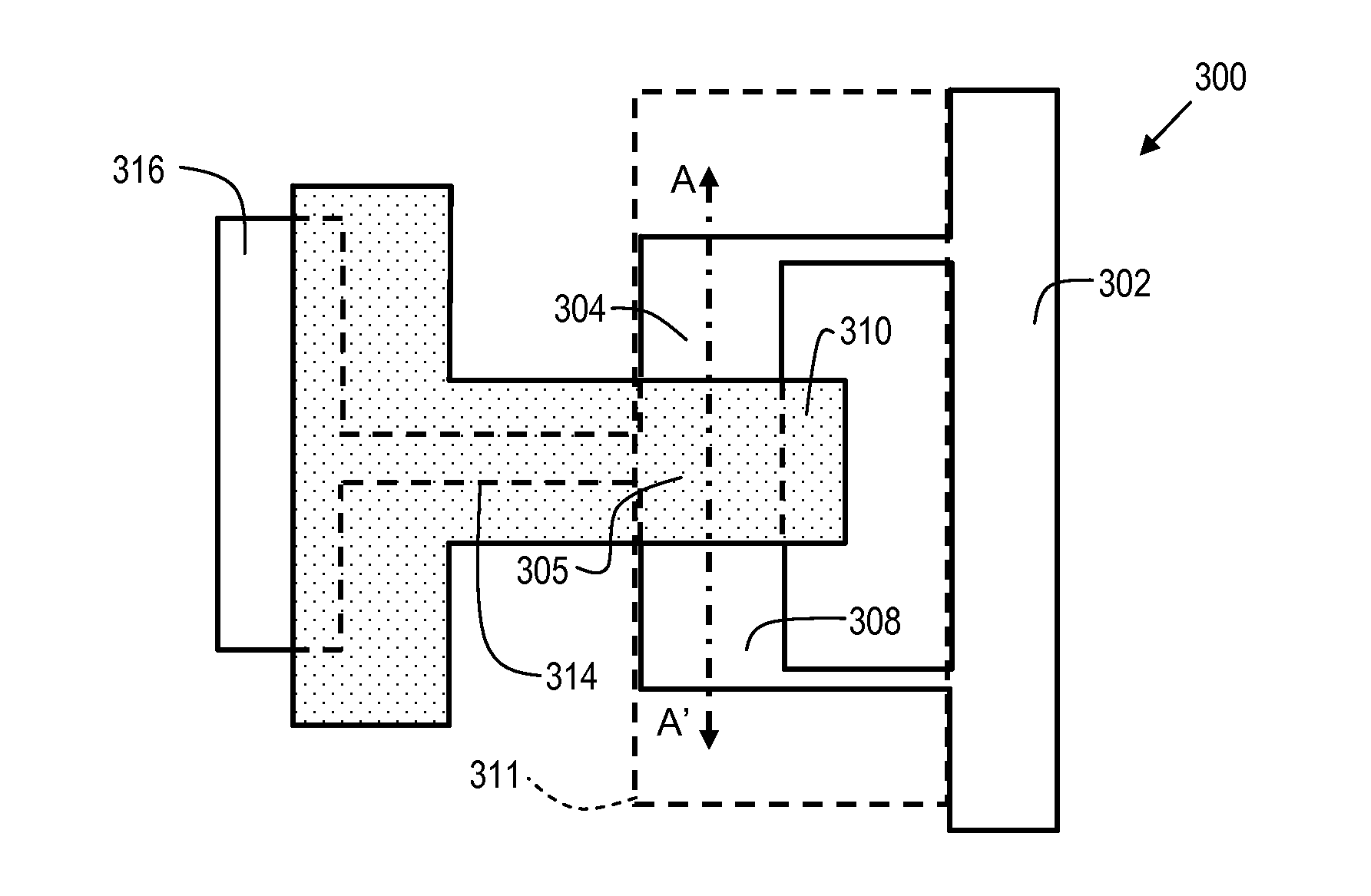

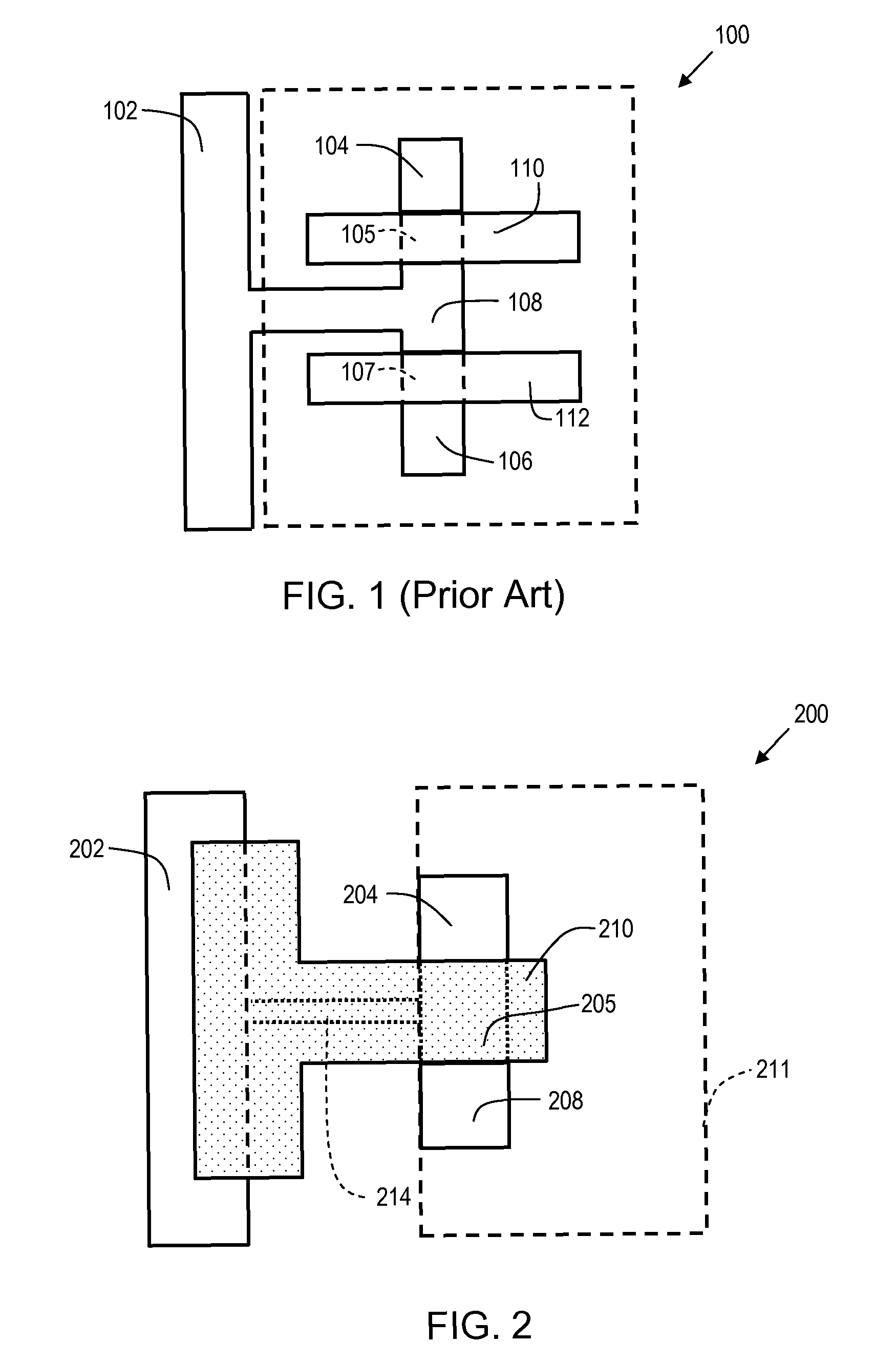

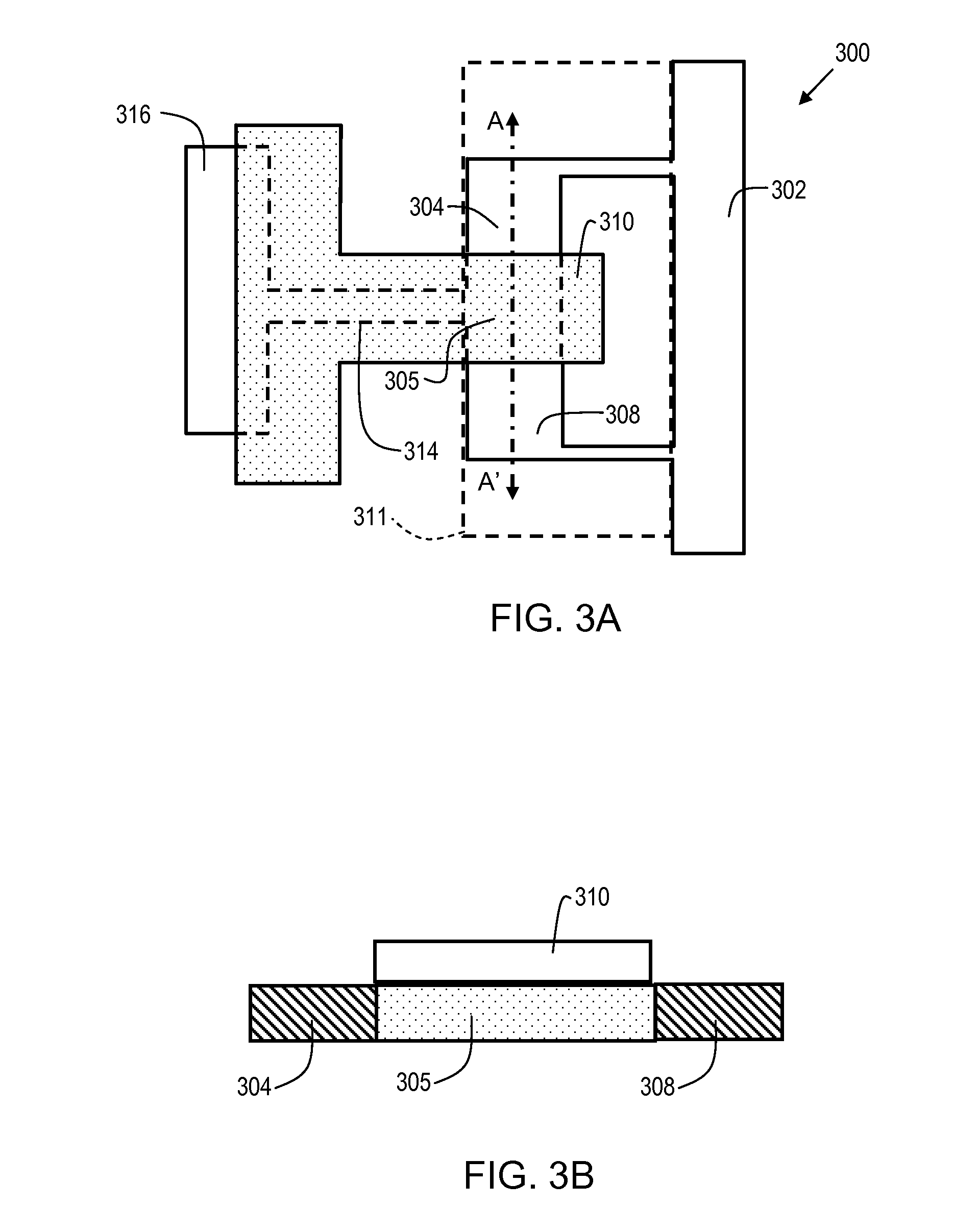

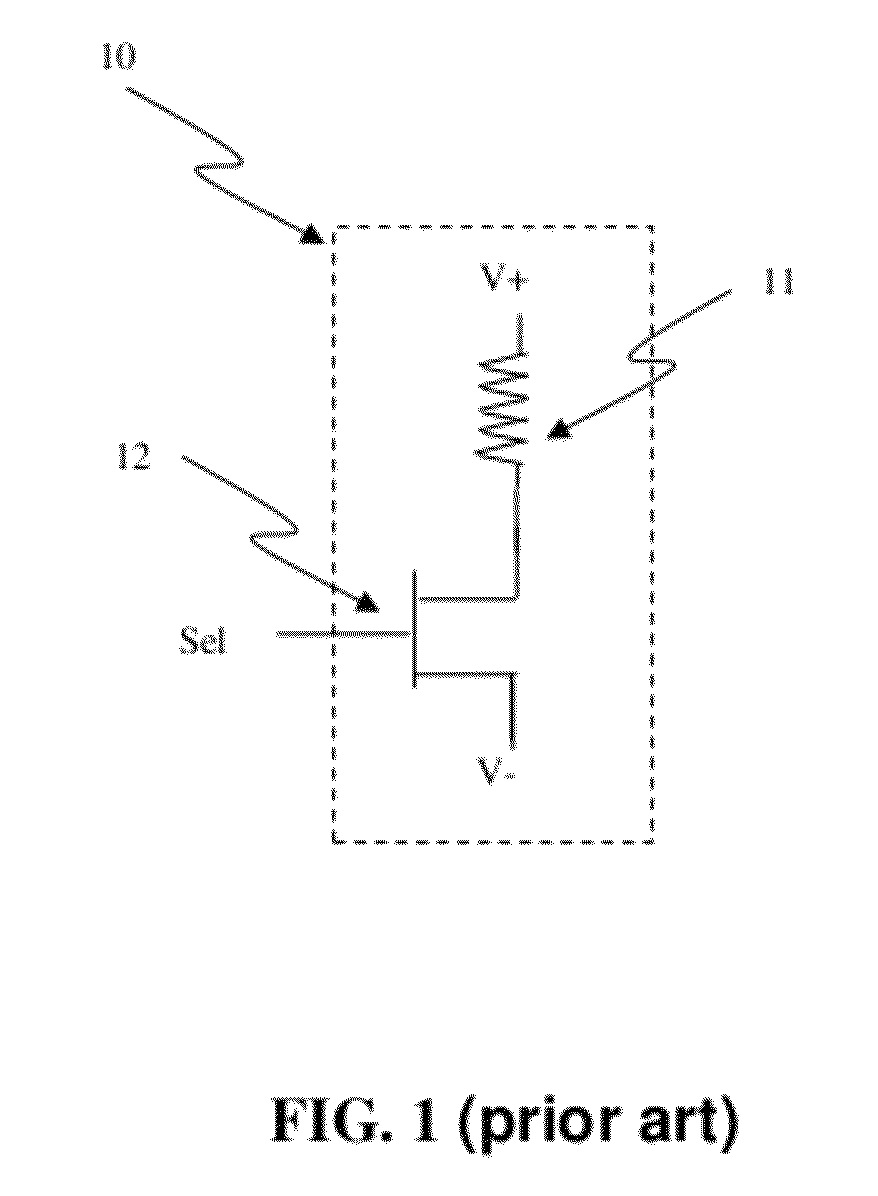

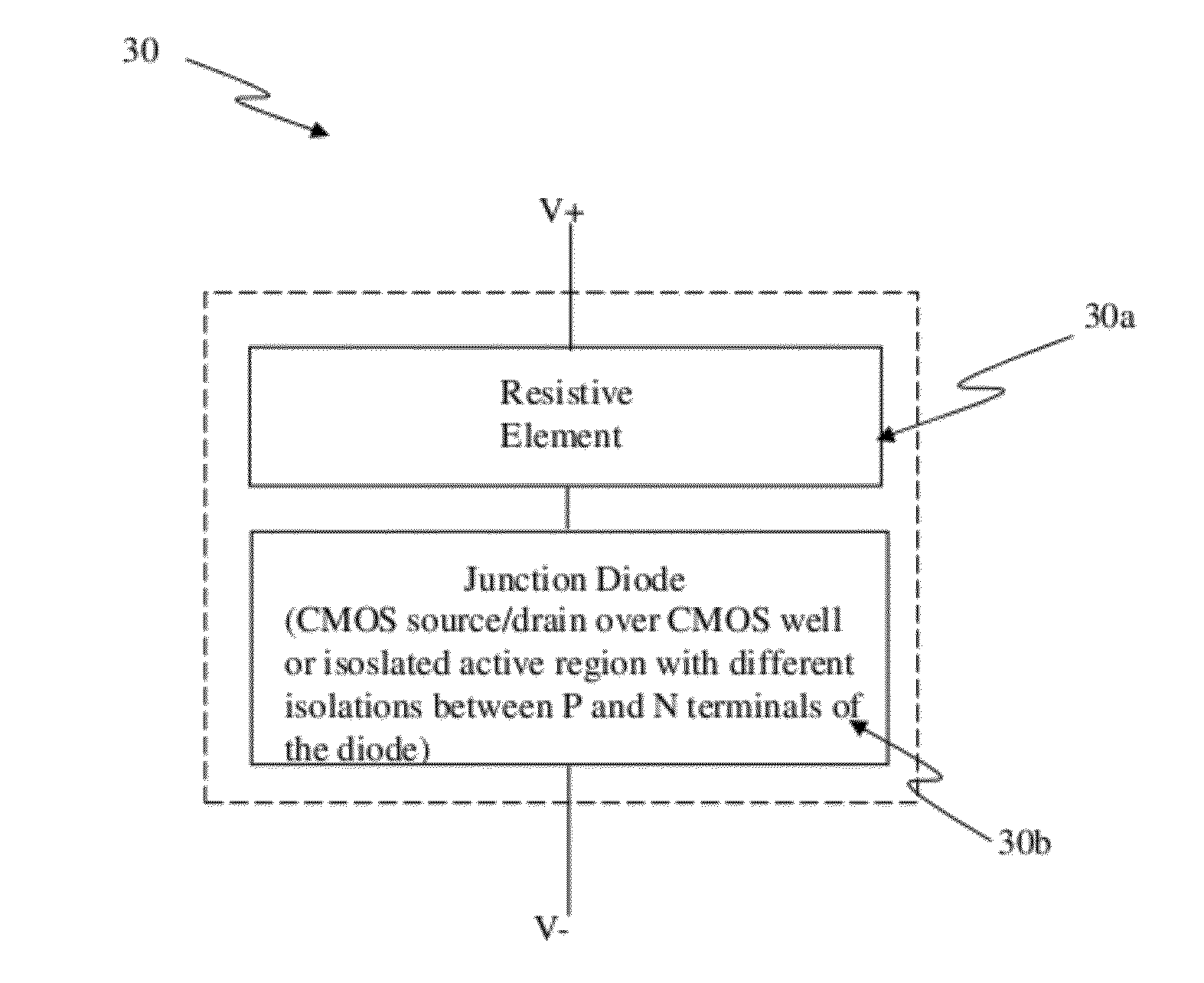

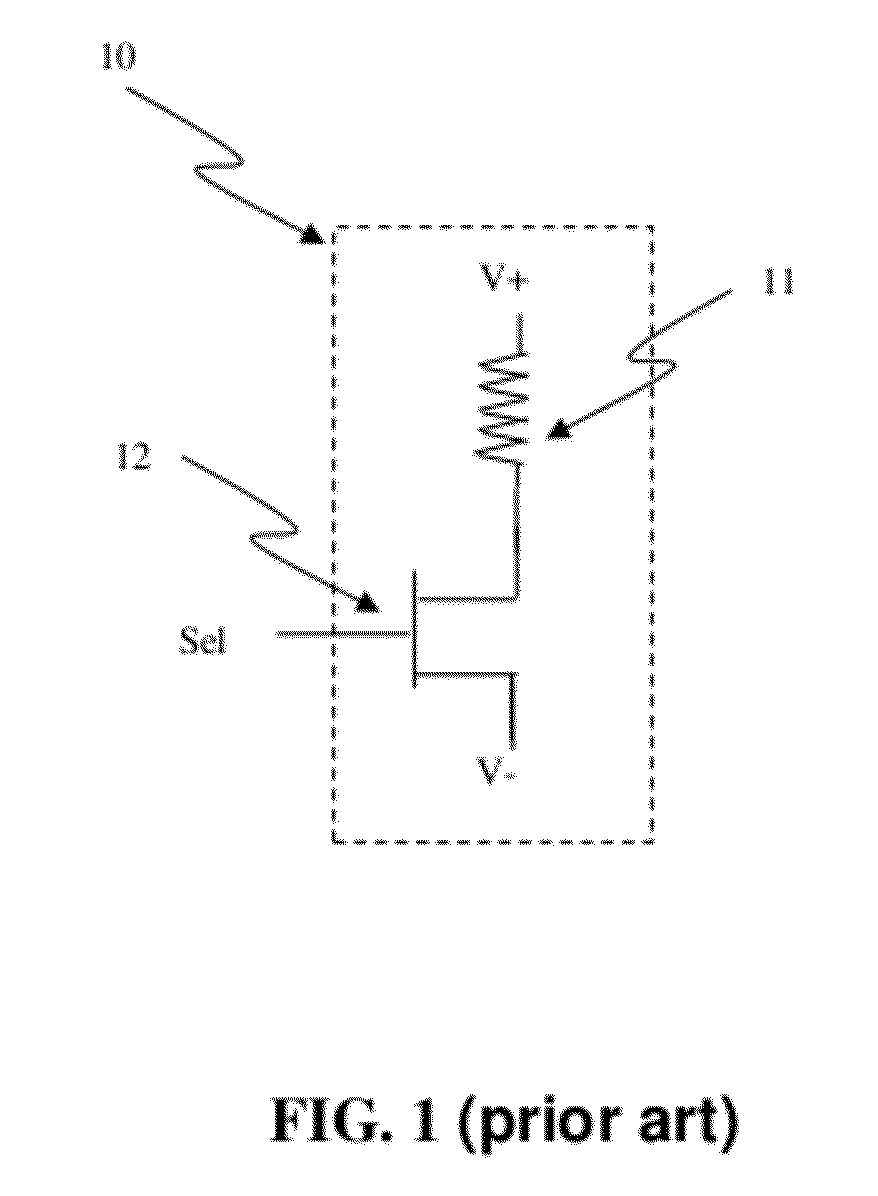

Circuit and system of using junction diode as program selector for one-time programmable devices

ActiveUS8488359B2Low costSmall sizeMagnetic-field-controlled resistorsSolid-state devicesCMOSMetal alloy

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP element can be polysilicon, silicided polysilicon, silicide, metal, metal alloy, local interconnect, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

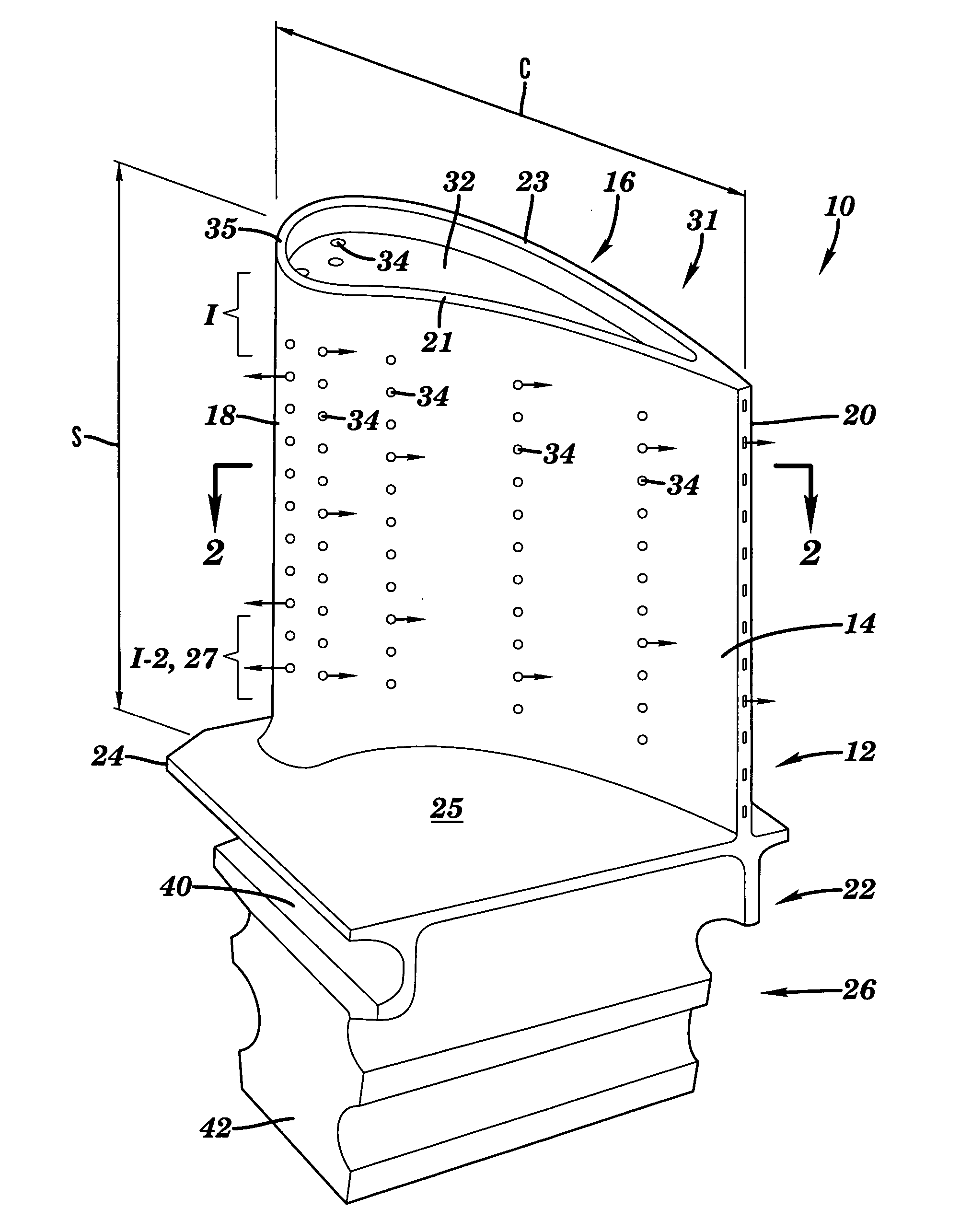

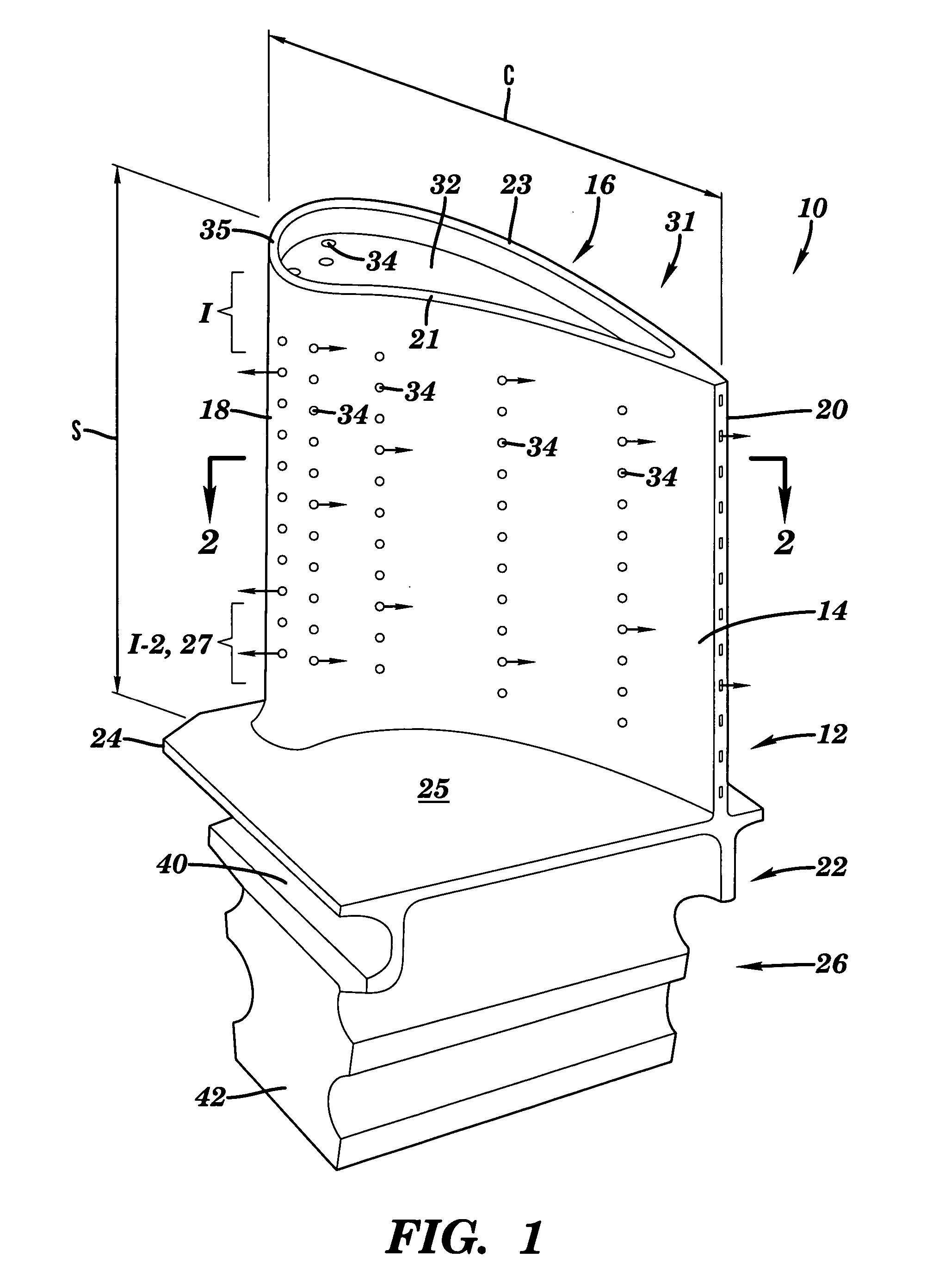

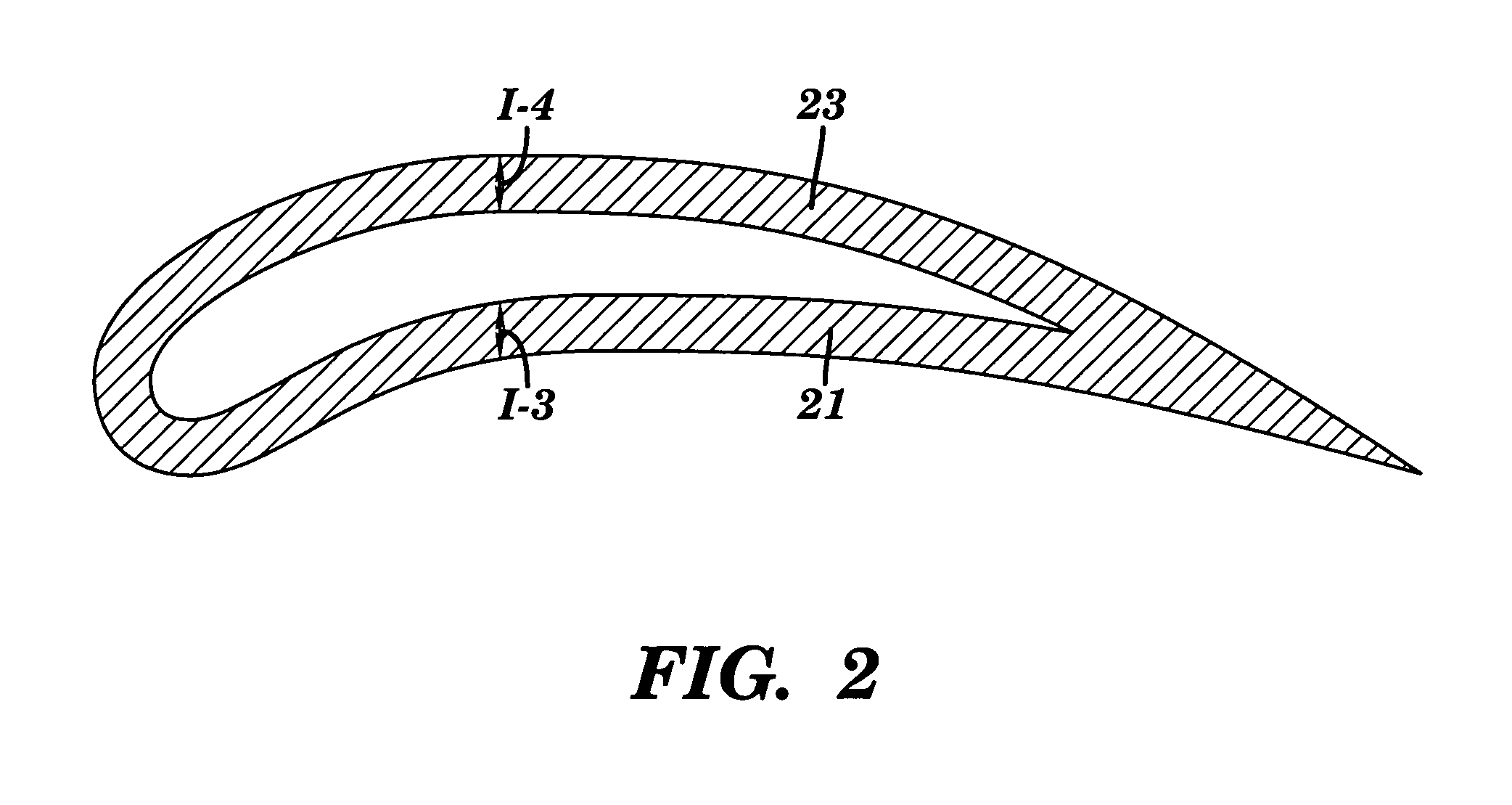

Niobium silicide-based turbine components, and related methods for laser deposition

A turbine component formed from a niobium silicide-based composition is described. The component can be compositionally-graded through at least a portion of its structure. A turbine blade formed from a composition which includes a niobium silicide alloy is also described. The blade includes an airfoil; an airfoil tip region; a platform on which the airfoil is mounted; and a dovetail root attached to an underside of the platform. The niobium silicide alloy in at least one portion of the turbine blade is compositionally different from the niobium silicide alloy in another portion of the blade. Processes for fabricating a niobium silicide-based turbine article are also described, using laser cladding techniques. Repair methods are also set forth in the application.

Owner:GENERAL ELECTRIC CO

Circuit and System of Using Junction Diode as Program Selector for One-Time Programmable Devices

ActiveUS20120224406A1Small cell sizeLow costMagnetic-field-controlled resistorsSolid-state devicesHemt circuitsEngineering

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP element can be polysilicon, silicided polysilicon, silicide, metal, metal alloy, local interconnect, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com