Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

869 results about "Double gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

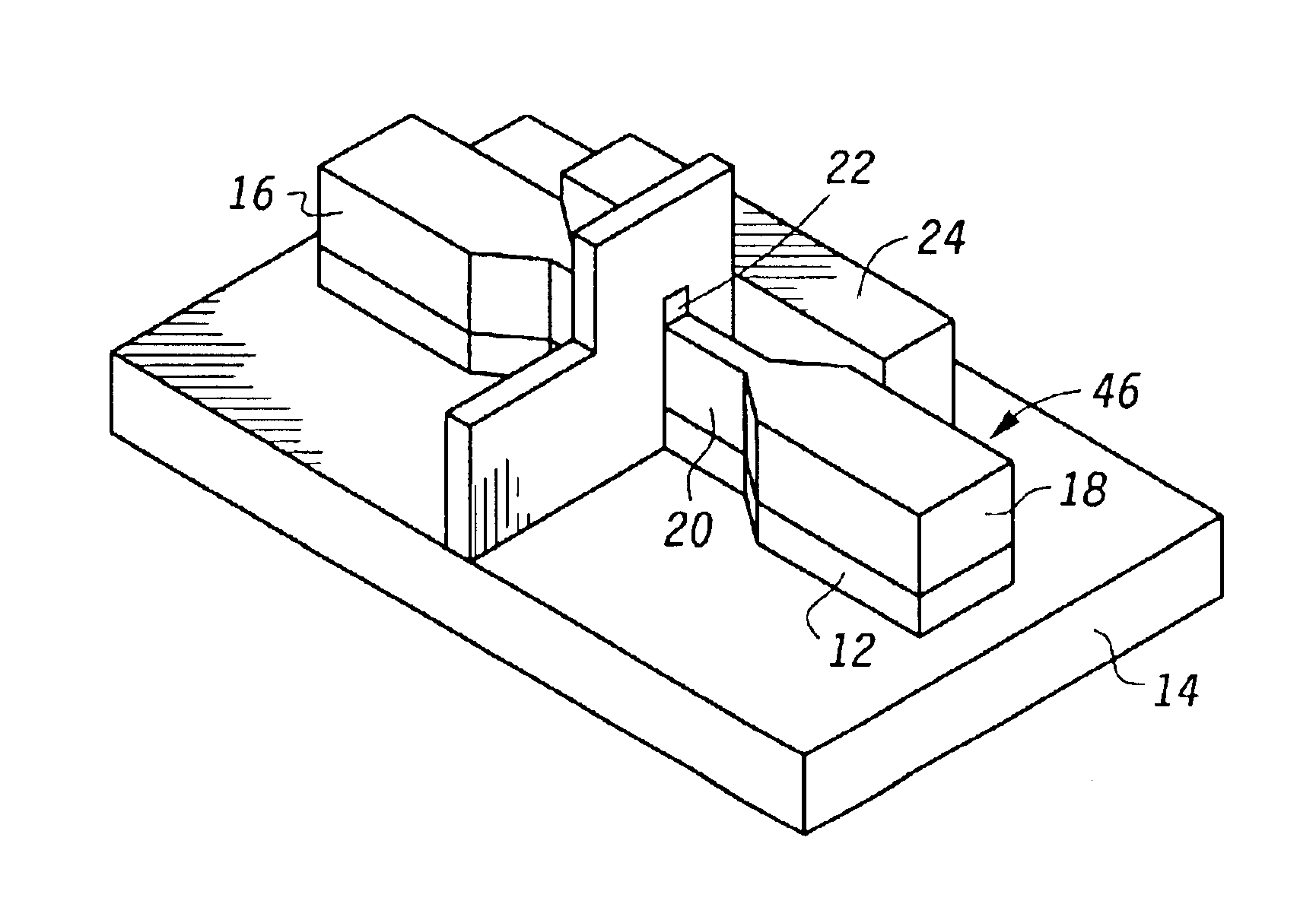

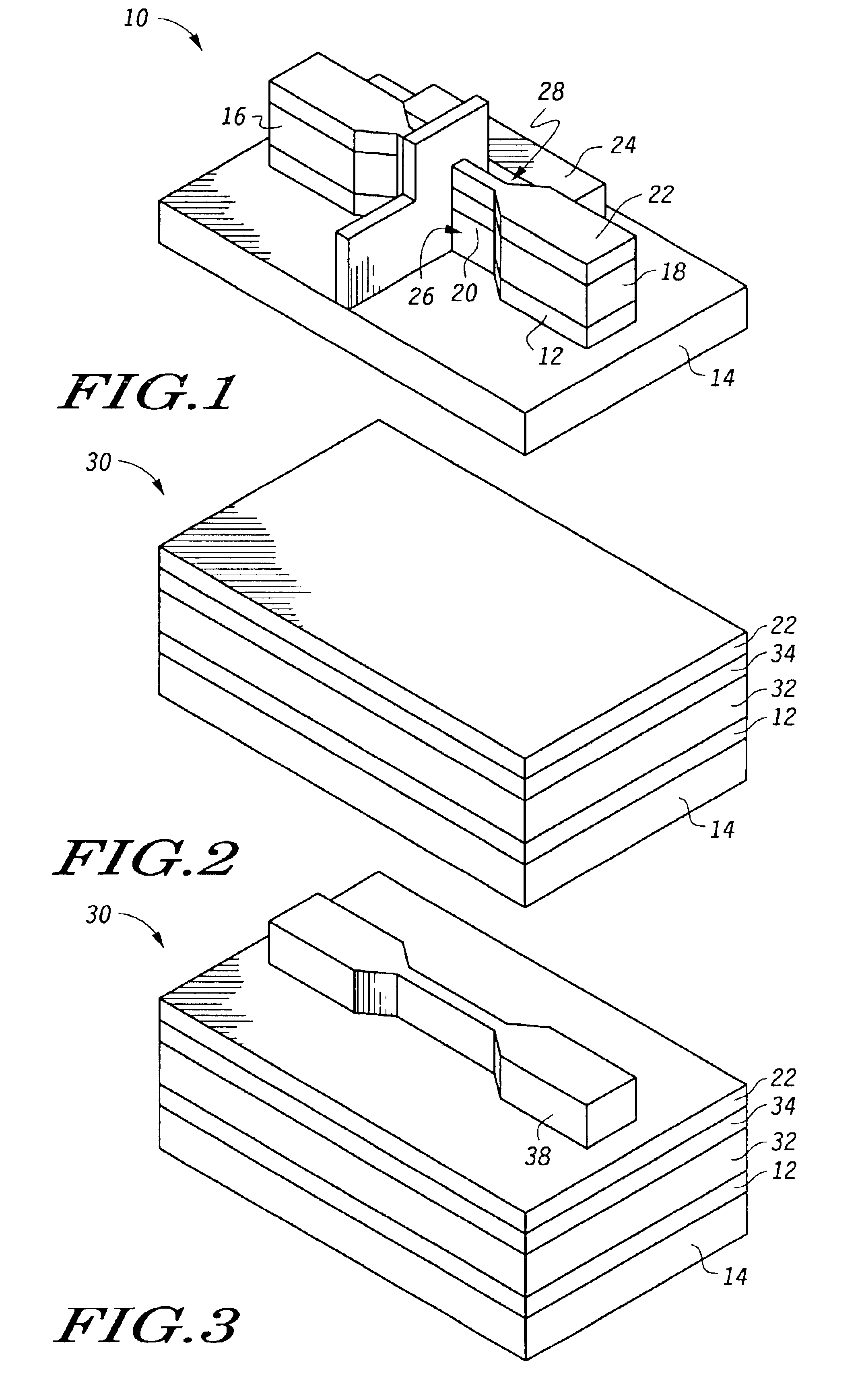

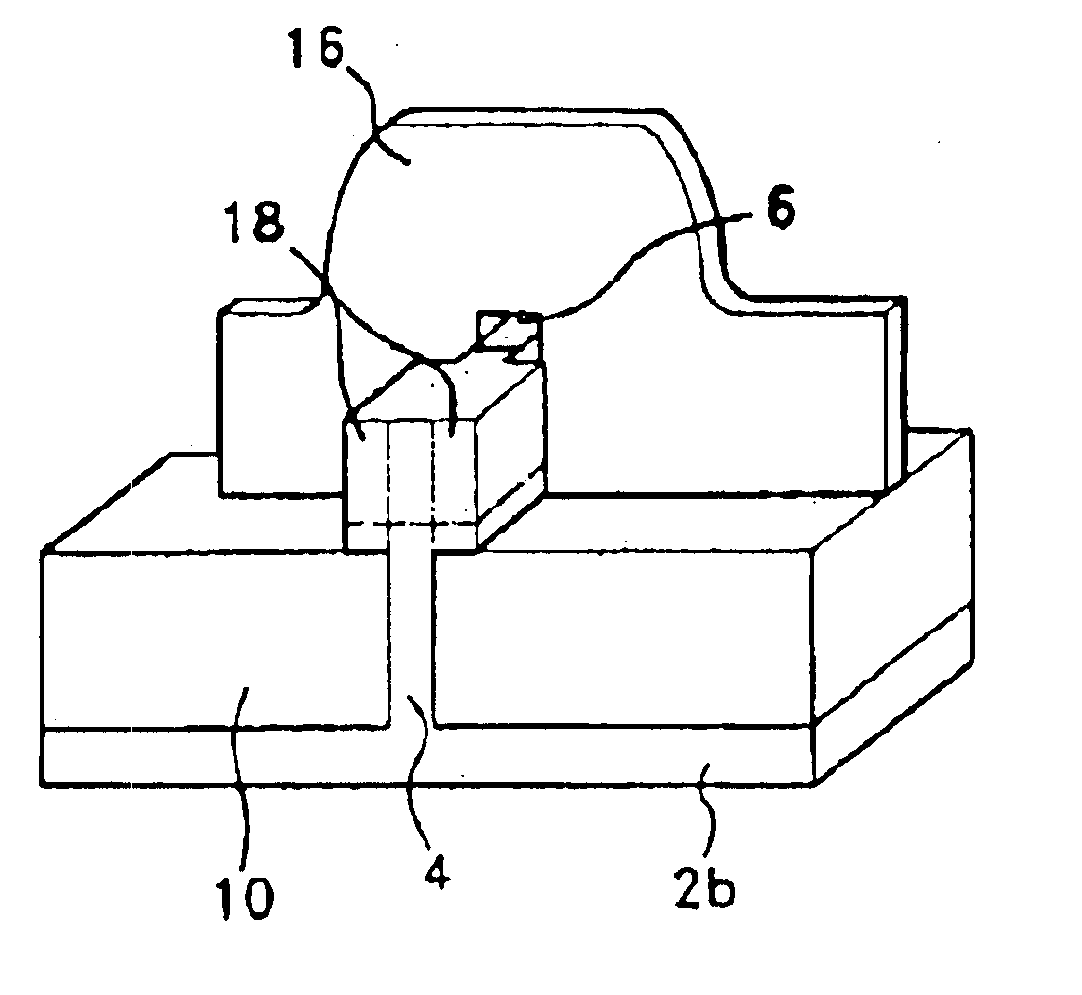

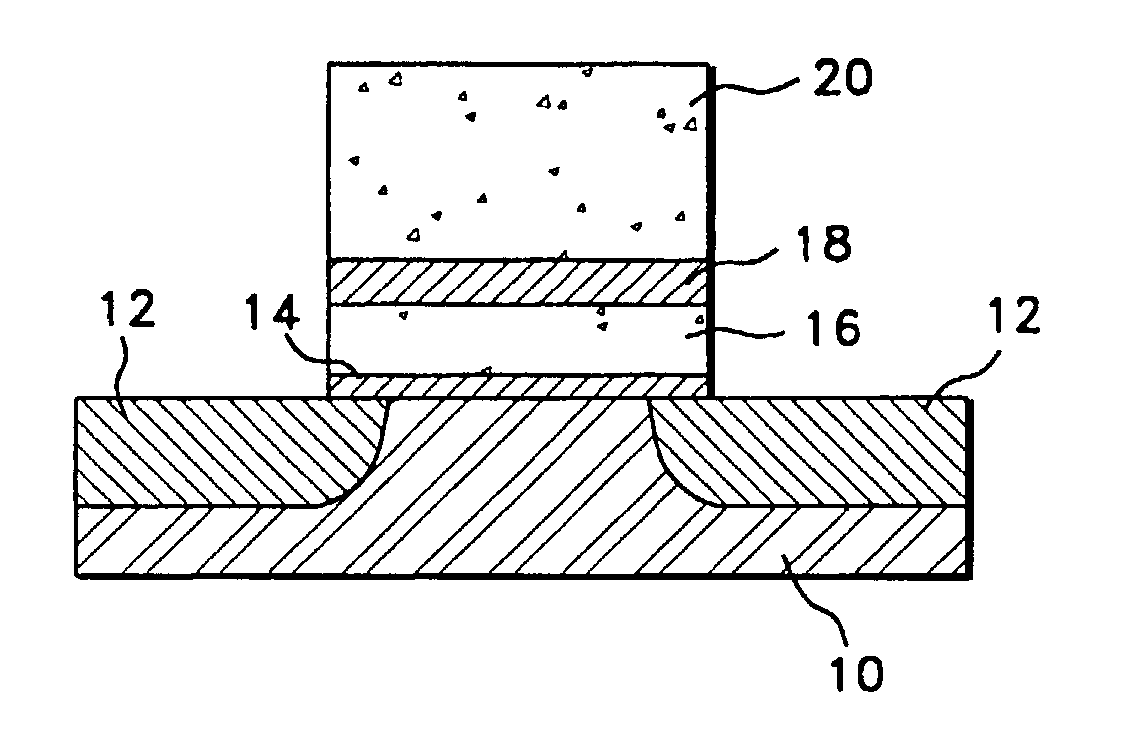

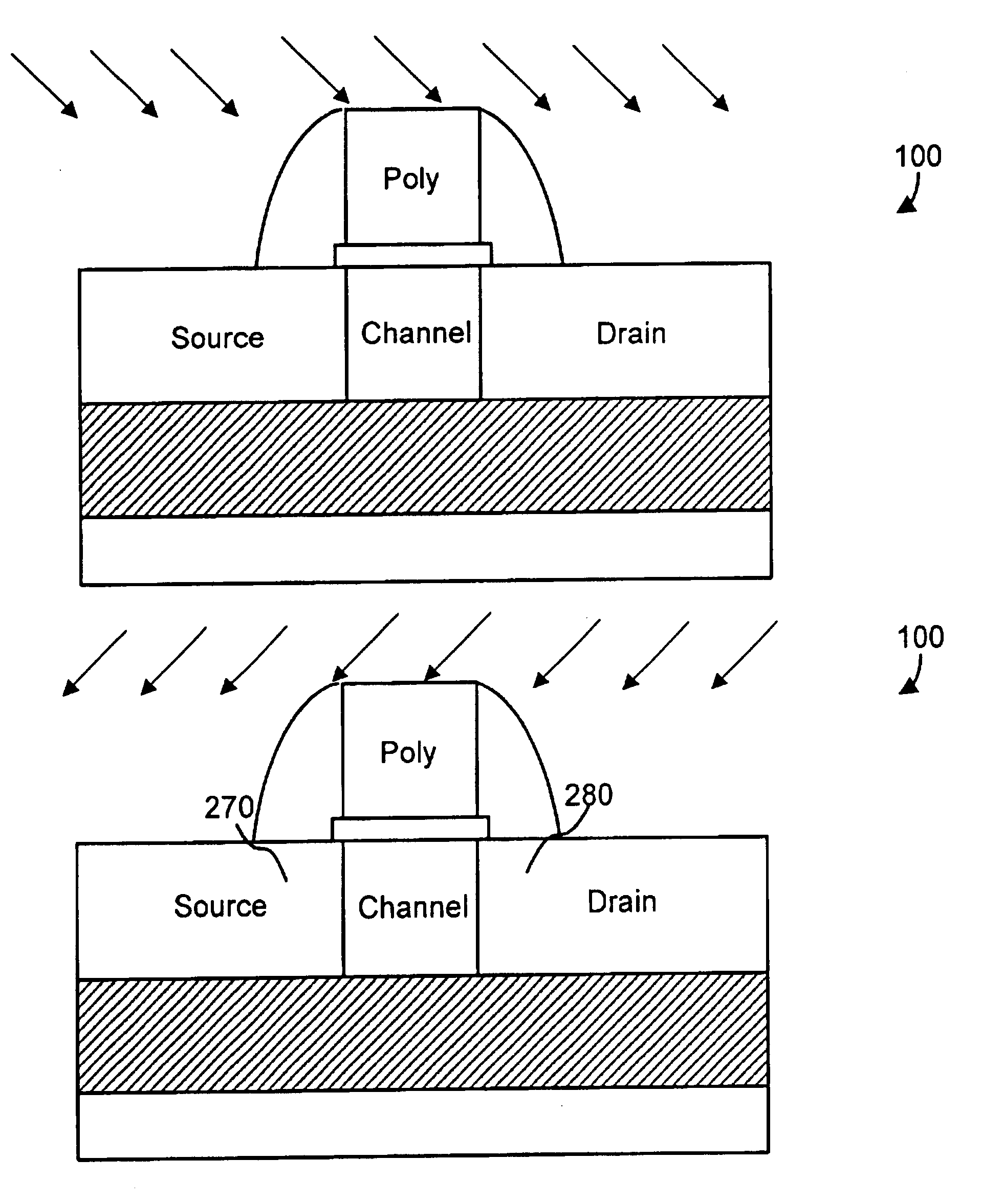

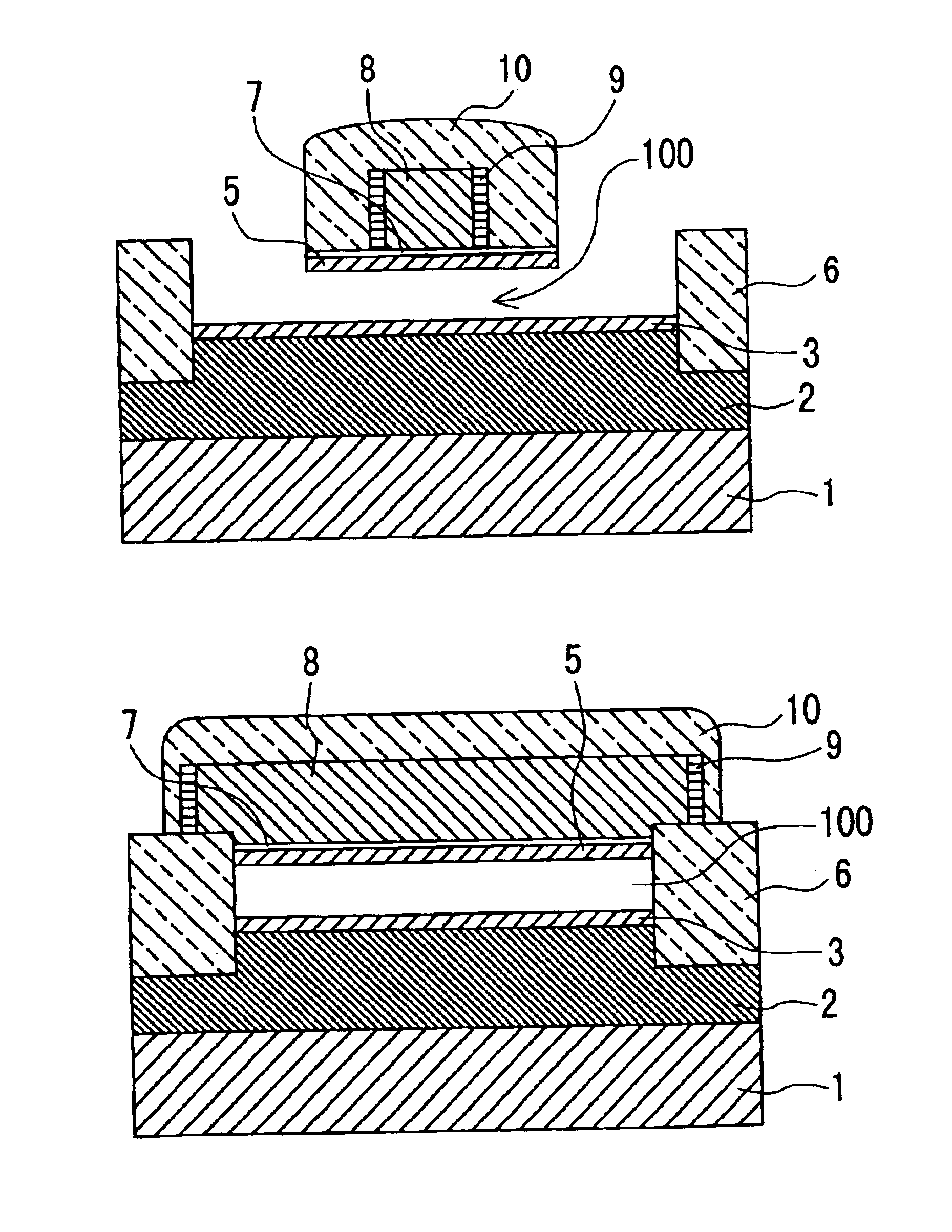

Method for forming a double-gated semiconductor device

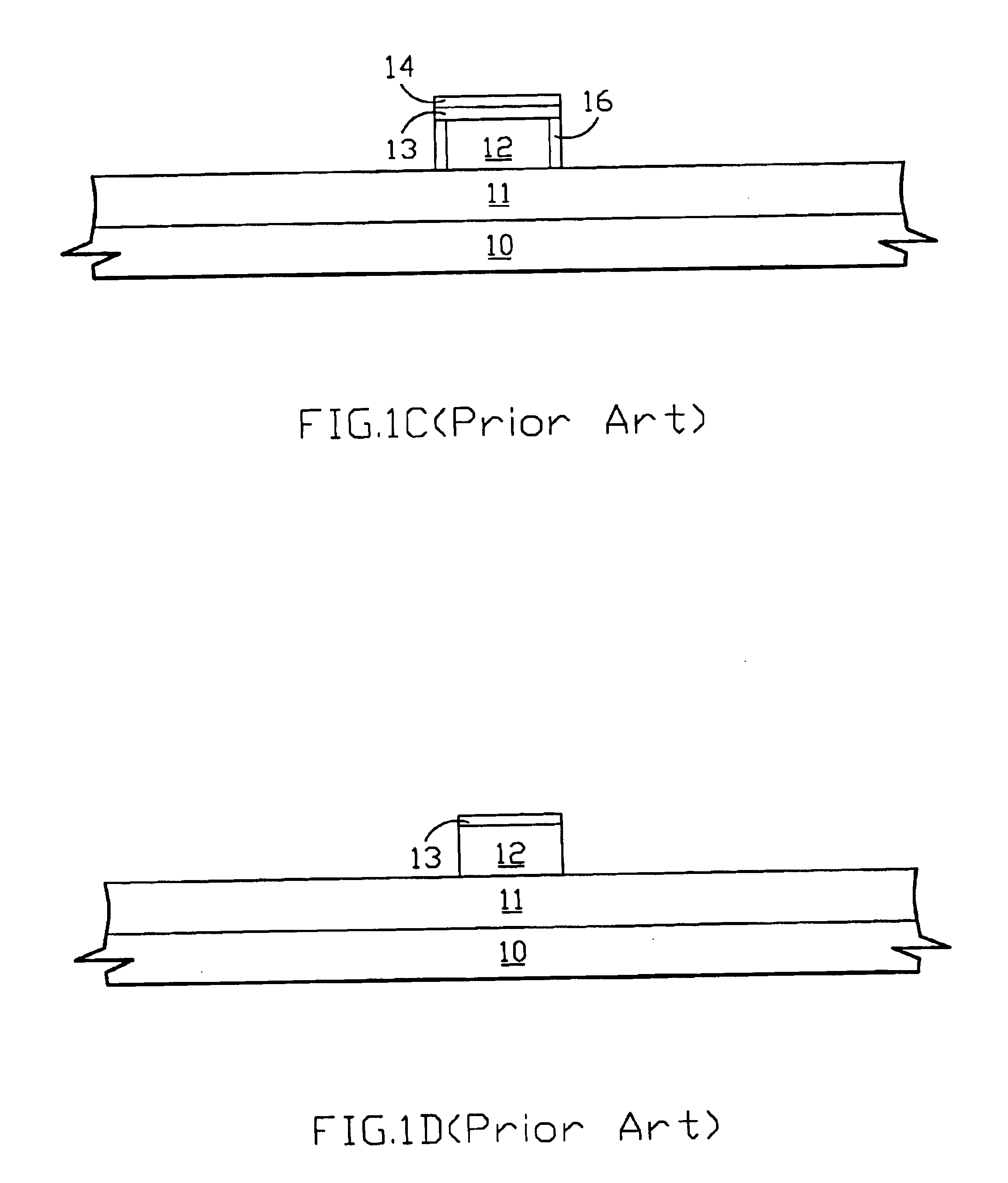

A method for forming a polysilicon FinFET (10) or other thin film transistor structure includes forming an insulative layer (12) over a semiconductor substrate (14). An amorphous silicon layer (32) forms over the insulative layer (12). A silicon germanium seed layer (44) forms in association with the amorphous silicon layer (32) for controlling silicon grain growth. The polysilicon layer arises from annealing the amorphous silicon layer (32). During the annealing step, silicon germanium seed layer (44), together with silicon germanium layer (34), catalyzes silicon recrystallization to promote growing larger crystalline grains, as well as fewer grain boundaries within the resulting polysilicon layer. Source (16), drain (18), and channel (20) regions are formed within the polysilicon layer. A double-gated region (24) forms in association with source (16), drain (18), and channel (20) to produce polysilicon FinFET (10).

Owner:NORTH STAR INNOVATIONS

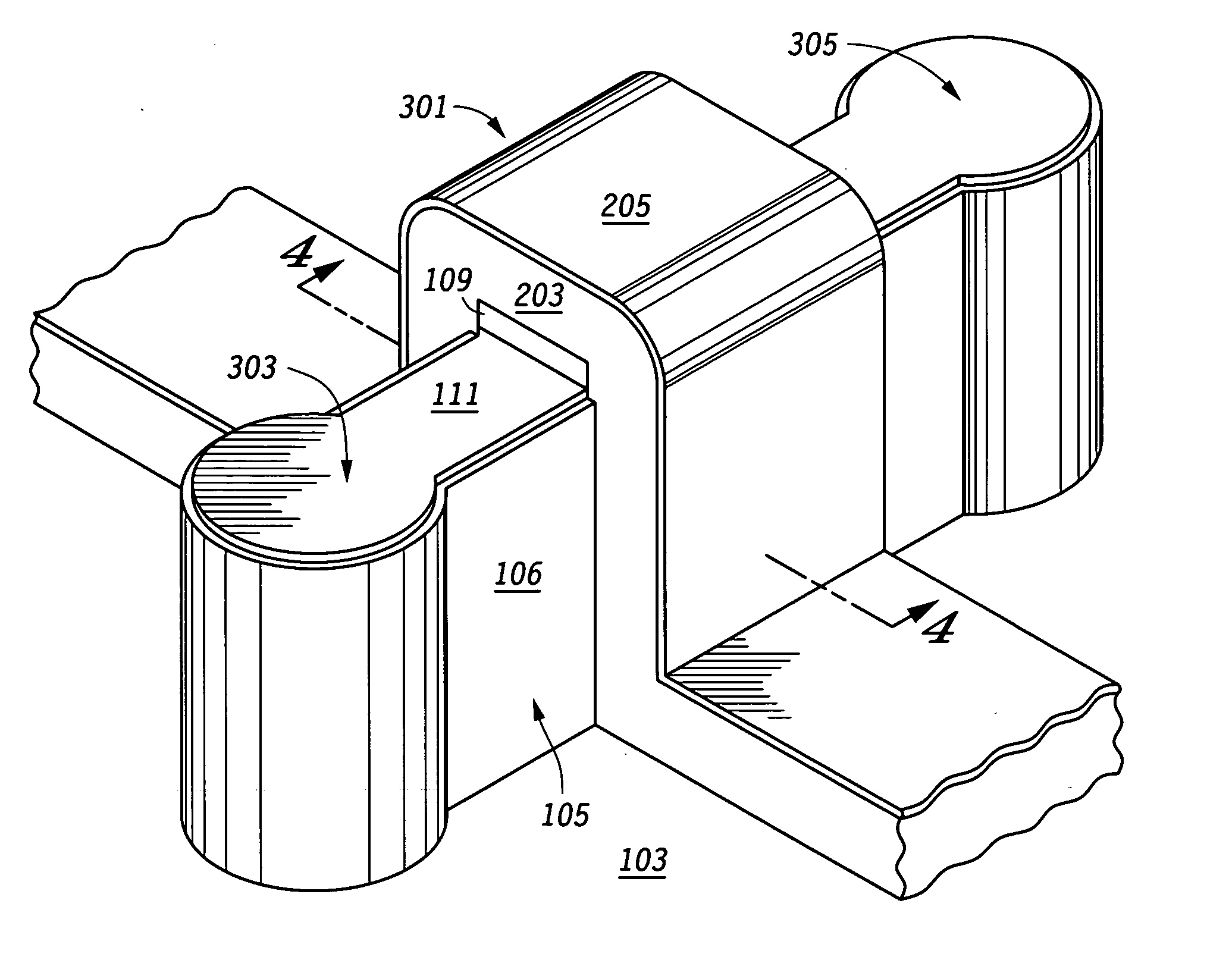

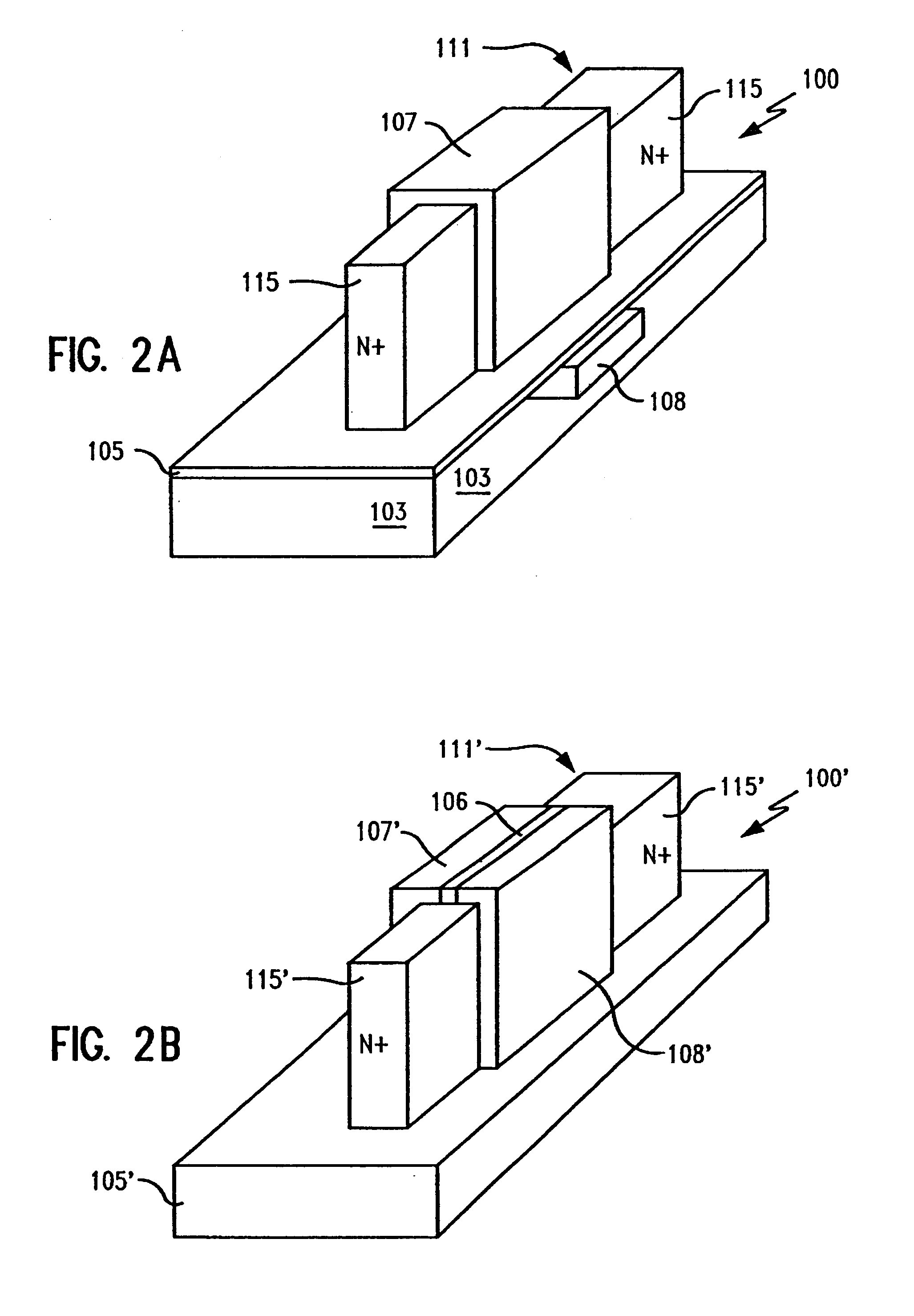

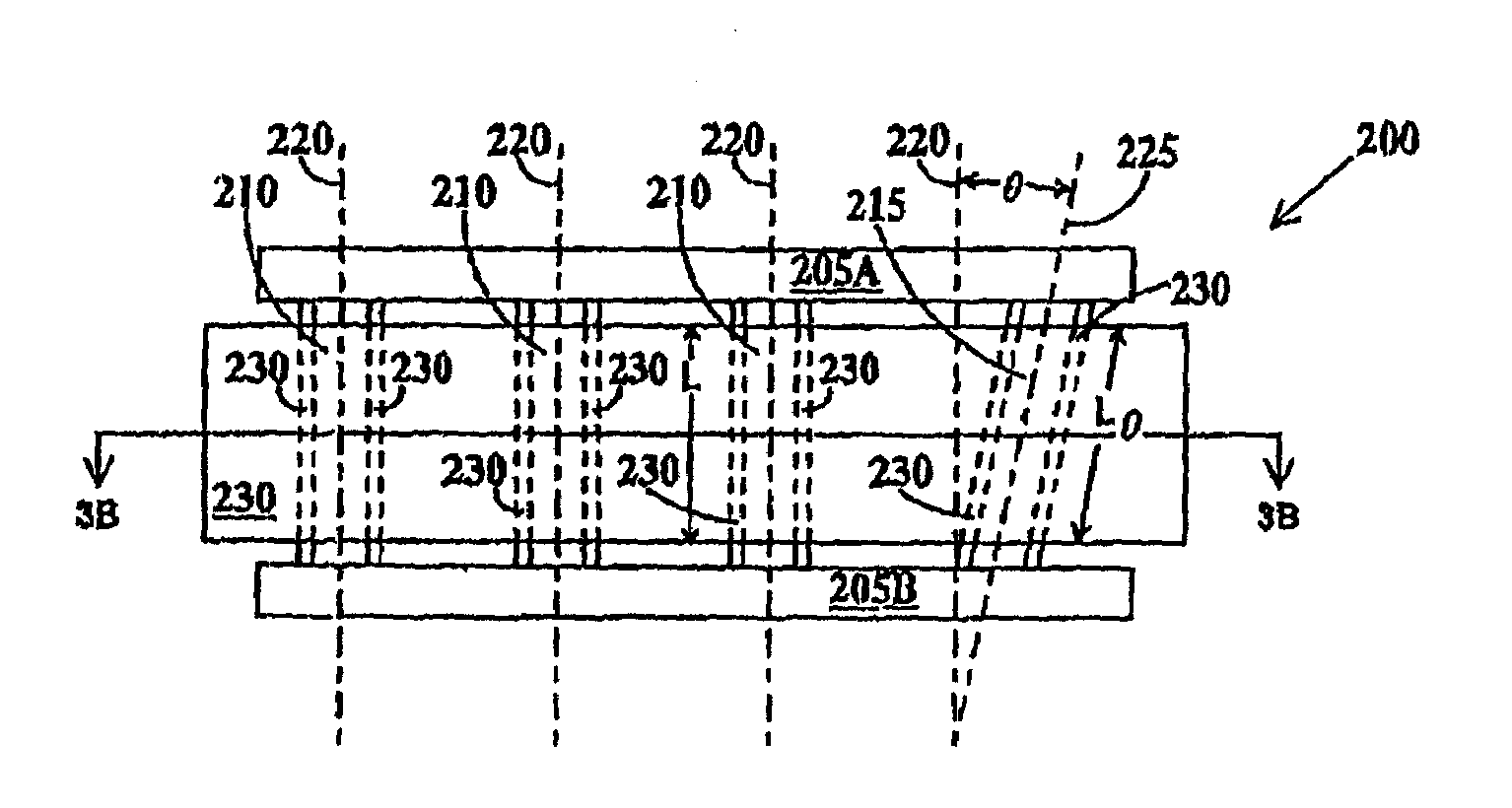

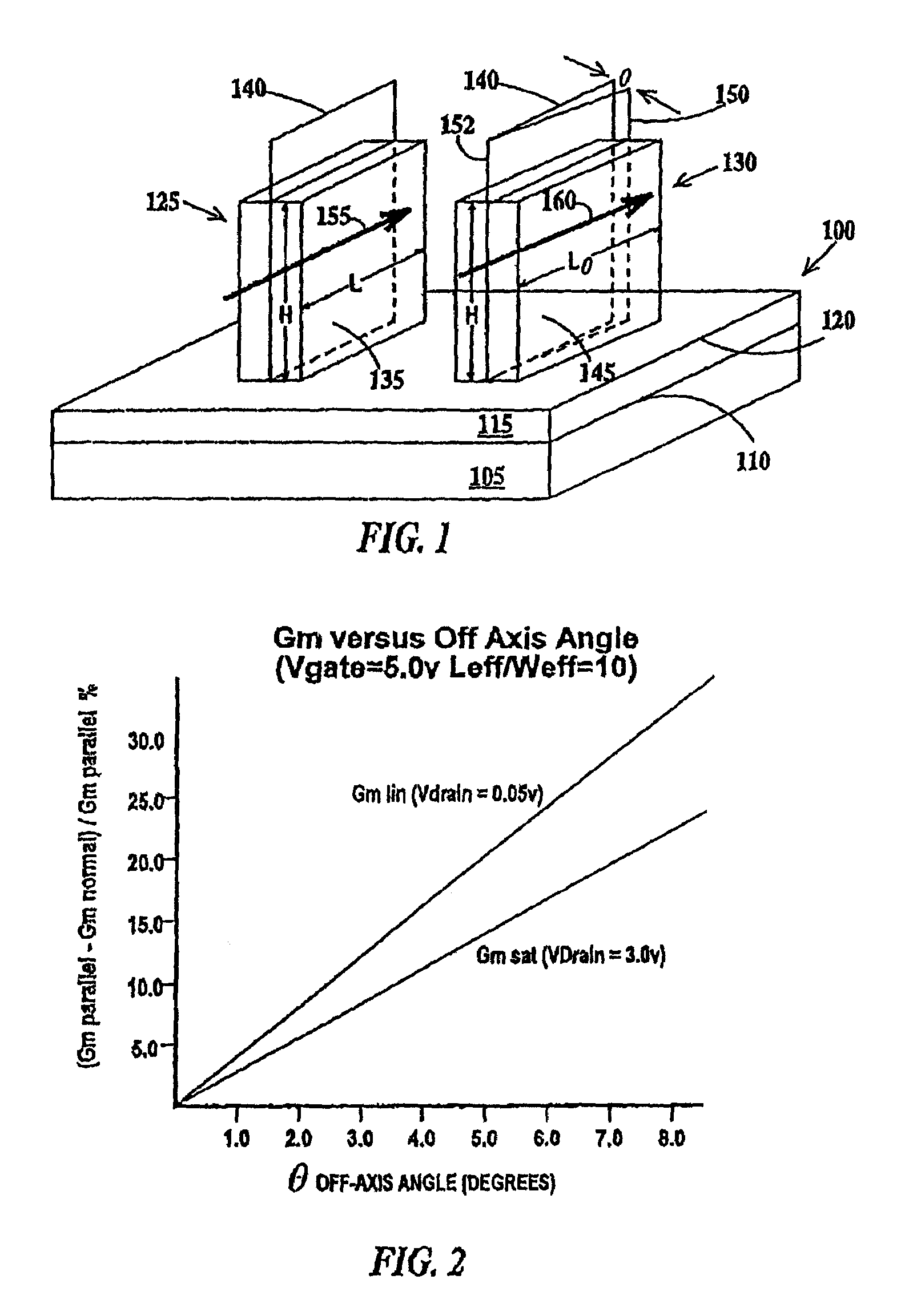

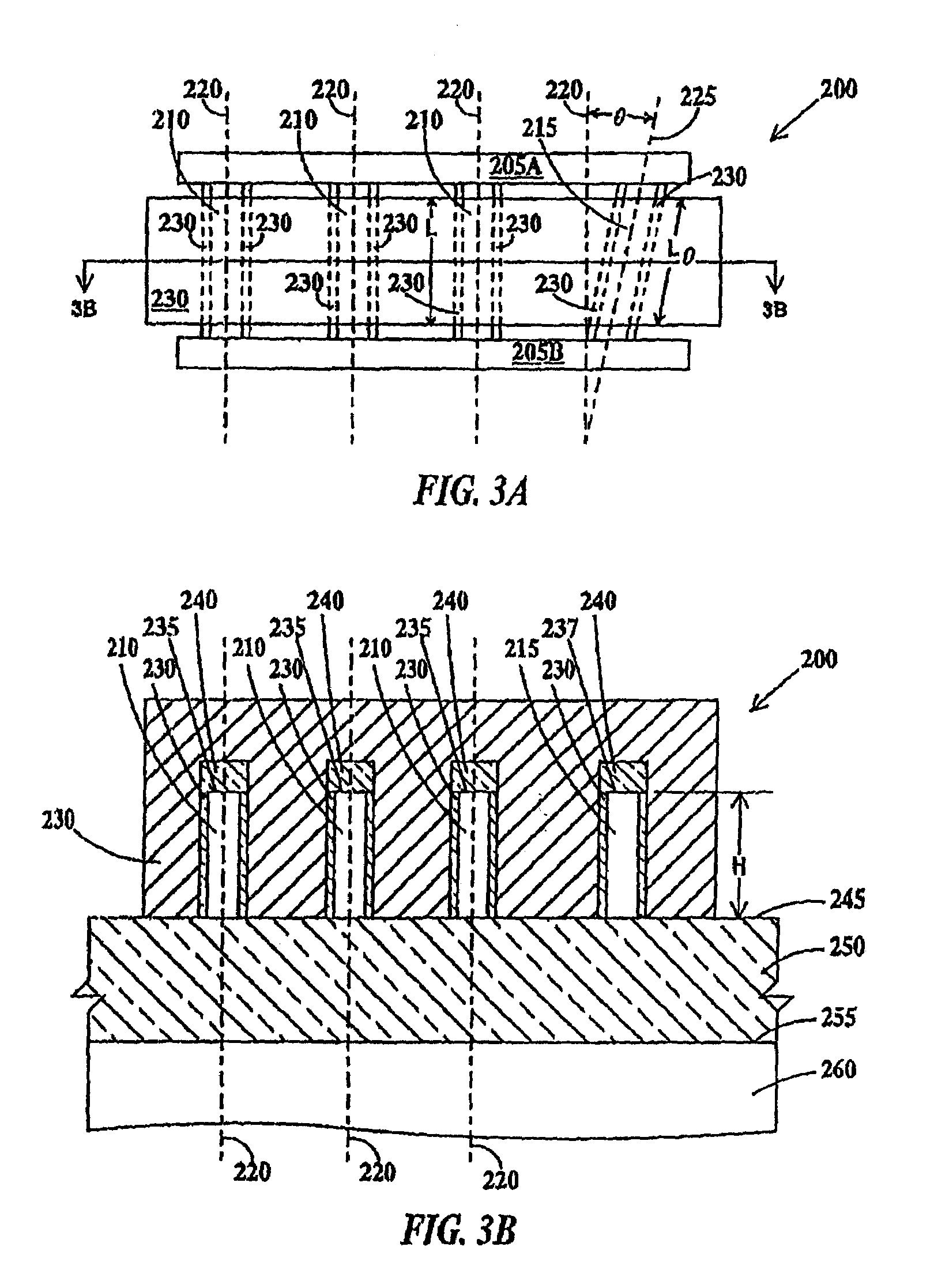

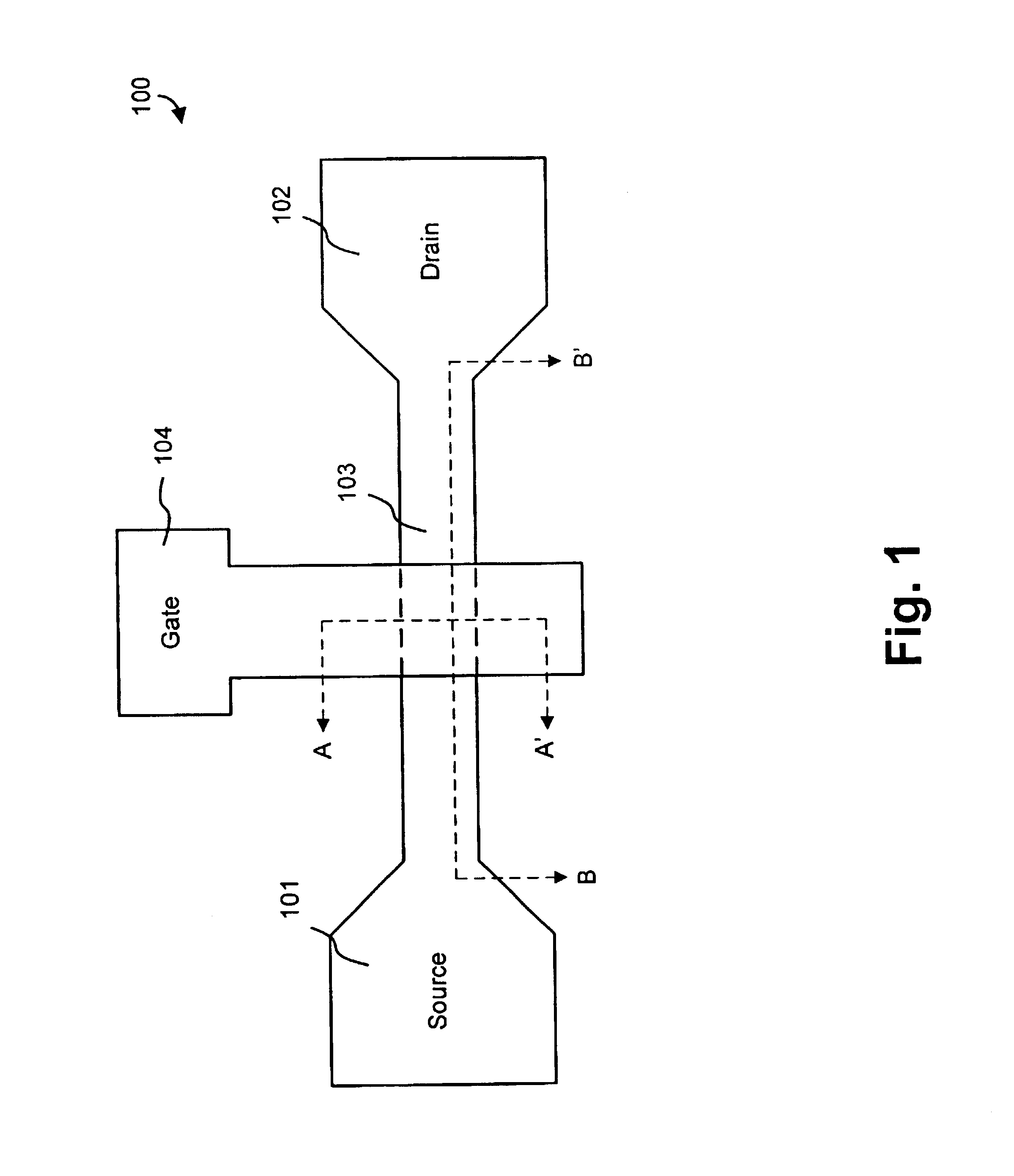

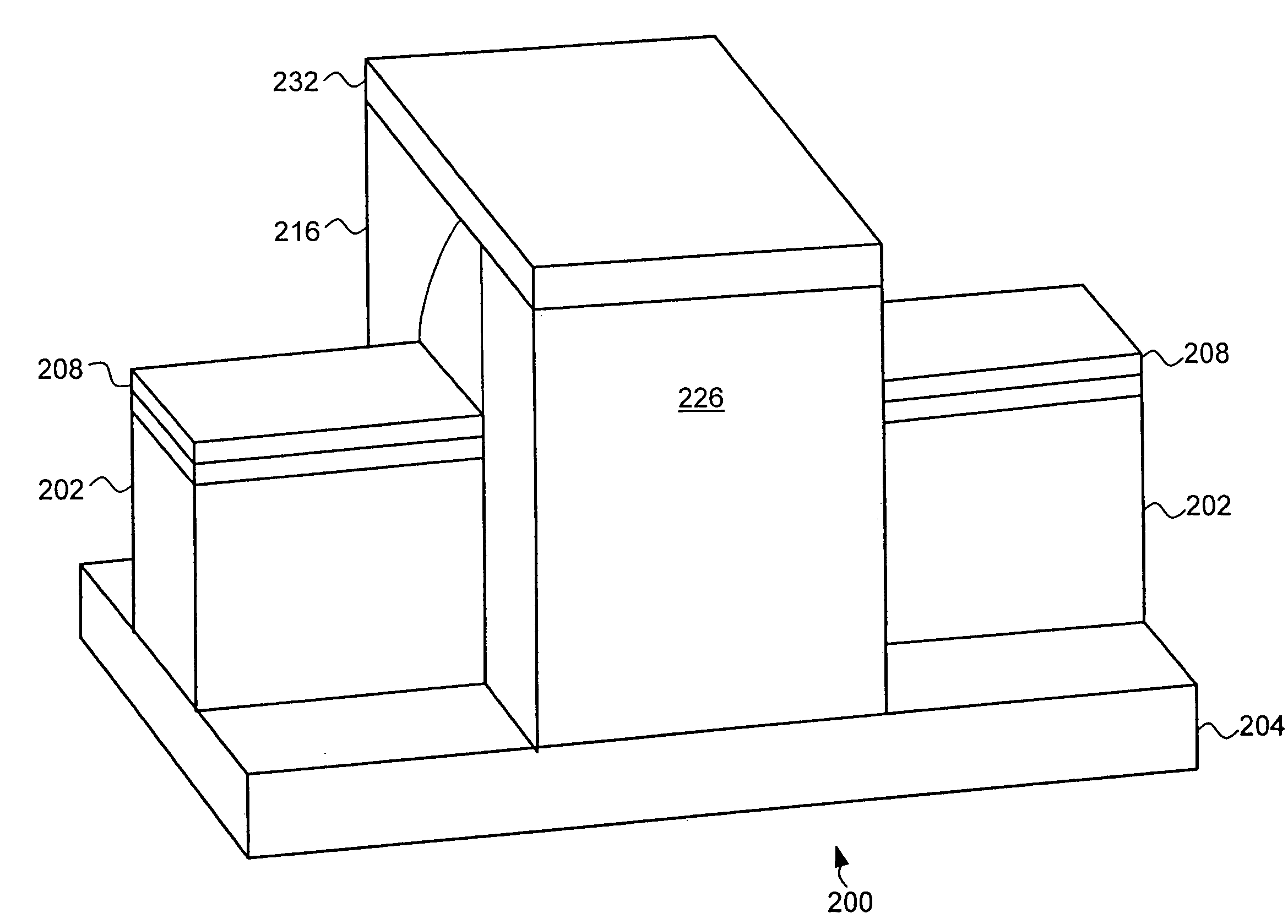

Method and circuit for multiplying signals with a transistor having more than one independent gate structure

A double gate semiconductor device (2006) is used beneficially as a multiplier (2000). The double gate semiconductor device (2006) has a lateral fin (105) as the channel region with the gates formed opposite each other on both sides of the fin. The lateral positioning of the fin provides symmetry between the two gates. To increase drive current, multiple transistors are easily connected in parallel by having a continuous fin structure (2106) with alternating source / drain terminals (2120, 2122, 2124, 2126) in which the sources are connected together and the drains are connected together. Gates (2116, 2110) are positioned between each pair of adjacent source / drain terminals and electrically connected together. The multiplier (2000) may also be used as a mixer and further as a phase detector.

Owner:NORTH STAR INNOVATIONS

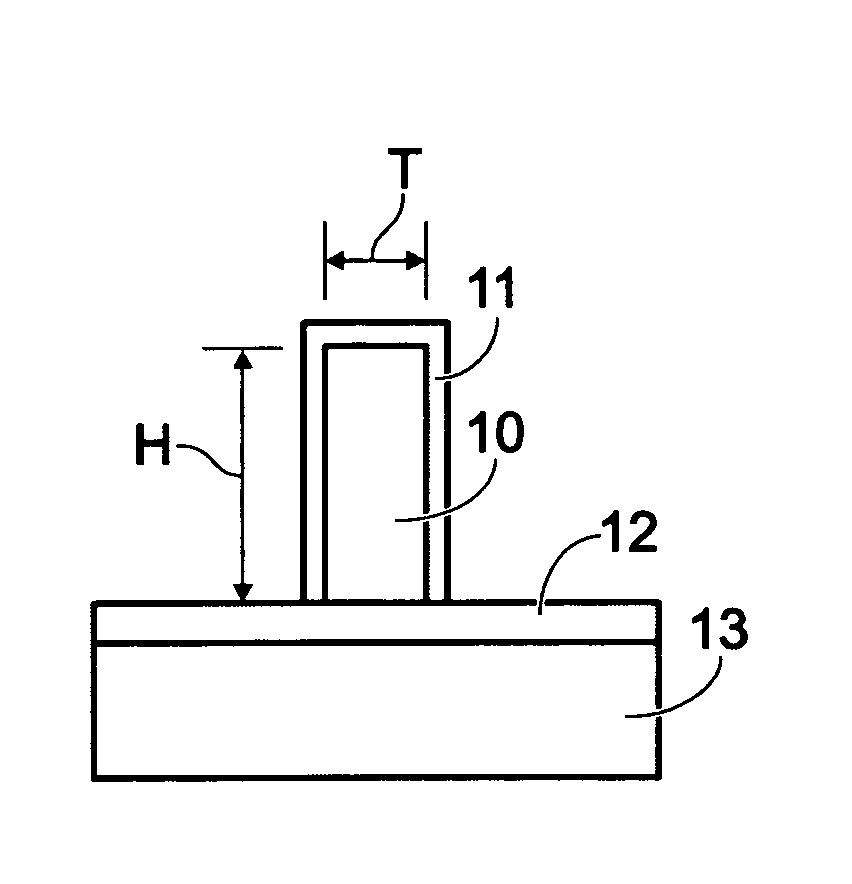

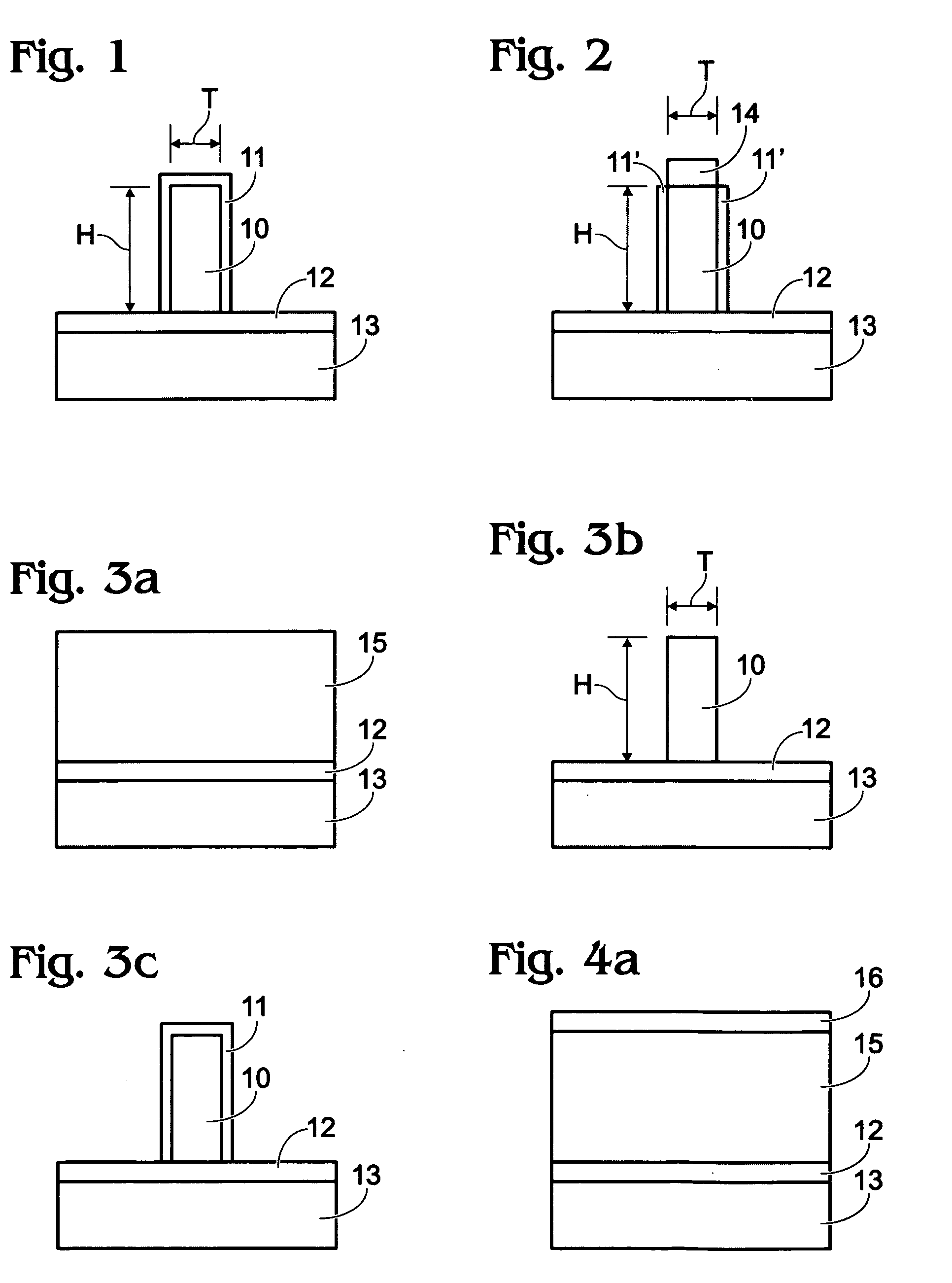

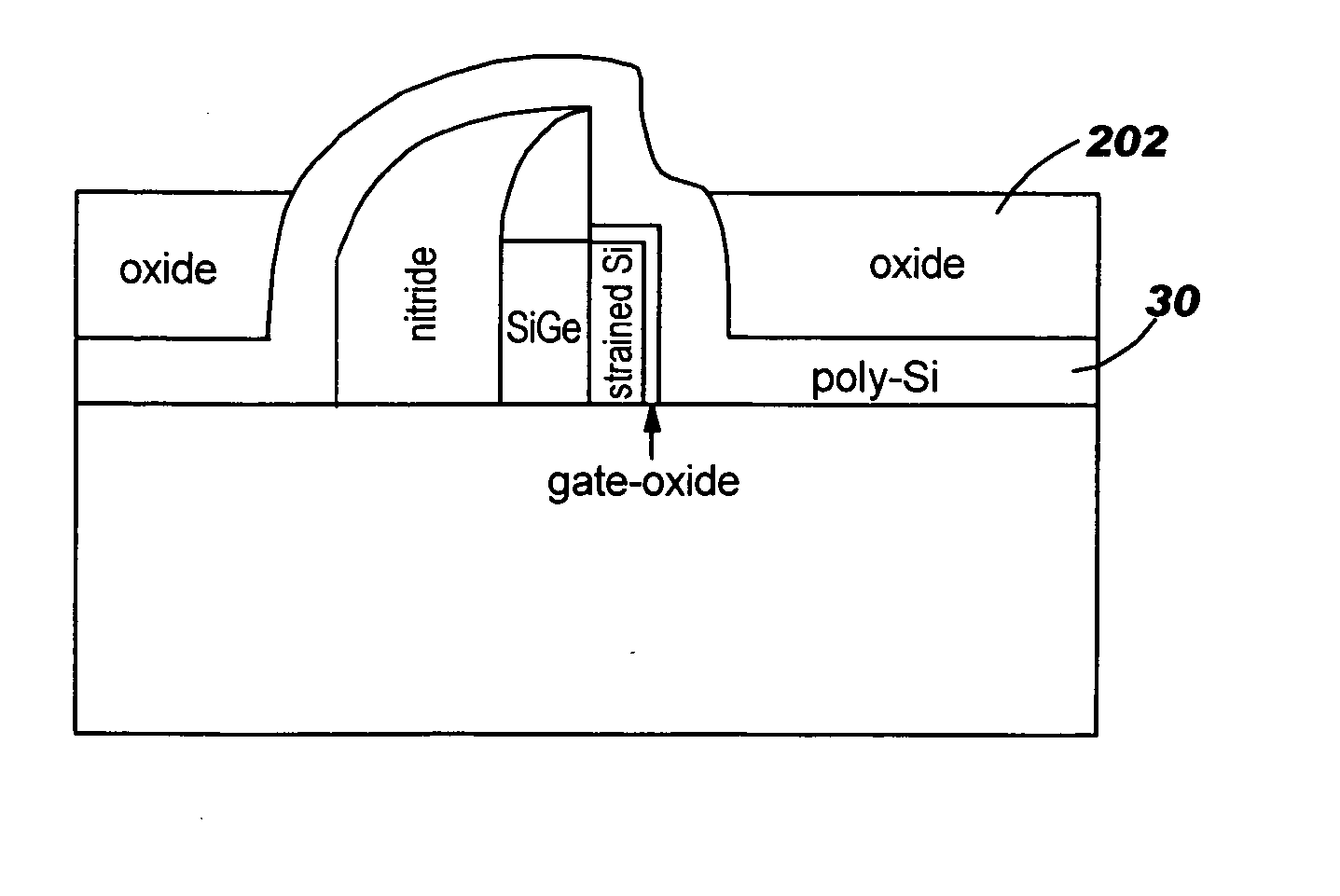

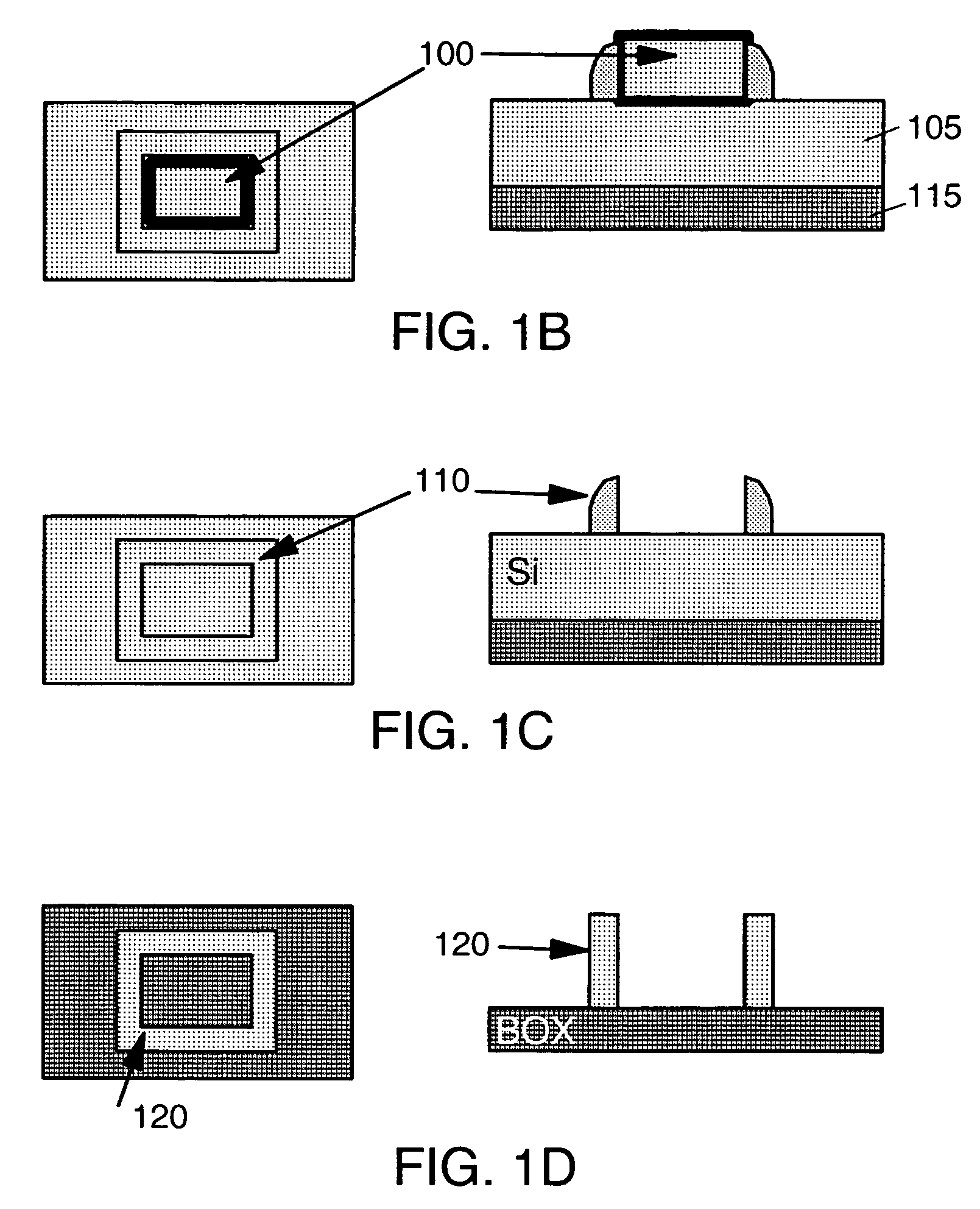

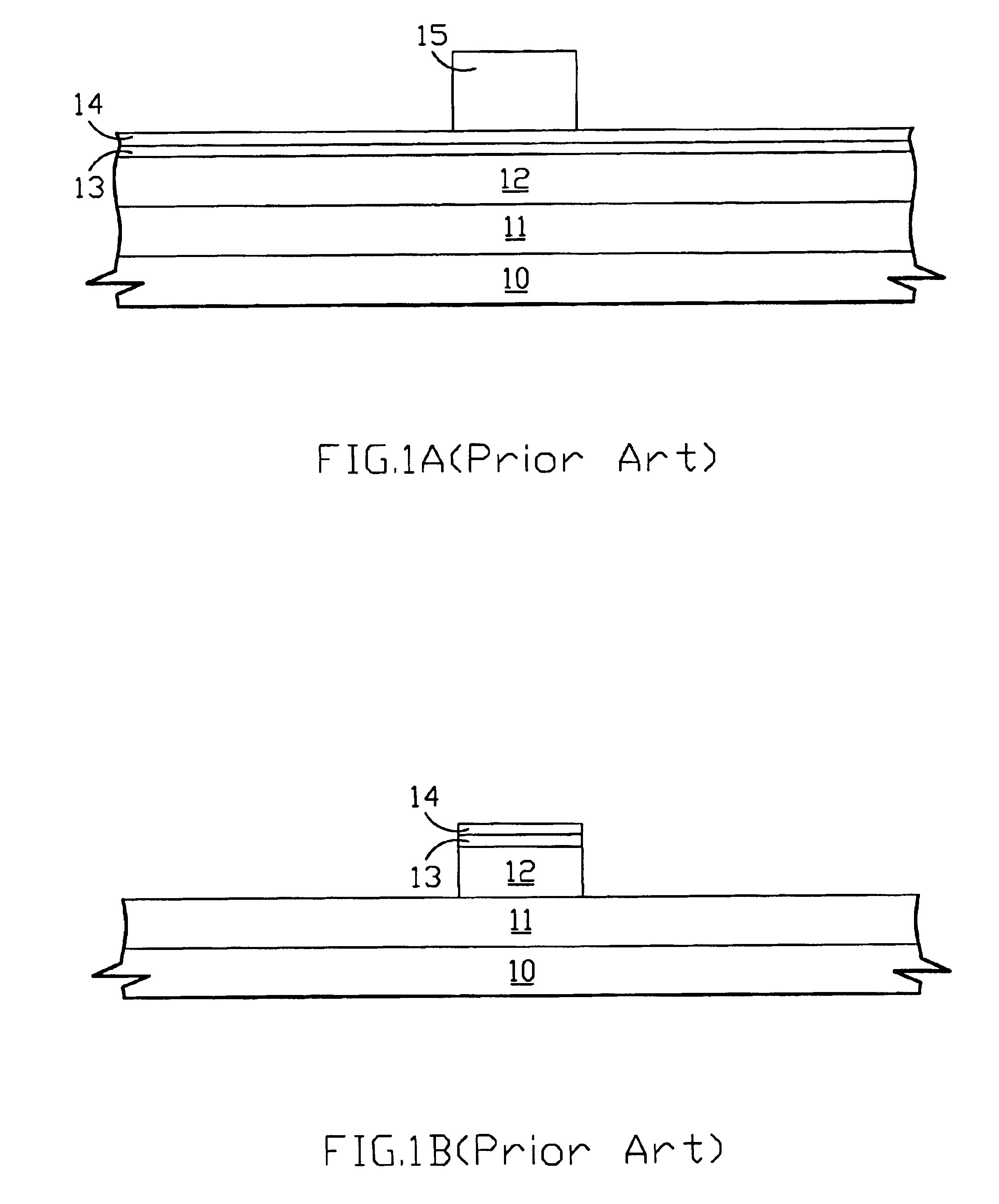

Strained silicon fin structure

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

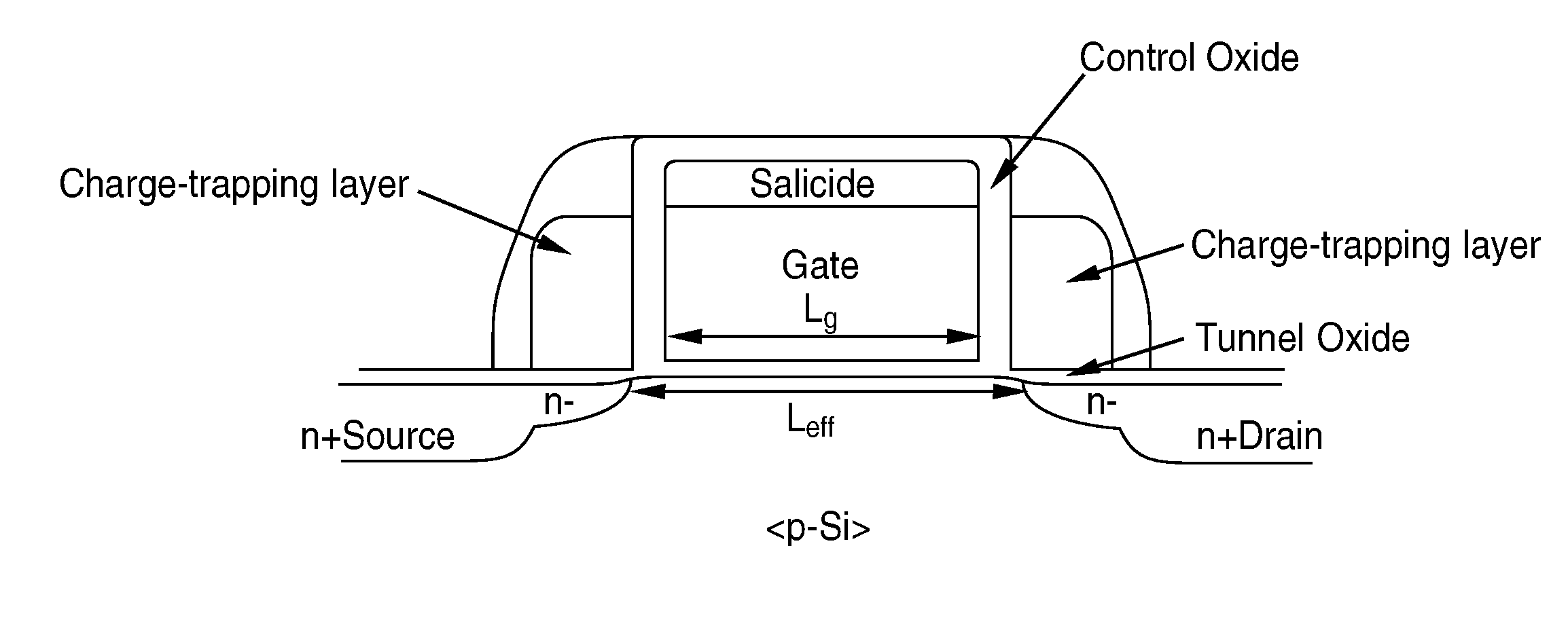

Multi-bit-per-cell nvm structures and architecture

InactiveUS20070164352A1High sensitivityReduce sensitivitySolid-state devicesRead-only memoriesGate dielectricEngineering

A transistor structure, such as a Double-gated FET (DG FET), that has been modified to include a charge-trapping region used to store either 2- or 4-bits of information. The charge-trapping region can, for example, be embedded in the gate dielectric stack underneath each gate electrode, or placed on the sidewalls of each gate electrode.

Owner:RGT UNIV OF CALIFORNIA

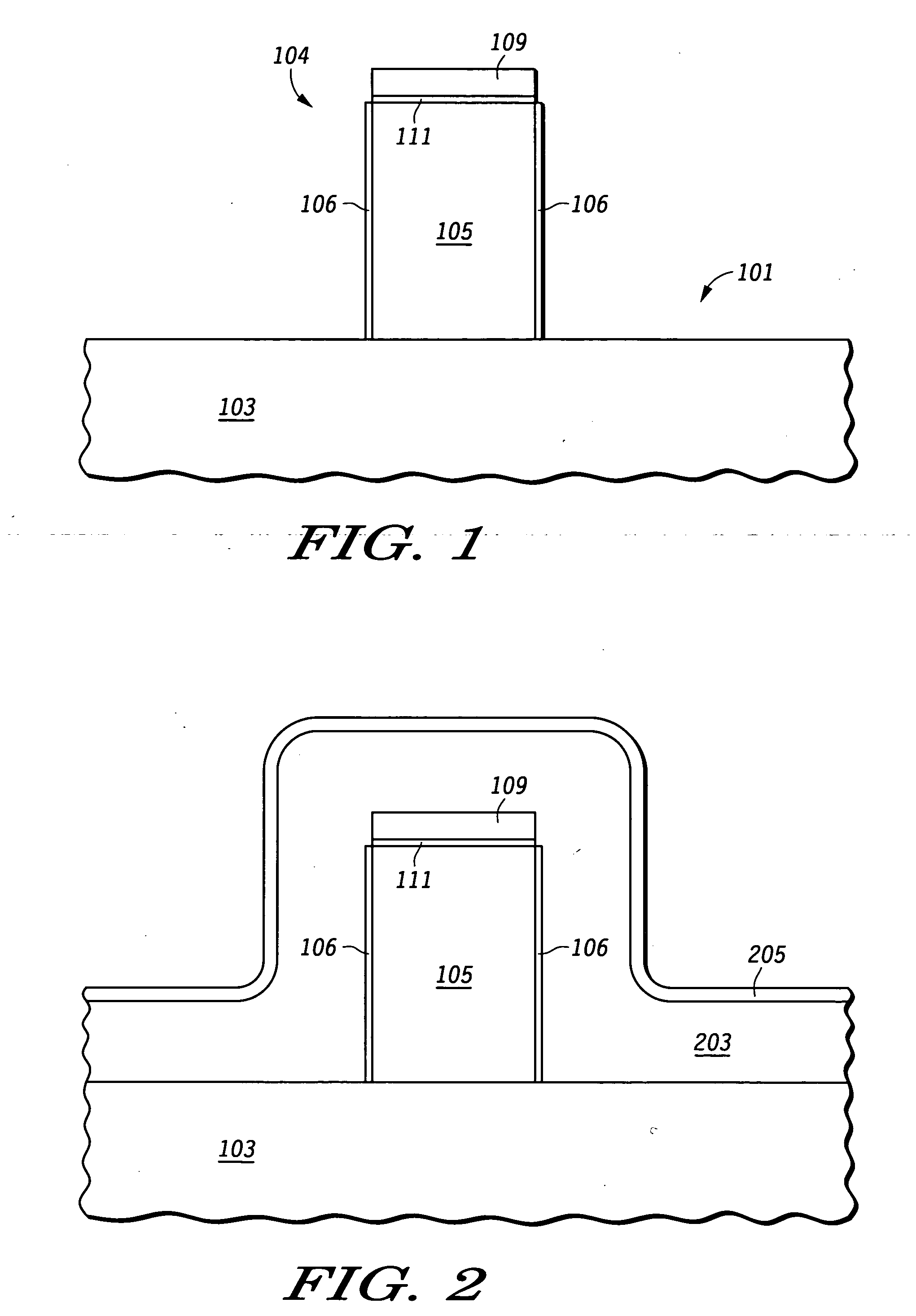

Double-gate FinFET device and fabricating method thereof

InactiveUS6885055B2Cost of wafer is decreasedImprove featuresTransistorSemiconductor/solid-state device detailsNano sizeFloating body effect

The present invention relates to double-gate FinFET devices and fabricating methods thereof. More particularly, the invention relates to an electrically stable double-gate FinFET device and the method of fabrication in which the Fin active region on a bulk silicon substrate where device channel and the body are to be formed has a nano-size width and is connected to the substrate and is formed with the shape of a wall along the channel length direction.The conventional double-gate MOS devices are fabricated using SOI wafers which are more expensive than bulk silicon wafers. It also has problems including the floating body effects, larger source / drain parasitic resistance, off-current increase, and deterioration in heat transfer to the substrate.

Owner:KIPB LLC

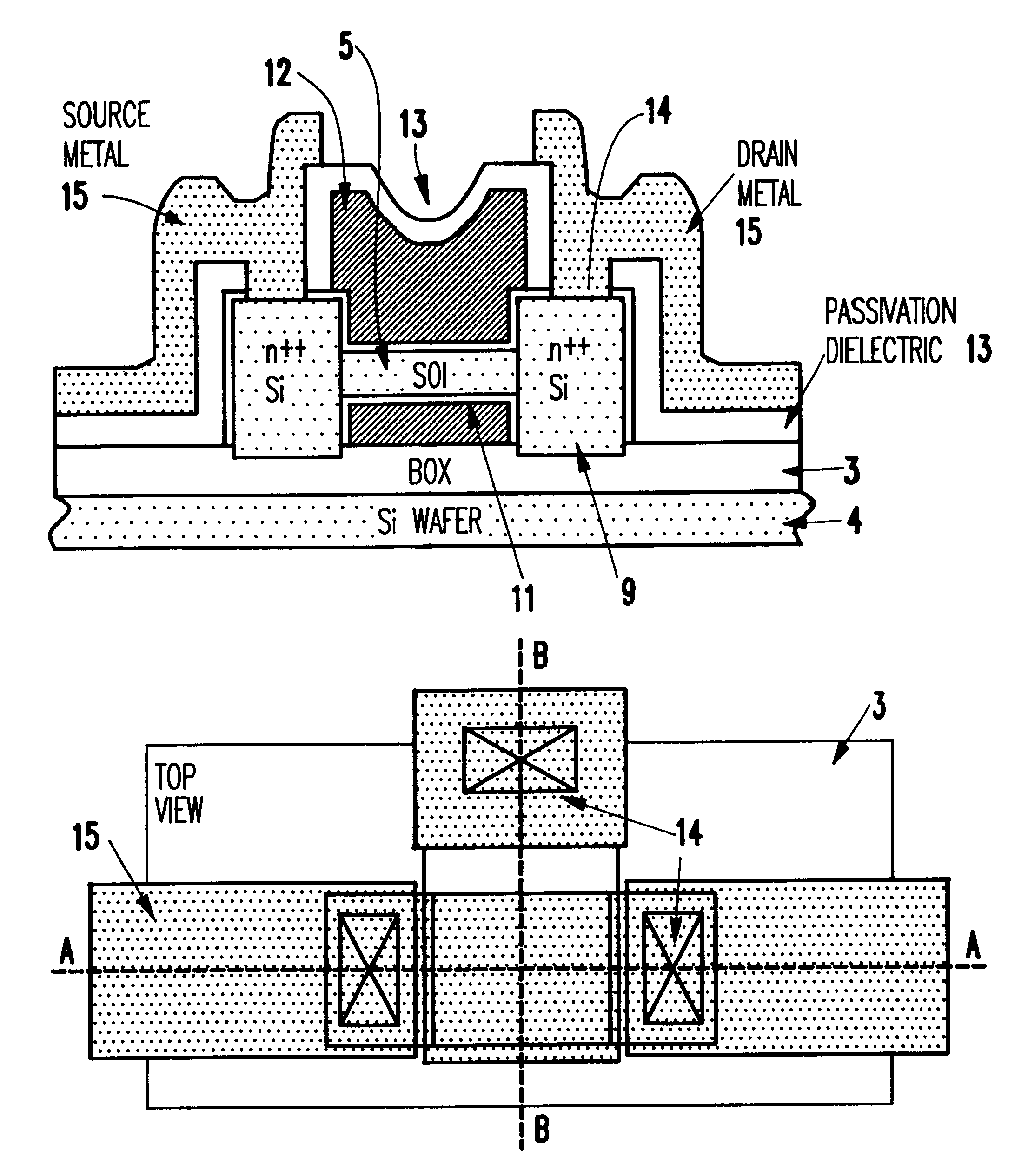

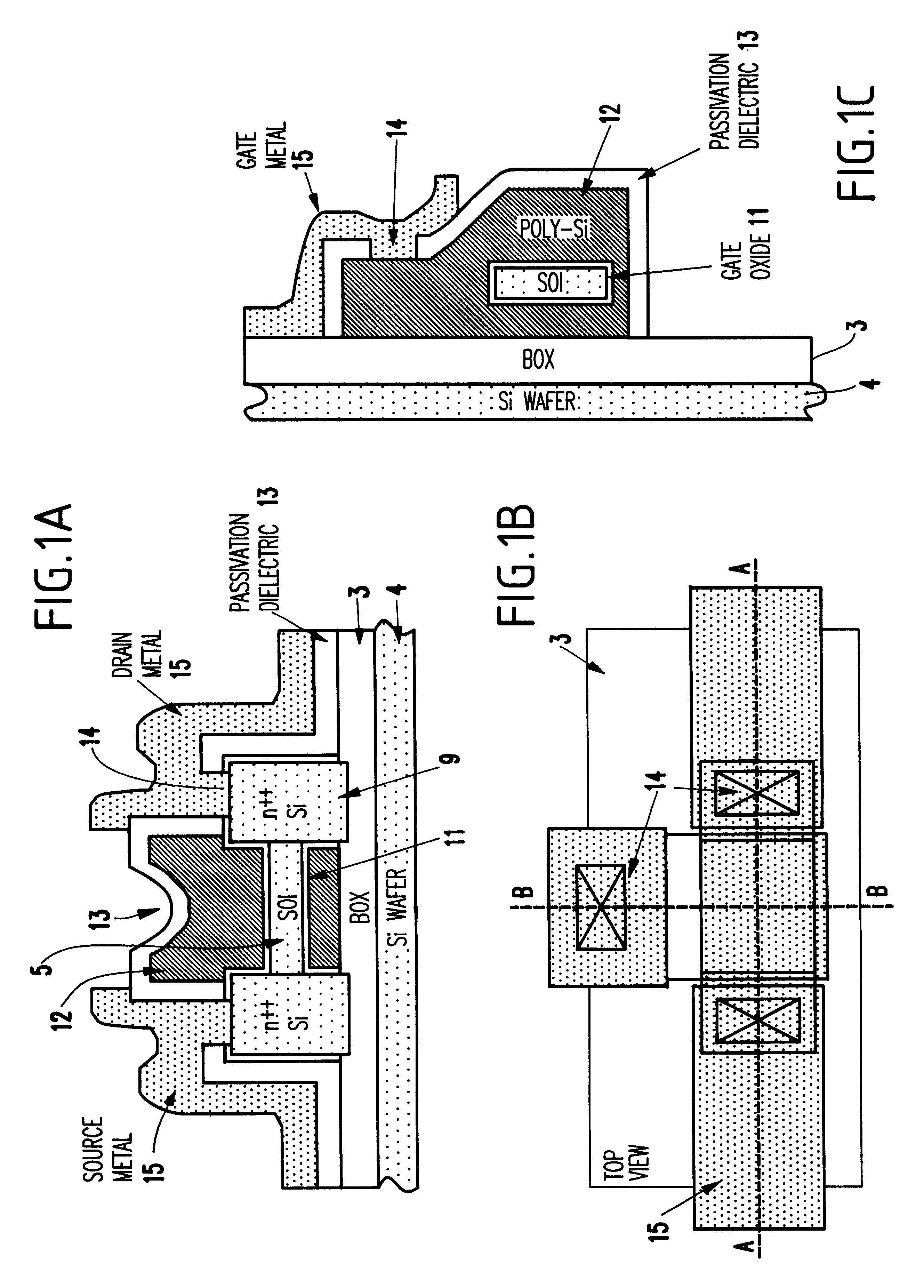

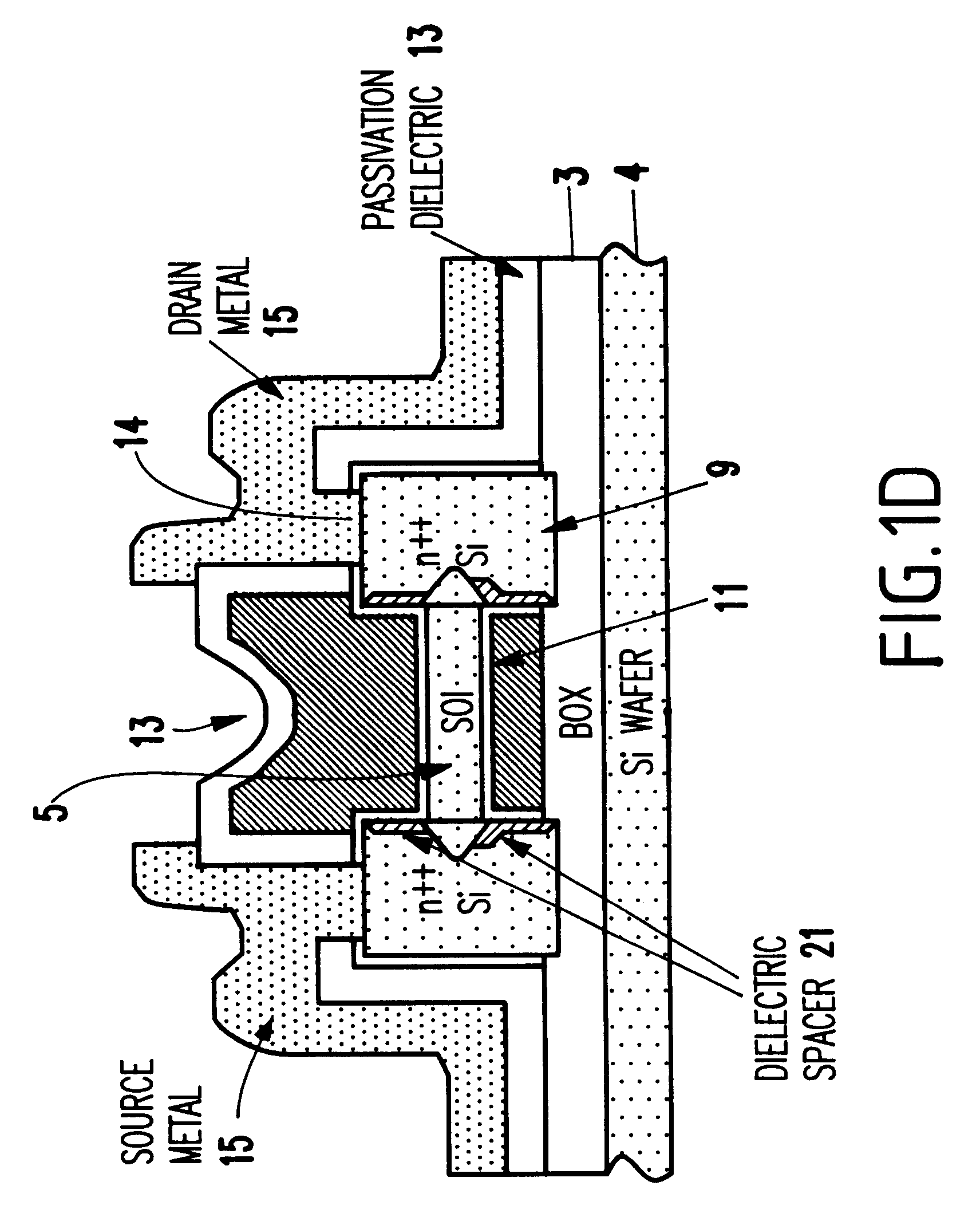

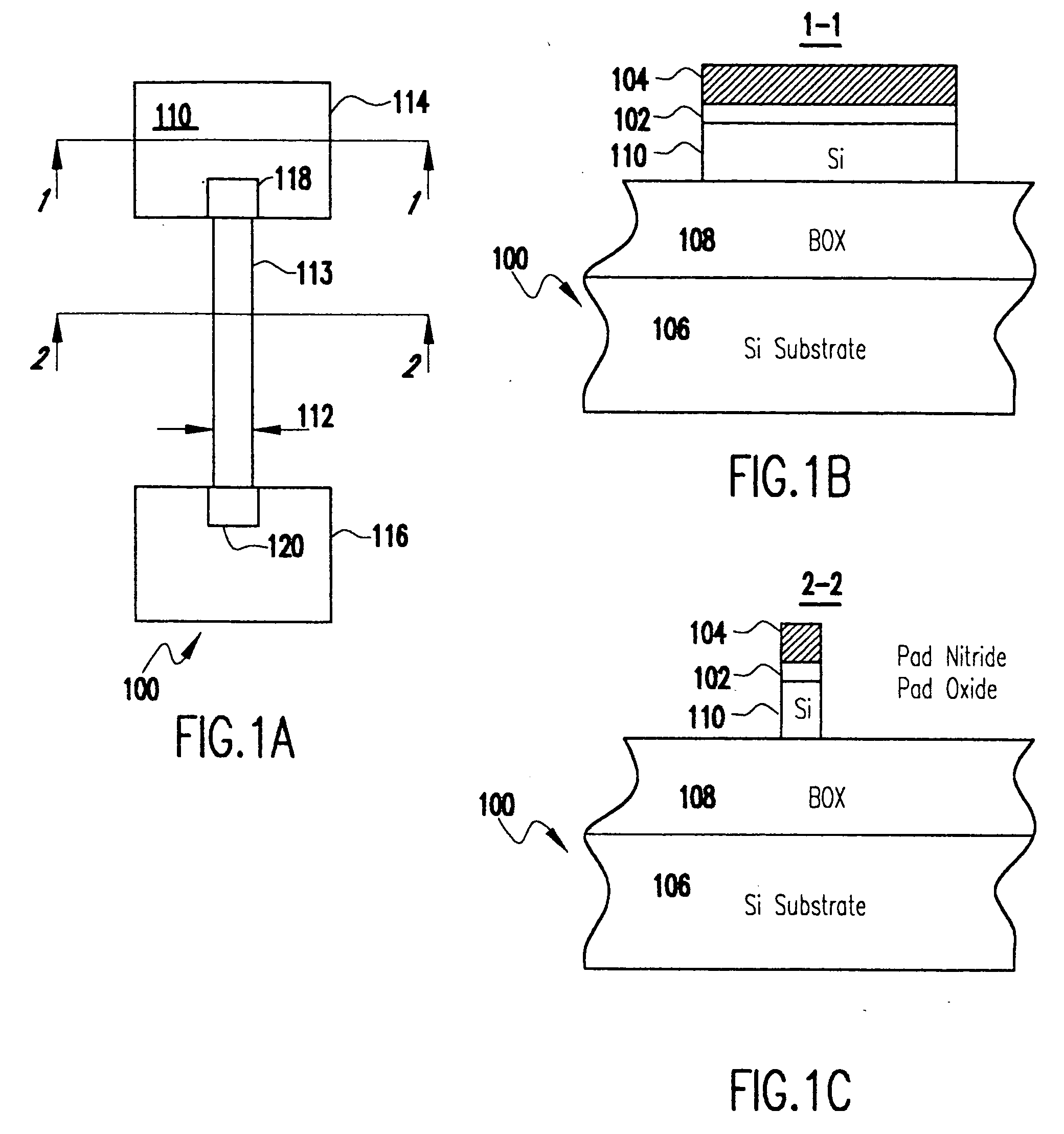

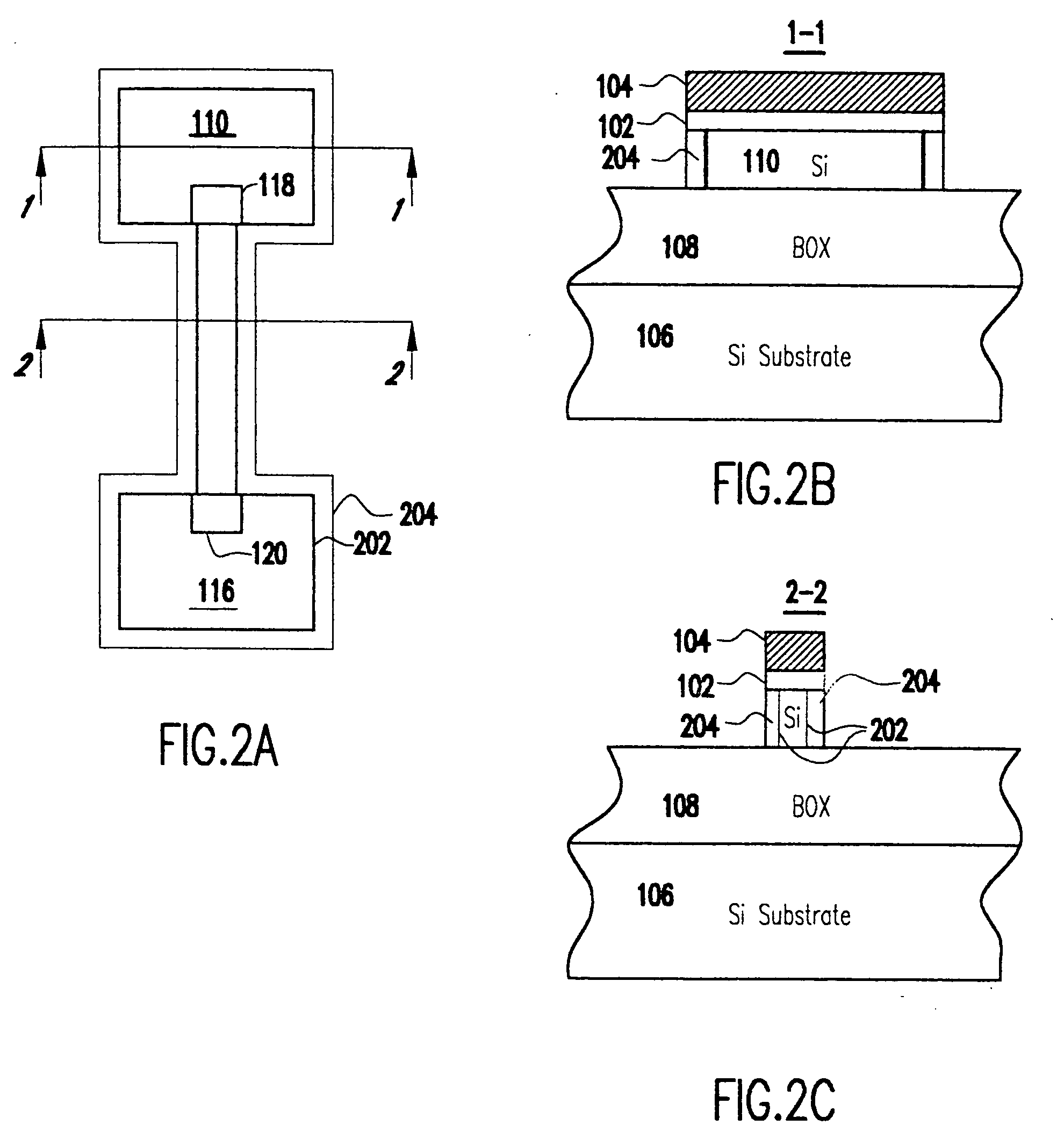

Double planar gated SOI MOSFET structure

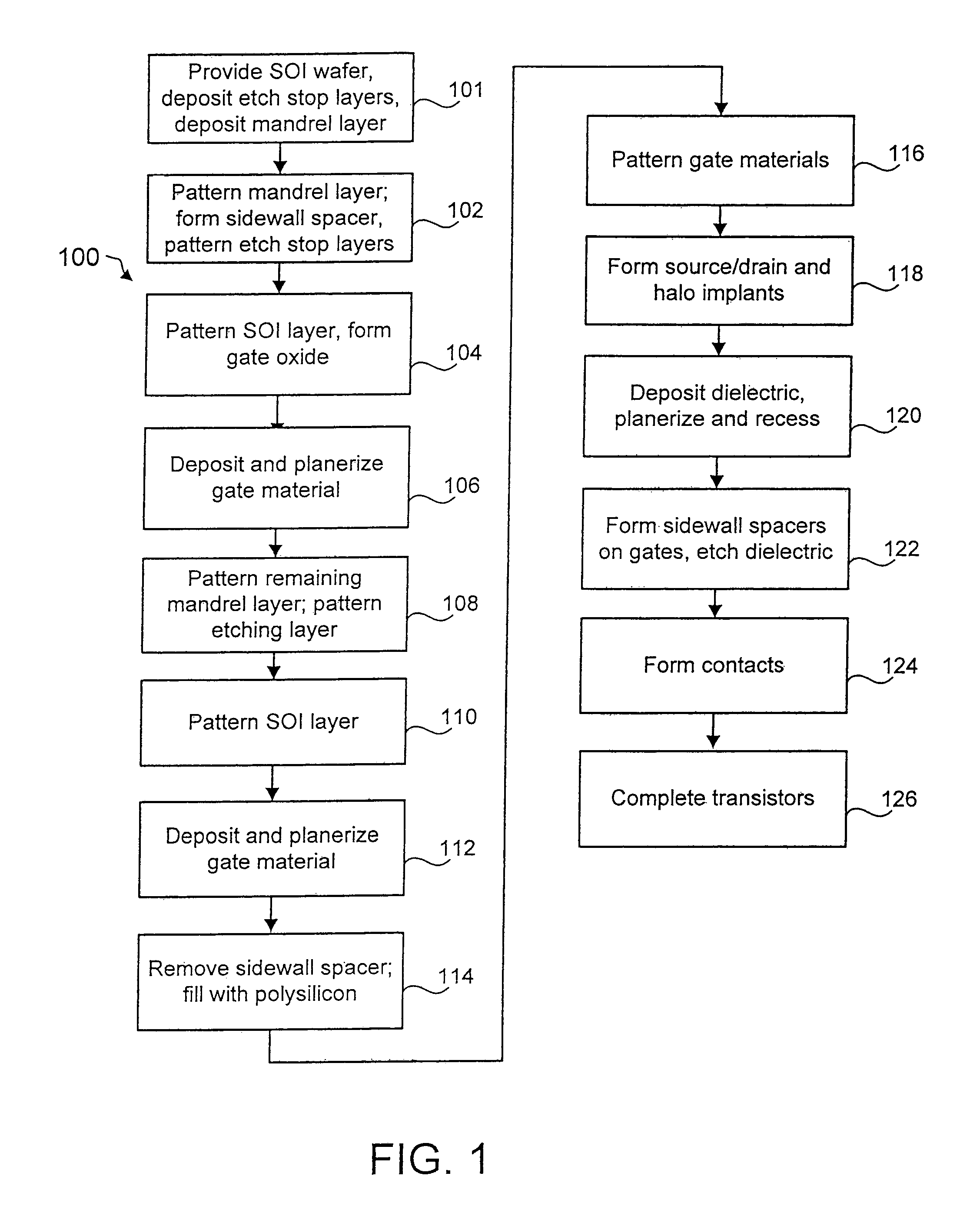

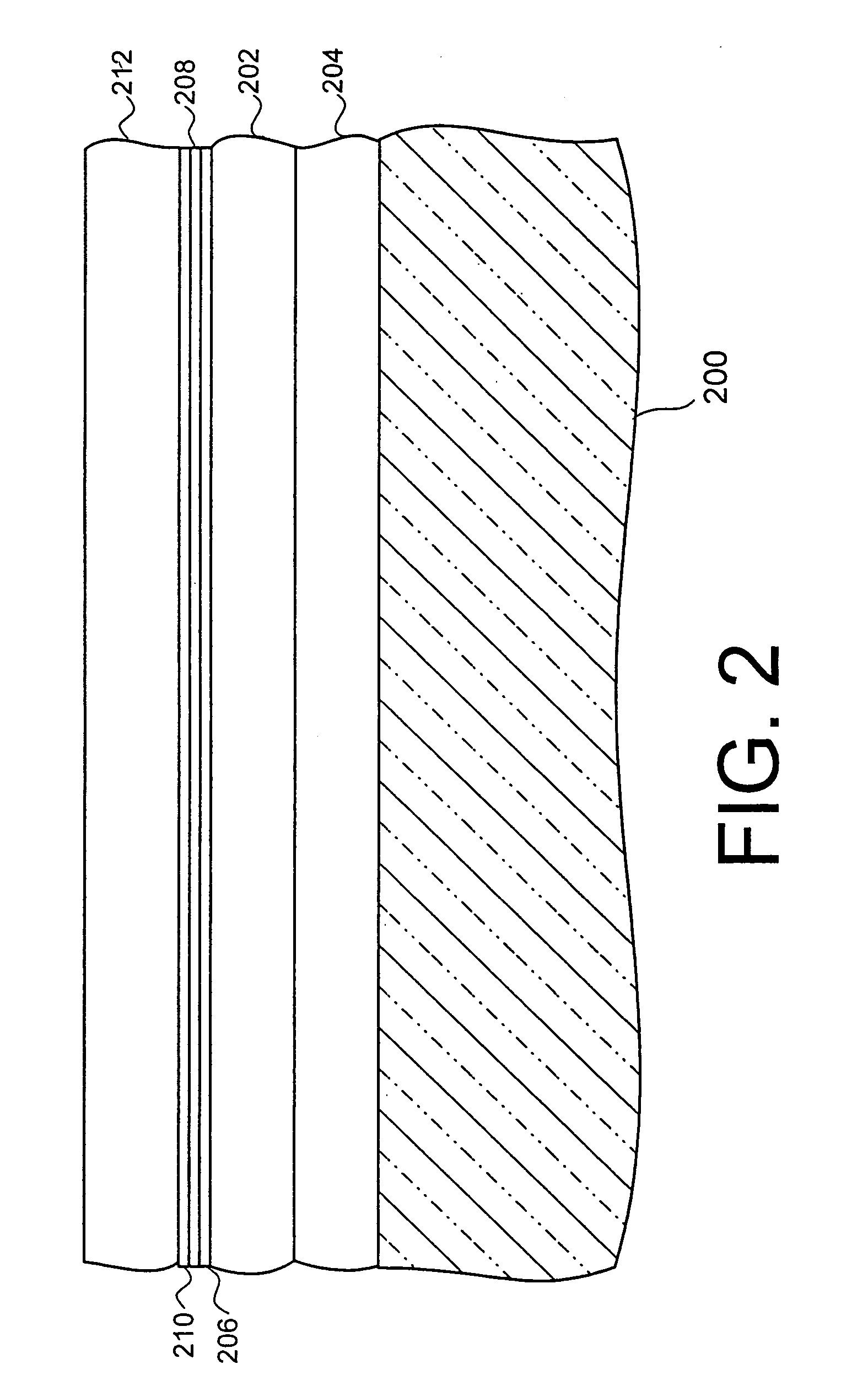

A double gated silicon-on-insulator (SOI) MOSFET is fabricated by using a mandrel shallow trench isolation formation process, followed by a damascene gate. The double gated MOSFET features narrow diffusion lines defined sublithographically or lithographically and shrunk, damascene process defined by an STI-like mandrel process. The double gated SOI MOSFET increases current drive per layout width and provides low out conductance.

Owner:GLOBALFOUNDRIES INC

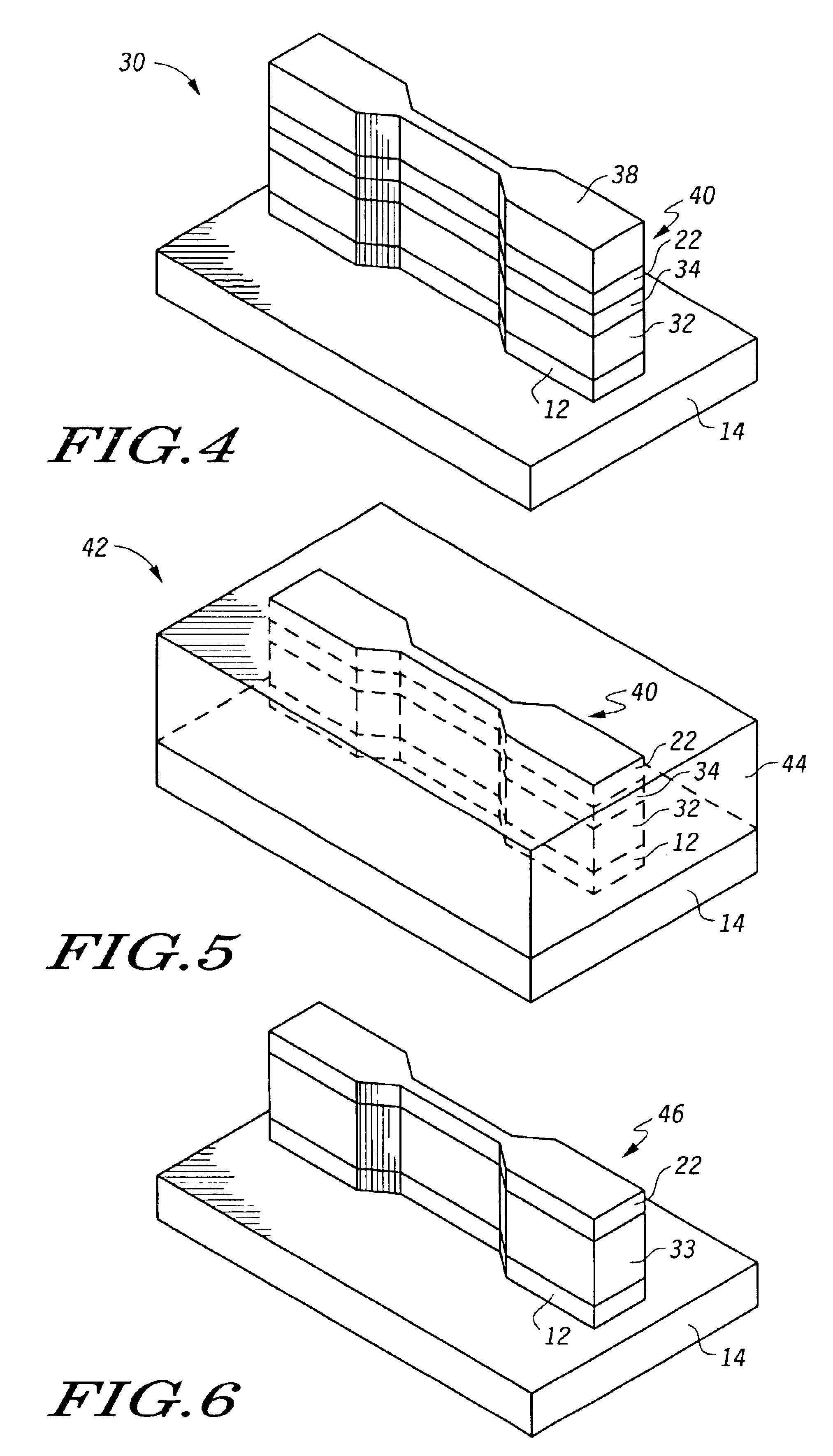

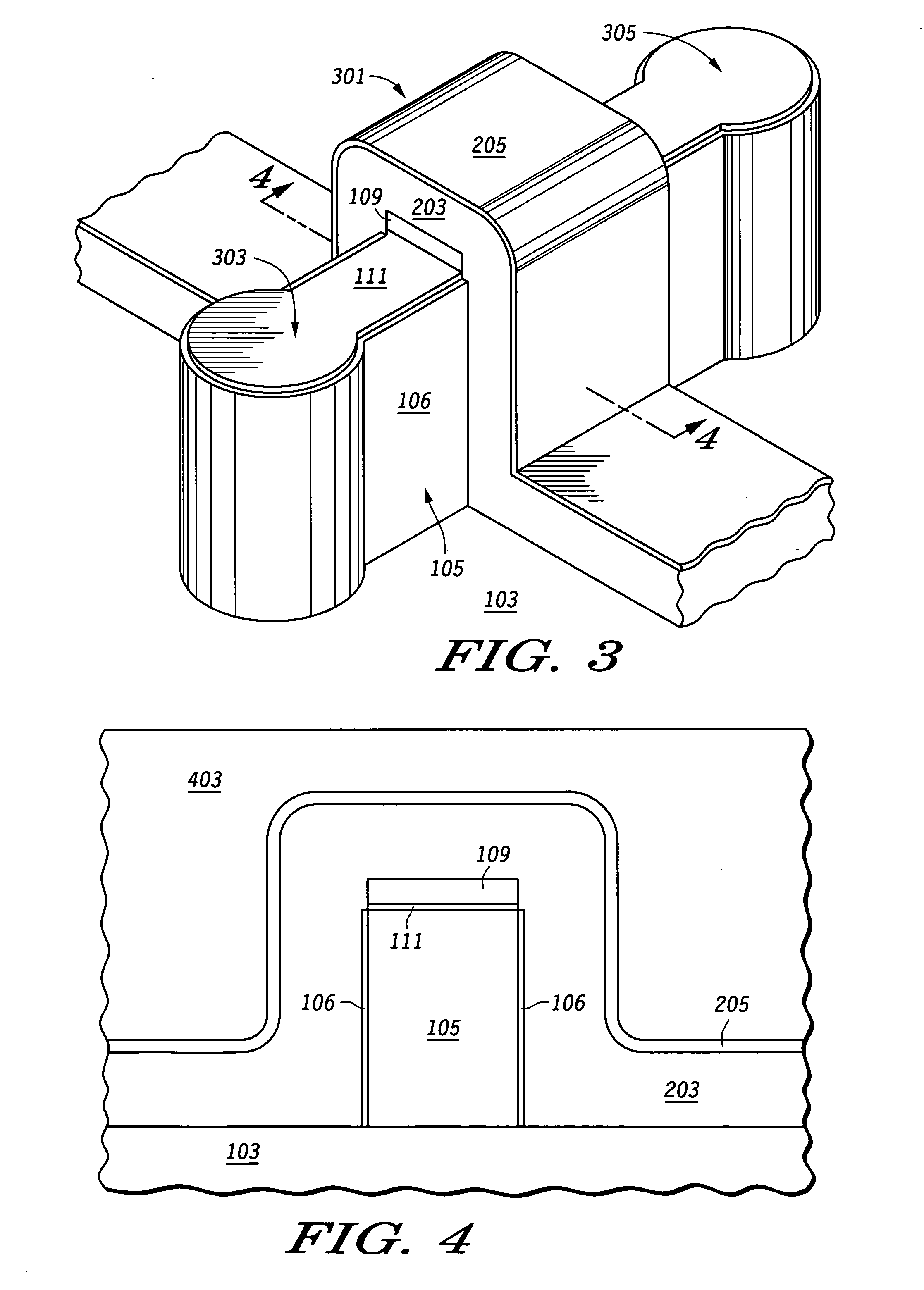

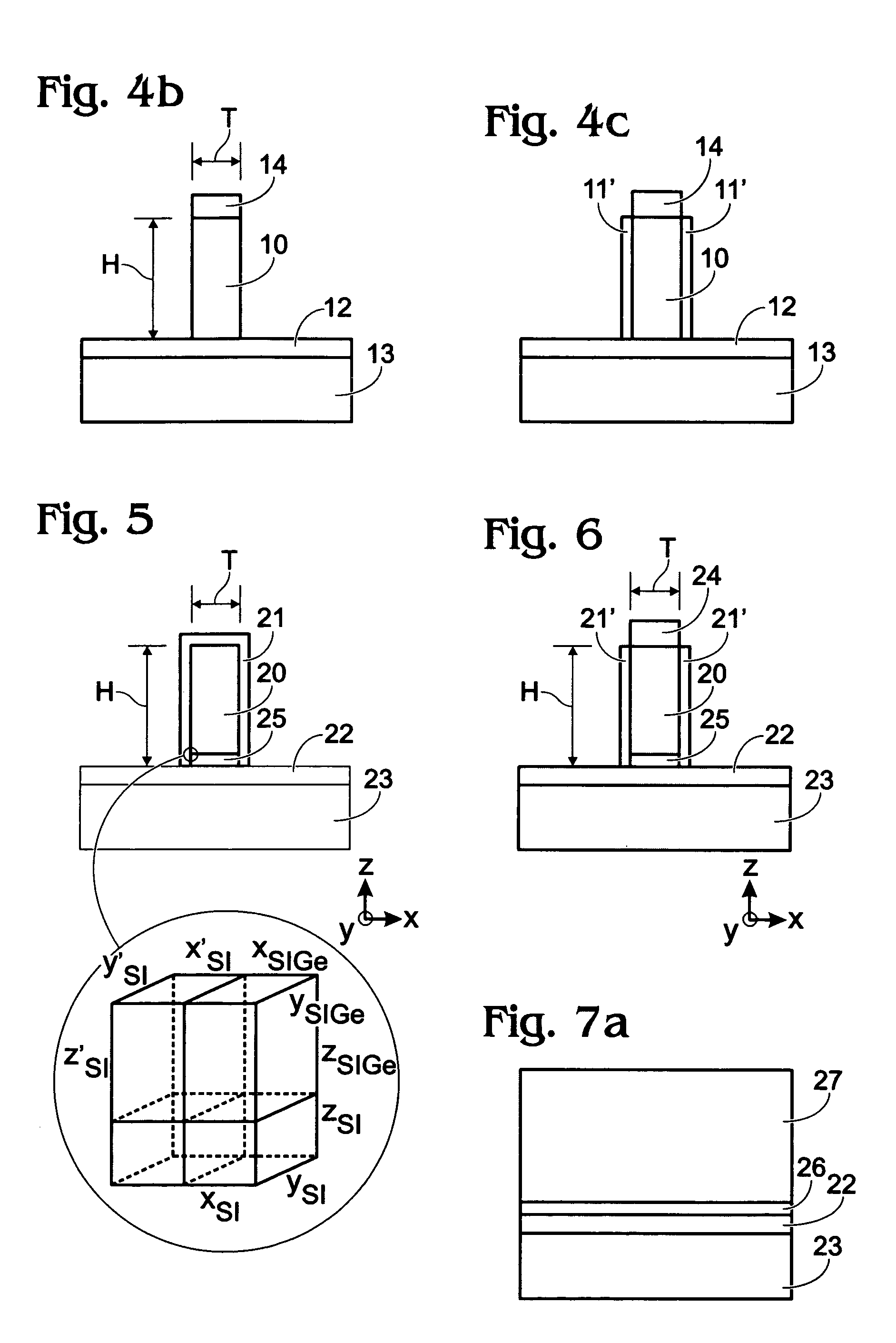

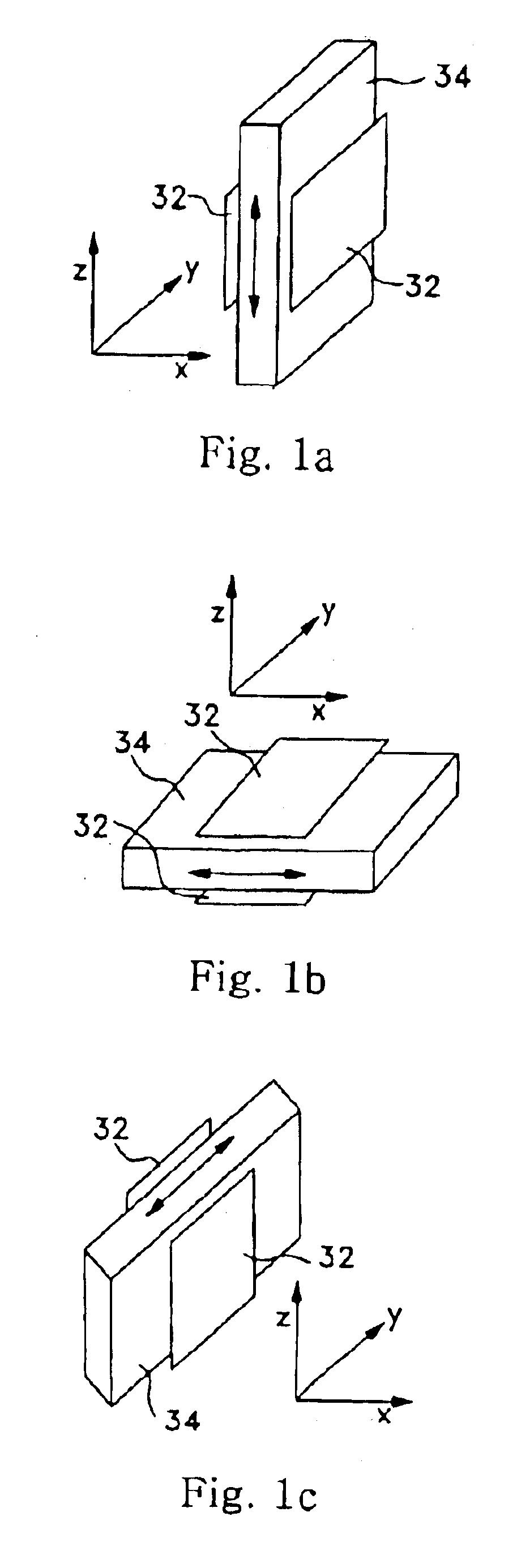

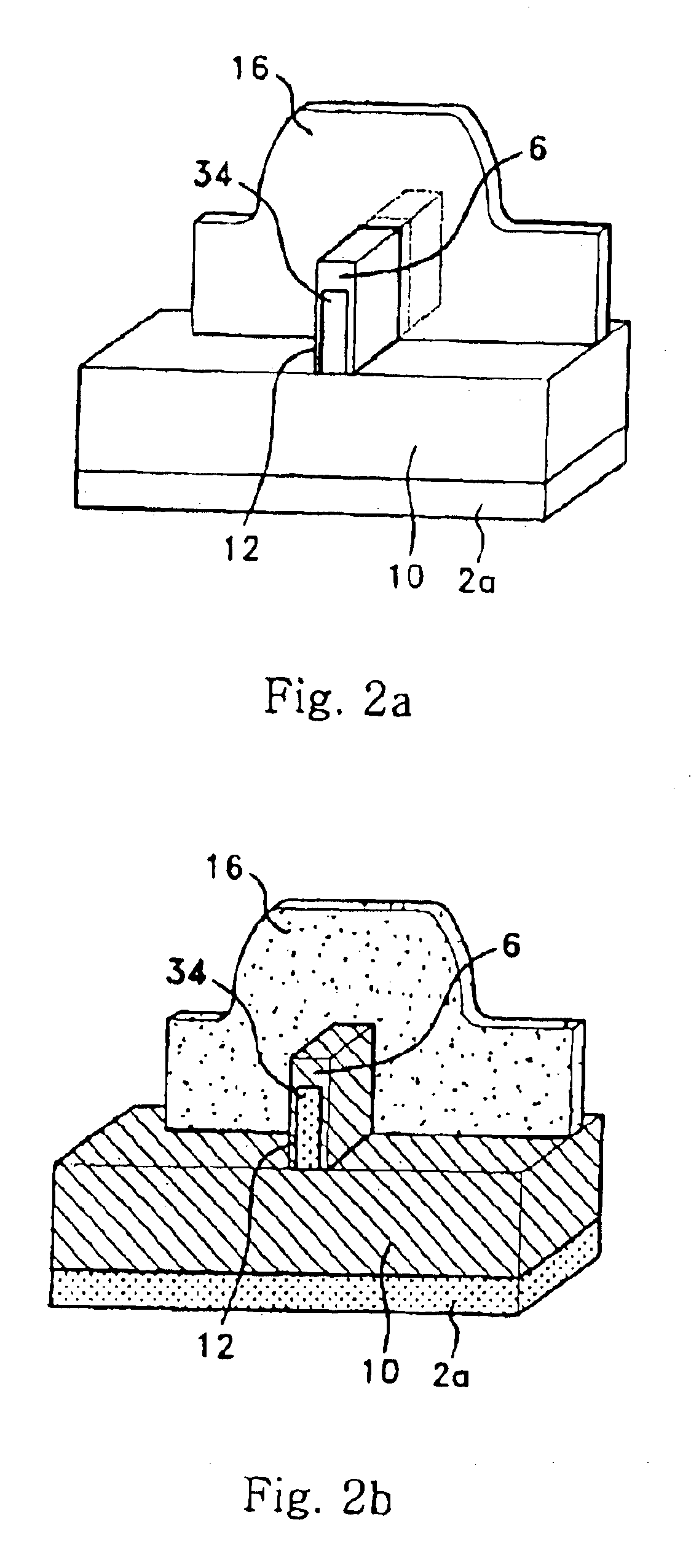

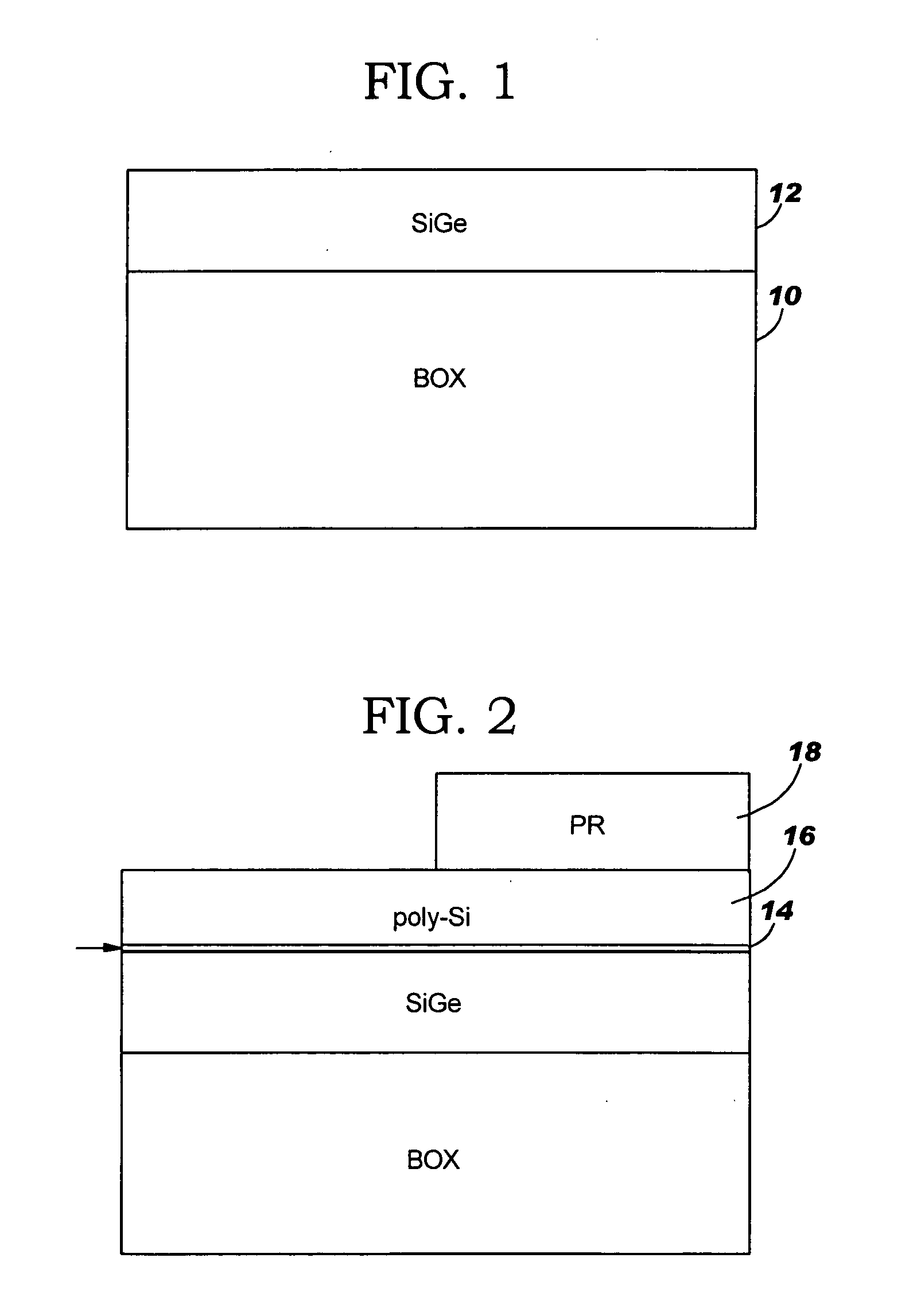

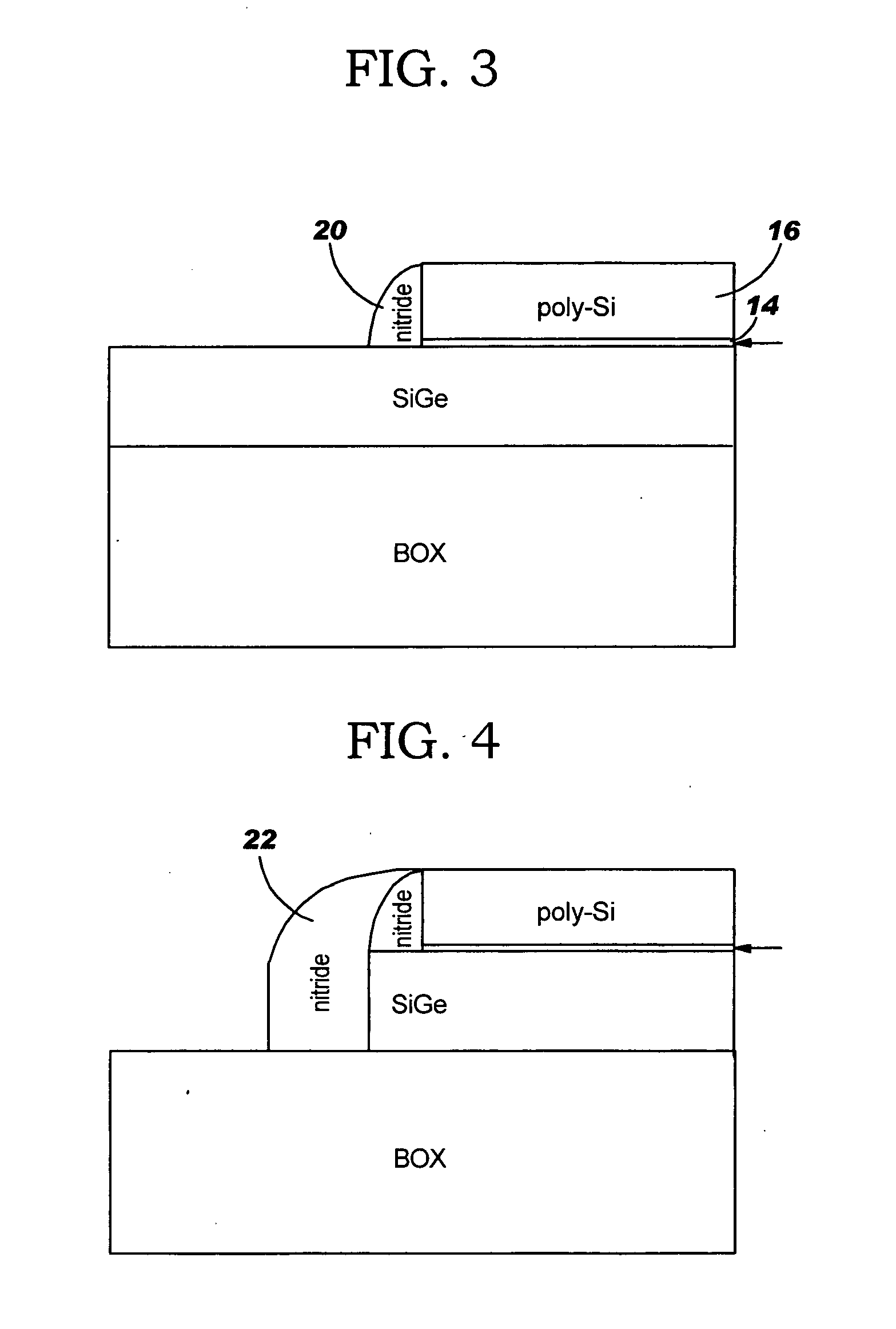

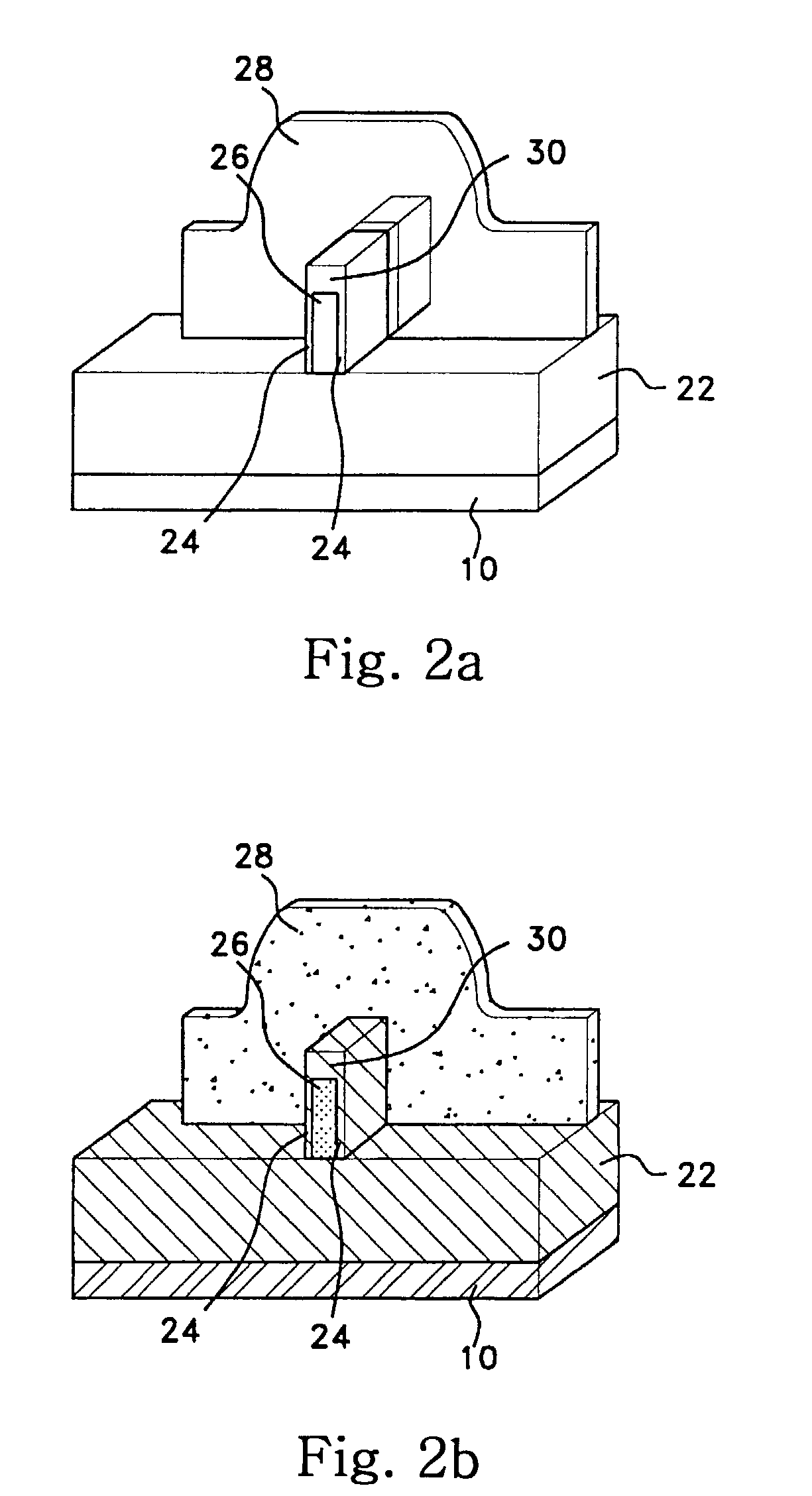

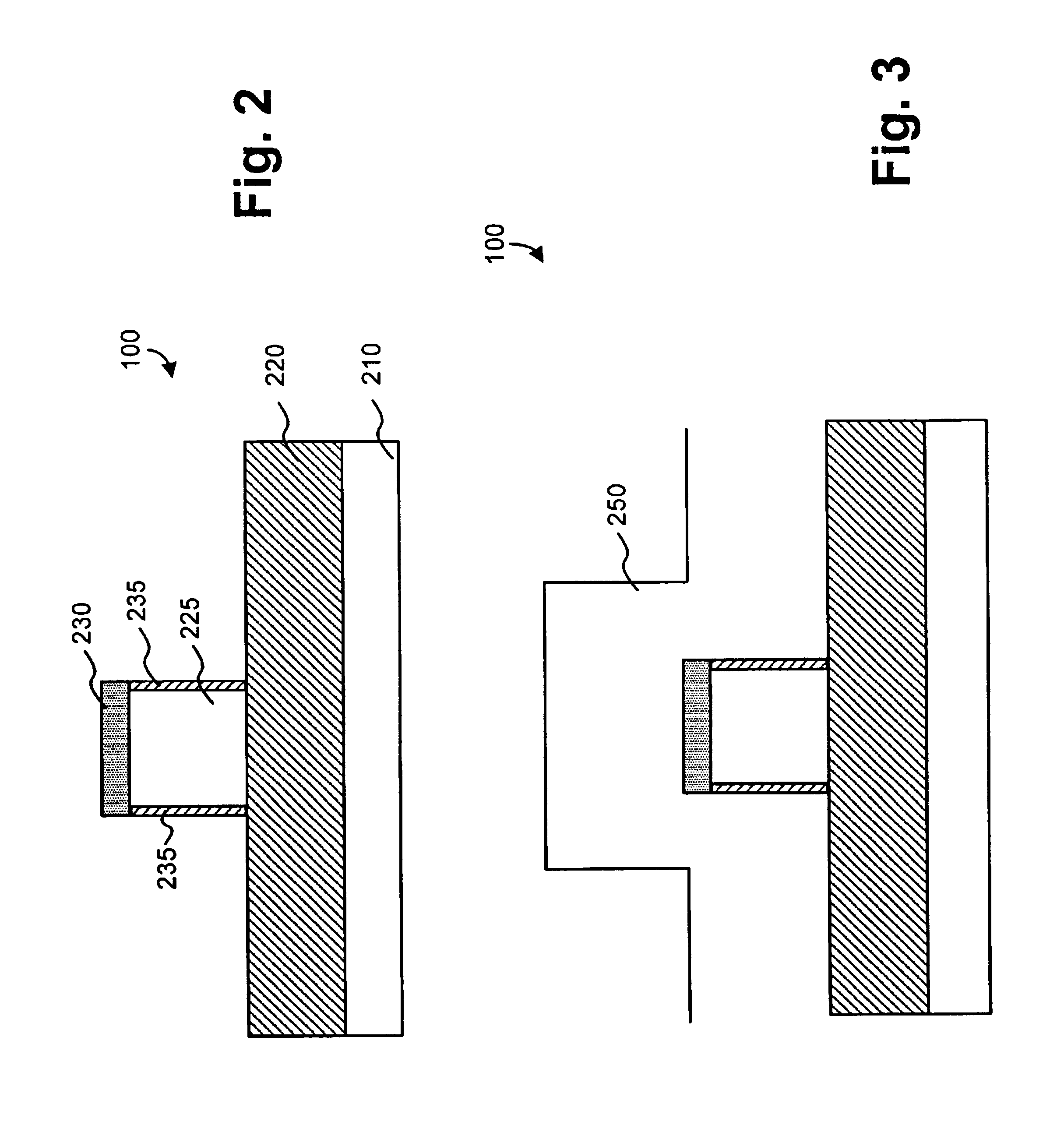

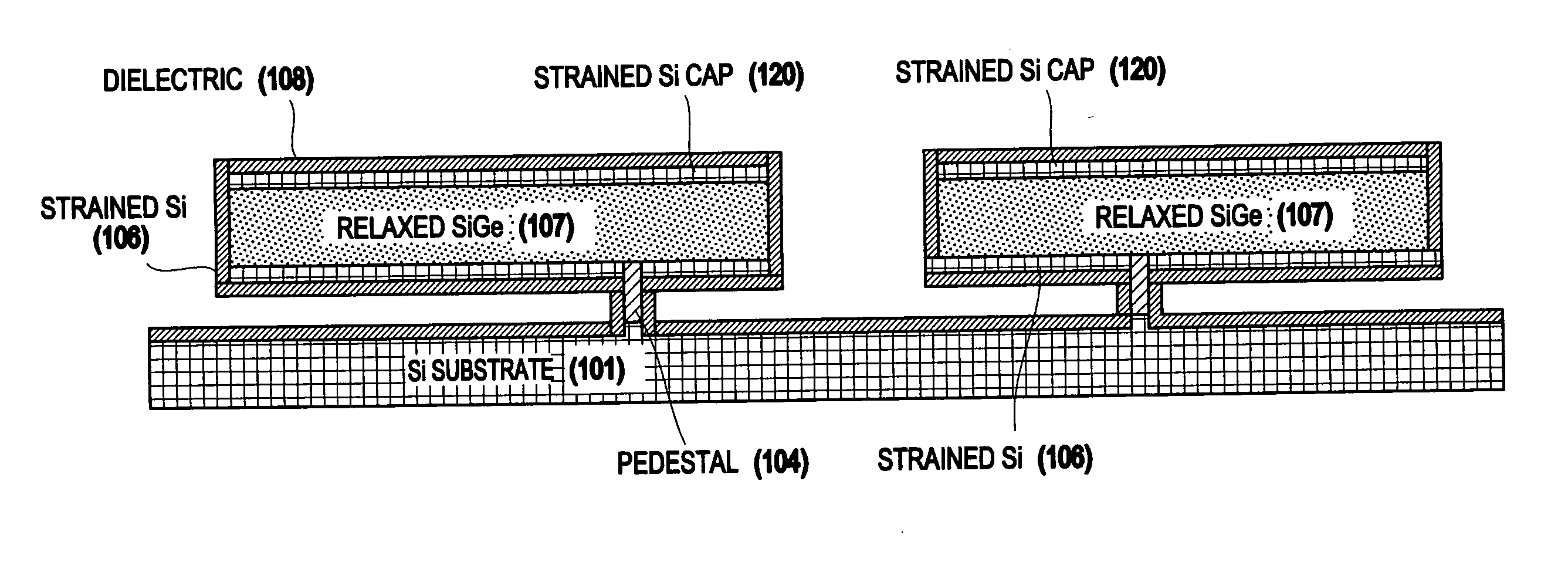

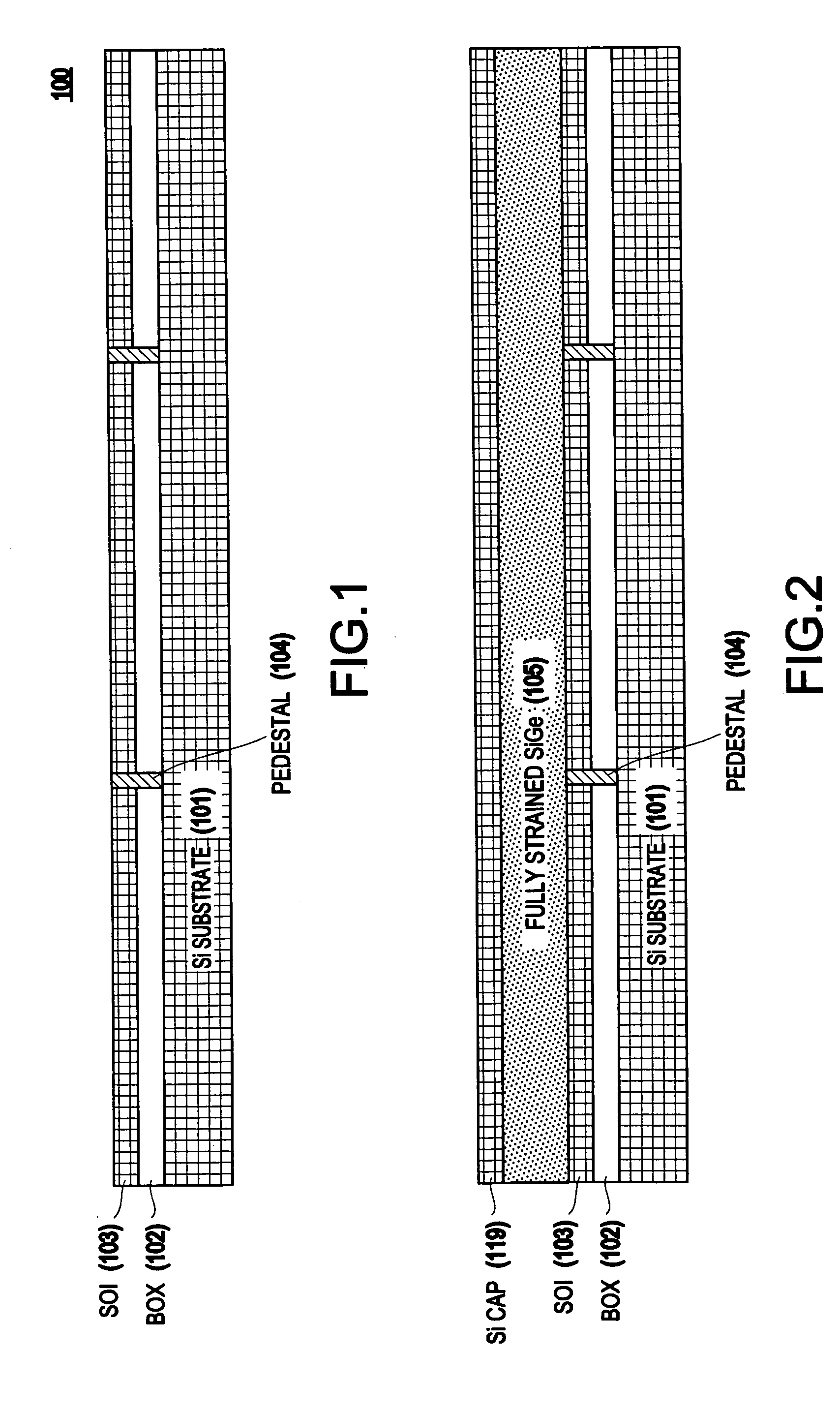

Structures and methods for making strained mosfets

A method and device providing a strained Si film with reduced defects is provided, where the strained Si film forms a fin vertically oriented on a surface of a non-conductive substrate. The strained Si film or fin may form a semiconductor channel having relatively small dimensions while also having few defects. The strained Si fin is formed by growing Si on the side of a relaxed SiGe block. A dielectric gate, such as, for example, an oxide, a high “k” material, or a combination of the two, may be formed on a surface of the strained Si film. Additionally, without substantially affecting the stress in the strained Si film, the relaxed SiGe block may be removed to allow a second gate oxide to be formed on the surface previously occupied by the relaxed SiGe block. Accordingly, a semiconductor device having a strained Si fin vertically oriented on a non-conductive substrate may be formed where the strained Si film is oriented such that it may form a channel of small dimensions allowing access to both sides and top in order to from single gate, double gate, or more gate MOSFETs and finFETs with a channel having a reduced number of defects and / or reduced dimensions.

Owner:GLOBALFOUNDRIES US INC

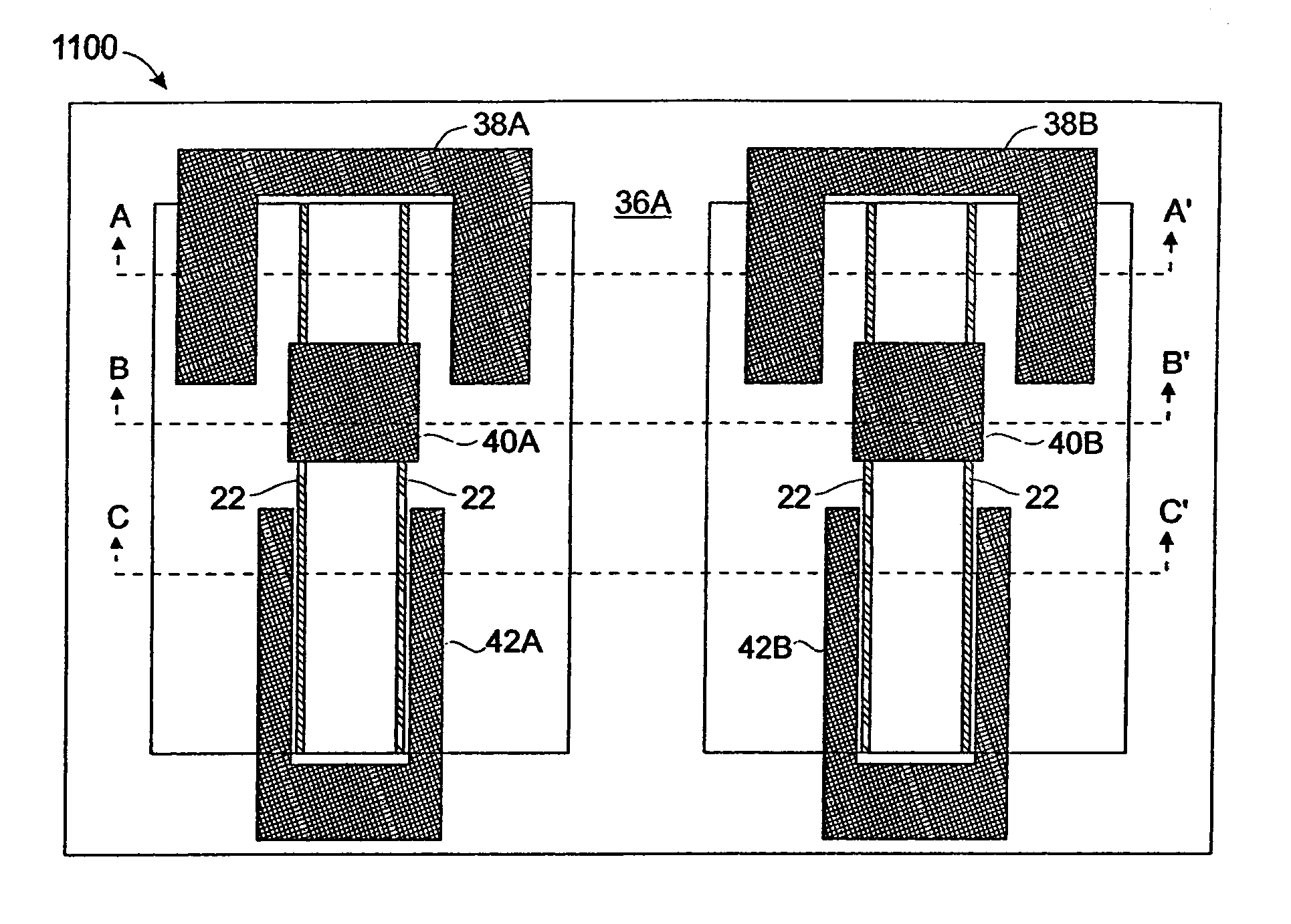

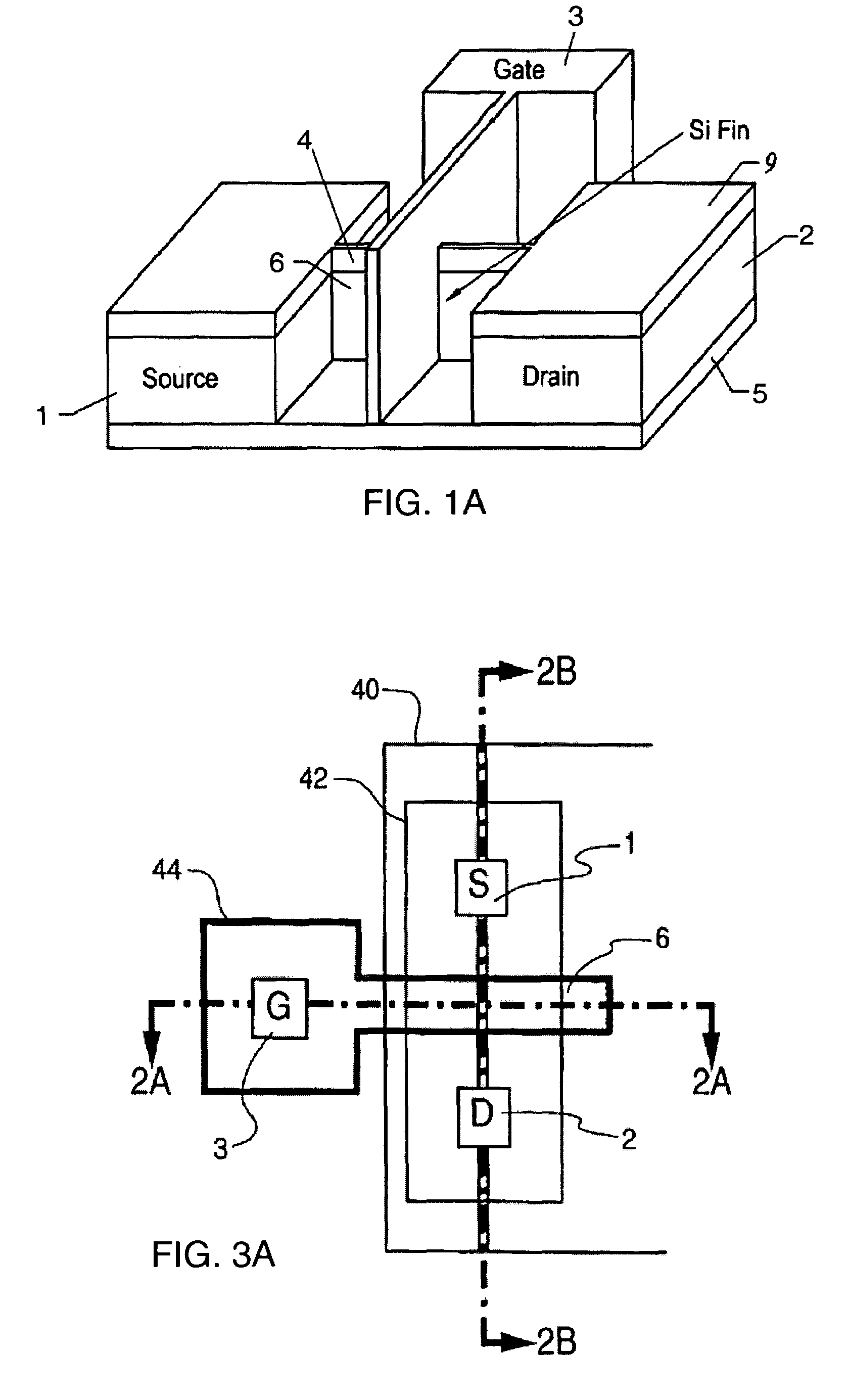

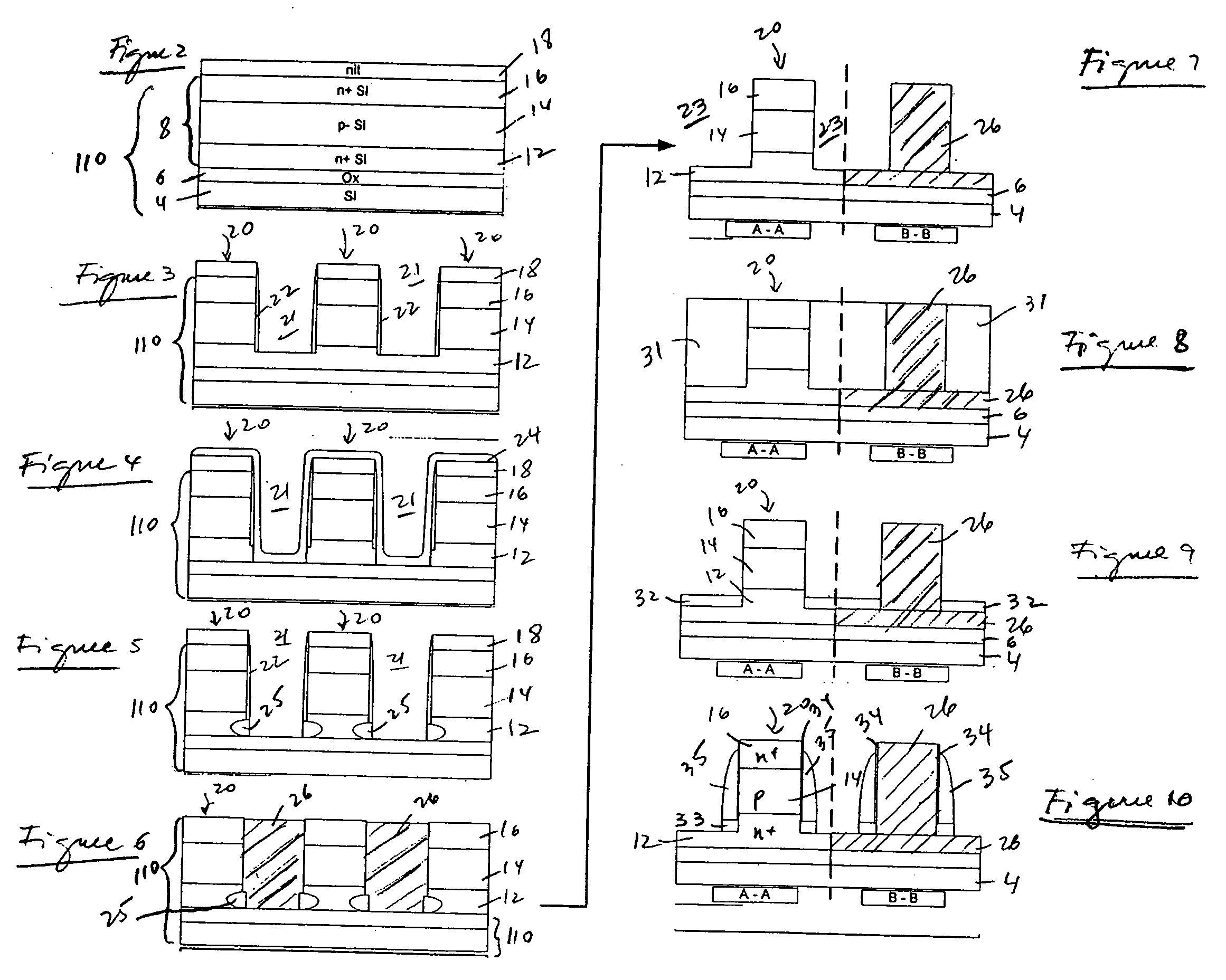

Vertical Fin-FET MOS devices

ActiveUS7683428B2Improve current carrying capacityImprove rendering capabilitiesTransistorSolid-state devicesHigh densityDouble gate

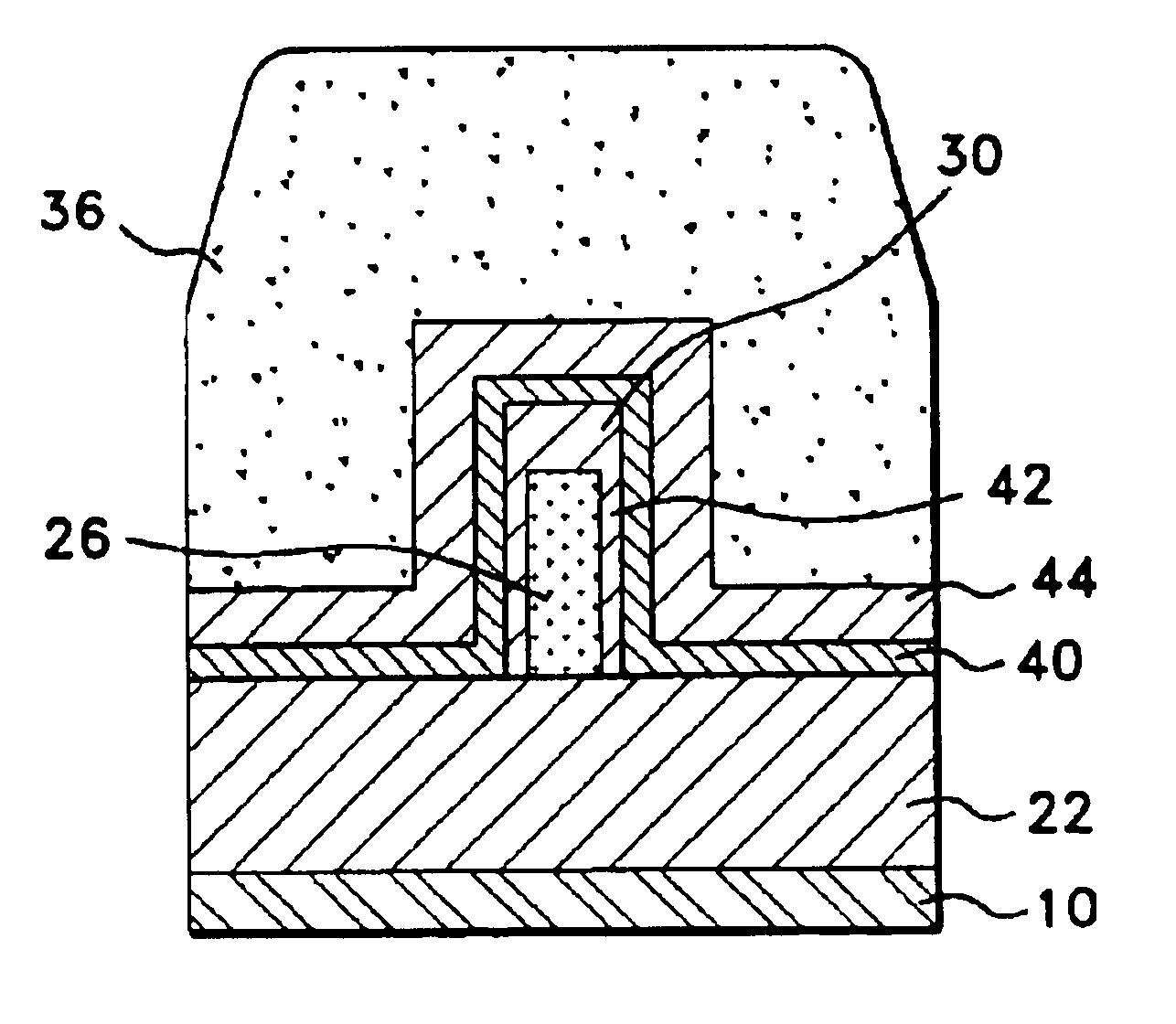

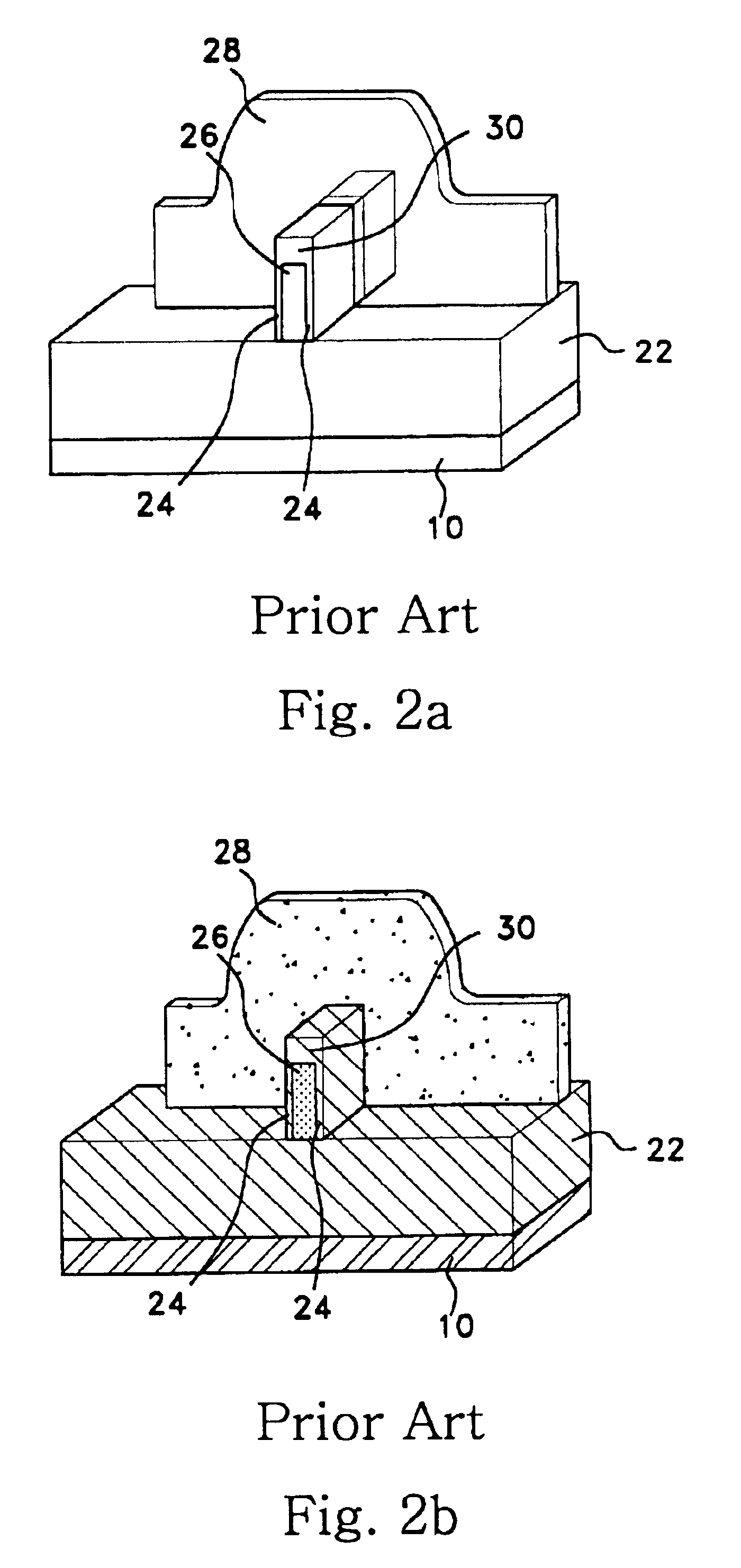

A new class of high-density, vertical Fin-FET devices that exhibit low contact resistance is described. These vertical Fin-FET devices have vertical silicon “fins” (12A) that act as the transistor body. Doped source and drain regions (26A, 28A) are formed at the bottoms and tops, respectively, of the fins (12A). Gates (24A, 24B) are formed along sidewalls of the fins. Current flows vertically through the fins (12A) between the source and drain regions (26A, 28A) when an appropriate bias is applied to the gates (24A, 24B). An integrated process for forming pFET, nFET, multi-fin, single-fin, multi-gate and double-gate vertical Fin-FETs simultaneously is described.

Owner:GLOBALFOUNDRIES US INC

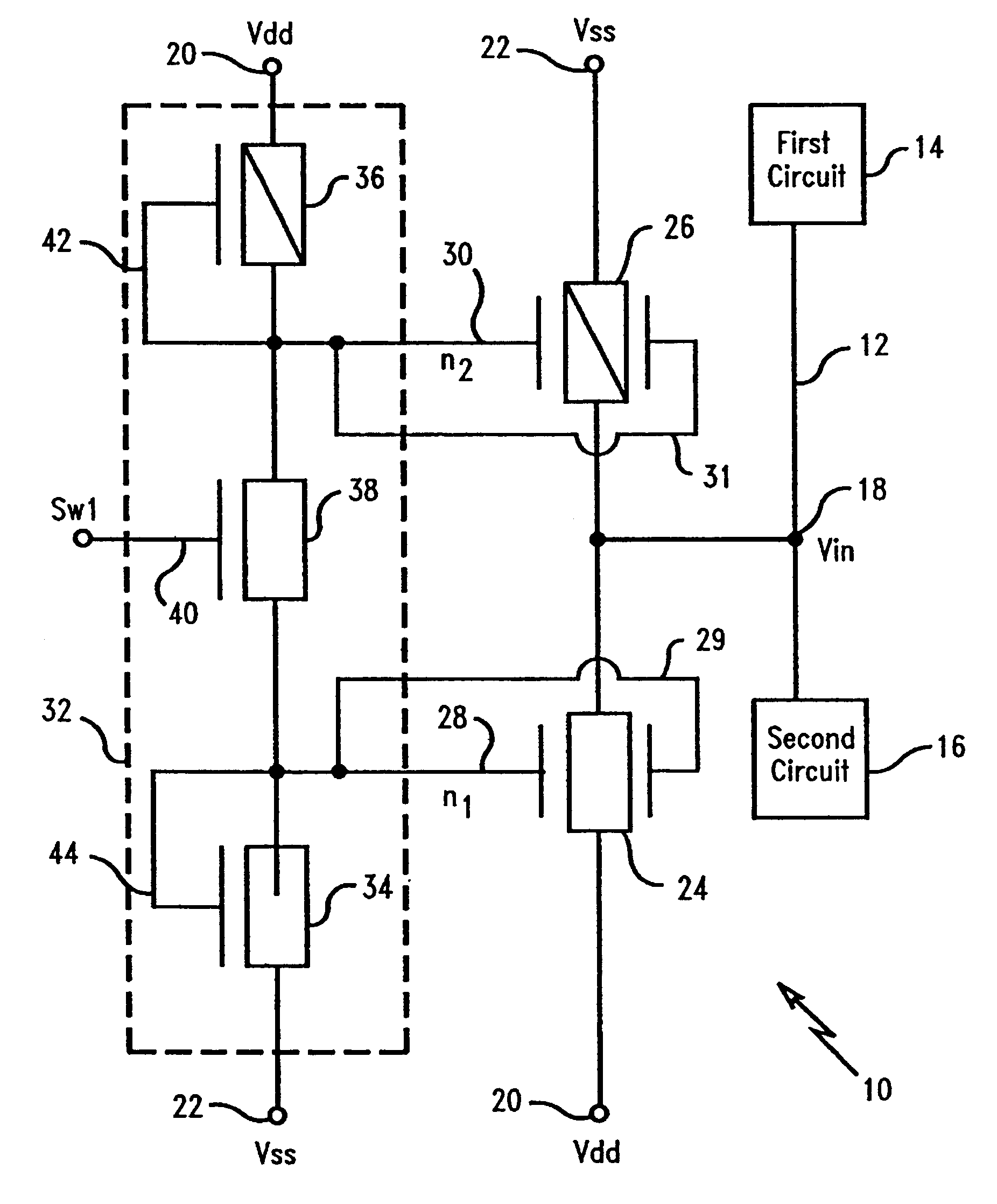

Double-gate low power SOI active clamp network for single power supply and multiple power supply applications

InactiveUS6433609B1Improve performanceReduce power consumptionTransistorPulse automatic controlActive clampLow voltage

A double-gated low power active clamp circuit for digital circuits includes a first double-gated MOSFET serially connected between an upper power supply voltage and an input terminal to be clamped, and a second double-gated MOSFET serially connected between a lower voltage power supply and the input terminal. The voltages at the gates of the first and second double-gated MOSFETs are held at constant reference voltages by a single or double reference circuits. The clamping action can be switched on or off. The double-gated active clamping network can be implemented with a single power supply voltage, or with multiple power supply voltages. The use of the back gates of the double-gated active clamping network enables additional clamping and ESD protection for smaller generations of transistors, such as, those having dimensions below 0.1 micron. The device is particularly suited for use with dynamic threshold double-gated silicon-on-insulator, FINFET, and bulk triple well technologies.

Owner:GLOBALFOUNDRIES US INC

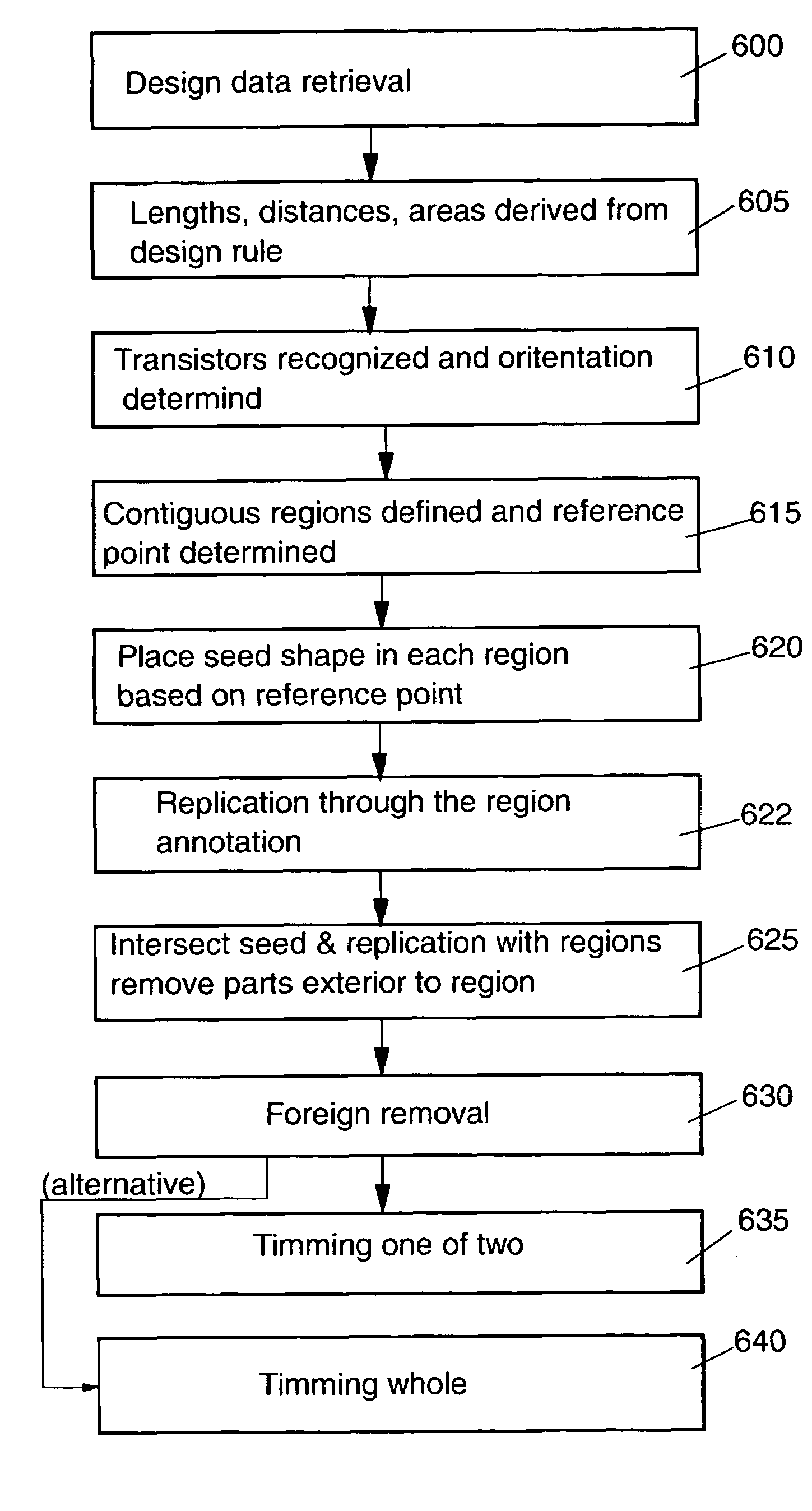

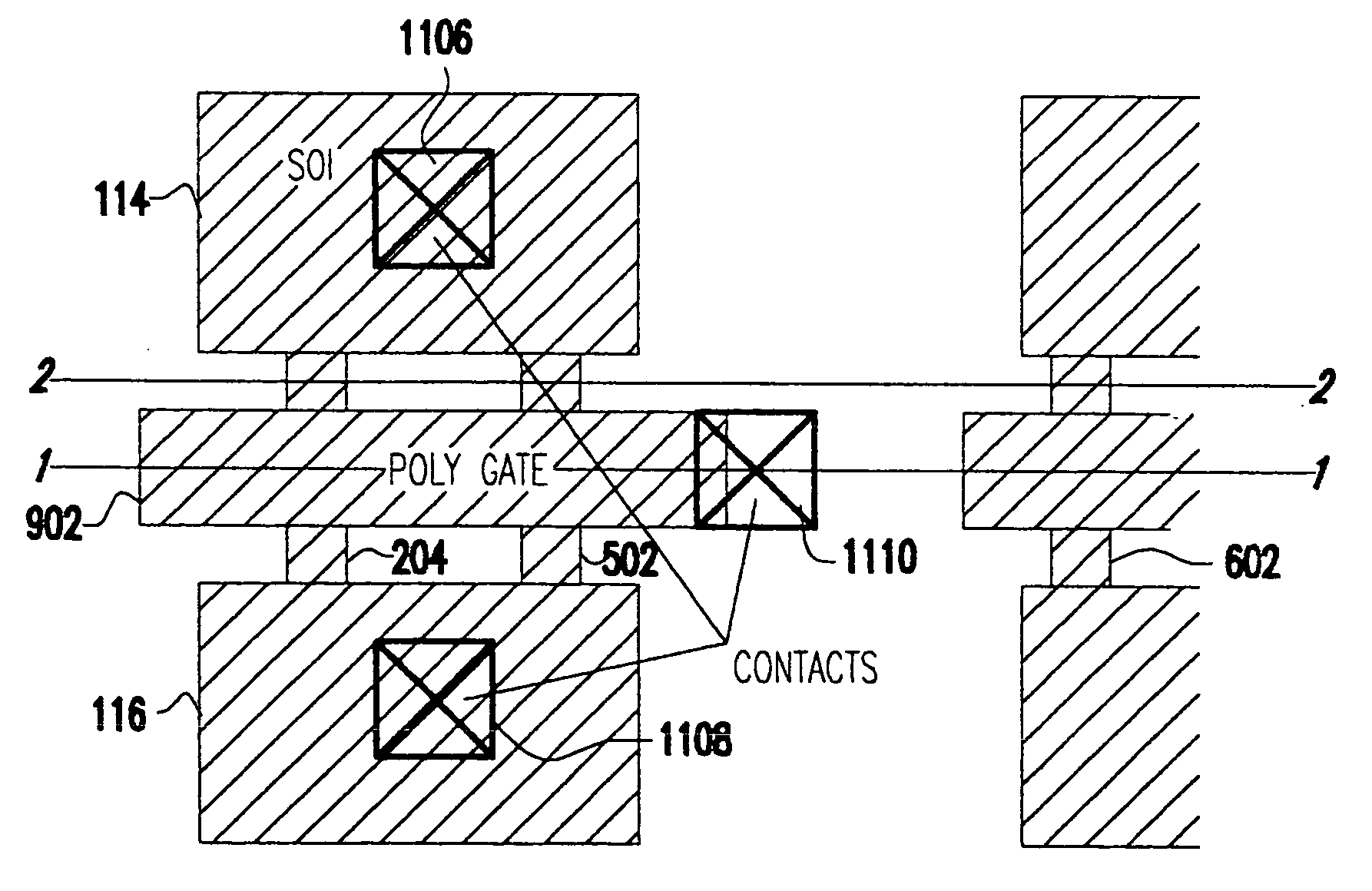

Method and device for automated layer generation for double-gate FinFET designs

InactiveUS7315994B2Reduce effortEnhance layeringTransistorSolid-state devicesEngineeringUnit structure

Owner:INT BUSINESS MASCH CORP

Self-aligned double-gate MOSFET by selective epitaxy and silicon wafer bonding techniques

InactiveUS6365465B1Controlled diffusionReduce diffuseTransistorSemiconductor/solid-state device manufacturingElectrical conductorEngineering

A structure and a method of manufacturing a double-gate metal oxide semiconductor transistor includes forming a laminated structure having a single crystal silicon channel layer and insulating oxide and nitride layers on each side of the single crystal silicon channel, forming openings in the laminated structure, forming drain and source regions in the openings, doping the drain and source regions, forming a mask over the laminated structure, removing portions of the laminated structure not protected by the mask, removing the mask and the insulating oxide and nitride layers to leave the single crystal silicon channel layer suspended from the drain and source regions, forming an oxide layer to cover the drain and source regions and the channel layer, and forming a double-gate conductor over the oxide layer such that the double-gate conductor includes a first conductor on a first side of the single crystal silicon channel layer and a second conductor on a second side of the single crystal silicon channel layer.

Owner:IBM CORP

FinFET transistor and circuit

Owner:GLOBALFOUNDRIES US INC

Flash memory element and manufacturing method thereof

The present invention provides a flash memory element and its manufacturing method having improved overall memory characteristics by constituting a double-gate element for improving the scaling down characteristic of flash memory element. A flash memory element comprises: a first oxide film formed on a surface of a silicon substrate; a fin active area vertically formed on the first oxide film; a gate tunneling oxide film formed on the fin active area; a floating electrode formed on the surfaces of the gate tunneling oxide film and the first oxide film; a inter-gates oxide film formed on the surface of the floating electrode; and a control electrode formed on the surface of the inter-gates oxide film. With the above double-gate flash memory structure, a flash memory element in the present invention improves the scaling down characteristic and the programming and retention characteristic of a flash memory element.

Owner:SMARTISM CO LTD

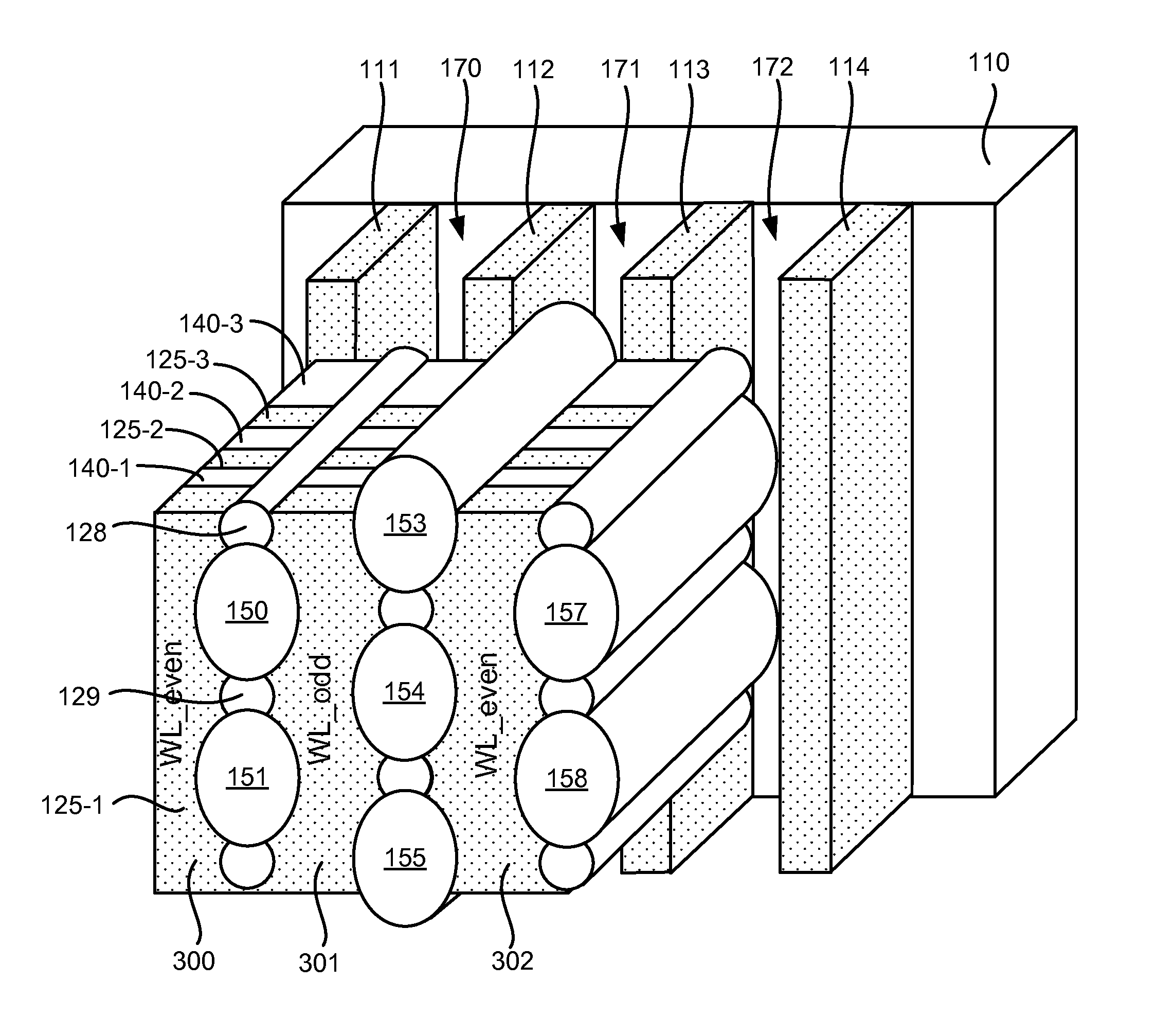

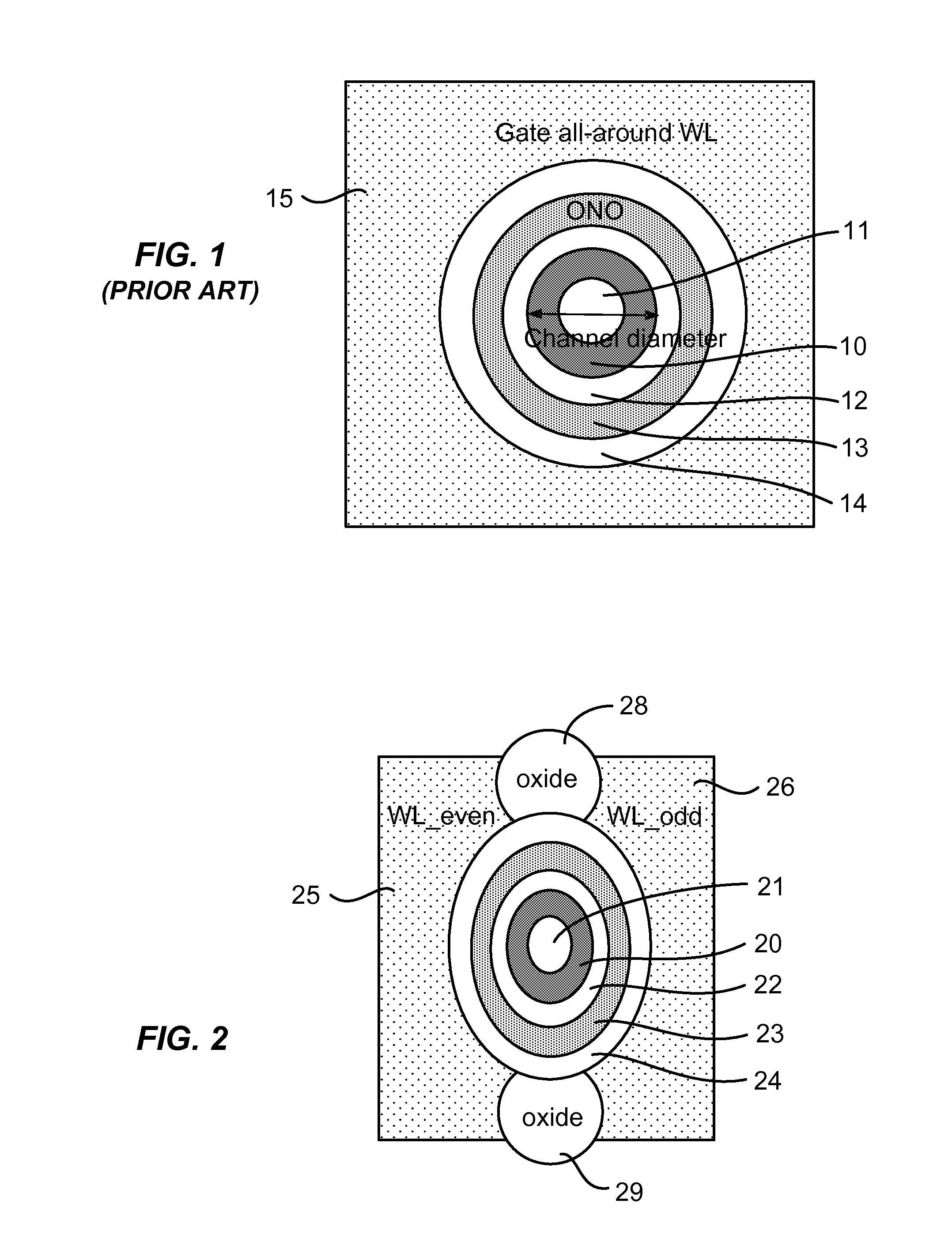

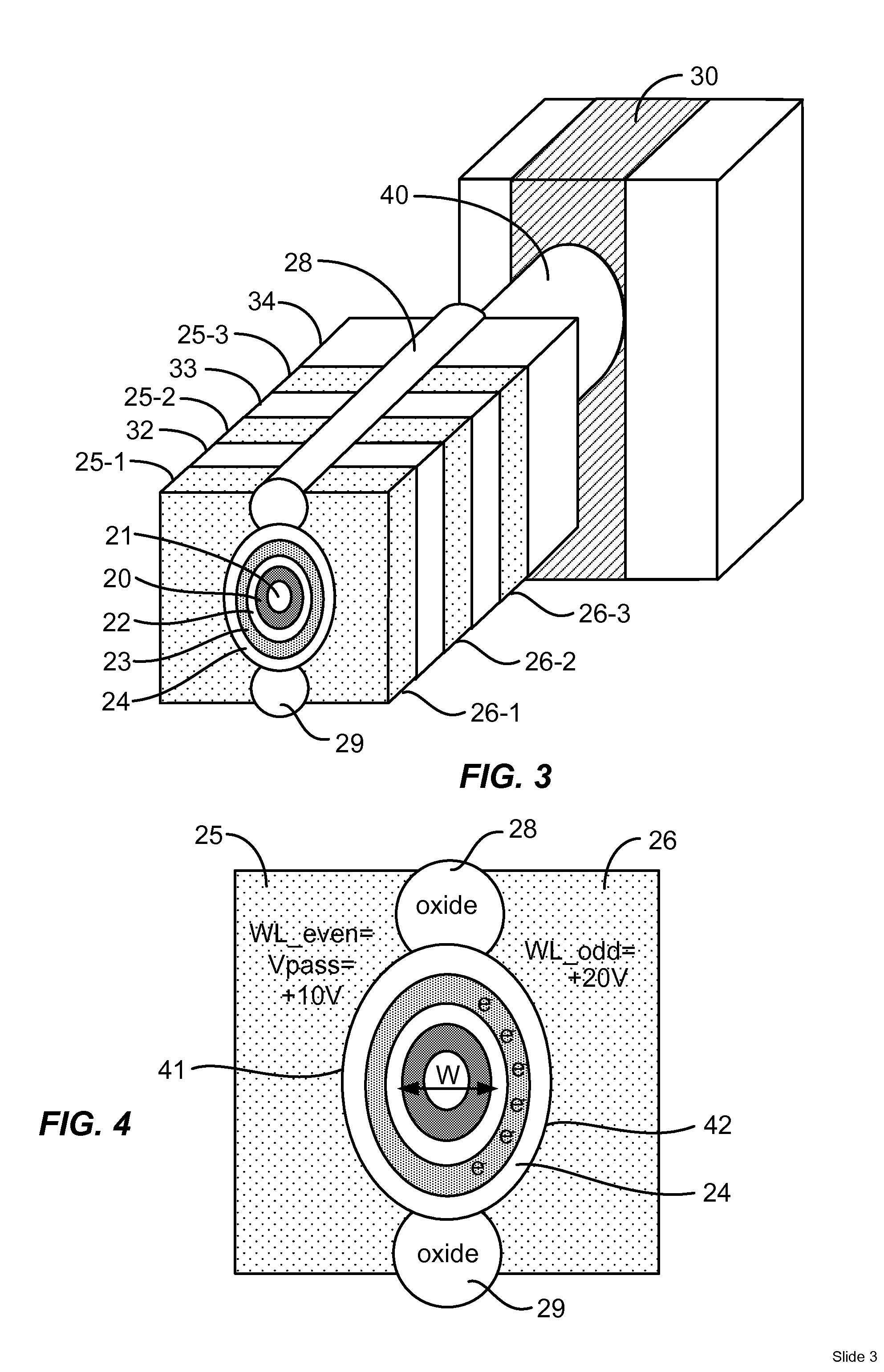

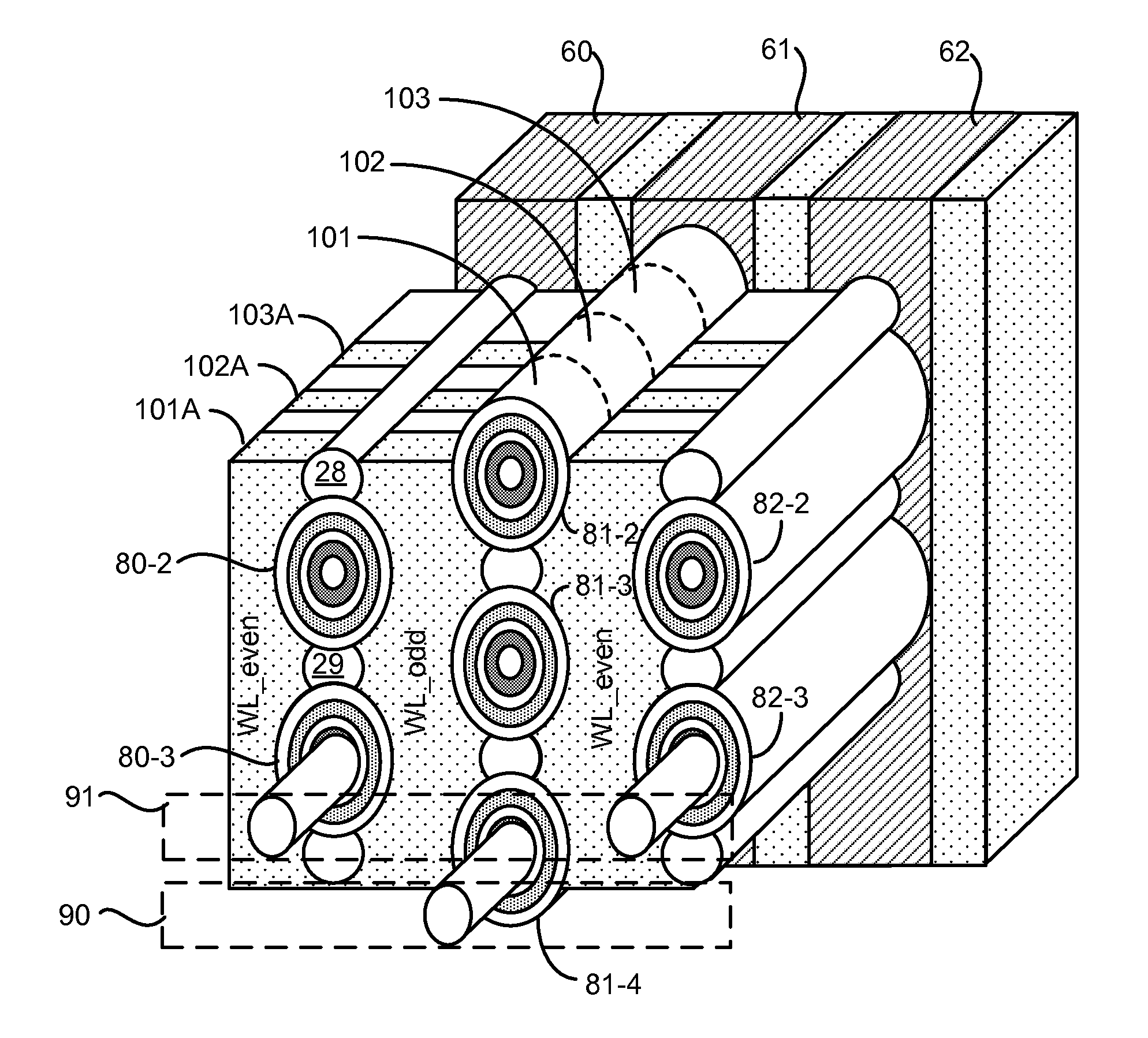

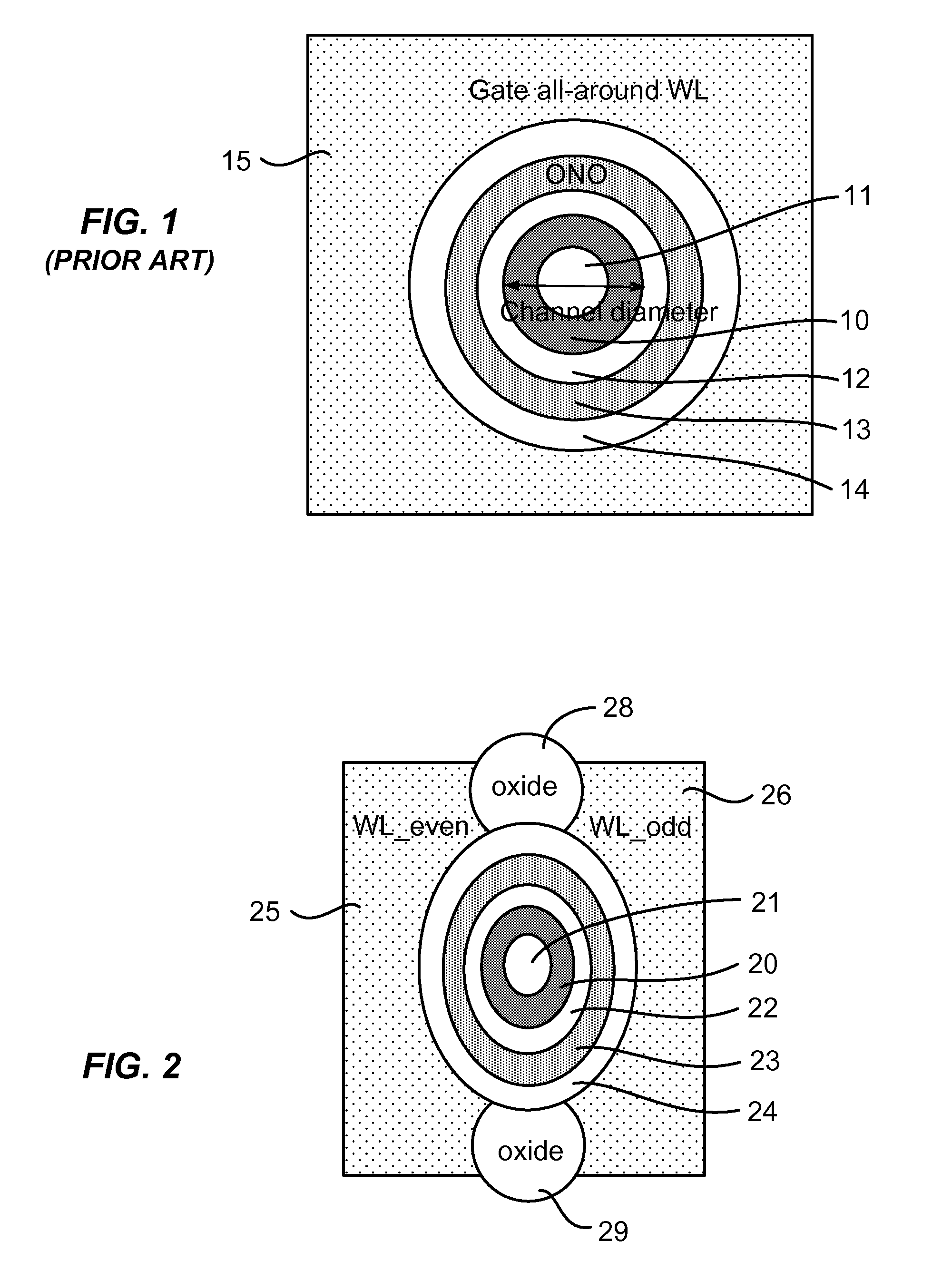

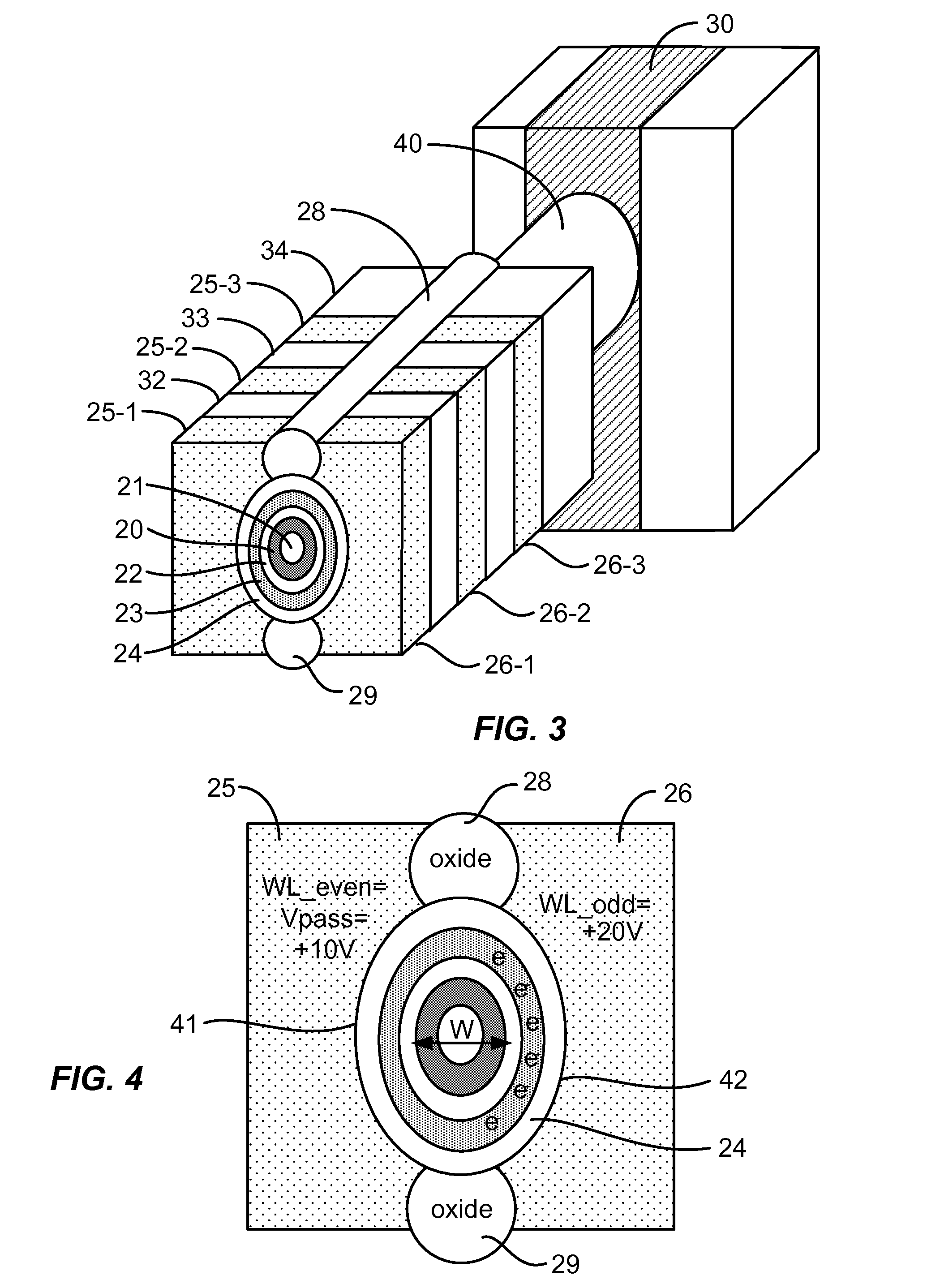

3D independent double gate flash memory

ActiveUS20150340369A1High density data storageIncrease data storageSolid-state devicesRead-only memoriesVertical channelDouble gate

A memory device configurable for independent double gate cells, storing multiple bits per cell includes multilayer stacks of conductive strips configured as word lines. Active pillars are disposed between pairs of first and second stacks, each active pillar comprising a vertical channel structure, a charge storage layer and an insulating layer. The insulating layer in a frustum of an active pillar contacts a first arcuate edge of a first conductive strip in a layer of the first stack and a second arcuate edge of a second conductive strip in a same layer of the second stack. A plurality of insulating columns serve, with the active pillars, to divide the stacks of word lines into even and odd lines contacting opposing even and odd sides of each active pillar. The active pillar can be generally elliptical with a major axis parallel with the first and second conductive strips.

Owner:MACRONIX INT CO LTD

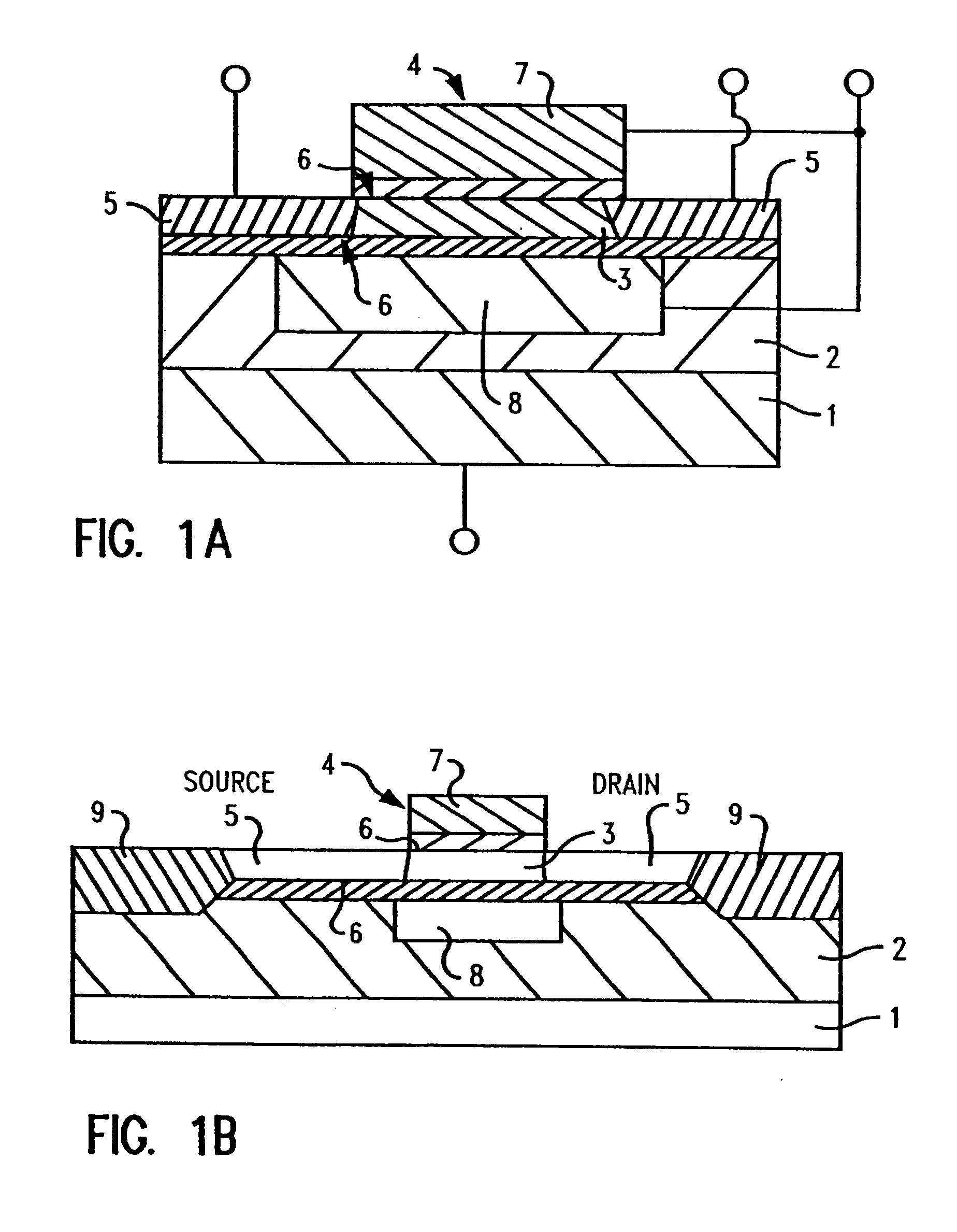

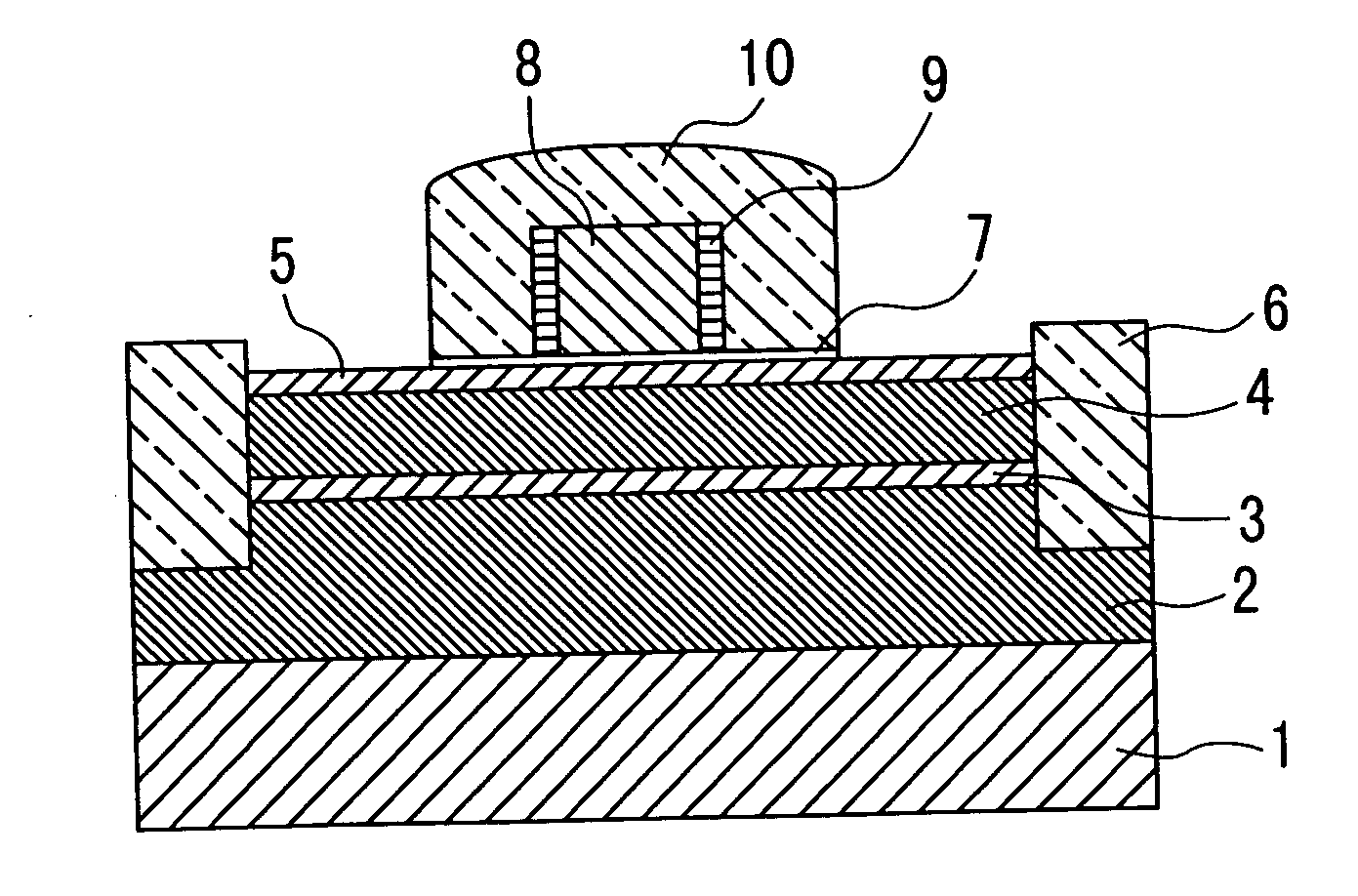

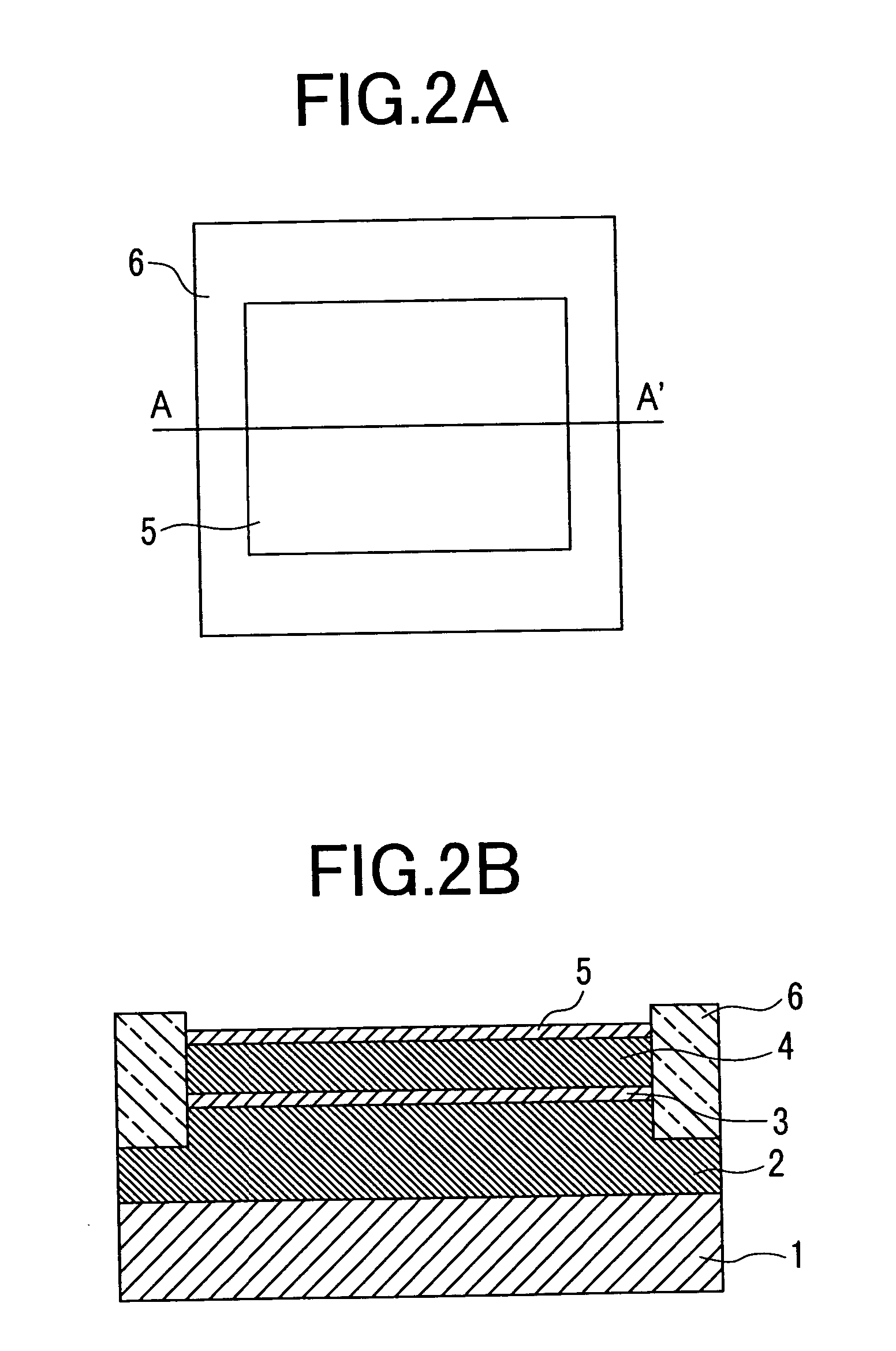

Insulated-gate field-effect transistor, method of fabricating same, and semiconductor device employing same

With the invention, it is possible to avoid deterioration in short-channel characteristics, caused by a silicon germanium layer coming into contact with the channel of a strained SOI transistor. Further, it is possible to fabricate a double-gate type of strained SOI transistor or to implement mixedly mounting the strained SOI transistor and a conventional silicon or SOI transistor on the same wafer. According to the invention, for example, a strained silicon layer is grown on a strain-relaxed silicon germanium layer, and subsequently, portions of the silicon germanium layer are removed, thereby constituting a channel layer in the strained silicon layer.

Owner:RENESAS ELECTRONICS CORP

Method of fabricating a MOSFET device with metal containing gate structures

InactiveUS6869868B2Improve device performanceLow working voltageTransistorSemiconductor/solid-state device manufacturingTitanium nitrideTwo step

A method of forming a composite gate structure for a planar MOSFET device, as well as for vertical, double gate, FINFET device, has been developed. The method features a composite gate structure comprised of an overlying silicon gate structure shape, and an underlying titanium nitride gate structure shape. The titanium nitride component allows a lower work function, and thus lower device operating voltages to be realized when compared to counterpart gate structures formed with only polysilicon. A novel, two step gate structure definition procedure, featuring an anisotropic first etch procedure for definition of the polysilicon gate structure shape, followed by a wet or dry isotopic second etch procedure for definition of the titanium nitride gate structure shape, is employed.

Owner:TAIWAN SEMICON MFG CO LTD

Double gated transistor and method of fabrication

InactiveUS7288445B2High densityImprove performanceTransistorSemiconductor/solid-state device manufacturingNon symmetricLow voltage cmos

Owner:GLOBALFOUNDRIES INC

Flash memory element and manufacturing method thereof

InactiveUS6768158B2Highly-improved memory characteristicsImprove integrityTransistorNanoinformaticsScale downDouble gate

Owner:SMARTISM CO LTD

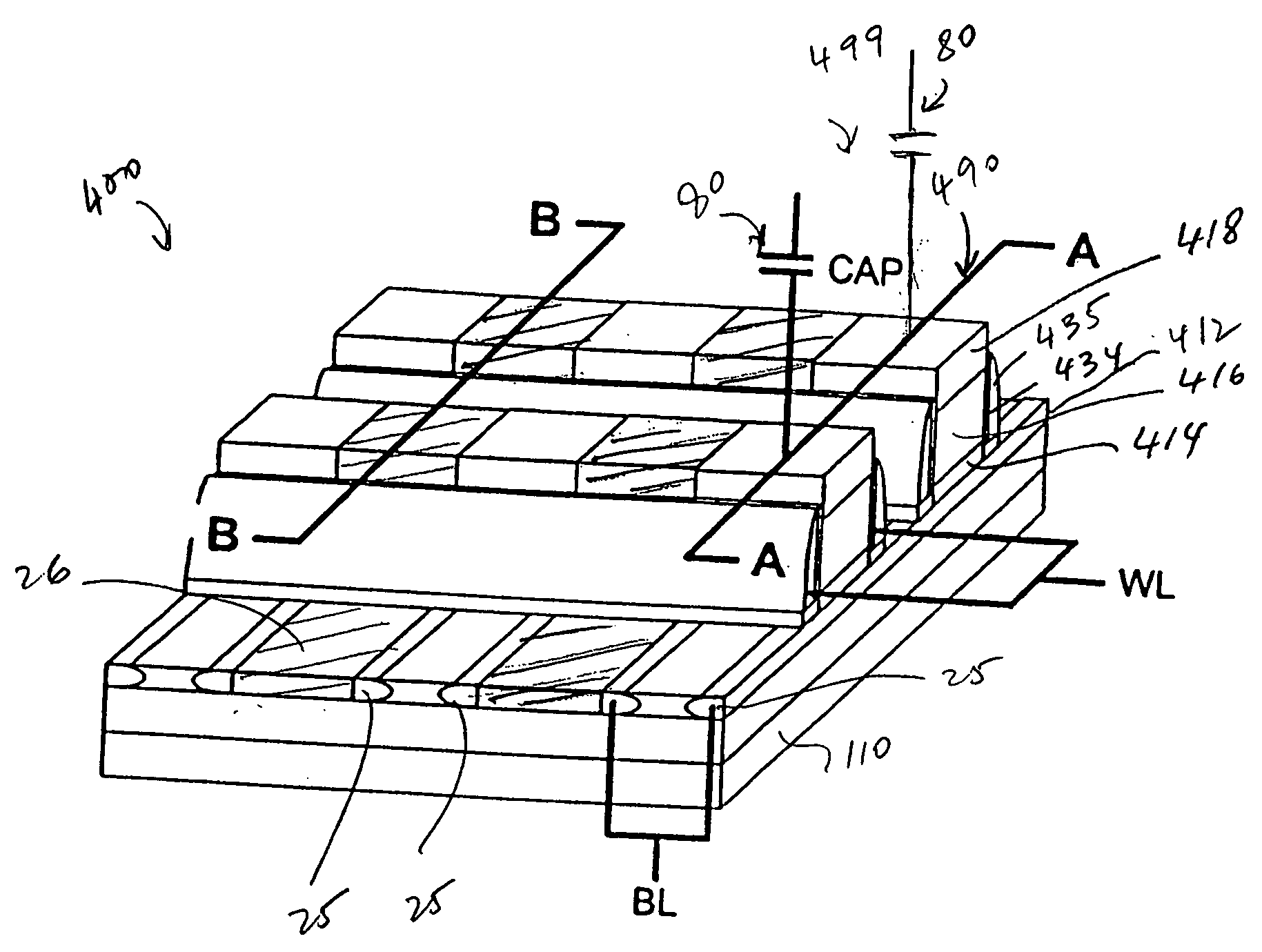

DRAM layout with vertical FETS and method of formation

DRAM cell arrays having a cell area of about 4F2 comprise an array of vertical transistors with buried bit lines and vertical double gate electrodes. The buried bit lines comprise a silicide material and are provided below a surface of the substrate. The word lines are optionally formed of a silicide material and form the gate electrode of the vertical transistors. The vertical transistor may comprise sequentially formed doped polysilicon layers or doped epitaxial layers. At least one of the buried bit lines is orthogonal to at least one of the vertical gate electrodes of the vertical transistors.

Owner:MICRON TECH INC

3D independent double gate flash memory on bounded conductor layer

ActiveUS20150340371A1High density data storageIncrease data storageSolid-state devicesRead-only memoriesElectrical conductorVertical channel

A memory device configurable for independent double gate cells, storing multiple bits per cell, includes multilayer stacks of conductive strips configured as word lines. Active pillars are disposed between pairs of first and second stacks, each active pillar comprising a vertical channel structure extending from an underlying bounded conductive layer, a charge storage layer and an insulating layer. The insulating layer in a frustum of an active pillar contacts a first arcuate edge of a first conductive strip in a layer of the first stack and a second arcuate edge of a second conductive strip in a same layer of the second stack. The conductive strips can comprise a metal. The active pillar can be generally elliptical with a major axis parallel with the first and second conductive strips.

Owner:MACRONIX INT CO LTD

Insulated-gate field-effect transistor, method of fabricating same, and semiconductor device employing same

InactiveUS6936875B2Improve mobilityShorten the lengthTransistorSolid-state devicesDevice materialField-effect transistor

With the invention, it is possible to avoid deterioration in short-channel characteristics, caused by a silicon germanium layer coming into contact with the channel of a strained SOI transistor. Further, it is possible to fabricate a double-gate type of strained SOI transistor or to implement mixedly mounting the strained SOI transistor and a conventional silicon or SOI transistor on the same wafer. According to the invention, for example, a strained silicon layer is grown on a strain-relaxed silicon germanium layer, and subsequently, portions of the silicon germanium layer are removed, thereby constituting a channel layer in the strained silicon layer.

Owner:RENESAS ELECTRONICS CORP

Strained-silicon-on-insulator single-and double-gate MOSFET and method for forming the same

InactiveUS20040253792A1Eliminate difficultiesSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A method of forming a semiconductor structure (and the resulting structure), includes straining a free-standing semiconductor, and fixing the strained, free-standing semiconductor to a substrate.

Owner:IBM CORP

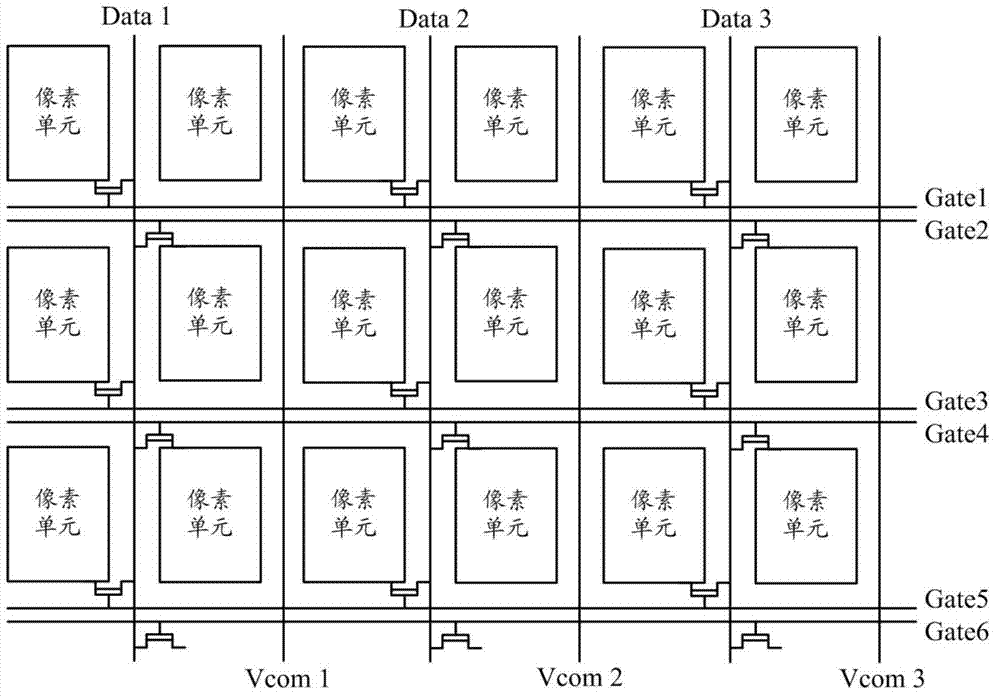

Capacitance-type built-in touch screen, driving method thereof and display device

ActiveCN102955637AConducive to narrow bezel designImprove transmission efficiencyStatic indicating devicesNon-linear opticsCapacitanceTime delays

The invention discloses a capacitance-type built-in touch screen, a driving method thereof and a display device. A touch induction electrode is arranged on a colorful film substrate; a whole-surface connection public electrode layer in a TFT (thin film transistor) array substrate is divided into strips to be used as touch driving electrodes; touch driving signal lines are arranged in a display area by a double-gate structure, thereby being favorable for the narrow frame design of the touch screen relative to that the touch driving signal lines are arranged in the non-display area of the touch screen; at least one touch driving signal line is electrically connected with one touch driving electrode; and multiple touch driving signal lines simultaneously provide a driving electric signal to one touch driving electrode so as to furthest improve the transmission efficiency of the driving electric signal and reduce the time delay of the driving electric signal. In addition, because the touch stage and the display stage adopt a time-sharing driving mode, a display driving chip and a touch driving chip can be integrated into a whole, and the production cost is lowered. According to the time-sharing driving, mutual interference between display and touch can be lowered, and the picture quality and the touch accuracy can be improved.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

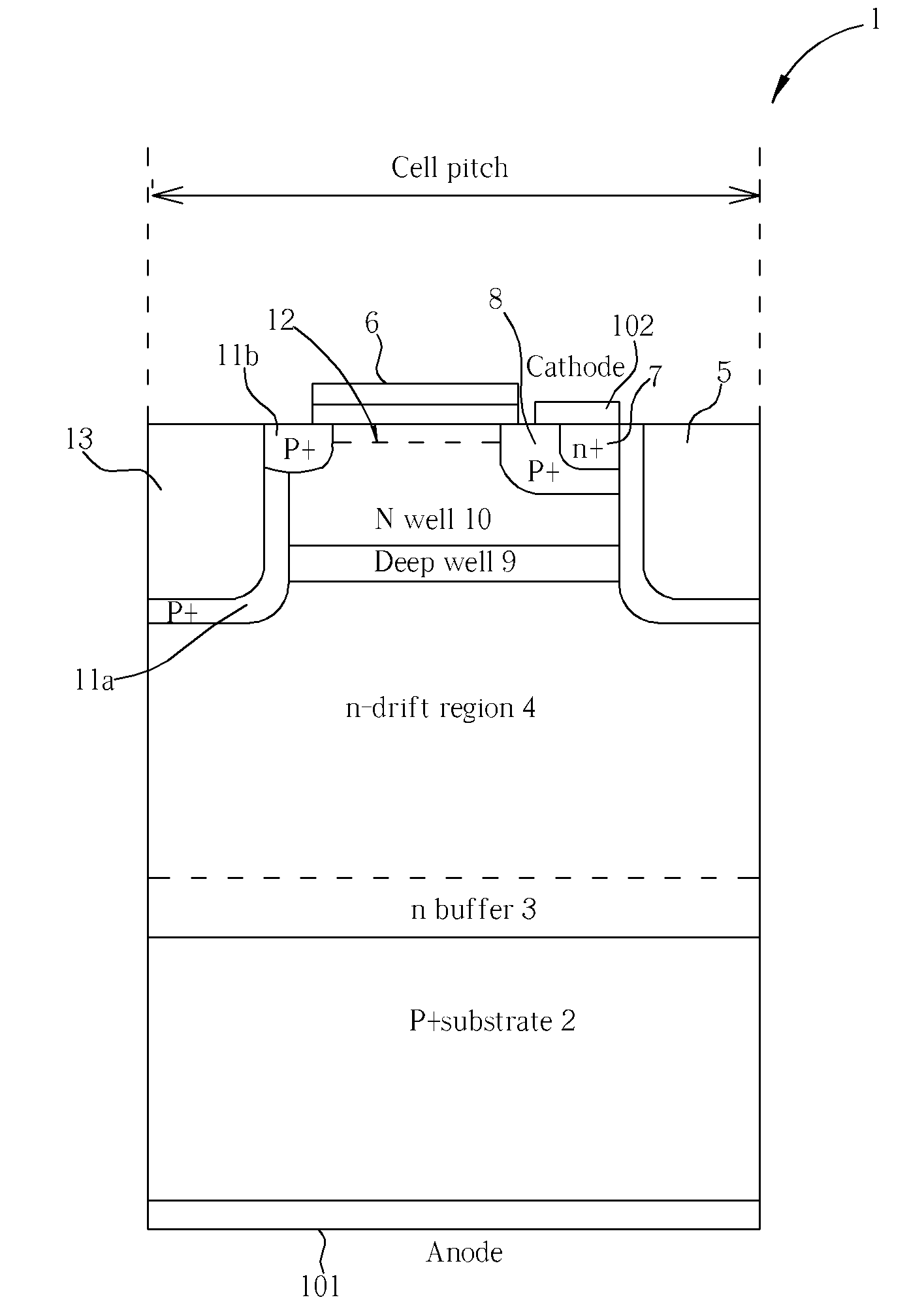

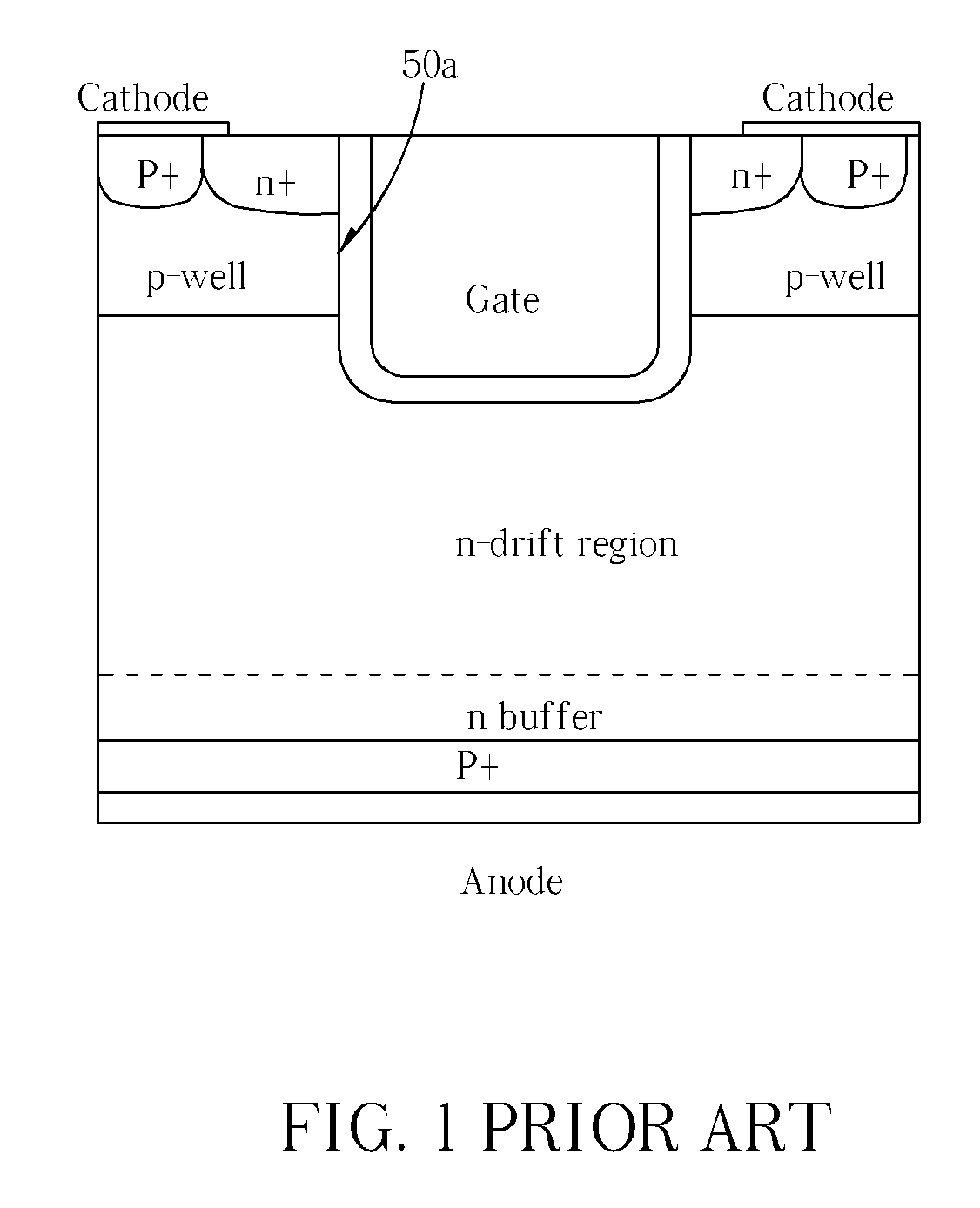

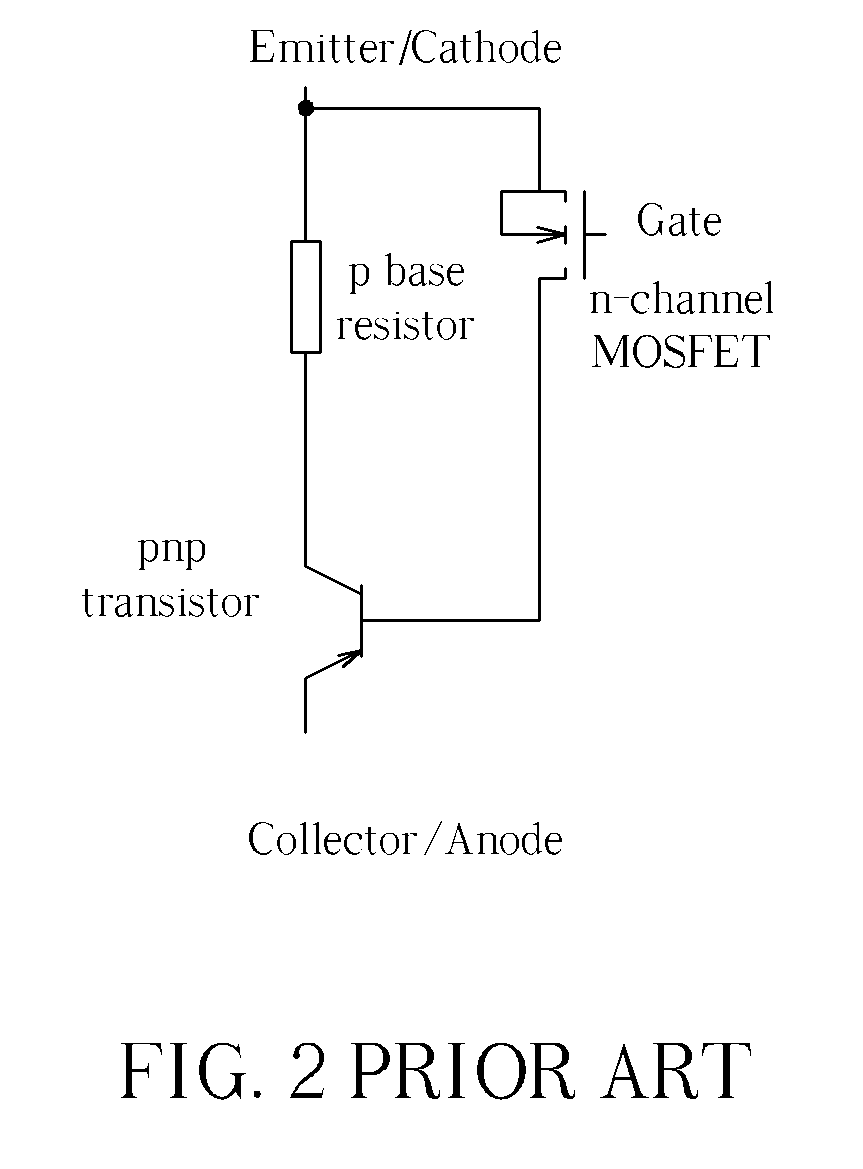

Double gate insulated gate bipolar transistor

InactiveUS20090008674A1Reduce the number of holesReduce transportationTransistorSolid-state devicesParasitic bipolar transistorEngineering

Double gate IGBT having both gates referred to a cathode in which a second gate is for controlling flow of hole current. In on-state, hole current can be largely suppressed. While during switching, hole current is allowed to flow through a second channel. Incorporating a depletion-mode p-channel MOSFET having a pre-formed hole channel that is turned ON when 0V or positive voltages below a specified threshold voltage are applied between second gate and cathode, negative voltages to the gate of p-channel are not used. Providing active control of holes amount that is collected in on-state by lowering base transport factor through increasing doping and width of n well or by reducing injection efficiency through decreasing doping of deep p well. Device includes at least anode, cathode, semiconductor substrate, n− drift region, first & second gates, n+ cathode region; p+ cathode short, deep p well, n well, and pre-formed hole channel.

Owner:ANPEC ELECTRONICS CORPORATION

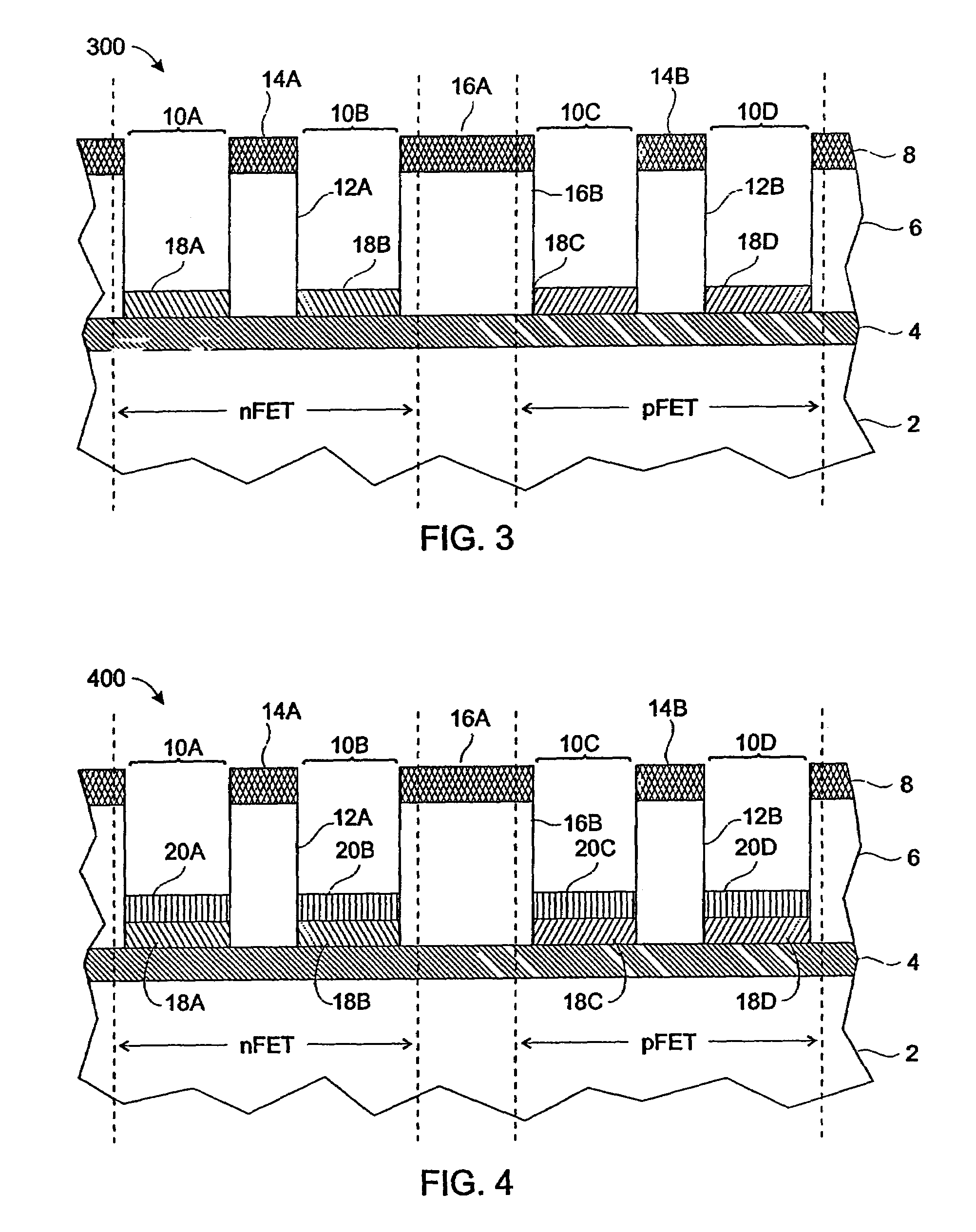

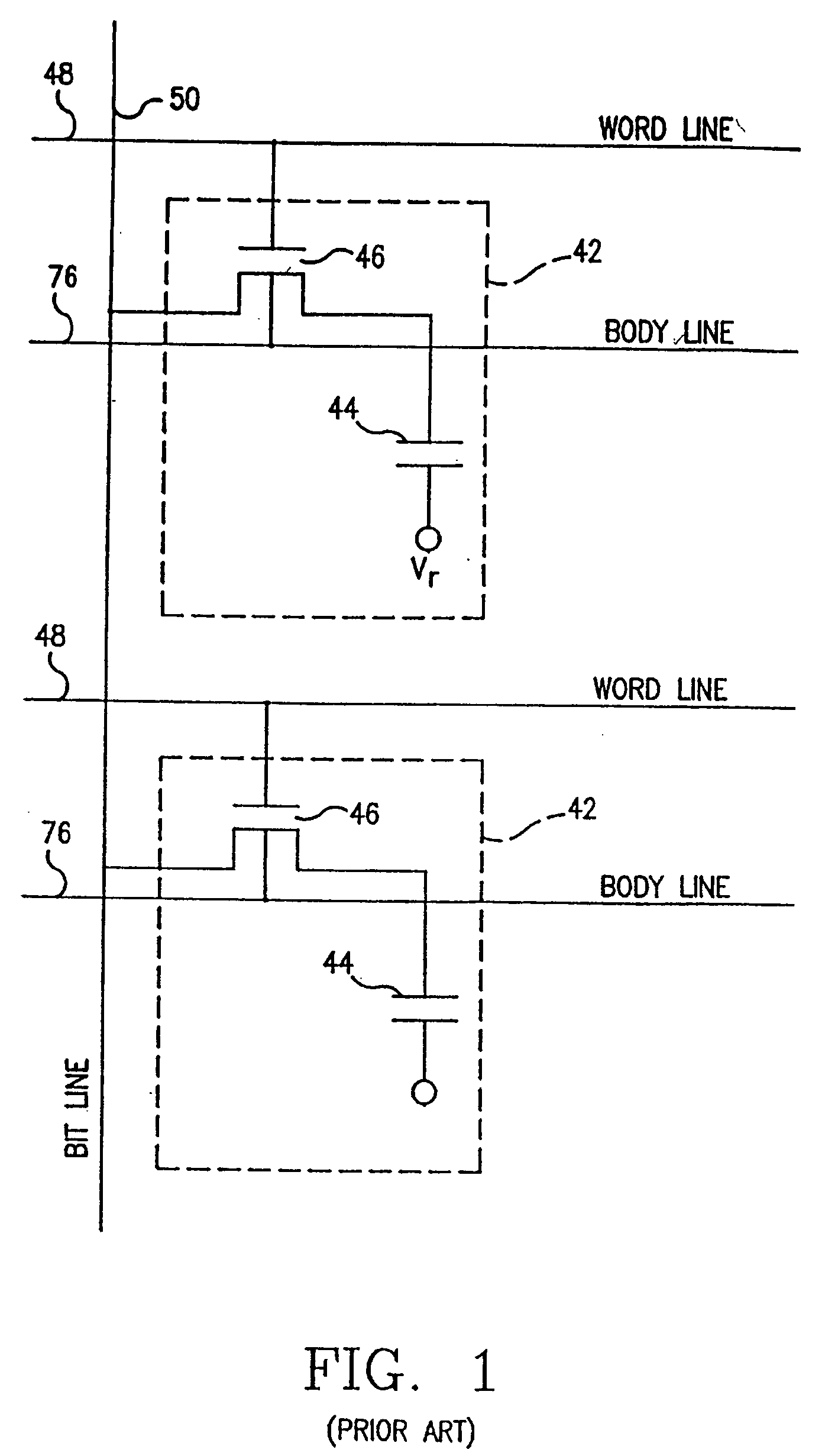

Semiconductor device including back-gated transistors and method of fabricating the device

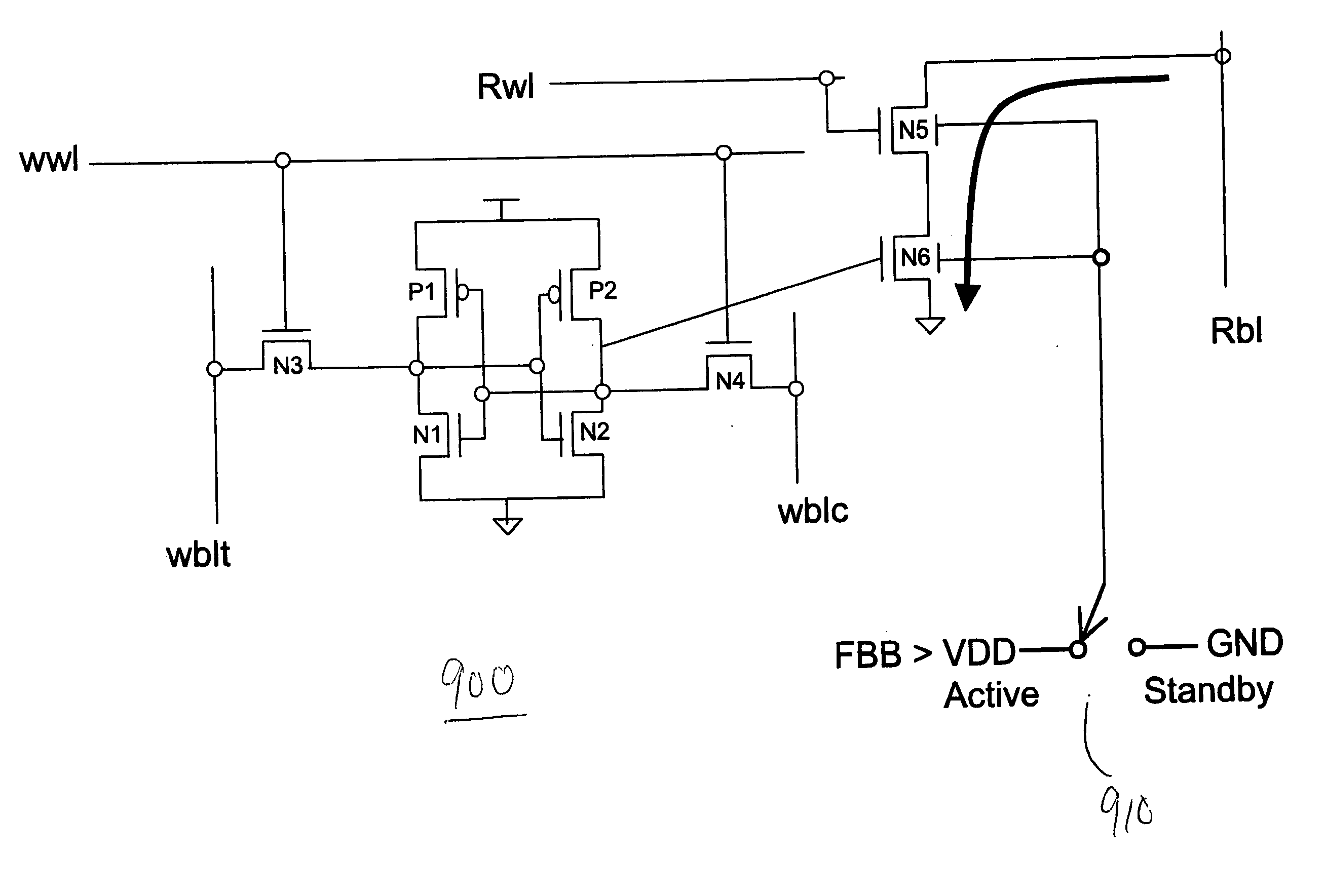

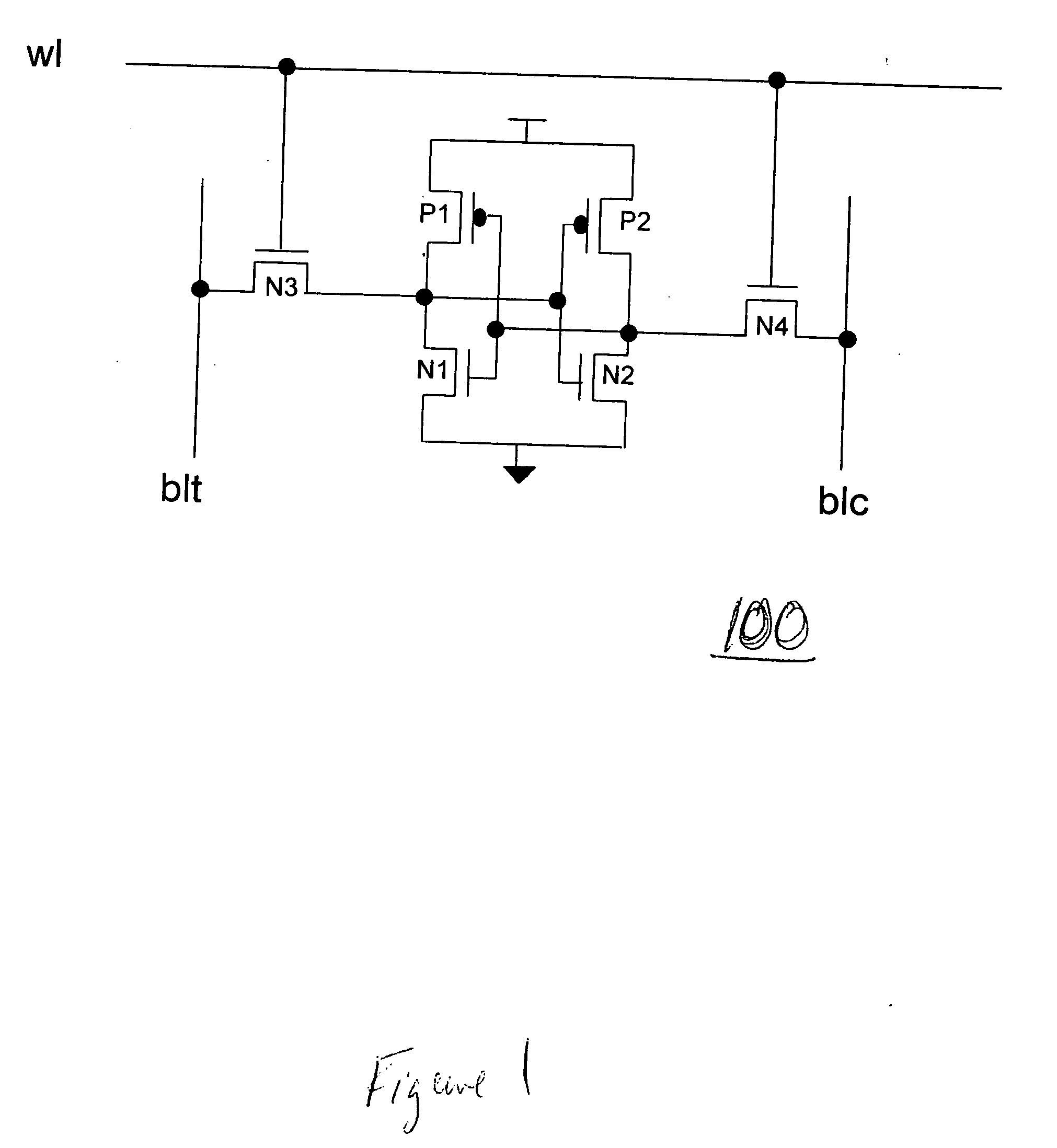

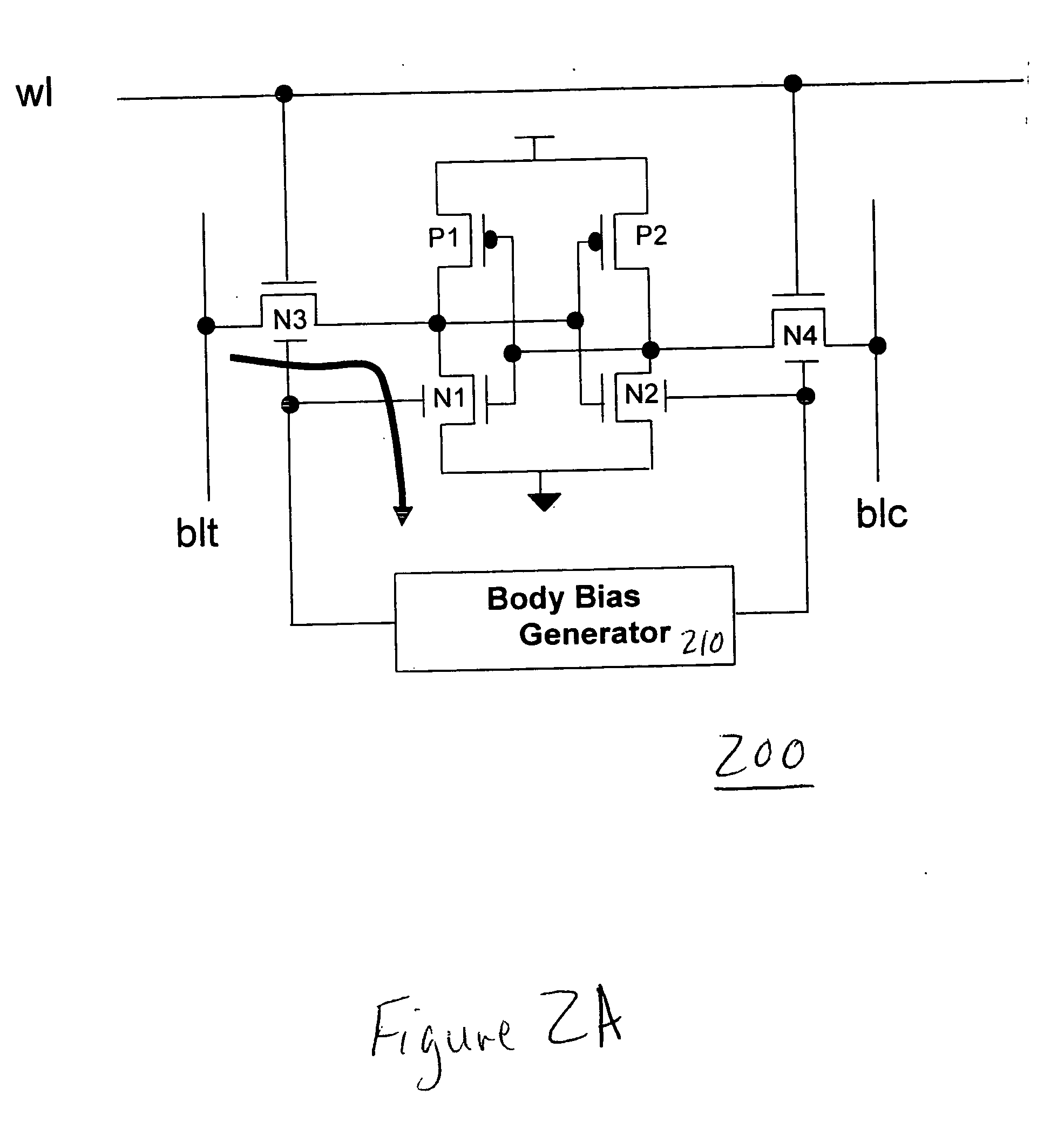

ActiveUS20060274569A1Improve device densityImprove device stabilityTransistorSolid-state devicesStatic random-access memoryDevice material

A memory cell (e.g., static random access memory (SRAM) cell) includes a plurality of back-gated n-type field effect transistors (nFETs), and a plurality of double-gated p-type field effect transistors (pFETs) operatively coupled to the plurality of nFETs.

Owner:GLOBALFOUNDRIES US INC

CMOS compatible low band offset double barrier resonant tunneling diode

InactiveUS20050056827A1Good I-V characteristicRaise the ratioTransistorNanoinformaticsCMOSElectrical resistance and conductance

Three configurations of double barrier resonant tunneling diodes (RTD) are provided along with methods of their fabrication. The tunneling barrier layers of the diode are formed of low band offset dielectric materials and produce a diode with good I-V characteristics including negative differential resistance (NDR) with good peak-to-valley ratios (PVR). Fabrication methods of the RTD start with silicon-on-insulator substrates (SOI), producing silicon quantum wells, and are, therefore, compatible with main stream CMOS technologies such as those applied to SOI double gate transistor fabrication. Alternatively, Ge-on-insulator or SiGe-on-insulator substrates can be used if the quantum well is to be formed of Ge or SiGe. The fabrication methods include the formation of both vertical and horizontal silicon quantum well layers. The vertically formed layer may be oriented so that its vertical sides are in any preferred crystallographic plane, such as the 100 or 110 planes.

Owner:AGENCY FOR SCI TECH & RES +1

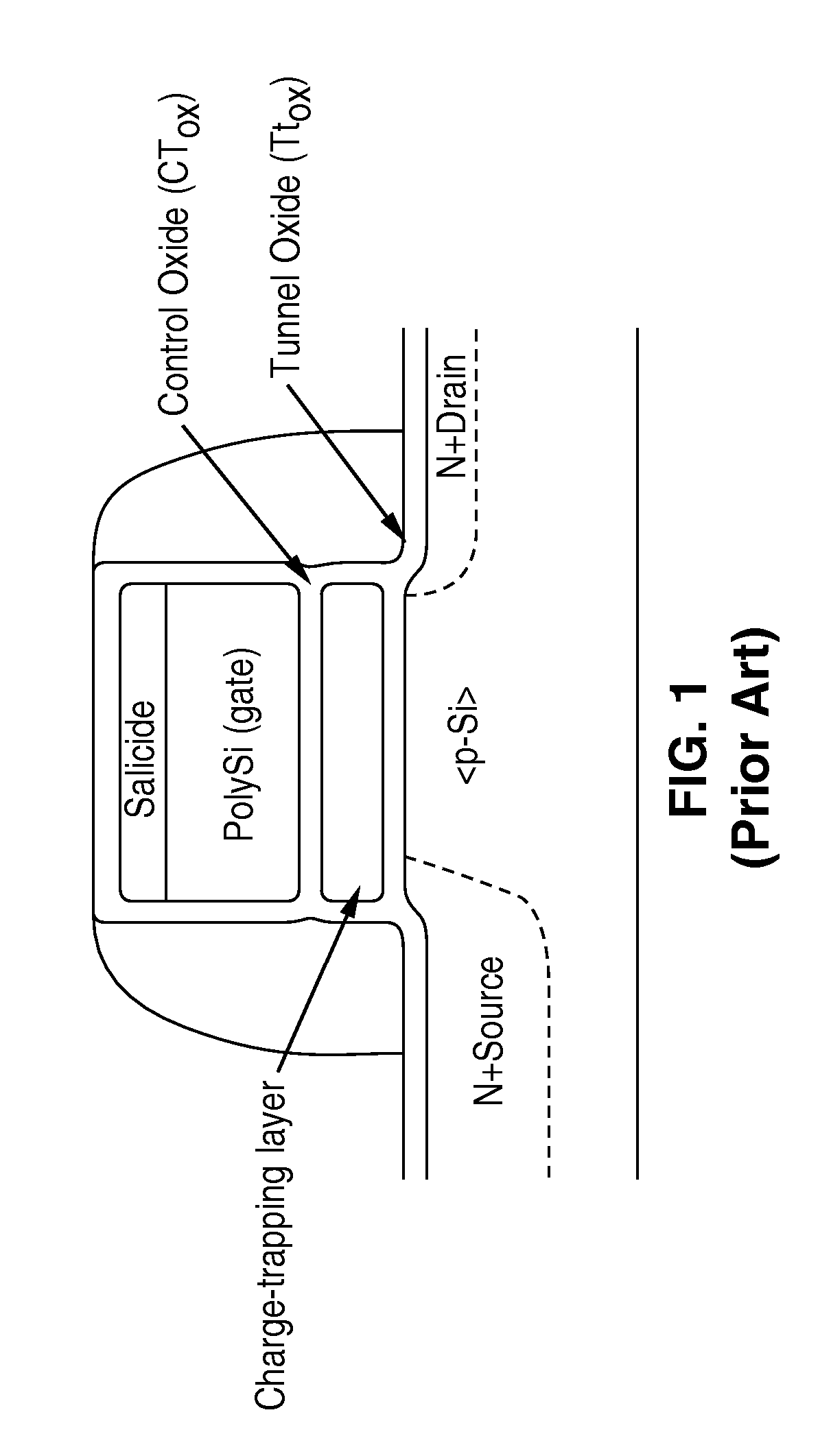

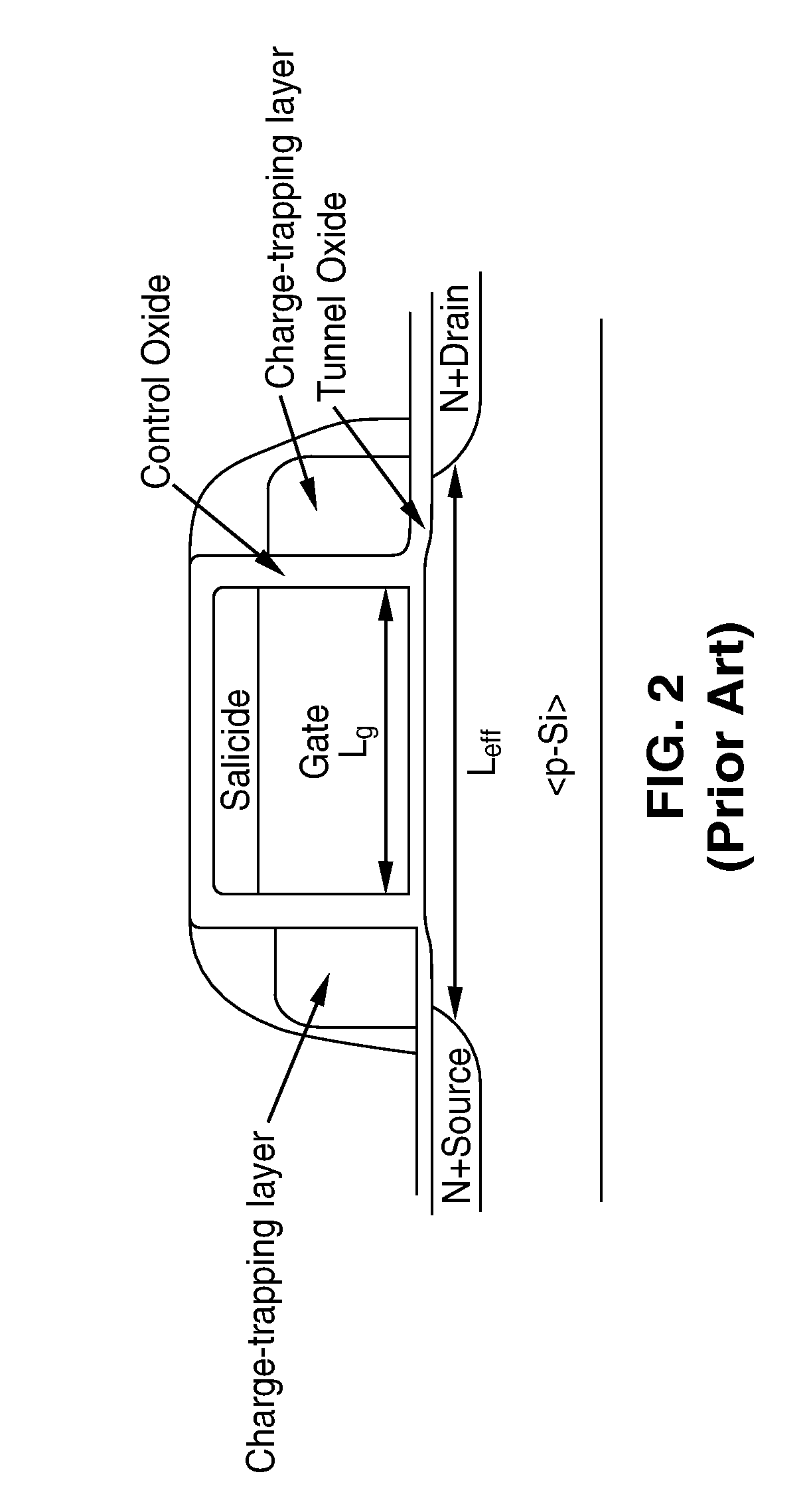

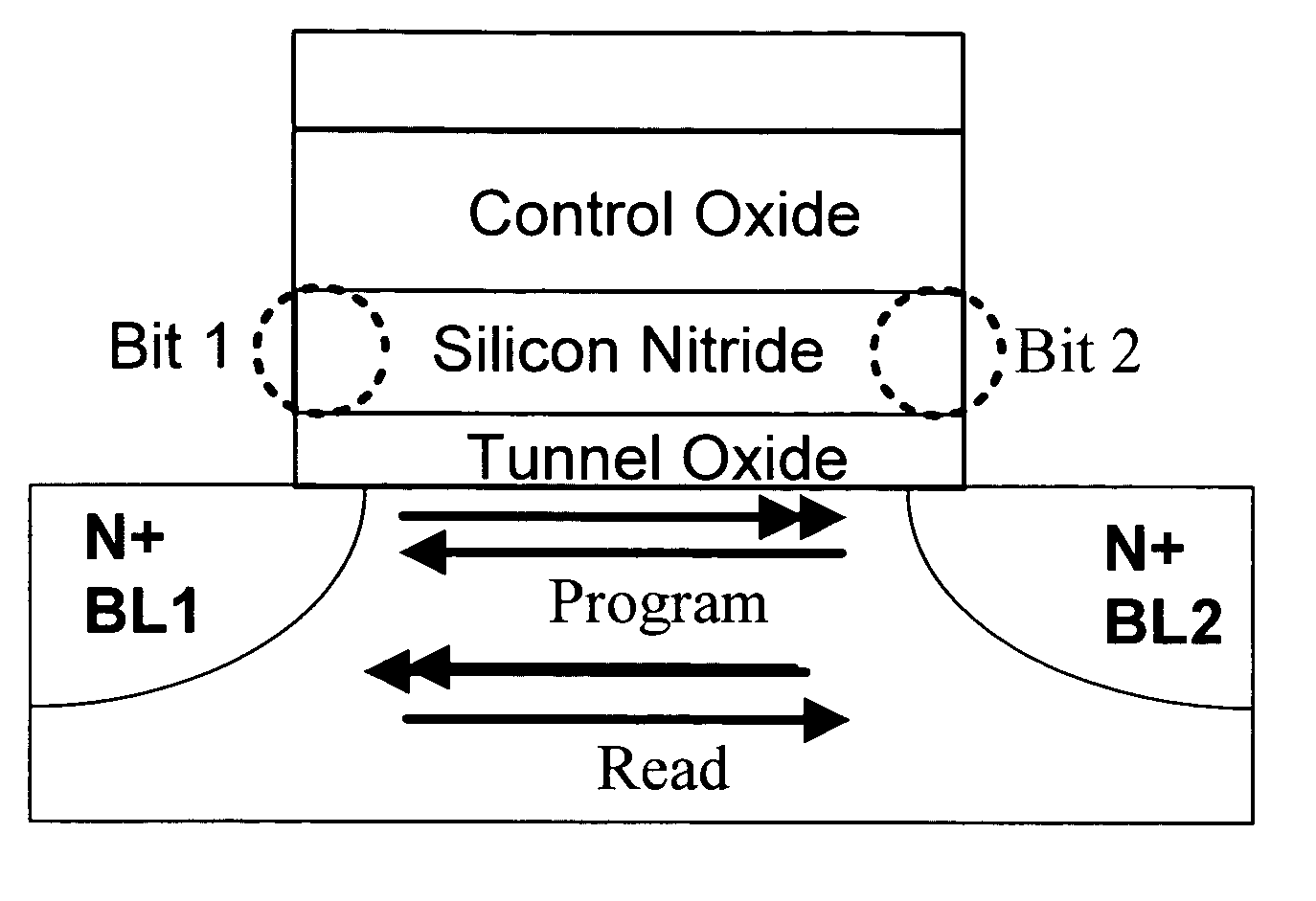

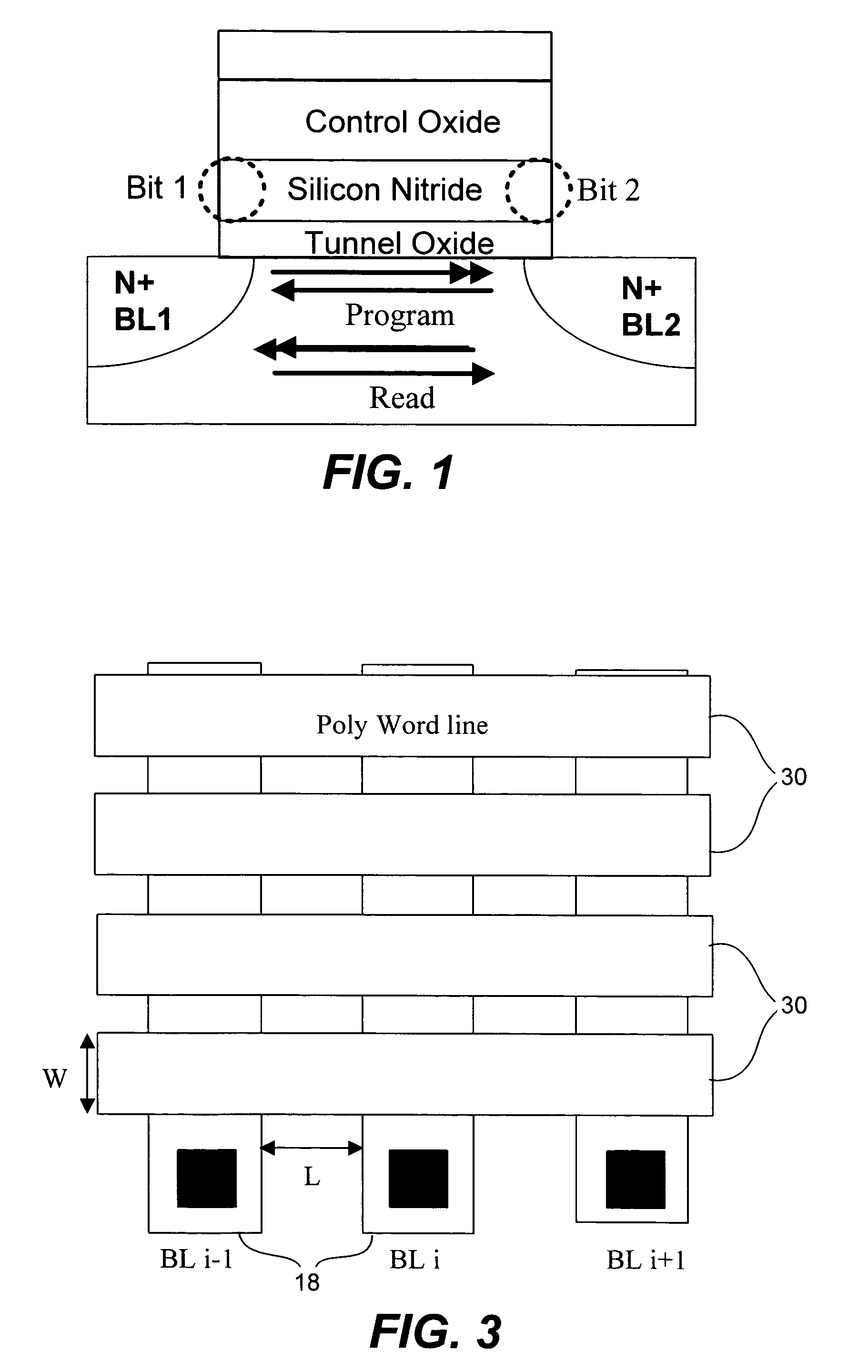

Two bit/four bit SONOS flash memory cell

InactiveUS20050242391A1Prevent lateral charge migrationMore charge injectionSolid-state devicesRead-only memoriesEngineeringMaterial physics

Charge migration in a SONOS memory cell is eliminated by physically separating nitride layer storage sites with dielectric material. Increased storage in a cell is realized with a double gate structure for controlling bit storage in line channels between a source and a drain, such as with a FinFET structure in which the gates are folded over the channels on sides of a fin.

Owner:RGT NIVERSITY OF CALIFORNIA THE

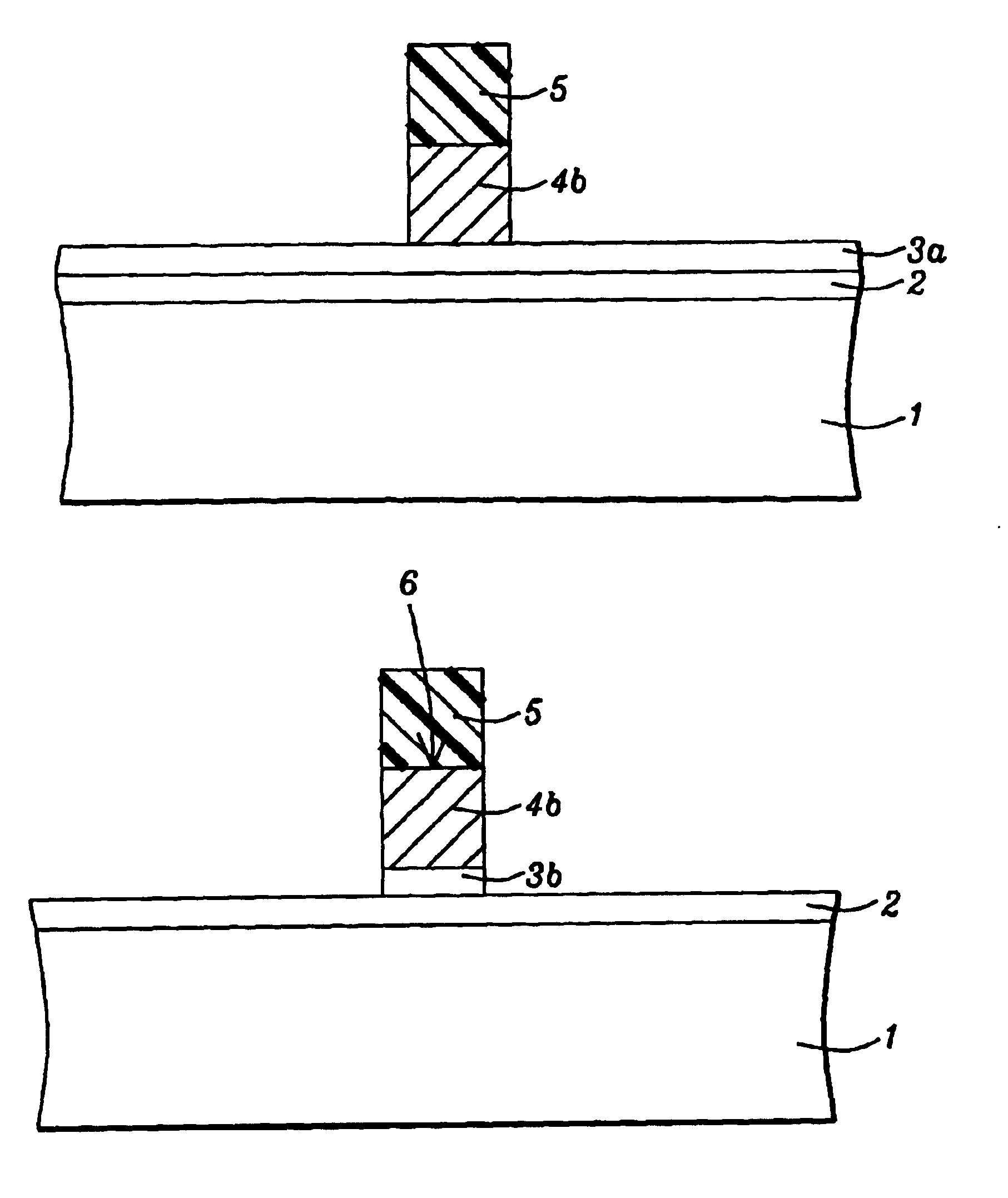

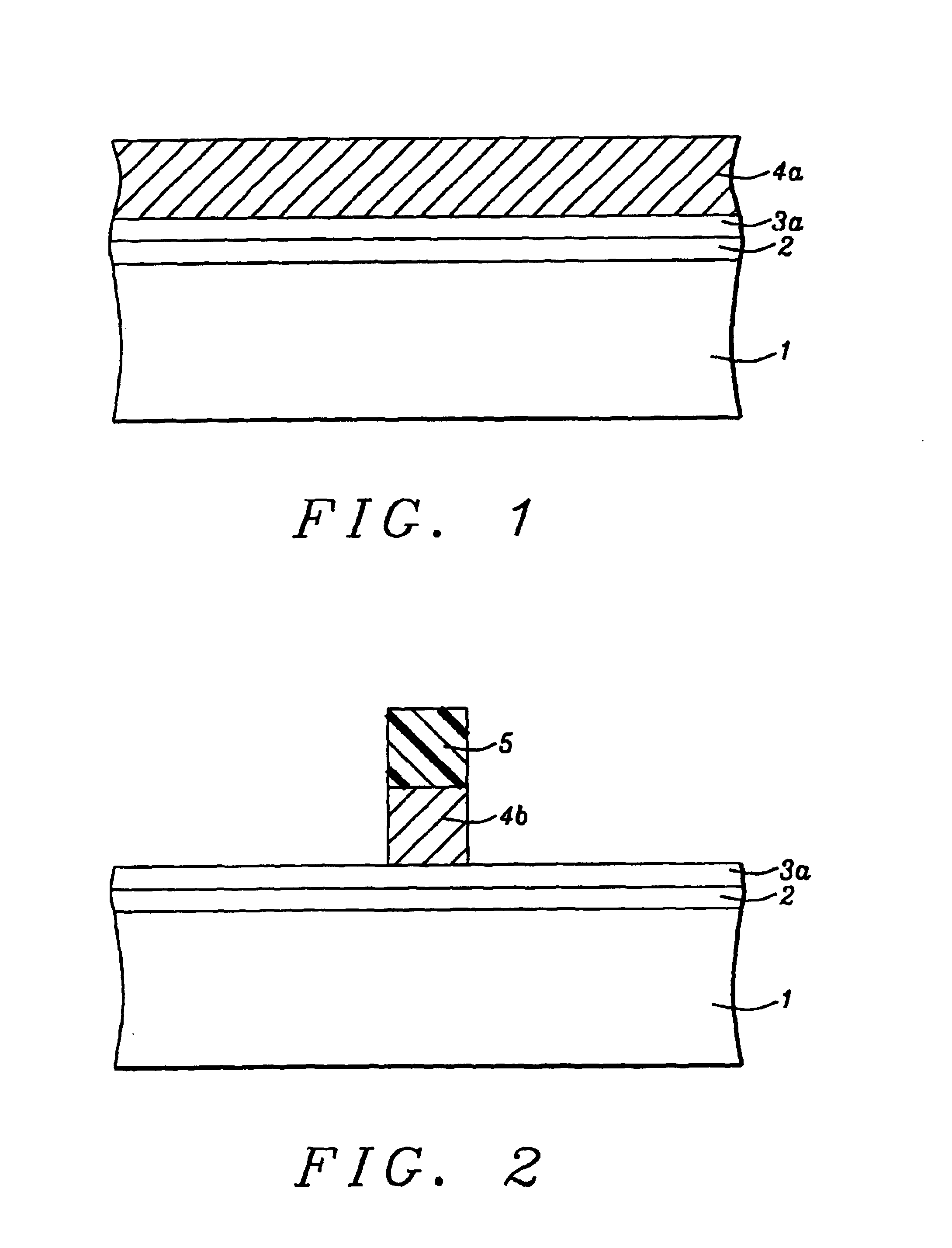

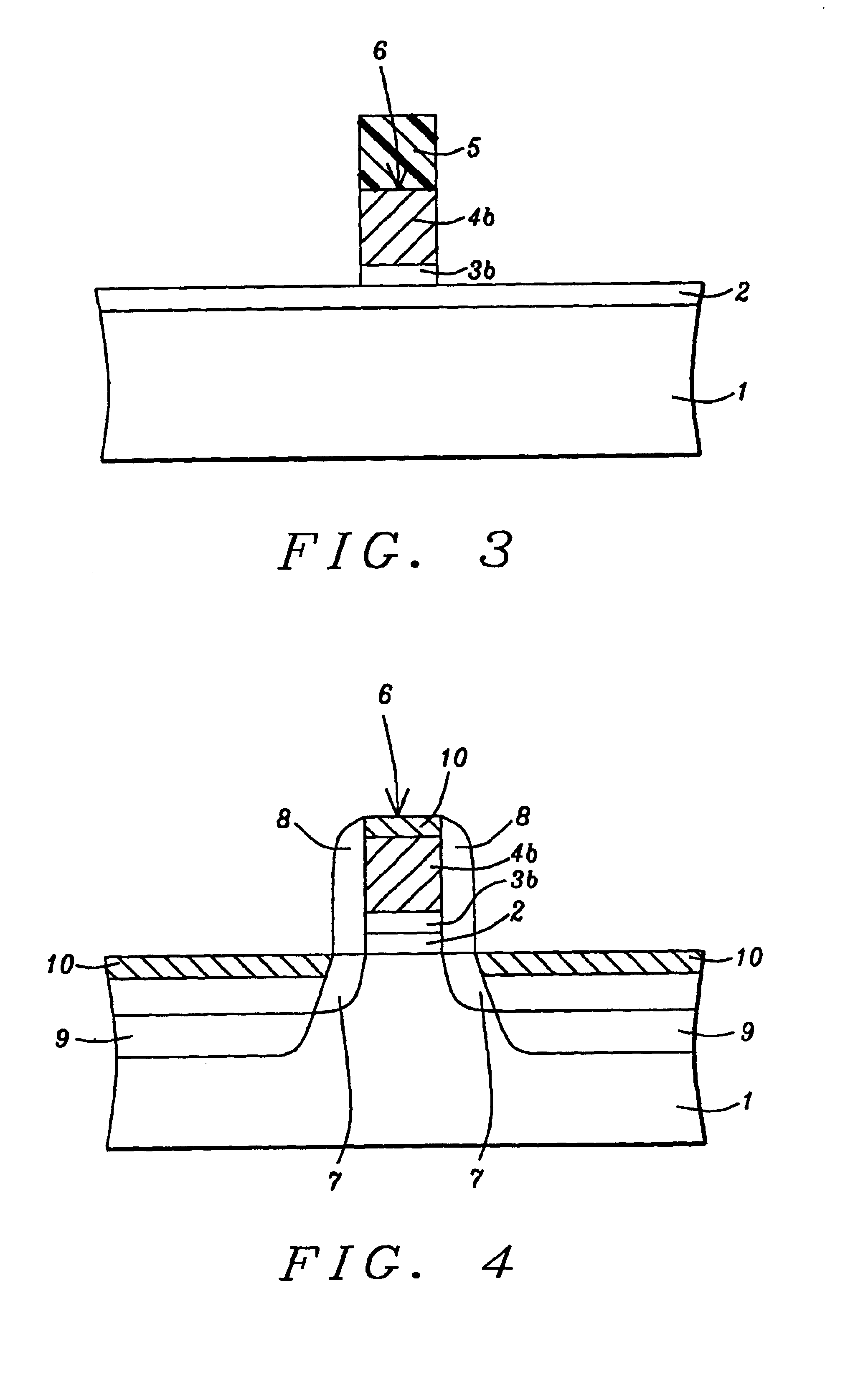

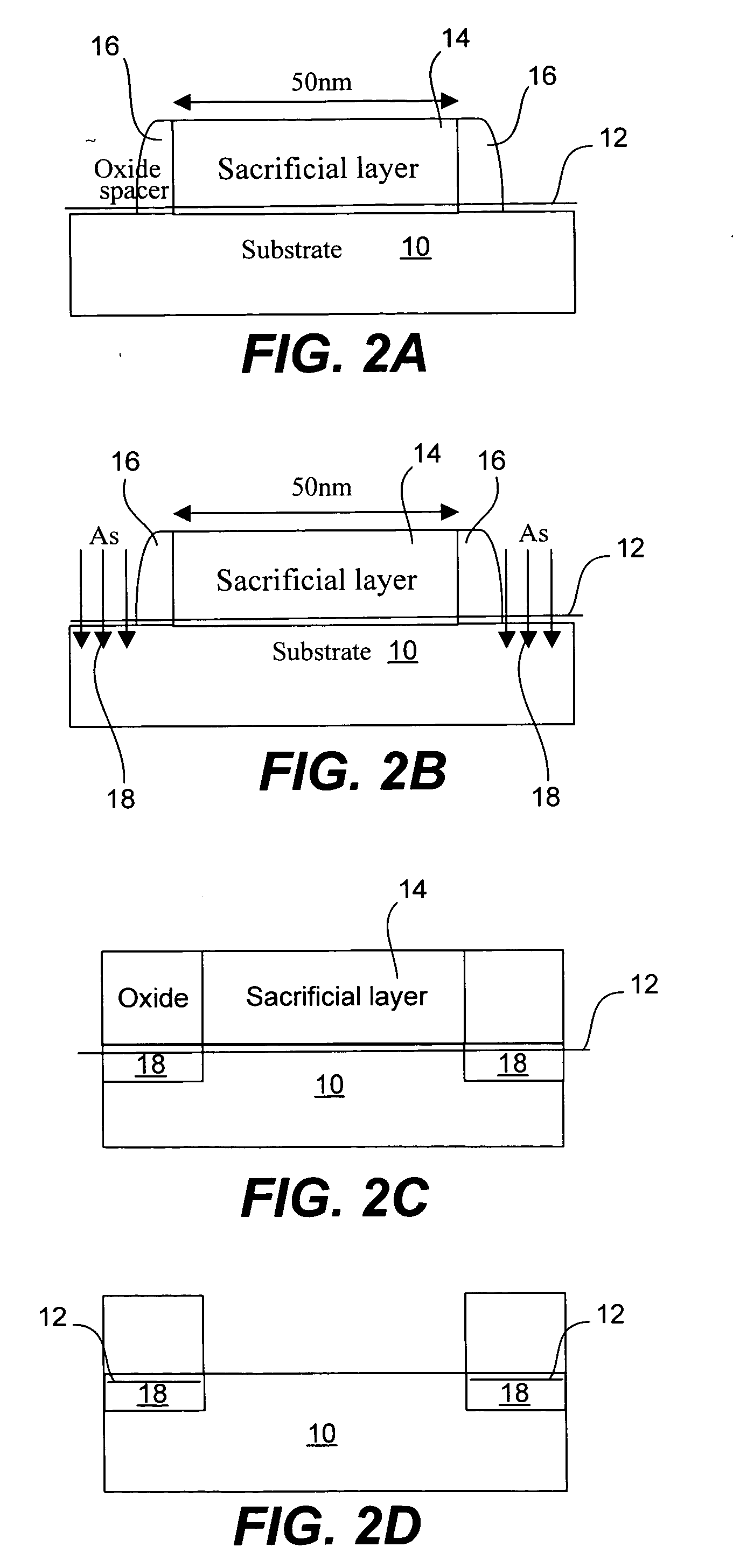

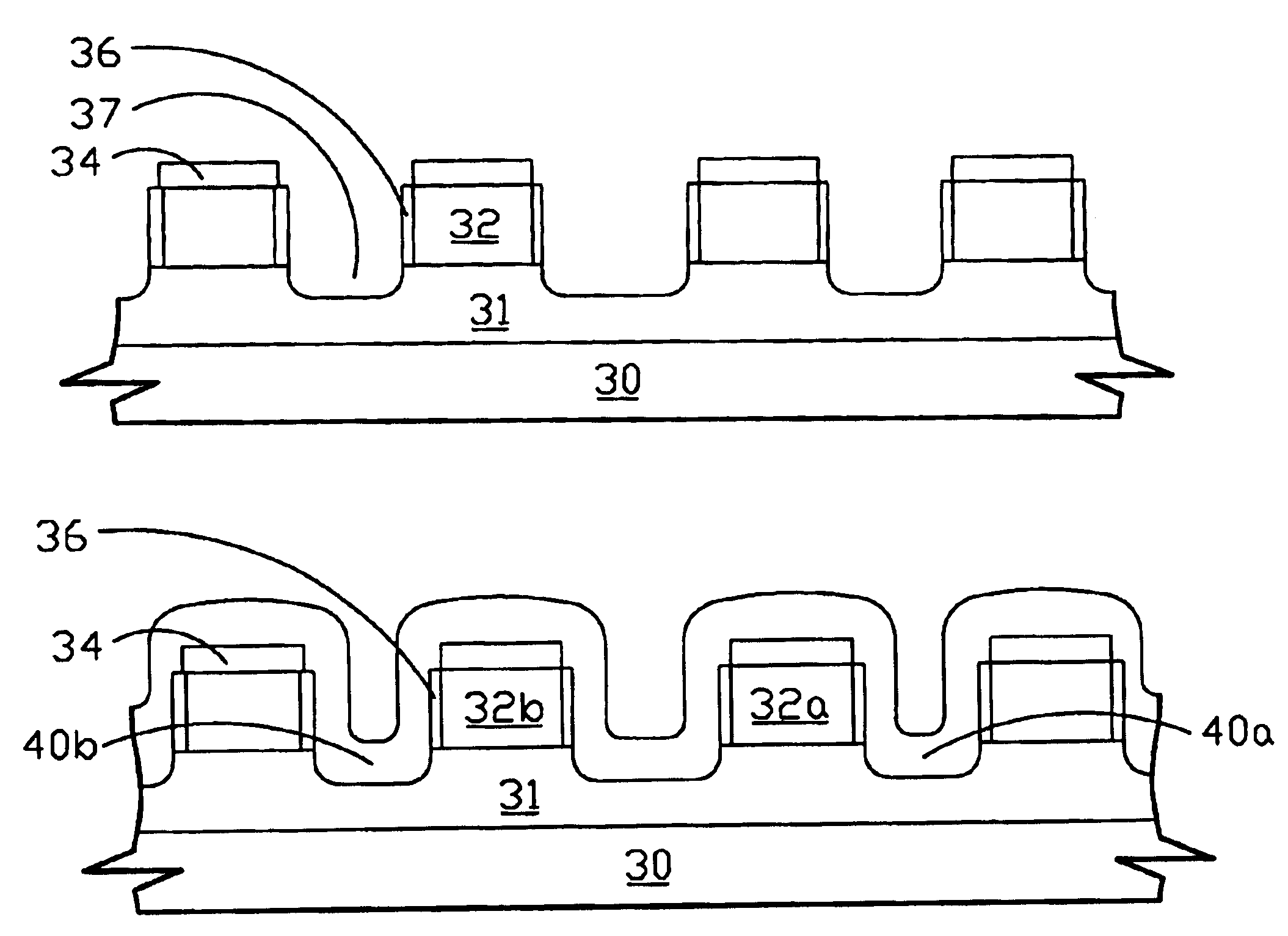

Method of fabricating a double gate MOSFET device

ActiveUS6855588B1Excellent short channel behaviorBetter gate controlTransistorSemiconductor/solid-state device manufacturingDriving currentDouble gate

A method of fabricating a double gate MOSFET device is provided. The present invention overetches a silicon layer overlying a buried oxide layer using a hard mask of cap oxide on the silicon layer as an etching mask. As a result, source, drain and channel regions are formed extending from the buried oxide layer, and a pair of recesses are formed under the channel regions in the buried oxide layer. The channel is a fin structure with a top surface and two opposing parallelly sidewalls. The bottom recess is formed under each opposing sidewall of the fin structure. A conductive gate layer is formed straddling the fin structures. The topography of the conductive gate layer significantly deviates from the conventional plainer profile due to the bottom recess structures under the channel regions, and a more uniformly distributed doped conductive gate layer can be obtained. Hence, the depletion effect of the conductive polysilicon gate while operating the device can be suppressed and the device drive-on currents can be further enhanced.

Owner:UNITED MICROELECTRONICS CORP

Method of fabricating semiconductor side wall fin

InactiveUS20050001216A1Tolerance channel thicknessGrowth is not complicatedTransistorSolid-state devicesGate insulatorEngineering

Owner:GLOBALFOUNDRIES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com