Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1234 results about "Lattice mismatch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

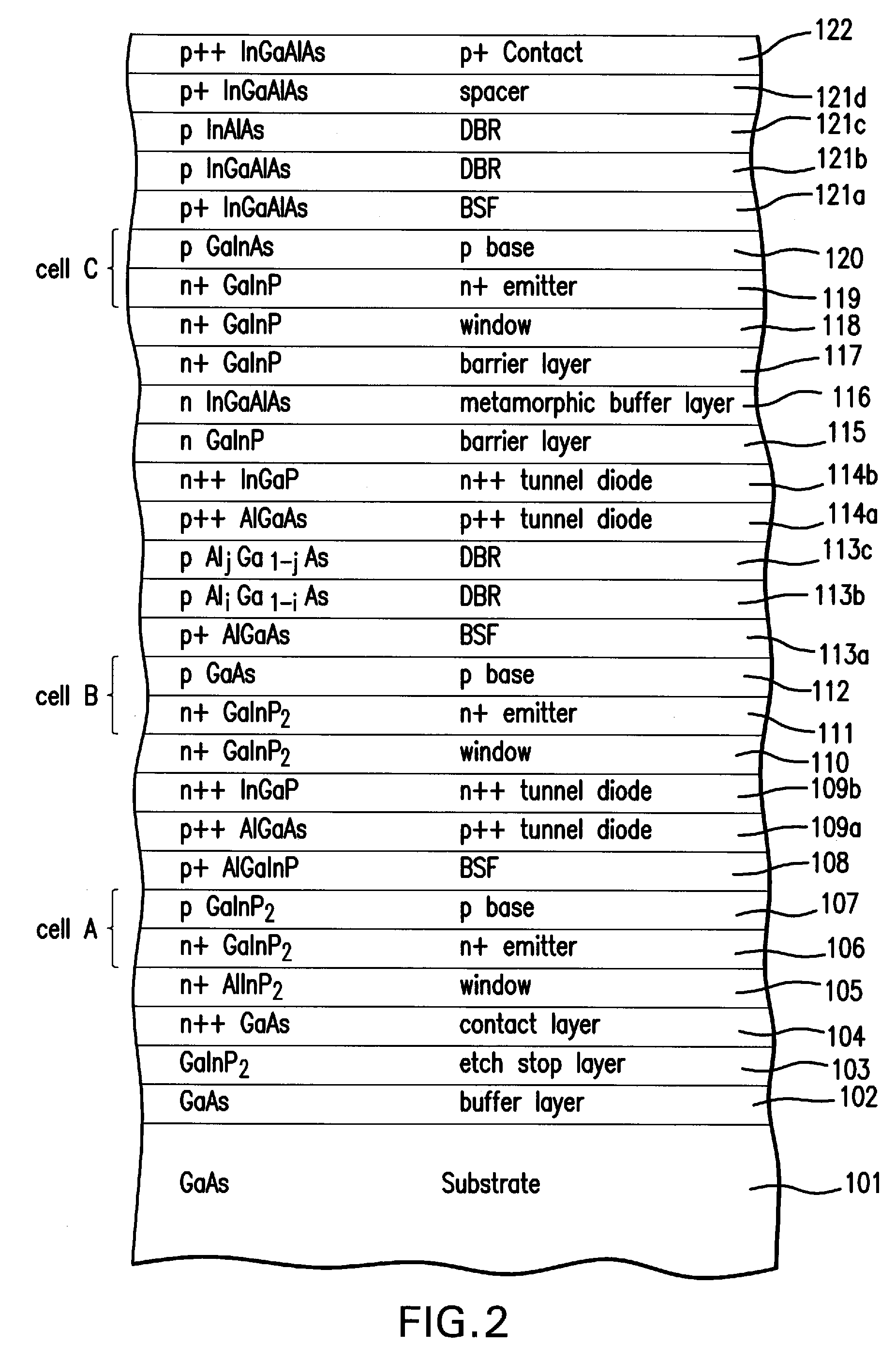

High-efficiency, monolithic, multi-bandgap, tandem photovoltaic energy converters

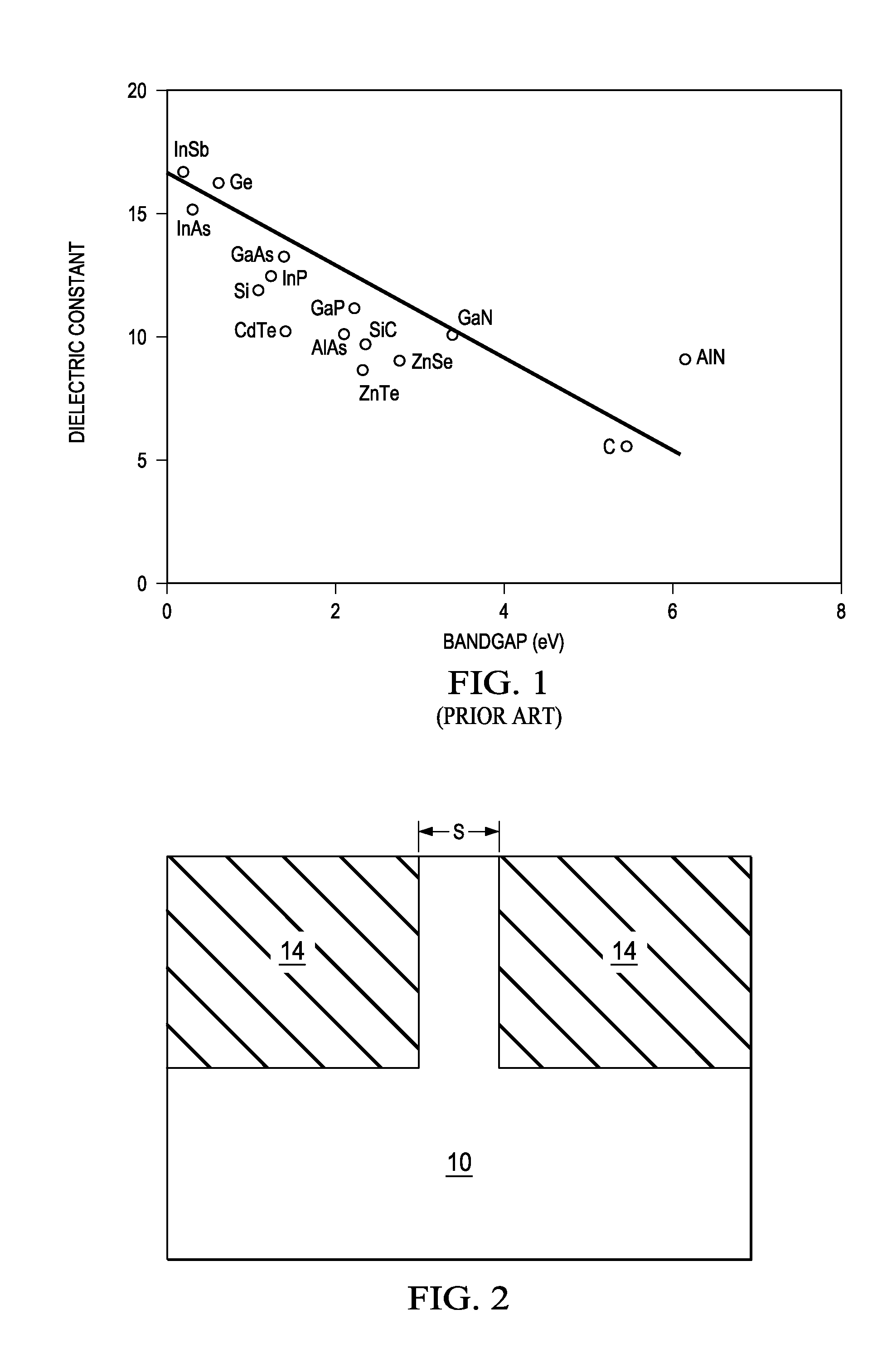

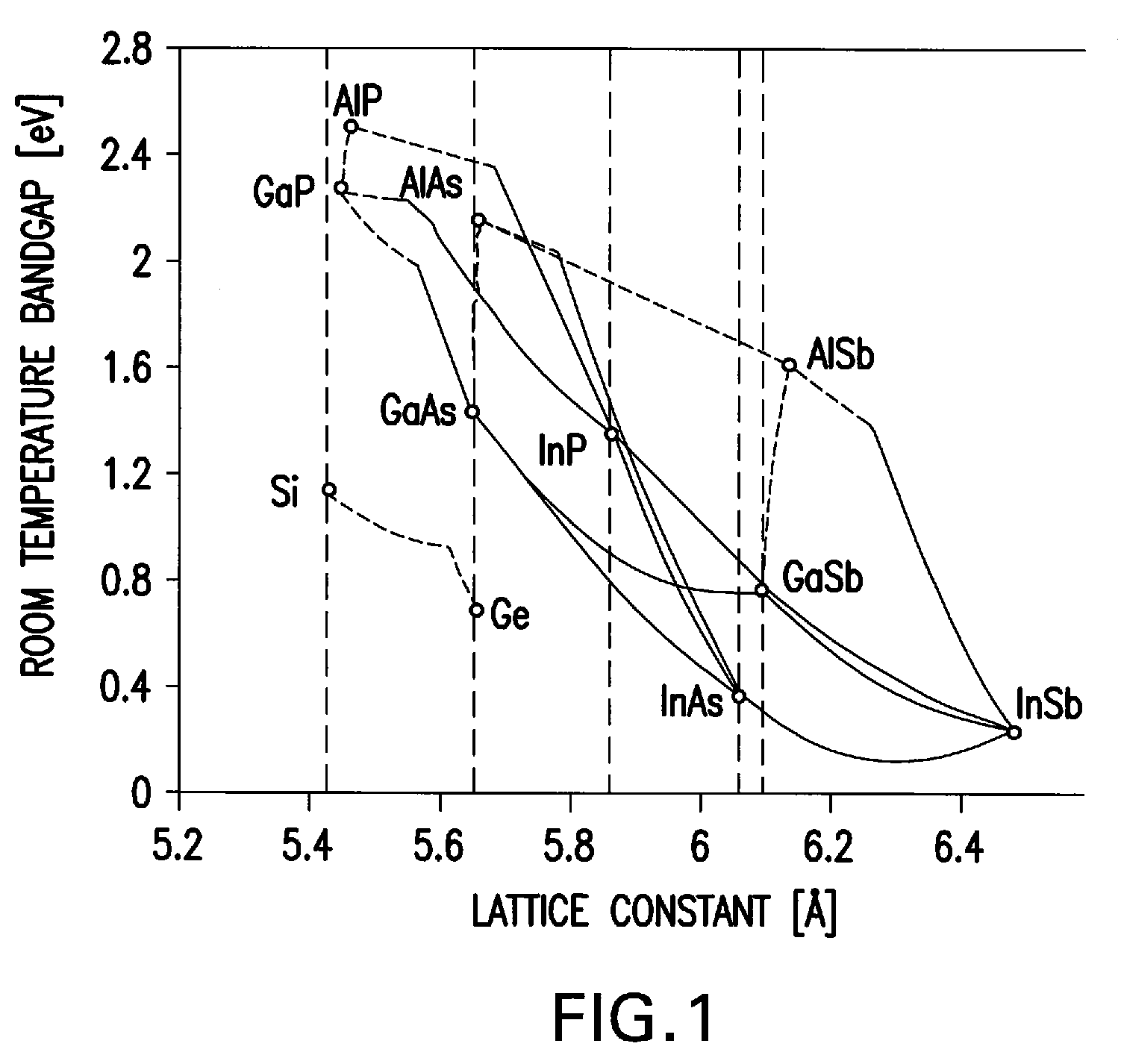

ActiveUS20060144435A1Improved thermal managementIncrease flexibilityPV power plantsSemiconductor/solid-state device manufacturingHigh energyLattice mismatch

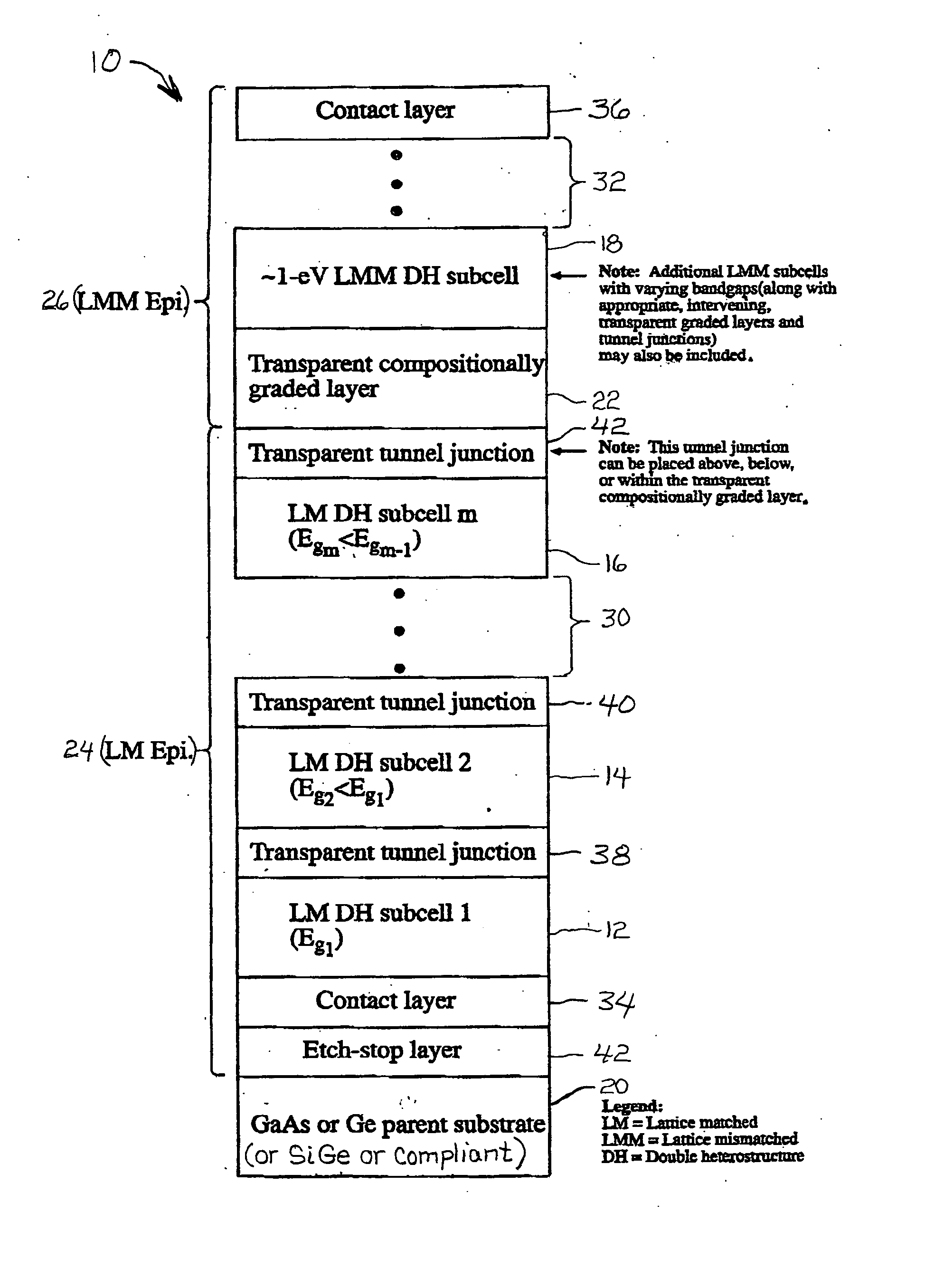

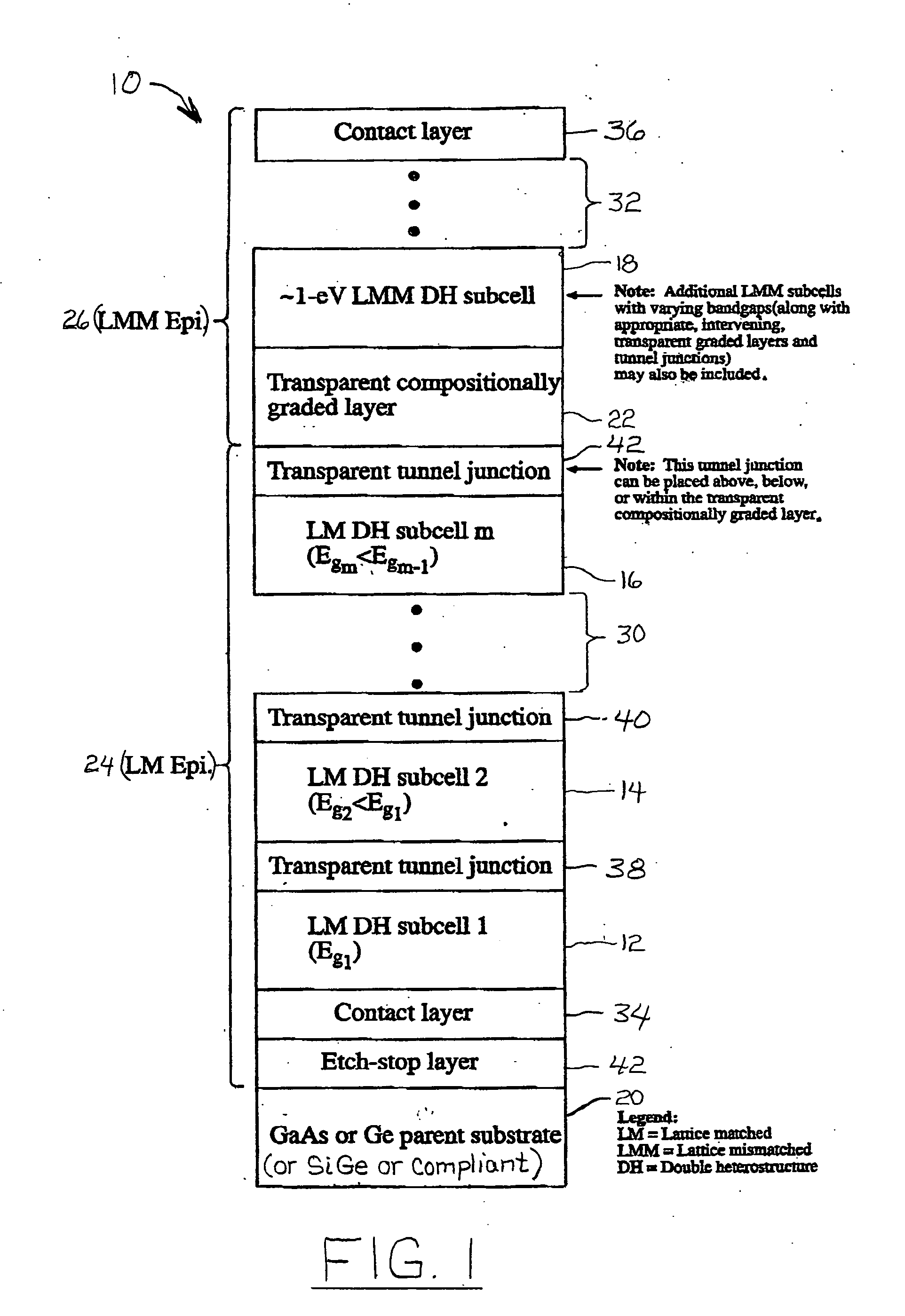

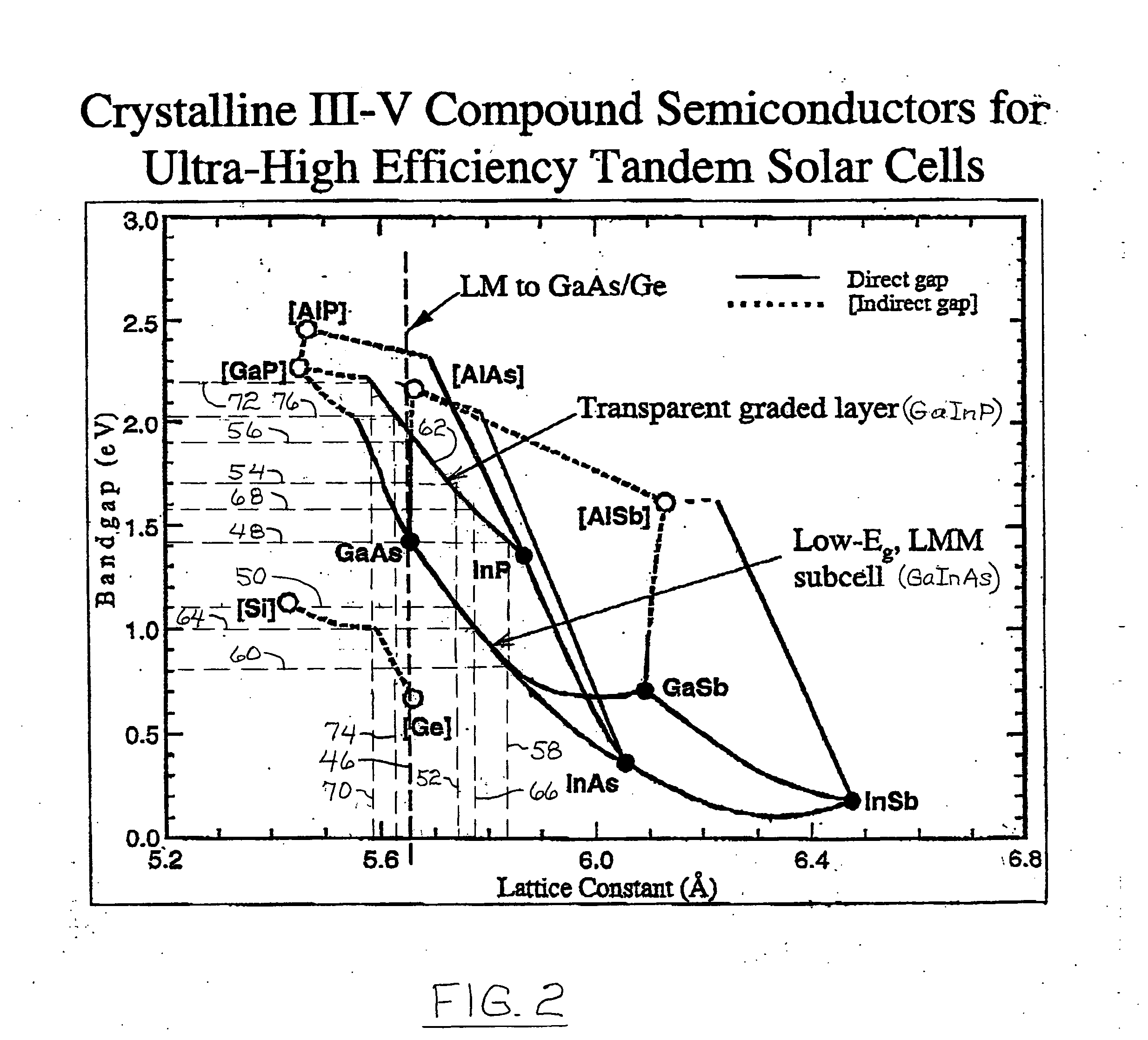

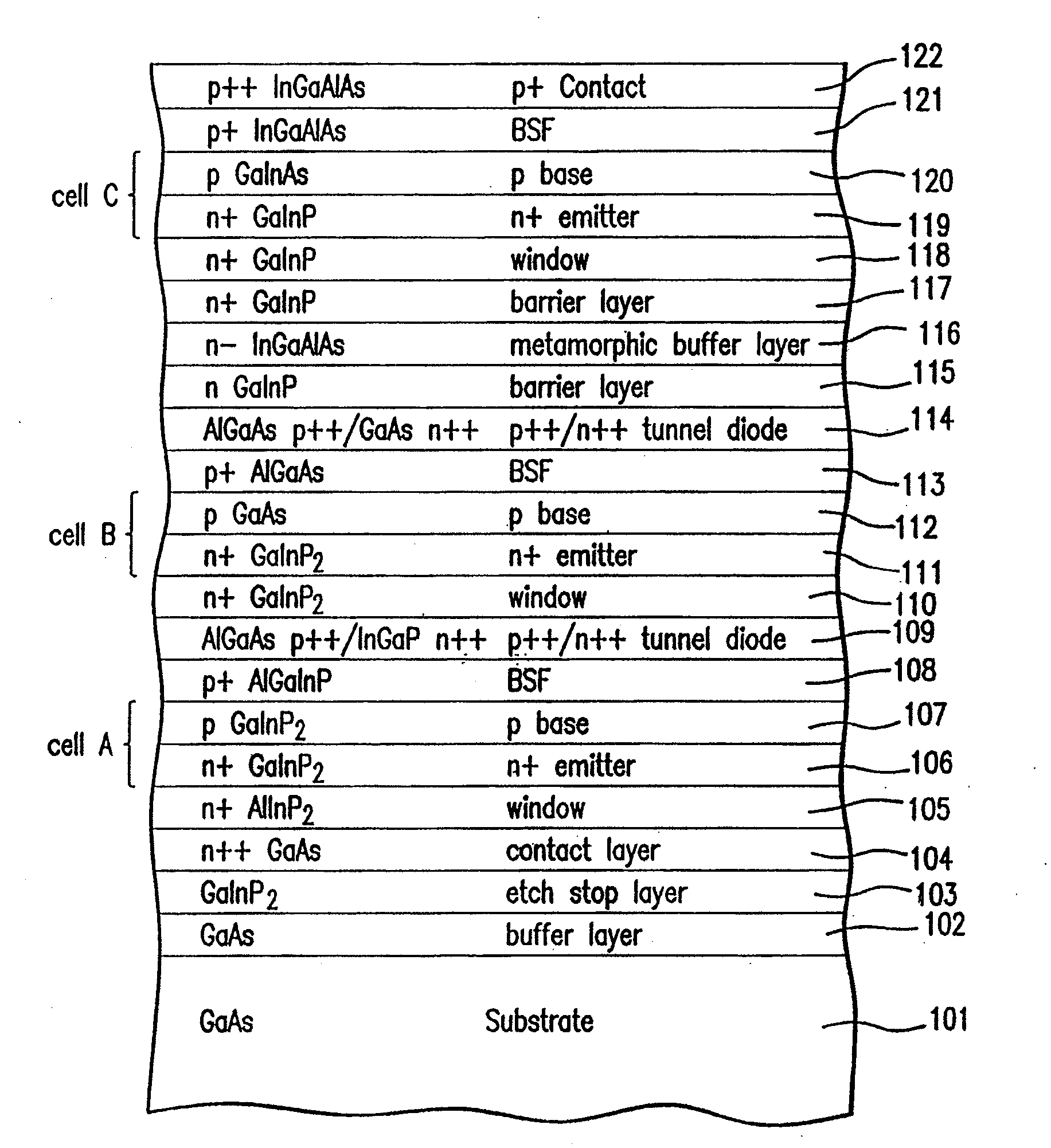

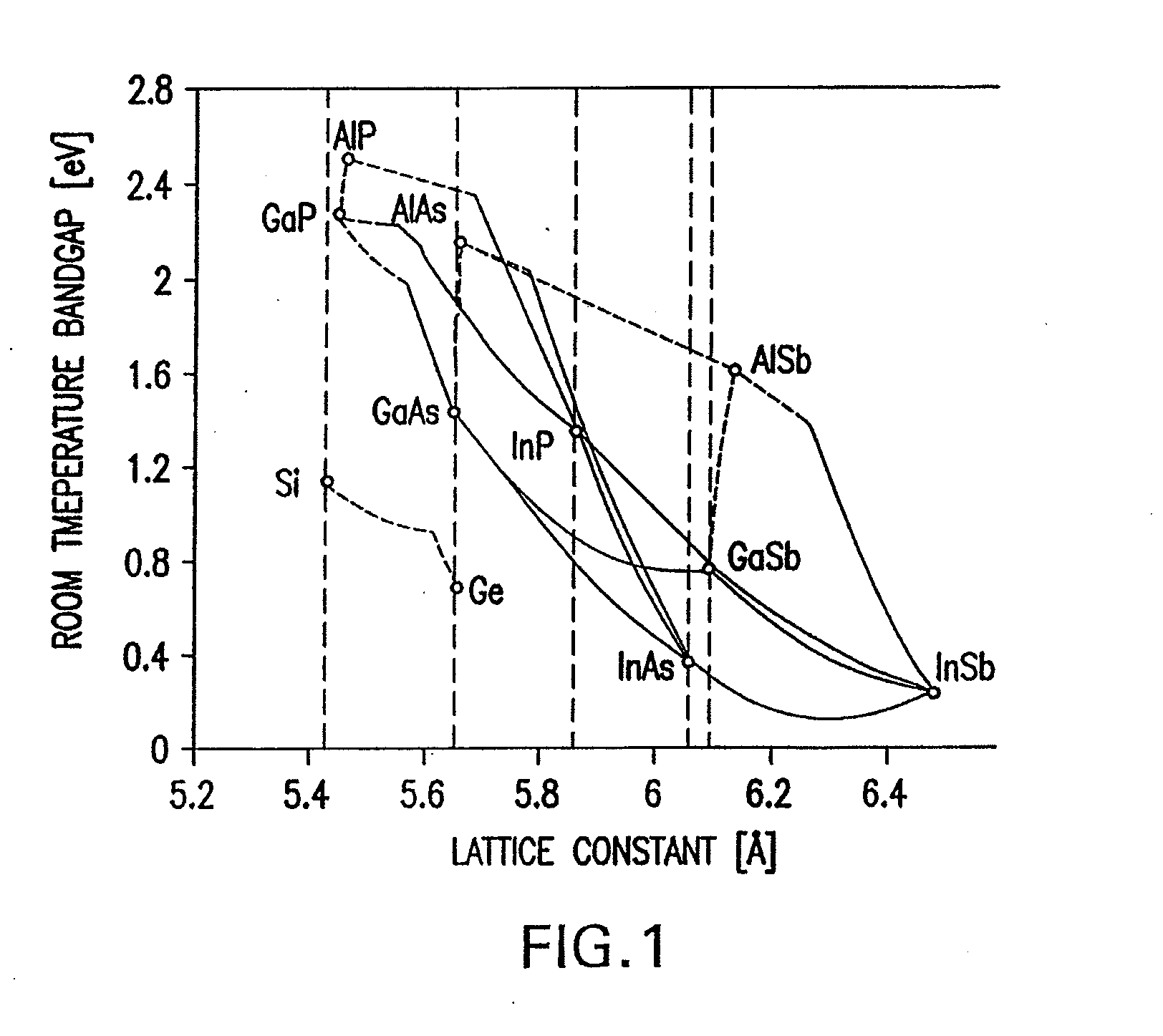

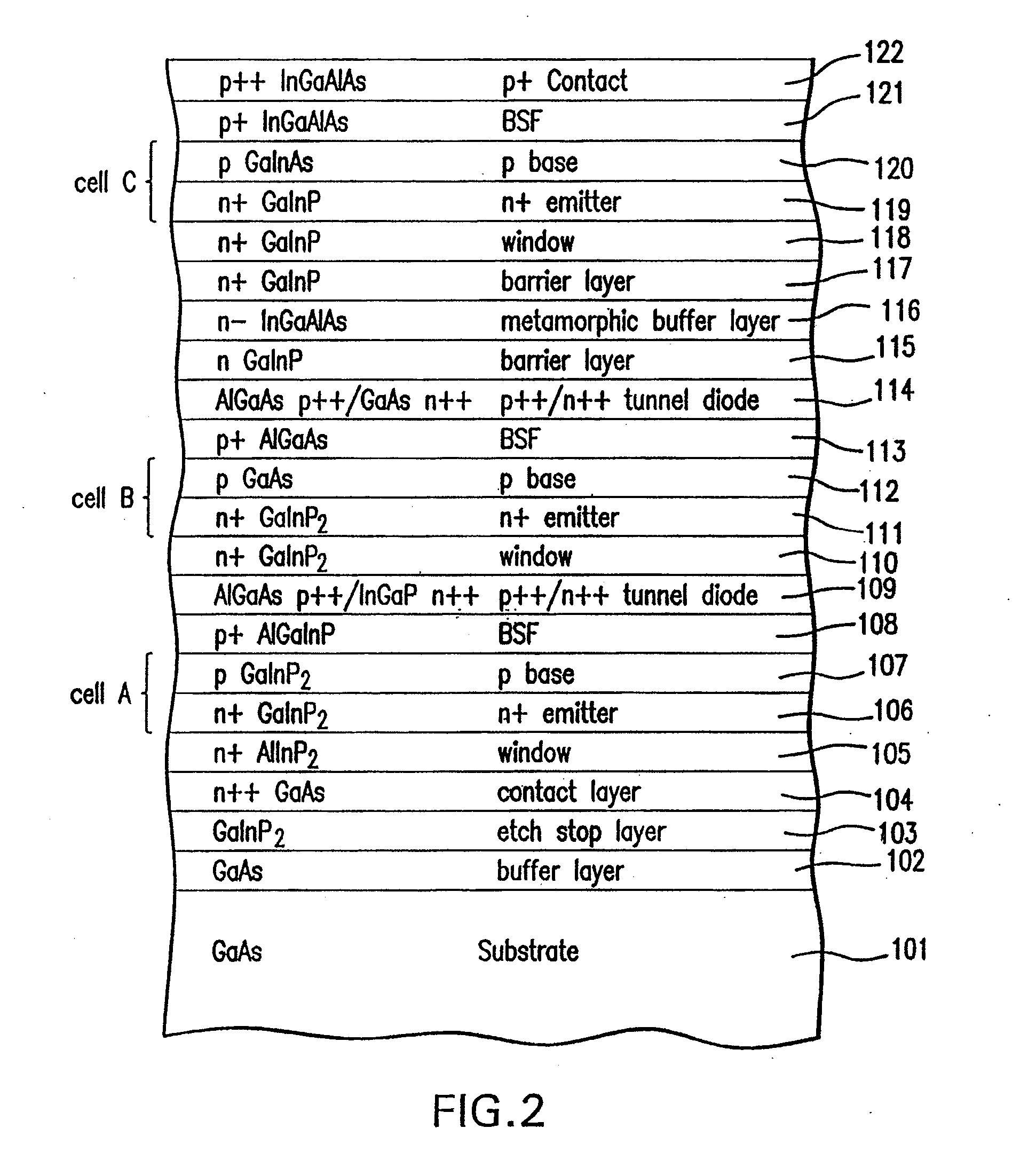

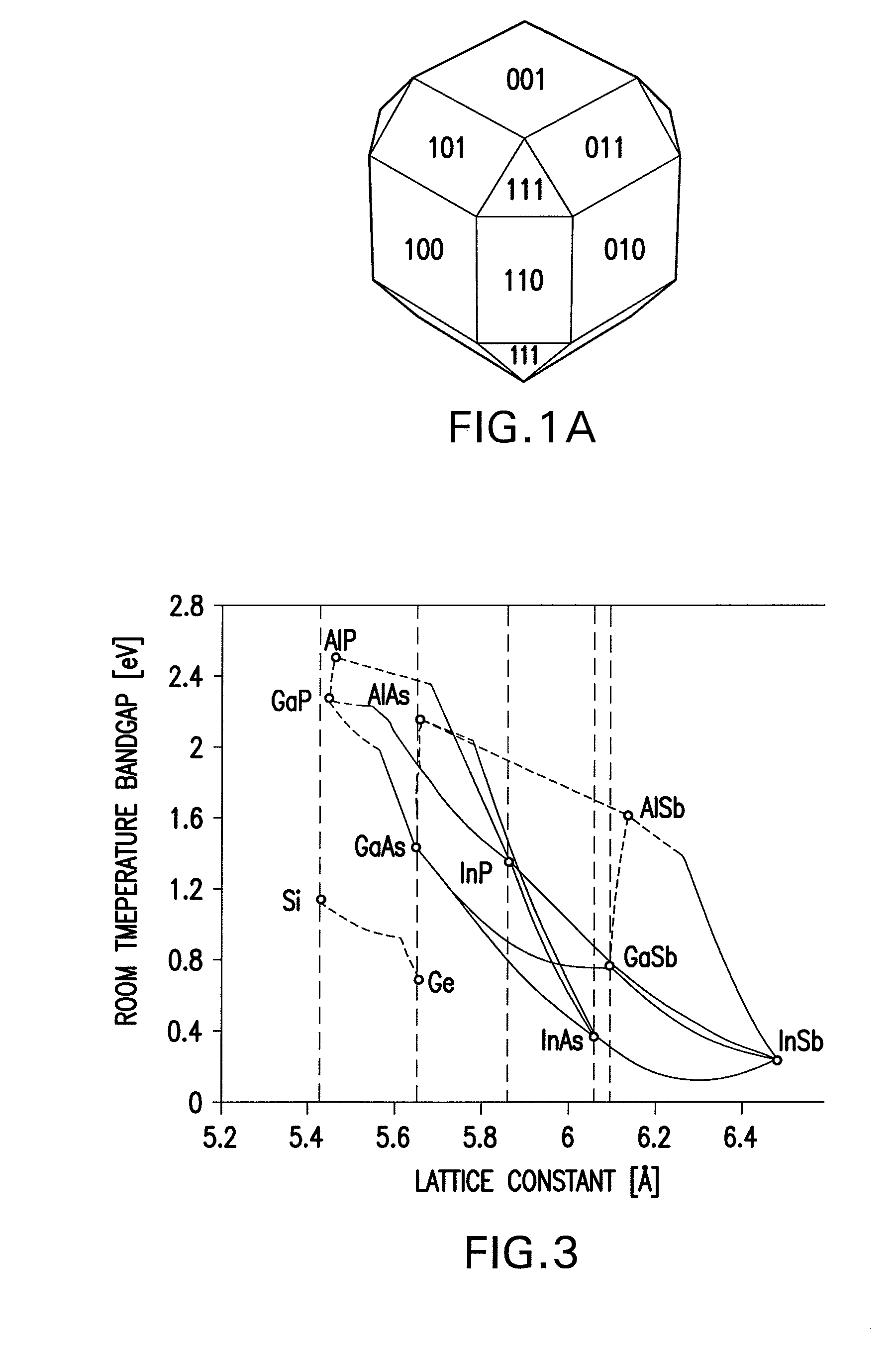

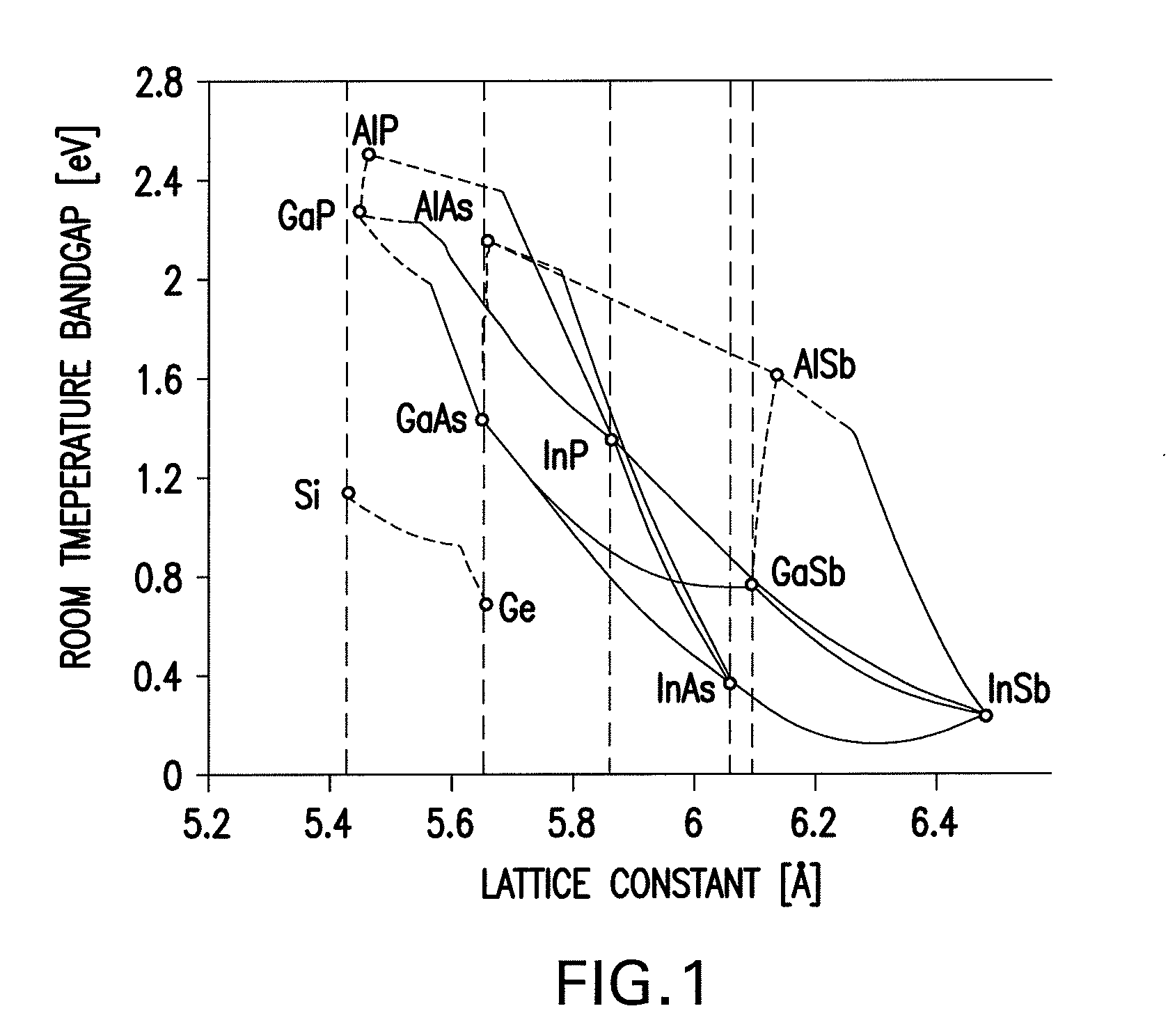

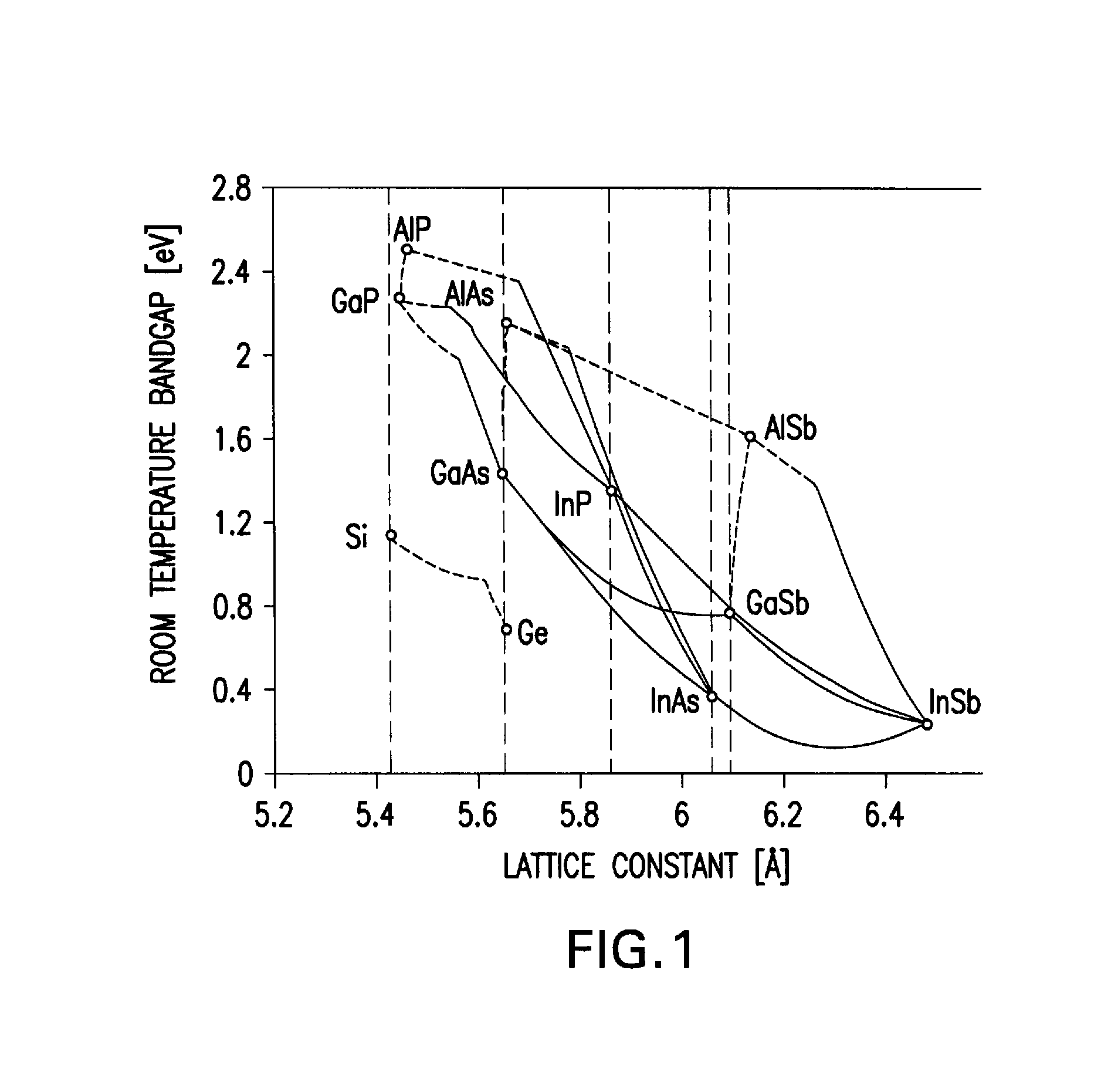

A monolithic, multi-bandgap, tandem solar photovoltaic converter has at least one, and preferably at least two, subcells grown lattice-matched on a substrate with a bandgap in medium to high energy portions of the solar spectrum and at least one subcell grown lattice-mismatched to the substrate with a bandgap in the low energy portion of the solar spectrum, for example, about 1 eV.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

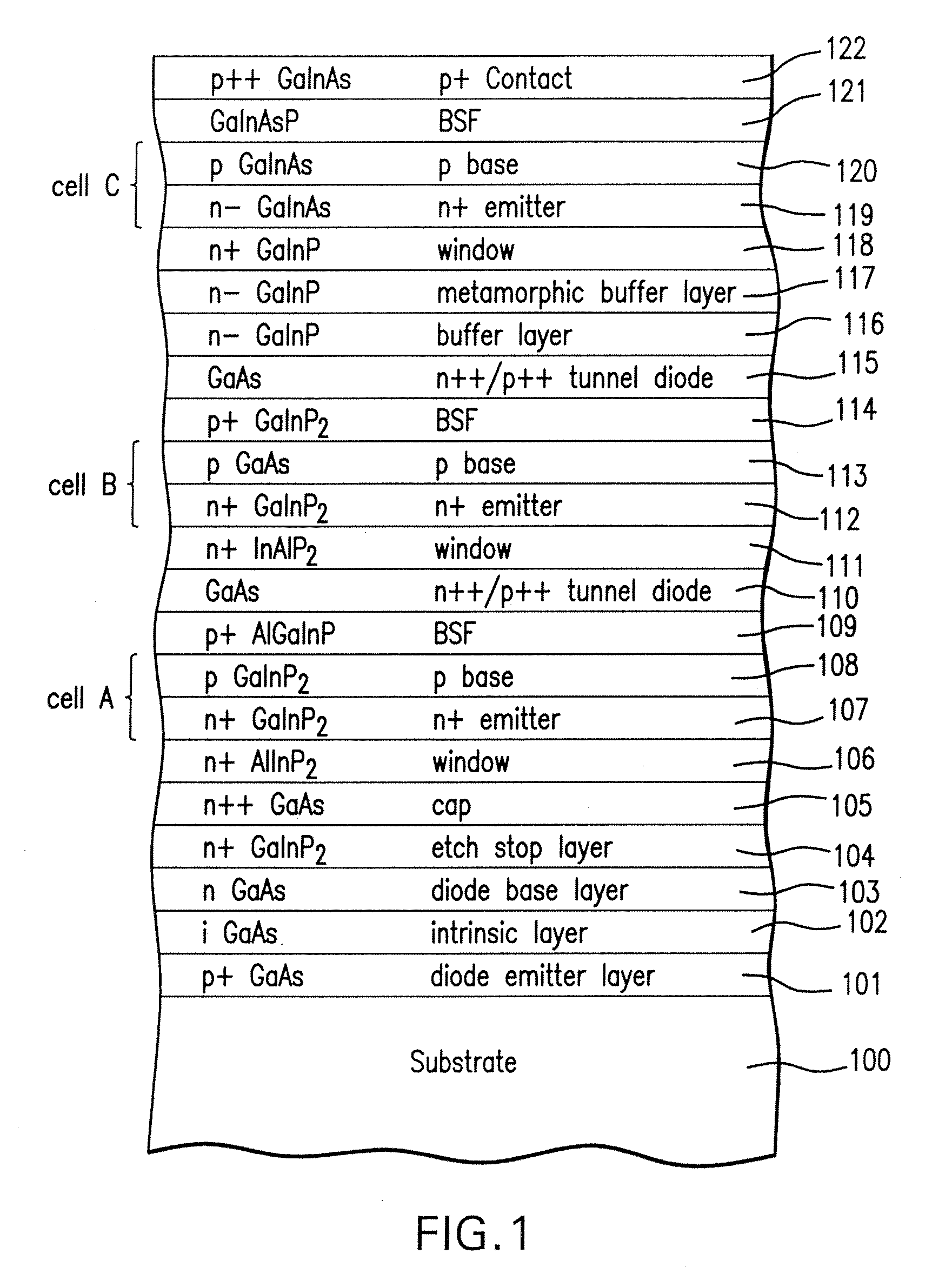

High efficiency, monolithic multijunction solar cells containing lattice-mismatched materials and methods of forming same

ActiveUS6951819B2Improve performanceRelieve pressureSemiconductor/solid-state device manufacturingPhotovoltaic energy generationLattice mismatchSemiconductor

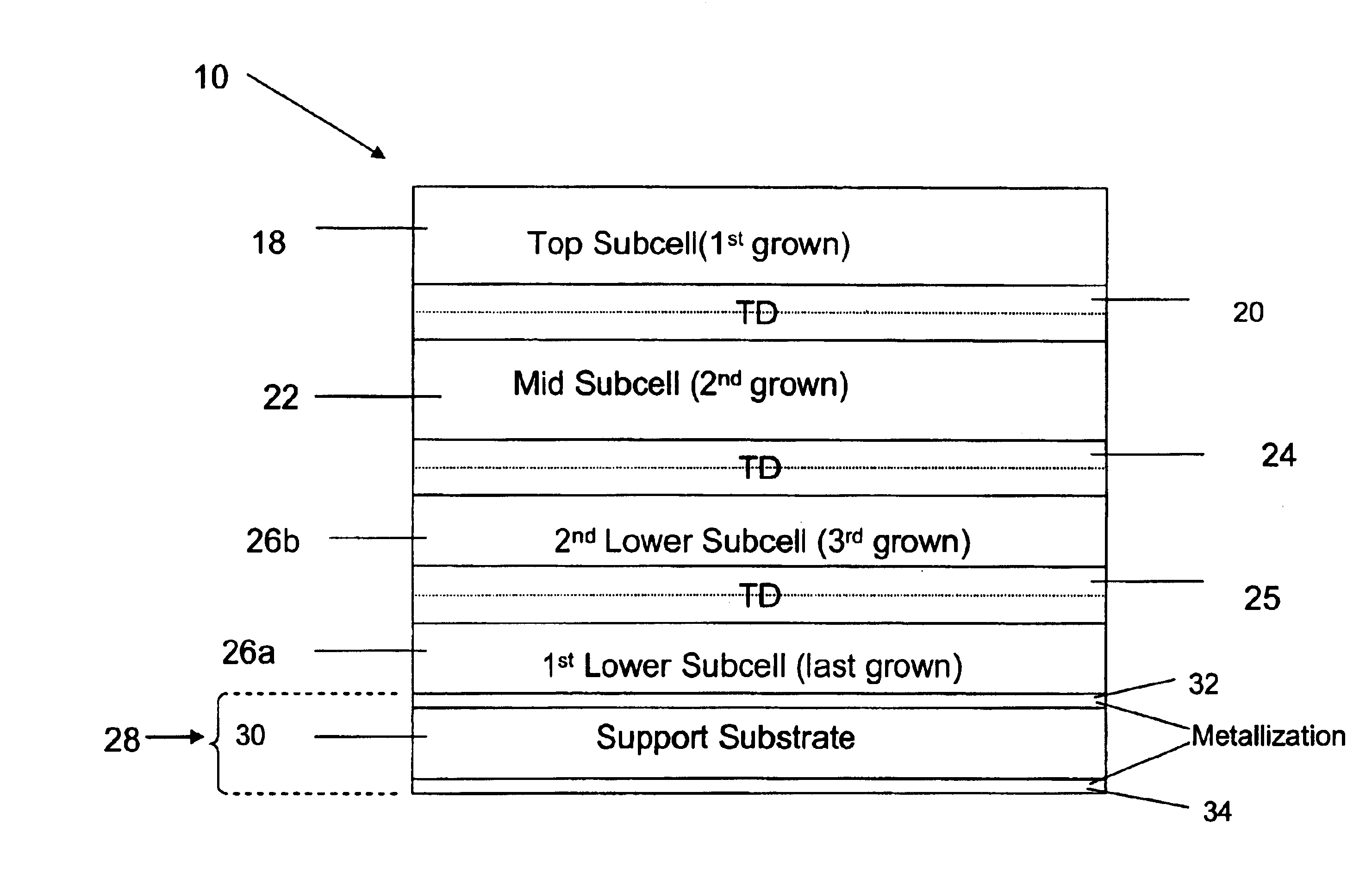

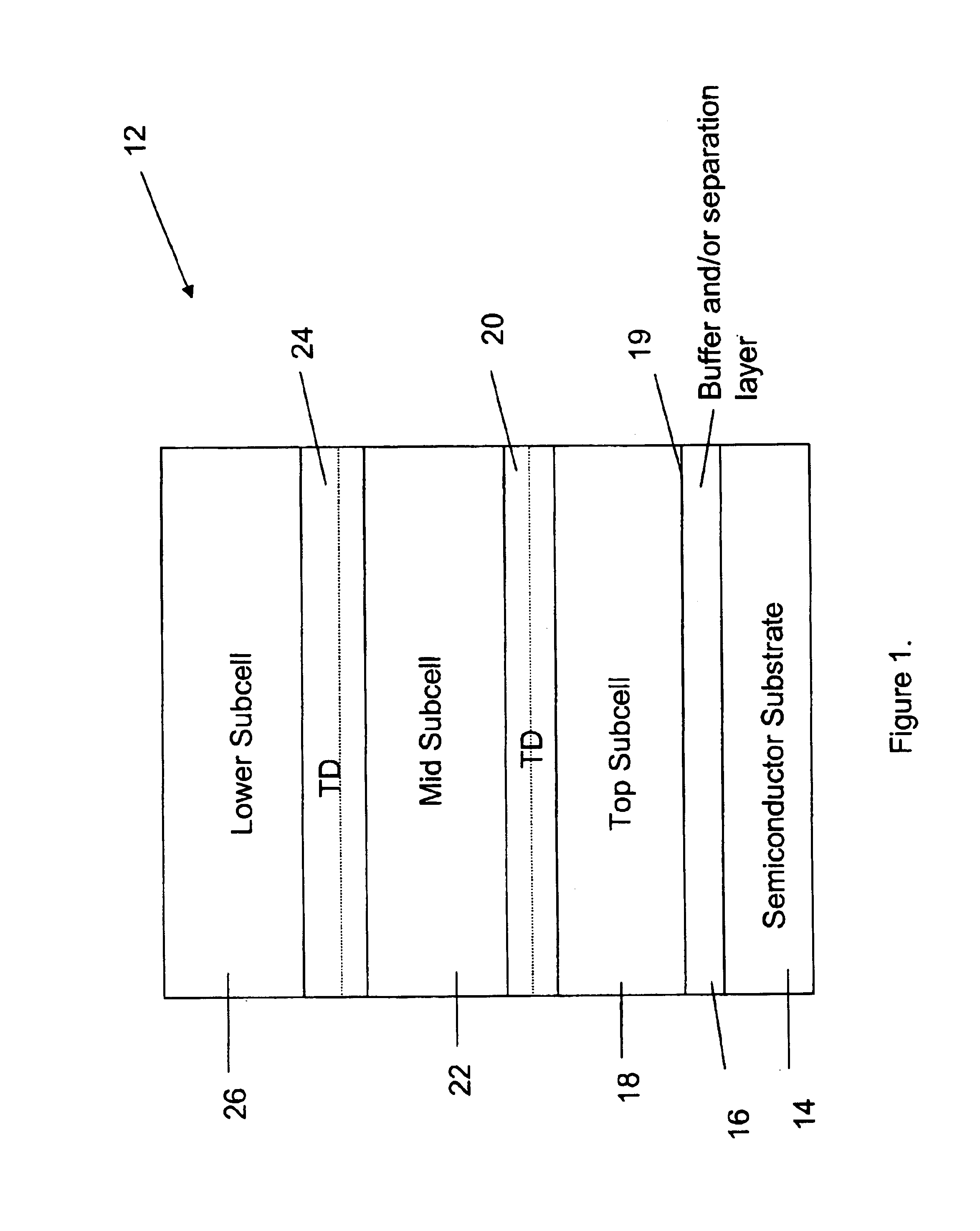

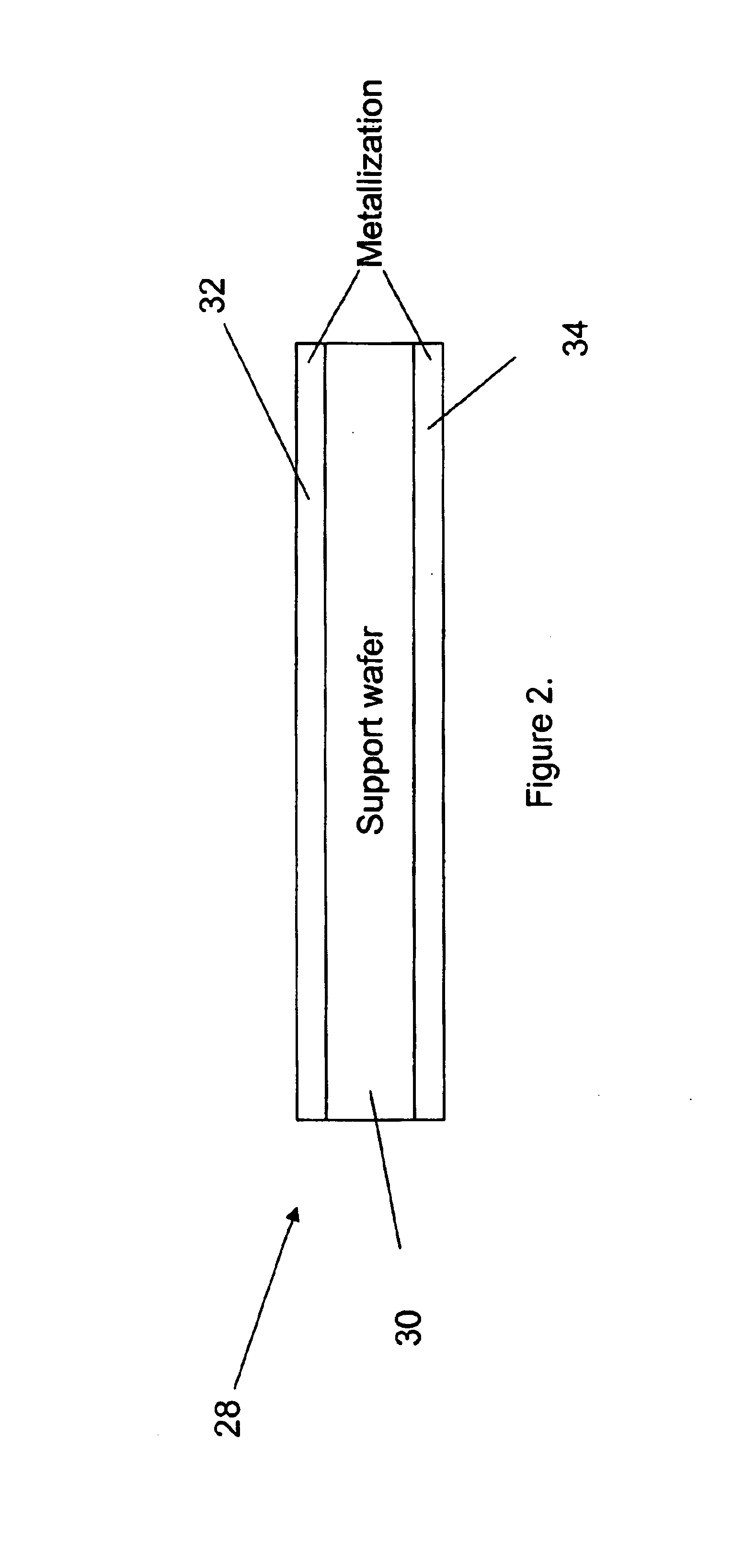

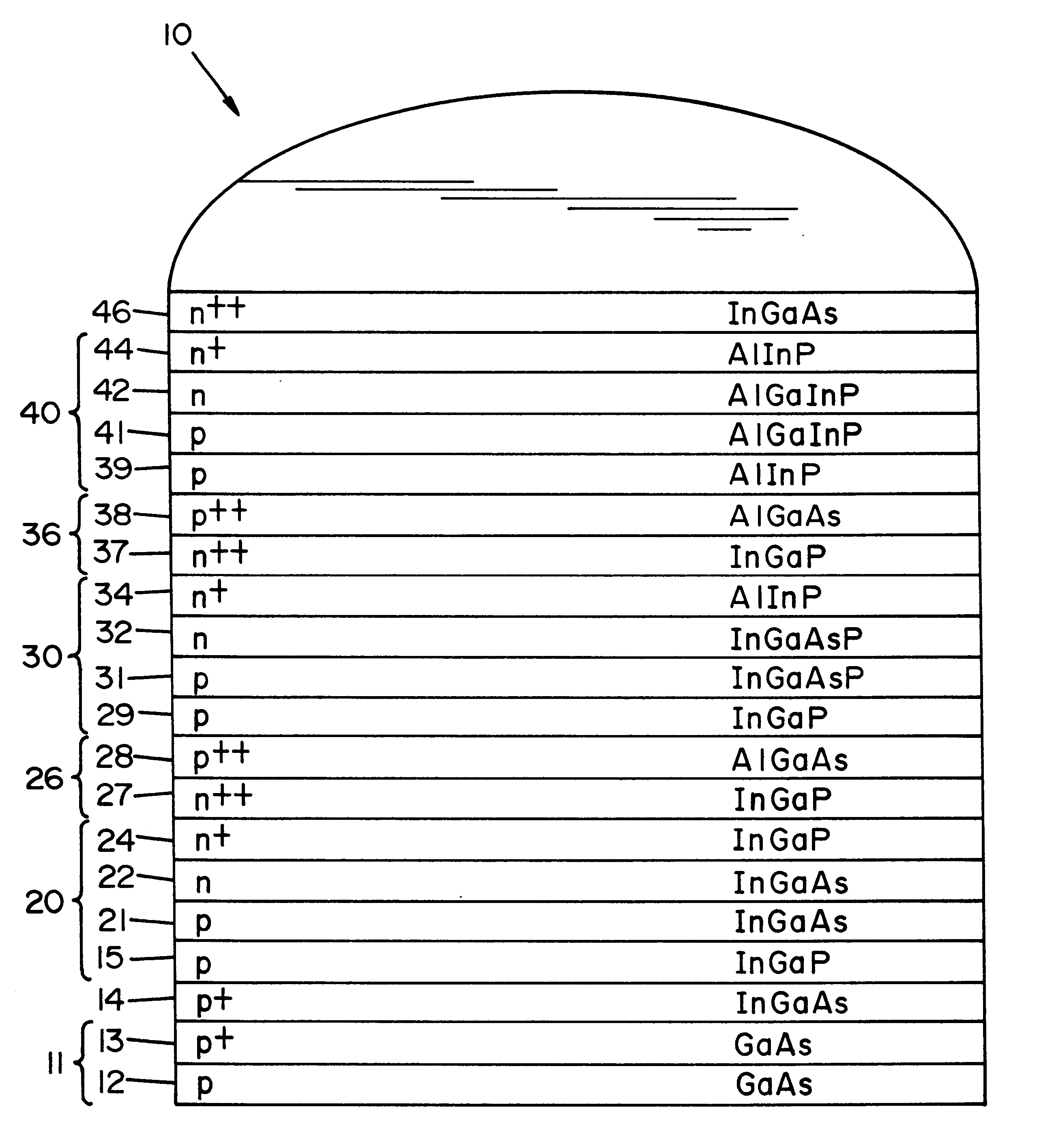

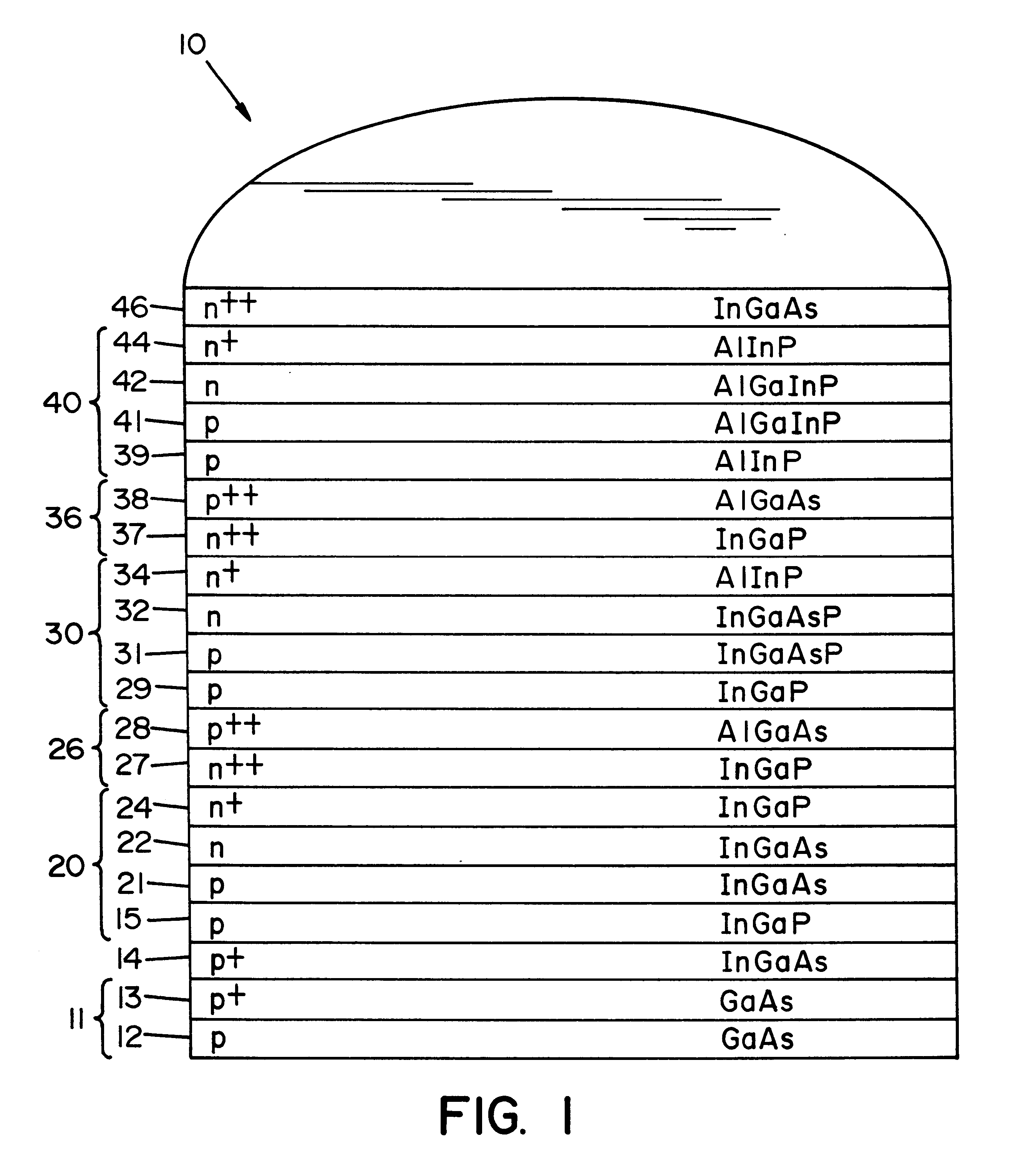

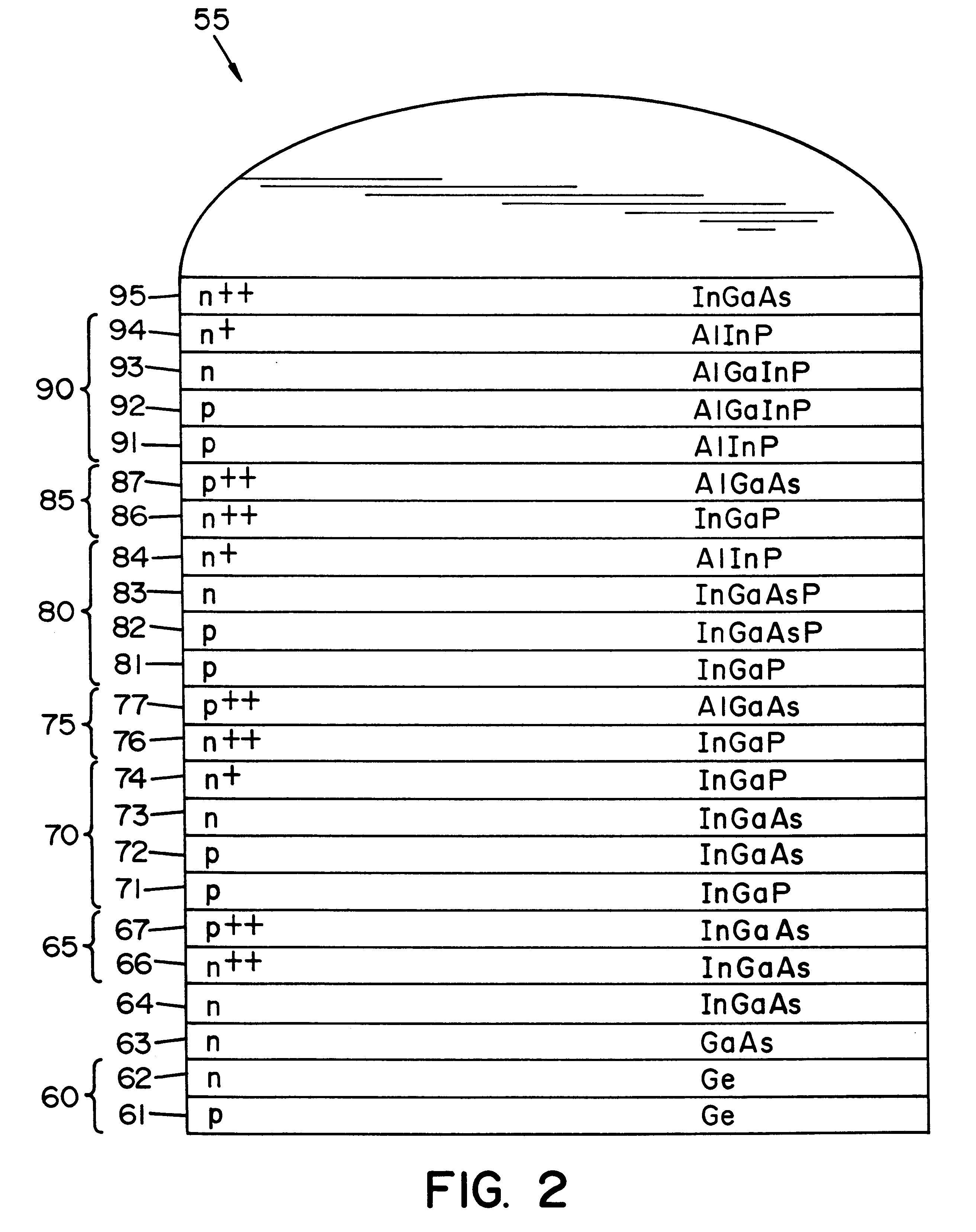

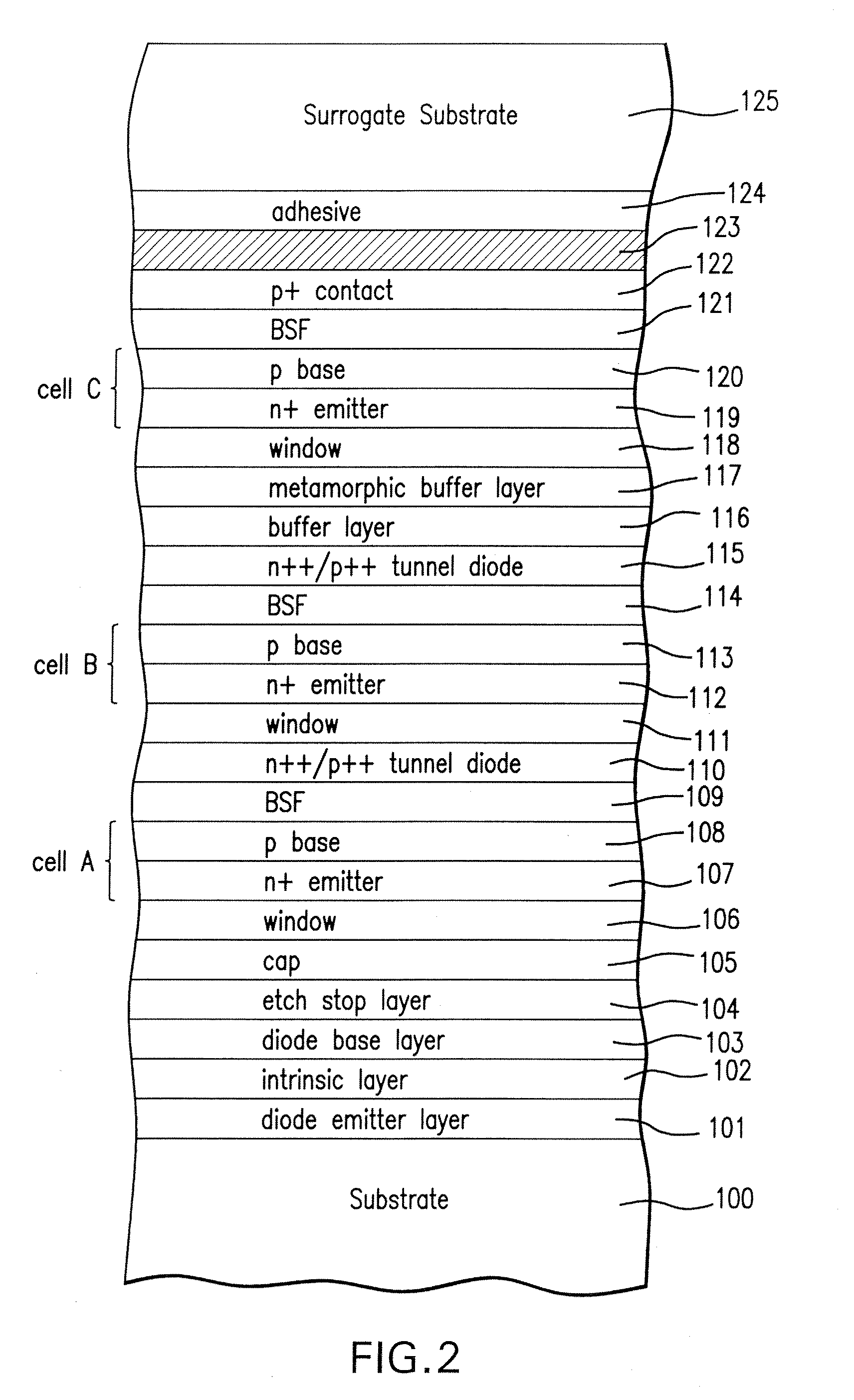

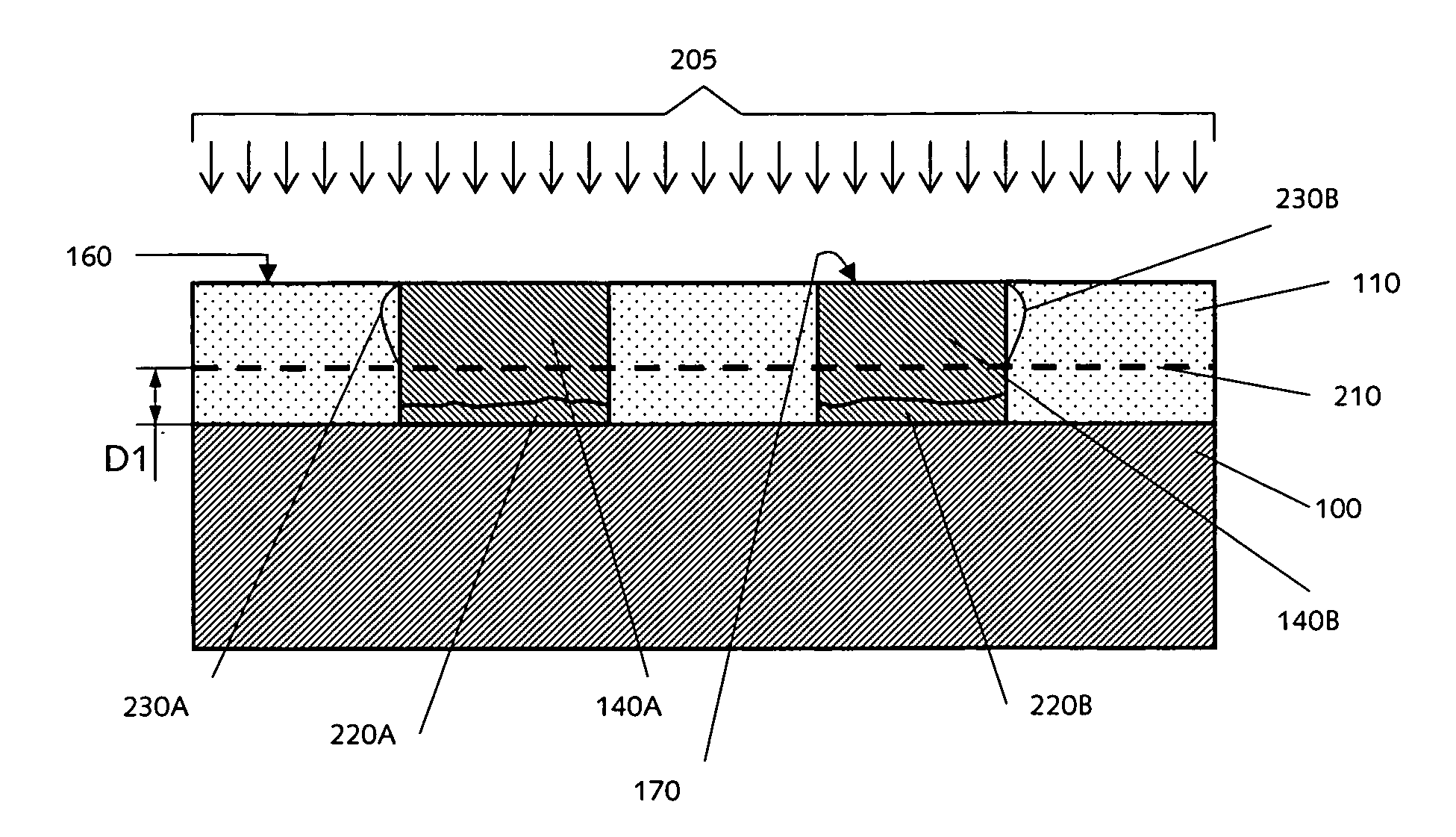

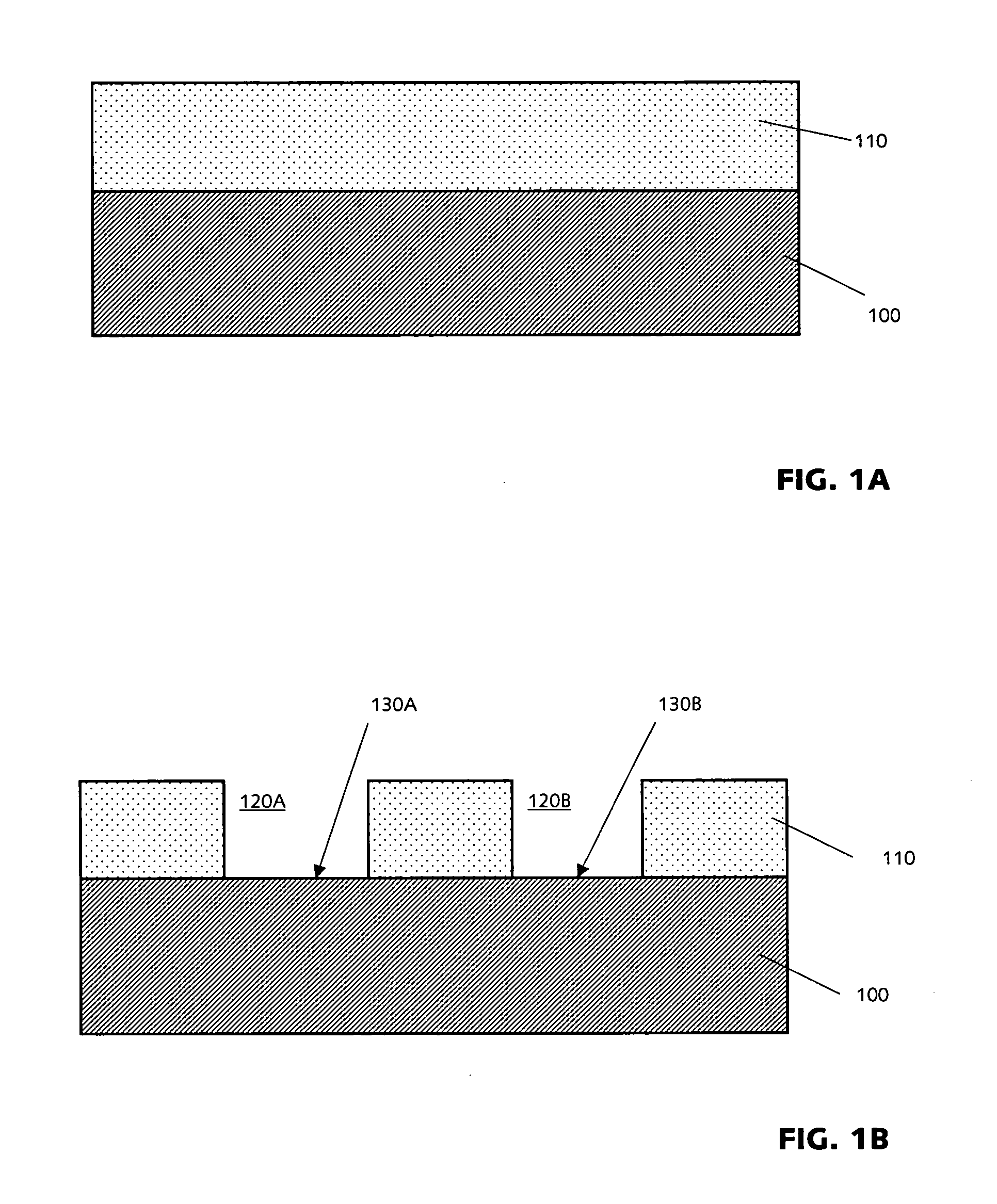

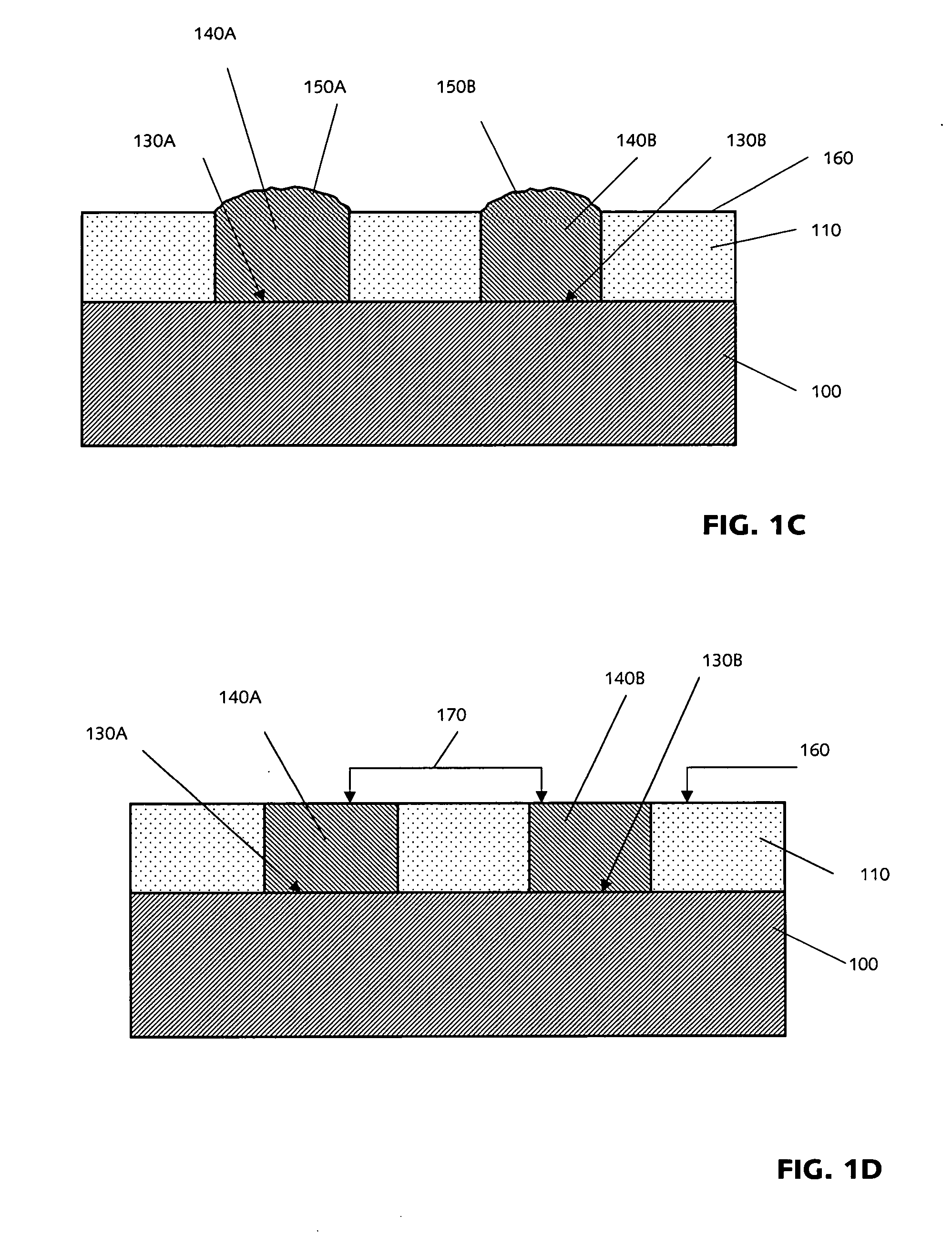

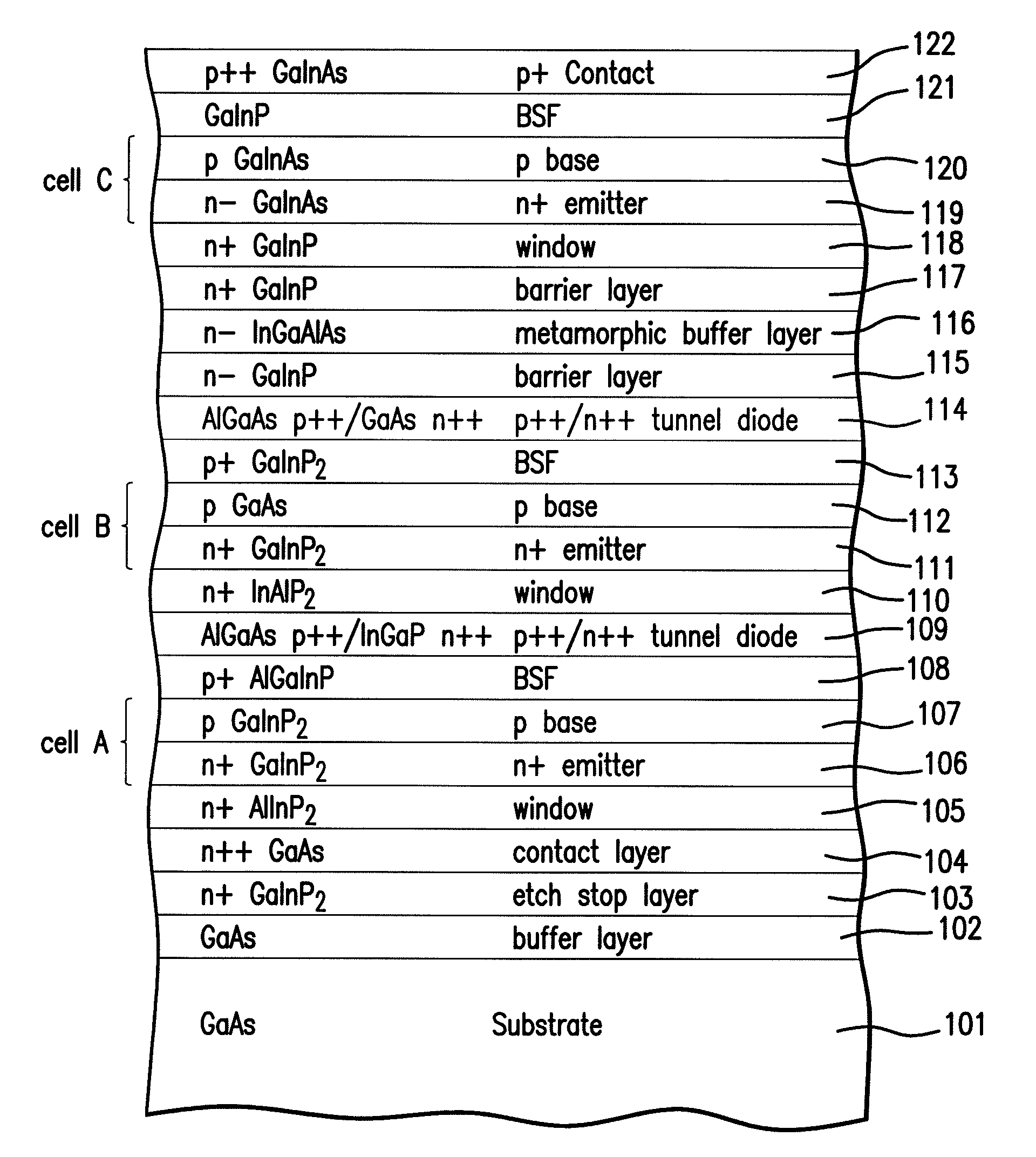

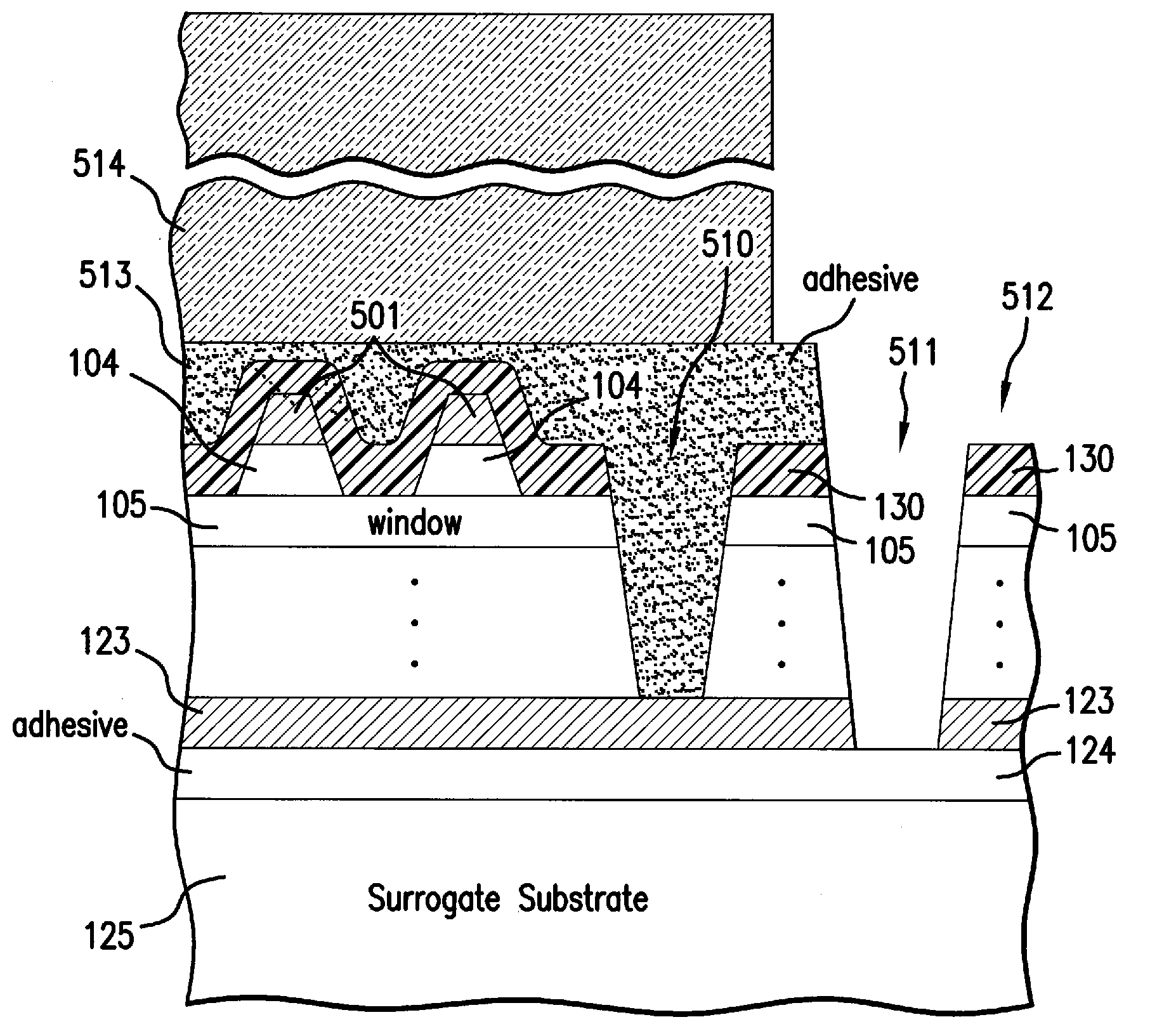

In one embodiment, a method of forming a multijunction solar cell having lattice mismatched layers and lattice-matched layers comprises growing a top subcell having a first band gap over a growth semiconductor substrate. A middle subcell having a second band gap is grown over the top subcell, and a lower subcell having a third band gap is grown over the middle subcell. The lower subcell is substantially lattice-mismatched with respect to the growth semiconductor substrate. The first band gap of the top subcell is larger than the second band gap of the middle subcell. The second band gap of the middle subcell is larger than the third band gap of the lower subcell. A support substrate is formed over the lower subcell, and the growth semiconductor substrate is removed. In various embodiments, the multijunction solar cell may further comprise additional lower subcells. A parting layer may also be provided between the growth substrate and the top subcell in certain embodiments. Embodiments of this reverse process permit the top and middle subcells to have high performance by having atomic lattice spacing closely matched to that of the growth substrate. Lower subcells can be included with appropriate band gap, but with lattice spacing mismatched to the other subcells. The reduced performance caused by strain resulting from mismatch can be mitigated without reducing the performance of the upper subcells.

Owner:OSTENDO TECH INC

Low bandgap, monolithic, multi-bandgap, optoelectronic devices

InactiveUS20060162768A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationPhotovoltaic detectorsPhotodetector

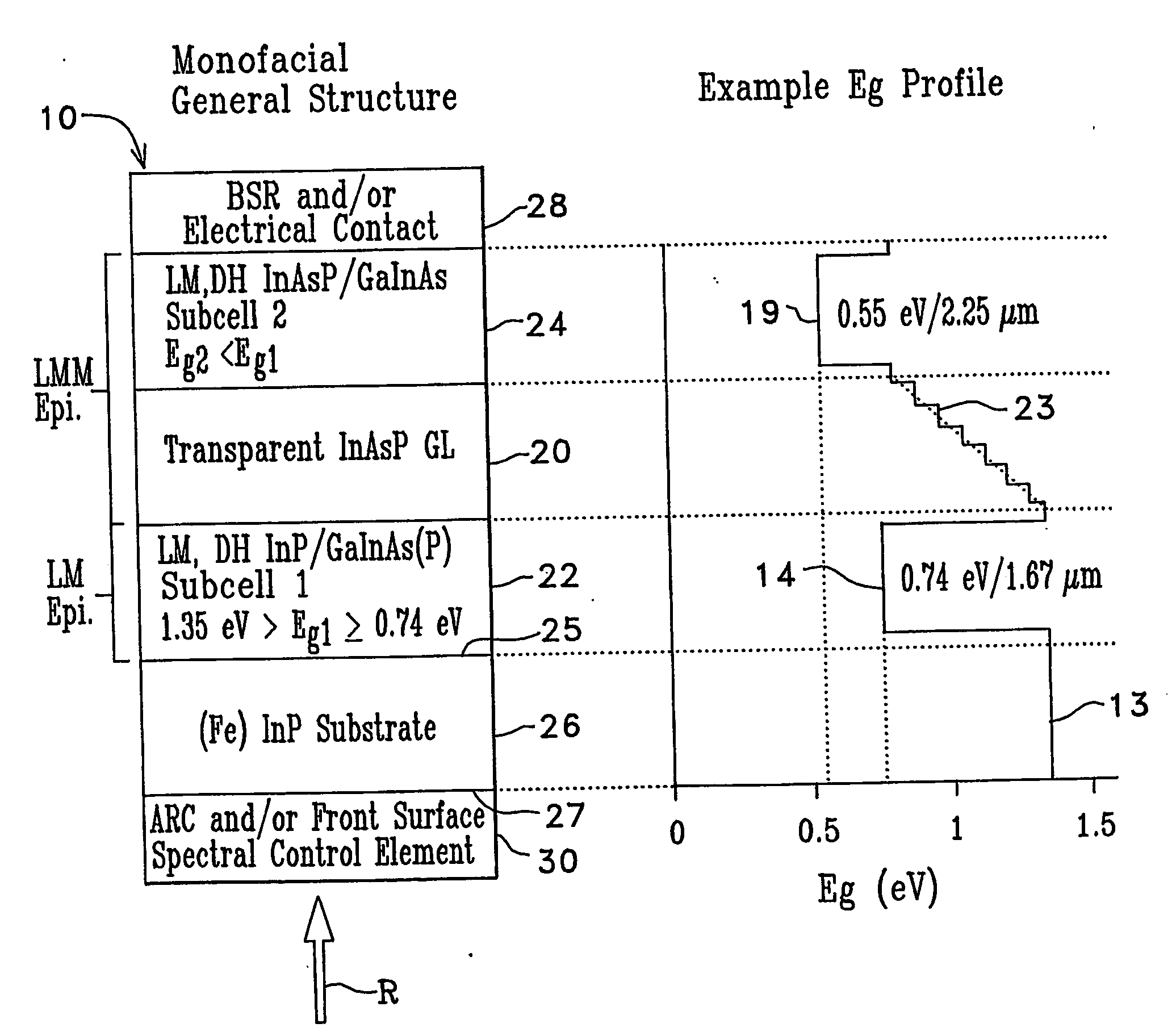

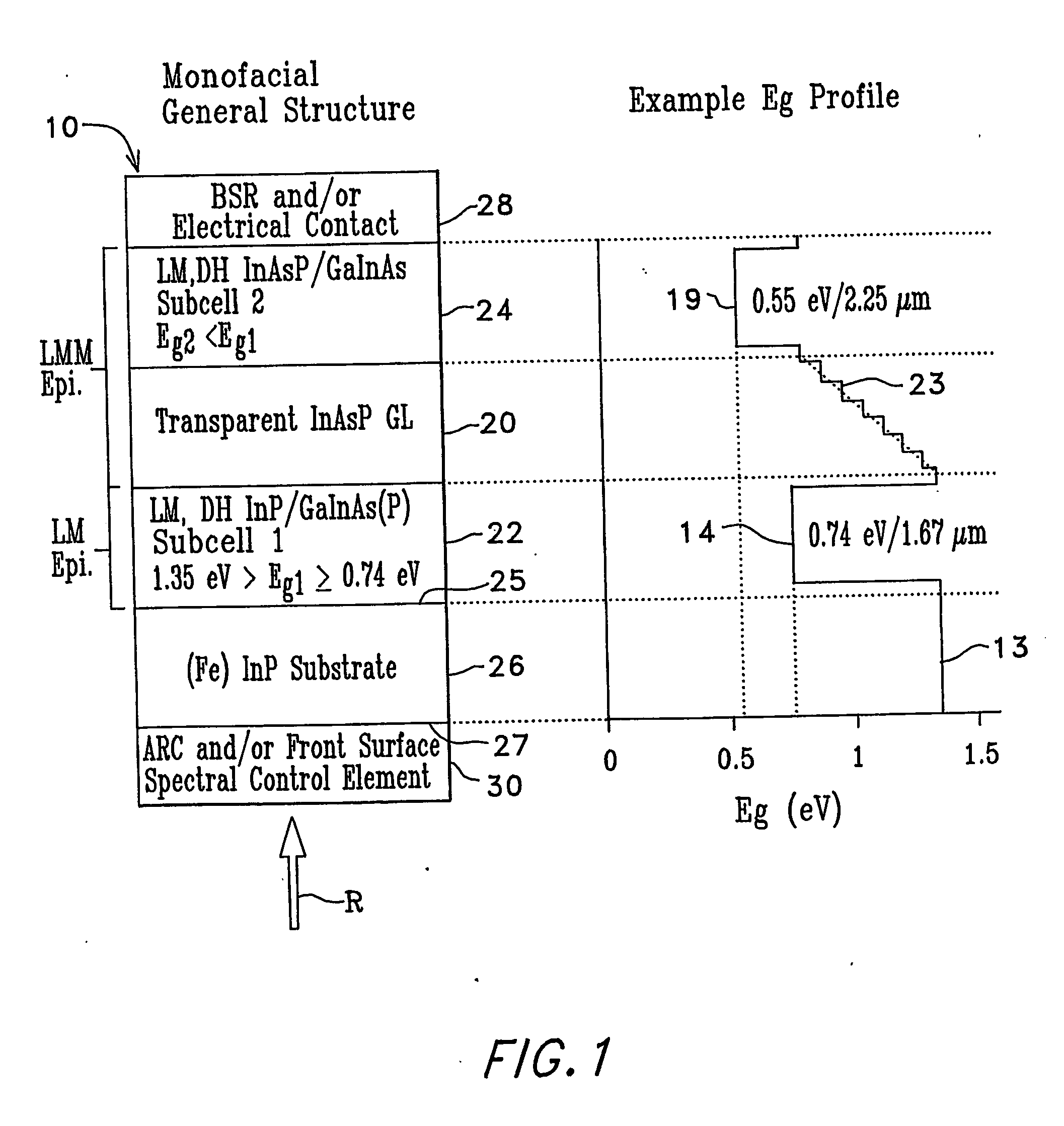

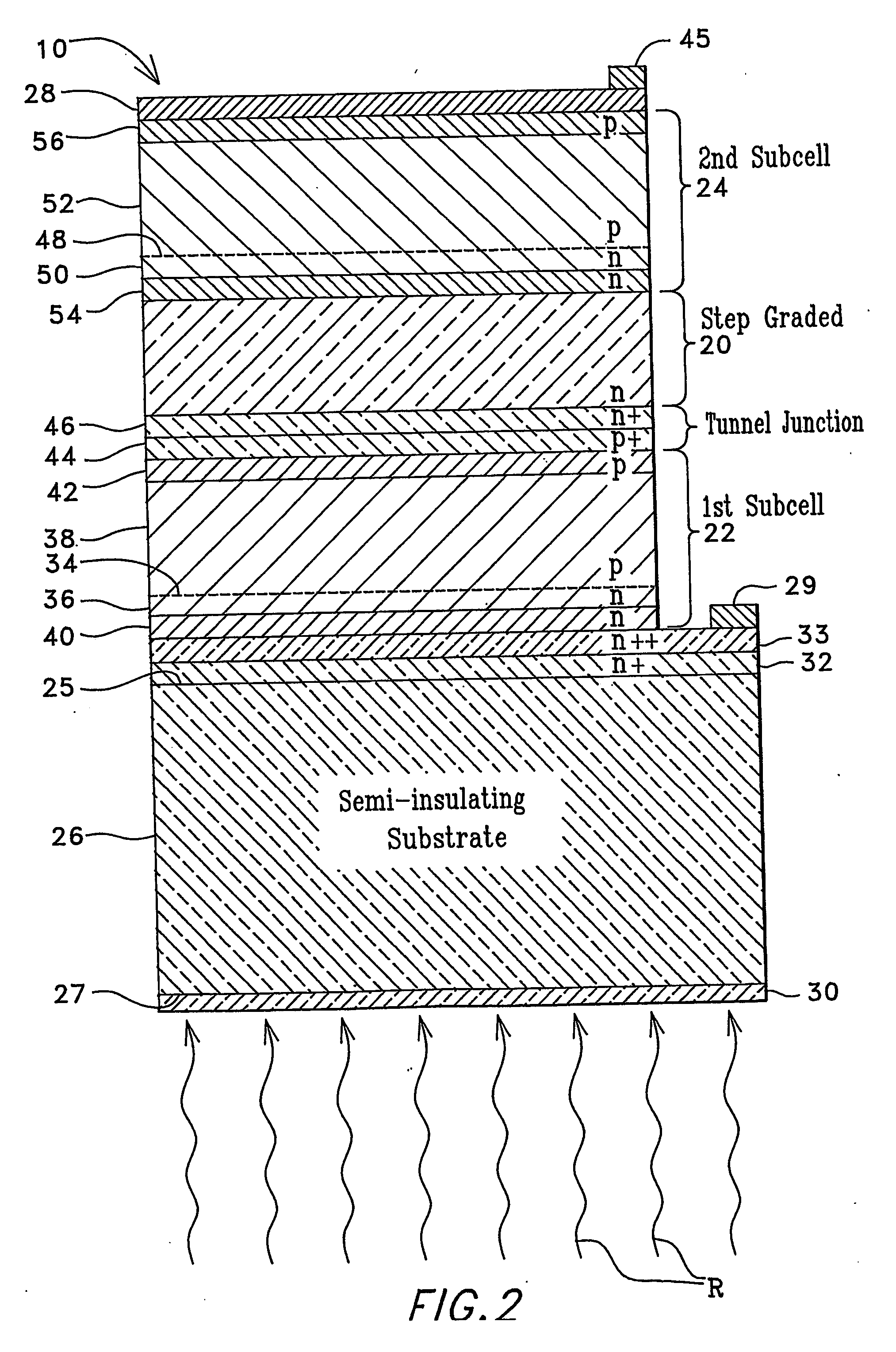

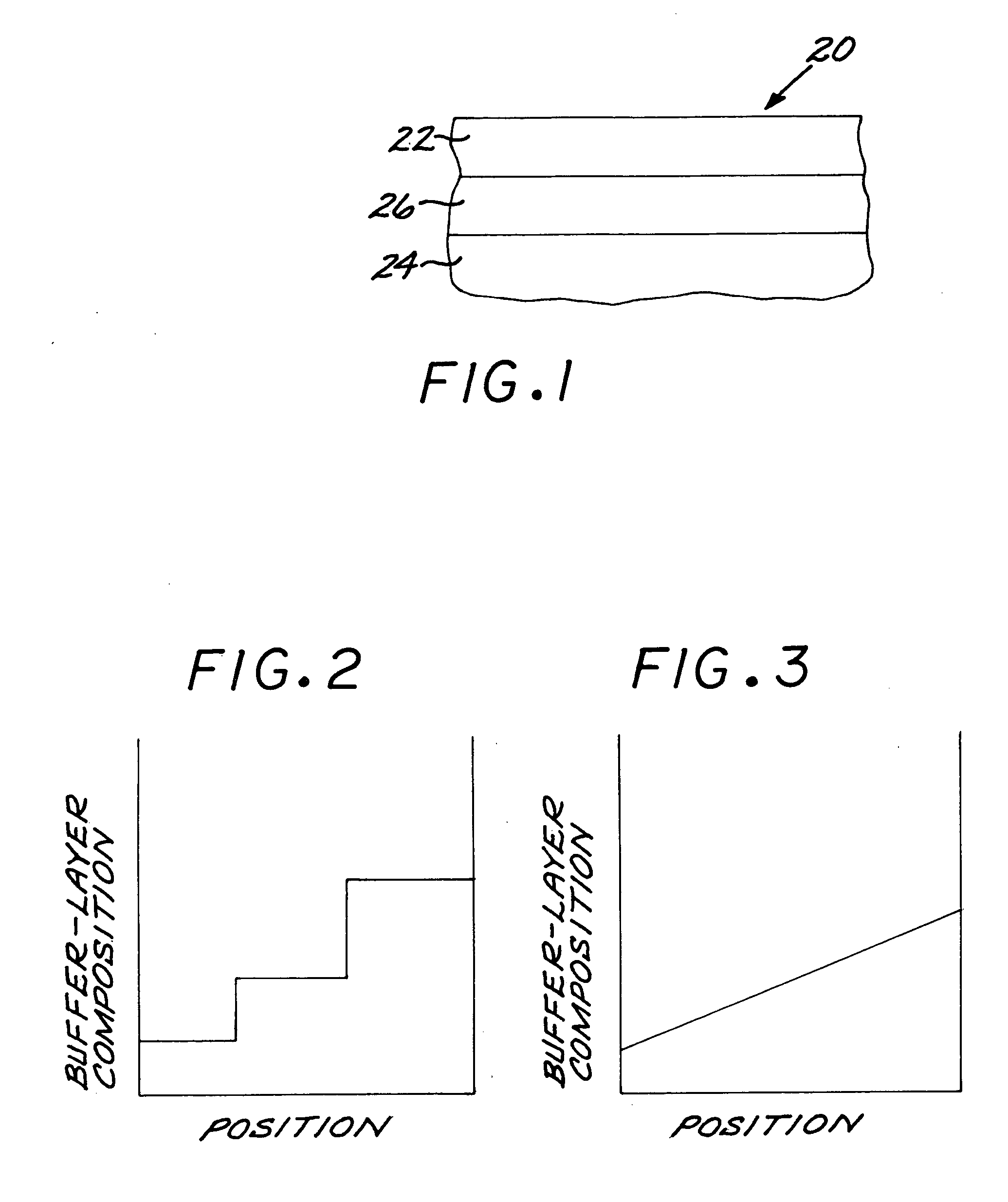

Low-bandgap, monolithic, multi-bandgap, optoelectronic devices (10), including PV converters, photodetectors, and LED's, have lattice-matched (LM), double-heterostructure (DH), low-bandgap GaInAs(P) subcells (22, 24) including those that are lattice-mismatched (LMM) to InP, grown on an InP substrate (26) by use of at least one graded lattice constant transition layer (20) of InAsP positioned somewhere between the InP substrate (26) and the LMM subcell(s) (22, 24). These devices are monofacial (10) or bifacial (80) and include monolithic, integrated, modules (MIMs) (190) with a plurality of voltage-matched subcell circuits (262, 264, 266, 270, 272) as well as other variations and embodiments.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

Multi-junction photovoltaic cell

InactiveUS6660928B1Useful radiation hardnessCell efficiency and power densityPV power plantsSolid-state devicesLattice mismatchSolar cell

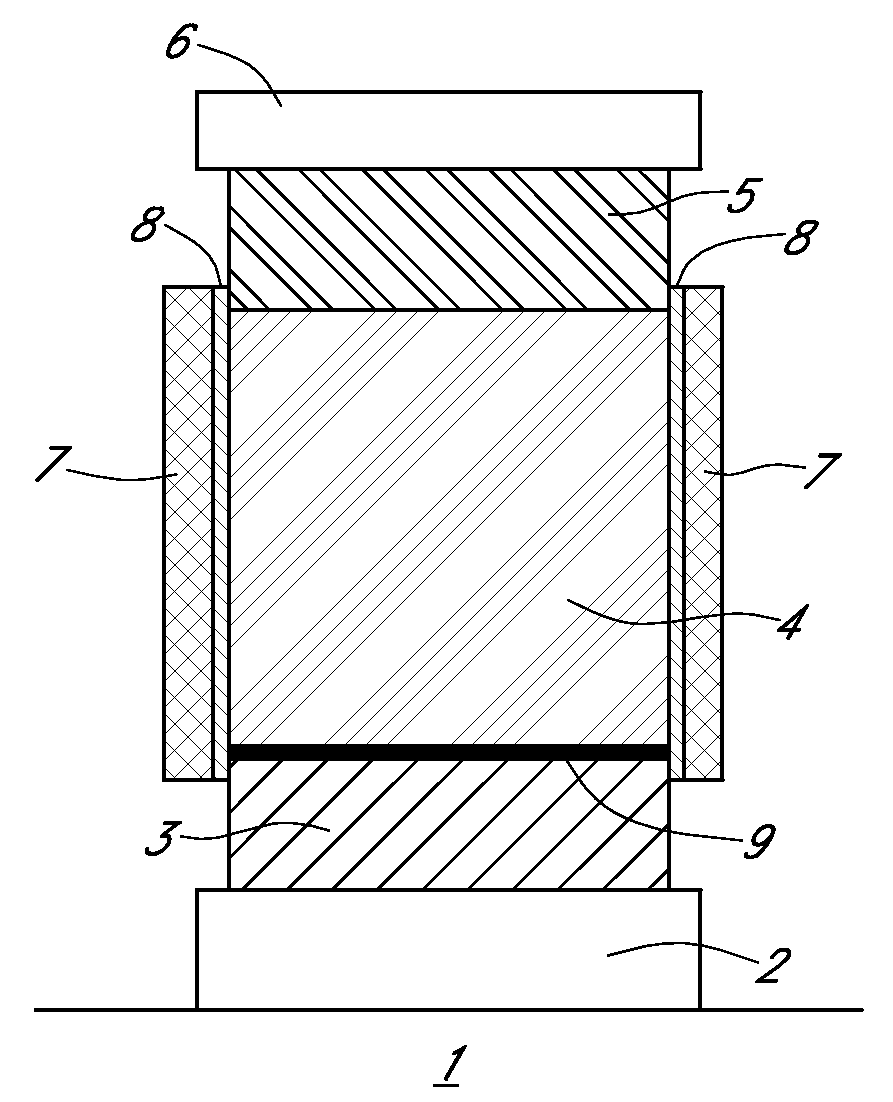

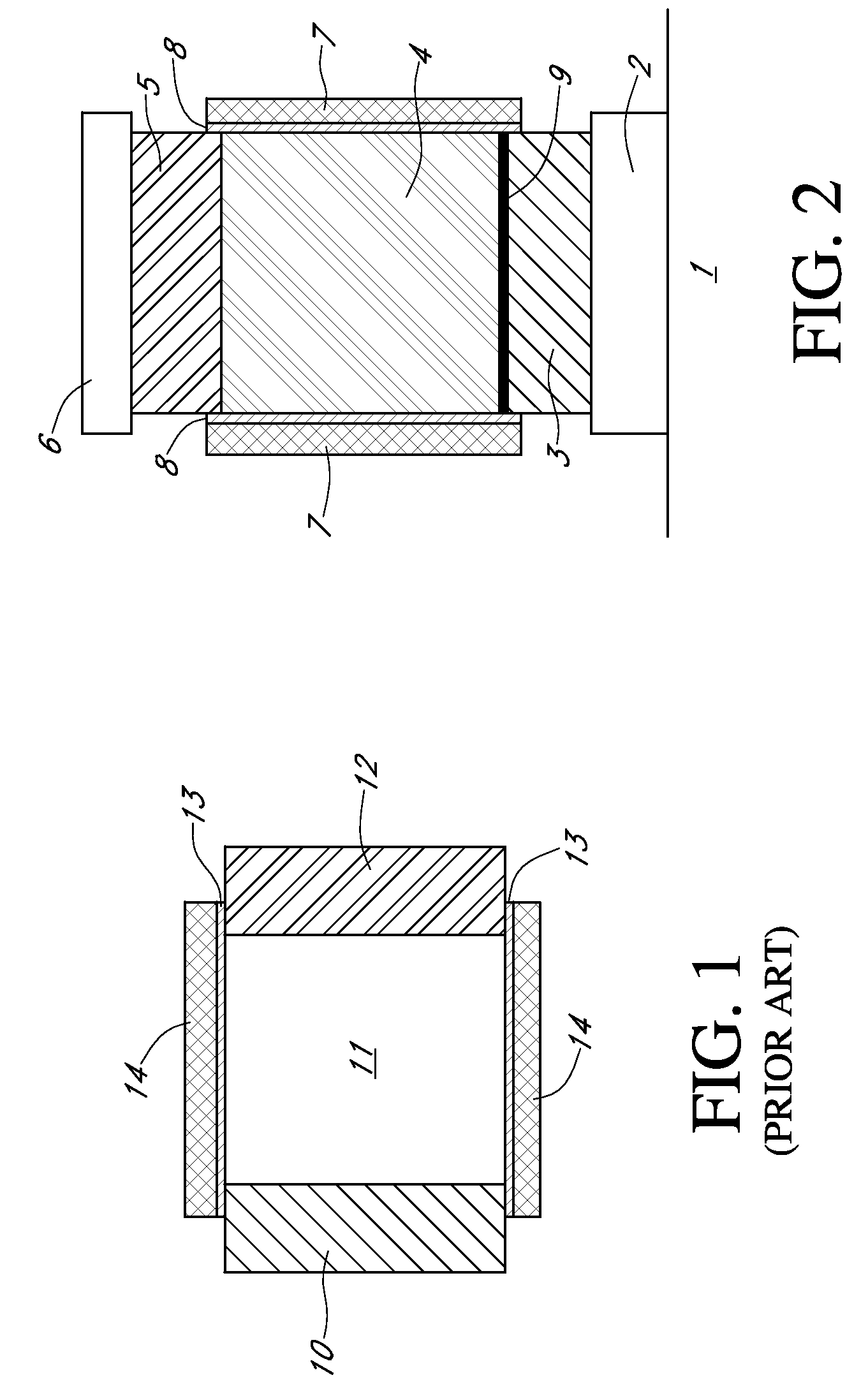

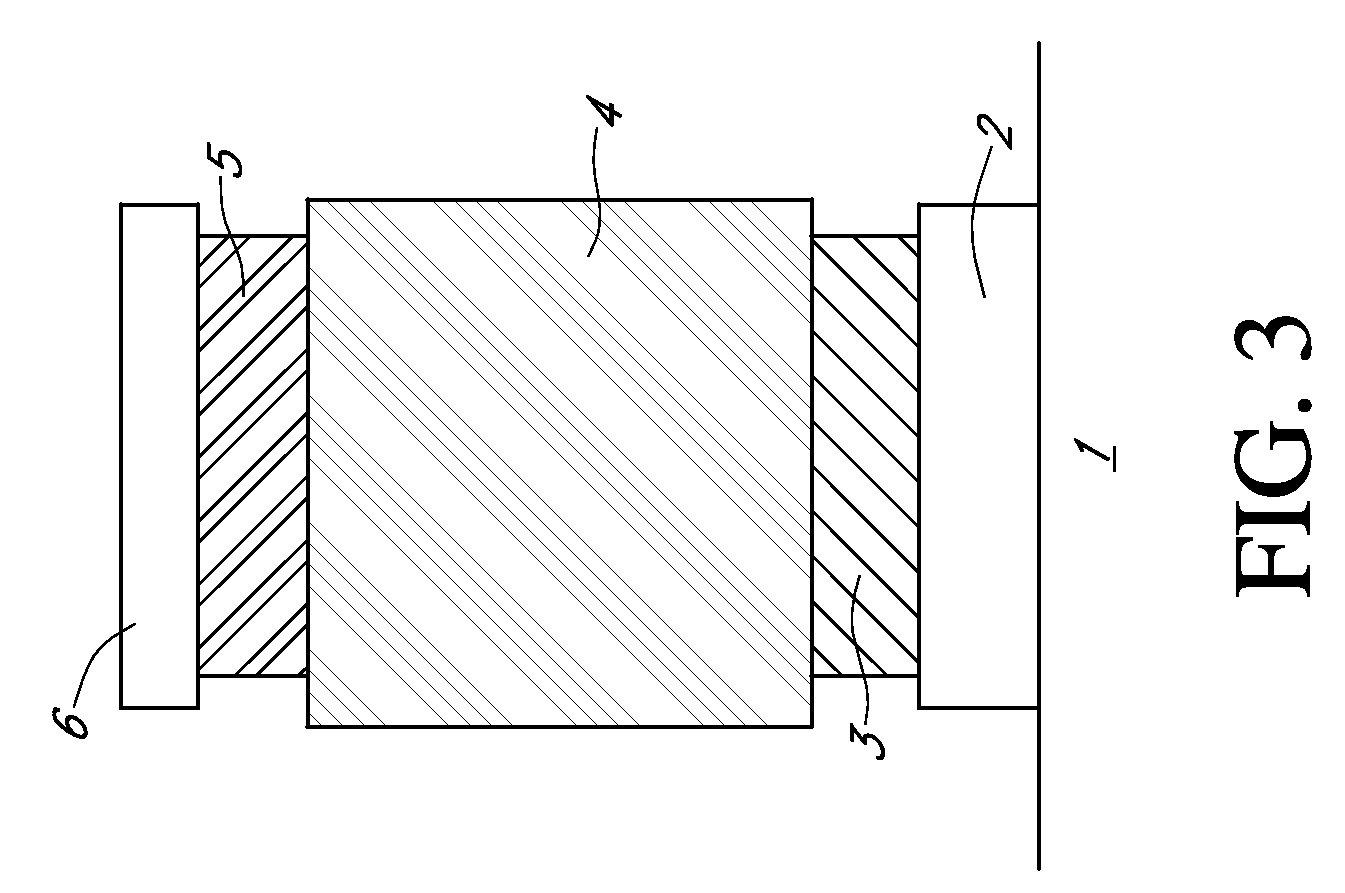

A solar cell comprising a substrate, a buffer layer, a first subcell, a second subcell, and a third subcell, where said first subcell, said second subcell, and said third subcell are lattice matched, and where said substrate is lattice mismatched with said first, second, and third subcells.

Owner:ESSENTIAL RES

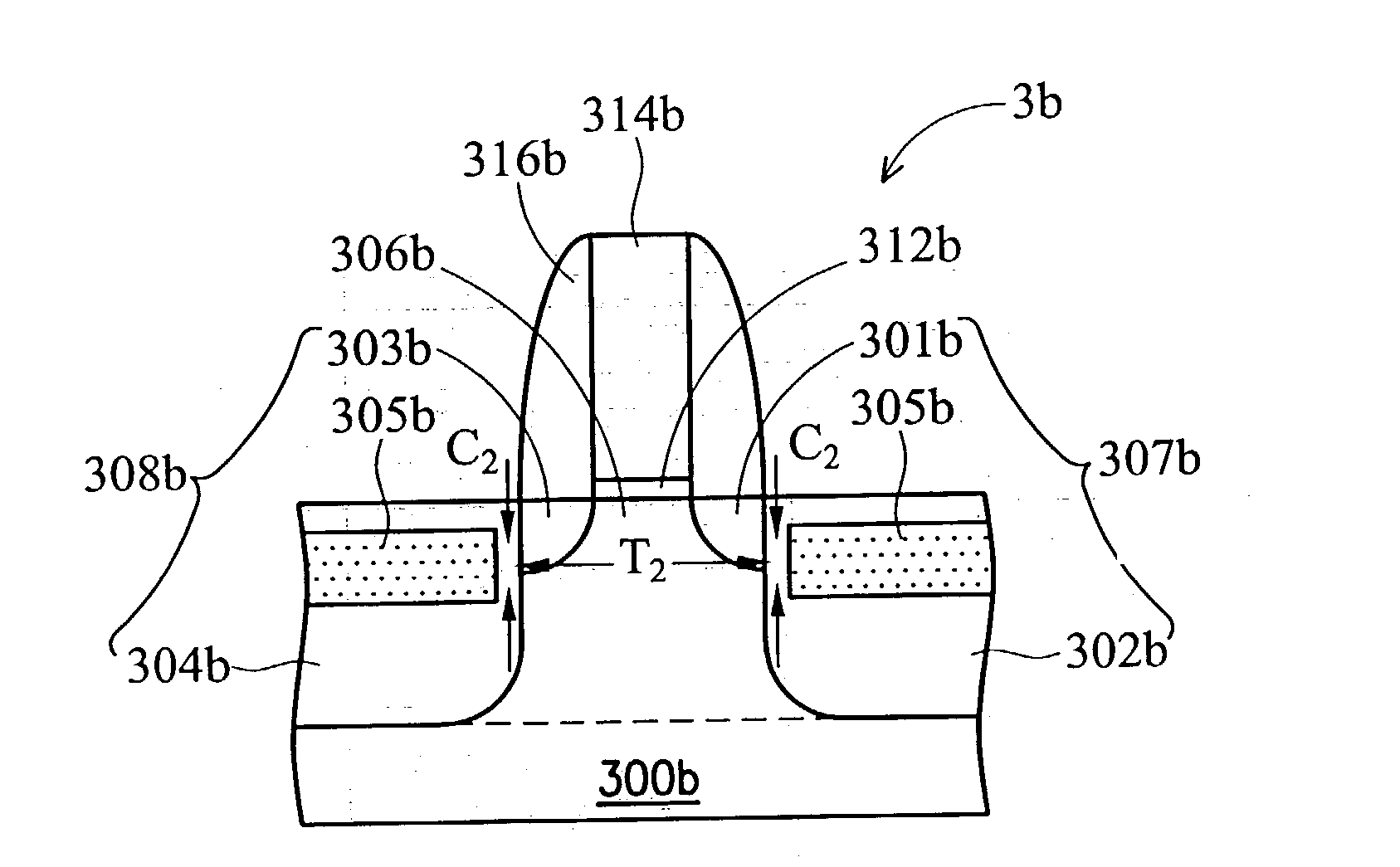

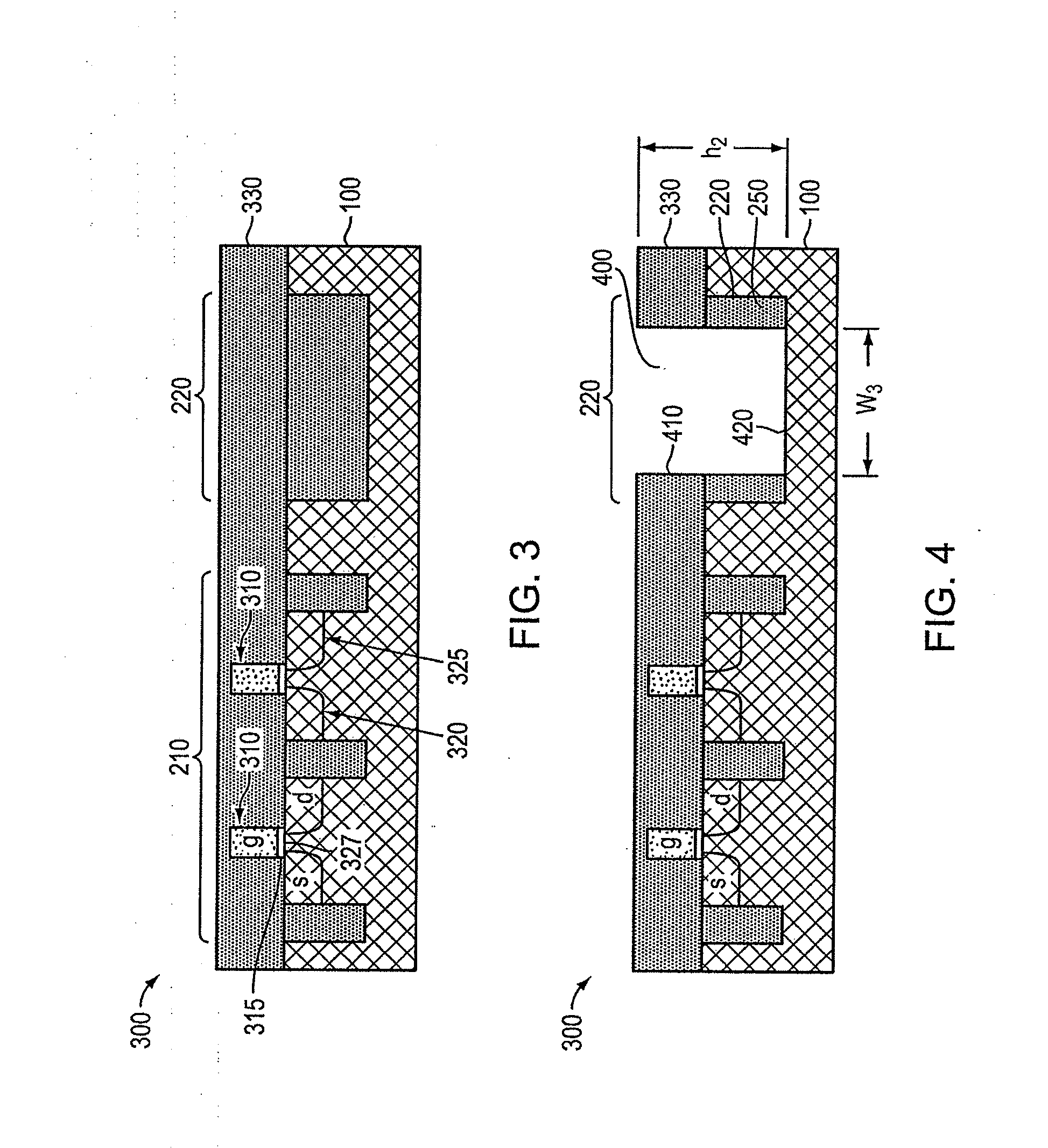

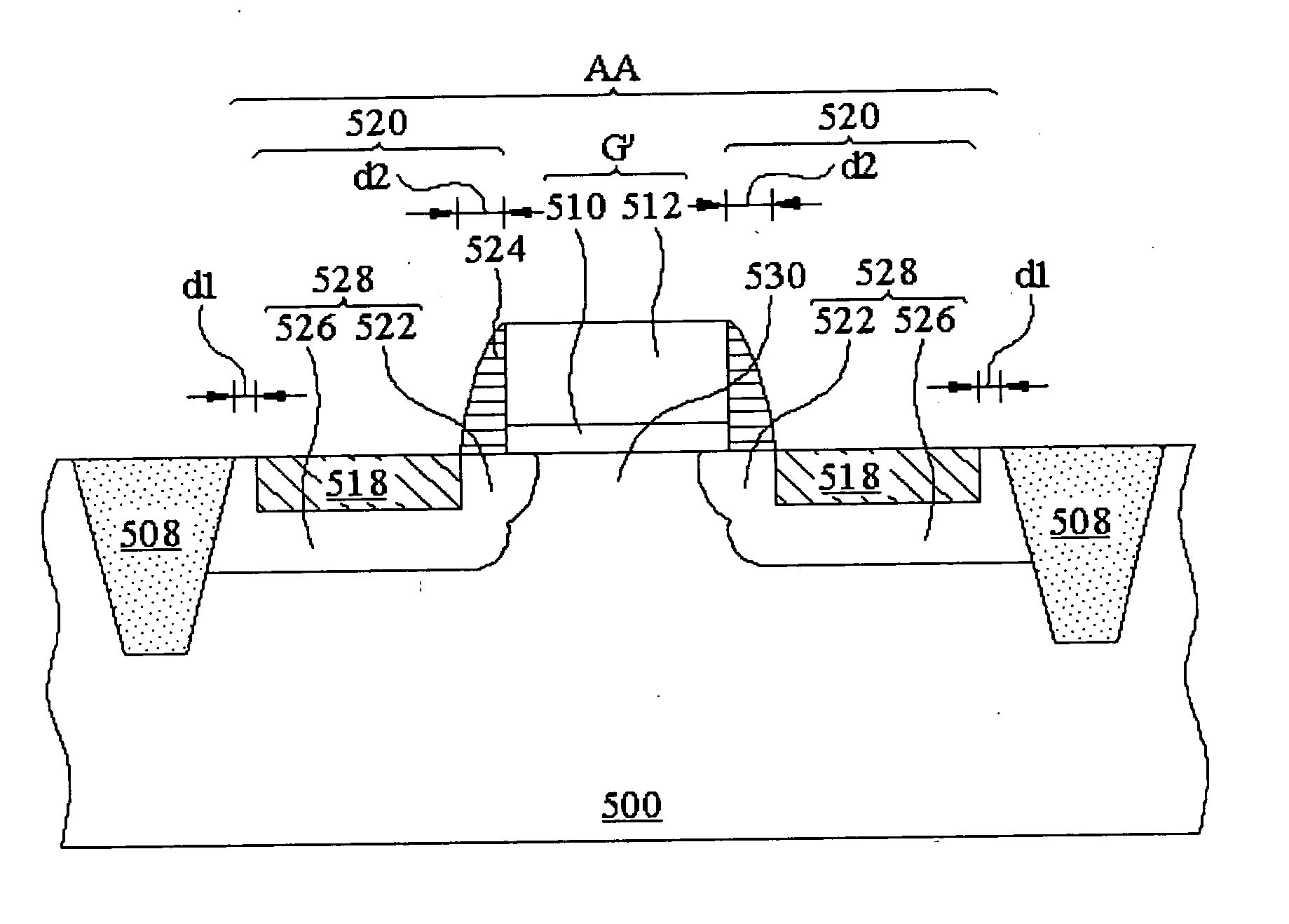

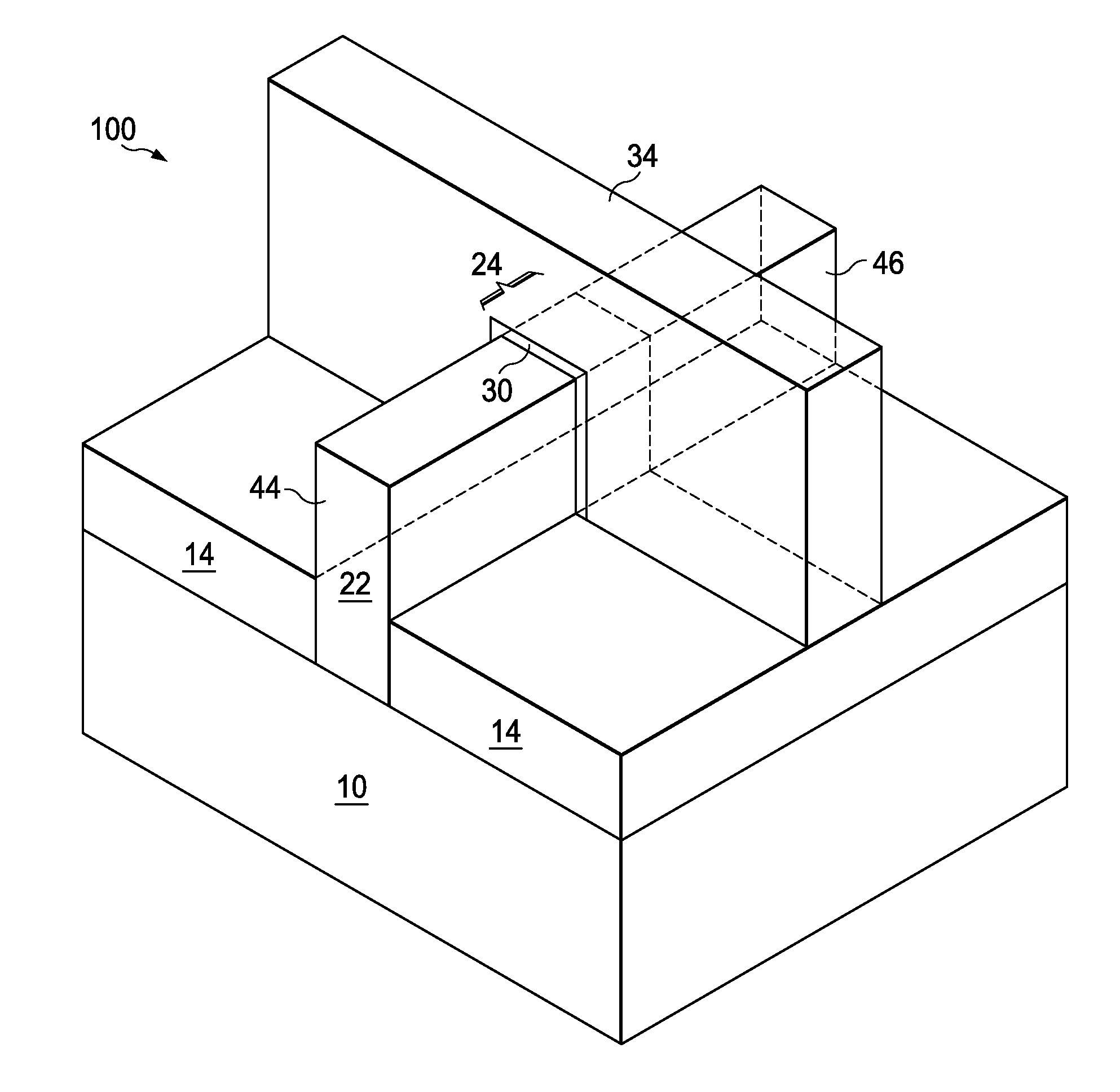

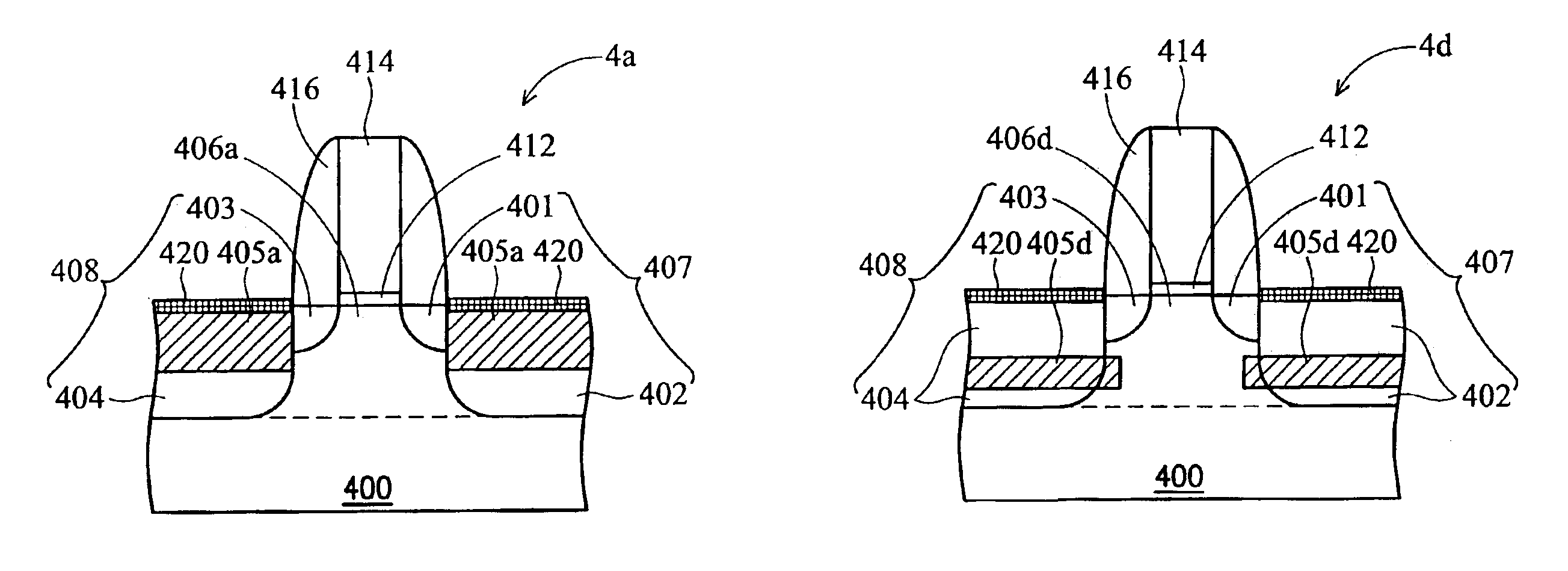

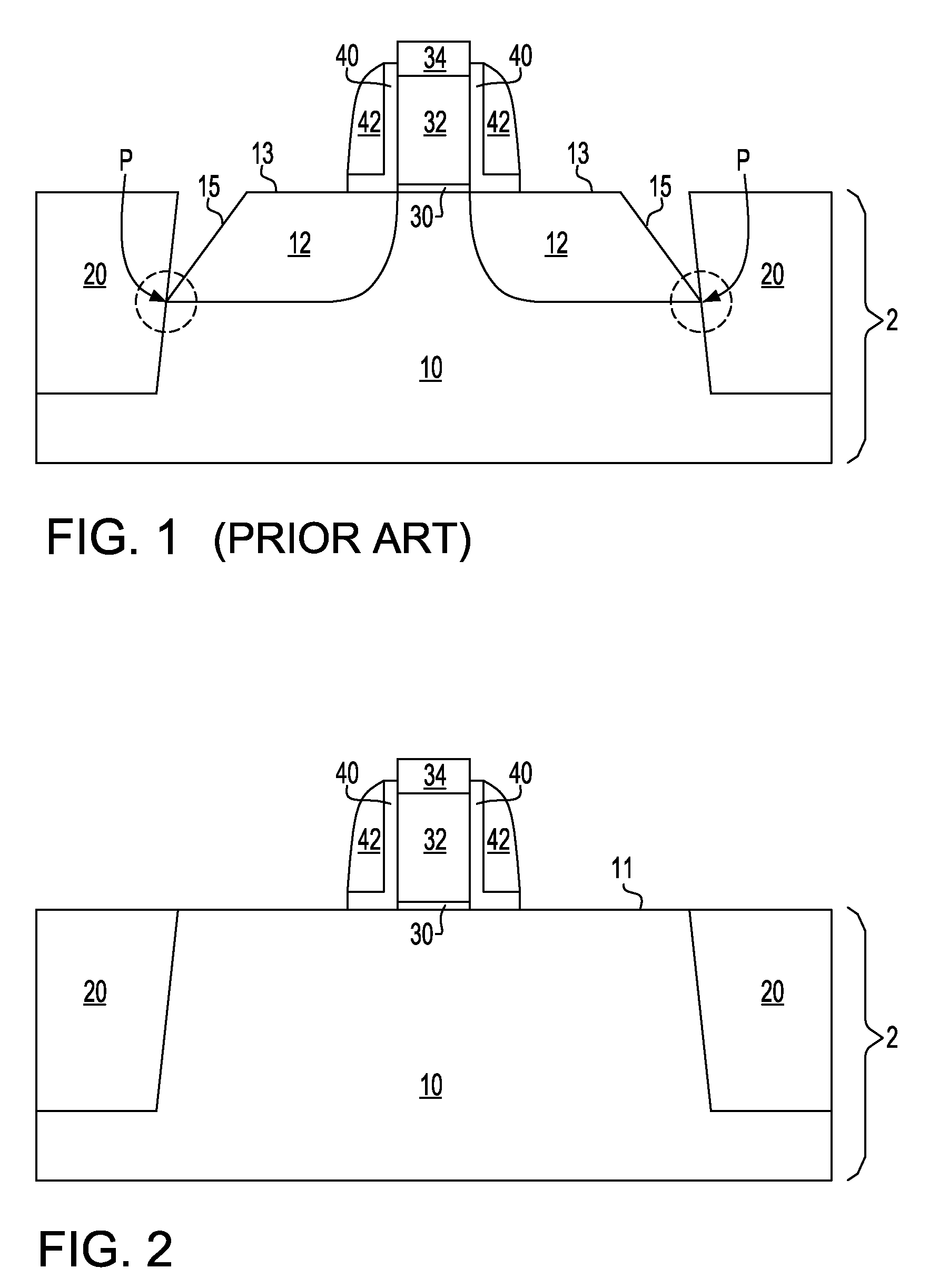

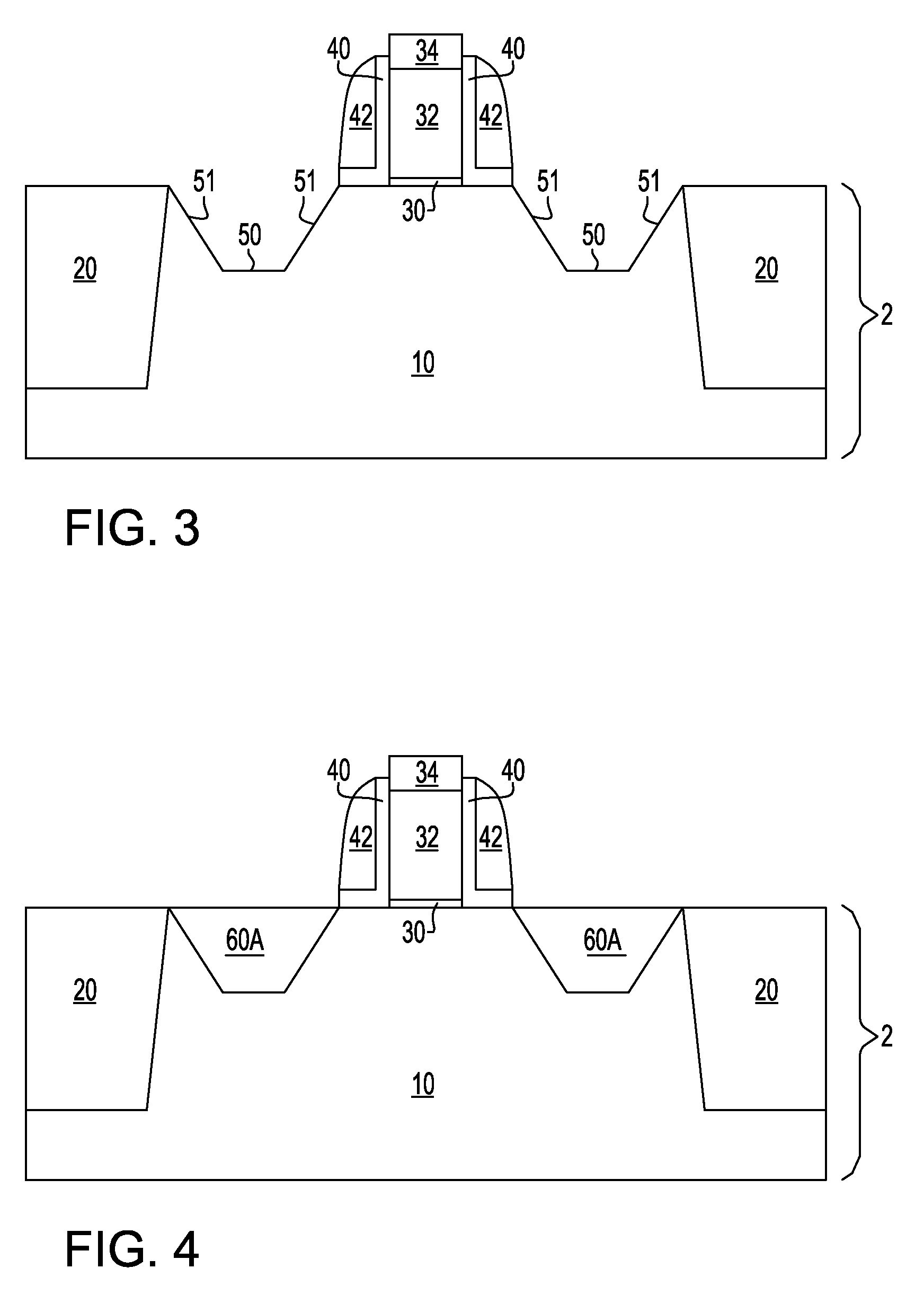

Strained-channel transistor structure with lattice-mismatched zone

InactiveUS20040173815A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor materials

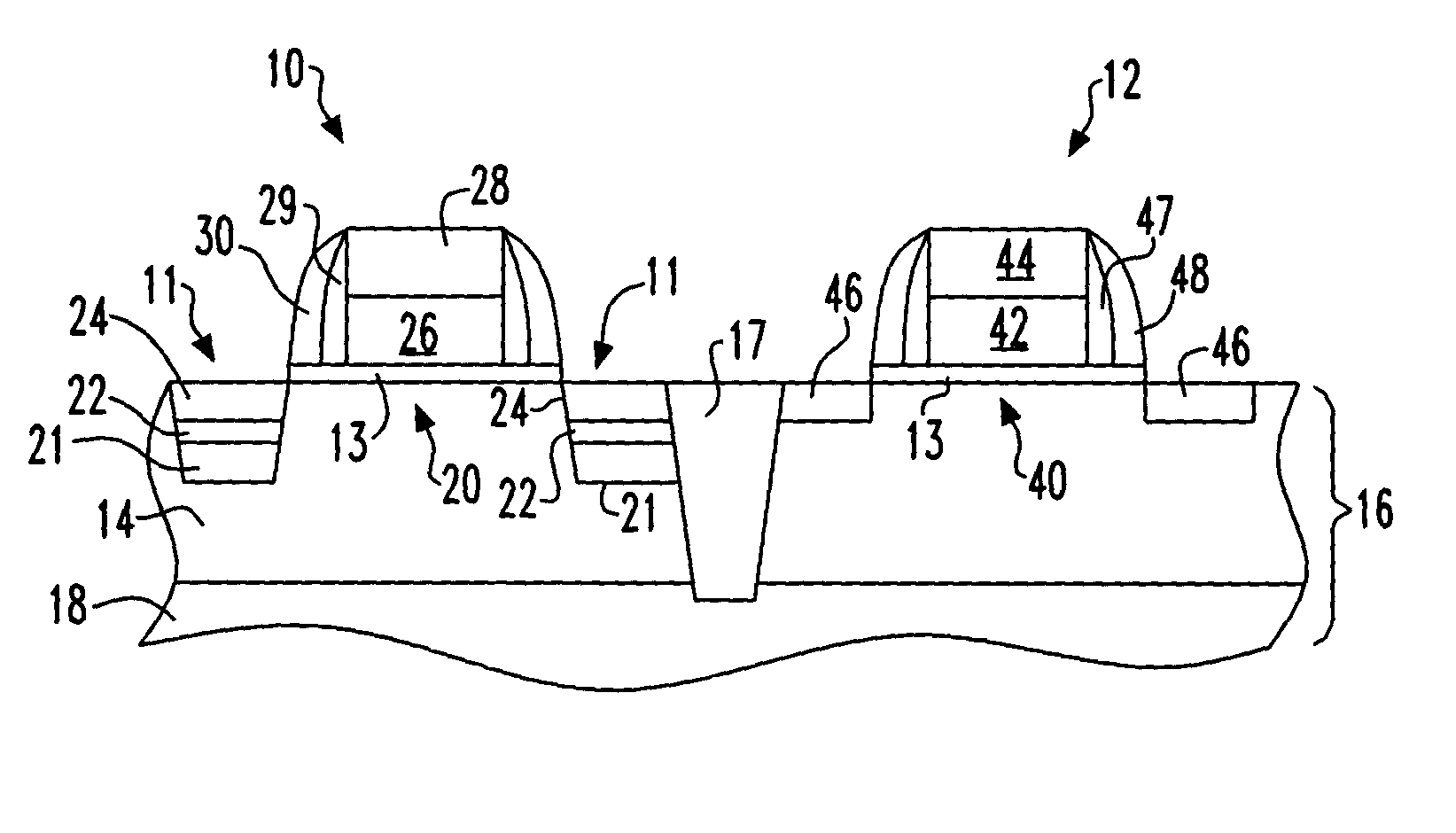

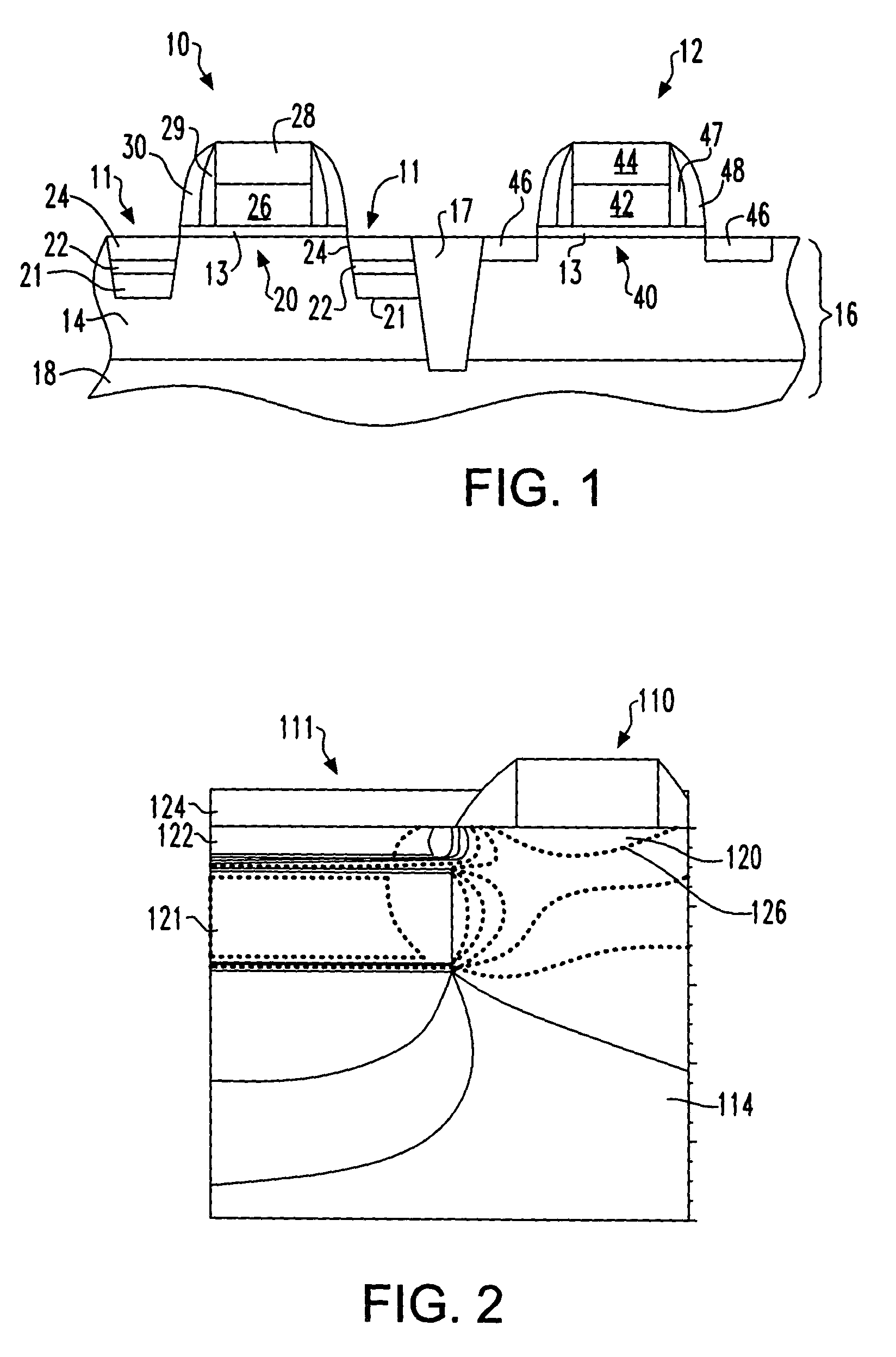

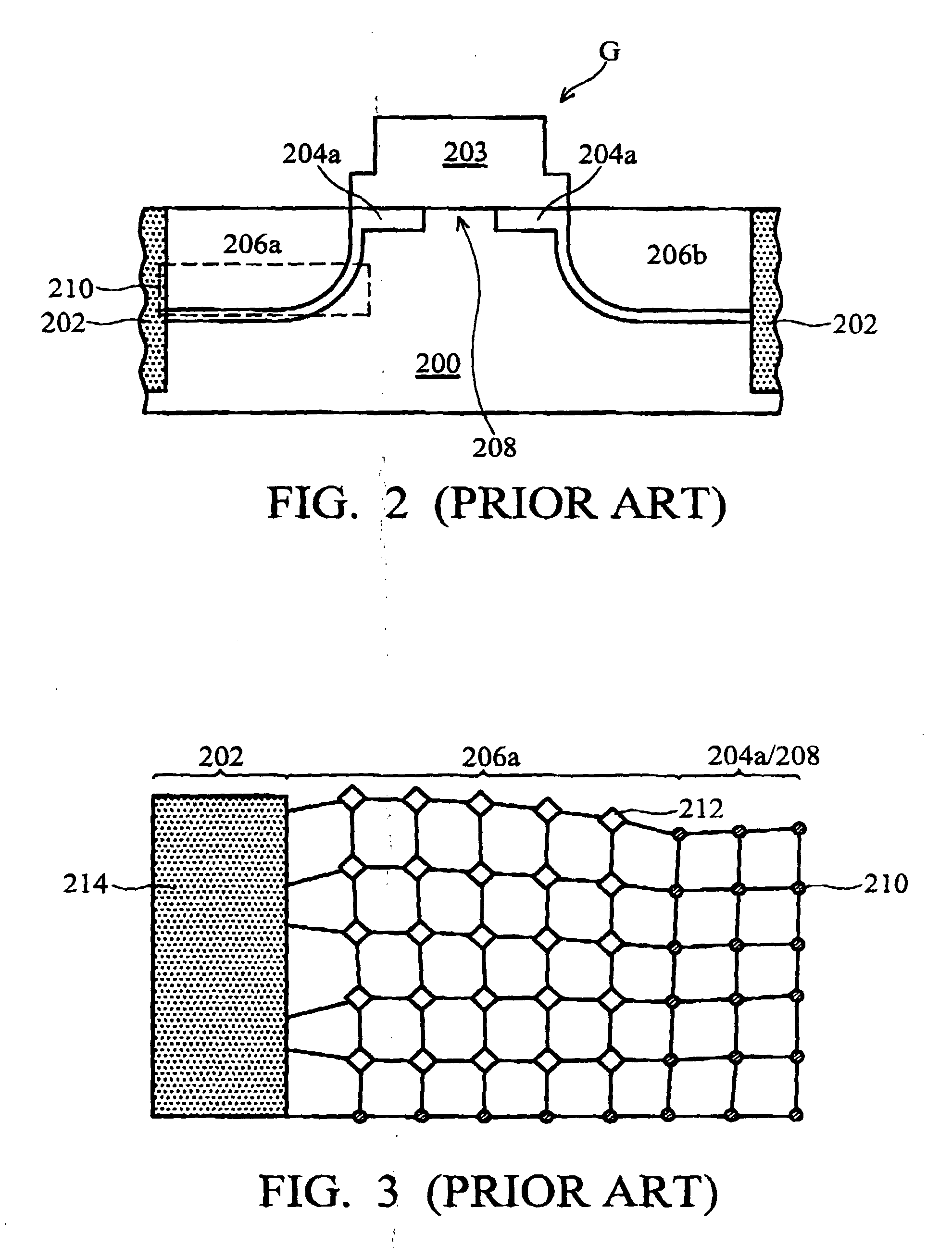

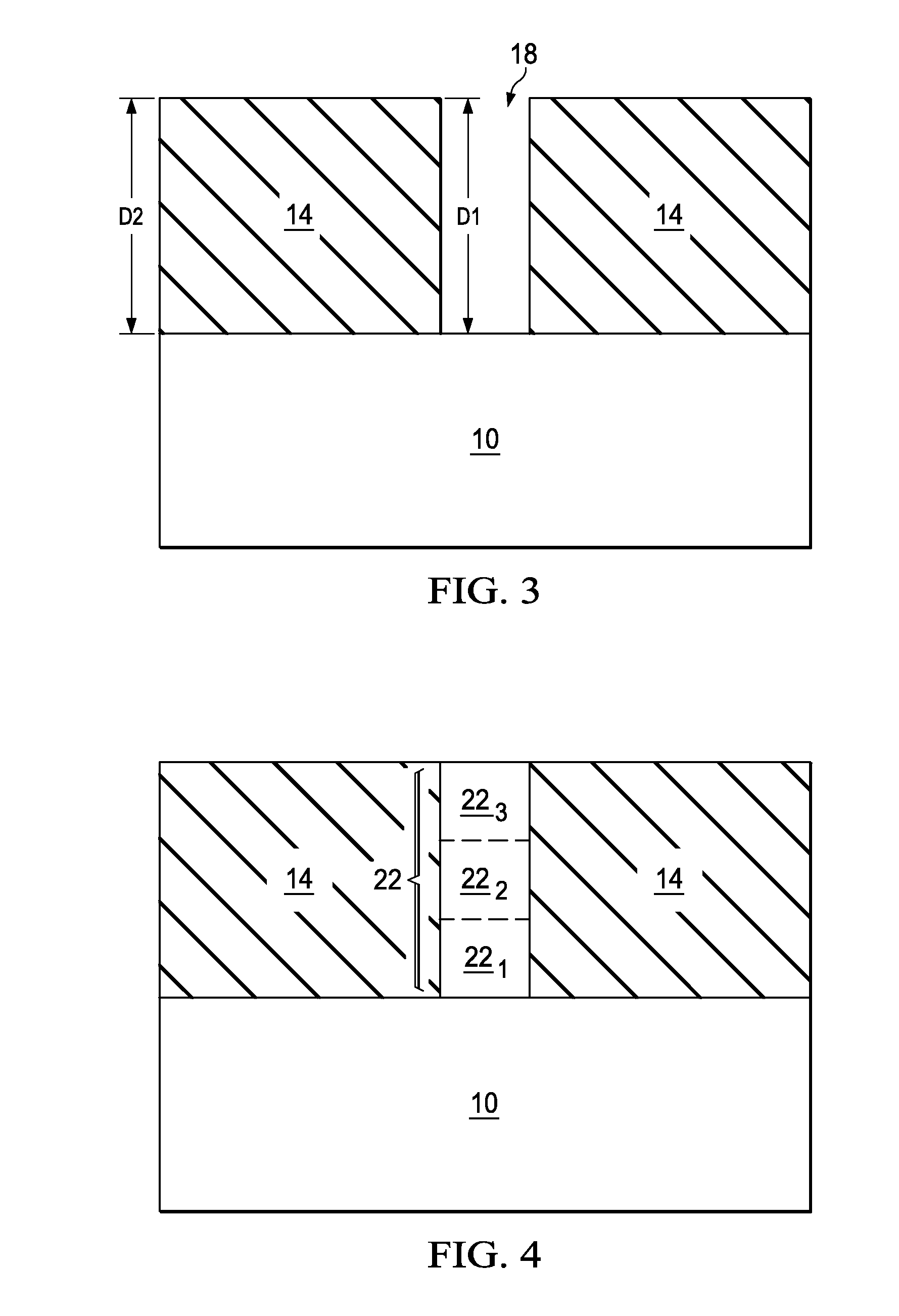

A strained-channel transistor structure with lattice-mismatched zone and fabrication method thereof. The transistor structure includes a substrate having a strained channel region, comprising a first semiconductor material with a first natural lattice constant, in a surface, a gate dielectric layer overlying the strained channel region, a gate electrode overlying the gate dielectric layer, and a source region and drain region oppositely adjacent to the strained channel region, with one or both of the source region and drain region comprising a lattice-mismatched zone comprising a second semiconductor material with a second natural lattice constant different from the first natural lattice constant.

Owner:TAIWAN SEMICON MFG CO LTD

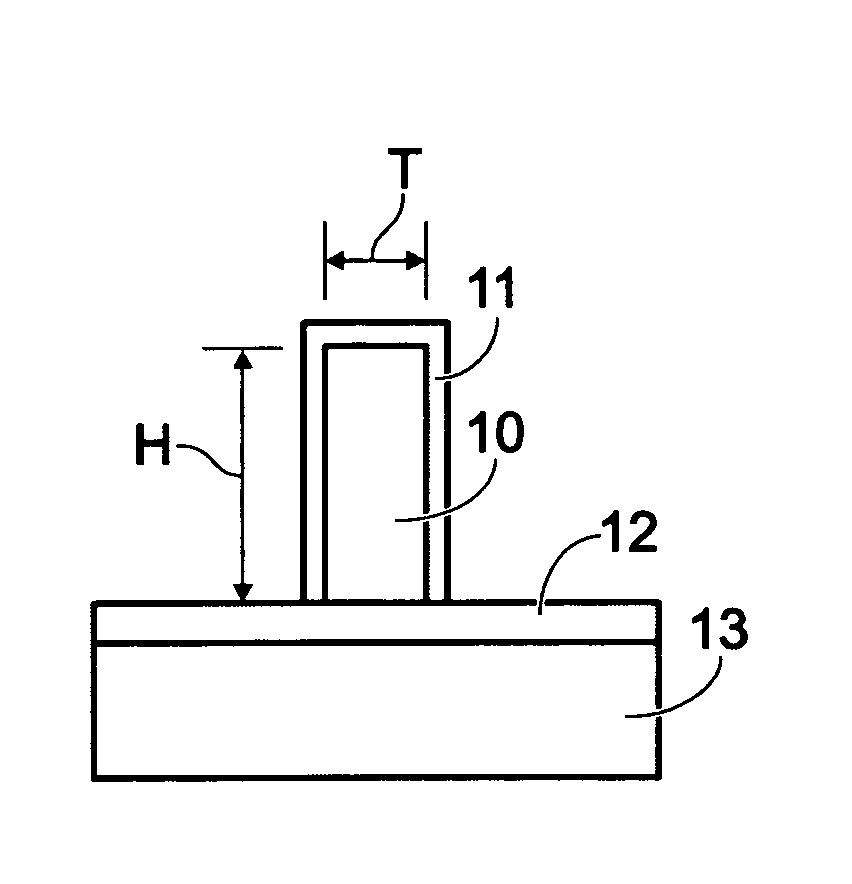

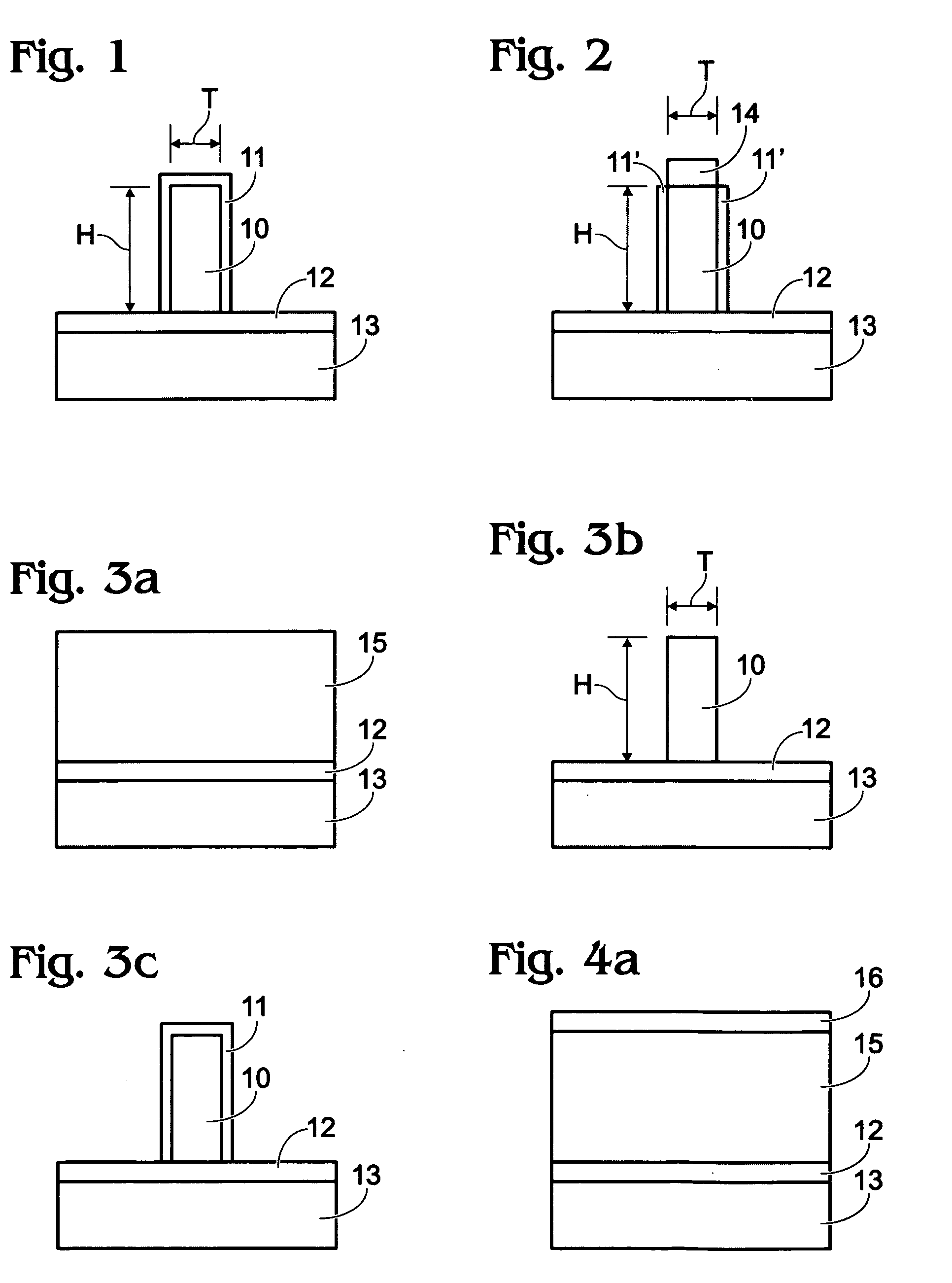

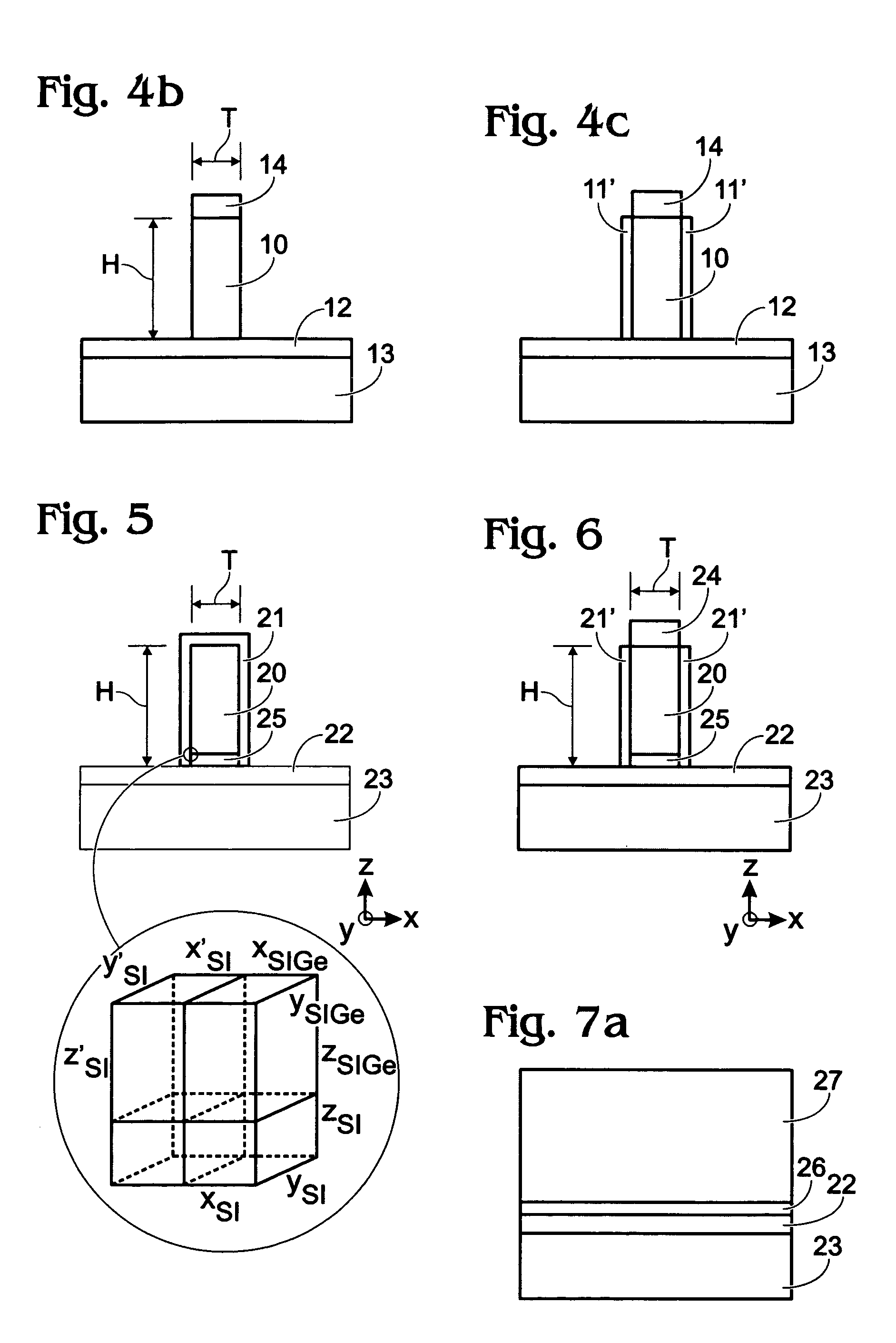

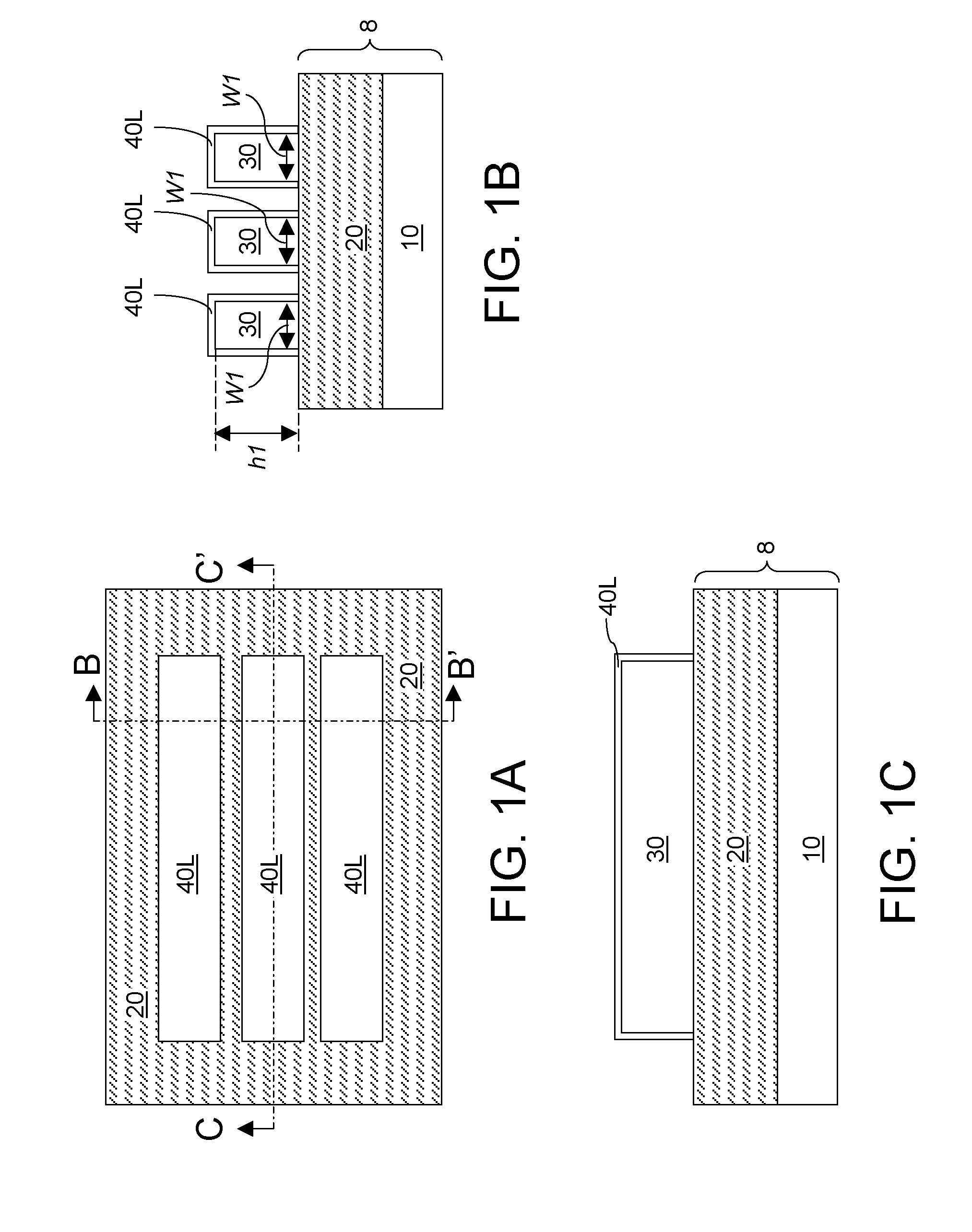

Strained silicon fin structure

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

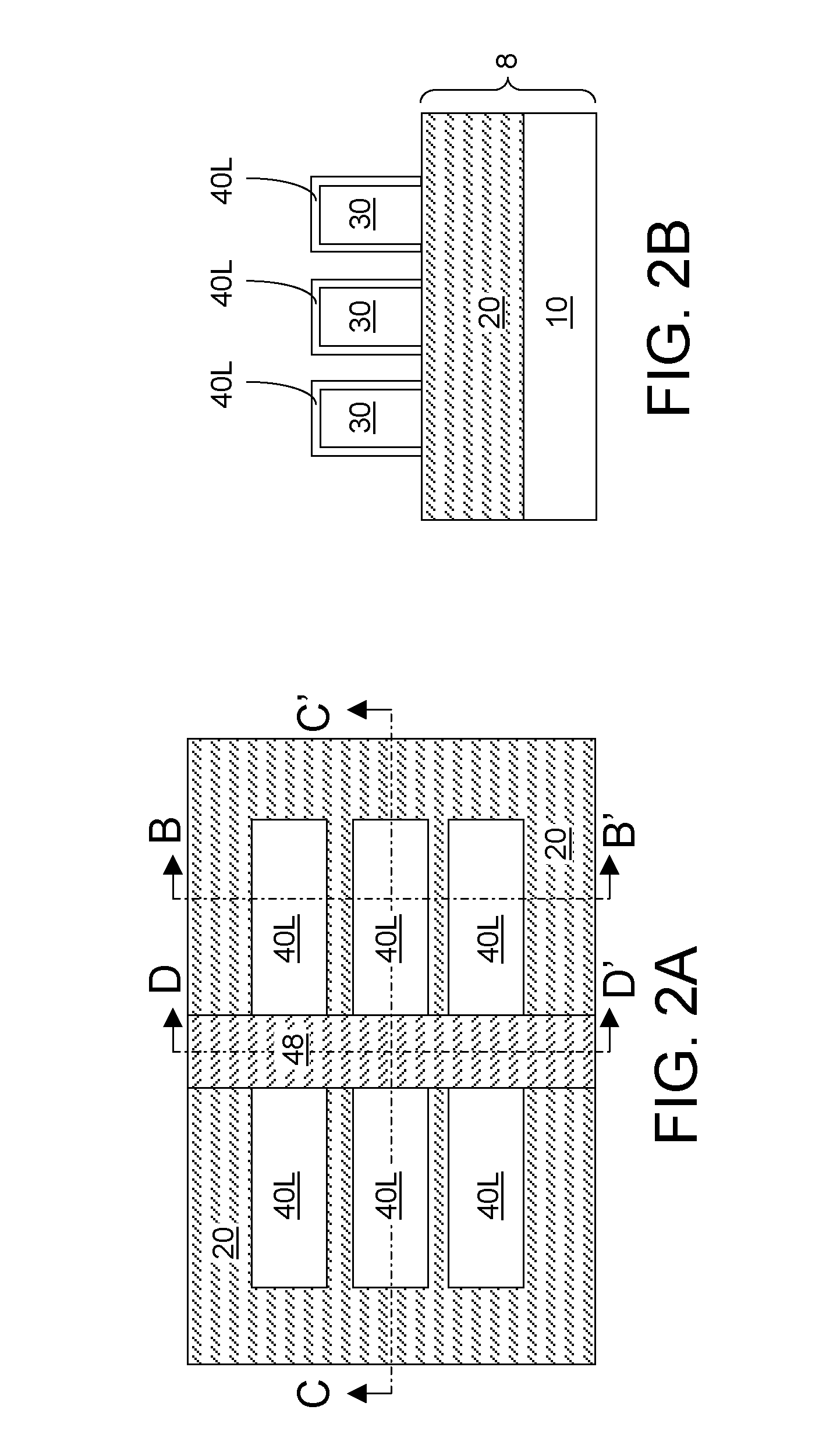

Aspect ratio trapping for mixed signal applications

InactiveUS20080070355A1Suitable for integrationReduce complicationsSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsTrapping

Structures and methods for their formation include a substrate comprising a first semiconductor material, with a second semiconductor material disposed thereover, the first semiconductor material being lattice mismatched to the second semiconductor material. Defects are reduced by using an aspect ratio trapping approach.

Owner:AMBERWAVE SYST

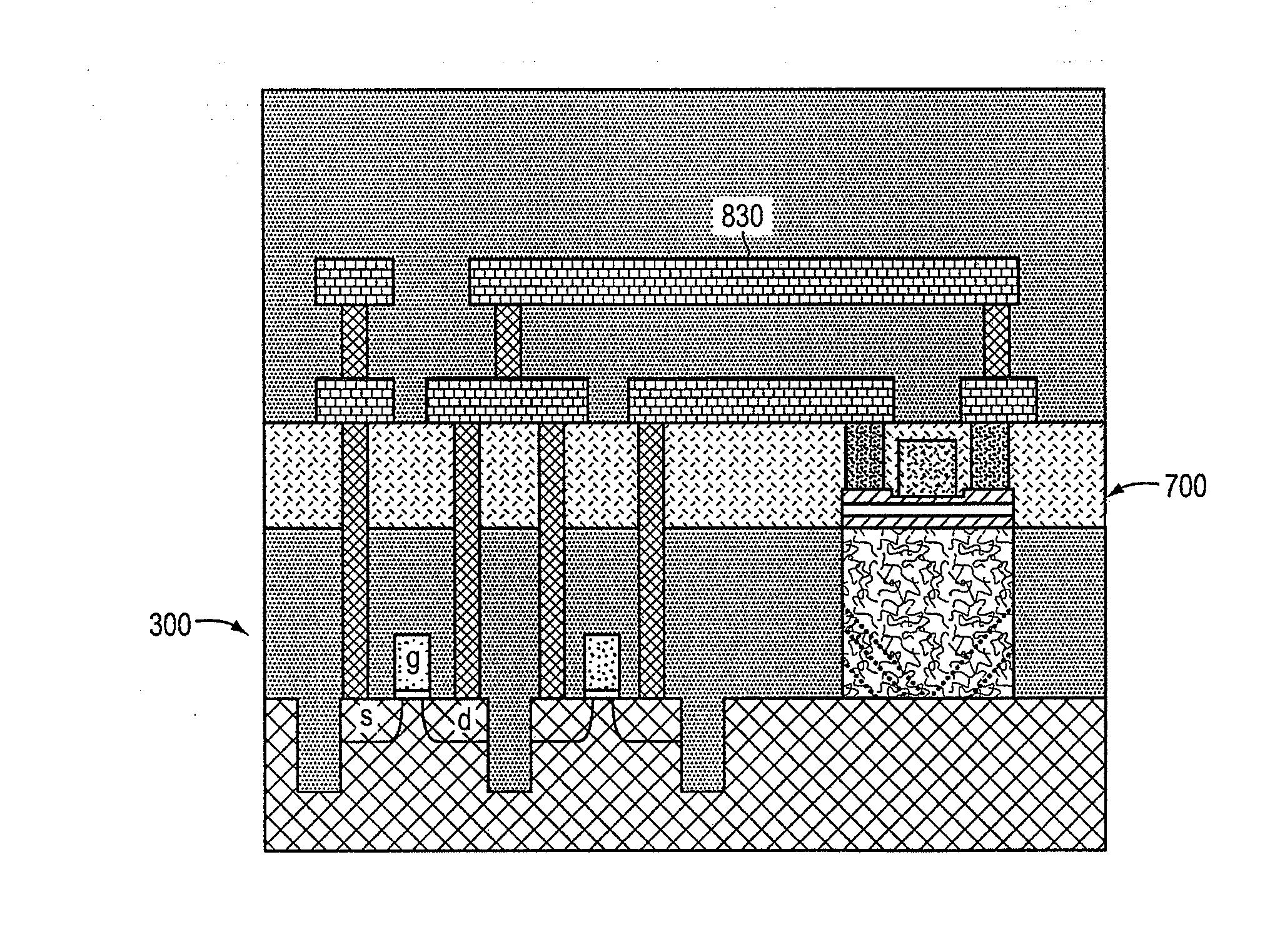

Structure and method of making strained semiconductor CMOS transistors having lattice-mismatched semiconductor regions underlying source and drain regions

Owner:SEMICON MFG INT (SHANGHAI) CORP

Metamorphic layers in multijunction solar cells

ActiveUS20070277873A1Maximize energy efficiencyFinal product manufacturePhotovoltaic energy generationSemiconductor materialsLattice mismatch

A method of forming a multijunction solar cell comprising an upper subcell, a middle subcell, and a lower subcell comprising providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on said substrate having a first band gap; forming a second solar subcell over said first subcell having a second band gap smaller than said first band gap; and forming a grading interlayer over said second subcell having a third band gap larger than said second band gap forming a third solar subcell having a fourth band gap smaller than said second band gap such that said third subcell is lattice mismatched with respect to said second subcell.

Owner:SOLAERO TECH CORP

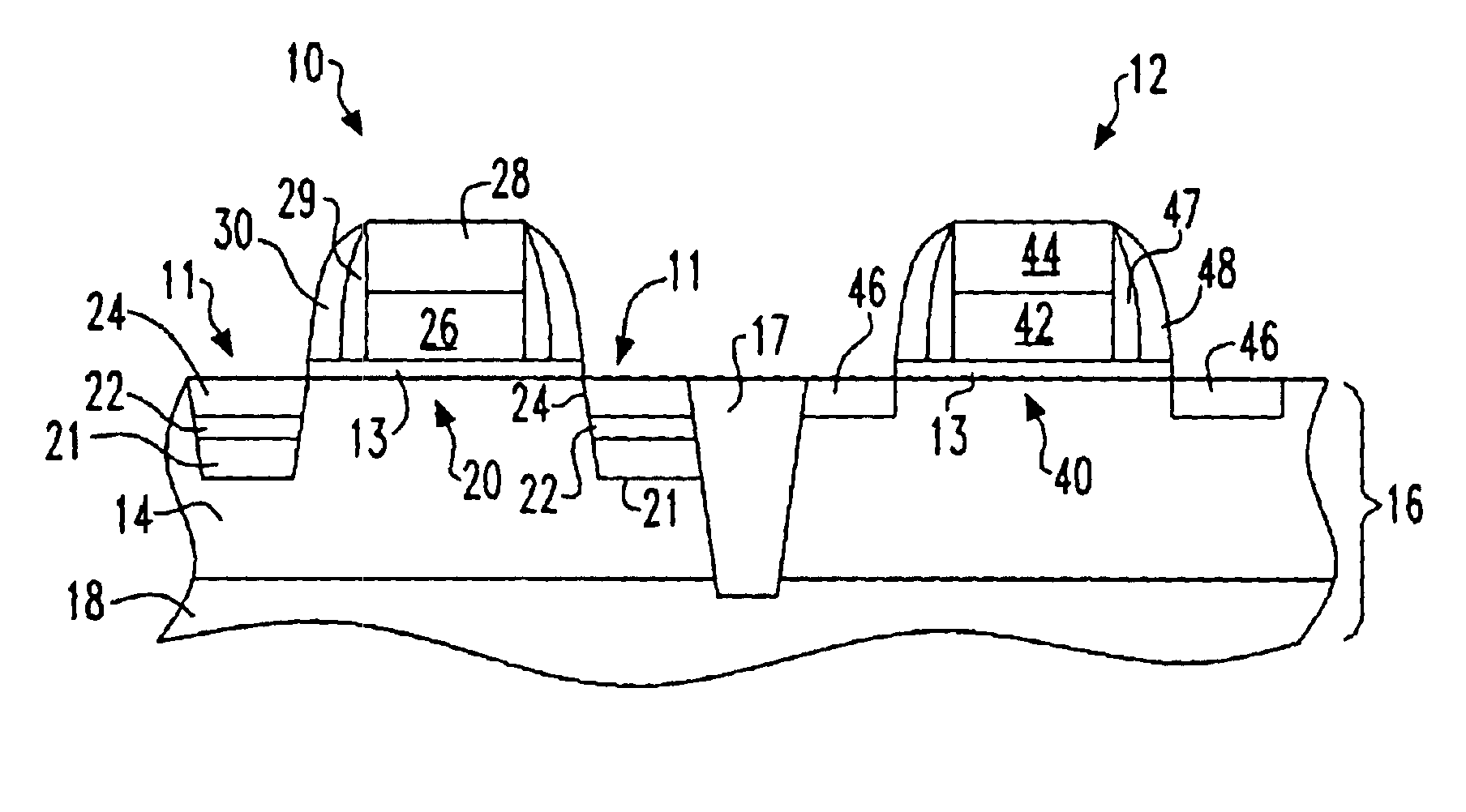

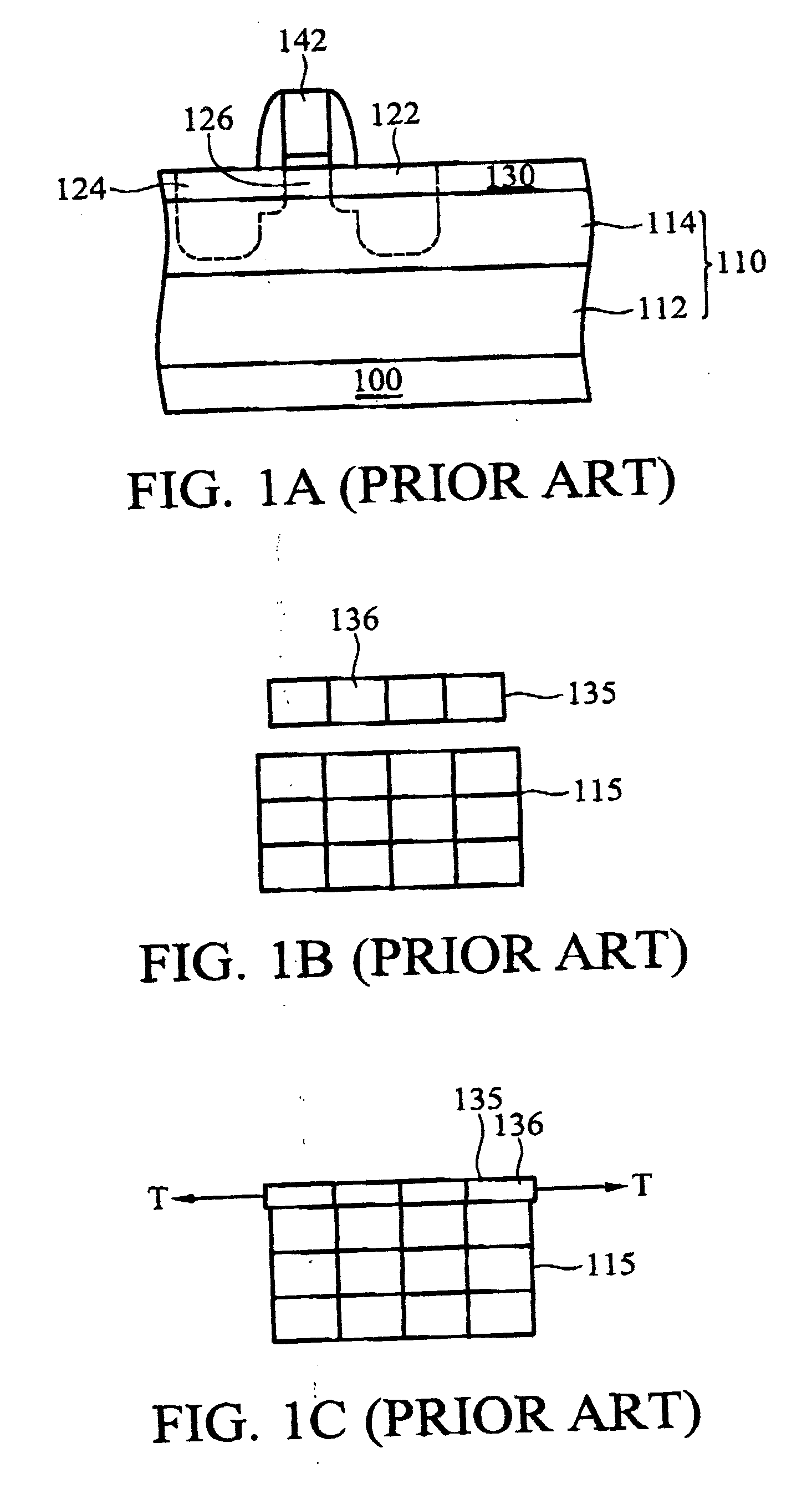

Structure and method of making strained semiconductor CMOS transistors having lattice-mismatched source and drain regions

A p-type field effect transistor (PFET) and an n-type field effect transistor (NFET) of an integrated circuit are provided. A first strain is applied to the channel region of the PFET but not the NFET via a lattice-mismatched semiconductor layer such as silicon germanium disposed in source and drain regions of only the PFET and not of the NFET. A process of making the PFET and NFET is provided. Trenches are etched in the areas to become the source and drain regions of the PFET and a lattice-mismatched silicon germanium layer is grown epitaxially therein to apply a strain to the channel region of the PFET adjacent thereto. A layer of silicon can be grown over the silicon germanium layer and a salicide formed from the layer of silicon to provide low-resistance source and drain regions.

Owner:SEMICON MFG INT (SHANGHAI) CORP

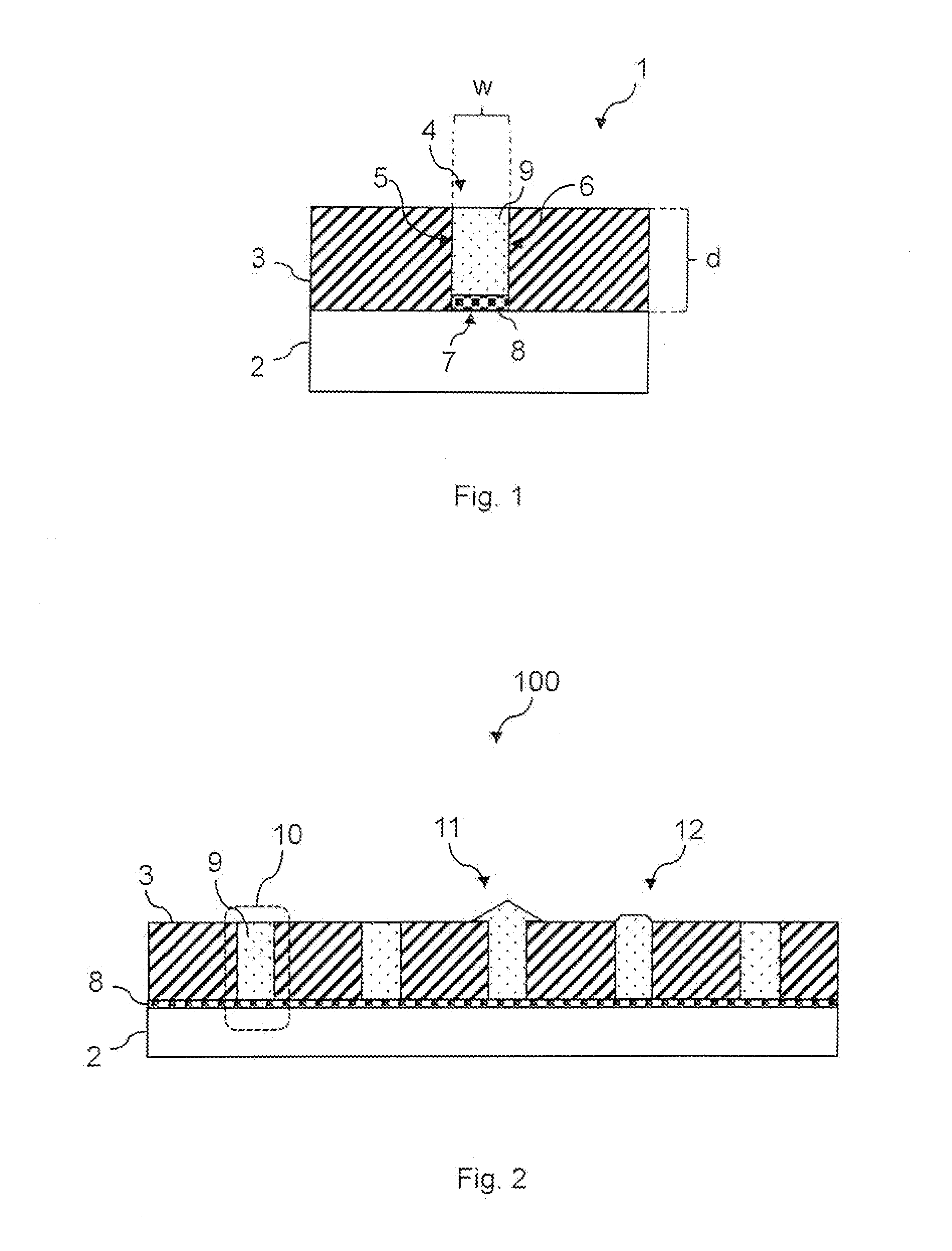

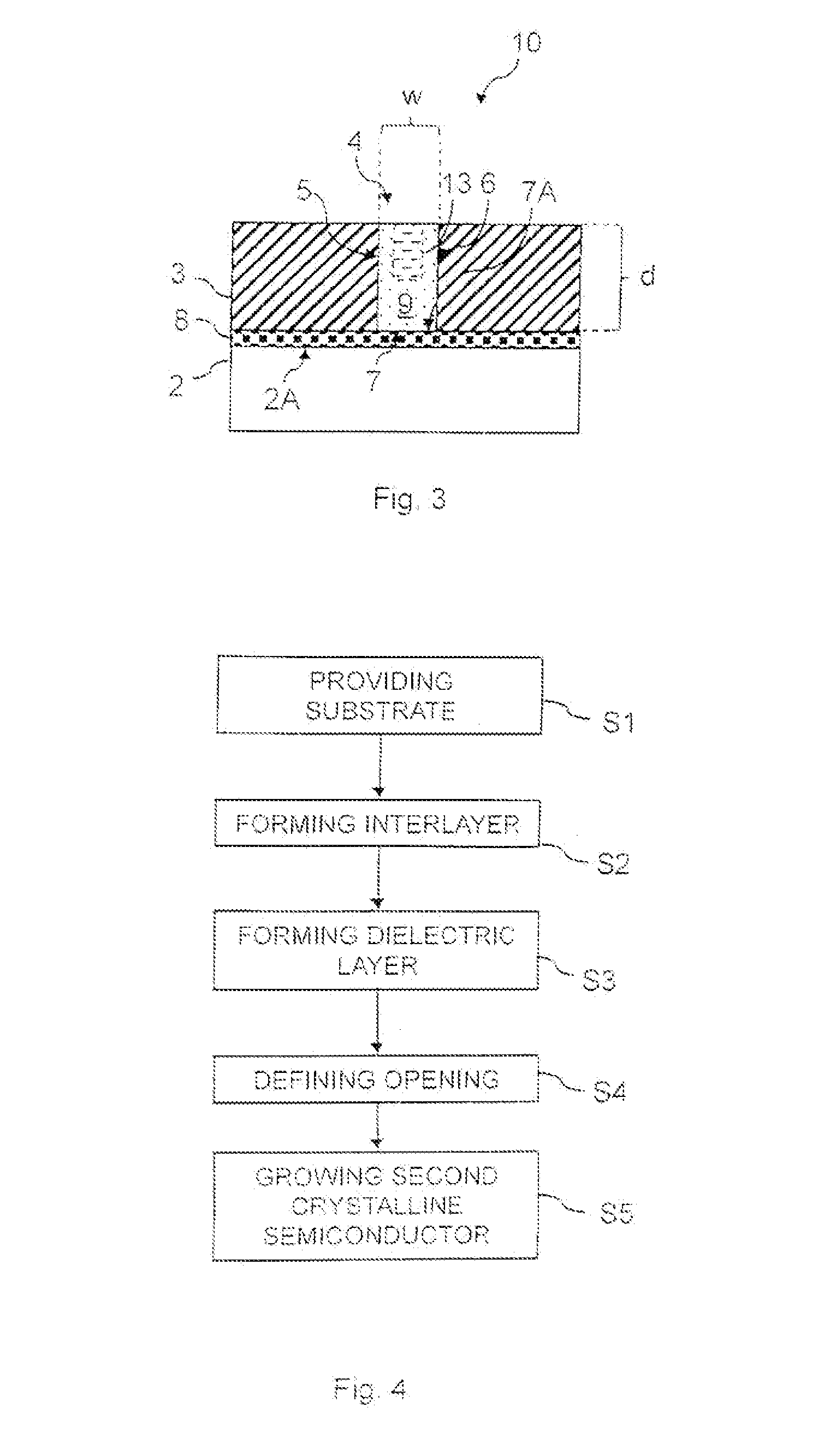

Compound semiconductor structure

InactiveUS20150061078A1Semiconductor/solid-state device manufacturingSemiconductor devicesCrystallographySemiconductor materials

A semiconductor structure comprises a substrate comprising a first crystalline semiconductor material, a dielectric layer, above the substrate, defining an opening, a second crystalline semiconductor material at least partially filling the opening, and a crystalline interlayer between the substrate and the second crystalline semiconductor material. The first crystalline semiconductor material and the second crystalline semiconductor material are lattice mismatched, and the crystalline interlayer comprises an oxygen compound. A method for fabricating semiconductor structure comprises the steps of providing a substrate including a first crystalline semiconductor material, patterning an opening in a dielectric layer above the substrate, the opening having a bottom, forming a crystalline interlayer on the substrate at least partially covering the bottom, and growing a second crystalline semiconductor material on the crystalline interlayer thereby at least partially filling the opening. The crystalline semiconductor materials are lattice mismatched, and the crystalline interlayer comprises an oxygen compound.

Owner:ALSEPHINA INNOVATIONS INC

Strained-channel semiconductor structure and method of fabricating the same

A strained-channel semiconductor structure and method of fabricating the same. The strained-channel semiconductor structure comprises a substrate composed of a first semiconductor material with a first natural lattice constant. A channel region is disposed in the substrate and a gate stack is disposed over the strained channel region A pair of source / drain regions are oppositely disposed in the substrate adjacent to the channel region, wherein each of the source / drain regions comprises a lattice-mismatched zone comprising a second semiconductor material with a second natural lattice constant rather than the first natural lattice constant, an inner side and an outer side corresponding to the gate stack, and at least one outer sides laterally contacts the first semiconductor material of the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

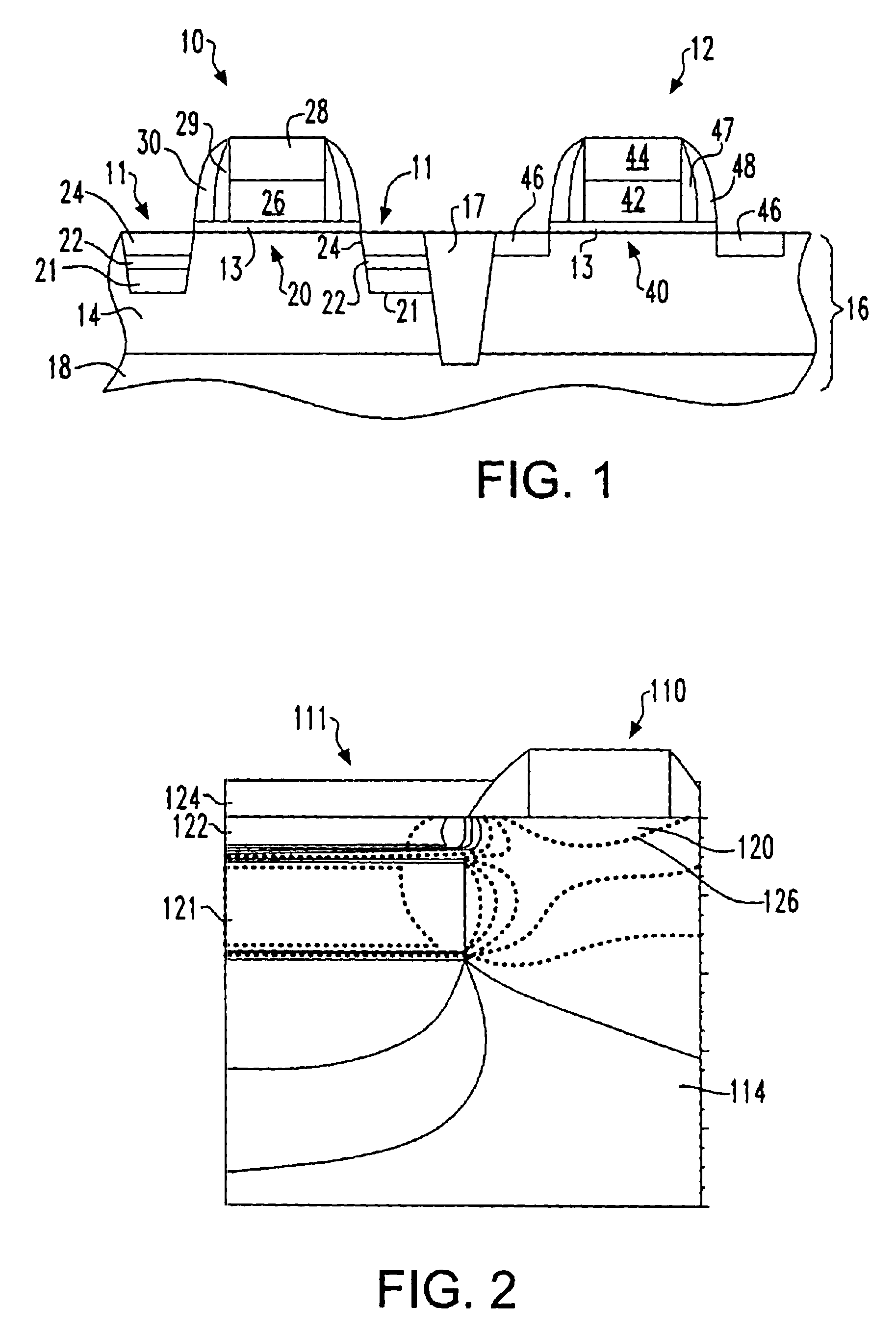

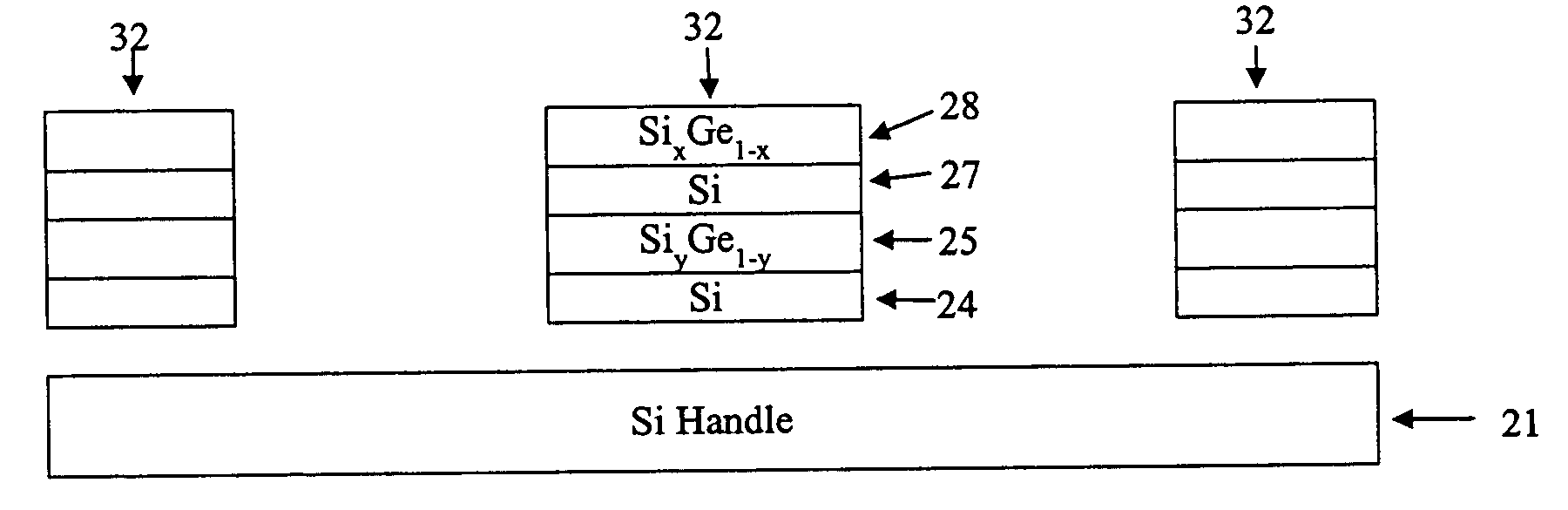

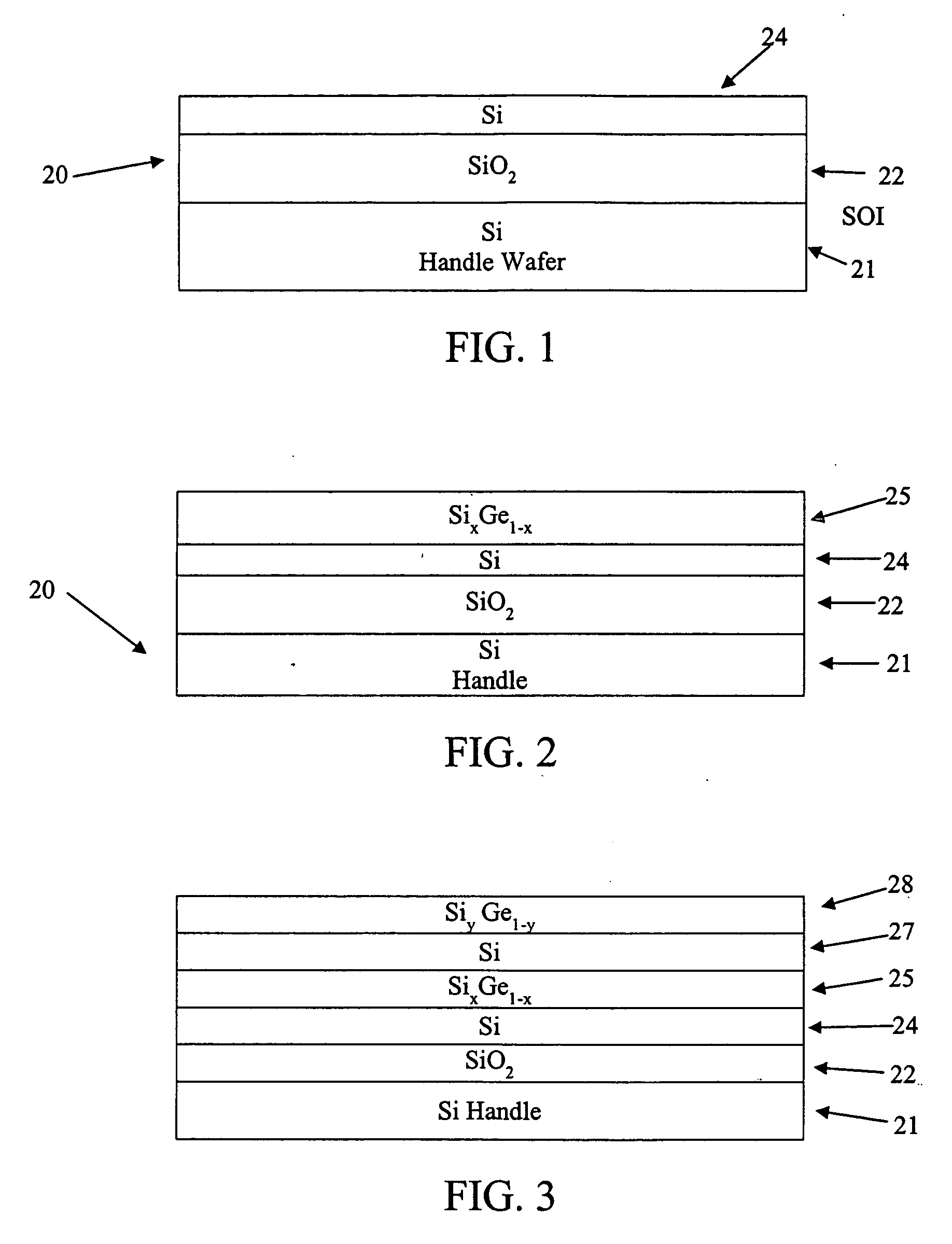

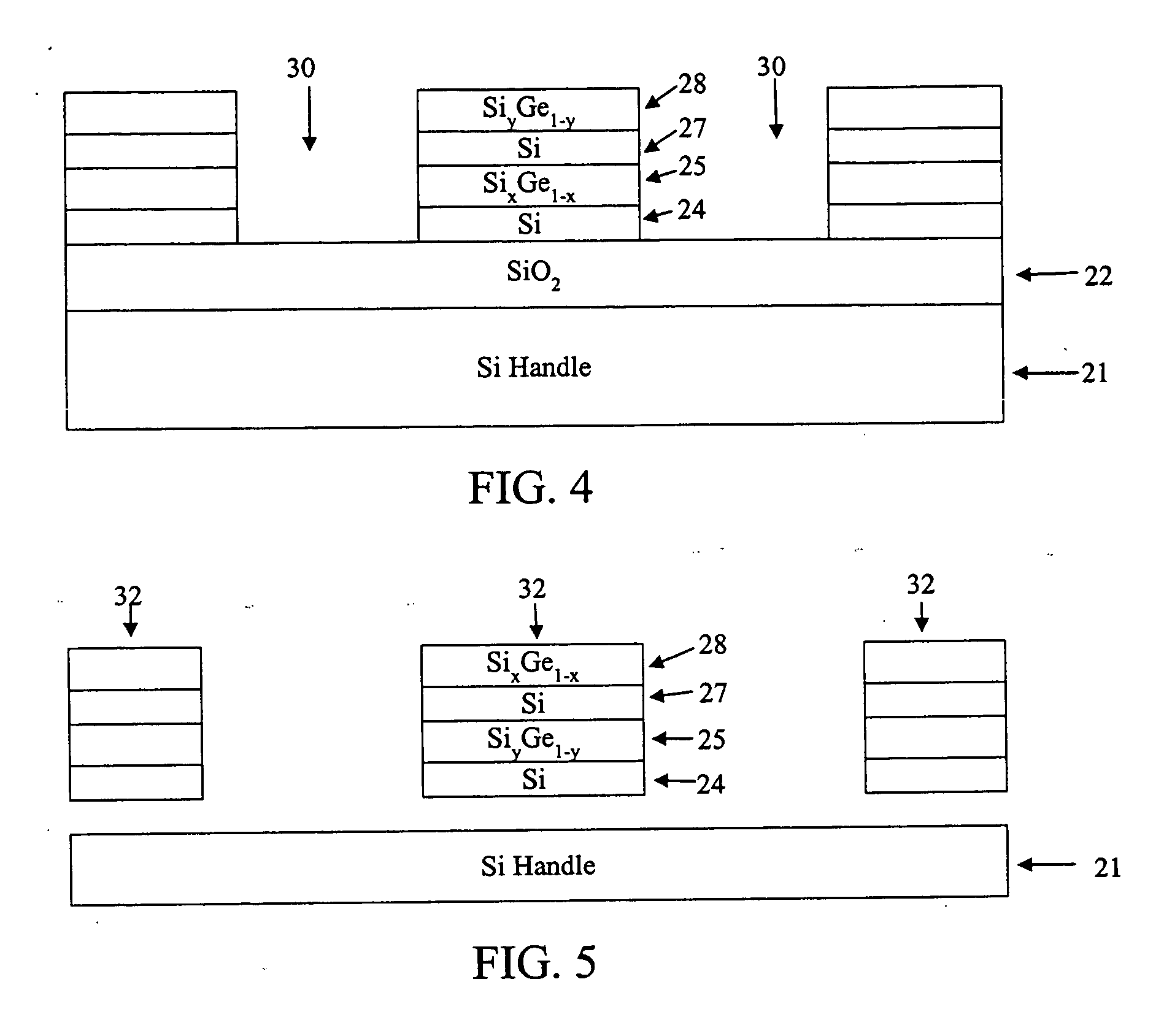

Fabrication of strained heterojunction structures

ActiveUS20060134893A1Improve featuresHigh carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionLayer interface

Growth of multilayer films is carried out in a manner which allows close control of the strain in the grown layers and complete release of the grown films to allow mounting of the released multilayer structures on selected substrates. A layer of material, such as silicon-germanium, is grown onto a template layer, such as silicon, of a substrate having a sacrificial layer on which the template layer is formed. The grown layer has a lattice mismatch with the template layer so that it is strained as deposited. A top layer of crystalline material, such as silicon, is grown on the alloy layer to form a multilayer structure with the grown layer and the template layer. The sacrificial layer is preferentially etched away to release the multilayer structure from the sacrificial layer, relaxing the grown layer and straining the crystalline layers interfaced with it.

Owner:WISCONSIN ALUMNI RES FOUND

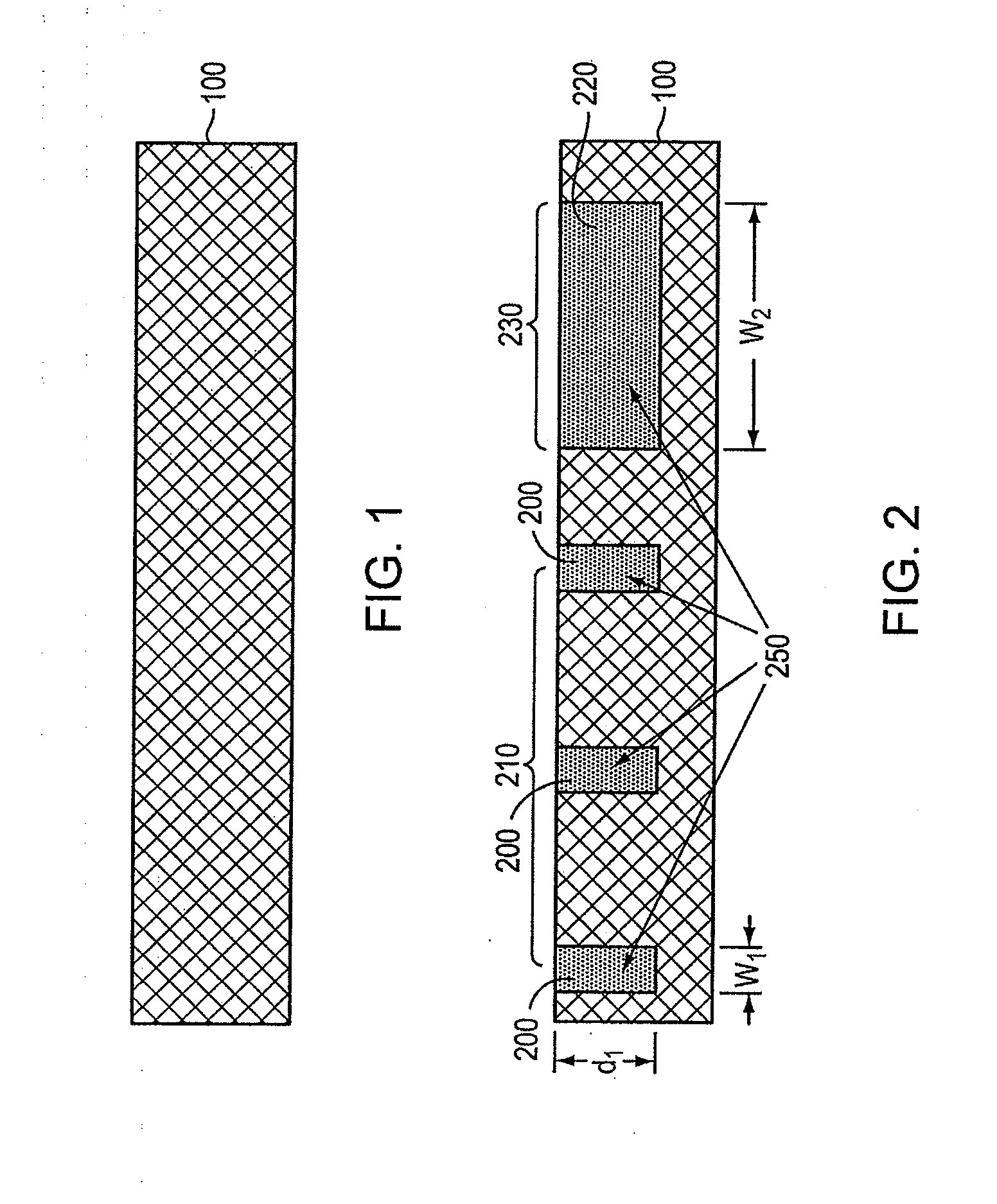

Methods for integrating lattice-mismatched semiconductor structure on insulators

InactiveUS20070054467A1Improve functionalityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsSemiconductor structure

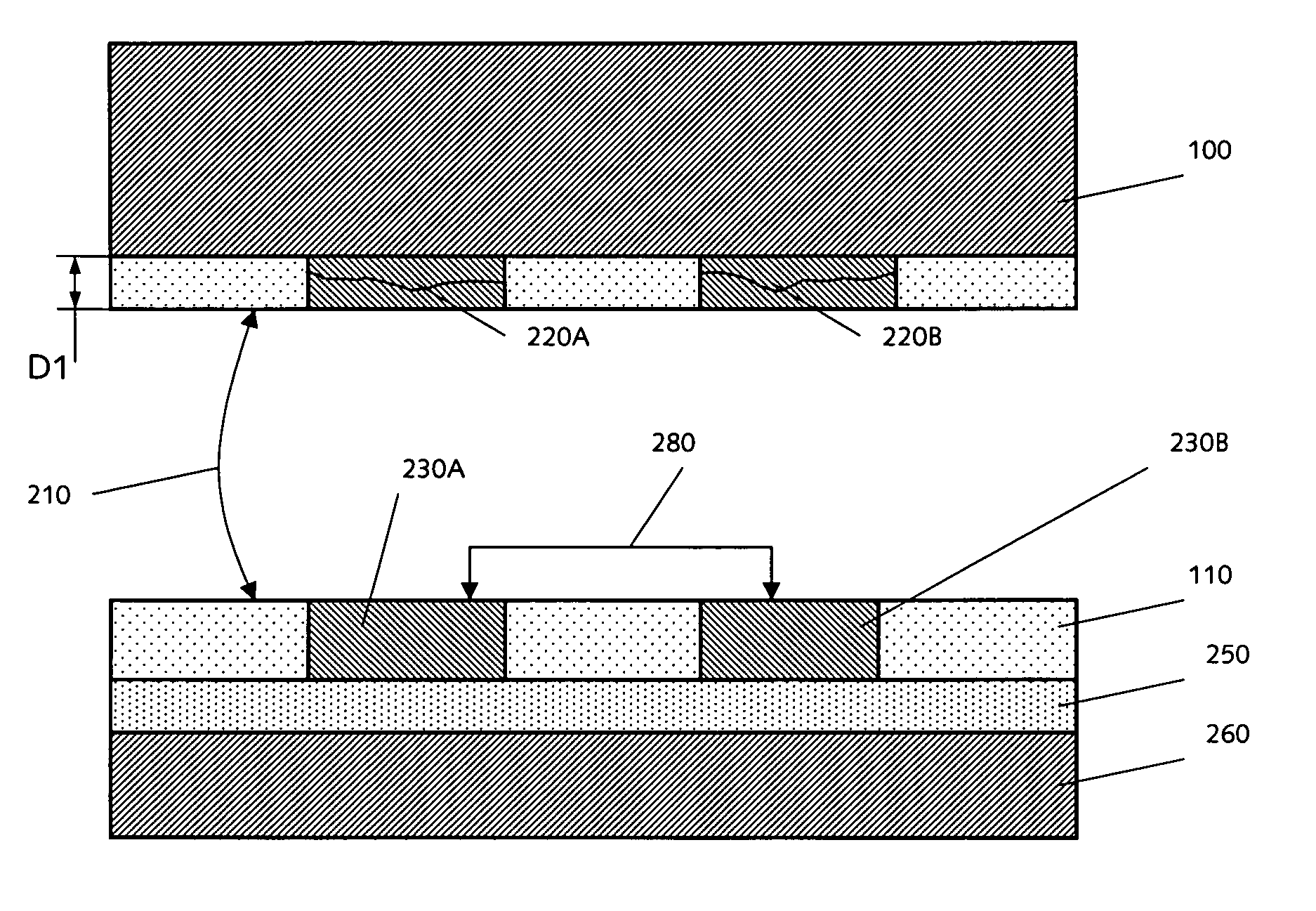

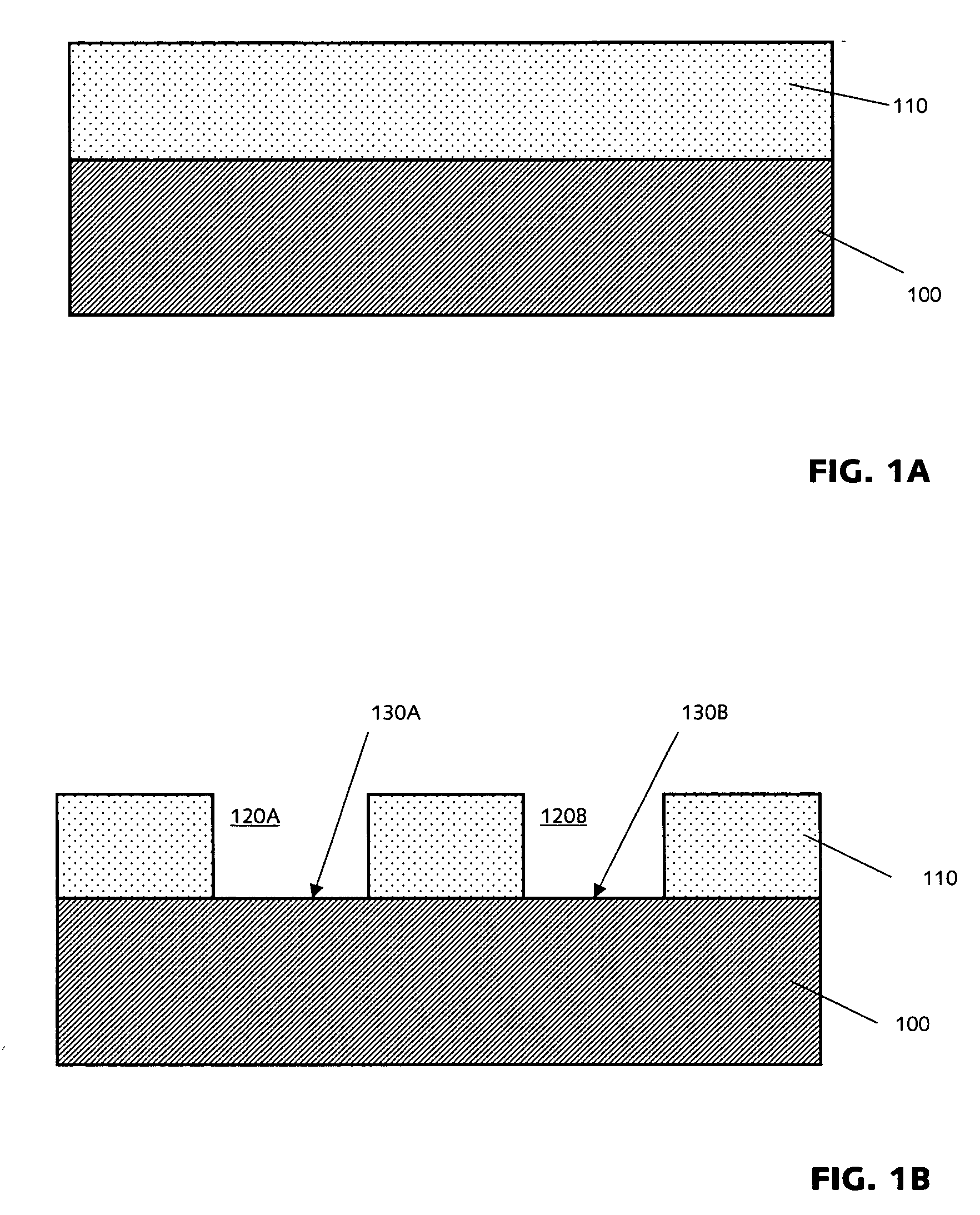

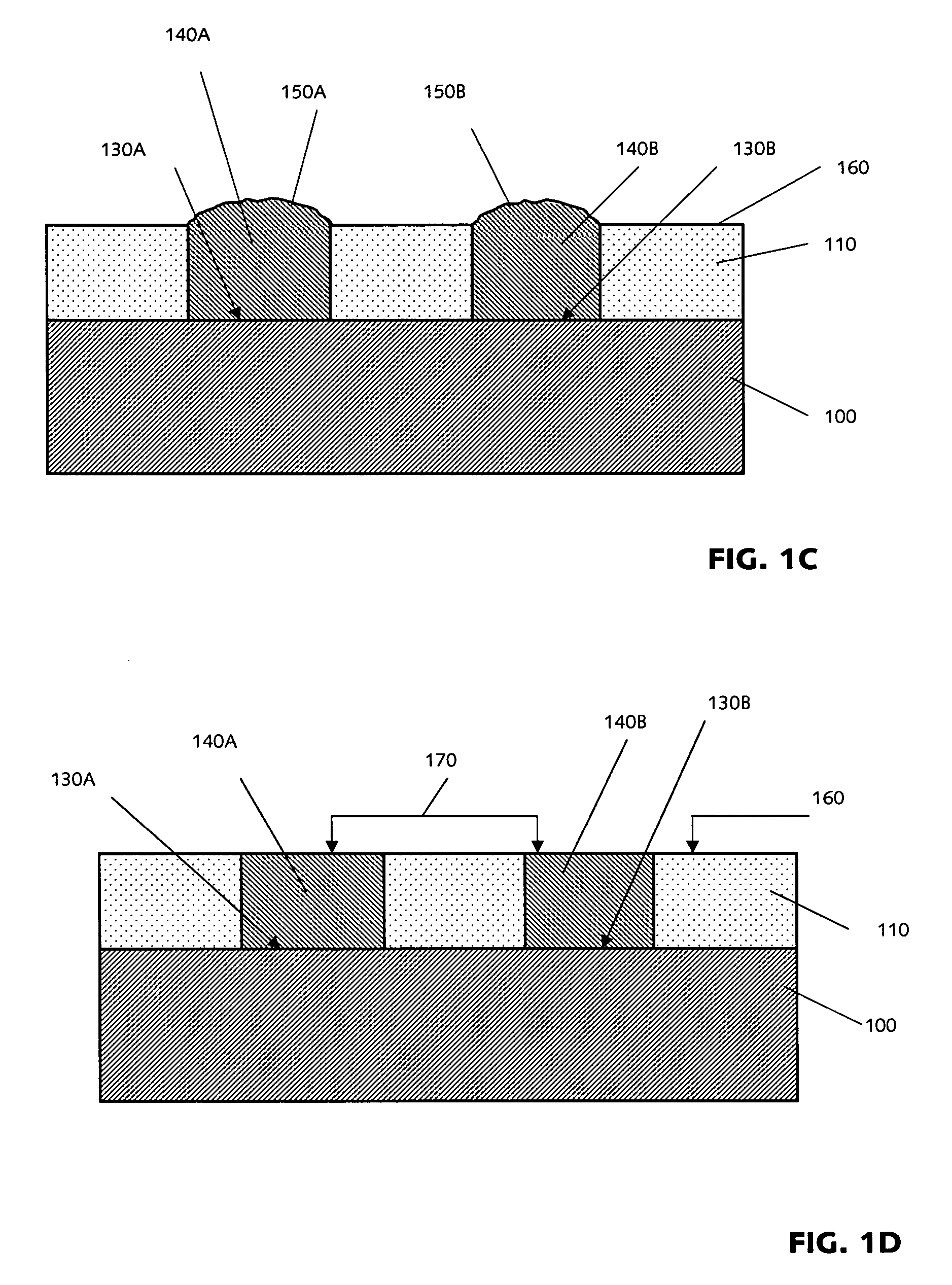

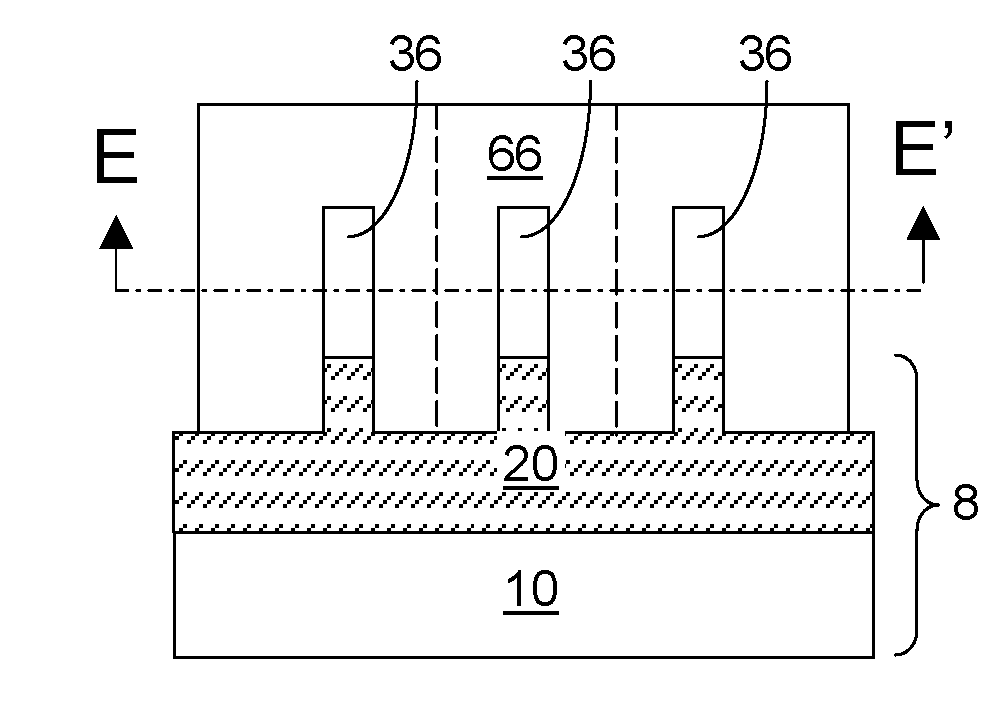

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:AMBERWAVE SYST

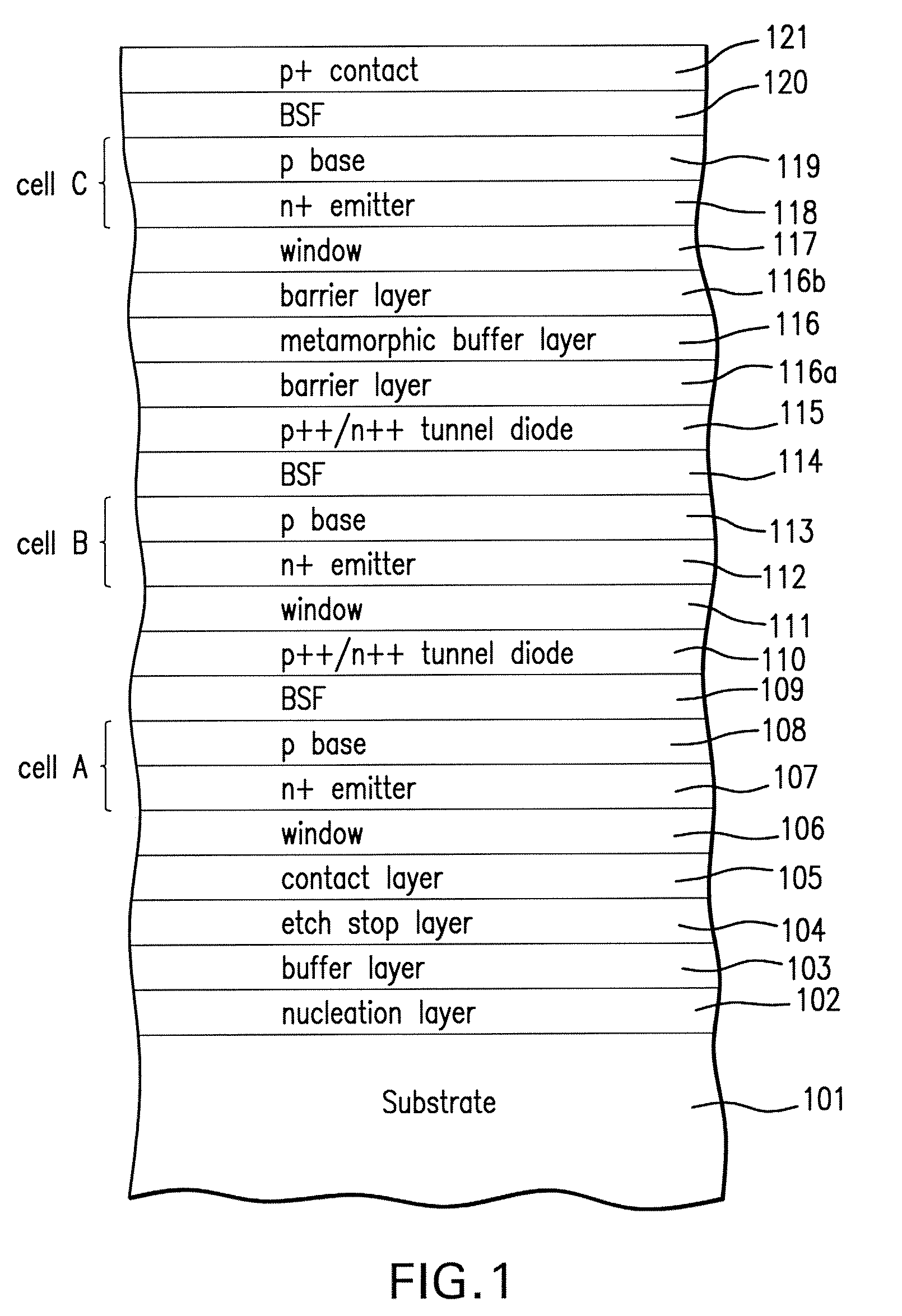

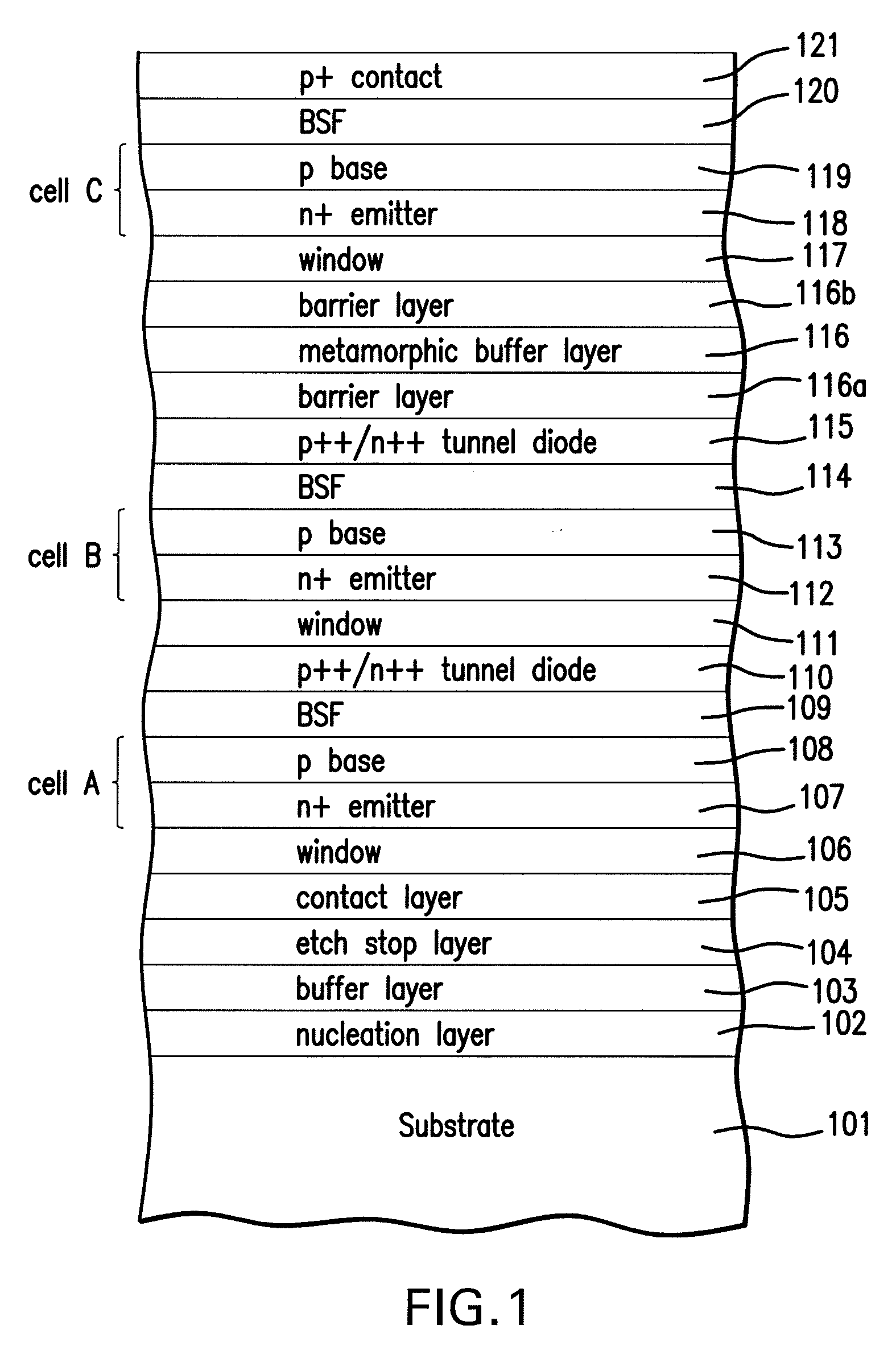

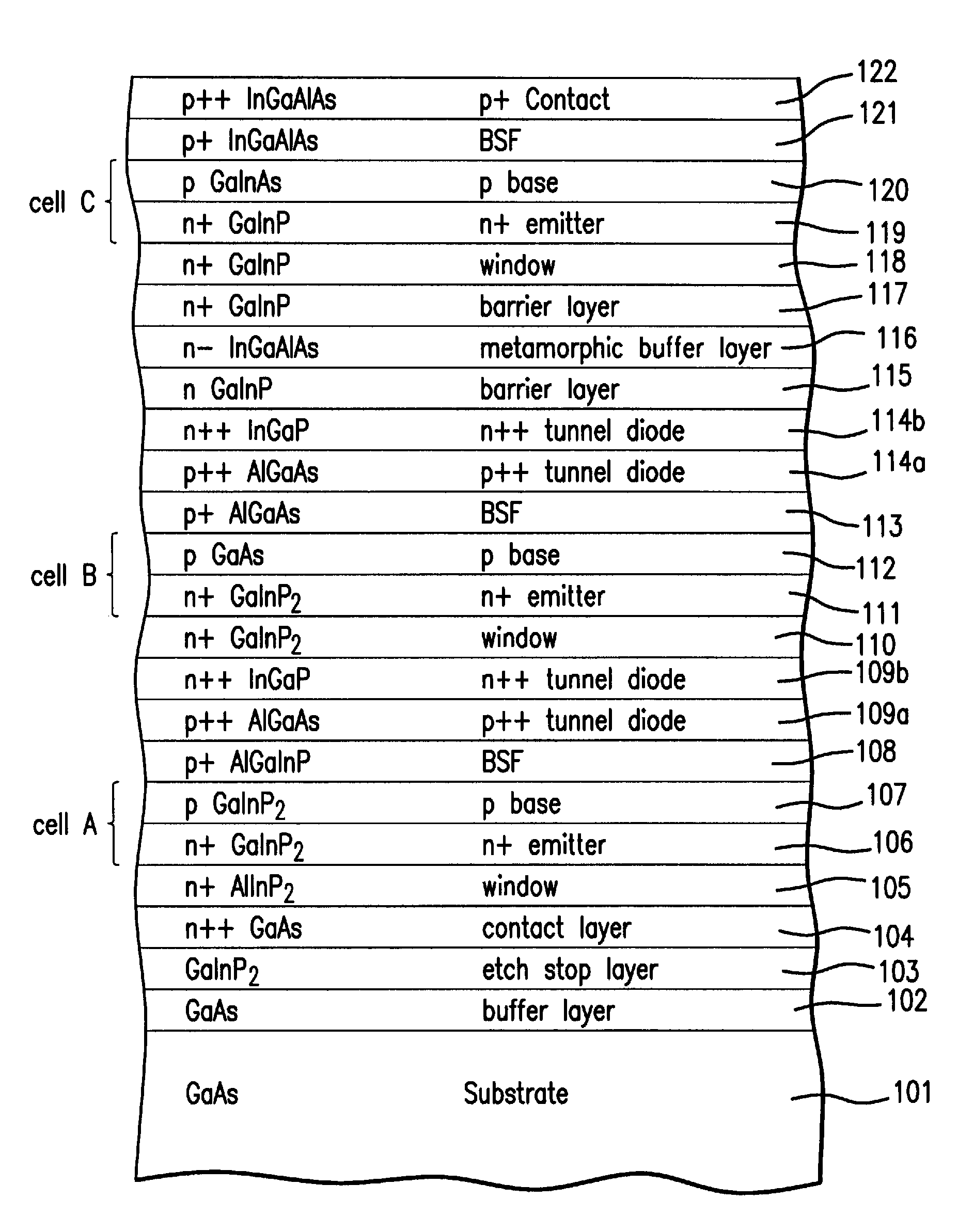

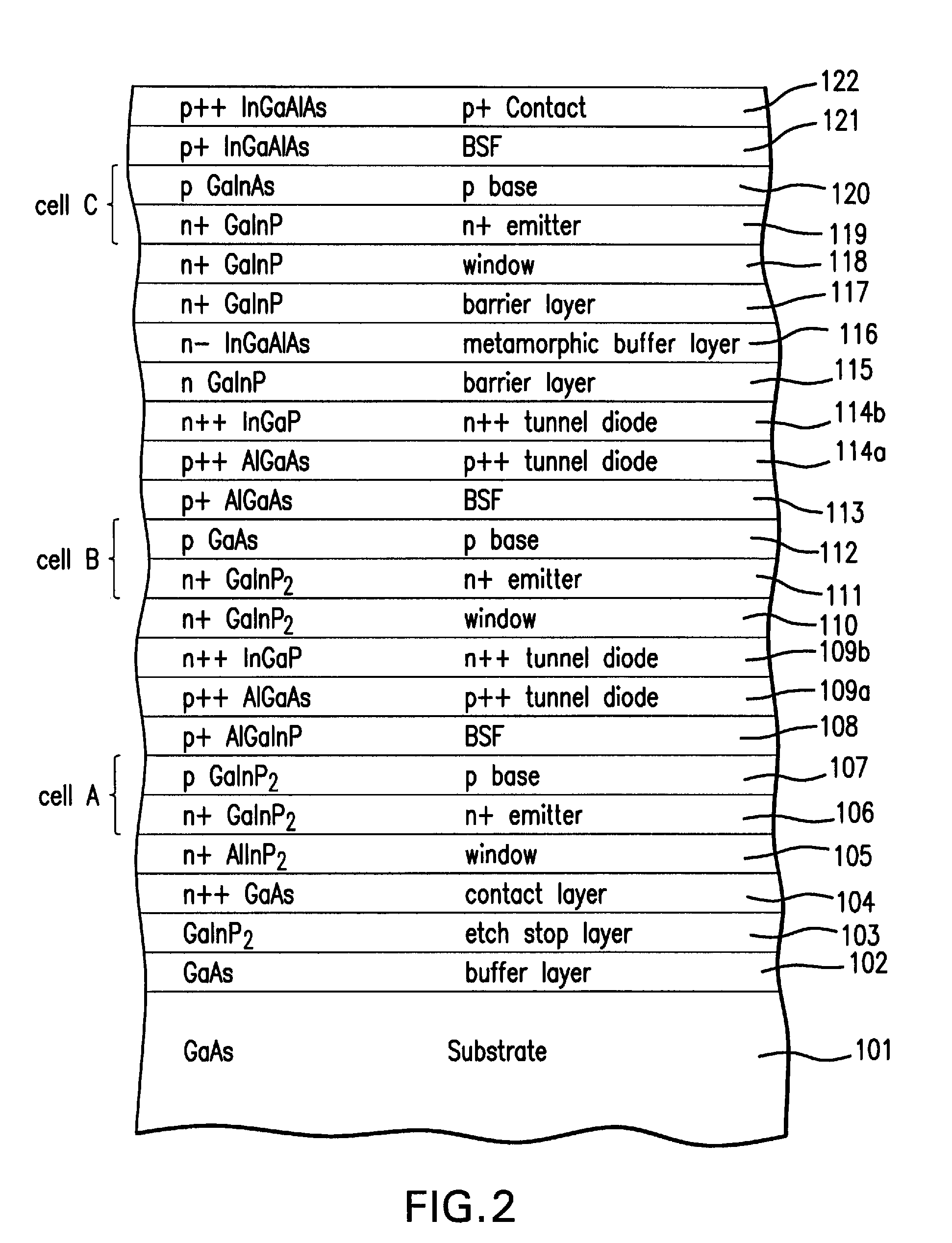

Barrier Layers In Inverted Metamorphic Multijunction Solar Cells

InactiveUS20090078309A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationThreading dislocationsSemiconductor materials

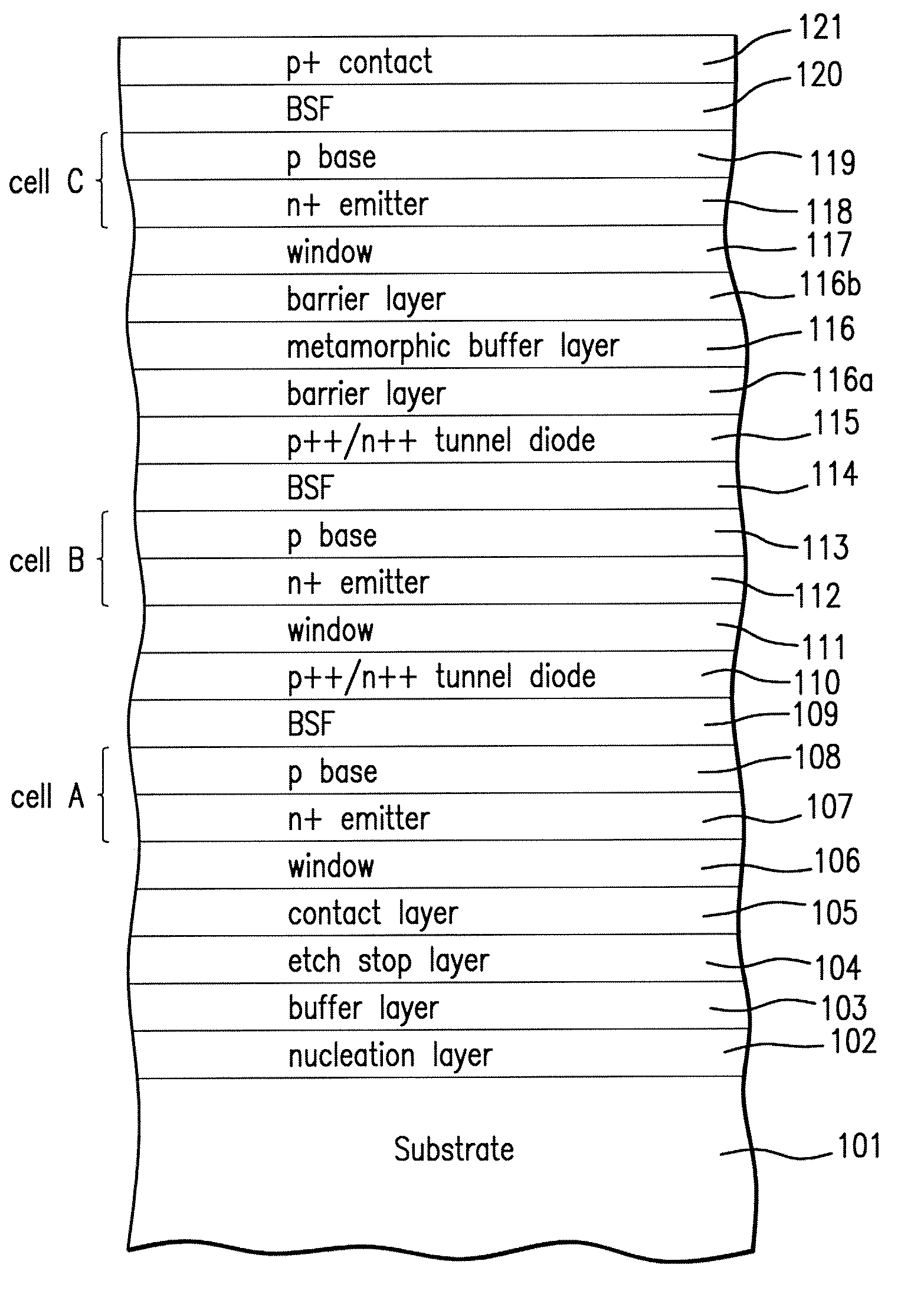

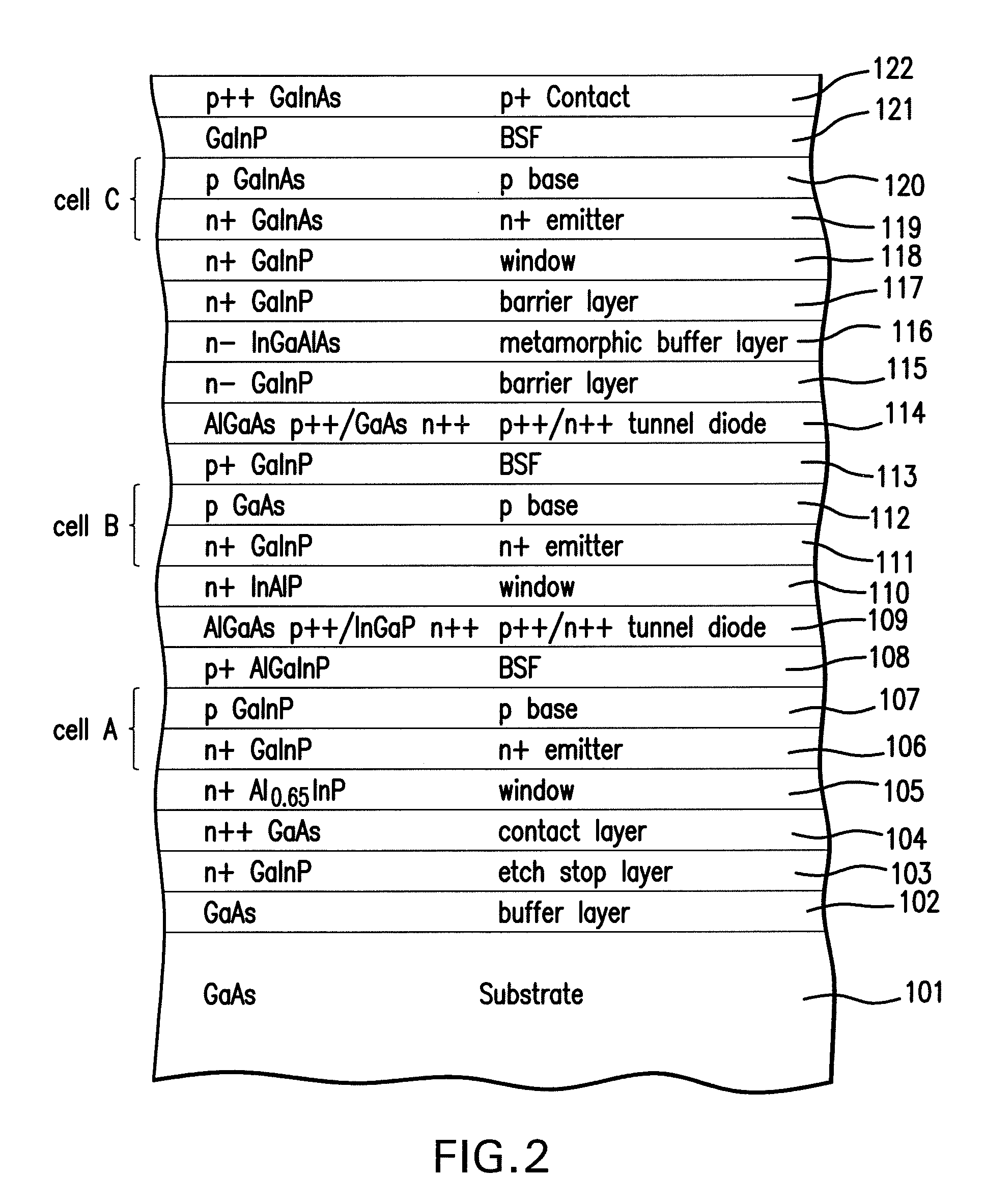

A method of forming a multijunction solar cell including an upper subcell, a middle subcell, and a lower subcell, the method including: providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a barrier layer over the second subcell to reduce threading dislocations; forming a grading interlayer over the barrier layer, the grading interlayer having a third band gap greater than the second band gap; and forming a third solar subcell over the grading interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell.

Owner:SOLAERO TECH CORP

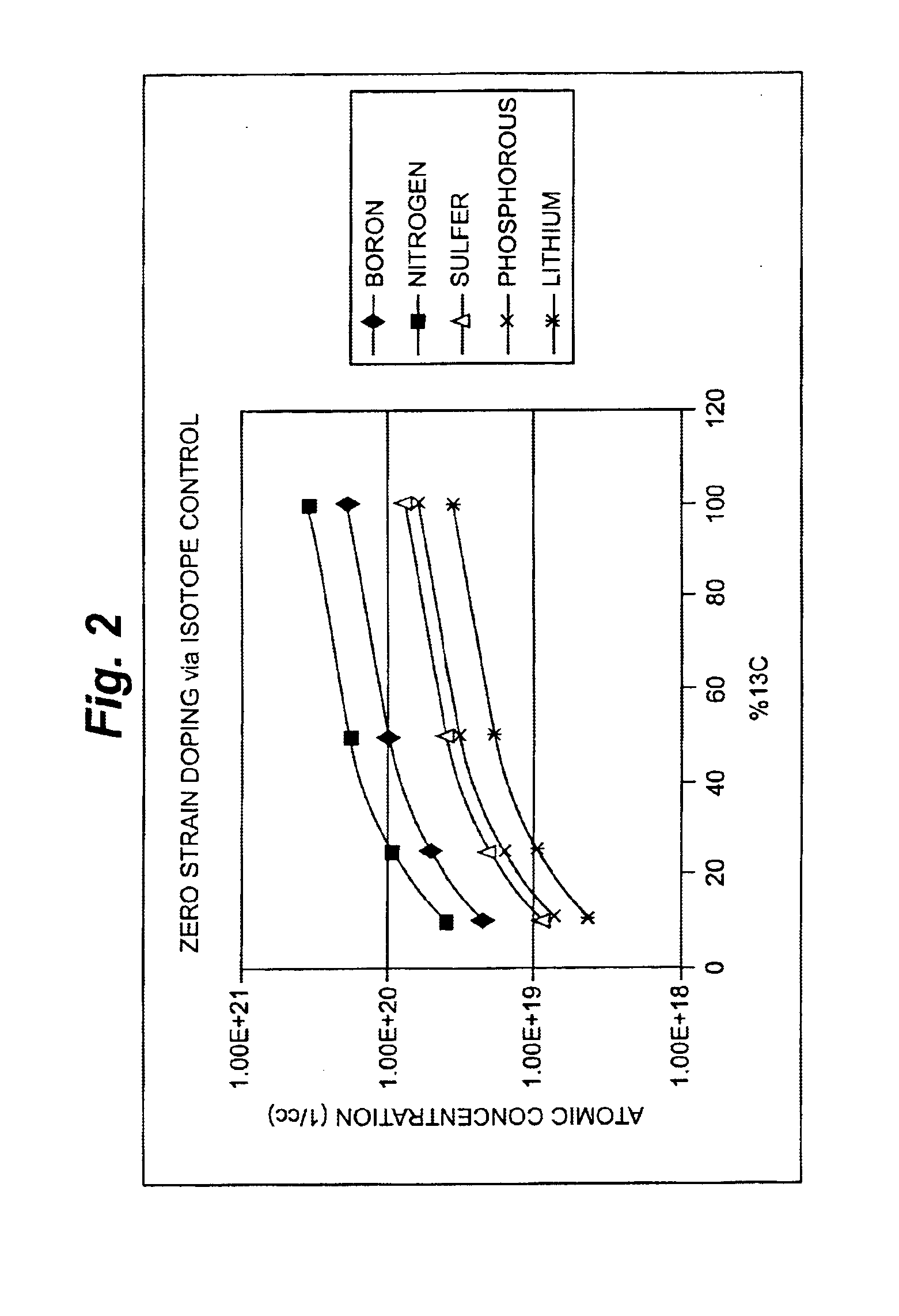

Exponentially Doped Layers In Inverted Metamorphic Multijunction Solar Cells

InactiveUS20090155952A1Increase currentFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsLattice mismatch

A method of forming a multifunction solar cell including an upper subcell, a middle subcell, and a lower subcell, including providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a grading interlayer over the second subcell, the grading interlayer having a third band gap greater than the second band gap; and forming a third solar subcell over the grading interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell, wherein at least one of the bases of a solar subcell has an exponentially doped profile.

Owner:EMCORE SOLAR POWER

Tunnel effect transistors based on silicon nanowires

InactiveUS20080067495A1Optimize architectureReduce power consumptionTransistorNanoinformaticsMOSFETLattice mismatch

Tunnel field-effect transistors (TFETs) are regarded as successors of metal-oxide semiconductor field-effect transistors (MOSFETs), but silicon-based TFETs typically suffer from low on-currents, a drawback related to the large resistance of the tunnel barrier. To achieve higher on-currents a nanowire-based TFET with a germanium (Ge) tunnel barrier in an otherwise silicon (Si) channel is used. A nanowire is introduced such that the lattice mismatch between silicon and germanium does not result in a highly defective interface. A dynamic power reduction as well as a static power reduction can result, compared to conventional MOSFET configurations. Multiple layers of logic can therefore be envisioned with these nanowire Si / Ge TFETs resulting in ultra-high on-chip transistor densities.

Owner:KATHOLIEKE UNIV LEUVEN

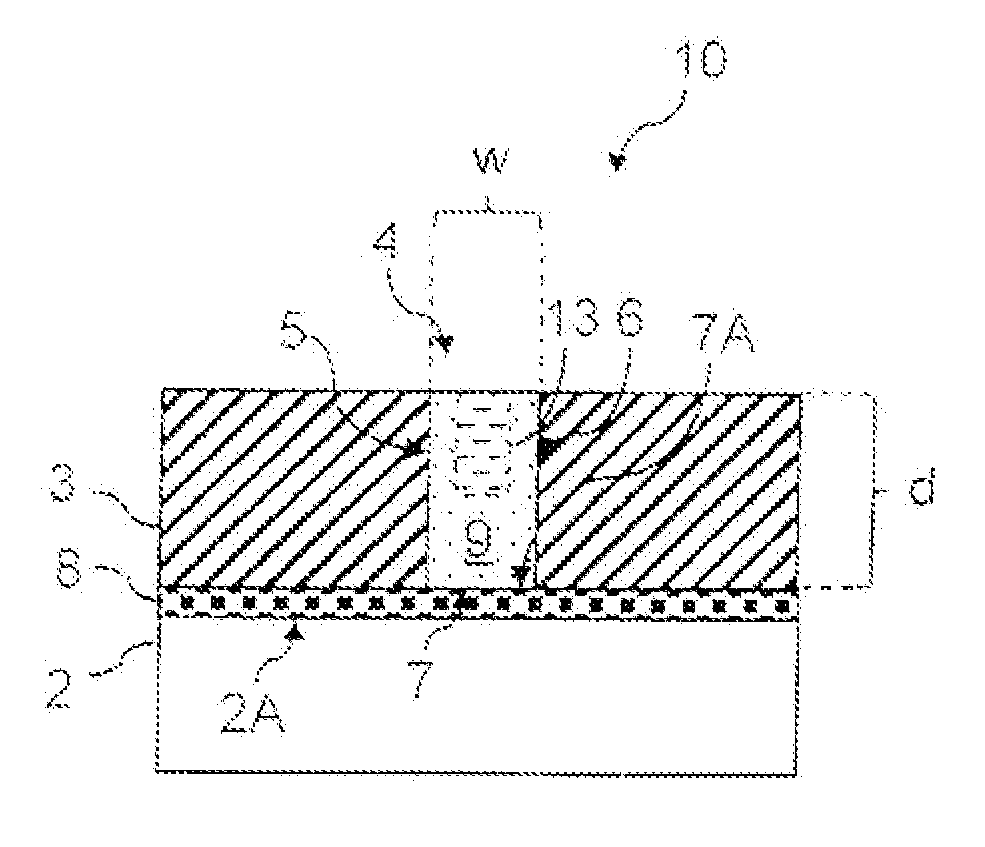

Finfet with longitudinal stress in a channel

ActiveUS20100038679A1Improve device performanceReduce the overall heightSolid-state devicesSemiconductor/solid-state device manufacturingDielectricGate dielectric

At least one gate dielectric, a gate electrode, and a gate cap dielectric are formed over at least one channel region of at least one semiconductor fin. A gate spacer is formed on the sidewalls of the gate electrode, exposing end portions of the fin on both sides of the gate electrode. The exposed portions of the semiconductor fin are vertically and laterally etched, thereby reducing the height and width of the at least one semiconductor fin in the end portions. Exposed portions of the insulator layer may also be recessed. A lattice-mismatched semiconductor material is grown on the remaining end portions of the at least one semiconductor fin by selective epitaxy with epitaxial registry with the at least one semiconductor fin. The lattice-mismatched material applies longitudinal stress along the channel of the finFET formed on the at least one semiconductor fin.

Owner:GLOBALFOUNDRIES US INC

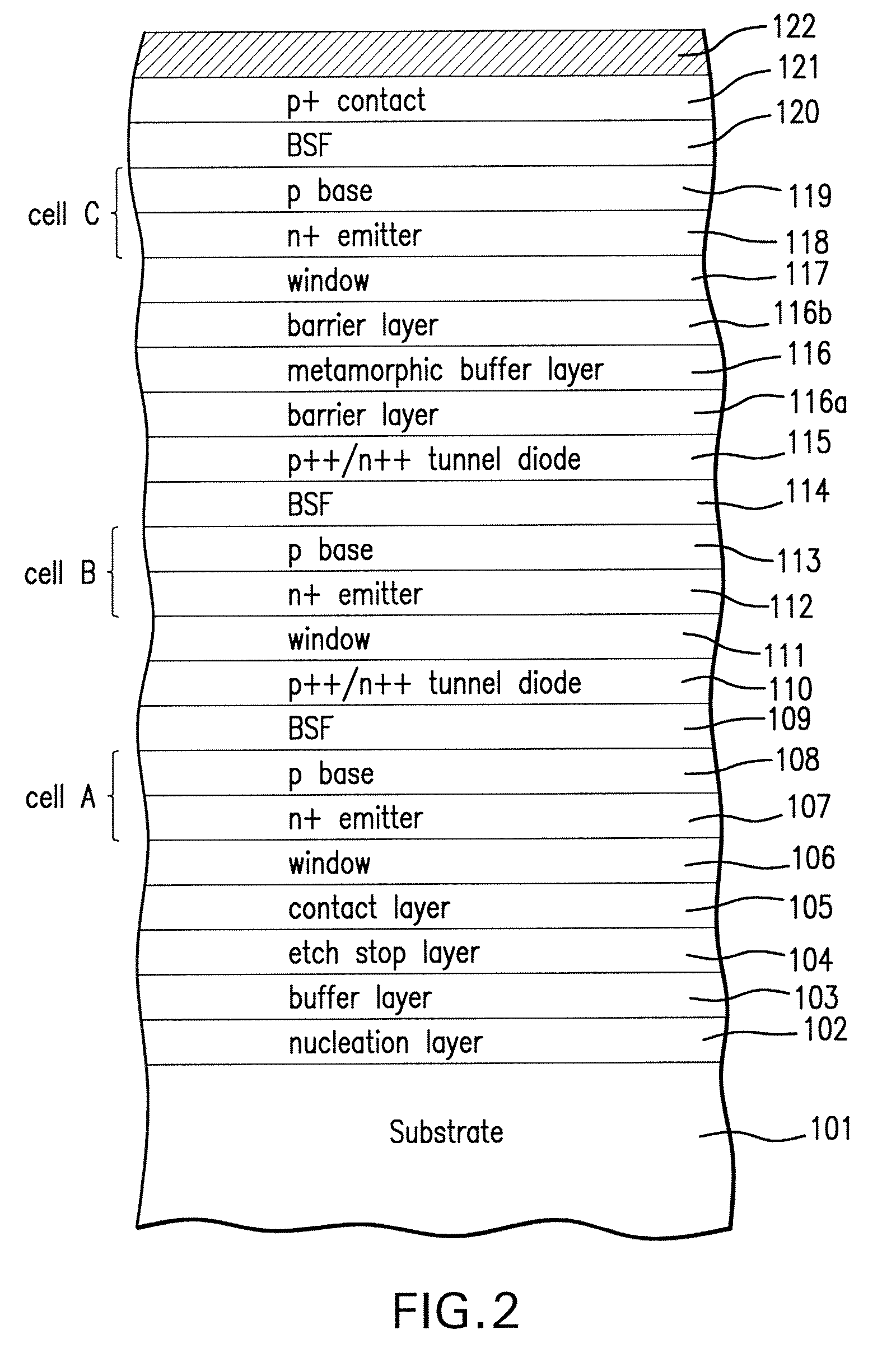

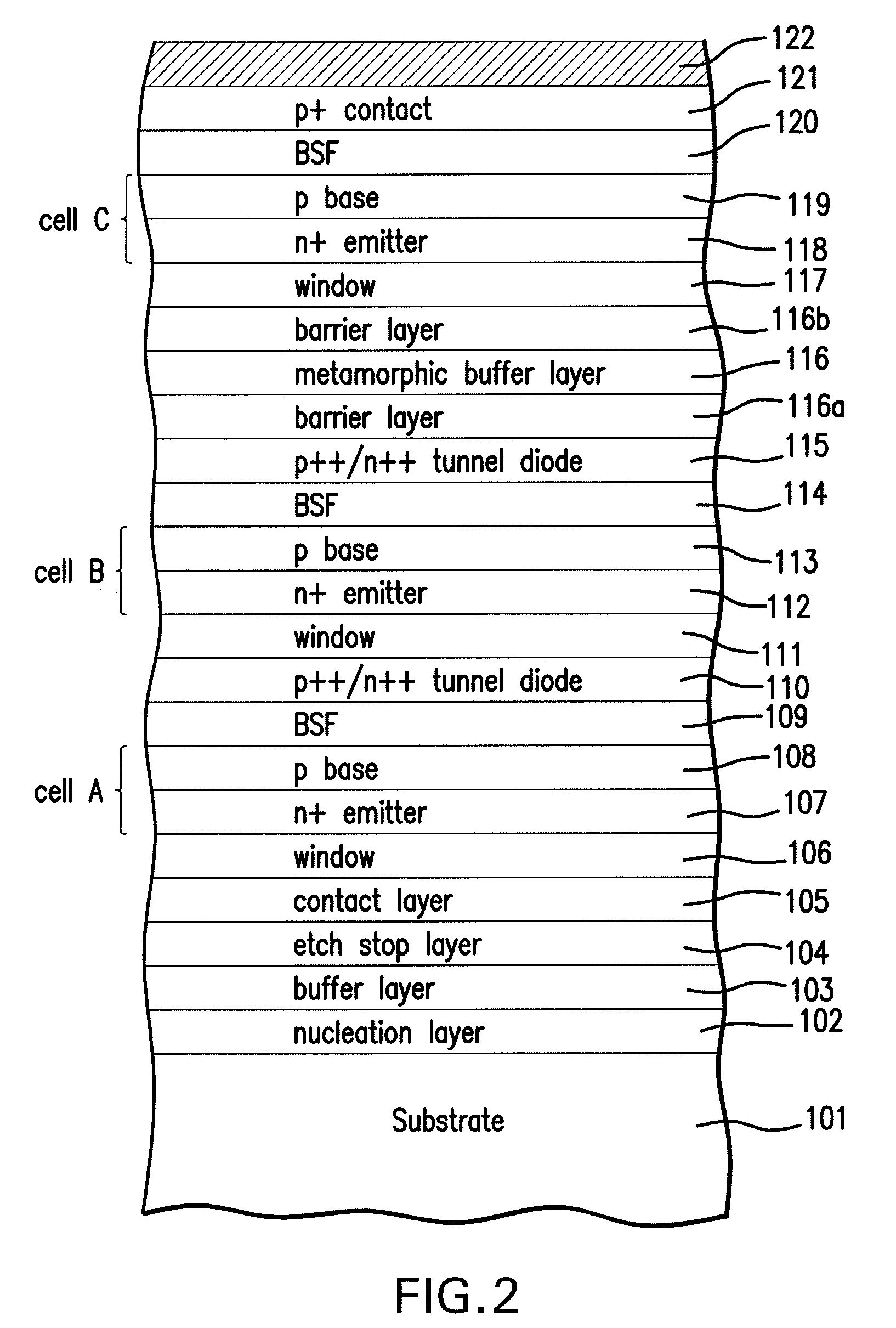

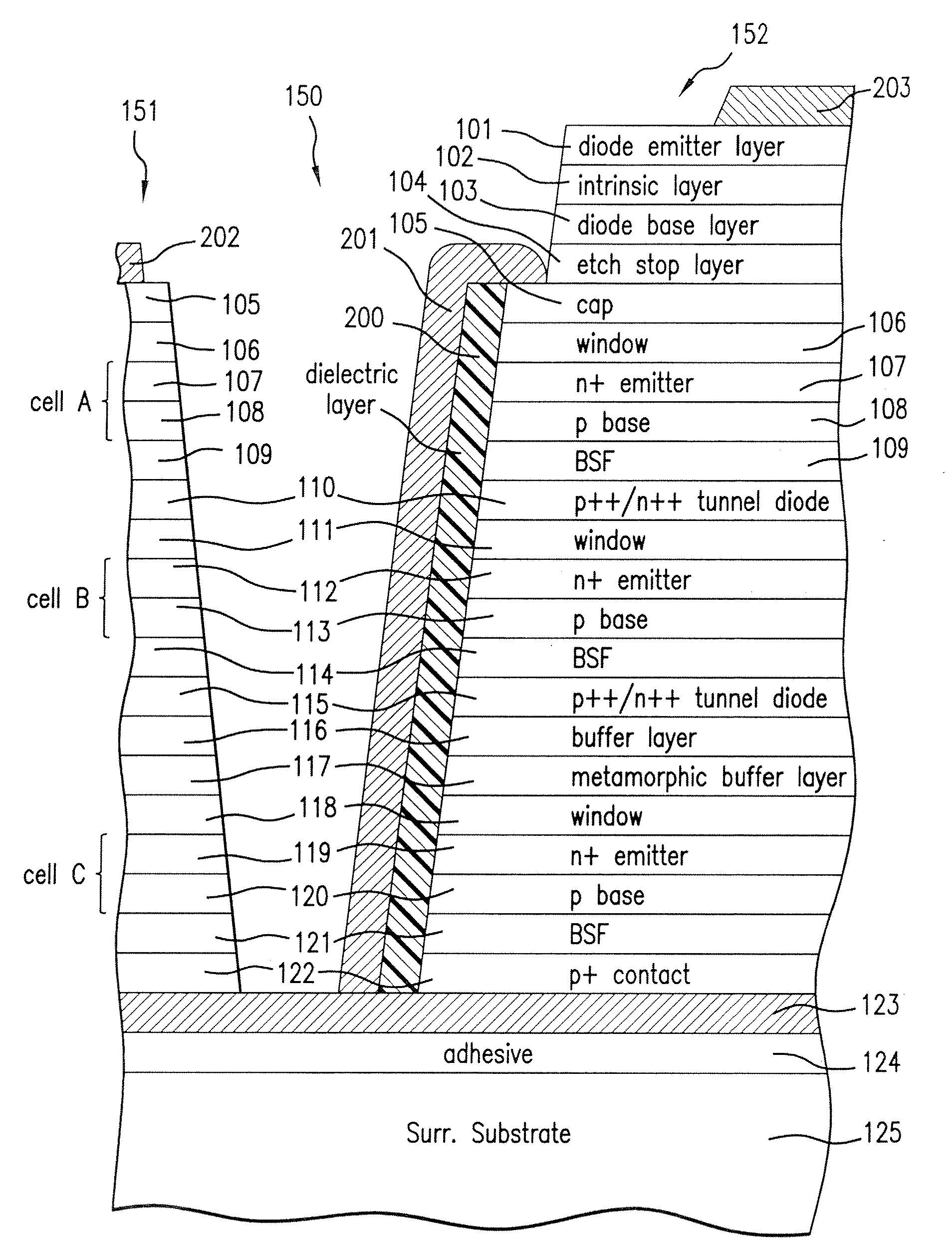

Inverted metamorphic solar cell with bypass diode

InactiveUS20080149173A1Maximize energy efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor structure

A method of forming a semiconductor structure including a multijunction solar cell with an upper subcell, a middle subcell, and a lower subcell, by providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on said substrate having a first band gap; forming a second solar subcell over said first subcell having a second band gap smaller than said first band gap; and forming a grading interlayer over said second subcell having a third band gap larger than said second band gap; forming a third solar subcell having a fourth band gap smaller than said second band gap such that said third subcell is lattice mismatched with respect to said second subcell. A bypass diode is further provided in the semiconductor structure with a region of first polarity of the solar cell connected with a region of second polarity of the bypass diode.

Owner:EMCORE SOLAR POWER

Lattice-mismatched semiconductor structures on insulators

ActiveUS20070054465A1Improve functionalityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsLattice mismatch

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:TAIWAN SEMICON MFG CO LTD

Ohmic n-contact formed at low temperature in inverted metamorphic multijunction solar cells

InactiveUS20100012175A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationSemiconductor materialsLattice mismatch

A method of forming a multifunction solar cell including an upper subcell, a middle subcell, and a lower subcell by providing a substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a graded interlayer over the second subcell, the graded interlayer having a third band gap greater than the second band gap; forming a third solar subcell over the graded interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell; and forming a contact composed of a sequence of layers over the first subcell at a temperature of 280° C. or less and having a contact resistance of less than 5×10−4 ohms-cm2.

Owner:EMCORE SOLAR POWER

Gradient Ternary or Quaternary Multiple-Gate Transistor

ActiveUS20100301390A1Improve performanceReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesLattice mismatchIntegrated circuit

An integrated circuit structure includes a semiconductor substrate; insulation regions over the semiconductor substrate; and an epitaxy region over the semiconductor substrate and having at least a portion in a space between the insulation regions. The epitaxy region includes a III-V compound semiconductor material. The epitaxy region also includes a lower portion and an upper portion over the lower portion. The lower portion and the semiconductor substrate have a first lattice mismatch. The upper portion and the semiconductor substrate have a second lattice mismatch different from the first lattice mismatch.

Owner:TAIWAN SEMICON MFG CO LTD

Off-Cut Substrates In Inverted Metamorphic Multijunction Solar Cells

InactiveUS20090229662A1Final product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsLattice mismatch

A method of forming a multijunction solar cell including an upper subcell, a middle subcell, and a lower subcell, including: providing a substrate having an off-cut of 15° from the (001) plane to the (111)A plane for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a grading interlayer over the second subcell layer, the grading interlayer having a third band gap greater than the second band gap; and forming a third solar subcell over the grading interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell.

Owner:EMCORE SOLAR POWER

Wide Band Gap Window Layers In Inverted Metamorphic Multijunction Solar Cells

InactiveUS20090288703A1Increase currentSemiconductor/solid-state device manufacturingPhotovoltaic energy generationSemiconductor materialsLattice mismatch

A method of forming a multijunction solar cell including an upper subcell, a middle subcell, and a lower subcell, the method including: providing a substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap and including a pseudomorphic window layer; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a graded interlayer over the second subcell, the graded interlayer having a third band gap greater than the second band gap; and forming a third solar subcell over the graded interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second solar subcell.

Owner:SOLAERO TECH CORP

Inverted Metamorphic Multijunction Solar Cells with Distributed Bragg Reflector

InactiveUS20100147366A1Final product manufactureSemiconductor/solid-state device manufacturingLattice mismatchDistributed Bragg reflector

A multijunction solar cell including an upper first solar subcell having a first band gap; a middle second solar subcell adjacent to the first solar subcell and having a second band gap smaller than the first band gap, and having a base layer and an emitter layer, a graded interlayer adjacent to the second solar subcell; the graded interlayer having a third band gap greater than said second band gap; a third solar subcell adjacent to the interlayer, the third subcell having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell; and a distributed Bragg reflector (DBR) adjacent the second or third subcell.

Owner:EMCORE SOLAR POWER

Strained-channel transistor structure with lattice-mismatched zone

InactiveUS6921913B2Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor materials

A strained-channel transistor structure with lattice-mismatched zone and fabrication method thereof. The transistor structure includes a substrate having a strained channel region, comprising a first semiconductor material with a first natural lattice constant, in a surface, a gate dielectric layer overlying the strained channel region, a gate electrode overlying the gate dielectric layer, and a source region and drain region oppositely adjacent to the strained channel region, with one or both of the source region and drain region comprising a lattice-mismatched zone comprising a second semiconductor material with a second natural lattice constant different from the first natural lattice constant.

Owner:TAIWAN SEMICON MFG CO LTD

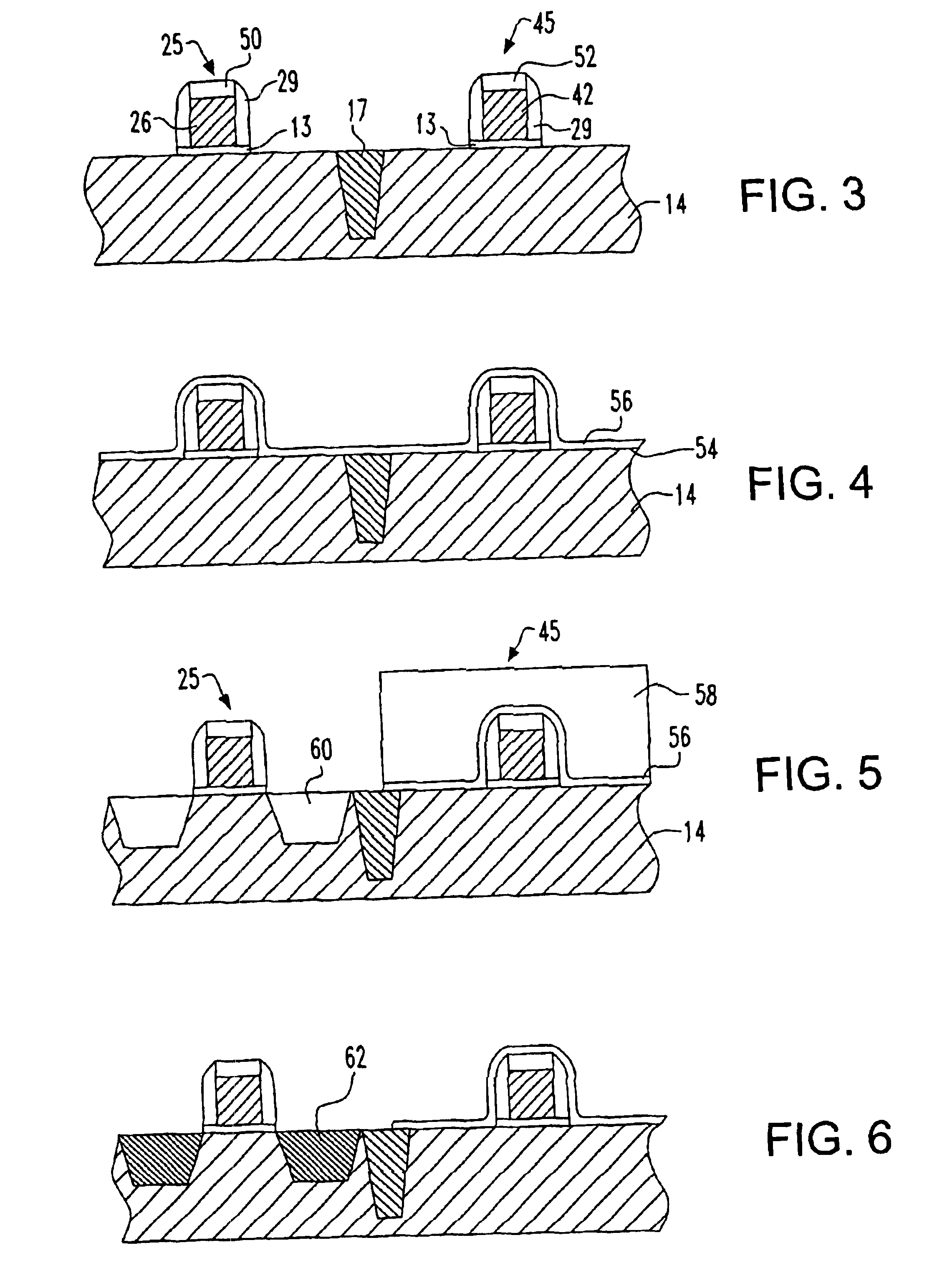

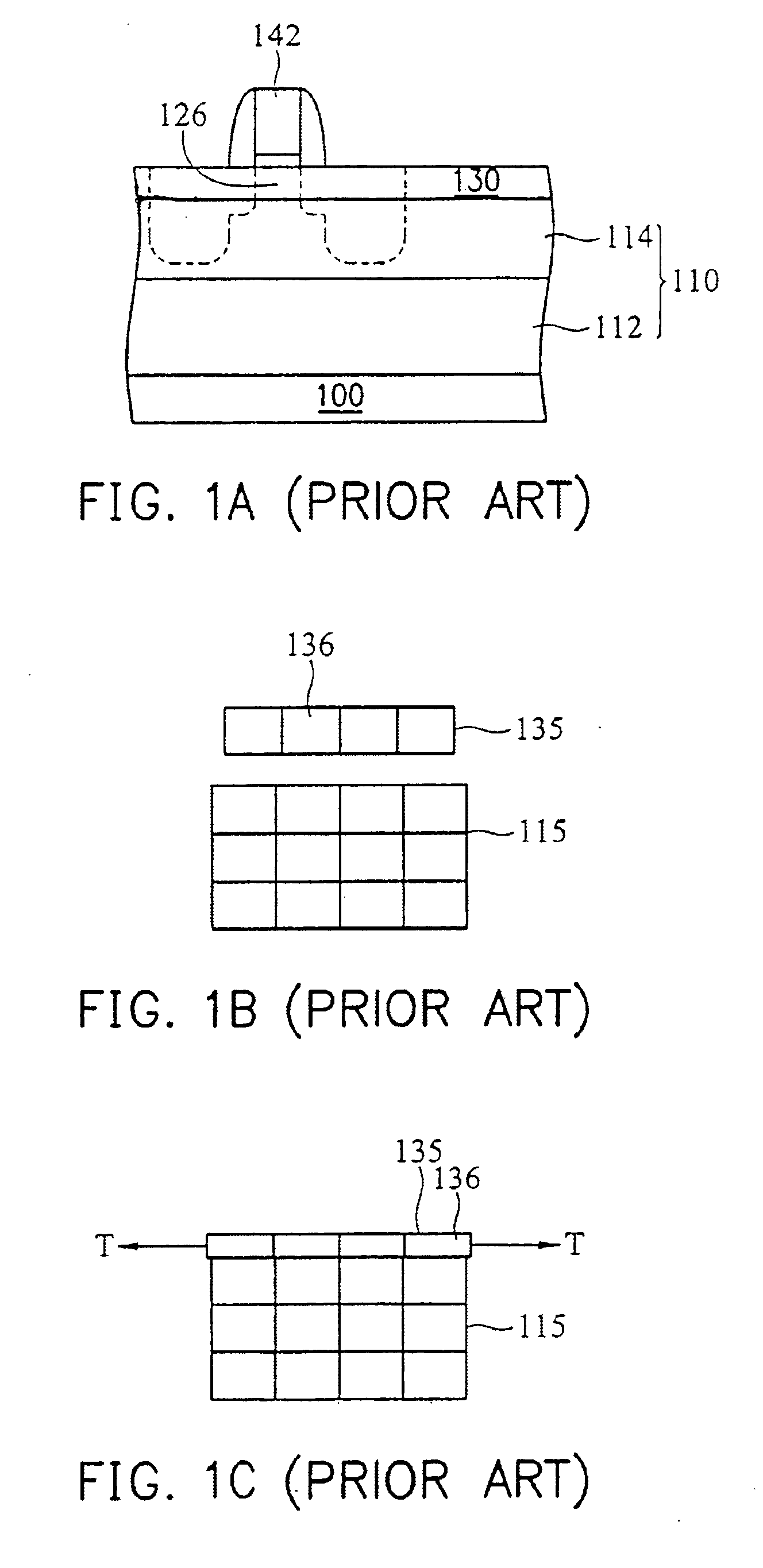

Crystallographic recess etch for embedded semiconductor region

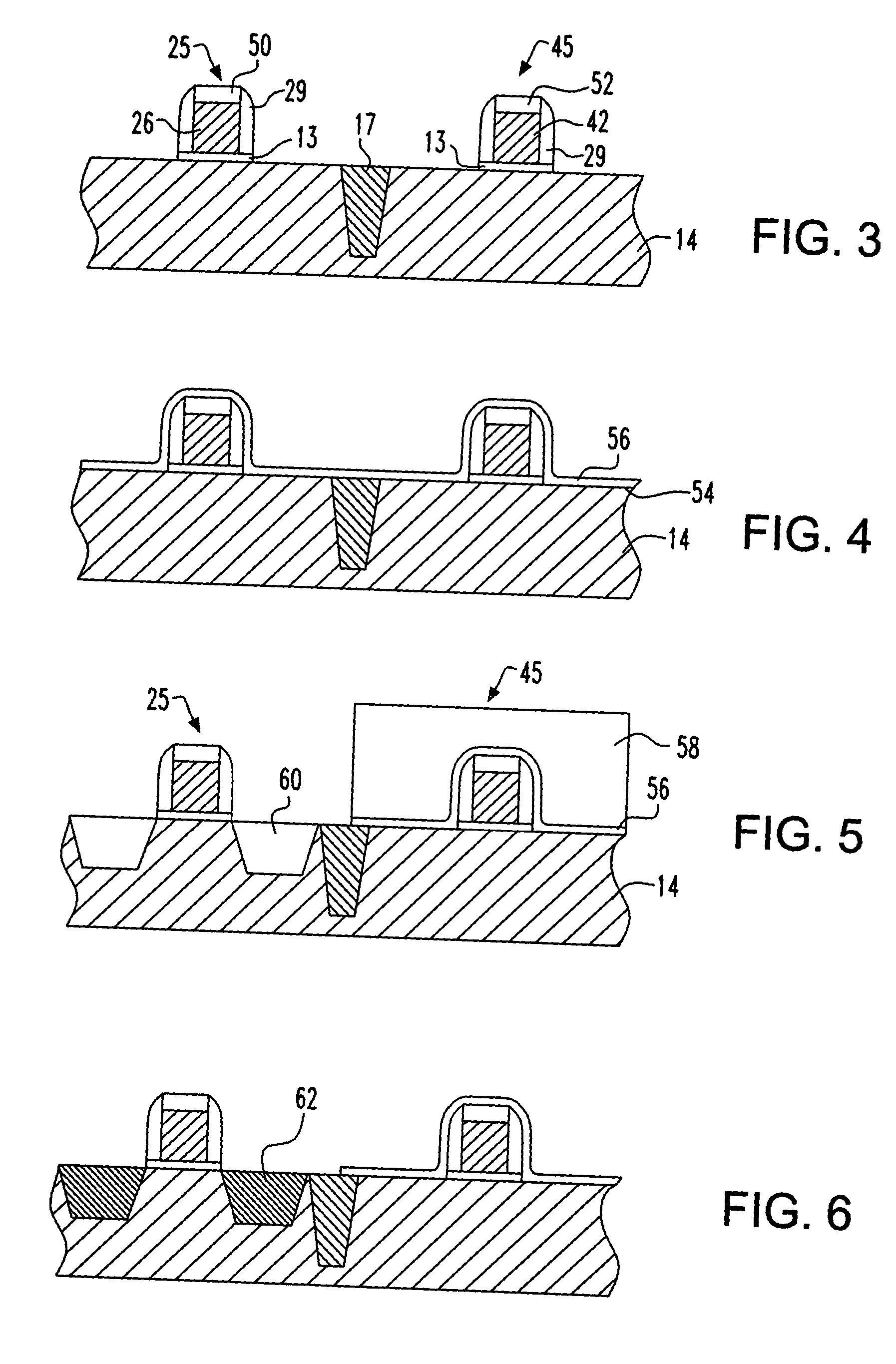

InactiveUS20080237634A1Enhanced inhibitory effectRelieve pressureSemiconductor/solid-state device manufacturingSemiconductor devicesLattice mismatchSemiconductor

Source and drain regions of an FET are etched by a crystallographic anisotropic etch to form a cavity surrounded by crystallographic facets. The exposure of the sidewalls of shallow trench isolation (STI) is avoided or reduced compared to the prior art. The crystallographic anisotropic etch may be combined with an isotropic etch or a recess etch to create undercuts beneath gate spacers and / or a pegging line beneath a top surface of the STI. The at least one cavity is then filled with a lattice-mismatched embedded material so that stress is applied to the channel of the FET. The resulting structure has increased containment of the embedded semiconductor region by shallow trench isolation. A reduction in stress due to the unconstrained sidewall area and an increase in the junction current due to the recessing of the pegging line are eliminated or alleviated.

Owner:IBM CORP

Tunable CVD diamond structures

InactiveUS6858080B2Improve propertiesPolycrystalline material growthUltra-high pressure processesLattice mismatchMonocrystalline silicon

Monocrystalline diamond, adapted for use as in applications such as semiconductor devices, optical waveguides, and industrial applications, in the form of a single crystalline diamond structure having one or more diamond layers, at least one of which is formed by a CVD process. The diamond layers are “lattice-matched” or “lattice-mismatched” to each other to provide a desired level of strain.

Owner:SCIO DIAMOND TECHNOLOGY CORPORATION

Refractive Index Matching in Inverted Metamorphic Multijunction Solar Cells

InactiveUS20090272430A1Final product manufactureSemiconductor/solid-state device manufacturingLattice mismatchRefractive index matching

A multijunction solar cell including an upper first solar subcell having a first band gap; a middle second solar subcell adjacent to the first solar subcell and having a second band gap smaller than the first band gap and having a base layer and an adjacent emitter layer, wherein the other layer adjacent to the emitter layer has an index of refraction substantially equal to that of the emitter layer; a graded interlayer adjacent to the second solar having a third band gap greater than said second band gap; and a lower solar subcell adjacent to the interlayer, and having a fourth band gap smaller than the second band gap, the third subcell being lattice mismatched with respect to the second subcell.

Owner:EMCORE SOLAR POWER

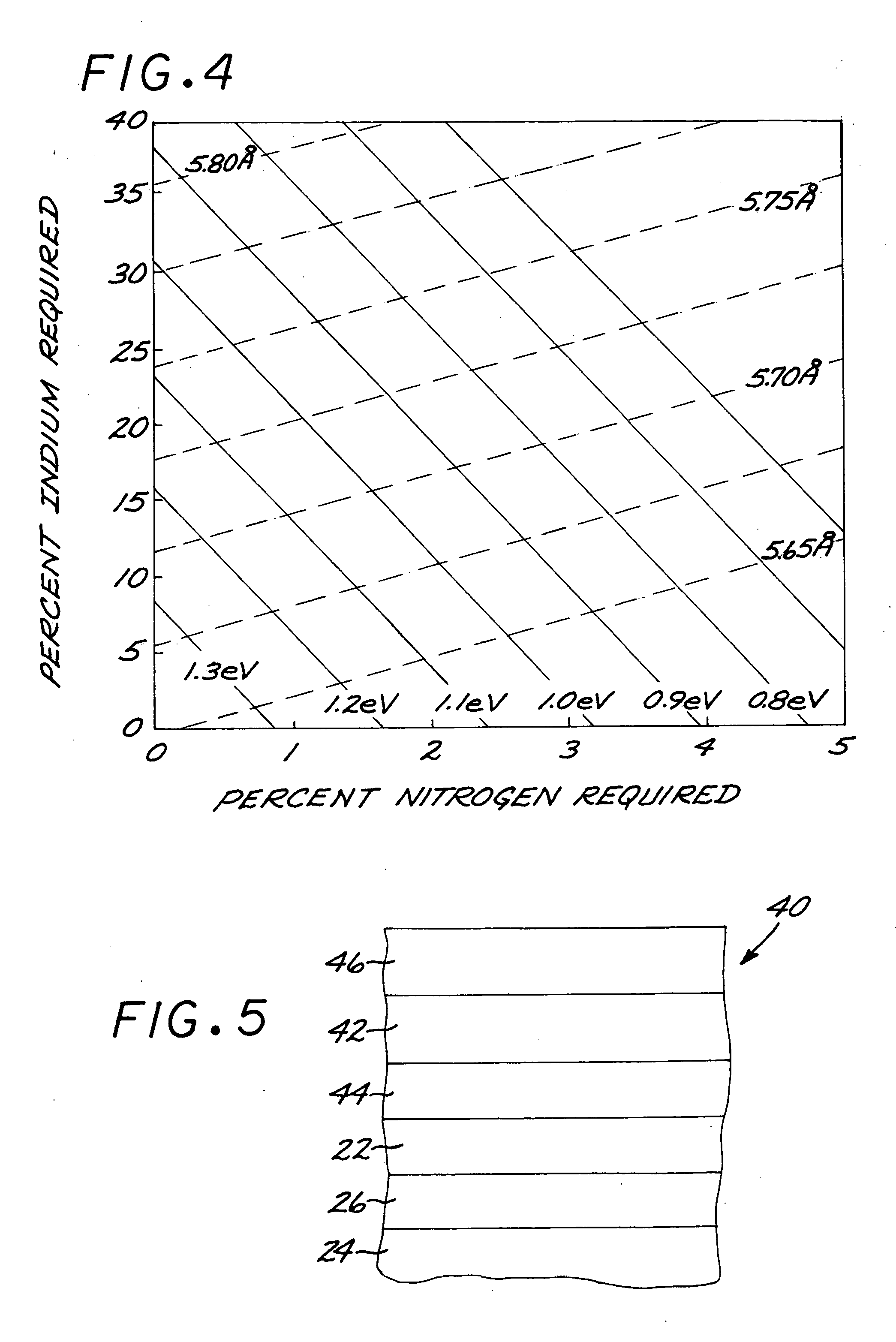

Multijunction solar cell having a lattice mismatched GrIII-GrV-X layer and a composition-graded buffer layer

ActiveUS20050274409A1Improve performancePV power plantsPhotovoltaic energy generationLattice mismatchNitrogen

A multijunction solar cell includes a first photoactive subcell layer having a first-subcell lattice parameter and a composition including (a) at least one Group III element, at least one Group V element other than (nitrogen, phosphorus), and (nitrogen, phosphorus), or (b) a material selected from the group including GaInAsBi, GaInAsSb, GaInAsP, ZnGeAs2, or BGaInAs. The multijunction solar cell also has a substrate having a substrate lattice parameter different from the first-subcell lattice parameter, and a composition-graded buffer layer between the first photoactive subcell layer and the substrate and having a buffer-layer lattice parameter graded between the first-subcell lattice parameter and the substrate lattice parameter. The substrate may be a second photoactive subcell layer having a second-subcell lattice parameter different from the first-subcell lattice parameter and sensitive to a second-photoactive-subcell-layer wavelength, and the buffer layer is transparent to the second-photoactive-subcell-layer wavelength.

Owner:THE BOEING CO

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com