Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3814 results about "Shallow trench isolation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Shallow trench isolation (STI), also known as box isolation technique, is an integrated circuit feature which prevents electric current leakage between adjacent semiconductor device components. STI is generally used on CMOS process technology nodes of 250 nanometers and smaller. Older CMOS technologies and non-MOS technologies commonly use isolation based on LOCOS.

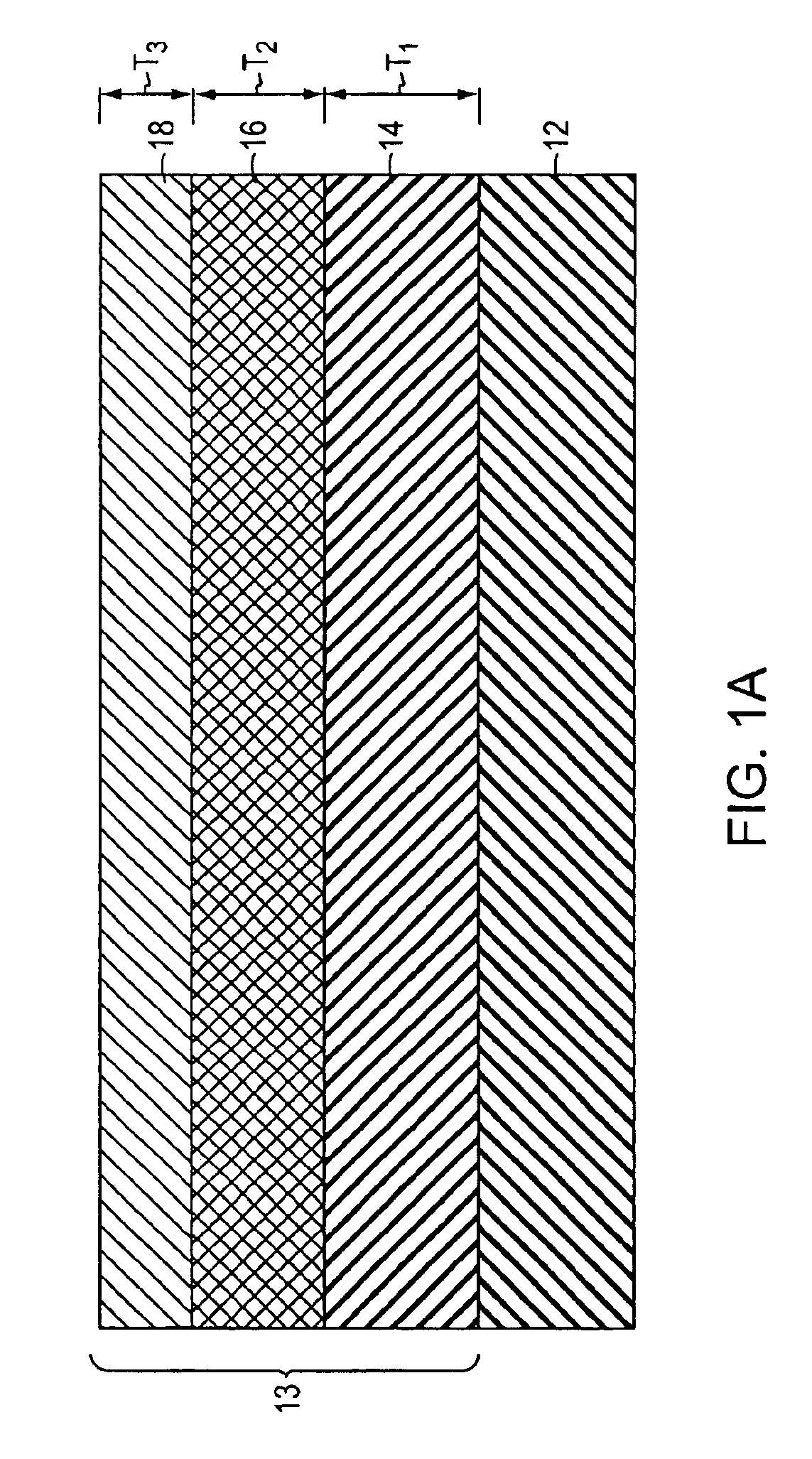

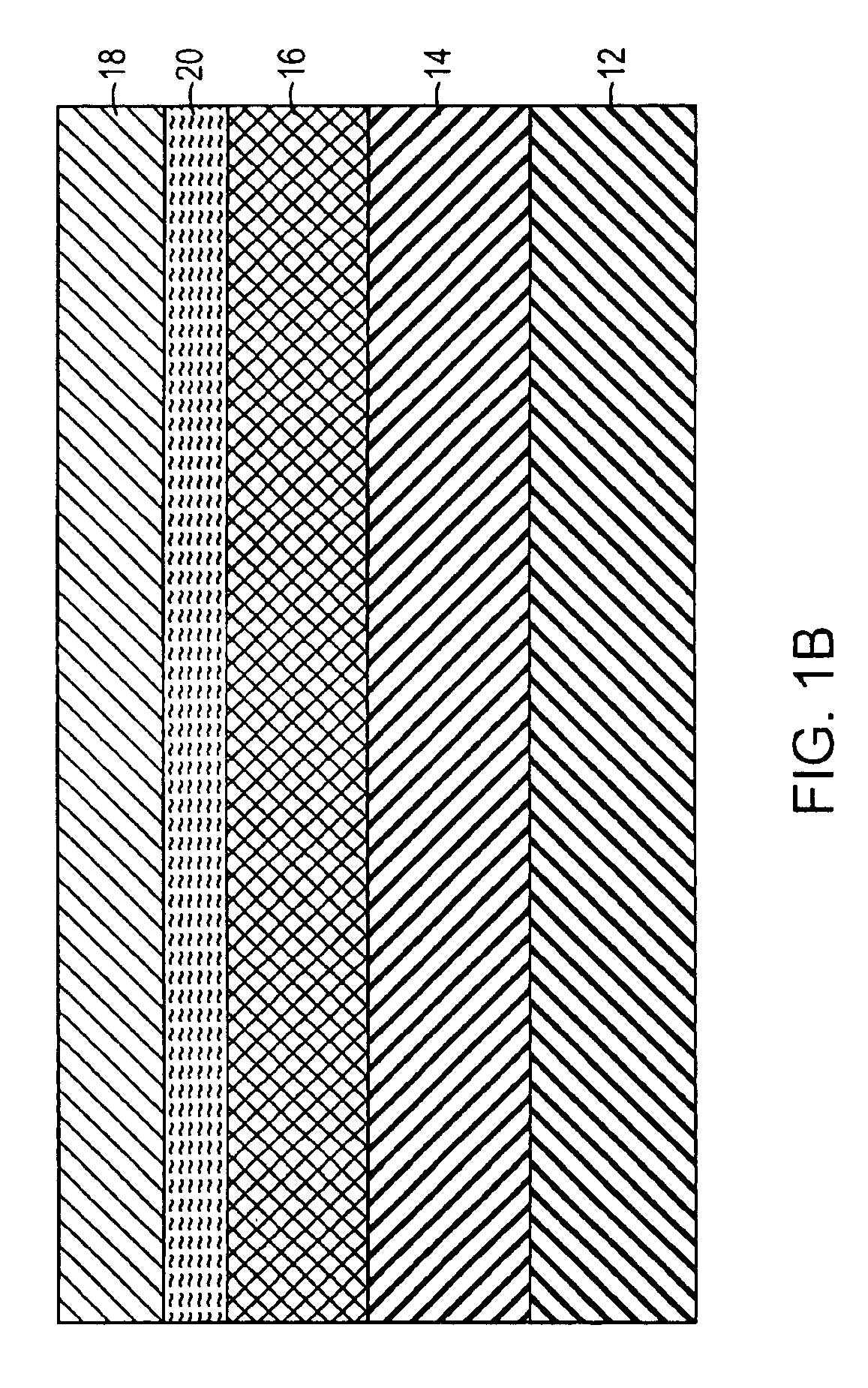

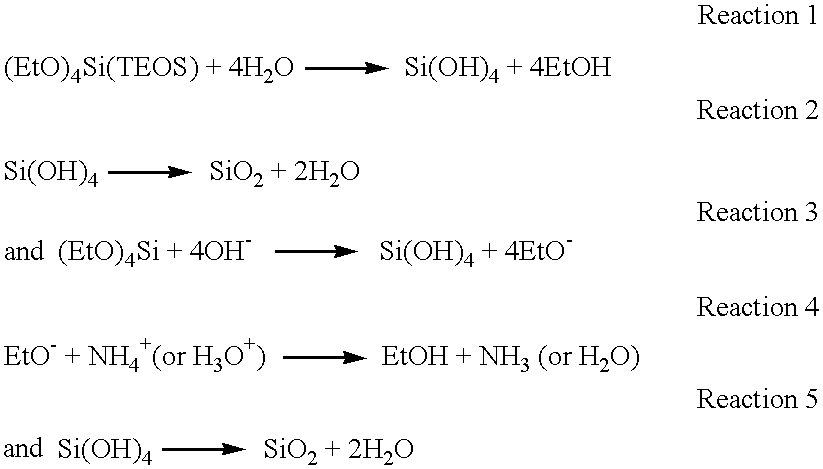

Formation of a liquid-like silica layer by reaction of an organosilicon compound and a hydroxyl forming compound

InactiveUS6413583B1Semiconductor/solid-state device detailsSolid-state devicesSilicon oxideSilicon dioxide

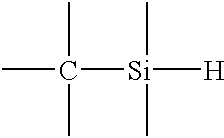

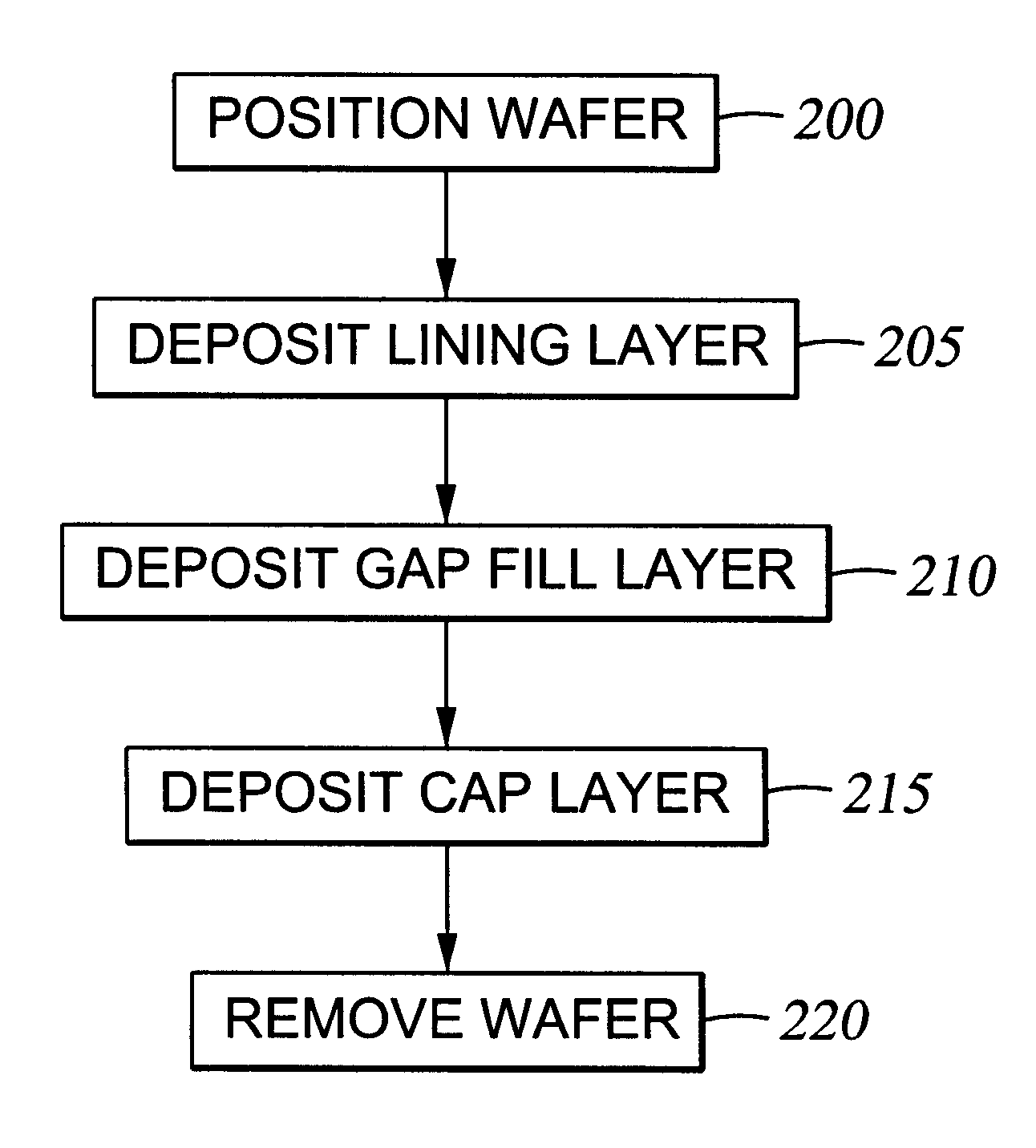

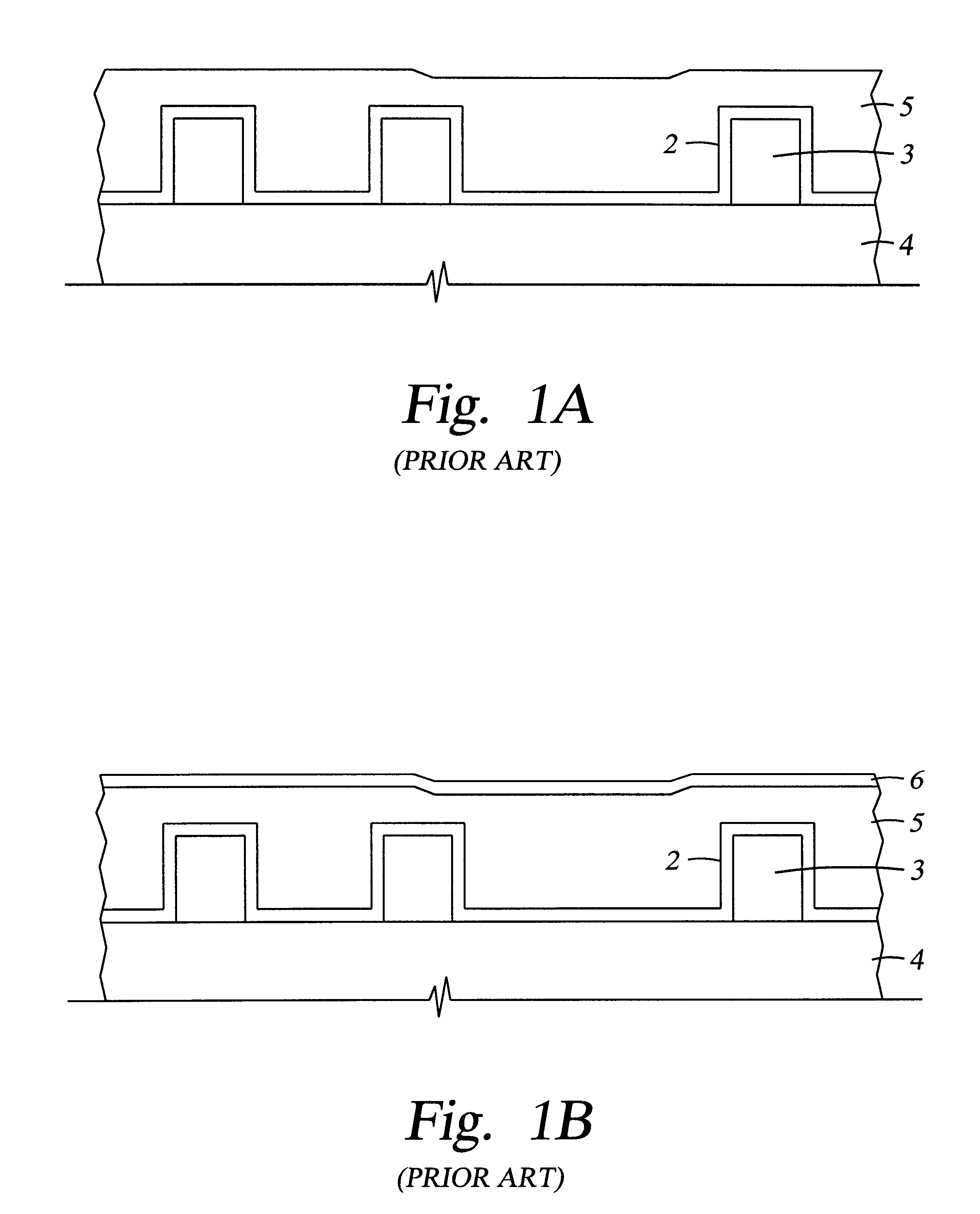

A method for depositing silicon oxide layers having a low dielectric constant by reaction of an organosilicon compound and a hydroxyl forming compound at a substrate temperature less than about 400° C. The low dielectric constant films contain residual carbon and are useful for gap fill layers, pre-metal dielectric layers, inter-metal dielectric layers, and shallow trench isolation dielectric layers in sub-micron devices. The hydroxyl compound can be prepared prior to deposition from water or an organic compound. The silicon oxide layers are preferably deposited at a substrate temperature less than about 40° C. onto a liner layer produced from the organosilicon compound to provide gap fill layers having a dielectric constant less than about 3.0.

Owner:APPLIED MATERIALS INC

Semiconductor structure and device and methods of forming same using selective epitaxial process

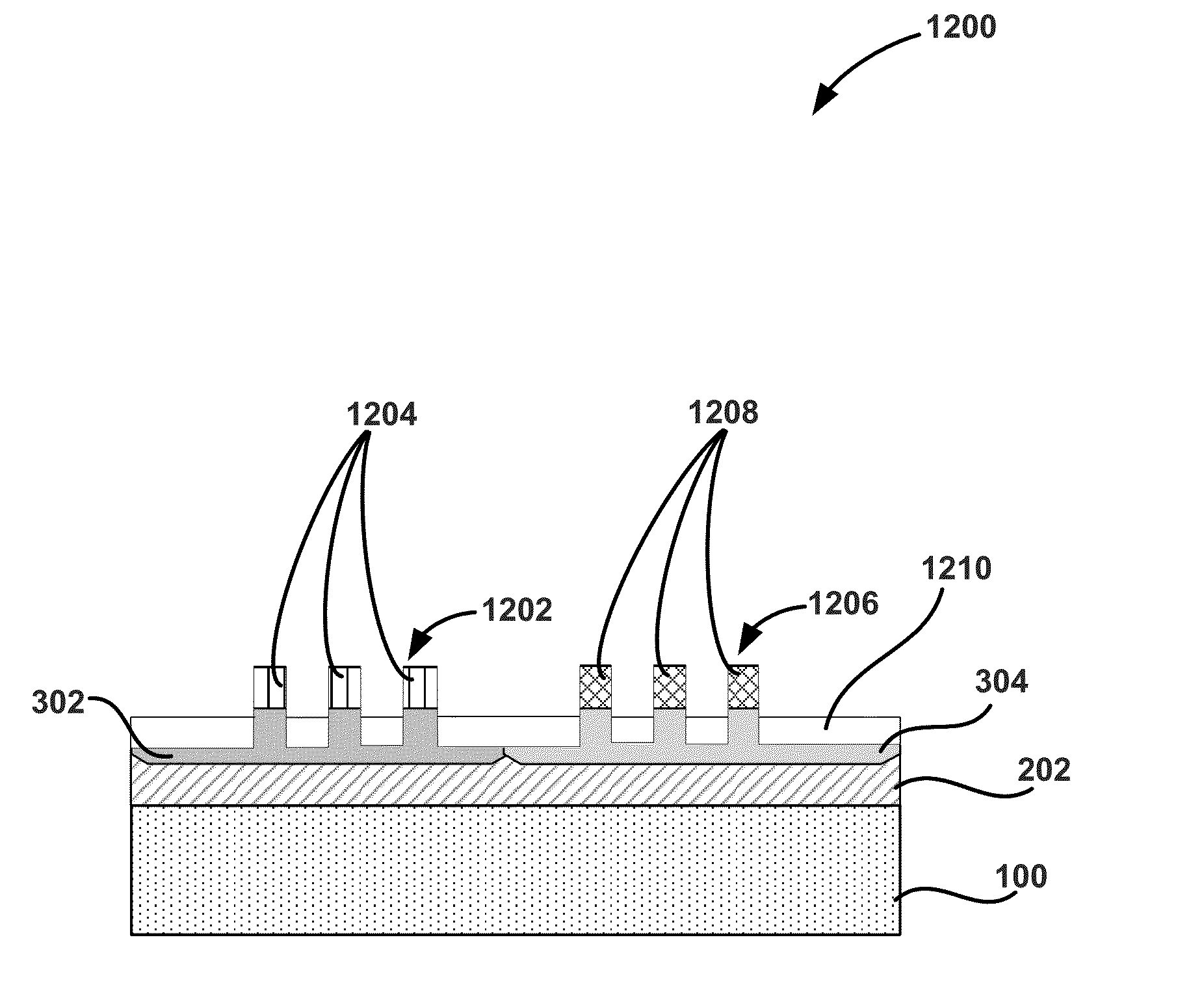

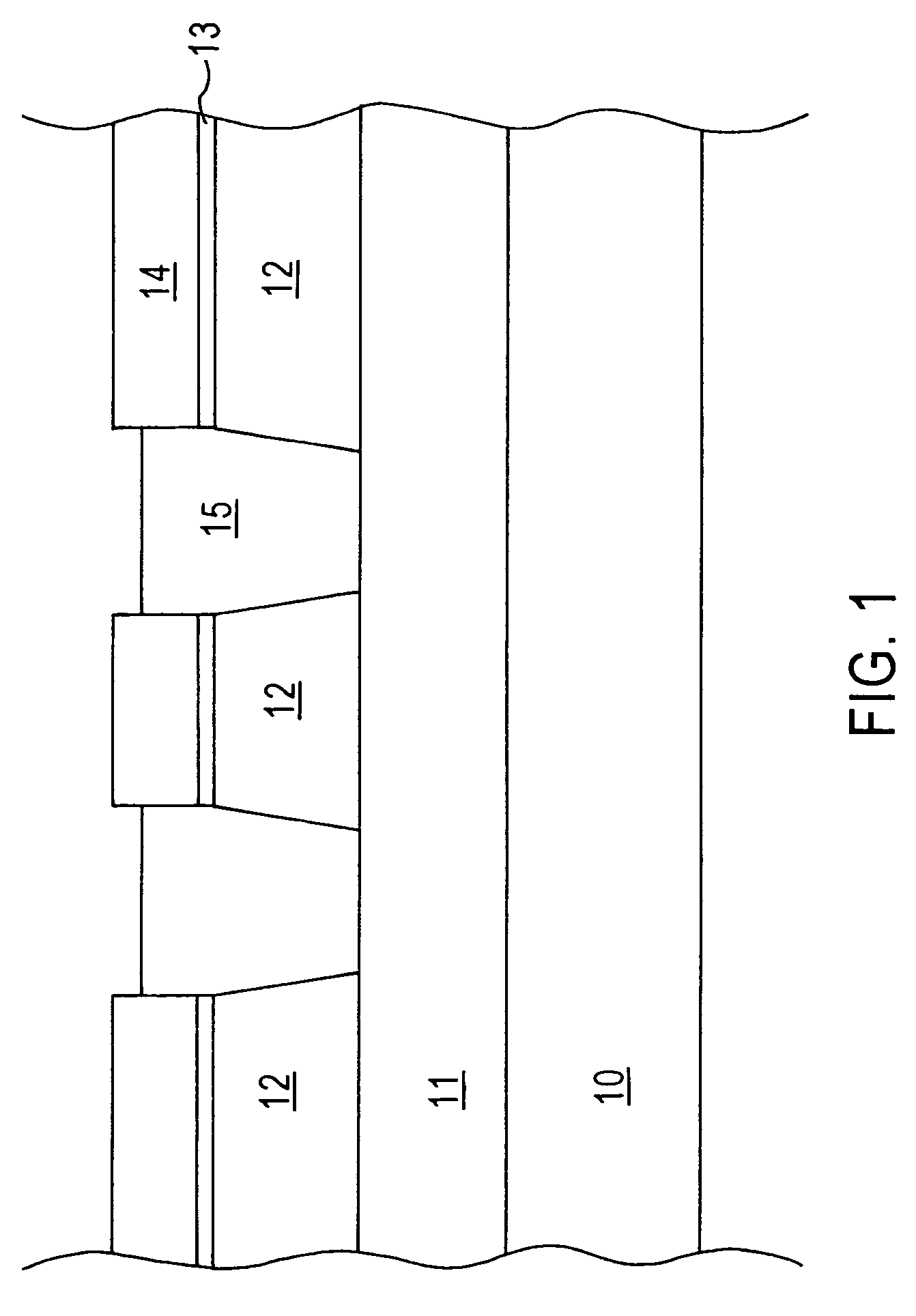

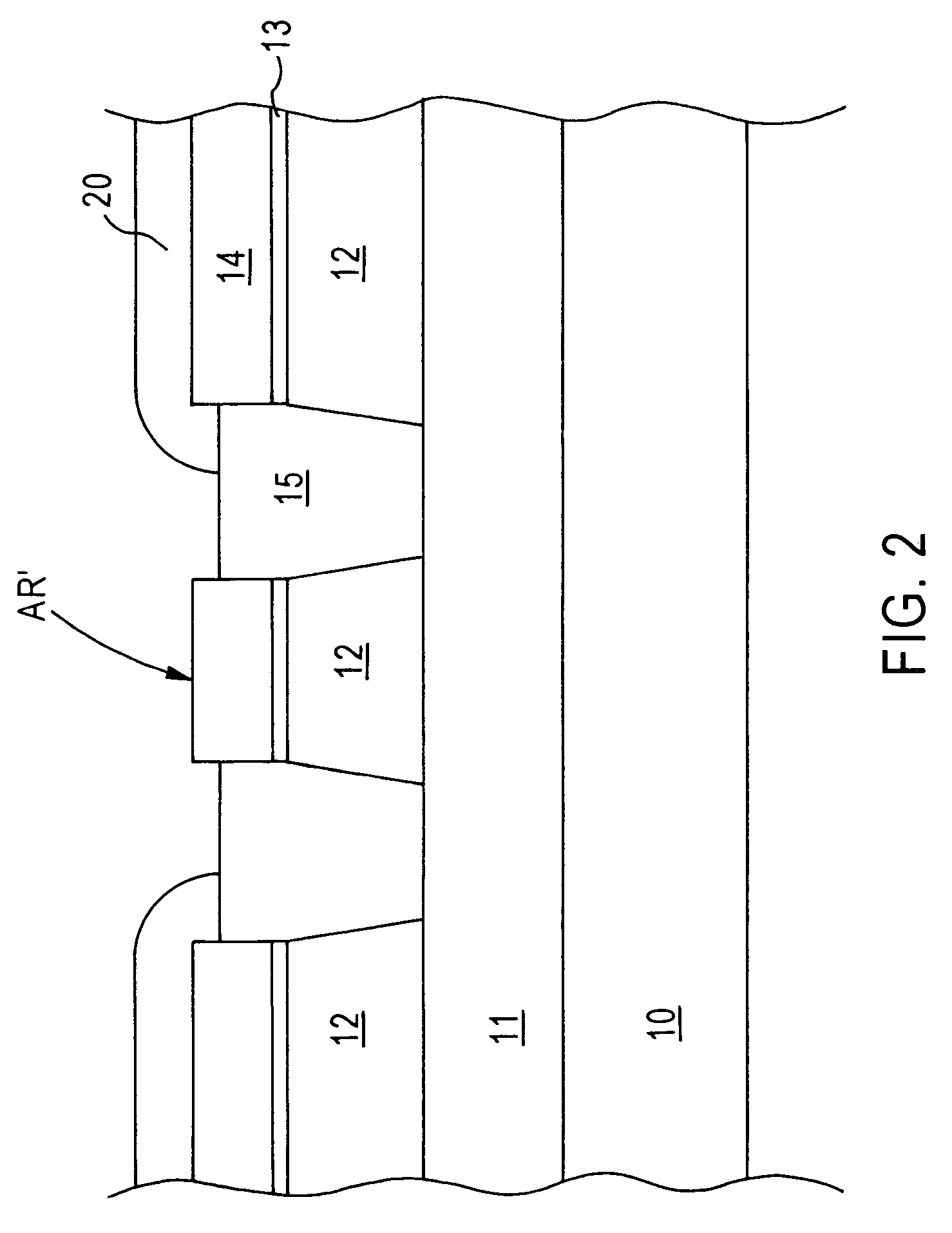

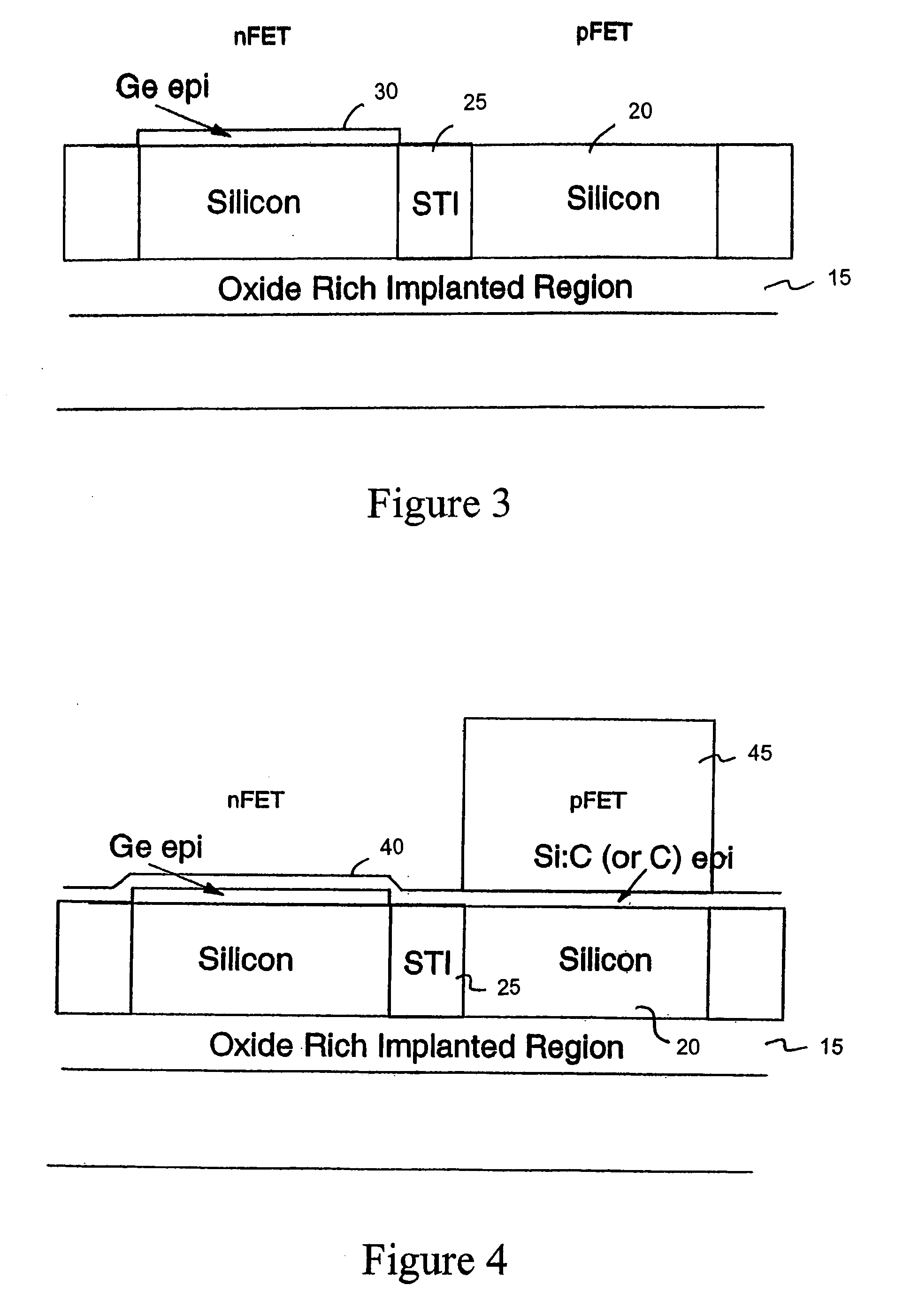

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both n-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both re-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

Semiconductor structure and device and methods of forming same using selective epitaxial process

Owner:ASM IP HLDG BV

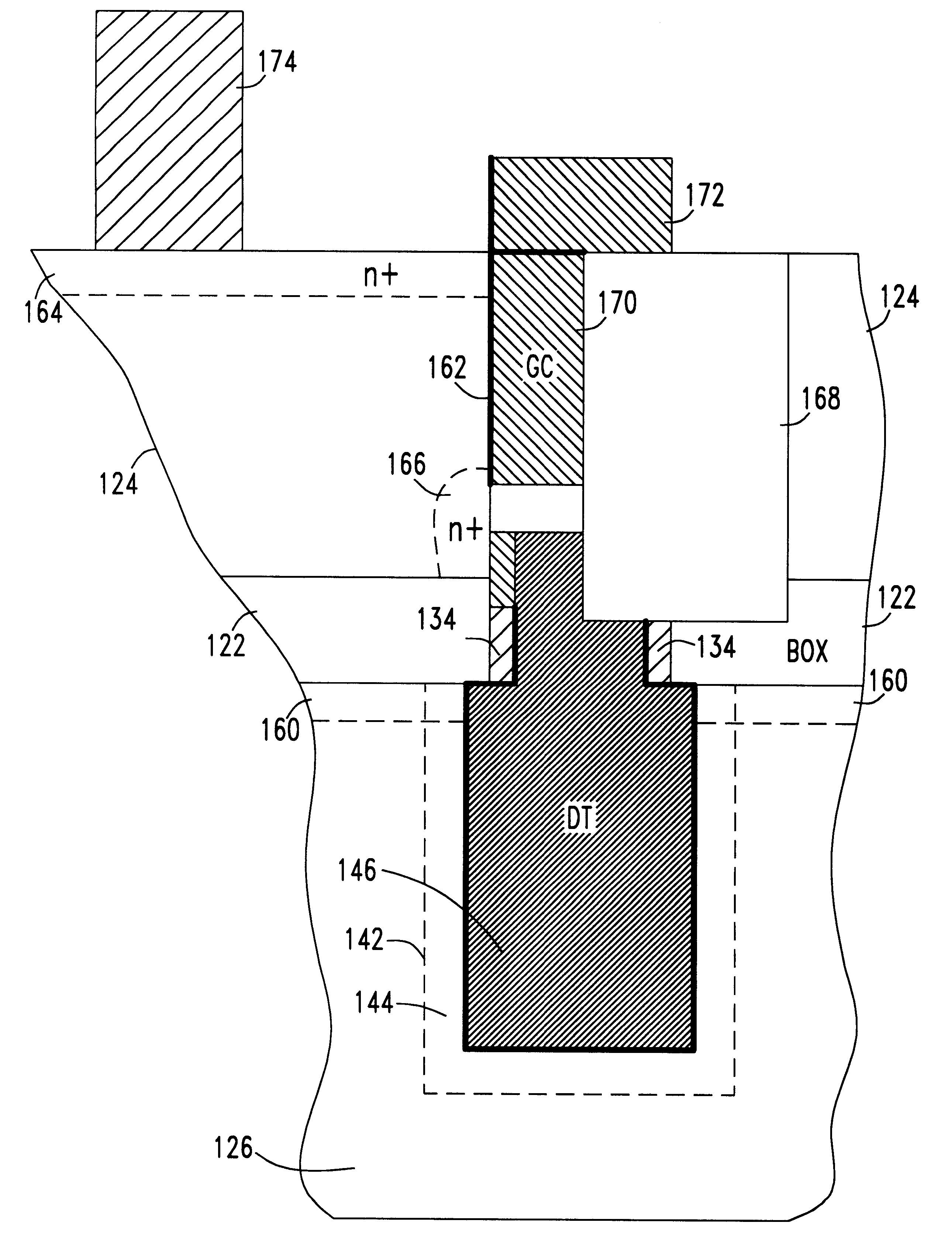

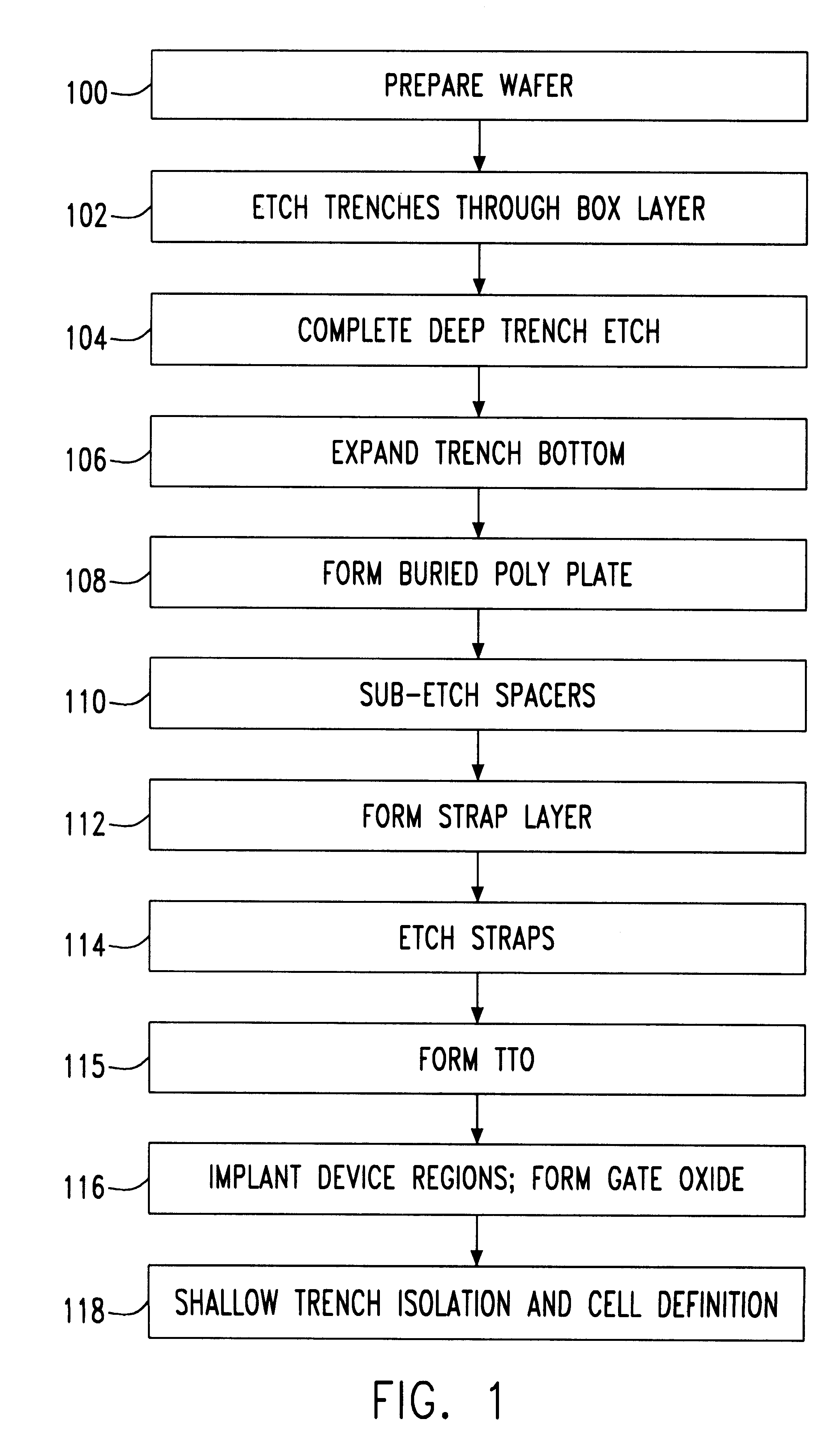

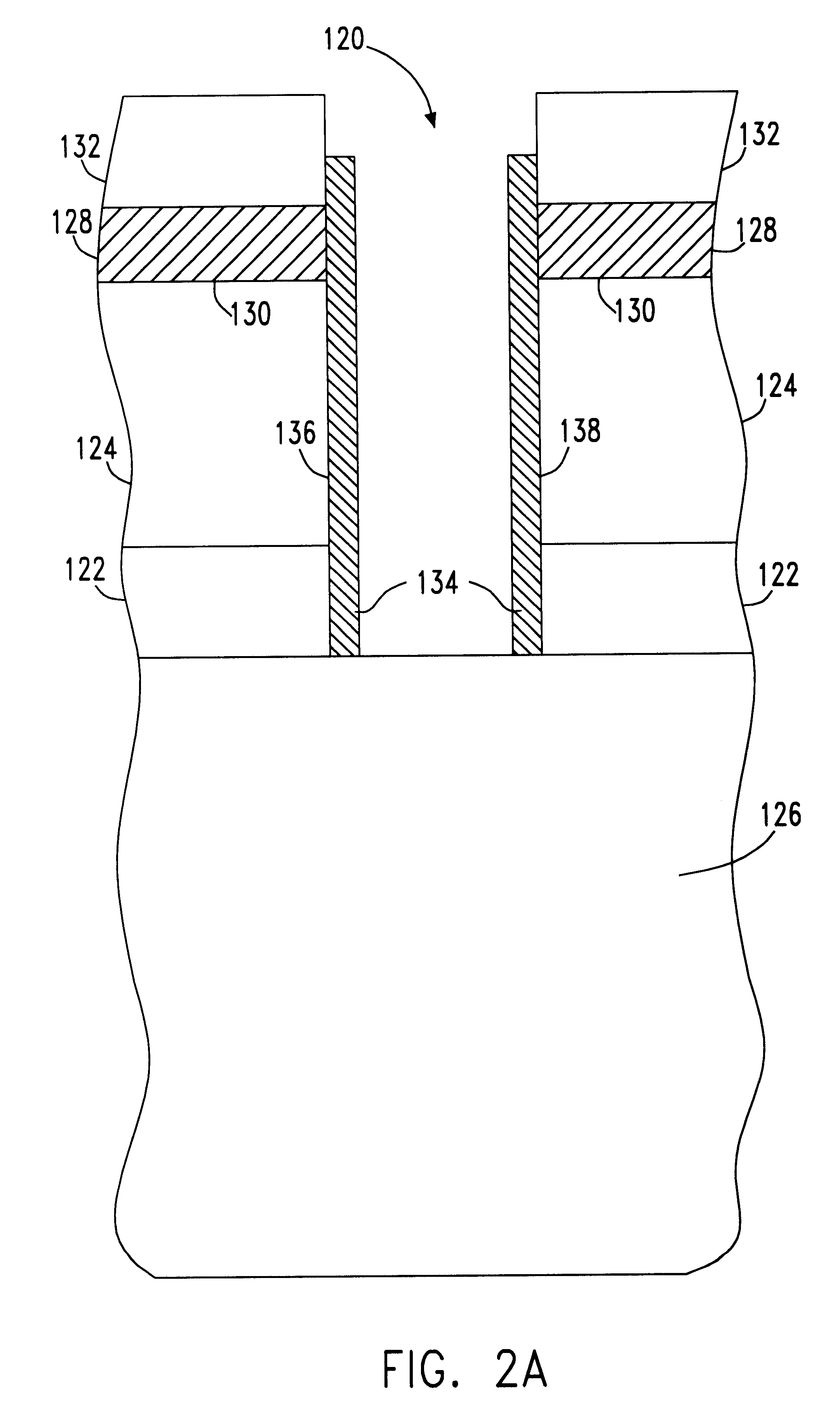

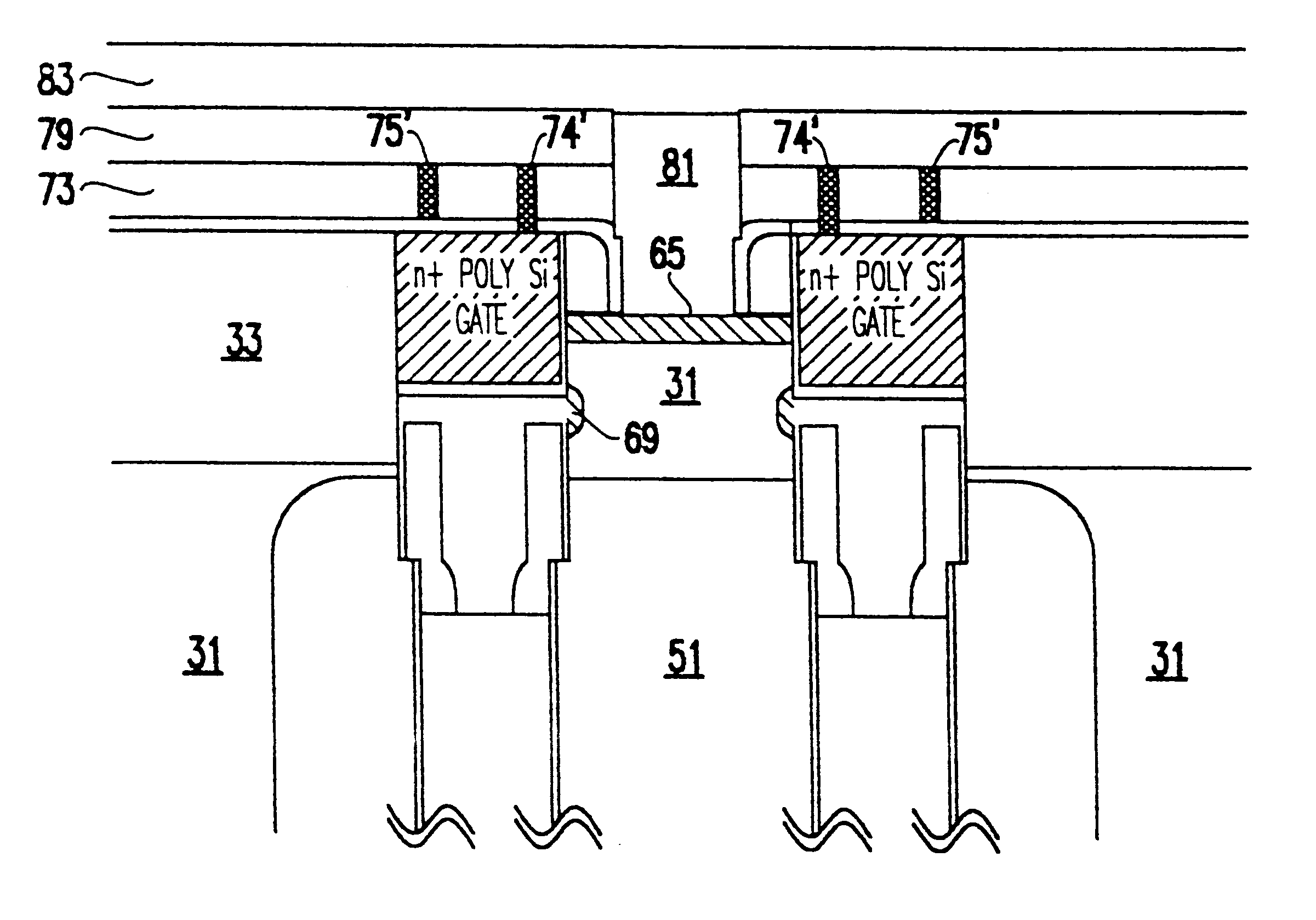

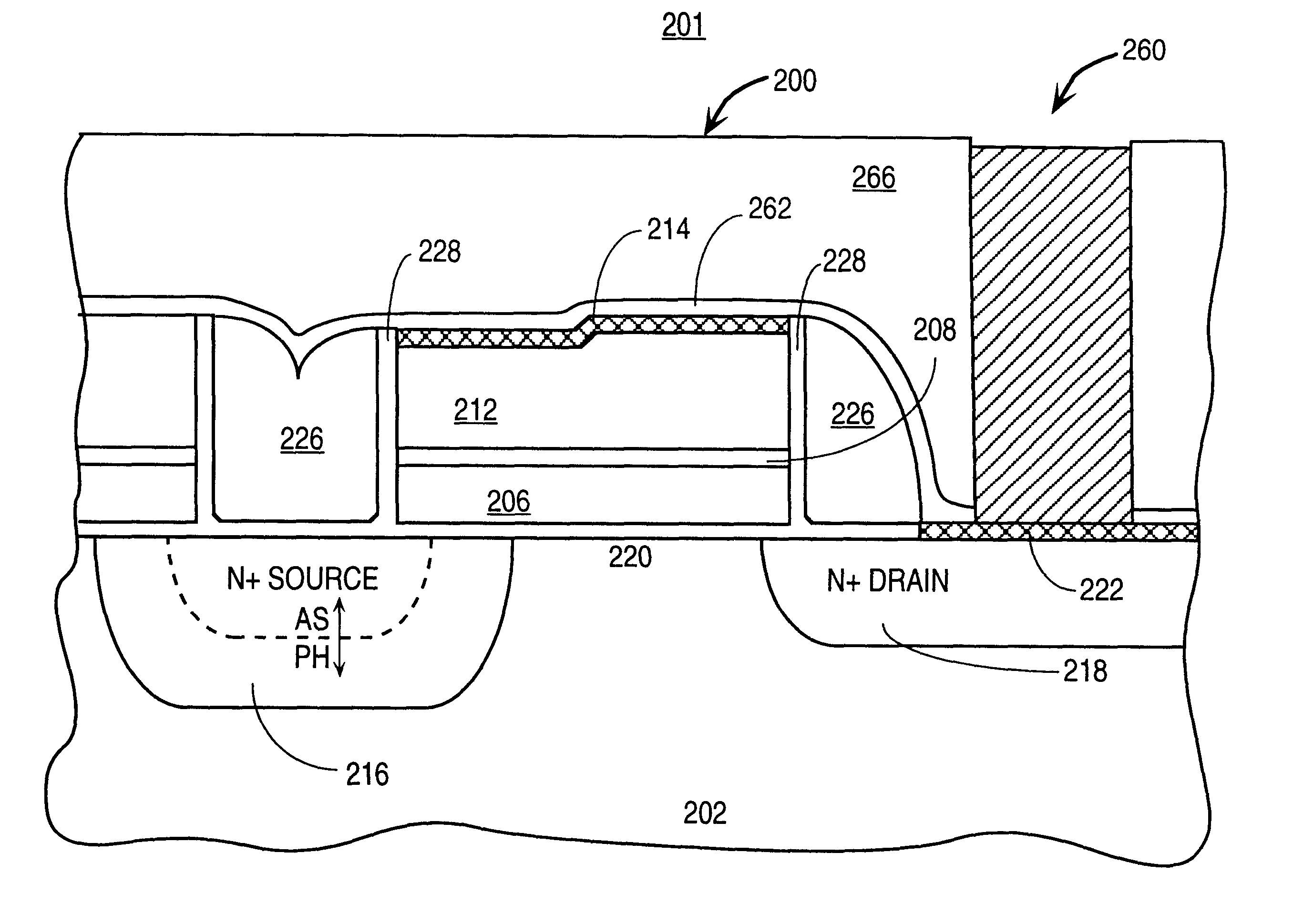

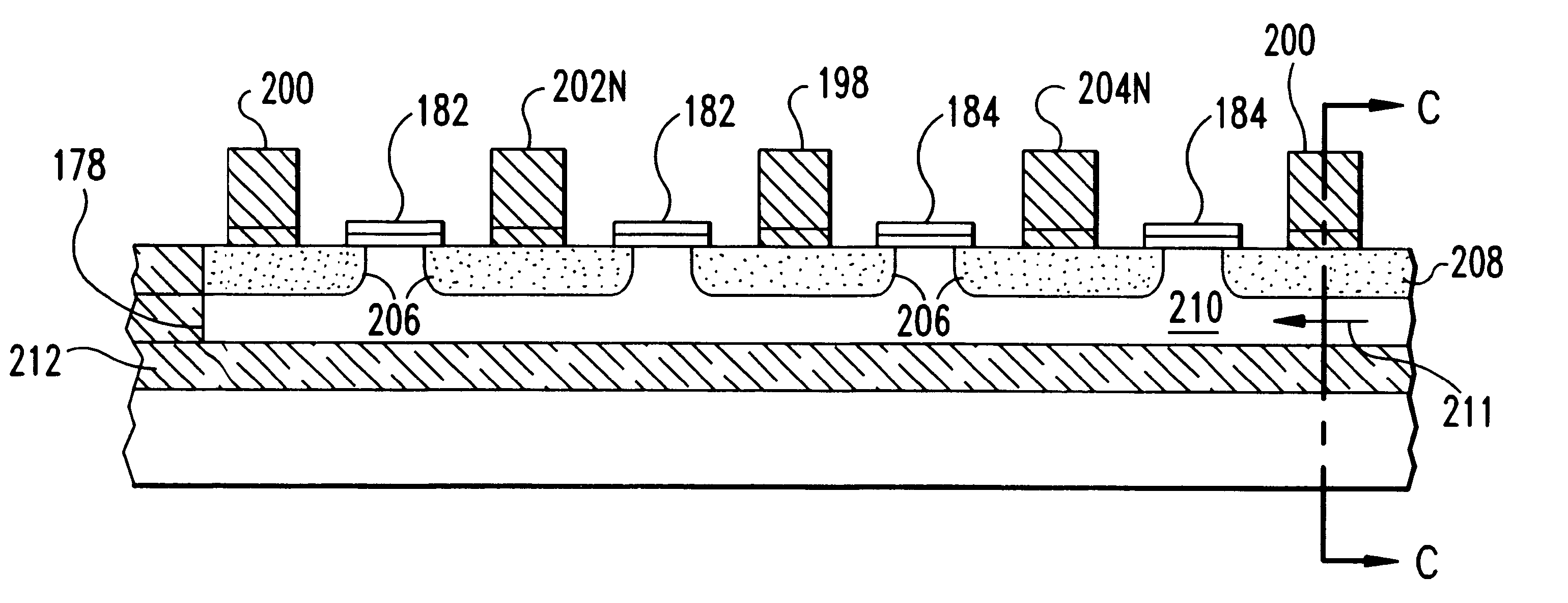

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

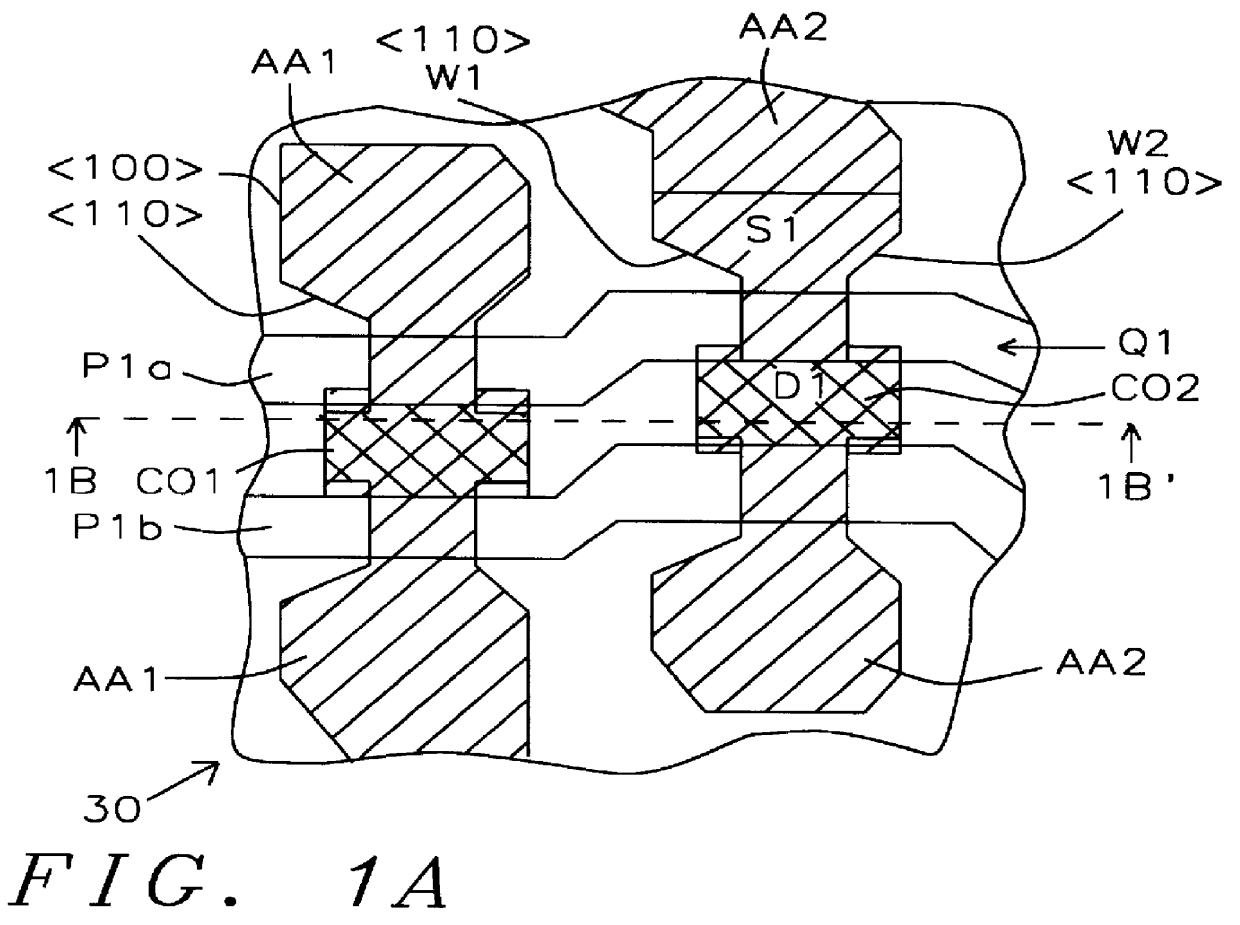

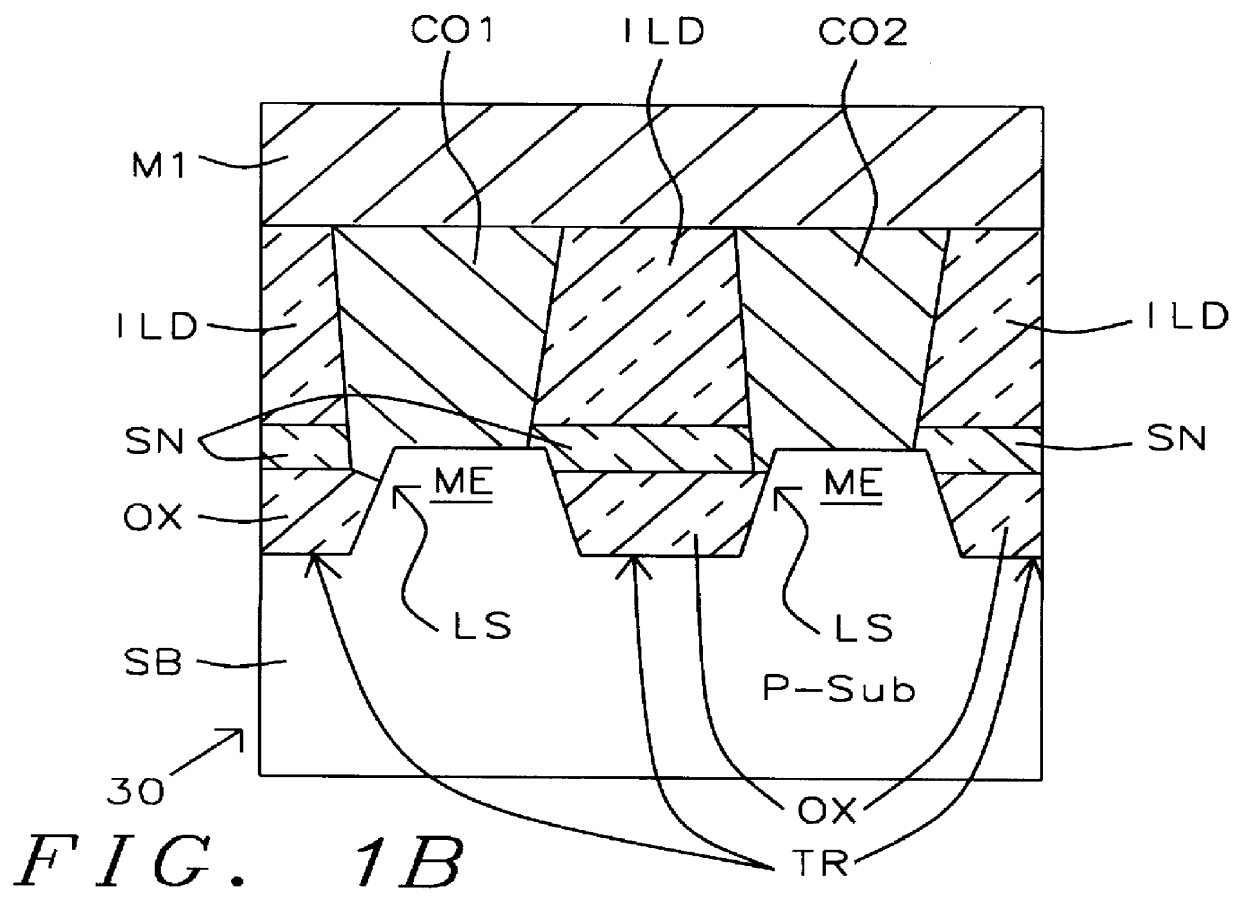

SRAM layout for relaxing mechanical stress in shallow trench isolation technology and method of manufacture thereof

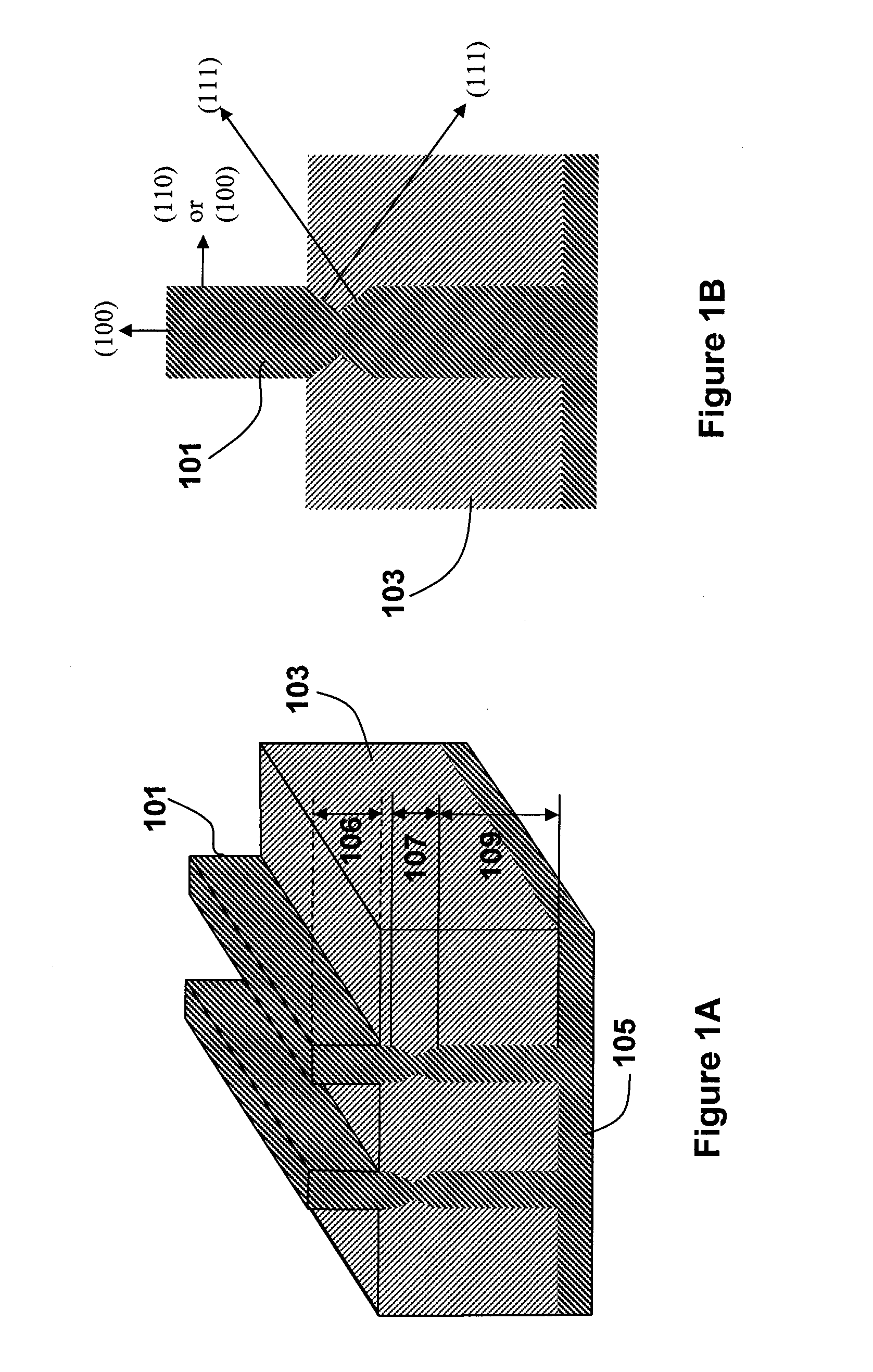

InactiveUS6117722ARelieve pressureSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorCrystal plane

An SRAM device has STI regions separated by mesas and doped regions including source / drain regions, active areas, wordline conductors and contacts in a semiconductor substrate is made with a source region has 90 DEG transitions in critical locations. Form a dielectric layer above the active areas. Form the wordline conductors above the active areas transverse to the active areas. The source and drain regions of a pass gate transistor are on the opposite sides of a wordline conductor. Form the sidewalls along the <100> crystal plane. Form the contacts extending down through to the dielectric layer to the mesas. Substrate stress is reduced because the large active area region formed in the substrate assures that the contacts are formed on the <100> surfaces of the mesas are in contact with the mesas formed on the substrate and that the <110> surfaces of the silicon of the mesas are shielded from the contacts.

Owner:TAIWAN SEMICON MFG CO LTD

Shallow trench isolation process

ActiveUS6960781B2Improve performanceTrench sidewallTransistorSolid-state devicesEngineeringTransistor

A structure including a transistor and a trench structure, with the trench structure inducing only a portion of the strain in a channel region of the transistor.

Owner:TAIWAN SEMICON MFG CO LTD

Double planar gated SOI MOSFET structure

A double gated silicon-on-insulator (SOI) MOSFET is fabricated by using a mandrel shallow trench isolation formation process, followed by a damascene gate. The double gated MOSFET features narrow diffusion lines defined sublithographically or lithographically and shrunk, damascene process defined by an STI-like mandrel process. The double gated SOI MOSFET increases current drive per layout width and provides low out conductance.

Owner:GLOBALFOUNDRIES INC

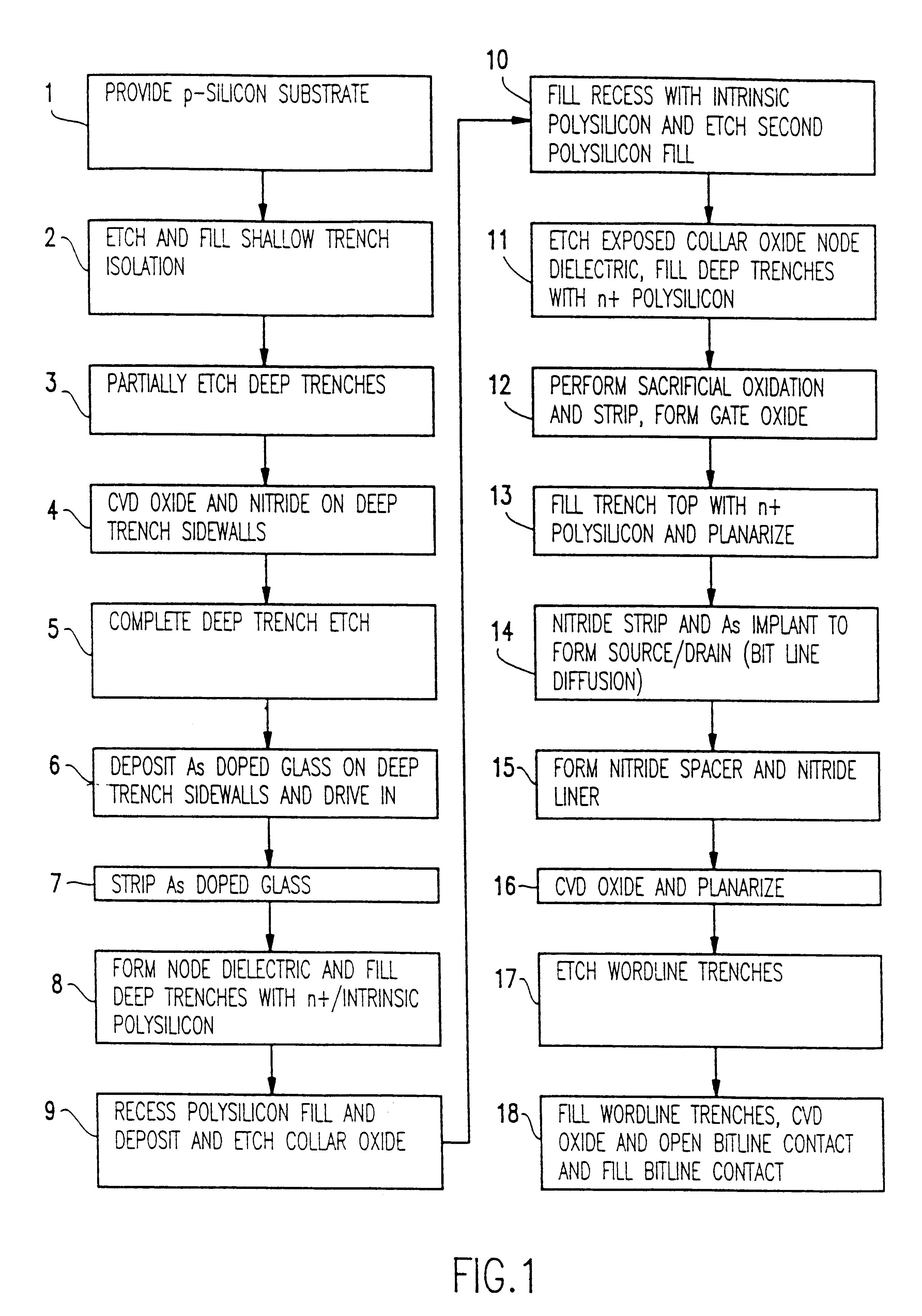

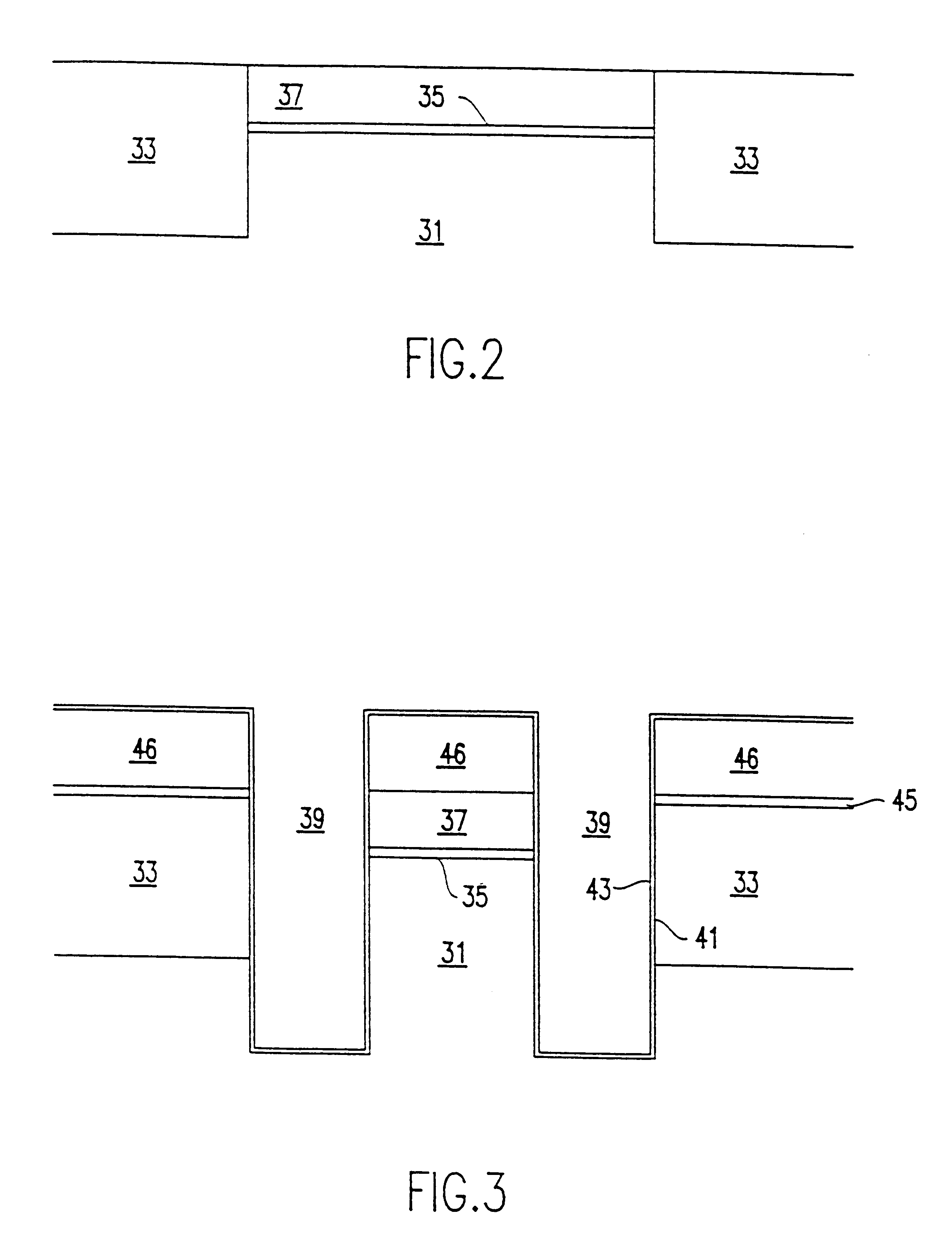

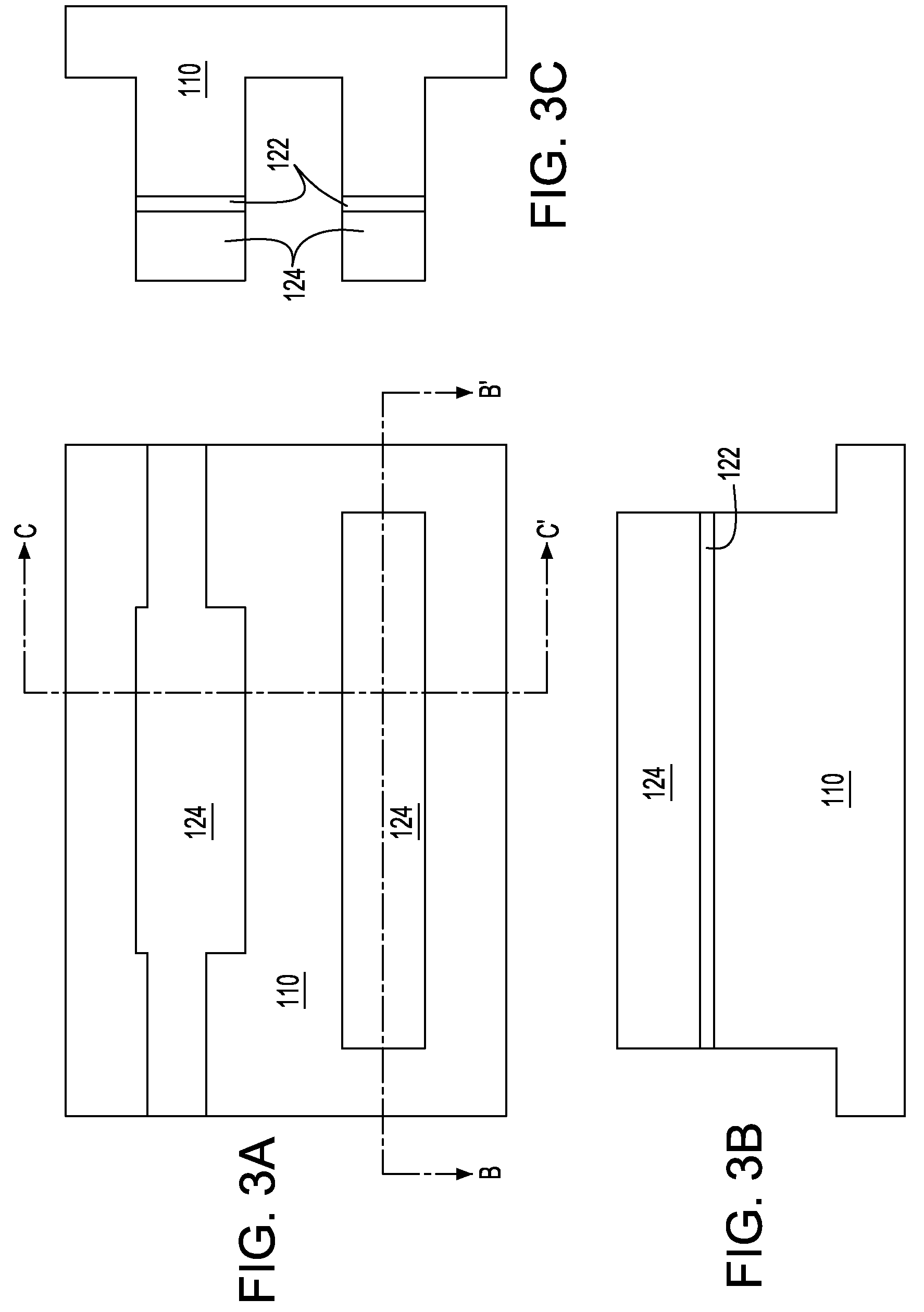

Trench storage dynamic random access memory cell with vertical transfer device

InactiveUS6225158B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringDeep trench

A trench storage dynamic random access memory cell with vertical transfer device can be formed in a wafer having prepared shallow trench isolation. Vertical transfer device is built as the deep trenches are formed. Using square printing to form shallow trench isolation and deep trenches, allows for scaling of the cell to very small dimensions.

Owner:GLOBALFOUNDRIES INC

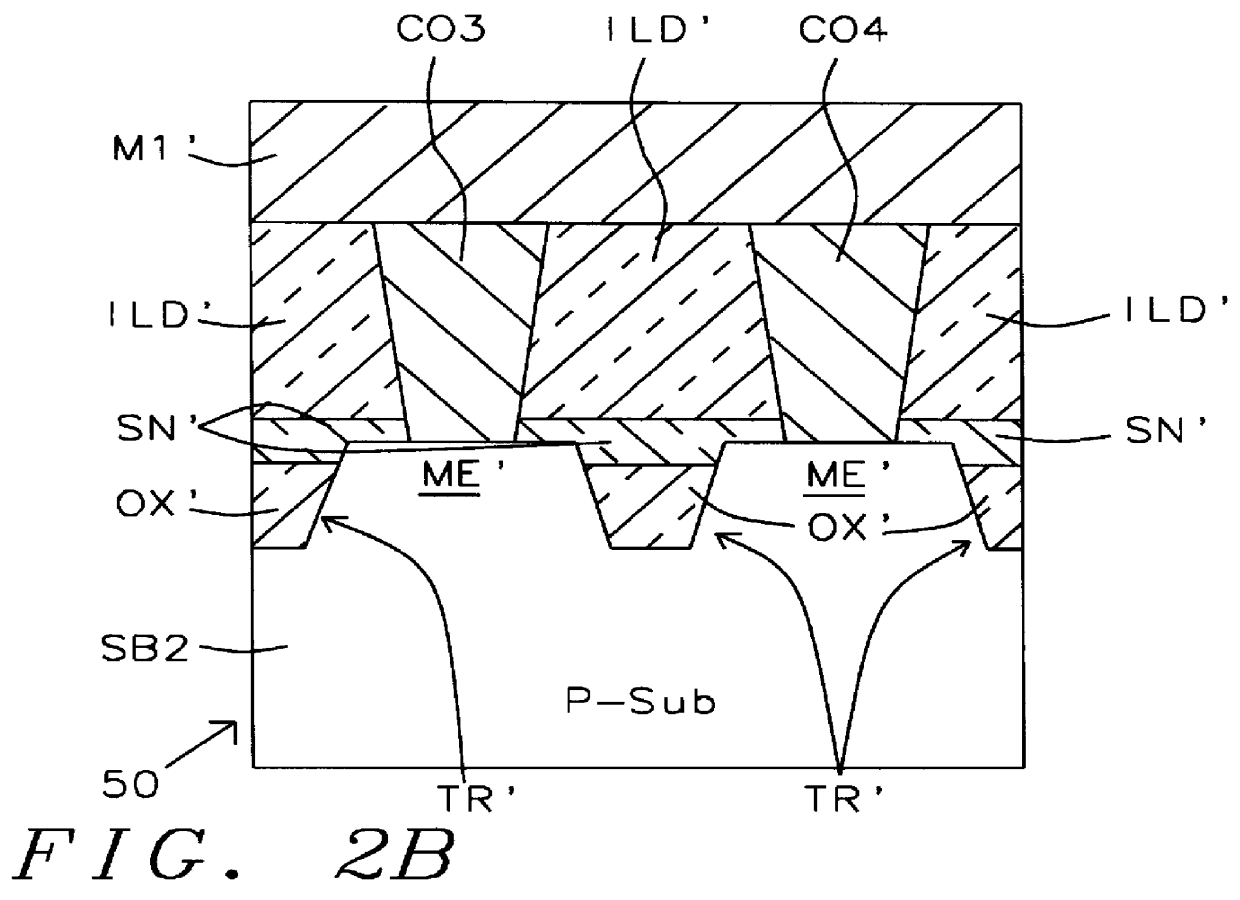

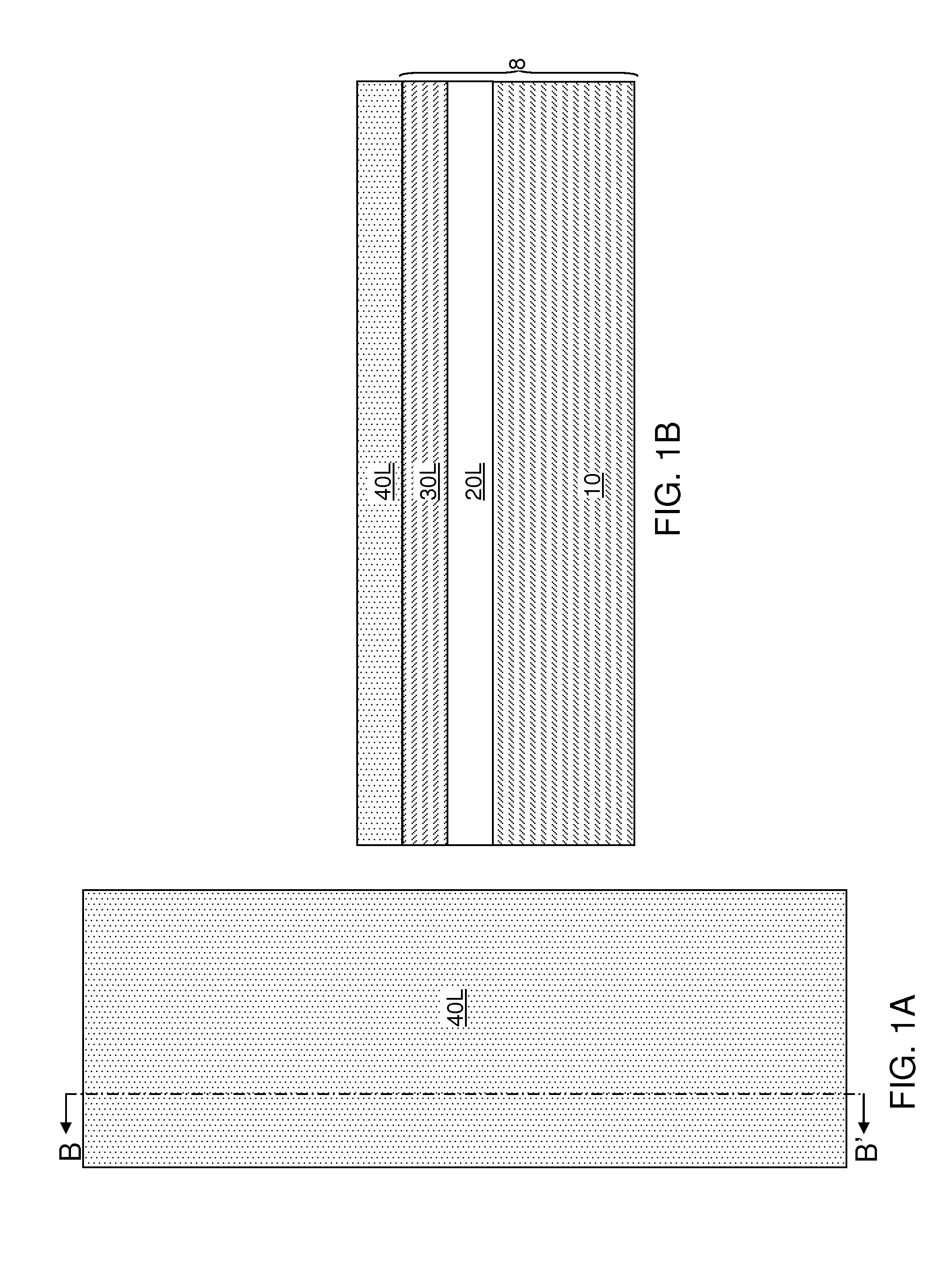

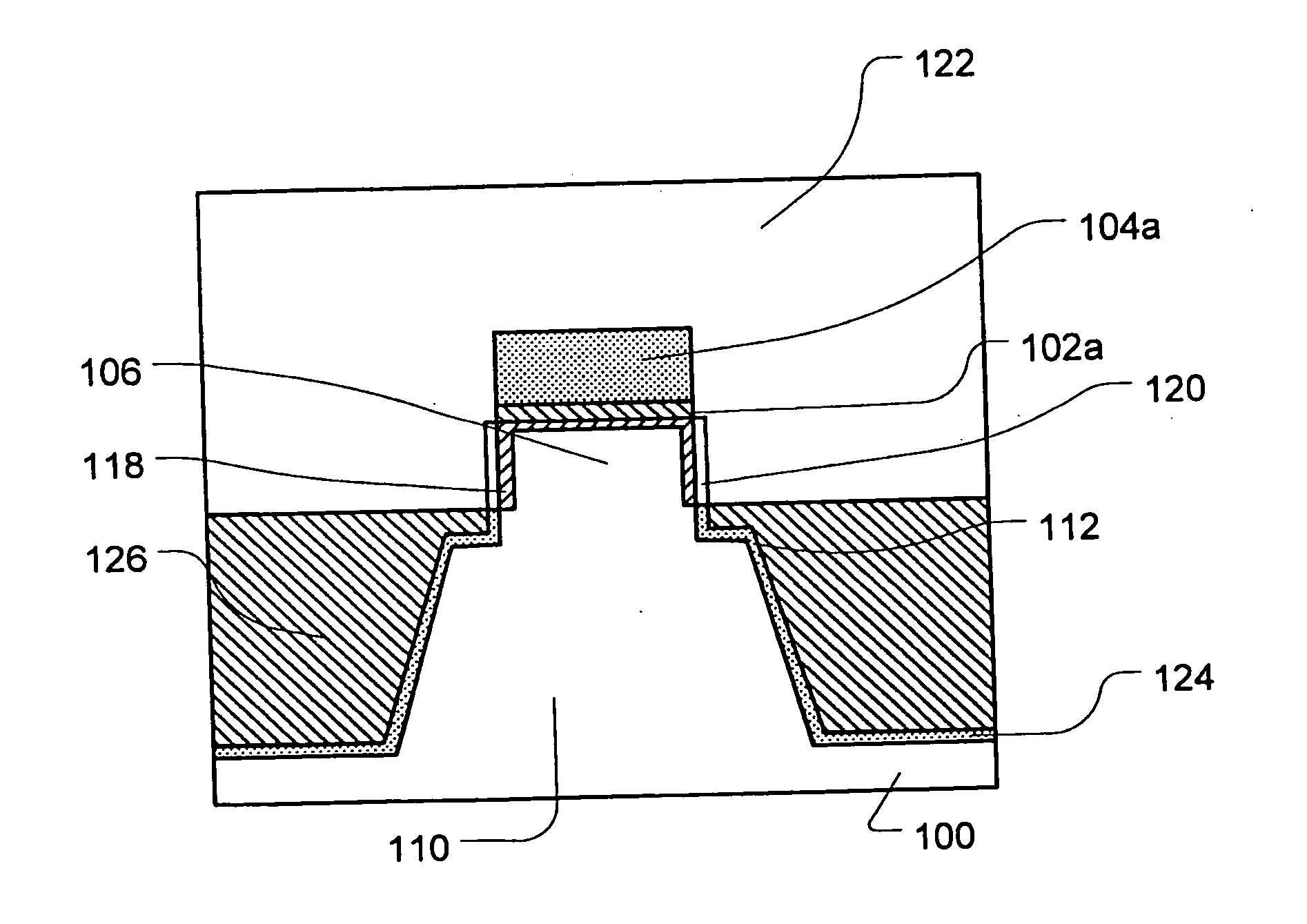

Dual-depth self-aligned isolation structure for a back gate electrode

InactiveUS20120256260A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Doped semiconductor back gate regions self-aligned to active regions are formed by first patterning a top semiconductor layer and a buried insulator layer to form stacks of a buried insulator portion and a semiconductor portion. Oxygen is implanted into an underlying semiconductor layer at an angle so that oxygen-implanted regions are formed in areas that are not shaded by the stack or masking structures thereupon. The oxygen implanted portions are converted into deep trench isolation structures that are self-aligned to sidewalls of the active regions, which are the semiconductor portions in the stacks. Dopant ions are implanted into the portions of the underlying semiconductor layer between the deep trench isolation structures to form doped semiconductor back gate regions. A shallow trench isolation structure is formed on the deep trench isolation structures and between the stacks.

Owner:IBM CORP

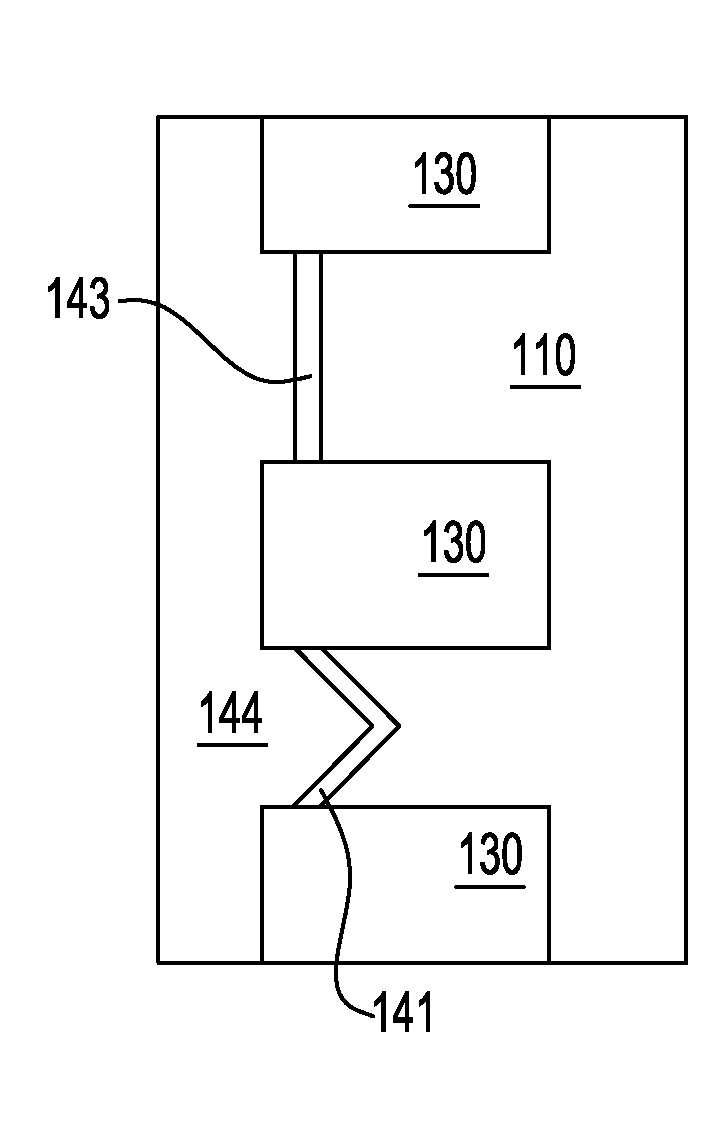

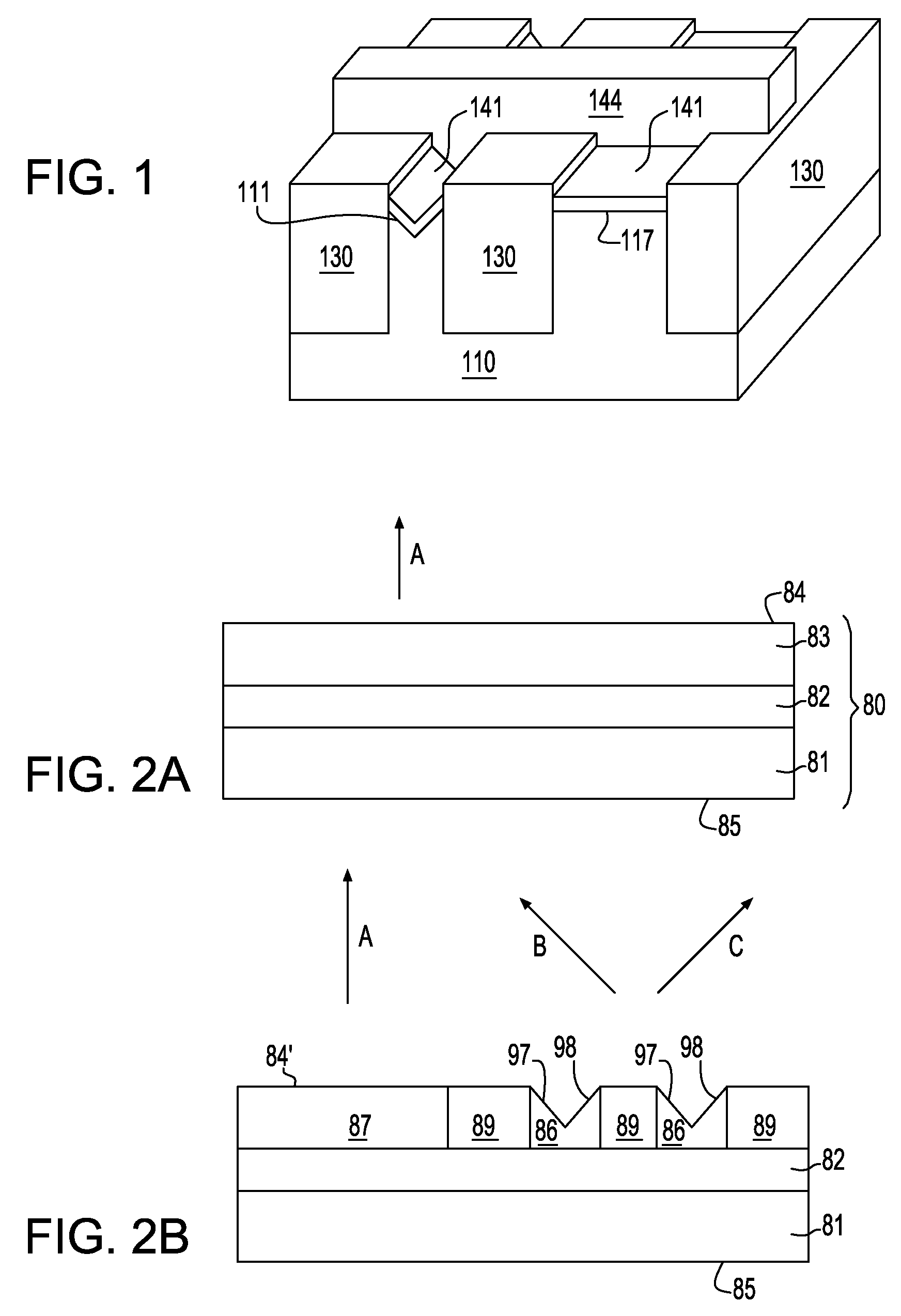

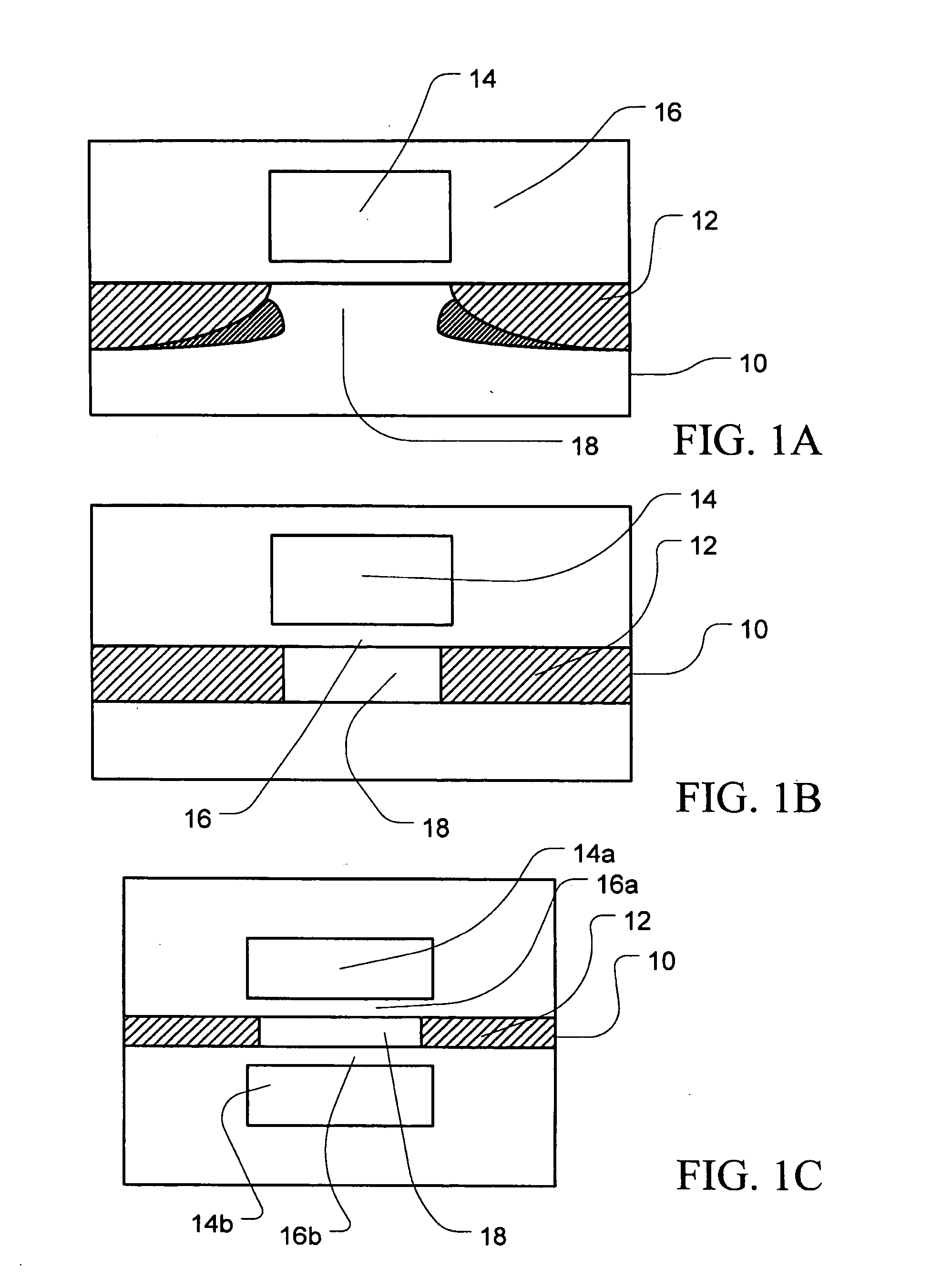

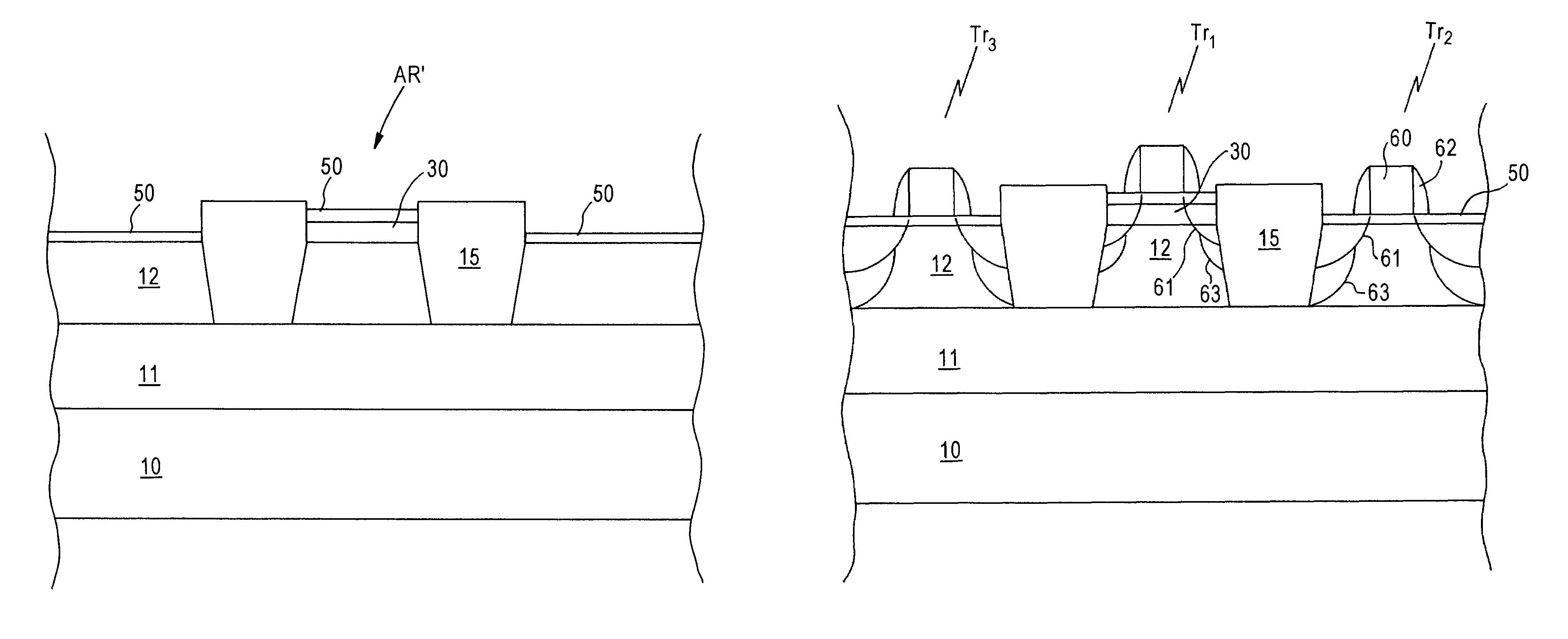

Enhanced mobility CMOS transistors with a v-shaped channel with self-alignment to shallow trench isolation

InactiveUS20080173906A1Improve performanceIncrease the on-currentTransistorSolid-state devicesCMOSCharge carrier mobility

The present invention provides structures and methods for a transistor formed on a V-shaped groove. The V-shaped groove contains two crystallographic facets joined by a ridge. The facets have different crystallographic orientations than what a semiconductor substrate normally provides such as the substrate orientation or orientations orthogonal to the substrate orientation. Unlike the prior art, the V-shaped groove is formed self-aligned to the shallow trench isolation, eliminating the need to precisely align the V-shaped grooves with lithographic means. The electrical properties of the new facets, specifically, the enhanced carrier mobility, are utilized to enhance the performance of transistors. In a transistor with a channel on the facets that are joined to form a V-shaped profile, the current flows in the direction of the ridge joining the facets avoiding any inflection in the direction of the current.

Owner:GLOBALFOUNDRIES INC

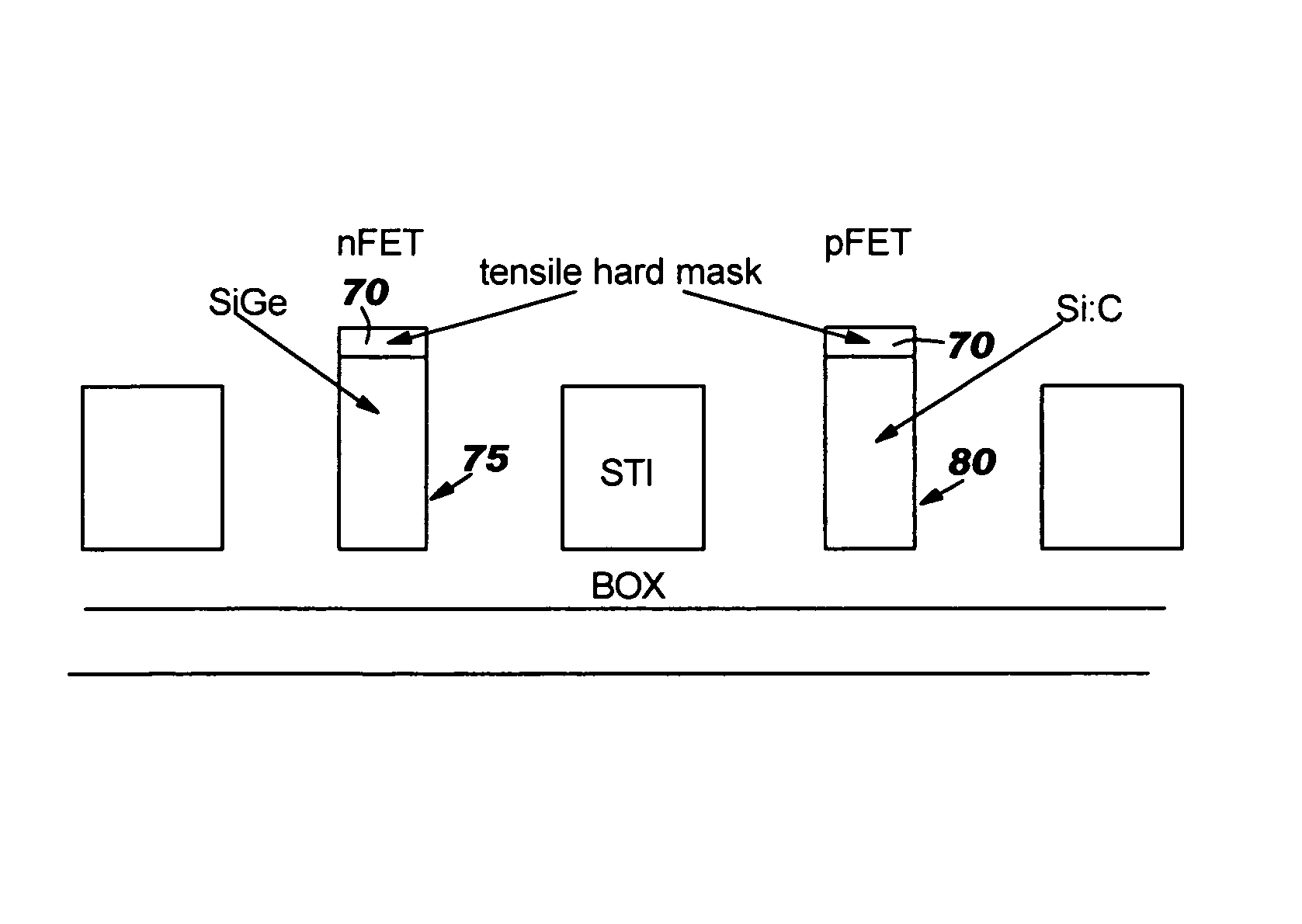

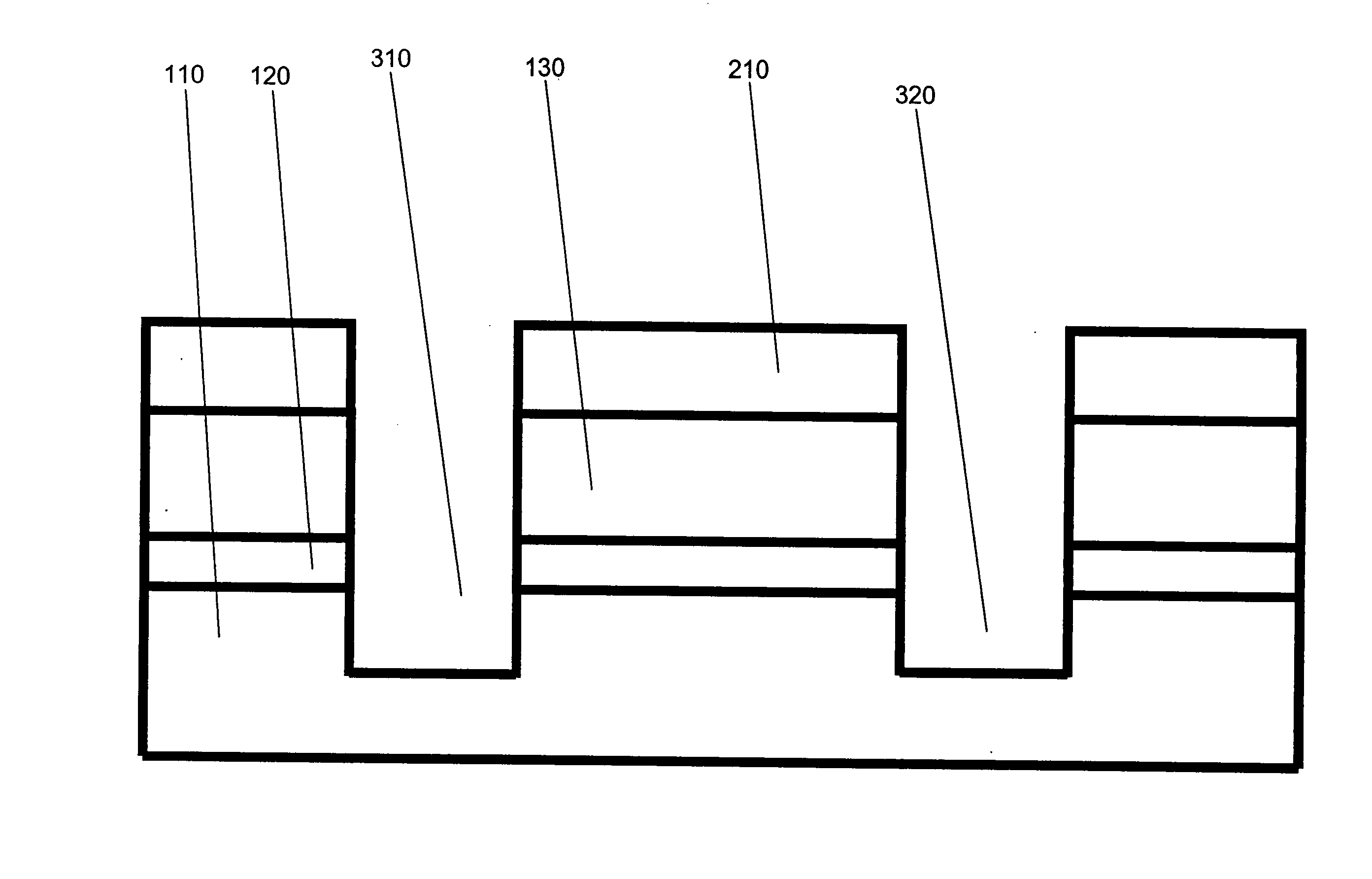

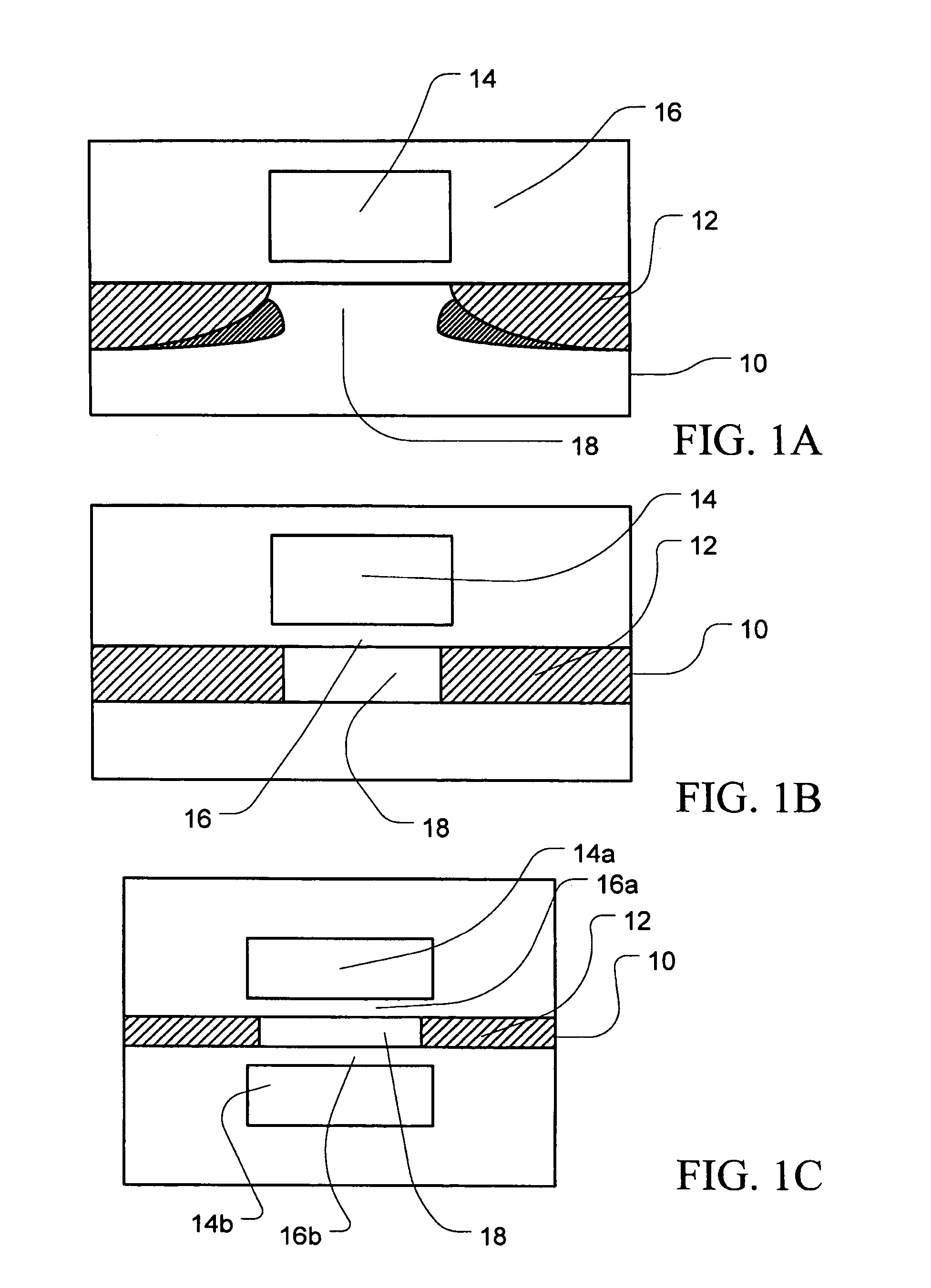

Strained finFETs and method of manufacture

A semiconductor structure and method of manufacturing is provided. The method of manufacturing includes forming shallow trench isolation (STI) in a substrate and providing a first material and a second material on the substrate. The first material and the second material form a first island and second island at an pFET region and a nFET region, respectively. A tensile hard mask is formed on the first and the second island layer prior to forming finFETs. An Si epitaxial layer is grown on the sidewalls of the finFETs with the hard mask, now a capping layer which is under tension, preventing lateral buckling of the nFET fin.

Owner:GLOBALFOUNDRIES U S INC

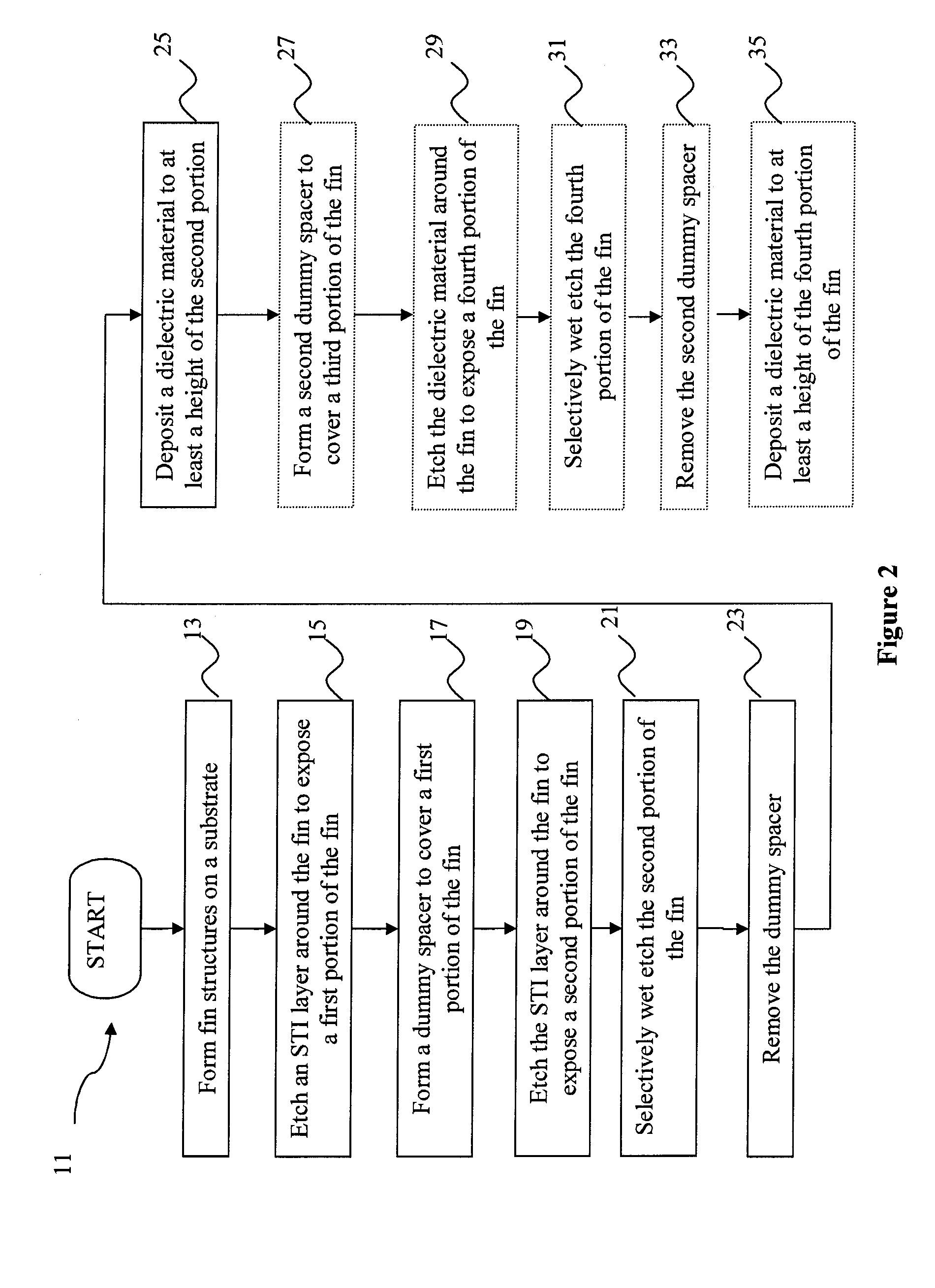

Transistor having notched fin structure and method of making the same

ActiveUS20120086053A1Semiconductor/solid-state device manufacturingSemiconductor devicesTetramethylammonium hydroxideEtching

A transistor includes a notched fin covered under a shallow trench isolation layer. One or more notch may be used, the size of which may vary along a lateral direction of the fin. In some embodiments, The notch is formed using anisotropic wet etching that is selective according to silicon orientation. Example wet etchants are tetramethylammonium hydroxide (TMAH) or potassium hydroxide (KOH).

Owner:TAIWAN SEMICON MFG CO LTD

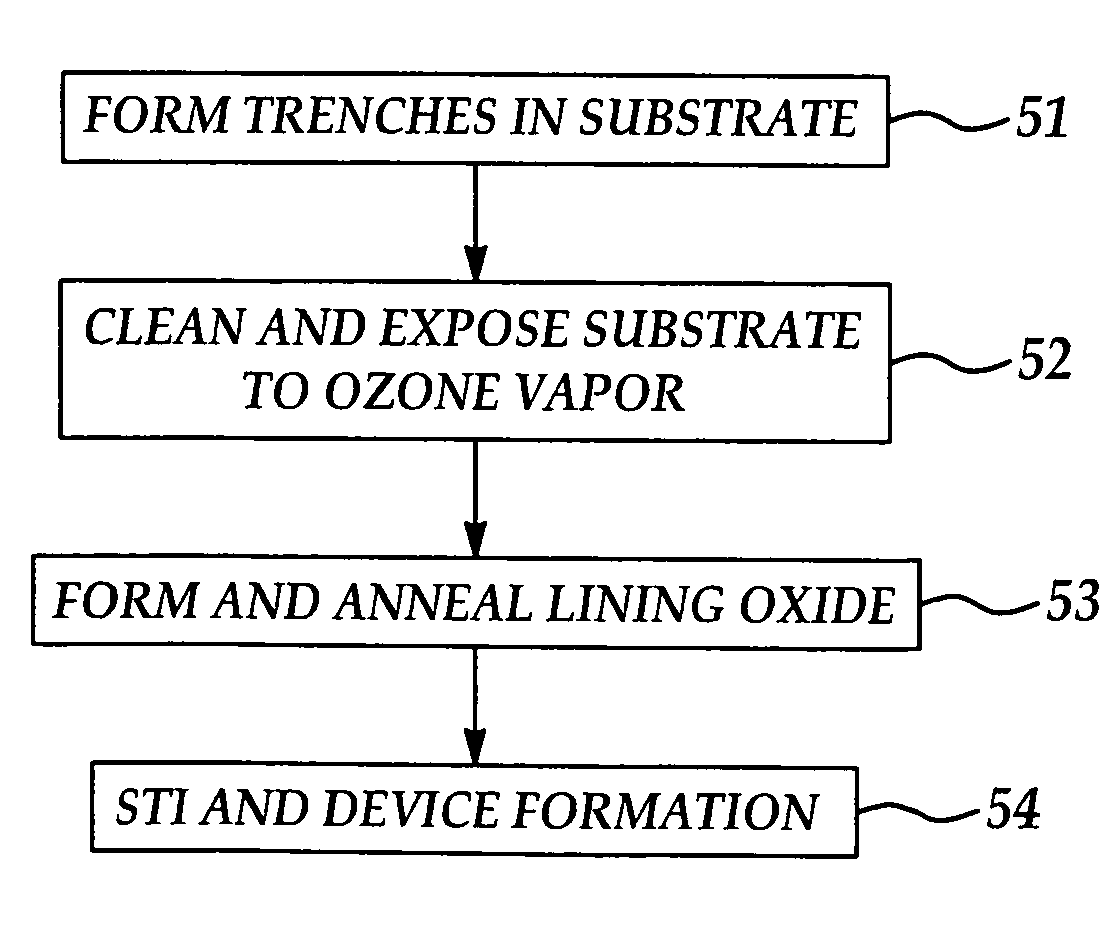

Ozone vapor clean method

Owner:TAIWAN SEMICON MFG CO LTD

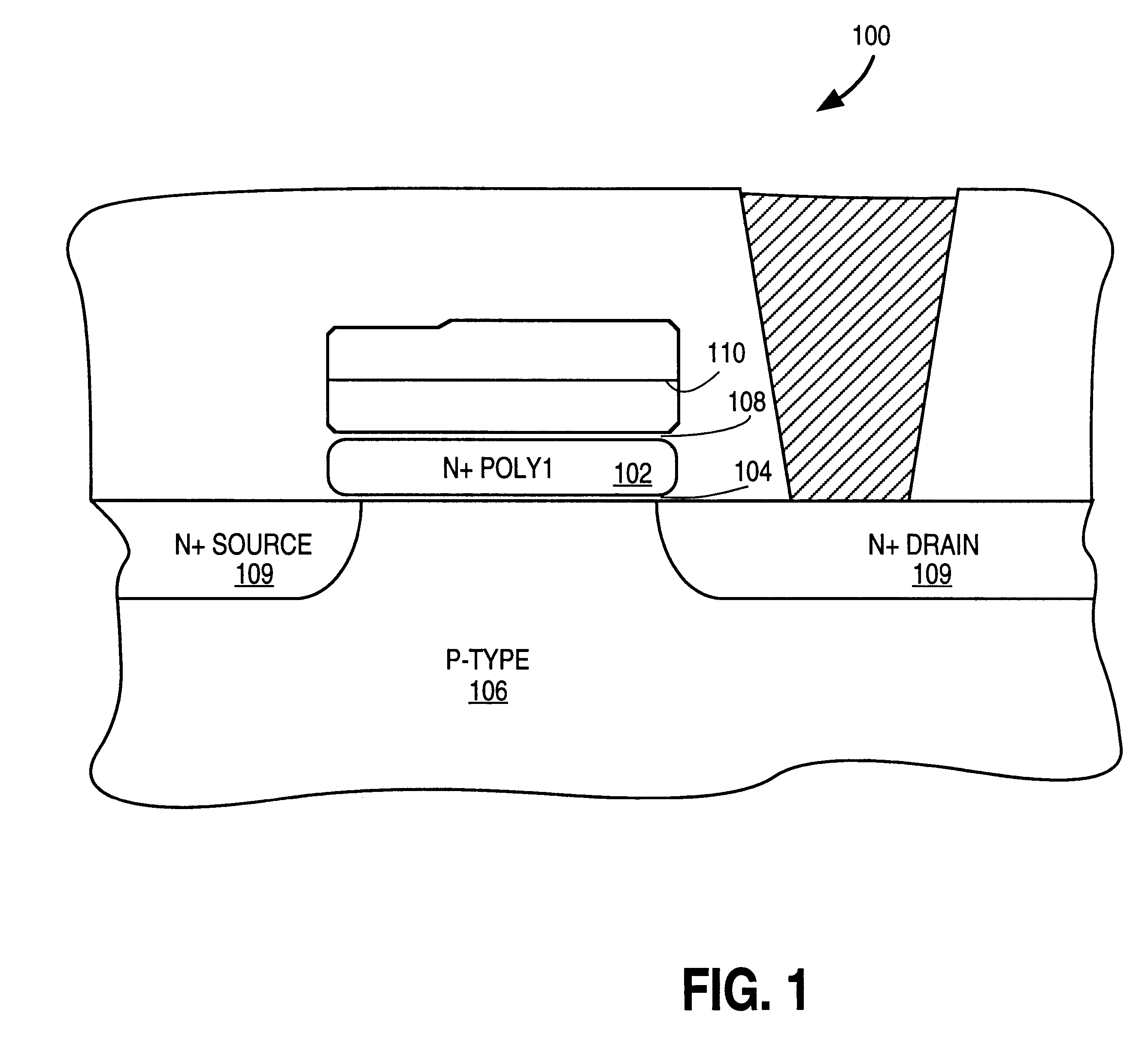

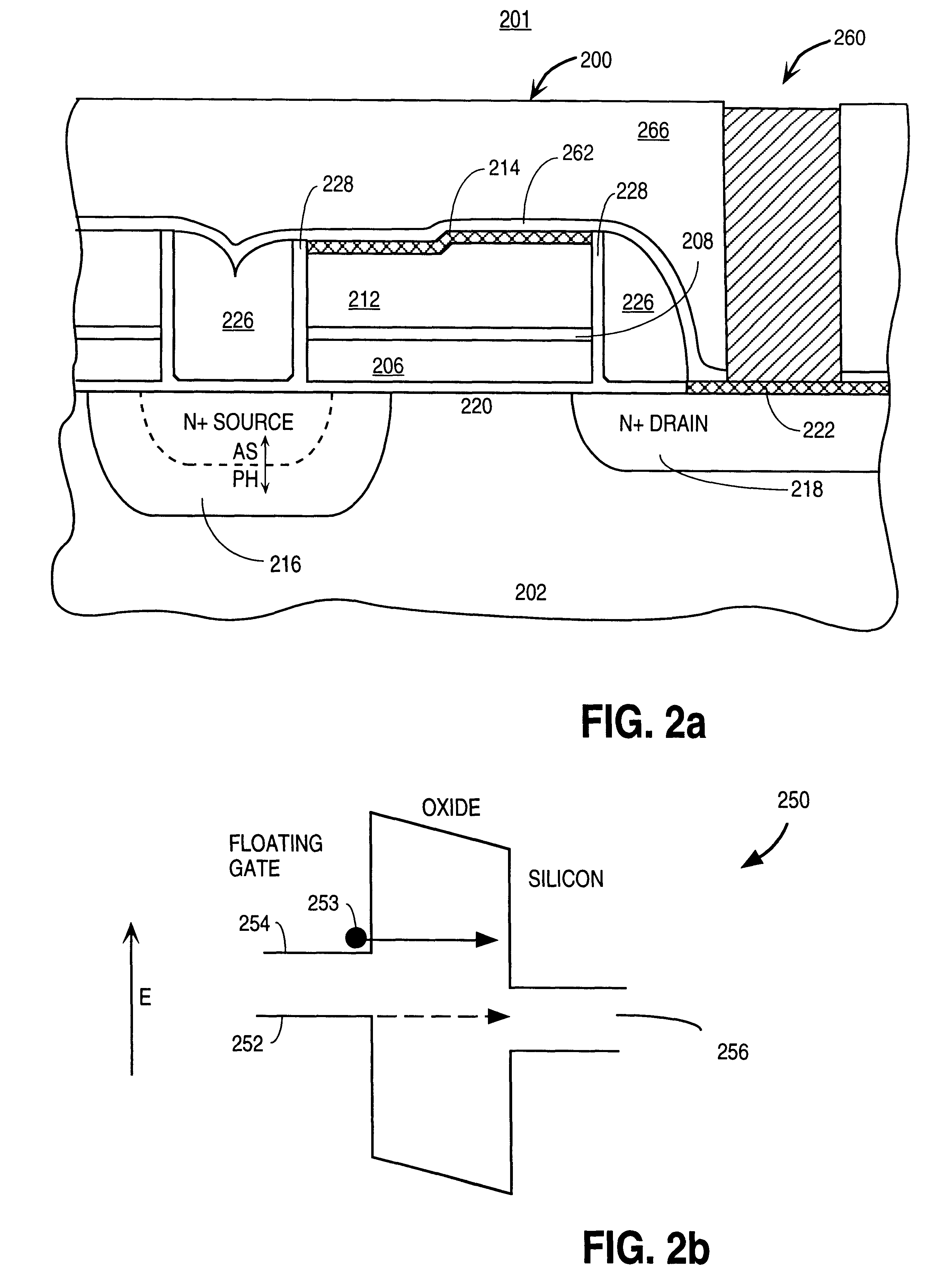

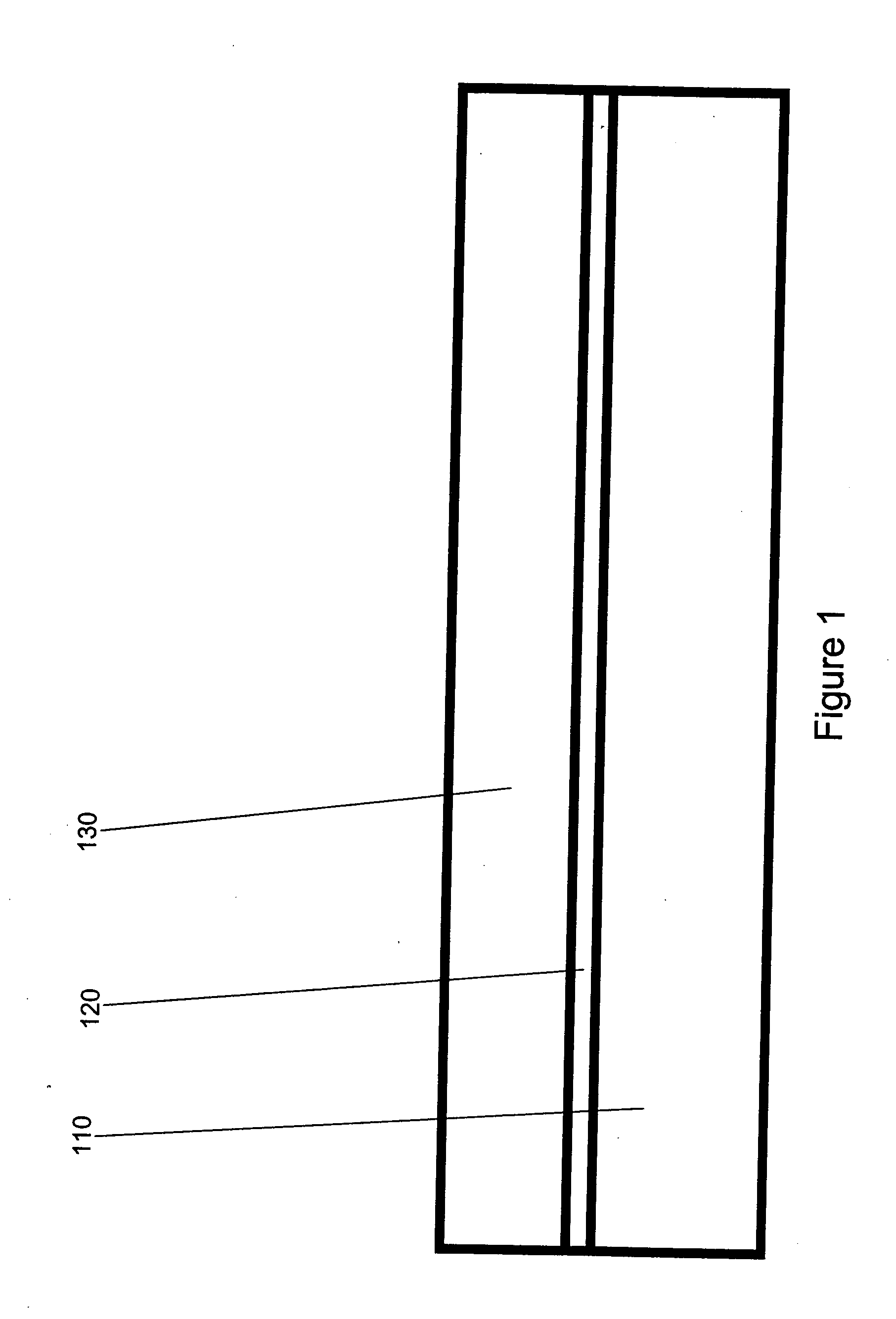

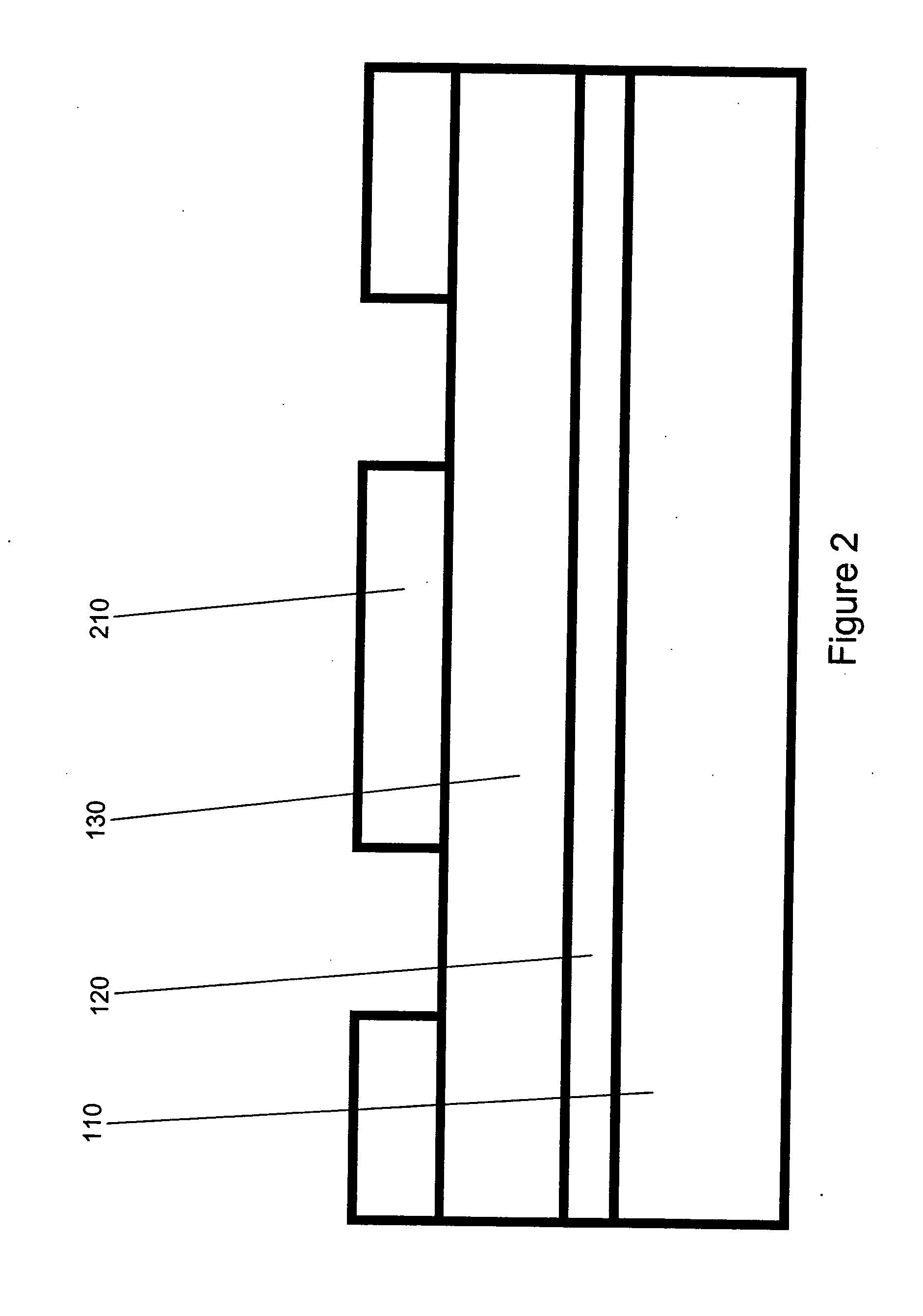

Integrated memory cell and method of fabrication

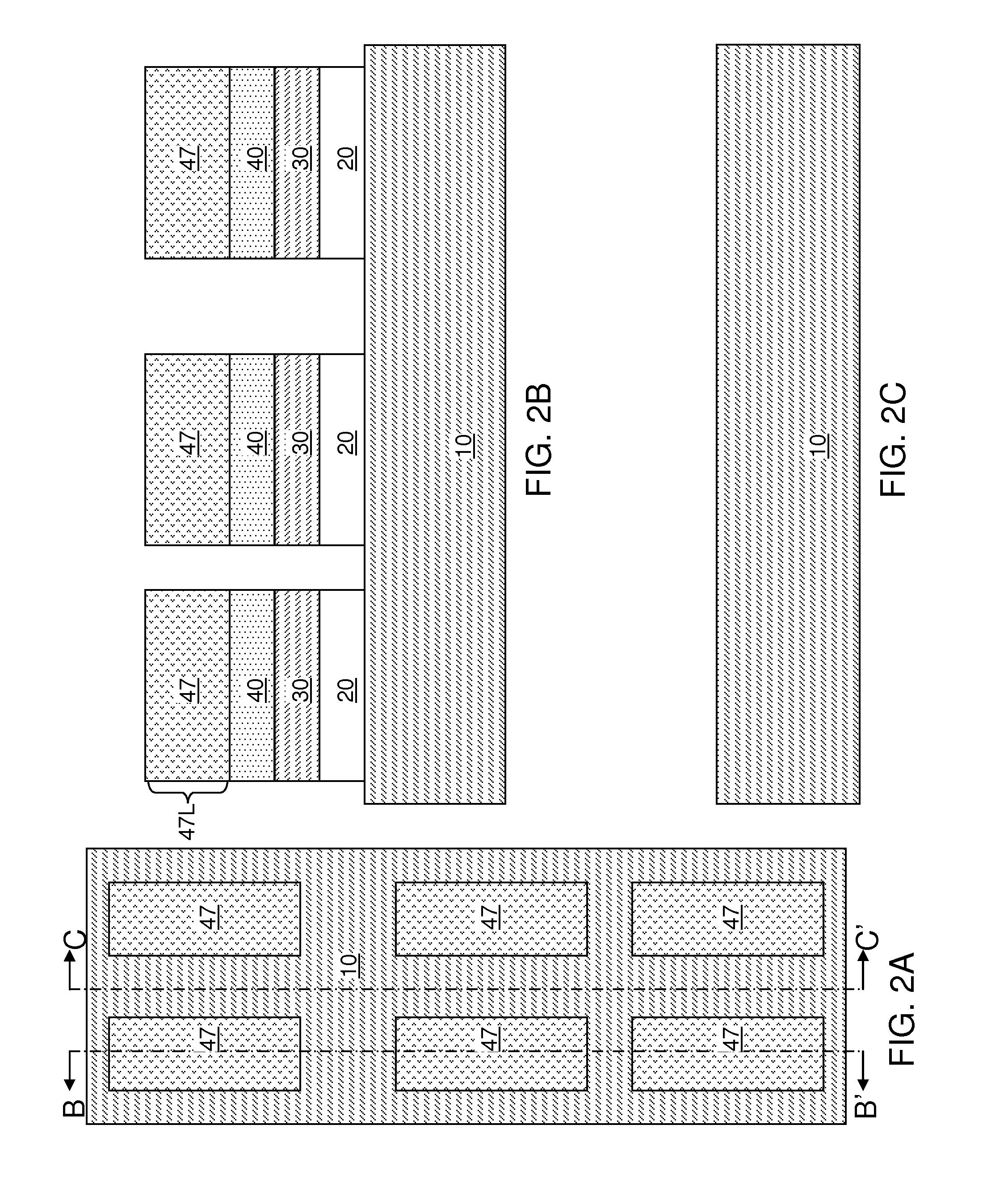

A nonvolatile memory cell comprising a pair of spaced apart shallow trench isolation regions formed in a substrate and defining a substrate active region. A tunnel dielectric is formed on the substrate active region. A floating gate is formed on the tunnel dielectric and is self aligned between the spaced apart shallow trench isolation regions. A dielectric layer is formed on the floating gate and a control gate formed on the dielectric layer. A source region and a drain region are formed in the substrate active region on opposite sides of the floating gate.

Owner:INTEL CORP

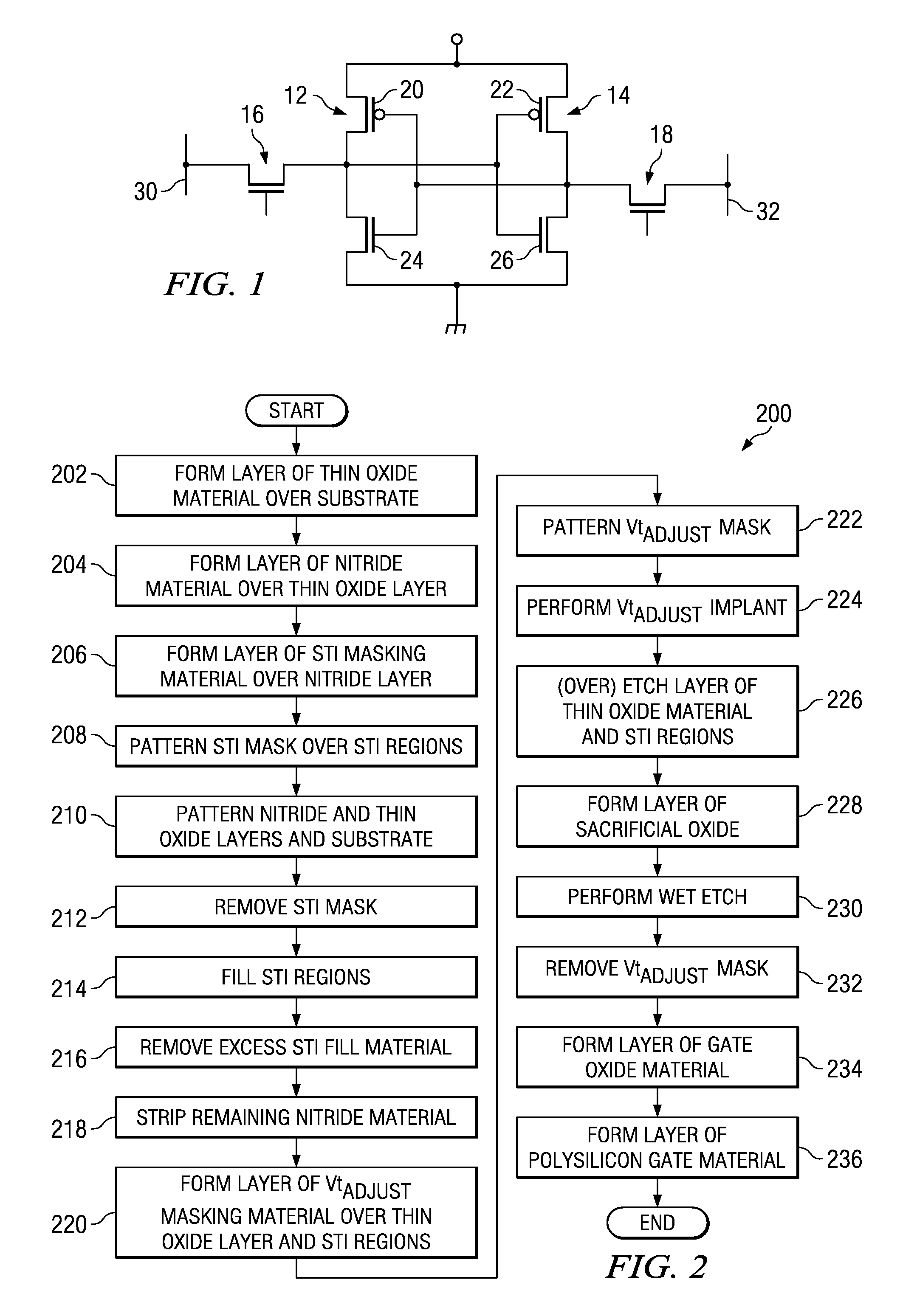

Method to improve SRAM performance and stability

Owner:TEXAS INSTR INC

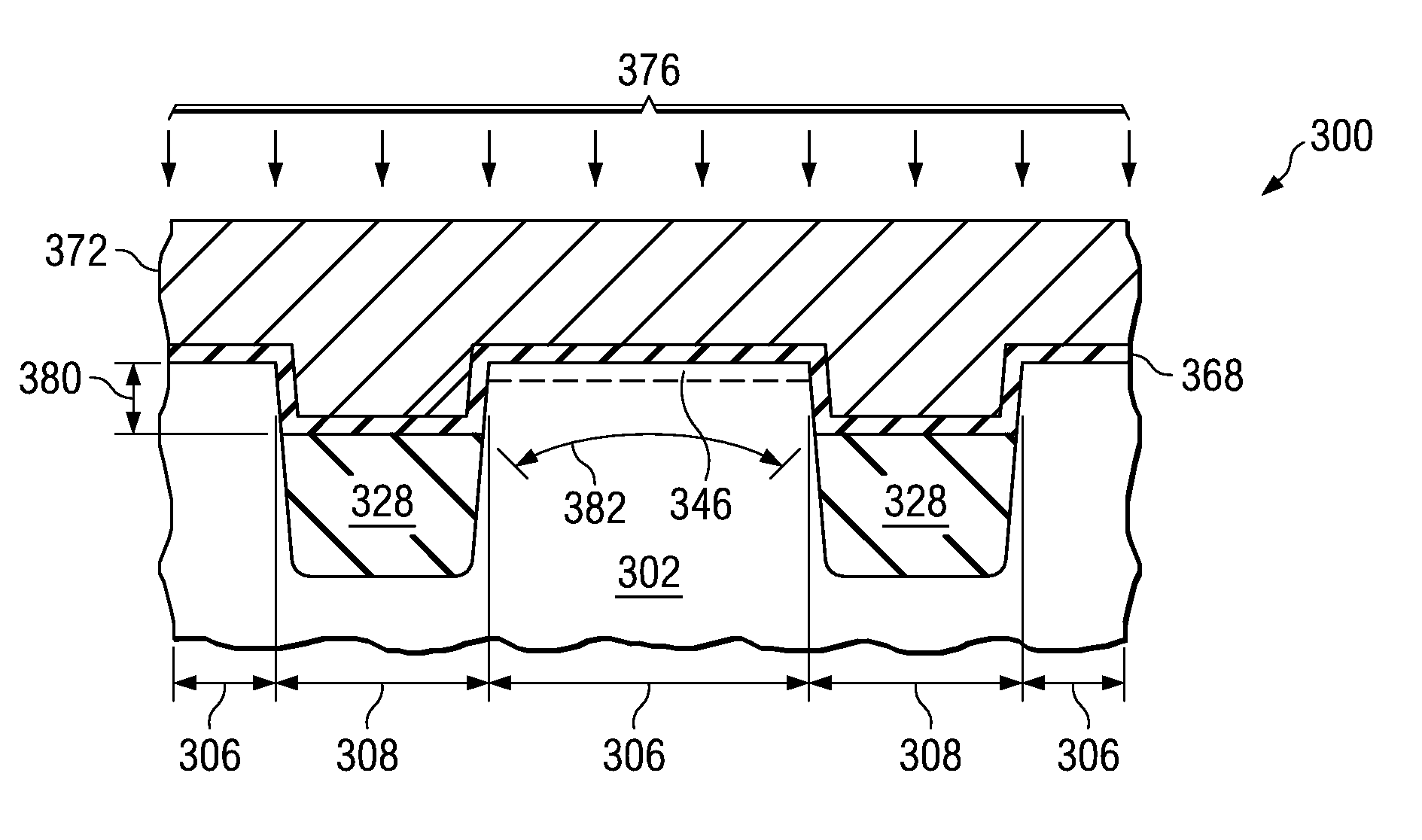

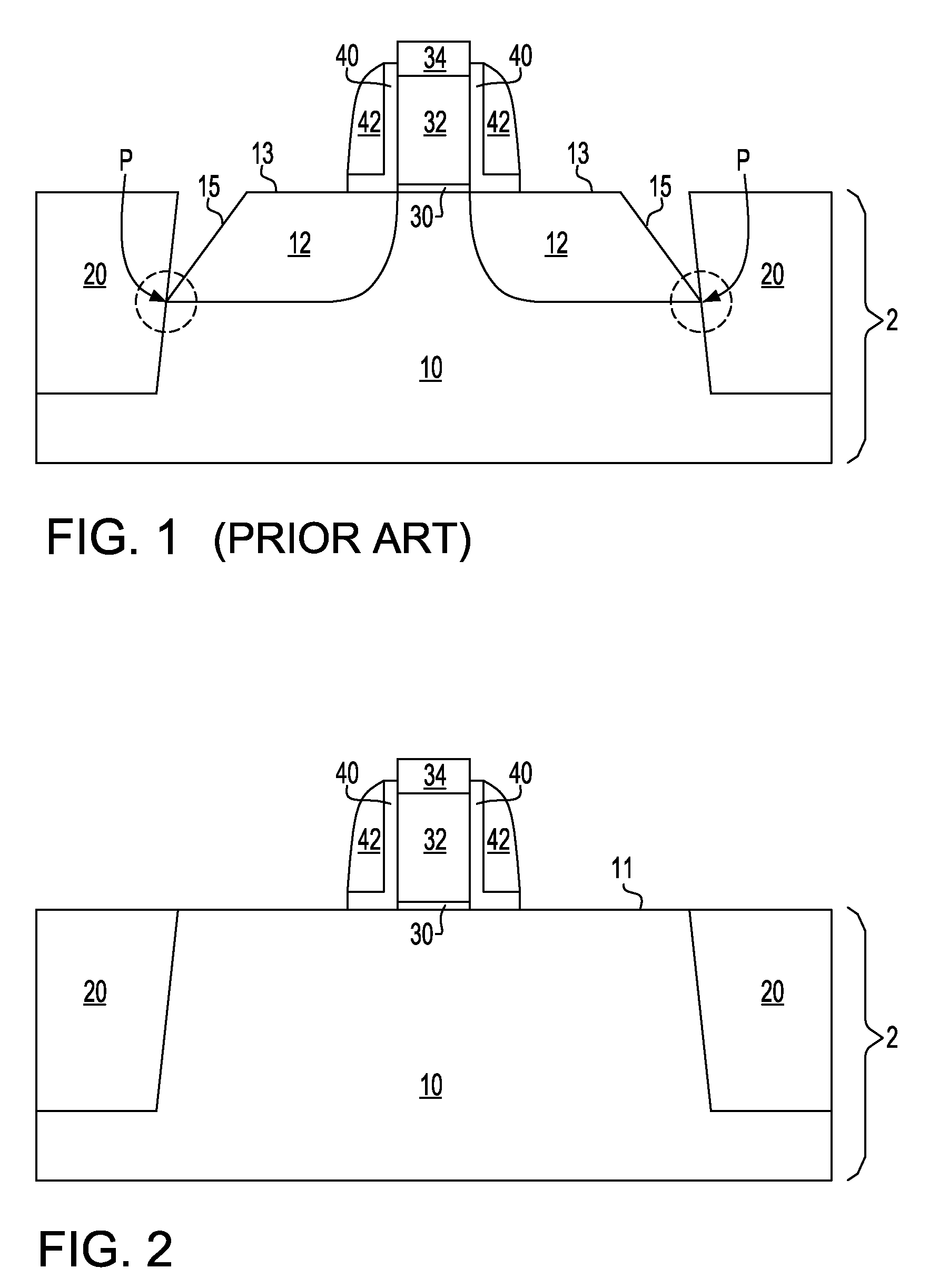

High performance strained CMOS devices

InactiveUS20050148146A1Semiconductor/solid-state device manufacturingSemiconductor devicesCMOSEngineering

A semiconductor device and method of manufacture provide an n-channel field effect transistor (nFET) having a shallow trench isolation with overhangs that overhang Si—SiO2 interfaces in a direction parallel to the direction of current flow and in a direction transverse to current flow. The device and method also provide a p-channel field effect transistor (pFET) having a shallow trench isolation with an overhang that overhangs Si—SiO2 interfaces in a direction transverse to current flow. However, the shallow trench isolation for the pFET is devoid of overhangs, in the direction parallel to the direction of current flow.

Owner:GLOBALFOUNDRIES INC

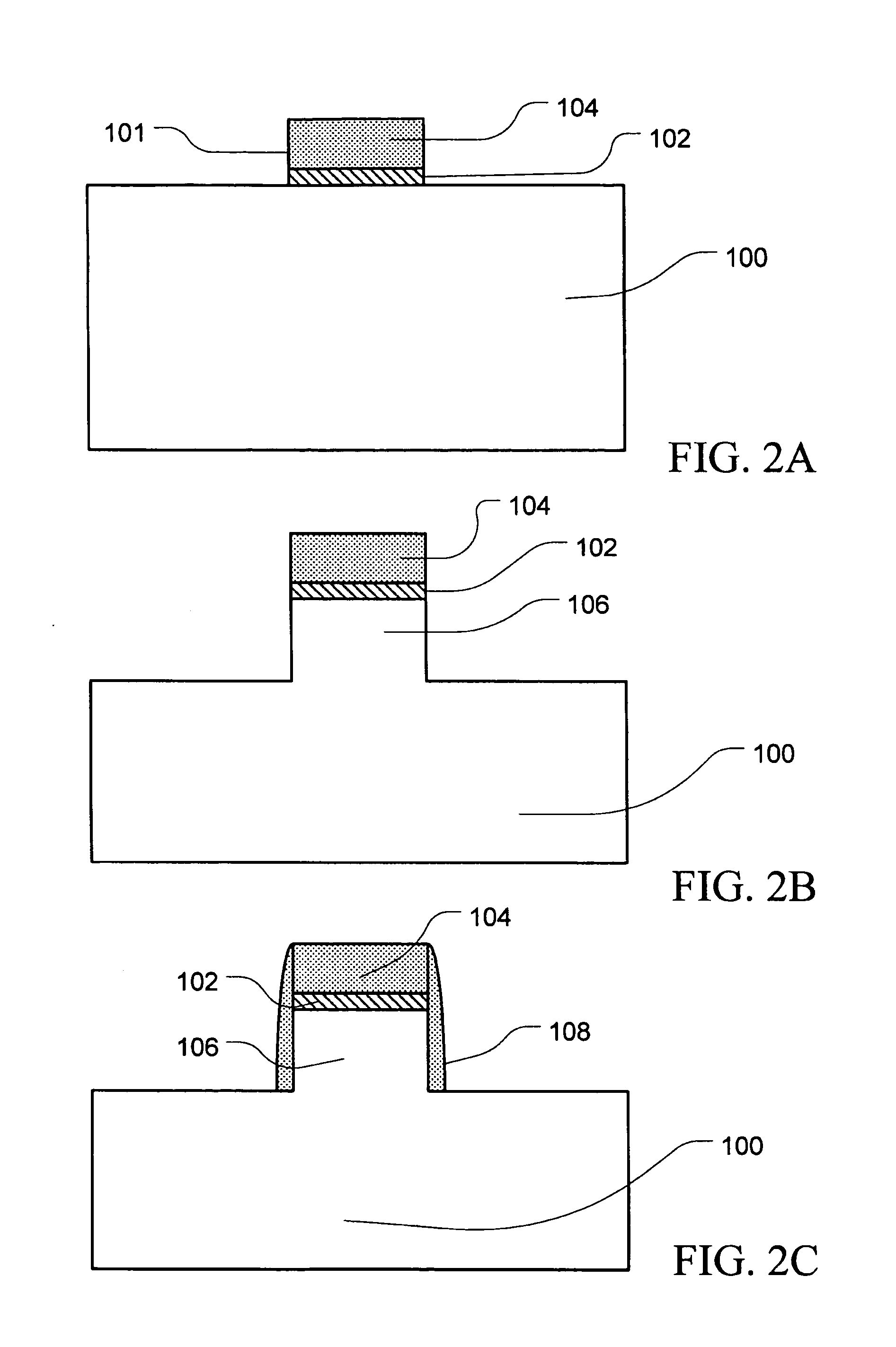

Multi-structured Si-fin and method of manufacture

InactiveUS20050035391A1Point becomes highGood planarityTransistorSemiconductor/solid-state device detailsDevice materialEngineering

Disclosed is a semiconductor fin construction useful in FinFET devices that incorporates an upper region and a lower region with wherein the upper region is formed with substantially vertical sidewalls and the lower region is formed with inclined sidewalls to produce a wider base portion. The disclosed semiconductor fin construction will also typically include a horizontal step region at the interface between the upper region and the lower region. Also disclosed are a series of methods of manufacturing semiconductor devices incorporating semiconductor fins having this dual construction and incorporating various combinations of insulating materials such as silicon dioxide and / or silicon nitride for forming shallow trench isolation (STI) structures between adjacent semiconductor fins.

Owner:SAMSUNG ELECTRONICS CO LTD

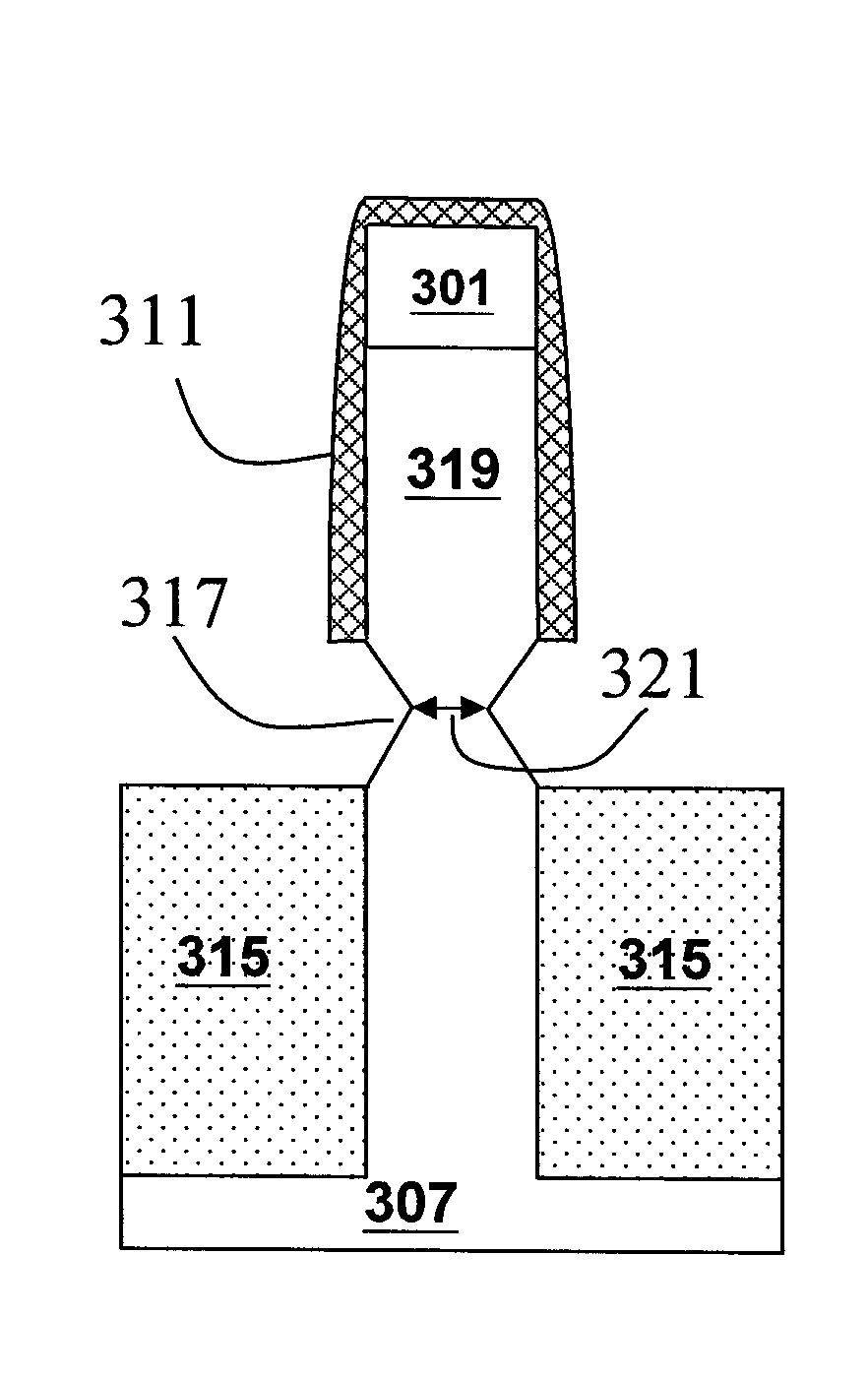

Tunneling effect transistor with self-aligned gate

ActiveUS7700466B2Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingField-effect transistorP–n junction

In one embodiment, a mandrel and an outer dummy spacer may be employed to form a first conductivity type region. The mandrel is removed to form a recessed region wherein a second conductivity type region is formed. In another embodiment, a mandrel is removed from within shallow trench isolation to form a recessed region, in which an inner dummy spacer is formed. A first conductivity type region and a second conductivity region are formed within the remainder of the recessed region. An anneal is performed so that the first conductivity type region and the second conductivity type region abut each other by diffusion. A gate electrode is formed in self-alignment to the p-n junction between the first and second conductivity regions. The p-n junction controlled by the gate electrode, which may be sublithographic, constitutes an inventive tunneling effect transistor.

Owner:TWITTER INC

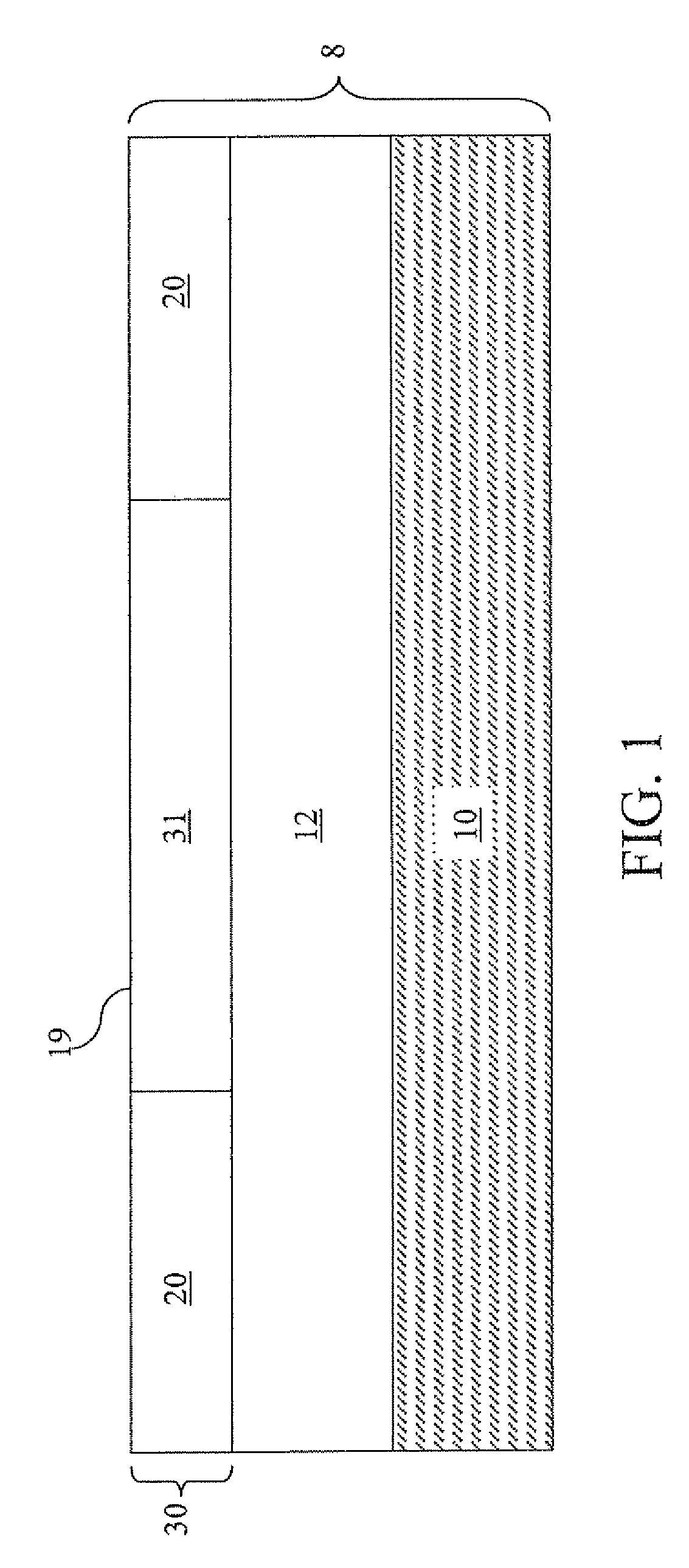

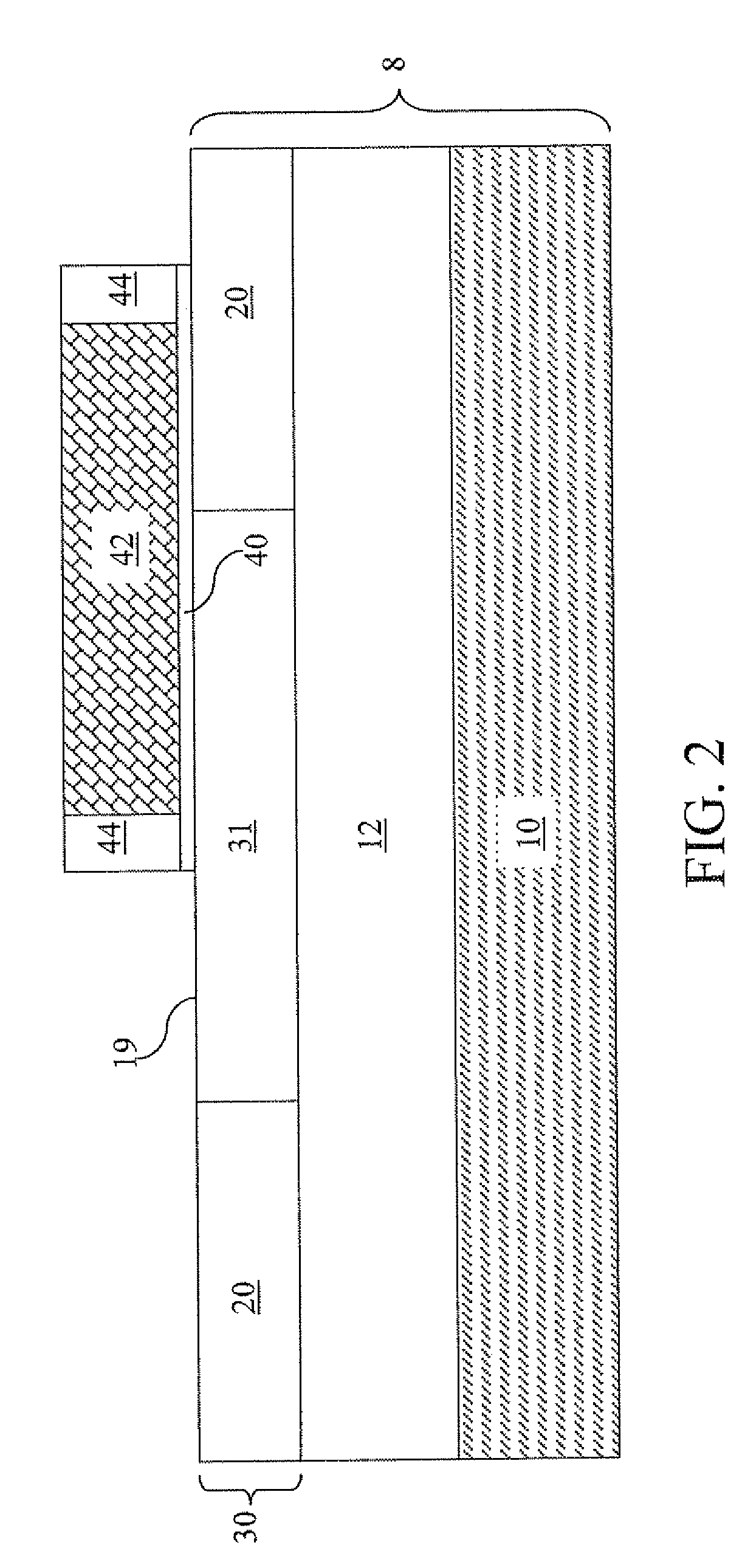

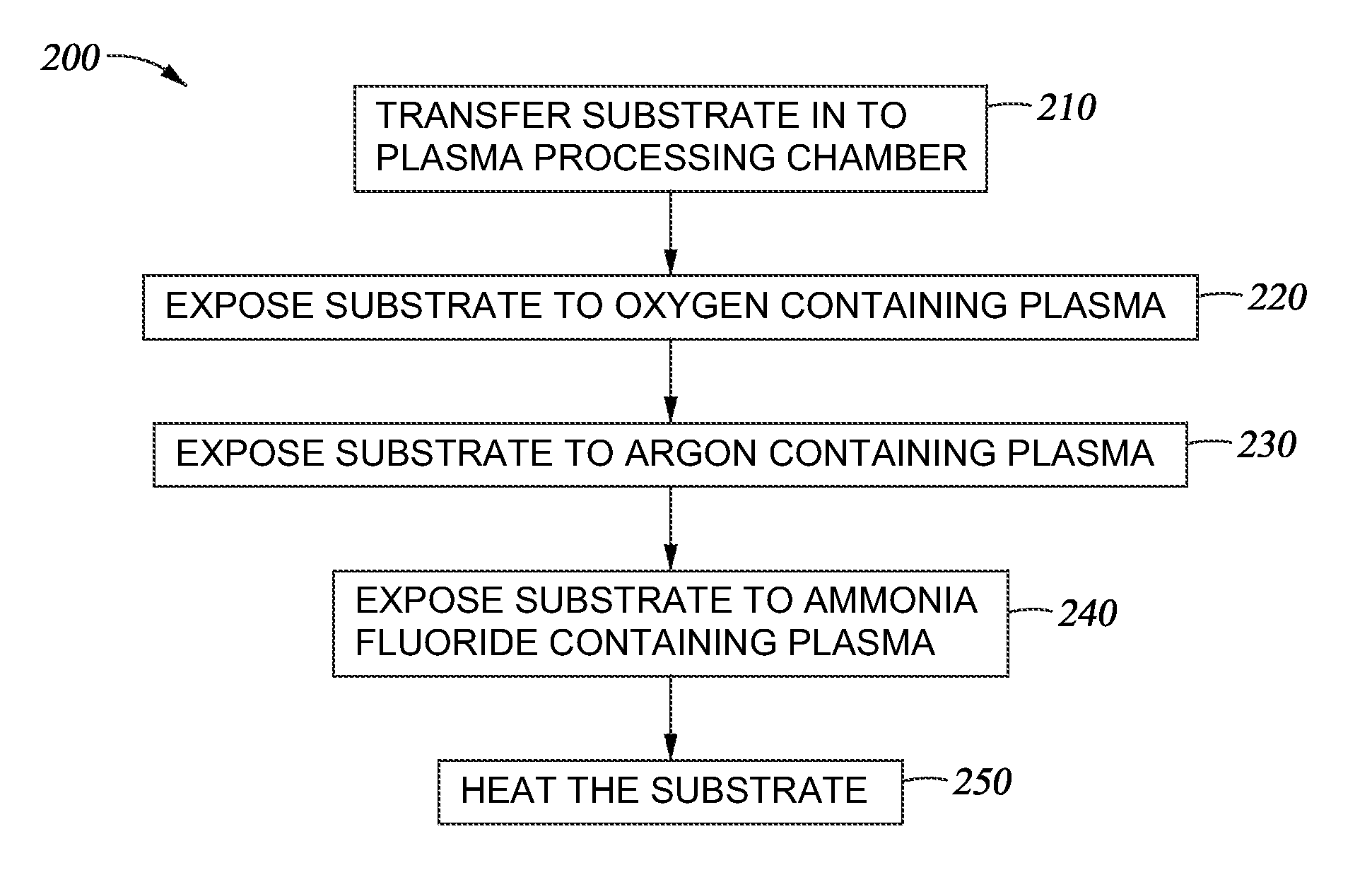

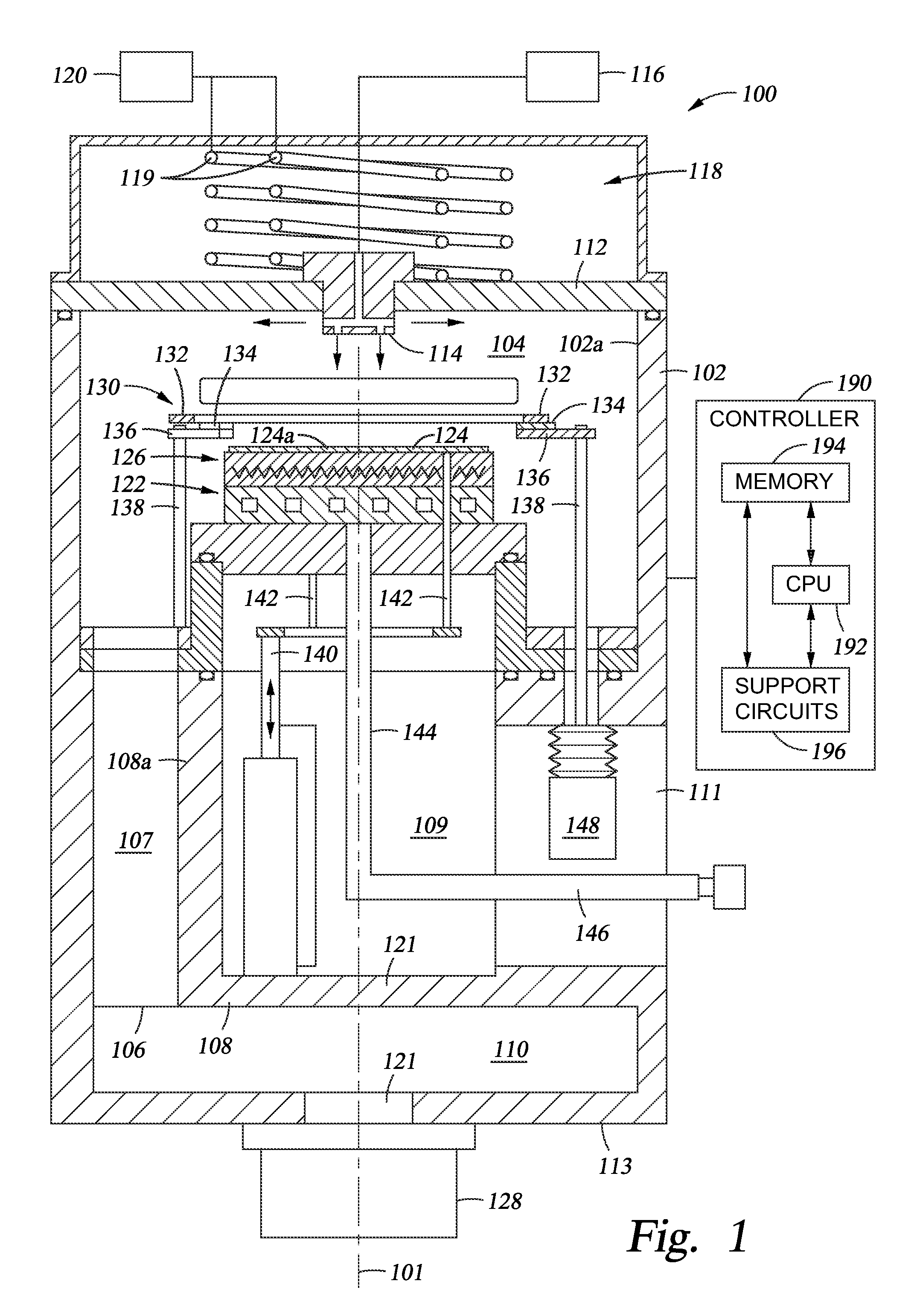

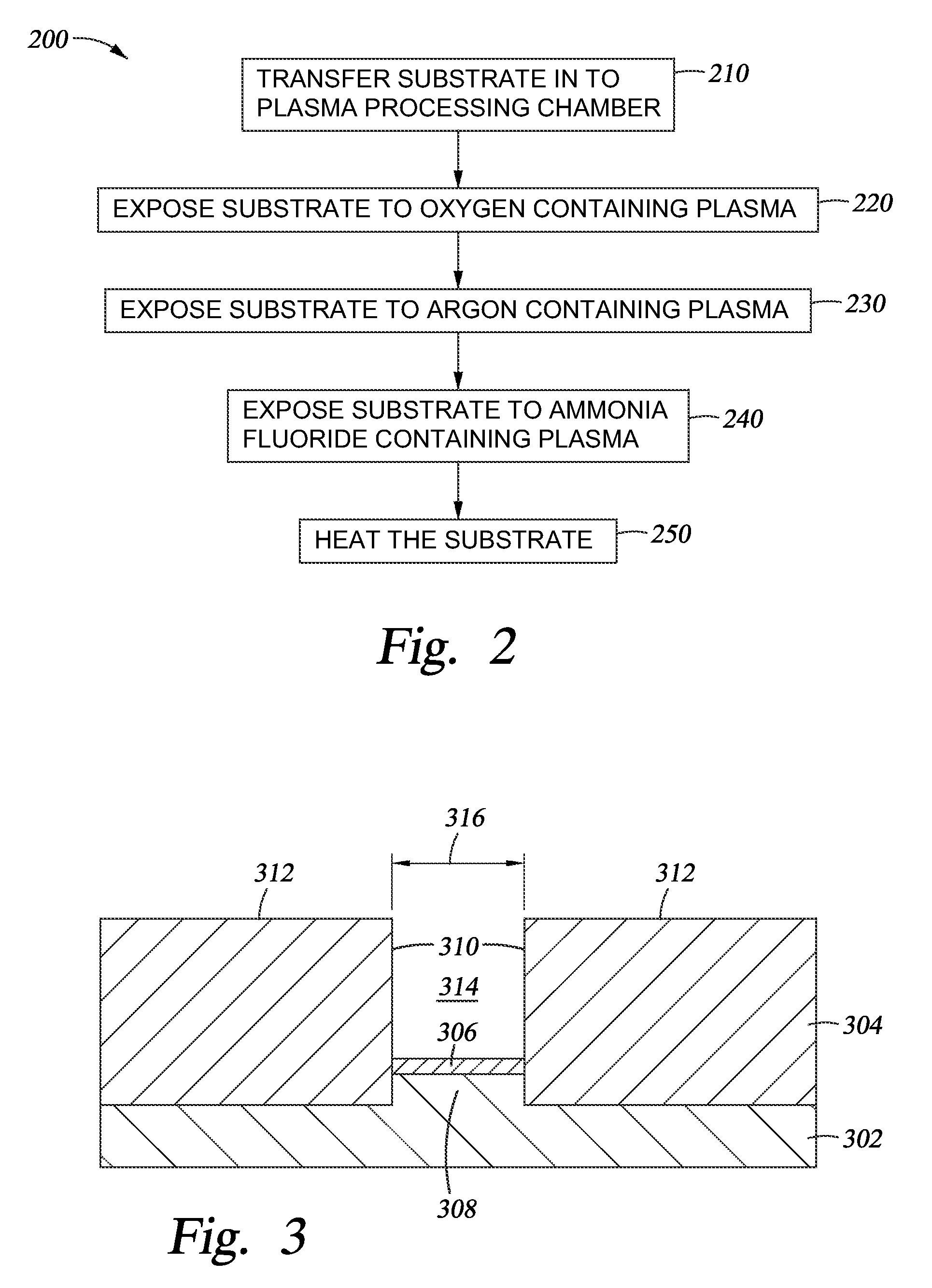

CVD oxide surface pre-conditioning by inductively coupled O2 plasma

A method and apparatus for conditioning an oxide surface during a semiconductor device formation process is provided herein. One or more plasma processing operations are performed on a substrate having a fin structure and shallow trench isolation structure (STI) formed thereon. An oxygen containing plasma process may modify surfaces of the STI structure in preparation for an argon containing plasma process. The argon containing plasma process may form a first layer on the fin structure and STI structure and an ammonia fluoride containing plasma process may form a second layer on the first layer. The first and second layers may be removed from the substrate during a subsequent heating process to provide a cleaned fin structure suitable for subsequent processing operations.

Owner:APPLIED MATERIALS INC

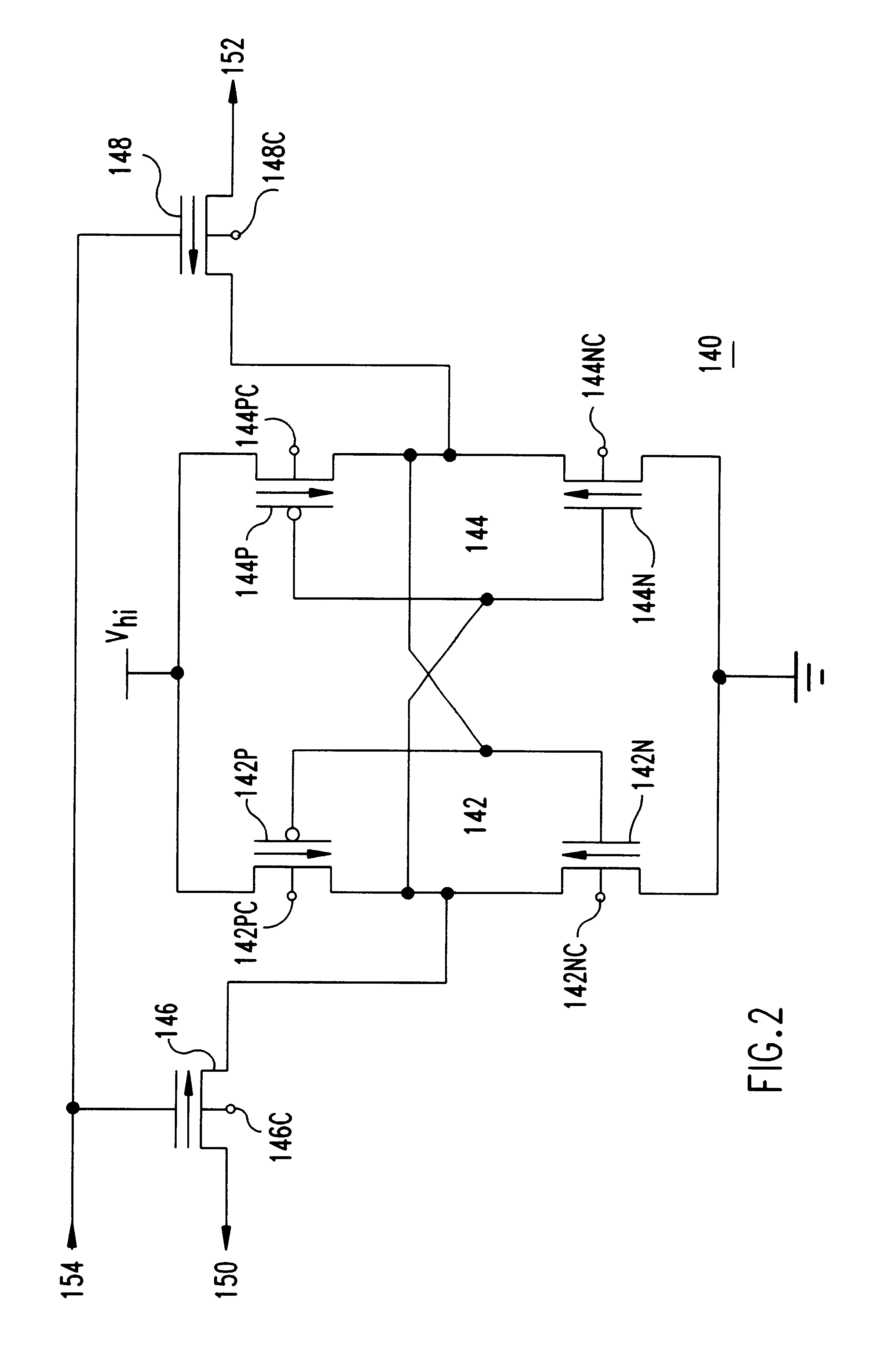

Semiconductor integrated circuit device

A semiconductor integrated circuit device contains a CMOS circuit that includes a plurality of N-channel transistors and a plurality of P-channel transistors. The plurality of N-channel transistors is provided with device isolation by one of a gate isolation structure and a shallow trench isolation structure. The plurality of P-channel transistors are provided with device isolation by the other of the gate isolation structure and the shallow trench isolation structure.

Owner:KK TOSHIBA

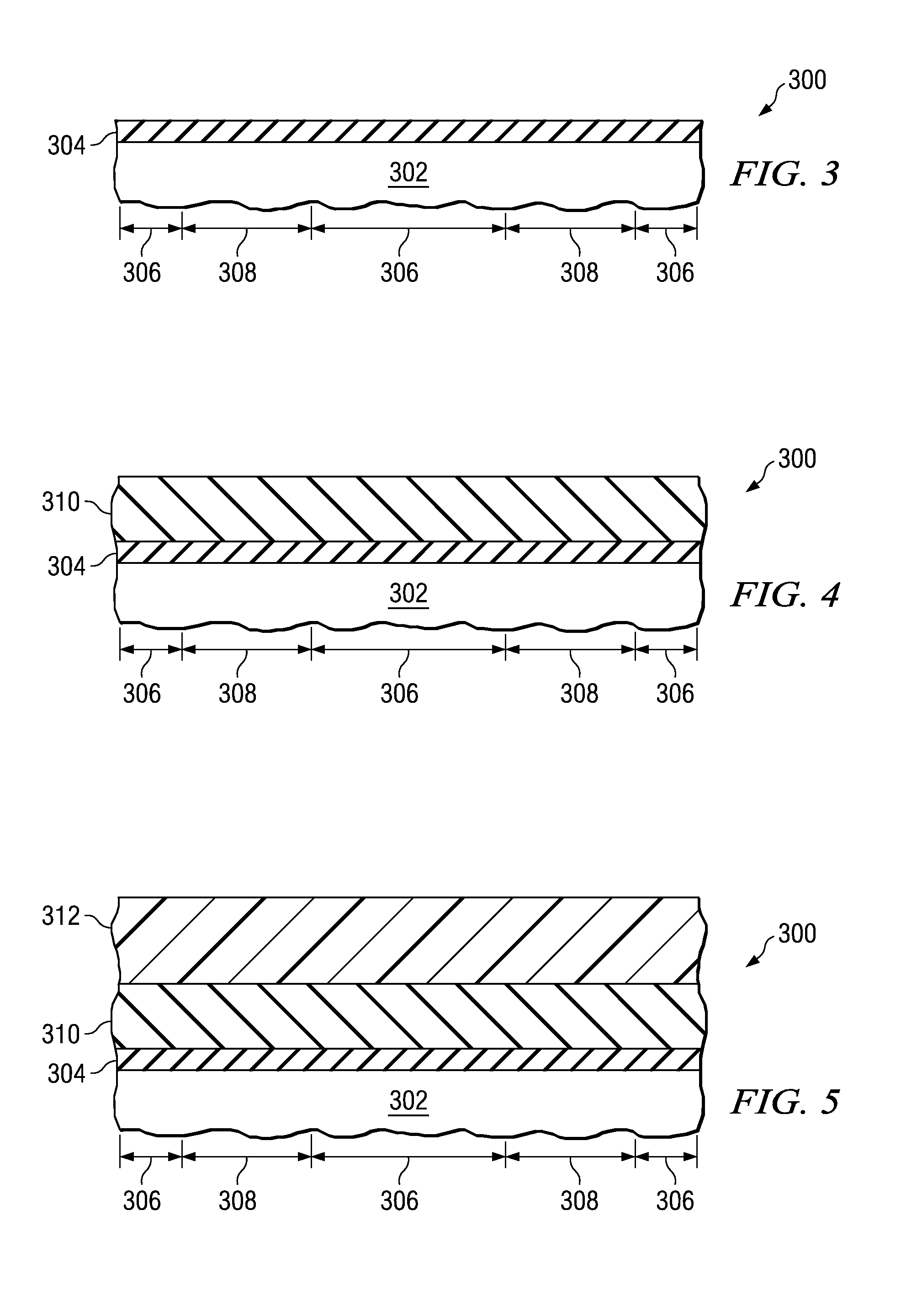

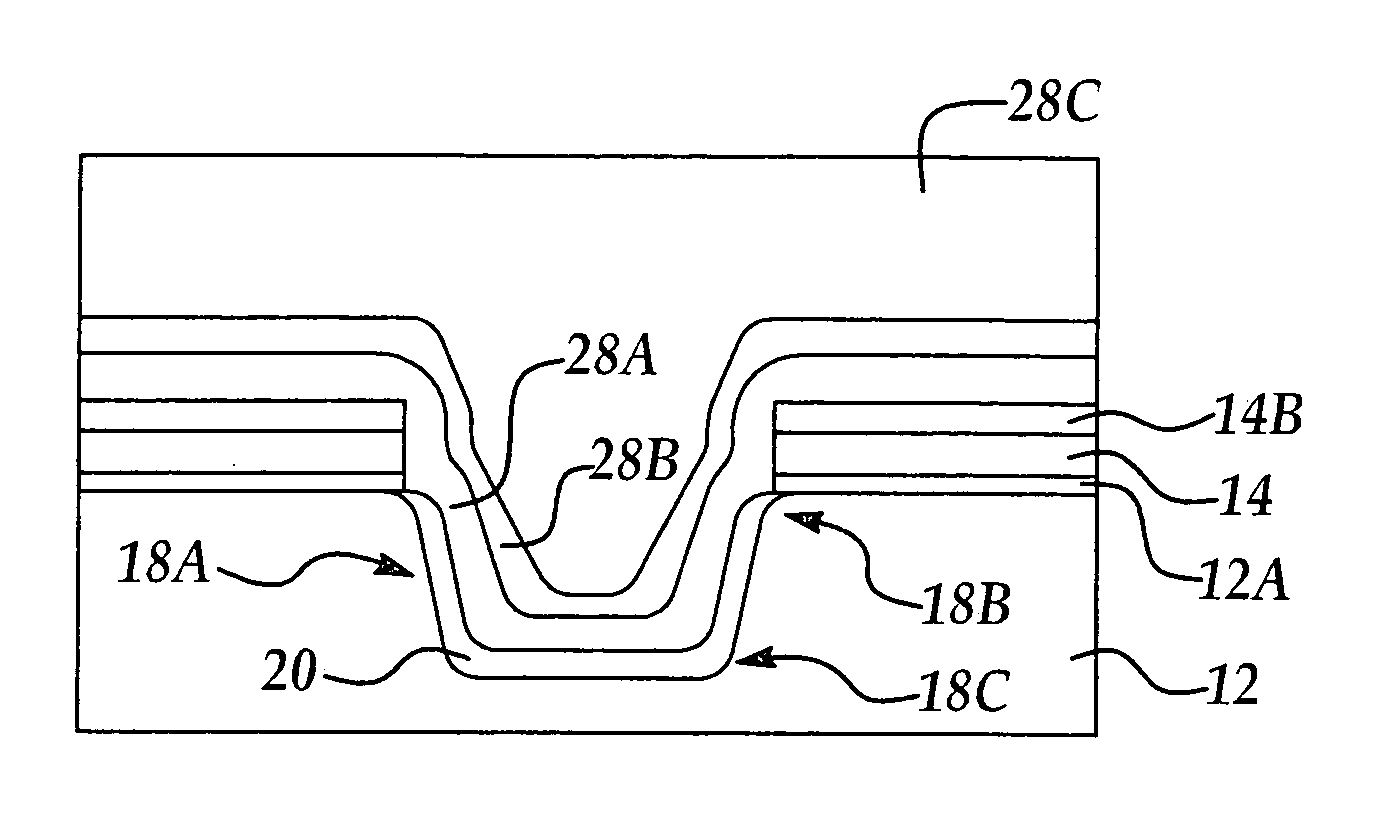

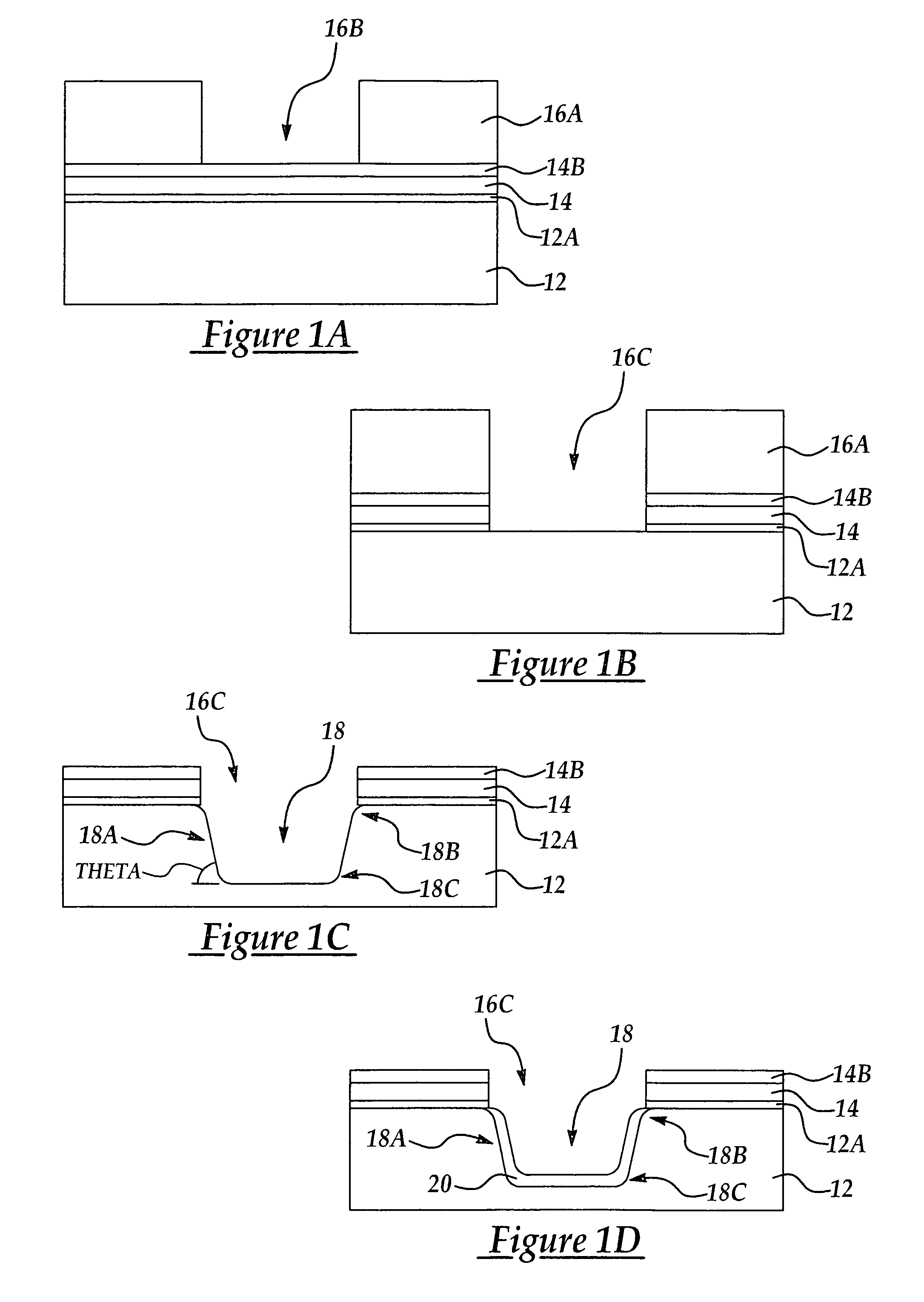

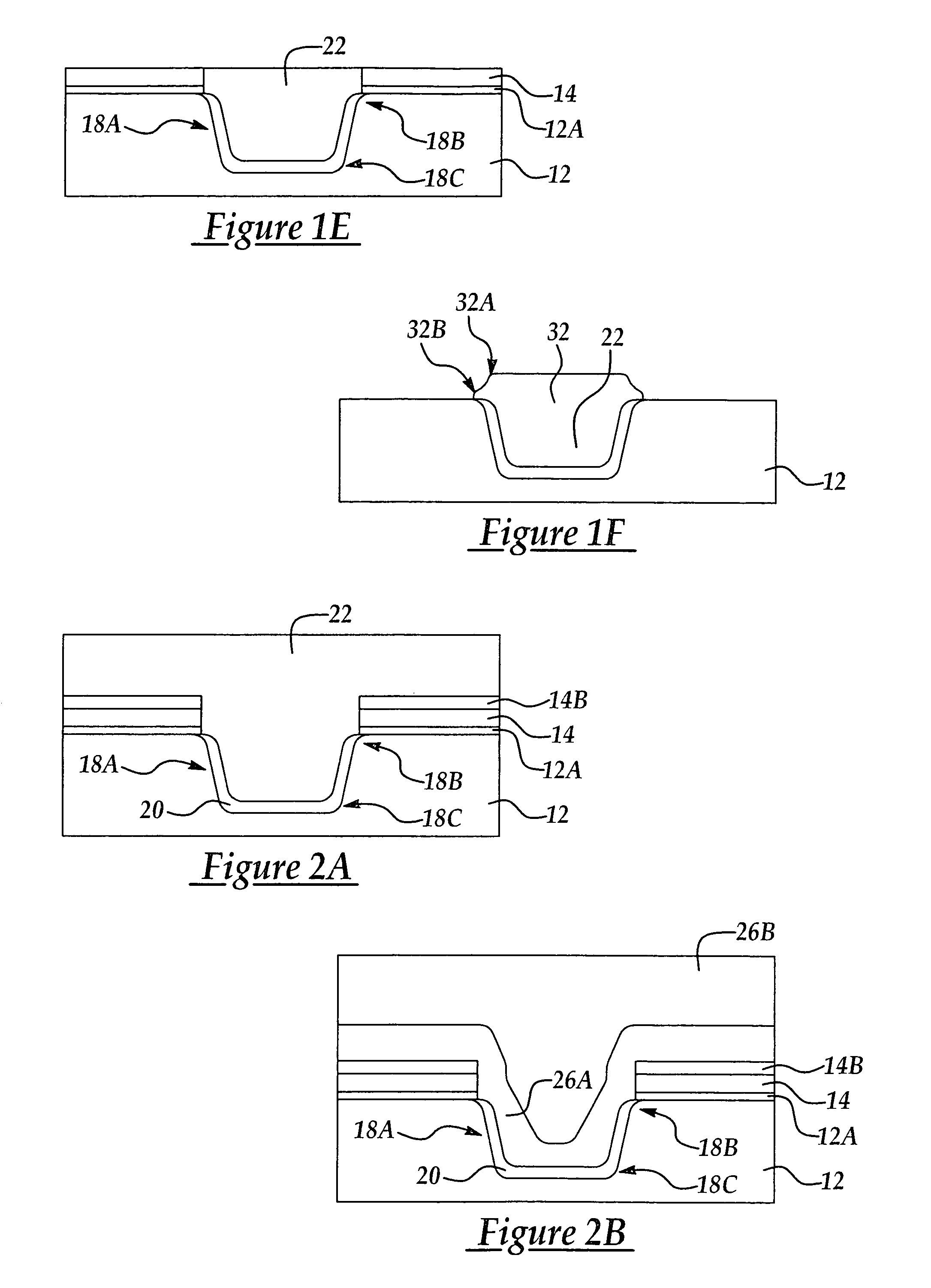

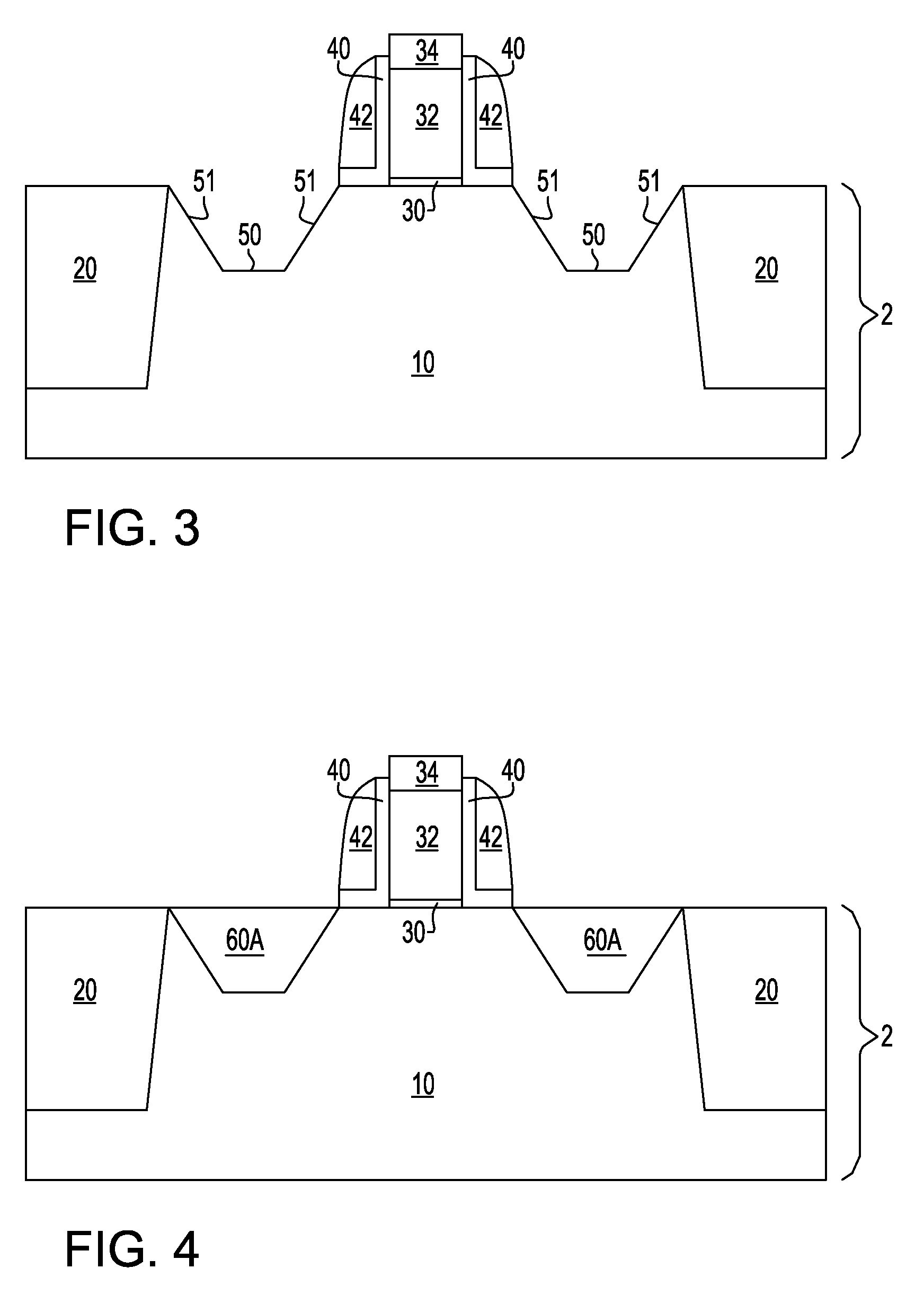

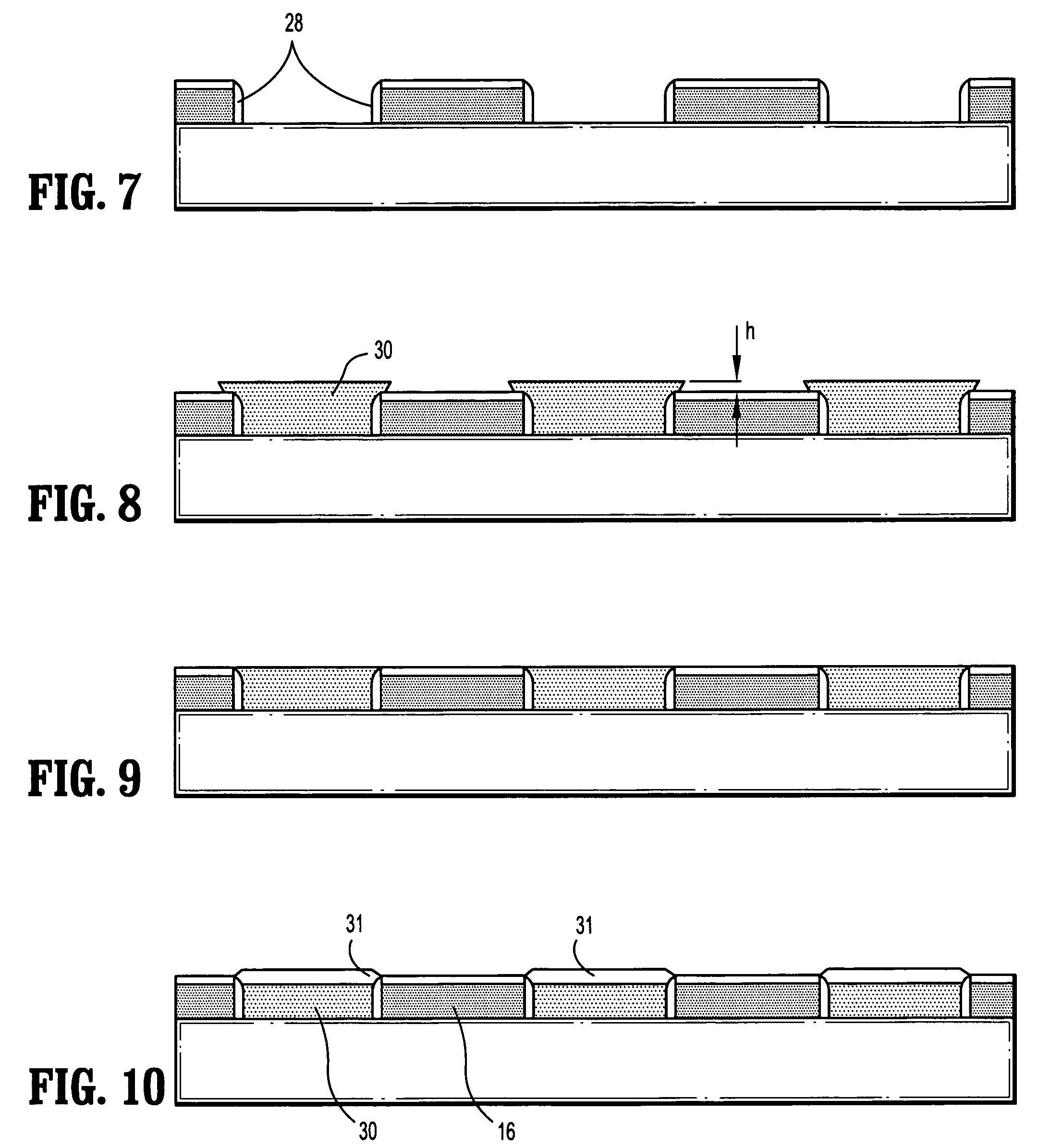

Method of achieving improved STI gap fill with reduced stress

InactiveUS7118987B2Relieve pressureIncrease charge mobilityStentsBalloon catheterEngineeringSilicon dioxide

A shallow trench isolation (STI) structure and method of forming the same with reduced stress to improve charge mobility the method including providing a semiconductor substrate comprising at least one patterned hardmask layer overlying the semiconductor substrate; dry etching a trench in the semiconductor substrate according to the at least one patterned hardmask layer; forming one or more liner layers to line the trench selected from the group consisting of silicon dioxide, silicon nitride, and silicon oxynitride; forming one or more layers of trench filling material comprising silicon dioxide to backfill the trench; carrying out at least one thermal annealing step to relax accumulated stress in the trench filling material; carrying out at least one of a CMP and dry etch process to remove excess trench filling material above the trench level; and, removing the at least one patterned hardmask layer.

Owner:TAIWAN SEMICON MFG CO LTD

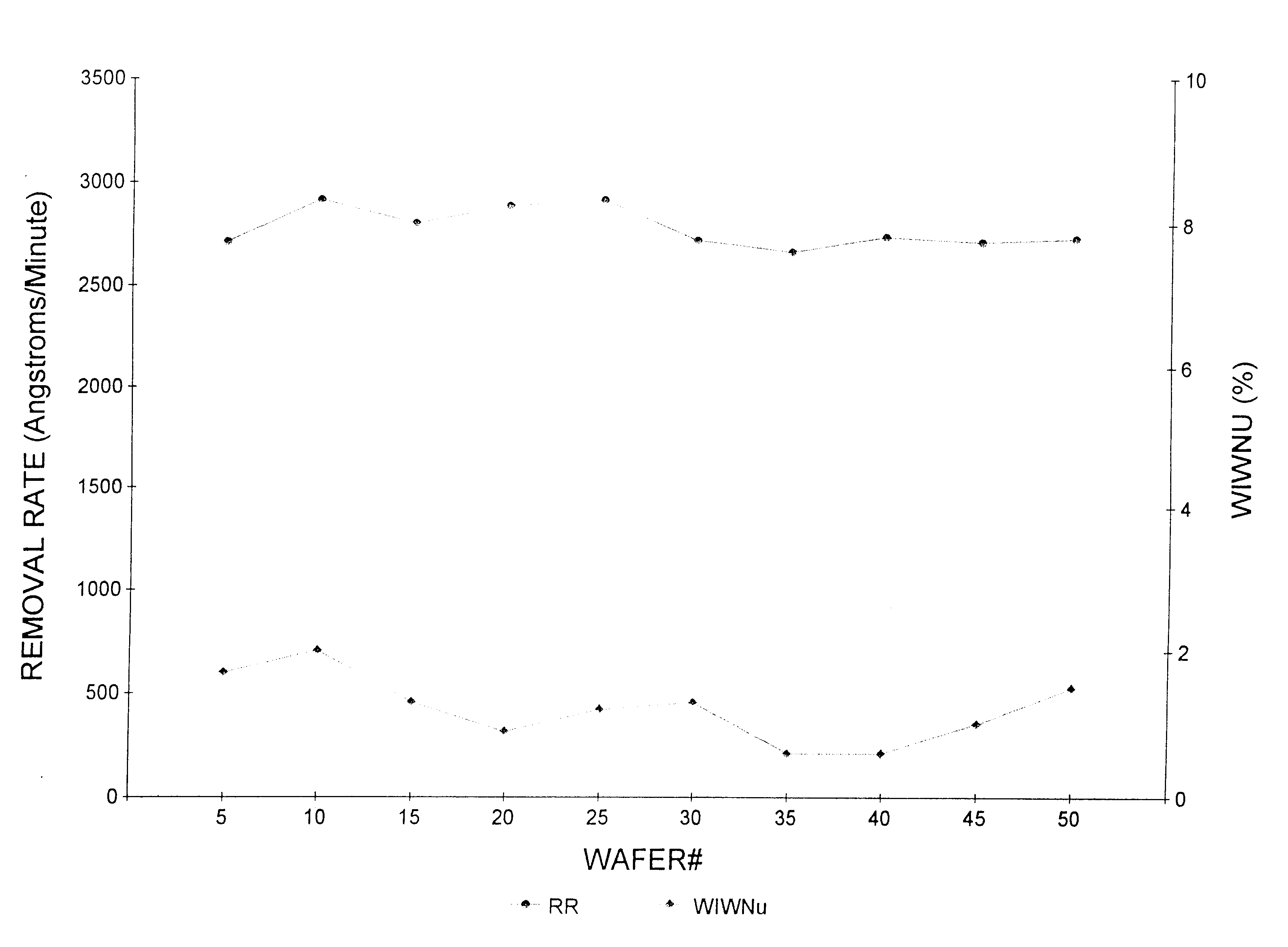

Planarization compositions and methods for removing interlayer dielectric films

InactiveUS6322600B1Improve planarization qualityQuality improvementPigmenting treatmentOther chemical processesThinningDielectric thin films

A planarization composition is set forth for chemical mechanical planarization of dielectric layers for semiconductor manufacture. The composition comprises spherical silica particles having an average diameter of from 30 nm to about 400 nm, and a narrow range of particle sizes, wherein about 90% of the particles is within 20% of the average particle diameter. The composition includes a liquid carrier comprising up to about 9% alcohol and an amine hydroxide in the amount of about 0.2 to about 9% by weight. The pH of the composition is in the range of about 9 to about 11.5, and the remainder of the solution is water. The composition has low amounts of metal ions, and the composition is used for thinning, polishing and planarizing interlayer dielectric thin films, shallow trench isolation structures, and isolation of gate structures. The invention also comprises methods for using the planarization composition in the manufacture of semiconductor devices.

Owner:ADVANCED TECH MATERIALS INC

Crystallographic recess etch for embedded semiconductor region

InactiveUS20080237634A1Enhanced inhibitory effectRelieve pressureSemiconductor/solid-state device manufacturingSemiconductor devicesLattice mismatchSemiconductor

Source and drain regions of an FET are etched by a crystallographic anisotropic etch to form a cavity surrounded by crystallographic facets. The exposure of the sidewalls of shallow trench isolation (STI) is avoided or reduced compared to the prior art. The crystallographic anisotropic etch may be combined with an isotropic etch or a recess etch to create undercuts beneath gate spacers and / or a pegging line beneath a top surface of the STI. The at least one cavity is then filled with a lattice-mismatched embedded material so that stress is applied to the channel of the FET. The resulting structure has increased containment of the embedded semiconductor region by shallow trench isolation. A reduction in stress due to the unconstrained sidewall area and an increase in the junction current due to the recessing of the pegging line are eliminated or alleviated.

Owner:IBM CORP

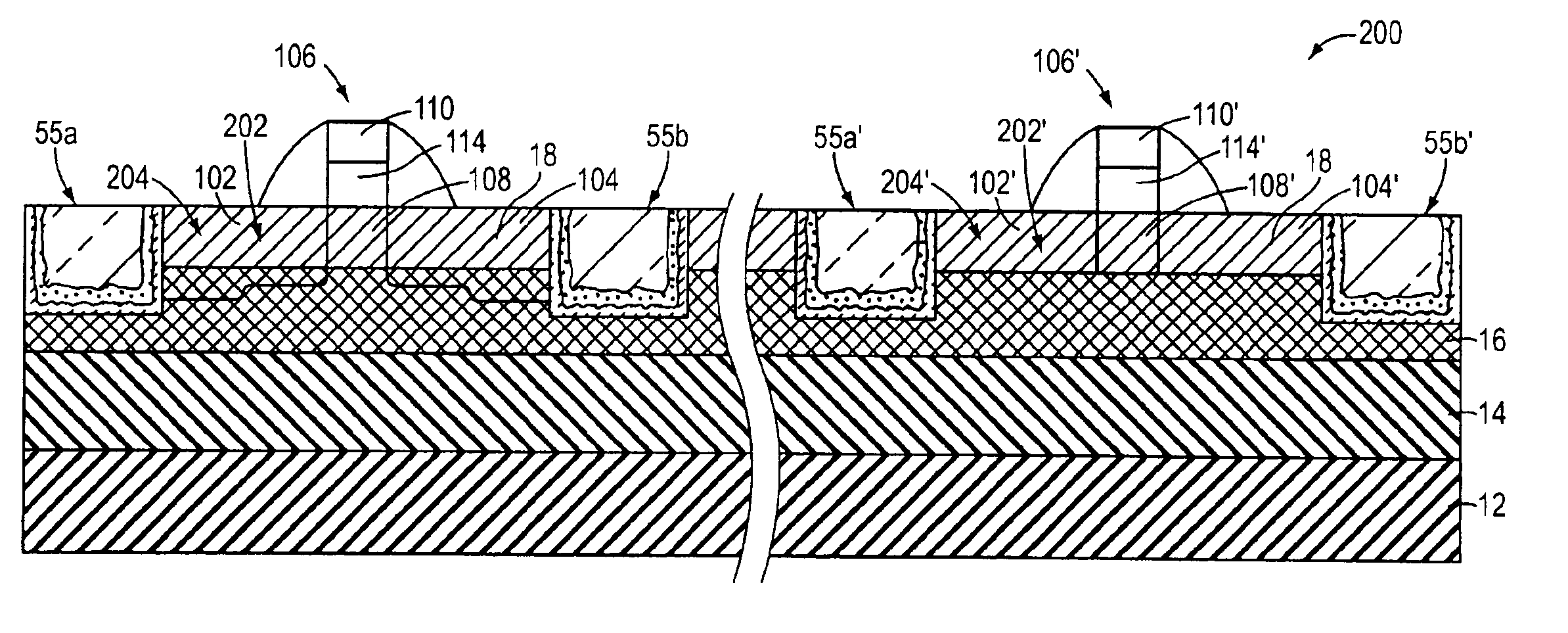

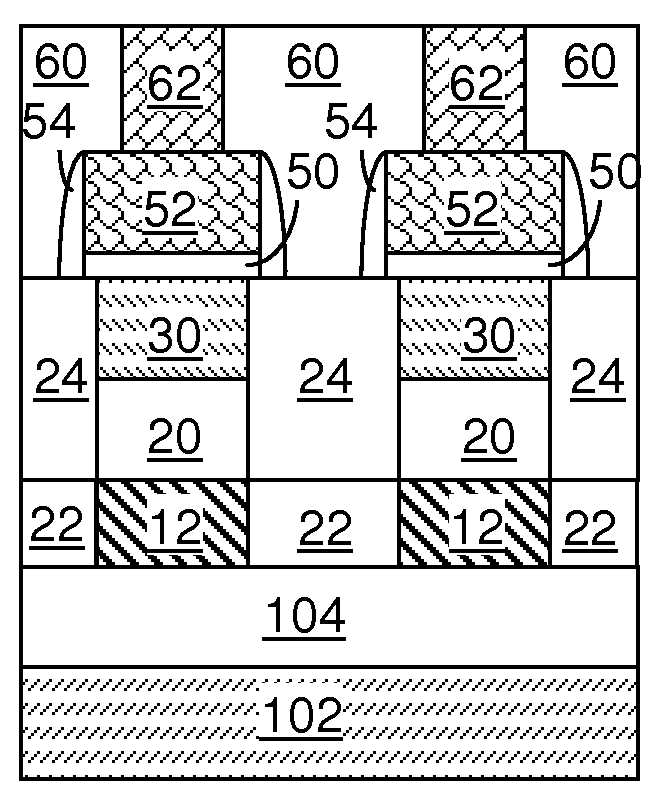

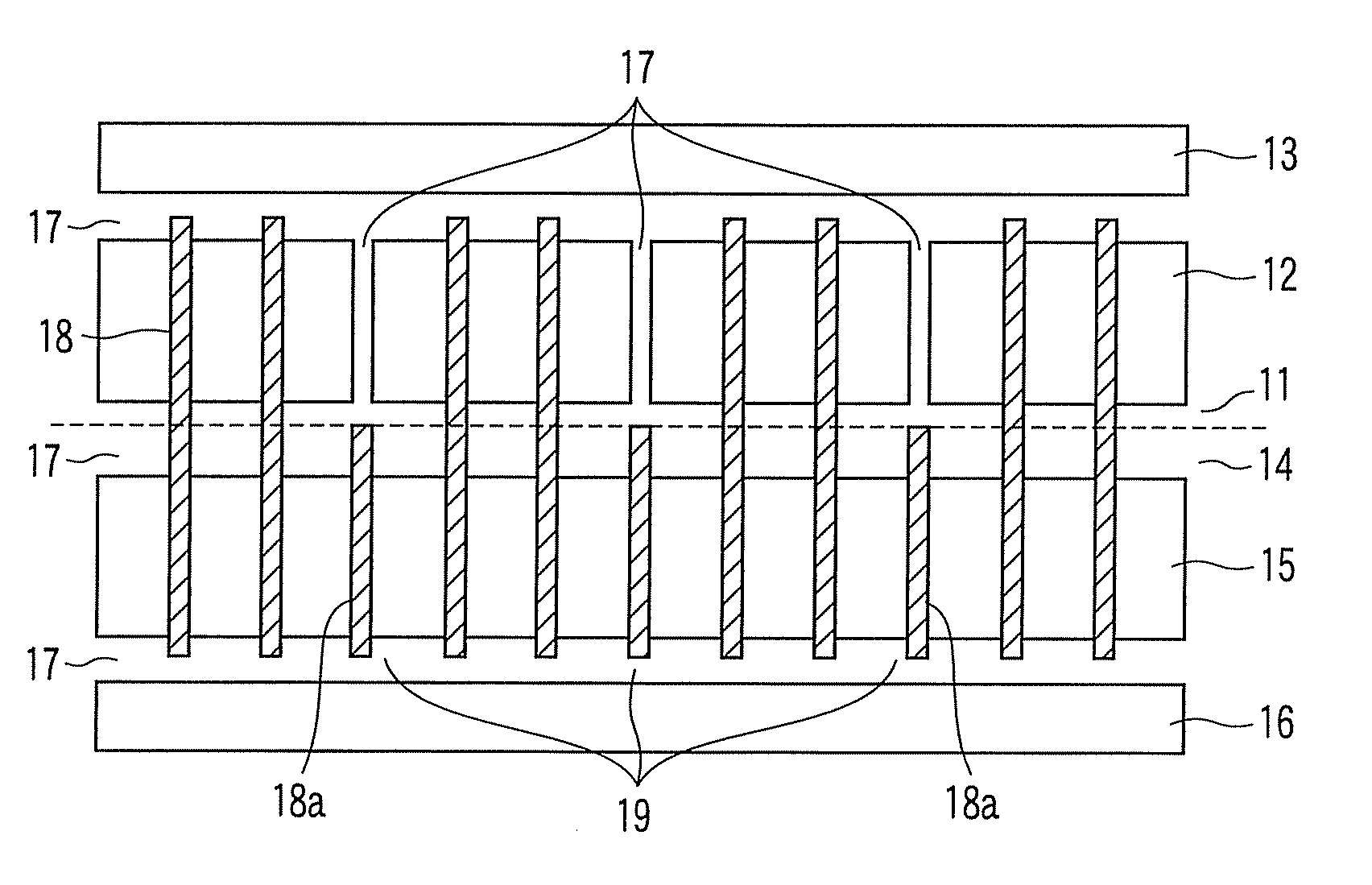

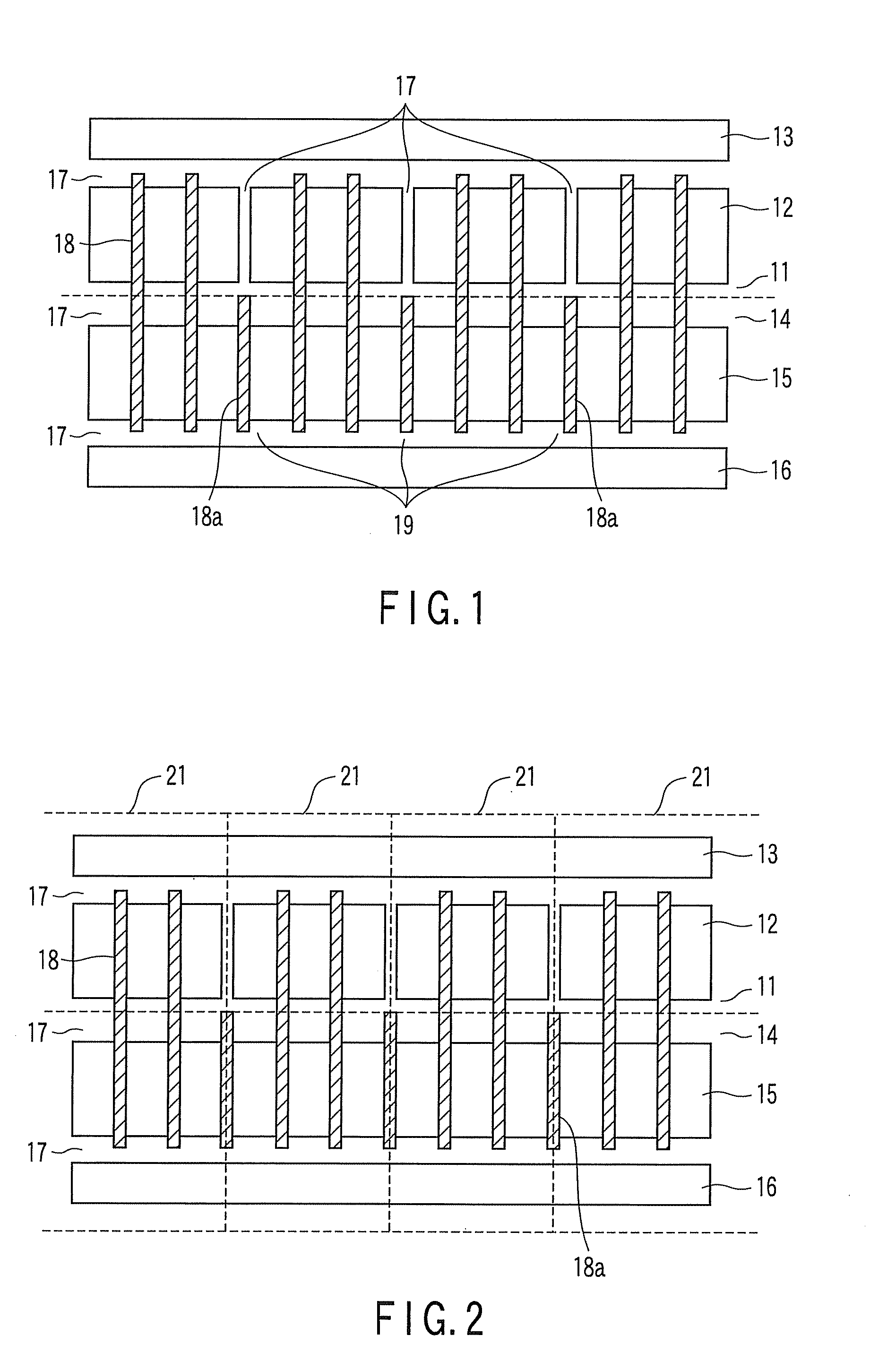

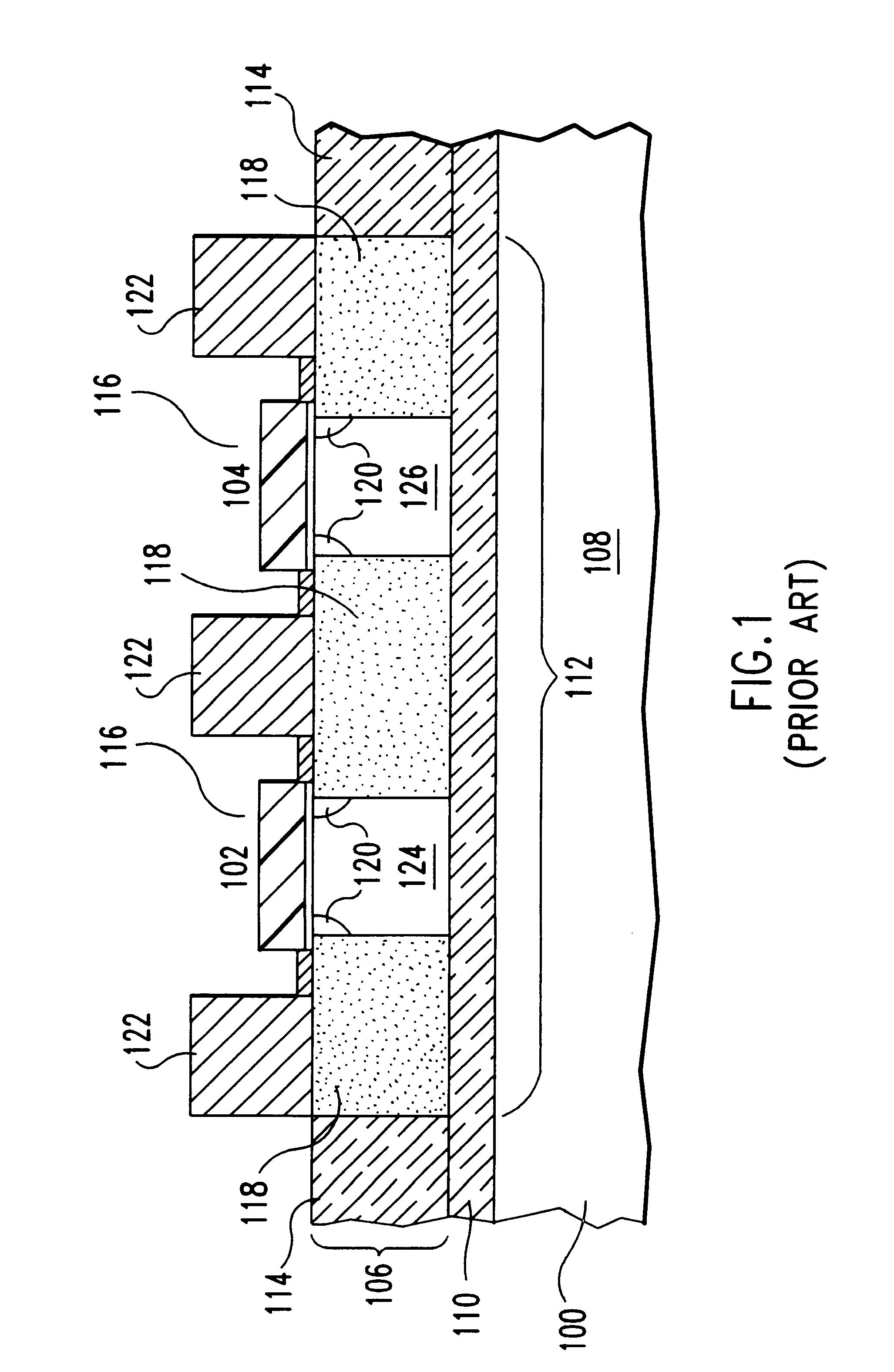

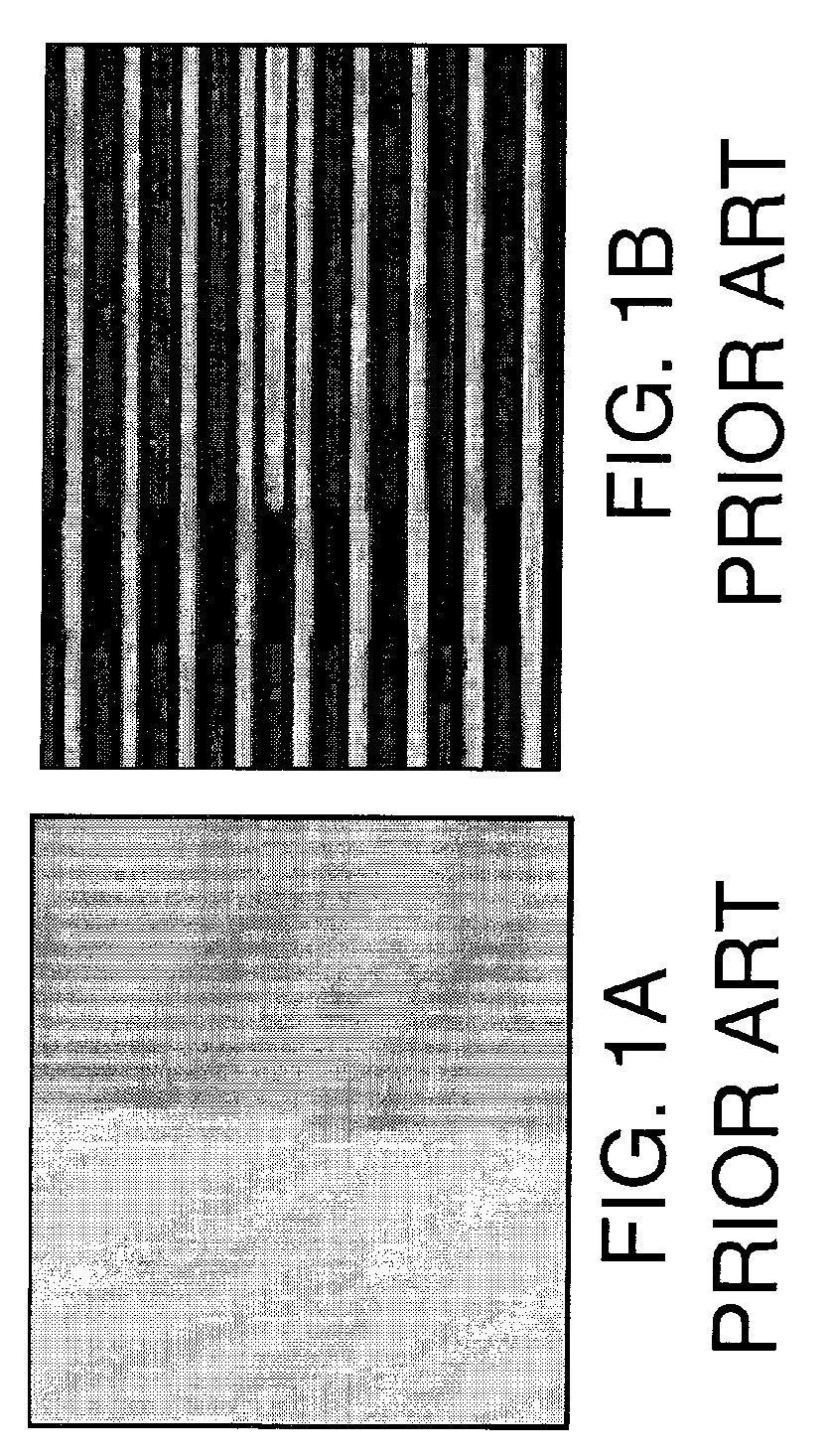

Silicon on insulator field effect transistors having shared body contact

InactiveUS6624459B1Improve memory cell stabilityImprove stabilityTransistorSolid-state devicesBit lineBody contact

Silicon on insulator (SOI) field effect transistors (FET) with a shared body contact, a SRAM cell and array including the SOI FETs and the method of forming the SOI FETs. The SRAM cell has a hybrid SOI / bulk structure wherein the source / drain diffusions do not penetrate to the underlying insulator layer, resulting in a FET in the surface of an SOI layer with a body or substrate contact formed at a shared contact. FETs are formed on SOI silicon islands located on a BOX layer and isolated by shallow trench isolation (STI). NFET islands in the SRAM cells include a body contact to a P-type diffusion in the NFET island. Each NFET in the SRAM cells include at least one shallow source / drain diffusion that is shallower than the island thickness. A path remains under the shallow diffusions between NFET channels and the body contact. The P-type body contact diffusion is a deep diffusion, the full thickness of the island. Bit line diffusions shared by SRAM cells on adjacent wordlines may be deep diffusions.

Owner:INT BUSIENSS MACHINES IBM +1

Selective epitaxial growth for tunable channel thickness

ActiveUS7105399B1Increasing the thicknessReadily apparentSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSoi substrate

Gate electrodes with selectively tuned channel thicknesses are formed by selective epitaxial growth. Embodiments include forming shallow trench isolation regions in an SOI substrate, selectively removing the nitride stop layer and pad oxide layer in an exposed particular active region, and implementing selective epitaxial growth to increase the thickness of the semiconductor layer in the particular active region. Subsequently, the remaining nitride stop and pad oxide layers in other active regions are removed, gate dielectric layers formed, as by thermal oxidation, and the transistors completed.

Owner:GLOBALFOUNDRIES US INC

Multi-structured Si-fin

InactiveUS7141856B2Point becomes highGood planarityTransistorSemiconductor/solid-state device detailsDevice materialEngineering

Disclosed is a semiconductor fin construction useful in FinFET devices that incorporates an upper region and a lower region with wherein the upper region is formed with substantially vertical sidewalls and the lower region is formed with inclined sidewalls to produce a wider base portion. The disclosed semiconductor fin construction will also typically include a horizontal step region at the interface between the upper region and the lower region. Also disclosed are a series of methods of manufacturing semiconductor devices incorporating semiconductor fins having this dual construction and incorporating various combinations of insulating materials such as silicon dioxide and / or silicon nitride for forming shallow trench isolation (STI) structures between adjacent semiconductor fins.

Owner:SAMSUNG ELECTRONICS CO LTD

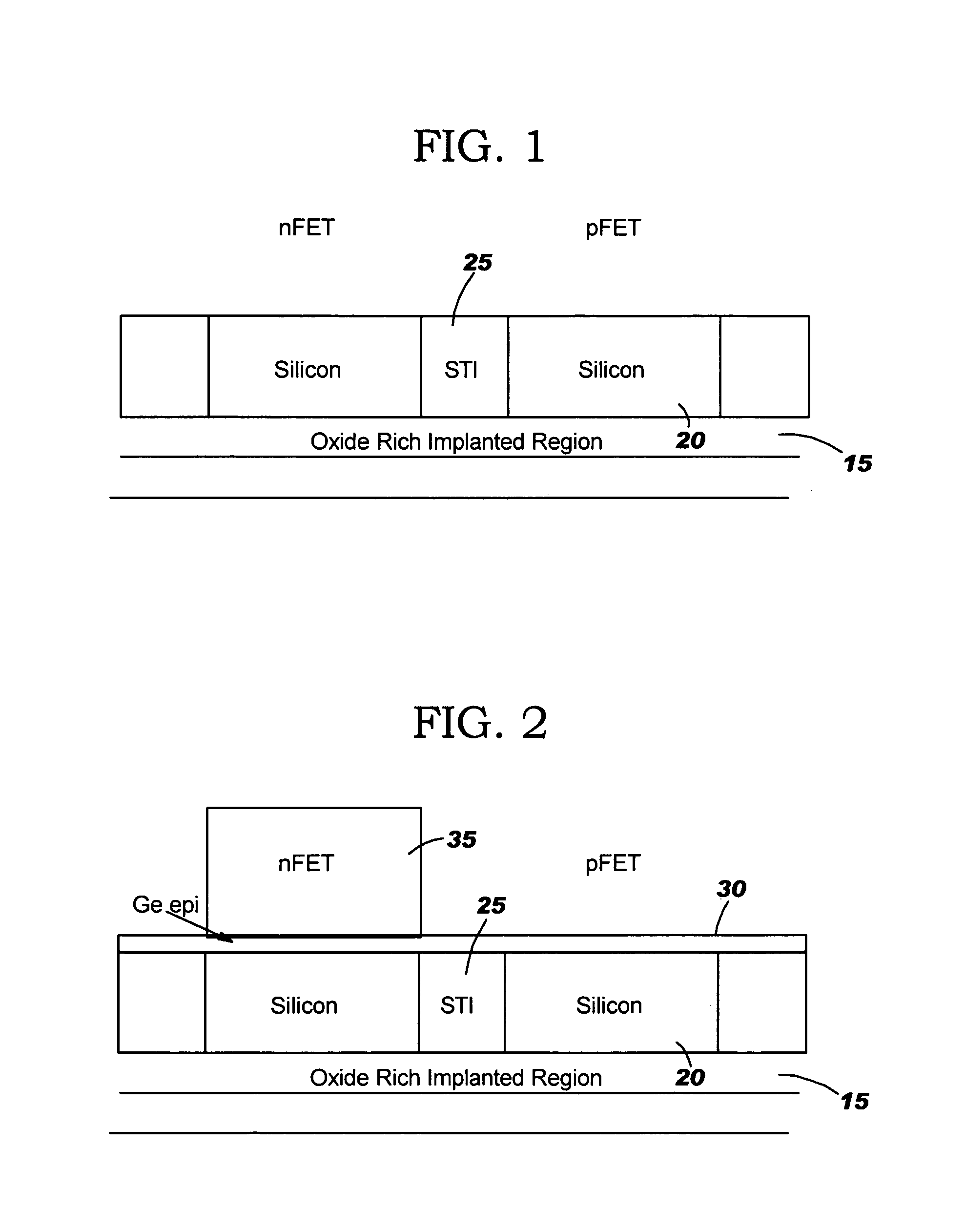

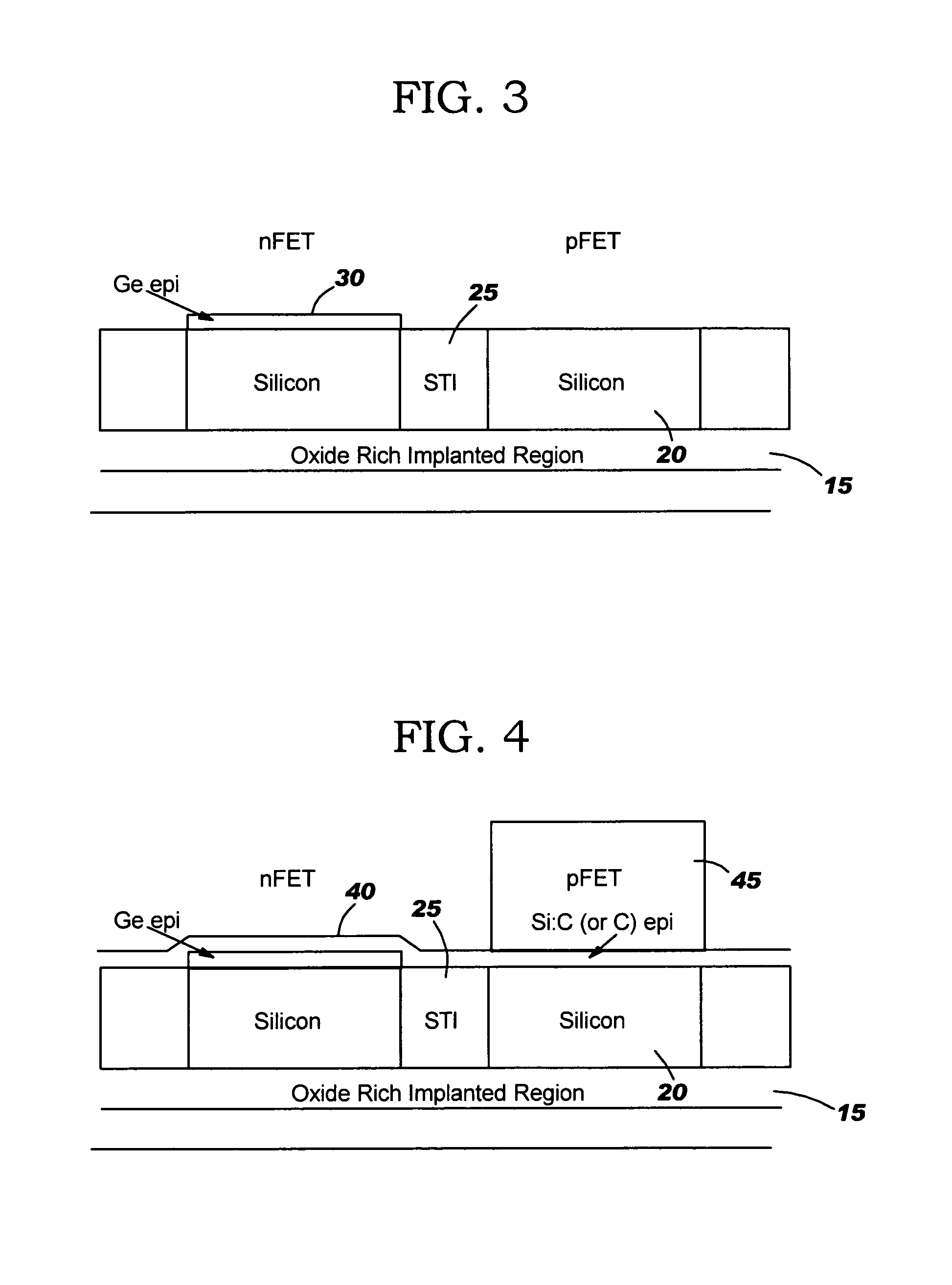

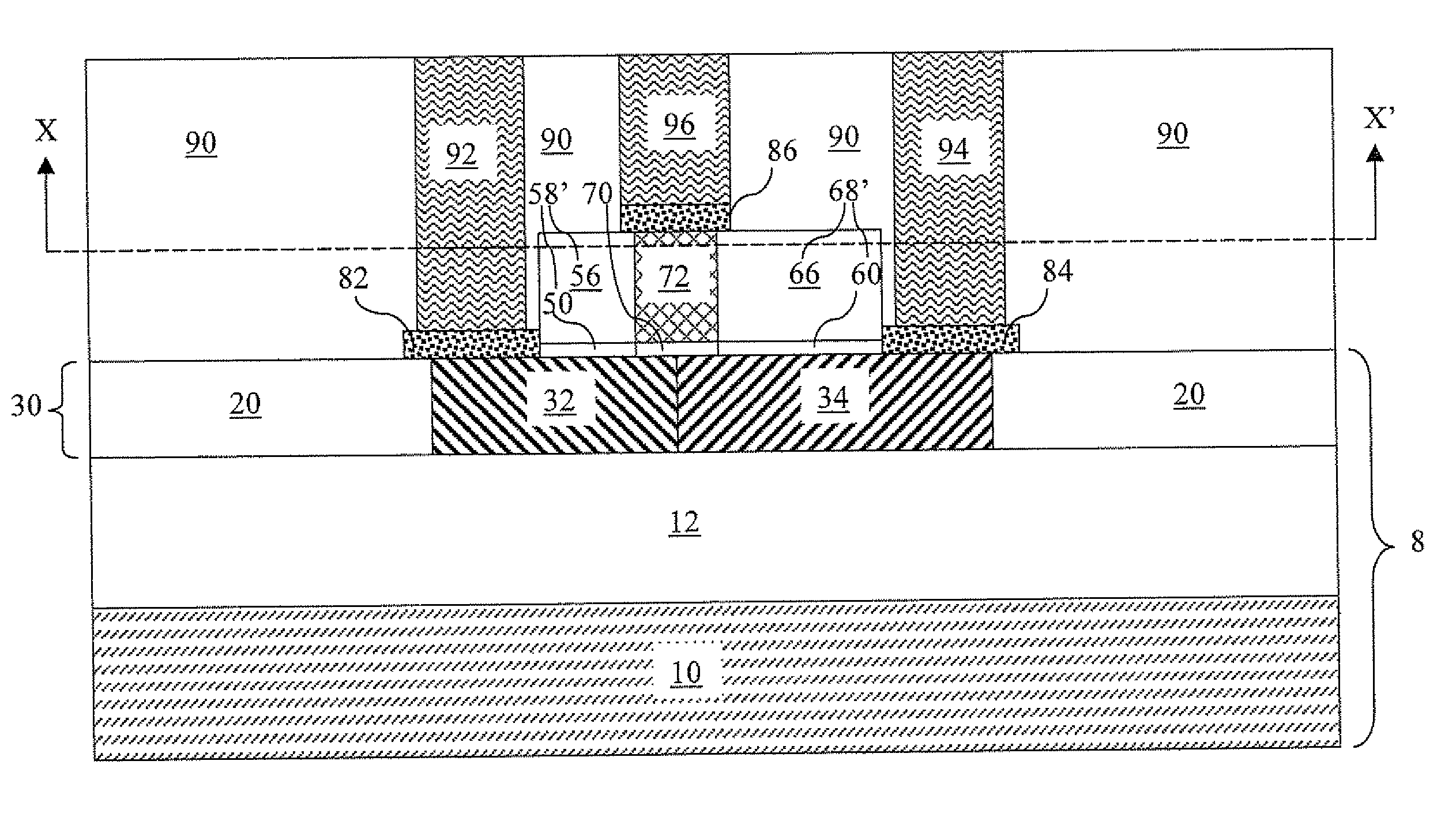

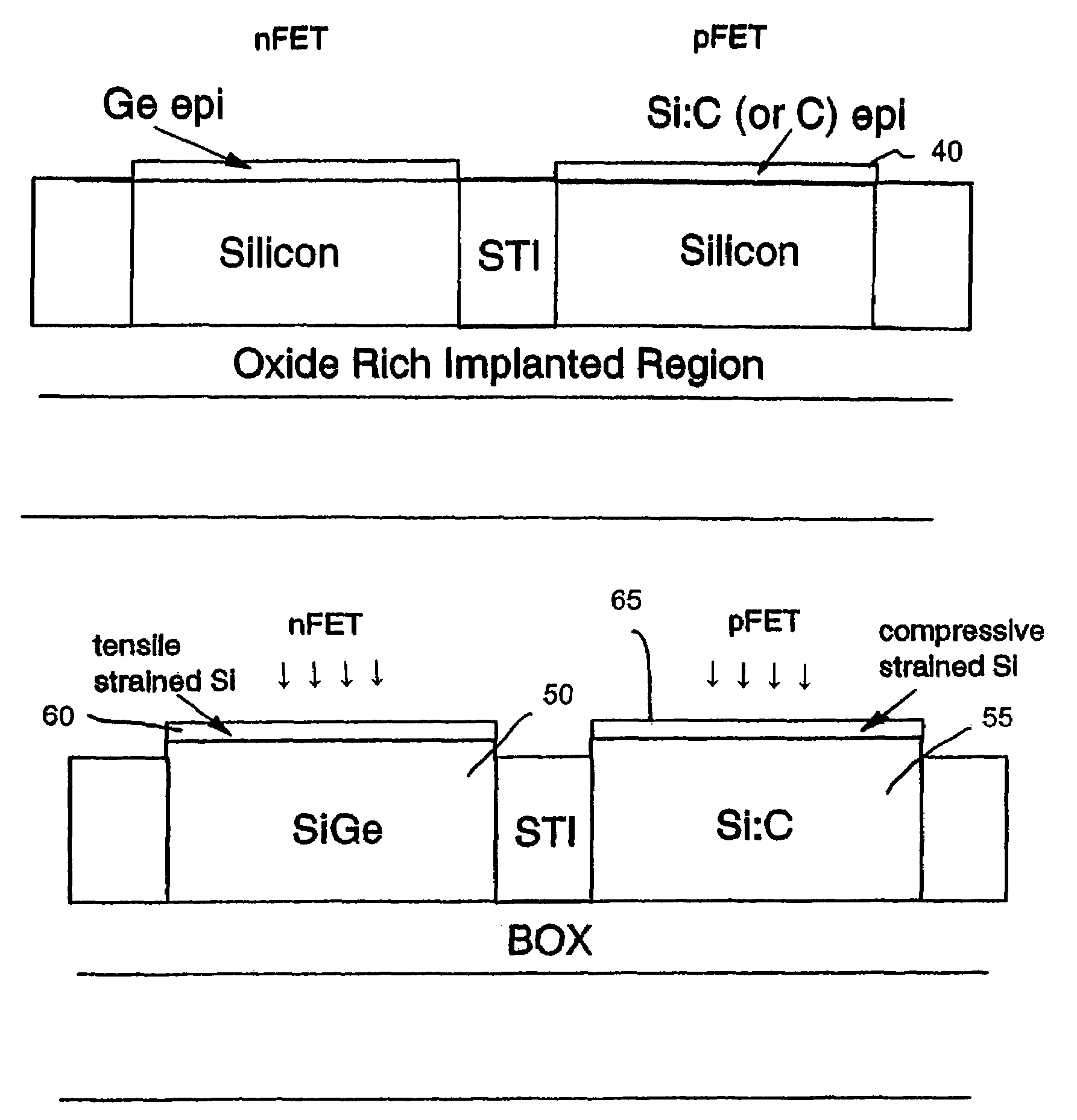

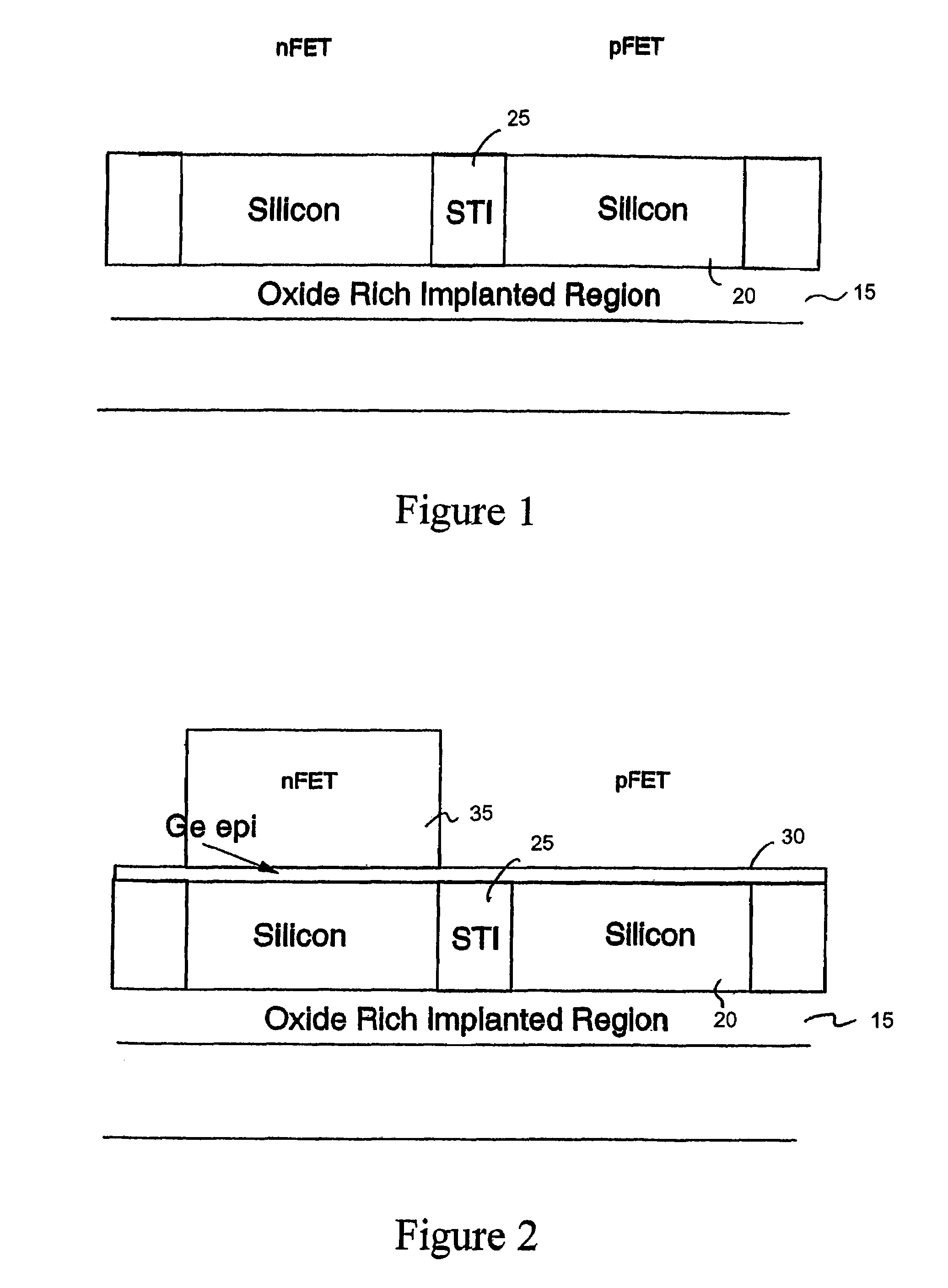

Silicon device on Si:C-OI and SGOI and method of manufacture

A semiconductor structure and method of manufacturing is provided. The method of manufacturing includes forming shallow trench isolation (STI) in a substrate and providing a first material and a second material on the substrate. The first material and the second material are mixed into the substrate by a thermal anneal process to form a first island and second island at an nFET region and a pFET region, respectively. A layer of different material is formed on the first island and the second island. The STI relaxes and facilitates the relaxation of the first island and the second island. The first material may be deposited or grown Ge material and the second material may deposited or grown Si:C or C. A strained Si layer is formed on at least one of the first island and the second island.

Owner:IBM CORP

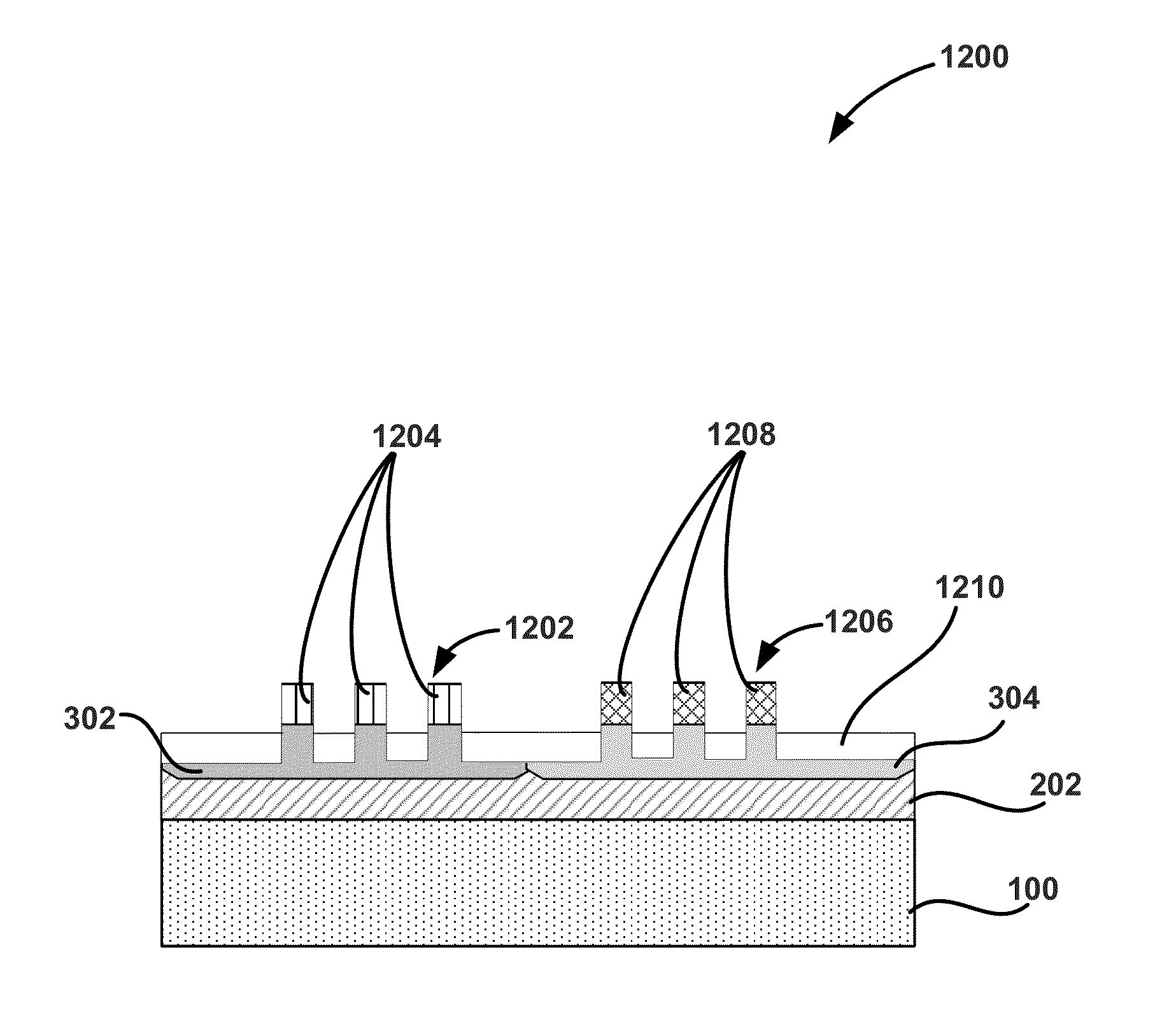

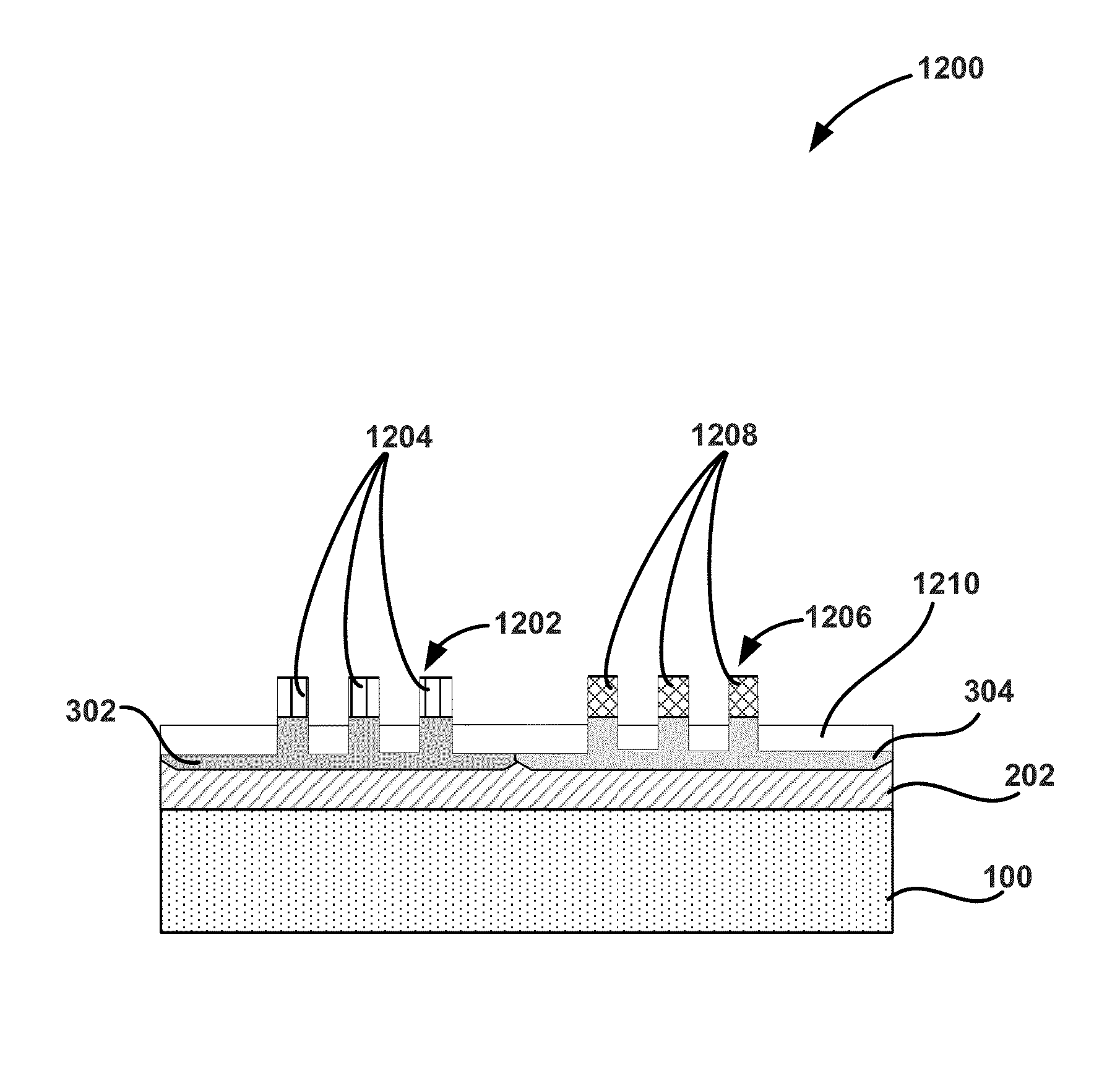

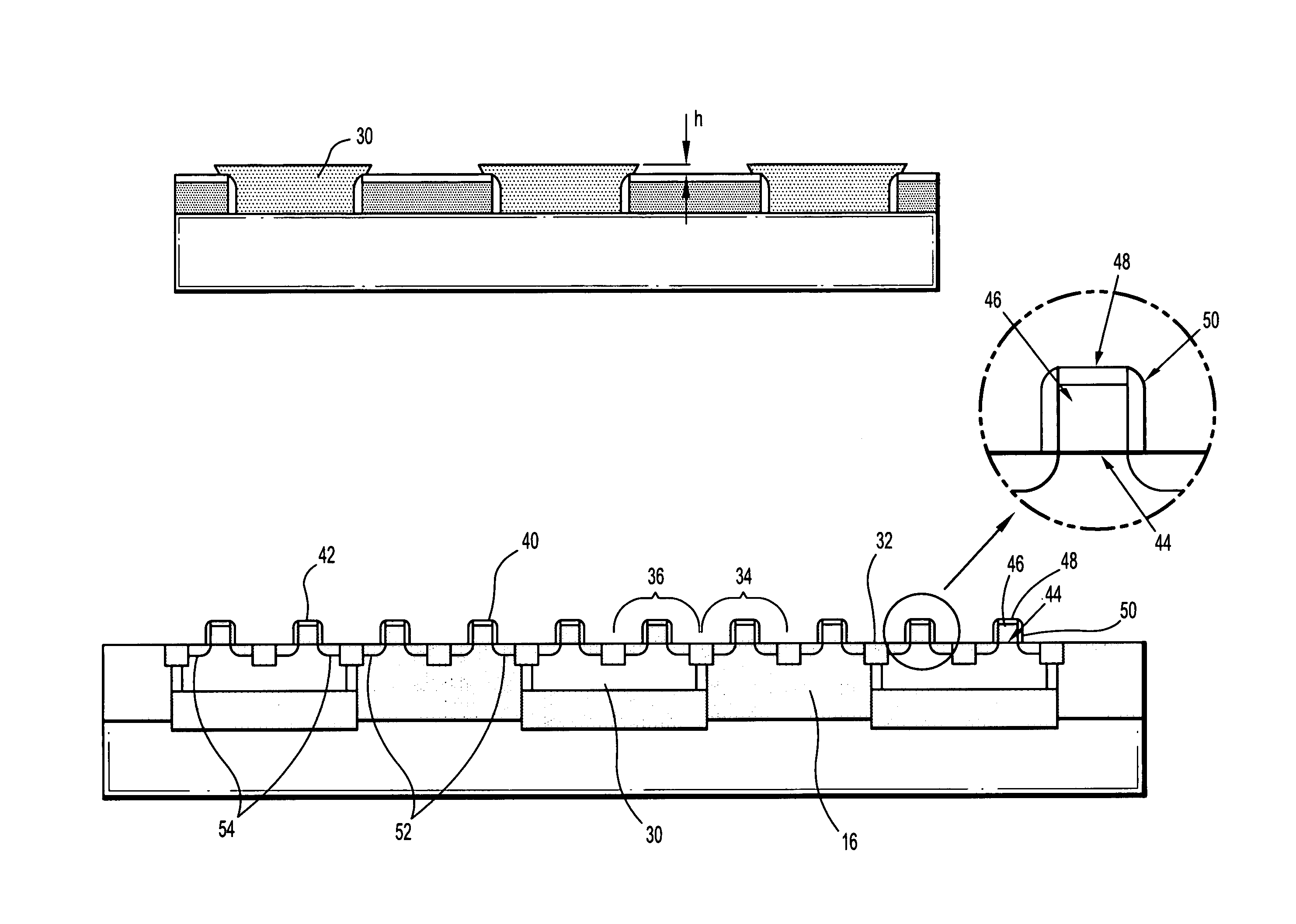

CMOS well structure and method of forming the same

A method for forming a CMOS well structure including forming a plurality of first conductivity type wells over a substrate, each of the plurality of first conductivity type wells formed in a respective opening in a first mask. A cap is formed over each of the first conductivity type wells, and the first mask is removed. Sidewall spacers are formed on sidewalls of each of the first conductivity type wells. A plurality of second conductivity type wells are formed, each of the plurality of second conductivity type wells are formed between respective first conductivity type wells. A plurality of shallow trench isolations are formed between the first conductivity type wells and second conductive type wells. The plurality of first conductivity type wells are formed by a first selective epitaxial growth process, and the plurality of second conductivity type wells are formed by a second selective epitaxial growth process.

Owner:GLOBALFOUNDRIES U S INC

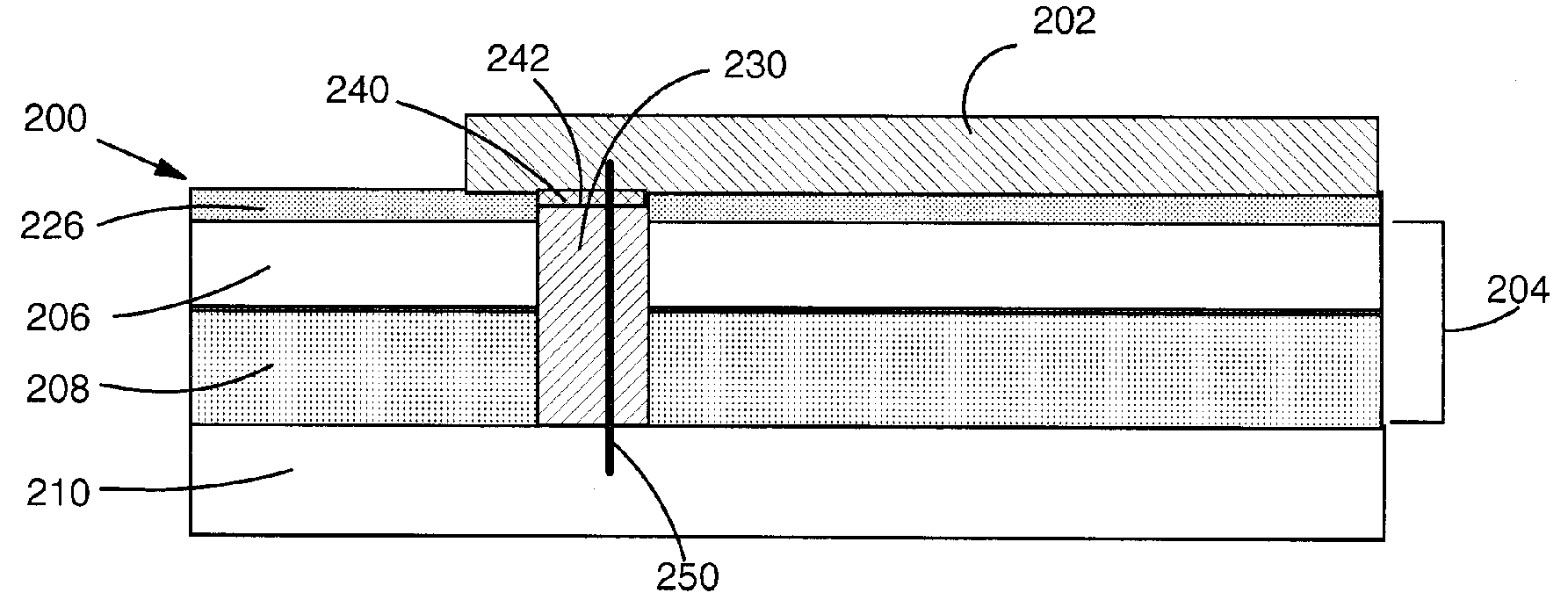

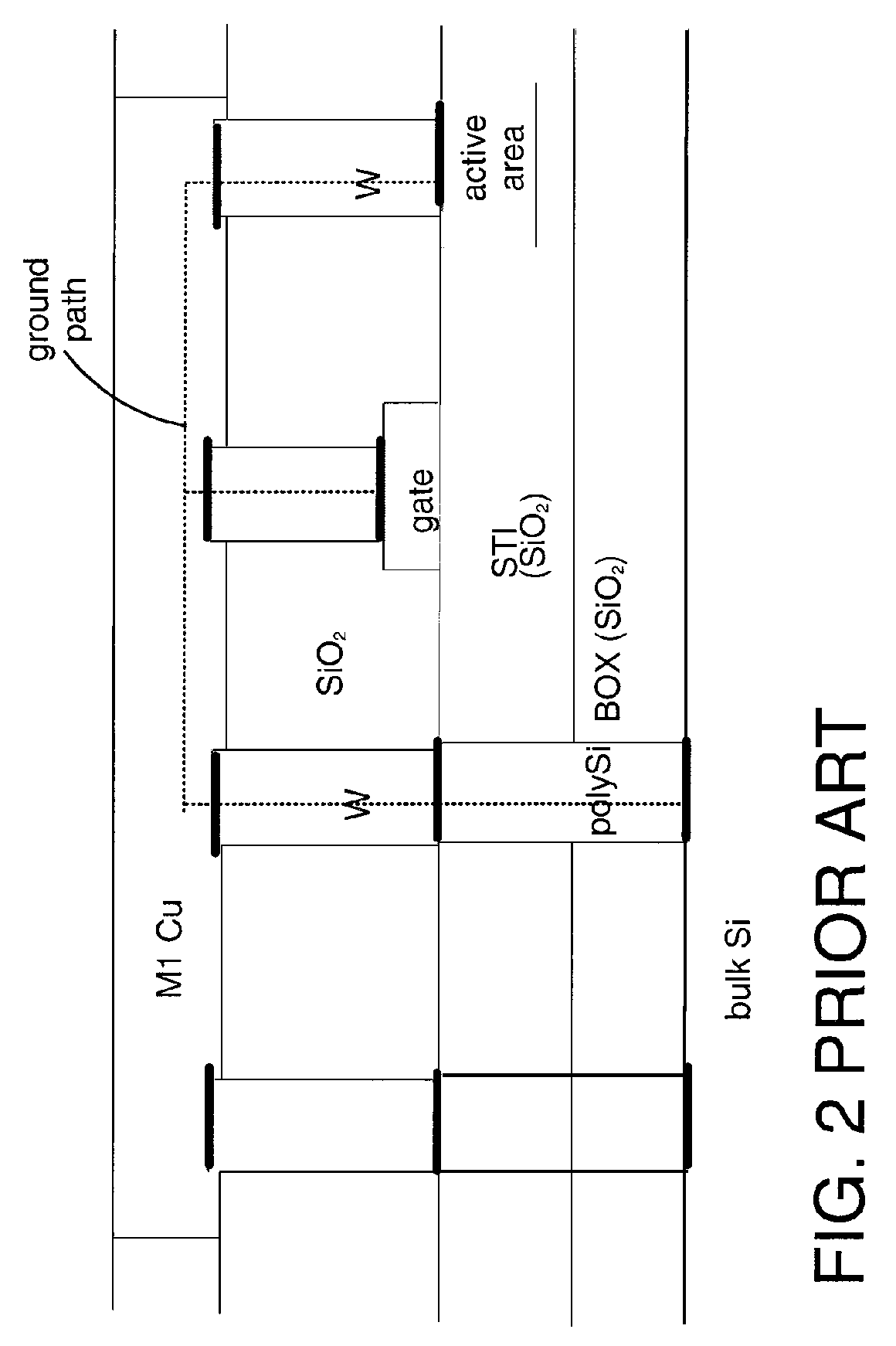

Grounding front-end-of-line structures on a SOI substrate

ActiveUS7518190B2Semiconductor/solid-state device detailsSolid-state devicesGround contactGate stack

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com