Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1871 results about "Deep trench" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

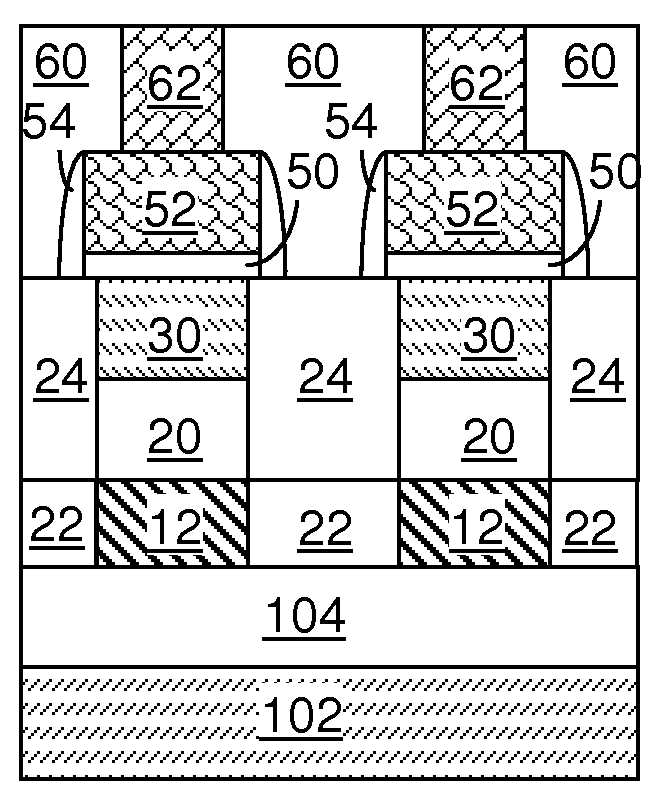

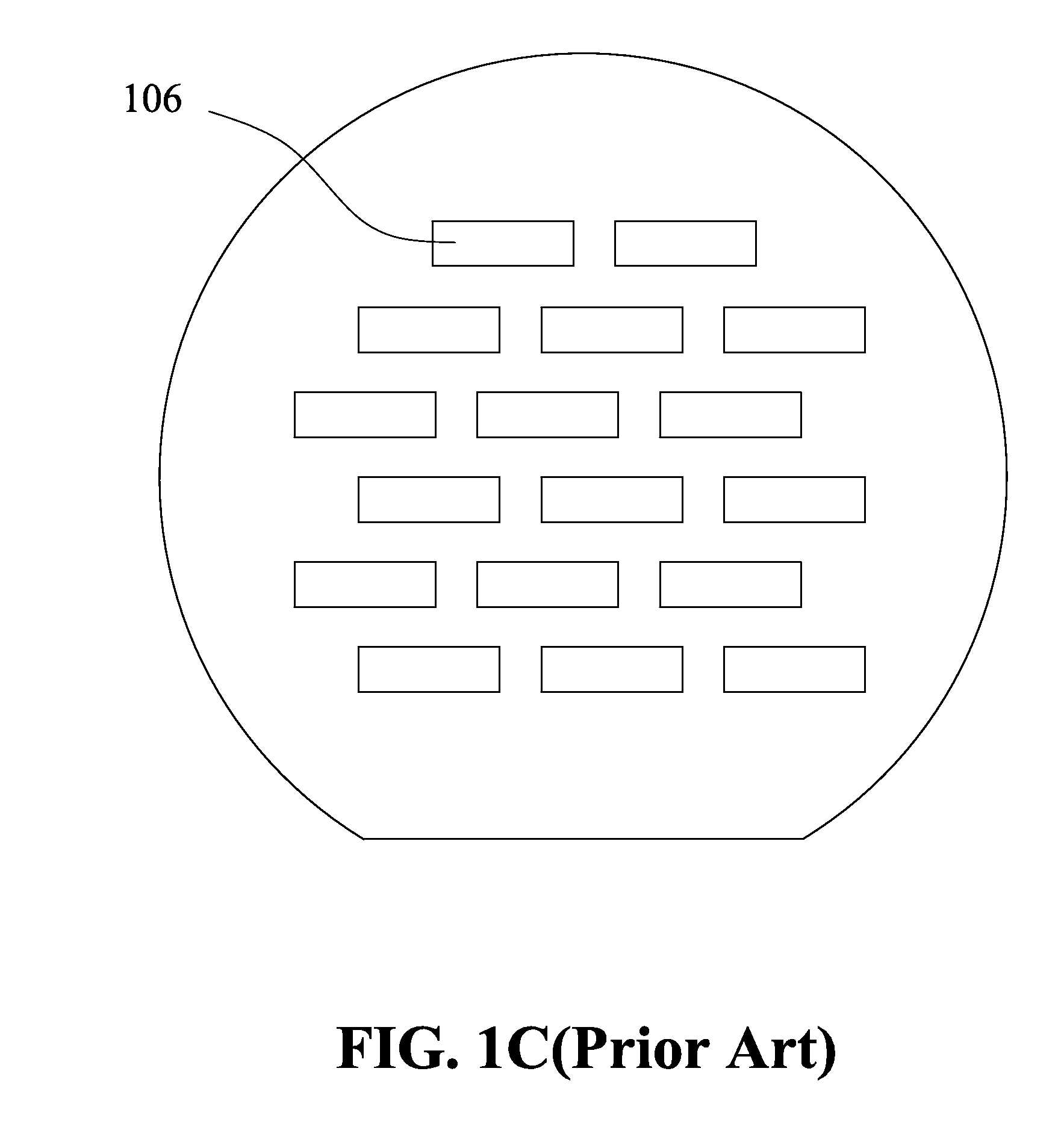

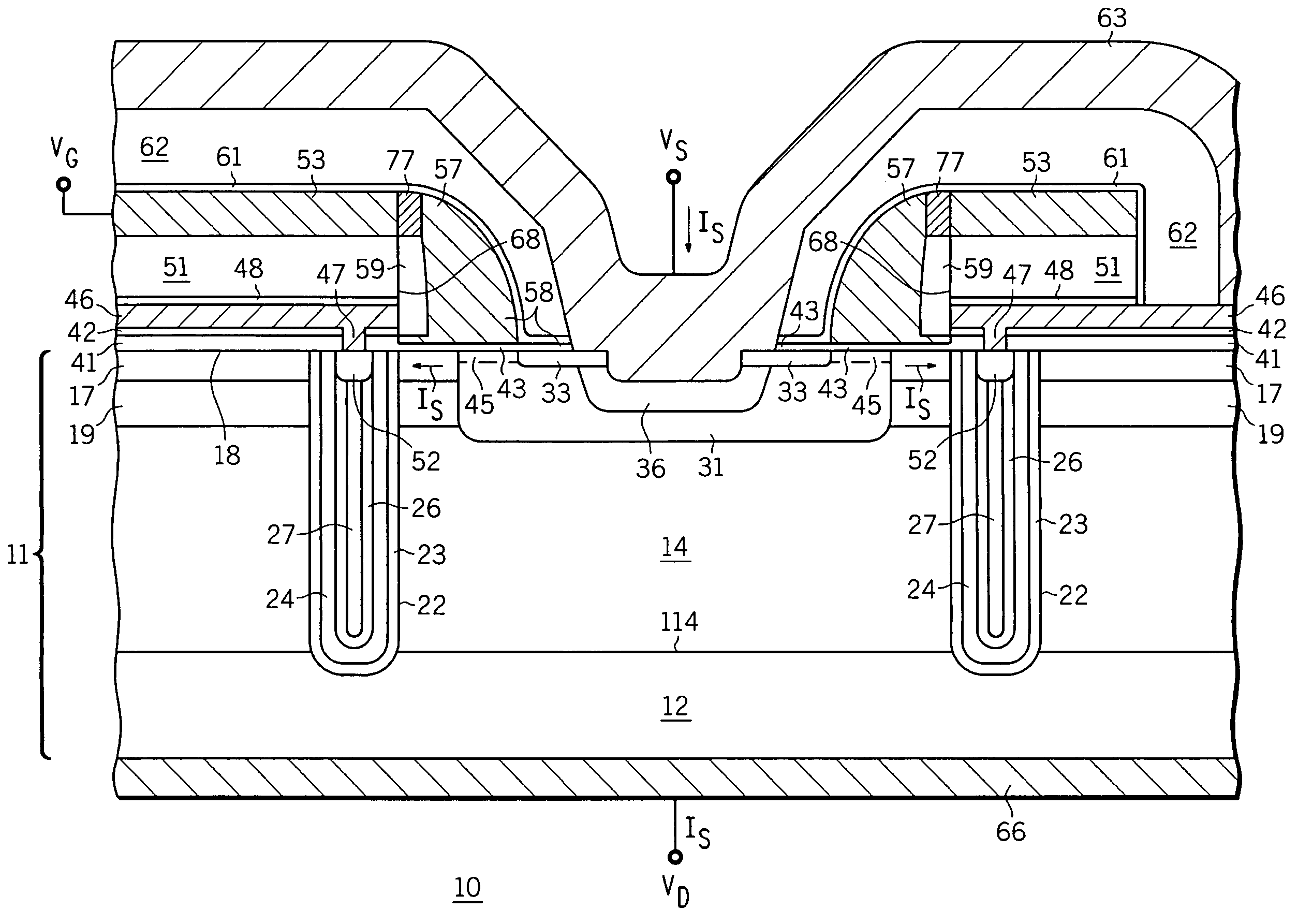

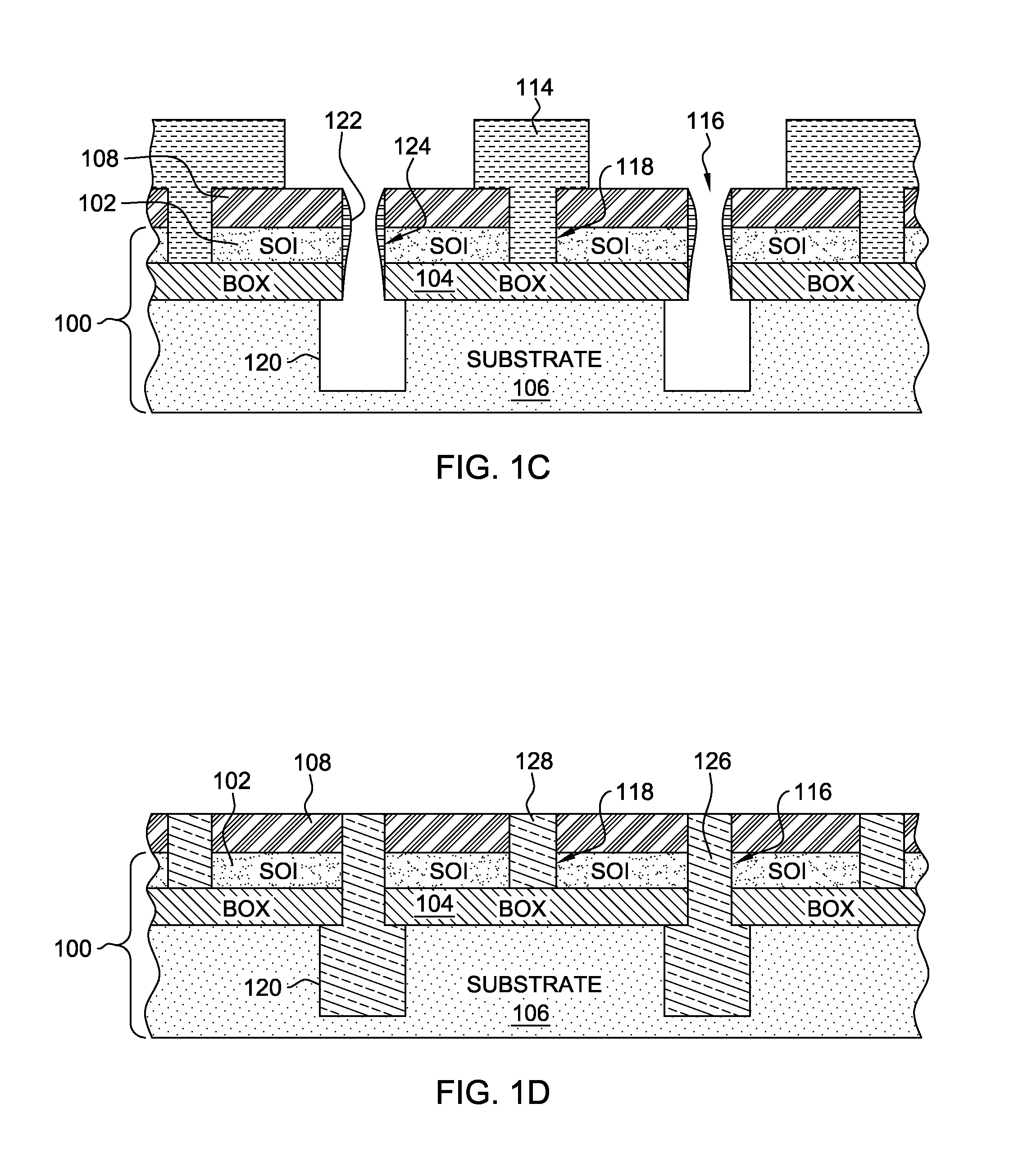

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

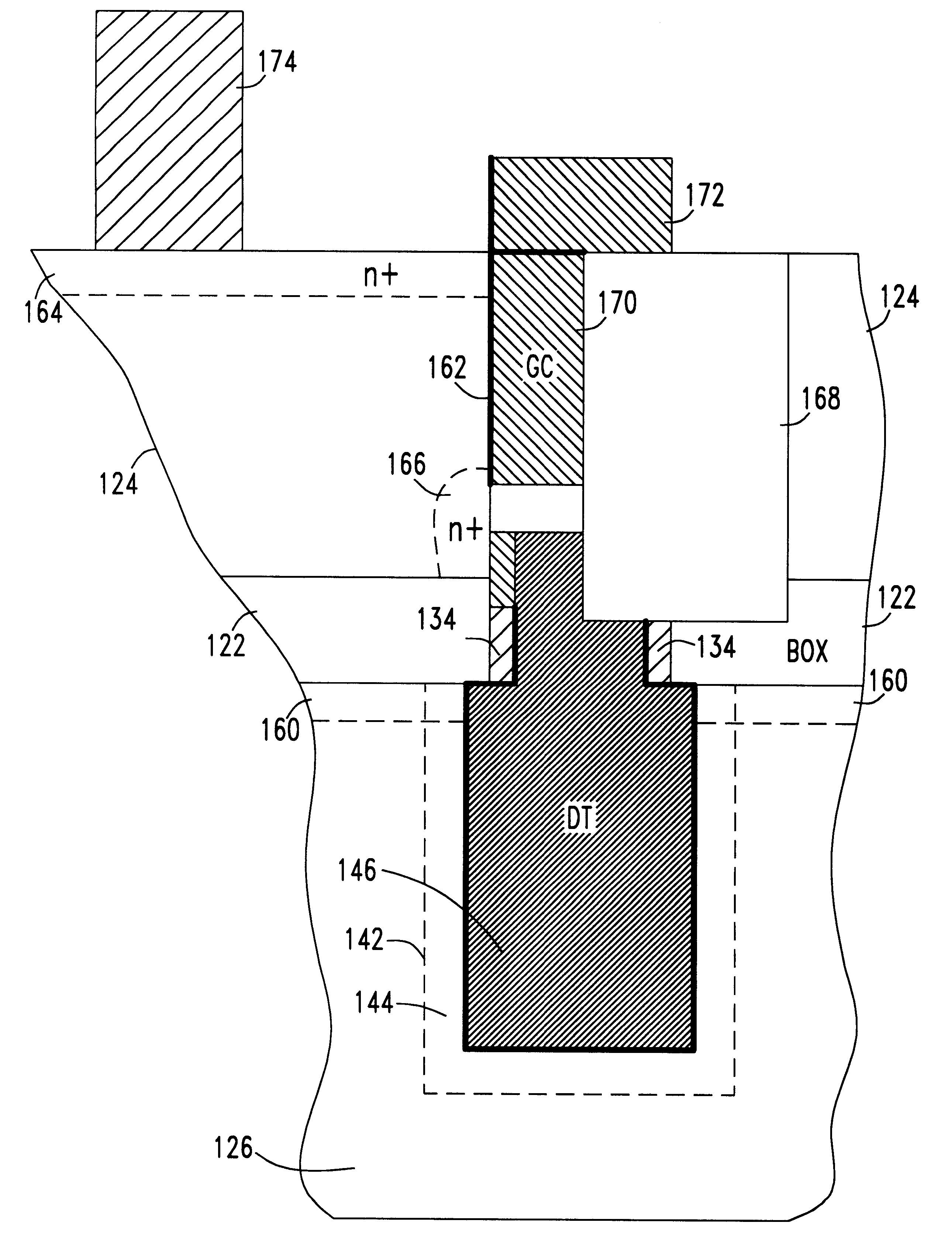

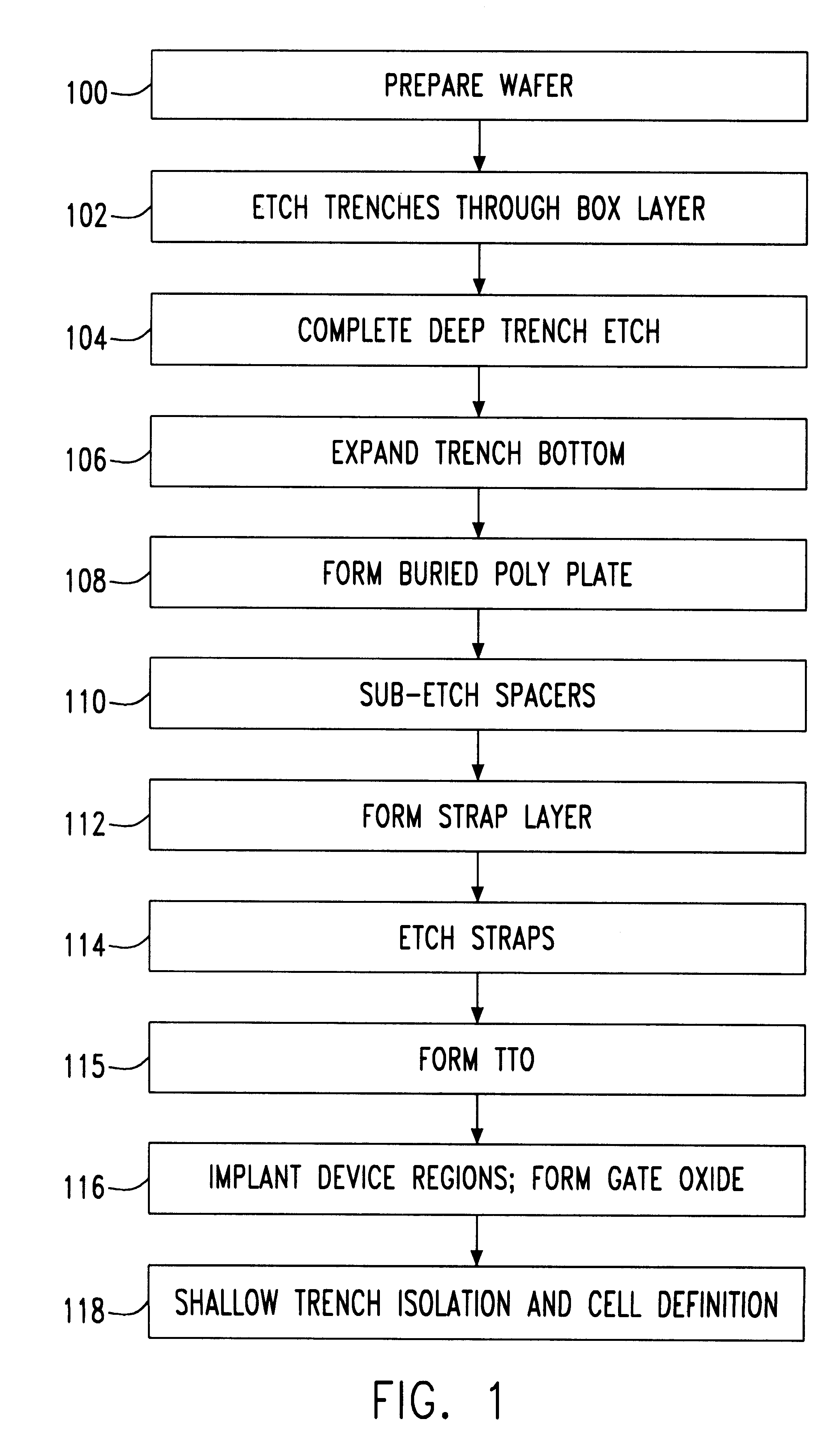

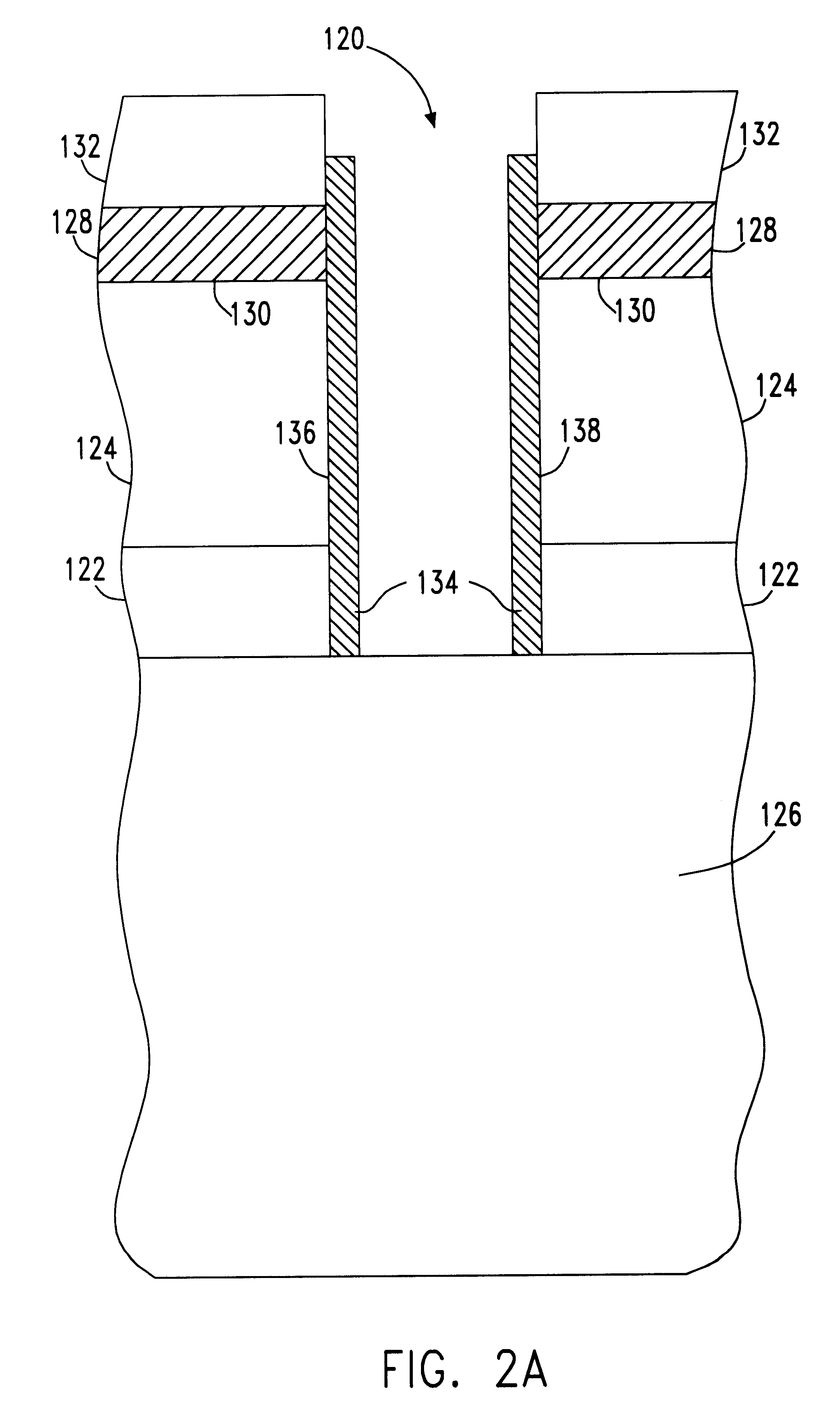

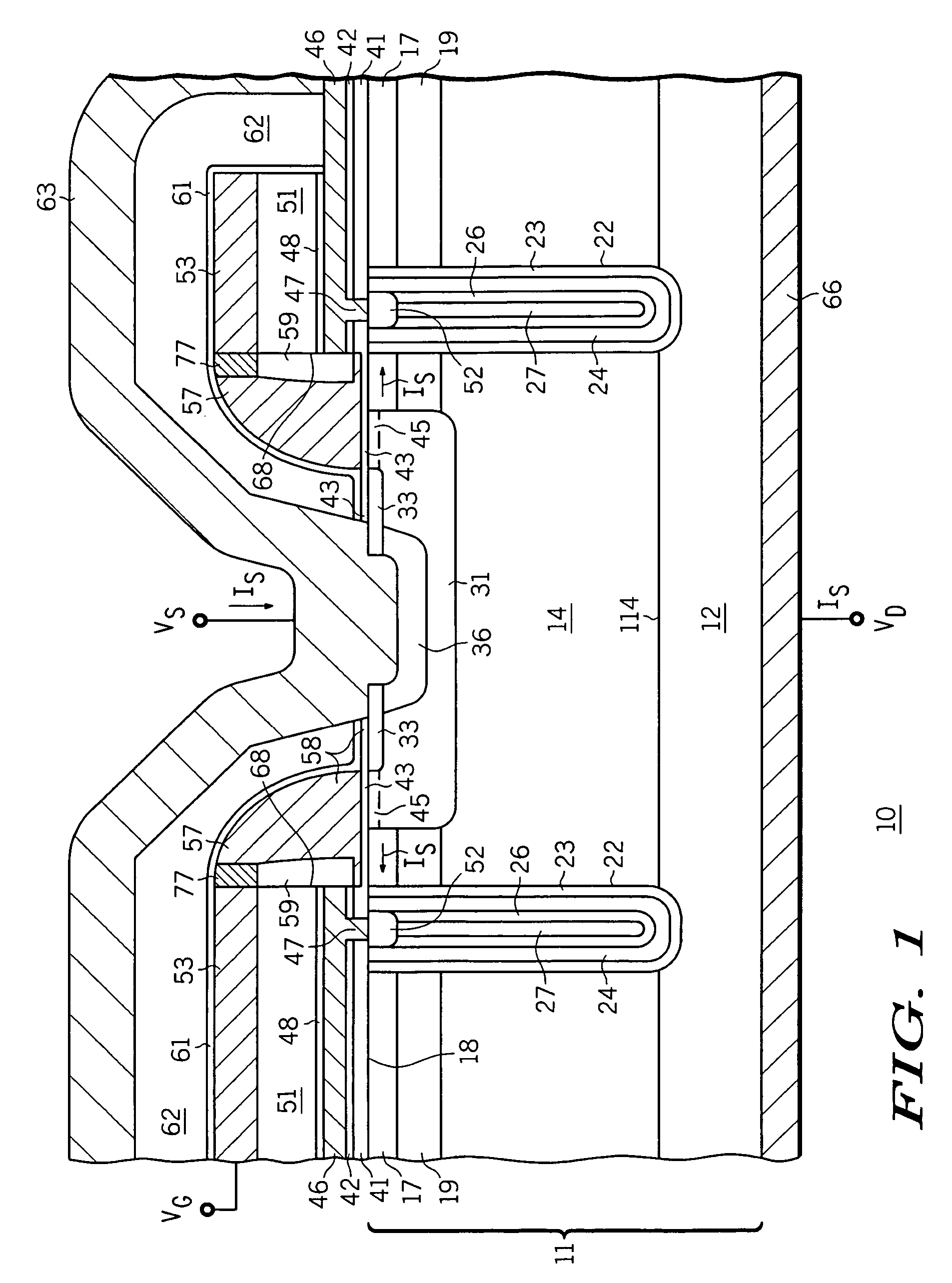

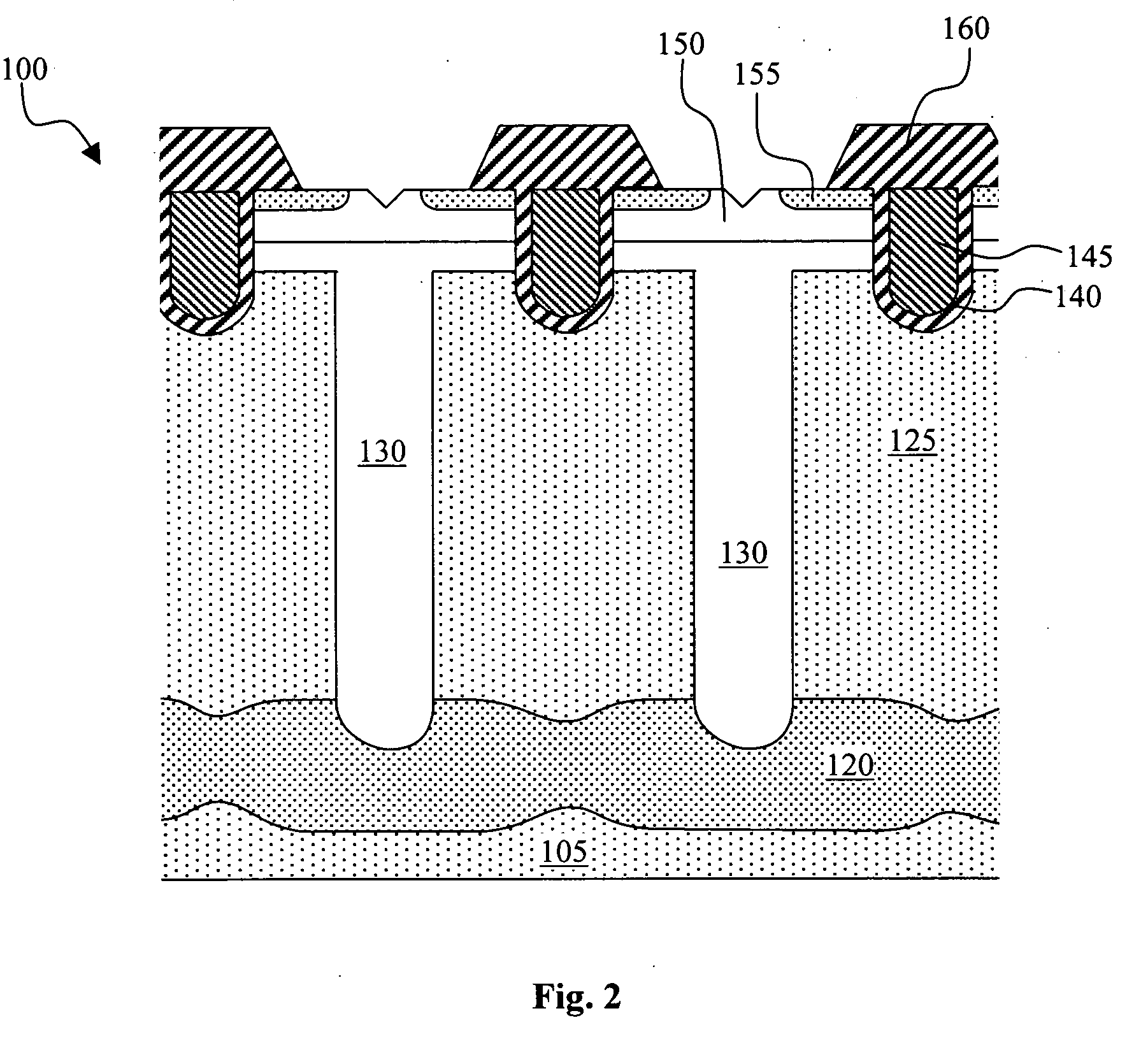

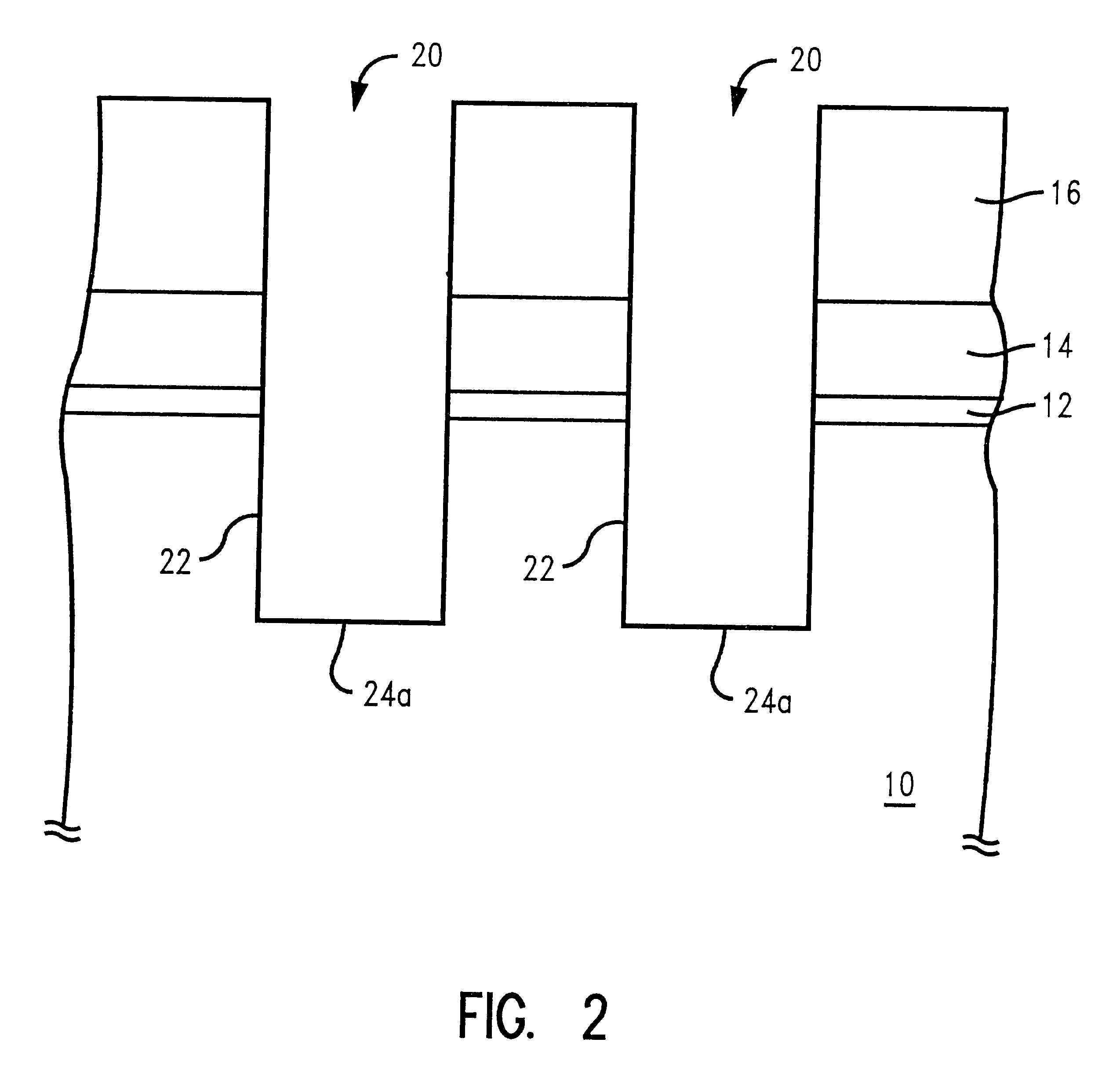

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

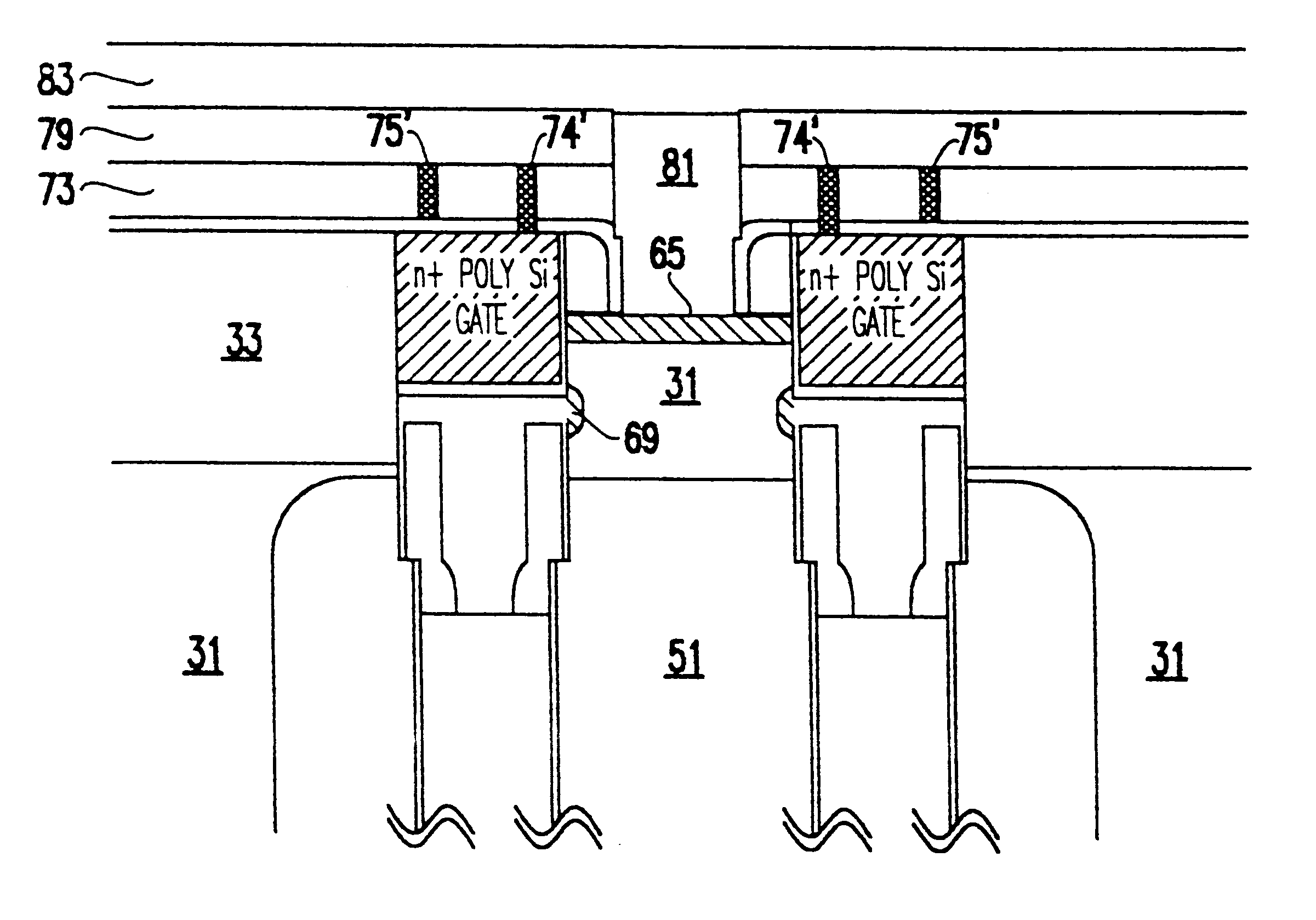

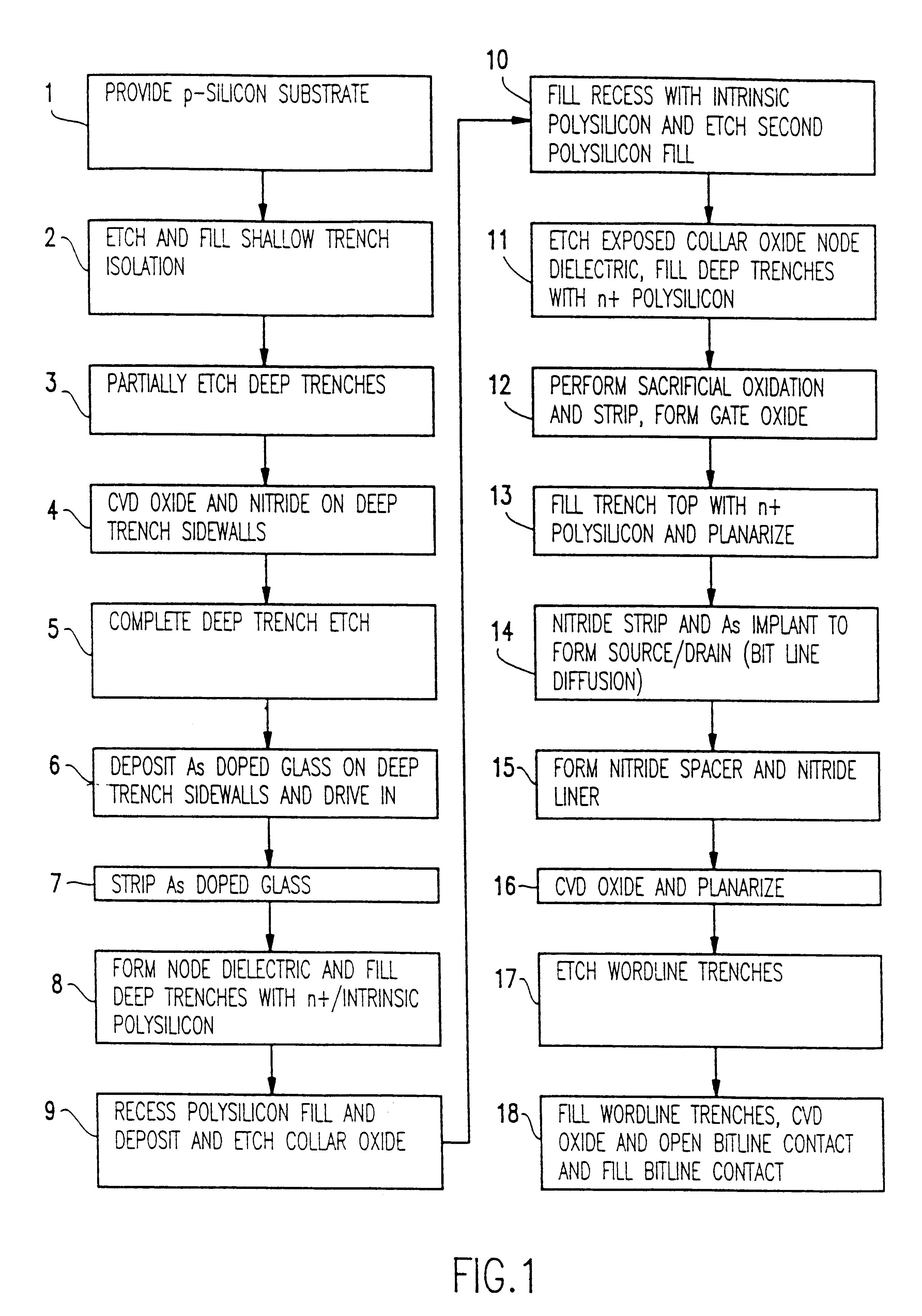

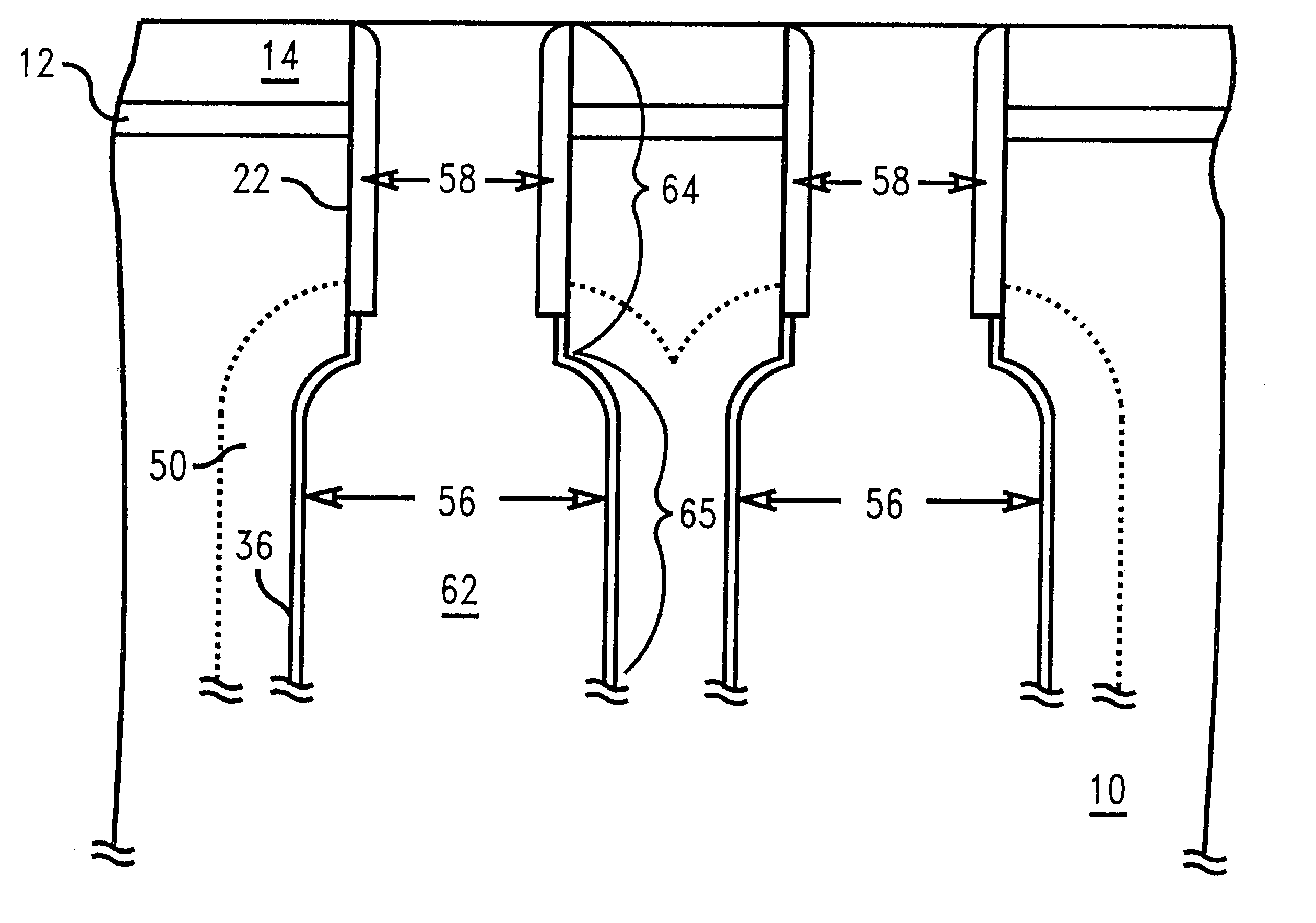

Trench storage dynamic random access memory cell with vertical transfer device

InactiveUS6225158B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringDeep trench

A trench storage dynamic random access memory cell with vertical transfer device can be formed in a wafer having prepared shallow trench isolation. Vertical transfer device is built as the deep trenches are formed. Using square printing to form shallow trench isolation and deep trenches, allows for scaling of the cell to very small dimensions.

Owner:GLOBALFOUNDRIES INC

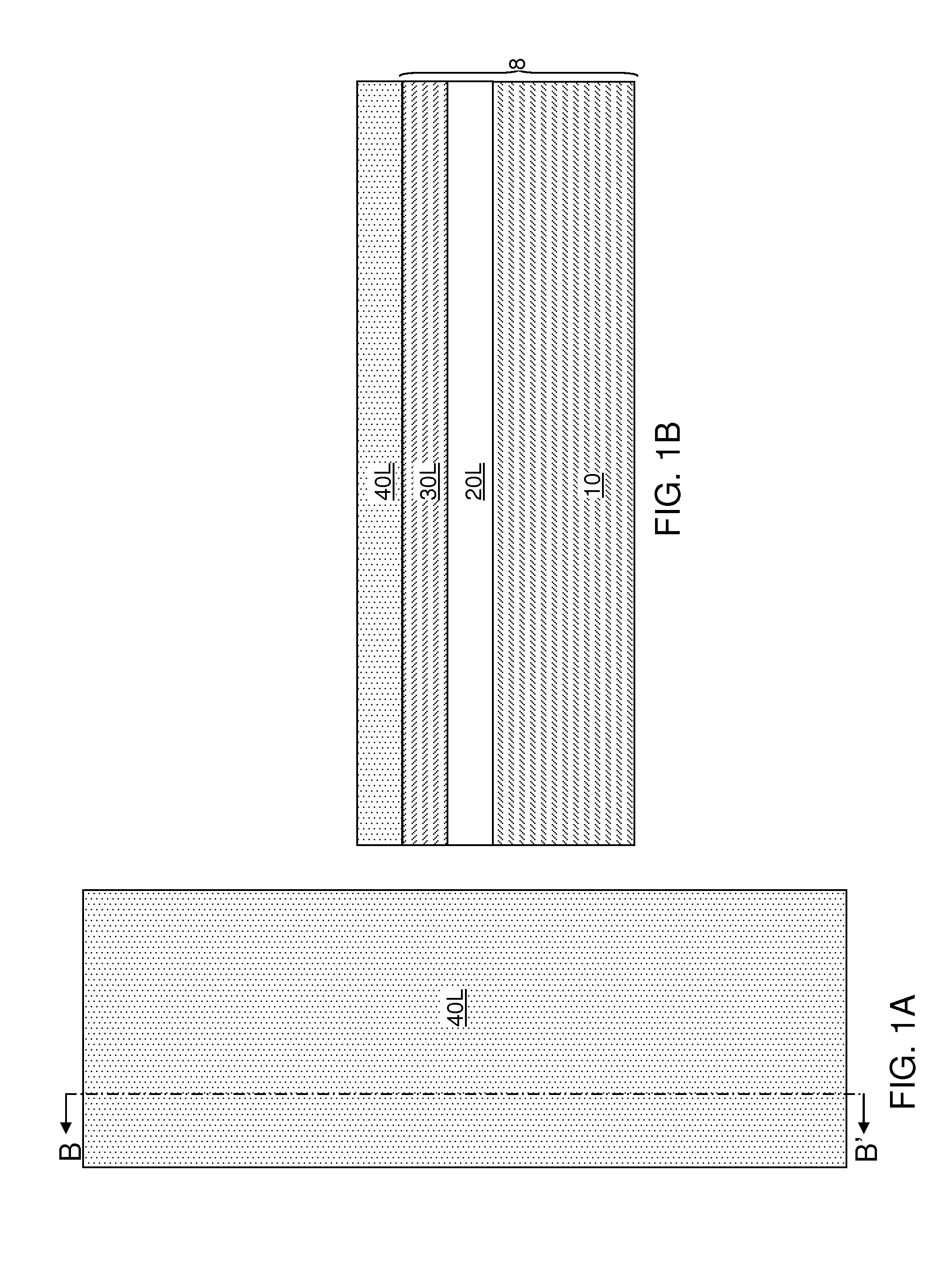

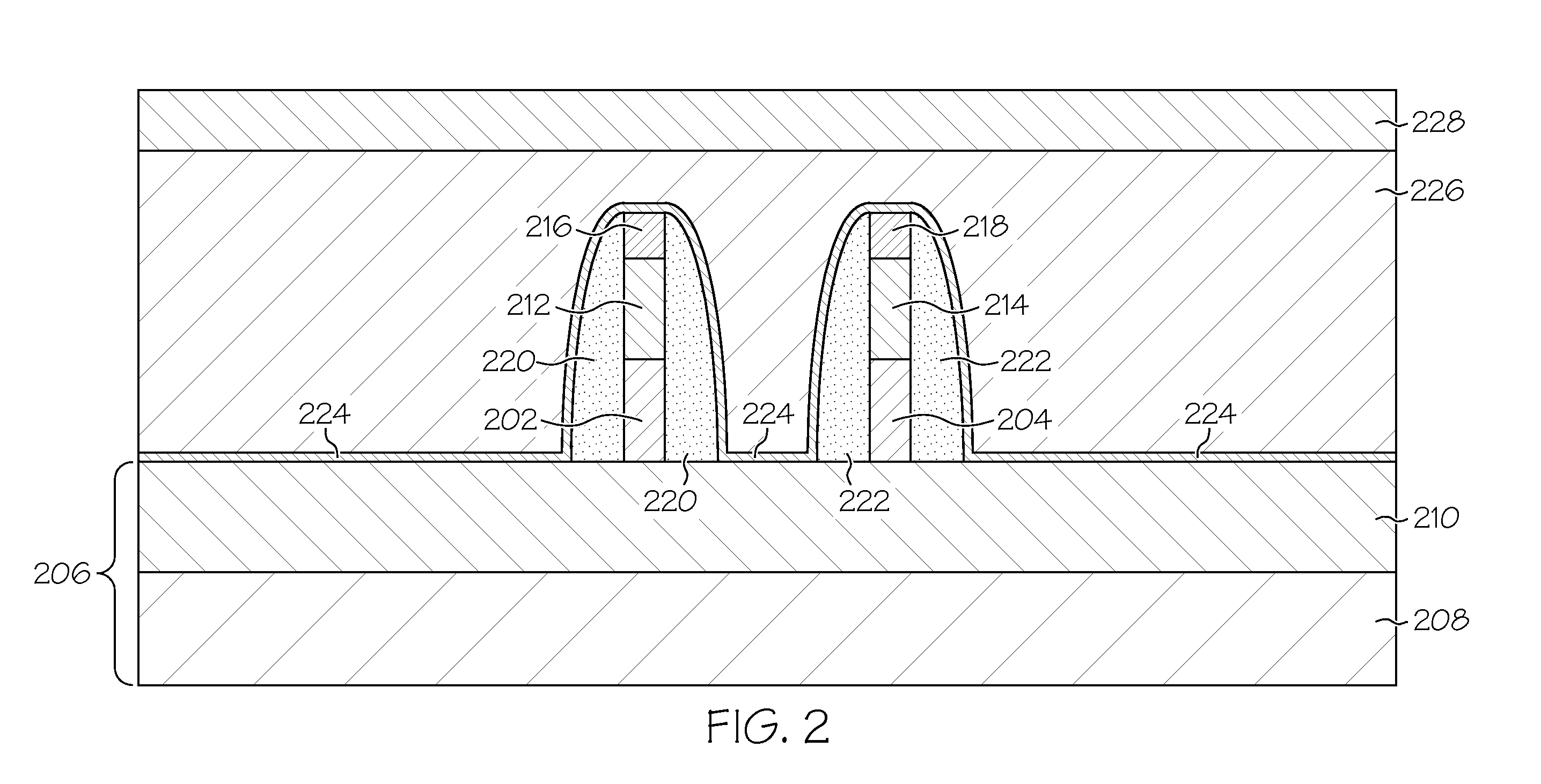

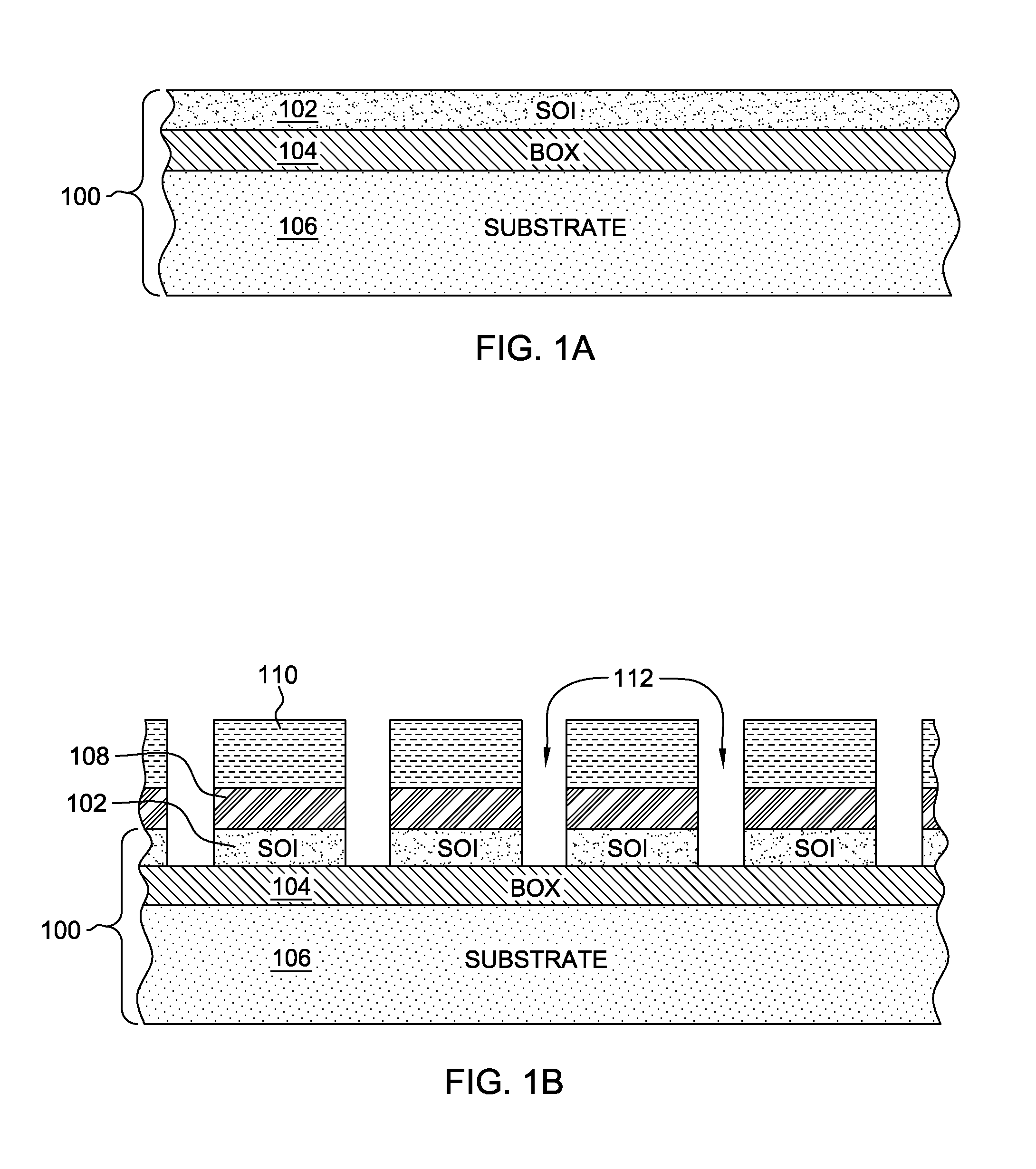

Dual-depth self-aligned isolation structure for a back gate electrode

InactiveUS20120256260A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

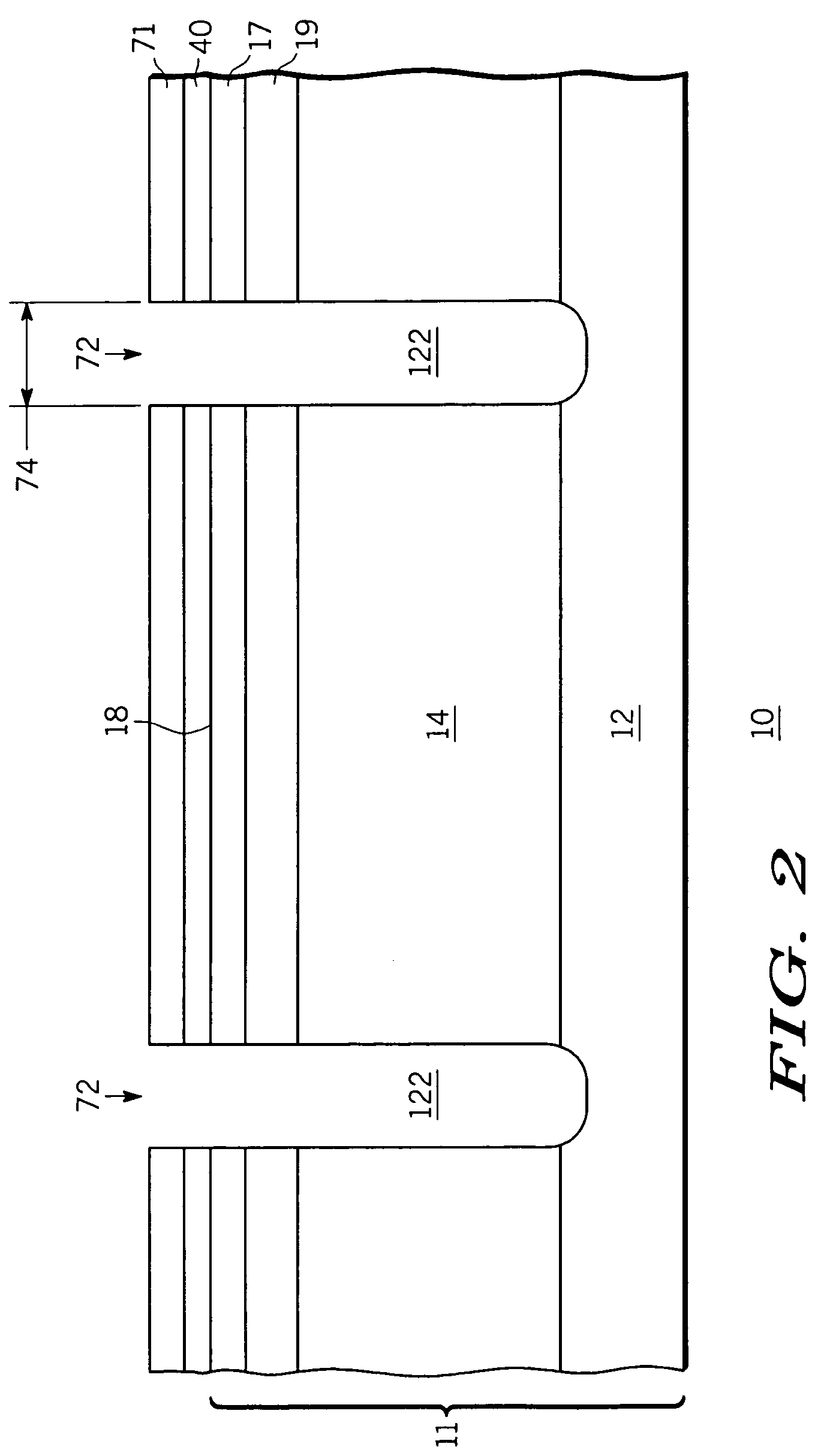

Doped semiconductor back gate regions self-aligned to active regions are formed by first patterning a top semiconductor layer and a buried insulator layer to form stacks of a buried insulator portion and a semiconductor portion. Oxygen is implanted into an underlying semiconductor layer at an angle so that oxygen-implanted regions are formed in areas that are not shaded by the stack or masking structures thereupon. The oxygen implanted portions are converted into deep trench isolation structures that are self-aligned to sidewalls of the active regions, which are the semiconductor portions in the stacks. Dopant ions are implanted into the portions of the underlying semiconductor layer between the deep trench isolation structures to form doped semiconductor back gate regions. A shallow trench isolation structure is formed on the deep trench isolation structures and between the stacks.

Owner:IBM CORP

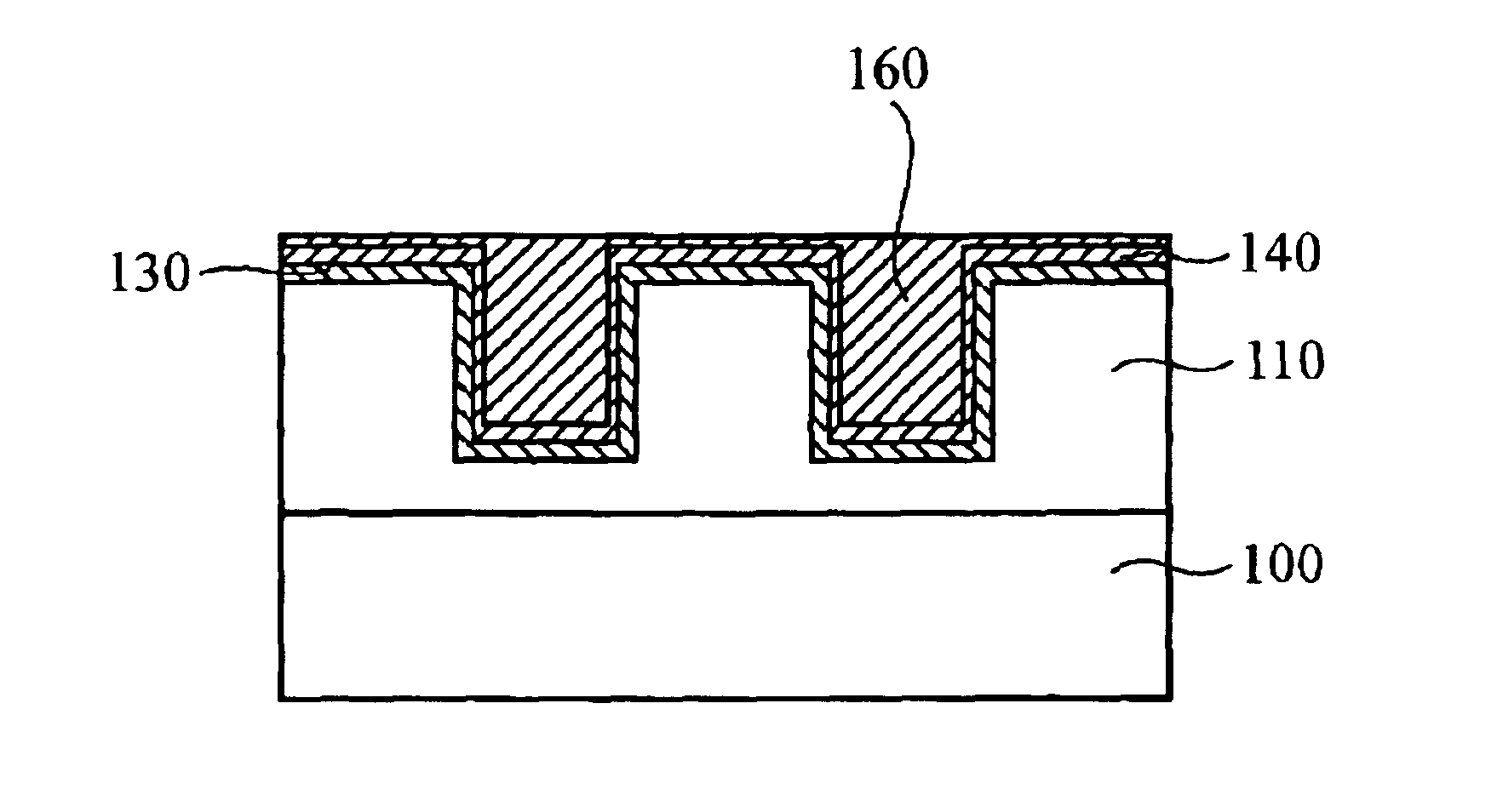

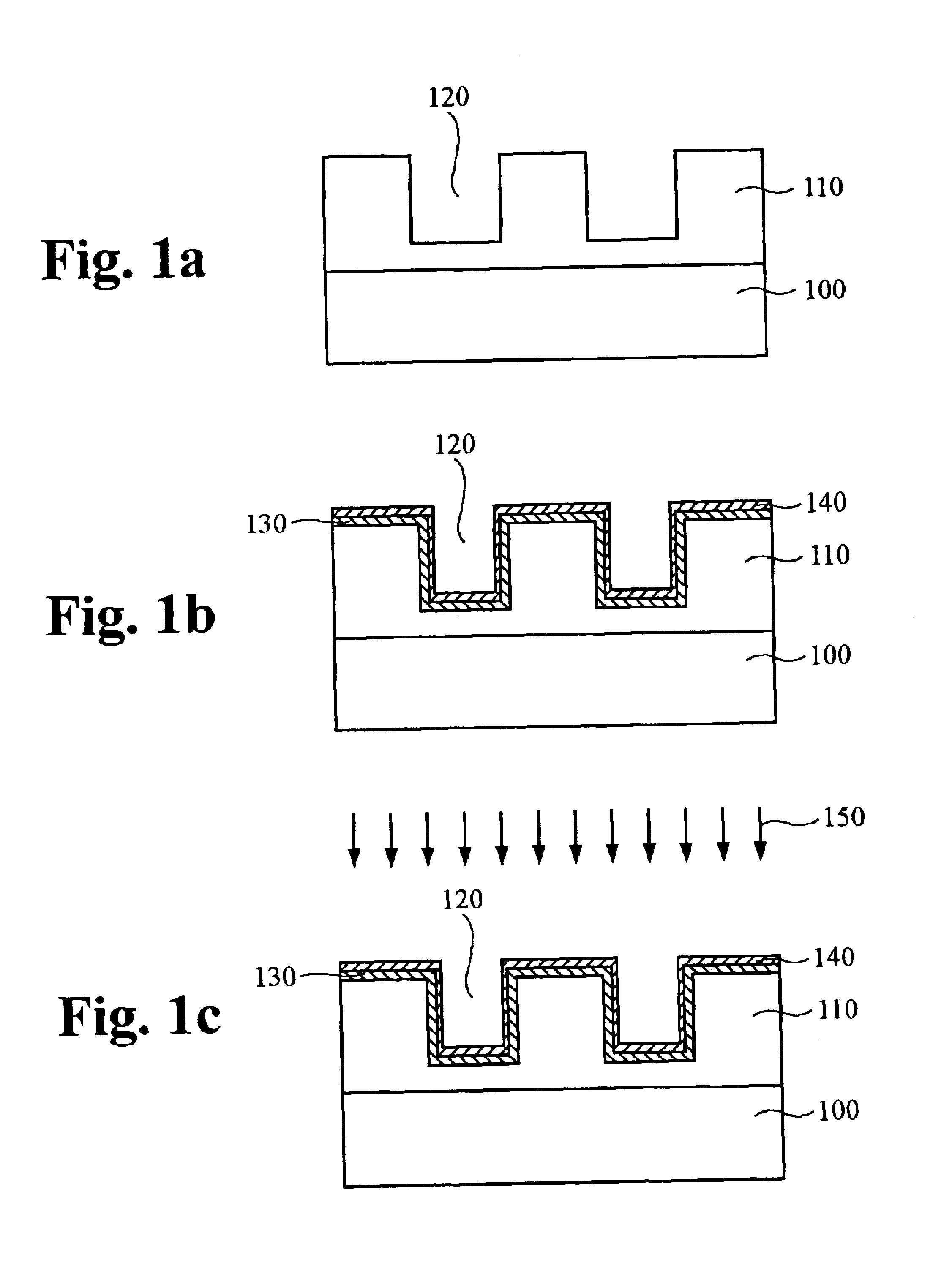

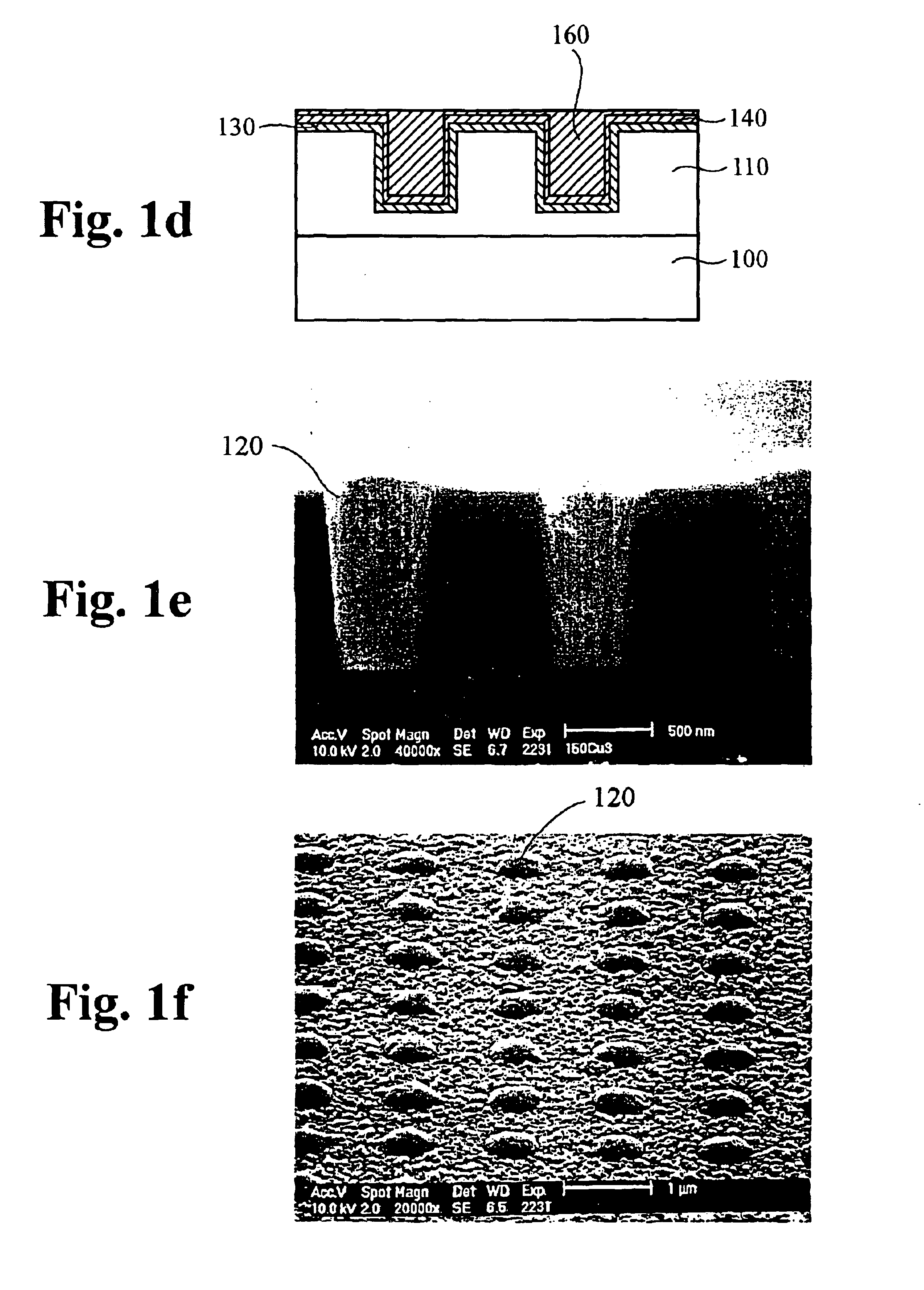

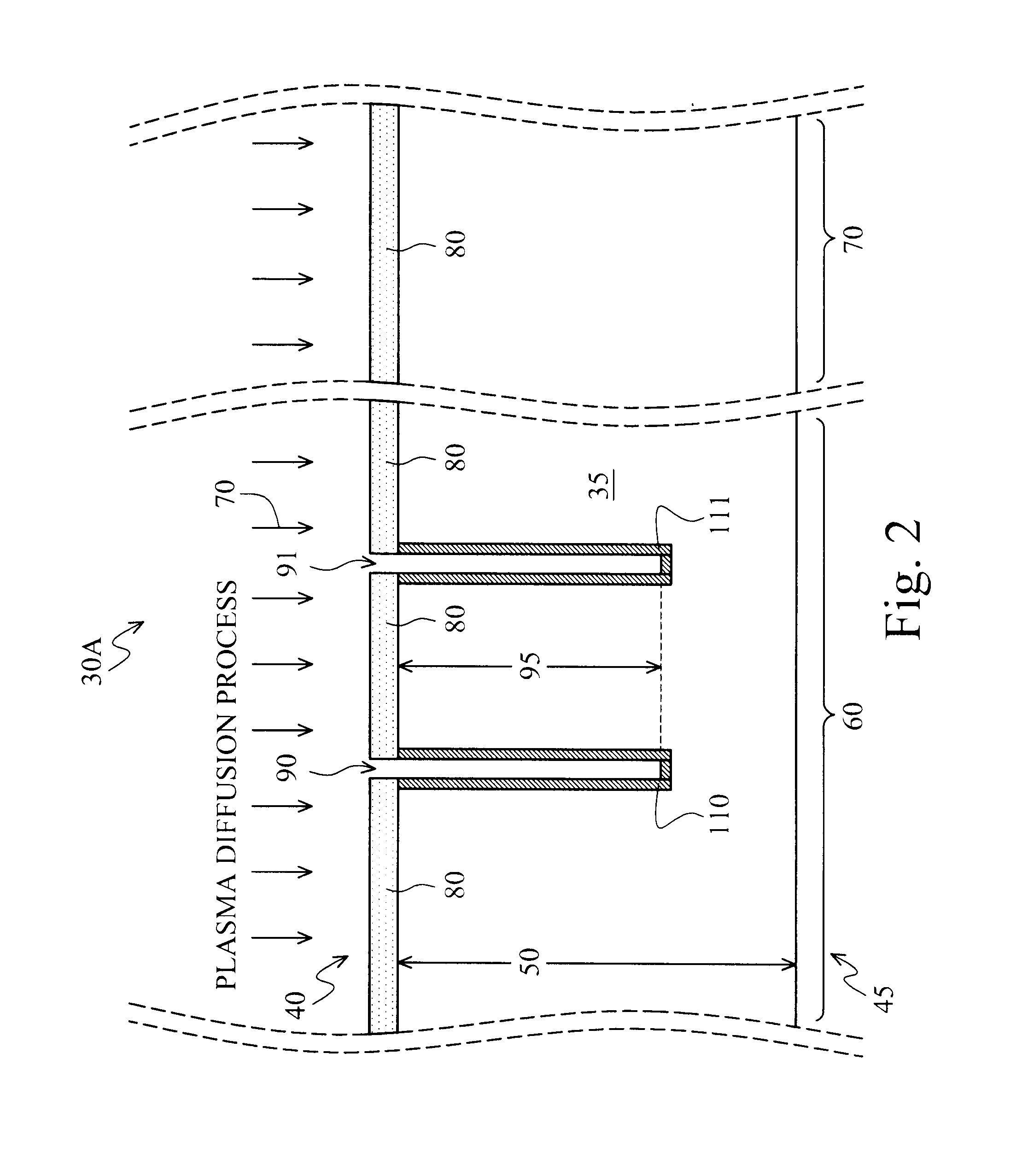

Method of forming copper interconnections and thin films using chemical vapor deposition with catalyst

InactiveUS6720262B2Semiconductor/solid-state device detailsSolid-state devicesCopper conductorSource material

A method of forming copper conductors for interconnecting active and passive elements as well as signal and power lines for circuits and devices on silicon wafers is disclosed. The method disclosed herein involves with using catalysts in conjunction with a chemical vapor deposition(CVD) process with typically using copper as a source material for forming interconnecting conductors. Interconnecting method for filling trenches, via holes, contacts, large trenches and holes for power devices and lines as well as for forming large passive elements is also disclosed. Disclosed herein are also a method of filling narrow and deep trenches and small in diameter and deep holes, and a method of forming very thin film on the flat top surface so that an etchback process, such as wet or dry etchback as well as plasma etchback processes, can be used for removing a thin film in preparation for subsequent processing steps, thereby rather expensive chemical mechanical polishing(CMP) process need not be used.

Owner:ASM KOREA LTD

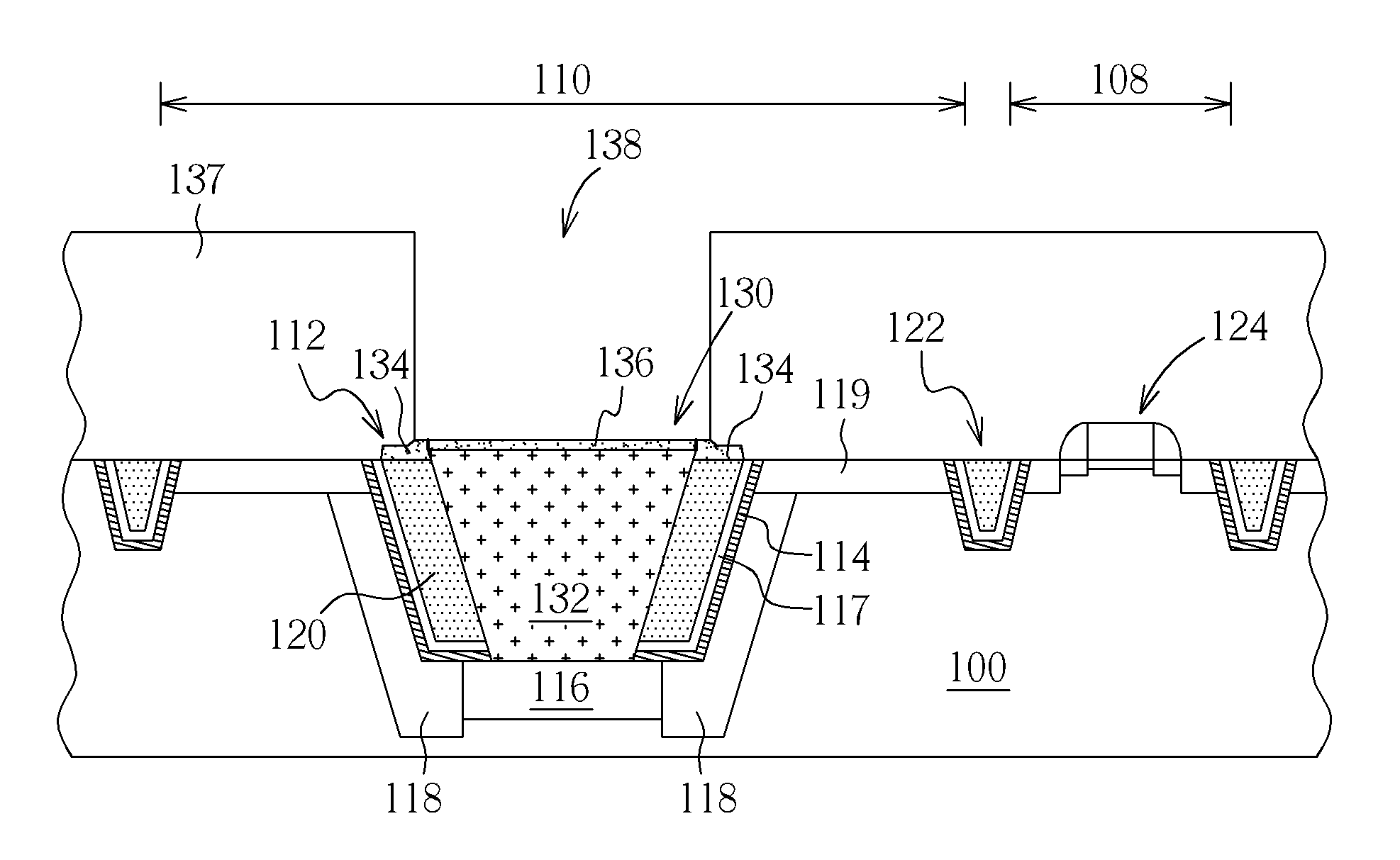

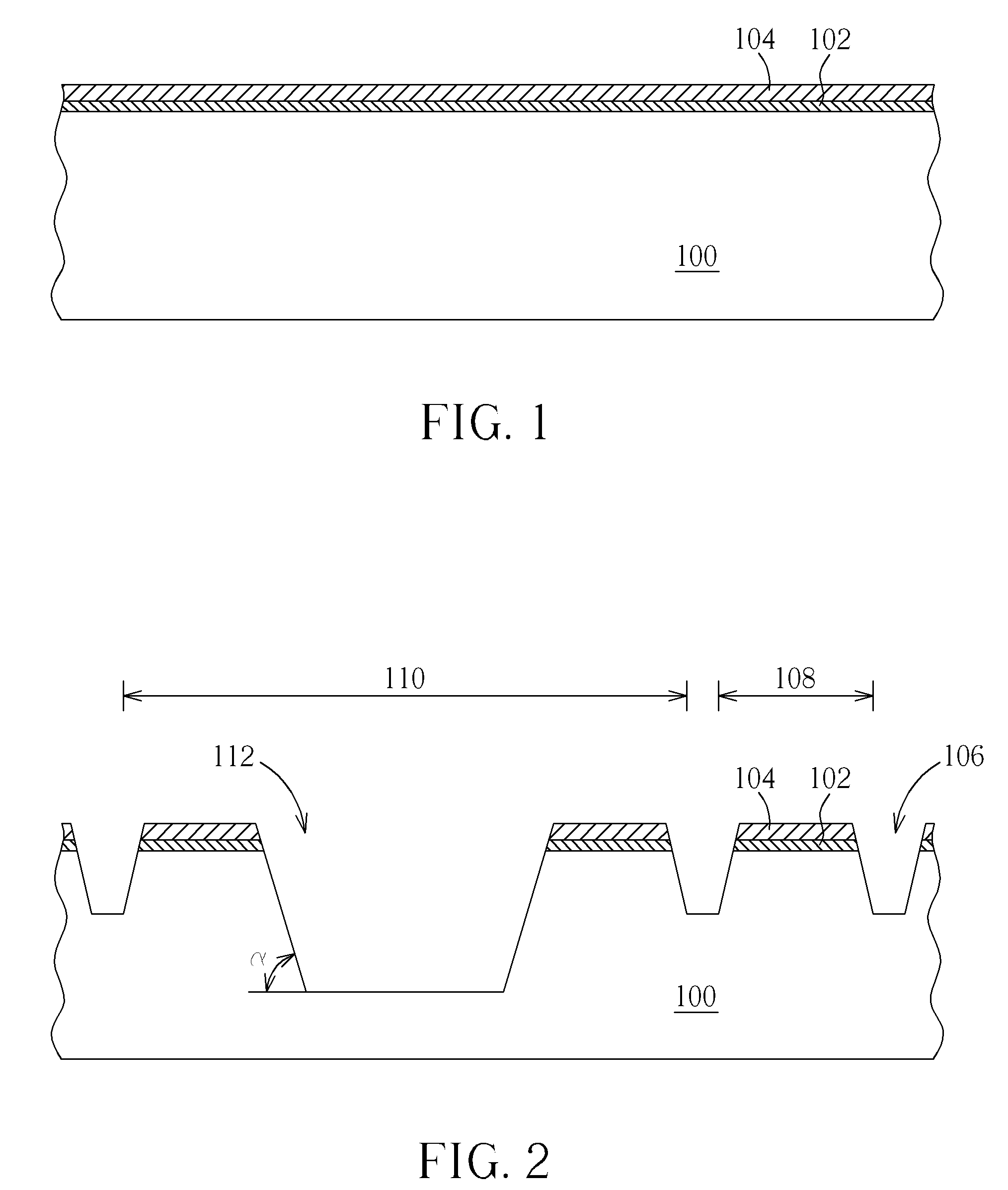

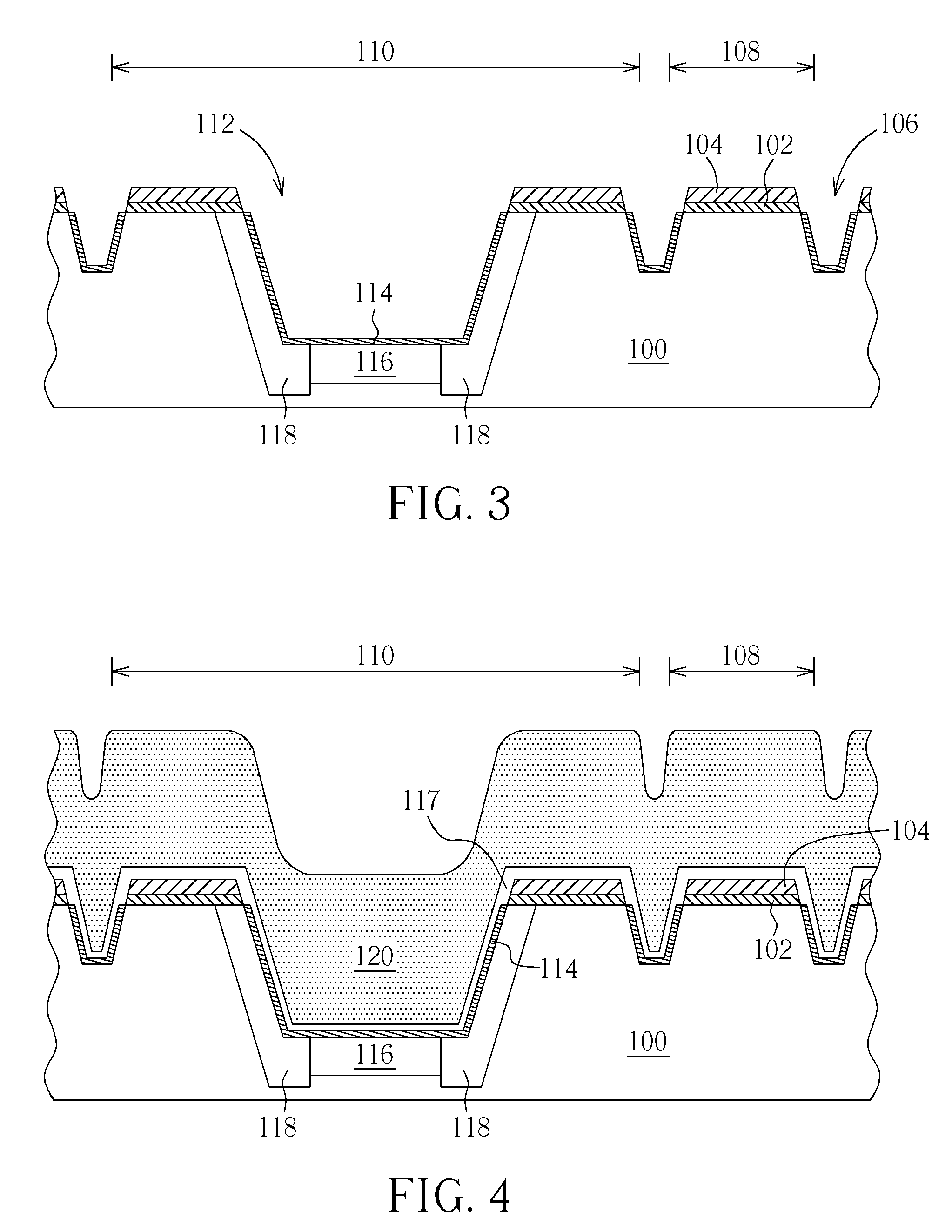

Semiconductor device and method of fabricating the same

ActiveUS20120104564A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering physics

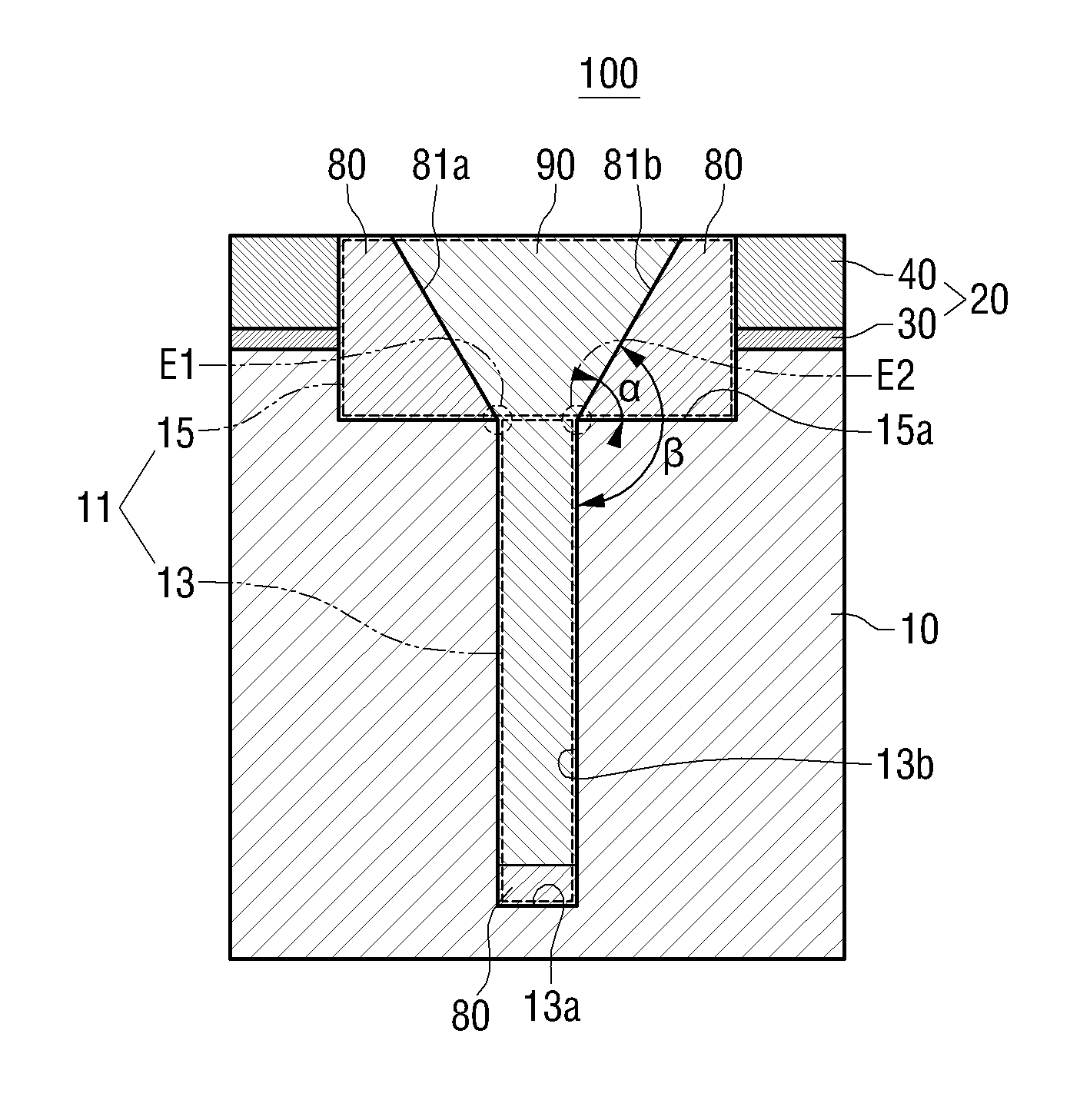

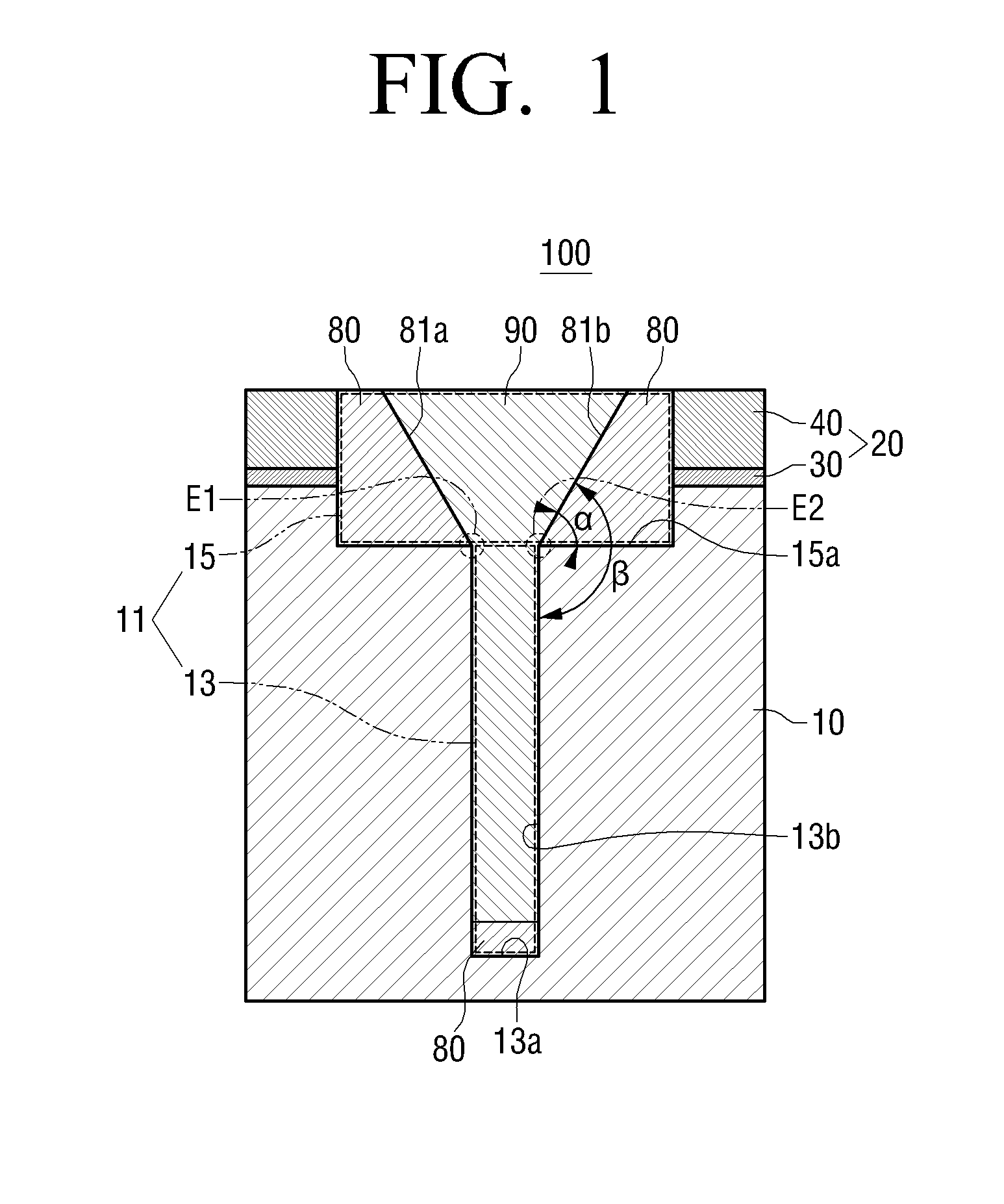

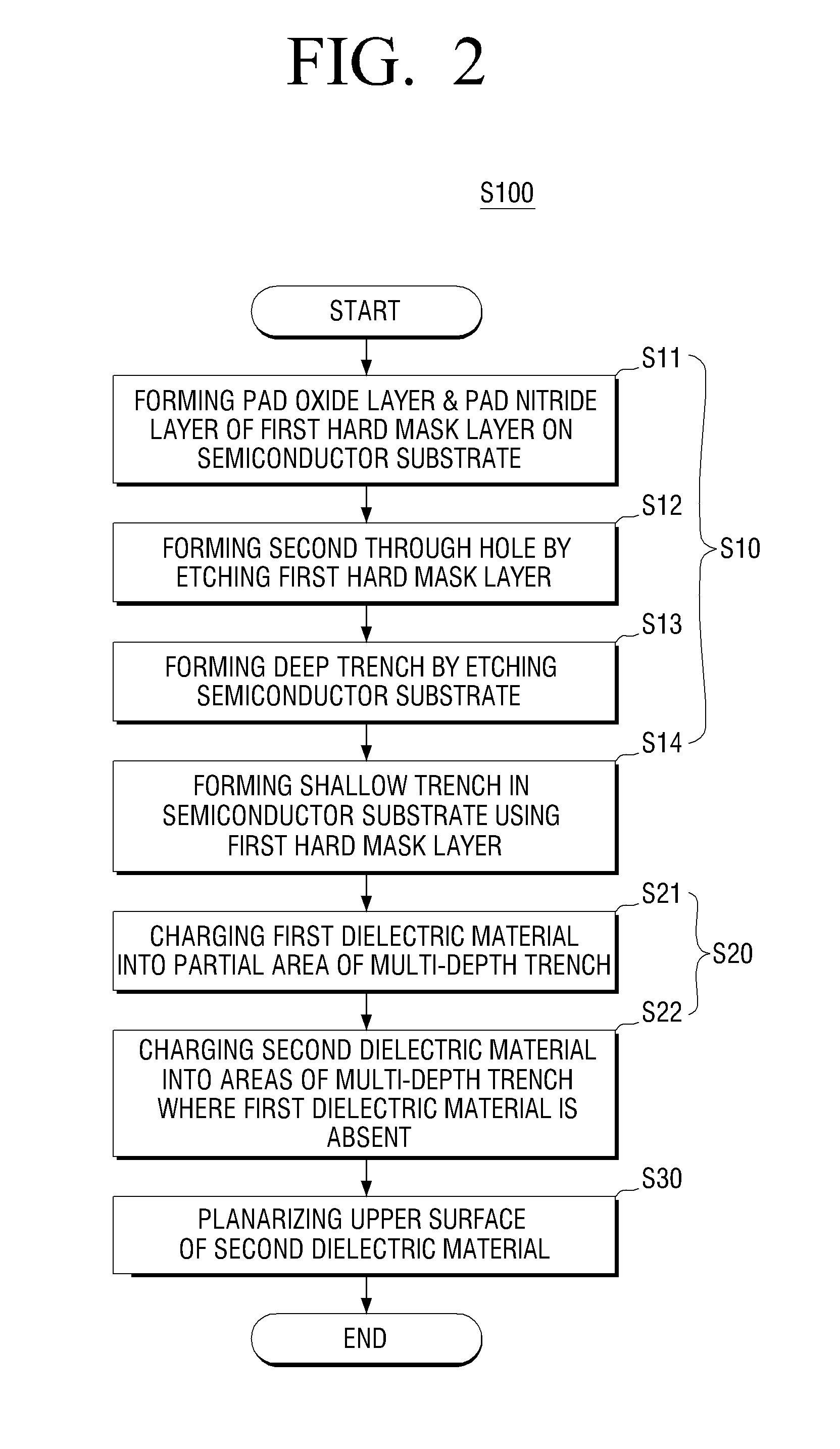

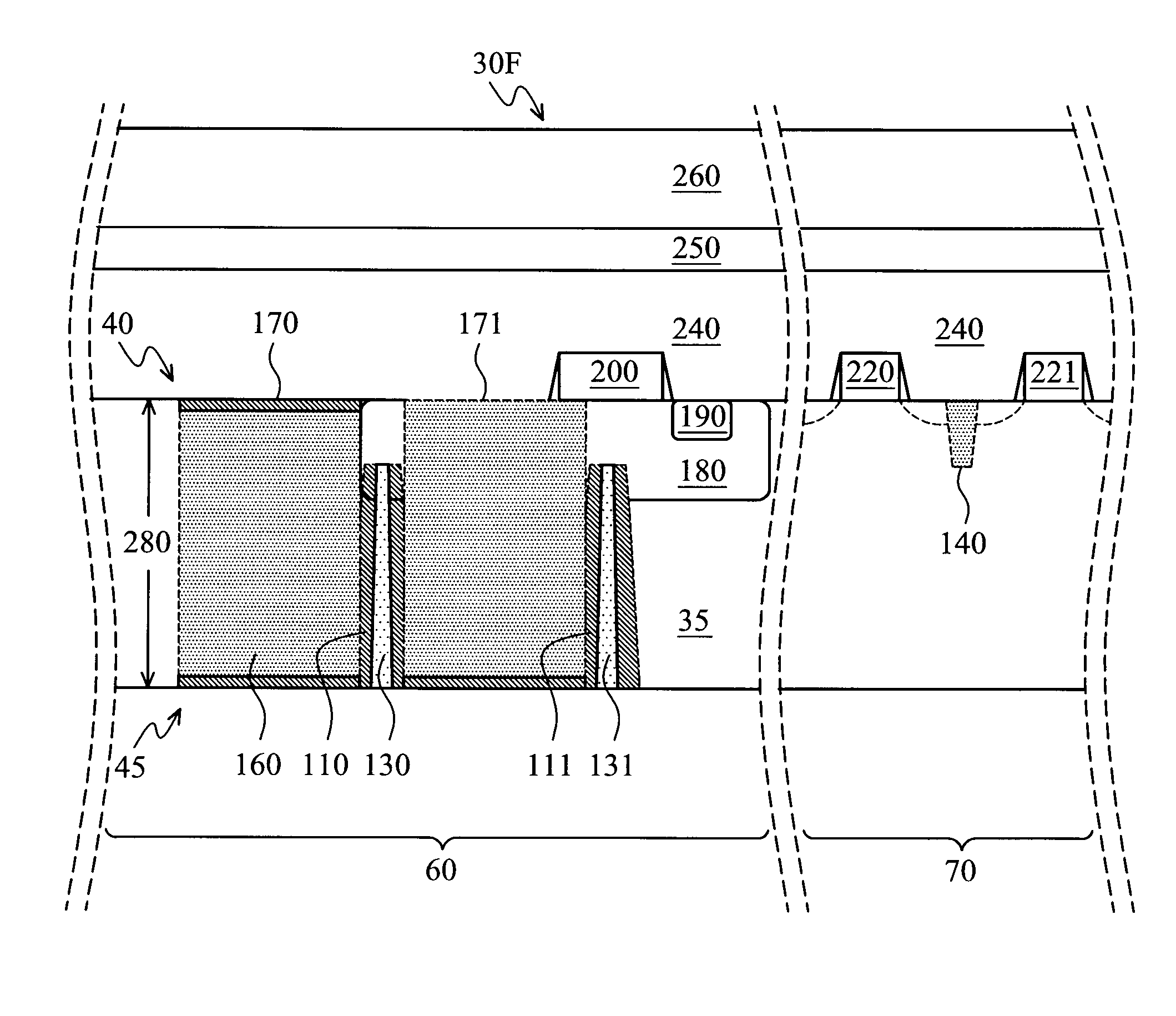

A semiconductor device and a method of fabricating the same are provided. The semiconductor device includes a semiconductor substrate in which a multi-depth trench is formed, the multi-depth trench including a shallow trench and a deep trench arranged below the shallow trench, a first dielectric material formed in partial area of the multi-depth trench, the first dielectric material including a slope in the shallow trench that extends upward from a corner where a bottom plane of the shallow trench and a sidewall of the deep trench meets, the slope being inclined with respect to the bottom plane of the shallow trench, and a second dielectric material formed in areas of the multi-depth trench in which the first dielectric material is absent.

Owner:KEY FOUNDRY CO LTD

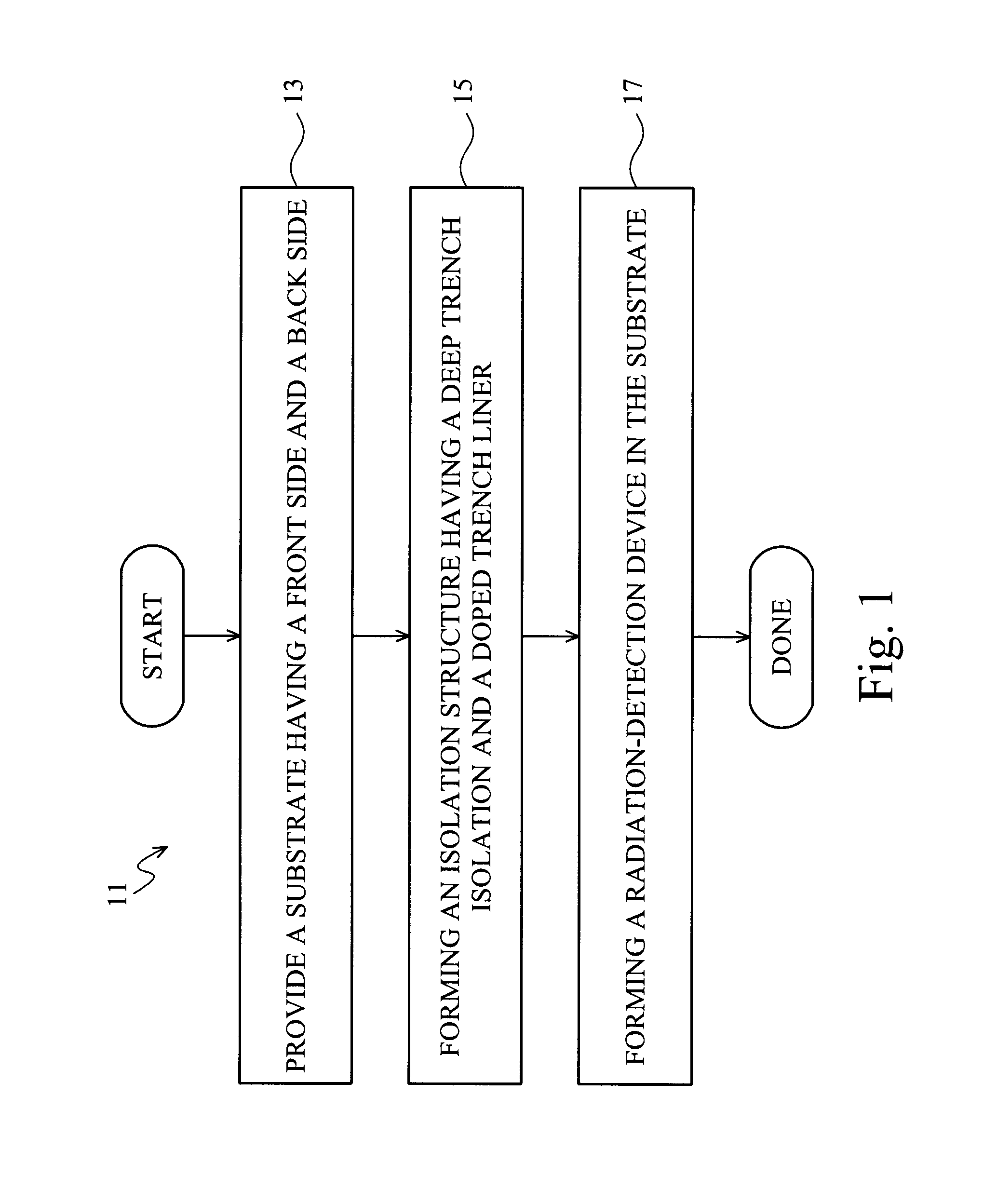

Image Sensor with Deep Trench Isolation Structure

ActiveUS20120025199A1Solid-state devicesSemiconductor/solid-state device manufacturingDeep trenchRadiation

Provided is a back side illuminated image sensor device. The image sensor device includes a substrate having a front side and a back side opposite the front side. The image sensor also includes a radiation-detection device that is formed in the substrate. The radiation-detection device is operable to detect a radiation wave that enters the substrate through the back side. The image sensor further includes a deep trench isolation feature that is disposed adjacent to the radiation-detection device. The image sensor device further includes a doped layer that at least partially surrounds the deep trench isolation feature in a conformal manner.

Owner:TAIWAN SEMICON MFG CO LTD

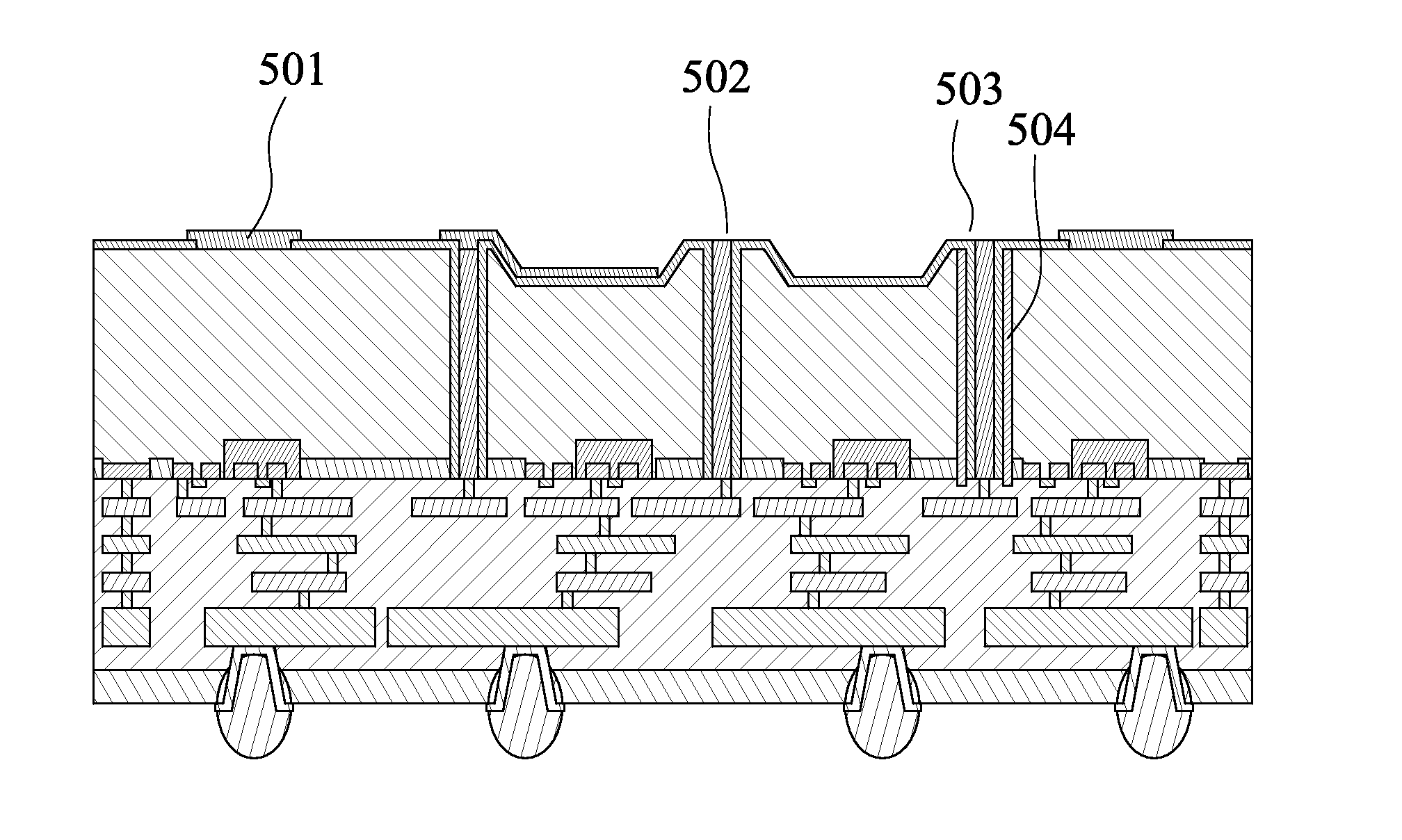

Integrated compact MEMS device with deep trench contacts

InactiveUS20130168740A1High aspect ratioIncrease contactSolid-state devicesSpeed/acceleration/shock instrument detailsCMOSSolder ball

A compact MEMS motion sensor device is provided, including a CMOS substrate layer, with plural anchor posts having an isolation oxide layer surrounding a conductive layer. On one side of CMOS substrate layer, the device further includes a field oxide (FOX) layer, a first set and a second set of implant doped silicon areas, a first polysilicon layer, an oxide layer embedded with plural metal layers interleaved with via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. On the other side of CMOS substrate layer, the present invention further includes a backside interconnect isolation oxide layer, a first MEMS bonding layer, a first metal compound layer, a second MEMS bonding layer, a MEMS layer, a first MEMS eutectic bonding layer, a second metal compound layer, a second MEMS eutectic bonding layer, and a MEMS cap layer.

Owner:WINDTOP TECH CORP

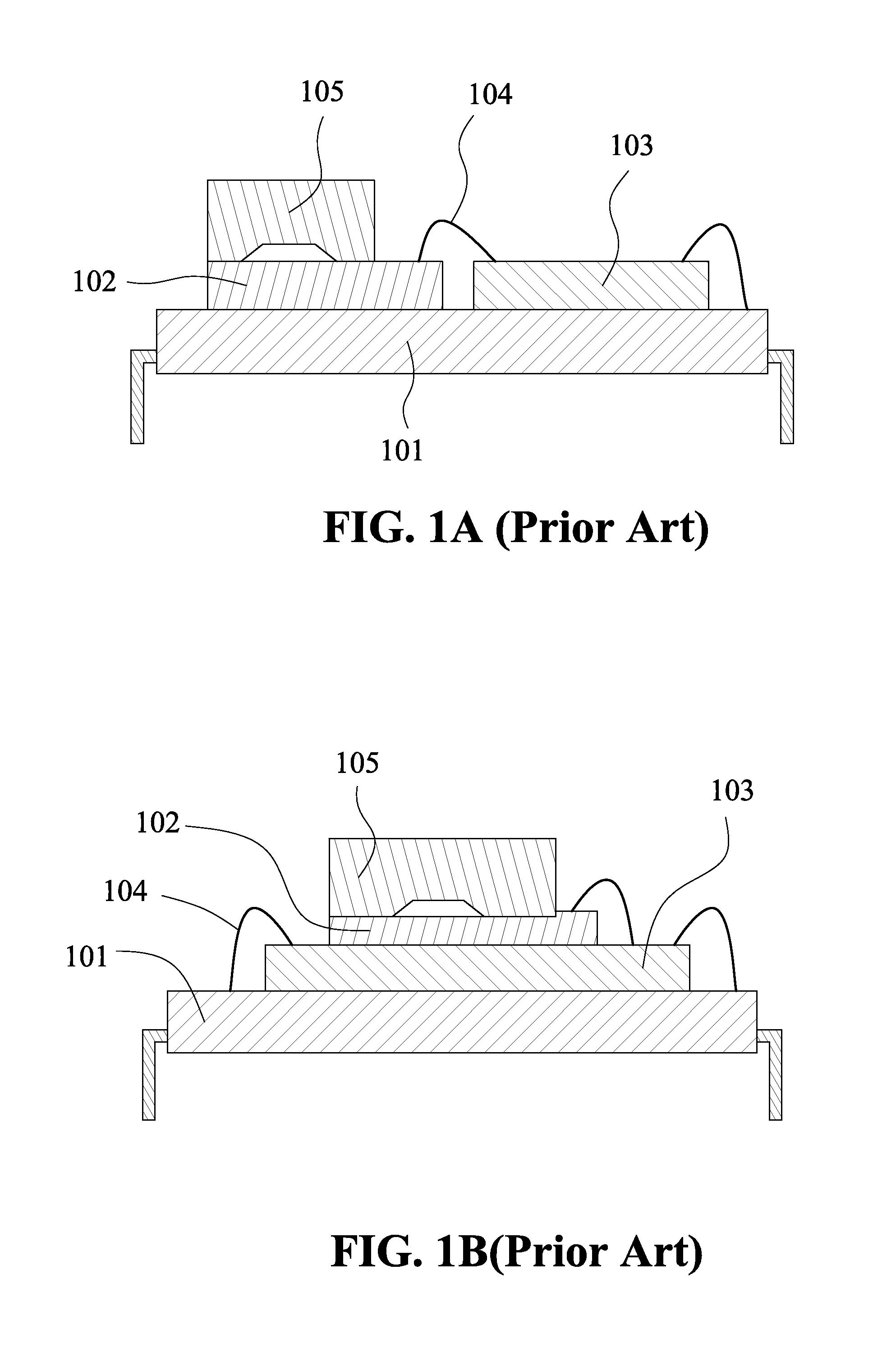

Semiconductor Photodetector Structure and the Fabrication Method Thereof

ActiveUS20110037133A1Photodetector qualityQuality improvementFinal product manufactureSolid-state devicesDopantSemiconductor materials

A semiconductor photodetector structure is provided. The structure includes a substrate, a photodetecting element and a semiconductor layer disposed on the photodetecting element. The substrate includes a first semiconductor material and includes a deep trench. The surface of the deep trench includes a first type dopant. The photodetecting element is disposed in the deep trench. The photodetecting element includes a second semiconductor material. The semiconductor layer includes a second type dopant.

Owner:UNITED MICROELECTRONICS CORP

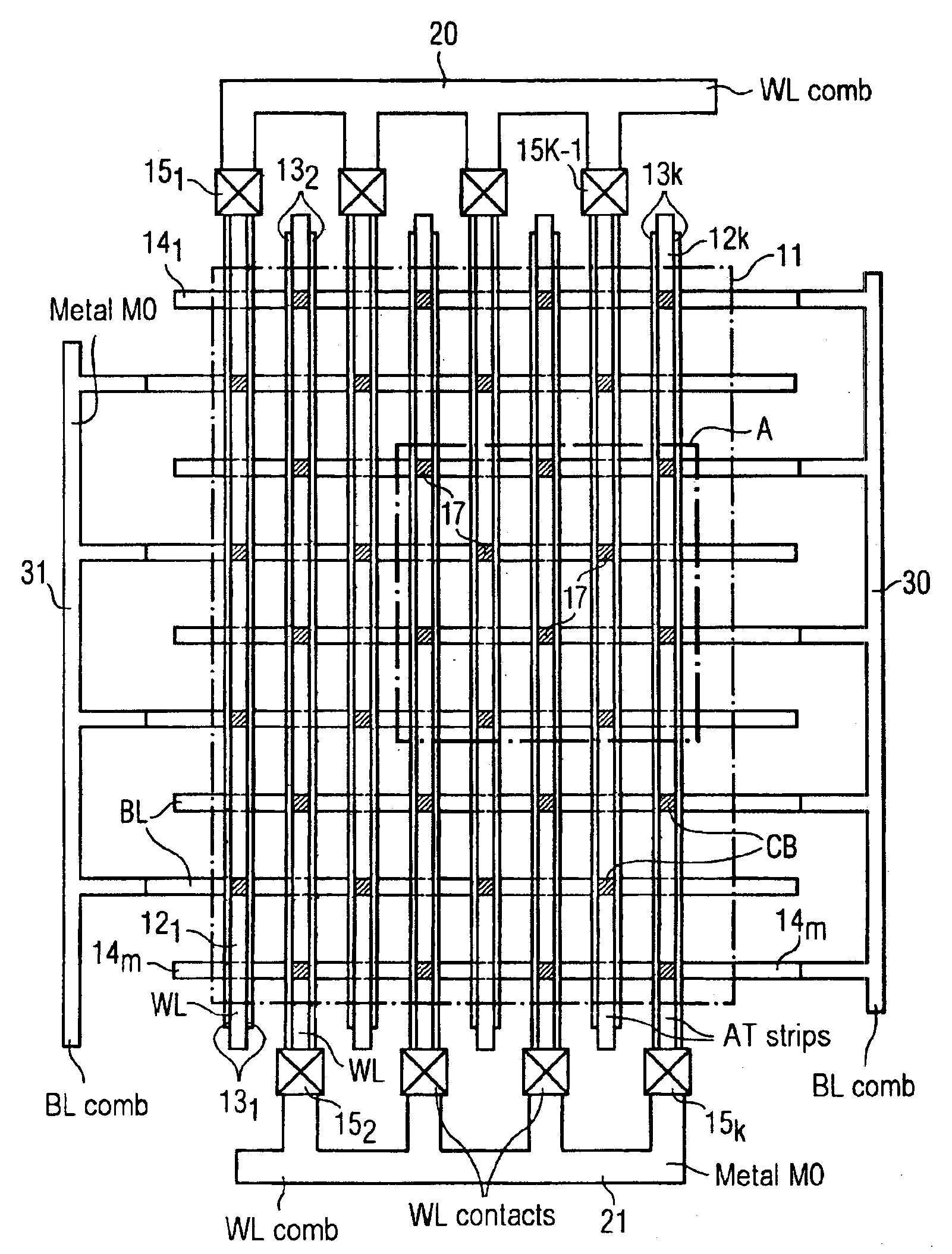

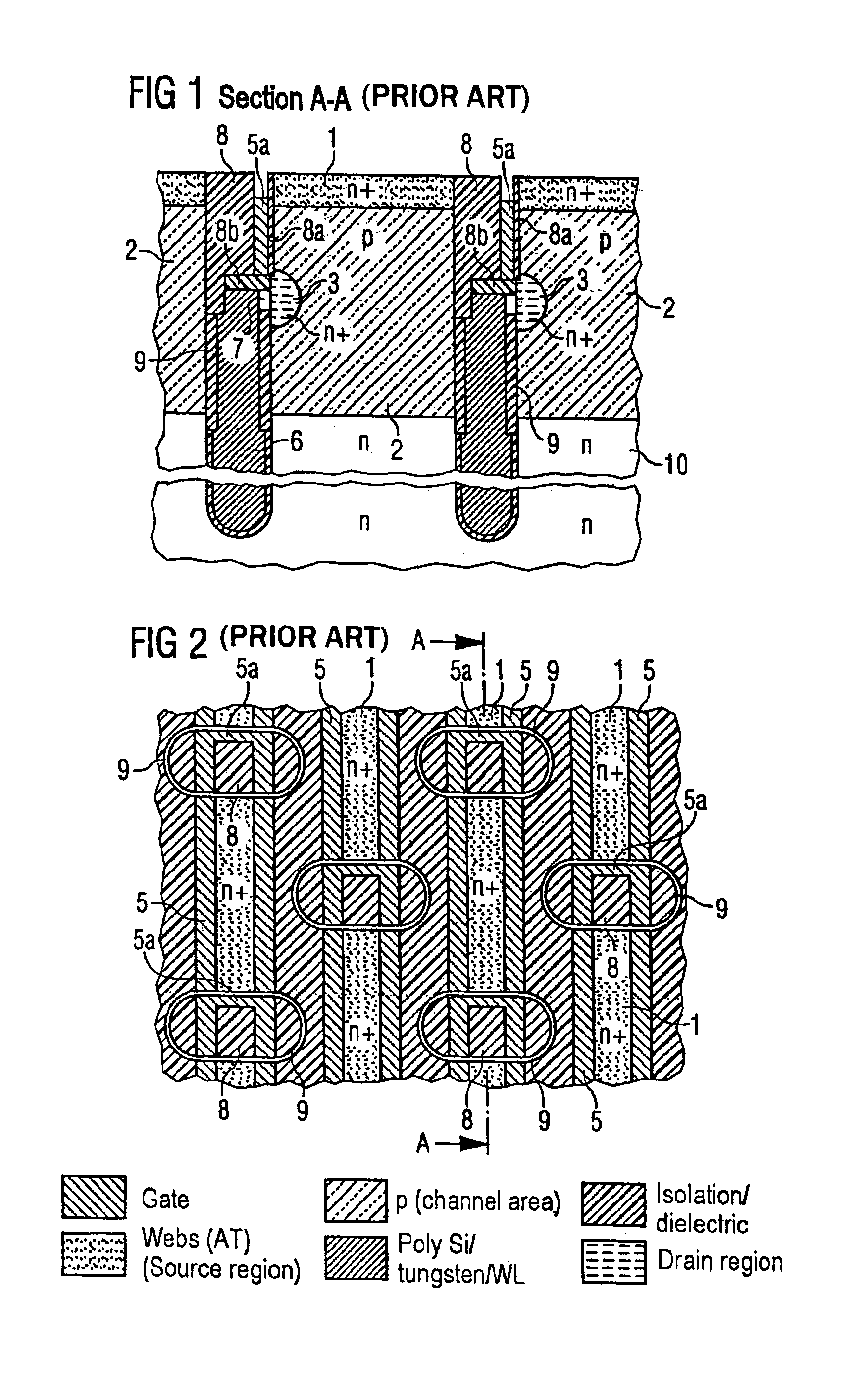

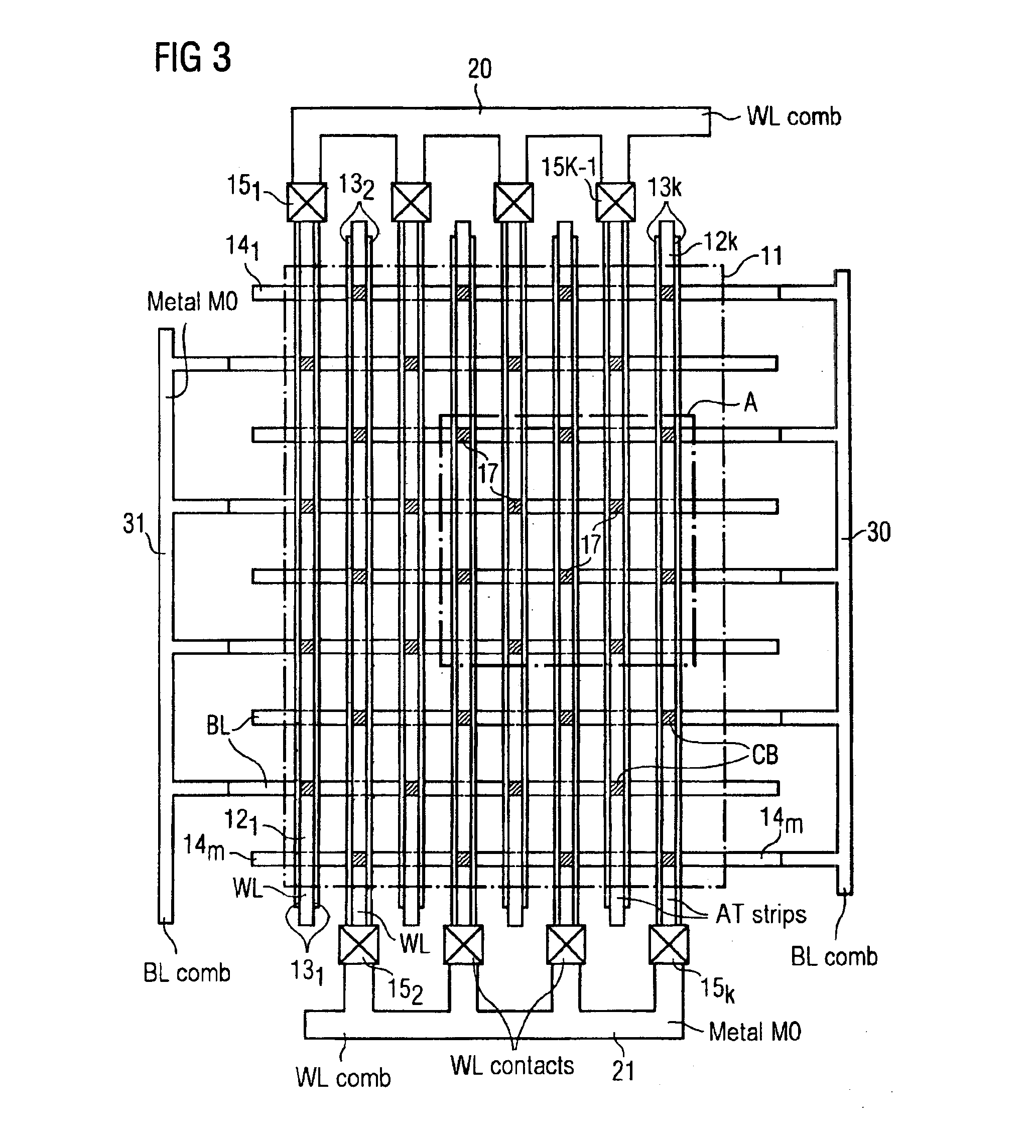

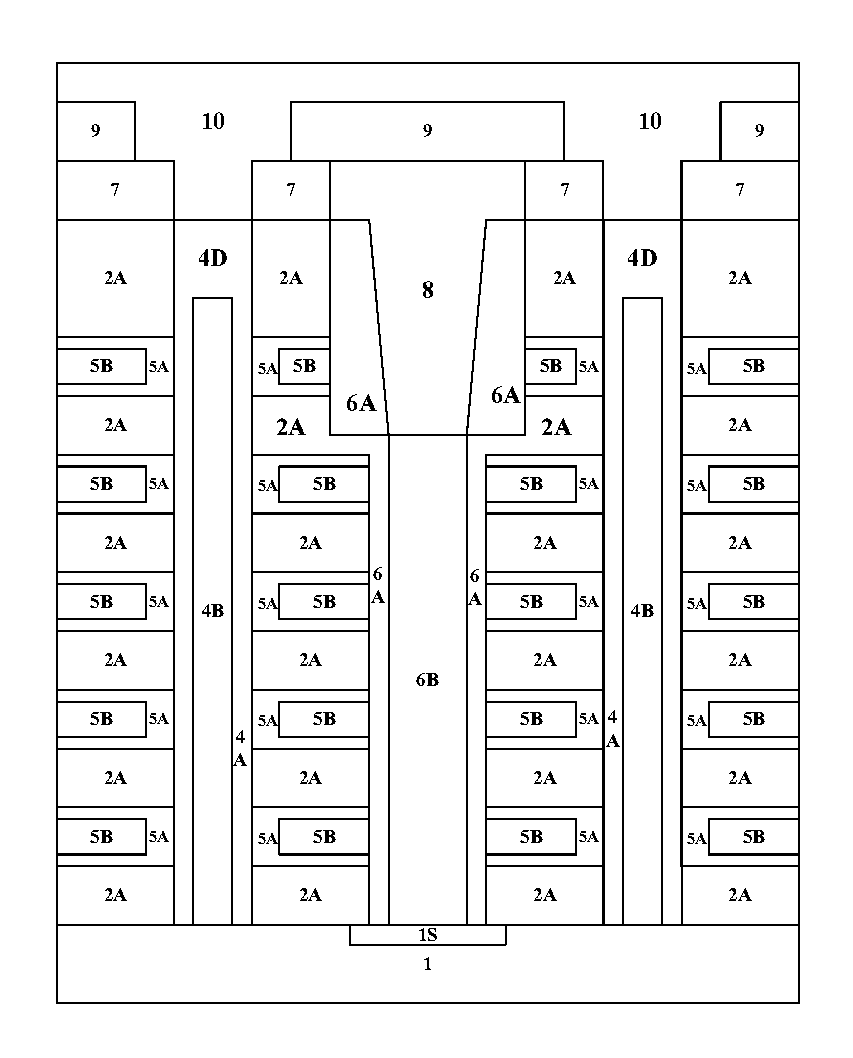

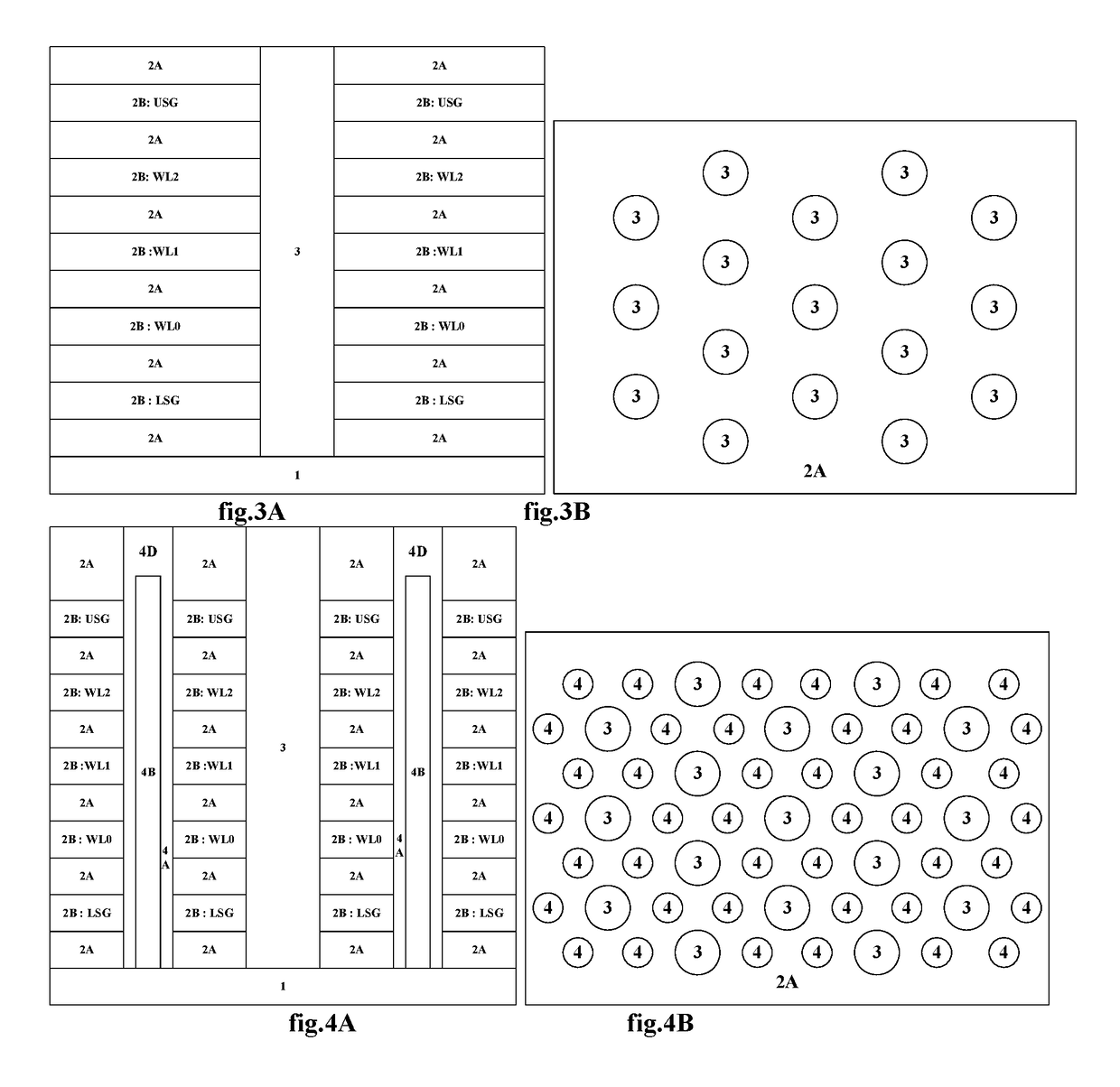

Device architecture and process for improved vertical memory arrays

InactiveUS6930324B2TransistorSemiconductor/solid-state device testing/measurementTransistor arrayDielectric

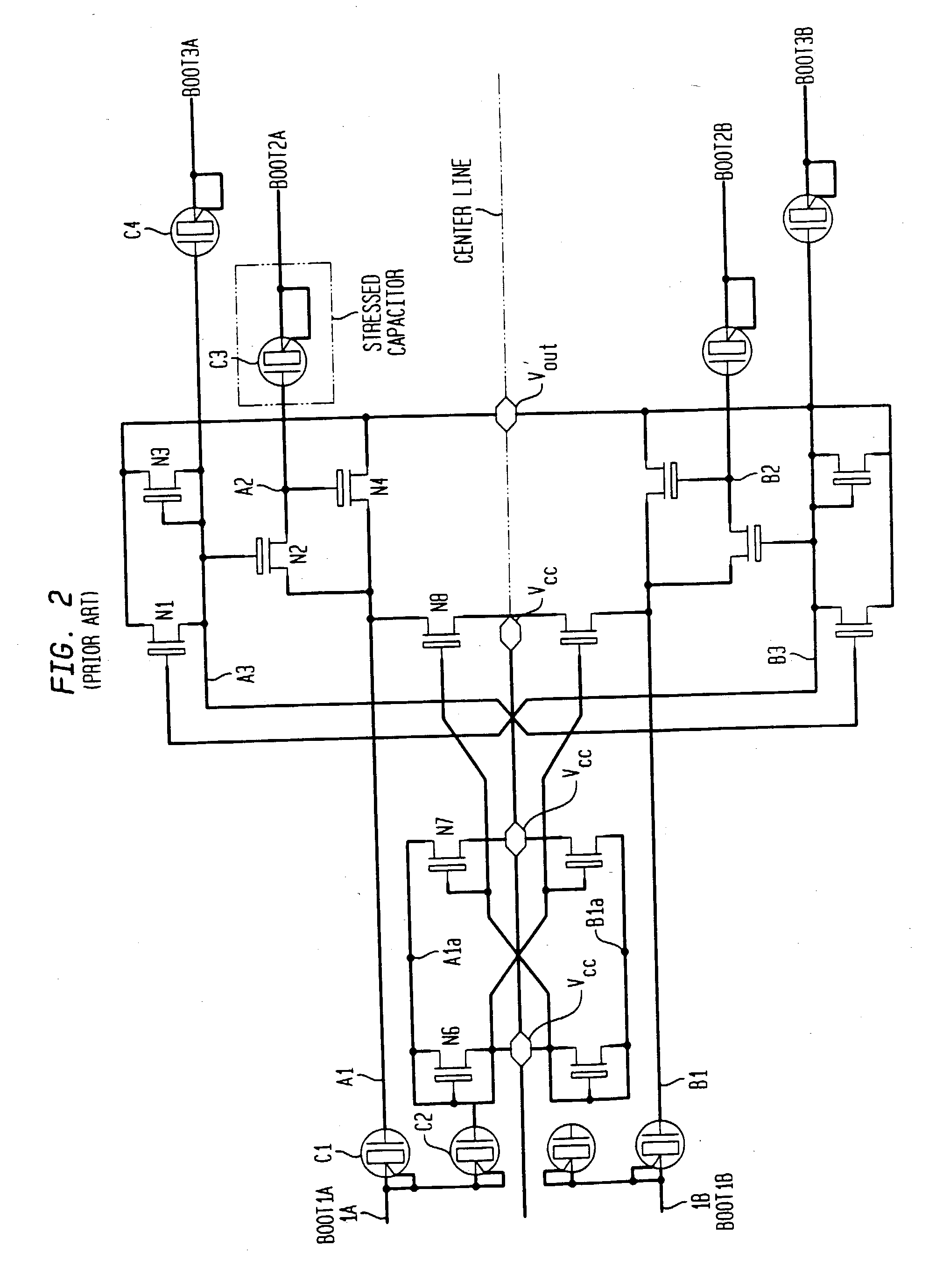

An array process diagnosis test structure for an integrated circuit including a transistor array composed of vertical FET memory cell access transistors, which are formed into the depth of a substrate in the form of active webs which run parallel in the lateral direction of the circuit is disclosed. Memory cell storage capacitors in the array test structure are formed in deep trenches on the end faces of those sections of the active webs which form the vertical FET transistors. Word lines are arranged along the webs and along parallel intersecting bit lines of the array, outside of which, and on two mutually opposite edges, are located a first and second word line comb. The wordline combs are offset and connected alternately to different word lines. In addition, a first and a second bit line comb are formed on the two other opposing edges of the transistor array mutually offset and each connected to different bit lines. The test structure provides a convenient means to carry out reliability investigations on the gate oxide of the vertical FET transistors and on the capacitor dielectric in the deep trenches, capacitance measurements between the word lines, and between the word lines and other circuit layers, as well as capacitance measurements between the bit lines and between the bit lines and other circuit layers, and thus facilitates diagnosis of possible fault sources arising during the production process.

Owner:POLARIS INNOVATIONS

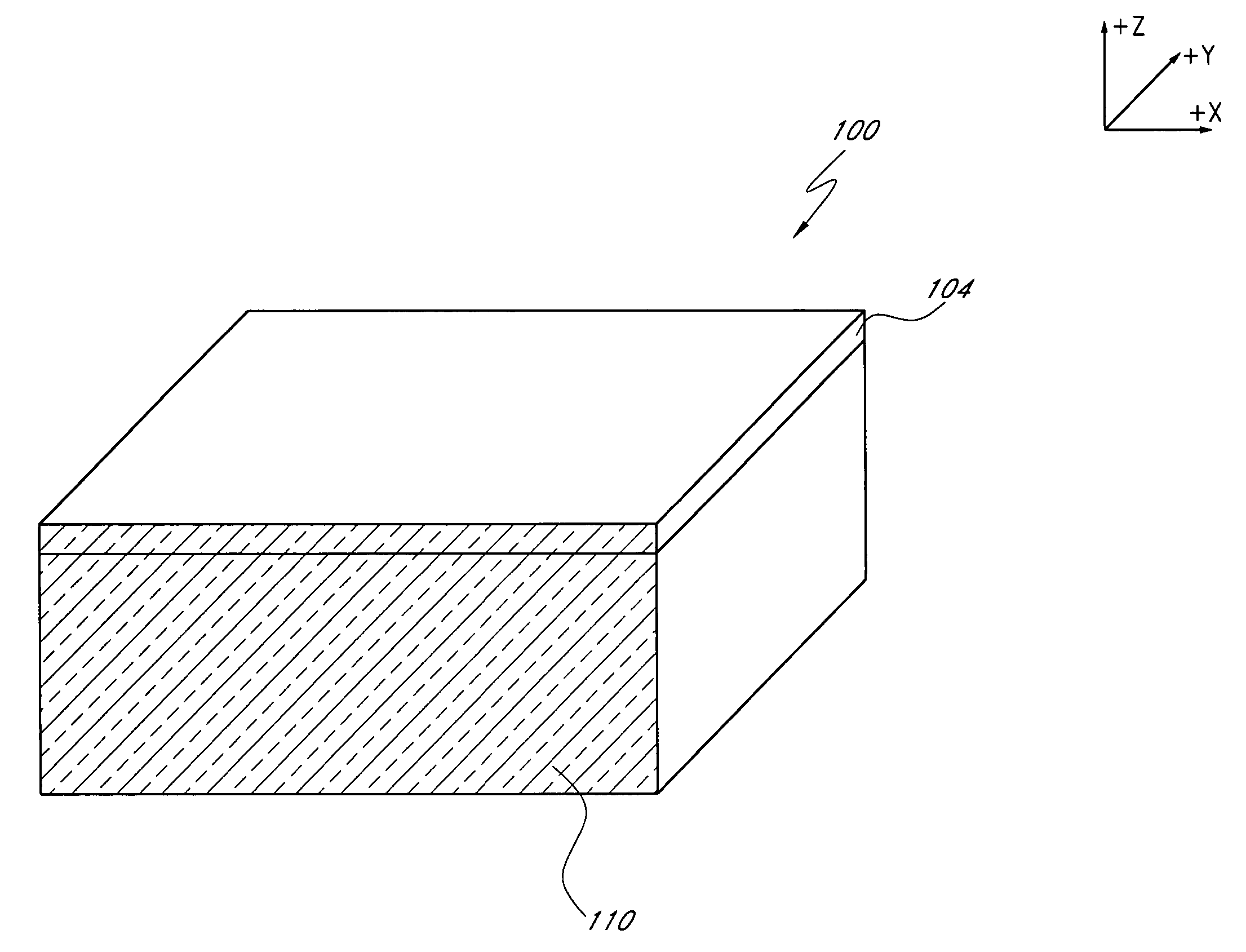

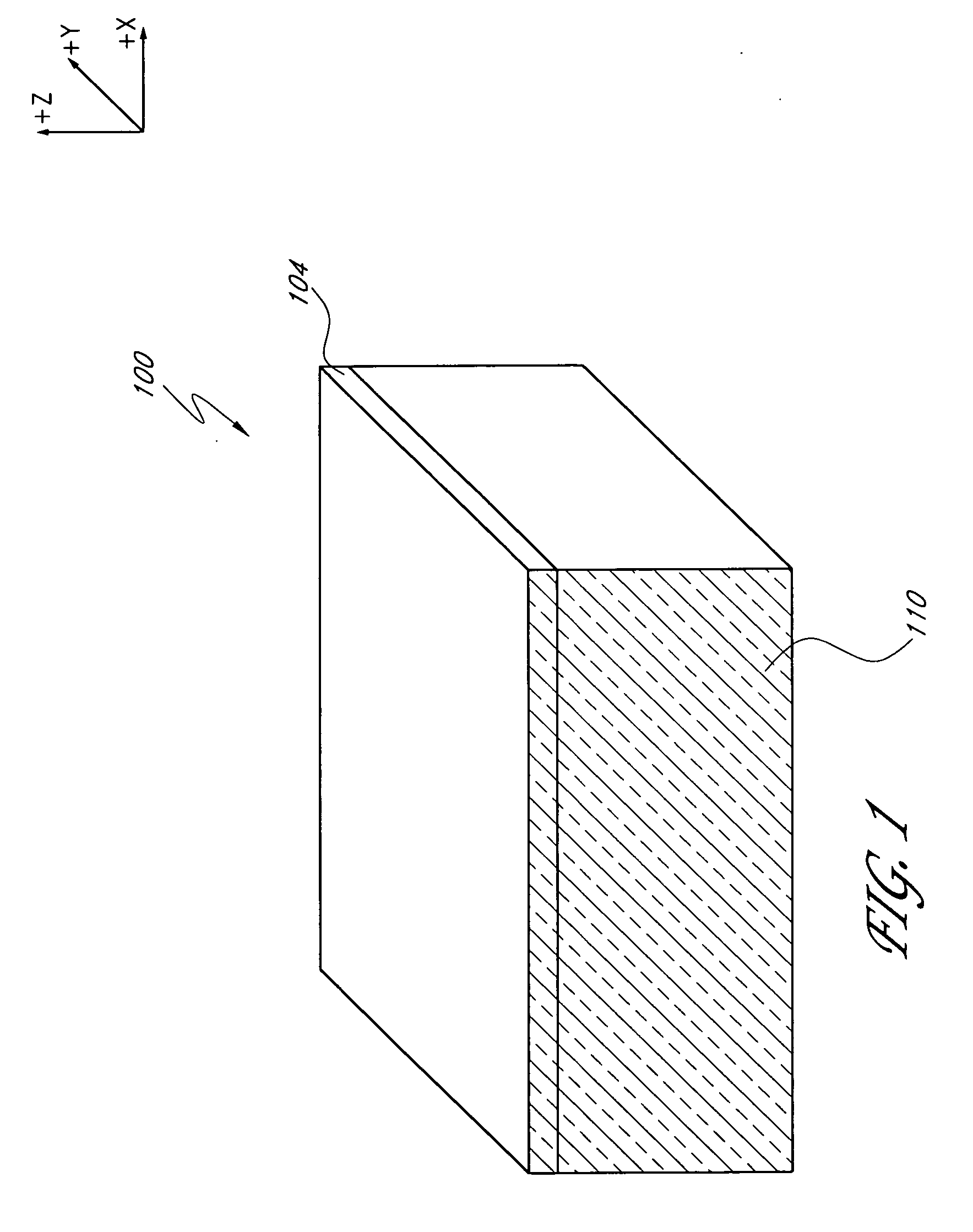

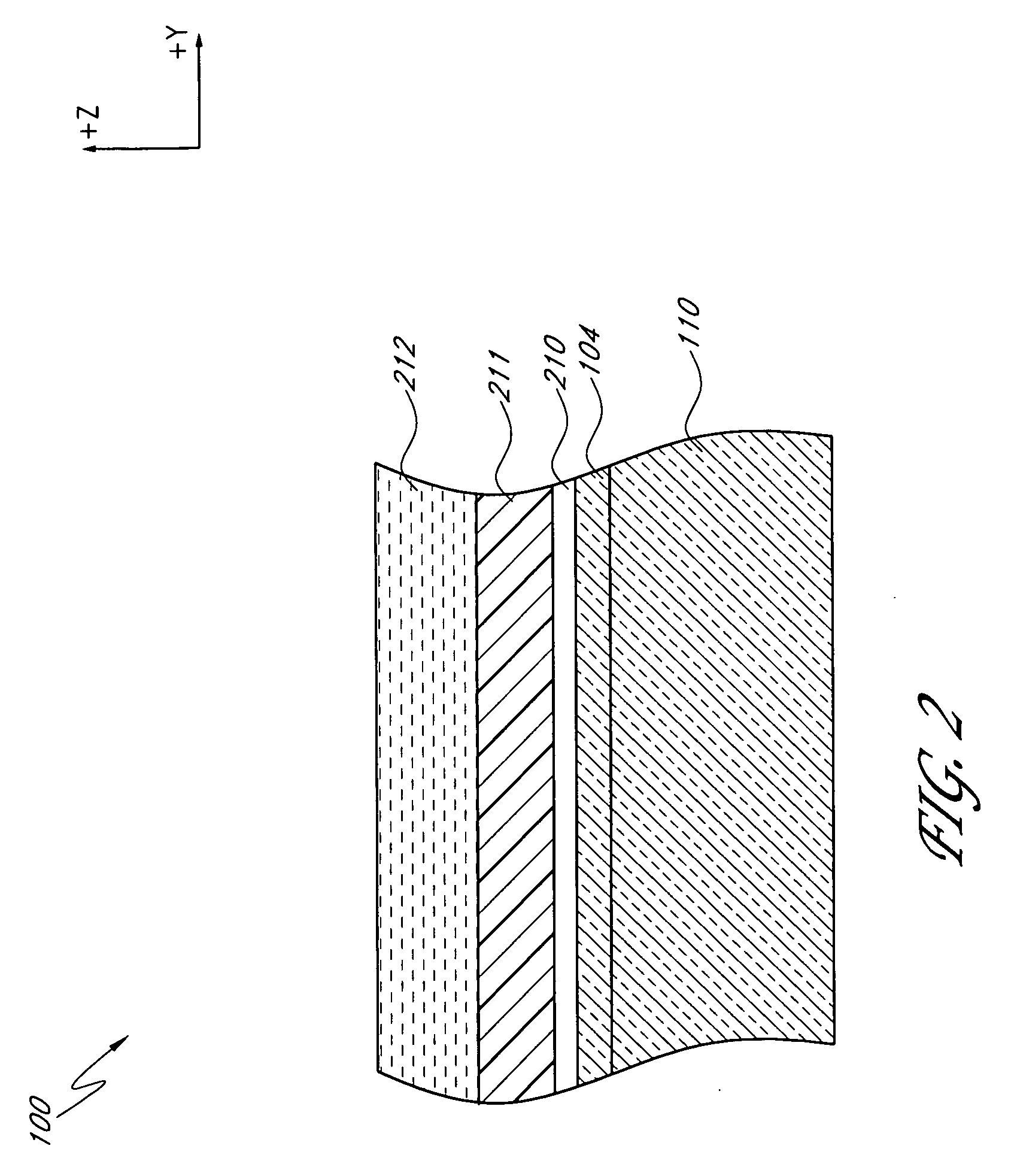

Semiconductor device having deep trench charge compensation regions and method

ActiveUS7176524B2Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsCharge compensation

In one embodiment, a semiconductor device is formed in a body of semiconductor material. The semiconductor device includes a charge compensating trench formed in proximity to active portions of the device. The charge compensating trench includes a trench filled with various layers of semiconductor material including opposite conductivity type layers.

Owner:SEMICON COMPONENTS IND LLC

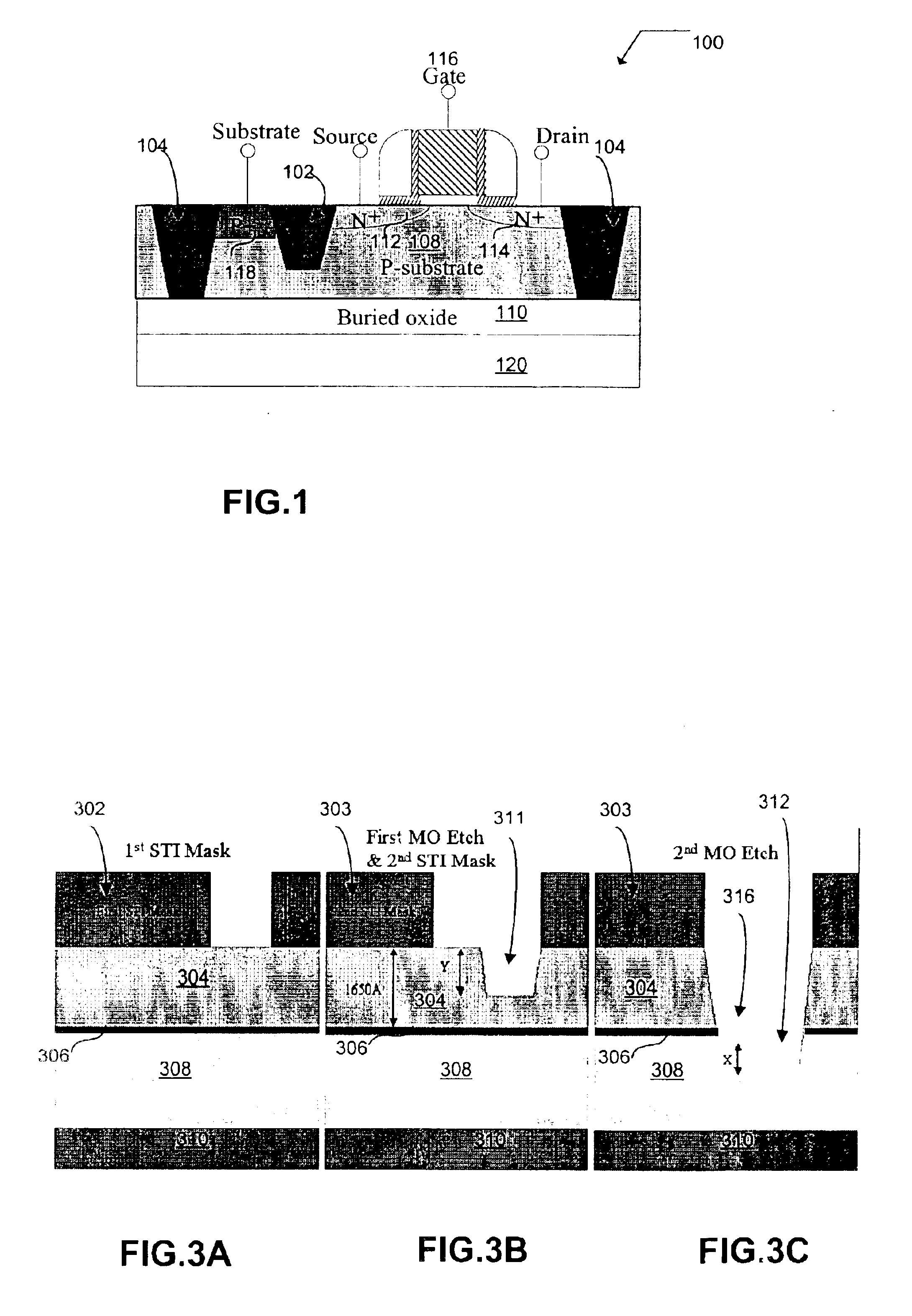

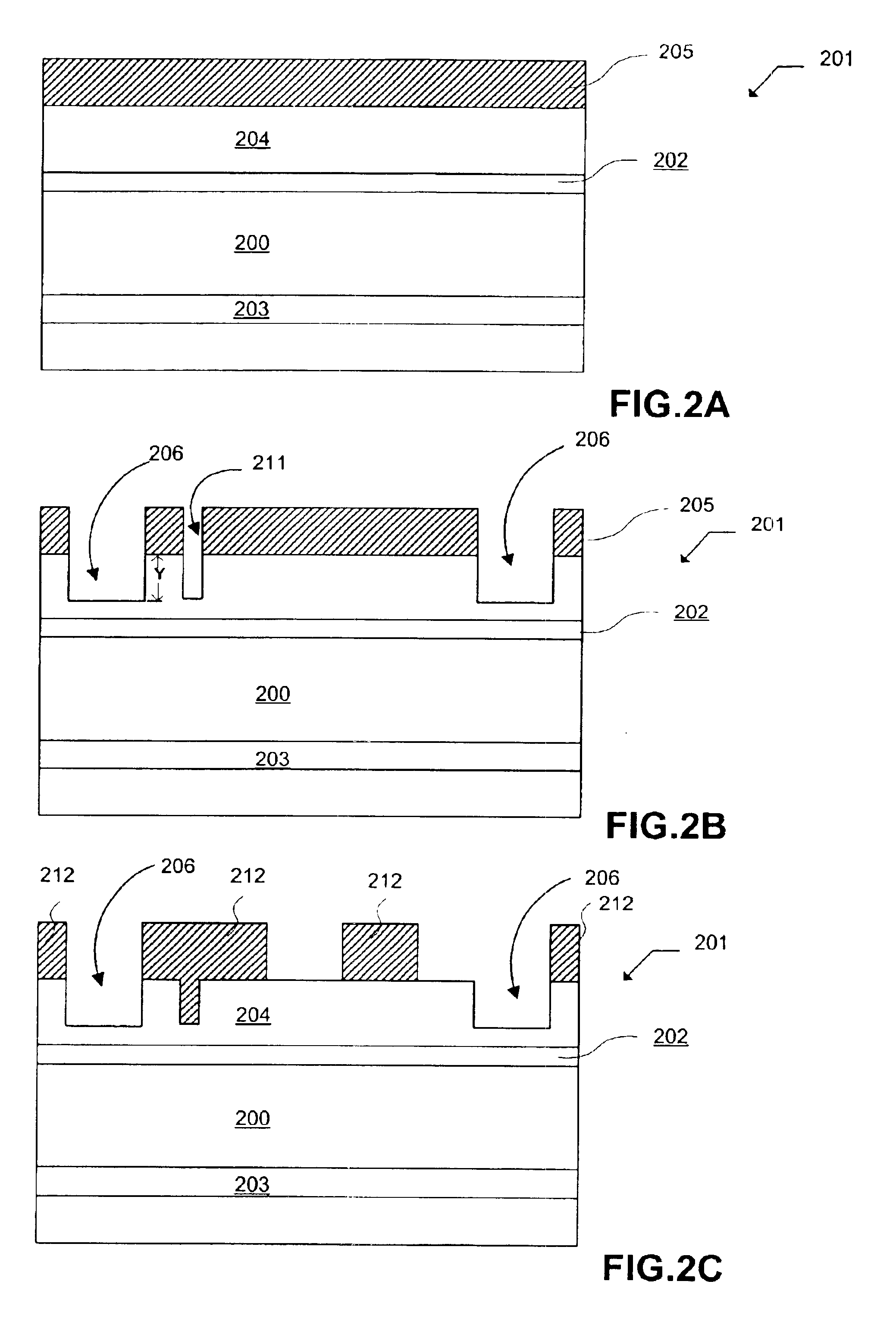

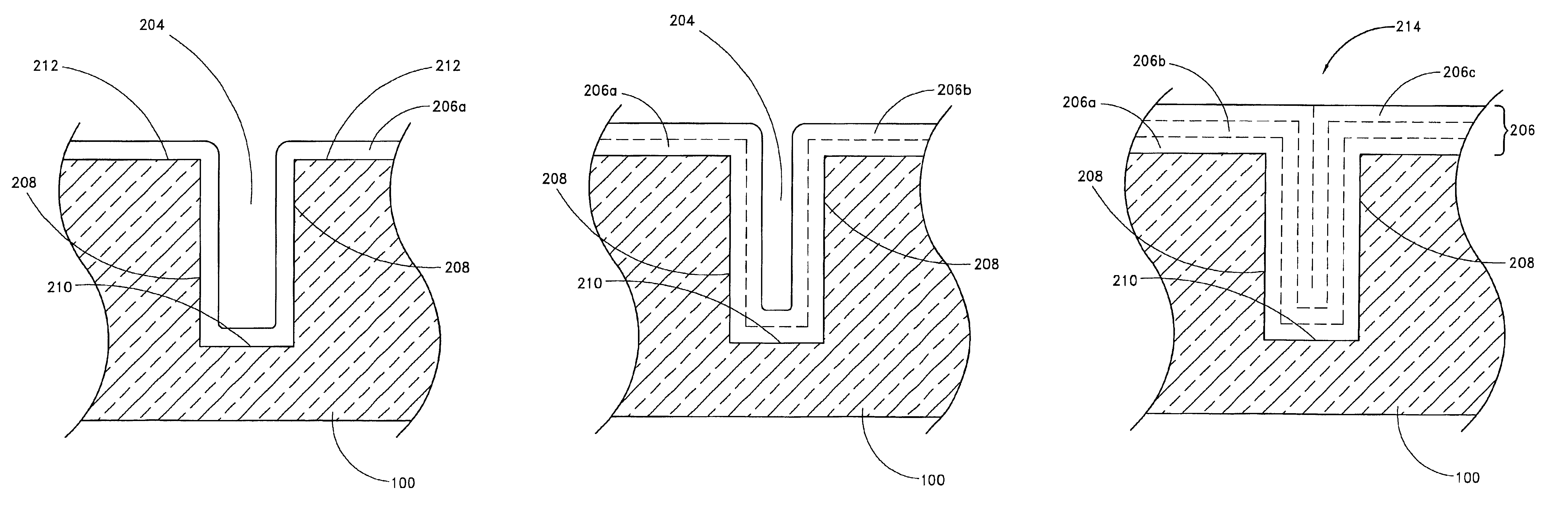

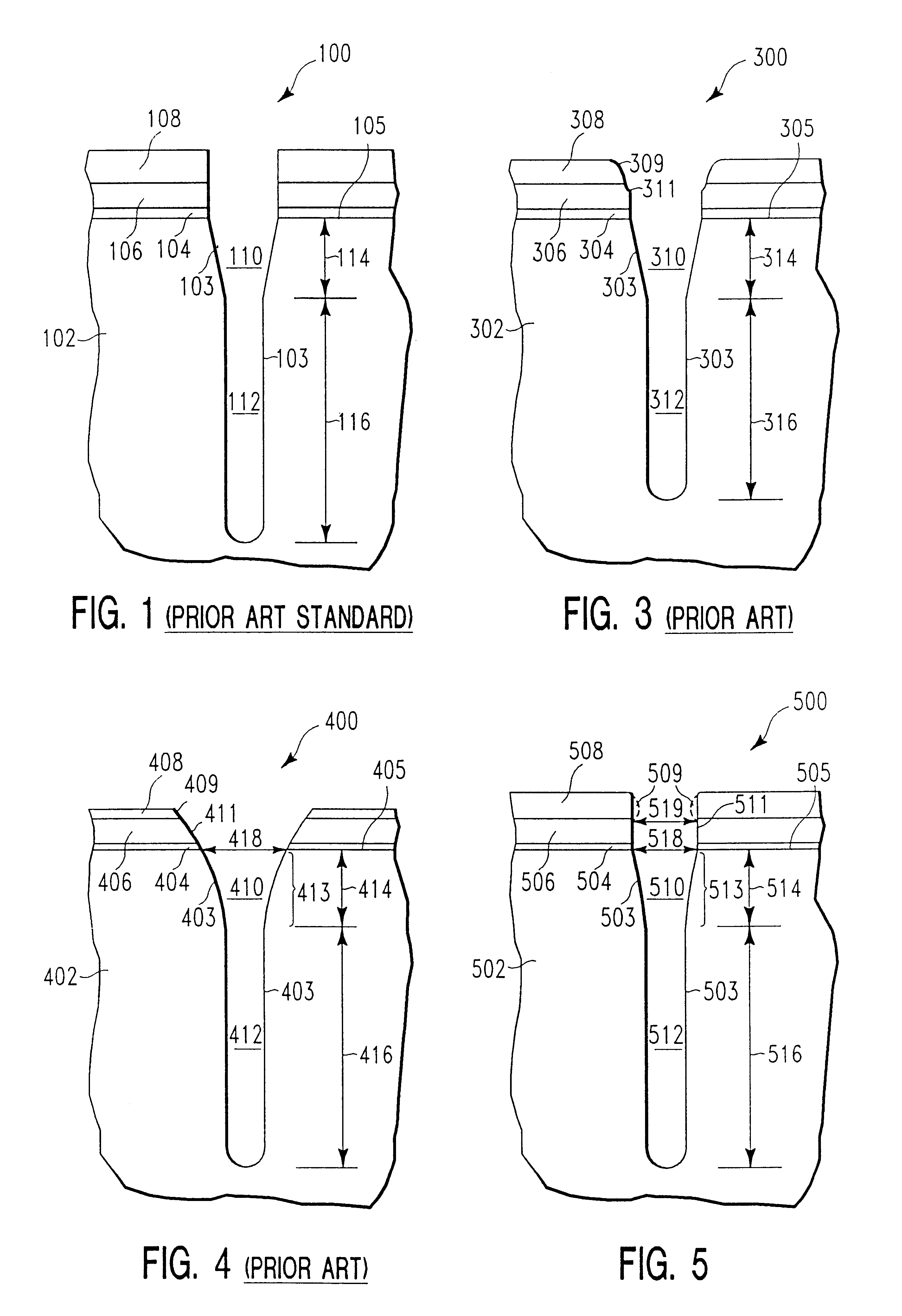

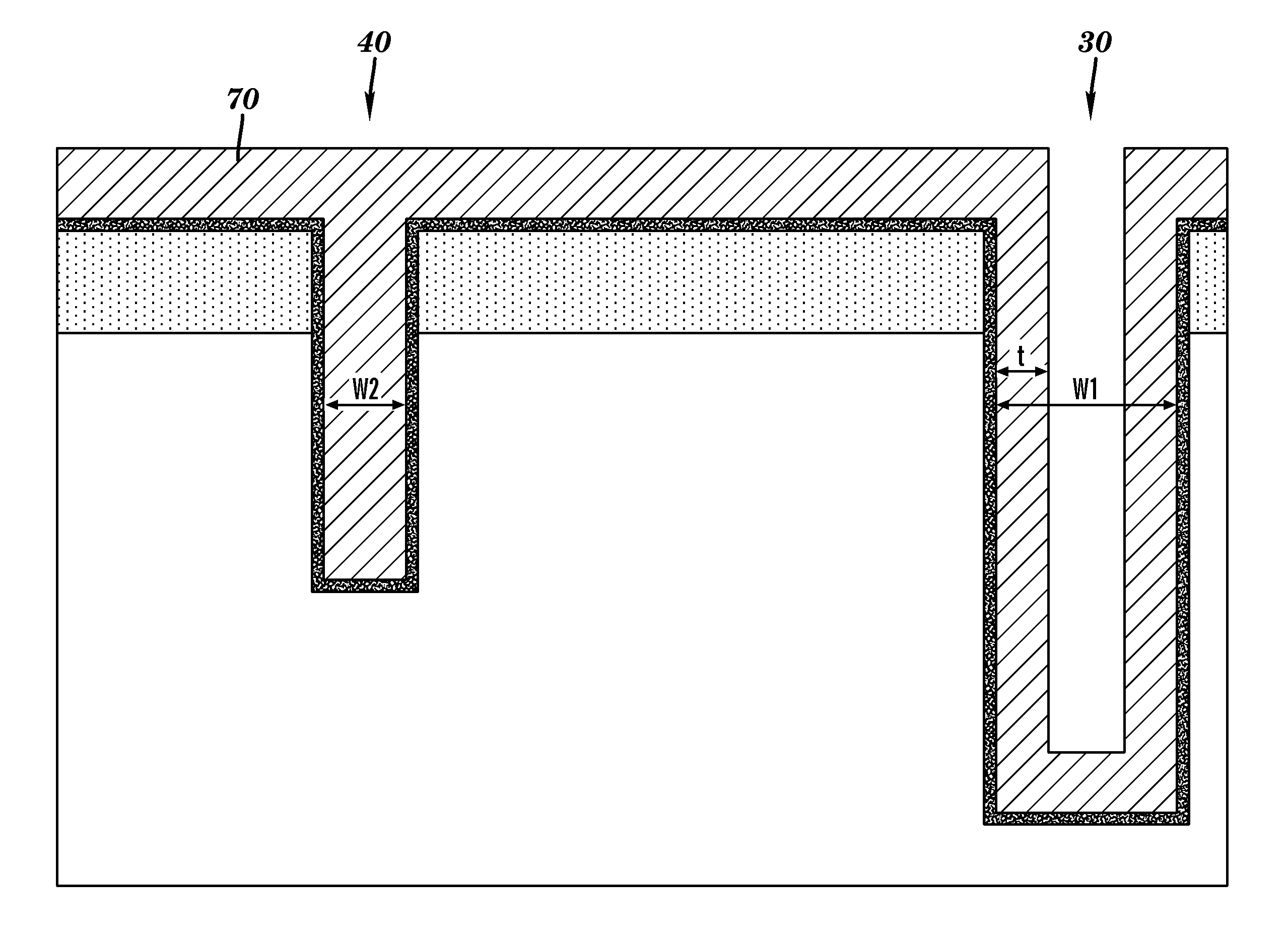

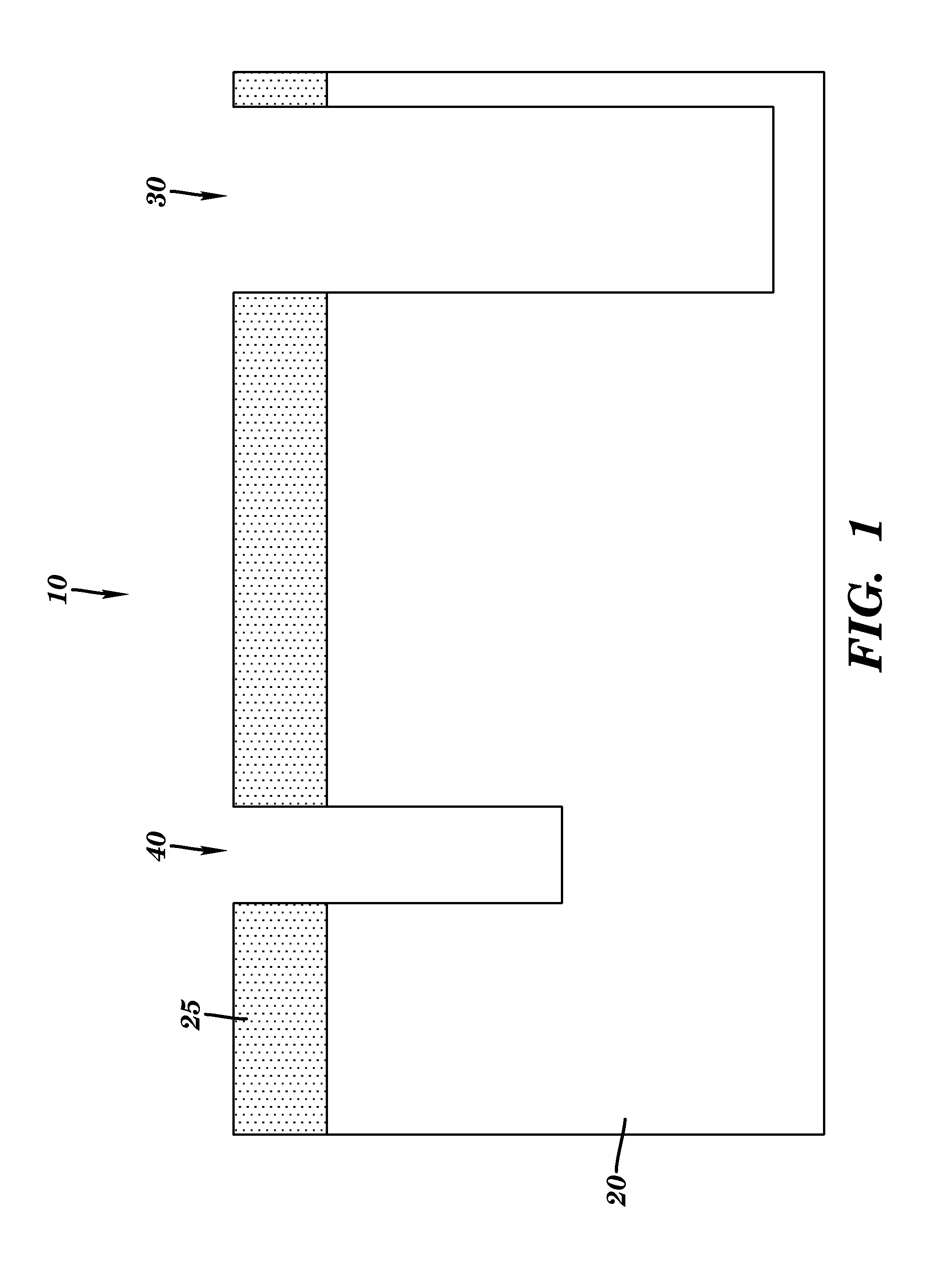

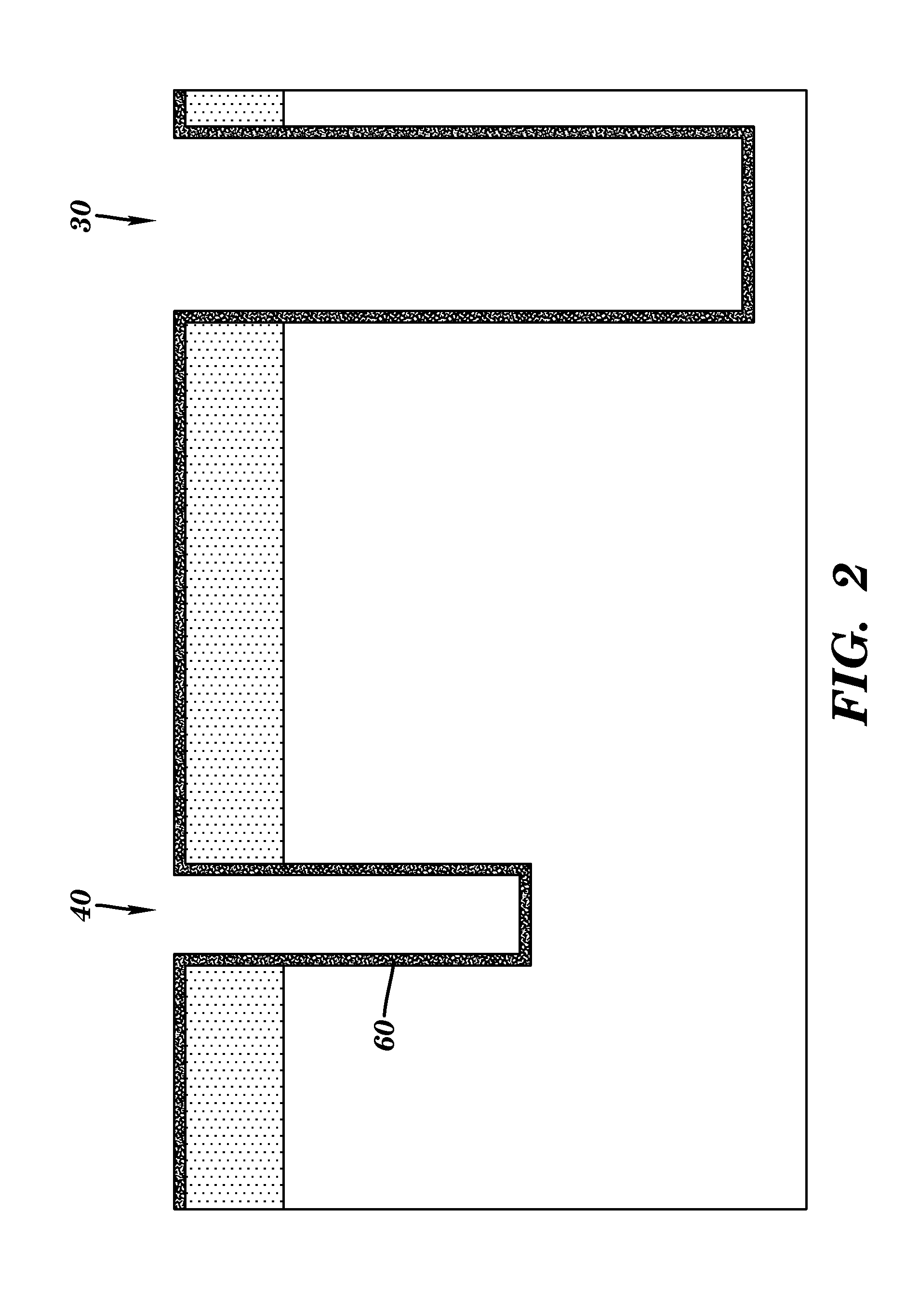

Fabrication of trenches with multiple depths on the same substrate

InactiveUS6864152B1Minimize changesProcess variationSemiconductor/solid-state device manufacturingEngineeringDeep trench

Dual trench depths are achieved on the same wafer by forming an initial trench having a depth corresponding to the difference in final depths of the shallow and deep trenches. A second mask is used to open areas for the deep trenches over the preliminary trenches and for the shallow trenches at additional locations. Etching of the shallow and deep trenches then proceeds simultaneously.

Owner:BELL SEMICON LLC

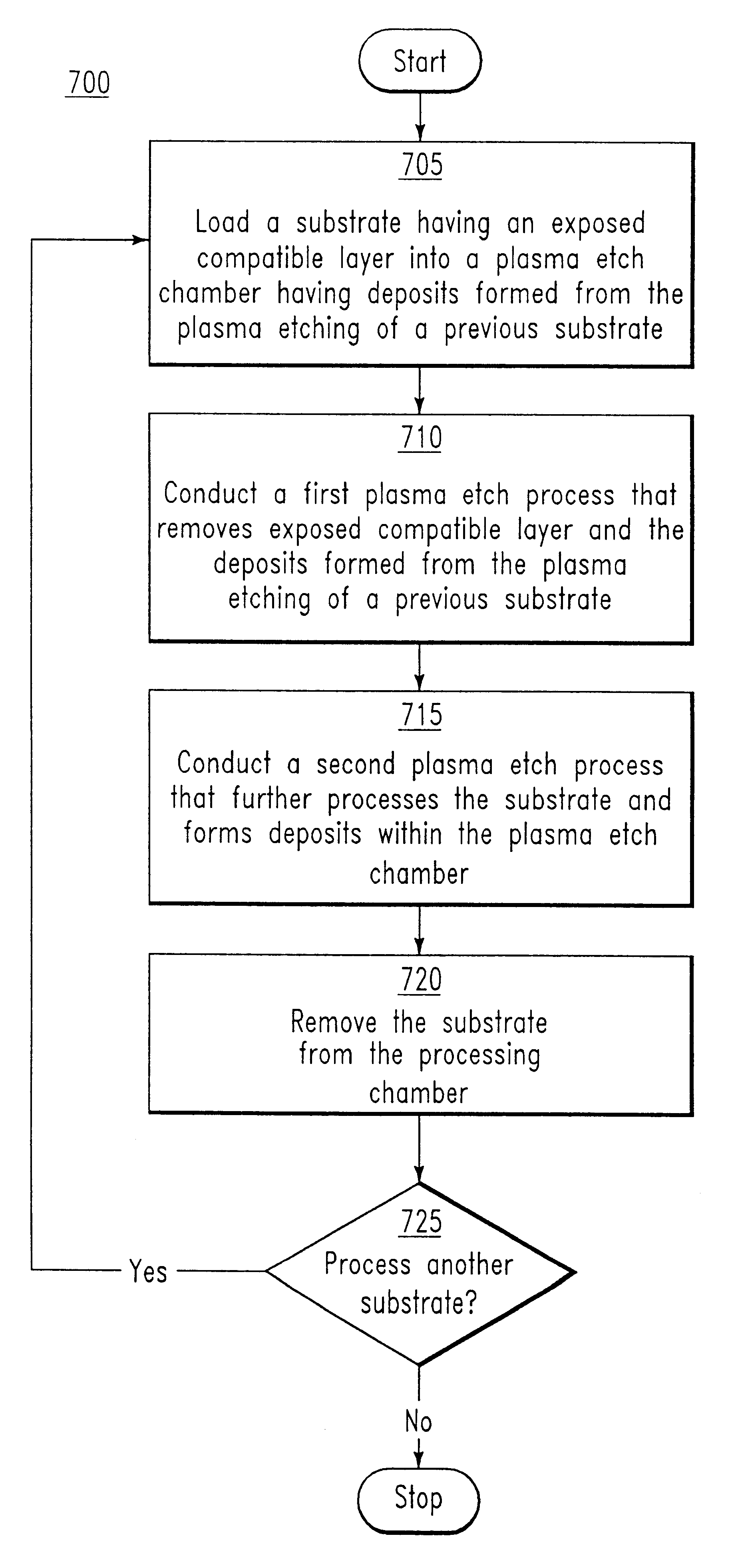

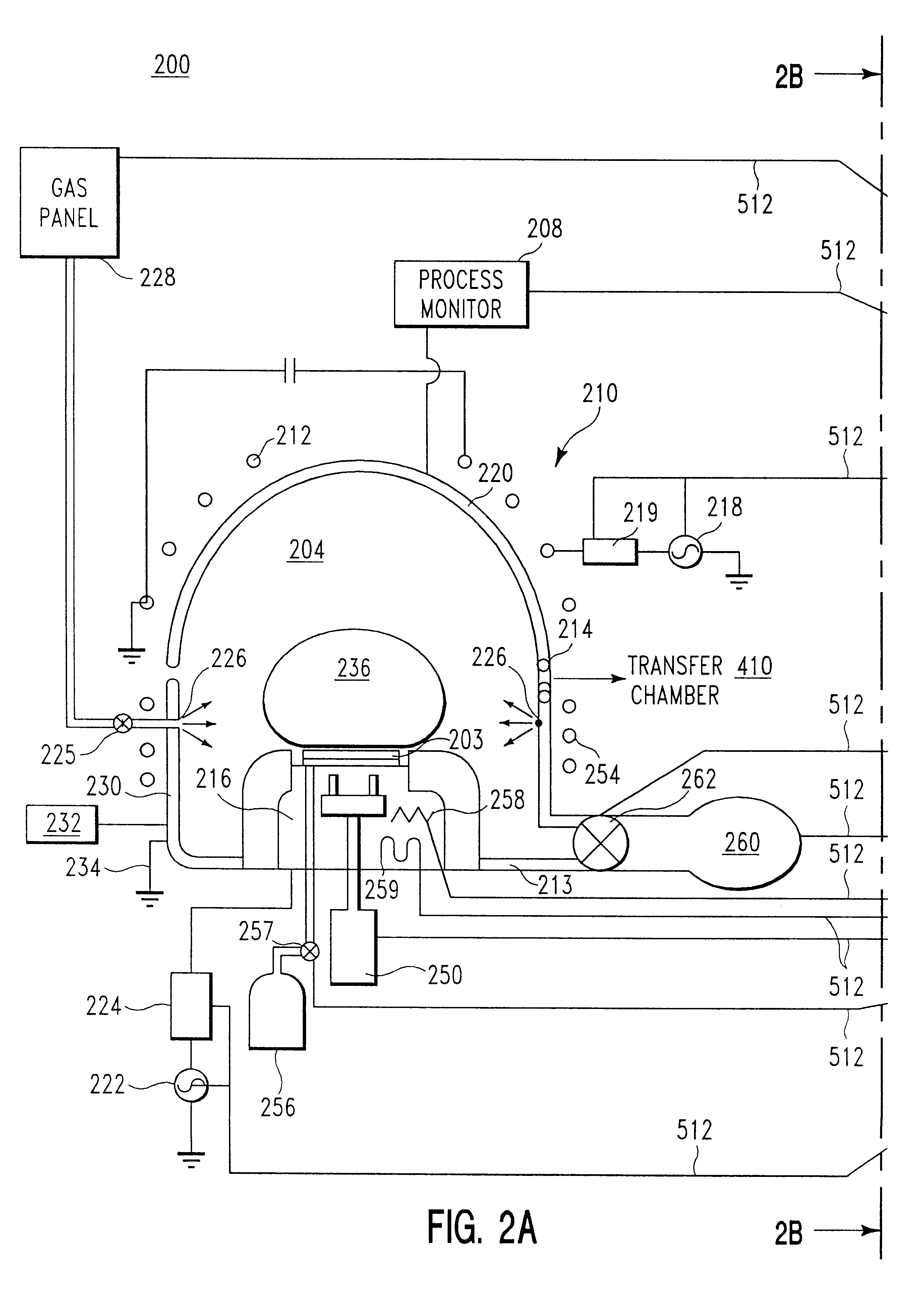

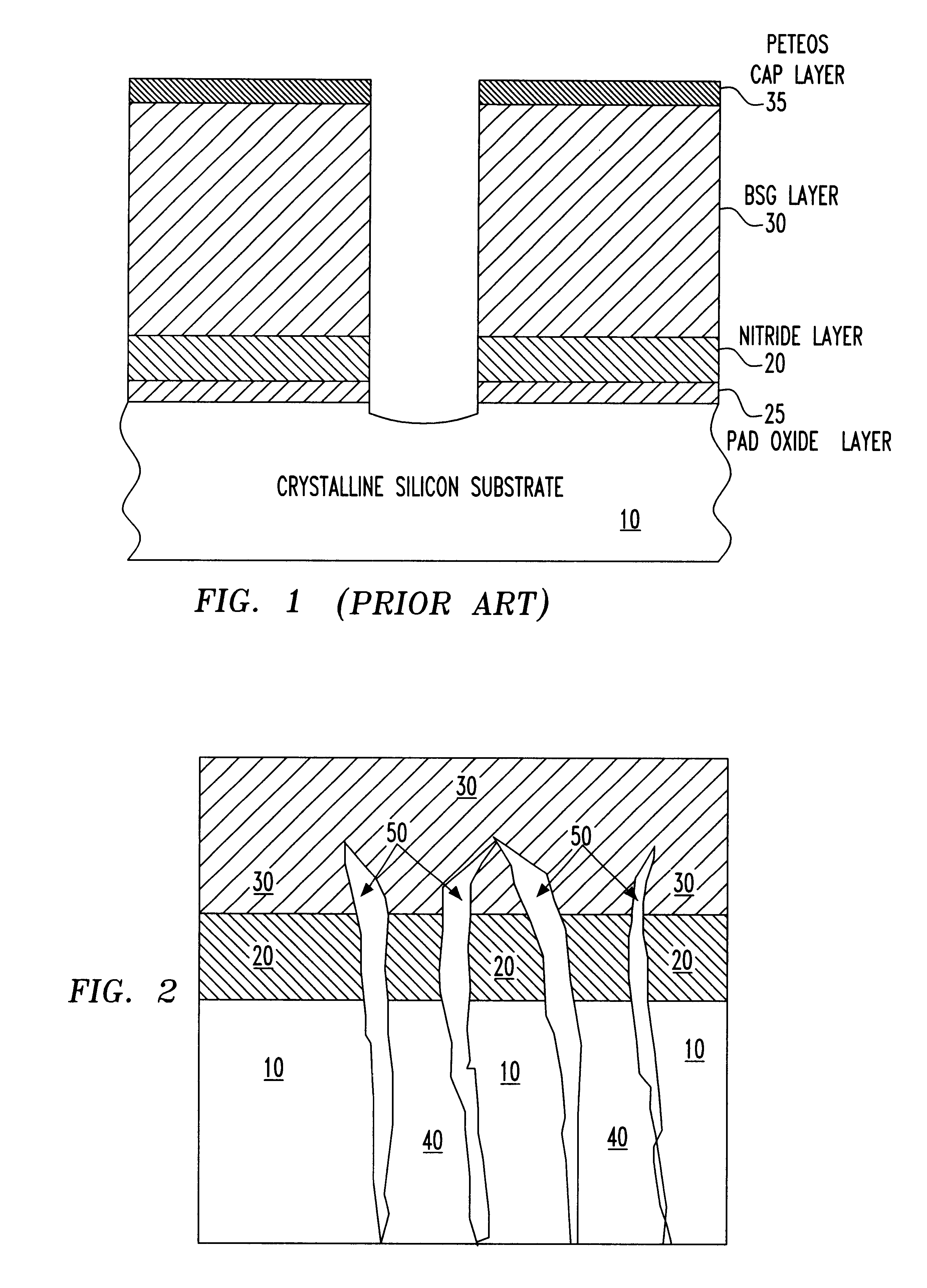

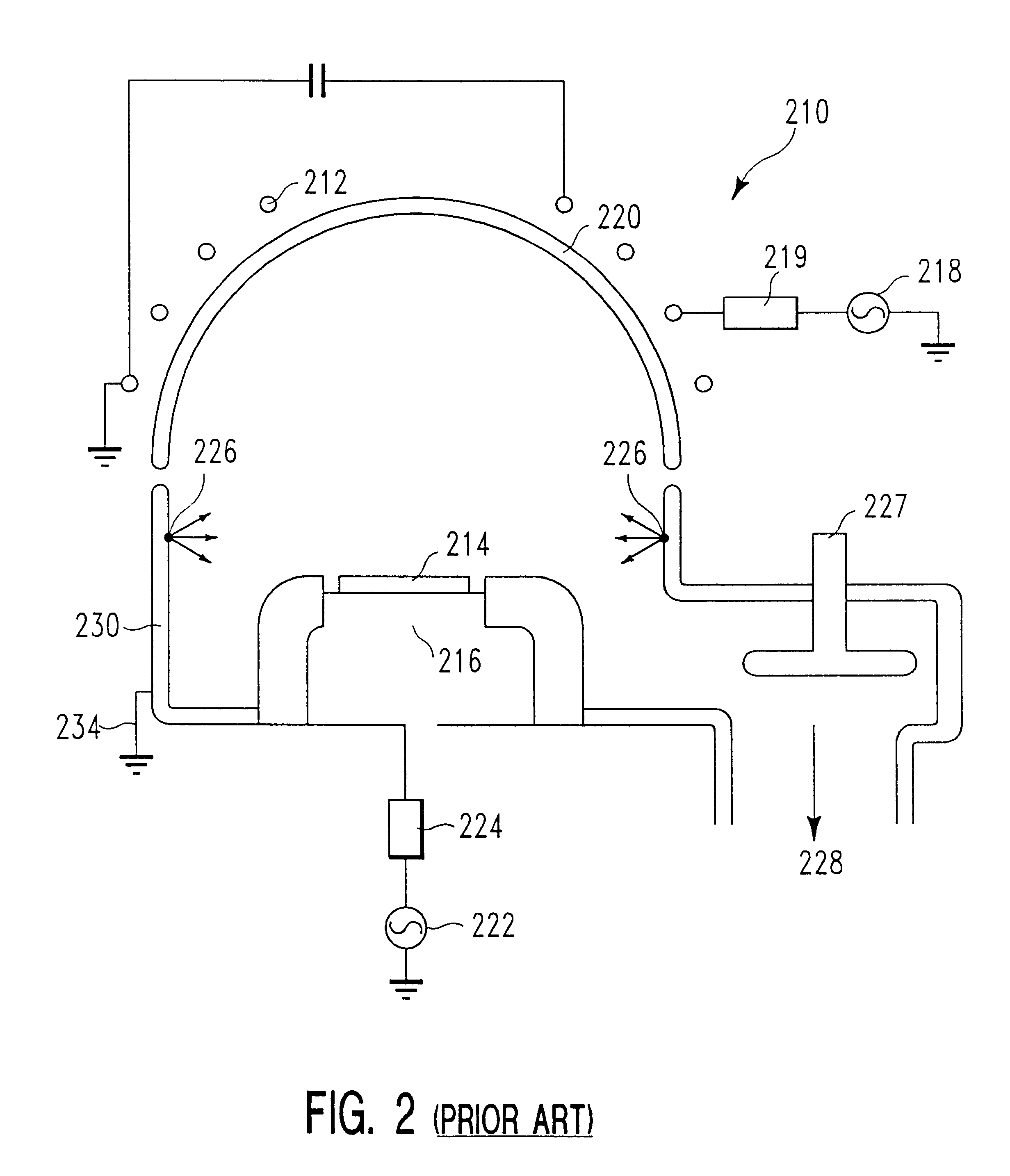

Self cleaning method of forming deep trenches in silicon substrates

This invention is directed to a method for etching films on semiconductor substrates and cleaning etch chambers. The method includes an improved processing sequence and cleaning method where residue formed from processing a previous substrate are cleaned by the etching process used to remove an exposed layer of material from the present substrate. The process provides improved substrate throughput by combining the step to clean residue from a previous substrate with an etch step conducted on the present substrate. Applicants have found the method particularly useful in processing structures such as DRAM stacks, especially where the residue is formed by a trench etched in the previous silicon substrate and the exposed layer etched from the present substrate is silicon nitride.

Owner:APPLIED MATERIALS INC

Method of fabricating trench isolation structures for integrated circuits using atomic layer deposition

InactiveUS6861334B2Semiconductor/solid-state device manufacturingSemiconductor devicesMulliteSilicon oxide

A dielectric film is formed by atomic layer deposition to conformally fill a narrow, deep trench for device isolation. The method of the illustrated embodiments includes alternately pulsing vapor-phase reactants in a string of cycles, where each cycle deposits no more than about a monolayer of material, capable of completely filling high aspect ratio trenches. Additionally, the trench-fill material composition can be tailored by processes described herein, particularly to match the coefficient of thermal expansion (CTE) to that of the surrounding substrate within which the trench is formed. Mixed phases of mullite and silica have been found to meet the goals of device isolation and matched CTE. The described process includes mixing atomic layer deposition cycles of aluminum oxide and silicon oxide in ratios selected to achieve the desired composition of the isolation material, namely on the order of 30% alumina and 70% silicon oxide by weight.

Owner:ASM INTERNATIONAL

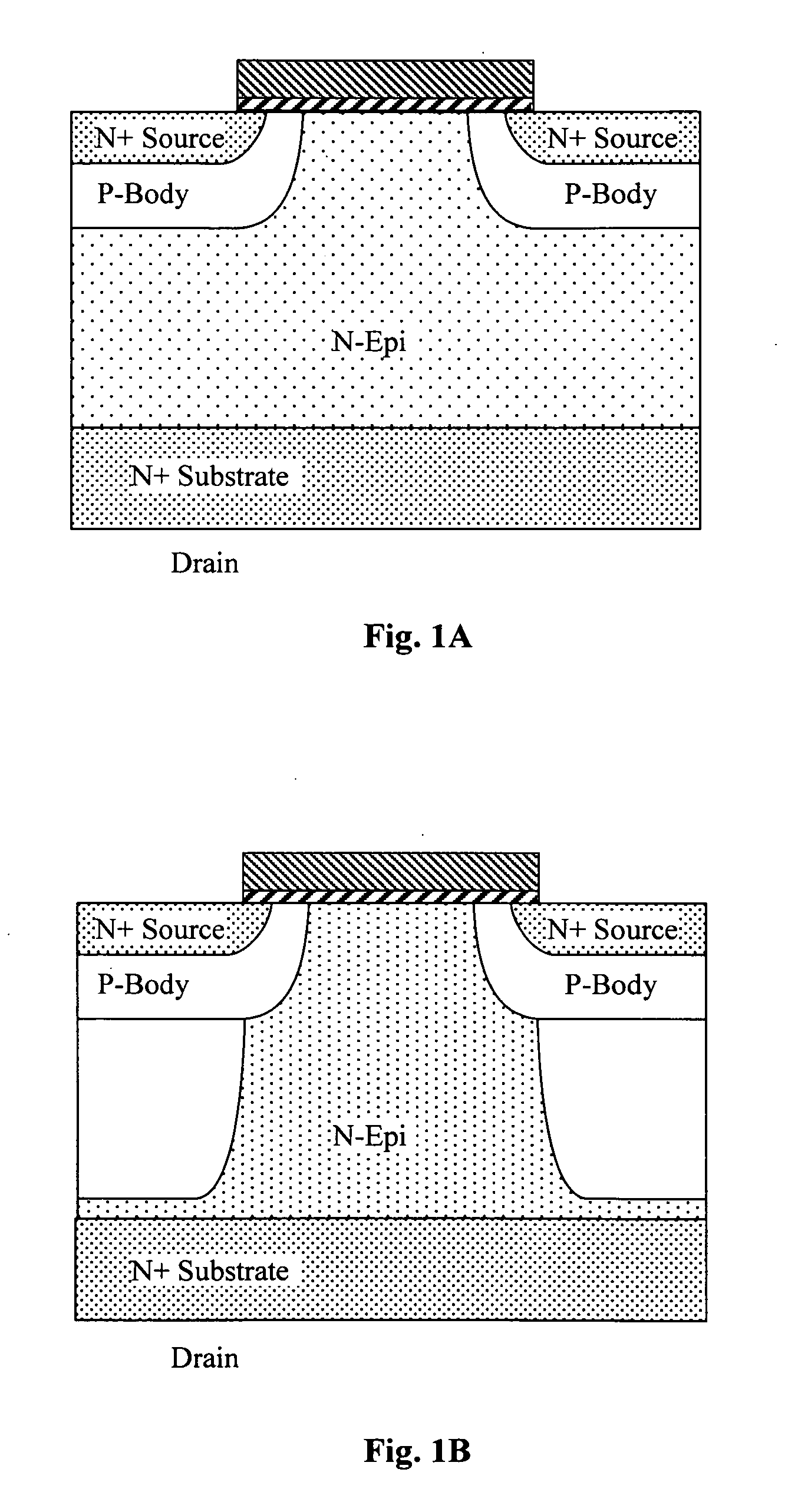

Configurations and methods for manufacturing charge balanced devices

ActiveUS20100044791A1Simple and convenient processing stepReduce processing stepsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricTrench gate

This invention discloses a semiconductor power device disposed in a semiconductor substrate and the semiconductor substrate has a plurality of deep trenches. The deep trenches are filled with an epitaxial layer thus forming a top epitaxial layer covering areas above a top surface of the deep trenches covering over the semiconductor substrate. The semiconductor power device further includes a plurality of transistor cells disposed in the top epitaxial layer whereby a device performance of the semiconductor power device is dependent on a depth of the deep trenches and not dependent on a thickness of the top epitaxial layer. Each of the plurality of transistor cells includes a trench DMOS transistor cell having a trench gate opened through the top epitaxial layer and filled with a gate dielectric material.

Owner:ALPHA & OMEGA SEMICON LTD

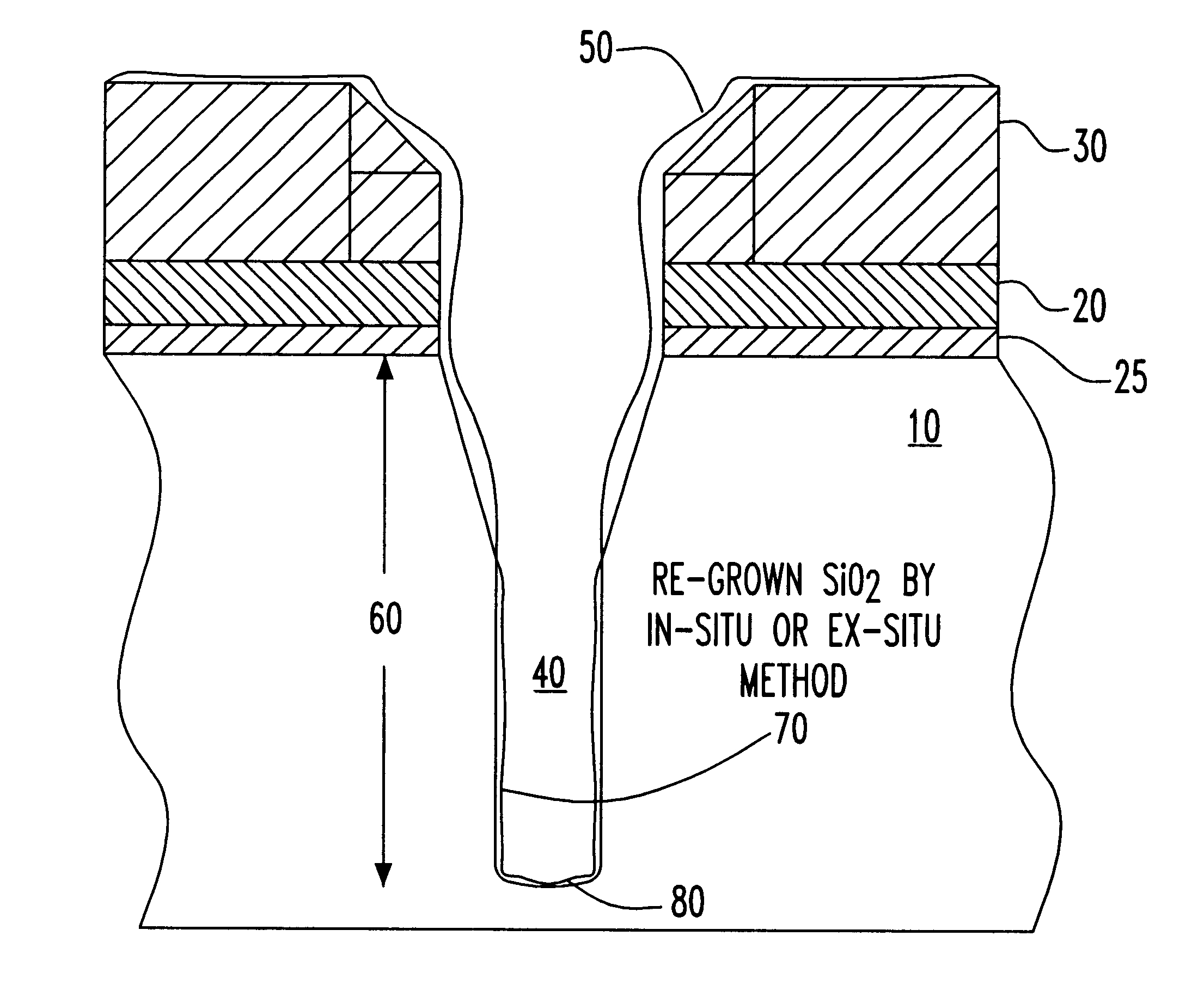

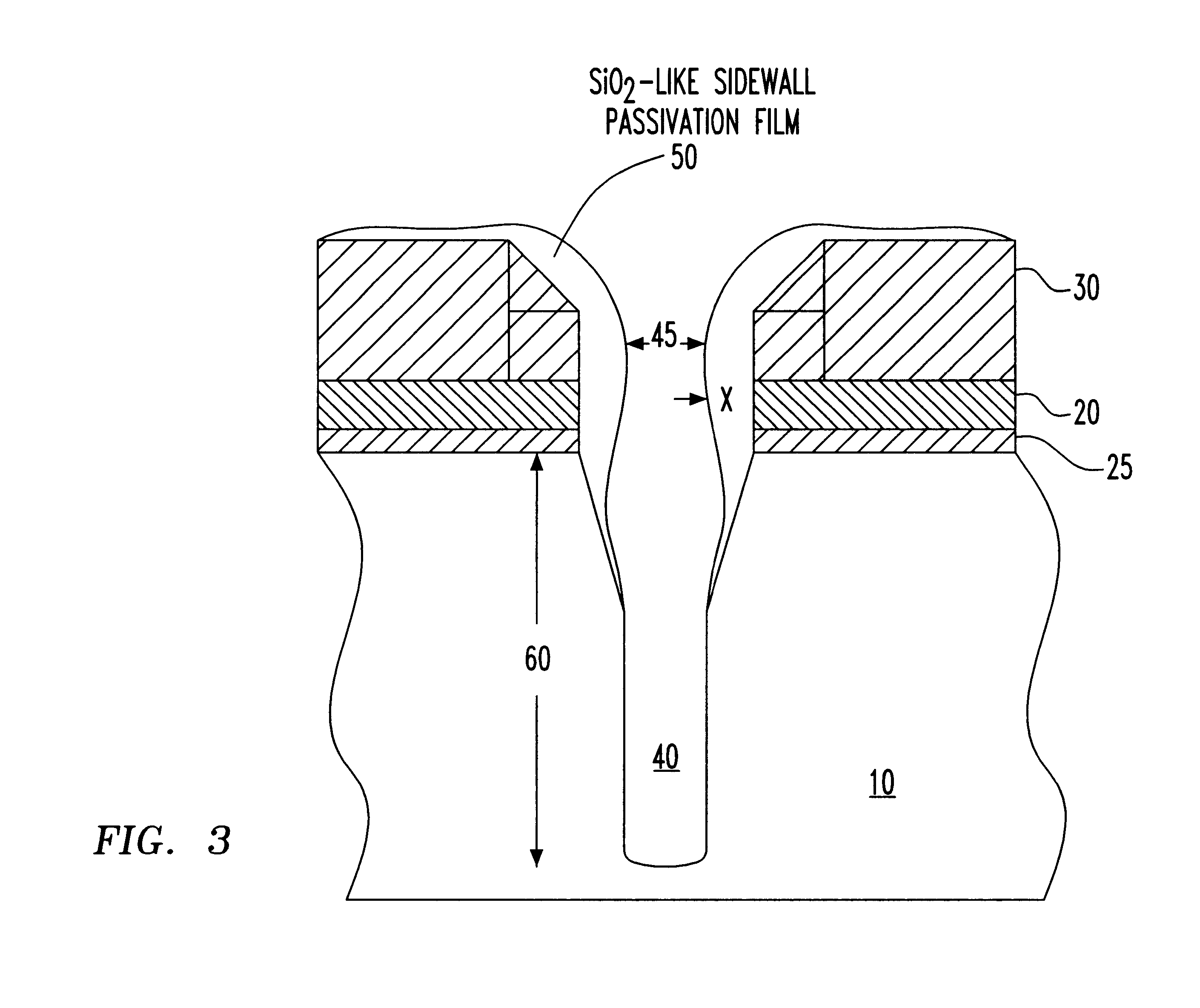

Method of reducing RIE lag for deep trench silicon etching

InactiveUS6284666B1Eliminating and at least minimizing RIE lagEliminating or at least minimizing RIE lagTransistorSemiconductor/solid-state device manufacturingHydrofluoric acidGas phase

A method of minimizing RIE lag (i.e., the neutral and ion fluxes at the bottom of a deep trench (DT) created during the construction of the trench opening using a side wall film deposition)) in DRAMs having a large aspect ratio (i.e., <30:1) is described. The method forms a passivation film to the extent necessary for preventing isotropic etching of the substrate, hence maintaining the required profile and the shape of the DT within the substrate. The RIE process described provides a partial DT etched into a substrate to achieve the predetermined depth. The passivation film is allowed to grow to a certain thickness still below the extent that it would close the opening of the deep trench. Alternatively, the passivation film is removed by a non-RIE etching process. The non-RIE process that removes the film can be wet etched with chemicals, such as hydrofluoric acid (buffered or non buffered) or, alternatively, using vapor phase and / or non-ionized chemicals, such as anhydrous hydrofluoric acid. The controlled thickness of the film allows achieving a predetermined DT depth for high aspect ratio structures.

Owner:INFINEON TECH AG +1

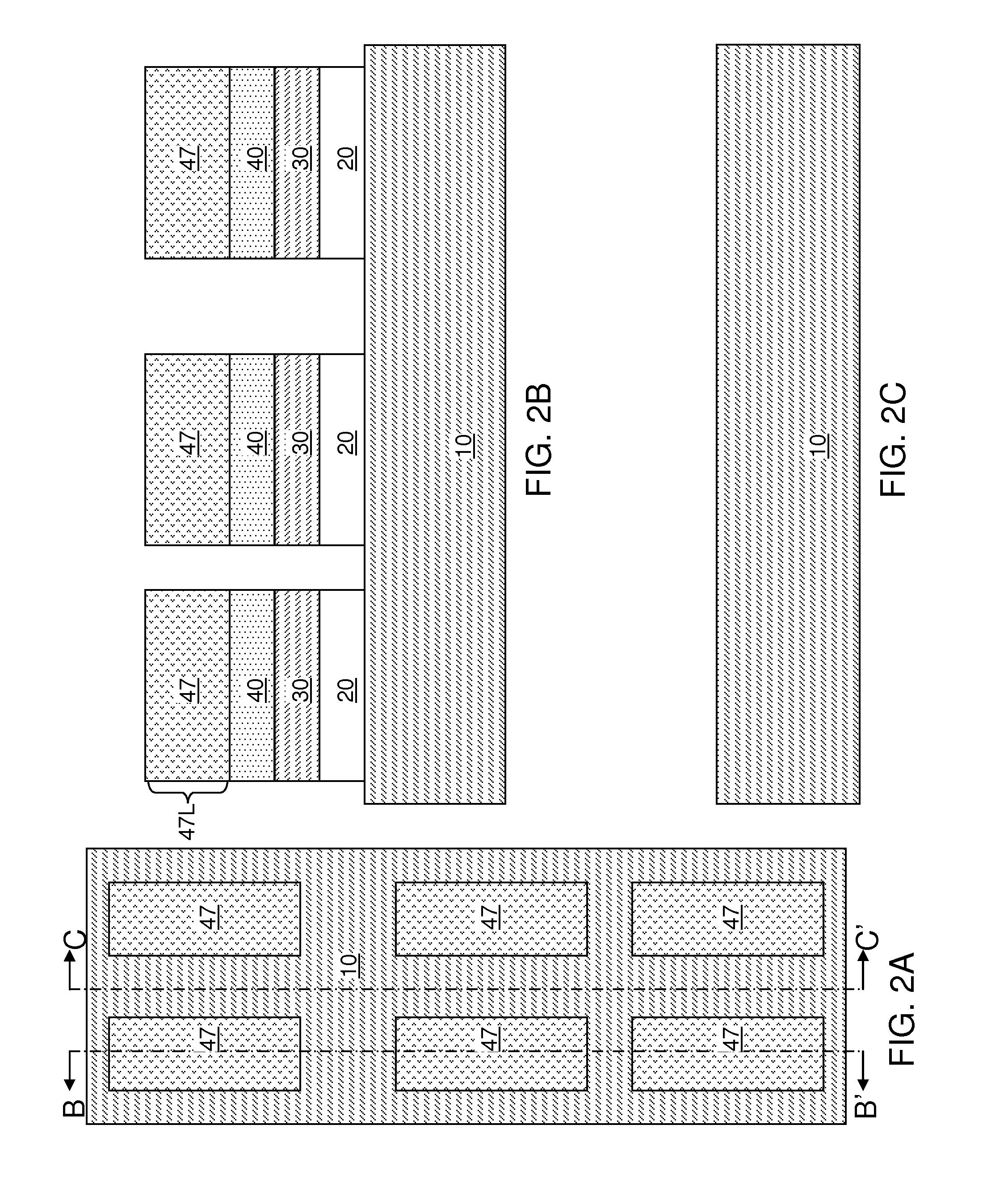

Vertical gated access transistor

According to one embodiment of the present invention, a method of forming an apparatus comprises forming a plurality of deep trenches and a plurality of shallow trenches in a first region of a substrate. At least one of the shallow trenches is positioned between two deep trenches. The plurality of shallow trenches and the plurality of deep trenches are parallel to each other. The method further comprises depositing a layer of conductive material over the first region and a second region of the substrate. The method further comprises etching the layer of conductive material to define a plurality of lines separated by a plurality of gaps over the first region of the substrate, and a plurality of active device elements over the second region of the substrate. The method further comprises masking the second region of the substrate. The method further comprises removing the plurality of lines from the first region of the substrate, thereby creating a plurality of exposed areas from which the plurality of lines were removed. The method further comprises etching a plurality of elongate trenches in the plurality of exposed areas while the second region of the substrate is masked.

Owner:MICRON TECH INC

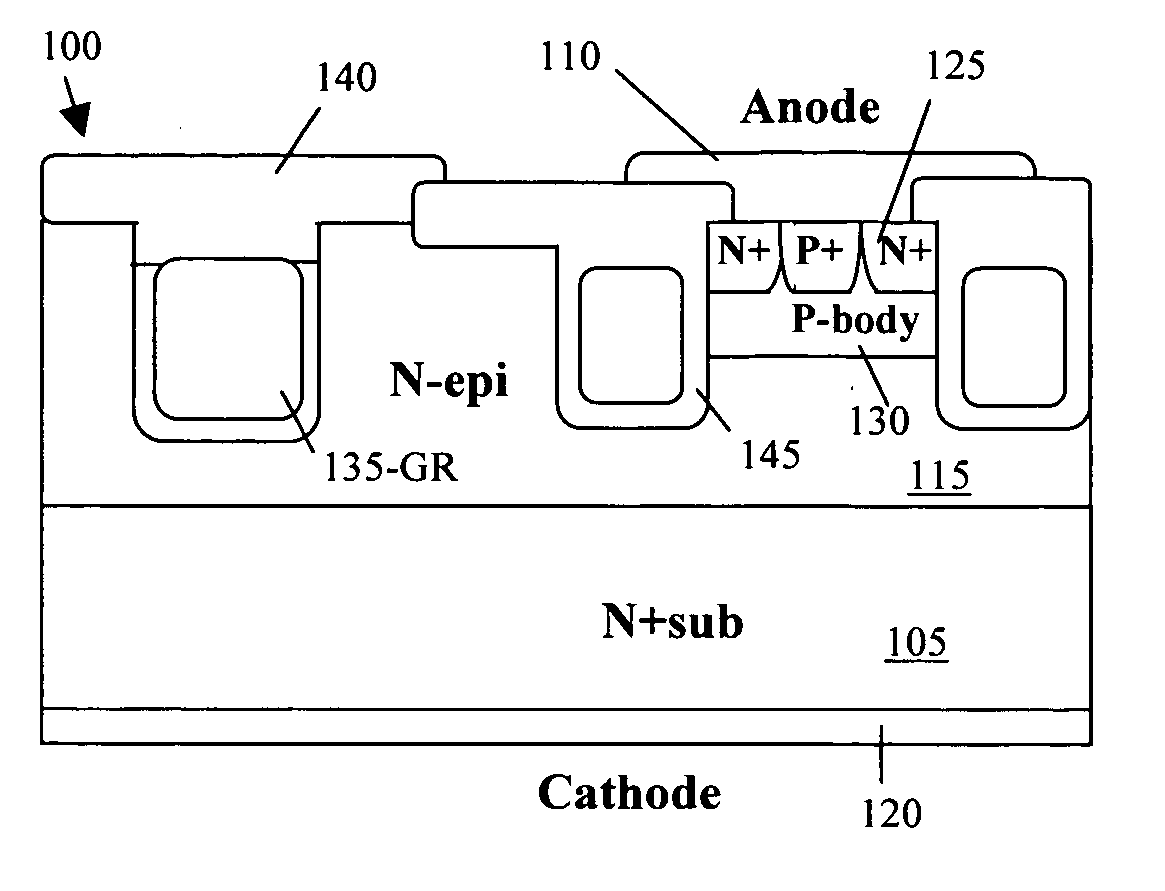

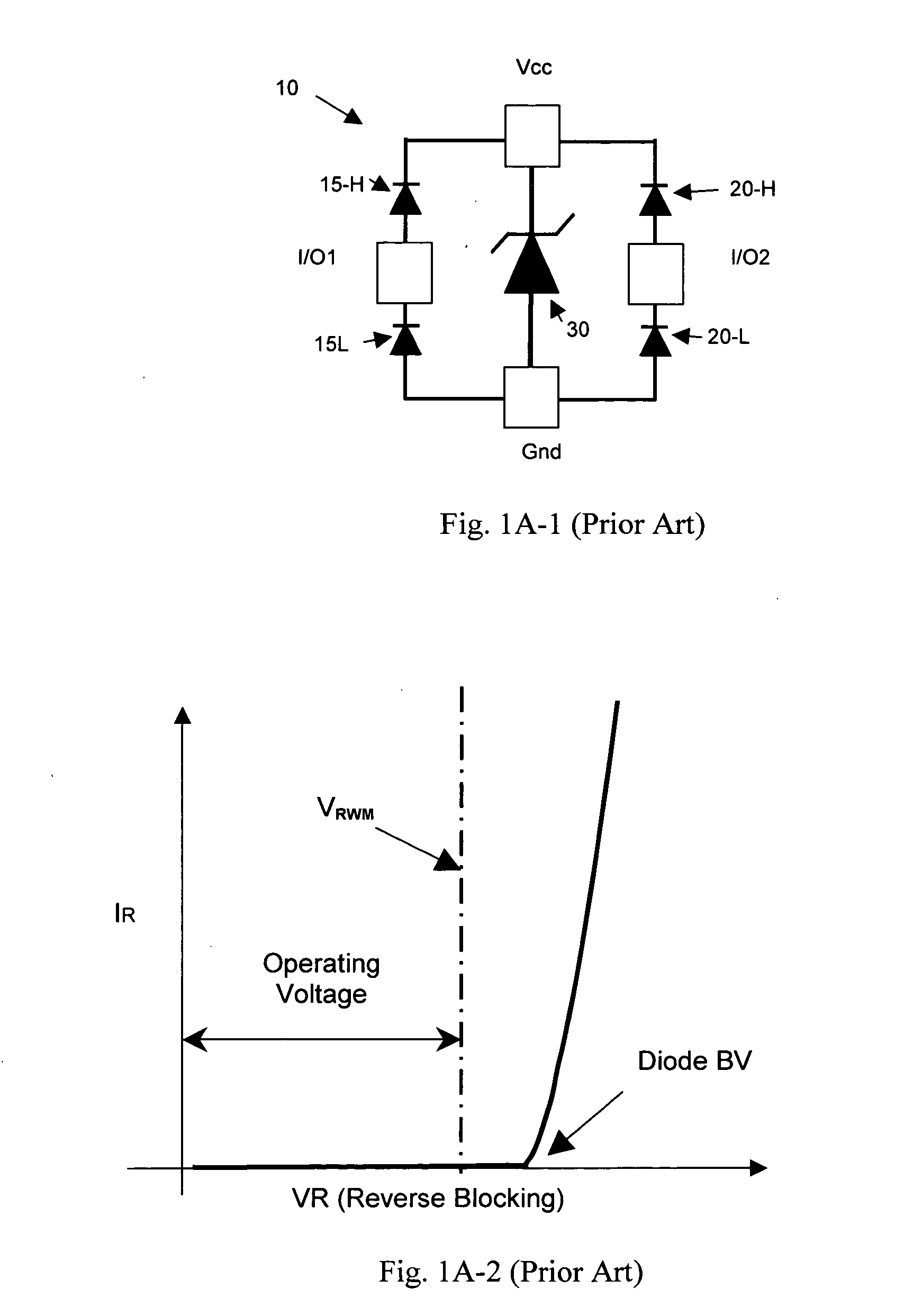

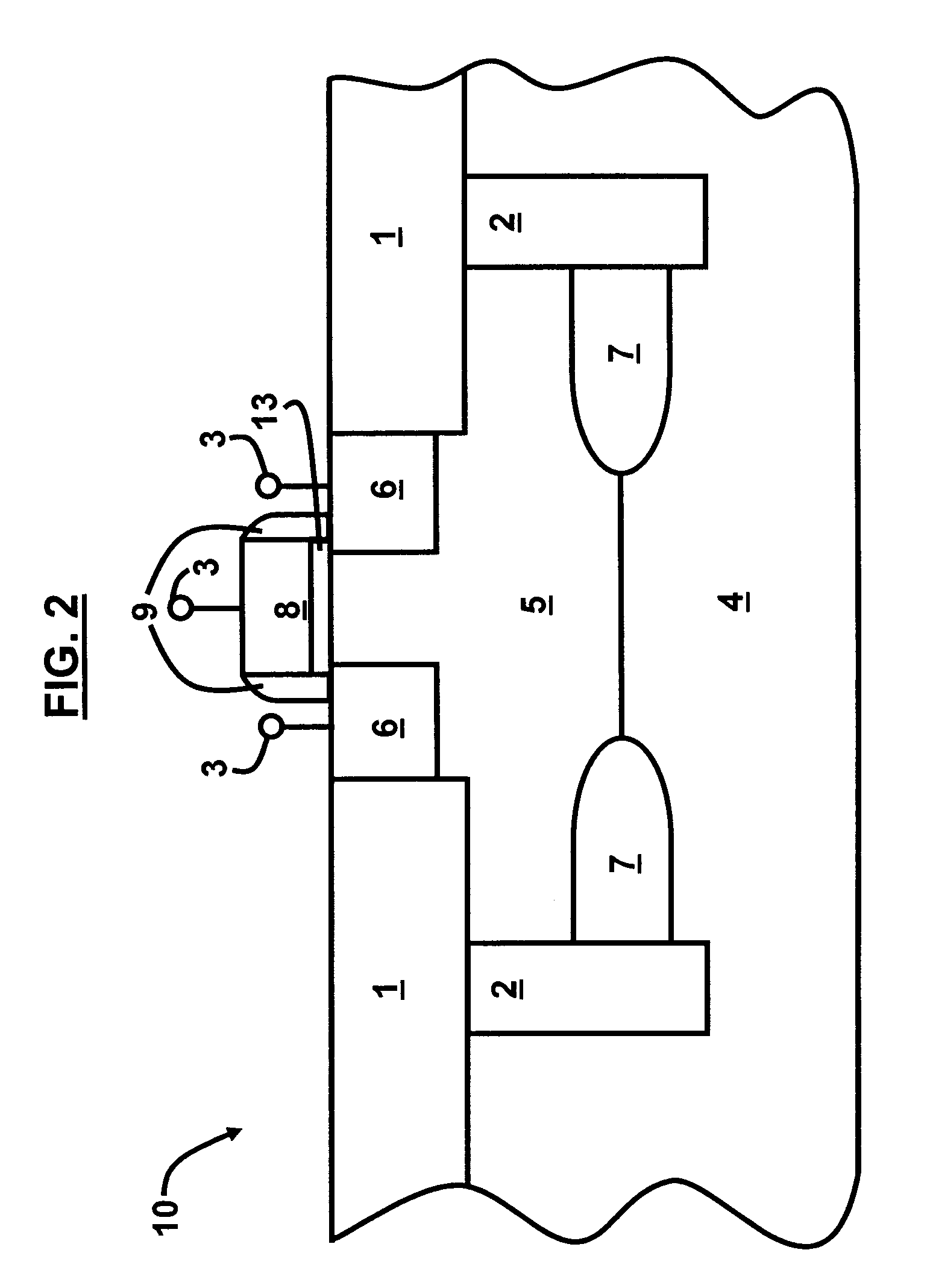

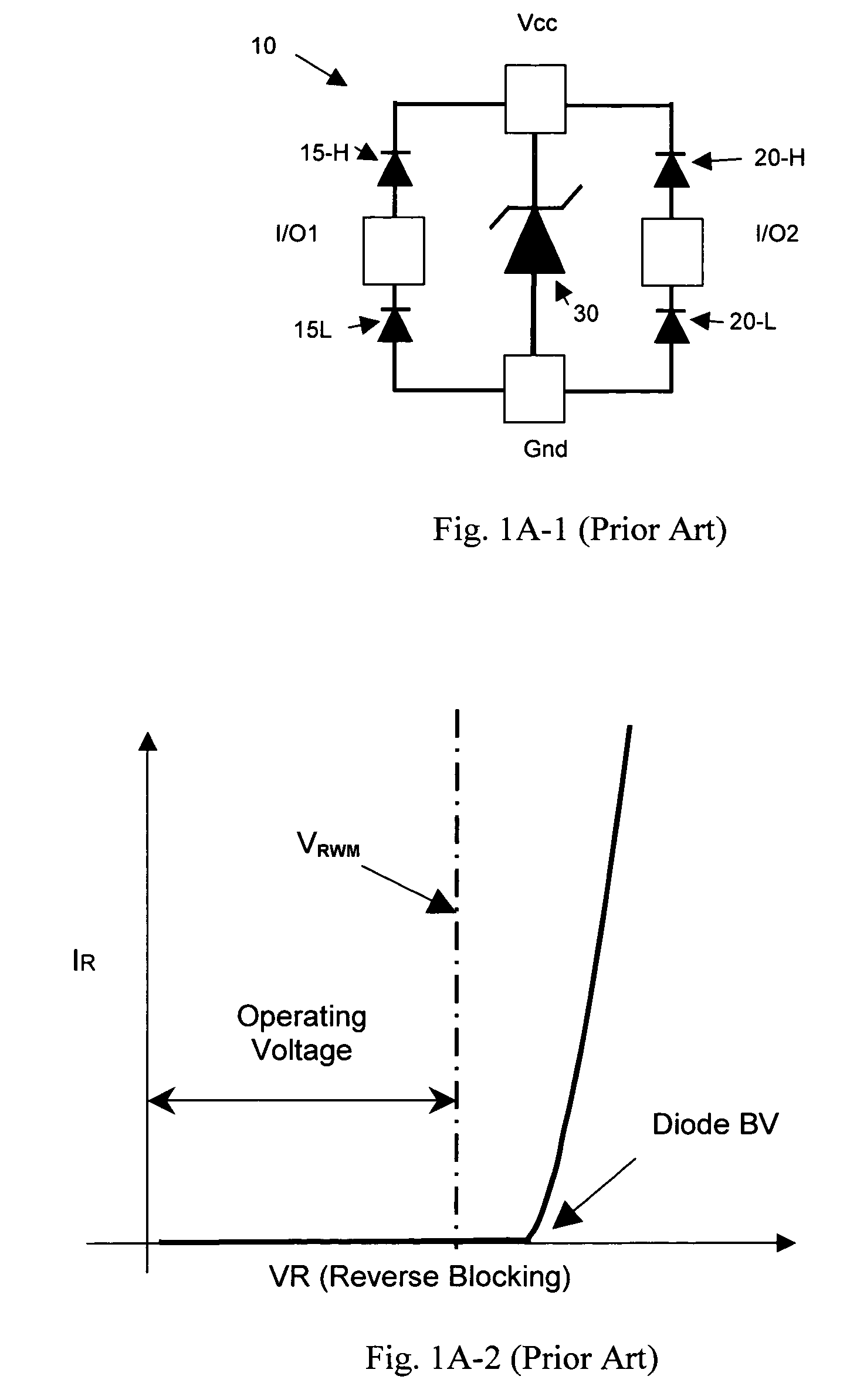

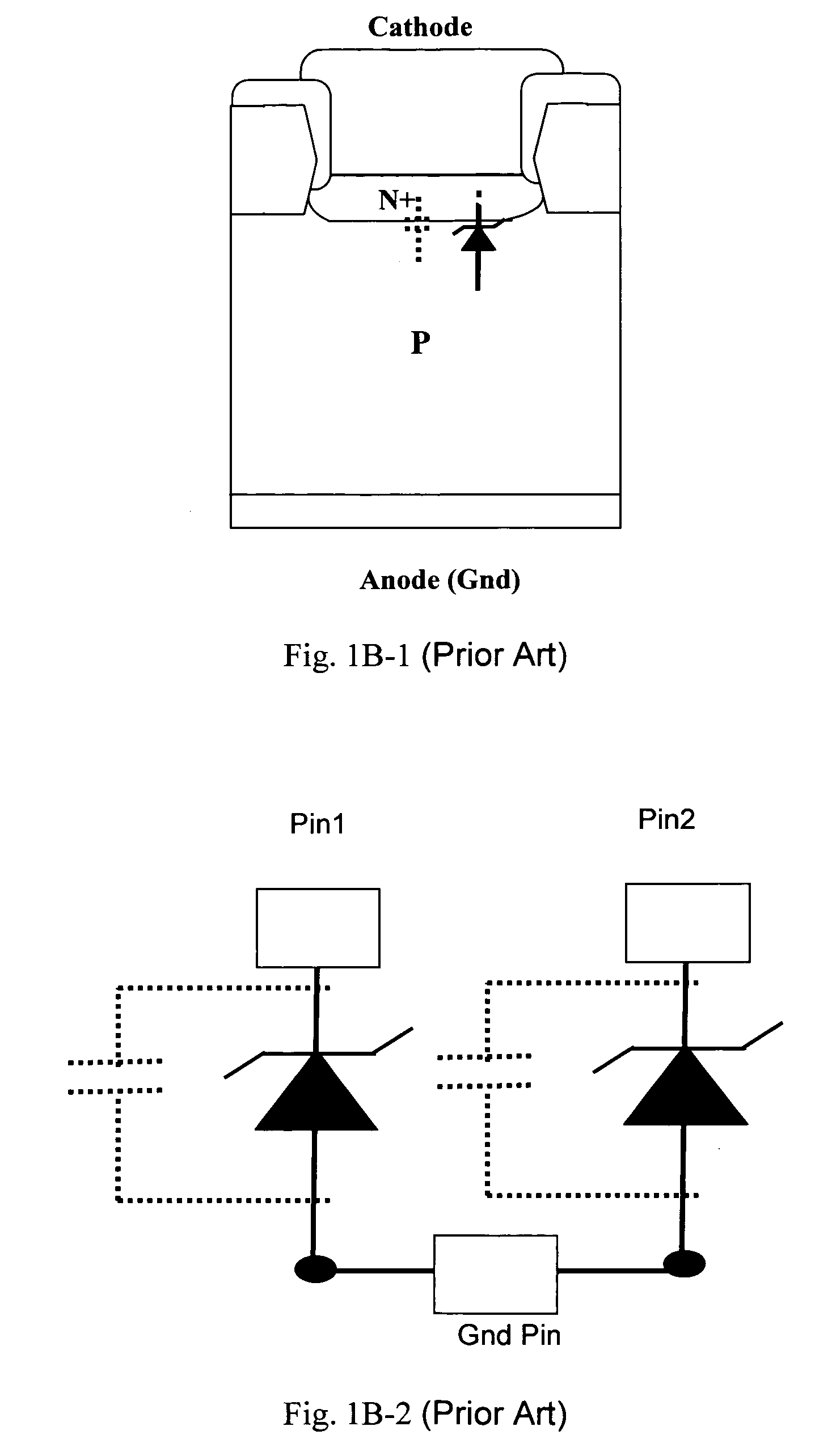

Circuit configuration and manufacturing processes for vertical transient voltage suppressor (TVS) and EMI filter

ActiveUS20080121988A1Small footprintLow costSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceTransient voltage suppressor

A vertical TVS (VTVS) circuit includes a semiconductor substrate for supporting the VTVS device thereon having a heavily doped layer extending to the bottom of substrate. Deep trenches are provided for isolation between multi-channel VTVS. Trench gates are also provided for increasing the capacitance of VTVS with integrated EMI filter.

Owner:ALPHA & OMEGA SEMICON LTD

Silicon trench etch using silicon-containing precursors to reduce or avoid mask erosion

The present invention pertains to an etch chemistry and method useful for the etching of silicon surfaces. The method is particularly useful in the deep trench etching of silicon where profile control is important. In the case of deep trench etching, at least a portion of the substrate toward the bottom of the trench is etched using a combination of reactive gases including a fluorine-containing compound which does not contain silicon (FC); a silicon-containing compound (SC) which does not contain fluorine; and oxygen (O2).

Owner:APPLIED MATERIALS INC

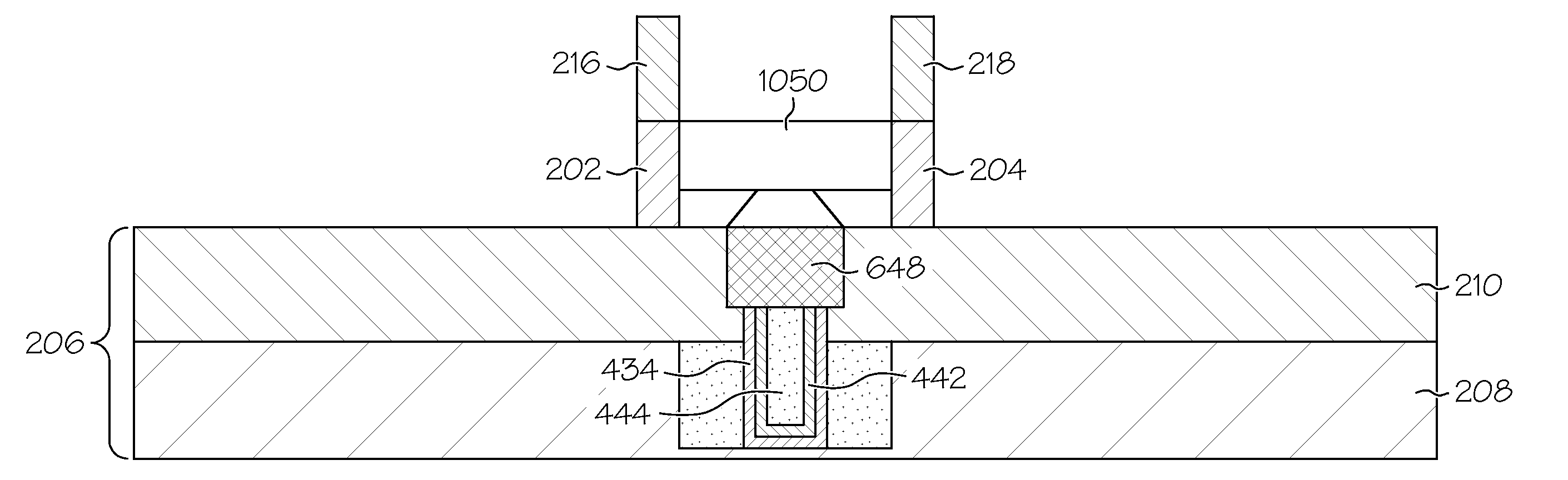

Structure and method for simultaneously forming a through silicon via and a deep trench structure

ActiveUS20120091593A1Semiconductor/solid-state device detailsSolid-state devicesOptoelectronicsReactive-ion etching

A through silicon via (TSV) and a deep trench capacitor (DTCap) or a deep trench isolation (DTI) are simultaneously formed on the same substrate by a single mask and a single reactive ion etching (RIE). The TSV trench is wider and deeper that the DTCap or DTI trench. The TSV and DTCap or DTI are formed with different dielectric materials on the trench sidewalls. The TSV and DTCap or DTI are perfectly aligned.

Owner:GLOBALFOUNDRIES US INC

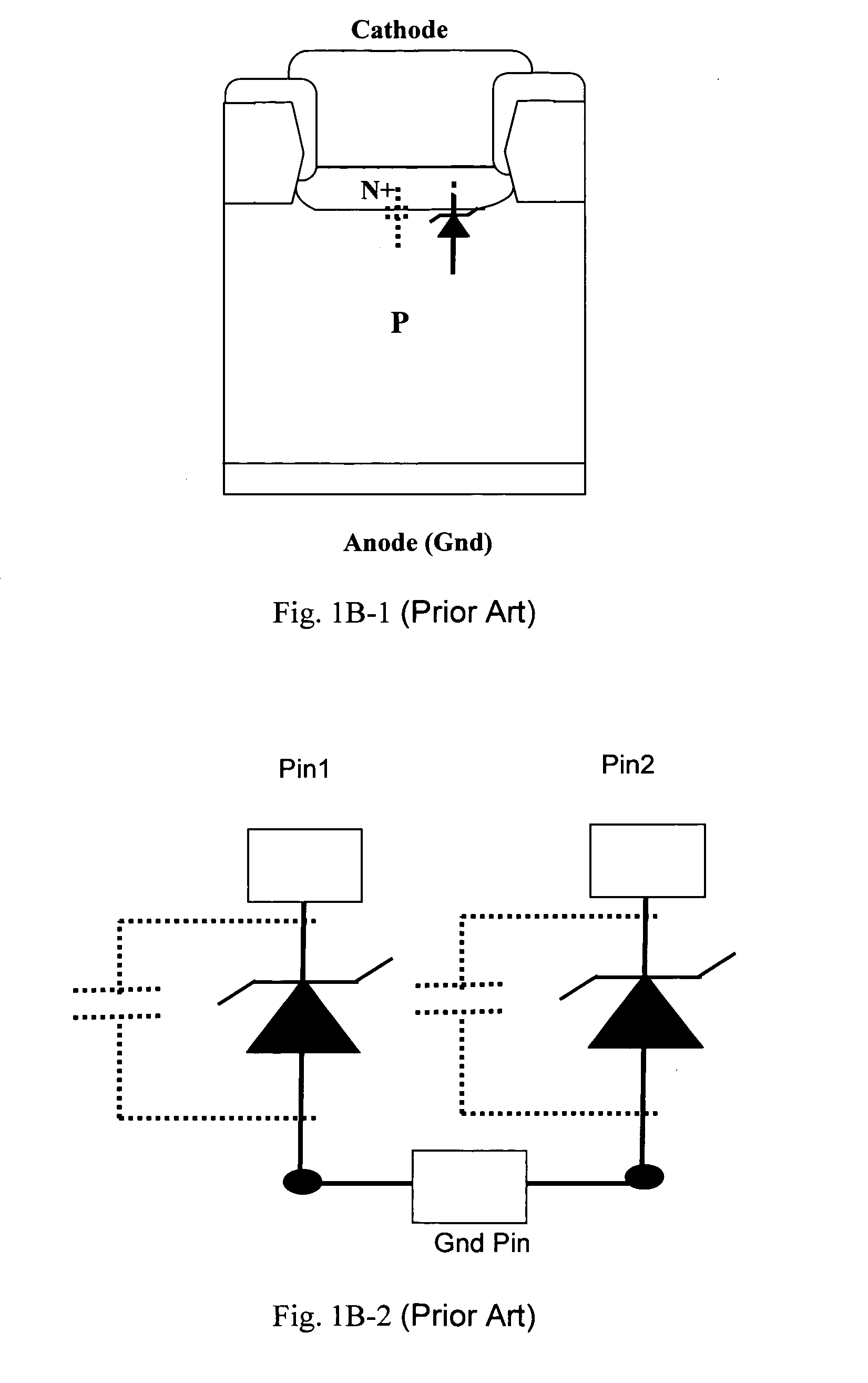

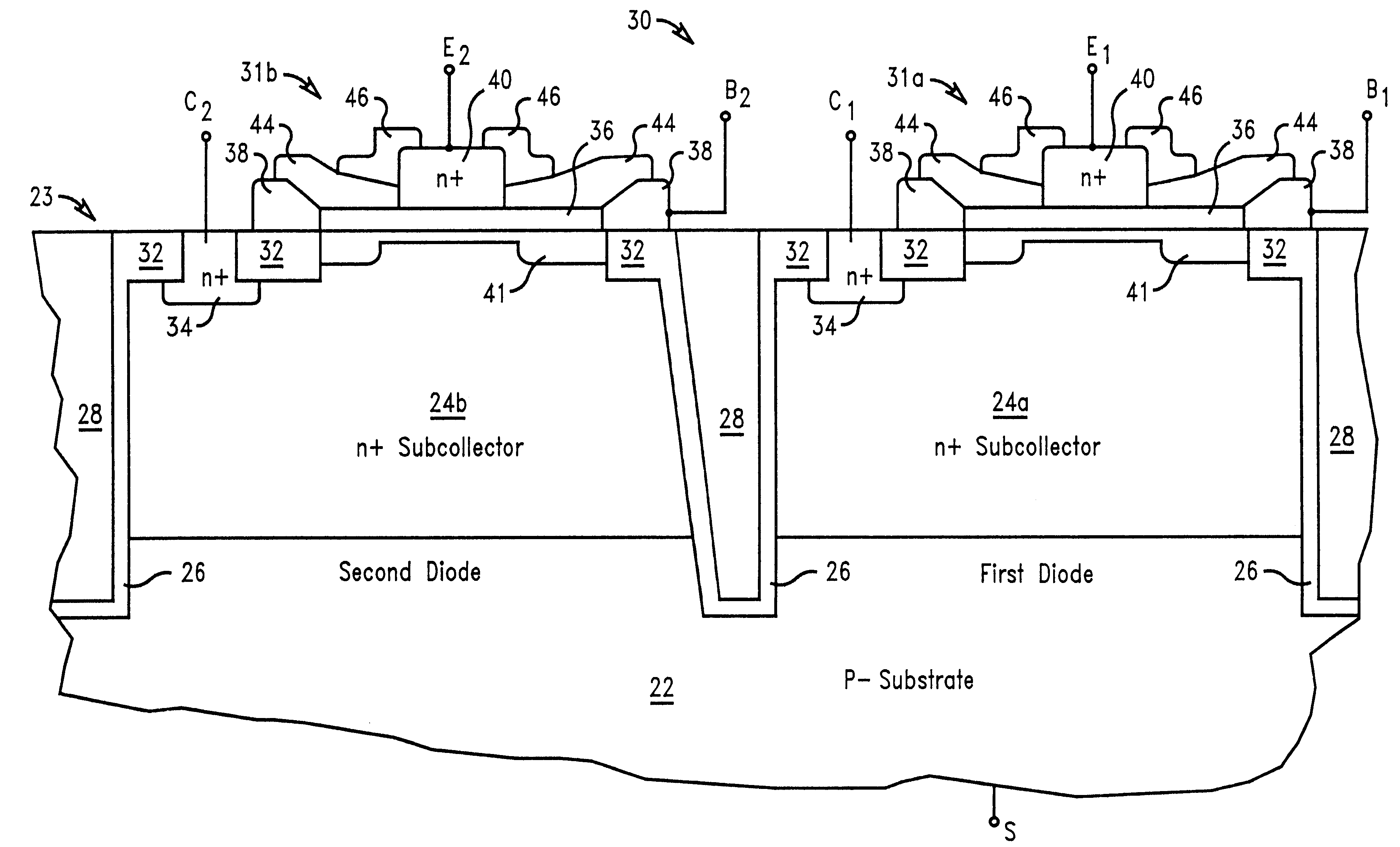

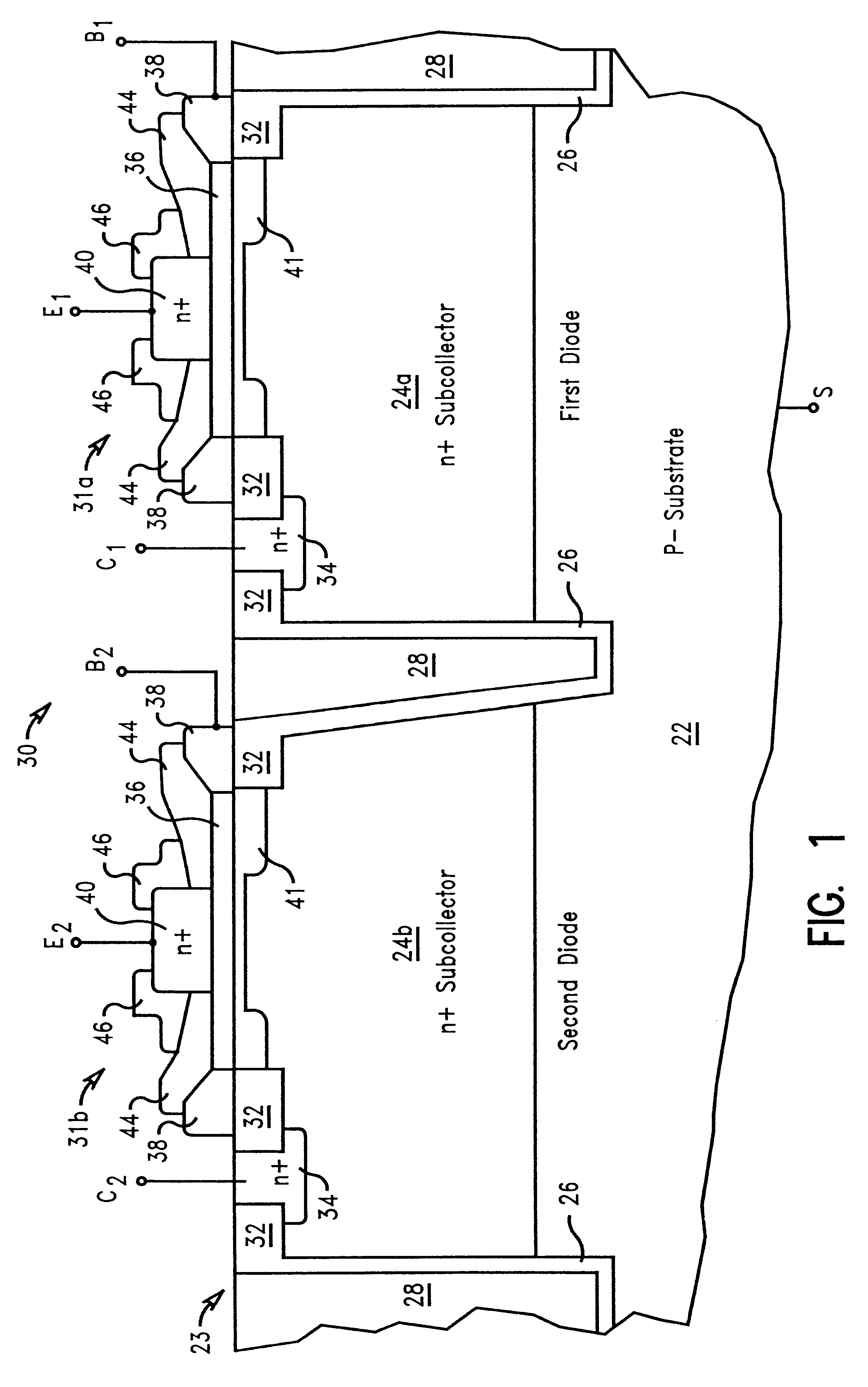

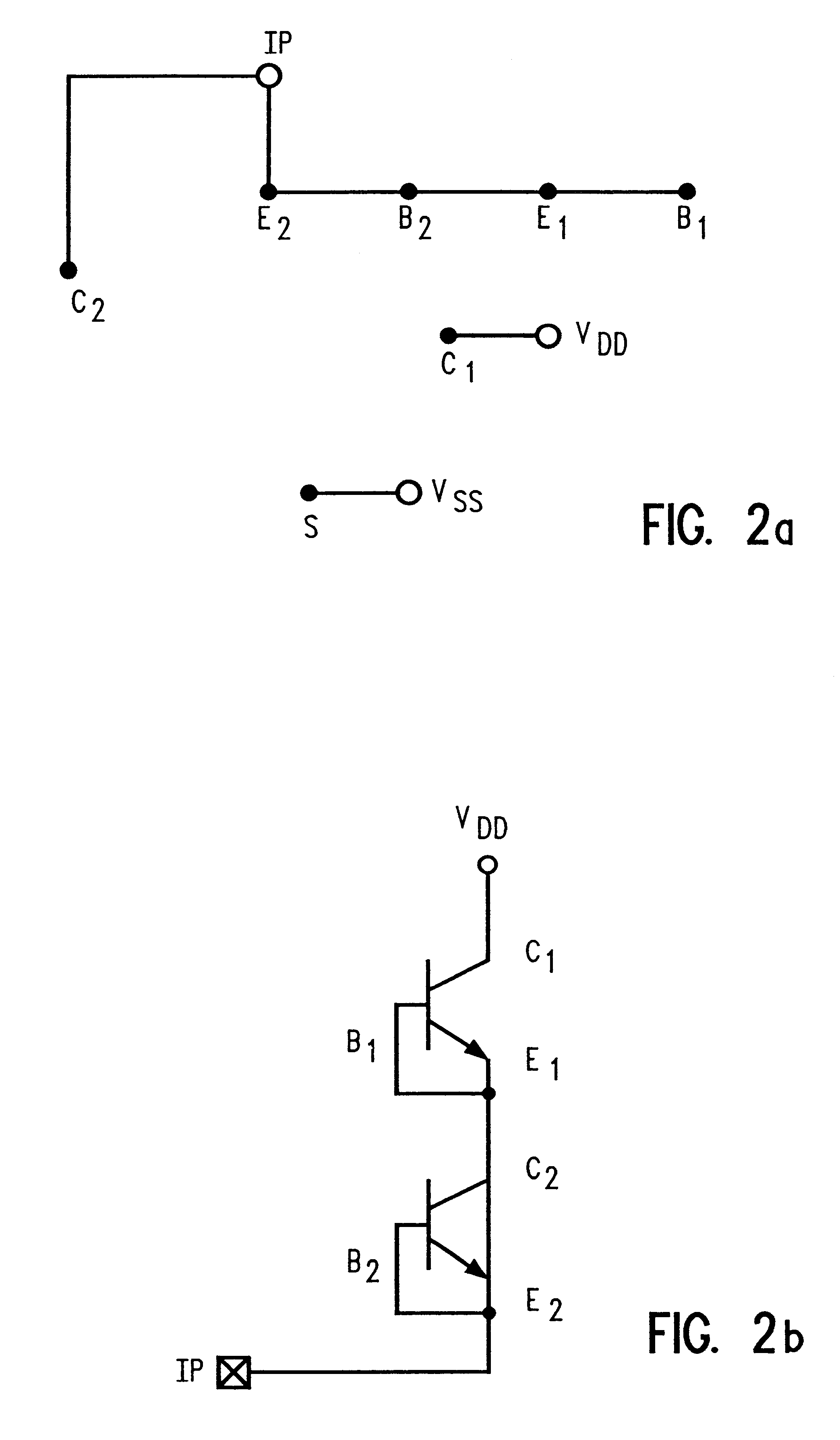

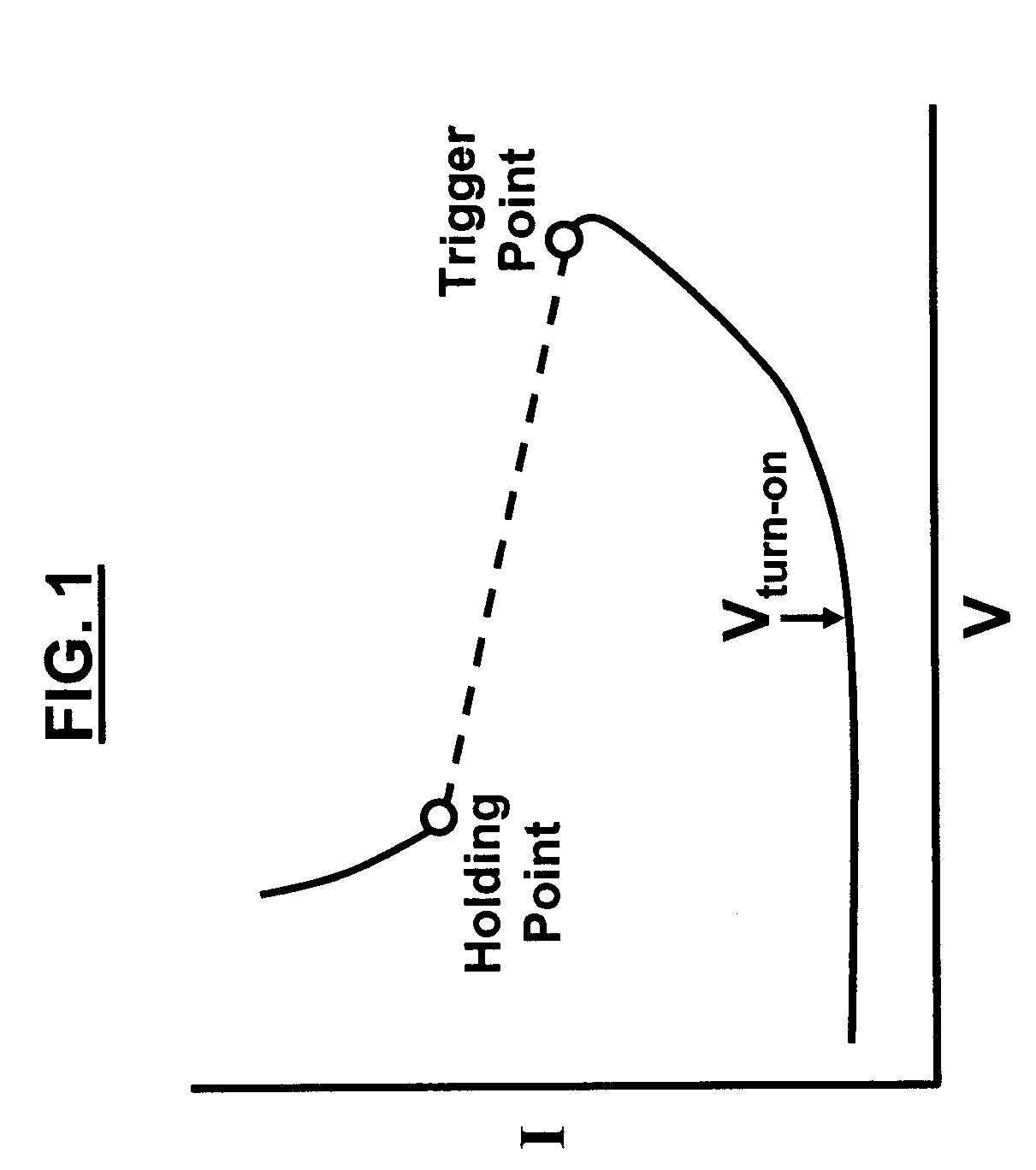

Trench-defined silicon germanium ESD diode network

InactiveUS6396107B1Harmful voltageHarmful current spikeTransistorSemiconductor/solid-state device detailsDopantSingle crystal

A silicon-germanium ESD element comprises a substrate of a first dopant type coupled to a first voltage terminal and a first diode-configured element. The first diode-configured element has a collector region of a second dopant type in the substrate, a SiGe base layer of the first dopant type on the collector region, with the SiGe base layer including a base contact region, and an emitter of the second dopant type on the SiGe base layer. Preferably, the SiGe base layer ion the collector region is an epitaxial SiGe layer and the second dopant type of the emitter is diffused in to the SiGe base layer. The ESD element of the present invention may further include a second diode-configured element of the same structure as the first diode-configured element, with an isolation region in the substrate separating the first and second diode-configured elements. The first and second diode-configured elements form a diode network. In each of the embodiments, the isolation regions may be disposed adjacent the collector regions of the diode elements and below a portion of the SiGe base layer of the diode elements. The SiGe base layer in the diode elements preferably comprises an active, single crystal layer in a portion directly over the collector region and a polycrystalline layer in portions directly over the isolation regions. The isolation regions may be shallow or deep trench isolations.

Owner:GLOBALFOUNDRIES US INC

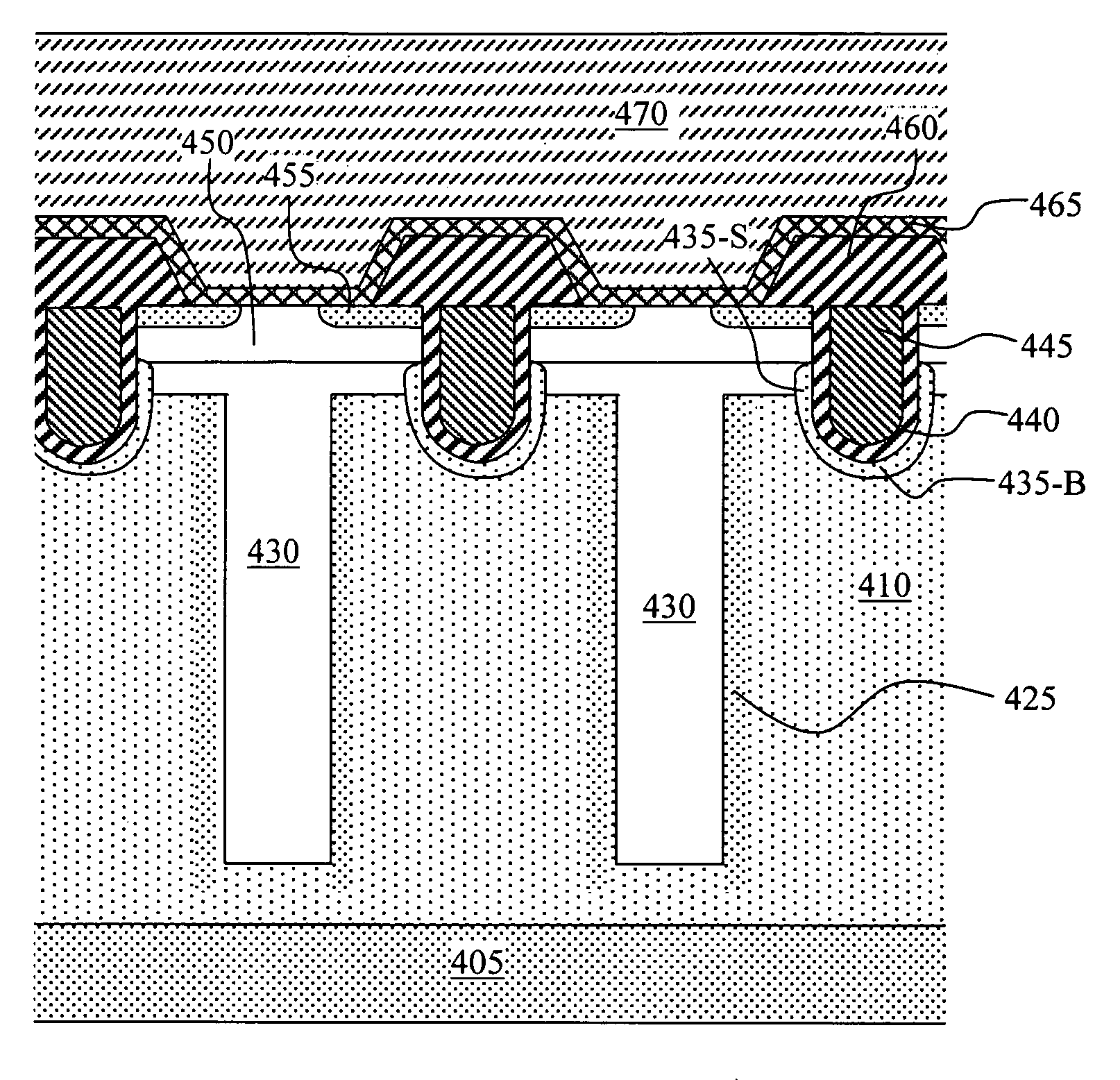

Structure and method to integrate embedded dram with finfet

A transistor includes a first fin structure and at least a second fin structure formed on a substrate. A deep trench area is formed between the first and second fin structures. The deep trench area extends through an insulator layer of the substrate and a semiconductor layer of the substrate. A high-k metal gate is formed within the deep trench area. A polysilicon layer is formed within the deep trench area adjacent to the metal layer. The polysilicon layer and the high-k metal layer are recessed below a top surface of the insulator layer. A poly strap in the deep trench area is formed on top of the high-k metal gate and the polysilicon material. The poly strap is dimensioned to be below a top surface of the first and second fin structures. The first fin structure and the second fin structure are electrically coupled to the poly strap.

Owner:IBM CORP

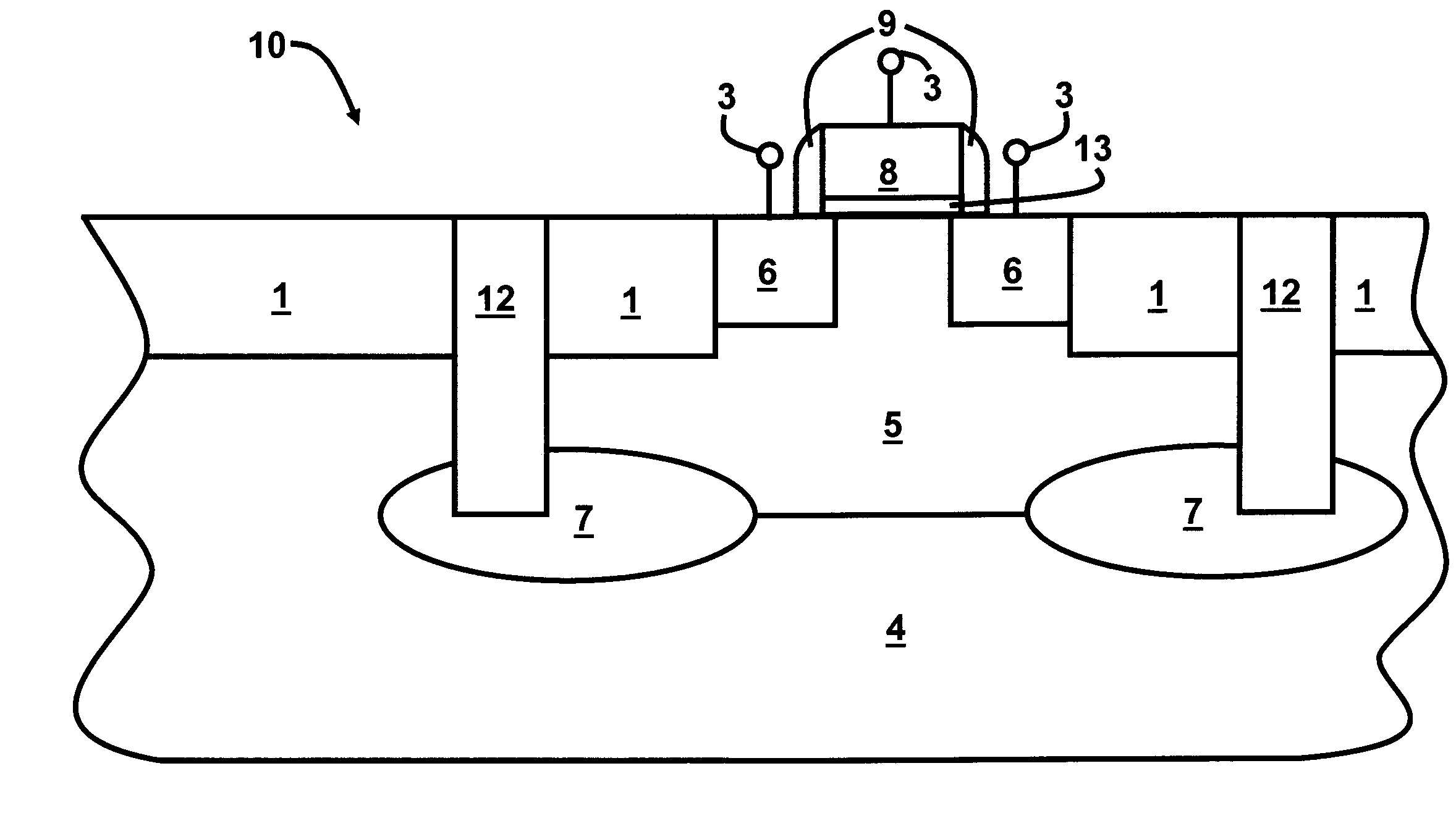

Structure and method for latchup suppression utilizing trench and masked sub-collector implantation

InactiveUS6956266B1Improve latchup robustnessImprove robustnessTransistorSolid-state devicesEngineeringP–n diode

A method and structure for an integrated circuit comprising a substrate of a first polarity; a trench structure in the substrate; a well region of a second polarity abutting the trench structure; and a heavily doped region of the second polarity abutting the trench structure, wherein the heavily doped region is adapted to suppress latch-up in the integrated circuit, wherein the heavily doped region comprises a sub-collector region, and wherein the trench structure comprises a deep trench structure or a trench isolation structure. The integrated circuit further comprises a p+ anode in the well region and a n+ cathode in the well region, wherein the integrated circuit is configured as a latchup robust p-n diode. In another embodiment, the integrated circuit further comprises a p+ anode in the well region; a n+ cathode in the well region; and a gate structure over the p+ anode and n+ cathode.

Owner:GLOBALFOUNDRIES INC

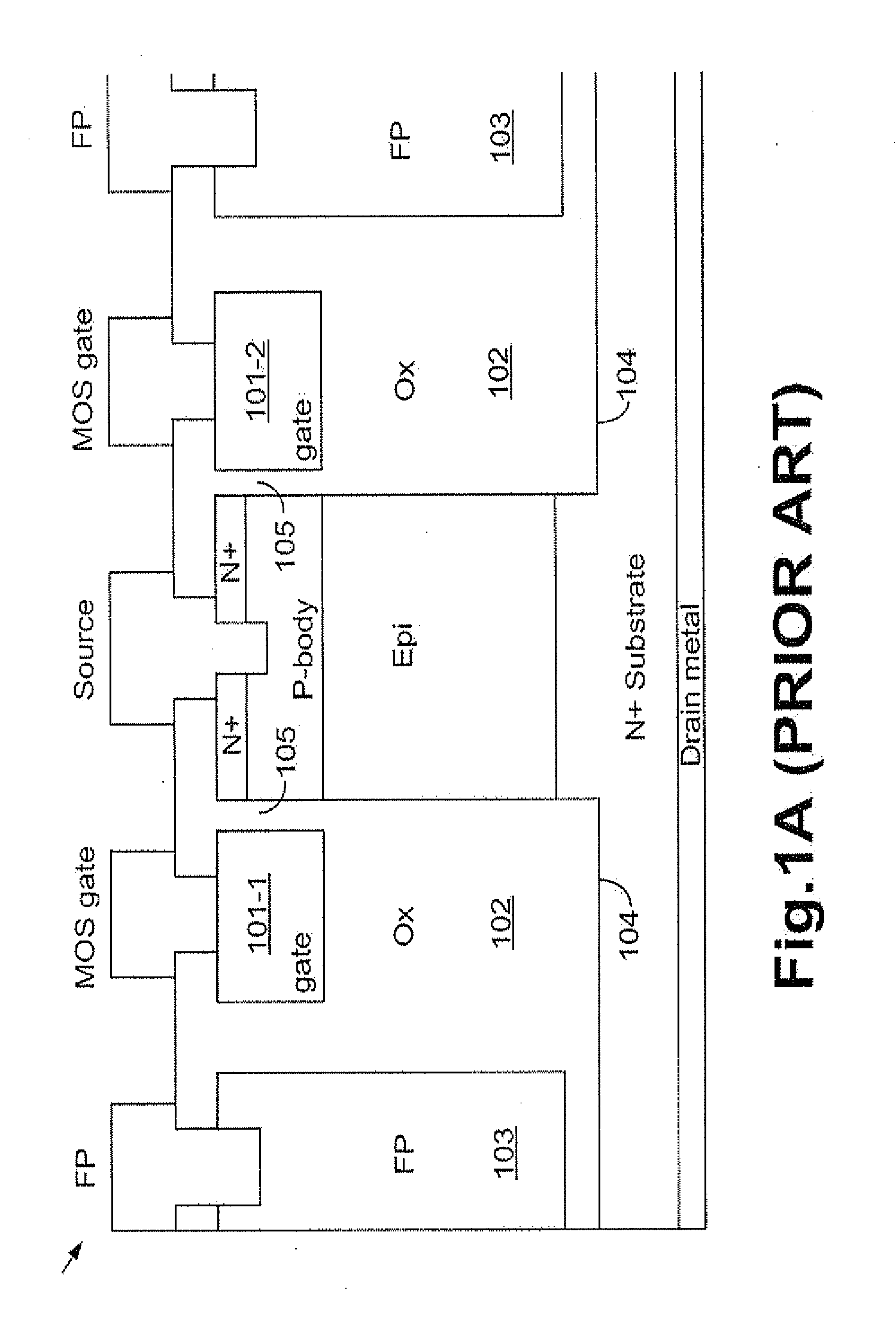

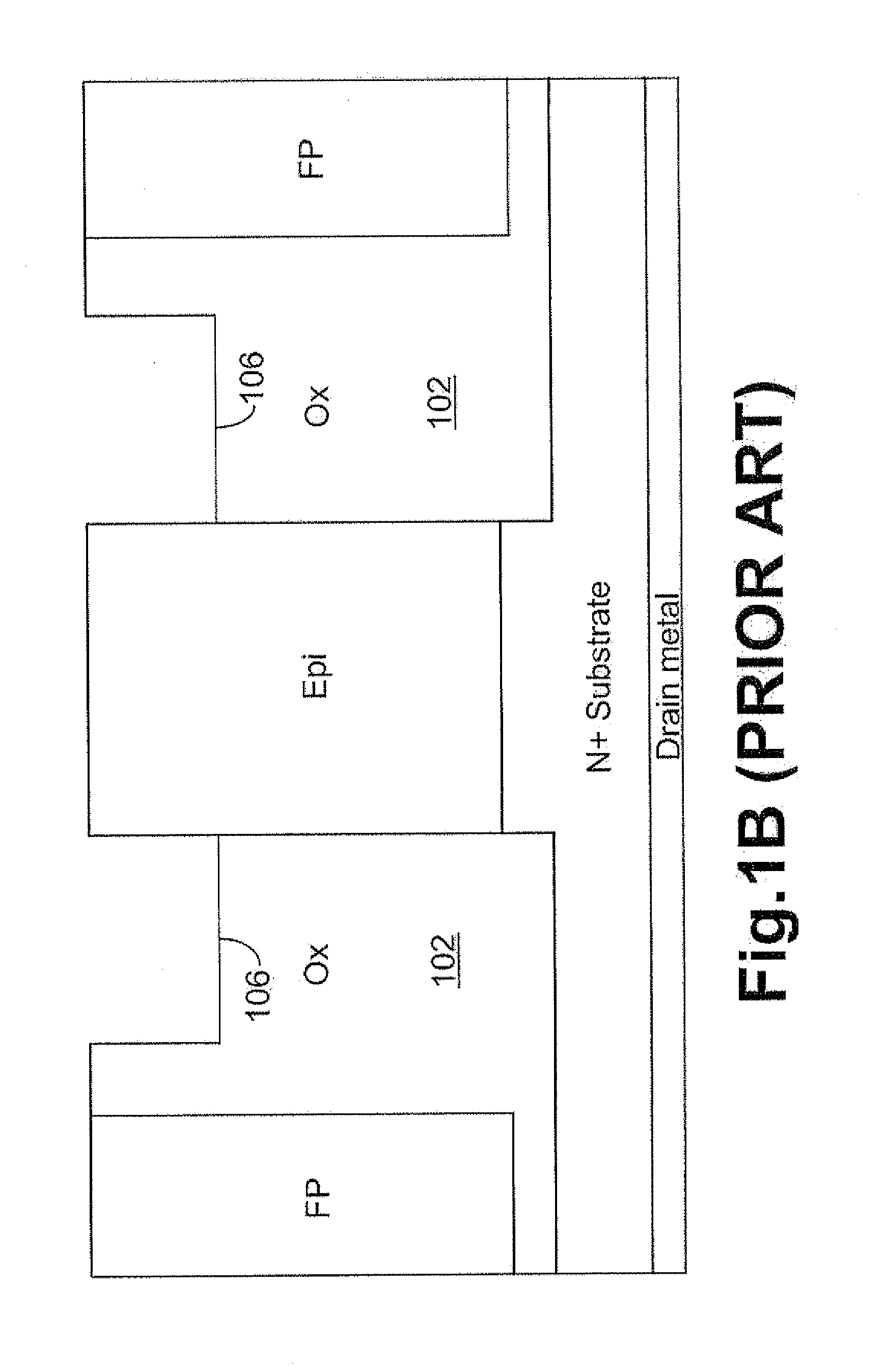

Trench mosfet with resurf stepped oxide and diffused drift region

ActiveUS20130168760A1Super cost-effectiveEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetEngineering

A trench MOSFET with split gates and diffused drift region for on-resistance reduction is disclosed. Each of the split gates is symmetrically disposed in the middle of the source electrode and adjacent trench sidewall of a deep trench. The inventive structure can save a mask for definition of the location of the split gate electrodes. Furthermore, the fabrication method can be implemented more reliably with lower cost.

Owner:FORCE MOS TECH CO LTD

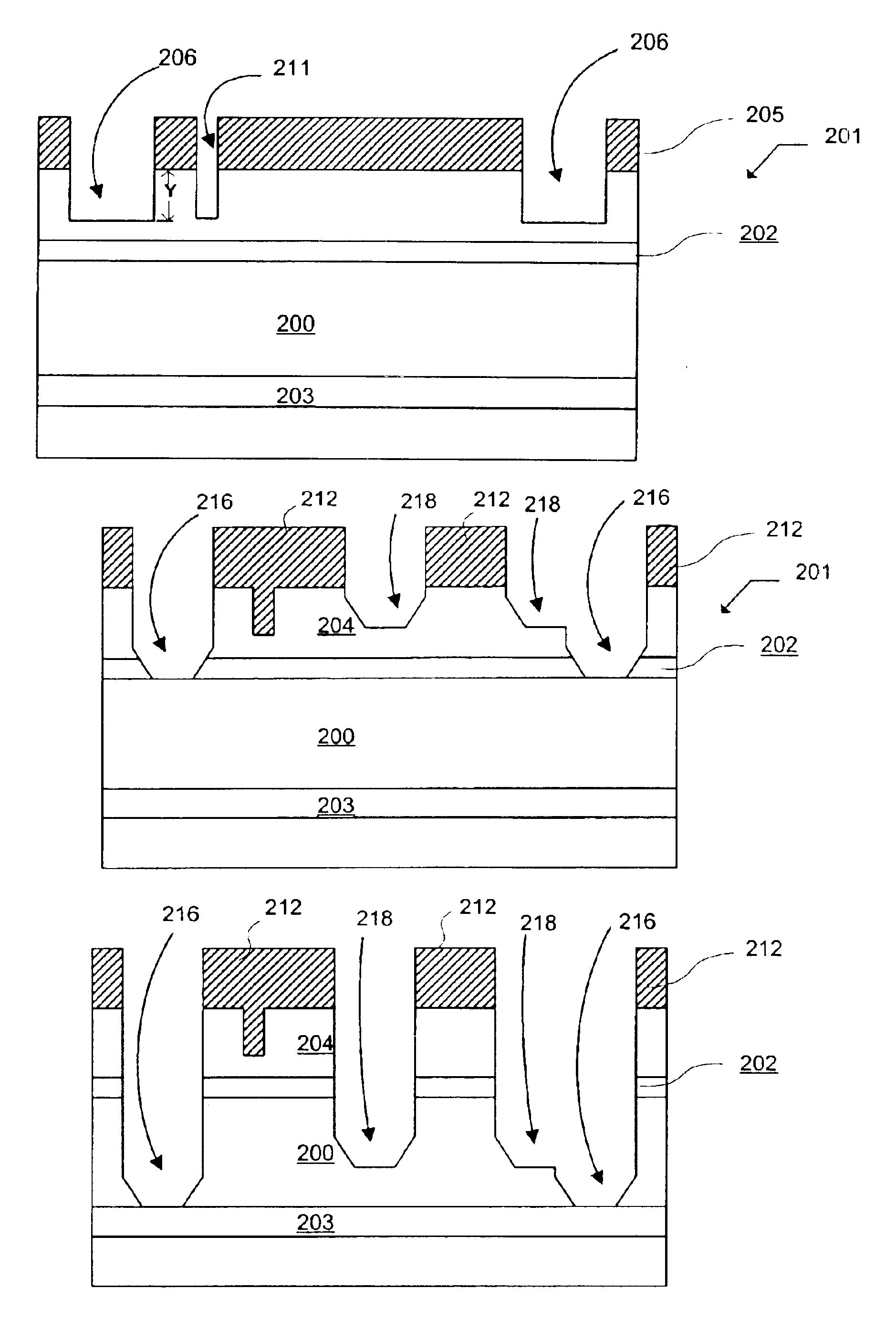

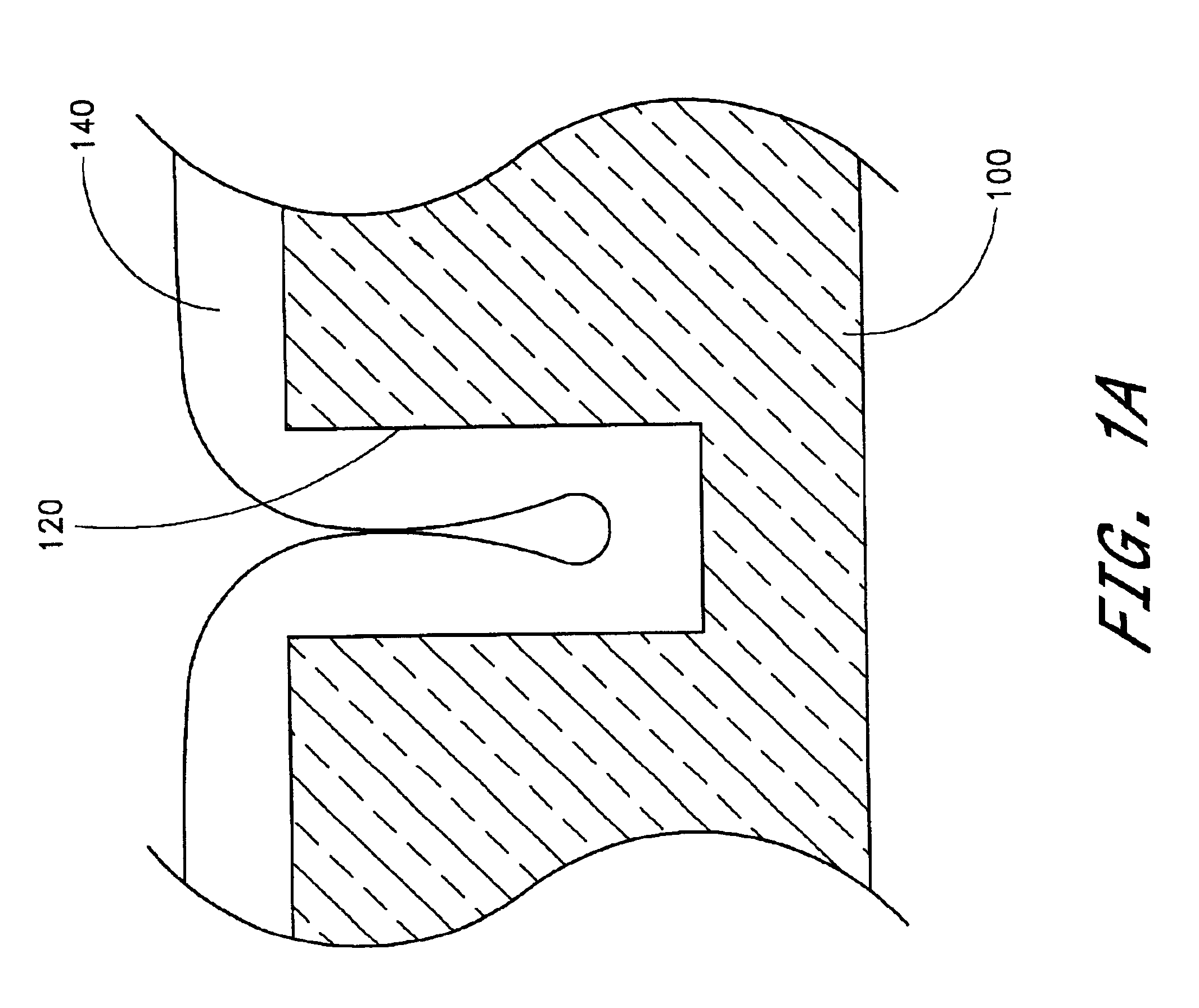

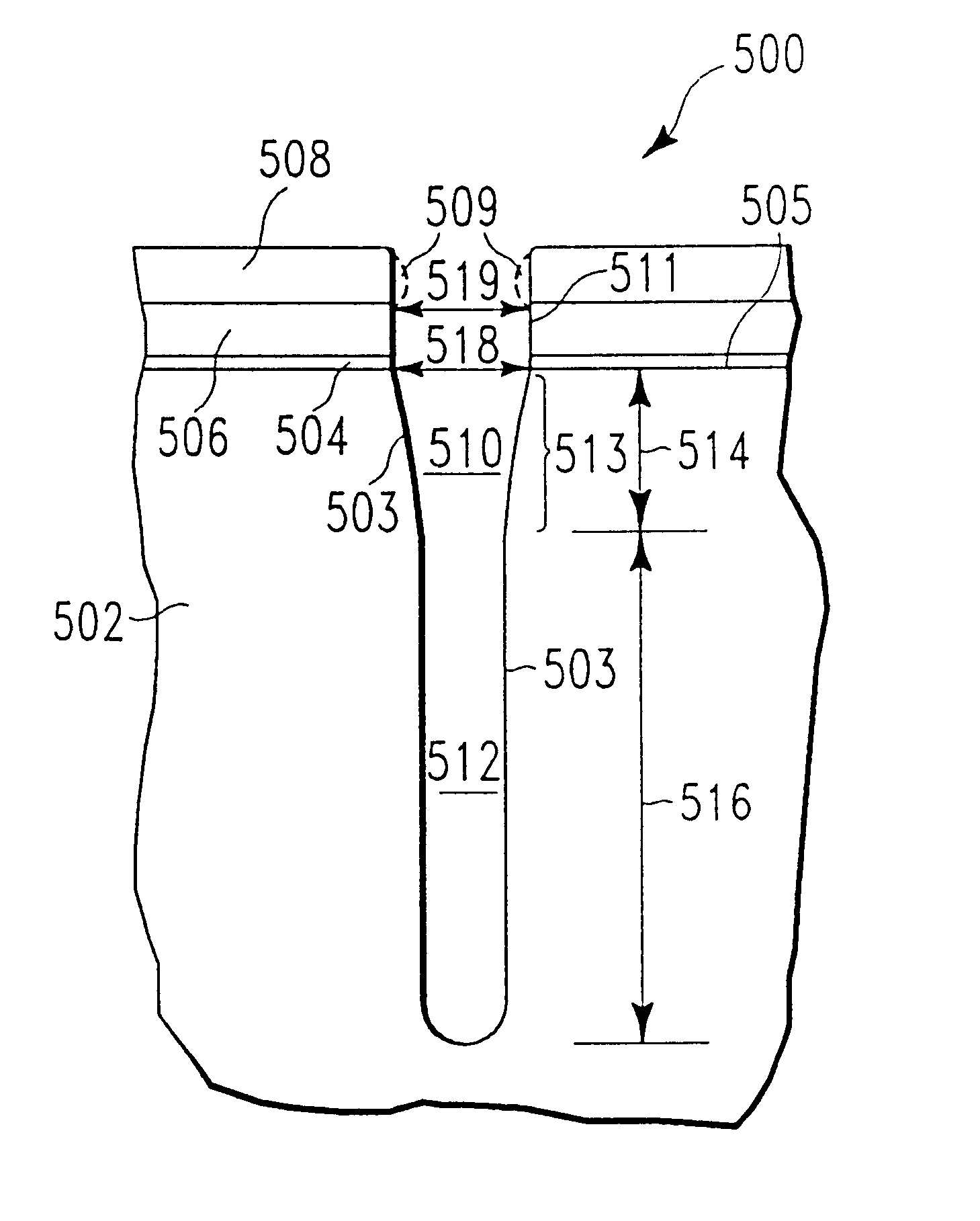

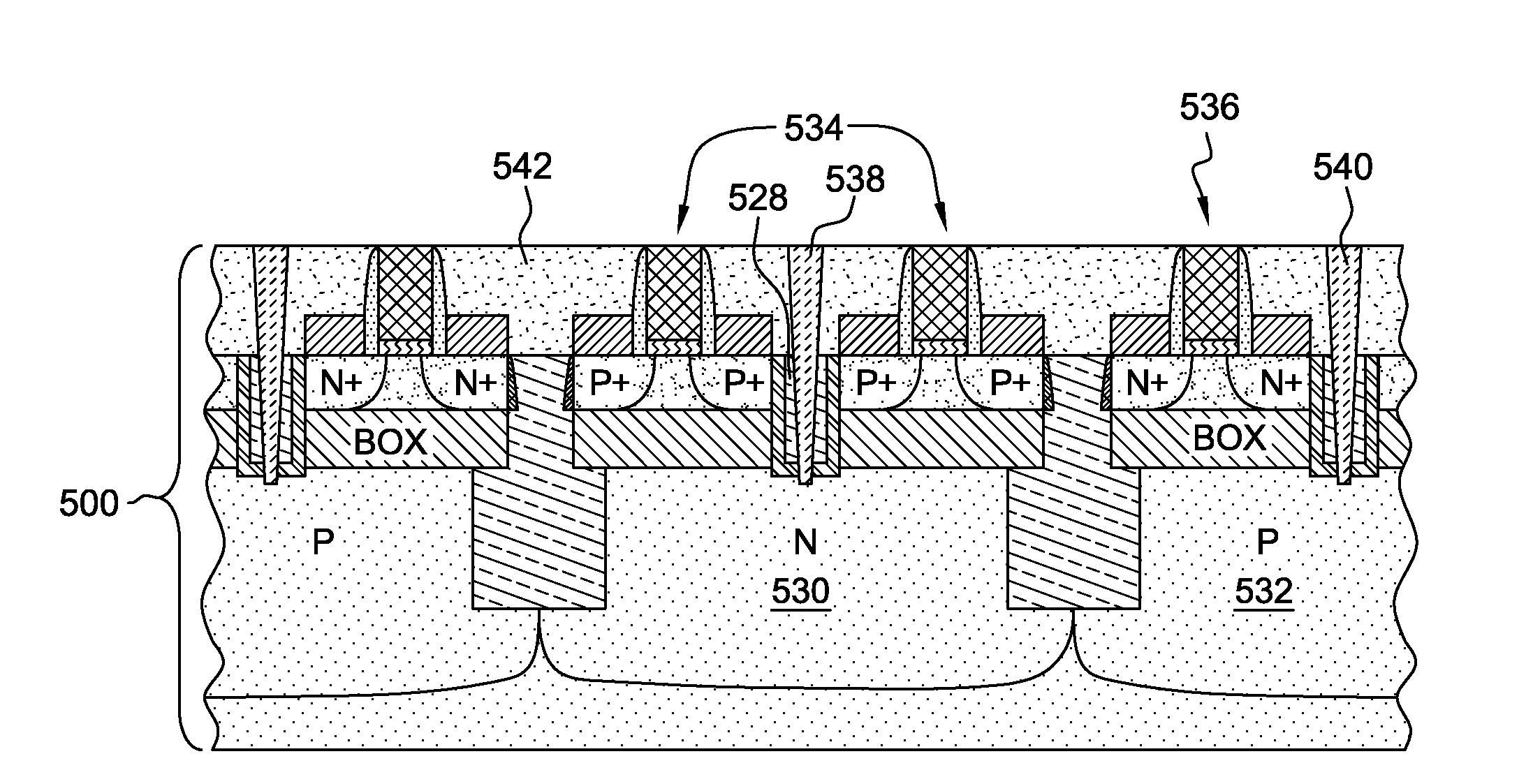

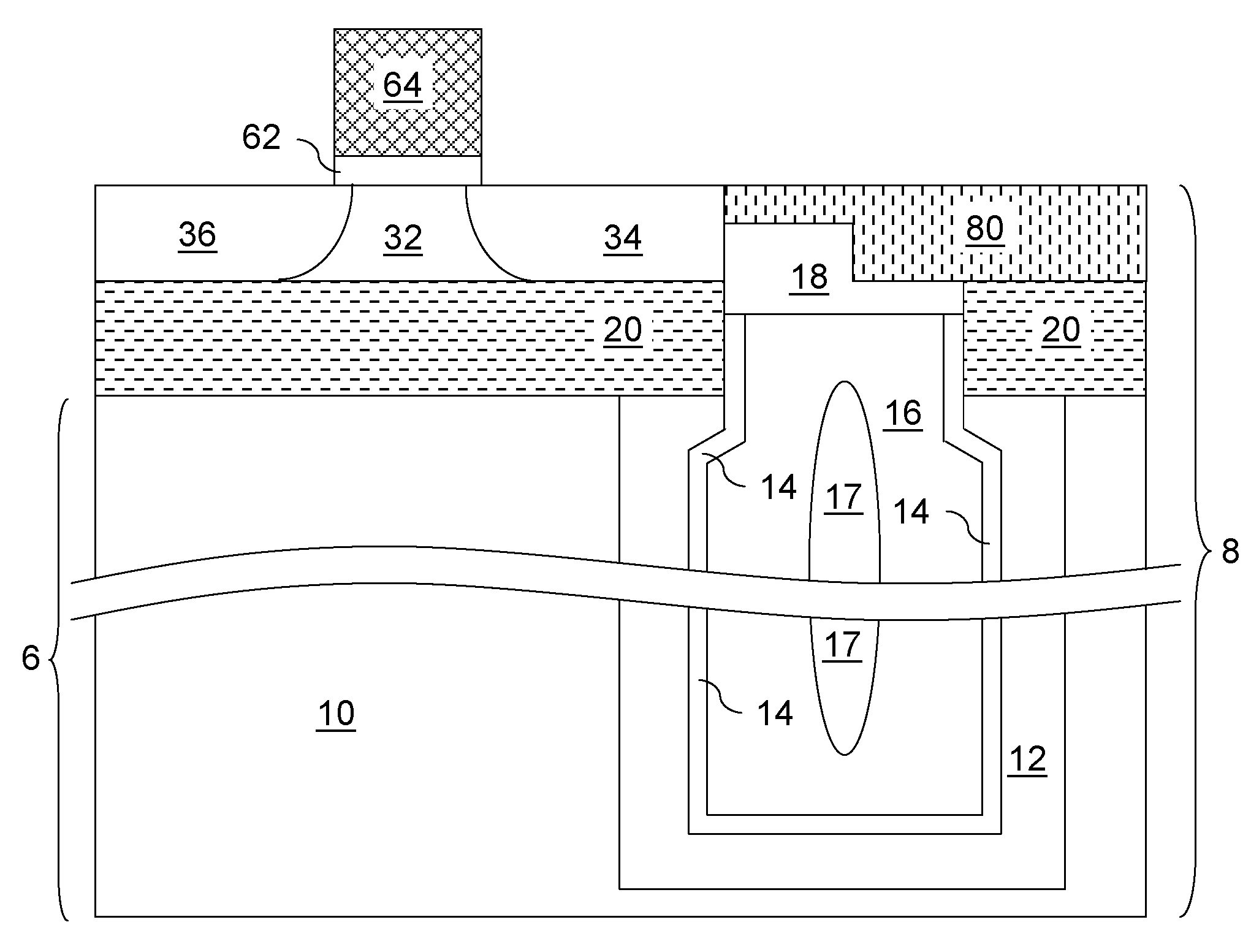

Soi device with dti and sti

ActiveUS20120261792A1Solid-state devicesSemiconductor/solid-state device manufacturingSiliconSemiconductor

An SOI structure including a semiconductor on insulator (SOI) substrate including a top silicon layer, an intermediate buried oxide (BOX) layer and a bottom substrate; at least two wells in the bottom substrate; a deep trench isolation (DTI) separating the two wells, the DTI having a top portion extending through the BOX layer and top silicon layer and a bottom portion within the bottom substrate wherein the bottom portion has a width that is larger than a width of the top portion; and at least two semiconductor devices in the silicon layer located over one of the wells, the at least two semiconductor devices being separated by a shallow trench isolation within the top silicon layer.

Owner:GLOBALFOUNDRIES US INC

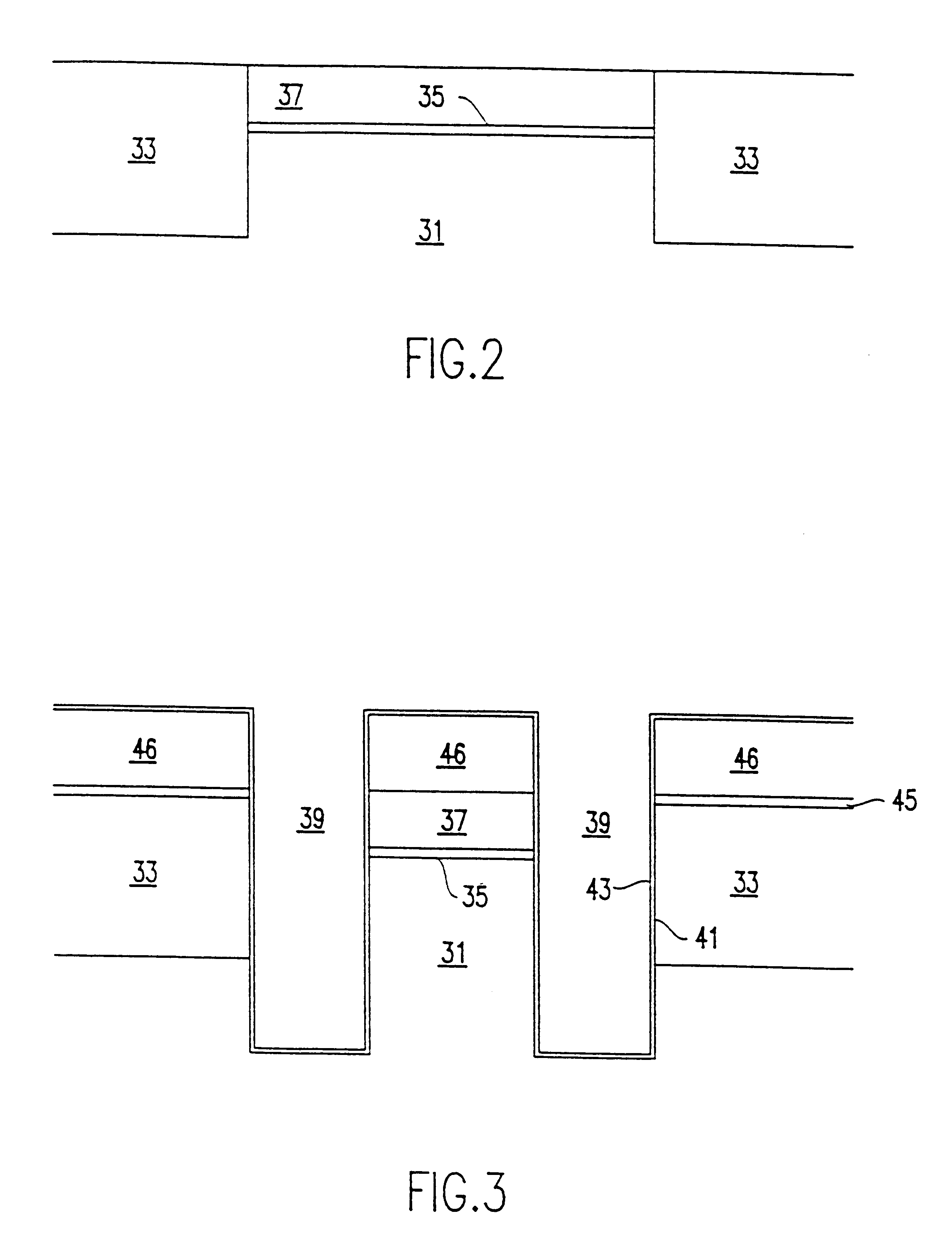

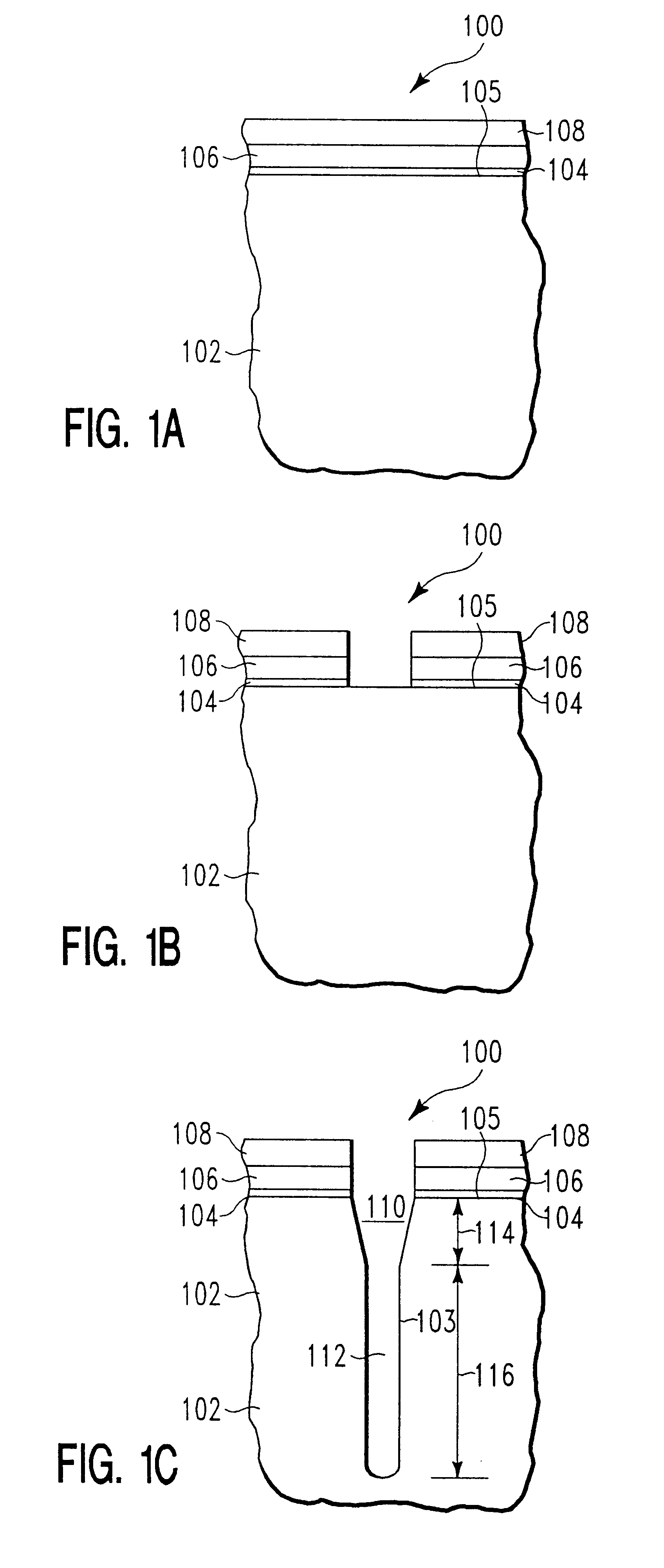

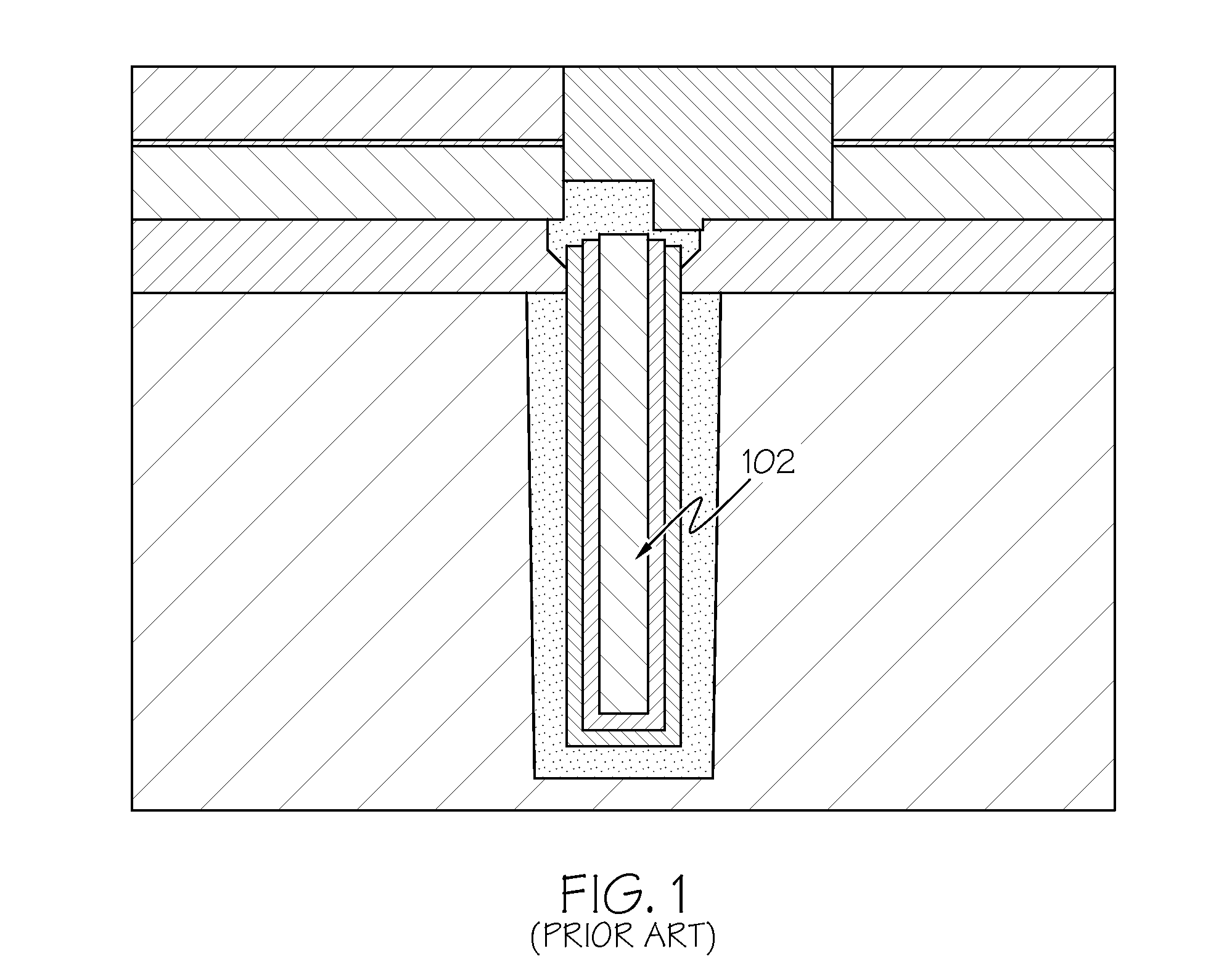

Method for a controlled bottle trench for a dram storage node

InactiveUS6190988B1Solid-state devicesSemiconductor/solid-state device manufacturingDopantElectrical conductor

A bottle-shaped trench capacitor with a buried plate is formed in a controlled etch process. The bottle-shape is fabricated by etching deep trenches from a layered substrate, using the layers as a mask, and covering the side walls of the substrate with protective oxide and nitride layers. With the side walls covered, deep trench etching is then resumed, and a lower trench portion, below the protective layers of the side wall are formed. By diffusing a first dopant in the lower portion of the deep trench region, using the side wall protective layers as a mask, an etch stop is established for a wet etch process at the p / n junction established by the first dopant. The width of the lower trench portion is regulated by the time and temperature of the diffusion. Removing the doped material and applying a second dopant to the lower trench portion establishes a continuous buried plate region between trenches. A capacitor is formed by applying an insulating layer to the trench and filling with a conductor.

Owner:IBM CORP

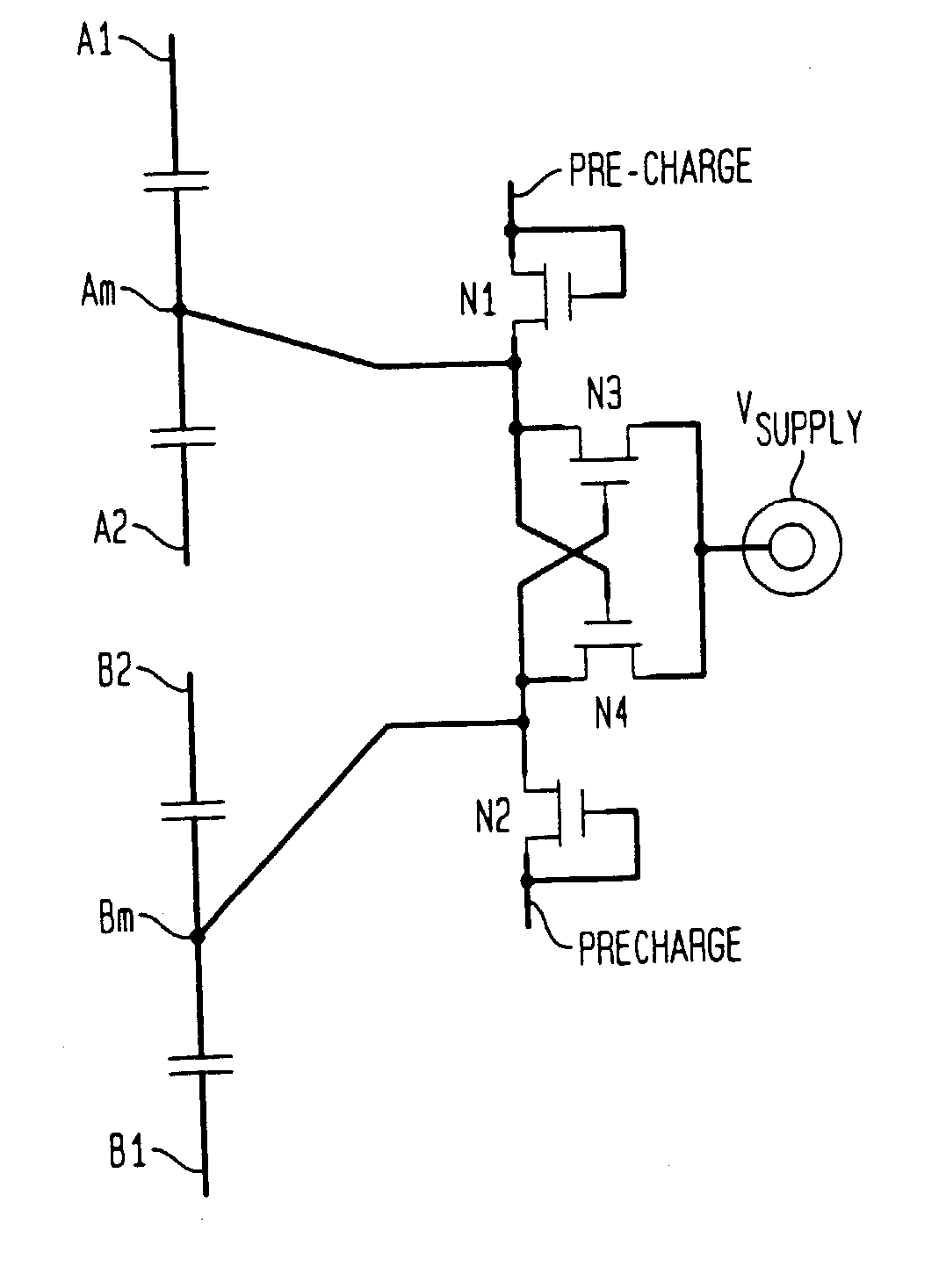

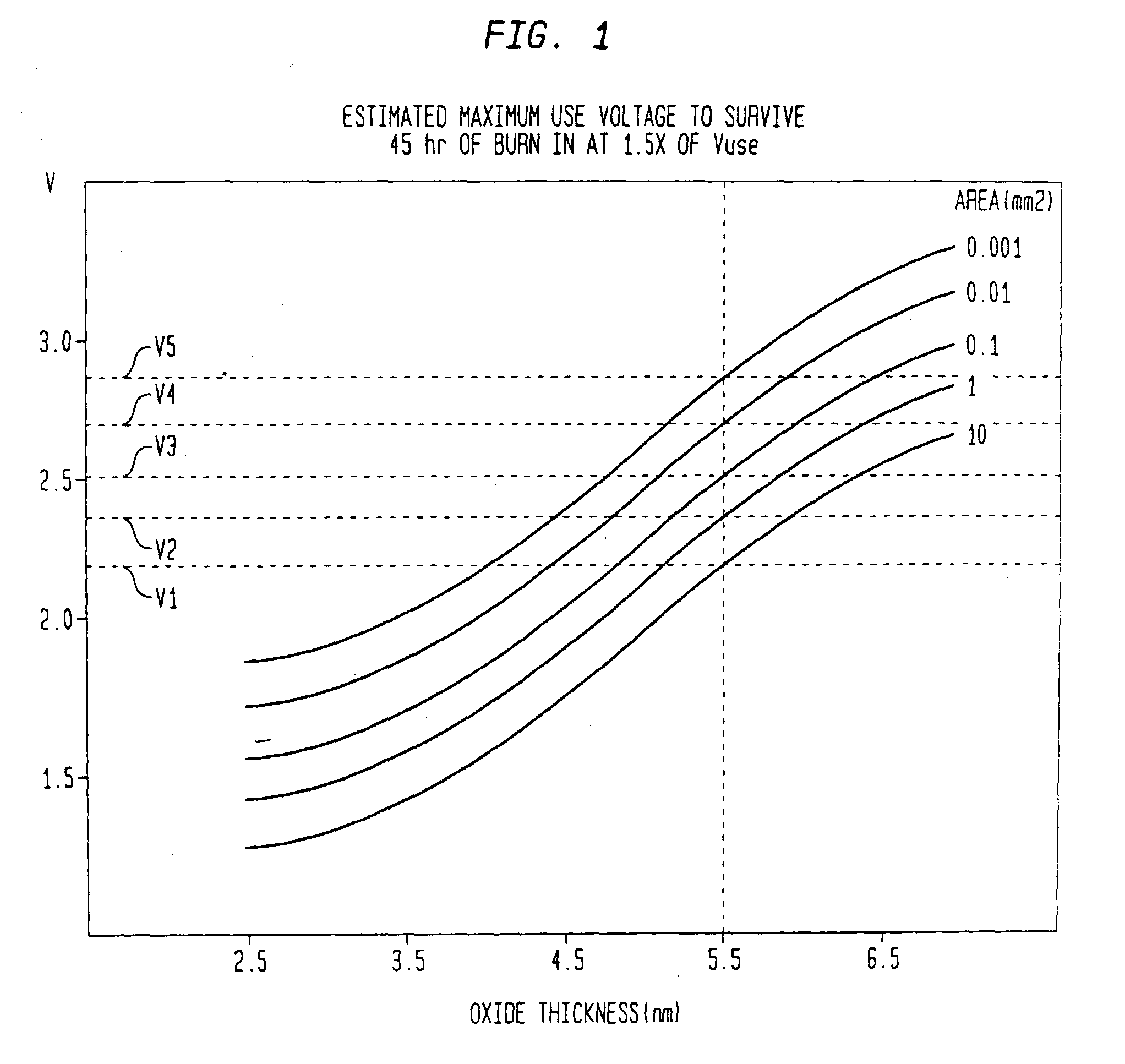

Method to improve charge pump reliability, efficiency and size

A dynamic clamp is used in conjunction with capacitors with thinner dielectric or with deep trench capacitors to solve the problem of dielectric breakdown in high stress capacitors. The dynamic clamp is realized using a two stage pump operation cycle such that, during a first stage pump cycle, a middle node of a pair of series connected capacitors is pre-charged to a supply voltage and, during a second stage pump cycle, the middle node is coupled by a boost clock. Thus, at any moment in the pump operation cycle, the voltage across the capacitors is held within a safety range.

Owner:INFINEON TECHNOLOGIES NORTH AMERICA CORPORATION

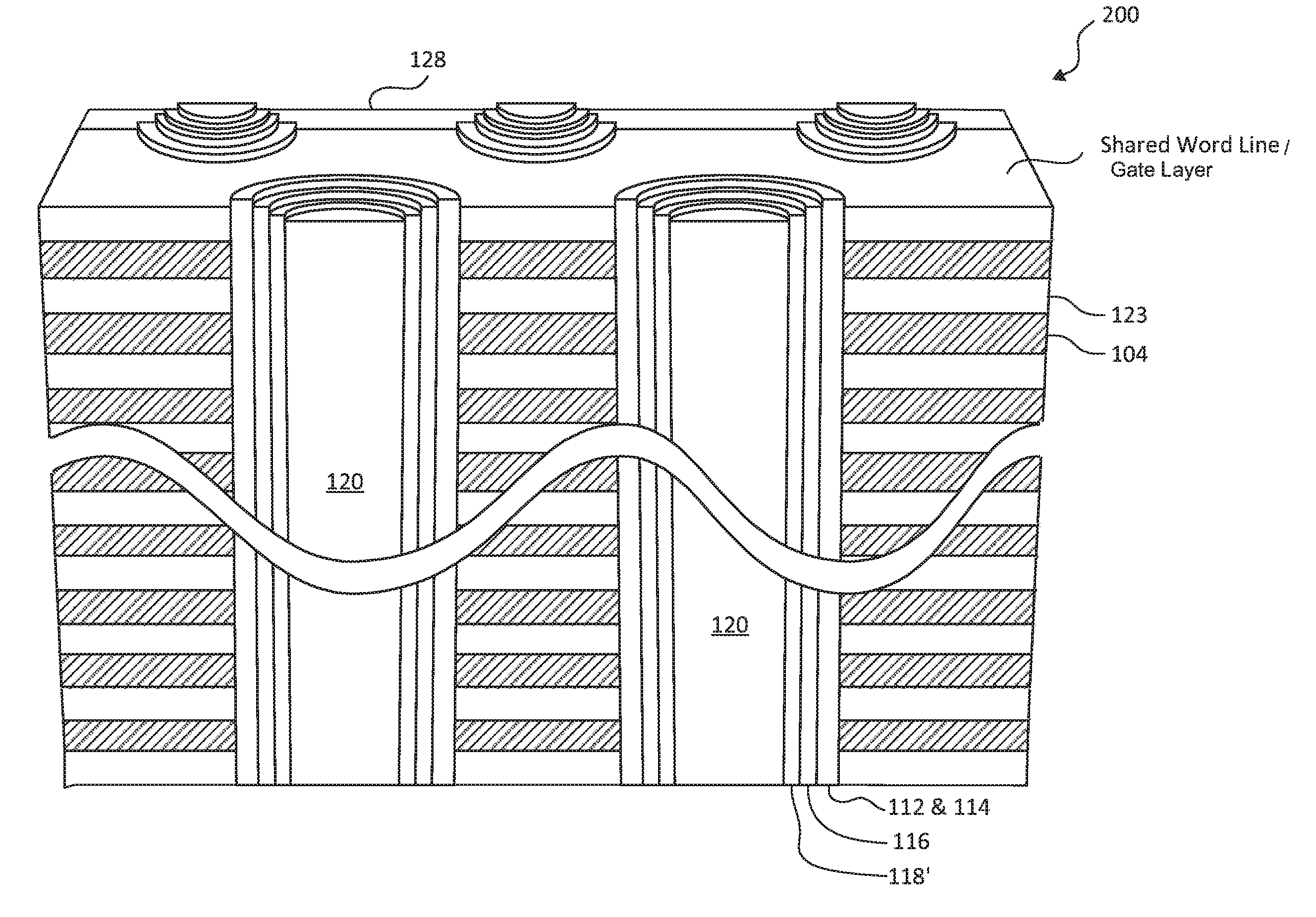

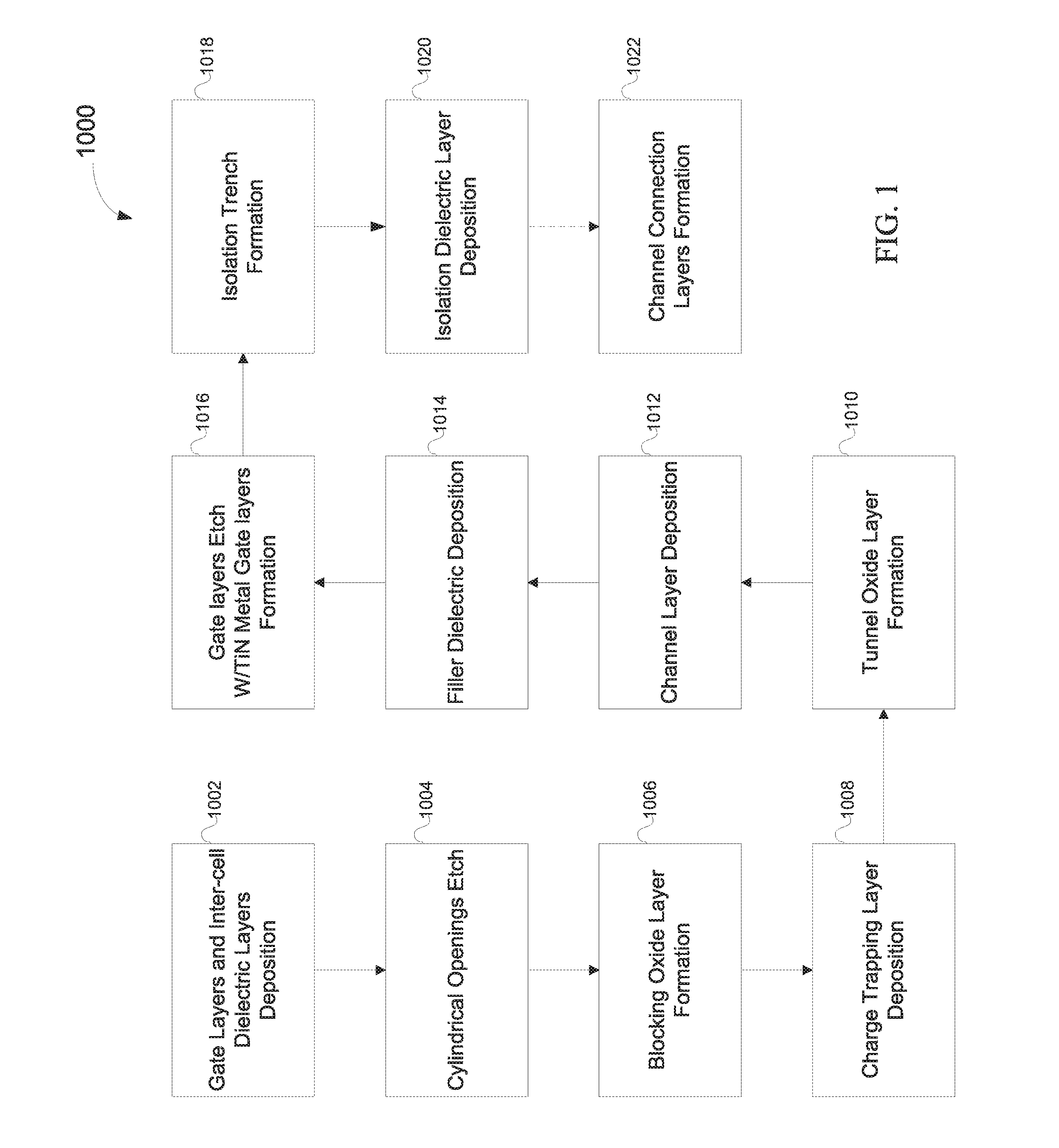

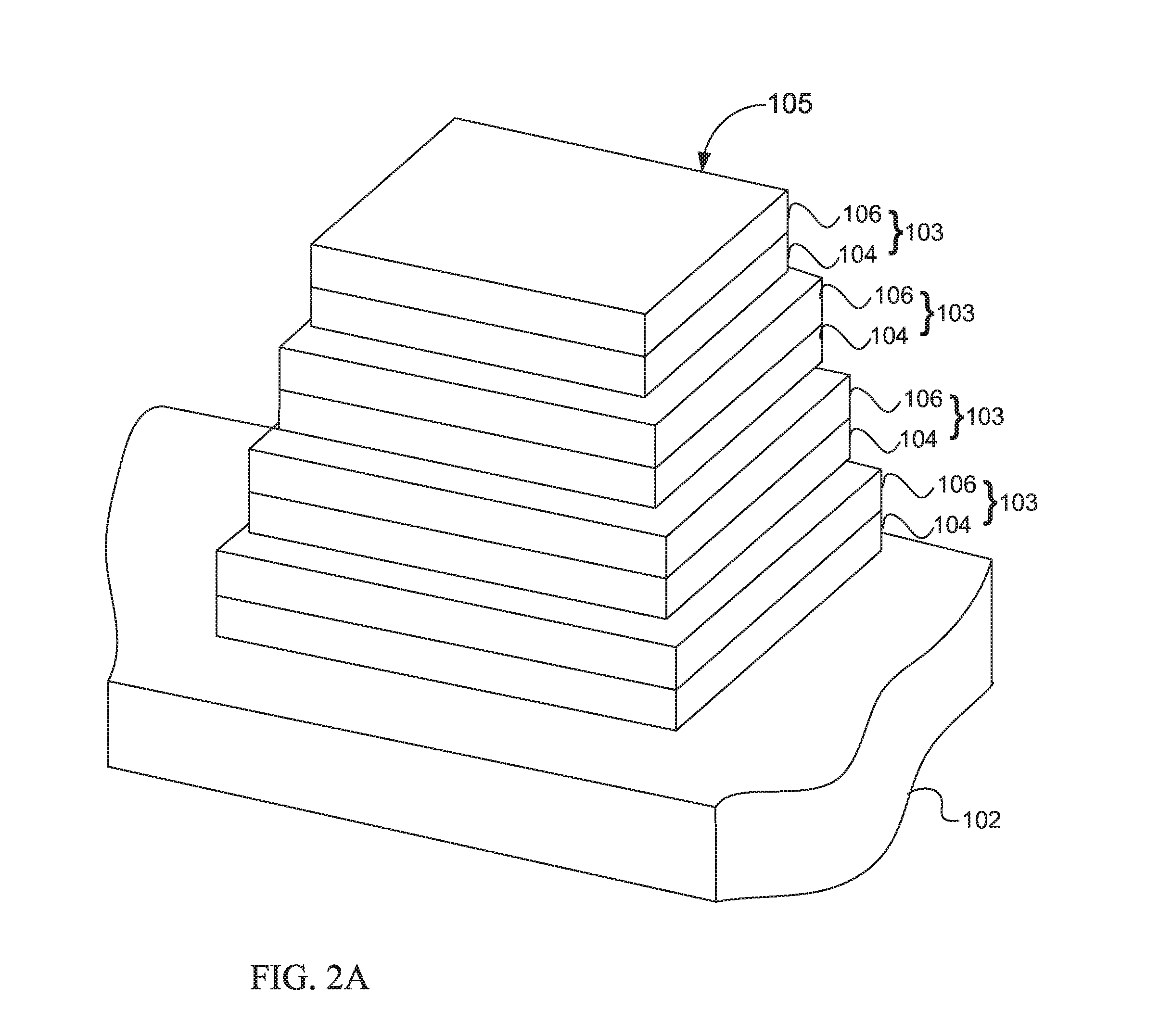

Vertical division of three-dimensional memory device

A method of forming a vertical non-volatile (NV) memory device such as 3-D NAND flash memory includes forming a vertical NV memory cell string within an opening disposed in a stack of alternating layers of a first layer and a second layer over a substrate, and dividing the vertical NV memory cell string into two halves with a first vertical deep trench and an isolation dielectric pillar formed in the first vertical deep trench, such that memory bit density of the divided vertical NV memory cell strings double the memory bits of the device.

Owner:CYPRESS SEMICON CORP

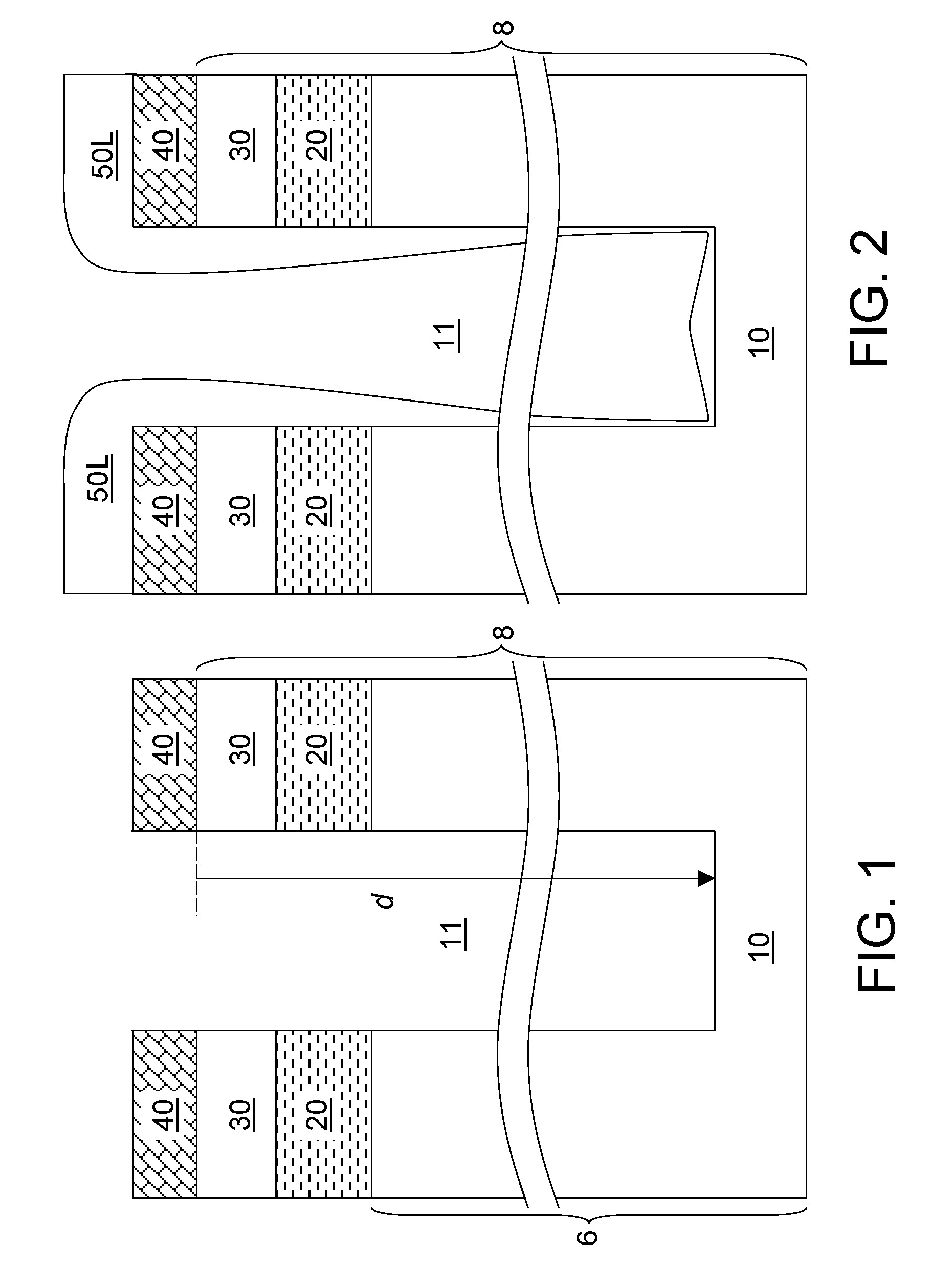

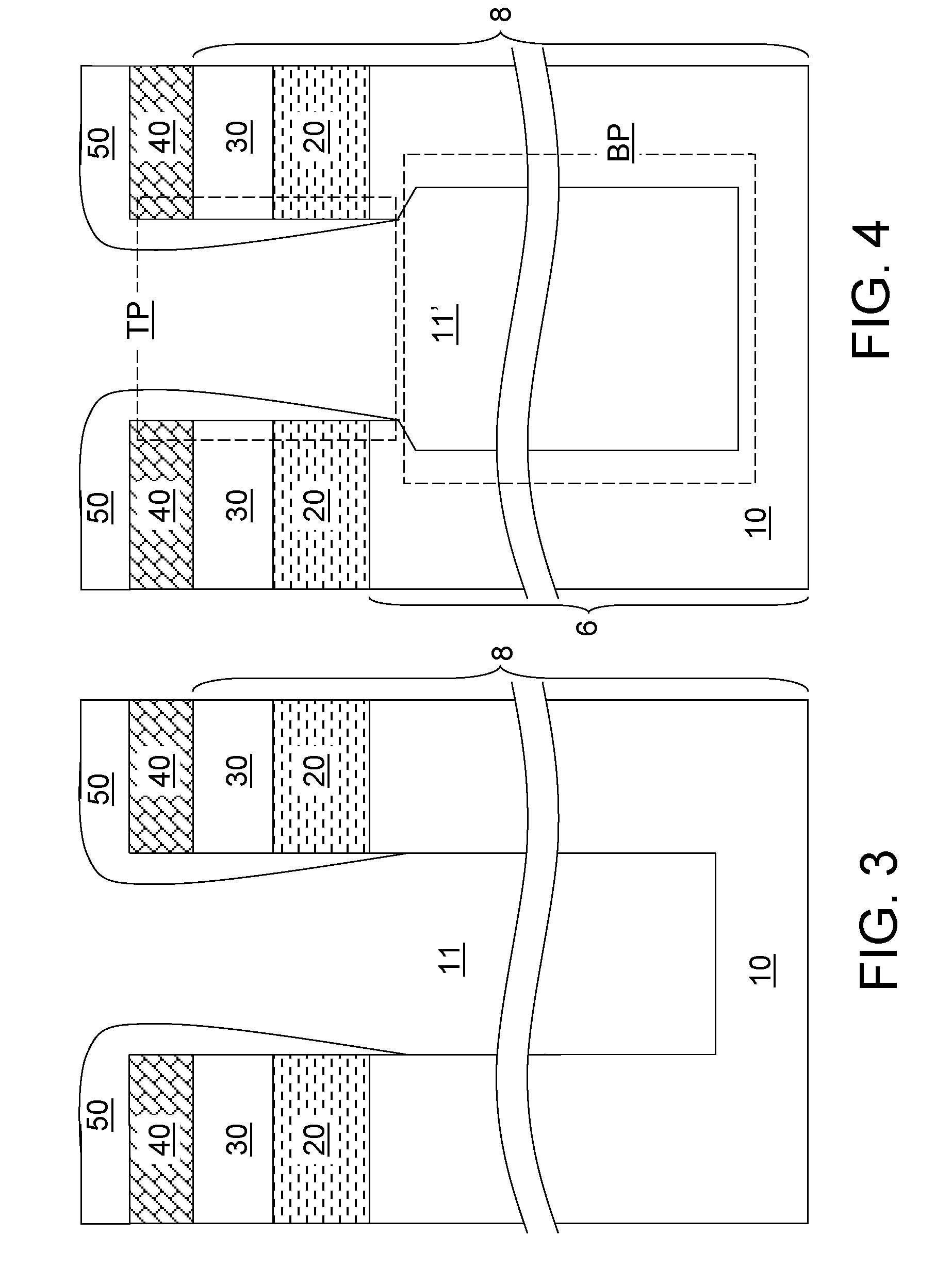

Soi deep trench capacitor employing a non-conformal inner spacer

InactiveUS20090289291A1Simplified and cost-effective manufacturing sequenceTransistorSolid-state devicesDielectricDiffusion barrier

A bottle shaped trench for an SOI capacitor is formed by a simple processing sequence. A non-conformal dielectric layer with an optional conformal dielectric diffusion barrier layer underneath is formed on sidewalls of a deep trench. Employing an isotropic etch, the non-conformal dielectric layer is removed from a bottom portion of the deep trench, leaving a dielectric spacer covering sidewalls of the buried insulator layer and the top semiconductor layer. The bottom portion of the deep trench is expanded to form a bottle shaped trench, and a buried plated is formed underneath the buried insulator layer. The dielectric spacer may be recessed during formation of a buried strap to form a graded thickness dielectric collar around the upper portion of an inner electrode. Alternately, the dielectric spacer may be removed prior to formation of a buried strap.

Owner:GLOBALFOUNDRIES INC

Three-dimensional Memory Device and Manufacturing Method Thereof

ActiveUS20170236836A1Improve integration densitySimplify the etch processSolid-state devicesSemiconductor devicesEtchingGate stack

A method for manufacturing three-dimensional memory, comprising the steps of: forming a stack structure composed of a plurality of first material layers and a plurality of second material layers on a substrate; etching the stack structure to expose the substrate, forming a plurality of first vertical openings; forming a filling layer in each of the first openings; etching the stack structure around each of the first openings to expose the substrate, forming a plurality of second vertical openings; forming a vertical channel layer and a drain in each of the second openings; removing the filling layer by selective etching, re-exposing the first openings; partially or completely removing the second material layers by lateral etching, leaving a plurality of recesses; forming a plurality of gate stack structure in the recesses; forming a plurality of common sources on and / or in the substrate at the bottom of each of the first openings. In accordance with the three-dimensional memory manufacturing method of the present invention, the deep trenches of word-line in the TCAT three-dimensional device are replaced with deep-hole etching to realize the same function, thereby improving the integration density, simplifying the etching process of stacked structure, and maintaining the control performance of the metal gate.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Circuit configuration and manufacturing processes for vertical transient voltage suppressor (TVS) and EMI filter

ActiveUS7781826B2Small footprintImproved TVS and EMI filter circuitSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

A vertical TVS (VTVS) circuit includes a semiconductor substrate for supporting the VTVS device thereon having a heavily doped layer extending to the bottom of substrate. Deep trenches are provided for isolation between multi-channel VTVS. Trench gates are also provided for increasing the capacitance of VTVS with integrated EMI filter.

Owner:ALPHA & OMEGA SEMICON LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com