Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6376 results about "Passivation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Passivation, in physical chemistry and engineering, refers to a material becoming "passive," that is, less affected or corroded by the environment of future use. Passivation involves creation of an outer layer of shield material that is applied as a microcoating, created by chemical reaction with the base material, or allowed to build from spontaneous oxidation in the air. As a technique, passivation is the use of a light coat of a protective material, such as metal oxide, to create a shell against corrosion. Passivation can occur only in certain conditions, and is used in microelectronics to enhance silicon. The technique of passivation strengthens and preserves the appearance of metallics. In electrochemical treatment of water, passivation reduces the effectiveness of the treatment by increasing the circuit resistance, and active measures are typically used to overcome this effect, the most common being polarity reversal, which results in limited rejection of the fouling layer. Other proprietary systems to avoid electrode passivation, several discussed below, are the subject of ongoing research and development.

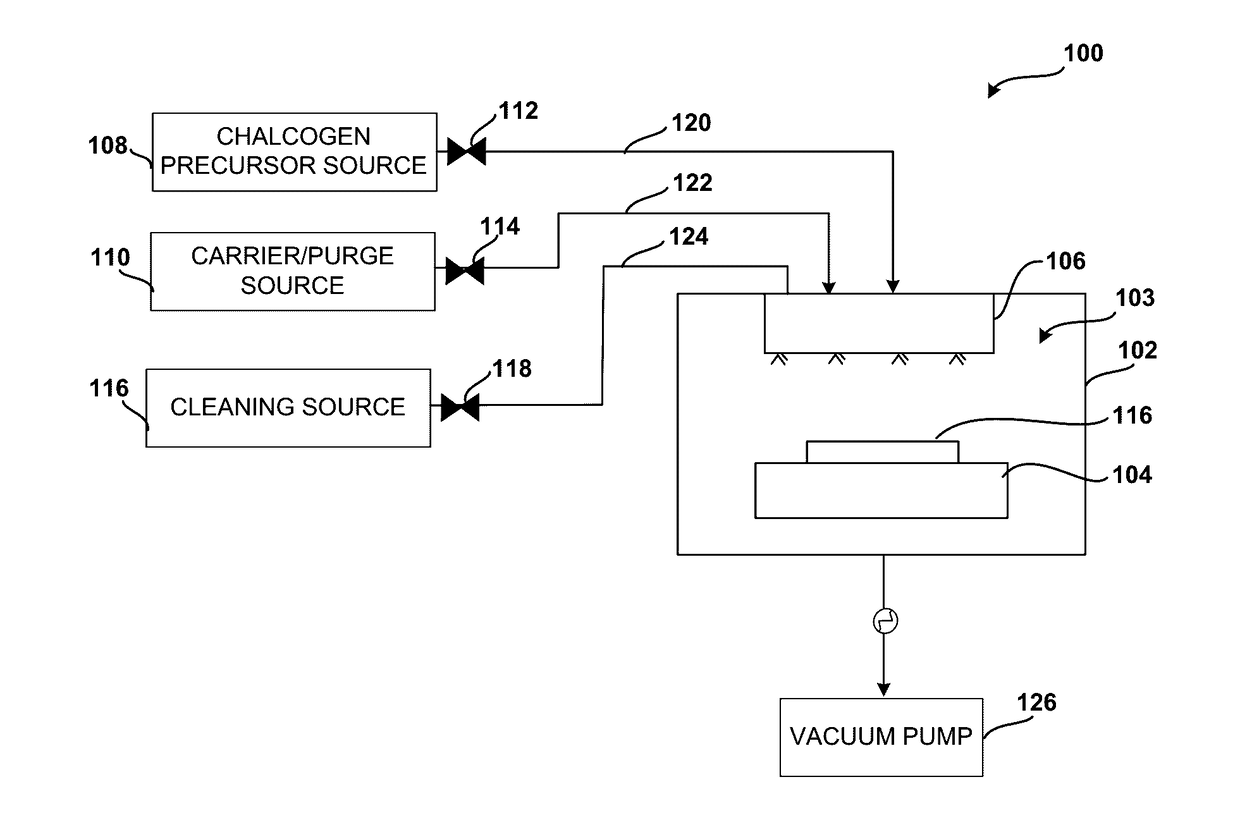

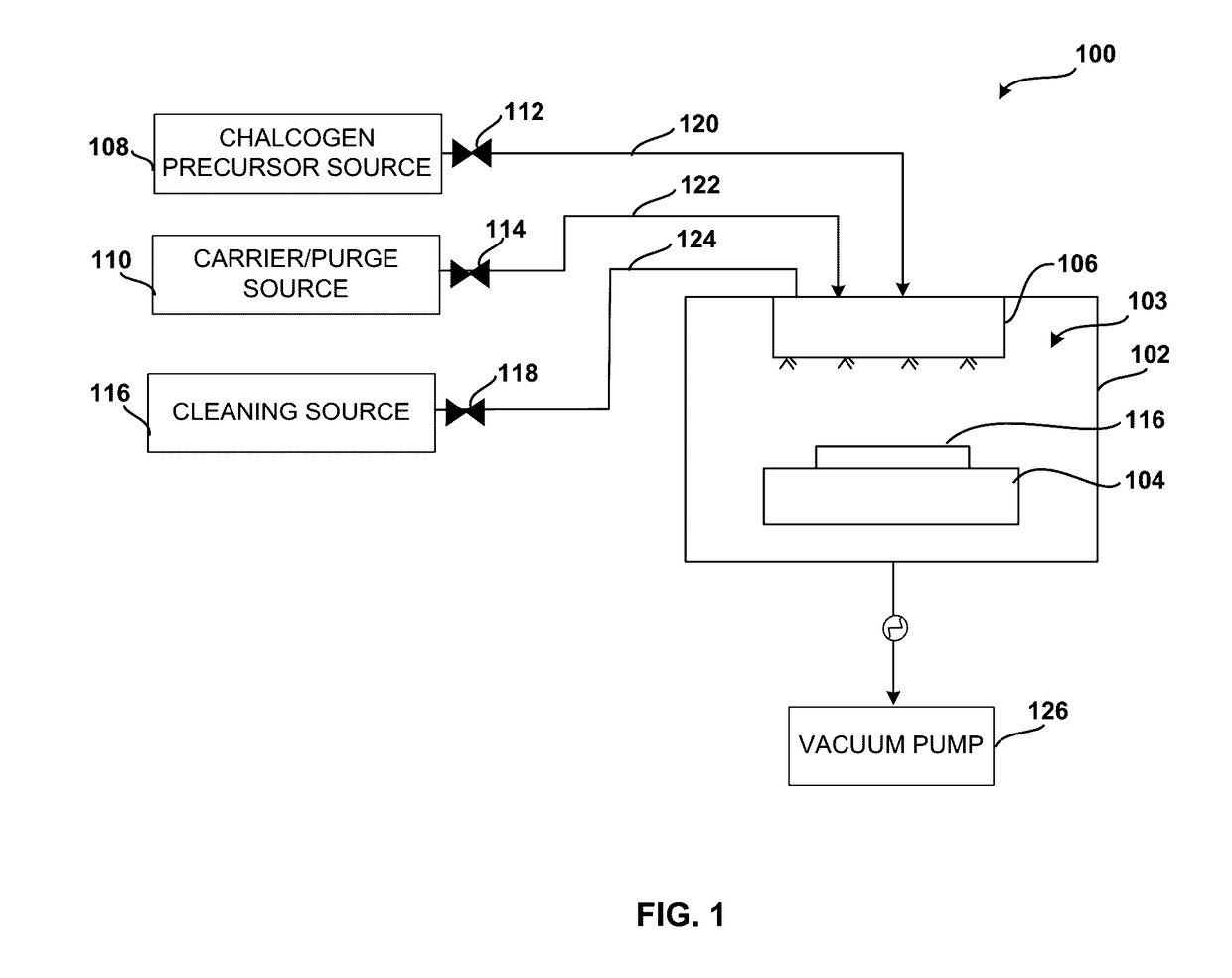

System and method for gas-phase passivation of a semiconductor surface

ActiveUS20170117203A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

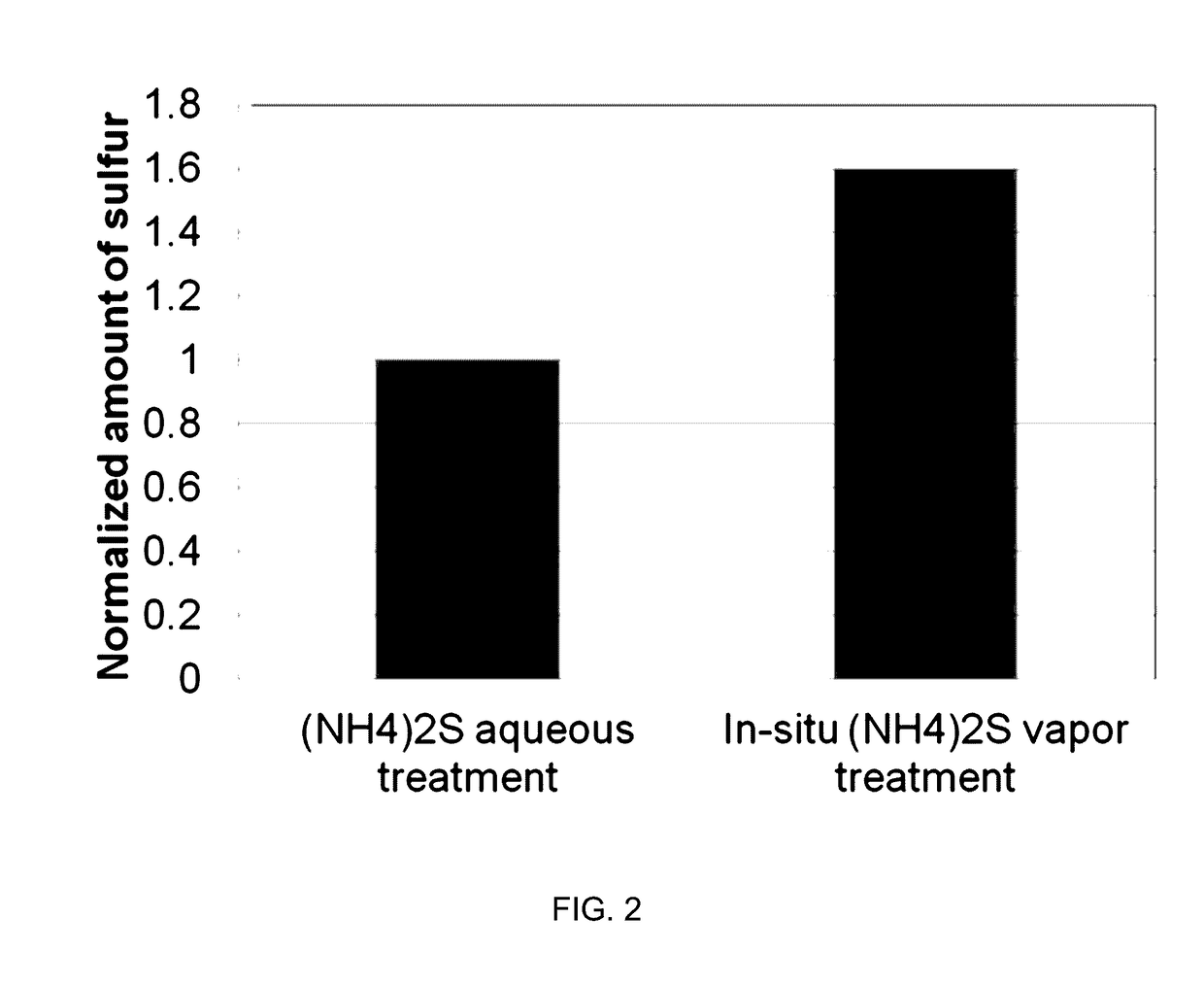

Improved methods and systems for passivating a surface of a high-mobility semiconductor and structures and devices formed using the methods are disclosed. The method includes providing a high-mobility semiconductor surface to a chamber of a reactor and exposing the high-mobility semiconductor surface to a gas-phase sulfur precursor to passivate the high-mobility semiconductor surface.

Owner:ASM IP HLDG BV

Back-contact photovoltaic cells

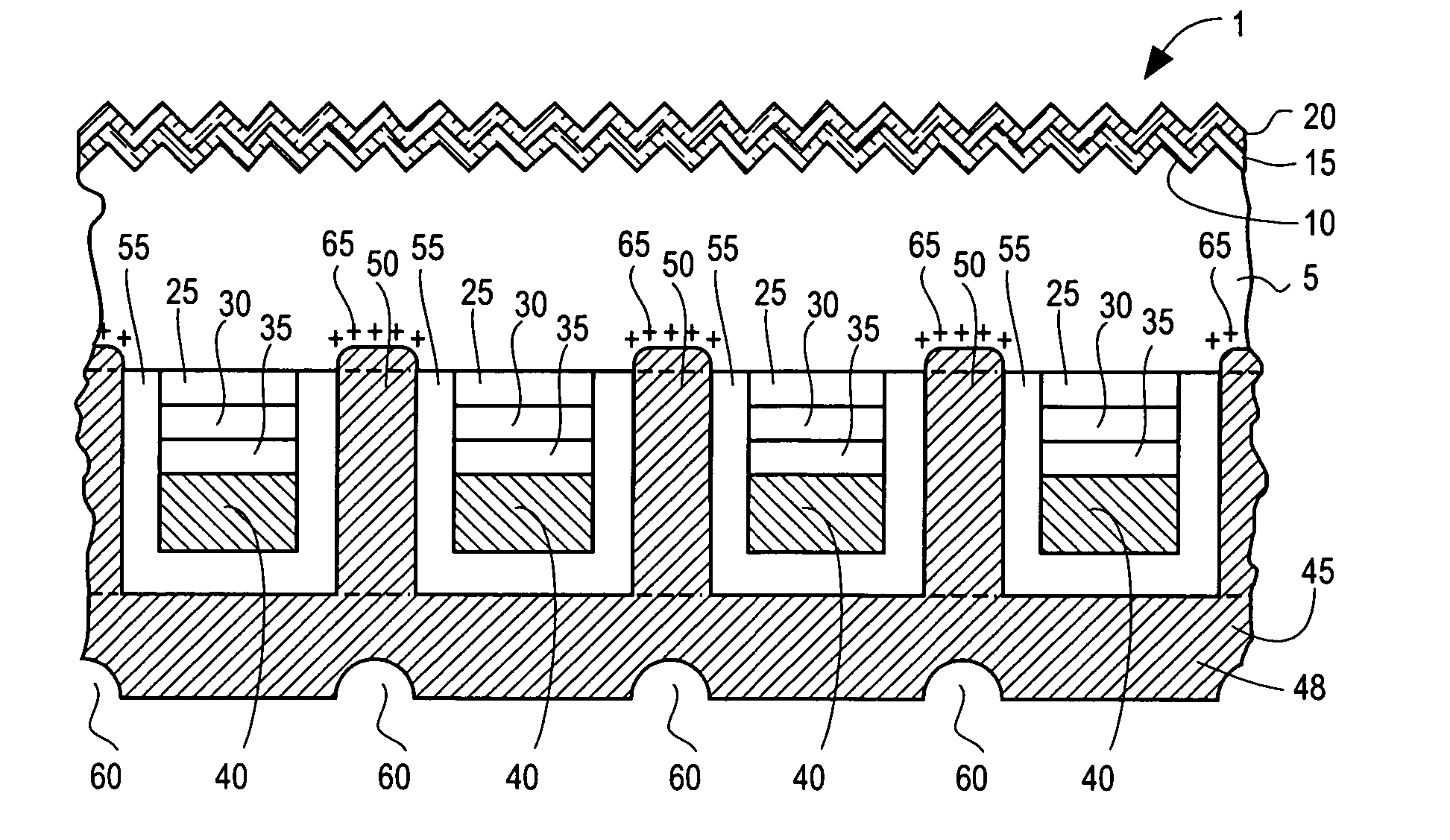

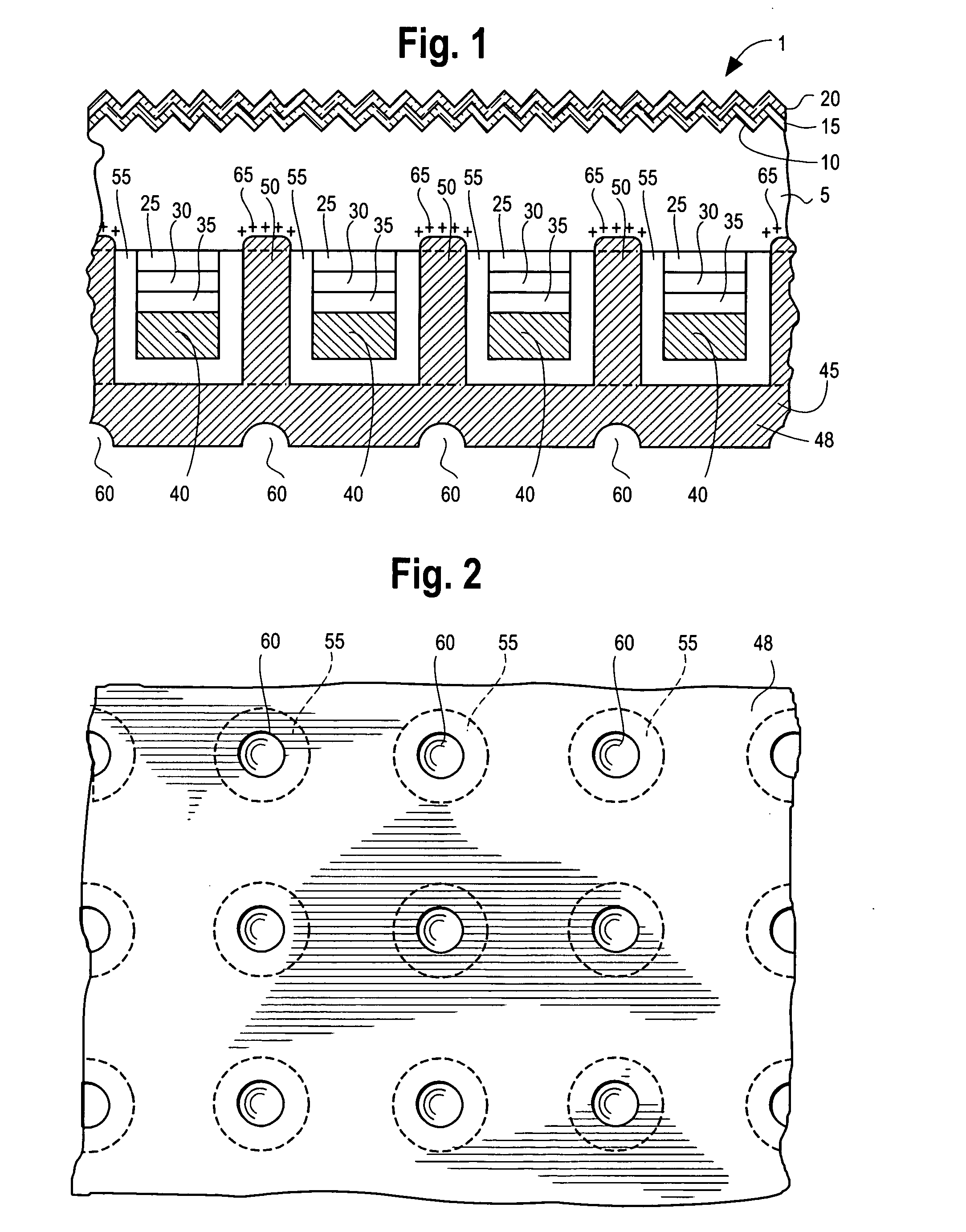

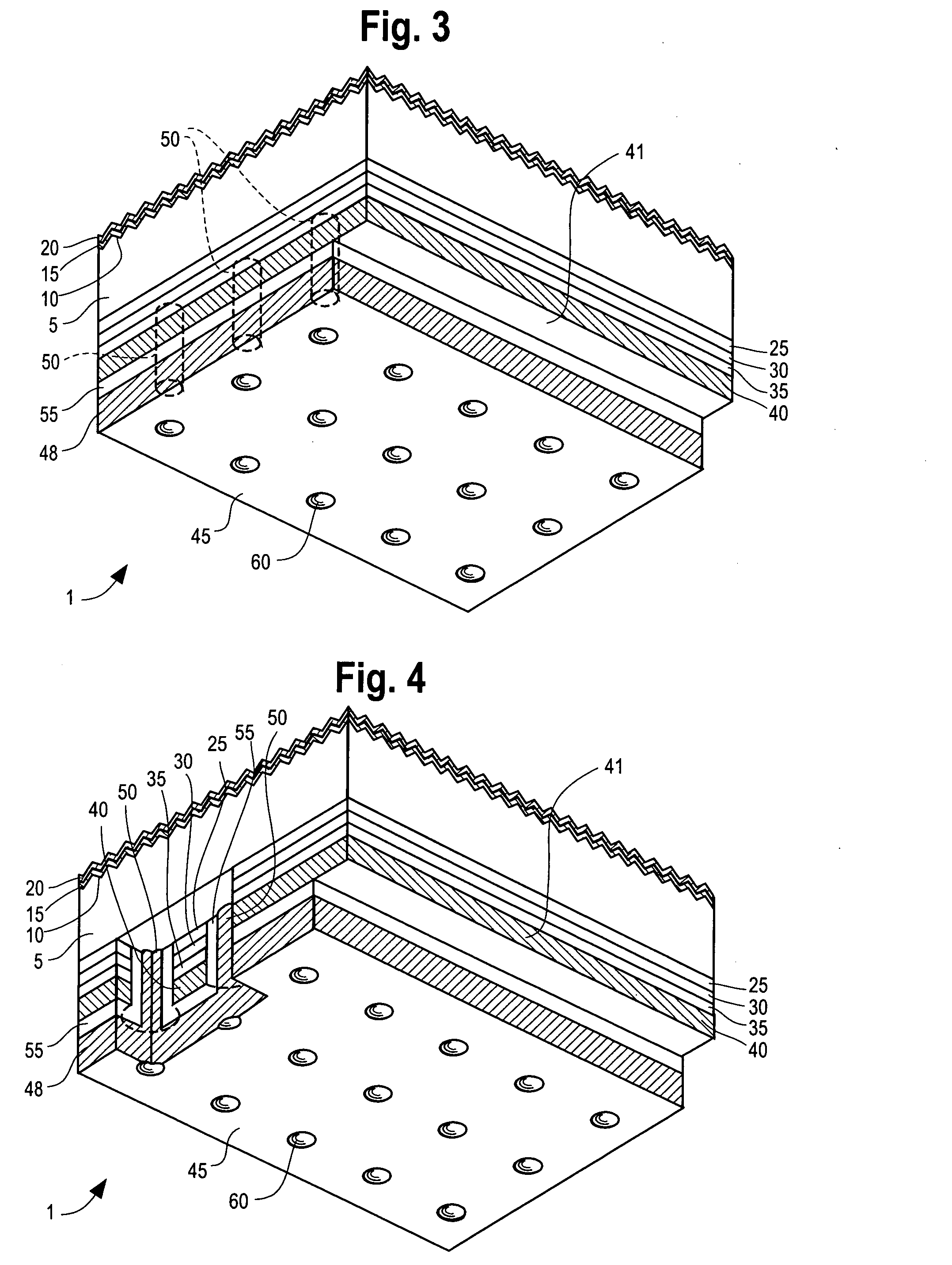

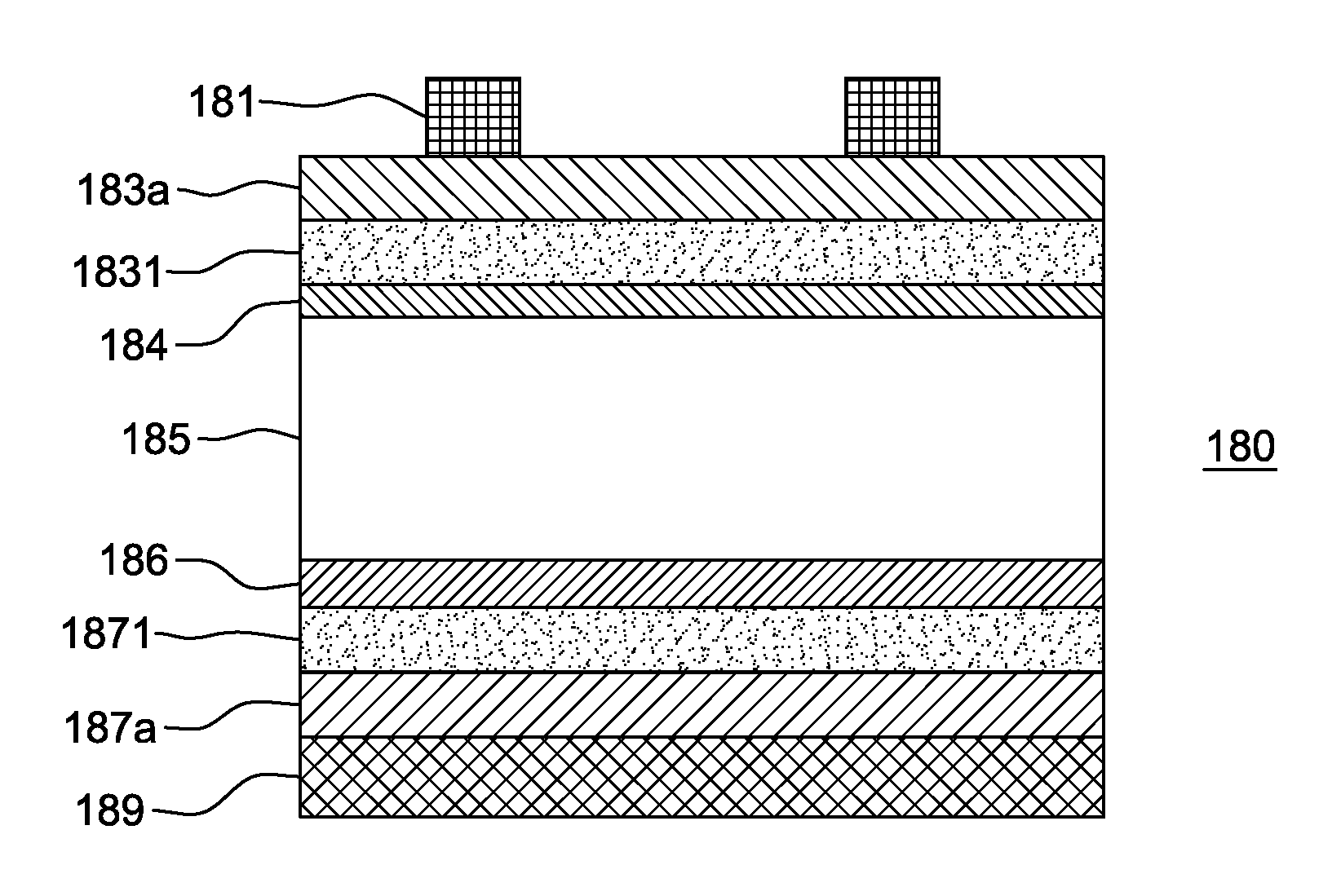

A photovoltaic cell comprising a wafer comprising a semiconductor material of a first conductivity type, the wafer comprising a first light receiving surface and a second surface opposite the first surface; a first passivation layer positioned over the first surface of the wafer; a first electrical contact positioned over the second surface of the wafer; a second electrical contact positioned over the second surface of the wafer and separated electrically from the first electrical contact; a second passivation layer positioned over the second surface of the wafer in the region on the wafer that is at least between the first electrical contact and the second surface of the wafer; and a layer comprising a semiconductor material of a conductivity opposite the conductivity of the wafer and positioned in the region between the second passivation layer and the first contact.

Owner:BP CORP NORTH AMERICA INC

System and method for gas-phase passivation of a semiconductor surface

ActiveUS20170117202A1Low Dit valueSemiconductor/solid-state device detailsSolid-state devicesGas phaseDevice form

Improved methods and systems for passivating a surface of a high-mobility semiconductor and structures and devices formed using the methods are disclosed. The method includes providing a high-mobility semiconductor surface to a chamber of a reactor and exposing the high-mobility semiconductor surface to a gas-phase chalcogen precursor to passivate the high-mobility semiconductor surface.

Owner:ASM IP HLDG BV

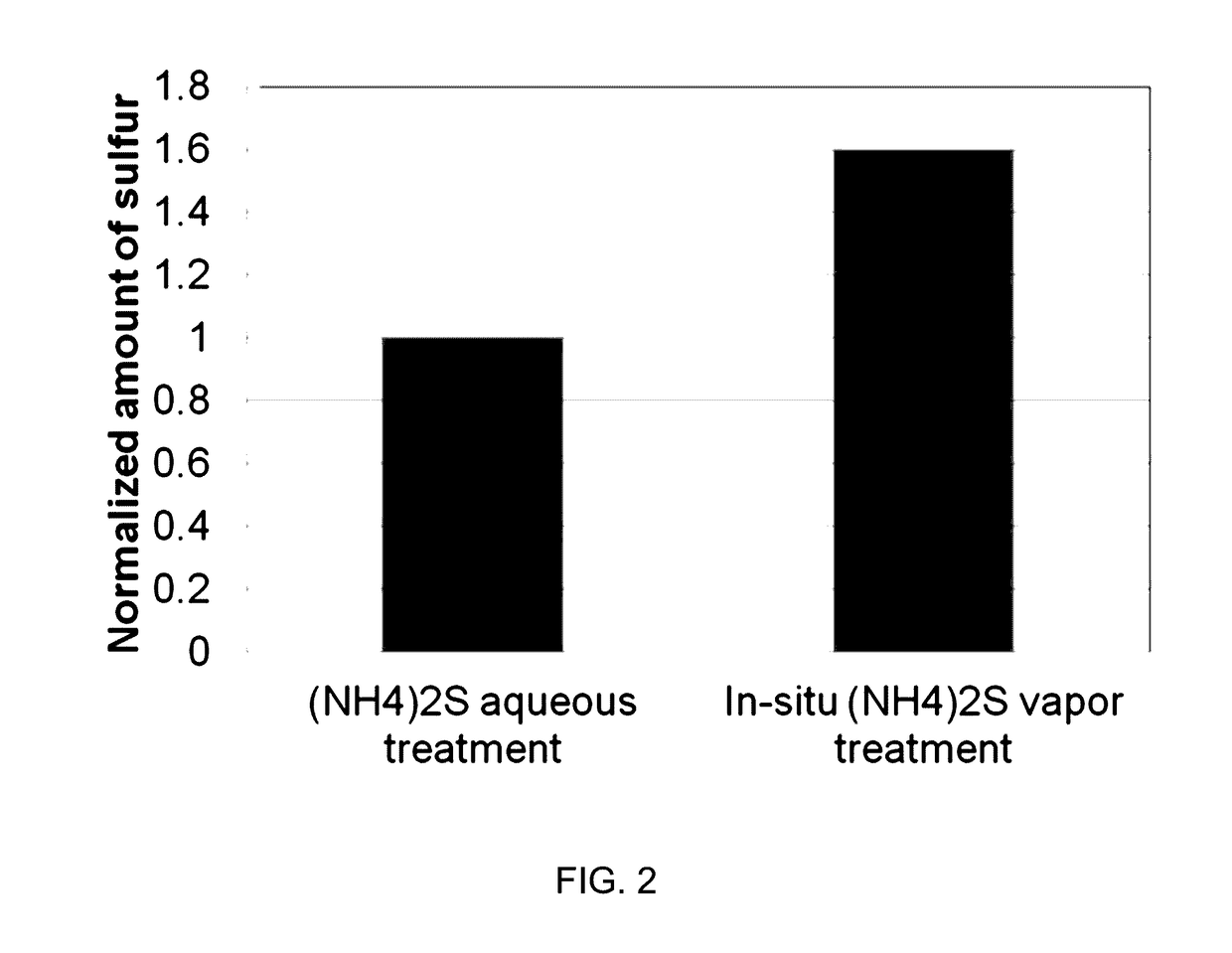

Water vapor passivation of a wall facing a plasma

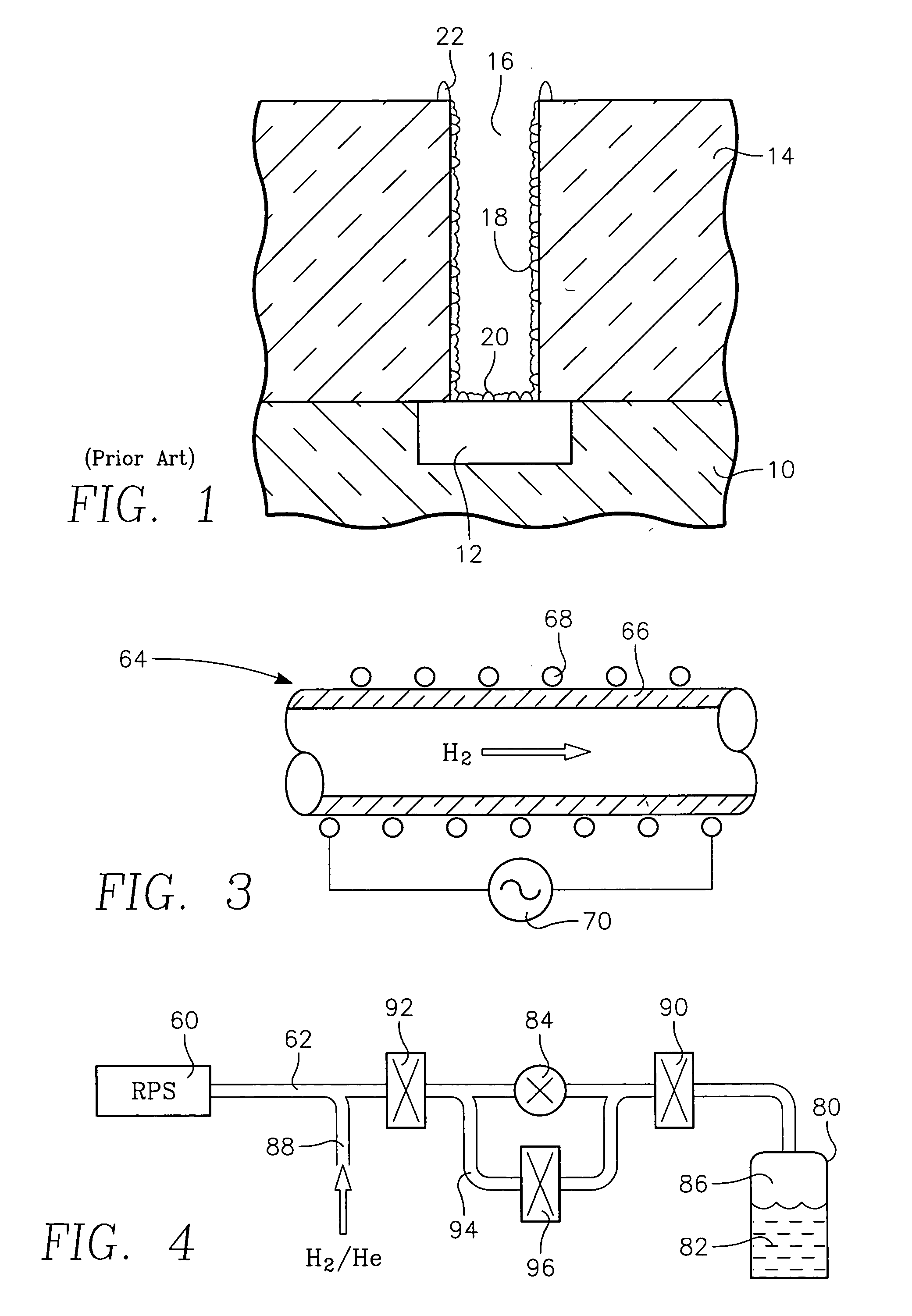

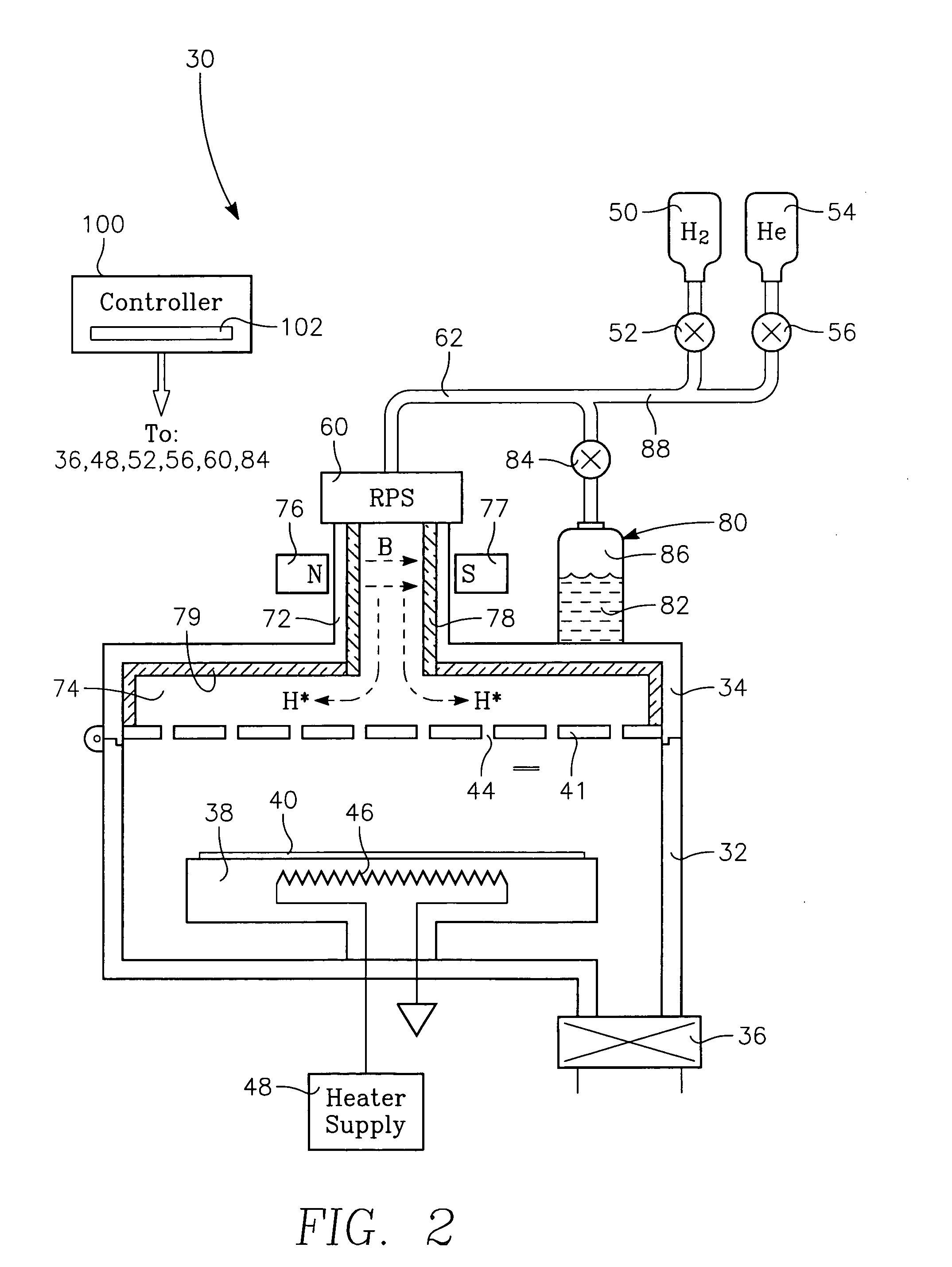

InactiveUS20070190266A1Easy to cleanHollow article cleaningVacuum evaporation coatingChemistryLow-k dielectric

A chamber passivation method particularly useful for hydrogen plasma cleaning of low-k dielectrics prior to coating a barrier layer into a via hole with hydrogen radicals are provided from a remote plasma source. For each wafer, the chamber is passivated with water vapor (or other gas even more chemabsorbed on plasma facing walls) passed through the remote plasma source prior to the ignition of the hydrogen plasma. The water vapor is absorbed on walls, such as alumina and quartz parts of the remote plasma source, and forms a protective mono-layer that endures sufficiently long to protect the walls during the generation of the hydrogen plasma. Thereby, the plasma facing walls, particularly of a dielectric such as alumina, are protected from etching.

Owner:APPLIED MATERIALS INC

Fuel cell platelet separators having coordinate features

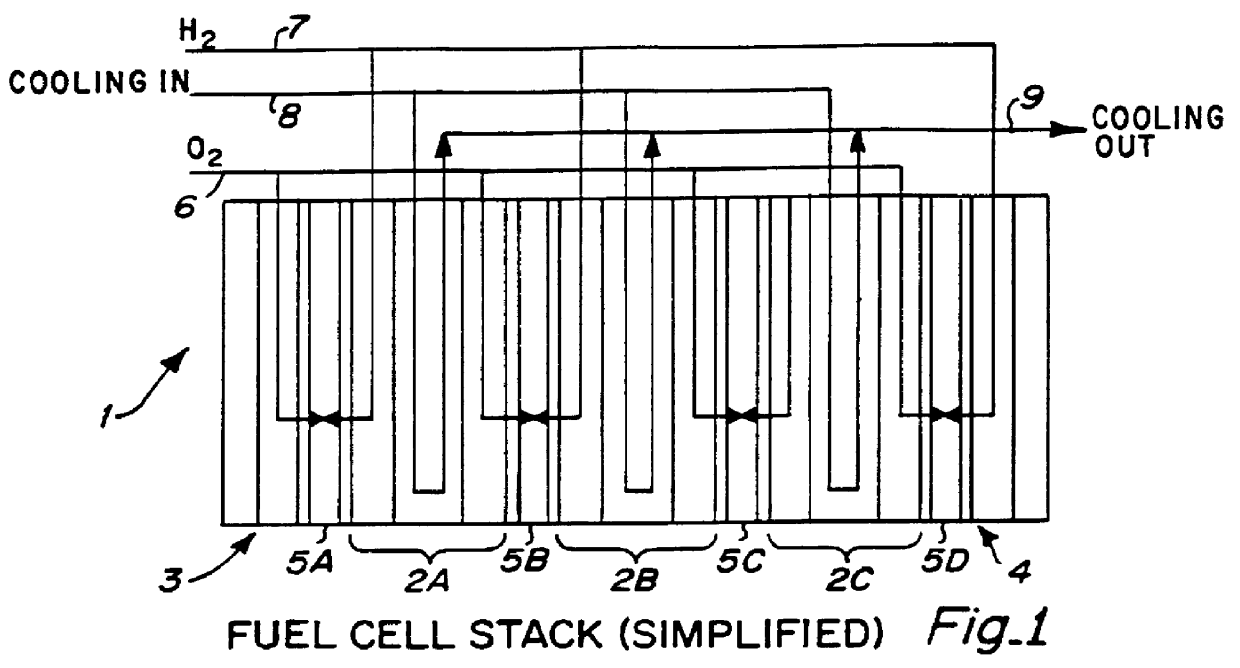

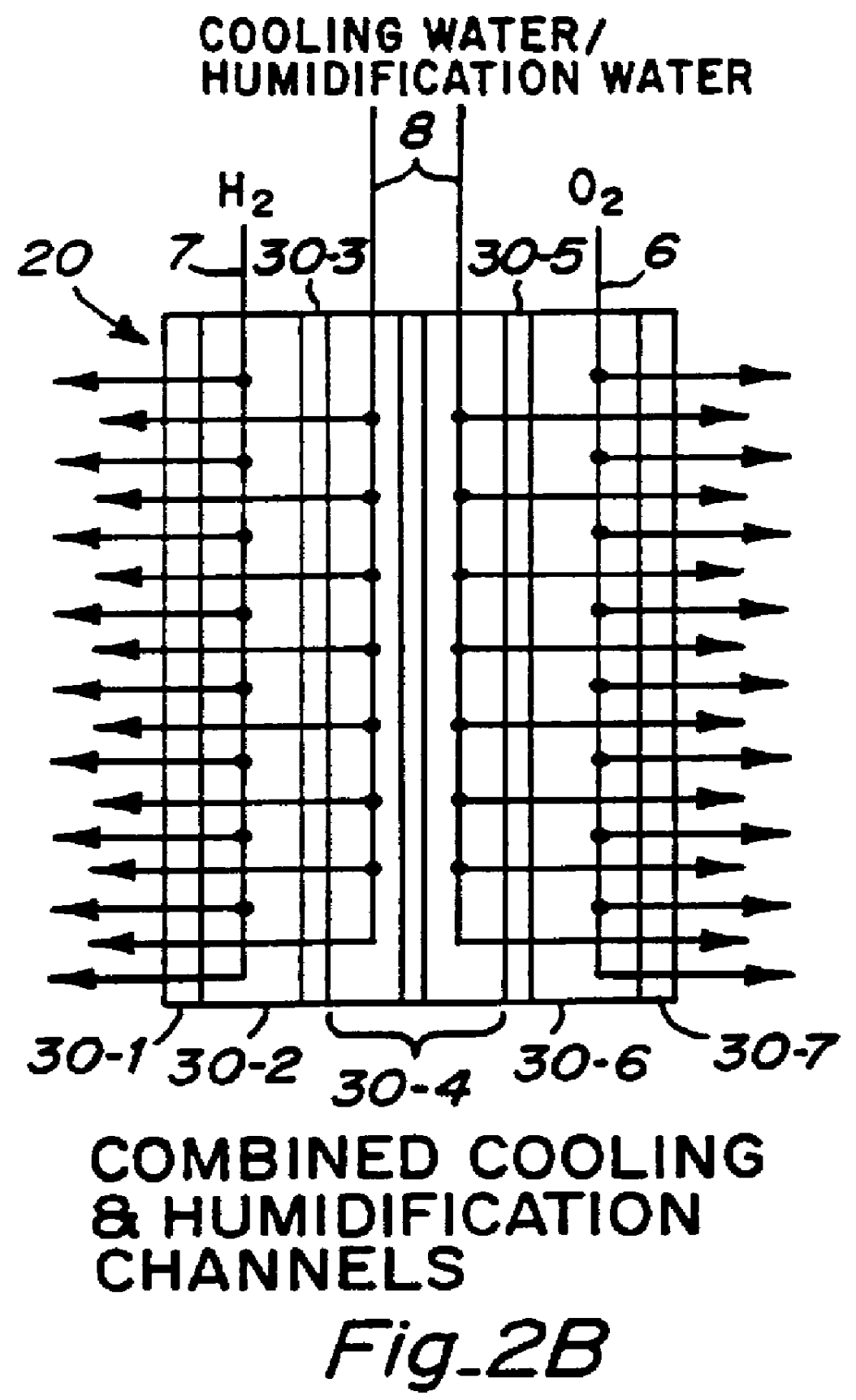

InactiveUS6051331ASimple designEvenly distributedSolid electrolytesFuel cells groupingLaser etchingFuel cells

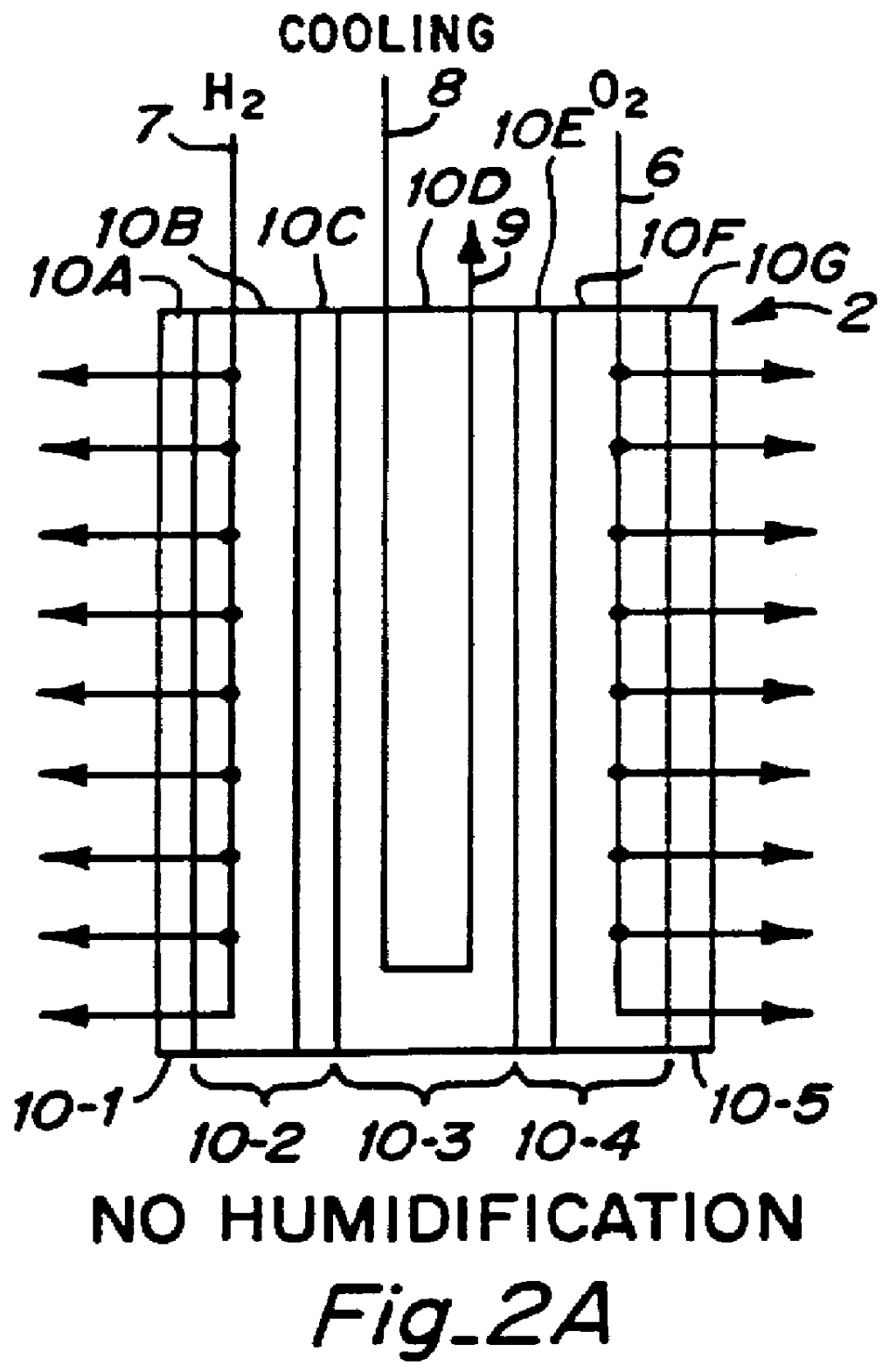

PCT No. PCT / US95 / 13325 Sec. 371 Date Sep. 28, 1997 Sec. 102(e) Date Sep. 28, 1997 PCT Filed Oct. 10, 1995 PCT Pub. No. WO96 / 12316 PCT Pub. Date Apr. 25, 1996Fuel cell stacks comprising stacked separator / membrane electrode assembly fuel cells in which the separators comprise a series of thin sheet platelets, having individually configured serpentine micro-channel reactant gas humidification active areas and cooling fields therein. The individual platelets are stacked with coordinate features aligned in contact with adjacent platelets and bonded to form a monolithic separator. Post-bonding processing includes passivation, such as nitriding. Preferred platelet material is 4-25 mil Ti, in which the features, serpentine channels, tabs, lands, vias, manifolds and holes, are formed by chemical and laser etching, cutting, pressing or embossing, with combinations of depth and through etching preferred. The platelet manufacturing process is continuous and fast. By employing CAD based platelet design and photolithography, rapid change in feature design can accommodate a wide range of thermal management and humidification techniques. One hundred H2-O2 / PEM fuel cell stacks of this IFMT platelet design will exhibit outputs on the order of 0.75 kW / kg, some 3-6 times greater than the current graphite plate PEM stacks.

Owner:H POWER

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

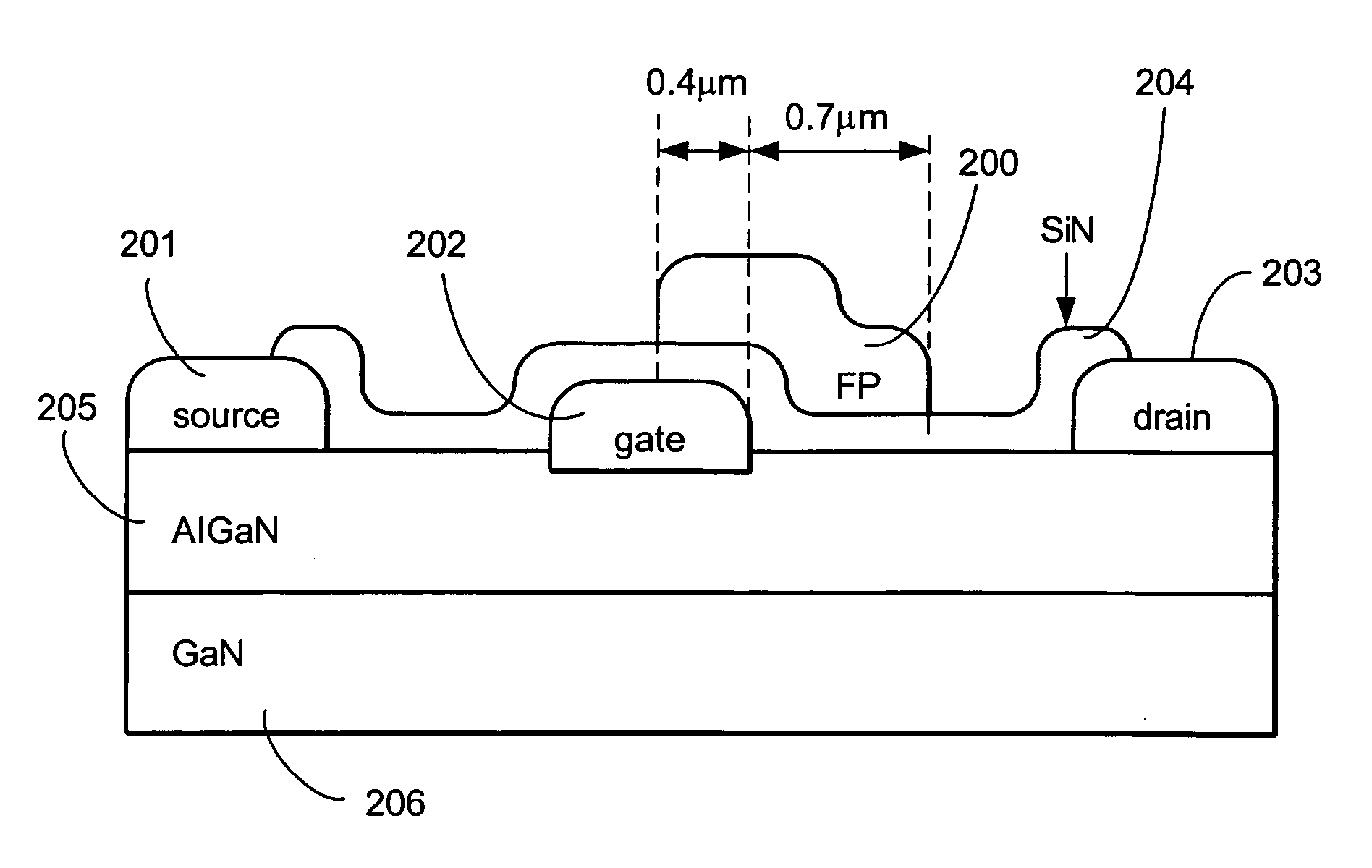

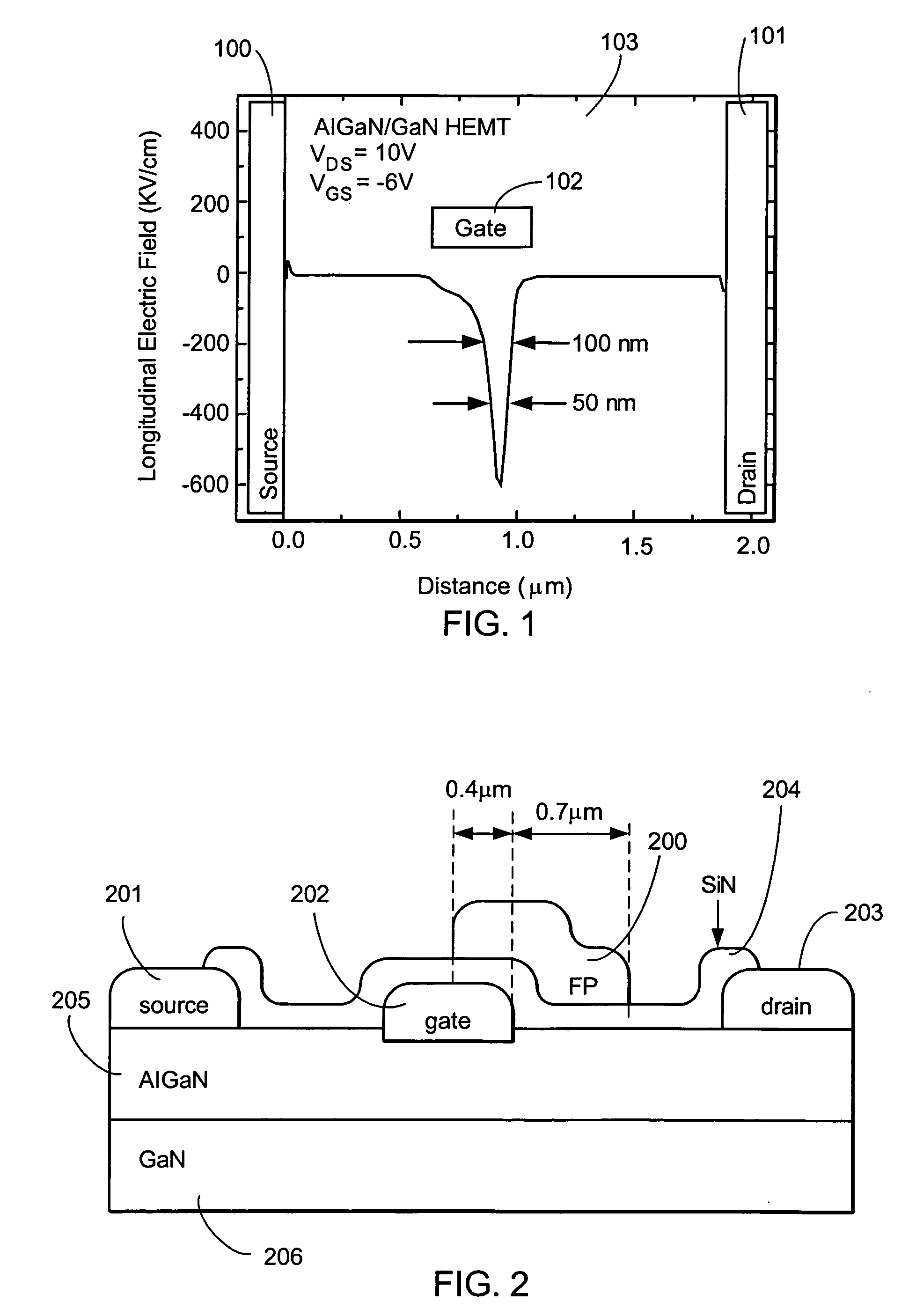

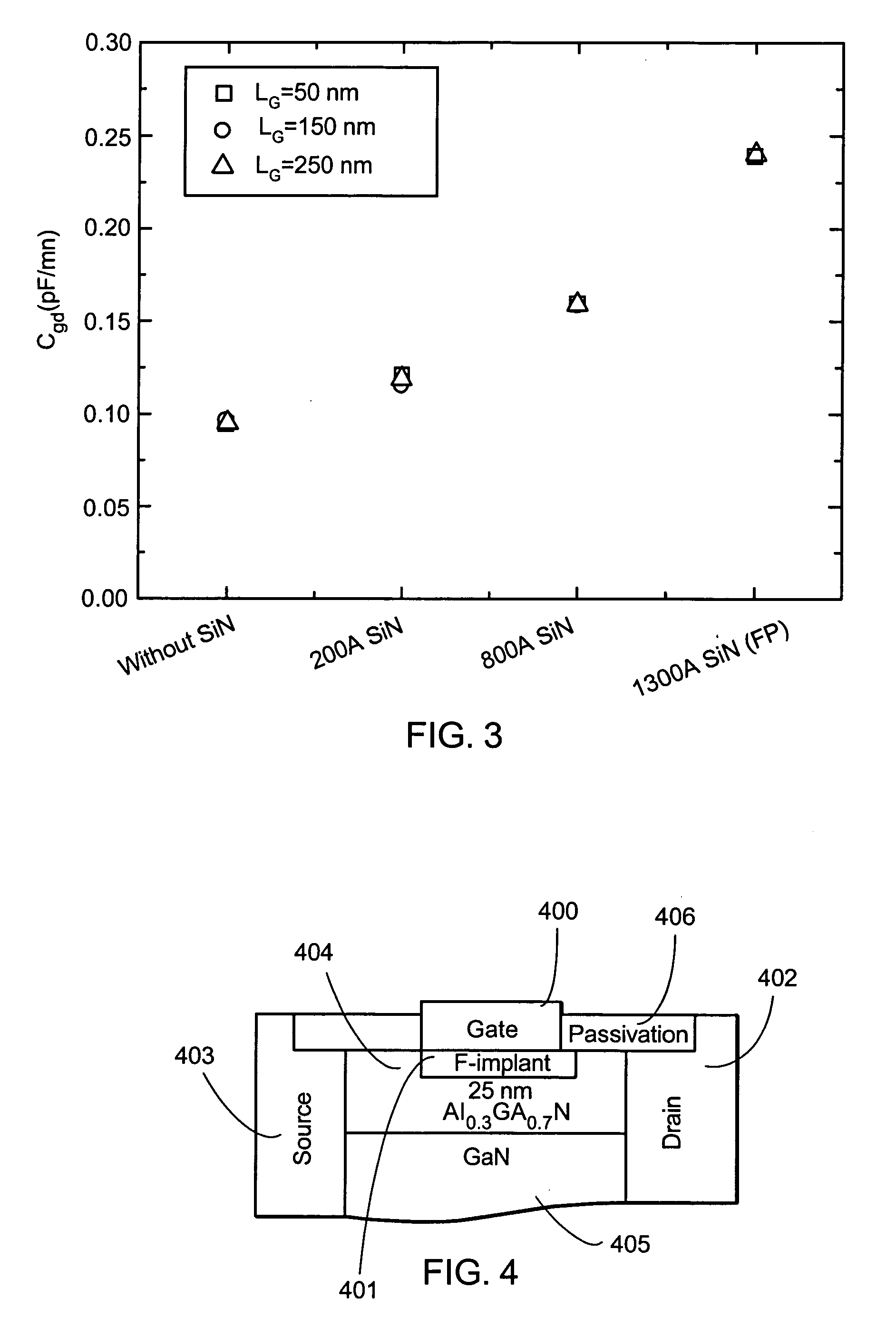

ActiveUS20070224710A1Increase output powerReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueDislocation

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

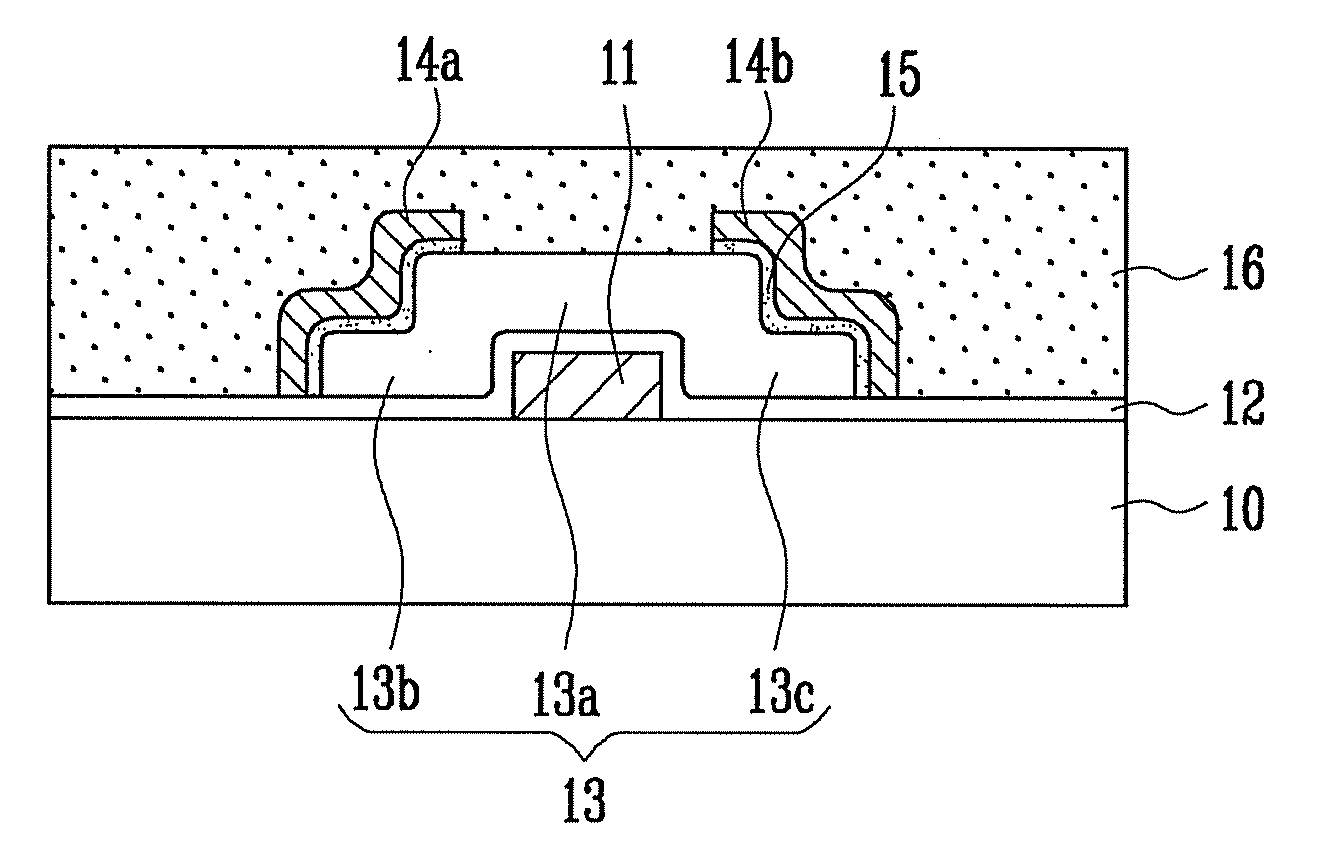

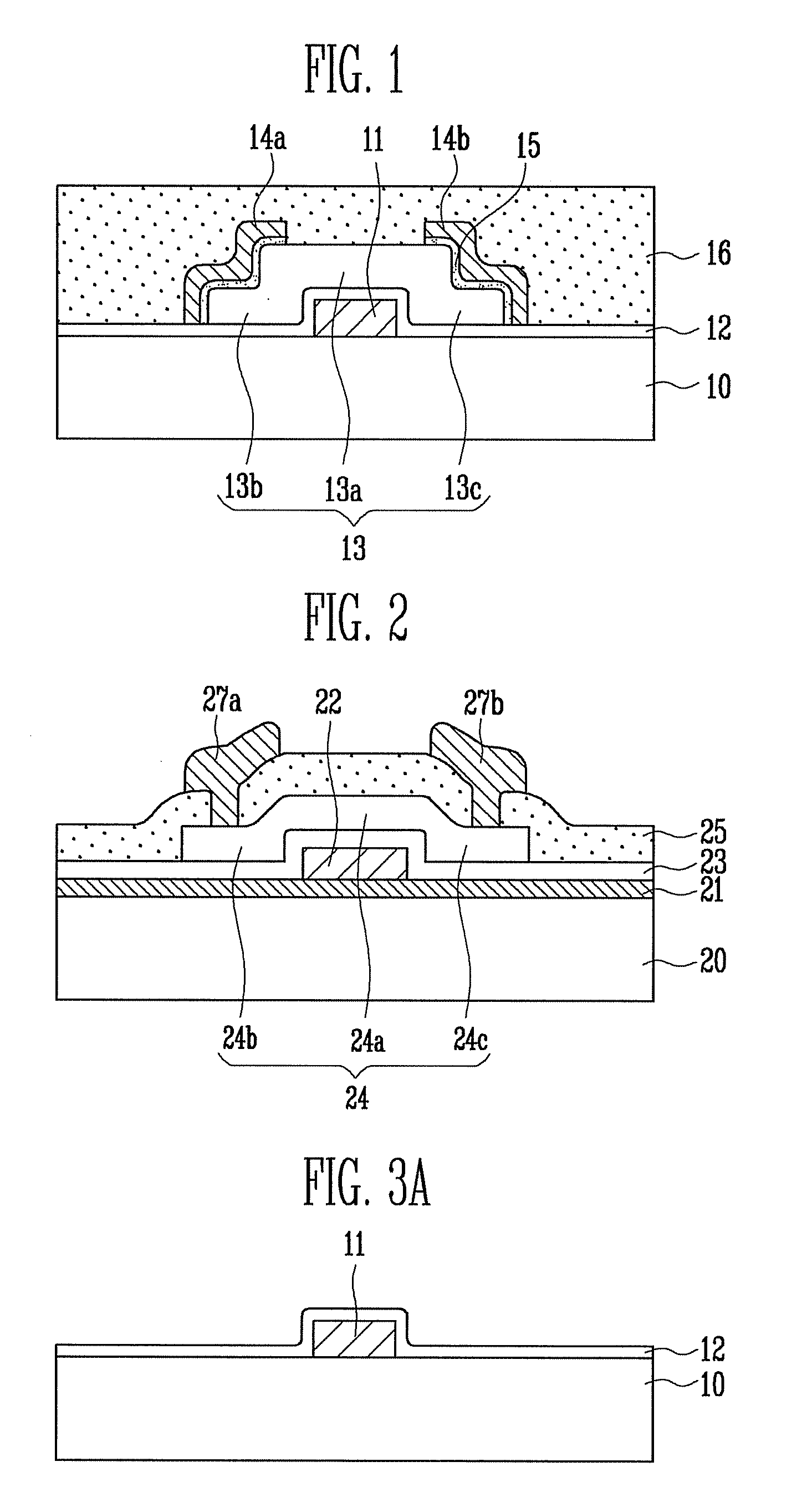

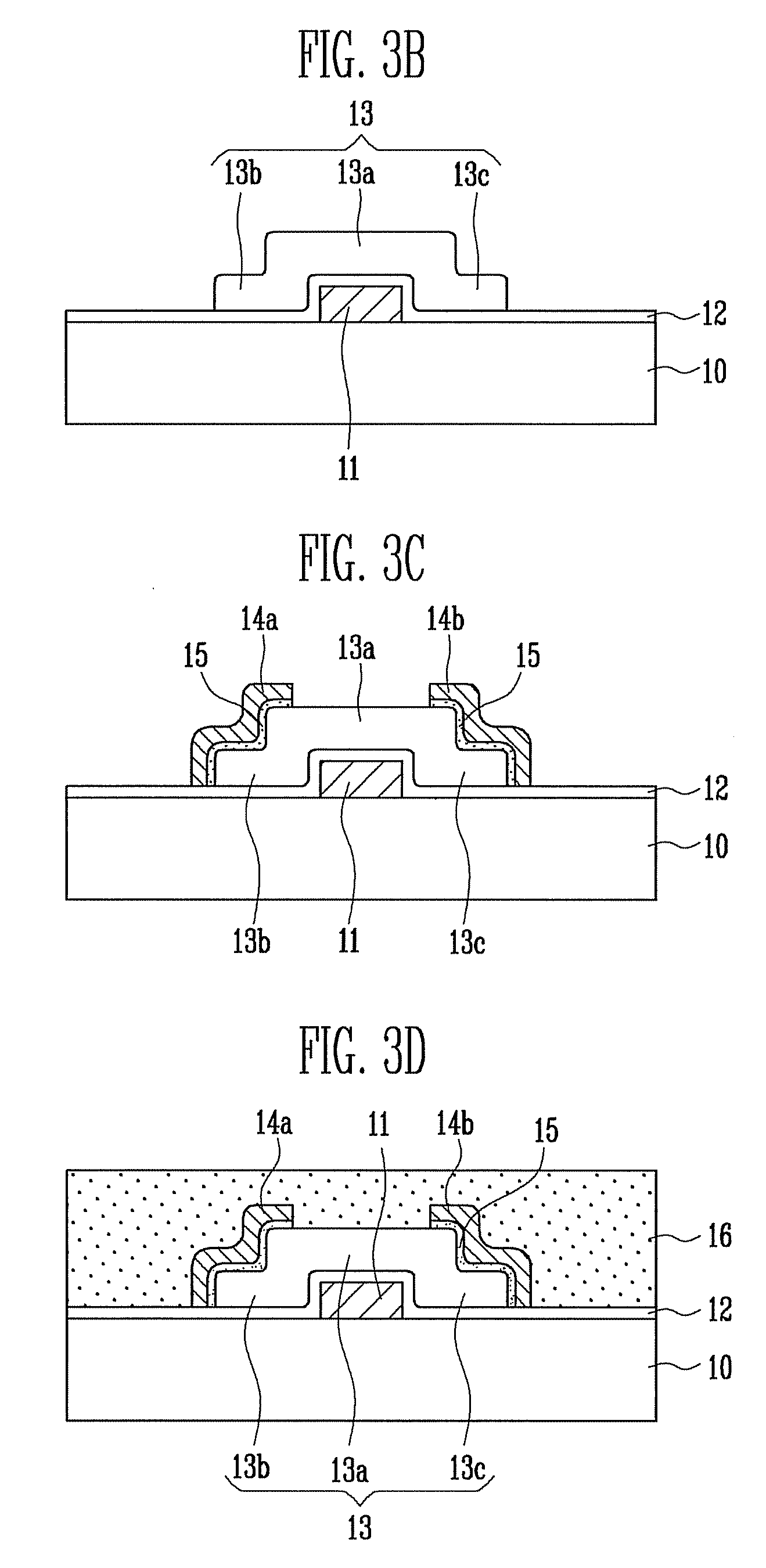

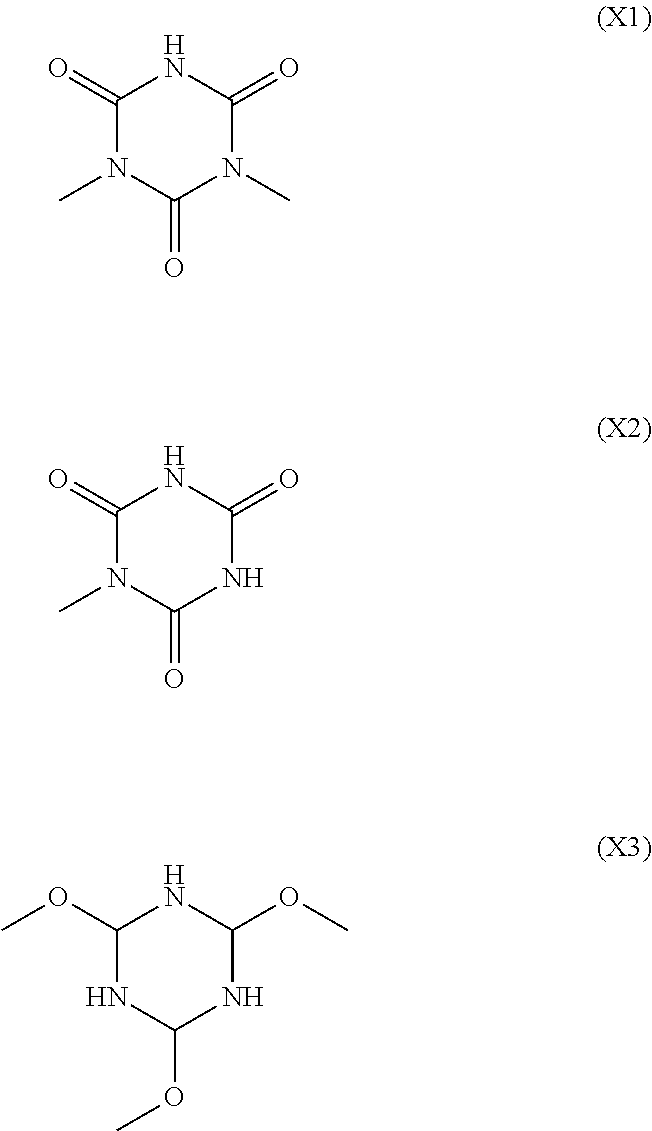

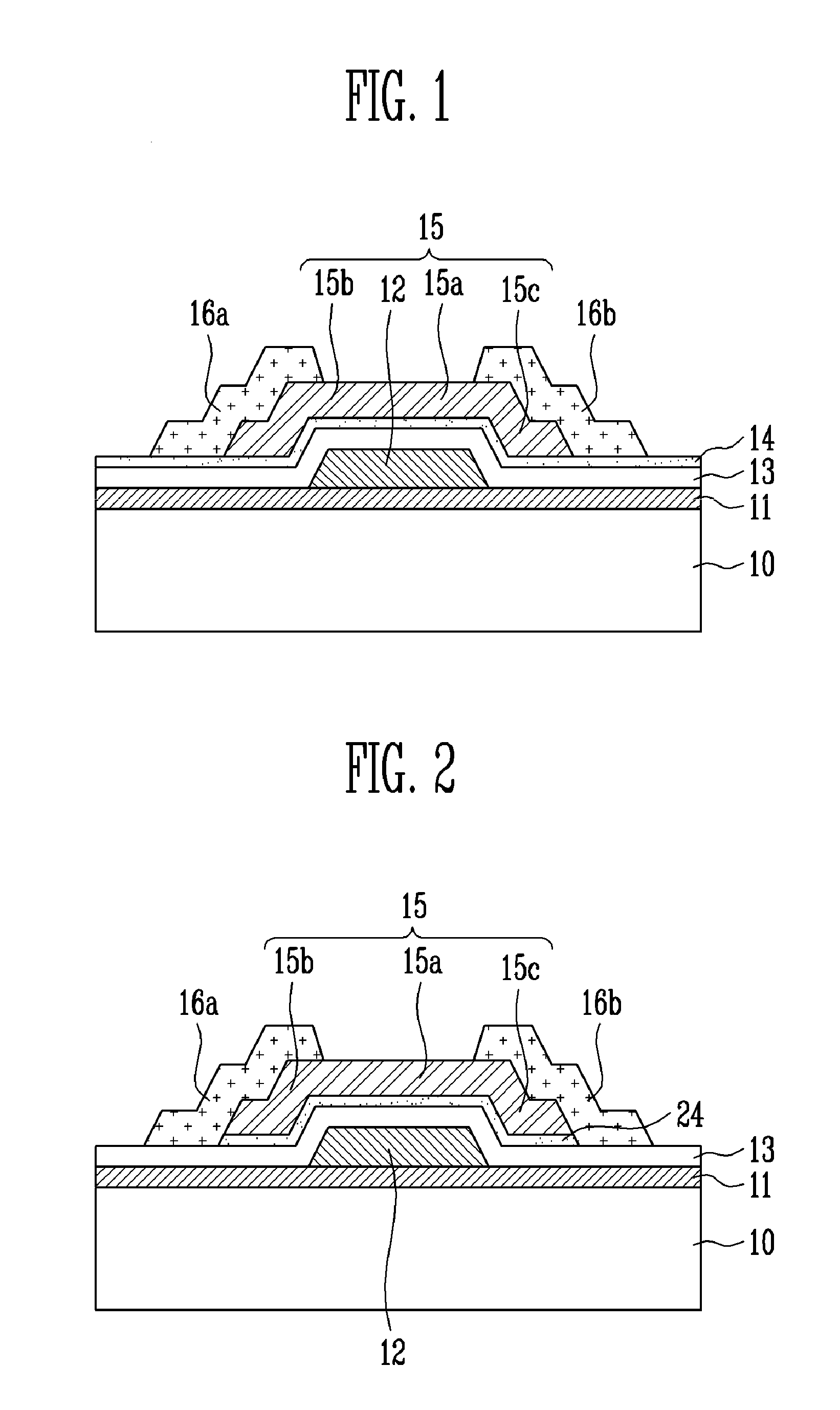

Method of manufacturing thin film transistor and method of manufacturing organic light emitting display having thin film transistor

ActiveUS20090155940A1Preventing and reducing property changeReliability and electrical property is raisedTransistorSolid-state devicesCharge-carrier densityOxygen ions

A method of manufacturing a thin film transistor having a compound semiconductor with oxygen as a semiconductor layer and a method of manufacturing an organic light emitting display having the thin film transistor include: forming a gate electrode on an insulating substrate; forming a gate insulating layer on the gate electrode; forming a semiconductor layer including oxygen ions on the gate insulating layer, and including a channel region, a source region, and a drain region; forming a source electrode and a drain electrode to contact the semiconductor layer in the source region and the drain region, respectively; and forming a passivation layer on the semiconductor layer by coating an organic material, wherein a carrier density of the semiconductor layer is maintained in the range of 1E+17 to 1E+18 / cm3 to have stable electrical property.

Owner:SAMSUNG DISPLAY CO LTD

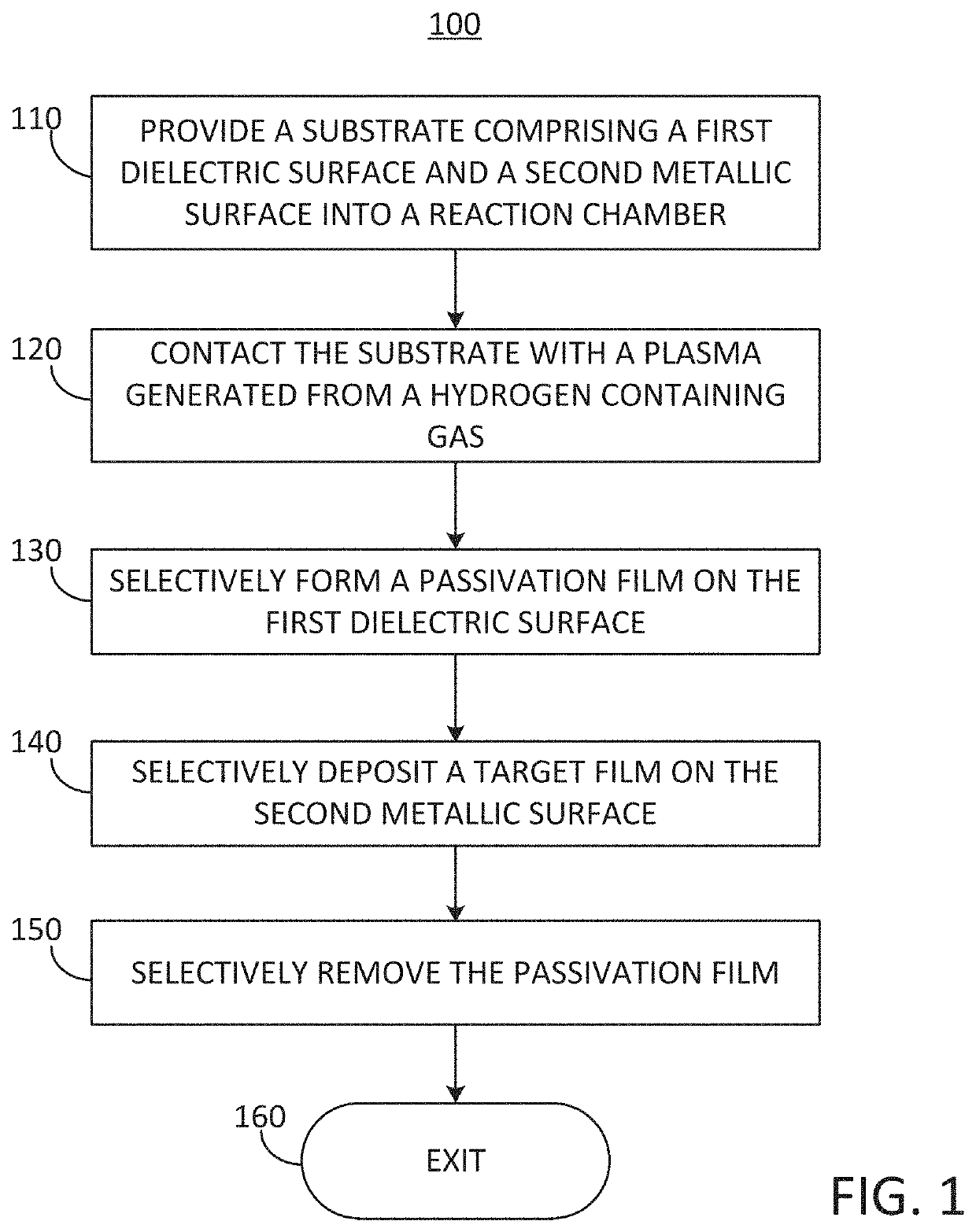

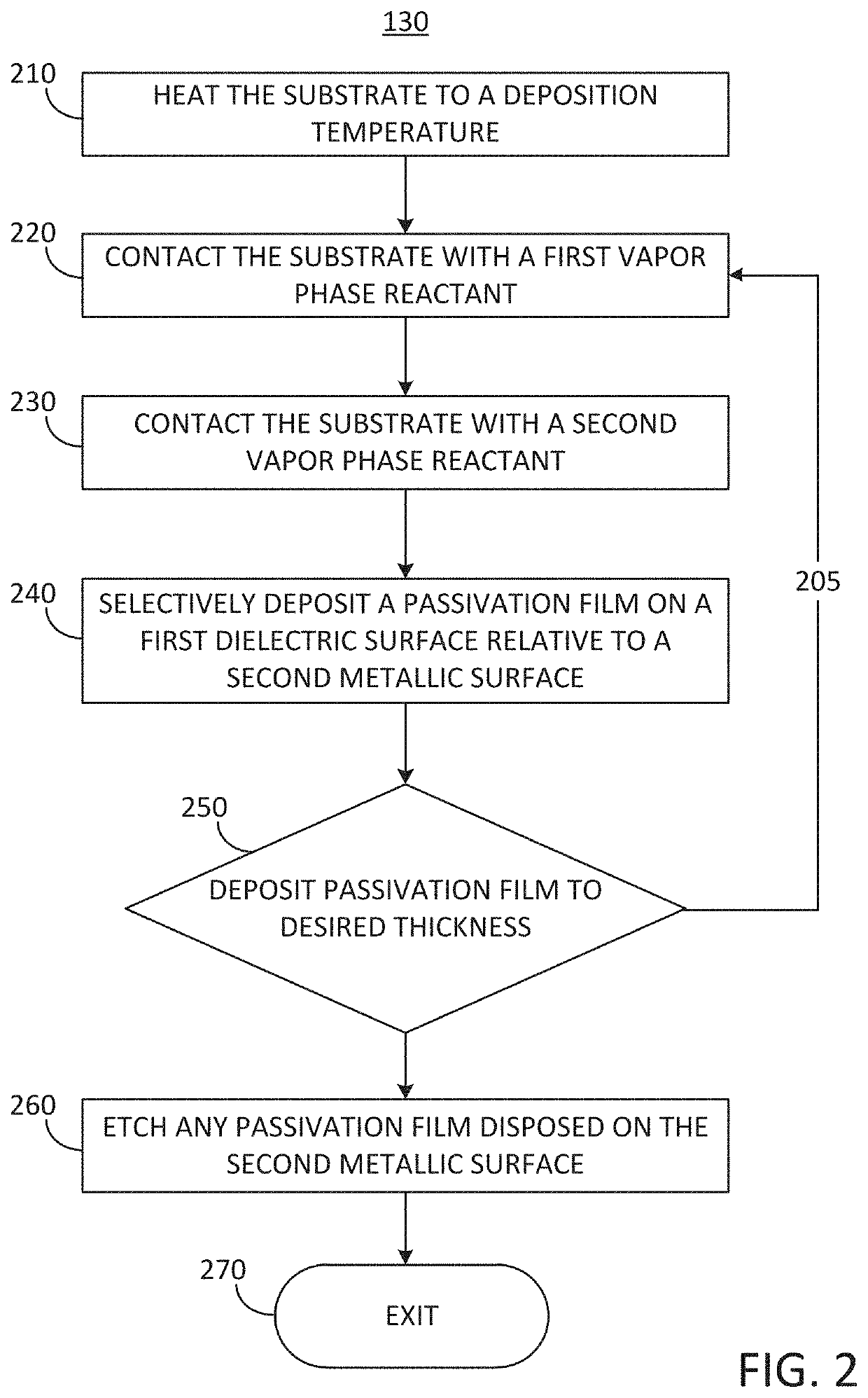

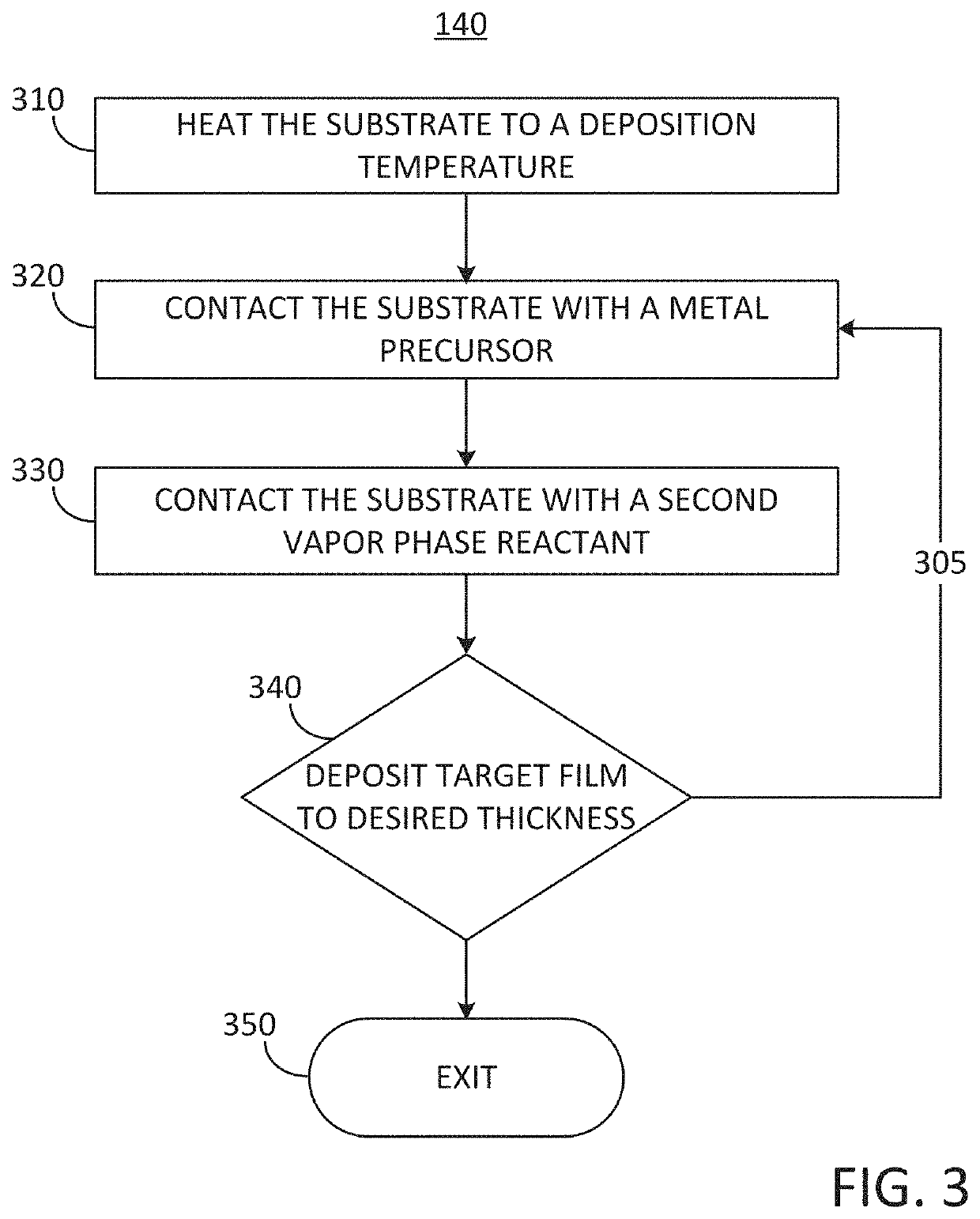

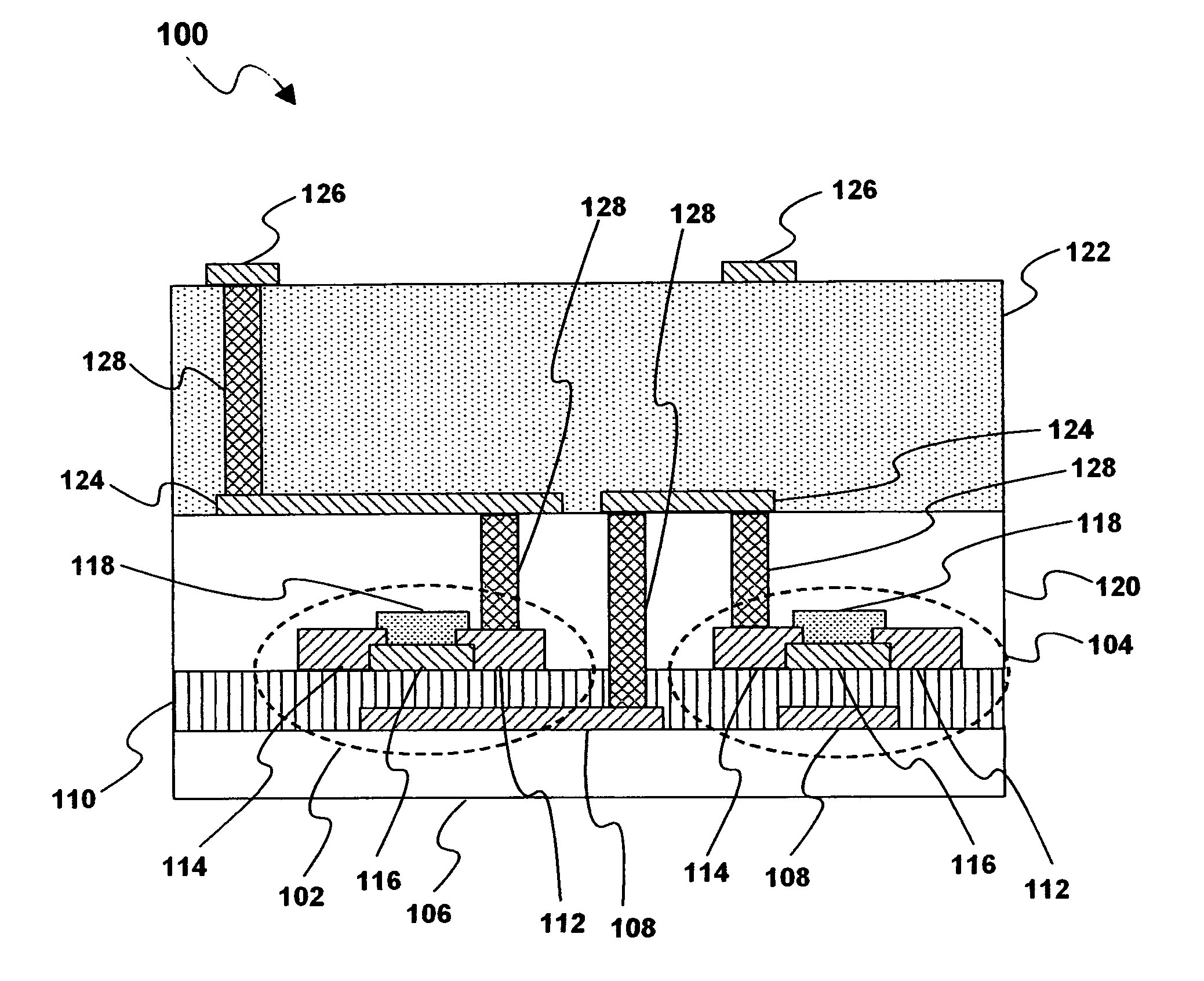

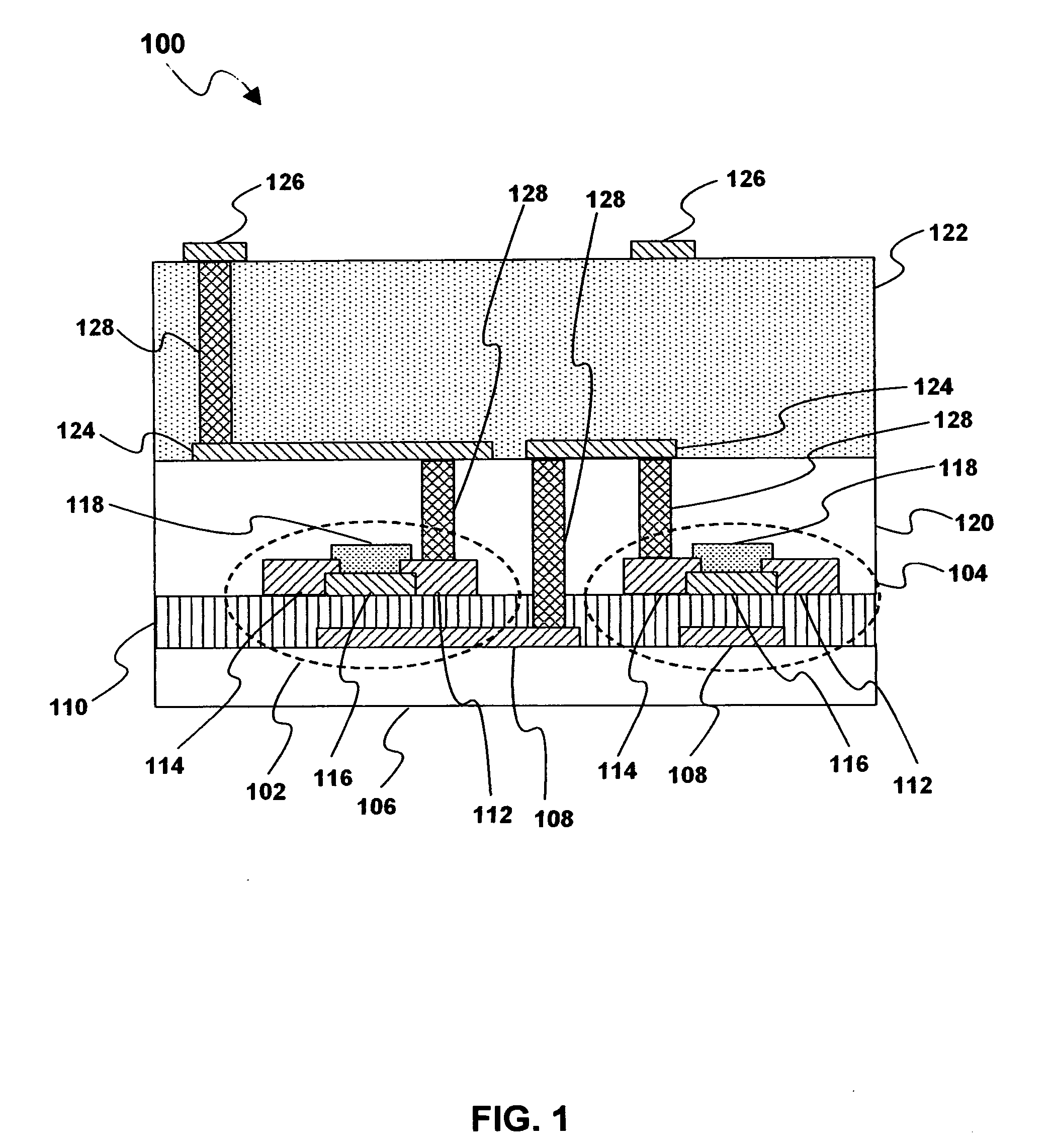

Methods for selectively forming a target film on a substrate comprising a first dielectric surface and a second metallic surface

ActiveUS20210159077A1Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingDielectric surfaceVapor phase

Methods for selectively forming a target film on a substrate comprising a first dielectric surface and a second metallic surface are disclosed. The methods may include: contacting the substrate with a plasma generated from a hydrogen containing gas, selectively forming a passivation film from vapor phase reactants on the first dielectric surface while leaving the second metallic surface free from the passivation film, and selectively depositing the target film from vapor phase reactants on the second metallic surface relative to the passivation film.

Owner:ASM IP HLDG BV

Method to form a passivation layer

ActiveUS20060079034A1Semiconductor/solid-state device manufacturingNon-linear opticsComputer scienceMaterials science

Embodiments of methods, apparatuses, devices, and / or systems for forming a passivation layer are described.

Owner:HEWLETT PACKARD DEV CO LP +1

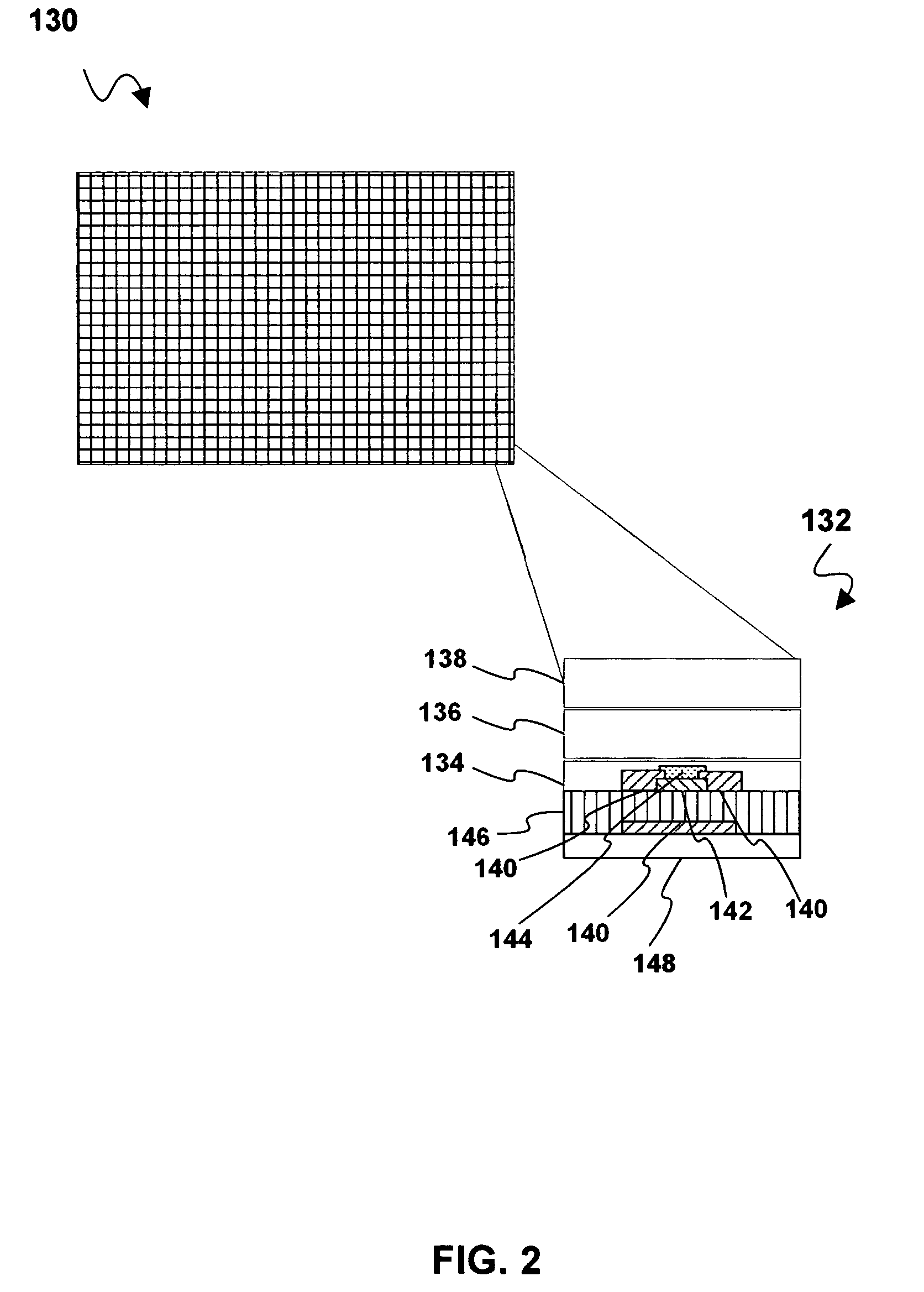

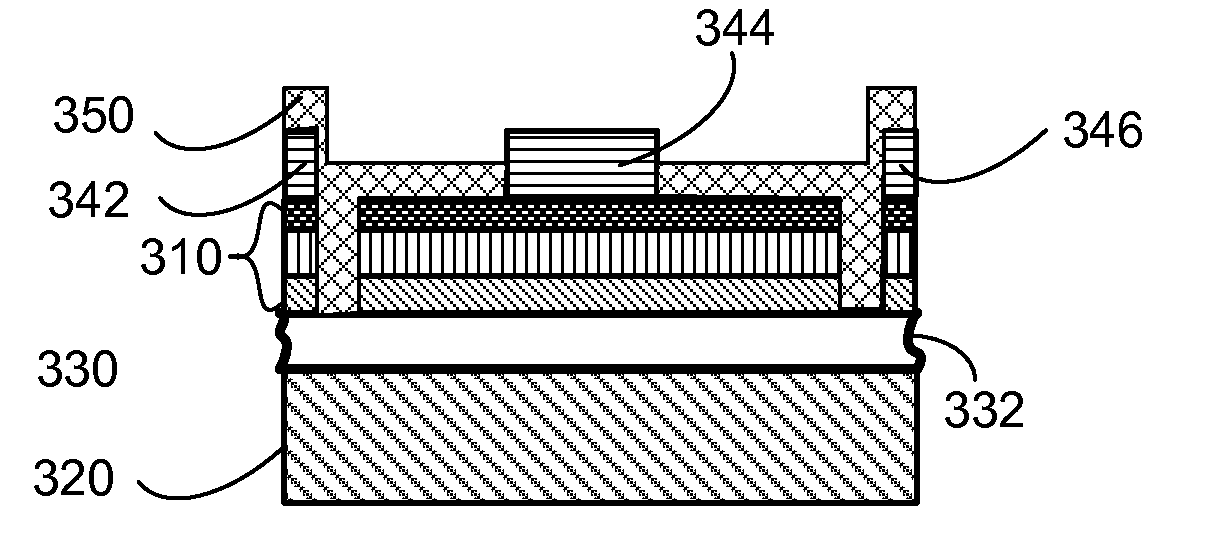

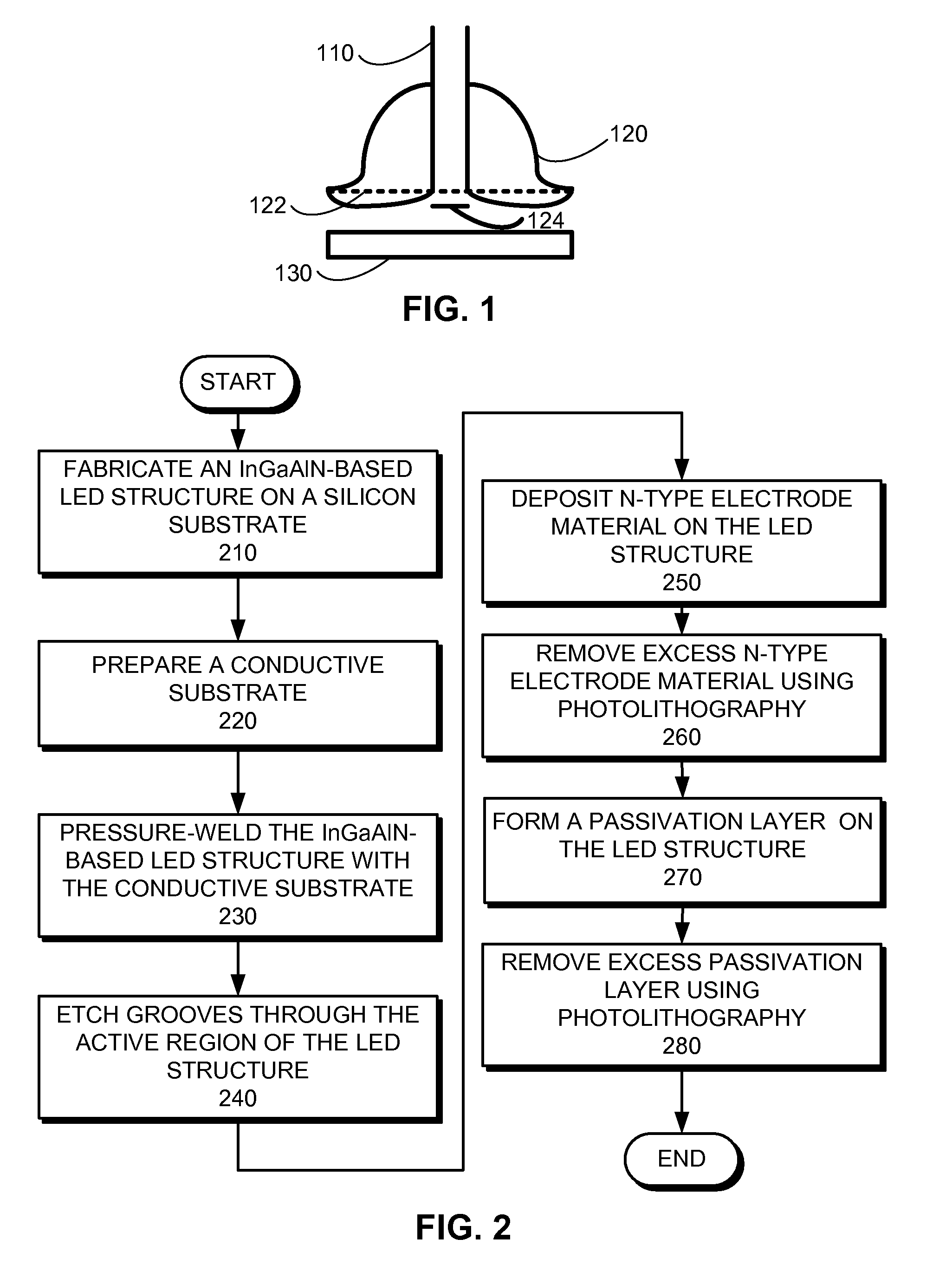

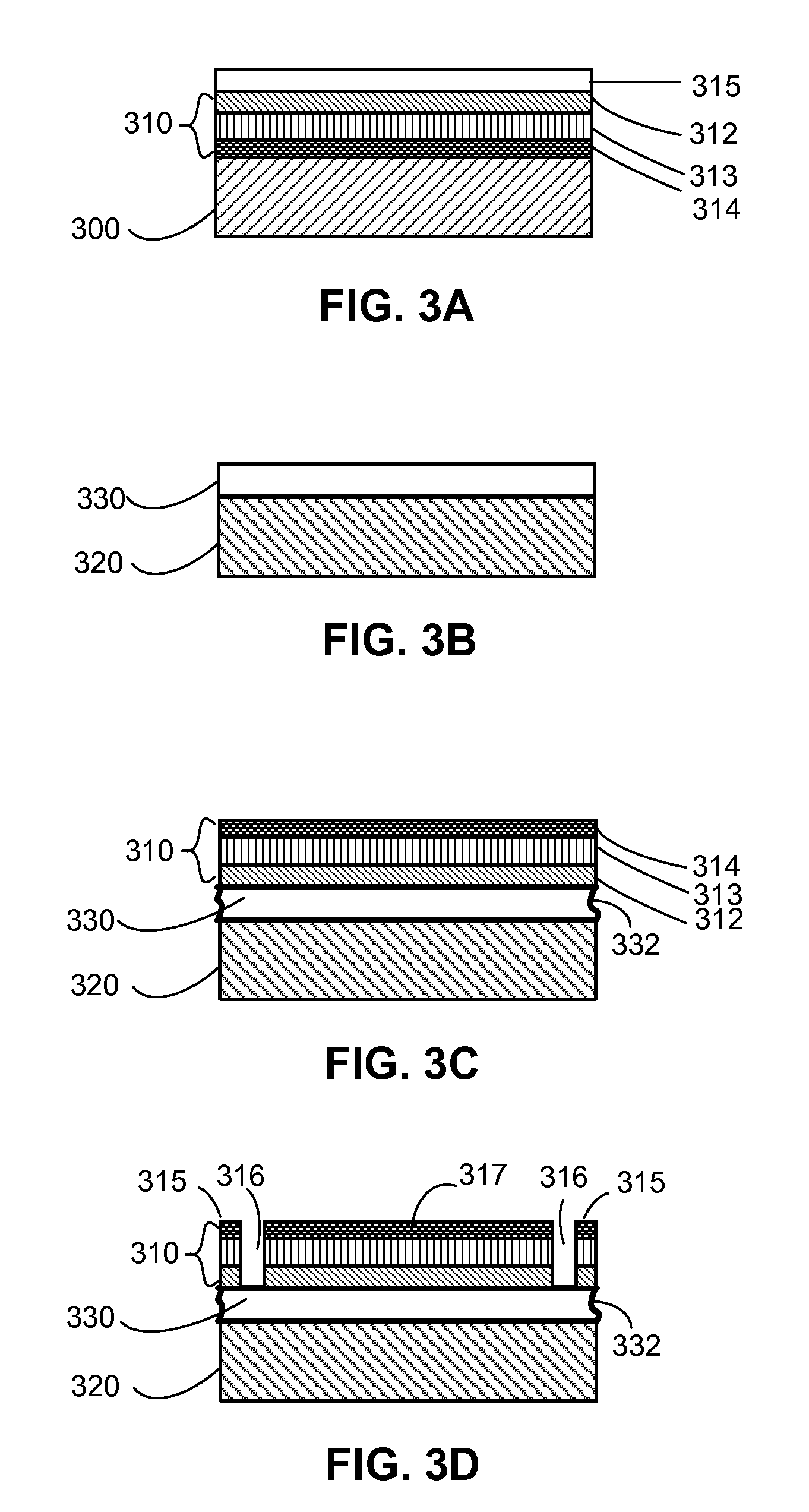

Method for fabricating robust light-emitting diodes

InactiveUS20110049540A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringLead structure

One embodiment of the present invention provides a method for fabricating light-emitting diodes (LEDs). The method includes fabricating an InGaAlN-based multilayer LED structure on a conductive substrate. The method further includes etching grooves of a predetermined pattern through the active region of the multilayer LED structure. The grooves separate a light-emitting region from non-light-emitting regions. In addition, the method includes depositing electrode material on the light-emitting and non-light-emitting regions, thereby creating an electrode. Furthermore, the method includes depositing a passivation layer covering the light-emitting and non-light-emitting regions. Moreover, the method includes removing the passivation layer on the electrode to allow the non-light-emitting regions which are covered with the electrode material and the passivation layer to be higher than the light-emitting region and the electrode, thereby protecting the light-emitting region from contact with test equipment.

Owner:LATTICE POWER (JIANGXI) CORP

Chromium-free passivation liquid for galvanized sheet and manufacture method thereof

InactiveCN101250699AImprove bindingImprove corrosion resistanceMetallic material coating processesChromium freeSealant

The invention in particular relates to passivation solution without chrome which is used for galvanized sheets and a method thereof. The technical scheme thereof comprises: firstly, dissolving inorganic salt corrosion inhibitor, then, adding the inorganic salt corrosion inhibitor into a stirred tank, adding dispersant, organic acid, sealant, silicone-acrylate emulsion and water while stirring, then, using inorganic acid or alkali to regulate the pH value to be 2.0-5.0, and then stirring for 1-2 hours under the condition that the temperature is 20-30 DEG C, the content of the components of each liter is: the inorganic salt corrosion inhibitor 10-55g, additive 4-10g, the organic acid 5-20g, the sealant 5-30g, the silicone-acrylate emulsion 150-300g, and the rest is the water. The method of the invention can additionally form a layer of organic resin separate layer on the basis of forming an inorganic metal compound precipitation film, additionally, since the silicon compound is added, not only the binding force between a passivation layer and zinc coating can be increased, but also the corrosion resistance, the scrubbing resistance and the wear resistance of the passivation layer can be increased, and the coating treatment after passivation can not be affected.

Owner:WUHAN UNIV OF SCI & TECH

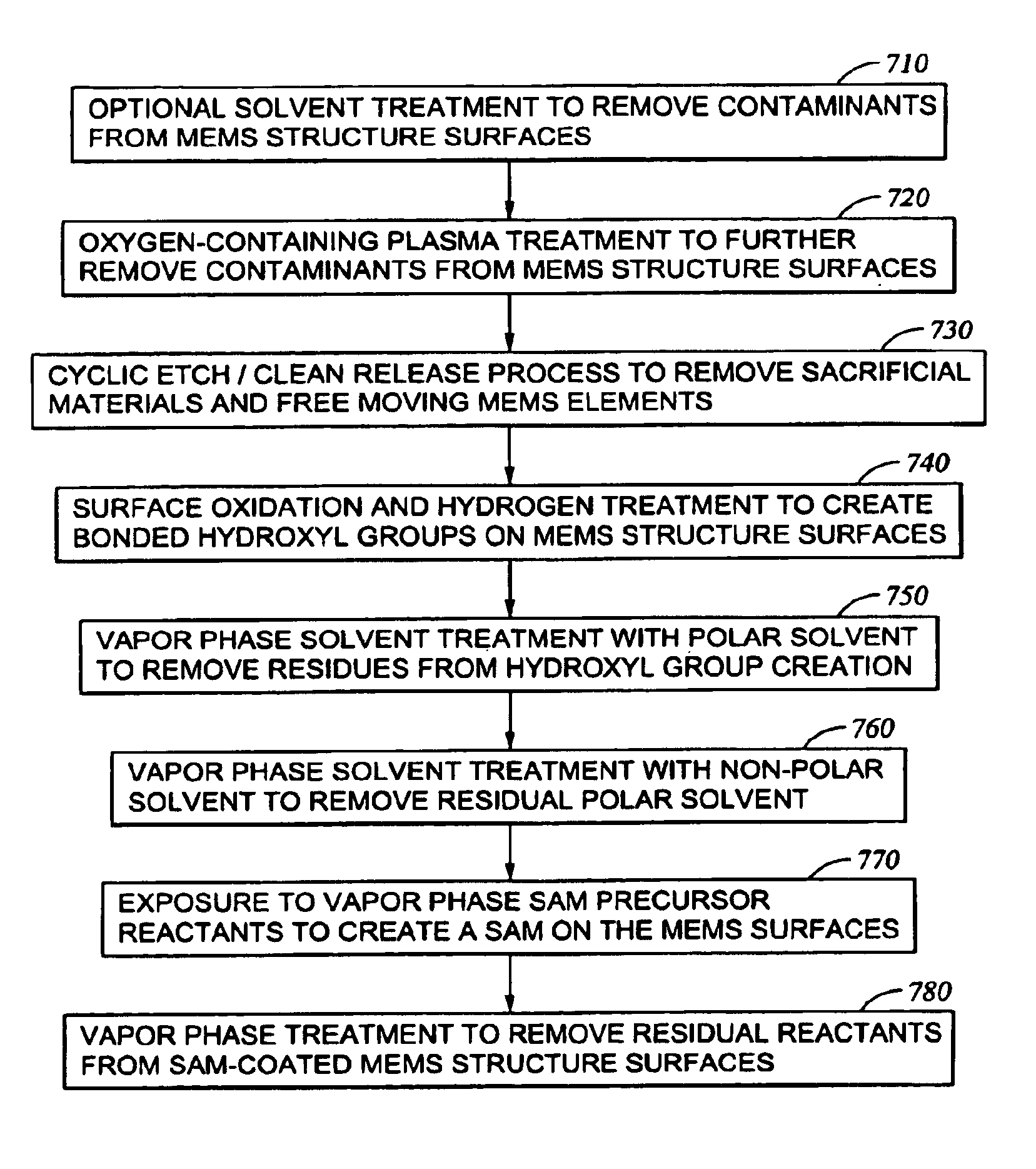

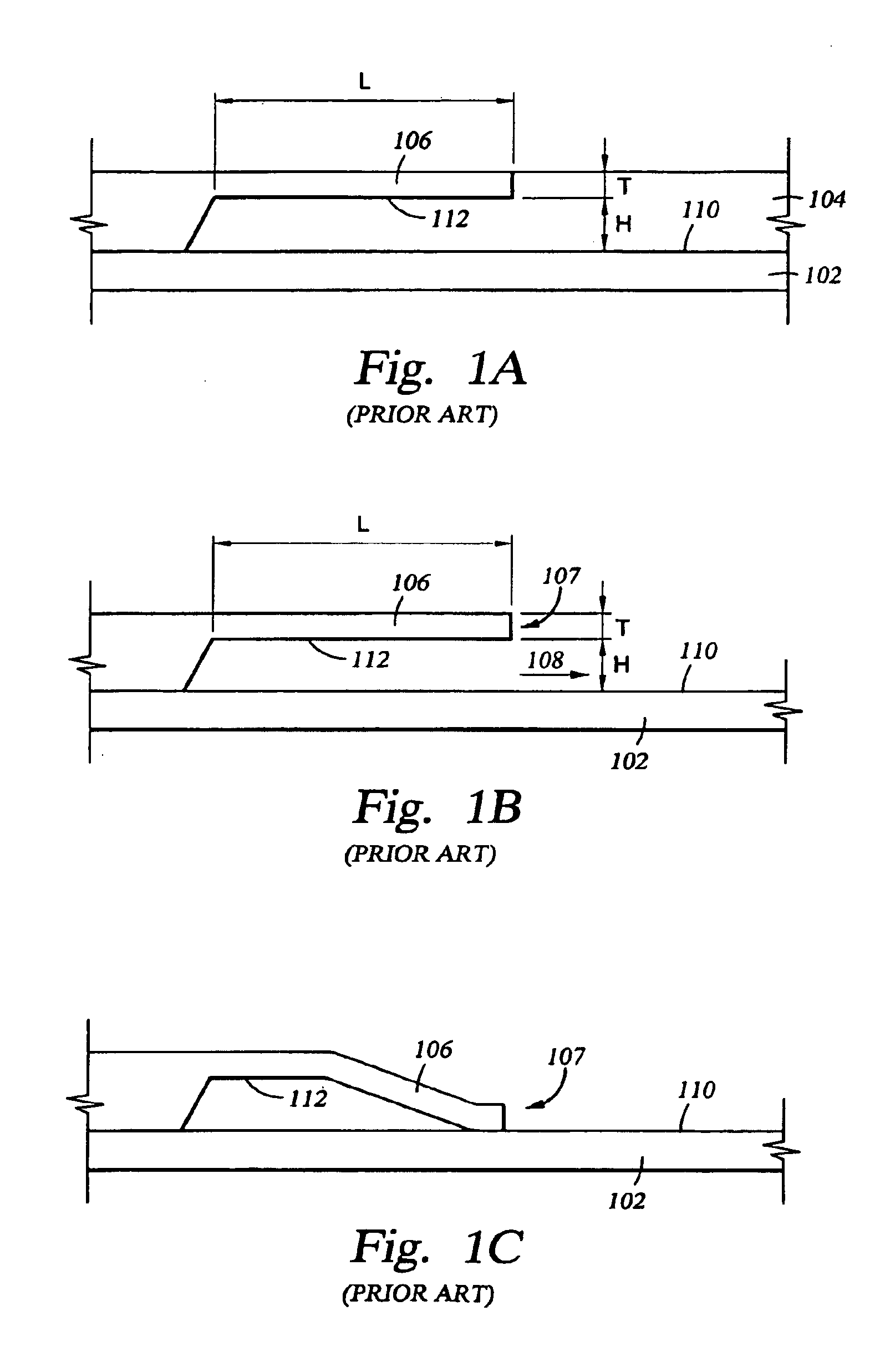

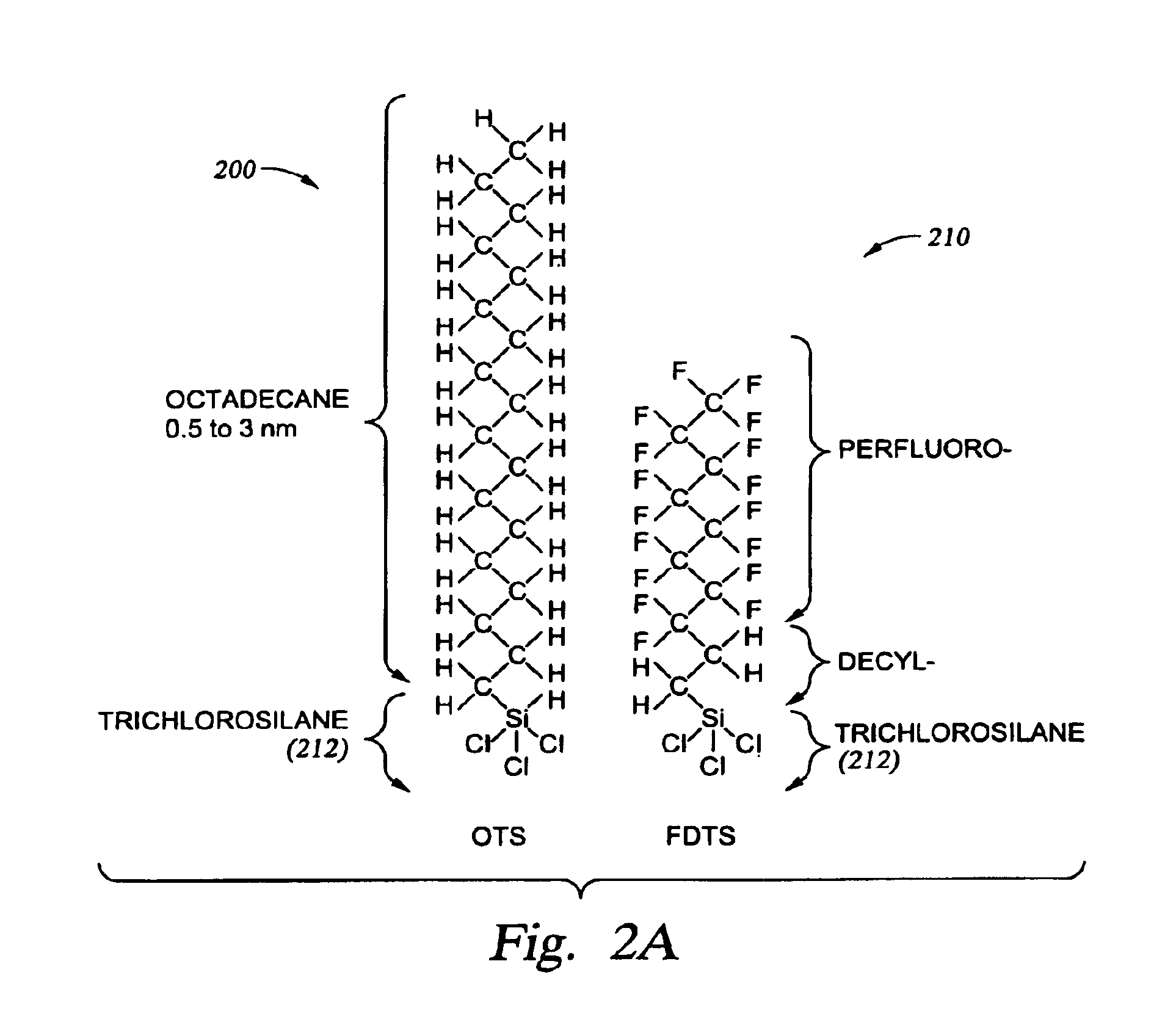

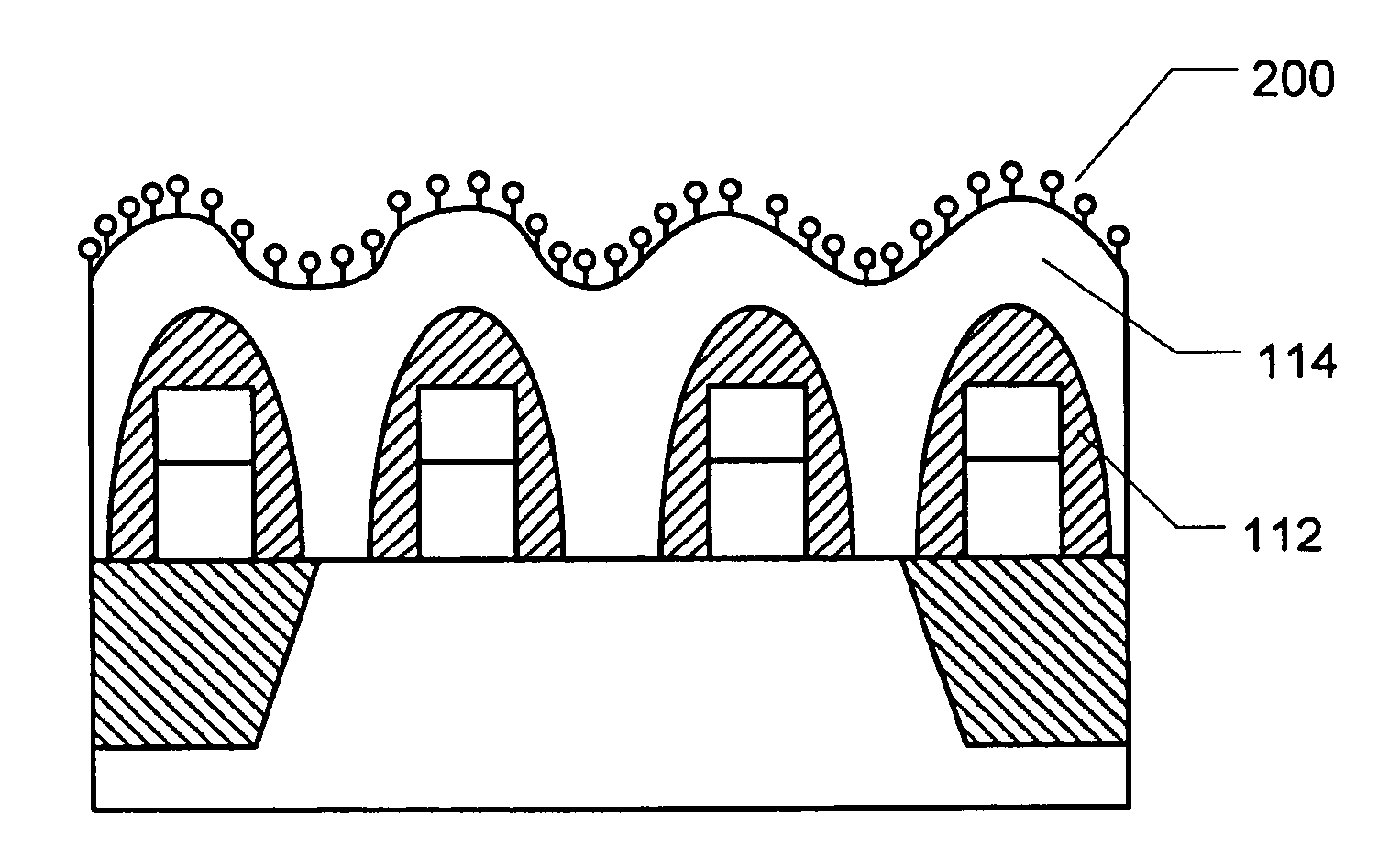

Integrated method for release and passivation of MEMS structures

InactiveUS6902947B2Preventing undesirable etchingHigh speedMaterial nanotechnologyDecorative surface effectsHydrogenSelf-assembled monolayer

Disclosed herein is a method of improving the adhesion of a hydrophobic self-assembled monolayer (SAM) coating to a surface of a MEMS structure, for the purpose of preventing stiction. The method comprises treating surfaces of the MEMS structure with a plasma generated from a source gas comprising oxygen and, optionally, hydrogen. The treatment oxidizes the surfaces, which are then reacted with hydrogen to form bonded OH groups on the surfaces. The hydrogen source may be present as part of the plasma source gas, so that the bonded OH groups are created during treatment of the surfaces with the plasma. Also disclosed herein is an integrated method for release and passivation of MEMS structures which may be adjusted to be carried out in a either a single chamber processing system or a multi-chamber processing system.

Owner:APPLIED MATERIALS INC

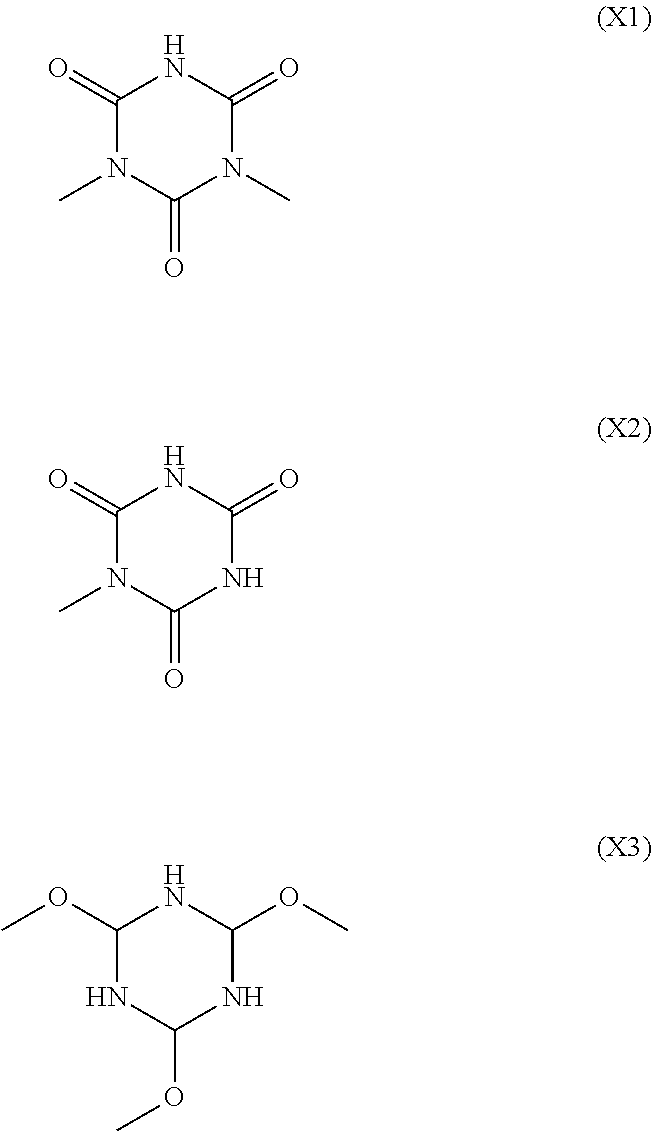

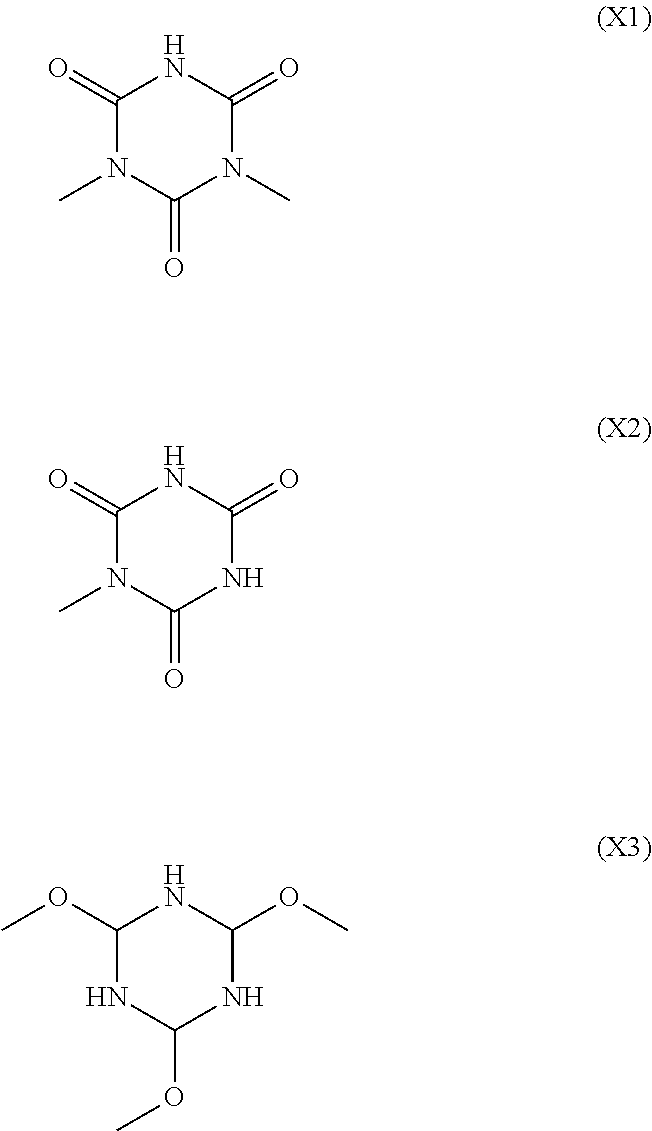

Slurry compositions and CMP methods using the same

InactiveUS20050130428A1Reduce and eliminate excessive removalOther chemical processesSemiconductor/solid-state device manufacturingArylSlurry

The exemplary embodiments of the present invention providing new slurry compositions suitable for use in processes involving the chemical mechanical polishing (CMP) of a polysilicon layer. The slurry compositions include one or more non-ionic polymeric surfactants that will selectively form a passivation layer on an exposed polysilicon surface in order to suppress the polysilicon removal rate relative to silicon oxide and silicon nitride and improve the planarity of the polished substrate. Exemplary surfactants include alkyl and aryl alcohols of ethylene oxide (EO) and propylene oxide (PO) block copolymers and may be present in the slurry compositions in an amount of up to about 5 wt %, although much smaller concentrations may be effective. Other slurry additives may include viscosity modifiers, pH modifiers, dispersion agents, chelating agents, and amine or imine surfactants suitable for modifying the relative removal rates of silicon nitride and silicon oxide.

Owner:SAMSUNG ELECTRONICS CO LTD

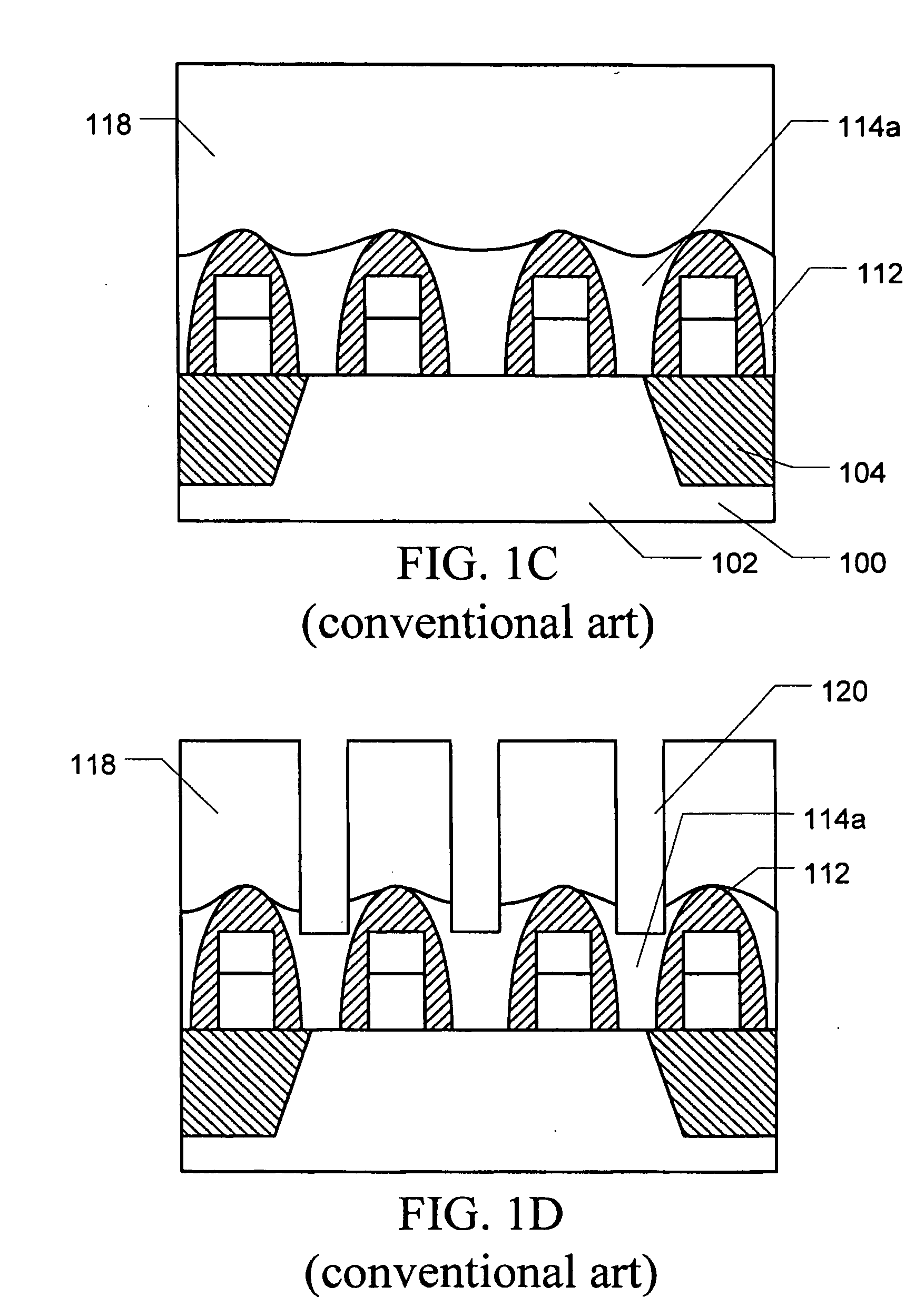

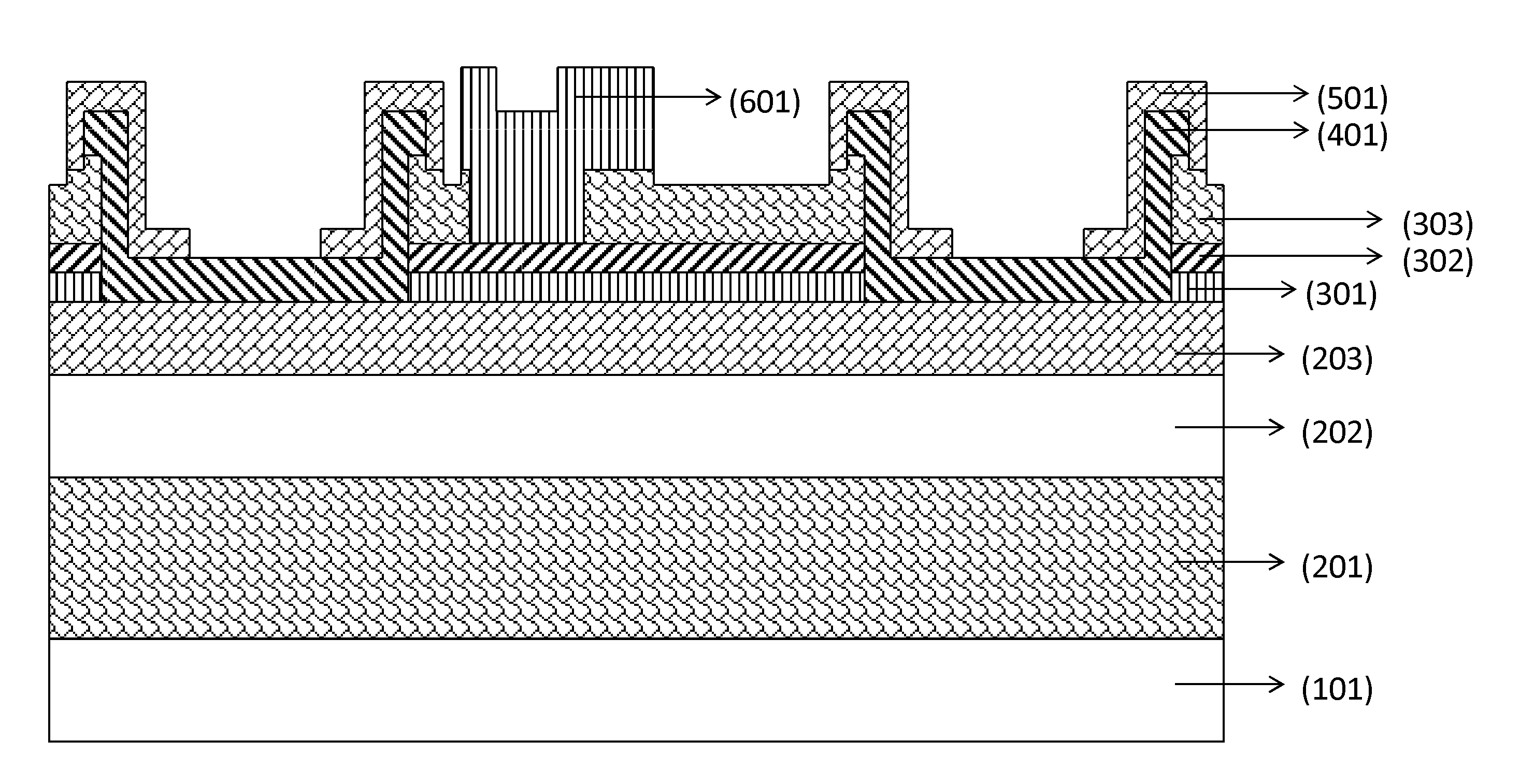

CMOS compatible method for manufacturing a HEMT device and the HEMT device thereof

ActiveUS20120319169A1Semiconductor/solid-state device detailsSolid-state devicesOhmic contactDielectric layer

A method for manufacturing a III-nitride HEMT having a gate electrode and source and drain ohmic contacts is provided, comprising providing a substrate; forming a stack of III-nitride layers on the substrate; forming a first passivation layer comprising silicon nitride overlying and in contact with an upper layer of the stack of III-nitride layers, wherein the first passivation layer is deposited in-situ with the stack of III-nitride layers; forming a dielectric layer overlying and in contact with the first passivation layer; forming a second passivation layer comprising silicon nitride overlying and in contact with the dielectric layer wherein the second passivation layer is deposited at a temperature higher than 450° C. by LPCVD or MOCVD or any equivalent technique; and thereafter forming the source and drain ohmic contacts and the gate electrode.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

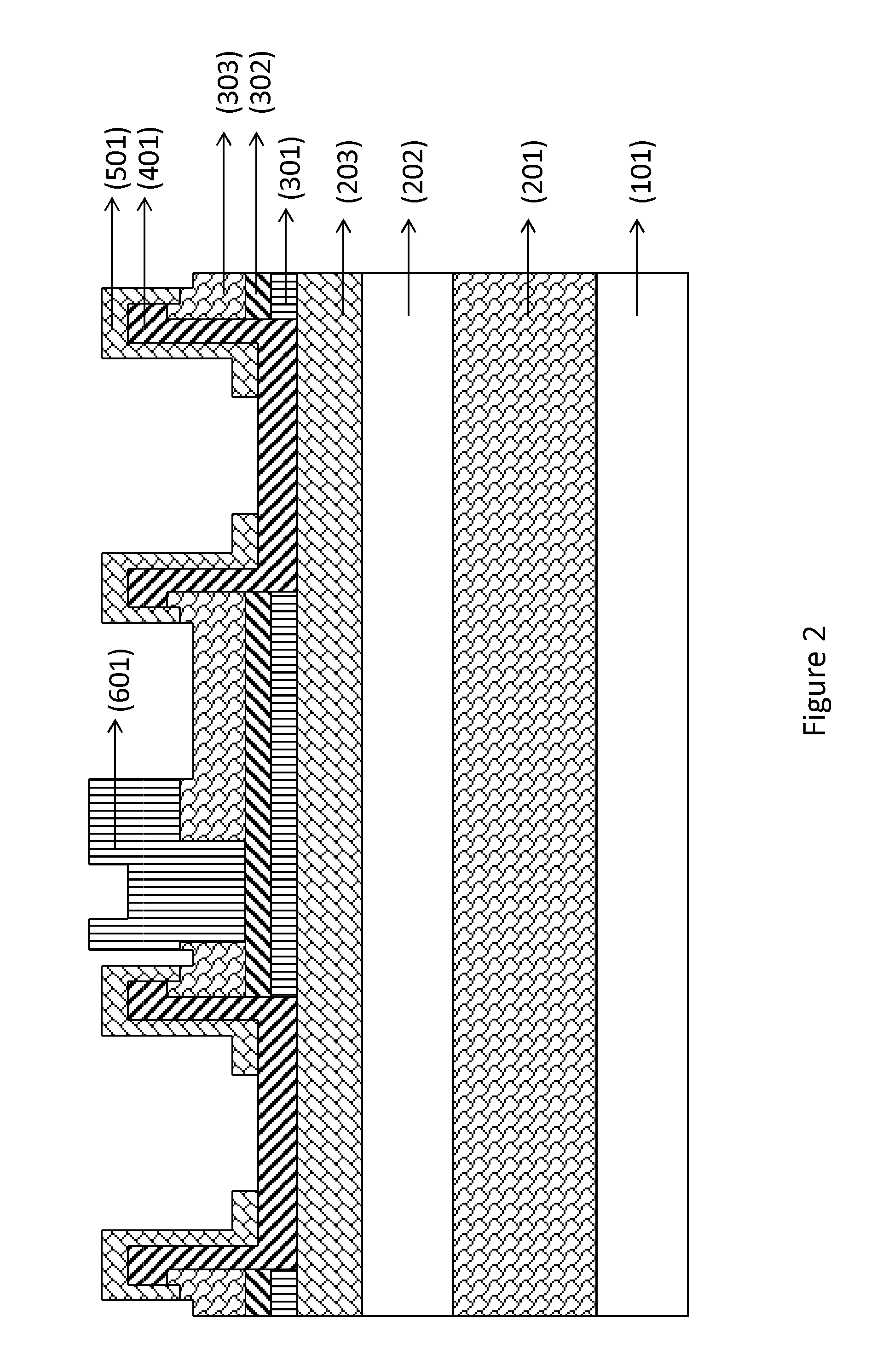

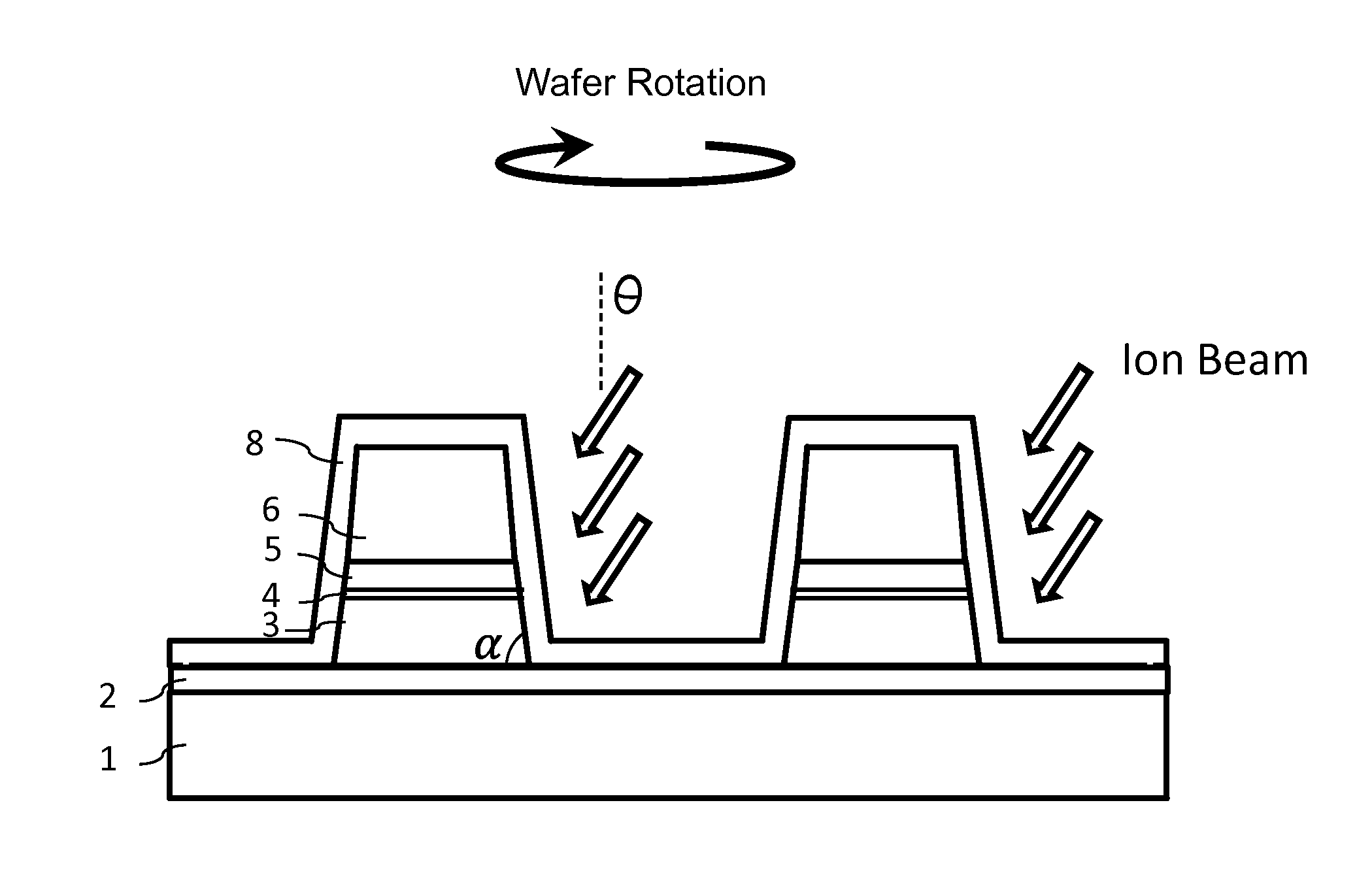

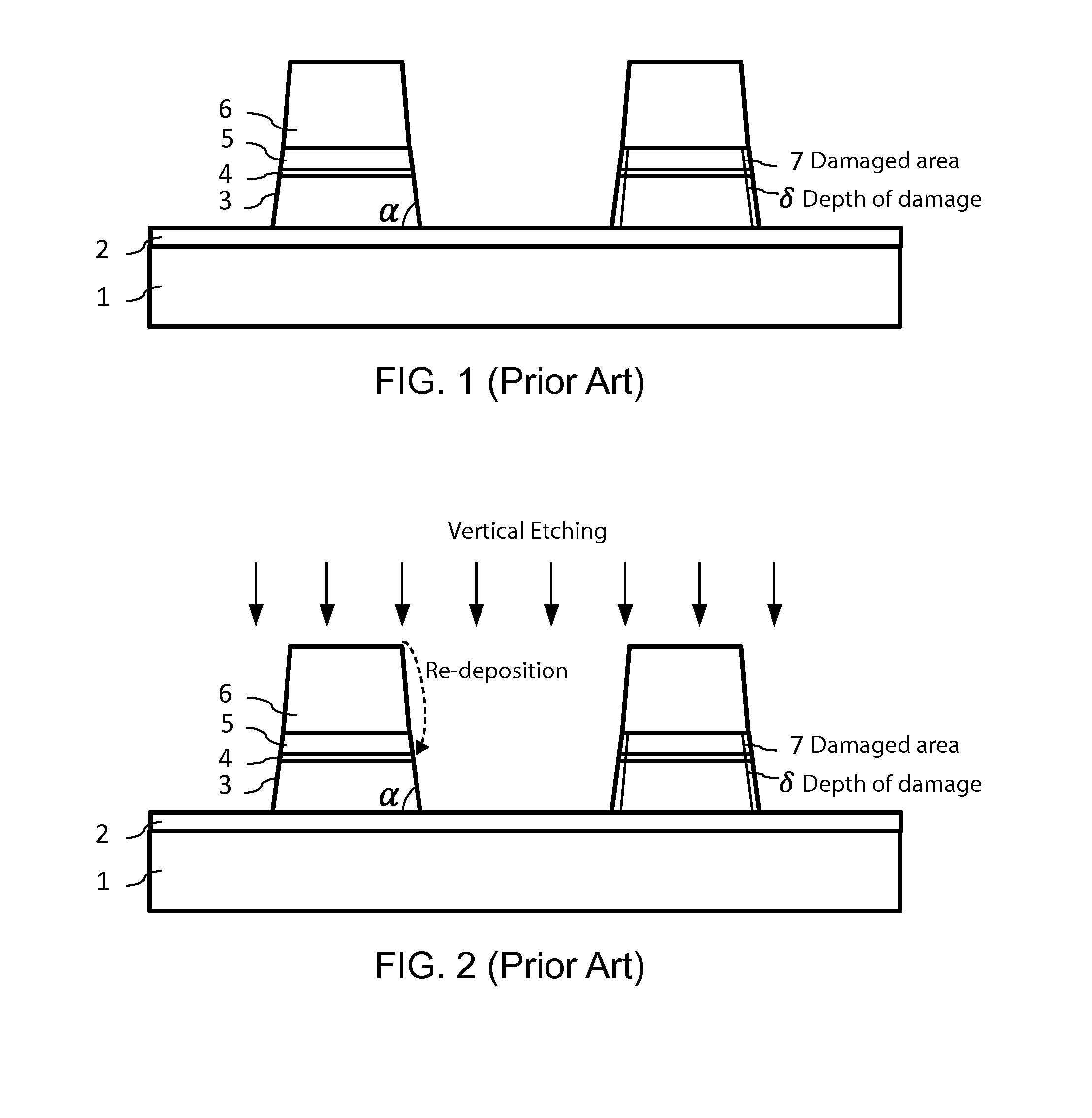

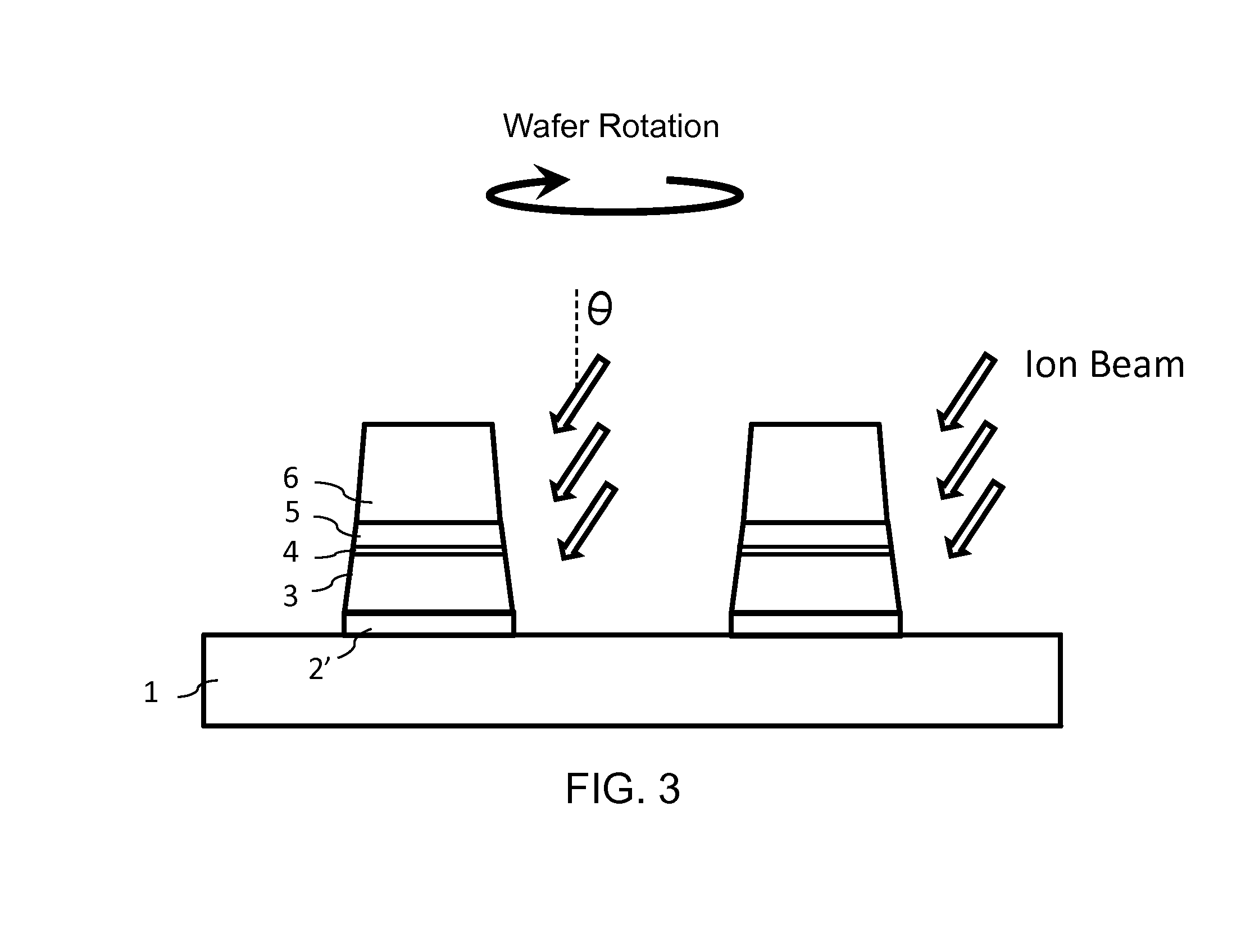

Mtj stack and bottom electrode patterning process with ion beam etching using a single mask

ActiveUS20140170776A1High selectivityAvoid damageSemiconductor/solid-state device manufacturingGalvano-magnetic device manufacture/treatmentEngineeringInductively coupled plasma

Fabrication methods using Ion Beam Etching (IBE) for MRAM cell memory elements are described. In embodiments of the invention the top electrode and MTJ main body are etched with one mask using reactive etching such as RIE or magnetized inductively coupled plasma (MICP) for improved selectivity, then the bottom electrode is etched using IBE as specified in various alternative embodiments which include selection of incident angles, wafer rotational rate profiles and optional passivation layer deposited prior to the IBE. The IBE according to the invention etches the bottom electrode without the need for an additional mask by using the layer stack created by the first etching phase as the mask. This makes the bottom electrode self-aligned to MTJ. The IBE also achieves MTJ sidewall cleaning without the need for an additional step.

Owner:AVALANCHE TECH

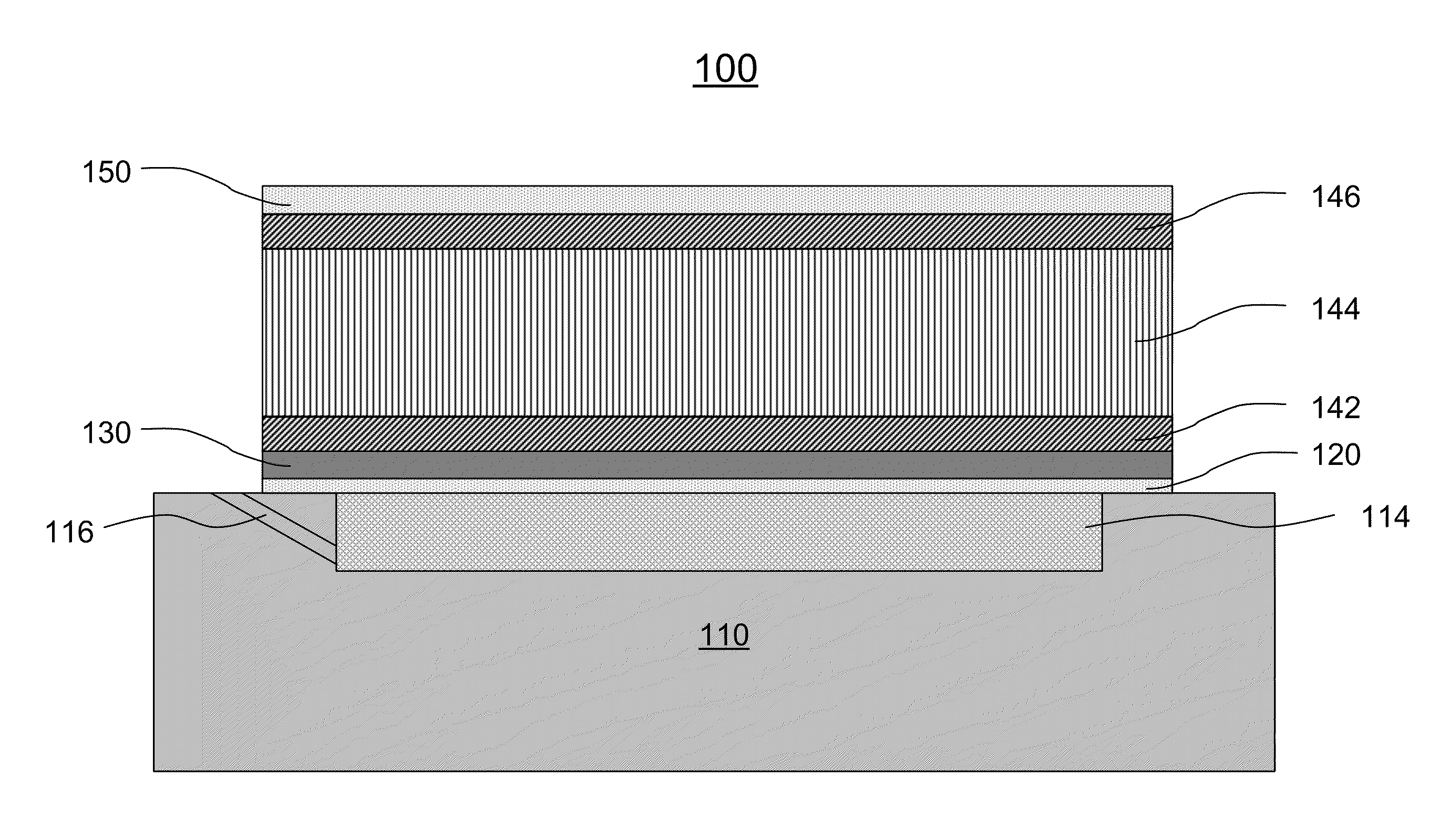

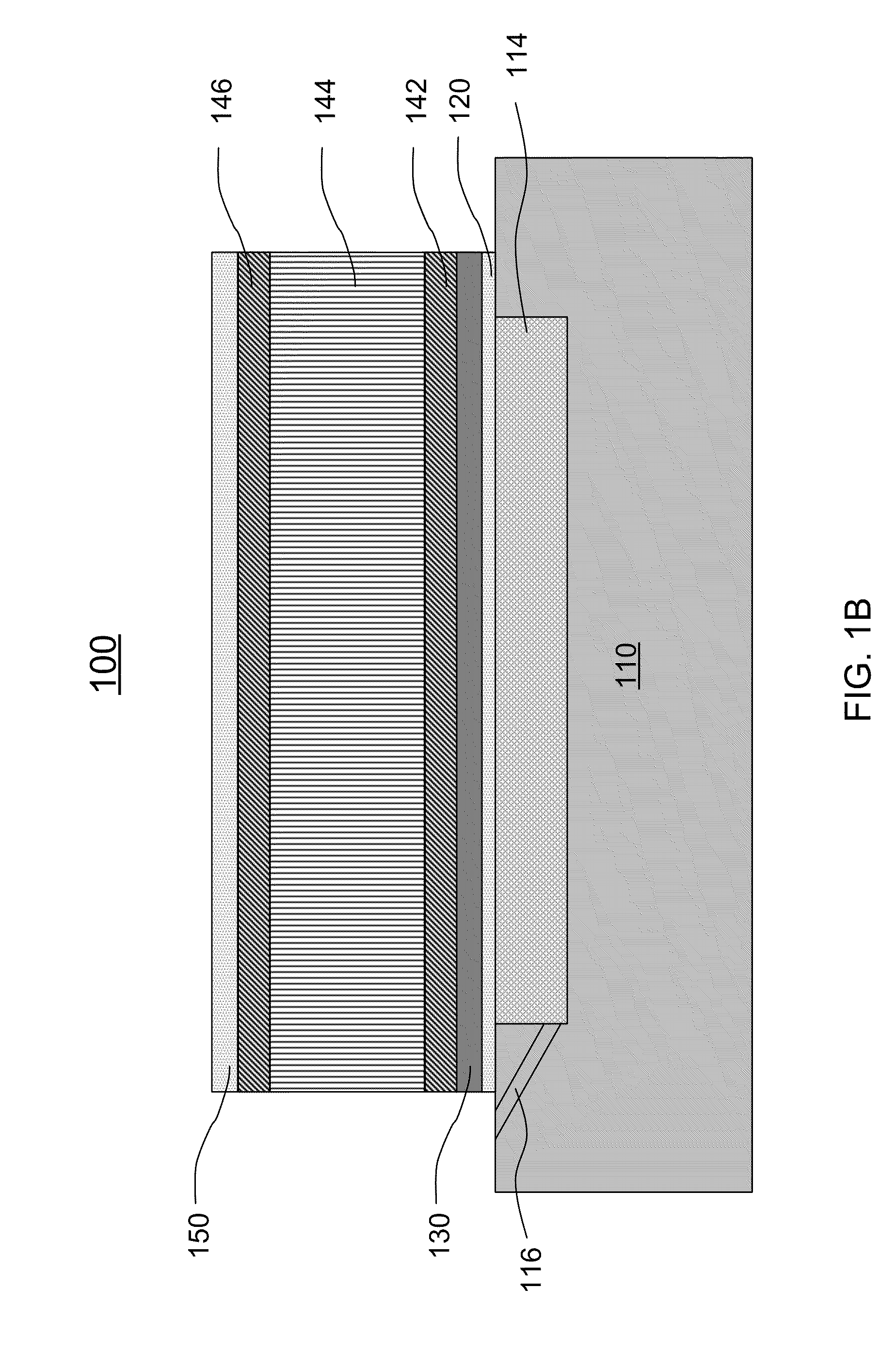

Acoustic Wave Resonators and Methods of Manufacturing Same

InactiveUS20110304412A1Eliminates and alleviates susceptibilityRelax packaging hermeticityPiezoelectric/electrostrictive device manufacture/assemblyImpedence networksAcoustic waveResonator

In one aspect of the invention, the acoustic wave resonator includes a substrate defined an air cavity, a first passivation layer formed on the substrate and over the air cavity, a seed layer formed on the passivation layer, a bottom electrode formed on the seed layer, a piezoelectric layer formed on the bottom electrode, a top electrode formed on the piezoelectric layer, and a second passivation layer formed on the top electrode.

Owner:AVAGO TECH INT SALES PTE LTD

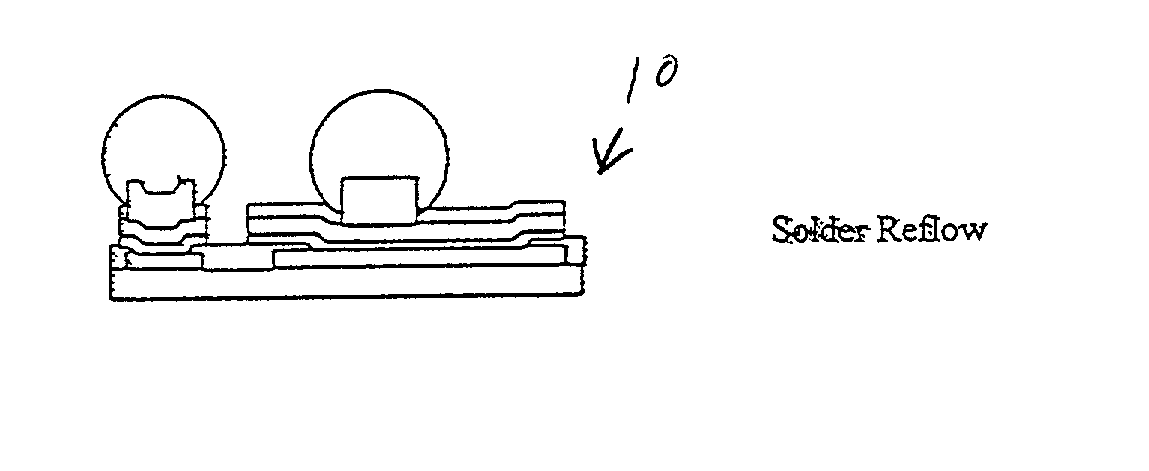

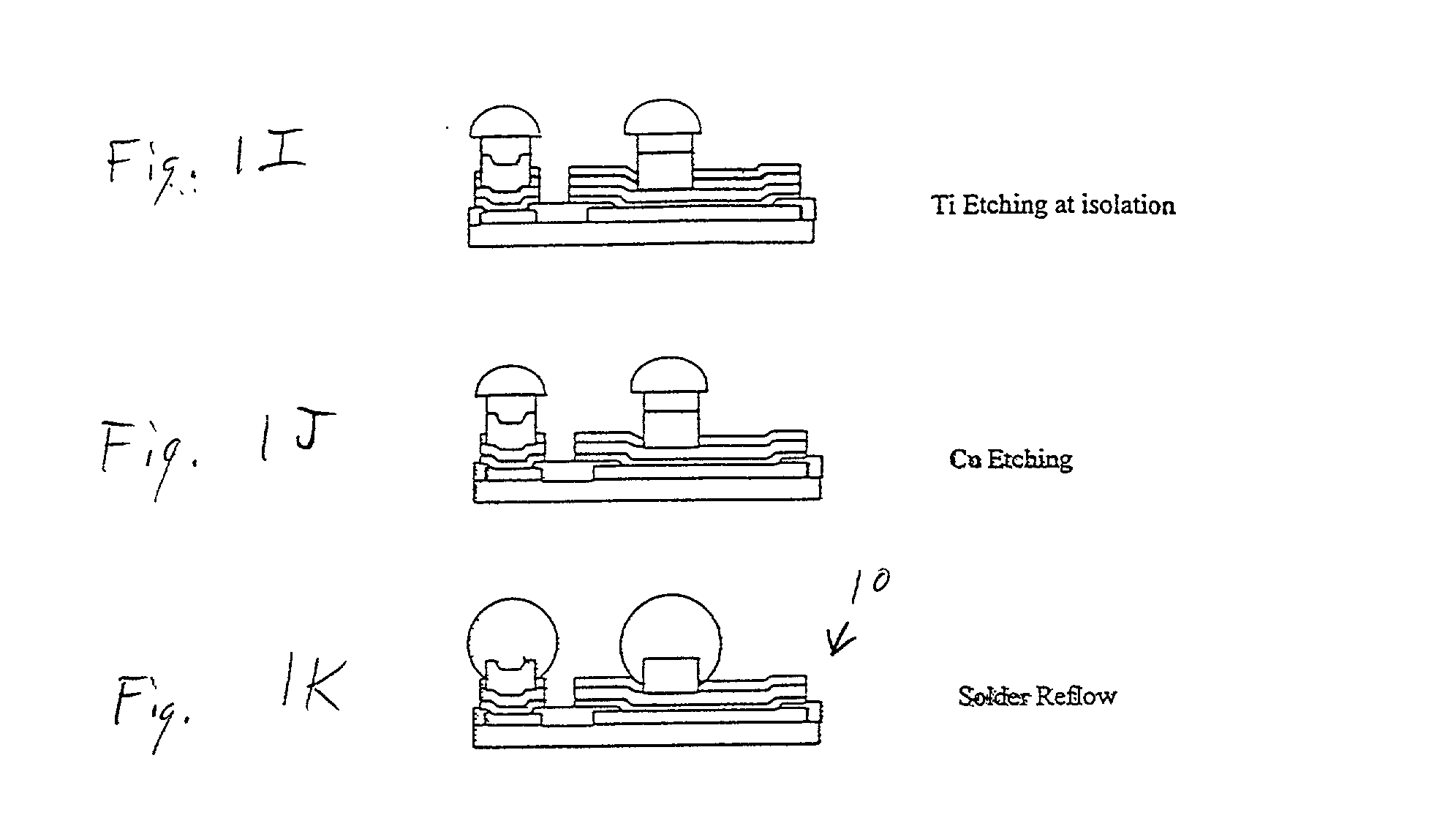

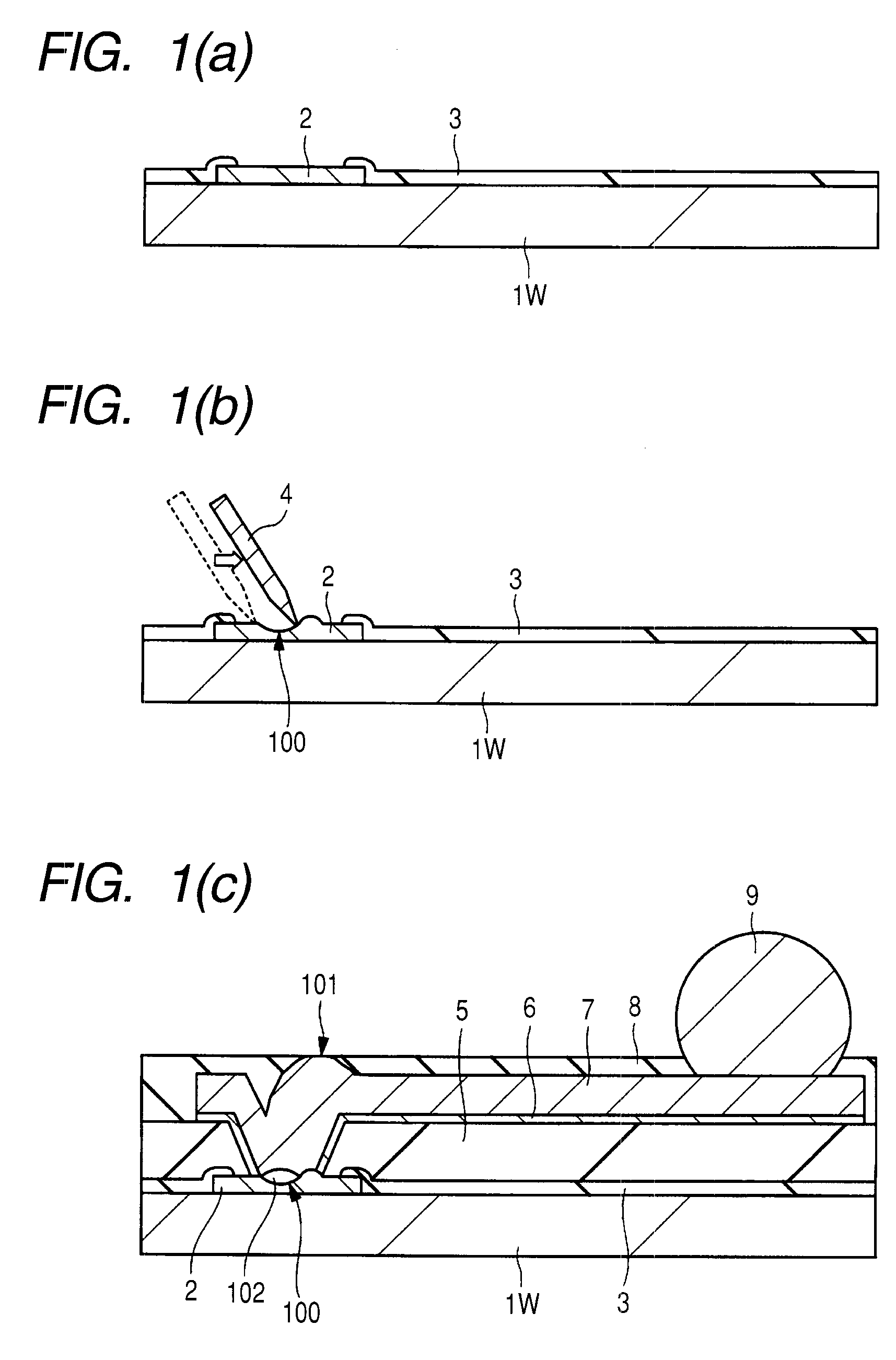

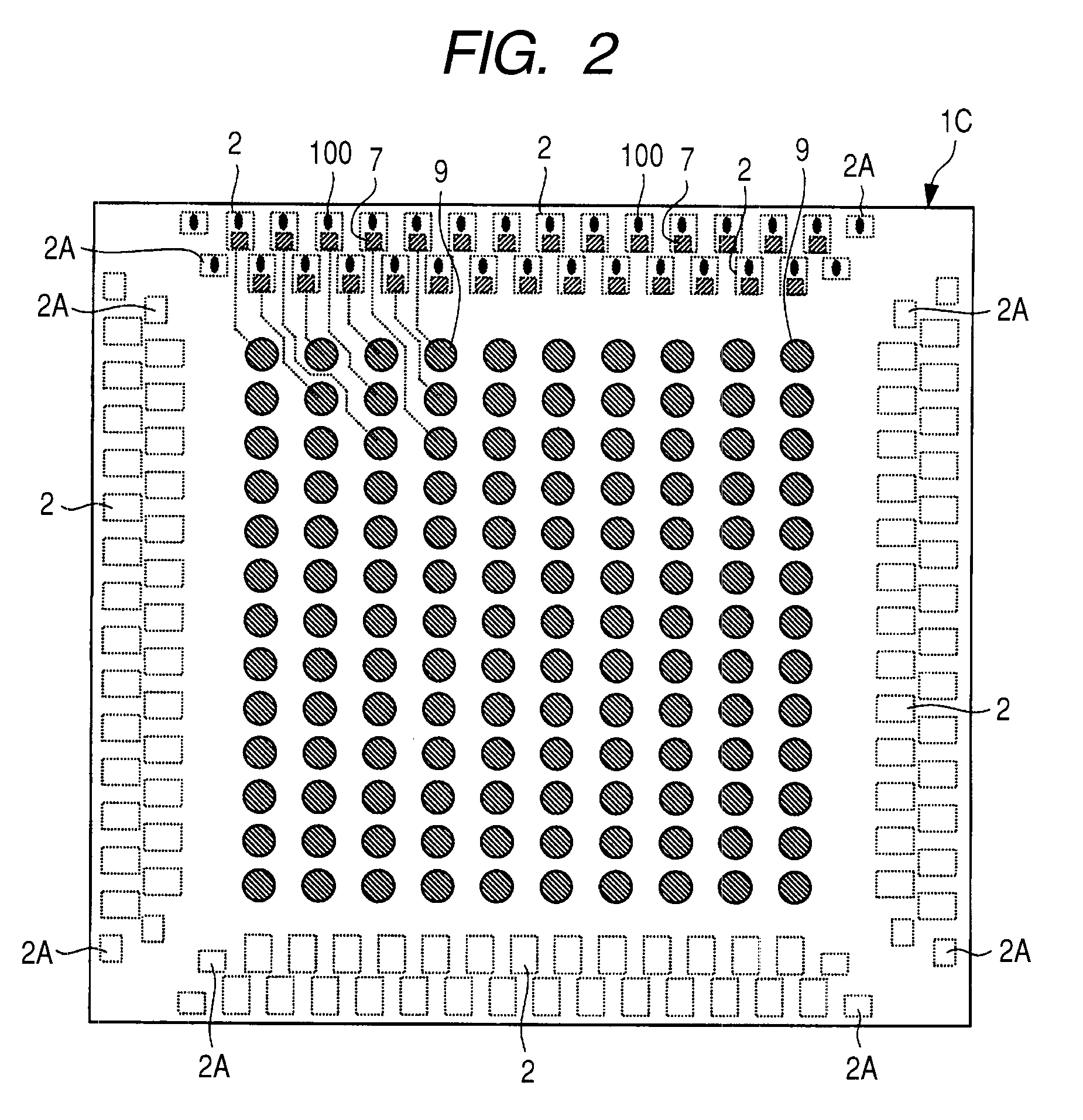

Passivation scheme for bumped wafers

InactiveUS20020066959A1Semiconductor/solid-state device detailsSolid-state devicesWaferingEngineering physics

Owner:SEMICON COMPONENTS IND LLC

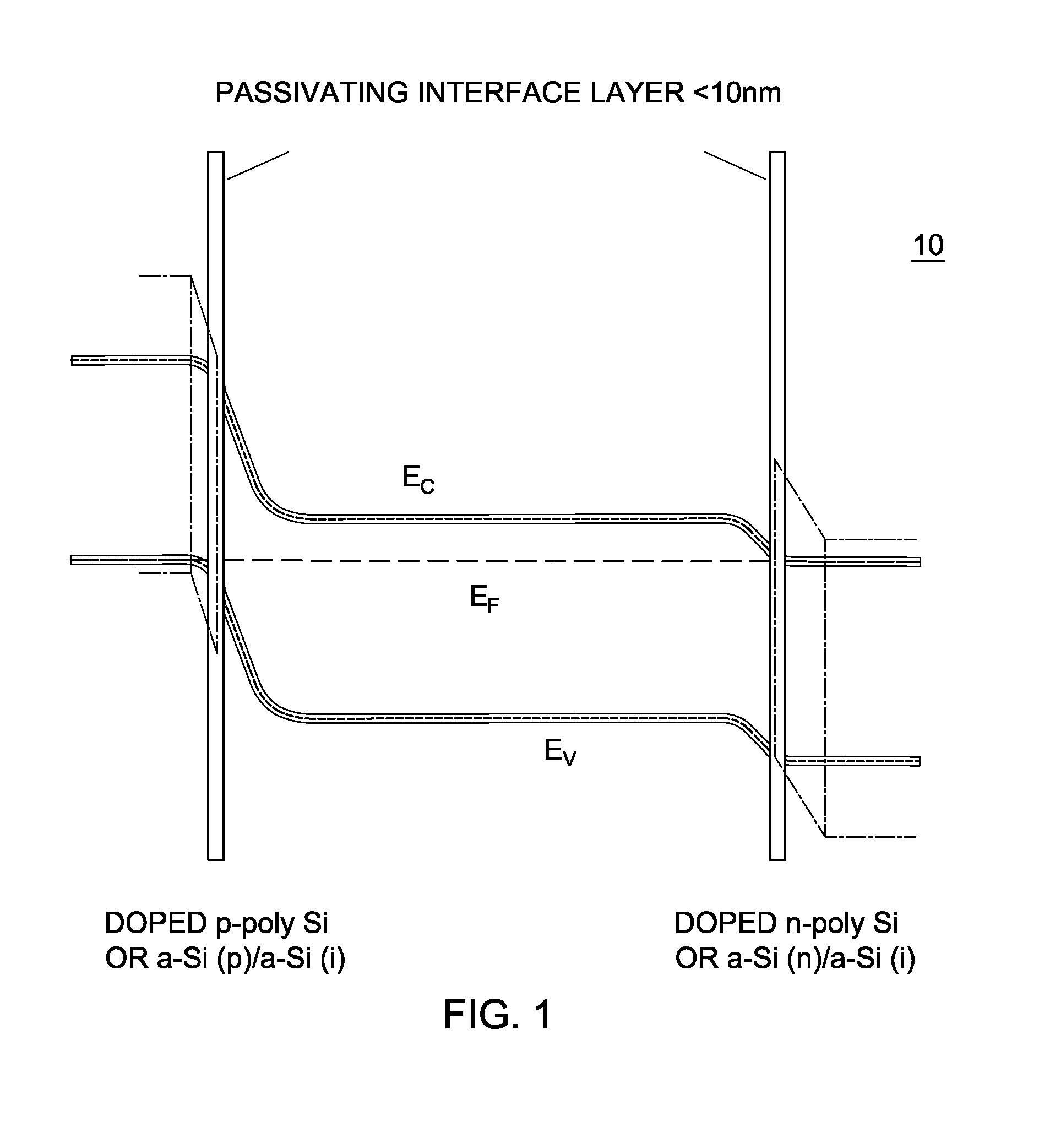

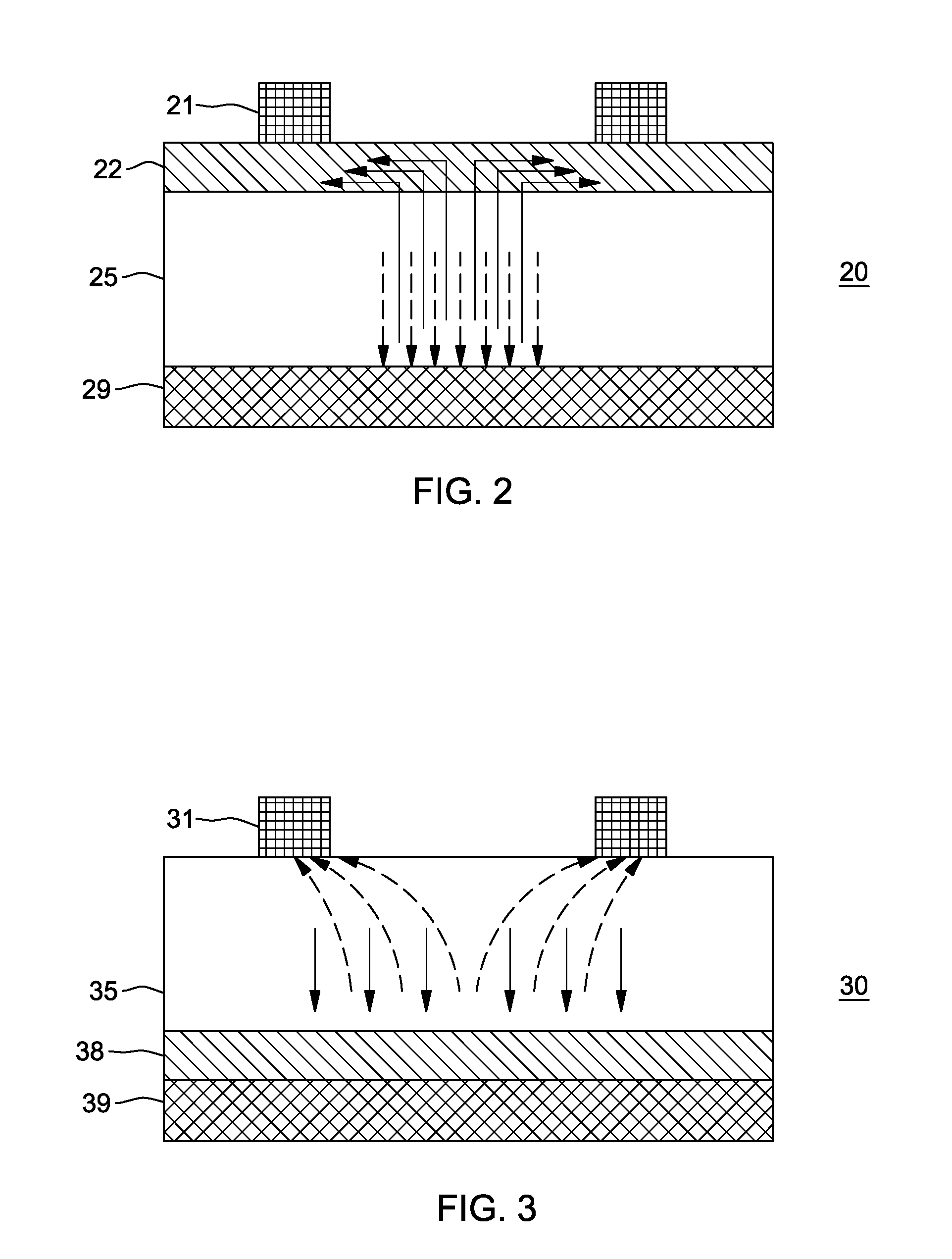

High-efficiency solar cell structures and methods of manufacture

ActiveUS20120055547A1High light transmittanceHigh transparencyFinal product manufactureSemiconductor/solid-state device manufacturingDeposition processSolar cell

Solar cells of varying composition are disclosed, generally including a central substrate, conductive layer(s), antireflection layers(s), passivation layer(s) and / or electrode(s). Multifunctional layers provide combined functions of passivation, transparency, sufficient conductivity for vertical carrier flow, the junction, and / or varying degrees of anti-reflectivity. Improved manufacturing methods including single-side CVD deposition processes and thermal treatment for layer formation and / or conversion are also disclosed.

Owner:TETRASUN

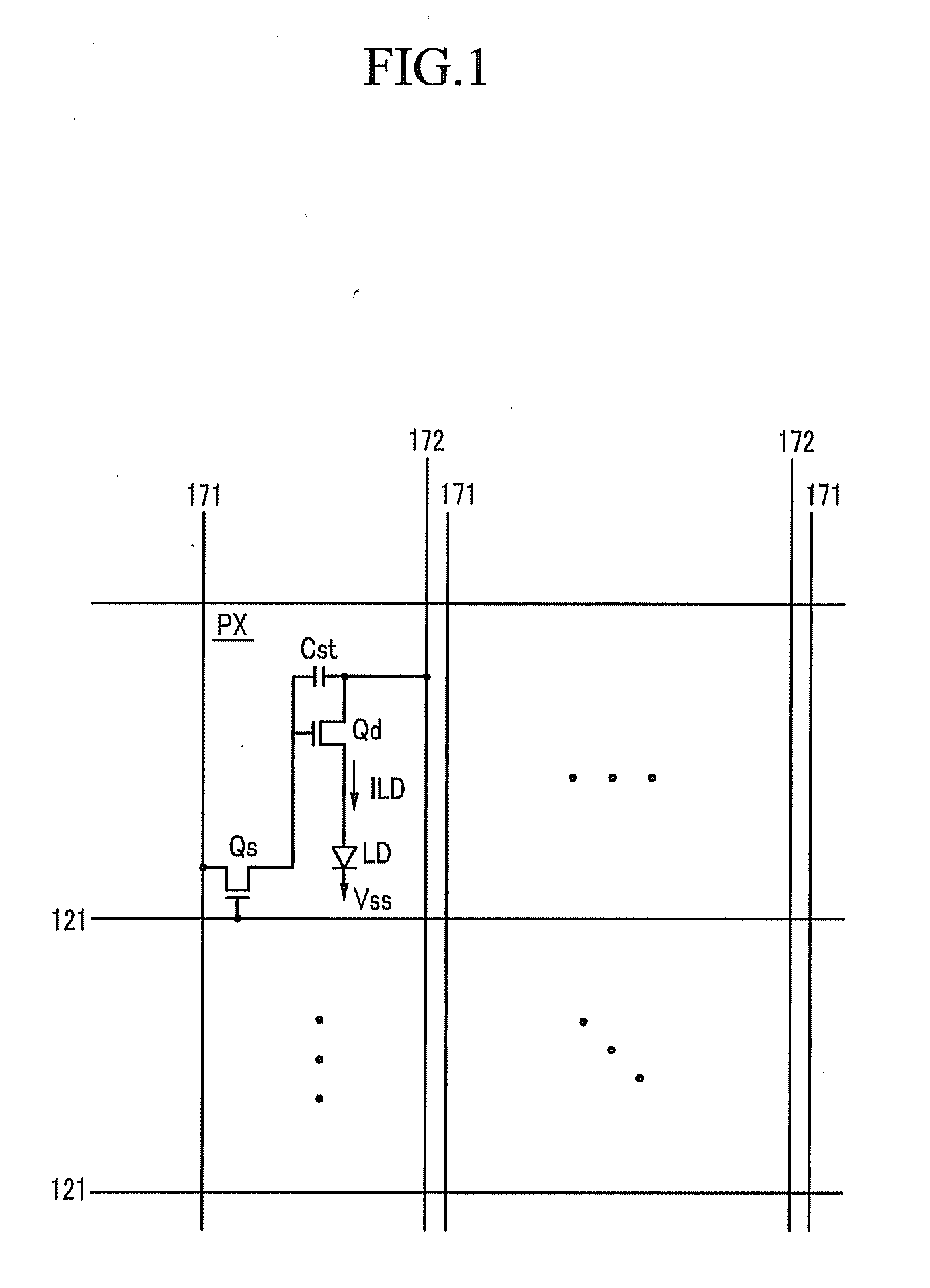

Alkali-developable curable composition, insulating thin film using the same, and thin film transistor

ActiveUS20110001190A1Excellent heat resistance and transparencyImprove insulation performanceSilicon organic compoundsPhotosensitive materialsGate insulatorAqueous solution

An object of the present invention is to provide a polysiloxane compound that can be developed in an aqueous alkali solution and can yield a cured product or thin film having superior heat-resistant transparency and insulating properties, a curable composition thereof, and a thin film transistor provided with a passivation layer or gate insulator using the same, and the present invention relates to a polysiloxane compound having at least one photopolymerizable functional group in a molecule thereof, and having at least one member selected from the group consisting of an isocyanuric acid backbone structure, a phenolic hydroxyl group and a carboxyl group within the same molecule, to a curable composition containing the polysiloxane compound, and to a cured product thereof.

Owner:KANEKA CORP

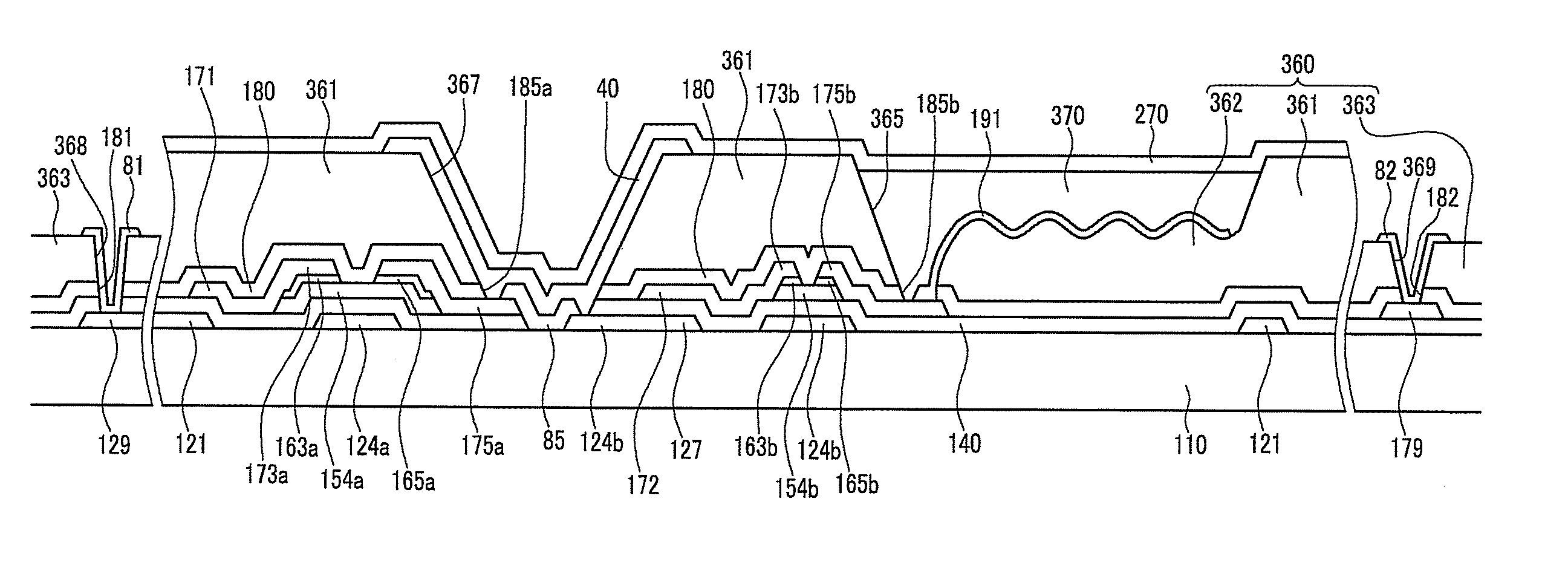

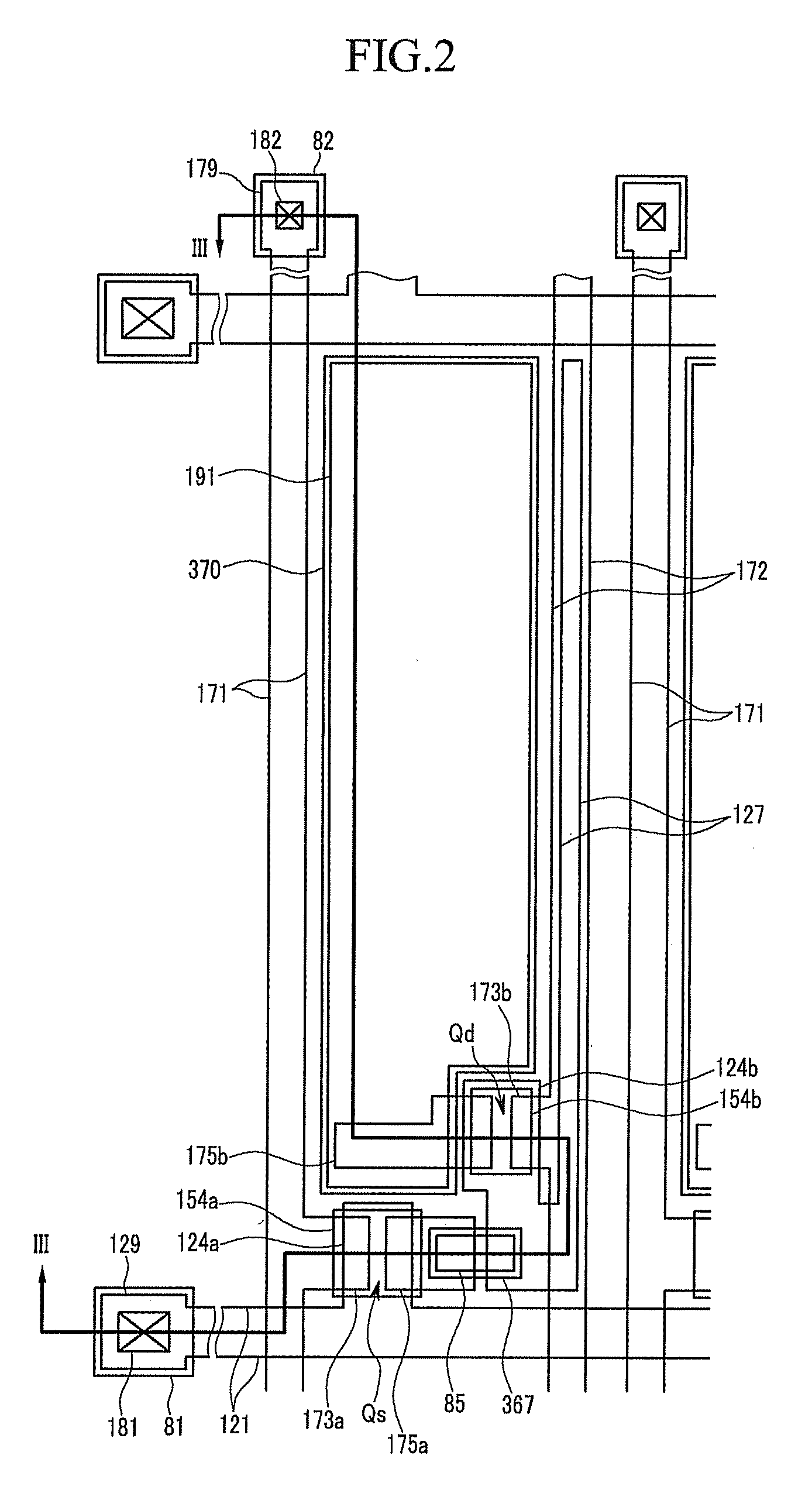

Organic light emitting diode display and method of manufacturing the same

InactiveUS20070096636A1Reduce in quantitySimple manufacturing processDischarge tube luminescnet screensElectroluminescent light sourcesDisplay deviceLight-emitting diode

A method of manufacturing an organic light emitting diode display includes forming a plurality of signal lines and a plurality of TFTs on a substrate, forming a passivation layer on the signal lines and the TFTs, forming a photosensitive layer having a plurality of openings on the passivation layer, etching the passivation layer using the photosensitive layer as a mask, forming a first electrode by depositing and etching a conductive layer on substantially the entire surface including the photosensitive layer, forming a light emitting member in portions of the openings, and forming a second electrode on the light emitting member and the photosensitive layer.

Owner:SAMSUNG DISPLAY CO LTD

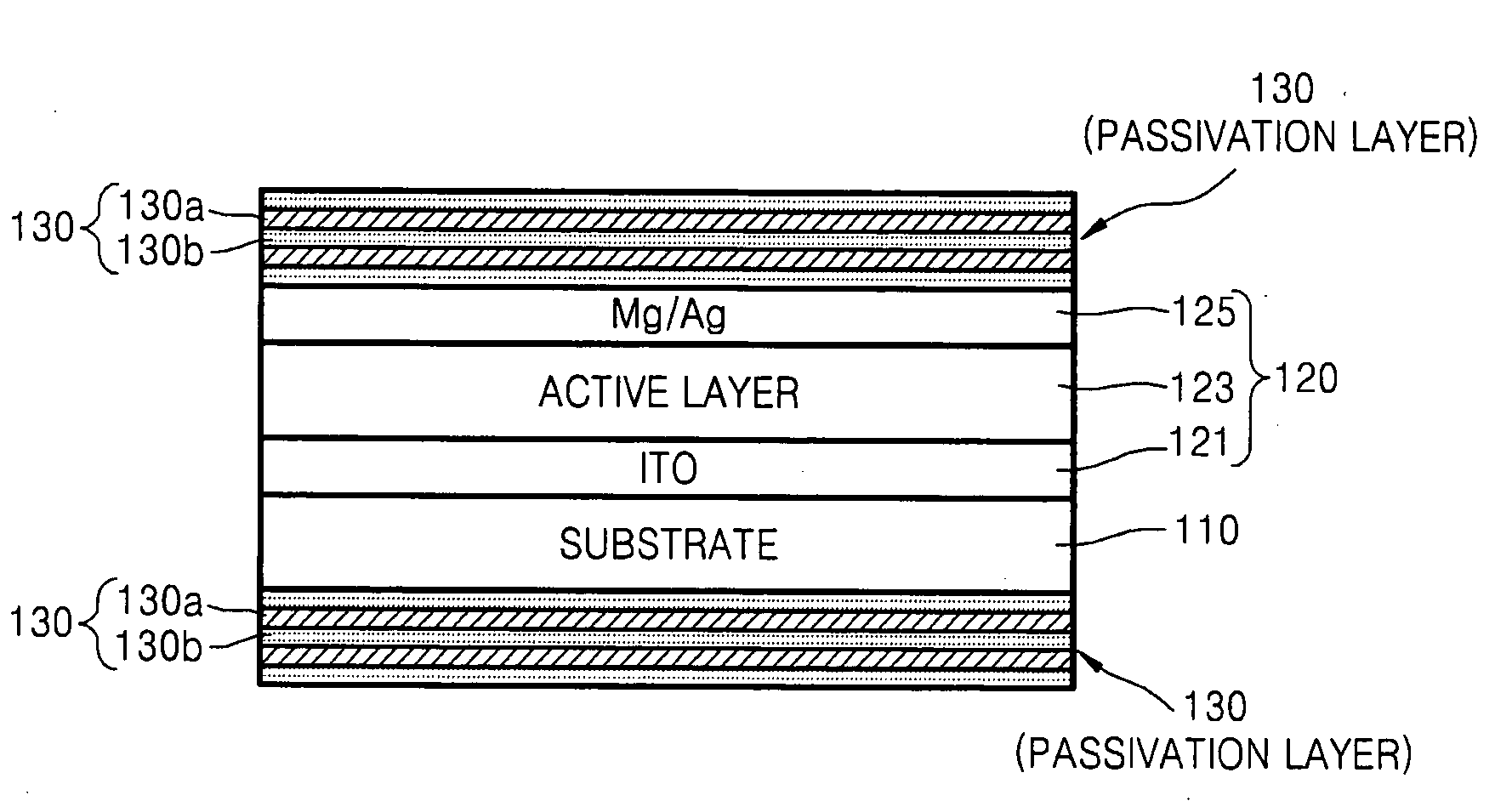

Organic light emitting device and organic electronic device

InactiveUS20070273280A1Prevent degradation in performanceAvoid performance degradationDischarge tube luminescnet screensElectroluminescent light sourcesOxidePolymer

An organic light emitting device has a structure in which the penetration of harmful materials into an inner functional layer is blocked to prevent the degradation of the performance of the organic light emitting device and an organic electronic device includes such an organic light emitting device. The organic light emitting device includes an insulating substrate; a light emitting unit arranged on the insulating substrate and including a first electrode layer to inject holes, a second electrode layer to inject electrons, and an active layer interposed between the first and second electrode layers to emit light by recombining the holes and electrons; and a passivation layer including alternately arranged barrier layers and buffer layers to seal the light emitting unit from an external atmosphere, each barrier layer including at least one material selected from a group consisting of an activated metal oxide, an activated metal nitride, or an activated metal oxynitride, and each buffer layer being of a polymer organic material.

Owner:SAMSUNG SDI CO LTD

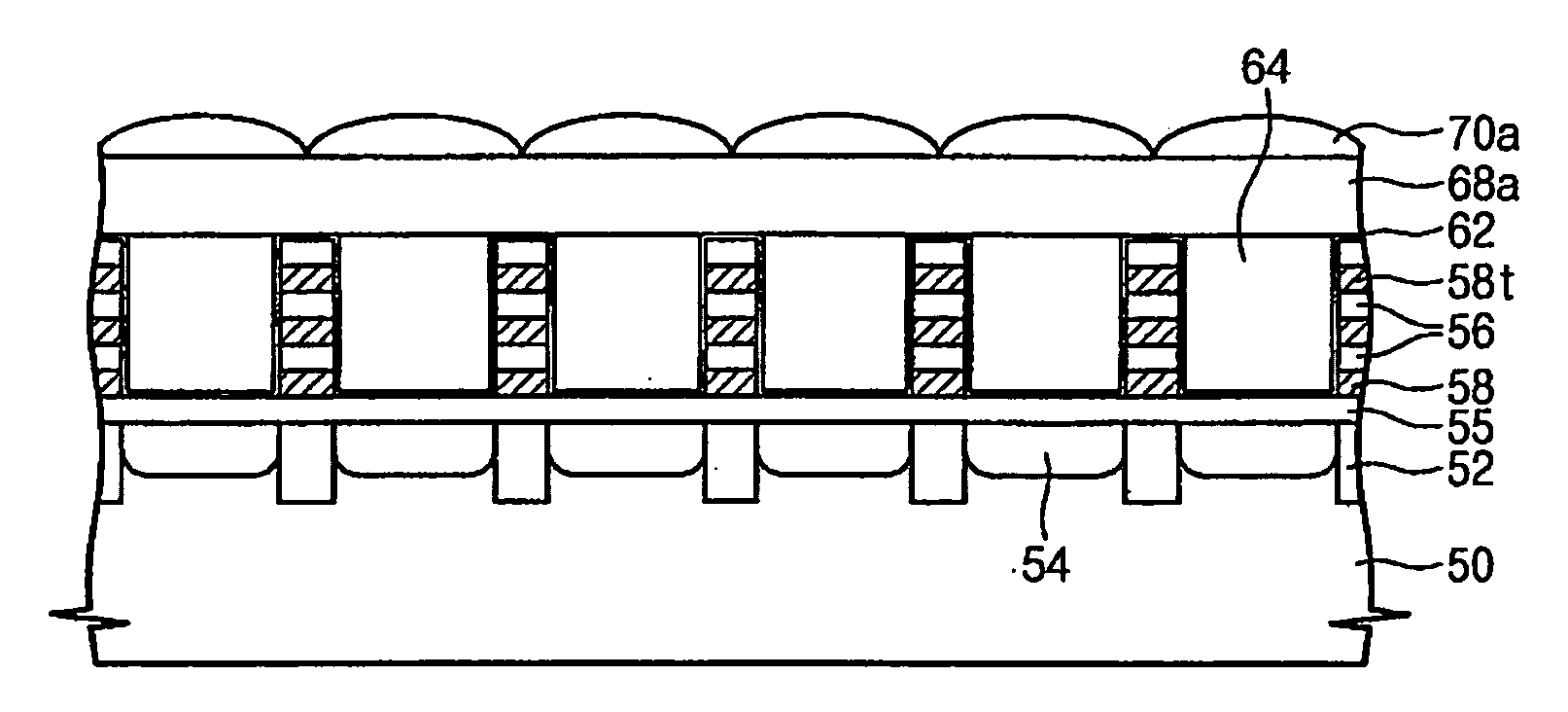

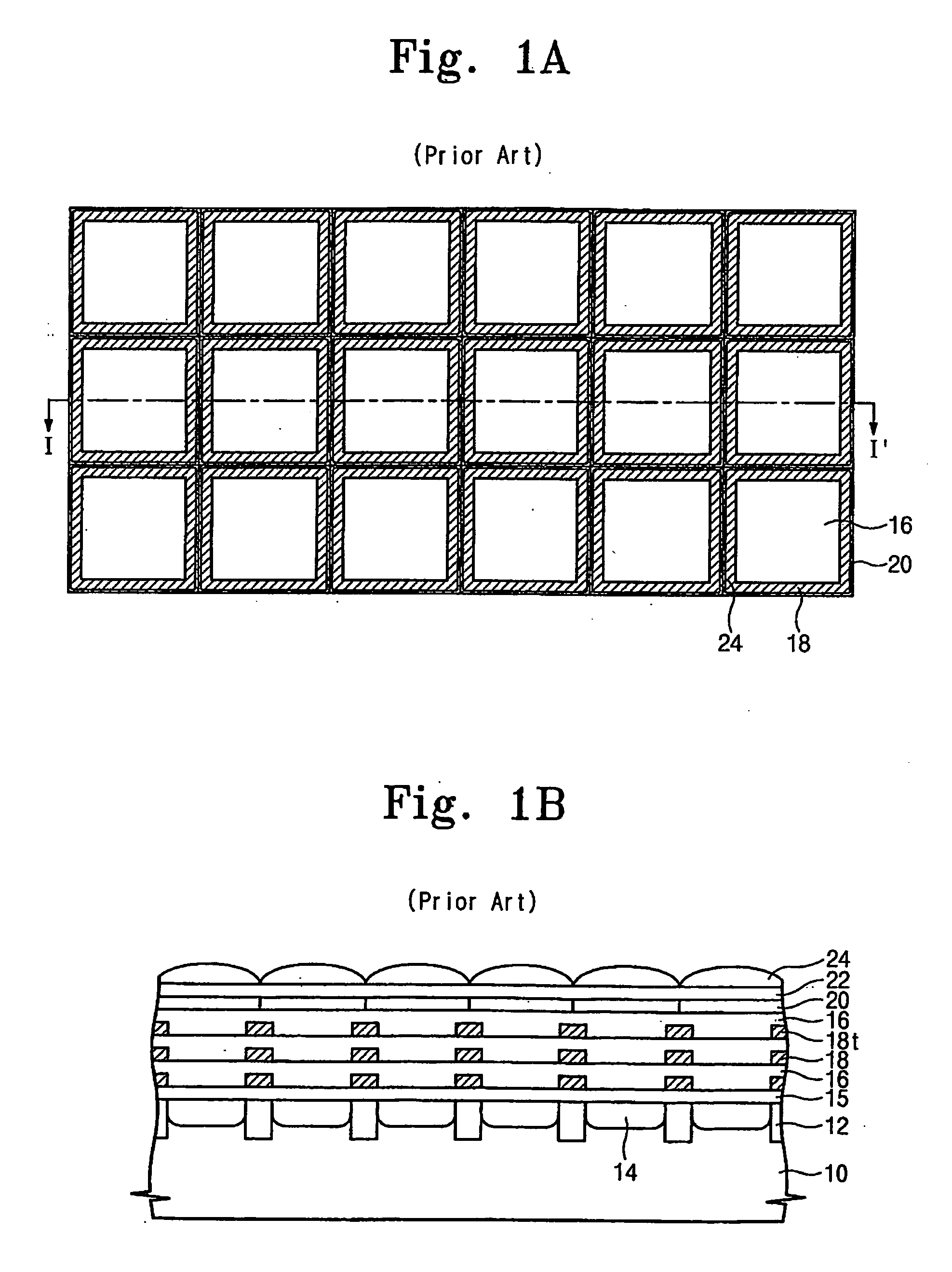

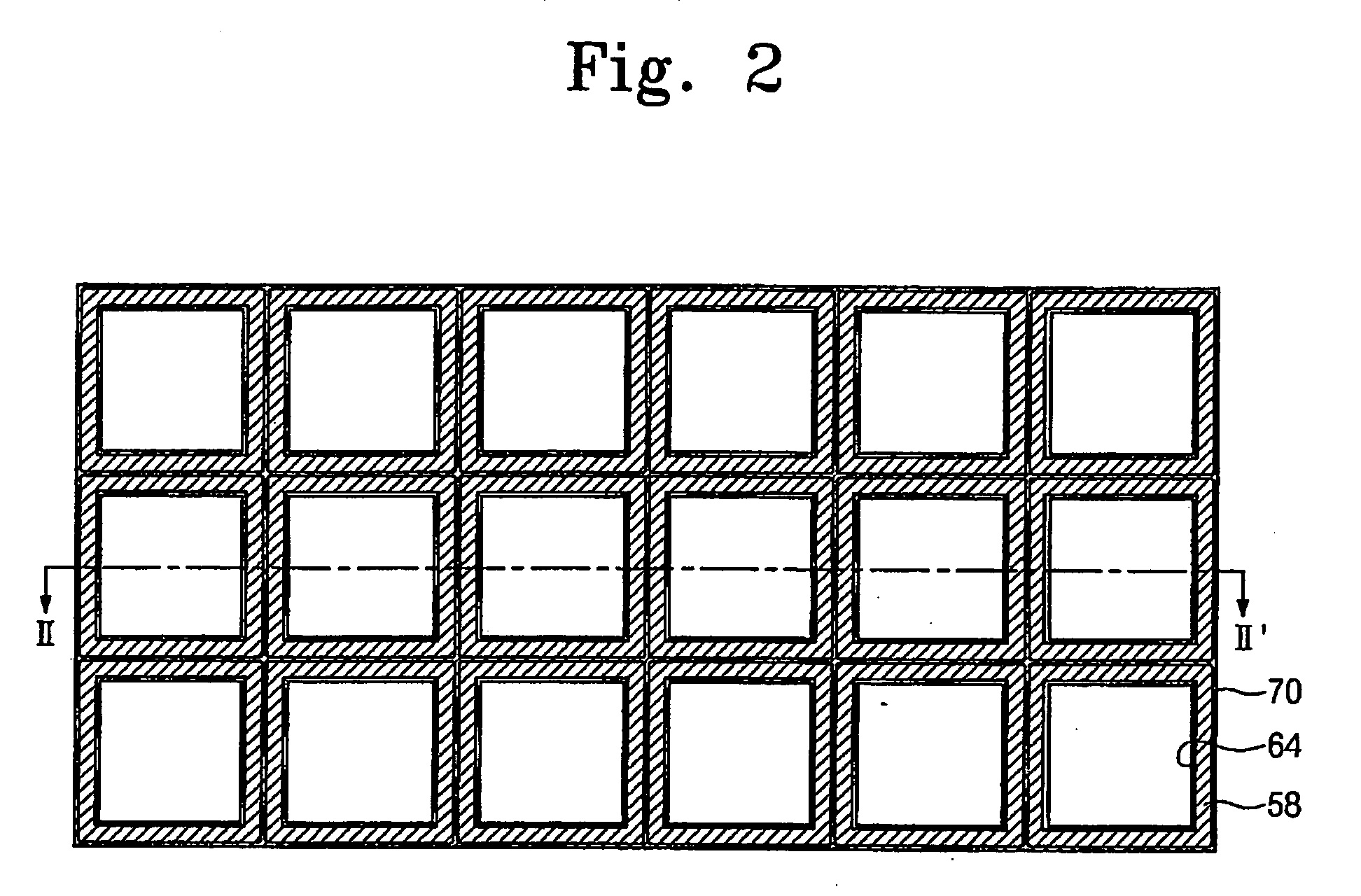

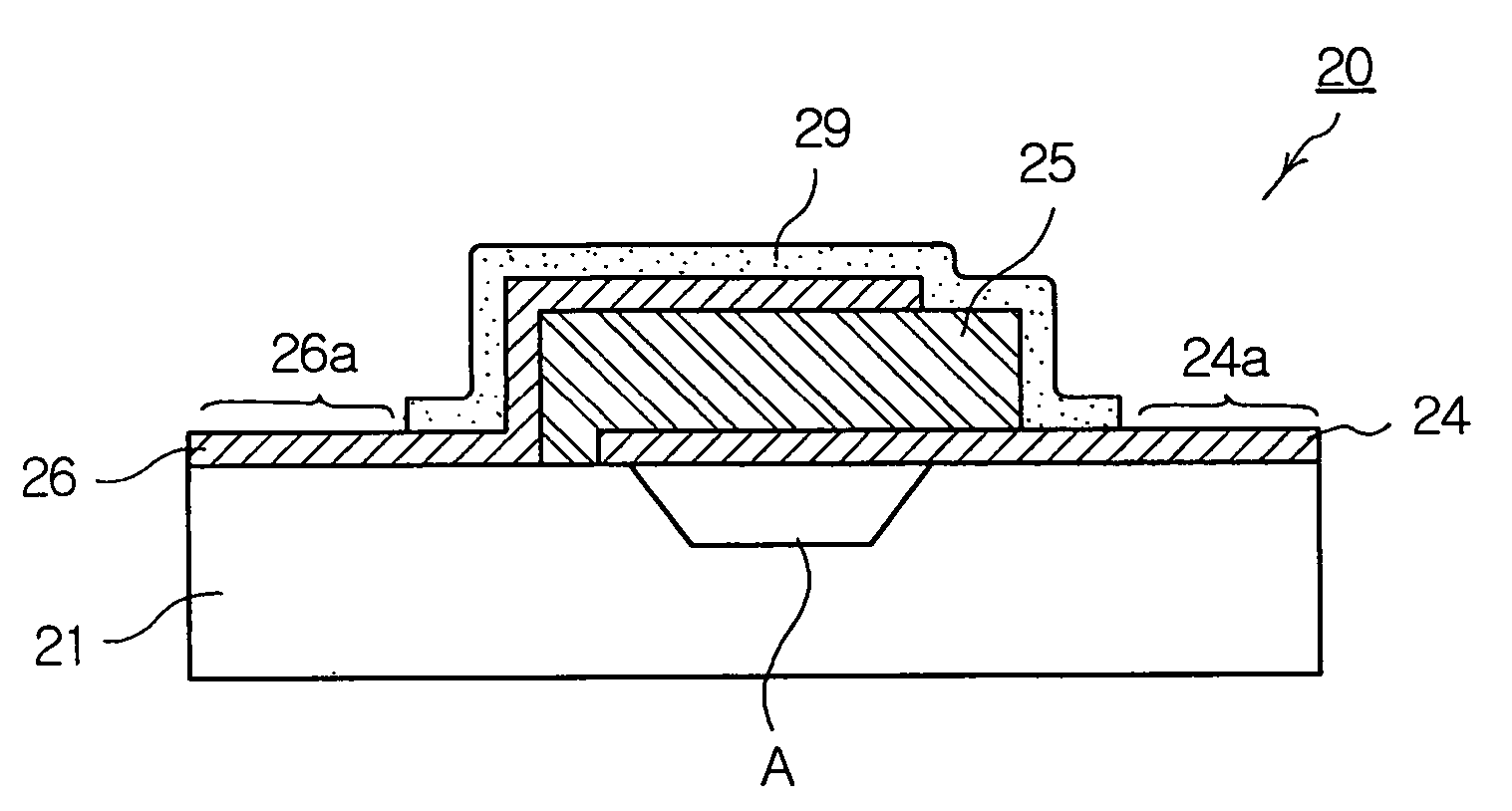

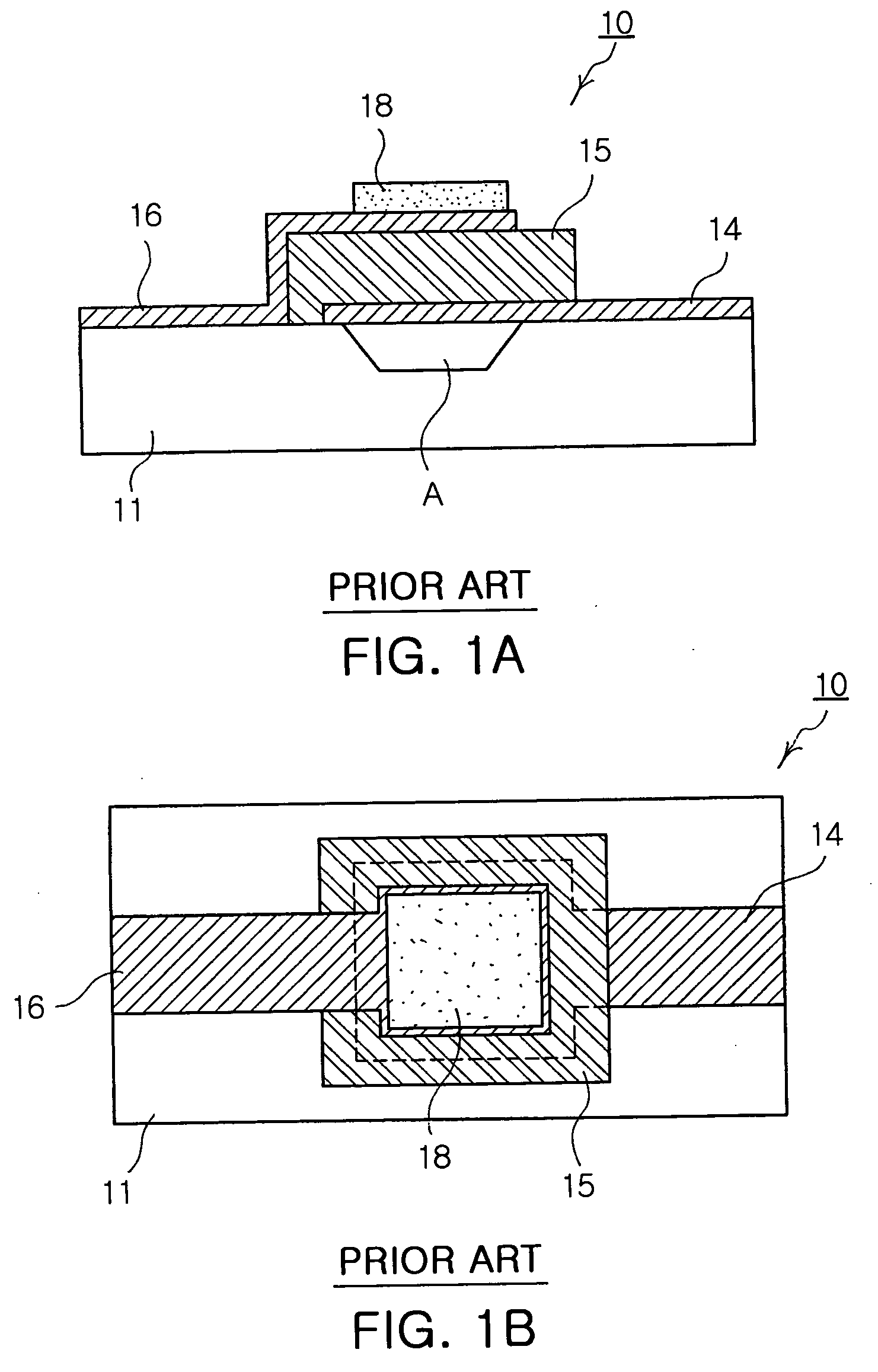

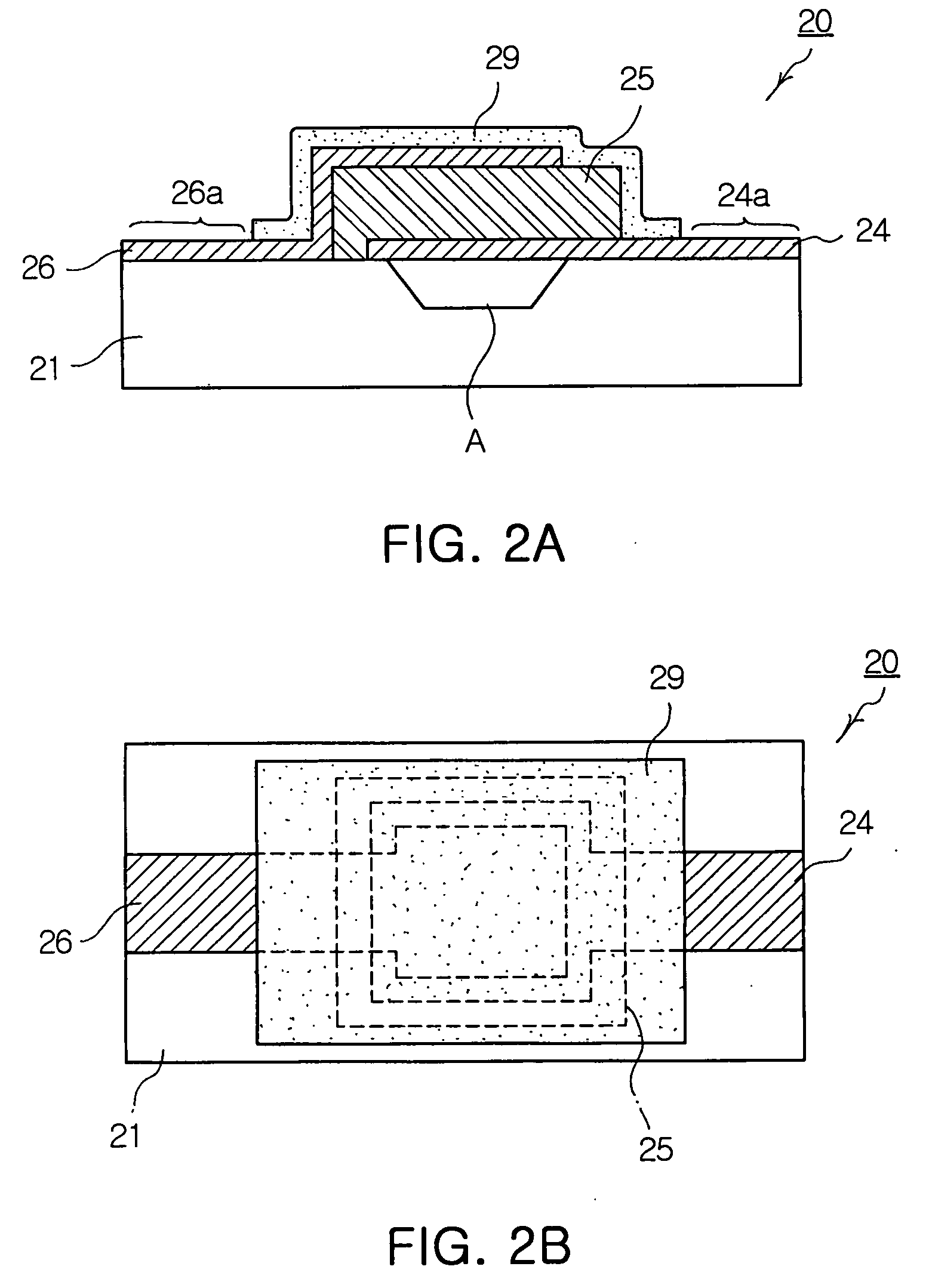

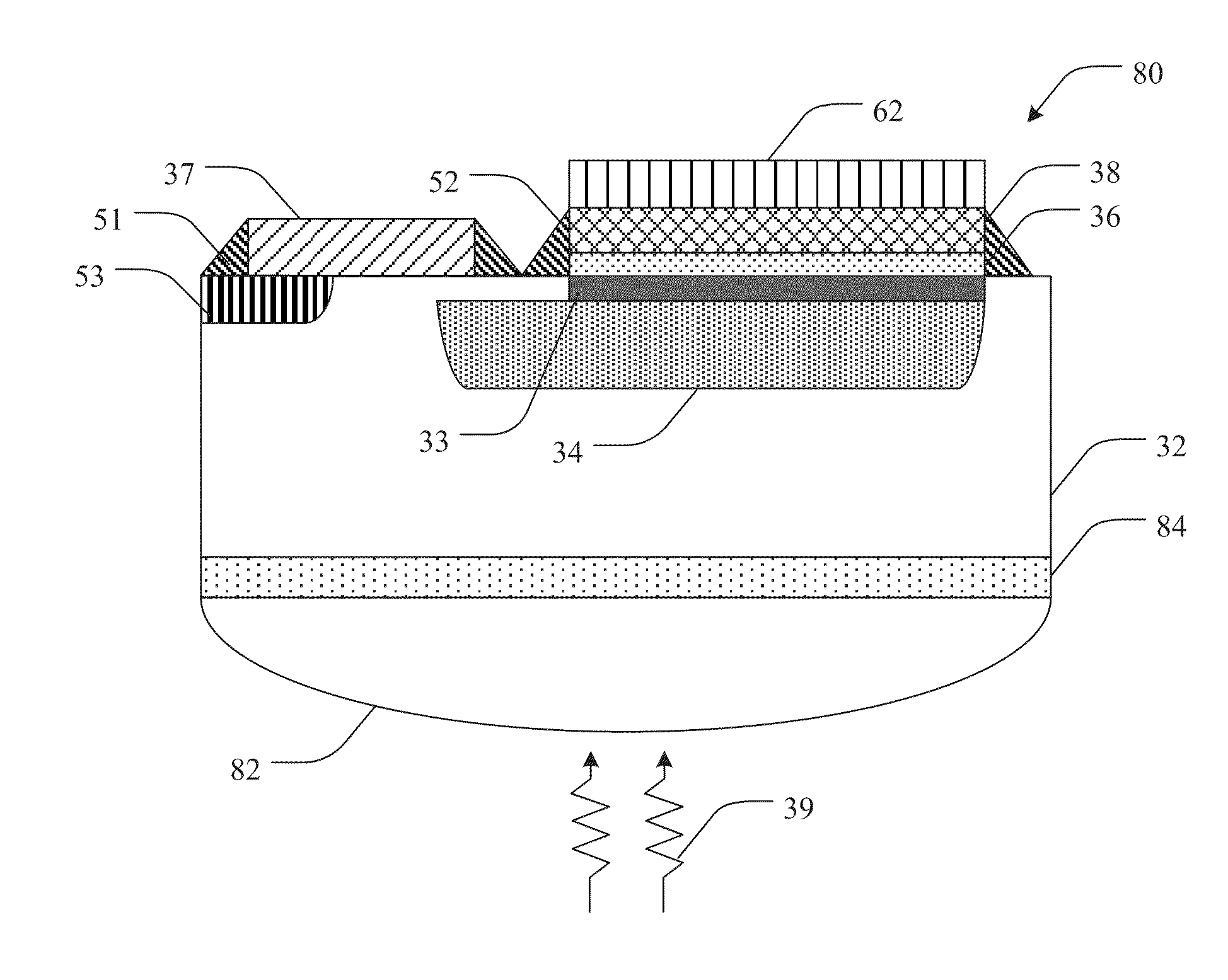

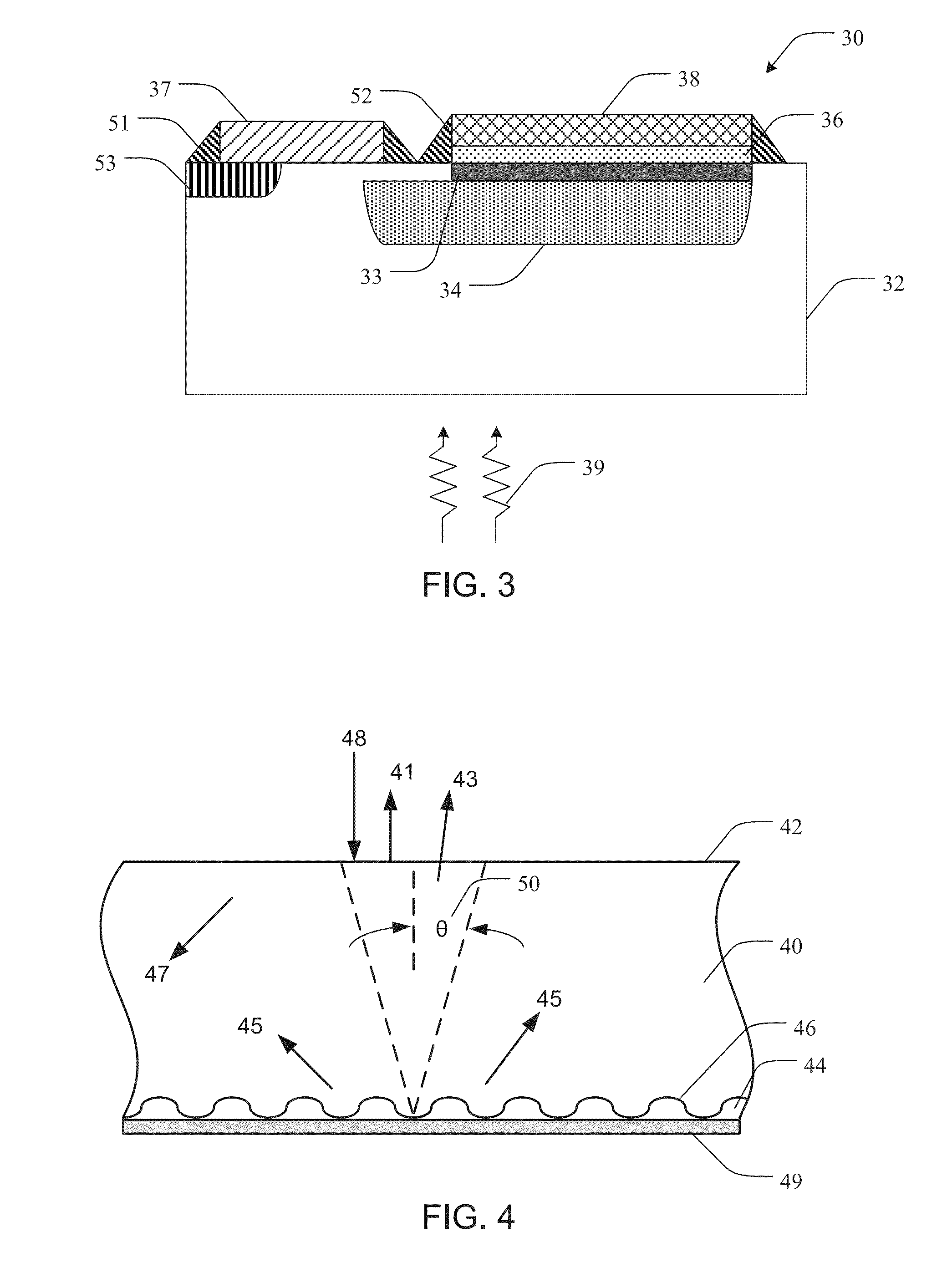

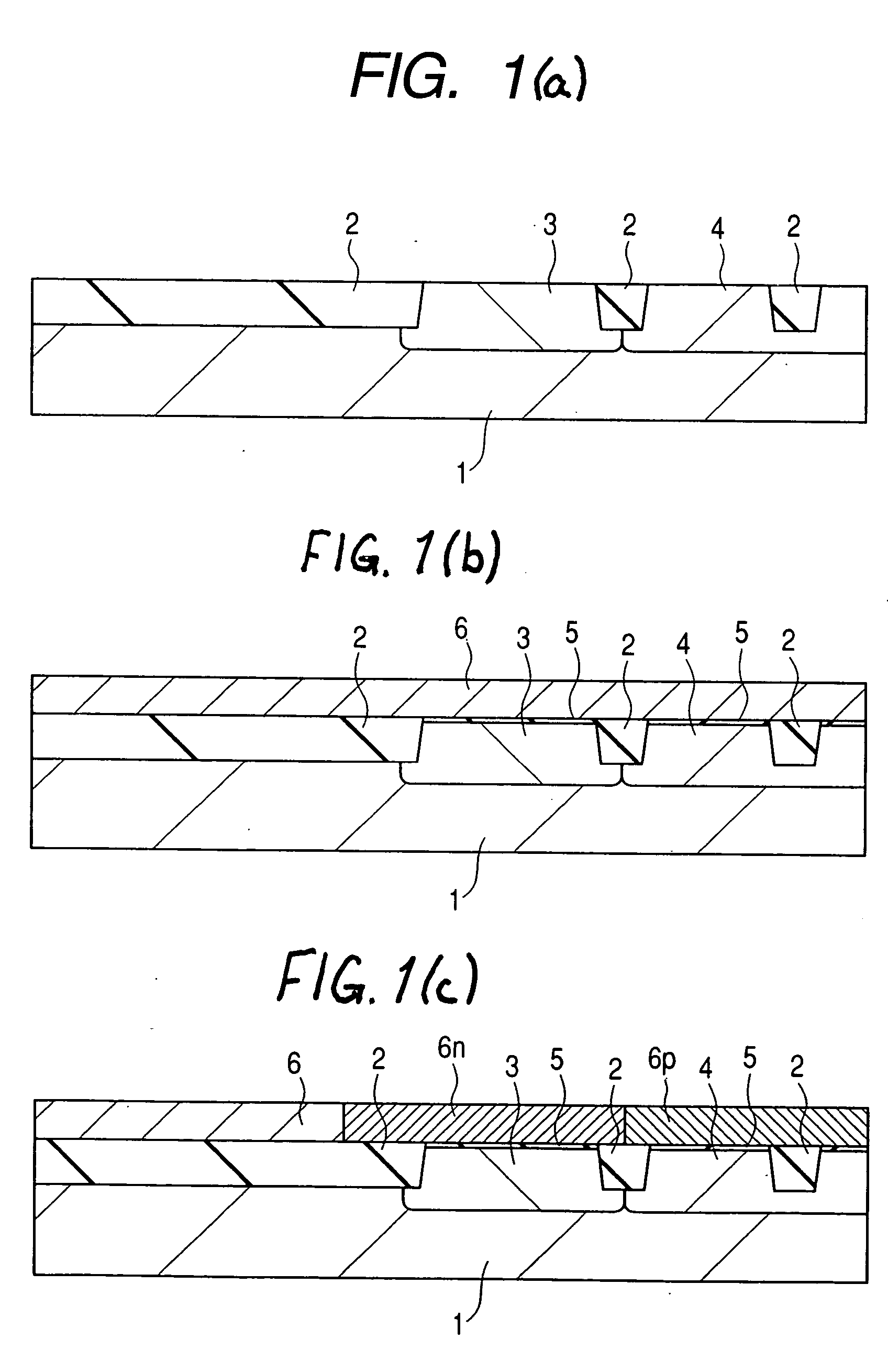

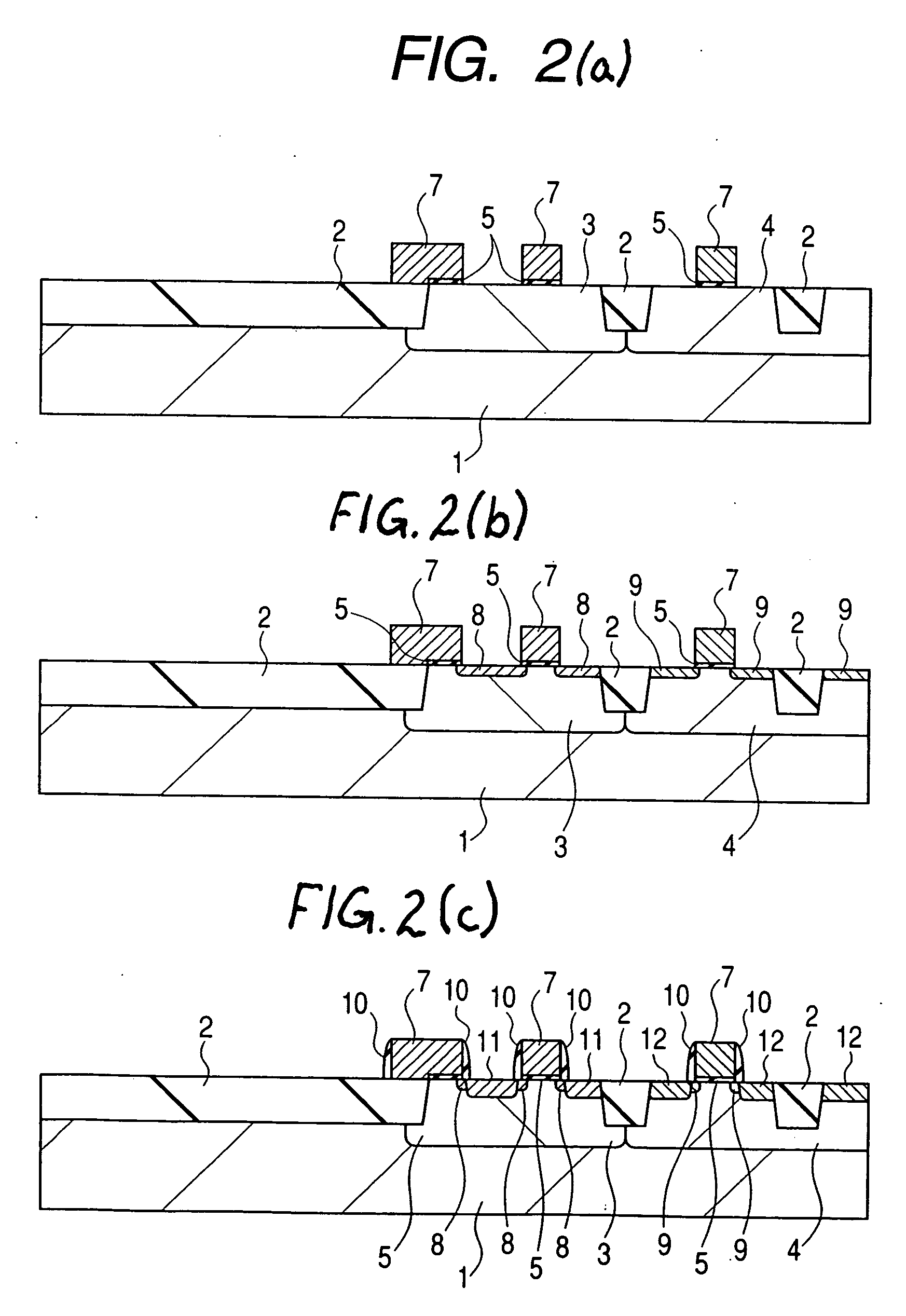

Image sensor and method of fabrication

InactiveUS20080251697A1Reduce light lossIncrease the number ofRadiation pyrometrySolid-state devicesDielectric membranePhotoelectric conversion

Disclosed is an image sensor and method of fabricating the same. The image sensor includes a photoelectric transformation region formed in a semiconductor substrate, and pluralities of interlayer dielectric films formed over the photoelectric transformation regions. The interlayer dielectric films contain multilevel interconnection layers. A color filter layer is disposed in a well region formed in the interlayer dielectric films over the photoelectric transformation region. A passivation layer is interposed between the color filter layer and the interlayer dielectric films.

Owner:SAMSUNG ELECTRONICS CO LTD

Film bulk acoustic wave resonator device and manufacturing method thereof

InactiveUS20050140247A1Stability protectionEasy to adjustPiezoelectric/electrostrictive device manufacture/assemblyImpedence networksThin-film bulk acoustic resonatorAcoustics

Disclosed herein is an FBAR (film bulk acoustic wave resonator) device and a manufacturing method thereof. The FBAR device comprises a substrate, a resonance unit including a lower electrode, a piezoelectric film, and an upper electrode, which are successively stacked on the substrate, and a passivation layer formed substantially throughout an upper surface and peripheral surface of the resonance unit in order to protect the resonance unit. A partial region of the passivation layer formed on at least the upper electrode has a thickness required to compensate for a difference between a resonant frequency of the resonance unit and a desired target resonant frequency.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Microbolometer for infrared detector or Terahertz detector and method for manufacturing the same

InactiveUS20110315981A1Improve business performanceLow costSemiconductor/solid-state device manufacturingPyrometry using electric radation detectorsComposite filmMicrobolometer

A microbolometer includes a micro-bridge structure for uncooling infrared or terahertz detectors. The thermistor and light absorbing materials of the micro-bridge structure are the vanadium oxide-carbon nanotube composite film formed by one-dimensional carbon nanotubes and two-dimensional vanadium oxide film. The micro-bridge is a three-layer sandwich structure consisting of a layer of amorphous silicon nitride base film as the supporting and insulating layer of the micro-bridge, a layer or multi-layer of vanadium oxide-carbon nanotube composite film in the middle of the micro-bridge as the heat sensitive and light absorbing layer of the microbolometer, and a layer of amorphous silicon nitride top film as the stress control layer and passivation of the heat sensitive film. The microbolometer and method for manufacturing the same can overcome the shortcomings of the prior art, improve the performance of the device, reduce the cost of raw materials and is suitable for large-scale industrial production.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

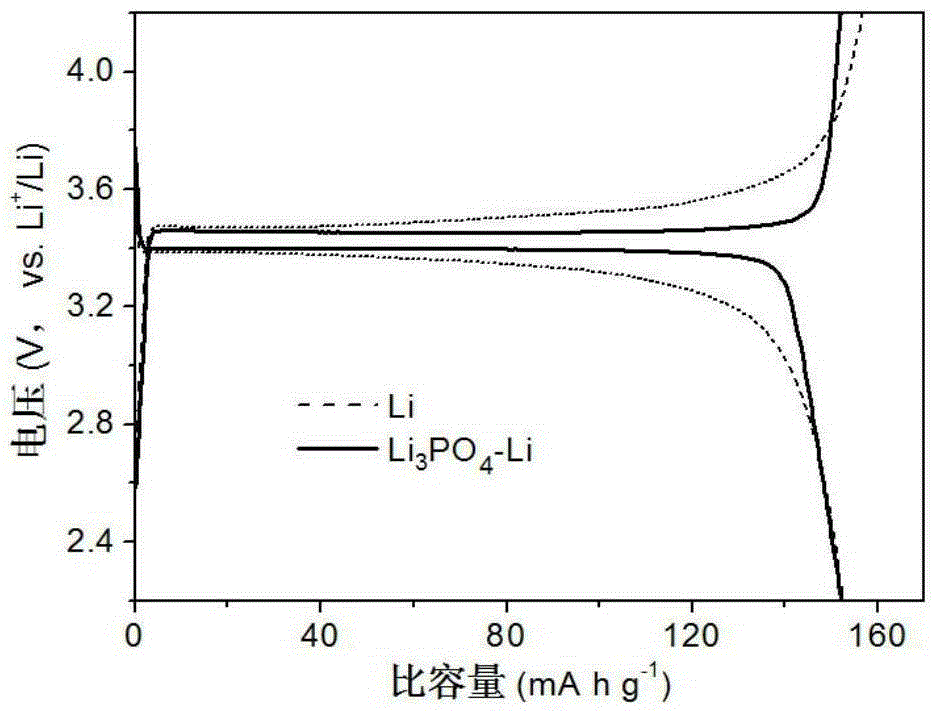

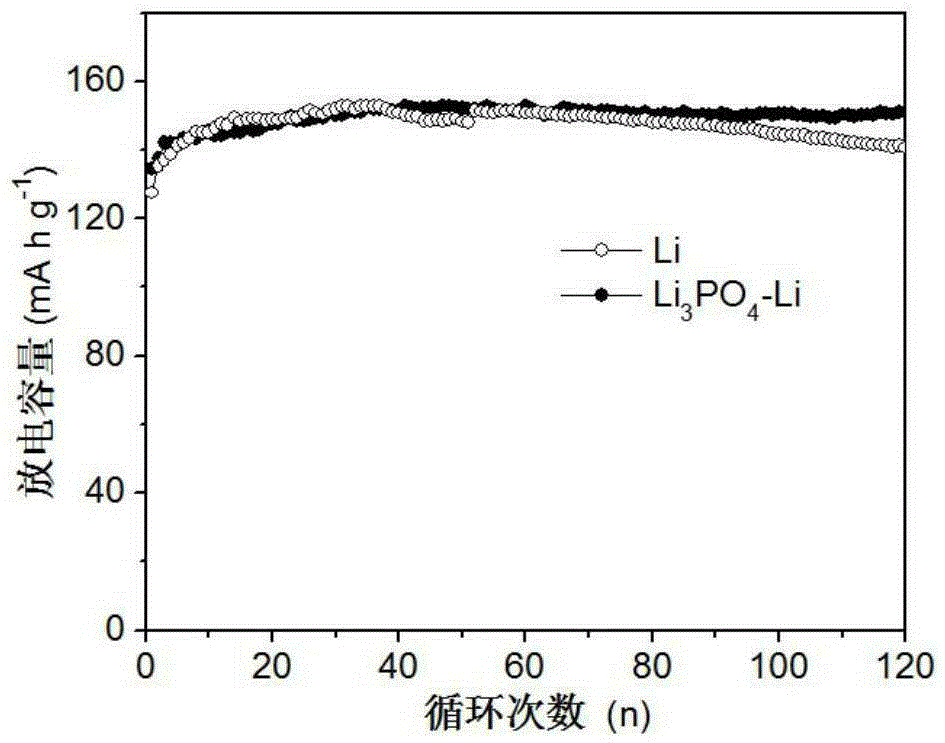

Surface in-situ processing method of metal lithium negative electrode and application

ActiveCN105280886ASolve the problem of uneven depositionSolution to constant ruptureCell electrodesSecondary cellsElectrical batteryPhosphoric acid

The invention discloses a surface in-situ processing method of a metal lithium negative electrode. And such metal lithium subjected to in-situ processing can be applicable for a high-performance metal lithium secondary battery. According to the surface in-situ processing method of the metal lithium negative electrode, provided by the invention, a processing liquid containing a few amount of phosphoric acid matters reacts with metal lithium and a passivation layer on the surface of the metal lithium to generate an interface protection layer taking lithium phosphate as a center. The in-situ processing technology has the advantages of simplicity in method, easiness in regulation and control and high practical degree; and the metal lithium negative electrode subjected to in-situ processing is used in the metal lithium secondary battery, the energy density and the cycle performance of the current battery can be substantially improved, and high practical value is achieved.

Owner:BEIJING IAMETAL NEW ENERGY TECH CO LTD

Photosensitive imaging devices and associated methods

ActiveUS20140197509A1Solid-state devicesRadiation controlled devicesEngineeringElectromagnetic radiation

Backside illuminated photosensitive devices and associated methods are provided. In one aspect, for example, a backside-illuminated photosensitive imager device can include a semiconductor substrate having multiple doped regions forming a least one junction, a textured region coupled to the semiconductor substrate and positioned to interact with electromagnetic radiation, and a passivation region positioned between the textured region and the at least one junction. The passivation region is positioned to isolate the at least one junction from the textured region, and the semiconductor substrate and the textured region are positioned such that incoming electromagnetic radiation passes through the semiconductor substrate before contacting the textured region. Additionally, the device includes an electrical transfer element coupled to the semiconductor substrate to transfer an electrical signal from the at least one junction.

Owner:SIONYX

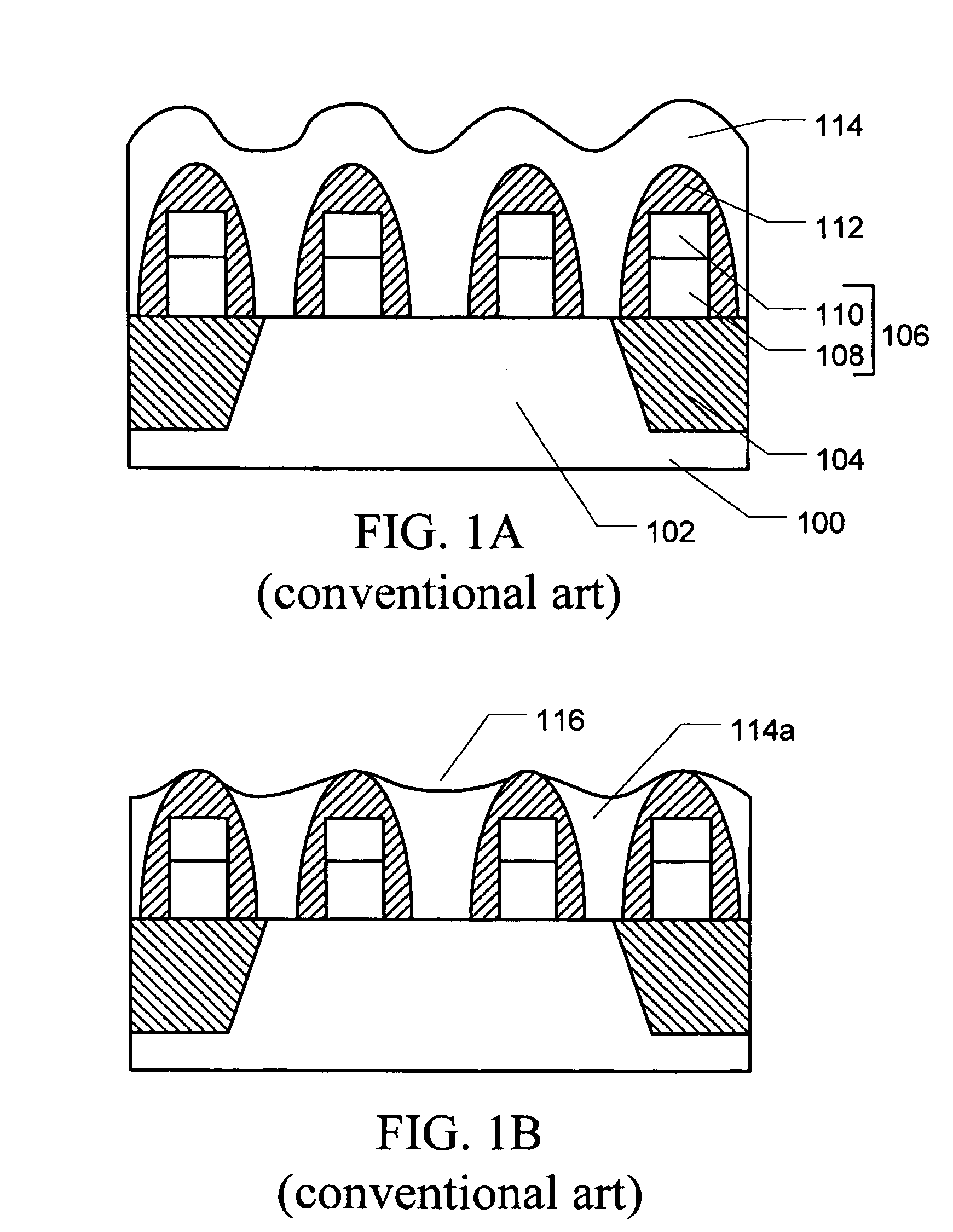

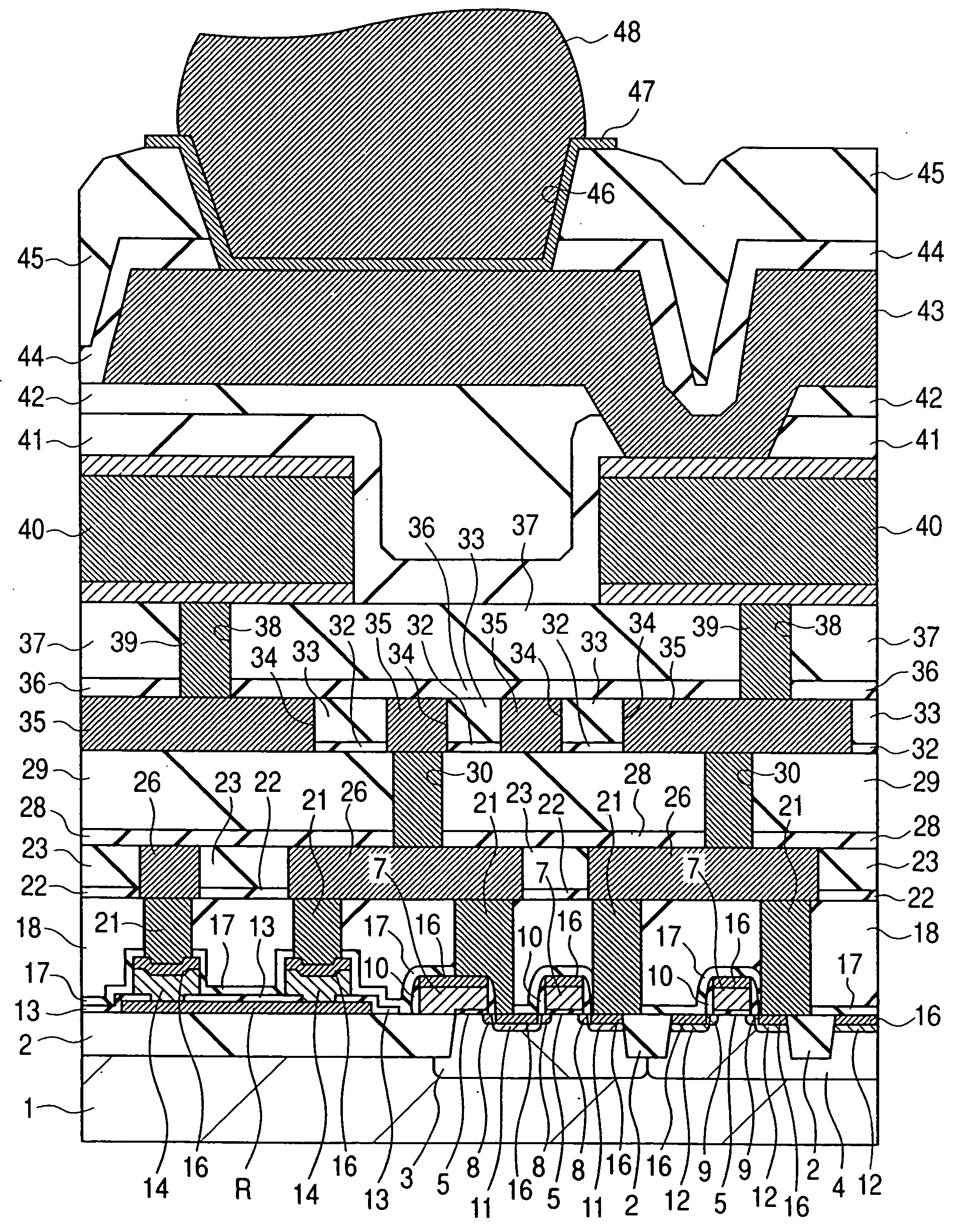

Semiconductor integrated circuit device and process for manufacturing the same

InactiveUS20050020021A1Image degradationLess fluctuationTransistorSolid-state devicesDevice materialHydrogen content

In the manufacture of a semiconductor device having a high-performance and high-reliability, a silicon nitride film 17 for self alignment, which film is formed to cover the gate electrode of a MISFET, is formed at a substrate temperature of 400° C. or greater by plasma CVD using a raw material gas including monosilane and nitrogen. A silicon nitride film 44 constituting a passivation film is formed at a substrate temperature of about 350° C. by plasma CVD using a raw material gas including monosilane, ammonia and nitrogen. The hydrogen content contained in the silicon nitride film 17 is smaller than that contained in the silicon nitride film 44, making it possible to suppress hydrogen release from the silicon nitride film 17.

Owner:RENESAS ELECTRONICS CORP

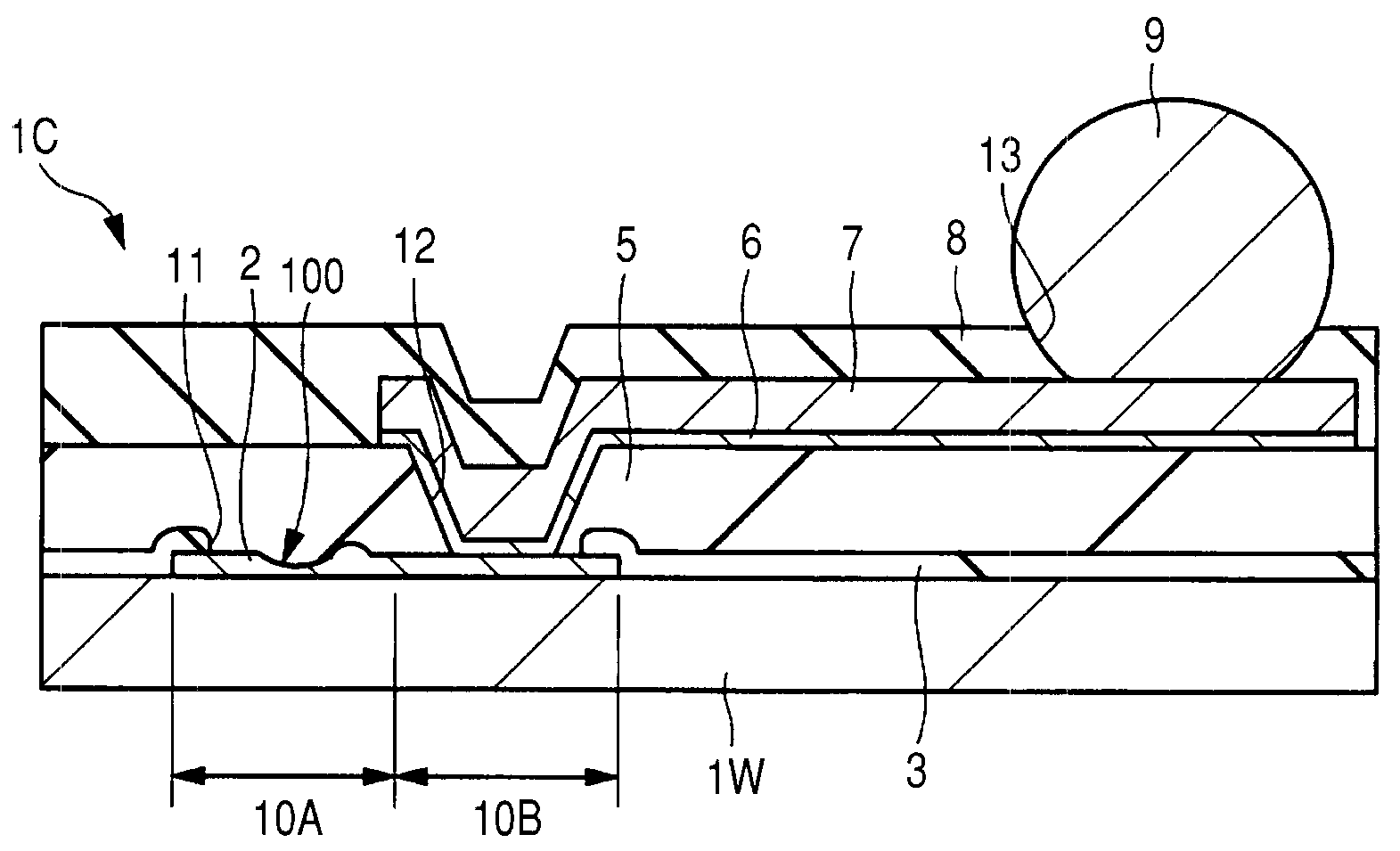

Semiconductor device and manufacturing method of the same

ActiveUS20090243118A1High pin-countImprove reliabilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCouplingSemiconductor chip

Provided is a semiconductor device having a pad on a semiconductor chip, a first passivation film formed over the semiconductor chip and having an opening portion on the pad of a probe region and a coupling region, a second passivation film formed over the pad and the first passivation film and having an opening portion on the pad of the coupling region, and a rewiring layer formed over the coupling region and the second passivation film and electrically coupled to the pad. The pad of the probe region placed on the periphery side of the semiconductor chip relative to the coupling region has a probe mark and the rewiring layer extends from the coupling region to the center side of the semiconductor chip. The present invention provides a technology capable of achieving size reduction, particularly pitch narrowing, of a semiconductor device.

Owner:RENESAS ELECTRONICS CORP

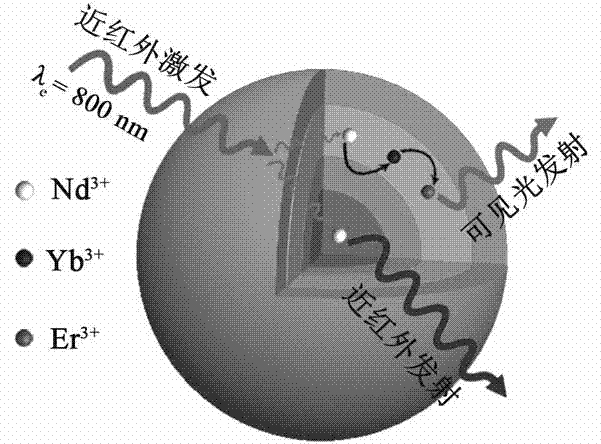

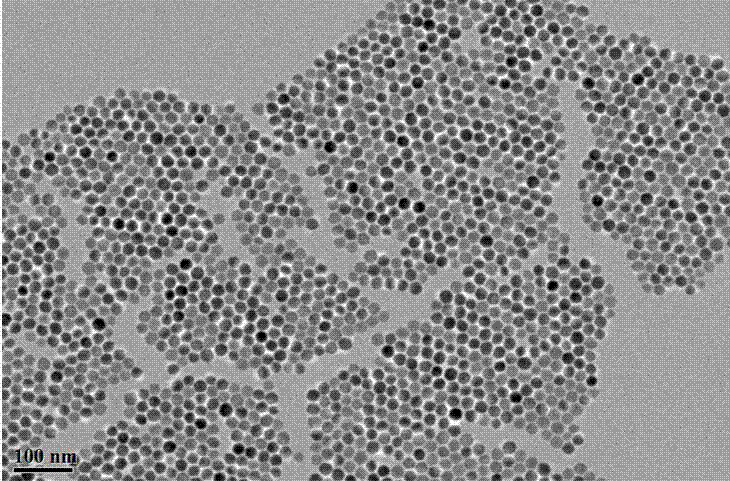

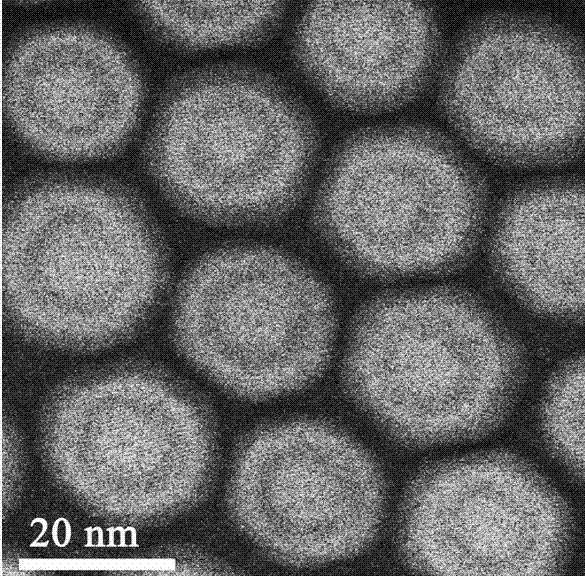

Up/down conversion dual-mode fluorescent nanomaterial for Nd<3+> sensitization and synthesis method thereof

The invention belongs to the technical field of nanometer biological materials, and particularly relates to an 800nm excitation-based up / down conversion dual-mode fluorescent nanomaterial for Nd<3+> sensitization and a synthesis method thereof. The synthetic up / down conversion dual-mode fluorescent nanomaterial for Nd<3+>sensitization designed by the invention has a multi-layer core-shell structure, and comprises a down conversion luminous layer, an up conversion luminous layer, an isolation layer and a passivation layer. Different layers of the material synergistically play respective different roles, and meanwhile, the dual-mode fluorescent probe with up conversion fluorescence and down conversion fluorescence is finally achieved under an 800nm of excitation light with a low-heat effect. The up conversion excitation light is expanded to about 800nm from 980nm by Nd<3+>, Yb<3+> and Er<3+>-doped NaGdF4:Nd, Yb, Er up conversion layer due to introduction of Nd<3+>, and the fluorescent process from a near infrared light to a visible light is achieved. The process meets the requirements of an in-vitro fluorescent probe. In addition, the typical down conversion fluorescence from the near infrared light to a far infrared light is also achieved in one nanoparticle due to the synergistic effect of the NaGdF4:Nd core.

Owner:FUDAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com