Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

79026 results about "Copper" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Copper is a chemical element with the symbol Cu (from Latin: cuprum) and atomic number 29. It is a soft, malleable, and ductile metal with very high thermal and electrical conductivity. A freshly exposed surface of pure copper has a pinkish-orange color. Copper is used as a conductor of heat and electricity, as a building material, and as a constituent of various metal alloys, such as sterling silver used in jewelry, cupronickel used to make marine hardware and coins, and constantan used in strain gauges and thermocouples for temperature measurement.

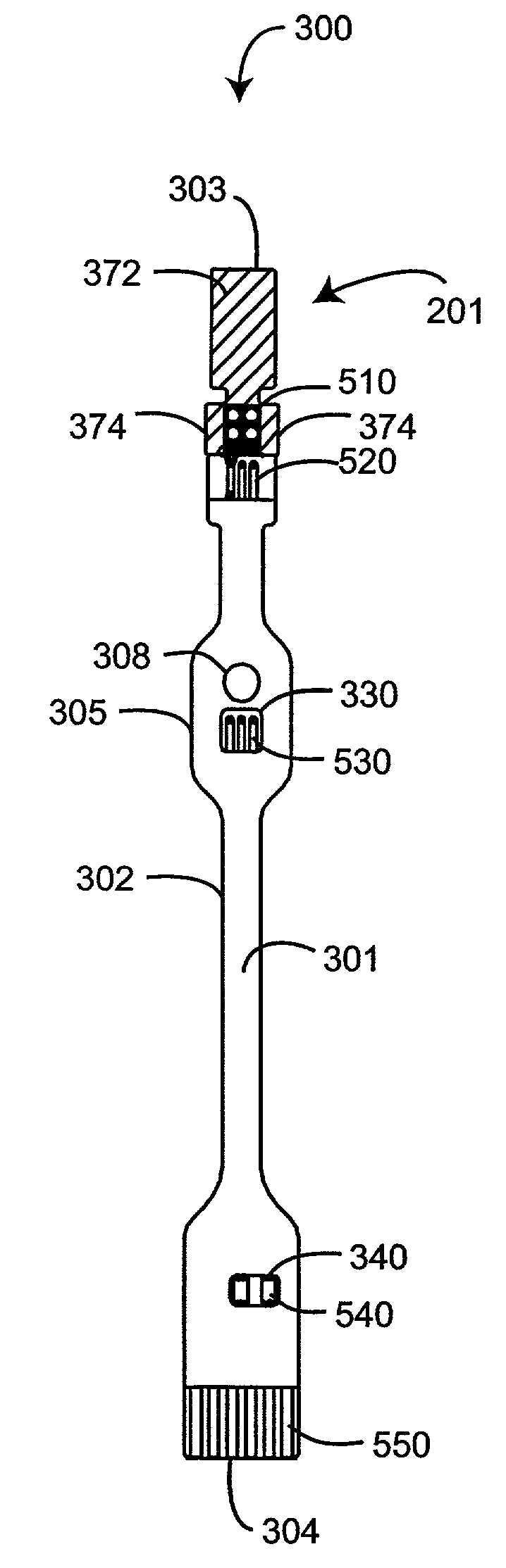

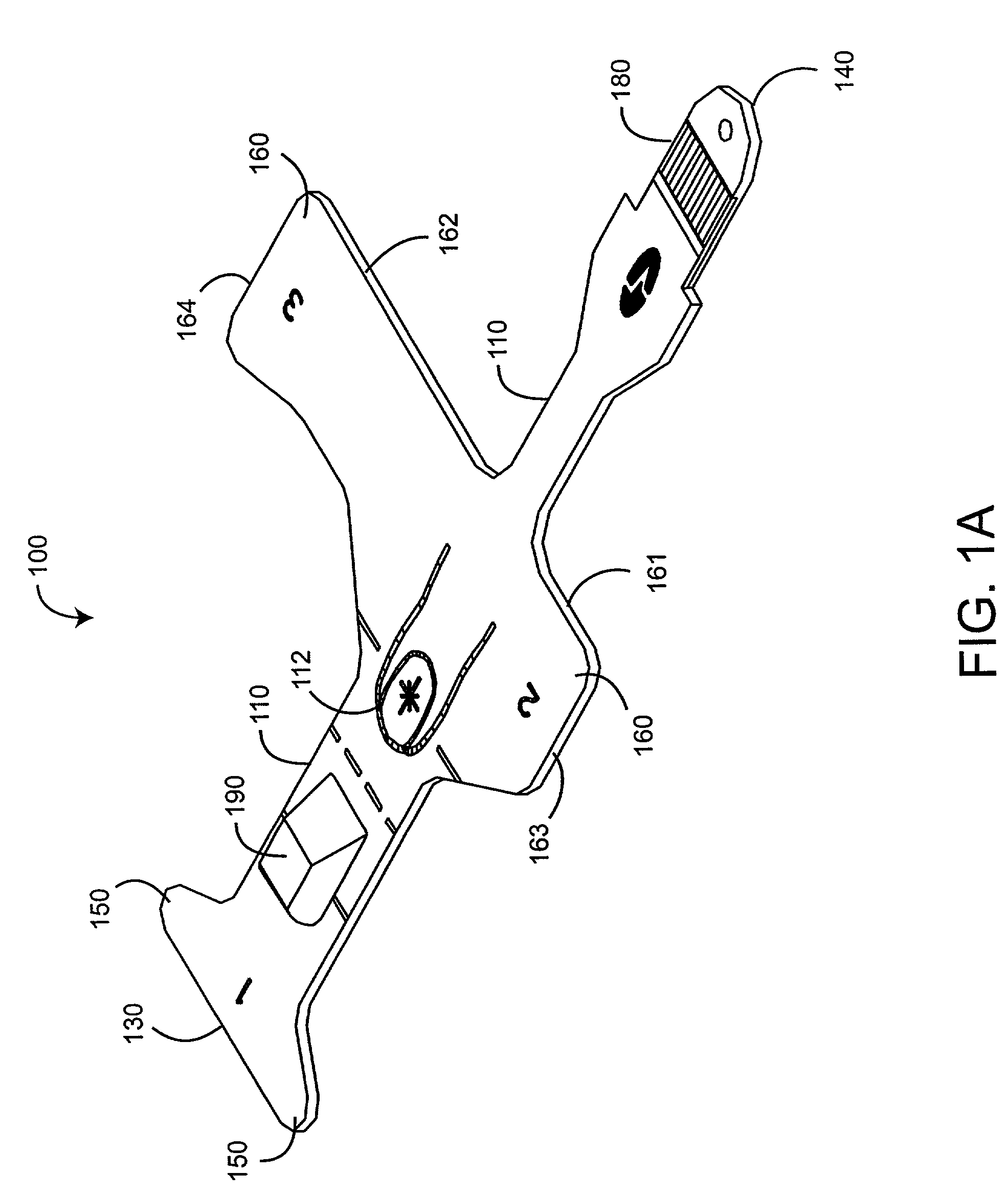

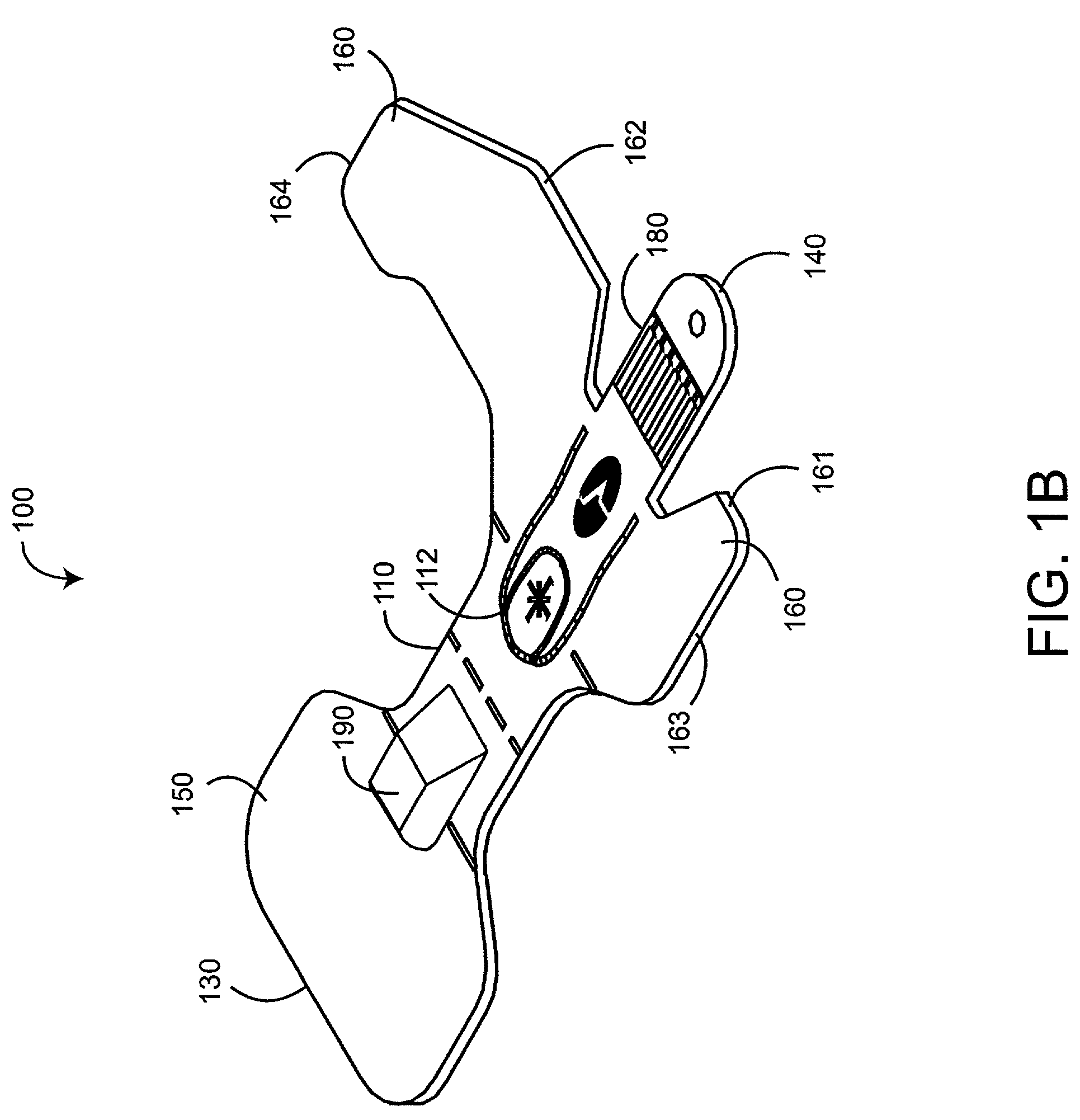

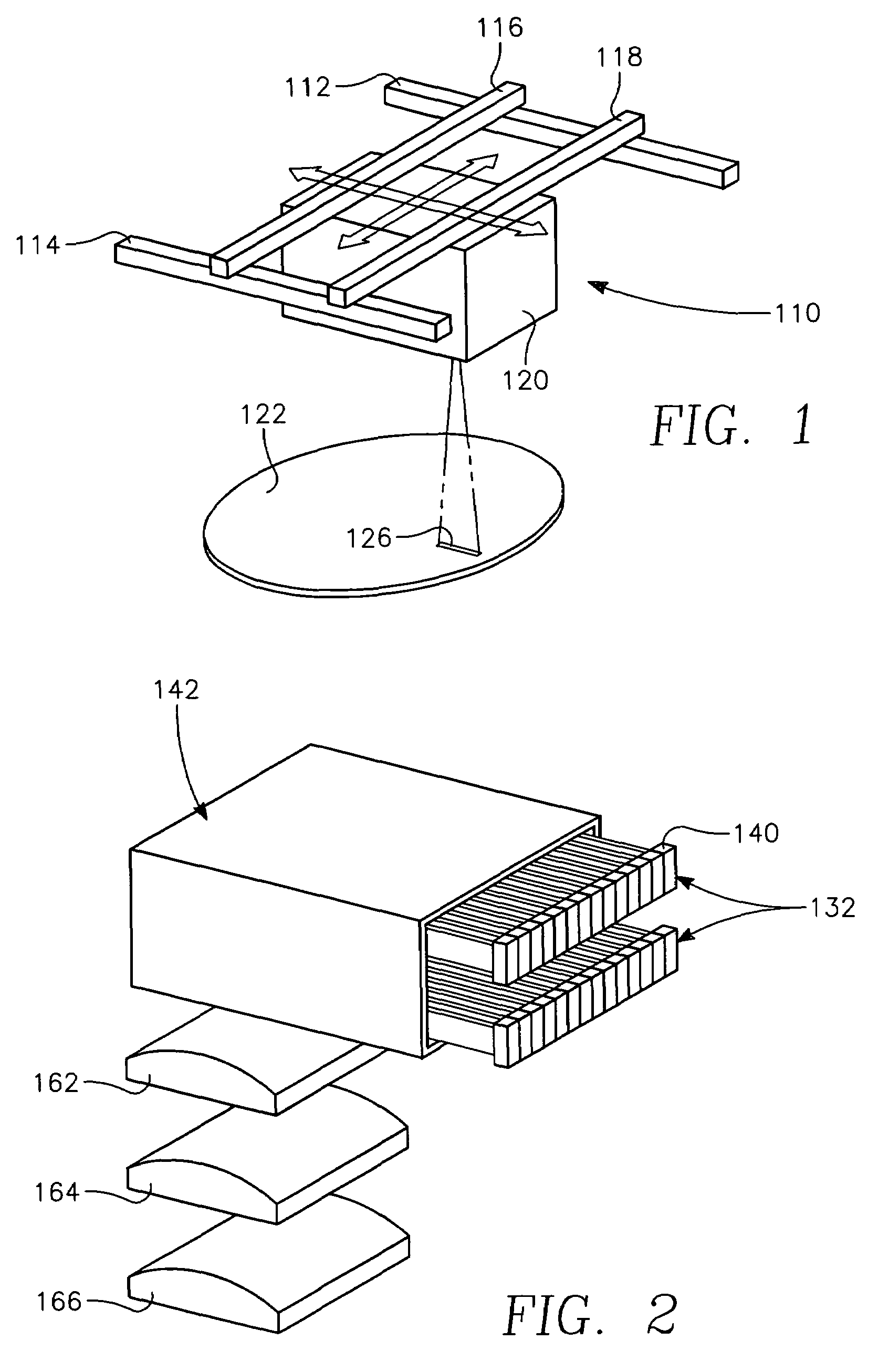

Flex circuit shielded optical sensor

InactiveUS6985764B2Cross-talk/noise/interference reductionColor/spectral properties measurementsPhotovoltaic detectorsPhotodetector

A flex circuit optical sensor has an integrated Faraday shield. A conductive trace layer disposed on a substrate is used to form a conductive grid which shields the face of a photodetector. A conductive ink layer is formed on a substrate side opposite the trace layer. The back and sides of the detector are shielded by flex circuit flaps that have the conductive ink layer but substantially exclude the trace layer so as to fold over and closely adhere to the detector body. The shielded substrate flaps advantageously eliminate a separate detector shield, which is typically fabricated with an etched copper part that must be attached to a flex circuit before mounting the detector.

Owner:JPMORGAN CHASE BANK NA

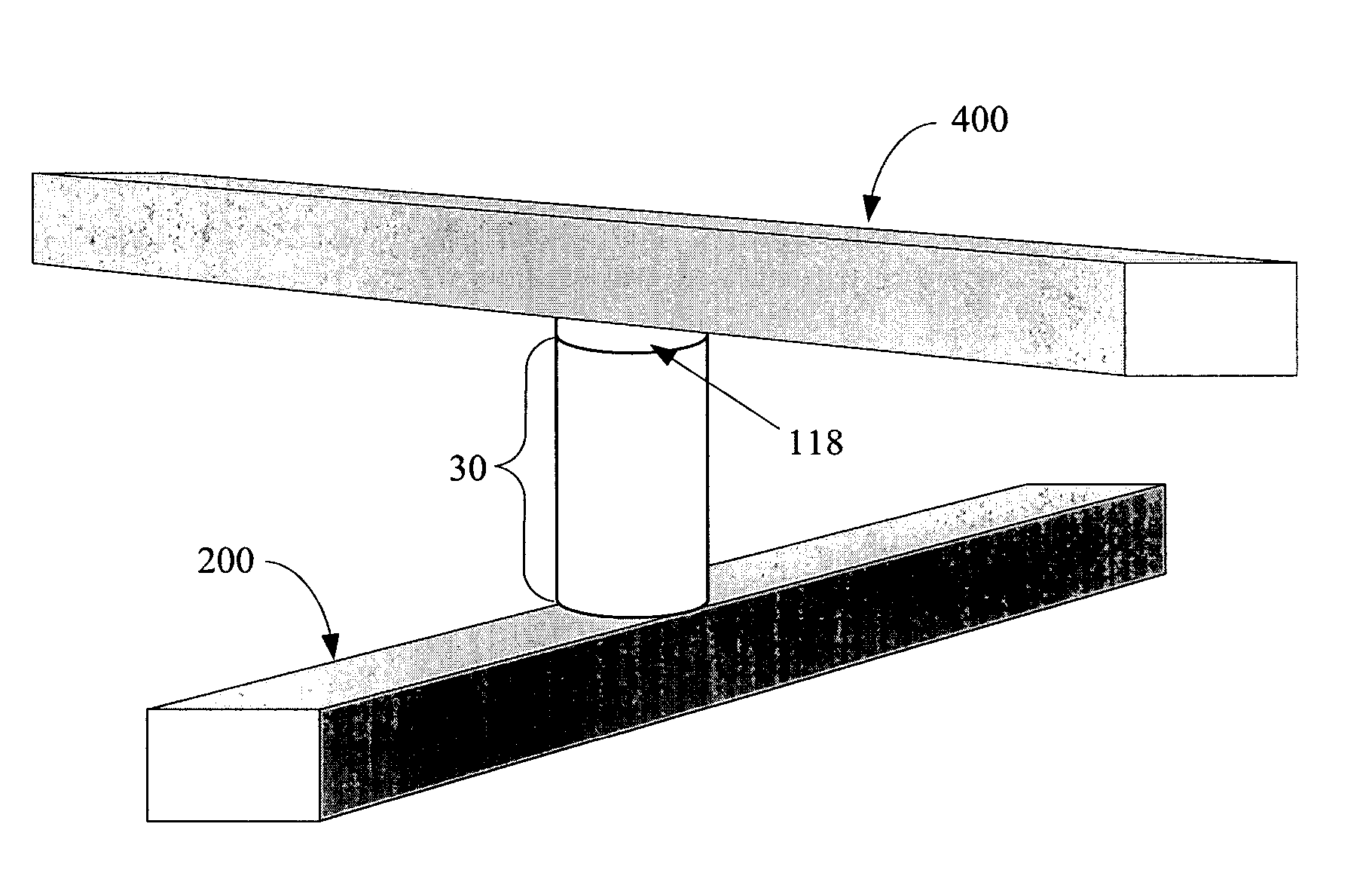

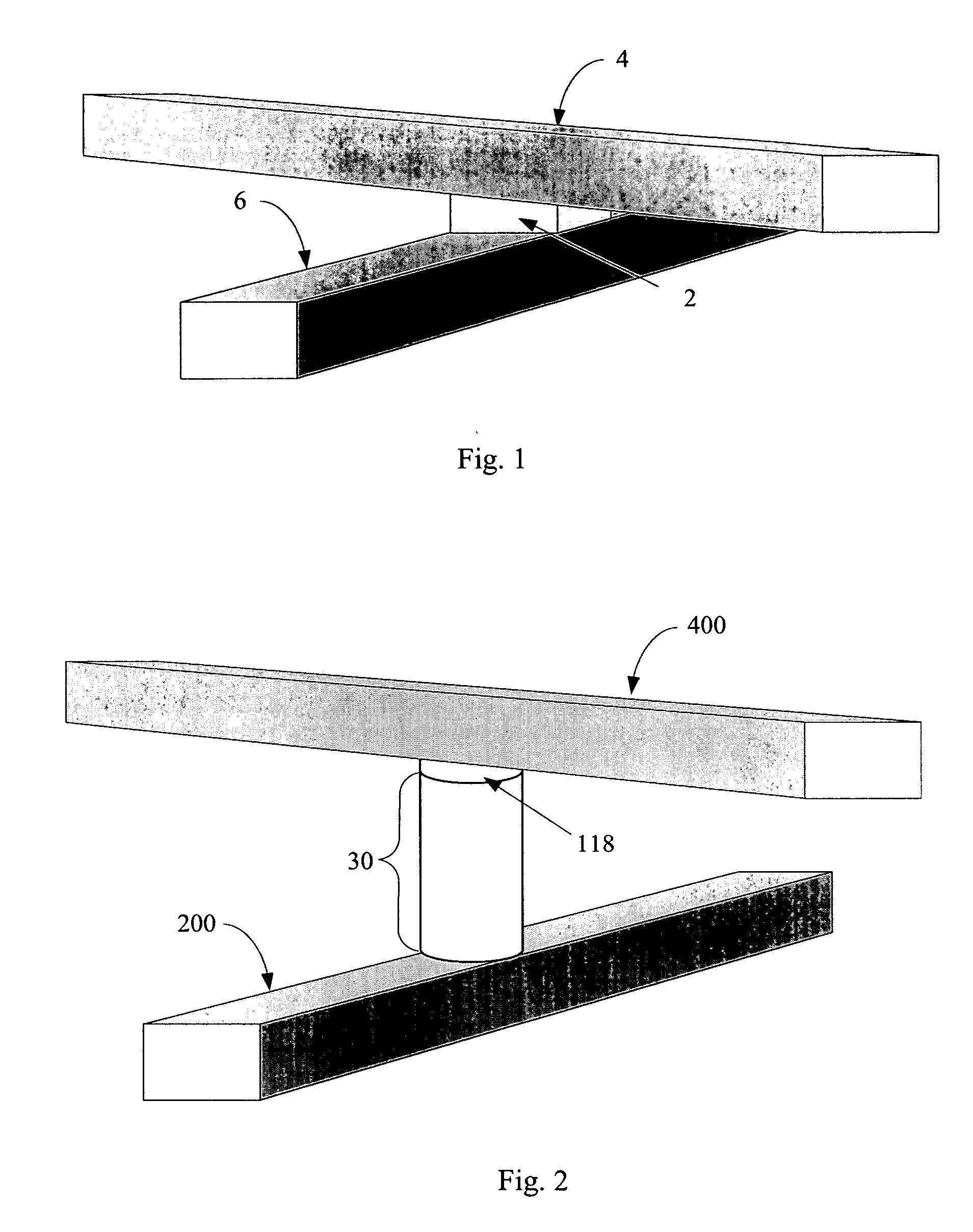

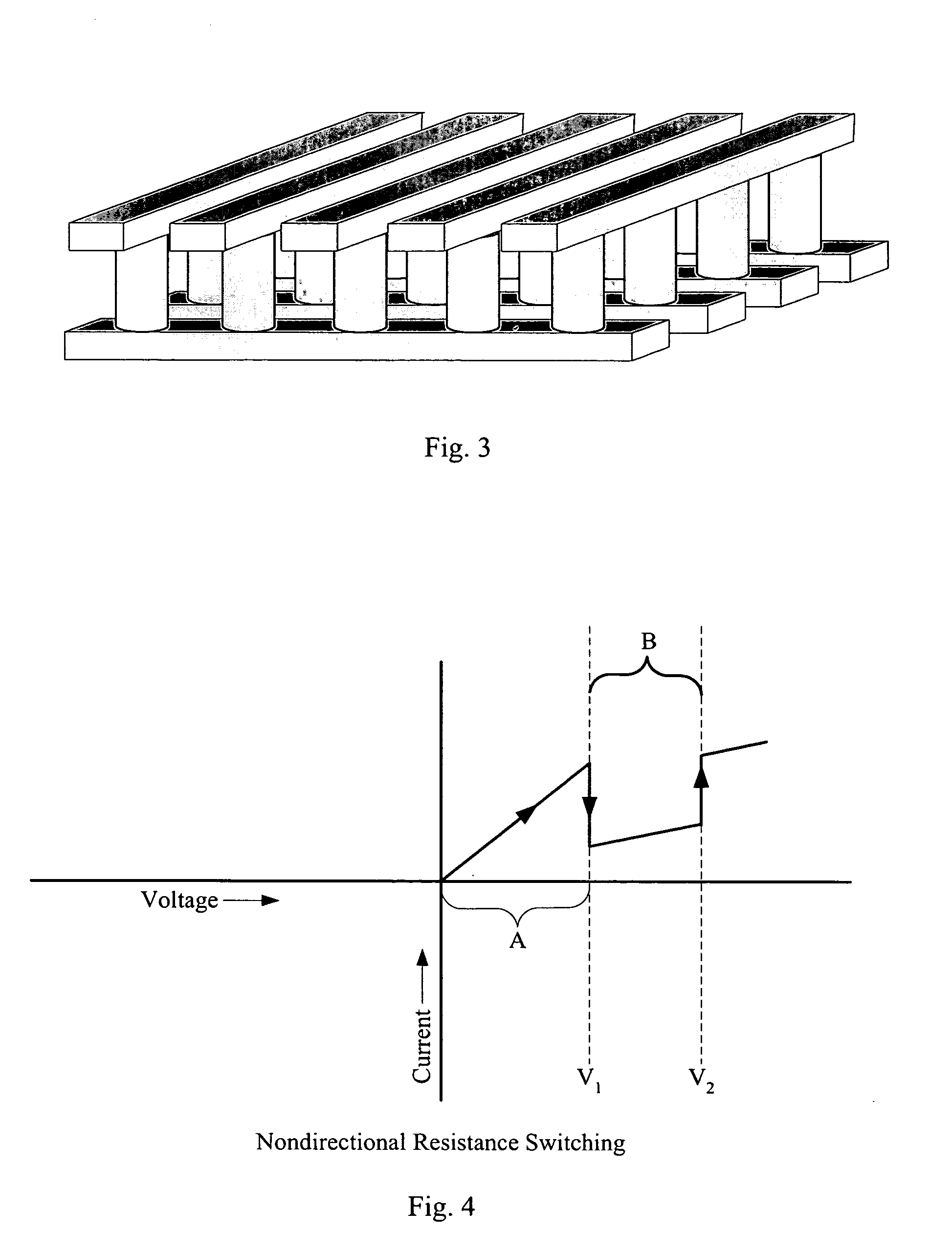

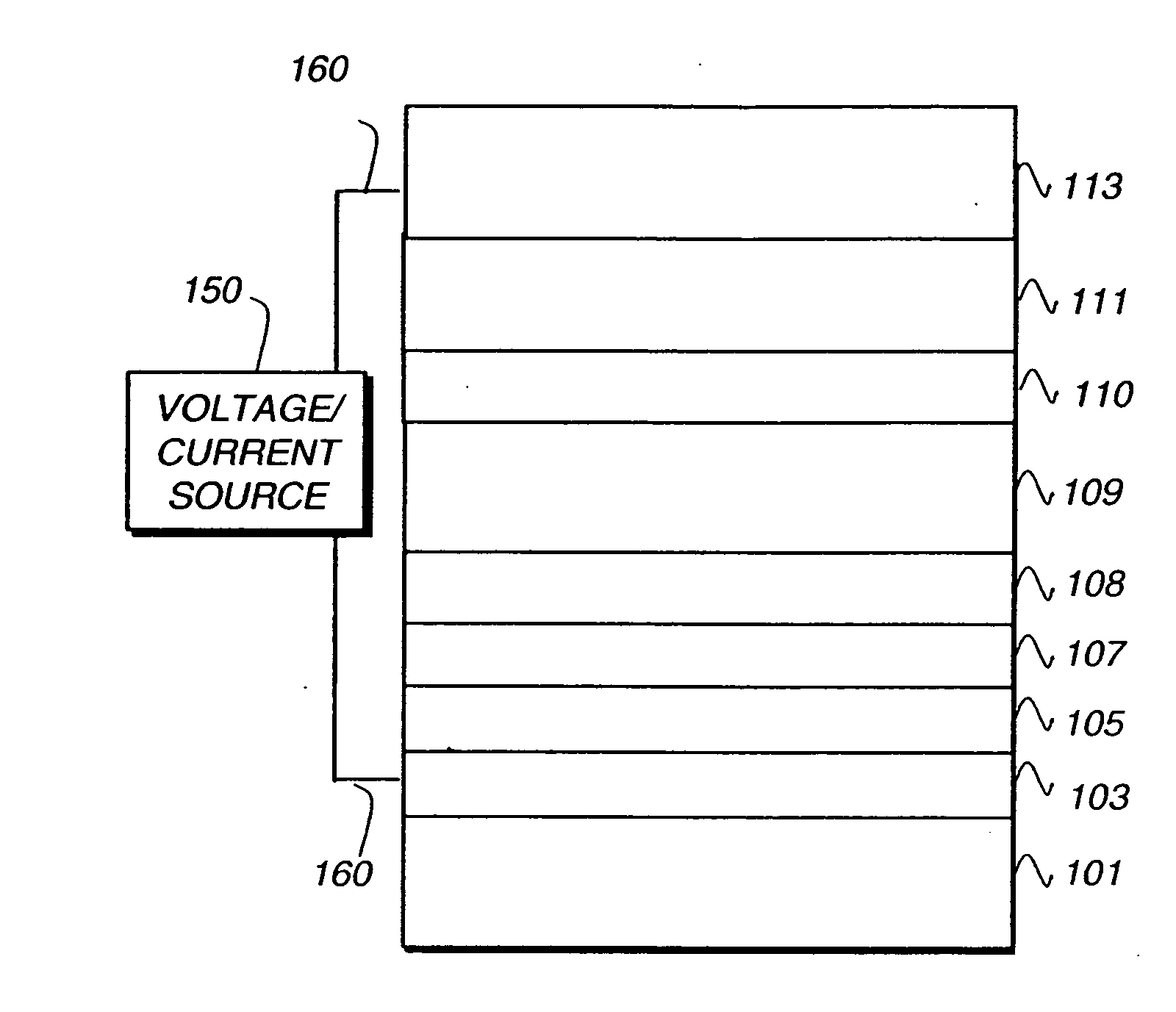

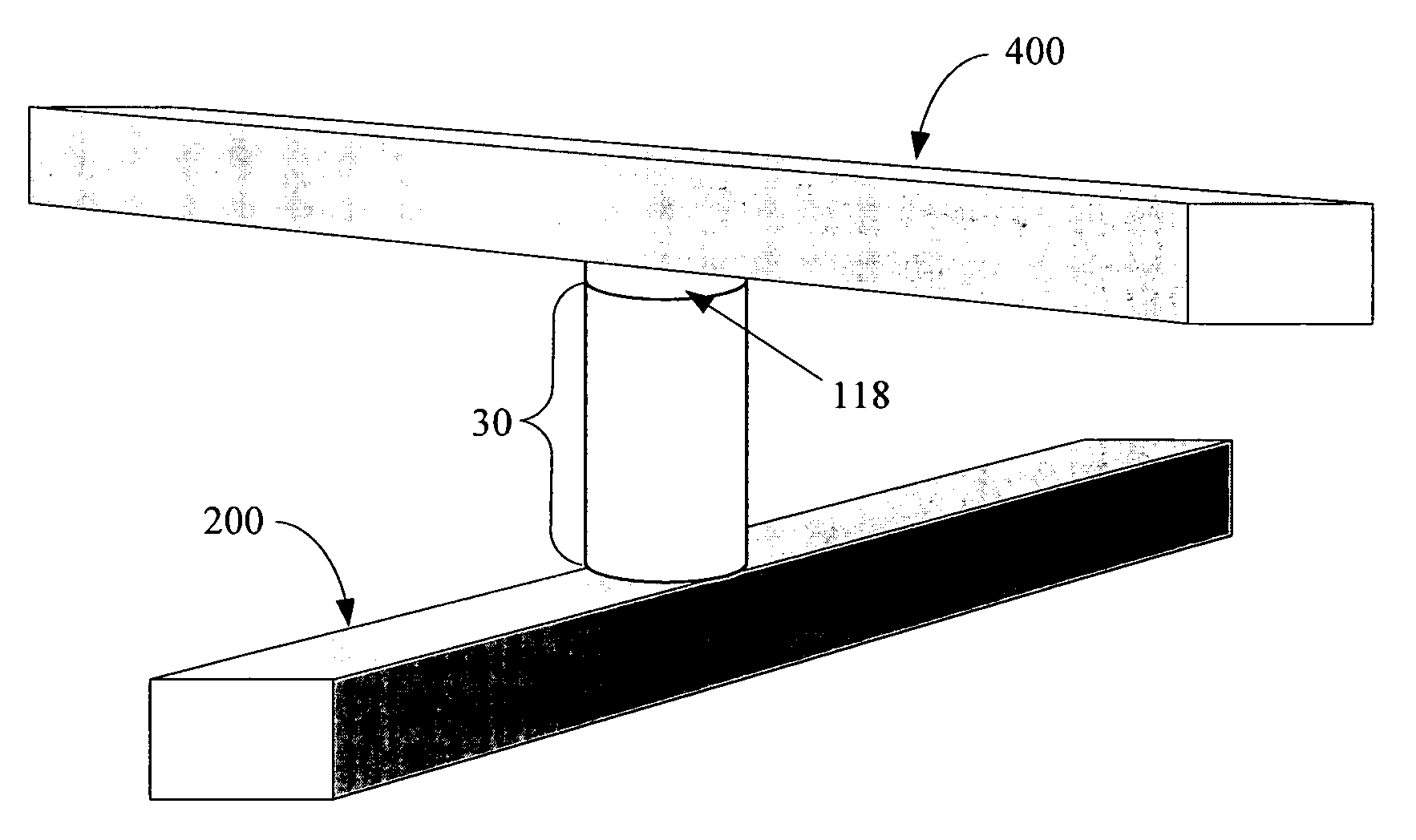

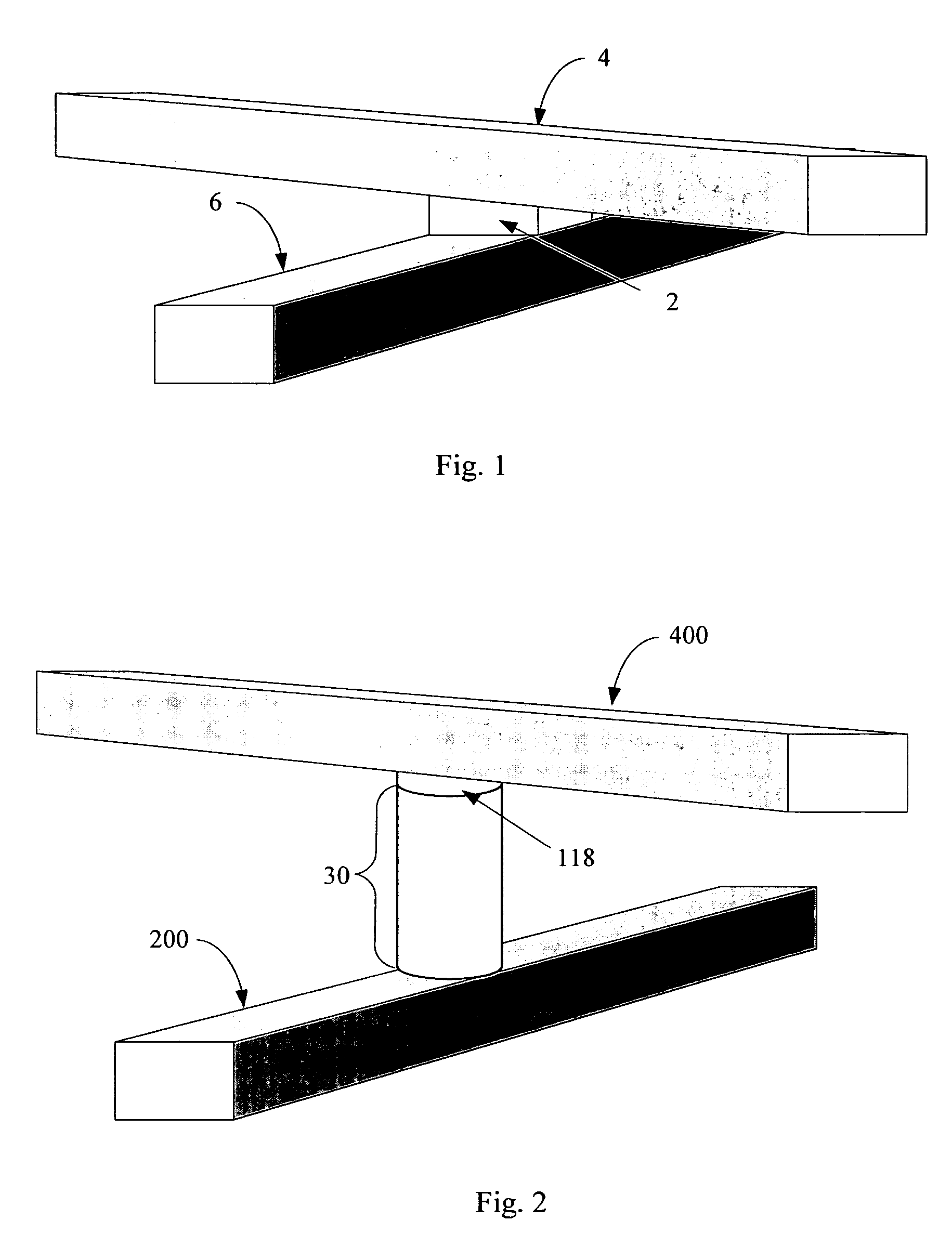

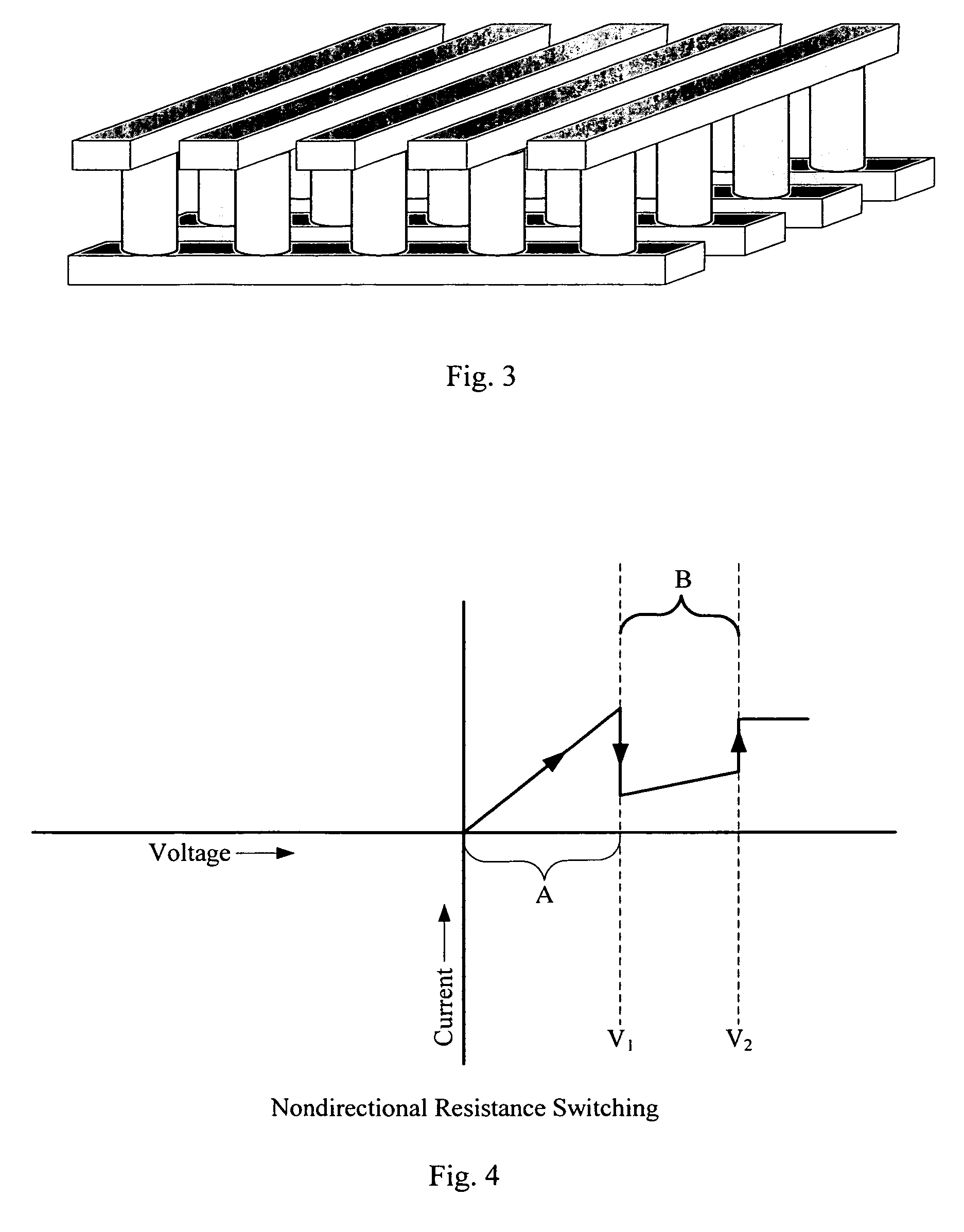

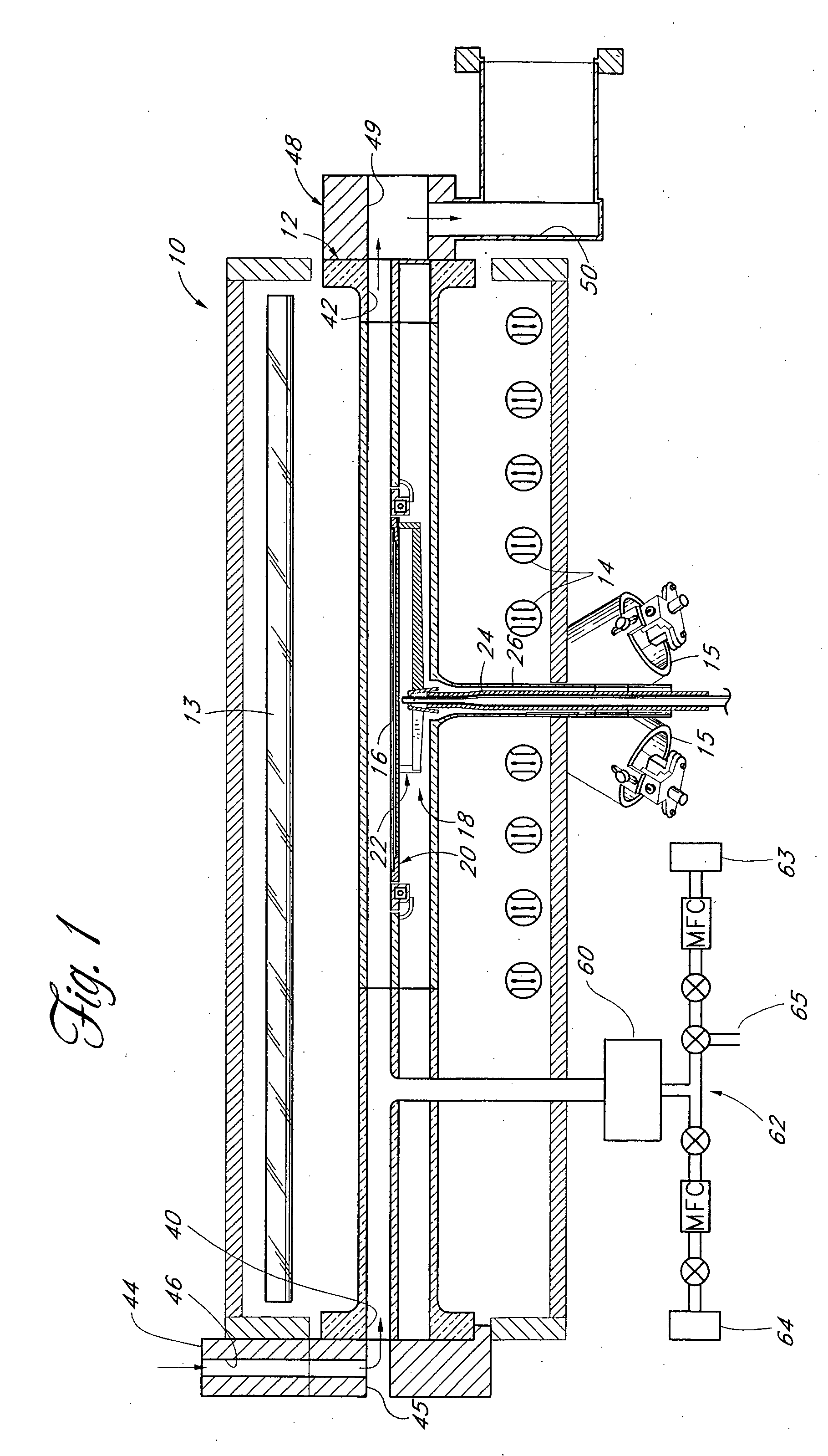

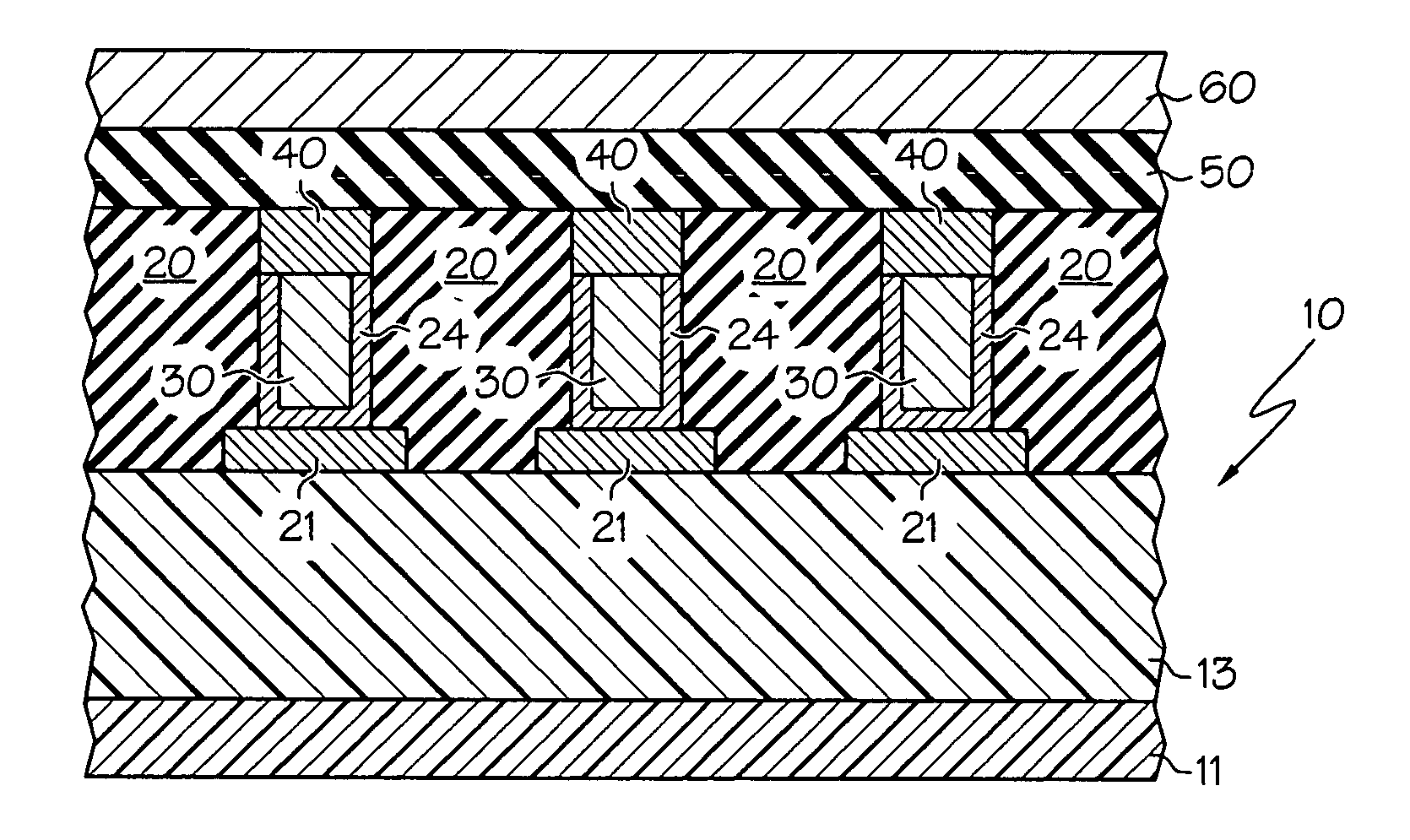

Rewriteable memory cell comprising a diode and a resistance-switching material

In a novel rewriteable nonvolatile memory cell formed above a substrate, a diode is paired with a reversible resistance-switching material, preferably a metal oxide or nitride such as, for example, NiO, Nb2O5, TiO2, HfO2, Al2O3, MgOx, CrO2, VO, BN, and AlN. In preferred embodiments, the diode is formed as a vertical pillar disposed between conductors. Multiple memory levels can be stacked to form a monolithic three dimensional memory array. In some embodiments, the diode comprises germanium or a germanium alloy, which can be deposited and crystallized at relatively low temperatures, allowing use of aluminum or copper in the conductors.

Owner:SANDISK TECH LLC

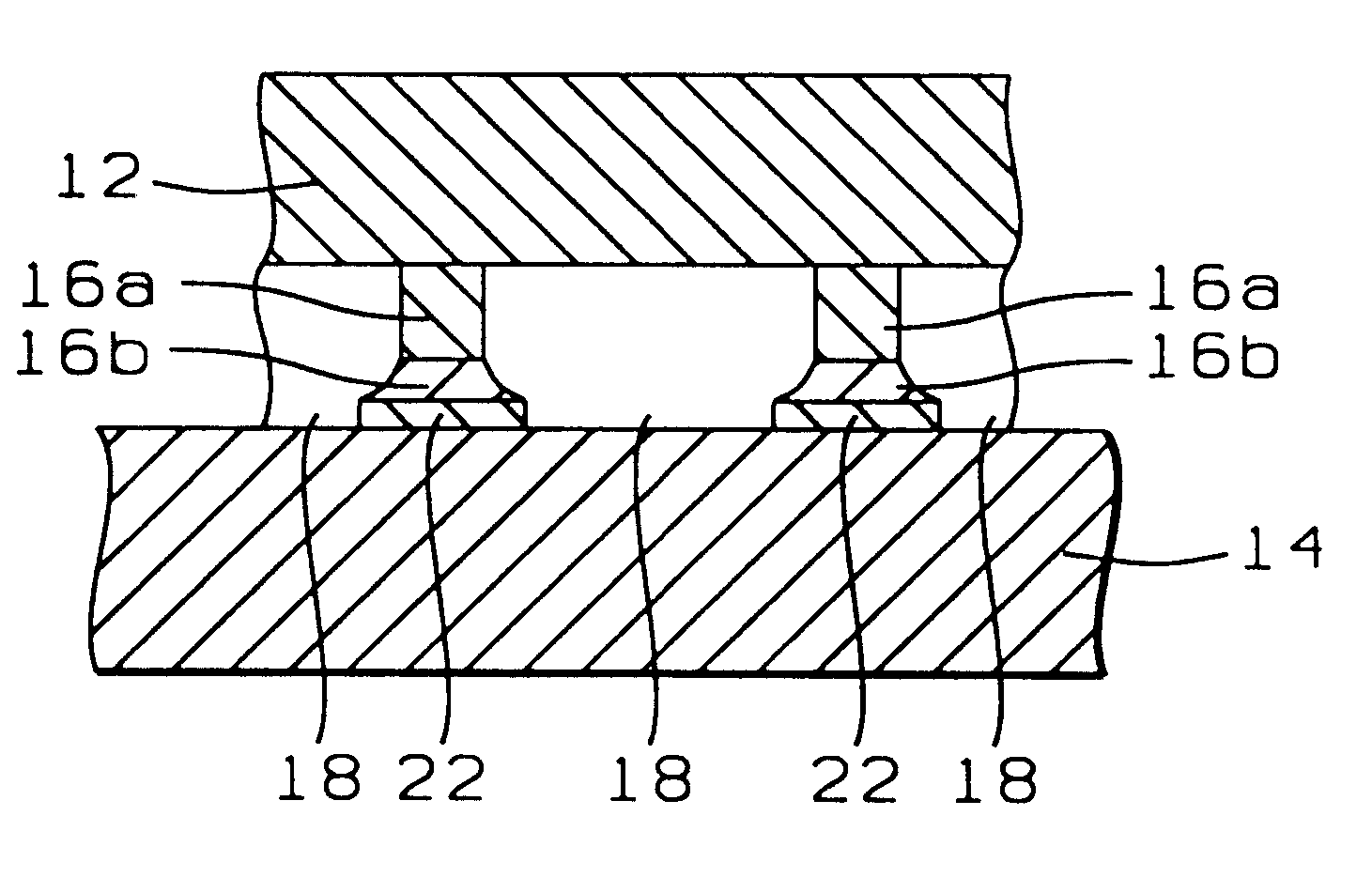

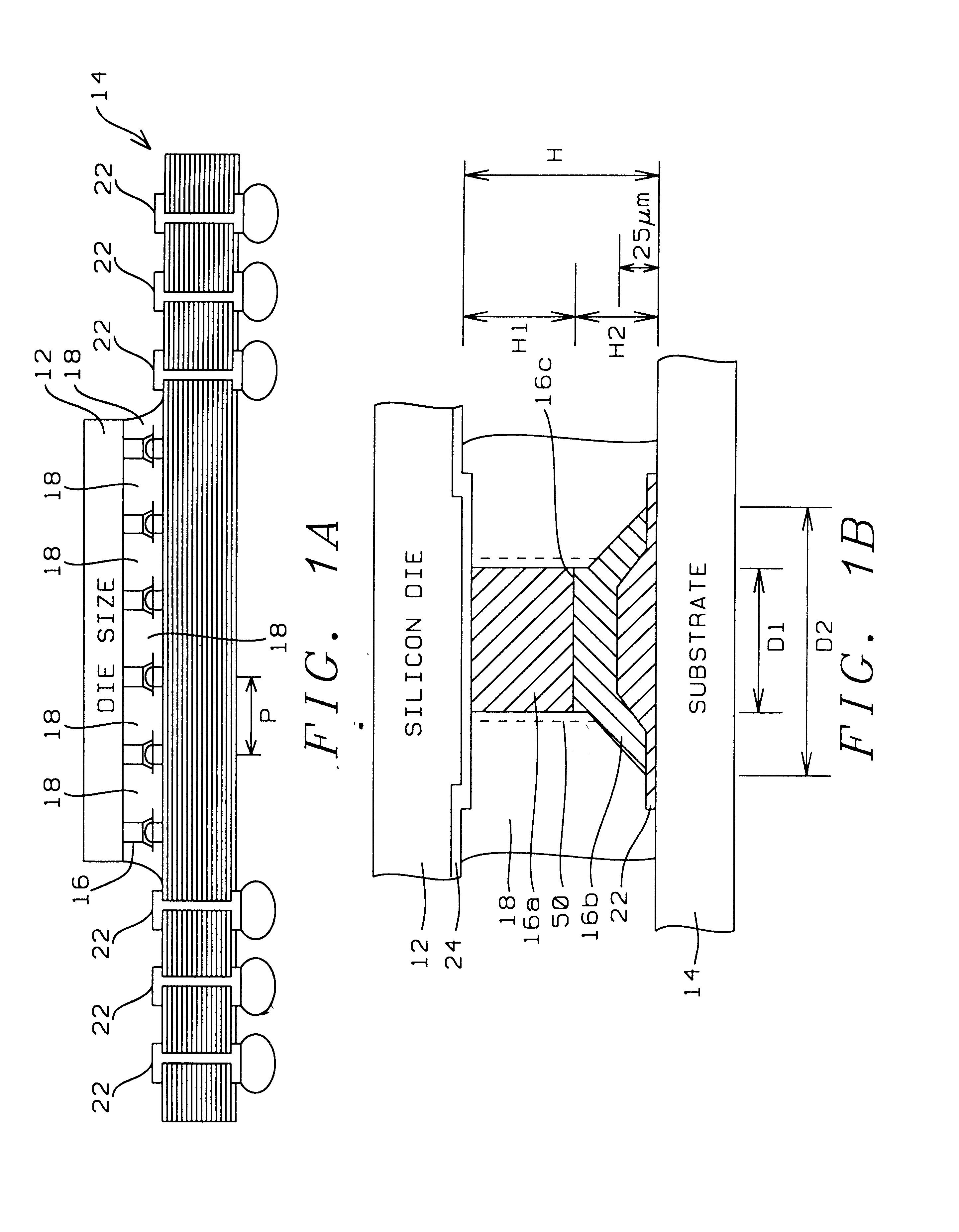

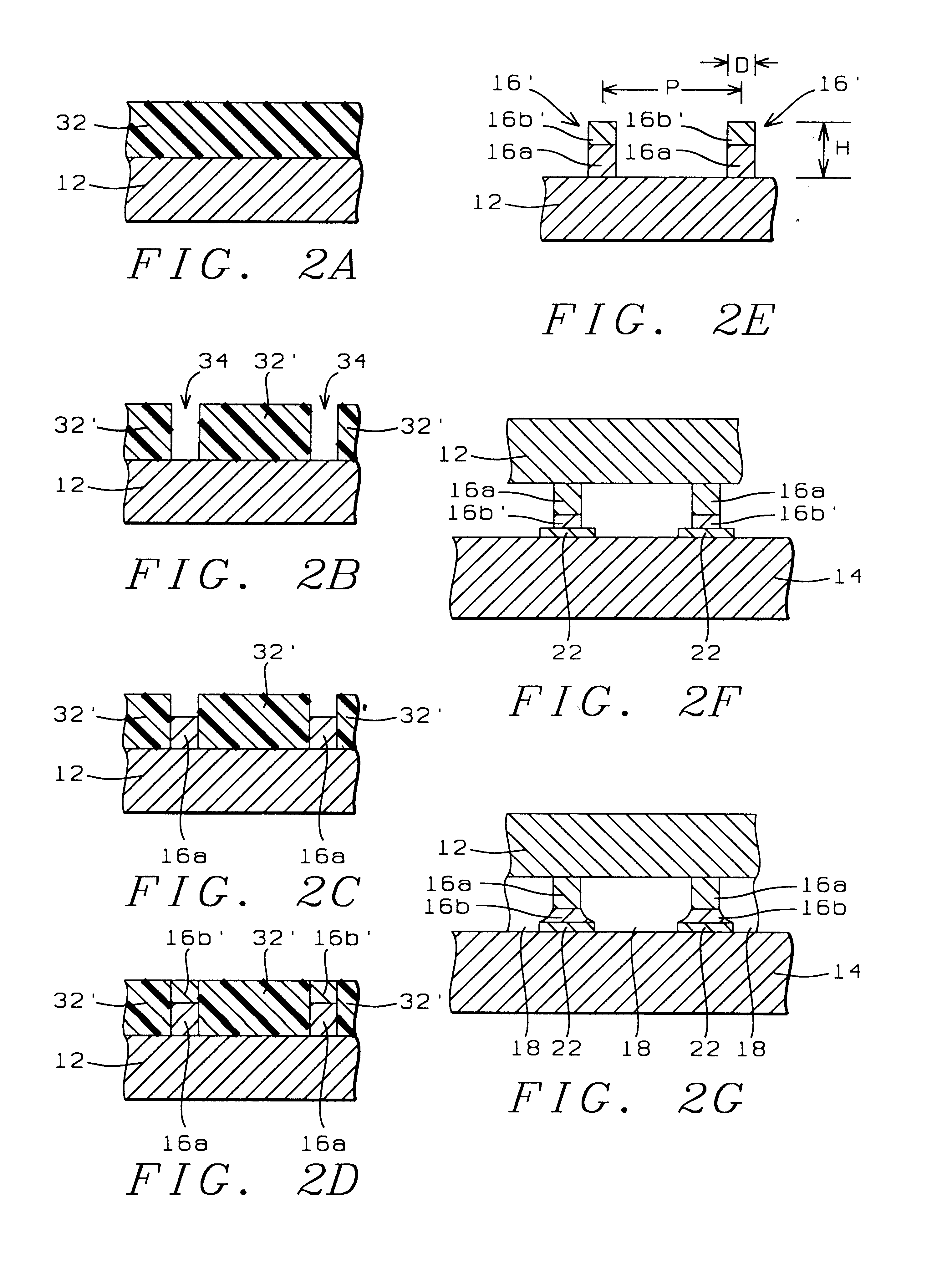

Pillar connections for semiconductor chips and method of manufacture

InactiveUS6578754B1Reduce chanceInduced in connectionSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor chip

A flip chip interconnect system comprises and elongated pillar comprising two elongated portions, one portion including copper and another portion including solder. The portion including copper is in contact with the semiconductor chip and has a length preferably of more than 55 microns to reduce the effect of .alpha. particles from the solder from affecting electronic devices on the chip. The total length of the pillar is preferably in the range of 80 to 120 microns.

Owner:ADVANPAK SOLUTIONS PTE

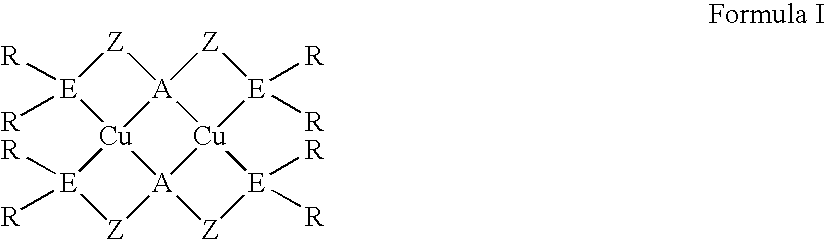

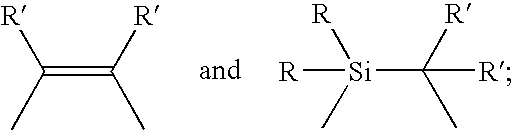

Oled devices with dinuclear copper compounds

ActiveUS20070111026A1Discharge tube luminescnet screensElectroluminescent light sourcesCompound (substance)Copper

An OLED device comprises an anode, a cathode and therebetween a light emitting layer containing a compound represented by Formula I below: wherein: each A is independently selected from N and P; each E is independently selected from N, P, and As; each Z is a radical independently selected from each R is an independently selected substituent; and each R′ is independently selected from H and a substituent; provided that two substituent groups can join to form a ring.

Owner:UNIVERSITY OF ROCHESTER +1

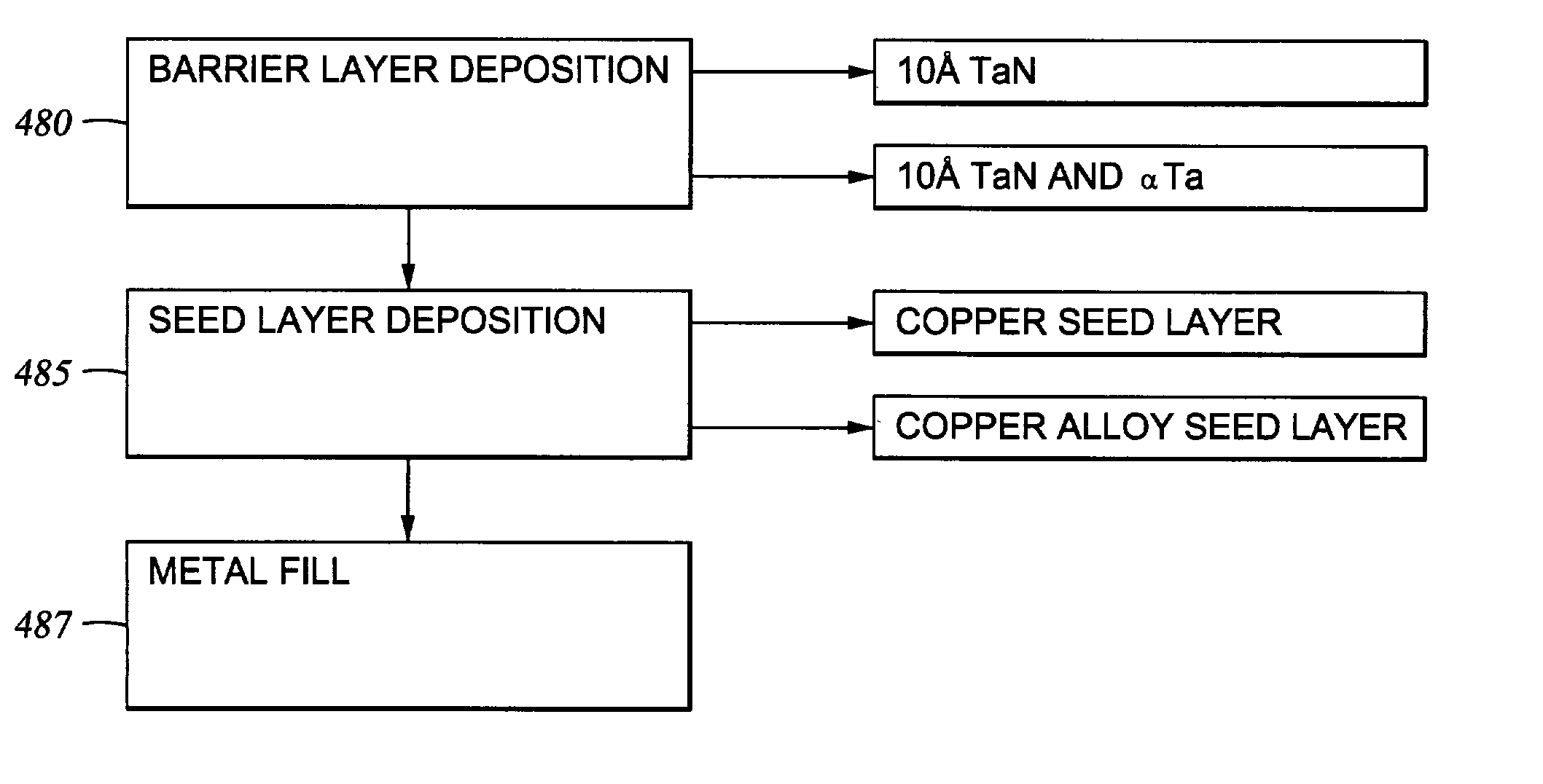

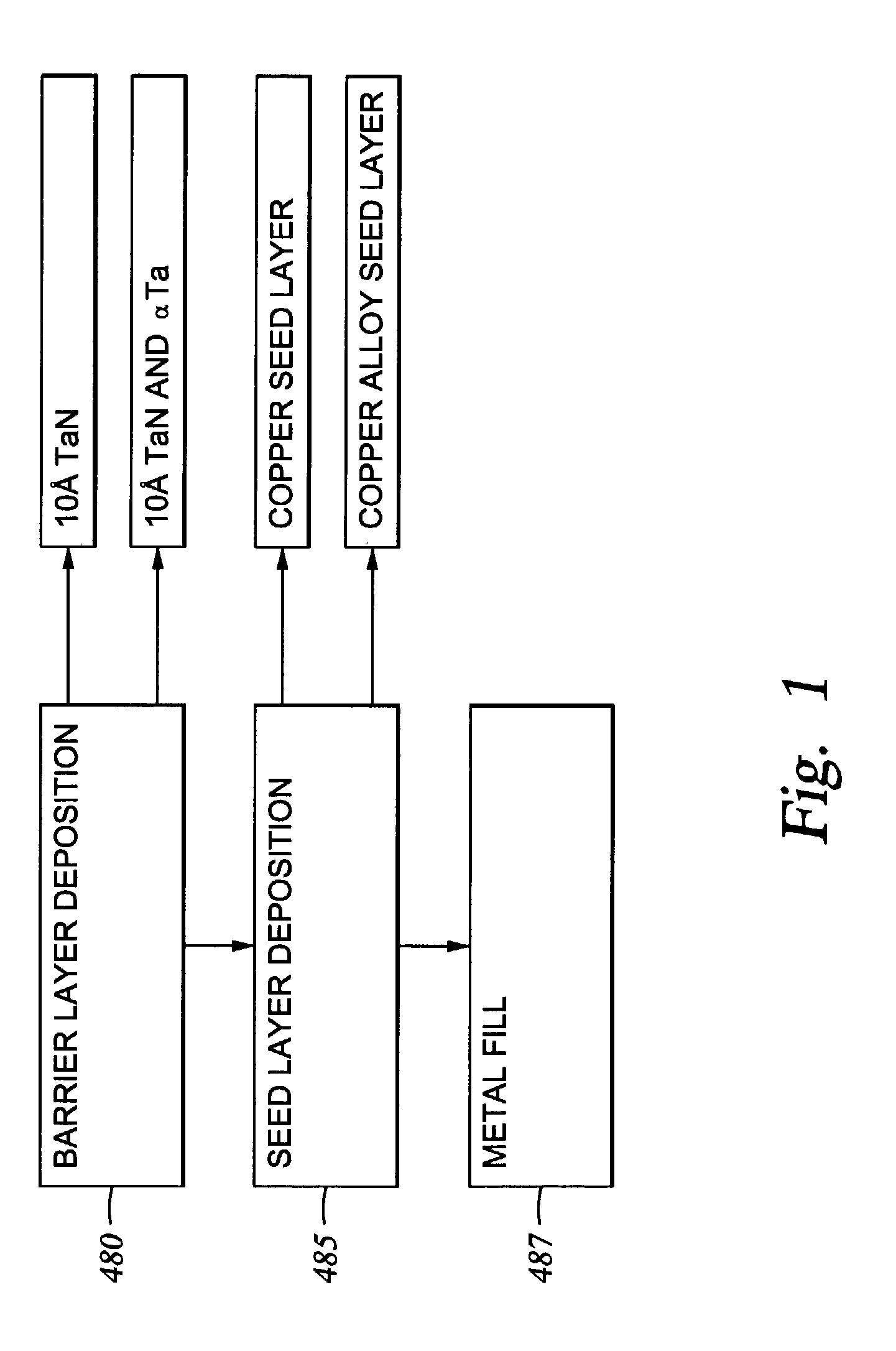

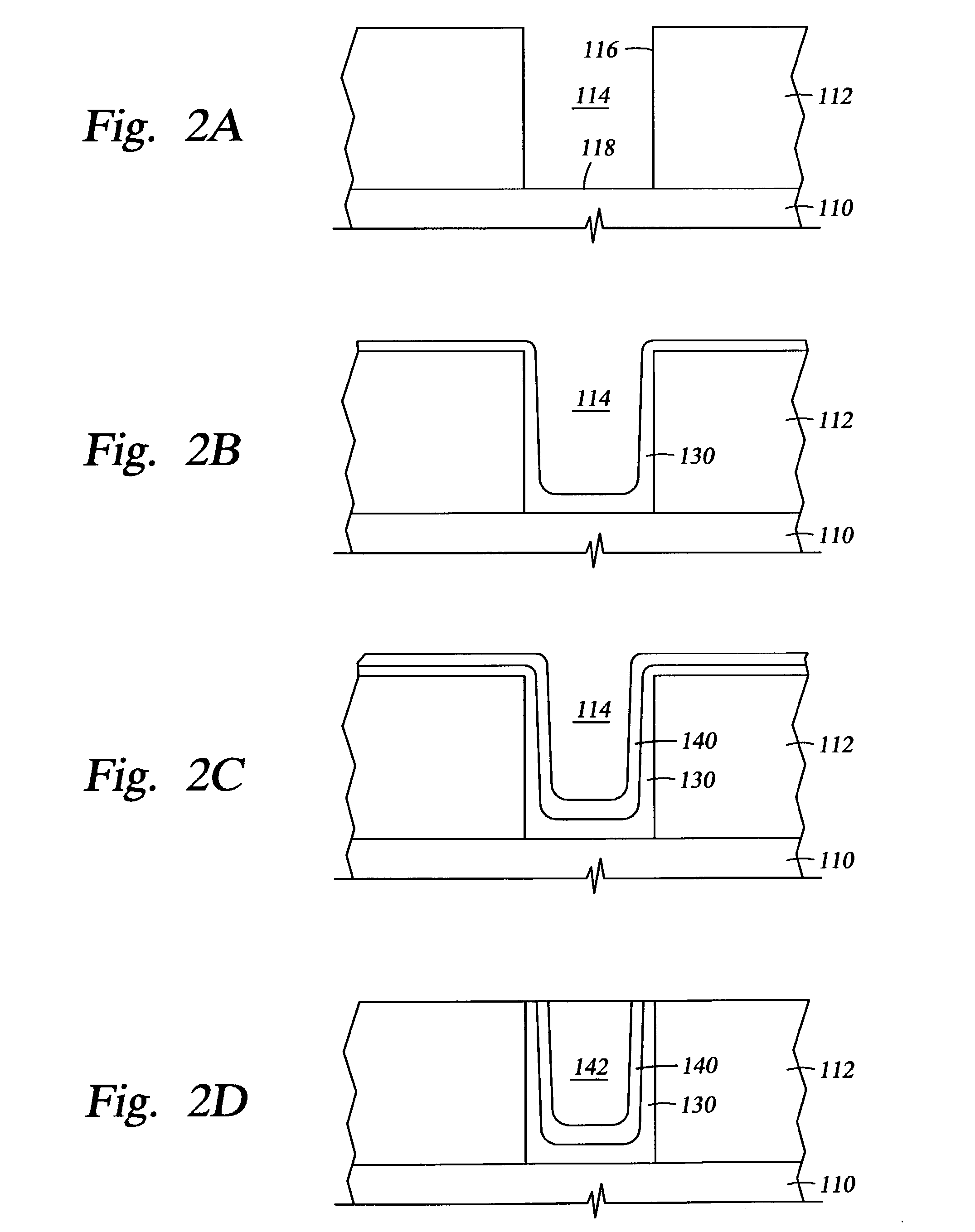

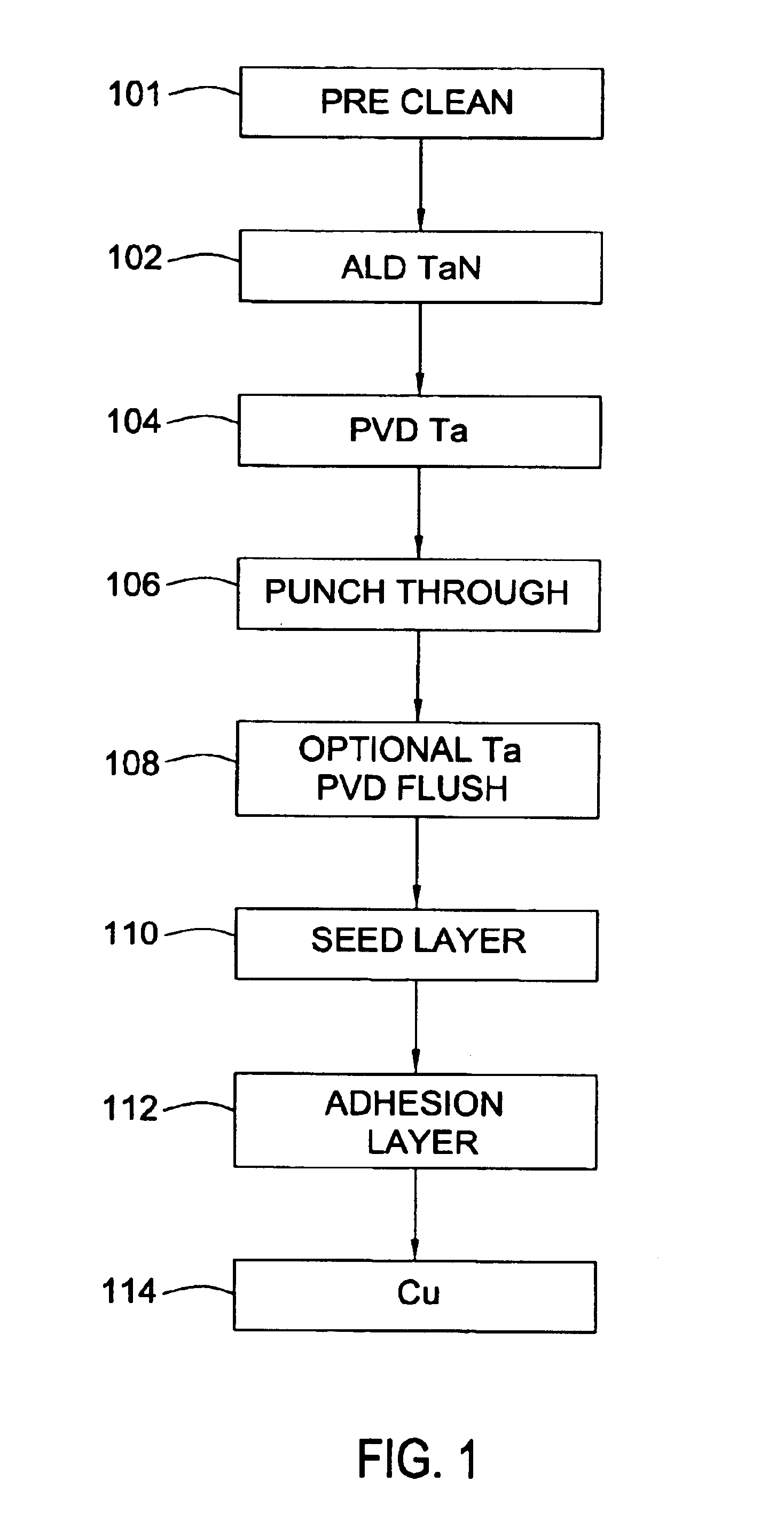

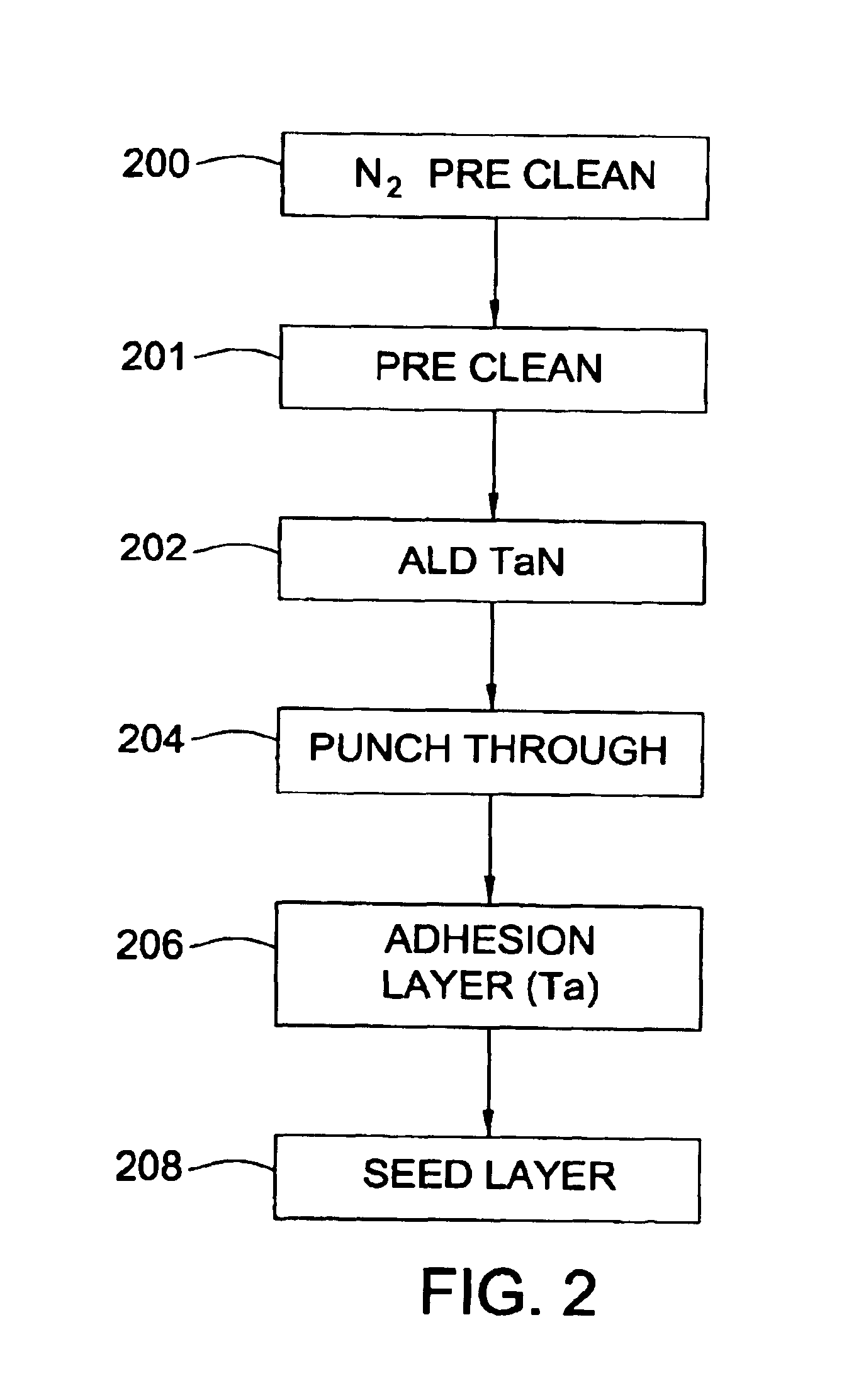

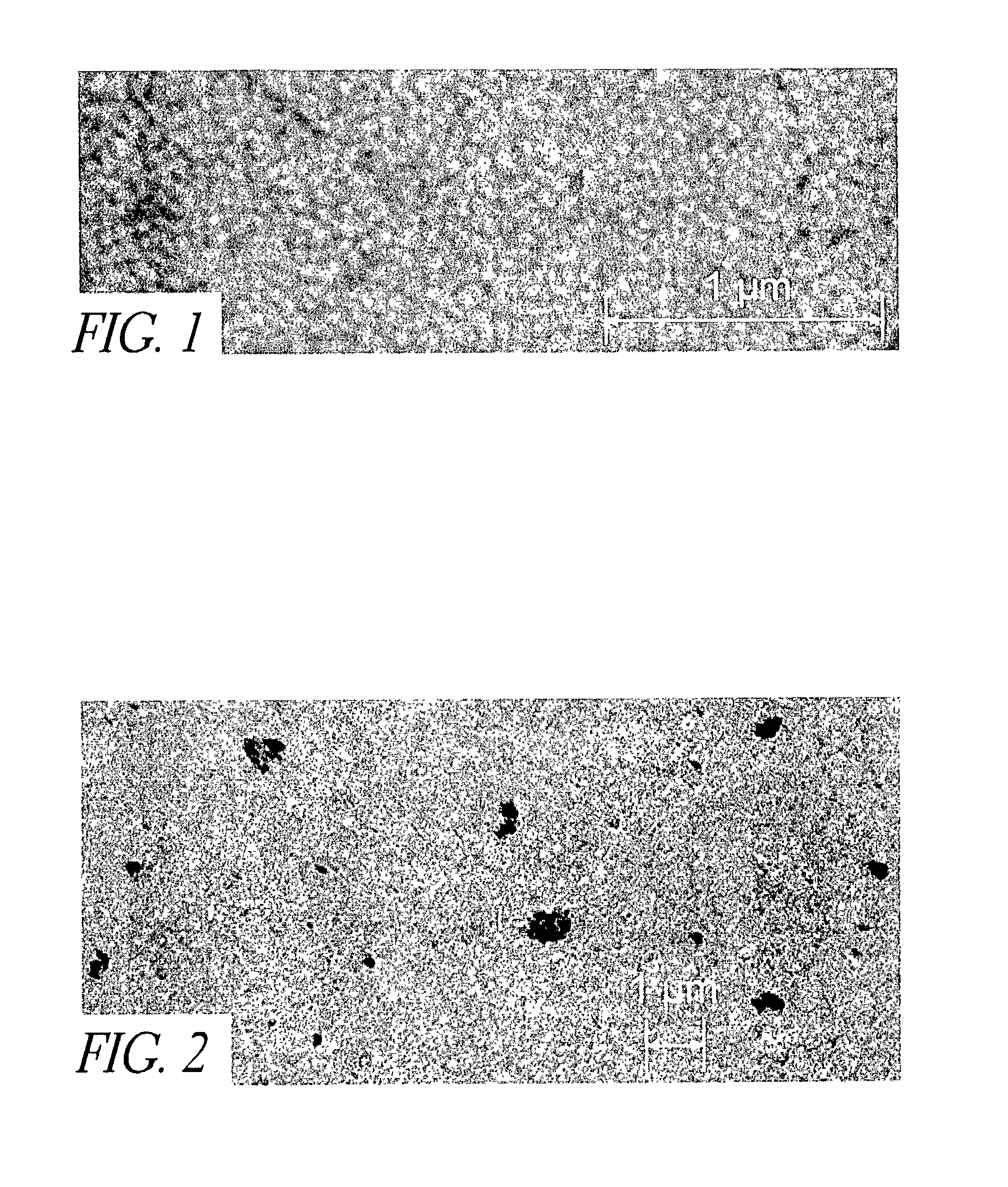

Integration of ALD tantalum nitride and alpha-phase tantalum for copper metallization application

InactiveUS20030082307A1Pretreated surfacesSemiconductor/solid-state device manufacturingMetal interconnectTantalum nitride

A method for forming a metal interconnect on a substrate is provided. The method includes depositing a refractory metal-containing barrier layer having a thickness less than about 20 angstroms on at least a portion of a metal layer by alternately introducing one or more pulses of a metal-containing compound and one or more pulses of a nitrogen-containing compound. The method also includes depositing a seed layer on at least a portion of the barrier layer, and depositing a second metal layer on at least a portion of the seed layer. The barrier layer provides adequate barrier properties and allows the grain growth of the metal layer to continue across the barrier layer into the second metal layer thereby enhancing the electrical performance of the interconnect.

Owner:APPLIED MATERIALS INC

Nonvolatile memory cell comprising a diode and a resistance-switching material

In a novel nonvolatile memory cell formed above a substrate, a diode is paired with a reversible resistance-switching material, preferably a metal oxide or nitride such as, for example, NixOy, NbxOy, TixOy, HFxOy, AlxOy, MgxOy, CoxOy, CrxOy, VxOy, ZnxOy, ZrxOy, BxNy, and AlxNy. In preferred embodiments, the diode is formed as a vertical pillar disposed between conductors. Multiple memory levels can be stacked to form a monolithic three dimensional memory array. In some embodiments, the diode comprises germanium or a germanium alloy, which can be deposited and crystallized at relatively low temperatures, allowing use of aluminum or copper in the conductors. The memory cell of the present invention can be used as a rewriteable memory cell or a one-time-programmable memory cell, and can store two or more data states.

Owner:SANDISK TECH LLC

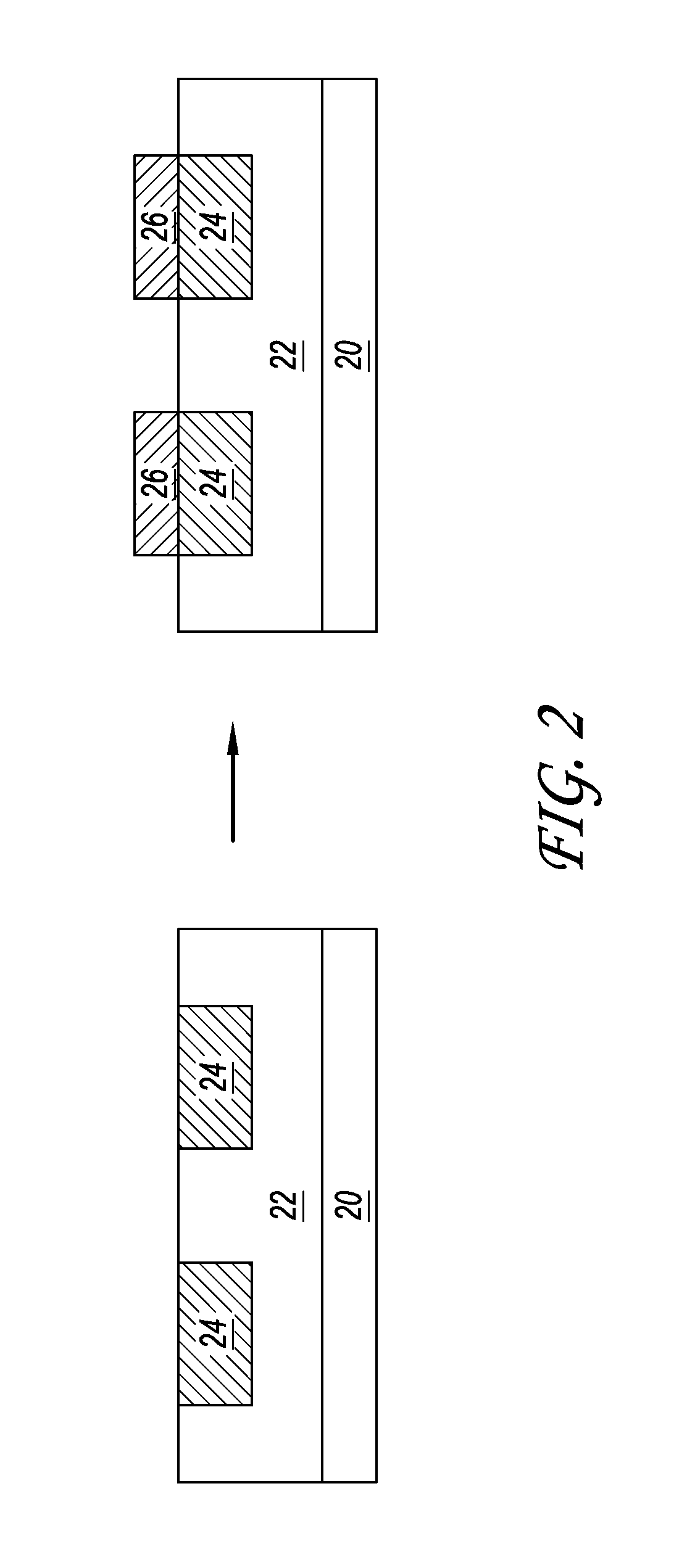

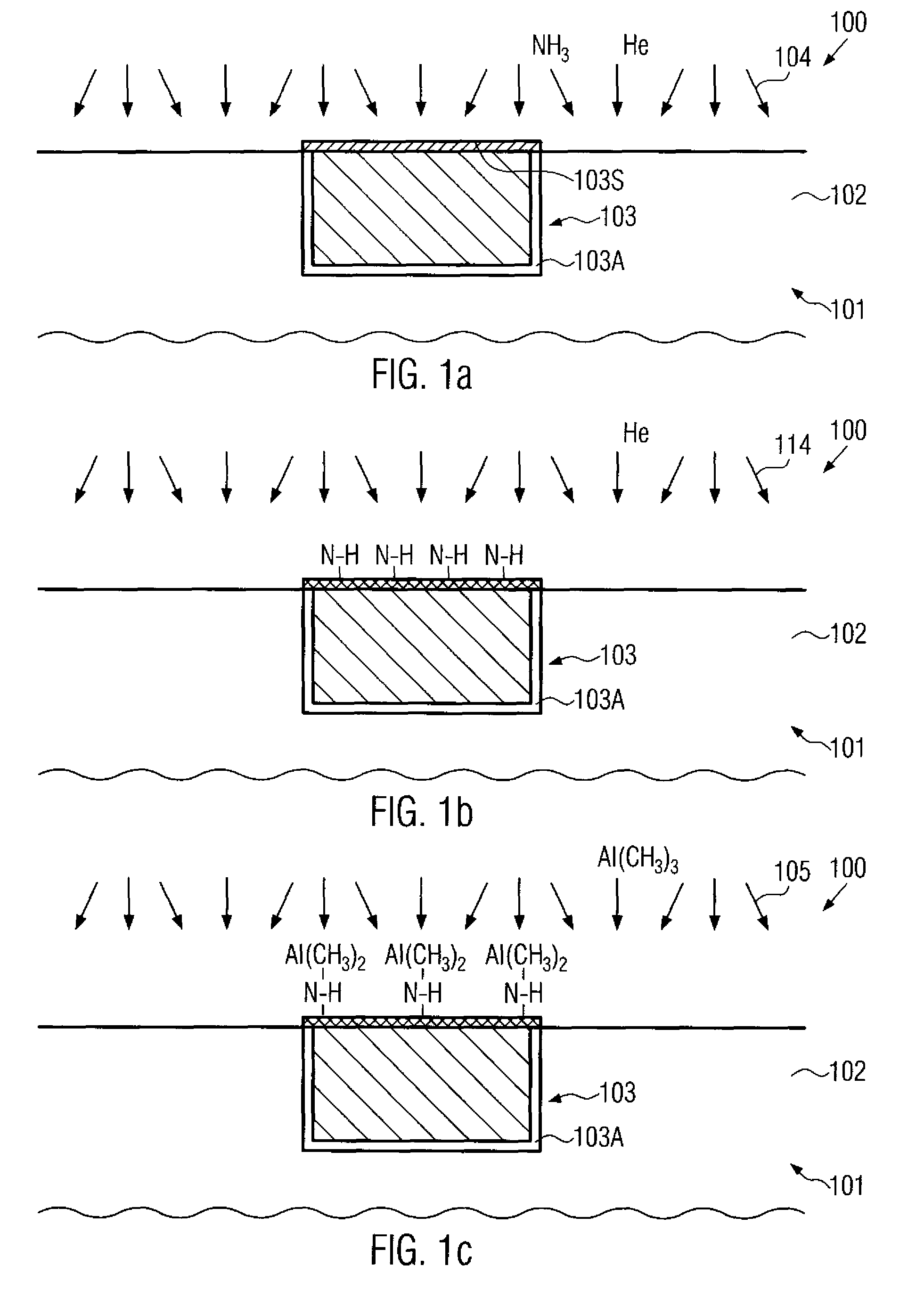

Forming capping layer over metal wire structure using selective atomic layer deposition

InactiveUS7084060B1Material nanotechnologySemiconductor/solid-state device detailsDielectricSemiconductor structure

Methods of forming a capping layer over a metal wire structure of a semiconductor device are disclosed. In one embodiment, the method includes providing a partially fabricated semiconductor device having exposed surfaces of the metal (e.g., copper) wire structure and a dielectric around the metal wire structure. The exposed surface of the metal wire structure is then activated by forming a seed layer thereon. The capping layer is then formed over the exposed surface of the metal wire structure by performing a selective atomic layer deposition (ALD) of a capping layer material onto the metal wire structure. As an alternative, the dielectric may be masked off to further assist the selectivity of the ALD. The invention also includes a semiconductor structure including the metal wire structure having an atomic layer deposition capping layer over an upper surface thereof.

Owner:IBM CORP

Thin films

InactiveUS20050181555A1Quality improvementHigh dielectric constantSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Thin films are formed by formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces. In some embodiments additional seed layers or additional transition layers are provided.

Owner:ASM INTERNATIONAL

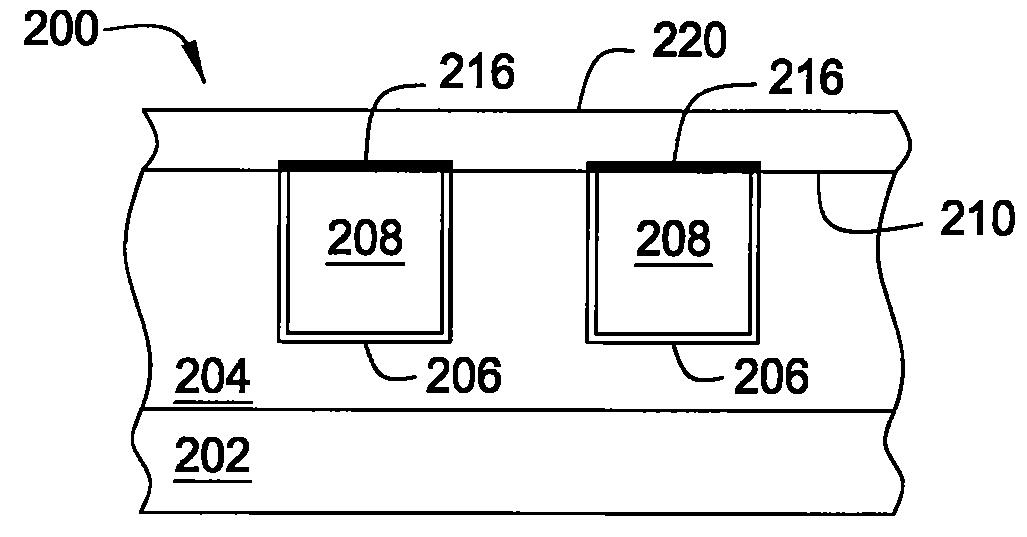

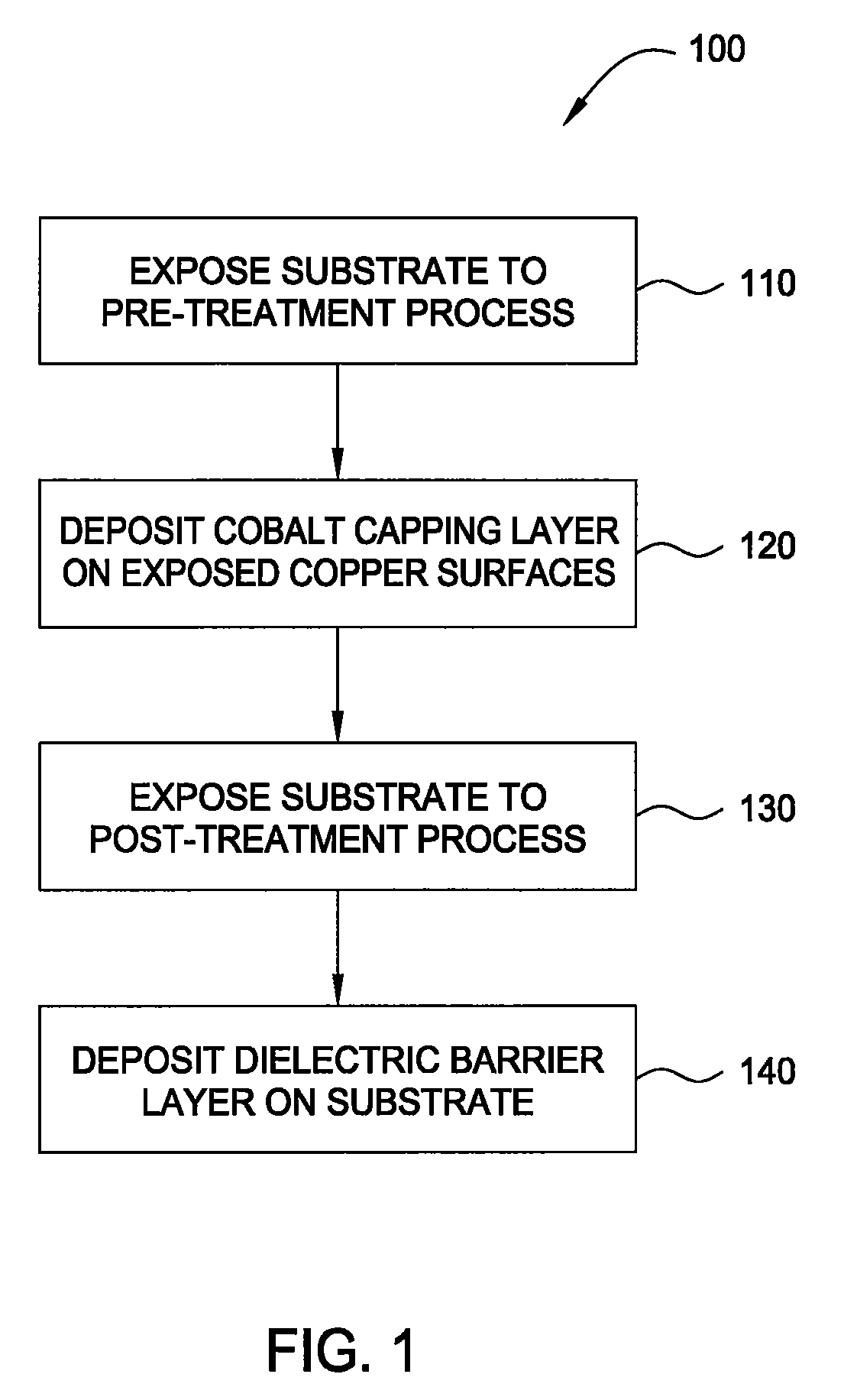

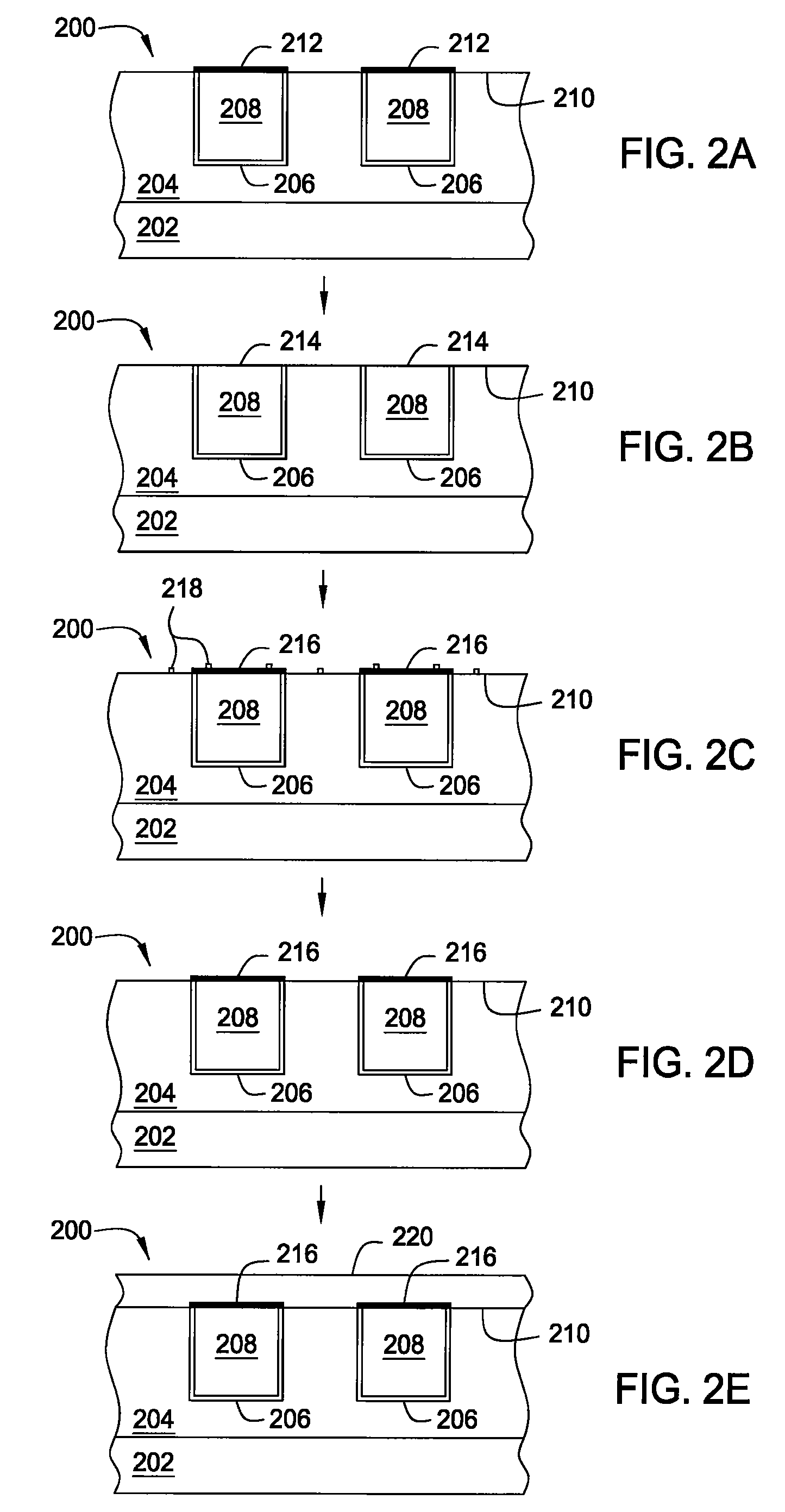

Selective cobalt deposition on copper surfaces

InactiveUS20090269507A1Pretreated surfacesSemiconductor/solid-state device manufacturingGas phaseDielectric surface

Embodiments of the invention provide processes to selectively form a cobalt layer on a copper surface over exposed dielectric surfaces. In one embodiment, a method for capping a copper surface on a substrate is provided which includes positioning a substrate within a processing chamber, wherein the substrate contains a contaminated copper surface and a dielectric surface, exposing the contaminated copper surface to a reducing agent while forming a copper surface during a pre-treatment process, exposing the substrate to a cobalt precursor gas to selectively form a cobalt capping layer over the copper surface while leaving exposed the dielectric surface during a vapor deposition process, and depositing a dielectric barrier layer over the cobalt capping layer and the dielectric surface. In another embodiment, a deposition-treatment cycle includes performing the vapor deposition process and subsequently a post-treatment process, which deposition-treatment cycle may be repeated to form multiple cobalt capping layers.

Owner:APPLIED MATERIALS INC

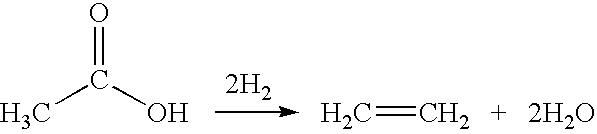

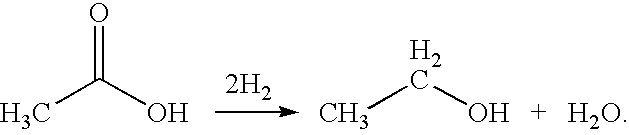

Process for catalytically producing ethylene directly from acetic acid in a single reaction zone

InactiveUS20100030001A1High selectivityHigh yieldHydrocarbonsBulk chemical productionAcetic acidHydrogen

A process for the selective production of ethylene by vapor phase reaction of acetic acid over a hydrogenating catalyst composition to form ethylene in a single reaction zone is disclosed and claimed. In an embodiment of this invention reaction of acetic acid and hydrogen over either a copper supported on iron oxide, copper-aluminum catalyst, cobalt supported on H-ZSM-5, ruthenium-cobalt supported on silica or cobalt supported on carbon selectively produces ethylene in a vapor phase at a temperature in the range of about 250° C. to 350° C.

Owner:CELANESE INT CORP

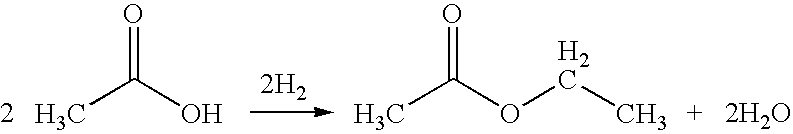

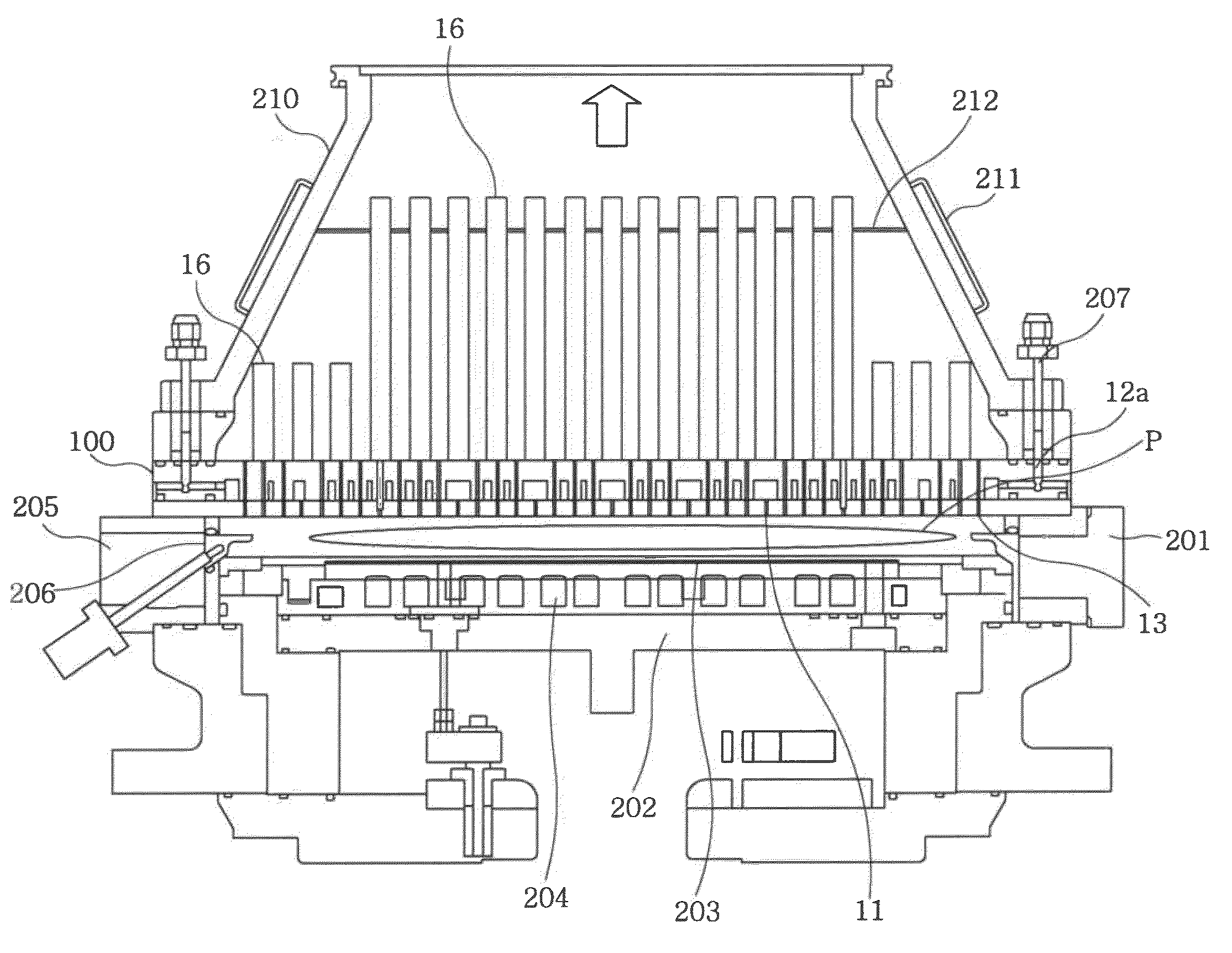

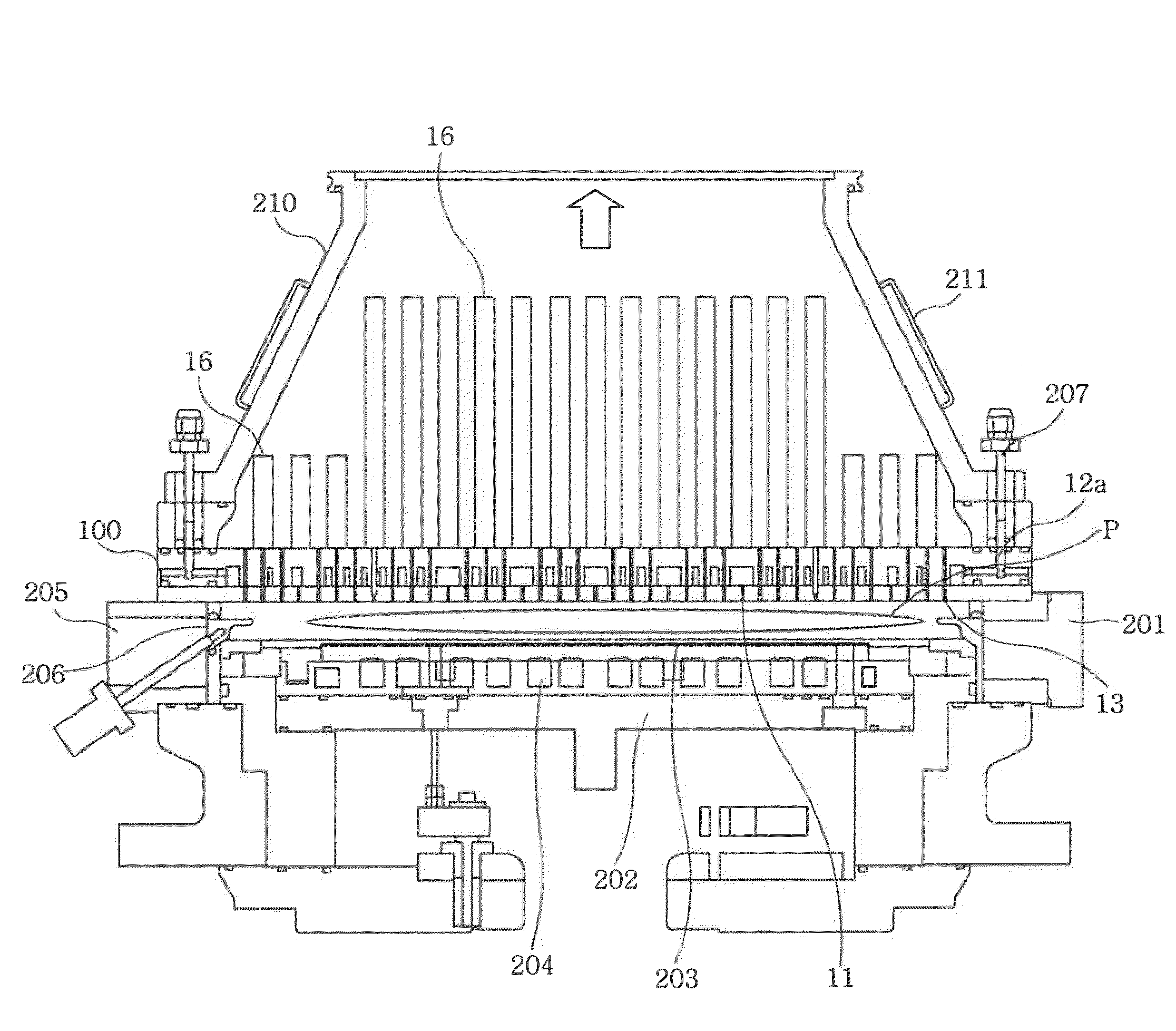

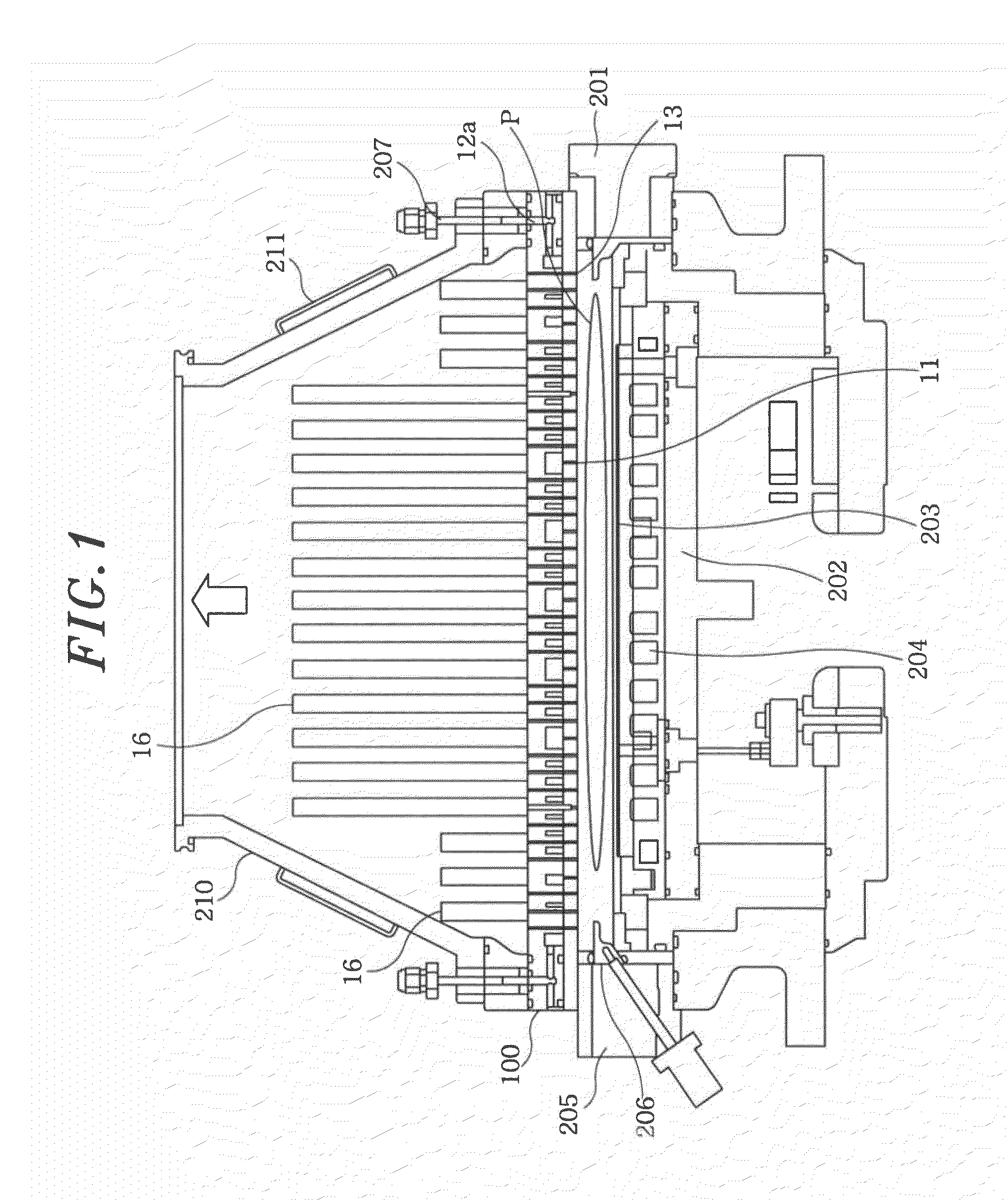

Shower head and plasma processing apparatus having same

InactiveUS8282769B2Avoid temperature riseImprove uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringCopper

A shower head is provided, in a processing chamber in which a substrate is processed, to face a mounting table for mounting the substrate thereon. The shower head includes: a facing surface that faces the mounting table to supply a gas to the substrate in a form of shower through a plurality of gas injection holes formed on the facing surface; an opposing surface provided opposite to the facing surface; and a plurality of bar-shaped heat transfer columns standing on the opposing surface. Here, the heat transfer columns have varying lengths and / or thicknesses to adjust heat capacities thereof. The heat transfer columns are made of one of aluminum, stainless steel, and copper.

Owner:TOKYO ELECTRON LTD

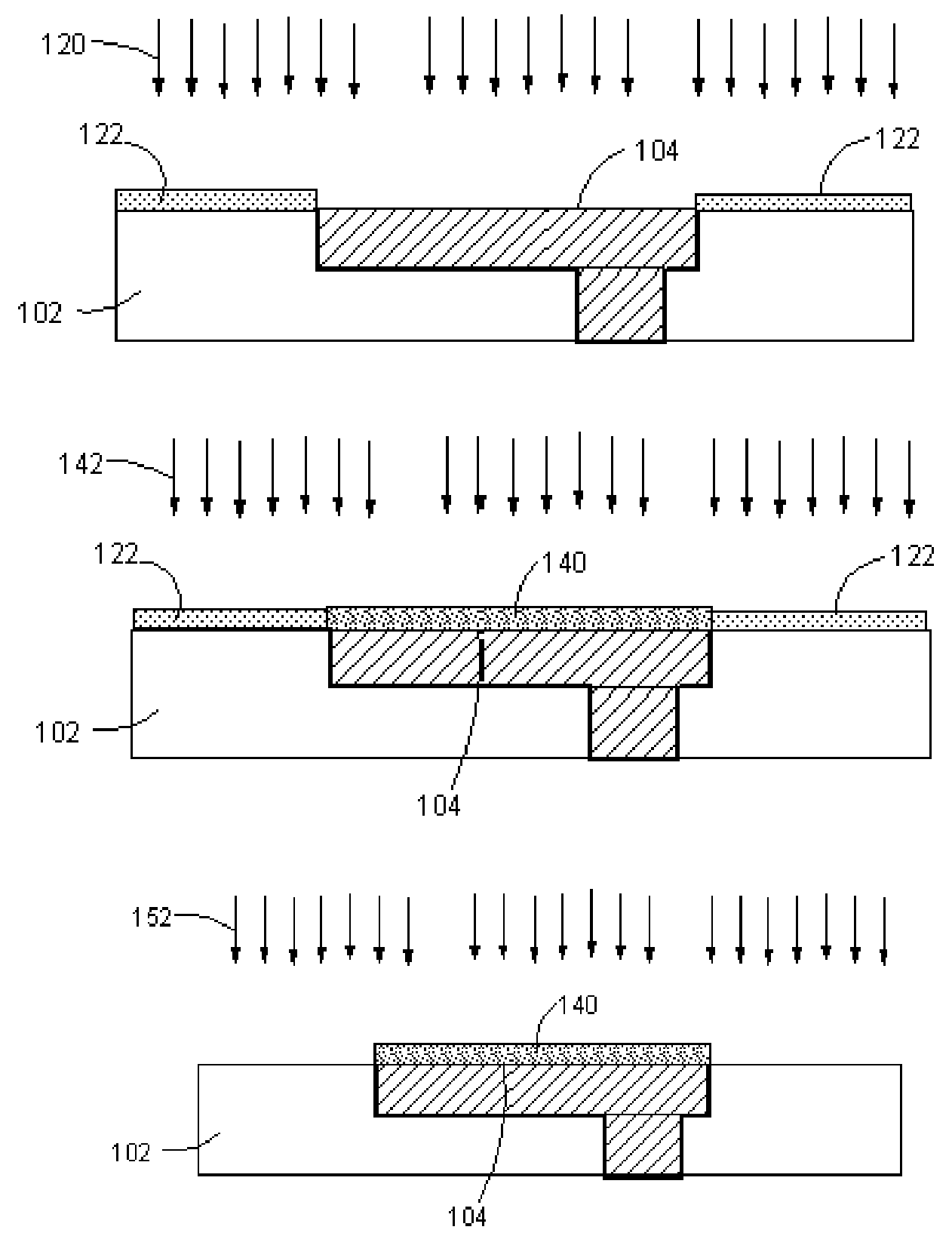

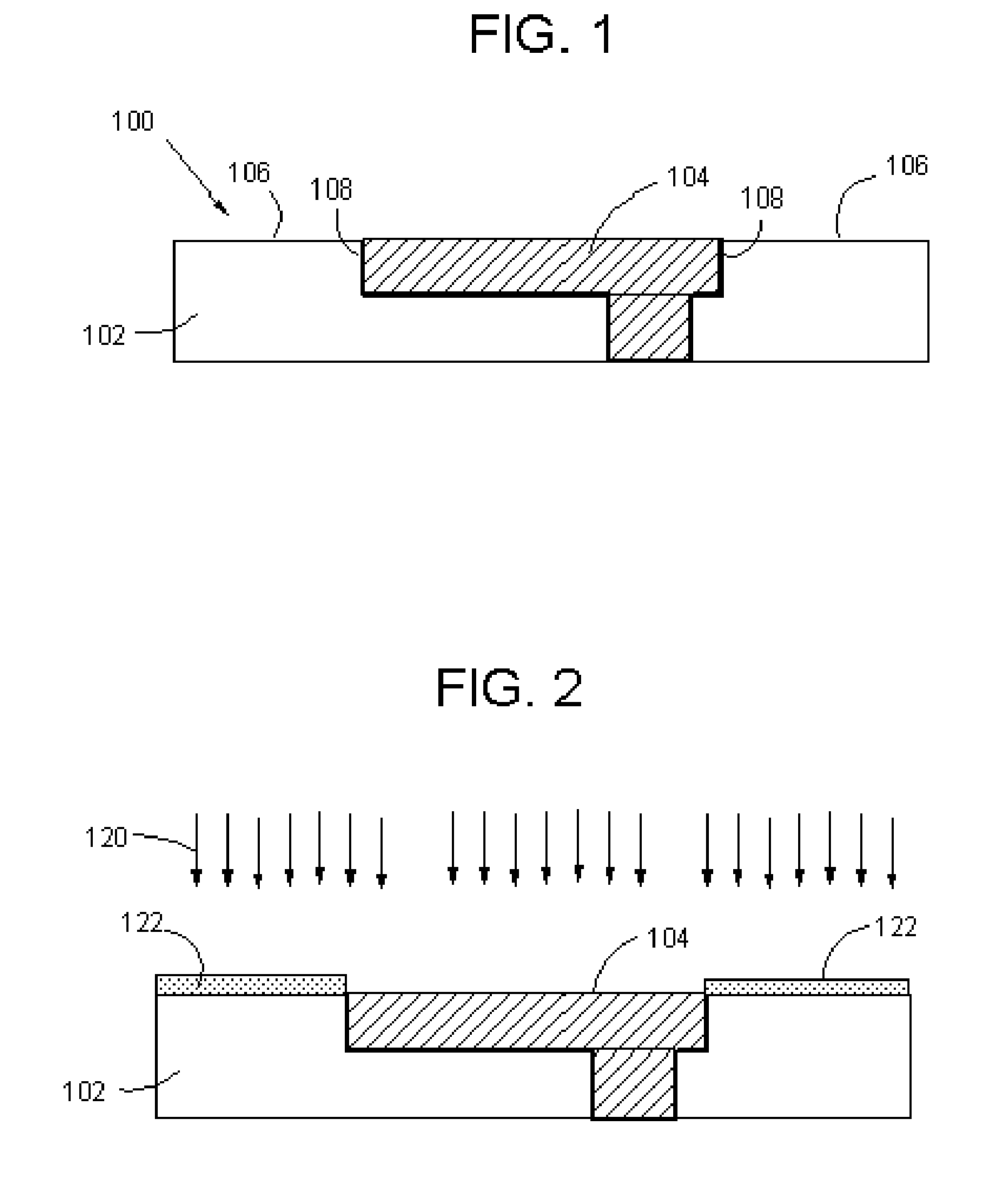

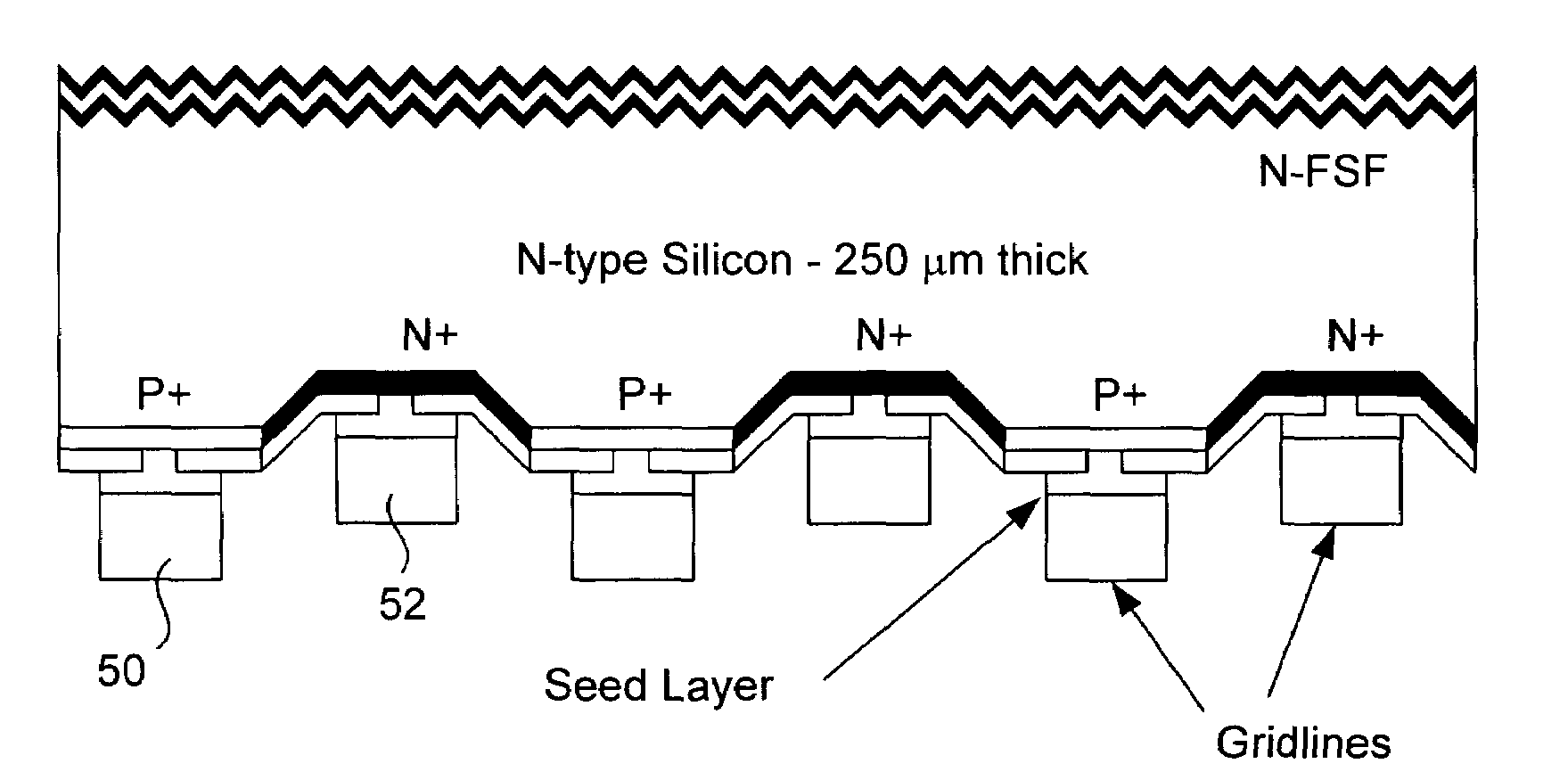

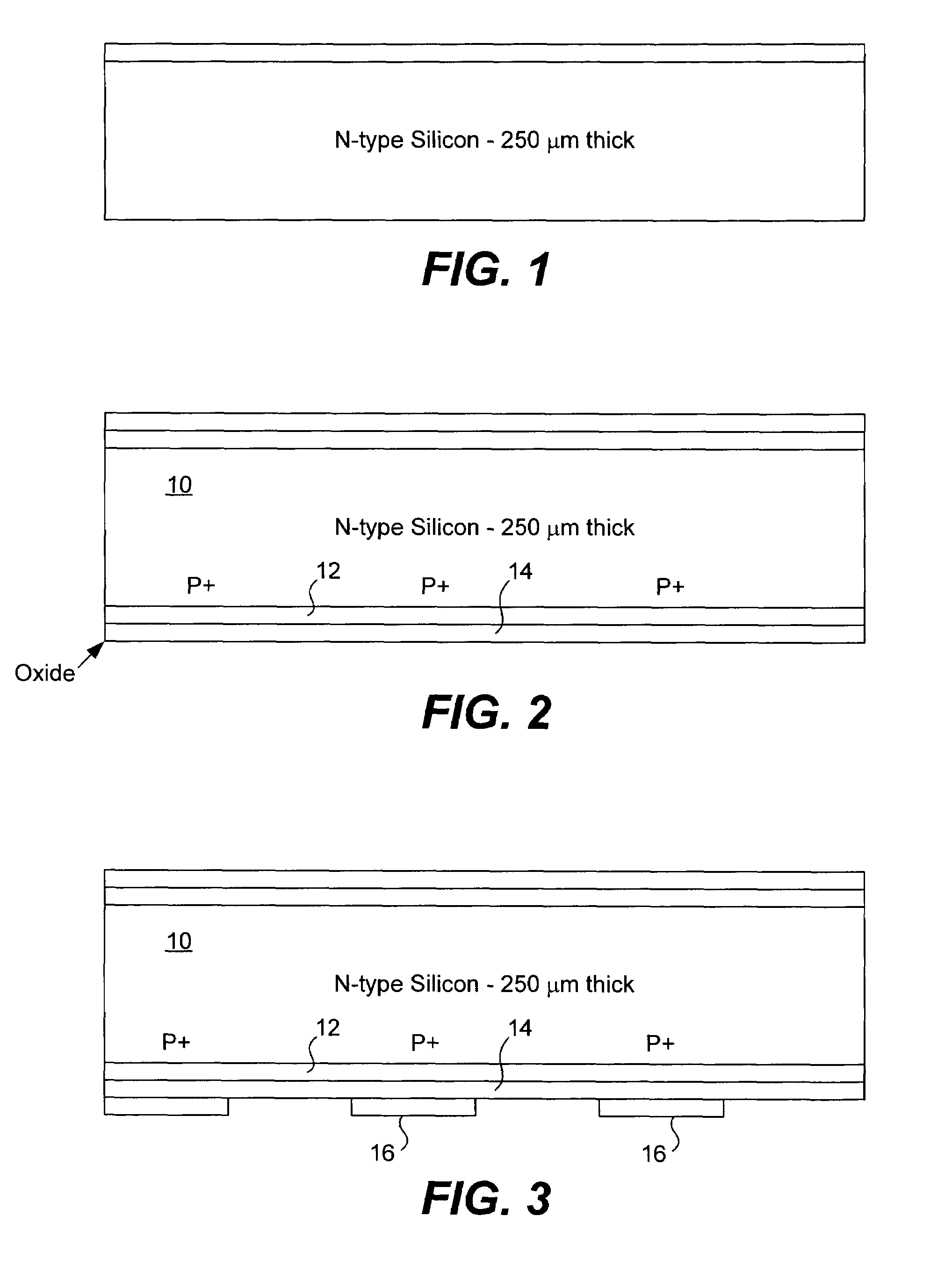

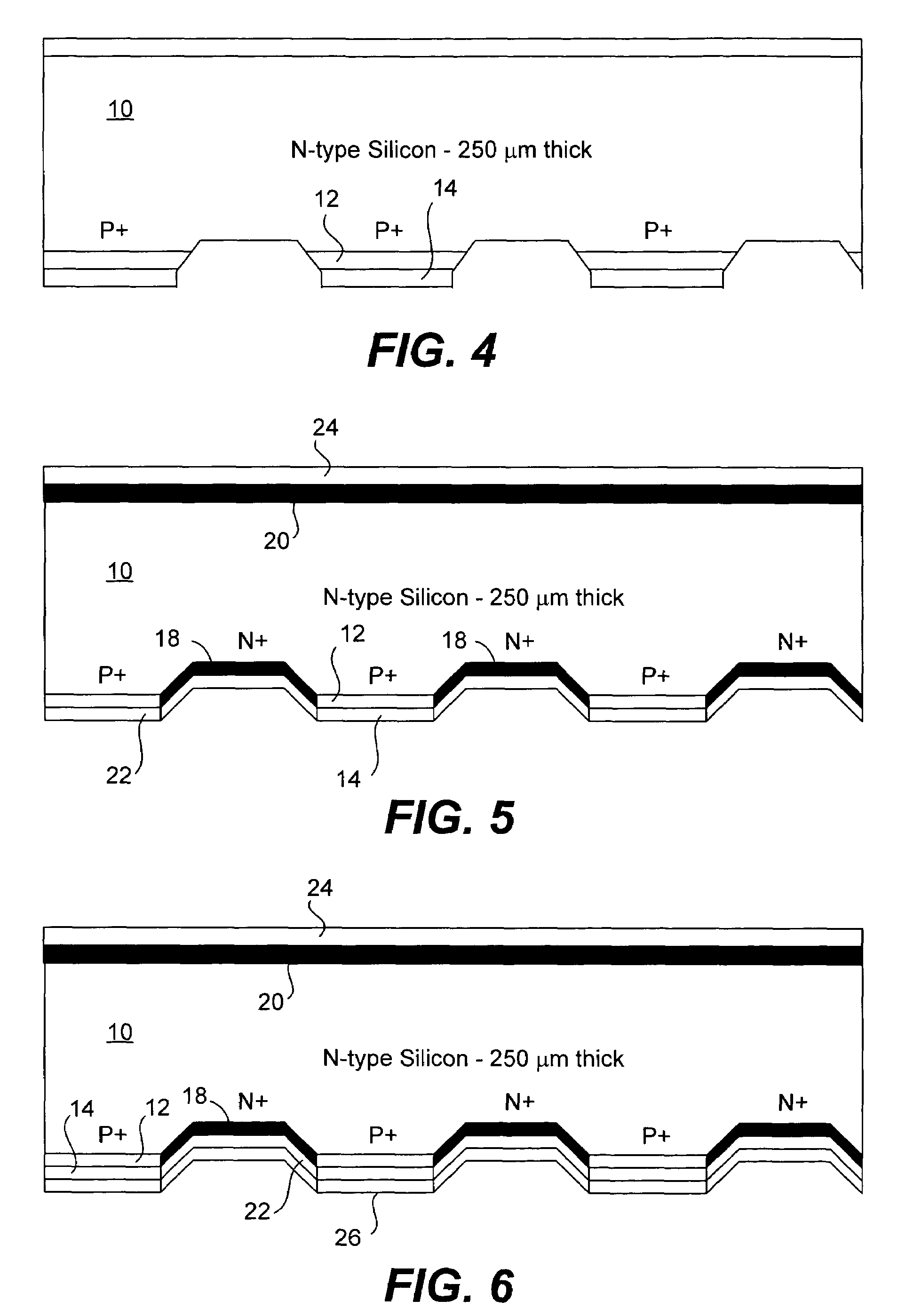

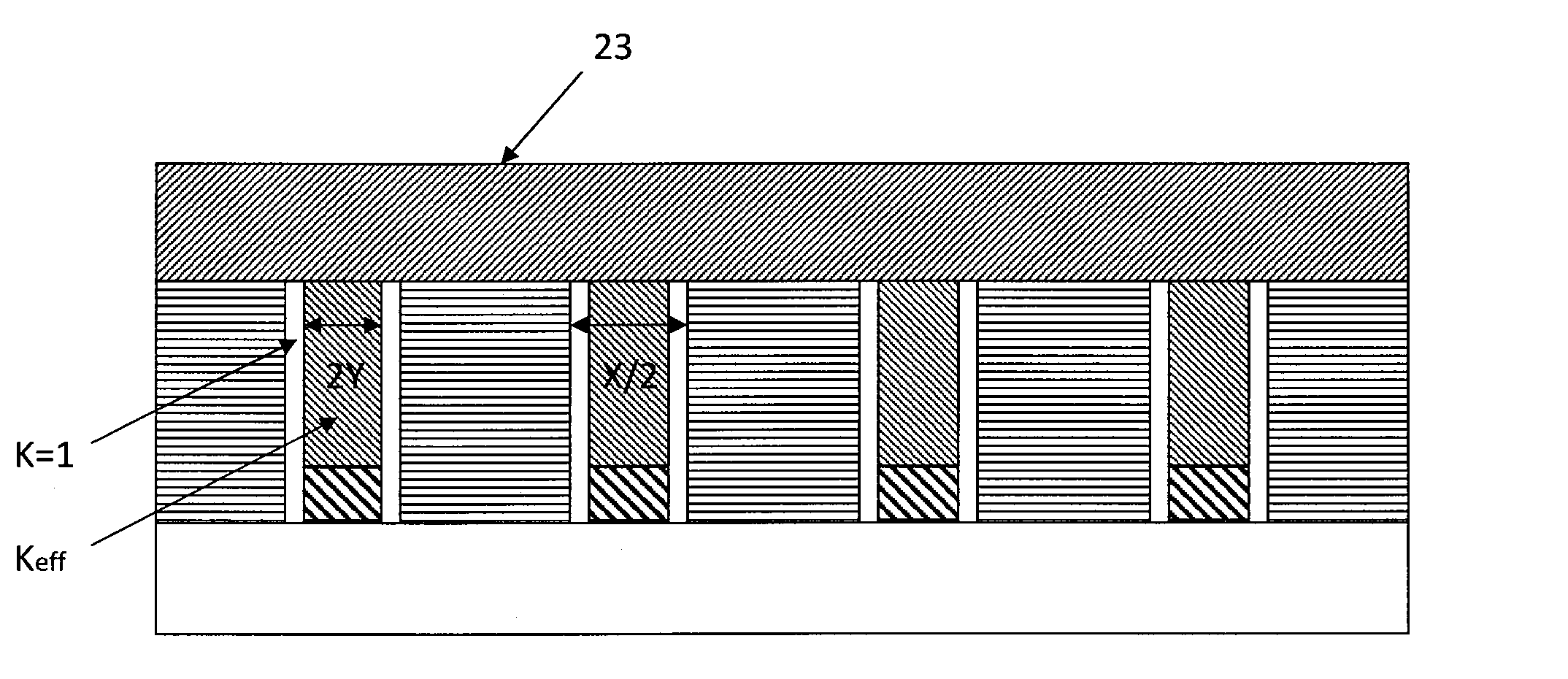

Solar cell and method of manufacture

ActiveUS7339110B1Easy to manufactureLess expensiveFinal product manufacturePhotovoltaic energy generationEngineeringSilicon oxide

A solar cell that is readily manufactured using processing techniques which are less expensive than microelectronic circuit processing. In preferred embodiments, printing techniques are utilized in selectively forming masks for use in etching of silicon oxide and diffusing dopants and in forming metal contacts to diffused regions. In a preferred embodiment, p-doped regions and n-doped regions are alternately formed in a surface of the wafer in offset levels through use of masking and etching techniques. Metal contacts are made to the p-regions and n-regions by first forming a seed layer stack that comprises a first layer such as aluminum that contacts silicon and functions as an infrared reflector, second layer such titanium tungsten that acts as diffusion barrier, and a third layer functions as a plating base. A thick conductive layer such as copper is then plated over the seed layer, and the seed layer between plated lines is removed. A front surface of the wafer is preferably textured by etching or mechanical abrasion with an antireflection layer provided over the textured surface. A field layer can be provided in the textured surface with the combined effect being a very low surface recombination velocity.

Owner:MAXEON SOLAR PTE LTD +1

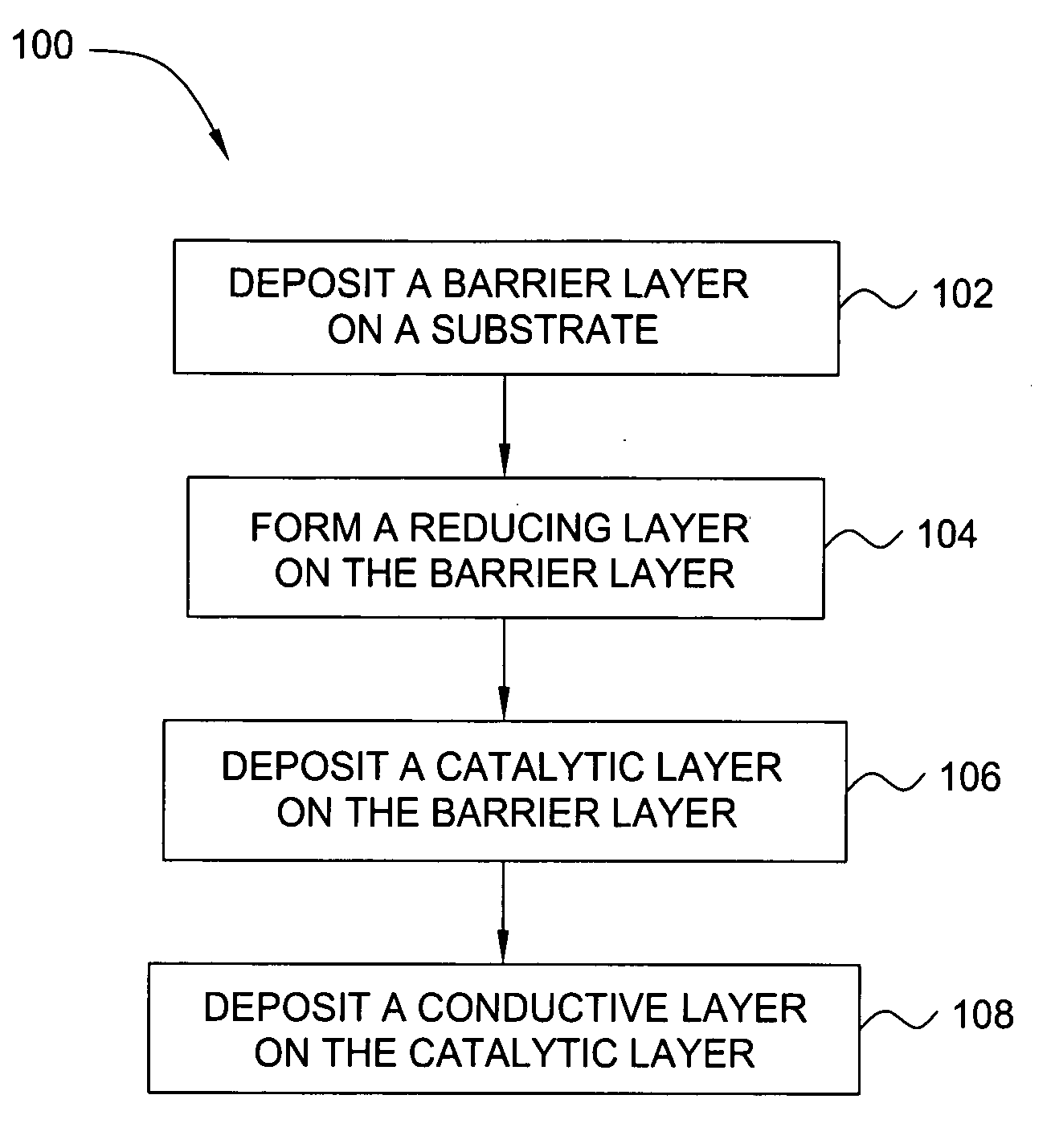

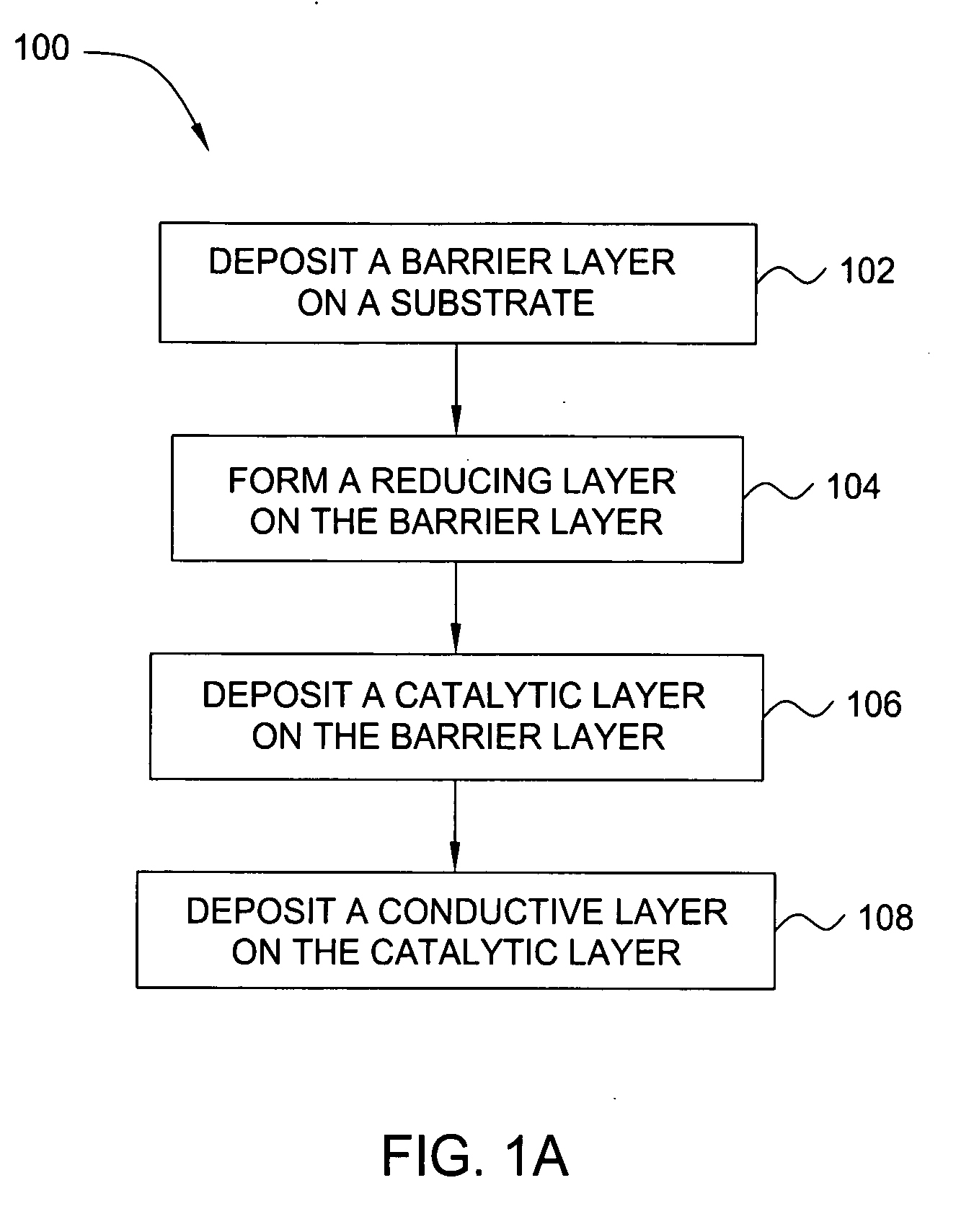

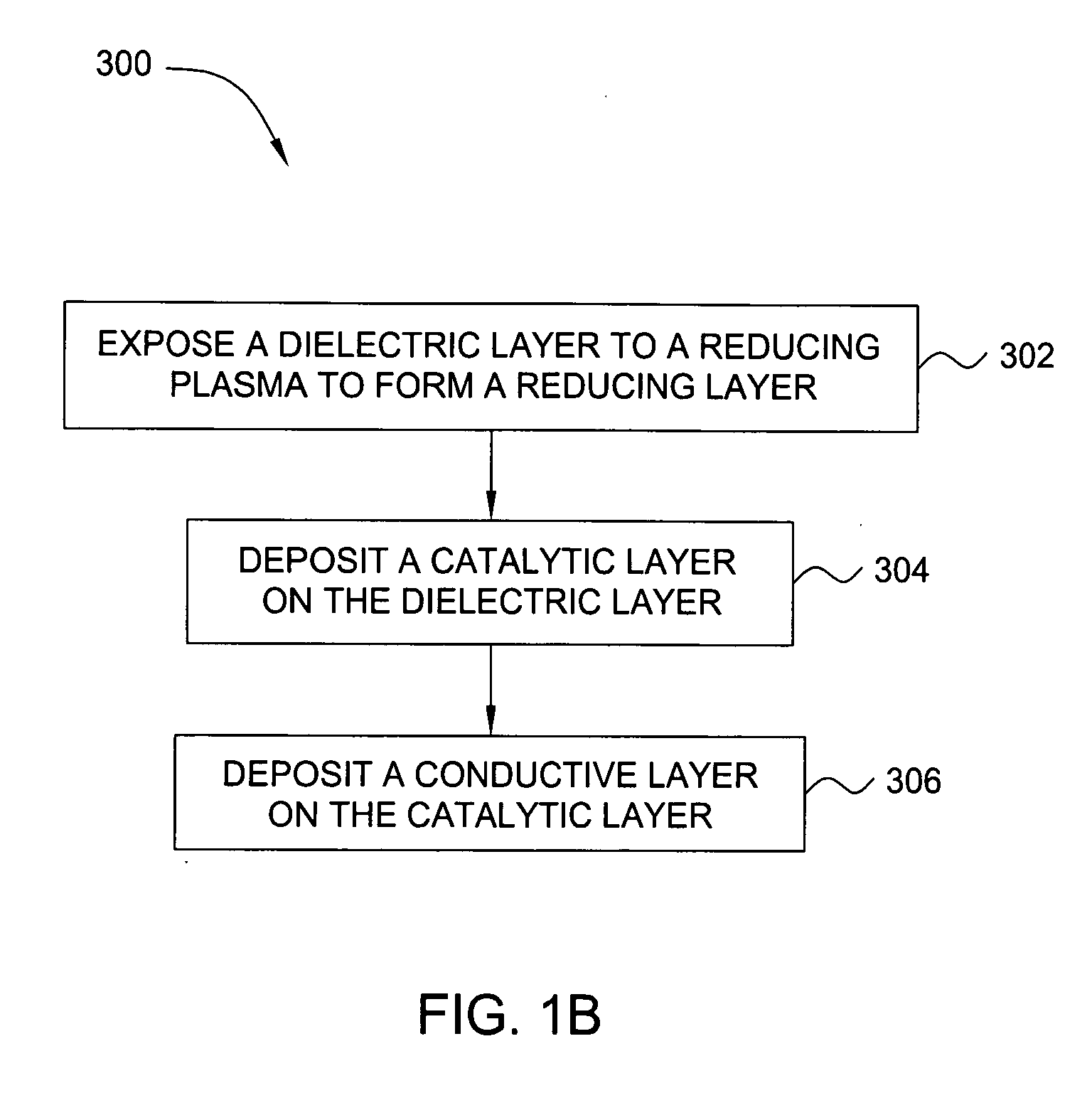

Deposition of an intermediate catalytic layer on a barrier layer for copper metallization

InactiveUS20060240187A1Solid-state devicesSemiconductor/solid-state device manufacturingIridiumSilanes

In one embodiment, a method for depositing a conductive material on a substrate is provided which includes exposing a substrate containing a barrier layer to a volatile reducing precursor to form a reducing layer during a soak process, exposing the reducing layer to a catalytic-metal precursor to deposit a catalytic metal-containing layer on the barrier layer, and depositing a conductive layer (e.g., copper) on the catalytic metal-containing layer. The volatile reducing precursor may include phosphine, diborane, silane, a plasma thereof, or a combination thereof and be exposed to the substrate for a time period within a range from about 1 second to about 30 seconds during the soak process. The catalytic metal-containing layer may contain ruthenium, cobalt, rhodium, iridium, nickel, palladium, platinum, silver, or copper. In one example, the catalytic metal-containing layer is deposited by a vapor deposition process utilizing ruthenium tetroxide formed by an in situ process.

Owner:APPLIED MATERIALS INC

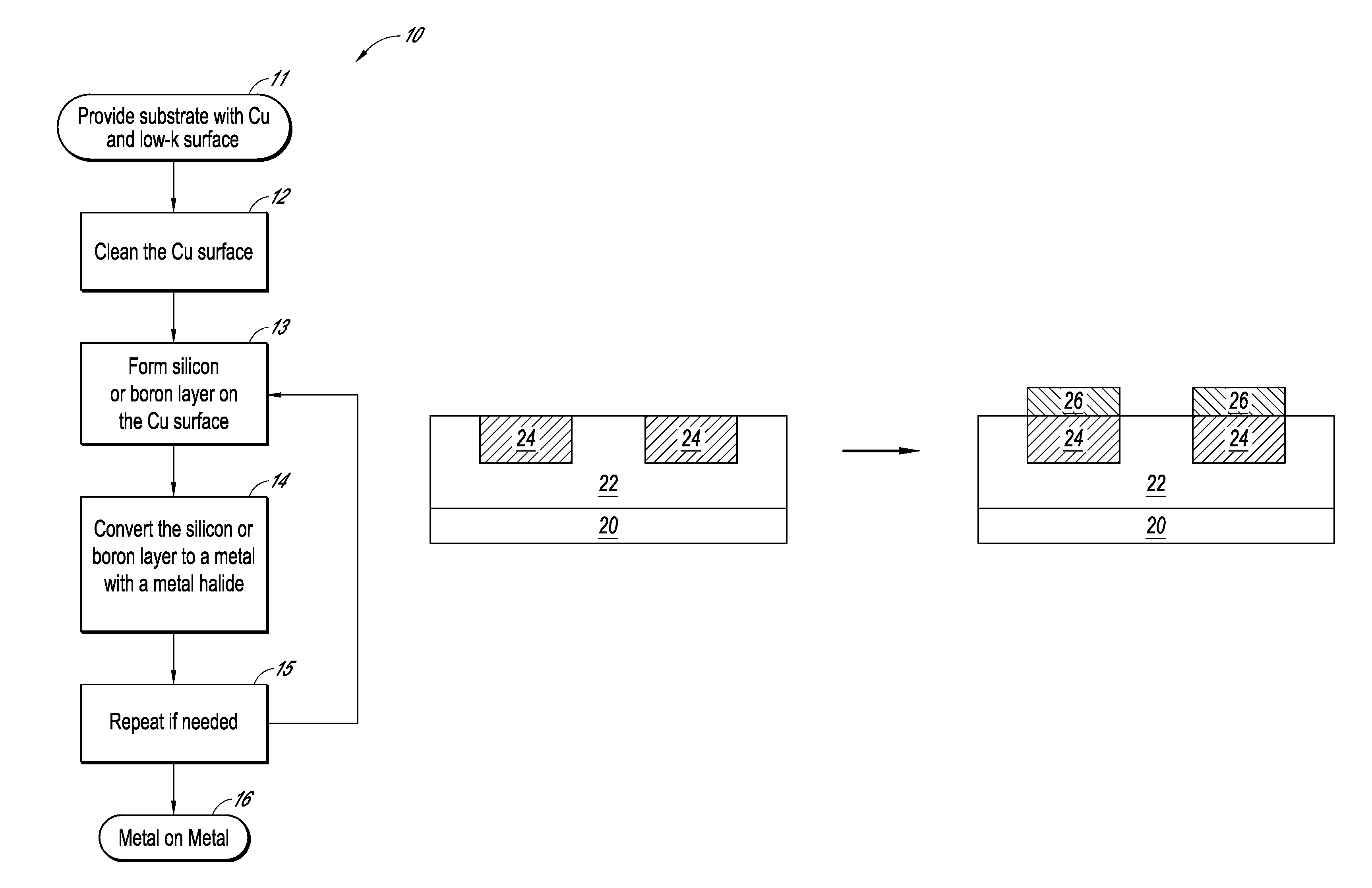

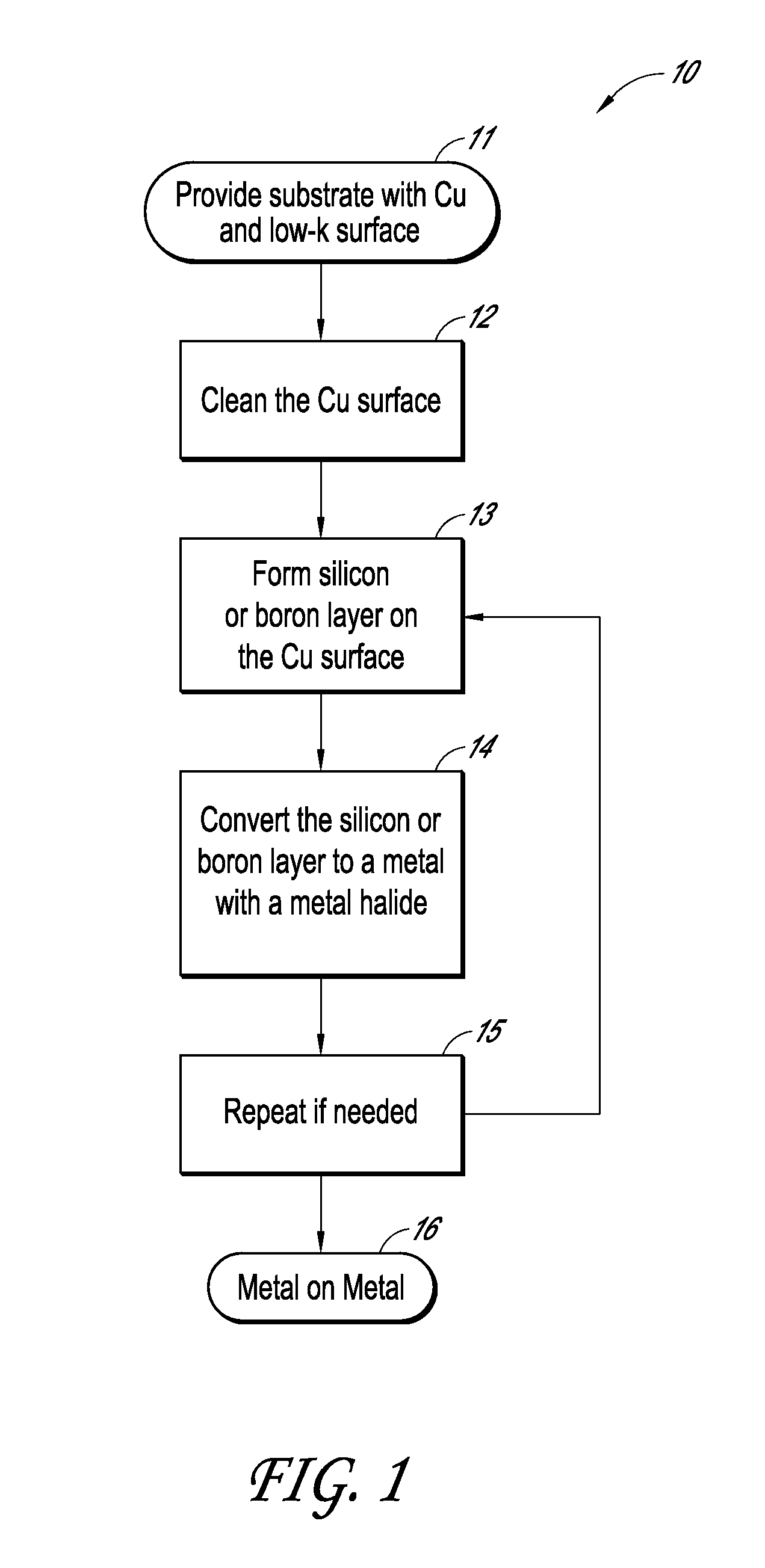

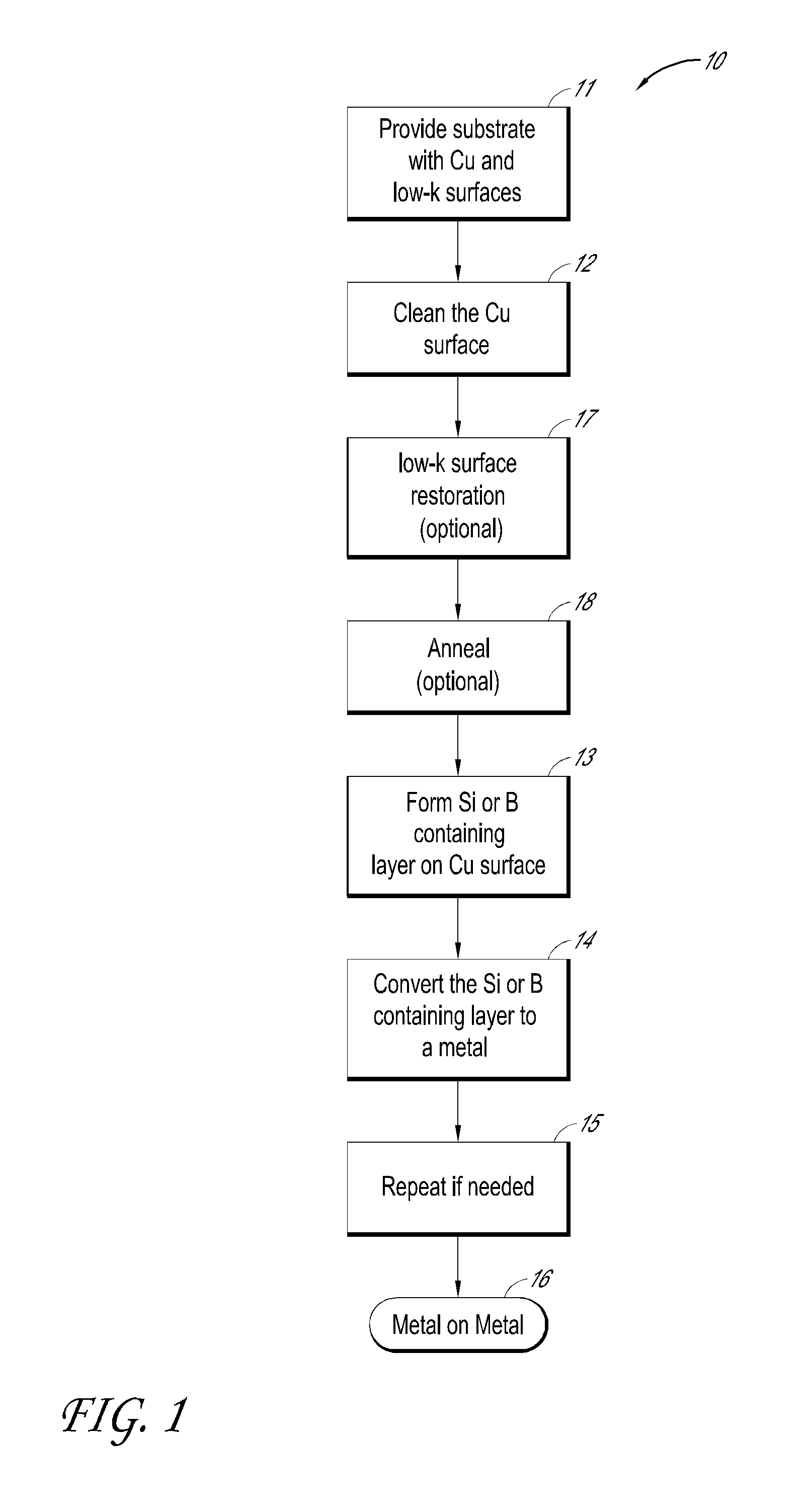

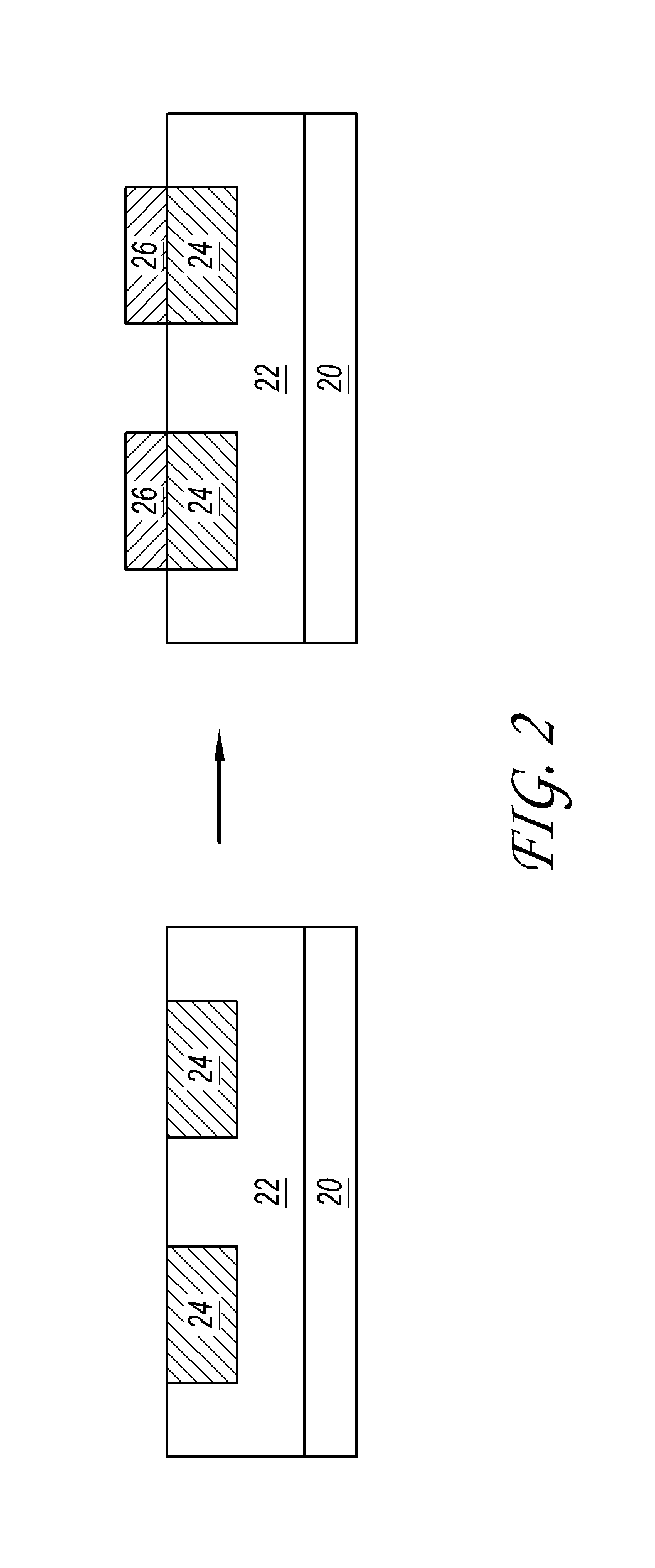

Selective formation of metallic films on metallic surfaces

ActiveUS8956971B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDeposition temperatureCopper

Owner:ASM INTERNATIONAL

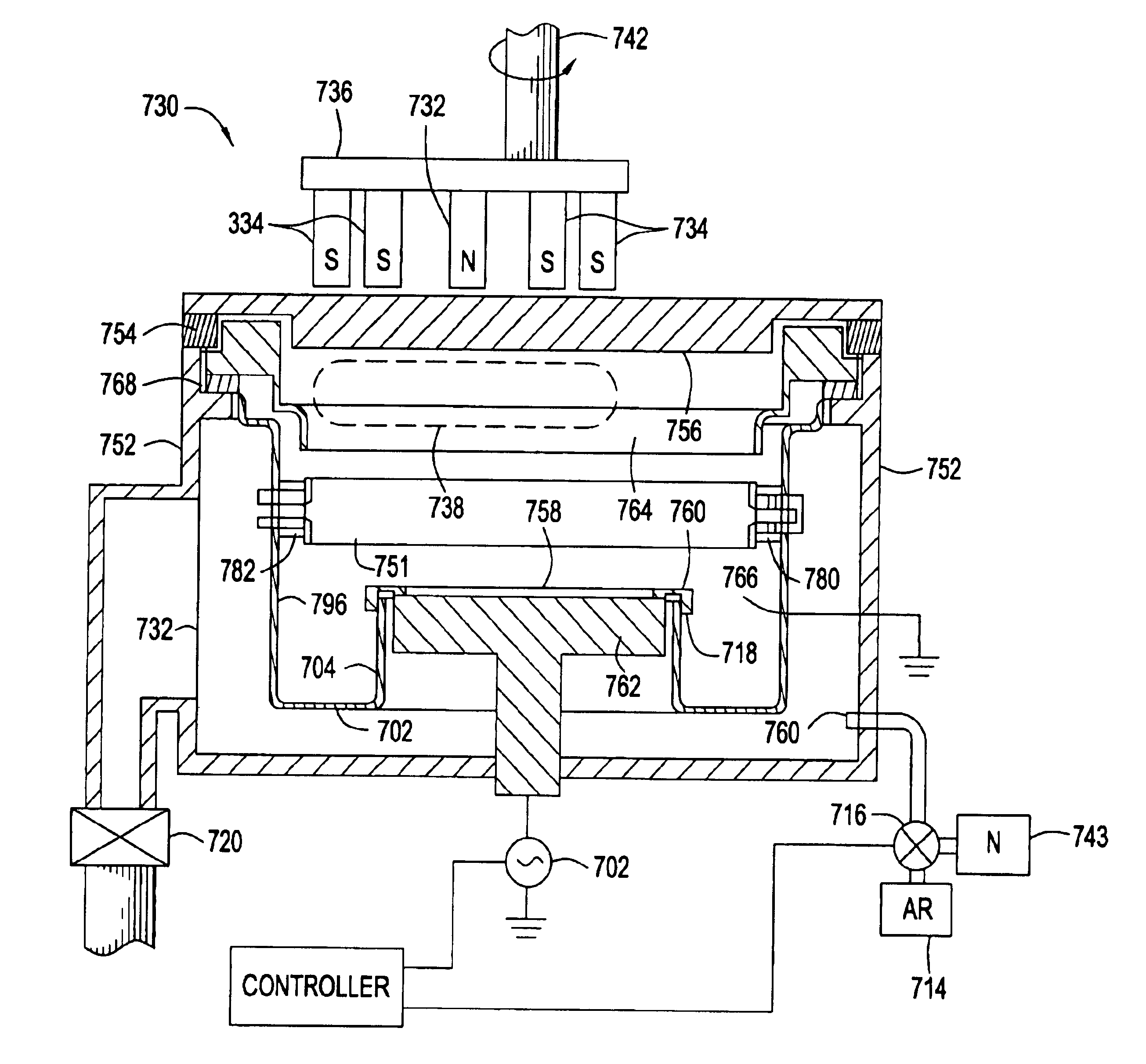

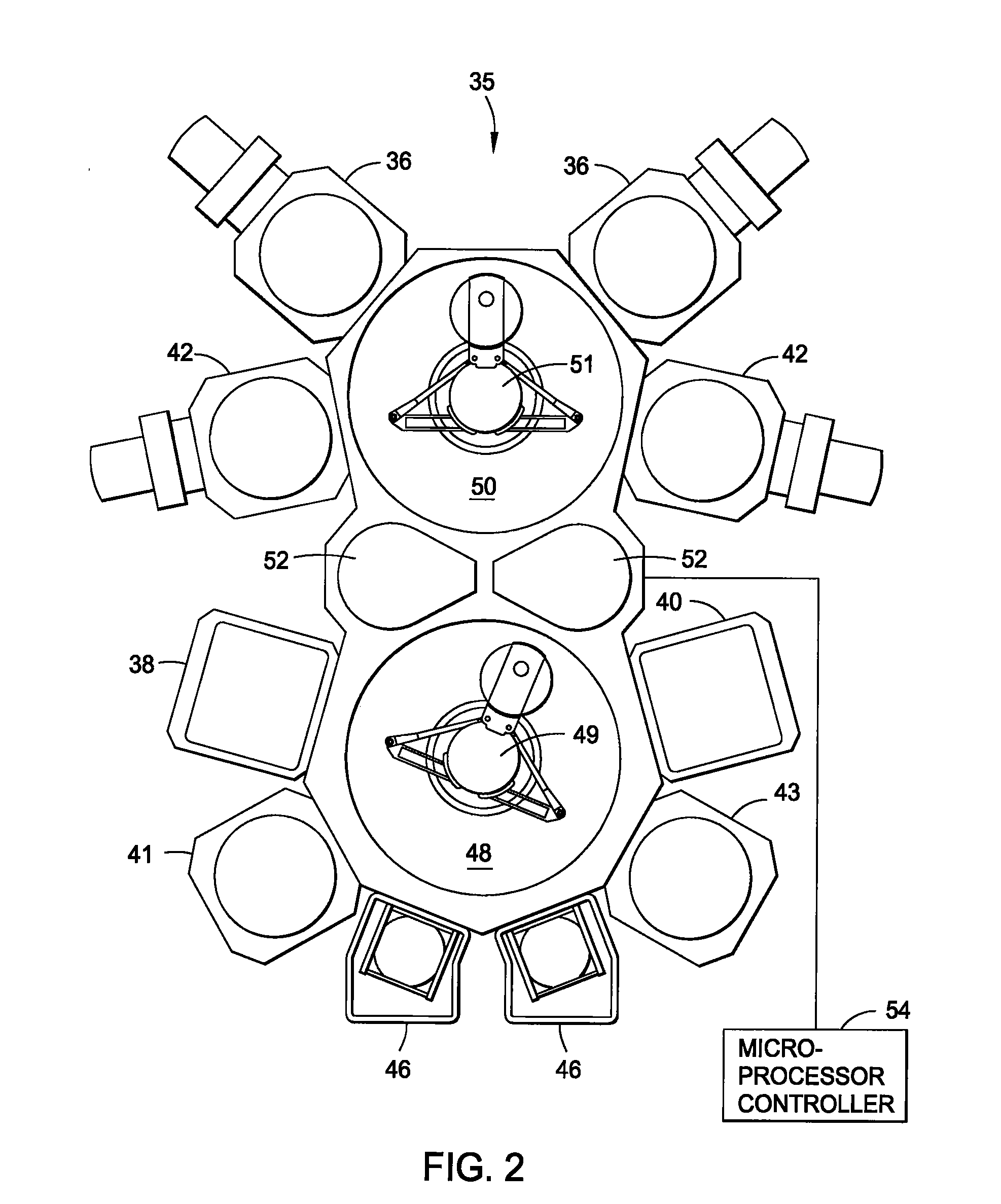

Integration of ALD tantalum nitride for copper metallization

InactiveUS7049226B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingTantalum nitrideConductive materials

A method and apparatus for depositing a tantalum nitride barrier layer is provided for use in an integrated processing tool. The tantalum nitride is deposited by atomic layer deposition. The tantalum nitride is removed from the bottom of features in dielectric layers to reveal the conductive material under the deposited tantalum nitride. Optionally, a tantalum layer may be deposited by physical vapor deposition after the tantalum nitride deposition. Optionally, the tantalum nitride deposition and the tantalum deposition may occur in the same processing chamber.

Owner:APPLIED MATERIALS INC

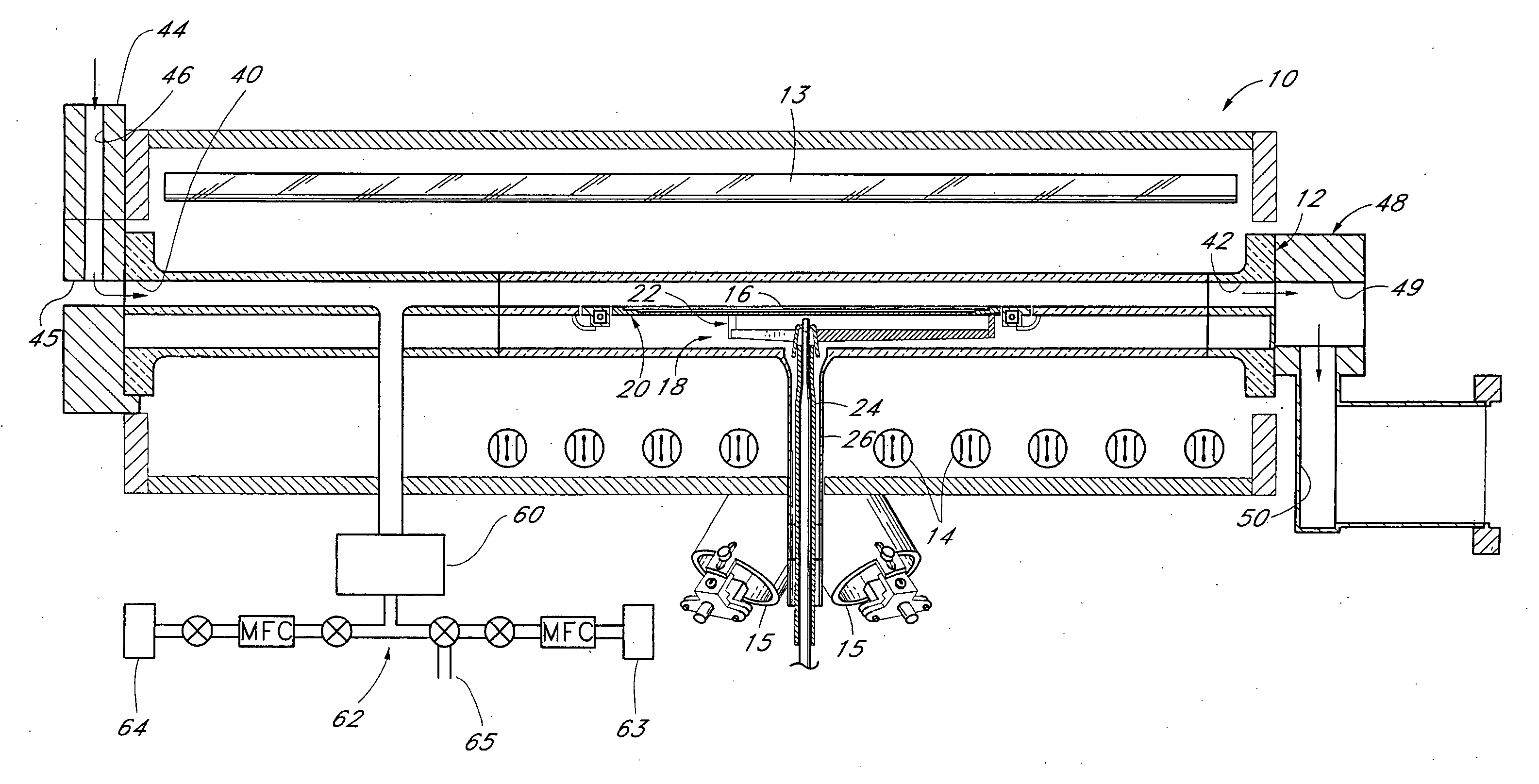

Shower head and plasma processing apparatus having same

InactiveUS20100230051A1Improve uniformityUniform temperature distributionElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringCopper

A shower head is provided, in a processing chamber in which a substrate is processed, to face a mounting table for mounting the substrate thereon. The shower head includes: a facing surface that faces the mounting table to supply a gas to the substrate in a form of shower through a plurality of gas injection holes formed on the facing surface; an opposing surface provided opposite to the facing surface; and a plurality of bar-shaped heat transfer columns standing on the opposing surface. Here, the heat transfer columns have varying lengths and / or thicknesses to adjust heat capacities thereof. The heat transfer columns are made of one of aluminum, stainless steel, and copper.

Owner:TOKYO ELECTRON LTD

Metal nitride carbide deposition by ALD

InactiveUS7410666B2Material nanotechnologySemiconductor/solid-state device detailsHydrogen halideCorrosive chemical

Owner:ASM INTERNATIONAL

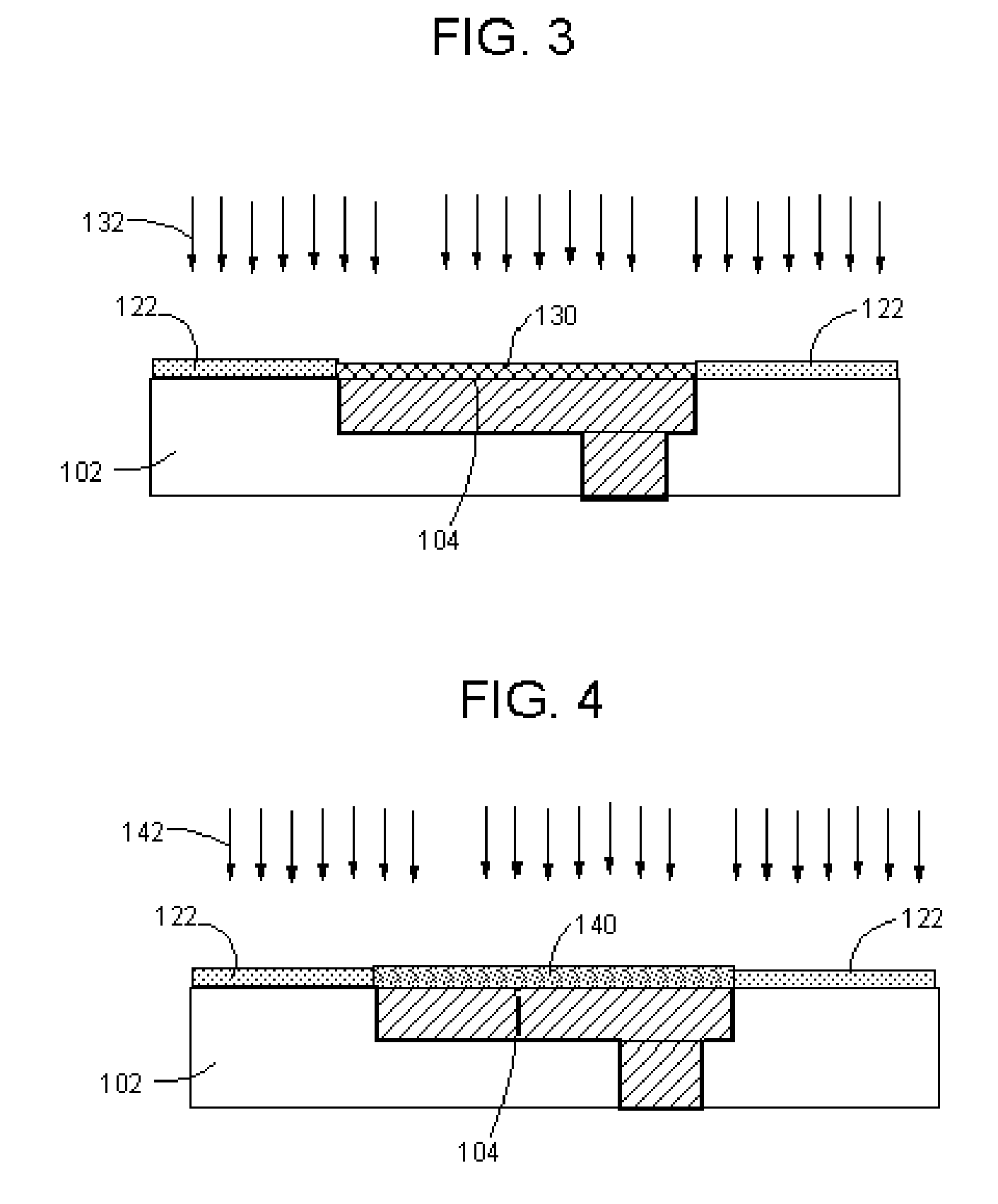

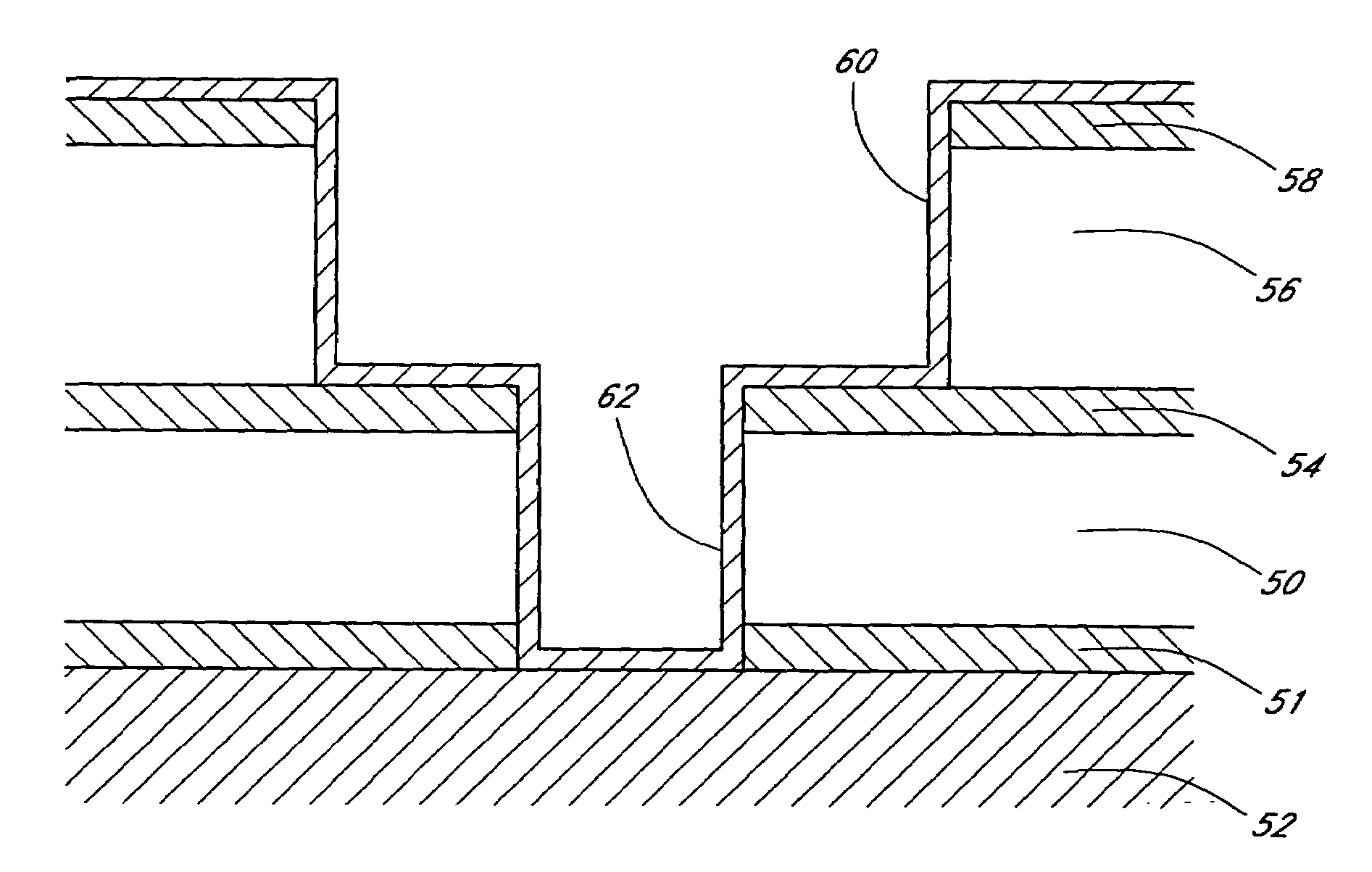

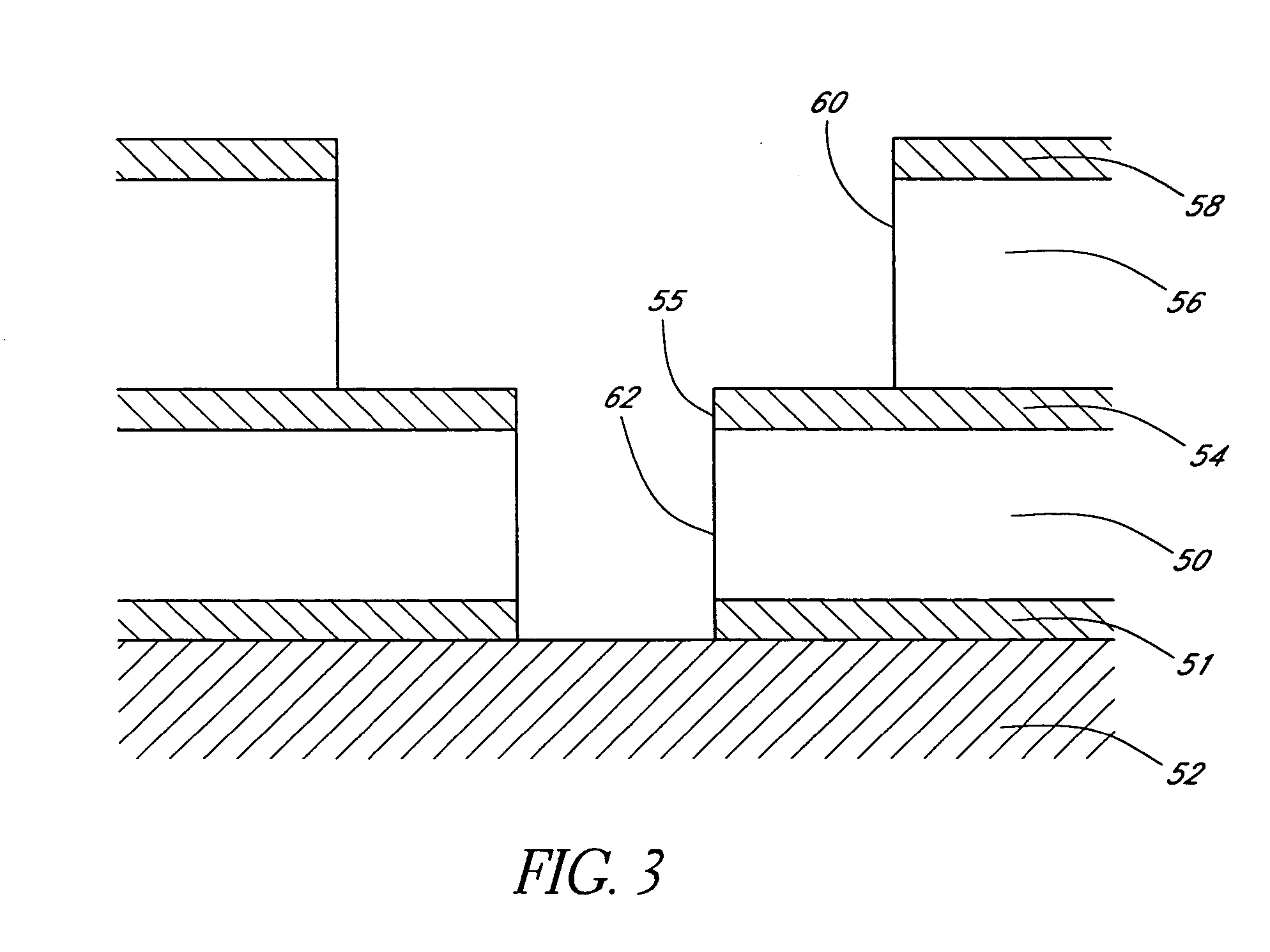

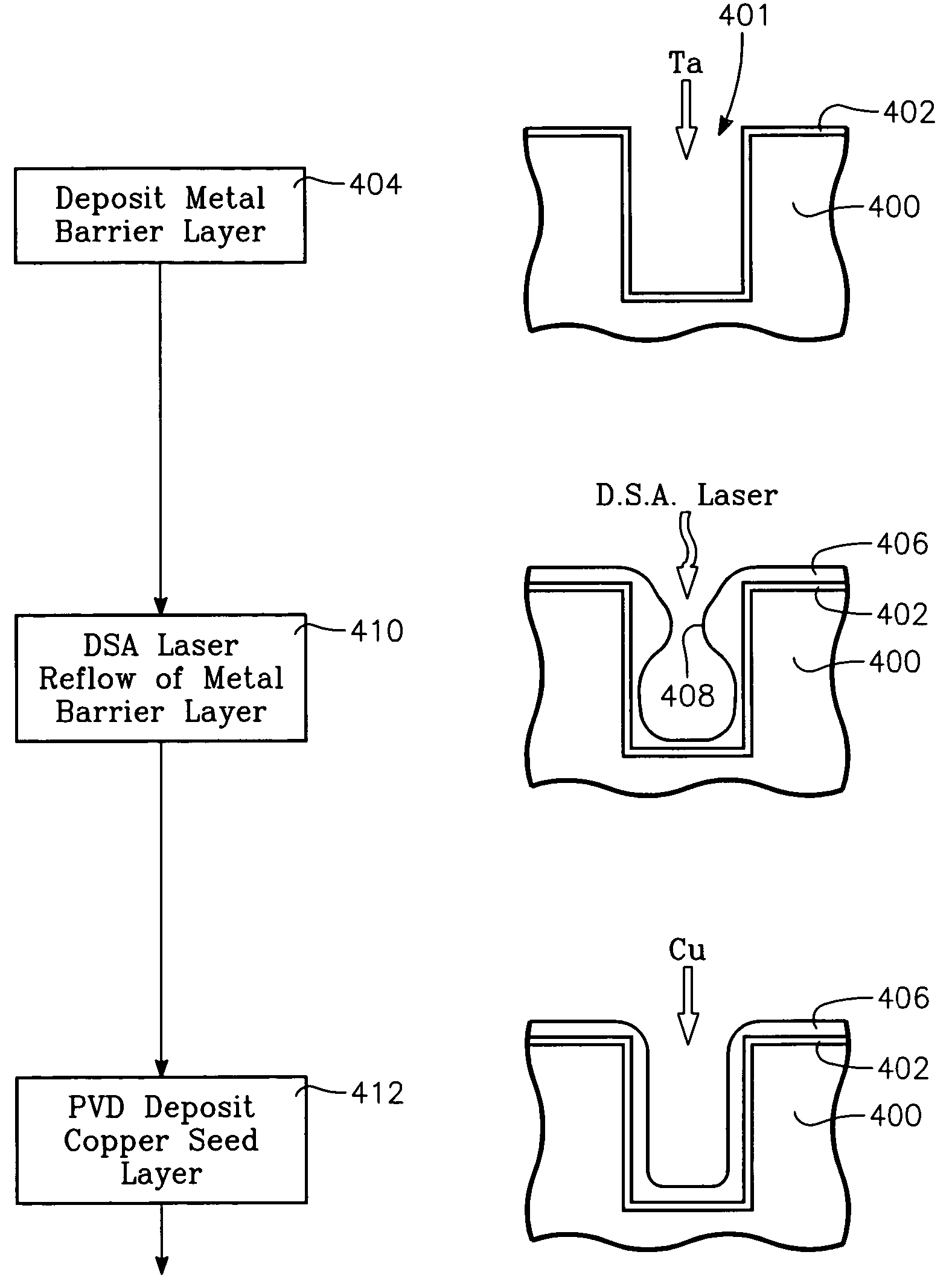

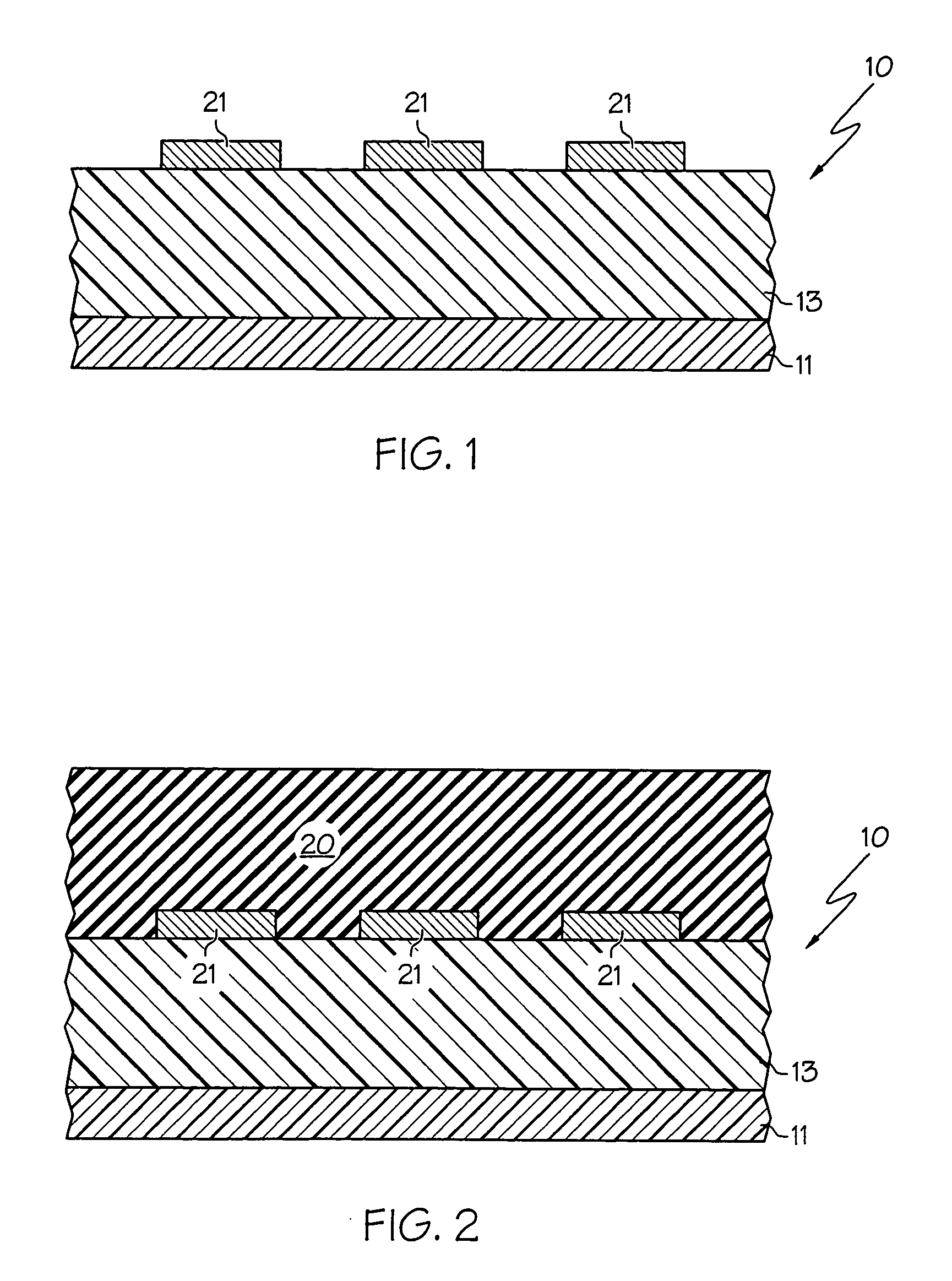

Copper barrier reflow process employing high speed optical annealing

A method of forming a barrier layer for a thin film structure on a semiconductor substrate includes forming high aspect ratio openings in a base layer having vertical side walls, depositing a dielectric barrier layer comprising a dielectric compound of a barrier metal on the surfaces of the high aspect ratio openings including the vertical side walls and depositing a metal barrier layer comprising the barrier metal on the first barrier layer. The method further includes reflowing the metal barrier layer by (a) directing light from an array of continuous wave lasers into a line of light extending at least partially across the thin film structure, and (b) translating the line of light relative to the thin film structure in a direction transverse to the line of light.

Owner:APPLIED MATERIALS INC

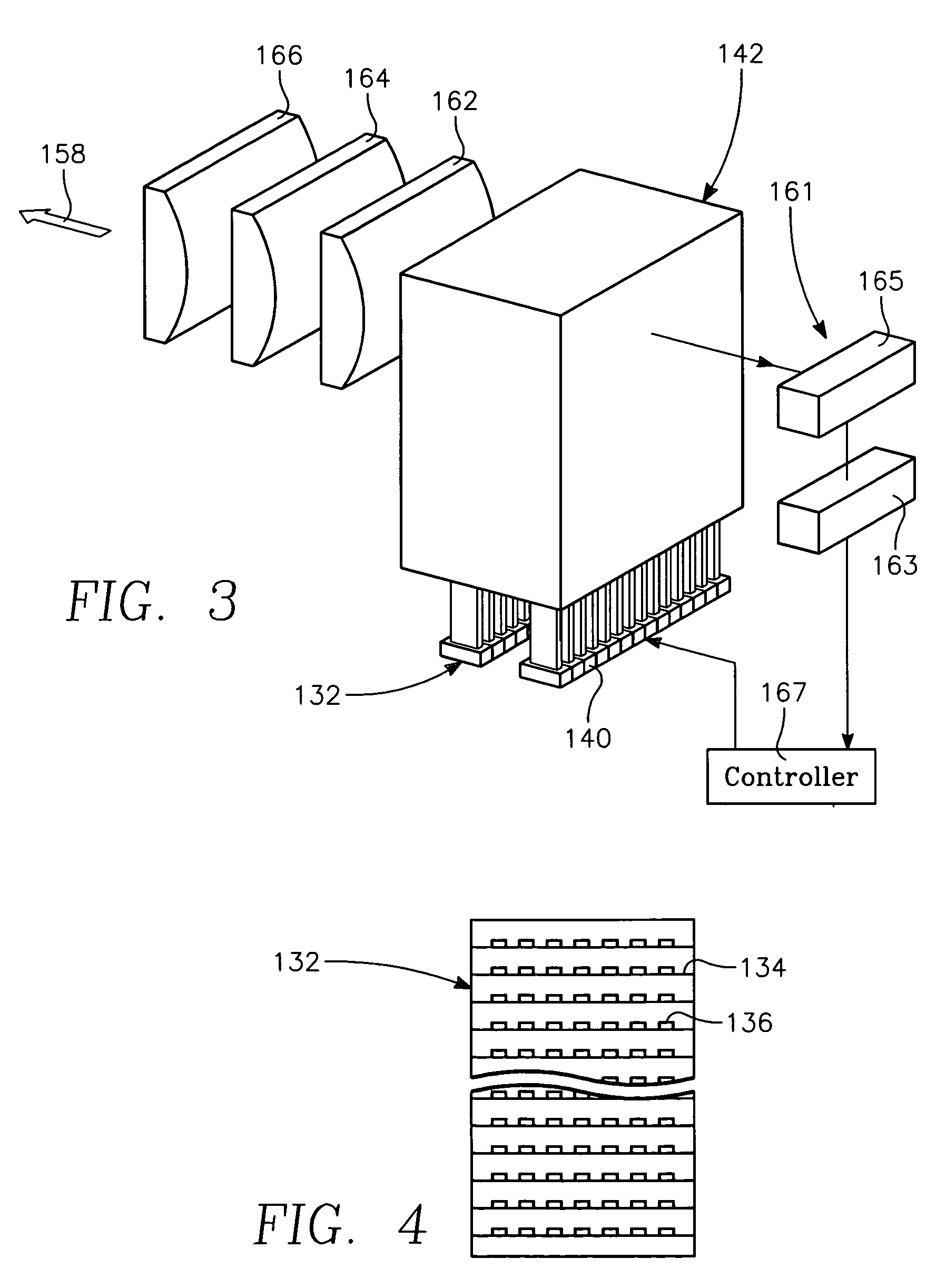

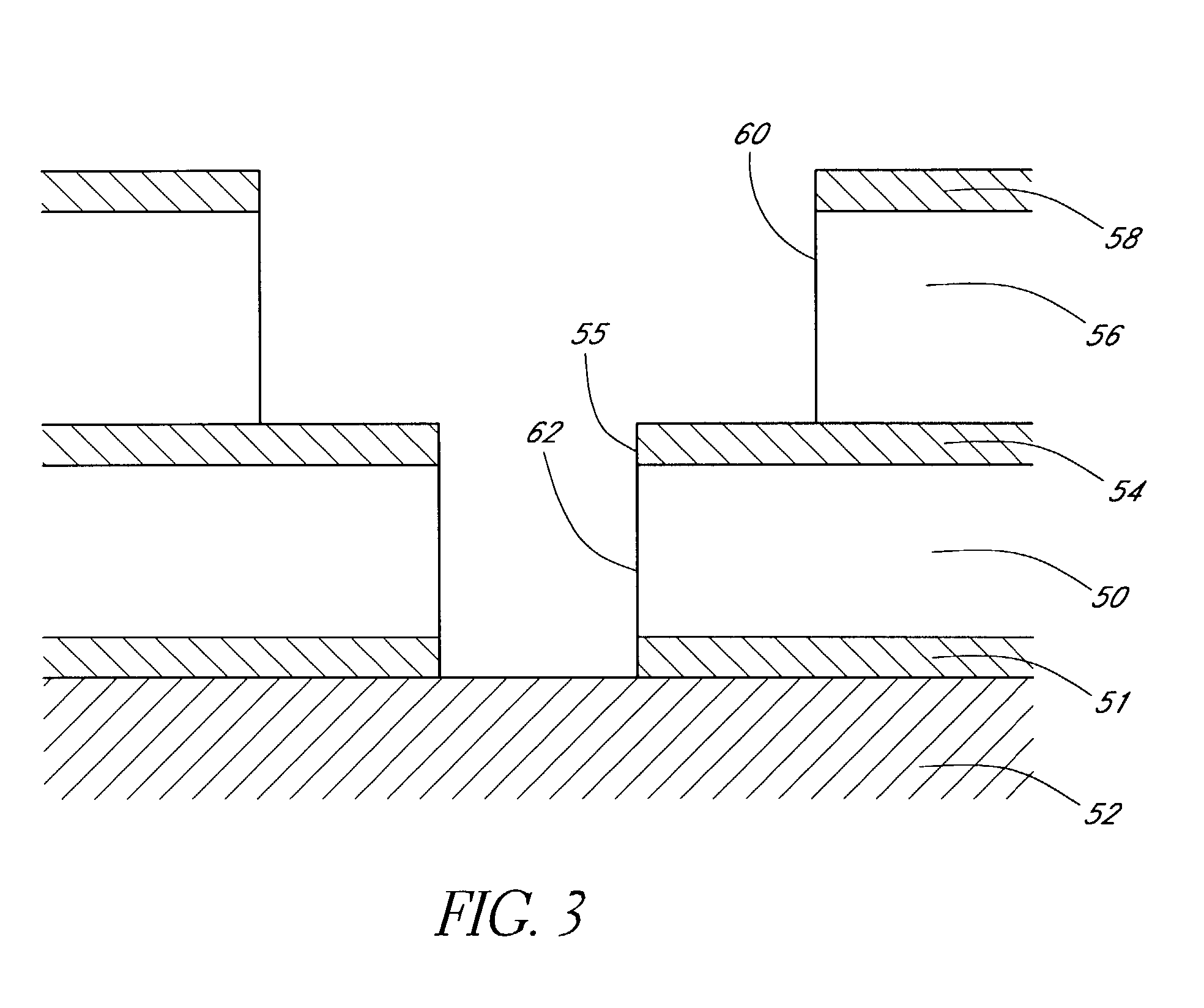

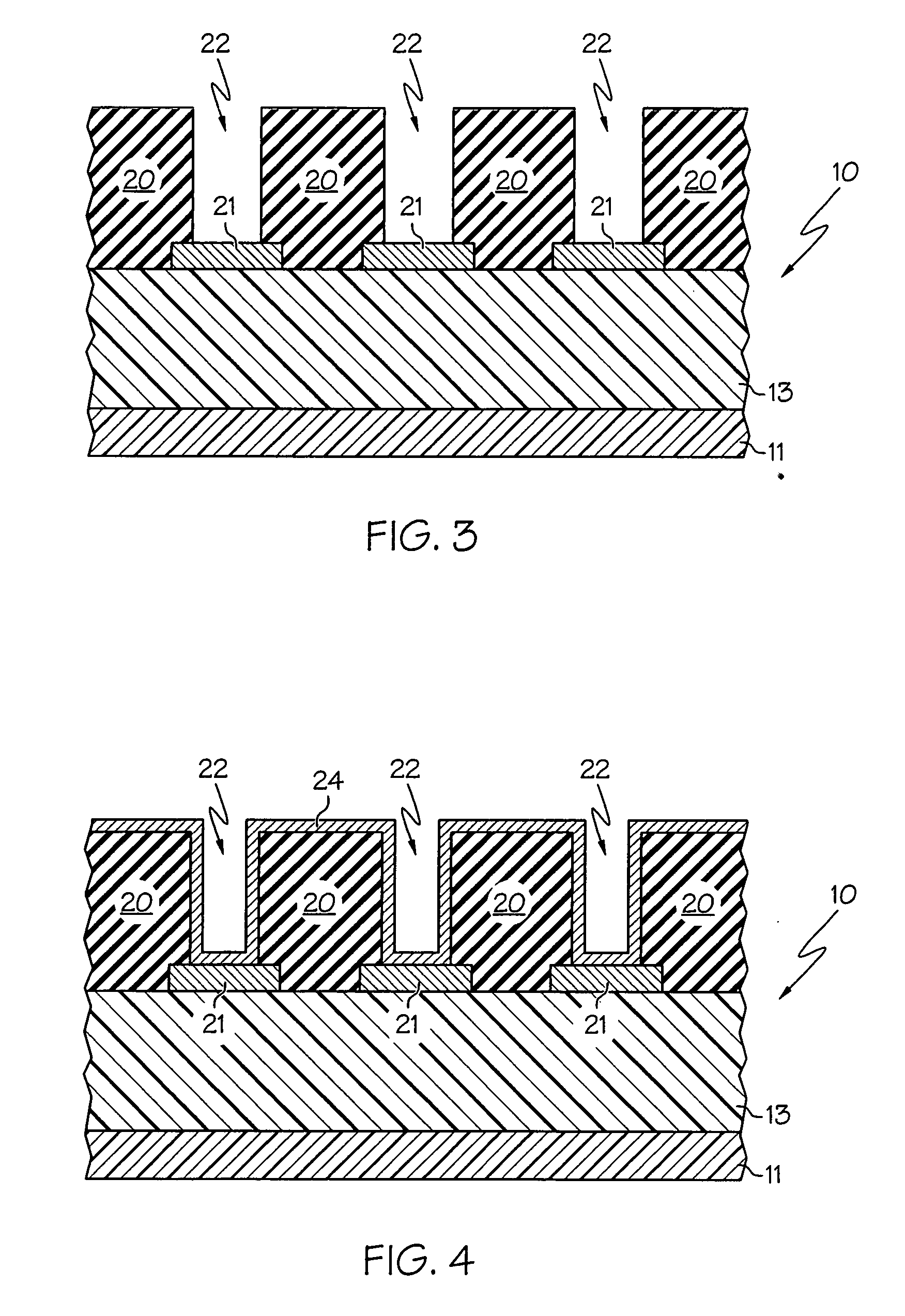

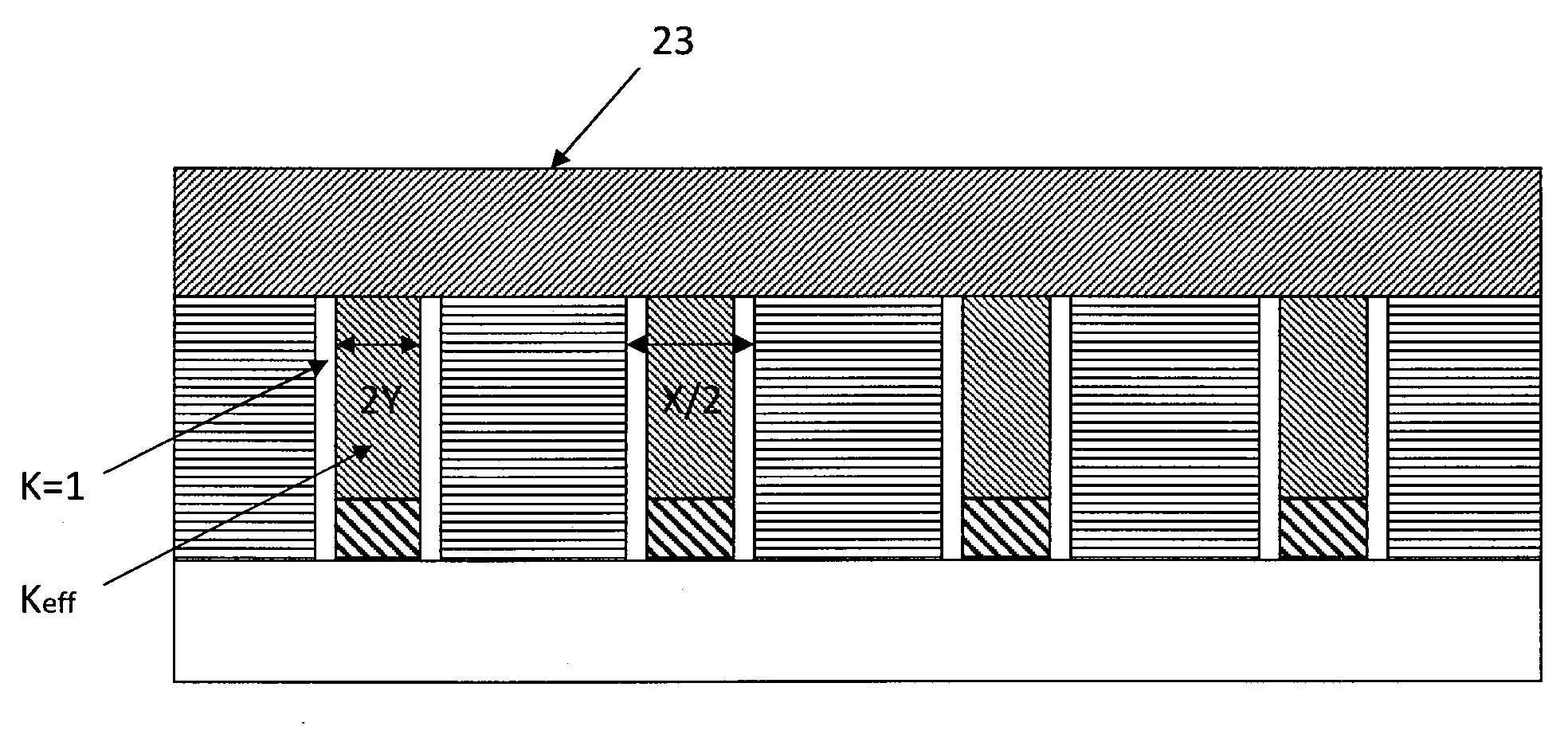

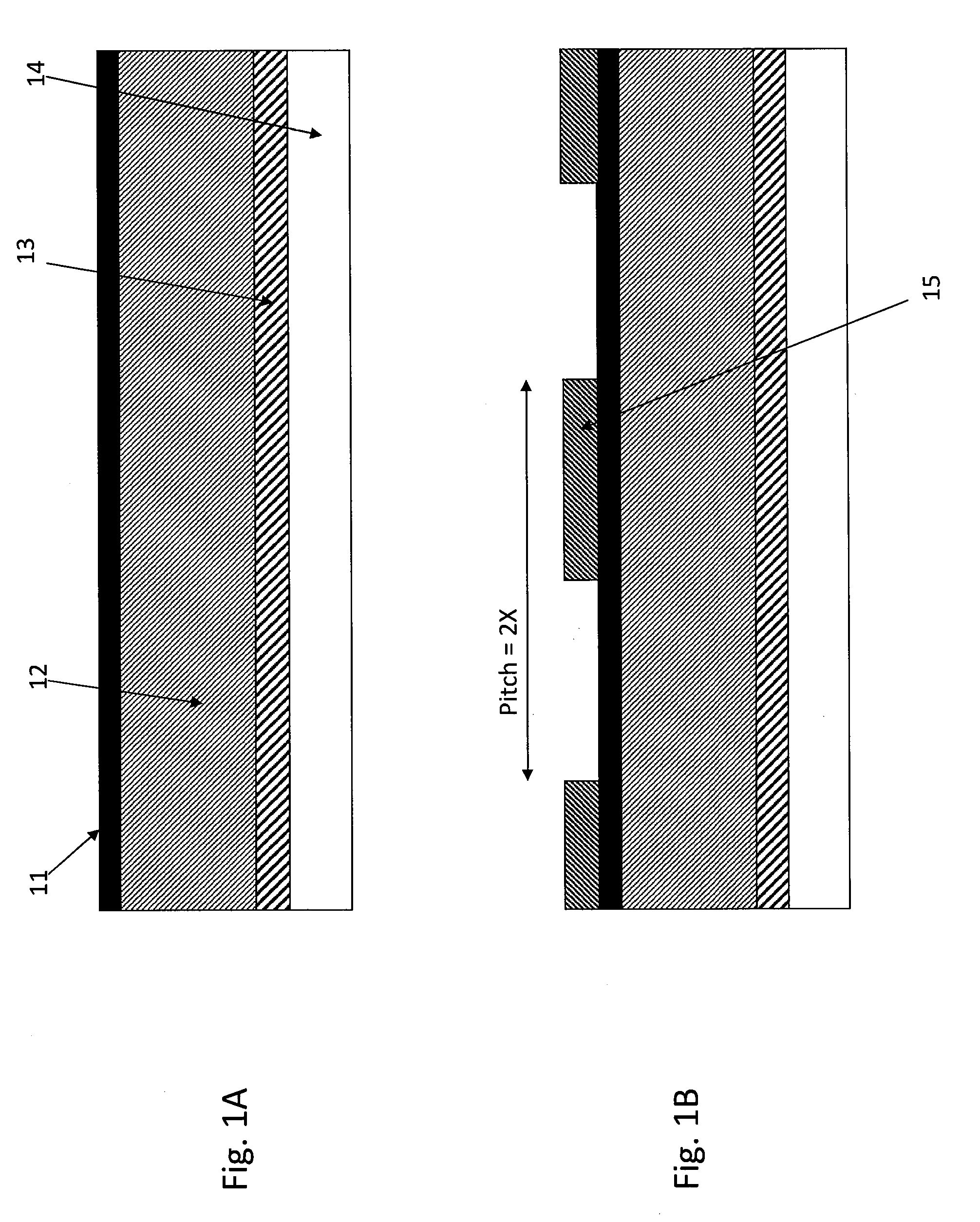

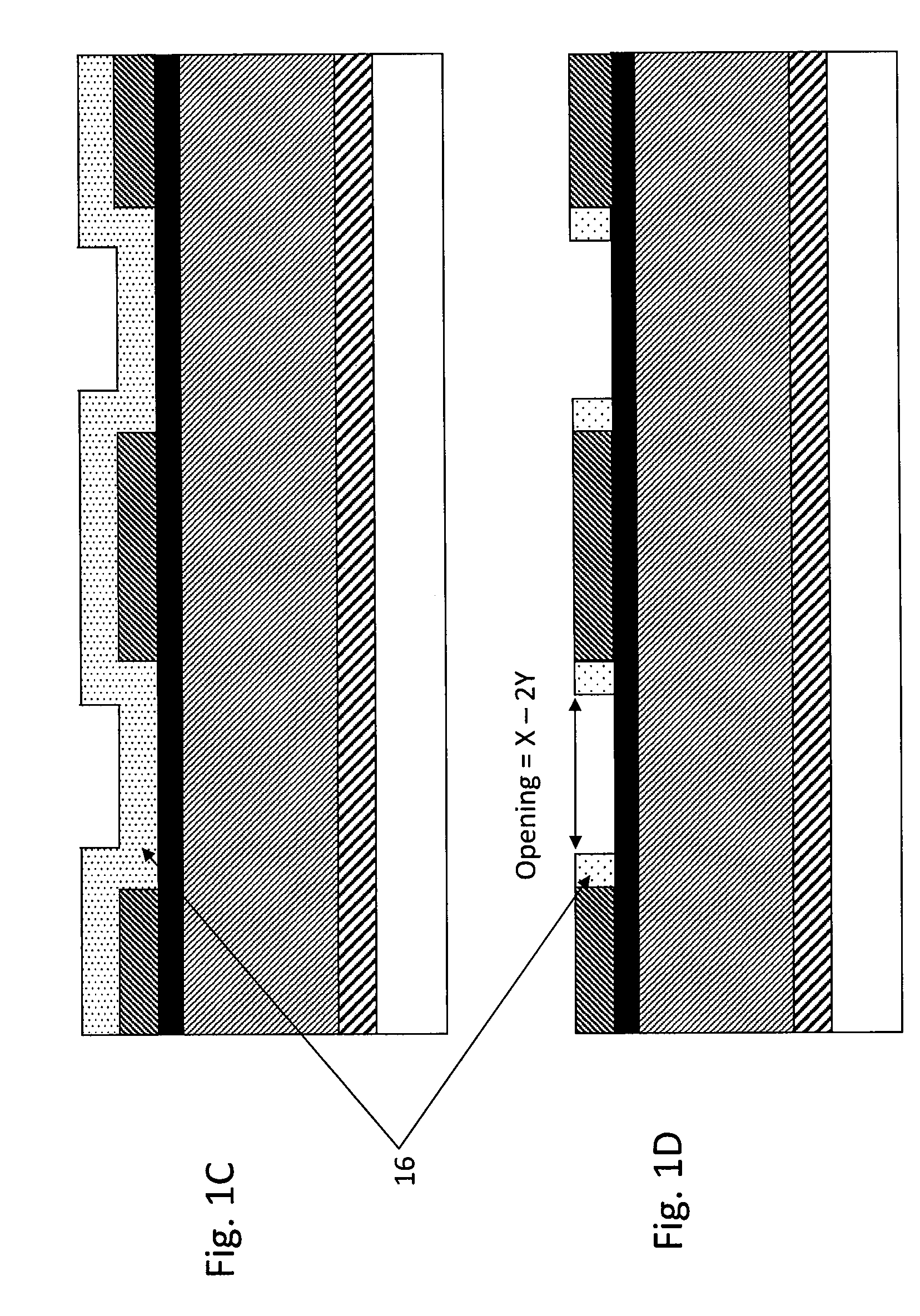

Method for forming interconnect structure having airgap

ActiveUS8241991B2Reducing KeffSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsCopper

A method for forming an interconnect structure with airgaps, includes: providing a structure having a trench formed on a substrate; depositing a spacer oxide layer on sidewalls of the trench as sidewall spacers by plasma enhanced atomic layer deposition; filling the trench having the sidewall spacers with copper; removing the sidewall spacers to form an airgap structure; and encapsulating the airgap structure, wherein airgaps are formed between the filled copper and the sidewalls of the trench.

Owner:ASM JAPAN

Process for forming cobalt and cobalt silicide materials in copper contact applications

InactiveUS20080268635A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingElectroless depositionCopper

Embodiments of the invention described herein generally provide methods for forming cobalt silicide layers and metallic cobalt layers by using various deposition processes and annealing processes. In one embodiment, a method for forming a cobalt silicide material on a substrate is provided which includes treating the substrate with at least one preclean process to expose a silicon-containing surface, depositing a cobalt silicide material over the silicon-containing surface, and depositing a copper material over the cobalt silicide material. In another embodiment, a metallic cobalt material may be deposited over the cobalt silicide material prior to depositing the copper material. In one example, the copper material may be formed by depositing a copper seed layer and a copper bulk layer on the substrate. The copper seed layer may be deposited by a PVD process and the copper bulk layer may be deposited by an ECP process or an electroless deposition process.

Owner:APPLIED MATERIALS INC

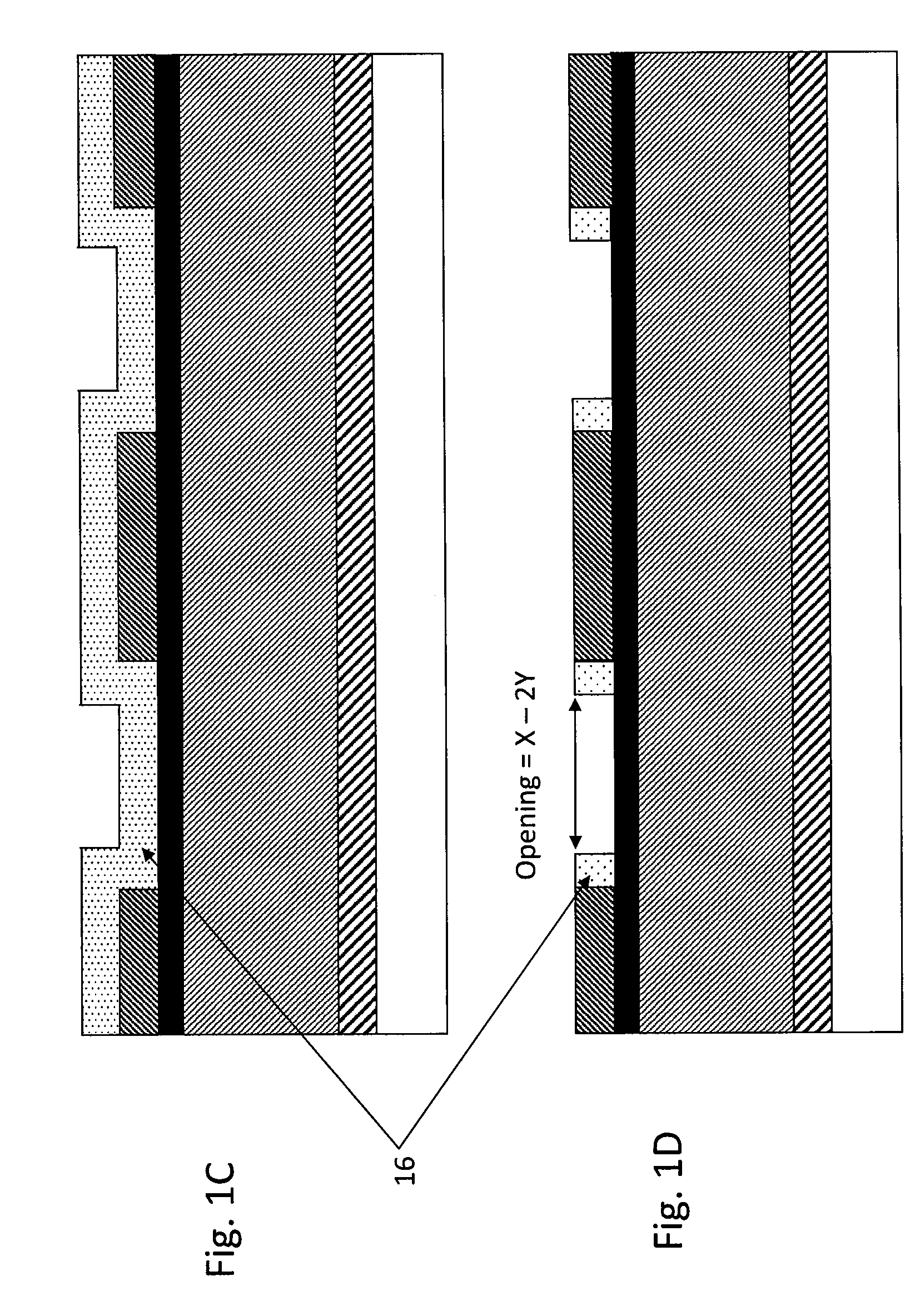

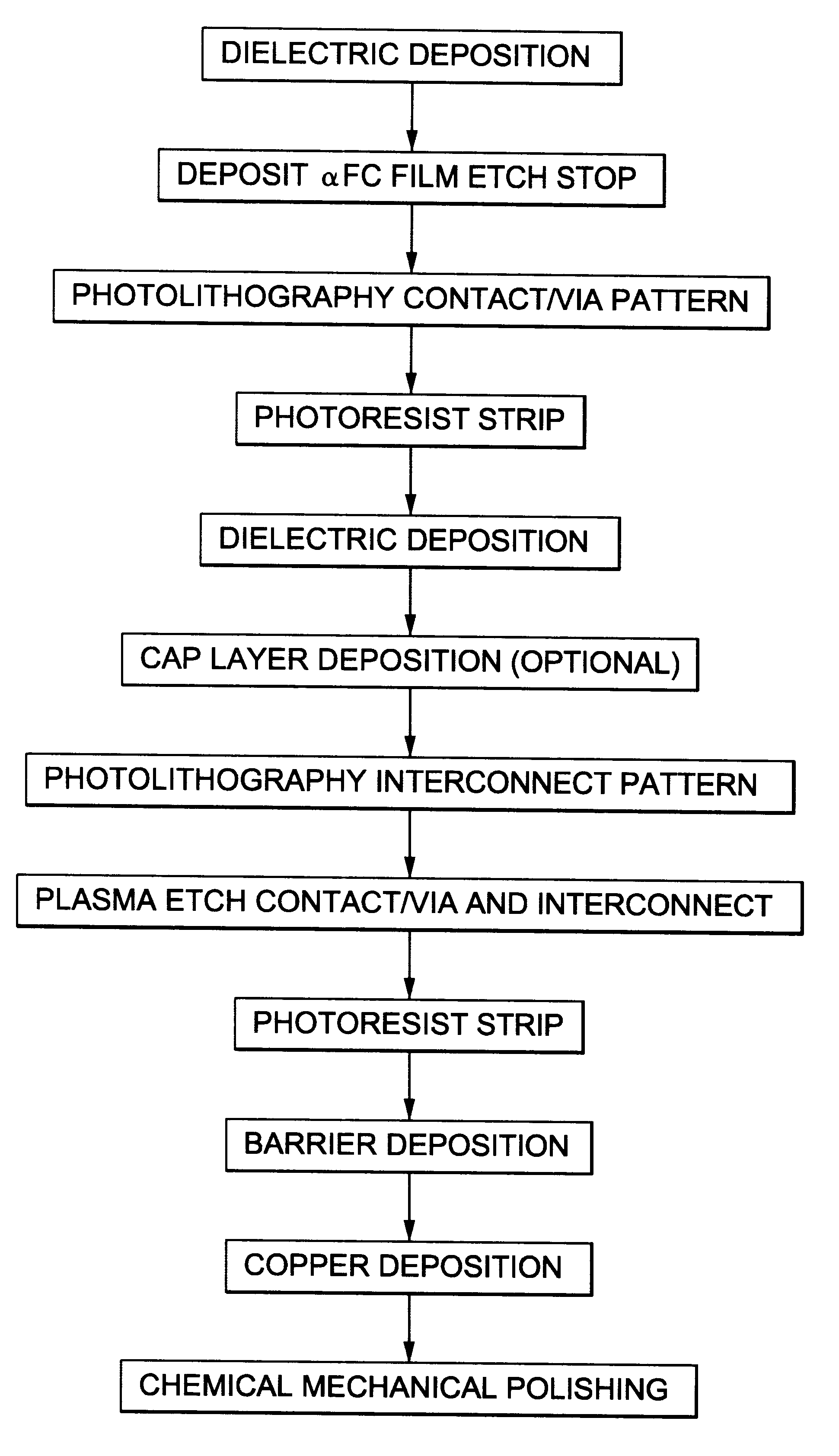

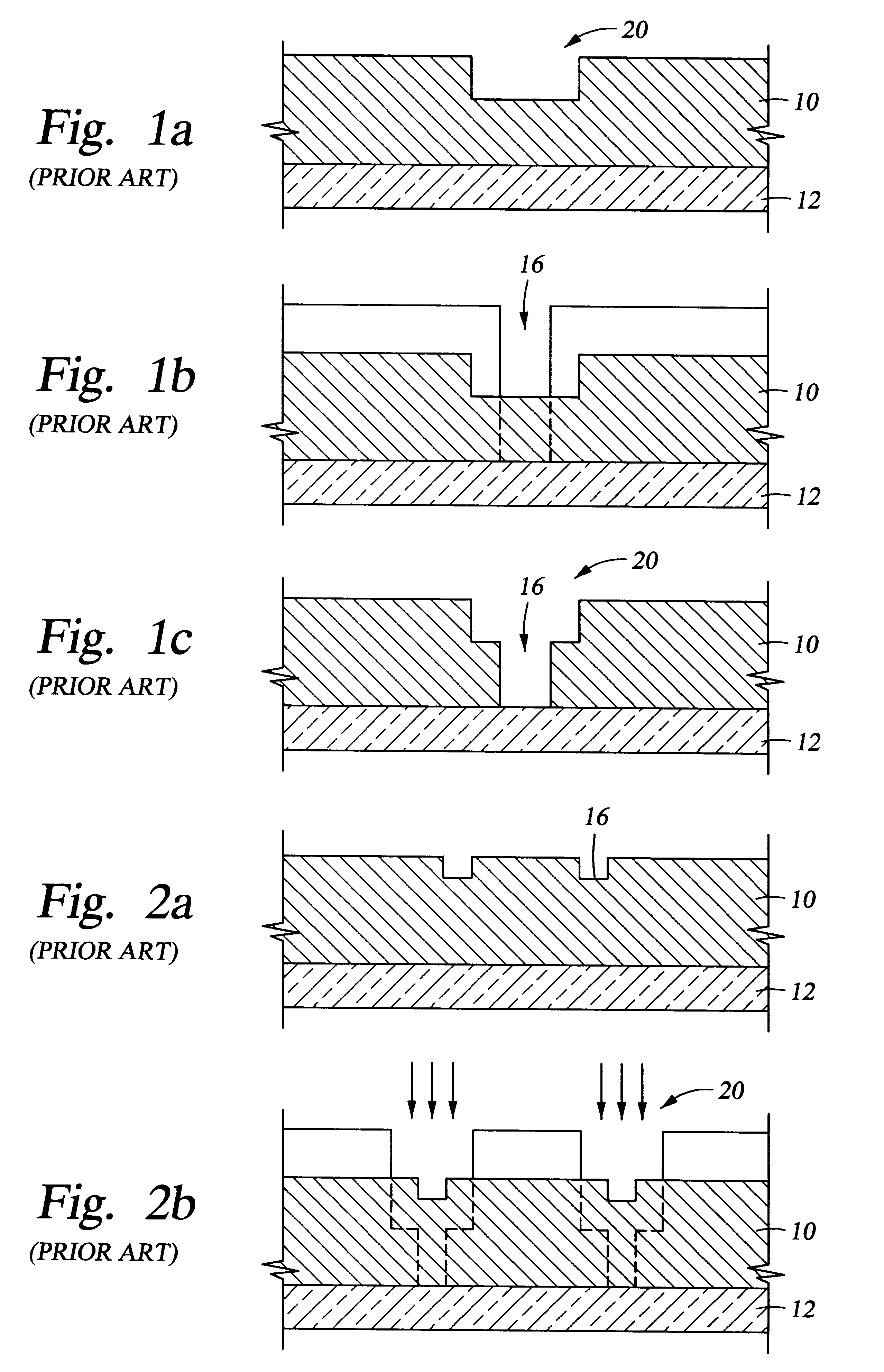

An etch stop layer for dual damascene process

The present invention provides a carbon based etch stop, such as a diamond like amorphous carbon, having a low dielectric constant and a method of forming a dual damascene structure. The low k etch stop is preferably deposited between two dielectric layers and patterned to define the underlying interlevel contacts / vias. The second or upper dielectric layer is formed over the etch stop and patterned to define the intralevel interconnects. The entire dual damascene structure is then etched in a single selective etch process which first etches the patterned interconnects, then etches the contact / vias past the patterned etch stop. The etch stop has a low dielectric constant relative to a conventional SiN etch stop, which minimizes the capacitive coupling between adjacent interconnect lines. The dual damascene structure is then filled with a suitable conductive material such as aluminum or copper and planarized using chemical mechanical polishing.

Owner:APPLIED MATERIALS INC

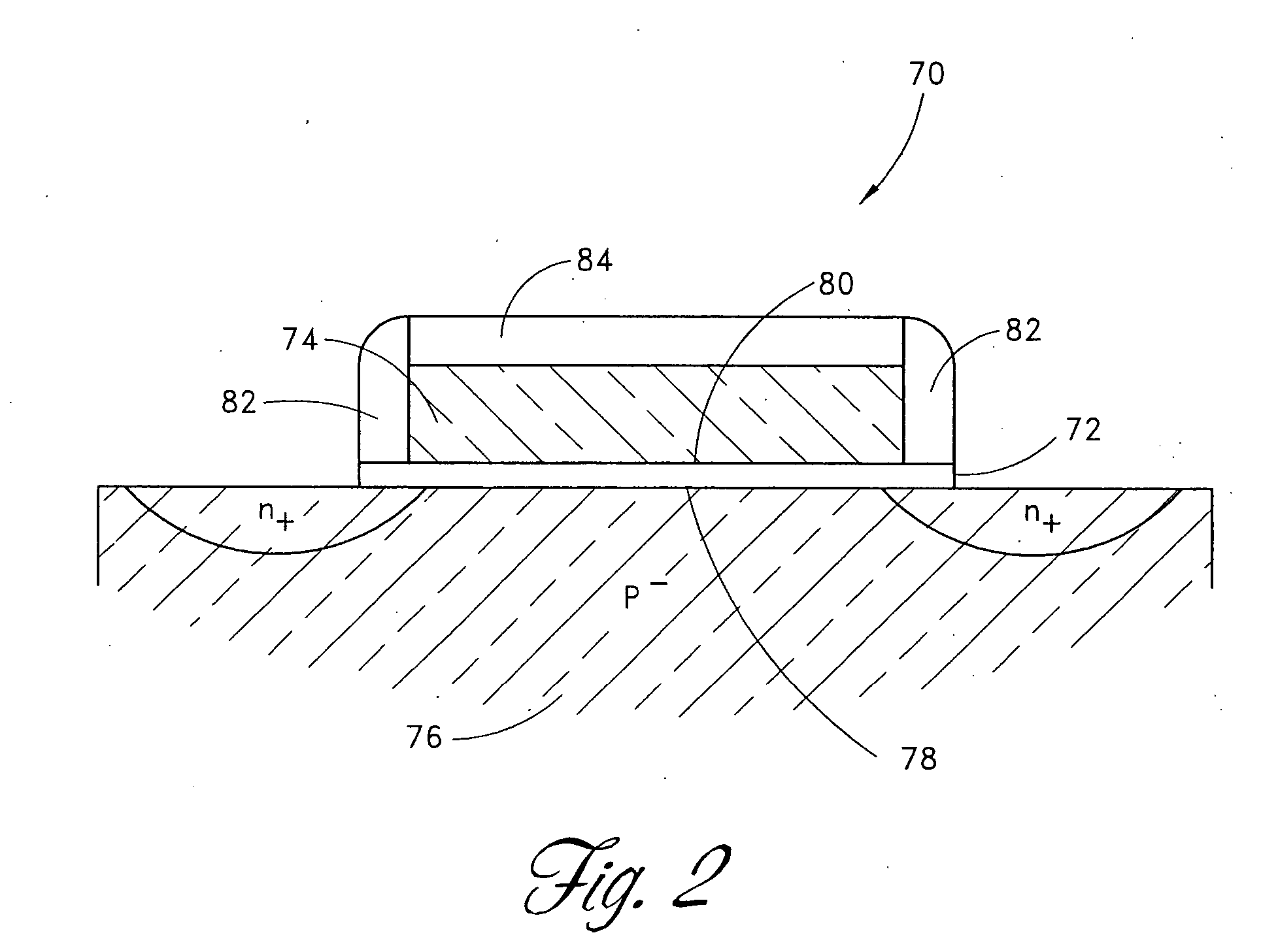

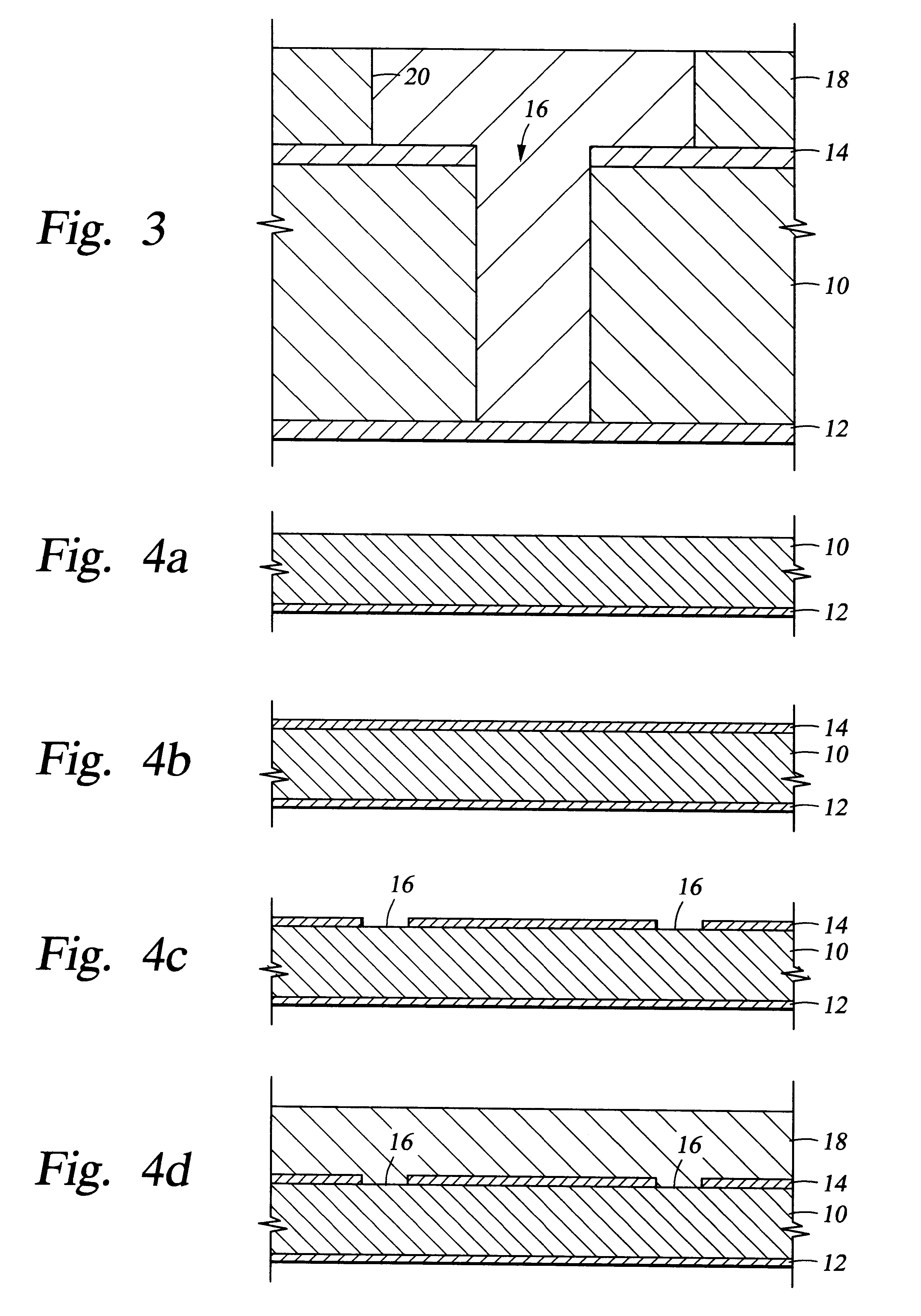

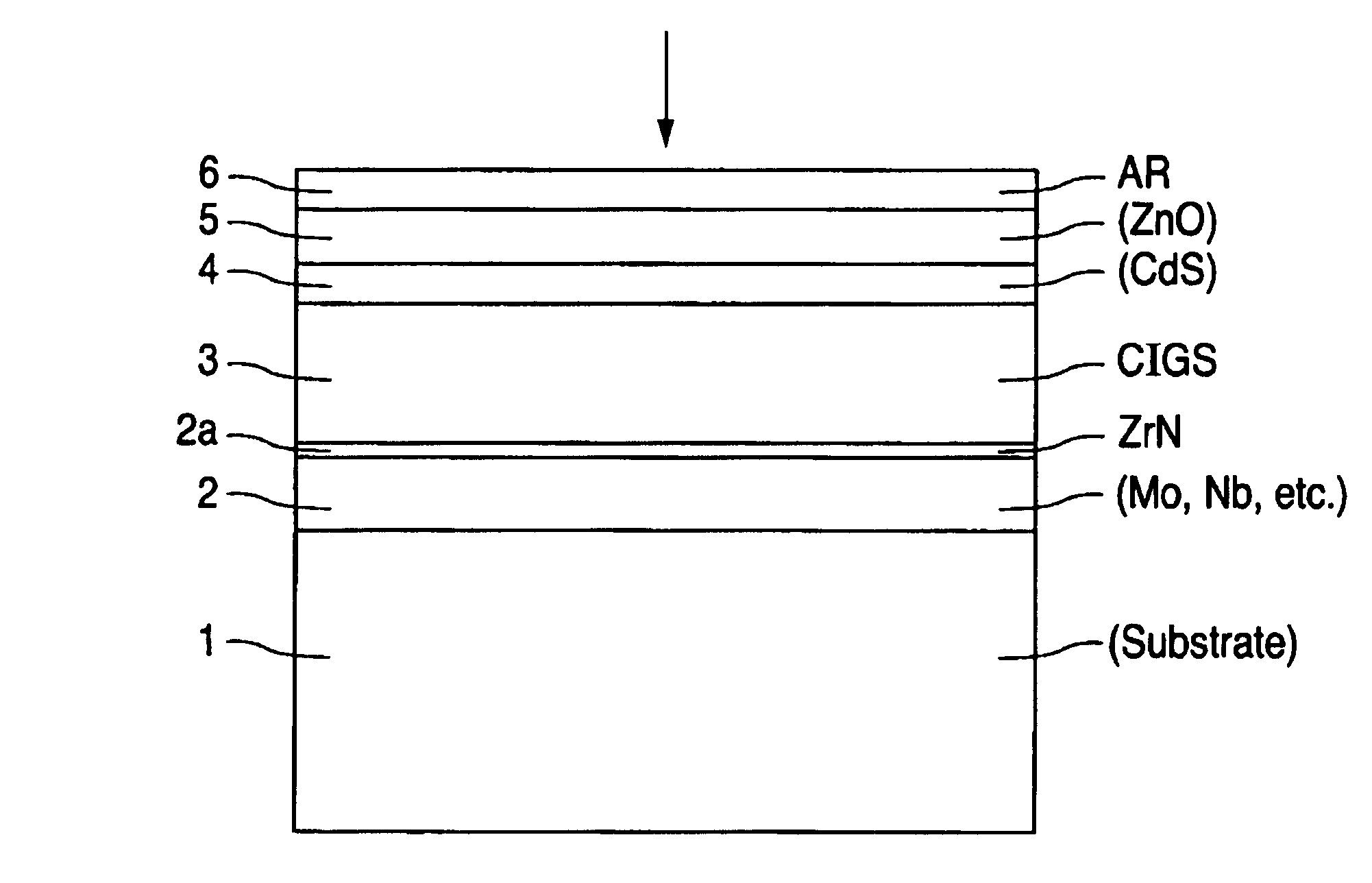

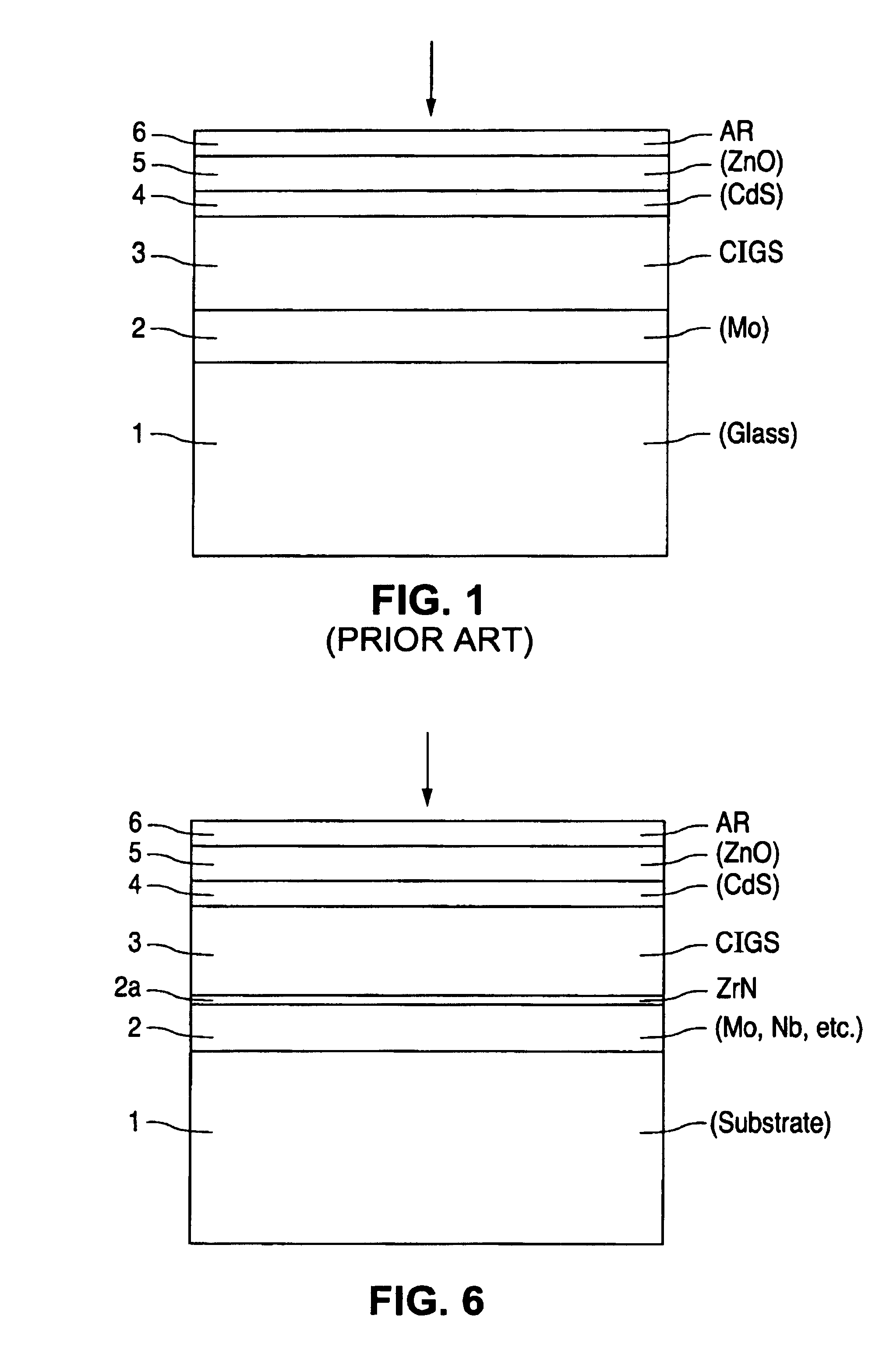

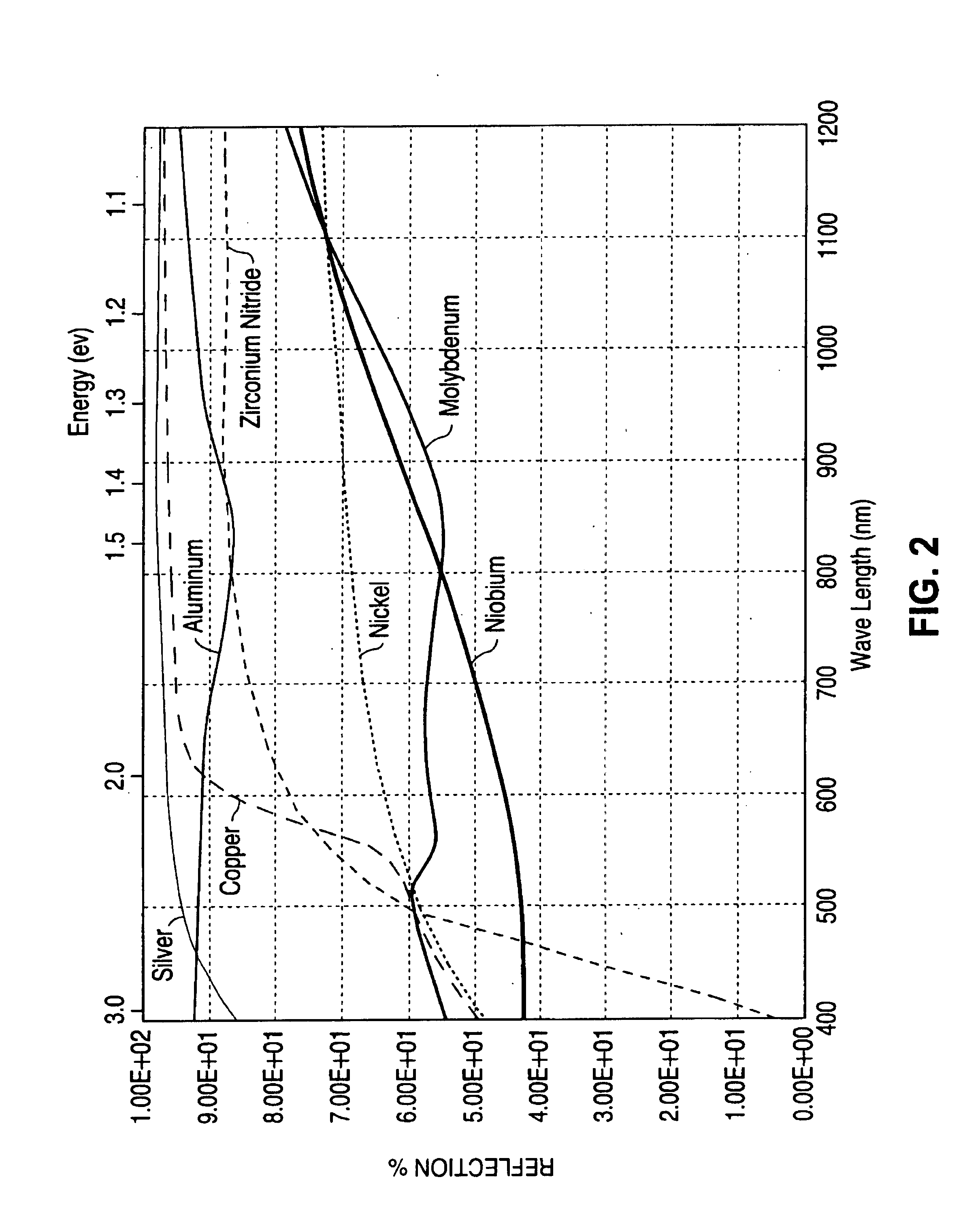

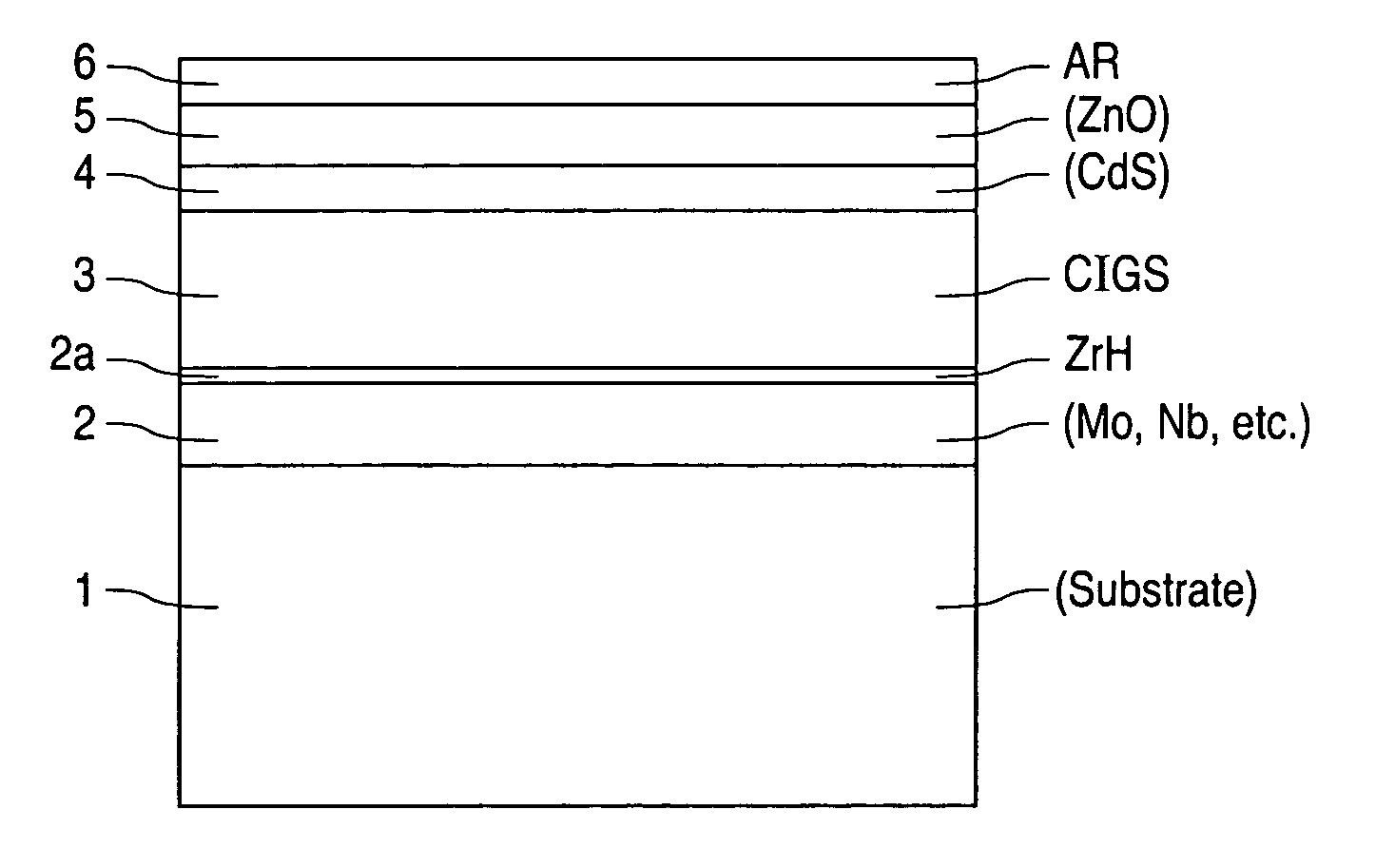

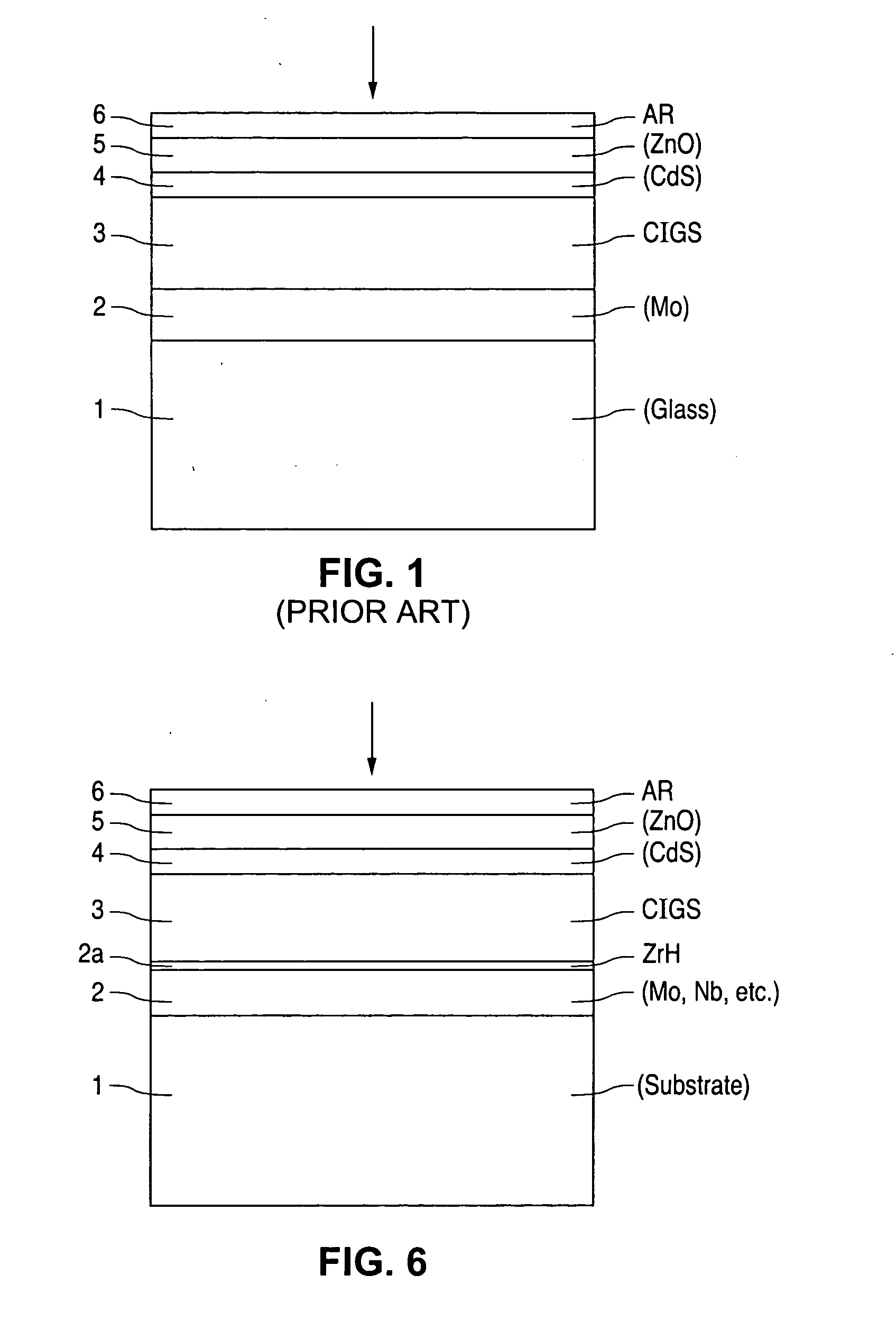

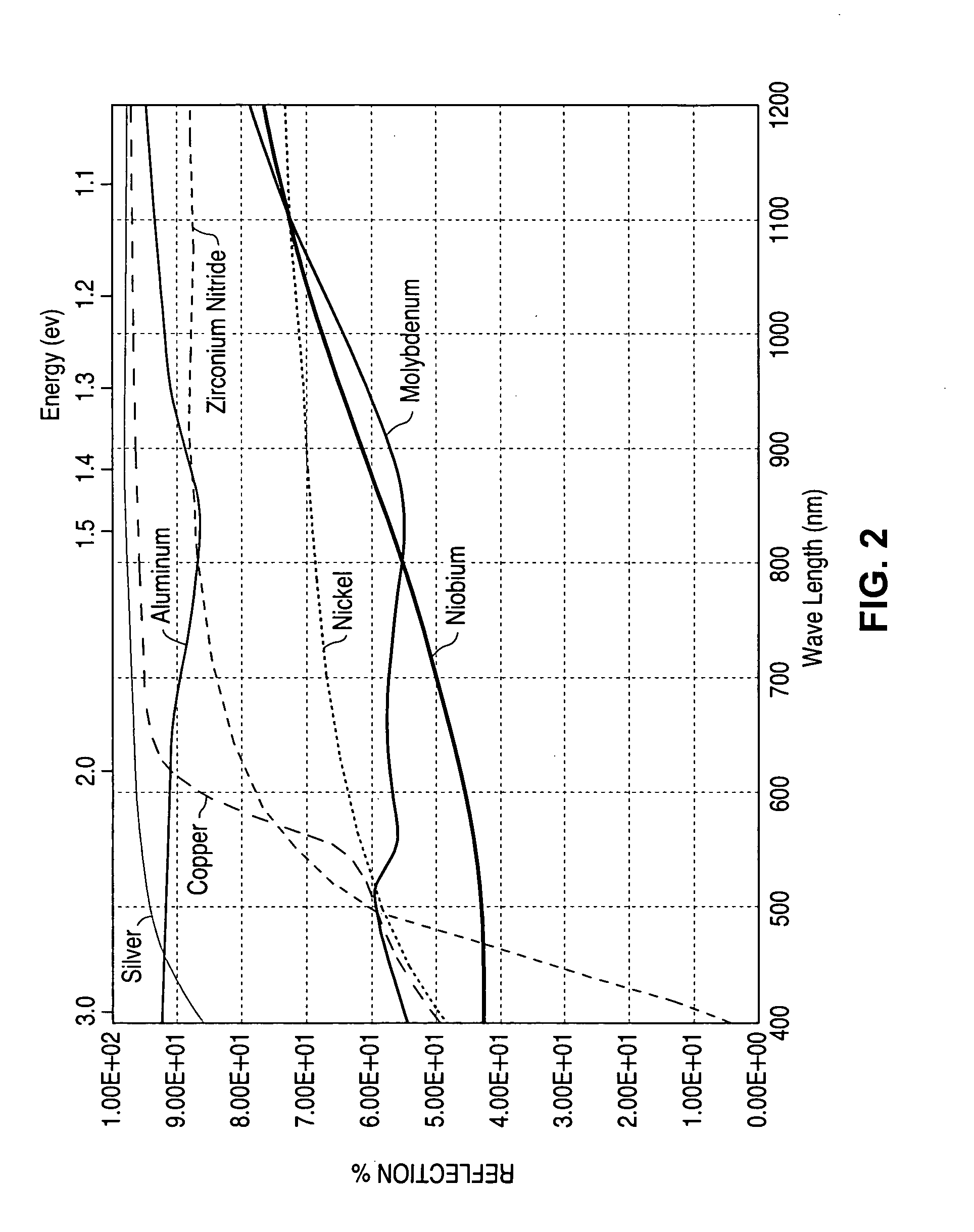

Thin-film solar cells

InactiveUS6974976B2Increase reflectionInhibition formationFinal product manufactureVacuum evaporation coatingIndiumElectrical battery

A method of manufacturing improved thin-film solar cells entirely by sputtering includes a high efficiency back contact / reflecting multi-layer containing at least one barrier layer consisting of a transition metal nitride. A copper indium gallium diselenide (Cu(InXGa1−X)Se2) absorber layer (X ranging from 1 to approximately 0.7) is co-sputtered from specially prepared electrically conductive targets using dual cylindrical rotary magnetron technology. The band gap of the absorber layer can be graded by varying the gallium content, and by replacing the gallium partially or totally with aluminum. Alternately the absorber layer is reactively sputtered from metal alloy targets in the presence of hydrogen selenide gas. RF sputtering is used to deposit a non-cadmium containing window layer of ZnS. The top transparent electrode is reactively sputtered aluminum doped ZnO. A unique modular vacuum roll-to-roll sputtering machine is described. The machine is adapted to incorporate dual cylindrical rotary magnetron technology to manufacture the improved solar cell material in a single pass.

Owner:BEIJING APOLLO DING RONG SOLAR TECH

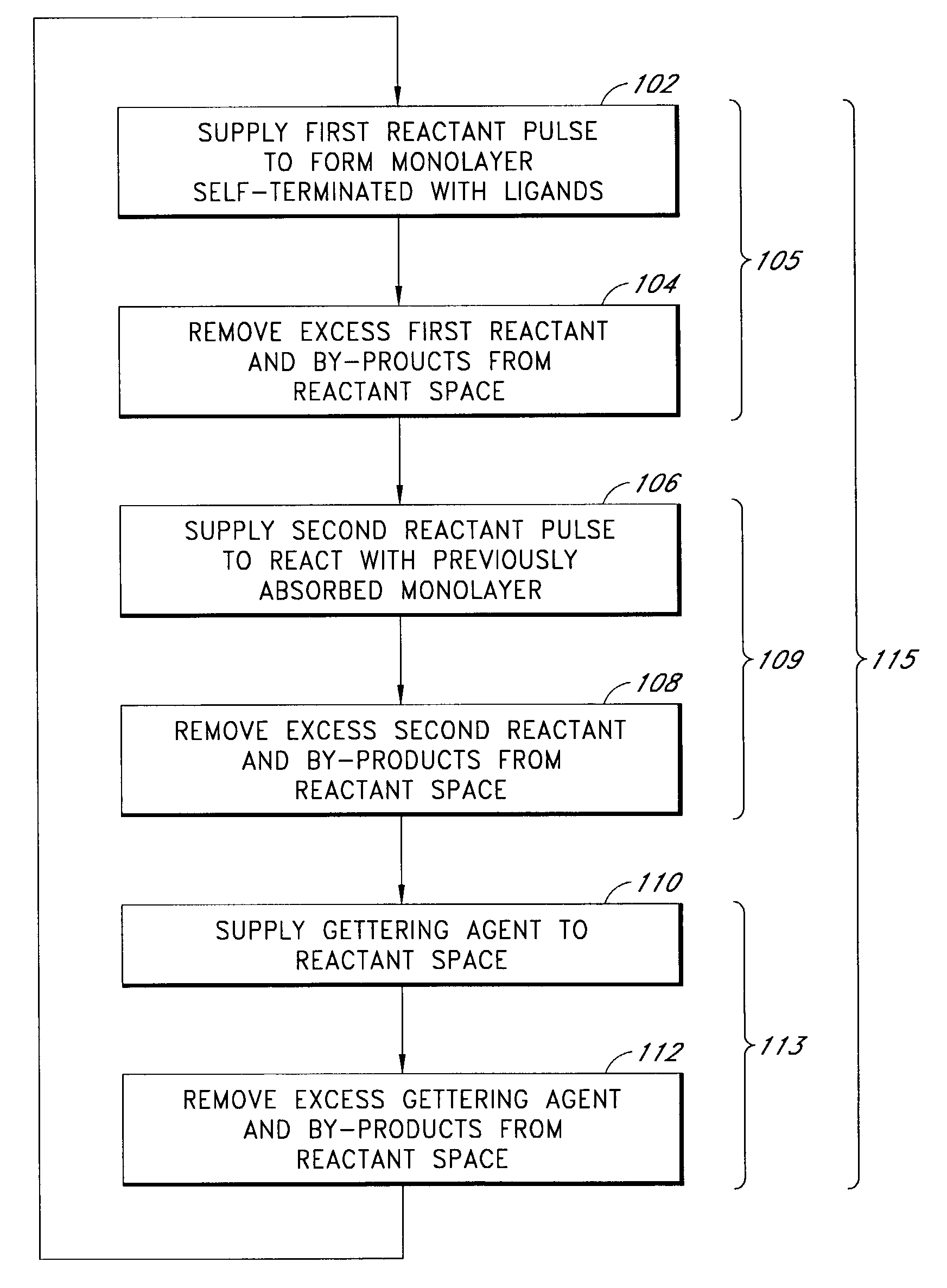

Metal nitride deposition by ALD with reduction pulse

The present methods provide tools for growing conformal metal thin films, including metal nitride, metal carbide and metal nitride carbide thin films. In particular, methods are provided for growing such films from aggressive chemicals. The amount of corrosive chemical compounds, such as hydrogen halides, is reduced during the deposition of transition metal, transition metal carbide, transition metal nitride and transition metal nitride carbide thin films on various surfaces, such as metals and oxides. Getter compounds protect surfaces sensitive to hydrogen halides and ammonium halides, such as aluminum, copper, silicon oxide and the layers being deposited, against corrosion. Nanolaminate structures incorporating metallic thin films, and methods for forming the same, are also disclosed.

Owner:ASM INTERNATIONAL

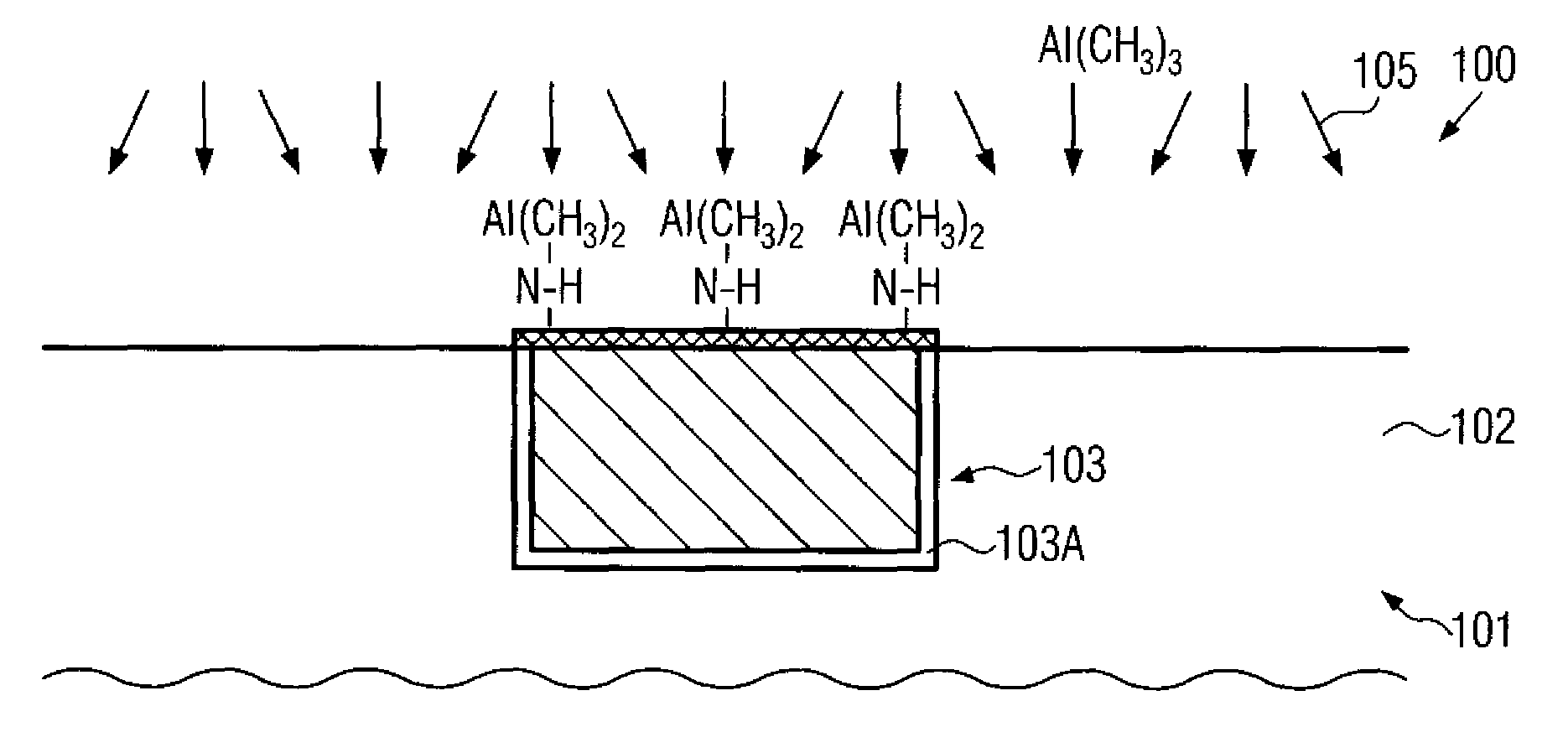

Method of manufracturing increasing reliability of copper-based metallization structures in a microstructure device by using aluminum nitride

ActiveUS7829460B2Reduce parasitic capacitanceEasy to controlSemiconductor/solid-state device detailsSolid-state devicesSelf limitingPermittivity

Owner:GLOBALFOUNDRIES U S INC

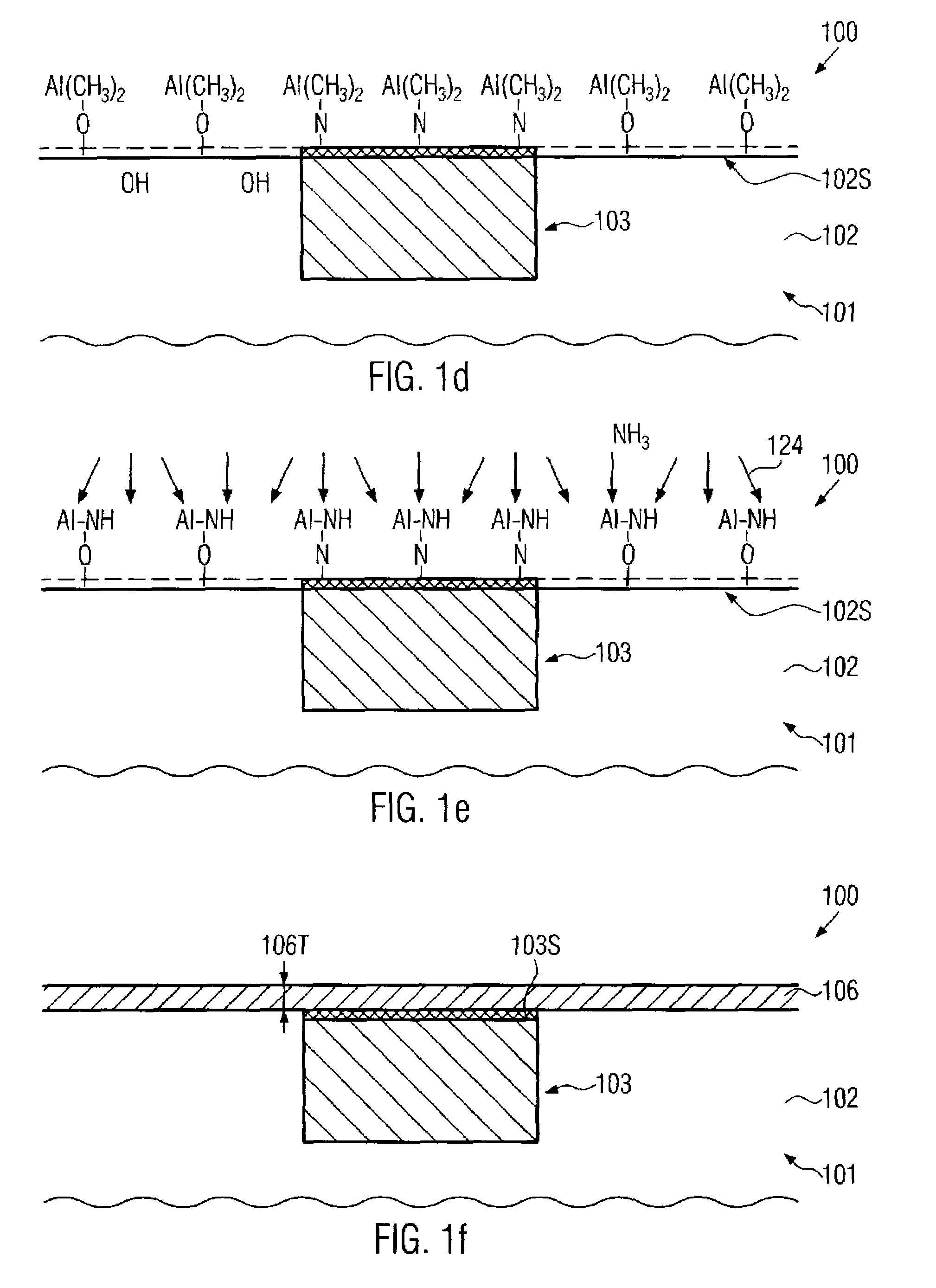

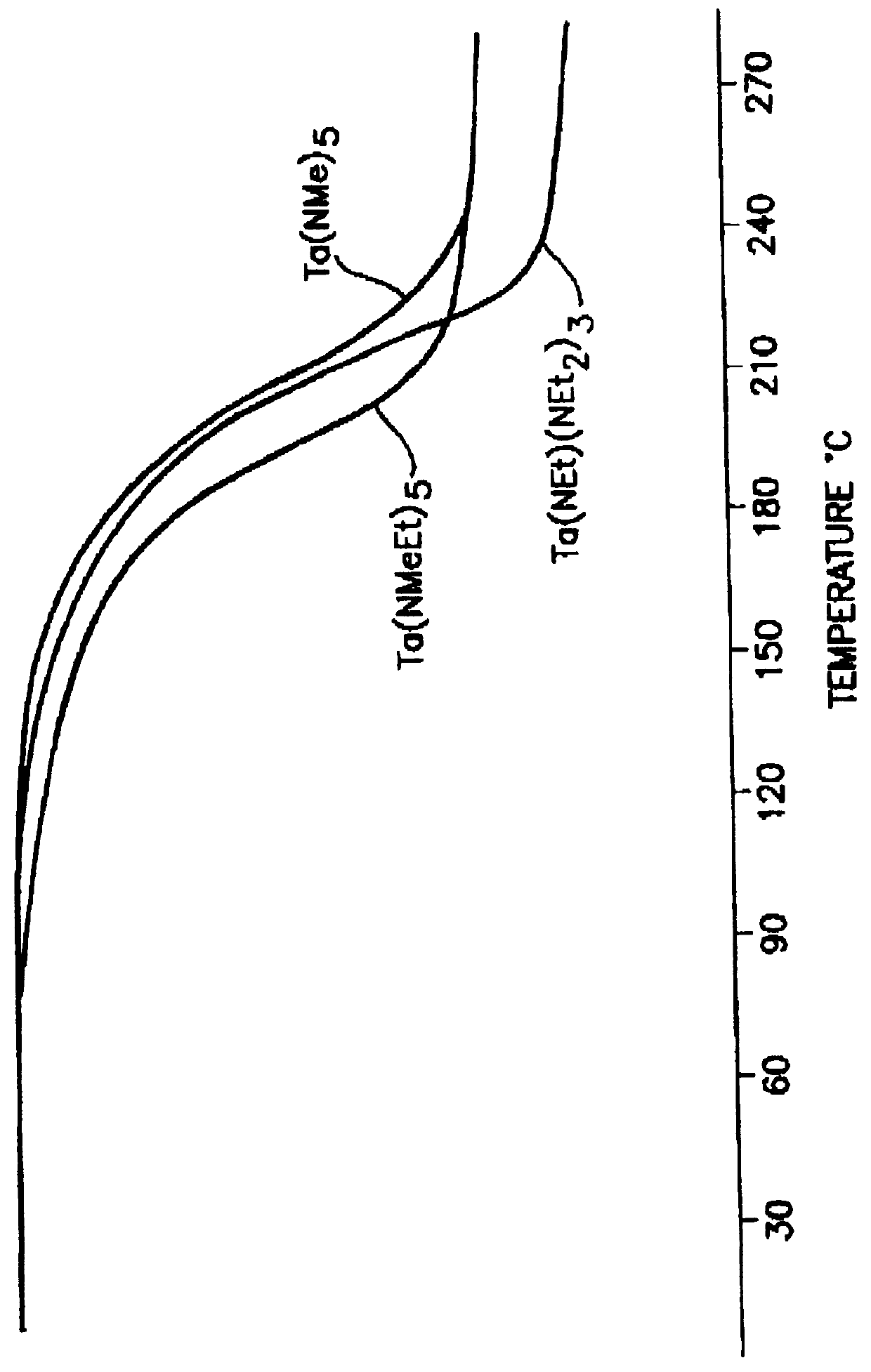

Tantalum amide precursors for deposition of tantalum nitride on a substrate

InactiveUS6015917ARapid heat treatmentSilicon organic compoundsPolycrystalline material growthFerroelectric thin filmsChemical vapor deposition

Tantalum and titanium source reagents are described, including tantalum amide and tantalum silicon nitride precursors for the deposition of tantalum nitride material on a substrate by processes such as chemical vapor deposition, assisted chemical vapor deposition, ion implantation, molecular beam epitaxy and rapid thermal processing. The precursors may be employed to form diffusion barrier layers on microlectronic device structures enabling the use of copper metallization and ferroelectric thin films in device construction.

Owner:ENTEGRIS INC

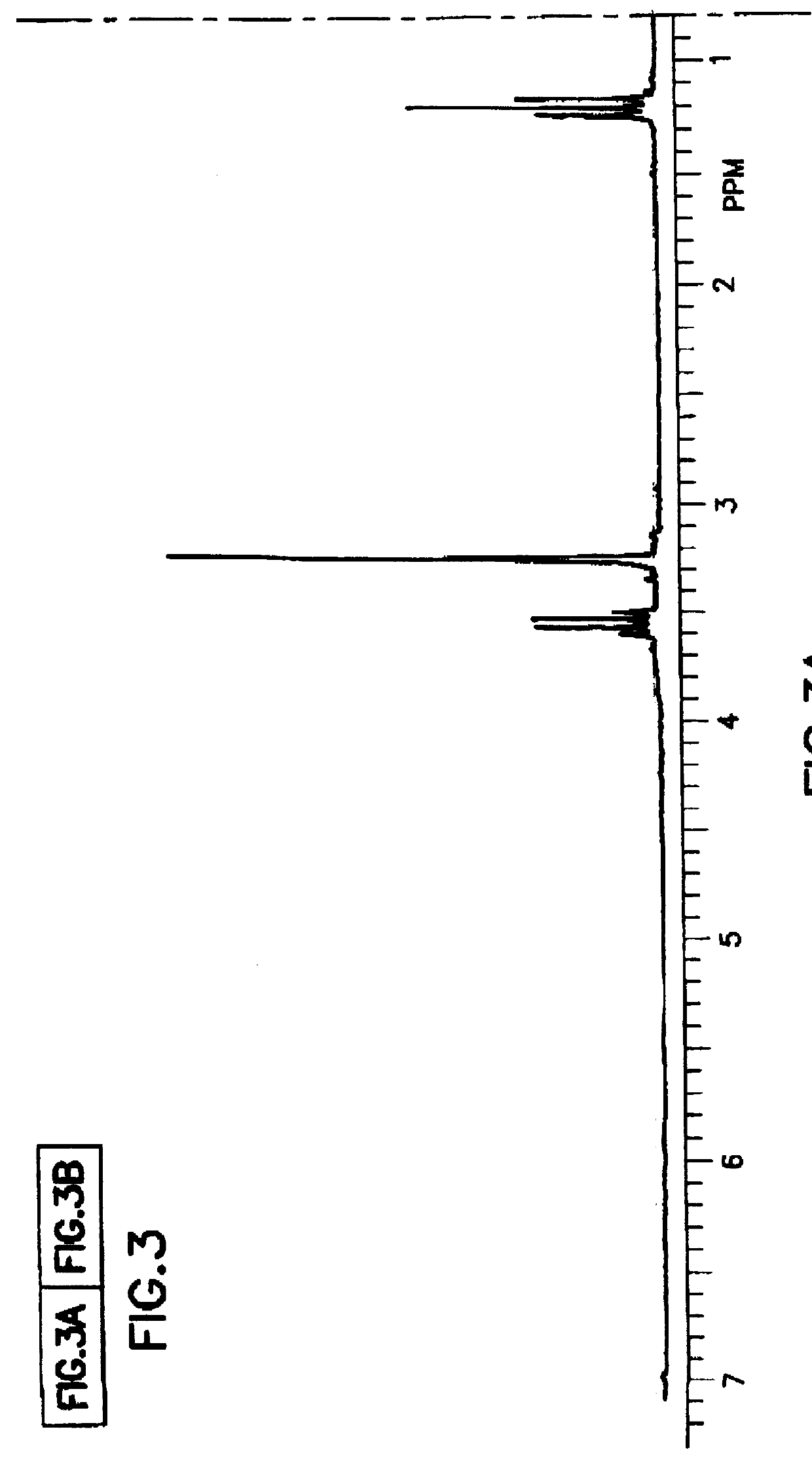

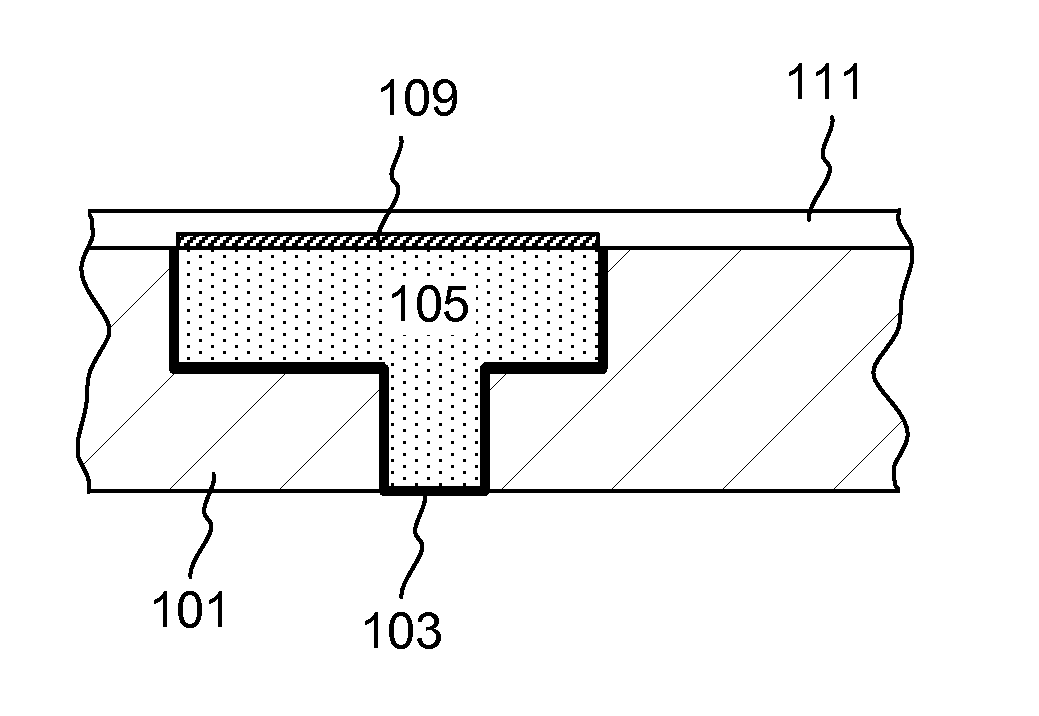

Selective formation of metallic films on metallic surfaces

ActiveUS20130196502A1Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingDeposition temperatureCopper

Metallic layers can be selectively deposited on one surface of a substrate relative to a second surface of the substrate. In some embodiments, the metallic layers are selectively deposited on copper instead of insulating or dielectric materials. In some embodiments, a first precursor forms a layer on the first surface and is subsequently reacted or converted to form a metallic layer. The deposition temperature may be selected such that a selectivity of above about 50% or even about 90% is achieved.

Owner:ASM INTERNATIONAL

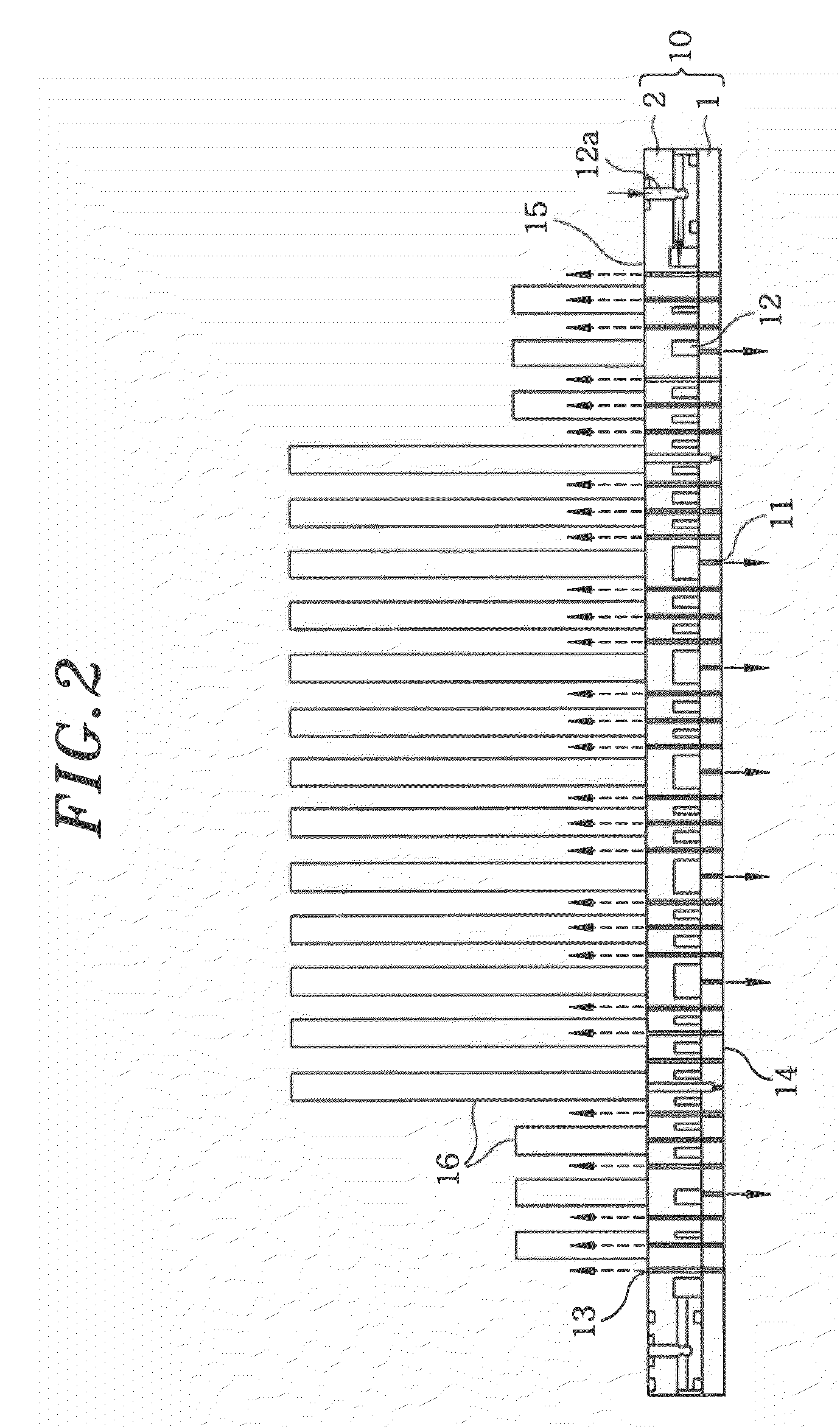

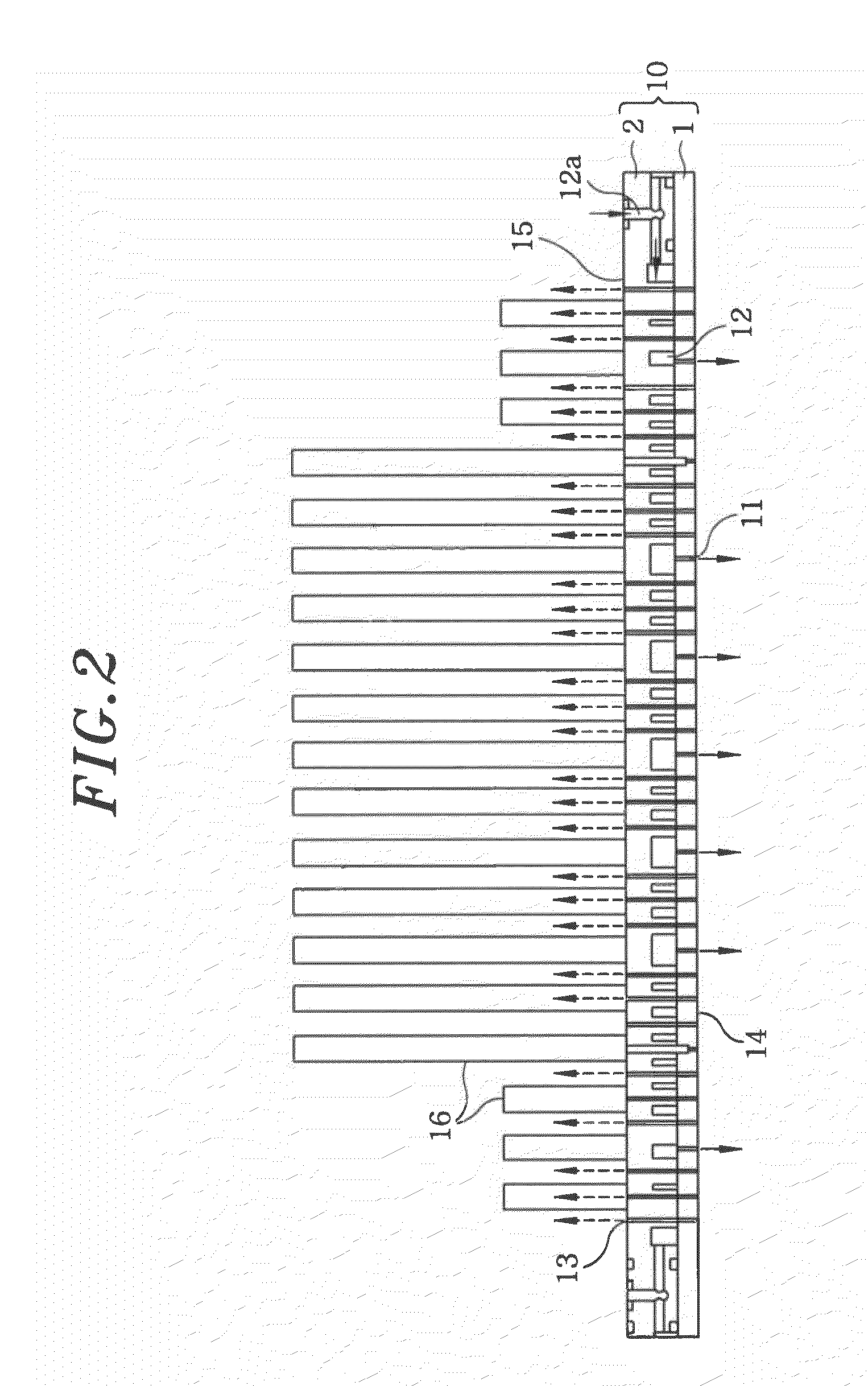

Manufacturing apparatus and method for large-scale production of thin-film solar cells

ActiveUS20050109392A1Cheap productionLow costPV power plantsFinal product manufactureIndiumElectrical battery

A method of manufacturing improved thin-film solar cells entirely by sputtering includes a high efficiency back contact / reflecting multi-layer containing at least one barrier layer consisting of a transition metal nitride. A copper indium gallium diselenide (Cu(InXGa1-x)Se2) absorber layer (X ranging from 1 to approximately 0.7) is co-sputtered from specially prepared electrically conductive targets using dual cylindrical rotary magnetron technology. The band gap of the absorber layer can be graded by varying the gallium content, and by replacing the gallium partially or totally with aluminum. Alternately the absorber layer is reactively sputtered from metal alloy targets in the presence of hydrogen selenide gas. RF sputtering is used to deposit a non-cadmium containing window layer of ZnS. The top transparent electrode is reactively sputtered aluminum doped ZnO. A unique modular vacuum roll-to-roll sputtering machine is described. The machine is adapted to incorporate dual cylindrical rotary magnetron technology to manufacture the improved solar cell material in a single pass.

Owner:BEIJING APOLLO DING RONG SOLAR TECH

Electroless plating of metal caps for chalcogenide-based memory devices

InactiveUS20060094236A1Good electrical contactSemiconductor/solid-state device manufacturingPlatinumSulfur

A method of forming a metal cap over a conductive interconnect in a chalcogenide-based memory device is provided and includes, forming a layer of a first conductive material over a substrate, depositing an insulating layer over the first conductive material and the substrate, forming an opening in the insulating layer to expose at least a portion of the first conductive material, depositing a second conductive material over the insulating layer and within the opening, removing portions of the second conductive material to form a conductive area within the opening, recessing the conductive area within the opening to a level below an upper surface of the insulating layer, forming a cap of a third conductive material over the recessed conductive area within the opening, the third conductive material selected from the group consisting of cobalt, silver, gold, copper, nickel, palladium, platinum, and alloys thereof, depositing a stack of a chalcogenide based memory cell material over the cap, and depositing a conductive material over the chalcogenide stack.

Owner:MICRON TECH INC

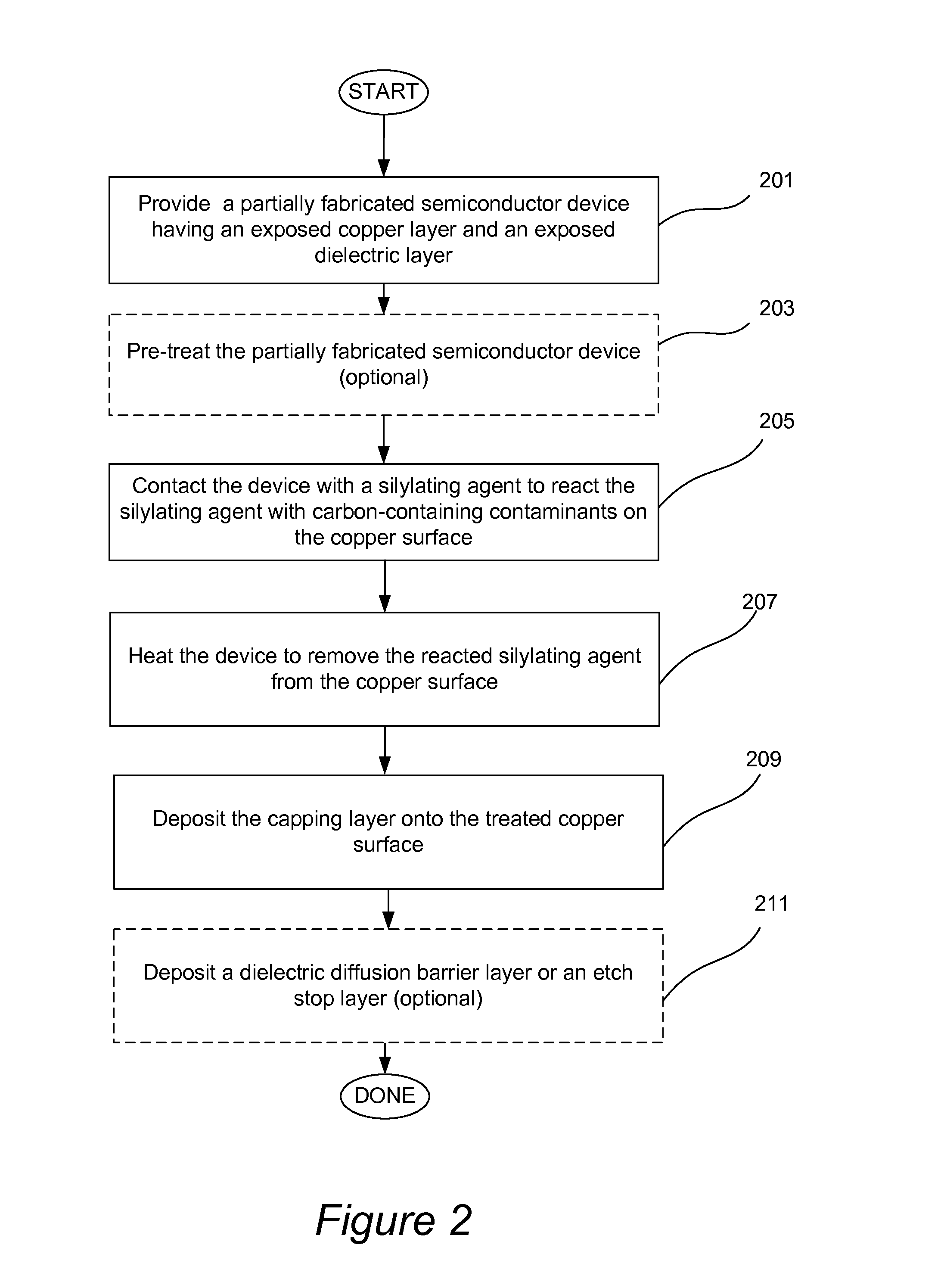

Cleaning of carbon-based contaminants in metal interconnects for interconnect capping applications

InactiveUS20150380296A1Avoid depositionLow deposition rateLiquid surface applicatorsSemiconductor/solid-state device manufacturingMetal interconnectSilylation

Protective caps residing at an interface between copper lines and dielectric diffusion barrier layers are used to improve various performance characteristics of interconnects. The caps, such as cobalt-containing caps or manganese-containing caps, are selectively deposited onto exposed copper lines in a presence of exposed dielectric using CVD or ALD methods. The deposition of the capping material is affected by the presence of carbon-containing contaminants on the surface of copper, which may lead to poor or uneven growth of the capping layer. A method of removing carbon-containing contaminants from the copper surface prior to deposition of caps involves contacting the substrate containing the exposed copper surface with a silylating agent at a first temperature to form a layer of reacted silylating agent on the copper surface, followed by heating the substrate at a higher temperature to release the reacted silylating agent from the copper surface.

Owner:LAM RES CORP

Method for forming interconnect structure having airgap

ActiveUS20110217838A1Limited spaceReducing KeffSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsCopper

A method for forming an interconnect structure with airgaps, includes: providing a structure having a trench formed on a substrate; depositing a spacer oxide layer on sidewalls of the trench as sidewall spacers by plasma enhanced atomic layer deposition; filling the trench having the sidewall spacers with copper; removing the sidewall spacers to form an airgap structure; and encapsulating the airgap structure, wherein airgaps are formed between the filled copper and the sidewalls of the trench.

Owner:ASM JAPAN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com