Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1666 results about "Metal interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

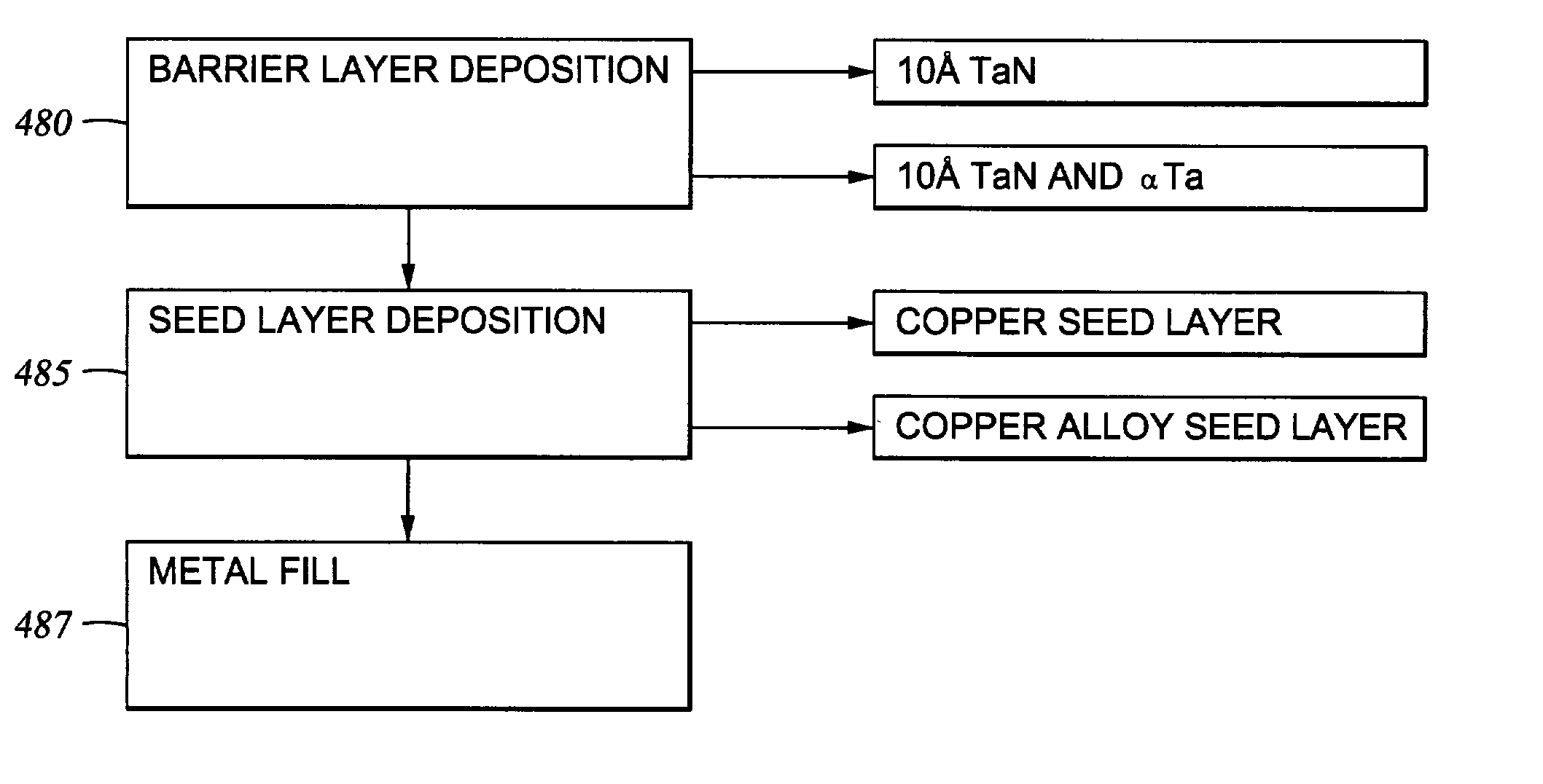

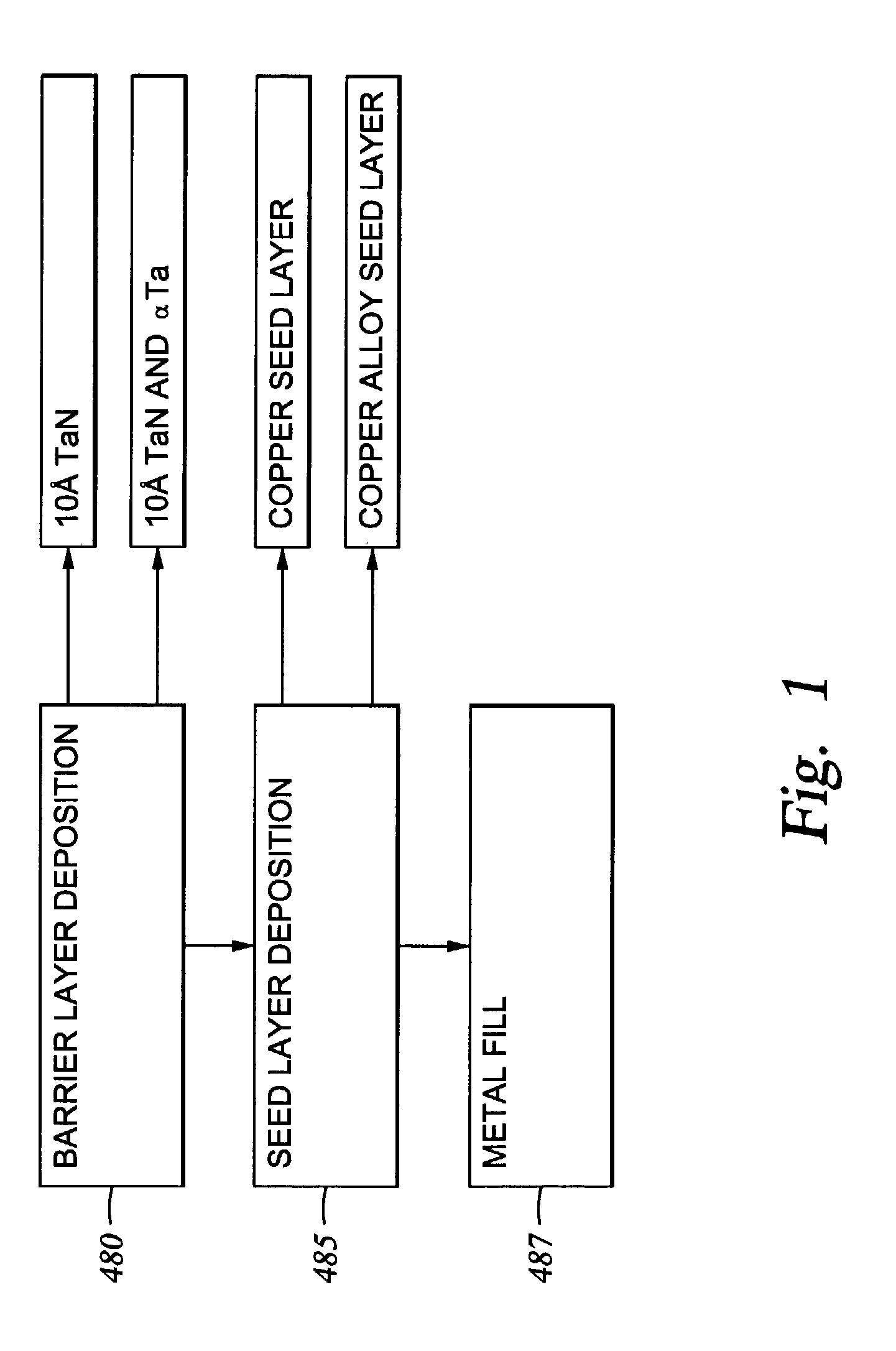

Integration of ALD tantalum nitride and alpha-phase tantalum for copper metallization application

InactiveUS20030082307A1Pretreated surfacesSemiconductor/solid-state device manufacturingMetal interconnectTantalum nitride

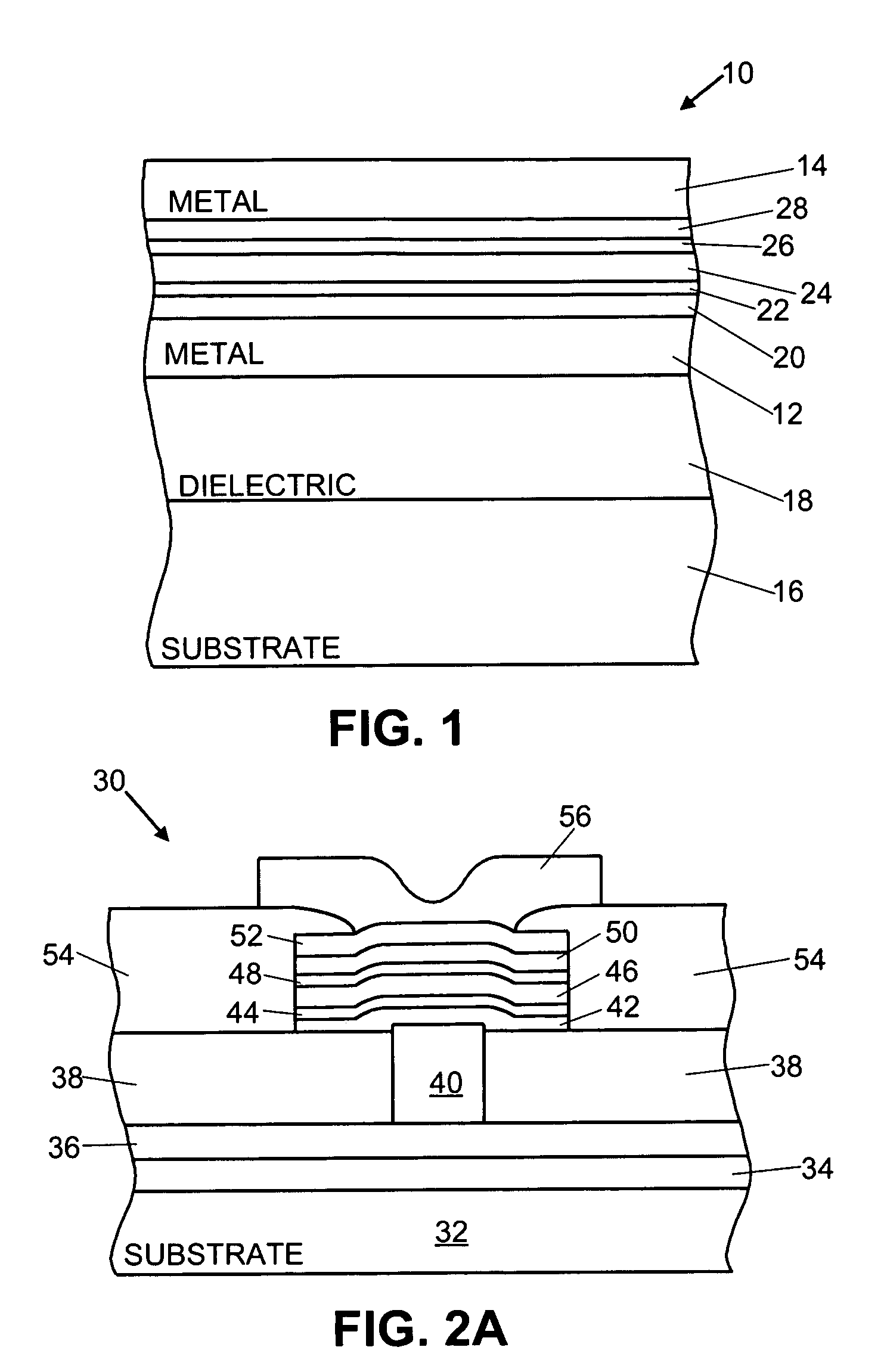

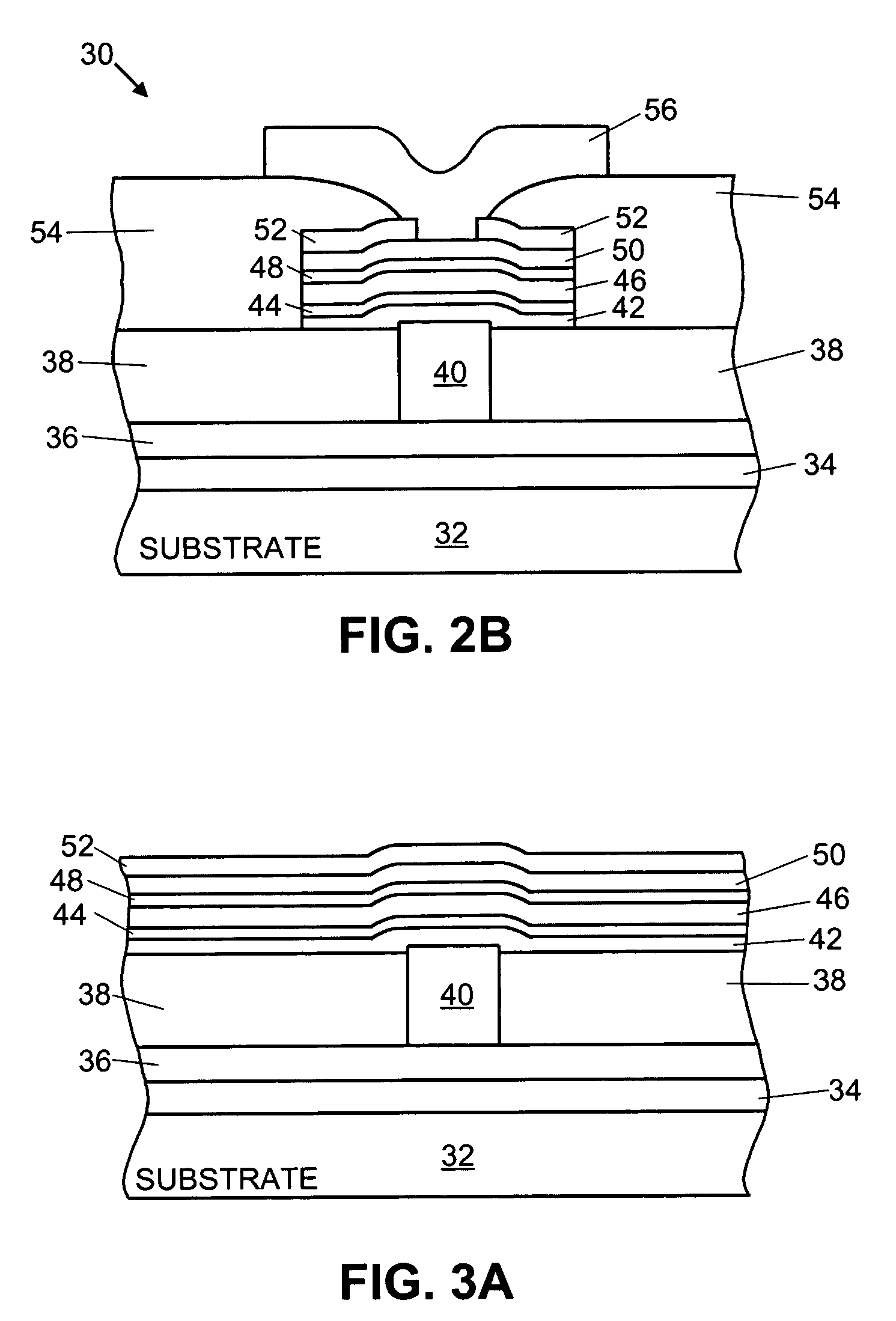

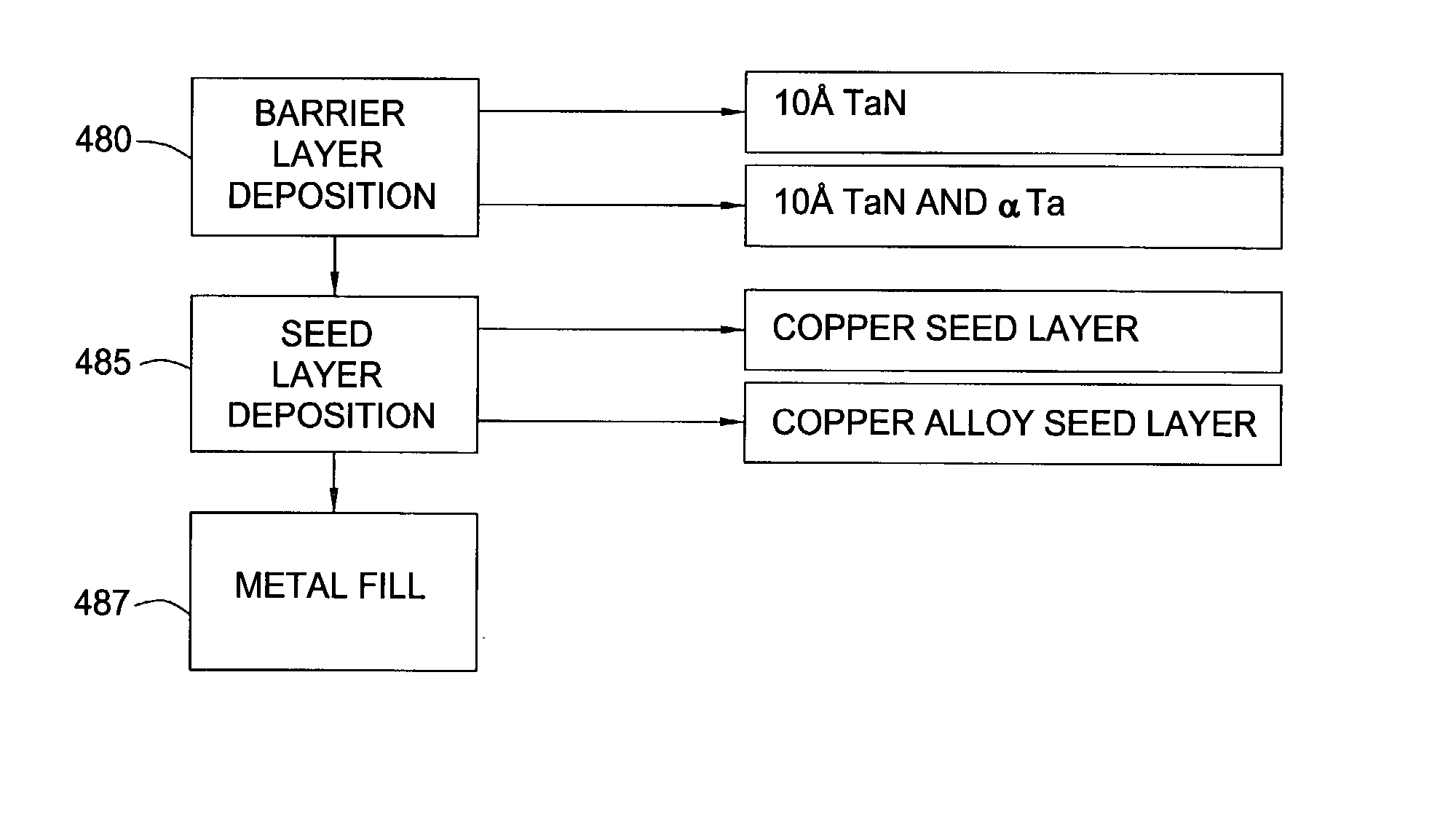

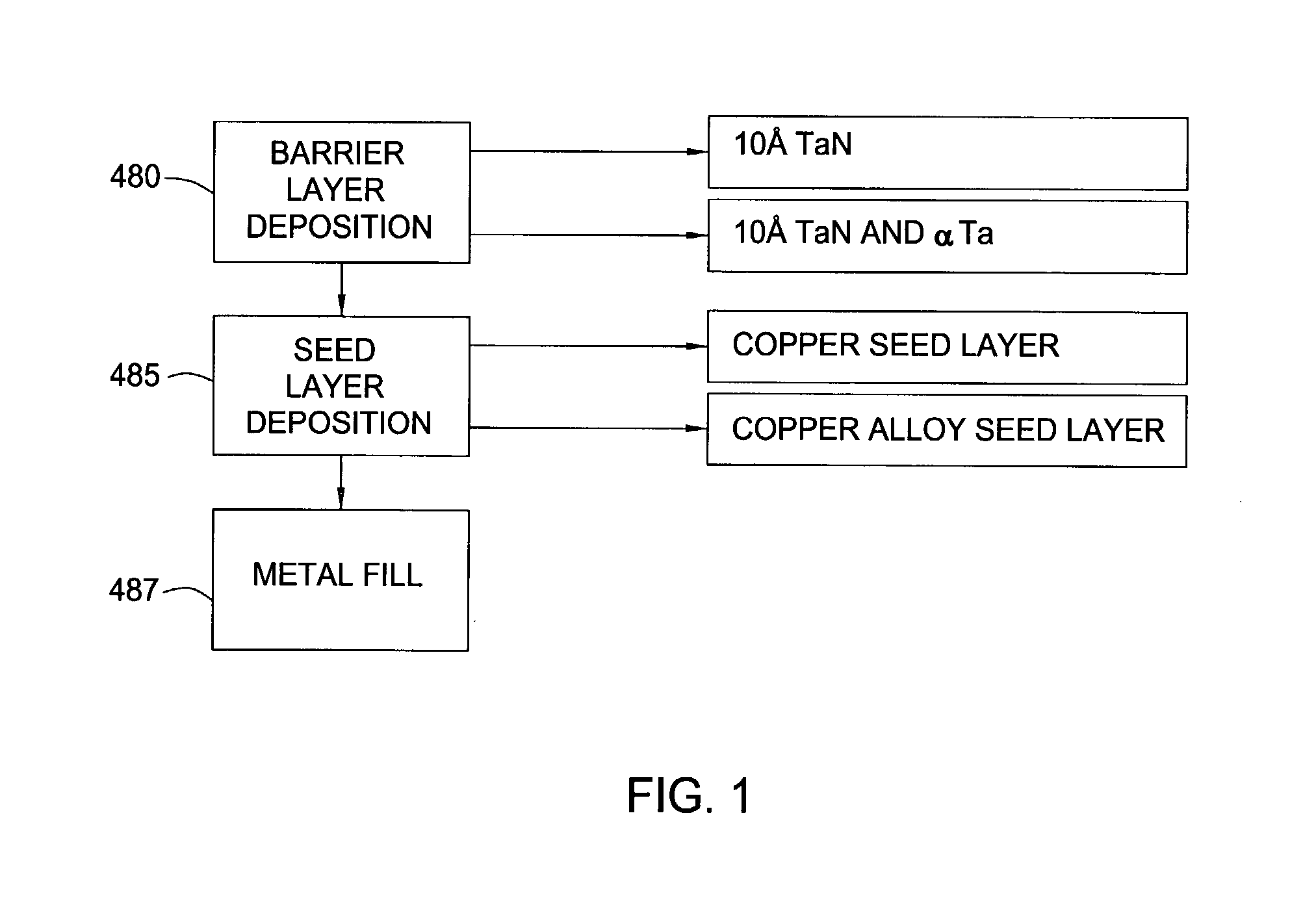

A method for forming a metal interconnect on a substrate is provided. The method includes depositing a refractory metal-containing barrier layer having a thickness less than about 20 angstroms on at least a portion of a metal layer by alternately introducing one or more pulses of a metal-containing compound and one or more pulses of a nitrogen-containing compound. The method also includes depositing a seed layer on at least a portion of the barrier layer, and depositing a second metal layer on at least a portion of the seed layer. The barrier layer provides adequate barrier properties and allows the grain growth of the metal layer to continue across the barrier layer into the second metal layer thereby enhancing the electrical performance of the interconnect.

Owner:APPLIED MATERIALS INC

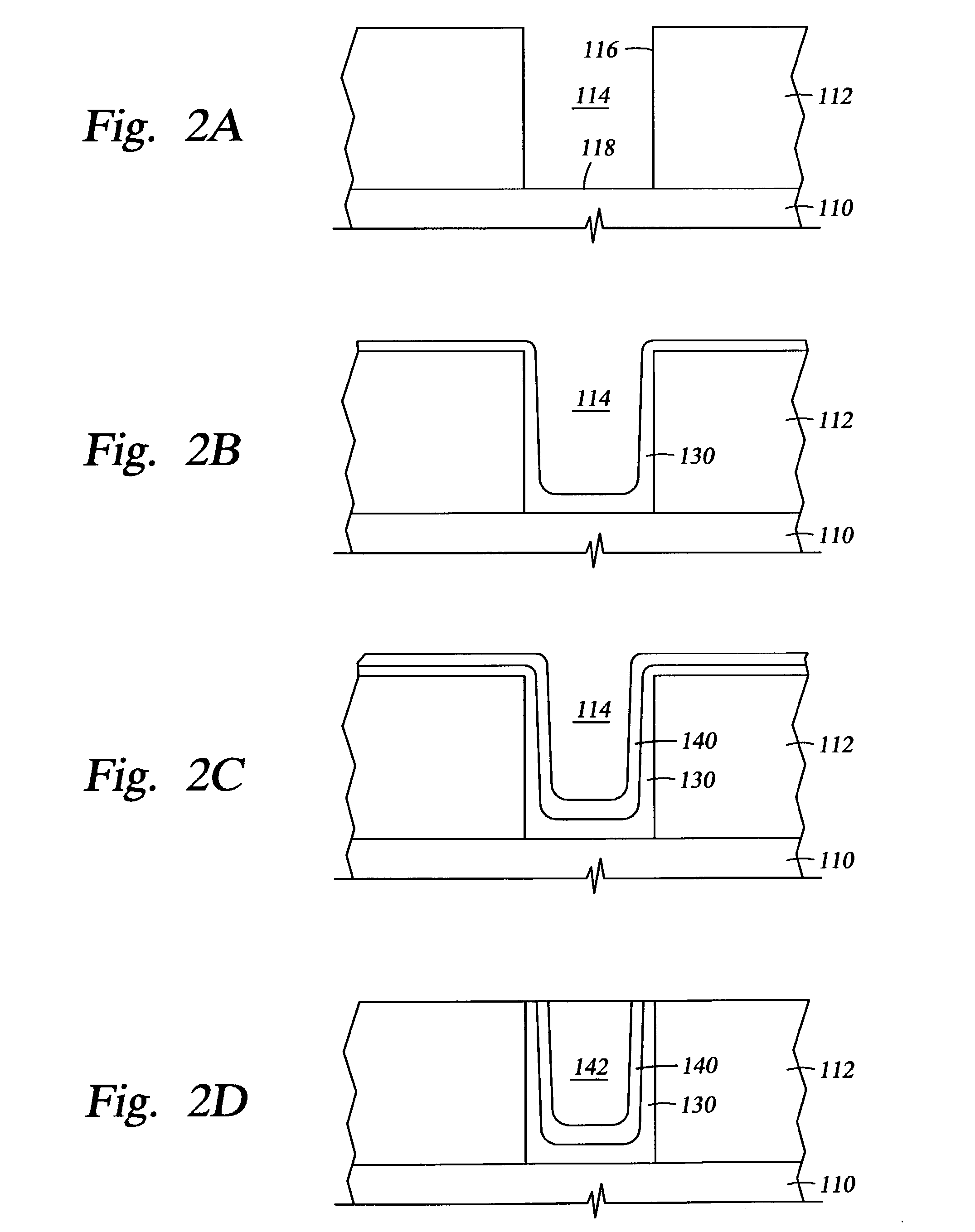

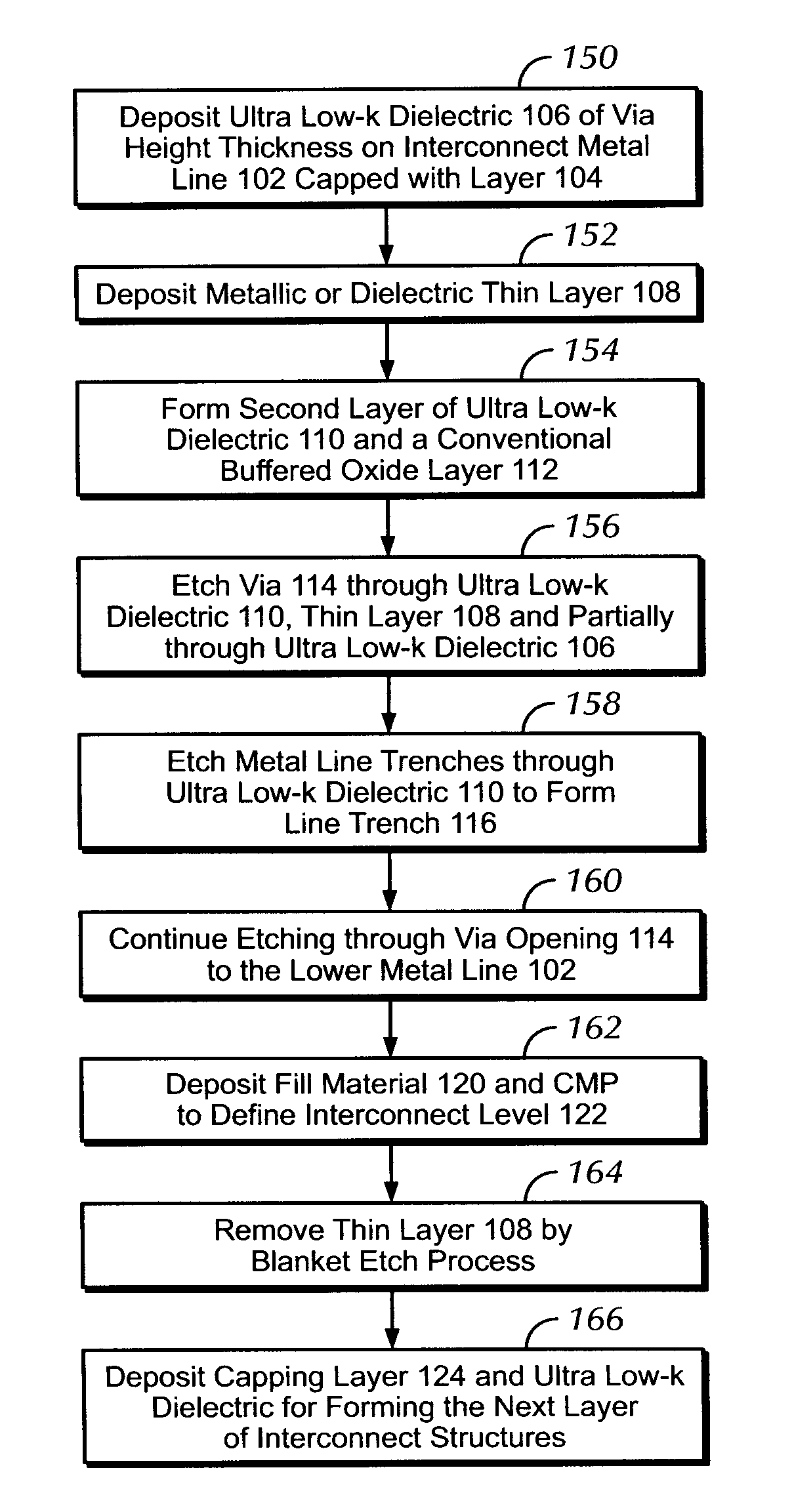

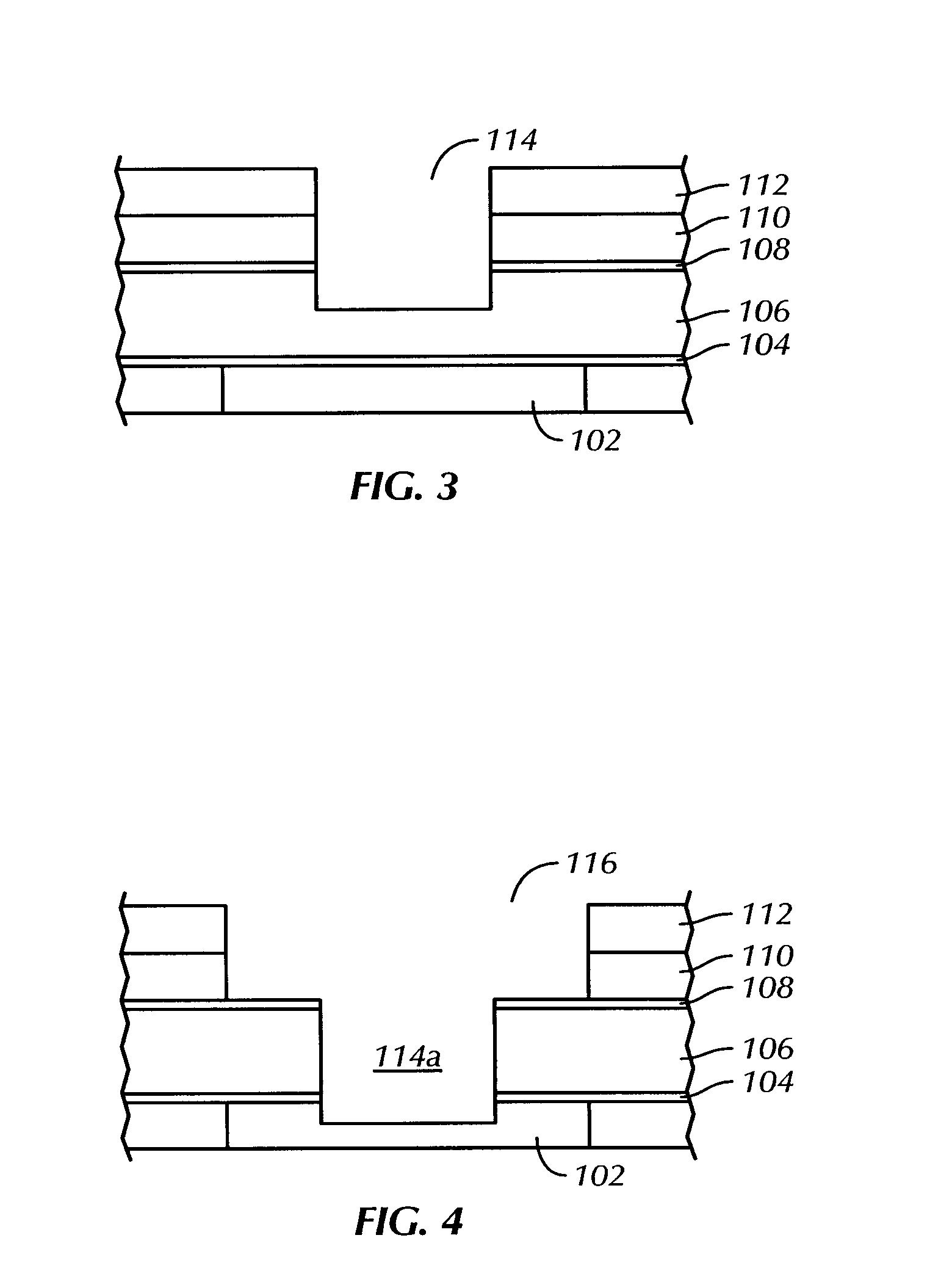

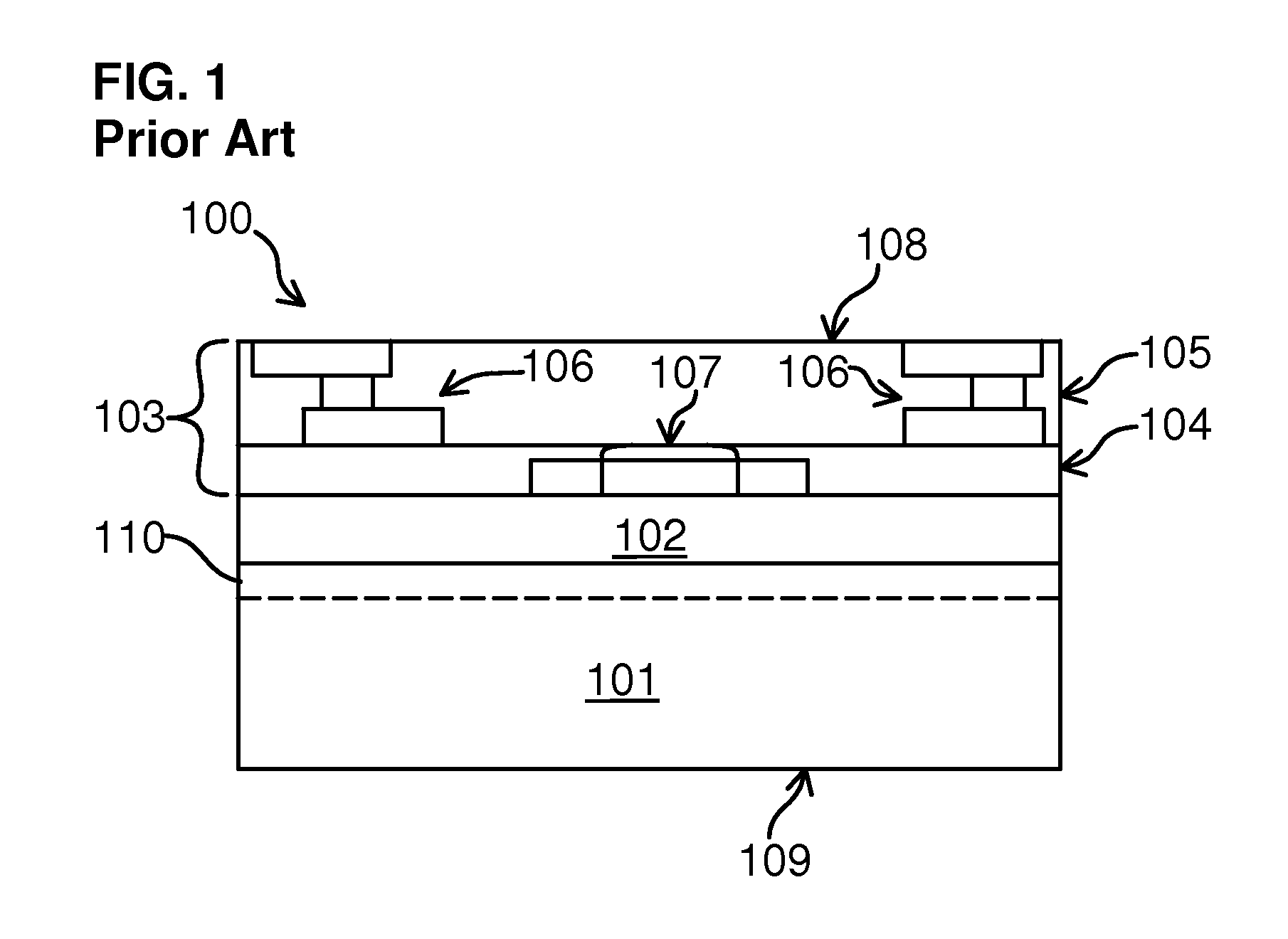

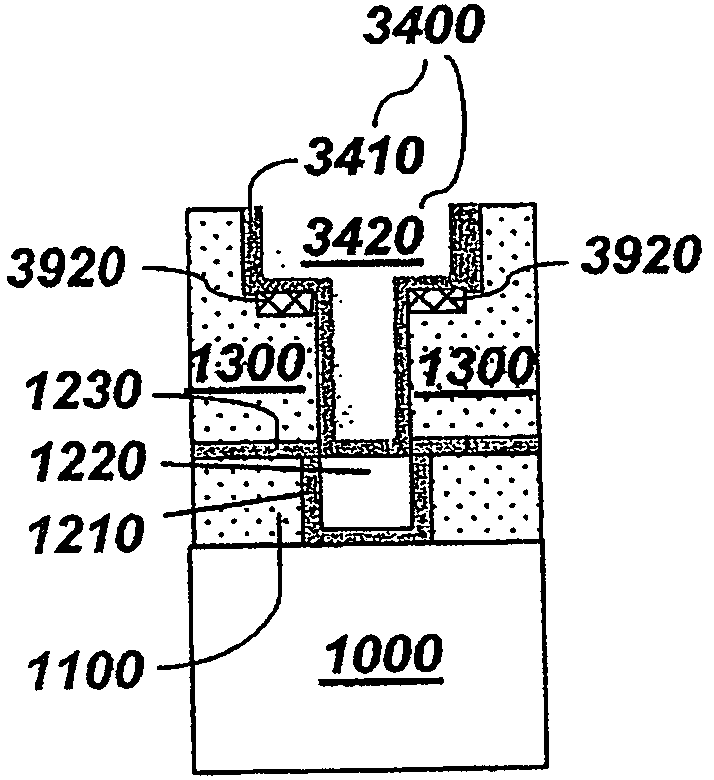

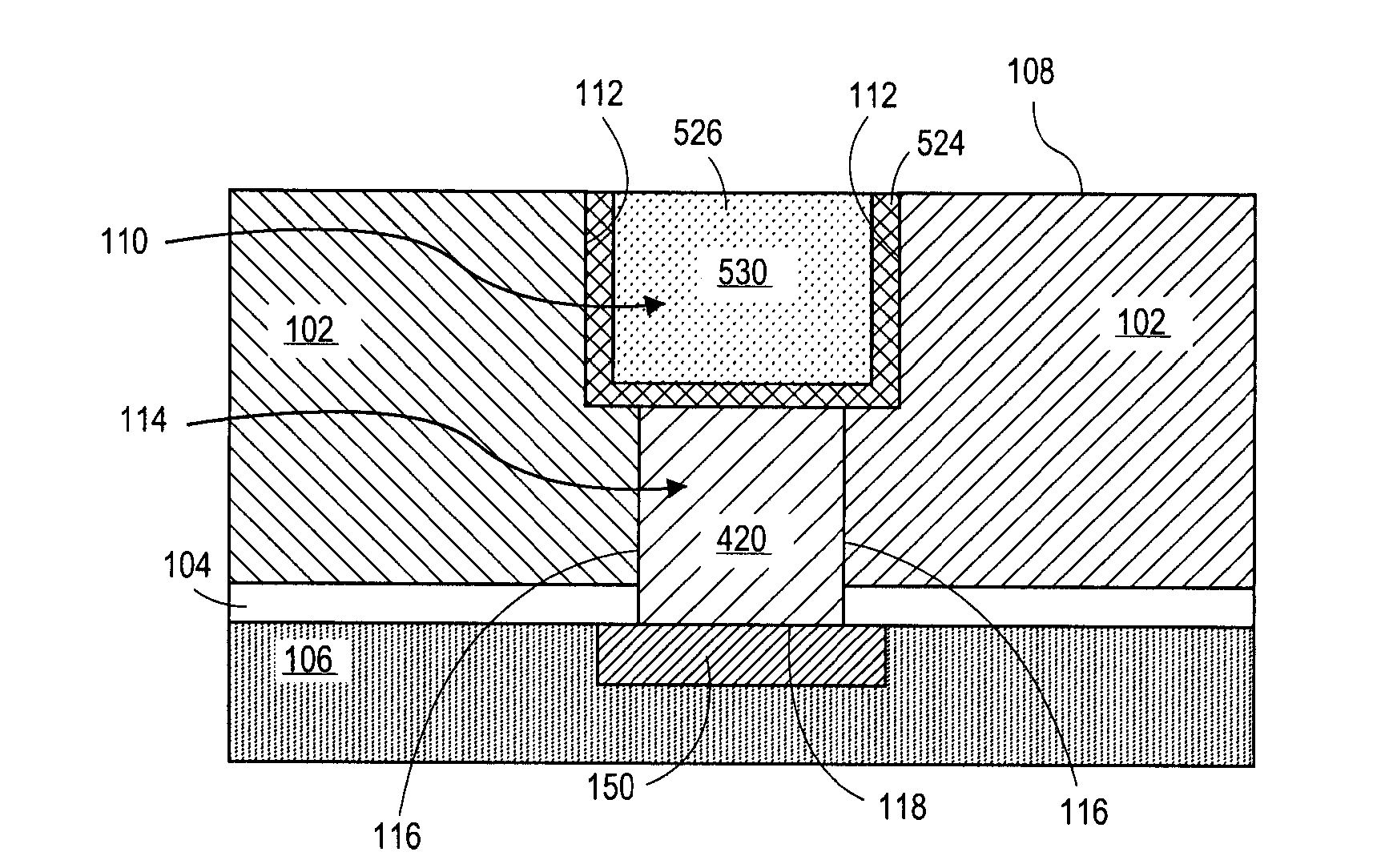

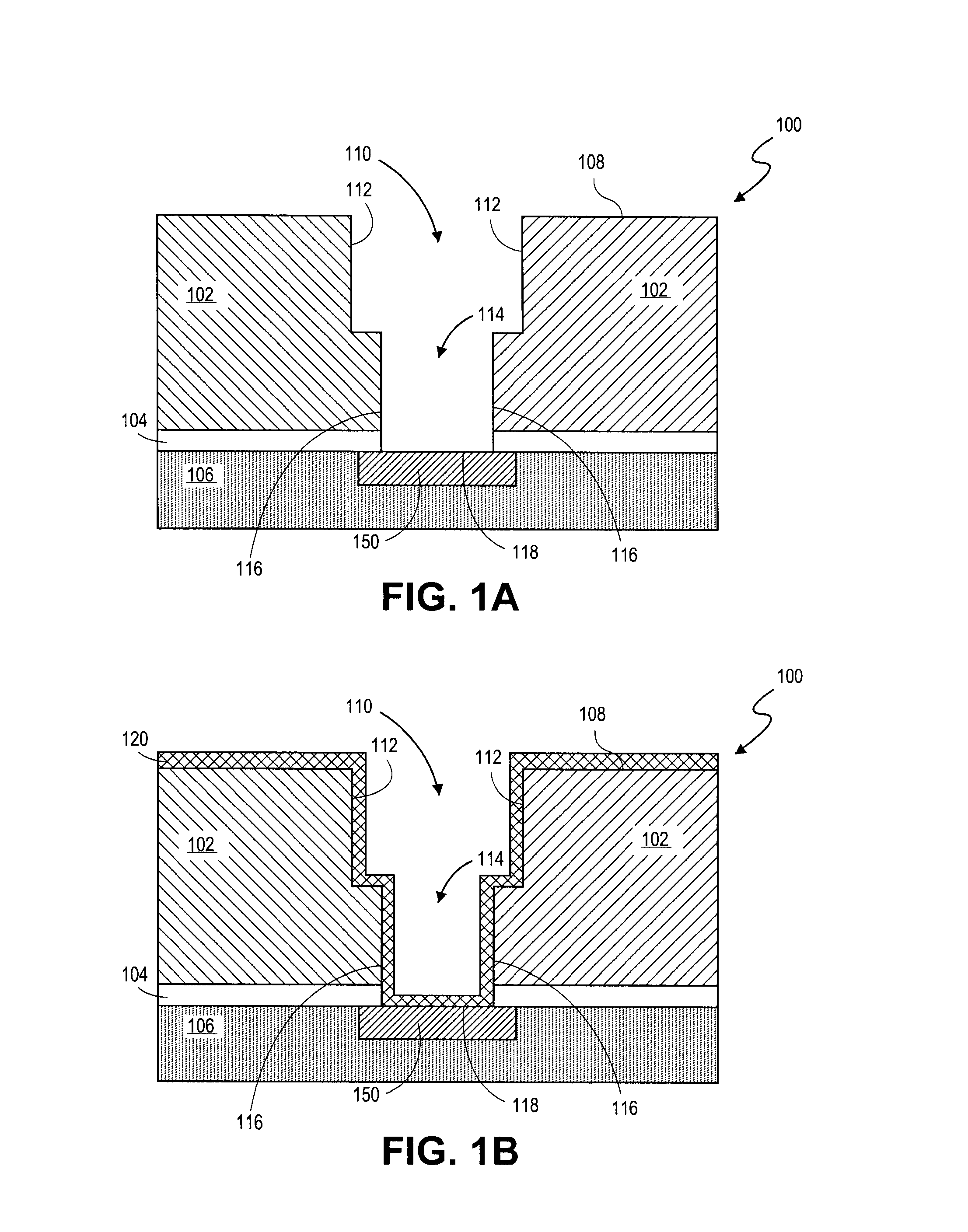

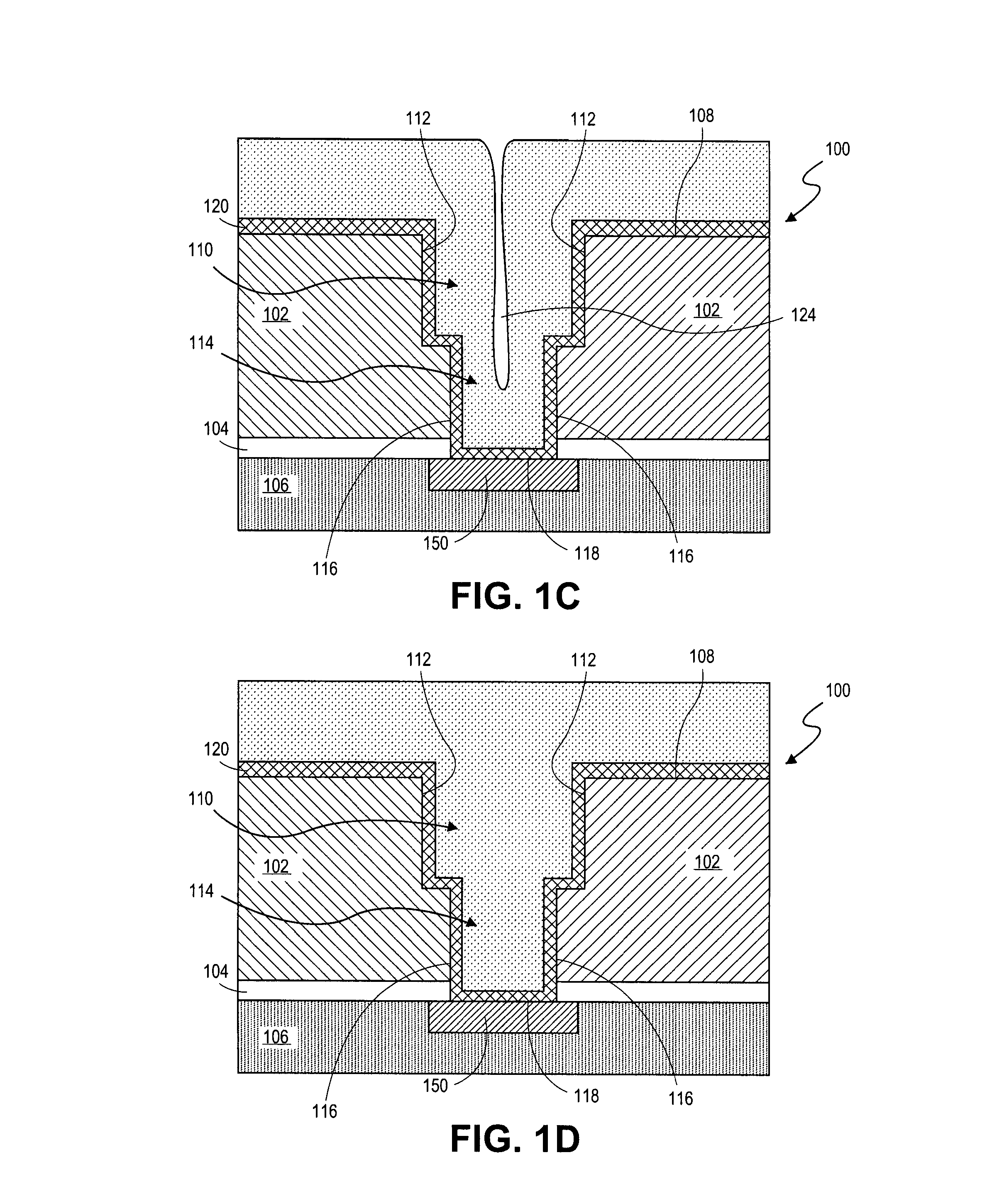

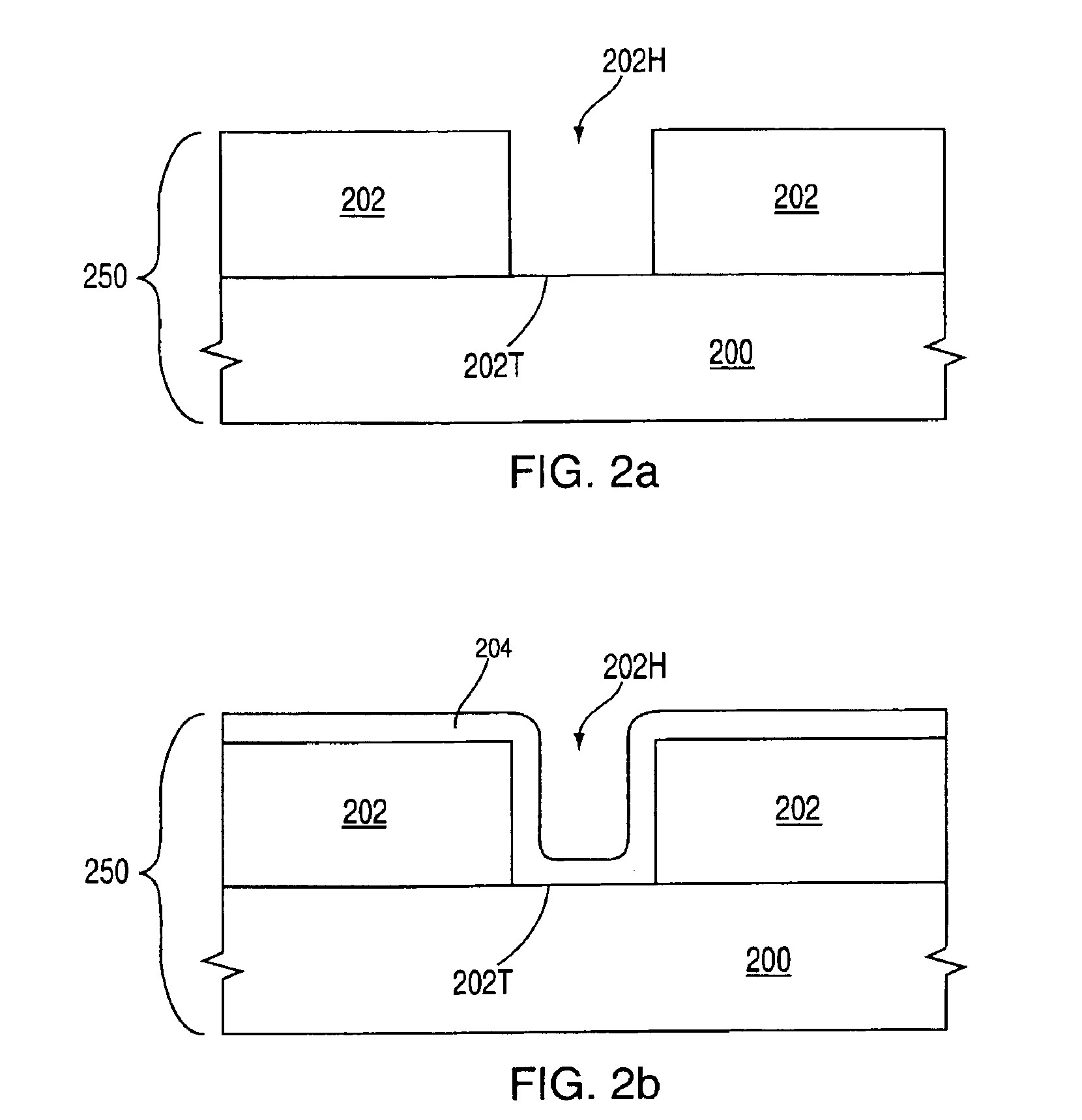

Method of Forming Metal Interconnect Structures in Ultra Low-K Dielectrics

ActiveUS20110117737A1Semiconductor/solid-state device manufacturingMetal interconnectConductive materials

A metal interconnect structure in ultra low-k dielectrics is described having a capped interconnect layer; an interconnect feature with a contact via and a contact line formed in a dielectric layer, where the via is partially embedded into the interconnect layer; and a thin film formed on the dielectric layer and separating the dielectric layer from the contact line. A method of fabricating the interconnect structure is also described and includes forming a first dielectric on a capped interconnect element; forming a thin film over the first dielectric; forming a second dielectric on the thin film; forming a via opening on the second dielectric, the thin film and extending into the first dielectric; forming a line trench on a portion of the second dielectric; and filling the via opening and the line trench with a conductive material for forming a contact via and a contact line, where the contact via is partially embedded in the interconnect element.

Owner:GLOBALFOUNDRIES US INC

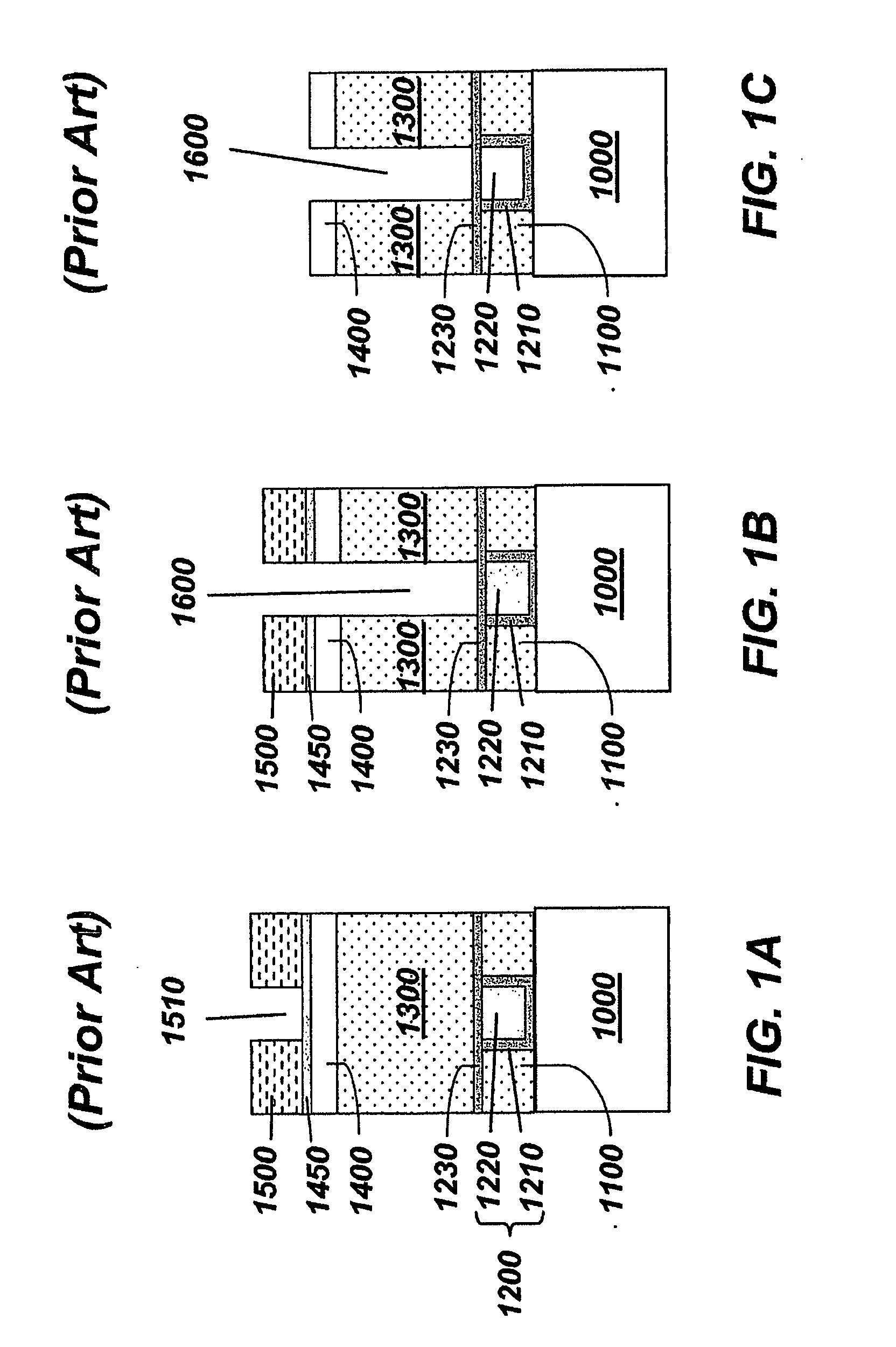

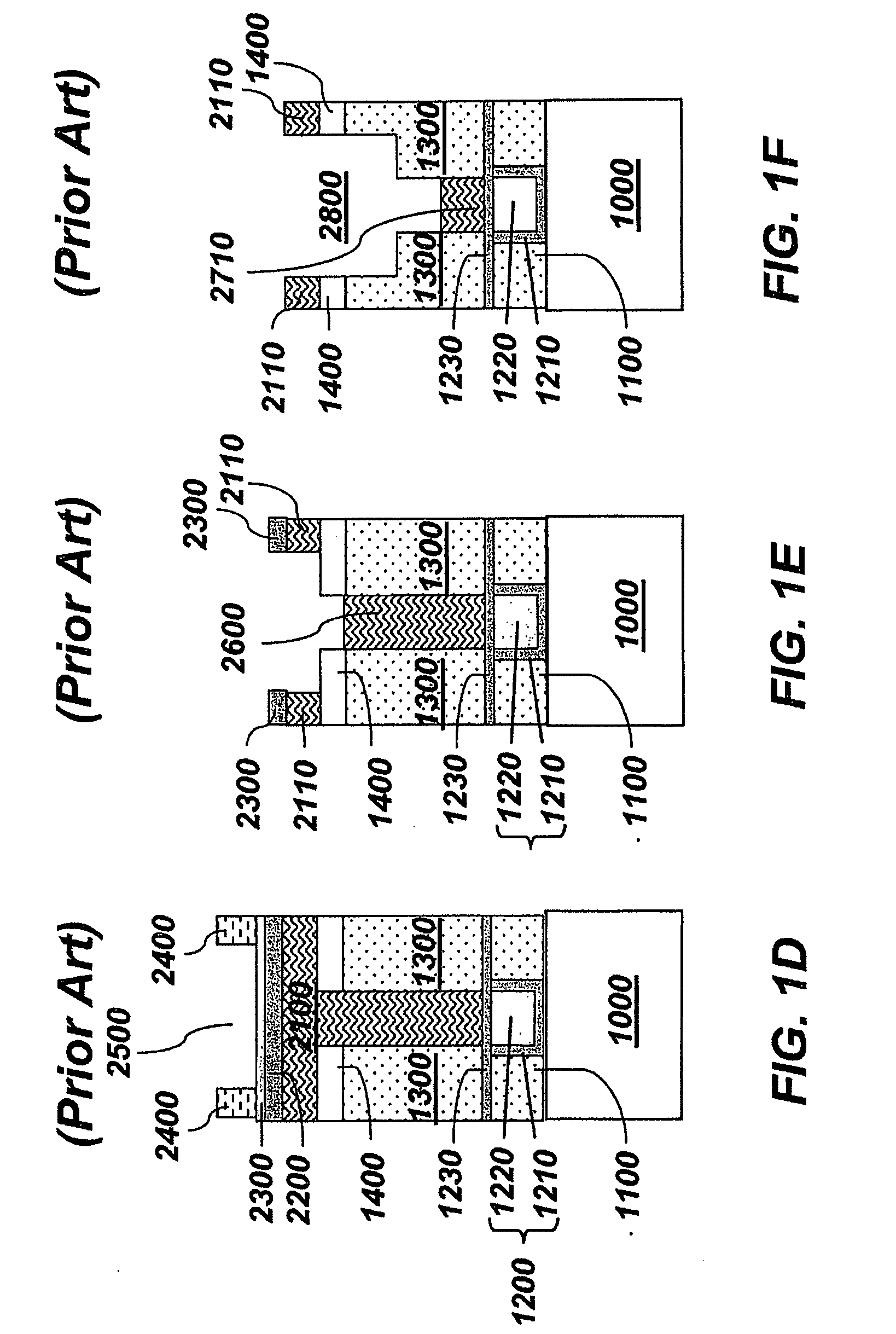

Low-carbon-doped silicon oxide film and damascene structure using same

ActiveUS20050260850A1Reduce electrical circuit lifetimeEnhance moisture intakeSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDevice material

A method of forming an interconnect for a semiconductor device using triple hard layers, comprises: forming a first hard layer serving as an etch stop layer on a metal interconnect-formed dielectric layer; forming a second hard layer on the first hard layer; forming a dielectric layer on the second hard layer; forming a third hard layer on the dielectric layer; forming a hole through the third and second hard layers, the dielectric layer, and the first hard layer; and filling the hole with metal to establish an interconnect. The second and third hard layers are each made of carbon-doped silicon oxide formed from a source gas and a redox gas, while controlling the carbon content in the second hard layer as a function of a flow rate of the redox gas.

Owner:ASM JAPAN

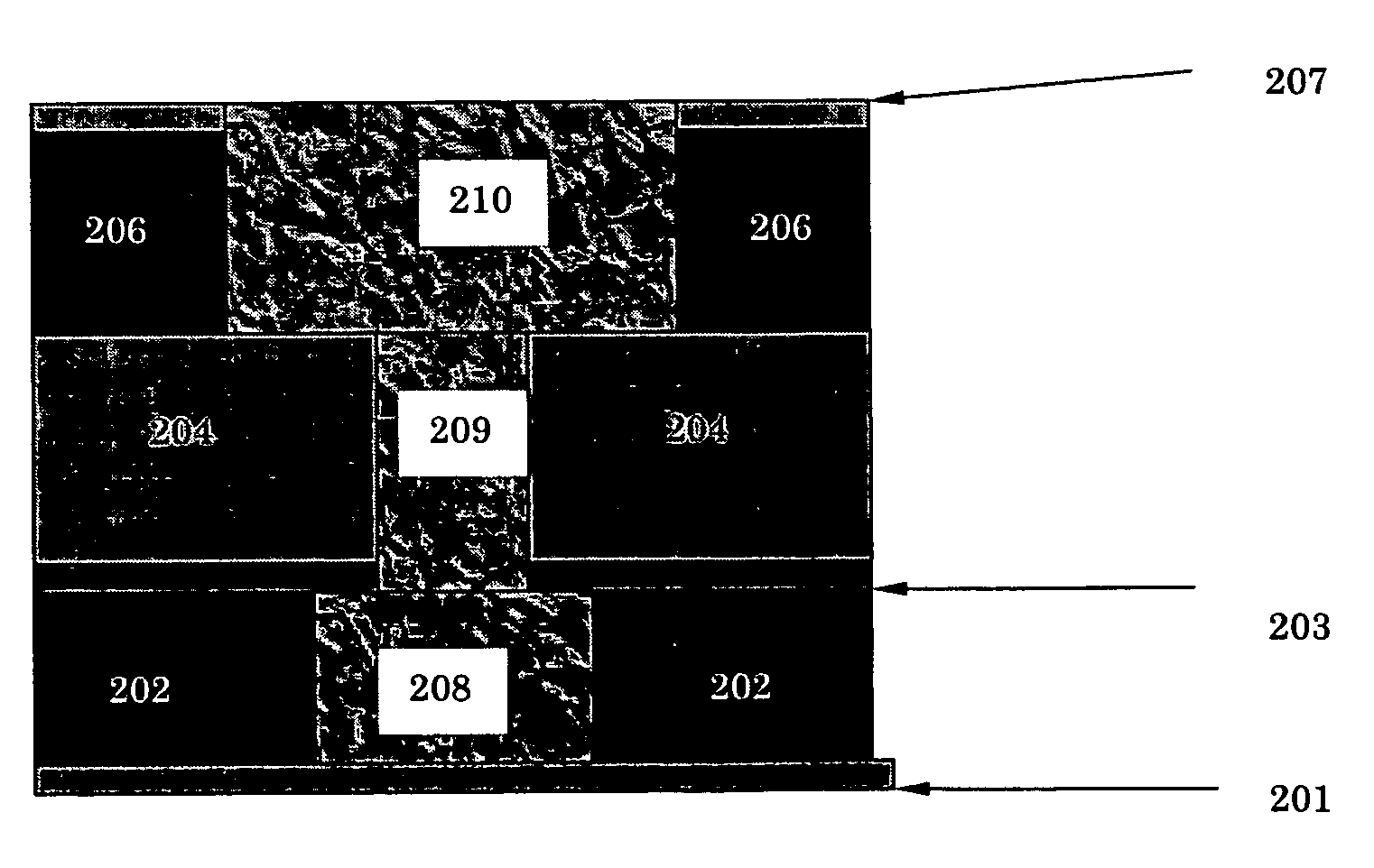

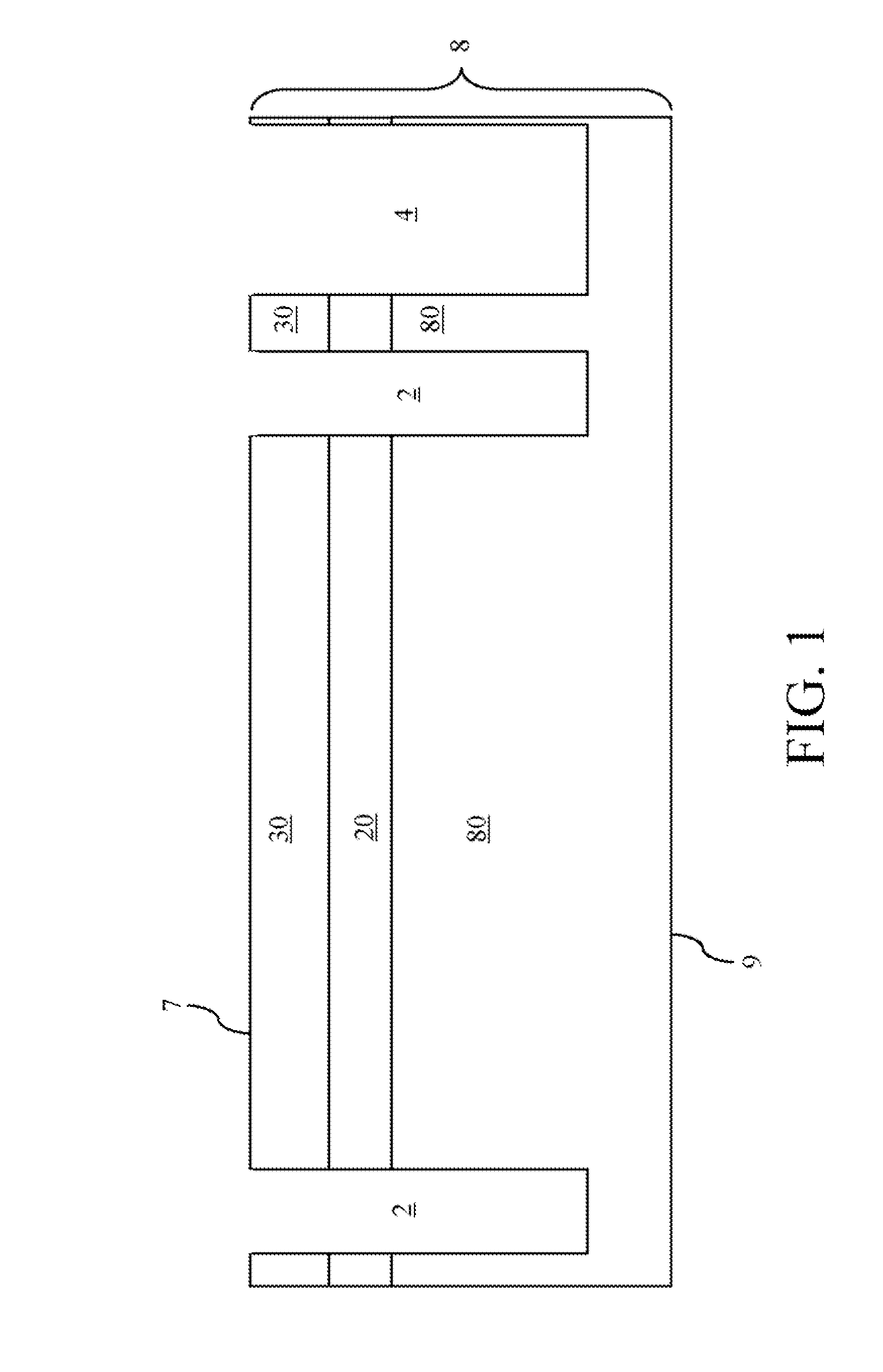

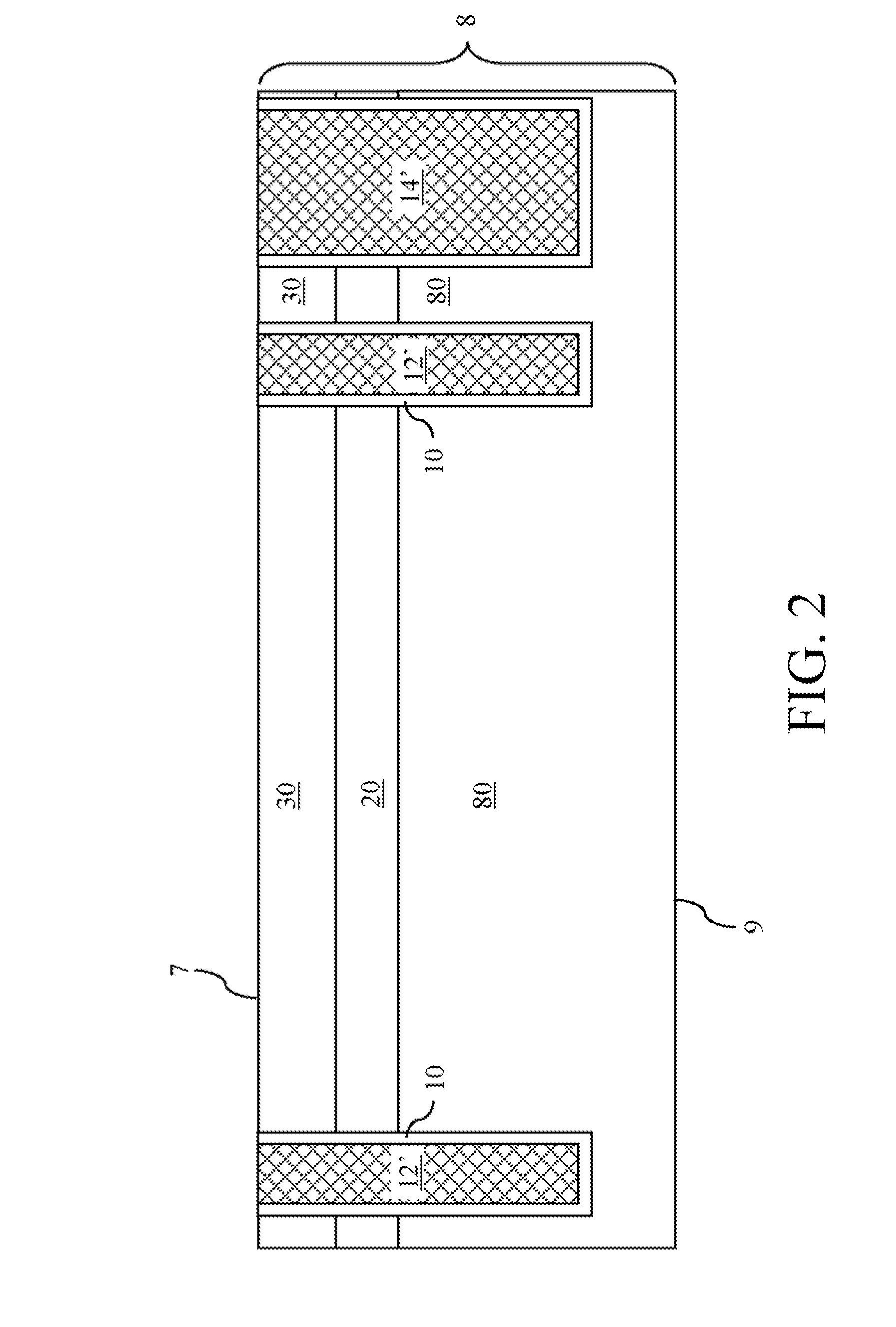

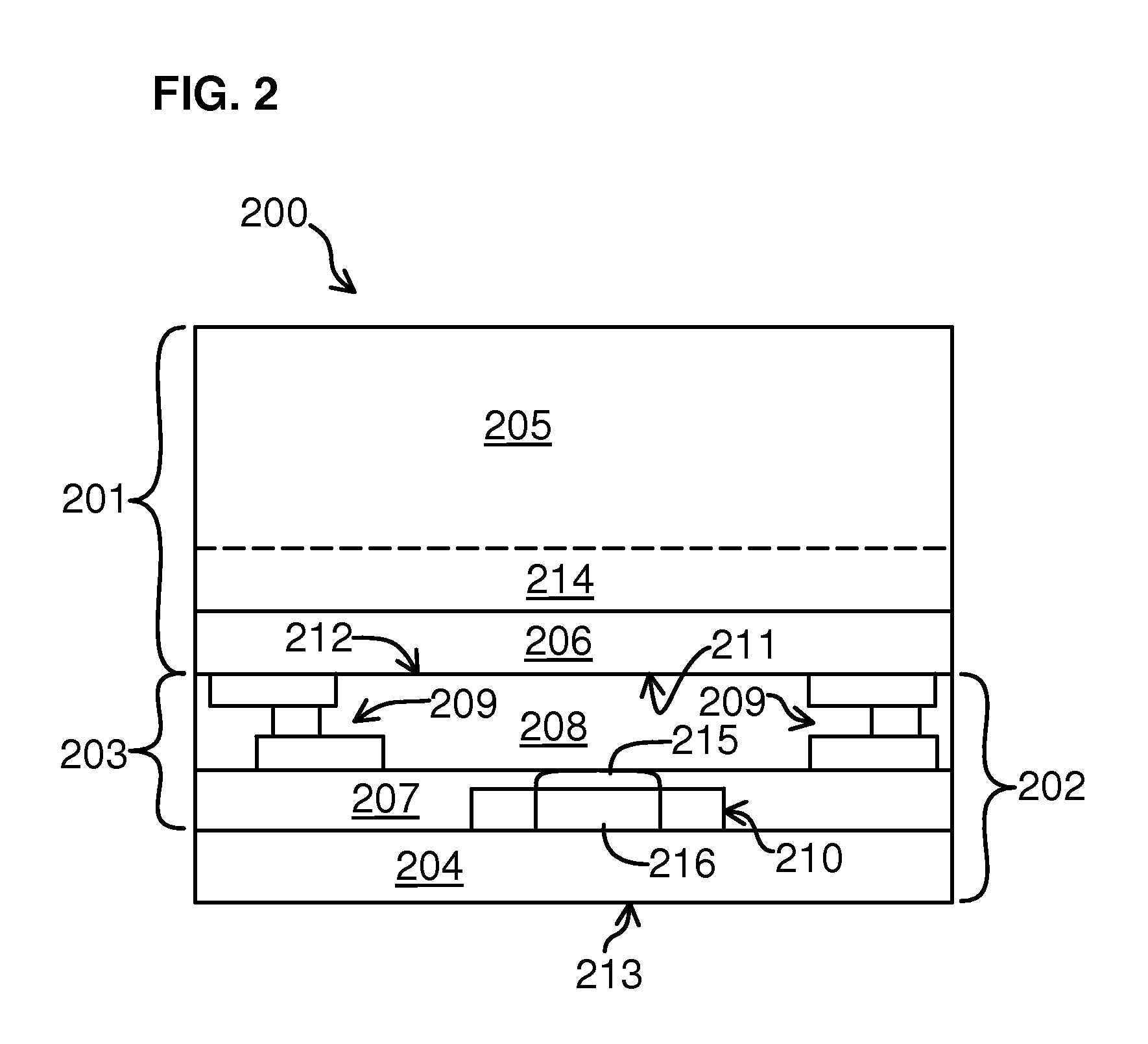

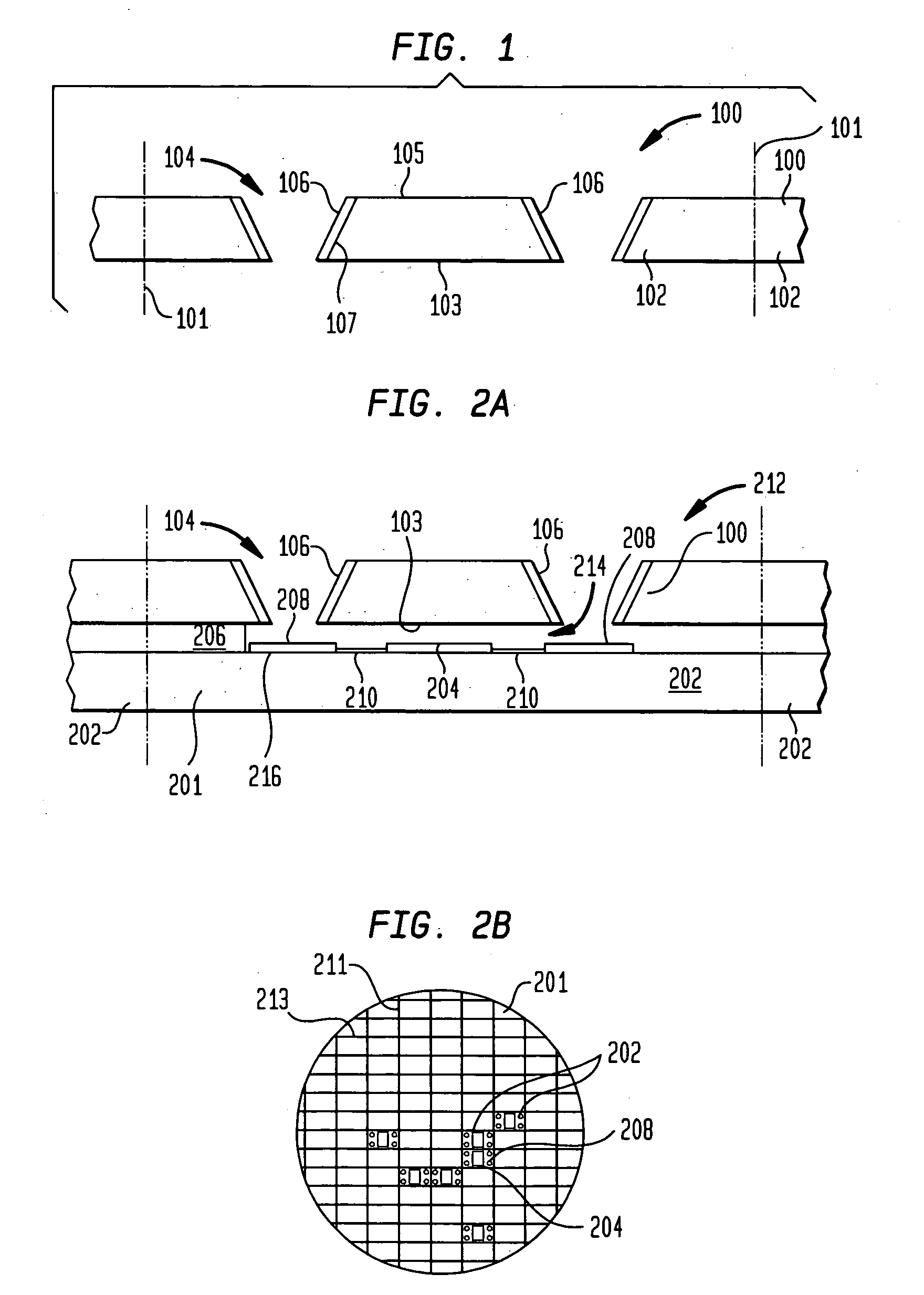

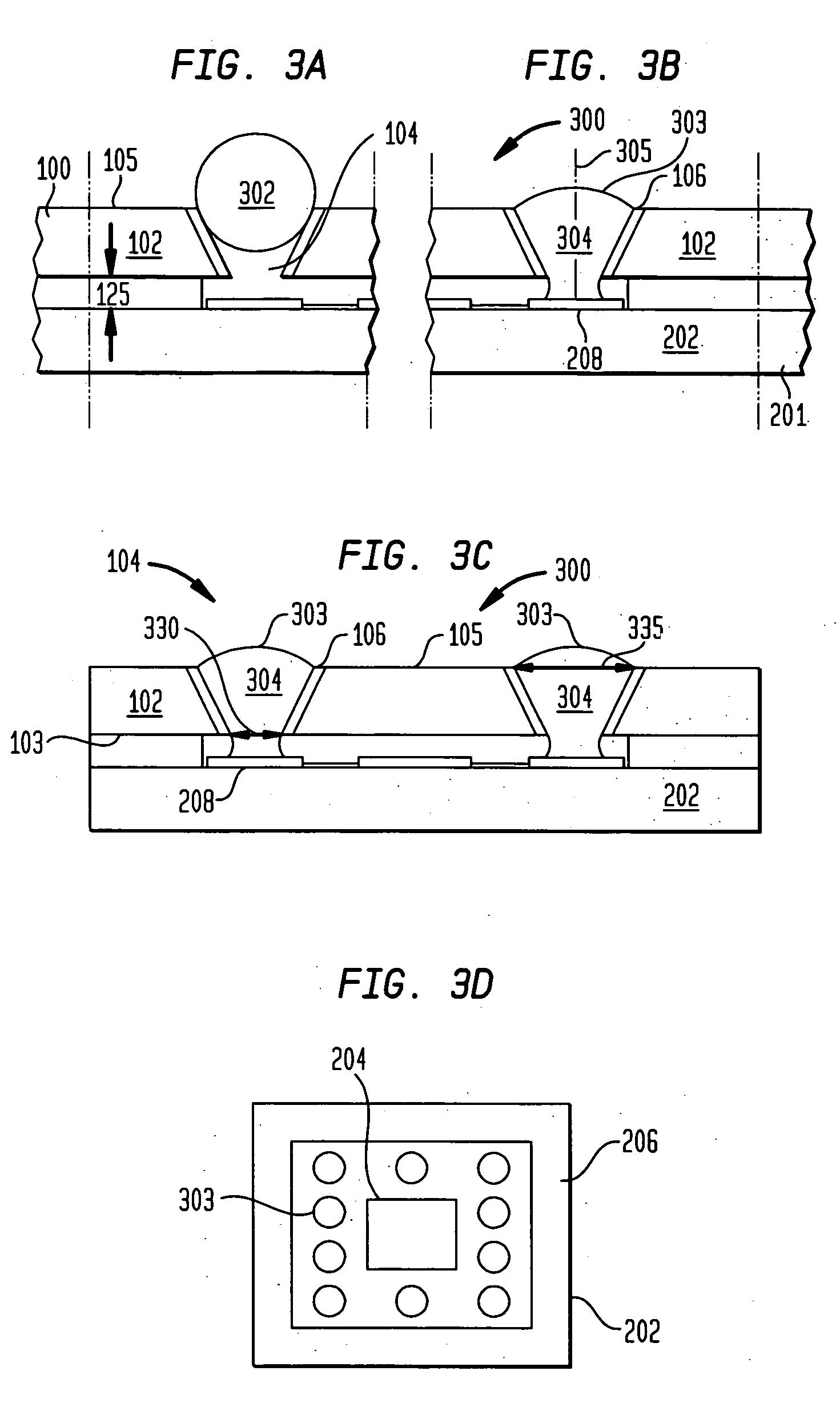

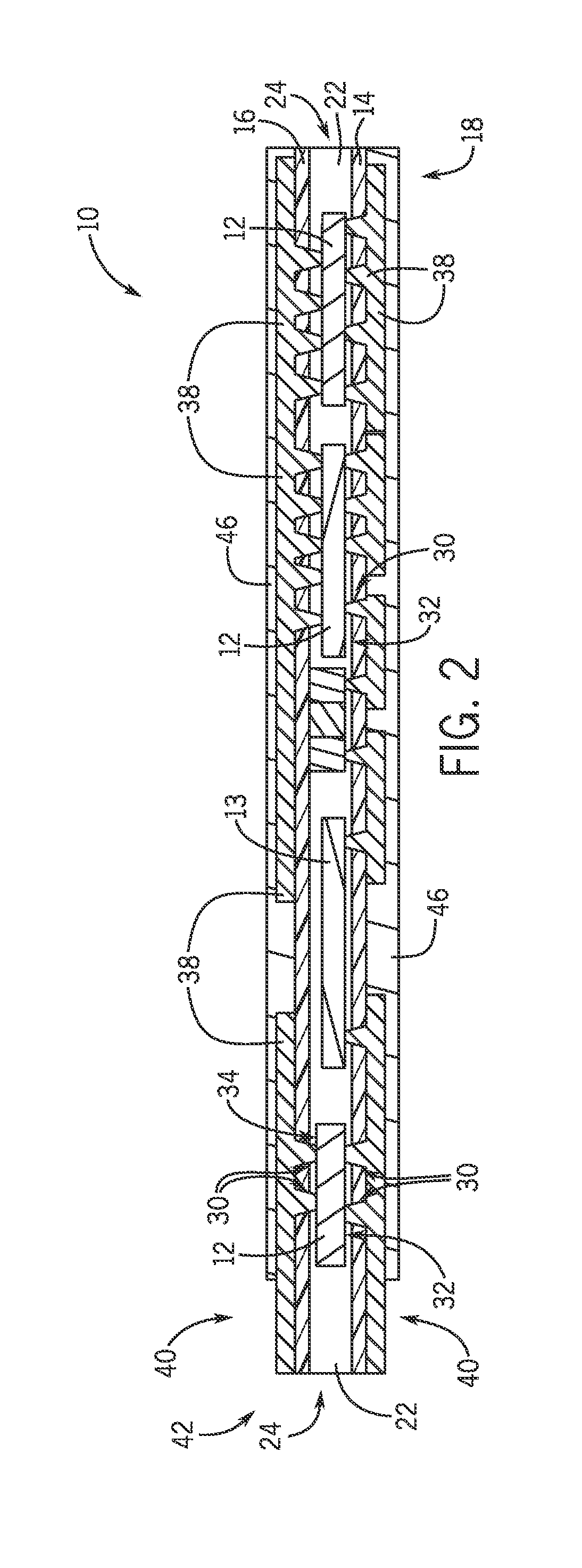

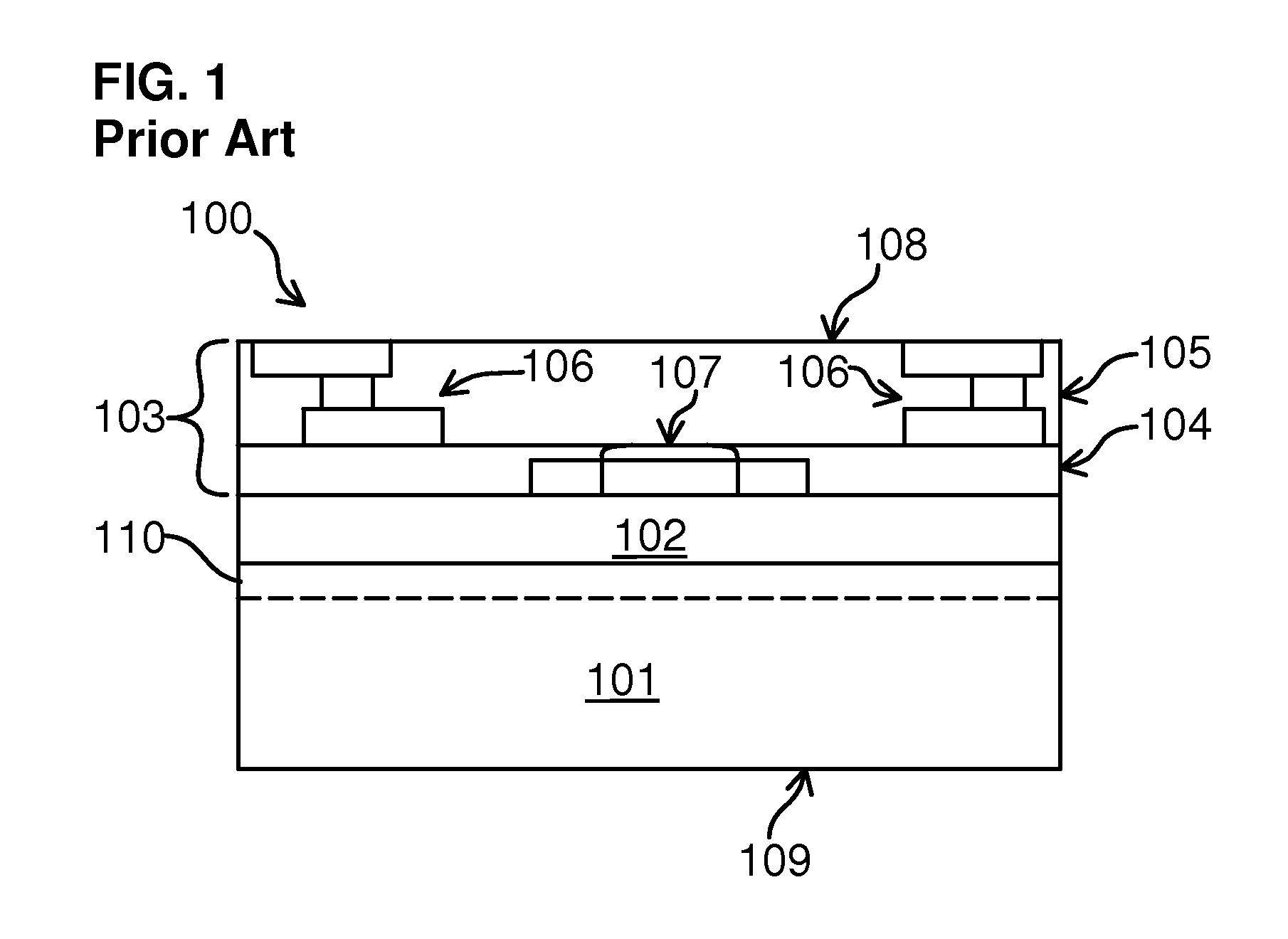

System-in packages

ActiveUS20110026232A1Improve uniformitySemiconductor/solid-state device detailsCircuit arrangements on support structuresMetal interconnectSystem in package

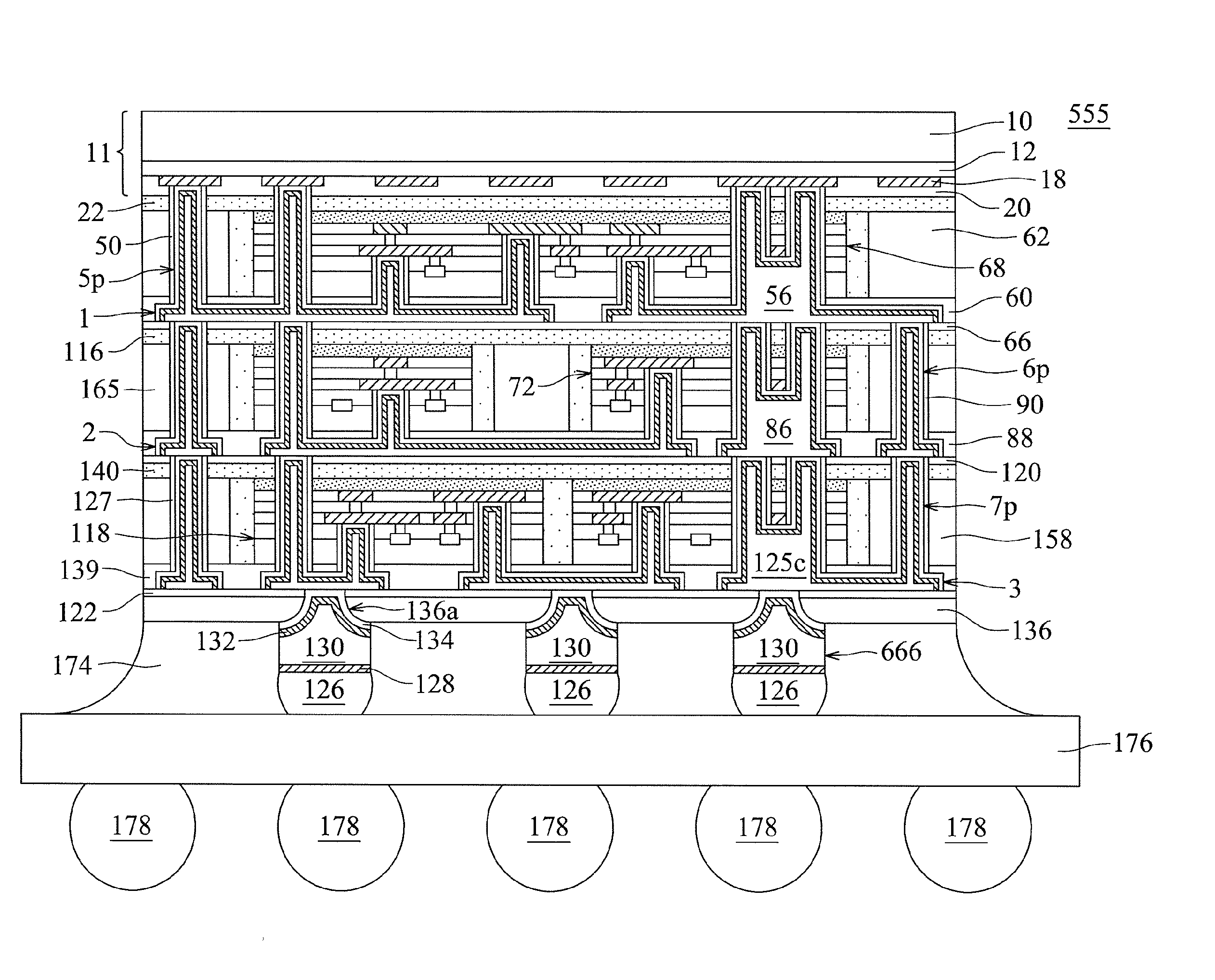

System-in packages, or multichip modules, are described which can include multi-layer chips and multi-layer dummy substrates over a carrier, multiple through vias blindly or completely through the multi-layer chips and completely through the multi-layer dummy substrates, multiple metal plugs in the through vias, and multiple metal interconnects, connected to the metal plugs, between the multi-layer chips. The multi-layer chips can be connected to each other or to an external circuit or structure, such as mother board, ball grid array (BGA) substrate, printed circuit board, metal substrate, glass substrate, or ceramic substrate, through the metal plugs and the metal interconnects.

Owner:QUALCOMM INC

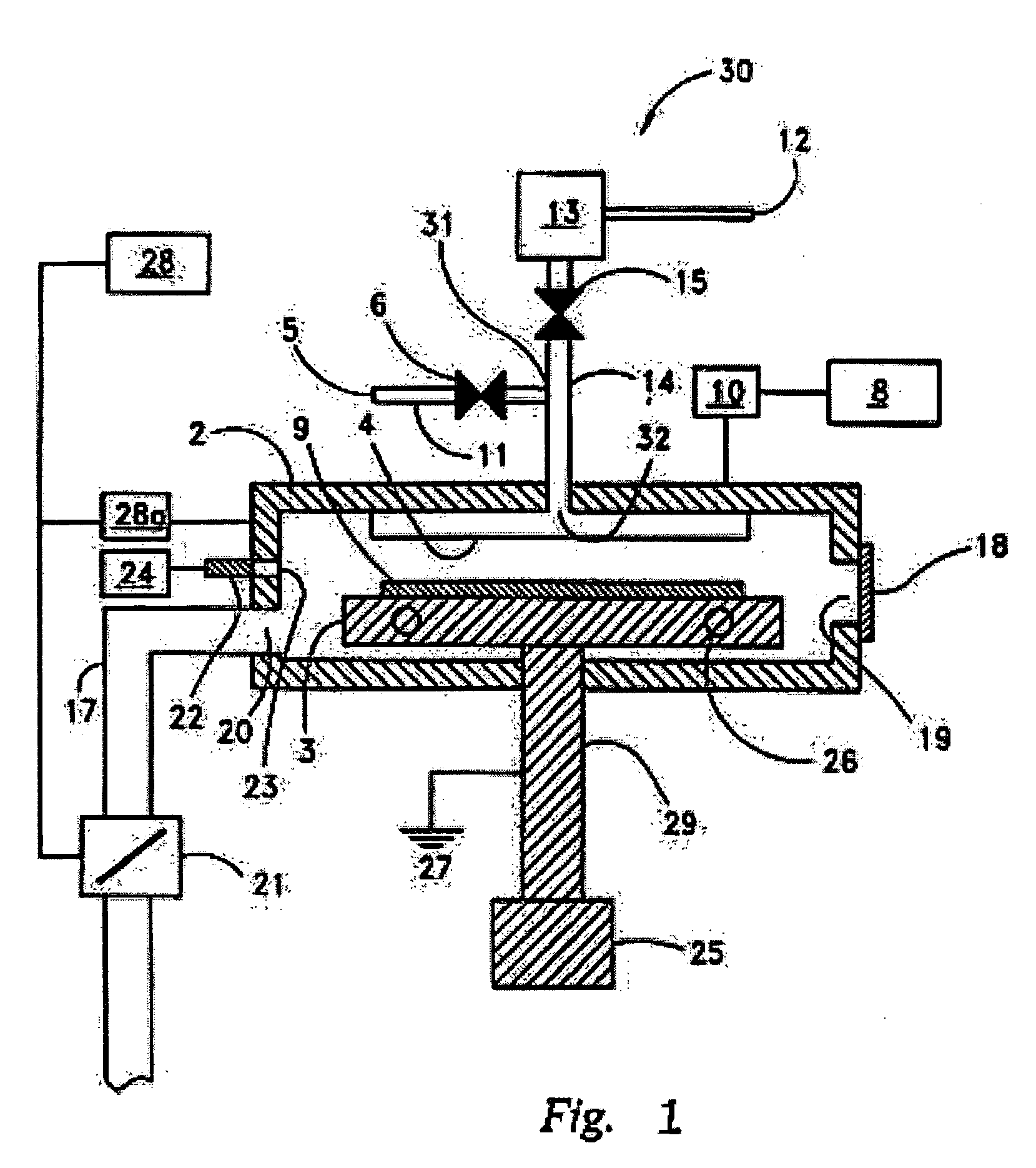

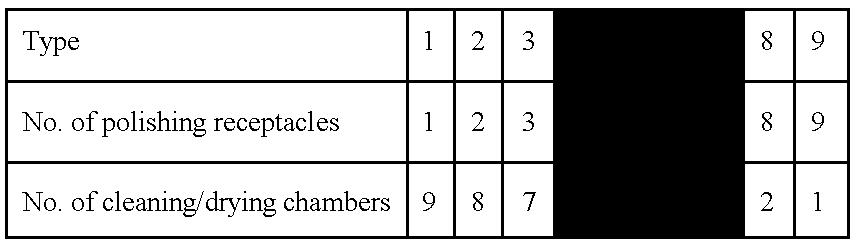

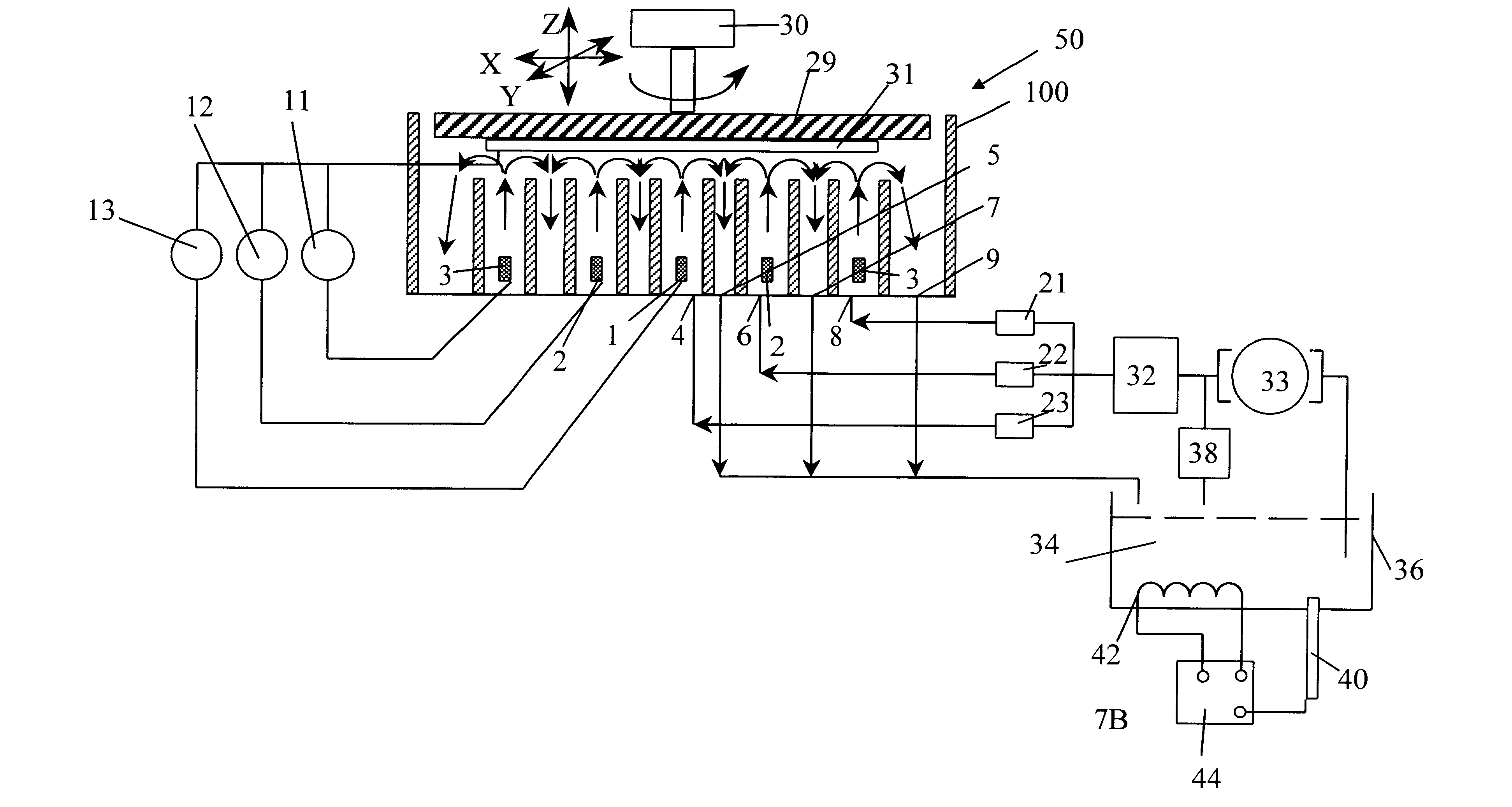

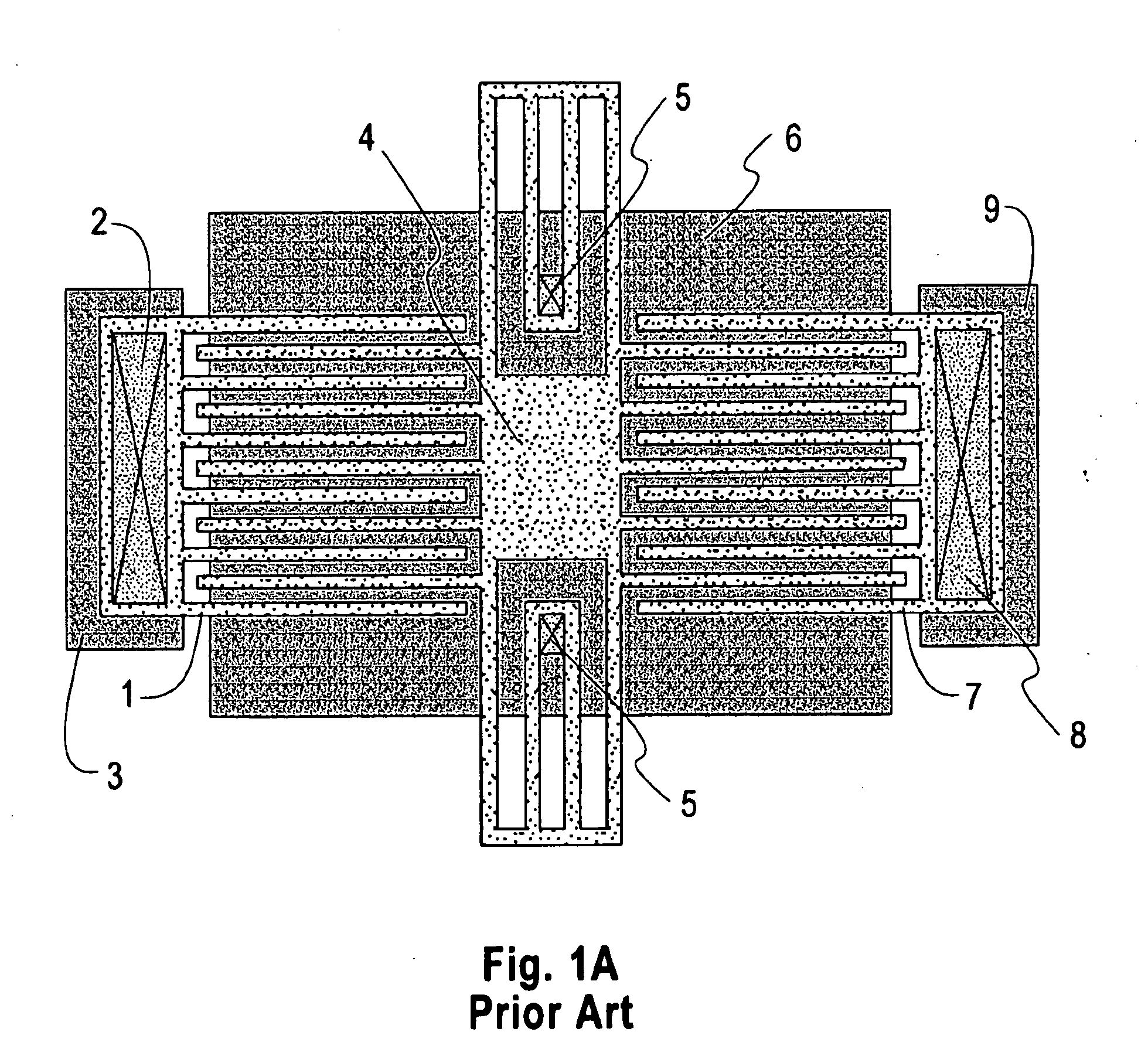

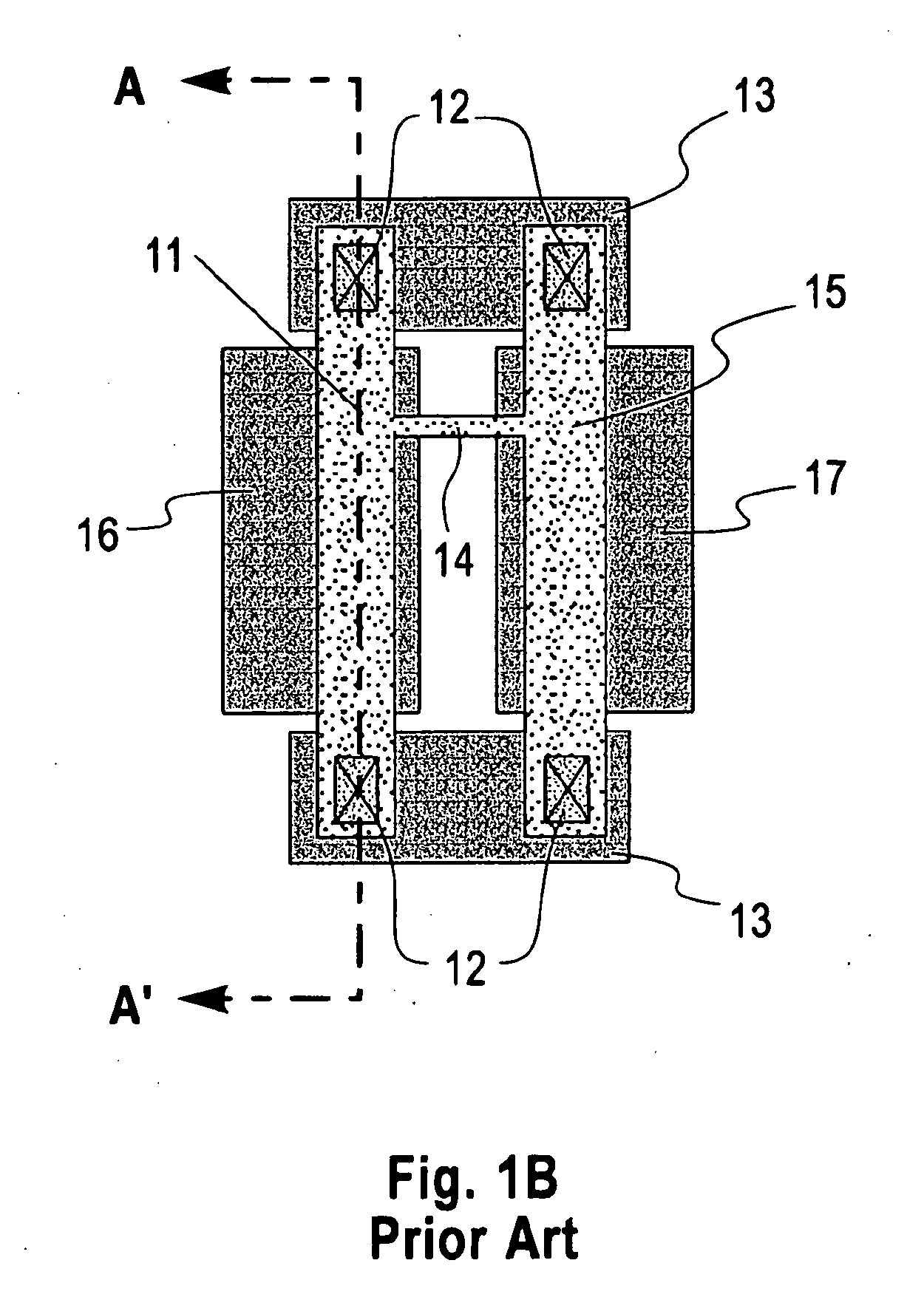

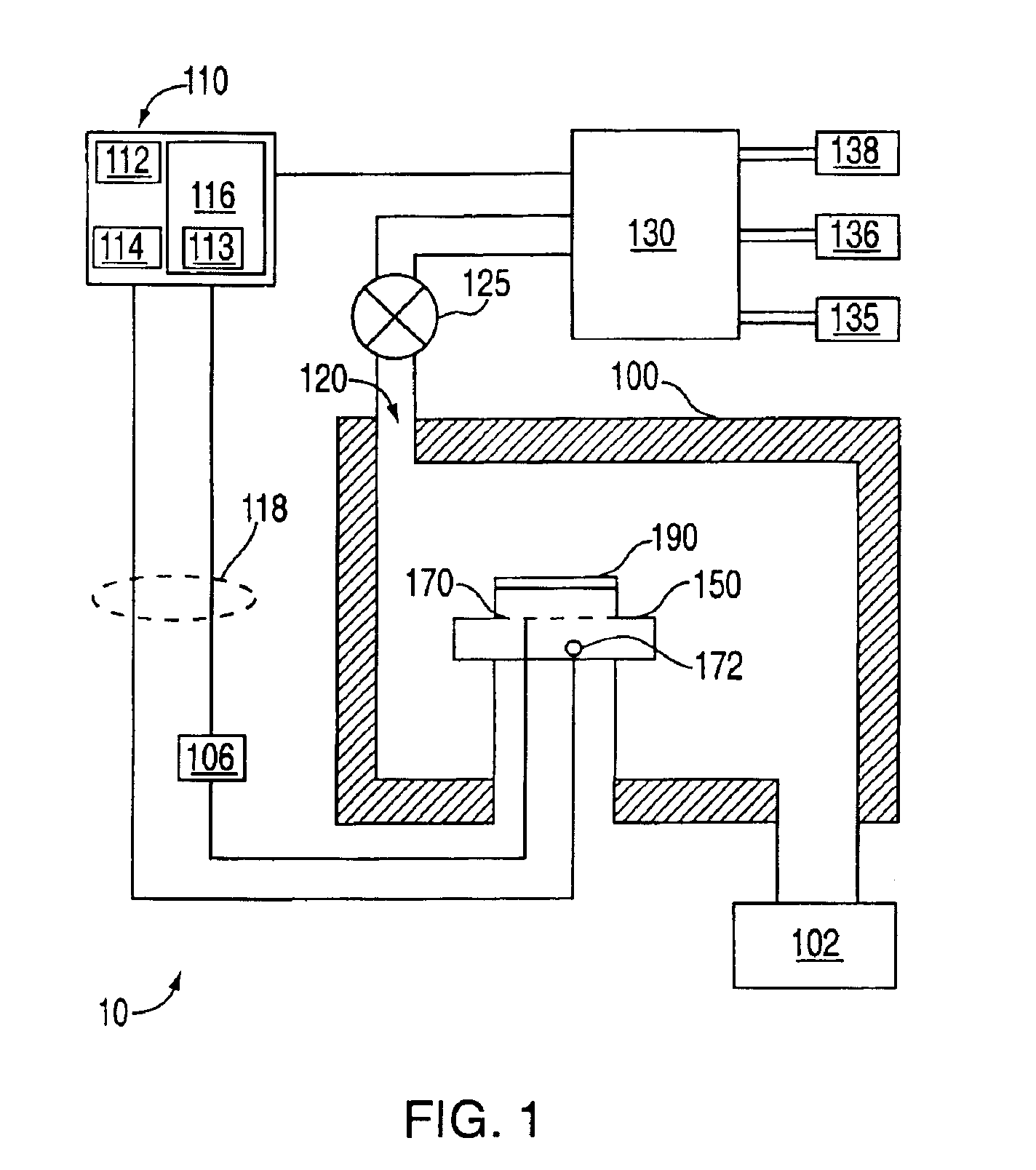

Methods and apparatus for electropolishing metal interconnections on semiconductor devices

InactiveUS6395152B1CellsSemiconductor/solid-state device manufacturingMetal interconnectSemiconductor

An electropolishing apparatus for polishing a metal layer formed on a wafer (31) includes an electrolyte (34), a polishing receptacle (100), a wafer chuck (29), a fluid inlet (5, 7, 9), and at least one cathode (1, 2, 3). The wafer chuck (29) holds and positions the wafer (31) within the polishing receptacle (100). The electrolyte (34) is delivered through the fluid inlet (5, 7, 9) into the polishing receptacle (100). The cathode (1, 2, 3) then applies an electropolishing current to the electrolyte to electropolish the wafer (31). In accordance with one aspect of the present invention, discrete portions of the wafer (31) can be electropolished to enhance the uniformity of the electropolished wafer.

Owner:ACM RES

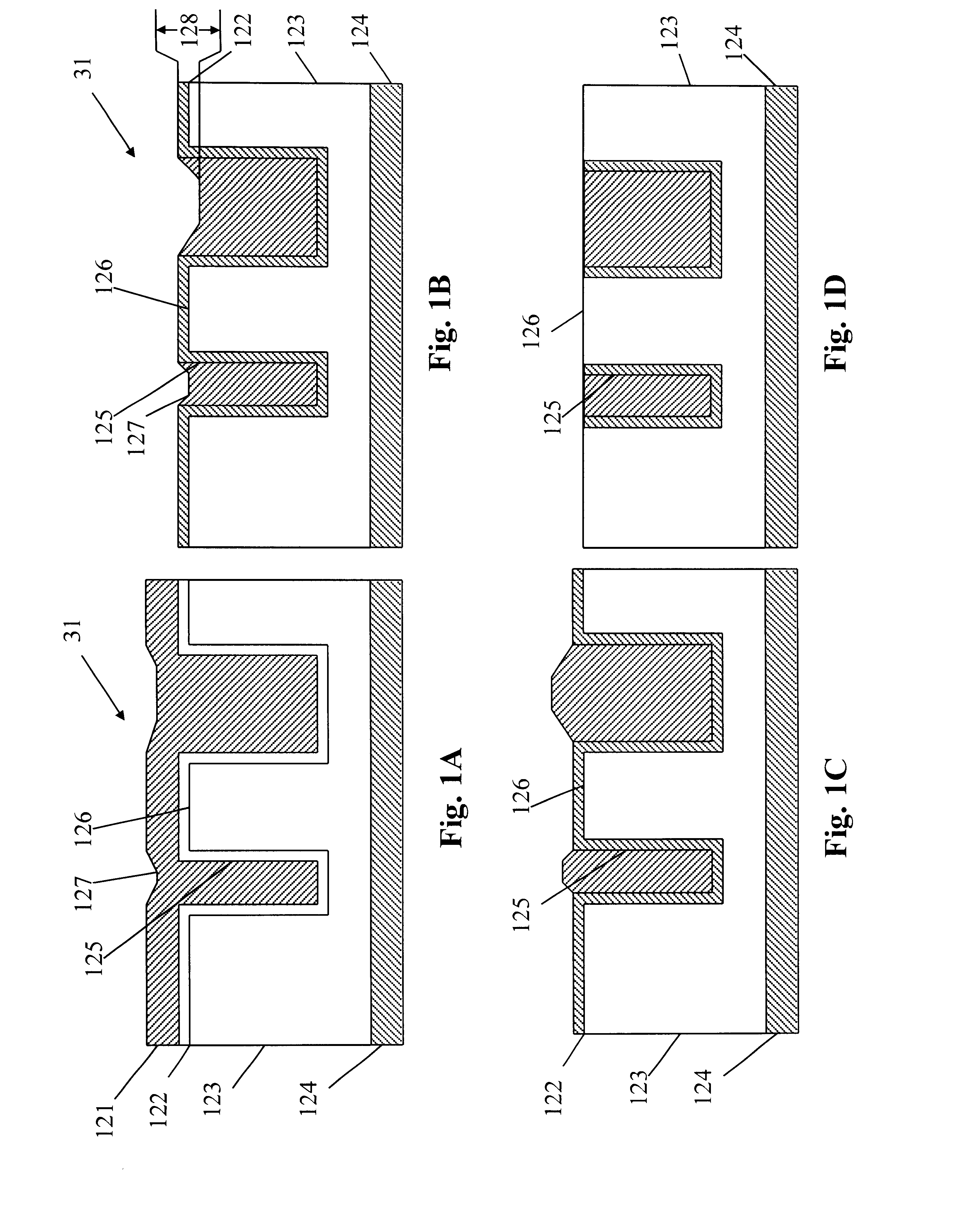

Method of selectively depositing a capping layer structure on a semiconductor device structure

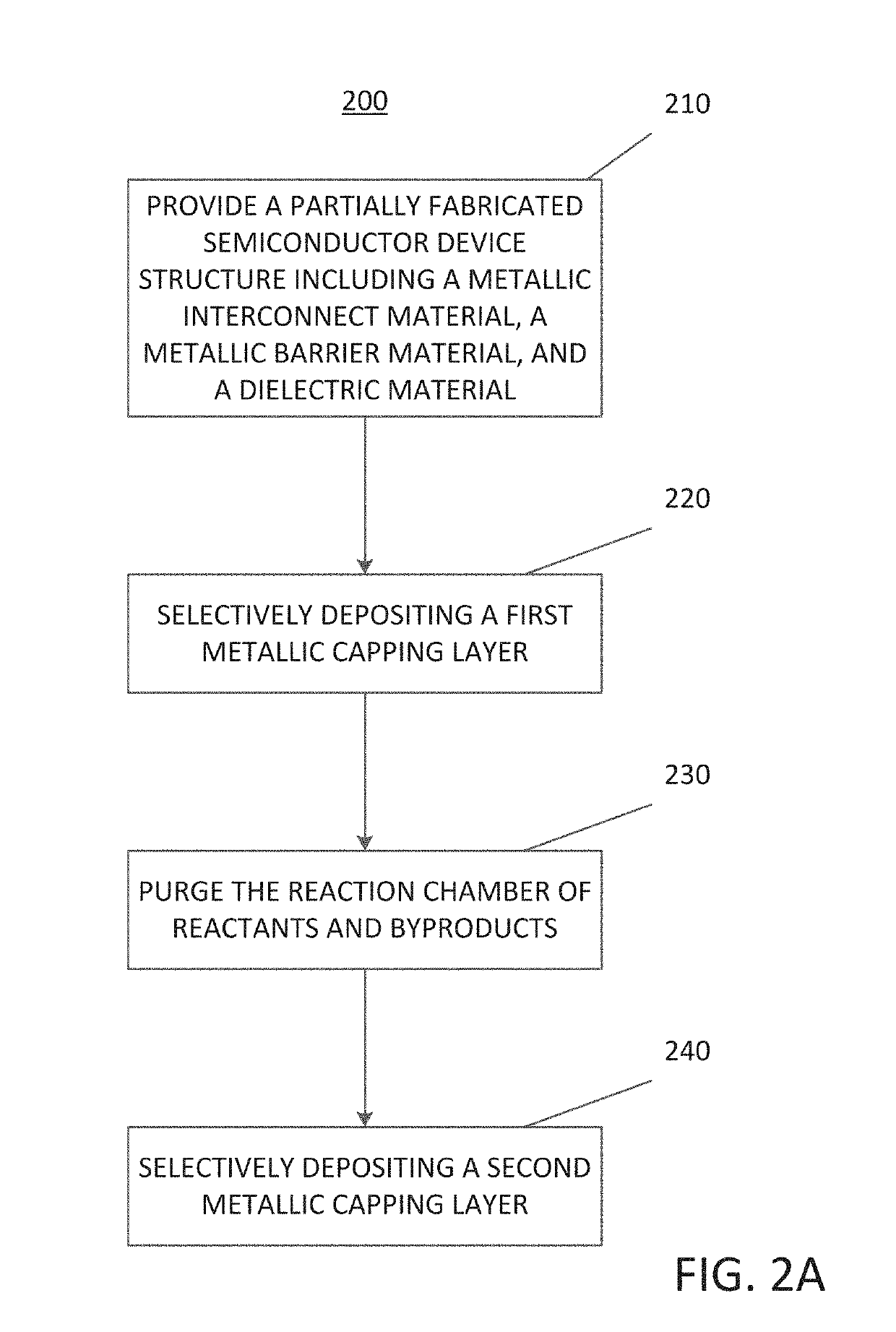

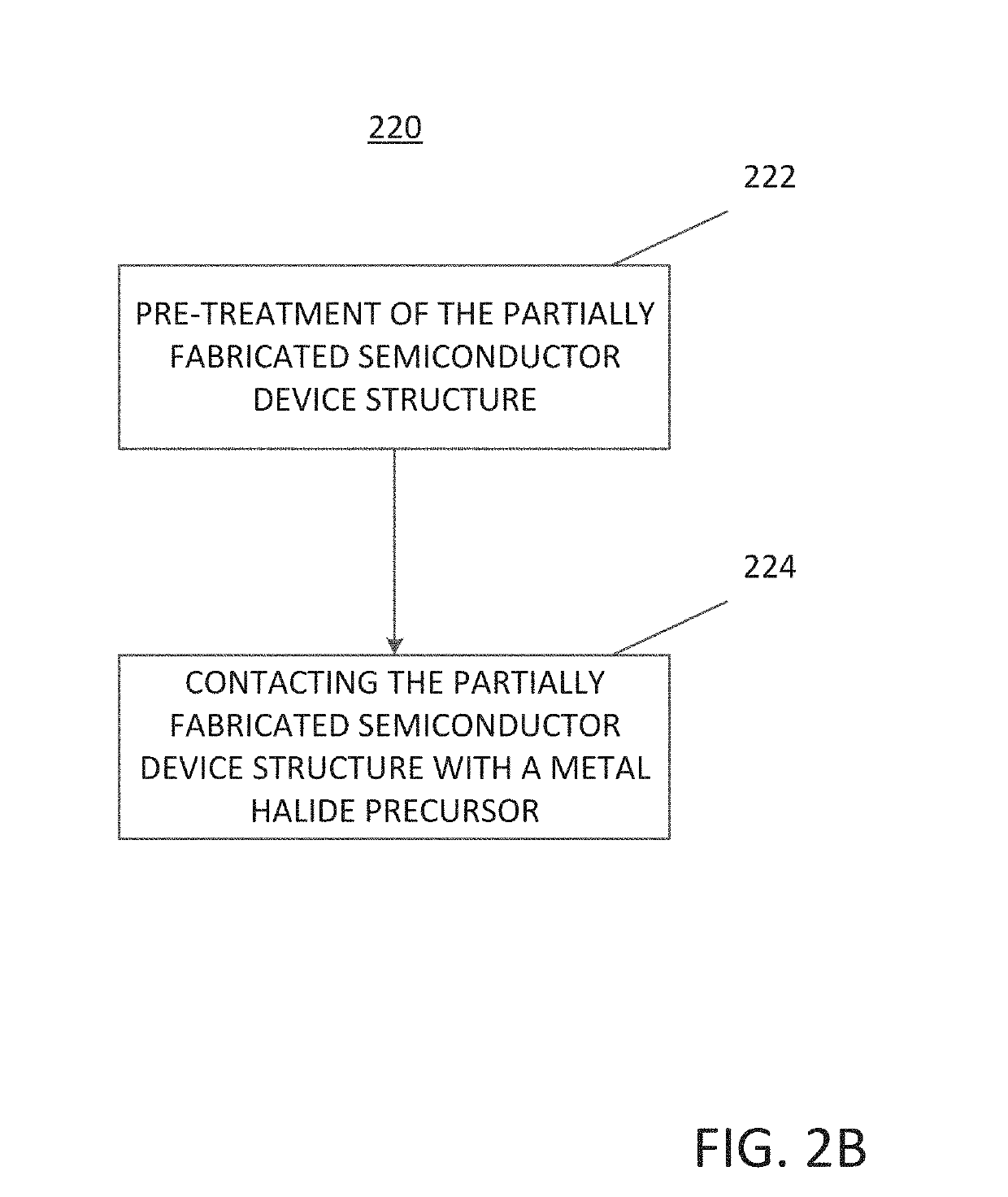

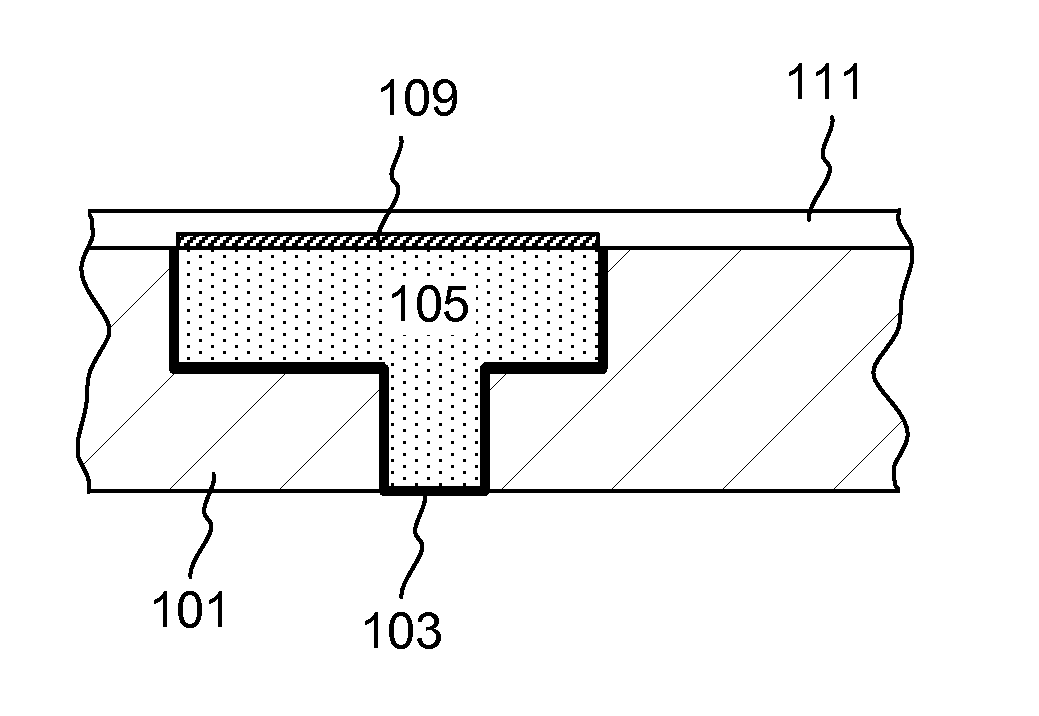

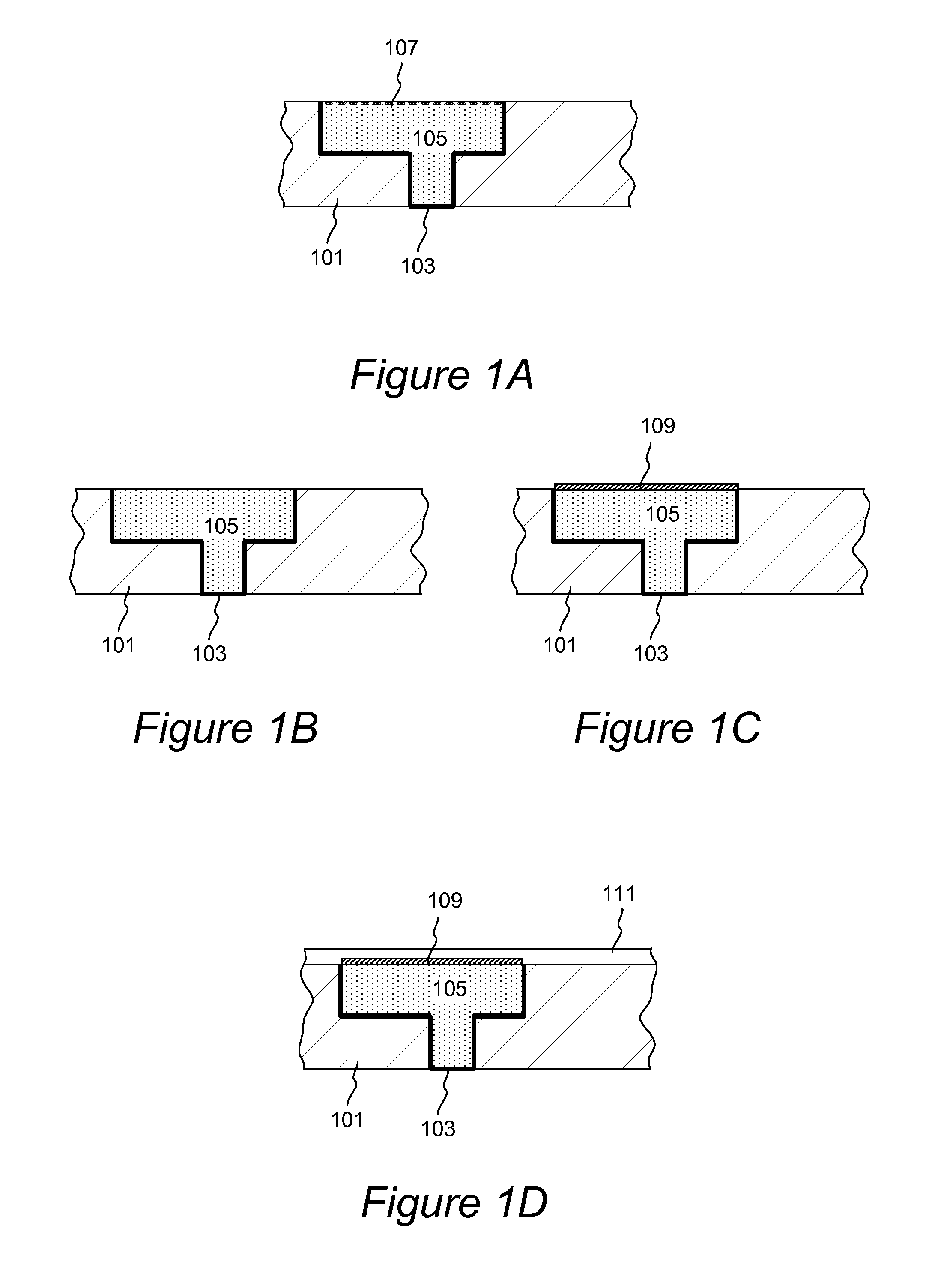

A method of selectively depositing a capping layer structure on a semiconductor device structure is disclosure. The method may include; providing a partially fabricated semiconductor device structure comprising a surface including a metallic interconnect material, a metallic barrier material, and a dielectric material. The method may also include; selectively depositing a first metallic capping layer over the metallic barrier material and over the metallic interconnect material relative to the dielectric material; and selectively depositing a second metallic capping layer over the first metallic capping layer relative to the dielectric material. Semiconductor device structures including a capping layer structure are also disclosed.

Owner:ASM IP HLDG BV

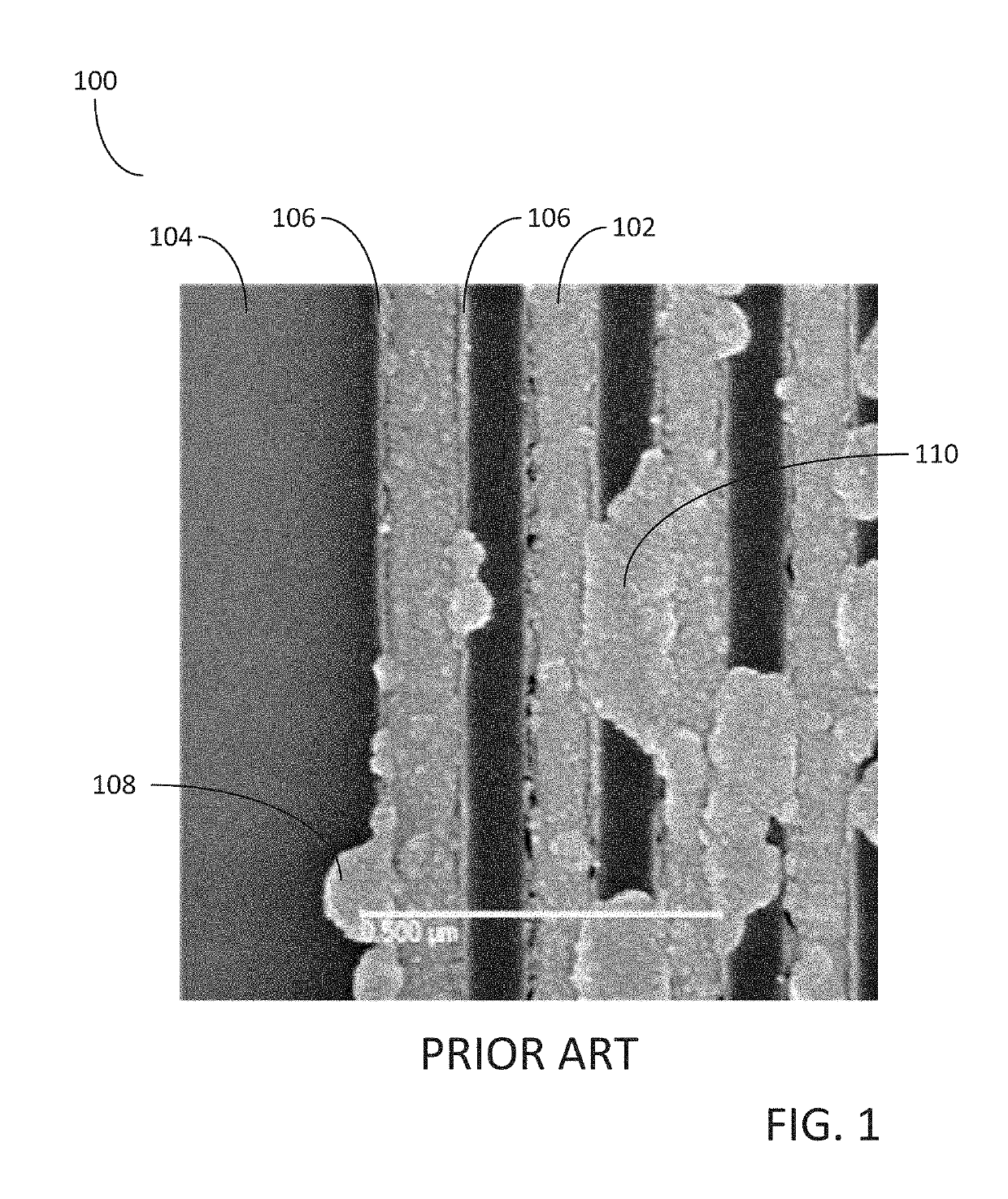

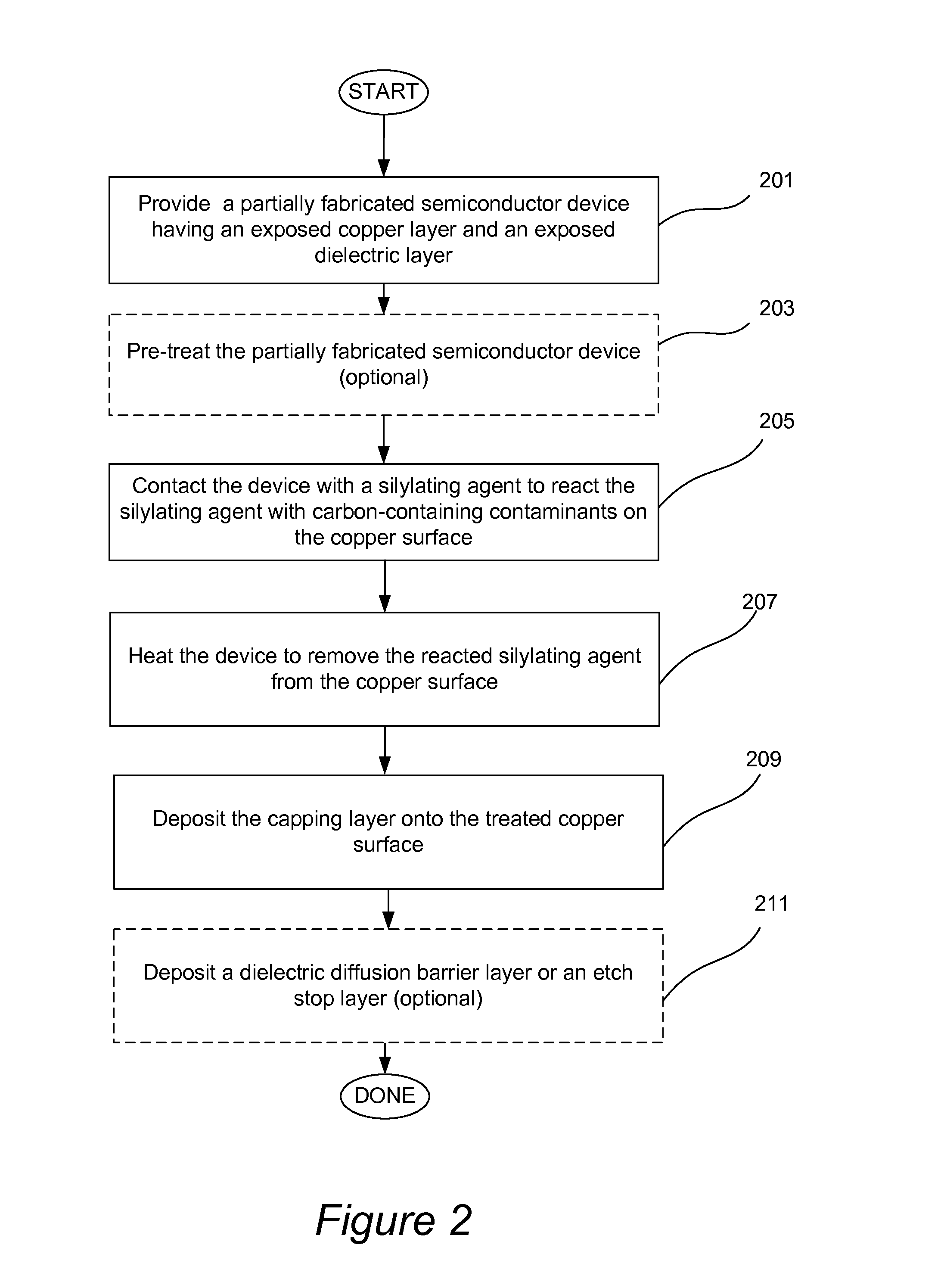

Cleaning of carbon-based contaminants in metal interconnects for interconnect capping applications

InactiveUS20150380296A1Avoid depositionLow deposition rateLiquid surface applicatorsSemiconductor/solid-state device manufacturingMetal interconnectSilylation

Protective caps residing at an interface between copper lines and dielectric diffusion barrier layers are used to improve various performance characteristics of interconnects. The caps, such as cobalt-containing caps or manganese-containing caps, are selectively deposited onto exposed copper lines in a presence of exposed dielectric using CVD or ALD methods. The deposition of the capping material is affected by the presence of carbon-containing contaminants on the surface of copper, which may lead to poor or uneven growth of the capping layer. A method of removing carbon-containing contaminants from the copper surface prior to deposition of caps involves contacting the substrate containing the exposed copper surface with a silylating agent at a first temperature to form a layer of reacted silylating agent on the copper surface, followed by heating the substrate at a higher temperature to release the reacted silylating agent from the copper surface.

Owner:LAM RES CORP

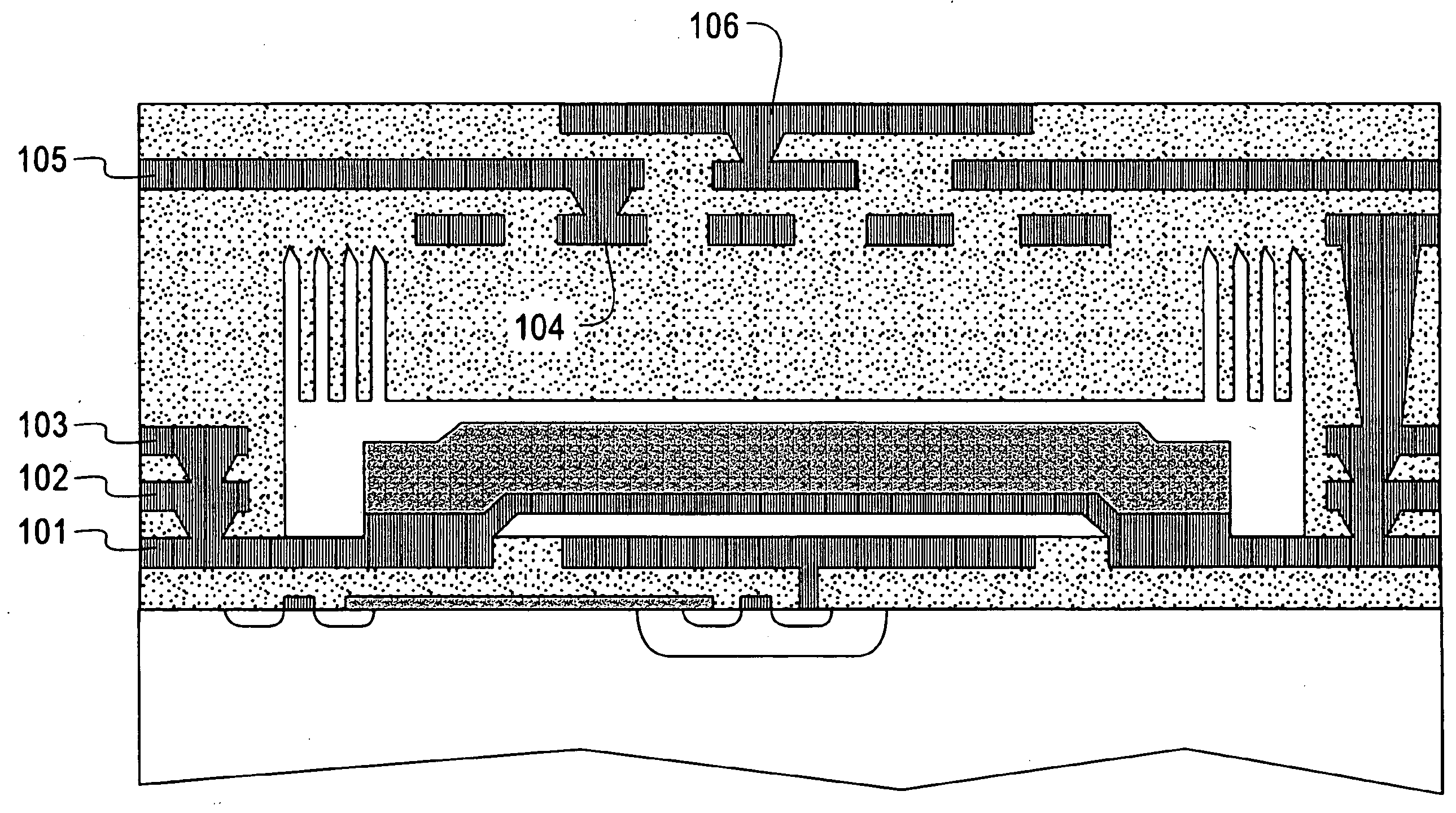

Low temperature bi-CMOS compatible process for MEMS RF resonators and filters

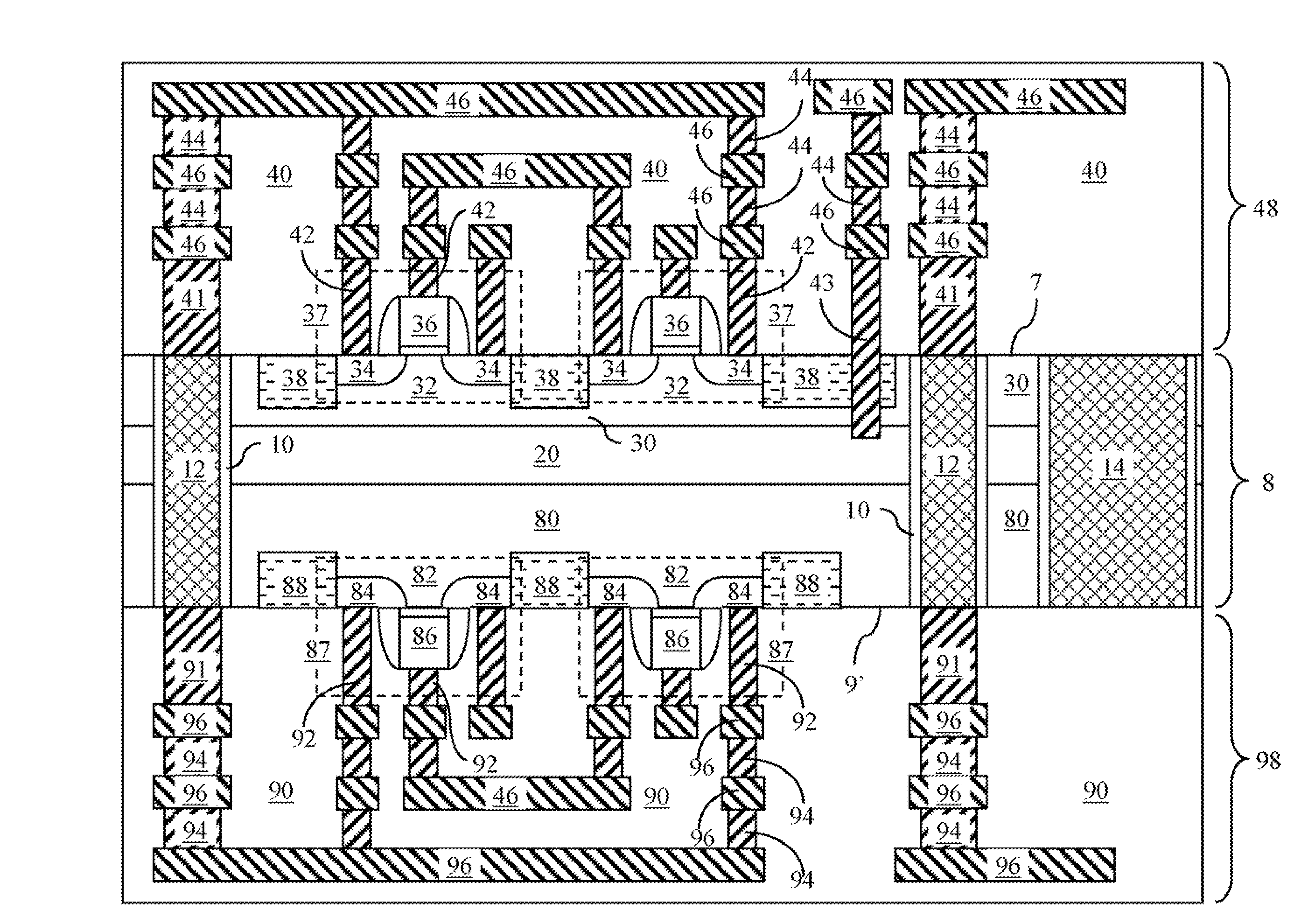

InactiveUS20090108381A1Impedence networksSemiconductor/solid-state device detailsMetal interconnectOxygen plasma

A method of formation of a microelectromechanical system (MEMS) resonator or filter which is compatible with integration with any analog, digital, or mixed-signal integrated circuit (IC) process, after or concurrently with the formation of the metal interconnect layers in those processes, by virtue of its materials of composition, processing steps, and temperature of fabrication is presented. The MEMS resonator or filter incorporates a lower metal level, which forms the electrodes of the MEMS resonator or filter, that may be shared with any or none of the existing metal interconnect levels on the IC. It further incorporates a resonating member that is comprised of at least one metal layer for electrical connection and electrostatic actuation, and at least one dielectric layer for structural purposes. The gap between the electrodes and the resonating member is created by the deposition and subsequent removal of a sacrificial layer comprised of a carbon-based material. The method of removal of the sacrificial material is by an oxygen plasma or an anneal in an oxygen containing ambient. A method of vacuum encapsulation of the MEMS resonator or filter is provided through means of a cavity containing the MEMS device, filled with additional sacrificial material, and sealed. Access vias are created through the membrane sealing the cavity; the sacrificial material is removed as stated previously, and the vias are re-sealed in a vacuum coating process.

Owner:IBM CORP

Two-Sided Semiconductor Structure

ActiveUS20100224876A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectSemiconductor structure

Deep via trenches and deep marker trenches are formed in a bulk substrate and filled with a conductive material to form deep conductive vias and deep marker vias. At least one first semiconductor device is formed on the first surface of the bulk substrate. A disposable dielectric capping layer and a disposable material layer are formed over the first surface of the bulk substrate. The second surface, located on the opposite side of the first surface, of the bulk substrate is polished to expose and planarize the deep conductive vias and deep marker vias, which become through-substrate vias and through-substrate alignment markers, respectively. At least one second semiconductor device and second metal interconnect structures are formed on the second surface of the bulk substrate. The disposable material layer and the disposable dielectric capping layer are removed and first metal interconnect structures are formed on the first surface.

Owner:IBM CORP

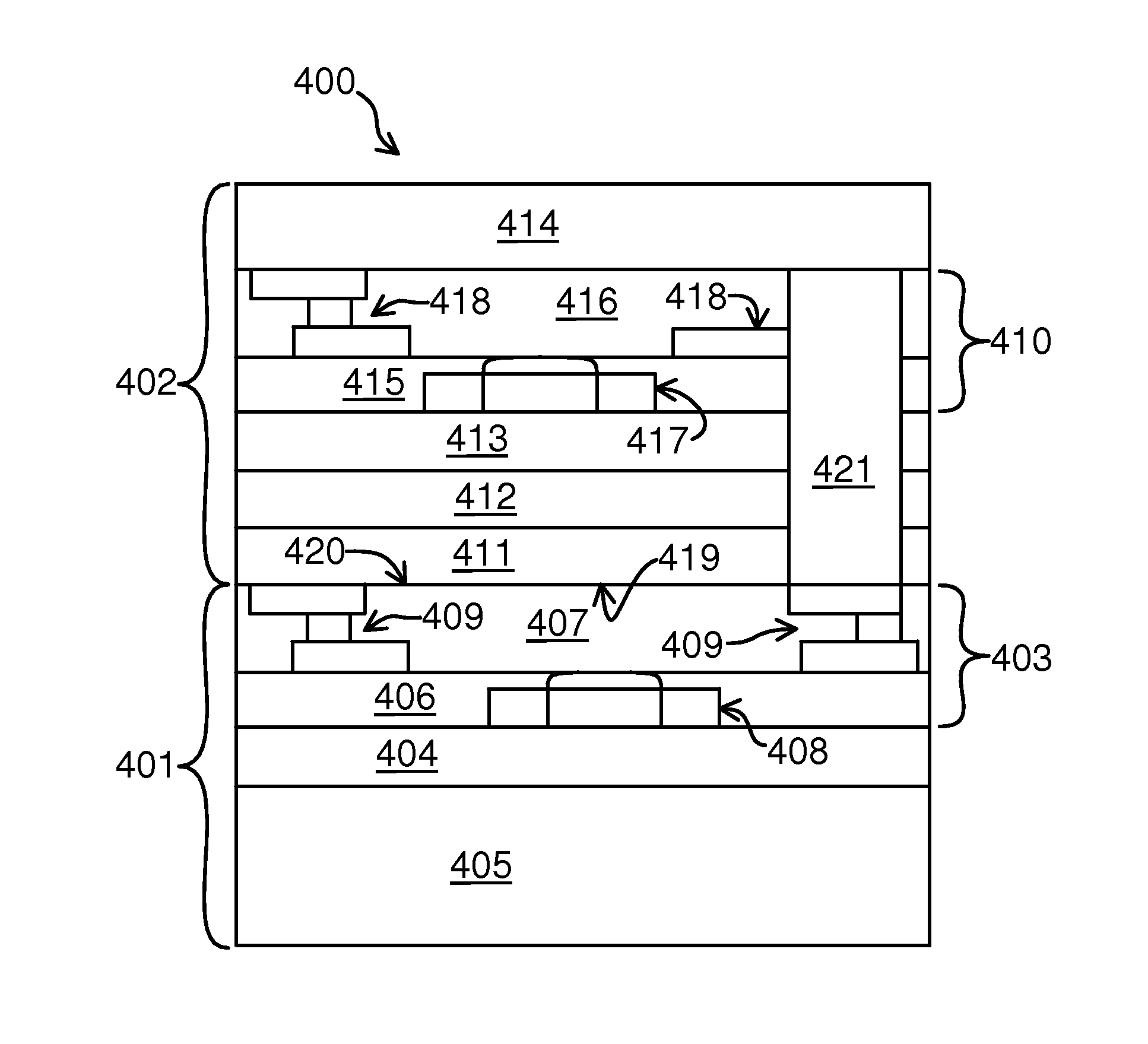

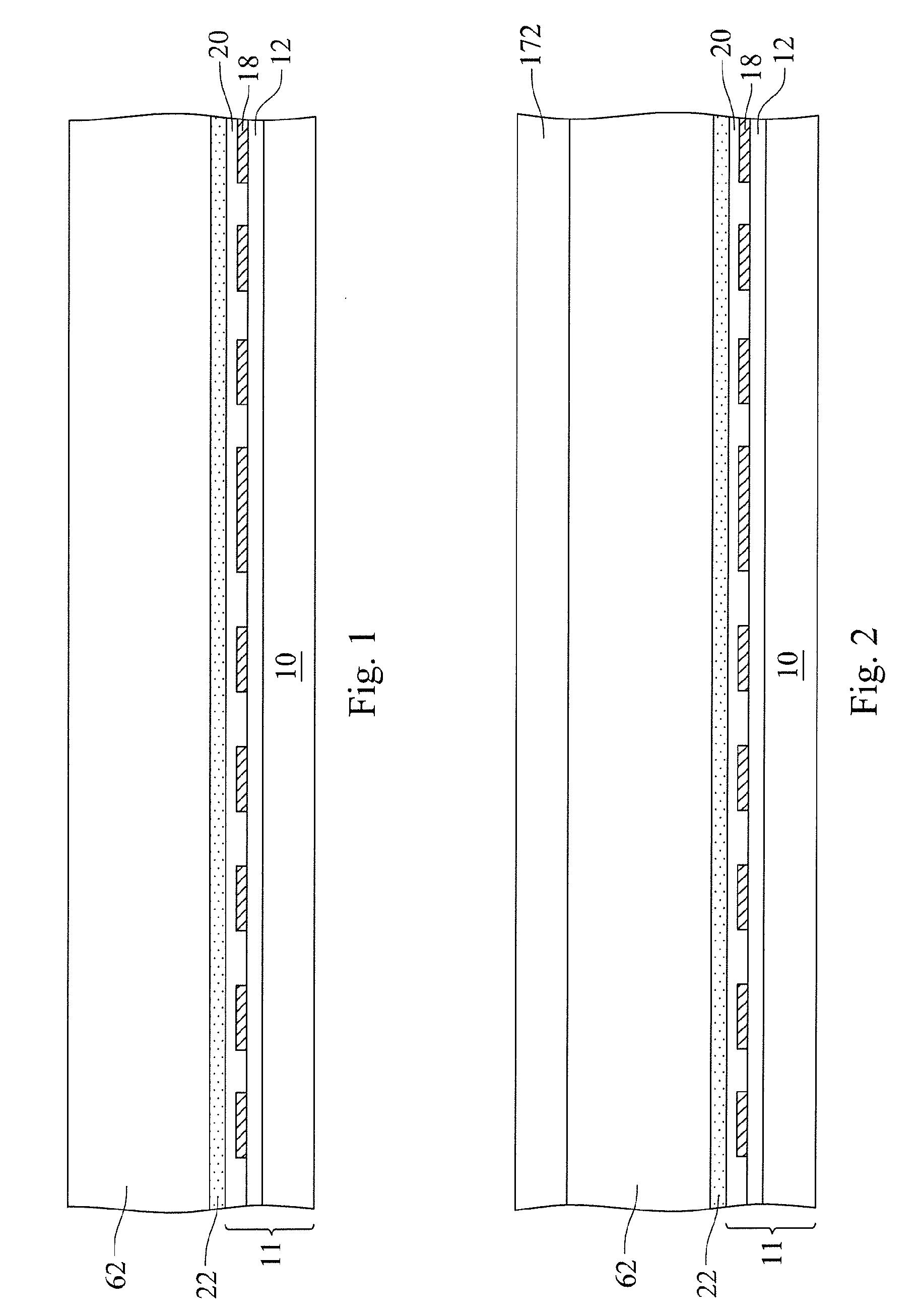

Trap Rich Layer for Semiconductor Devices

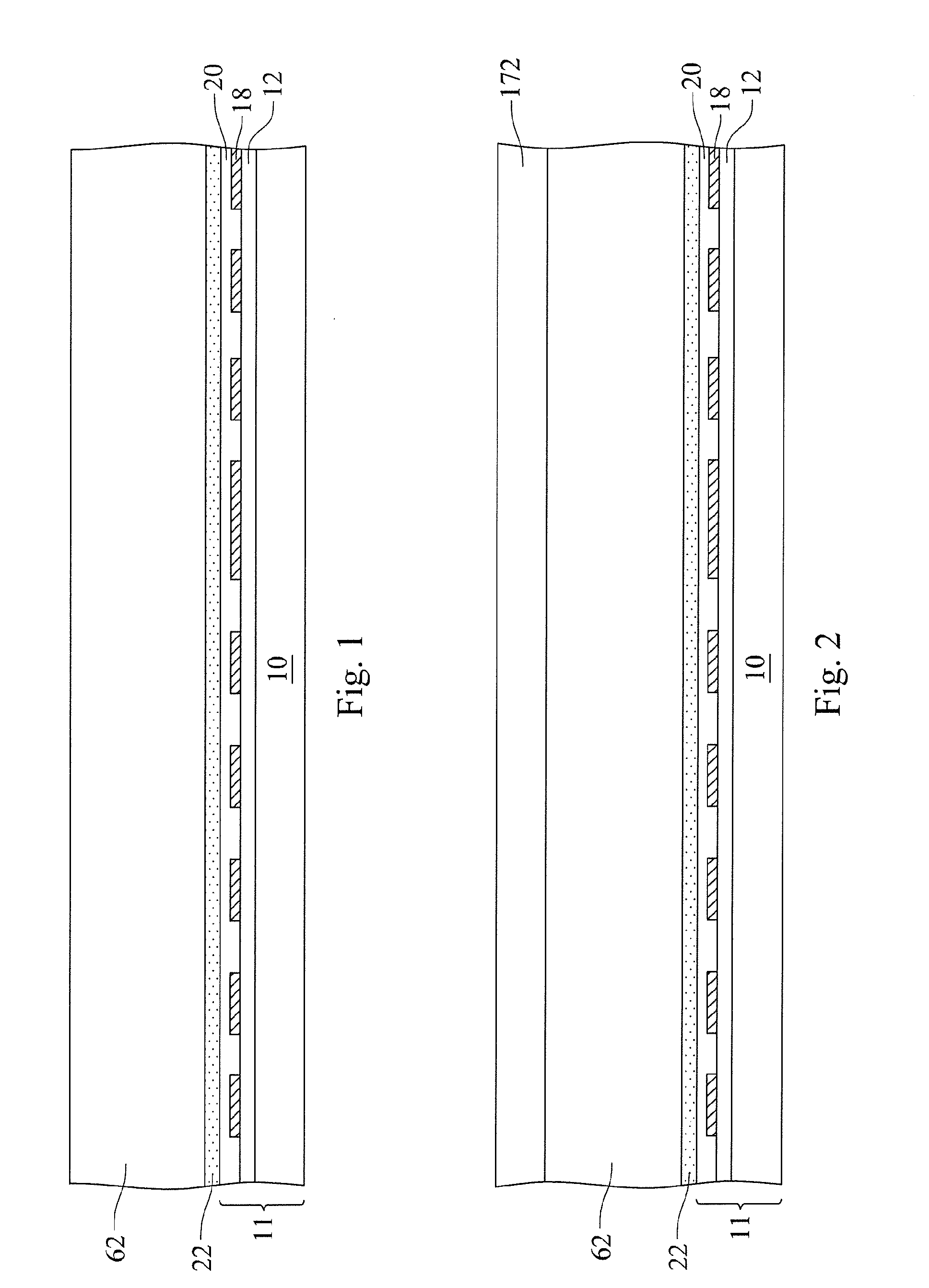

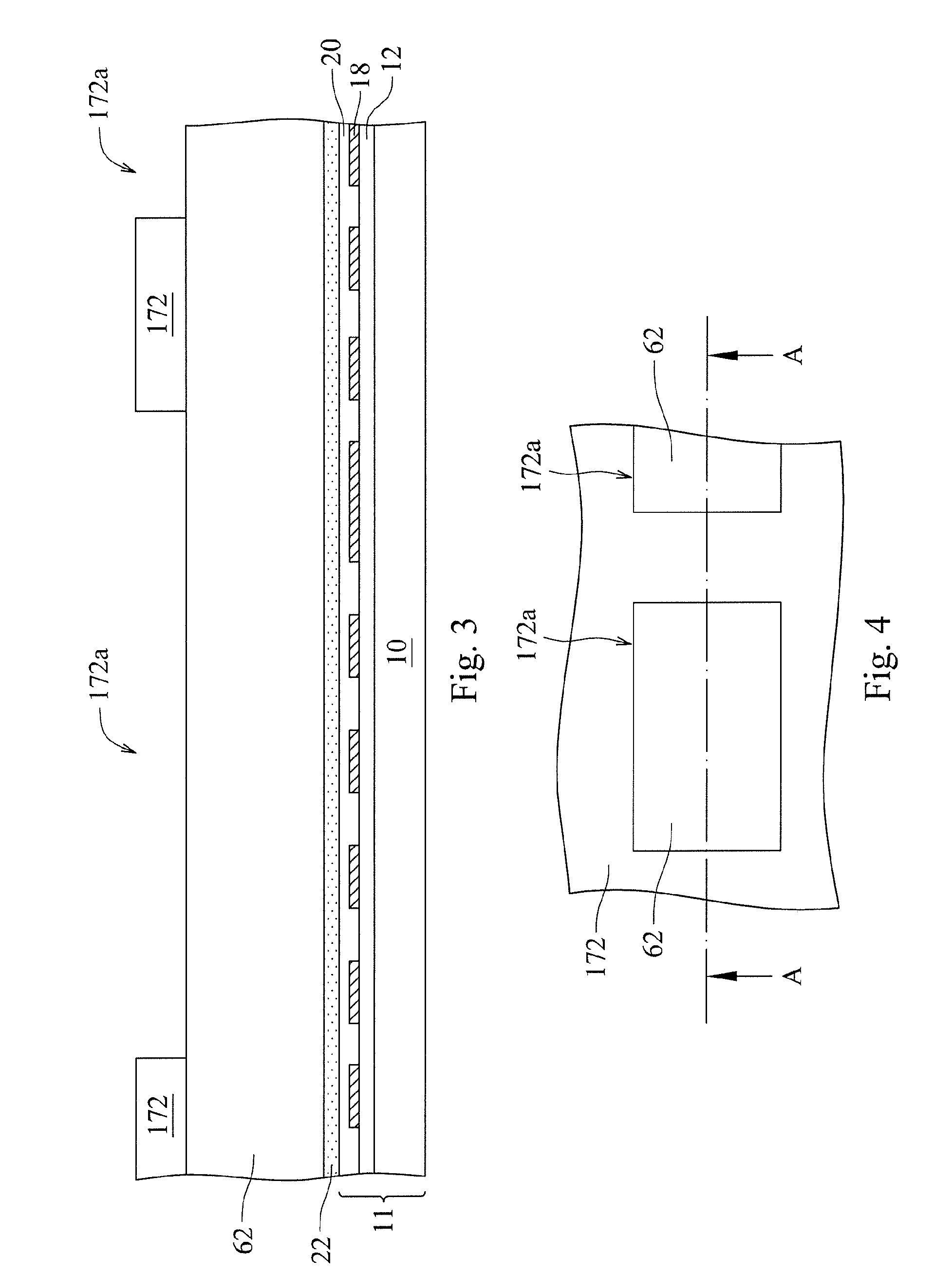

ActiveUS20120161310A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectActive layer

An integrated circuit chip is formed with an active layer and a trap rich layer. The active layer is formed with an active device layer and a metal interconnect layer. The trap rich layer is formed above the active layer. In some embodiments, the active layer is included in a semiconductor wafer, and the trap rich layer is included in a handle wafer.

Owner:QUALCOMM INC

System-in packages

ActiveUS8503186B2Improve uniformityCircuit arrangements on support structuresSemiconductor/solid-state device detailsMetal interconnectSystem in package

Owner:QUALCOMM INC

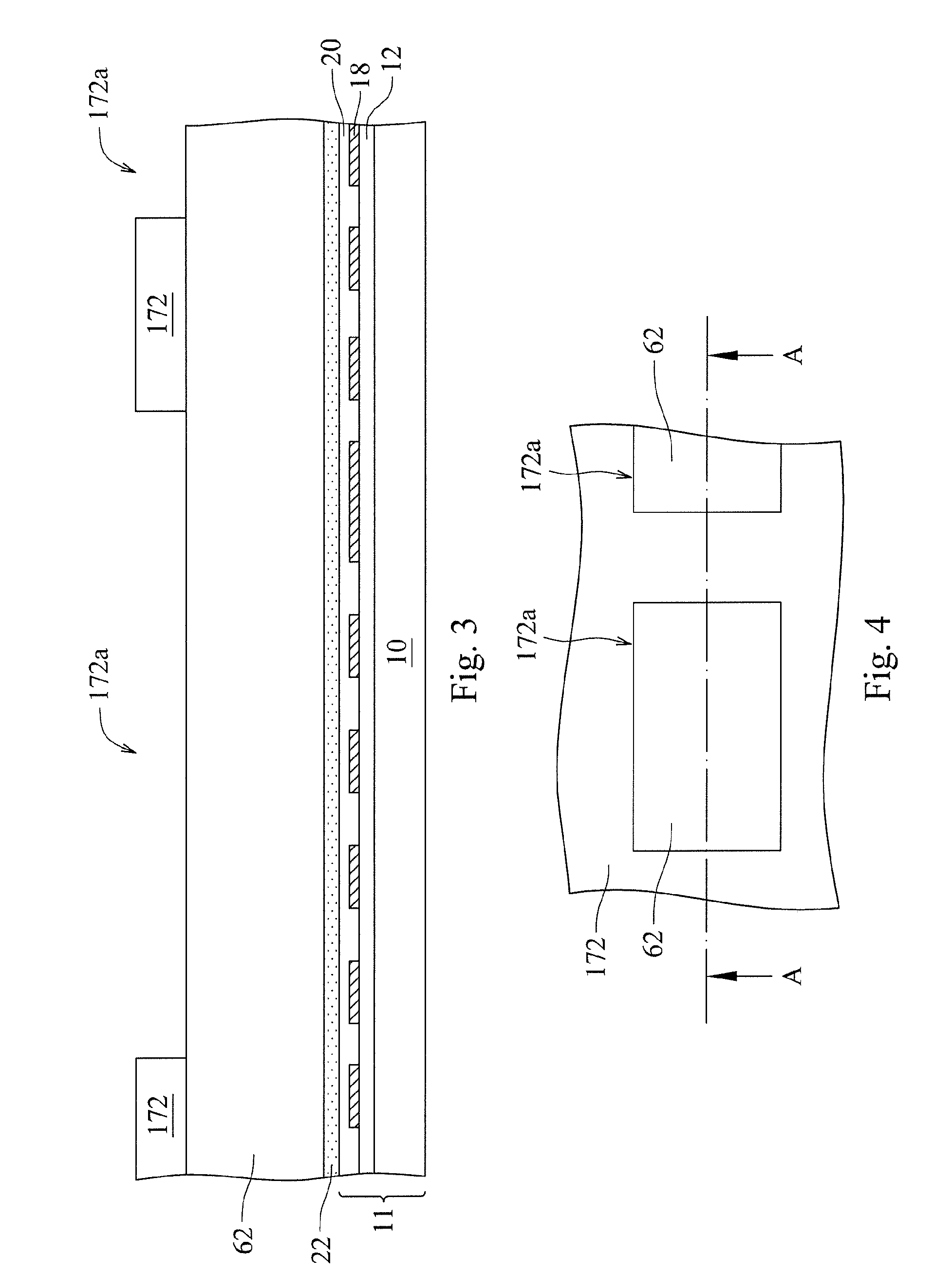

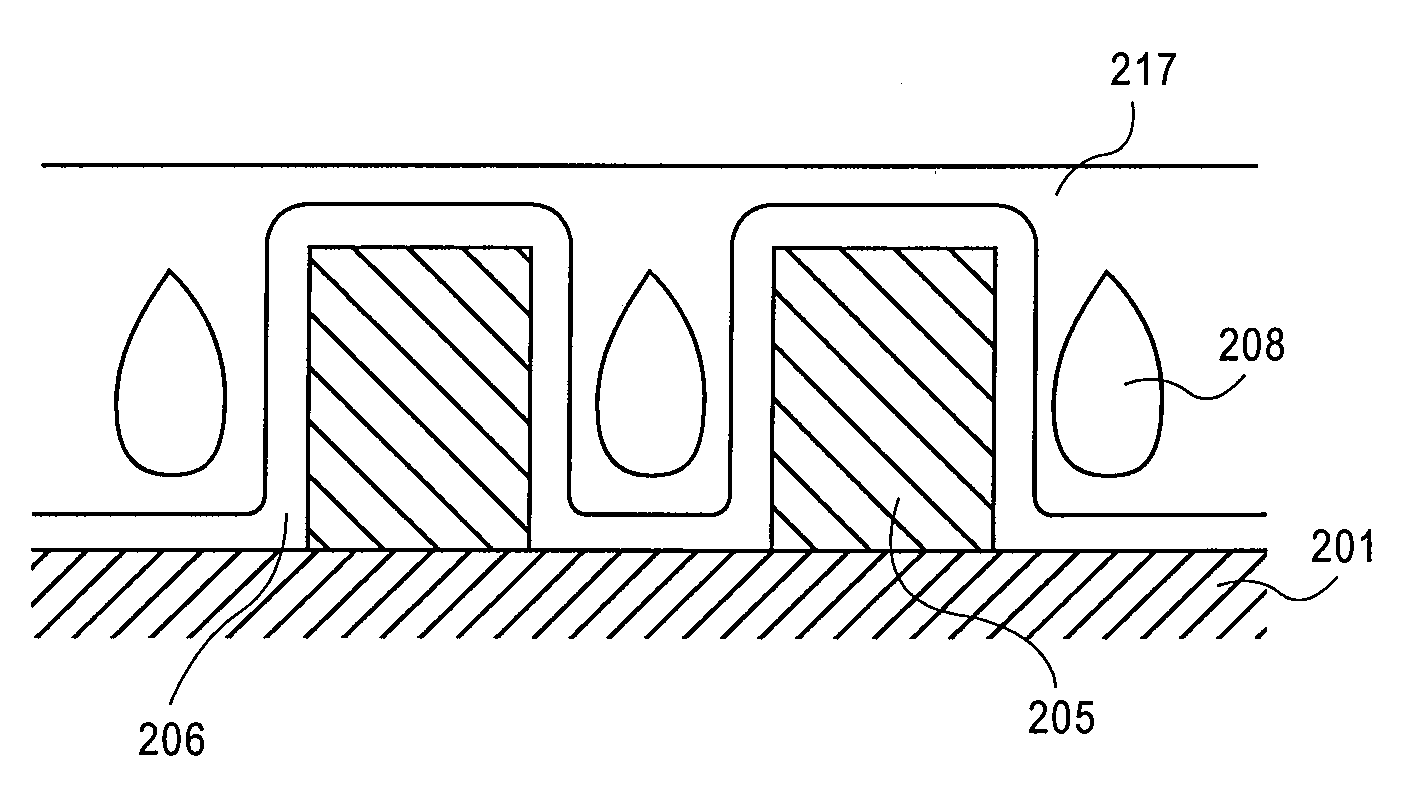

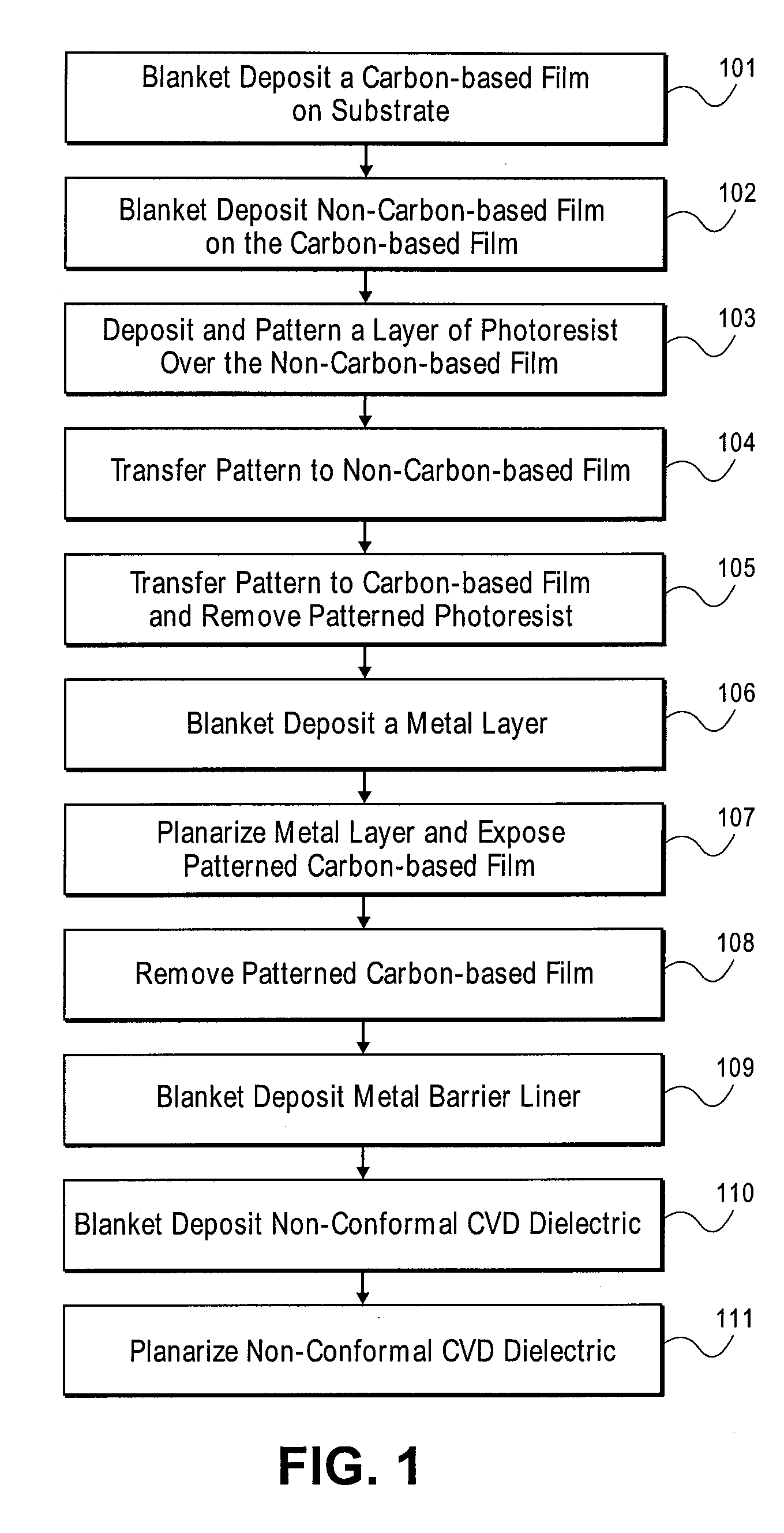

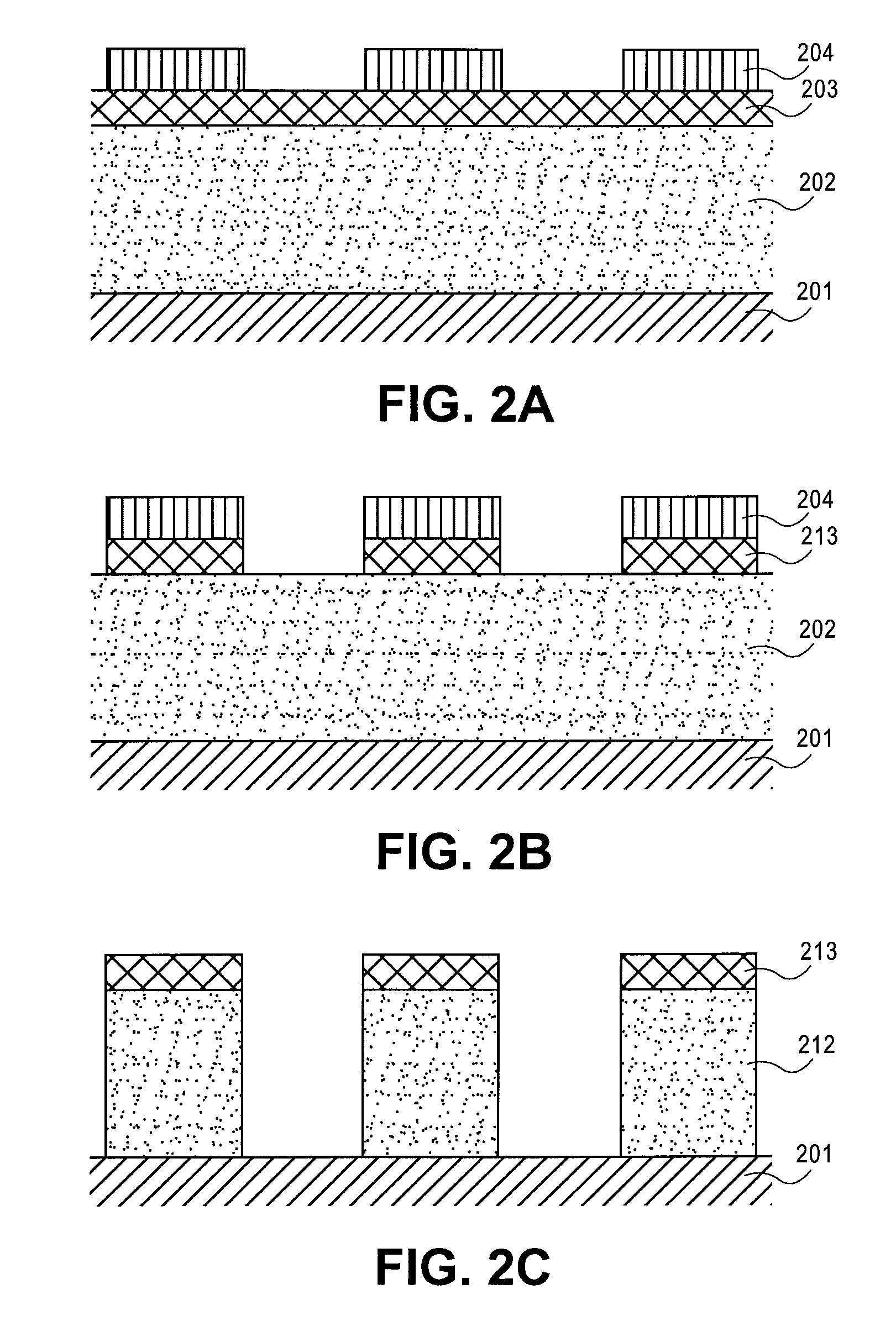

Air gap interconnects using carbon-based films

InactiveUS20100093168A1Improve electrical isolationSemiconductor/solid-state device manufacturingMetal interconnectPorous carbon

A method of forming an interconnect structure comprising: forming a sacrificial inter-metal dielectric (IMD) layer over a substrate, wherein the sacrificial IMD layer comprising a carbon-based film, such as amorphous carbon, advanced patterning films, porous carbon, or any combination thereof; forming a plurality of metal interconnect lines within the sacrificial IMD layer; removing the sacrificial IMD layer, with an oxygen based reactive process; and depositing a non-conformal dielectric layer to form air gaps between the plurality of metal interconnect lines. The metal interconnect lines may comprise copper, aluminum, tantalum, tungsten, titanium, tantalum nitride, titanium nitride, tungsten nitride, or any combination thereof. Carbon-based films and patterned photoresist layers may be simultaneously removed with the same reactive process. Highly reactive hydrogen radicals processes may be used to remove the carbon-based film and simultaneously pre-clean the metal interconnect lines prior to the deposition of a conformal metal barrier liner.

Owner:APPLIED MATERIALS INC

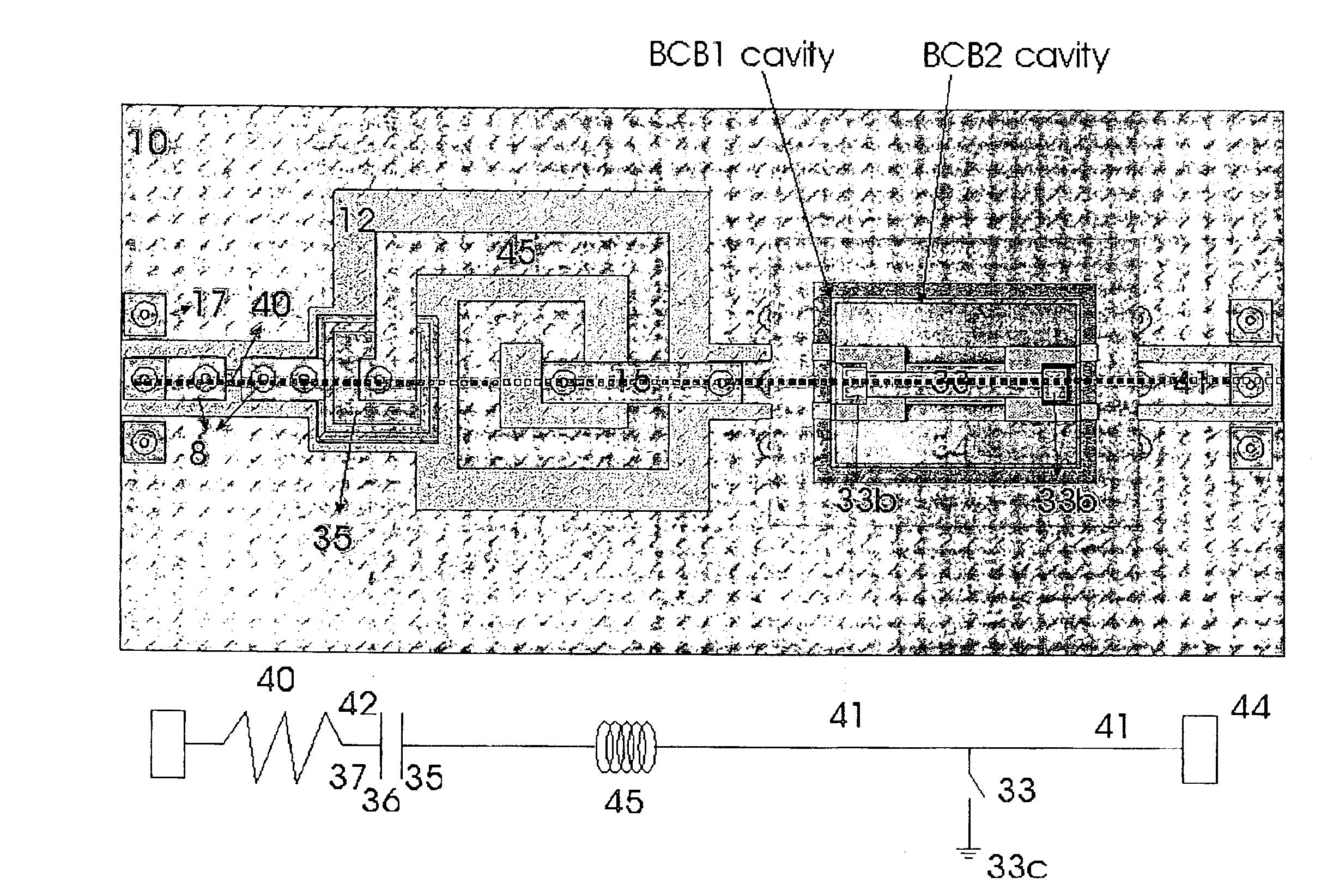

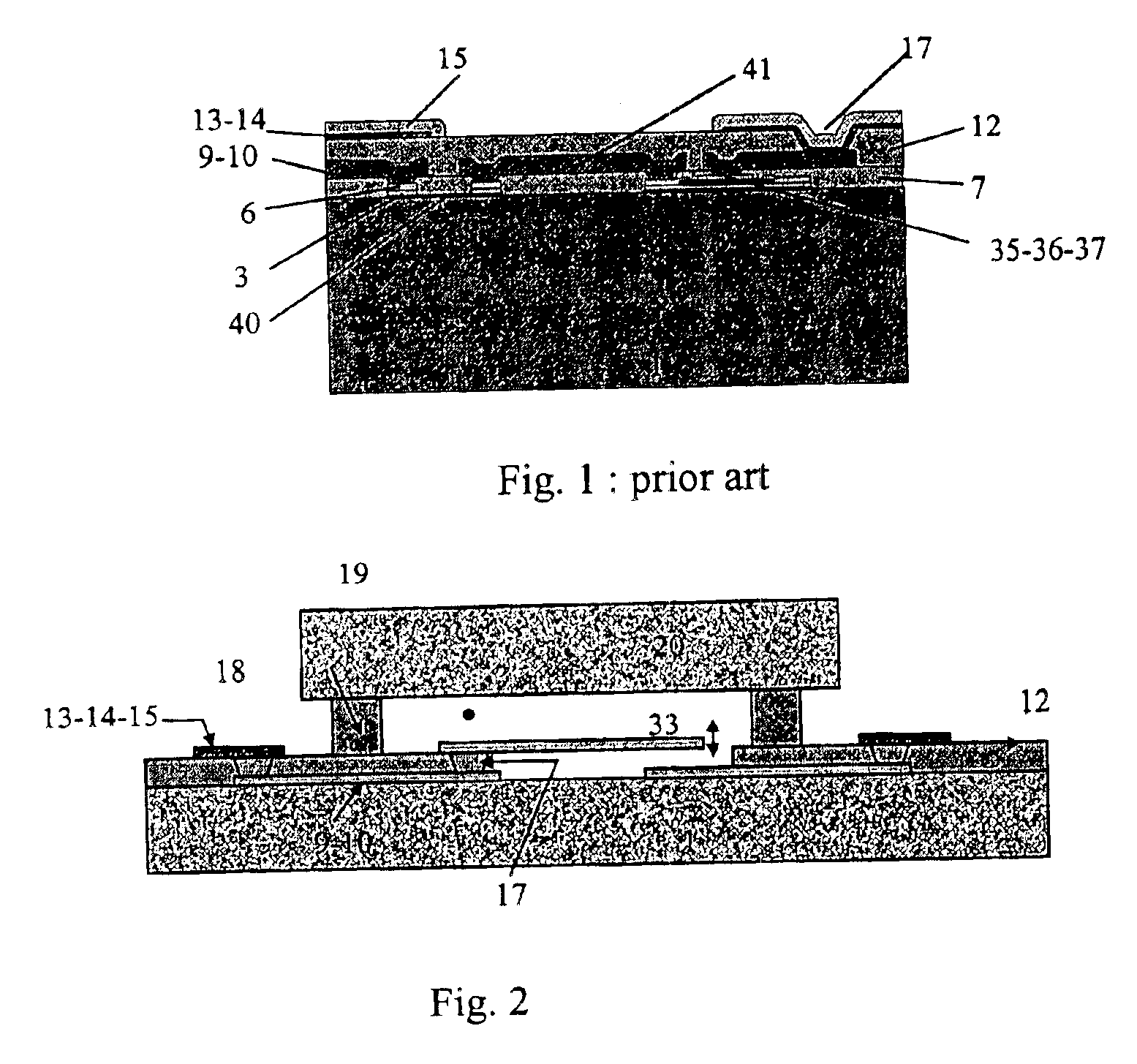

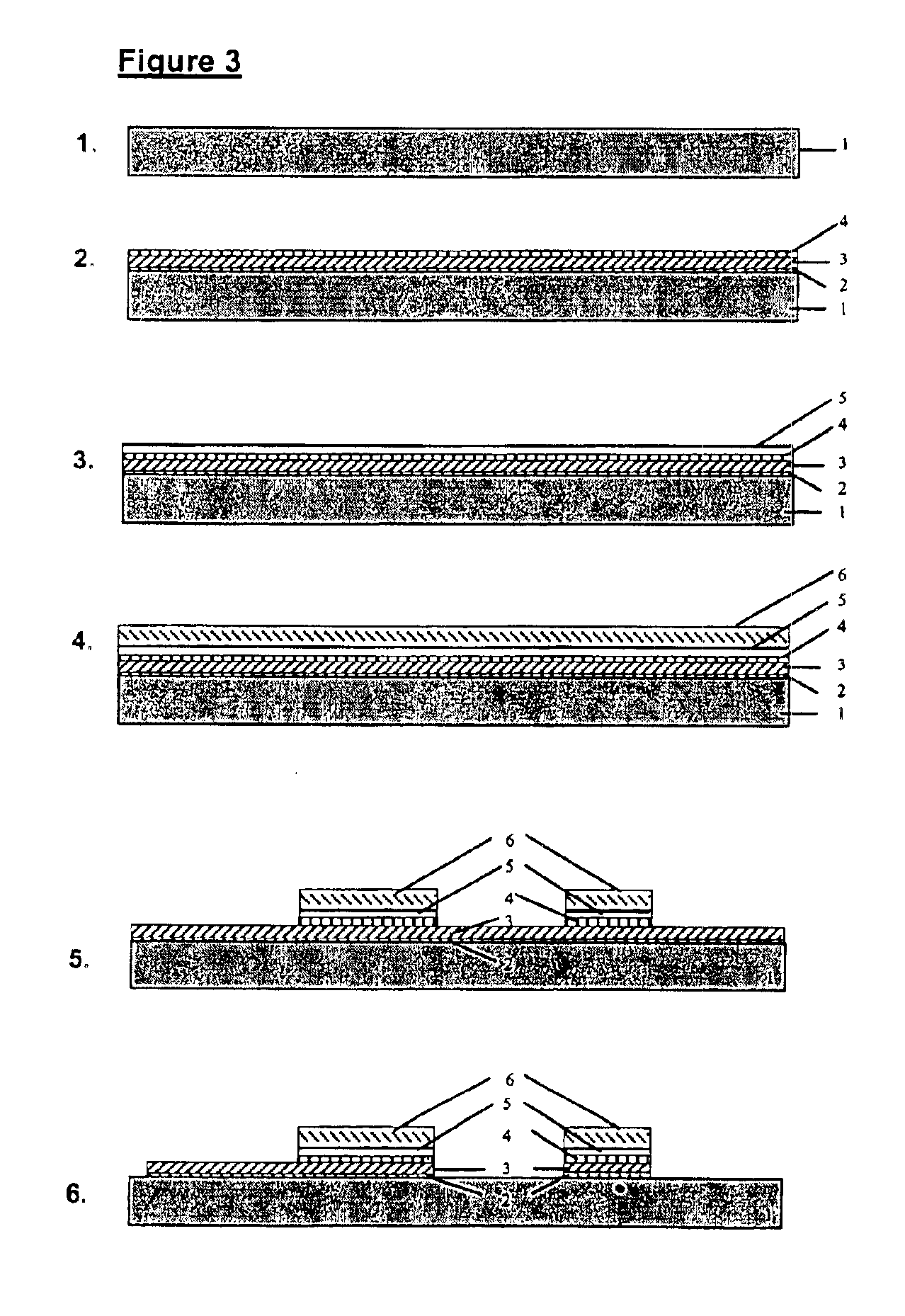

Method and system for fabrication of integrated tunable/switchable passive microwave and millimeter wave modules

InactiveUS6876056B2Electrostatic/electro-adhesion relaysSolid-state devicesMetal interconnectMicrowave

An interconnect module and a method of manufacturing the same is described comprising: a substrate, an interconnect section formed on the substrate, and a variable passive device section formed on the substrate located laterally adjacent to the interconnect section. The interconnect section has at least two metal interconnect layers separated by a dielectric layer and the variable passive device has at least one moveable element. The moveable element is formed from a metal layer which is formed from the same material and at the same time as one of the two interconnect layers. The moveable element is formed on the dielectric layer and is released by local removal of the dielectric layer. Additional interconnect layers and intermediate dielectric layers may be added.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

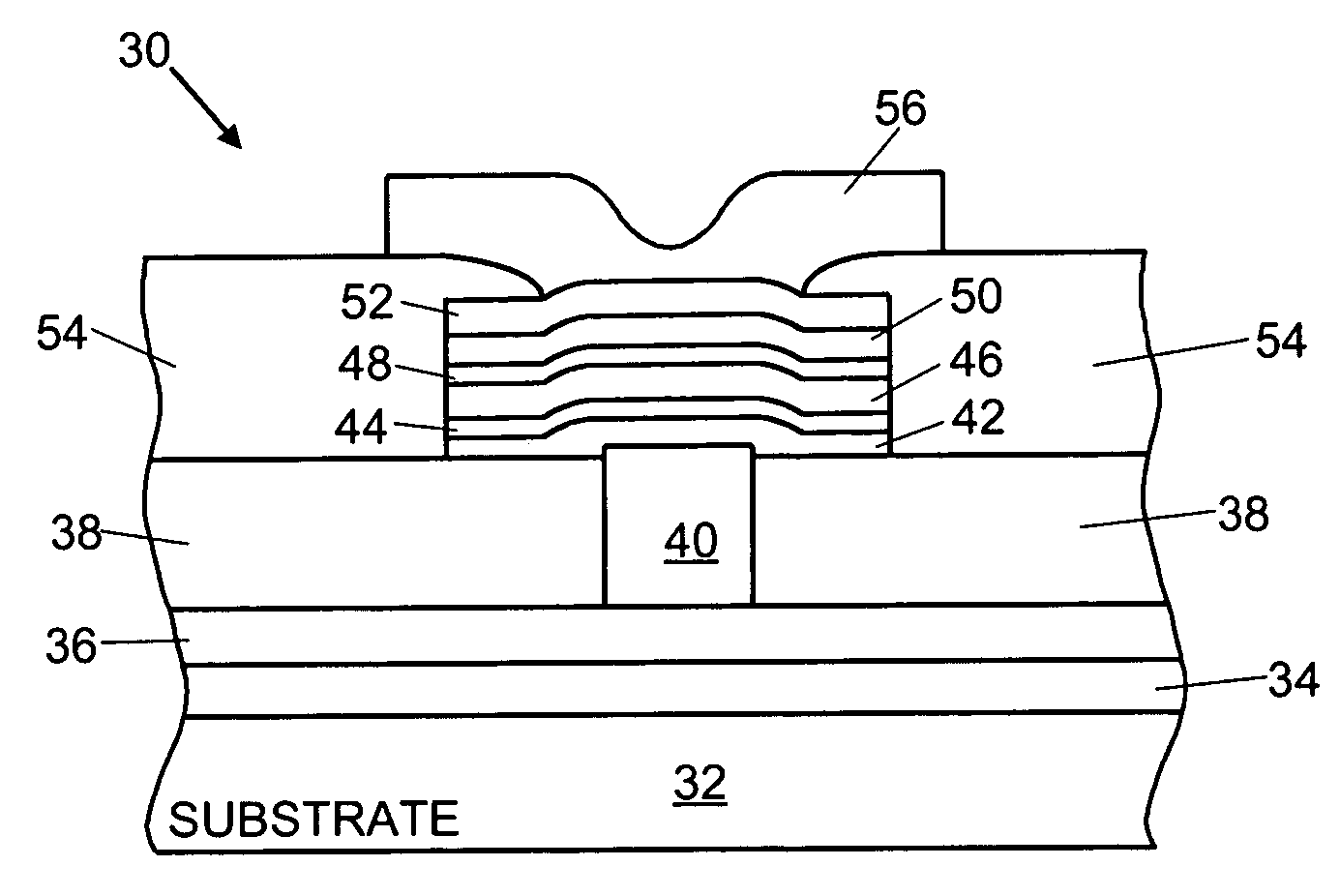

Reprogrammable metal-to-metal antifuse employing carbon-containing antifuse material

InactiveUS7459763B1Semiconductor/solid-state device detailsSolid-state devicesHydrogenMetal interconnect

A reprogrammable metal-to-metal antifuse is disposed between two metal interconnect layers in an integrated circuit. A lower barrier layer is formed from Ti. A lower adhesion-promoting layer is disposed over the lower Ti barrier layer. An antifuse material layer selected from a group comprising at least one of amorphous carbon and amorphous carbon doped with at least one of hydrogen and fluorine is disposed over the lower adhesion-promoting layer. An upper adhesion-promoting layer is disposed over the antifuse material layer. An upper Ti barrier layer is disposed over the upper adhesion-promoting layer.

Owner:MICROSEMI SOC

Integration of ALD tantalum nitride and alpha-phase tantalum for copper metallization application

InactiveUS20030124262A1Pretreated surfacesSemiconductor/solid-state device manufacturingMetal interconnectTantalum nitride

Owner:APPLIED MATERIALS INC

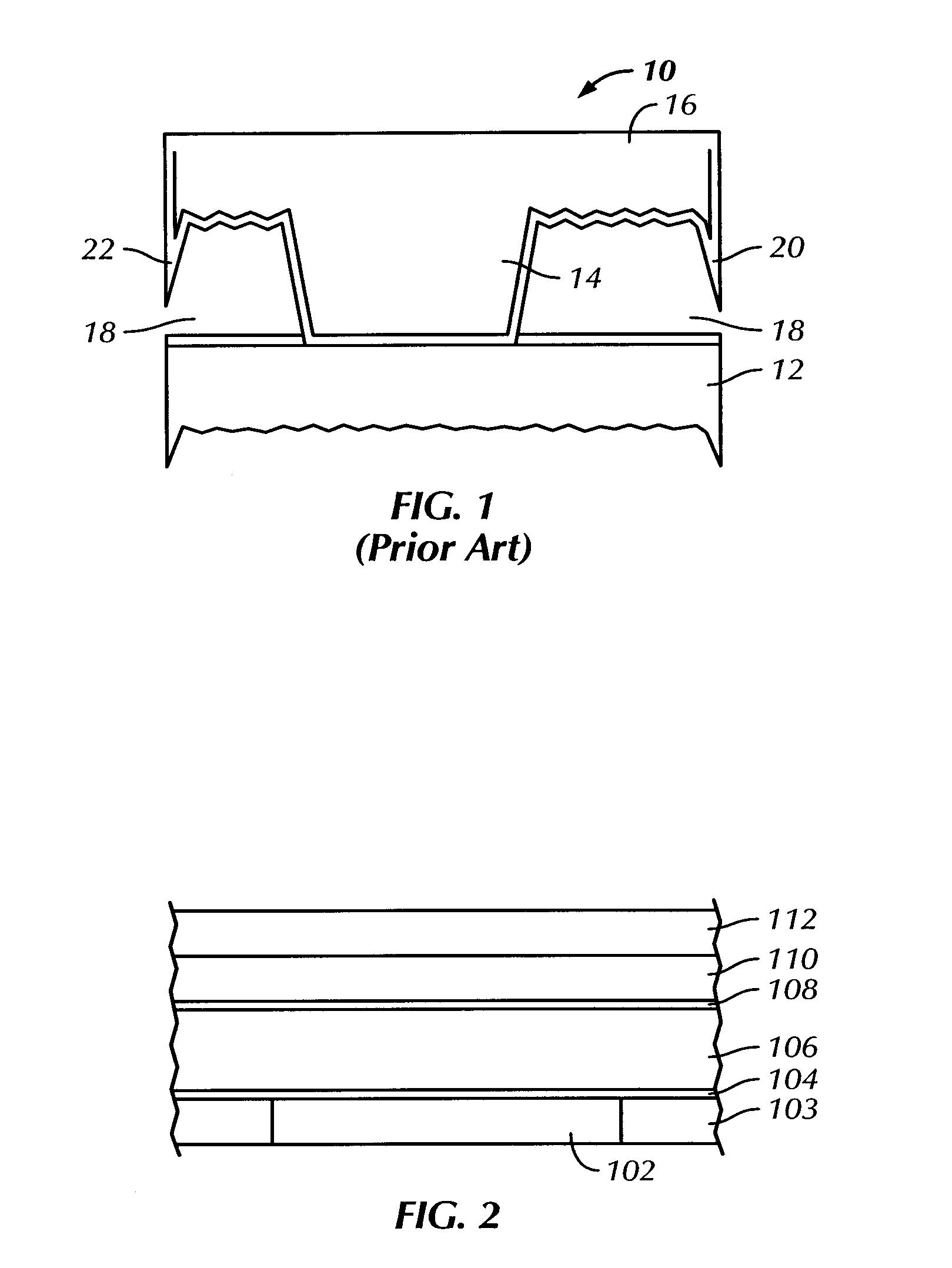

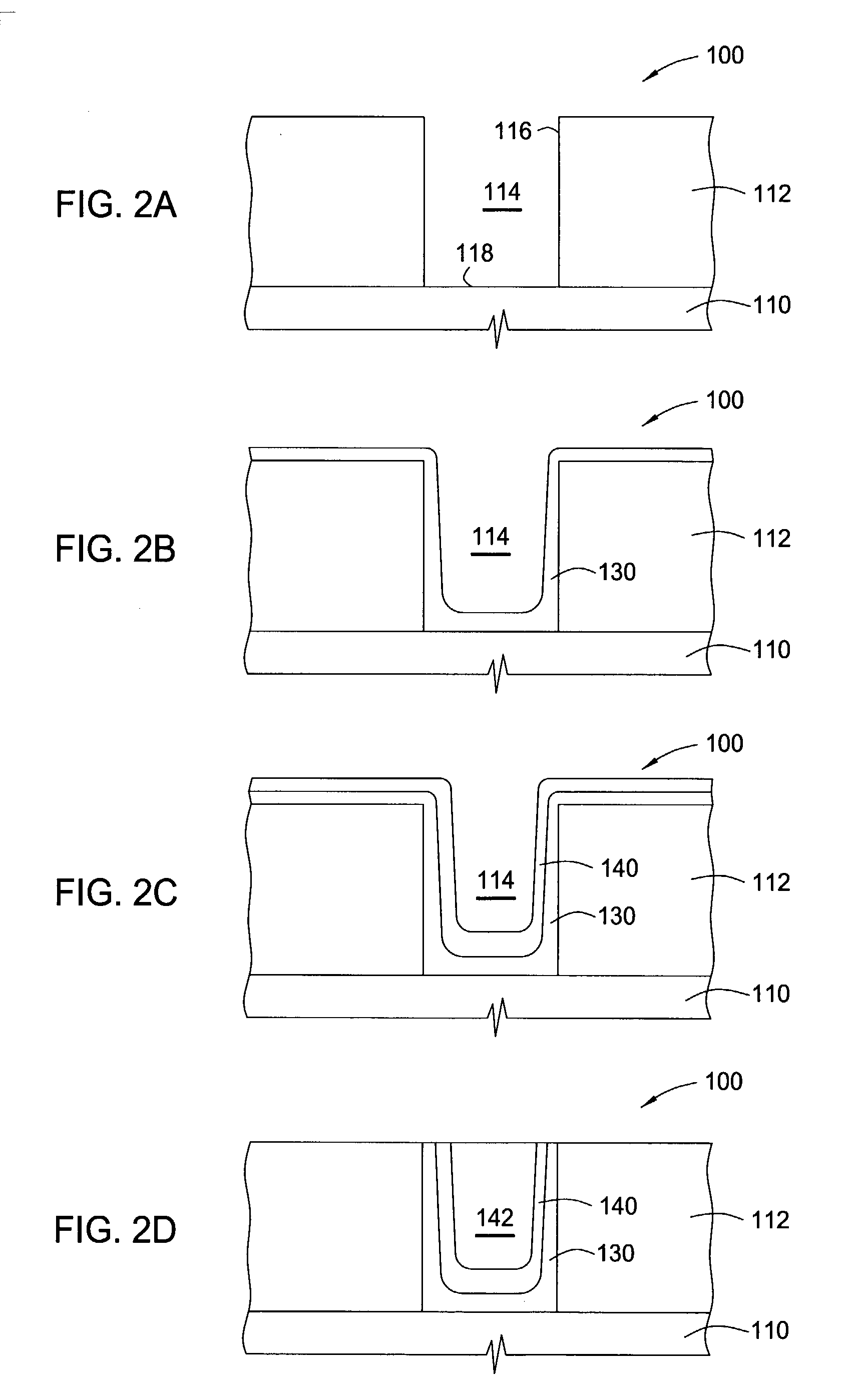

Methods to mitigate plasma damage in organosilicate dielectrics using a protective sidewall spacer

InactiveUS20090072401A1Reduce plasma damageIncrease line widthSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectEngineering

Plasma damage in ultra low k dielectric materials during formation of a dual damascene metal interconnect structure is reduced by providing a protective spacer on sidewalls of a line trench. A densified trench bottom region may be additionally formed directly beneath an exposed horizontal surface of the line trench. The protective spacer and / or the densified trench bottom region protects an ultra low k intermetal dielectric layer from plasma damage during a plasma strip process that is used to remove a disposable via fill plug employed in the dual damascene metal interconnect structure.

Owner:GLOBALFOUNDRIES INC

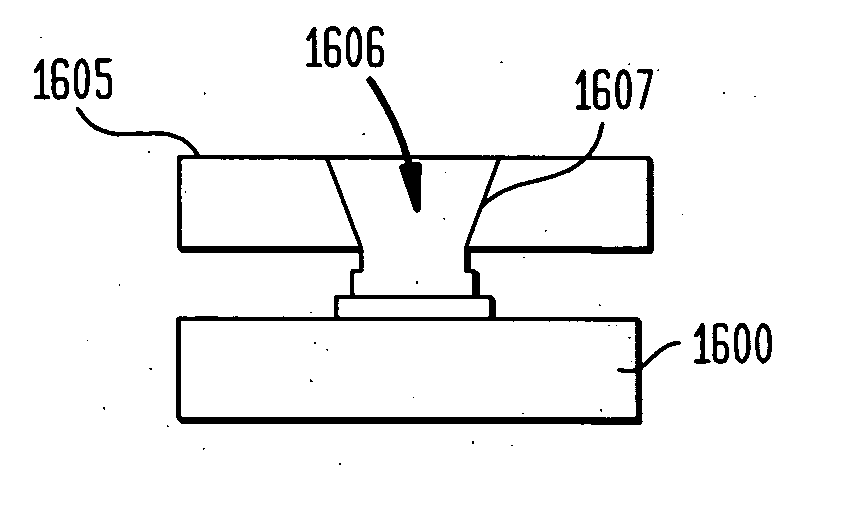

Structure and method of making capped chips including vertical interconnects having stud bumps engaged to surfaces of said caps

InactiveUS20050067688A1Impedence networksSemiconductor/solid-state device detailsEngineeringBiomedical engineering

A capped chip is provided which includes a chip and a cap member, the chip having a front surface and a plurality of bond pads exposed at the front surface, the cap member having a bottom surface facing the front surface of the chip and having a top surface opposite the front surface. A plurality of through holes extend from the bottom surface of the cap member to the top surface. The capped chip assembly further includes a plurality of metallic interconnects extending from the bond pads at least partially through the through holes, the metallic interconnects including stud bumps joined to the bond pads, the stud bumps contacting and engaging at least one of (i) the top surface of the cap member surrounding the through holes and (ii) inner surfaces of the through holes.

Owner:TESSERA INC

Cobalt based interconnects and methods of fabrication thereof

ActiveUS20140183738A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectFilling materials

A metal interconnect comprising cobalt and method of forming a metal interconnect comprising cobalt are described. In an embodiment, a metal interconnect comprising cobalt includes a dielectric layer disposed on a substrate, an opening formed in the dielectric layer such that the substrate is exposed. The embodiment further includes a seed layer disposed over the substrate and a fill material comprising cobalt formed within the opening and on a surface of the seed layer.

Owner:DAEDALUS PRIME LLC

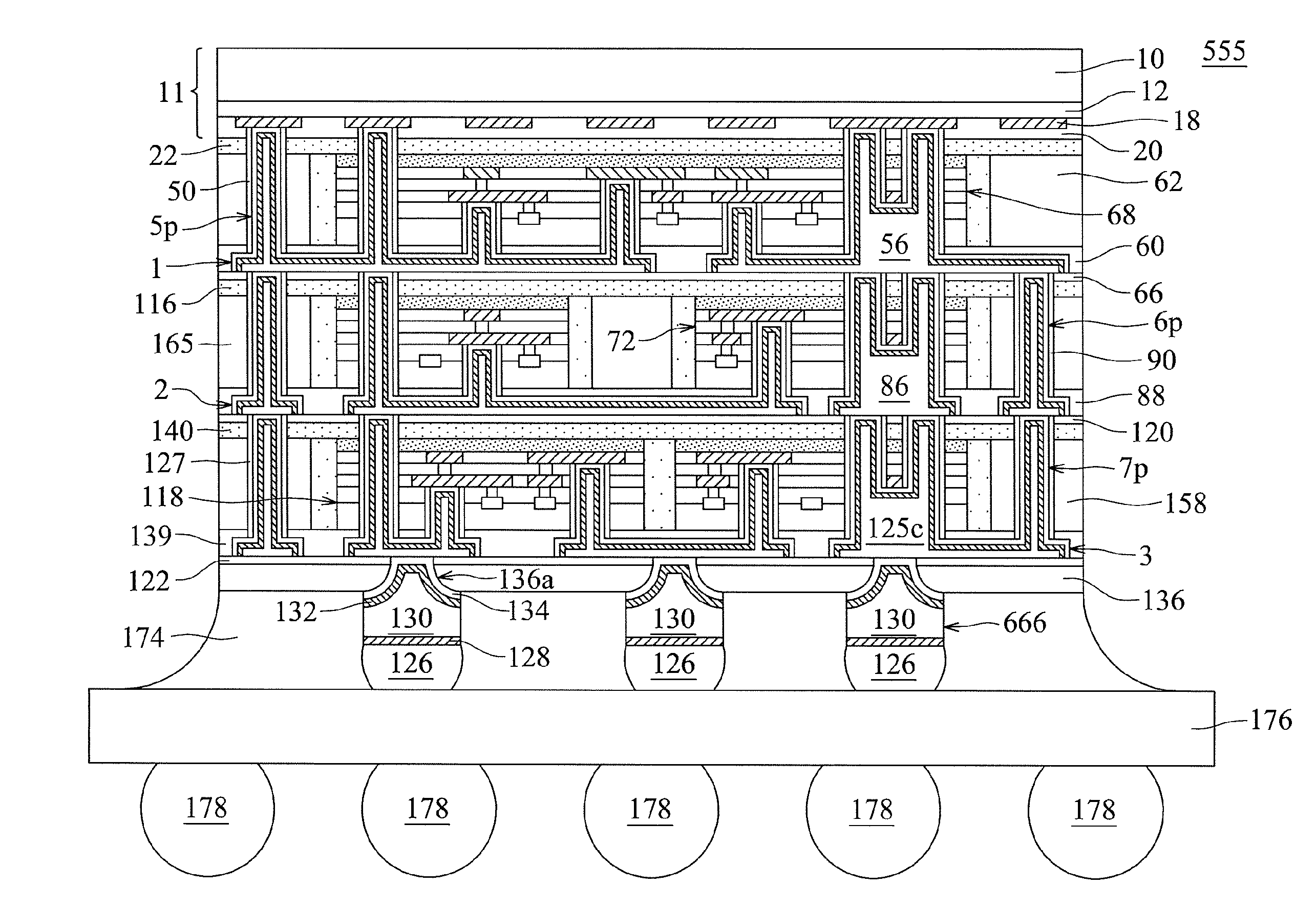

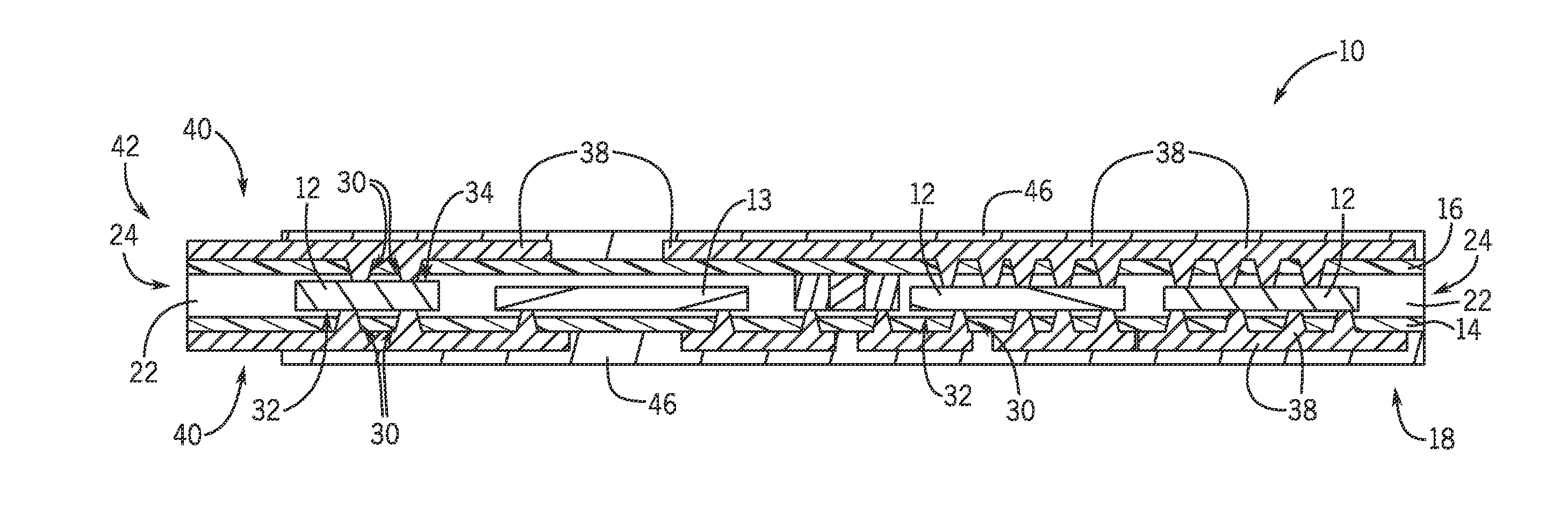

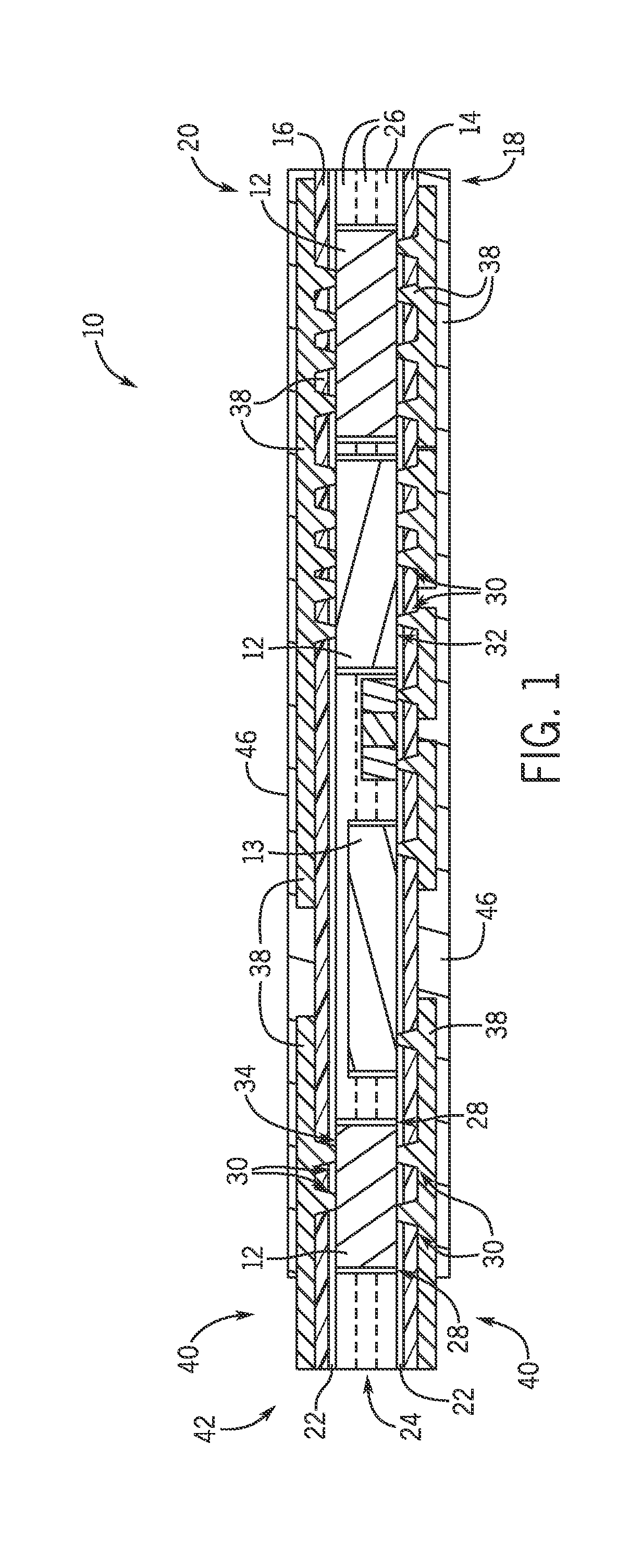

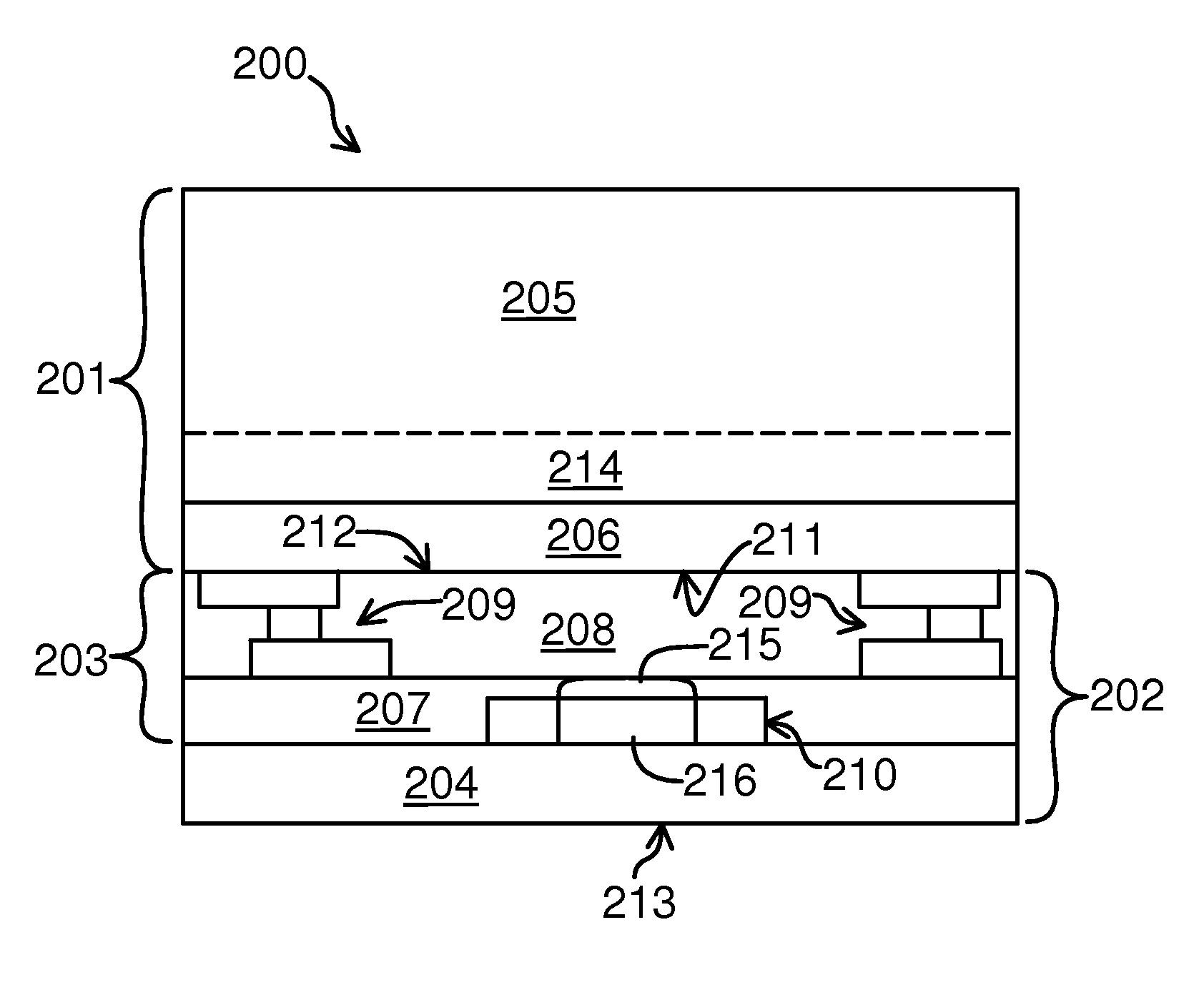

Ultra-thin embedded semiconductor device package and method of manufacturing thereof

ActiveUS20150255418A1Final product manufactureSemiconductor/solid-state device detailsMetal interconnectEngineering

A package structure includes a first dielectric layer, semiconductor device(s) attached to the first dielectric layer, and an embedding material applied to the first dielectric layer so as to embed the semiconductor device therein, the embedding material comprising one or more additional dielectric layers. Vias are formed through the first dielectric layer to the at least one semiconductor device, with metal interconnects formed in the vias to form electrical interconnections to the semiconductor device. Input / output (I / O) connections are located on one end of the package structure on one or more outward facing surfaces thereof to provide a second level connection to an external circuit. The package structure interfits with a connector on the external circuit to mount the package perpendicular to the external circuit, with the I / O connections being electrically connected to the connector to form the second level connection to the external circuit.

Owner:GENERAL ELECTRIC CO

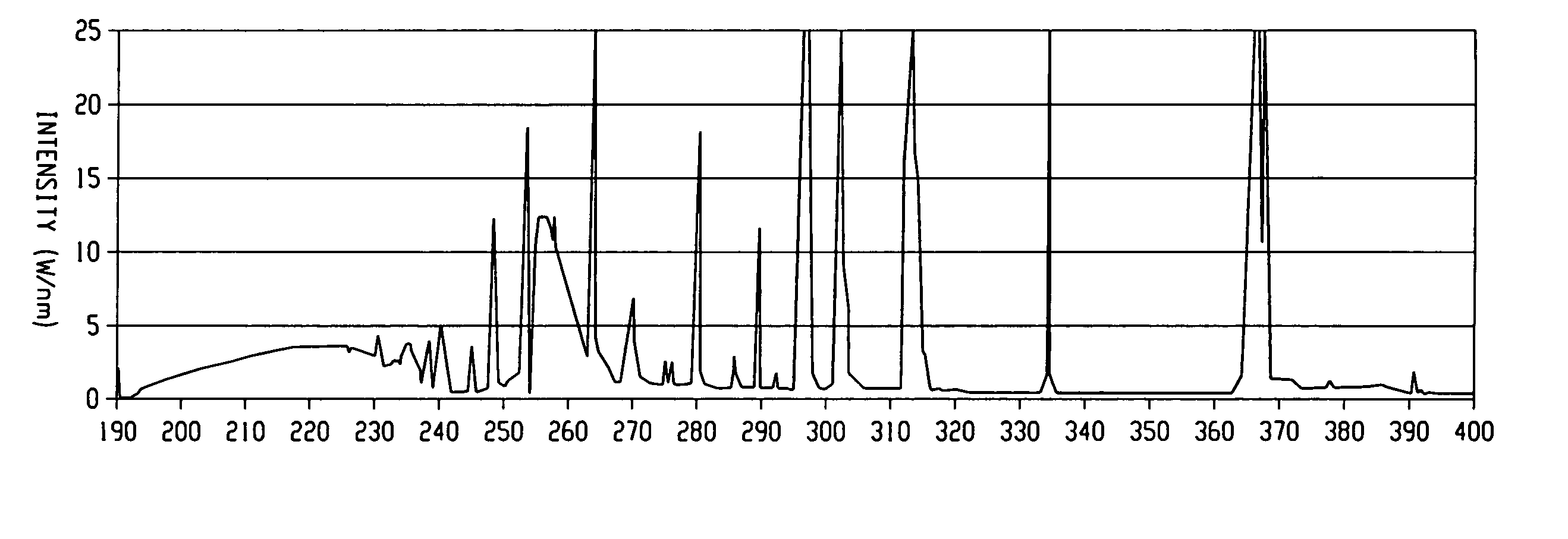

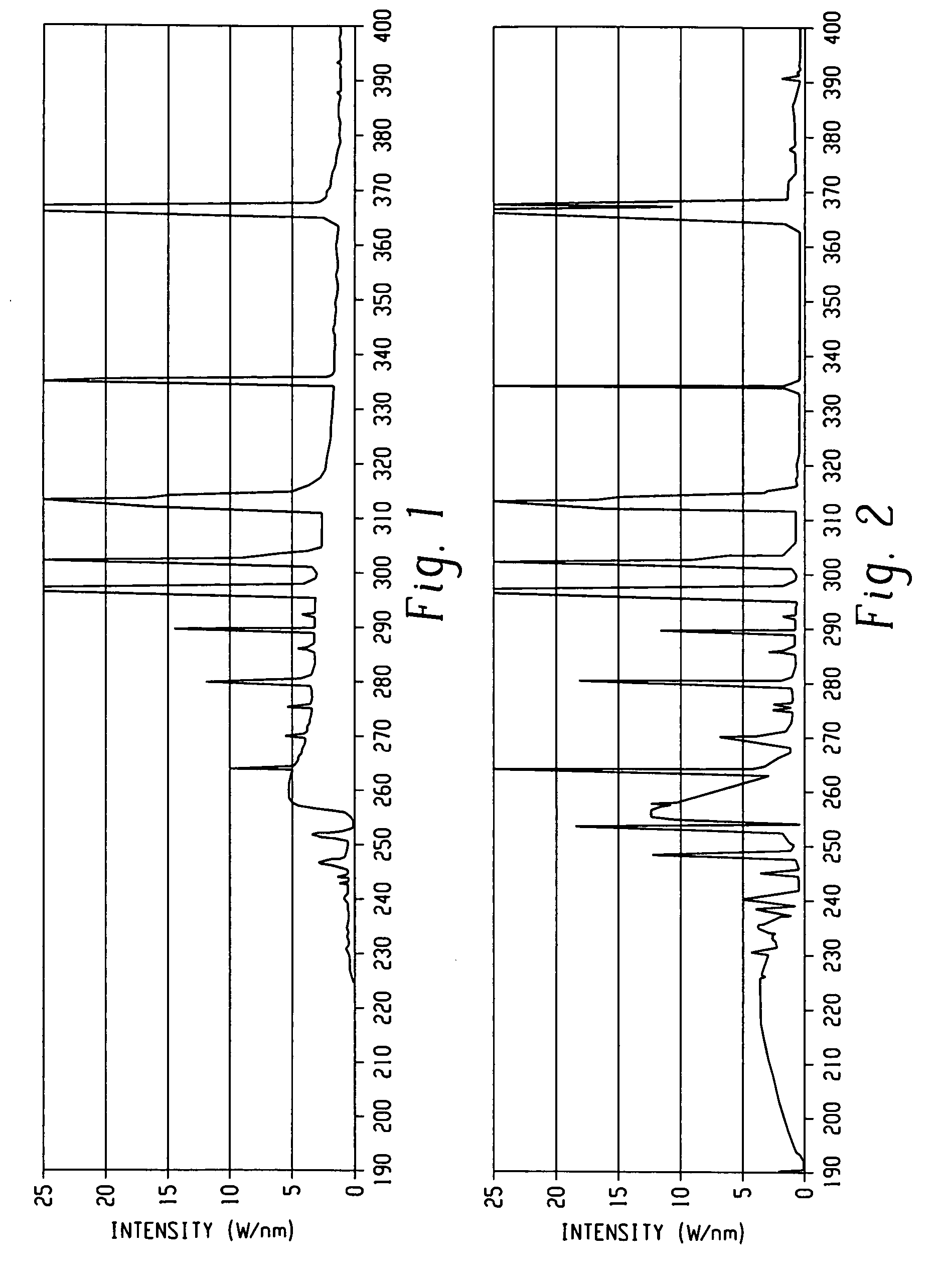

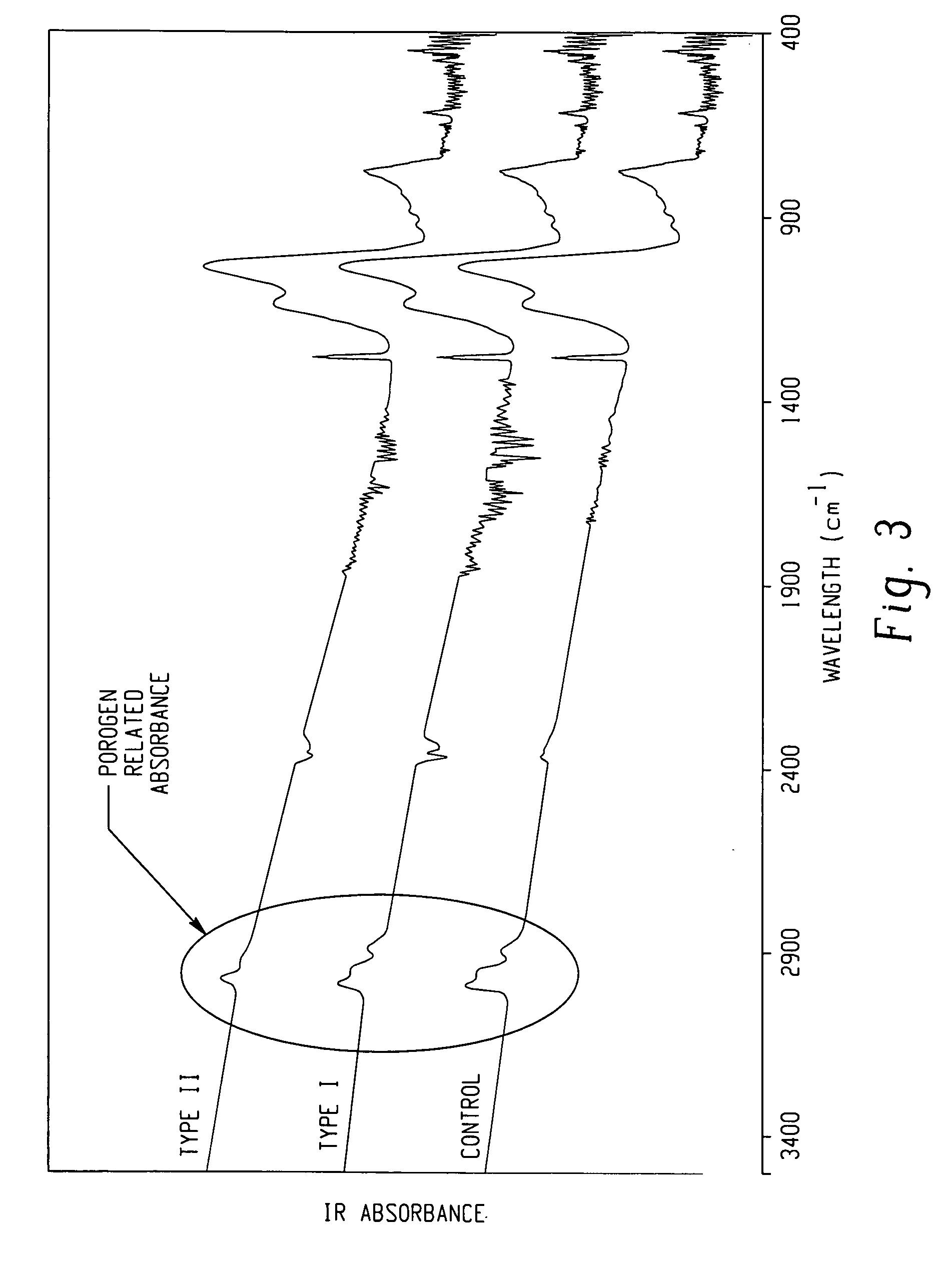

Ultraviolet assisted porogen removal and/or curing processes for forming porous low k dielectrics

InactiveUS20060024976A1Material removalIncrease crosslink densitySolid-state devicesSemiconductor/solid-state device manufacturingMetal interconnectUltraviolet radiation

Processes for forming porous low k dielectric materials from low k dielectric films containing a porogen material include exposing the low k dielectric film to ultraviolet radiation. In one embodiment, the film is exposed to broadband ultraviolet radiation of less than 240 nm for a period of time and intensity effective to remove the porogen material. In other embodiments, the low k dielectric film is exposed to a first ultraviolet radiation pattern effective to increase a crosslinking density of the film matrix while maintaining a concentration of the porogen material substantially the same before and after exposure to the first ultraviolet radiation pattern. The low k dielectric film can be then be processed to form a metal interconnect structure therein and subsequently exposed to a second ultraviolet radiation pattern effective to remove the porogen material from the low k dielectrics film and form a porous low k dielectric film.

Owner:AXCELIS TECHNOLOGIES

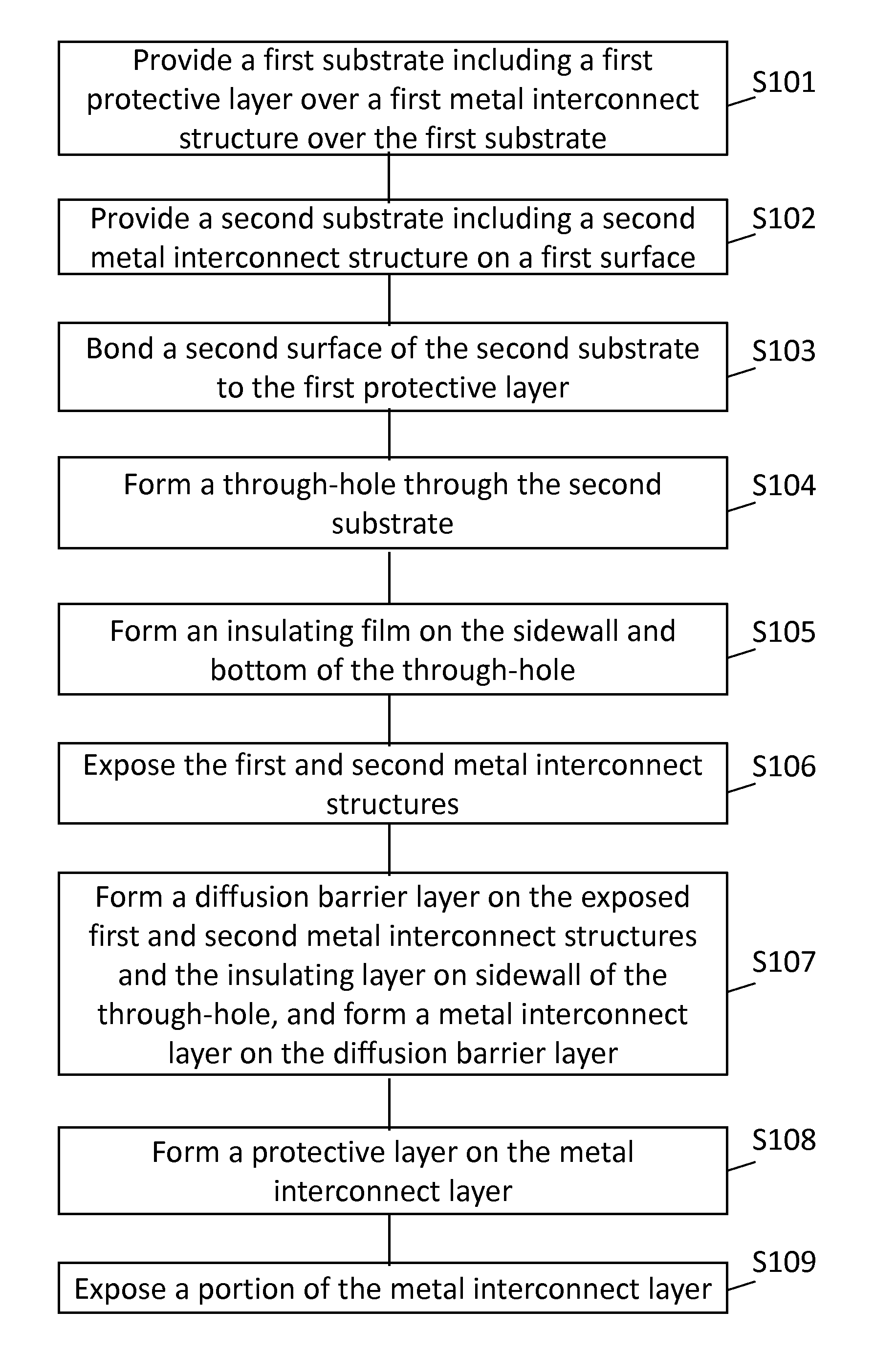

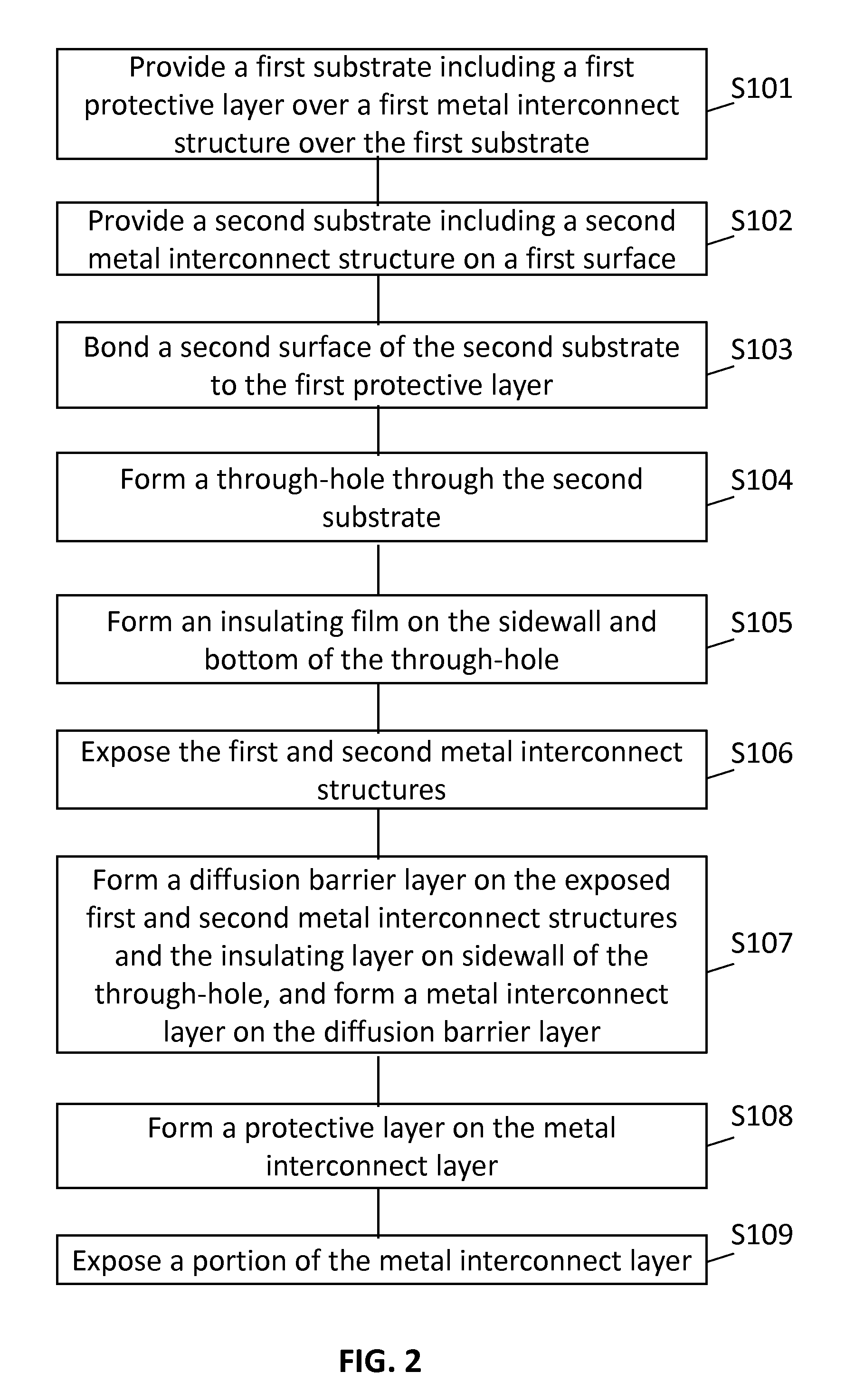

IC device including package structure and method of forming the same

ActiveUS20140015136A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectEngineering

Various embodiments provide semiconductor devices including a package structure and methods of forming the semiconductor devices. In one embodiment, the package structure can include a through-hole at least partially filled by one or more layers of material(s) to form a through-hole interconnect between semiconductor devices in the package structure. The through-hole can be filled by an insulating layer, a diffusion barrier layer, a metal interconnect layer, and / or a protective layer having a total thickness from the sidewall of the through-hole of less than or equal to the radius of the through-hole.

Owner:SEMICON MFG INT (SHANGHAI) CORP

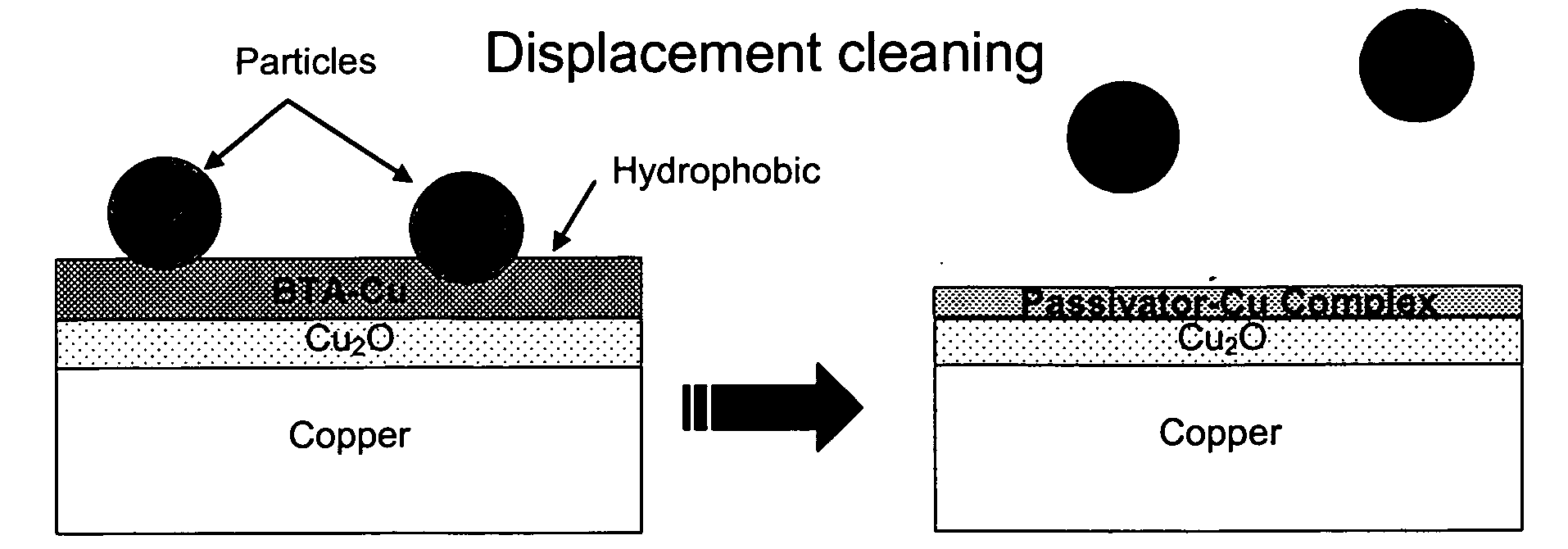

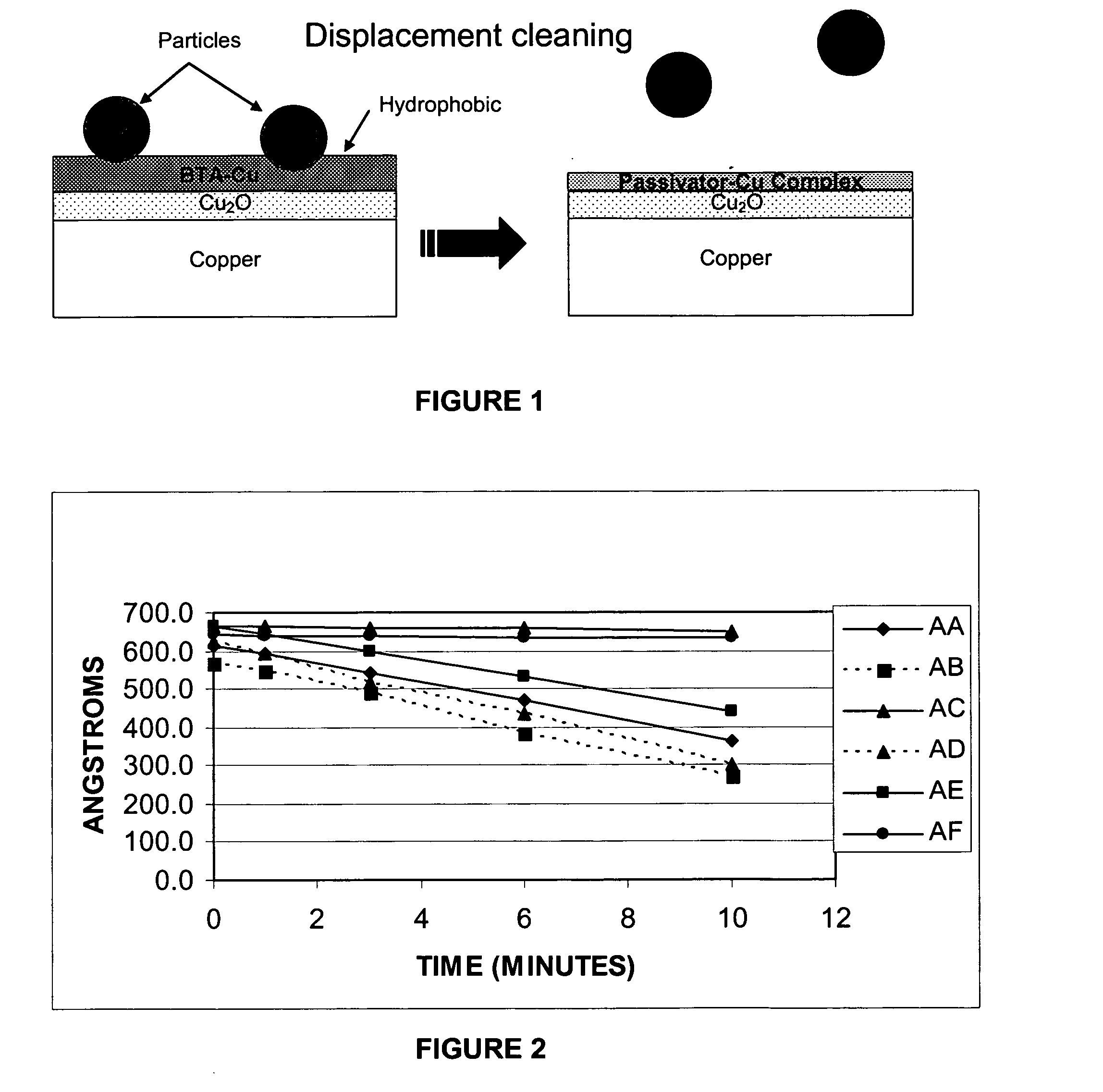

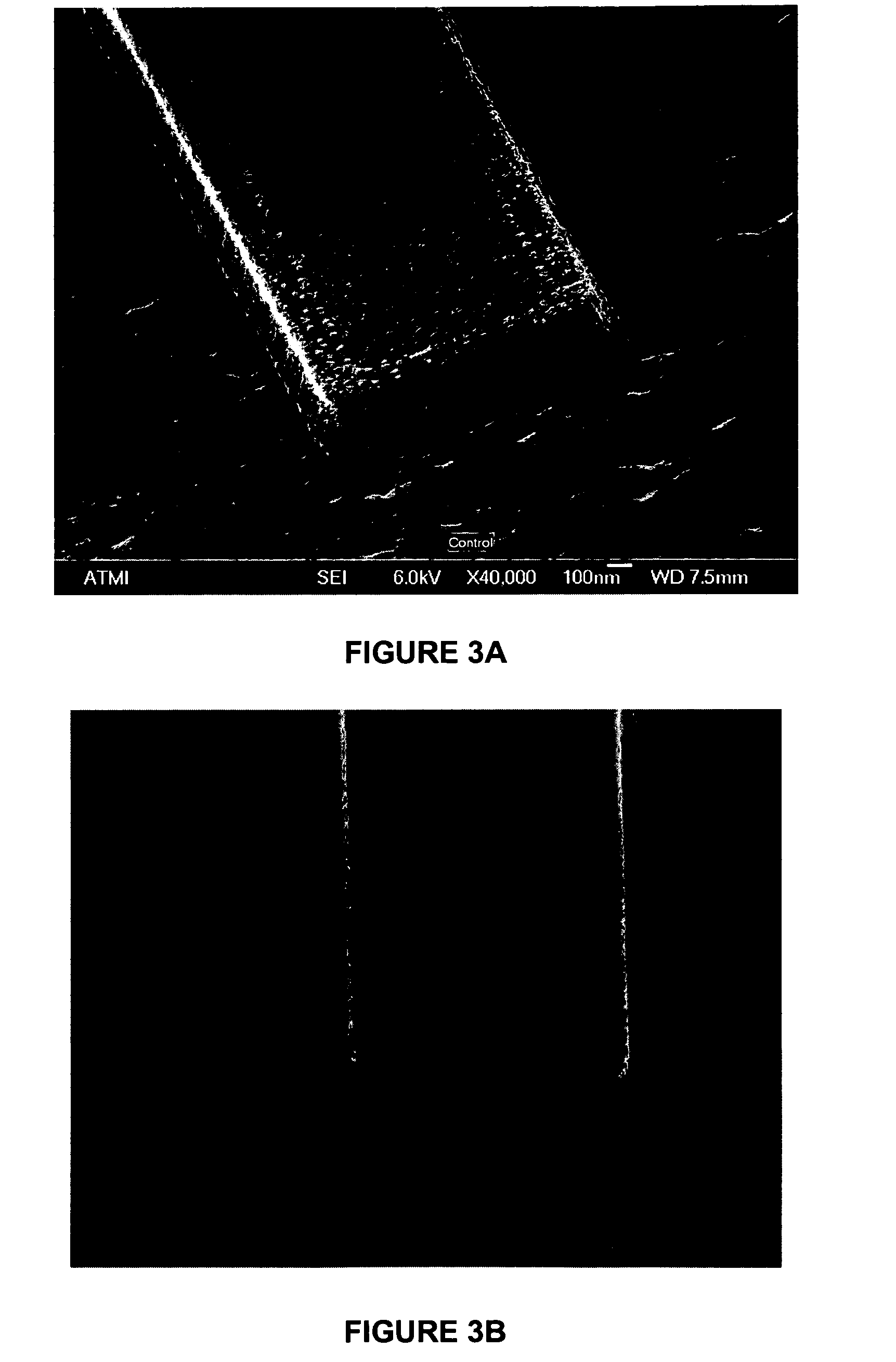

Copper passivating post-chemical mechanical polishing cleaning composition and method of use

InactiveUS20080076688A1Enough timeOrganic detergent compounding agentsNon-surface-active detergent compositionsMetal interconnectCompound (substance)

Alkaline aqueous cleaning compositions and processes for cleaning post-chemical mechanical polishing (CMP) residue, post-etch residue and / or contaminants from a microelectronic device having said residue and contaminants thereon. The alkaline aqueous cleaning compositions include amine, passivating agent, and water. The composition achieves highly efficacious cleaning of the residue and contaminant material from the microelectronic device while simultaneously passivating the metal interconnect material.

Owner:ADVANCED TECH MATERIALS INC

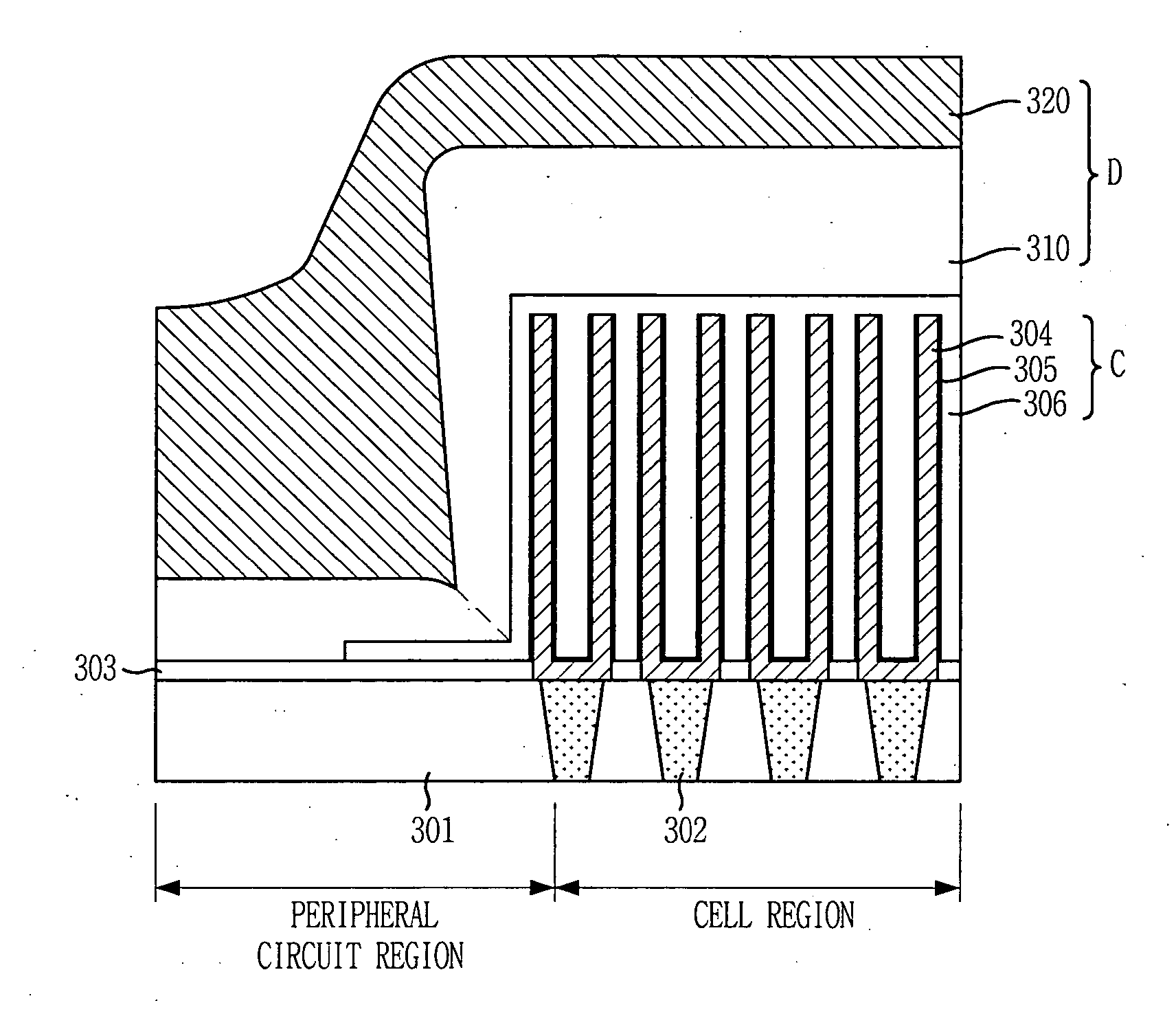

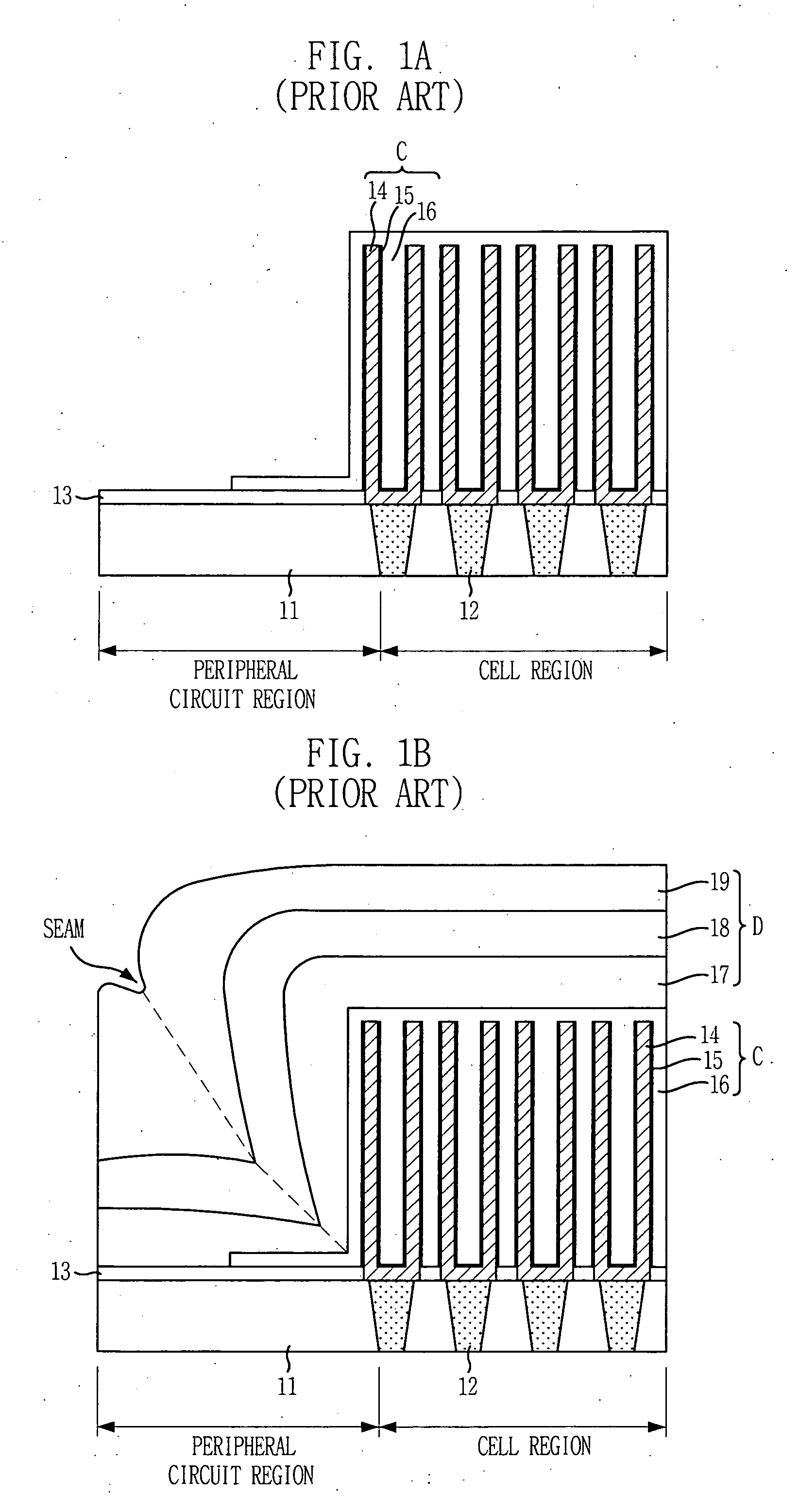

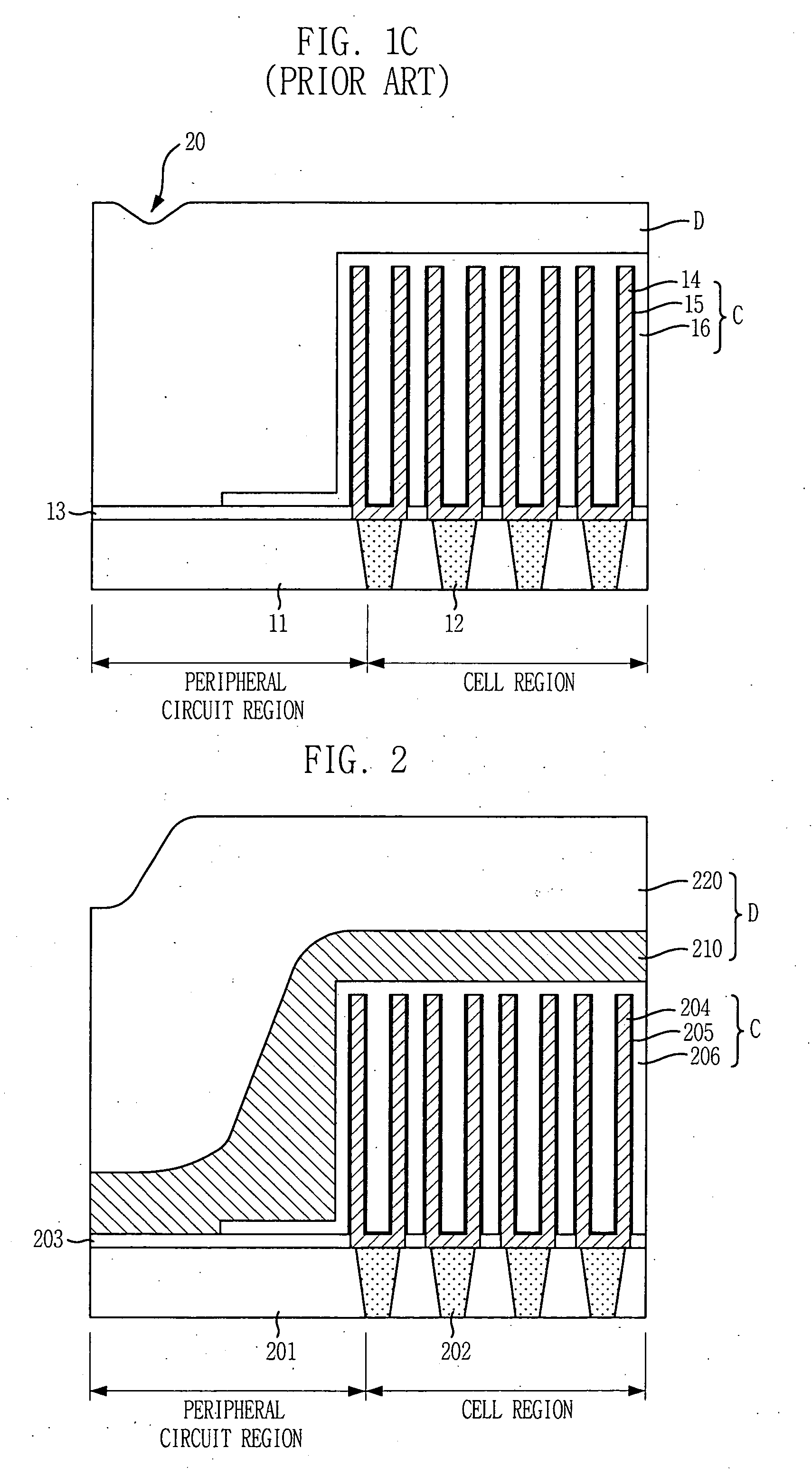

Semiconductor device with flowable insulation layer formed on capacitor and method for fabricating the same

ActiveUS20050266650A1Good planarization characteristicWithout degrading characteristicTransistorSemiconductor/solid-state device detailsMetal interconnectInsulation layer

Disclosed is a semiconductor device with a flowable insulation layer formed on a capacitor and a method for fabricating the same. Particularly, the semiconductor device includes: a capacitor formed on a predetermined portion of a substrate; an insulation layer formed by stacking a flowable insulation layer and an undoped silicate glass layer on a resulting substrate structure including the substrate and the capacitor; and a metal interconnection line formed on the insulation layer. The method includes the steps of: forming a capacitor on a predetermined portion of a substrate; forming an insulation layer by stacking a flowable insulation layer and an undoped silicate glass layer on a resulting substrate structure including the substrate and the capacitor; and forming a metal interconnection line on the insulation layer.

Owner:SK HYNIX INC

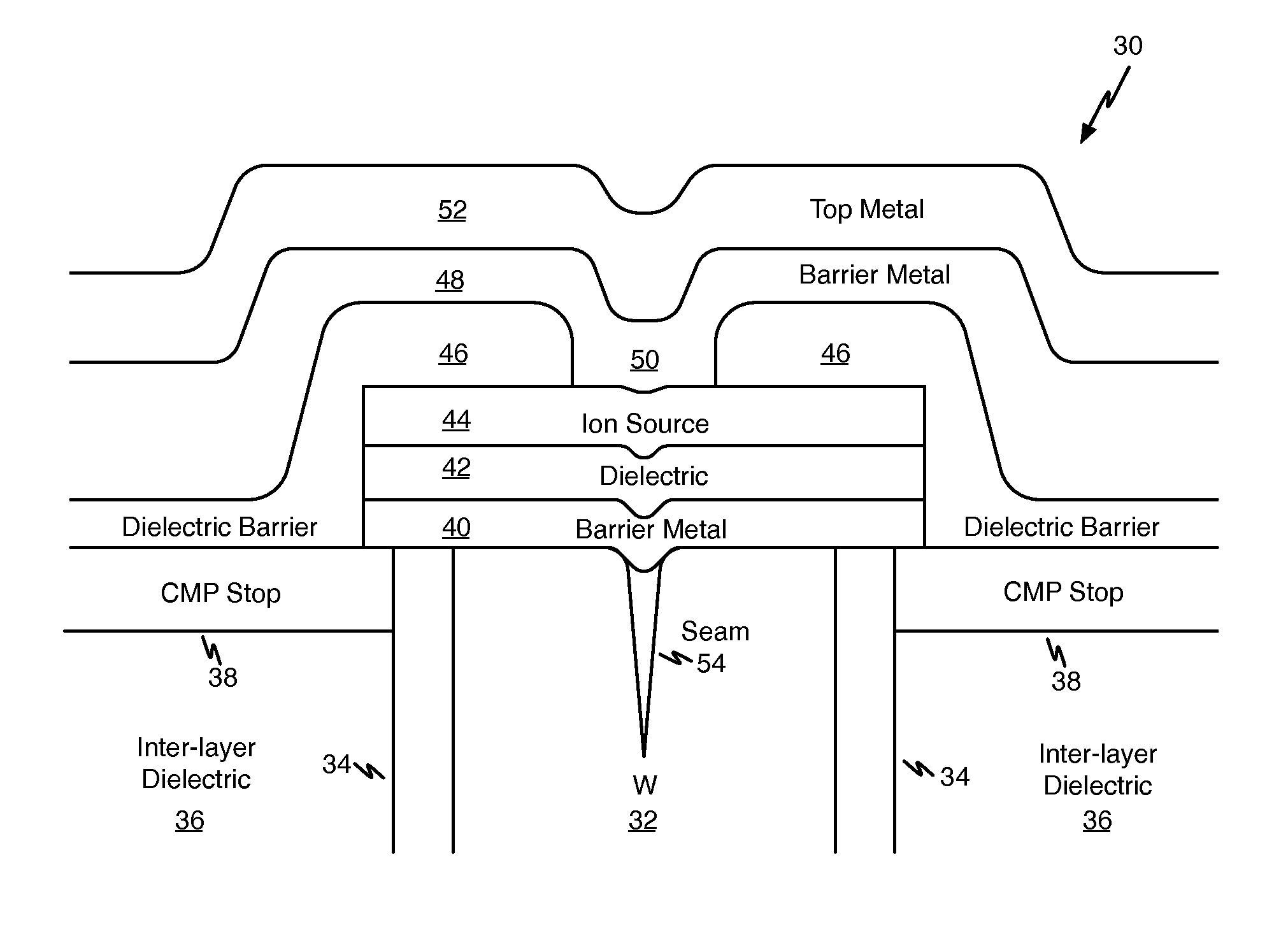

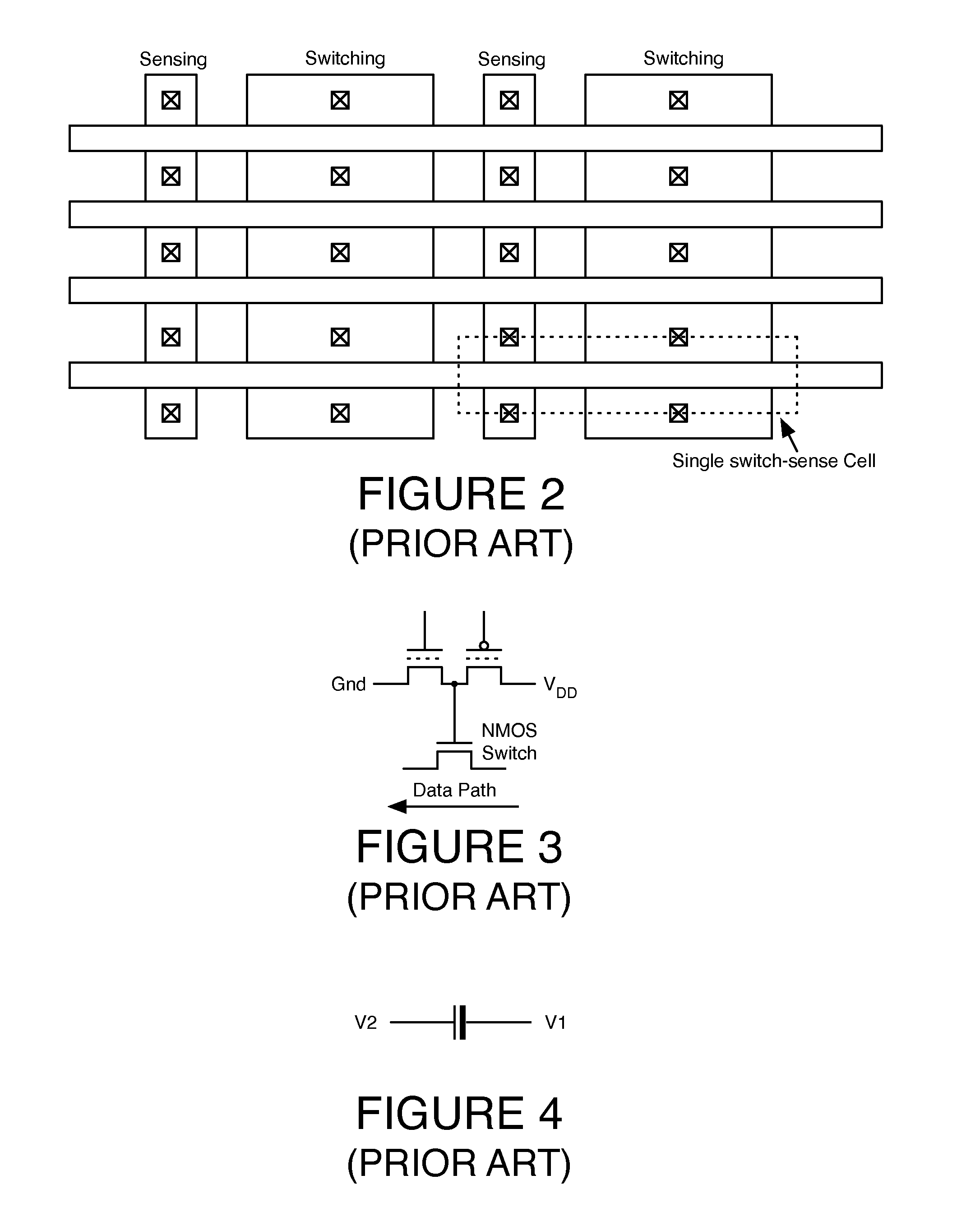

Front to back resistive random access memory cells

A resistive random access memory device formed on a semiconductor substrate comprises an interlayer dielectric having a via formed therethrough. A chemical-mechanical-polishing stop layer is formed over the interlayer dielectric. A barrier metal liner lines walls of the via. A conductive plug is formed in the via. A first barrier metal layer is formed over the chemical-mechanical-polishing stop layer and in electrical contact with the conductive plug. A dielectric layer is formed over the first barrier metal layer. An ion source layer is formed over the dielectric layer. A dielectric barrier layer is formed over the ion source layer, and includes a via formed therethrough communicating with the ion source layer. A second barrier metal layer is formed over the dielectric barrier layer and in electrical contact with the ion source layer. A metal interconnect layer is formed over the barrier metal layer.

Owner:MICROSEMI SOC

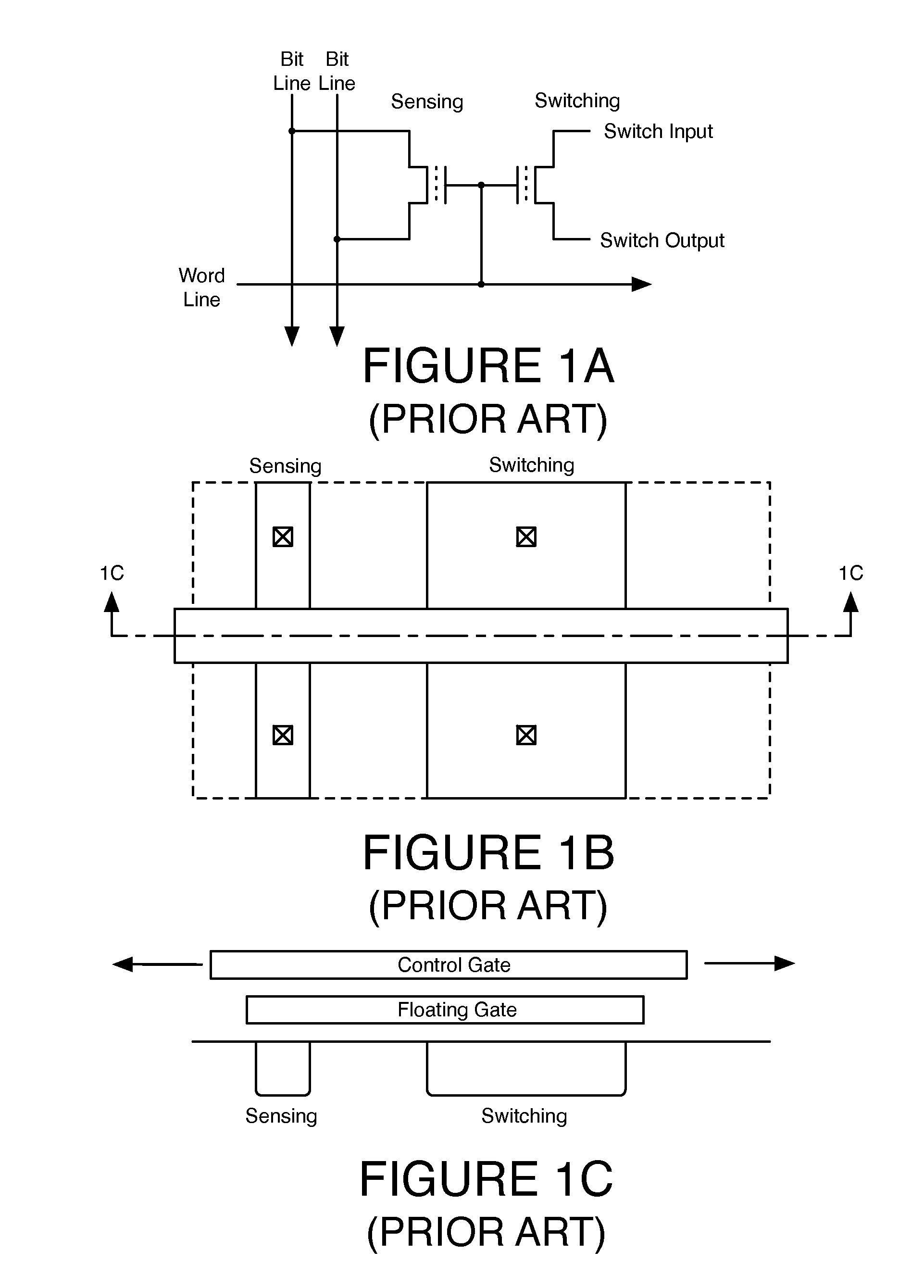

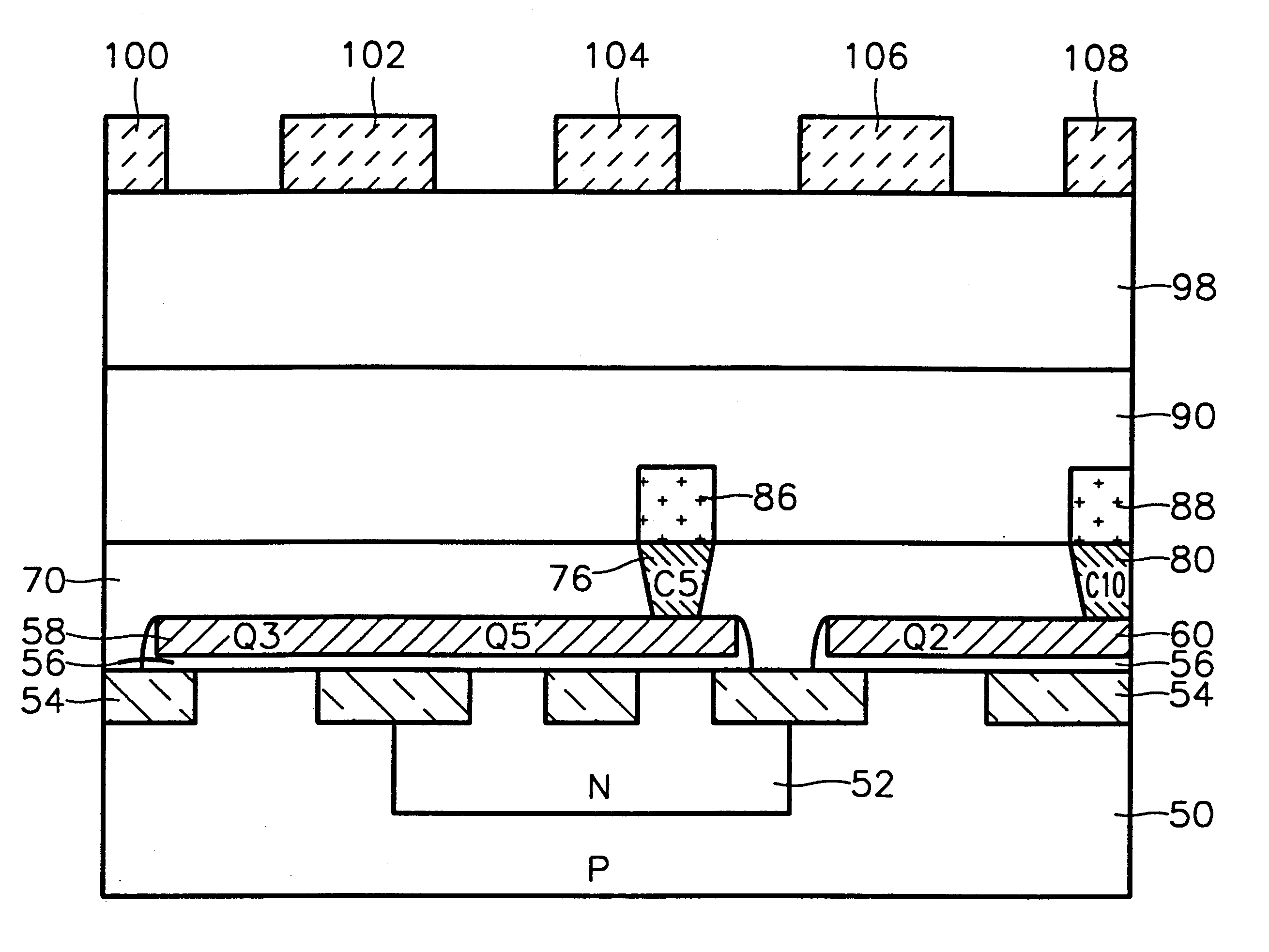

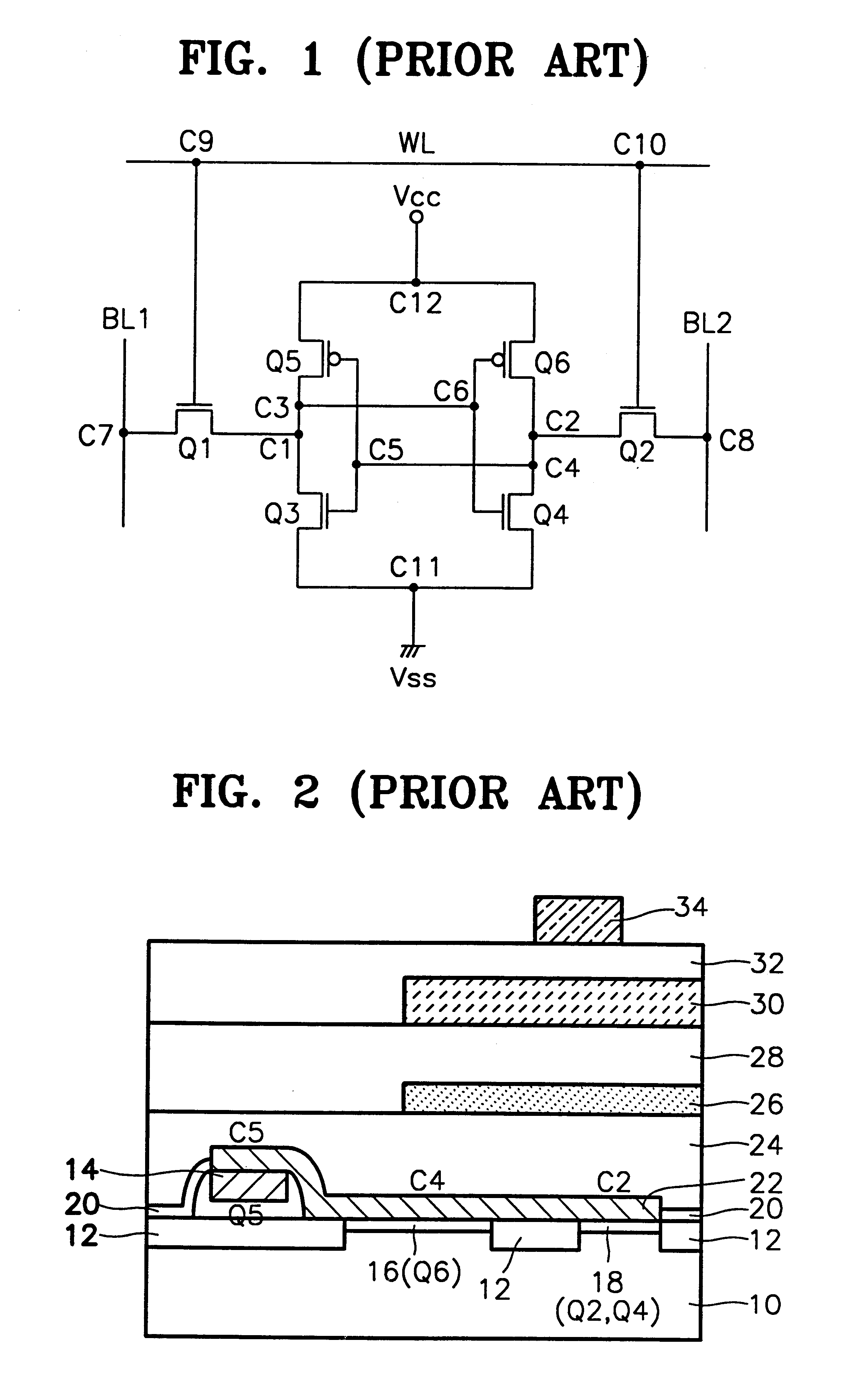

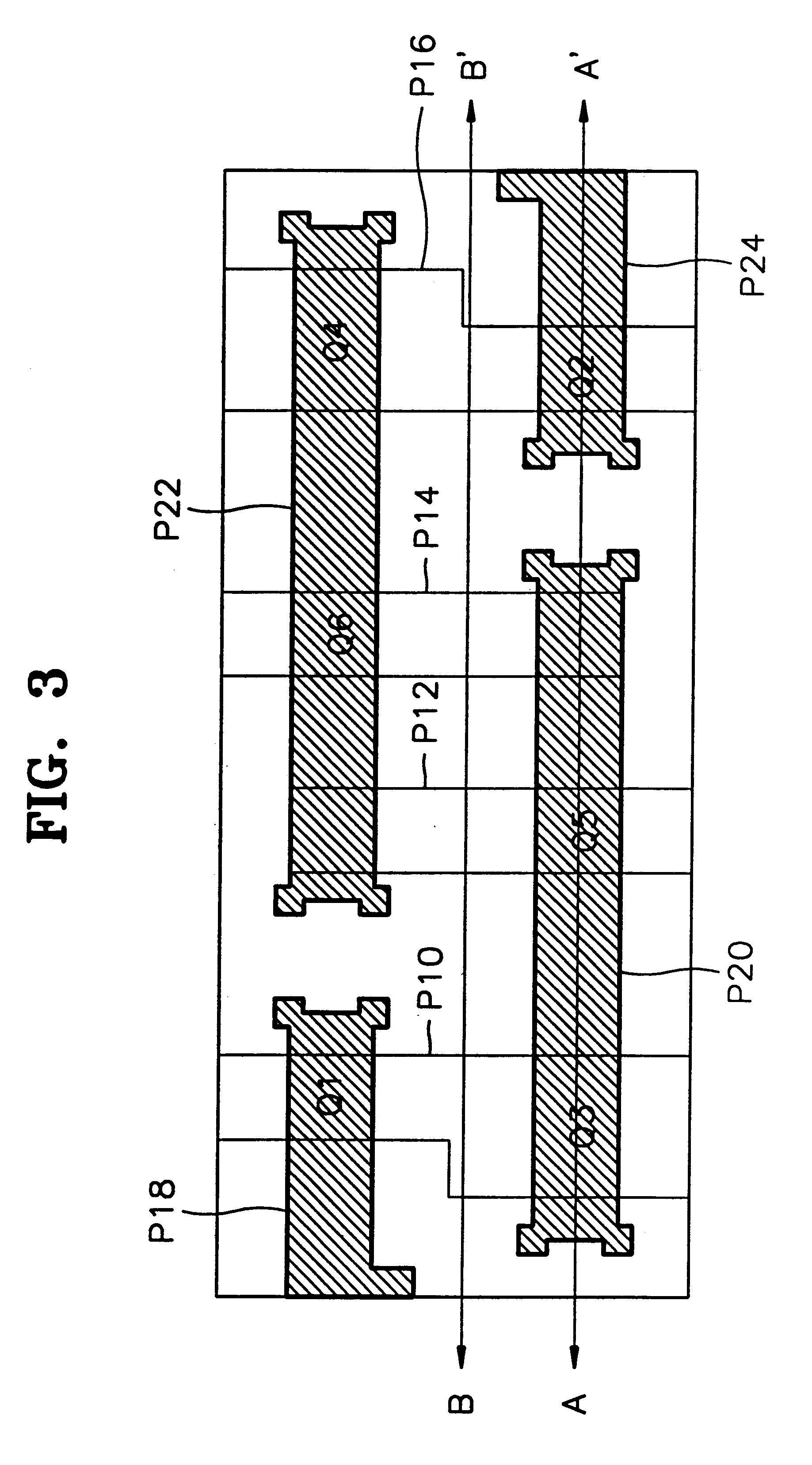

Static random access memory device and method for manufacturing the same

A static random access memory (SRAM) device and a method for manufacturing the same are disclosed. In the SRAM device including a flip-flop circuit including two access transistors and a pair of inverters, connection lines for connecting the inputs and outputs of the inverters, and a word line, power supply lines and bit lines are formed of a metal interconnection. The resistance of interconnection can be reduced and the SRAM device manufacturing process can be performed along with CMOS standard logic manufacturing process.

Owner:SAMSUNG ELECTRONICS CO LTD

Trap rich layer for semiconductor devices

ActiveUS8466036B2Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectActive layer

An integrated circuit chip is formed with an active layer and a trap rich layer. The active layer is formed with an active device layer and a metal interconnect layer. The trap rich layer is formed above the active layer. In some embodiments, the active layer is included in a semiconductor wafer, and the trap rich layer is included in a handle wafer.

Owner:QUALCOMM INC

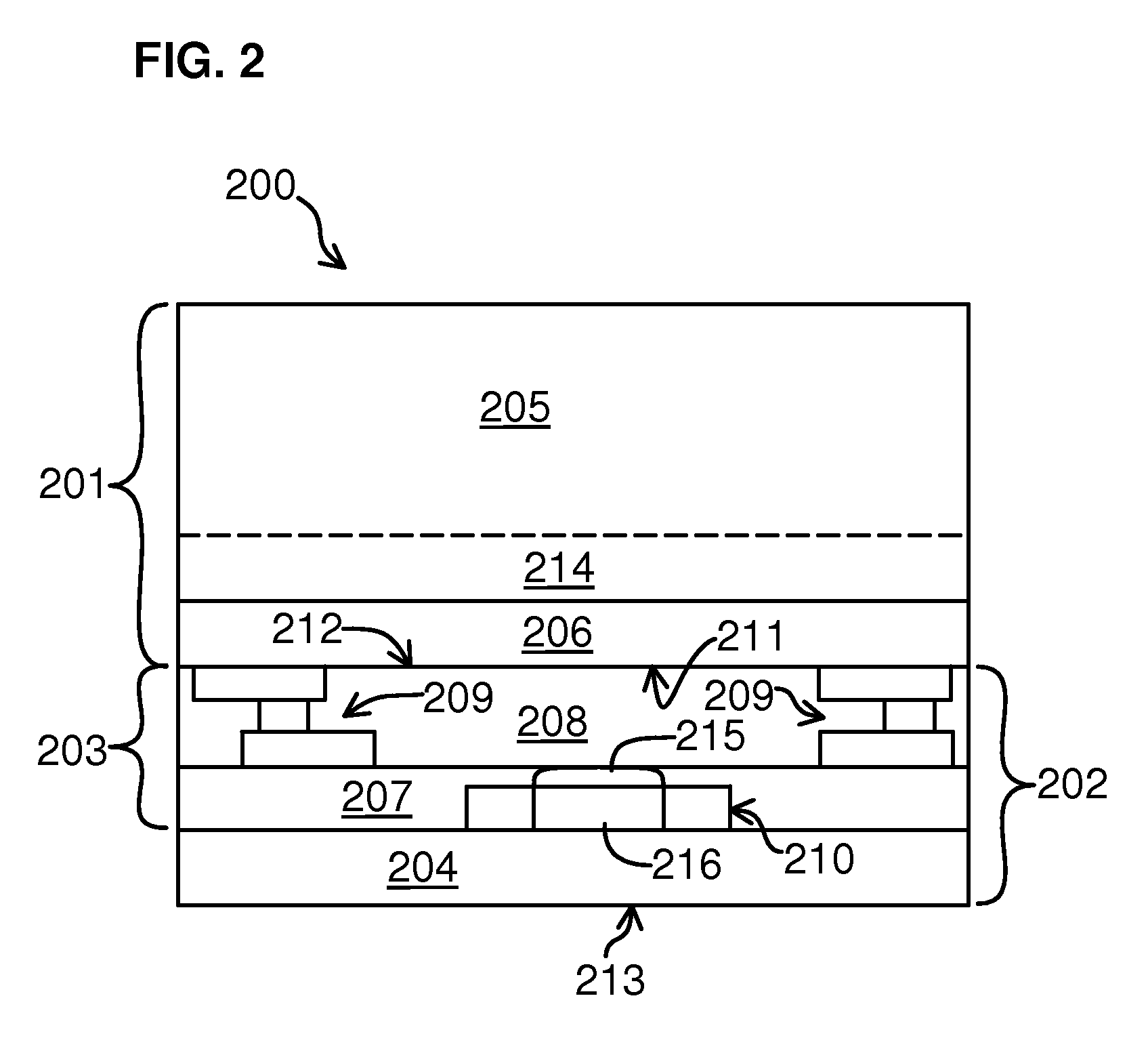

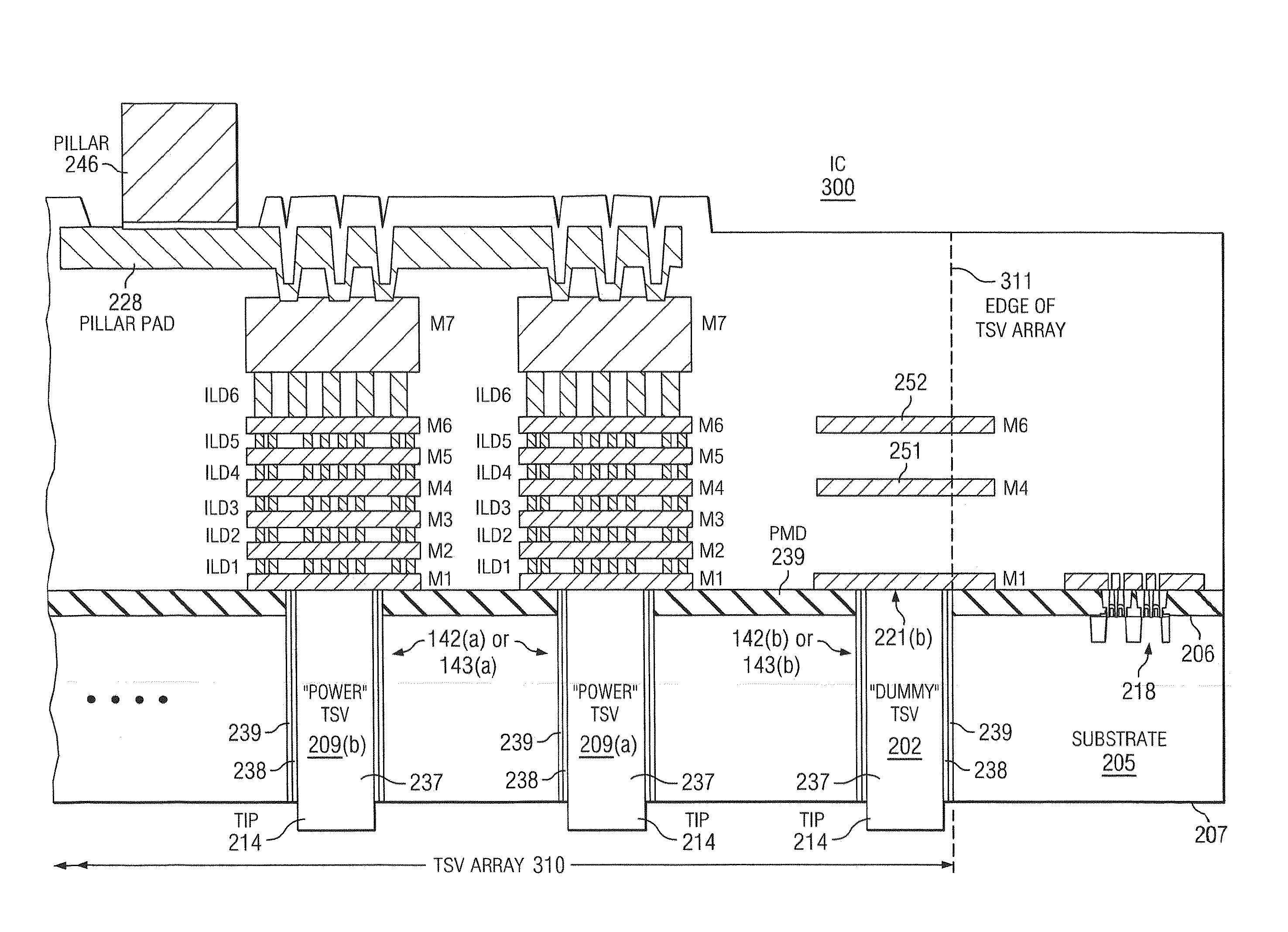

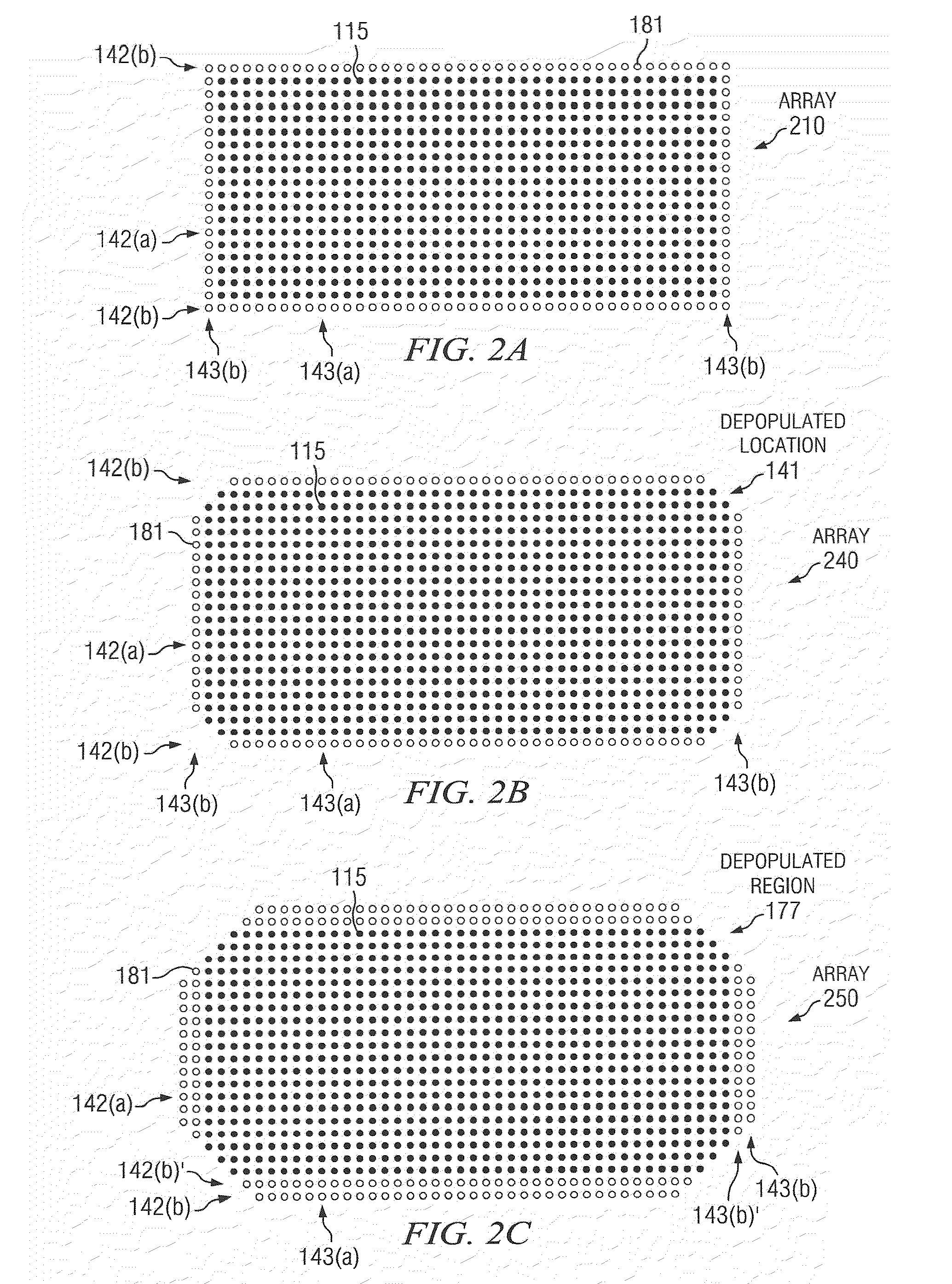

IC having TSV arrays with reduced TSV induced stress

ActiveUS20100171226A1Increase the areaEliminate needSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectEngineering

An integrated circuit (IC) includes a substrate having a top side having active circuitry thereon including a plurality of metal interconnect levels including a first metal interconnect level and a top metal interconnect level, and a bottom side. At least one TSV array includes a plurality of TSVs. The TSVs are positioned in rows including a plurality of interior rows and a pair of exterior rows and a plurality of columns including a plurality of interior columns and a pair of exterior columns. At least a portion of the TSVs in the array are electrically connected TSVs that are coupled to a TSV terminating metal interconnect level selected from the plurality of metal interconnect levels. At least one of the exterior rows or exterior columns include a lower number of electrically connected TSVs compared to a maximum number of electrically connected TSVs in the interior rows and interior columns, respectively.

Owner:TEXAS INSTR INC

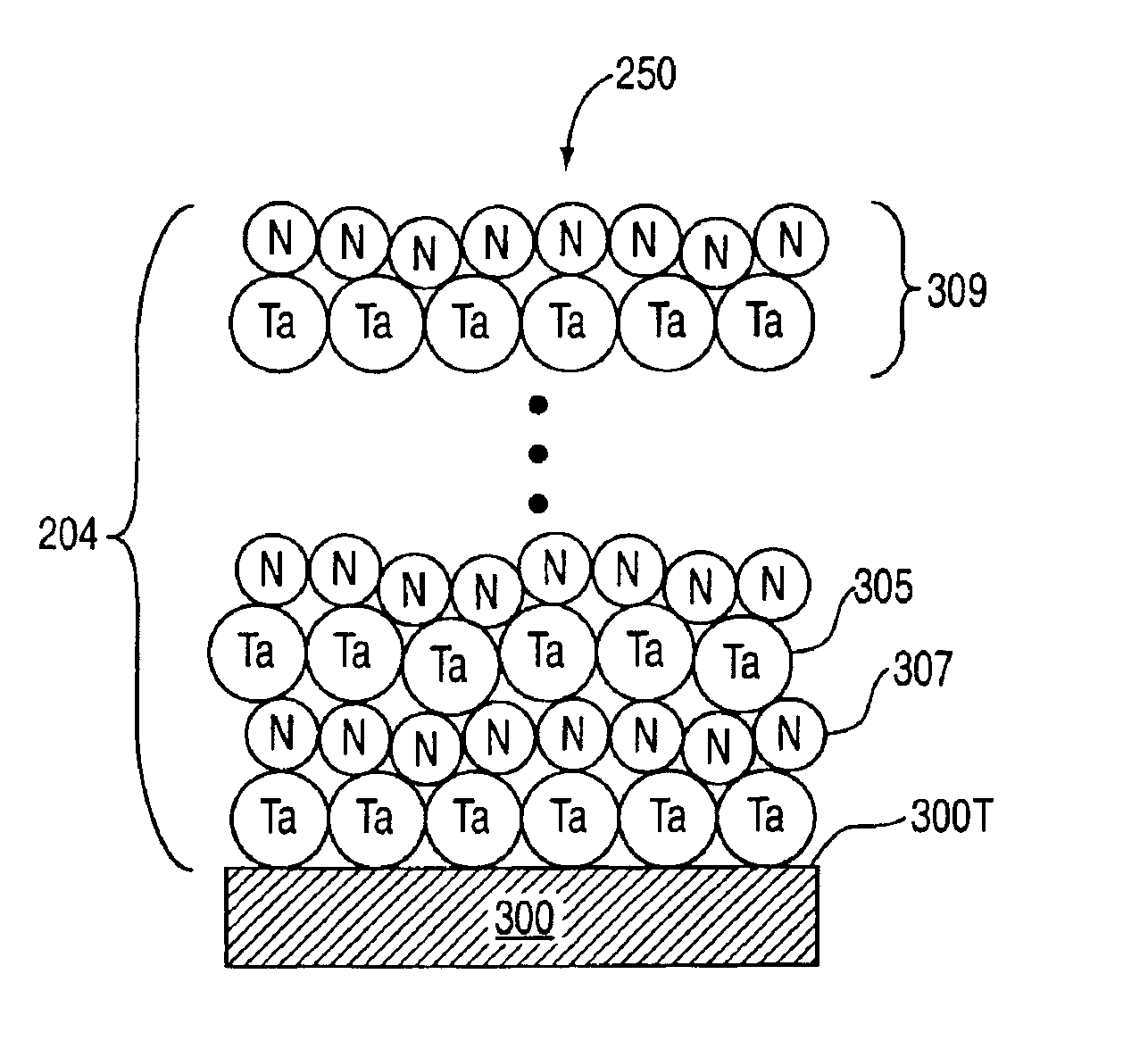

Formation of a tantalum-nitride layer

InactiveUS6951804B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMetal interconnectTantalum nitride

A method of forming a tantalum-nitride layer (204) for integrated circuit fabrication is disclosed. Alternating or co-reacting pulses of a tantalum containing precursor and a nitrogen containing precursor are provided to a chamber (100) to form layers (305, 307) of tantalum and nitrogen. The nitrogen precursor may be a plasma gas source. The resultant tantalum-nitride layer (204) may be used, for example, as a barrier layer. As barrier layers may be used with metal interconnect structures (206), at least one plasma anneal on the tantalum-nitride layer may be performed to reduce its resistivity and to improve film property.

Owner:APPLIED MATERIALS INC

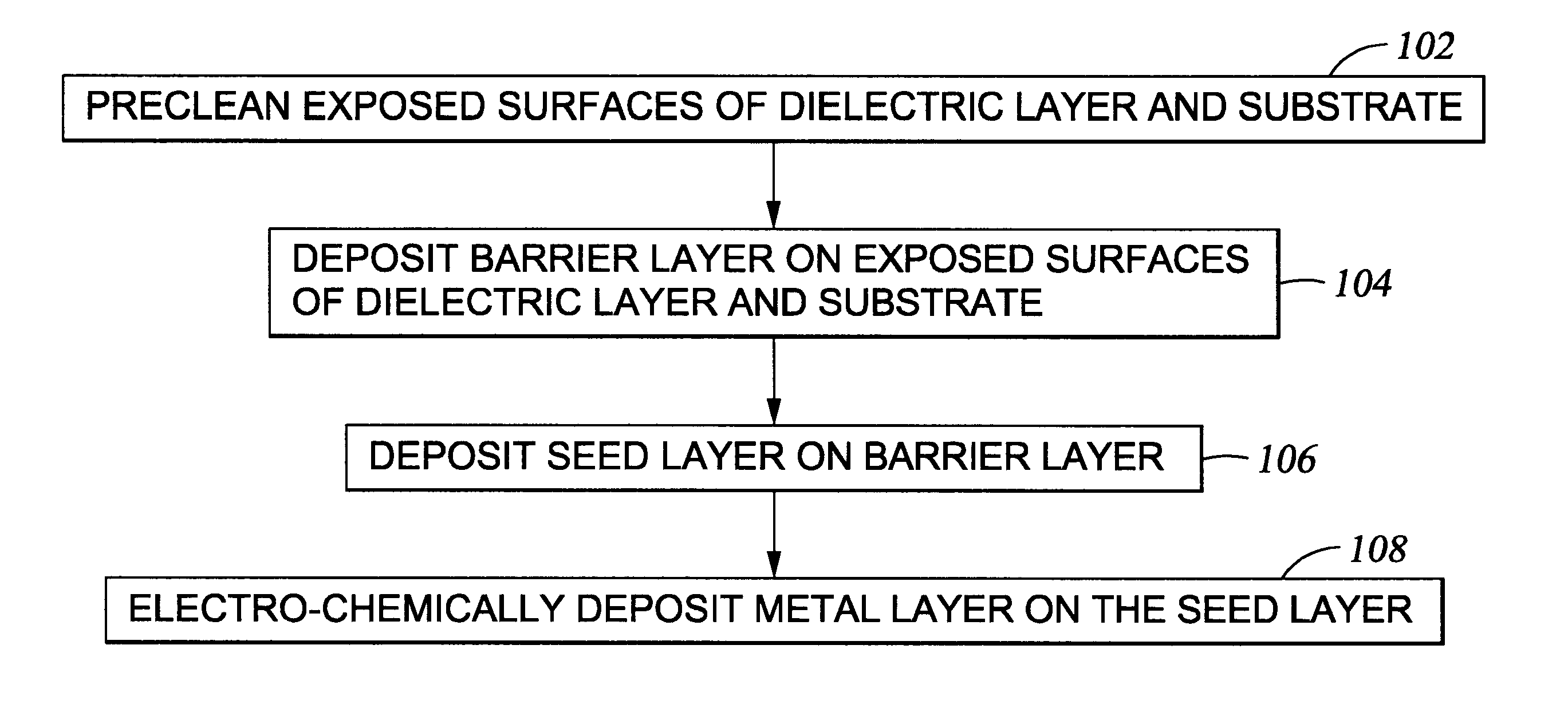

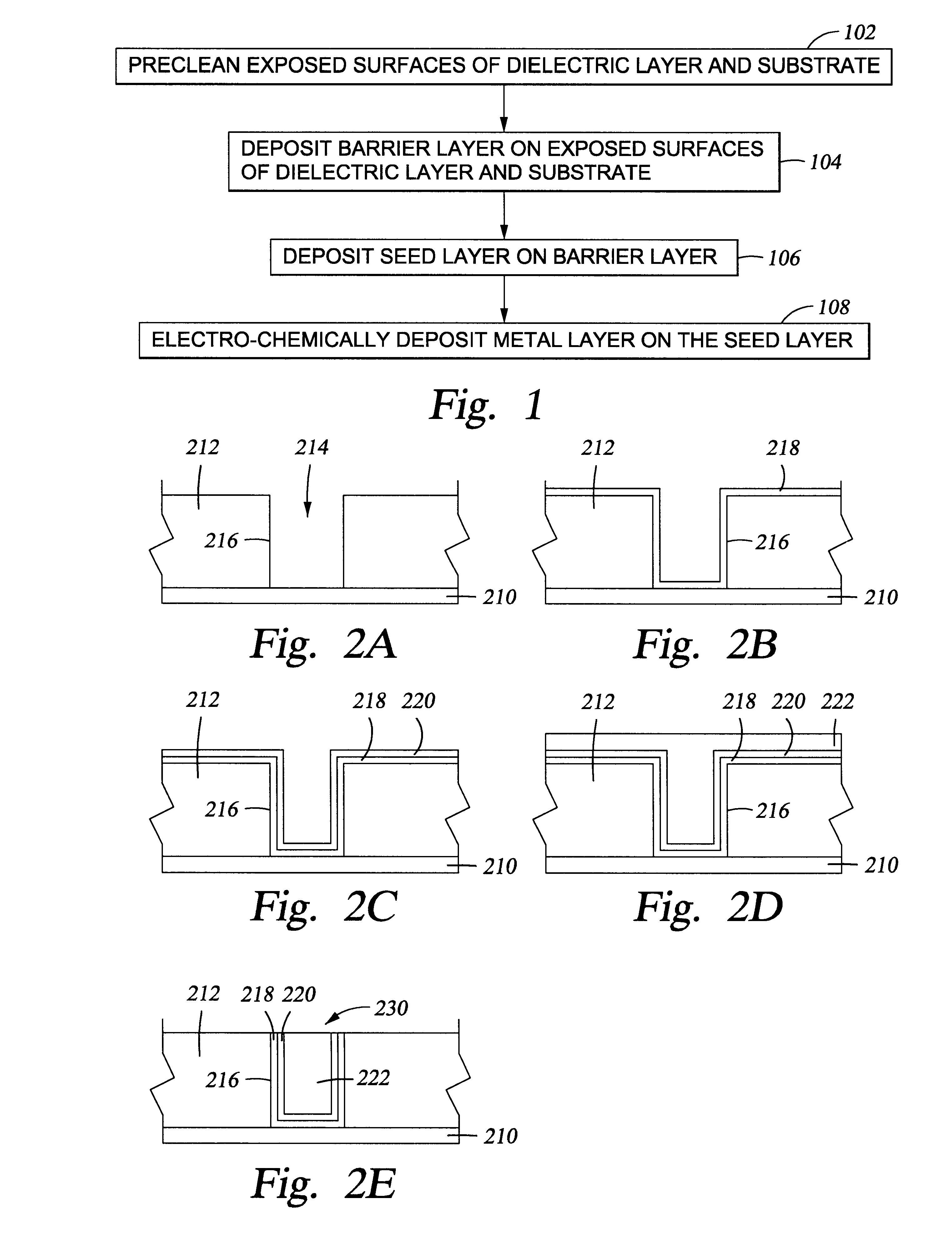

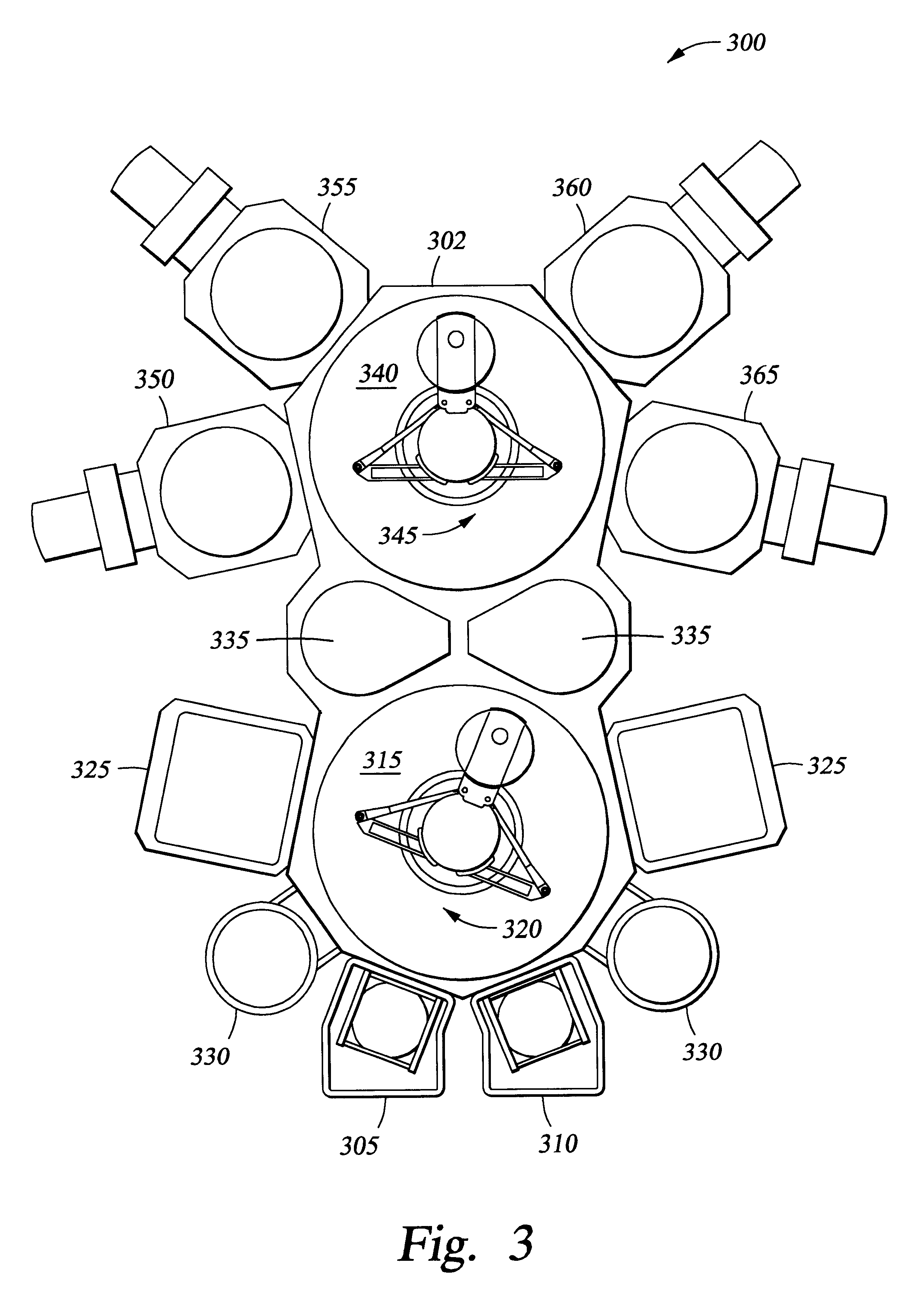

Method for achieving copper fill of high aspect ratio interconnect features

InactiveUS6436267B1AnodisationSemiconductor/solid-state device manufacturingMetal interconnectGas phase

One aspect of the invention provides a consistent metal electroplating technique to form void-less metal interconnects in sub-micron high aspect ratio features on semiconductor substrates. One embodiment of the invention provides a method for filling sub-micron features on a substrate, comprising reactive precleaning the substrate, depositing a barrier layer on the substrate using high density plasma physical vapor deposition; depositing a seed layer over the barrier layer using high density plasma physical vapor deposition; and electro-chemically depositing a metal using a highly resistive electrolyte and applying a first current density during a first deposition period followed by a second current density during a second period.

Owner:APPLIED MATERIALS INC

Liquid cleaner for the removal of post-etch residues

InactiveUS20100163788A1Cationic surface-active compoundsDetergent mixture composition preparationMetal interconnectTitanium nitride

Cleaning compositions and processes for cleaning post-plasma etch residue from a microelectronic device having said residue thereon. The composition achieves highly efficacious cleaning of the residue material, including titanium-containing, copper-containing, tungsten-containing, and / or cobalt-containing post-etch residue from the microelectronic device while simultaneously not damaging the interlevel dielectric, metal interconnect material, and / or capping layers also present thereon. In addition, the composition may be useful for the removal of titanium nitride layers from a microelectronic device having same thereon.

Owner:ENTEGRIS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com