Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

193 results about "Metallic interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Methods for forming a metallic film on a substrate by a cyclical deposition and related semiconductor device structures

ActiveUS20190252196A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrazine compoundOptoelectronics

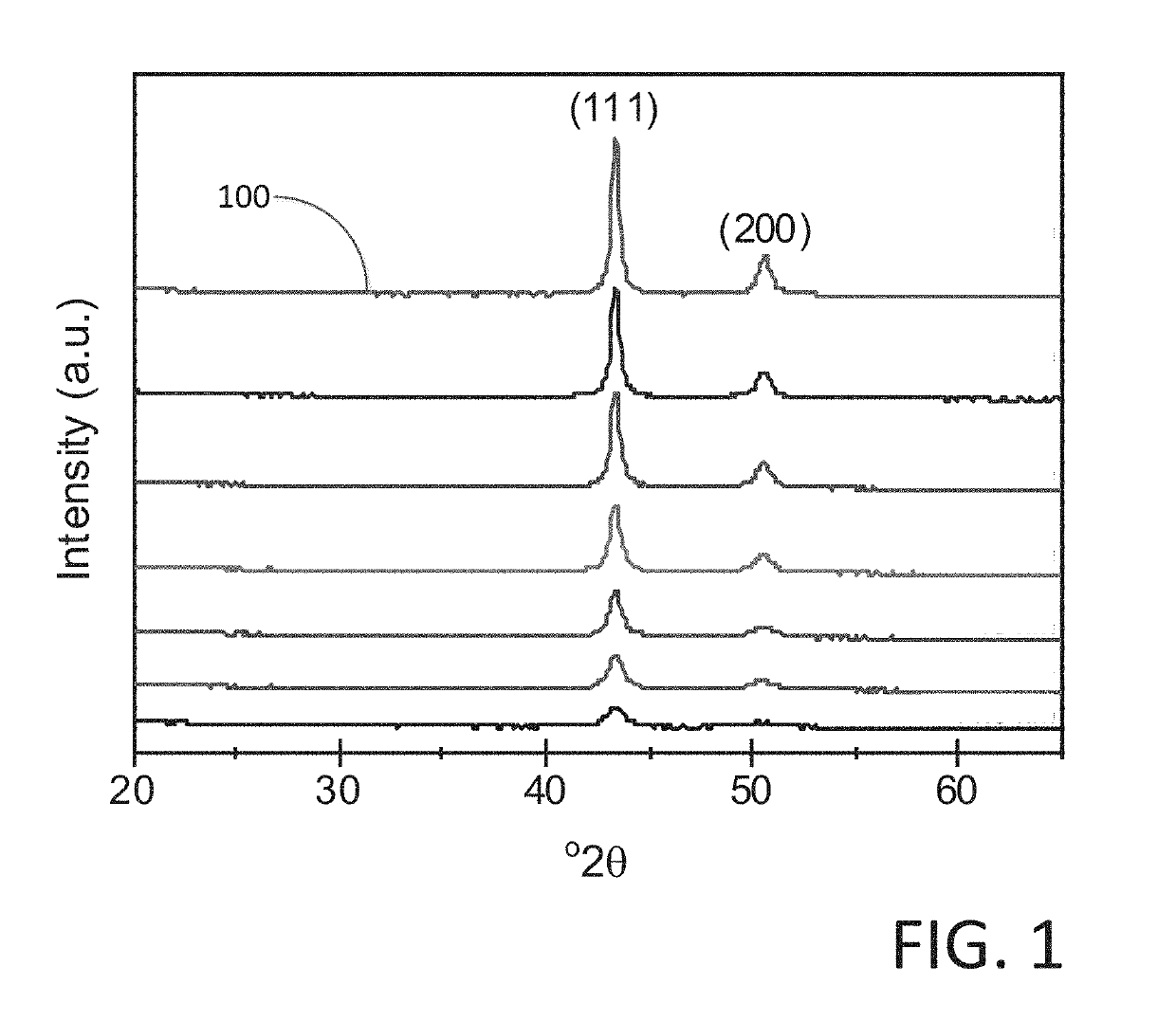

Methods for forming a metallic film on a substrate by cyclical deposition are provided. In some embodiments methods may include contacting the substrate with a first reactant comprising a non-halogen containing metal precursor comprising at least one of copper, nickel or cobalt and contacting the substrate with a second reactant comprising a hydrocarbon substituted hydrazine. In some embodiments related semiconductor device structures may include at least a portion of a metallic interconnect formed by cyclical deposition processes.

Owner:ASM IP HLDG BV

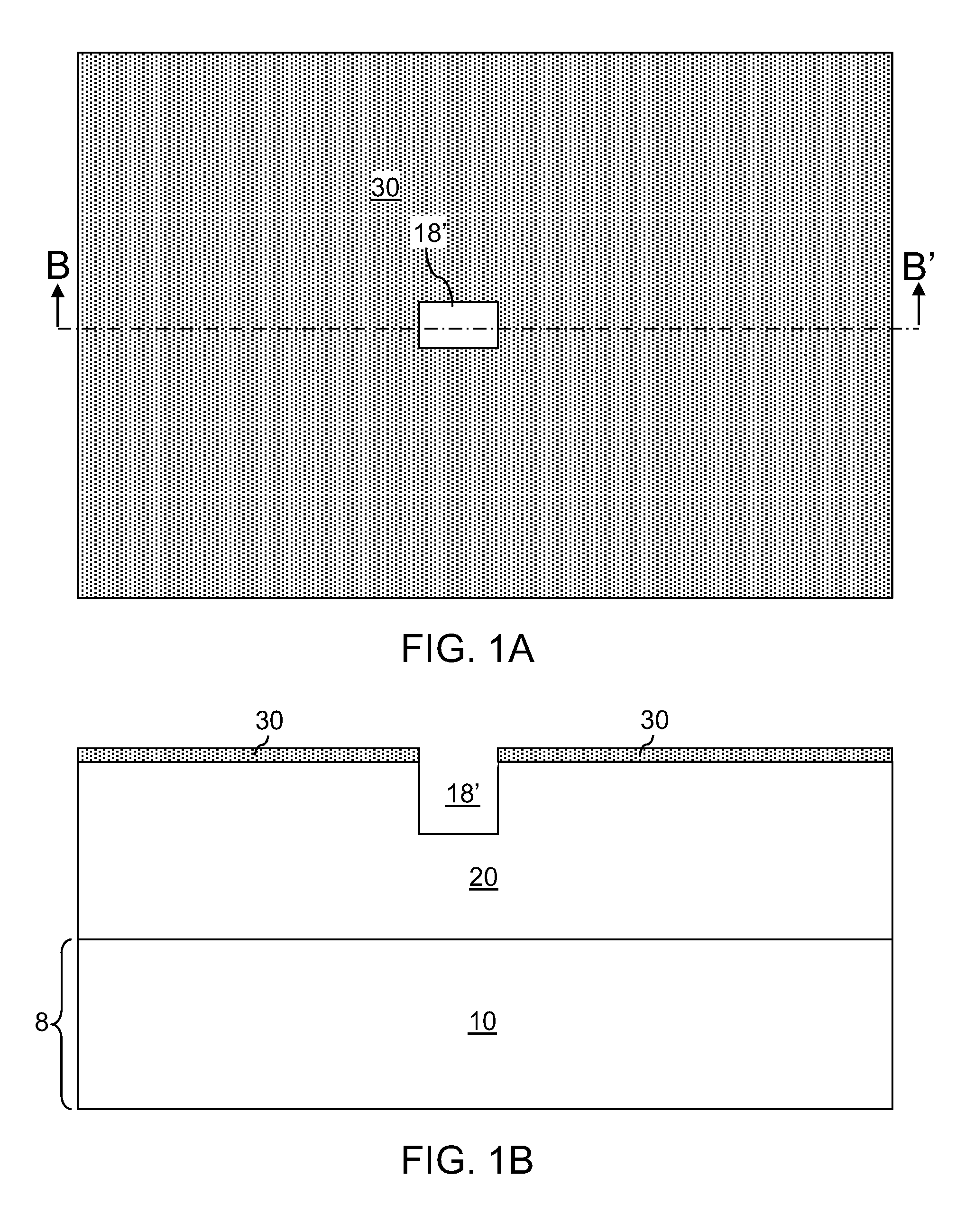

Method of selectively depositing a capping layer structure on a semiconductor device structure

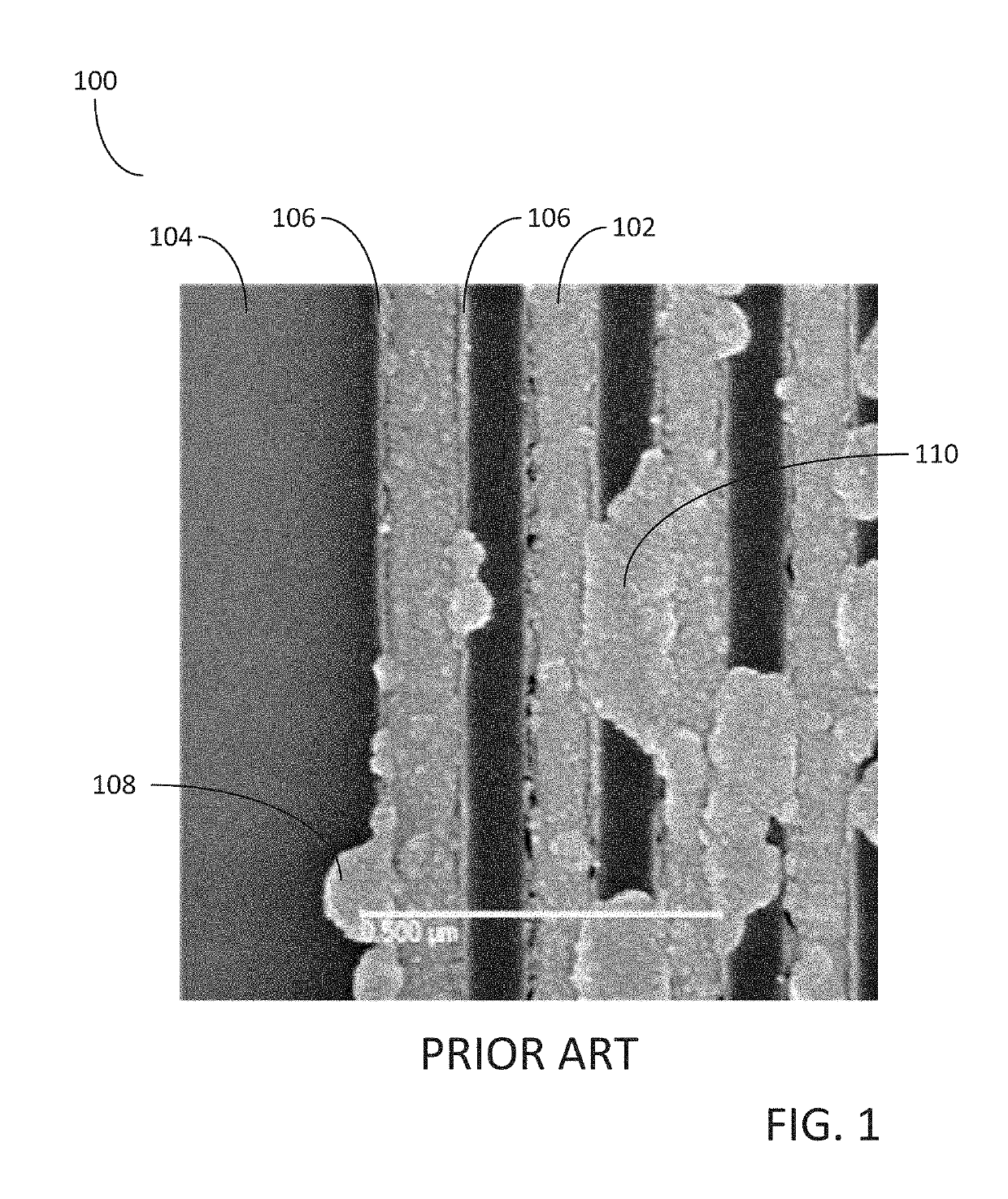

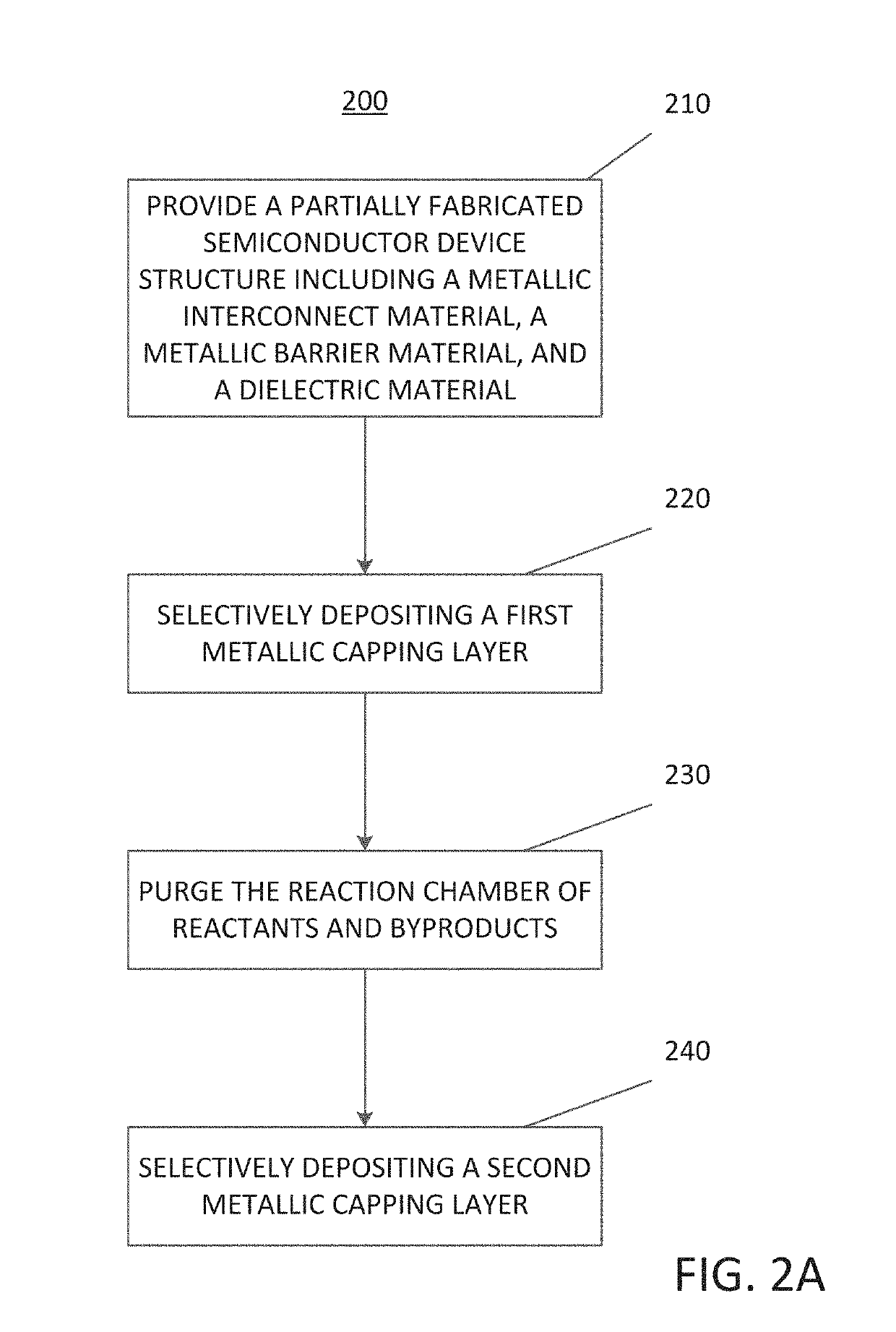

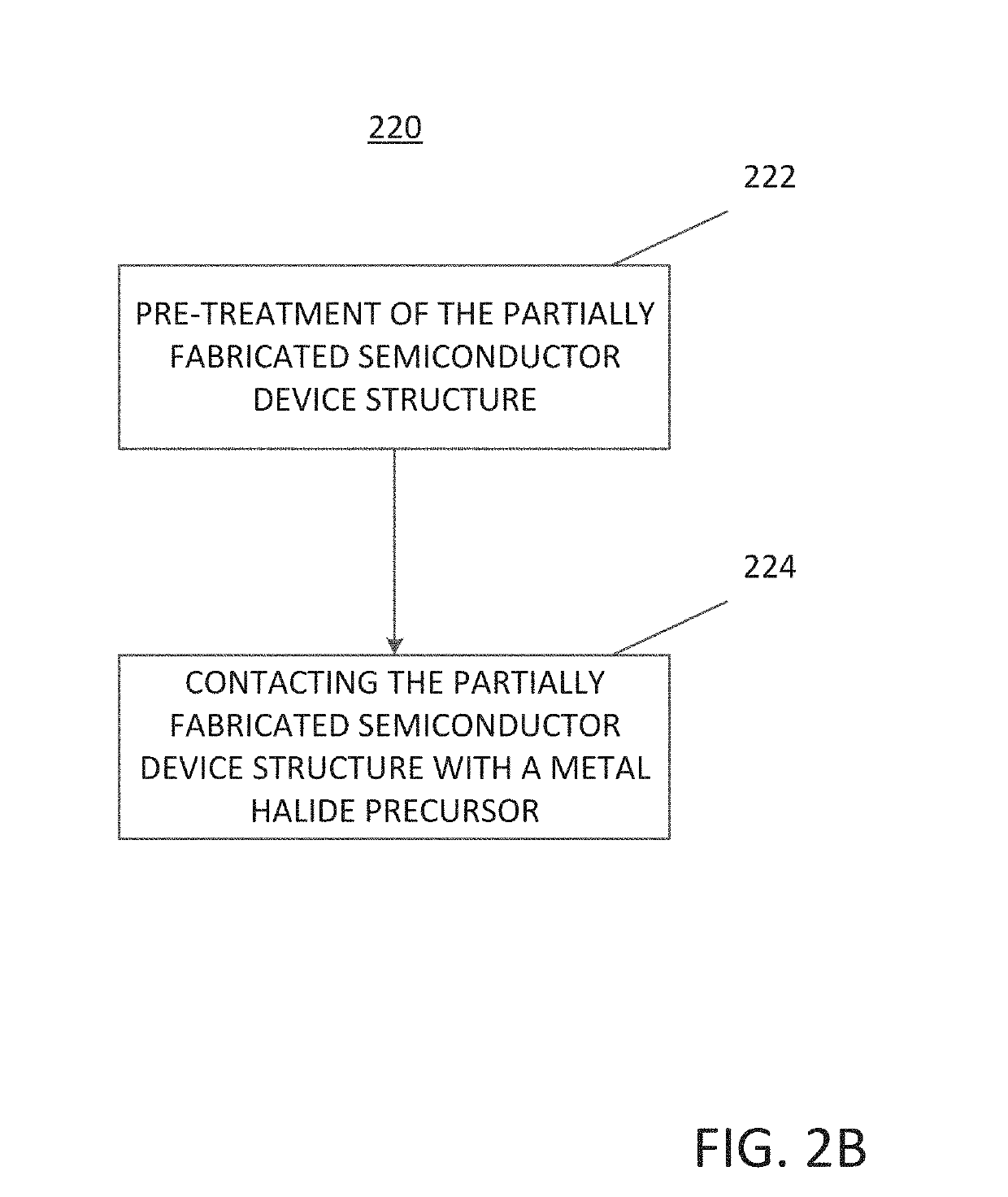

A method of selectively depositing a capping layer structure on a semiconductor device structure is disclosure. The method may include; providing a partially fabricated semiconductor device structure comprising a surface including a metallic interconnect material, a metallic barrier material, and a dielectric material. The method may also include; selectively depositing a first metallic capping layer over the metallic barrier material and over the metallic interconnect material relative to the dielectric material; and selectively depositing a second metallic capping layer over the first metallic capping layer relative to the dielectric material. Semiconductor device structures including a capping layer structure are also disclosed.

Owner:ASM IP HLDG BV

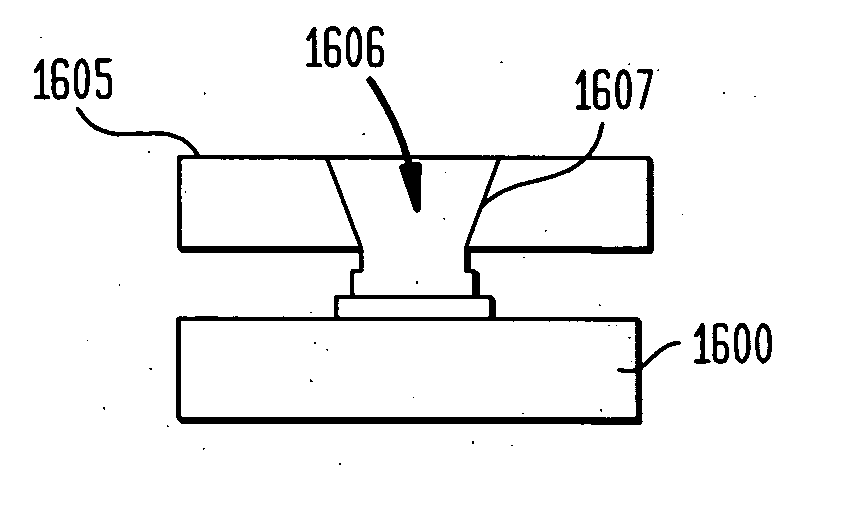

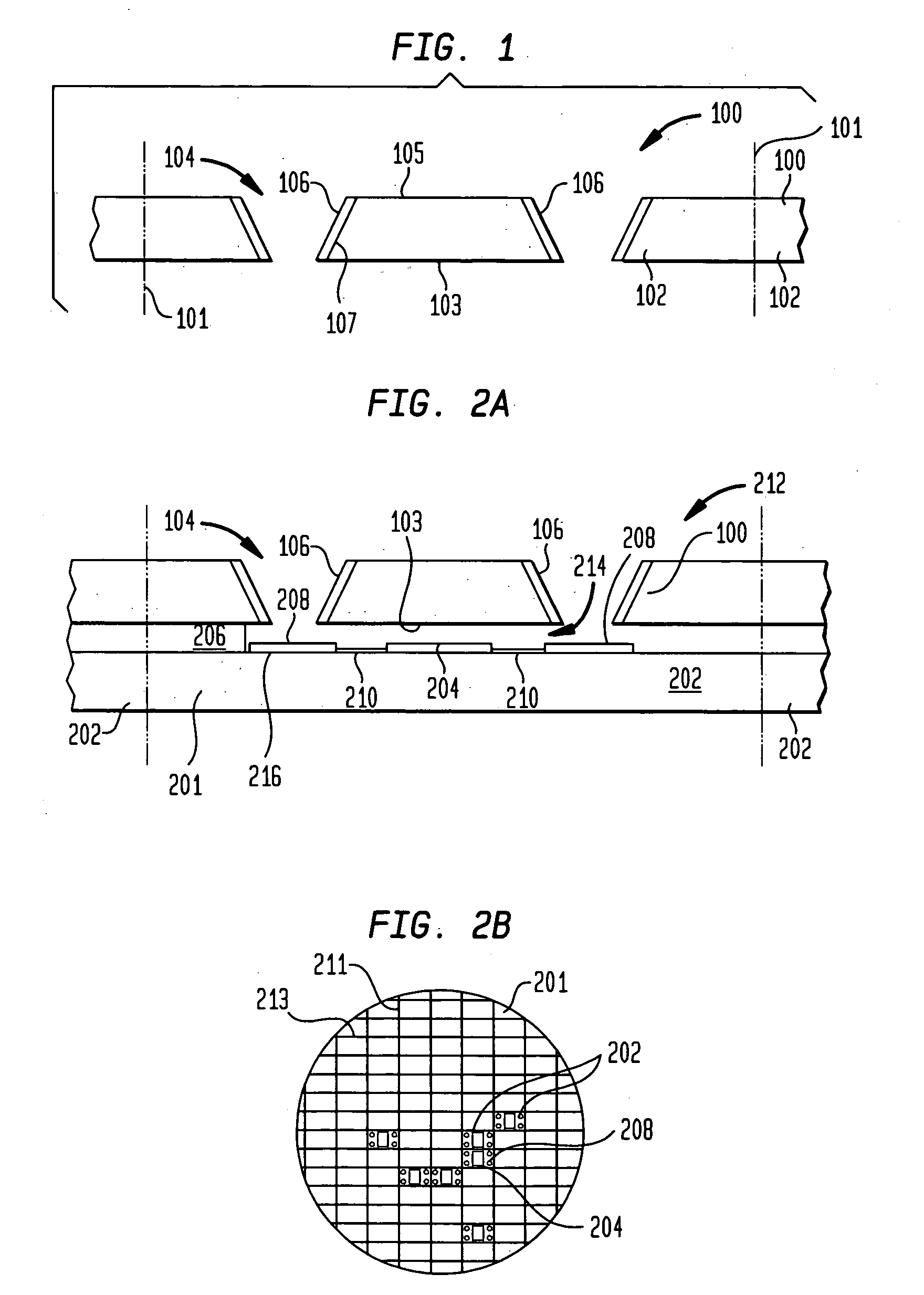

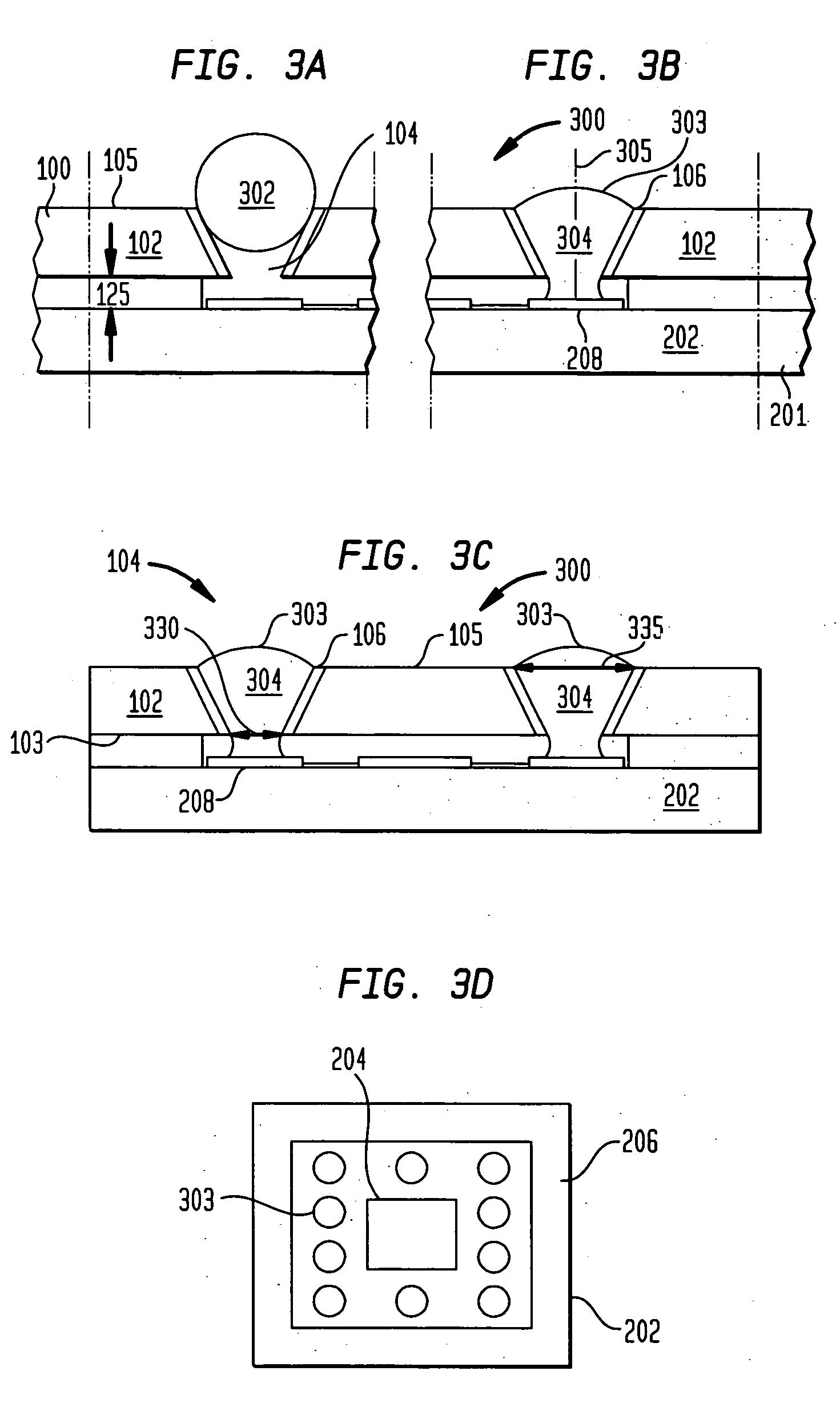

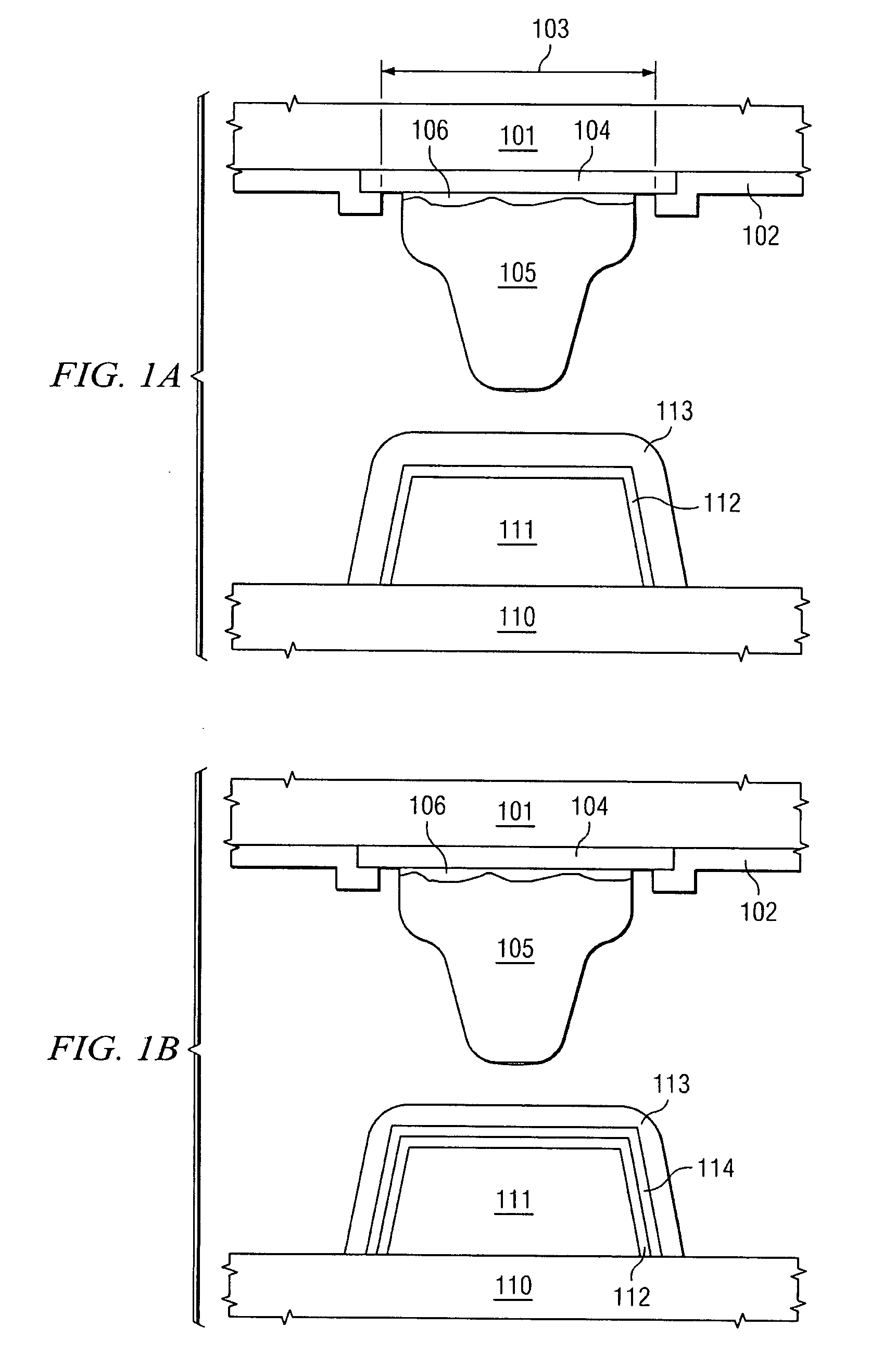

Structure and method of making capped chips including vertical interconnects having stud bumps engaged to surfaces of said caps

InactiveUS20050067688A1Impedence networksSemiconductor/solid-state device detailsEngineeringBiomedical engineering

A capped chip is provided which includes a chip and a cap member, the chip having a front surface and a plurality of bond pads exposed at the front surface, the cap member having a bottom surface facing the front surface of the chip and having a top surface opposite the front surface. A plurality of through holes extend from the bottom surface of the cap member to the top surface. The capped chip assembly further includes a plurality of metallic interconnects extending from the bond pads at least partially through the through holes, the metallic interconnects including stud bumps joined to the bond pads, the stud bumps contacting and engaging at least one of (i) the top surface of the cap member surrounding the through holes and (ii) inner surfaces of the through holes.

Owner:TESSERA INC

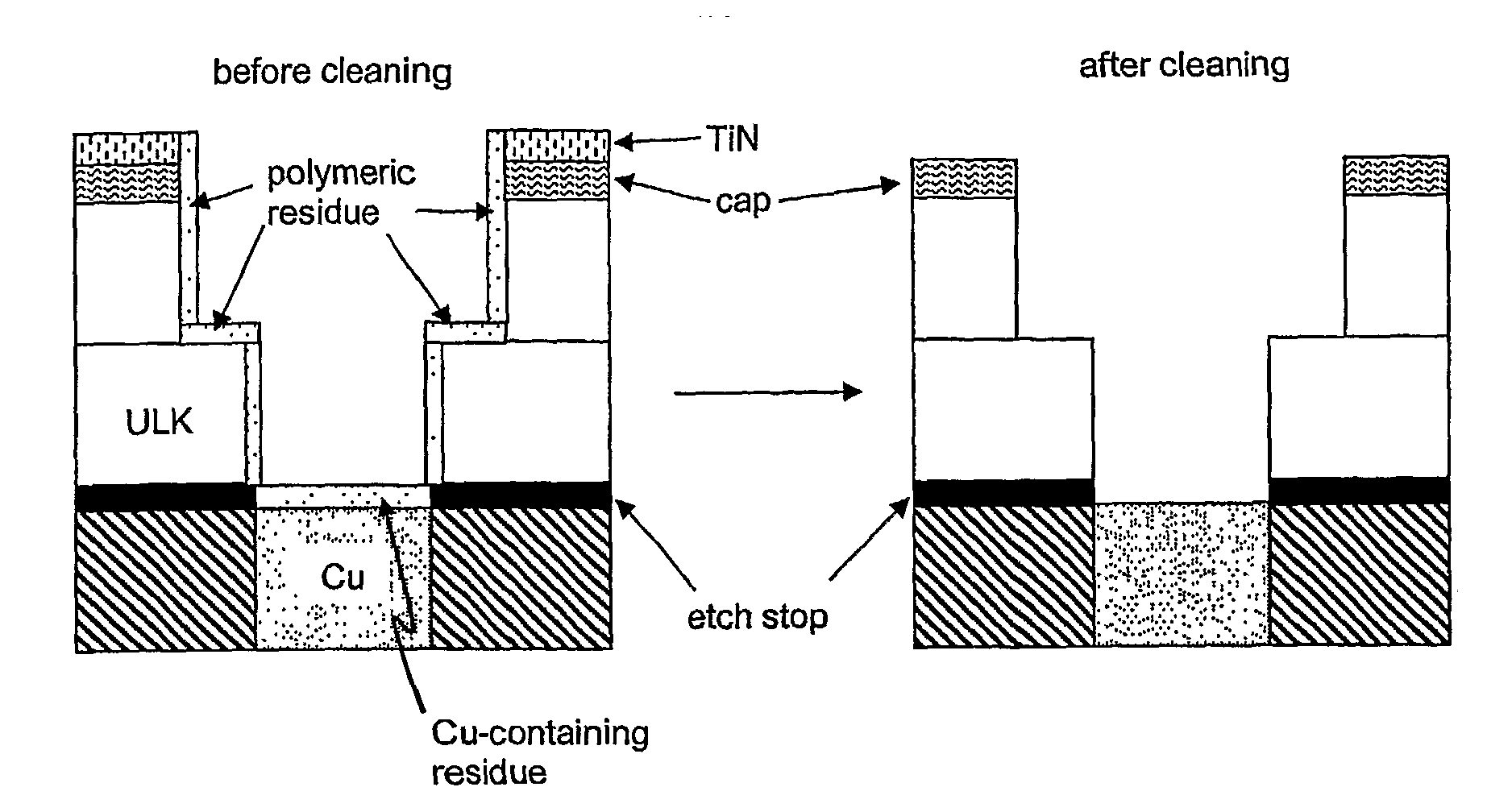

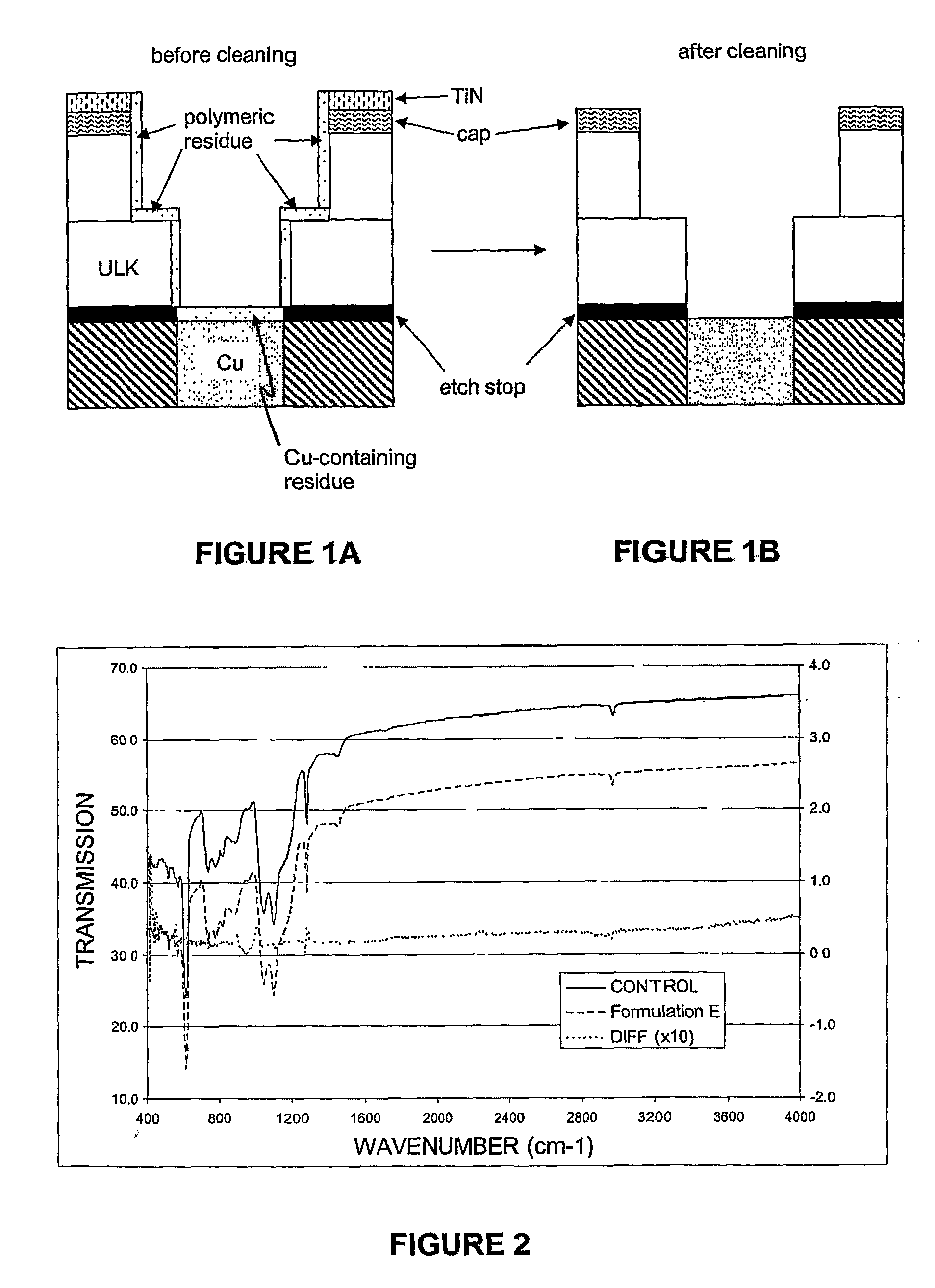

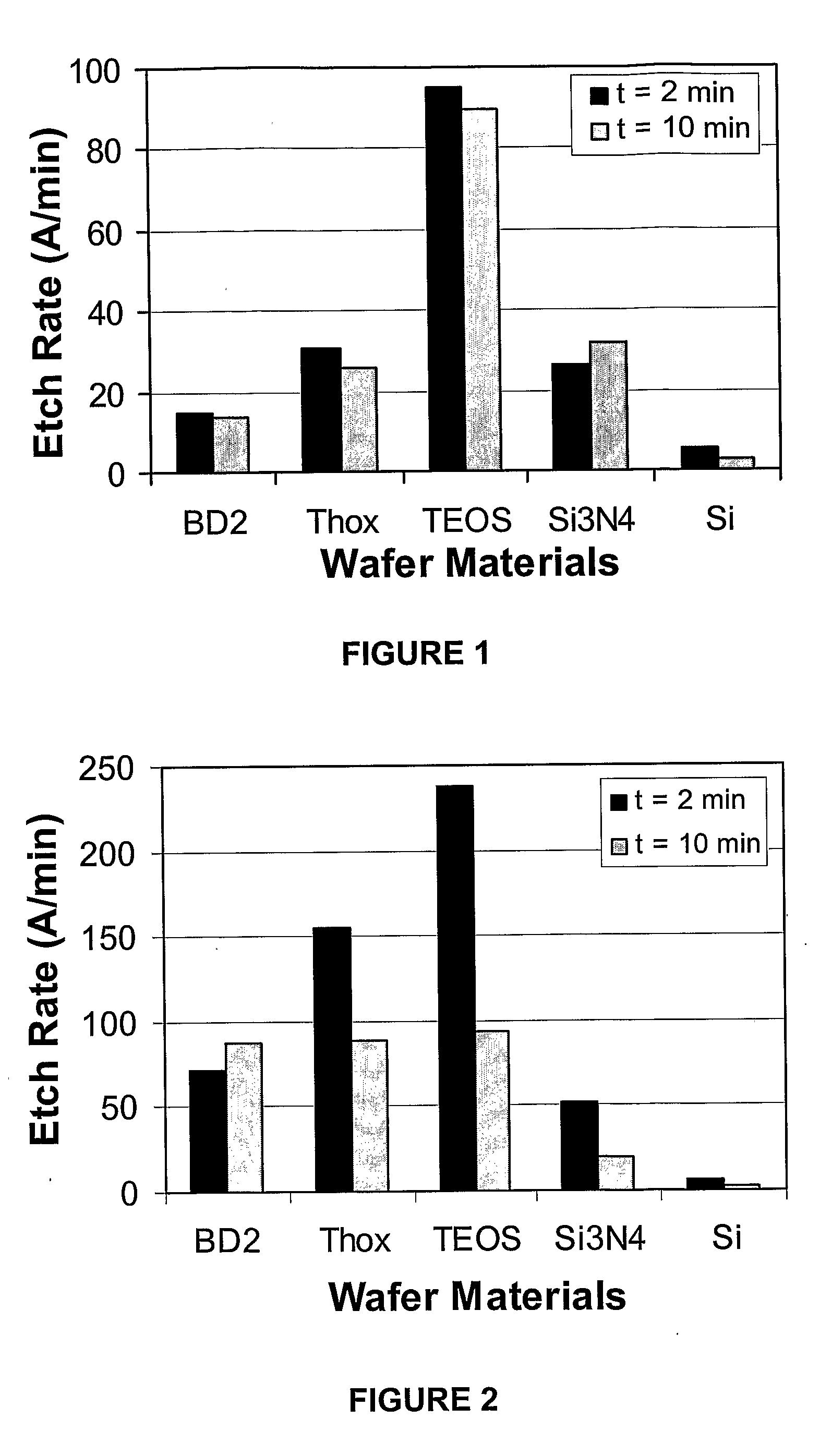

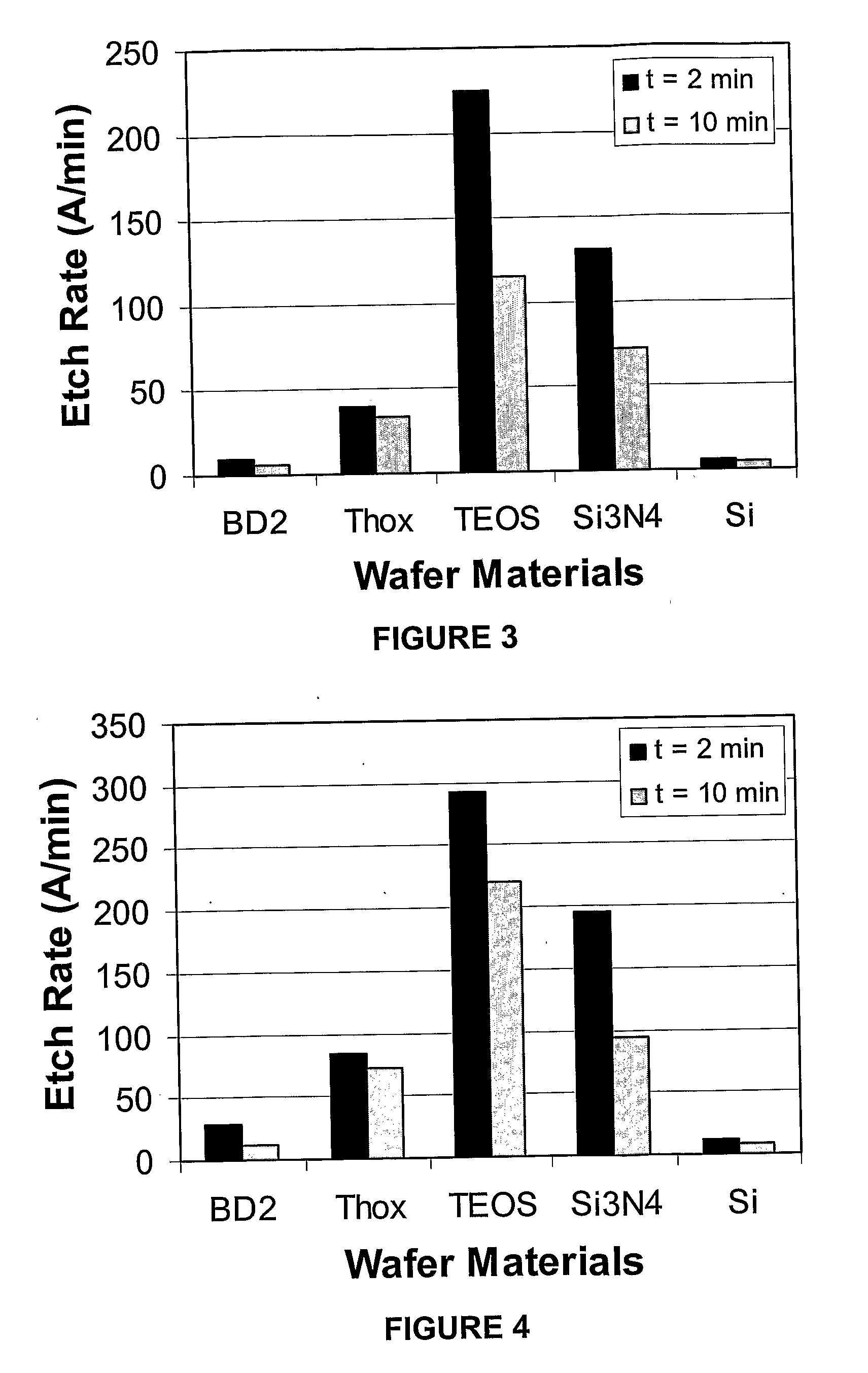

Aqueous cleaner for the removal of post-etch residues

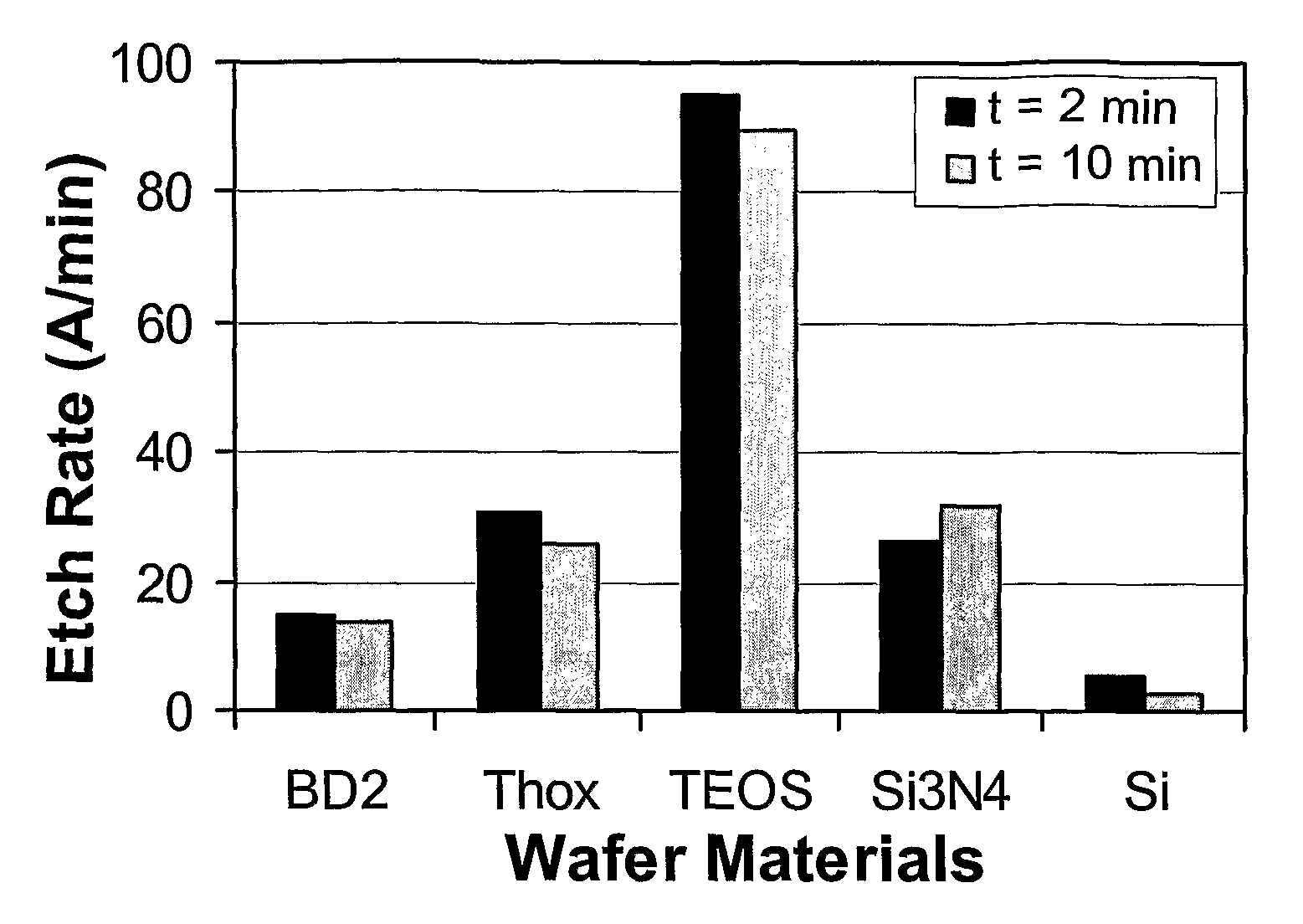

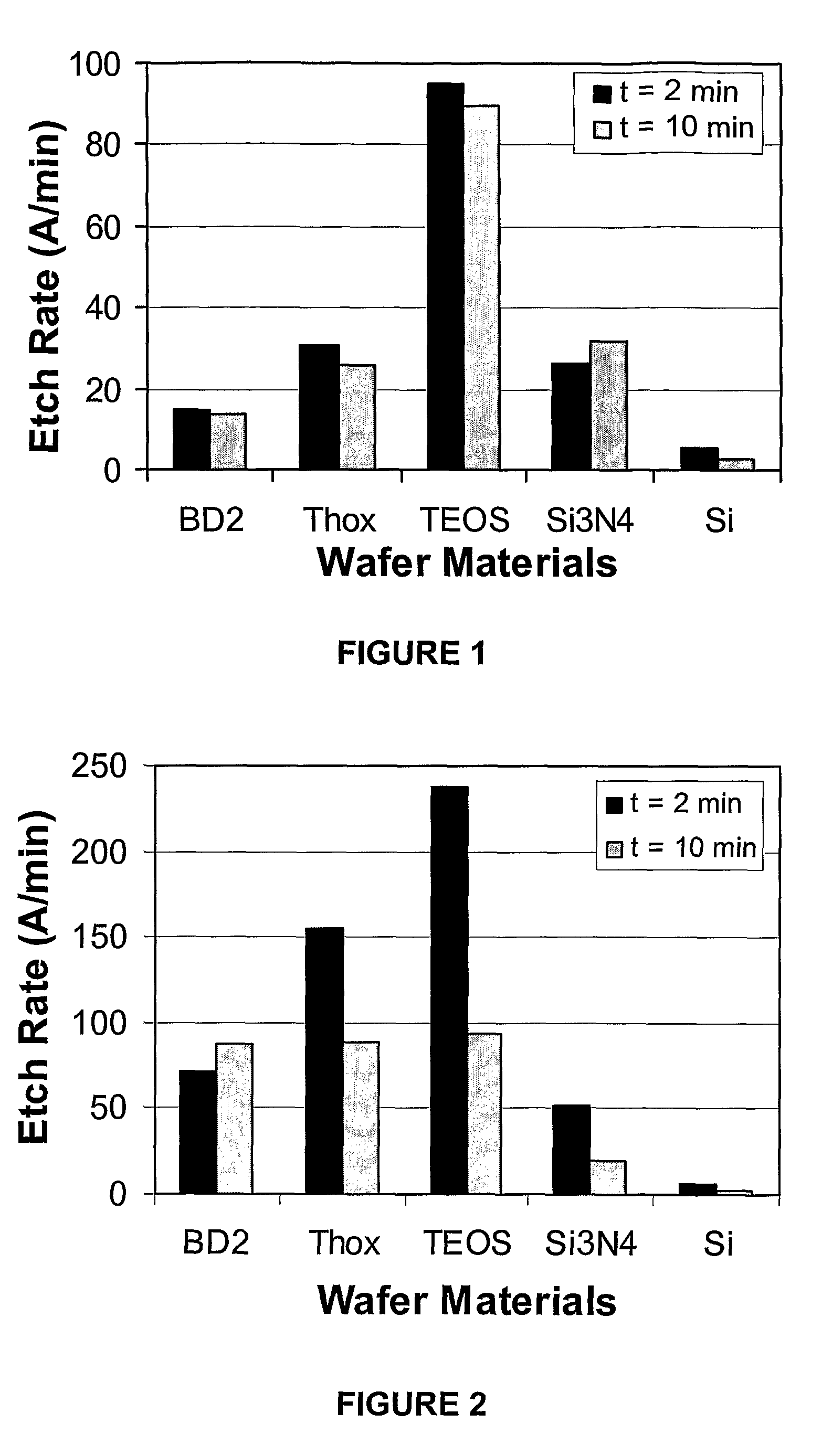

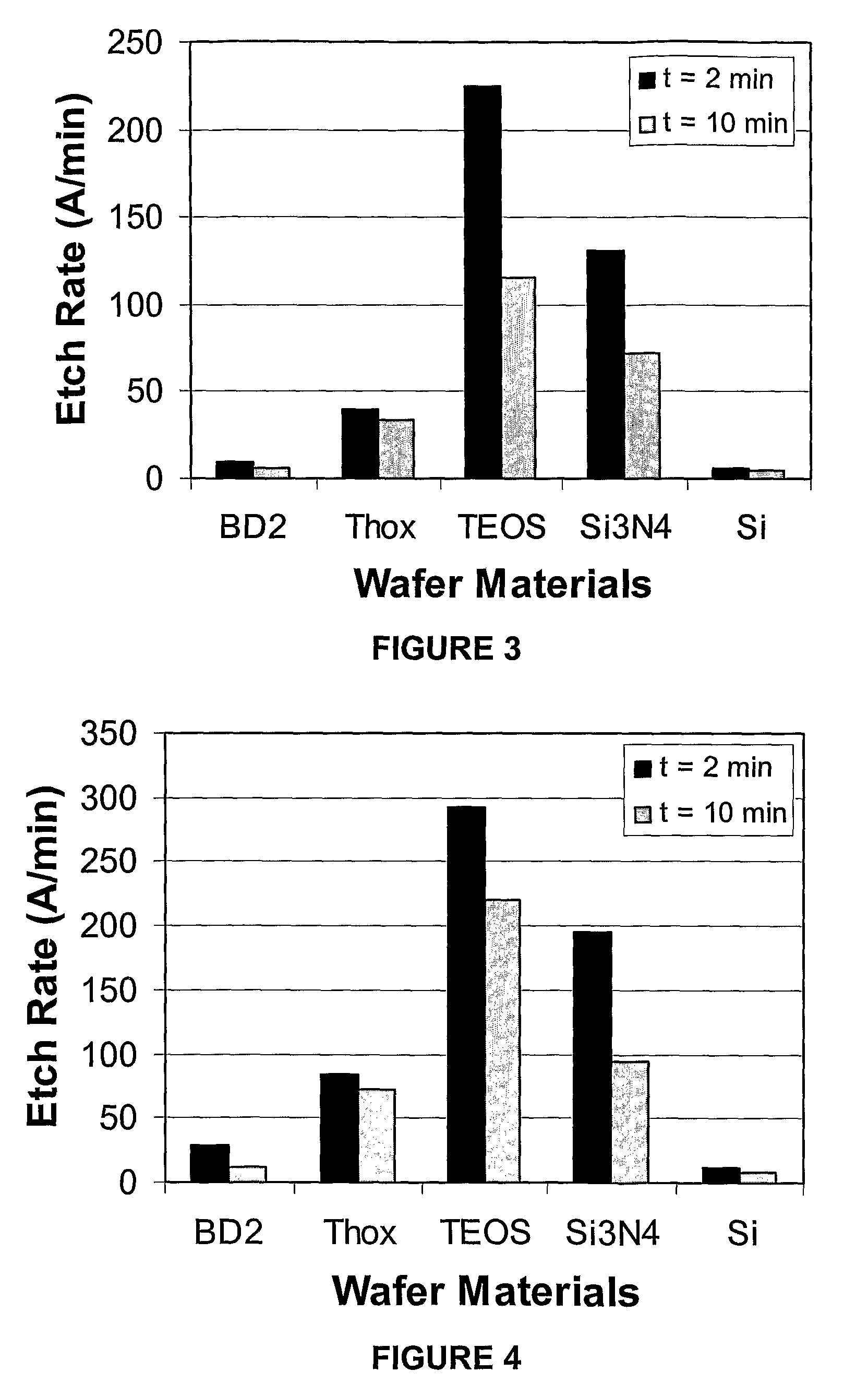

ActiveUS20130296214A1Suitable for cleaningDetergent mixture composition preparationSemiconductor/solid-state device manufacturingMetal interconnectTitanium

Cleaning compositions and processes for cleaning post-plasma etch residue from a microelectronic device having said residue thereon. The composition achieves highly efficacious cleaning of the residue material, including titanium-containing, copper-containing, tungsten-containing, and / or cobalt-containing post-etch residue from the microelectronic device while simultaneously not damaging the interlevel dielectric, metal interconnect material, and / or capping layers also present thereon.

Owner:ENTEGRIS INC

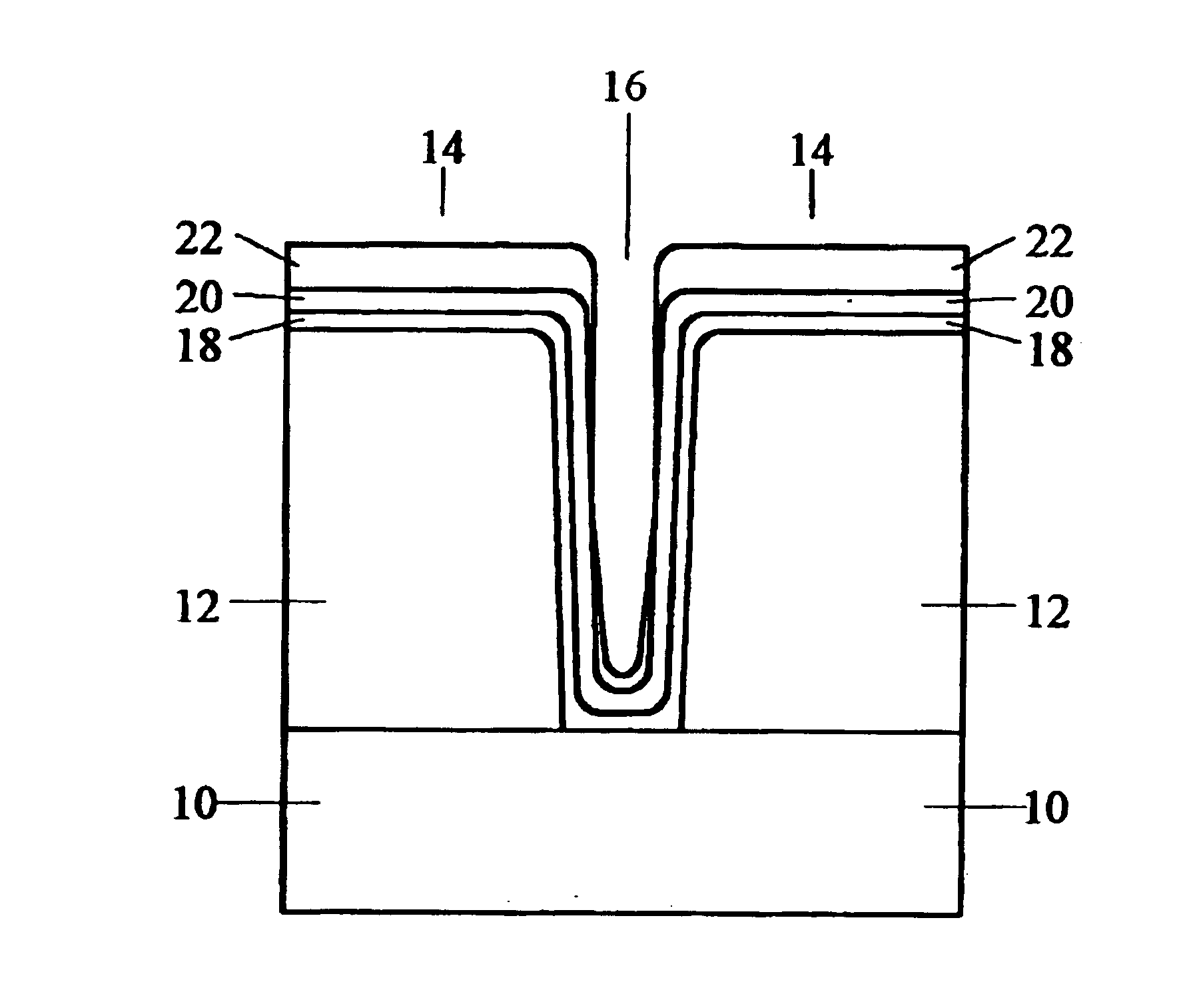

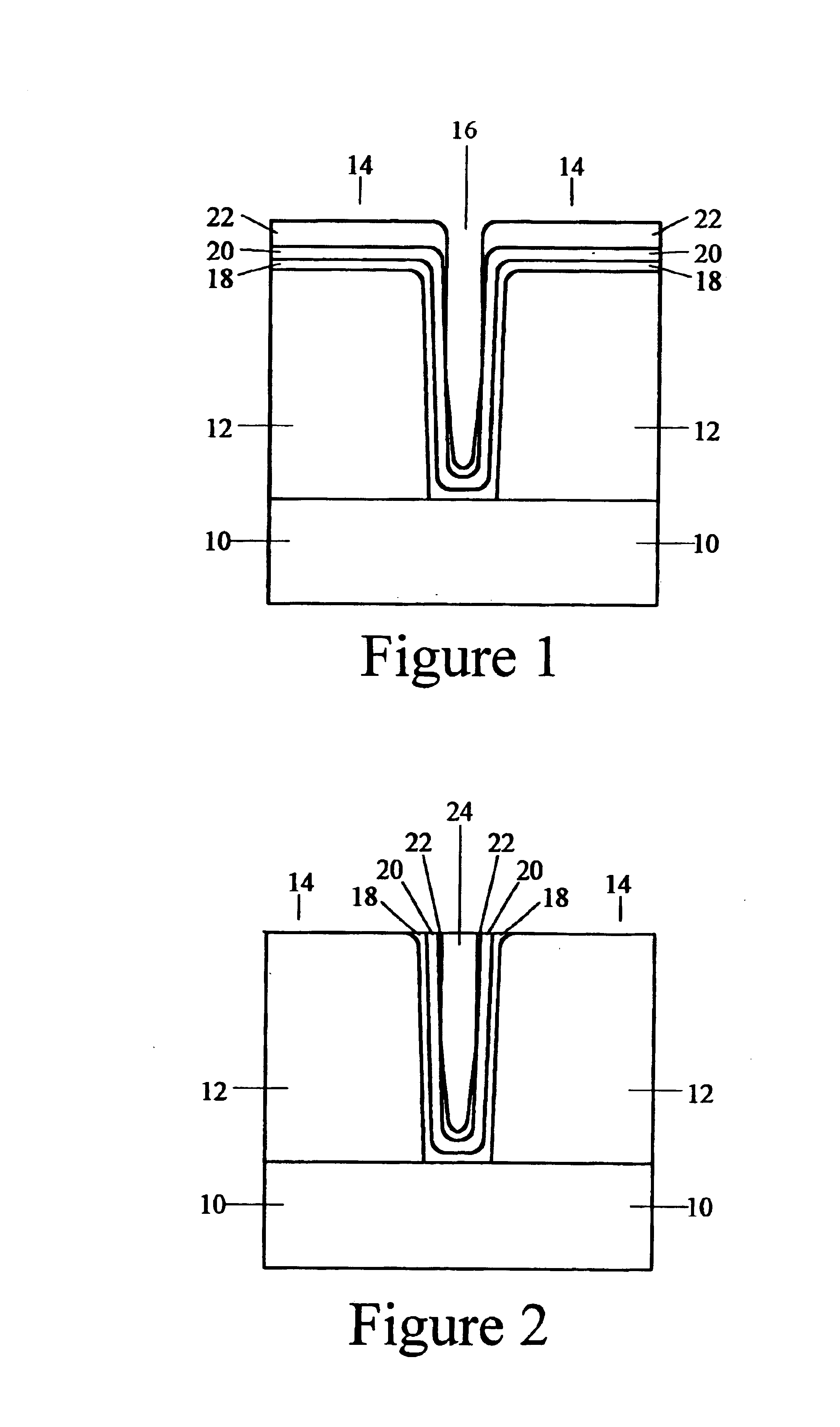

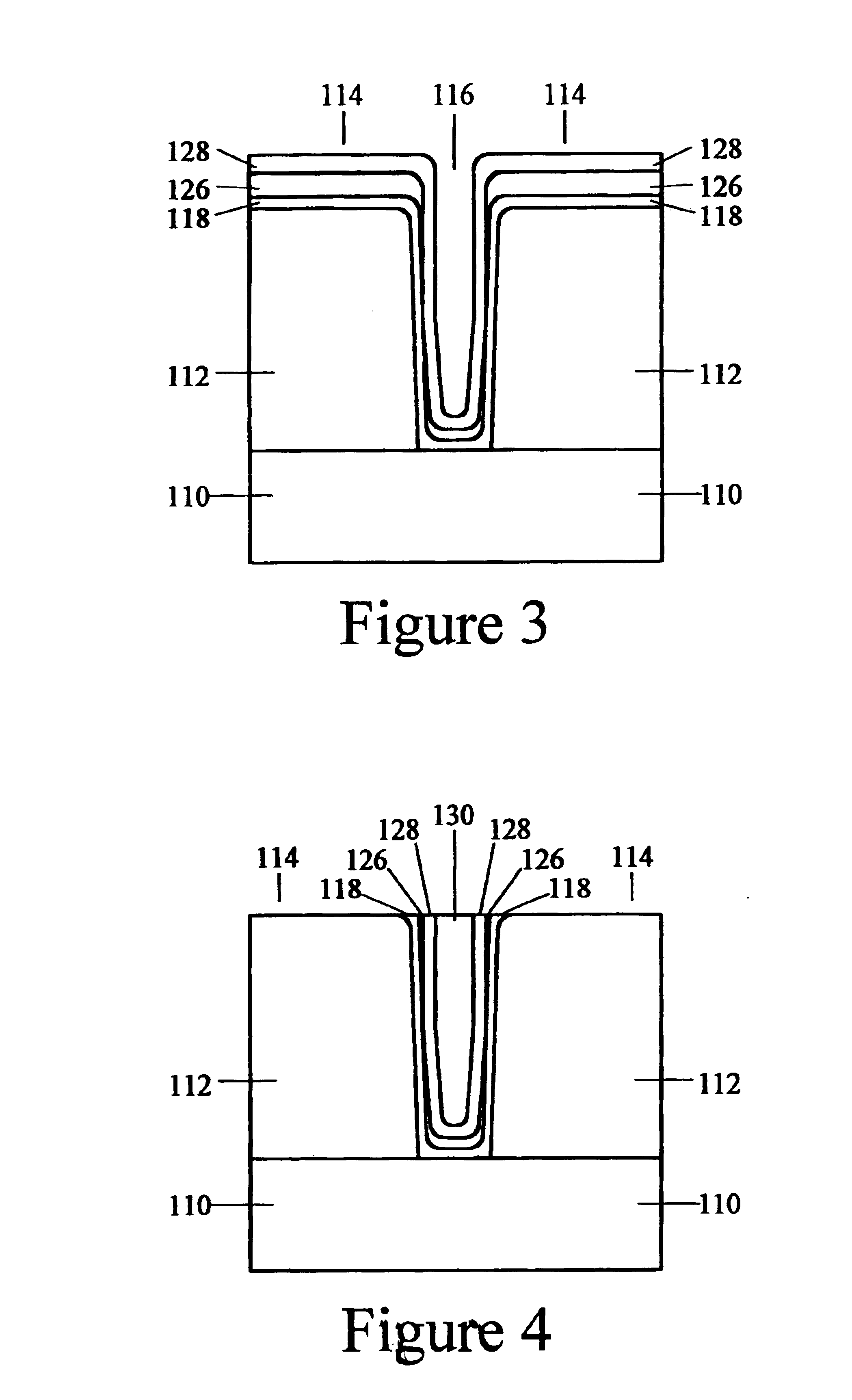

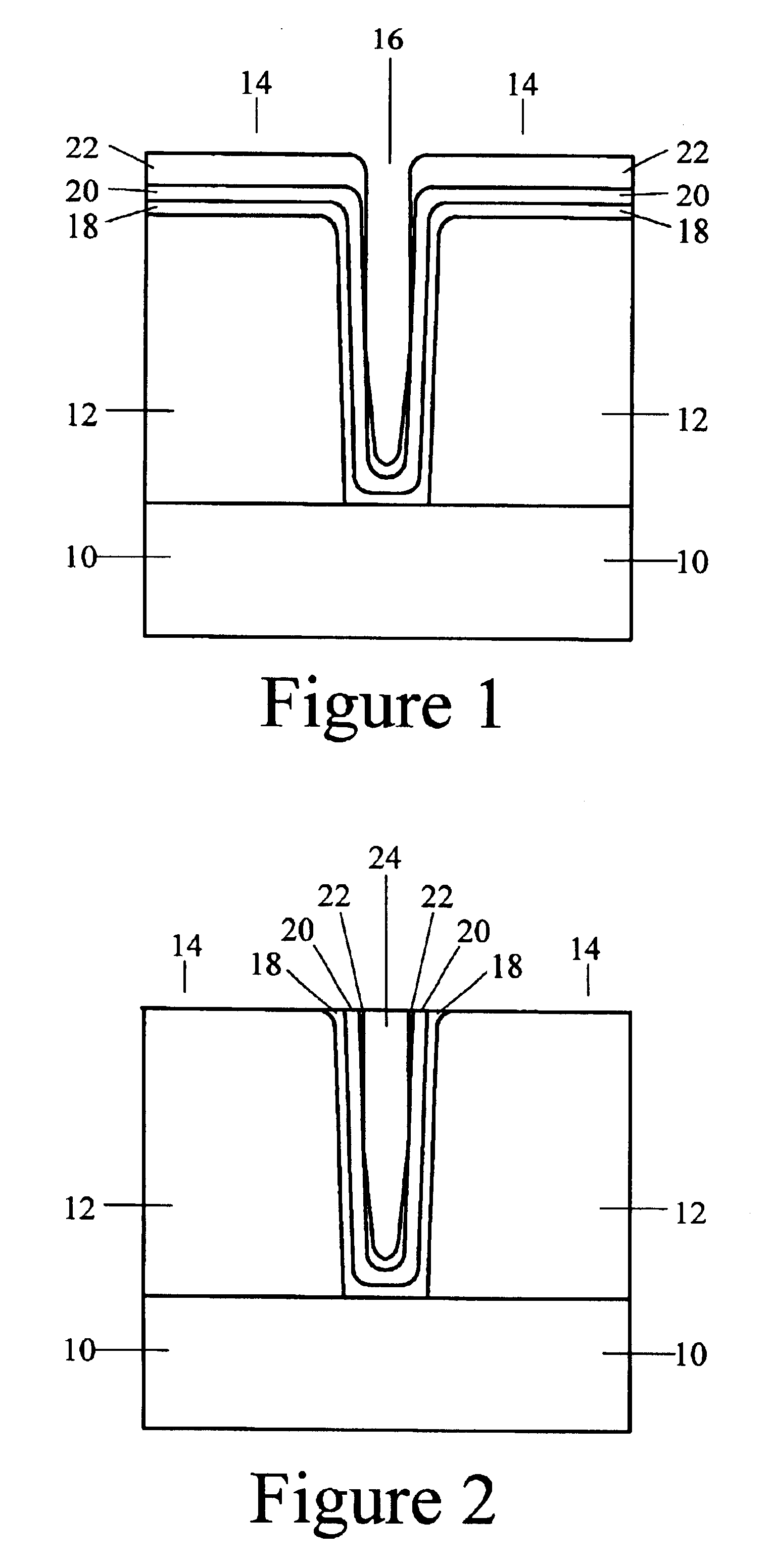

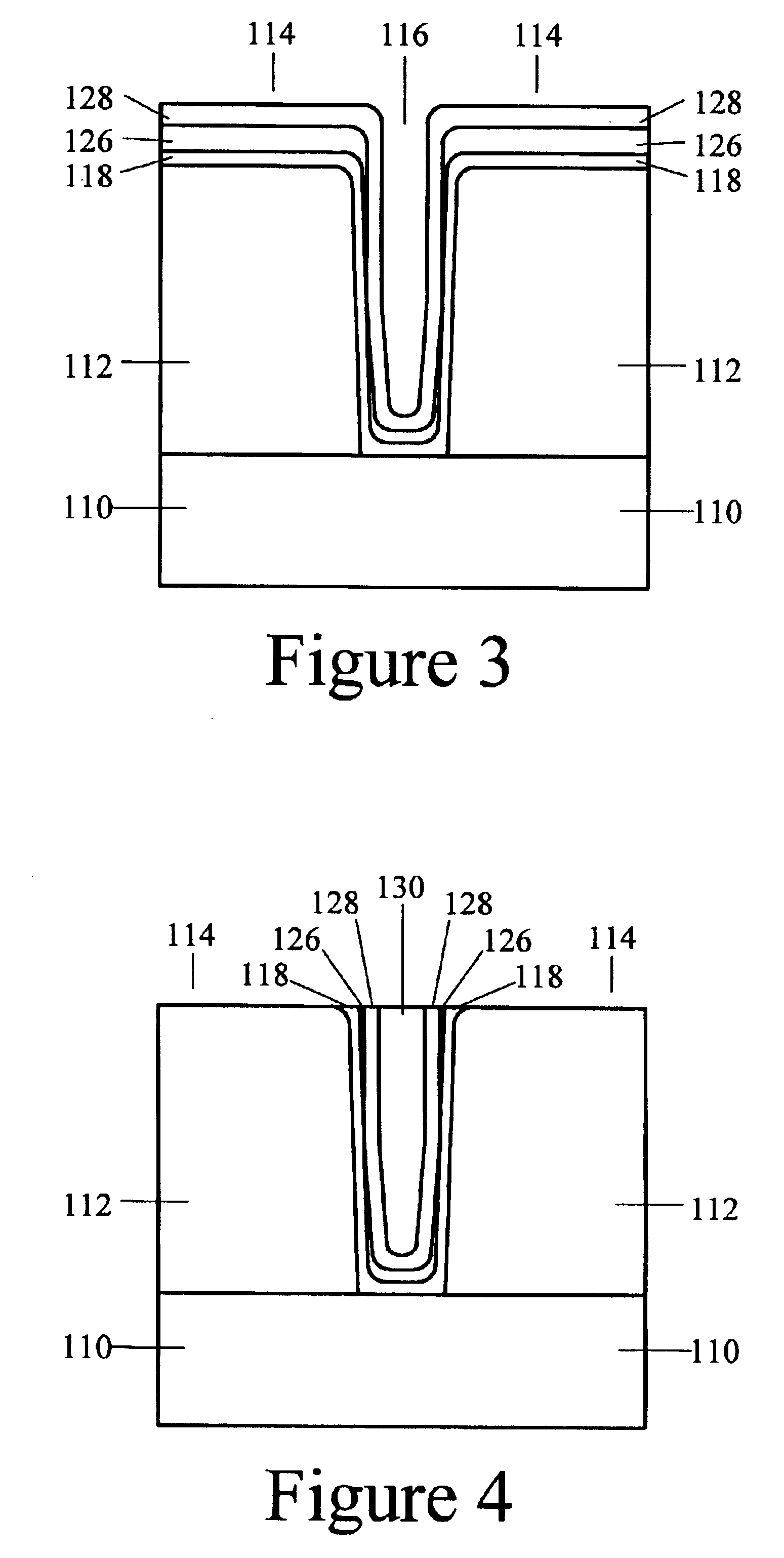

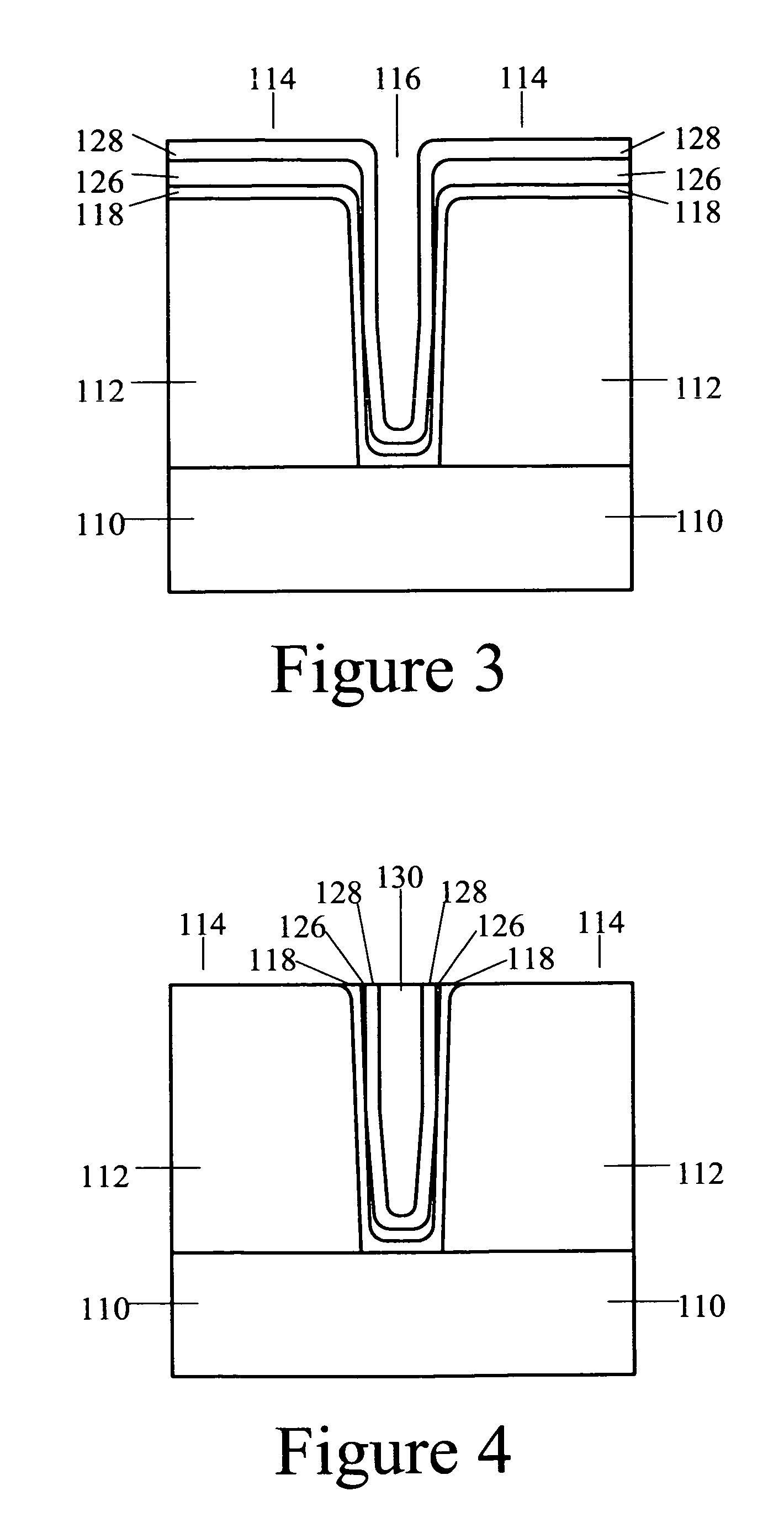

Combined conformal/non-conformal seed layers for metallic interconnects

InactiveUS6903016B2High aspect ratioSemiconductor/solid-state device detailsHeads using thin filmsCopper interconnectGas phase

One embodiment of the present invention in a method for making copper interconnects, which method includes: (a) forming a patterned insulating layer on a substrate, the patterned insulating layer including at least one opening and a field surrounding the at least one opening; (b) depositing a barrier layer over the field and inside surfaces of the at least one opening; (c) depositing a non-conformal first copper seed layer over the barrier layer using physical vapor deposition, wherein the first seed layer is thicker than about 500 Å over the field; (d) depositing a conformal second copper seed layer over the first seed layer using chemical vapor deposition; and (e) electroplating a copper layer over the second seed layer.

Owner:COHEN URI DR

Formulations for removing cooper-containing post-etch residue from microelectronic devices

InactiveUS20090301996A1Decorative surface effectsNon-surface-active detergent compositionsMetal interconnectDiluent

A method and composition for removing copper-containing post-etch and / or post-ash residue from patterned microelectronic devices is described. The removal composition includes a diluent, a solvent and a copper corrosion inhibitor, wherein the diluent may be a dense fluid or a liquid solvent. The removal compositions effectively remove the copper-containing post-etch residue from the microelectronic device without damaging exposed low-k dielectric and metal interconnect materials.

Owner:ADVANCED TECH MATERIALS INC

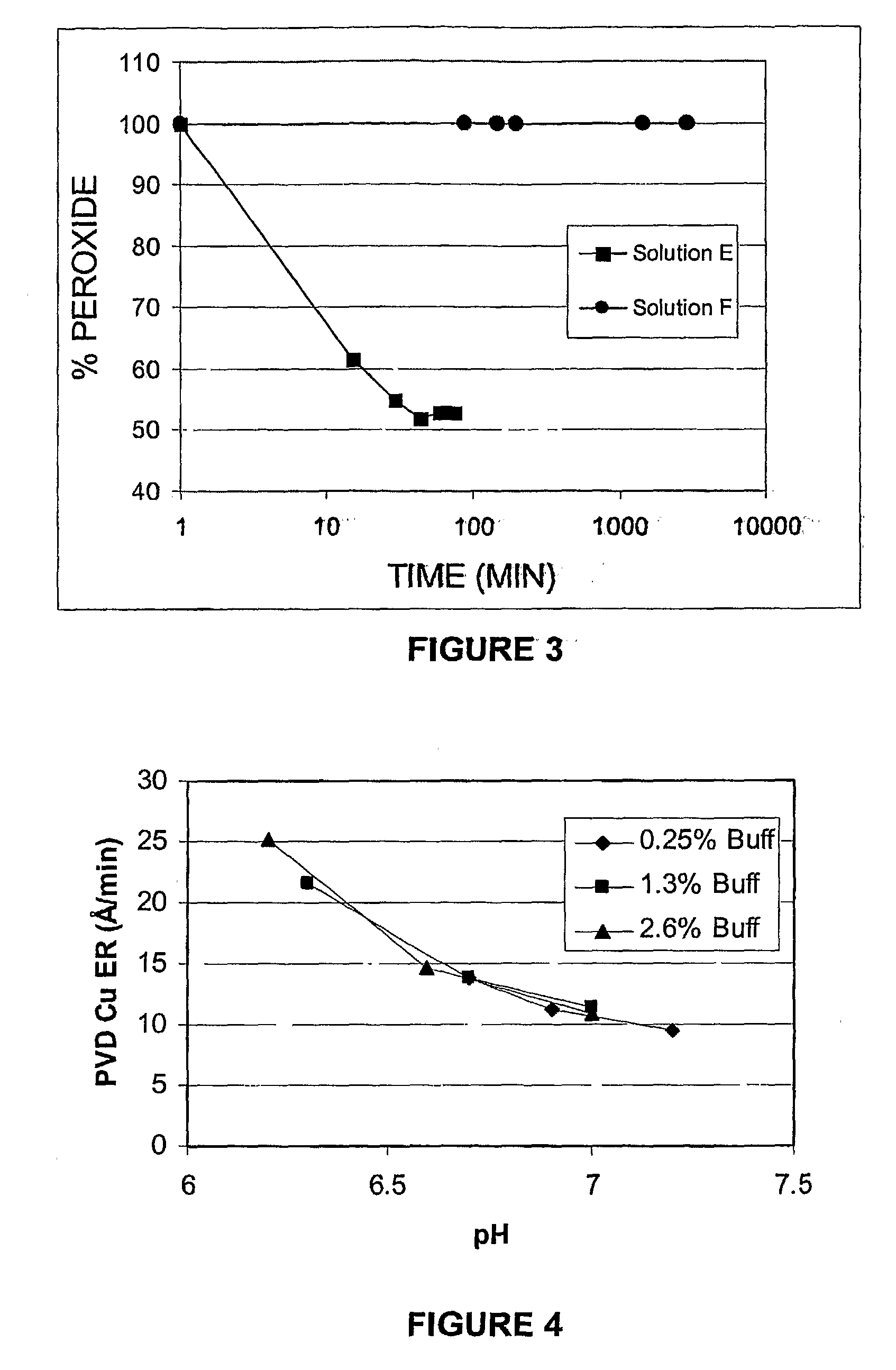

Oxidizing aqueous cleaner for the removal of post-etch residues

ActiveUS20090215658A1Organic detergent compounding agentsDetergent mixture composition preparationMetal interconnectOxygen

An oxidizing aqueous cleaning composition and process for cleaning post-plasma etch residue and / or hardmask material from a microelectronic device having said residue thereon. The oxidizing aqueous cleaning composition includes at least one oxidizing agent, at least one oxidizing agent stabilizer comprising an amine species selected from the group consisting of primary amines, secondary amines, tertiary amines and amine-N-oxides, optionally at least one co-solvent, optionally at least one metal-chelating agent, optionally at least one buffering species, and water. The composition achieves highly efficacious cleaning of the residue material from the microelectronic device while simultaneously not damaging the interlevel dielectric and metal interconnect material also present thereon.

Owner:ENTEGRIS INC

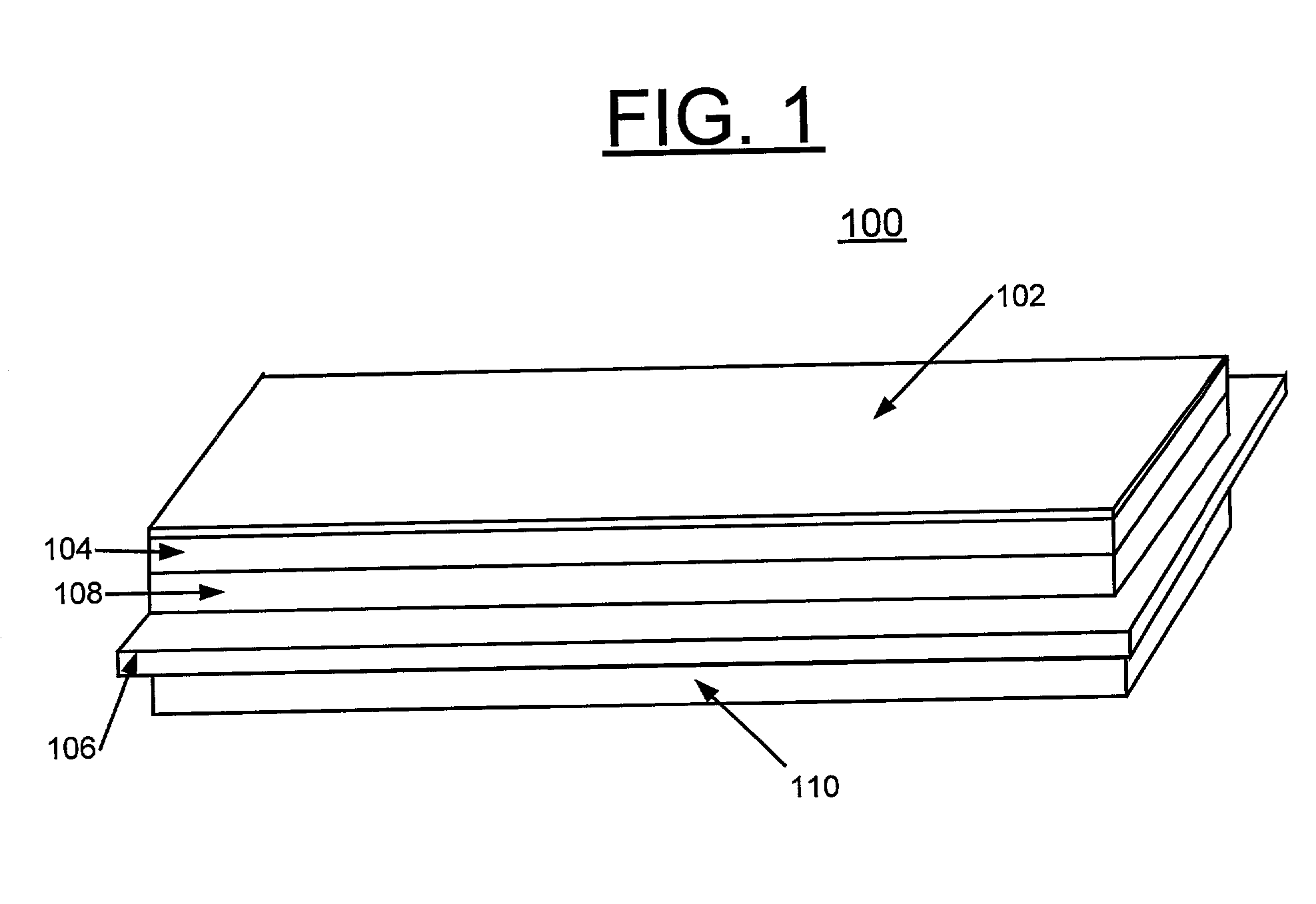

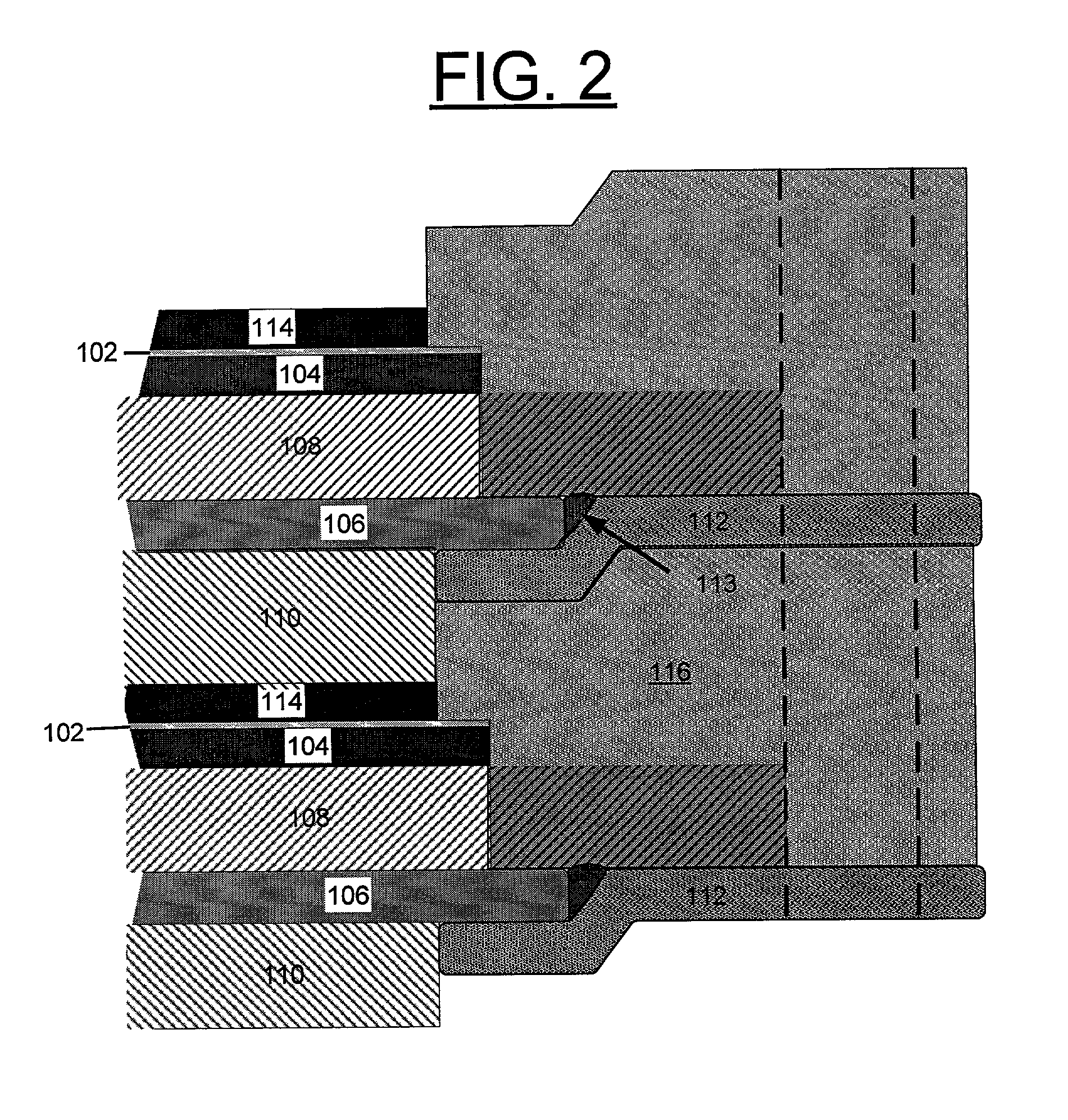

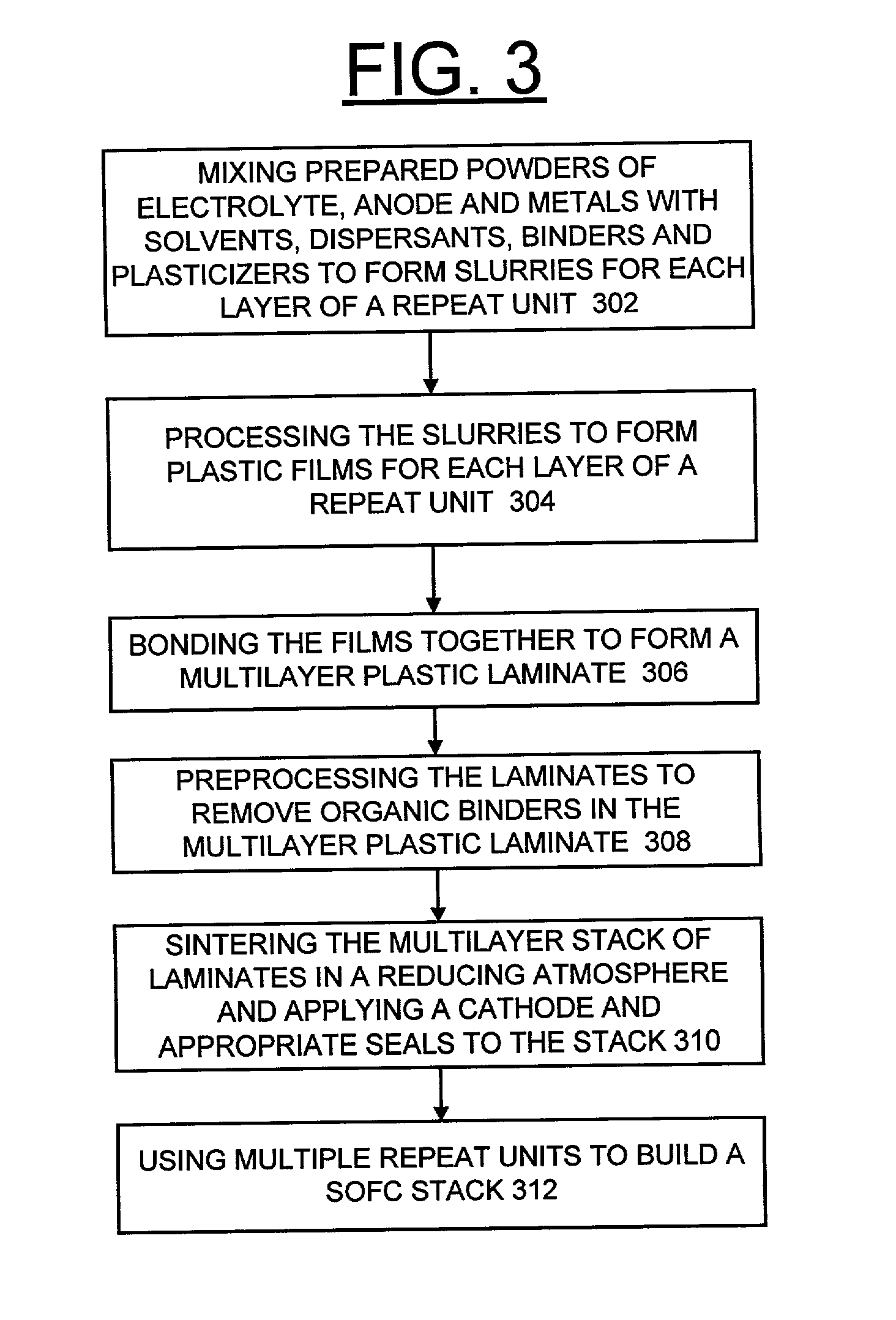

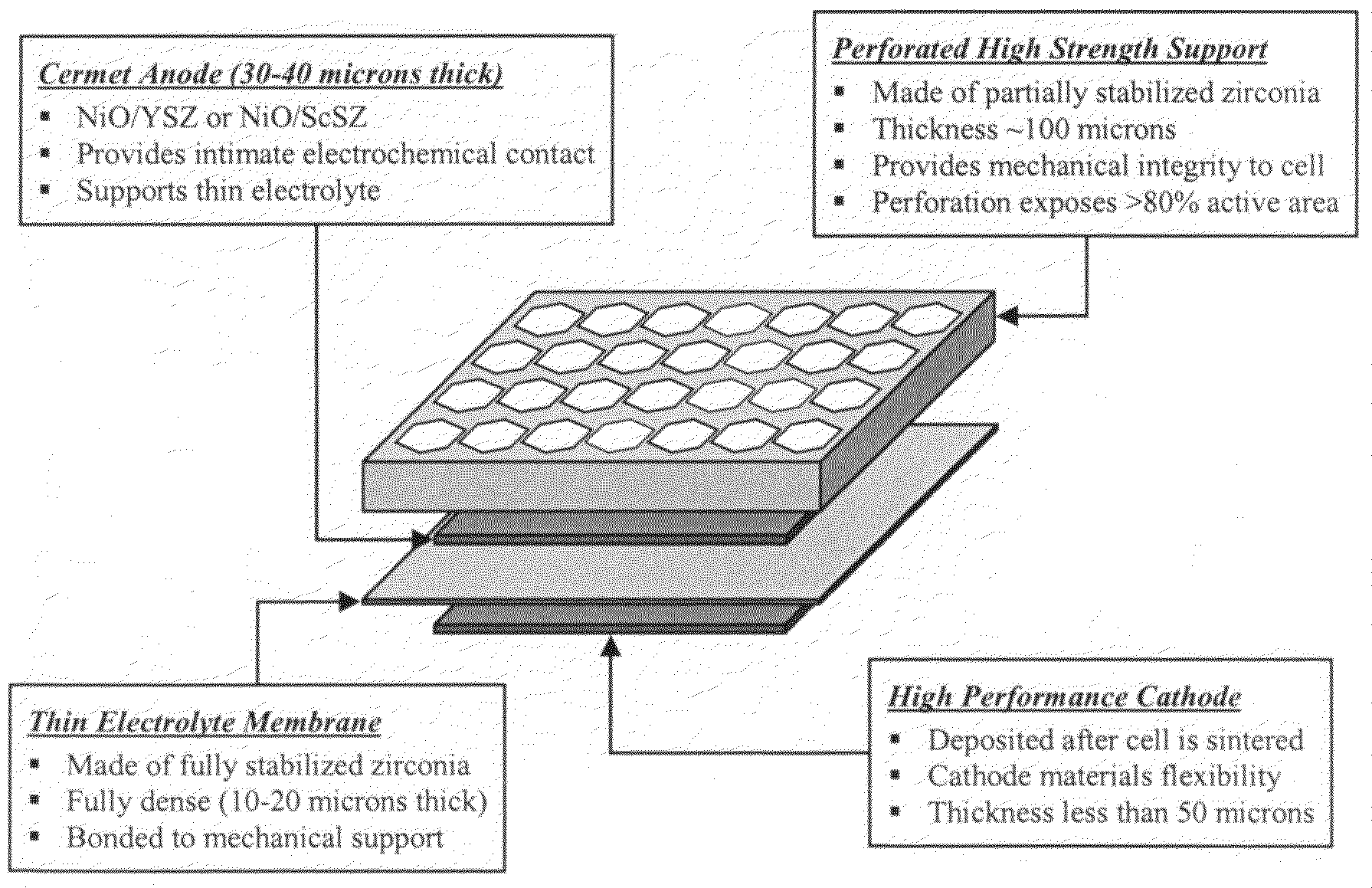

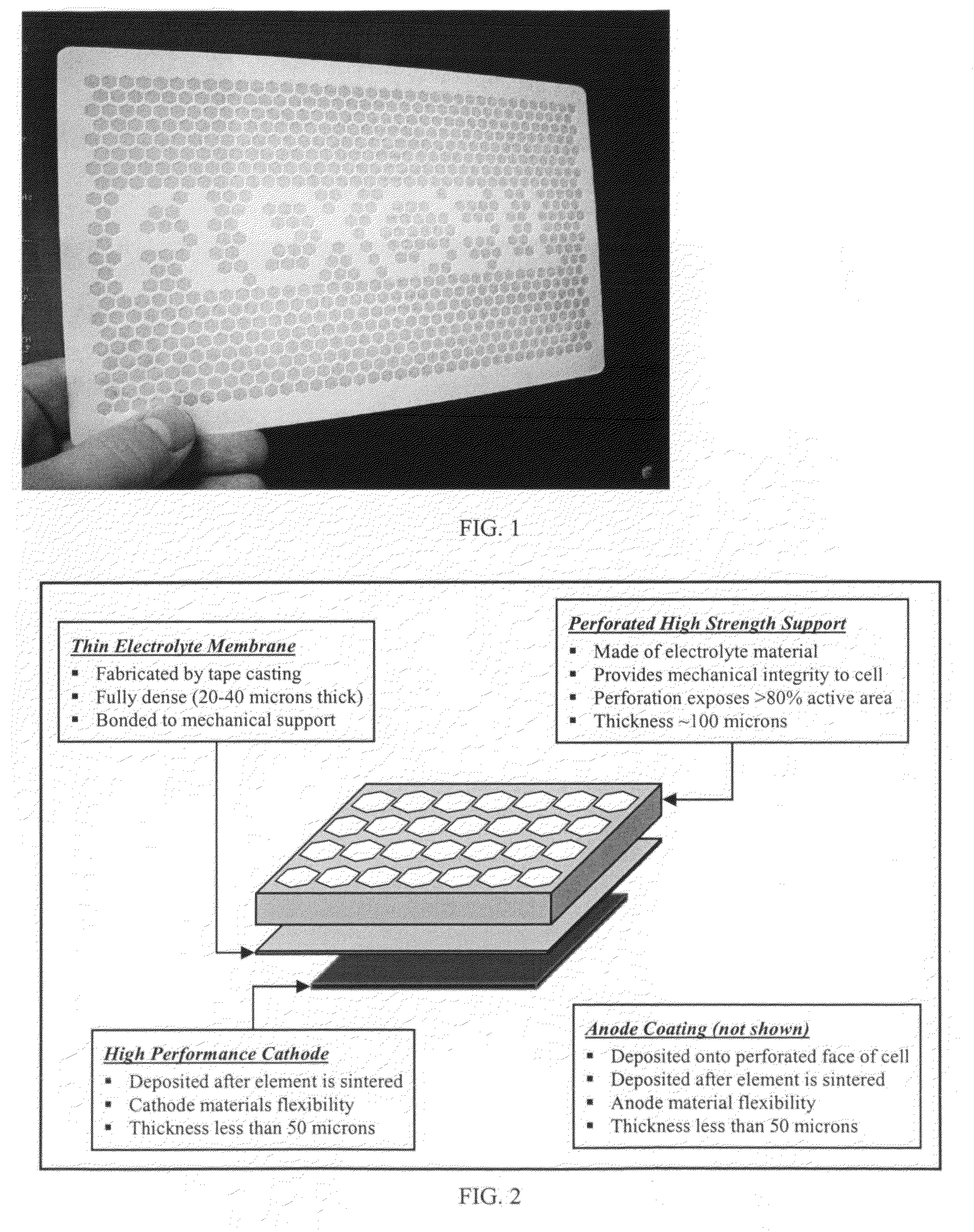

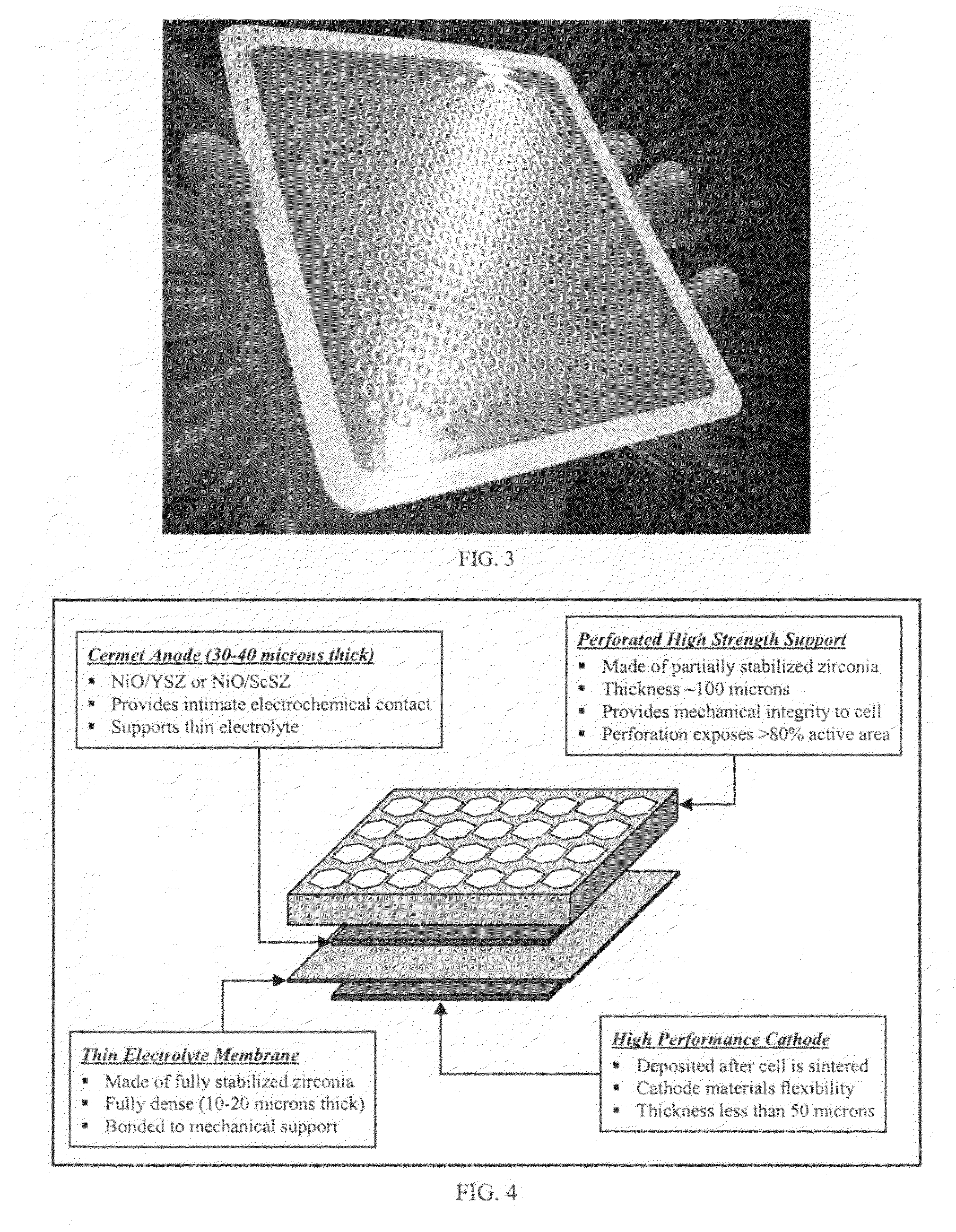

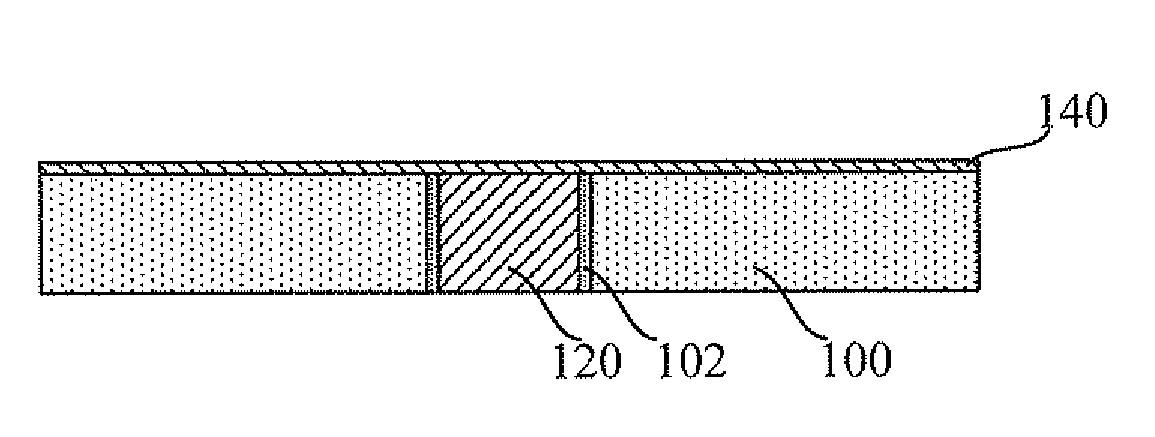

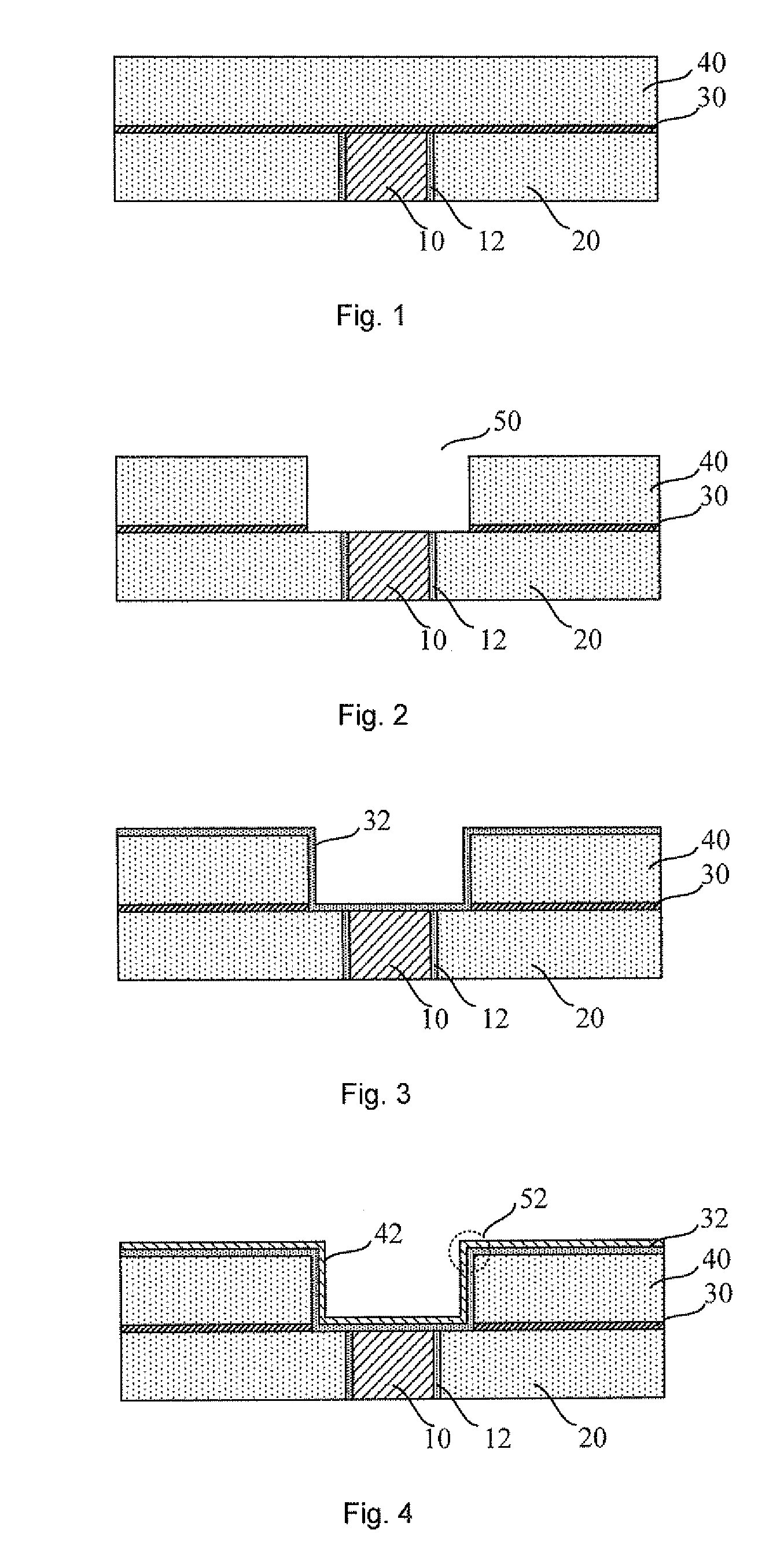

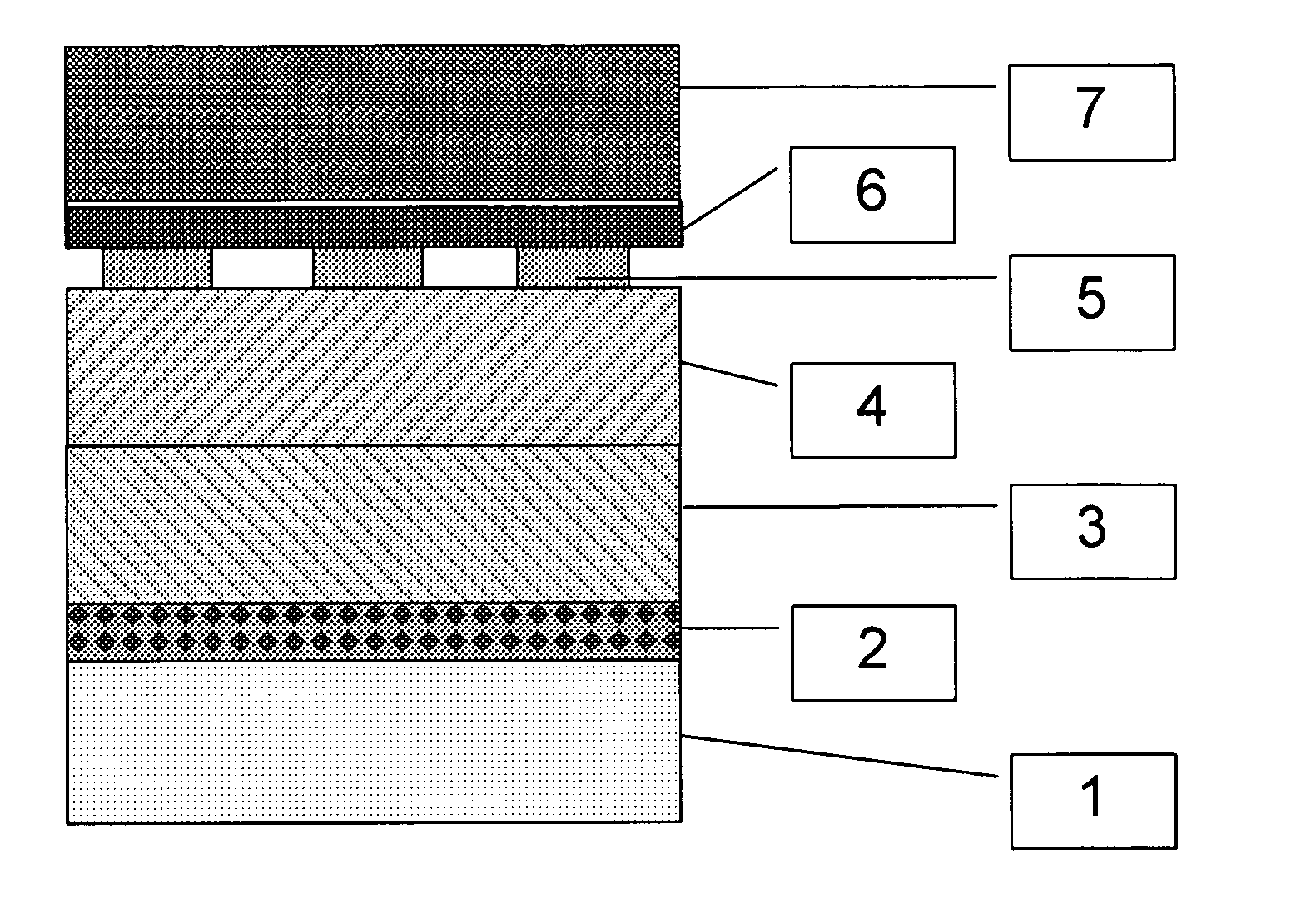

Solid oxide fuel cell with enhanced mechanical and electrical properties

InactiveUS20030232230A1Improve mechanical propertiesGood electrical propertiesFuel cells groupingCeramic shaping apparatusMechanical propertyContact resistance

A solid oxide fuel cell (SOFC) repeat unit includes an oxide electrolyte, an anode, a metallic fuel flow field, a metallic interconnect, and a metallic air flow field. The multilayer laminate is made by casting tapes of the different functional layers, laminating the tapes together and sintering the laminate in a reducing atmosphere. Solid oxide fuel cell stacks are made by applying a cathode layer, bonding the unit into a gas manifold plate, and then stacking the cells together. This process leads to superior mechanical properties in the SOFC due to the toughness of the supporting metallic layers. It also reduces contact resistances in stacking the cells since there is only one physical contact plane for each repeat unit.

Owner:UCHICAGO ARGONNE LLC

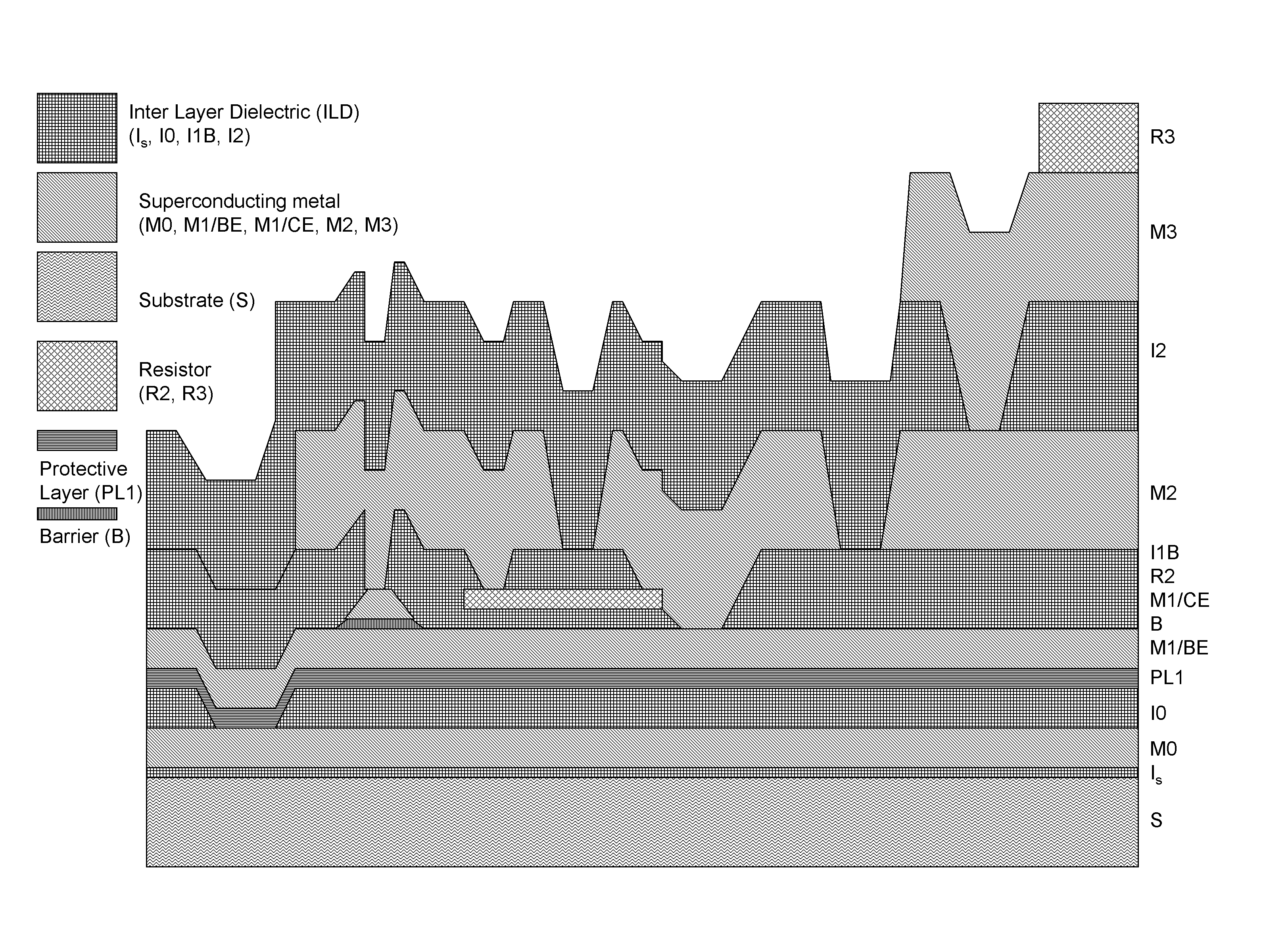

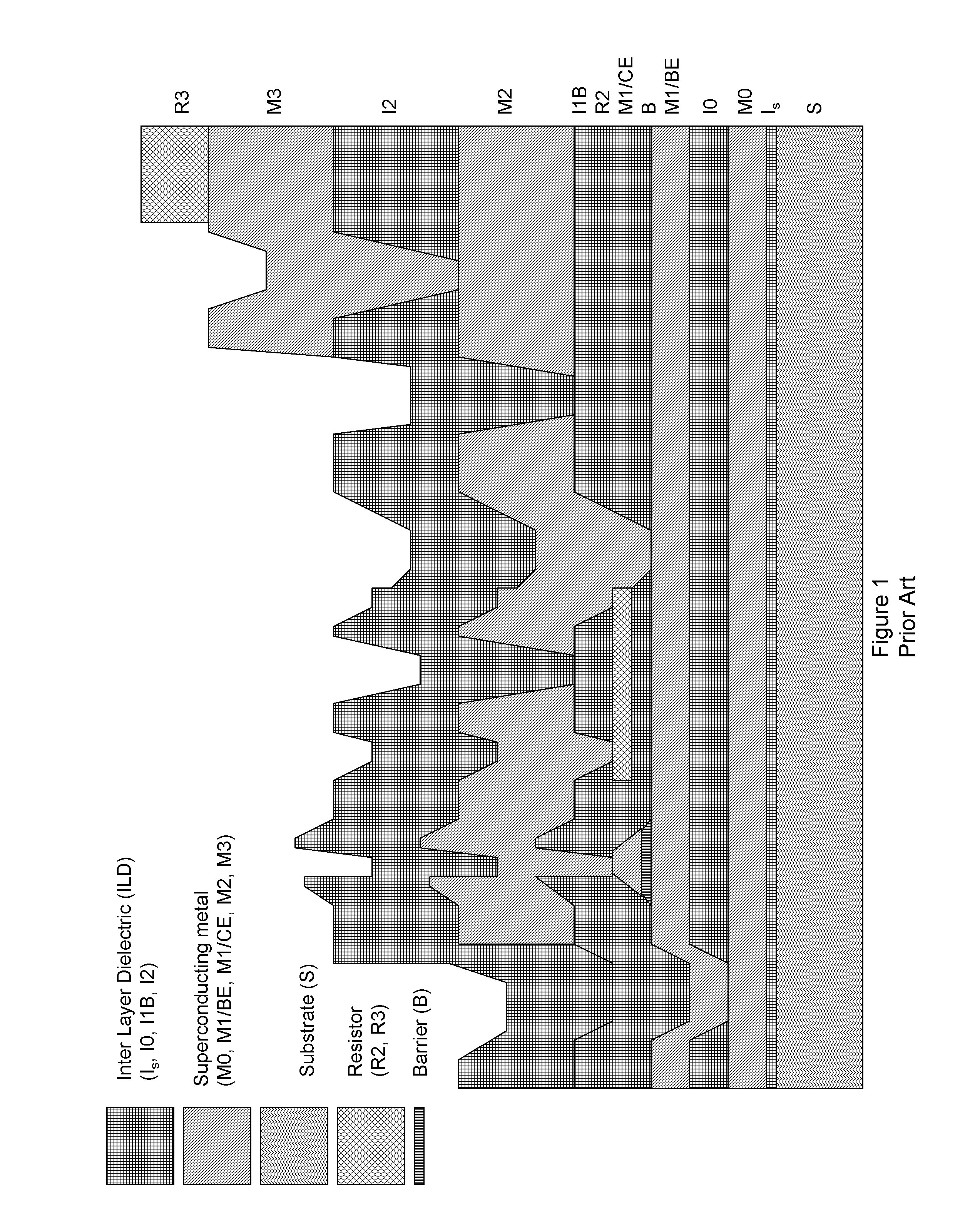

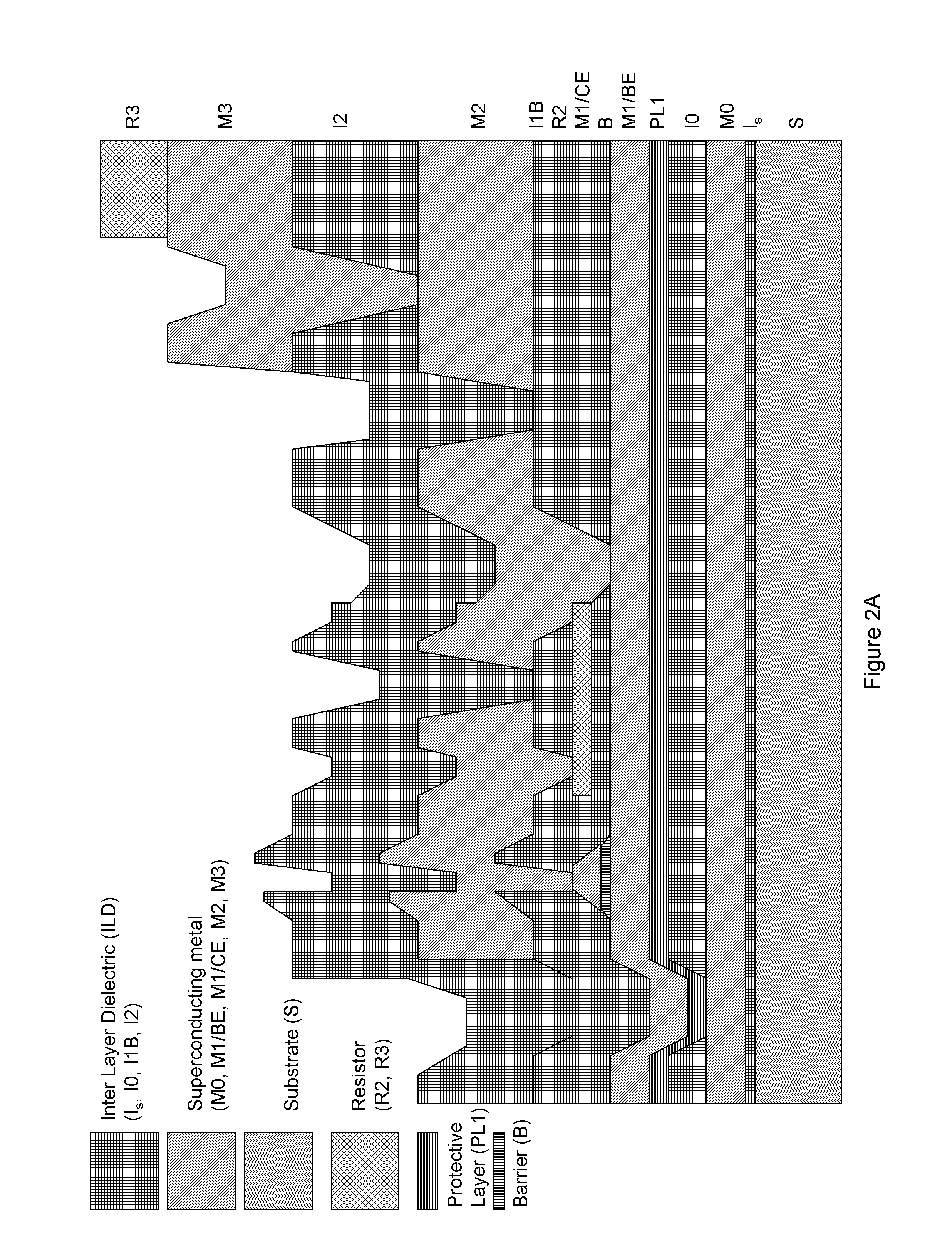

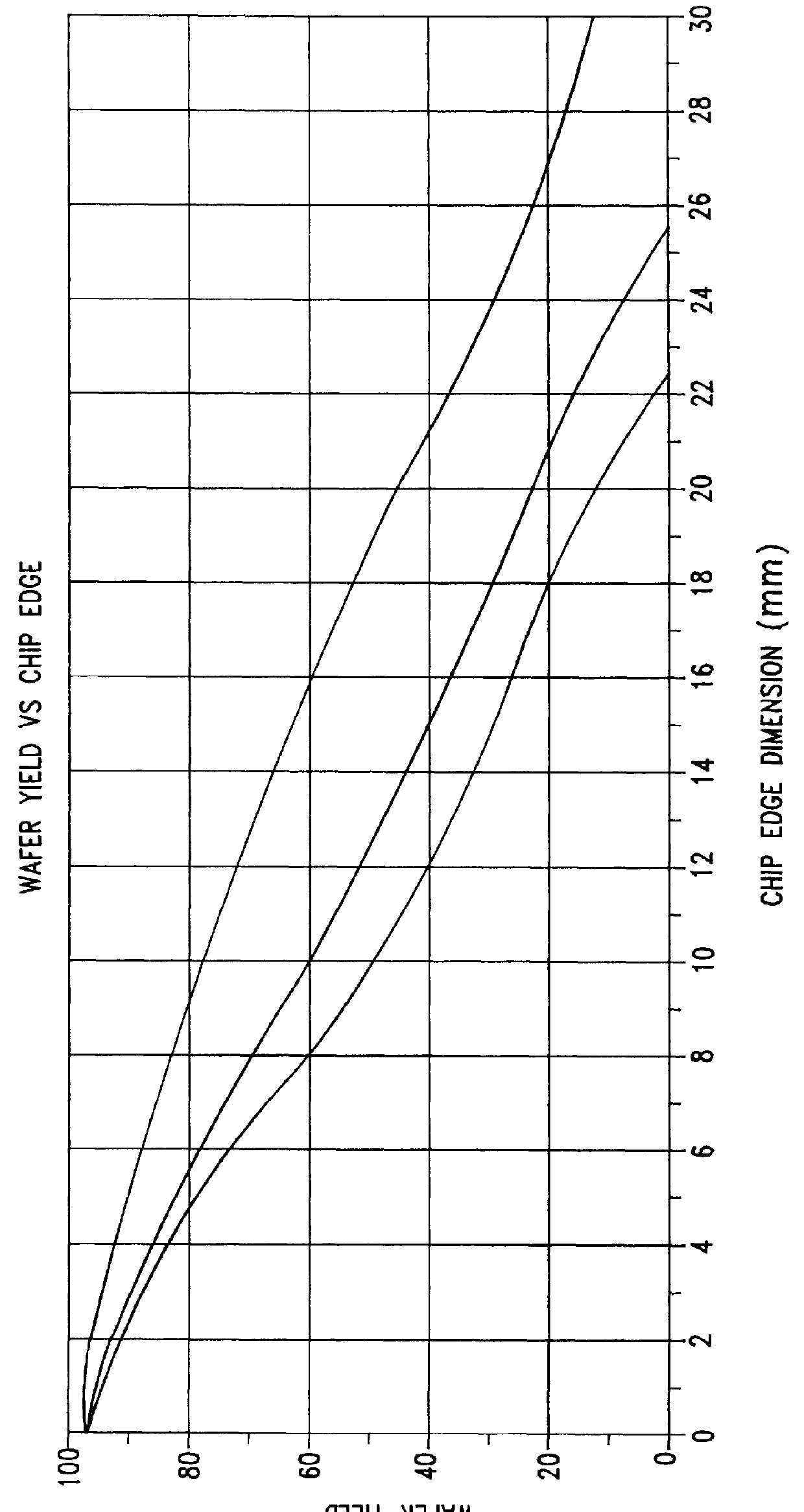

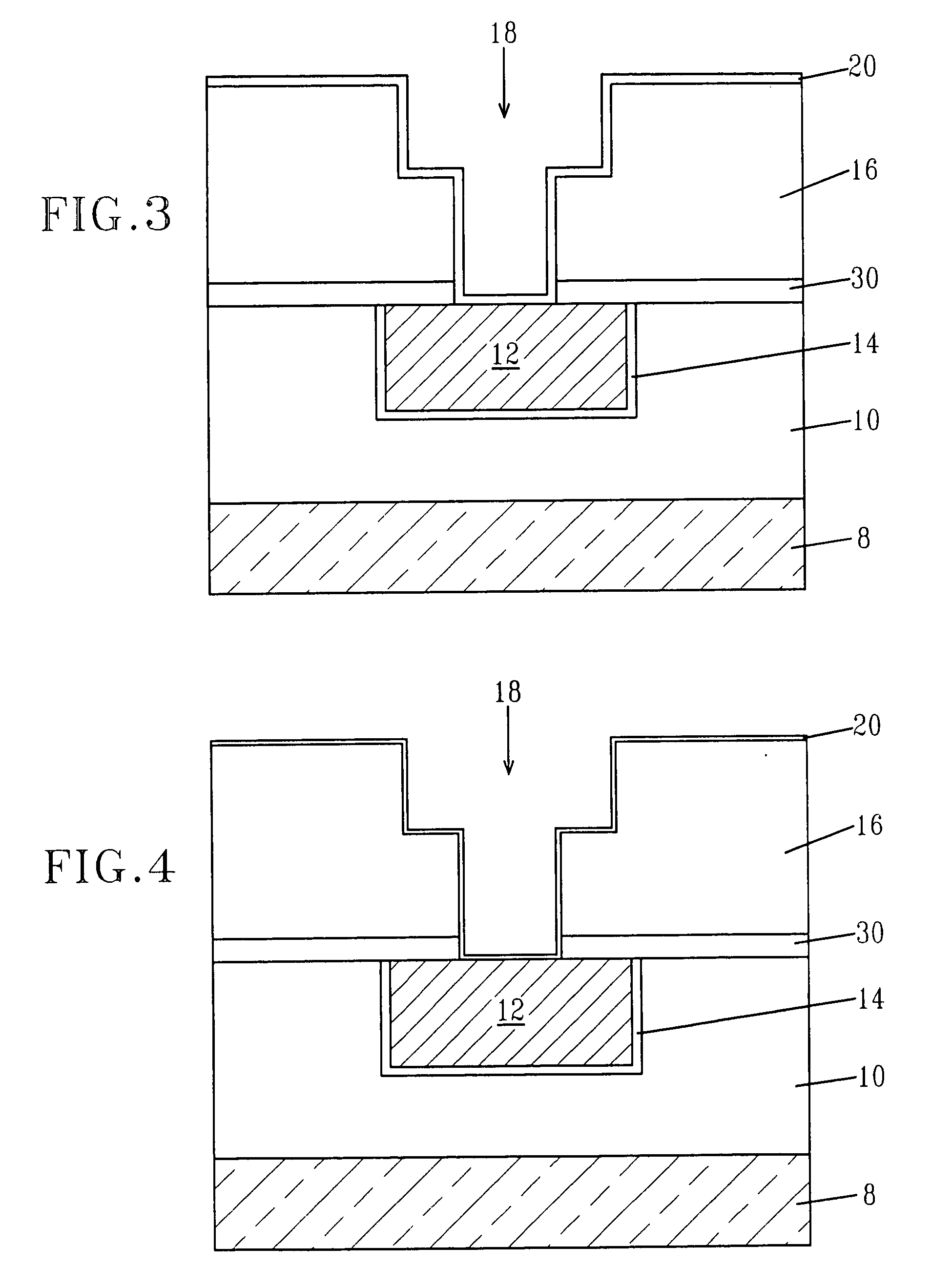

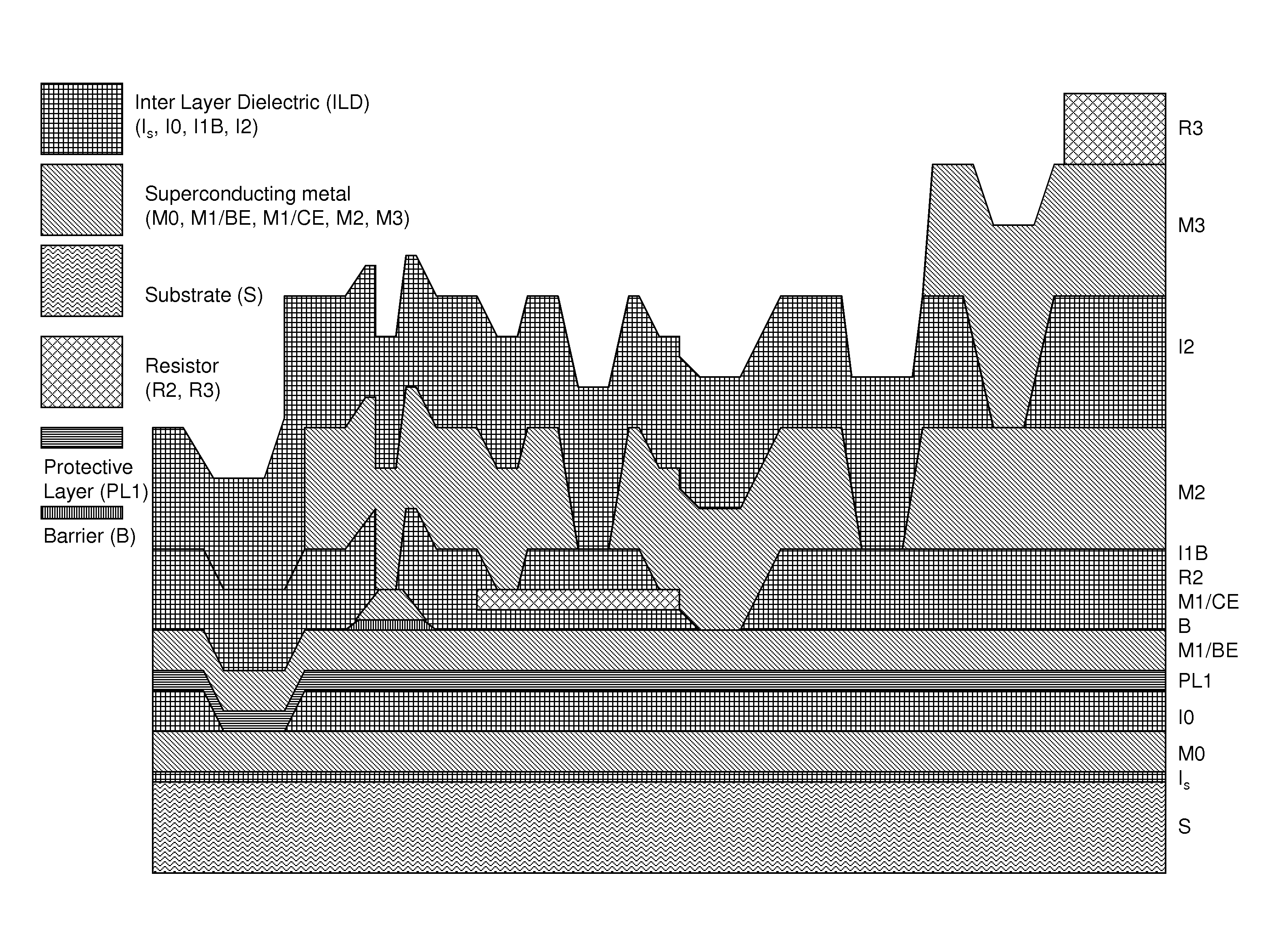

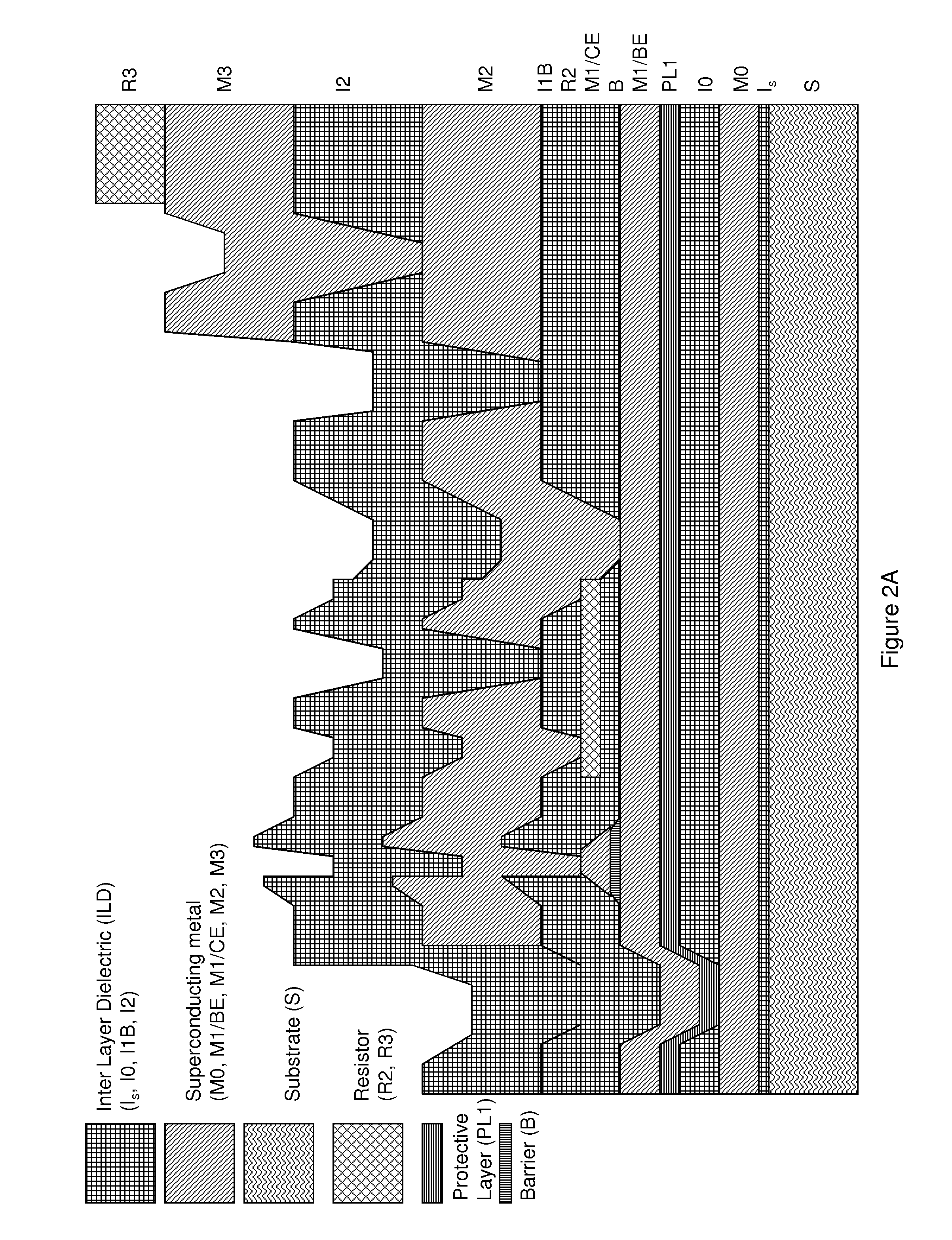

System and method for providing multi-conductive layer metallic interconnects for superconducting integrated circuits

ActiveUS8437818B1Reduce and prevent diffusion of impurityReduce non-uniformitySuperconductors/hyperconductorsSemiconductor/solid-state device detailsImpurity diffusionRapid single flux quantum

Superconducting integrated circuits require several wiring layers to distribute bias and signals across the circuit, which must cross each other both with and without contacts. All wiring lines and contacts must be fully superconducting, and in the prior art each wiring layer comprises a single metallic thin film. An alternative wiring layer is disclosed that comprises sequential layers of two or more different metals. Such a multi-metallic wiring layer may offer improved resistance to impurity diffusion, better surface passivation, and / or reduction of stress, beyond that which is attainable with a single-metallic wiring layer. The resulting process leads to improved margin and yield in an integrated circuit comprising a plurality of Josephson junctions. Several preferred embodiments are disclosed, for both planarized and non-planarized processes. These preferred and other methods may be applied to digital circuits based on Rapid Single Flux Quantum logic, and to quantum computing using Josephson junction qubits.

Owner:SEEQC INC

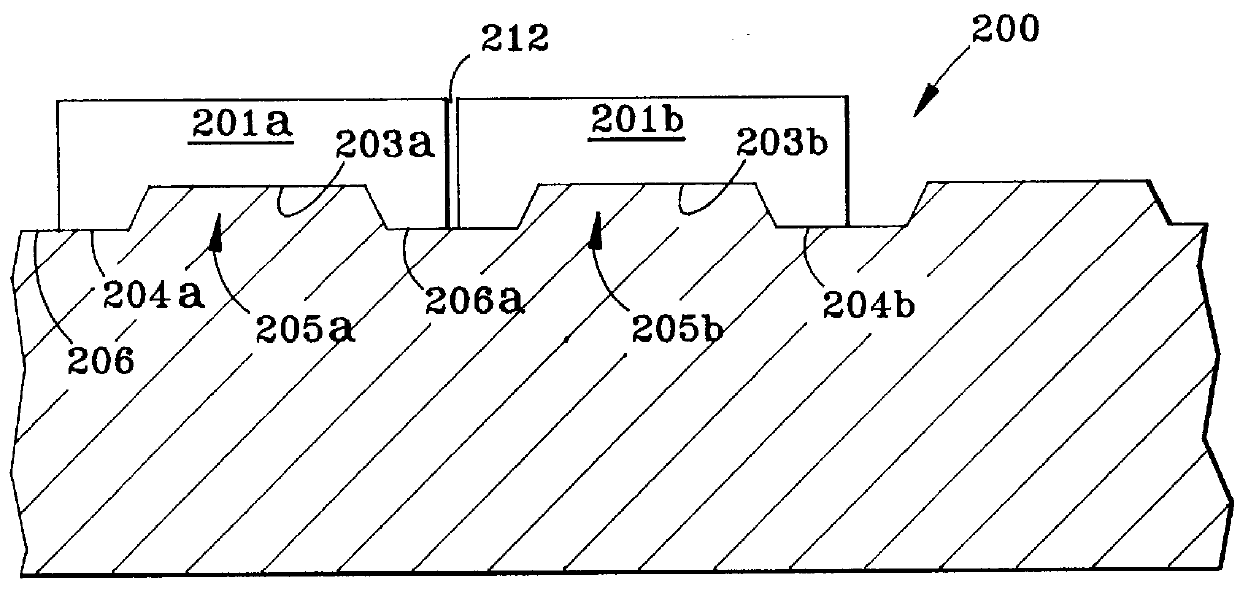

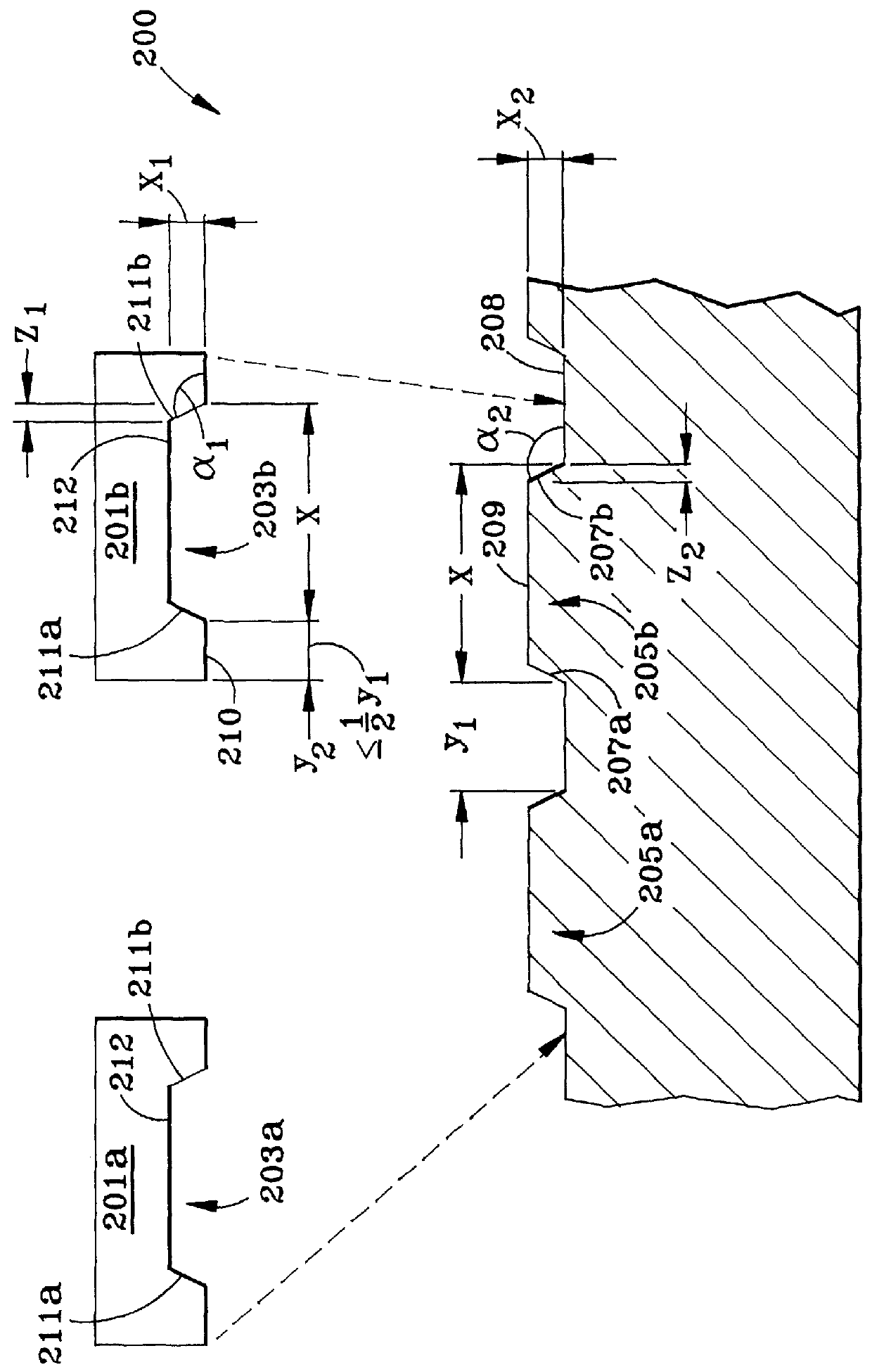

Method for fabricating a very dense chip package

InactiveUS6087199AConstant widthIncrease widthSemiconductor/solid-state device detailsSolid-state devicesIn planeTopography

A method for fabricating an integrated circuit package or arrangement includes providing a carrier having a surface topography of projections or recesses for supporting individual semiconductor circuit chips having conversely matching bottom surface topographies to permit self-aligned positioning of the chip on the carrier. Chips are provided such that top faces of neighboring chips lie substantially in planes separated by a distance of greater than 0.0 mu m. The carrier is arranged and dimensioned such that the neighboring chips are separated by a gap G or spacing in a range of 1 mu m<G< / =100 mu m. A metallic interconnect is provided over the top faces and the gap. Preferably, the interconnect has a gradual slope over the gap.

Owner:GOOGLE LLC

Process for forming an electrically conductive interconnect

InactiveUS20050118796A1Reduce field induced metal contaminationSemiconductor/solid-state device manufacturingDielectricMetallic materials

An electrically conductive metallic interconnect in a trench or via in a dielectric is provided by depositing a first liner layer on the walls and bottom of the trench or via; removing residual contamination from the bottom of the trench or via; depositing a second liner layer in the trench; depositing a seed layer and filling the trench with electrically conductive metallic material.

Owner:IBM CORP

System and method for providing multi-conductive layer metallic interconnects for superconducting integrated circuits

ActiveUS8301214B1Reduce and prevent diffusion of impurityReduce non-uniformitySuperconductors/hyperconductorsSemiconductor/solid-state device detailsImpurity diffusionRapid single flux quantum

Superconducting integrated circuits require several wiring layers to distribute bias and signals across the circuit, which must cross each other both with and without contacts. All wiring lines and contacts must be fully superconducting, and in the prior art each wiring layer comprises a single metallic thin film. An alternative wiring layer is disclosed that comprises sequential layers of two or more different metals. Such a multi-metallic wiring layer may offer improved resistance to impurity diffusion, better surface passivation, and / or reduction of stress, beyond that which is attainable with a single-metallic wiring layer. The resulting process leads to improved margin and yield in an integrated circuit comprising a plurality of Josephson junctions. Several preferred embodiments are disclosed, for both planarized and non-planarized processes. These preferred and other methods may be applied to digital circuits based on Rapid Single Flux Quantum logic, and to quantum computing using Josephson junction qubits.

Owner:SEEQC INC

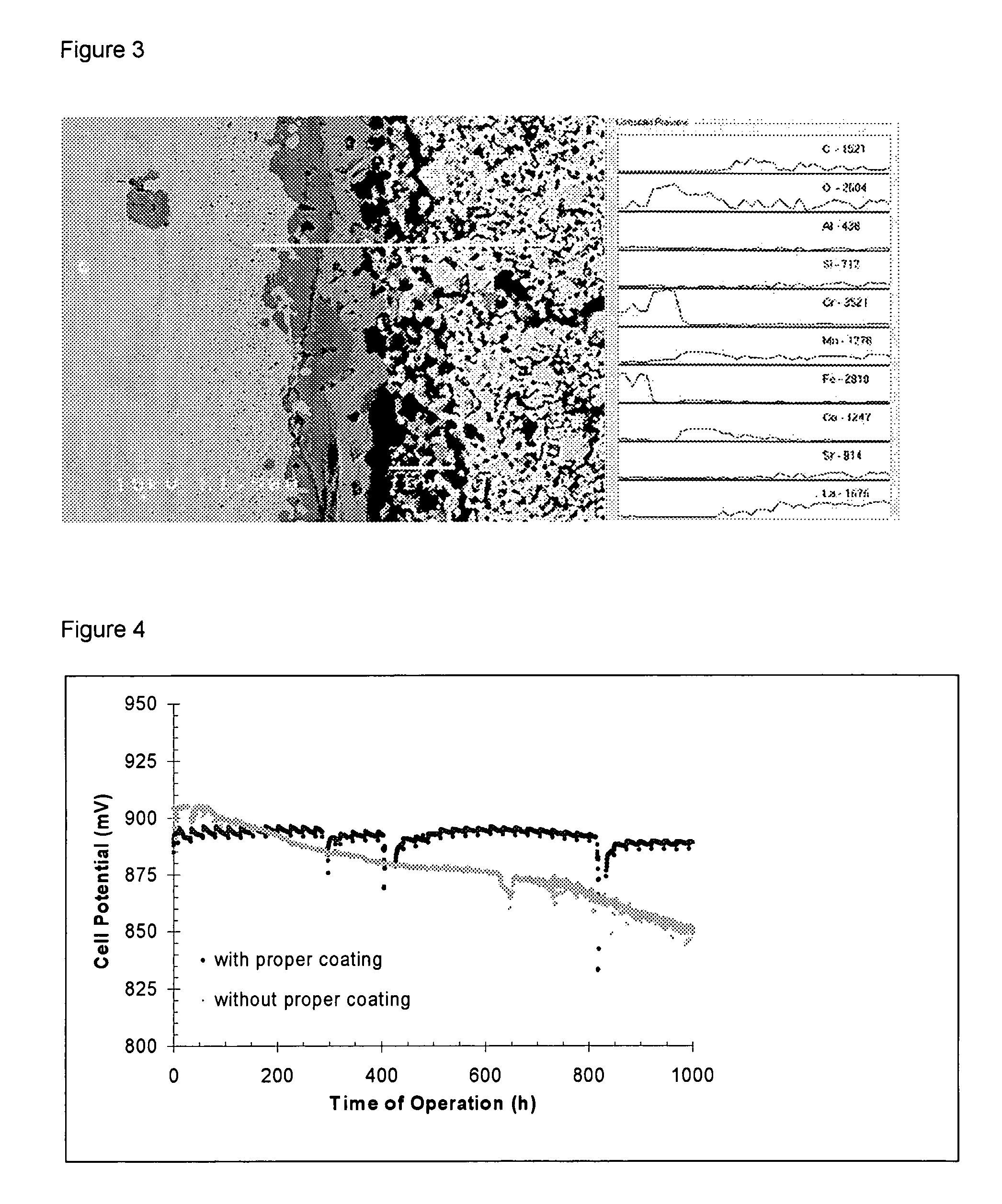

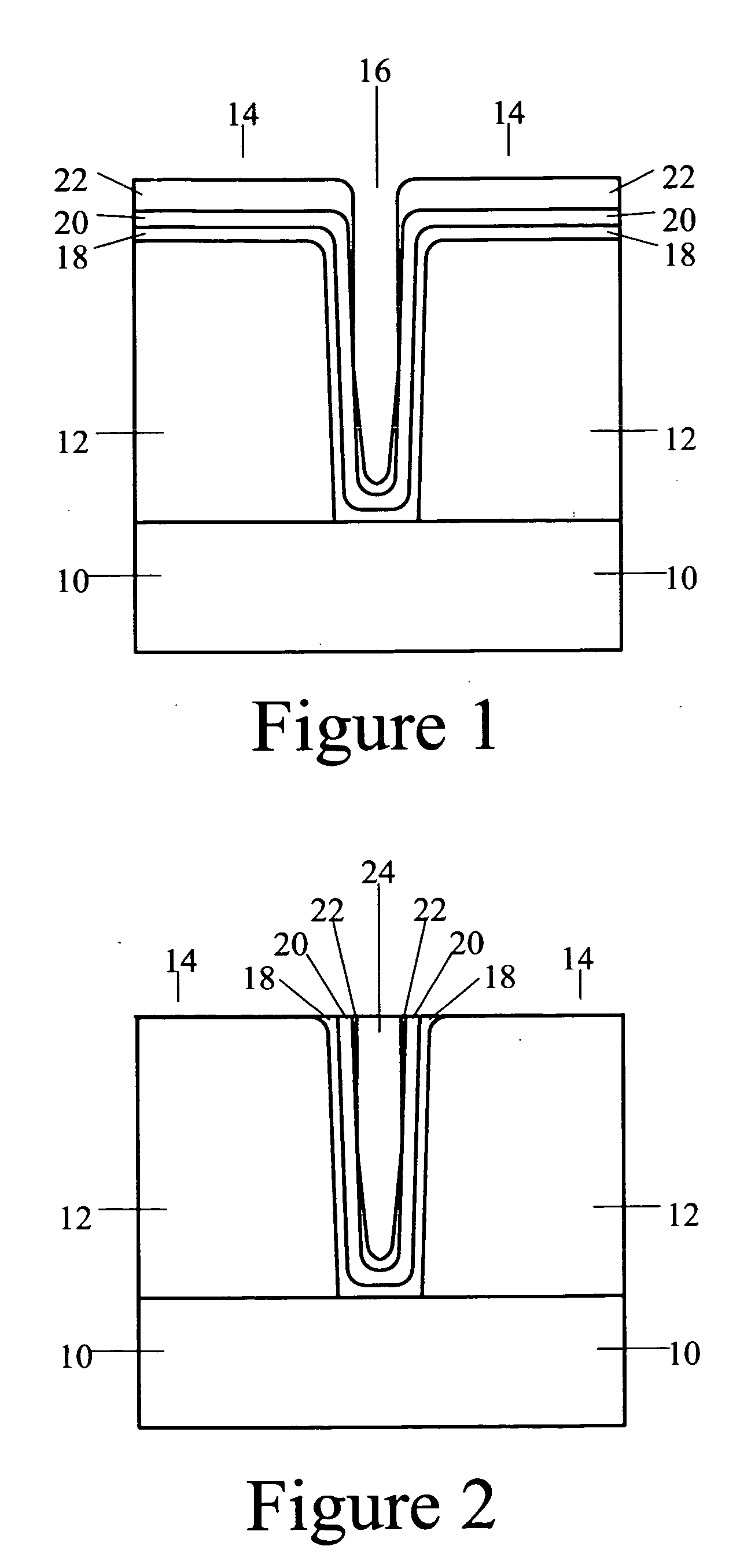

High performance multilayer electrodes for use in oxygen-containing gases

InactiveUS20090148743A1Final product manufactureNon-aqueous electrolyte accumulator electrodesCerium(IV) oxideLong term durability

Electrode materials systems for planar solid oxide fuel cells with high electrochemical performance including anode materials that provide exceptional long-term durability when used in reducing gases and cathode materials that provide exceptional long-term durability when used in oxygen-containing gases. The cathode materials comprise zinc-doped lanthanum strontium ferrite (LSZF) or an alternative ferrite, cobaltite or nickelate ceramic electrode material. The cathode material also may comprise a mixed-conducting ceria-based electrolyte material, a palladium dopant, or a combination of these. The cathode may have a bi-layer structure. A ceramic-based interfacial layer may be provided at the electrolyte / cathode interface. The multilayer cathode system and its palladium doped cathode material exhibit a high degree of tolerance to chromium contamination during operation with metallic interconnect materials.

Owner:NEXTECH MATERIALS

Cleaning Formulations

ActiveUS20140109931A1Semiconductor/solid-state device manufacturingPhotosensitive material processingOrganic acidOrganic solvent

A composition and method for removing copper-containing post-etch and / or post-ash residue from patterned microelectronic devices is described. The removal composition includes water, a water-miscible organic solvent, an amine compound, an organic acid, and a fluoride ion source. The compositions effectively remove the copper-containing post-etch residue from the microelectronic device without damaging exposed low-k dielectric and metal interconnect materials.

Owner:VERSUM MATERIALS US LLC

Metal Interconnection Structure and Method For Forming Metal Interlayer Via and Metal Interconnection Line

ActiveUS20120080792A1Difficult to fillReduce difficultySemiconductor/solid-state device detailsSolid-state devicesInterconnectionOptoelectronics

There is provided a method for forming a metal interlayer via, comprising: forming a seed layer on a first dielectric layer and a first metal layer embedded in the first dielectric layer; forming a mask pattern on the seed layer to expose a portion of the seed layer covering some of the first metal layer; growing a second metal layer on the exposed portion of the seed layer; removing the mask pattern and a portion of the seed layer carrying the mask pattern to expose side walls of the second metal layer, a portion of the first metal layer and the first dielectric layer; forming an insulating barrier layer on the side walls, the portion of the first metal layer and the first dielectric layer. There is also provided a method for forming a metal interconnection line. Both of them can suppress the occurrence of voids. There is further provided a metal interconnection structure comprising a contact plug, a via and a metal interconnection line, wherein the via is formed on the metal interconnection line, the metal gate and / or the contact plug.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

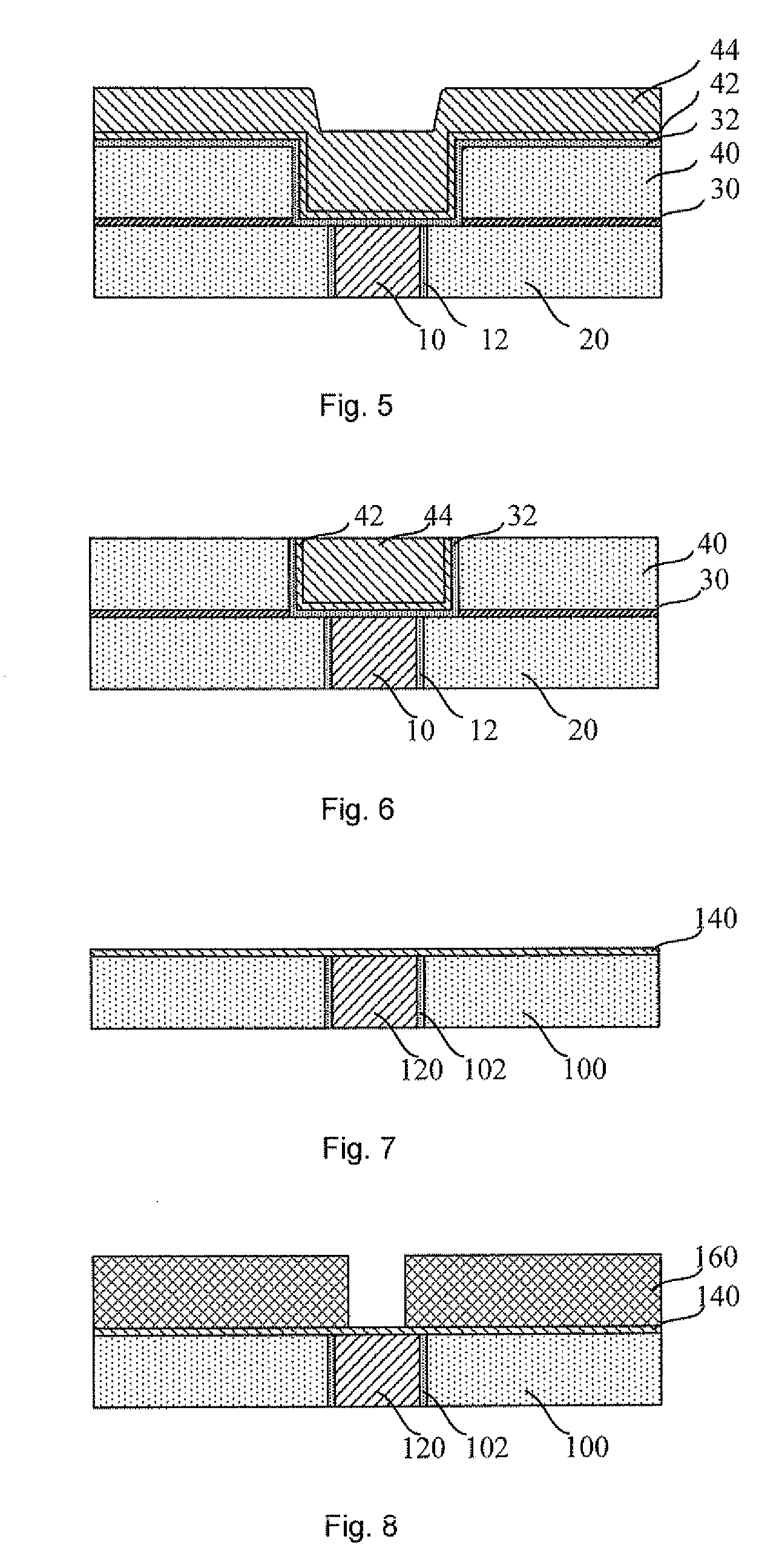

Method of producing a multilayer barrier structure for a solid oxide fuel cell

InactiveUS20100119886A1Minimized contact resistanceFuel cells groupingFinal product manufactureCurrent loadFuel cells

The present invention provides a method of producing a multilayer barrier structure in a solid oxide cell stack, comprising the steps of: -providing a metal interconnect; -applying a first metal oxide layer on said metal interconnect; -applying a second metal oxide layer on top of said first metal oxide layer; -applying a third metal oxide layer on top of said second metal oxide layer; -forming a solid oxide cell stack comprising said metal interconnect having said metal oxide layers thereon; and -reacting the metal oxide in said first metal oxide layer with the metal of said metal interconnect during the SOC-stack initialisation, and a solid oxide stack comprising an anode contact layer and support structure, an anode layer, an electrolyte layer, a cathode layer, a cathode contact layer, a metallic interconnect, and a multilayer barrier structure which is obtainable by the above method and through an initialisation step, which is carried out under controlled conditions for atmosphere composition and current load, which depends on the layer composition facilitating the formation of the desired reaction products as a dense barrier layer without chromium species migrating to the air-electrode.

Owner:TOPSOE FUEL CELL +1

Polishing pad

InactiveUS6705934B1Reduce global step heightDepression depressionOther chemical processesSemiconductor/solid-state device manufacturingSurface layerHardness

The present invention relates to a polishing pad which is characterized in that it is of micro rubber A-type hardness at least 80°, has closed cells of average cell diameter no more than 1000 mum, is of density in the range 0.4 to 1.1 and contains polyurethane and polymer produced from a vinyl compound. When planarizing local unevenness on a semiconductor substrate with the polishing pad relating to the present invention, the polishing rate is high, the global step height is low, dishing does not readily occur at the metallic interconnects, clogging and permanent set of the surface layer region do not readily occur and the polishing rate is stable.

Owner:TORAY IND INC

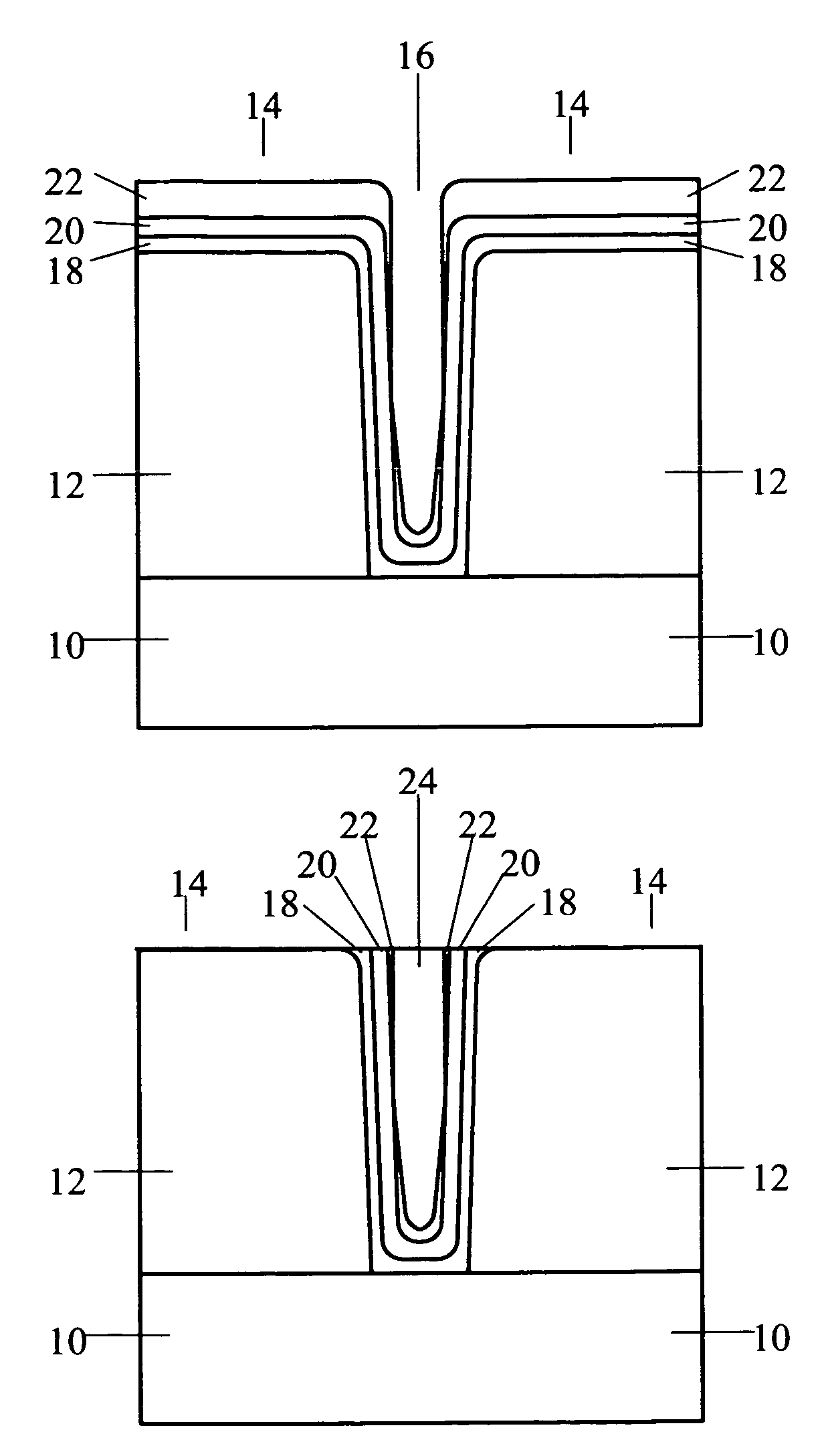

Advanced seed layery for metallic interconnects

One embodiment of the present invention is a method for making metallic interconnects, which method is utilized at a stage of processing a substrate having a patterned insulating layer which includes at least one opening and a field surrounding the at least one opening, the field and the at least one opening being ready for depositing one or more seed layers, which method includes steps of: (a) depositing by an ALD technique at least an initial portion of a substantially conformal seed layer on the field and inside surfaces of the at least one opening, wherein said at least one opening has a width of less than about 0.13 μm; (b) depositing by a PVD technique a substantially non-conformal seed layer over the substantially conformal seed layer, said substantially non-conformal seed layer being thicker than said substantially conformal seed layer over the field; and (c) electroplating a metallic layer over the substantially non-conformal seed layer, wherein the electroplated metallic layer consists of a material selected from a group consisting of Cu, Ag, or alloys comprising one or more of these metals.

Owner:COHEN URI DR

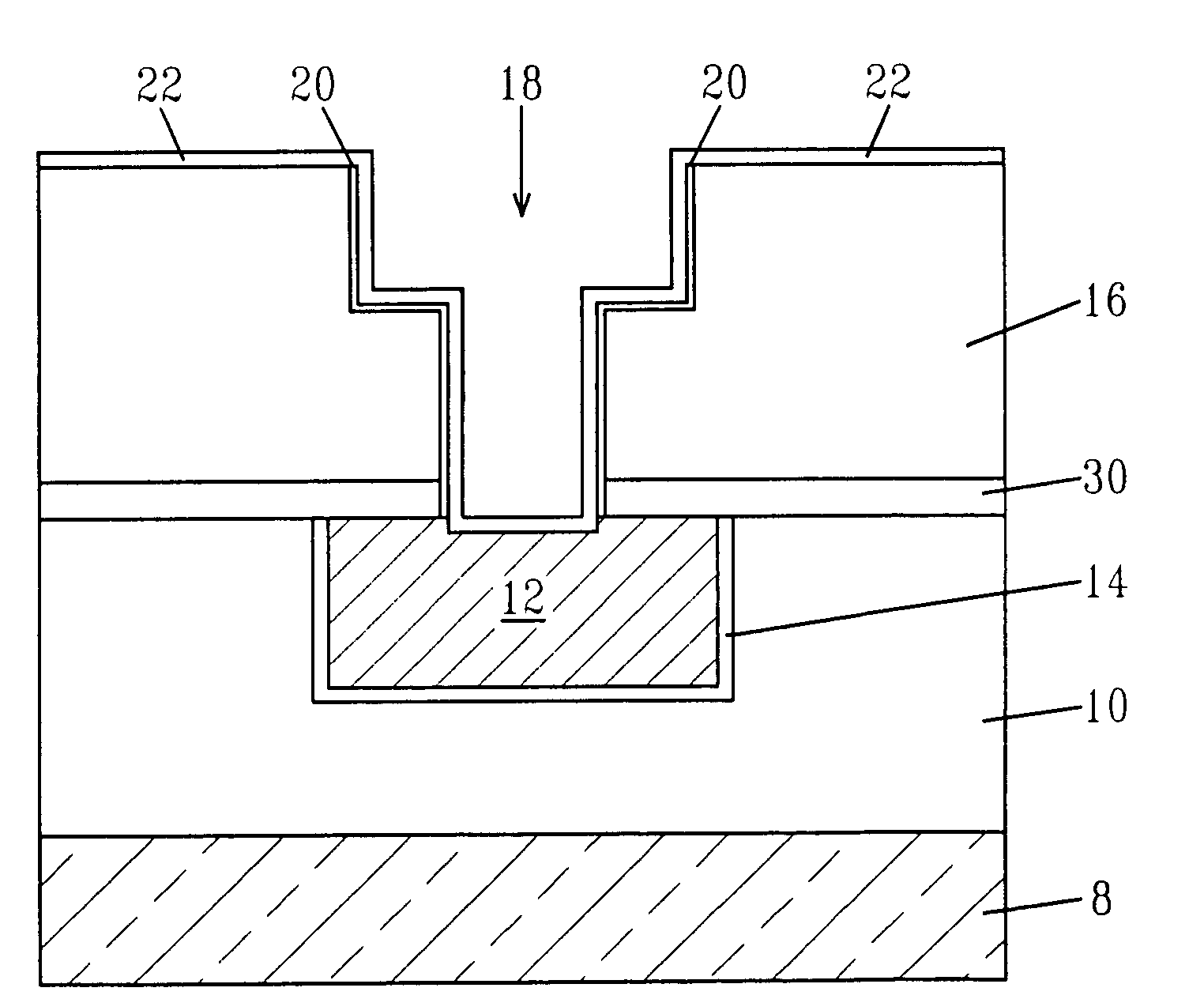

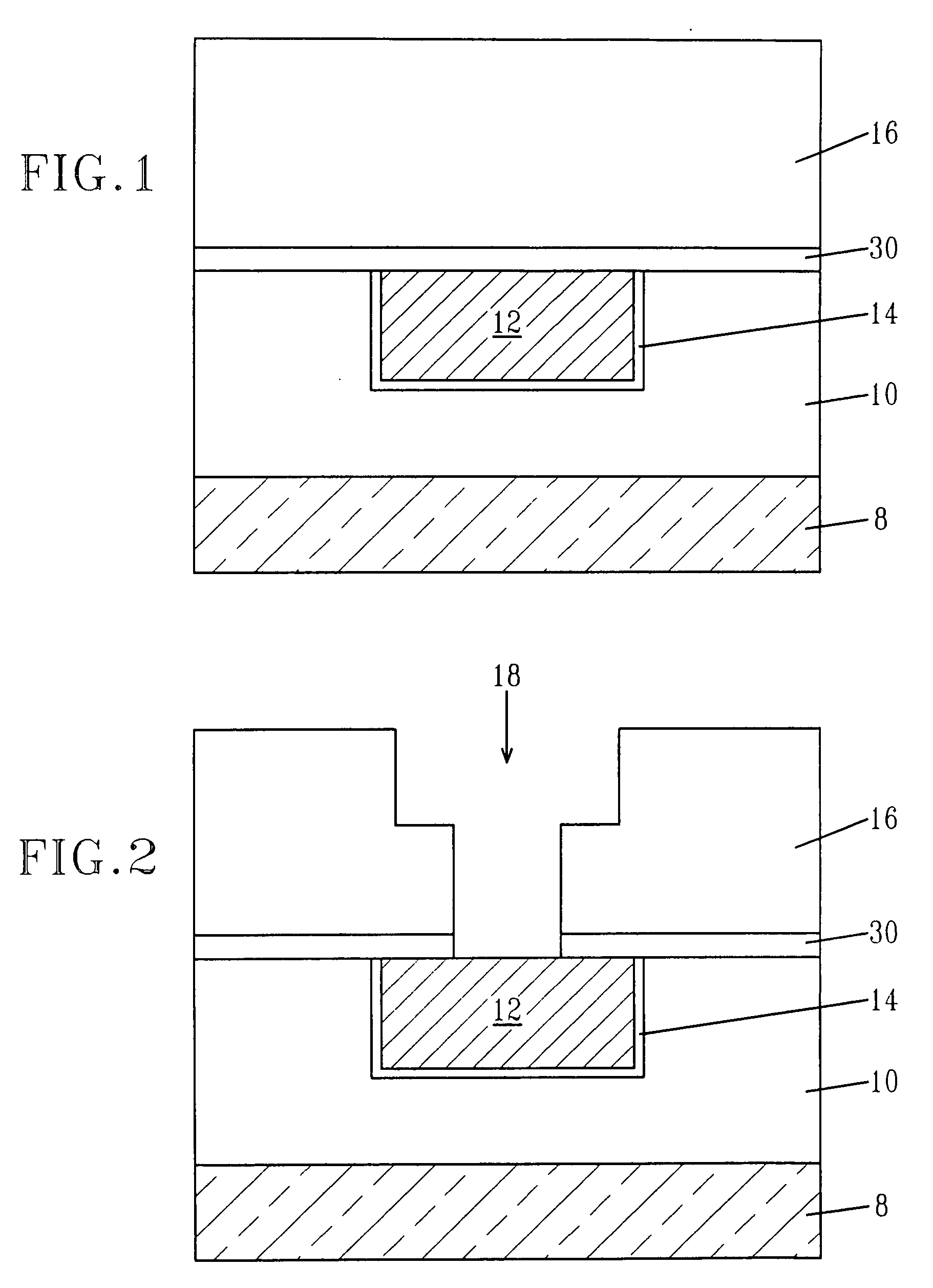

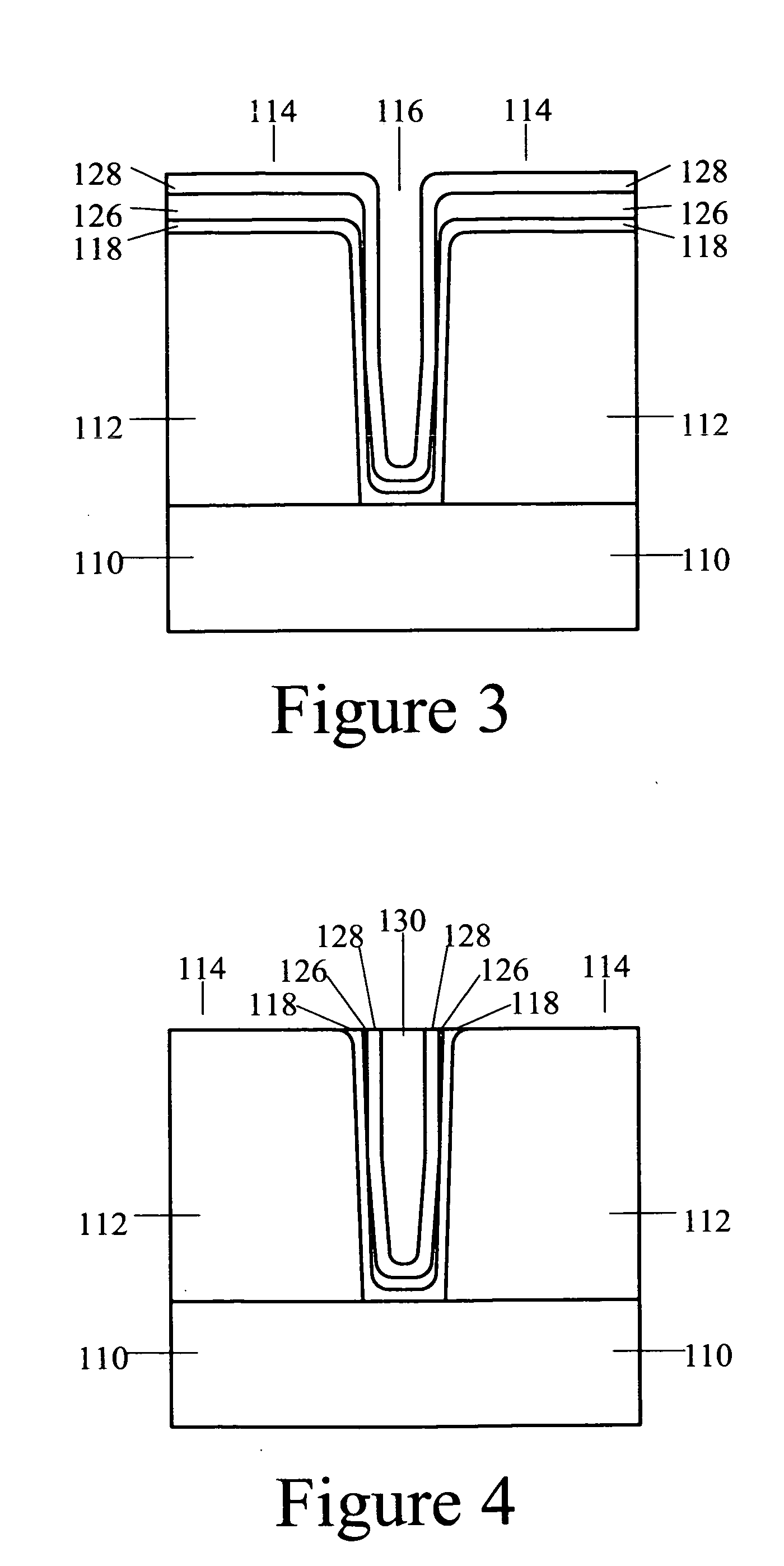

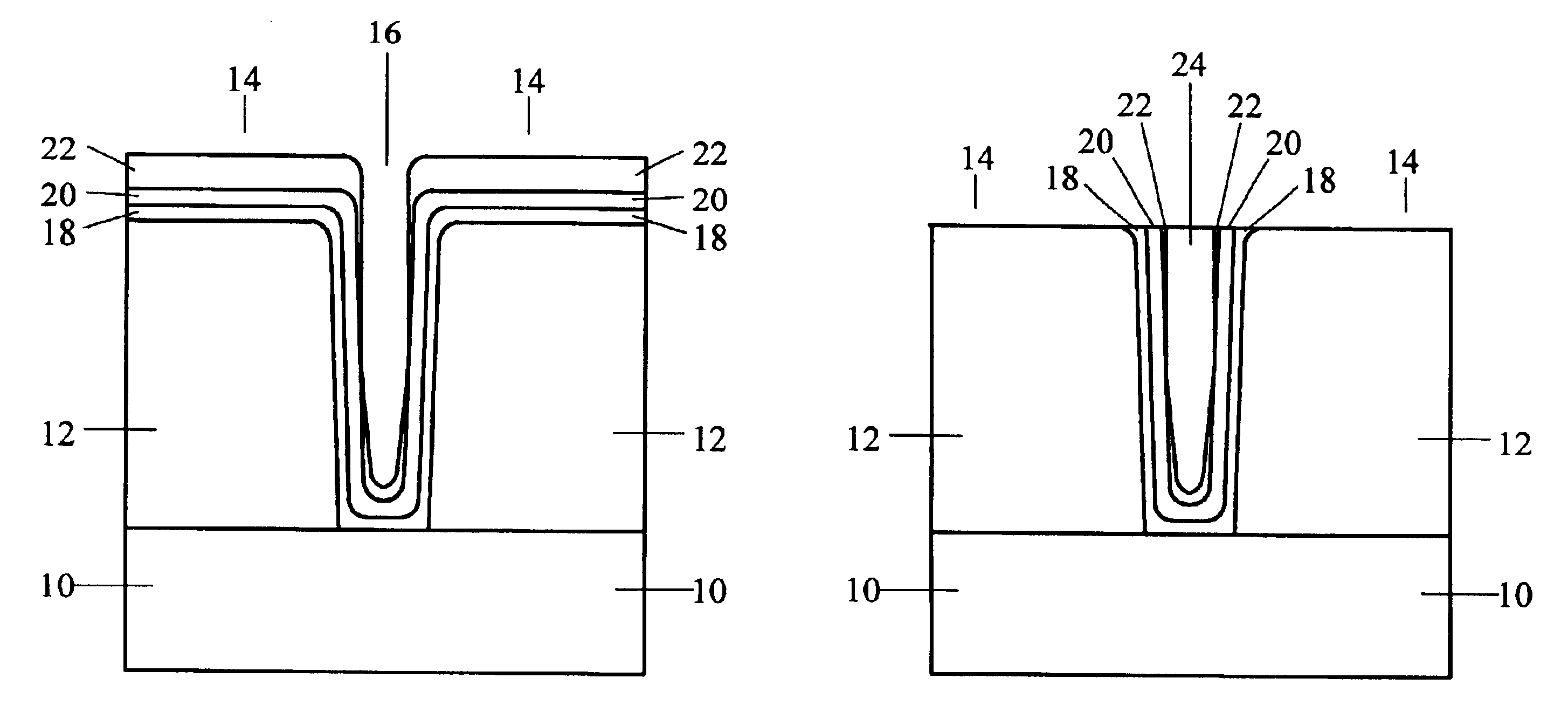

Methods for making multiple seed layers for metallic interconnects

InactiveUS6924226B2High aspect ratioSolid-state devicesSemiconductor/solid-state device manufacturingAlloyOptoelectronics

One embodiment of the present invention is a method for making metallic interconnects, which method is utilized at a stage of processing a substrate having a patterned insulating layer which includes at least one opening and a field surrounding the at least one opening, the field and the at least one opening being ready for depositing of one or more seed layers, which method includes steps of: (a) depositing a substantially conformal seed layer over the field and inside surfaces of the at least one opening; (b) depositing a substantially non-conformal seed layer over the substantially conformal seed layer, said substantially non-conformal seed layer being thicker than said substantially conformal seed layer over the field, wherein the substantially conformal and the substantially non-conformal seed layers do not seal the at least one opening; and (c) electroplating a metallic layer over the substantially non-conformal seed layer, wherein the electroplated metallic layer comprises a material selected from a group consisting of Cu, Ag, or alloys comprising one or more of these metals.

Owner:COHEN URI DR

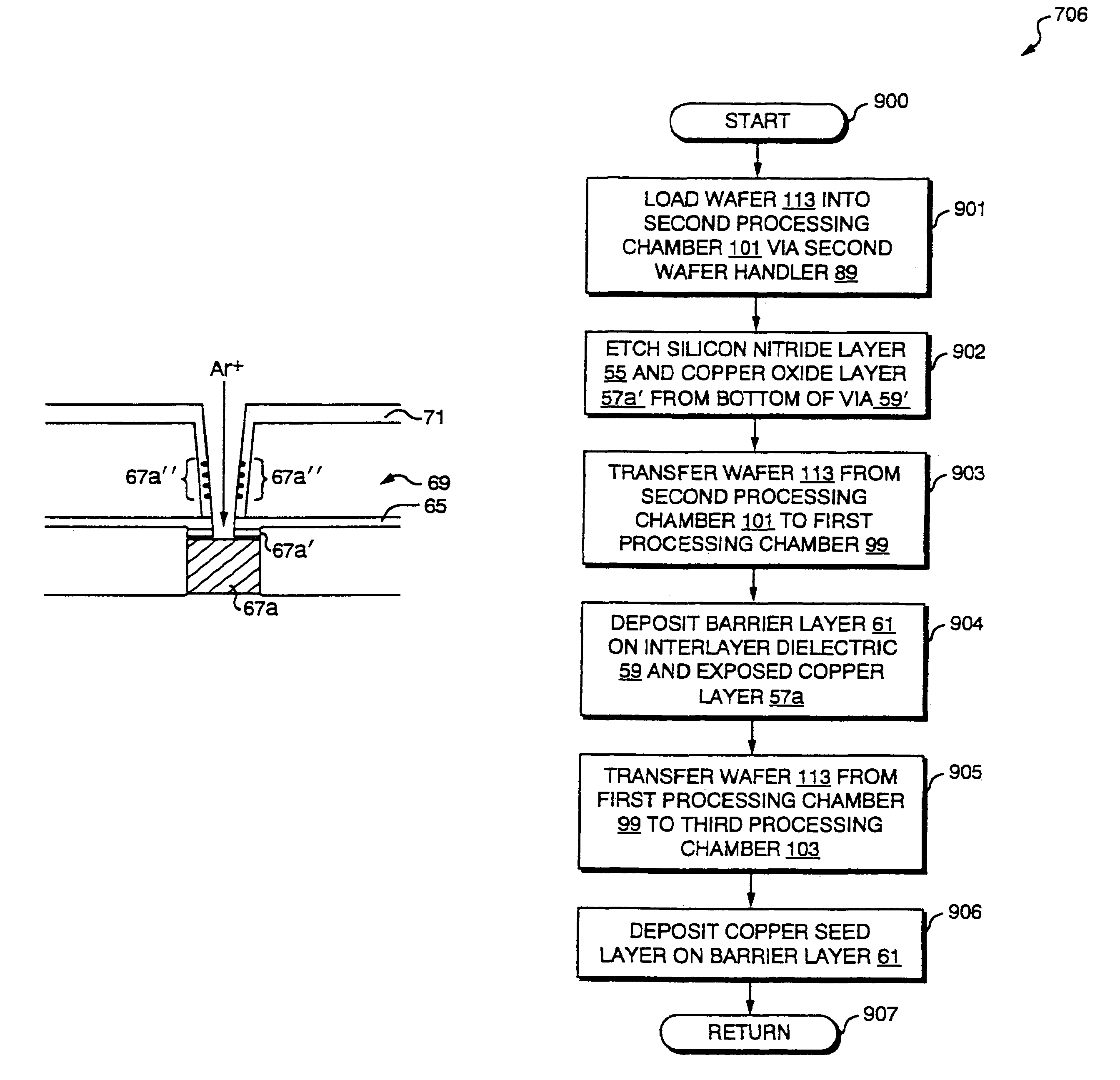

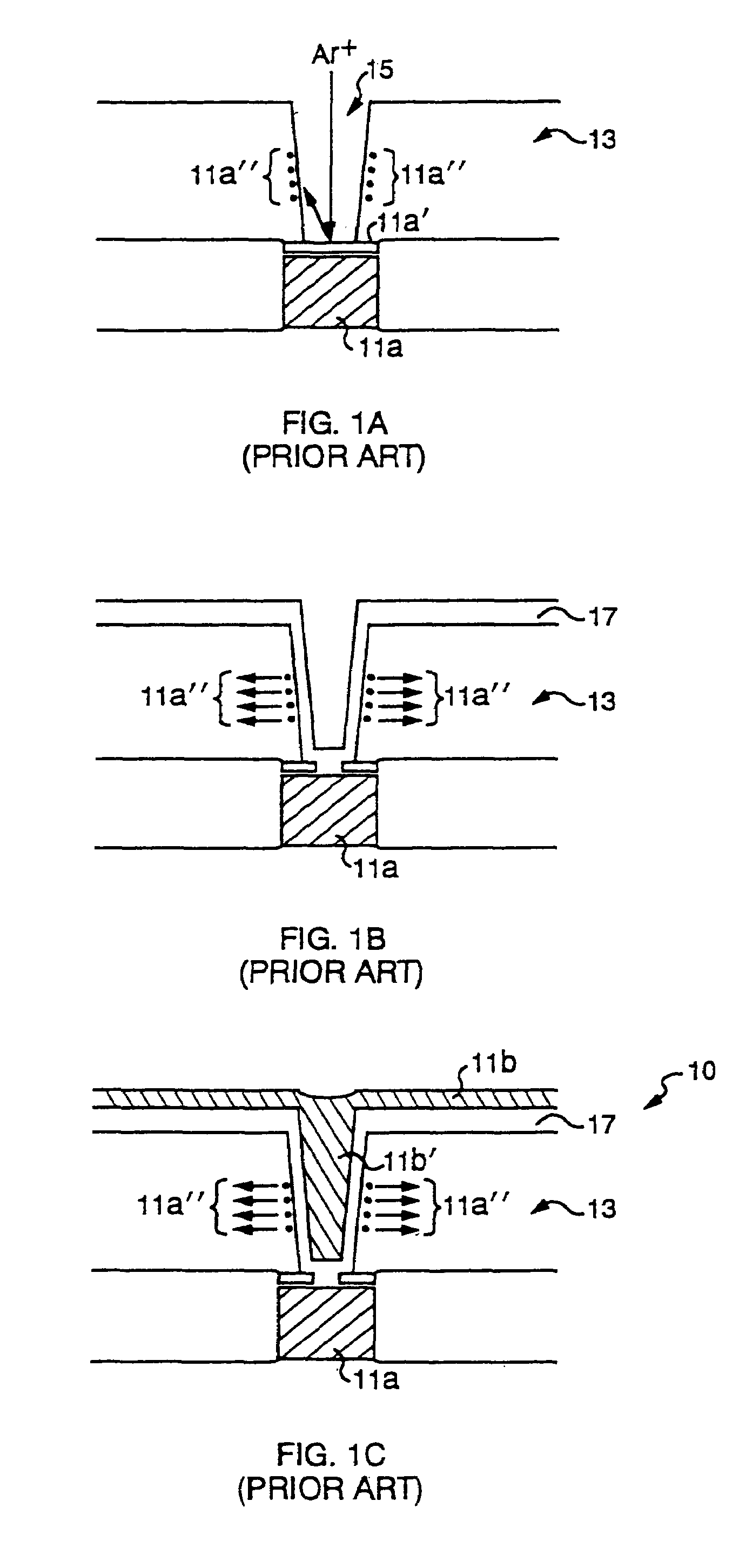

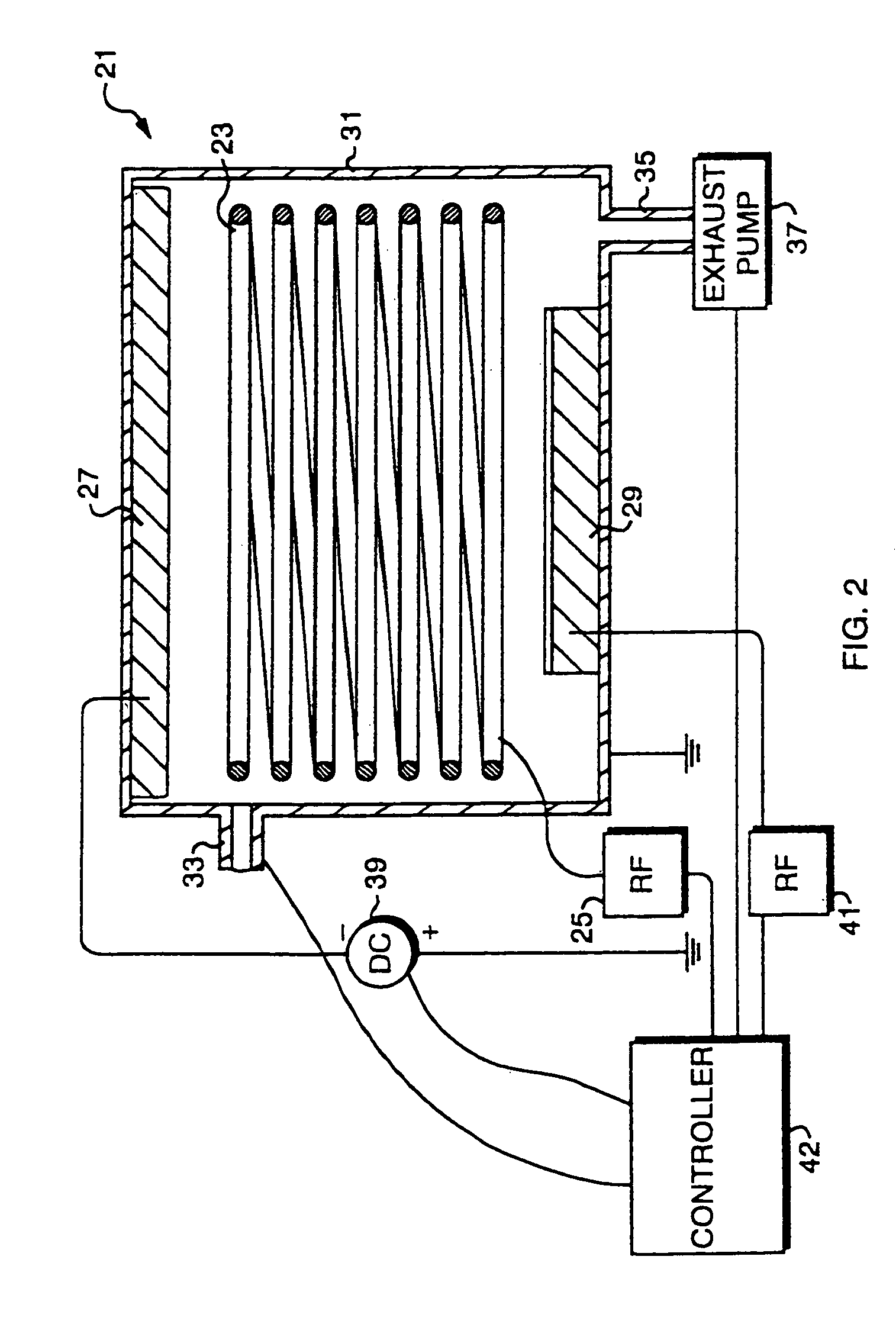

Method and apparatus for forming improved metal interconnects

InactiveUS6992012B2High resistivityLower resistanceSemiconductor/solid-state device detailsSolid-state devicesSputteringCopper atom

Methods of forming copper interconnects free from via-to-via leakage currents and having low resistances are disclosed. In a first aspect, a barrier layer is deposited on the first metal layer prior to copper oxide sputter-etching to prevent copper atoms from reaching the interlayer dielectric and forming via-to-via leakage current paths therein. In a second aspect, a capping dielectric barrier layer is deposited over the first metal layer prior to sputter etching. During sputter-etching, the capping dielectric barrier layer redistributes on the sidewalls of the interlayer dielectric, preventing sputter-etched copper atoms from reaching the interlayer dielectric and forming via-to-via leakage paths therein. In a third aspect, both a capping dielectric barrier layer and a barrier layer are deposited over the first metal layer prior to sputter-etching to prevent copper atoms produced during sputter-etching from reaching the interlayer dielectric and forming via-to-via leakage paths therein.

Owner:APPLIED MATERIALS INC

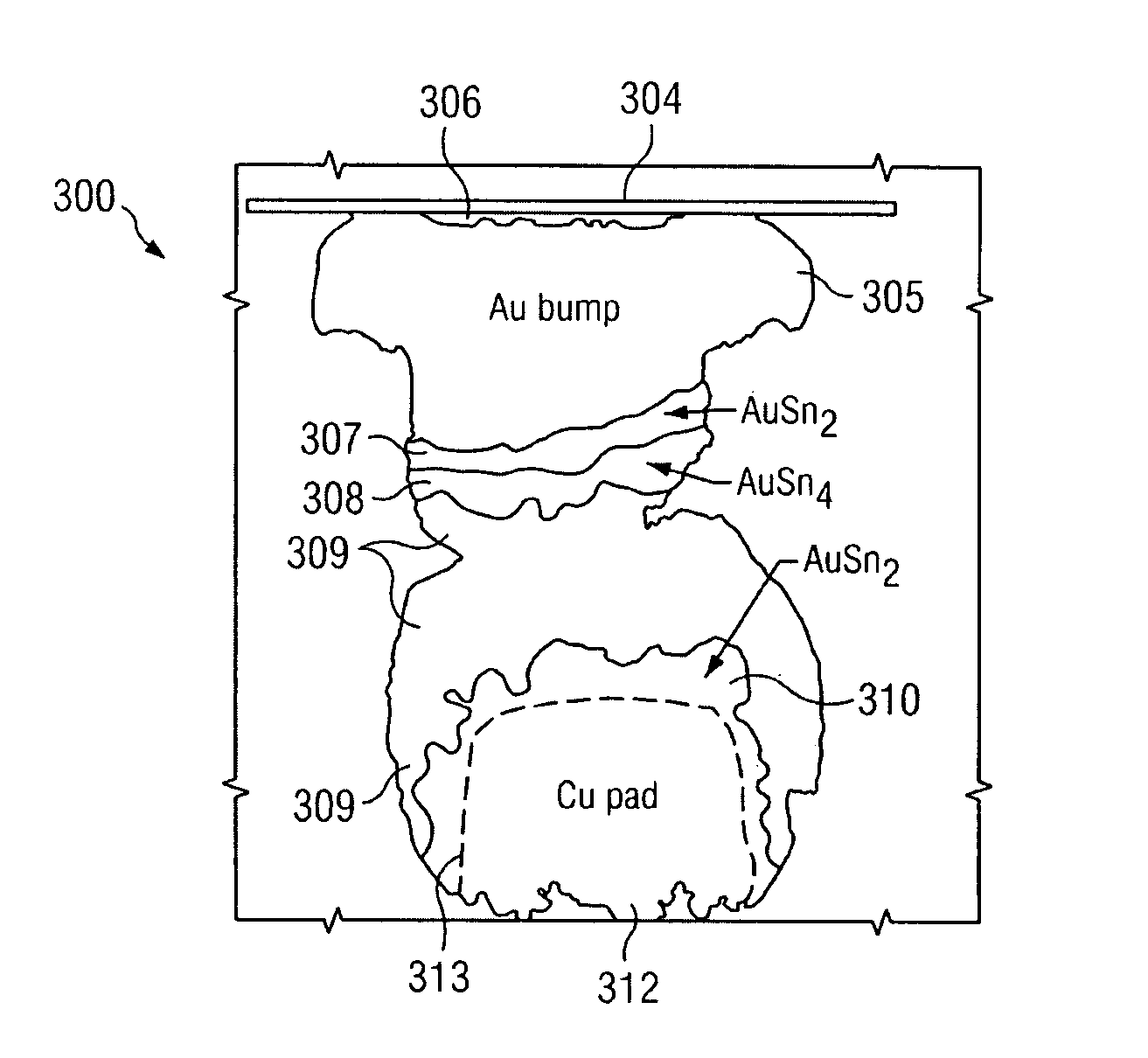

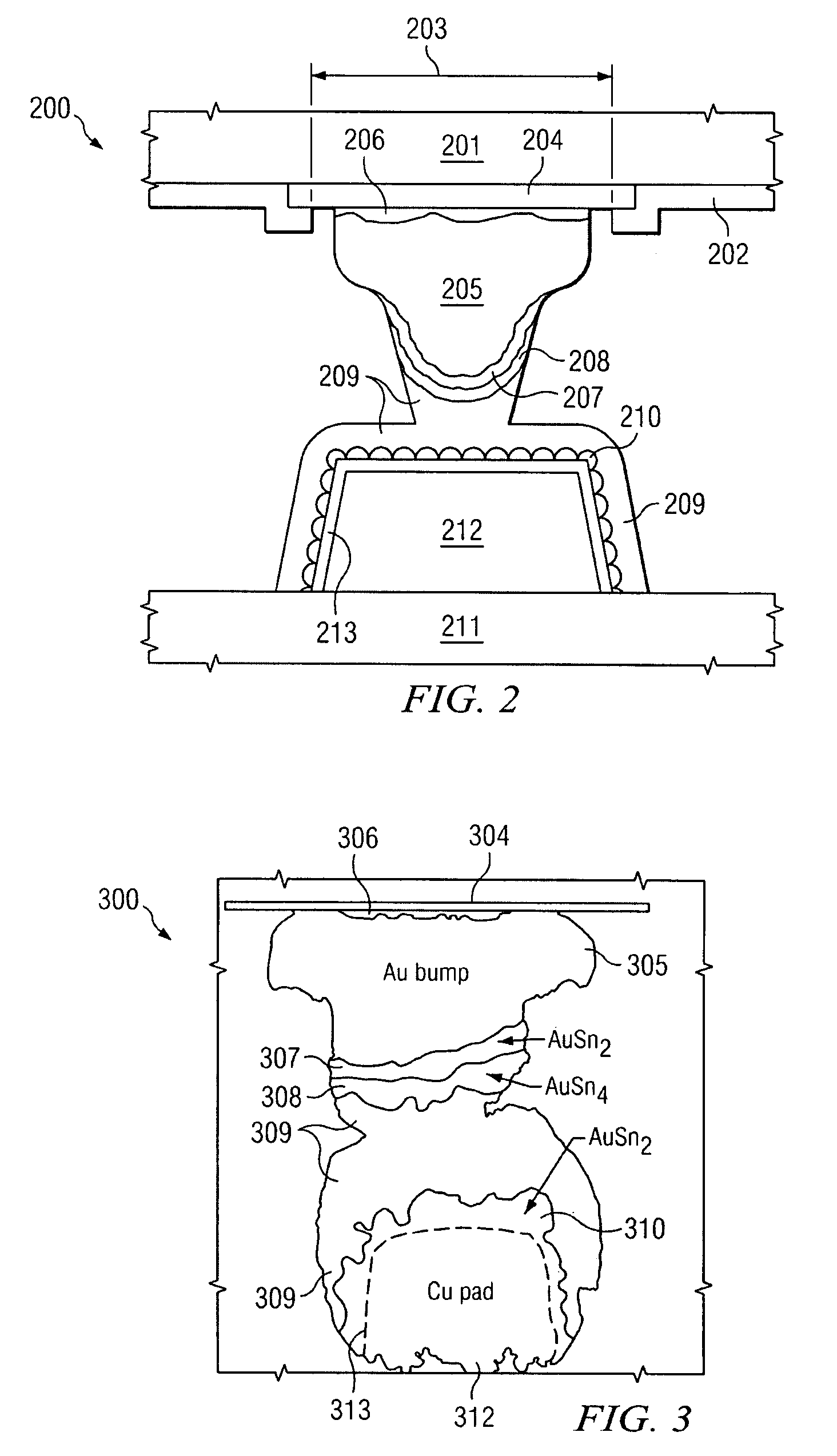

Stable gold bump solder connections

ActiveUS7939939B1High dissolution rateLess brittleSemiconductor/solid-state device detailsSolid-state devicesSolid solutionIntermetallic

A metallic interconnect structure (200) for connecting a gold bump (205) and a copper pad (212), as used for example in semiconductor flip-chip assembly. A first region (207) of binary AuSn2 intermetallic is adjacent to the gold bump. A region (208) of binary AuSn4 intermetallic is adjacent to the first AuSn2 region. Then, a region (209) of binary gold-tin solid solution is adjacent to the AuSn4 region, and a second region (210) of binary AuSn2 intermetallic is adjacent to the solid solution region. The second AuSn2 region is adjacent to a nickel layer (213) (preferred thickness about 0.08 μm), which covers the copper pad. The nickel layer insures that the gold / tin intermetallics and solutions remain substantially free of copper and thus avoid ternary compounds, providing stabilized gold bump / solder connections.

Owner:TEXAS INSTR INC

Formulations for Cleaning Ion-Implanted Photoresist Layers from Microelectronic Devices

InactiveUS20080269096A1Organic detergent compounding agentsAnionic surface-active compoundsSURFACTANT BLENDIon pairs

A method and composition for removing bulk and ion-implanted photoresist and / or post-etch residue material from densely patterned microelectronic devices is described. The composition includes a co-solvent, a chelating agent, optionally an ion pairing reagent, and optionally a surfactant. The composition may further include dense fluid. The compositions effectively remove the photoresist and / or post-etch residue material from the microelectronic device without substantially over-etching the underlying silicon-containing layer(s) and metallic interconnect materials.

Owner:ADVANCED TECH MATERIALS INC

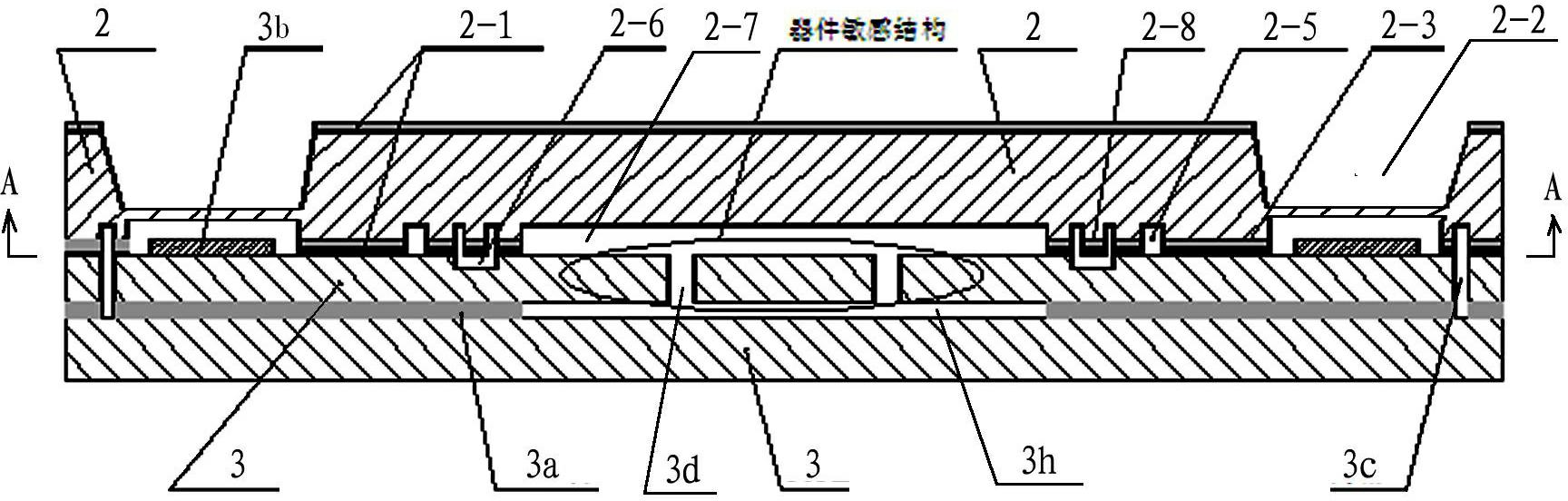

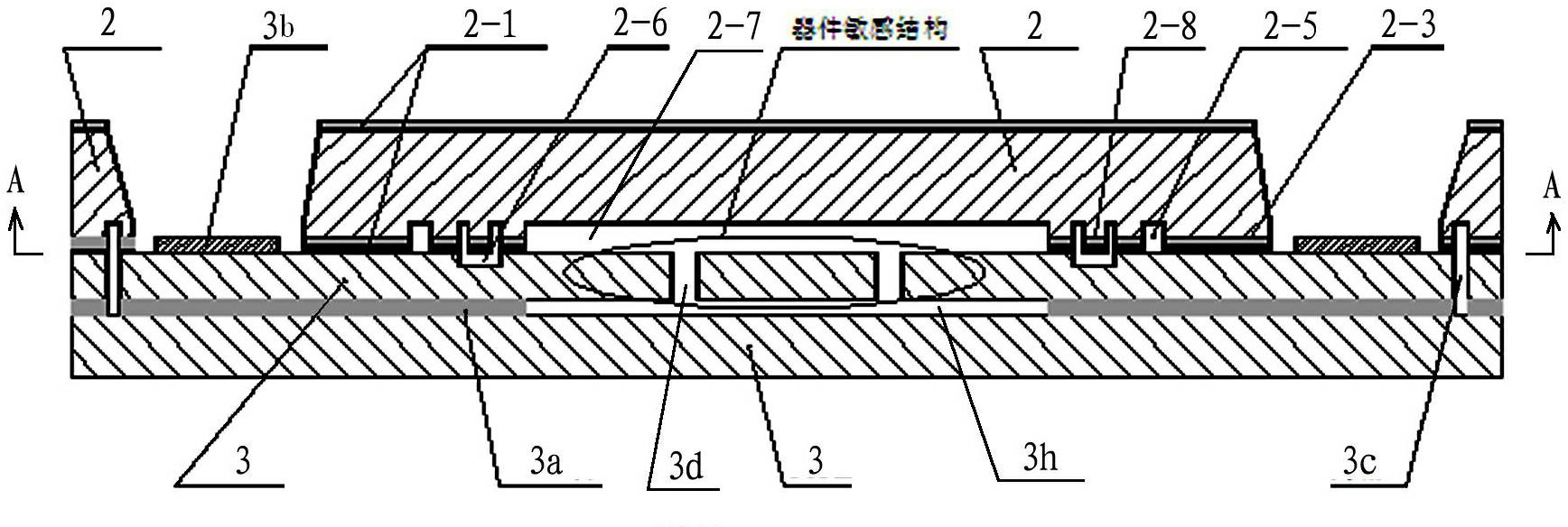

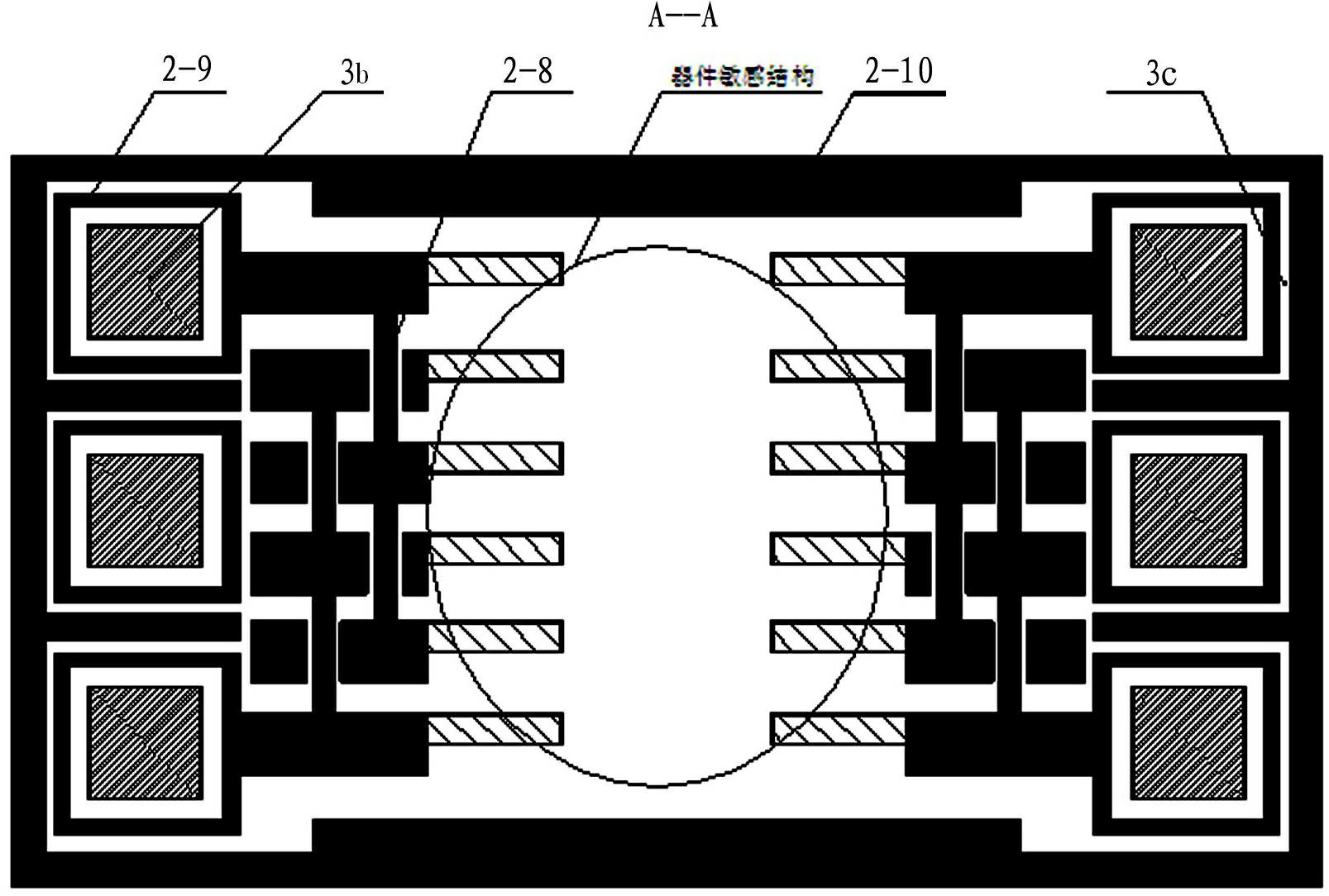

Method for interconnecting electrodes of MEMS (micro electro mechanical system) device based on SOI (silicon-on-insulator)

ActiveCN102367165ASuitable for productionSimple methodDecorative surface effectsChemical vapor deposition coatingElectricityEngineering

The invention relates to a method for interconnecting electrodes of an MEMS (micro electro mechanical system) device based on an SOI (silicon-on-insulator). In the method, a metal interconnection lead (2-8) and various electric isolation grooves (2-5, 2-6) are made on a silicon cover plate (2); and then, a structure layer (3) of the MEMS device is stuck with the silicon cover plate (2) through gold-silicon eutectic bonding, so that the electrodes of the MEMS device are interconnected together through the metal lead on the cover plate and led out to metal pressure welding points. The method provided by the invention overcomes the technical problems caused by the prior art adopting the techniques such as medium filling, flattening and the like, simplifies the techniques, is easy to operate, and is suitable for manufacturing various SOIMEMS devices.

Owner:EAST CHINA INST OF OPTOELECTRONICS INTEGRATEDDEVICE

Formulations for cleaning ion-implanted photoresist layers from microelectronic devices

InactiveUS8114220B2Organic detergent compounding agentsAnionic surface-active compoundsIon pairsSURFACTANT BLEND

A method and composition for removing bulk and ion-implanted photoresist and / or post-etch residue material from densely patterned microelectronic devices is described. The composition includes a co-solvent, a chelating agent, optionally an ion pairing reagent, and optionally a surfactant. The composition may further include dense fluid. The compositions effectively remove the photoresist and / or post-etch residue material from the microelectronic device without substantially over-etching the underlying silicon-containing layer(s) and metallic interconnect materials.

Owner:ADVANCED TECH MATERIALS INC

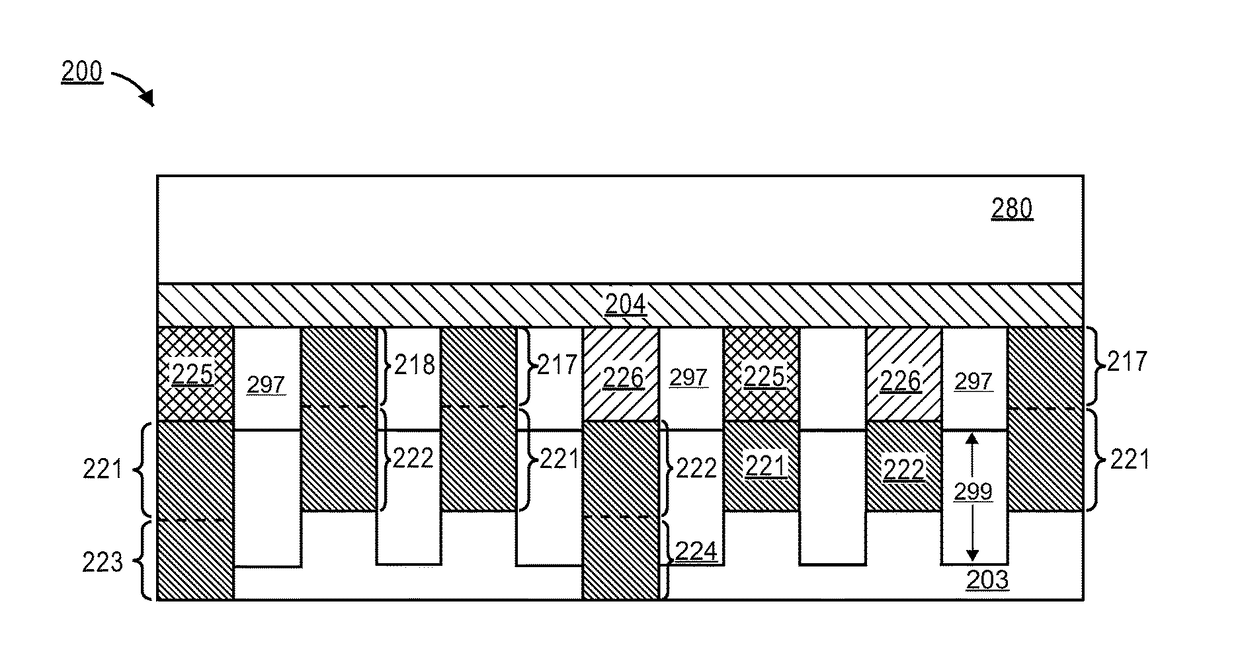

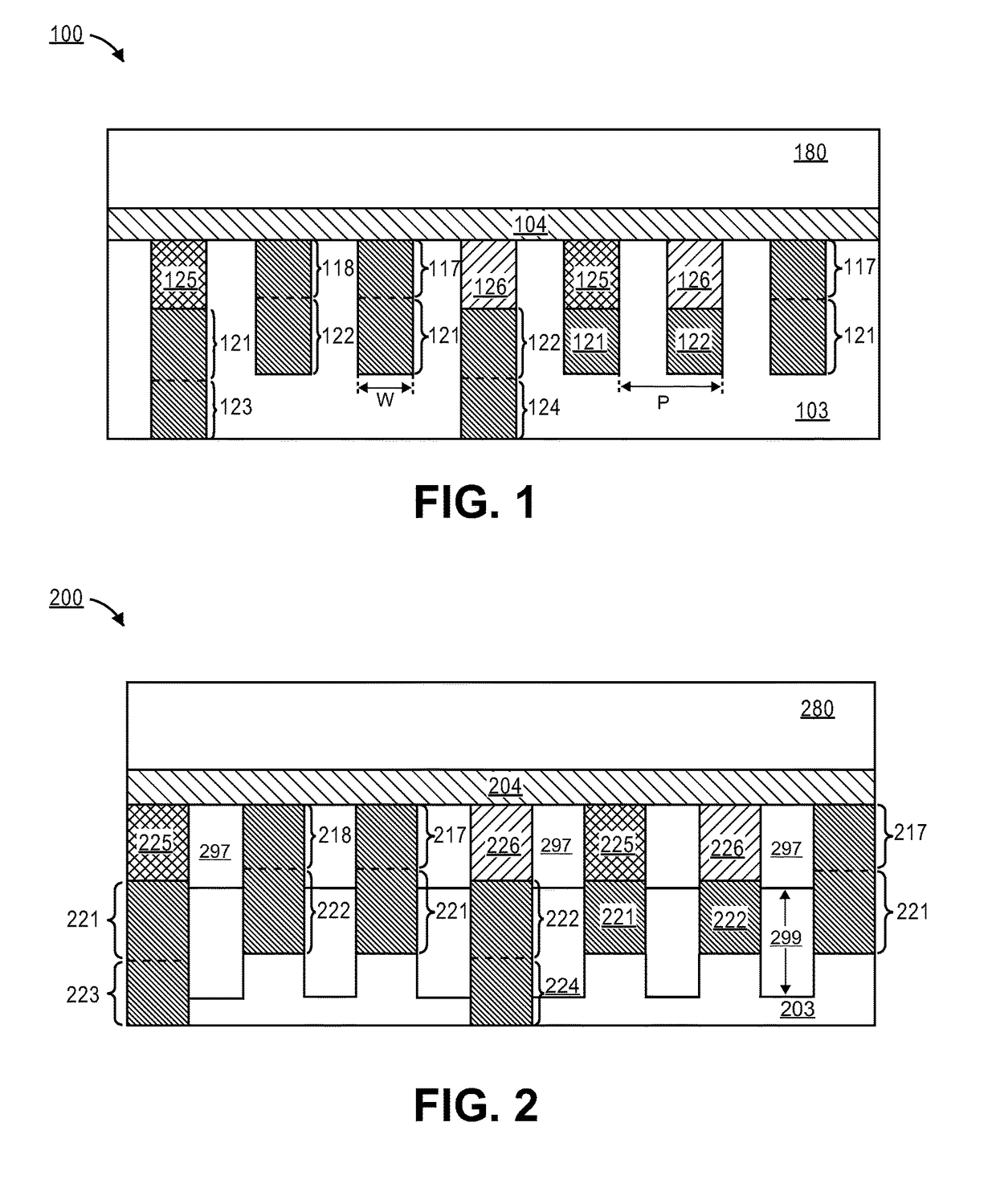

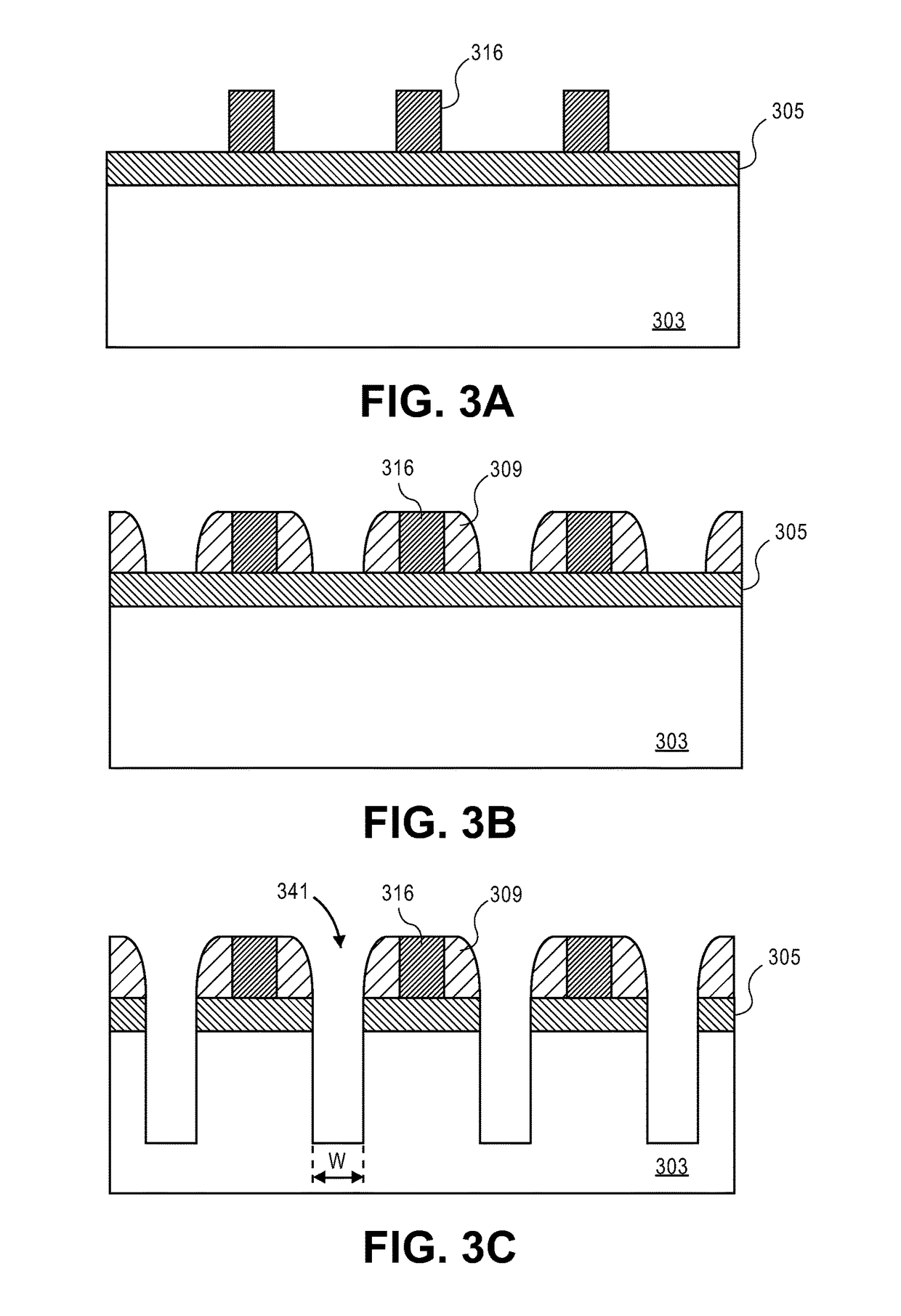

Structure and method to self align via to top and bottom of tight pitch metal interconnect layers

ActiveUS20170263553A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectEngineering

Embodiments of the invention include interconnect structures with overhead vias and through vias that are self-aligned with interconnect lines and methods of forming such structures. In an embodiment, an interconnect structure is formed in an interlayer dielectric (ILD). One or more first interconnect lines may be formed in the ILD. The interconnect structure may also include one or more second interconnect lines in the ILD that arranged in an alternating pattern with the first interconnect lines. Top surfaces of each of the first and second interconnect lines may be recessed below a top surface of the ILD. The interconnect structure may include a self-aligned overhead via formed over one or more of the first interconnect lines or over one or more of the second interconnect lines. In an embodiment, a top surface of the self-aligned overhead via is substantially coplanar with a top surface of the ILD.

Owner:INTEL CORP

Advanced seed layery for metallic interconnects

One embodiment of the present invention is a method for making metallic interconnects, which method is utilized at a stage of processing a substrate having a patterned insulating layer which includes at least one opening and a field surrounding the at least one opening, the field and the at least one opening being ready for depositing one or more seed layers, which method includes steps of: (a) depositing by an ALD technique at least an initial portion of a substantially conformal seed layer on the field and inside surfaces of the at least one opening, wherein said at least one opening has a width of less than about 0.13 μm; (b) depositing by a PVD technique a substantially non-conformal seed layer over the substantially conformal seed layer, said substantially non-conformal seed layer being thicker than said substantially conformal seed layer over the field; and (c) electroplating a metallic layer over the substantially non-conformal seed layer, wherein the electroplated metallic layer consists of a material selected from a group consisting of Cu, Ag, or alloys comprising one or more of these metals.

Owner:COHEN URI DR

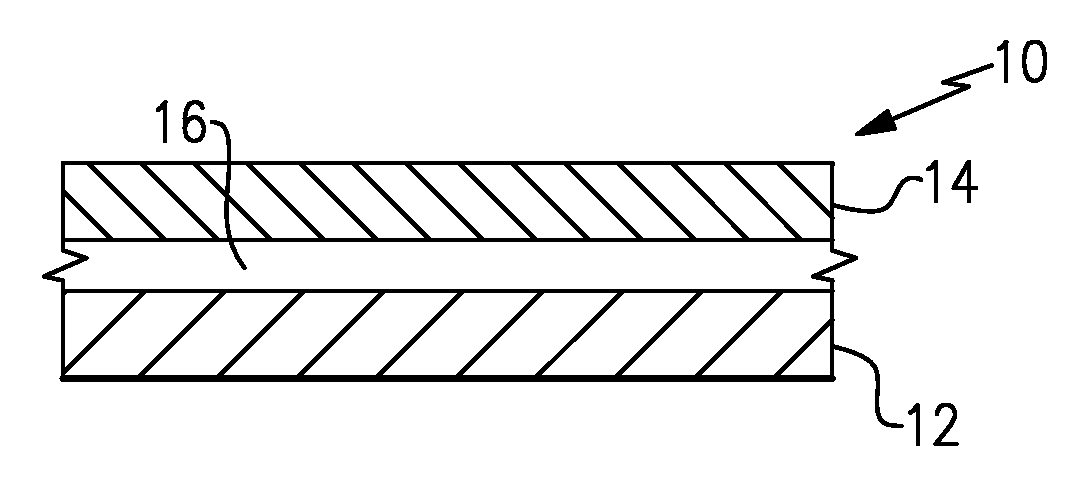

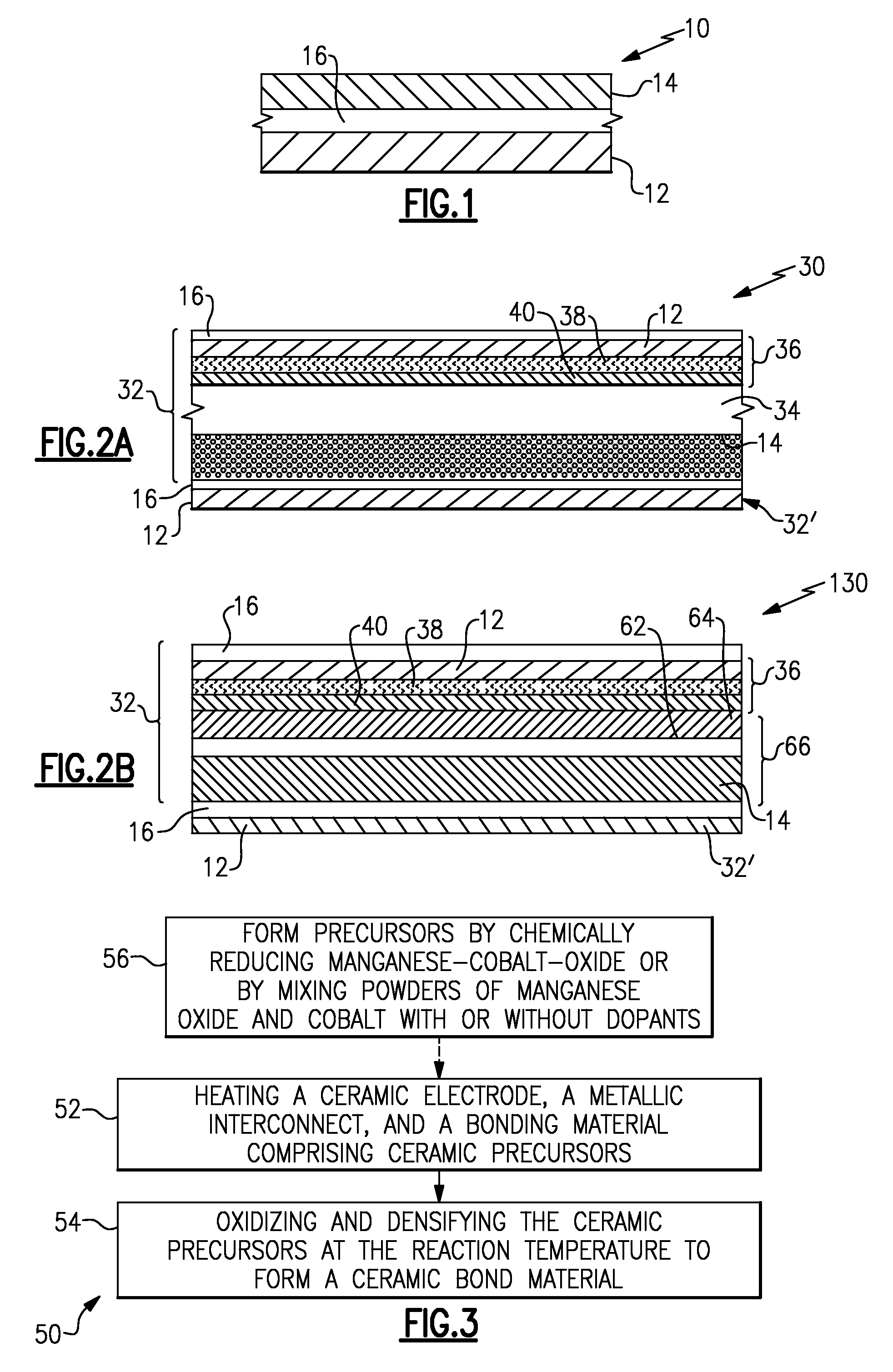

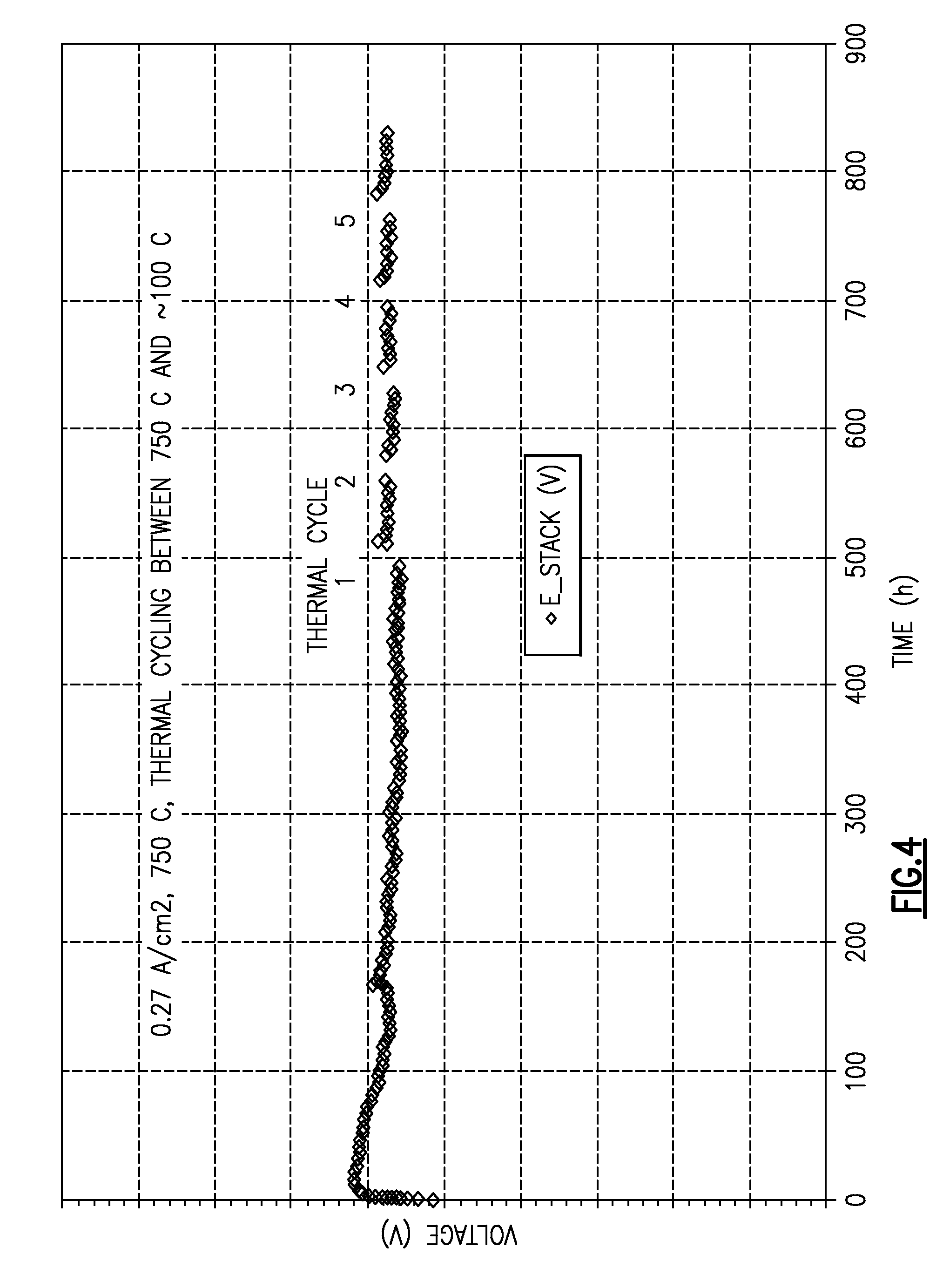

Method and device using a ceramic bond material for bonding metallic interconnect to ceramic electrode

An electrochemical device includes a ceramic electrode, a metallic interconnect, and a ceramic bond material that bonds the ceramic electrode and the metallic interconnect together. The ceramic material includes manganese-cobalt-oxide that is electrically conductive such that electric current can flow between the ceramic electrode and the metallic interconnect.

Owner:BALLARD POWER SYSTEMS

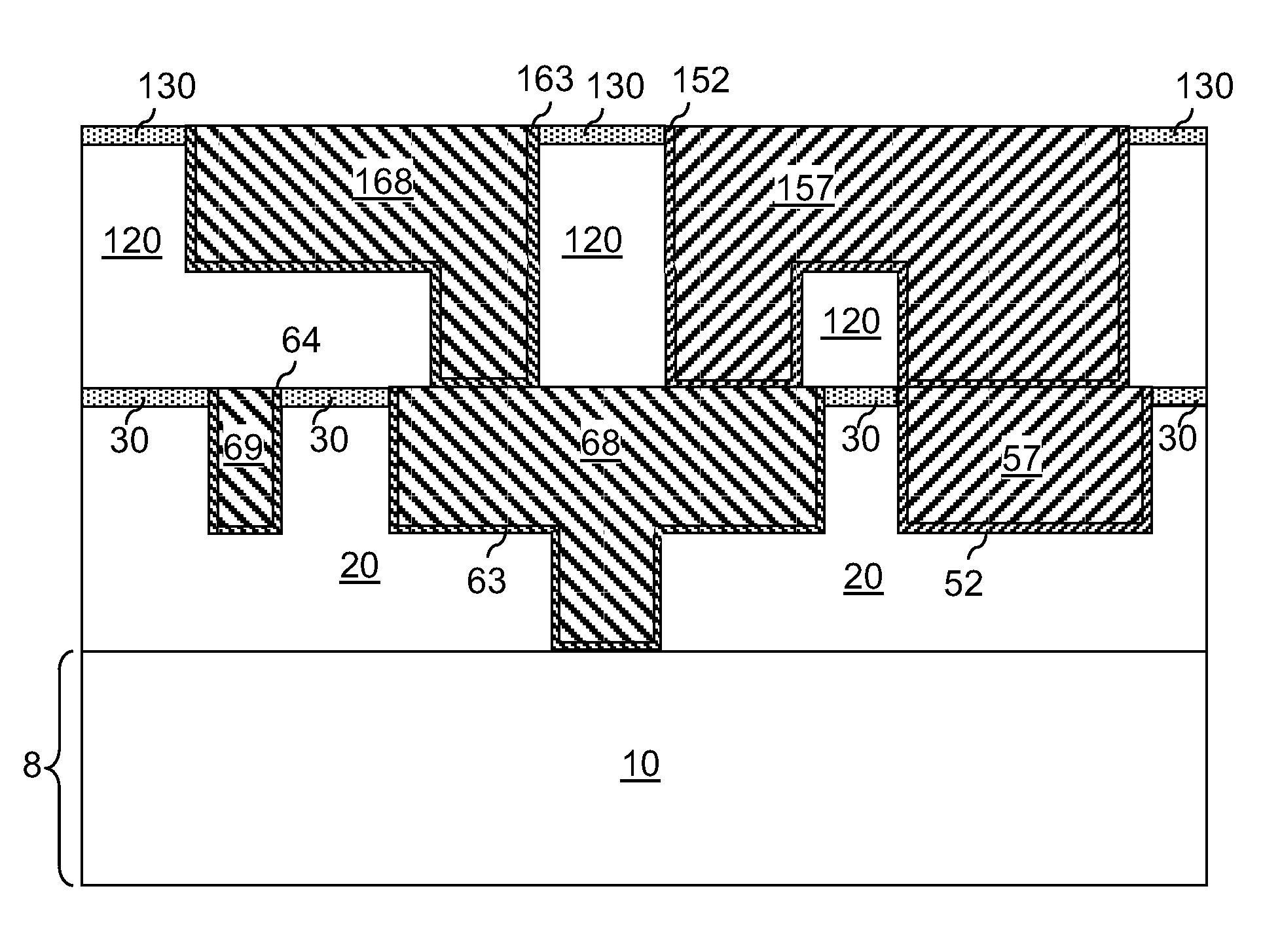

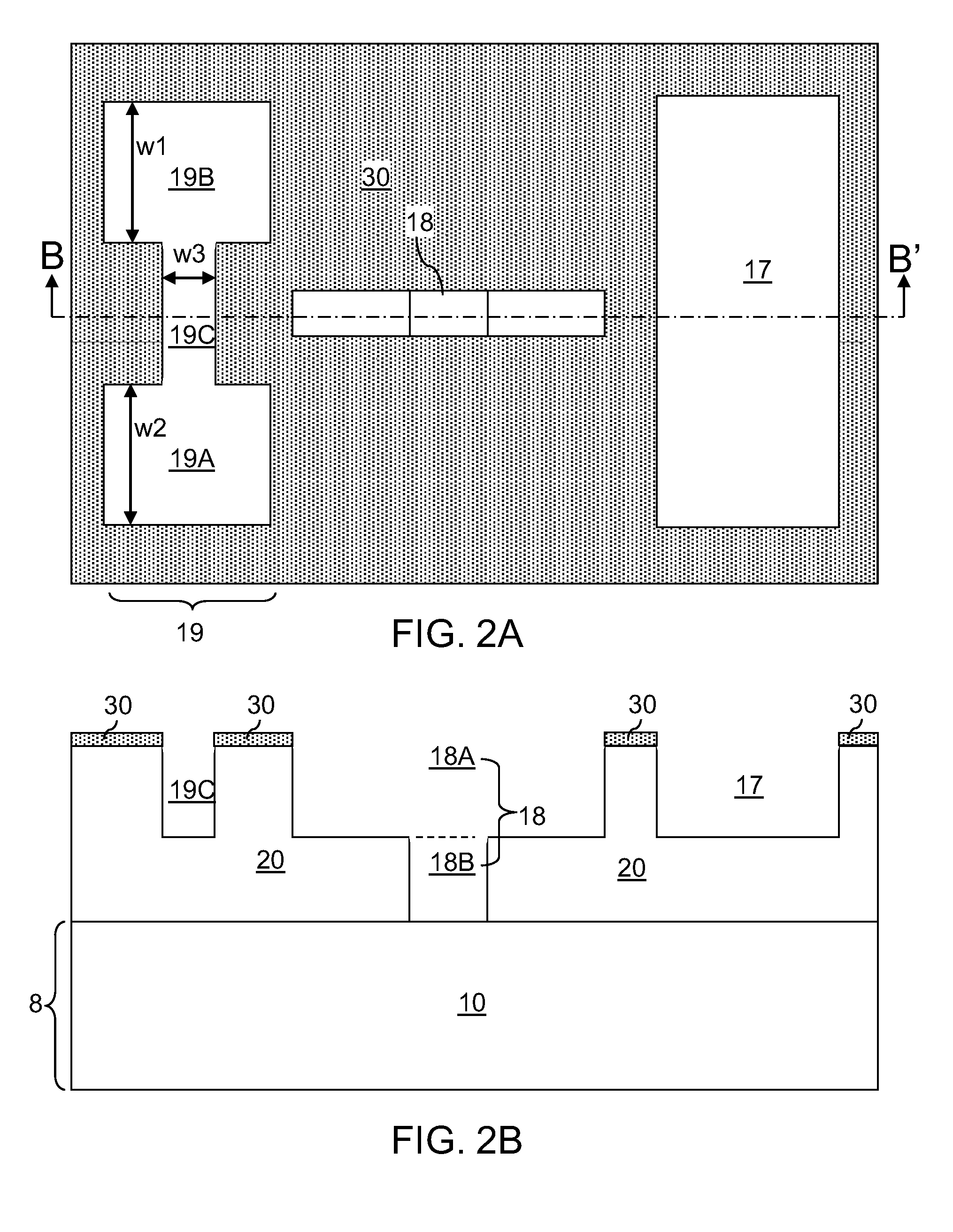

Size-filtered multimetal structures

InactiveUS20130043556A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectMaterials science

A size-filtered metal interconnect structure allows formation of metal structures having different compositions. Trenches having different widths are formed in a dielectric material layer. A blocking material layer is conformally deposited to completely fill trenches having a width less than a threshold width. An isotropic etch is performed to remove the blocking material layer in wide trenches, i.e., trenches having a width greater than the threshold width, while narrow trenches, i.e., trenches having a width less than the threshold width, remain plugged with remaining portions of the blocking material layer. The wide trenches are filled and planarized with a first metal to form first metal structures having a width greater than the critical width. The remaining portions of the blocking material layer are removed to form cavities, which are filled with a second metal to form second metal structures having a width less than the critical width.

Owner:IBM CORP

Contact-connection of nanotubes

InactiveUS20050148174A1Low possible resistanceThyristorSemiconductor/solid-state device detailsIt integrationNanotube

Owner:INFINEON TECH AG

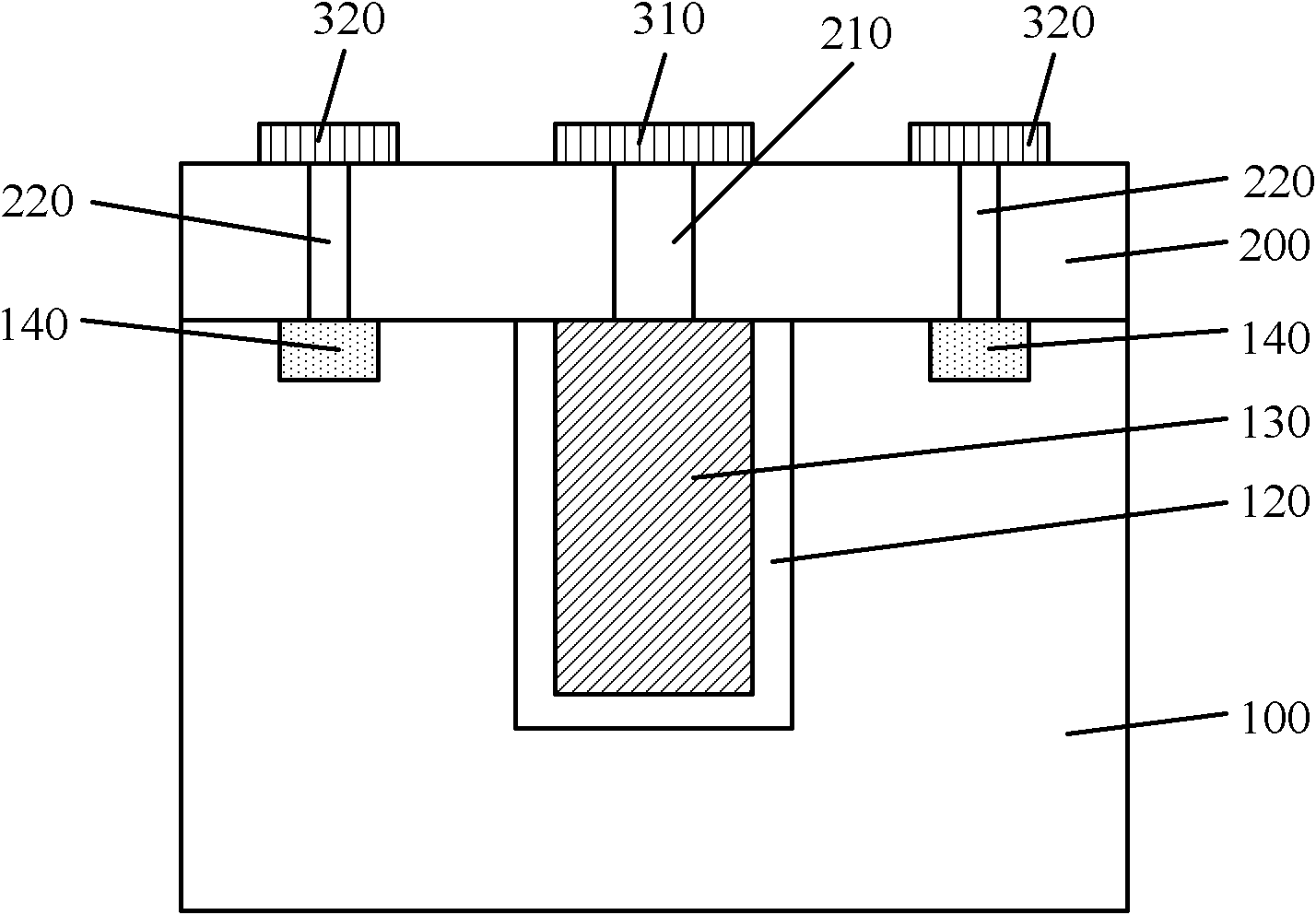

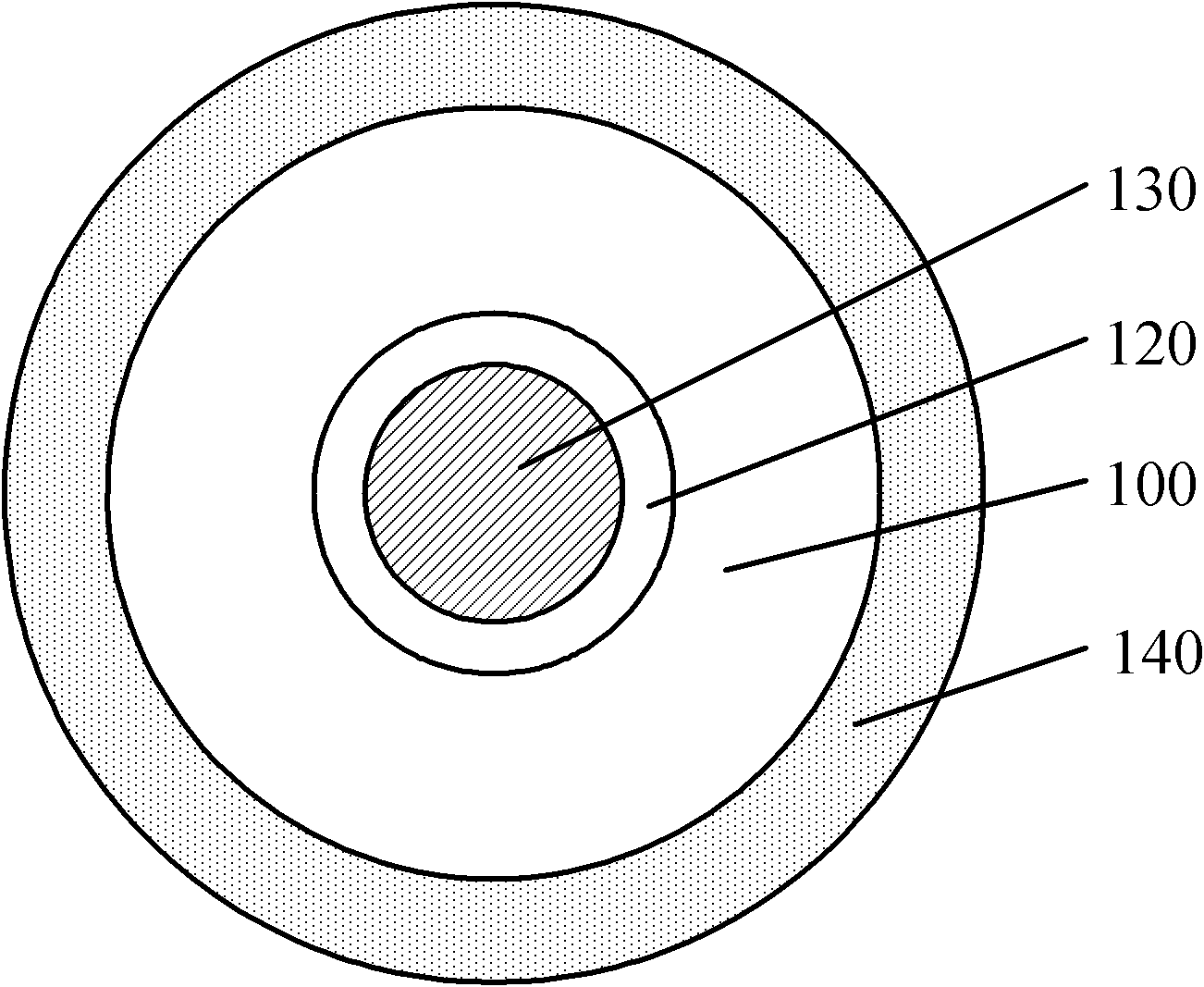

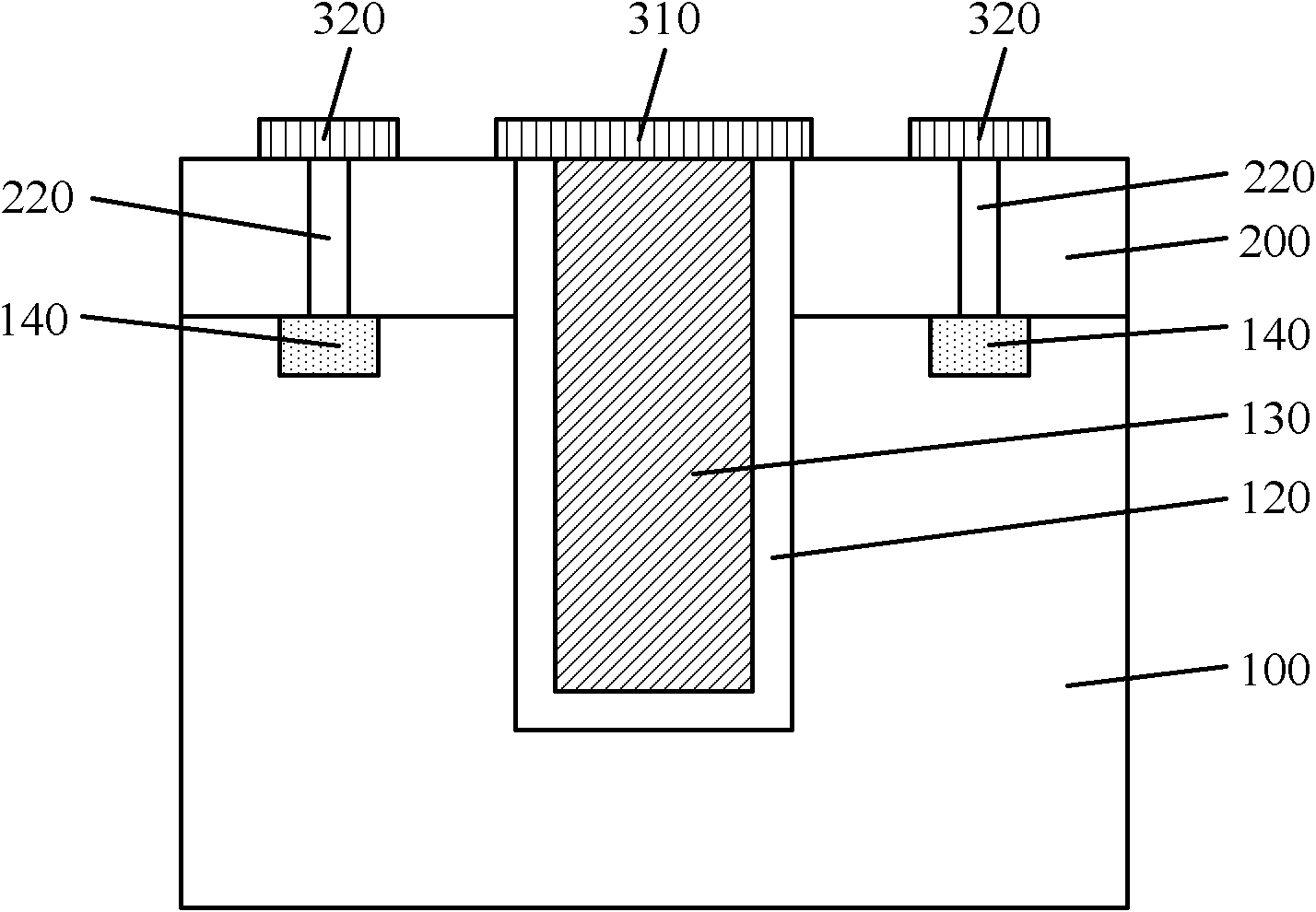

Silicon through-hole test structure and corresponding test method

ActiveCN103137511ASimple structureEasy to testSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCapacitanceInsulation layer

The invention discloses a silicon through-hole test structure which comprises a semi-conductor substrate, a silicon through hole, insulation layers, conducting materials, a heavily doped area, a dielectric layer and metal interconnection layers, wherein the silicon through hole is located inside the semi-conductor substrate, the insulation layers are located on the side wall and the bottom surface of the silicon through hole, the conducting materials are filled into the silicon through hole and located on the surfaces of the insulation layers, the heavily doped area is arranged to surround the silicon through hole and located inside the semi-conductor substrate, the dielectric layer is located on the surface of the semi-conductor substrate, and the metal interconnection layers are located on the surface of the dielectric layer. The conducting materials in the silicon through hole is in electricity connection with a first metal interconnection layer, and the heavily doped area is in electricity connection with a second metal interconnection layer, and the conducting materials in the silicon through hole is in electricity isolation with the heavily doped area. When polarization voltages are applied across the conducting materials of the silicon through hole and the heavily doped area, and then whether the insulation layers are judged complete or not through that whether leakage currents are measured between the conducting materials and the heavily doped area or not, and the depth of the silicon through hole is judged to reach a standard value or not through a measured capacitance value between the conducting materials and the heavily doped area, and the test process is simple and convenient.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com