Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

29190results about "Semiconductor/solid-state device testing/measurement" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

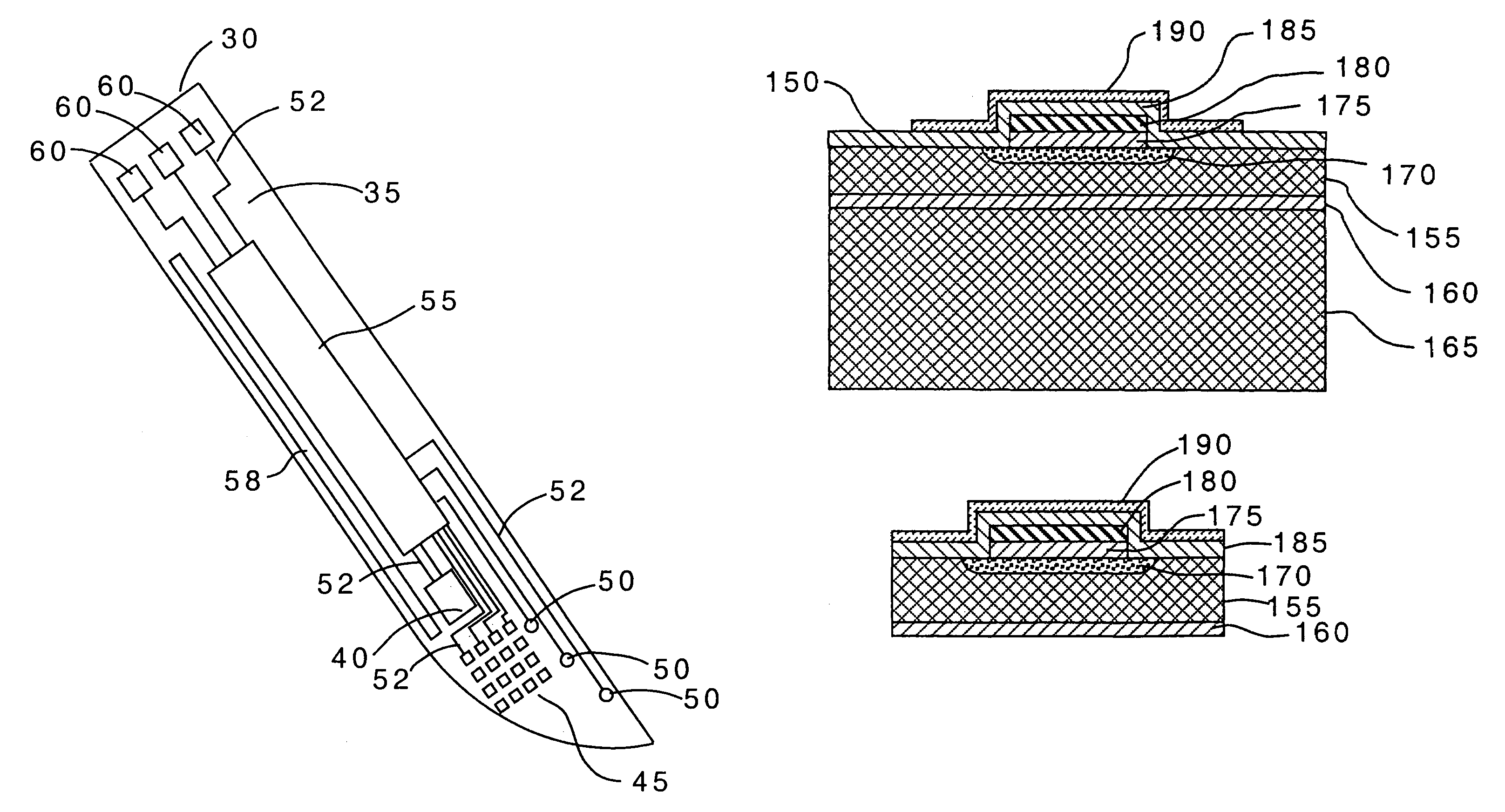

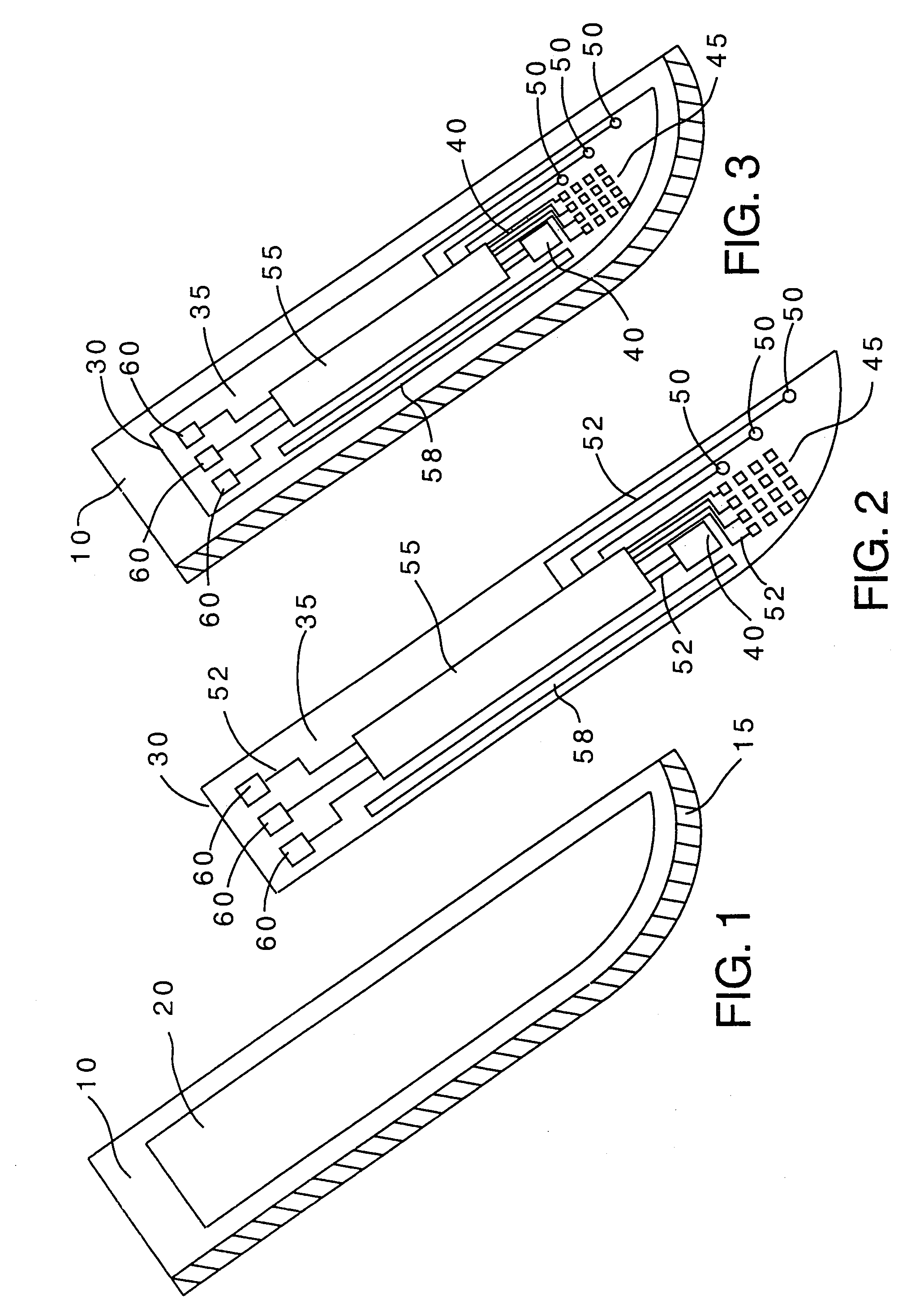

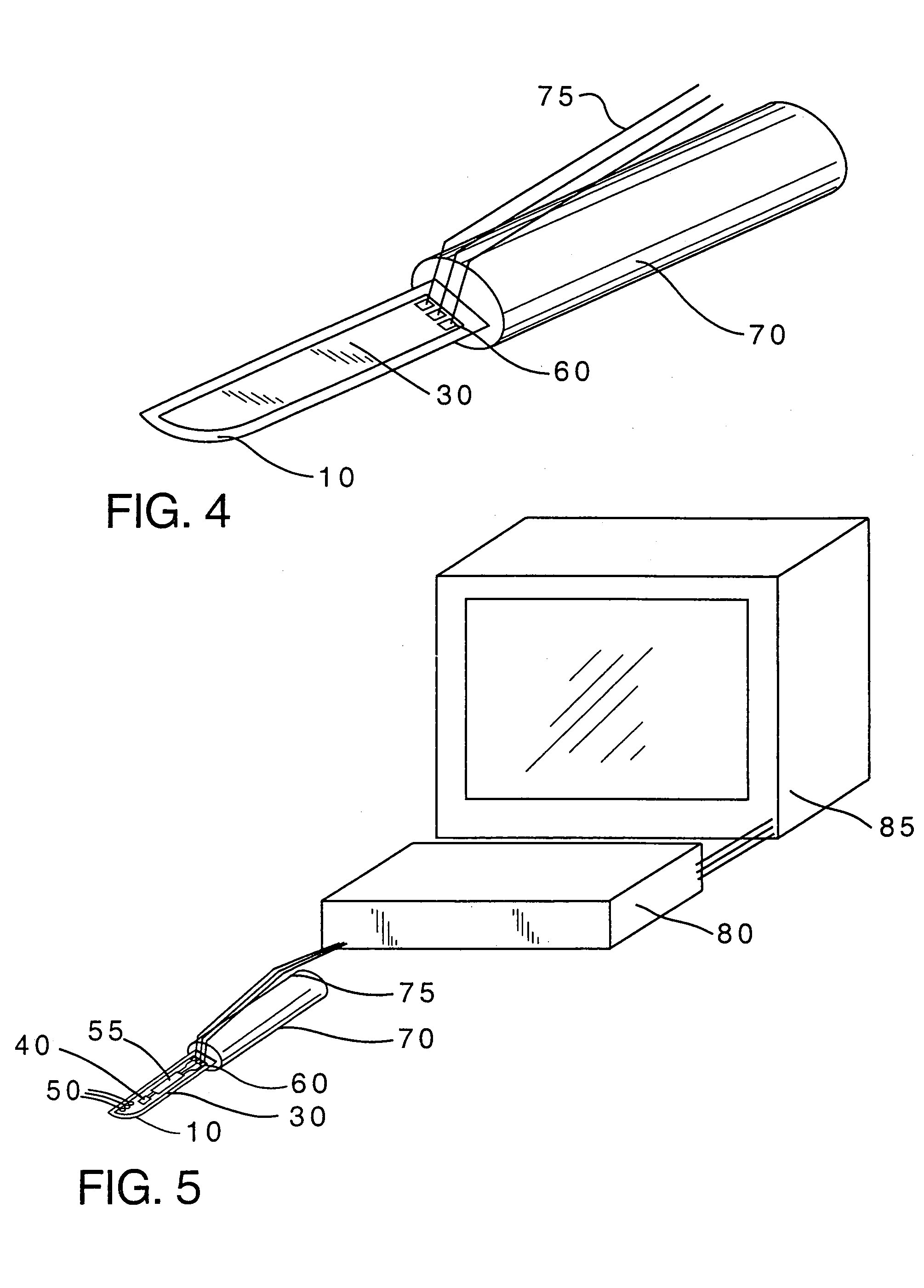

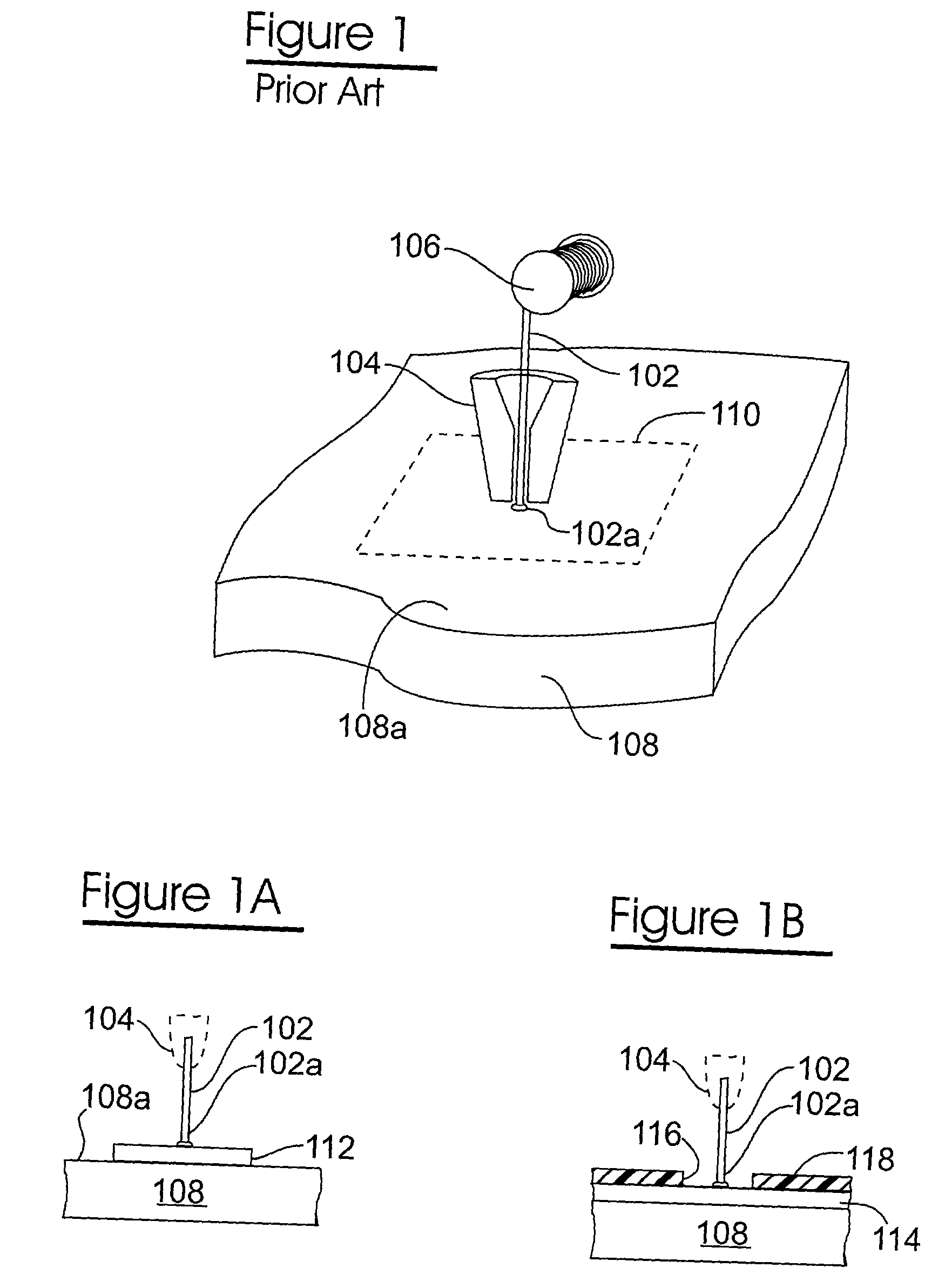

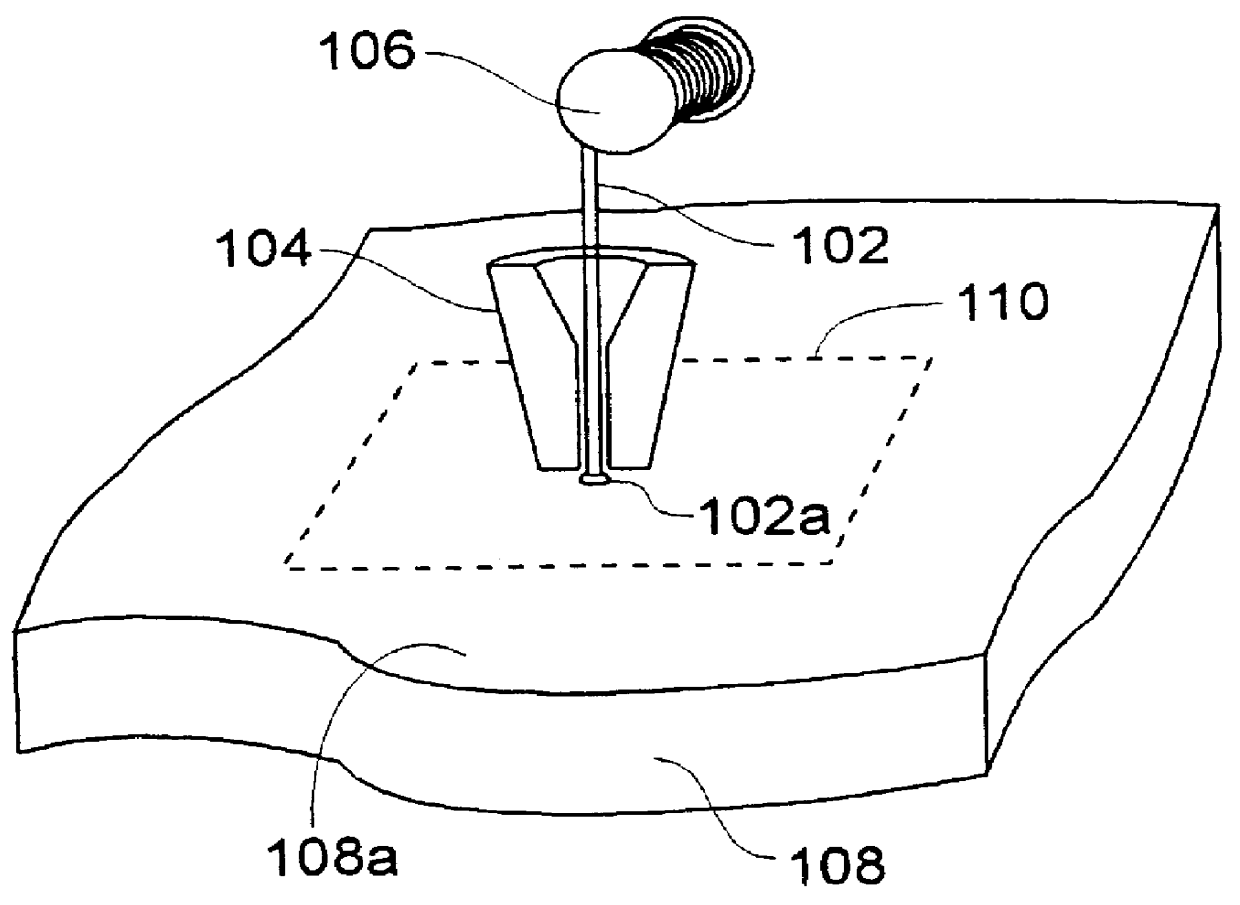

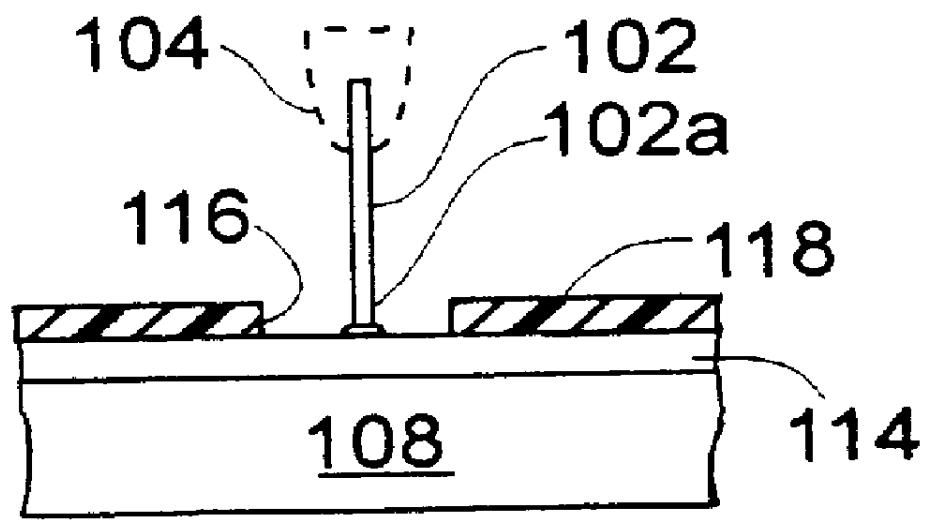

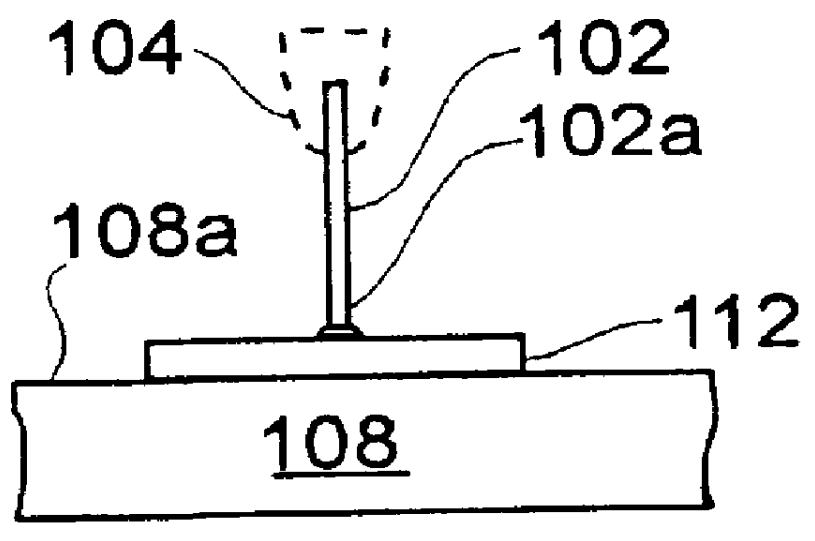

Method of making a cutting instrument having integrated sensors

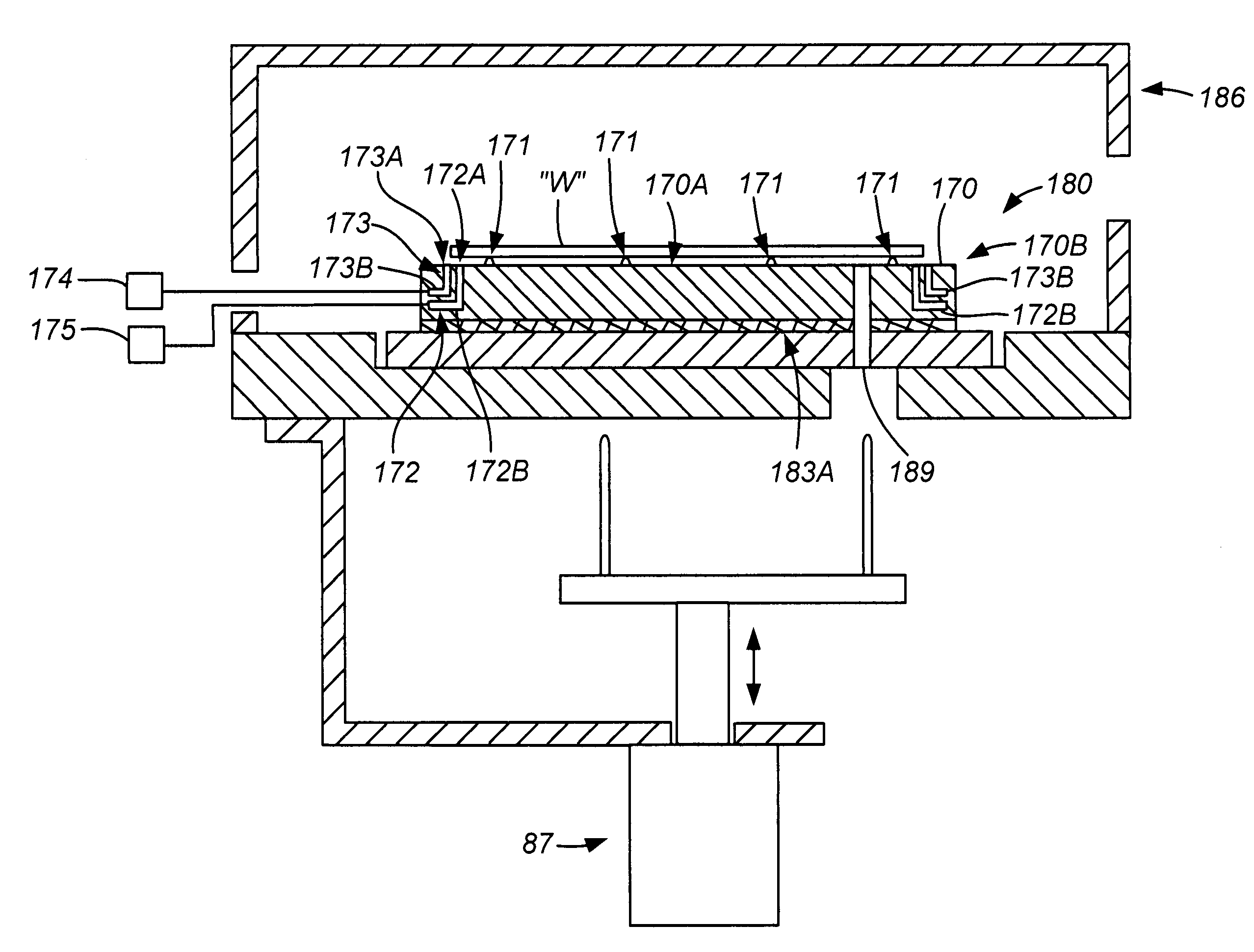

A cutting instrument including a metal blade has a recess formed therein and a semiconductor substrate affixed to the blade in the recess. The semiconductor substrate includes at least one sensor formed thereon. The sensor formed on the semiconductor substrate may comprise at least one or an array of a strain sensors, pressure sensors, nerve sensors, temperature sensors, density sensors, accelerometers, and gyroscopes. The cutting instrument may also further include a handle wherein the blade is affixed to the handle and the semiconductor substrate is electrically coupled to the handle. The handle may then be coupled, either physically or by wireless transmission, to a computer that is adapted to display information to a person using the cutting instrument based on signals generated by one or more of the sensors formed on the semiconductor substrate. The computer or handle may also be adapted to store data based on the signals generated by one or more of the sensors. A method of making said cutting instrument includes the steps of at least one sensor being formed on a semiconductor wafer and a layer of photoresist being applied on a top side of the semiconductor wafer according to a pattern that matches the defined shape of the semiconductor substrate. The portion of the semiconductor wafer not covered by the photoresist is removed and thereafter the photoresist is removed from the semiconductor wafer, thereby leaving the semiconductor substrate having a defined shape and at least one sensor formed thereon. The semiconductor substrate having a defined shape and at least one sensor formed thereon is then affixed to a metal blade in a recess formed in said blade.

Owner:VERIMETRA

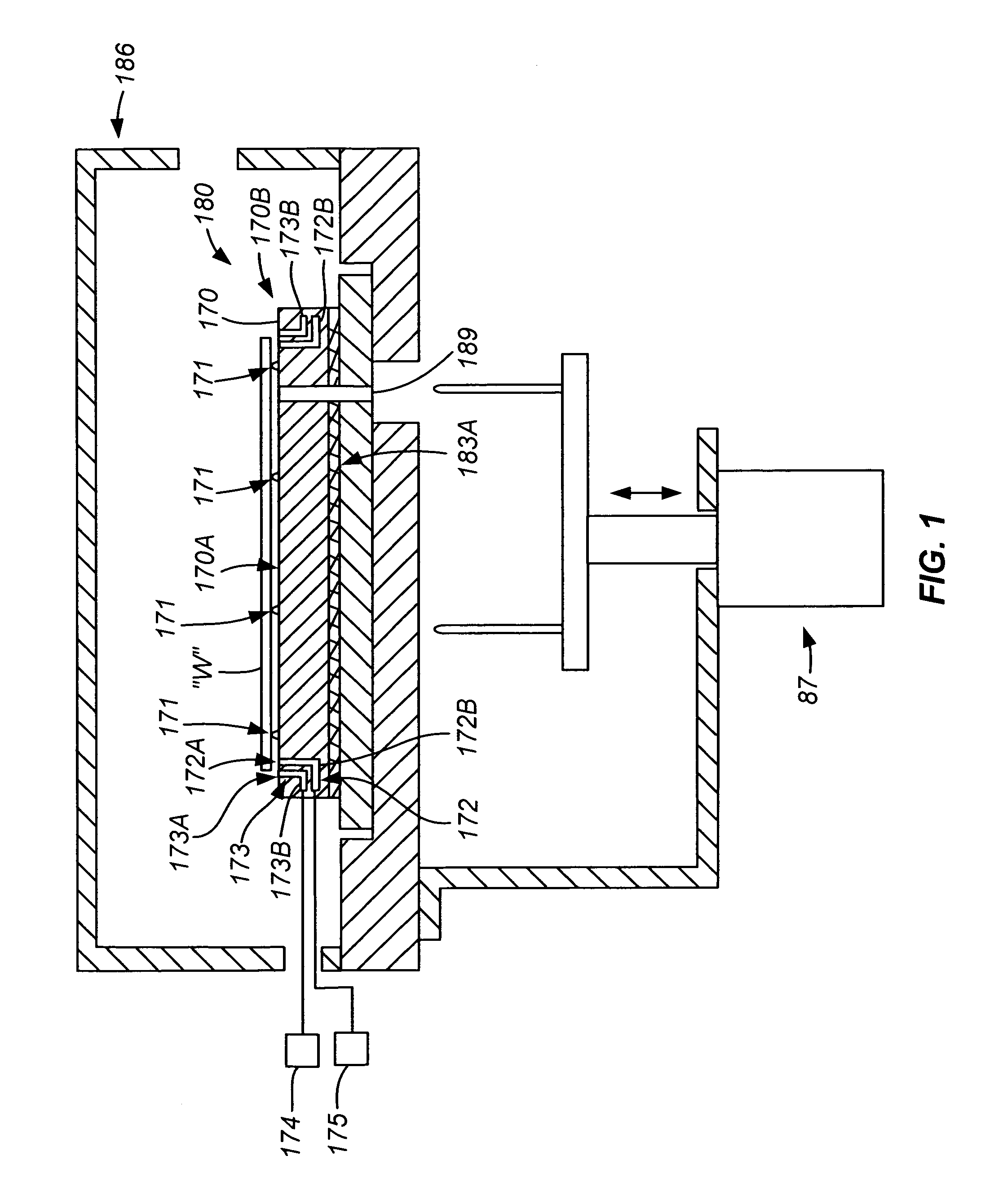

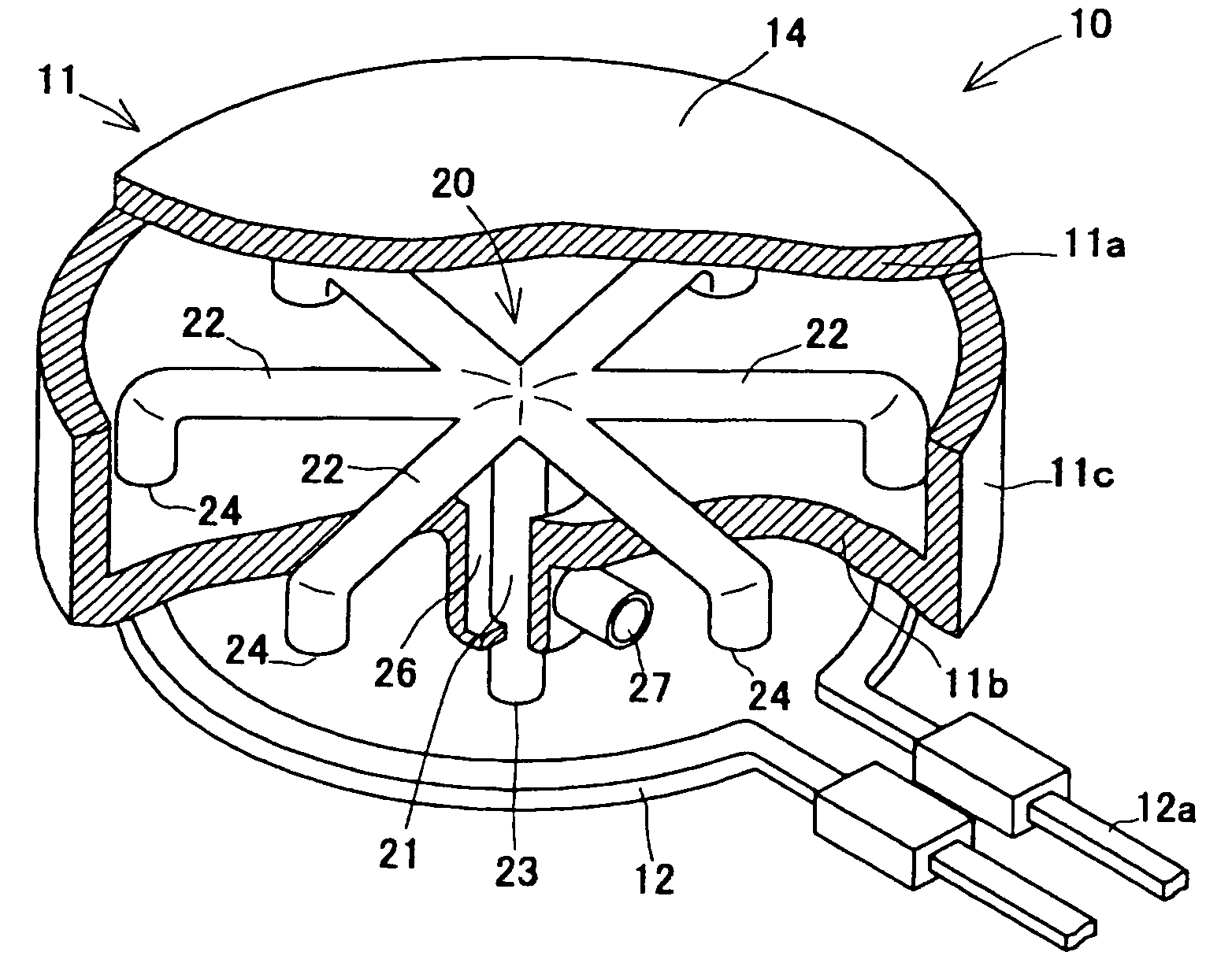

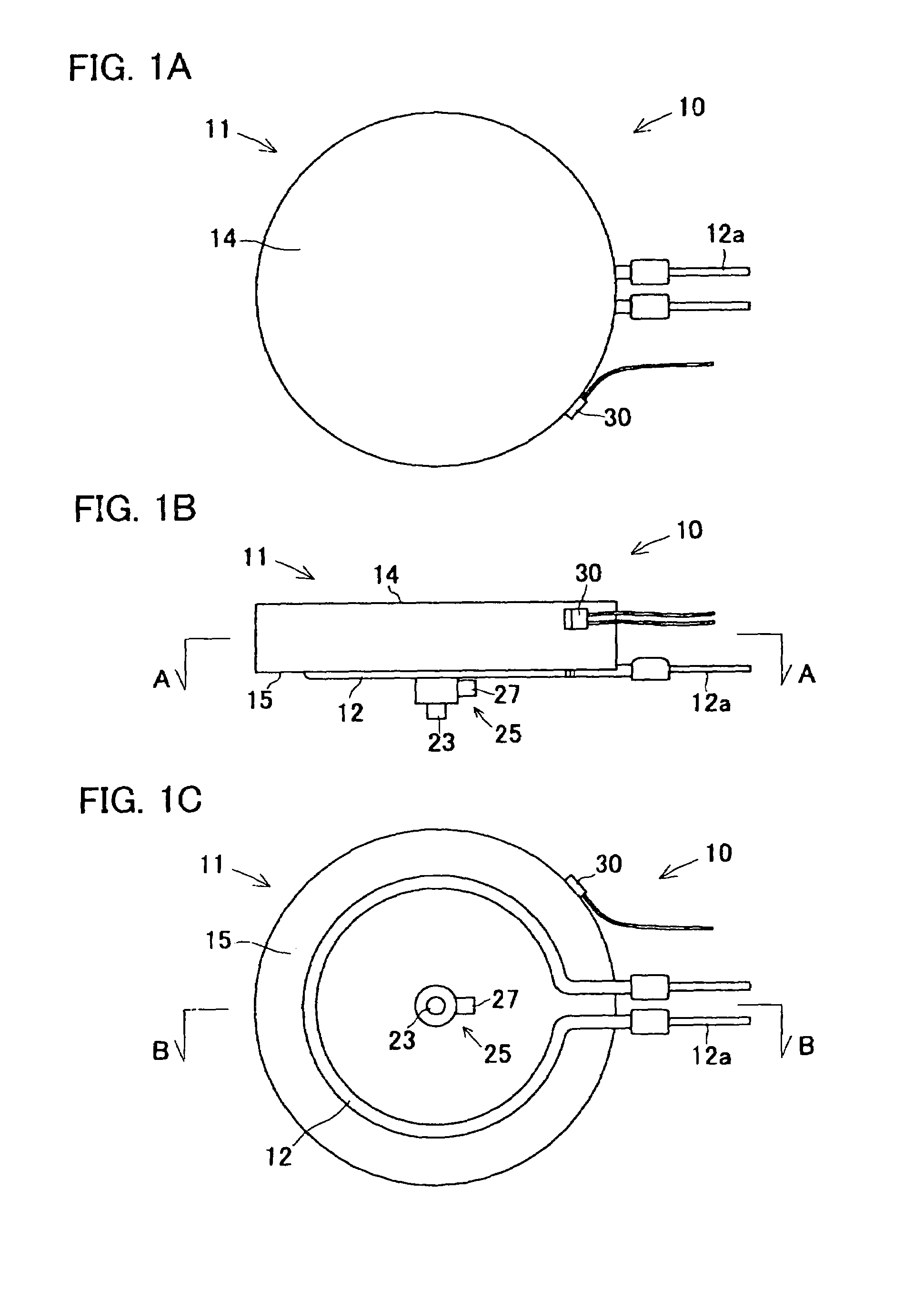

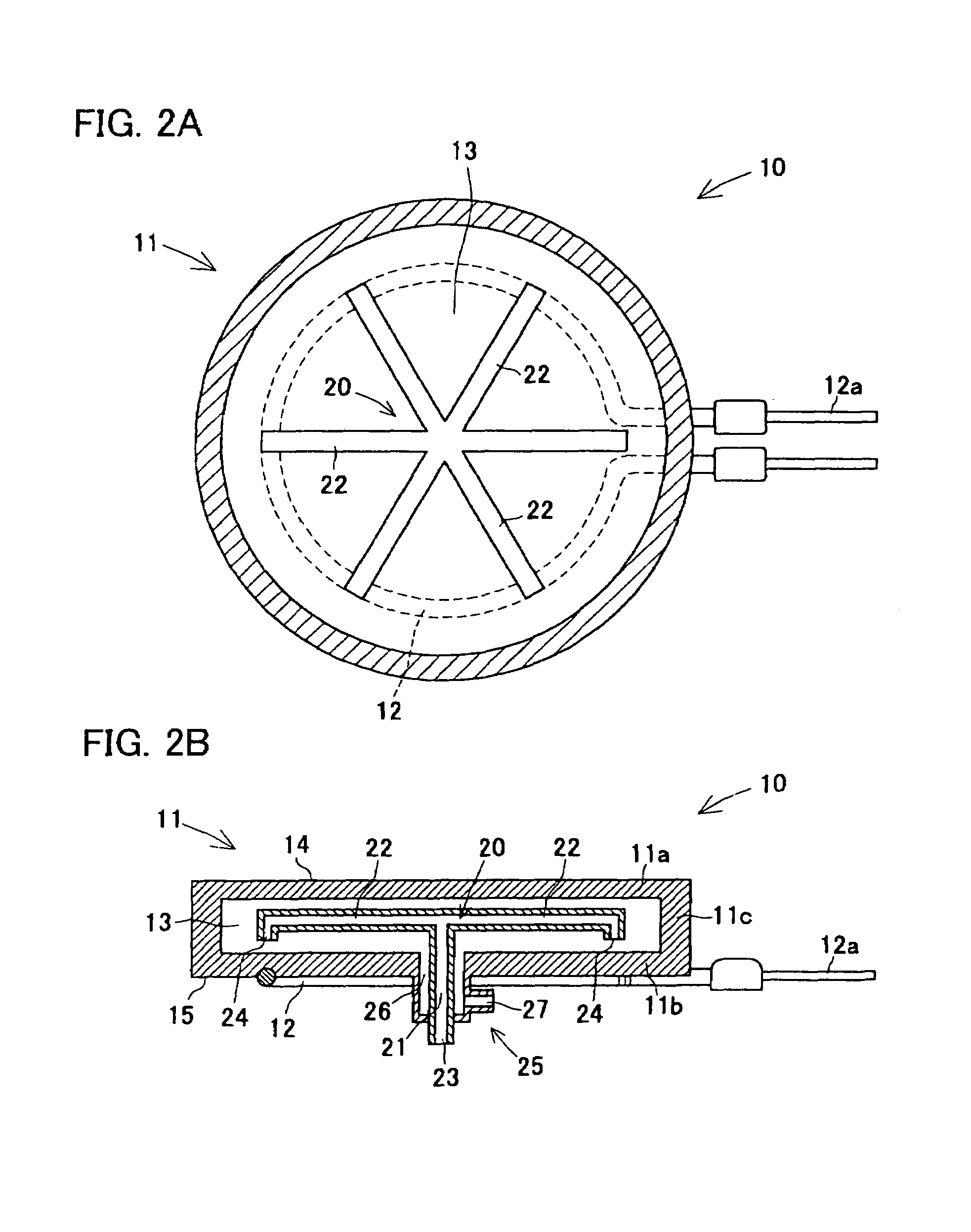

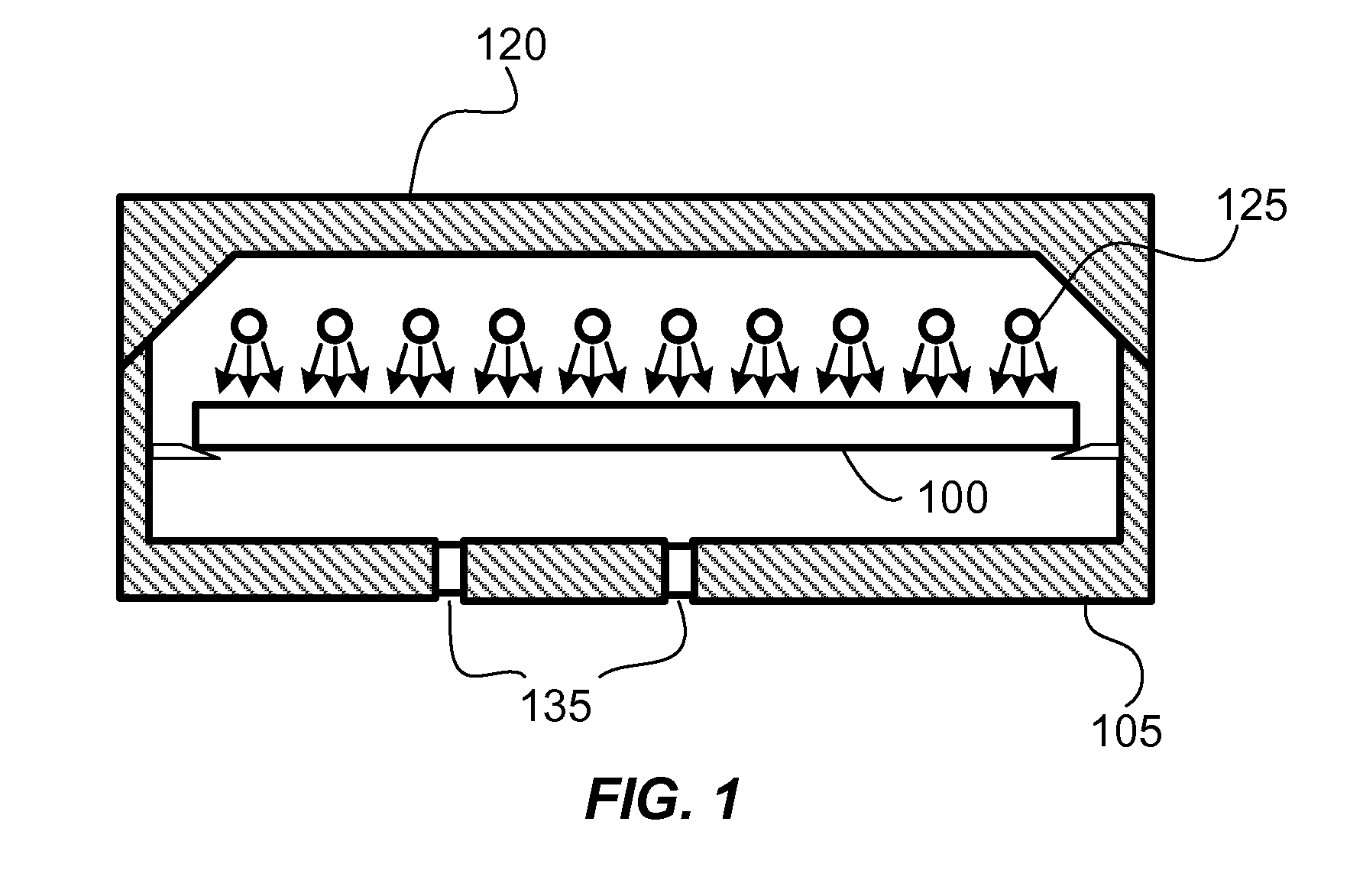

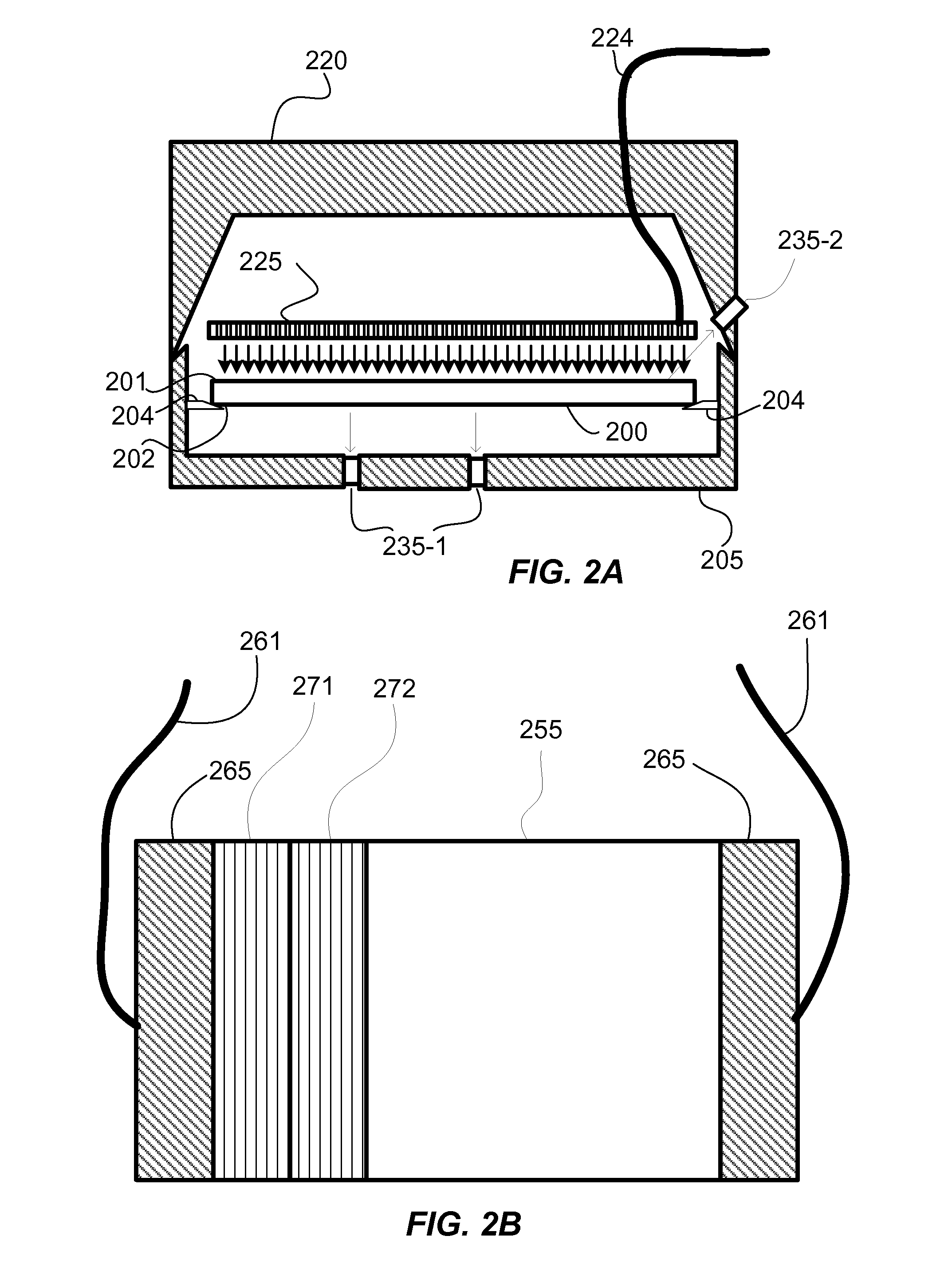

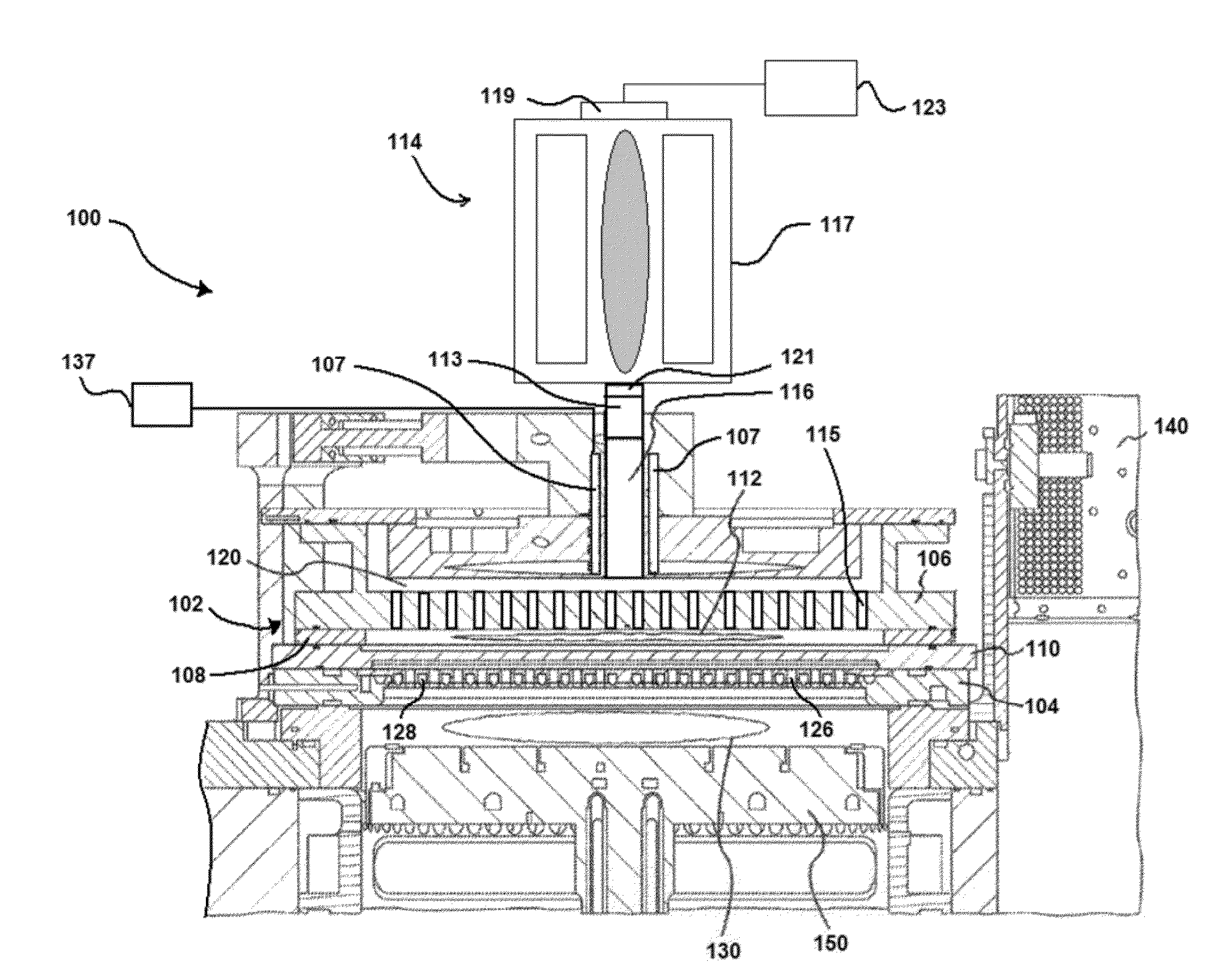

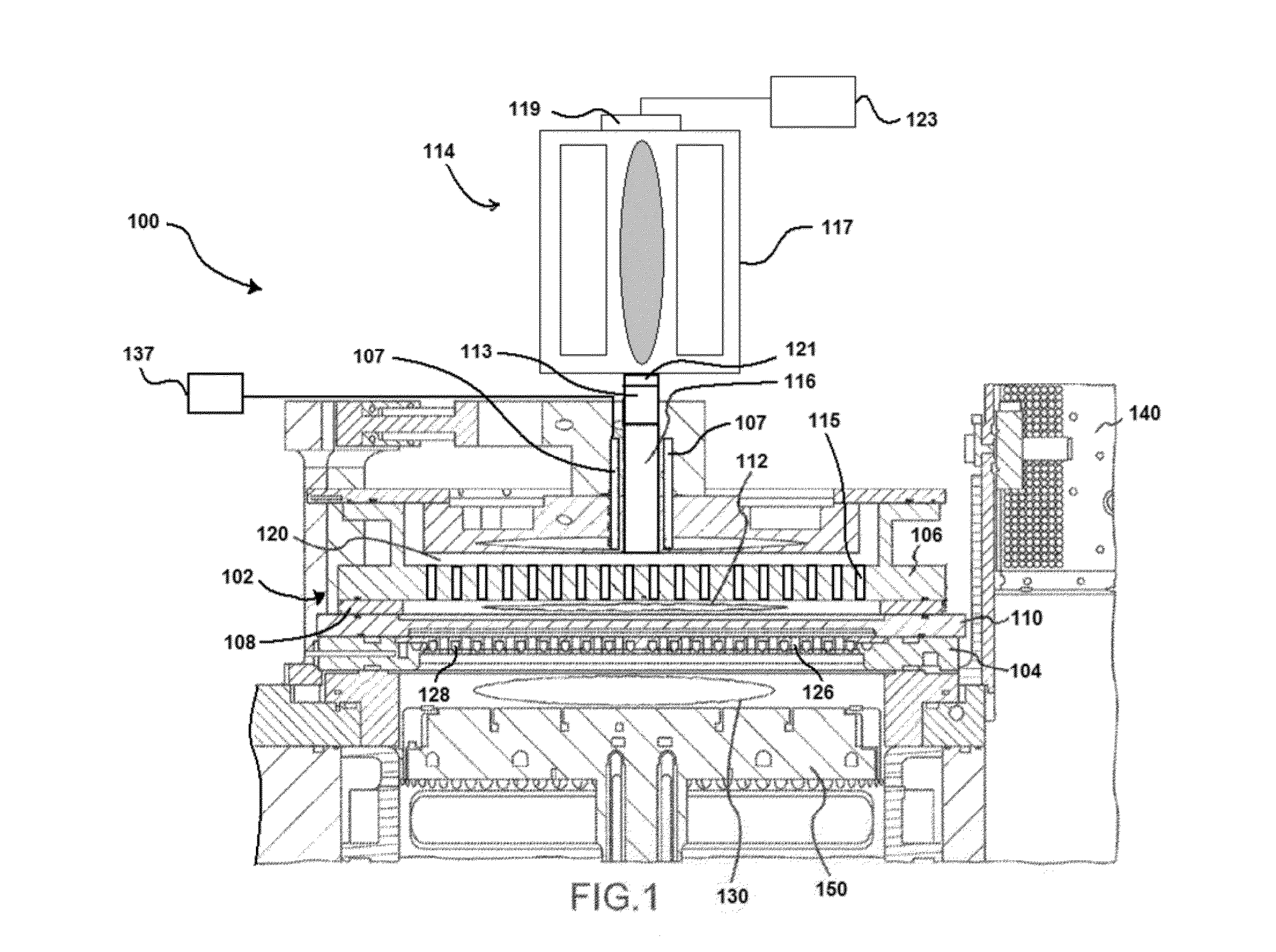

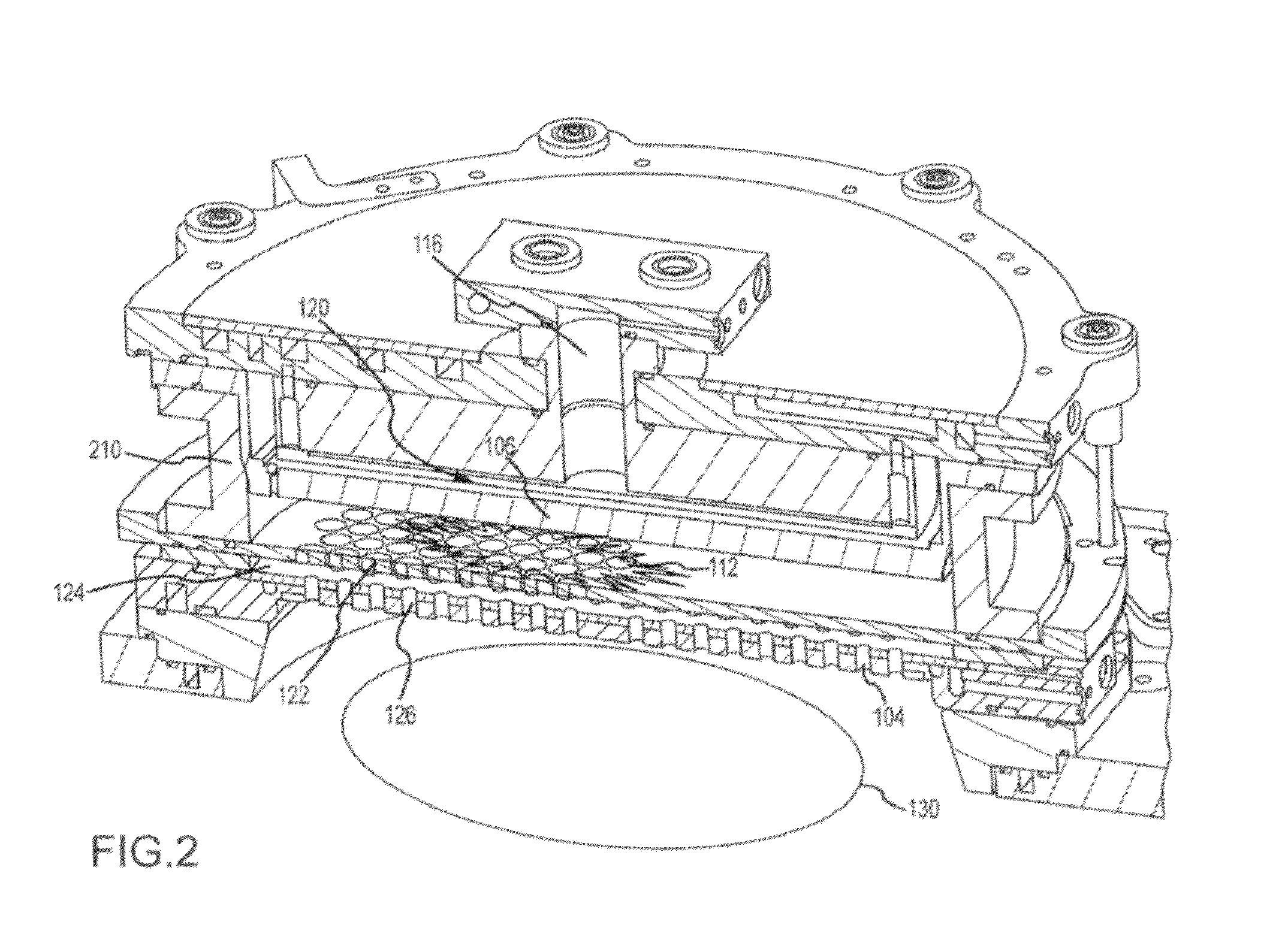

Purged vacuum chuck with proximity pins

InactiveUS20060130767A1Reduce the overall heightImprove heat transfer rateProgramme controlSemiconductor/solid-state device testing/measurementEngineeringFree space

A substrate support structure comprising a first surface and a second surface opposite the first surface. The substrate support structure also comprises a plurality of proximity pins projecting to a first height above the first surface, the first height being less than 100 μm. In addition, the substrate support structure further comprises a plurality of purge ports passing from the second surface to the first surface and a plurality of vacuum ports passing from the second surface to the first surface. In one embodiment, the plurality of purge ports are arranged in a first circular pattern, the first circular pattern having a first radial dimension less than the radius of the substrate support, and the plurality of vacuum ports are arranged in a second circular pattern, the second circular pattern having a second radial dimension less than the first radial dimension.

Owner:SOKUDO CO LTD

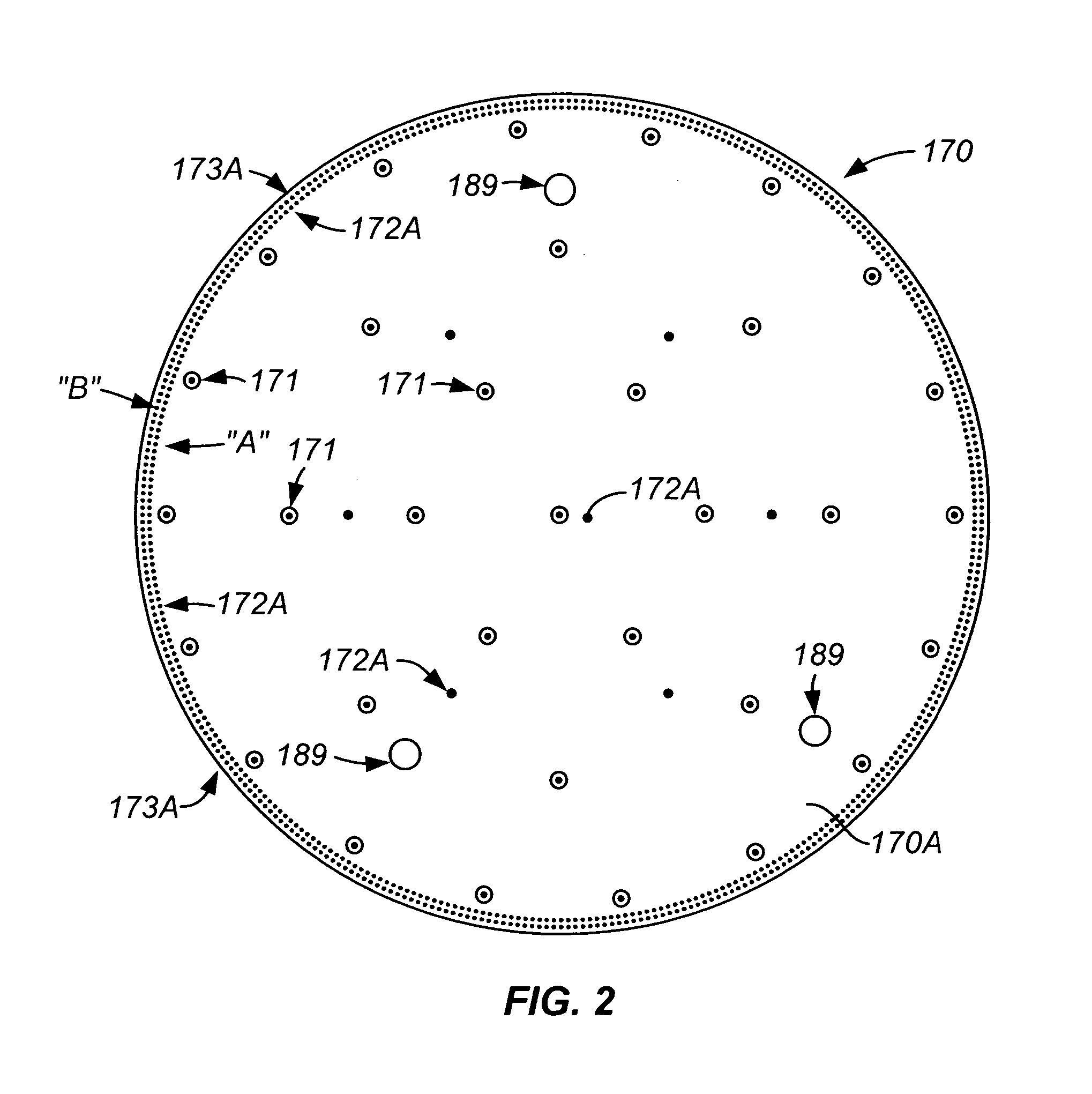

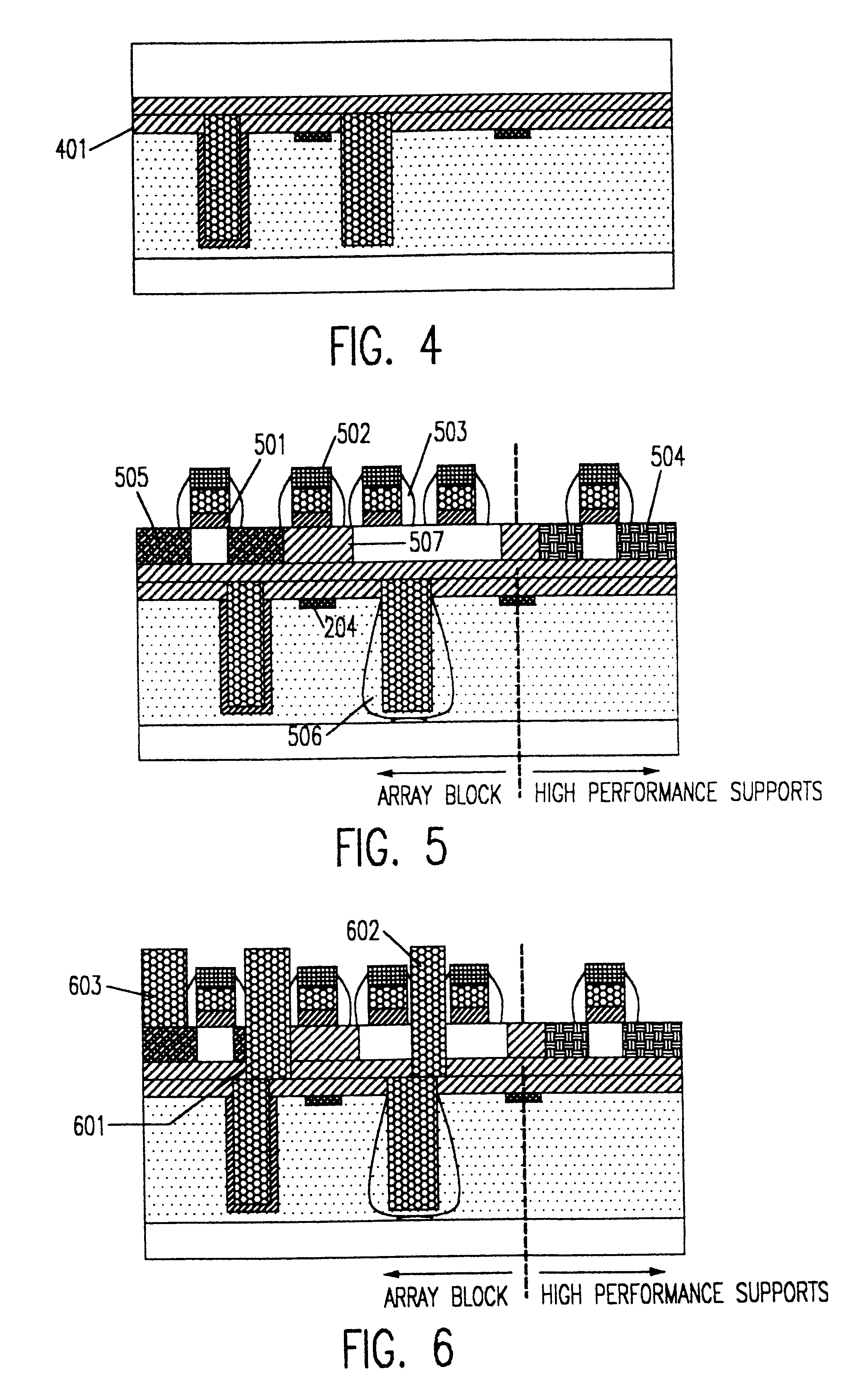

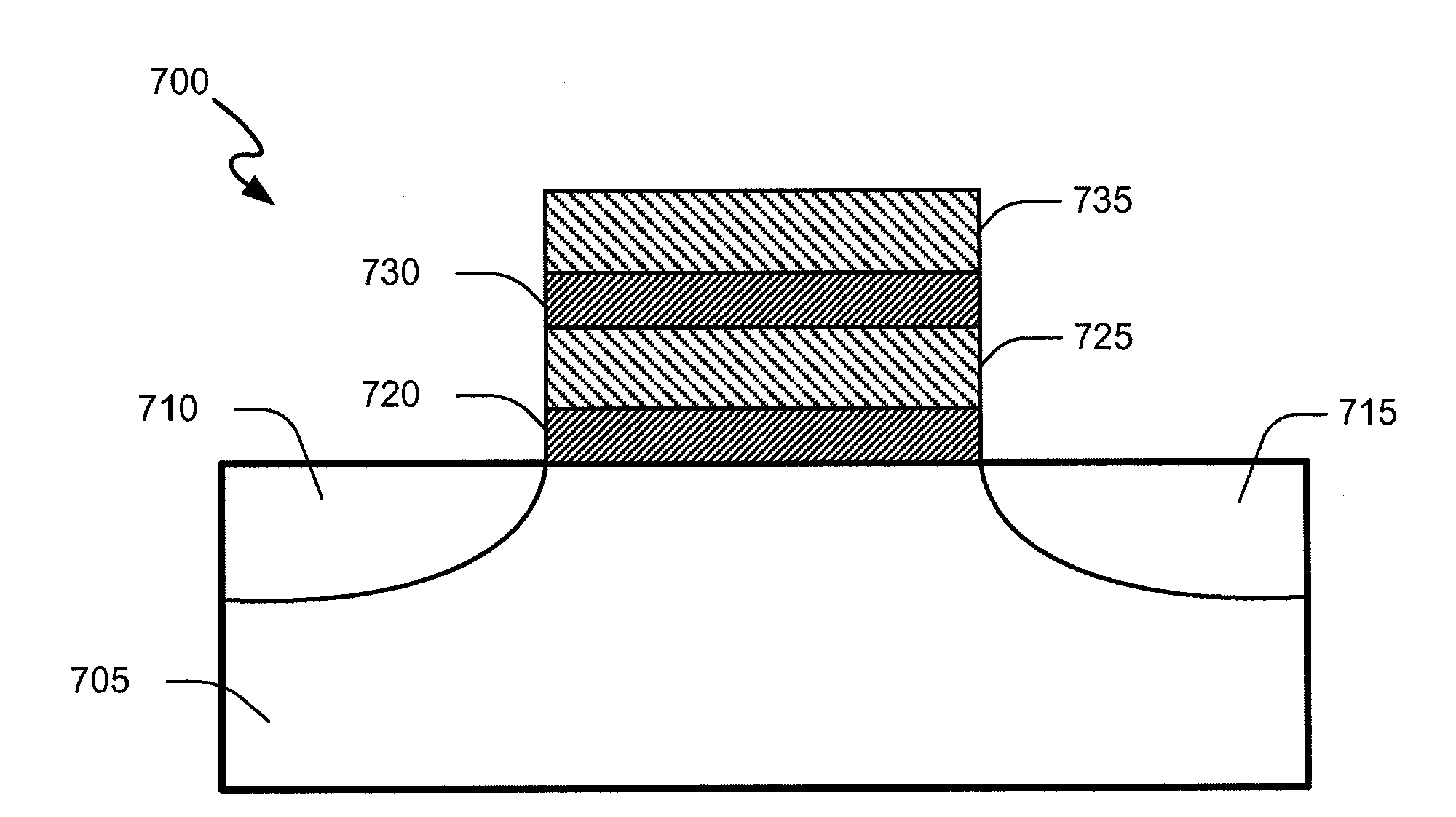

SOI stacked DRAM logic

A composite, layered, integrated circuit formed by bonding of insulator layers on wafers provides for combination of otherwise incompatible technologies such as trench capacitor DRAM arrays and high performance, low power, low voltage silicon on insulator (SOI) switching transistors and short signal propagation paths between devices formed on respective wafer layers of a chip. In preferred embodiments, an SOI wafer is formed by hydrophilic bonding of a wafer over an integrated circuit device and then cleaving a layer of the second wafer away using implanted hydrogen and low temperature heat treatment. Further wafers of various structures and compositions may be bonded thereover and connections between circuit elements and connection pads in respective wafers made using short vias that provide fast signal propagation as well as providing more numerous connections than can be provided on chip edges.

Owner:INT BUSINESS MASCH CORP

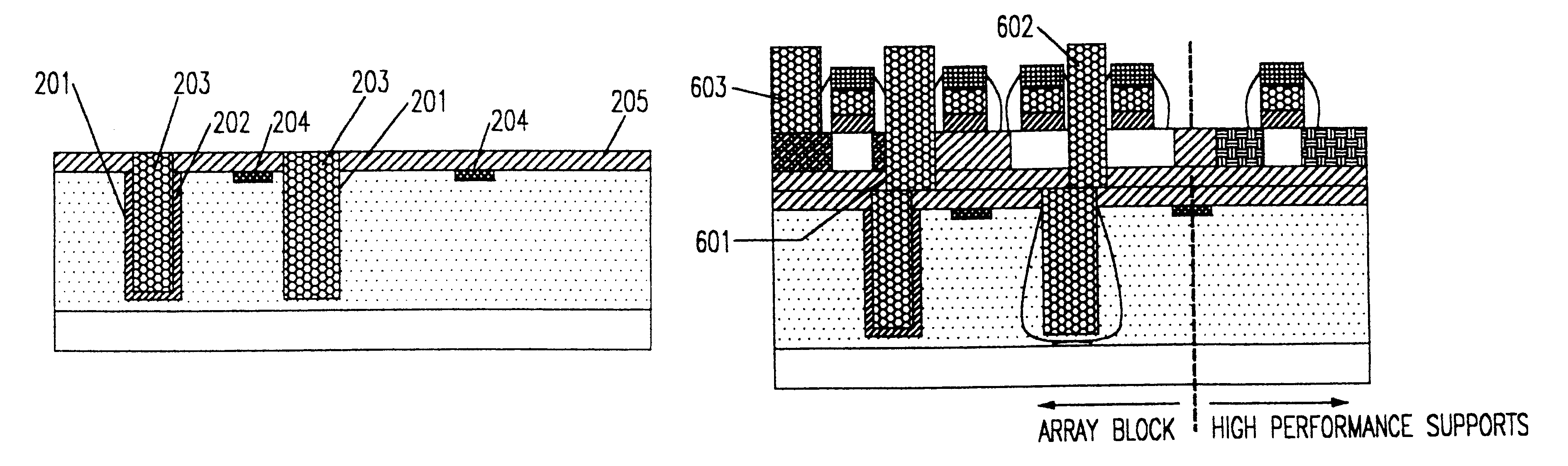

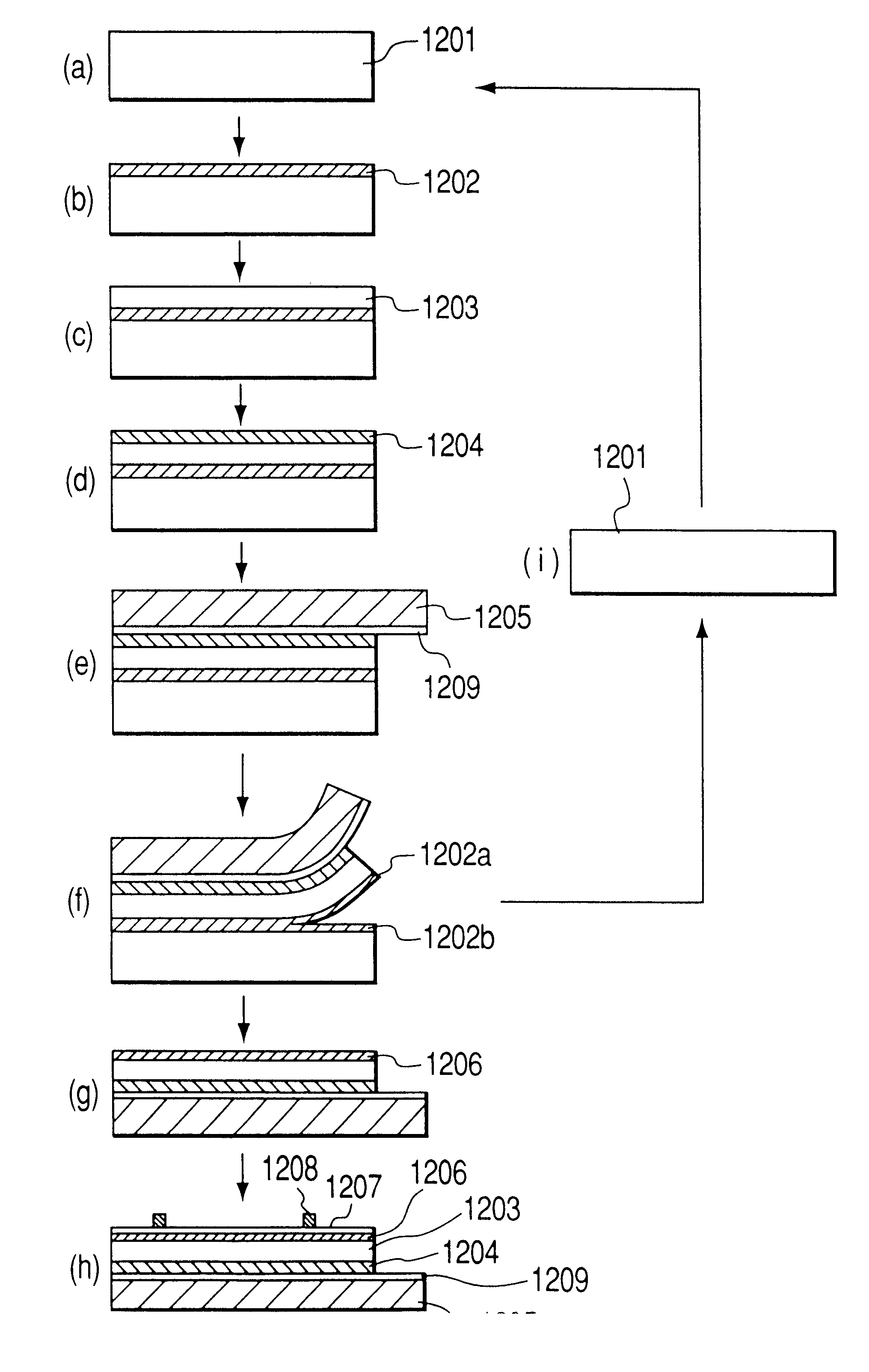

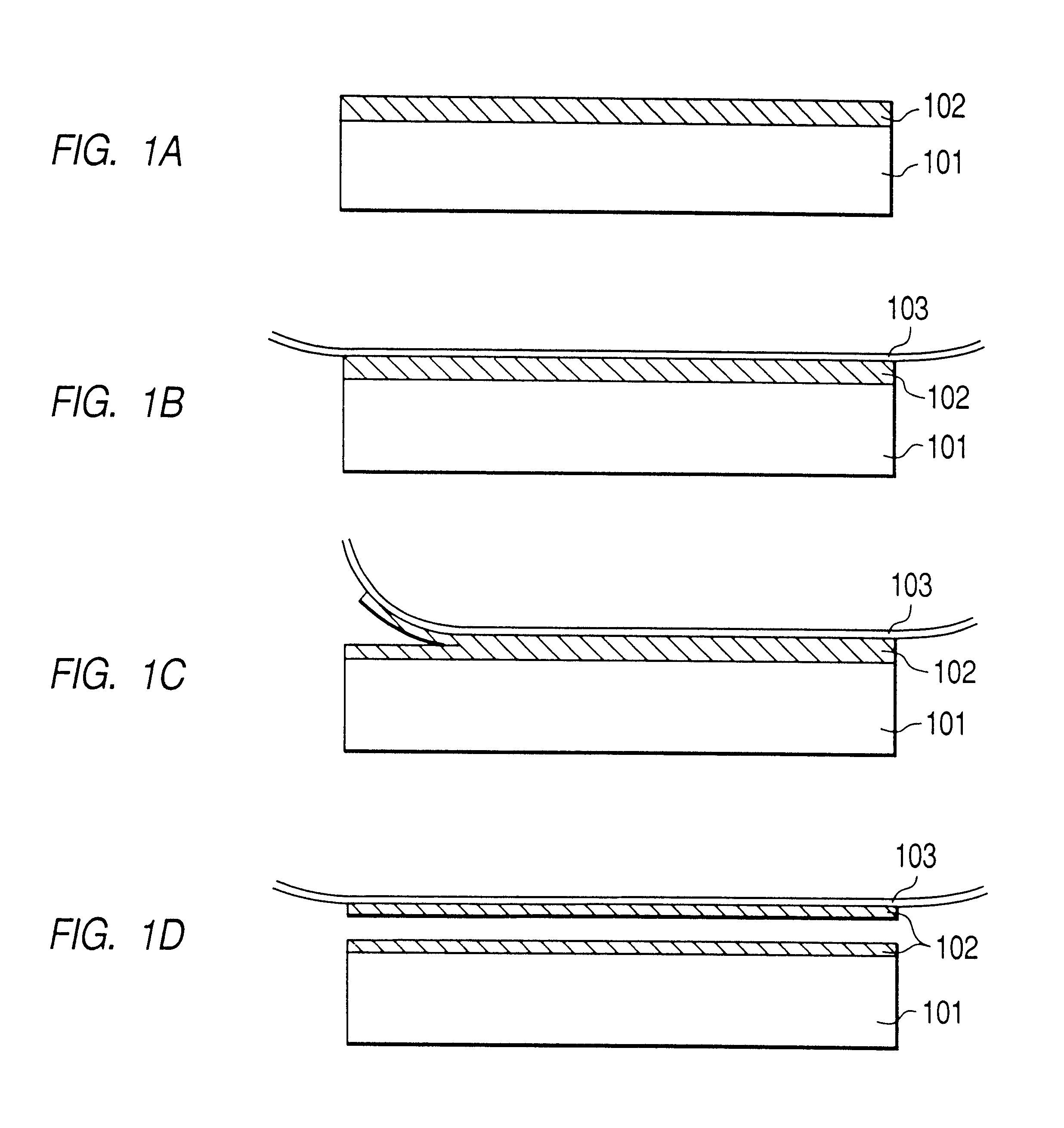

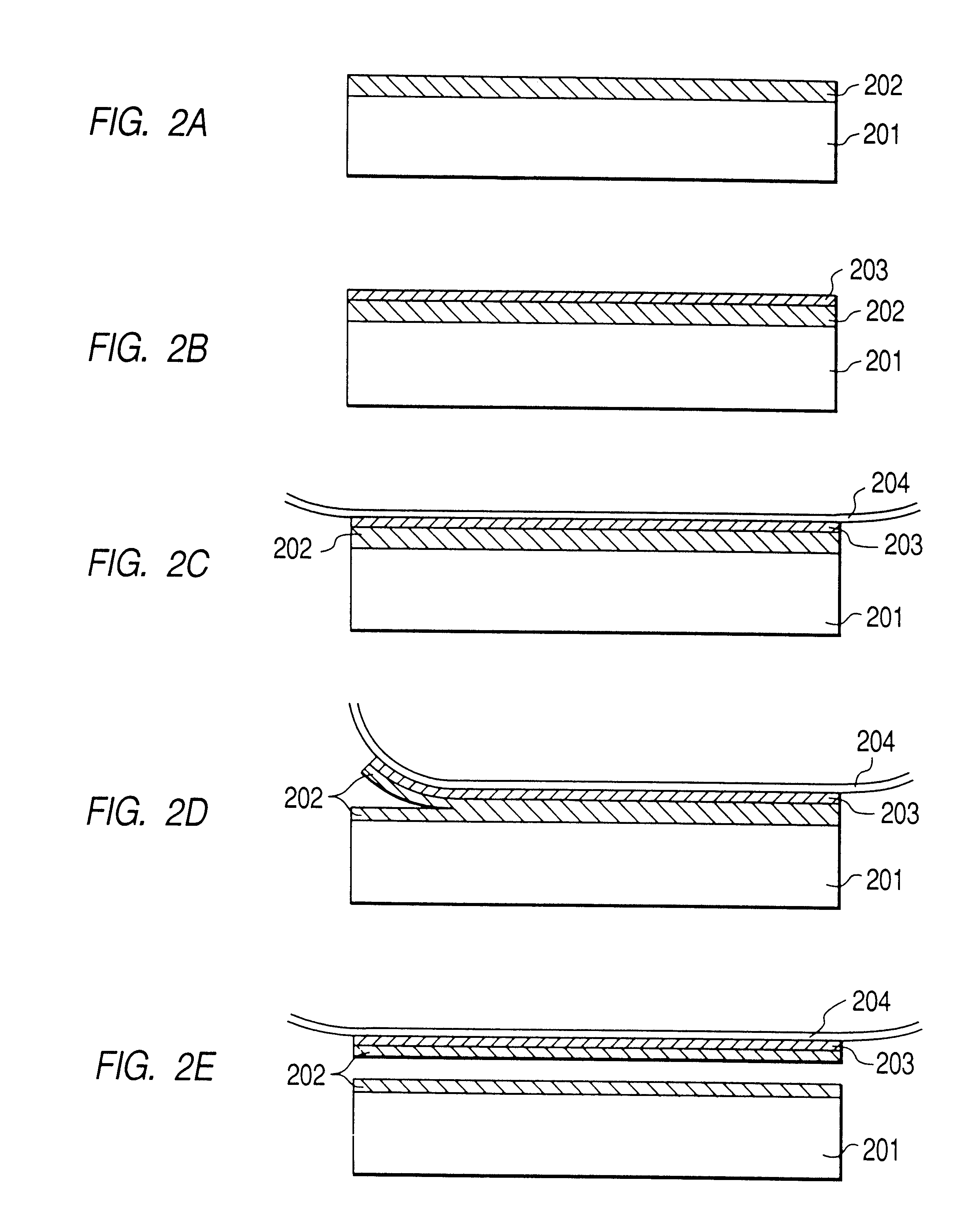

Process for producing semiconductor article

InactiveUS6534382B1Guaranteed high speed operationReduce power consumptionSemiconductor/solid-state device testing/measurementFinal product manufacturePorous semiconductorsSemiconductor

A process for producing a semiconductor article is provided which comprises the steps of bonding a film onto a substrate having a porous semiconductor layer, and separating the film from the substrate at the porous semiconductor layer by applying a force to the film in a peeling direction.

Owner:CANON KK

Unit for varying a temperature of a test piece and testing instrument incorporating same

ActiveUS7115838B2Easy to control temperatureUniform temperature distributionDrying solid materials with heatDomestic cooling apparatusInstrumentationCoolant

Owner:ESPEC CORP

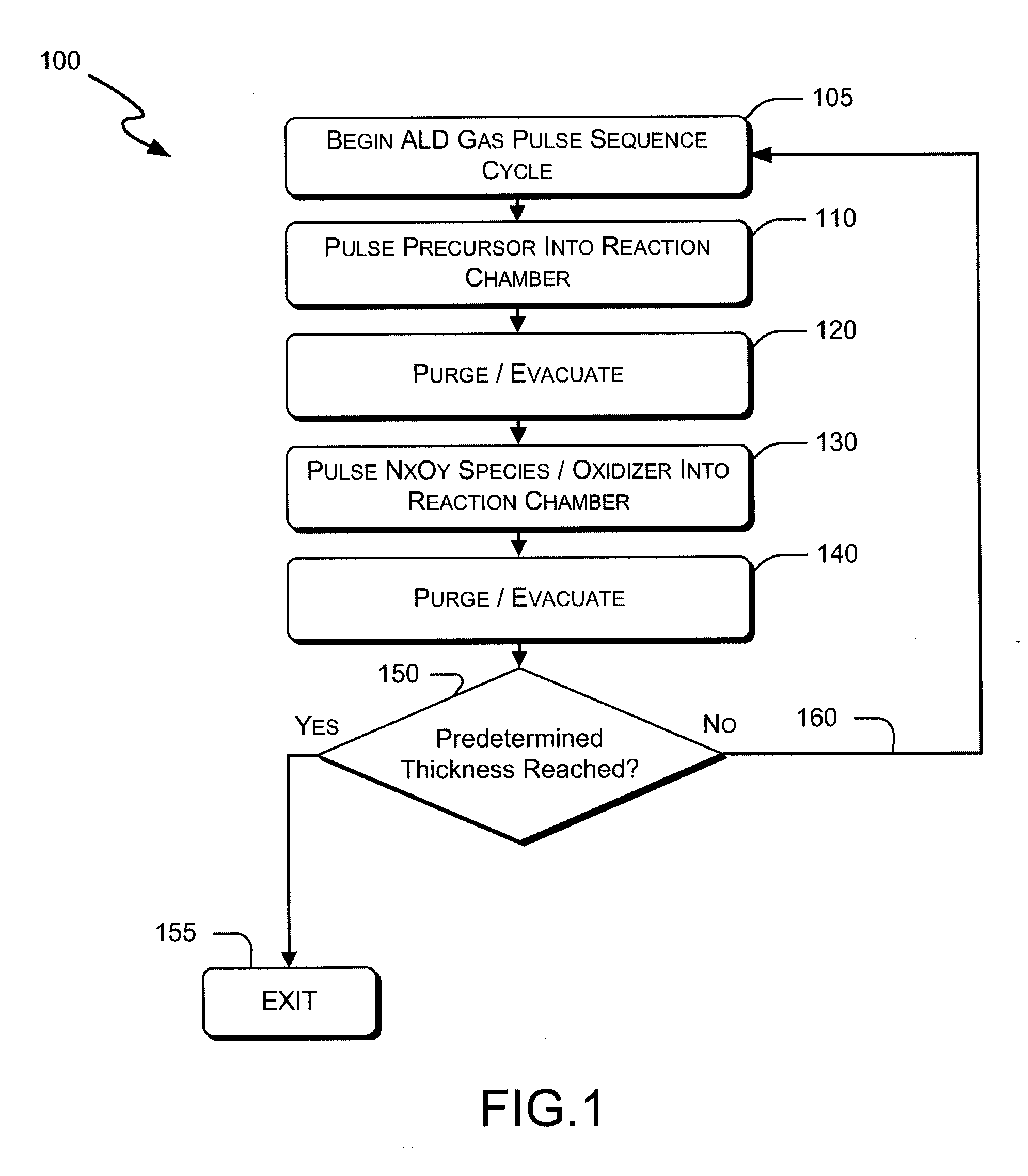

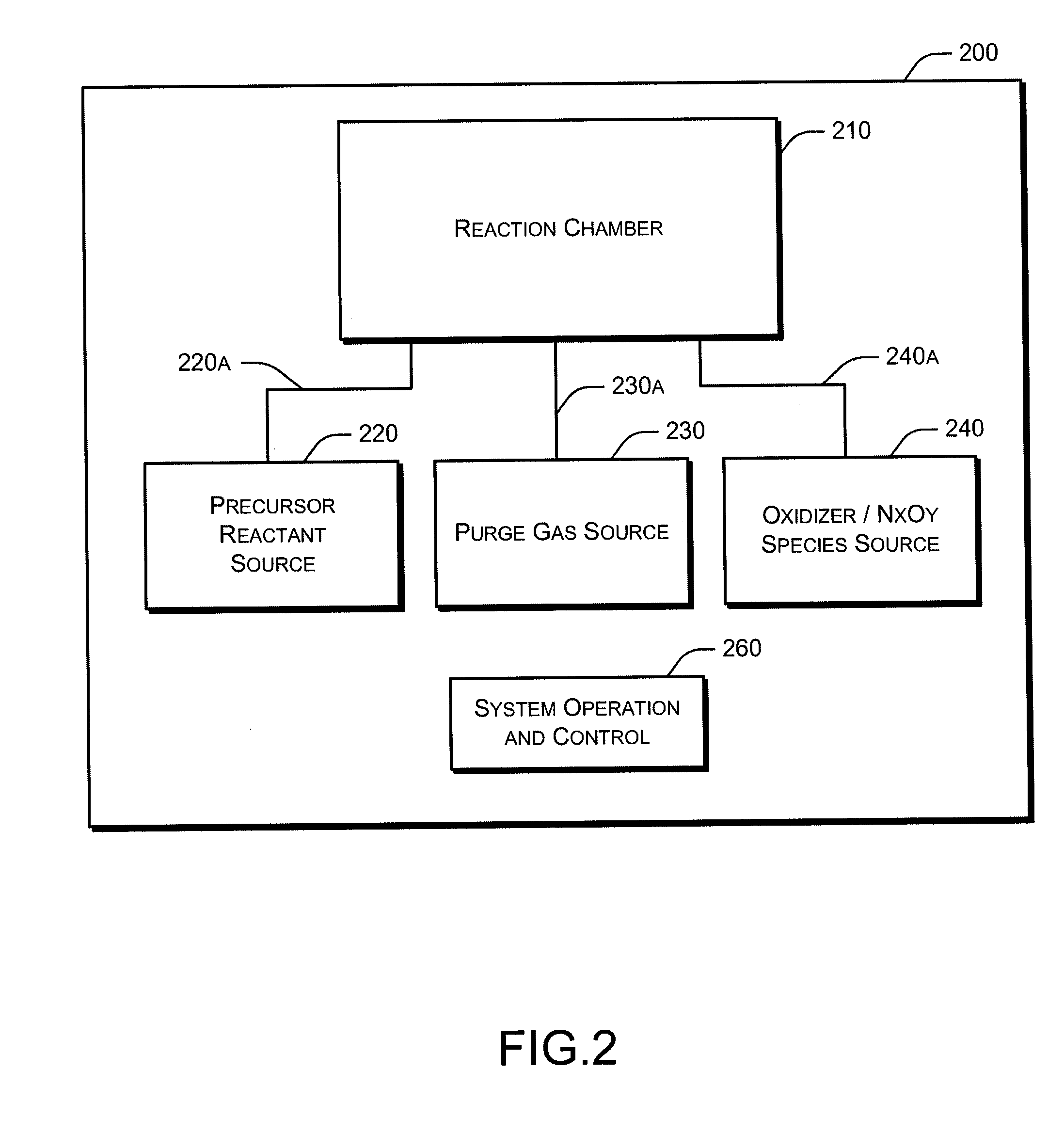

Systems and methods for thin-film deposition of metal oxides using excited nitrogen-oxygen species

ActiveUS20110275166A1Enhance growth rate and uniformityUniform growthLiquid surface applicatorsSemiconductor/solid-state device testing/measurementNitrogenOptoelectronics

The present invention relates to a process and system for depositing a thin film onto a substrate. One aspect of the invention is depositing a thin film metal oxide layer using atomic layer deposition (ALD).

Owner:ASM IP HLDG BV

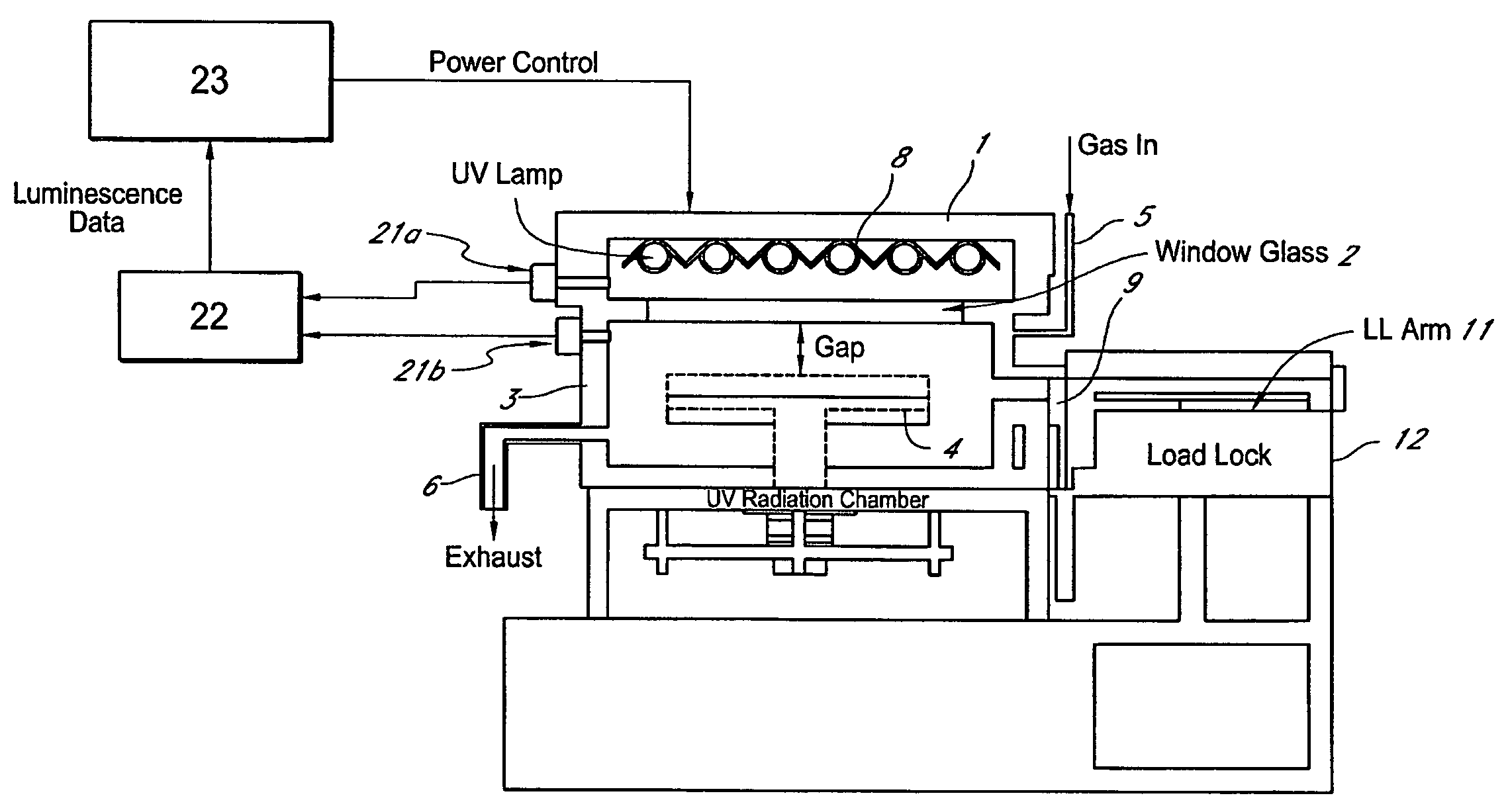

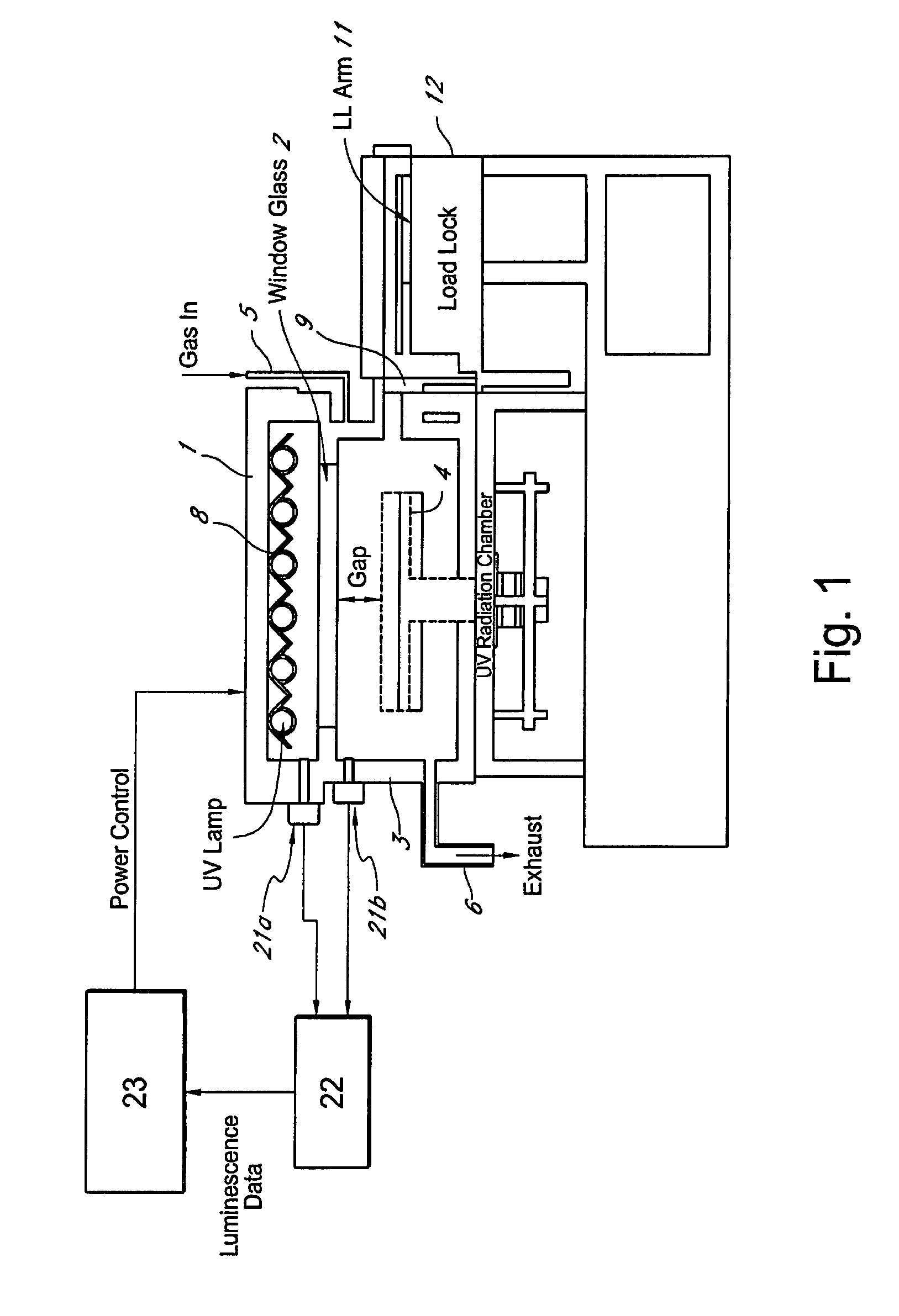

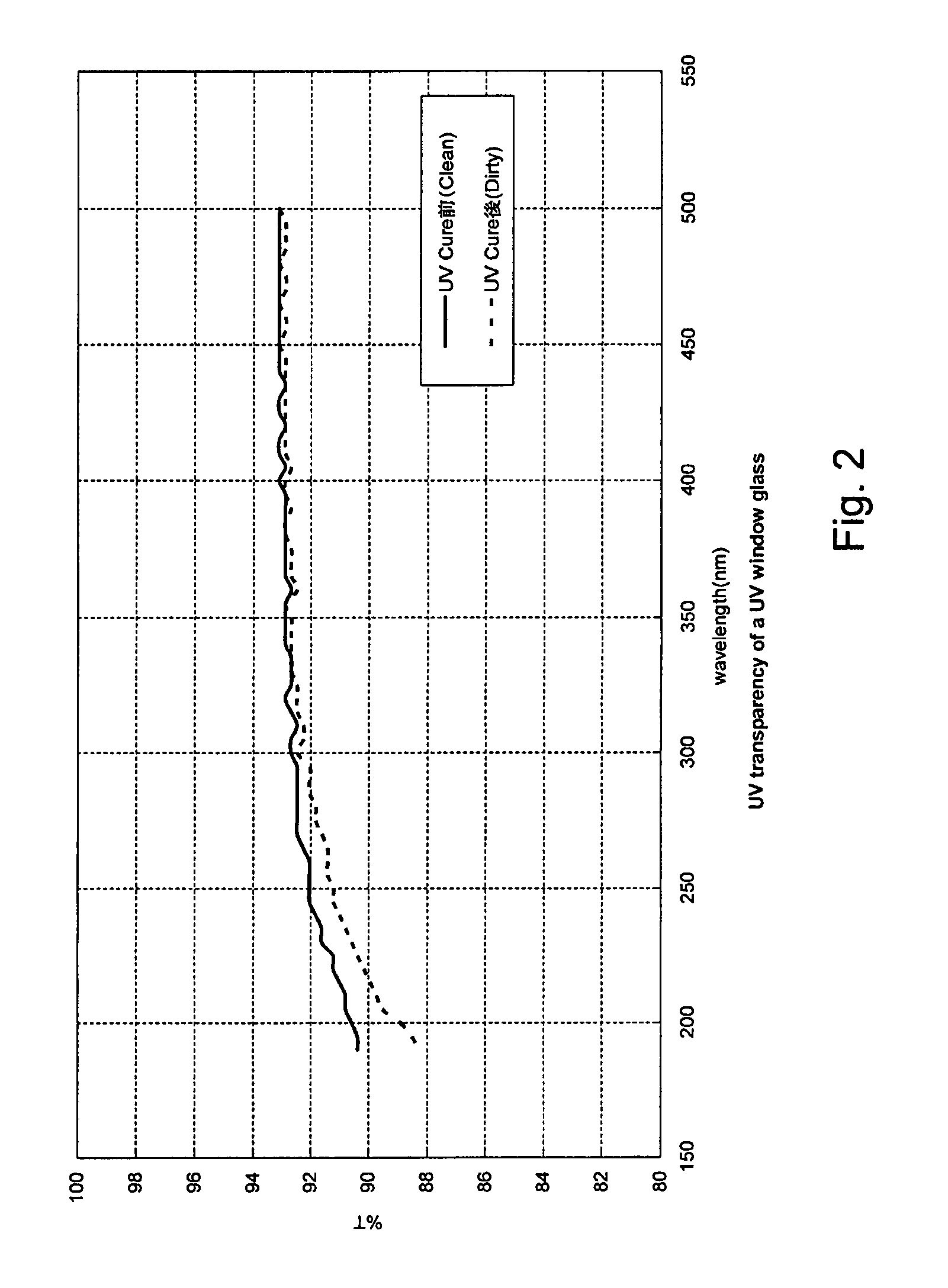

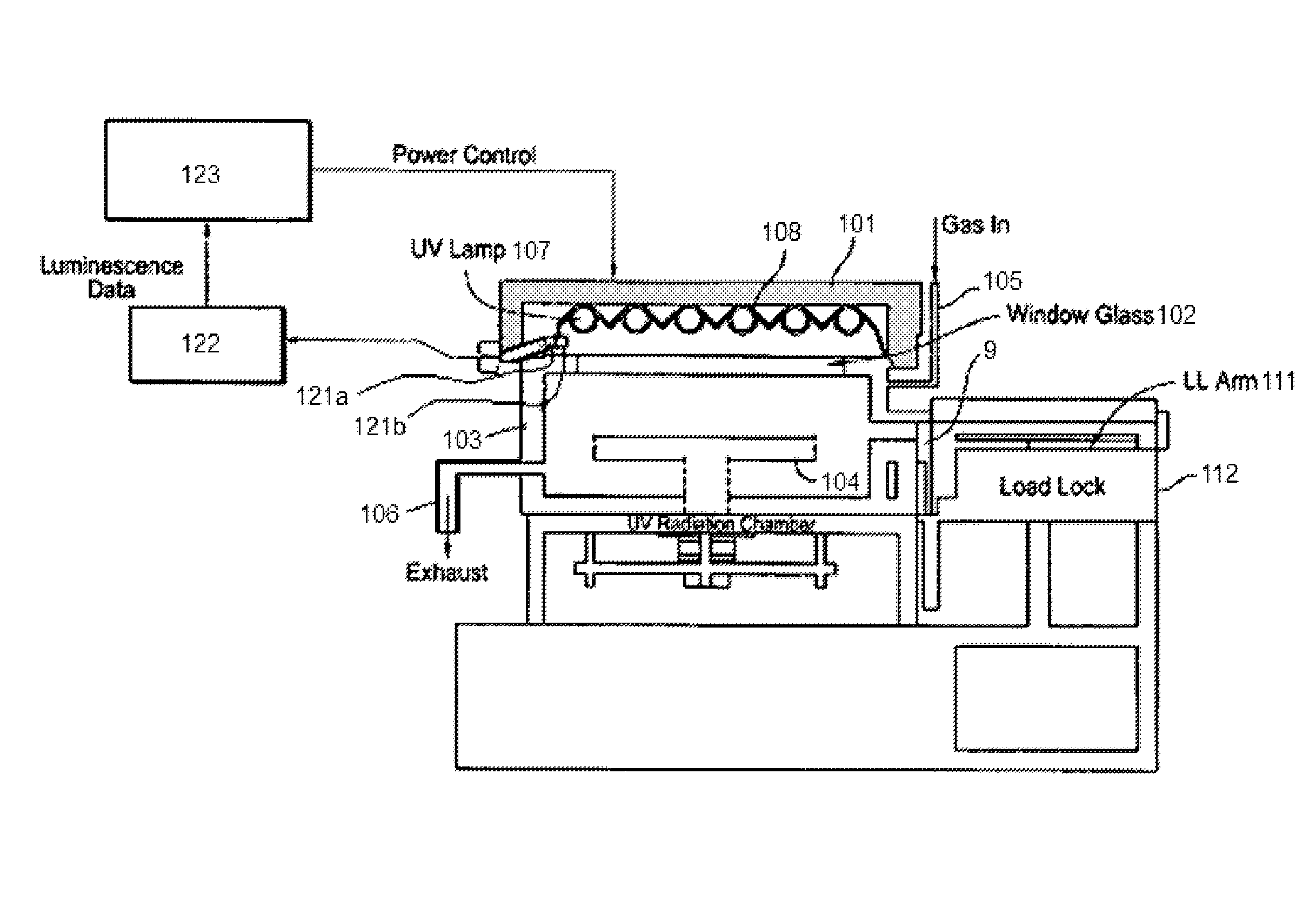

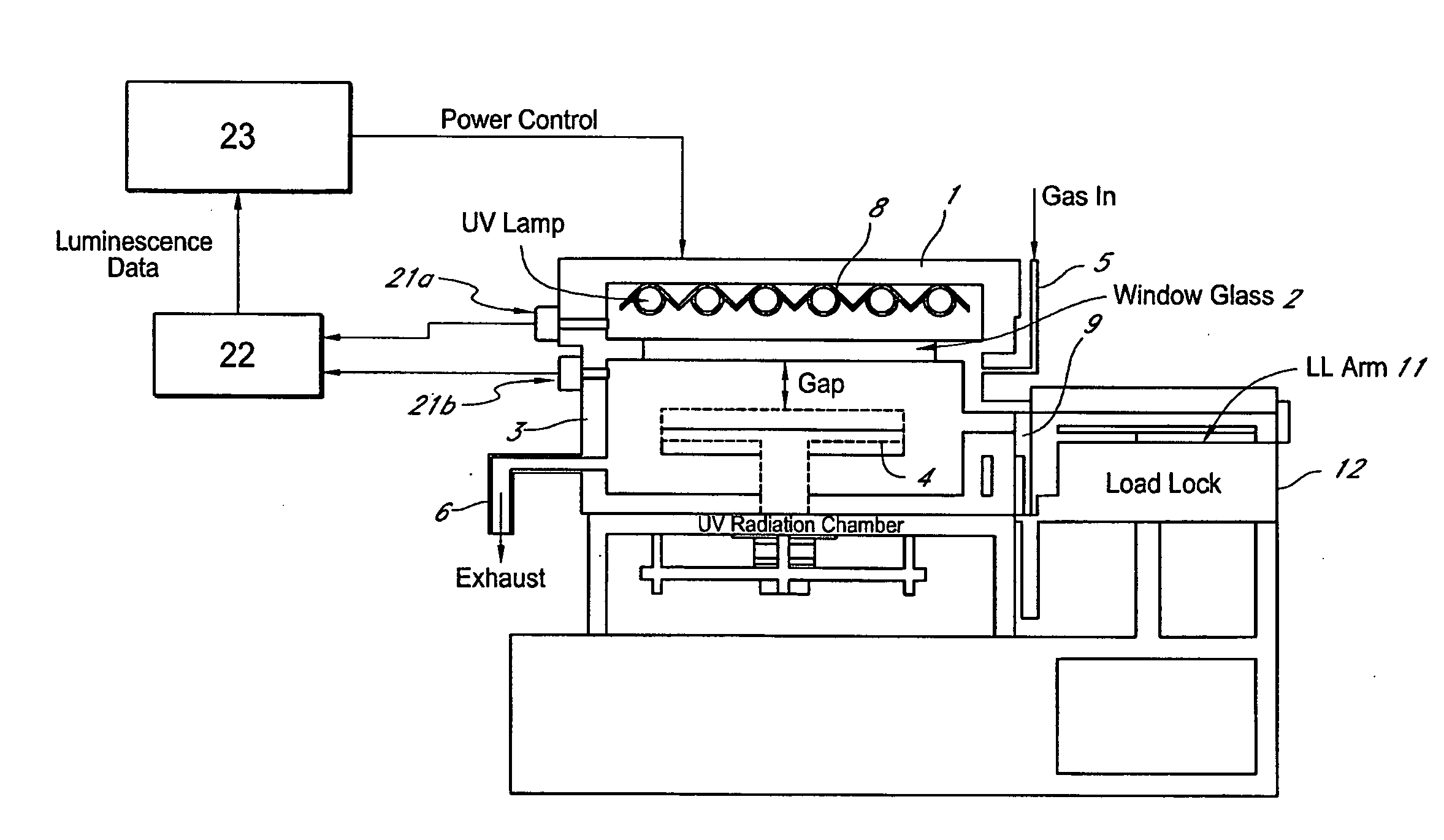

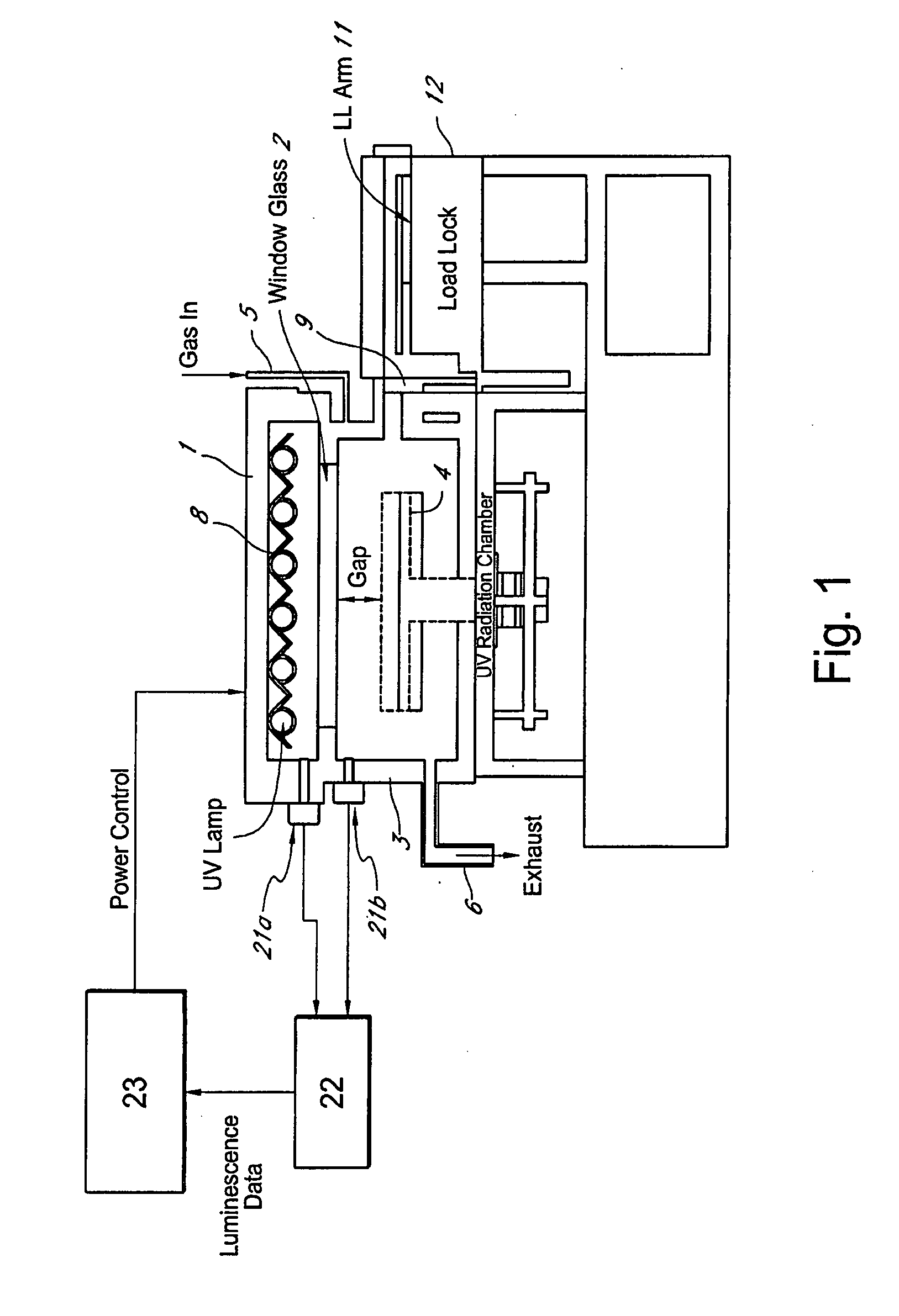

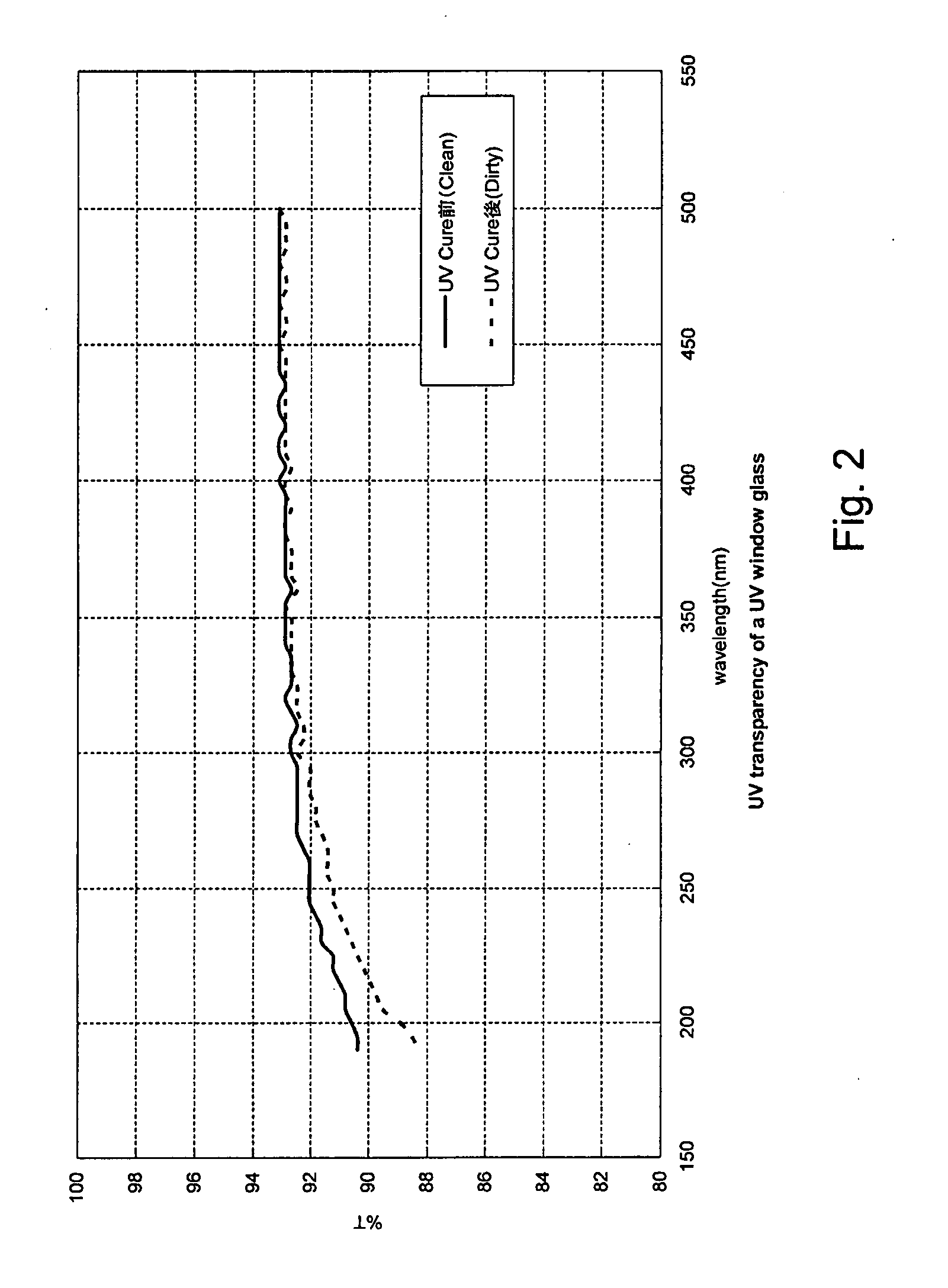

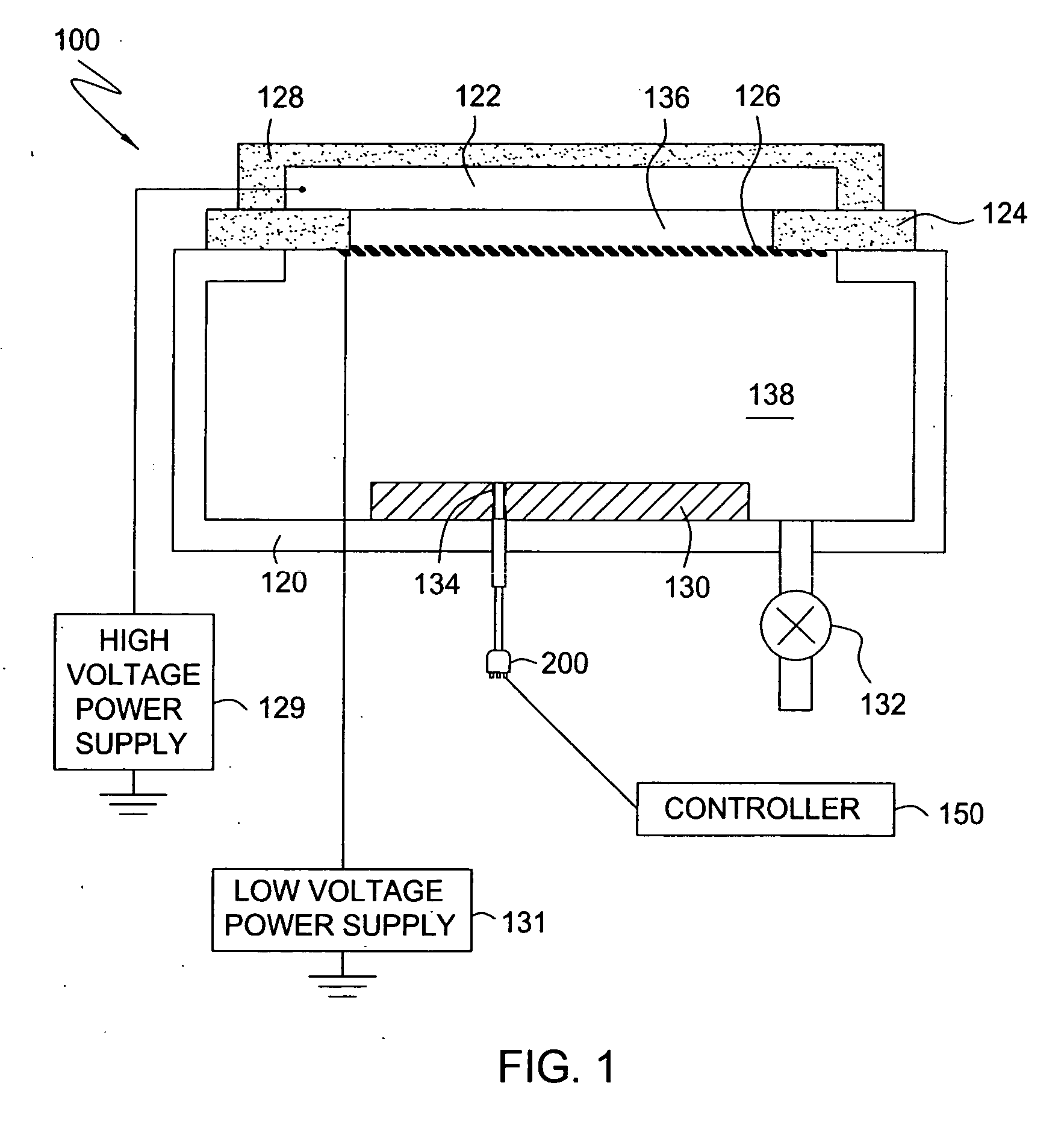

Method for managing UV irradiation for curing semiconductor substrate

ActiveUS7501292B2Maintain levelAutomatic controlSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingIlluminanceEngineering

A method for managing UV irradiation for curing a semiconductor substrate, includes: passing UV light through a transmission glass window provided in a chamber for curing a semiconductor substrate placed in the chamber; monitoring an illuminance upstream of the transmission glass window and an illuminance downstream of the transmission glass window; determining a timing and / or duration of cleaning of the transmission glass window, a timing of replacing the transmission glass window, a timing of replacing a UV lamp, and / or an output of the UV light based on the monitored illuminances.

Owner:ASM JAPAN

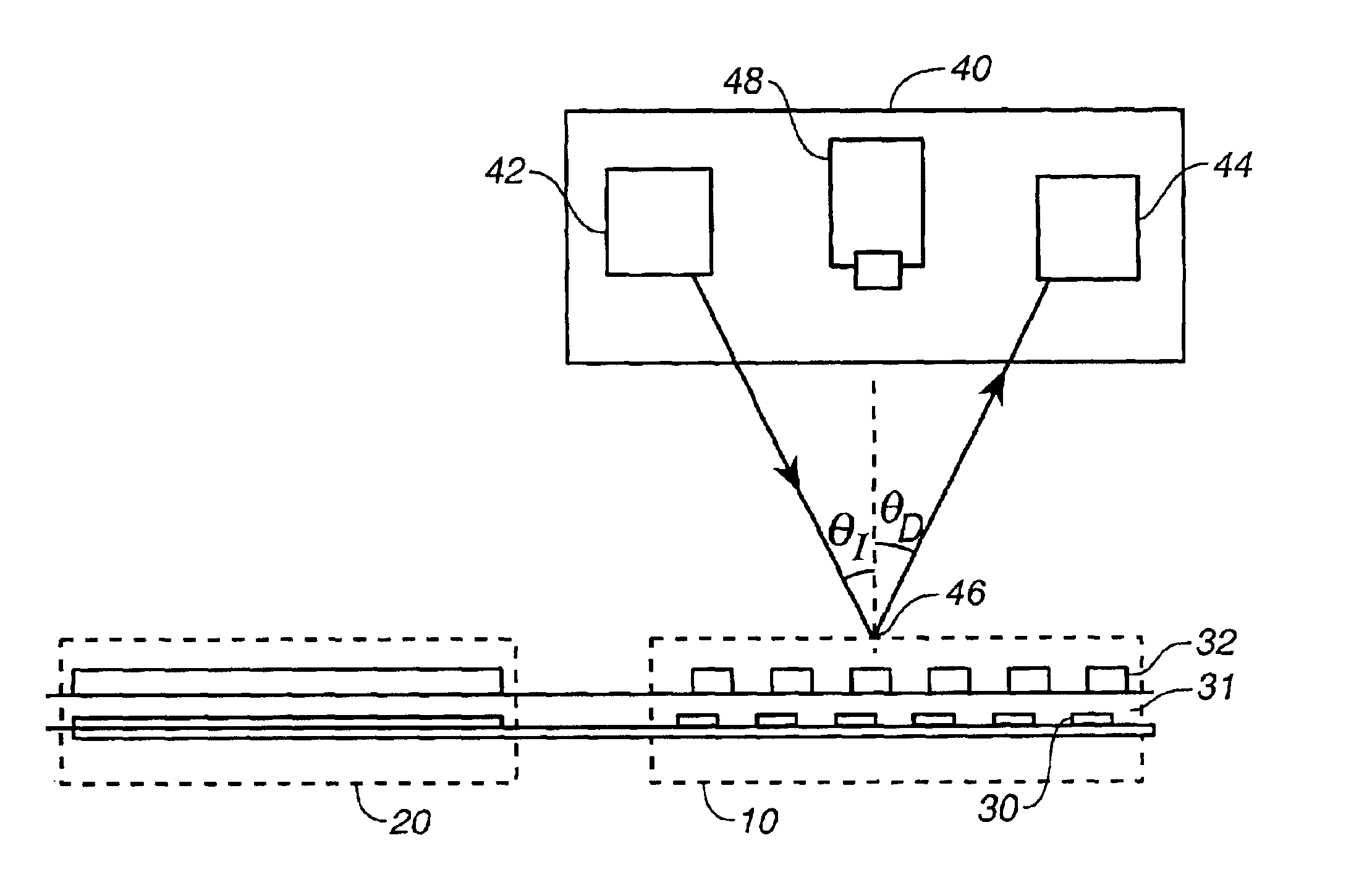

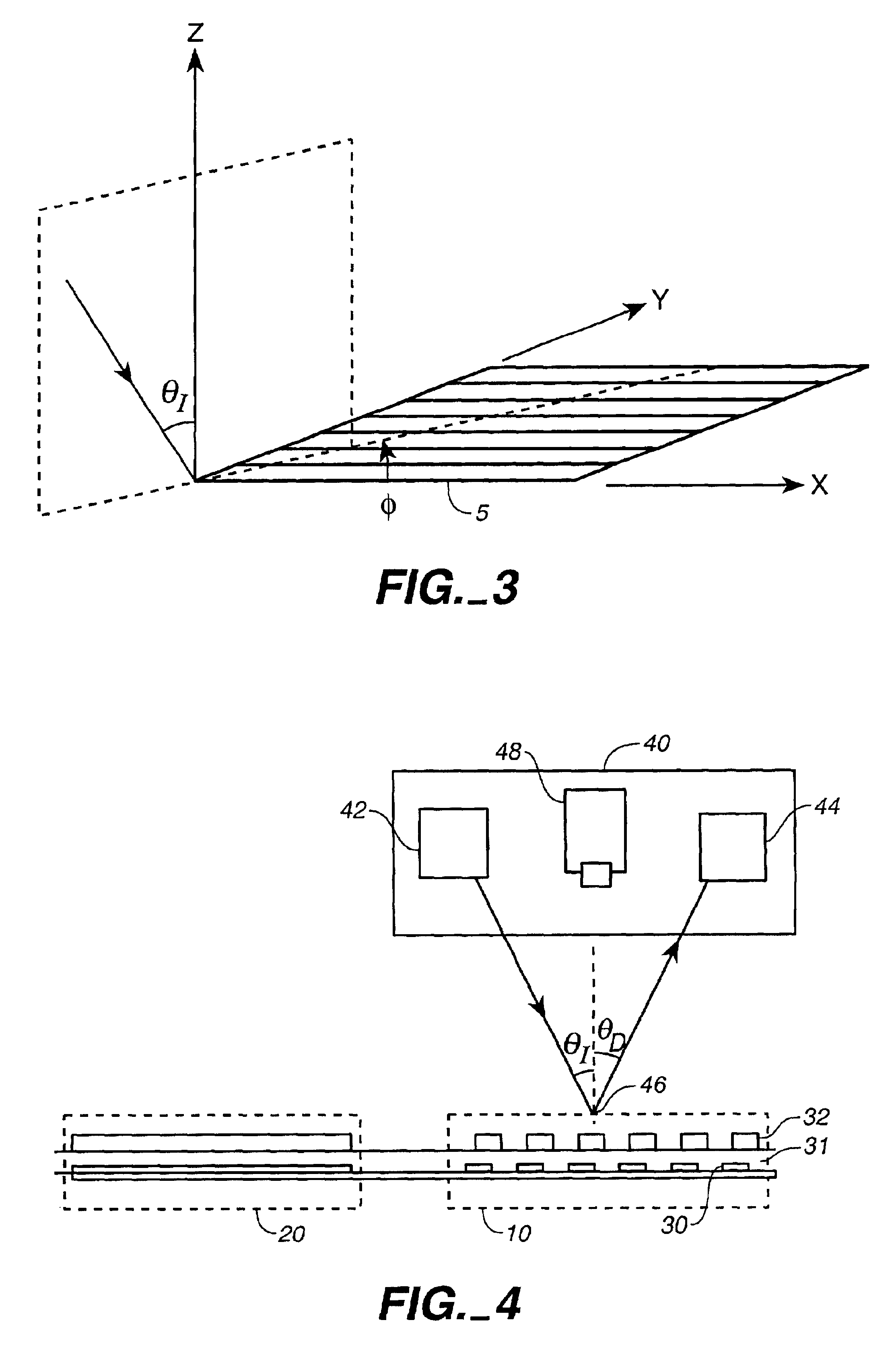

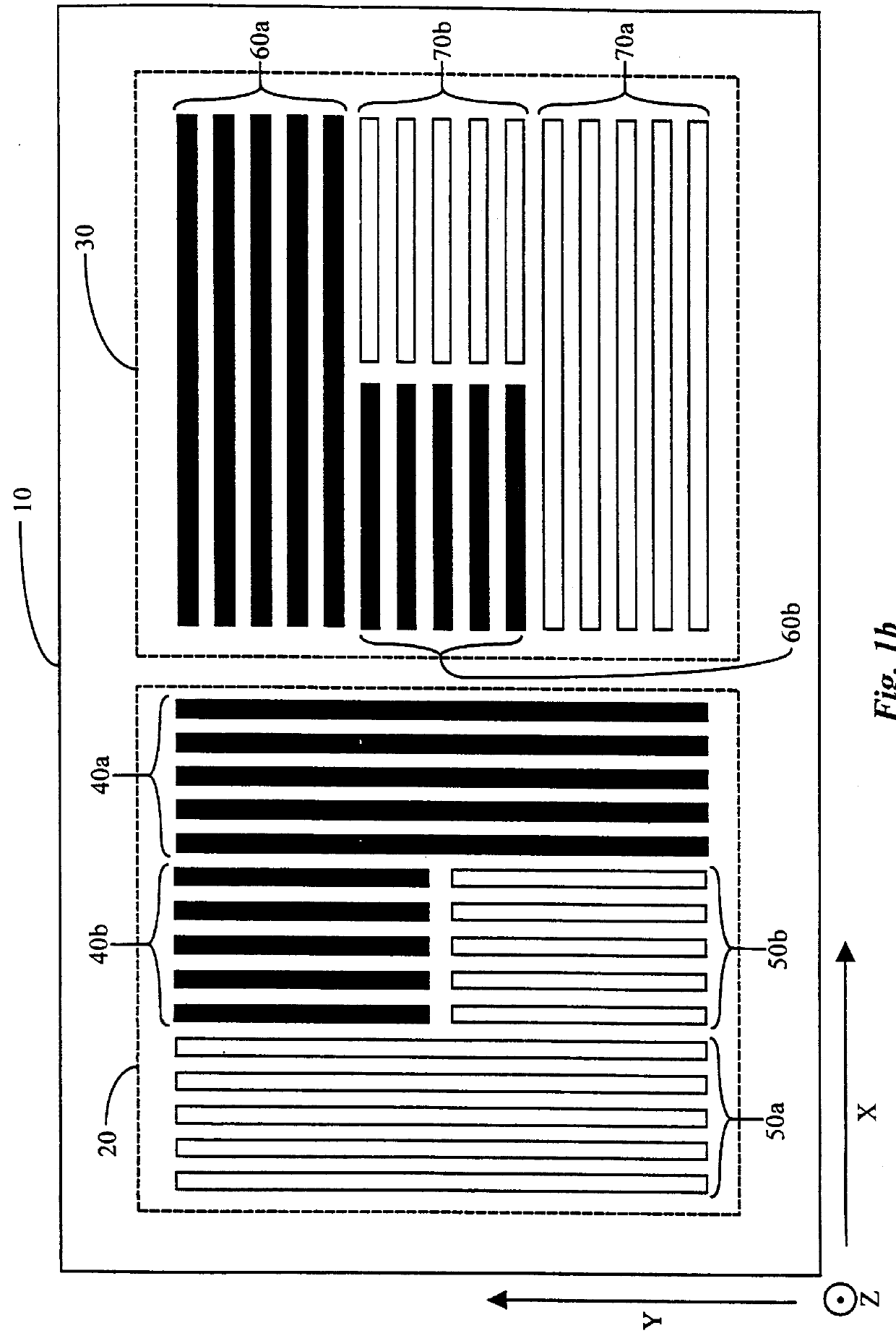

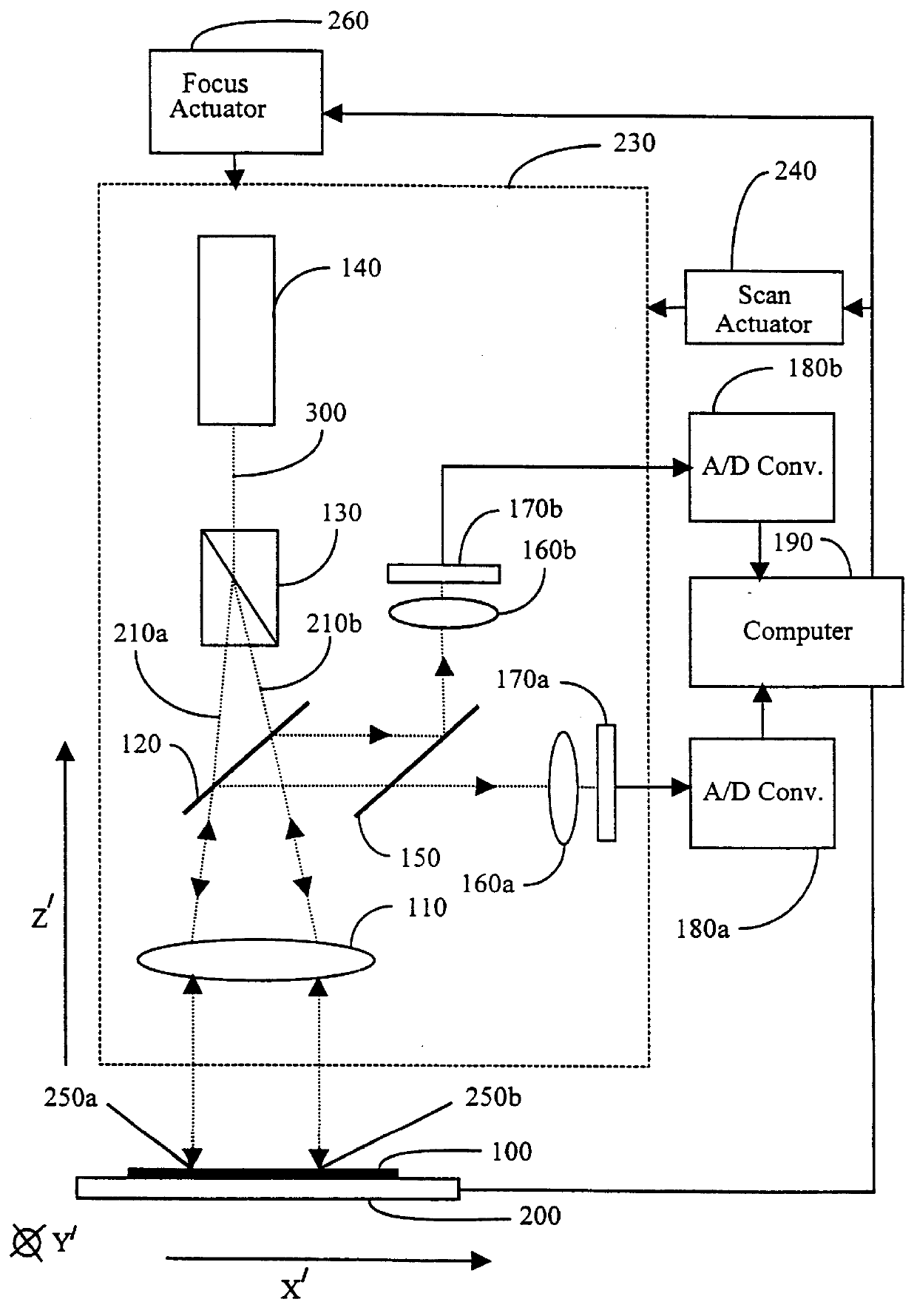

Overlay alignment metrology using diffraction gratings

InactiveUS6819426B2Accurate measurementLimited space availableSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMetrologyAngle of incidence

Alignment accuracy between two or more patterned layers is measured using a metrology target comprising substantially overlapping diffraction gratings formed in a test area of the layers being tested. An optical instrument illuminates all or part of the target area and measures the optical response. The instrument can measure transmission, reflectance, and / or ellipsometric parameters as a function of wavelength, polar angle of incidence, azimuthal angle of incidence, and / or polarization of the illumination and detected light. Overlay error or offset between those layers containing the test gratings is determined by a processor programmed to calculate an optical response for a set of parameters that include overlay error, using a model that accounts for diffraction by the gratings and interaction of the gratings with each others' diffracted field. The model parameters might also take account of manufactured asymmetries. The calculation may involve interpolation of pre-computed entries from a database accessible to the processor. The calculated and measured responses are iteratively compared and the model parameters changed to minimize the difference.

Owner:TOKYO ELECTRON LTD

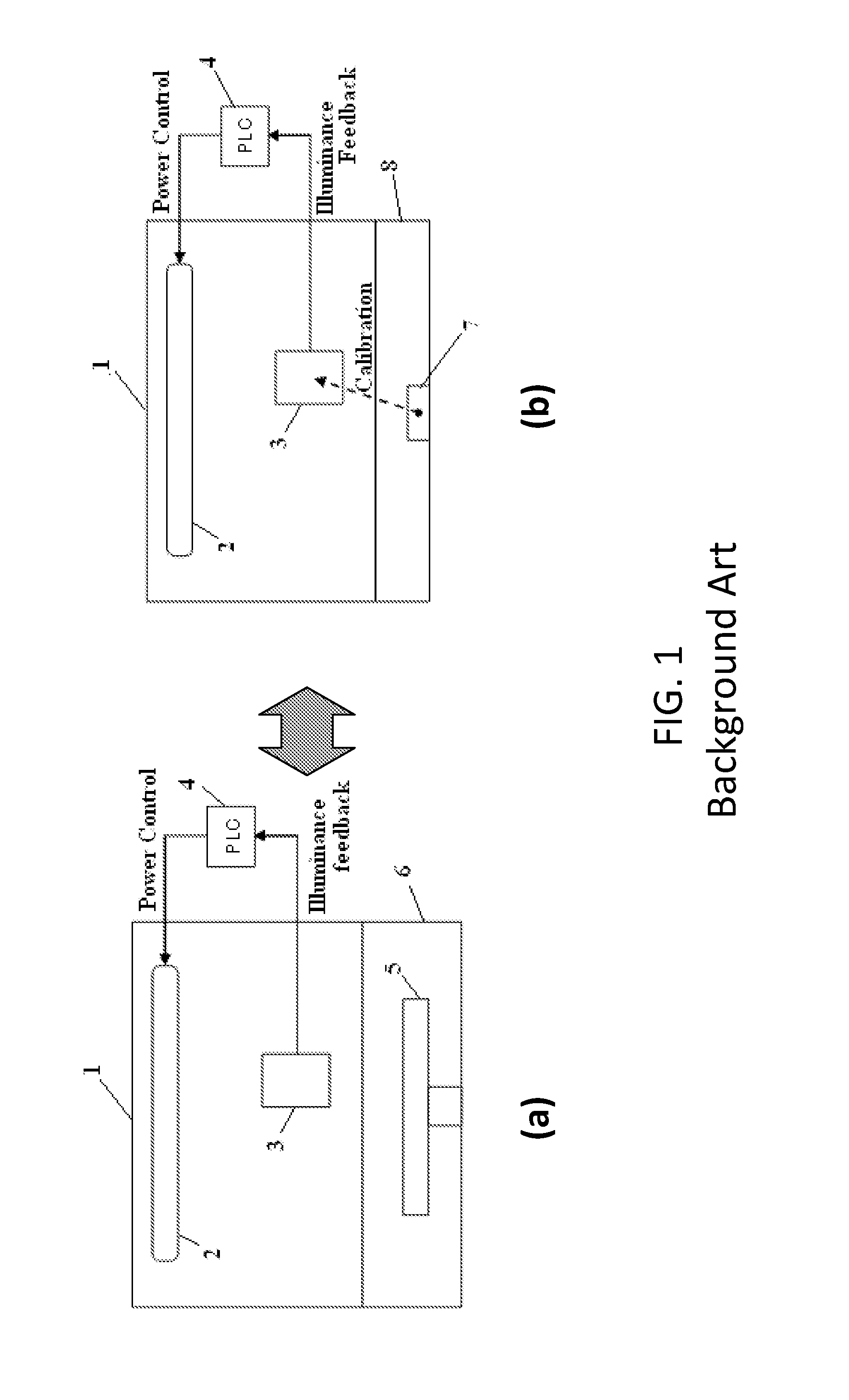

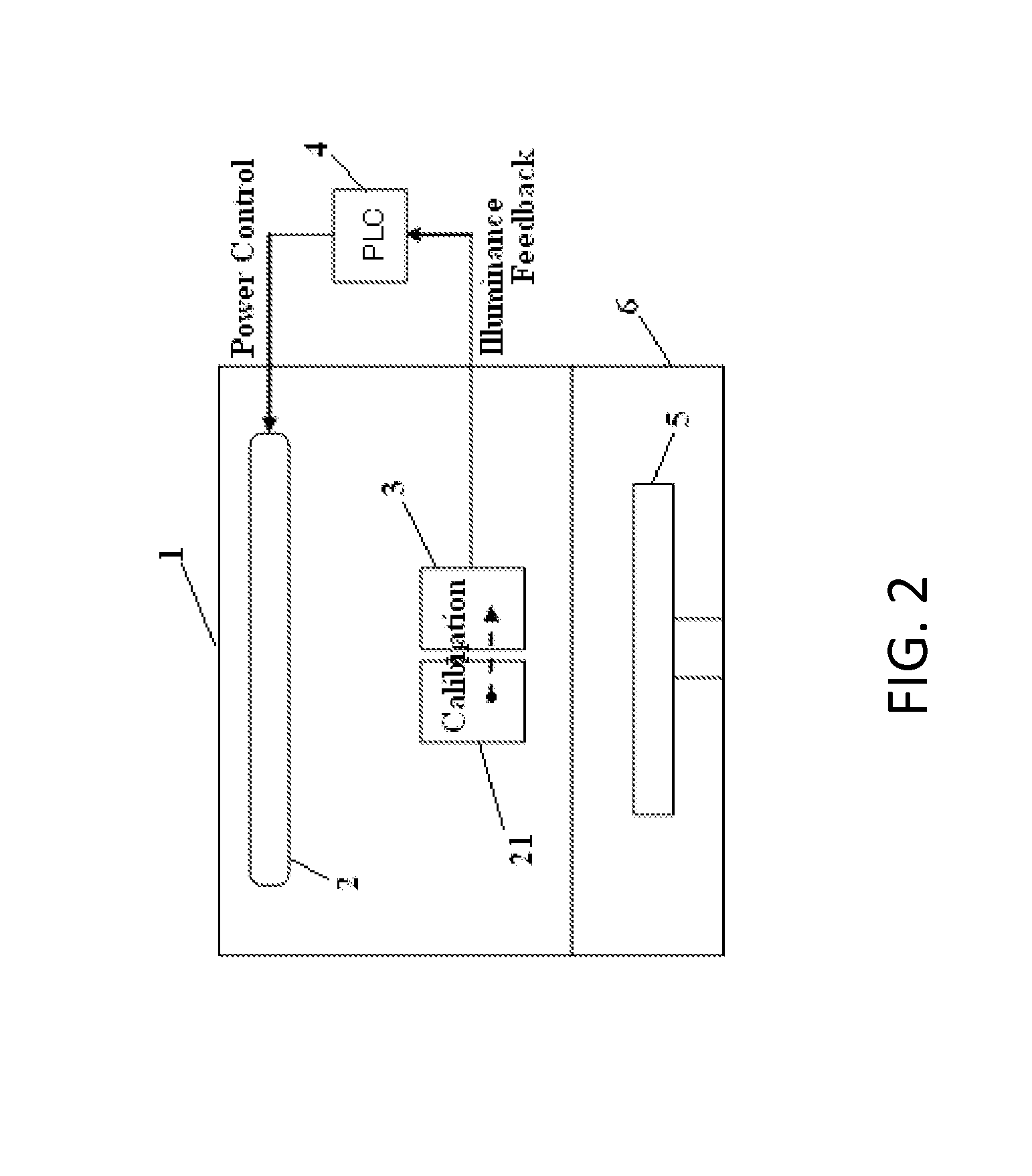

Calibration method of UV sensor for UV curing

ActiveUS8466411B2Reduce exposureEliminate errorsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingUV curingUltraviolet

A method for managing UV irradiation for treating substrates in the course of treating multiple substrates consecutively with UV light, includes: exposing a first UV sensor to the UV light at first intervals to measure illumination intensity of the UV light so as to adjust the illumination intensity to a desired level based on the measured illumination intensity; and exposing a second UV sensor to the UV light at second intervals to measure illumination intensity of the UV light so as to calibrate the first UV sensor by equalizing the illumination intensity measured by the first UV sensor substantially with the illumination intensity measured by the second UV sensor, wherein each second interval is longer than each first interval.

Owner:ASM JAPAN

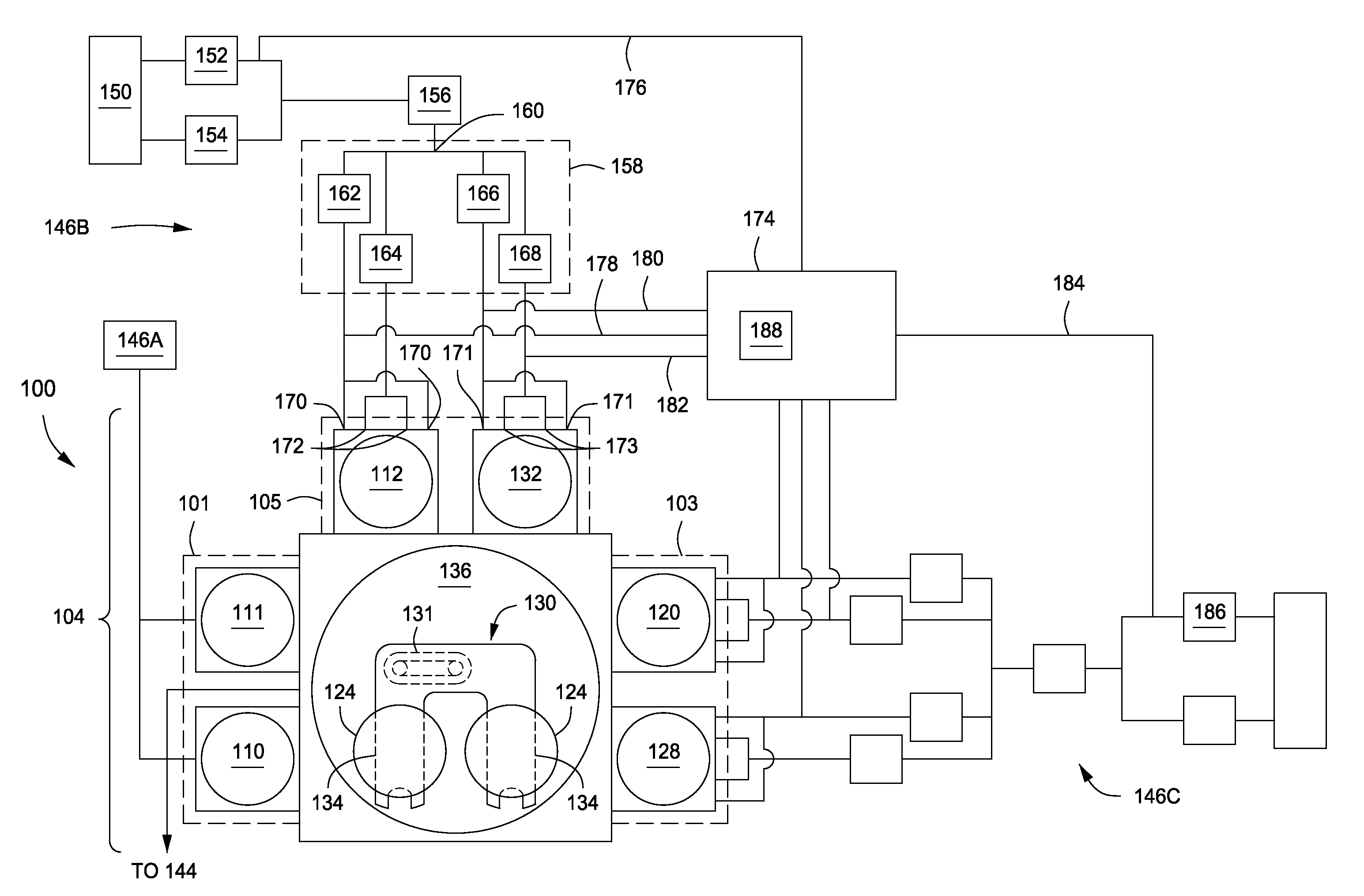

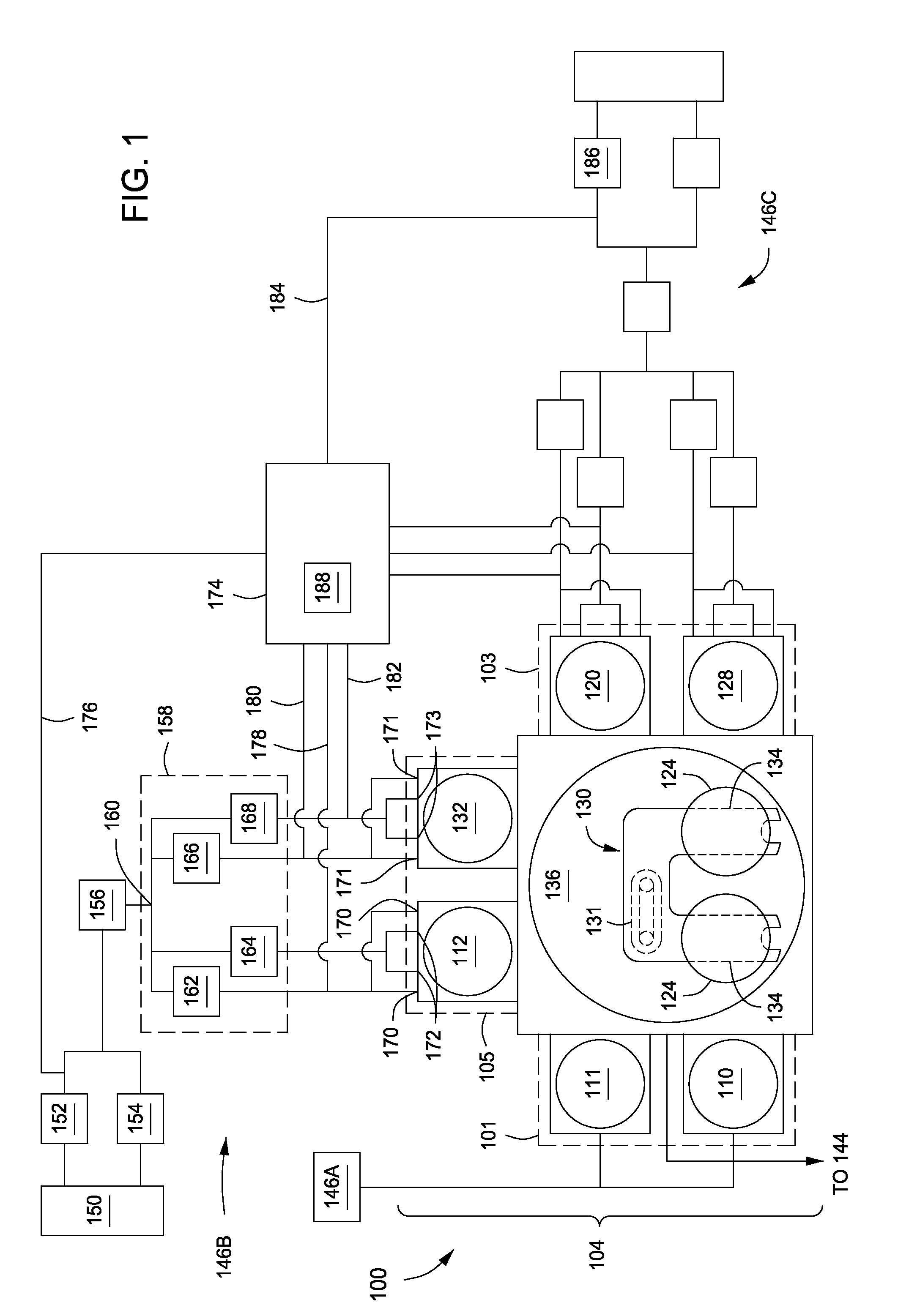

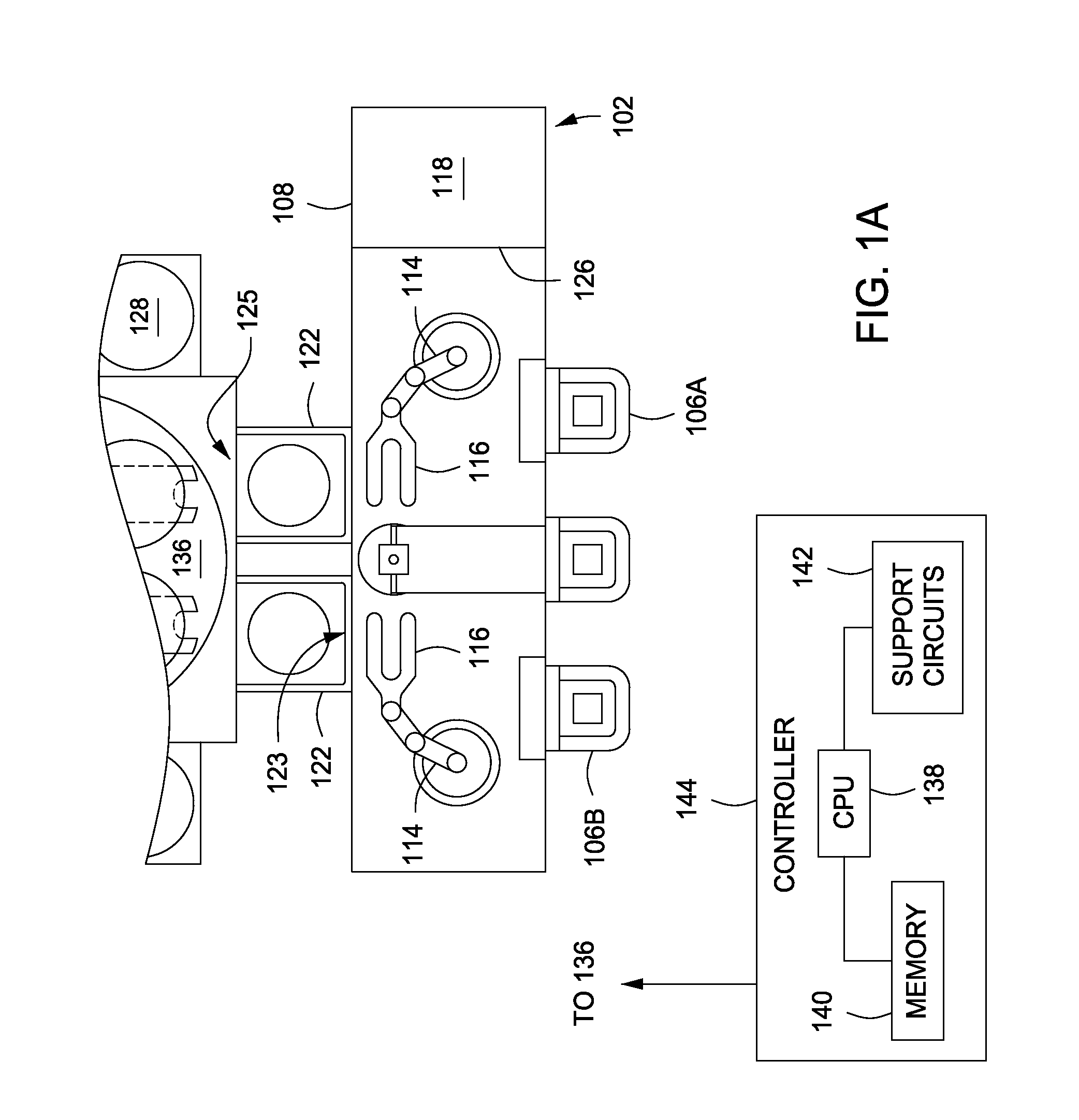

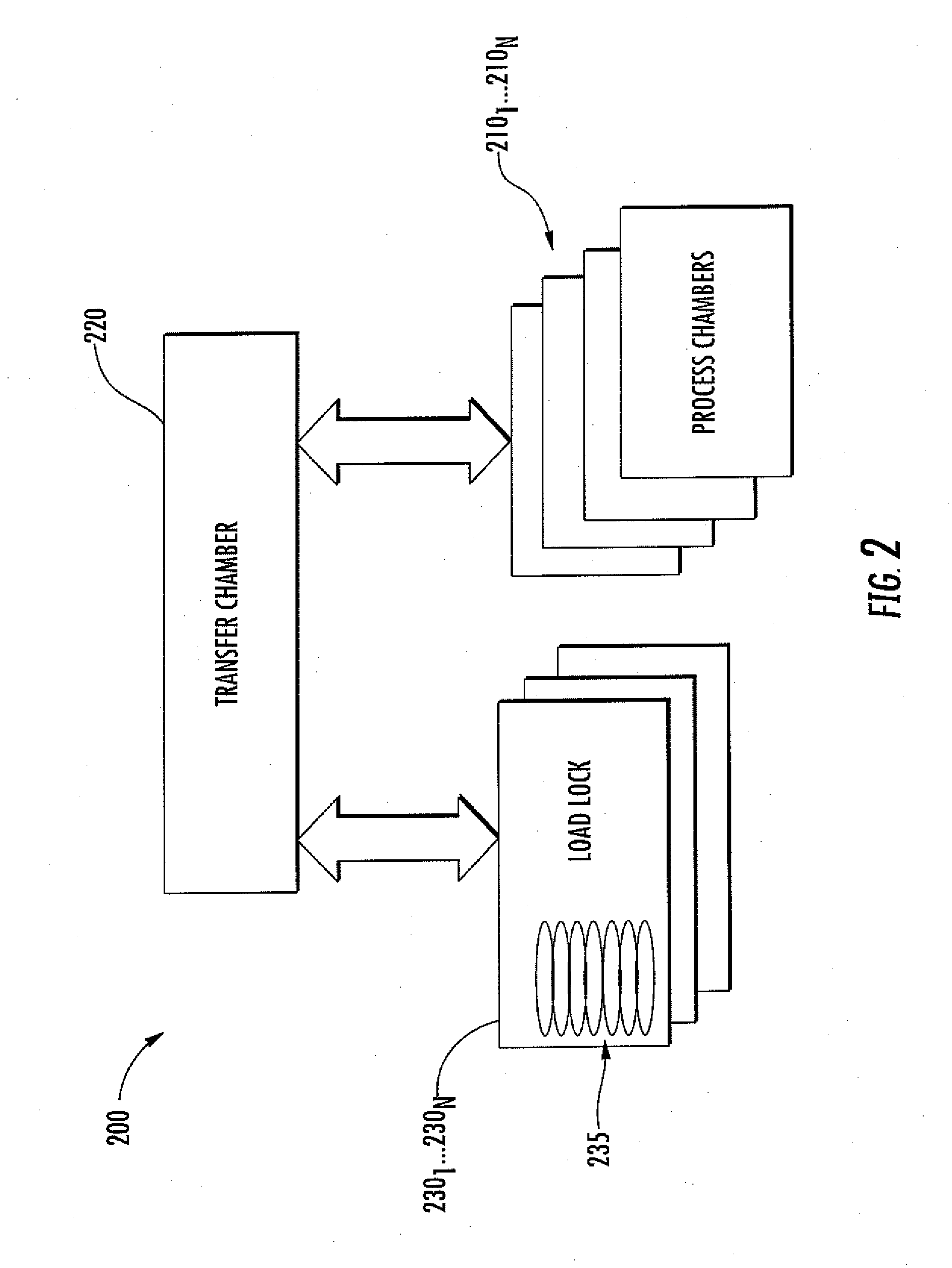

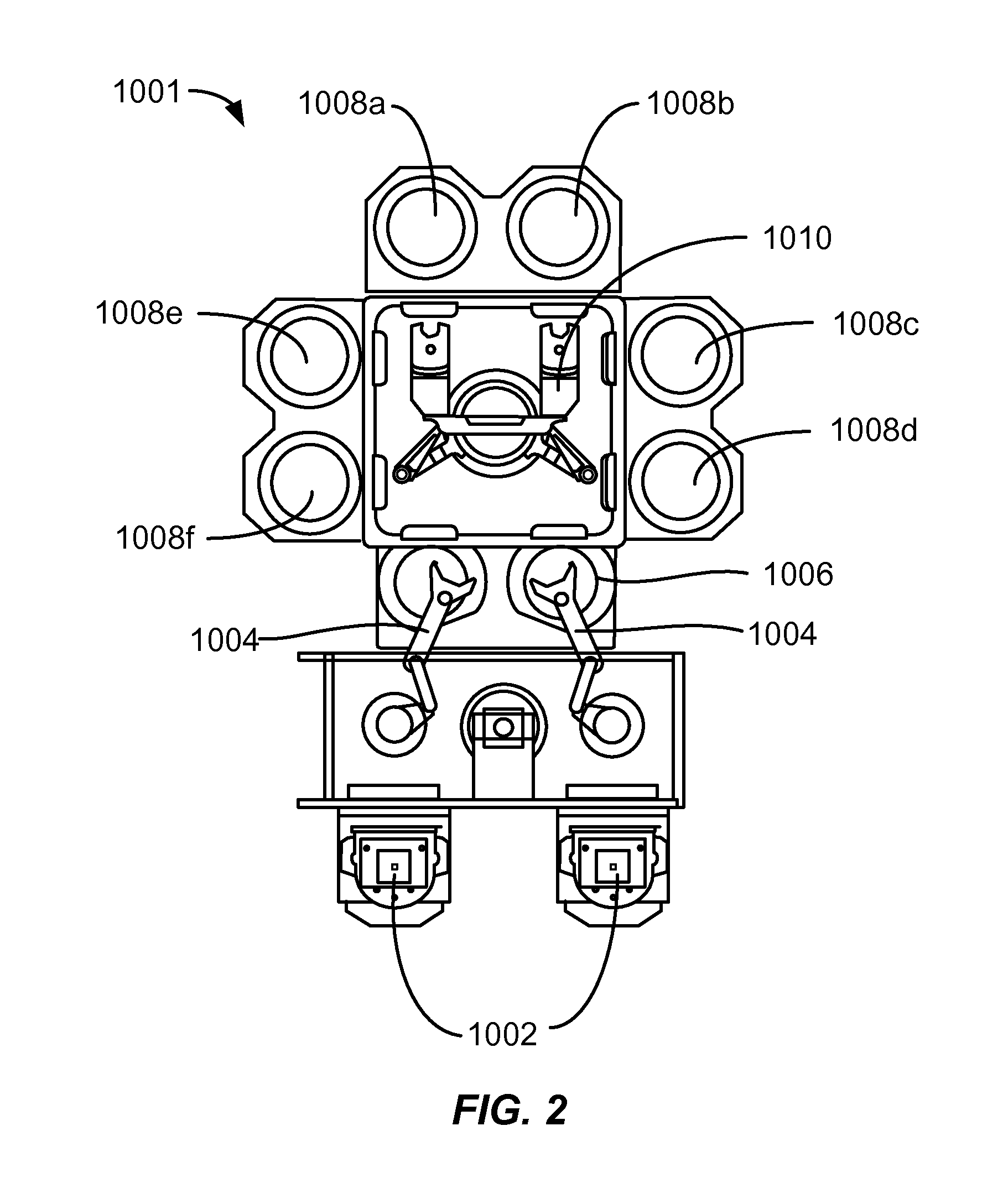

Methods and apparatus for calibrating flow controllers in substrate processing systems

Methods and apparatus for calibrating a plurality of gas flows in a substrate processing system are provided herein. In some embodiments, a substrate processing system may include a cluster tool comprising a first process chamber and a second process chamber coupled to a central vacuum transfer chamber; a first flow controller to provide a process gas to the first process chamber; a second flow controller to provide the process gas to the second process chamber; a mass flow verifier to verify a flow rate from each of the first and second flow controllers; a first conduit to selectively couple the first flow controller to the mass flow verifier; and a second conduit to selectively couple the second flow controller to the mass flow verifier.

Owner:APPLIED MATERIALS INC

Method for managing UV irradiation for curing semiconductor substrate

ActiveUS20090023229A1Automatic controlMaintain levelSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingIlluminanceEngineering

A method for managing UV irradiation for curing a semiconductor substrate, includes: passing UV light through a transmission glass window provided in a chamber for curing a semiconductor substrate placed in the chamber; monitoring an illuminance upstream of the transmission glass window and an illuminance downstream of the transmission glass window; determining a timing and / or duration of cleaning of the transmission glass window, a timing of replacing the transmission glass window, a timing of replacing a UV lamp, and / or an output of the UV light based on the monitored illuminances.

Owner:ASM JAPAN

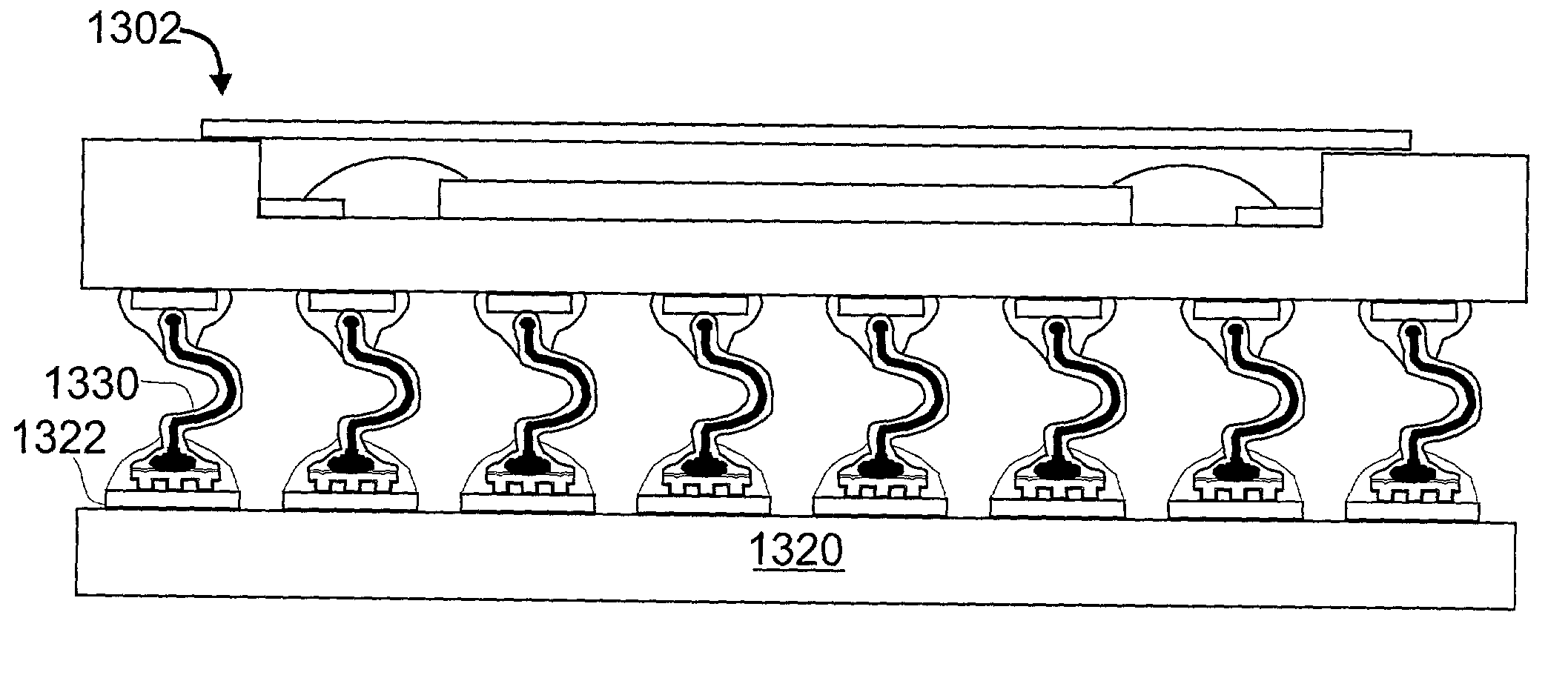

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

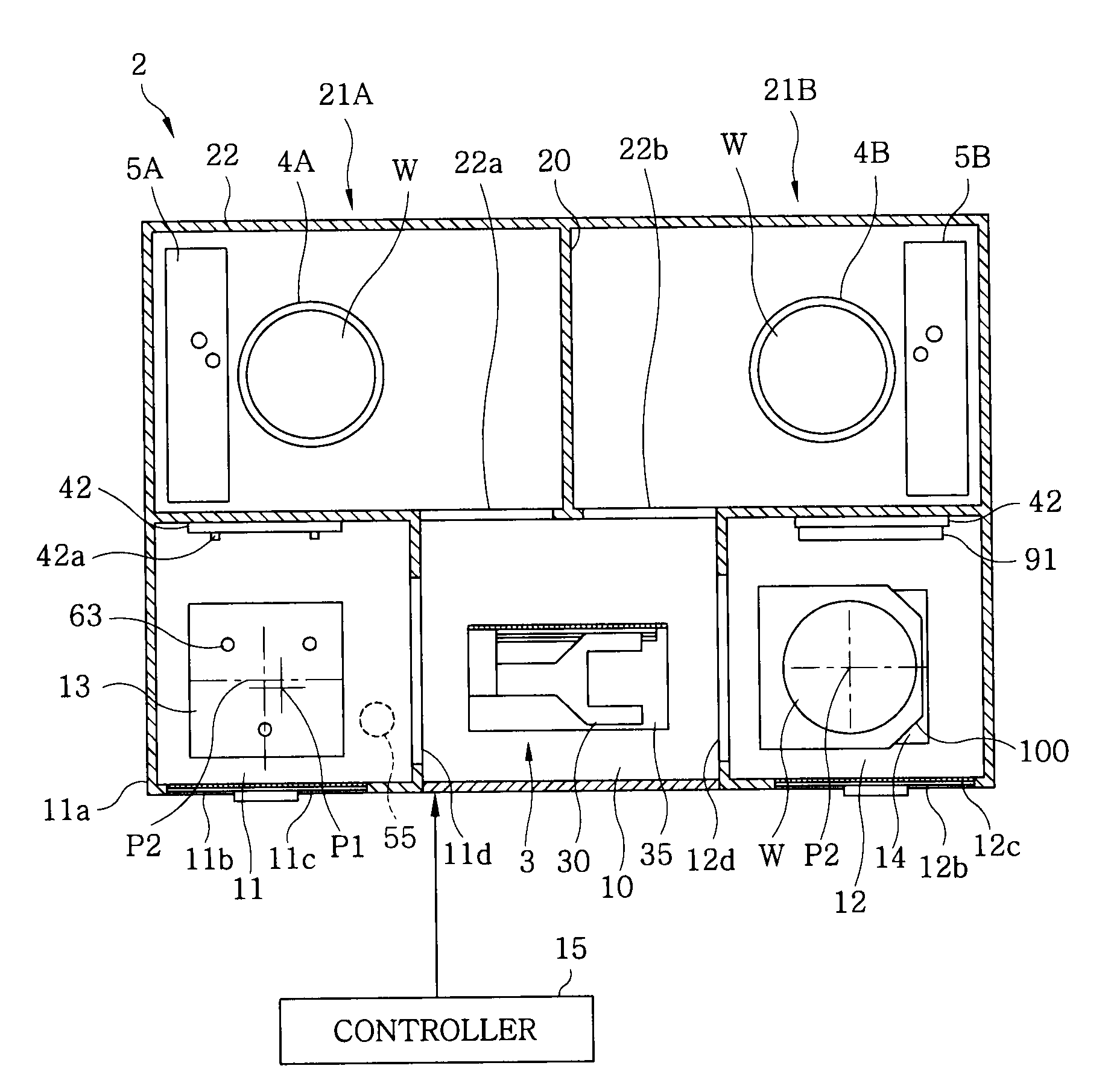

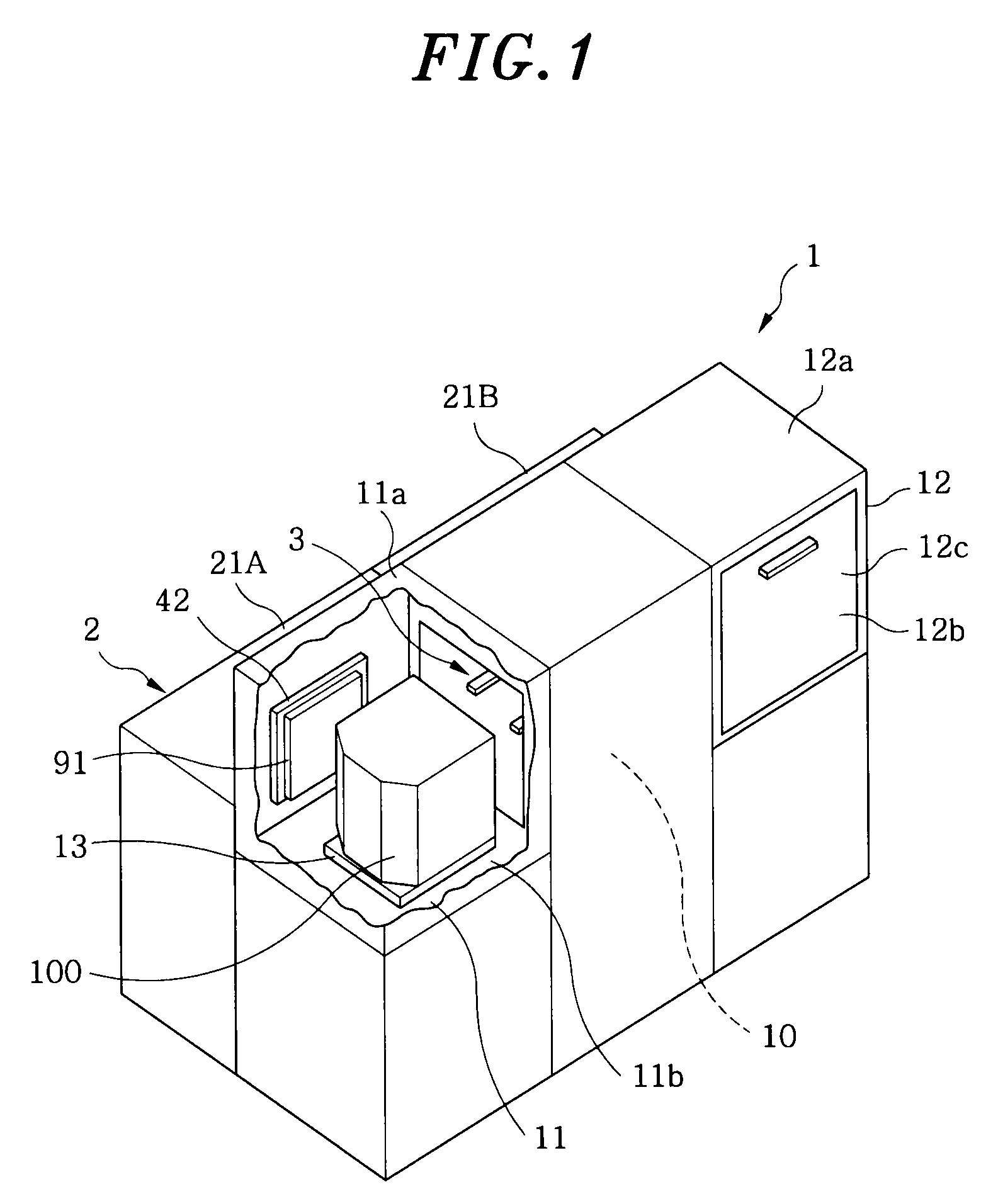

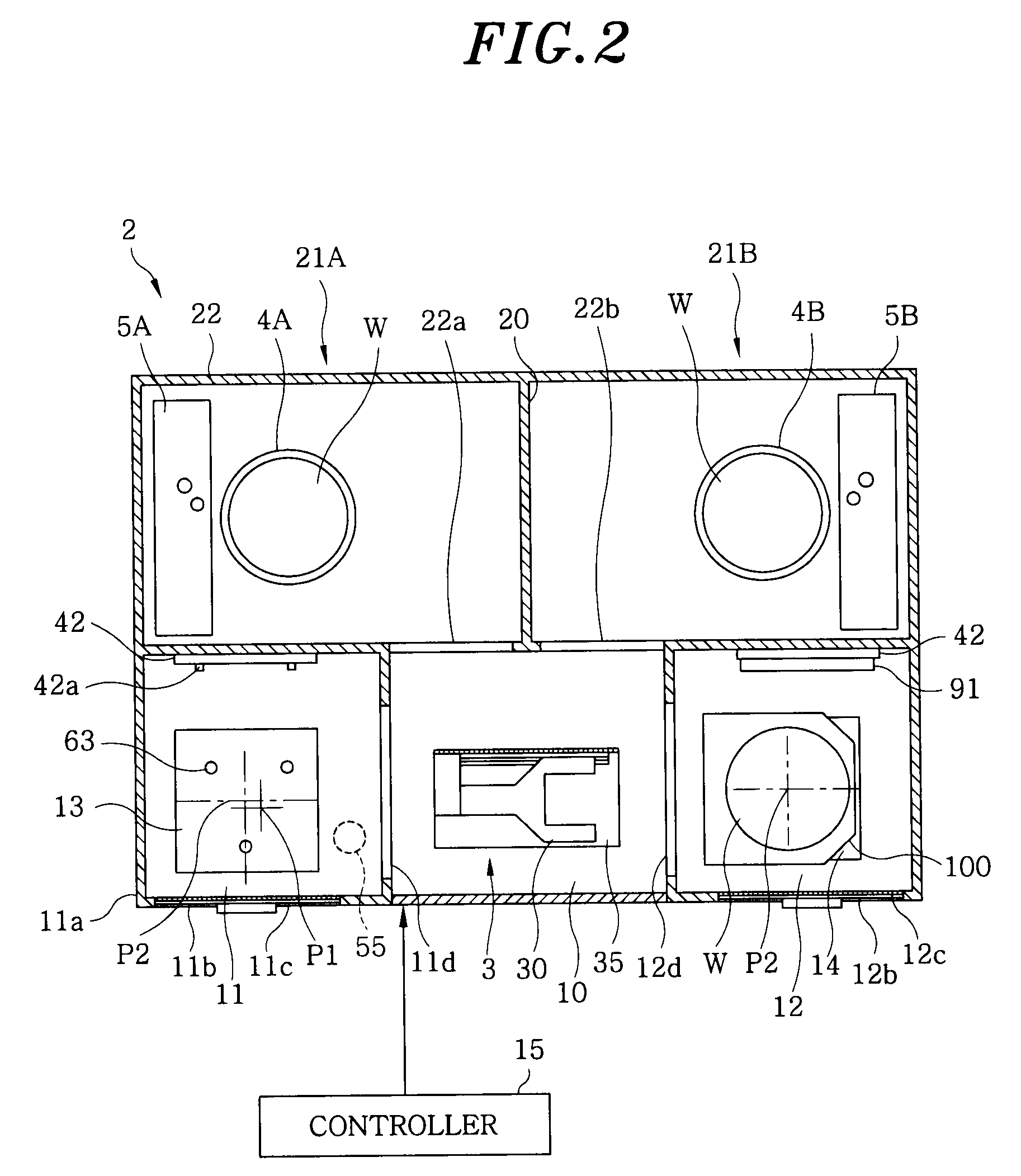

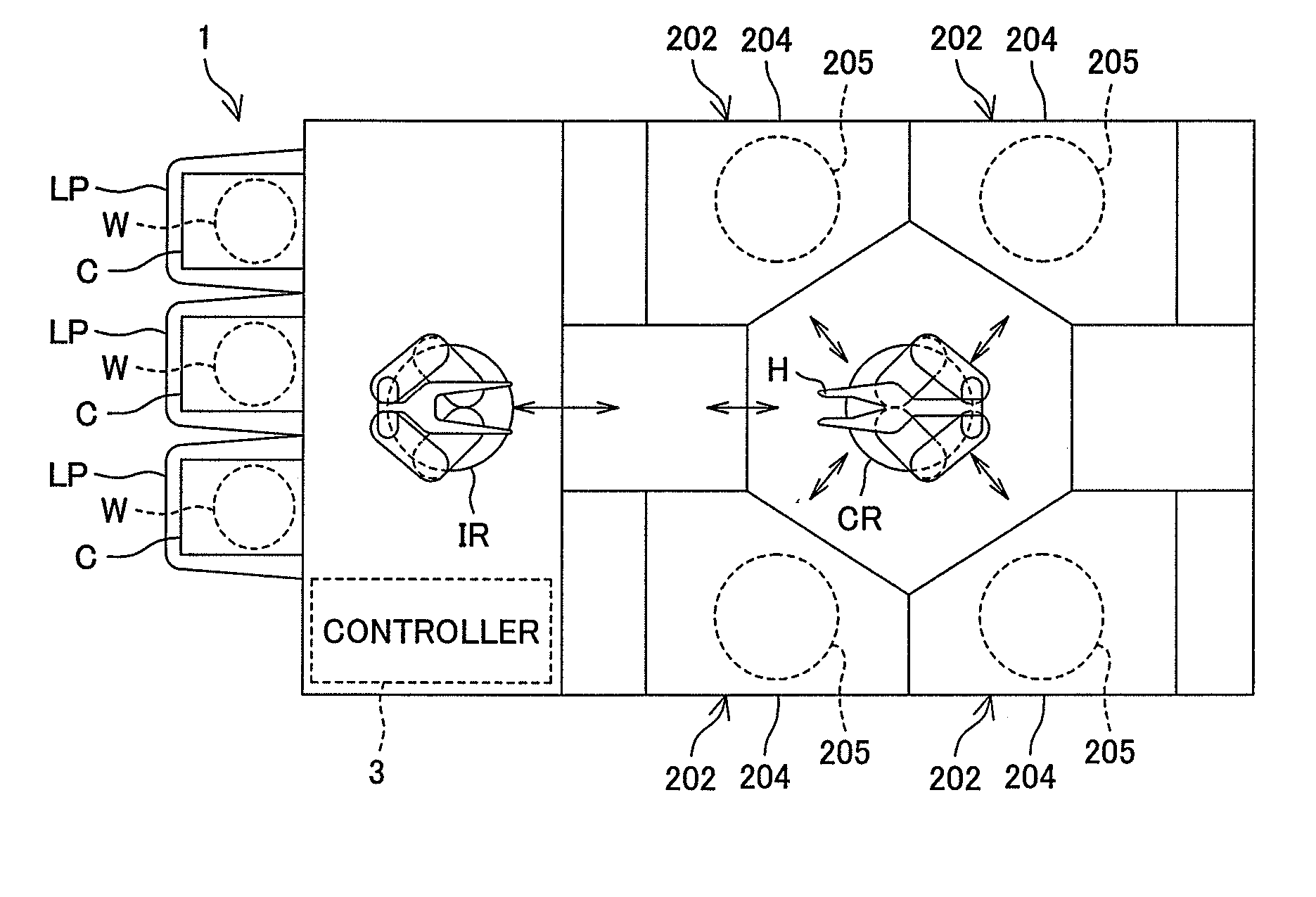

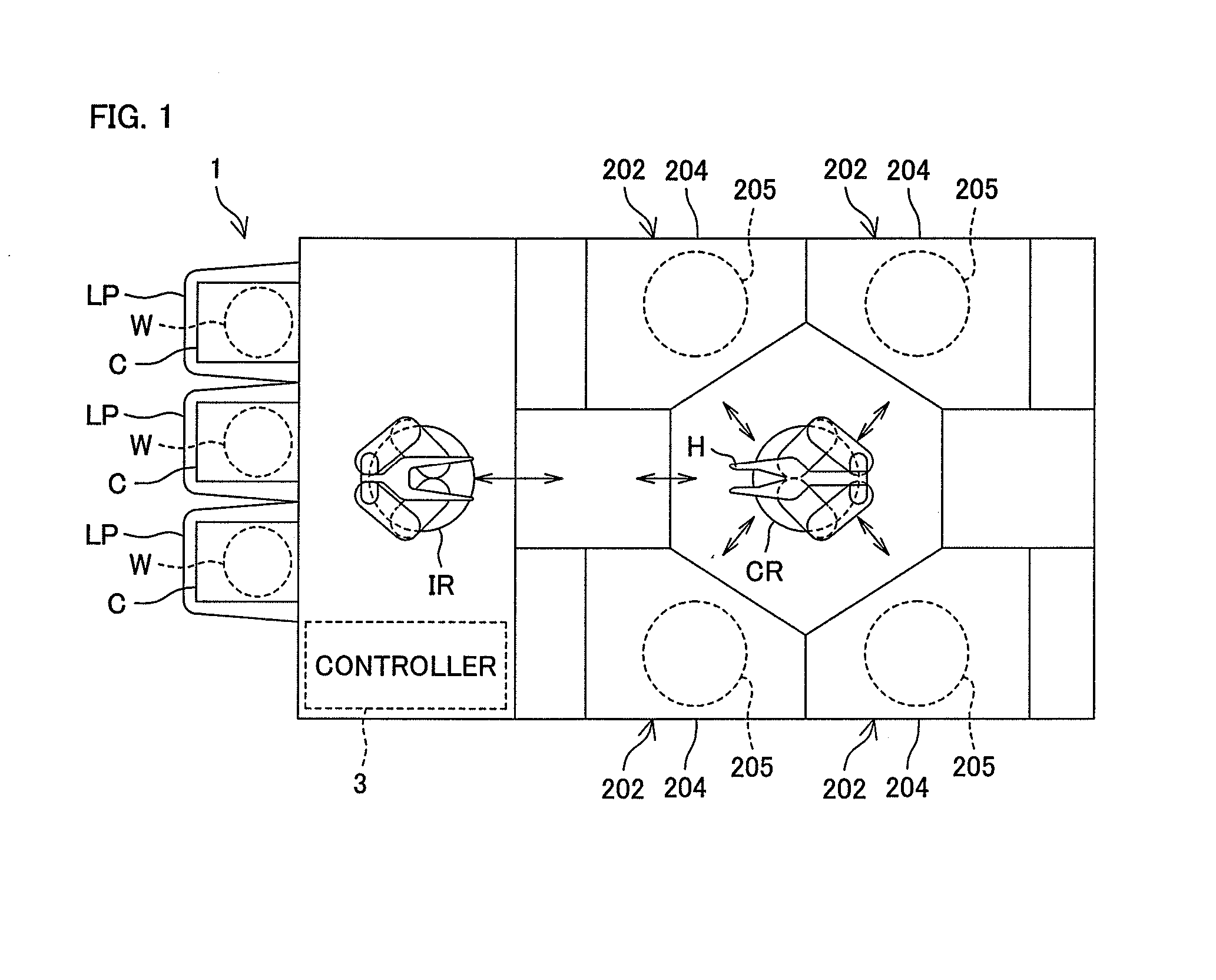

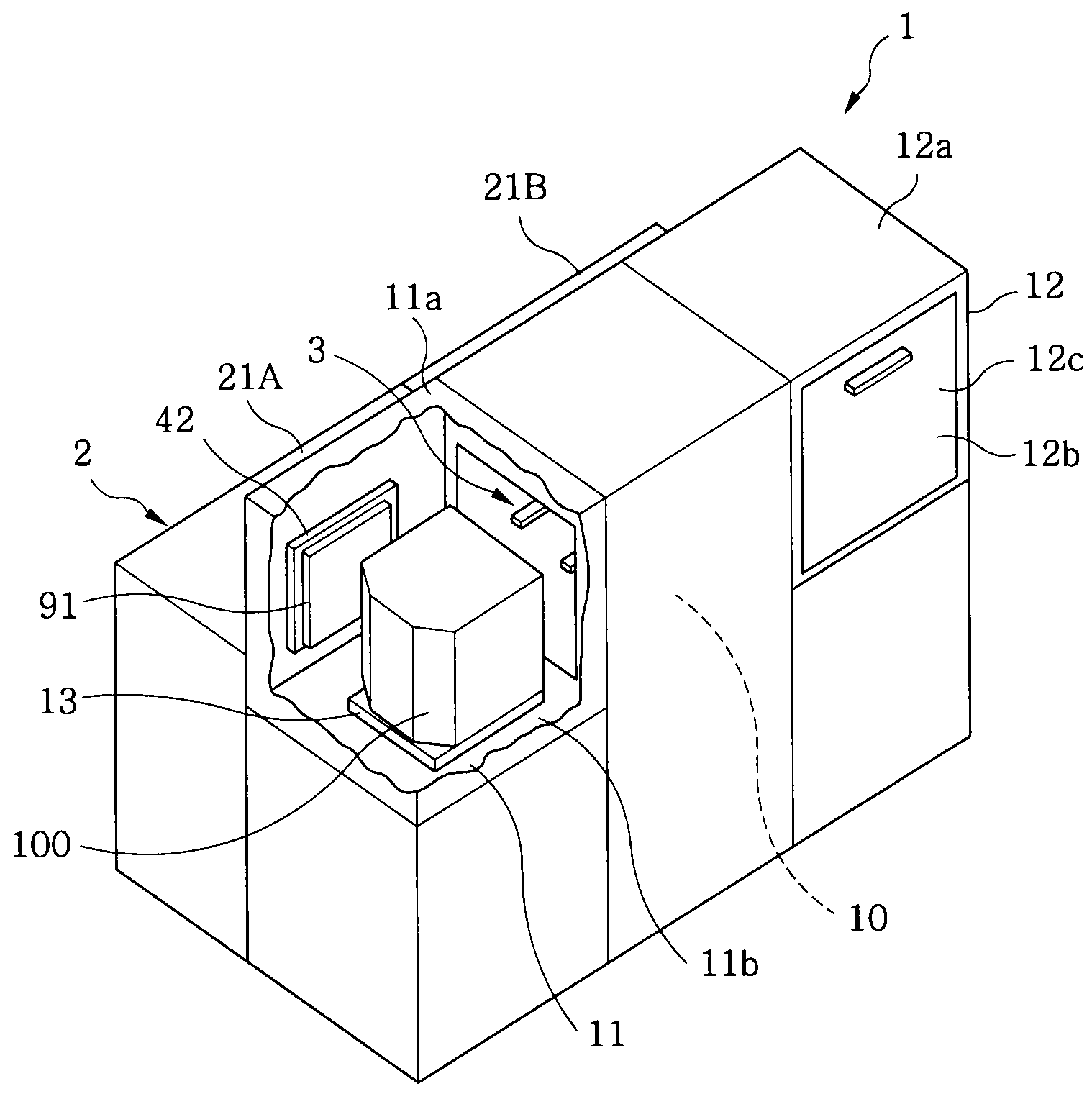

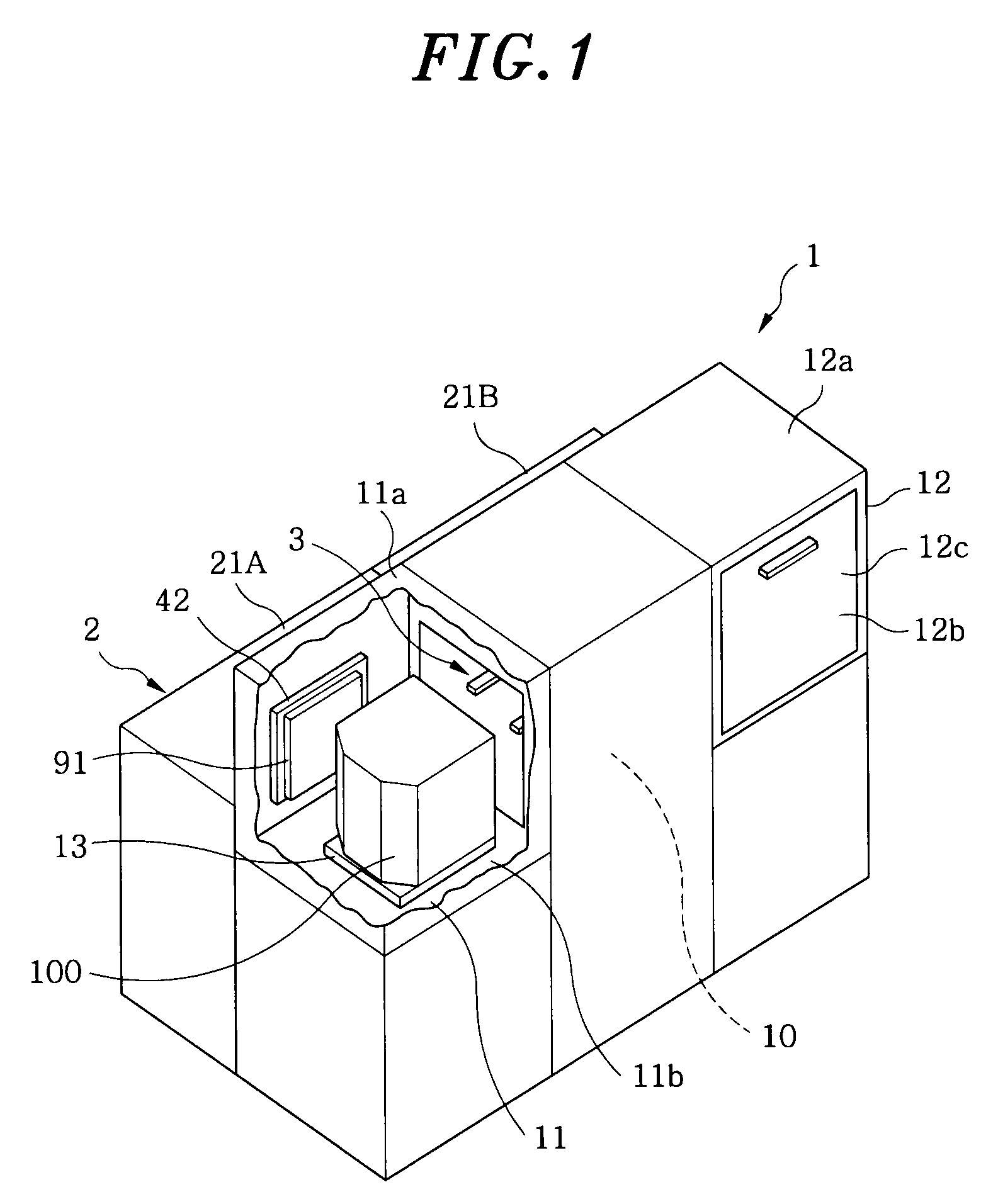

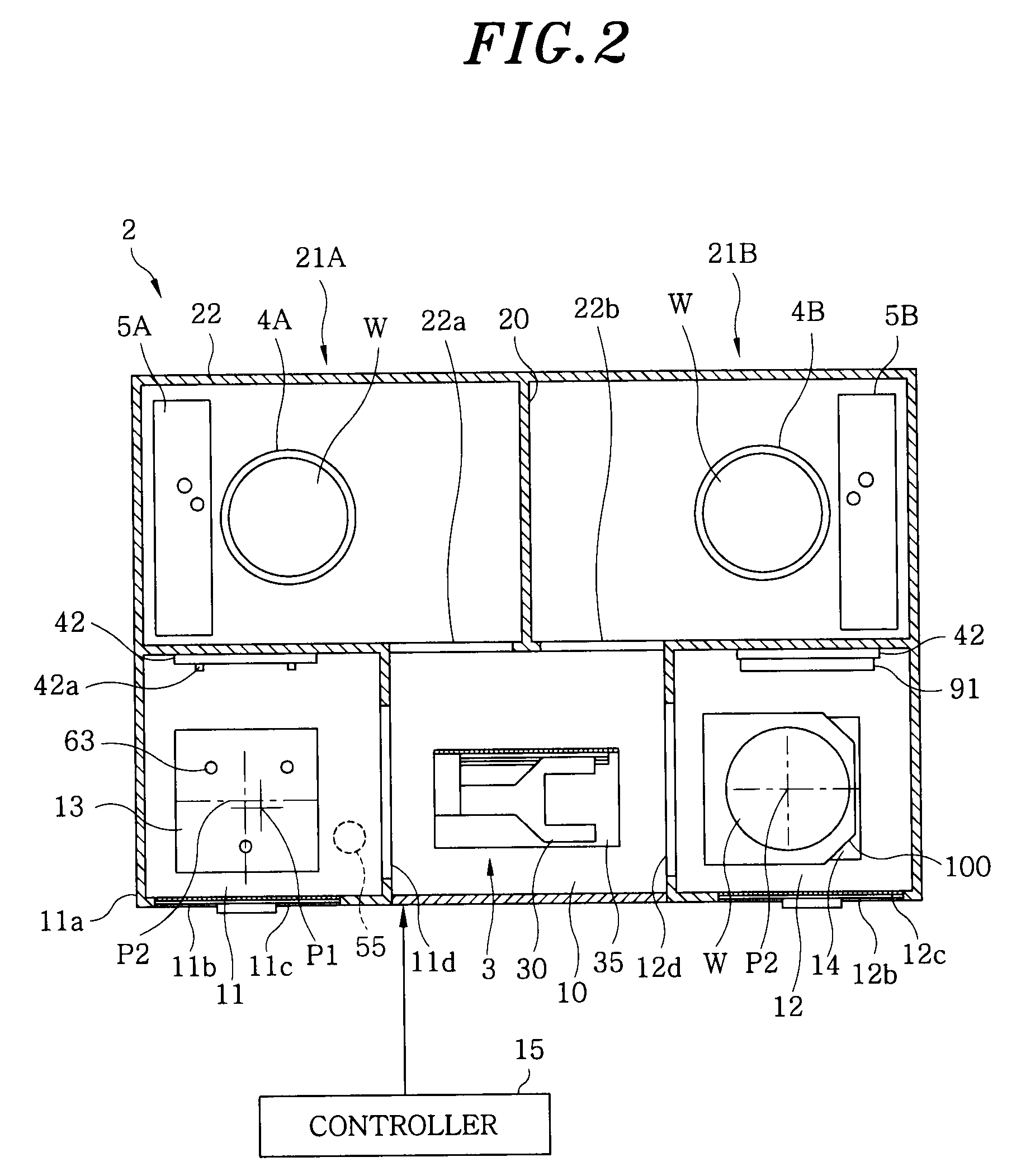

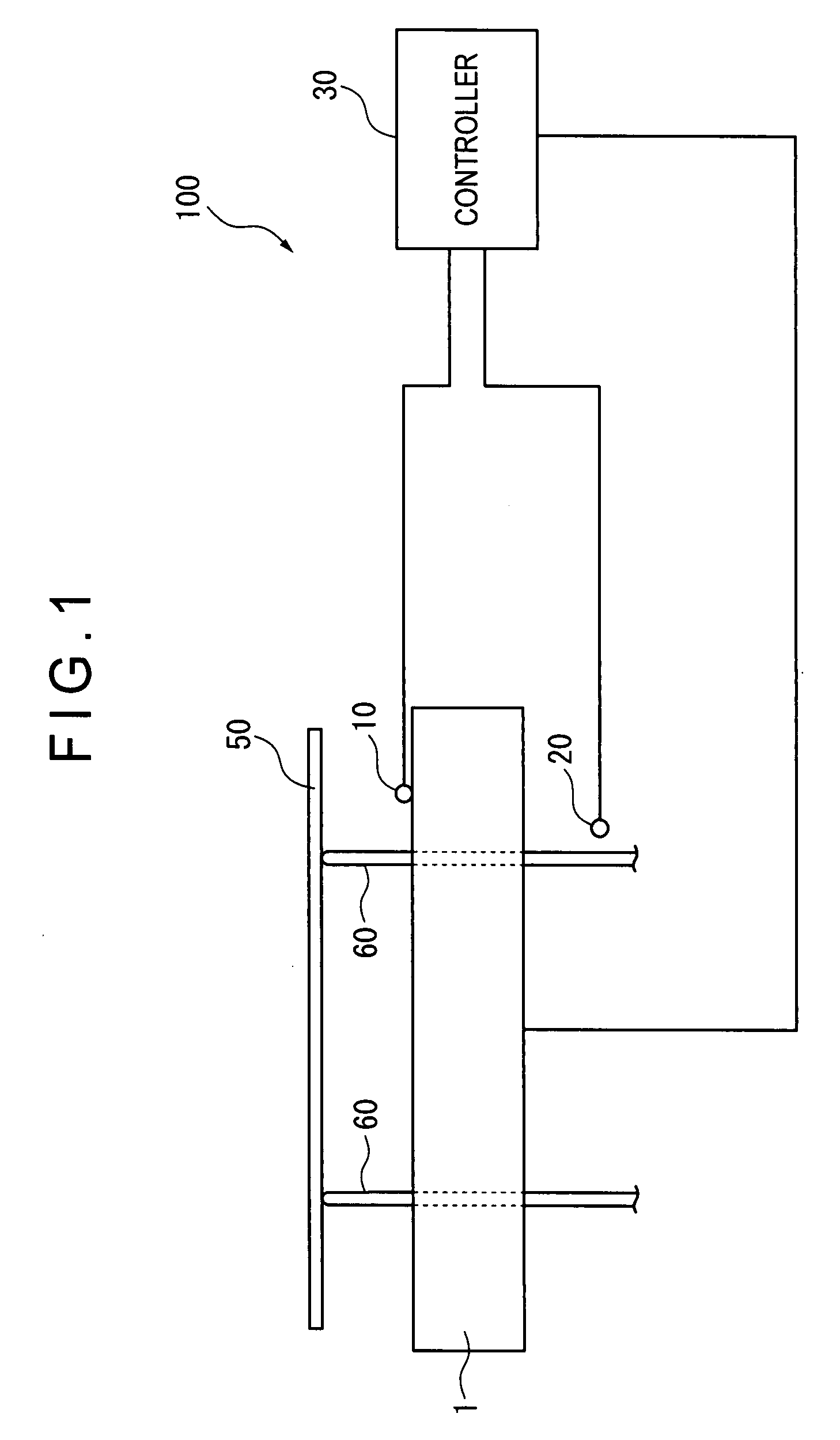

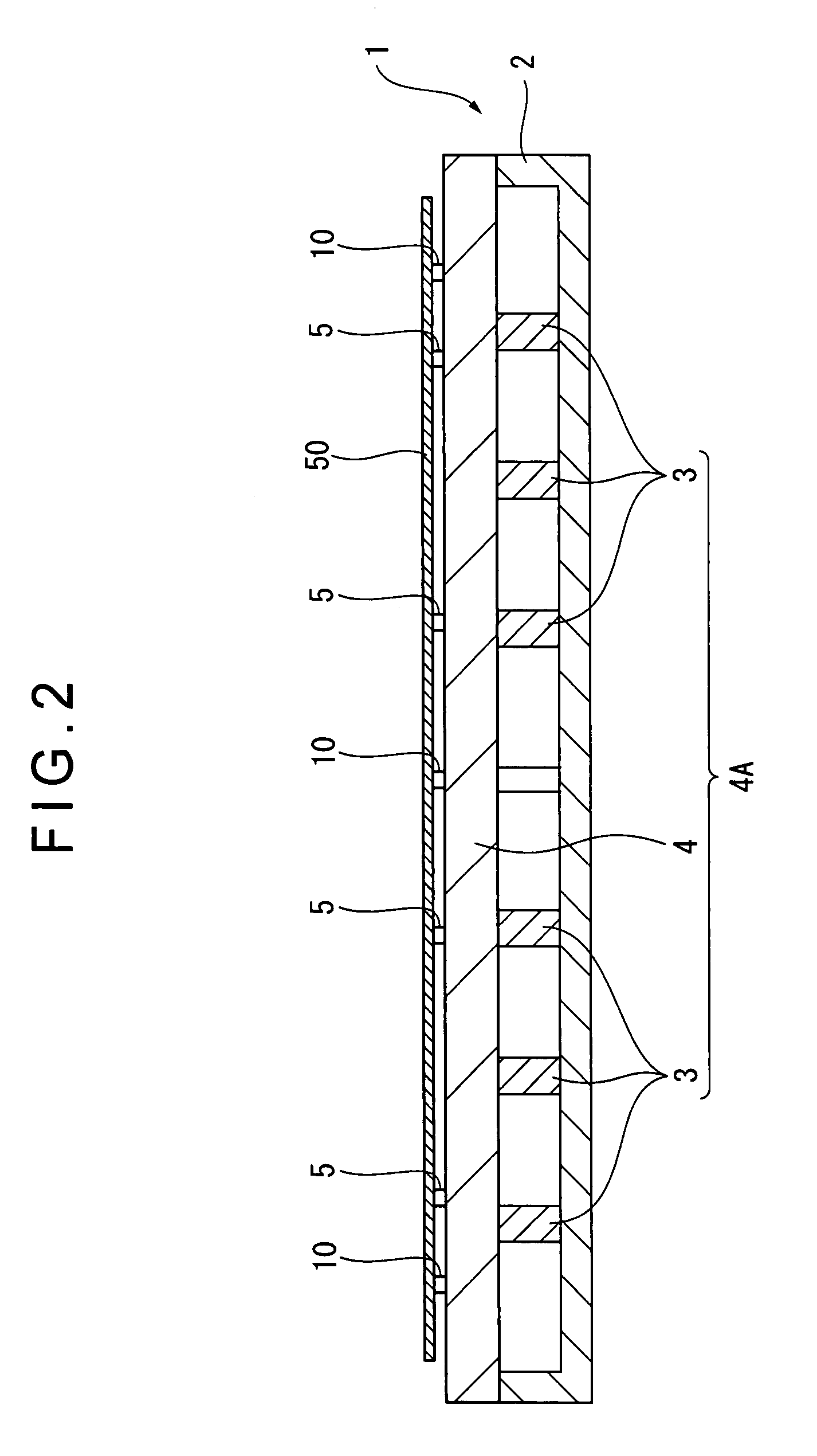

FOUP opening/closing device and probe apparatus

ActiveUS8267633B2Assure great degree of freedomEfficient comprehensive utilizationSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingControl signalFOUP

A FOUP opening / closing device includes a housing containing a mounting table for mounting the FOUP thereon, an FOUP loading opening, and a delivery opening. The device further includes a rotator for rotating the mounting table, a door opening / closing unit to open or close the door of the FOUP and keep the door open, a mover for moving the FOUP and the door opening / closing unit in a reciprocating manner, to allow the FOUP and the door opening / closing unit to be connected to or separated from each other, and a controller to output control signals for moving the FOUP and the door opening / closing unit via operation of the mover to mount the door of the FOUP to the door opening / closing unit, separating the door from the FOUP, moving the FOUP and the door opening / closing unit away from each other, and rotating the mounting table to make the FOUP face the delivery opening.

Owner:TOKYO ELECTRON LTD

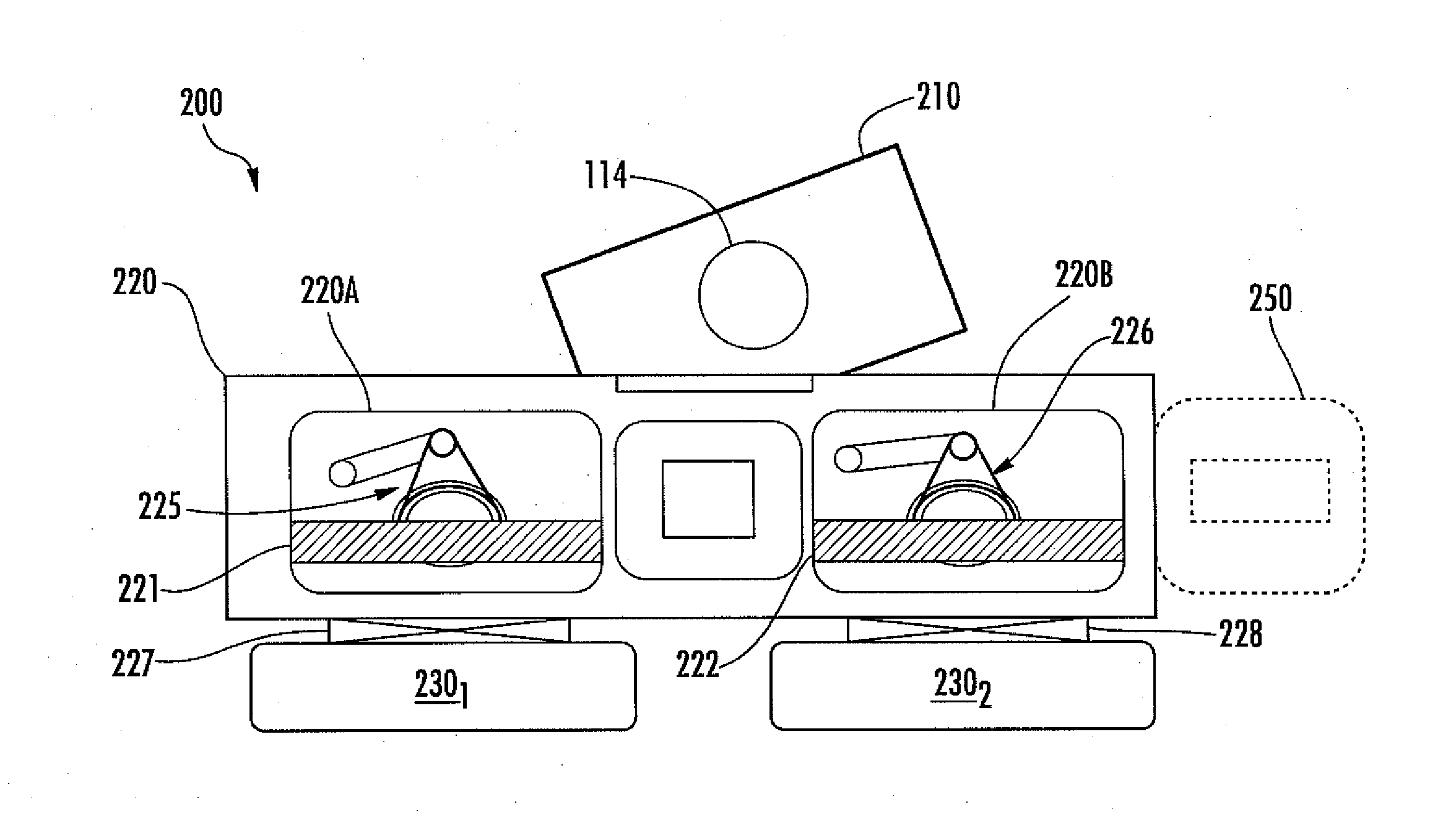

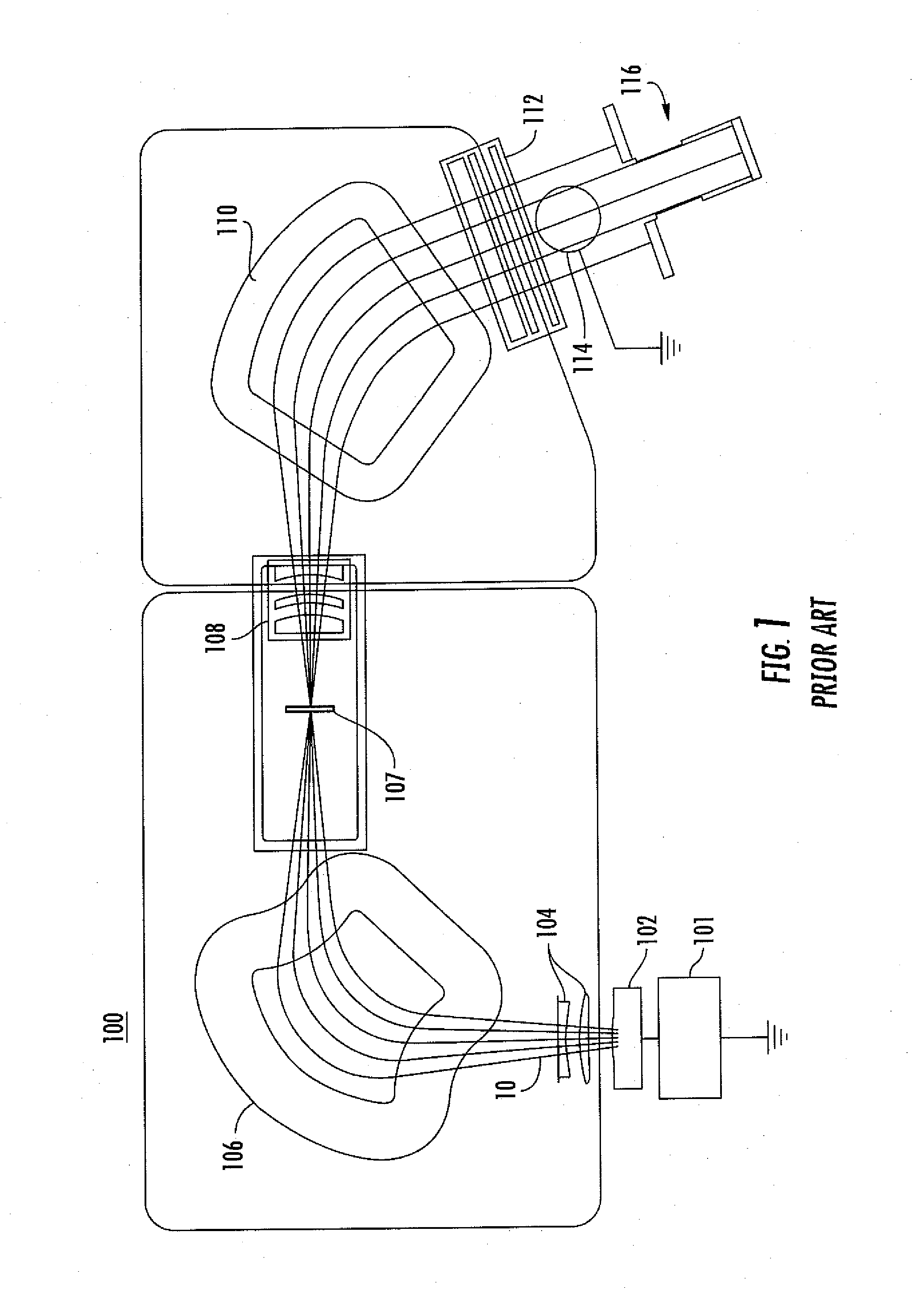

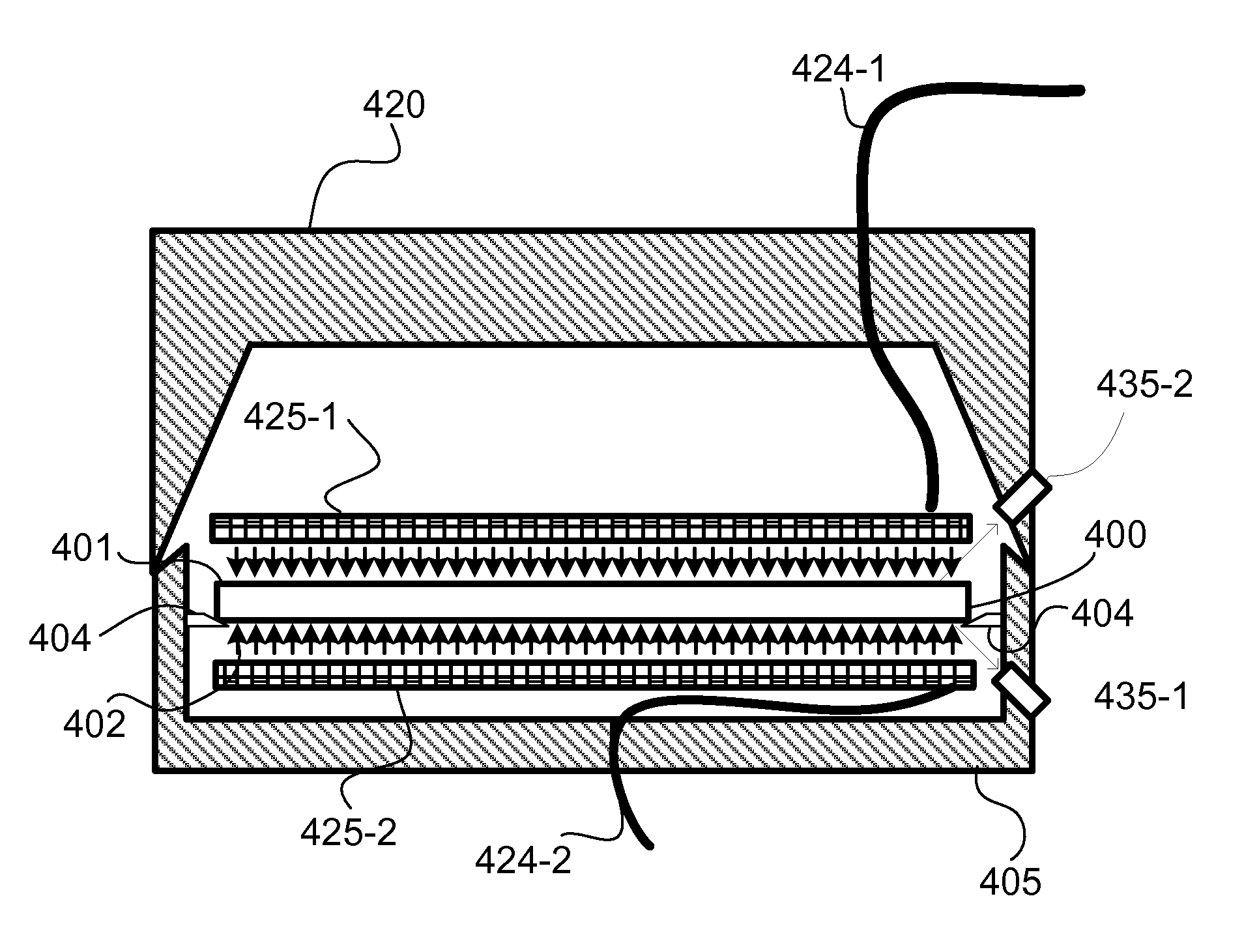

In vacuum optical wafer heater for cryogenic processing

ActiveUS20110143461A1Prevent unwanted condensationConveyorsSemiconductor/solid-state device testing/measurementEngineeringMoisture

A vacuum assembly used for warming processed substrates above the dew point to prevent unwanted moisture on the processed substrate surfaces as well as reducing negative impact on manufacturing throughput. The vacuum assembly includes a processing chamber, a substrate handling robot, and a heater which may be an optical heater. The processing chamber is configured to cryogenically process one or more substrates. The transfer chamber is connected to the processing chamber and houses the substrate handling robot. The substrate handling robot is configured to displace one or more substrates from the processing chamber to the transfer chamber. The heater is connected to the transfer chamber above the substrate handling robot such that the heater emits energy incident on the substrate when the substrate handling robot displaces the substrate in the transfer chamber.

Owner:VARIAN SEMICON EQUIP ASSOC INC

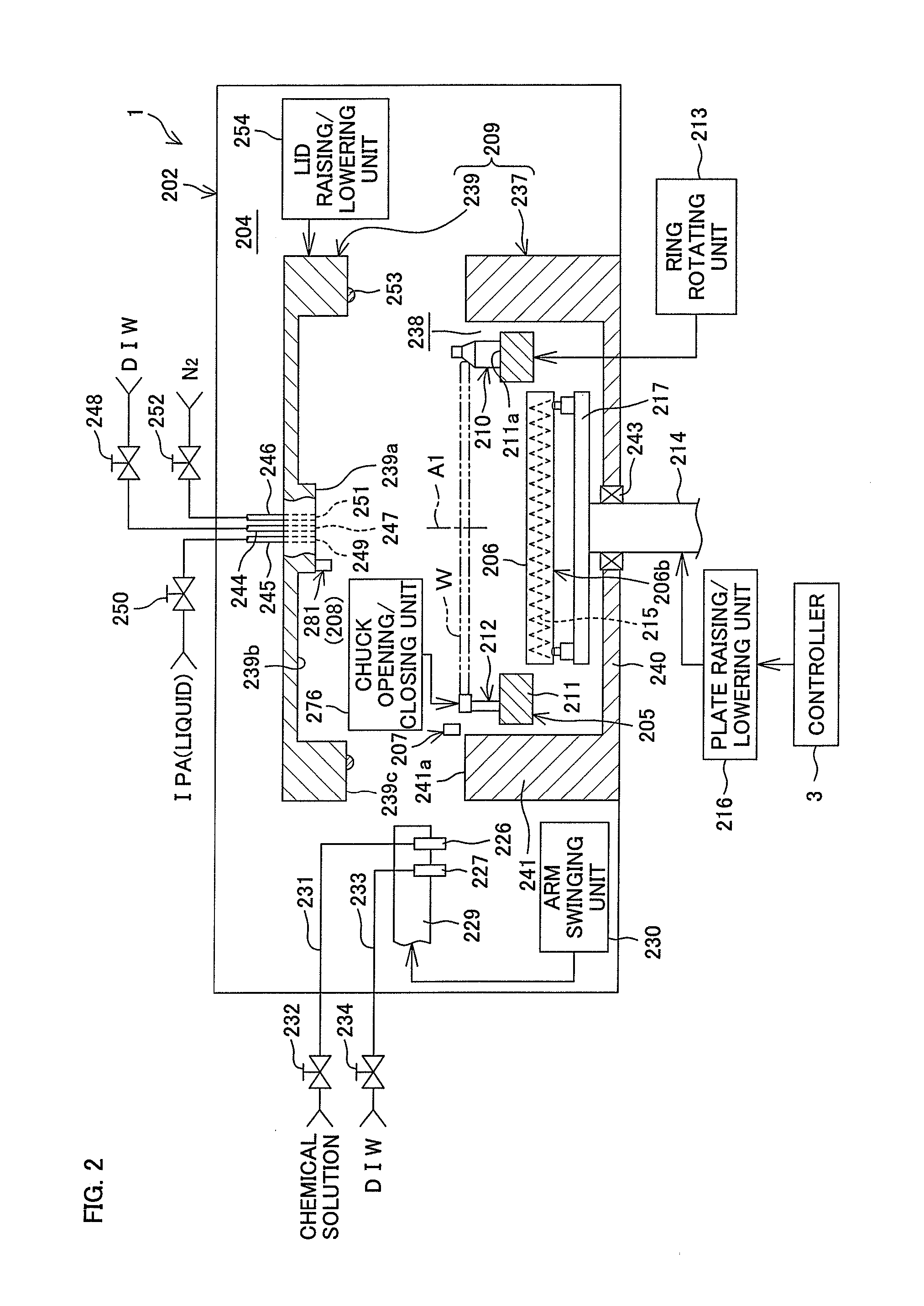

Substrate processing apparatus and substrate processing method

InactiveUS20150270146A1Supply is stoppedDry surfaceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOrganic solventEngineering

In parallel with a substrate heating step, a liquid surface sensor is used to monitor the raising of an IPA liquid film. An organic solvent removing step is started in response to the raising of the IPA liquid film over the upper surface of the substrate. At the end of the organic solvent removing step, a visual sensor is used to determine whether or not IPA droplets remain on the upper surface of the substrate.

Owner:DAINIPPON SCREEN MTG CO LTD

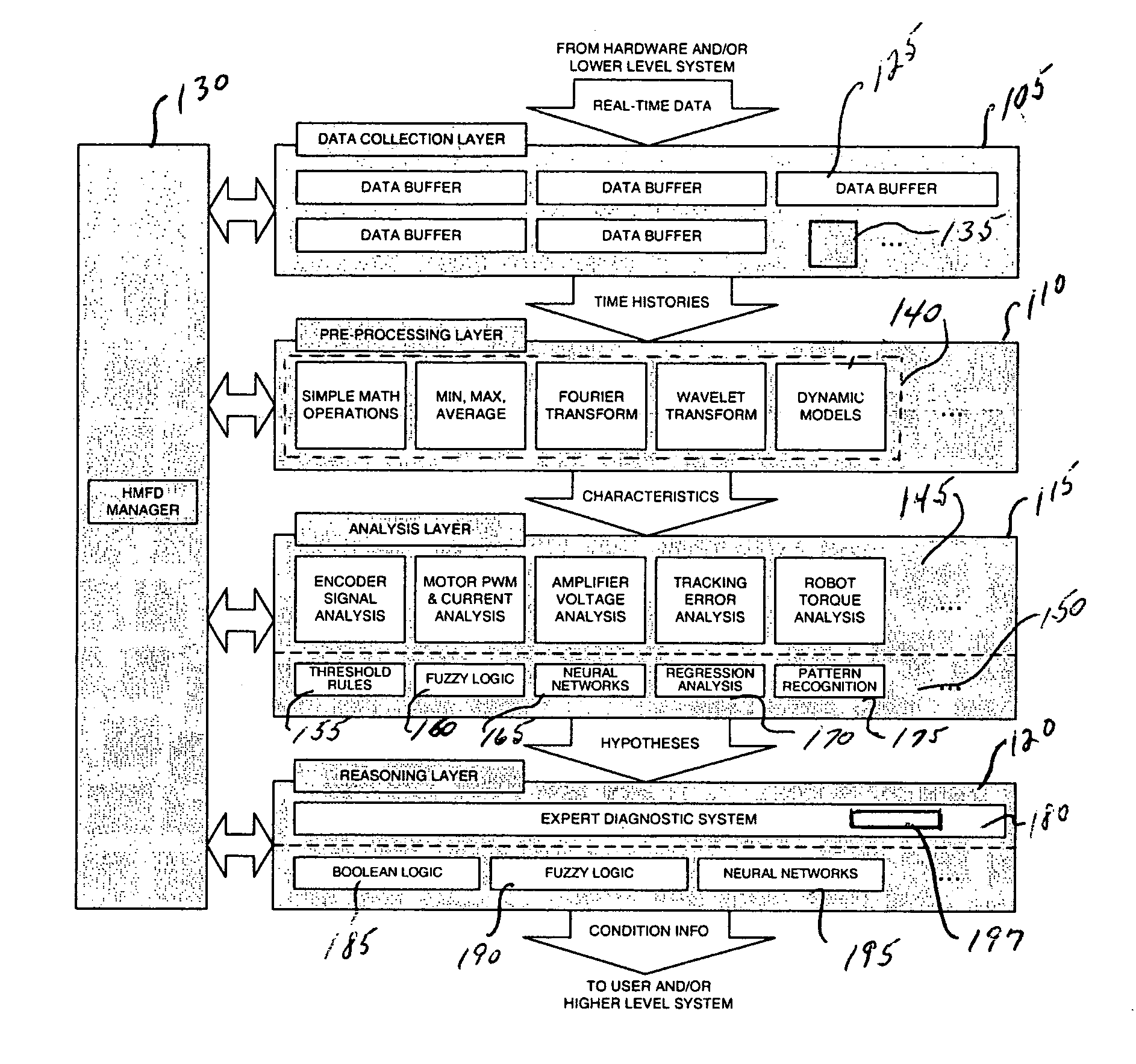

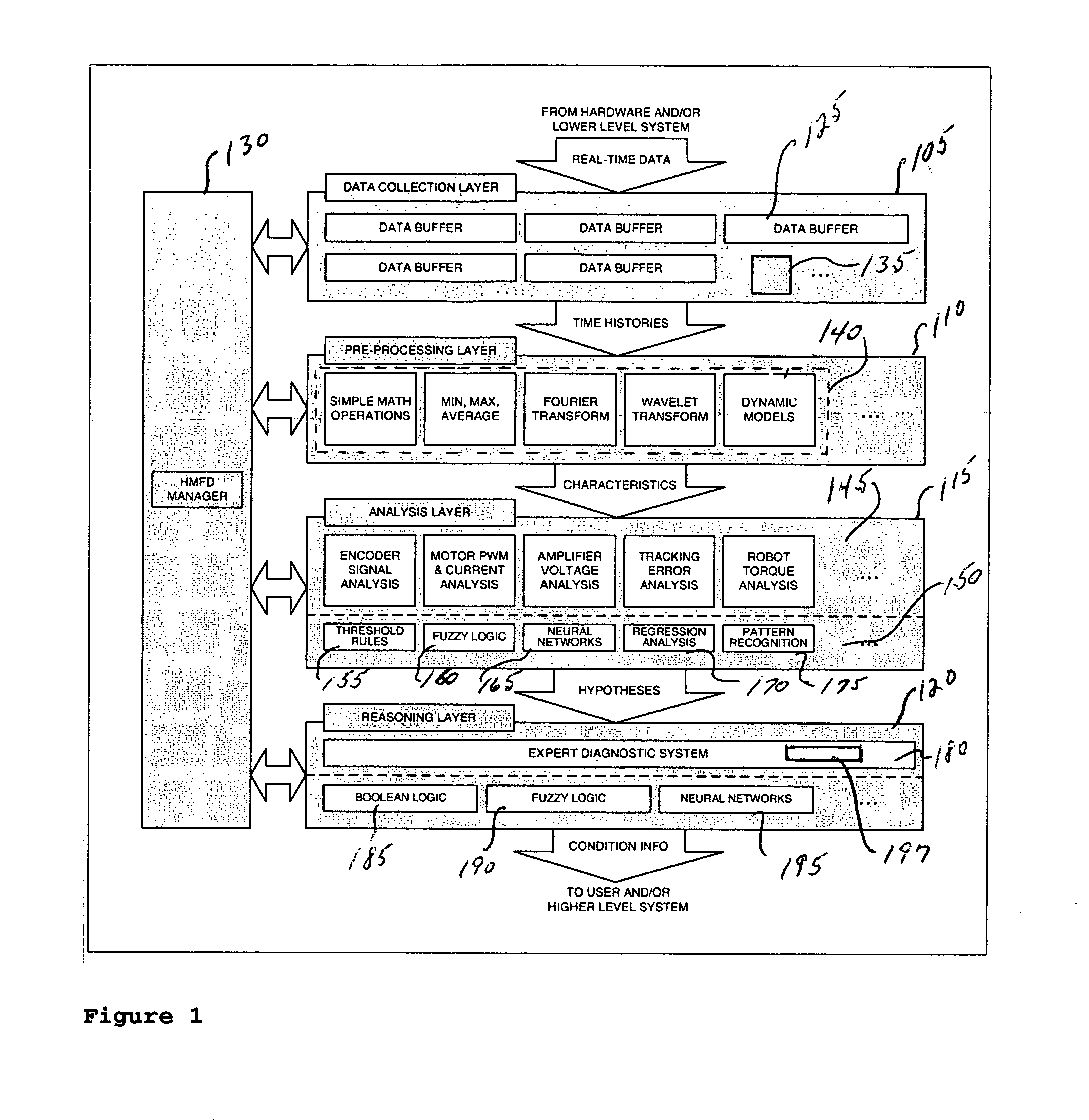

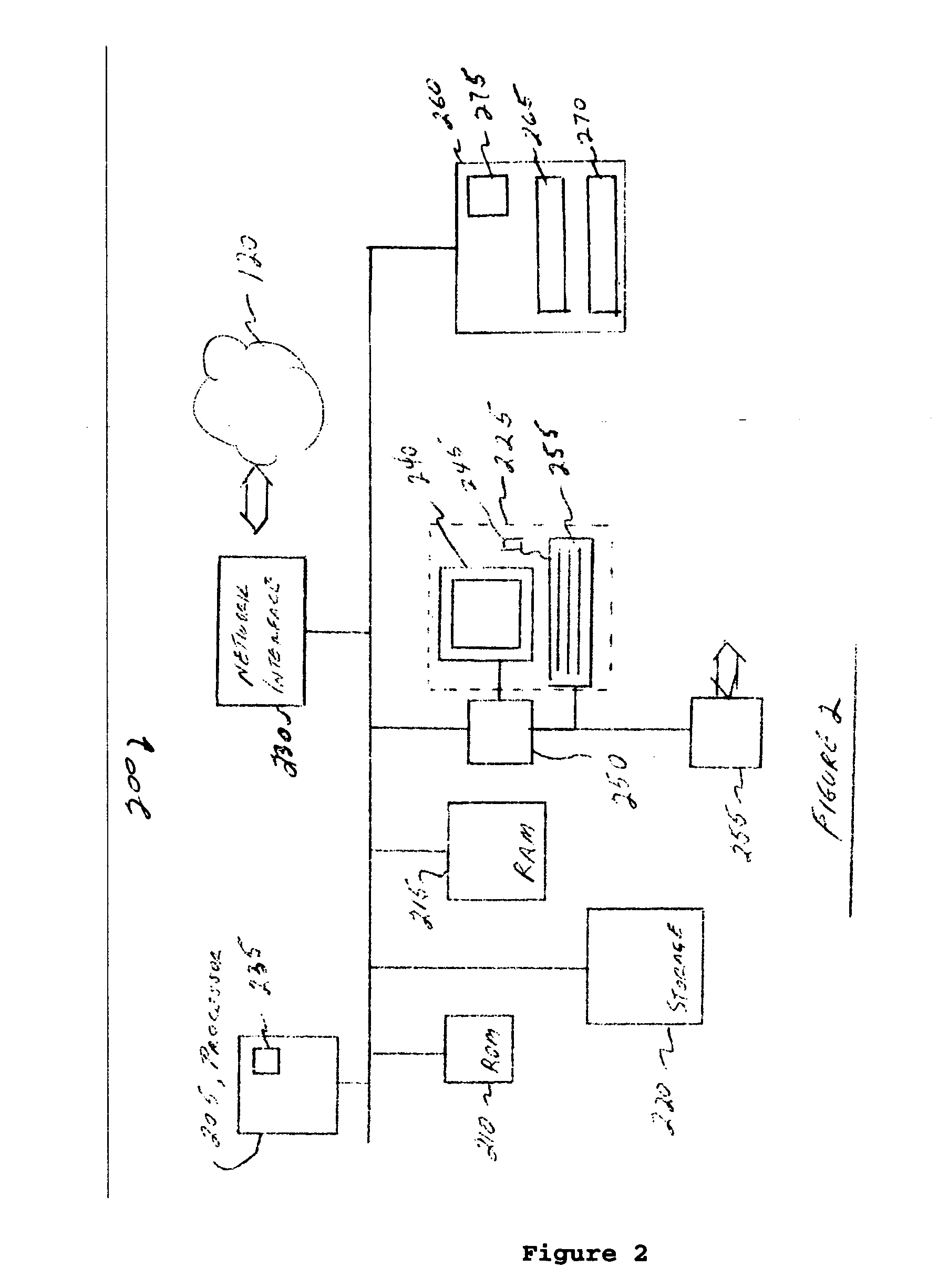

Intelligent condition-monitoring and fault diagnostic system for predictive maintenance

ActiveUS20070067678A1Sufficient weightFacilitates isolation of faultSemiconductor/solid-state device testing/measurementRegistering/indicating working of machinesPredictive maintenanceDiagnostic system

A system for condition monitoring and fault diagnosis includes a data collection function that acquires time histories of selected variables for one or more of the components, a pre-processing function that calculates specified characteristics of the time histories, an analysis function for evaluating the characteristics to produce one or more hypotheses of a condition of the one or more components, and a reasoning function for determining the condition of the one or more components from the one or more hypotheses.

Owner:BOOKS AUTOMATION US LLC

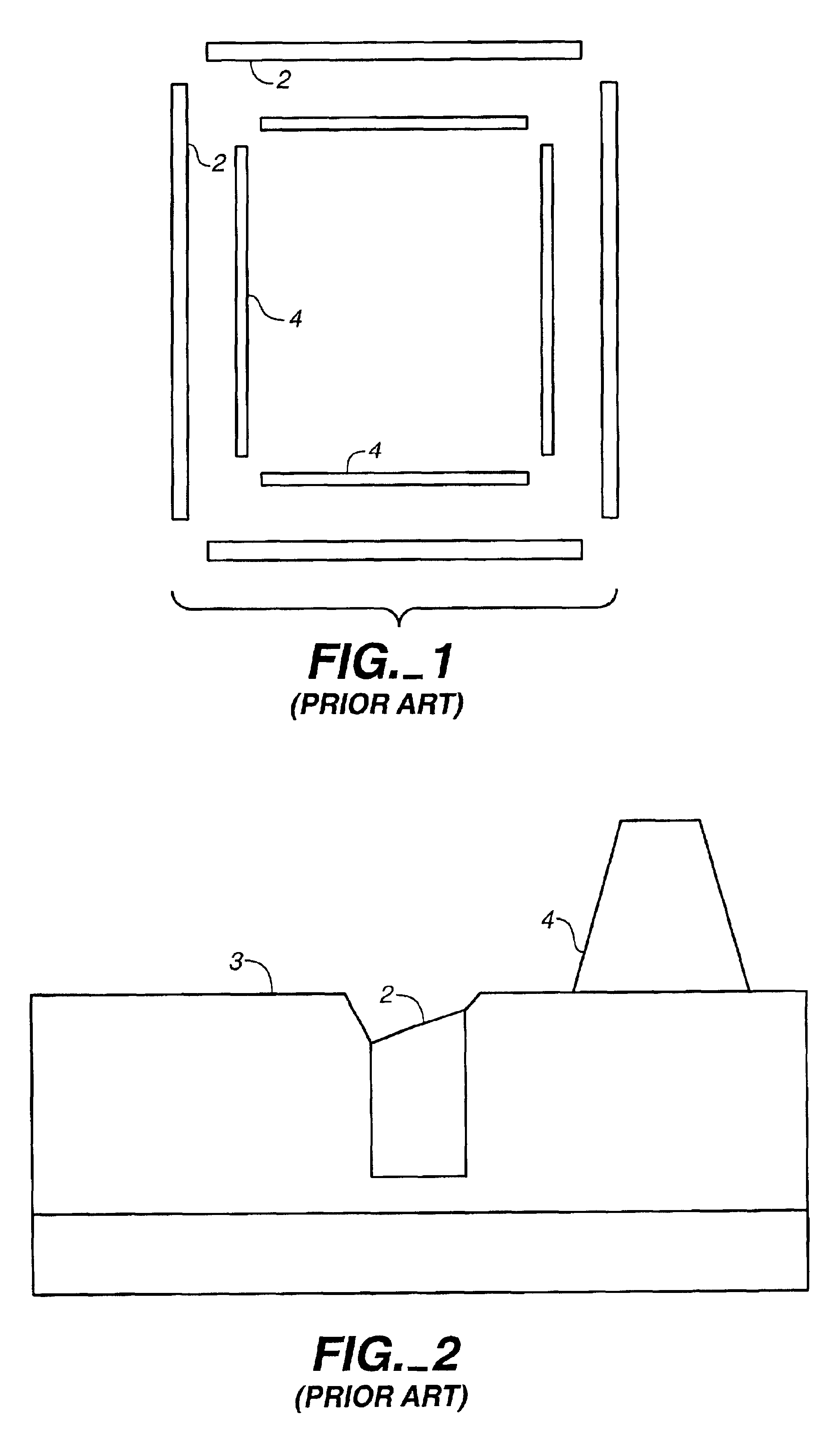

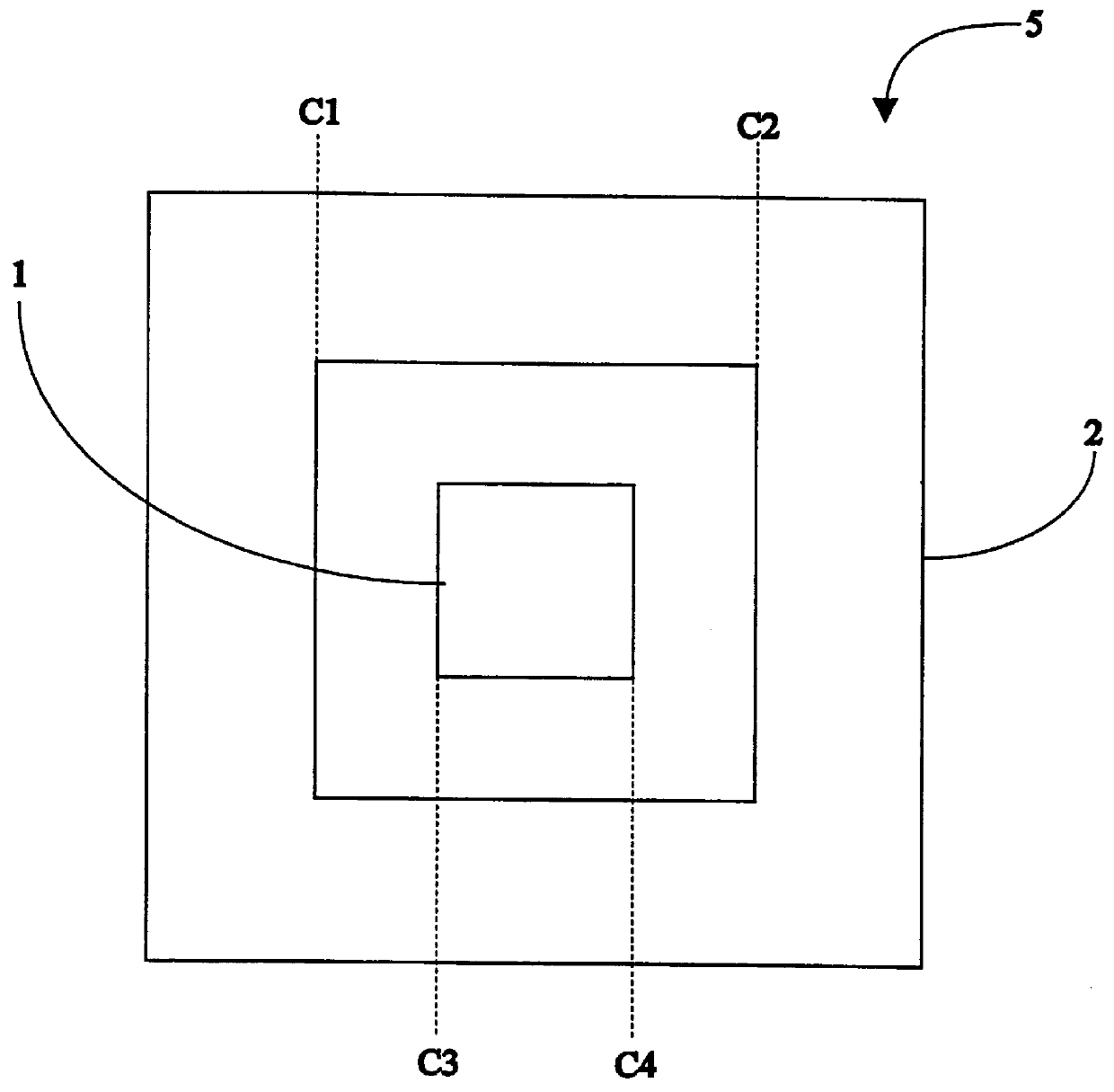

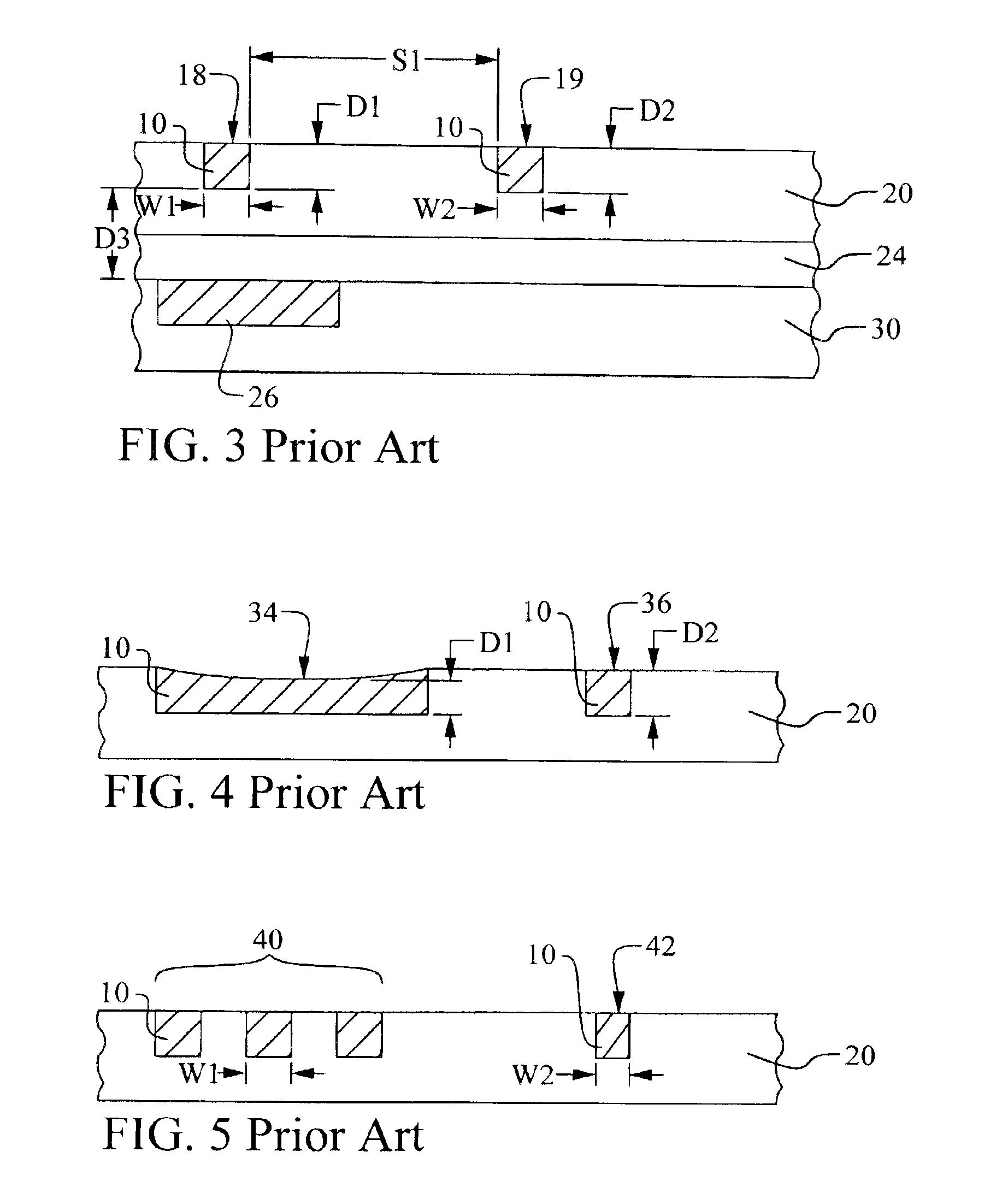

Overlay alignment measurement of wafers

InactiveUS6023338ASemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringElectron

The present invention is a new target, and associated apparatus and methods, for determining offset between adjacent layers of a semiconductor device. The target disclosed here includes a first periodic structure to be placed on a first layer of the device and a second periodic structure, that complements the first periodic structure, placed on a second layer of the device at a location that is adjacent the first periodic structure when the second layer is placed on the first layer. Any offset that may occur is detected by the present invention either optically, micro-mechanically or with electron beams using any of various methods and system embodiments.

Owner:KLA INSTR

LED substrate processing

ActiveUS8404499B2Improve efficiencyFast response timeSemiconductor/solid-state device testing/measurementMuffle furnacesLong pulseLight-emitting diode

Embodiments of the present invention pertain to substrate processing equipment and methods incorporating light emitting diodes (LEDs) for thermally processing substrates. Such light sources offer a variety of advantages including higher efficiency and more rapid response times. Pulse widths are selectable down to under a millisecond but can be for long pulses up to and exceeding a second. LEDs are preferable to tungsten-halogen lamps even in circumstances that allow longer processing times, since LEDs produce light with greater than 50% efficiency and tungsten-halogen lamps operate with less than 5% efficiency.

Owner:APPLIED MATERIALS INC

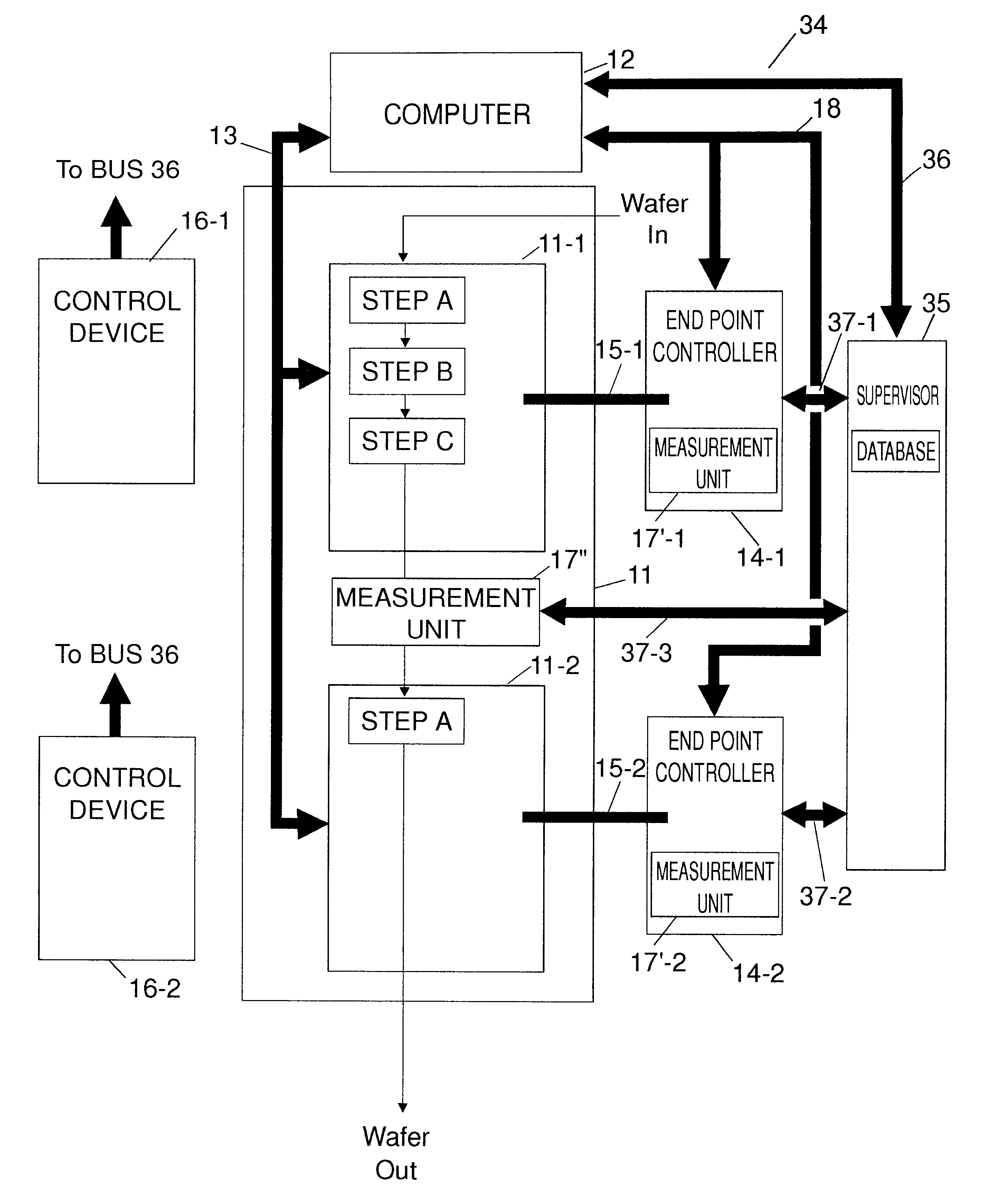

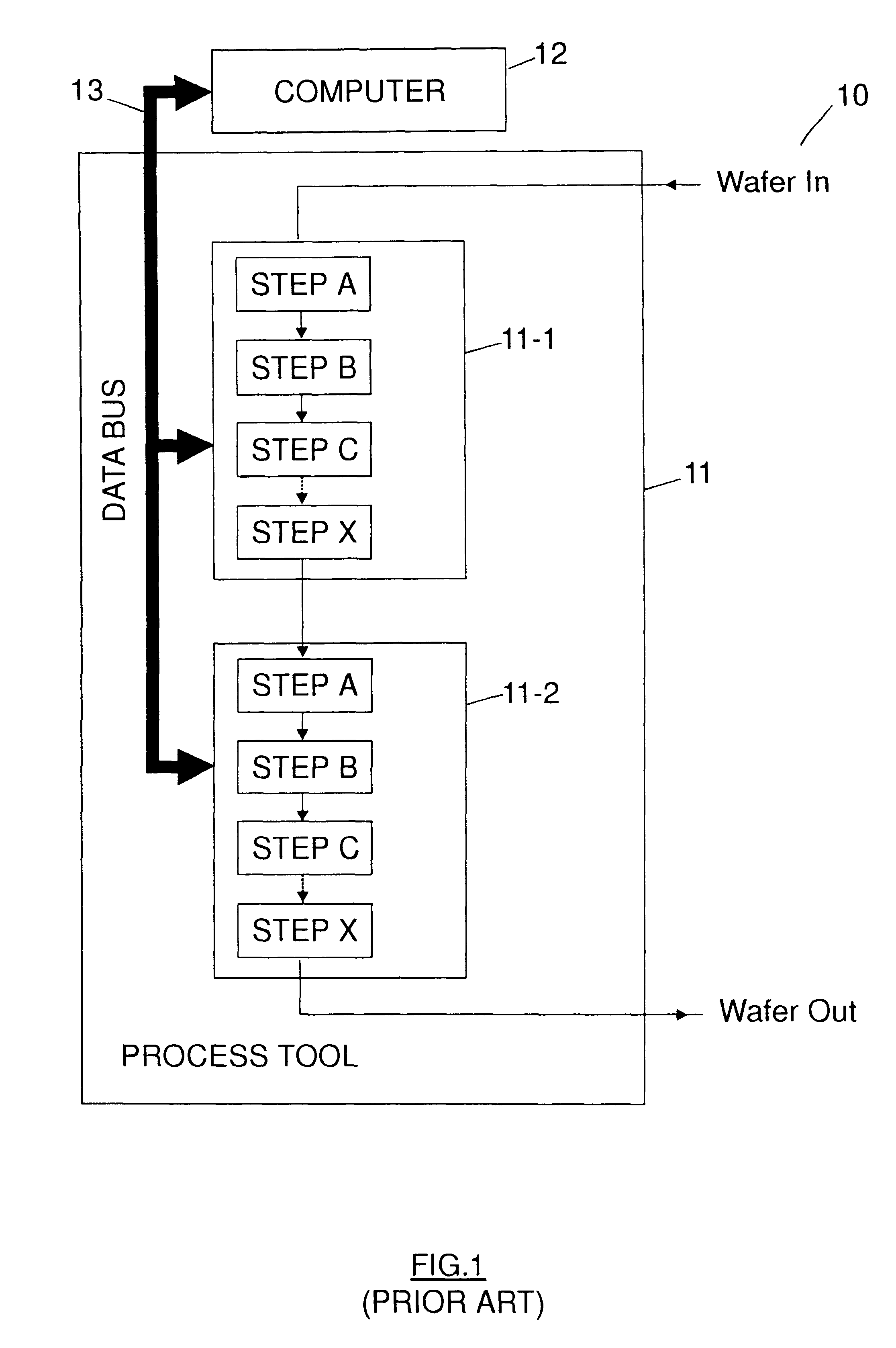

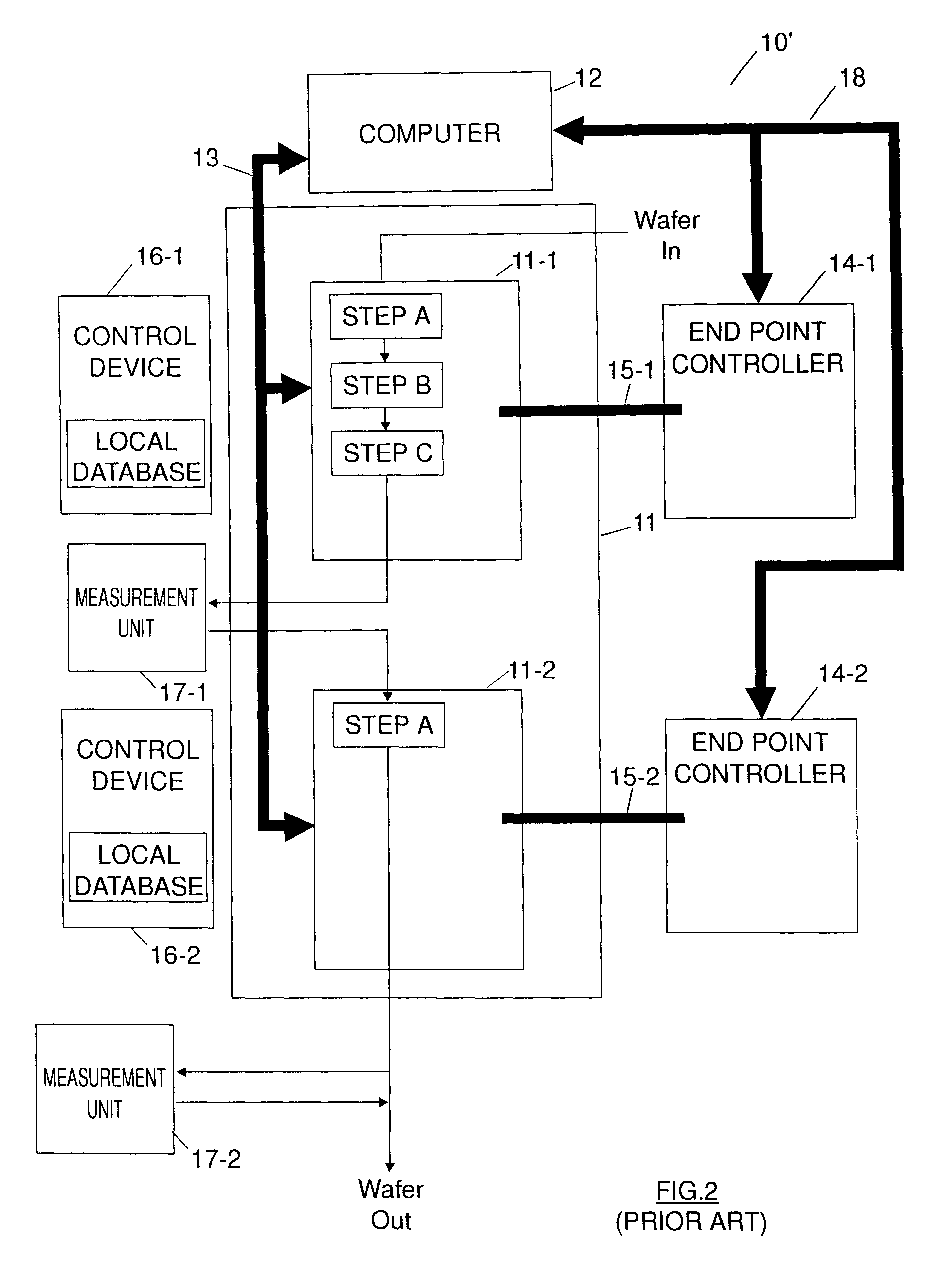

Method and system for semiconductor wafer fabrication process real-time in-situ interactive supervision

InactiveUS6363294B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingWafer fabricationEngineering

Method and system for real-time in-situ interactive supervision of a step performed in a tool during semiconductor wafer fabrication process. The system includes a tool and the computer attached thereto, an end point detection controller, a database and a supervisor to supervise the whole wafer processing for that step. The controller is used to monitor a key process parameter of the step and is adapted to perform in-situ measurements. The database contains the evolution of said process parameter in normal operating conditions and in all the identified deviations. It further contains the history of the wafer until this step and a reference to the batch and process names for this step and the wafer identification number. At the end of the step, the important process parameters and any alert code are stored in the database to up-date the wafer history. This technique allows a total clusterized wafer fabrication process and prevents wafer rejection.

Owner:IBM CORP

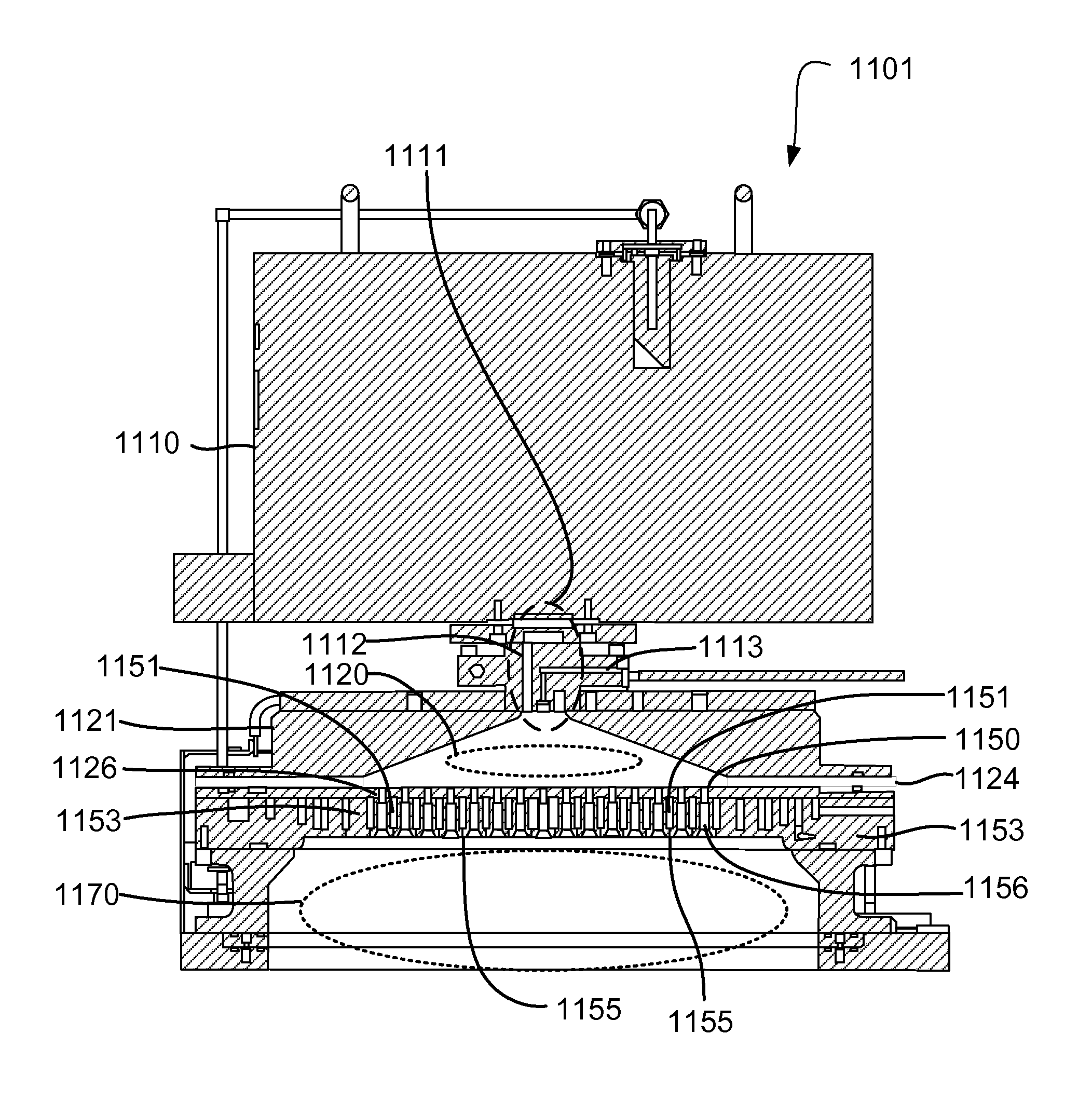

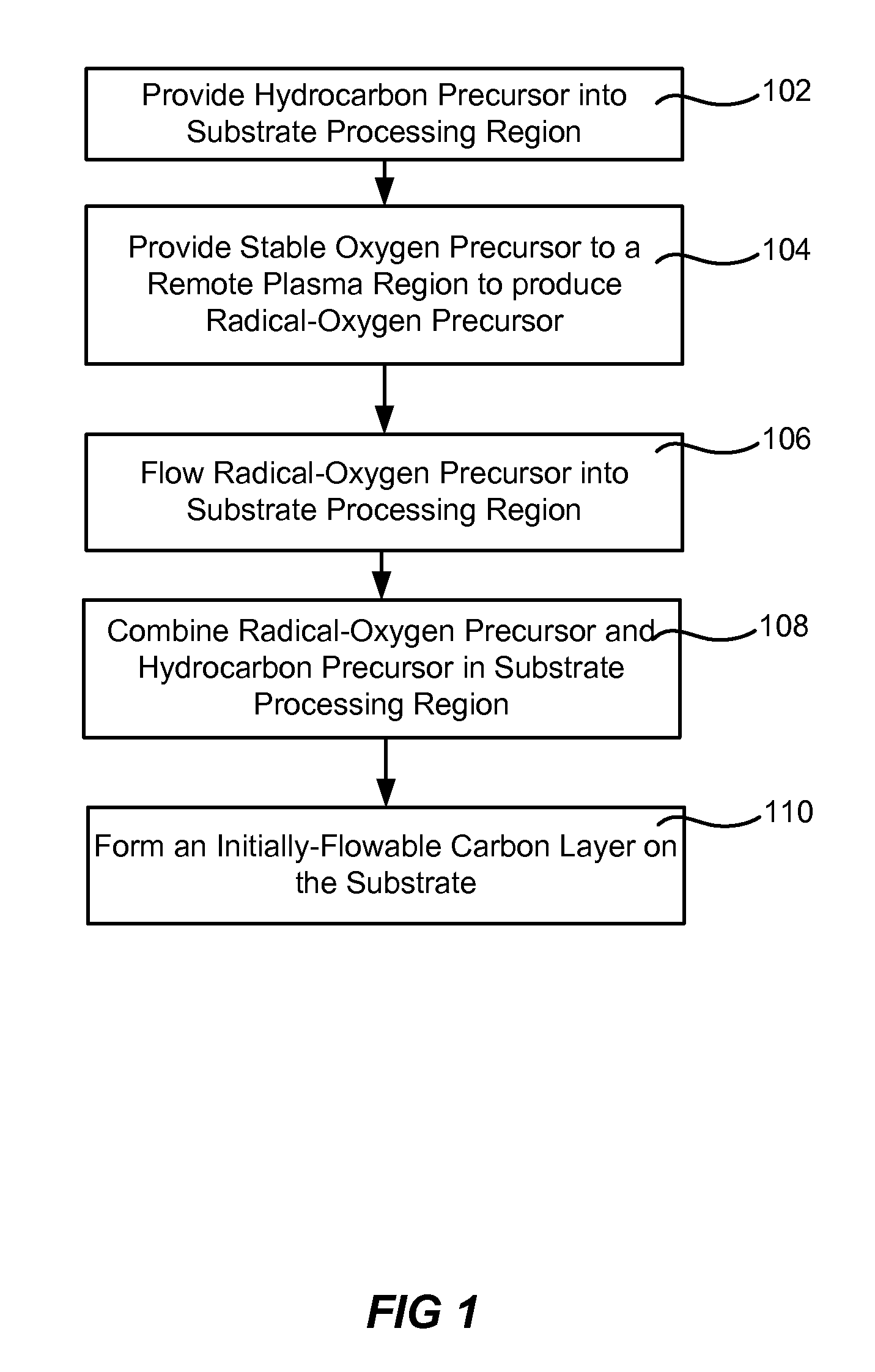

Flowable carbon for semiconductor processing

ActiveUS9514932B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingCarbon layerSemiconductor

Methods are described for forming flowable carbon layers on a semiconductor substrate. A local excitation (such as a hot filament in hot wire CVD, a plasma in PECVD or UV light) may be applied as described herein to a silicon-free carbon-containing precursor containing a hydrocarbon to form a flowable carbon-containing film on a substrate. A remote excitation method has also been found to produce flowable carbon-containing films by exciting a stable precursor to produce a radical precursor which is then combined with unexcited silicon-free carbon-containing precursors in the substrate processing region.

Owner:APPLIED MATERIALS INC

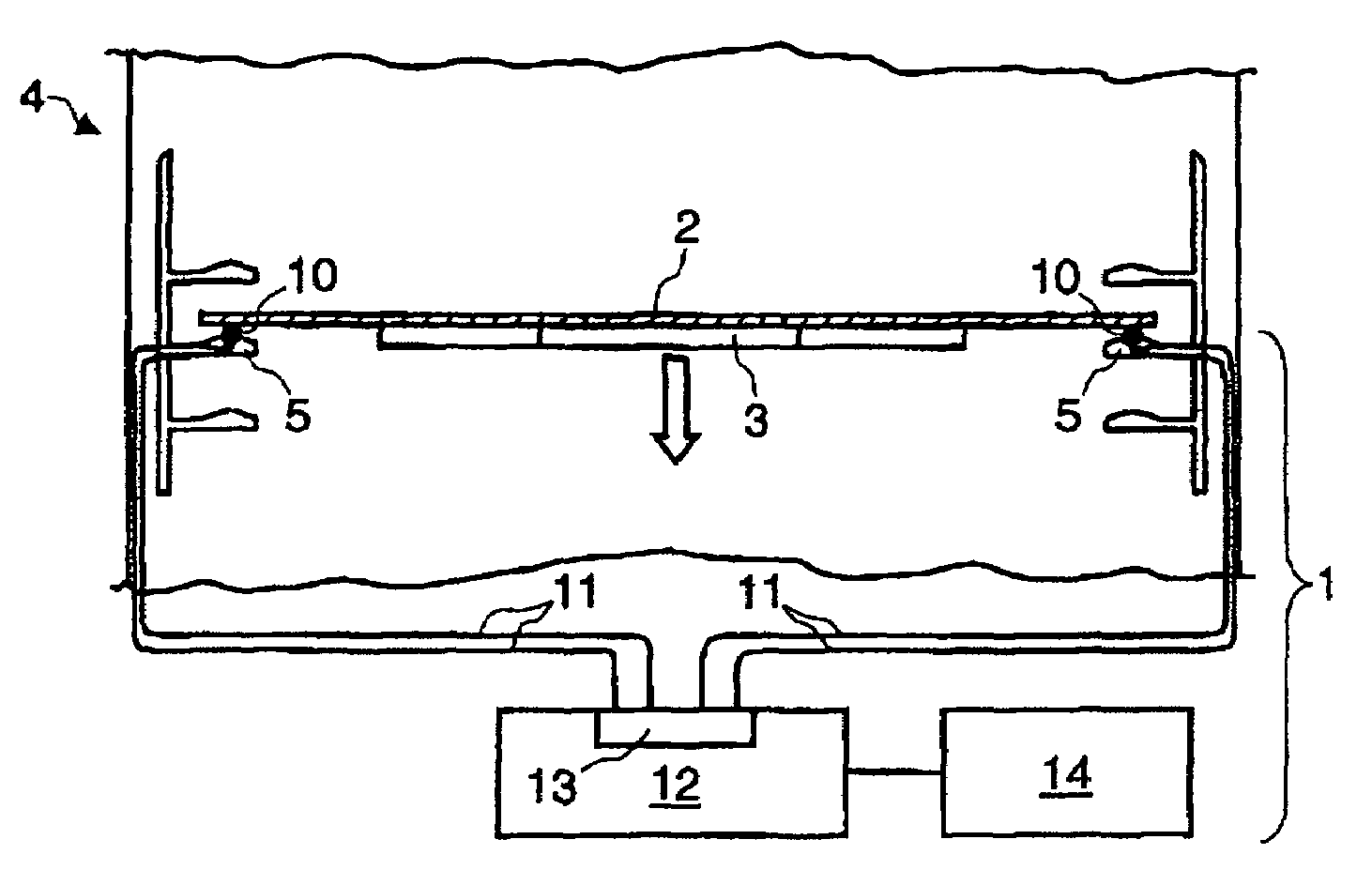

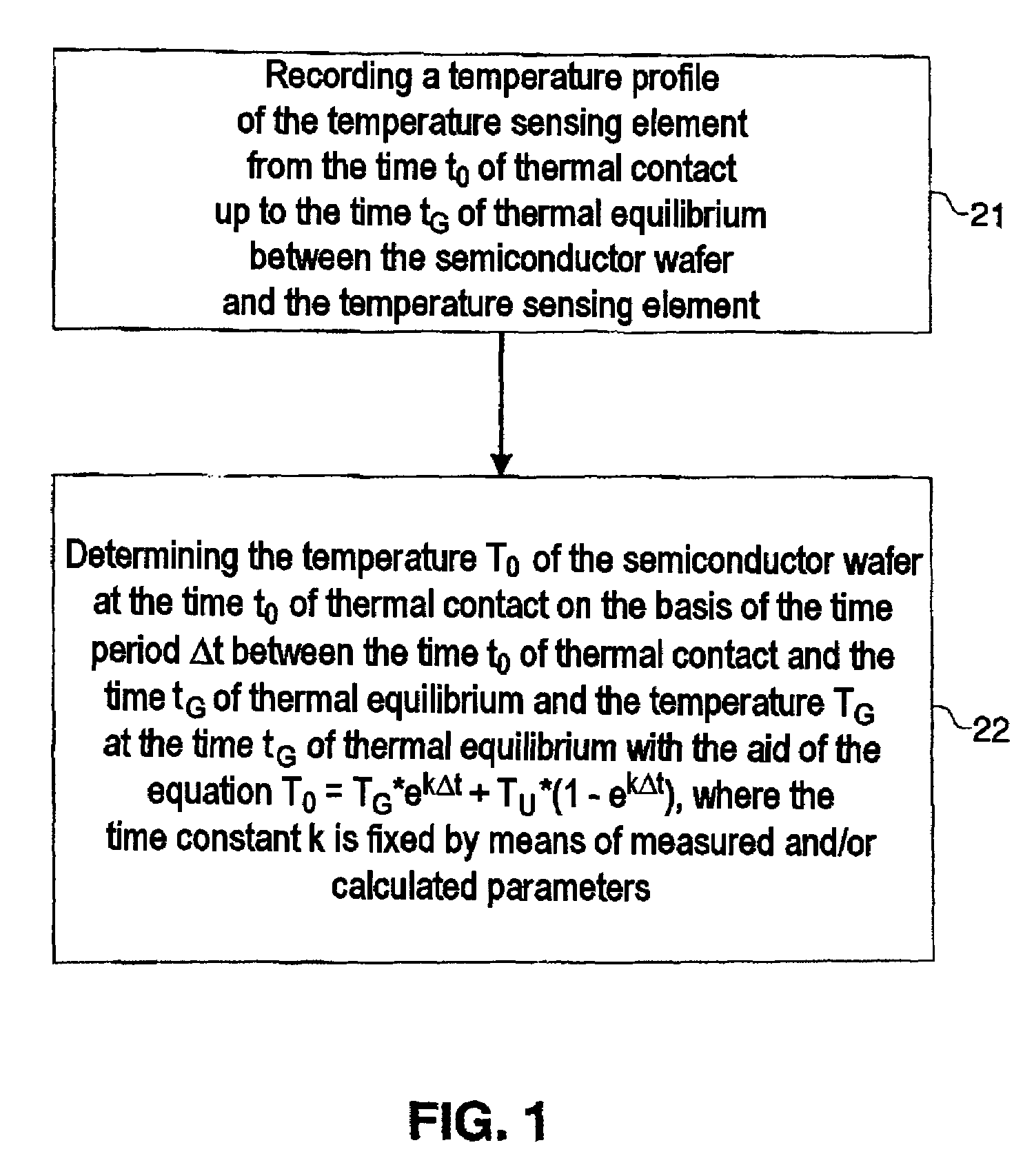

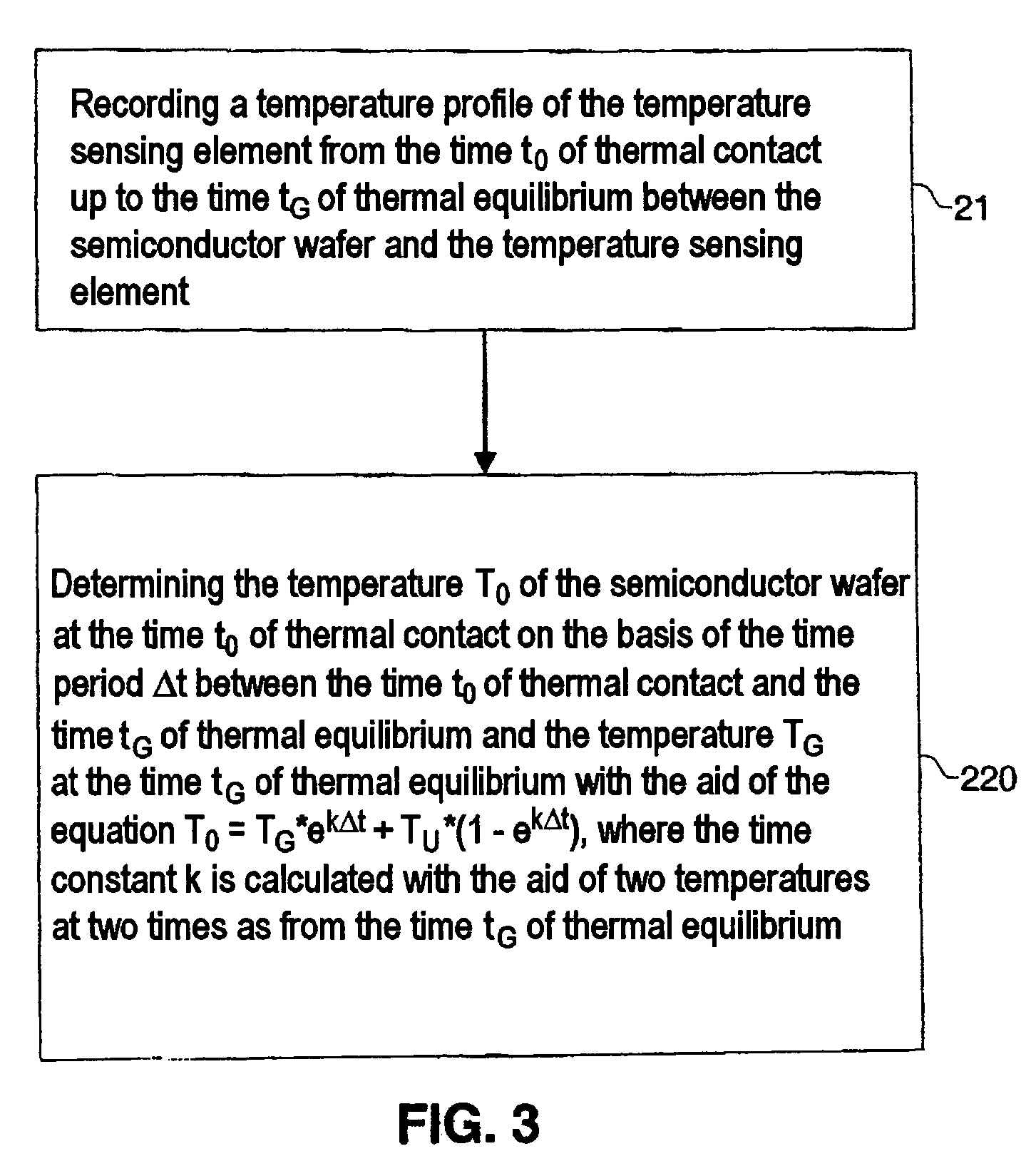

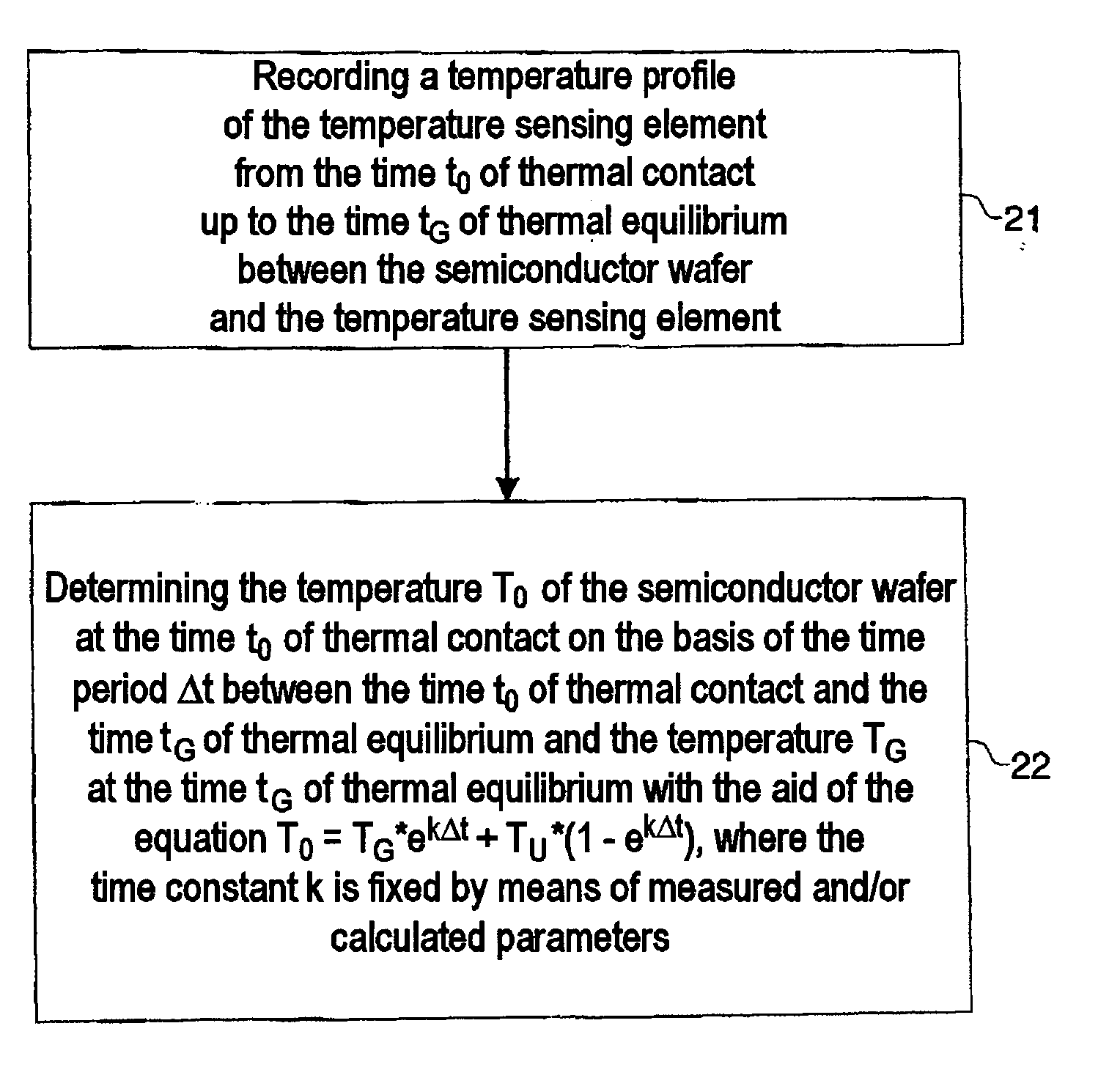

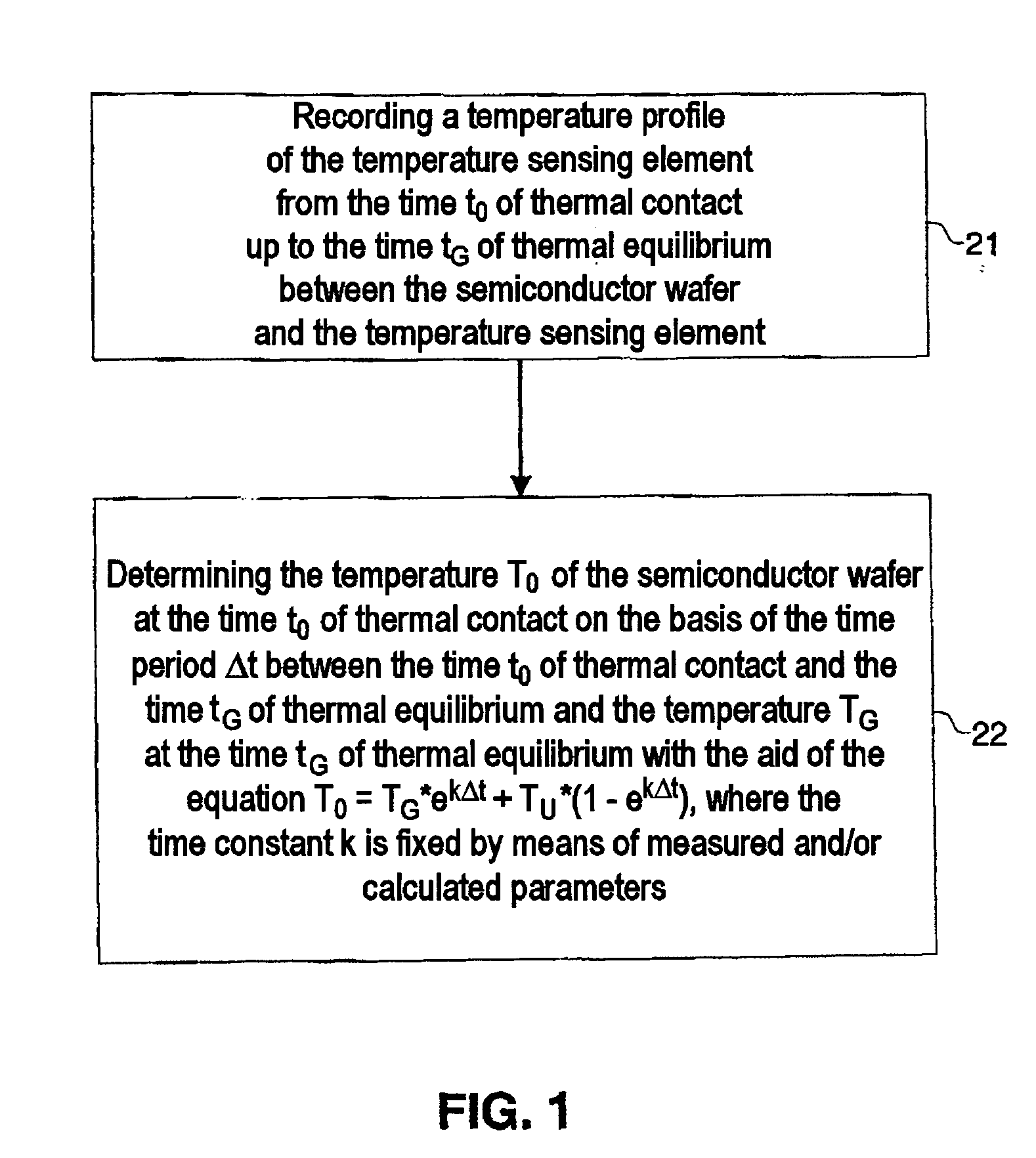

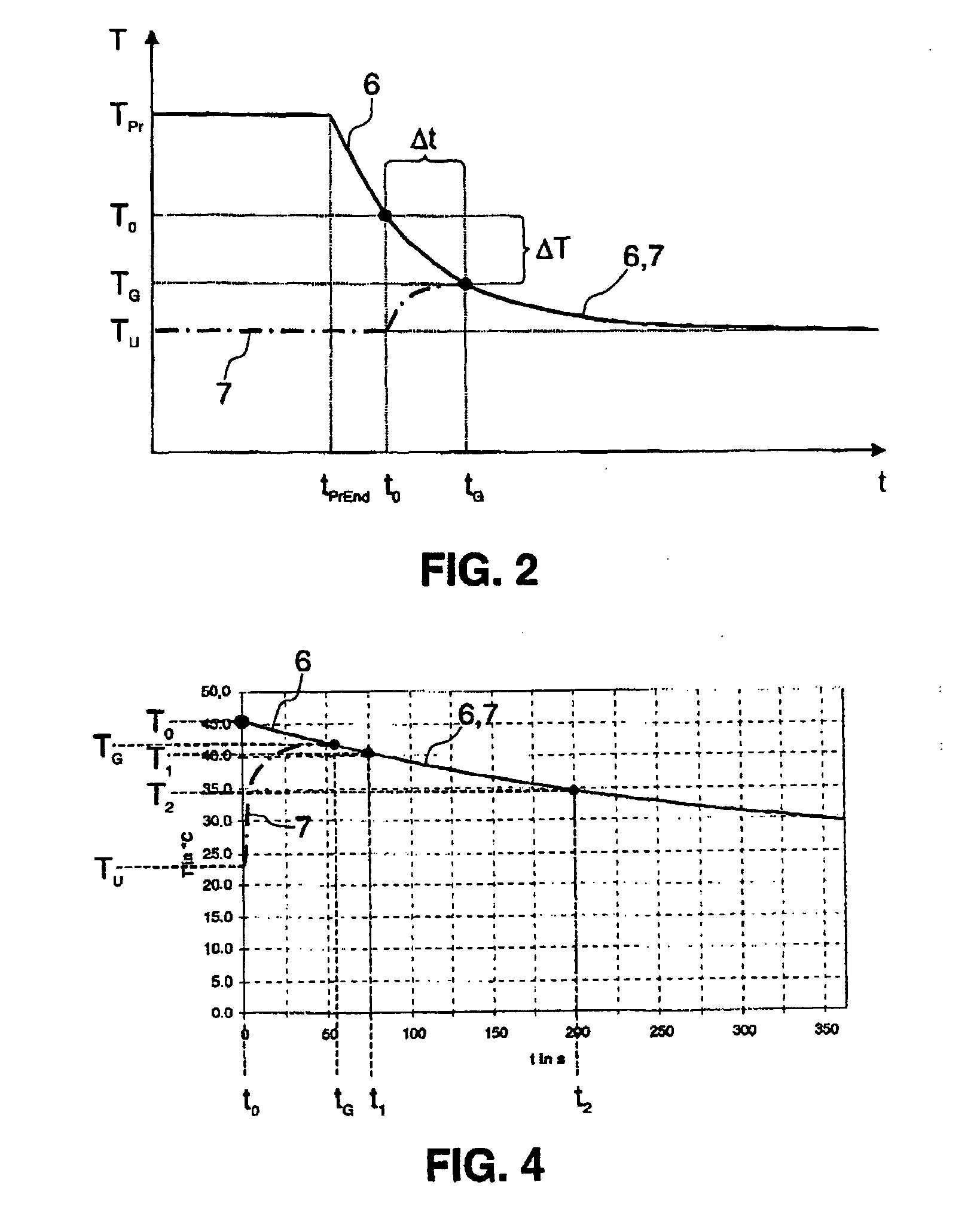

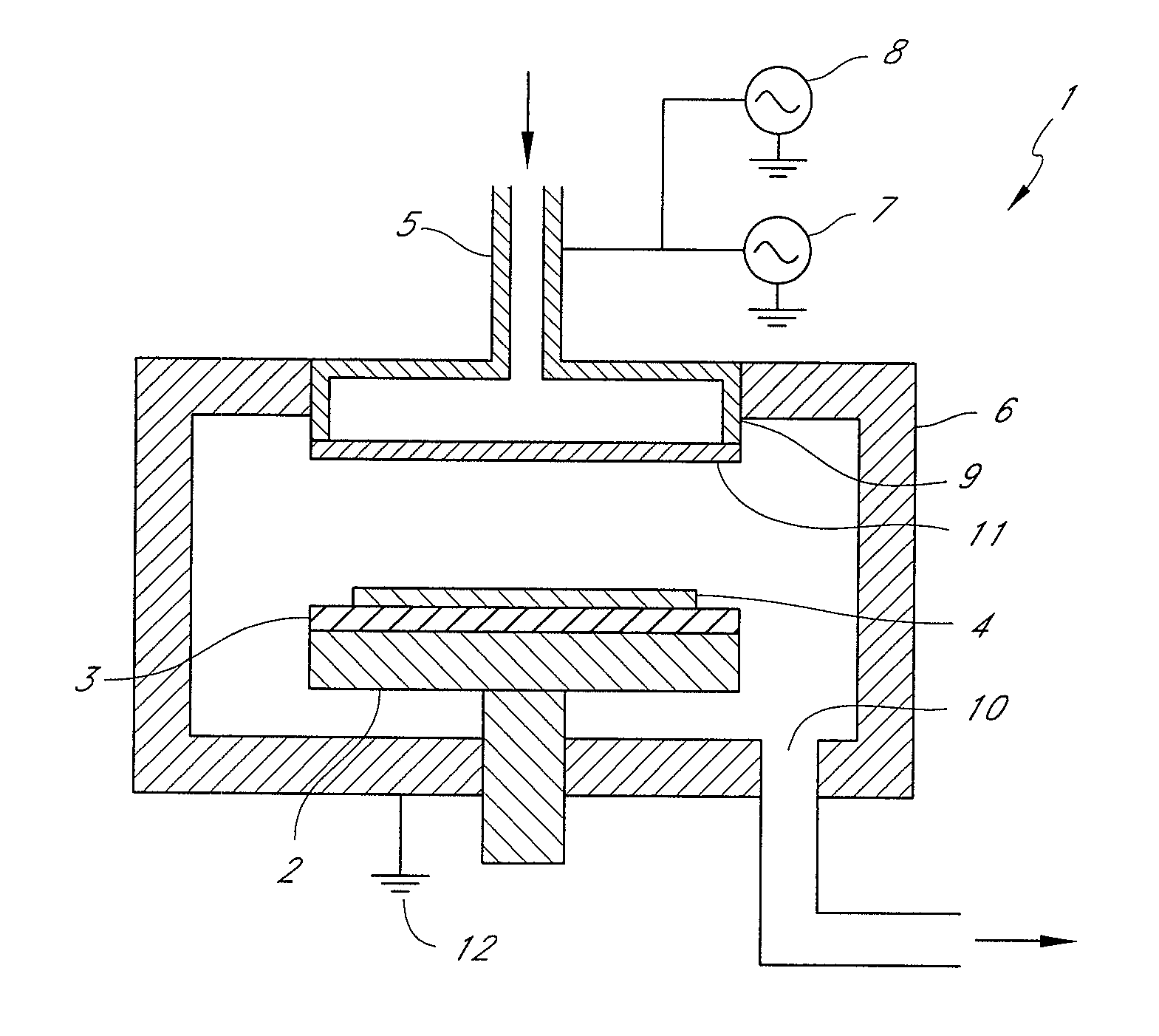

System and method for determining the temperature of a semiconductor wafer

InactiveUS7274867B2High precisionImprove convenienceDrying solid materials with heatSemiconductor/solid-state device testing/measurementTime segmentBack calculation

A system and method for determining the temperature of a semiconductor wafer at the time of thermal contact of the semiconductor wafer with a temperature sensing element. According to the invention, a temperature profile of the temperature sensing element is recorded from the time of thermal contact up to the time of thermal equilibrium between the semiconductor wafer and the temperature sensing element and the temperature of the semiconductor wafer at the time of thermal contact is determined on the basis of a time period between the time of thermal contact and the time of thermal equilibrium and the temperature TG of the semiconductor wafer reached at the time tG of thermal equilibrium is determined by back calculation with the aid of an equation derived from Newton's law of cooling.

Owner:POLARIS INNOVATIONS LTD

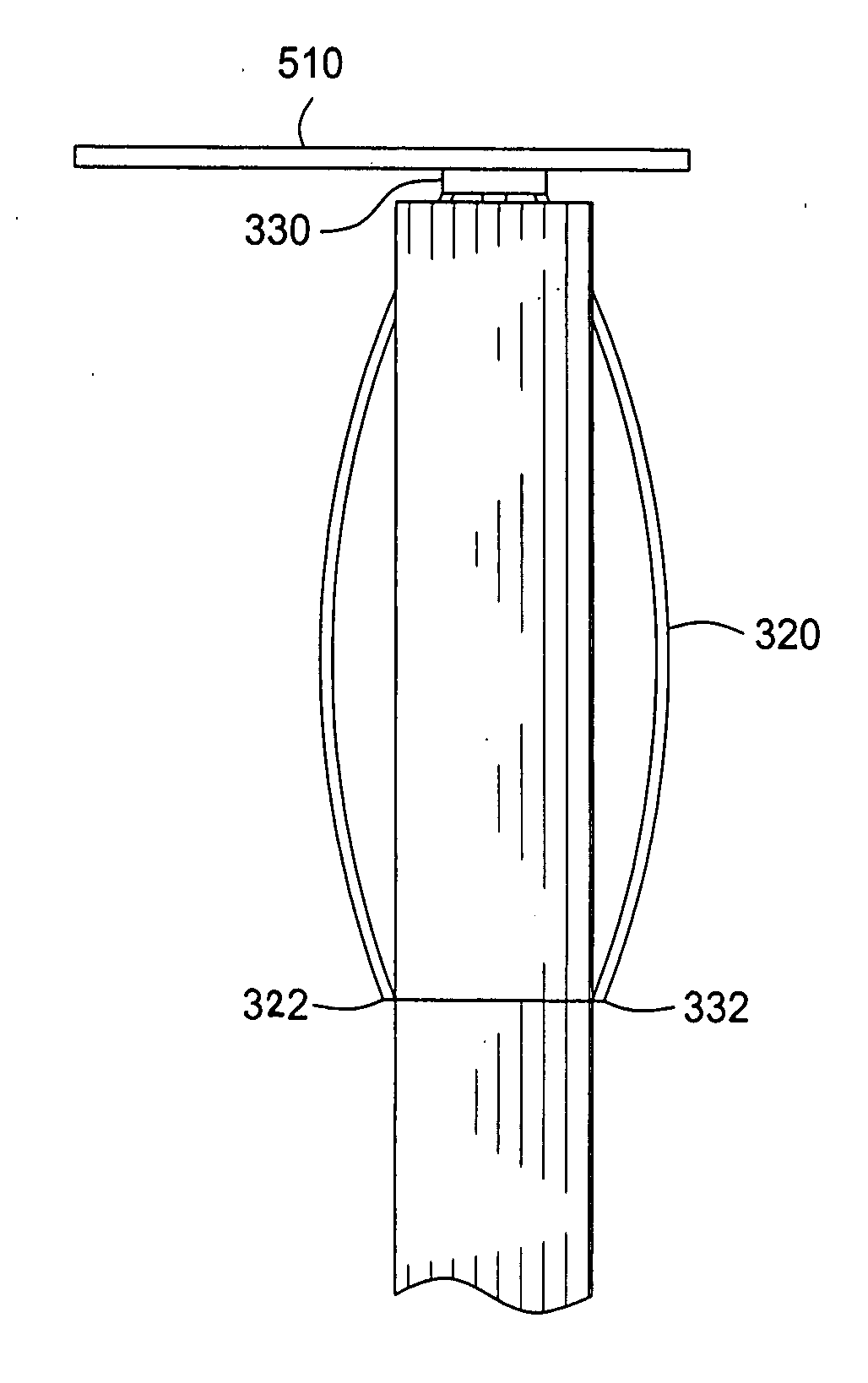

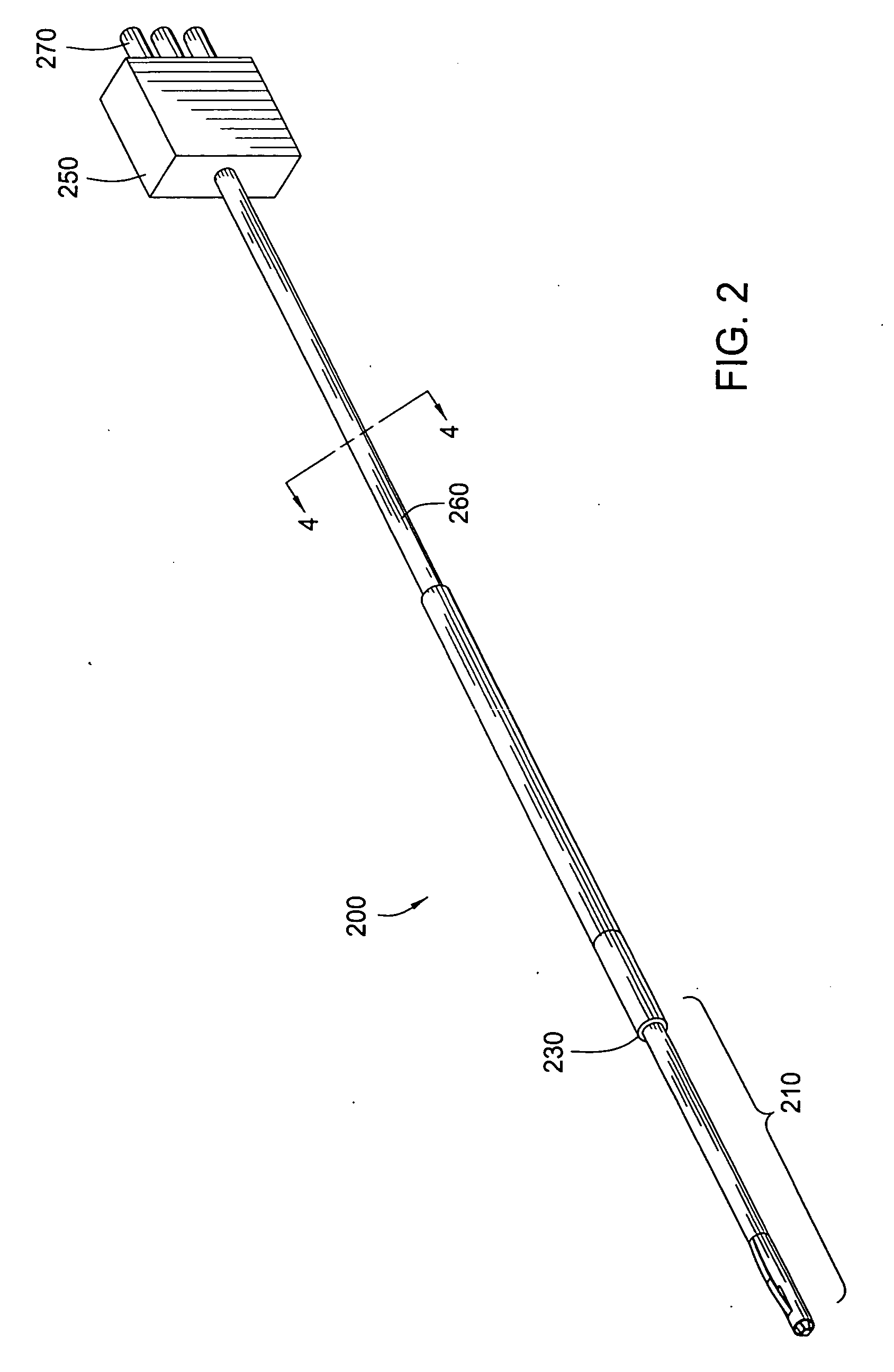

Thermally conductive ceramic tipped contact thermocouple

InactiveUS20060275933A1Thermometer detailsSemiconductor/solid-state device testing/measurementThermocoupleMaterials science

An apparatus for processing a substrate. The apparatus comprising a tubular member with a first end and a second end. The first end comprising an opening; and a temperature sensor disposed in the opening. The temperature sensor comprising a resilient member. The resilient member comprising a surface made of a ceramic material wherein the surface made of a ceramic material extends through the opening to provide a substrate contact surface.

Owner:APPLIED MATERIALS INC

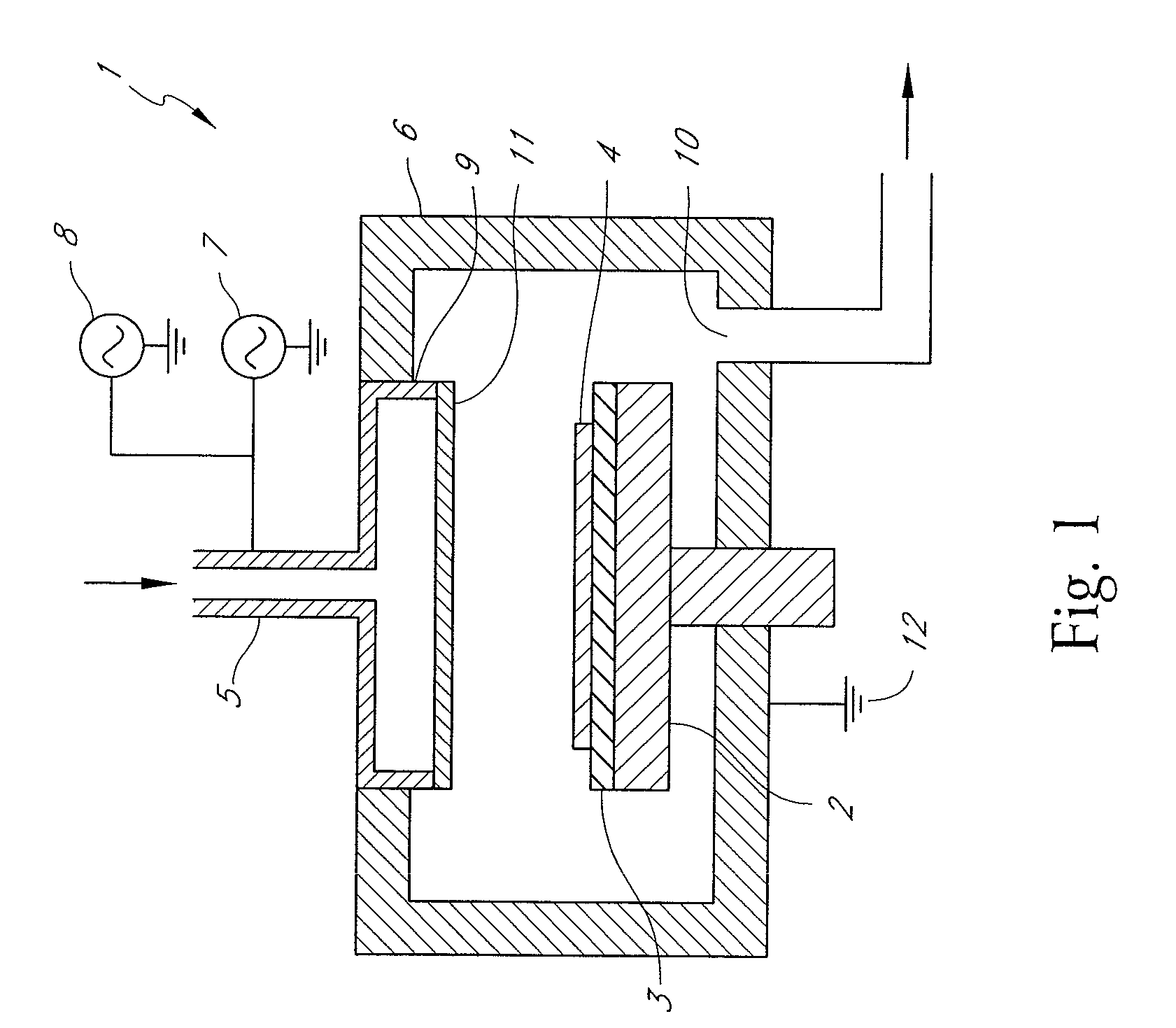

Rps assisted RF plasma source for semiconductor processing

ActiveUS20150221479A1CellsSemiconductor/solid-state device testing/measurementCapacitanceRemote plasma

Owner:APPLIED MATERIALS INC

Foup opening/closing device and probe apparatus

ActiveUS20100040441A1Efficient space utilizationThe degree of freedom becomes largerSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingControl signalEngineering

A FOUP opening / closing device includes a housing containing a mounting table for mounting the FOUP thereon, an FOUP loading opening, and a delivery opening. The device further includes a rotator for rotating the mounting table, a door opening / closing unit to open or close the door of the FOUP and keep the door open, a mover for moving the FOUP and the door opening / closing unit in a reciprocating manner, to allow the FOUP and the door opening / closing unit to be connected to or separated from each other, and a controller to output control signals for moving the FOUP and the door opening / closing unit via operation of the mover to mount the door of the FOUP to the door opening / closing unit, separating the door from the FOUP, moving the FOUP and the door opening / closing unit away from each other, and rotating the mounting table to make the FOUP face the delivery opening.

Owner:TOKYO ELECTRON LTD

System and method for determining the temperature of a semiconductor wafer

InactiveUS20050042778A1High precisionImprove convenienceDrying solid materials with heatSemiconductor/solid-state device testing/measurementBack calculationThermal contact

A system and method for determining the temperature of a semiconductor wafer at the time of thermal contact of the semiconductor wafer with a temperature sensing element. According to the invention, a temperature profile of the temperature sensing element is recorded from the time of thermal contact up to the time of thermal equilibrium between the semiconductor wafer and the temperature sensing element and the temperature of the semiconductor wafer at the time of thermal contact is determined on the basis of a time period between the time of thermal contact and the time of thermal equilibrium and the temperature TG of the semiconductor wafer reached at the time tG of thermal equilibrium is determined by back calculation with the aid of an equation derived from Newton's law of cooling.

Owner:POLARIS INNOVATIONS LTD

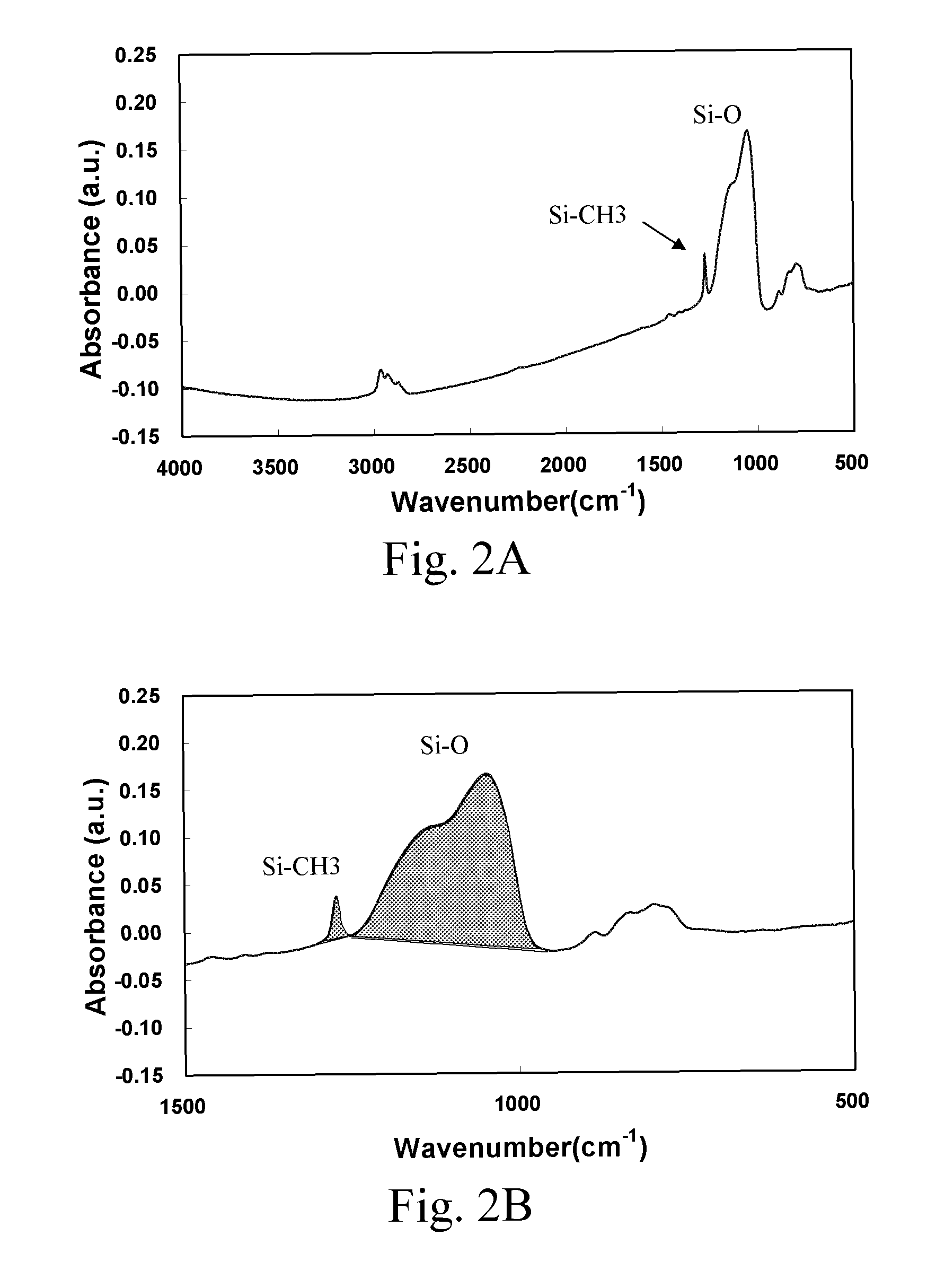

Method for forming dielectric SiOCH film having chemical stability

ActiveUS7807566B2Good chemical stabilityLow dielectric constantSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDielectricSusceptor

A method for determining conditions for forming a dielectric SiOCH film, includes: (i) forming a dielectric SiOCH film on a substrate under conditions; (ii) evaluating the conditions using a ratio of Si—CH3 bonding strength to Si—O bonding strength of the film as formed in step (i); (iii) if the ratio is 2.50 % or higher, confirming the conditions, and if the ratio is less than 2.50 %, changing the conditions by changing at least one of the susceptor temperature, the distance between upper and lower electrodes, the RF power, and the curing time; and (iv) repeating steps (i) to (iii) until the ratio is 2.50 % or higher.

Owner:ASM JAPAN

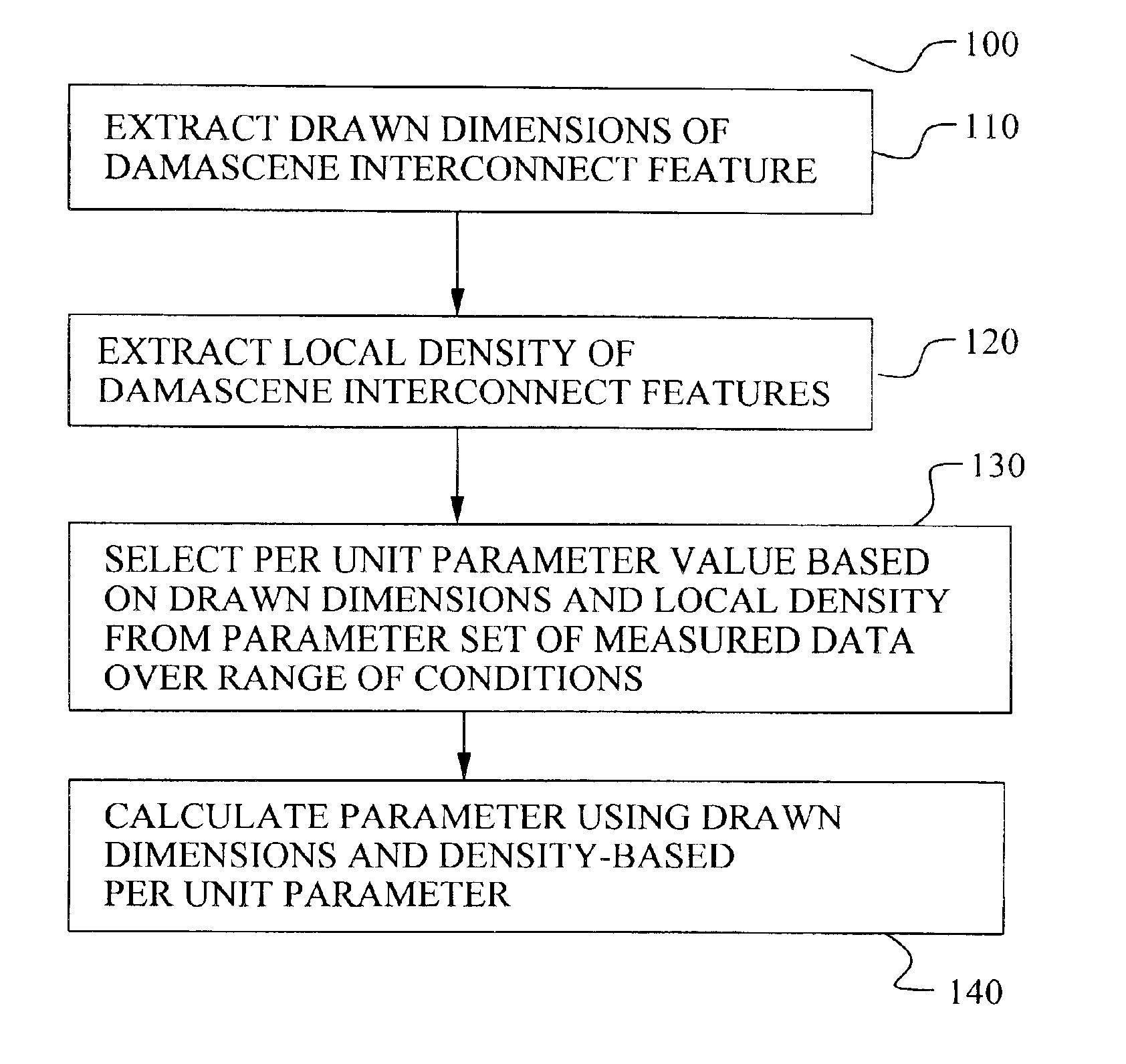

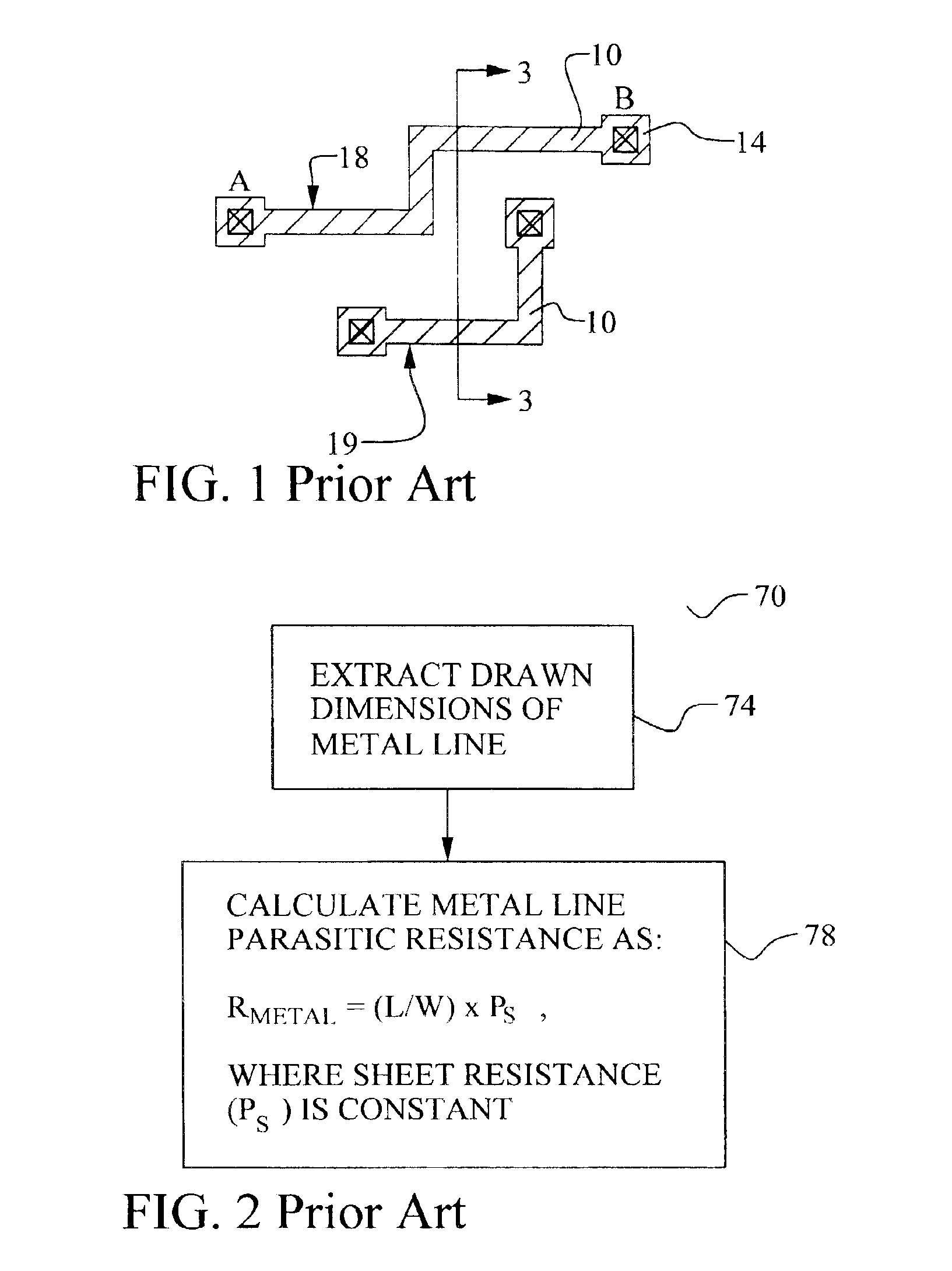

Methodology to characterize metal sheet resistance of copper damascene process

InactiveUS6854100B1Efficiently determinedSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareCopper damasceneIntegrated circuit

A new method to determine a parameter of a damascene interconnect in an integrated circuit device is achieved. Drawn dimensions and local pattern density of a damascene interconnect are extracted in an integrated circuit device. A parameter of the damascene interconnect is calculating using the drawn dimensions and the local pattern density to select a per unit value from a set of per unit values measured over a range of drawn dimension and pattern density combinations. The method may be used to improve the accuracy of extracted damascene metal line resistance and parasitic capacitance.

Owner:TAIWAN SEMICON MFG CO LTD

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

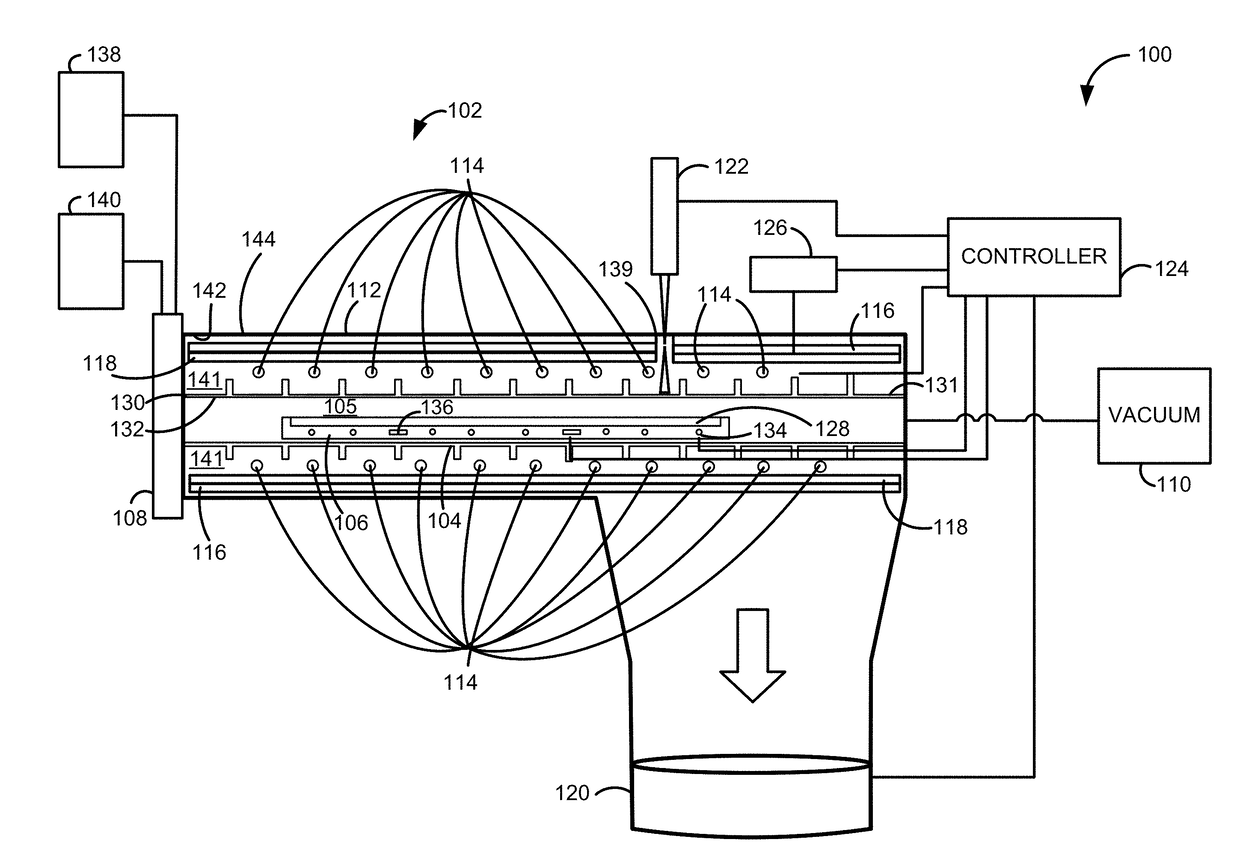

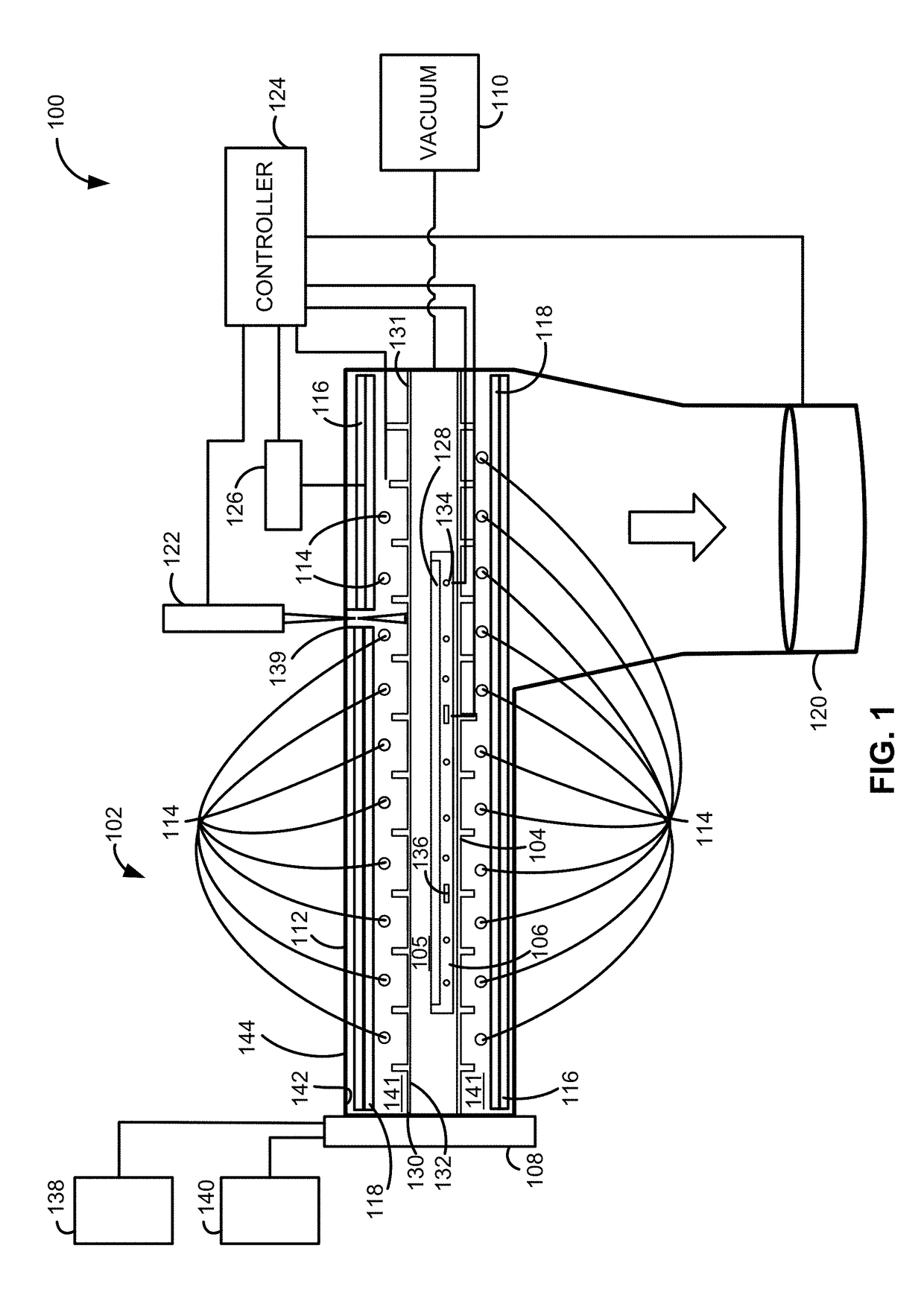

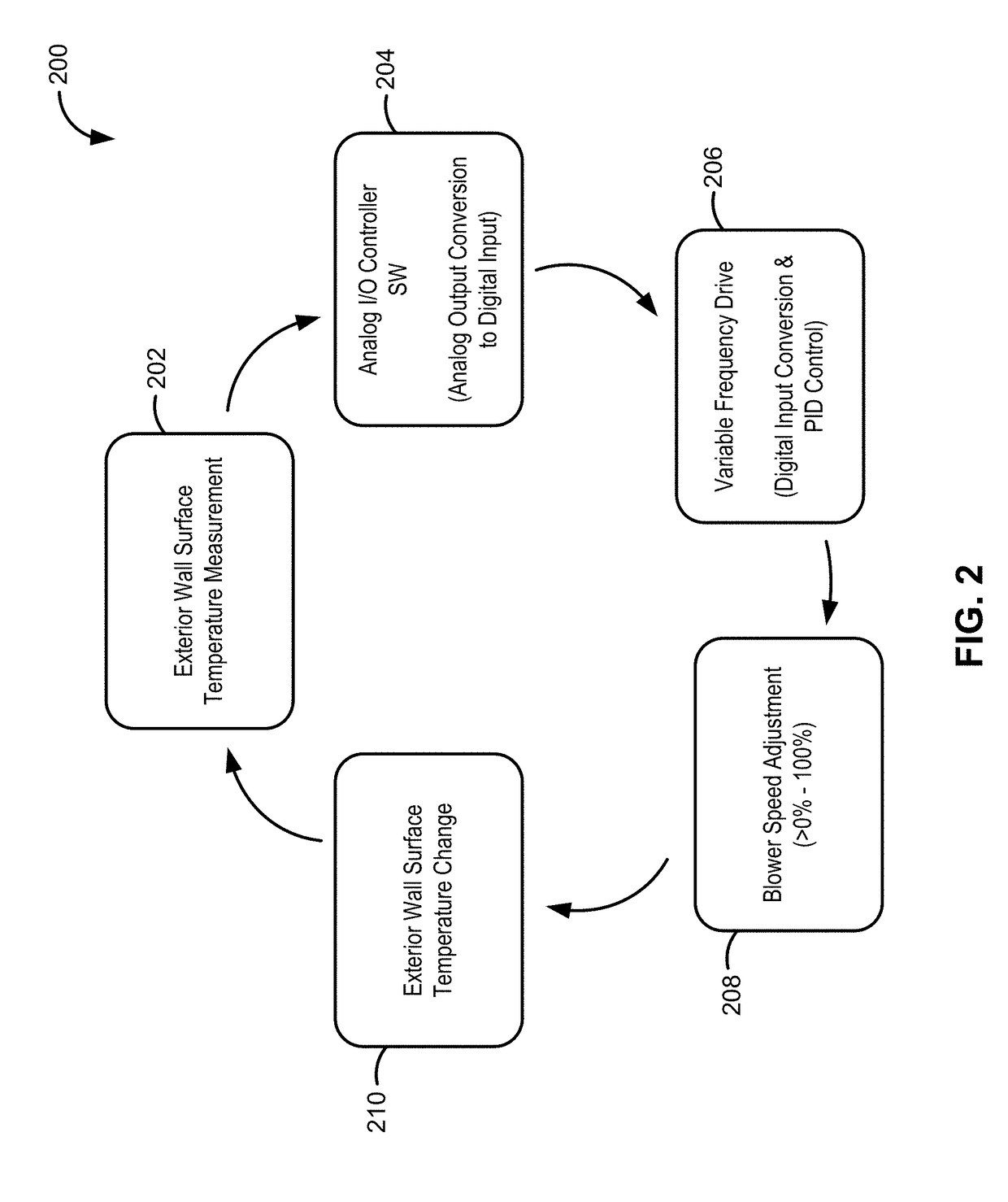

Reactor system and method to reduce residue buildup during a film deposition process

ActiveUS20180195174A1Mitigate formation of residueSubstrate throughput can be increasedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEtchingReactor system

A system and method for depositing a film within a reaction chamber are disclosed. An exemplary system includes a temperature measurement device, such as a pyrometer, to measure an exterior wall surface of the reaction chamber. A temperature of the exterior wall surface can be controlled to mitigate cleaning or etching of an interior wall surface of the reaction chamber.

Owner:ASM IP HLDG BV

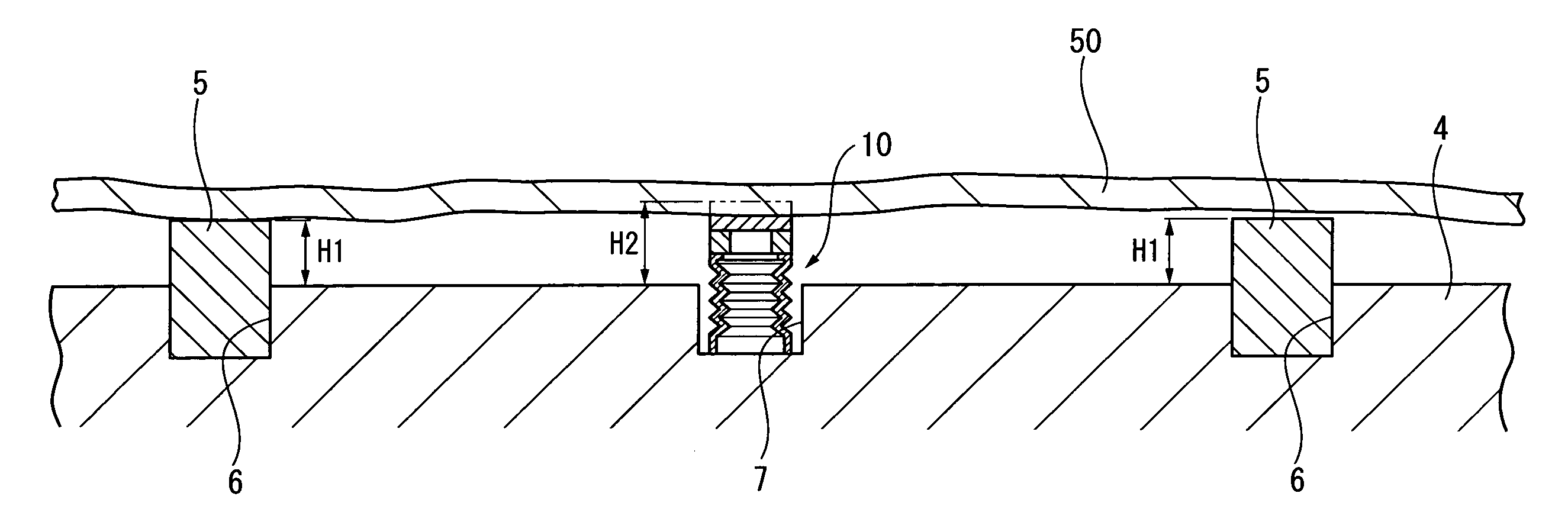

Temperature sensor, temperature control device, temperature controller and temperature-control method

ActiveUS20080043803A1High measurement accuracyThermometer detailsMechanical apparatusTemperature controlEngineering

A temperature sensor (10) includes: a temperature-sensing portion for measuring a temperature of an object (50) by contacting the object; and a supporting portion for supporting the temperature-sensing portion from a side opposite to a contact surface, the supporting portion having a space at a portion partially corresponding to the temperature-sensing portion. A temperature controller includes: a temperature control device; the temperature sensor (10) for measuring the temperature by contacting the object (50); and a controller for controlling the temperature control device. The controller includes: a mounting-state judging means for judging a mounting-state of the object (50); a switching means for switching a control gain and a target temperature of the temperature control device based on the judging result; and a control-command generating means for generating a control command based on the control gain, the target temperature and a measurement value of the temperature sensor (10).

Owner:KOMATSU LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com