Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

86355 results about "Optoelectronics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Optoelectronics (or optronics) is the study and application of electronic devices and systems that source, detect and control light, usually considered a sub-field of photonics. In this context, light often includes invisible forms of radiation such as gamma rays, X-rays, ultraviolet and infrared, in addition to visible light. Optoelectronic devices are electrical-to-optical or optical-to-electrical transducers, or instruments that use such devices in their operation. Electro-optics is often erroneously used as a synonym, but is a wider branch of physics that concerns all interactions between light and electric fields, whether or not they form part of an electronic device.

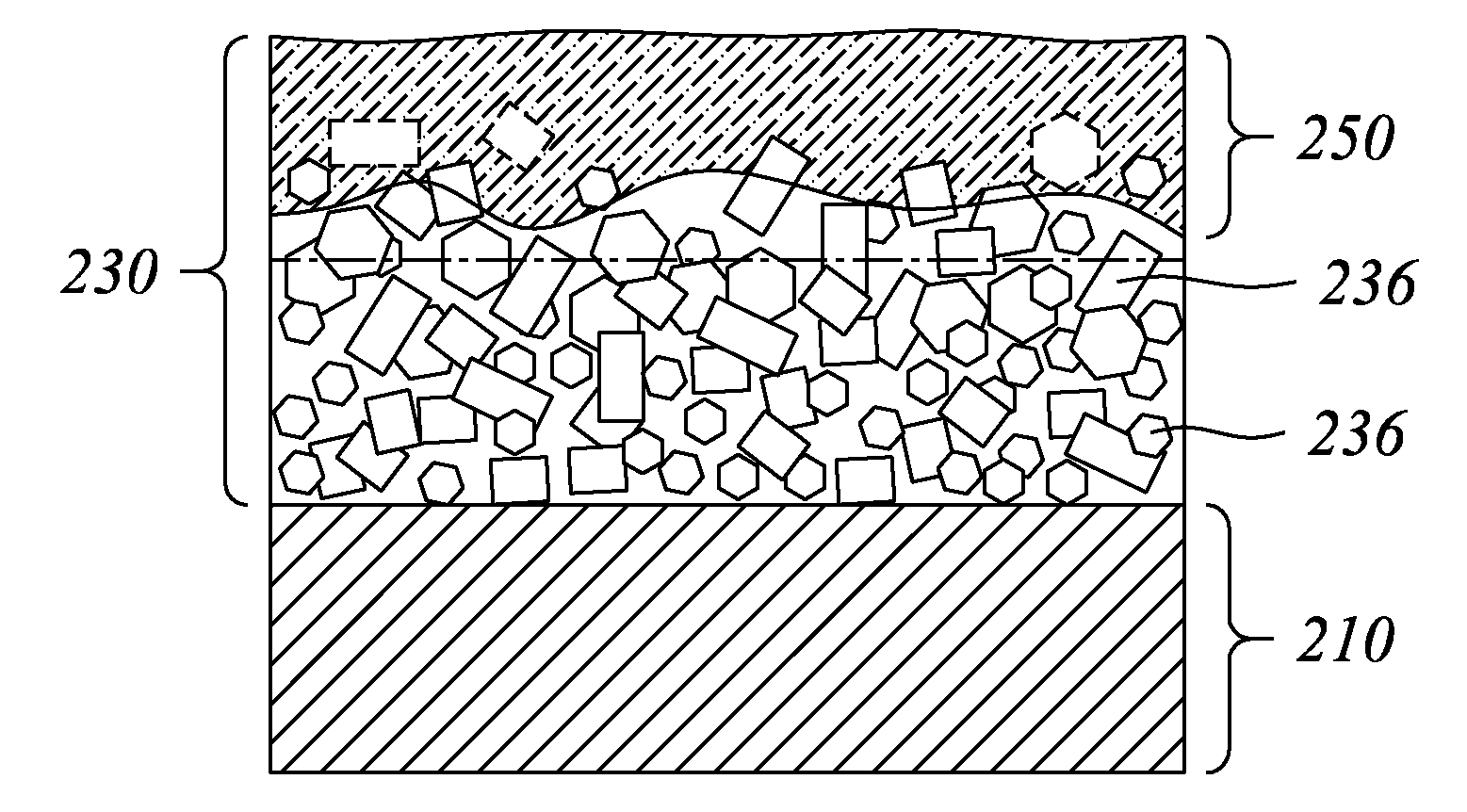

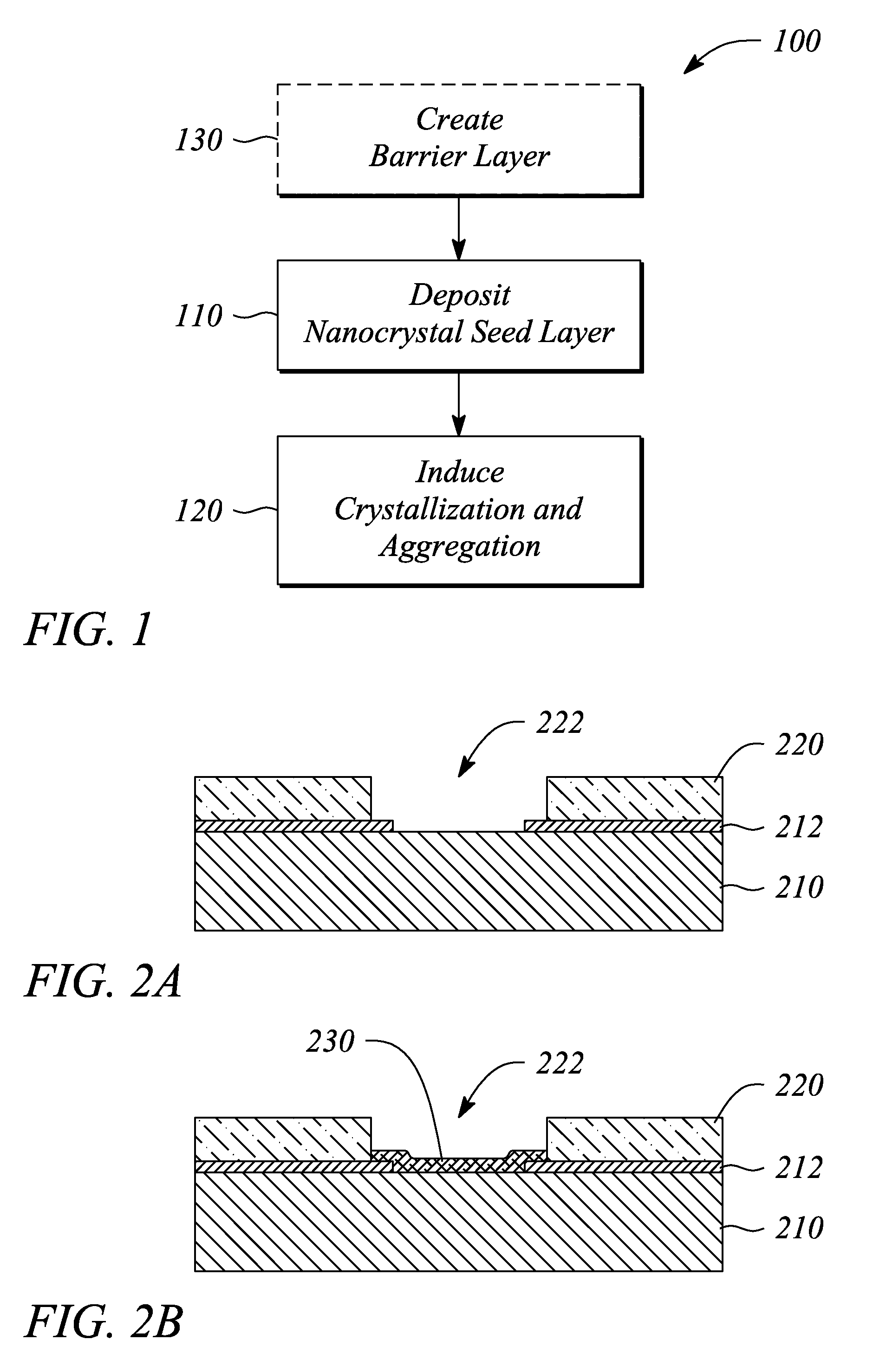

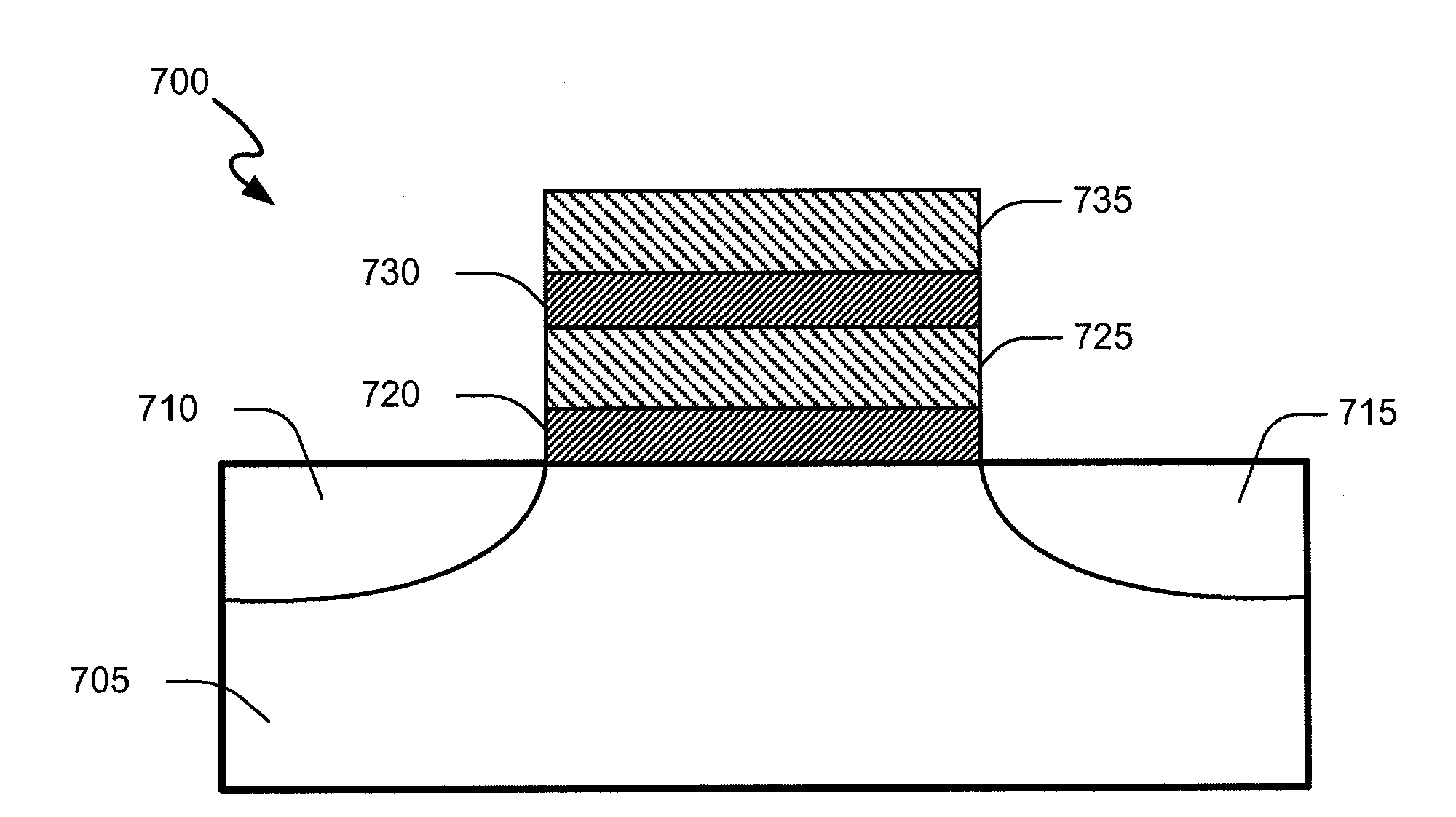

Fused nanocrystal thin film semiconductor and method

A thin film semiconductor and a method of its fabrication use induced crystallization and aggregation of a nanocrystal seed layer to form a merged-domain layer. The nanocrystal seed layer is deposited onto a substrate surface within a defined boundary. A reaction temperature below a boiling point of a reaction solution is employed. A thin film metal-oxide transistor and a method of its production employ the thin film semiconductor as a channel of the transistor. The merged-domain layer exhibits high carrier mobility.

Owner:HEWLETT PACKARD DEV CO LP

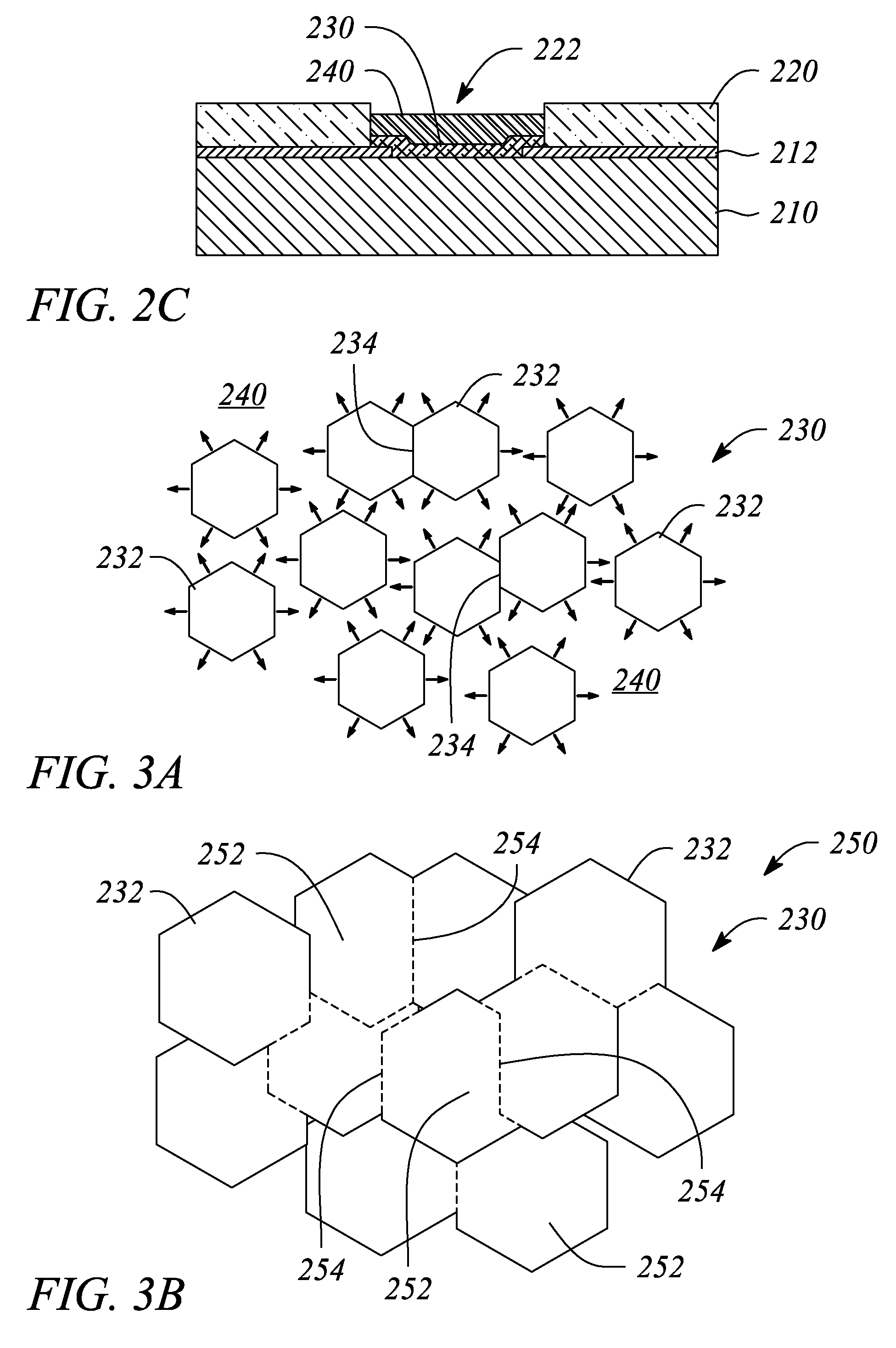

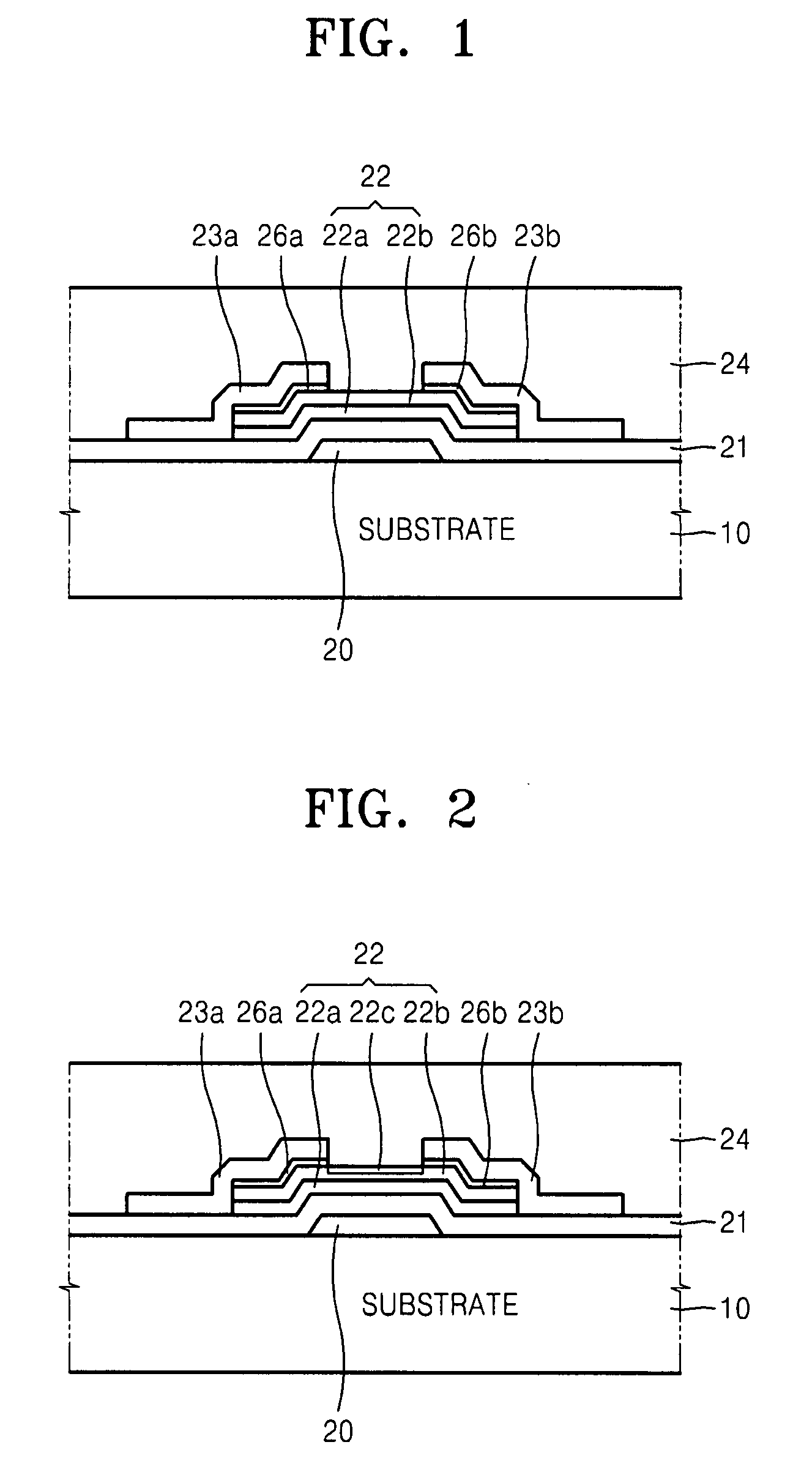

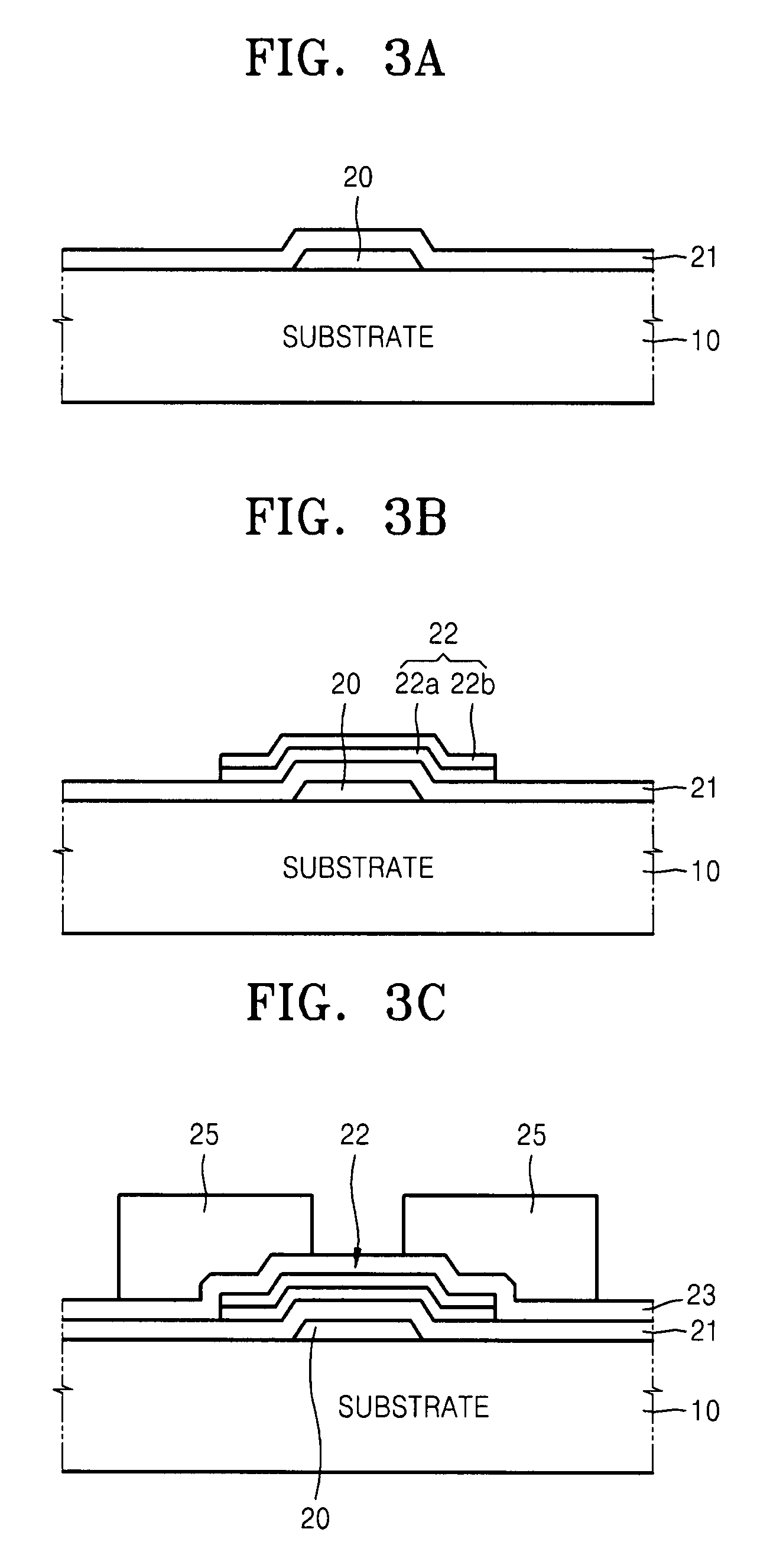

Thin film transistors and methods of manufacturing the same

ActiveUS20080296568A1Suppress and prevent damageAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesOxygen vacancyFluoride salt

A TFT includes a zinc oxide (ZnO)-based channel layer having a plurality of semiconductor layers. An uppermost of the plurality of semiconductor layers has a Zn concentration less than that of a lower semiconductor layer to suppress an oxygen vacancy due to plasma. The uppermost semiconductor layer of the channel layer also has a tin (Sn) oxide, a chloride, a fluoride, or the like, which has a relatively stable bonding energy against plasma. The uppermost semiconductor layer is relatively strong against plasma shock and less decomposed when being exposed to plasma, thereby suppressing an increase in carrier concentration.

Owner:SAMSUNG ELECTRONICS CO LTD

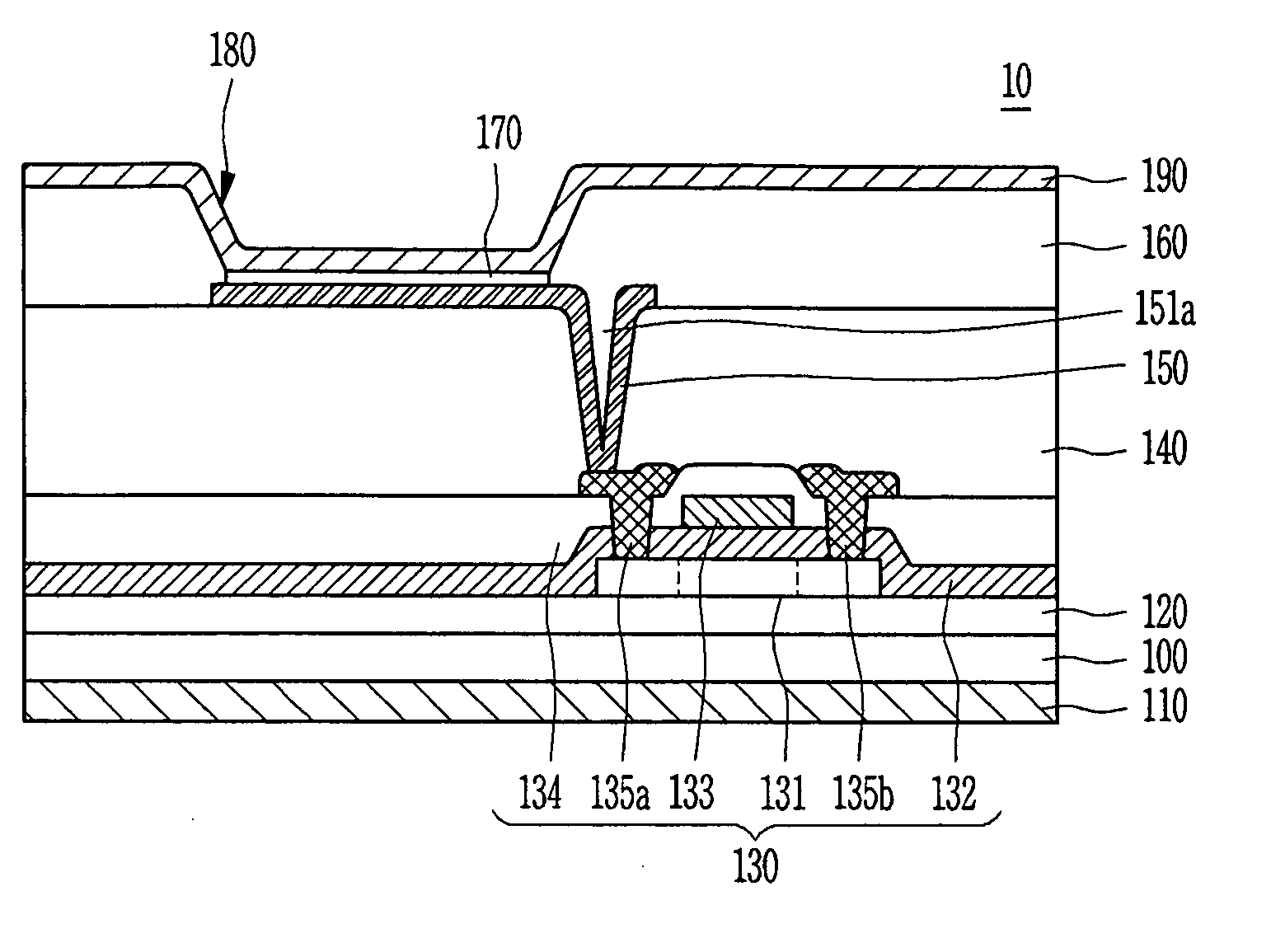

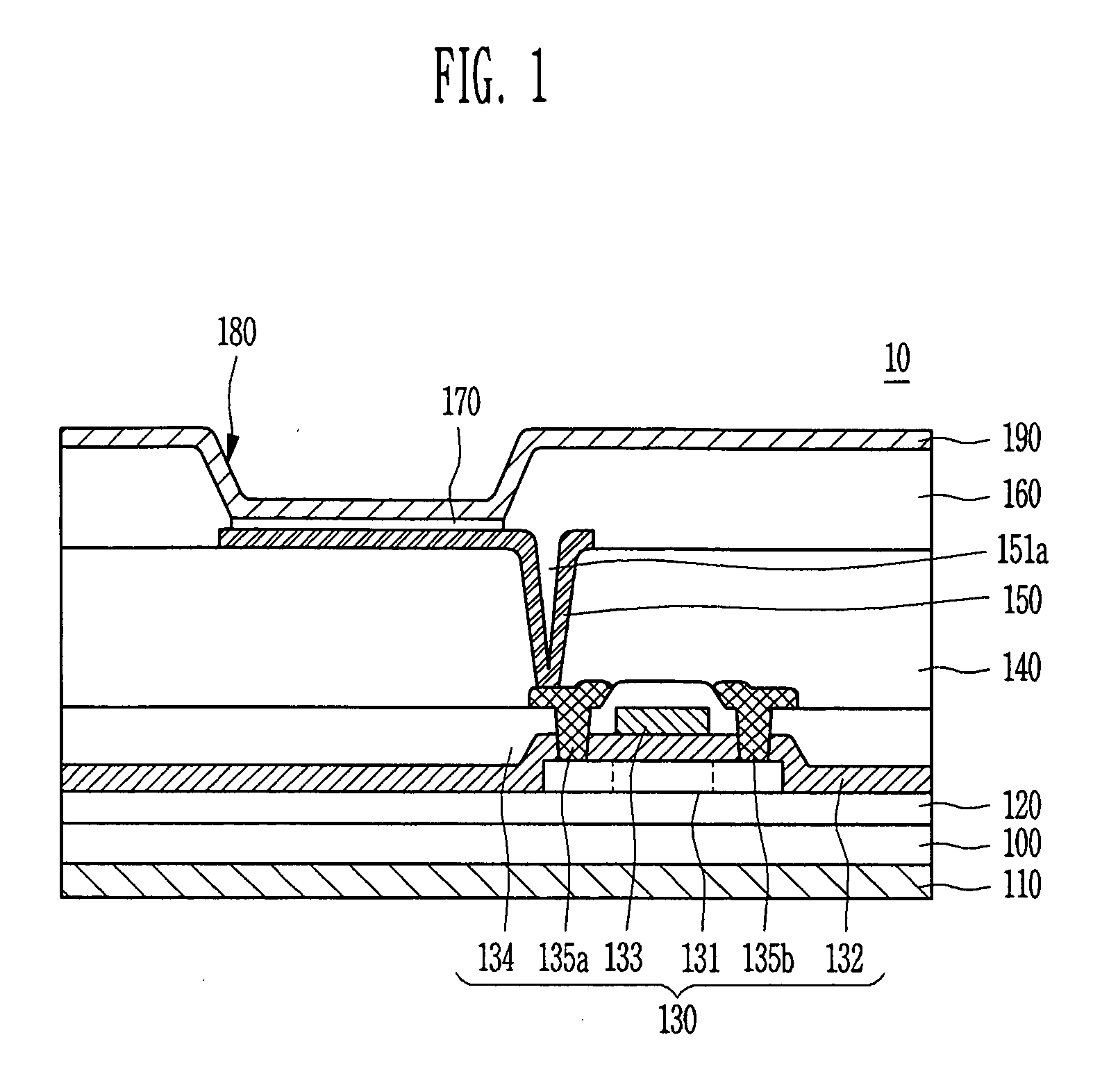

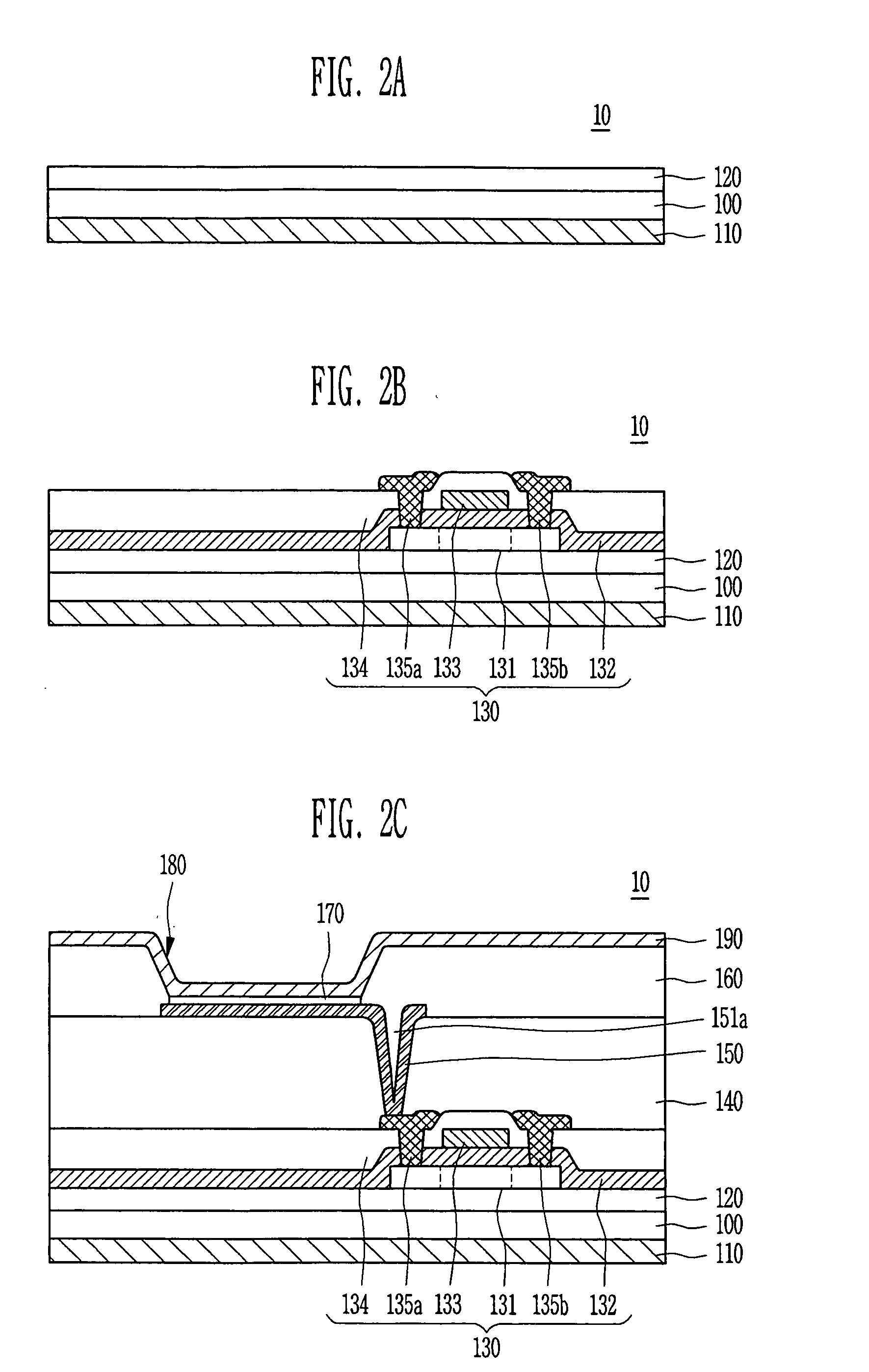

Organic light emitting display (OLED) and its method of fabrication

ActiveUS20070024187A1Improve visibilityIncrease contrastDischarge tube luminescnet screensElectroluminescent light sourcesOrganic light emitting deviceOptoelectronics

An Organic Light Emitting Display (OLED) and its method of fabrication includes: a transparent substrate; a photochromatic layer formed on a first surface of the transparent substrate; at least one transparent Thin Film Transistor (TFT) formed on a first surface of the transparent substrate, and an organic light emitting device formed on and electrically connected to the transparent TFT.

Owner:SAMSUNG DISPLAY CO LTD

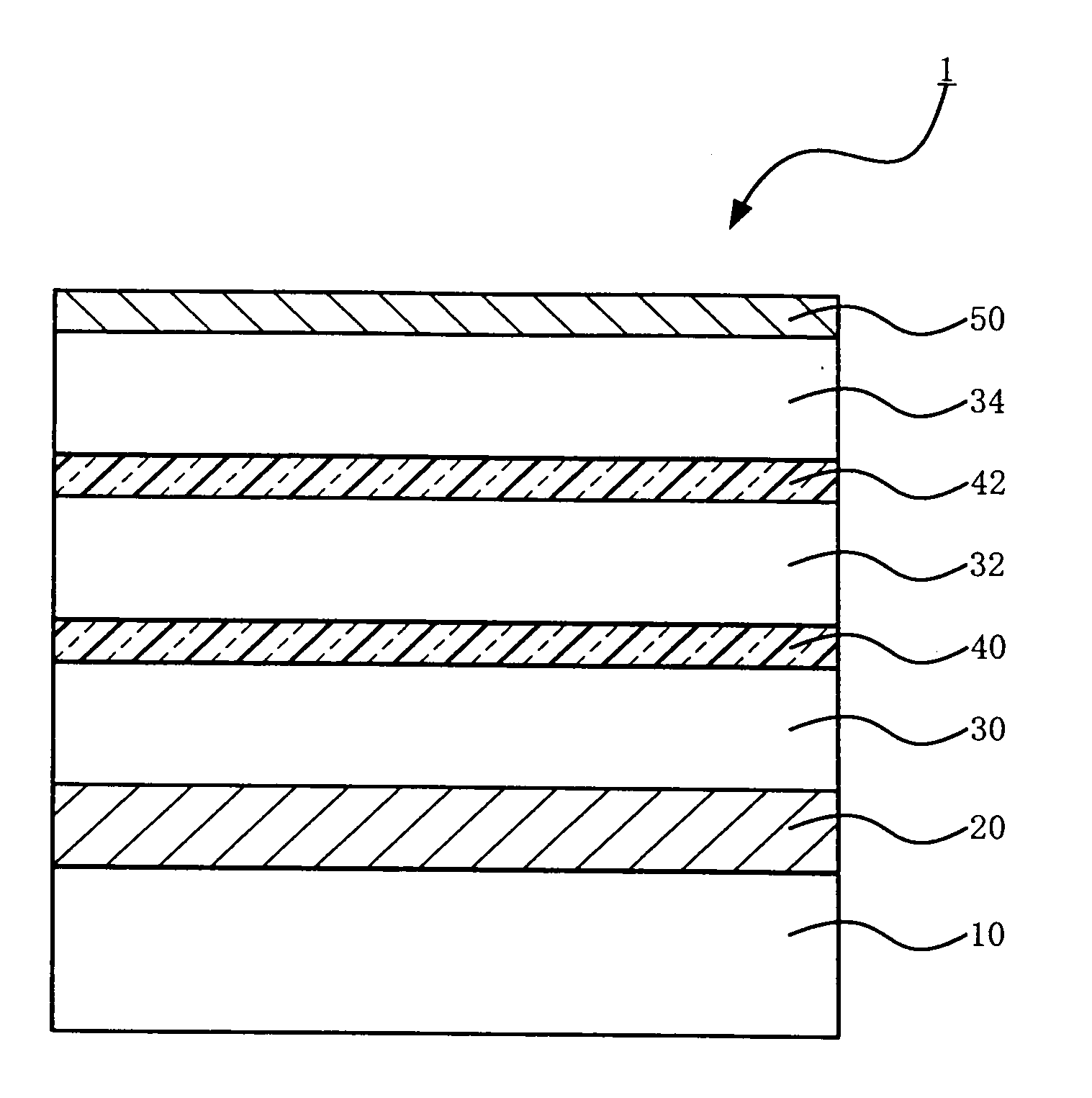

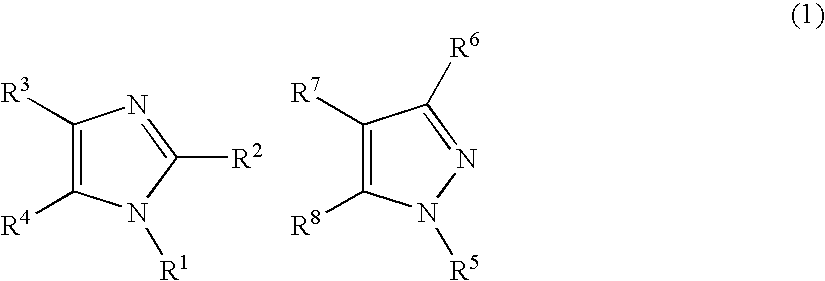

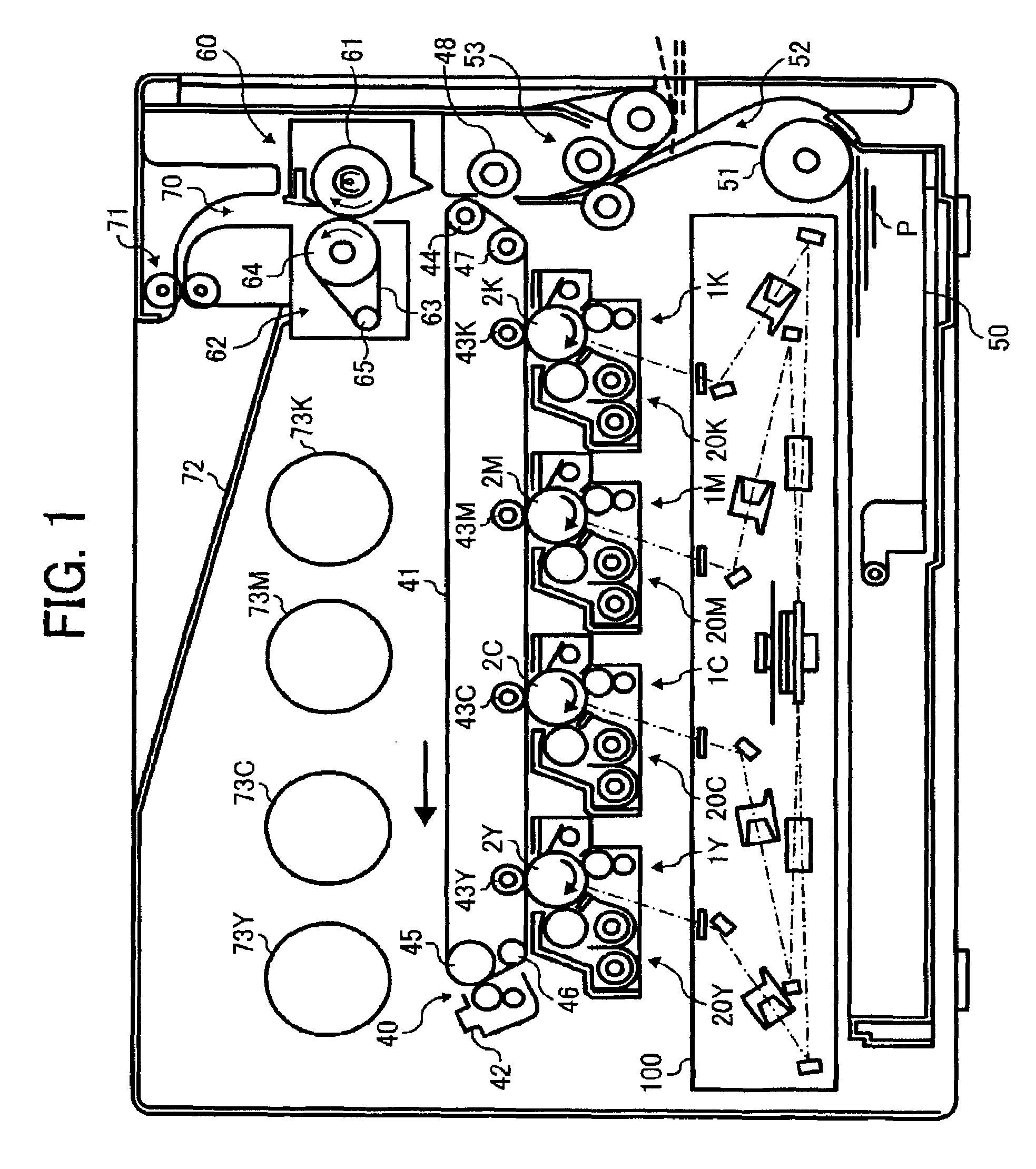

Organic electroluminescent device

ActiveUS20090179554A1Improve efficiencyReduce the driving voltageDischarge tube luminescnet screensLamp detailsNitrogenOptoelectronics

An organic electroluminescence device (1) including: an anode (20) and a cathode (50), at least two organic emitting layers (30), (32) and (34) interposed between the anode and the cathode, and at least one intermediate connection layer (40) and (42) being provided between the organic emitting layers (30), (32) and (34), the intermediate connection layer (40) and (42) comprising an acceptor layer, a donor layer and an electron-transporting material layer being stacked in this order from the cathode (50), the electron-transporting material layer containing a non-complex compound with a nitrogen-containing heterocyclic structure.

Owner:IDEMITSU KOSAN CO LTD

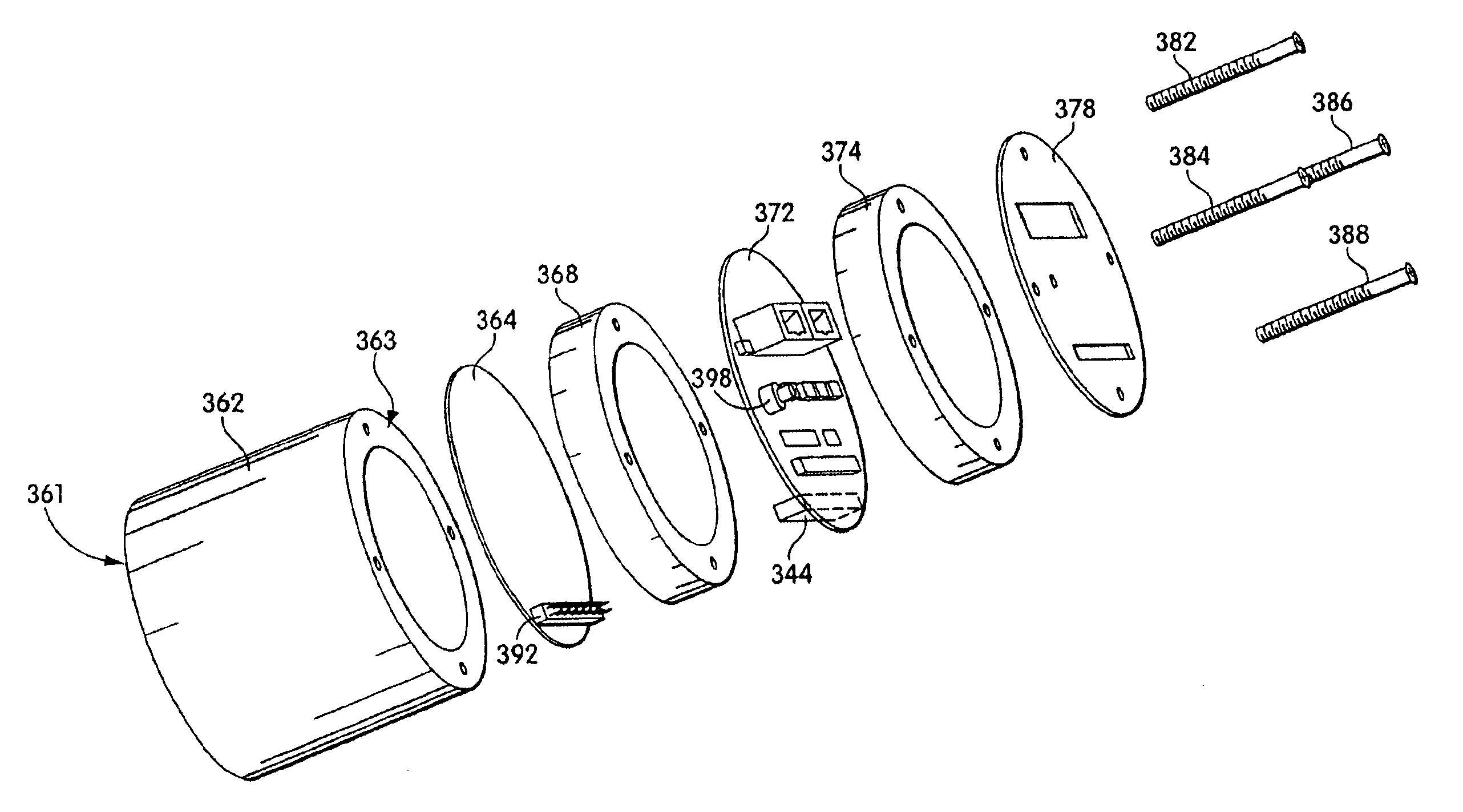

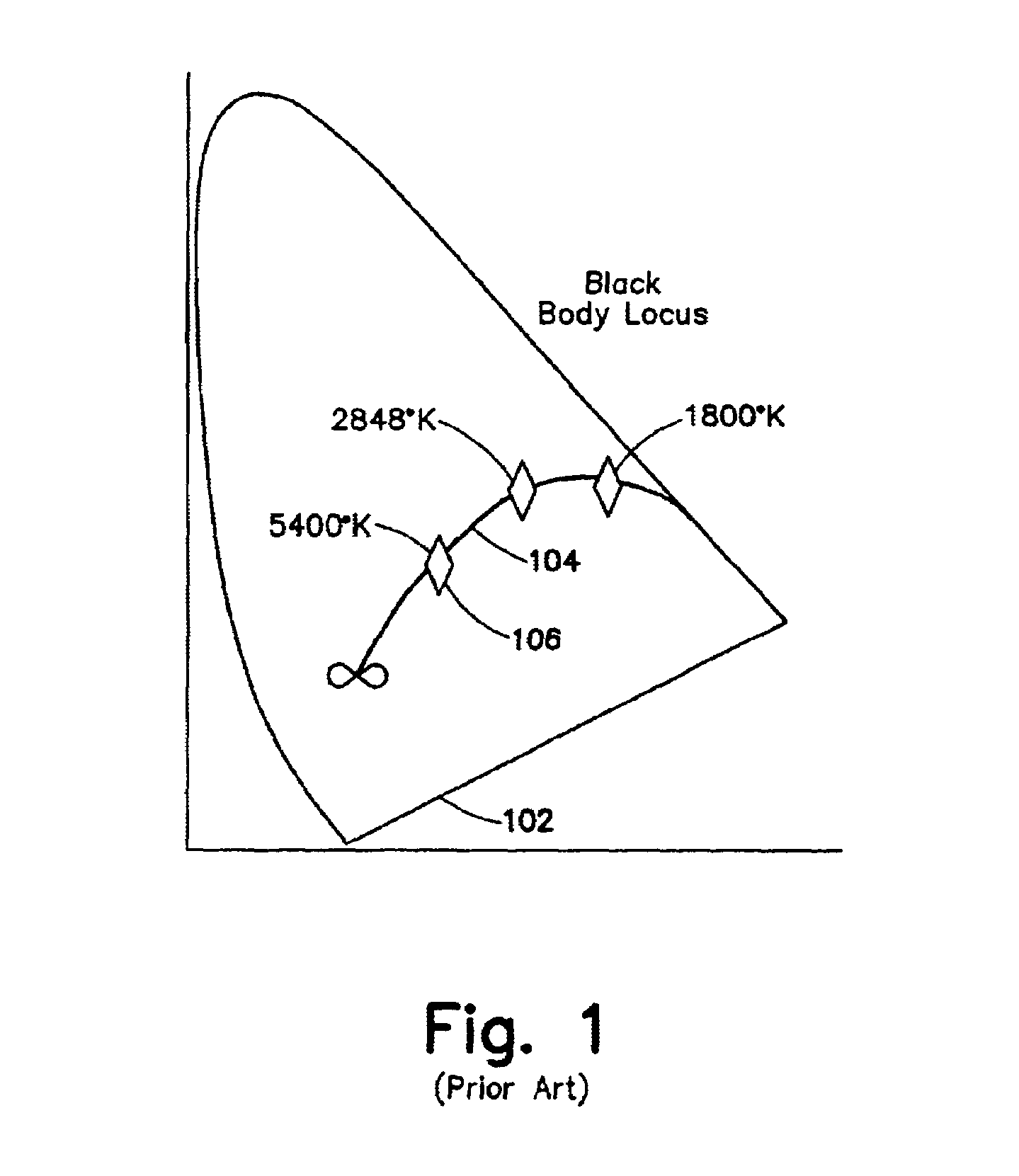

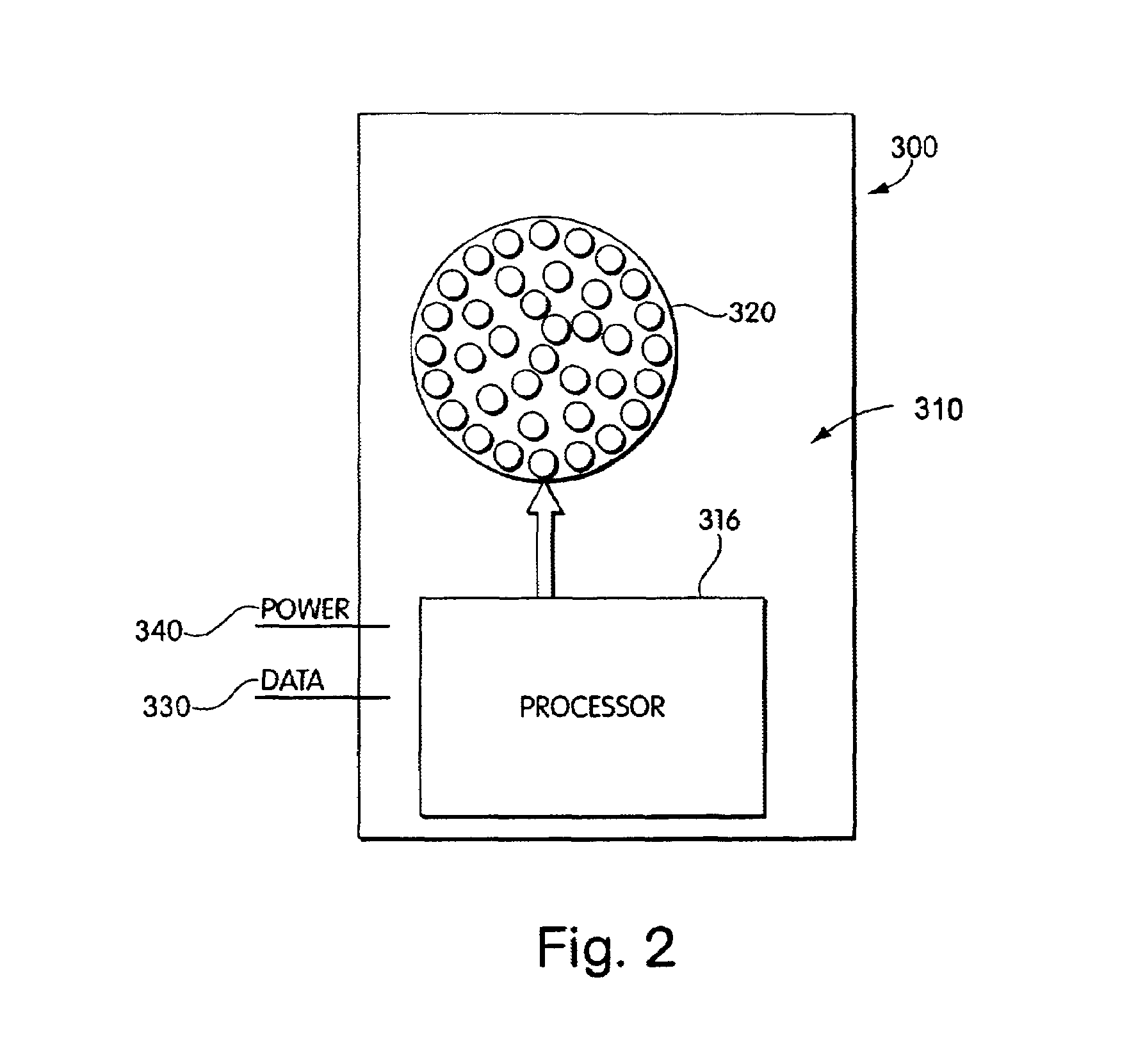

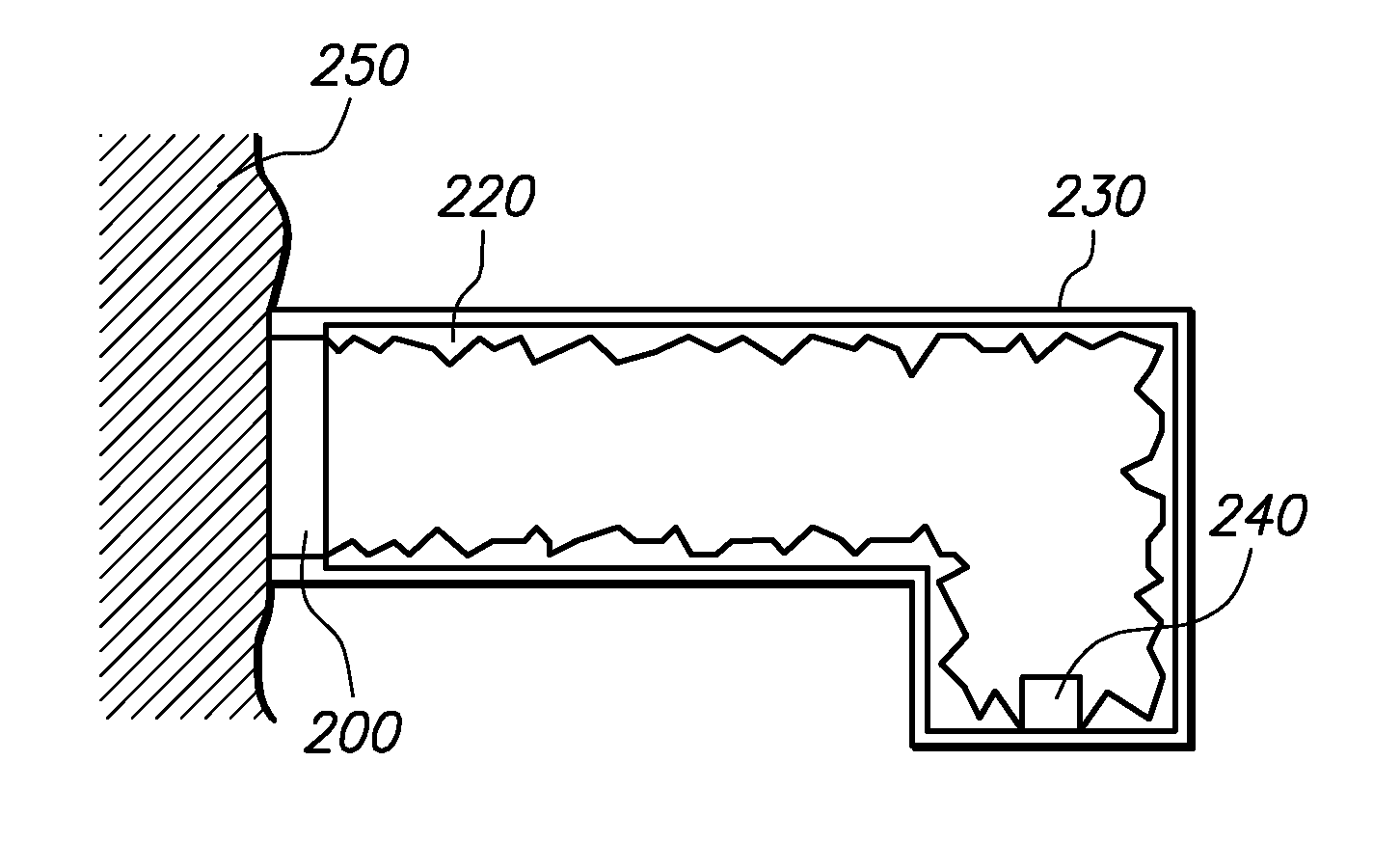

Systems and methods for generating and modulating illumination conditions

The present invention relates to systems and methods for generating and / or modulating illumination conditions to generate high-quality light of a desired and controllable color, for creating lighting fixtures for producing light in desirable and reproducible colors, and for modifying the color temperature or color shade of light within a prespecified range after a lighting fixture is constructed. In one embodiment, LED lighting units capable of generating light of a range of colors are used to provide light or supplement ambient light to afford lighting conditions suitable for a wide range of applications.

Owner:SIGNIFY NORTH AMERICA CORP

Eye-Safe Dermatologic Treatment Apparatus and Method

InactiveUS20090204109A1Reduce radiationEffective treatmentDiagnosticsSurgical instrument detailsRadianceOptoelectronics

A dermatologic treatment apparatus is disclosed which includes one or more housings with at least one housing configured for manipulation in a dermatologic treatment procedure, a light source, and an electrical circuit. The circuit energizes the light source to produce output light pulses. A light path includes an aperture through which eye-safe light pulses are propagated having properties sufficient for providing efficacious treatment. An optical diffuser is disposed along the light path to reduce the integrated radiance to an eye-safe level. The apparatus produces an output fluence not less than 4 J / cm2.

Owner:TRIA BEAUTY

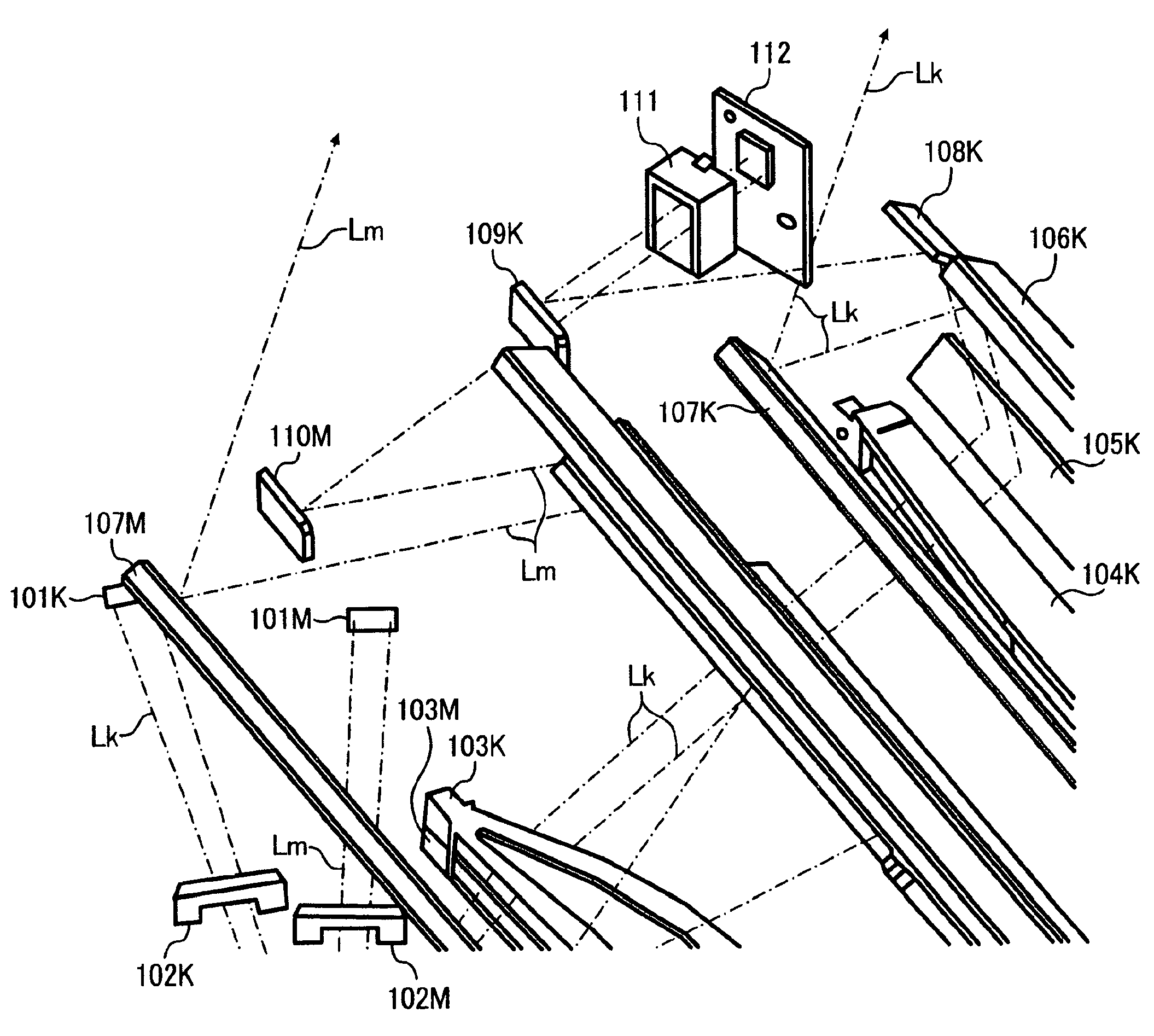

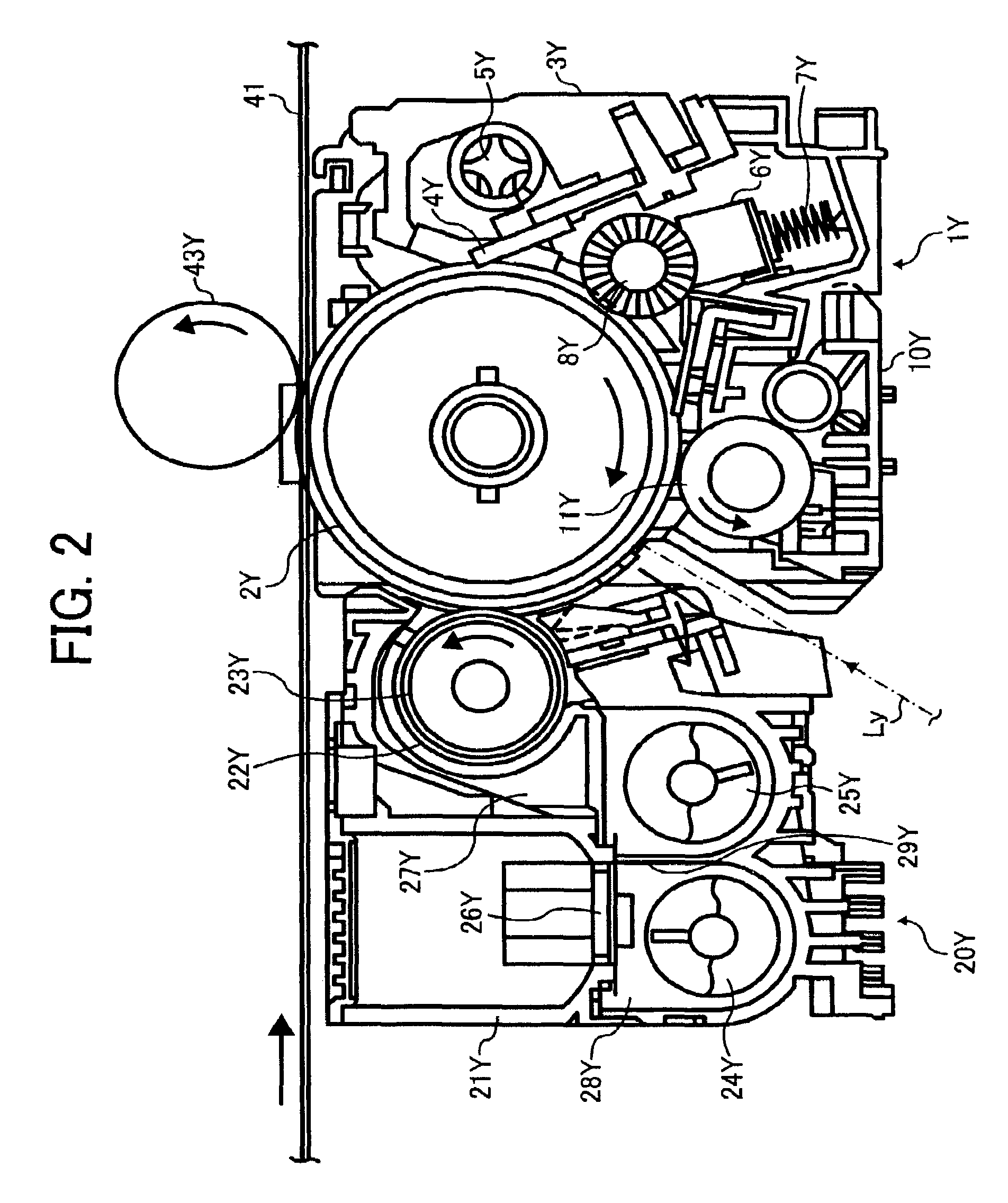

Optical scanning device and image forming apparatus

A deflecting unit deflects a light beam emitted by each of a plurality of light-beam emitting units independently to scan surfaces of different bodies to be scanned. Each of a plurality of light-receiving units receives the deflected light beam at a predetermined position in a direction of the deflection. An incident angle of the deflected light beam with respect to a scanning line extending in a direction of scanning on a light-receiving surface of the light-receiving unit is set to be identical for all of the light-receiving units.

Owner:RICOH KK

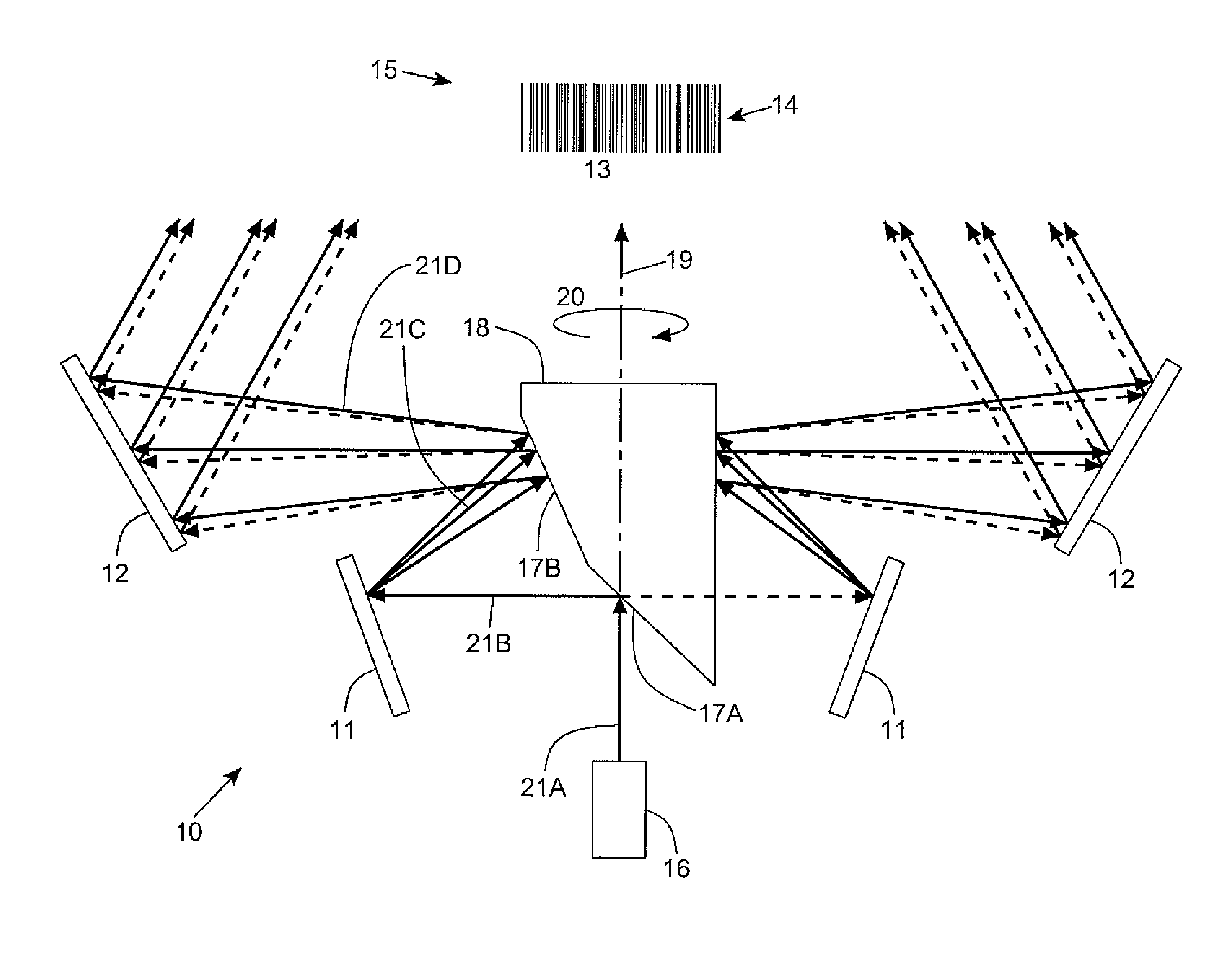

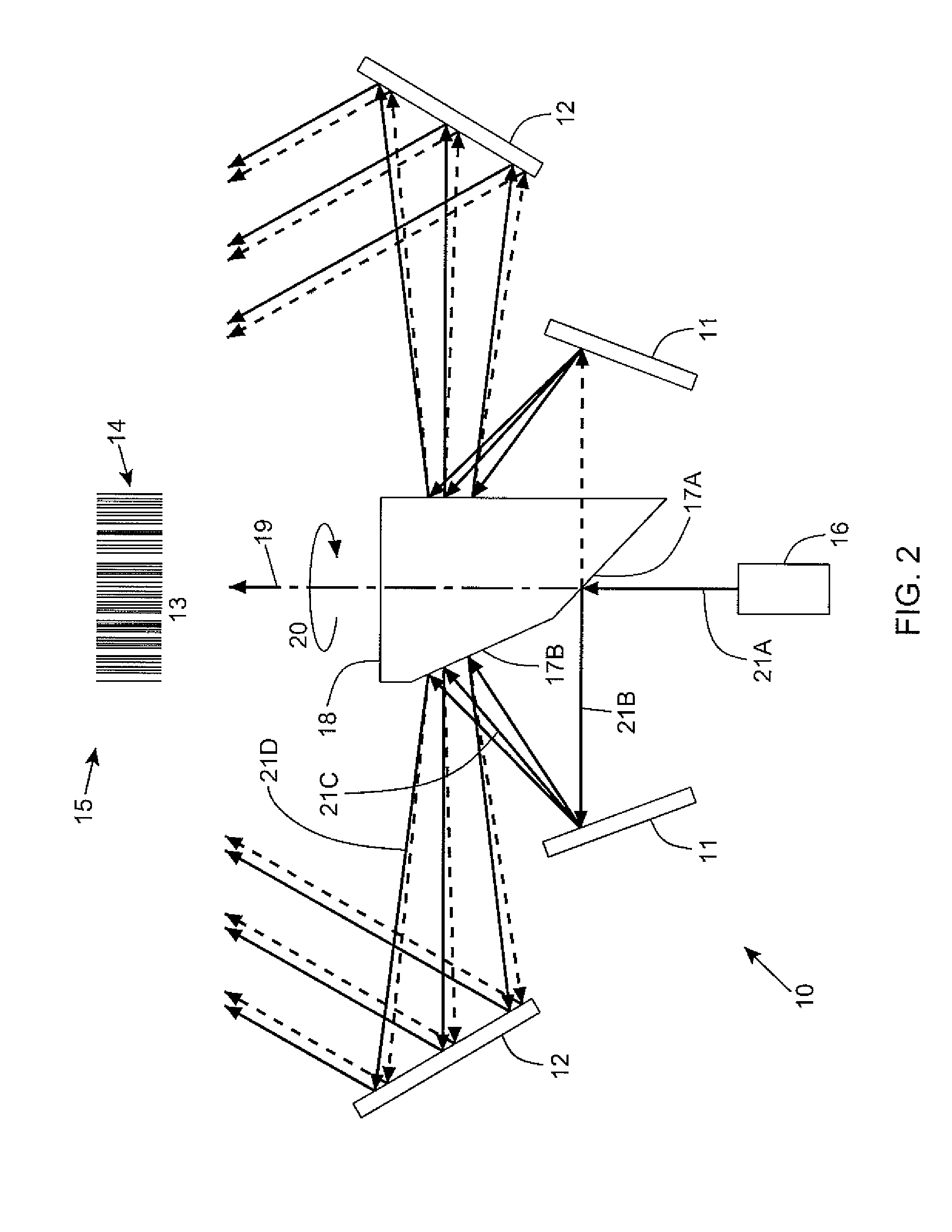

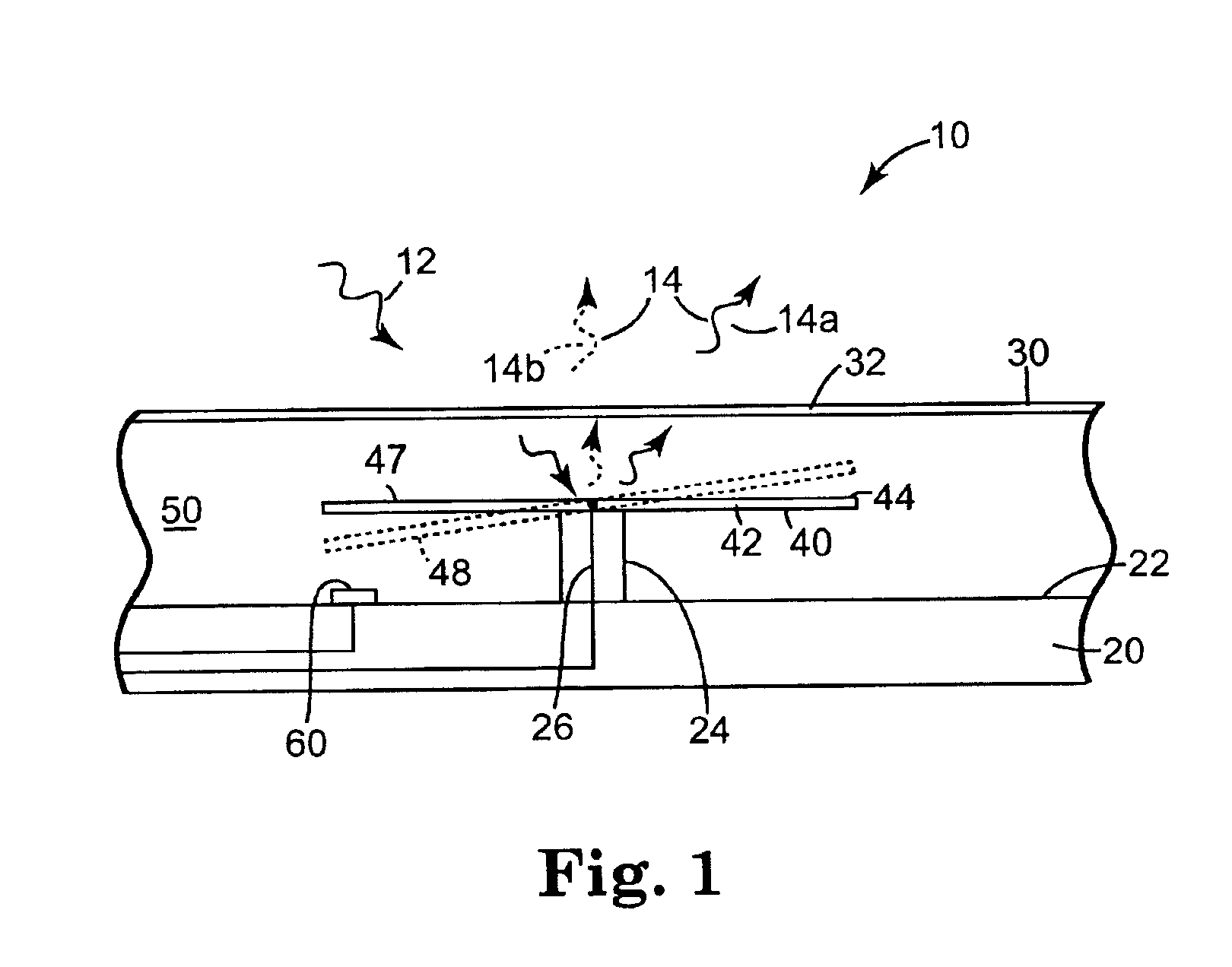

Laser scanning assembly having an improved scan angle-multiplication factor

InactiveUS8408469B2Increase multipleUniform collectionMirrorsBeam/ray focussing/reflecting arrangementsRotational axisAcute angle

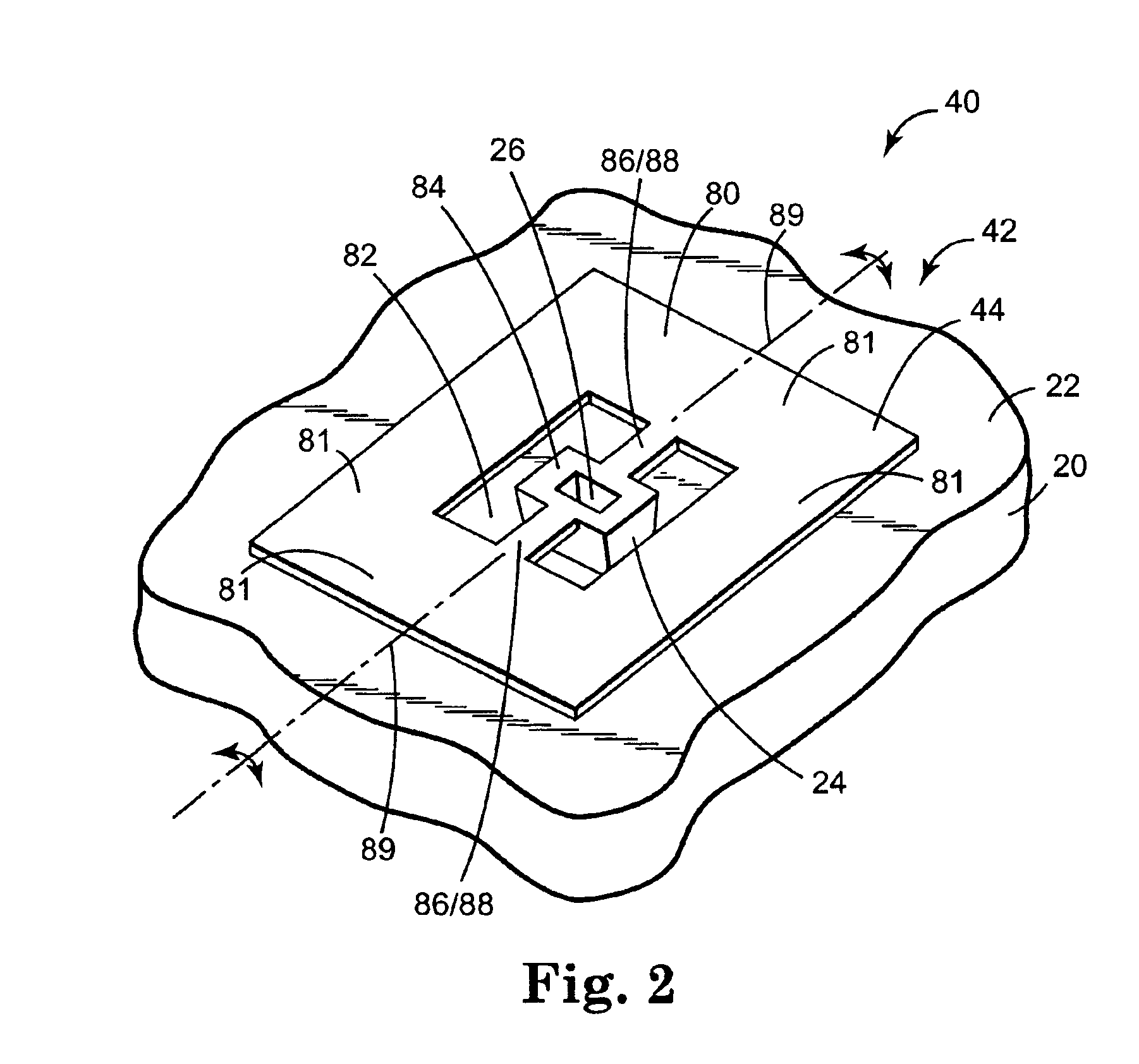

A laser scanning system for generating a laser scanning pattern in a scanning field, while amplifying the scan-angle multiplication factor of rotating mirrors employed therein. The laser scanning system employs rotatable laser scanning assembly having an axis of rotation and first and second rotating mirrors with normal vectors that are coplanar with each other and said rotational axis, and which form an acute angle substantially less than 90 degrees so as to provide a laser scanning assembly with a scan angle multiplication factor that is greater than 2.0. A cluster of stationary mirrors mounted about the first and second rotating mirrors, for sweeping a laser beam off the cluster of stationary mirrors after a laser beam has been reflected off the first rotating mirror, then reflected off the second rotating mirror, and then directed outwardly towards an array of pattern mirrors, so as to generate a resultant laser scanning pattern within the scanning field.

Owner:METROLOGIC INSTR INC

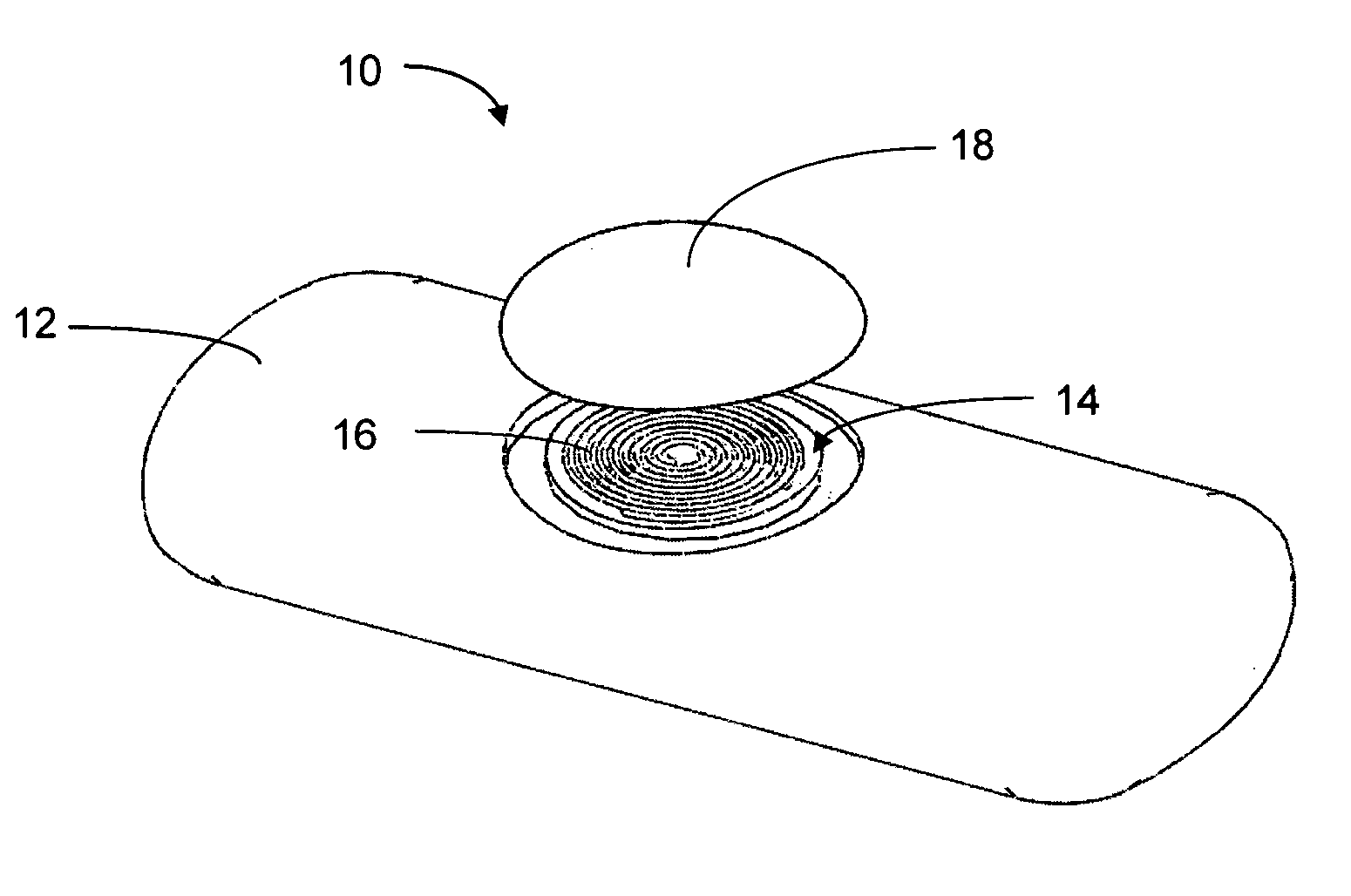

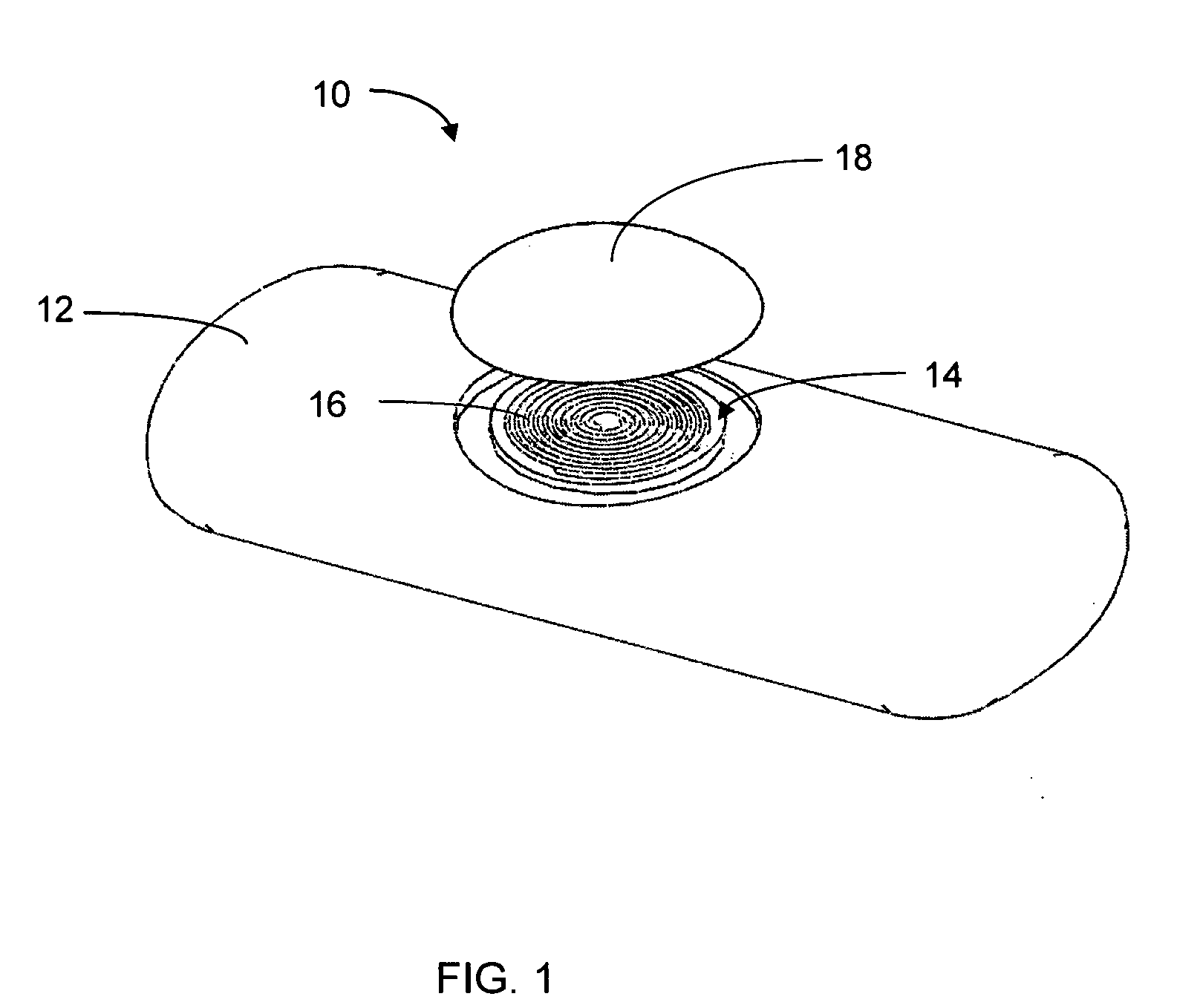

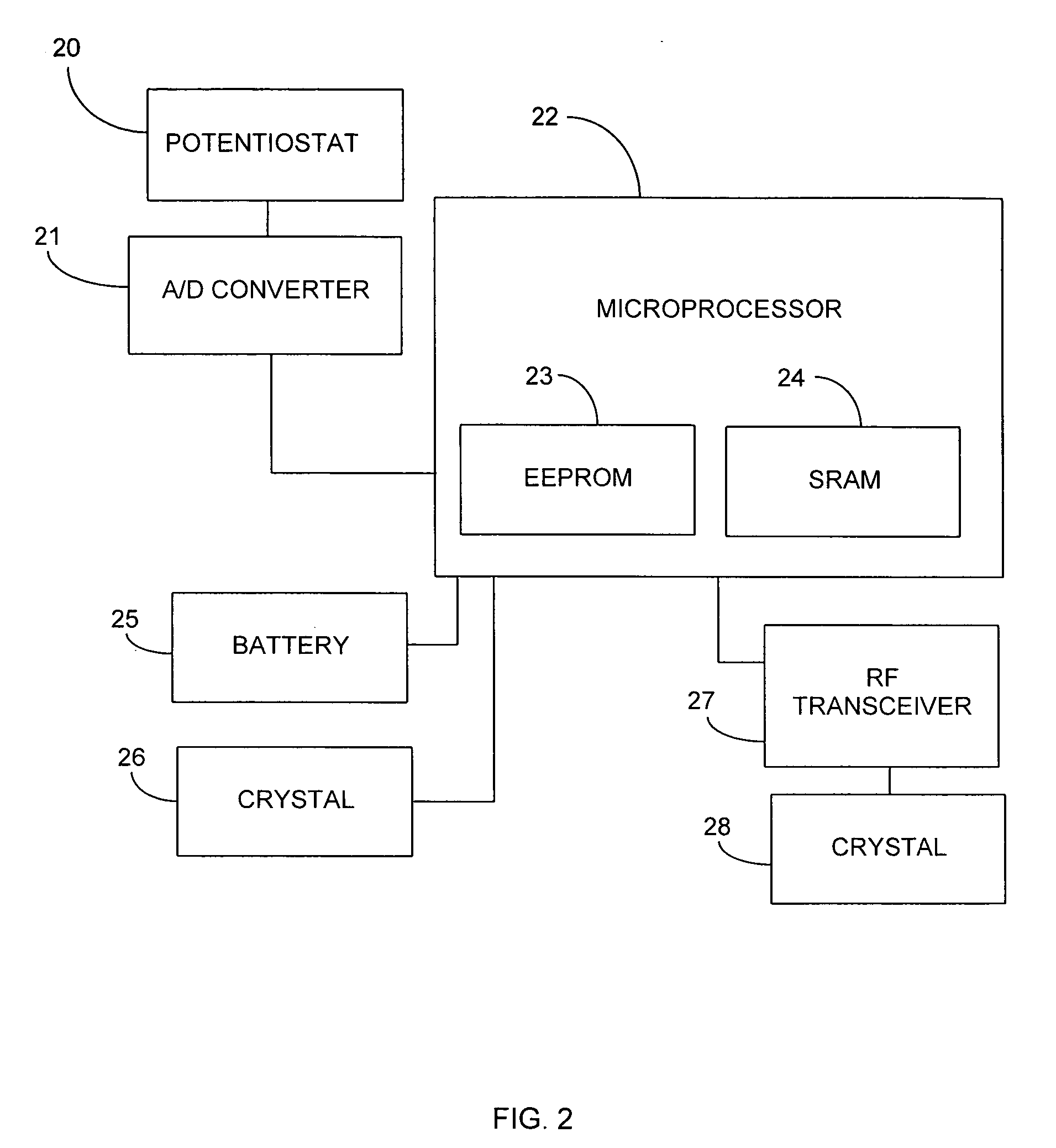

Rolled electrode array and its method for manufacture

InactiveUS20050051427A1Long-term robustnessSemiconductor/solid-state device manufacturingEndoradiosondesOptoelectronicsElectrode array

An electrode array for use in an electrochemical device is provided. The electrode array includes at least one electrode material and at least one insulating material arranged in a spiral configuration. The electrode array is manufactured by forming a composite stack of the at least one electrode material and the at least one insulating material, such that the insulating material(s) surrounds the electrode material(s) after which the stack is rolled into a spiral roll. The spiral roll can be cut, sliced, and / or dissected in numerous ways to form the electrode array of the preferred embodiments. Optionally, the sections can be further processed by machining, polishing, etching, or the like, to produce a curvature or stepped configuration.

Owner:DEXCOM

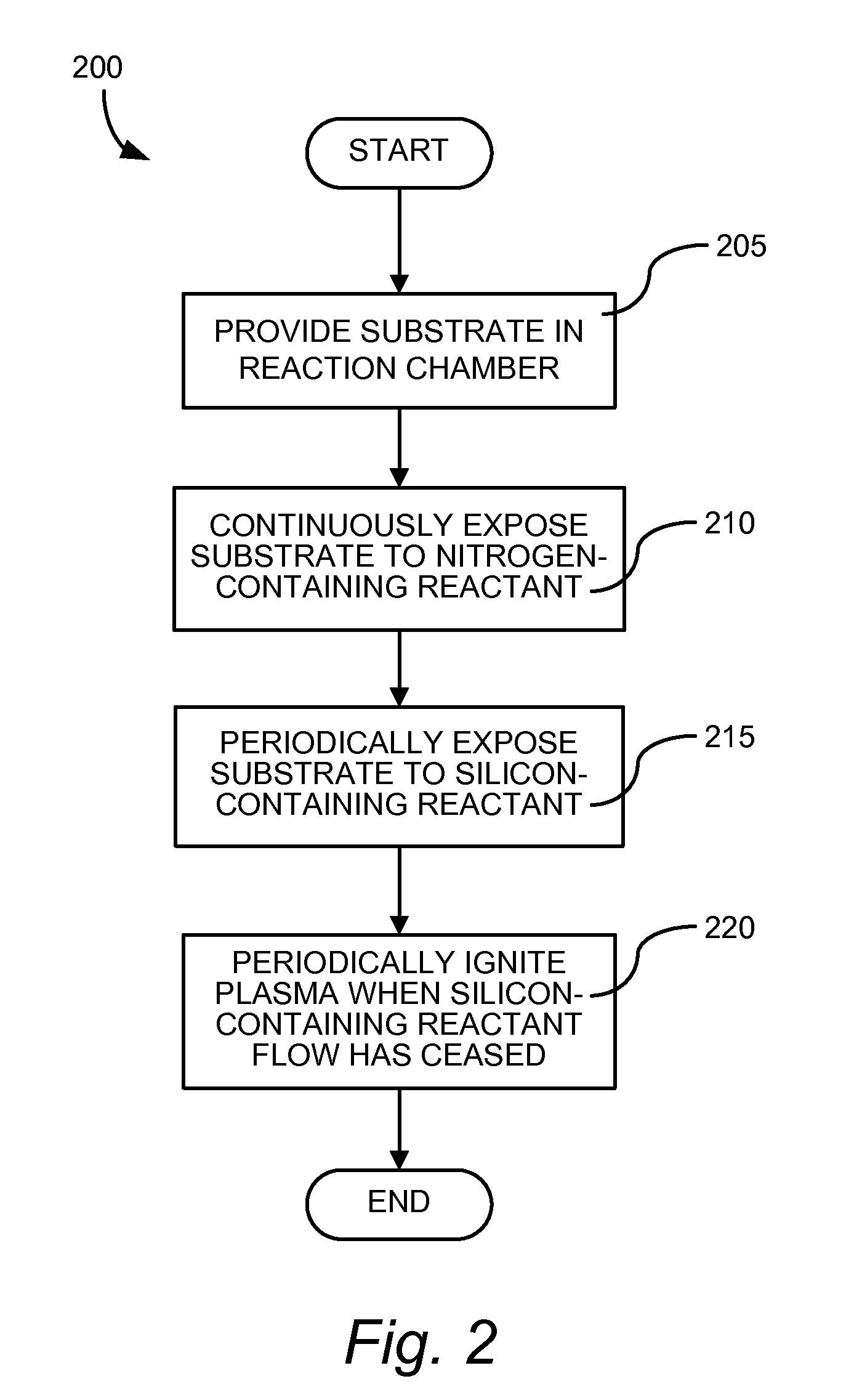

Silicon nitride films and methods

InactiveUS20110256734A1Reduce carbon contentSemiconductor/solid-state device manufacturingChemical vapor deposition coatingOptoelectronicsSemiconductor

Described are methods of making SiN materials on substrates, particularly SiN thin films on semiconductor substrates. Improved SiN films made by the methods are also included.

Owner:NOVELLUS SYSTEMS

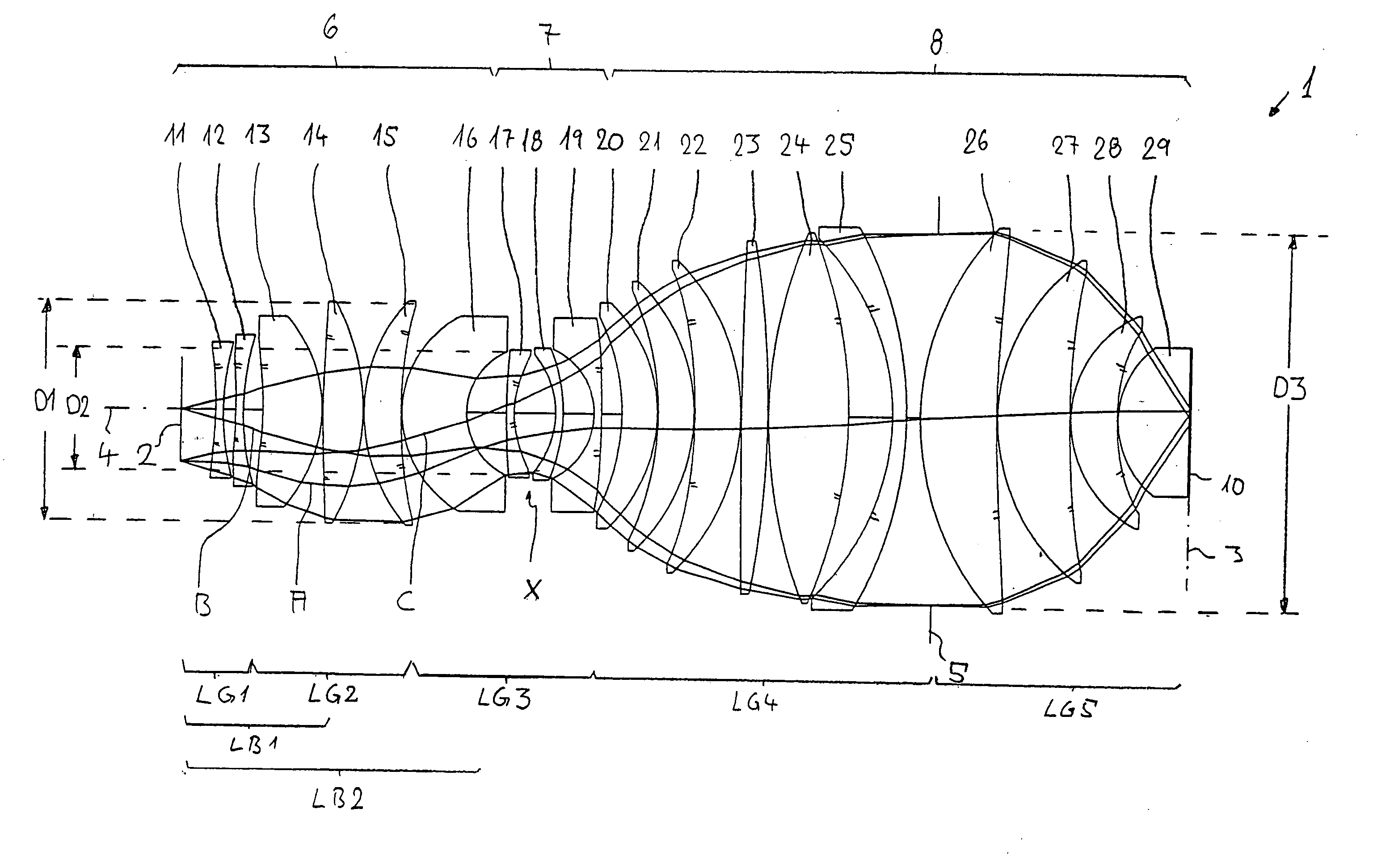

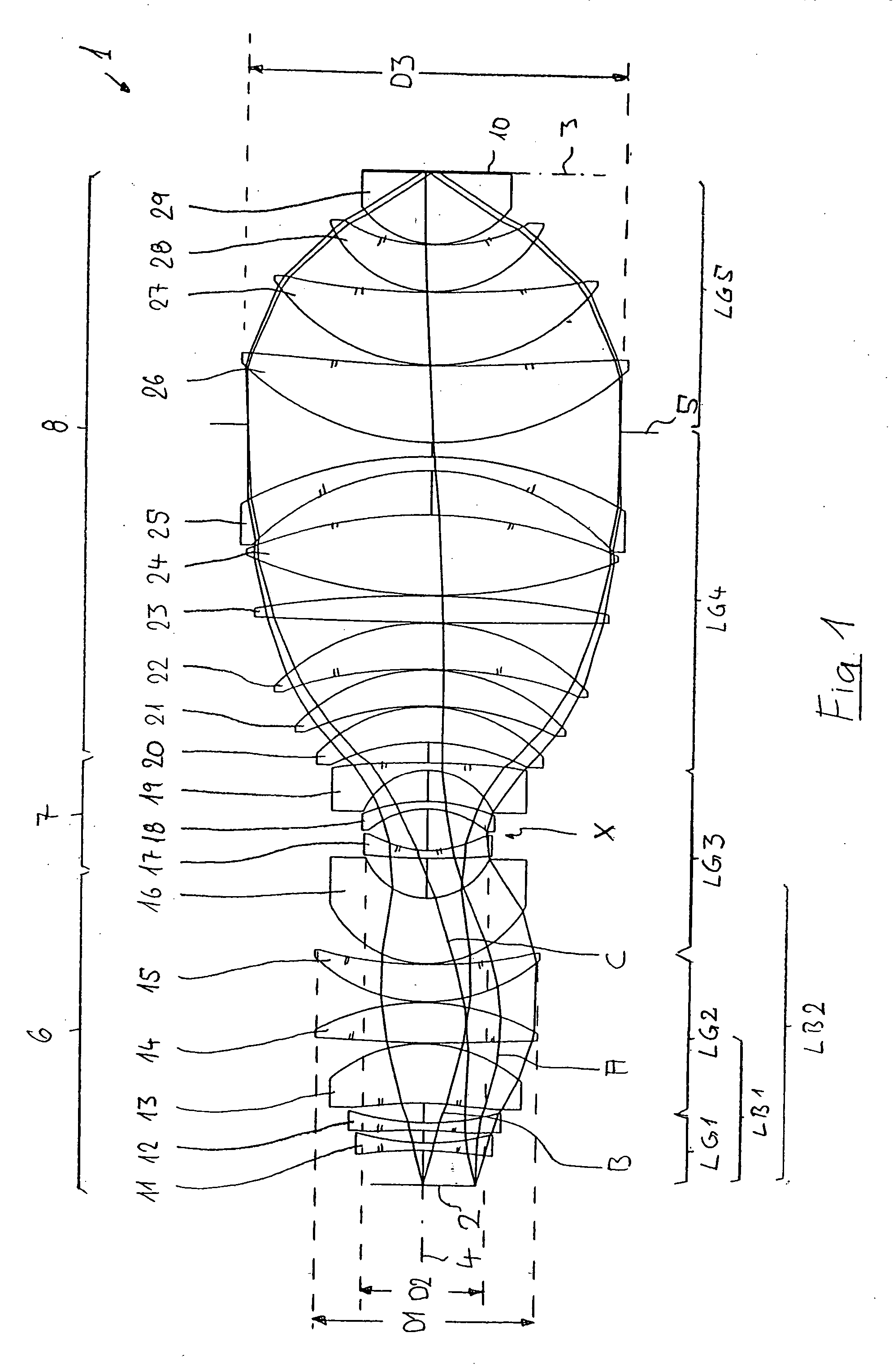

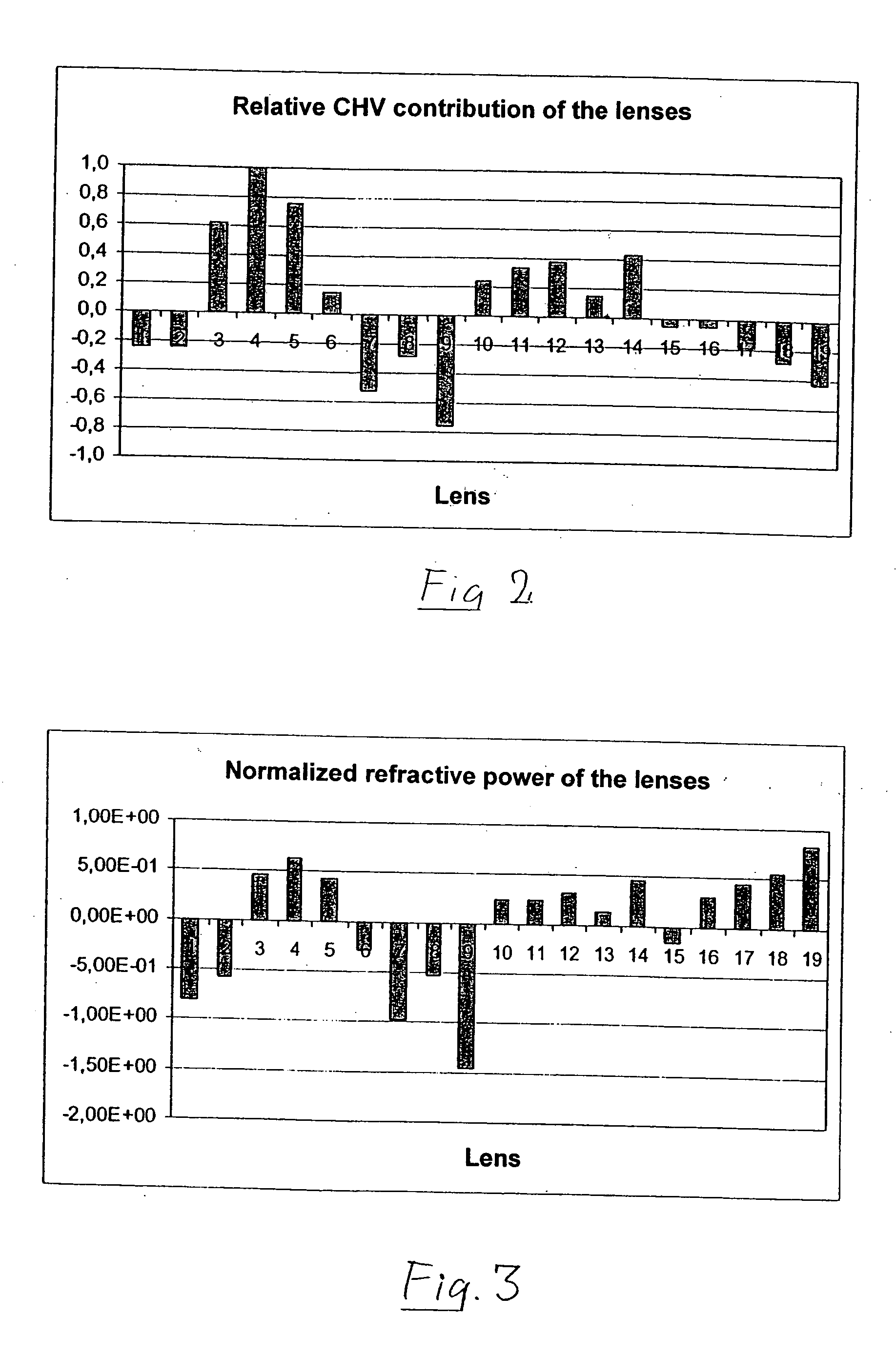

Refractive projection objective for immersion lithography

InactiveUS20050190455A1Small sizeGood correction stateMicroscopesPhotomechanical exposure apparatusHigh numerical apertureOptoelectronics

A purely refractive projection objective suitable for immersion microlithography is designed as a single-waist system with five lens groups, in the case of which a first lens group with negative refractive power, a second lens group with positive refractive power, a third lens group with negative refractive power, a fourth lens group with positive refractive power and a fifth lens group with positive refractive power are provided. A constriction site of narrowest constriction of the beam bundle lies in the region of the waist. A waist distance AT exists between the object plane and the constriction site X. The condition AT / L≦0.4 holds for a distance ratio AT / L between the waist distance AT and an object-image distance L of the projection objective. Embodiments of inventive projection objectives reach very high numerical apertures NA>1.1 in conjunction with a large image field and are distinguished by a compact overall size and good correction of the lateral chromatic aberration.

Owner:CARL ZEISS SMT GMBH

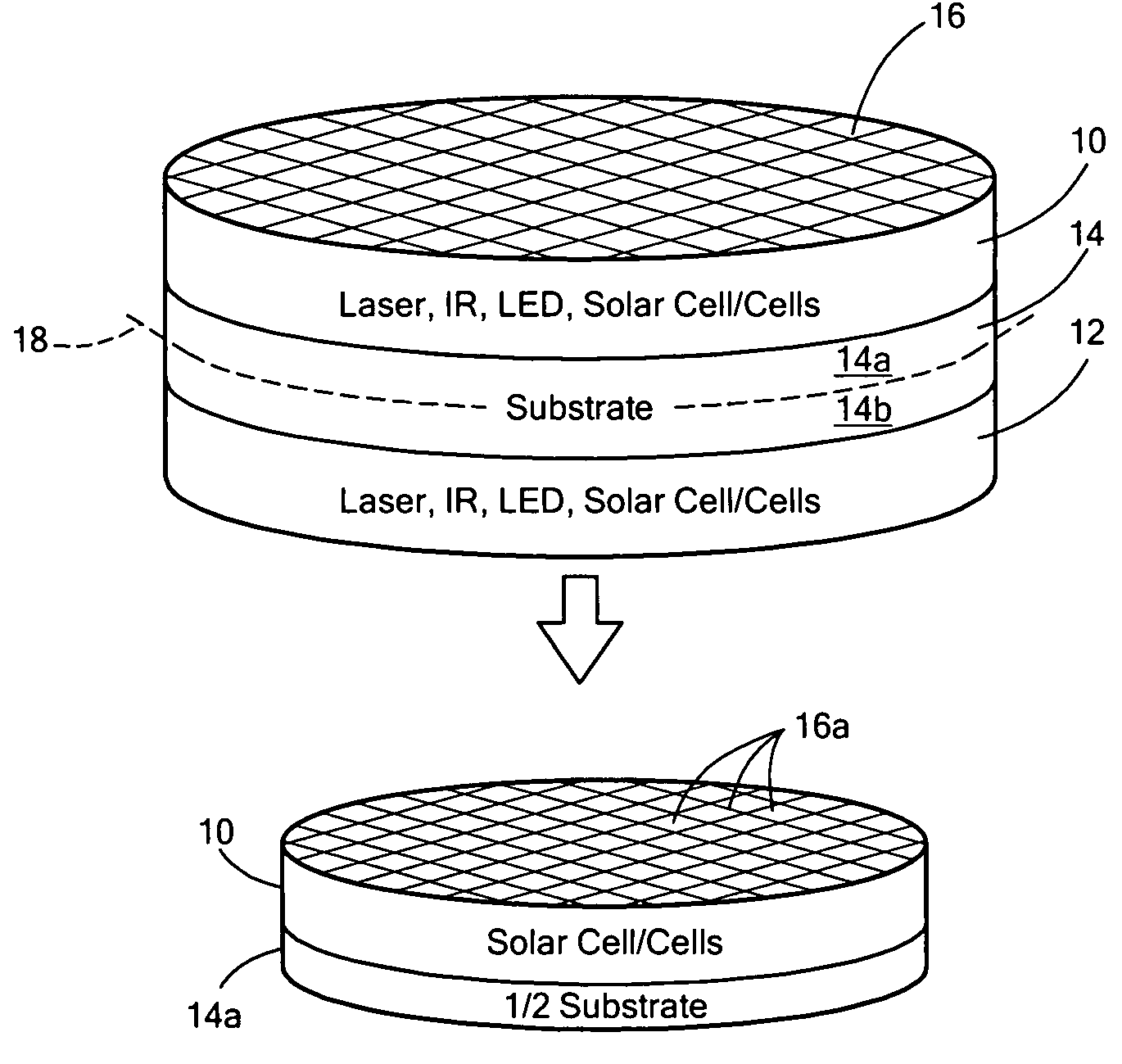

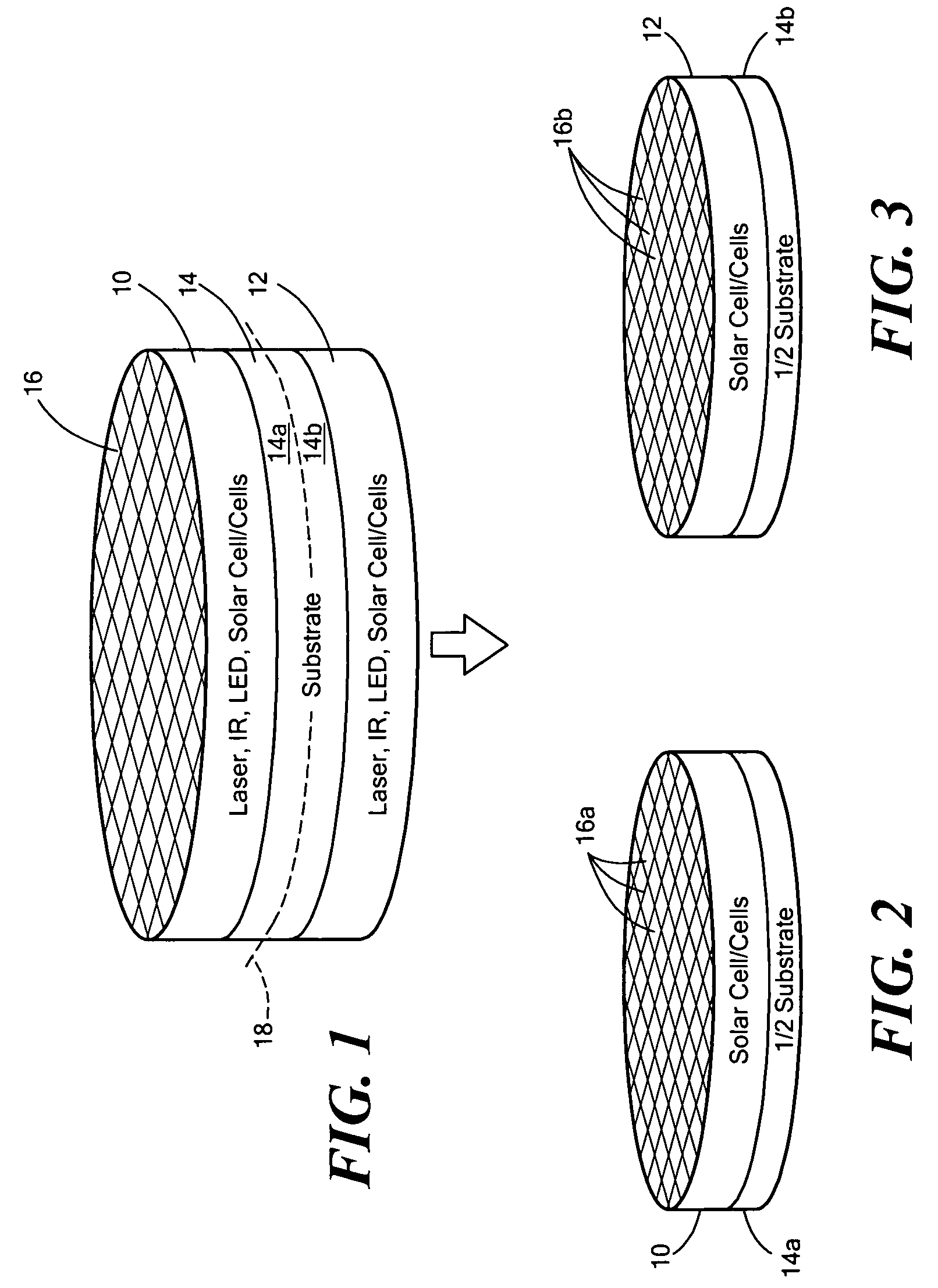

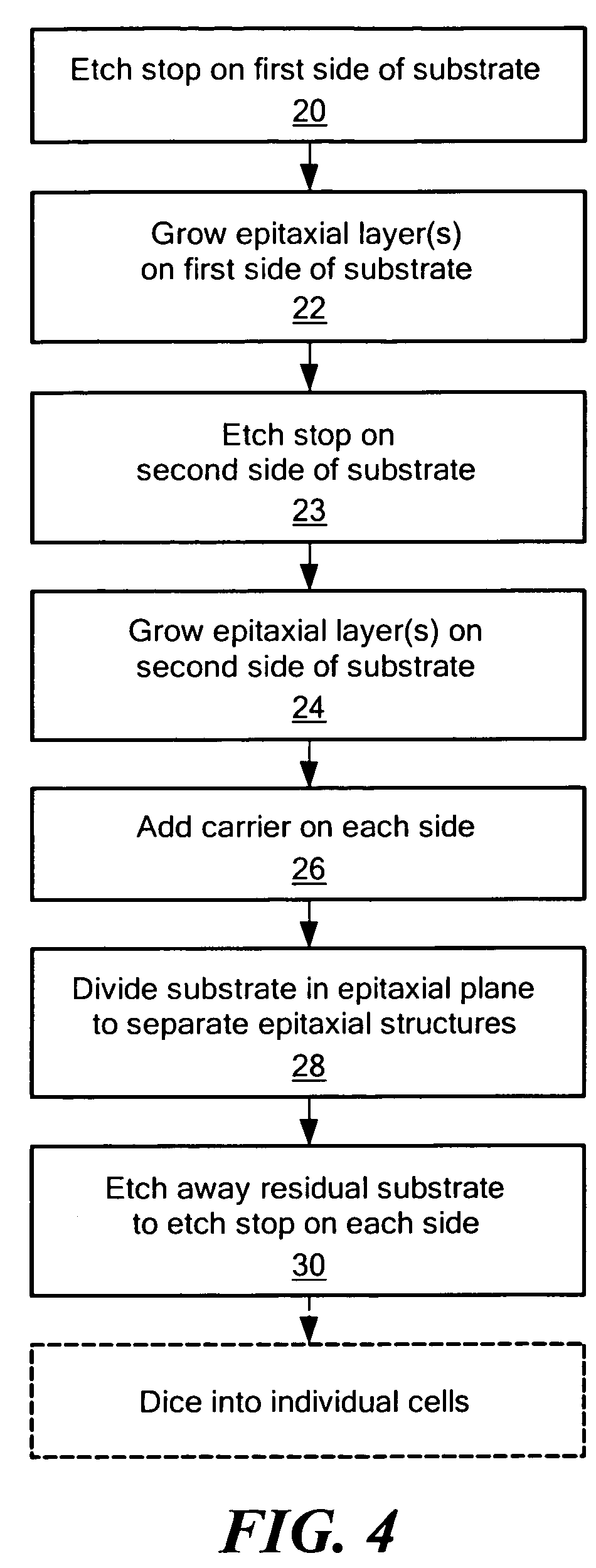

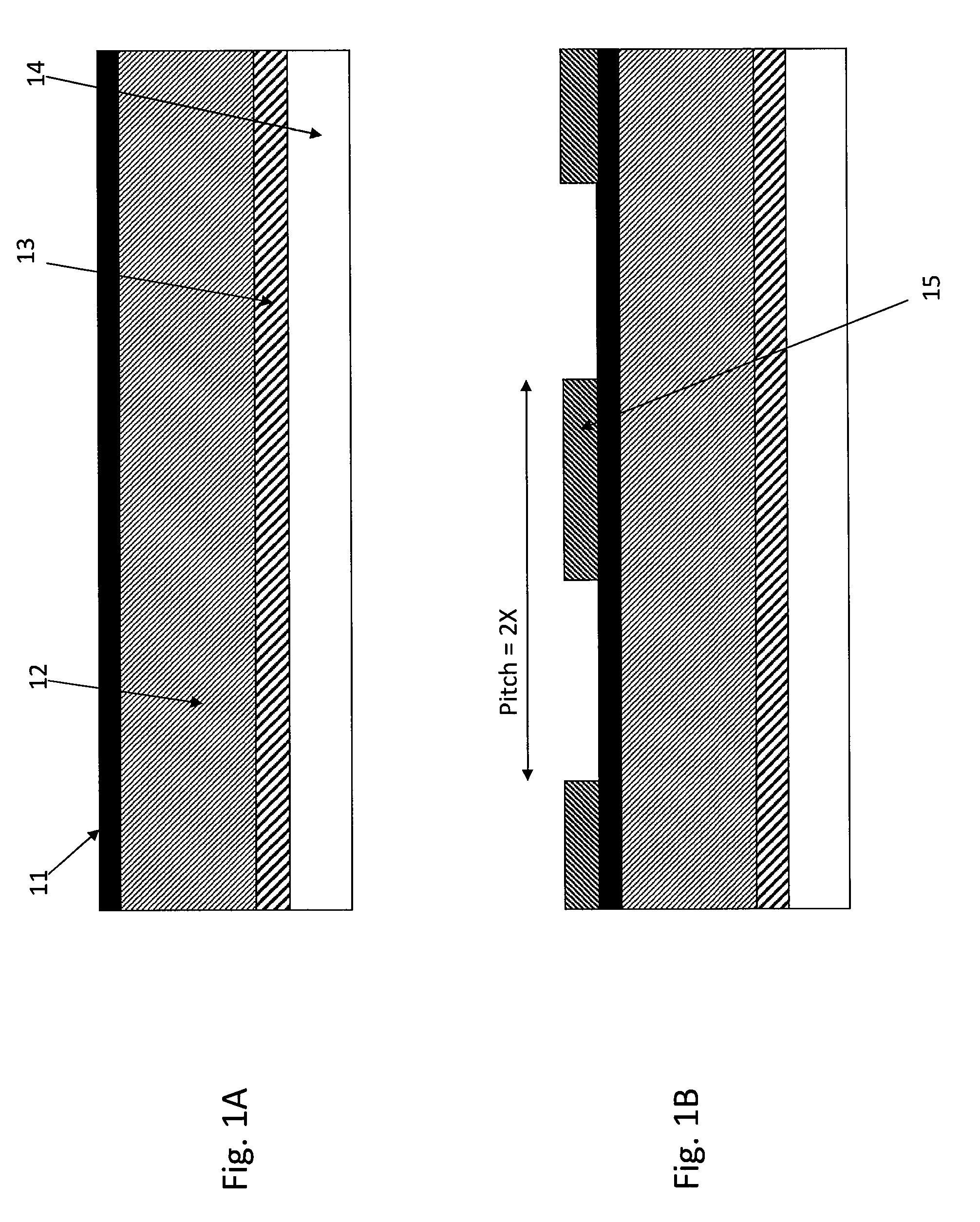

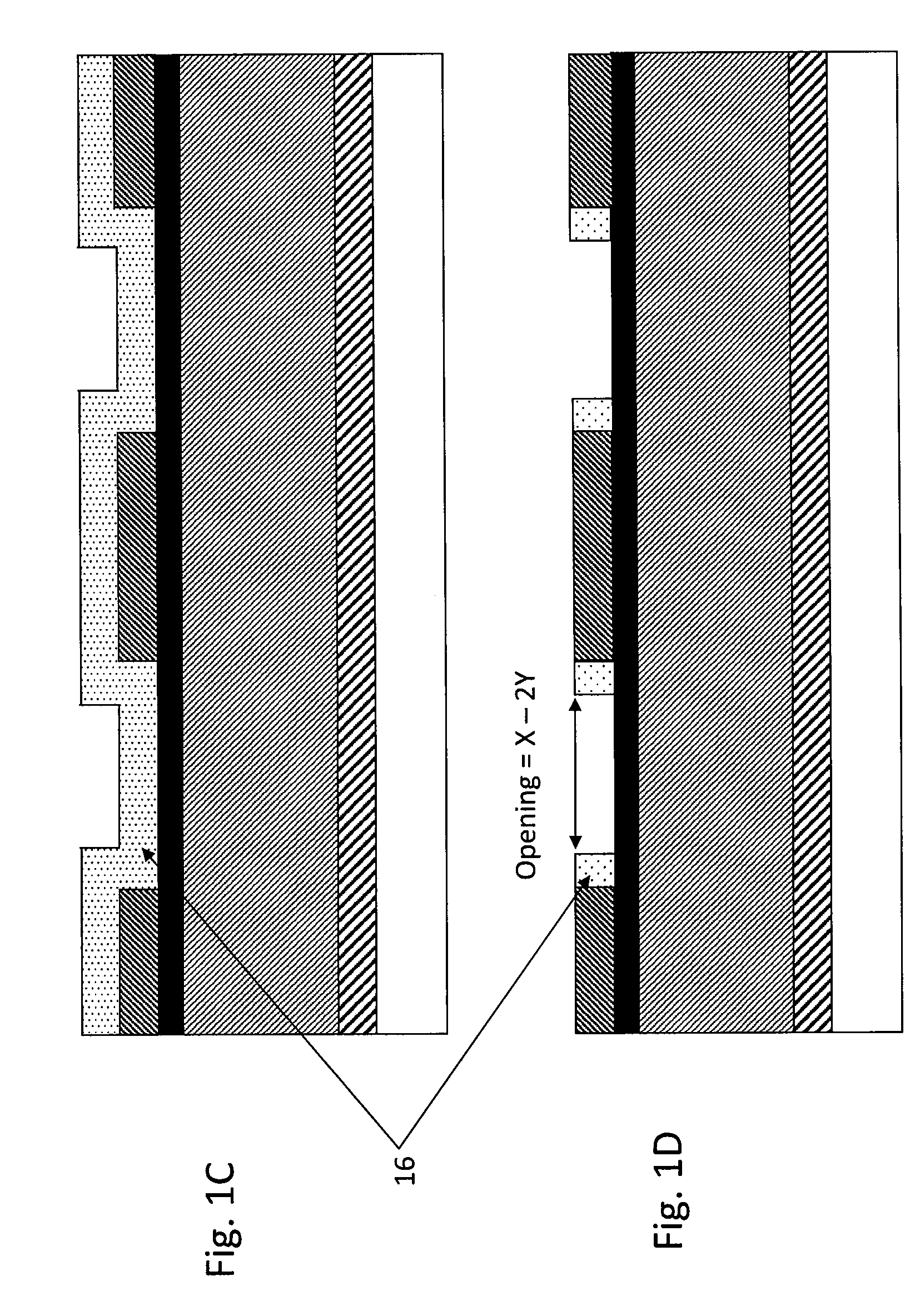

Method of fabricating epitaxial structures

ActiveUS8455290B2Reduce in quantitySimple and direct removalFinal product manufactureSemiconductor/solid-state device manufacturingOptoelectronicsPhysics

Owner:JPMORGAN CHASE BANK NA +1

Post treatment of low k dielectric films

ActiveUS7018941B2Semiconductor/solid-state device manufacturingOptoelectronicsDielectric permittivity

A method of depositing a low dielectric constant film on a substrate and post-treating the low dielectric constant film is provided. The post-treatment includes rapidly heating the low dielectric constant film to a desired high temperature and then rapidly cooling the low dielectric constant film such that the low dielectric constant film is exposed to the desired high temperature for about five seconds or less. In one aspect, the post-treatment also includes exposing the low dielectric constant film to an electron beam treatment and / or UV radiation.

Owner:APPLIED MATERIALS INC

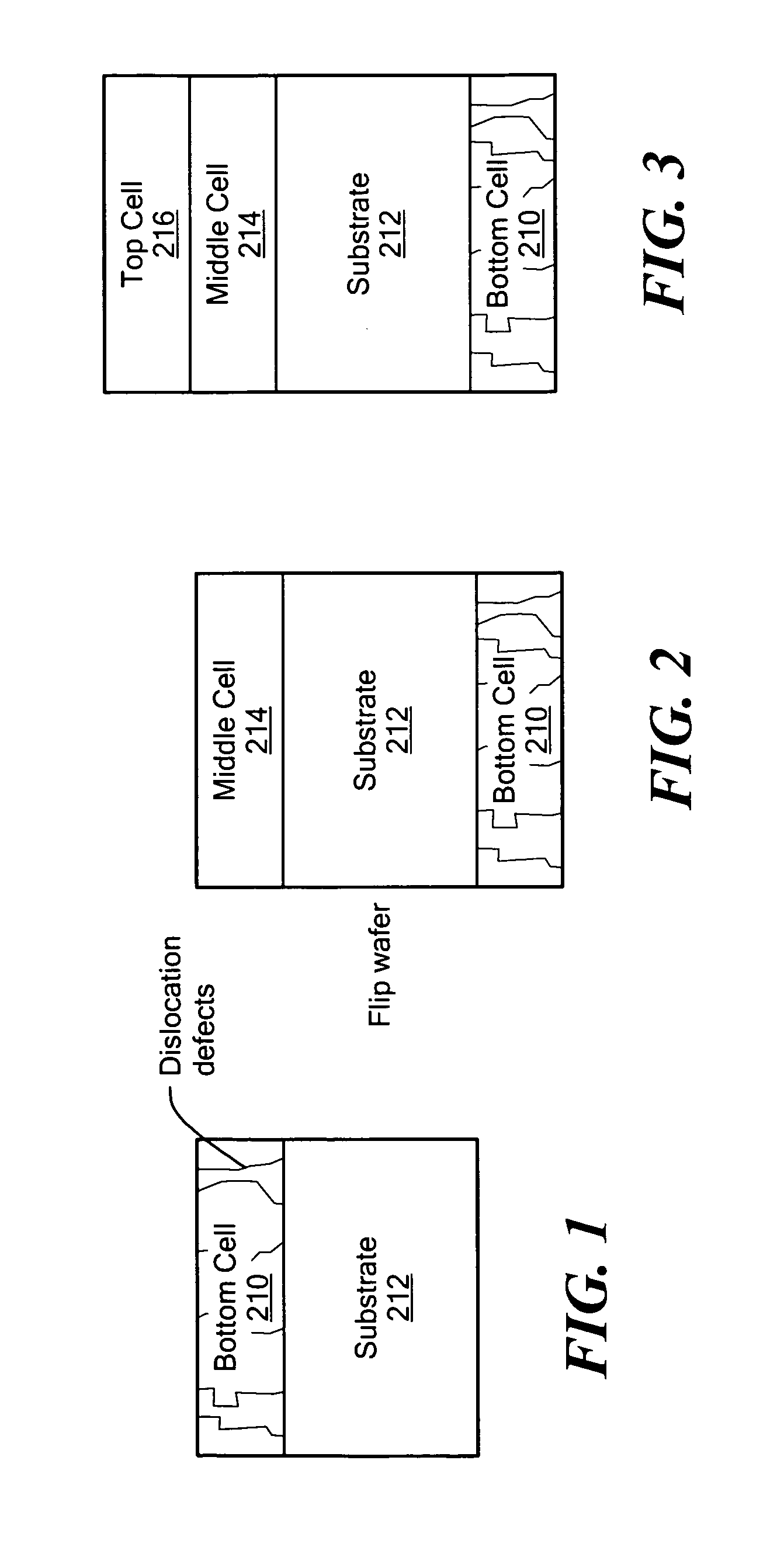

Method of fabricating bifacial tandem solar cells

ActiveUS8852994B2Easy and simpler and reliableSemiconductor/solid-state device manufacturingPhotovoltaic energy generationTandem solar cellOptoelectronics

A method of fabricating on a semiconductor substrate bifacial tandem solar cells with semiconductor subcells having a lower bandgap than the substrate bandgap on one side of the substrate and with subcells having a higher bandgap than the substrate on the other including, first, growing a lower bandgap subcell on one substrate side that uses only the same periodic table group V material in the dislocation-reducing grading layers and bottom subcells as is present in the substrate and after the initial growth is complete and then flipping the substrate and growing the higher bandgap subcells on the opposite substrate side which can be of different group V material.

Owner:MASIMO SEMICON +1

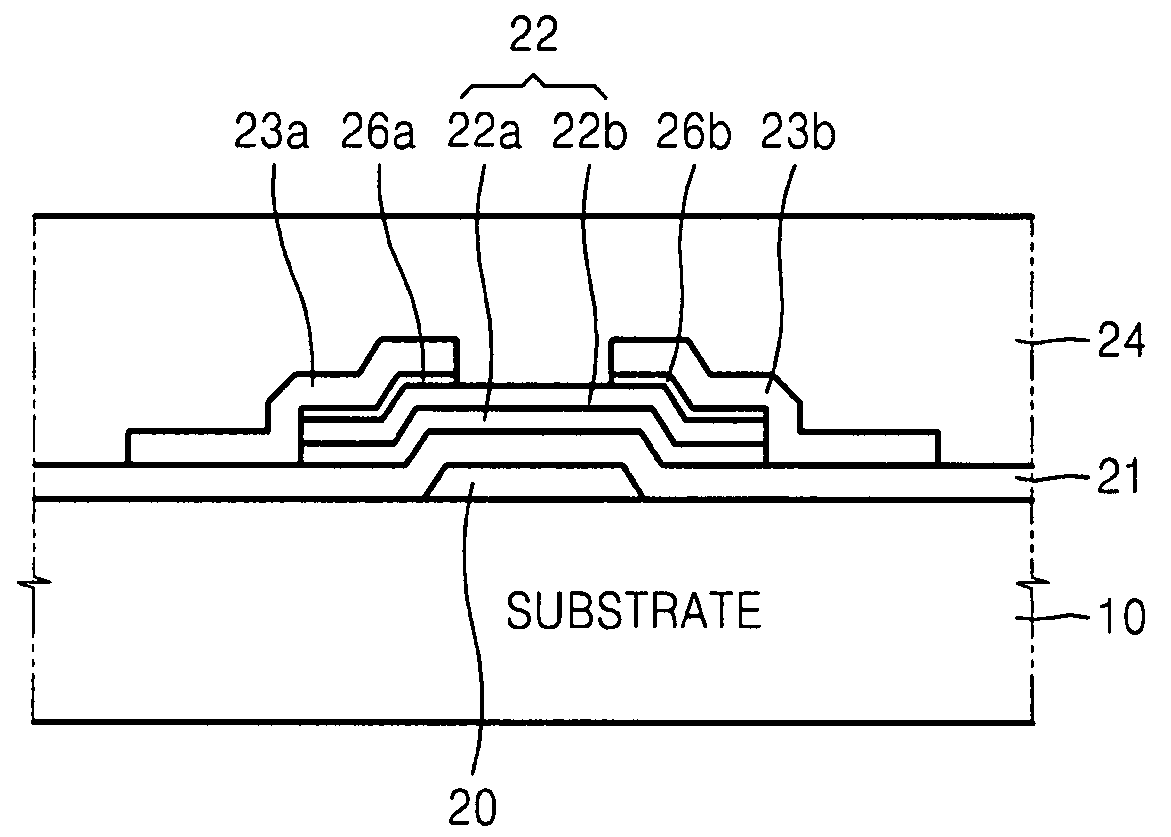

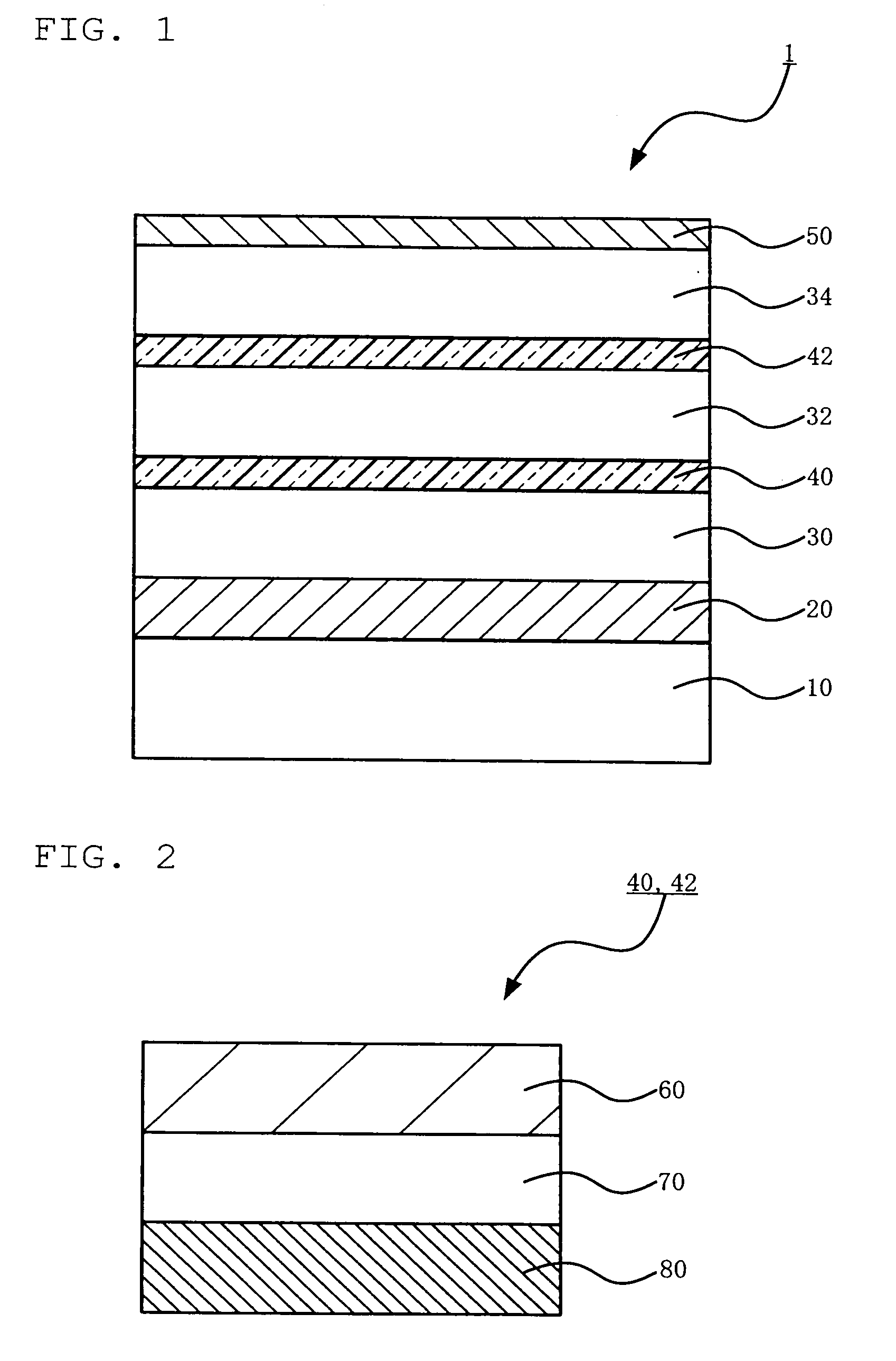

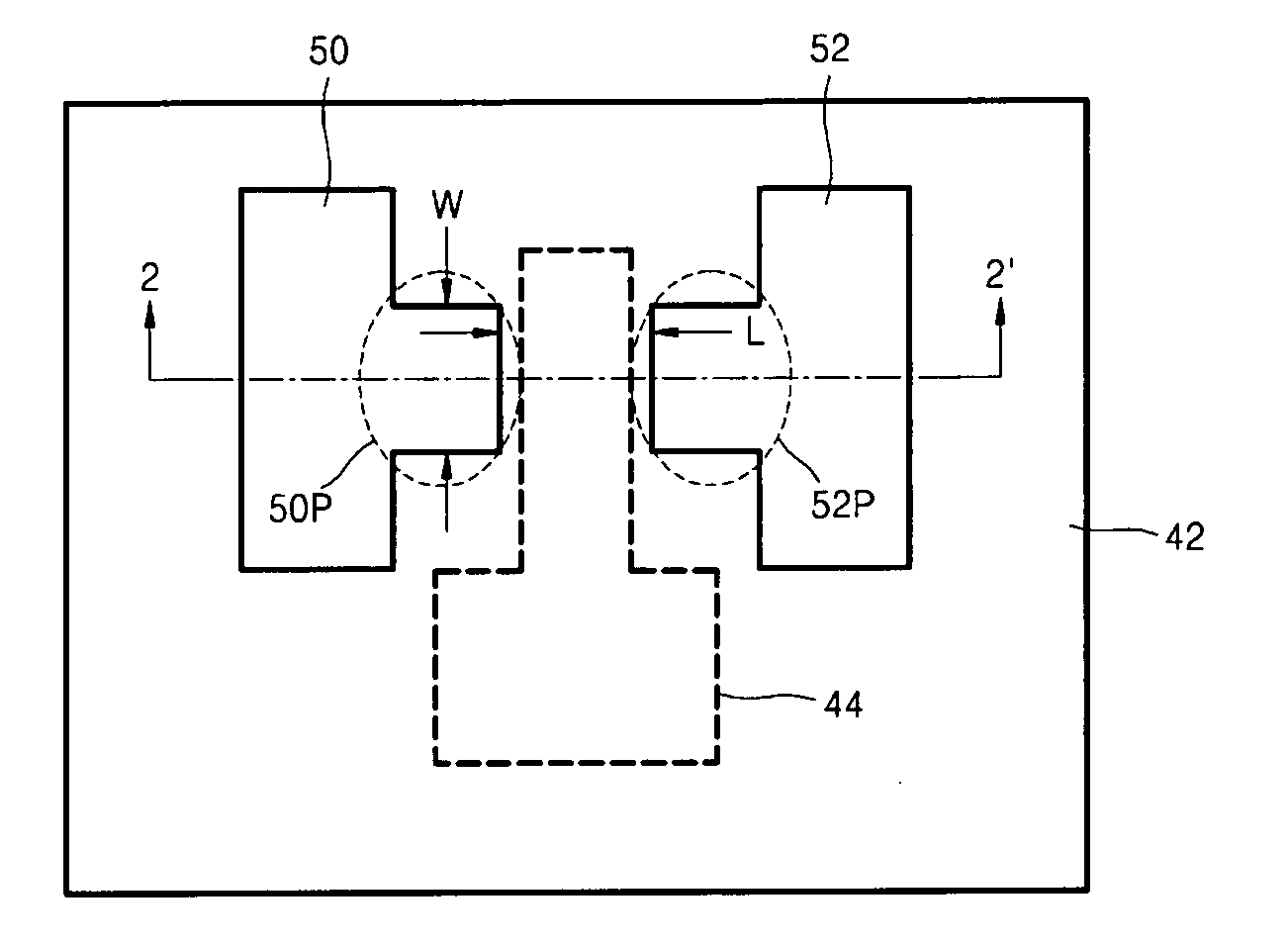

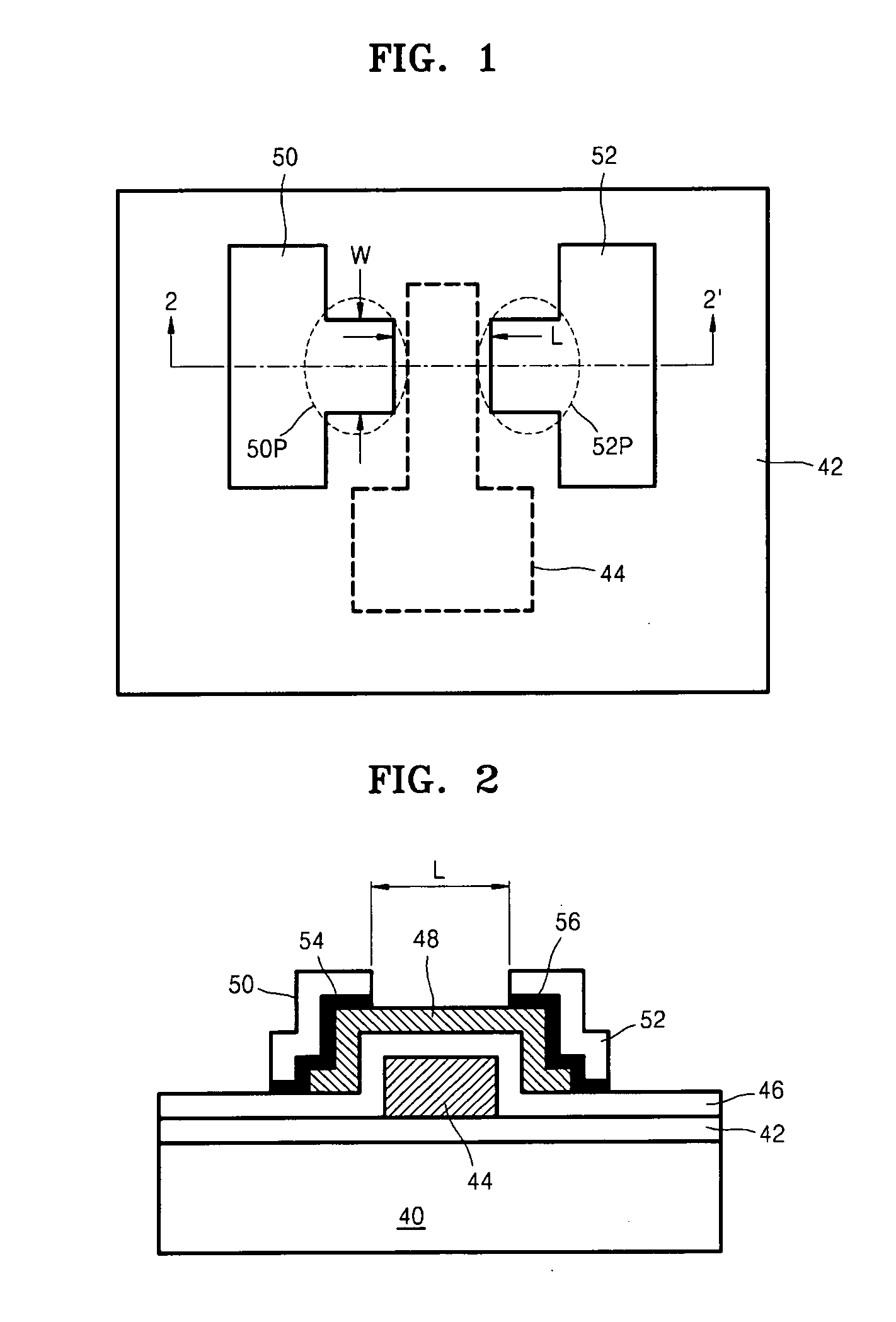

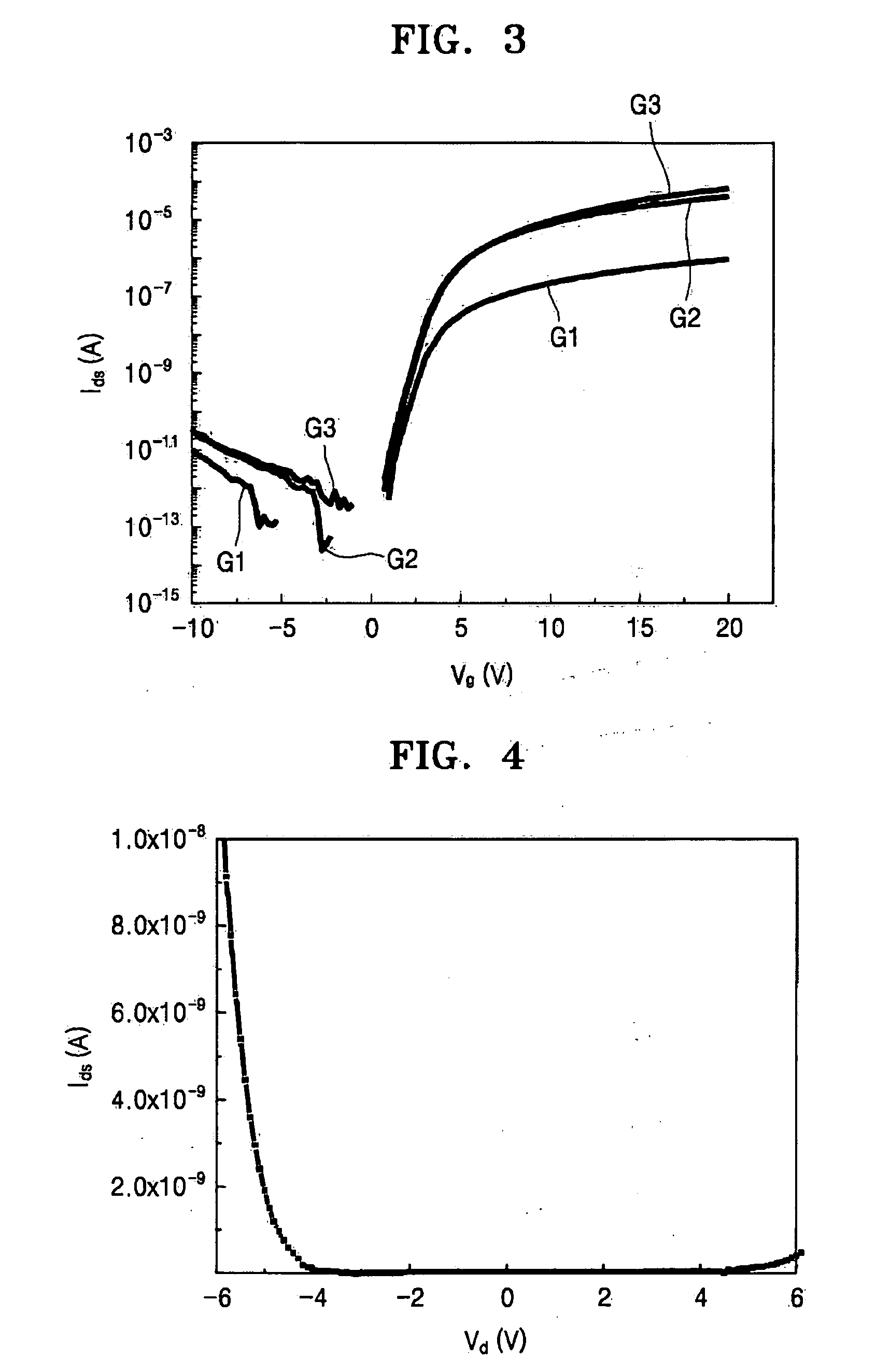

Thin film transistor and method of manufacturing the same

ActiveUS20080203387A1Improve featuresSmooth connectionTransistorSolid-state devicesOptoelectronicsMaterials science

Provided are a thin film transistor and a method of manufacturing the same. The thin film transistor may include a gate; a channel layer; a source and a drain, the source and the drain being formed of metal; and a metal oxide layer, the metal oxide layer being formed between the channel layer and the source and the drain. The metal oxide layer may have a gradually changing metal content between the channel layer and the source and the drain.

Owner:SAMSUNG ELECTRONICS CO LTD

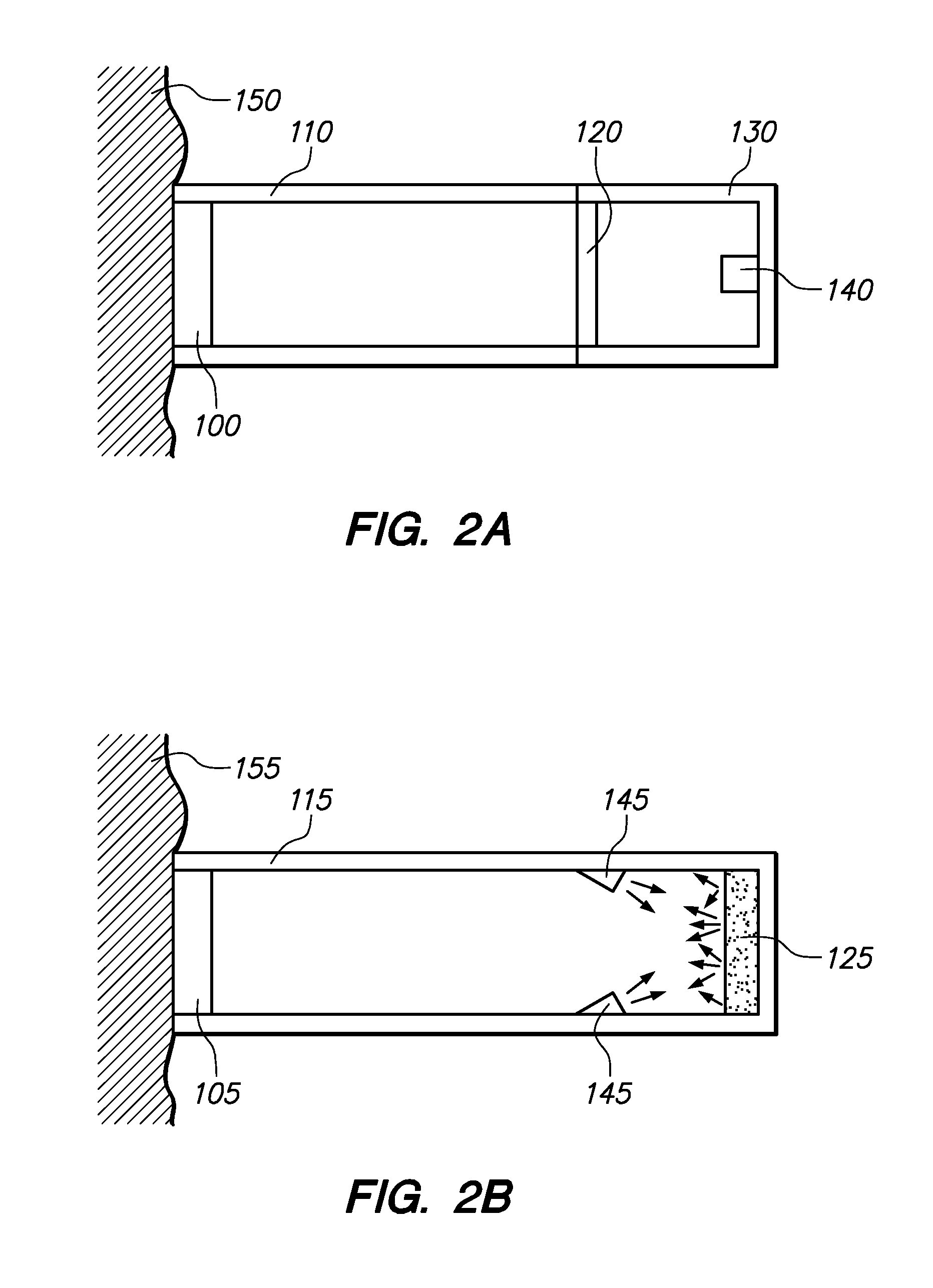

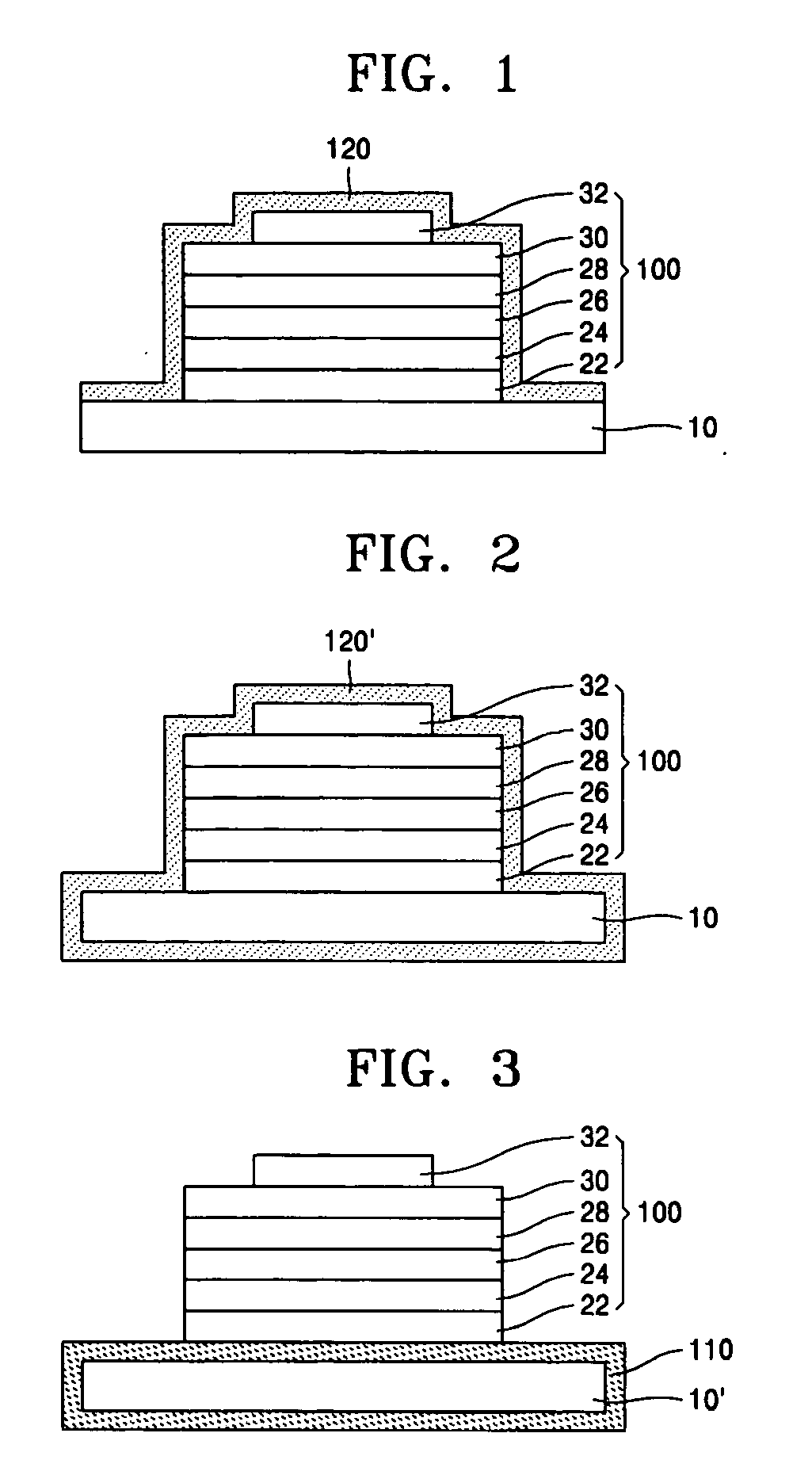

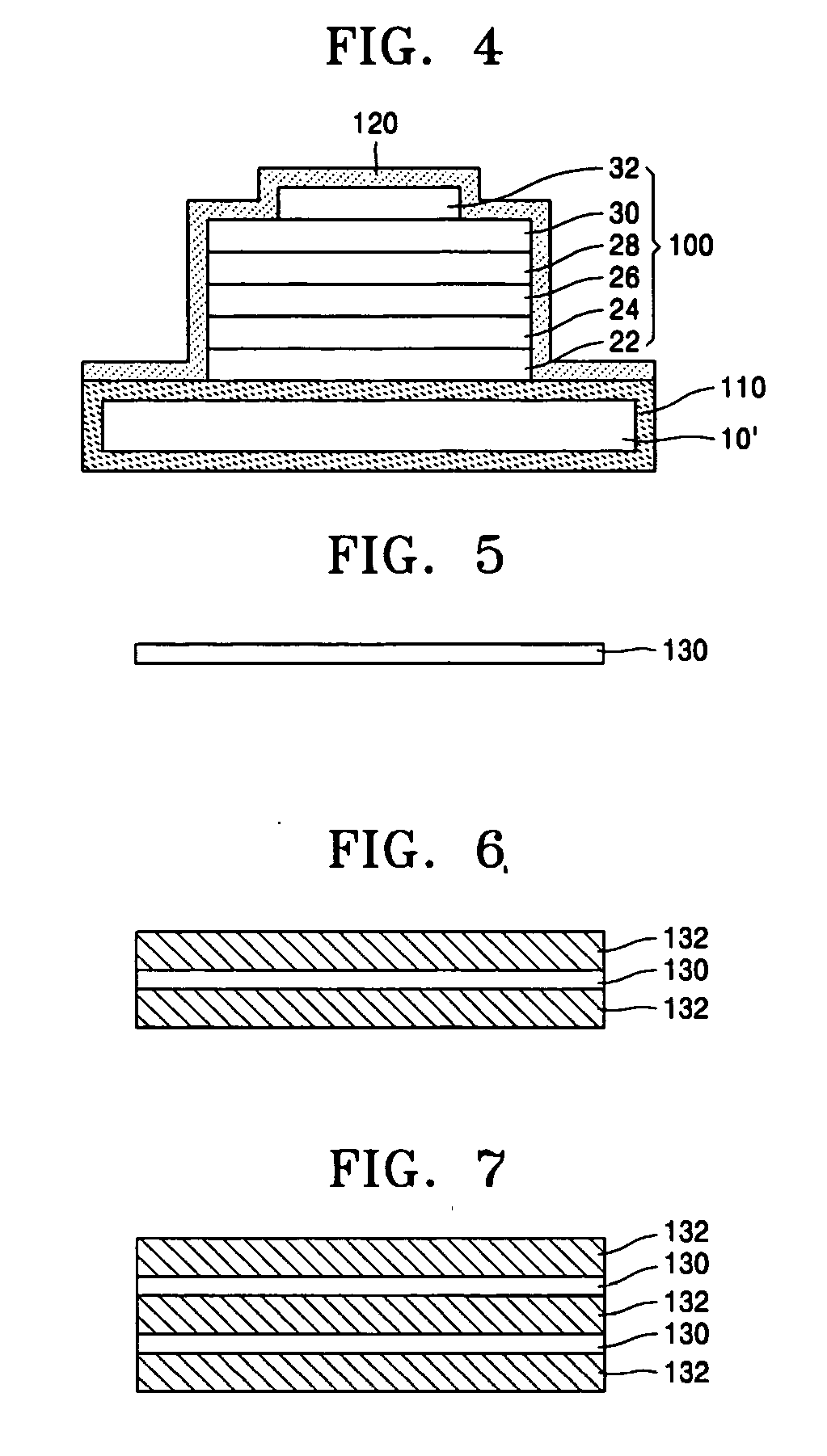

Method of fabricating passivation layer for organic devices

InactiveUS20050181535A1Reduce heatEasily deterioratedSolid-state devicesSemiconductor/solid-state device manufacturingOrganic devicesOptoelectronics

Provided is a method of fabricating a passivation layer for an organic device, including: forming the organic device on a substrate; and forming a passivation layer on the organic device. Here, forming the passivation layer on the organic device includes forming an inorganic thin film by thin film deposition using pulsed plasma.

Owner:ELECTRONICS & TELECOMM RES INST

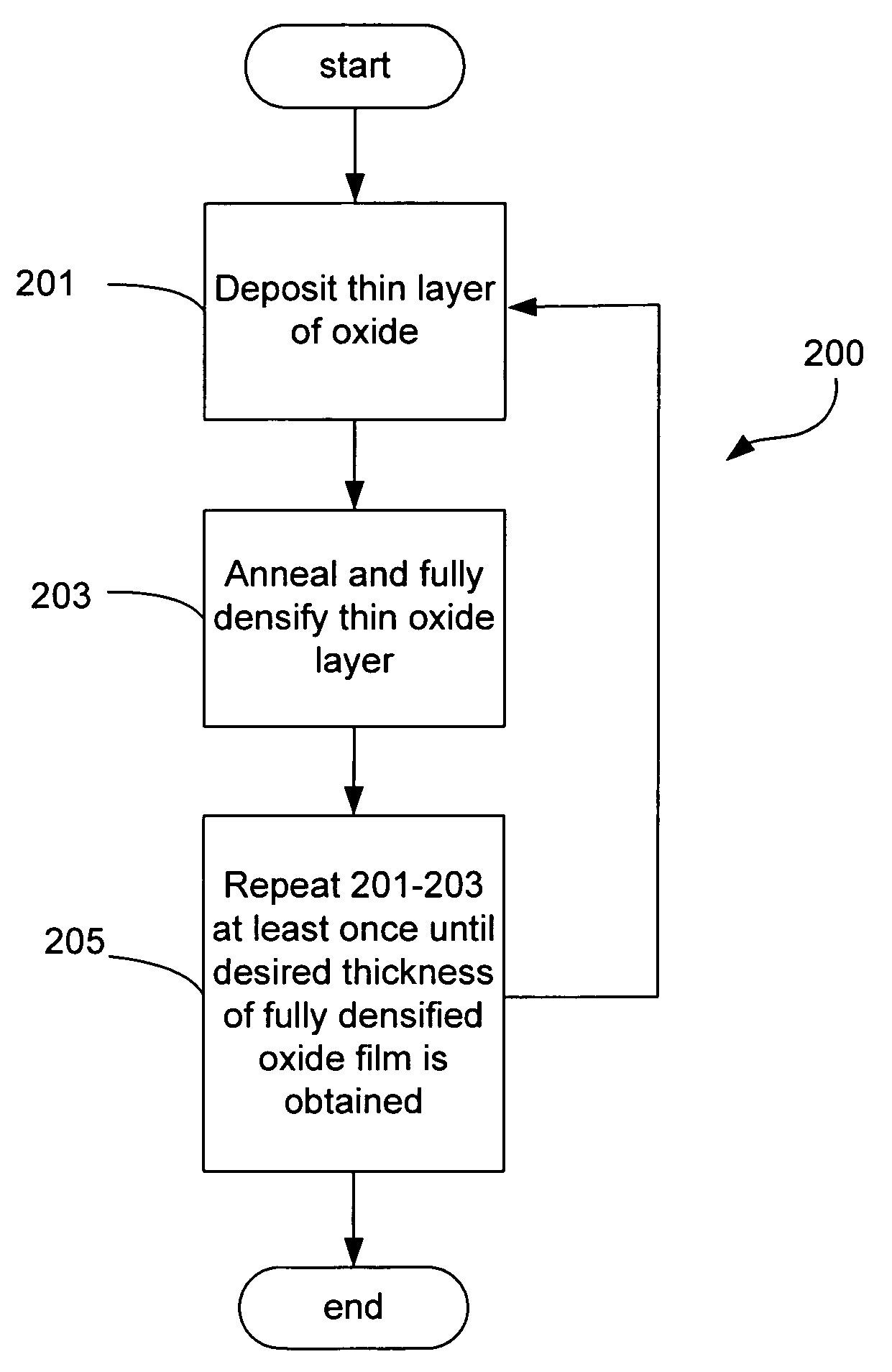

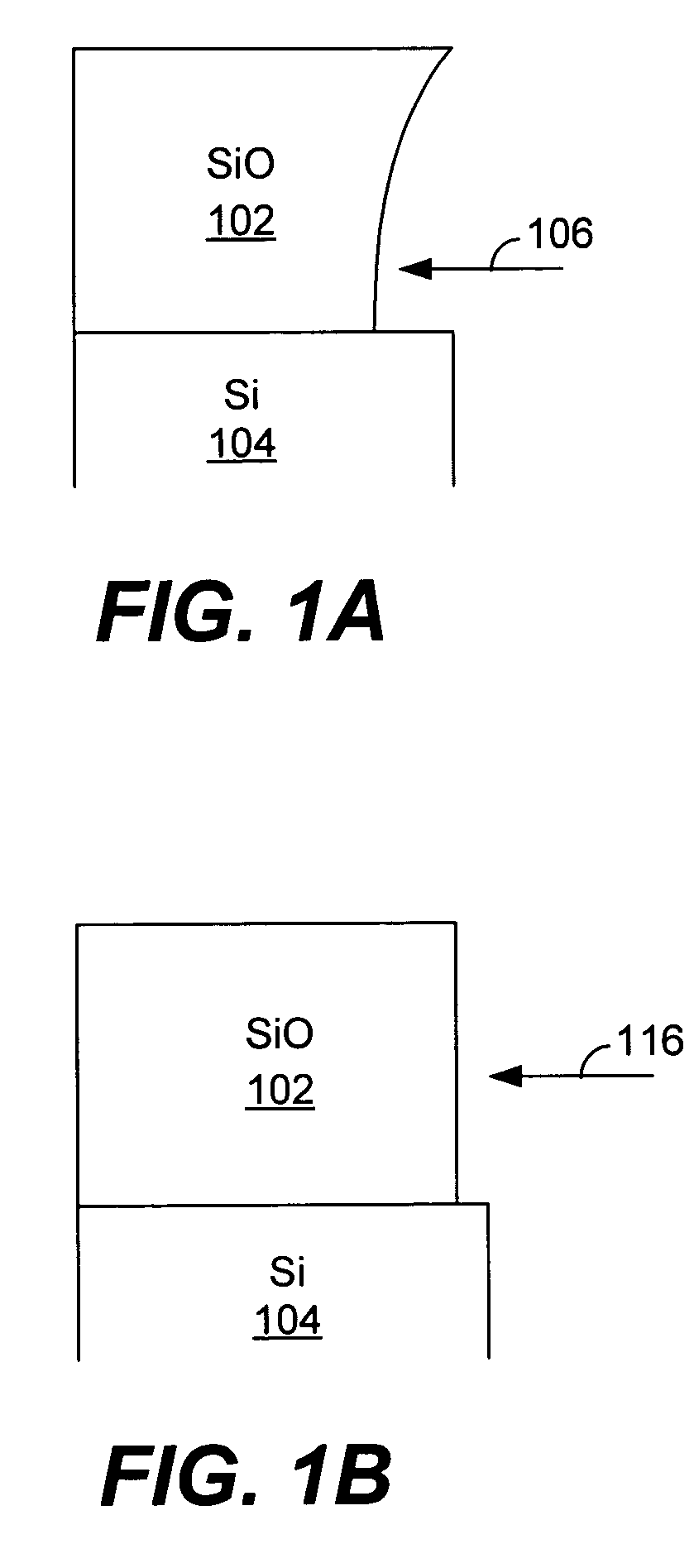

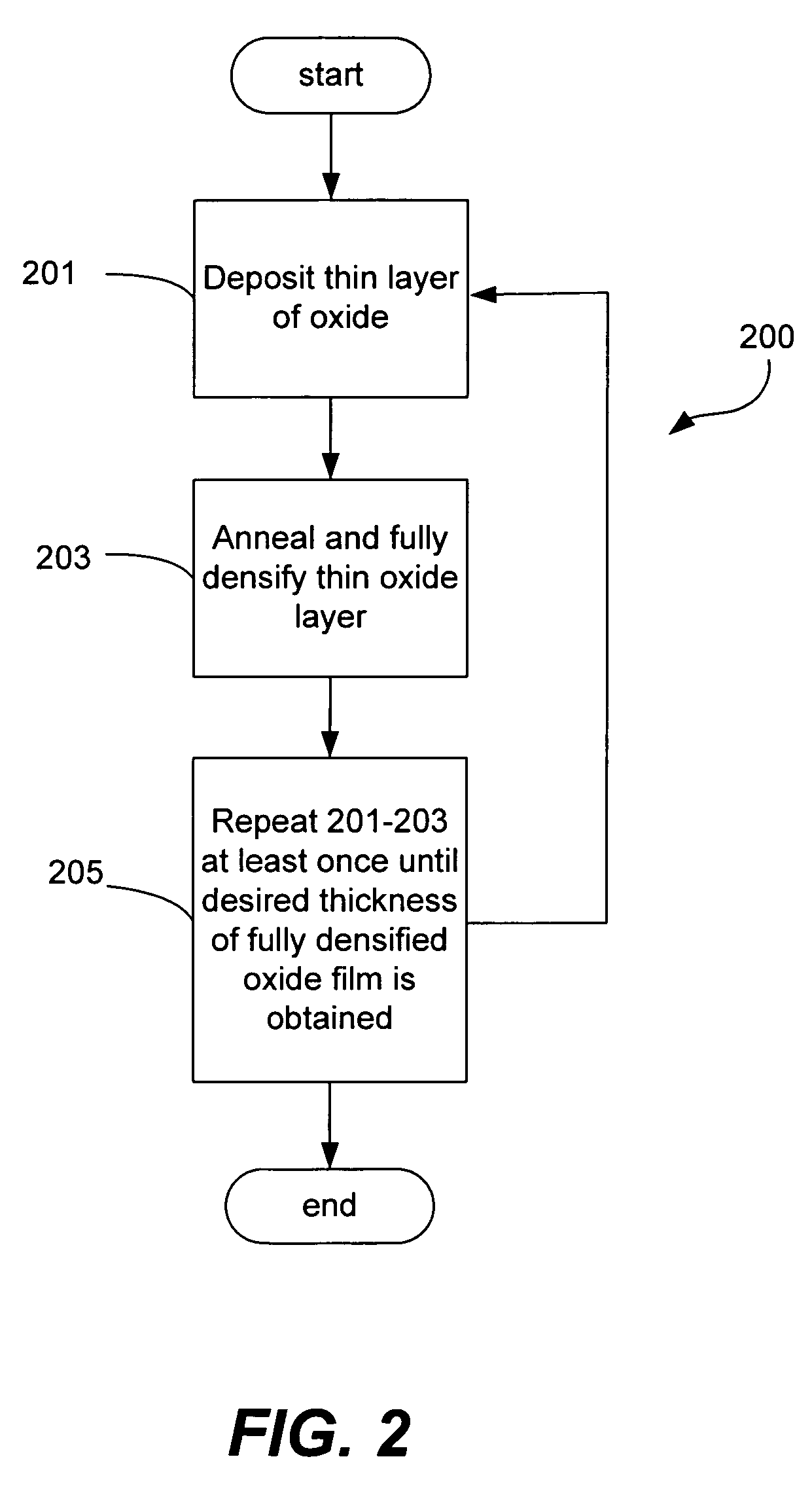

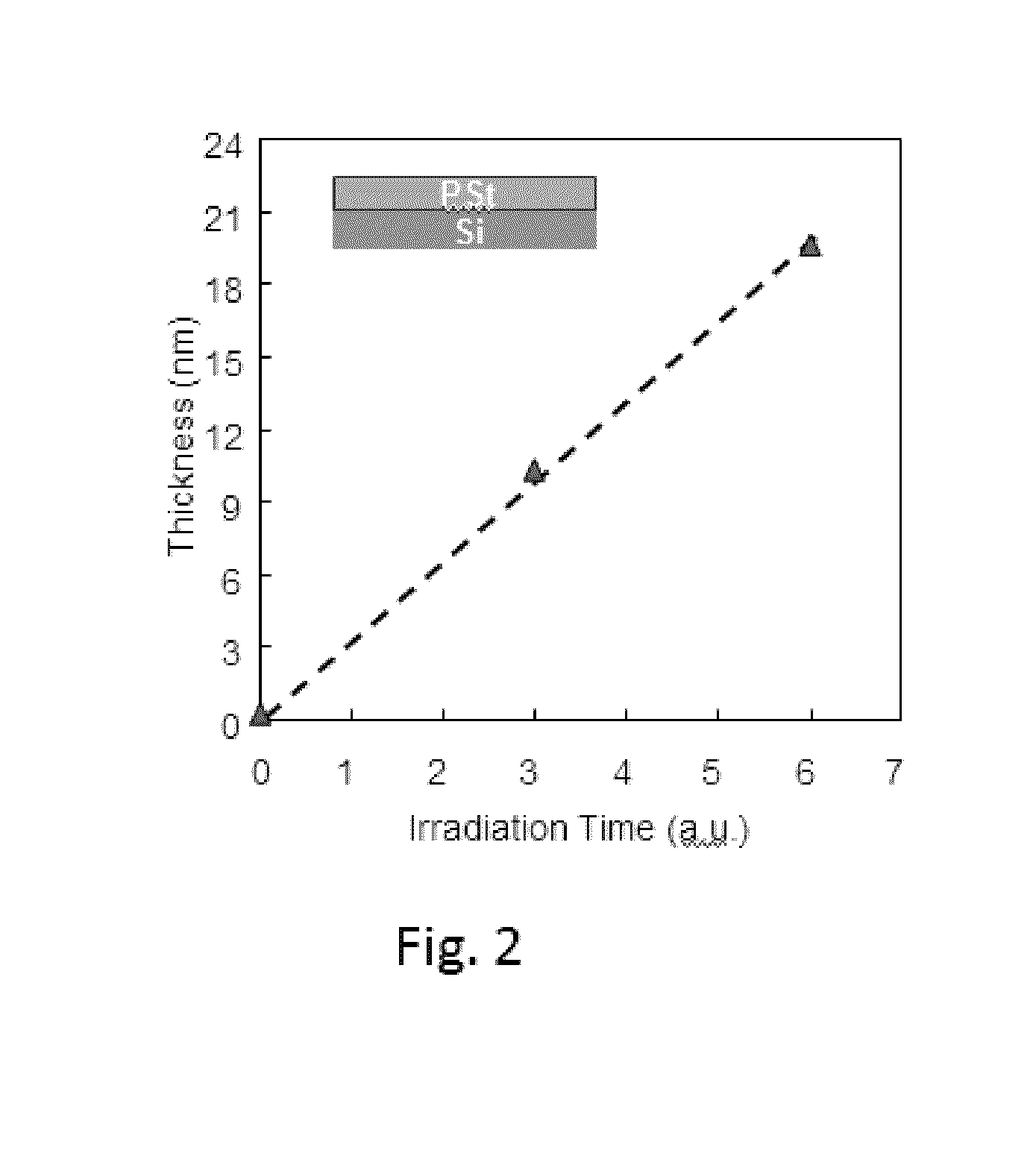

Sequential deposition/anneal film densification method

ActiveUS7790633B1Maintaining film propertyMaintain propertiesSemiconductor/solid-state device manufacturingProcedure AgentsOptoelectronics

A silicon dioxide-based dielectric layer is formed on a substrate surface by a sequential deposition / anneal technique. The deposited layer thickness is insufficient to prevent substantially complete penetration of annealing process agents into the layer and migration of water out of the layer. The dielectric layer is then annealed, ideally at a moderate temperature, to remove water and thereby fully densify the film. The deposition and anneal processes are then repeated until a desired dielectric film thickness is achieved.

Owner:NOVELLUS SYSTEMS

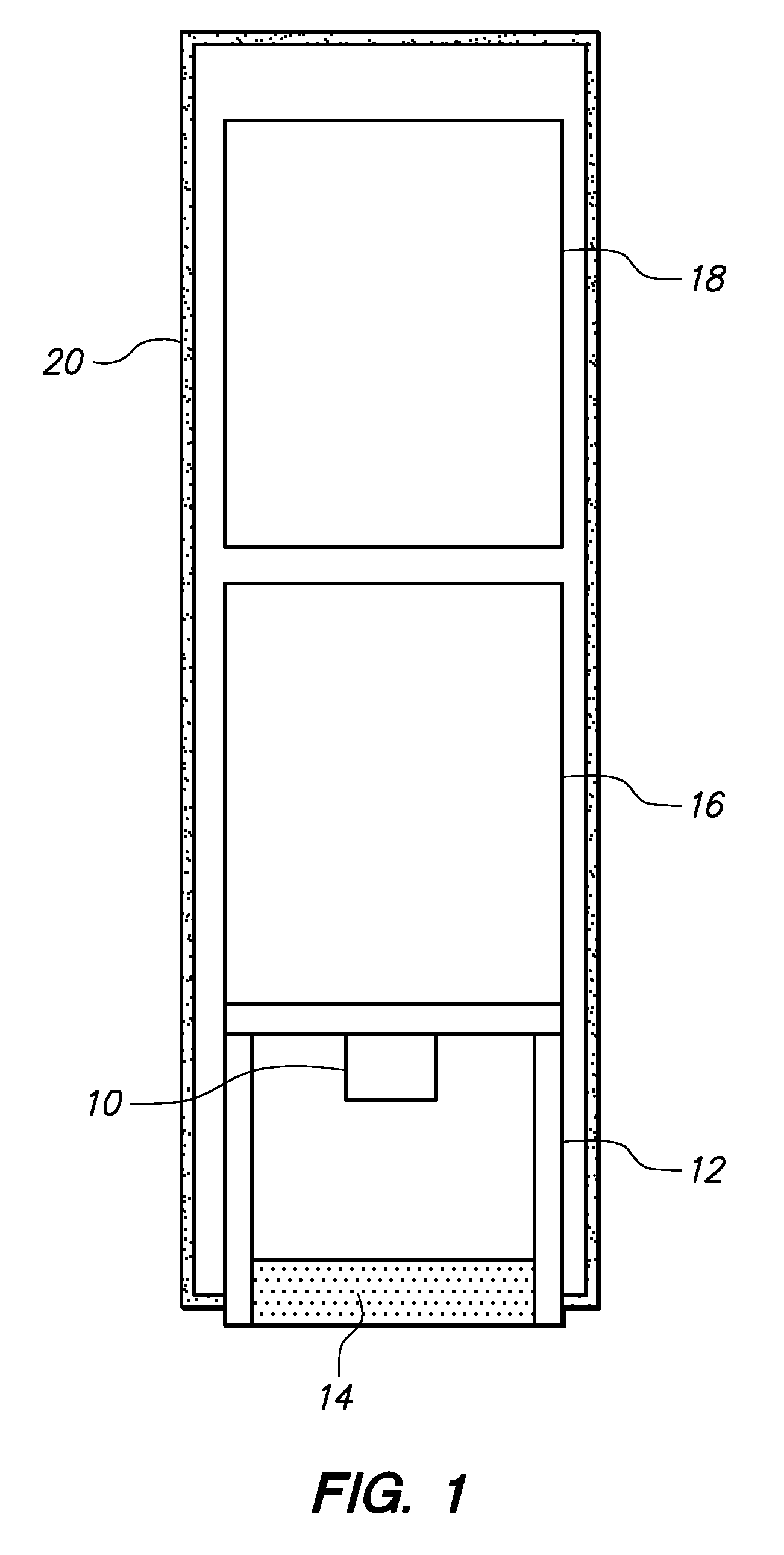

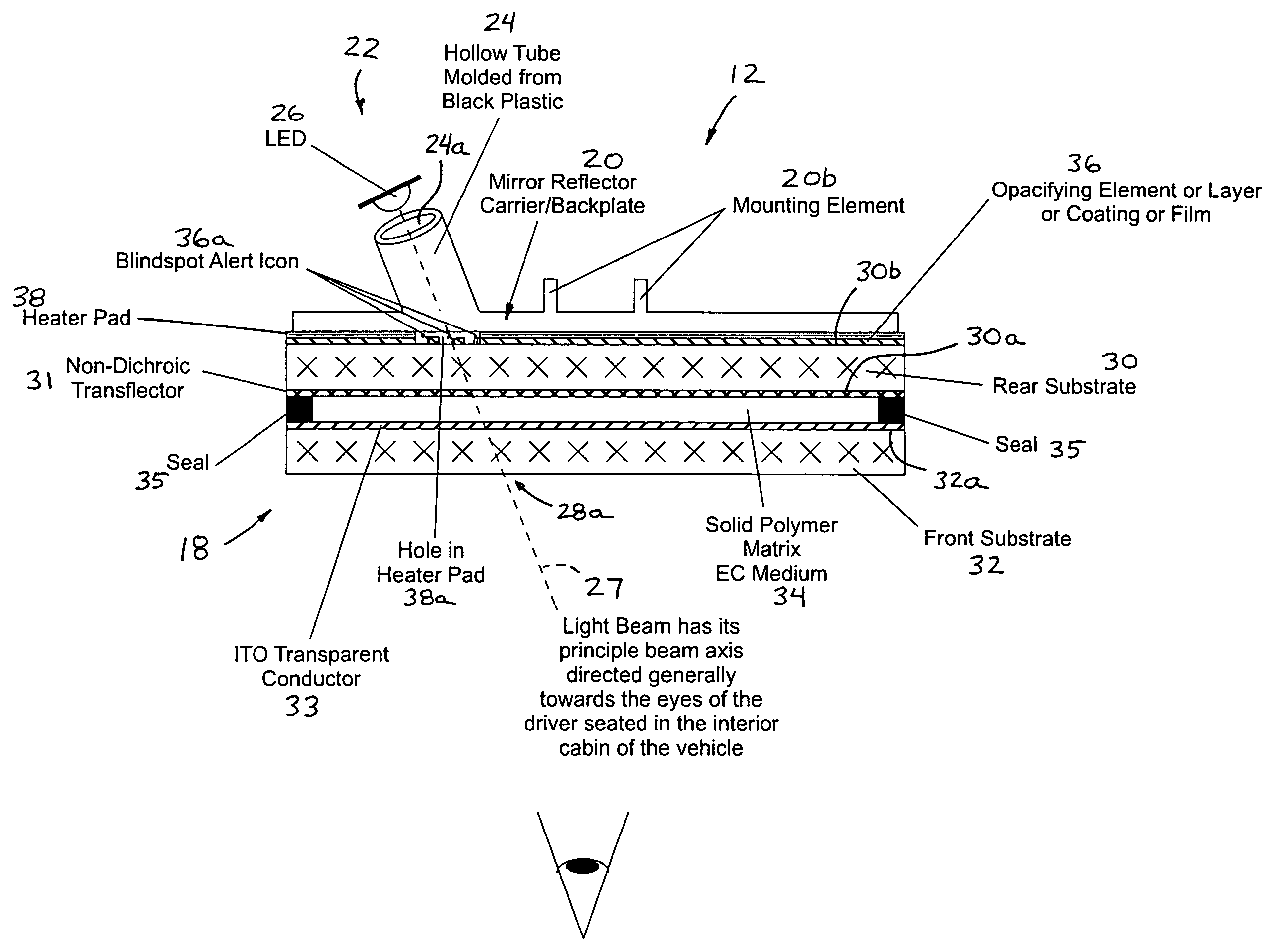

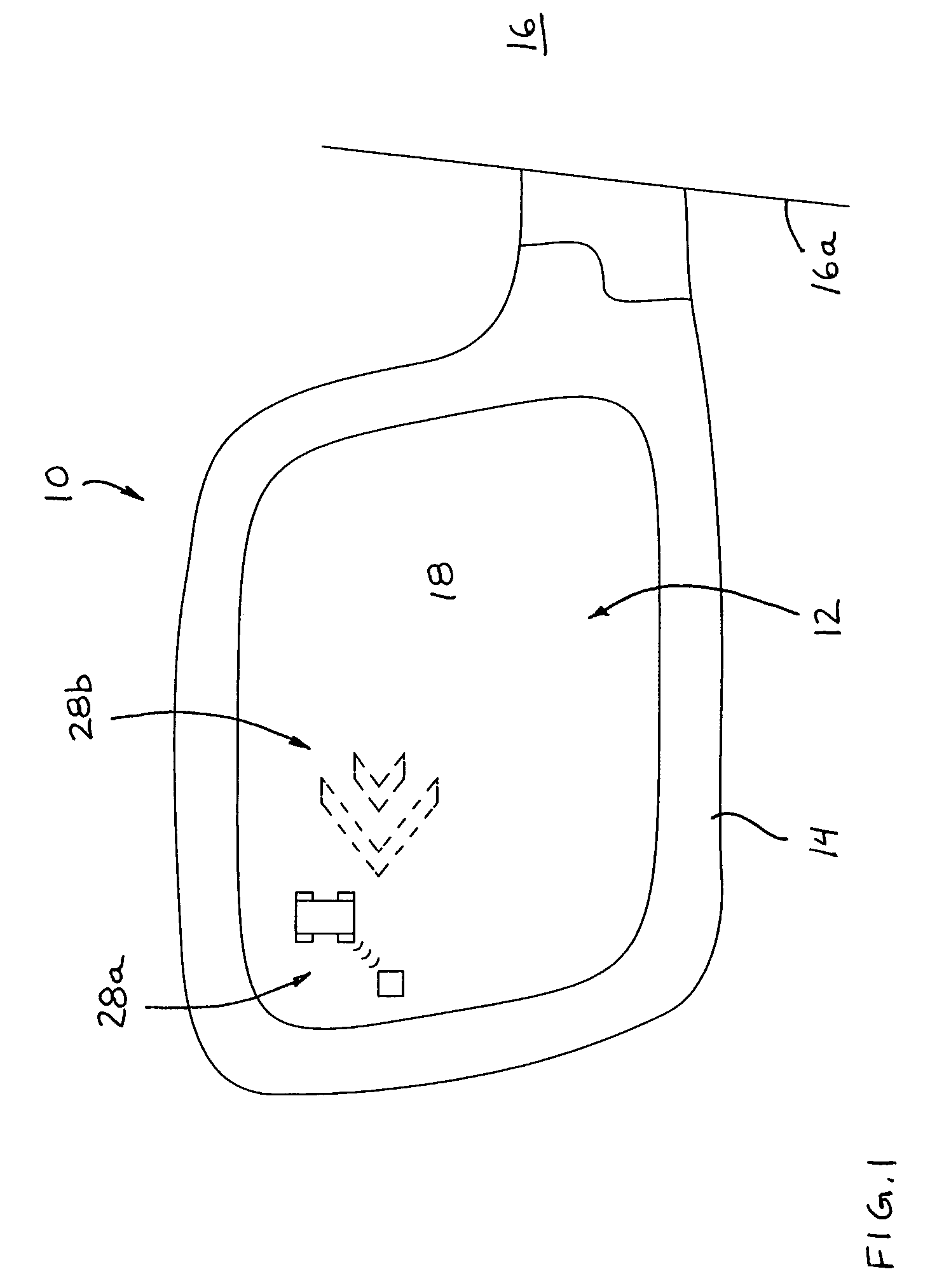

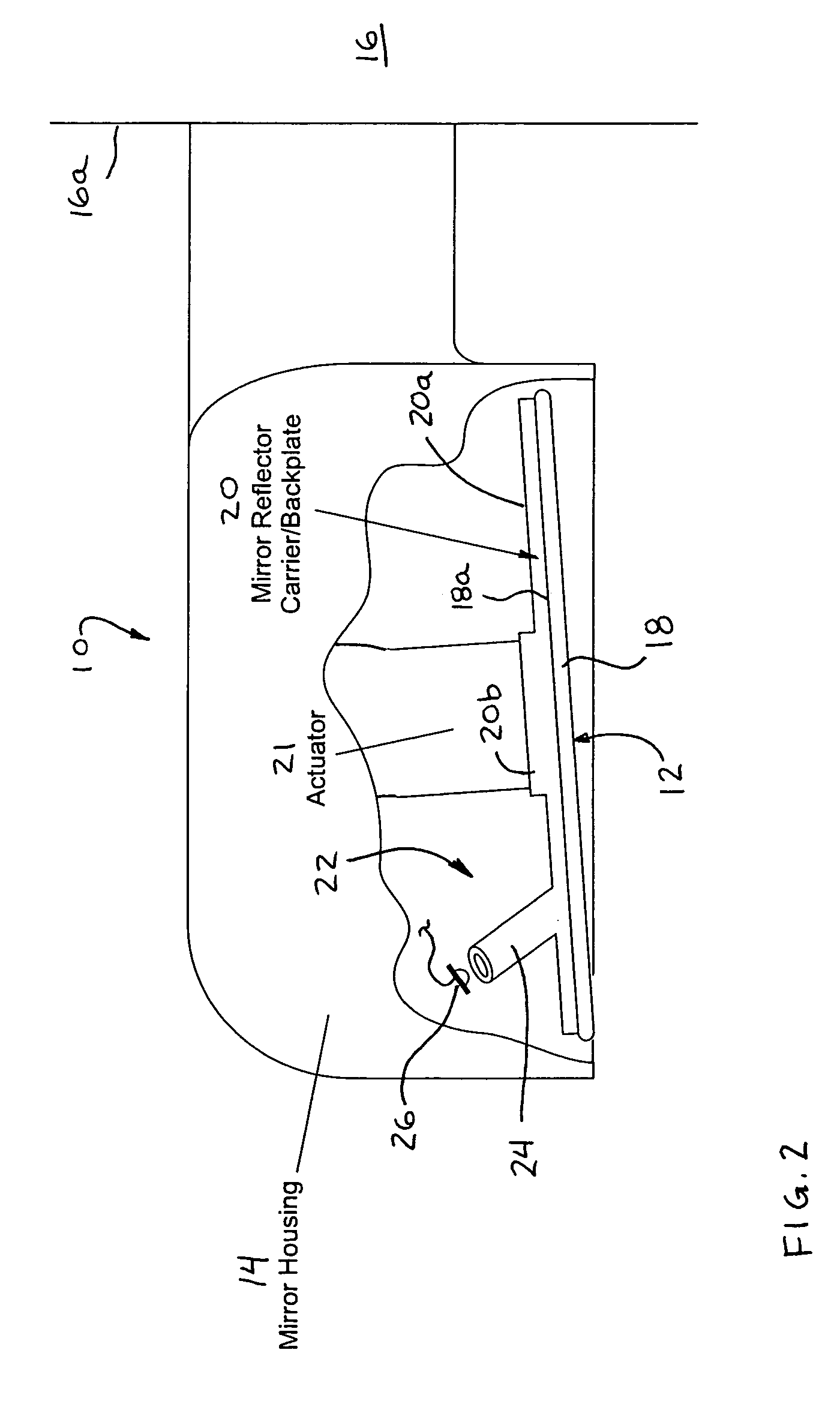

Display device for exterior rearview mirror

InactiveUS7581859B2Good adhesionEasy to assembleOptical signallingOptical viewingDisplay deviceOptoelectronics

An exterior mirror sub-assembly includes a reflective element, a back plate, and a display element having a light source that is activatable to emit light. The display element attaches to a display receiving portion of the back plate and the light source is activatable to emit light through the display receiving portion. The display receiving portion may be configured to orient the display element at a predetermined angle so that light exiting the display element when the light source is activated may be directed (a) generally away from the vehicle when the mirror assembly is mounted to the vehicle so as to be principally viewed by drivers of other vehicles or (b) generally toward the driver of the vehicle when the mirror assembly is mounted to the vehicle so as to be principally viewed by the driver of the host vehicle.

Owner:MAGNA MIRRORS OF AMERICA INC

Method for Sealing Pores at Surface of Dielectric Layer by UV Light-Assisted CVD

InactiveUS20110159202A1Improve controllabilityReduce throughputPretreated surfacesSemiconductor/solid-state device manufacturingOptoelectronicsIrradiation

A method for sealing pores at a surface of a dielectric layer formed on a substrate, includes: providing a substrate on which a dielectric layer having a porous surface is formed as an outermost layer; placing the substrate in an evacuatable chamber; irradiating the substrate with UV light in an atmosphere of hydrocarbon and / or oxy-hydrocarbon gas; sealing pores at the porous surface of the dielectric layer as a result of the irradiation; and continuously irradiating the substrate with UV light in the atmosphere of hydrocarbon and / or oxy-hydrocarbon gas until a protective film having a desired thickness is formed on the dielectric layer as a result of the irradiation.

Owner:ASM JAPAN

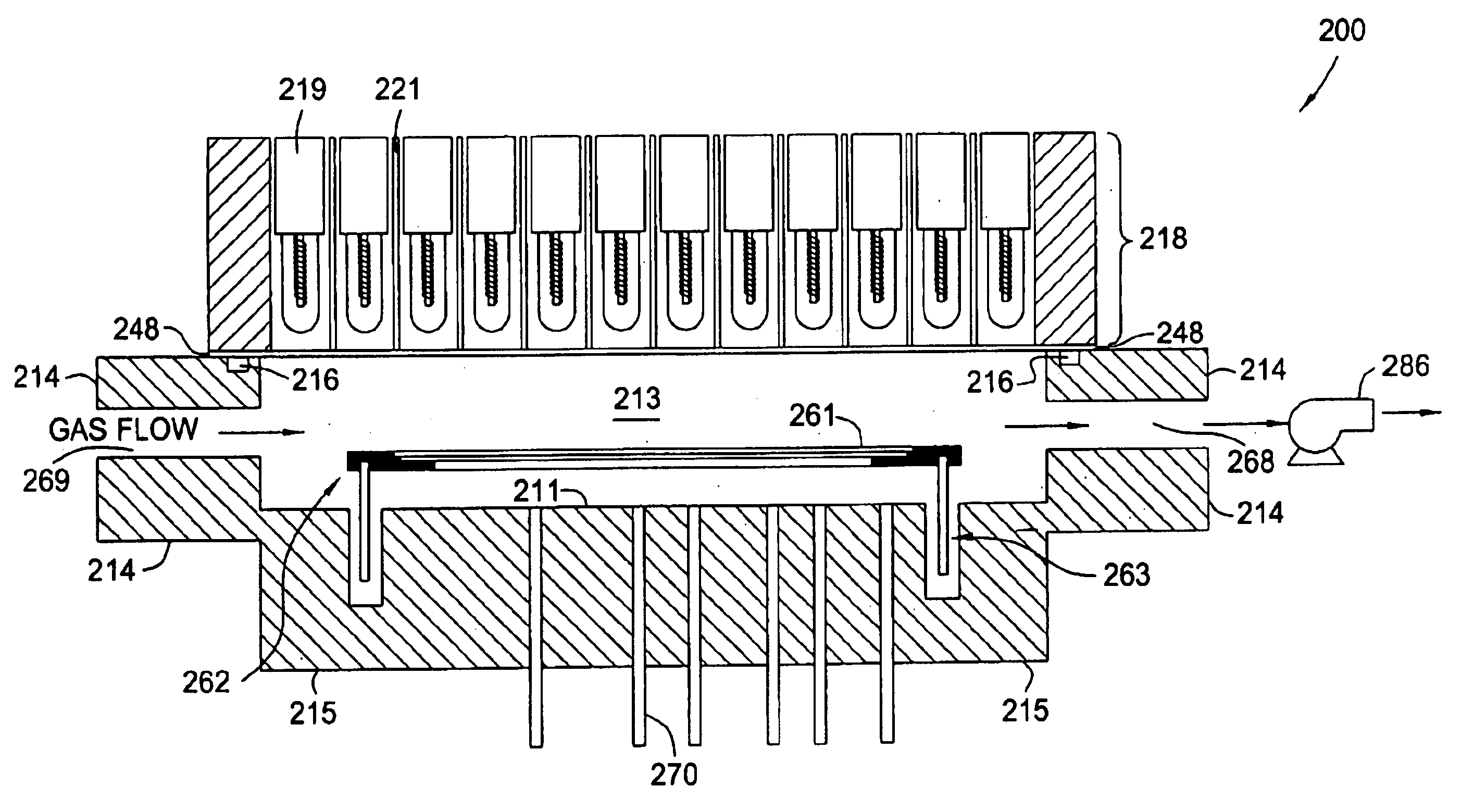

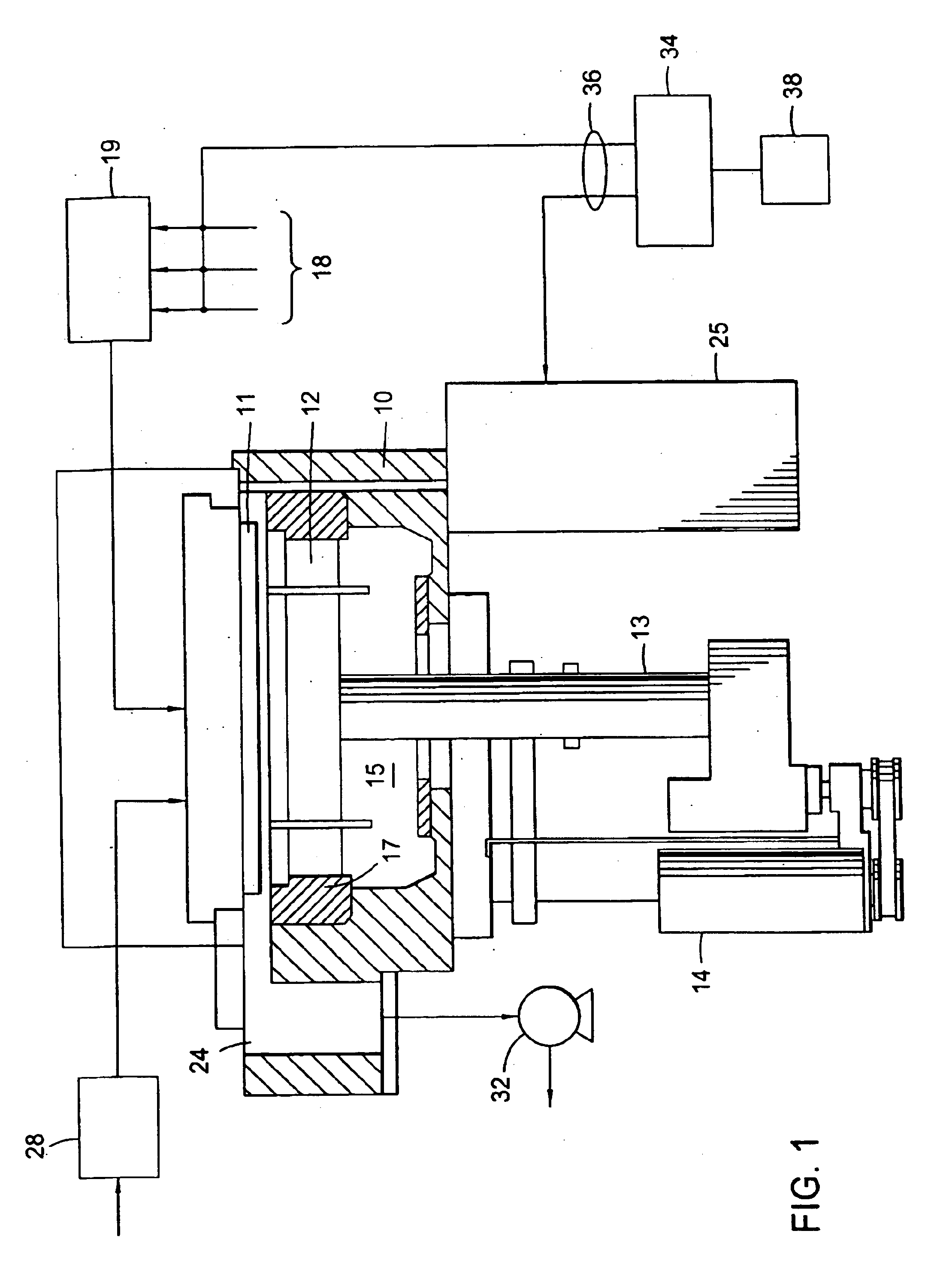

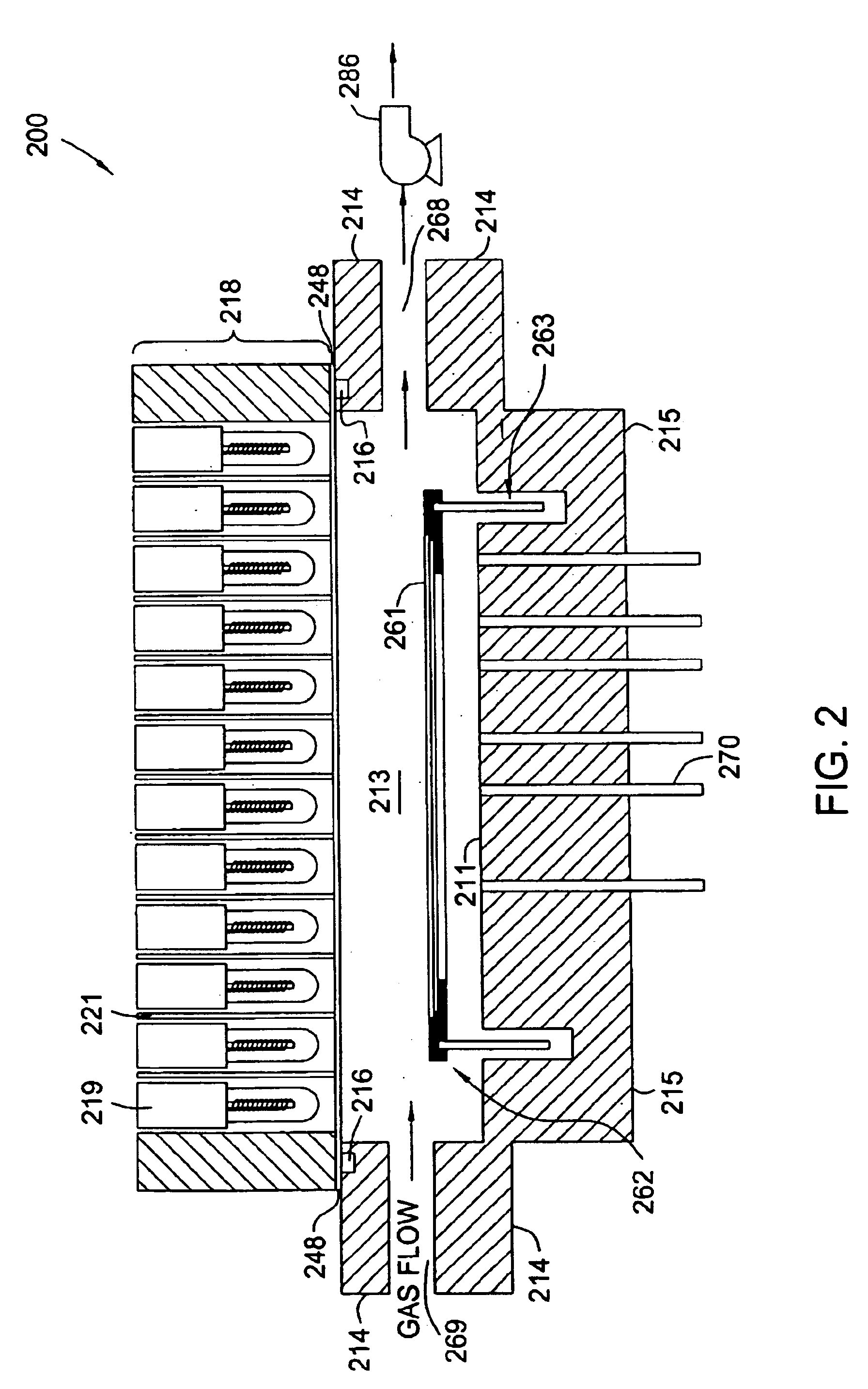

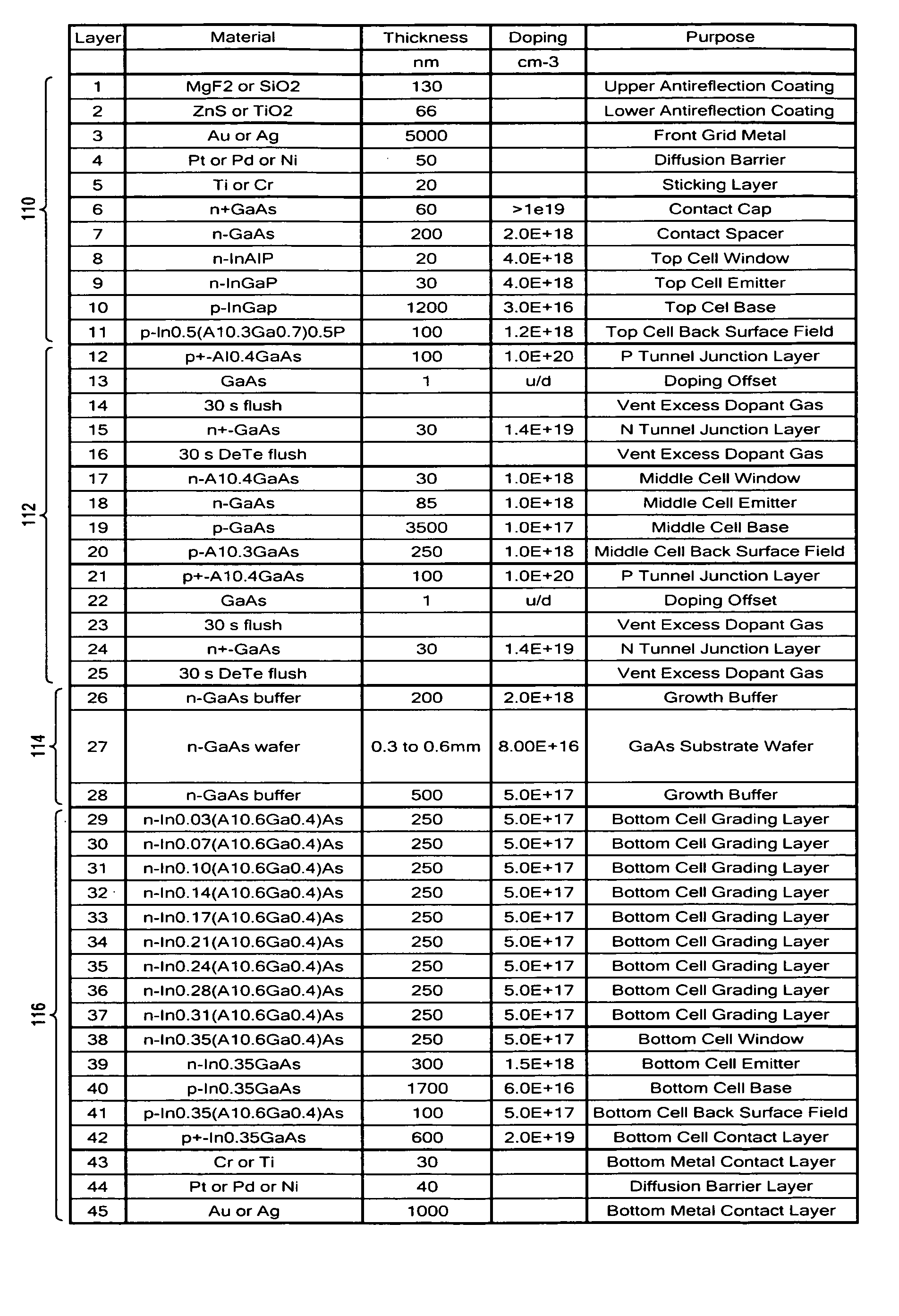

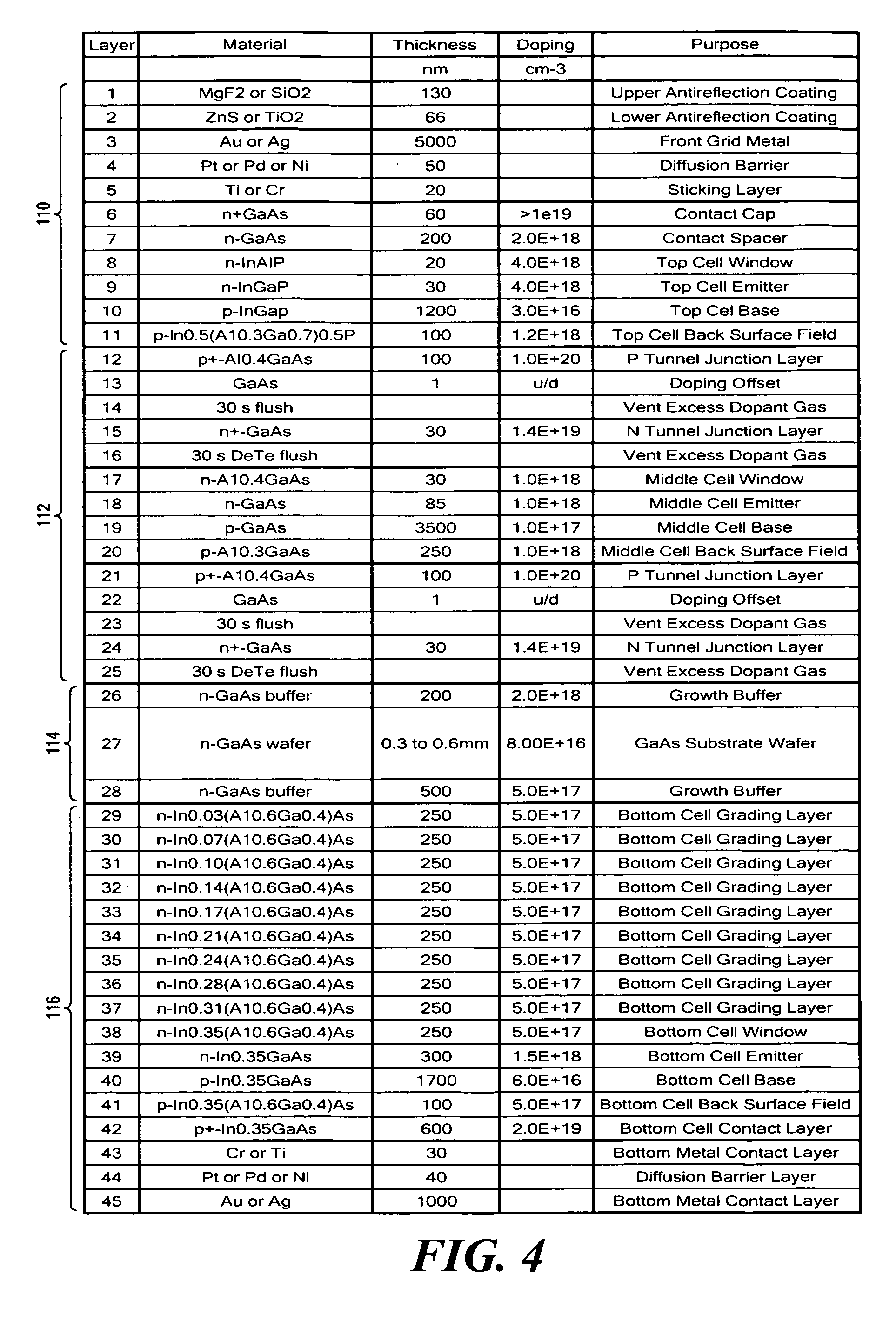

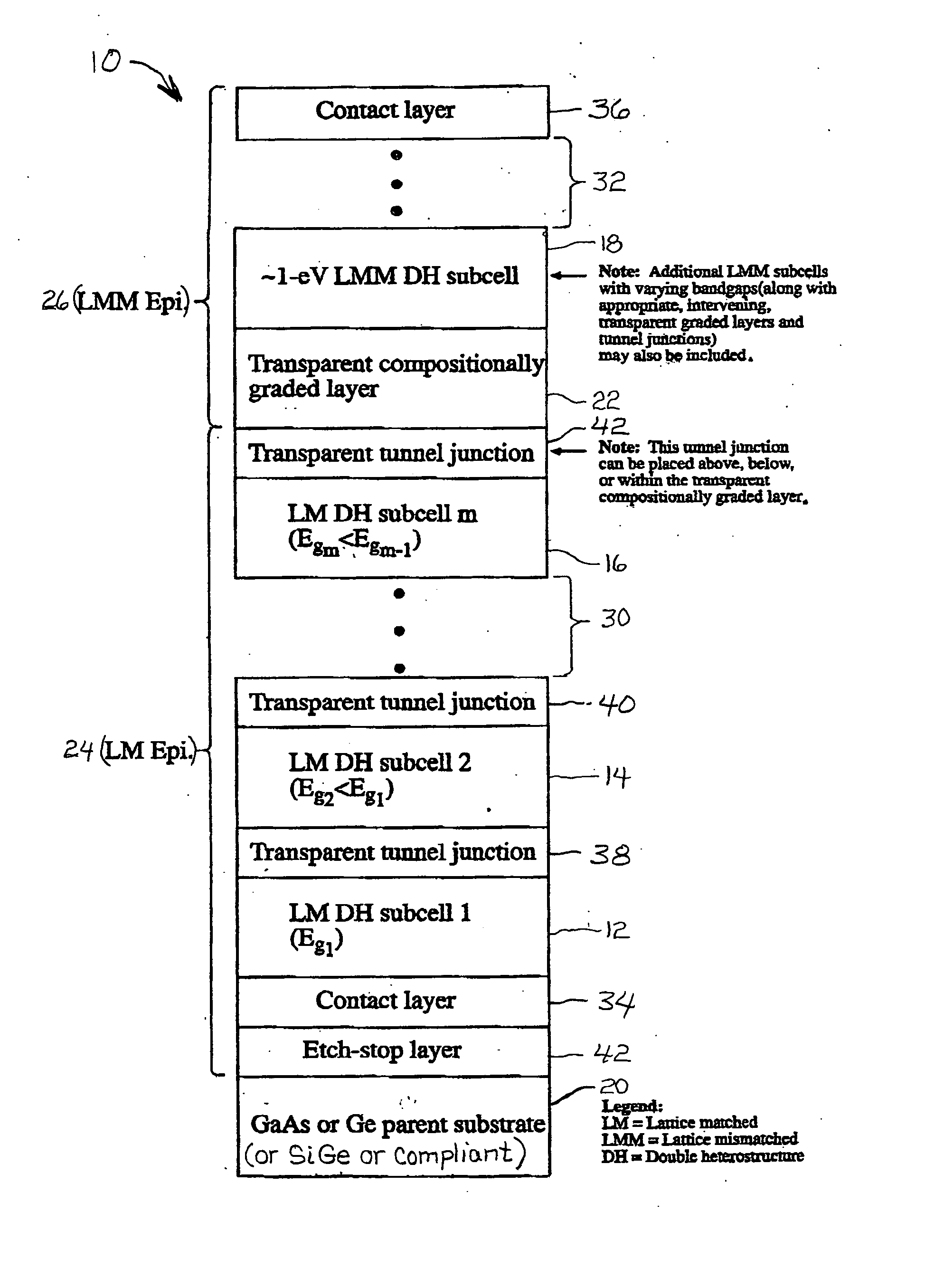

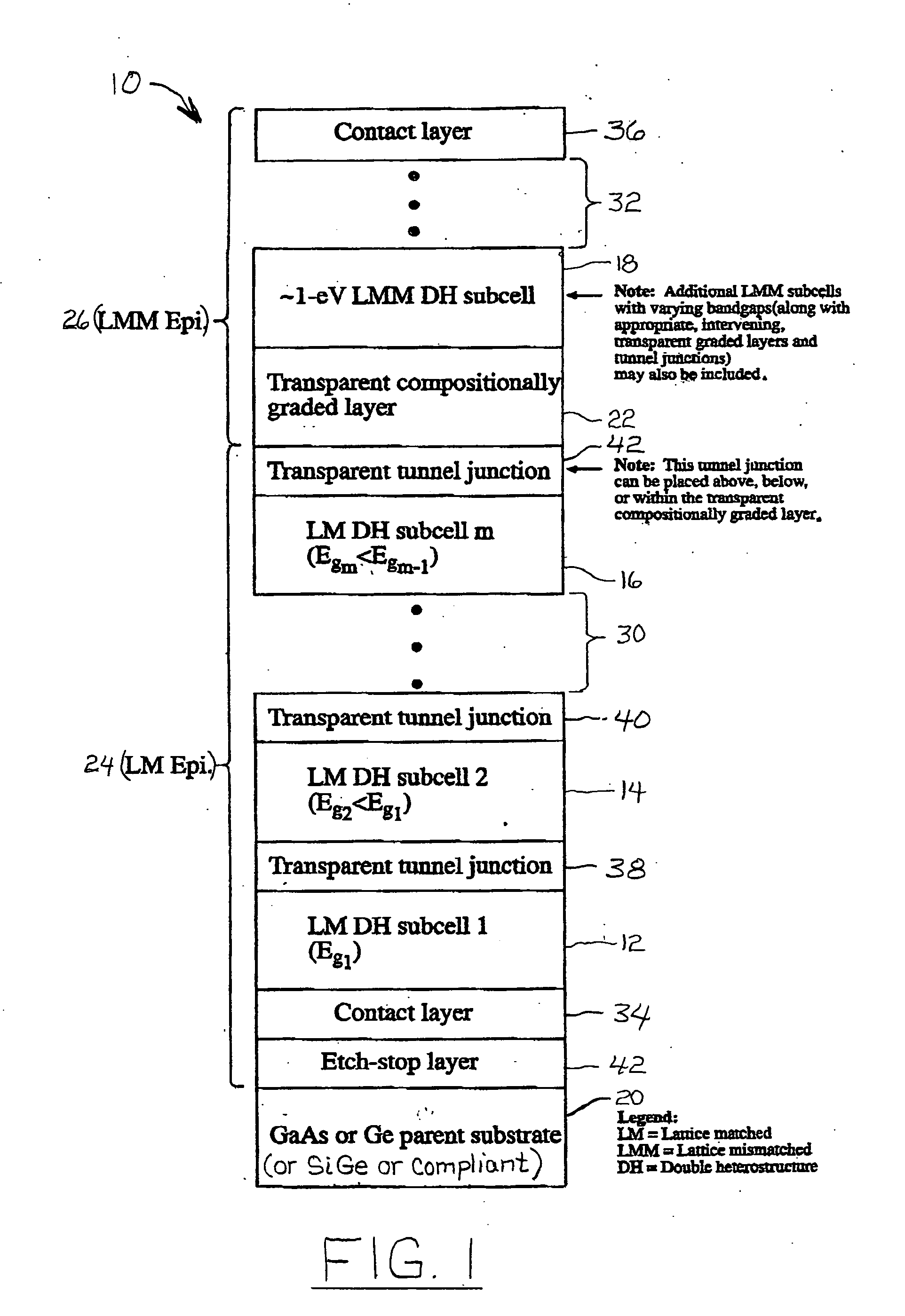

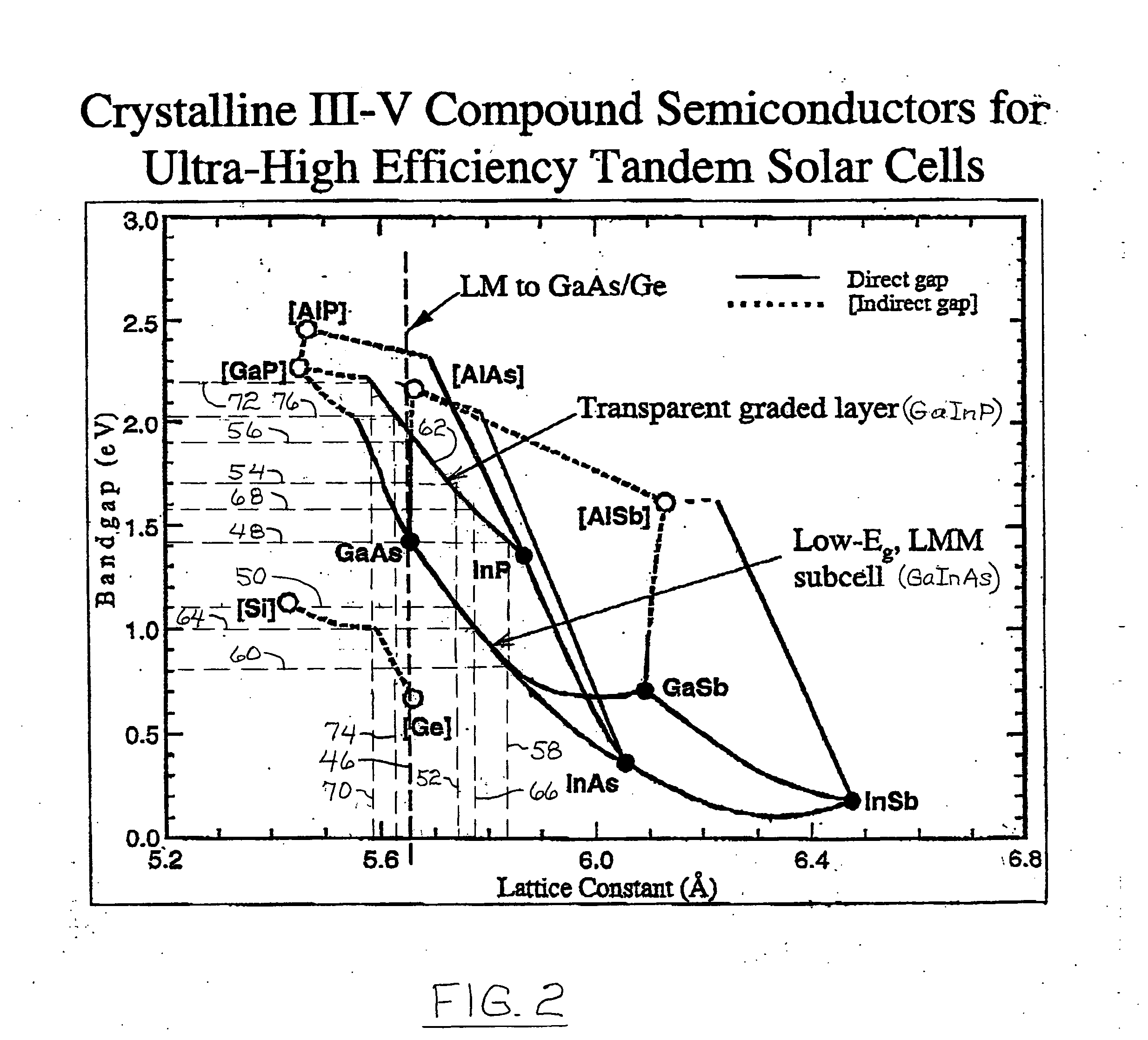

High-efficiency, monolithic, multi-bandgap, tandem photovoltaic energy converters

ActiveUS20060144435A1Improved thermal managementIncrease flexibilityPV power plantsSemiconductor/solid-state device manufacturingHigh energyLattice mismatch

A monolithic, multi-bandgap, tandem solar photovoltaic converter has at least one, and preferably at least two, subcells grown lattice-matched on a substrate with a bandgap in medium to high energy portions of the solar spectrum and at least one subcell grown lattice-mismatched to the substrate with a bandgap in the low energy portion of the solar spectrum, for example, about 1 eV.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

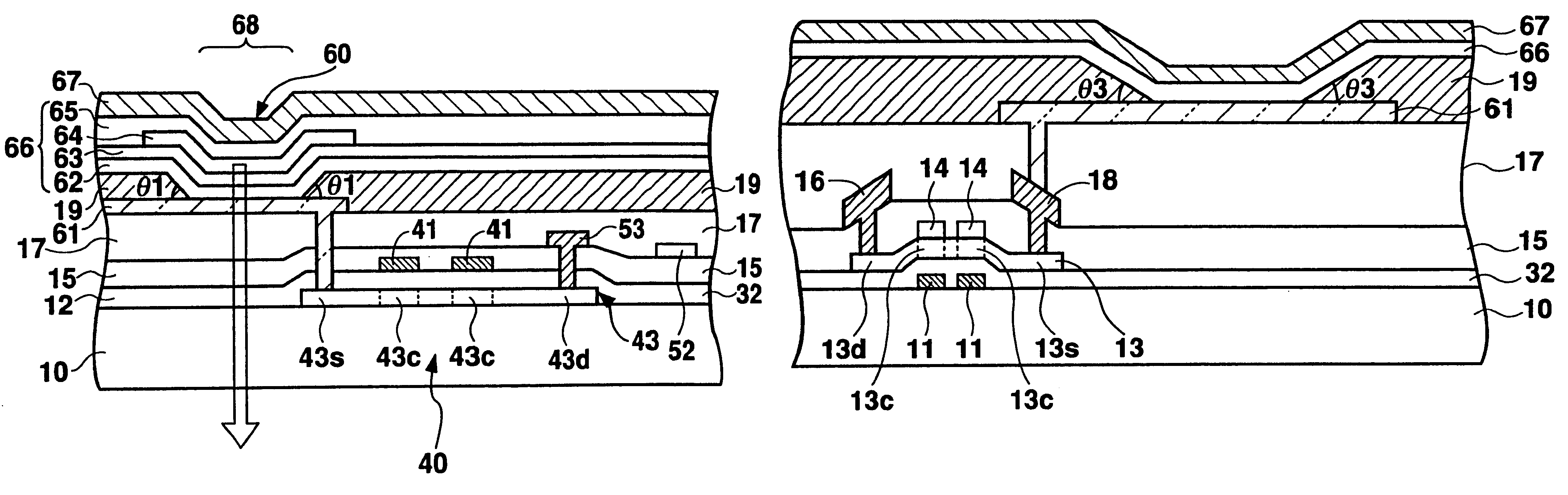

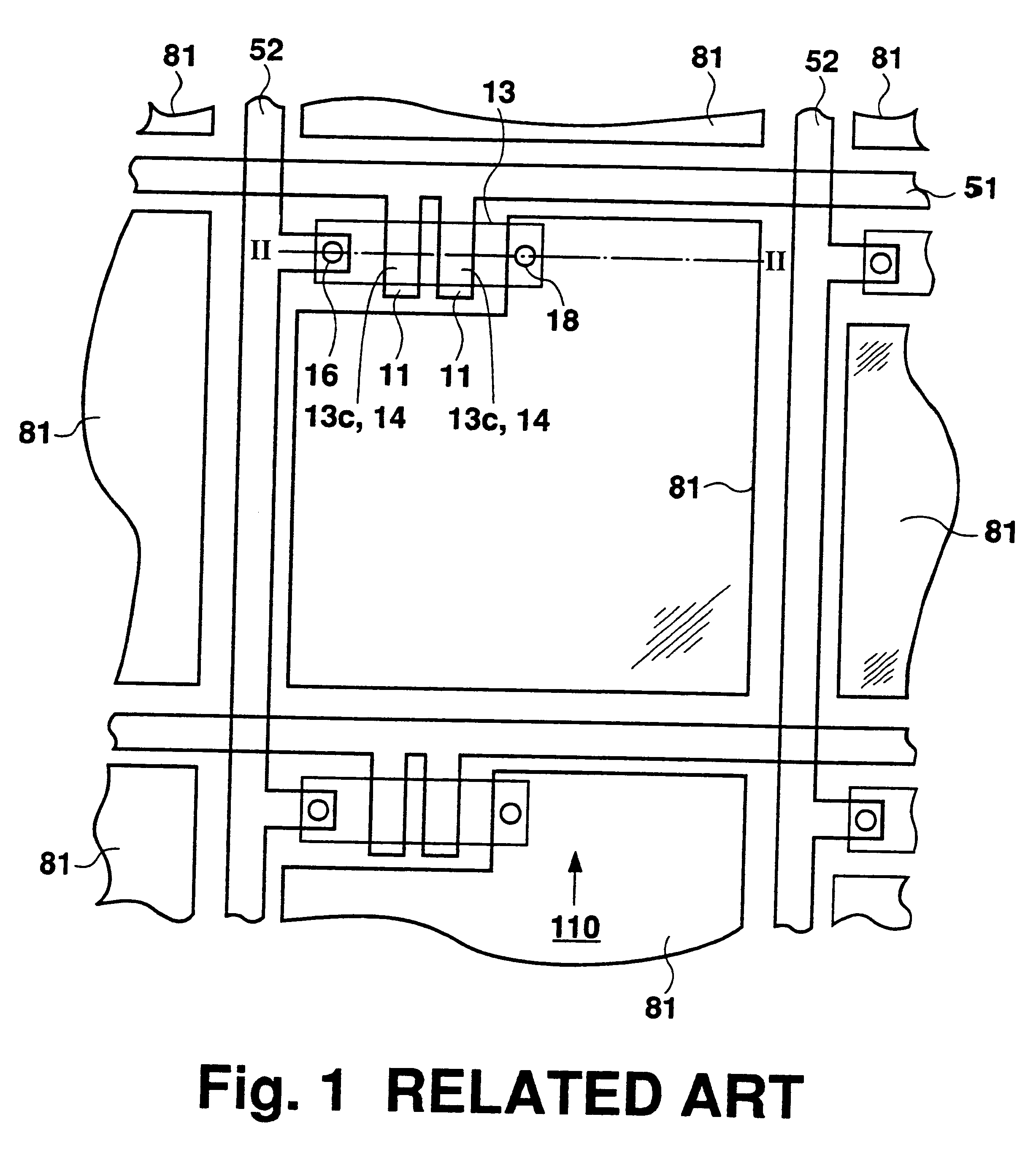

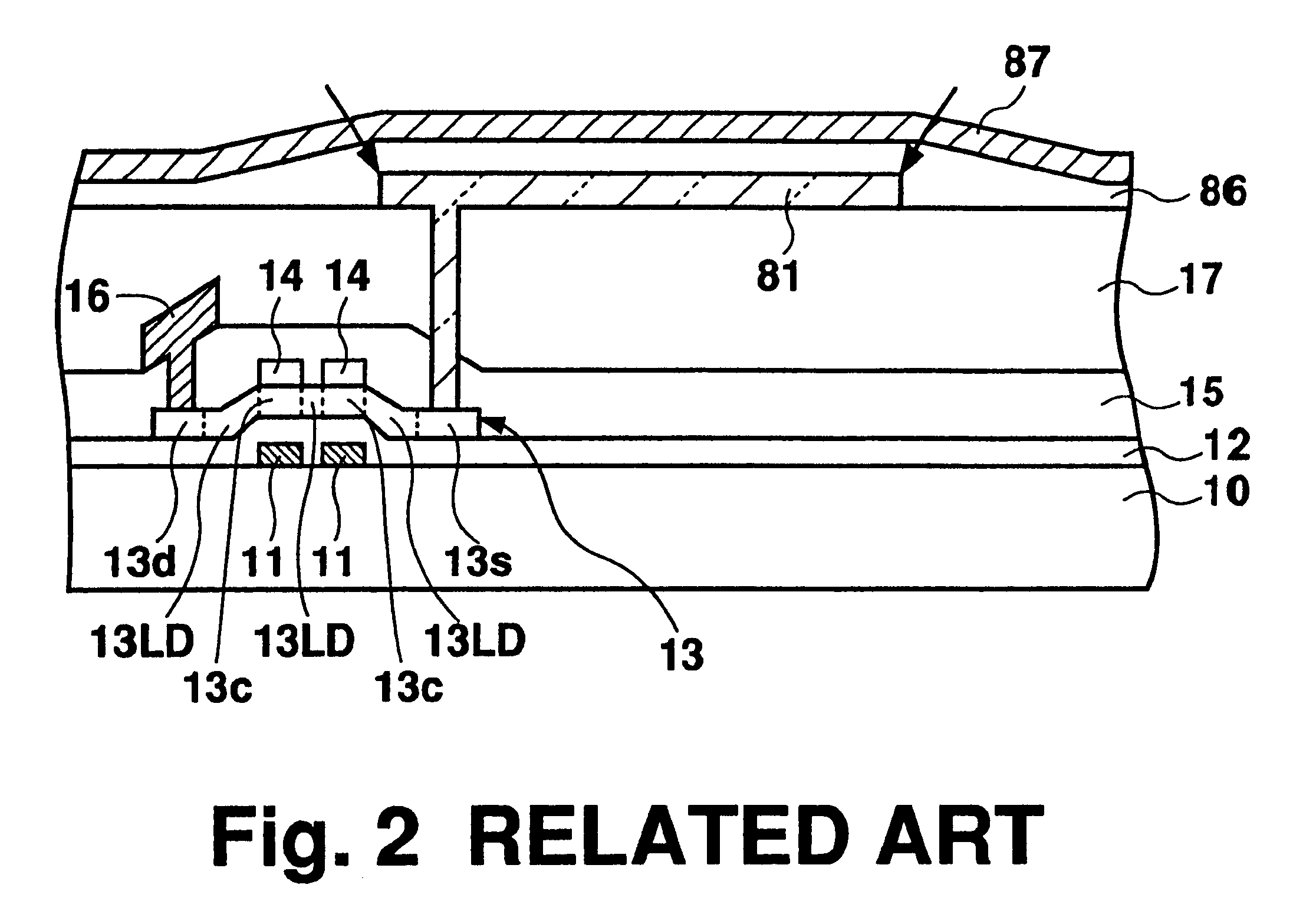

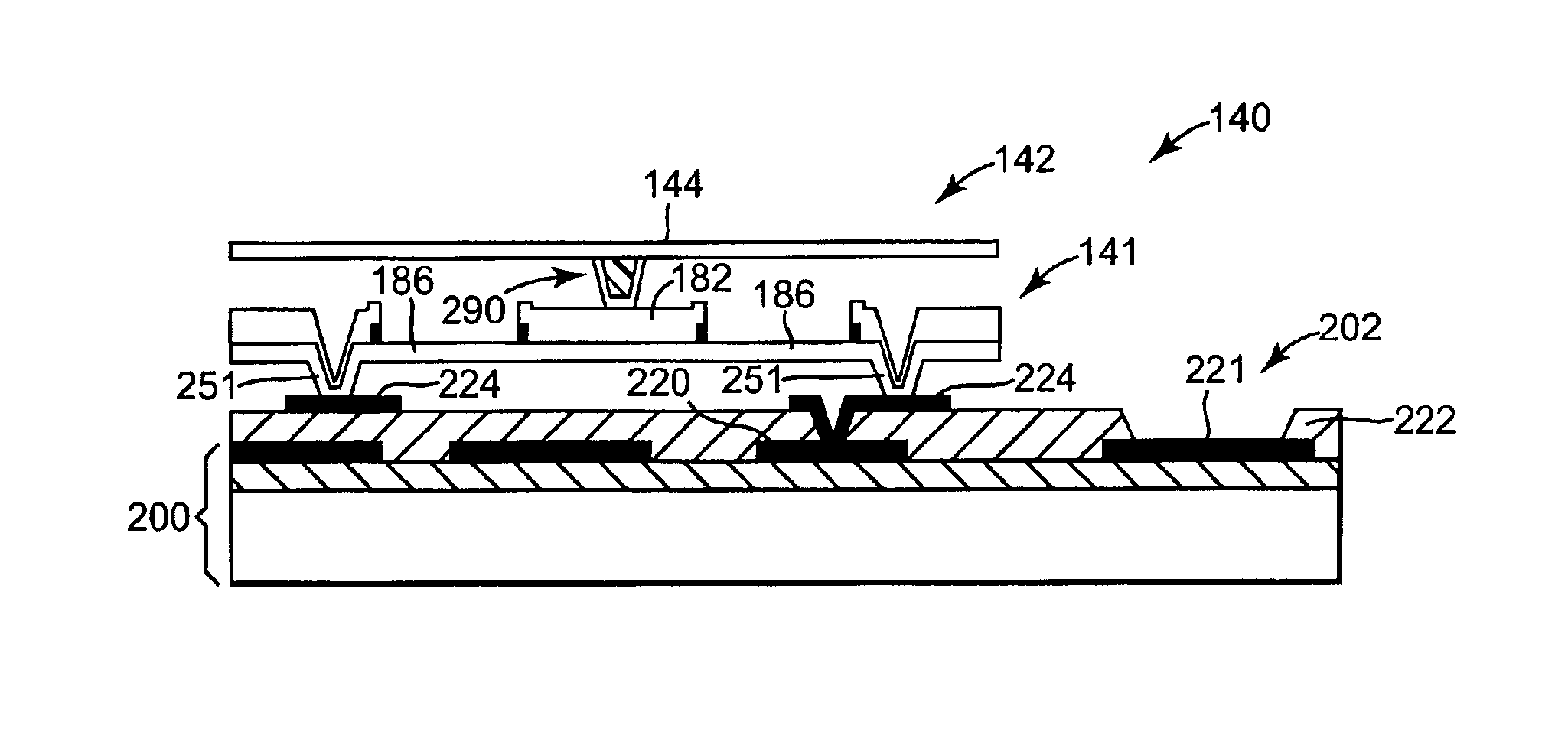

Emissive element and display device using such element

InactiveUS6246179B1Avoid it happening againLayer deterioratesDischarge tube luminescnet screensStatic indicating devicesDisplay deviceOptoelectronics

An EL element (60) comprises an anode (61), a cathode (67), and an emissive element layer (66) interposed between the two electrodes. A TFT is connected to the anode (61) at its source electrode (33s). The peripheral portion of the anode (61) and the entire region over the TFT are covered with a planarizing insulating film (17), and a part of the exposed portion of the anode (61) is connected to the emissive element layer (66). According to the above arrangement, it is possible to prevent disconnection of the emissive element layer (66) which may be caused by an uneven surface created by the thickness of the anode (61), and to avoid formation of a short circuit between the anode (61) and the cathode (67).

Owner:SANYO ELECTRIC CO LTD

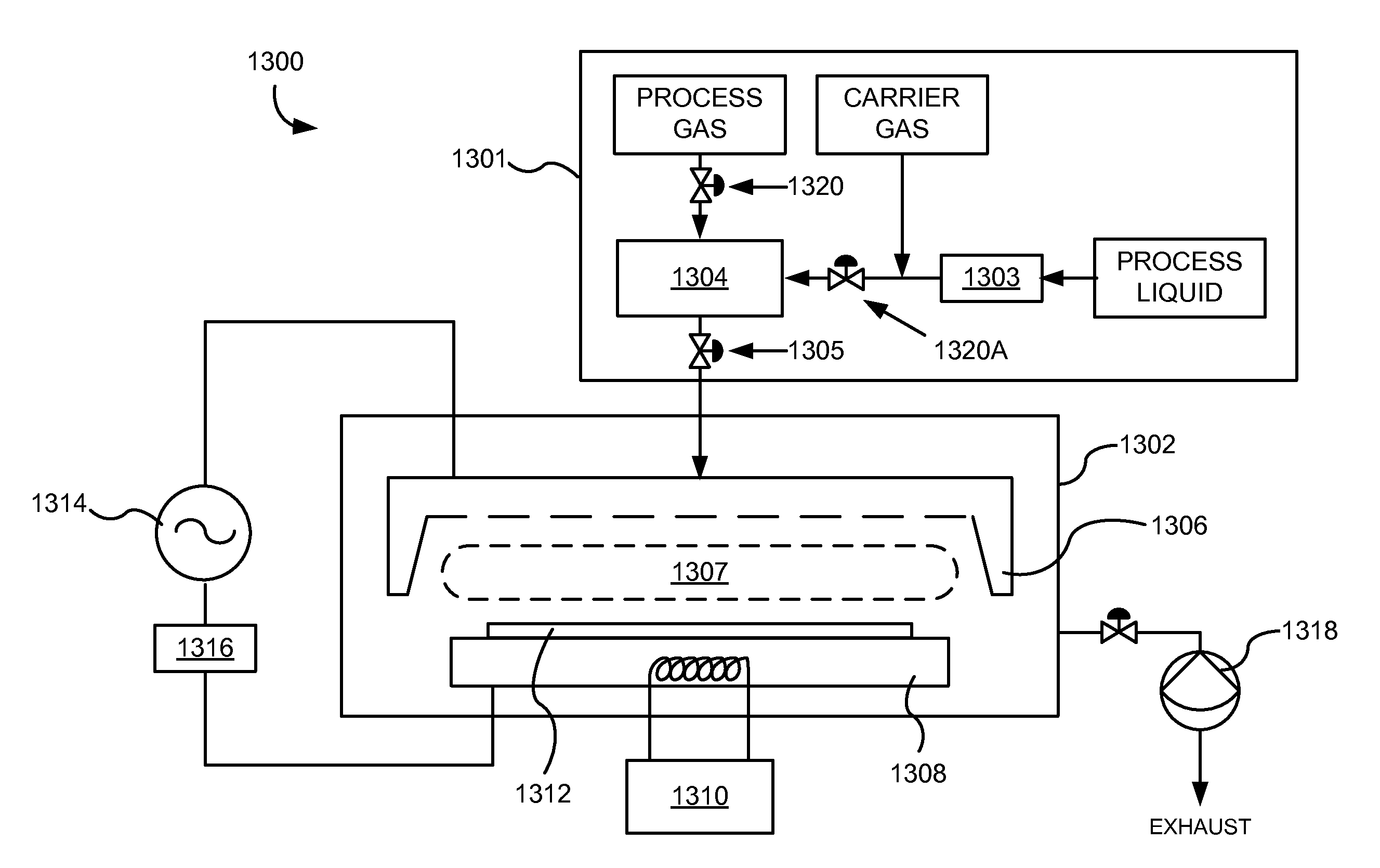

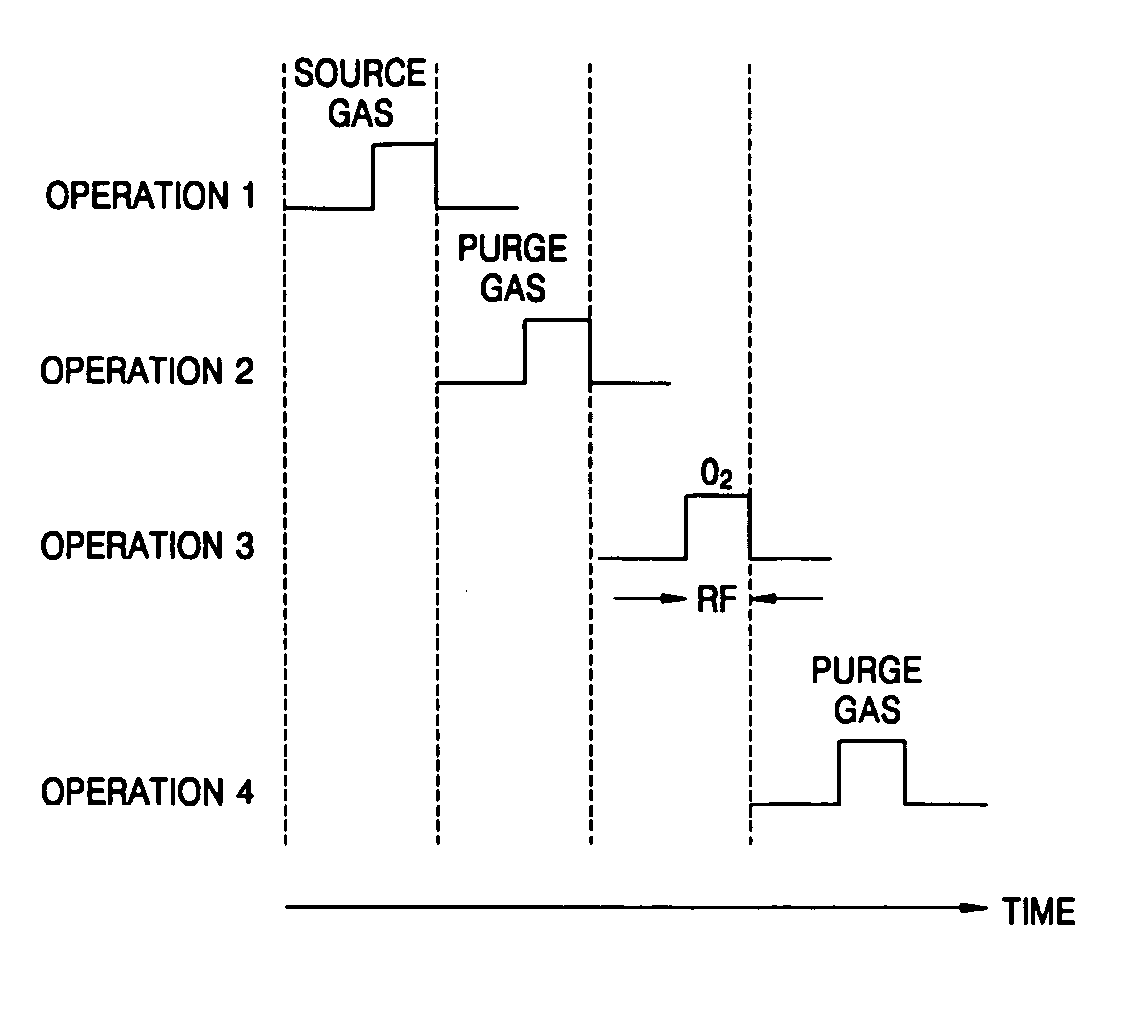

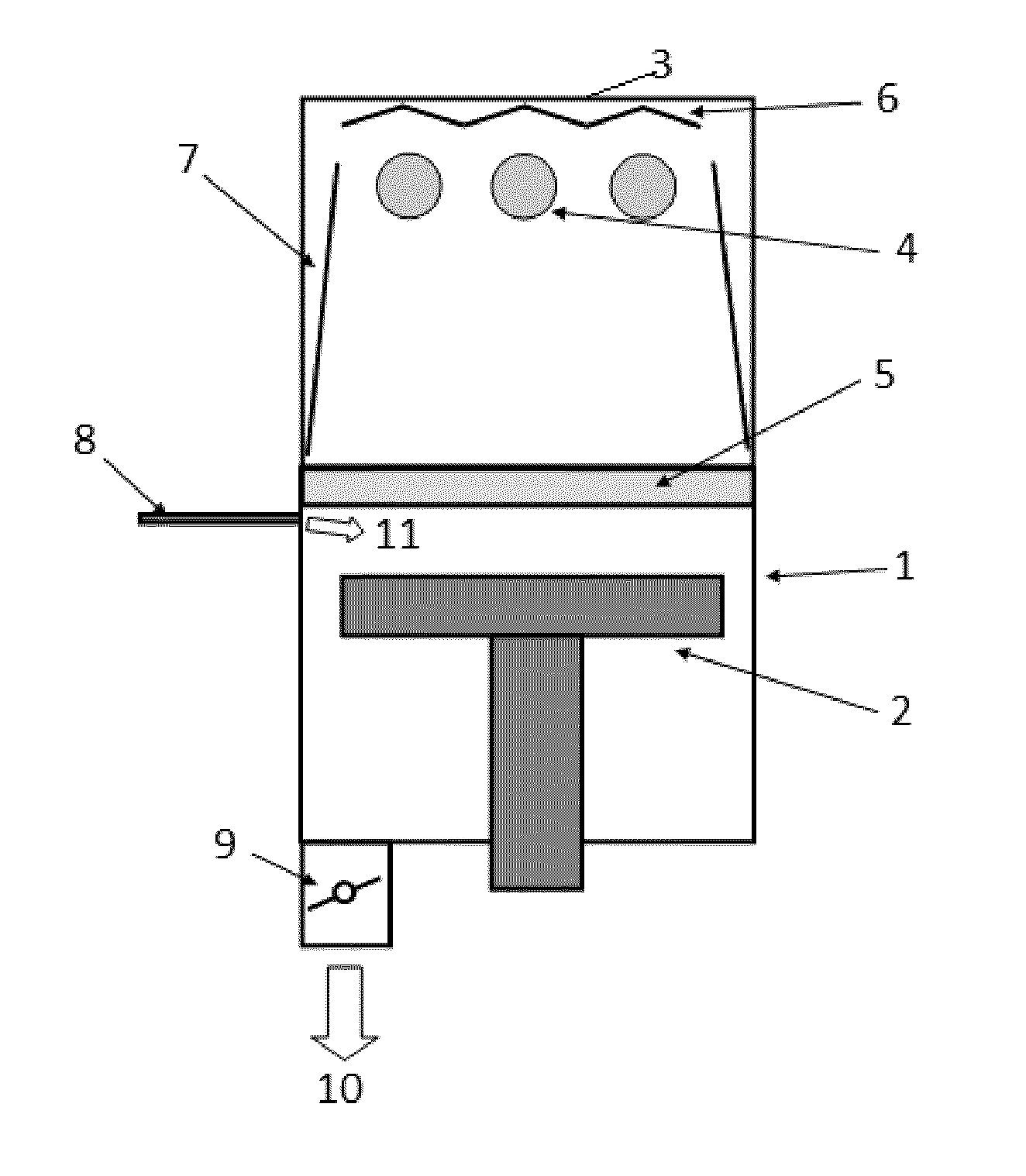

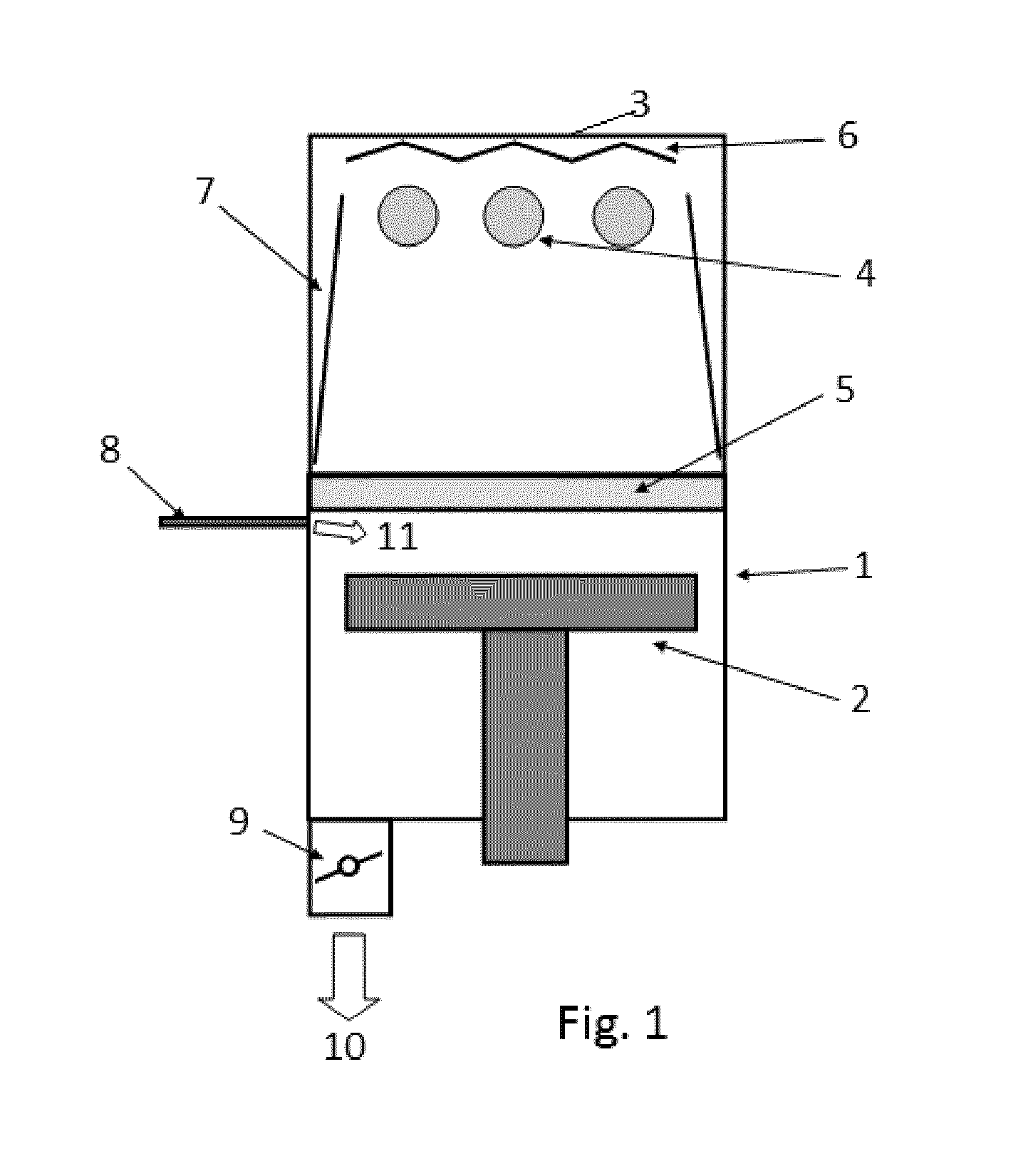

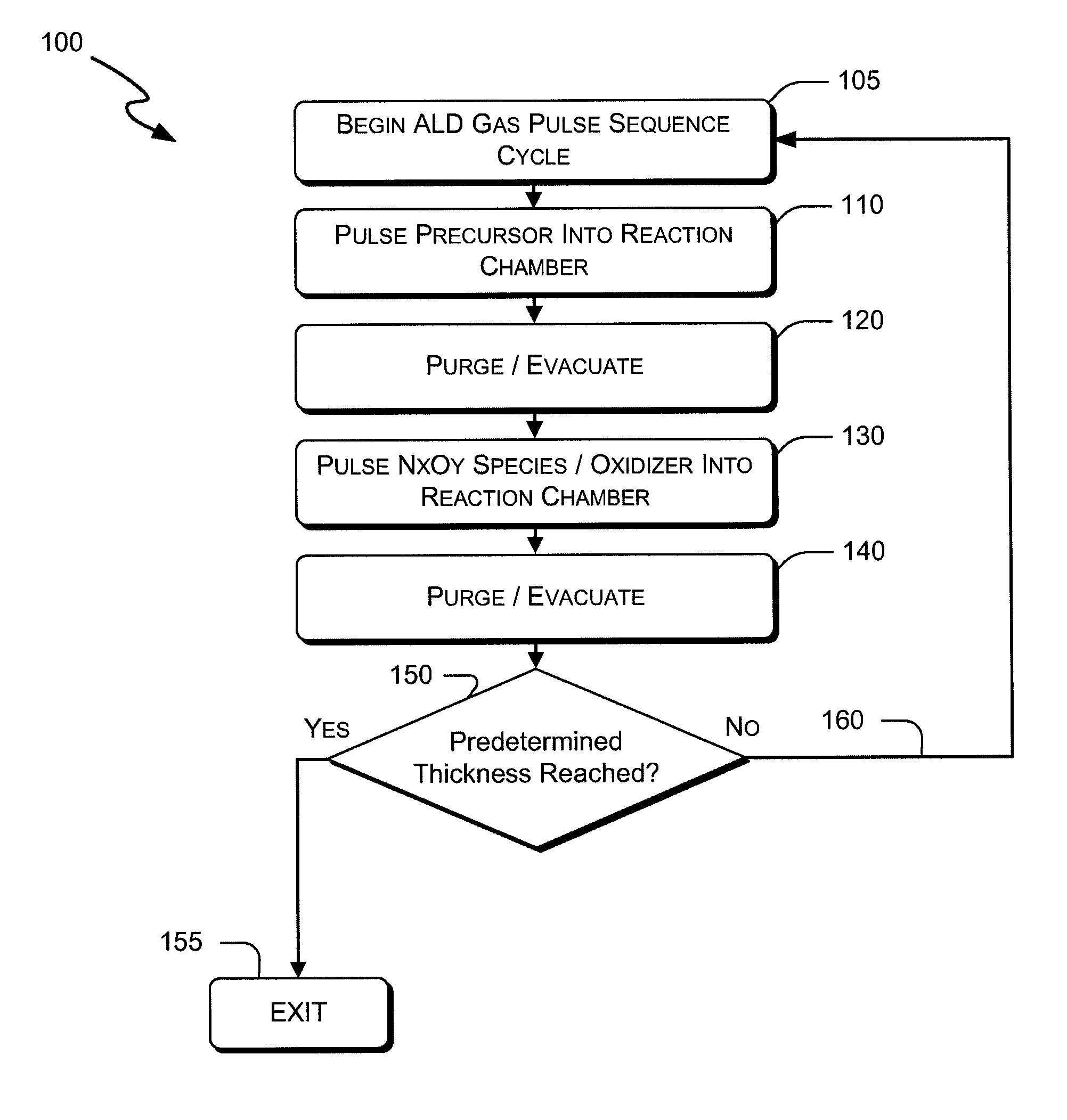

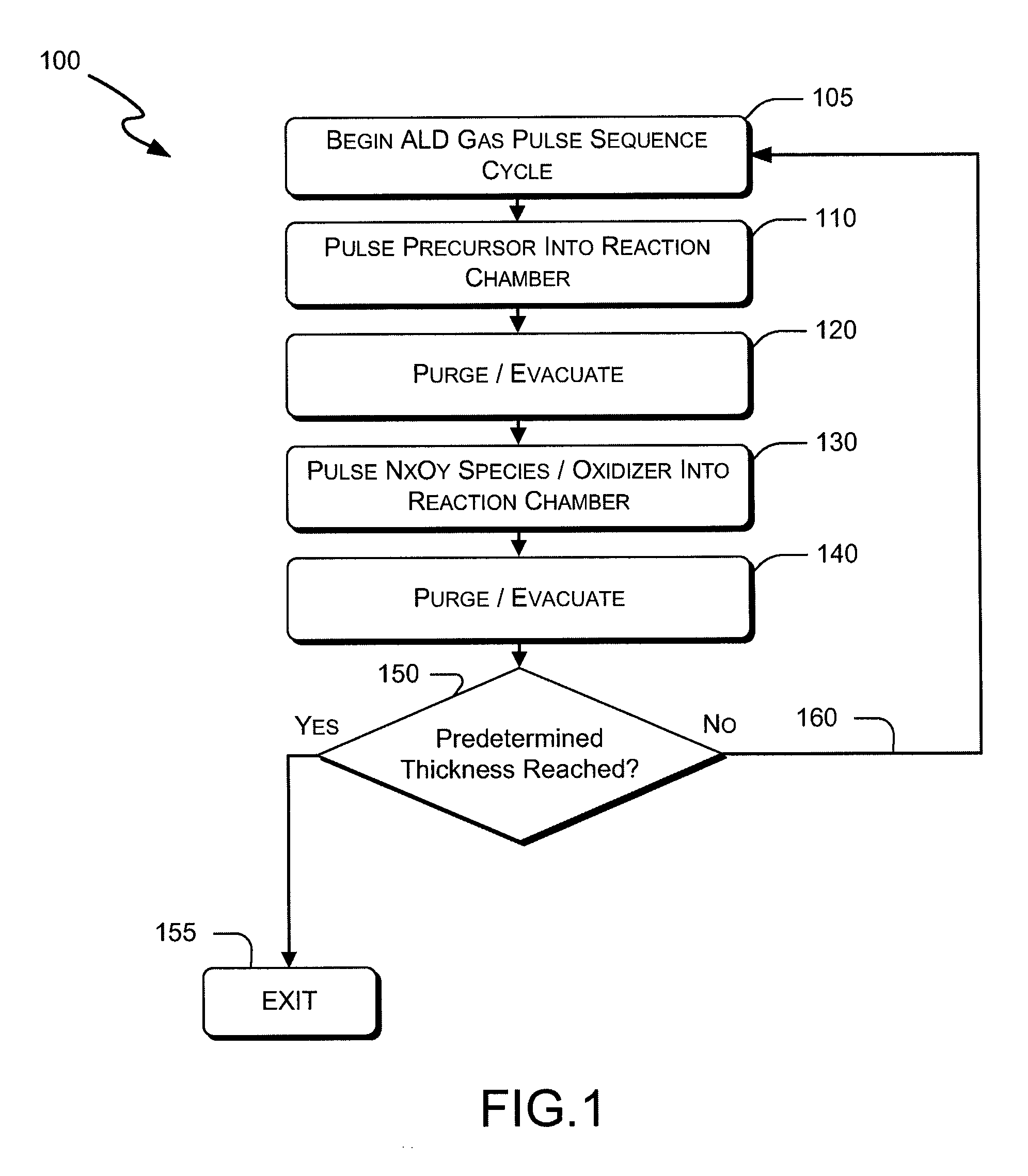

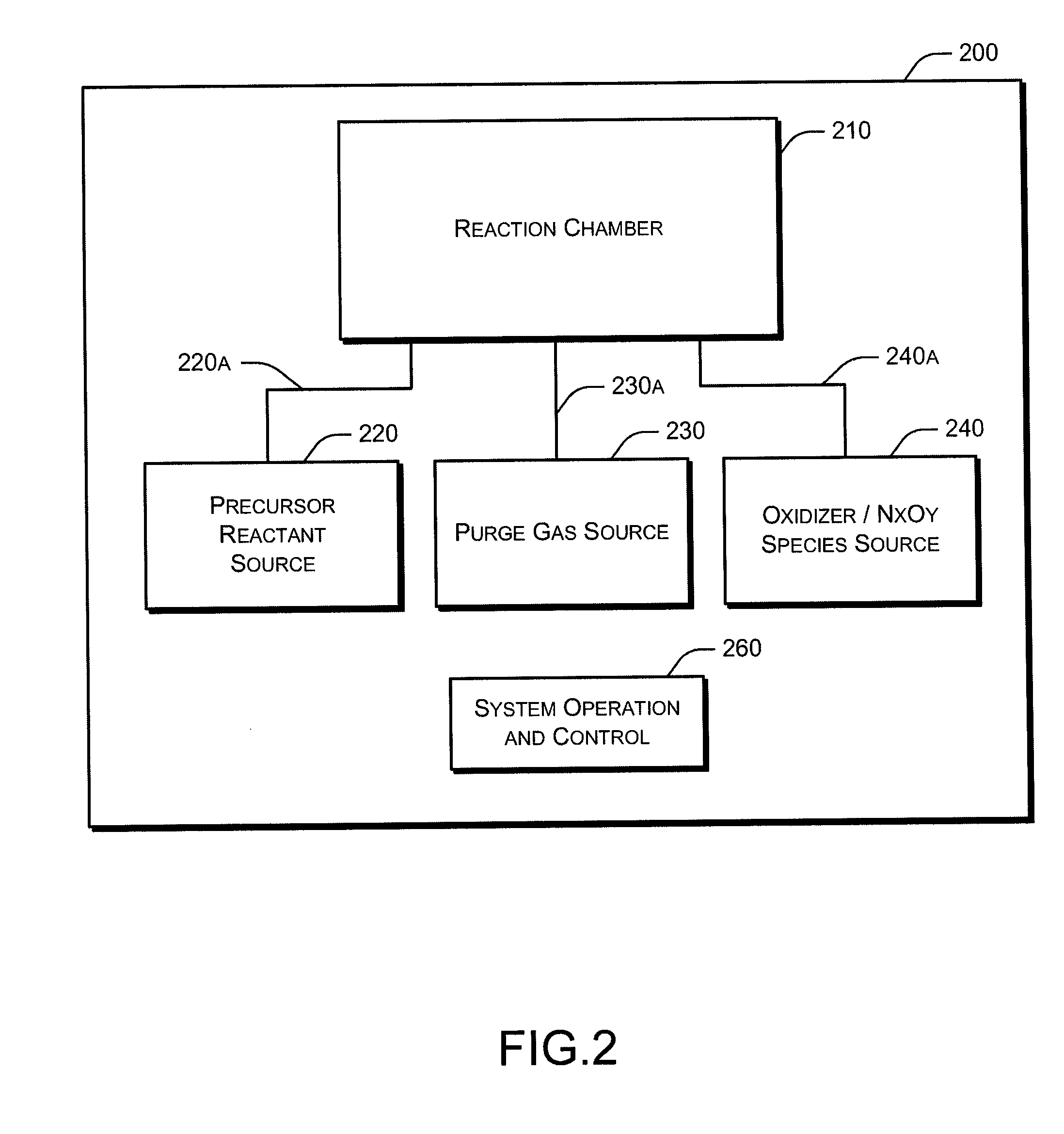

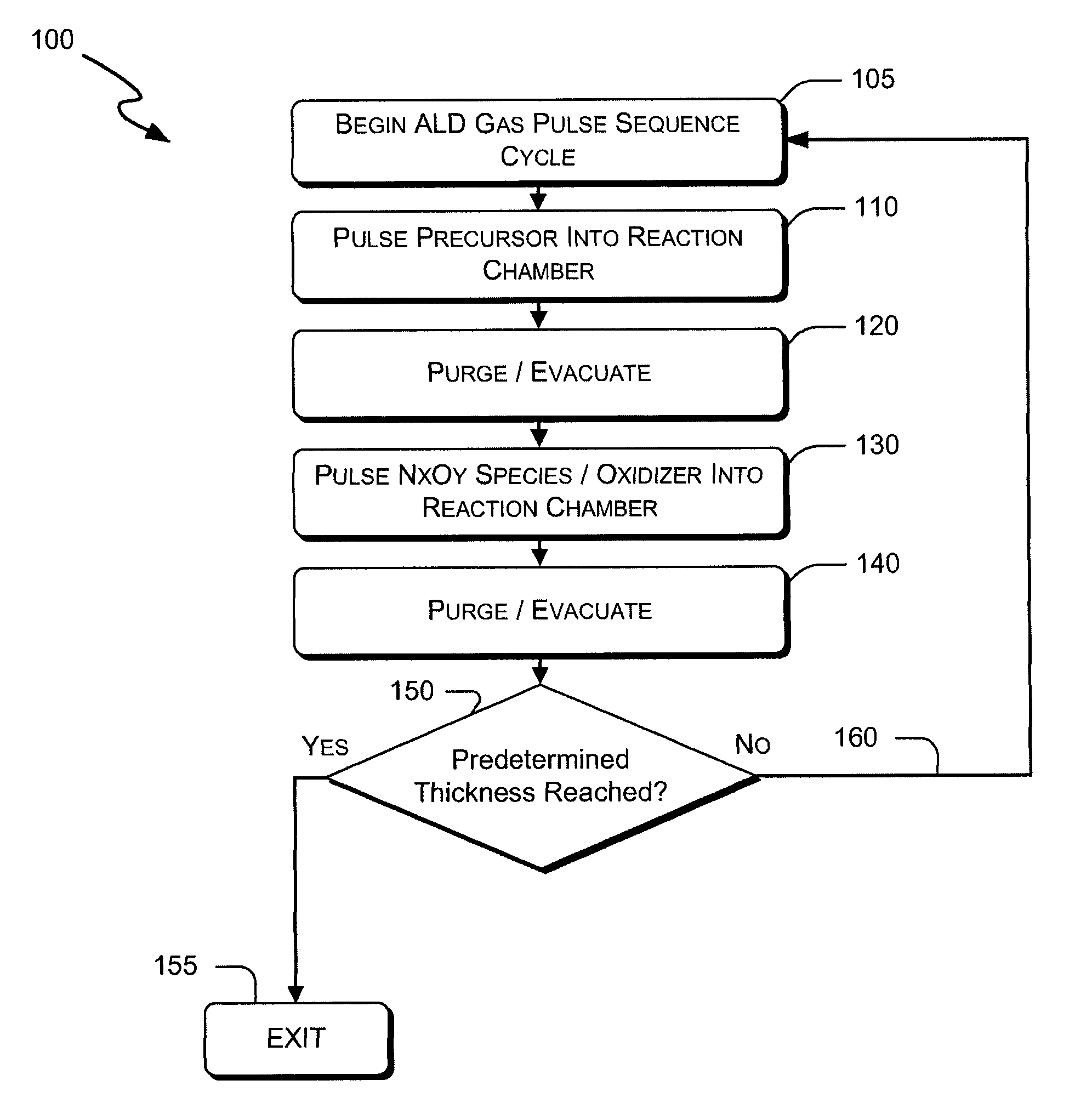

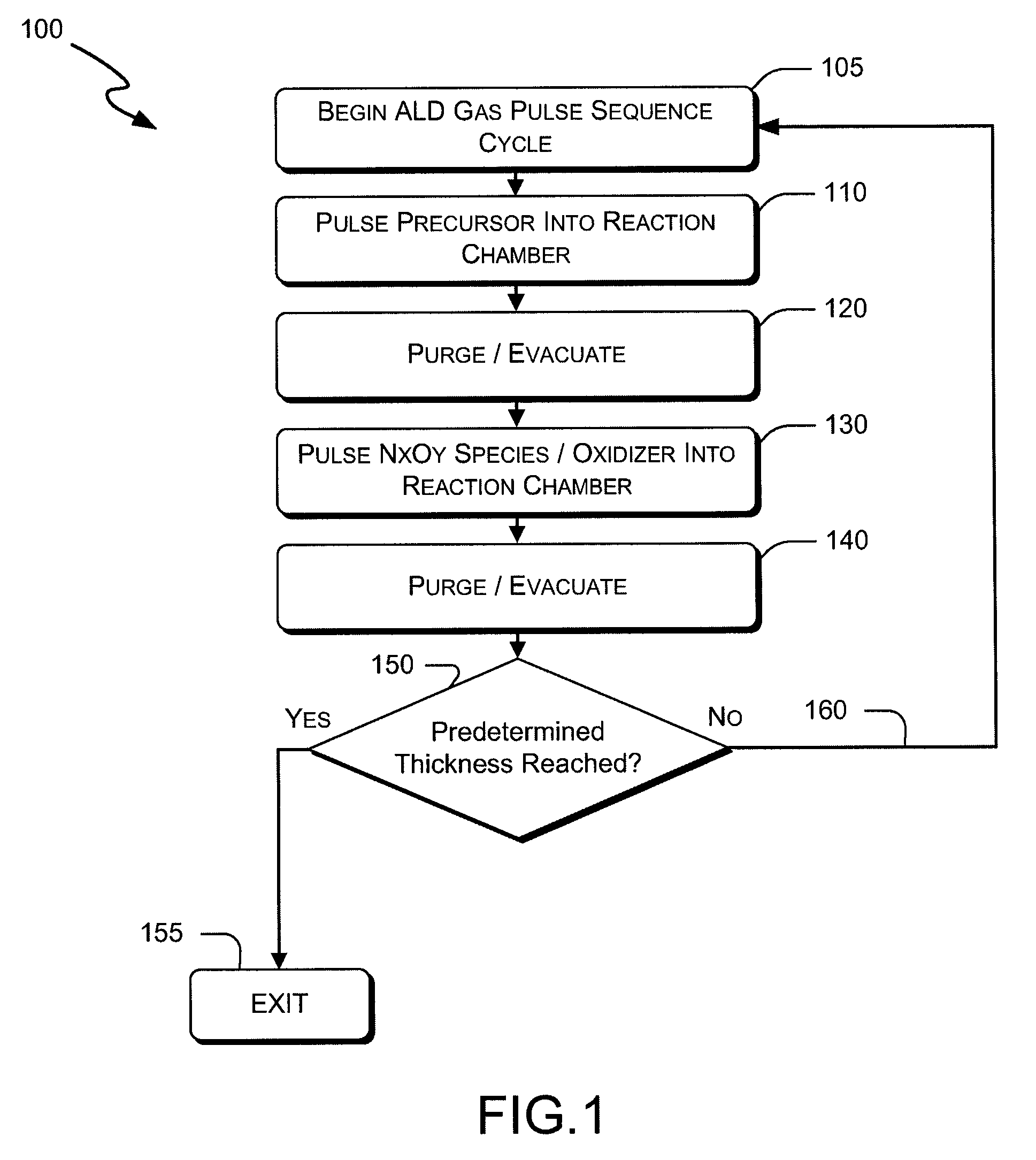

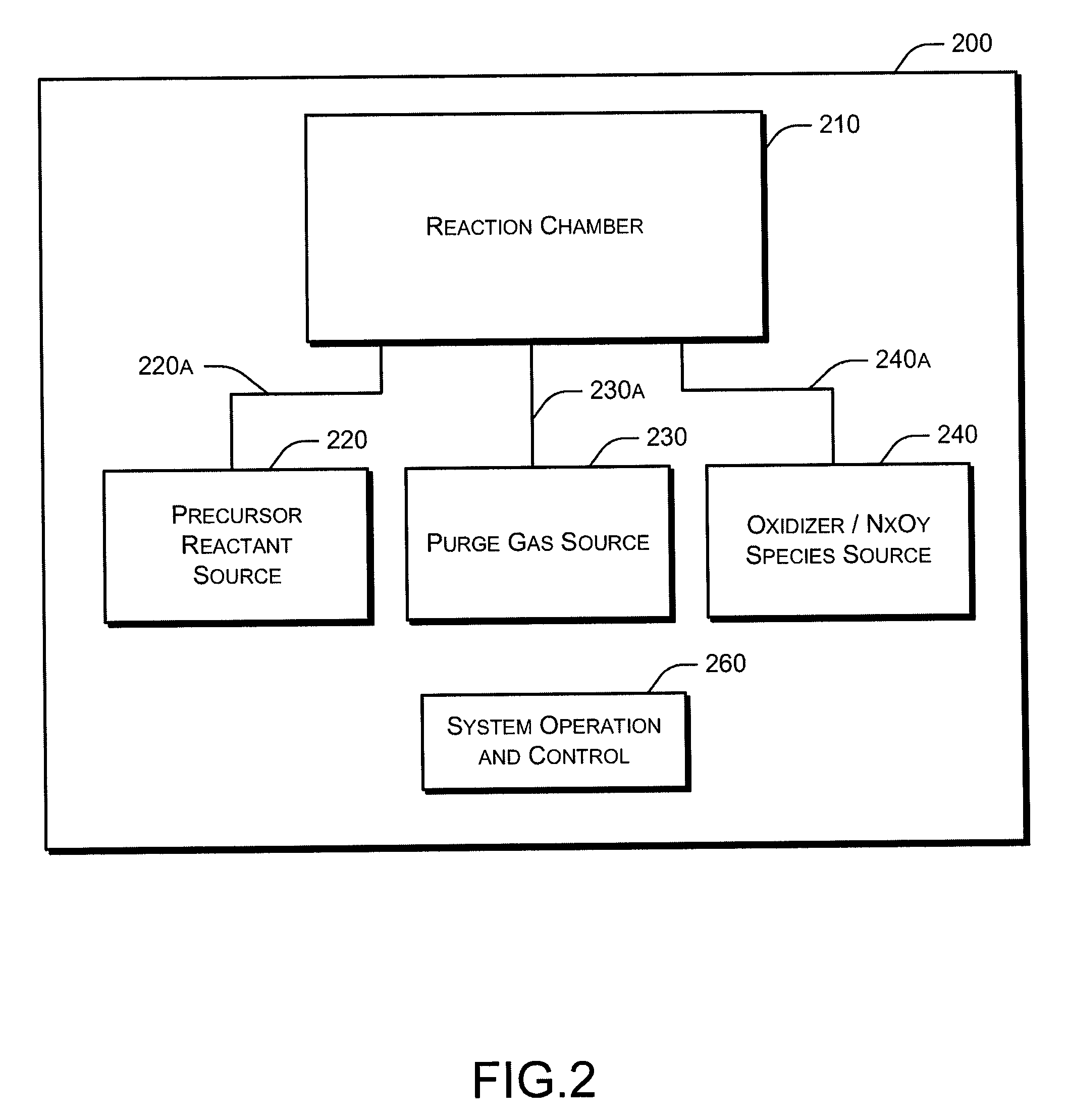

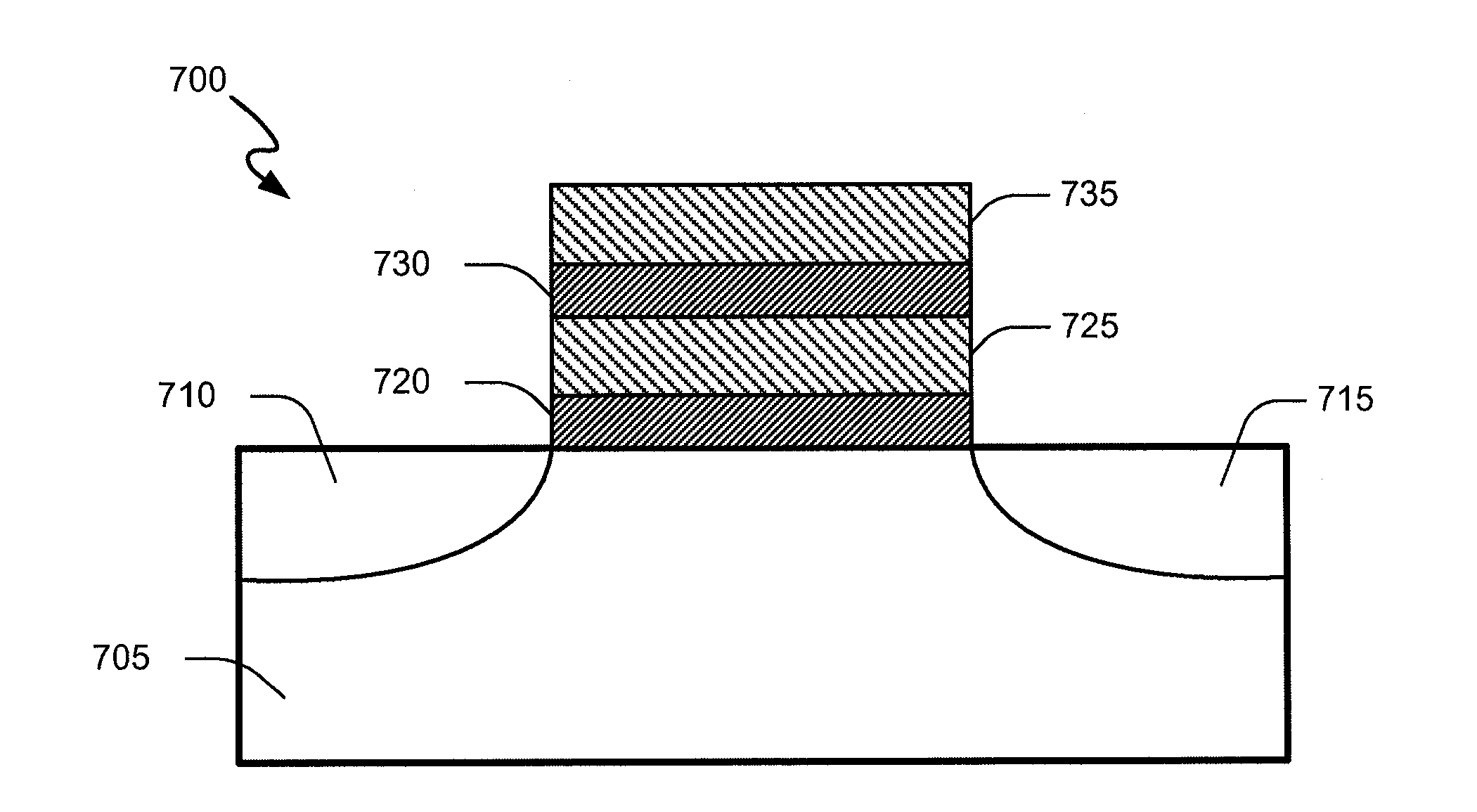

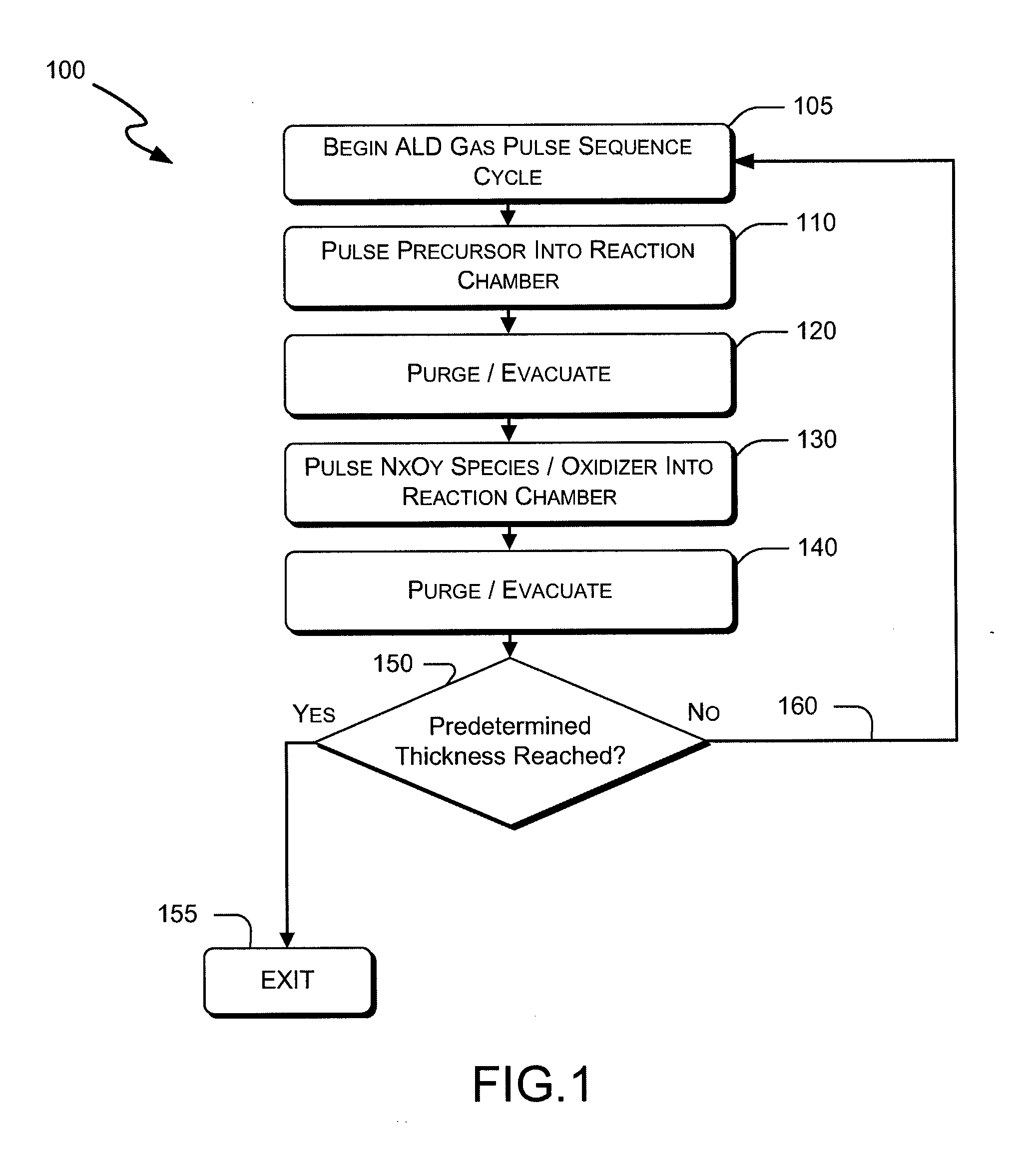

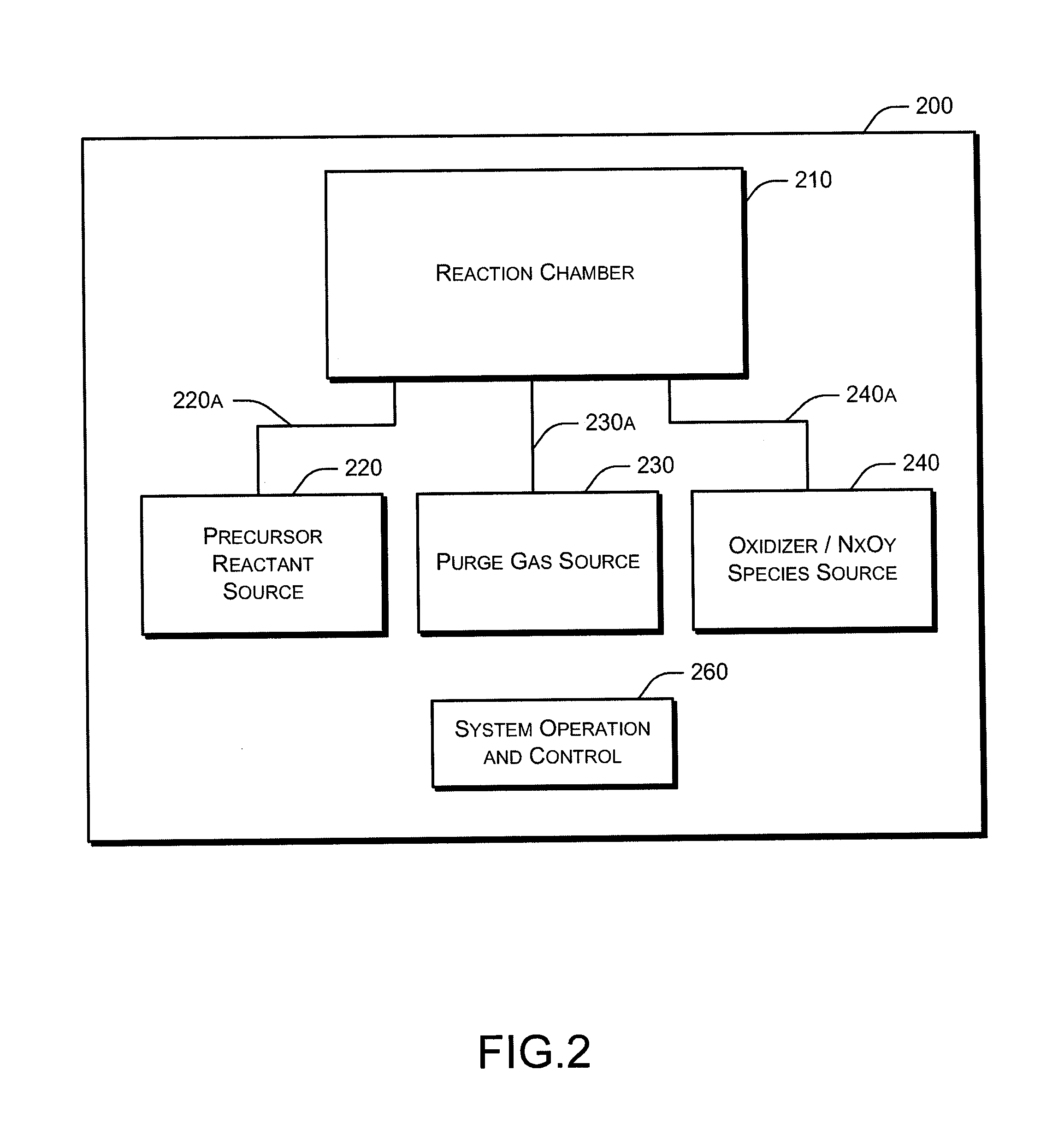

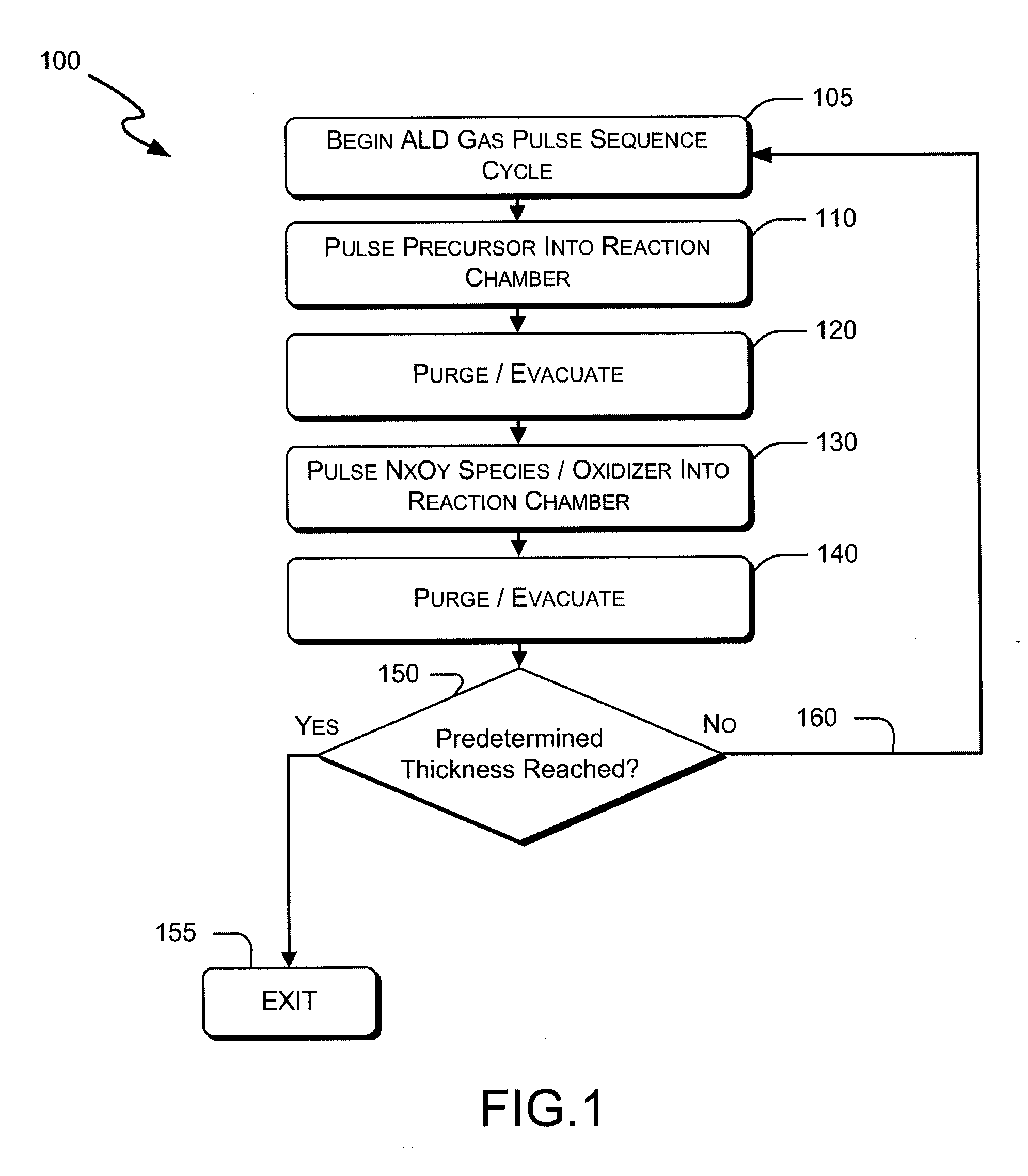

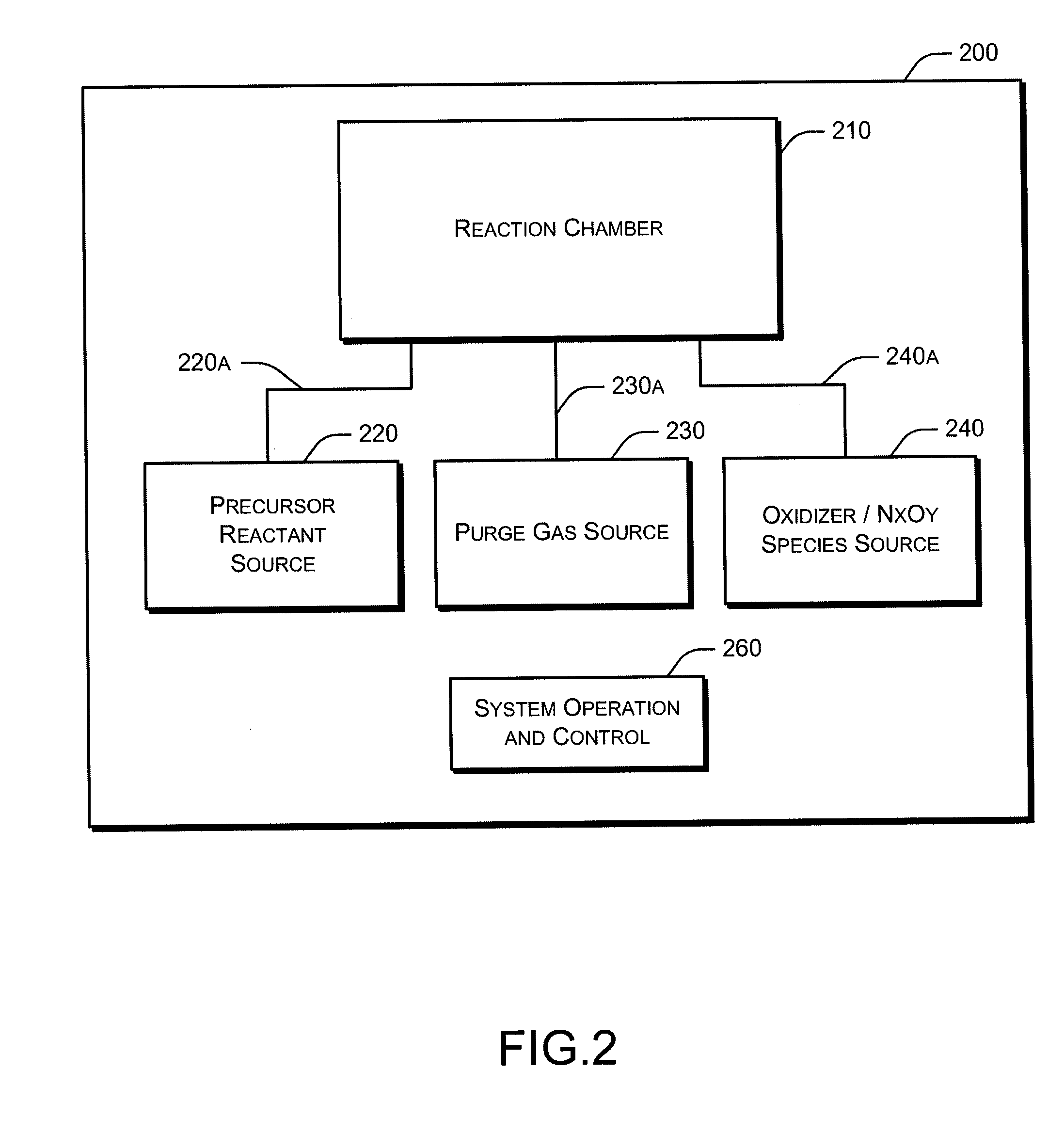

Systems and methods for thin-film deposition of metal oxides using excited nitrogen-oxygen species

ActiveUS8877655B2Enhance growth rate and uniformityUniform growthLiquid surface applicatorsSemiconductor/solid-state device manufacturingNitrogenOptoelectronics

The present invention relates to a process and system for depositing a thin film onto a substrate. One aspect of the invention is depositing a thin film metal oxide layer using atomic layer deposition (ALD).

Owner:ASM IP HLDG BV

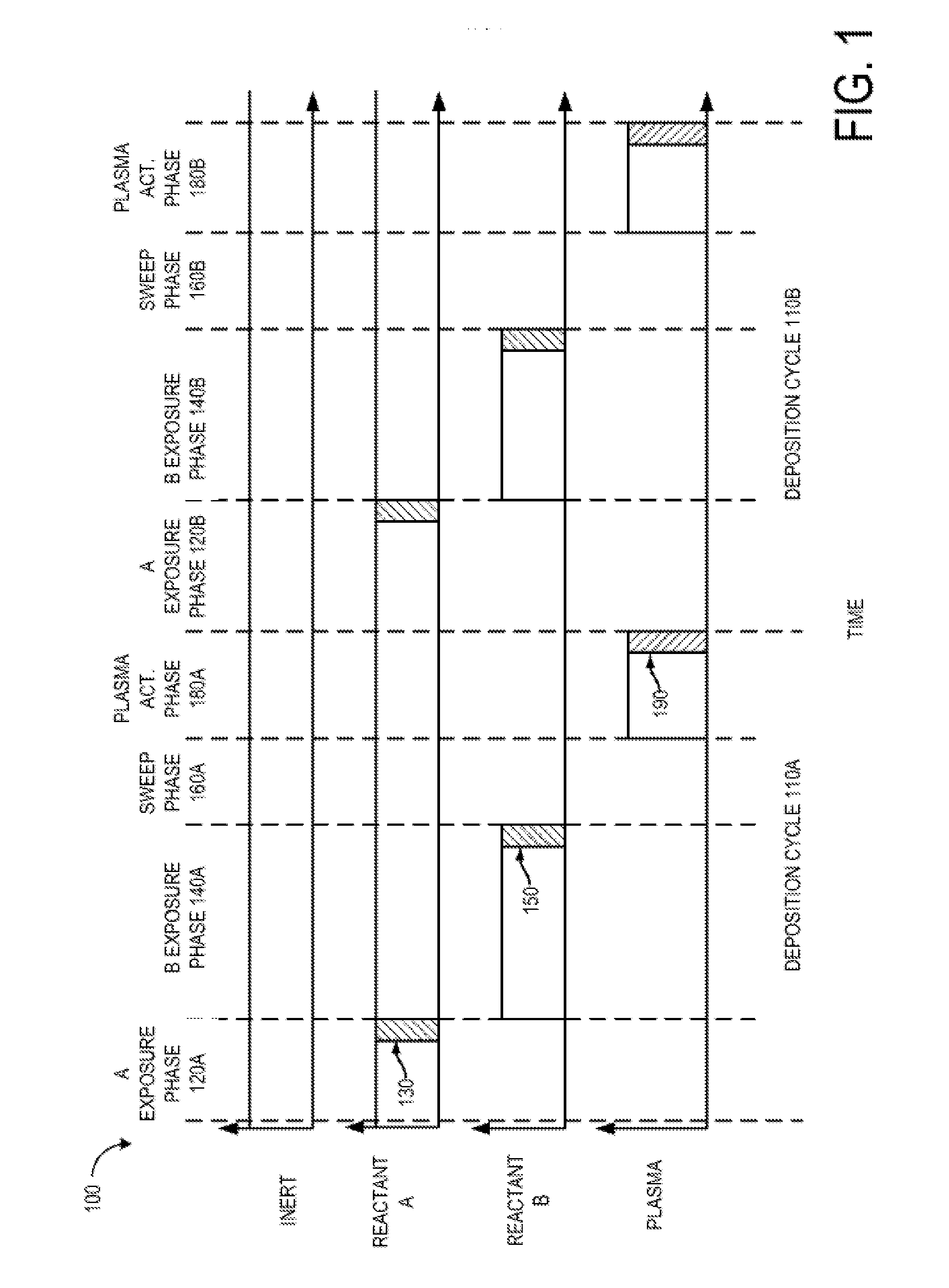

Systems and methods for thin-film deposition of metal oxides using excited nitrogen-oxygen species

ActiveUS8802201B2Enhance growth rate and uniformityUniform growthSemiconductor/solid-state device detailsSolid-state devicesNitrogenOptoelectronics

The present invention relates to a process and system for depositing a thin film onto a substrate. One aspect of the invention is depositing a thin film metal oxide layer using atomic layer deposition (ALD).

Owner:ASM IP HLDG BV

Systems and methods for thin-film deposition of metal oxides using excited nitrogen-oxygen species

ActiveUS20120098107A1Enhance growth rate and uniformityUniform growthSemiconductor/solid-state device detailsSolid-state devicesNitrogenOptoelectronics

The present invention relates to a process and system for depositing a thin film onto a substrate. One aspect of the invention is depositing a thin film metal oxide layer using atomic layer deposition (ALD).

Owner:ASM IP HLDG BV

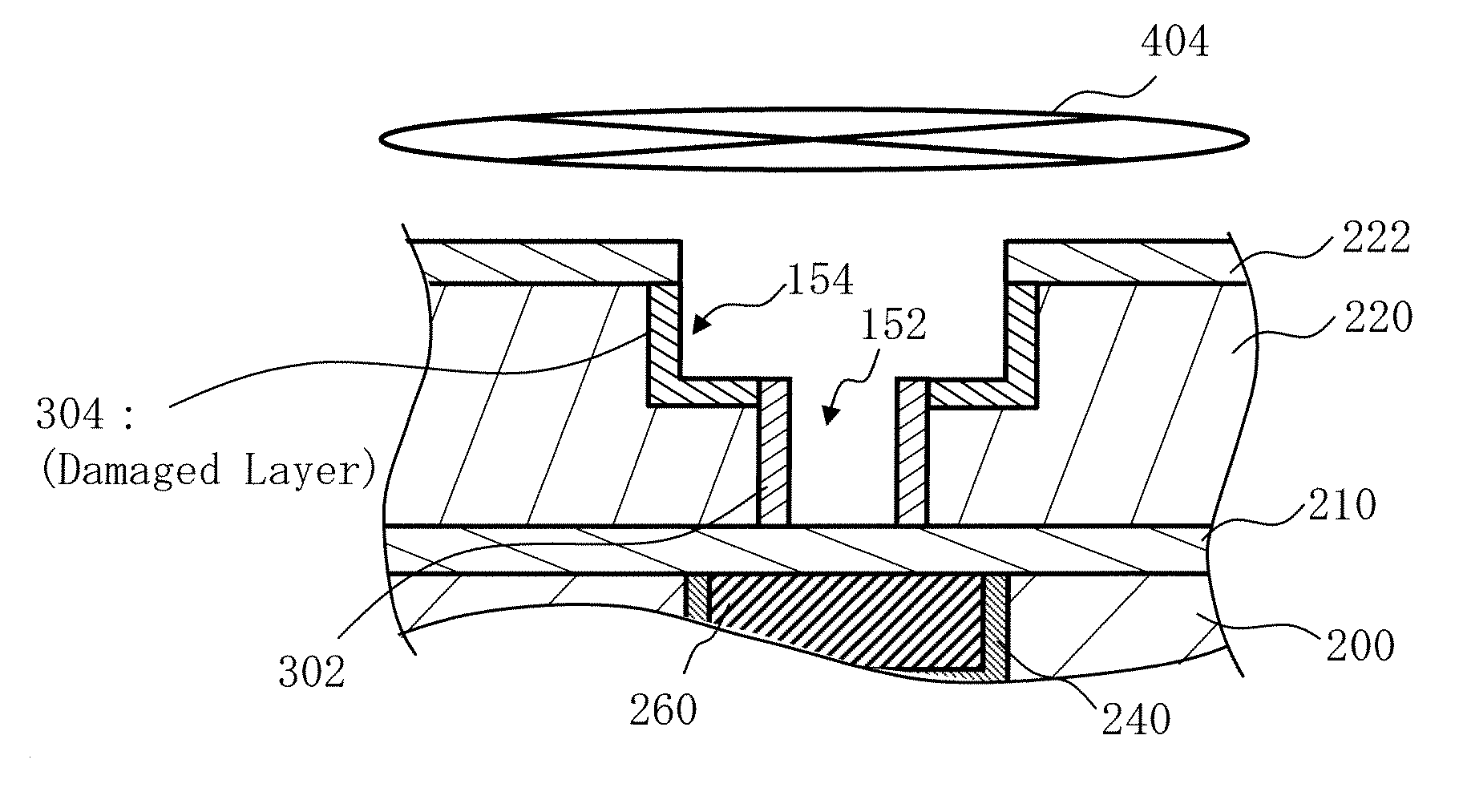

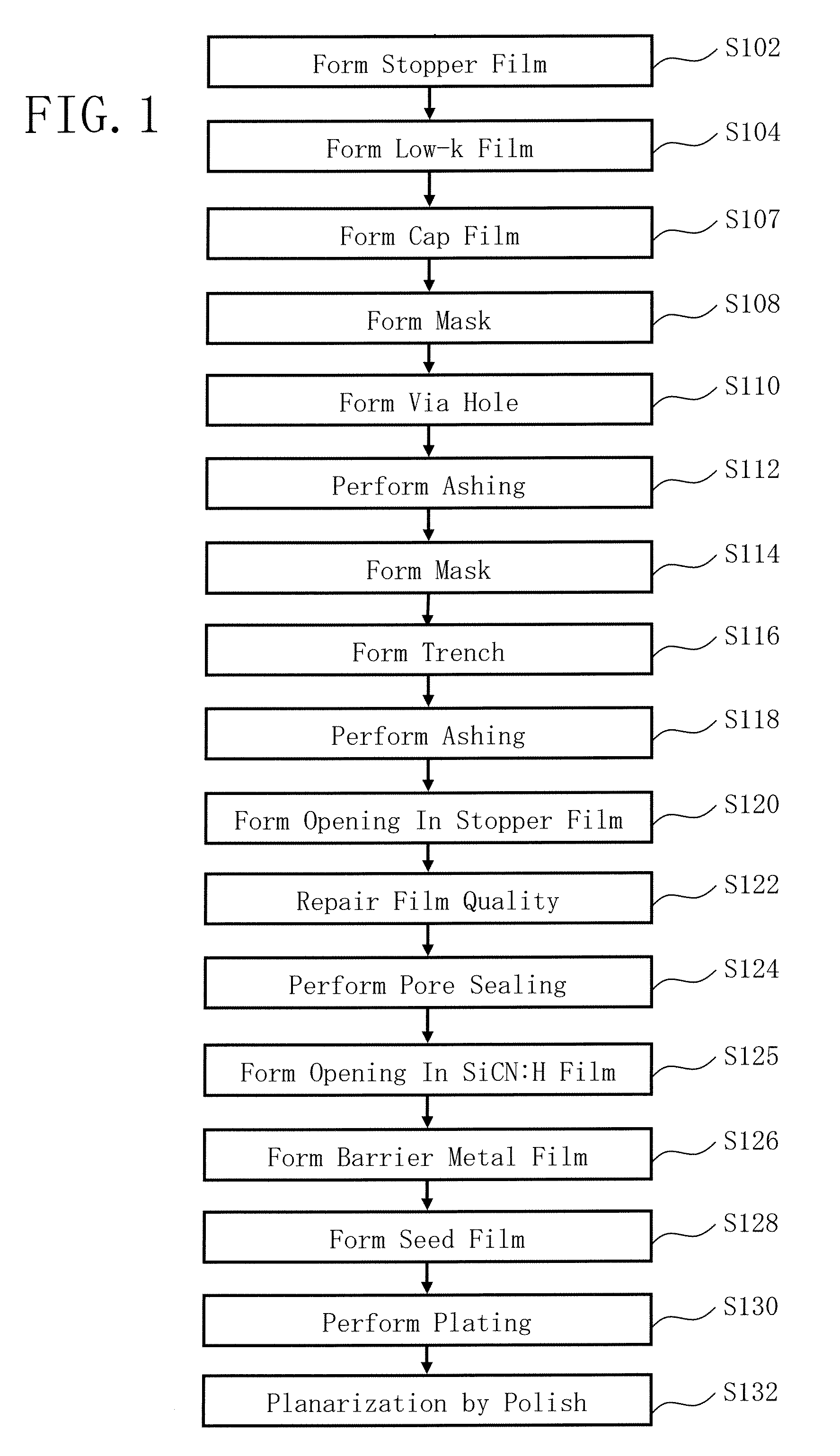

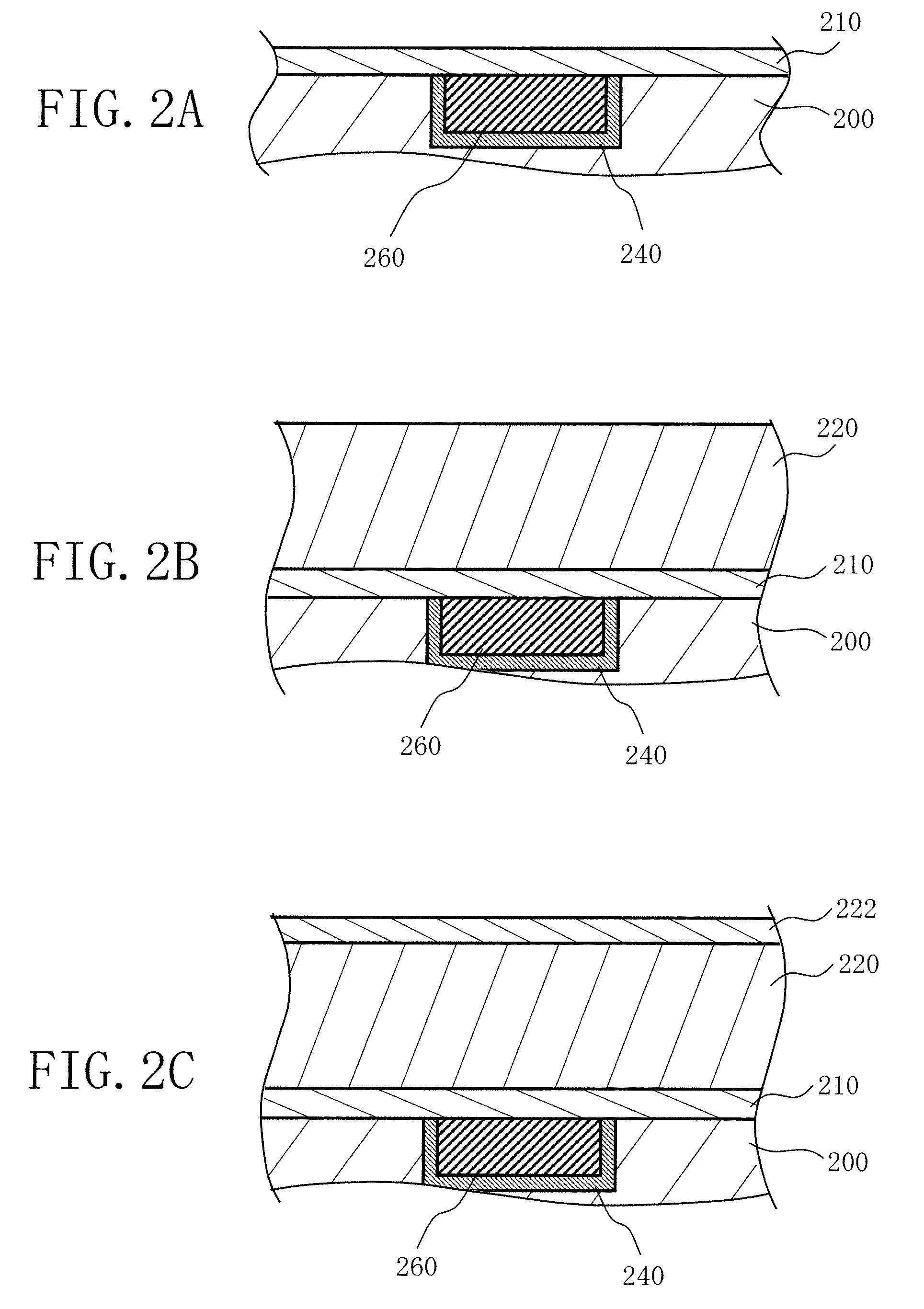

Method for fabricating semiconductor device

InactiveUS7842518B2Semiconductor/solid-state device detailsSolid-state devicesOptoelectronicsSemiconductor

A method for fabricating a semiconductor device, includes forming a porous dielectric film above a substrate using a porous insulating material, forming an opening in the porous dielectric film, repairing film quality of the porous dielectric film on a surface of the opening by feeding a predetermined gas replacing a Si—OH group to the opening, and performing pore sealing of the surface of the opening using the same predetermined gas as that used for film quality repairs after repairing the film quality.

Owner:KK TOSHIBA

Systems and methods for thin-film deposition of metal oxides using excited nitrogen-oxygen species

ActiveUS20110275166A1Enhance growth rate and uniformityUniform growthLiquid surface applicatorsSemiconductor/solid-state device testing/measurementNitrogenOptoelectronics

The present invention relates to a process and system for depositing a thin film onto a substrate. One aspect of the invention is depositing a thin film metal oxide layer using atomic layer deposition (ALD).

Owner:ASM IP HLDG BV

Method of forming MEMS device

InactiveUS6861277B1Decorative surface effectsSemiconductor/solid-state device manufacturingConductive materialsOptoelectronics

A method of forming a MEMS device includes depositing a conductive material on a substructure, forming a first sacrificial layer over the conductive material, including forming a substantially planar surface of the first sacrificial layer, and forming a first element over the substantially planar surface of the first sacrificial layer, including communicating the first element with the conductive material through the first sacrificial layer. In addition, the method includes forming a second sacrificial layer over the first element, including forming a substantially planar surface of the second sacrificial layer, forming a support through the second sacrificial layer to the first element after forming the second sacrificial layer, including filling the support, and forming a second element over the support and the substantially planar surface of the second sacrificial layer. As such, the method further includes substantially removing the first sacrificial layer and the second sacrificial layer, thereby supporting the second element relative to the first element with the support.

Owner:TAIWAN SEMICON MFG CO LTD

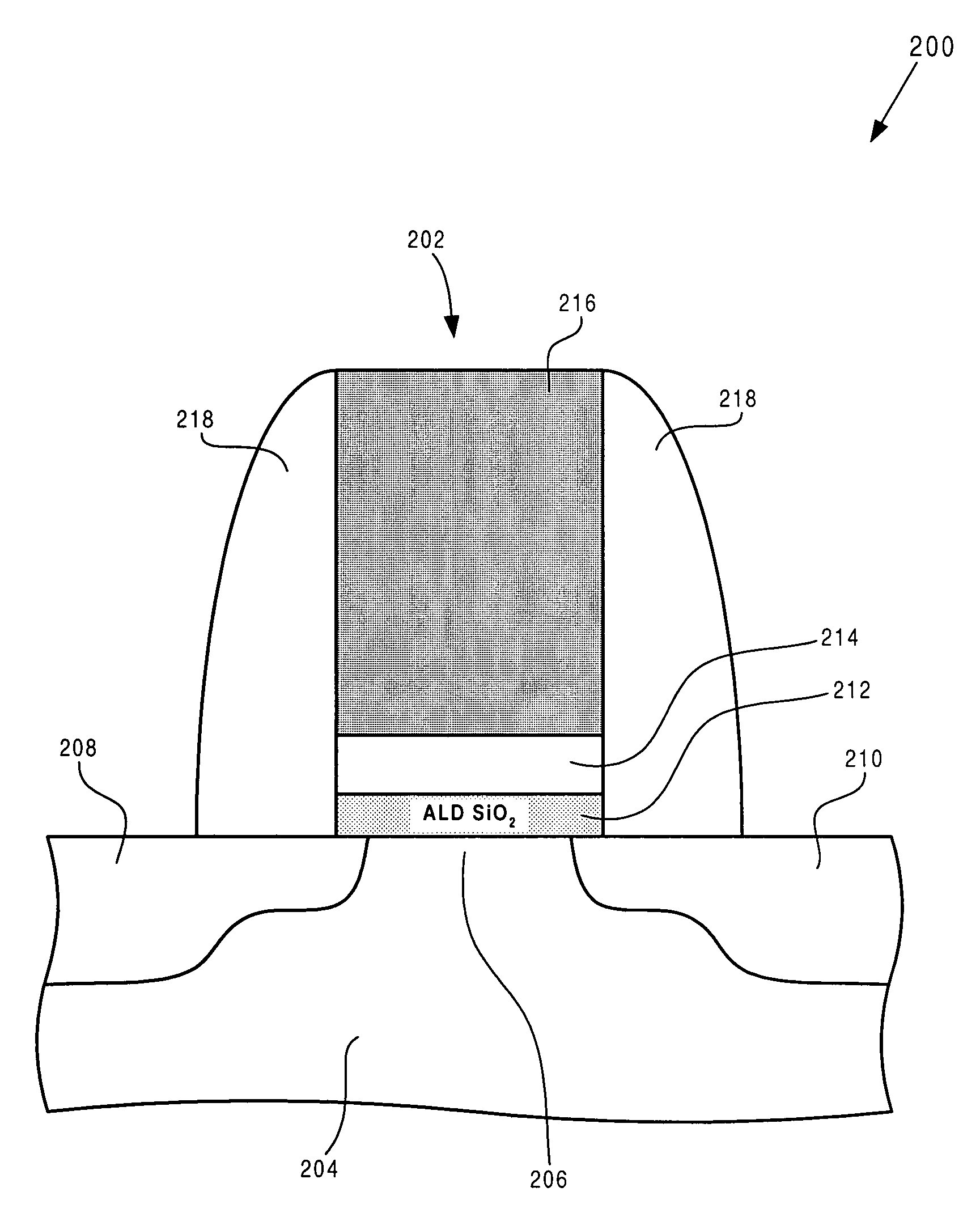

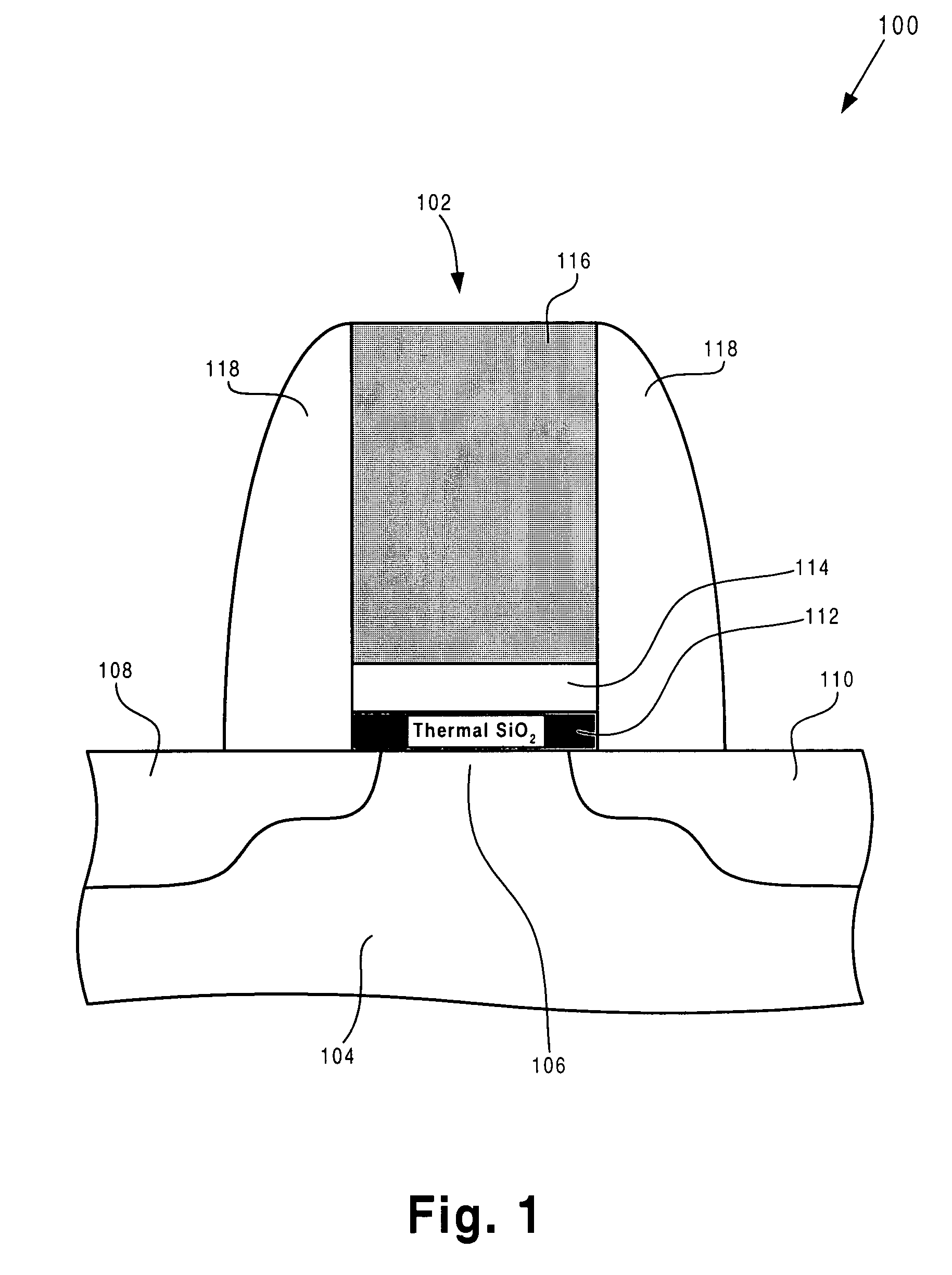

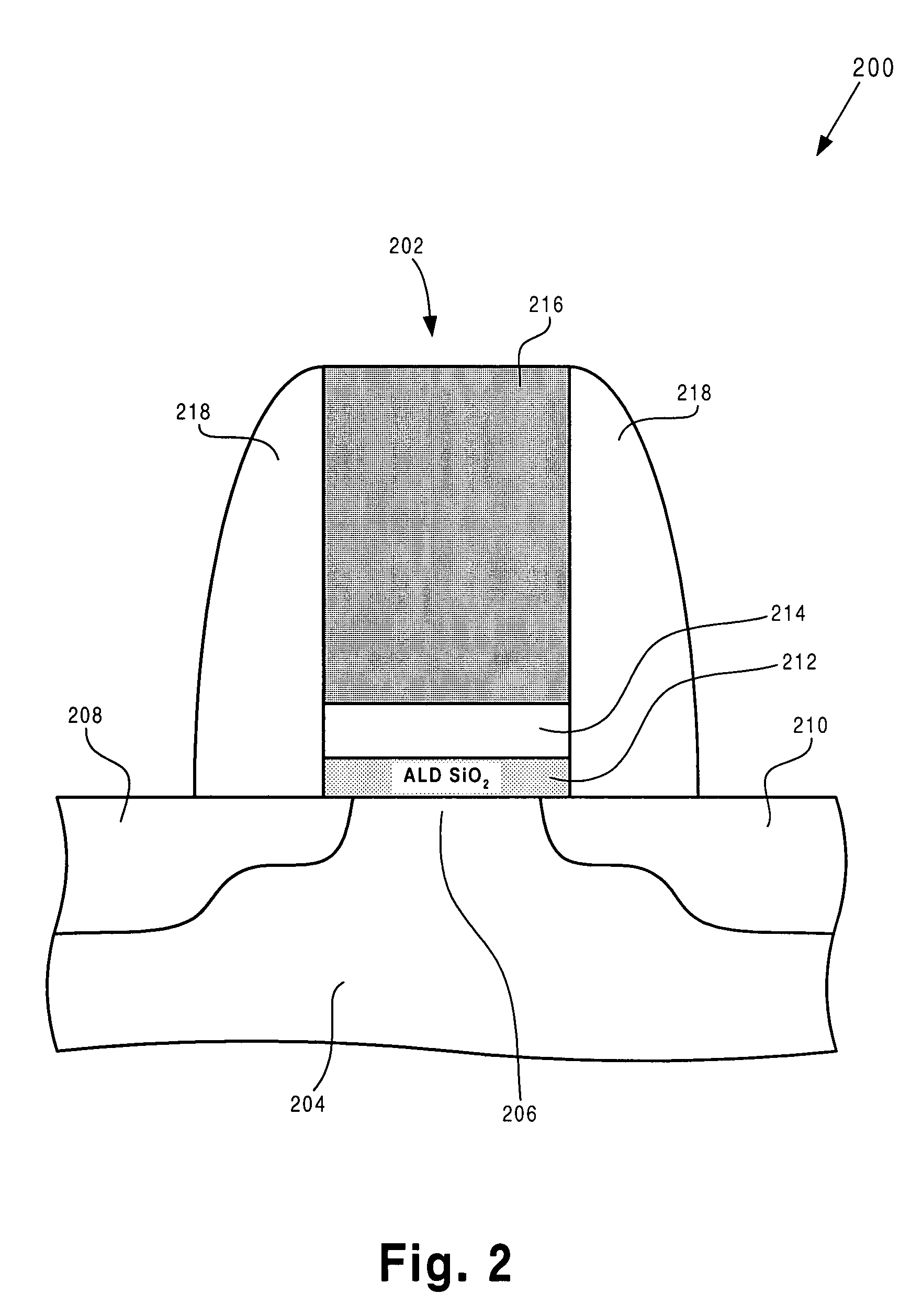

Method for forming a thin, high quality buffer layer in a field effect transistor and related structure

ActiveUS7071051B1Readily apparentSemiconductor/solid-state device manufacturingSemiconductor devicesOrganic field-effect transistorOptoelectronics

According to one exemplary embodiment, a method for forming a field-effect transistor on a substrate comprises a step of forming a buffer layer on the substrate, where the buffer layer comprises ALD silicon dioxide. The buffer layer can be formed by utilizing a silicon tetrachloride precursor in an atomic layer deposition process, for example. The buffer layer comprises substantially no pin-hole defects and may have a thickness, for example, that is less than approximately 5.0 Angstroms. The method further comprises forming a high-k dielectric layer over the buffer layer. The high-k dielectric layer may be, for example, hafnium oxide, zirconium oxide, or aluminum oxide. According to this exemplary embodiment, the method further comprises forming a gate electrode layer over the high-k dielectric layer. The gate electrode layer may be polycrystalline silicon, for example.

Owner:GLOBALFOUNDRIES US INC

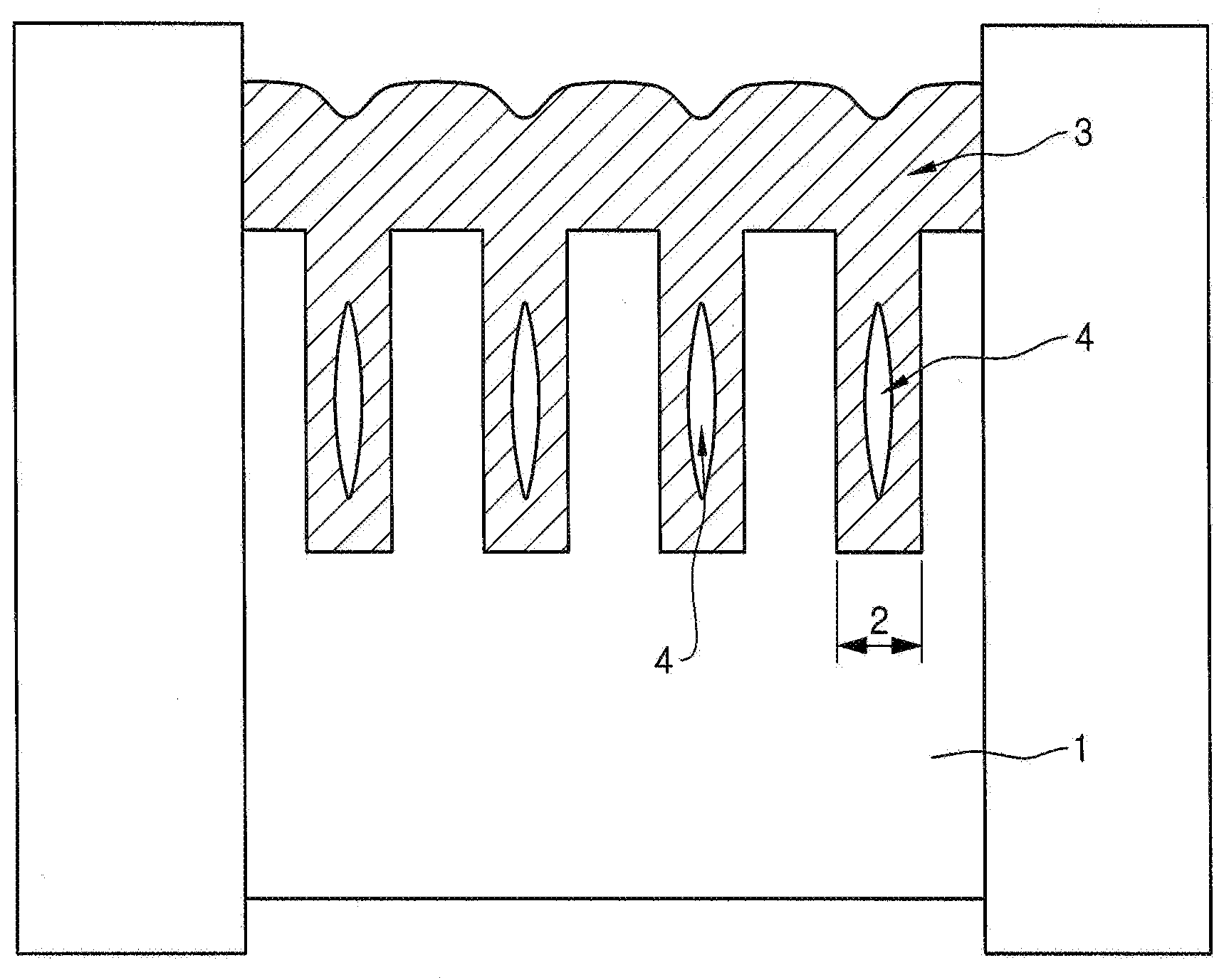

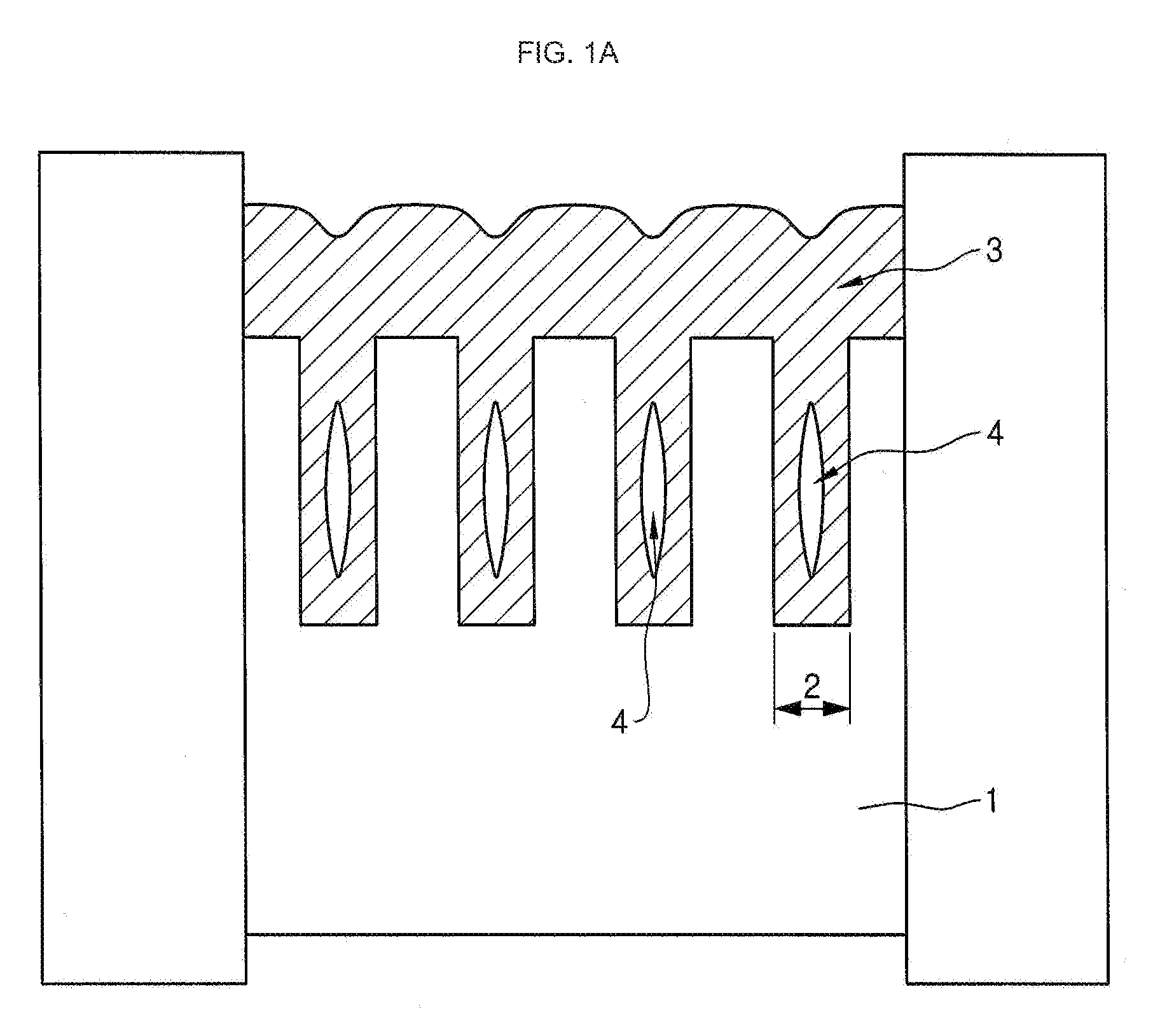

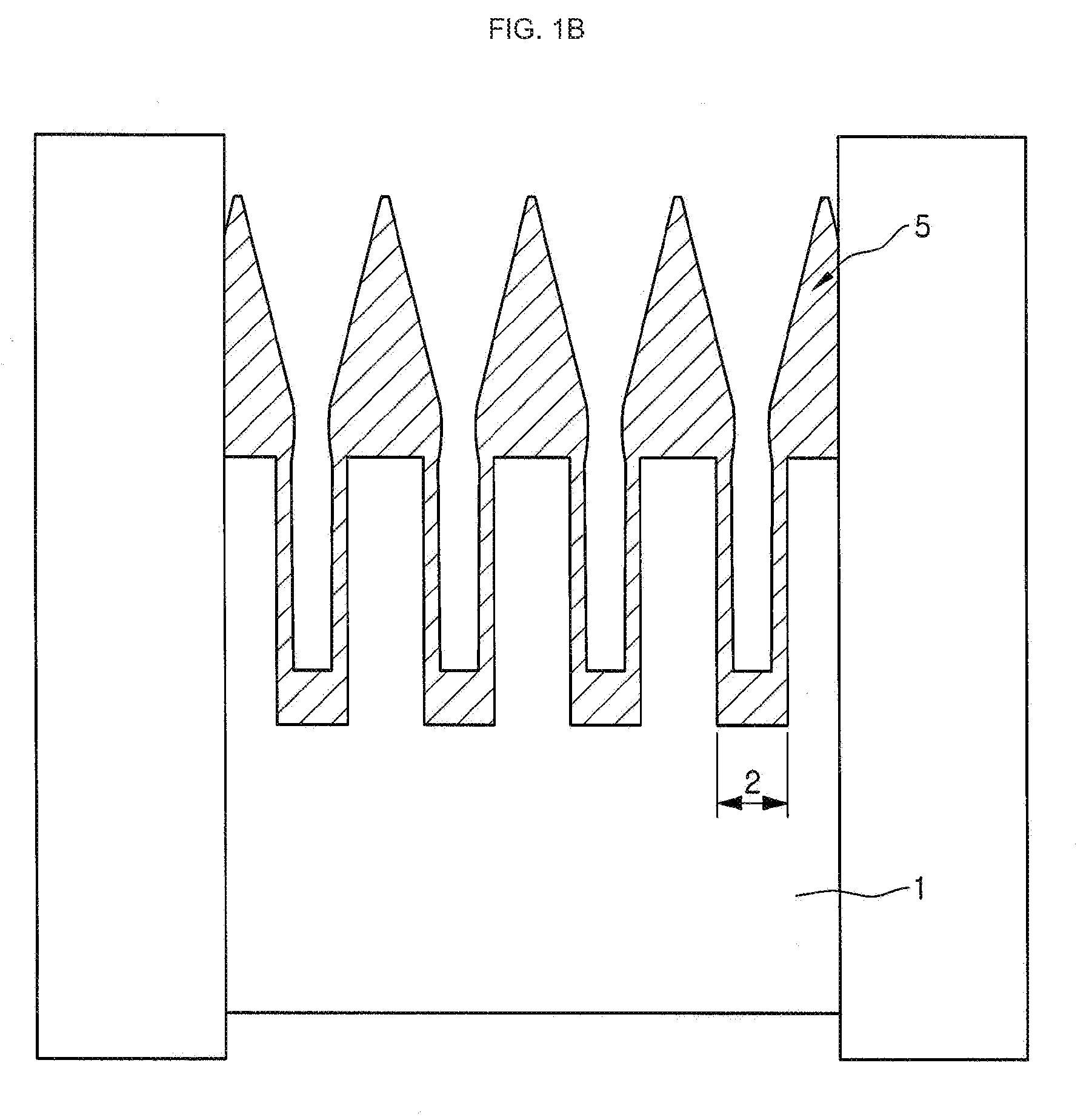

Forming Substrate Structure by Filling Recesses with Deposition Material

InactiveUS20100041179A1Semiconductor/solid-state device manufacturingOptoelectronicsMaterials science

Owner:VEECO ALD

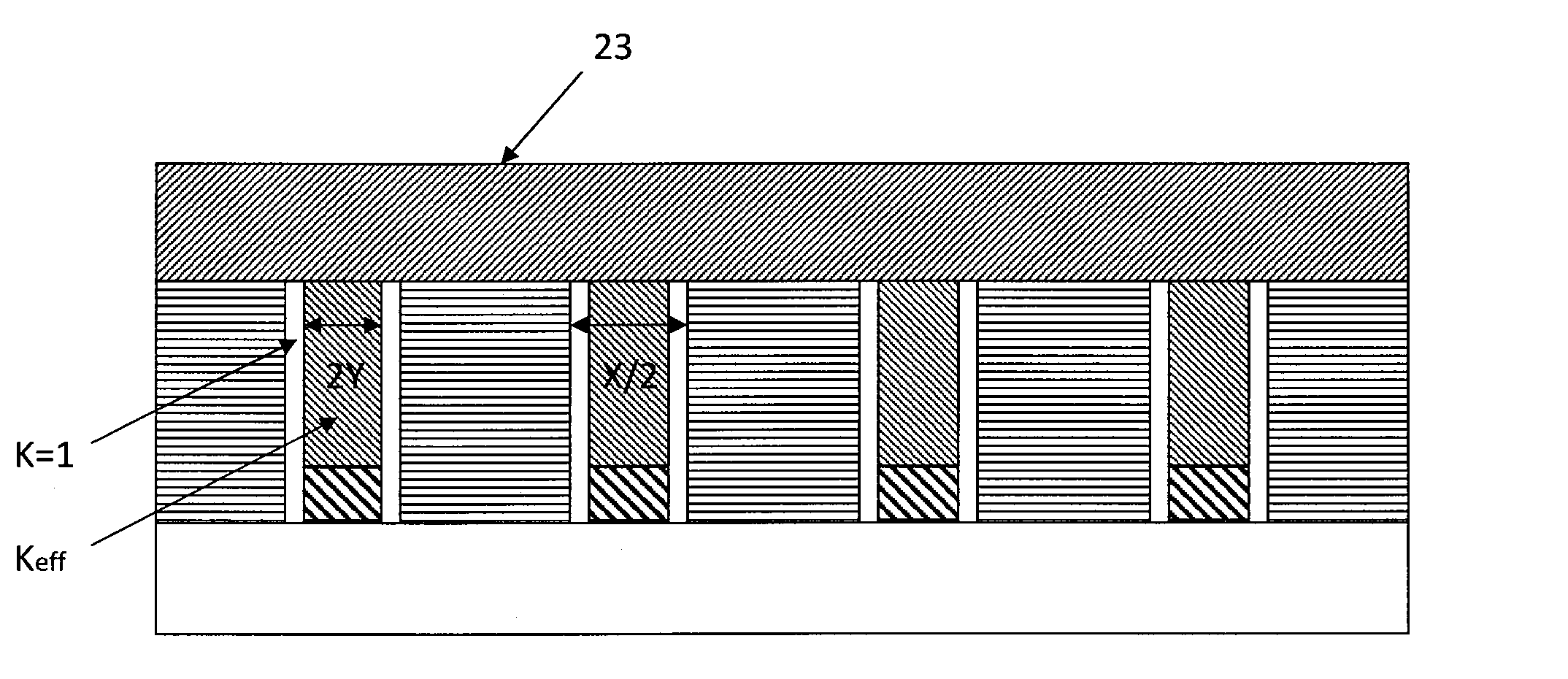

Method for forming interconnect structure having airgap

ActiveUS8241991B2Reducing KeffSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsCopper

A method for forming an interconnect structure with airgaps, includes: providing a structure having a trench formed on a substrate; depositing a spacer oxide layer on sidewalls of the trench as sidewall spacers by plasma enhanced atomic layer deposition; filling the trench having the sidewall spacers with copper; removing the sidewall spacers to form an airgap structure; and encapsulating the airgap structure, wherein airgaps are formed between the filled copper and the sidewalls of the trench.

Owner:ASM JAPAN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com