Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6074 results about "Dielectric permittivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dielectric Permittivity. Dielectric permittivity (ε) is grounded in complex physics but in simple terms it can be described as the ability of a substance to hold an electrical charge.

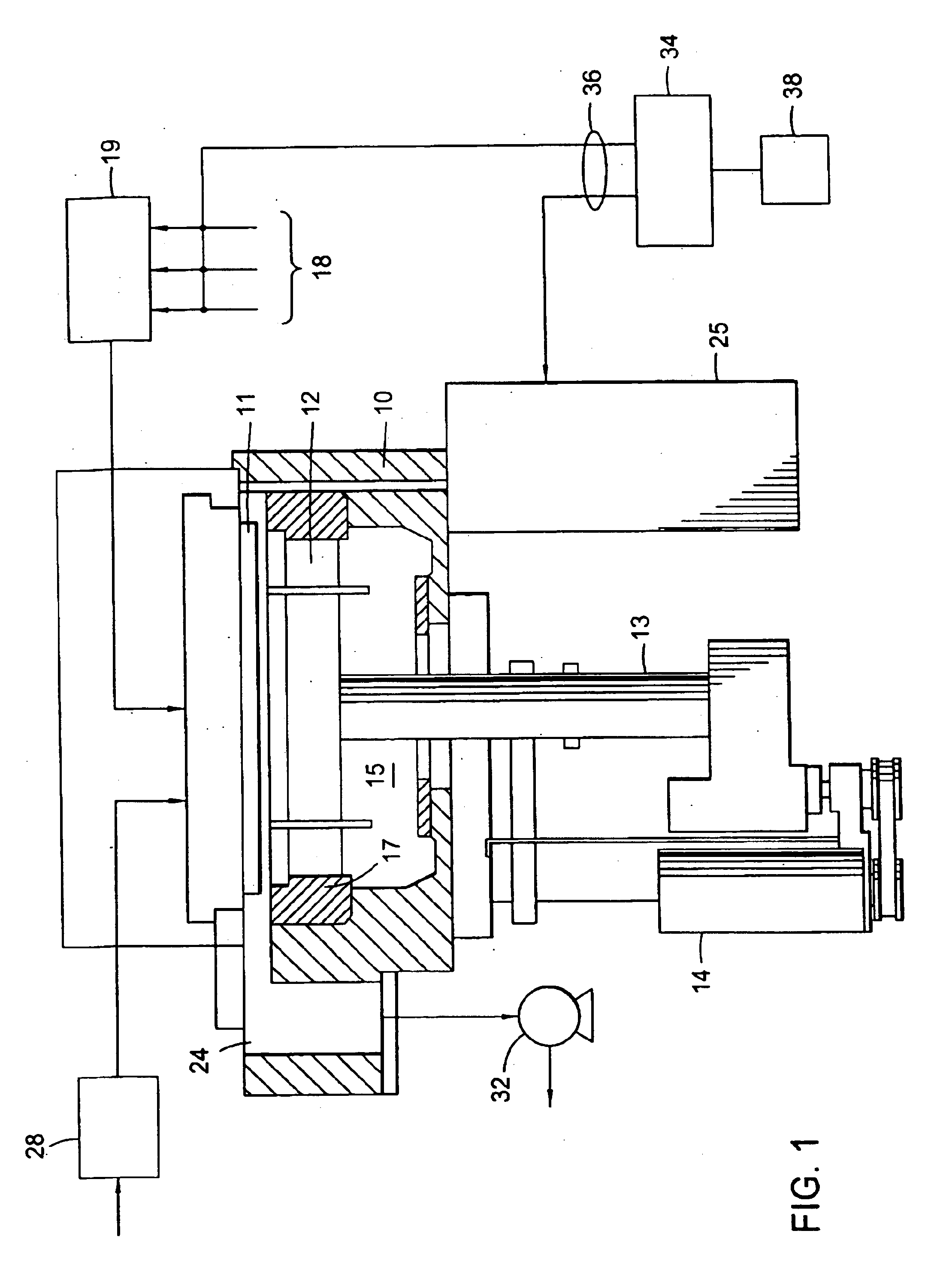

Formation of a liquid-like silica layer by reaction of an organosilicon compound and a hydroxyl forming compound

InactiveUS6413583B1Semiconductor/solid-state device detailsSolid-state devicesSilicon oxideSilicon dioxide

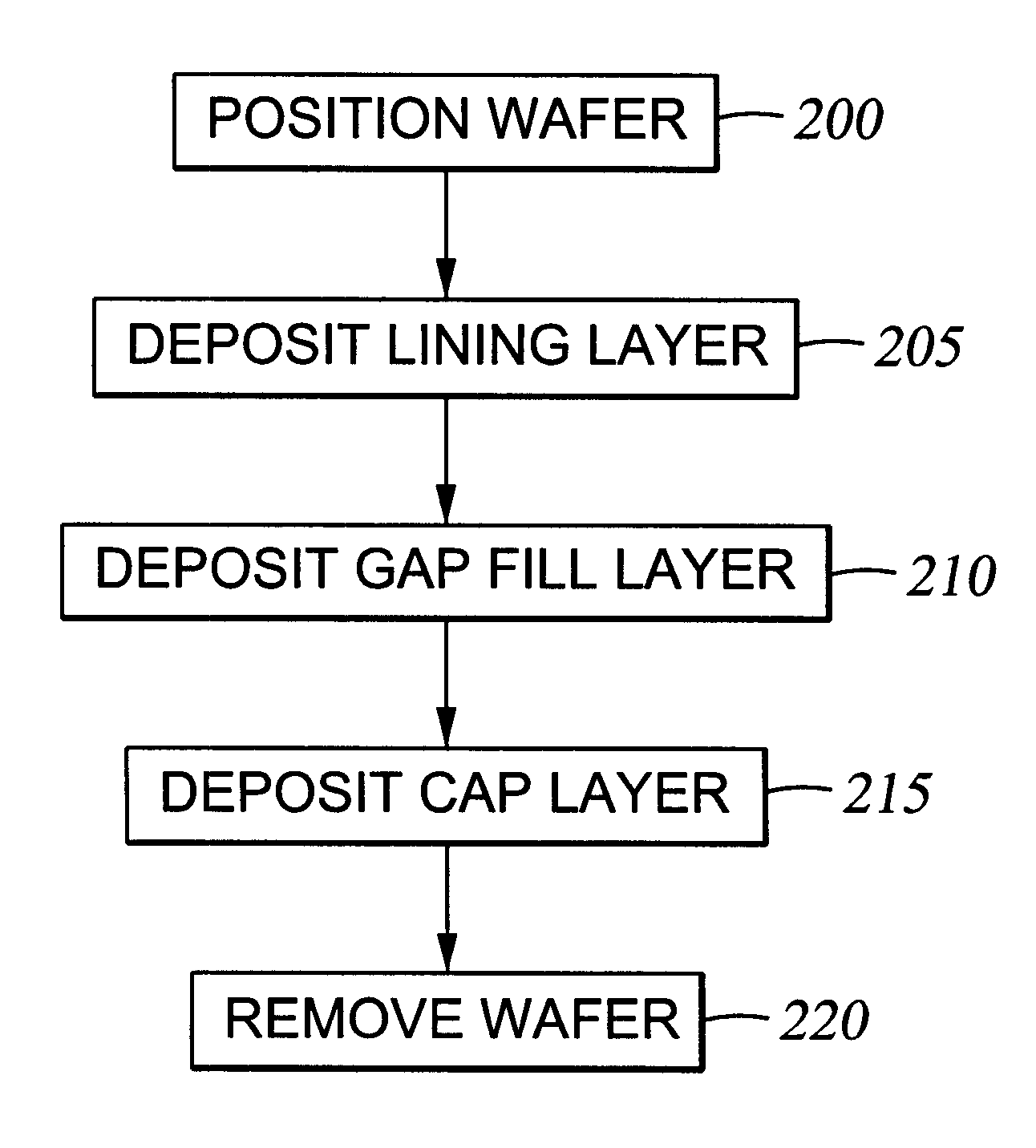

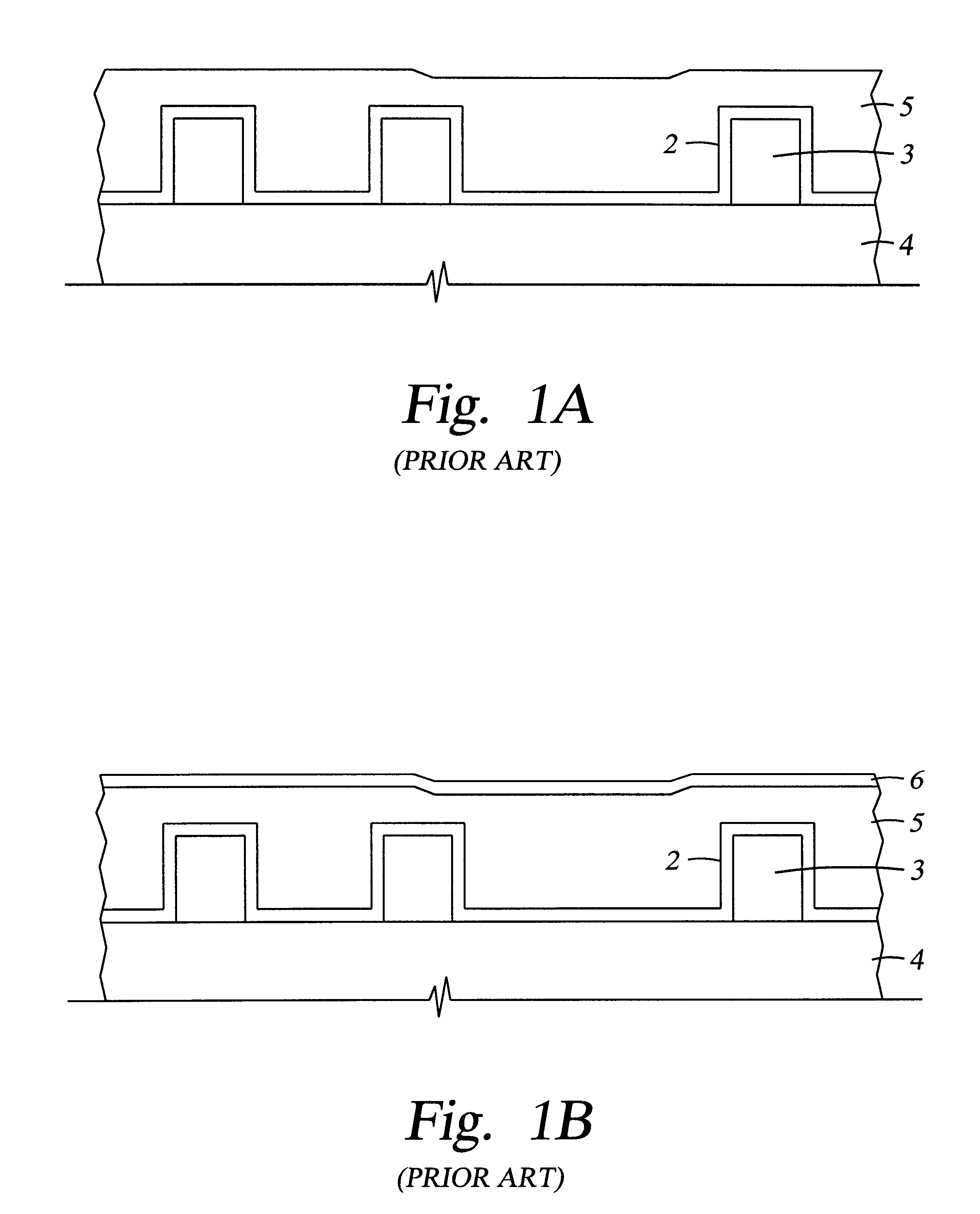

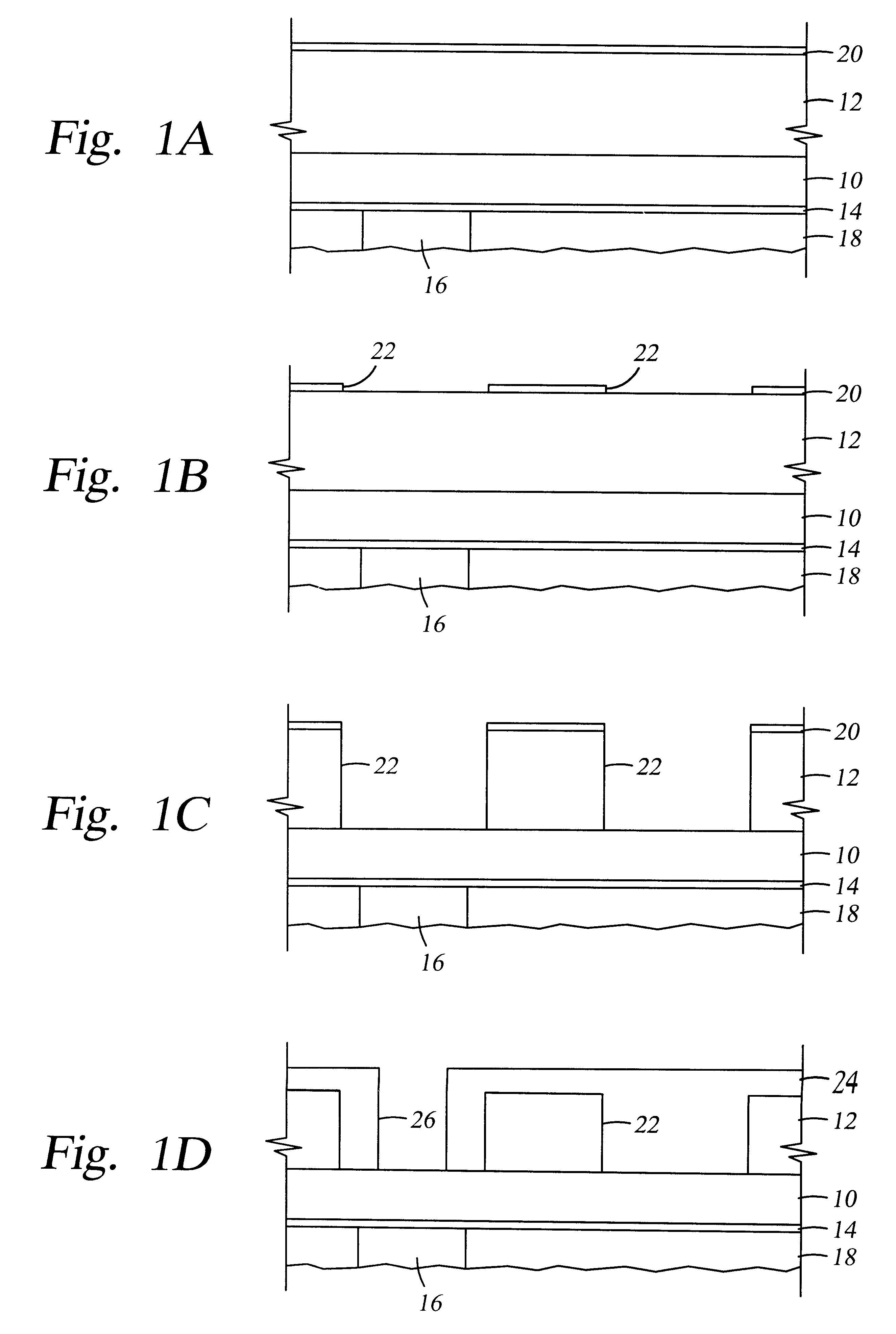

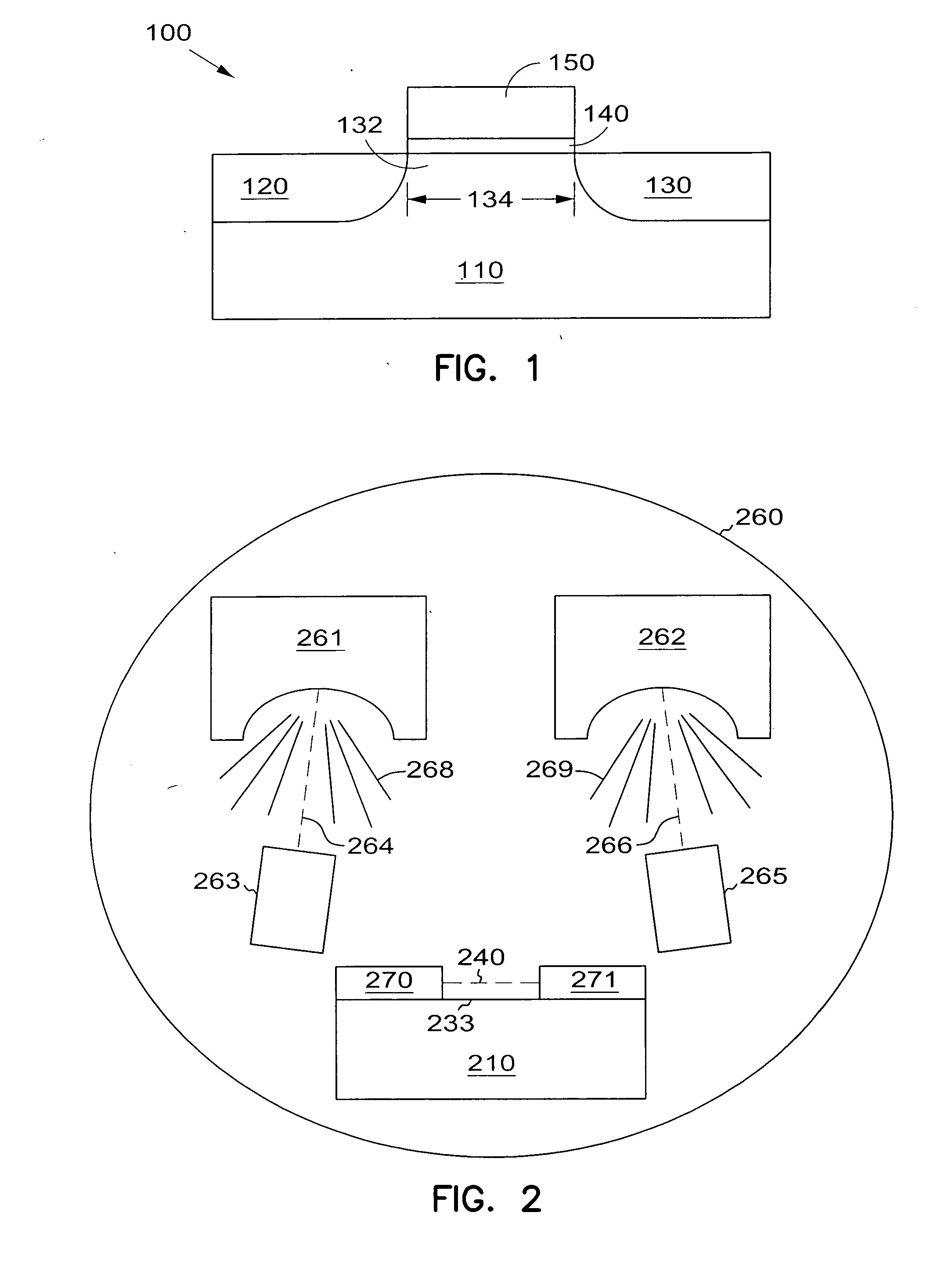

A method for depositing silicon oxide layers having a low dielectric constant by reaction of an organosilicon compound and a hydroxyl forming compound at a substrate temperature less than about 400° C. The low dielectric constant films contain residual carbon and are useful for gap fill layers, pre-metal dielectric layers, inter-metal dielectric layers, and shallow trench isolation dielectric layers in sub-micron devices. The hydroxyl compound can be prepared prior to deposition from water or an organic compound. The silicon oxide layers are preferably deposited at a substrate temperature less than about 40° C. onto a liner layer produced from the organosilicon compound to provide gap fill layers having a dielectric constant less than about 3.0.

Owner:APPLIED MATERIALS INC

Integrated low K dielectrics and etch stops

InactiveUS6340435B1Decorative surface effectsSemiconductor/solid-state device detailsHydrogenFluorocarbon

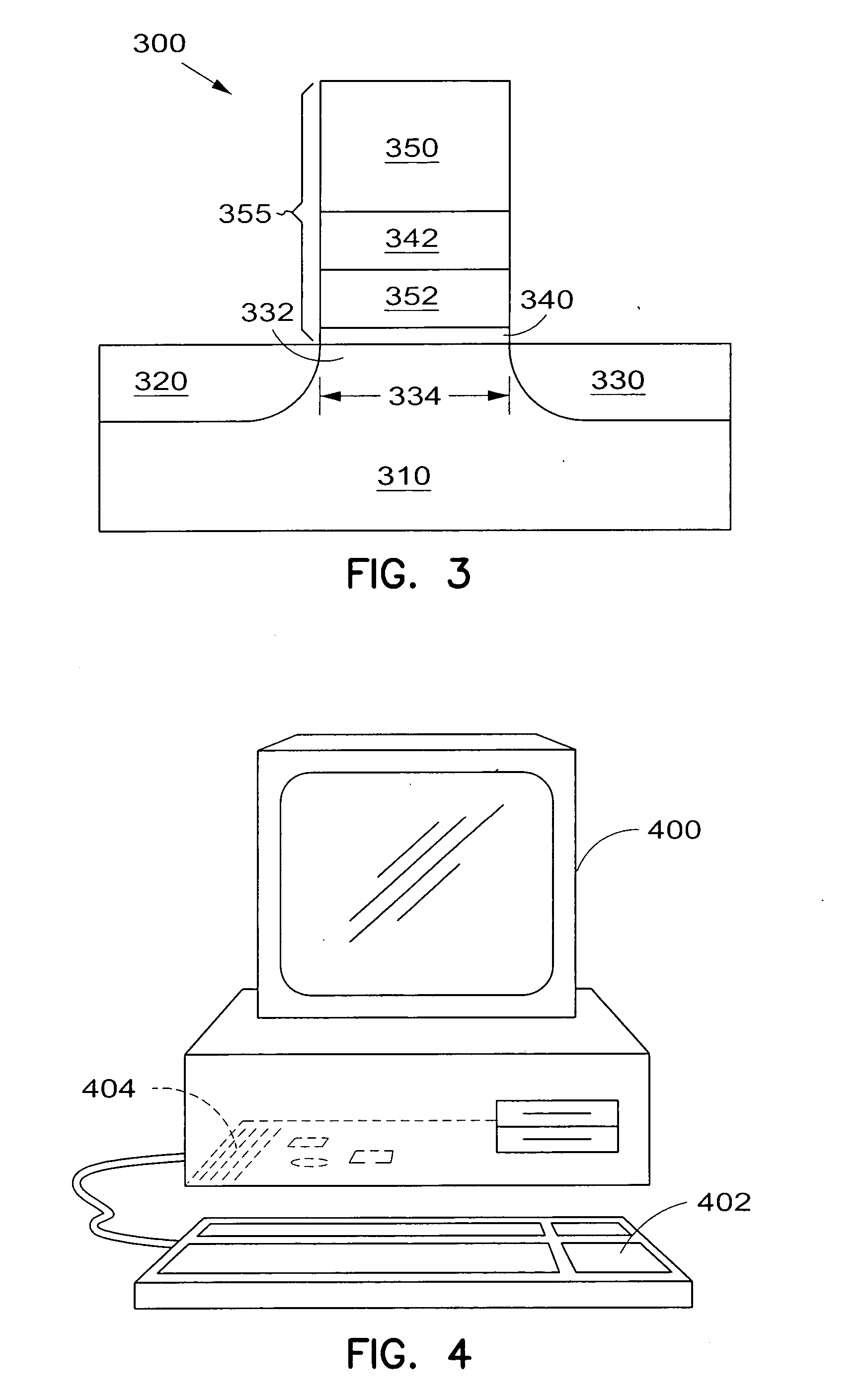

A method of depositing and etching dielectric layers having low dielectric constants and etch rates that vary by at least 3:1 for formation of horizontal interconnects. The amount of carbon or hydrogen in the dielectric layer is varied by changes in deposition conditions to provide low k dielectric layers that can replace etch stop layers or conventional dielectric layers in damascene applications. A dual damascene structure having two or more dielectric layers with dielectric constants lower than about 4 can be deposited in a single reactor and then etched to form vertical and horizontal interconnects by varying the concentration of a carbon:oxygen gas such as carbon monoxide. The etch gases for forming vertical interconnects preferably comprises CO and a fluorocarbon, and CO is preferably excluded from etch gases for forming horizontal interconnects.

Owner:APPLIED MATERIALS INC

Post treatment of low k dielectric films

ActiveUS7018941B2Semiconductor/solid-state device manufacturingOptoelectronicsDielectric permittivity

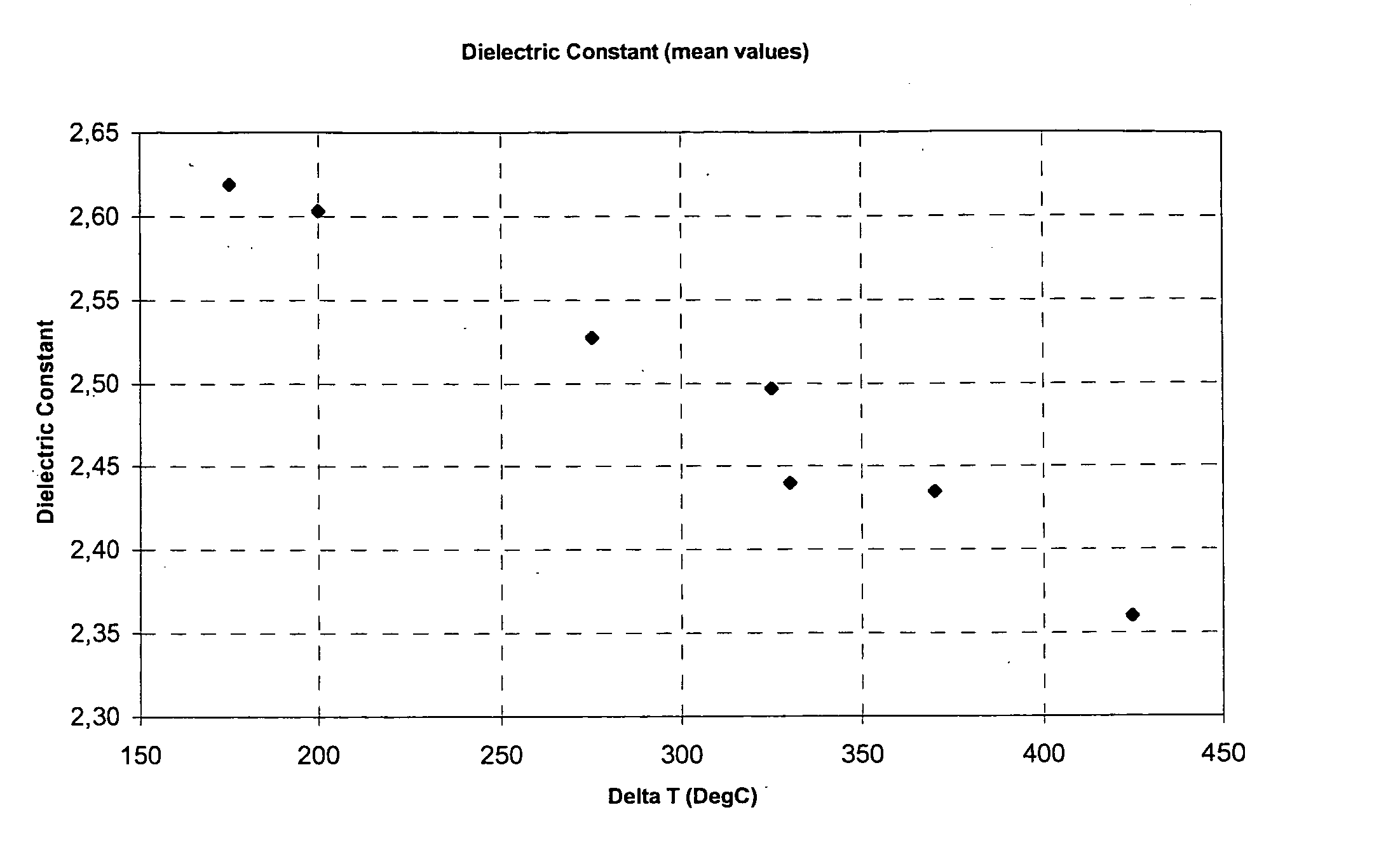

A method of depositing a low dielectric constant film on a substrate and post-treating the low dielectric constant film is provided. The post-treatment includes rapidly heating the low dielectric constant film to a desired high temperature and then rapidly cooling the low dielectric constant film such that the low dielectric constant film is exposed to the desired high temperature for about five seconds or less. In one aspect, the post-treatment also includes exposing the low dielectric constant film to an electron beam treatment and / or UV radiation.

Owner:APPLIED MATERIALS INC

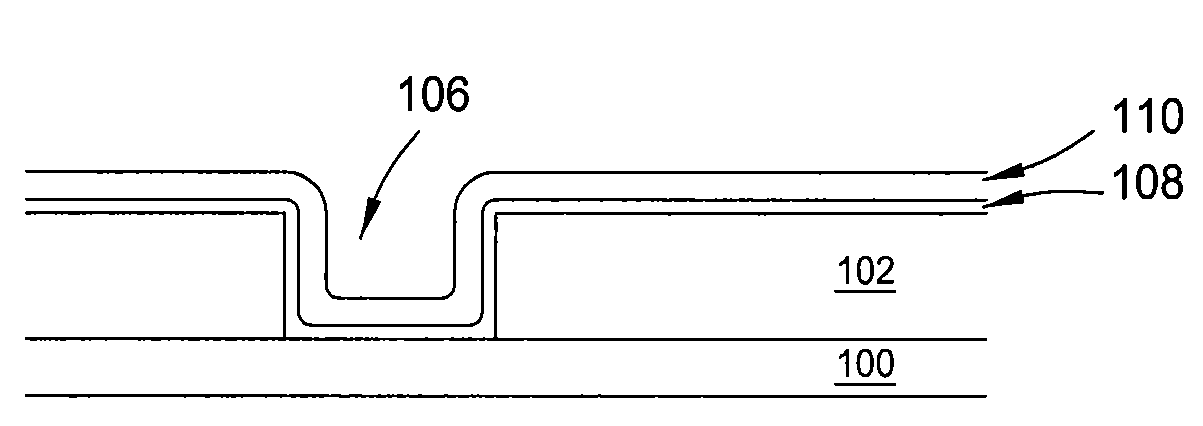

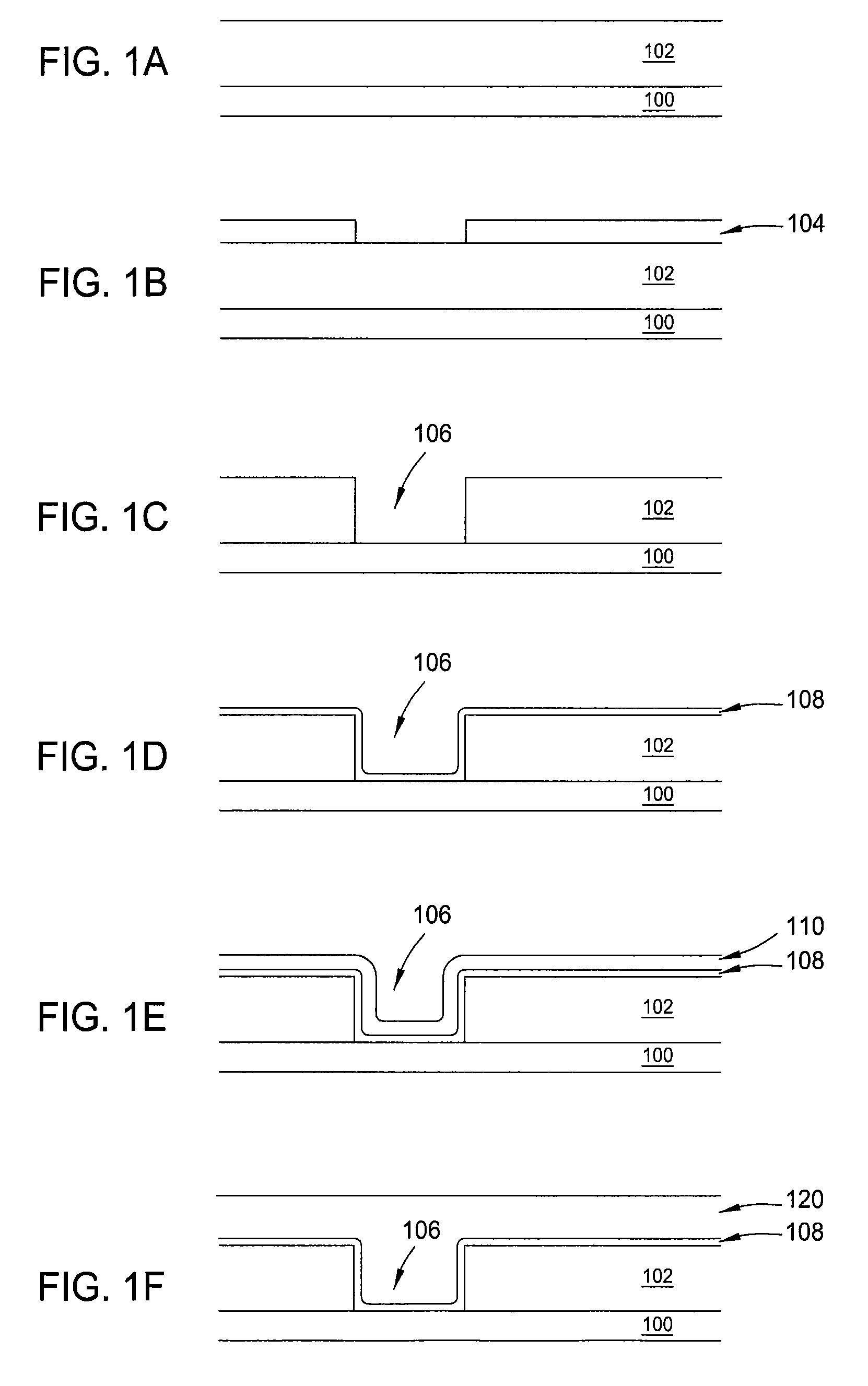

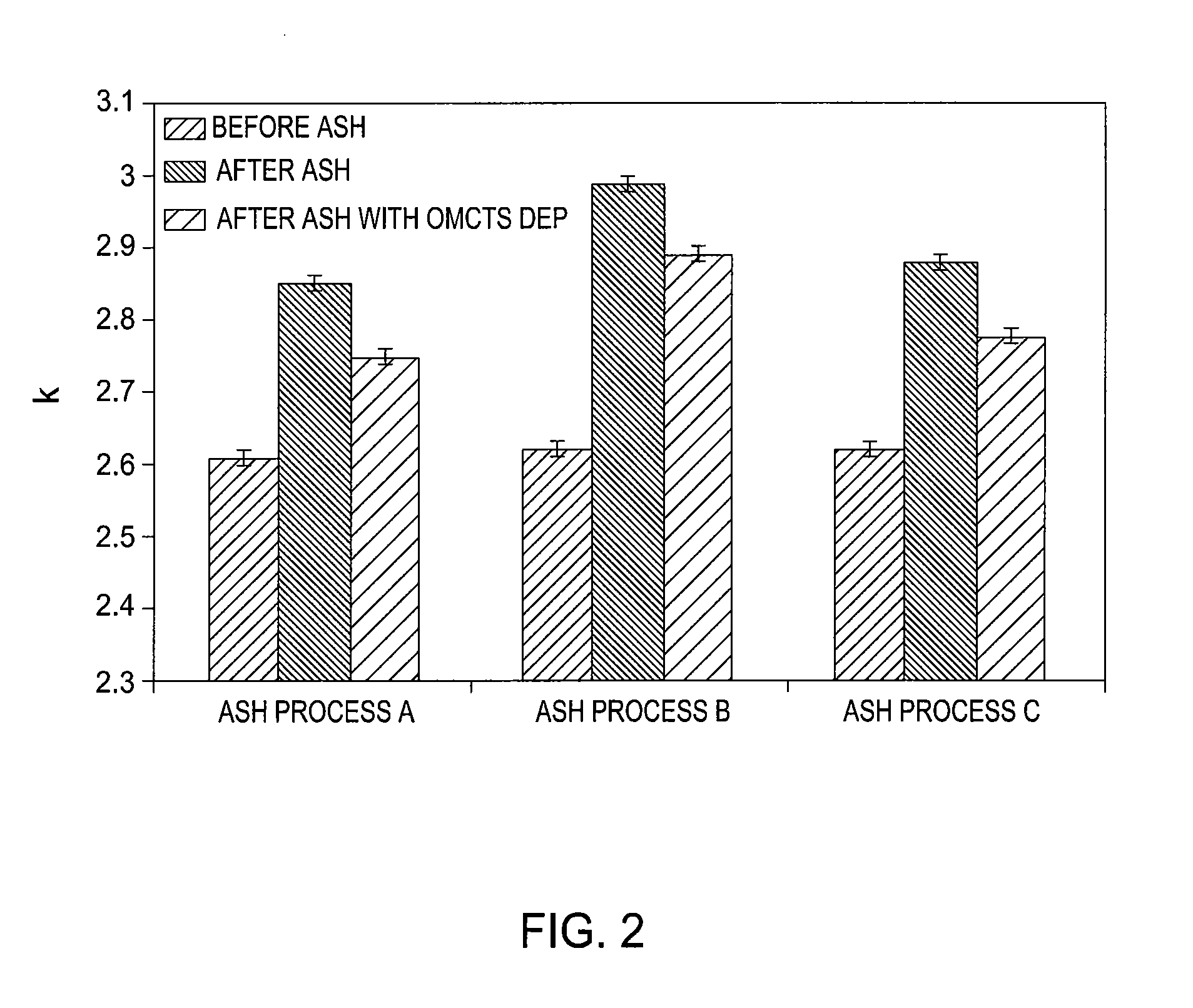

Method to minimize wet etch undercuts and provide pore sealing of extreme low k (k<2.5) dielectrics

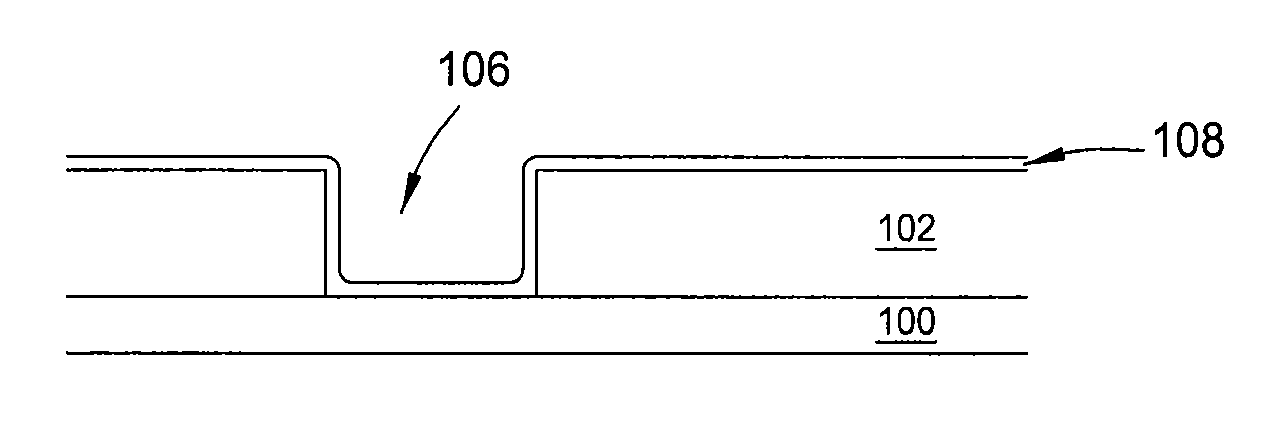

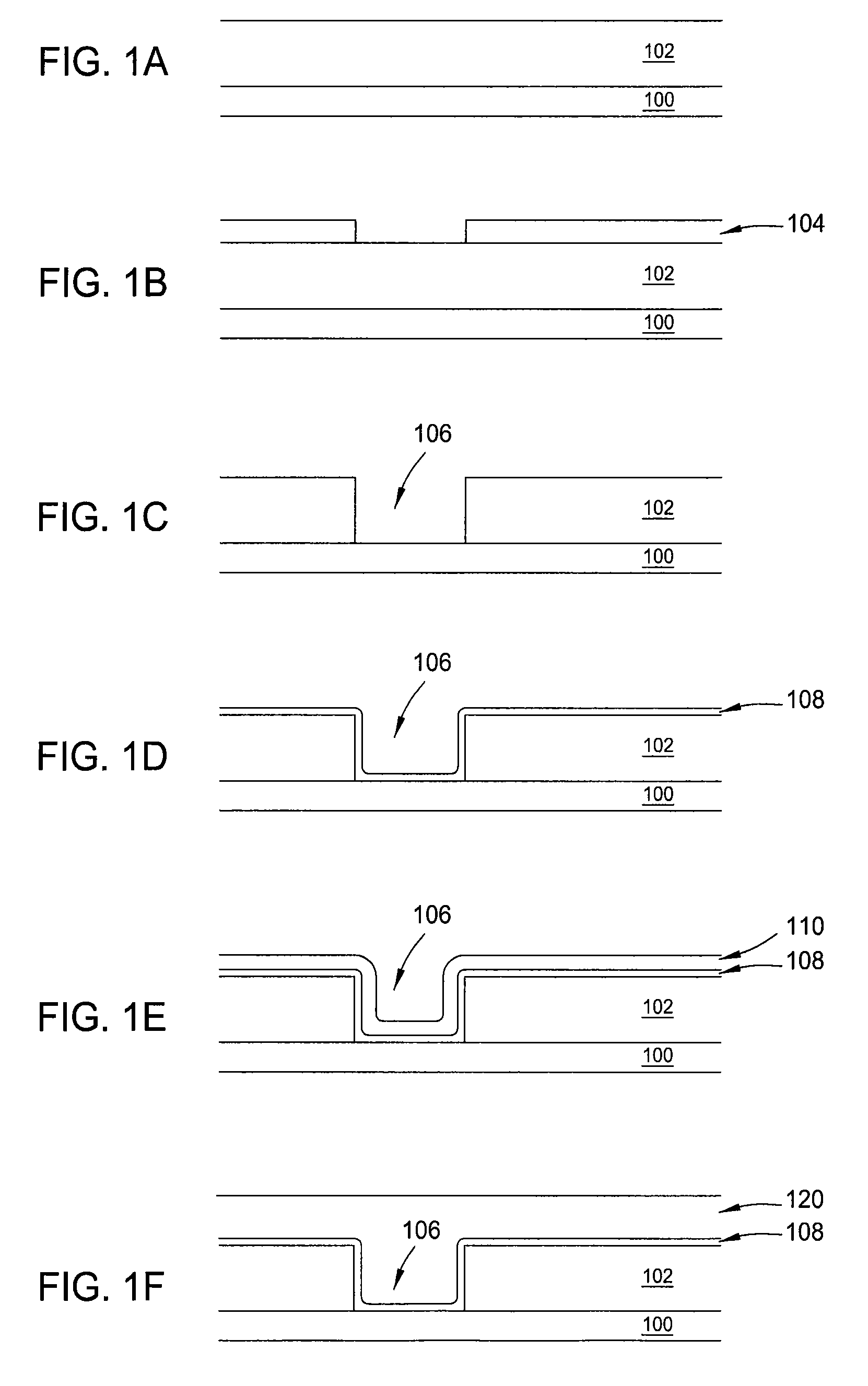

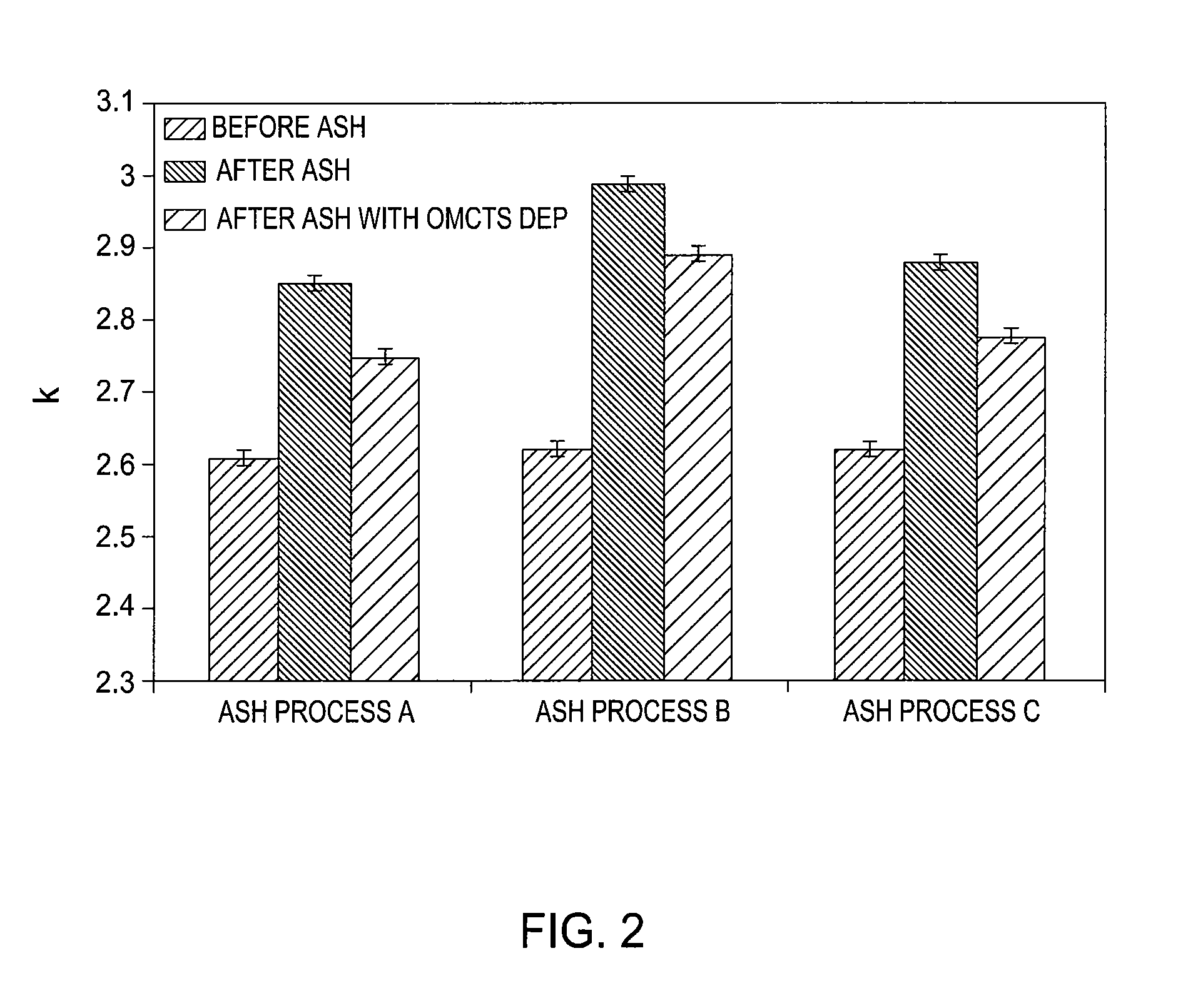

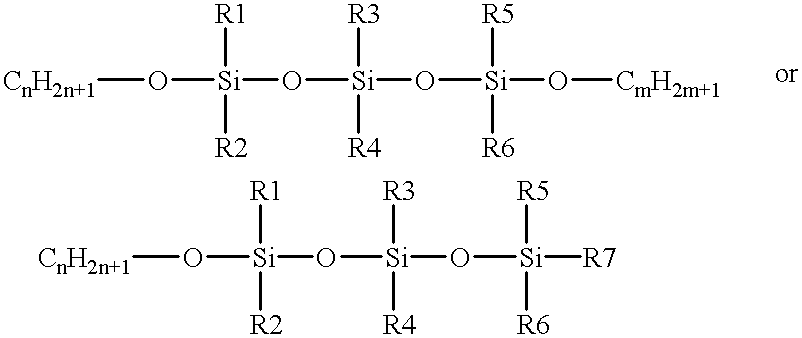

ActiveUS8445075B2Constant ratePrevents undercuts and CD lossVacuum evaporation coatingPretreated surfacesNitrogenThin layer

Methods of processing films on substrates are provided. In one aspect, the methods comprise treating a patterned low dielectric constant film after a photoresist is removed from the film by depositing a thin layer comprising silicon, carbon, and optionally oxygen and / or nitrogen on the film. The thin layer provides a carbon-rich, hydrophobic surface for the patterned low dielectric constant film. The thin layer also protects the low dielectric constant film from subsequent wet cleaning processes and penetration by precursors for layers that are subsequently deposited on the low dielectric constant film.

Owner:APPLIED MATERIALS INC

Method for fabricating an ultralow dielectric constant material as an intralevel or interlevel dielectric in a semiconductor device and electronic device made

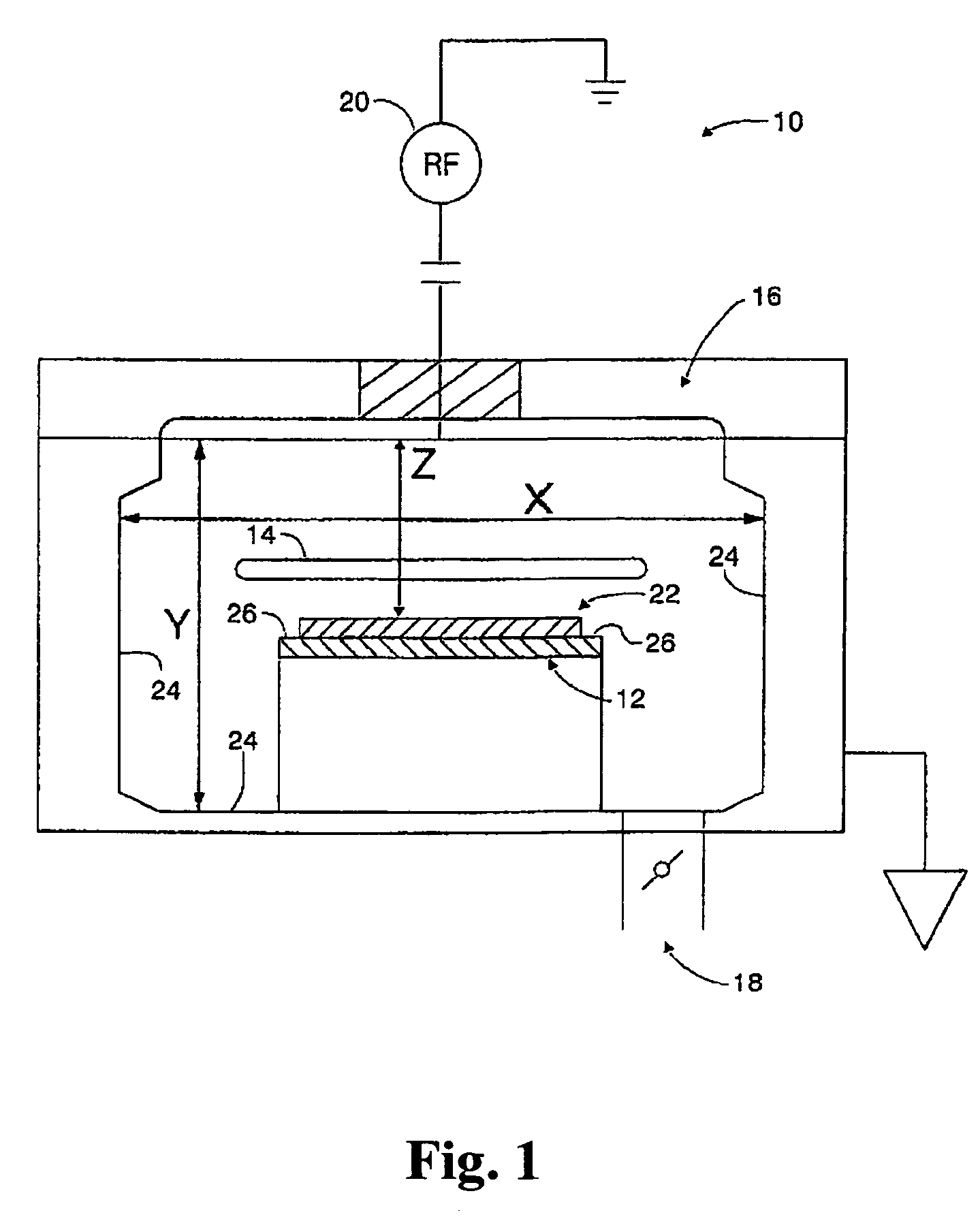

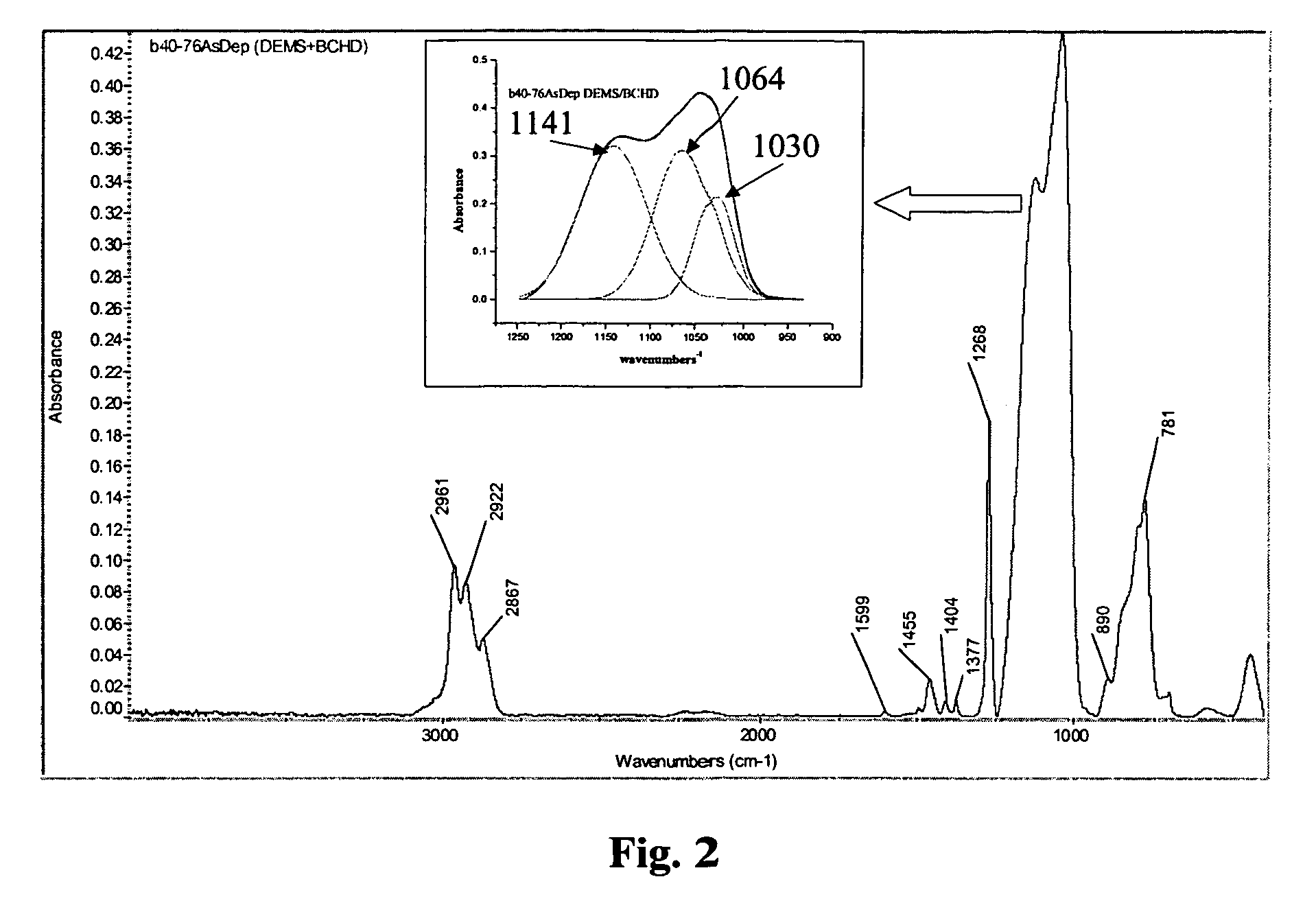

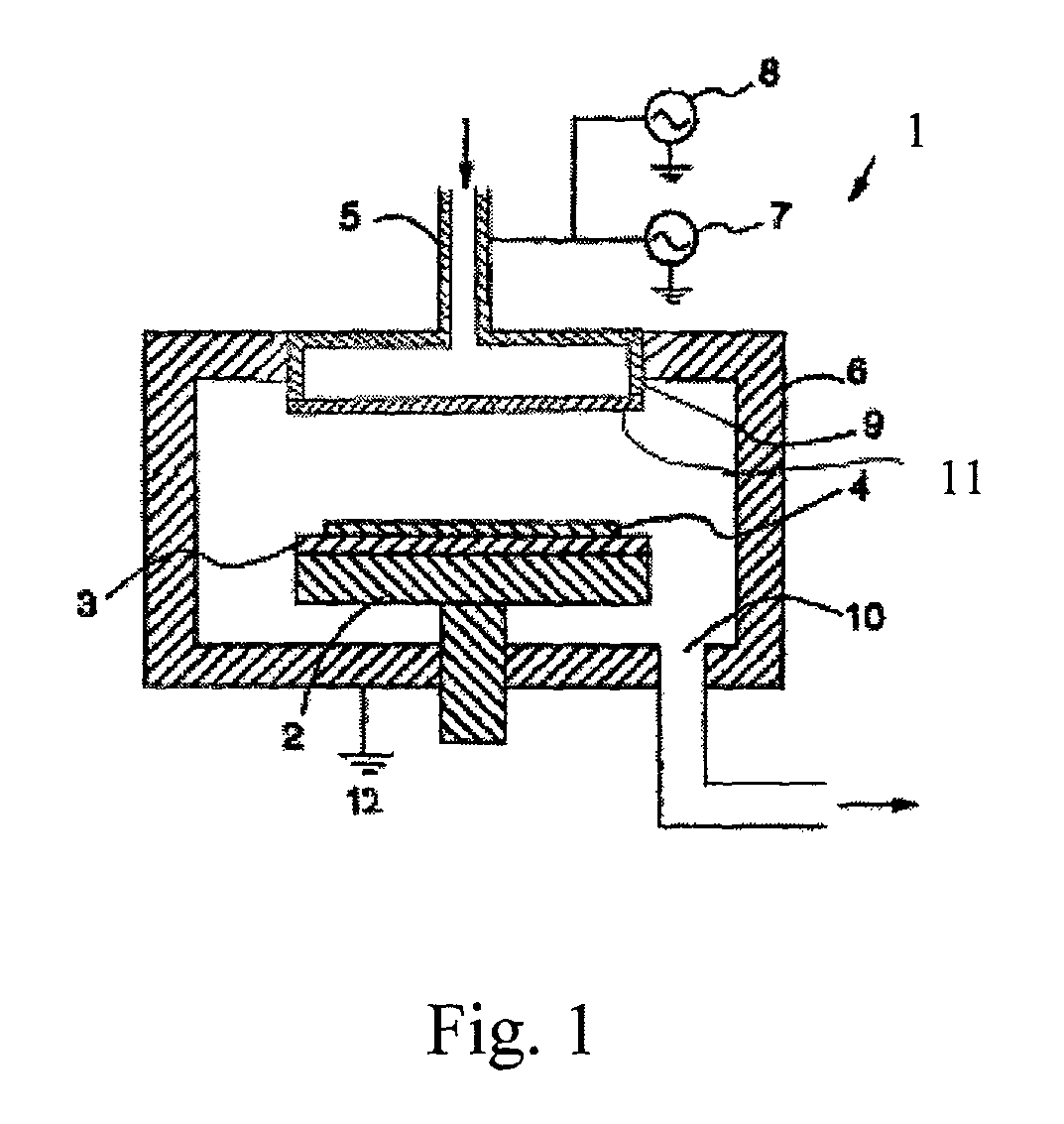

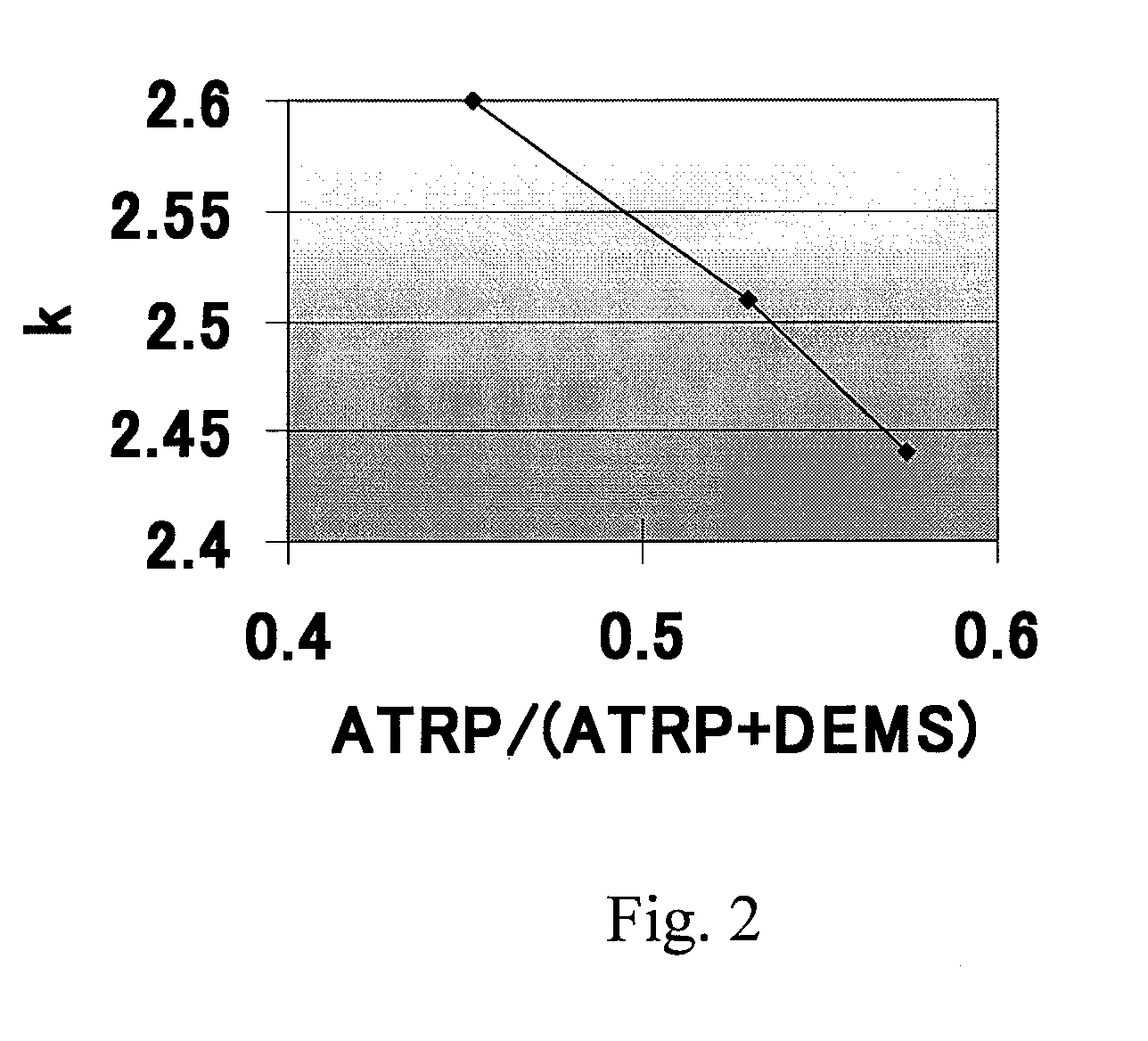

InactiveUS7049247B2Low costReduce tensile stressSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseParallel plate

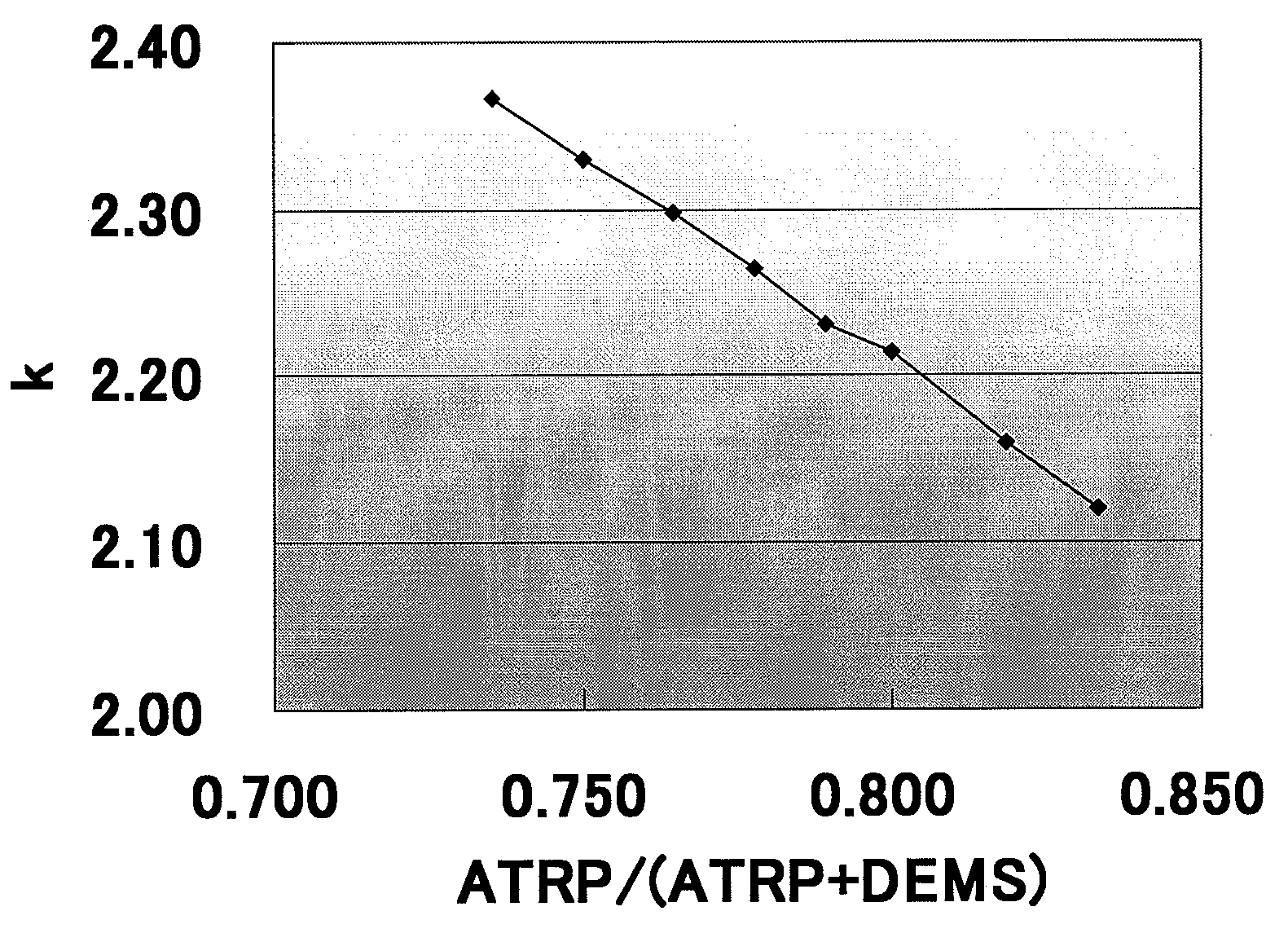

A method for fabricating a thermally stable ultralow dielectric constant film comprising Si, C, O and H atoms in a parallel plate chemical vapor deposition process utilizing a plasma enhanced chemical vapor deposition (“PECVD”) process is disclosed. Electronic devices containing insulating layers of thermally stable ultralow dielectric constant materials that are prepared by the method are further disclosed. To enable the fabrication of a thermally stable ultralow dielectric constant film, specific precursor materials are used, such as, silane derivatives, for instance, diethoxymethylsilane (DEMS) and organic molecules, for instance, bicycloheptadiene and cyclopentene oxide.

Owner:INTEL CORP

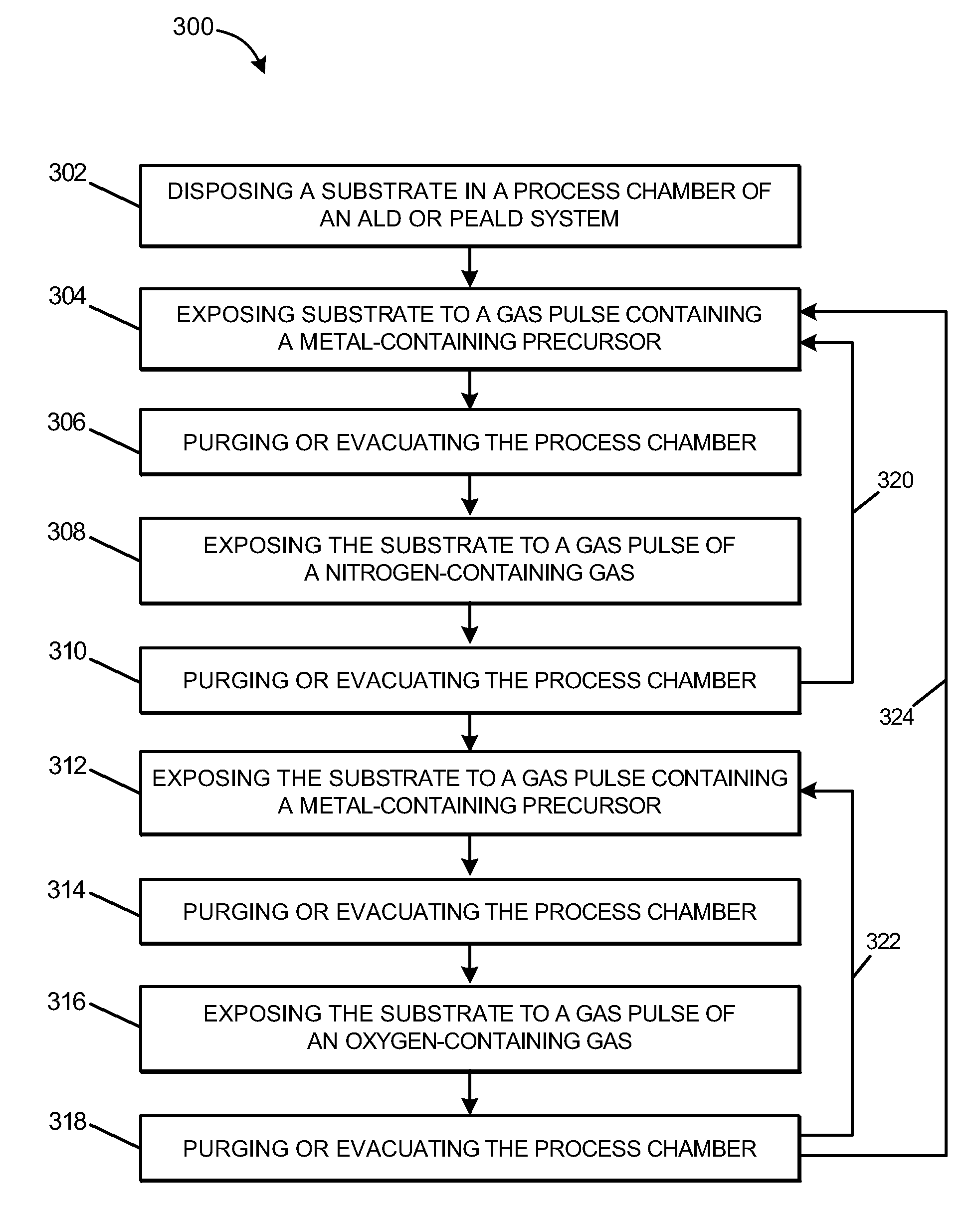

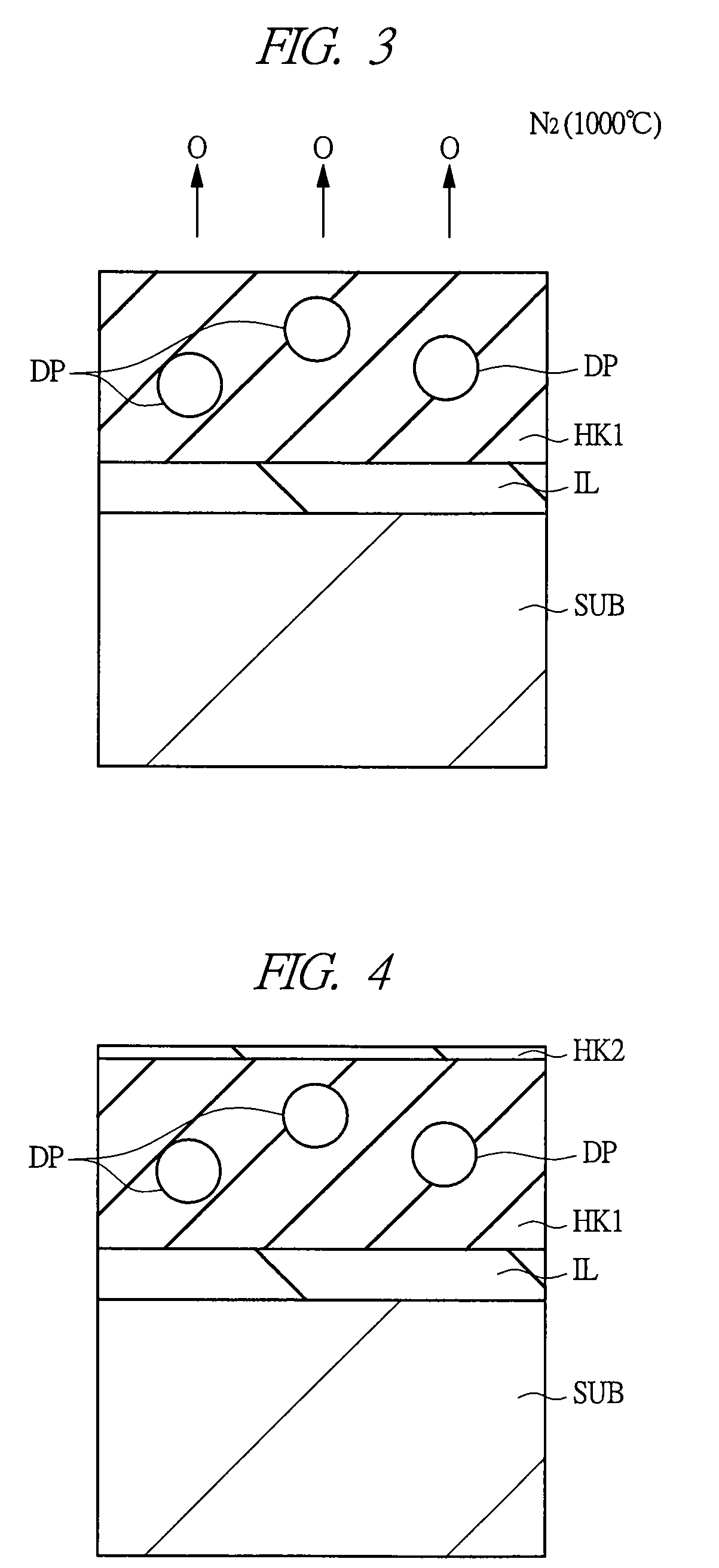

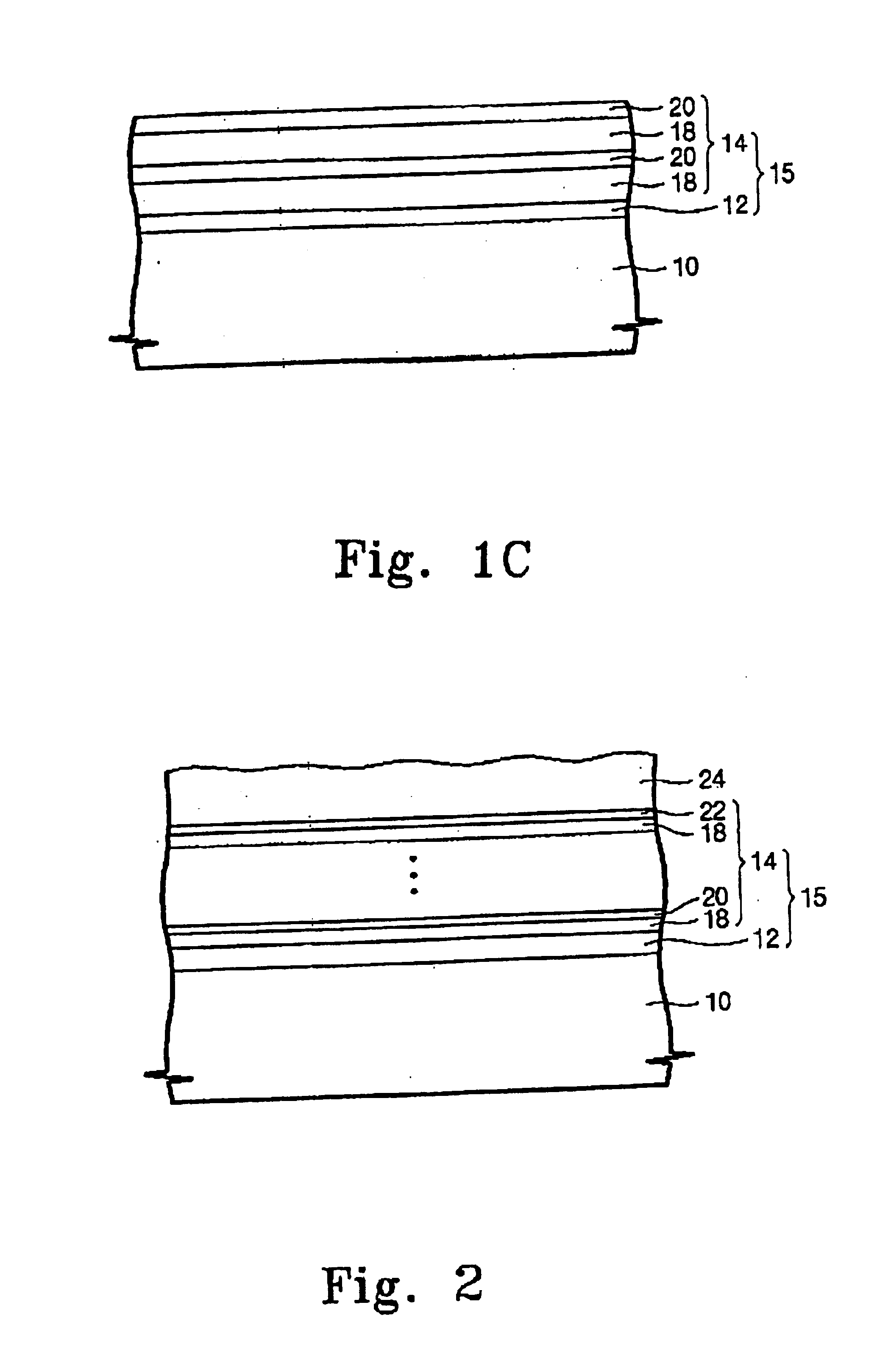

Nitrogen profile engineering in nitrided high dielectric constant films

InactiveUS20080081113A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingRare-earth elementNitrogen

A method of forming a nitrided high-k film by disposing a substrate in a process chamber and forming the nitrided high-k film on the substrate by a) depositing a nitrogen-containing film, and b) depositing an oxygen-containing film, wherein steps a) and b) are performed in any order, any number of times, so as to oxidize at least a portion of the thickness of the nitrogen-containing film. The oxygen-containing film and the nitrogen-containing film contain the same one or more metal elements selected from alkaline earth elements, rare earth elements, and Group IVB elements of the Periodic Table, and optionally aluminum, silicon, or aluminum and silicon. According to one embodiment, the method includes forming a nitrided hafnium based high-k film. The nitrided high-k film can be formed by atomic layer deposition (ALD) or plasma-enhanced ALD (PEALD).

Owner:TOKYO ELECTRON LTD

Manufacturing method of semiconductor device

InactiveUS20090011608A1Reduce hypoxiaSuppression of interface silicon oxide growthSemiconductor/solid-state device manufacturingSemiconductor devicesTantalum nitrideSilicon oxide

The transistor characteristics of a MIS transistor provided with a gate insulating film formed to contain oxide with a relative dielectric constant higher than that of silicon oxide are improved. After a high dielectric layer made of hafnium oxide is formed on a main surface of a semiconductor substrate, the main surface of the semiconductor substrate is heat-treated in a non-oxidation atmosphere. Next, an oxygen supplying layer made of hafnium oxide deposited by ALD and having a thickness smaller than that of the high dielectric layer is formed on the high dielectric layer, and a cap layer made of tantalum nitride is formed. Thereafter, the main surface of the semiconductor substrate is heat-treated.

Owner:RENESAS TECH CORP

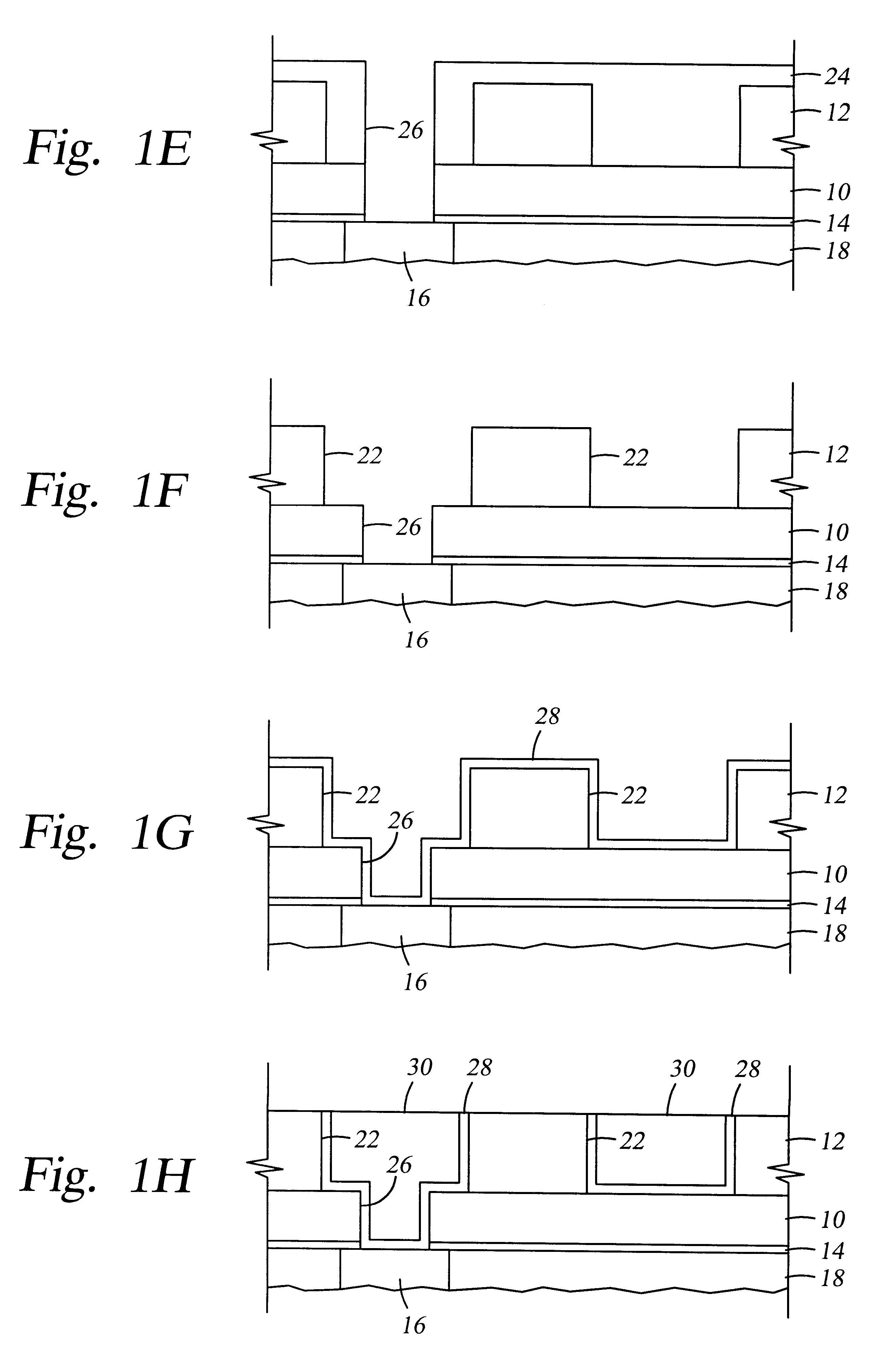

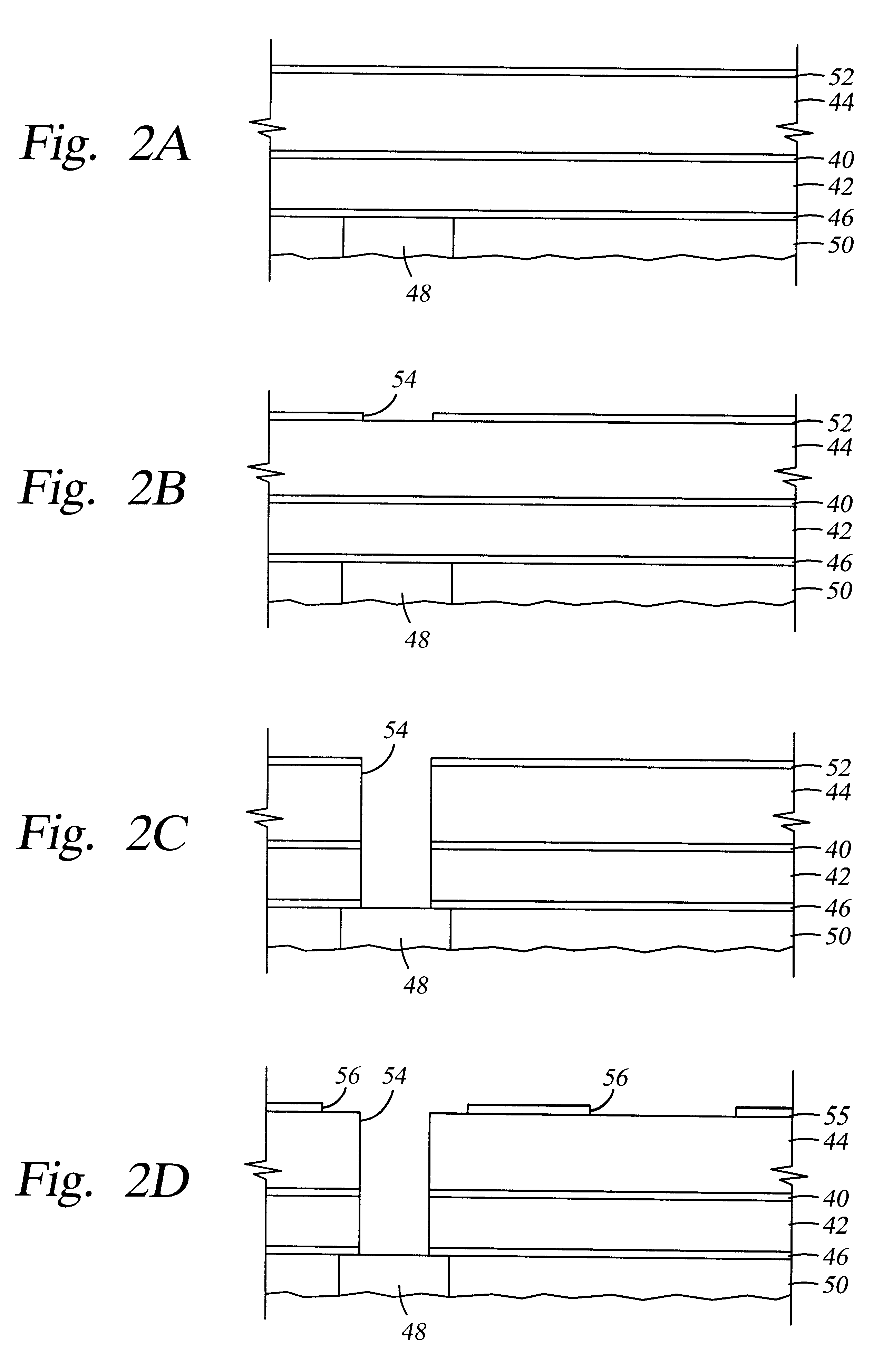

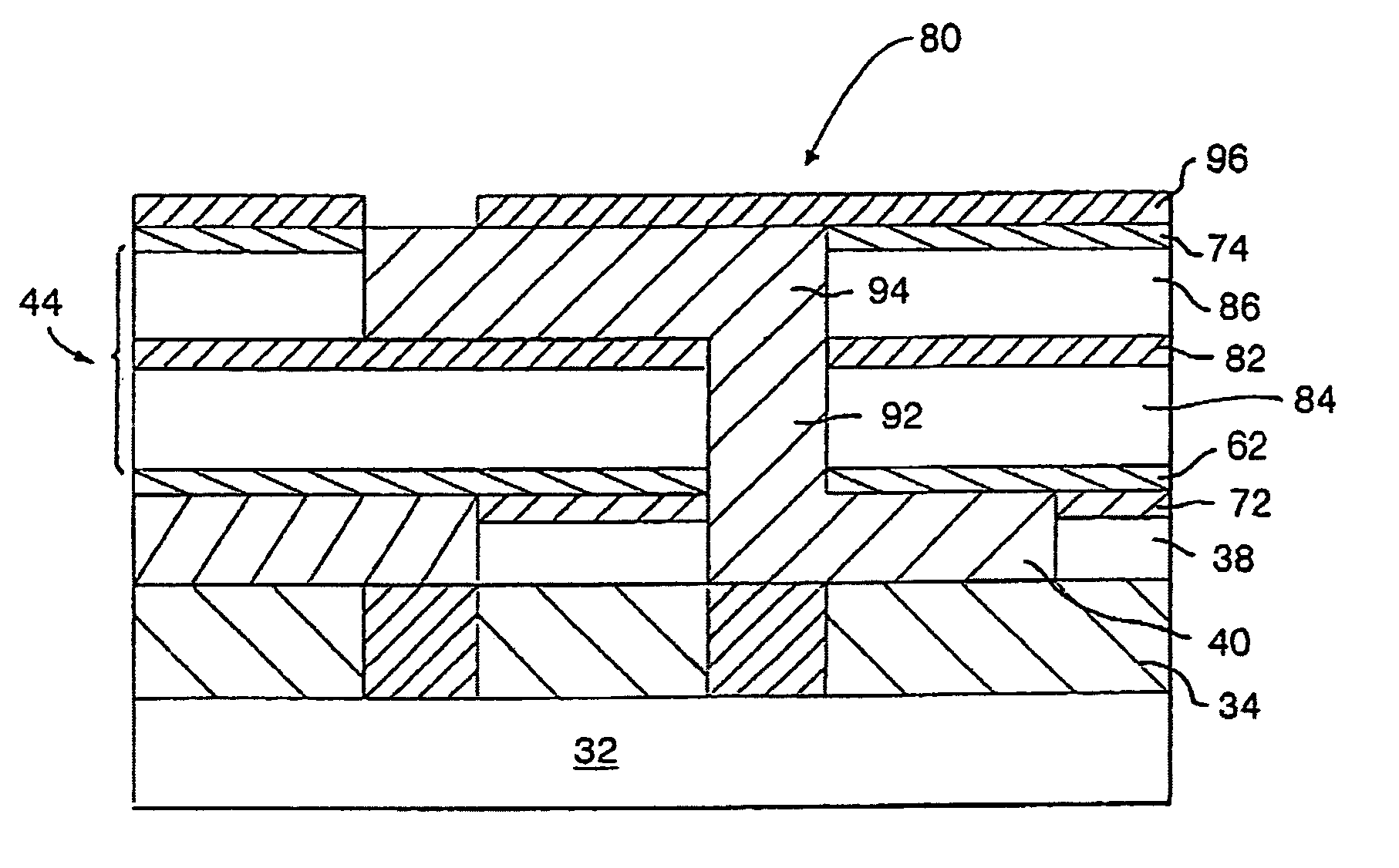

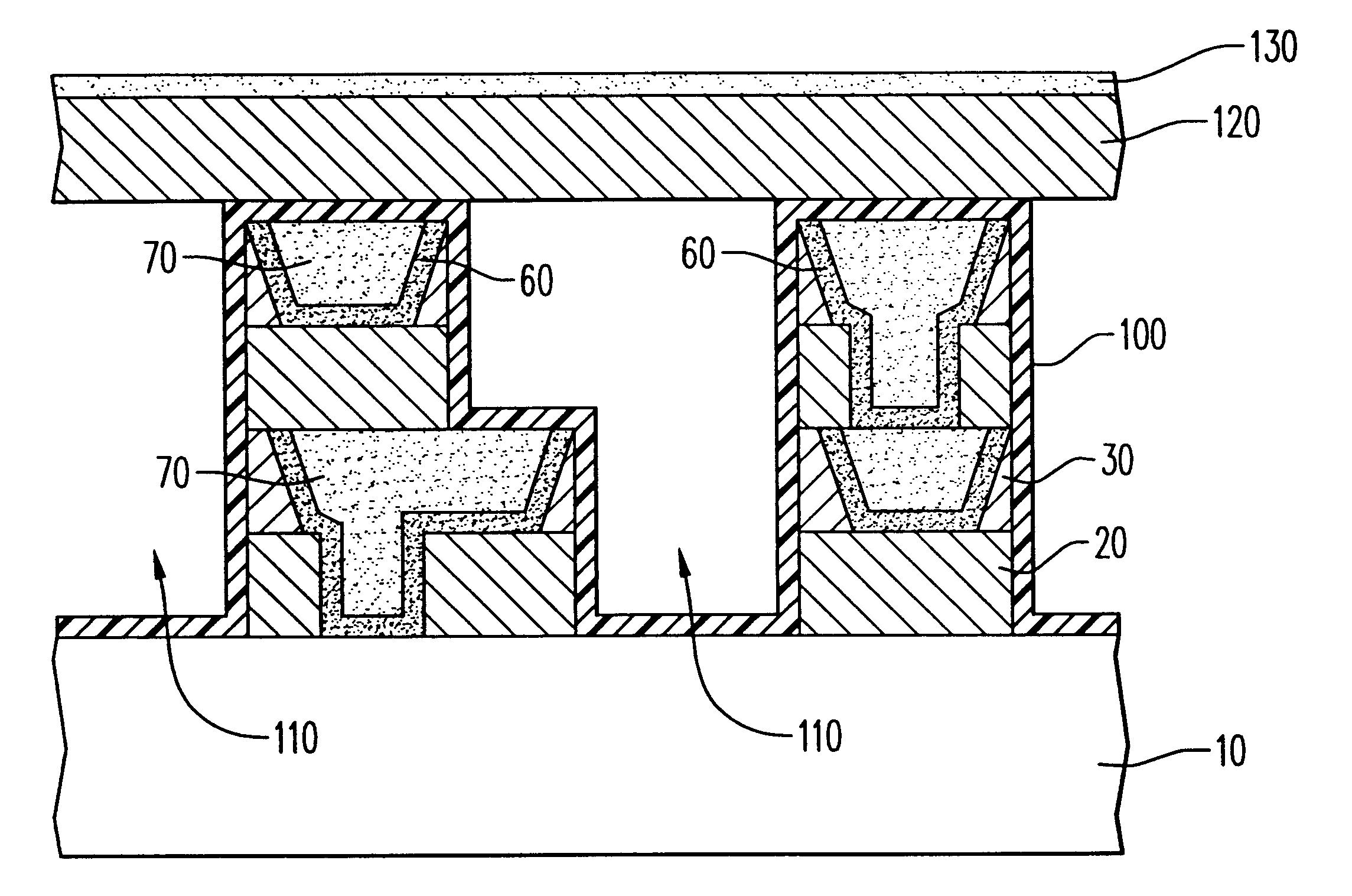

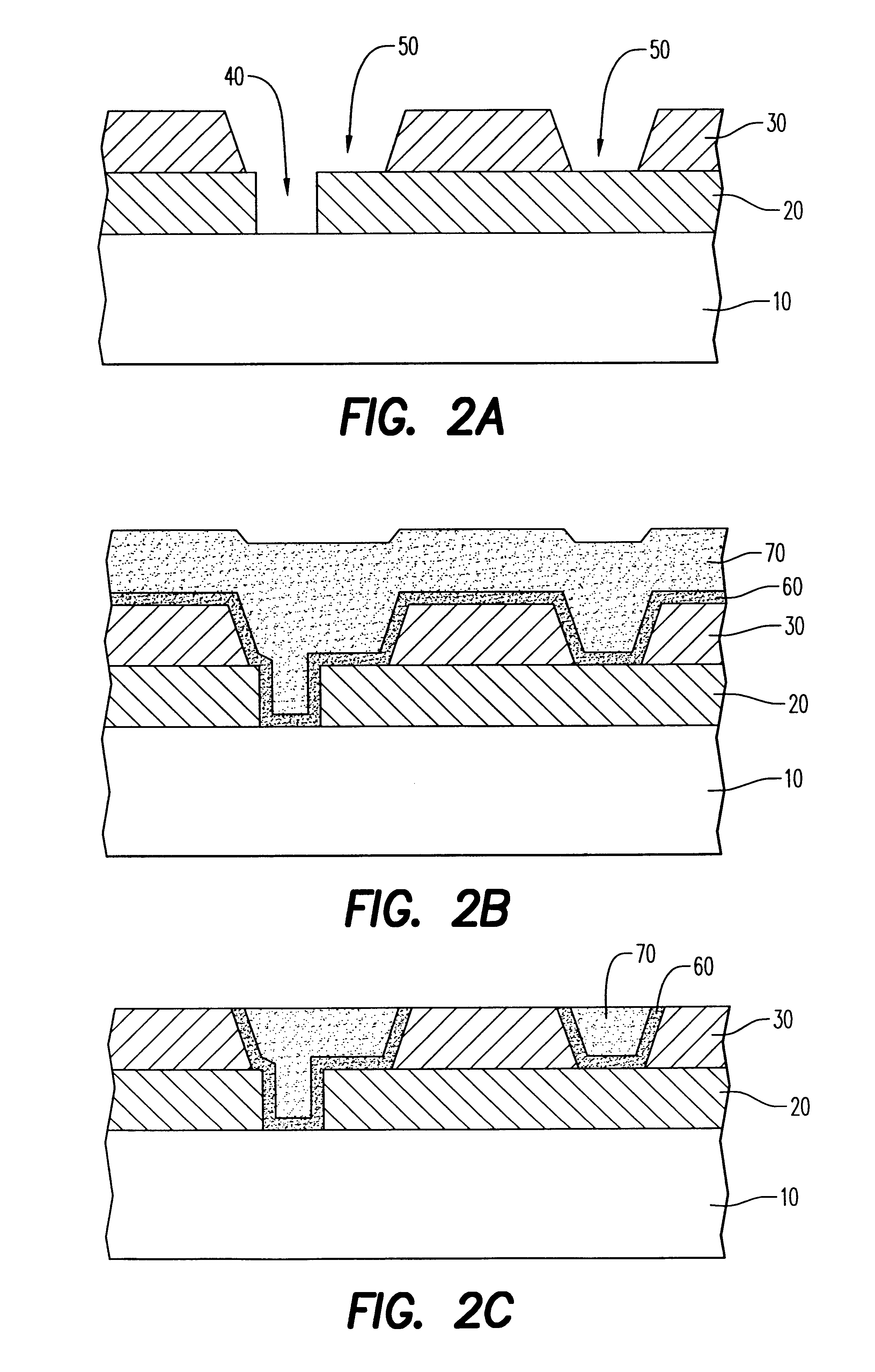

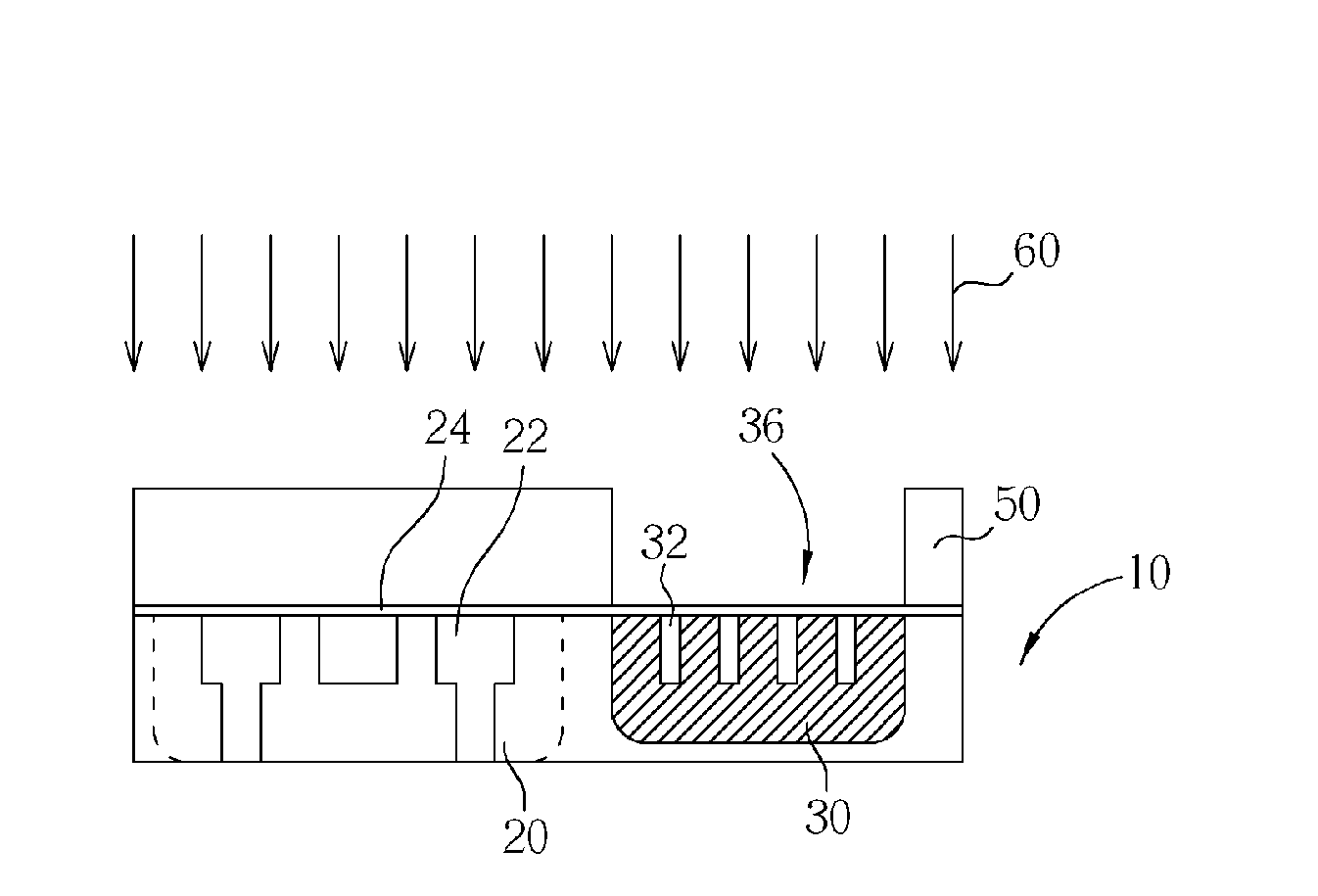

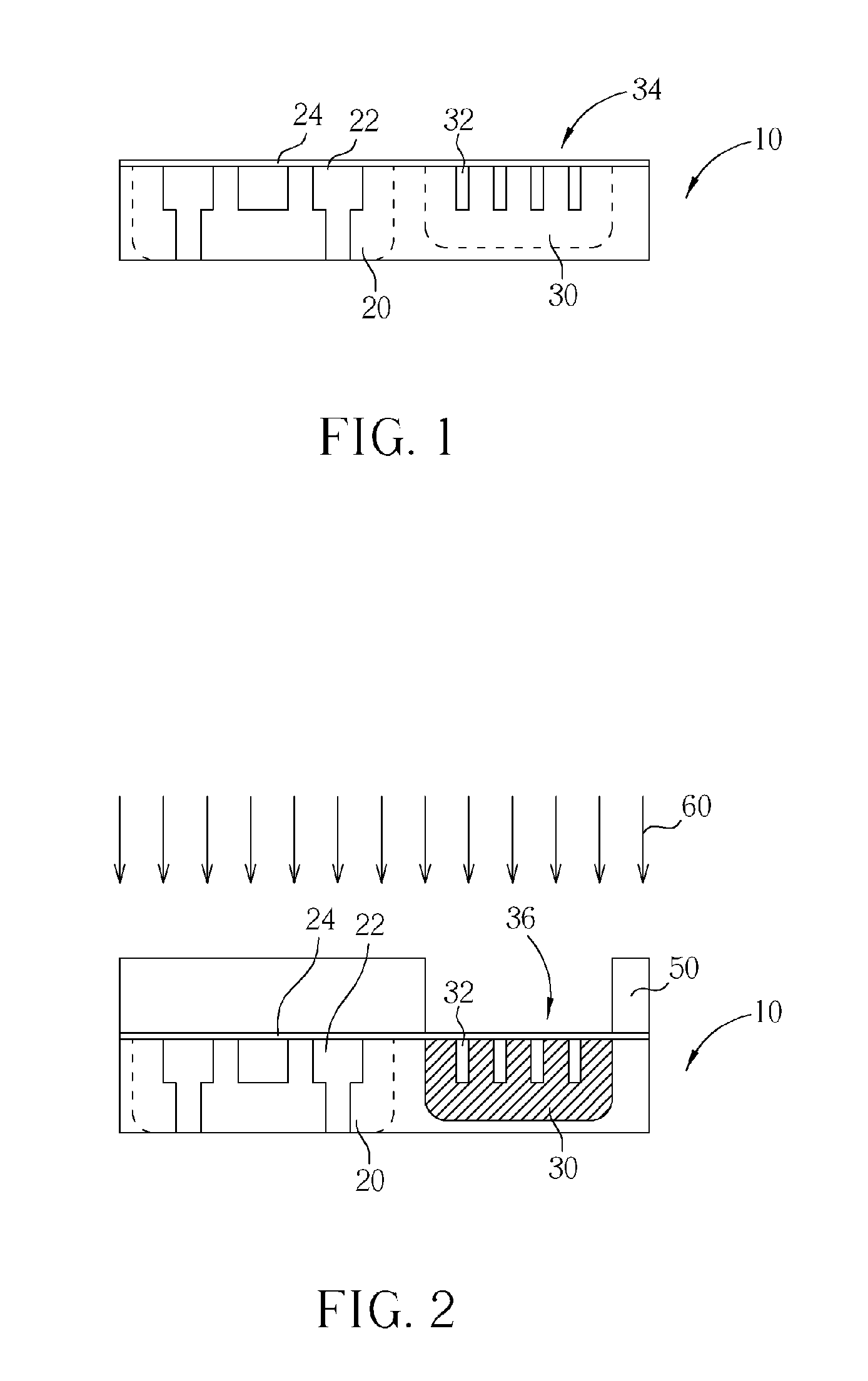

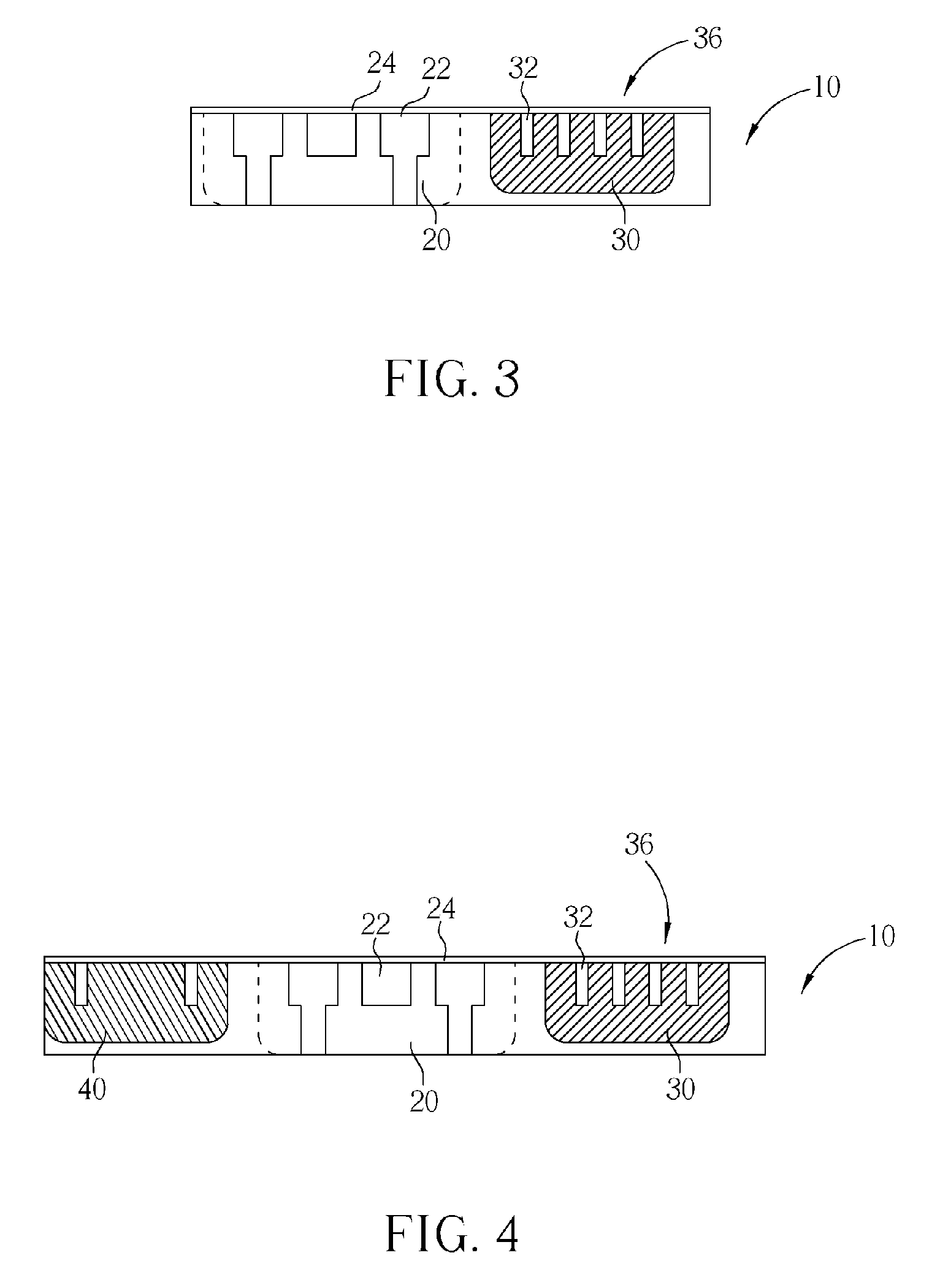

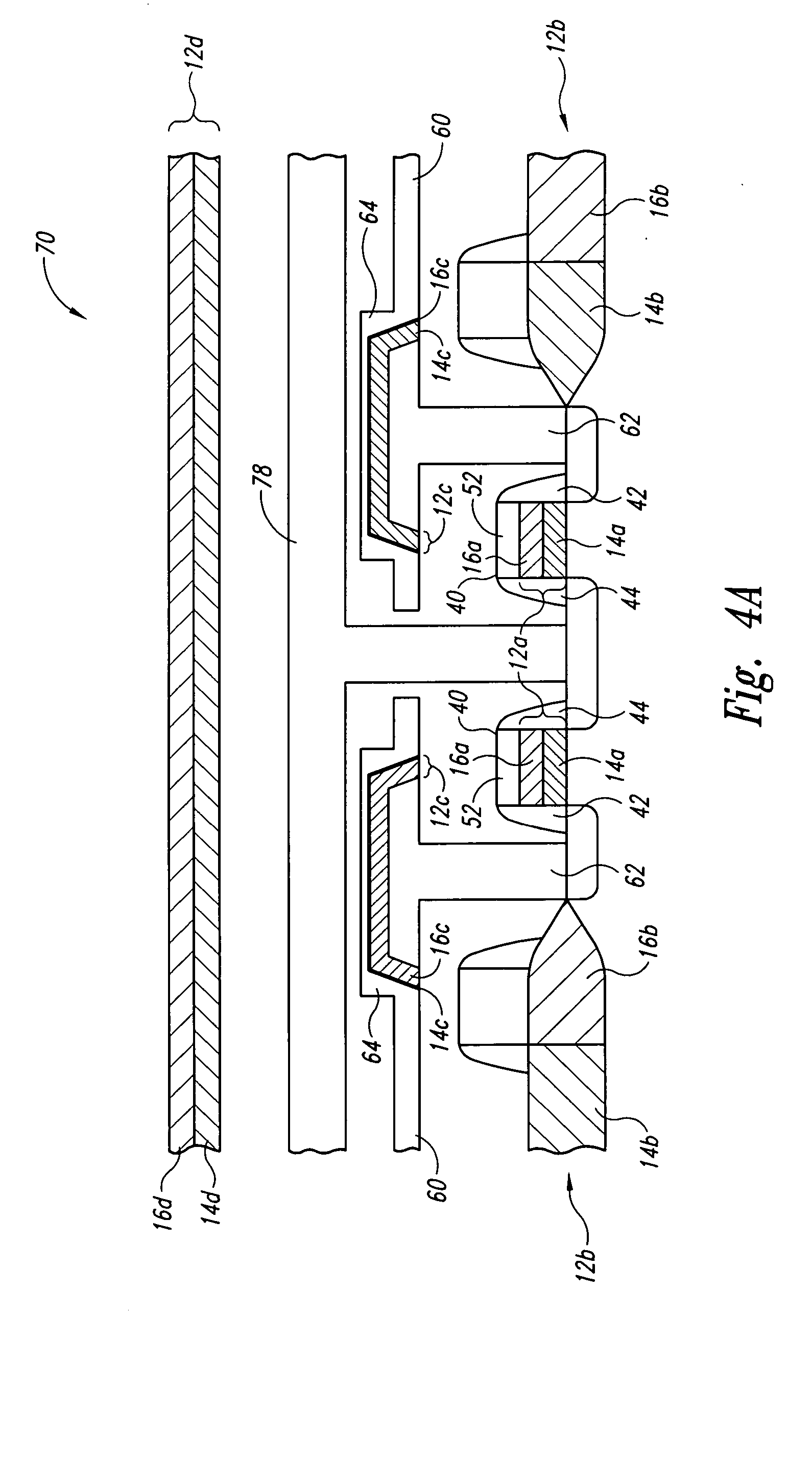

Chip interconnect wiring structure with low dielectric constant insulator and methods for fabricating the same

A method to achieve a very low effective dielectric constant in high performance back end of the line chip interconnect wiring and the resulting multilayer structure are disclosed. The process involves fabricating the multilayer interconnect wiring structure by methods and materials currently known in the state of the art of semiconductor processing; removing the intralevel dielectric between the adjacent metal features by a suitable etching process; applying a thin passivation coating over the exposed etched structure; annealing the etched structure to remove plasma damage; laminating an insulating cover layer to the top surface of the passivated metal features; optionally depositing an insulating environmental barrier layer on top of the cover layer; etching vias in the environmental barrier layer, cover layer and the thin passivation layer for terminal pad contacts; and completing the device by fabricating terminal input / output pads. The method obviates issues such as processability and thermal stability associated with low dielectric constant materials by avoiding their use. Since air, which has the lowest dielectric constant, is used as the intralevel dielectric the structure created by this method would possess a very low capacitance and hence fast propagation speeds. Such structure is ideally suitable for high density interconnects required in high performance microelectronic device chips.

Owner:GLOBALFOUNDRIES INC

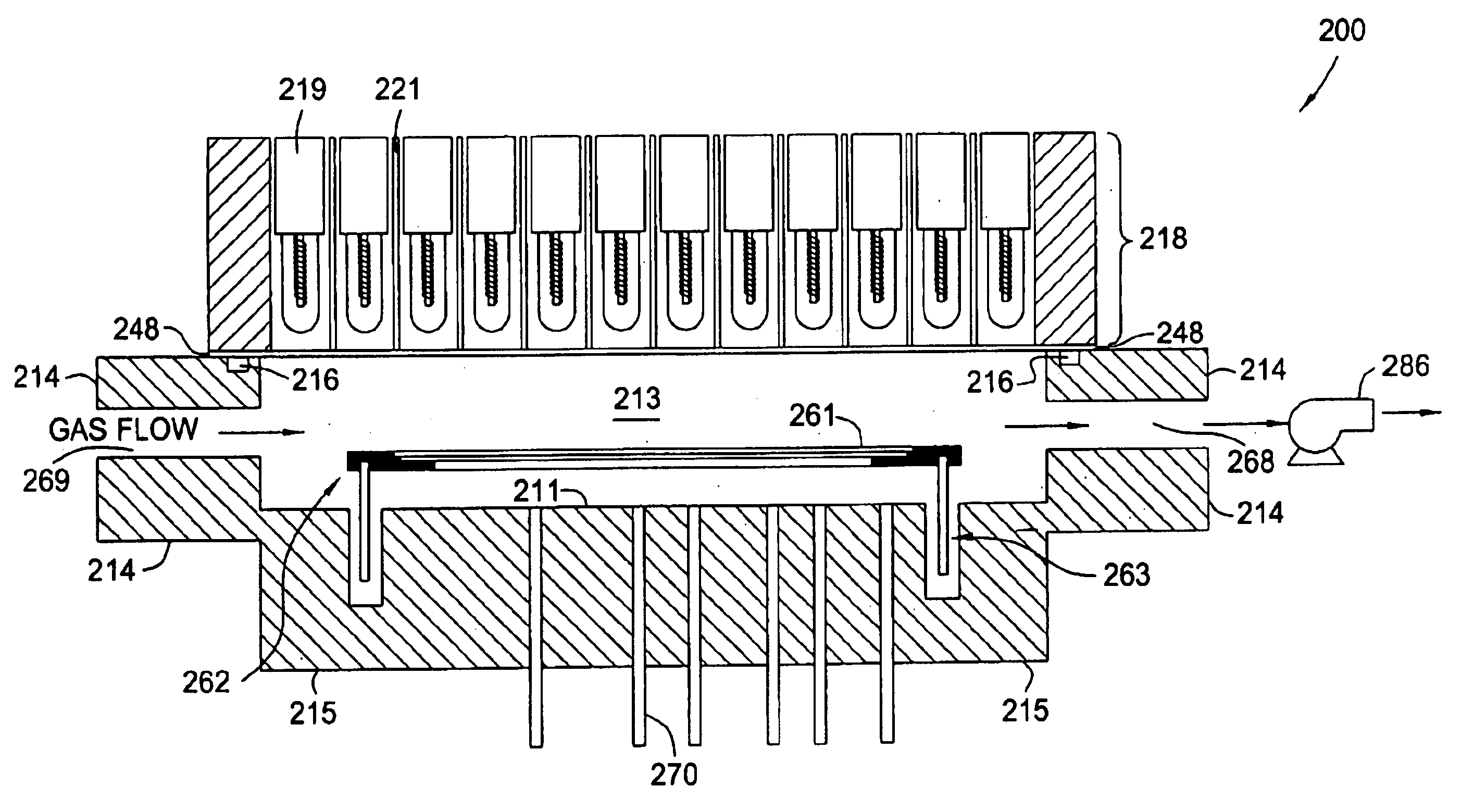

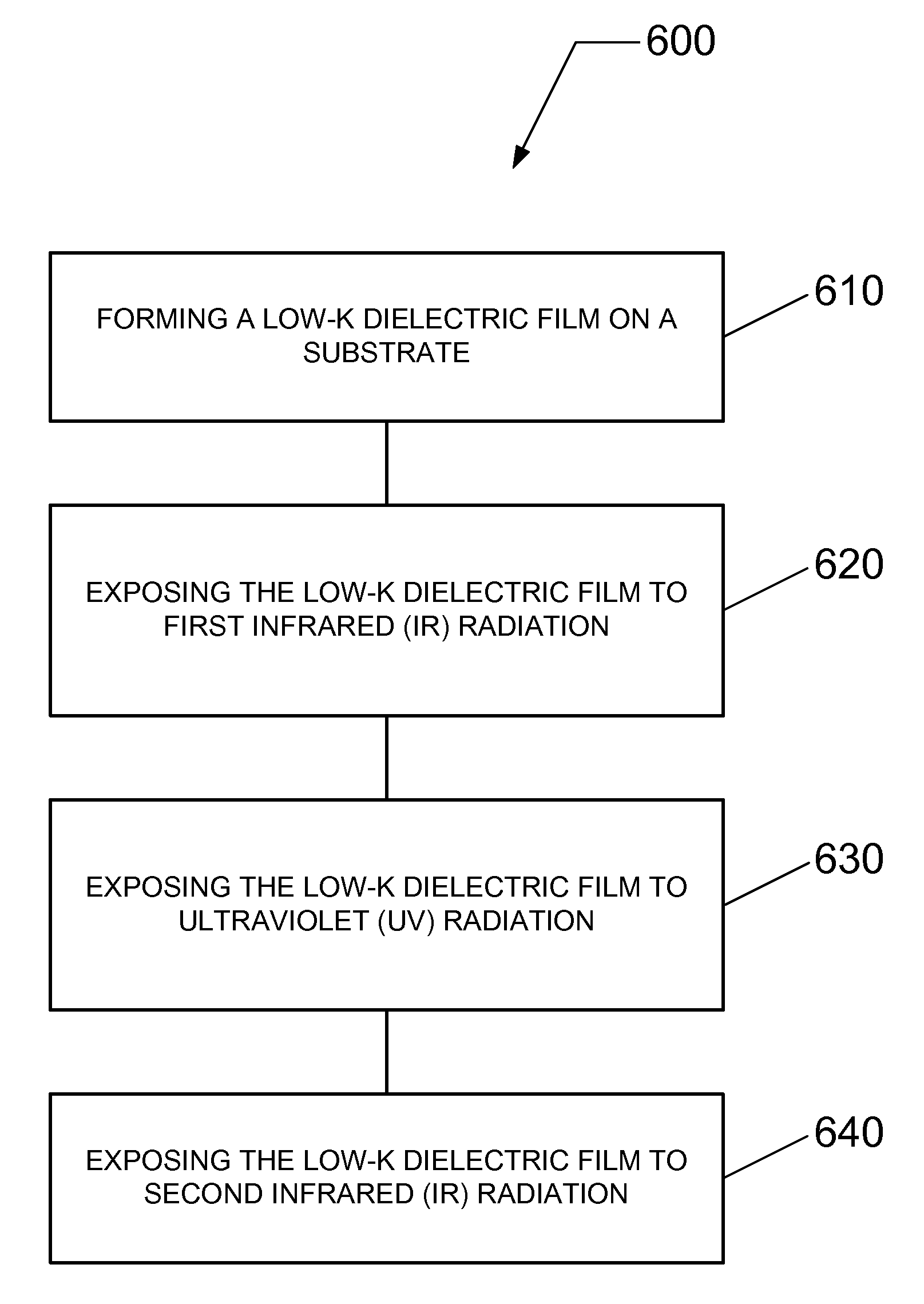

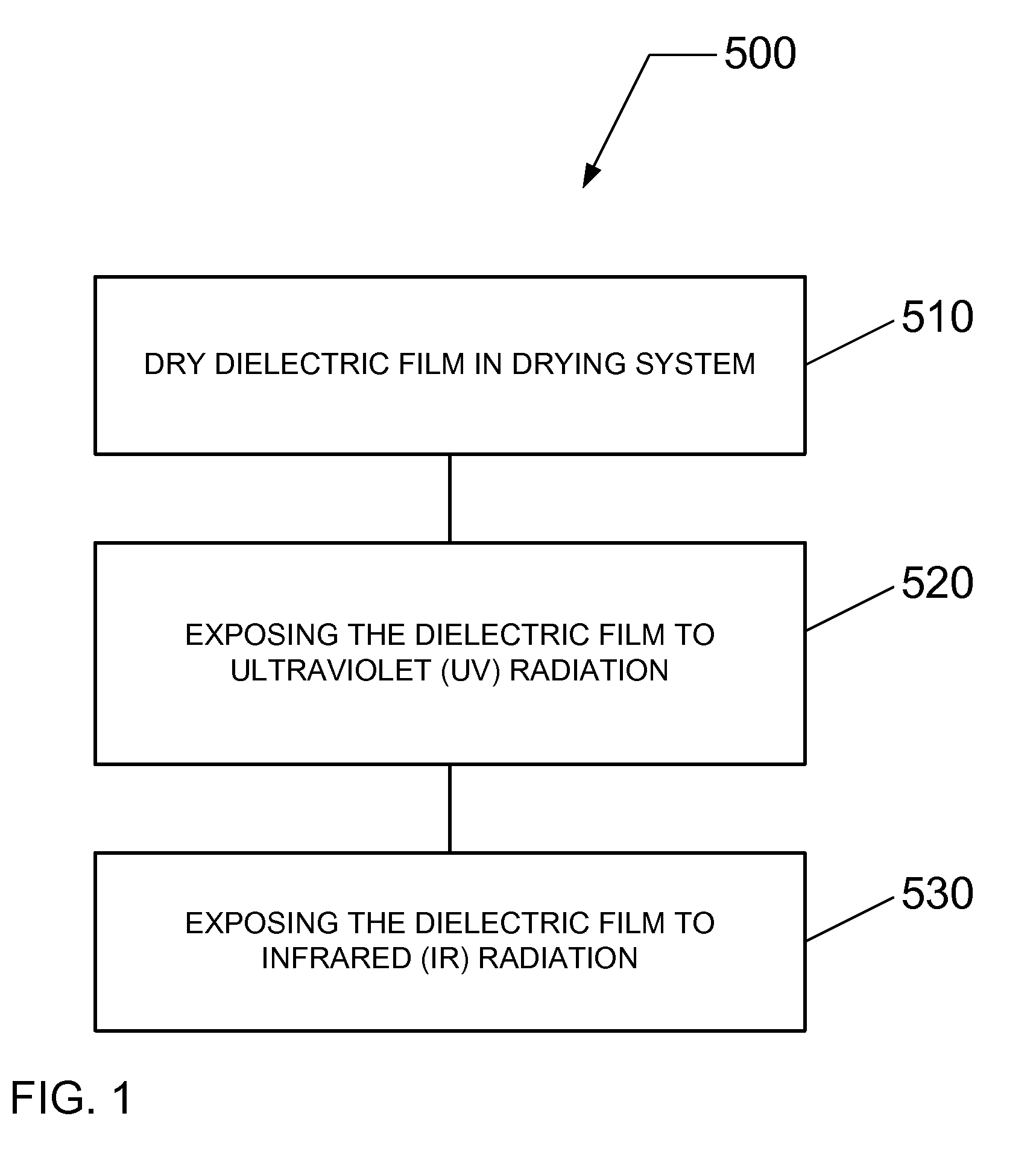

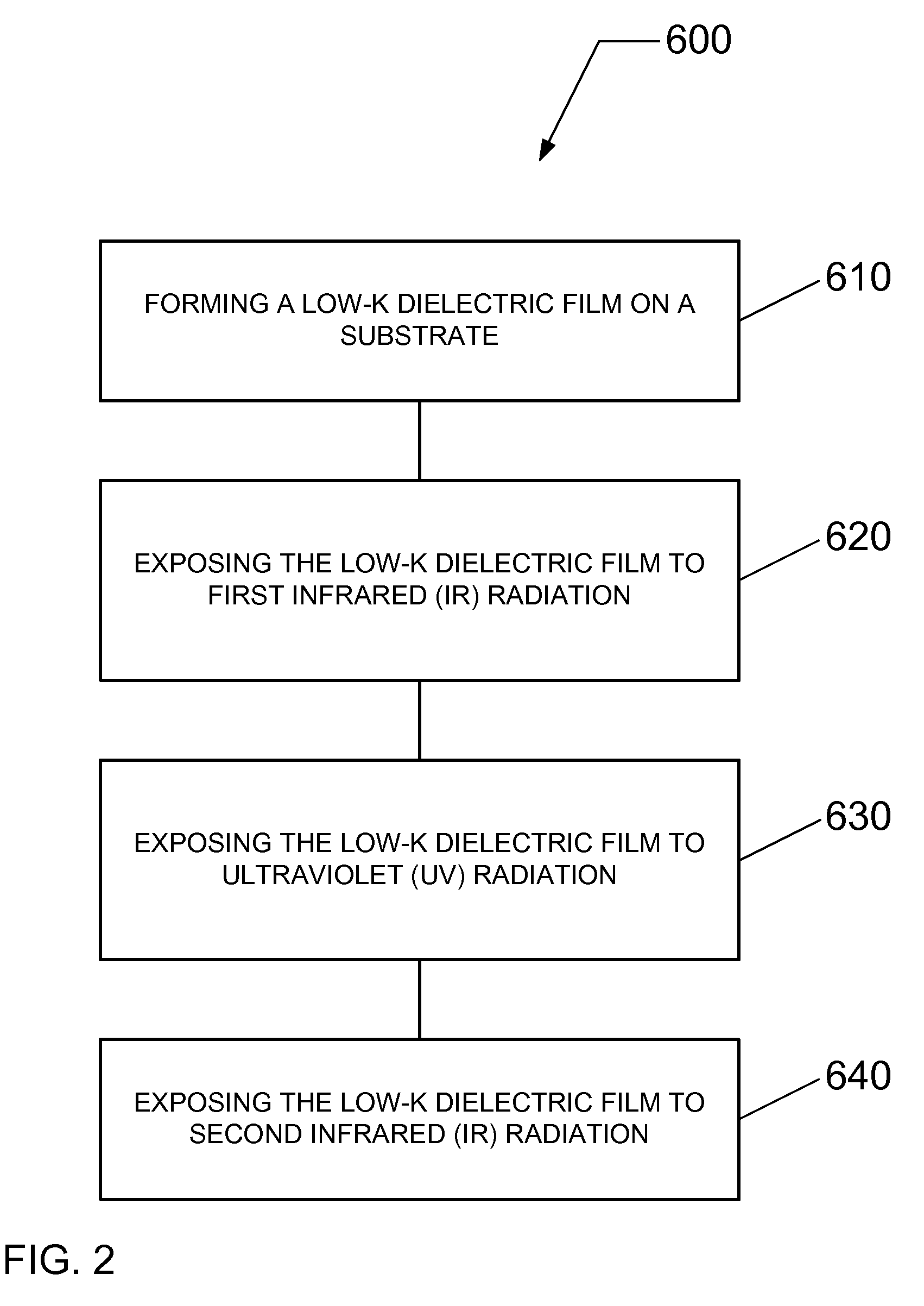

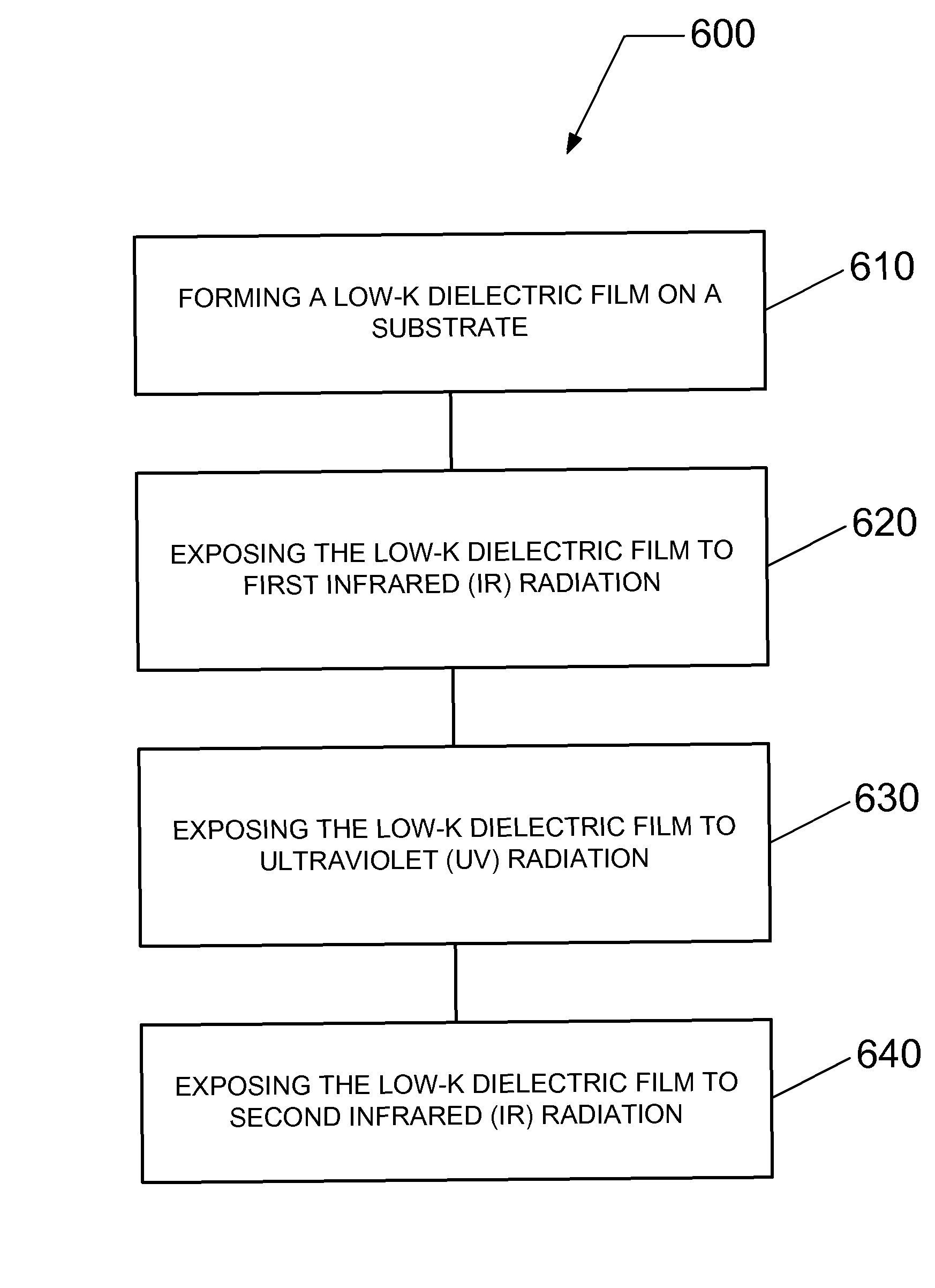

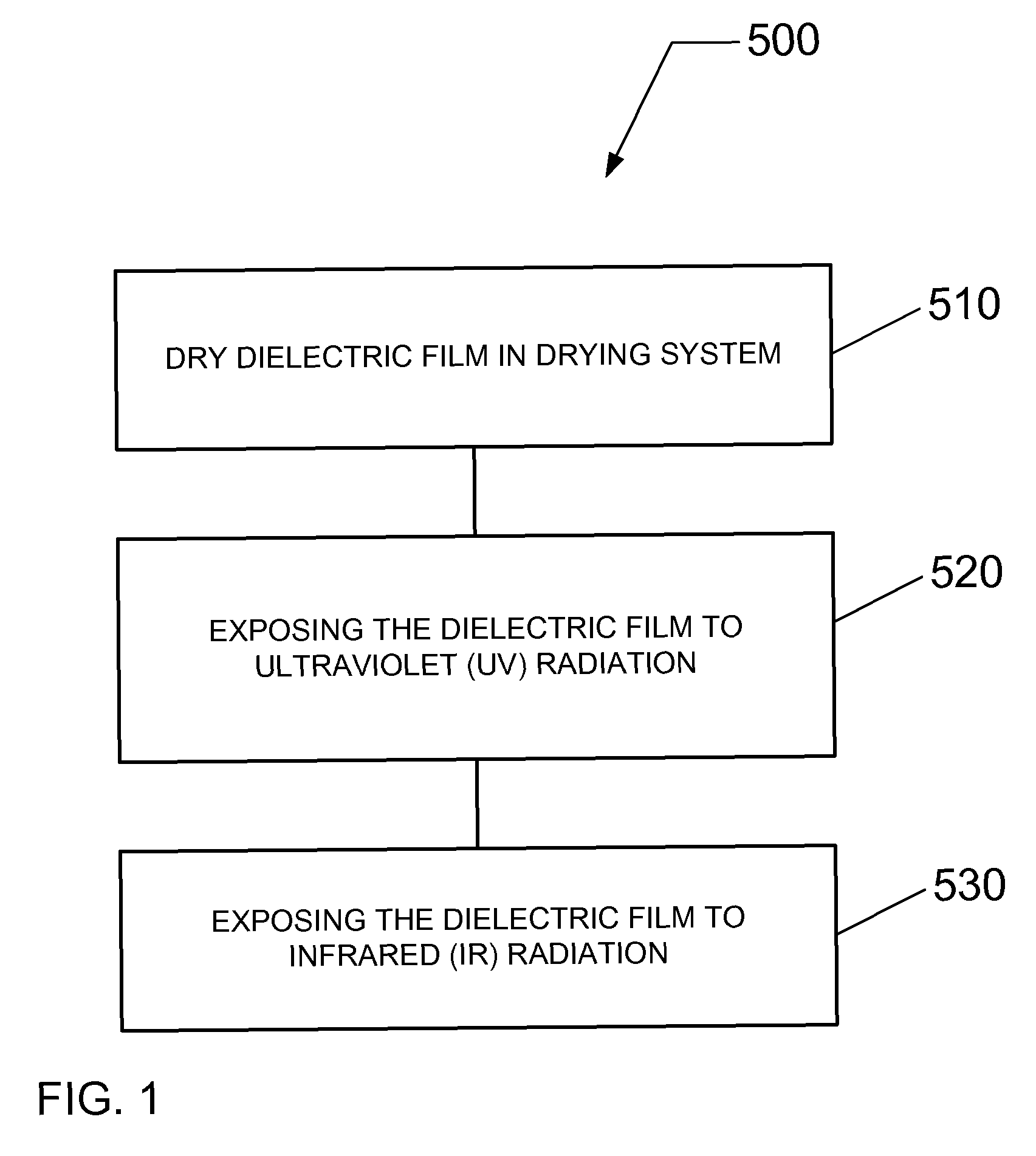

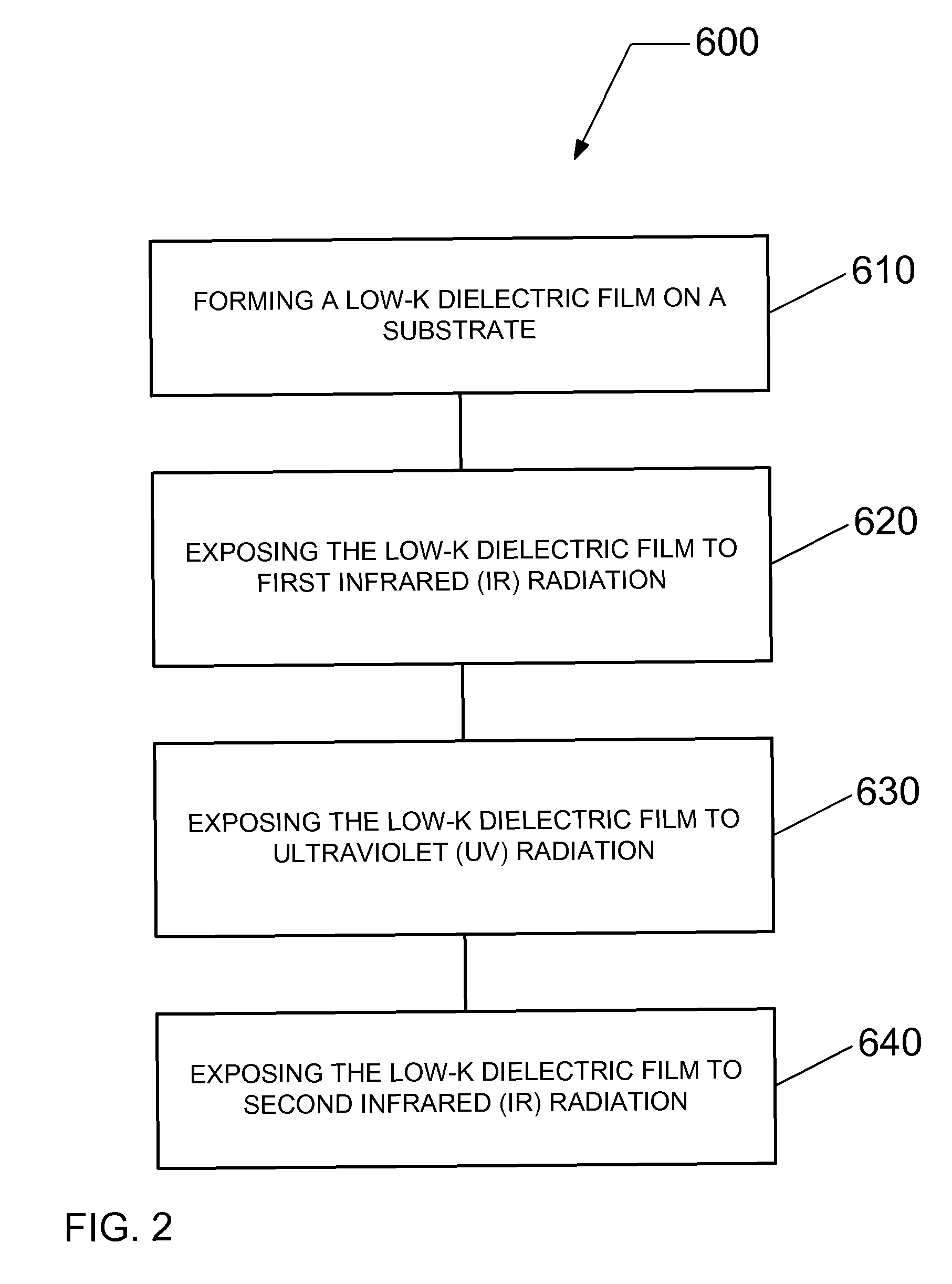

Method for curing a porous low dielectric constant dielectric film

A method of curing a low dielectric constant (low-k) dielectric film on a substrate is described, wherein the dielectric constant of the low-k dielectric film is less than a value of approximately 4. The method comprises exposing the low-k dielectric film to infrared (IR) radiation and ultraviolet (UV) radiation.

Owner:TOKYO ELECTRON LTD

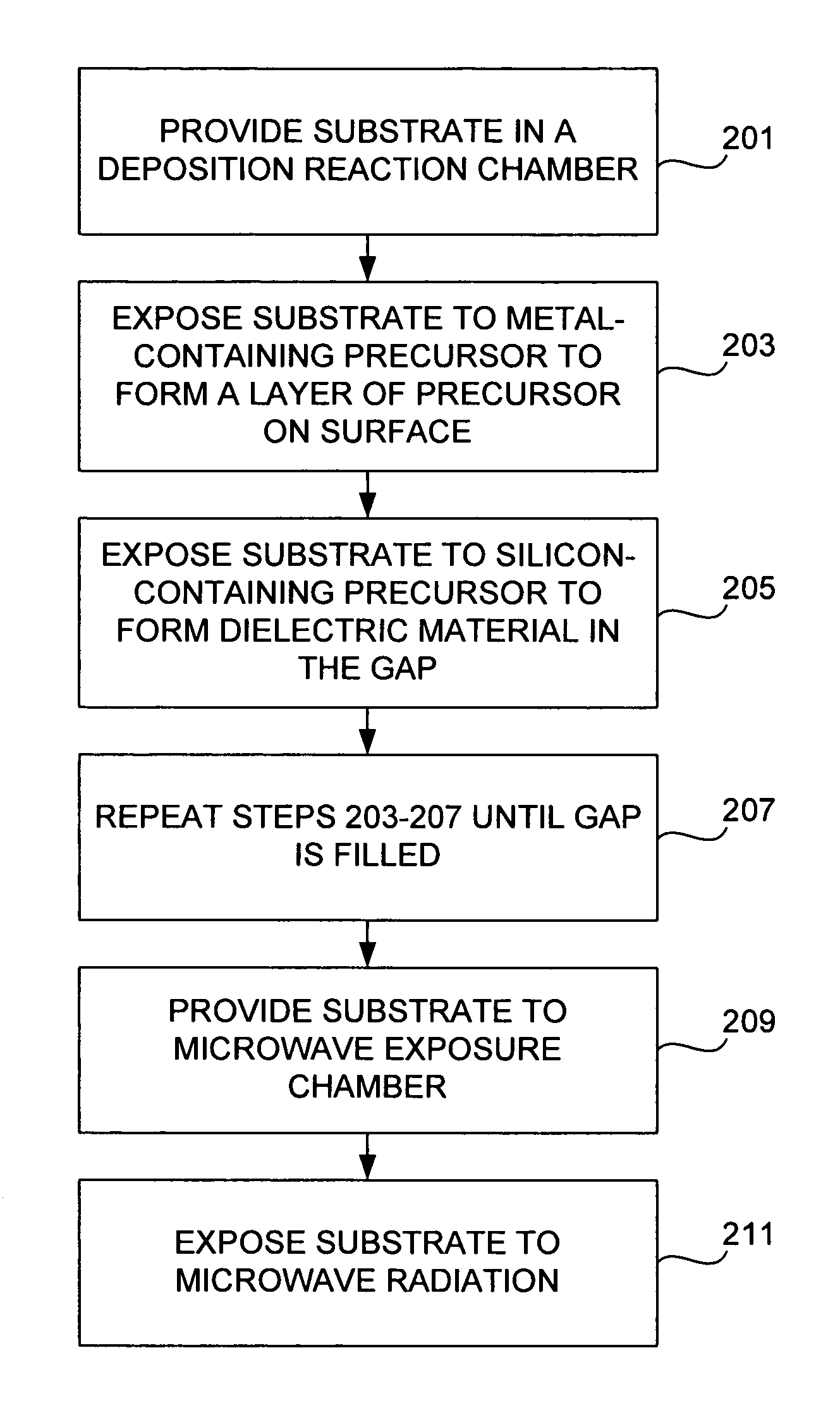

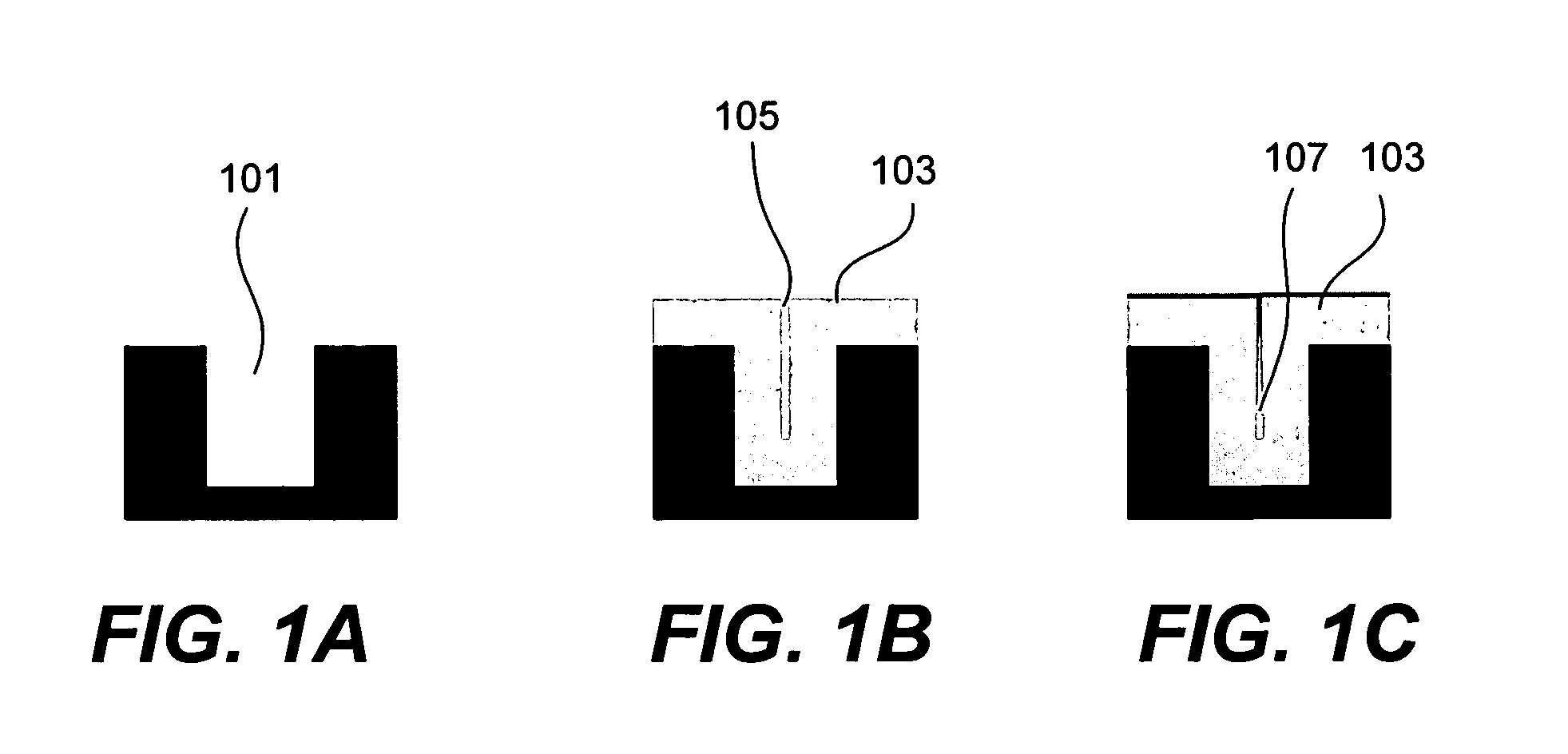

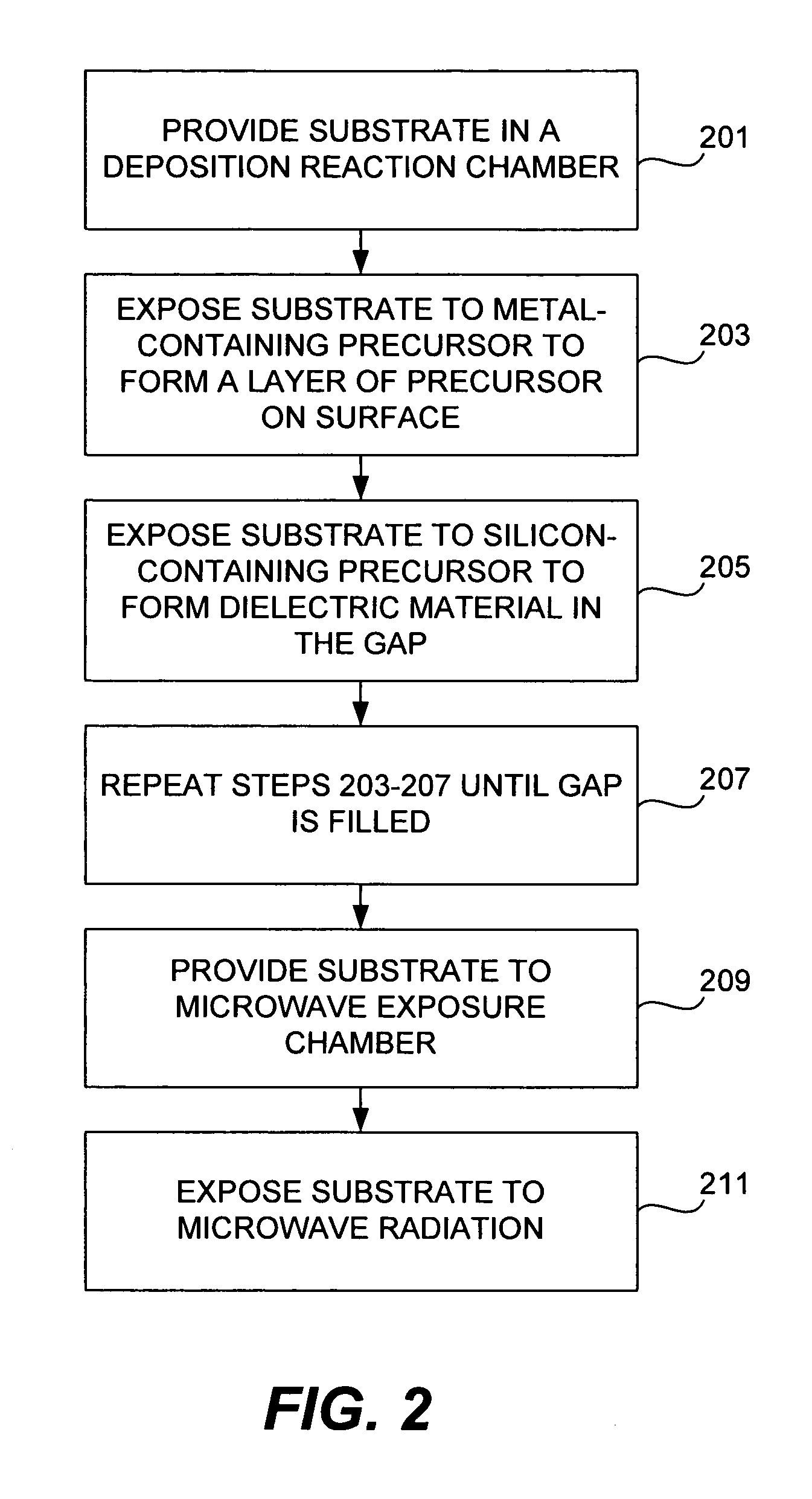

Hydroxyl bond removal and film densification method for oxide films using microwave post treatment

ActiveUS7589028B1High densityImprove film propertiesRadiation applicationsSemiconductor/solid-state device manufacturingDielectricMicrowave

Methods of forming dielectric films with increased density and improved film properties are provided. The methods involve exposing dielectric films to microwave radiation. According to various embodiments, the methods may be used to remove hydroxyl bonds, increase film density, reduce or eliminate seams and voids, and optimize film properties such as dielectric constant, refractive index and stress for particular applications. In certain embodiments, the methods are used to form conformal films deposited by a technique such as PDL. The methods may be used in applications requiring low thermal budgets.

Owner:NOVELLUS SYSTEMS

Method for removing a pore-generating material from an uncured low-k dielectric film

A method of forming a porous low dielectric constant (low-k) dielectric film on a substrate is described, wherein the dielectric constant of the low-k dielectric film is less than a value of approximately 4. The method comprises exposing the low-k dielectric film to infrared (IR) radiation and adjusting a residual amount of cross-linking inhibitor, such as pore-generating material, within the low-k dielectric film.

Owner:TOKYO ELECTRON LTD

Field effect transistors and materials and methods for their manufacture

A field effect transistor in which a continuous semiconductor layer comprises:a) an organic semiconductor; and,b) an organic binder which has an inherent conductivity of less than 10−6Scm−1 and a permittivity at 1,000 Hz of less than 3.3and a process for its production comprising:coating a substrate with a liquid layer which comprises the organic semiconductor and a material capable of reacting to form the binder; and,converting the liquid layer to a solid layer comprising the semiconductor and the binder by reacting the material to form the binder.

Owner:MERCK PATENT GMBH

Metal capacitor and method of making the same

ActiveUS8114734B2Increase capacitanceAvoid delaySemiconductor/solid-state device detailsSolid-state devicesCapacitanceInterconnection

A method of making a metal capacitor includes the following steps. A dielectric layer having a metal interconnection and a capacitor electrode is provided. Then, a treatment is performed to increase the dielectric constant of the dielectric layer surrounding the capacitor electrode. The treatment can be UV radiation, a plasma treatment or an ion implantation. Accordingly, the metal capacitor will have a higher capacitance and RC delay between the metal interconnection and the dielectric layer can be prevented.

Owner:MARLIN SEMICON LTD

Method for forming dielectric film using porogen gas

ActiveUS7955650B2Low mechanical strengthIncrease equipment costSemiconductor/solid-state device manufacturingSpecial surfacesDielectric permittivityGas formation

Owner:ASM JAPAN

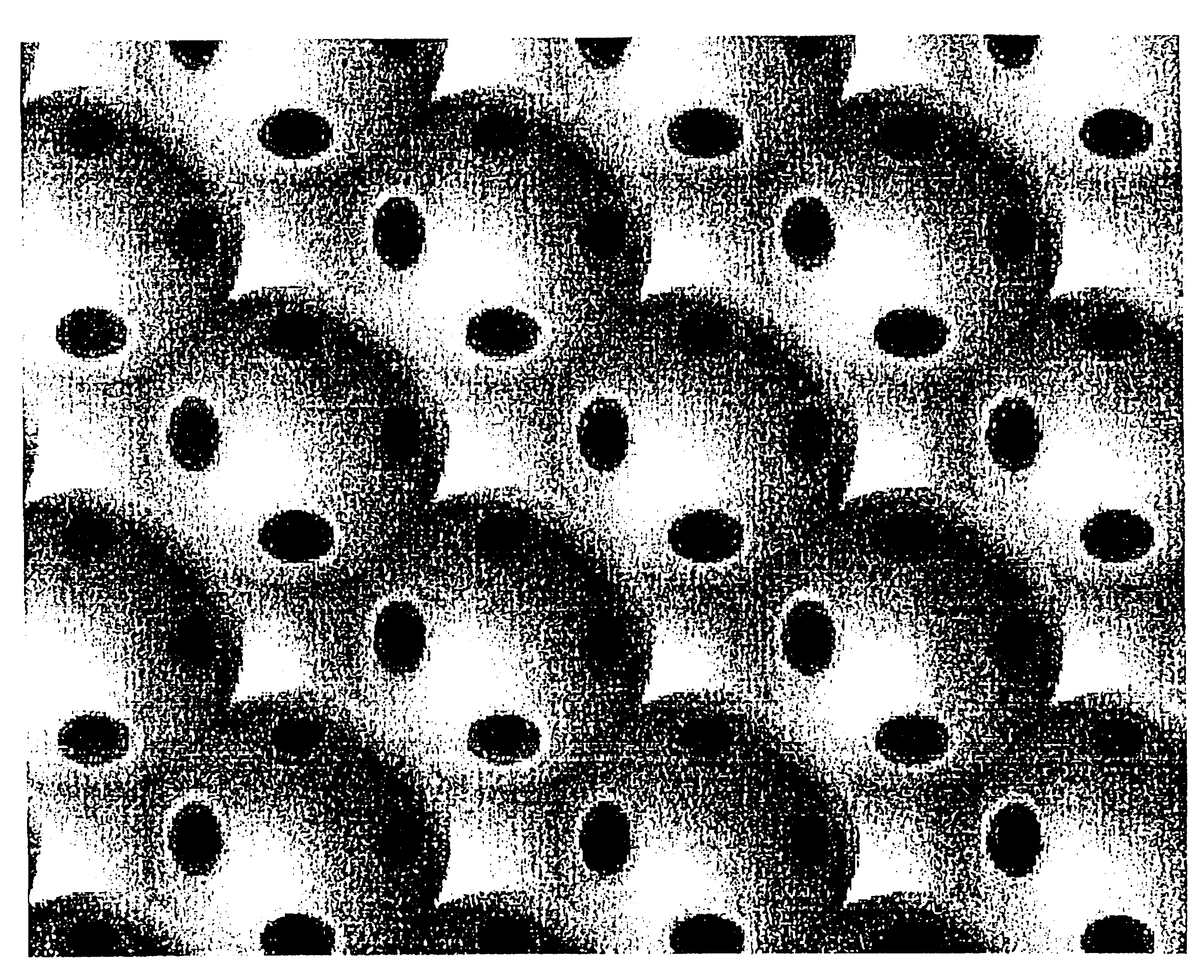

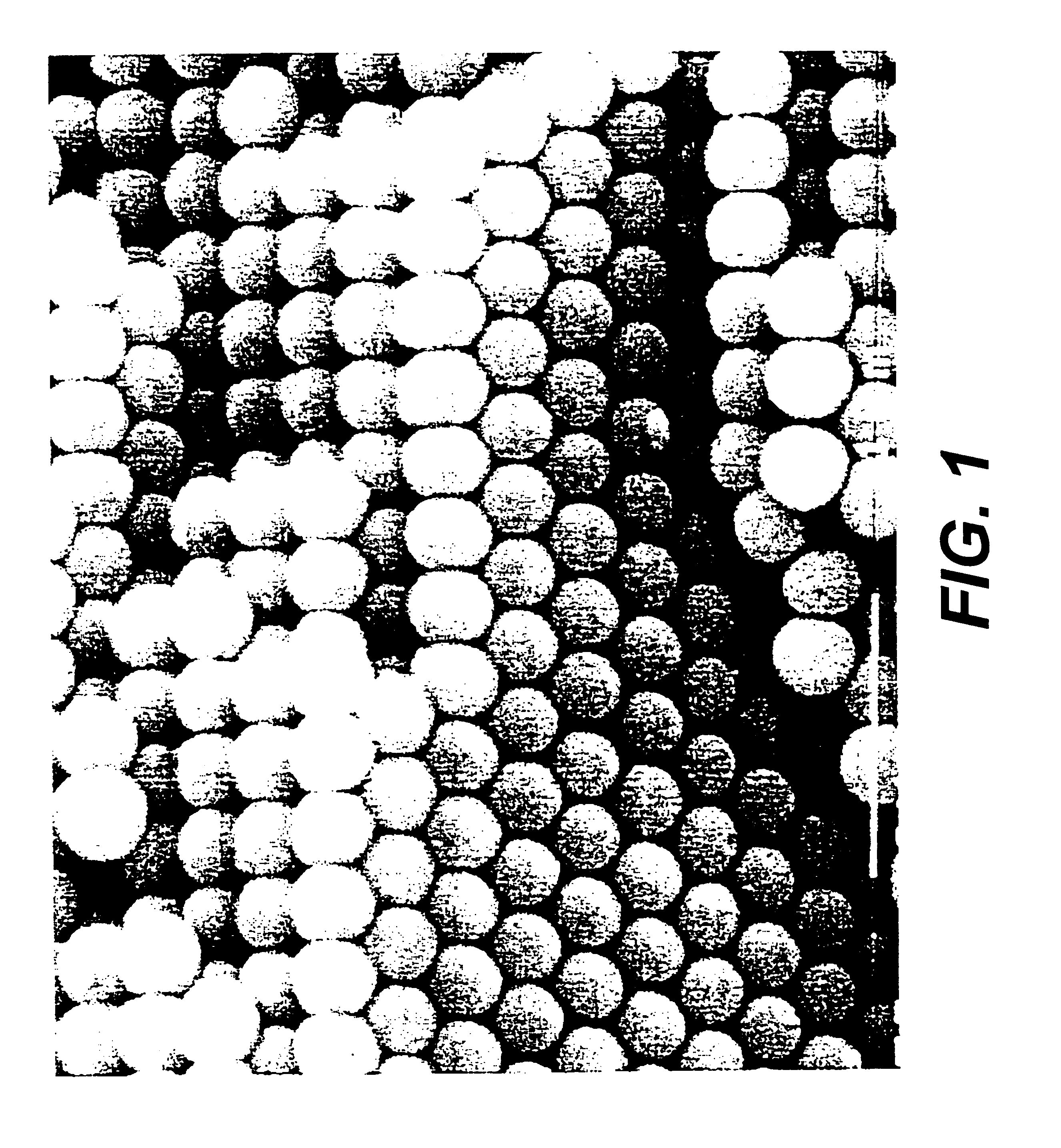

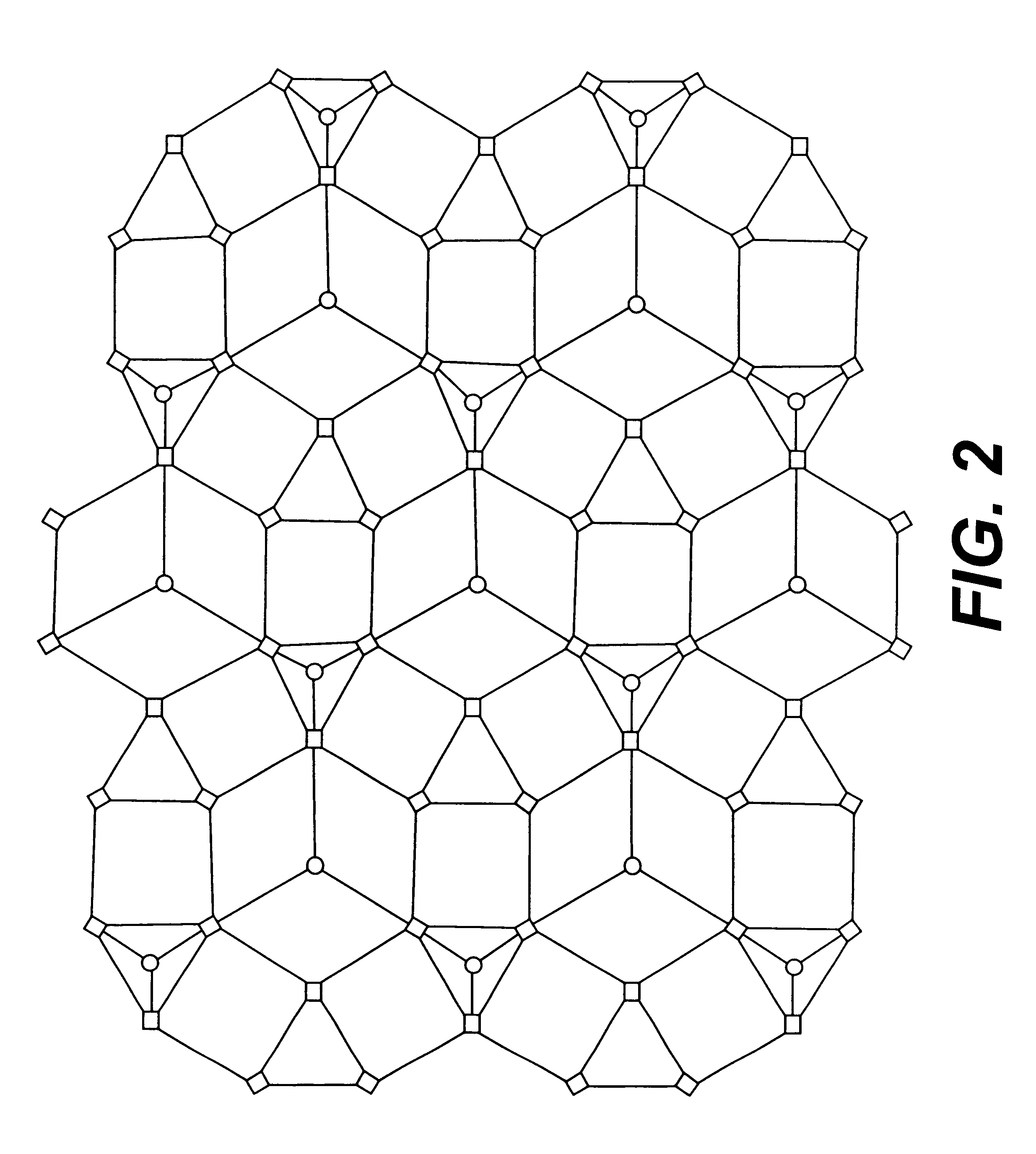

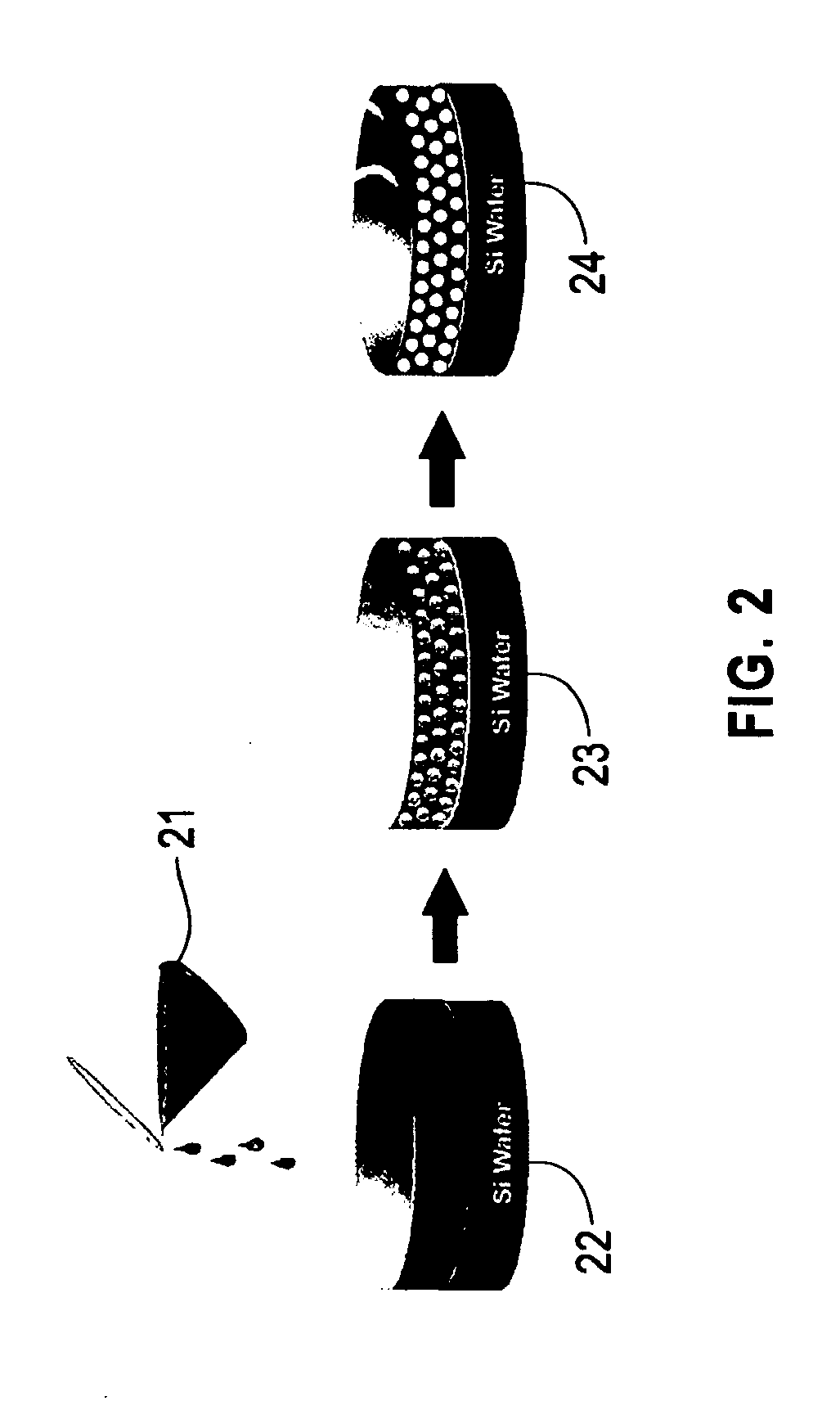

Three dimensionally periodic structural assemblies on nanometer and longer scales

InactiveUS6261469B1Low melting pointEasily de-infiltrateSilicaPaper/cardboard articlesChromatographic separationThermoelectric materials

This invention relates to processes for the assembly of three-dimensional structures having periodicities on the scale of optical wavelengths, and at both smaller and larger dimensions, as well as compositions and applications therefore. Invention embodiments involve the self assembly of three-dimensionally periodic arrays of spherical particles, the processing of these arrays so that both infiltration and extraction processes can occur, one or more infiltration steps for these periodic arrays, and, in some instances, extraction steps. The product articles are three-dimensionally periodic on a scale where conventional processing methods cannot be used. Articles and materials made by these processes are useful as thermoelectrics and thermionics, electrochromic display elements, low dielectric constant electronic substrate materials, electron emitters (particularly for displays), piezoelectric sensors and actuators, electrostrictive actuators, piezochromic rubbers, gas storage materials, chromatographic separation materials, catalyst support materials, photonic bandgap materials for optical circuitry, and opalescent colorants for the ultraviolet, visible, and infrared regions.

Owner:ALLIEDSIGNAL INC

Method to minimize wet etch undercuts and provide pore sealing of extreme low k (k<2.5) dielectrics

ActiveUS20110092077A1Constant ratePrevents undercuts and CD lossVacuum evaporation coatingSemiconductor/solid-state device manufacturingThin layerNitrogen

Methods of processing films on substrates are provided. In one aspect, the methods comprise treating a patterned low dielectric constant film after a photoresist is removed form the film by depositing a thin layer comprising silicon, carbon, and optionally oxygen and / or nitrogen on the film. The thin layer provides a carbon-rich, hydrophobic surface for the patterned low dielectric constant film. The thin layer also protects the low dielectric constant film from subsequent wet cleaning processes and penetration by precursors for layers that are subsequently deposited on the low dielectric constant film.

Owner:APPLIED MATERIALS INC

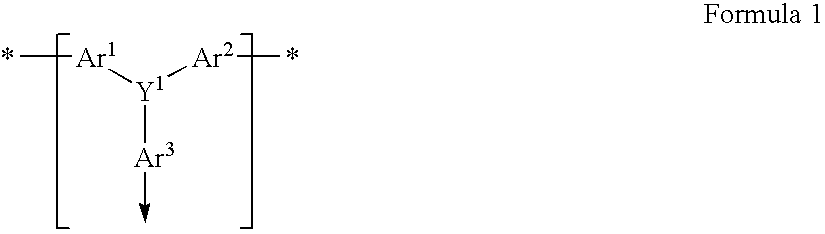

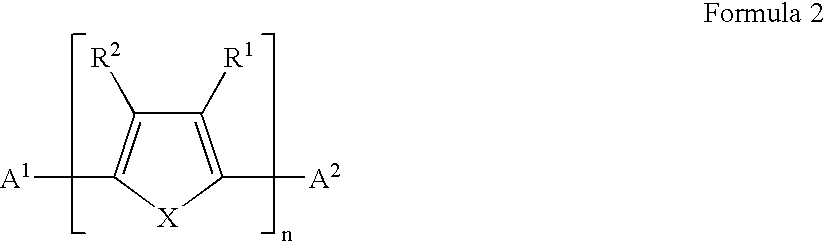

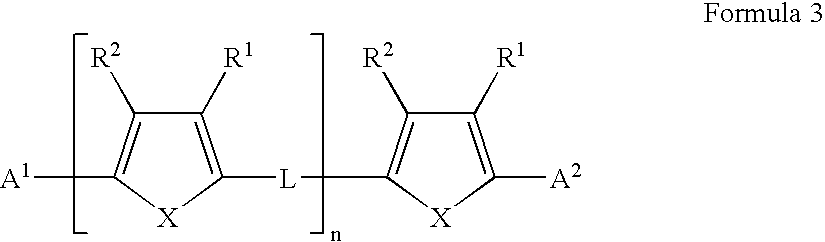

Low dielectric constant materials and method

InactiveUS6051321AImprove rotational flexibilityTightly boundSemiconductor/solid-state device detailsSynthetic resin layered productsElectrical conductorCopper

Intermetal dielectric (IMD) and interlevel dielectric (ILD) that have dielectric constants (K) ranging from 2.0 to 2.6 are prepared from plasma or photon assisted CVD (PACVD) or transport polymerization (TP). The low K dielectric (LKD) materials are prepared from PACVD or TP of some selected siloxanes and F-containing aromatic compounds. The thin films combine barrier and adhesion layer functions with low dielectric constant functions, thus eliminating the necessity for separate adhesion and barrier layers, and layers of low dielectric constant. The LKD materials disclosed in this invention are particularly useful for <0.18 .mu.m ICs, or when copper is used as conductor in future ICs.

Owner:CANON USA

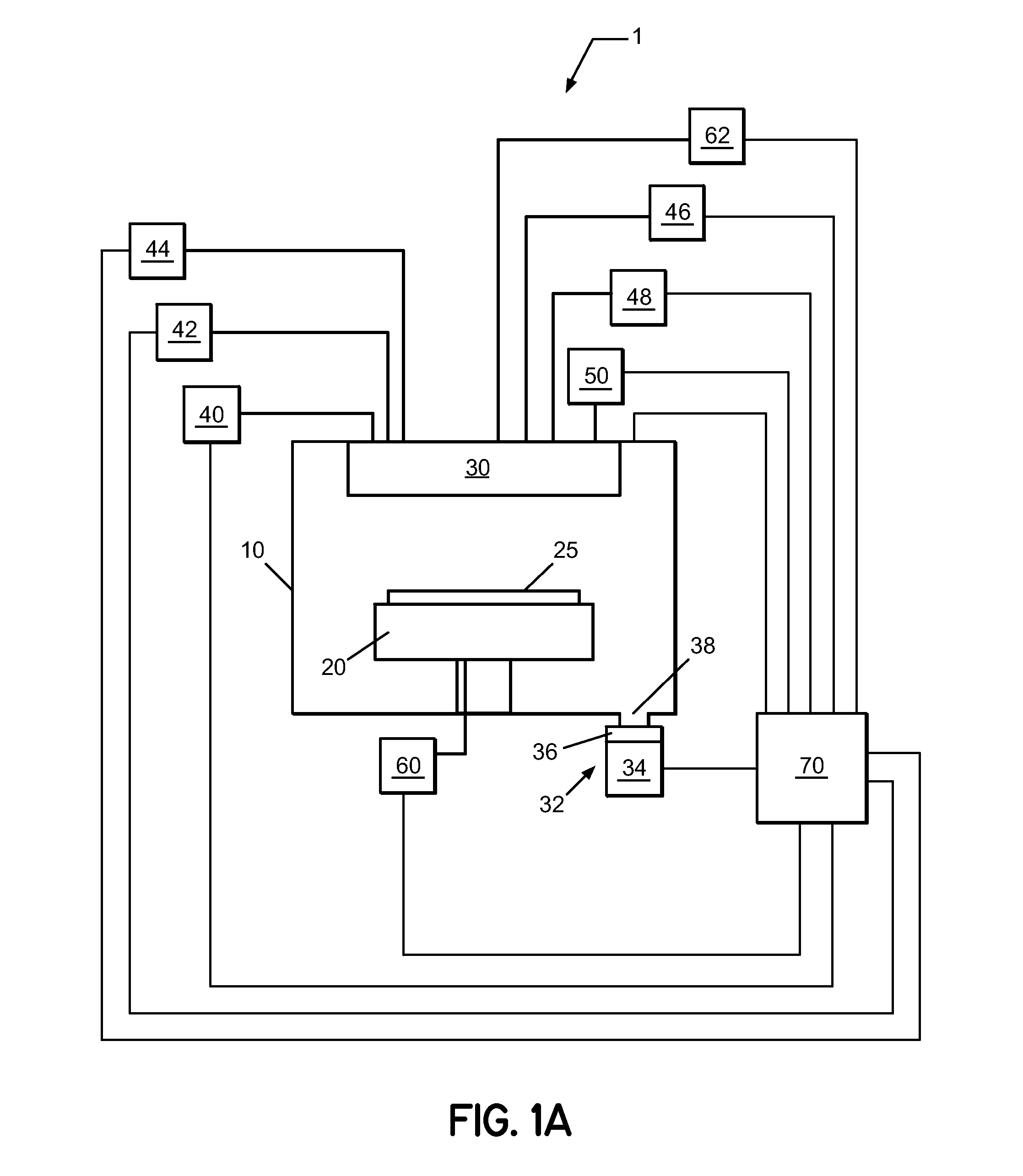

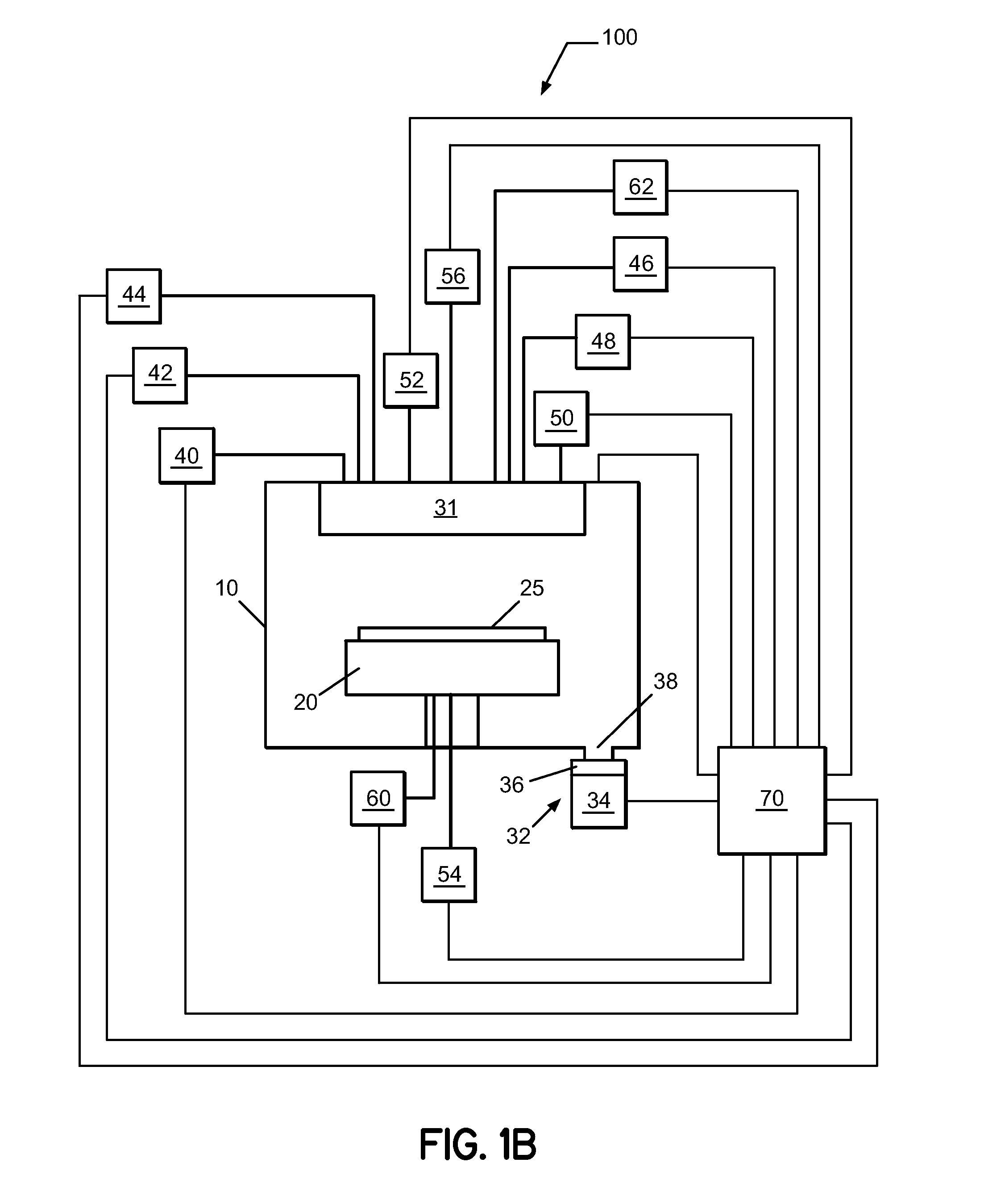

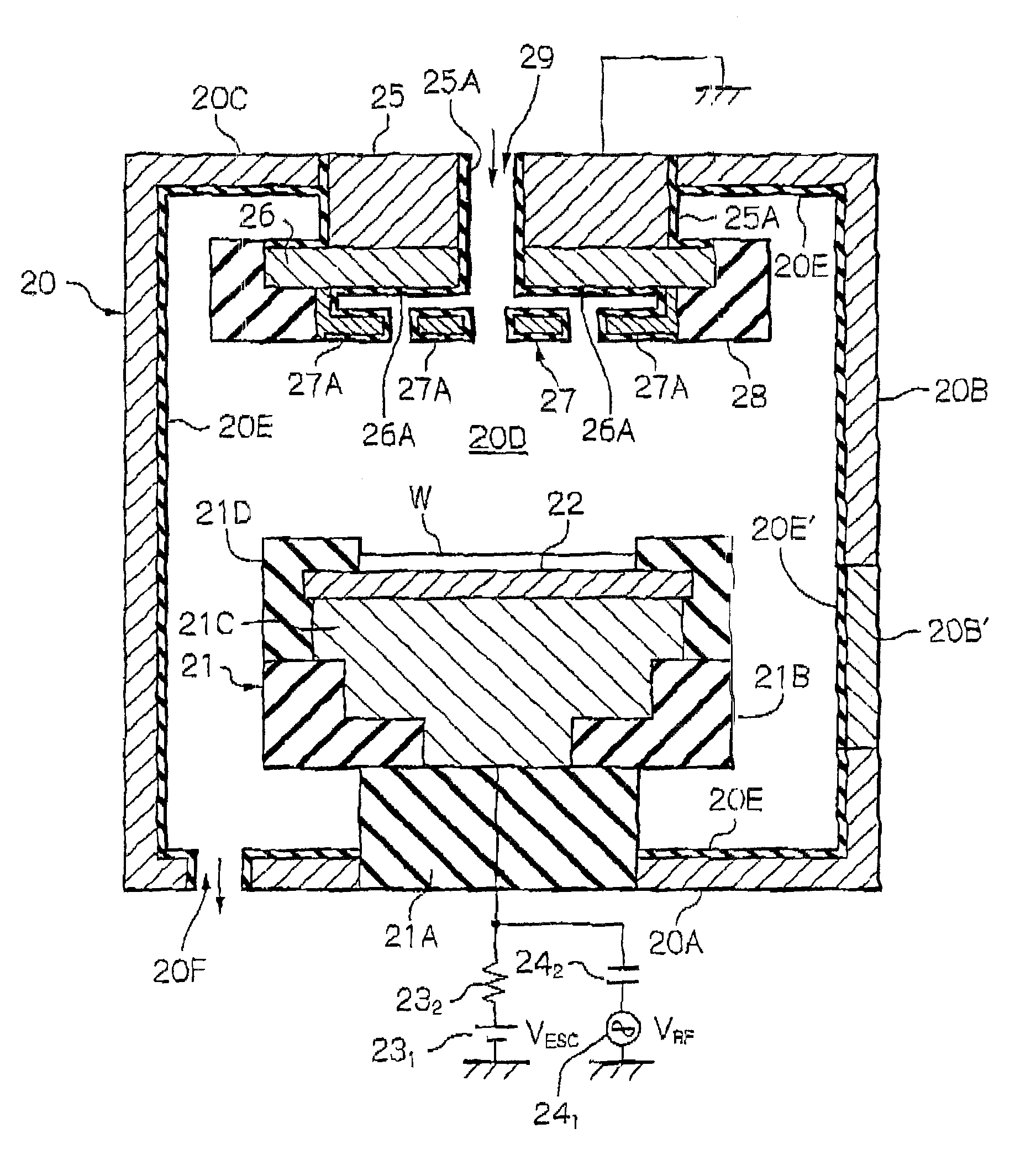

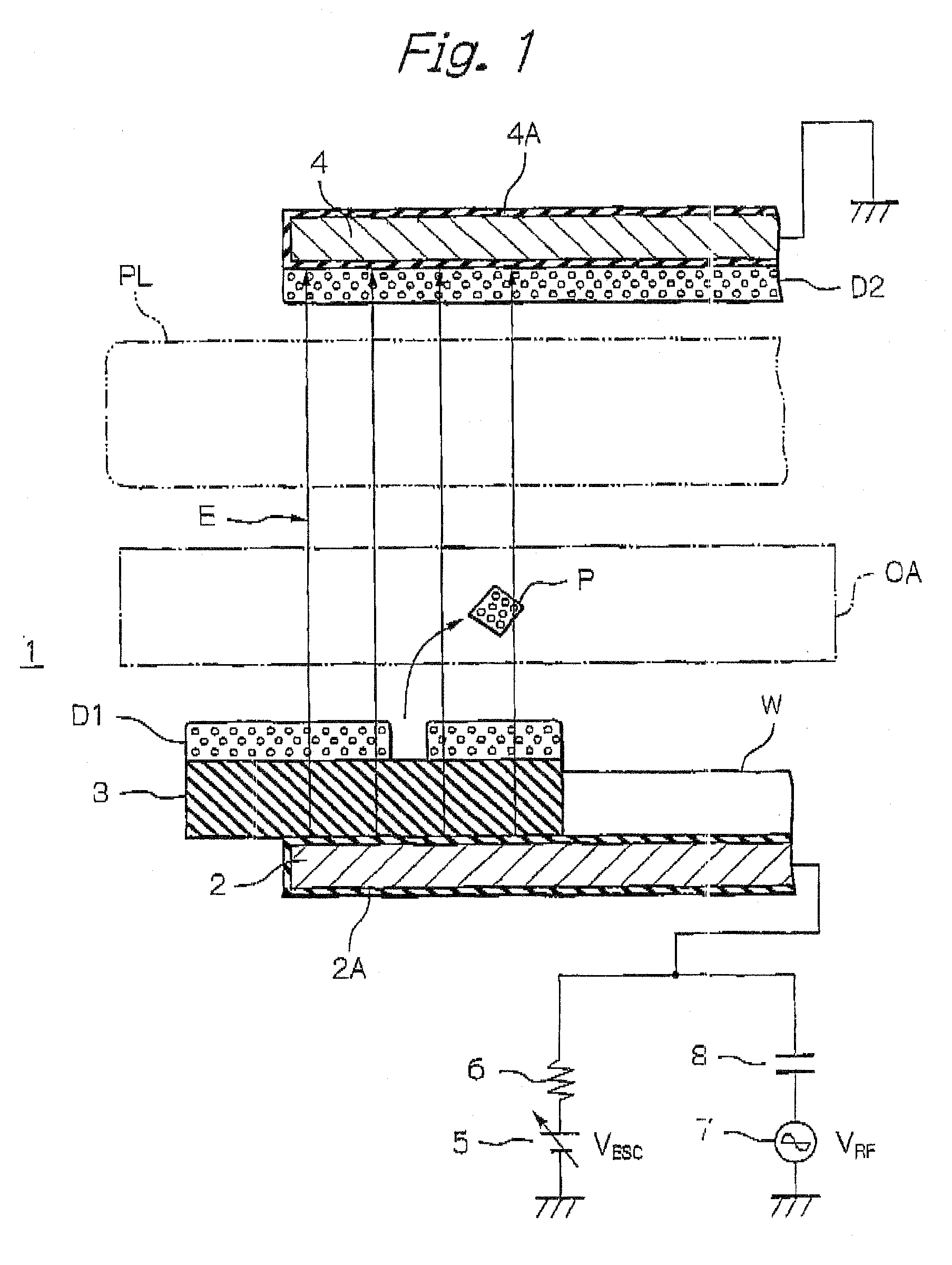

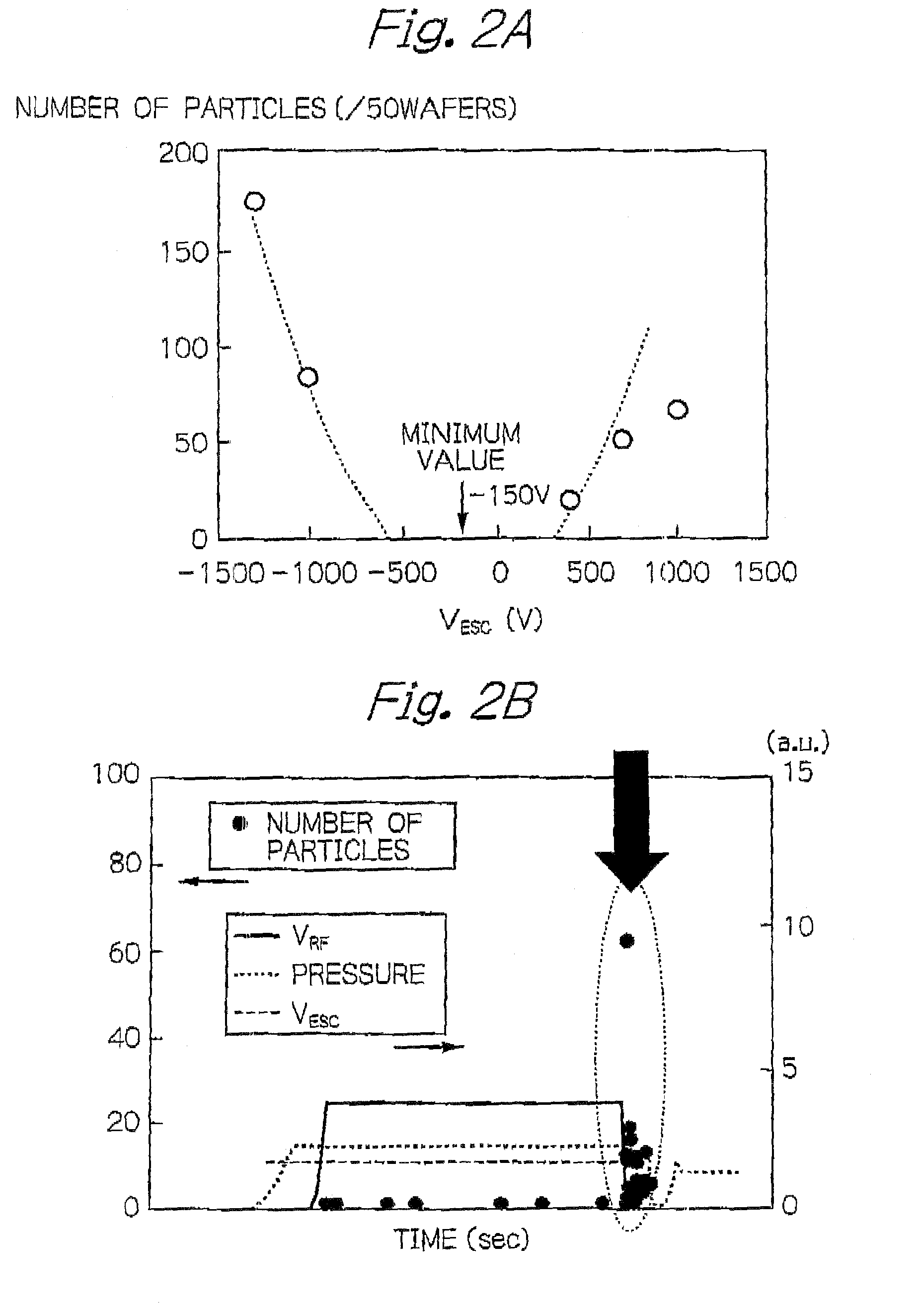

Object-processing apparatus controlling production of particles in electric field or magnetic field

InactiveUS8051799B2Liquid surface applicatorsElectric discharge tubesElectricityVolumetric Mass Density

Owner:RENESAS ELECTRONICS CORP

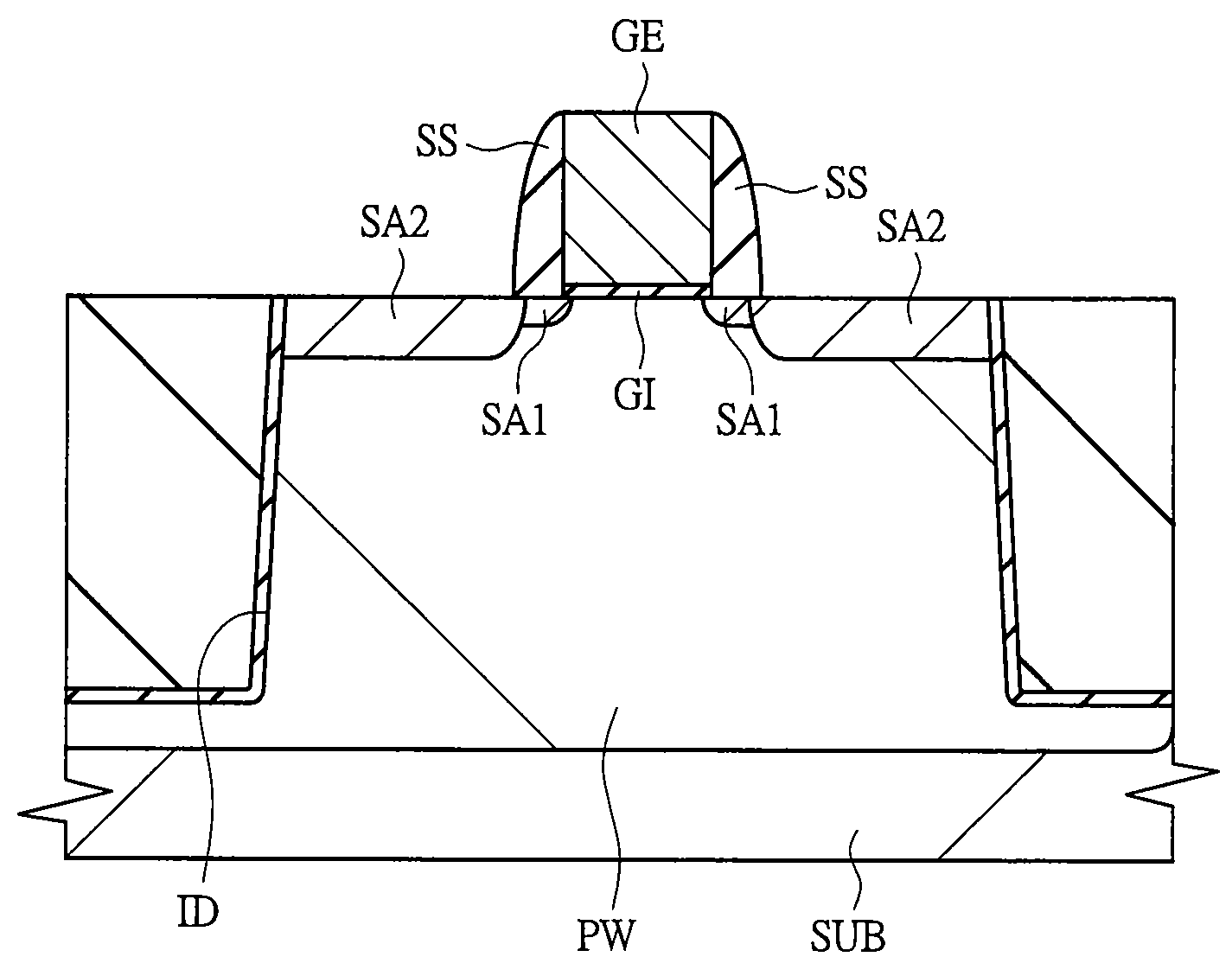

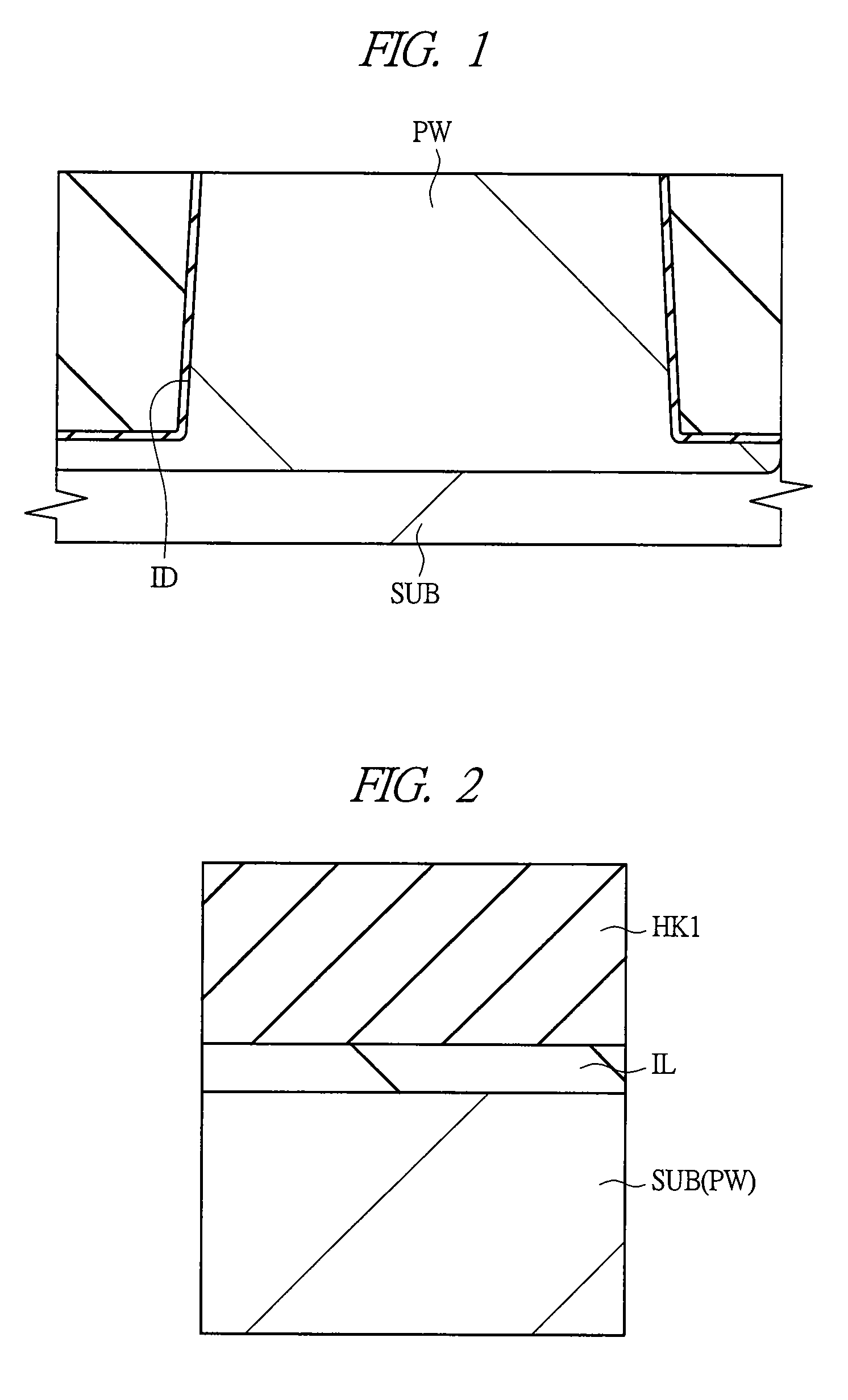

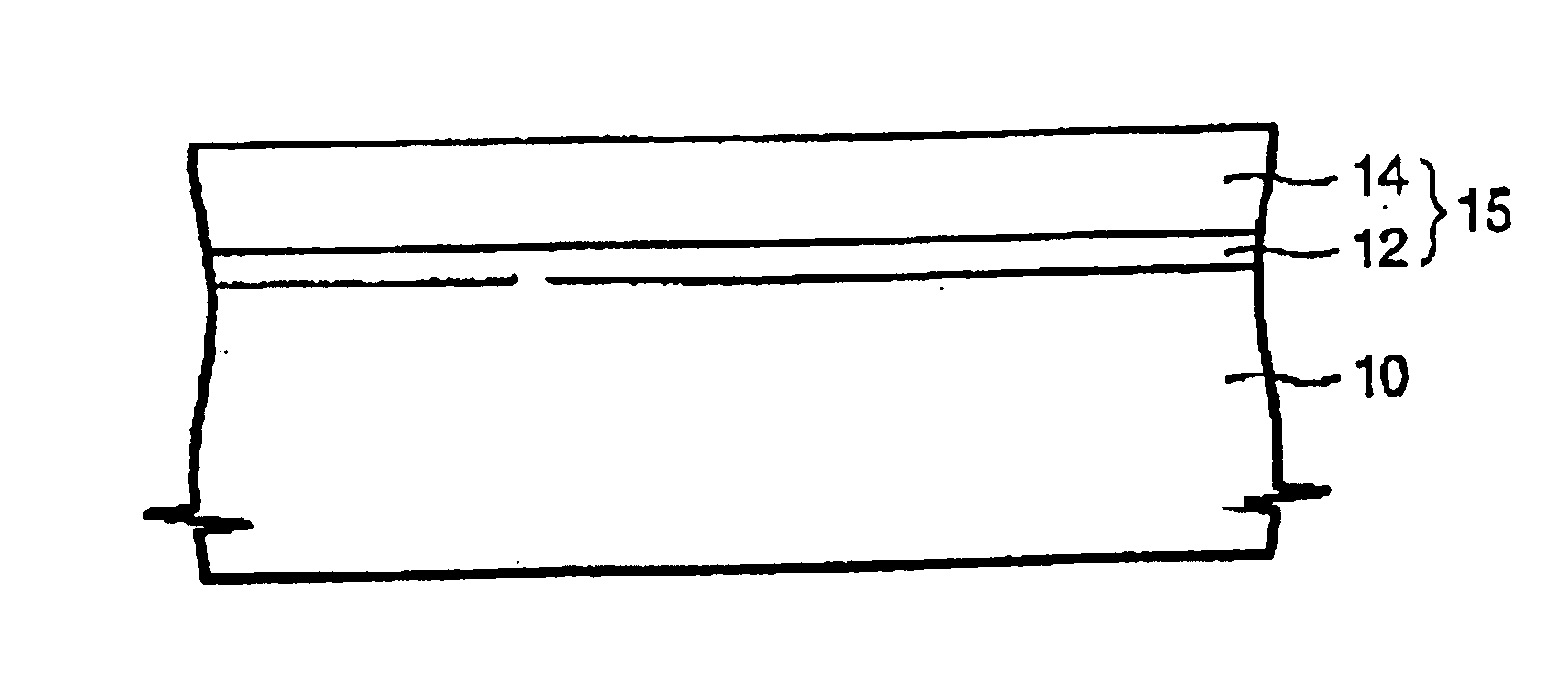

Dielectric layer for semiconductor device and method of manufacturing the same

InactiveUS6844604B2Improving interface characteristicReduce maintenanceTransistorSolid-state devicesDevice materialInterface layer

A multi-layer dielectric layer structure for a semiconductor device. The multi-layer dielectric layer structure comprises a silicate interface layer having a dielectric constant greater than that of silicon nitride and a high-k dielectric layer overlying the silicate interface layer. The high-k dielectric layer comprises one or more ordered pairs of first and second layers. With the present invention, the dielectric constant of the high-k dielectric layer can be optimized while improving interface characteristics. With a higher crystallization temperature realized by forming the multi-layer structure, each of whose layers is not more than the critical thickness, leakage current can be reduced, thereby improving device performance.

Owner:SAMSUNG ELECTRONICS CO LTD

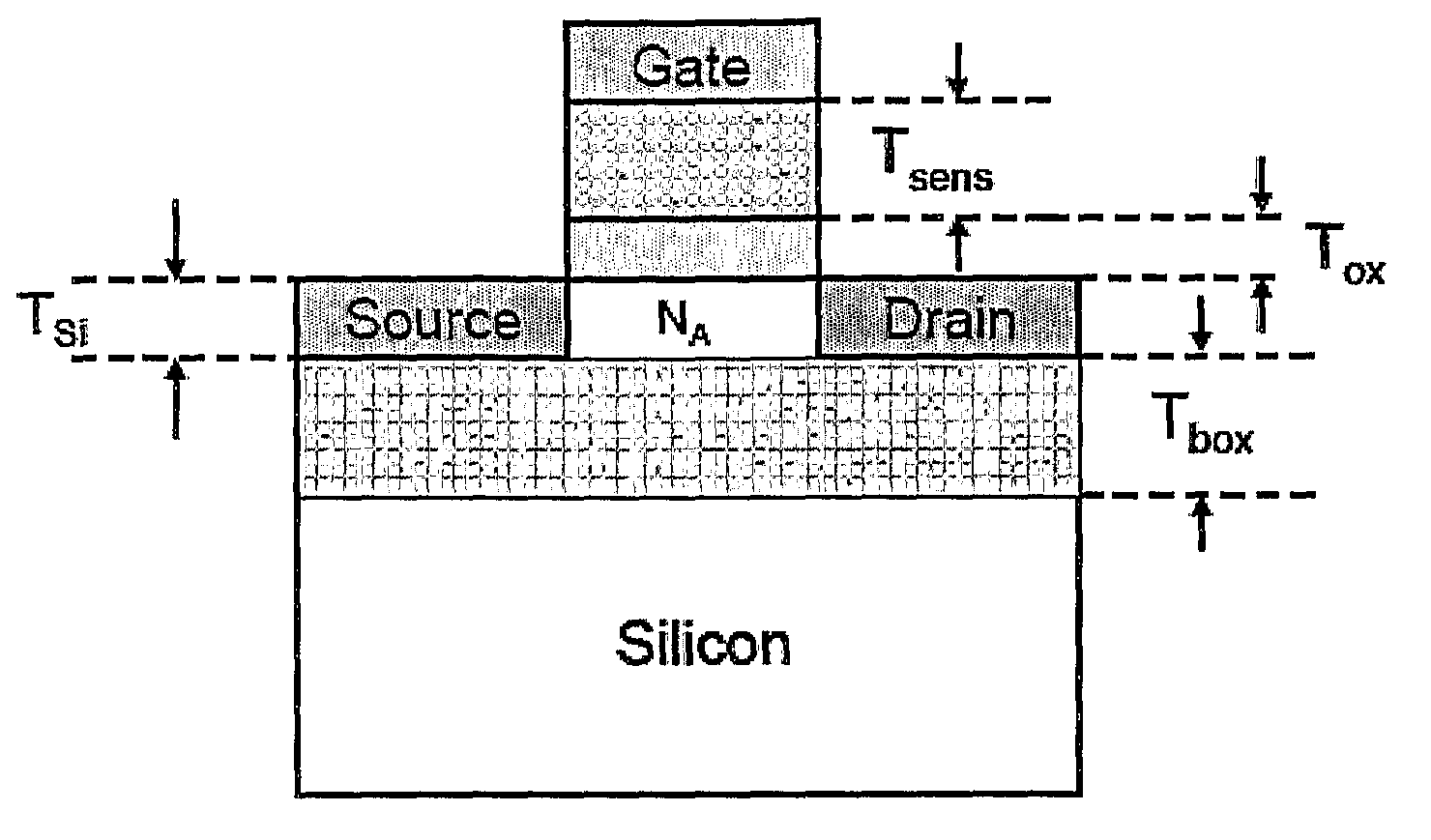

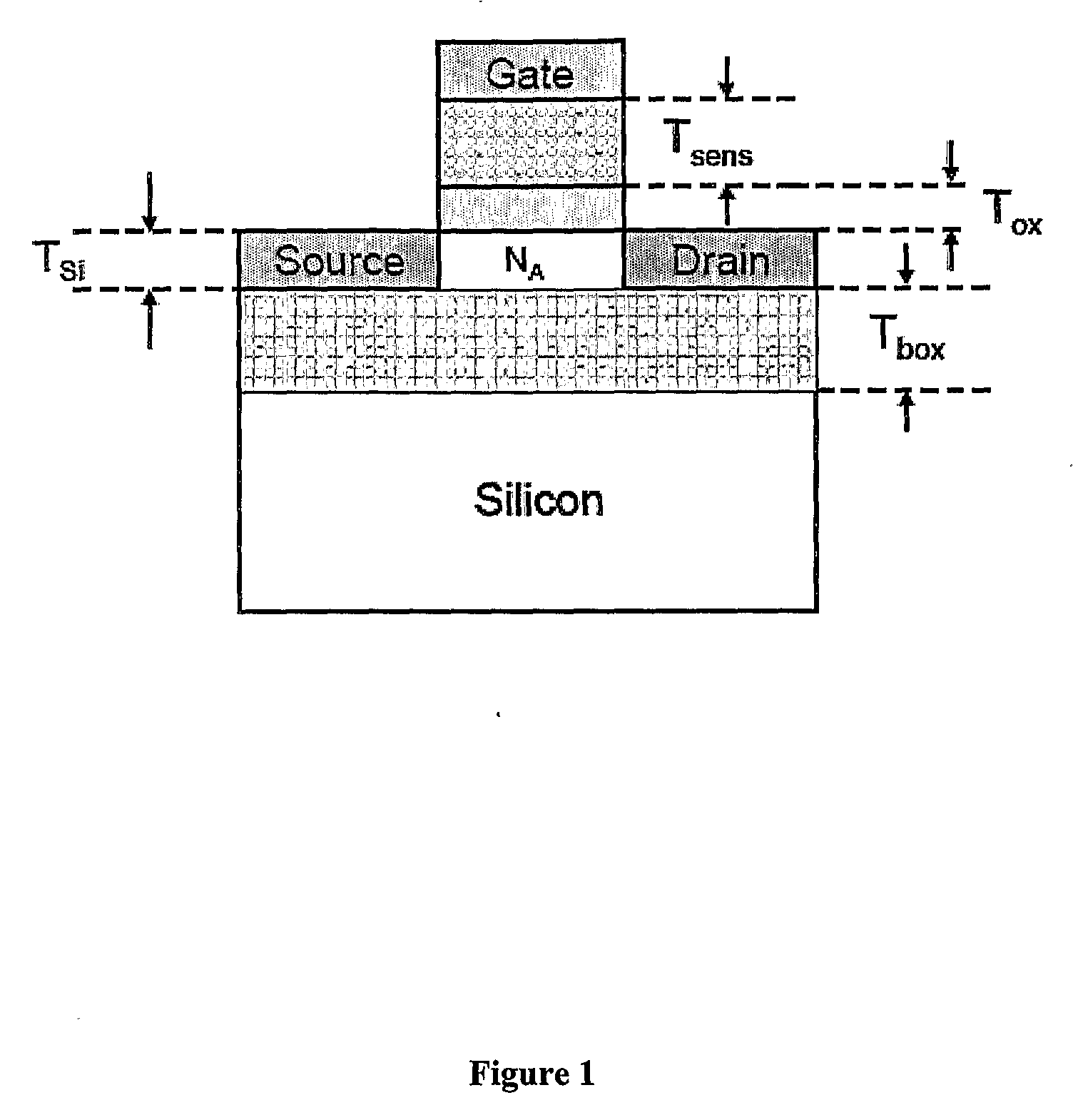

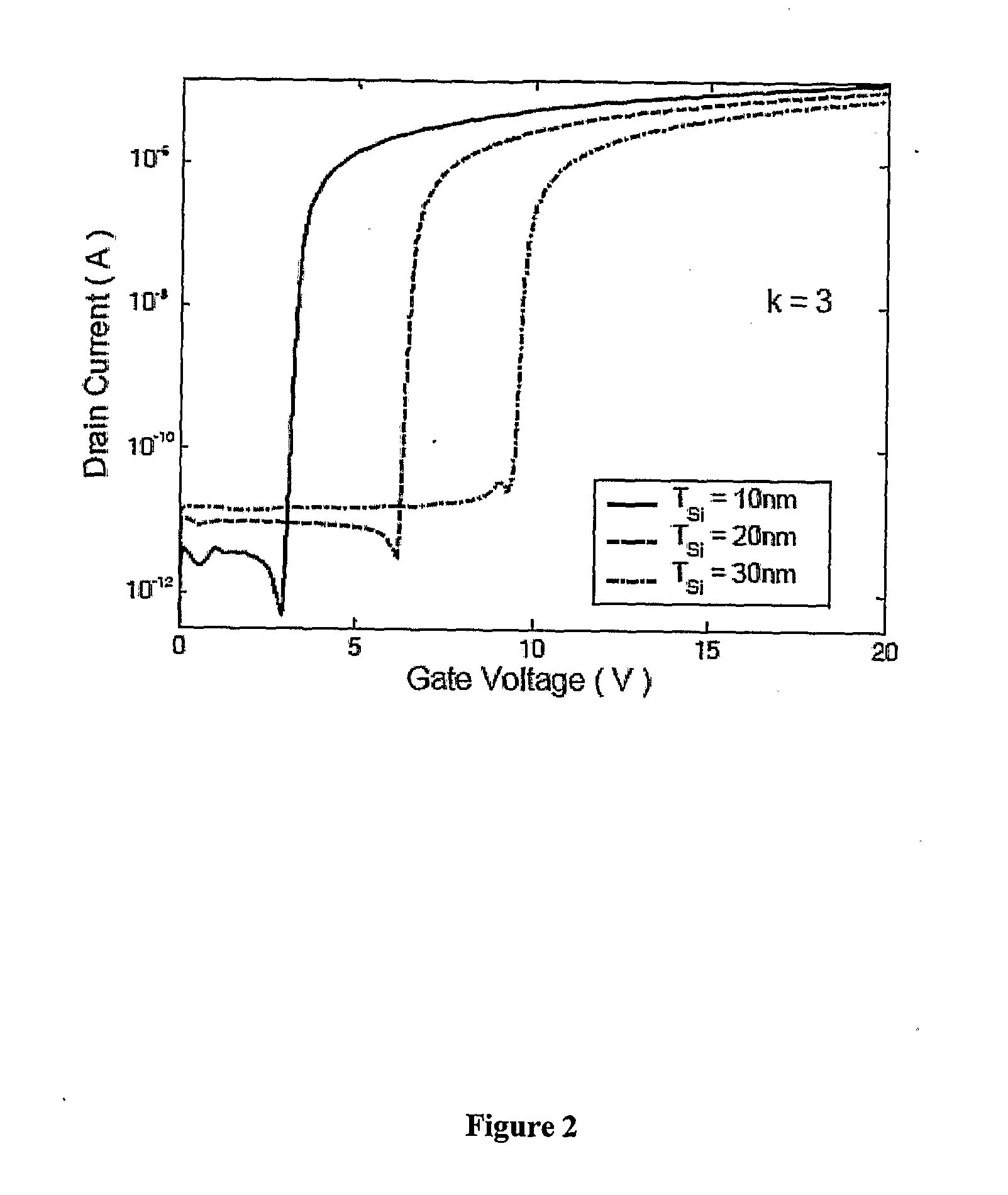

Sub-Threshold Capfet Sensor for Sensing Analyte, A Method and System Thereof

The present invention relates to high sensitivity chemical sensors, more particularly relates to high sensitivity chemical sensors which are capacitively coupled, FET based analyte sensors. A sub-threshold capacitively coupled Field Effect Transistor (CapFET) sensor for sensing an analyte comprises fixed dielectric placed on substrate of the CapFET and second dielectric sensitive to the analyte, placed between gate terminal of the CapFET and the fixed dielectric, wherein presence of the analyte alters either dielectric constant of the second dielectric or work function of the gate.

Owner:INDIAN INSTITUTE OF SCIENCE

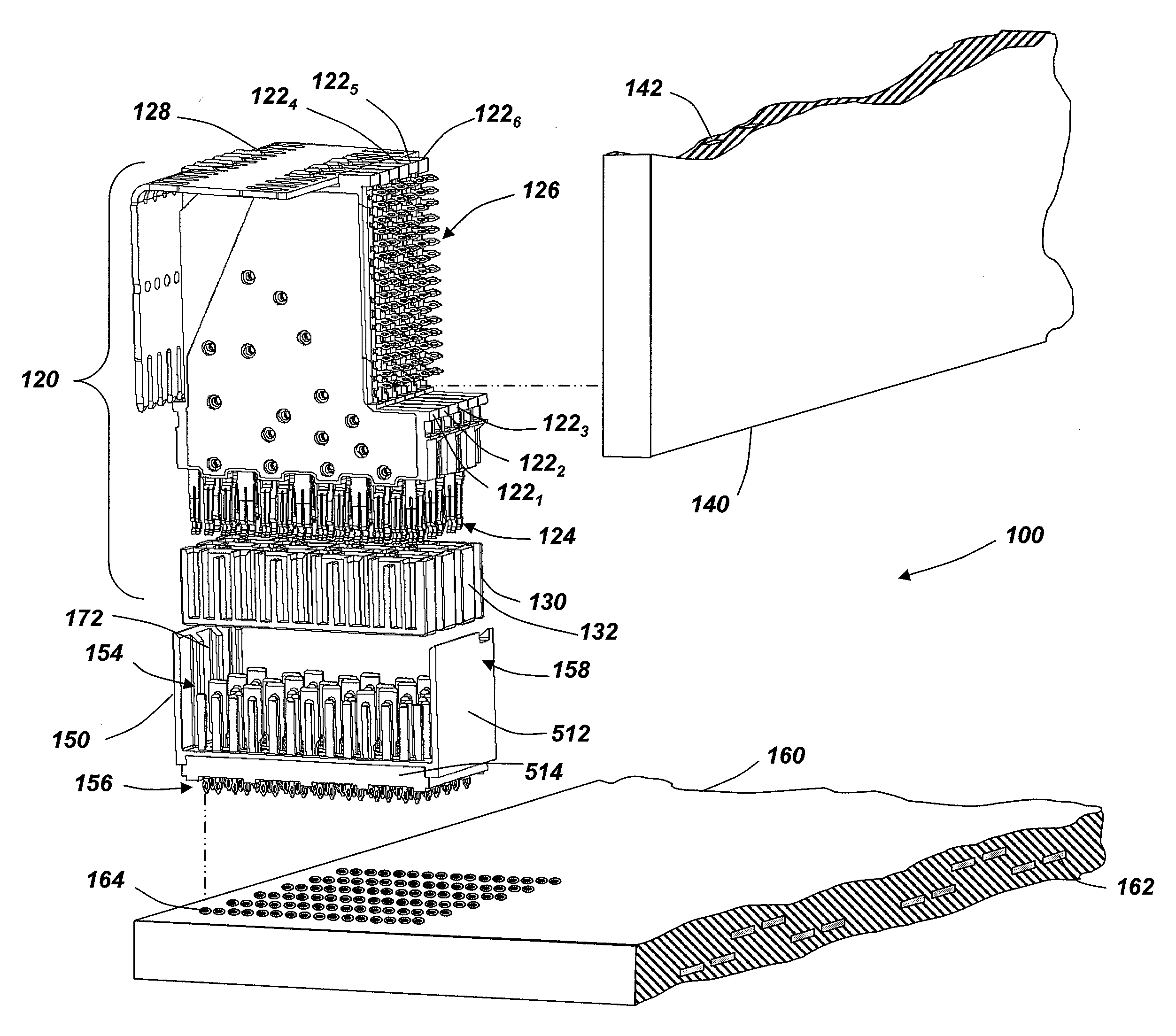

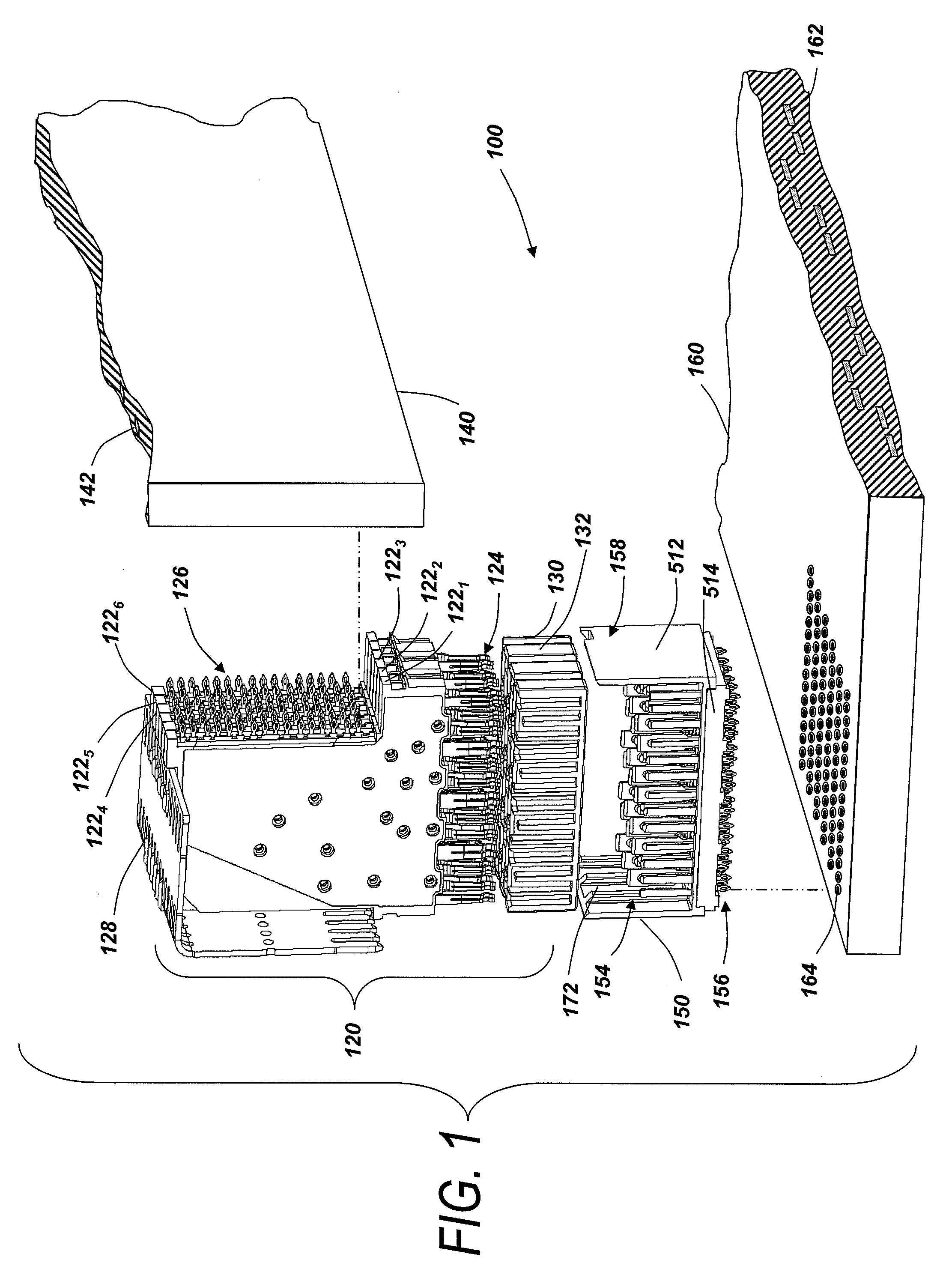

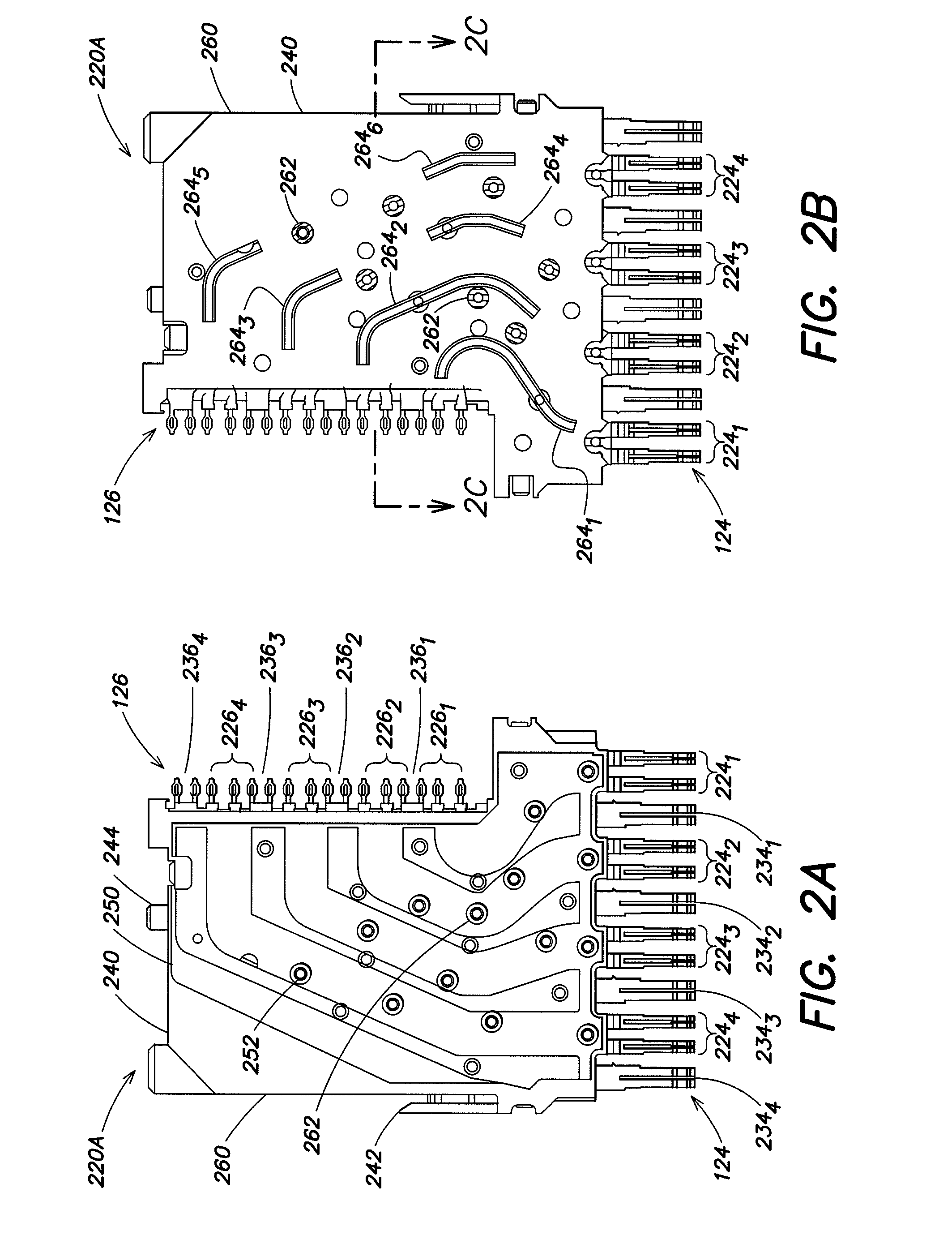

Differential electrical connector with skew control

ActiveUS20080246555A1Selective positioningCoupling devicesCoupling protective earth/shielding arrangementsElectrical conductorRegioselectivity

An electrical interconnection system with high speed, differential electrical connectors. The connector is assembled from wafers each containing a column of conductive elements, some of which form differential pairs. A housing for the wafer is formed with regions of higher and lower dielectric constant material. The regions of lower dielectric constant material are selectively positioned adjacent longer signal conductors of the differential pairs. The material may be preferentially placed along curved segments of the differential pair to reduce crosstalk in the connector while reducing skew.

Owner:AMPHENOL CORP

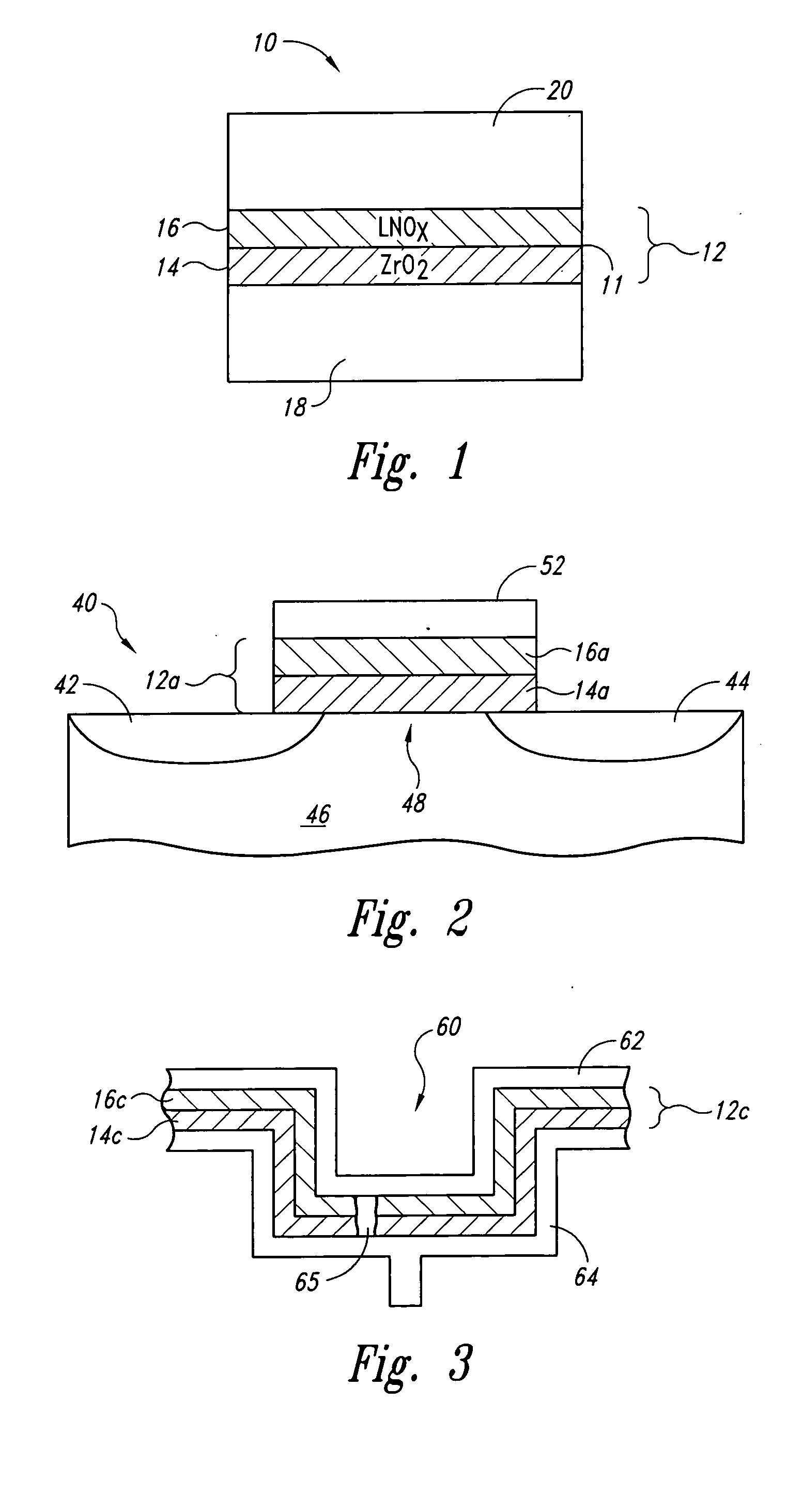

Lanthanide oxide/zirconium oxide atomic layer deposited nanolaminate gate dielectrics

The invention provides a laminated dielectric layer for semiconductor devices formed by a combination of ZrO2 and a lanthanide oxide on a semiconductor substrate and methods of making the same. In certain methods, the ZrO2 is deposited by multiple cycles of reaction sequence atomic layer deposition (RS-ALD) that includes depositing a ZrI4 precursor onto the surface of the substrate in a first pulse followed by exposure to H2O / H2O2 in a second pulse, thereby forming a thin ZrO2 layer on the surface. After depositing the ZrO2 layer, the lanthanide oxide layer is deposited by electron beam evaporation. The composite laminate zirconium oxide / lanthanide oxide dielectric layer has a relatively high dielectric constant and can be formed in layers of nanometer dimensions. It is useful for a variety of semiconductor applications, particularly for DRAM gate dielectric layers and DRAM capacitors.

Owner:MICRON TECH INC

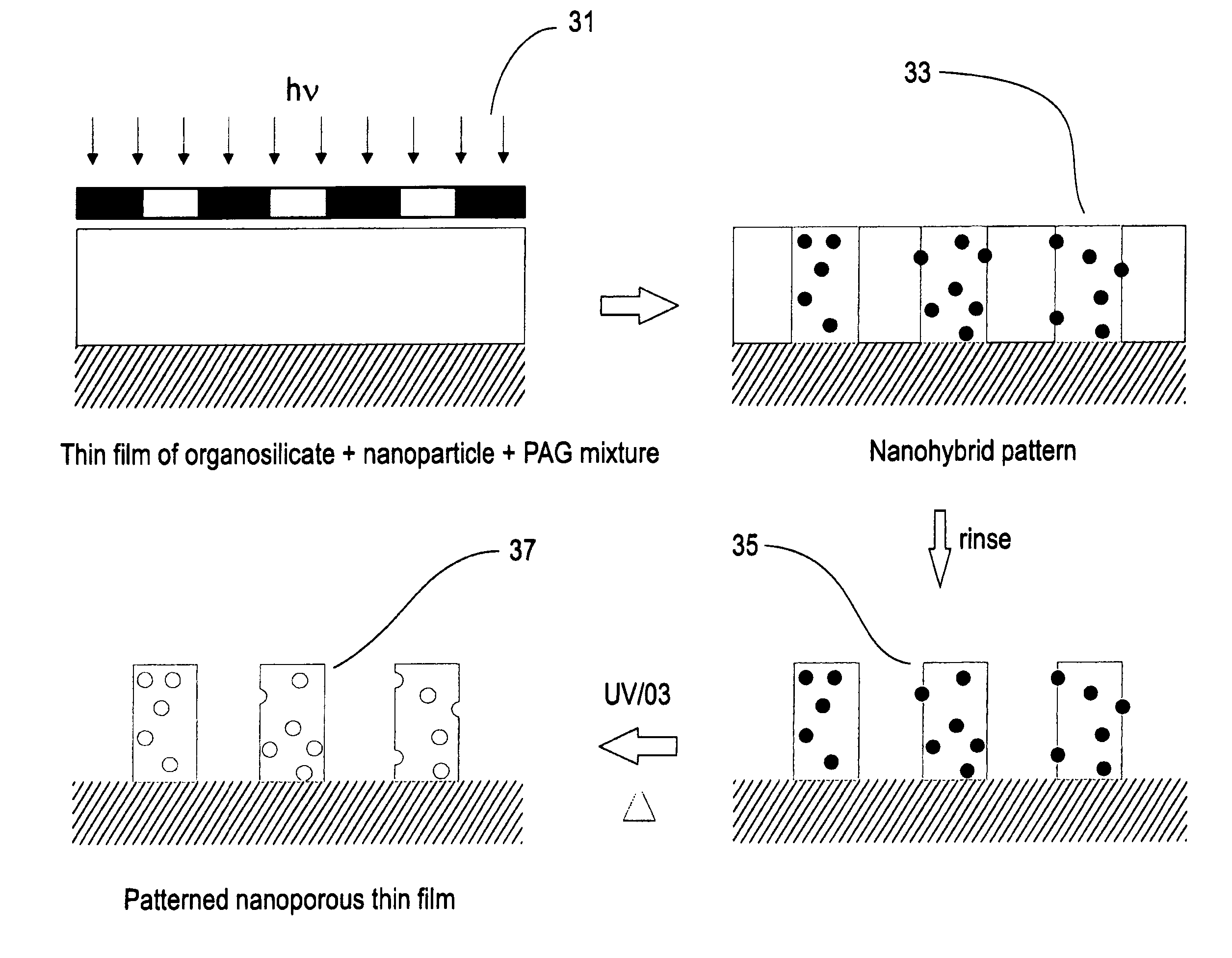

Direct photo-patterning of nanoporous organosilicates, and method of use

InactiveUS7056840B2Simple methodOrganic-compounds/hydrides/coordination-complexes catalystsSemiconductor/solid-state device manufacturingElectromagnetic radiationDielectric permittivity

A low dielectric constant, patterned, nanoporous material and a method of forming the material. The material is formed by depositing a layer onto a substrate, said layer comprising a reactive organosilicate material, a porogen, an initiator, and a solvent; exposing portions of the layer to energy (e.g., thermal energy or electromagnetic radiation) to change the solubility of portions of the organosilicate material with respect to the solvent; selectively removing more soluble portions of the layer to generate a relief pattern; and decomposing the porogen to thereby generate a nanoporous organosilicate layer.

Owner:INT BUSINESS MASCH CORP

Structures including dielectric layers and methods of forming same

PendingUS20210066075A1Readily apparentSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectric membraneDeposition process

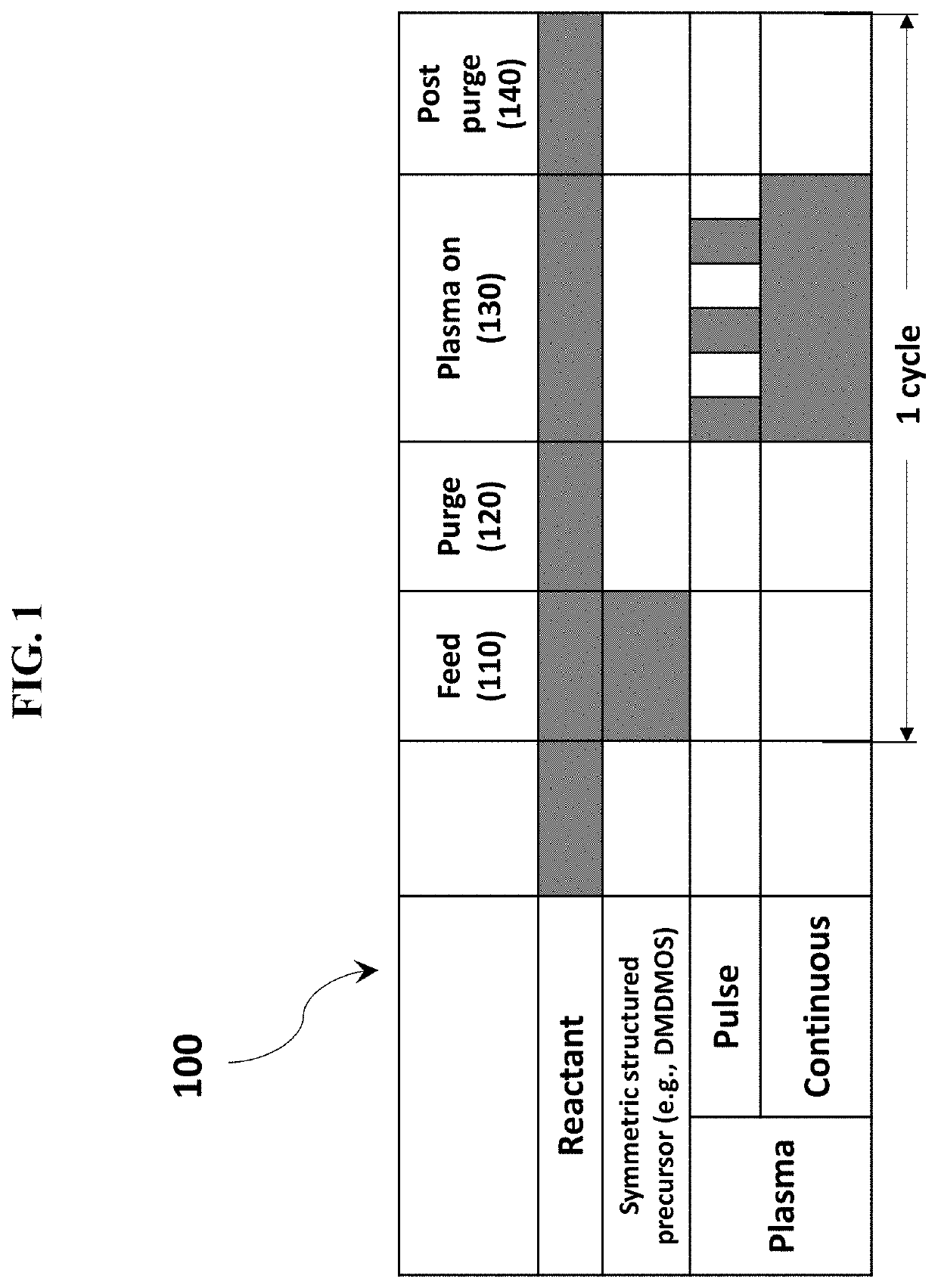

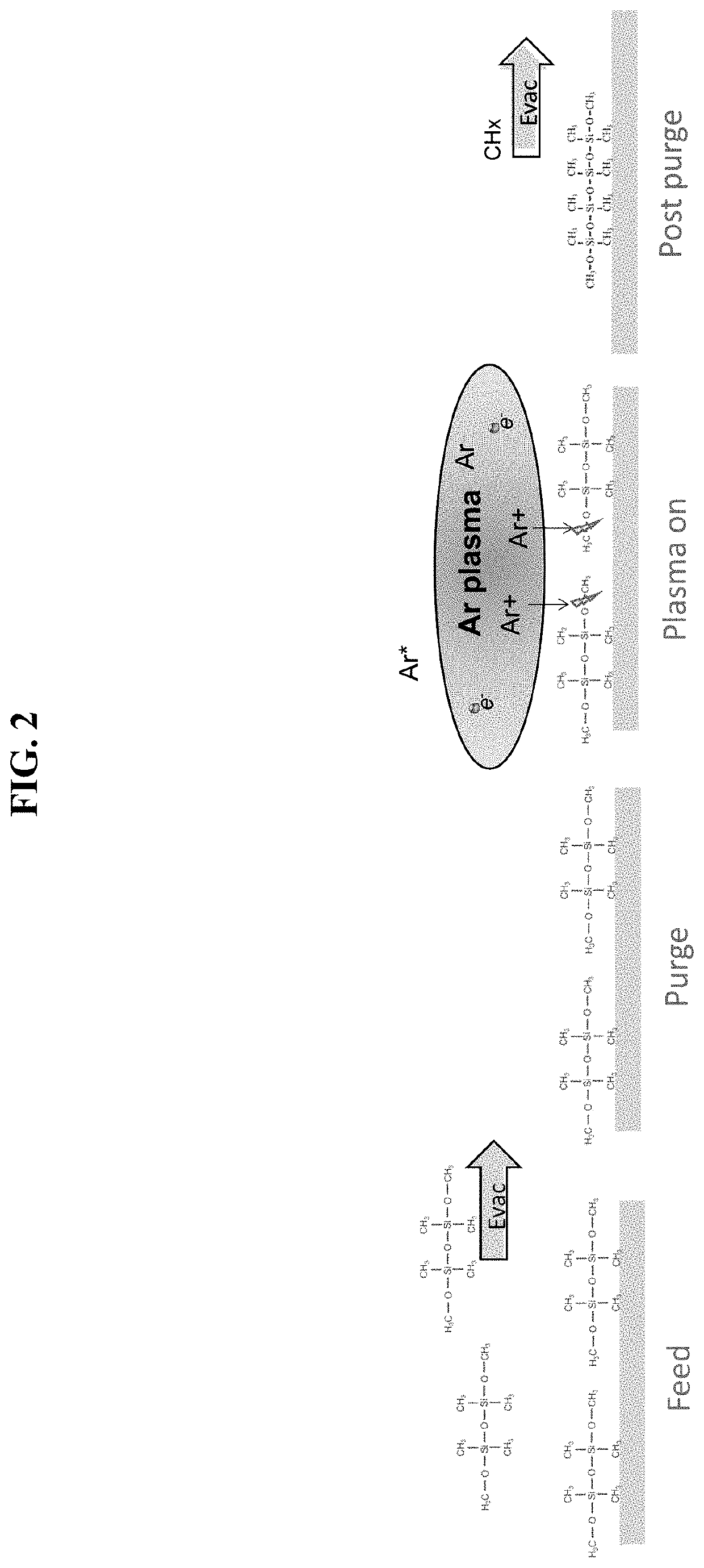

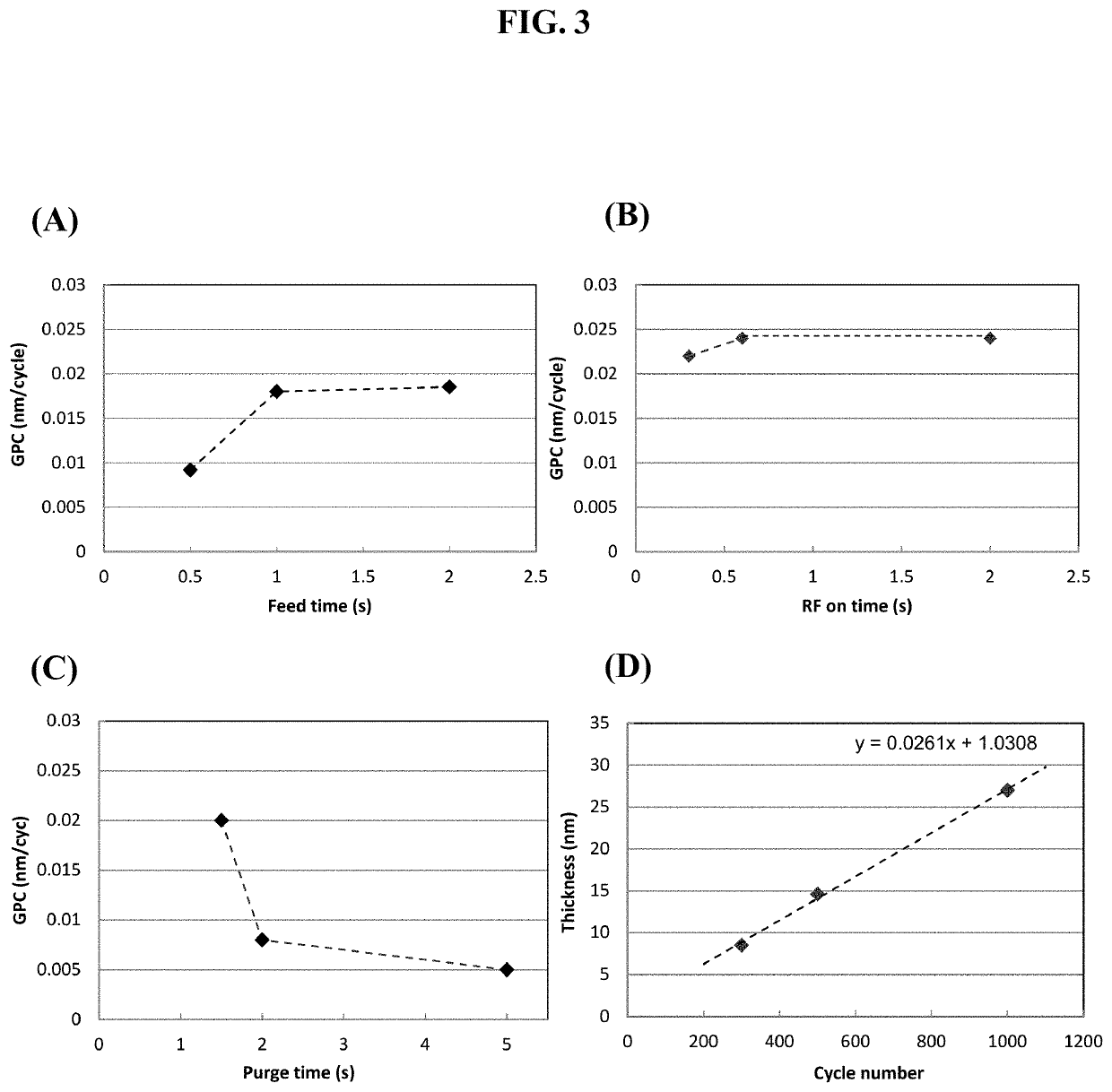

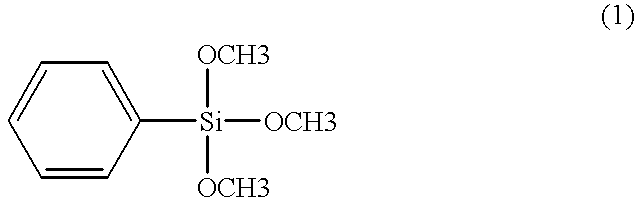

Methods of forming structures having dielectric films with improved properties, such as, for example, improved elastic modulus and / or dielectric constant are disclosed. Exemplary films can be formed using a cyclic deposition process. Exemplary methods use activated species to cleave (e.g., symmetric-structured) precursor molecules to form the high quality dielectric layers.

Owner:ASM IP HLDG BV

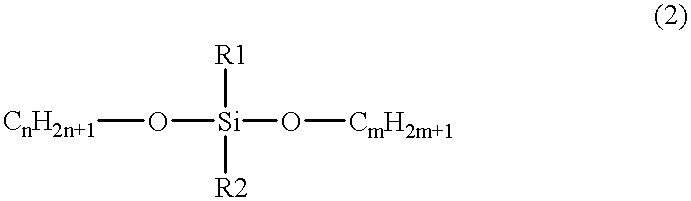

Silicone polymer insulation film on semiconductor substrate and method for forming the film

InactiveUS6432846B1Low dielectric constantImprove thermal stabilitySolid-state devicesPretreated surfacesPolymer scienceHigh humidity

A method for forming a silicone polymer insulation film having low relative dielectric constant, high thermal stability and high humidity-resistance on a semiconductor substrate is applied to a plasma CVD apparatus. The first step is vaporizing a silicon-containing hydrocarbon compound expressed by the general formula SialphaObetaCxHy (alpha=3, beta=3 or 4, x, and y are integers) and then introducing the vaporized compound to the reaction chamber of the plasma CVD apparatus. The next step is introducing additive gas into the reaction chamber. The residence time of the material gas is lengthened by reducing the total flow of the reaction gas, in such a way as to formed a silicone polymer film having a micropore porous structure with low relative dielectric constant.

Owner:ASM JAPAN

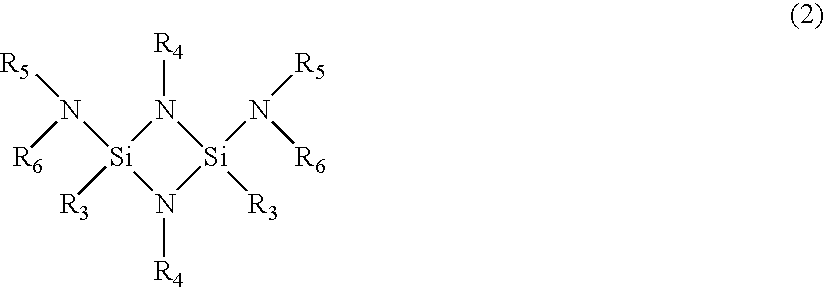

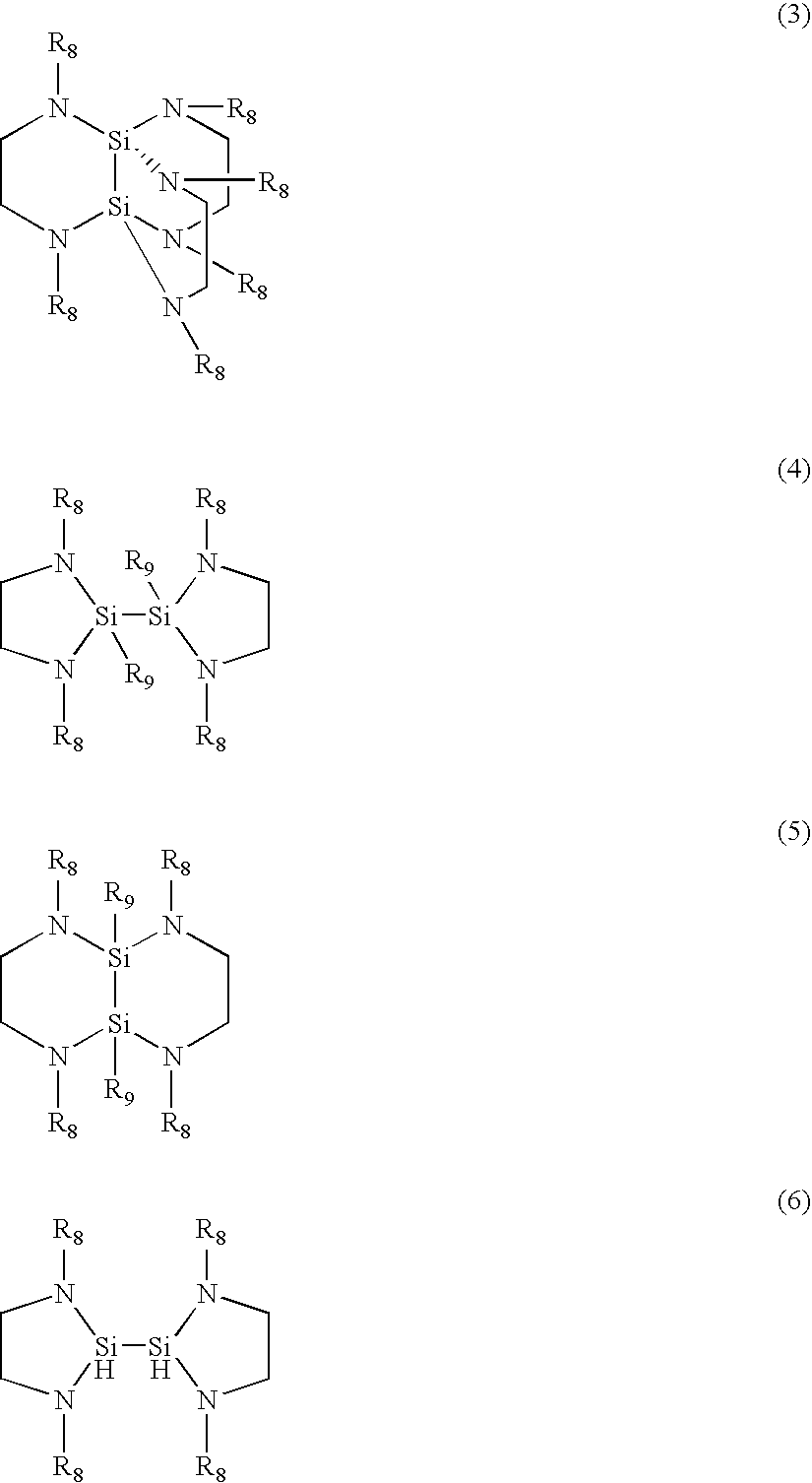

Composition and method for low temperature deposition of silicon-containing films such as films including silicon nitride, silicon dioxide and/or silicon-oxynitride

ActiveUS20040096582A1Silicon organic compoundsPolycrystalline material growthLow temperature depositionGas phase

Silicon precursors for forming silicon-containing films in the manufacture of semiconductor devices, such as low dielectric constant (k) thin films, high k gate silicates, low temperature silicon epitaxial films, and films containing silicon nitride (Si3N4), siliconoxynitride (SiOxNy) and / or silicon dioxide (SiO2). The precursors of the invention are amenable to use in low temperature (e.g., <500° C.) chemical vapor deposition processes, for fabrication of ULSI devices and device structures.

Owner:ENTEGRIS INC

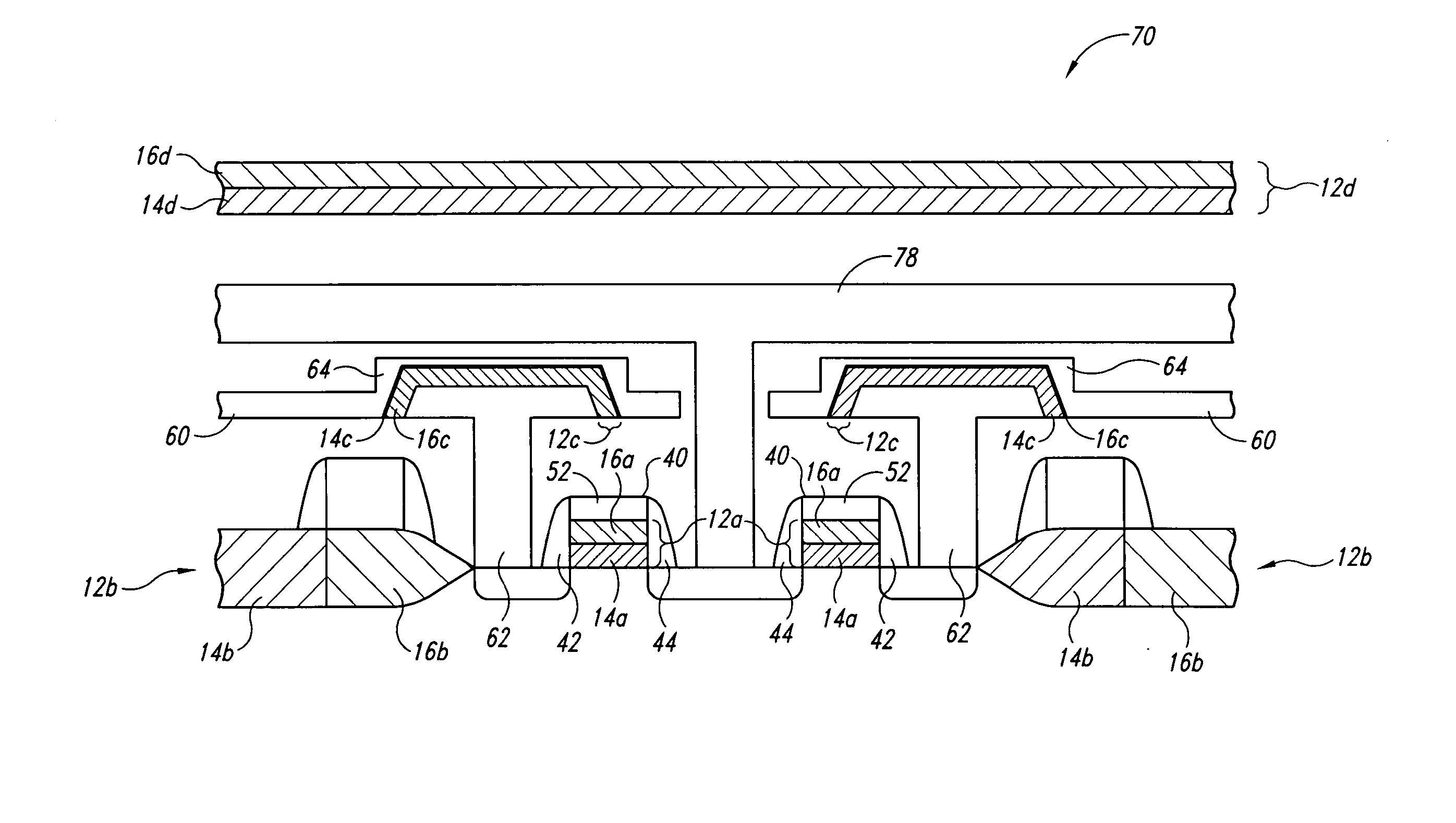

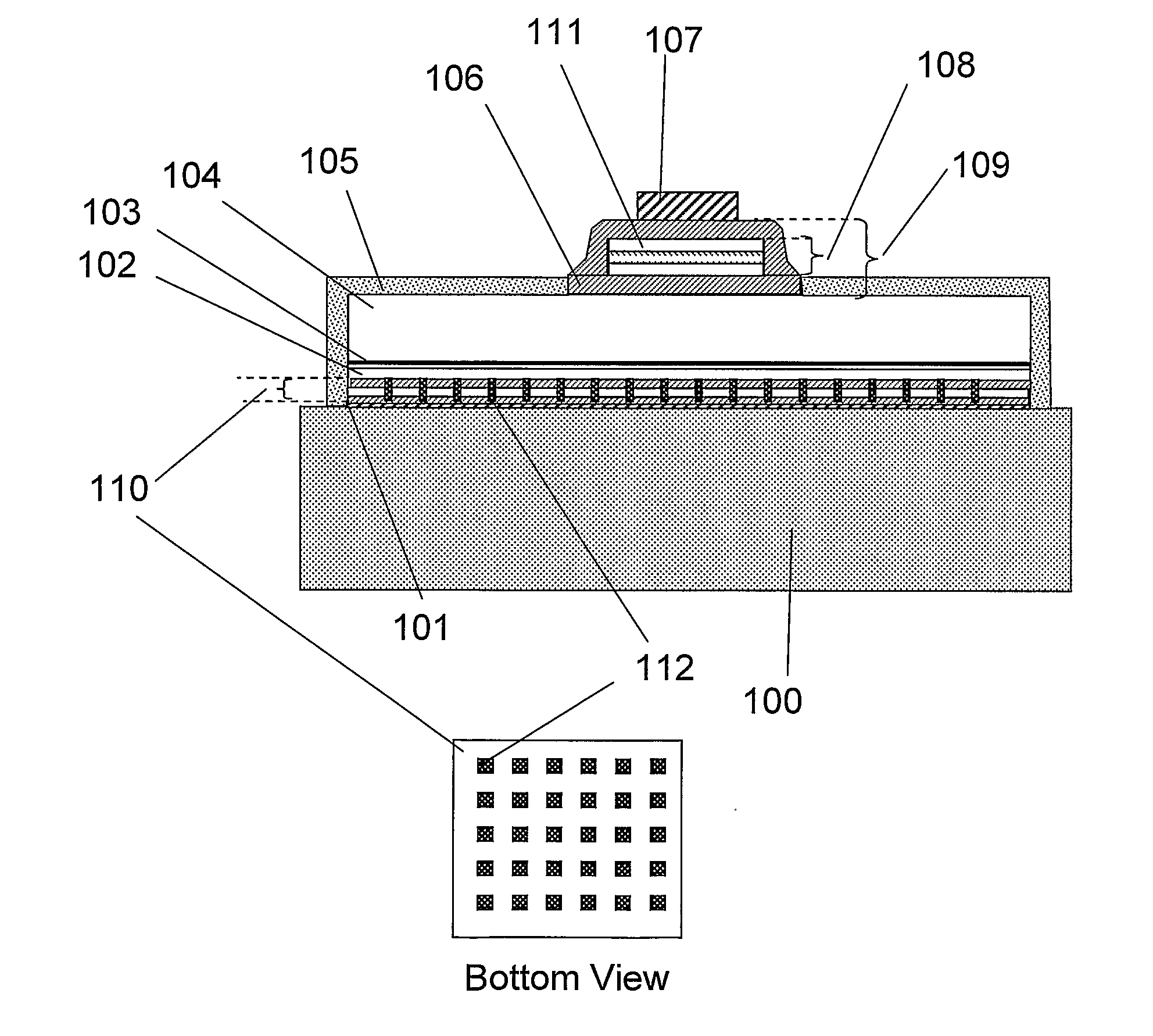

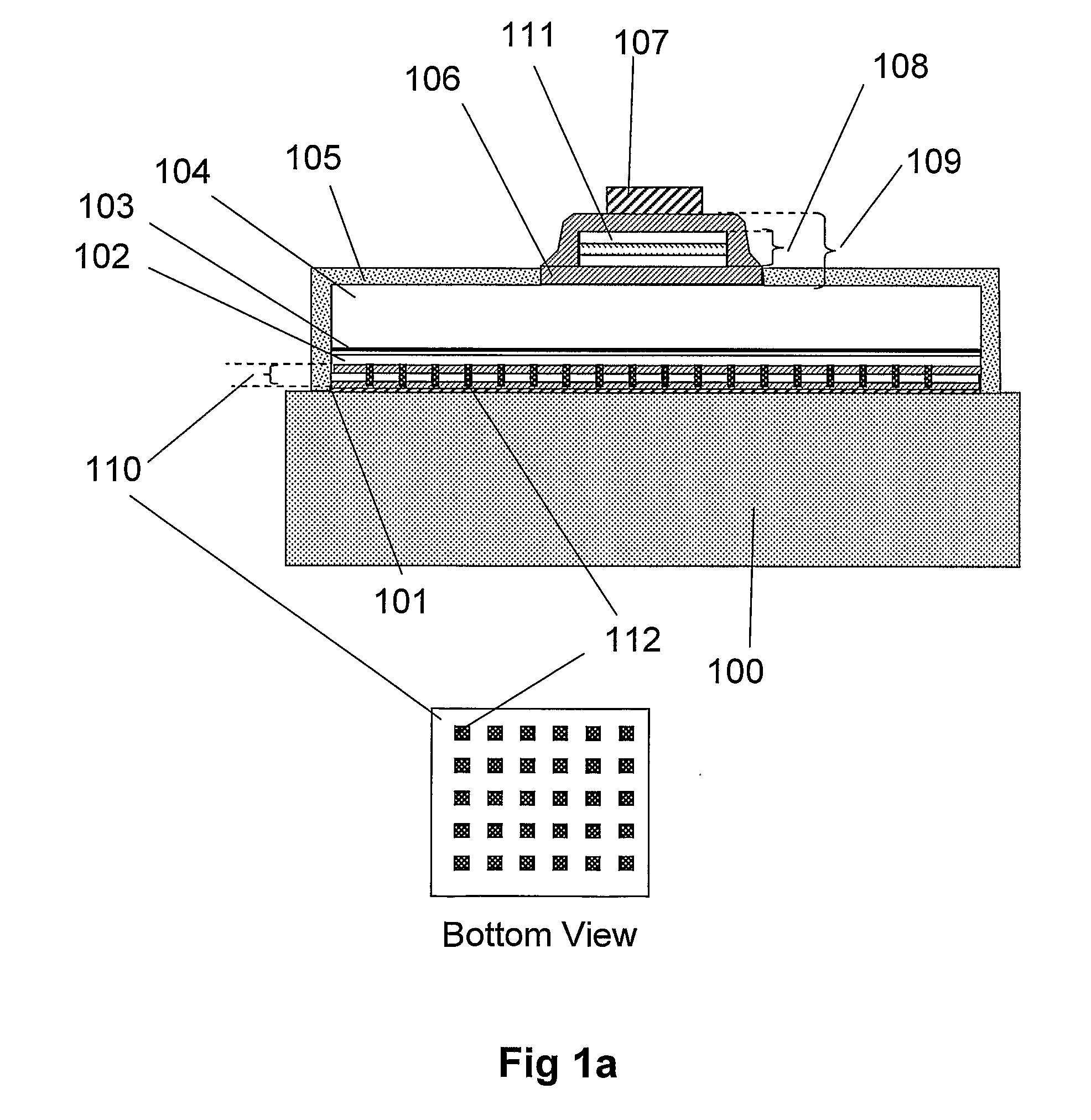

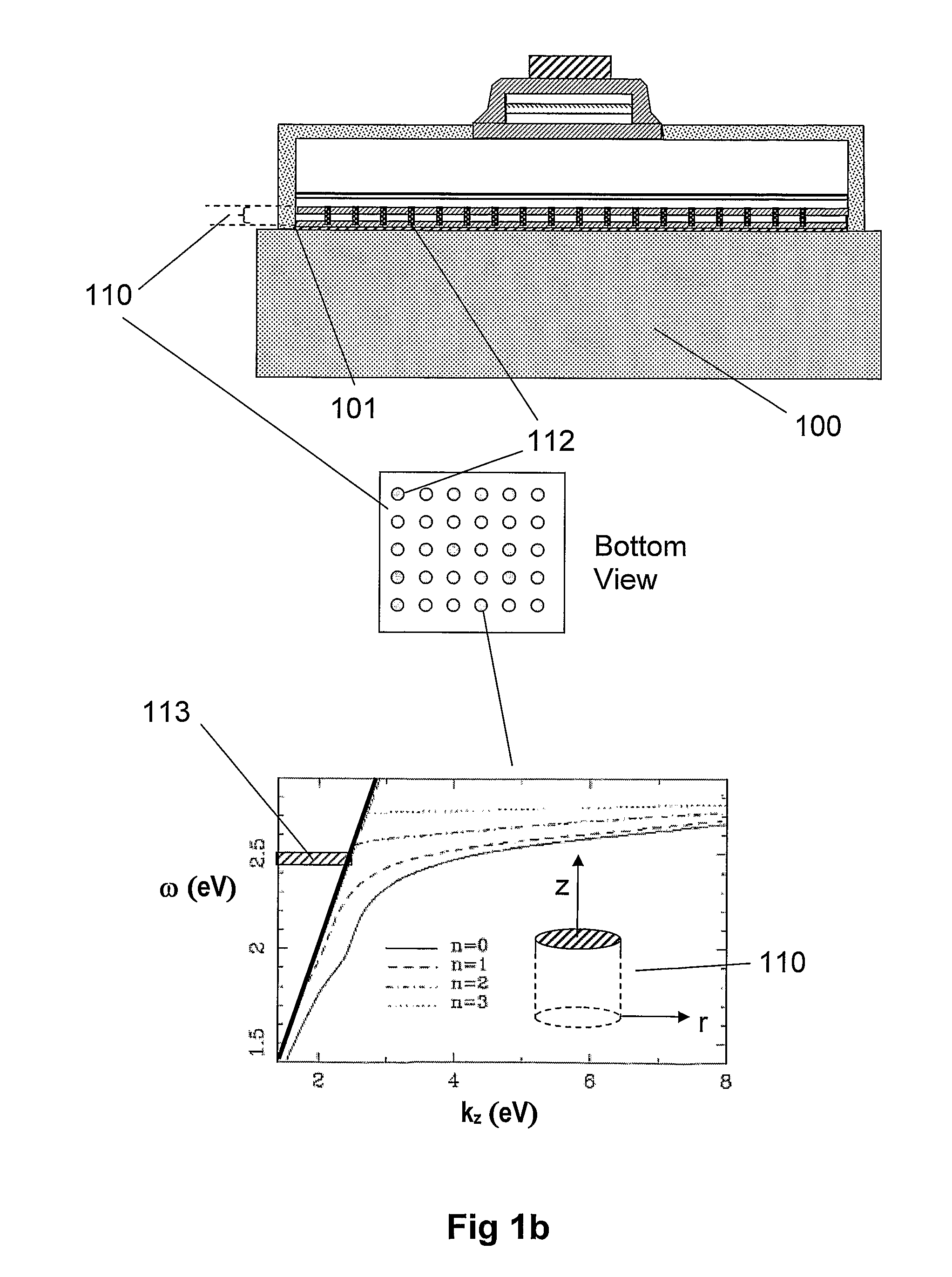

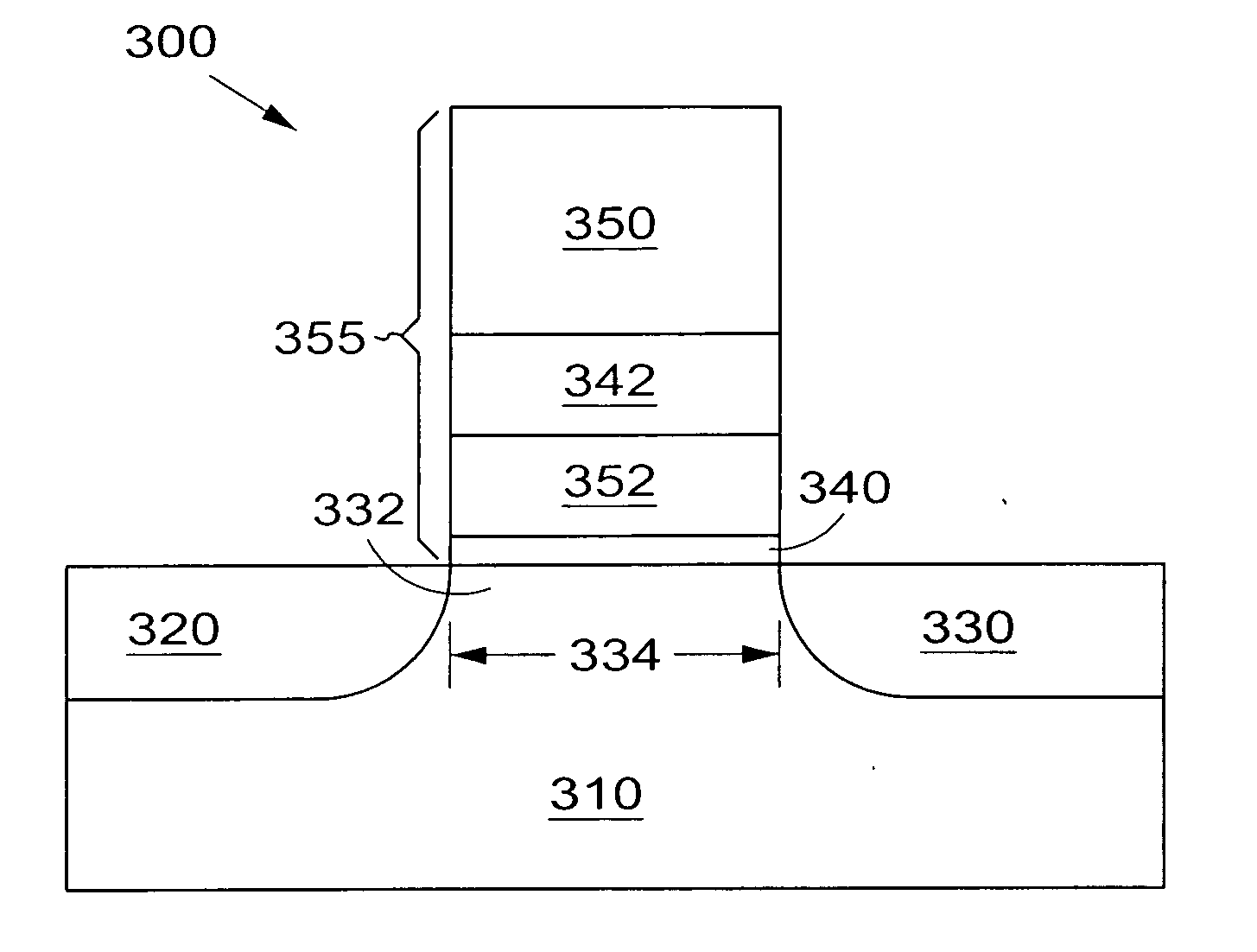

Vertical LED with conductive vias

ActiveUS20100213485A1Maximizing light extractionLight extraction efficiency can be improvedSolid-state devicesSemiconductor/solid-state device manufacturingSurface plasmonHigh reflectivity

A light emitting device comprises a novel low-loss array of conductive vias embedded in a dielectric multilayer stack, to act as an electrically-conductive, low-loss, high-reflectivity reflector layer (CVMR). In one example the CVMR stack is employed between a reflective metal bottom contact and a p-GaN semiconductor flip chip layer. The CVMR stack comprises at least (3) layers with at least (2) differing dielectric constants. The conductive vias are arranged such that localised and propagating surface plasmons associated with the structure reside within the electromagnetic stopband of the CVMR stack, which in turn inhibits trapped LED modes coupling into these plasmonic modes, thereby increasing the overall reflectivity of the CVM R. This technique improves optical light extraction and provides a vertical conduction path for optimal current spreading in a semiconductor light emitting device. A light emitting module and method of manufacture are also described.

Owner:LUMILEDS HLDG BV

Evaporated LaAlO3 films for gate dielectrics

InactiveUS20050145957A1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

A gate dielectric containing LaAlO3 and method of fabricating a gate dielectric contained LaAlO3 produce a reliable gate dielectric having a thinner equivalent oxide thickness than attainable using SiO2. The LaAlO3 gate dielectrics formed are thermodynamically stable such that these gate dielectrics will have minimal reactions with a silicon substrate or other structures during processing. A LaAlO3 gate dielectric is formed by evaporating Al2O3 at a given rate, evaporating La2O3 at another rate, and controlling the two rates to provide an amorphous film containing LaAlO3 on a transistor body region. The evaporation deposition of the LaAlO3 film is performed using two electron guns to evaporate dry pellets of Al2O3 and La2O3. The two rates for evaporating the materials are selectively chosen to provide a dielectric film composition having a predetermined dielectric constant ranging from the dielectric constant of an Al2O3 film to the dielectric constant of a La2O3 film. In addition to forming a LaAlO3 gate dielectric for a transistor, memory devices, and information handling devices such as computers include elements having a LaAlO3 gate electric with a thin equivalent oxide thickness.

Owner:MICRON TECH INC

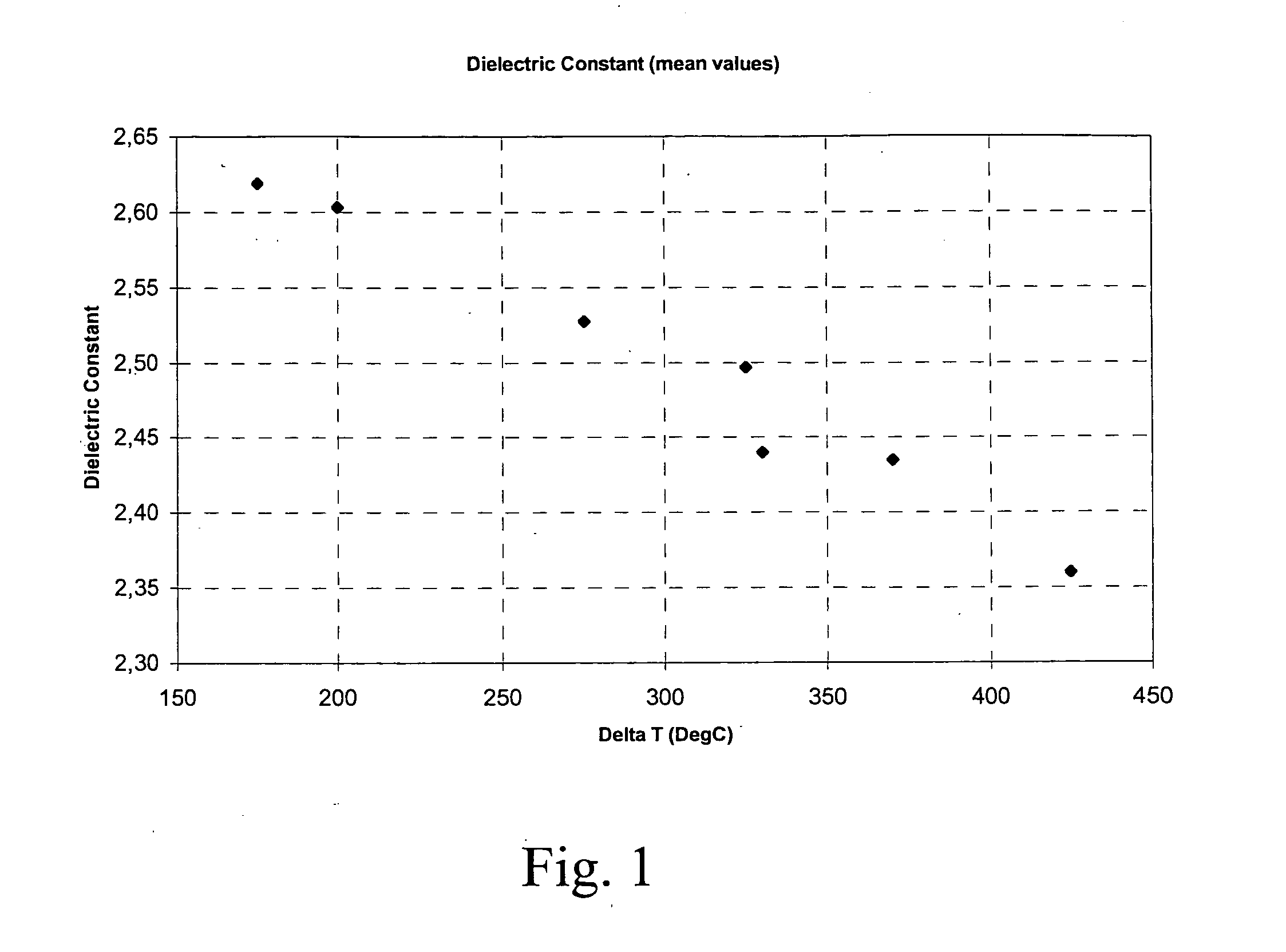

Method of forming low-k dielectrics

InactiveUS20050064726A1Improve performanceFast curingPretreated surfacesSemiconductor/solid-state device manufacturingDielectric permittivityMaterials science

A method of forming a low dielectric constant structure. The method comprises providing at a first temperature a dielectric material having a first dielectric constant and a first elastic modulus, and curing the dielectric material by a thermal curing process, in which the material is heated to a second temperature by increasing the temperature at an average rate of at least 1° C. per second. As a result a densified, dielectric material is obtained which has a low dielectric constant.

Owner:SILECS OY

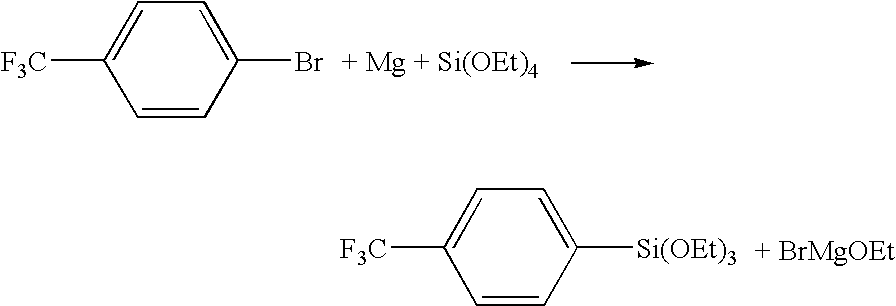

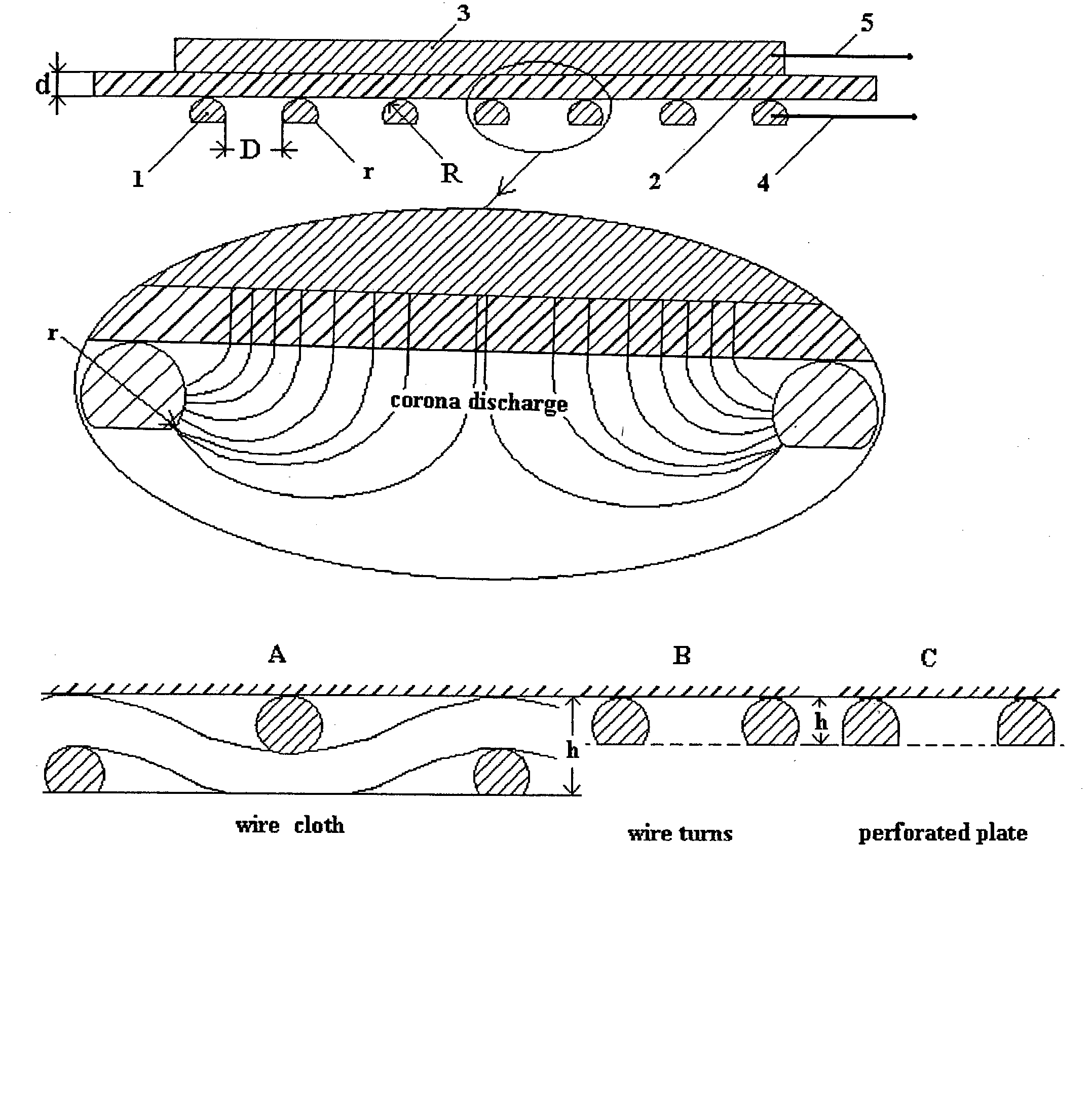

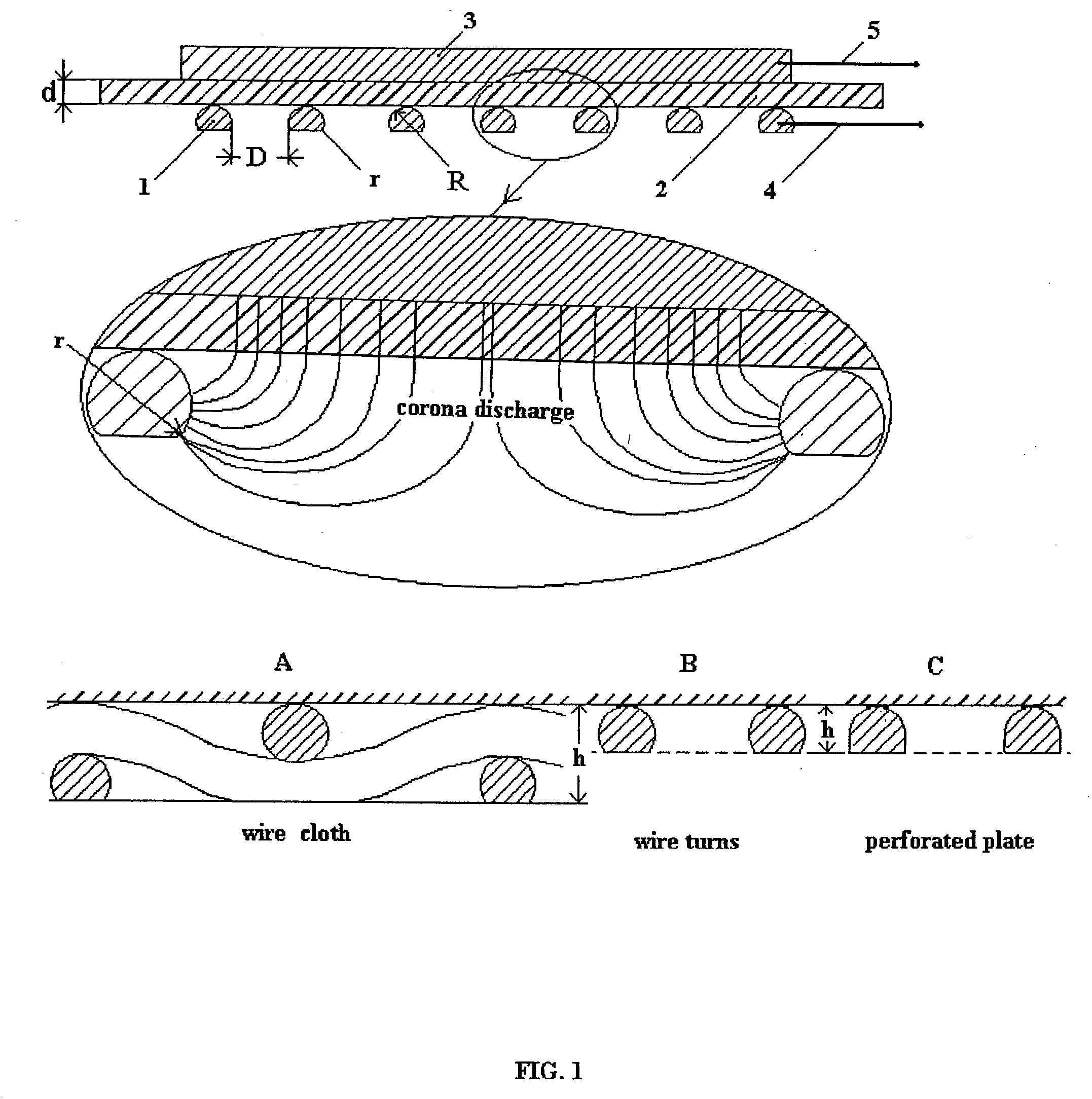

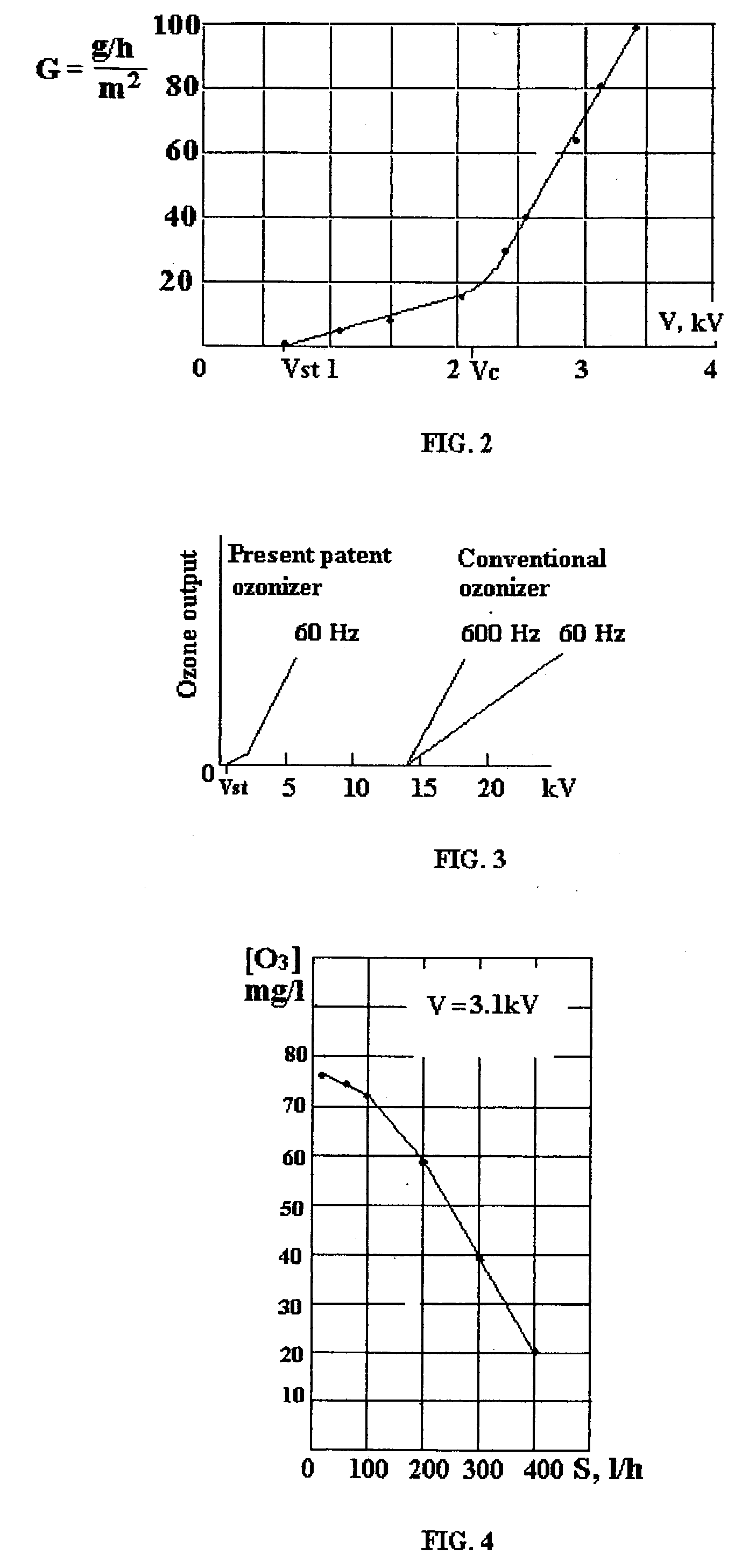

Method for surface corona/ozone making, devices utilizing the same and methods for corona and ozone applications

A method for making surface corona discharge, which produces ozone gas and apparatus for producing the same are disclosed, in which a dielectric spacer / film having a specific capacity C' equal to or more than 200 nanofarad per square meter positioned between the base electrode and the net electrode. Said net electrode is a wire net or a perforated metal or a wire winding having an open area not less than about 70%, and a size of hole D equals to or less than about 0.7V / P, where V is a voltage in kilovolts and P is pressure of an ambient air or an oxygen in atmospheres. Net electrode has radius R of wire or radius of an edge of openings in the perforated metal equal to or more than about 1.6d, where d is the thickness of the said dielectric spacer / film, which is determined by a fundamental formula d=9k / C', where d is in millimeters, C' is in nF / m2, and k is dimensionless dielectric constant k of given material. Under disclosed parameters said surface corona is safe for human contact if said net electrode is grounded. Start voltage Vst of ozone production is determined by experimental formula Vst=0.7+60 / C', kV, here C' in nF / m2. The even and high intensity corona surface and high ozone output takes place if the operating voltage is more than about 3Vst. AC power supply is applied to produce ozone gas at "home" voltage 0.7-1.0 kV and produces ozone gas more effectively at 2,5-3.6 kV. A method for disinfection and decontamination of objects by using the direct corona contact and apparatus for making the same is disclosed, in which safe corona surface is placed on said object and is acting by ozone, ultraviolet and ion bombing simultaneously in the unique environment, which takes place inside of the safe corona. A method for ozone disinfection and decontamination and devices for making the same is disclosed, in which said ozone generating element is placed in a closed container / room with or without treated objects and produce a high ozone concentration due to effective ozone dispersion from corona surface without blowing of air / oxygen through said container / room.

Owner:ANDREEV SERGEY I +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com