Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2989 results about "Work function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In solid-state physics, the work function (sometimes spelled workfunction) is the minimum thermodynamic work (i.e., energy) needed to remove an electron from a solid to a point in the vacuum immediately outside the solid surface. Here "immediately" means that the final electron position is far from the surface on the atomic scale, but still too close to the solid to be influenced by ambient electric fields in the vacuum. The work function is not a characteristic of a bulk material, but rather a property of the surface of the material (depending on crystal face and contamination).

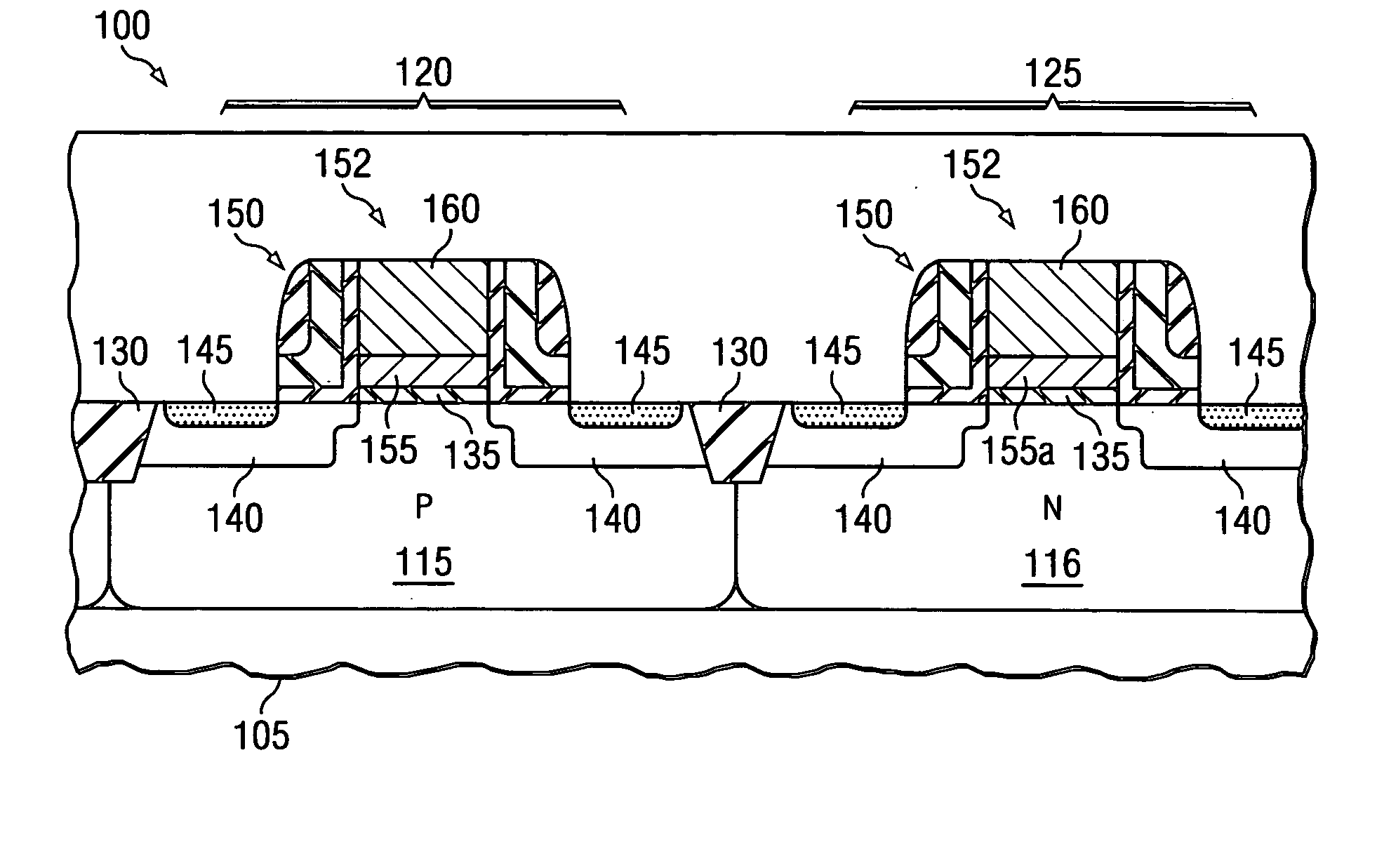

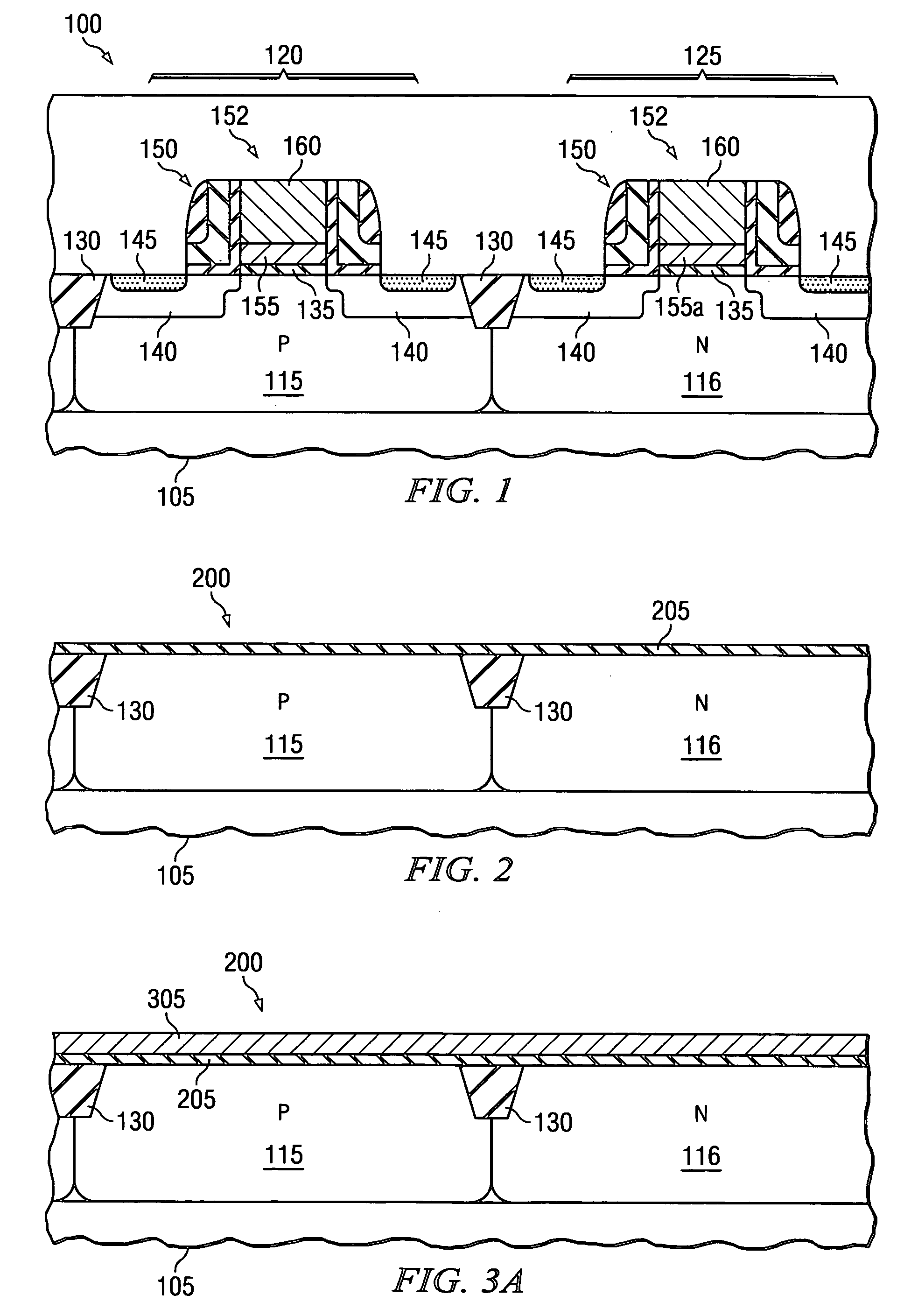

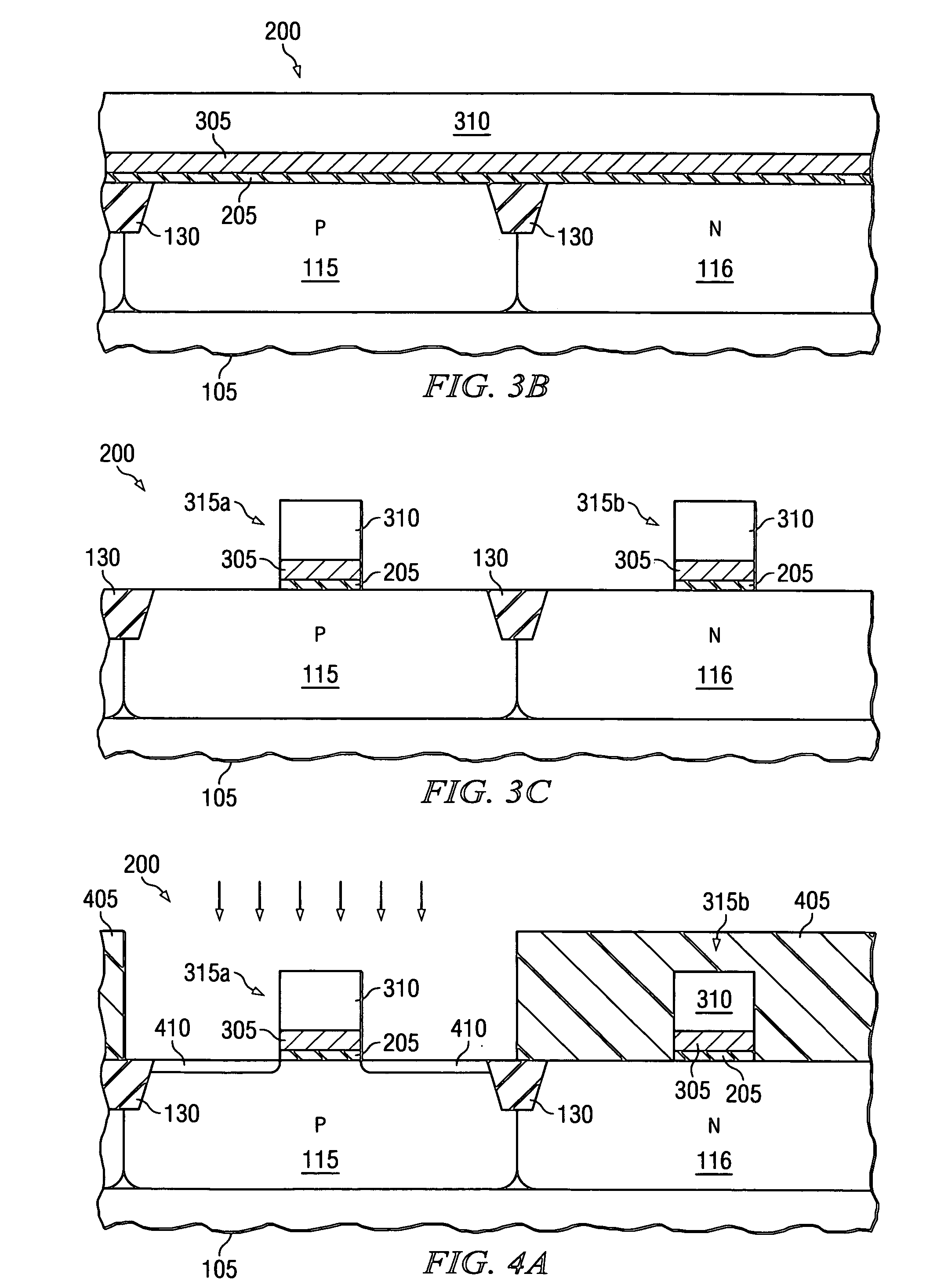

Process for manufacturing dual work function metal gates in a microelectronics device

ActiveUS20070037343A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricWork function

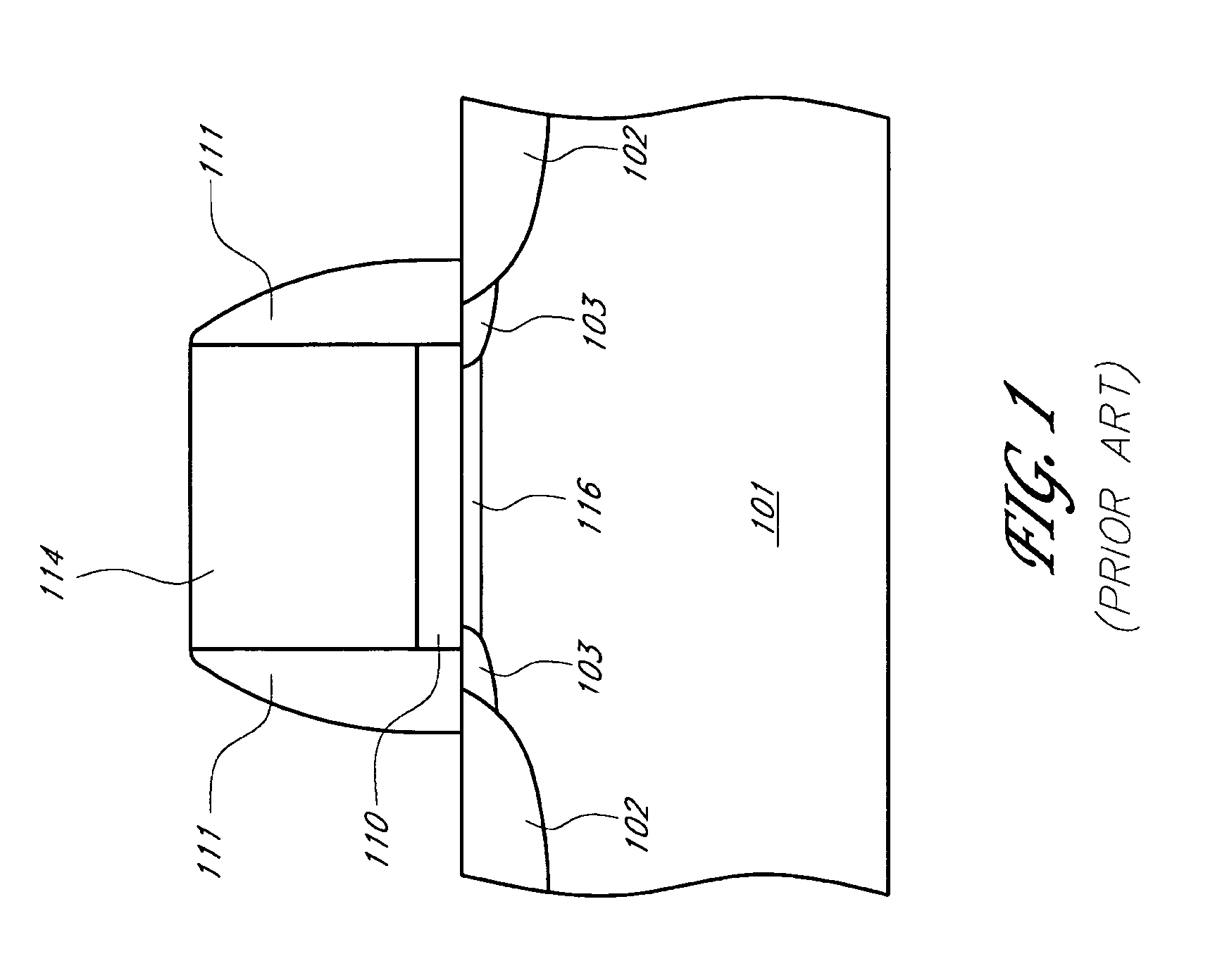

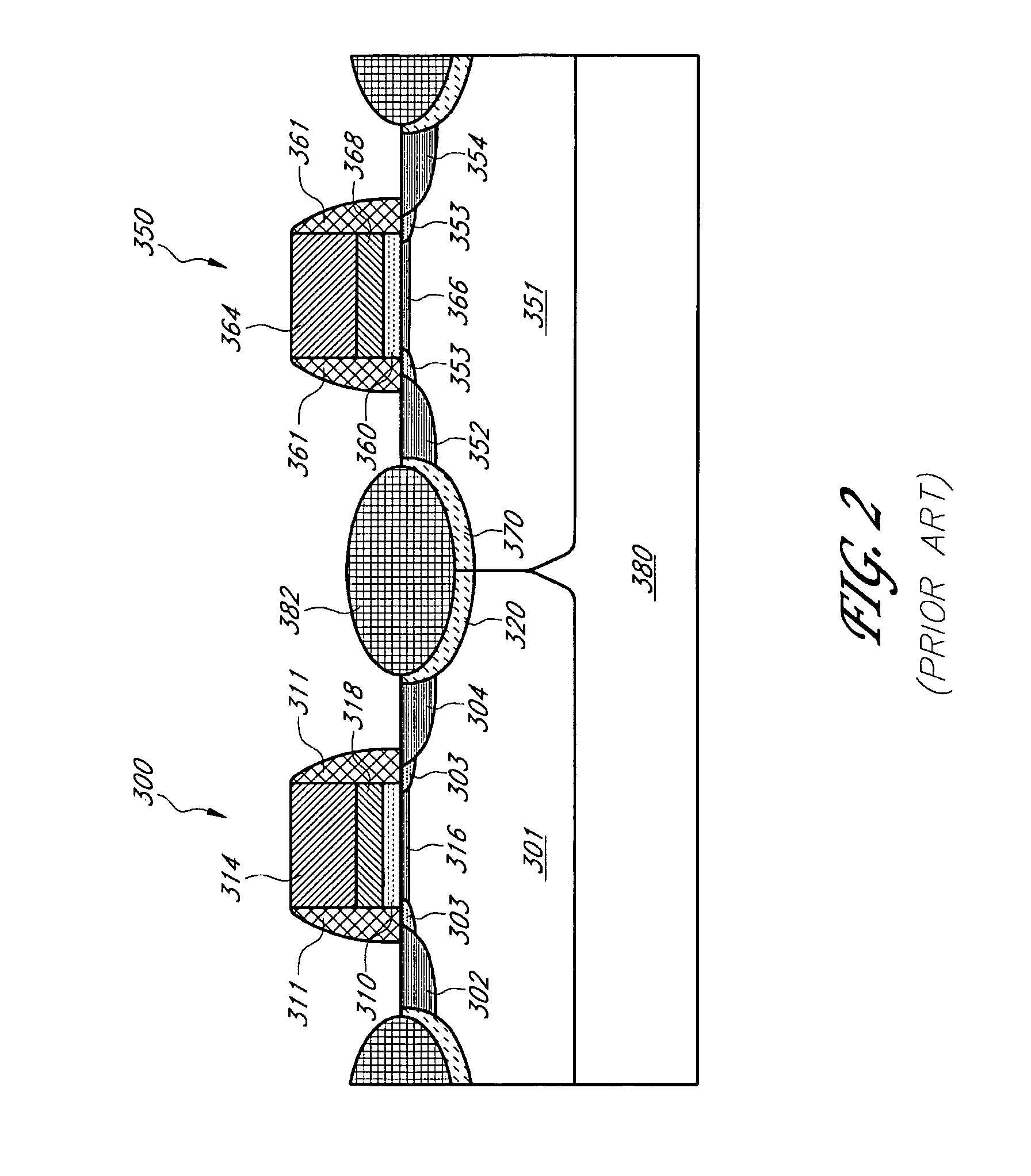

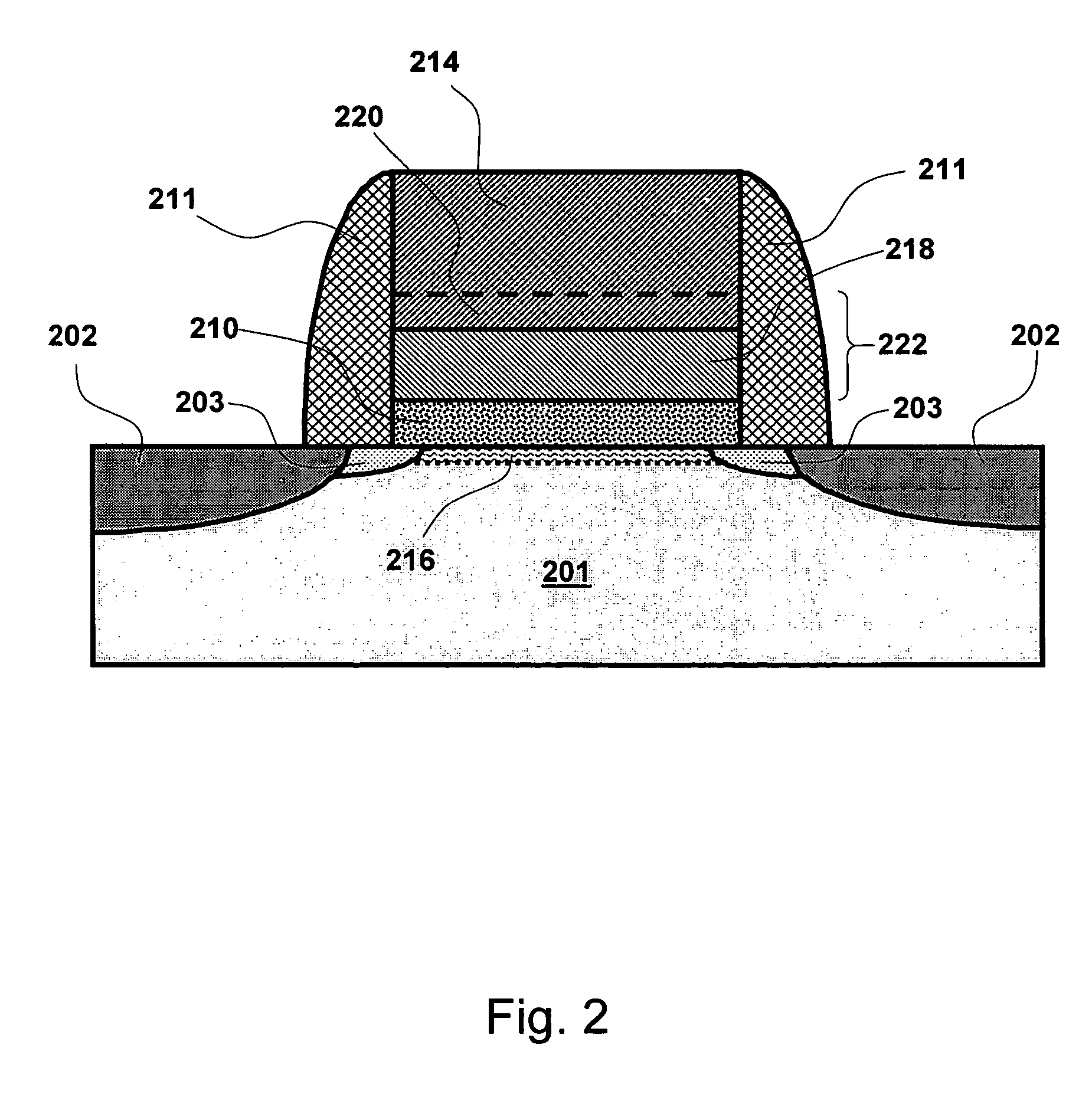

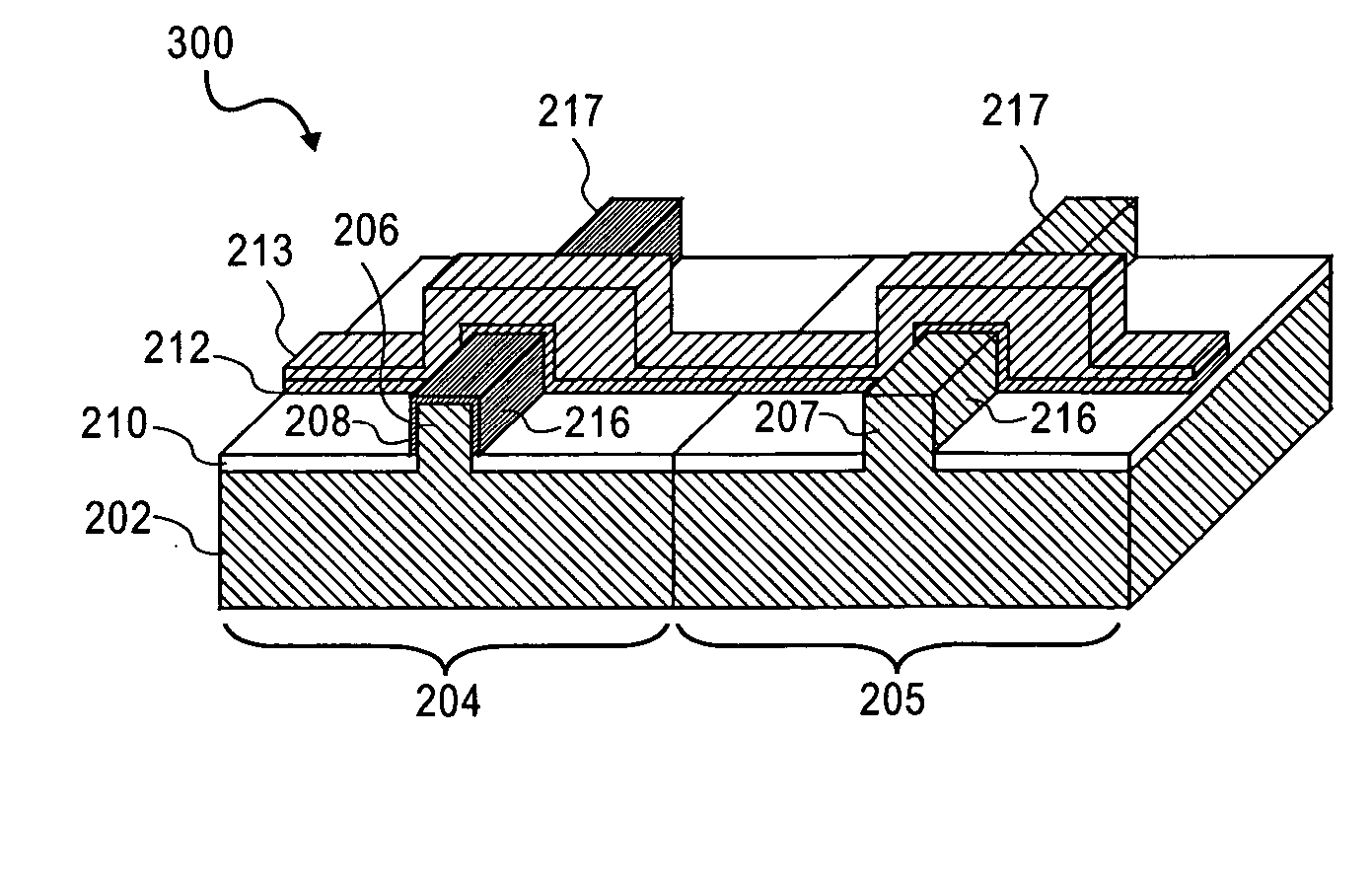

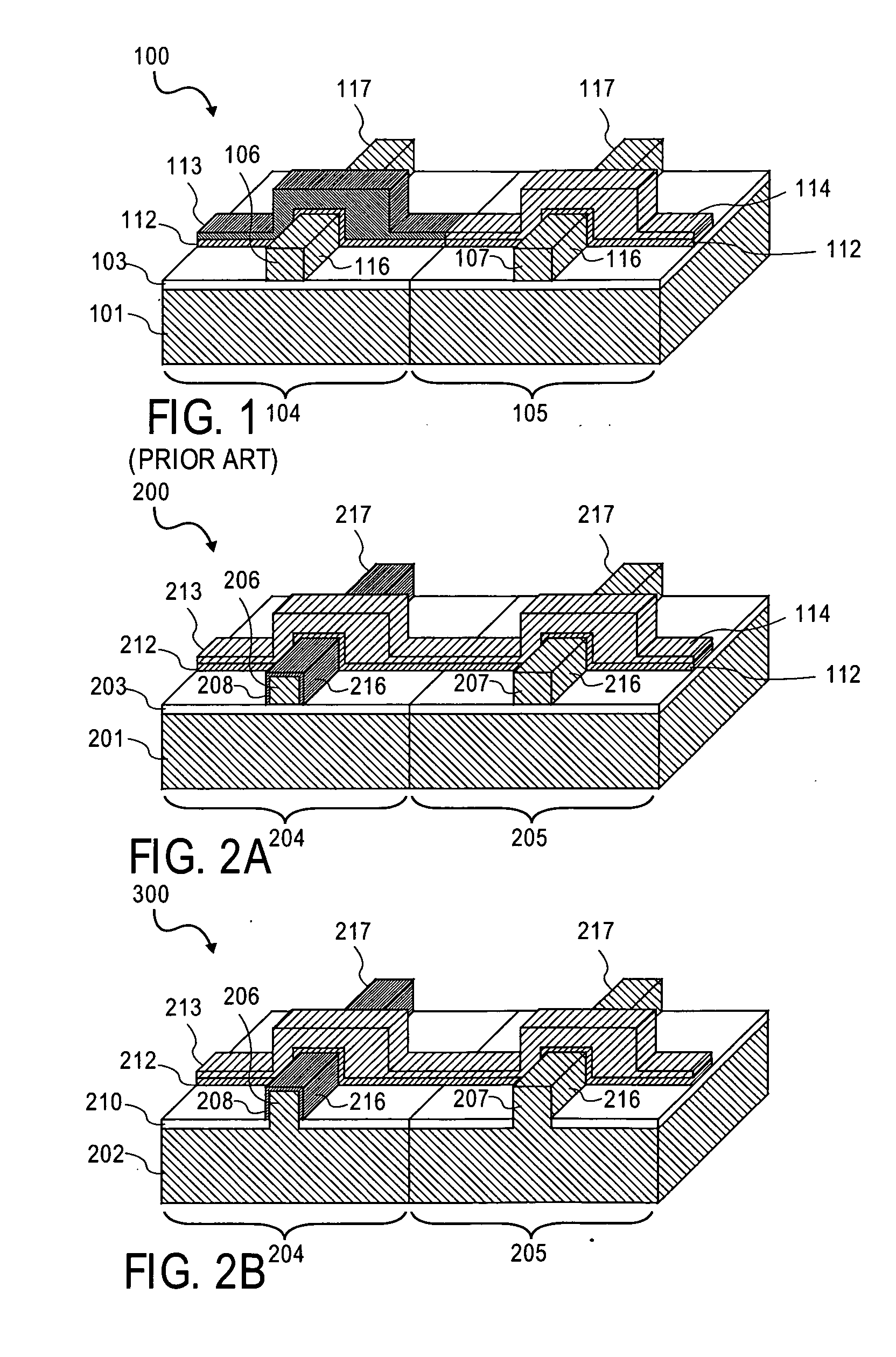

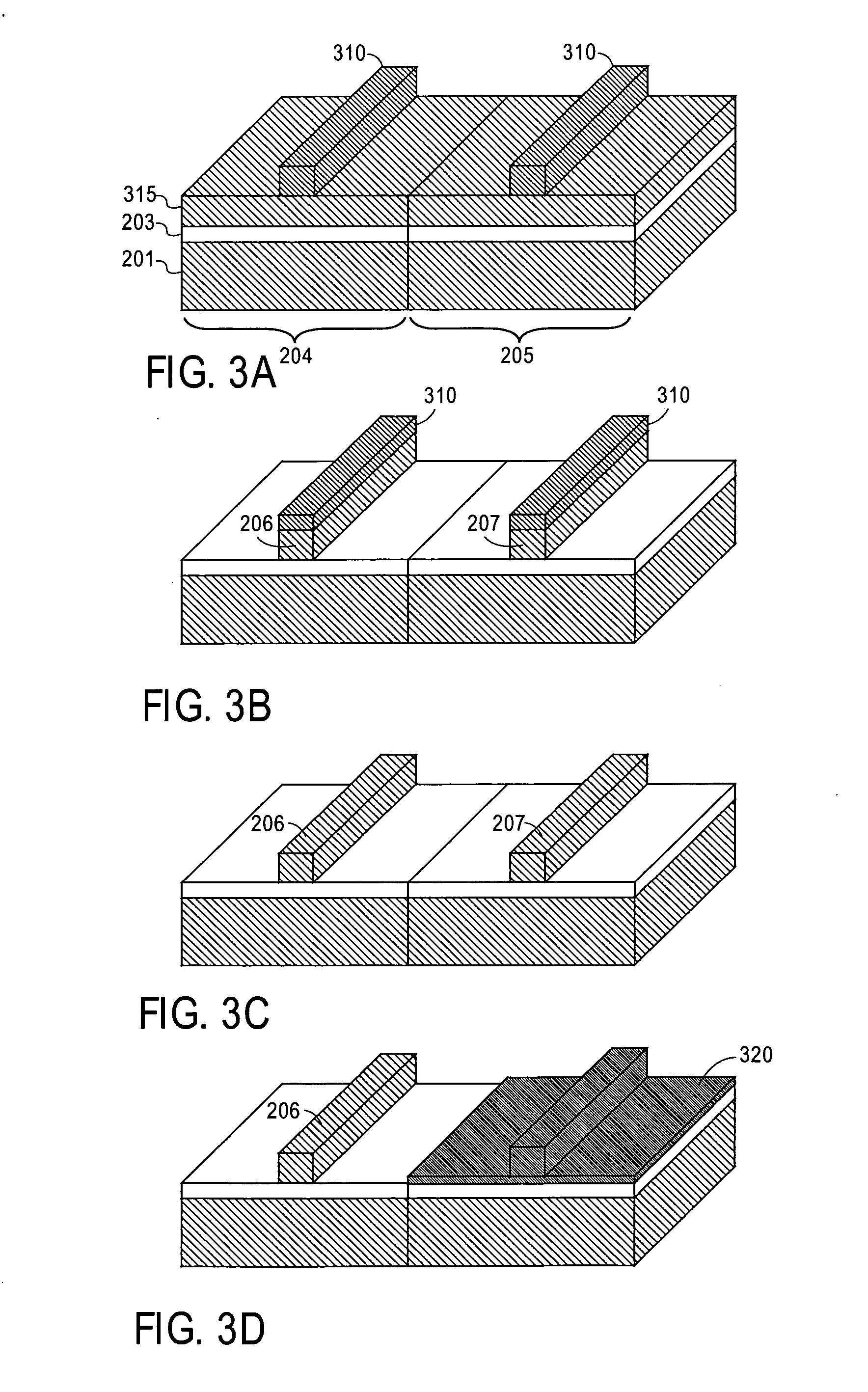

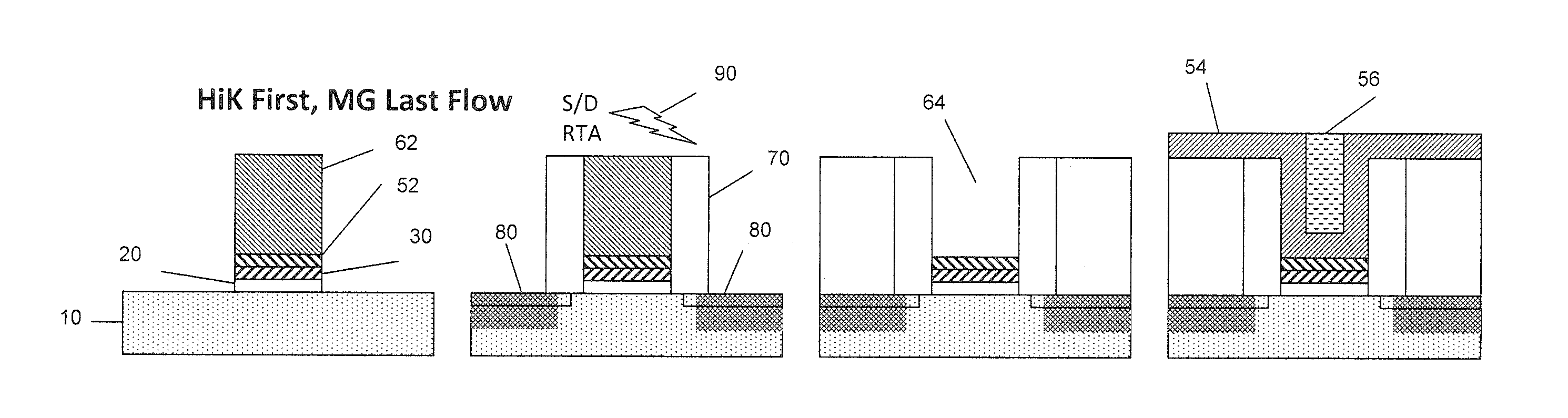

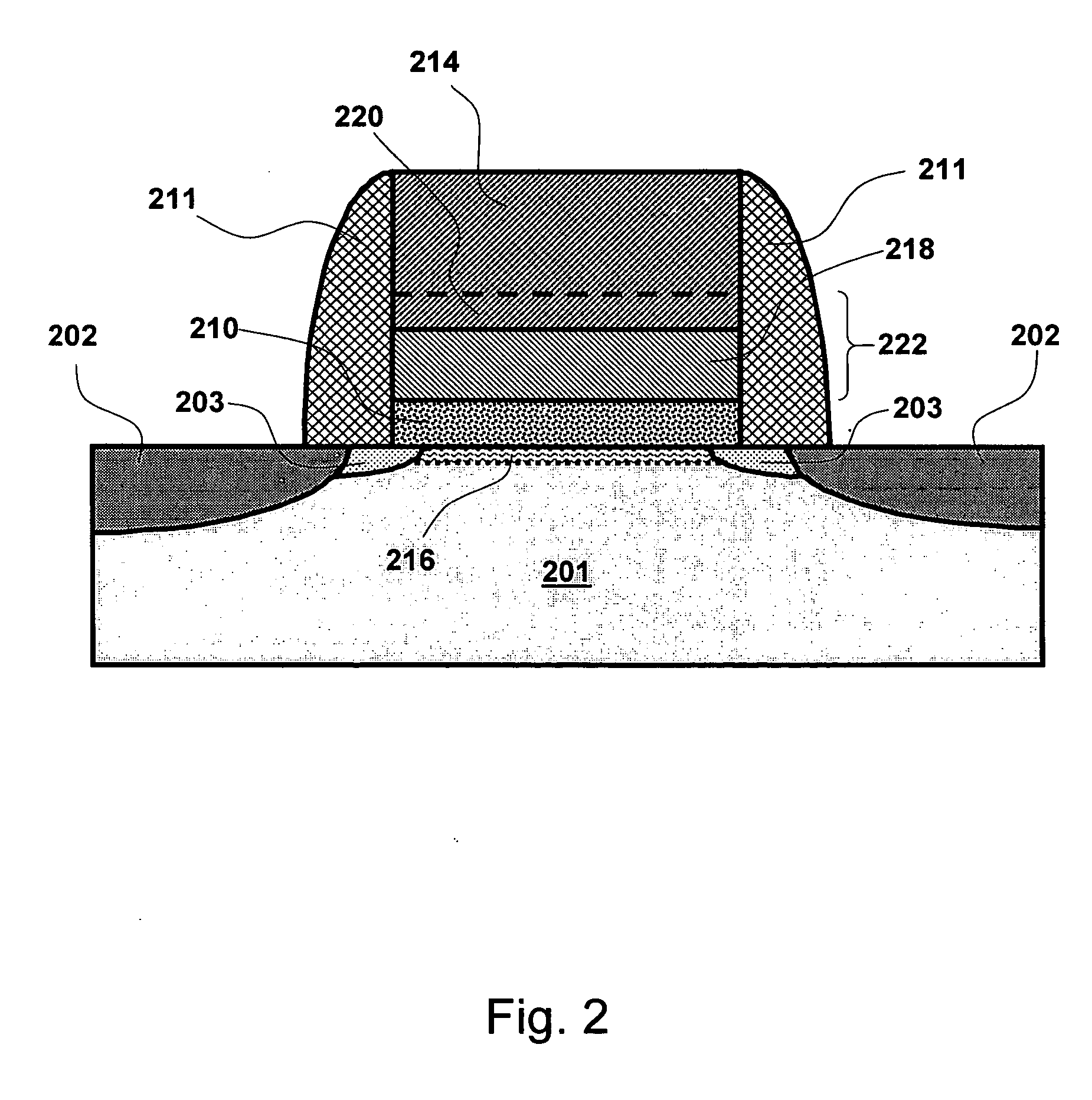

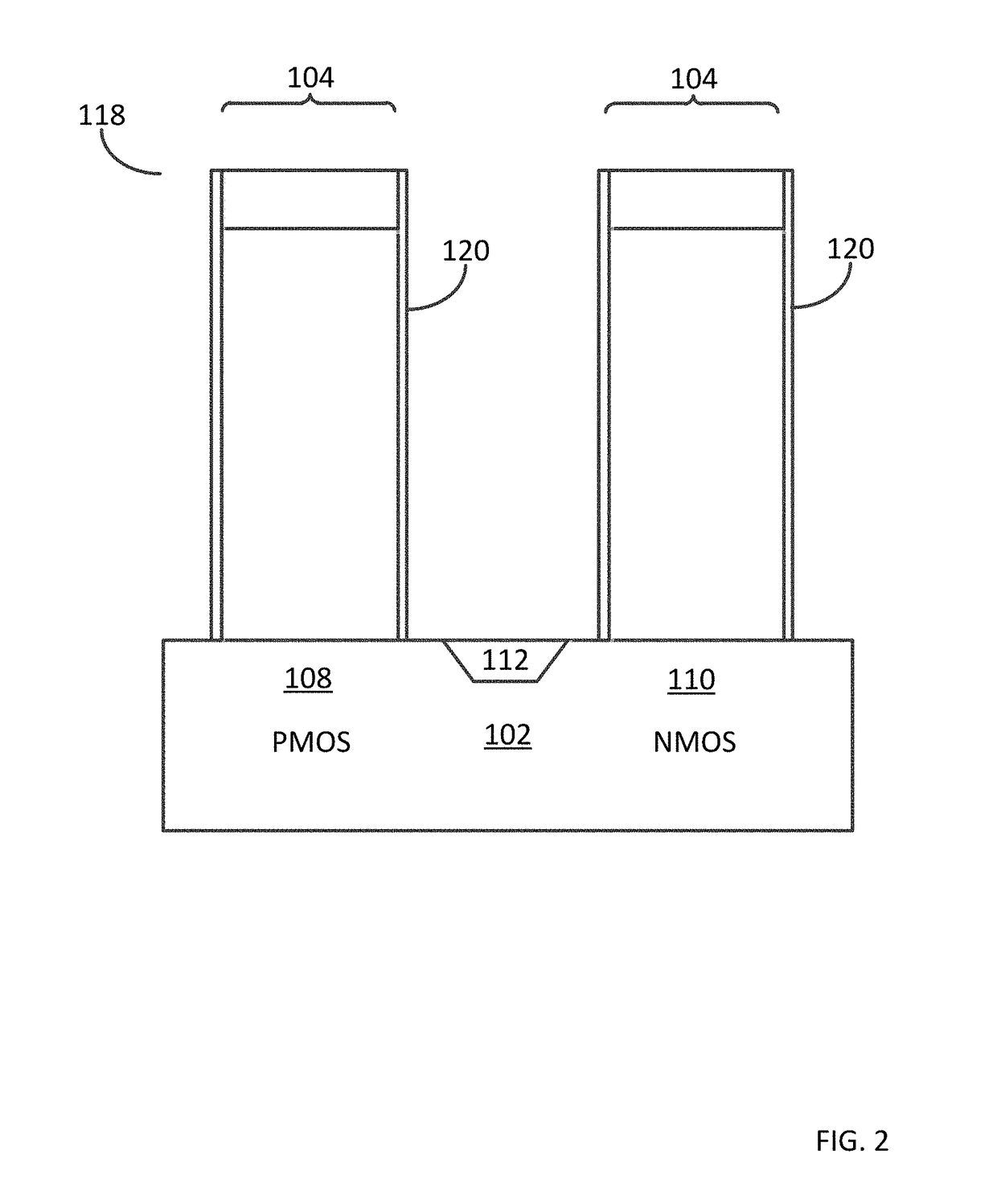

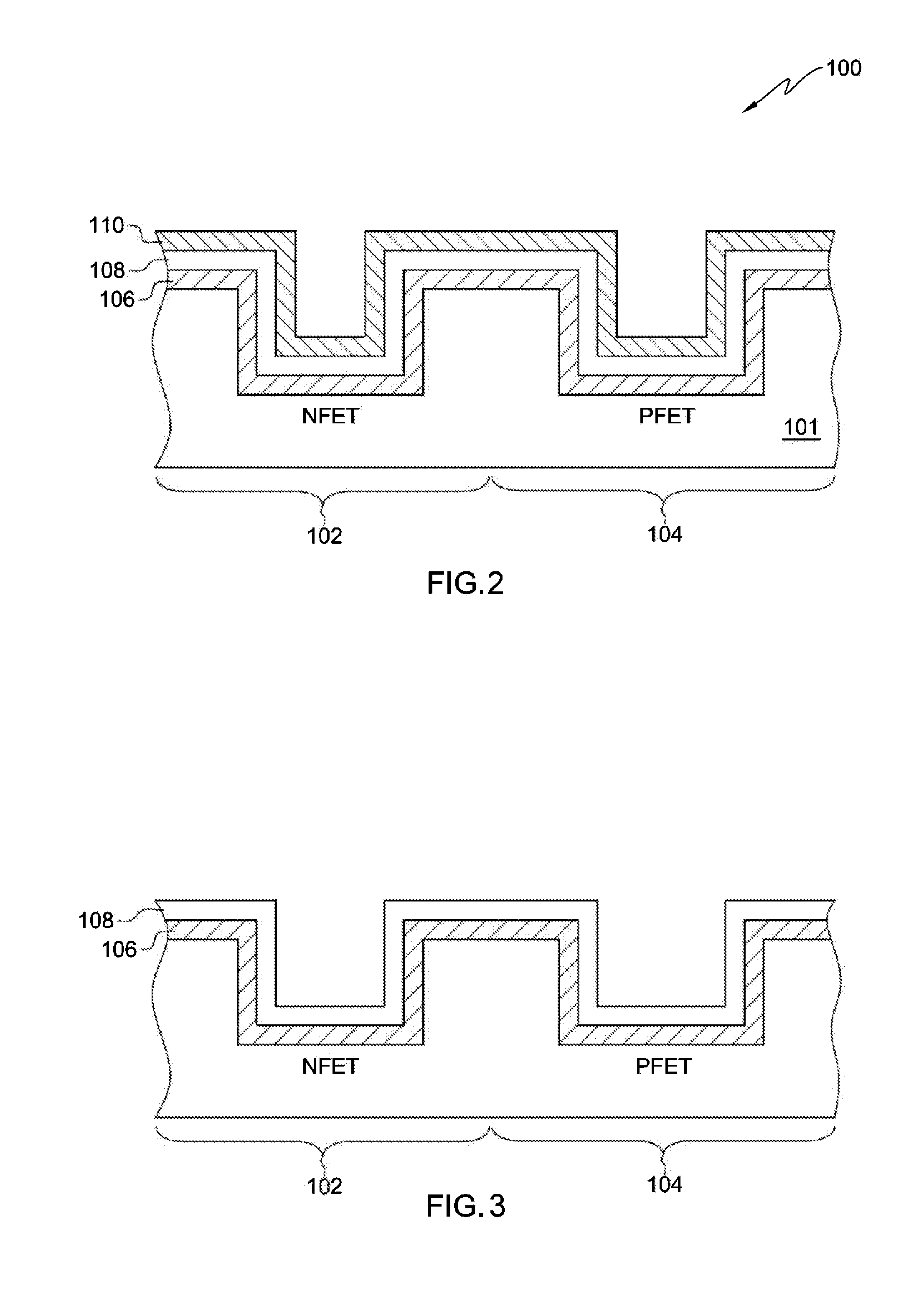

The present invention provides a method of forming a dual work function metal gate microelectronics device 200. In one aspect, the method includes forming nMOS and pMOS stacked gate structures 315a and 315b. The nMOS and pMOS stacked gate structures 315a and 315b each comprise a gate dielectric 205, a first metal layer, 305 located over the gate dielectric 205 and a sacrificial gate layer 310 located over the first metal layer 305. The method further includes removing the sacrificial gate layer 310 in at least one of the nMOS or pMOS stacked gate structures, thereby forming a gate opening 825 and modifying the first metal layer 305 within the gate opening 825 to form a gate electrode with a desired work function.

Owner:TEXAS INSTR INC

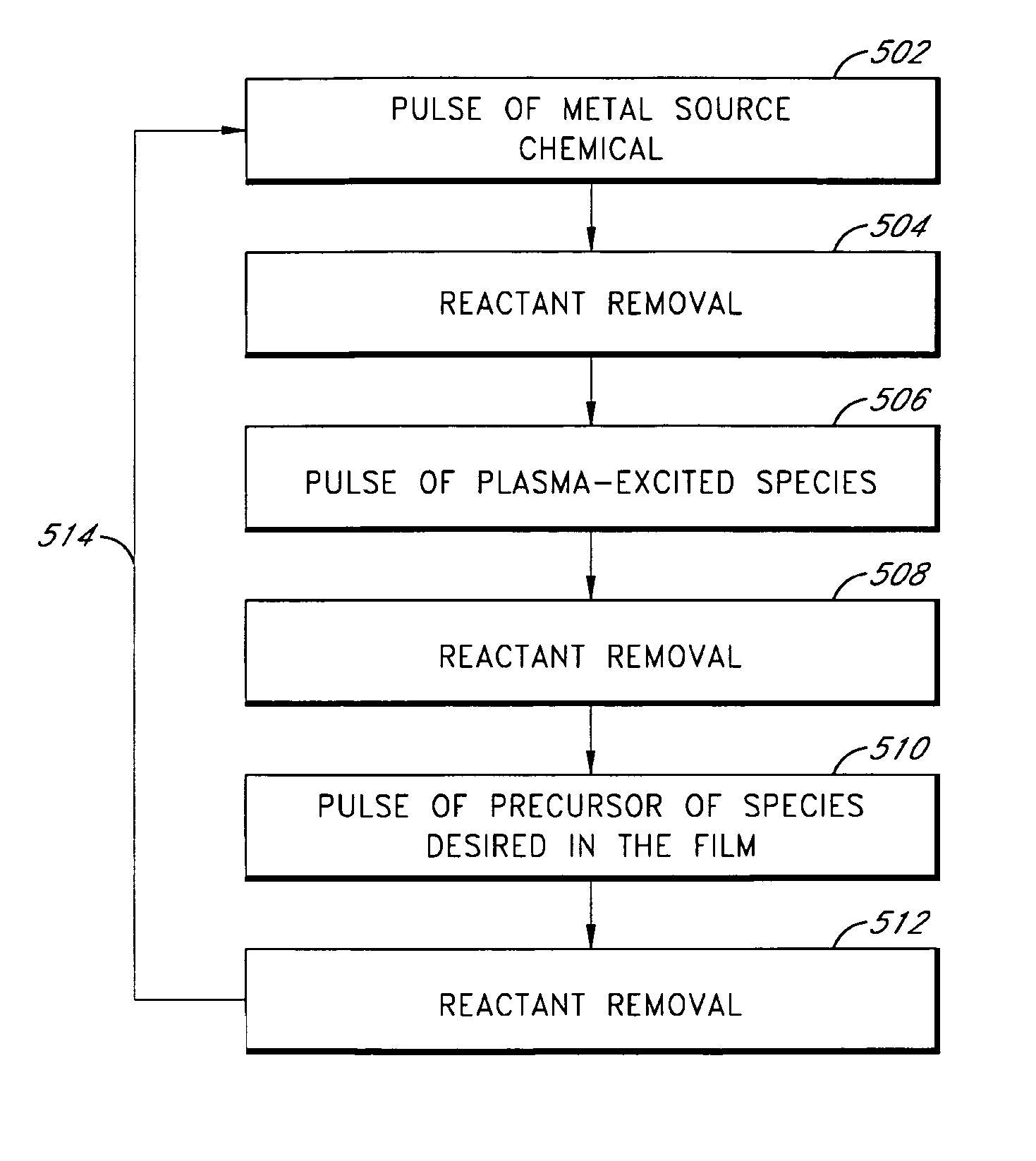

Controlled composition using plasma-enhanced atomic layer deposition

ActiveUS7727864B2Easily and accurately adjusted to a desired valueSemiconductor/solid-state device manufacturingChemical vapor deposition coatingOxidation stateWork function

Metallic-compound films are formed by plasma-enhanced atomic layer deposition (PEALD). According to preferred methods, film or thin film composition is controlled by selecting plasma parameters to tune the oxidation state of a metal (or plurality of metals) in the film. In some embodiments, plasma parameters are selected to achieve metal-rich metallic-compound films. The metallic-compound films can be components of gate stacks, such as gate electrodes. Plasma parameters can be selected to achieve a gate stack with a predetermined work function.

Owner:ASM IP HLDG BV

Method of producing thin films

ActiveUS7563715B2Lower work functionReduce crystallinityTransistorSemiconductor/solid-state device manufacturingWork functionMetal electrodes

Owner:ASM INTERNATIONAL

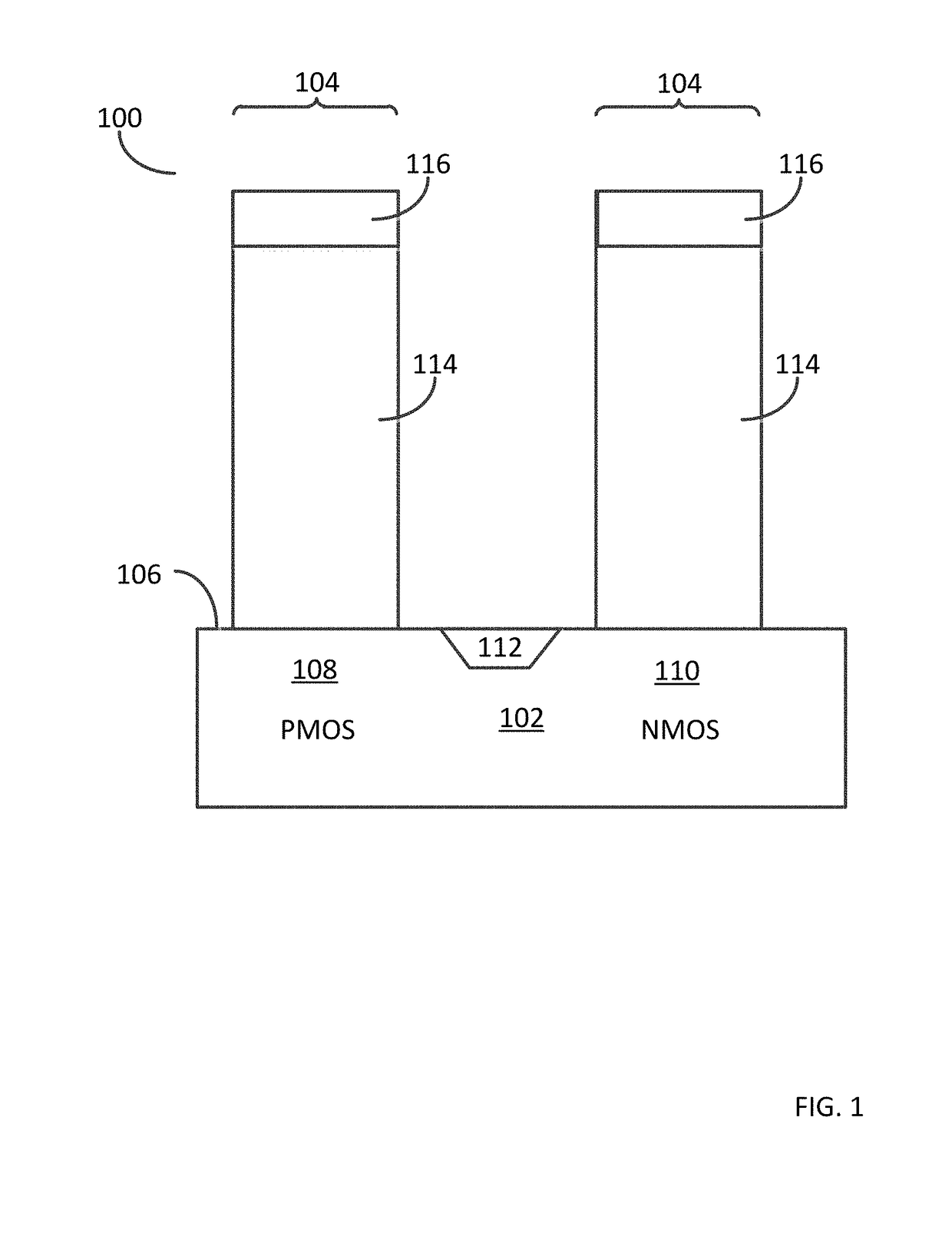

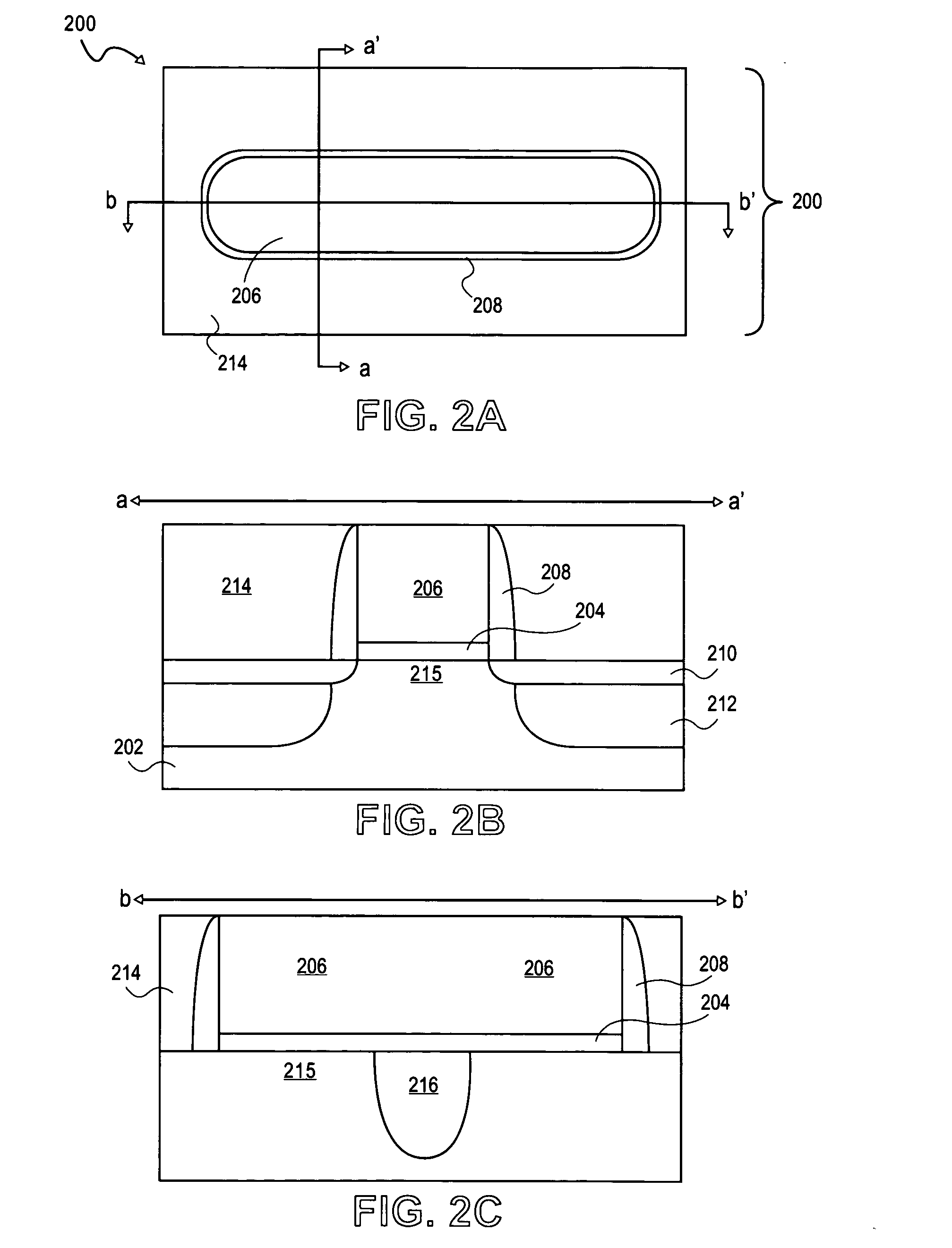

CMOS devices with a single work function gate electrode and method of fabrication

InactiveUS20070090416A1Lower threshold voltageEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingCMOSDevice form

Described herein are a device utilizing a gate electrode material with a single work function for both the pMOS and nMOS transistors where the magnitude of the transistor threshold voltages is modified by semiconductor band engineering and article made thereby. Further described herein are methods of fabricating a device formed of complementary (pMOS and nMOS) transistors having semiconductor channel regions which have been band gap engineered to achieve a low threshold voltage.

Owner:TAHOE RES LTD

Formation of boron-doped titanium metal films with high work function

ActiveUS10083836B2Solid-state devicesSemiconductor/solid-state device manufacturingHalogenTitanium metal

Owner:ASM IP HLDG BV

Process for depositing electrode with high effective work function

ActiveUS9136180B2Semiconductor/solid-state device manufacturingSemiconductor devicesHydrogenGate dielectric

Owner:ASM IP HLDG BV

Method of producing thin films

ActiveUS20070128858A1Lower work functionReduce crystallinityTransistorSemiconductor/solid-state device manufacturingWork functionMetal electrodes

Owner:ASM INTERNATIONAL

NbMC LAYERS

ActiveUS20170117141A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice PropertiesWork function

Methods of forming thin-film structures including one or more NbMC layers, and structures and devices including the one or more NbMC layers are disclosed. The NbMC layers enable tuning of various structure and device properties, including resistivity, current leakage, and work function.

Owner:ASM IP HLDG BV

Formation of boron-doped titanium metal films with high work function

ActiveUS20170025280A1Solid-state devicesSemiconductor/solid-state device manufacturingTitanium metalWork function

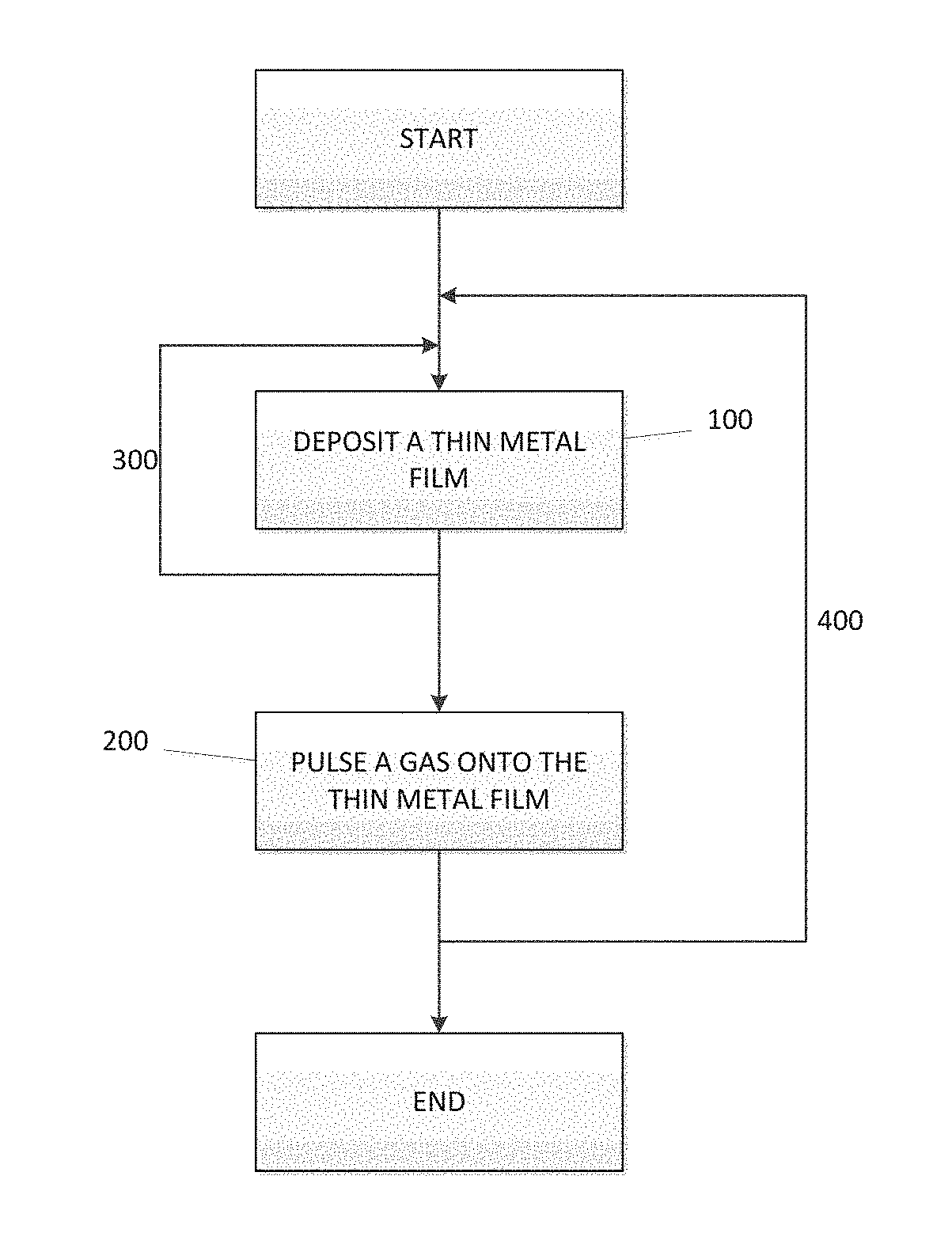

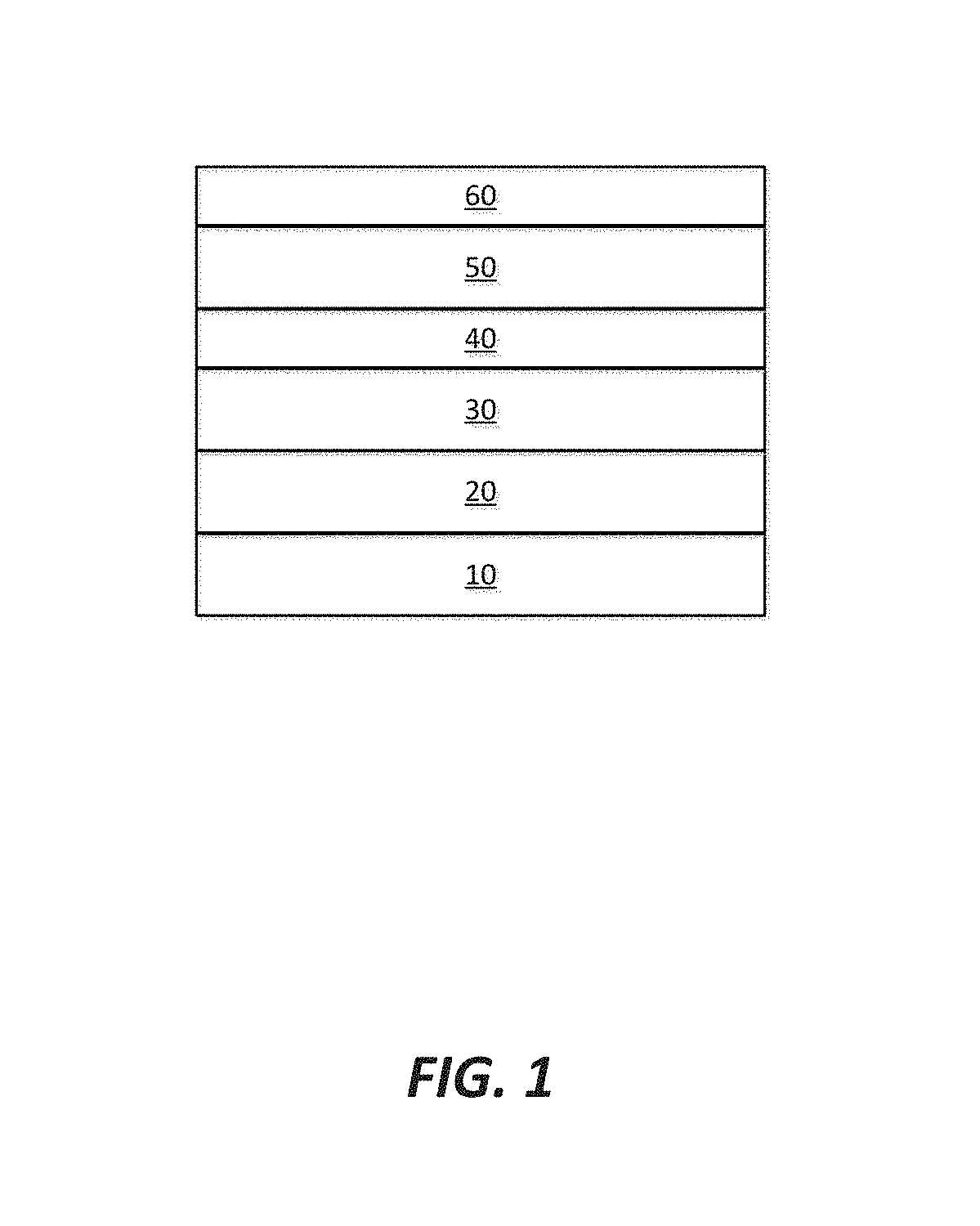

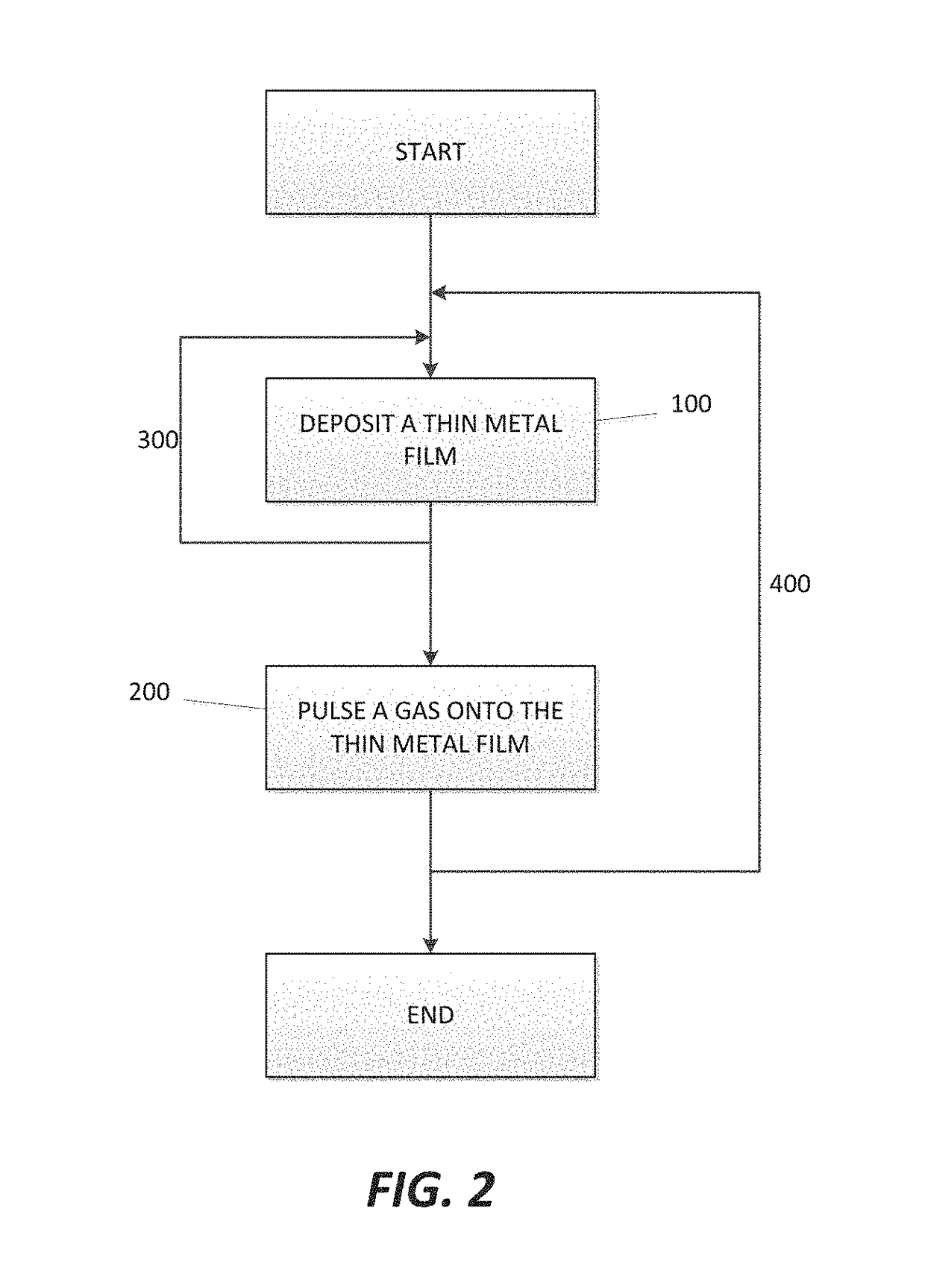

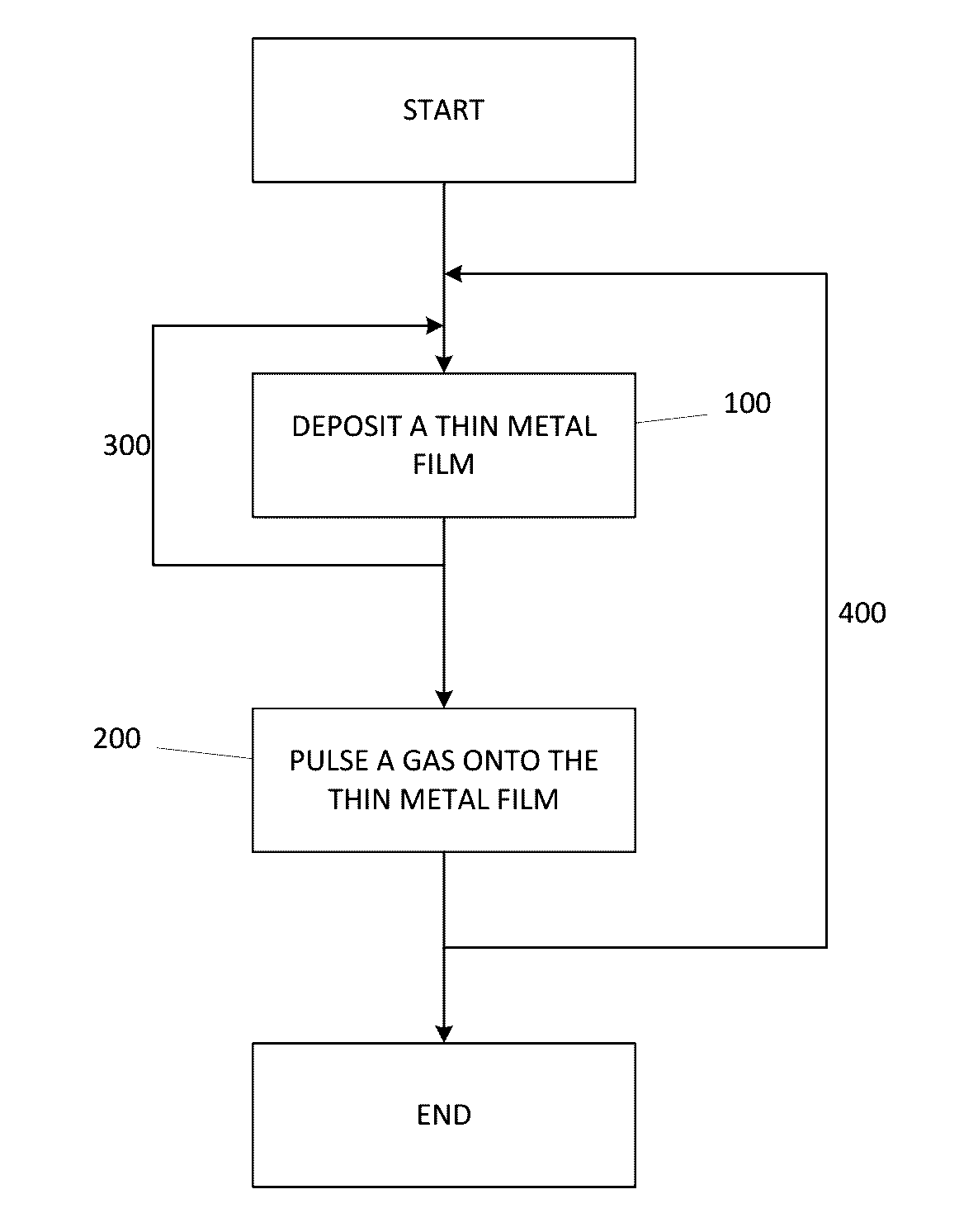

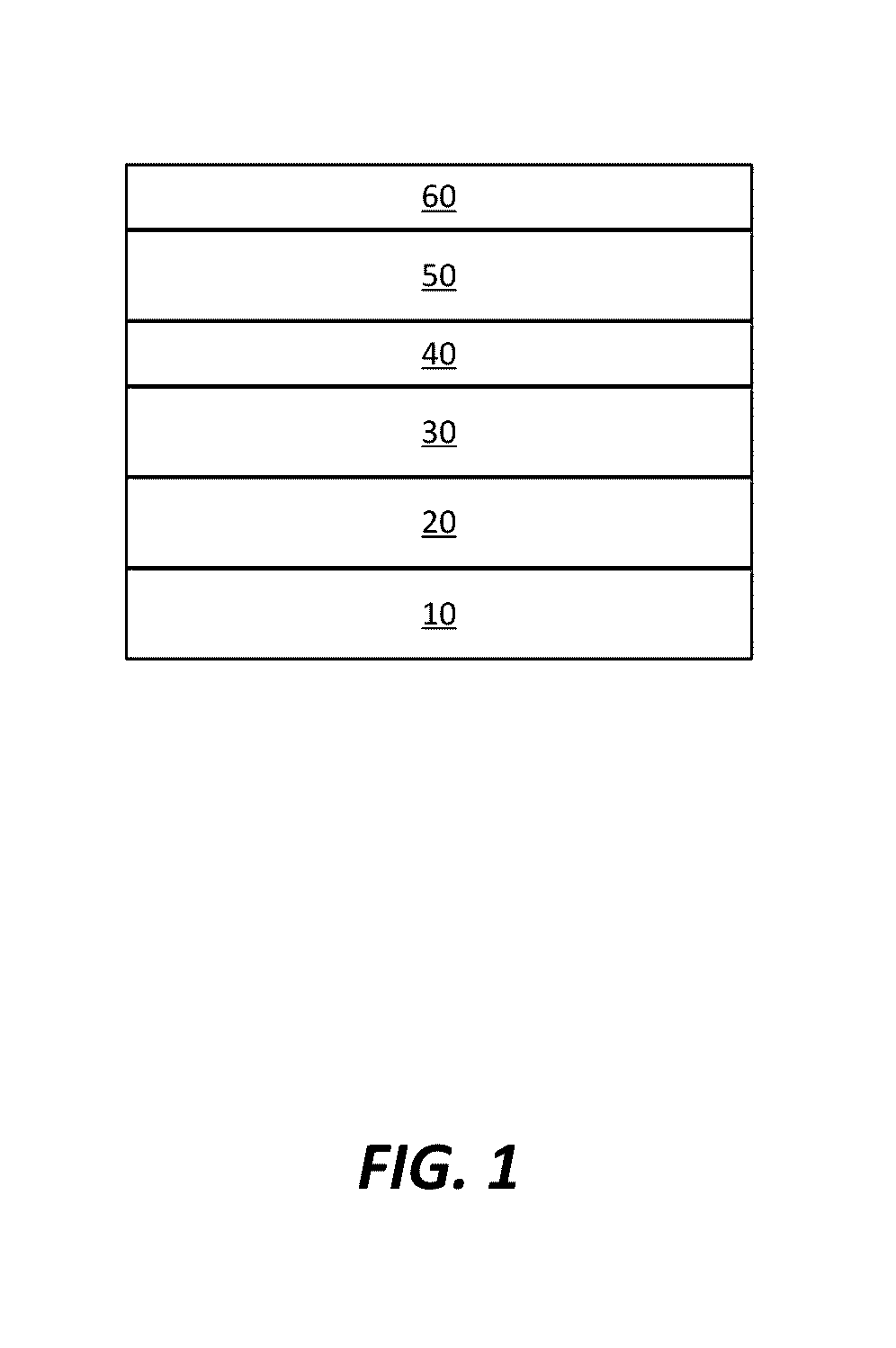

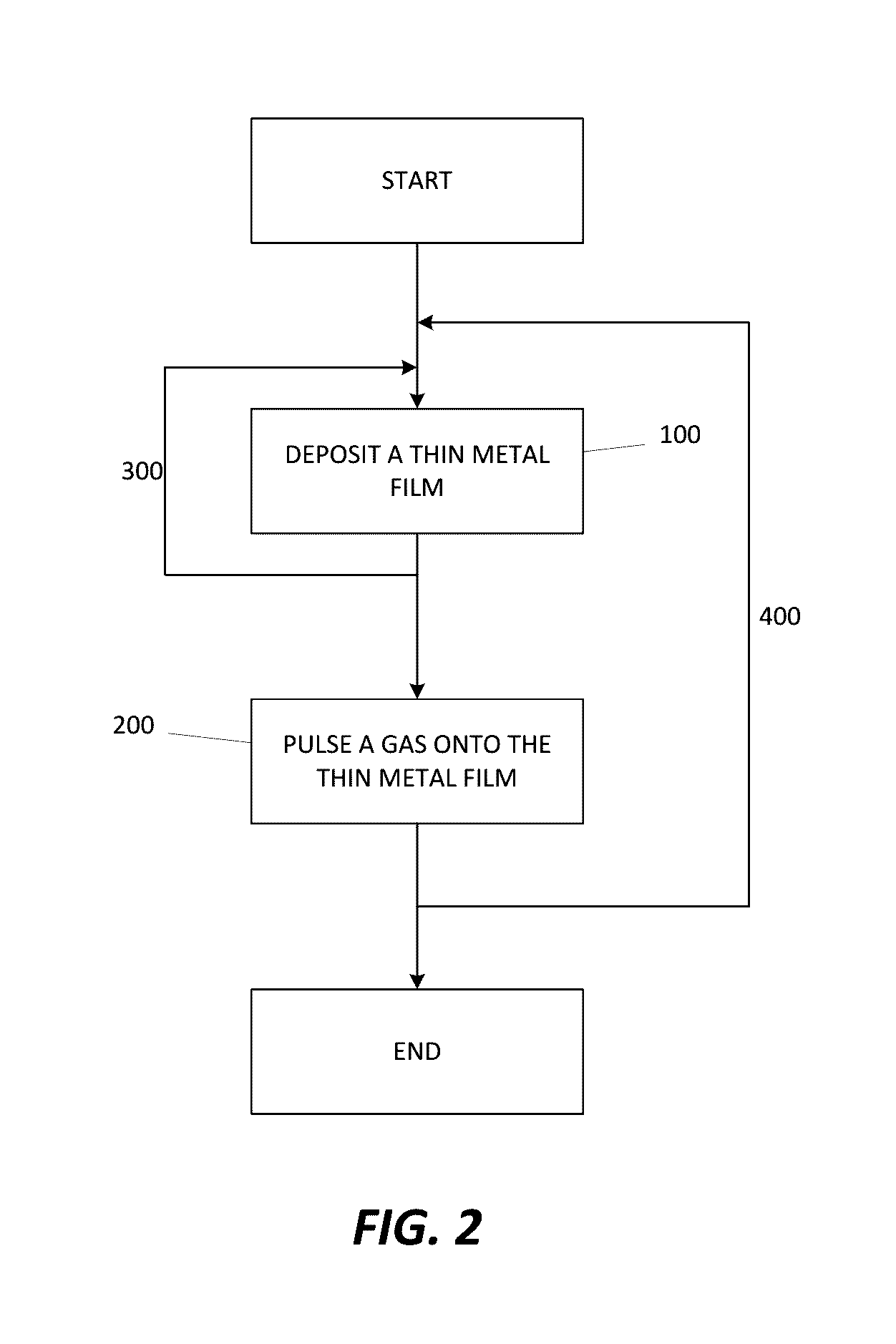

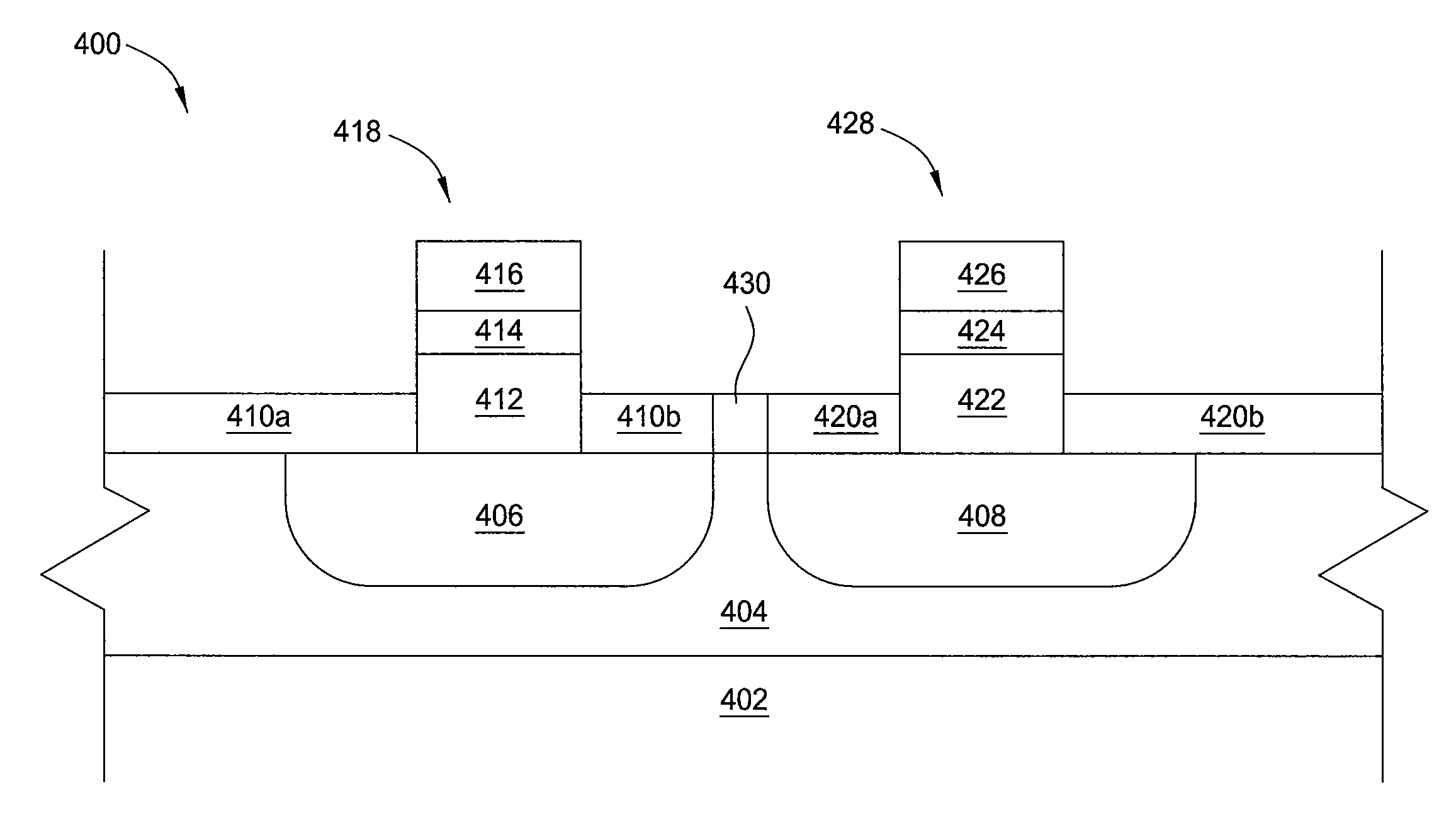

A method for forming a Boron doped metallic film, such as Titanium Boron Nitride, is disclosed. The method allows for creation of the metallic film with a high work function and low resistivity, while limiting the increase in effective oxide thickness. The method comprises a thin metallic layer deposition step as well as a Boron-based gas pulse step. The Boron-based gas pulse deposits Boron and allows for the removal of excess halogens within the metallic film. The steps may be repeated in order to achieve a desired thickness of the metallic film.

Owner:ASM IP HLDG BV

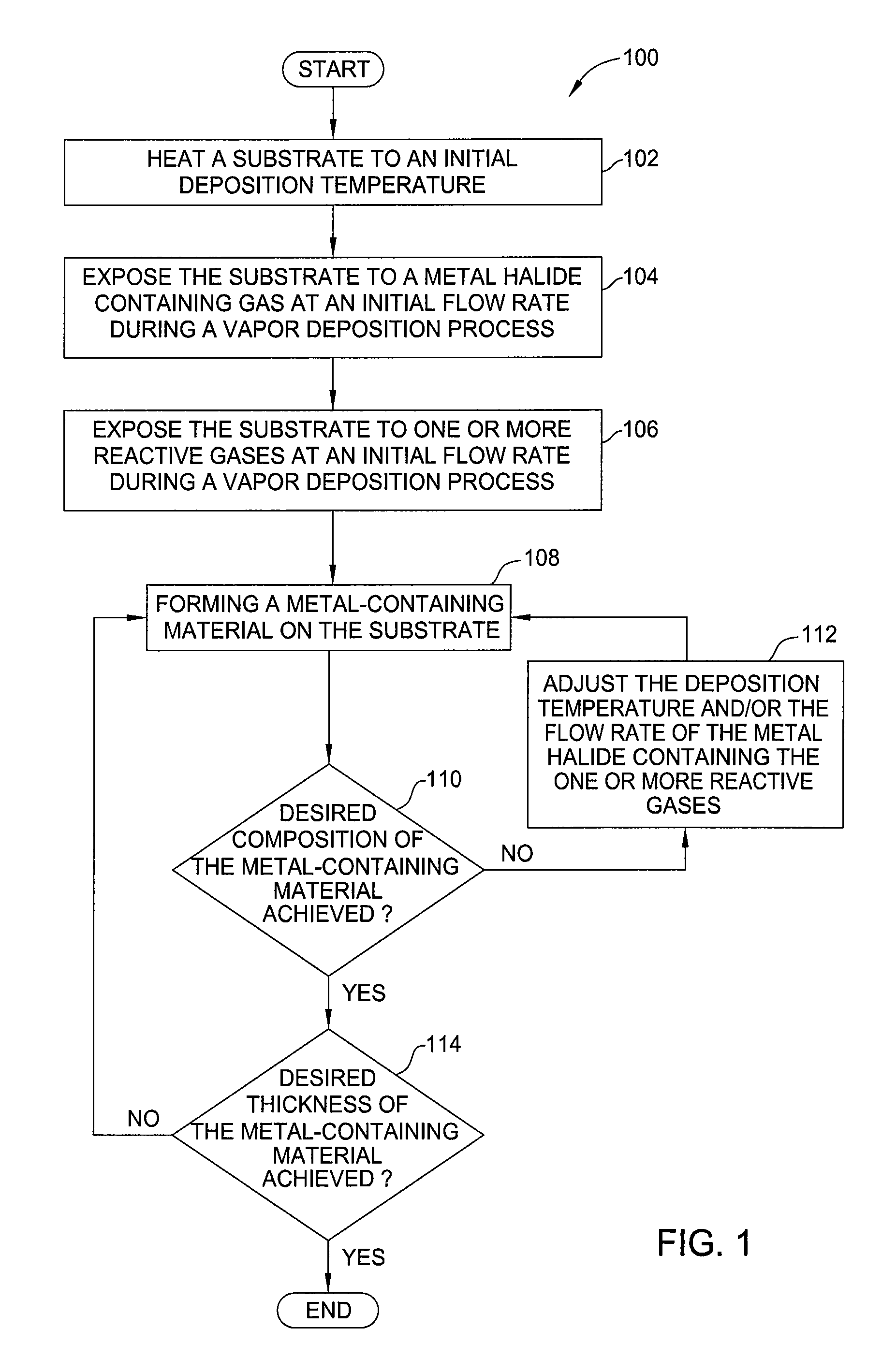

Nmos metal gate materials, manufacturing methods, and equipment using CVD and ald processes with metal based precursors

ActiveUS20110263115A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseMetallic materials

Embodiments of the invention generally provide methods for depositing metal-containing materials and compositions thereof. The methods include deposition processes that form metal, metal carbide, metal silicide, metal nitride, and metal carbide derivatives by a vapor deposition process, including thermal decomposition, CVD, pulsed-CVD, or ALD. In one embodiment, a method for processing a substrate is provided which includes depositing a dielectric material having a dielectric constant greater than 10, forming a feature definition in the dielectric material, depositing a work function material conformally on the sidewalls and bottom of the feature definition, and depositing a metal gate fill material on the work function material to fill the feature definition, wherein the work function material is deposited by reacting at least one metal-halide precursor having the formula MXY, wherein M is tantalum, hafnium, titanium, and lanthanum, X is a halide selected from the group of fluorine, chlorine, bromine, or iodine, and y is from 3 to 5.

Owner:APPLIED MATERIALS INC

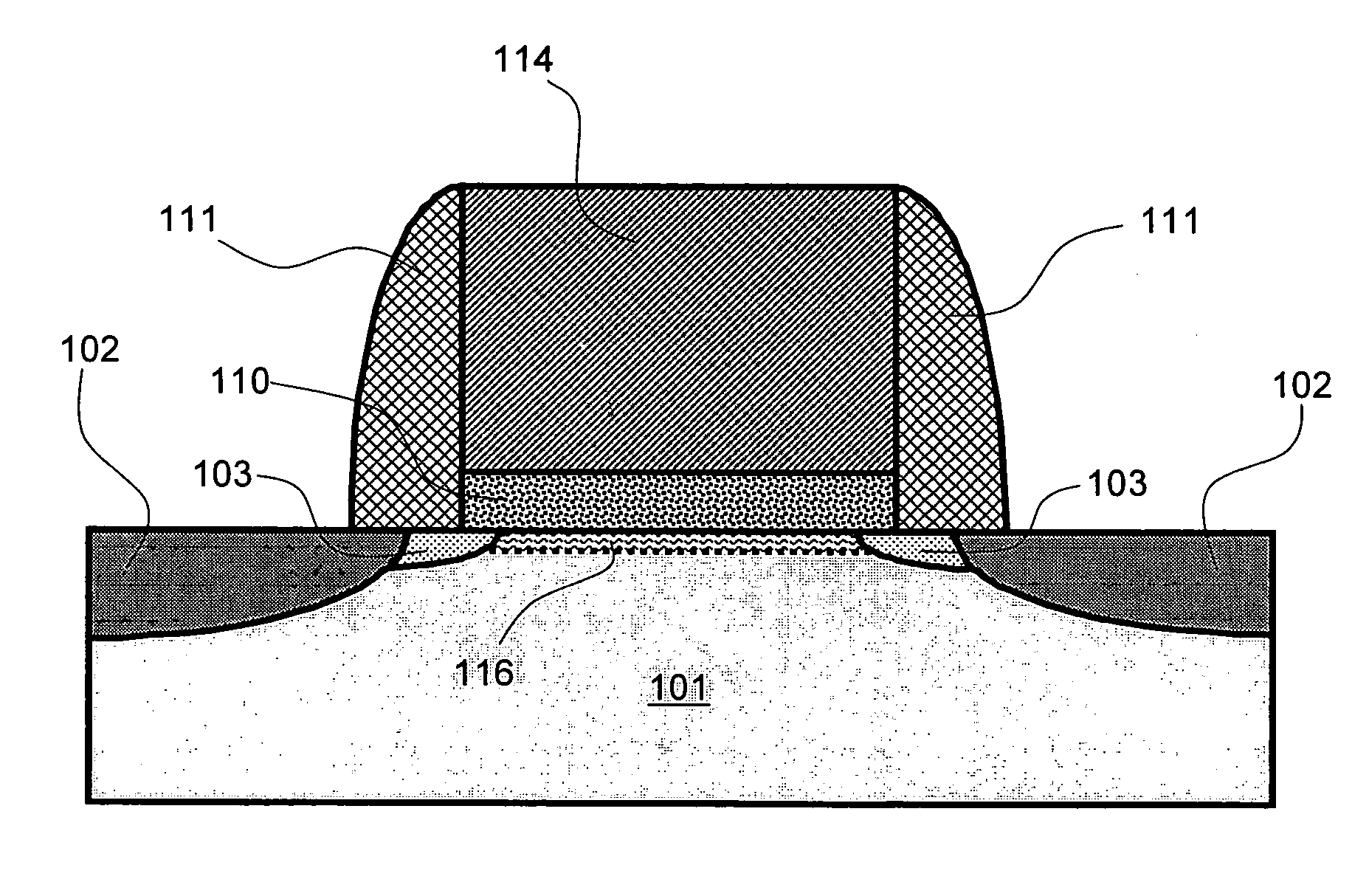

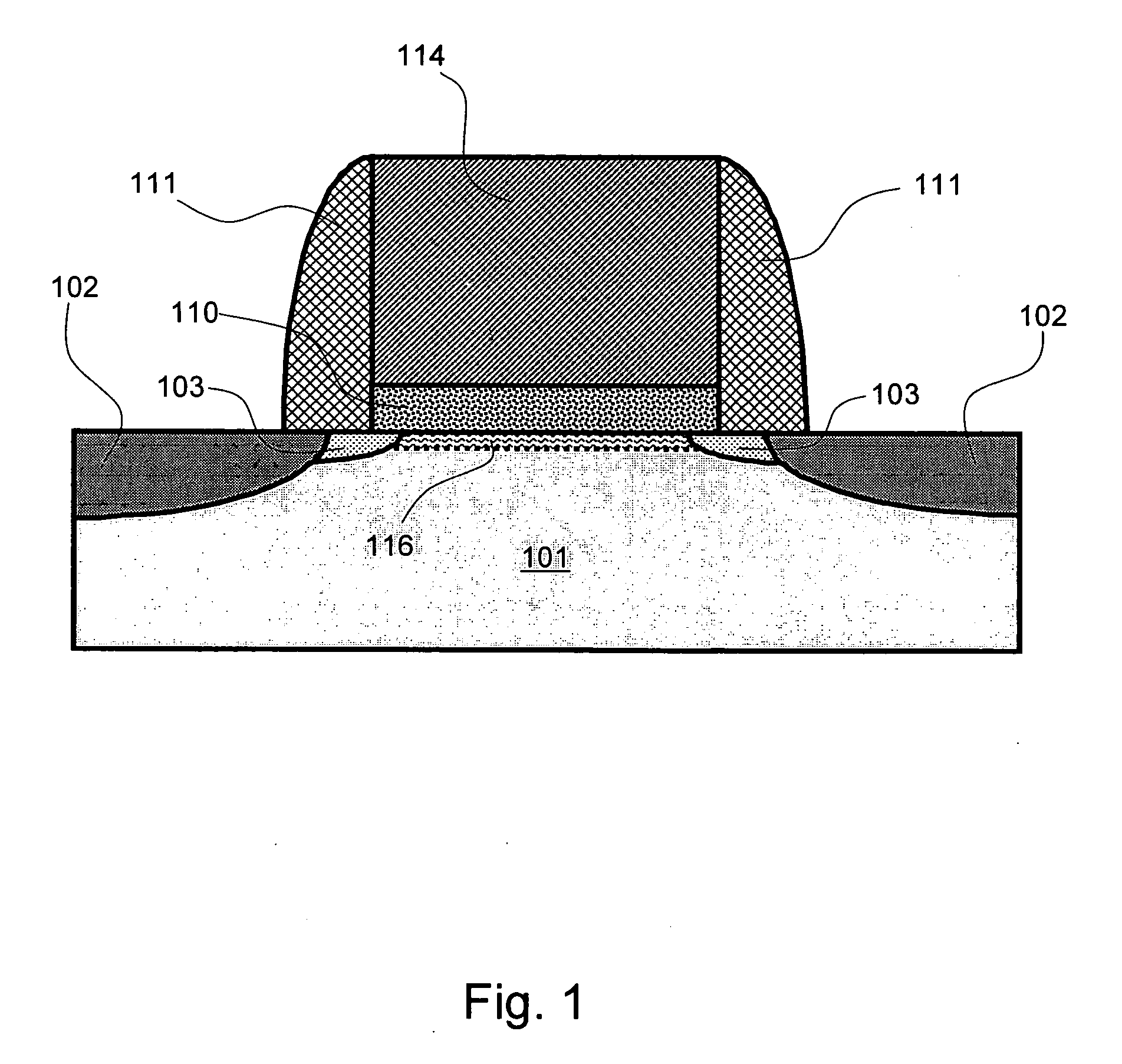

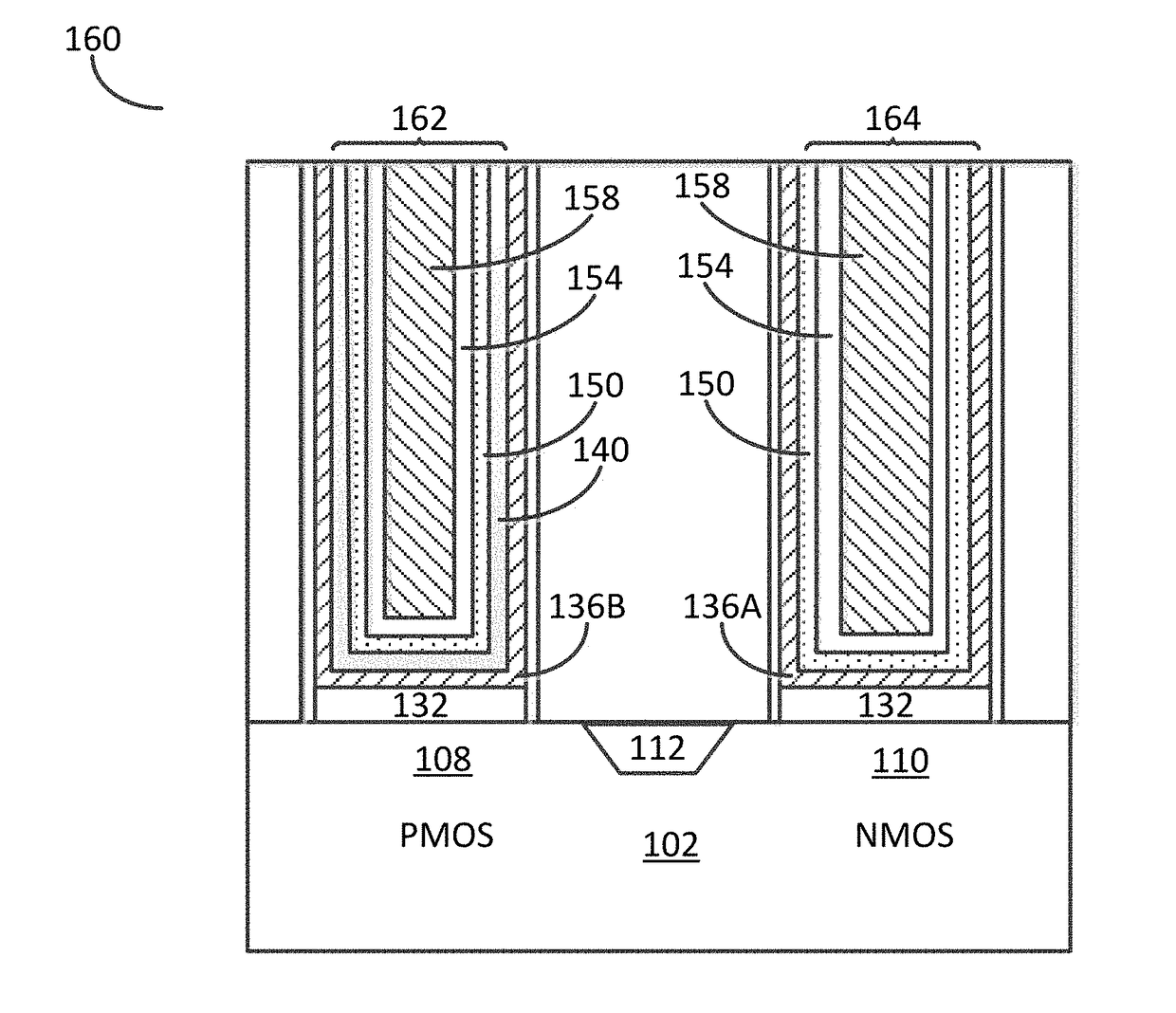

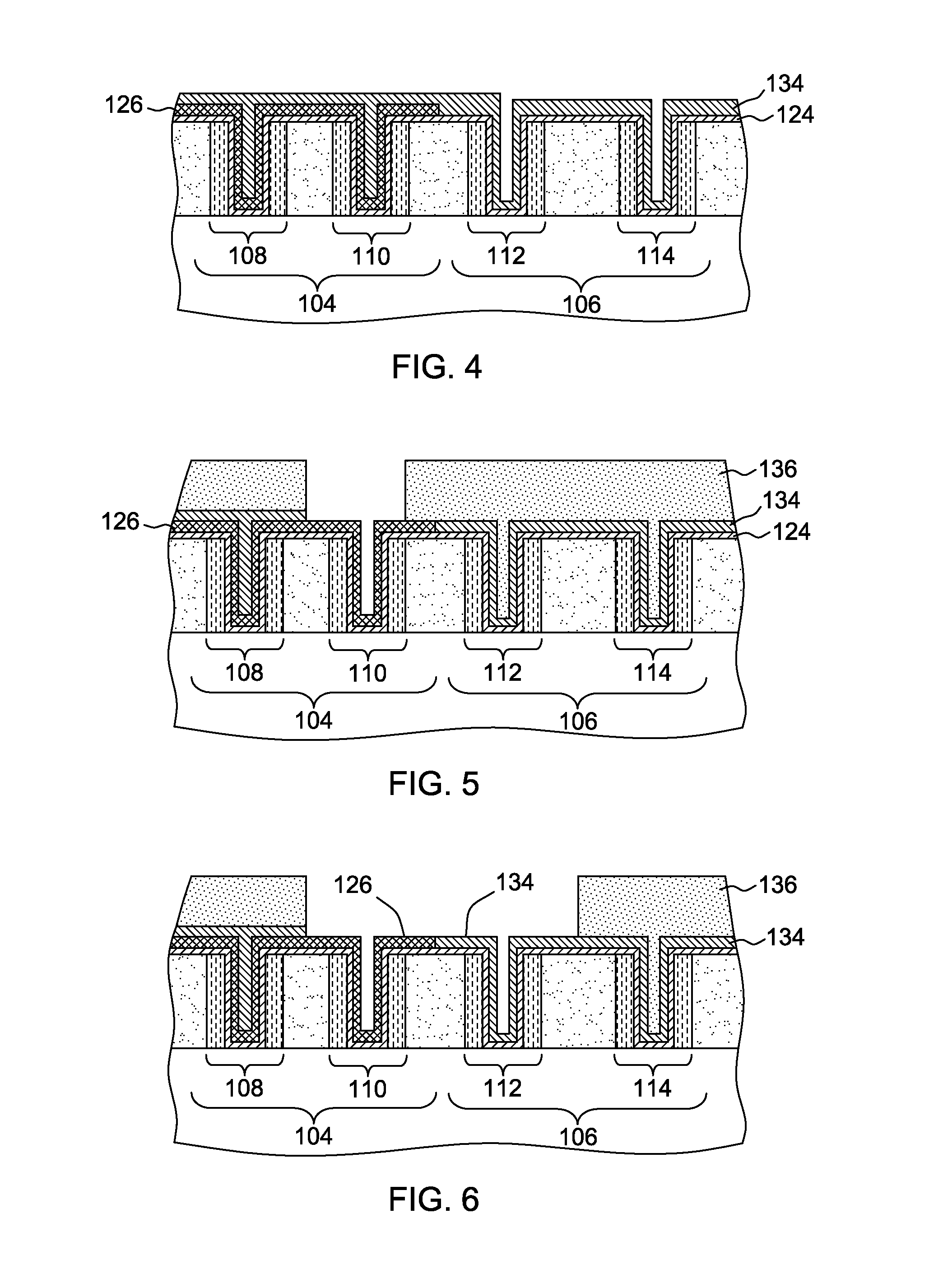

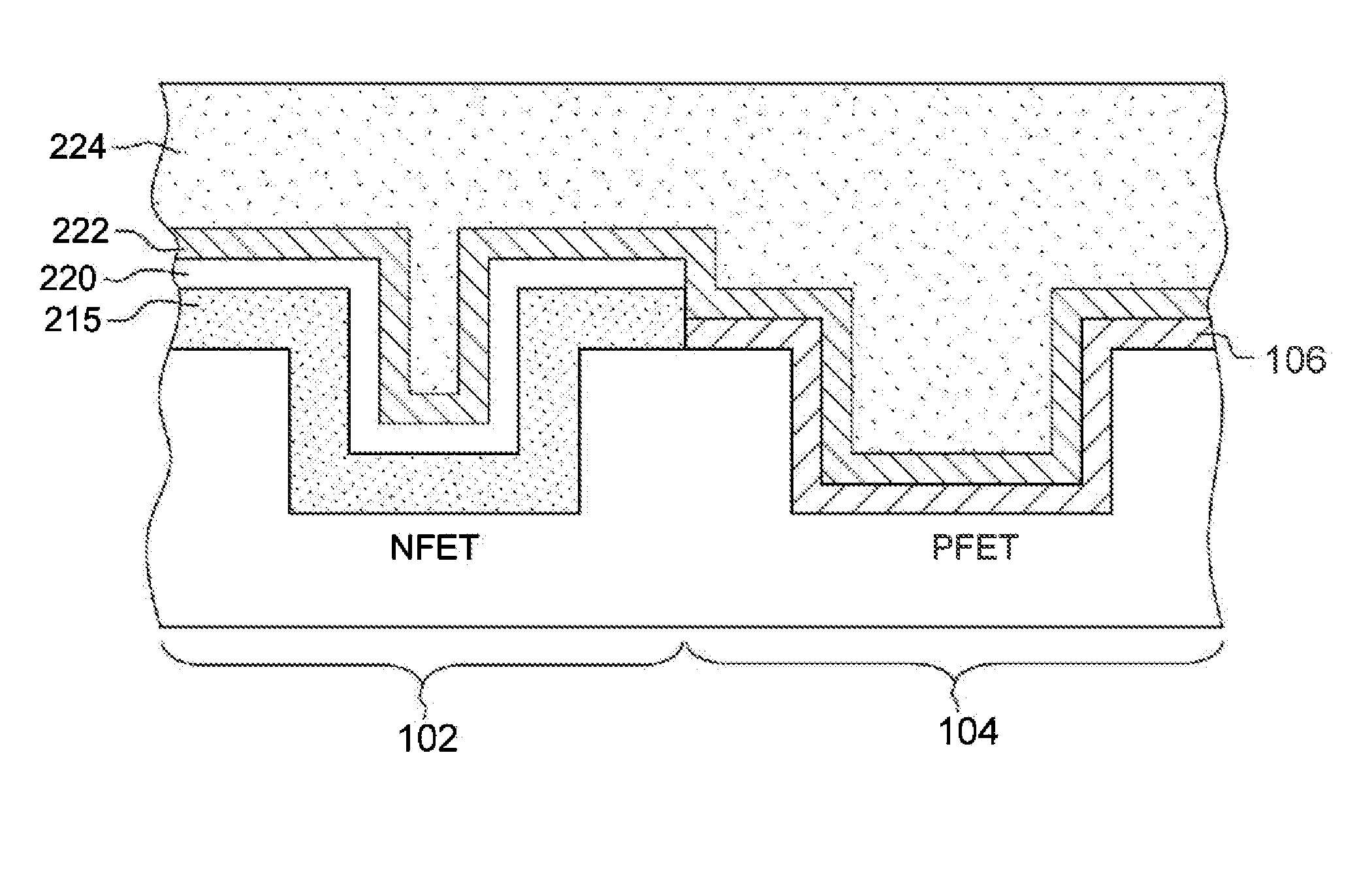

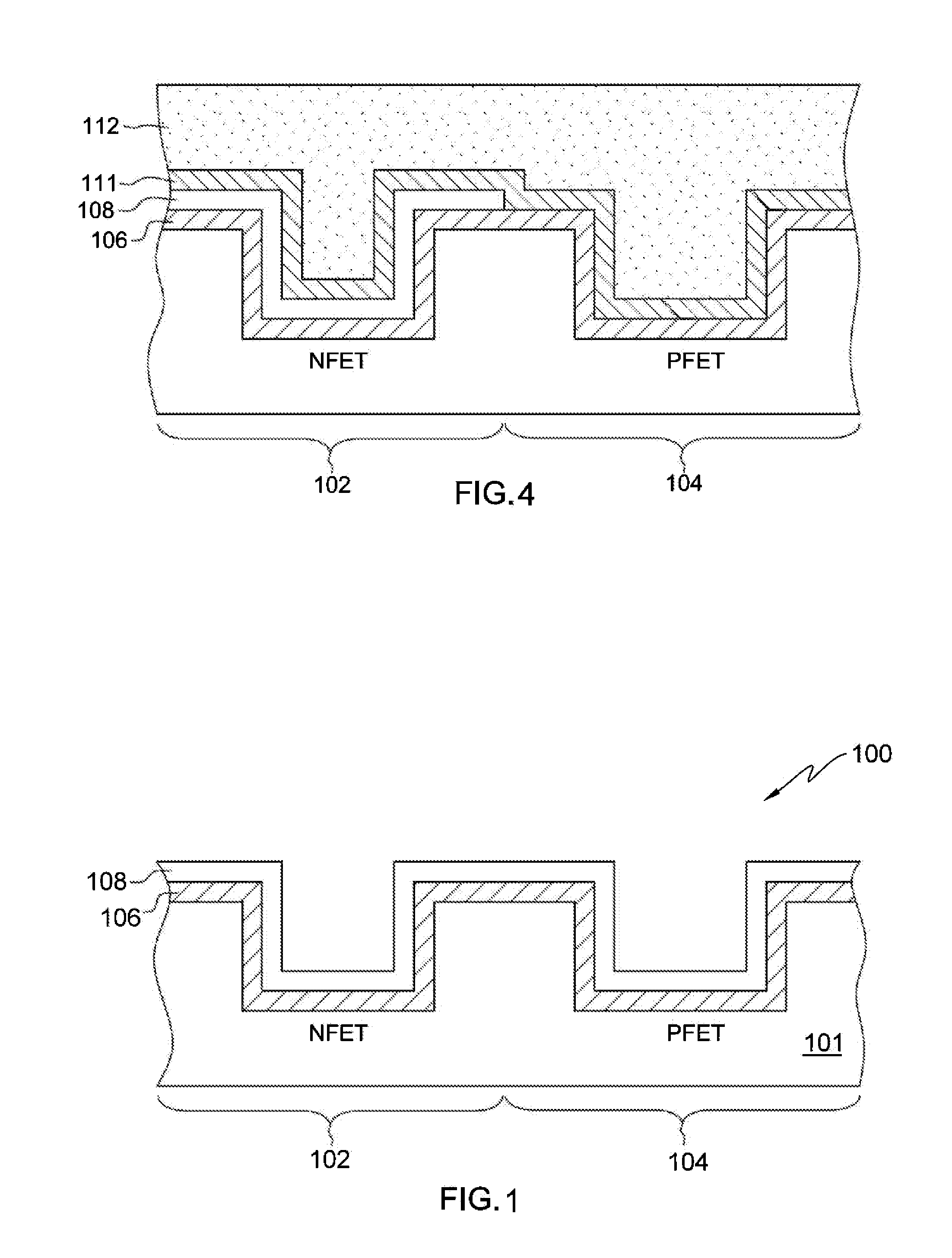

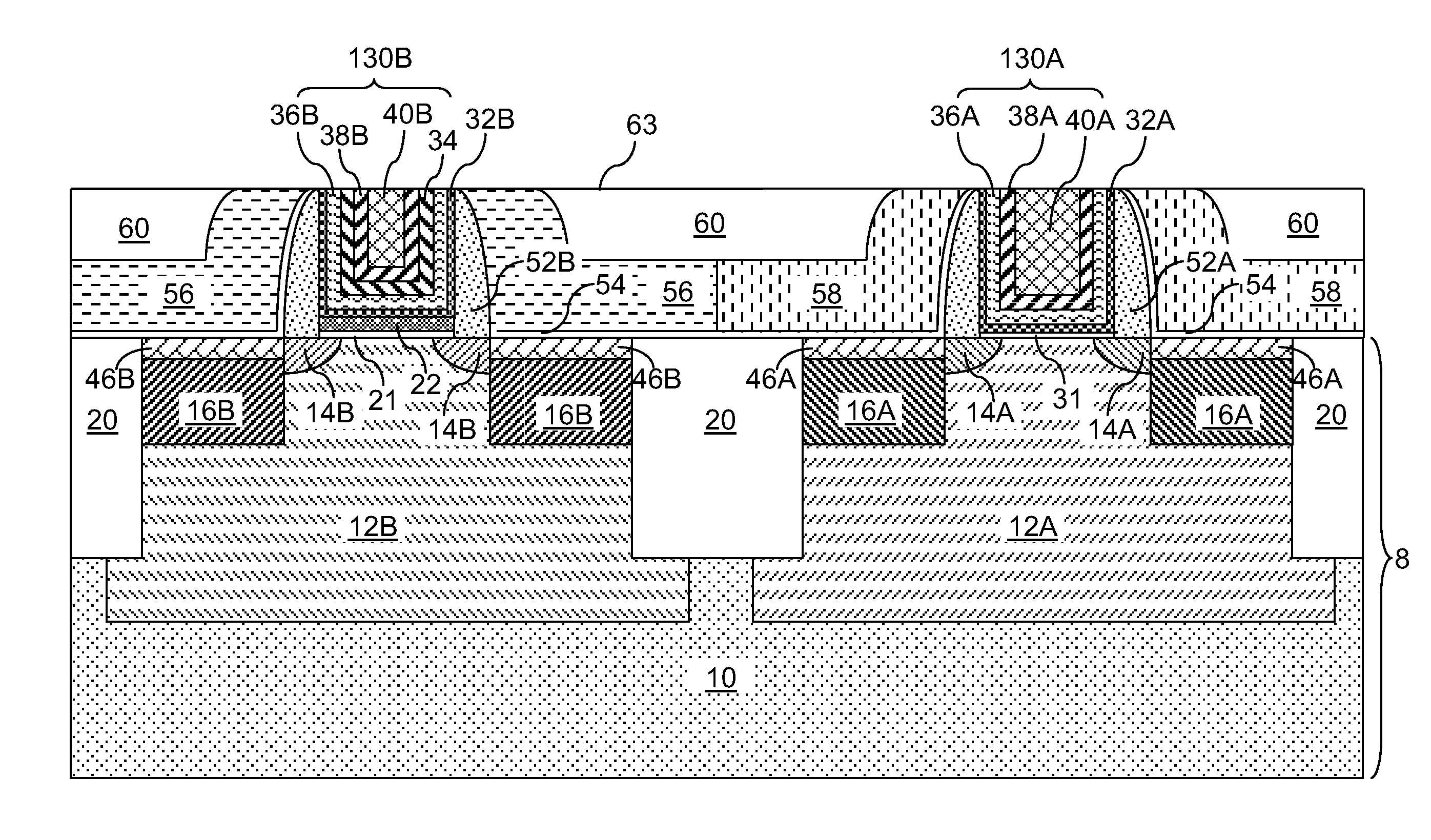

Methods for forming a semiconductor device and related semiconductor device structures

ActiveUS20180122709A1Well formedTransistorSolid-state devicesPower semiconductor deviceGate dielectric

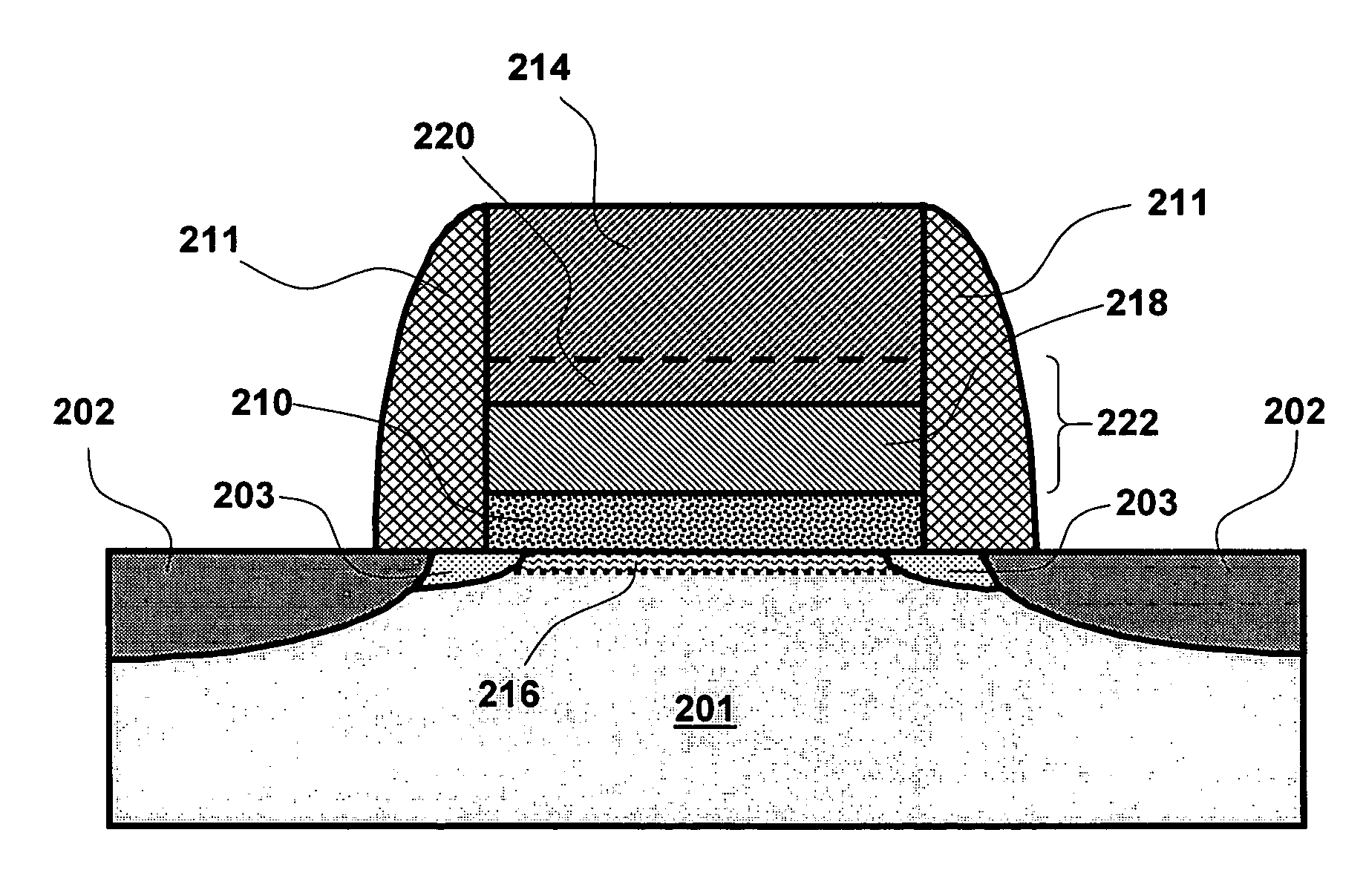

Methods for forming a semiconductor device and related semiconductor device structures are provided. In some embodiments, methods may include forming an NMOS gate dielectric and a PMOS gate dielectric over a substrate and forming a first work function metal over the NMOS gate dielectric and over the PMOS gate dielectric. In some embodiments, methods may also include, removing the first work function metal over the NMOS gate dielectric and forming a second work function metal over the NMOS gate dielectric and over the PMOS gate dielectric. In some embodiments, related semiconductor device structures may include an NMOS gate dielectric and a PMOS gate dielectric disposed over a semiconductor substrate. A PMOS gate electrode may be disposed over the PMOS gate dielectric and the PMOS gate electrode may include a first work function metal disposed over the PMOS gate dielectric and a second work function metal disposed over the first work function metal. A NMOS gate electrode may be disposed over the NMOS gate dielectric and the NMOS gate electrode may include the second work function metal.

Owner:ASM IP HLDG BV

Common fabrication of different semiconductor devices with different threshold voltages

A multi-device semiconductor structure including a p-type logic device, a p-type memory device, a n-type logic device and a n-type memory device are provided on a bulk silicon substrate. Each of these devices includes a dielectric layer and either a n-type or a p-type work function layer disposed over the dielectric layer. Some of the various device types of the multi-device semiconductor structure are protected, and impurities, such as aluminum and / or nitrogen, are added to the exposed work function layers to achieve one or more other desired work functions with different threshold voltages.

Owner:GLOBALFOUNDRIES INC

NbMC layers

ActiveUS10211308B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice PropertiesWork function

Methods of forming thin-film structures including one or more NbMC layers, and structures and devices including the one or more NbMC layers are disclosed. The NbMC layers enable tuning of various structure and device properties, including resistivity, current leakage, and work function.

Owner:ASM IP HLDG BV

Method for forming a semiconductor device structure and related semiconductor device structures

ActiveUS20190088555A1TransistorSemiconductor/solid-state device manufacturingWork functionEngineering

A method for forming a semiconductor device structure is disclosure. The method may include, depositing an NMOS gate dielectric and a PMOS gate dielectric over a semiconductor substrate, depositing a first work function metal over the NMOS gate dielectric and over the PMOS gate dielectric, removing the first work function metal over the PMOS gate dielectric, and depositing a second work function metal over the NMOS gate dielectric and over the PMOS gate dielectric. Semiconductor device structures including desired metal gate electrodes deposited by the methods of the disclosure are also disclosed.

Owner:ASM IP HLDG BV

Semiconductor device incorporating a multi-function layer into gate stacks

InactiveUS8859368B2Reduce in quantityReduce complexityTransistorSolid-state devicesWork functionGate stack

Approaches are provided for forming a semiconductor device (e.g., a FET) having a multi-function layer (e.g., niobium carbide (NbC)) that serves as a work function layer and a gate metal layer in gate stacks of solid state applications. By introducing a single layer with multiple functions, total number of layers that needs processing (e.g., recessing) may be decreased. As such, the complexity of device integration and resulting complications may be reduced.

Owner:GLOBALFOUNDRIES INC

Transistors, integrated circuits, systems, and processes of manufacture with improved work function modulation

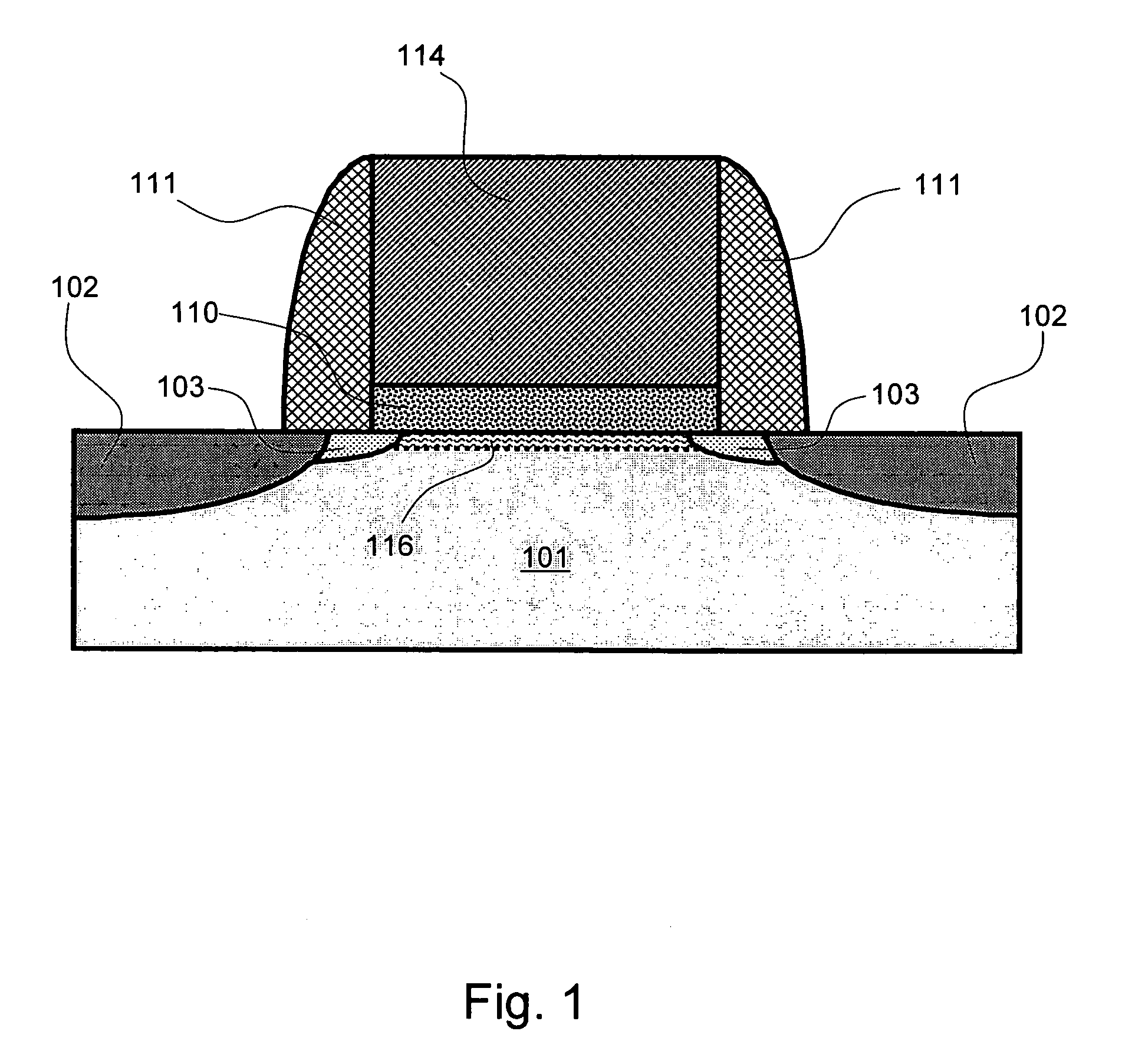

ActiveUS20060084247A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

A process (200) for making integrated circuits with a gate, uses a doped precursor (124, 126N and / or 126P) on barrier material (118) on gate dielectric (116). The process (200) involves totally consuming (271) the doped precursor (124, 126N and / or 126P) thereby driving dopants (126N and / or 126P) from the doped precursor (124) into the barrier material (118). An integrated circuit has a gate dielectric (116), a doped metallic barrier material (118, 126N and / or 126P) on the gate dielectric (116), and metal silicide (180) on the metallic barrier material (118). Other integrated circuits, transistors, systems and processes of manufacture are disclosed.

Owner:TEXAS INSTR INC

Semiconductor gate structure for threshold voltage modulation and method of making same

InactiveUS20140231922A1Lower work functionSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricTitanium nitride

A gate structure of a semiconductor device having a NFET and a PFET, includes a lower layer of a hafnium-based dielectric over the gates of the NFET and PFET, and an upper layer of a lanthanide dielectric. The dielectrics are annealed to mix them above the NFET resulting in a lowered work function, and corresponding threshold voltage reduction. An annealed, relatively thick titanium nitride cap over the mixed dielectric above the NFET gate also lowers the work function and threshold voltage. Above the TiN cap and the hafnium-based dielectric over the PFET gate, is another layer of titanium nitride that has not been annealed. A conducting layer of tungsten covers the structure.

Owner:GLOBALFOUNDRIES US INC

Methods for forming a semiconductor device structure and related semiconductor device structures

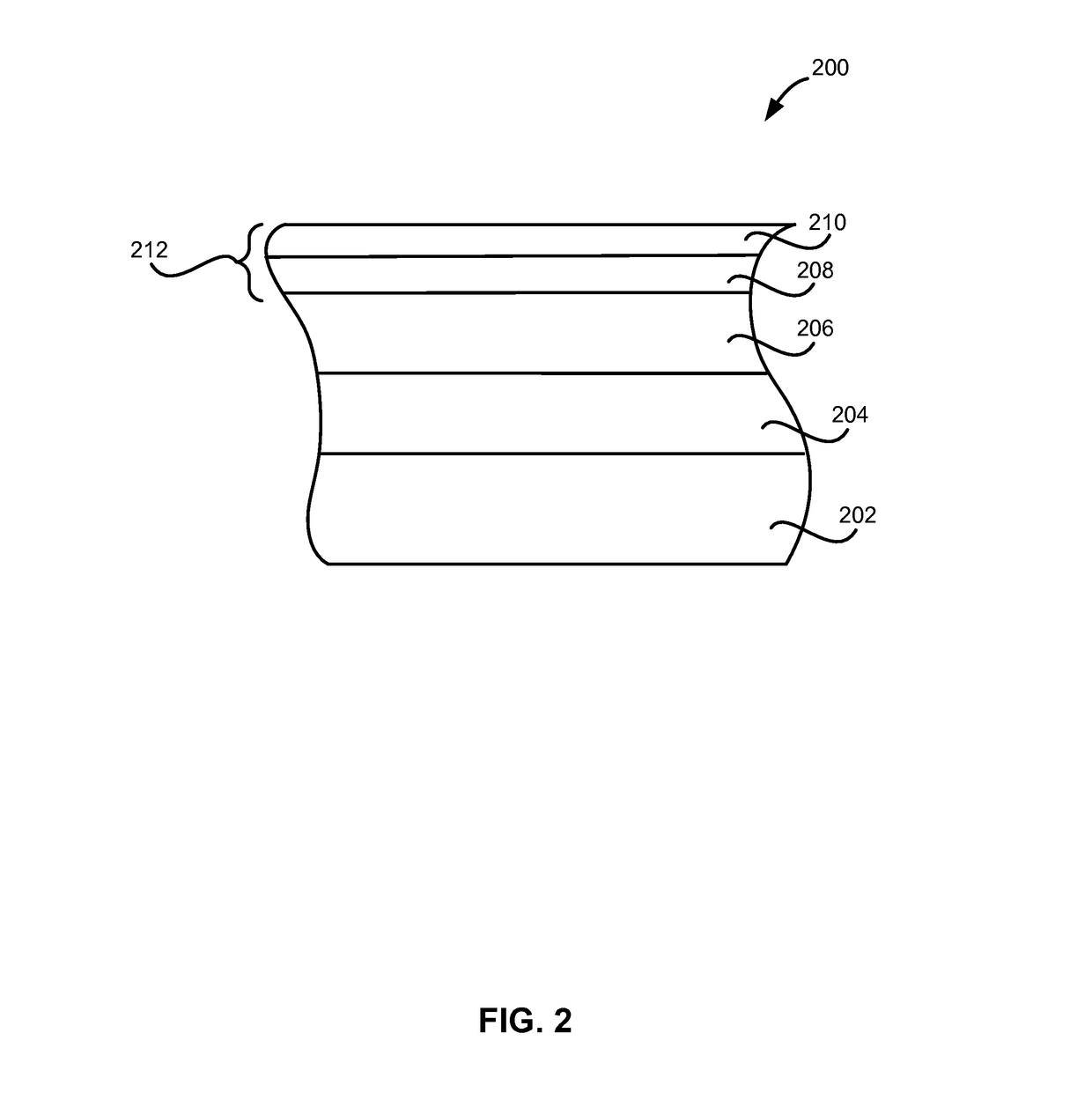

Methods for forming a semiconductor device structure are provided. The methods may include forming a molybdenum nitride film on a substrate by atomic layer deposition by contacting the substrate with a first vapor phase reactant comprising a molybdenum halide precursor, contacting the substrate with a second vapor phase reactant comprise a nitrogen precursor, and contacting the substrate with a third vapor phase reactant comprising a reducing precursor. The methods provided may also include forming a gate electrode structure comprising the molybdenum nitride film, the gate electrode structure having an effective work function greater than approximately 5.0 eV. Semiconductor device structures including molybdenum nitride films are also provided.

Owner:ASM IP HLDG BV

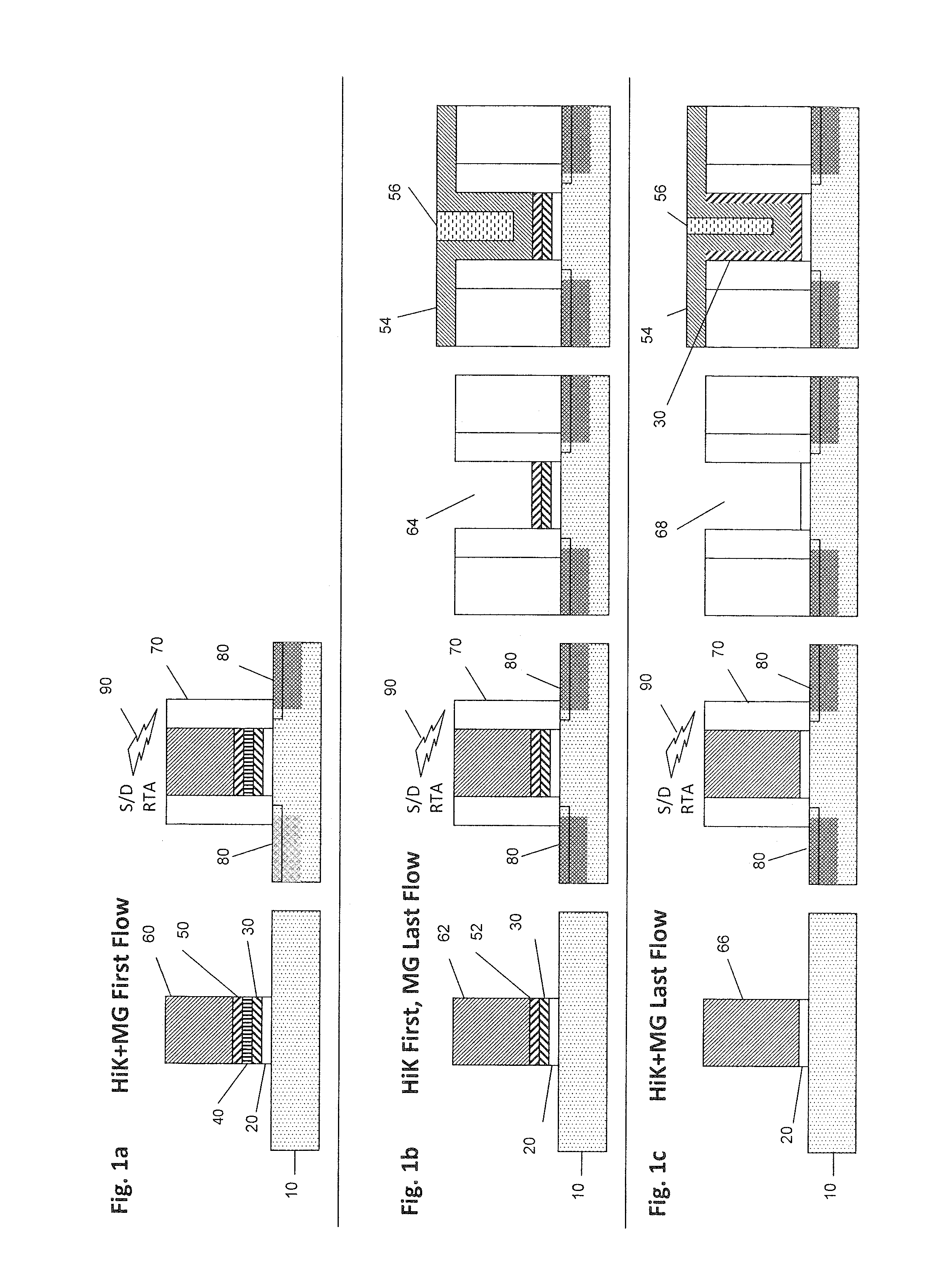

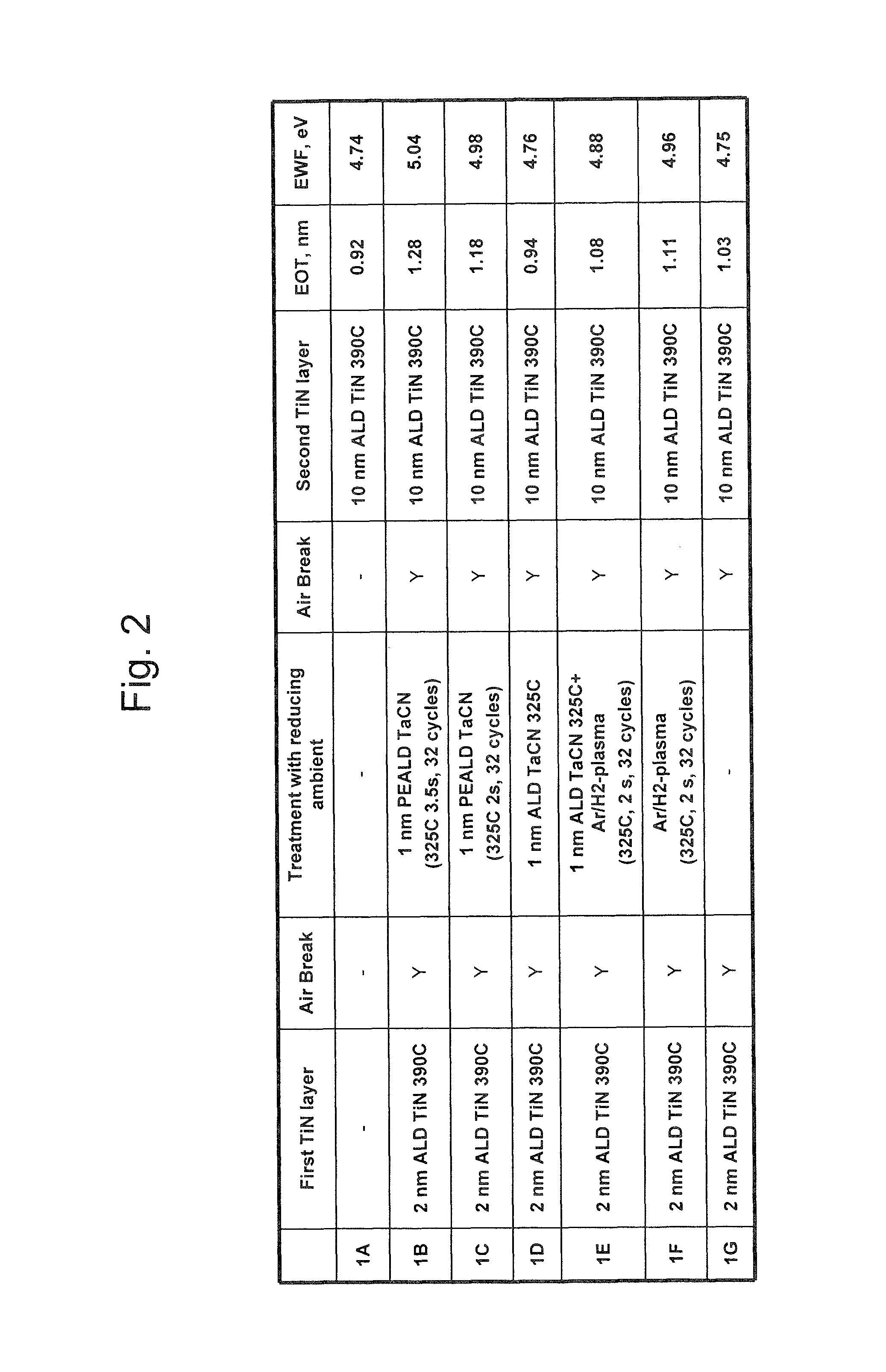

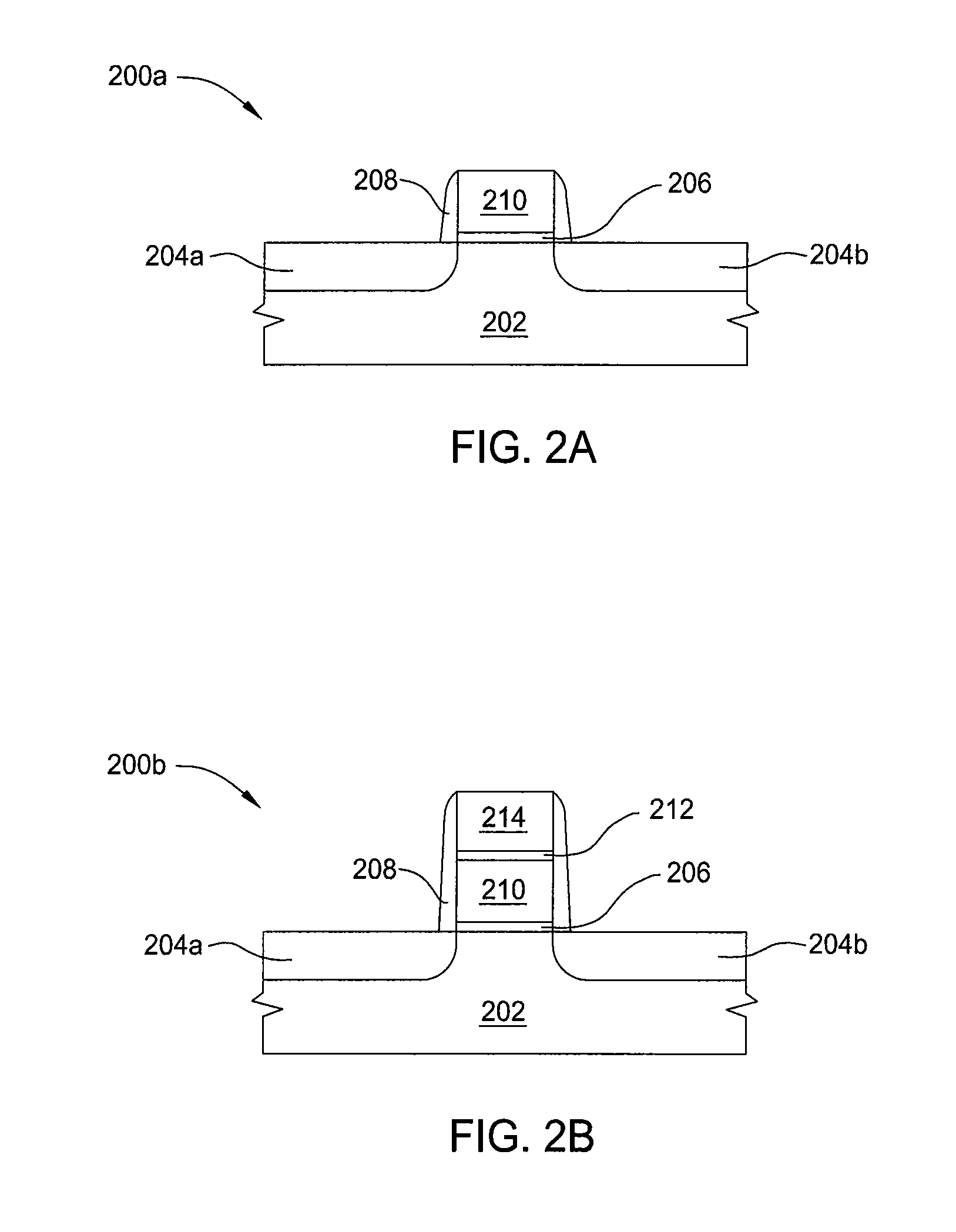

Process for depositing electrode with high effective work function

ActiveUS20120309181A1Semiconductor/solid-state device manufacturingSemiconductor devicesWork functionPhysics

According to some embodiments, an electrode have a high effective work function is formed. The electrode may be the gate electrode of a transistor and may be formed on a high-k gate dielectric by depositing a first layer of conductive material, exposing that first layer to a hydrogen-containing gas, and depositing a second layer of conductive material over the first layer. The first layer may be deposited using a non-plasma process in which the substrate is not exposed to plasma or plasma-generated radicals. The hydrogen-containing gas to which the first layer is exposed may include an excited hydrogen species, which may be part of a hydrogen-containing plasma, and may be hydrogen-containing radicals. The first layer may also be exposed to oxygen before depositing the second layer. The work function of the gate electrode in the gate stack may be about 5 eV or higher in some embodiments.

Owner:ASM IP HLDG BV

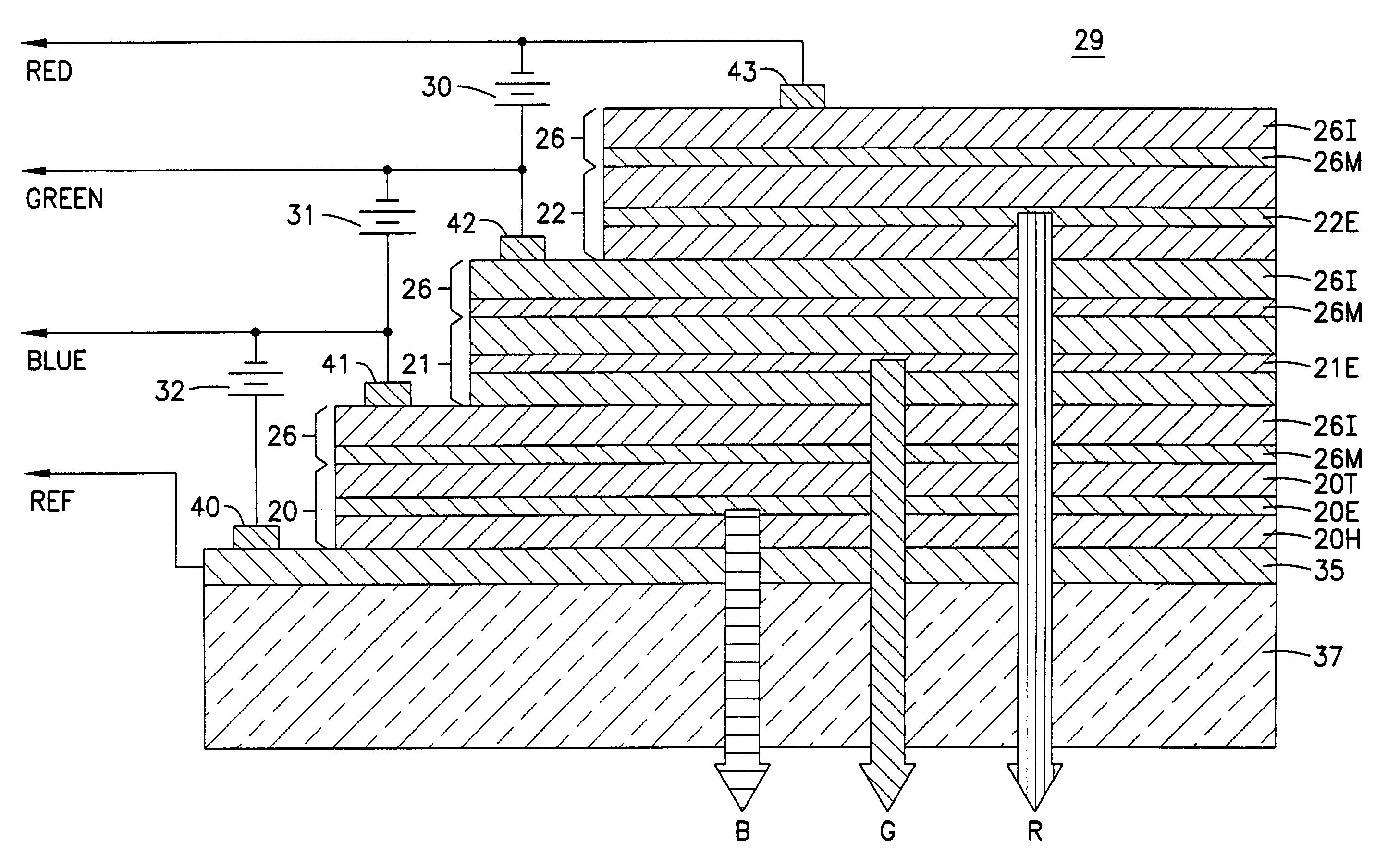

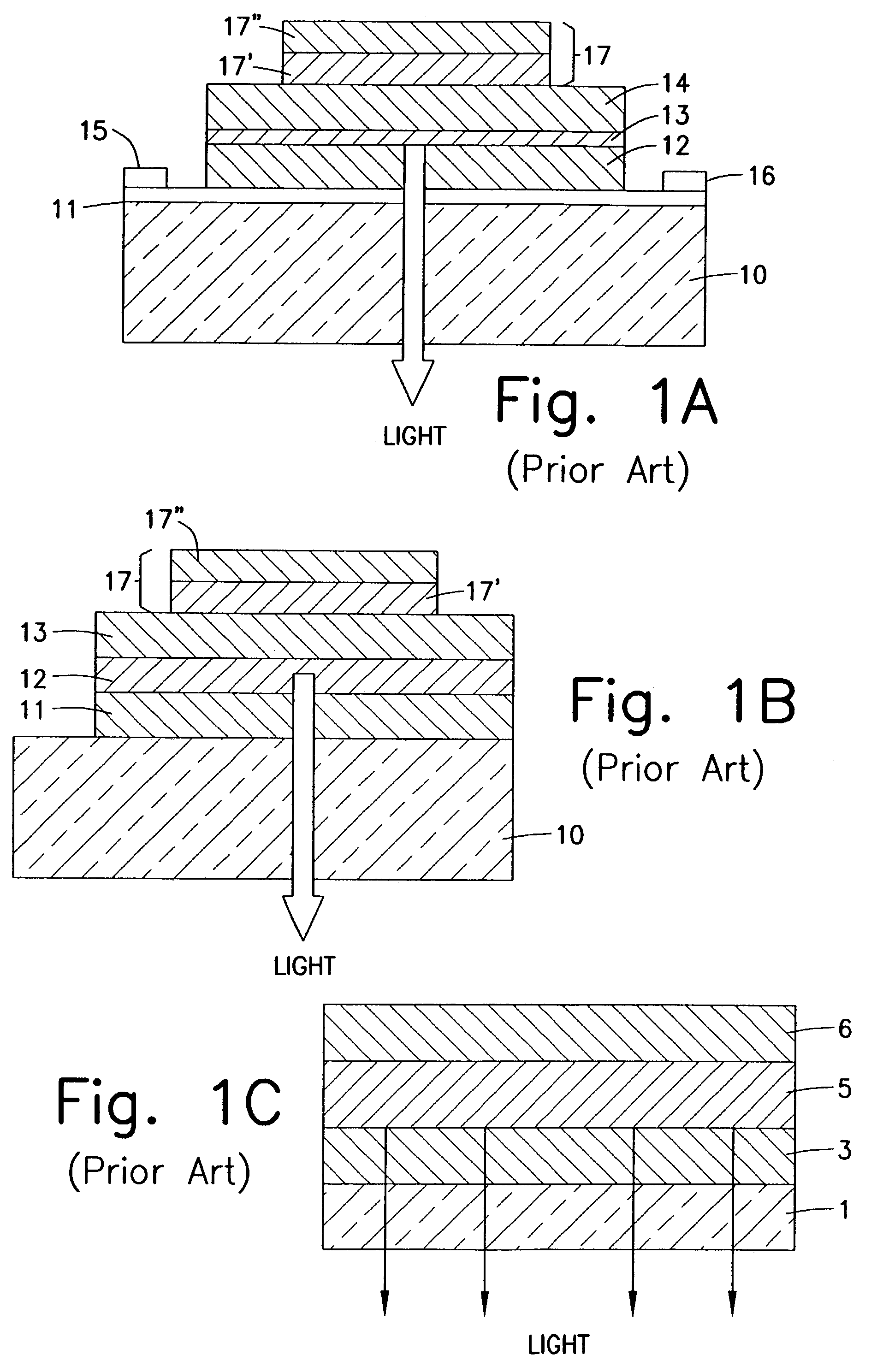

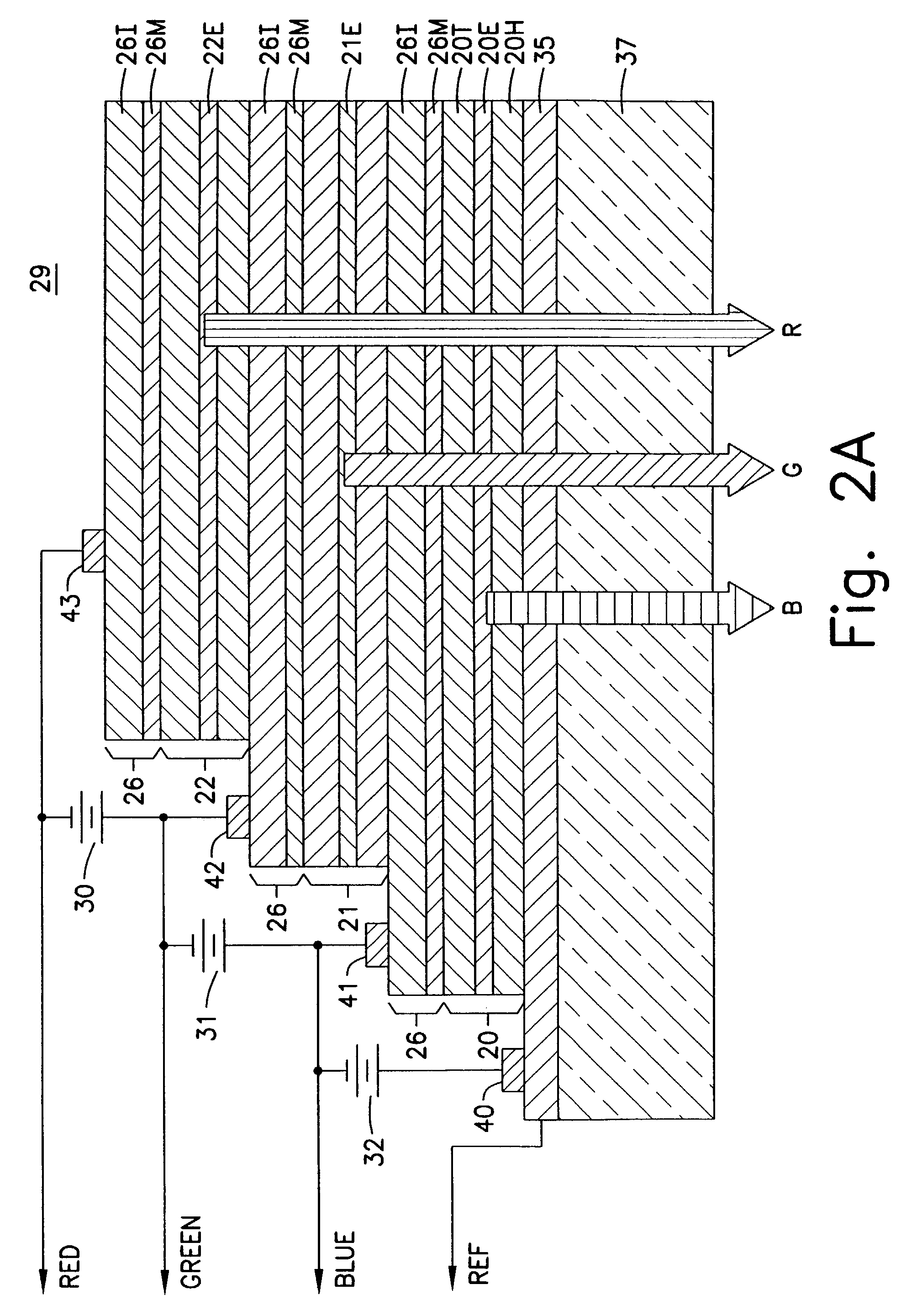

Transparent contacts for organic devices

InactiveUS7173369B2Low production costReduce the driving voltageStatic indicating devicesSolid-state devicesOrganic light emitting deviceWork function

An organic light emitting device structure includes a substrate, a first electrically conductive layer formed over the substrate wherein the first electrically conductive layer has a positive polarity, and a transparent organic light emitting device formed over the first electrically conductive layer. The structure also includes a transparent electrically conductive metal layer formed over the transparent organic light emitting device wherein the metal has a work function less than 4 eV, and a second electrically conductive layer formed over the transparent electrically conductive metal layer, wherein the second electrically conductive layer has a negative polarity, and wherein the second electrically conductive layer comprises a material selected from the group consisting of a transparent electrically conductive oxide and a transparent electrically conductive polymer.

Owner:THE TRUSTEES FOR PRINCETON UNIV

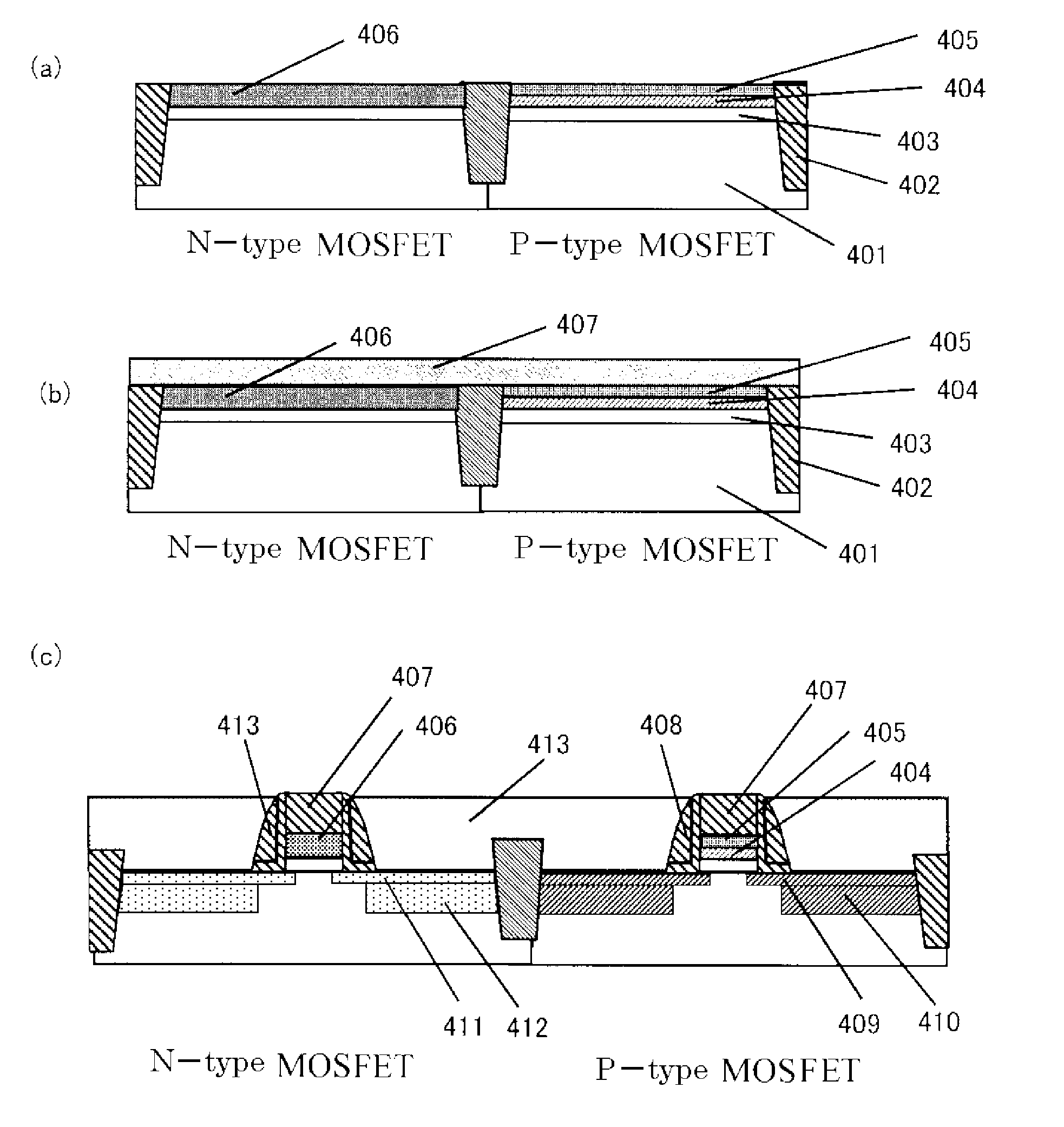

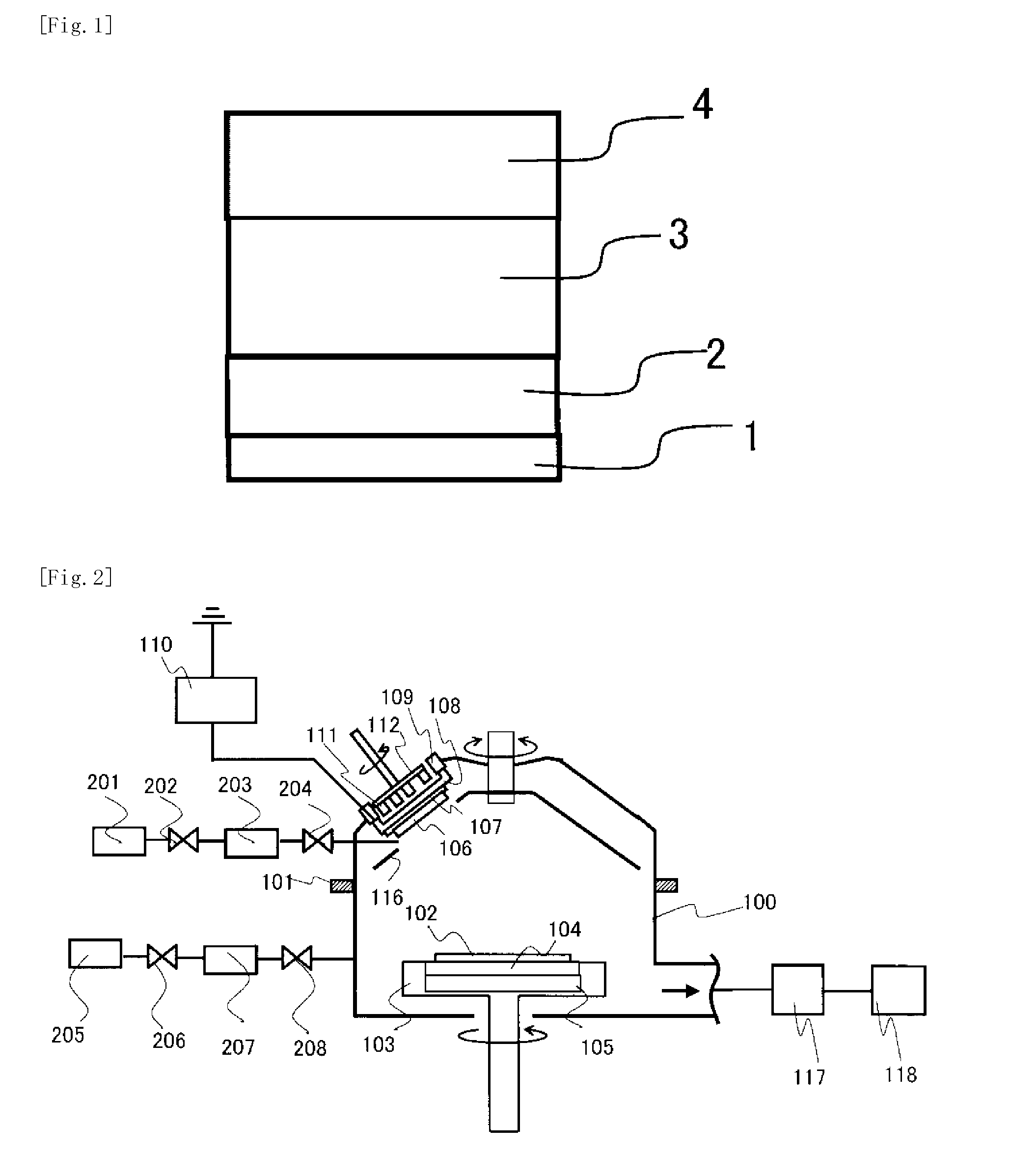

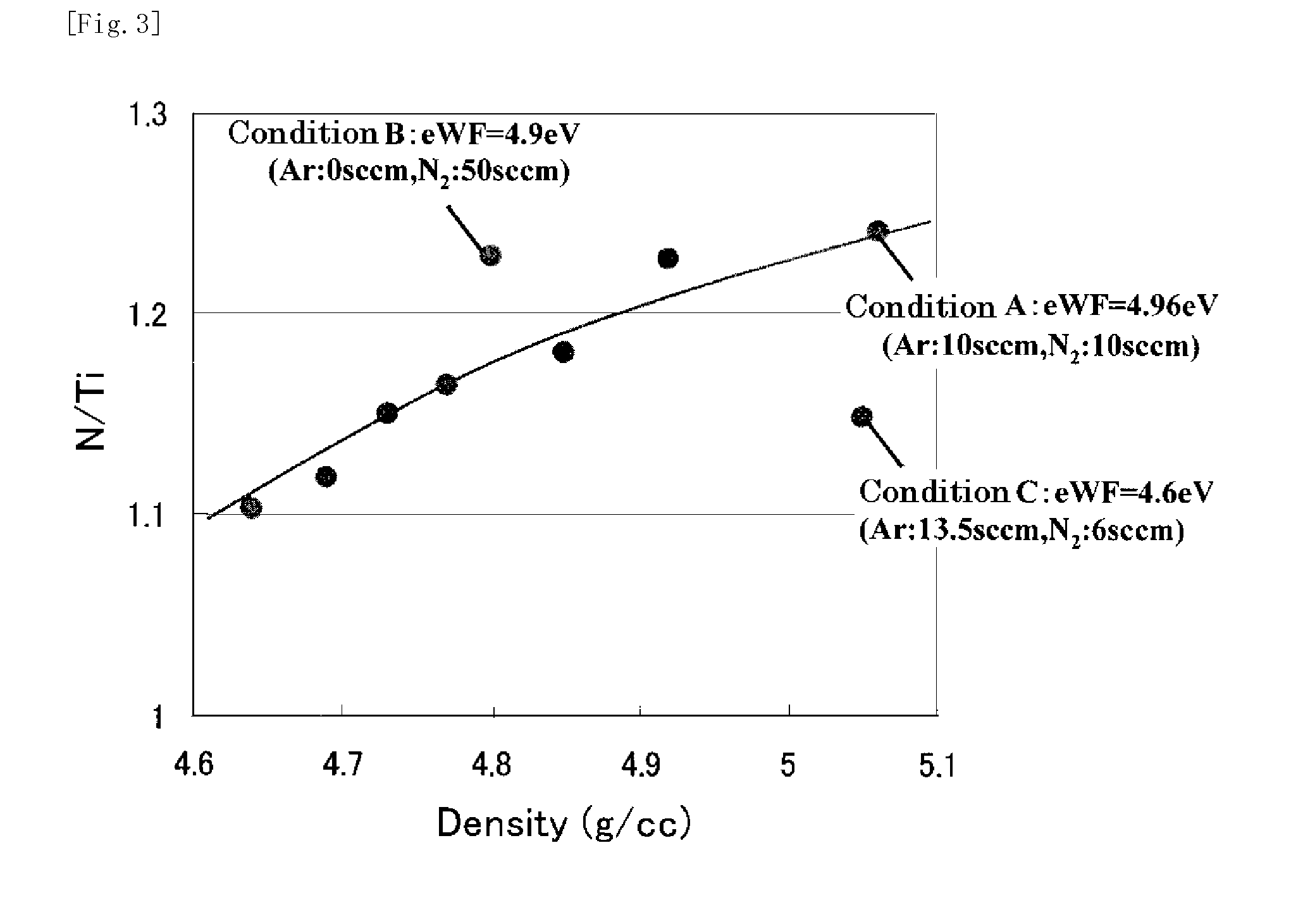

Semiconductor device and method of manufacturing the same

ActiveUS20120043617A1Work lessTransistorSemiconductor/solid-state device manufacturingDevice materialPermittivity

This invention provides a semiconductor device having a field effect transistor comprising agate electrode comprising a metal nitride layer and a polycrystalline silicon layer, and the gate electrode is excellent in thermal stability and realizes a desired work function.In the semiconductor device, a gate insulating film 6 on a silicon substrate 5 has a high-permittivity insulating film formed of a metal oxide, a metal silicate, a metal oxide introduced with nitrogen, or a metal silicate introduced with nitrogen,the gate electrode has a first metal nitride layer 7 provided on the gate insulating film 6 and containing Ti and N, a second metal nitride layer 8 containing Ti and N, and a polycrystalline silicon layer 9, in the first metal nitride layer 7, a molar ratio between Ti and N (N / Ti) is not less than 1.1, and a crystalline orientation X1 is 1.1<X1<1.8, andin the second metal nitride layer 8, the molar ratio between Ti and N (N / Ti) is not less than 1.1, and a crystalline orientation X2 is 1.8≦X2.

Owner:CANON ANELVA CORP

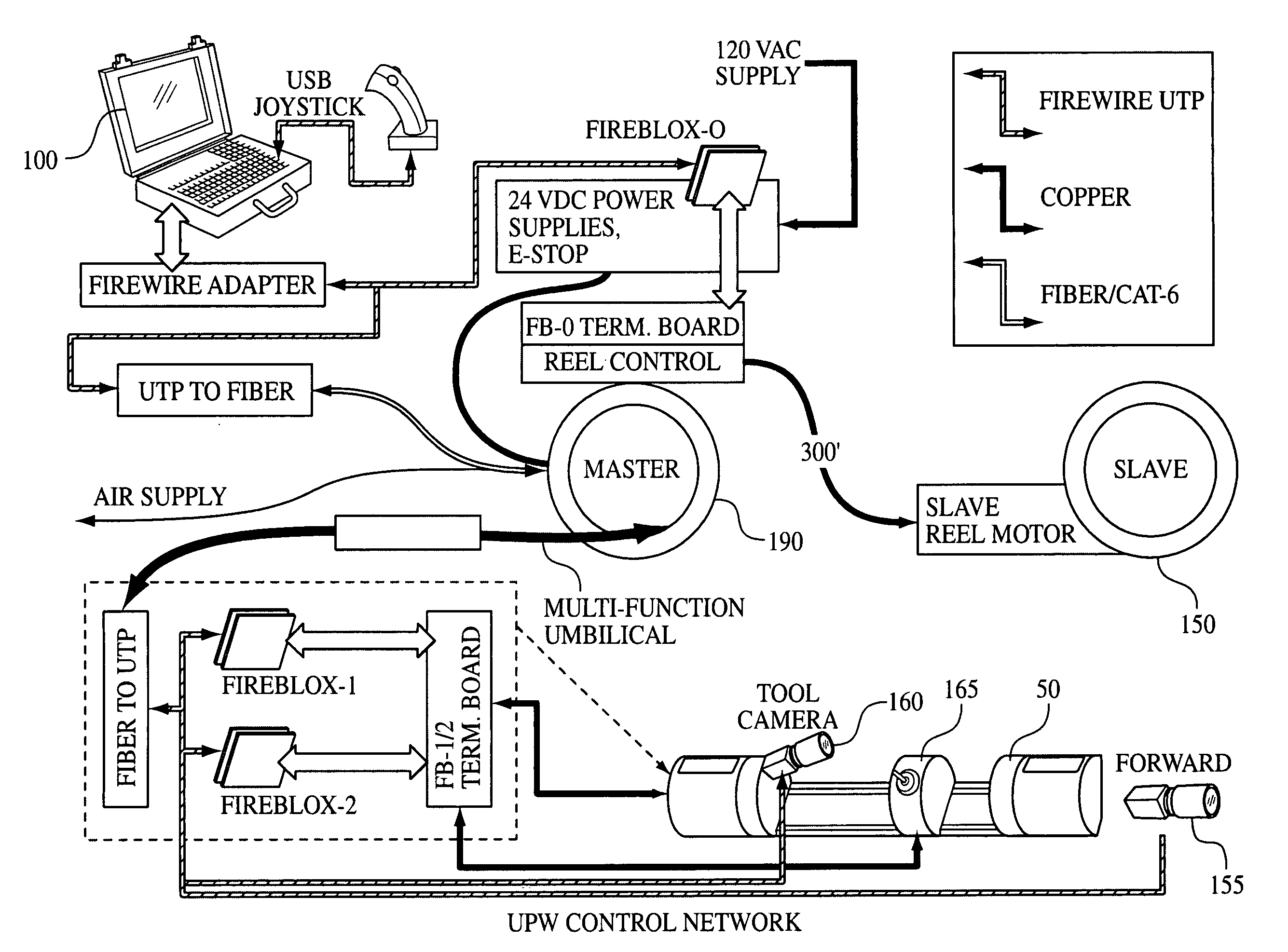

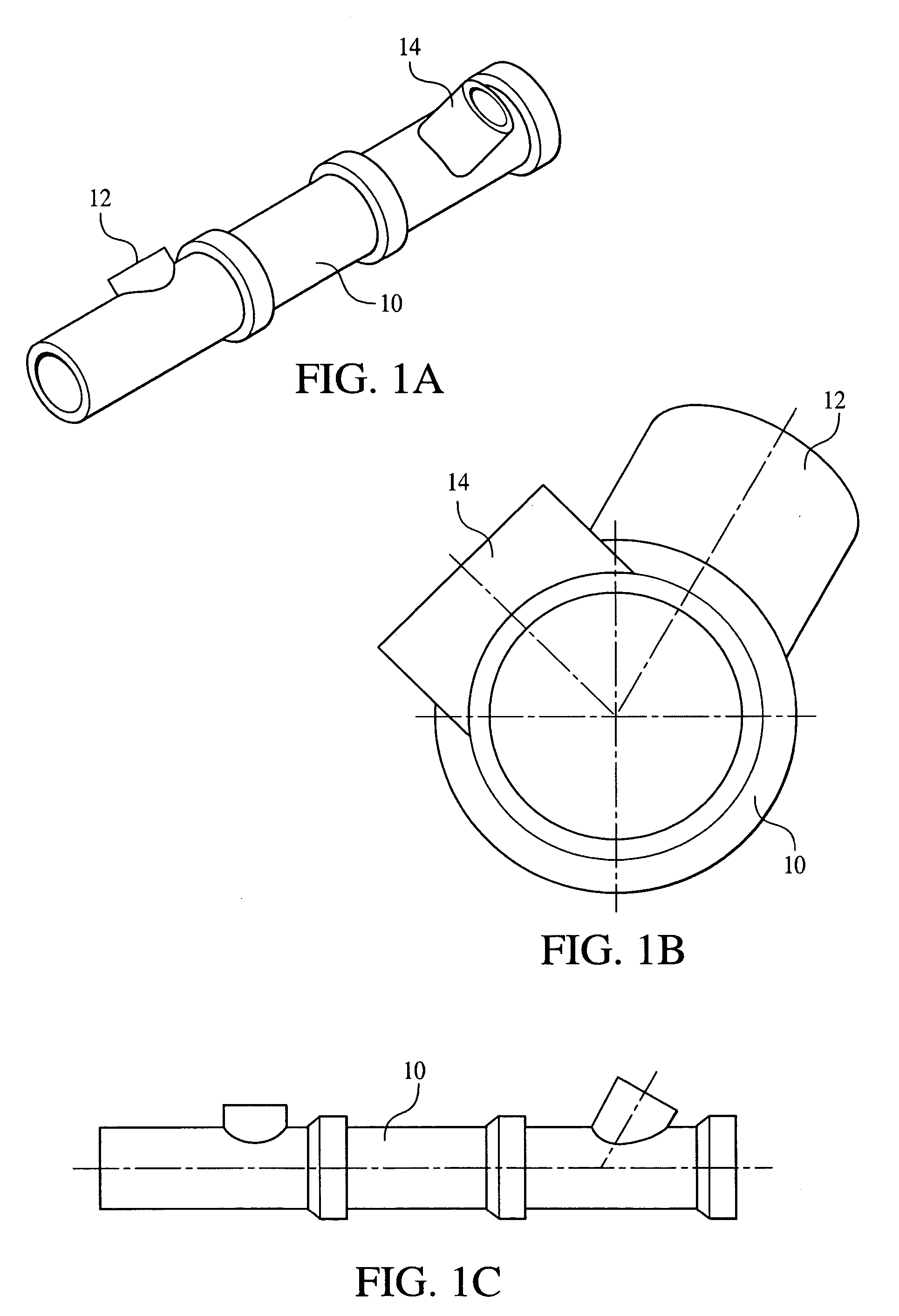

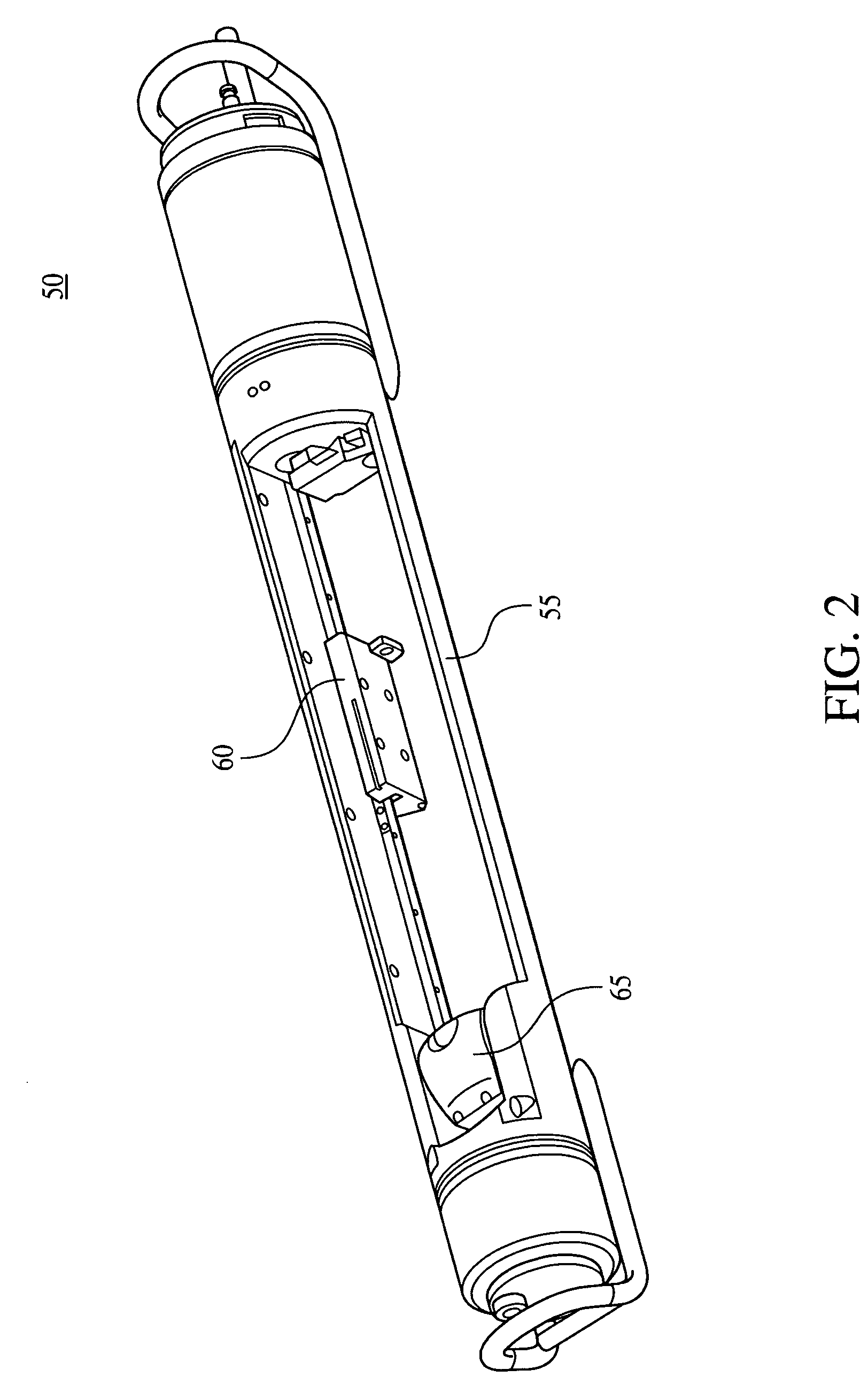

Network architecture for remote robot with interchangeable tools

ActiveUS20060074525A1Slow feedback loopLess time-critical decisionProgramme controlProgramme-controlled manipulatorDigital feedbackAuto-configuration

Systems, methods and devices for the remote control of a robot which incorporates interchangeable tool heads. Although applicable to many different industries, the core structure of the system includes a robot with a tool head interface for mechanically, electrically and operatively interconnecting a plurality of interchangeable tool heads to perform various work functions. The robot and tool head may include several levels of digital feedback (local, remote and wide area) depending on the application. The systems include a single umbilical cord to send power, air, and communications signals between the robot and a remote computer. Additionally, all communication (including video) is preferably sent in a digital format. Finally, a GUI running on the remote computer automatically queries and identifies all of the various devices on the network and automatically configures its user options to parallel the installed devices. Systems according to the preferred embodiments find particular application in the pipeline arts. For example, interchangeable tool heads may be designed to facilitate inspection, debris clearing, cleaning, relining, lateral cutting after relining, mapping, and various other common pipeline-related tasks.

Owner:REDZONE ROBOTICS

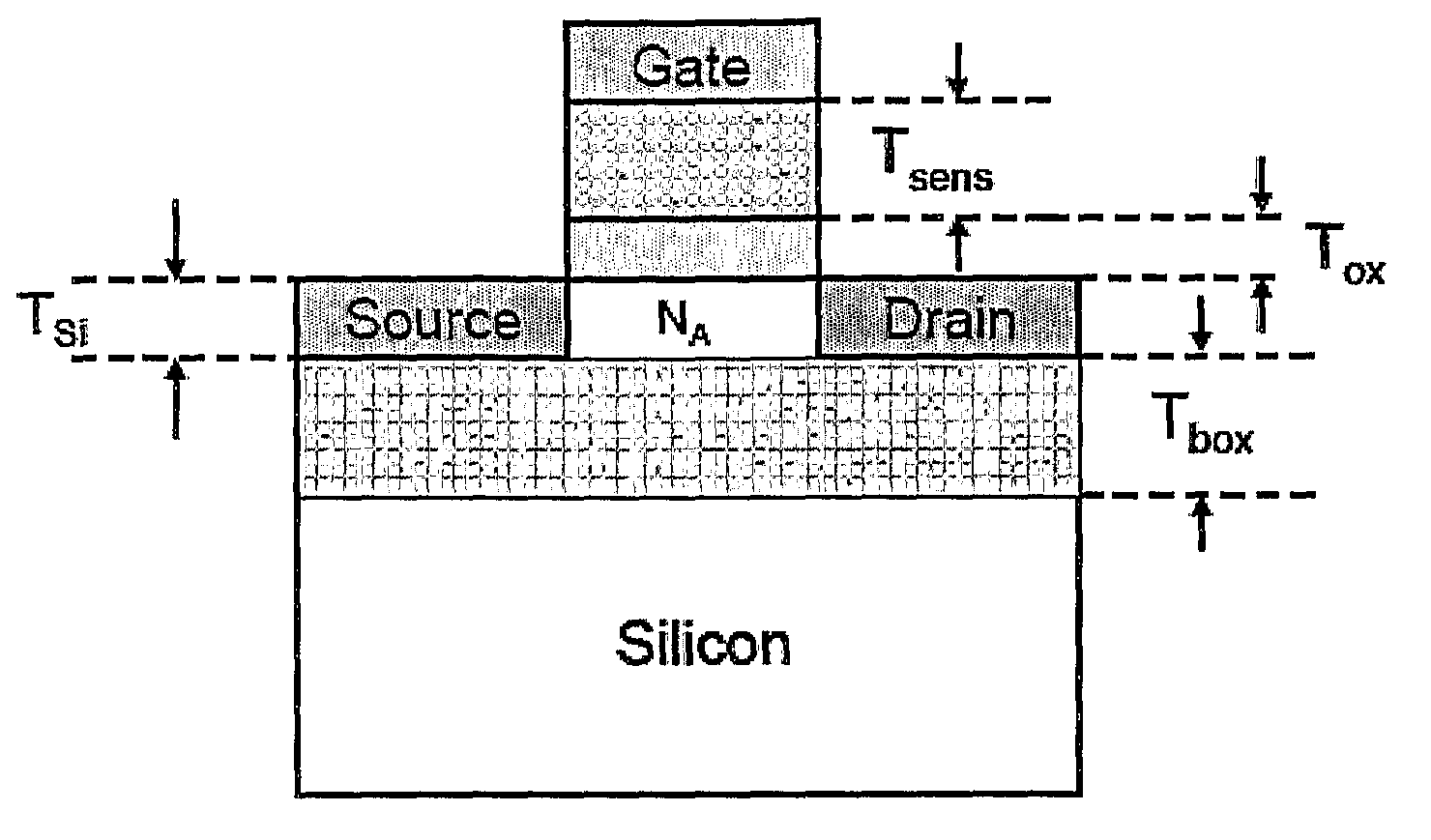

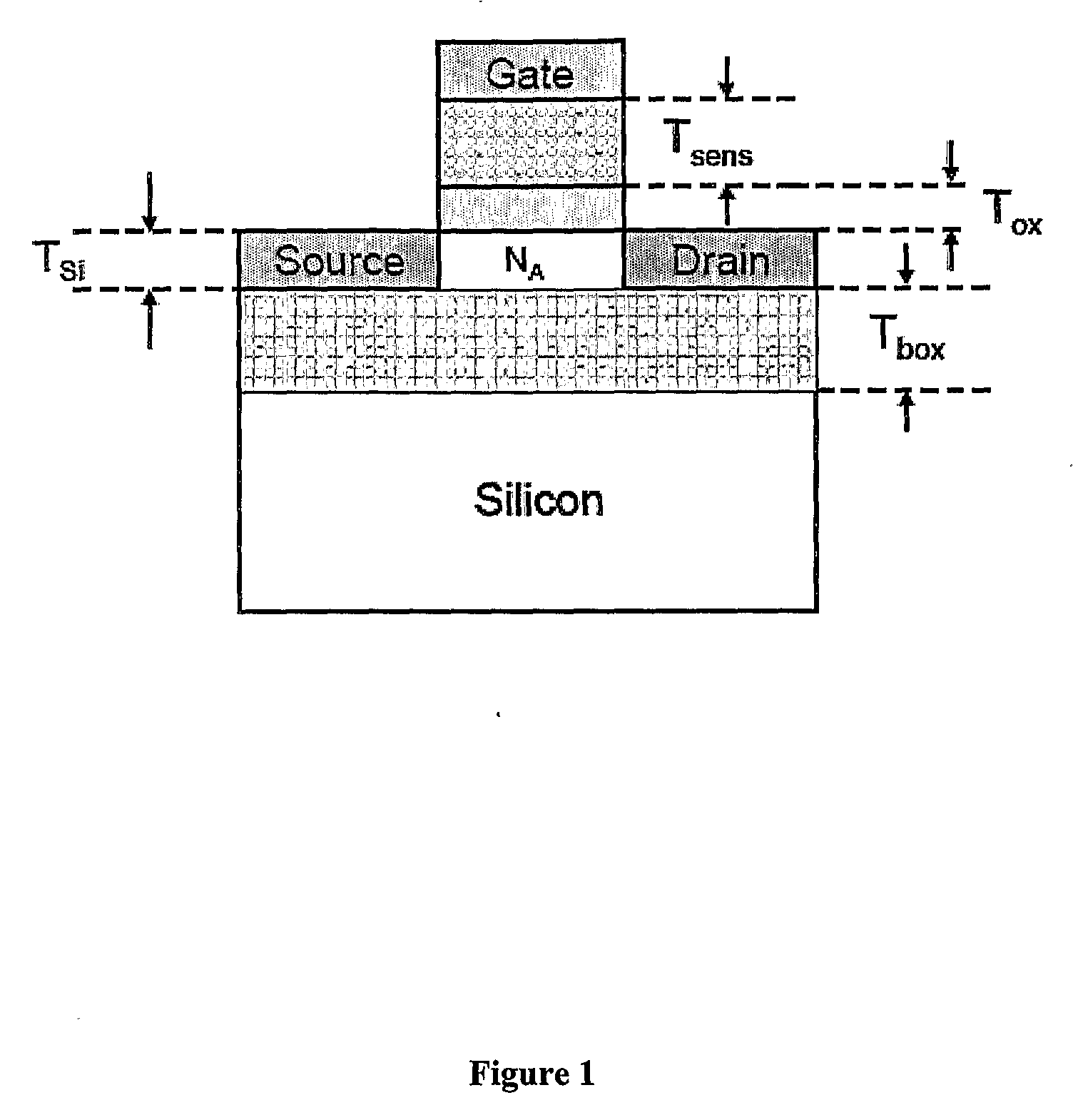

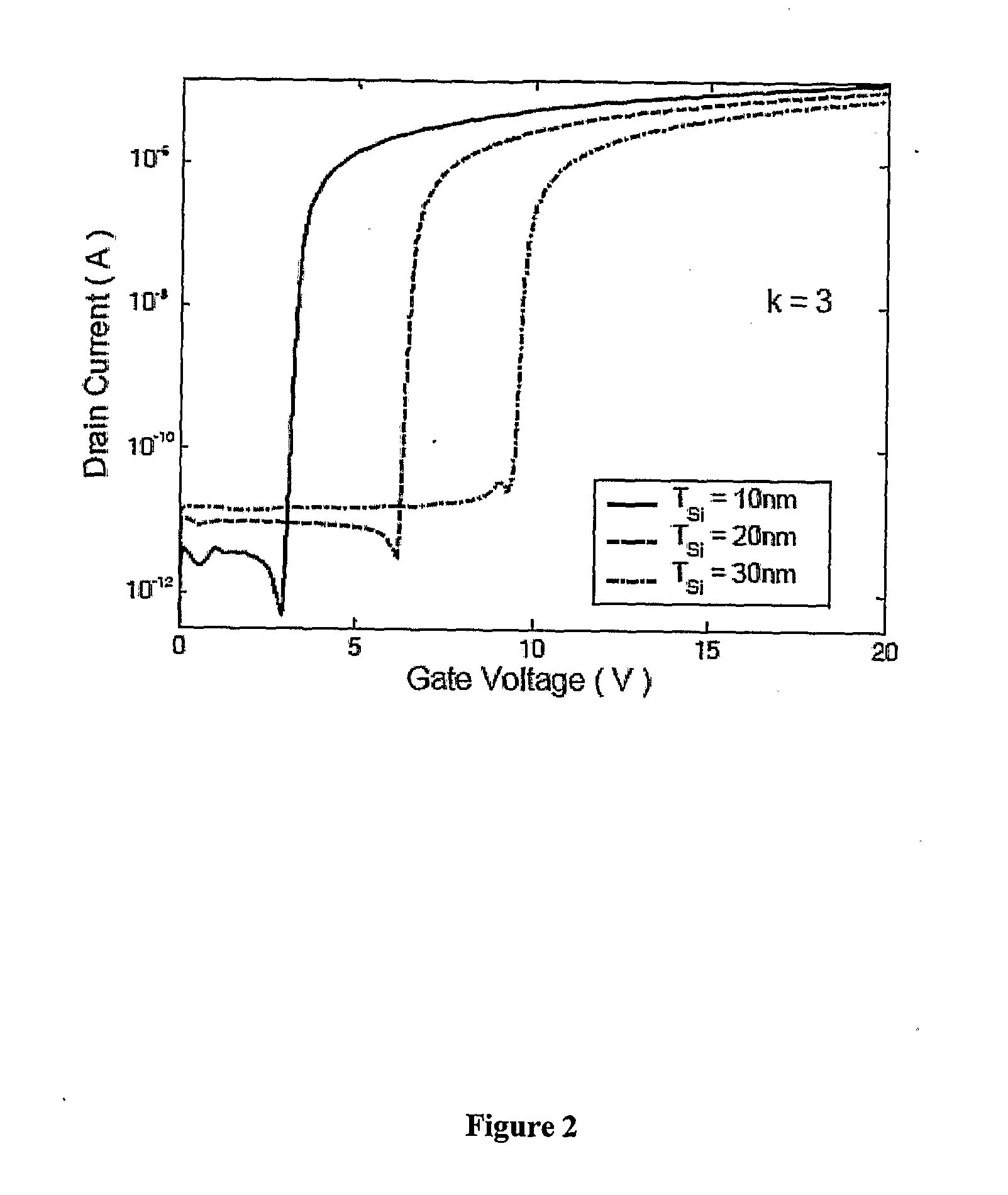

Sub-Threshold Capfet Sensor for Sensing Analyte, A Method and System Thereof

The present invention relates to high sensitivity chemical sensors, more particularly relates to high sensitivity chemical sensors which are capacitively coupled, FET based analyte sensors. A sub-threshold capacitively coupled Field Effect Transistor (CapFET) sensor for sensing an analyte comprises fixed dielectric placed on substrate of the CapFET and second dielectric sensitive to the analyte, placed between gate terminal of the CapFET and the fixed dielectric, wherein presence of the analyte alters either dielectric constant of the second dielectric or work function of the gate.

Owner:INDIAN INSTITUTE OF SCIENCE

Tunable gate electrode work function material for transistor applications

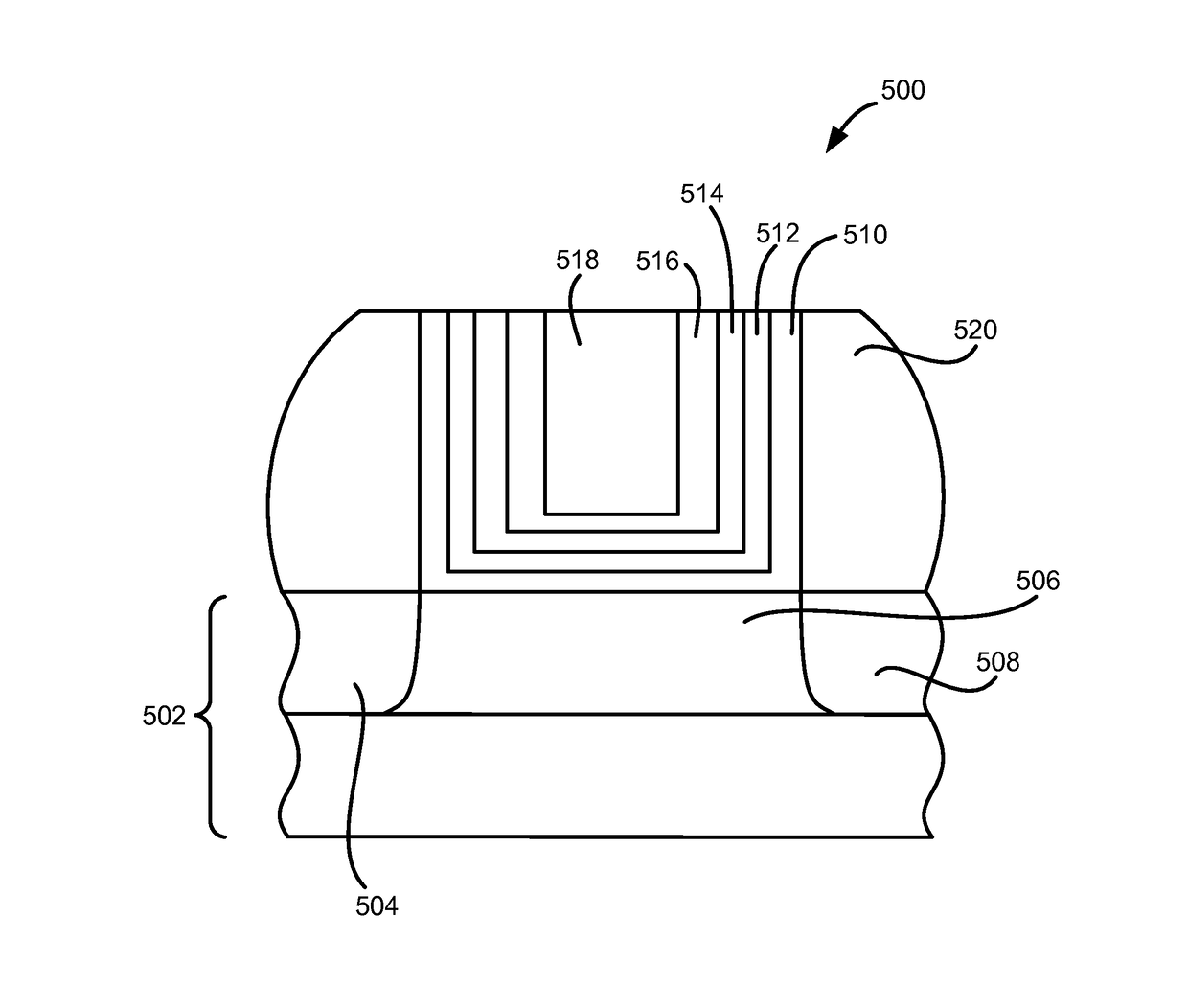

Described herein are metal gate electrode stacks including a low resistance metal cap in contact with a metal carbonitride diffusion barrier layer, wherein the metal carbonitride diffusion barrier layer is tuned to a particular work function to also serve as a work function metal for a pMOS transistor. In an embodiment, the work function-tuned metal carbonitride diffusion barrier prohibits a low resistance metal cap layer of the gate electrode stack from migrating into the MOS junction. In a further embodiment of the present invention, the work function of the metal carbonitride barrier film is modulated to be p-type with a pre-selected work function by altering a nitrogen concentration in the film.

Owner:TAHOE RES LTD

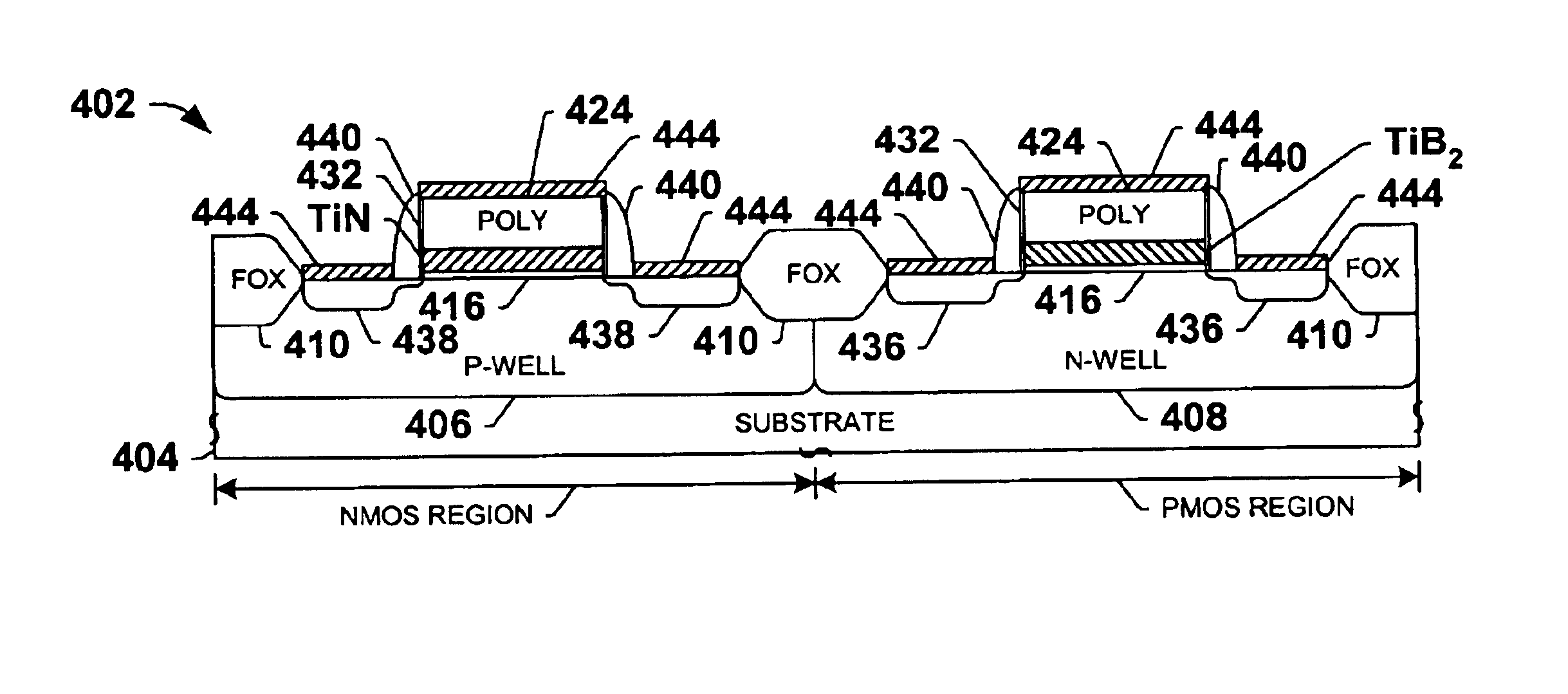

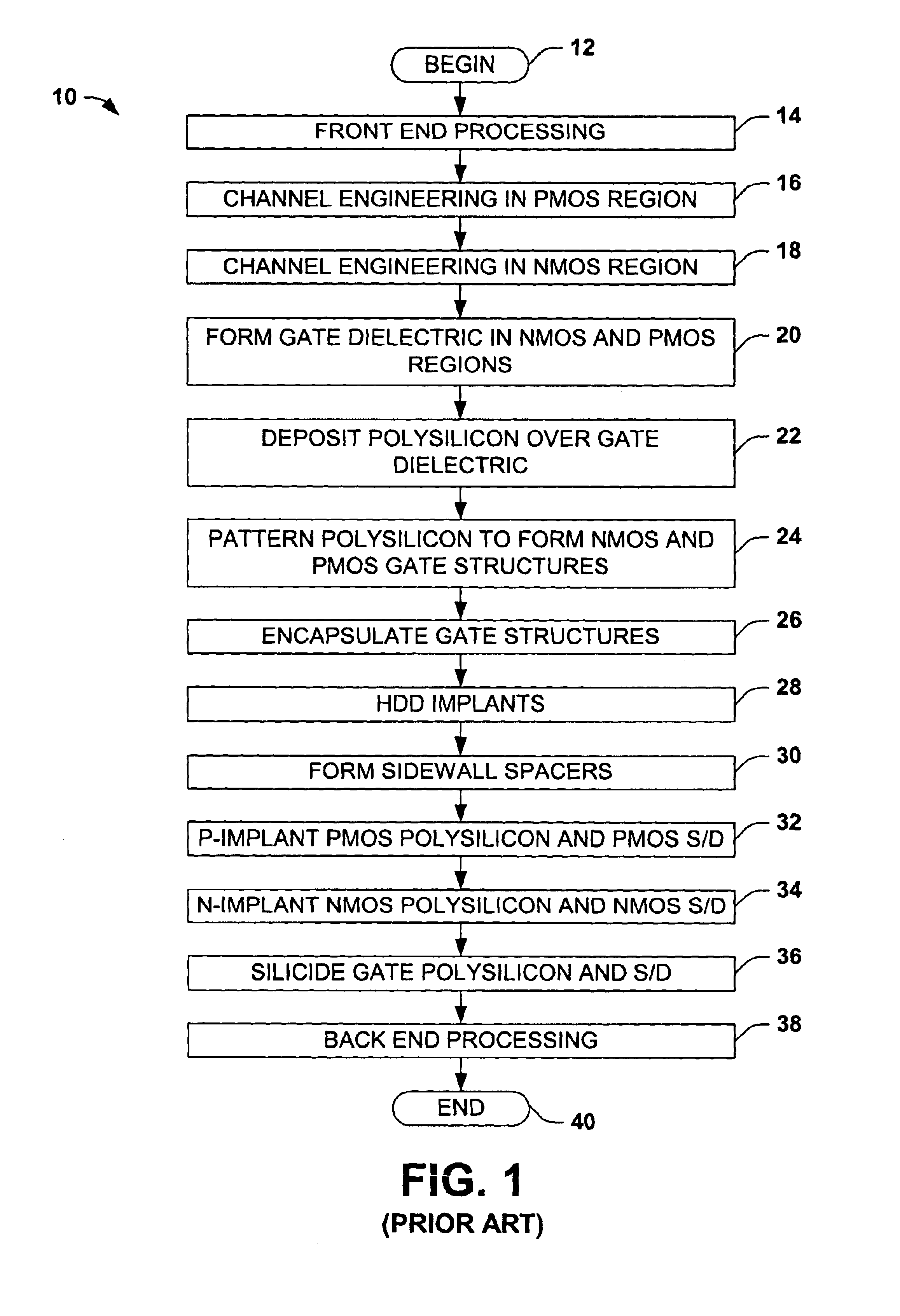

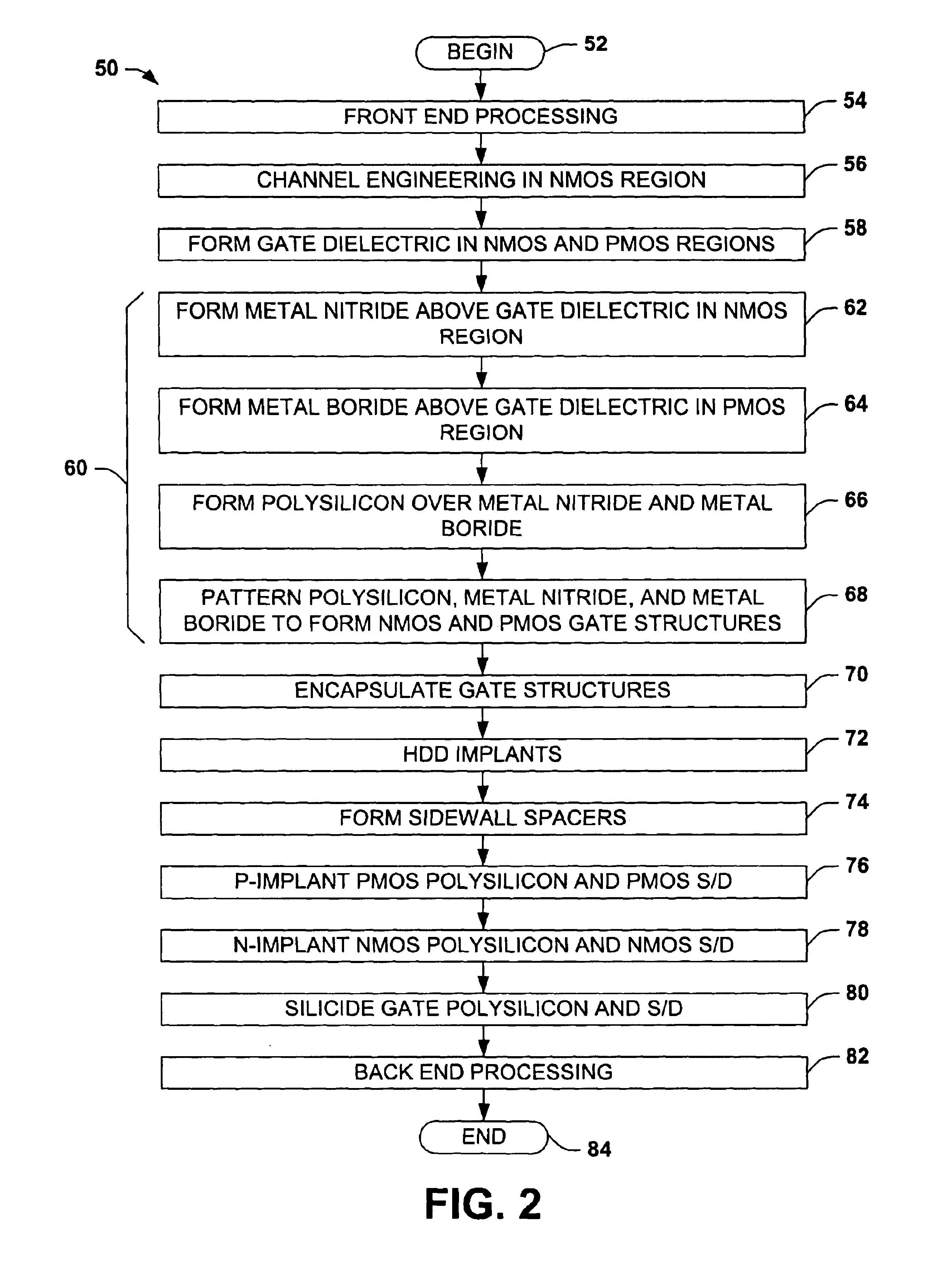

Metal gate MOS transistors and methods for making the same

InactiveUS6936508B2Less dopantsReduce complexitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNitrogen

Semiconductor devices and fabrication methods are provided, in which metal transistor gates are provided for MOS transistors. Metal boride is formed above a gate dielectric to create PMOS gate structures and metal nitride is formed over a gate dielectric to provide NMOS gate structures. The metal portions of the gate structures are formed from an initial starting material that is either a metal boride or a metal nitride, after which the starting material is provided with boron or nitrogen in one of the PMOS and NMOS regions through implantation, diffusion, or other techniques, either before or after formation of the conductive upper material, and before or after gate patterning. The change in the boron or nitrogen content of the starting material provides adjustment of the material work function, thereby tuning the threshold voltage of the resulting PMOS or NMOS transistors.

Owner:TEXAS INSTR INC

Crosspoint resistor memory device with back-to-back Schottky diodes

InactiveUS20070015348A1Inhibit currentHigh voltageSolid-state devicesSemiconductor/solid-state device manufacturingWork functionAmorphous silicon

A metal / semiconductor / metal (MSM) back-to-back Schottky diode, a resistance memory device using the MSM diode, and associated fabrication processes are provided. The method includes: providing a substrate; forming a metal bottom electrode overlying the substrate, having a first work function; forming a semiconductor layer overlying the metal bottom electrode, having a second work function, less than the first work function; and, forming a metal top electrode overlying the semiconductor layer, having a third work function, greater than the second work function. The metal top and bottom electrodes can be materials such as Pt, Au, Ag, TiN, Ta, Ru, or TaN. In one aspect, the metal top electrode and metal bottom electrode are made from the same material and, therefore, have identical work functions. The semiconductor layer can be a material such as amorphous silicon (a:Si), polycrystalline Si, InOx, or ZnO.

Owner:SHARP LAB OF AMERICA INC

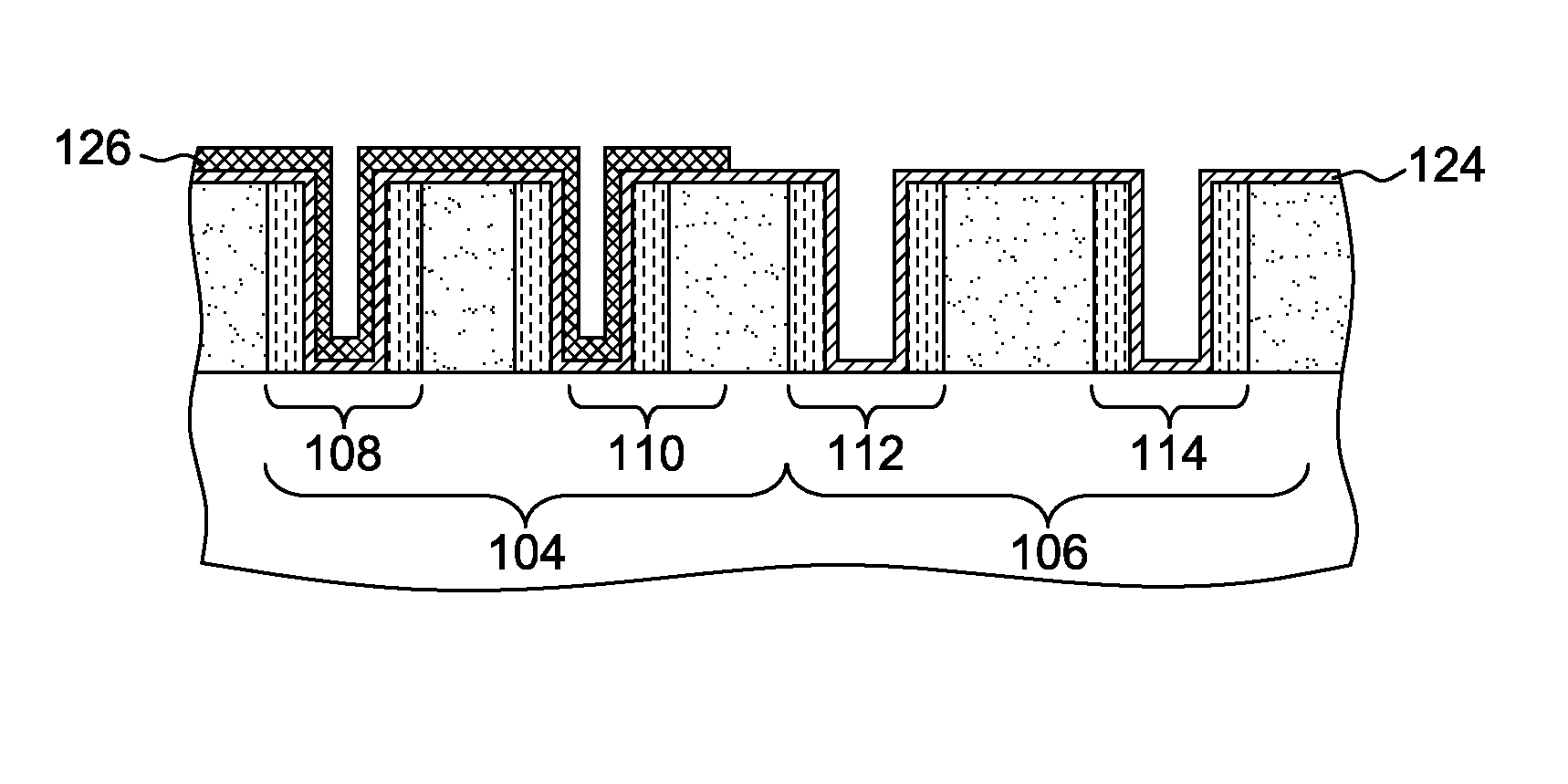

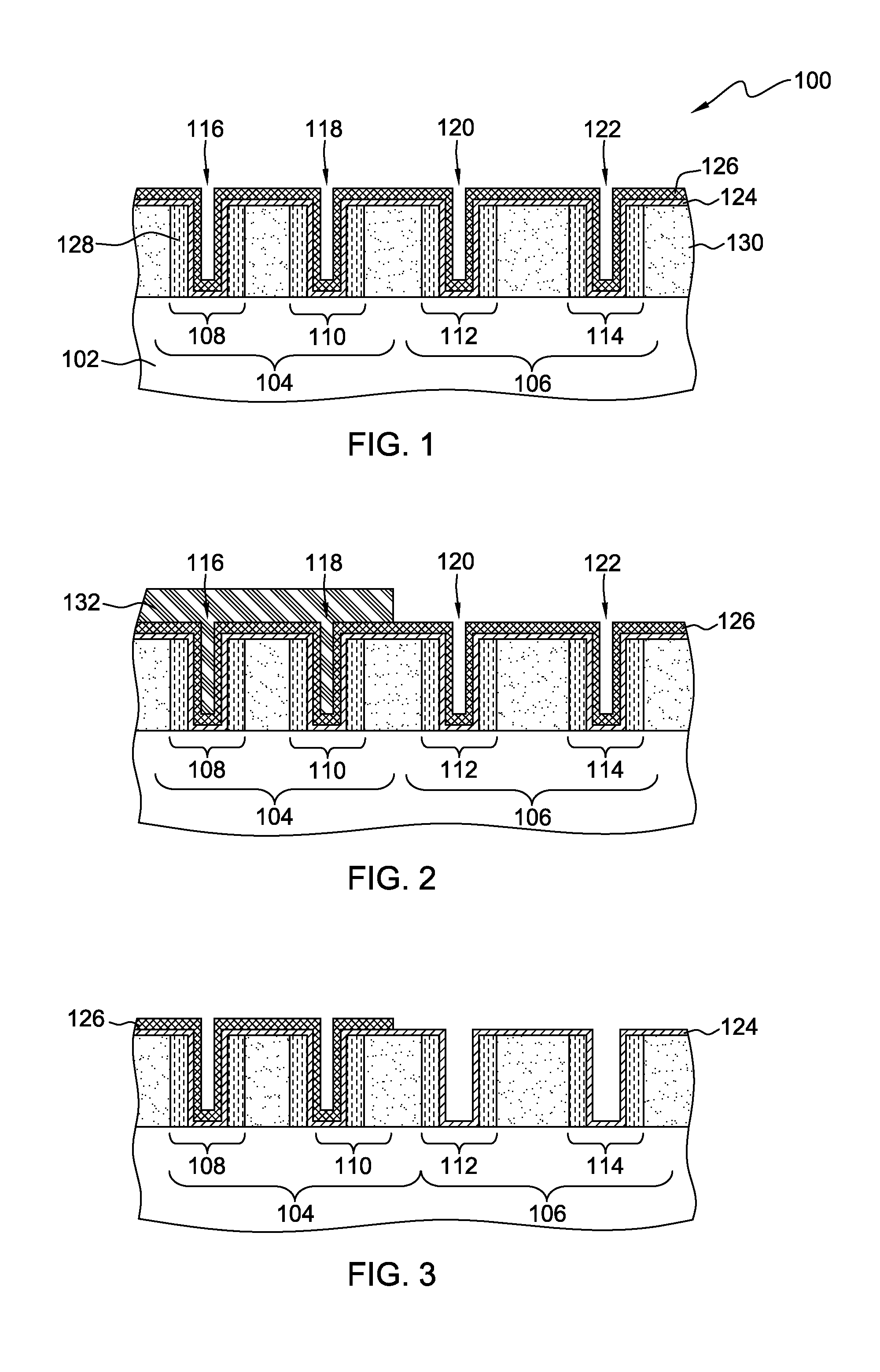

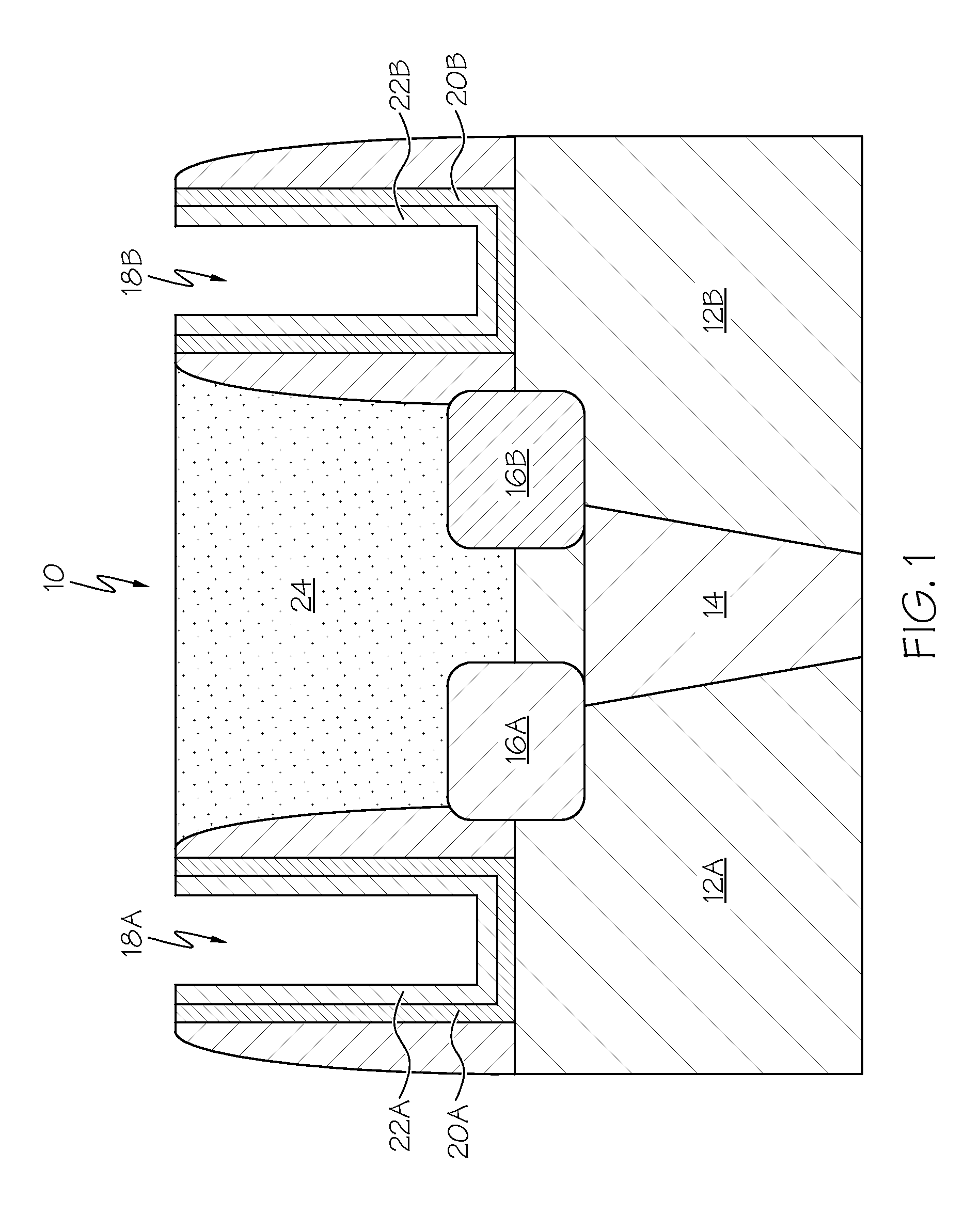

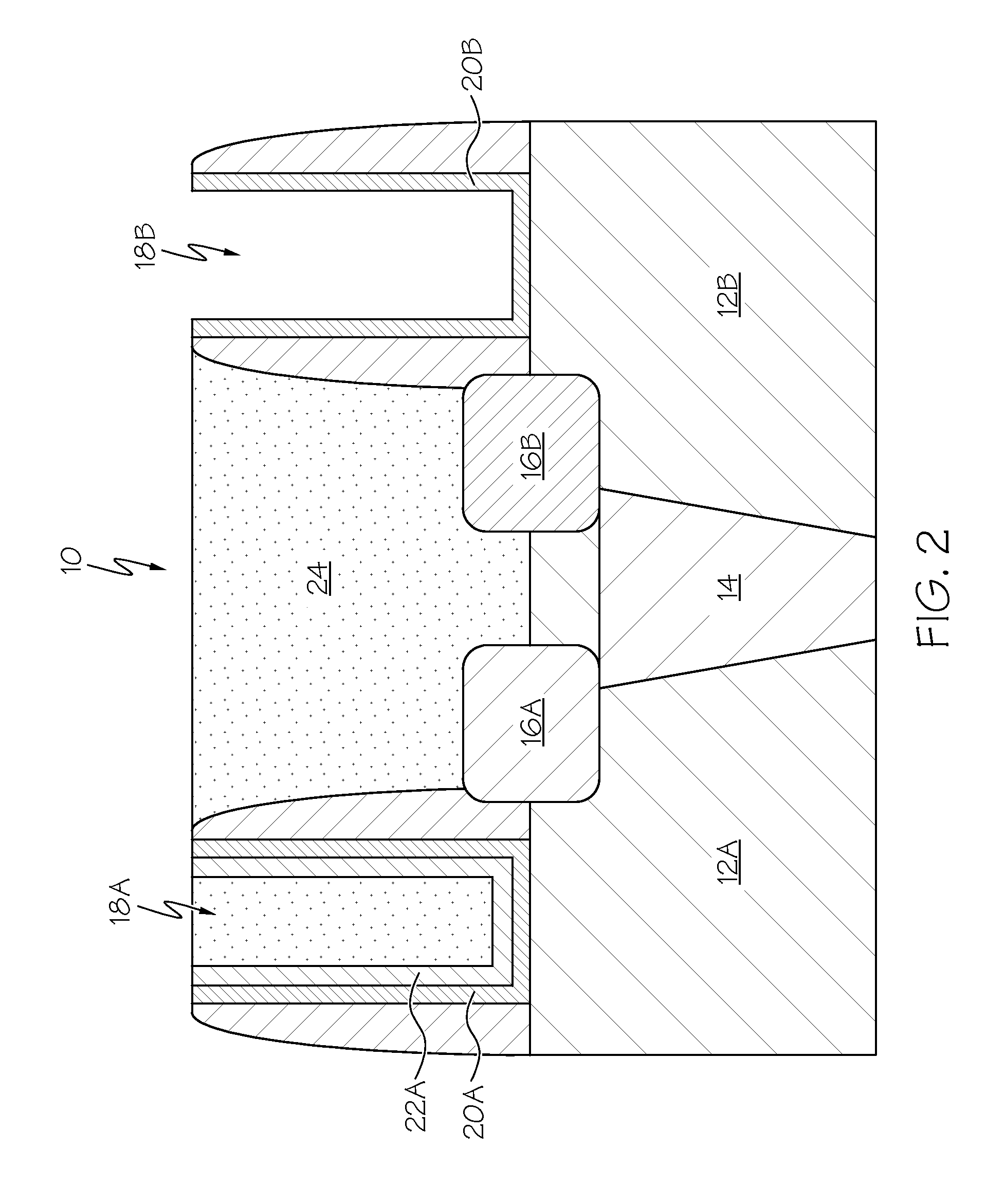

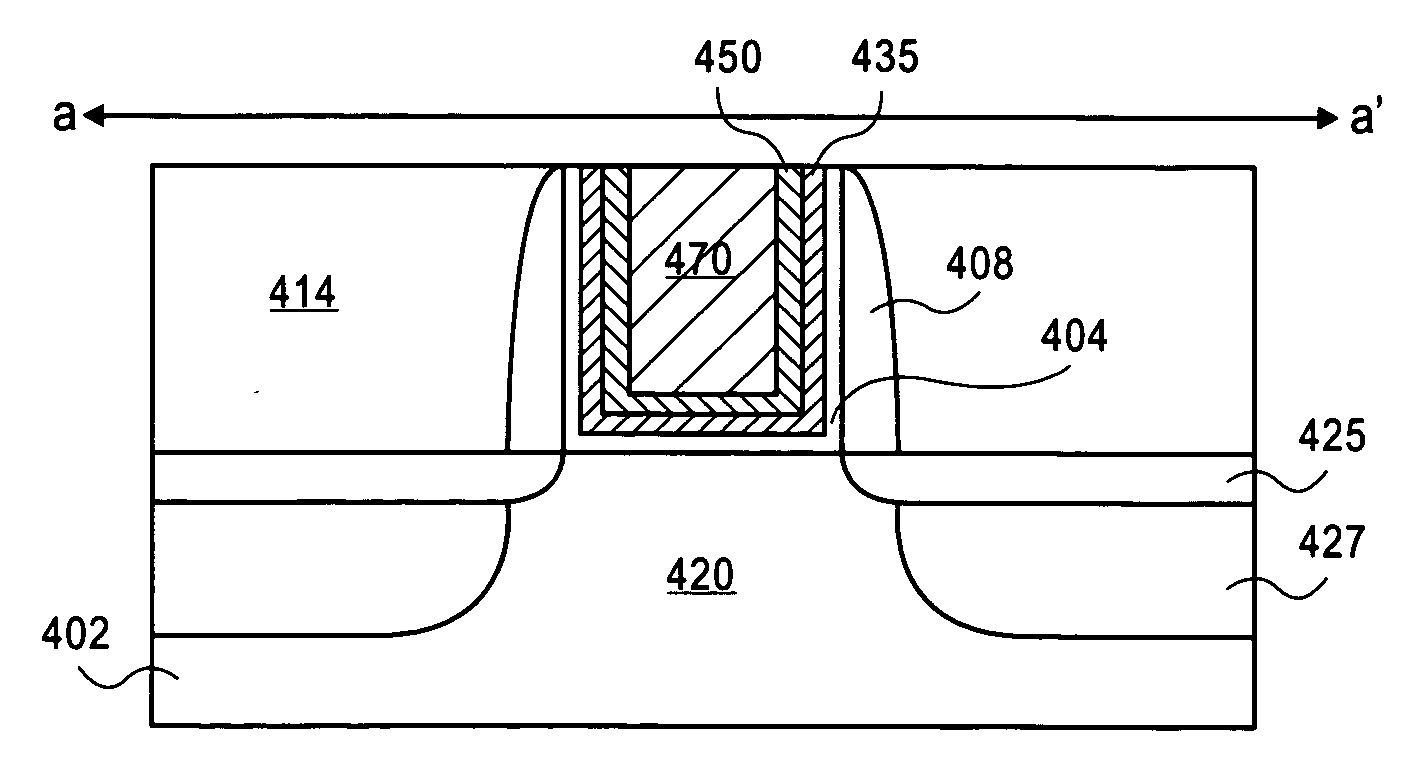

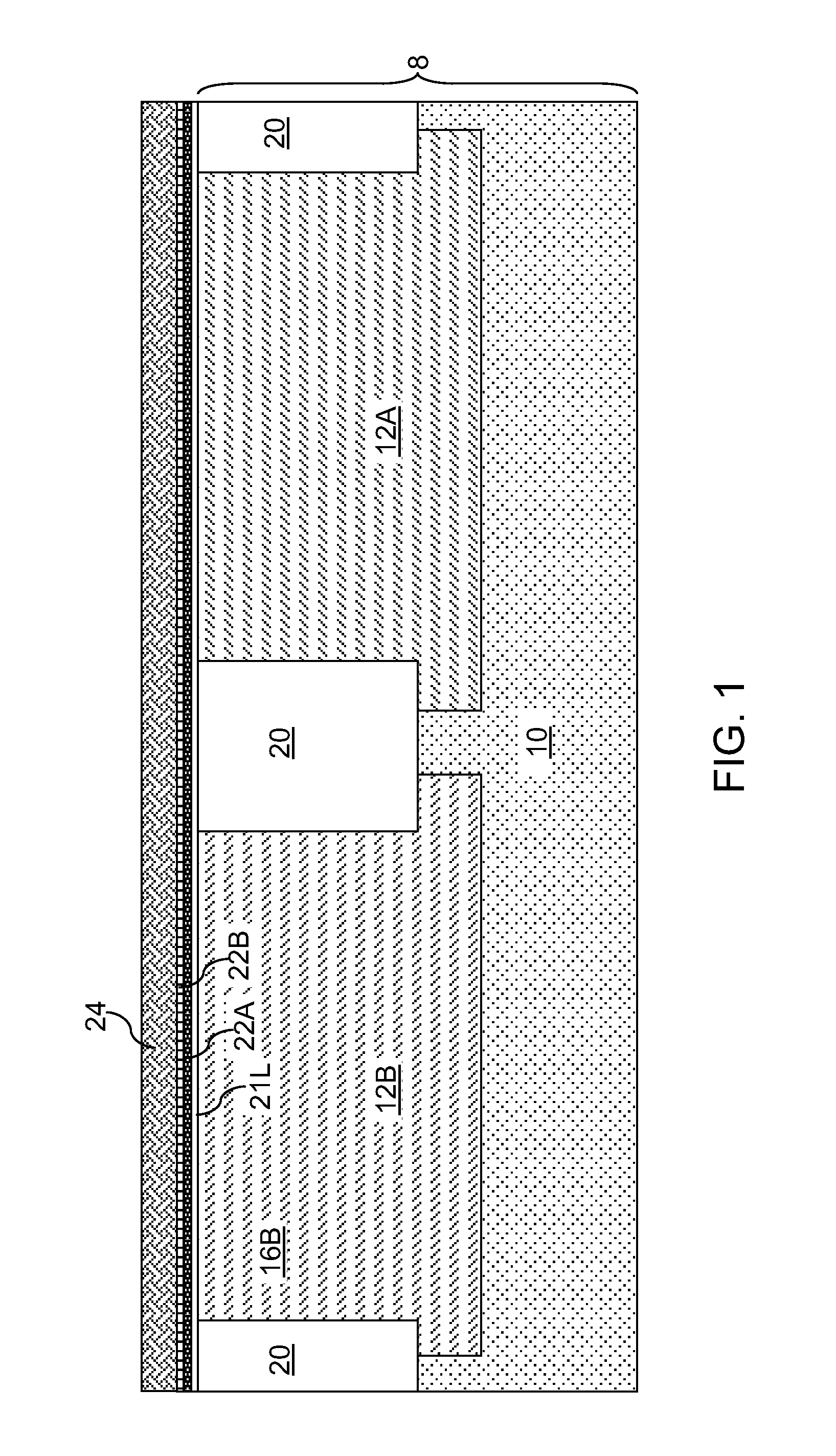

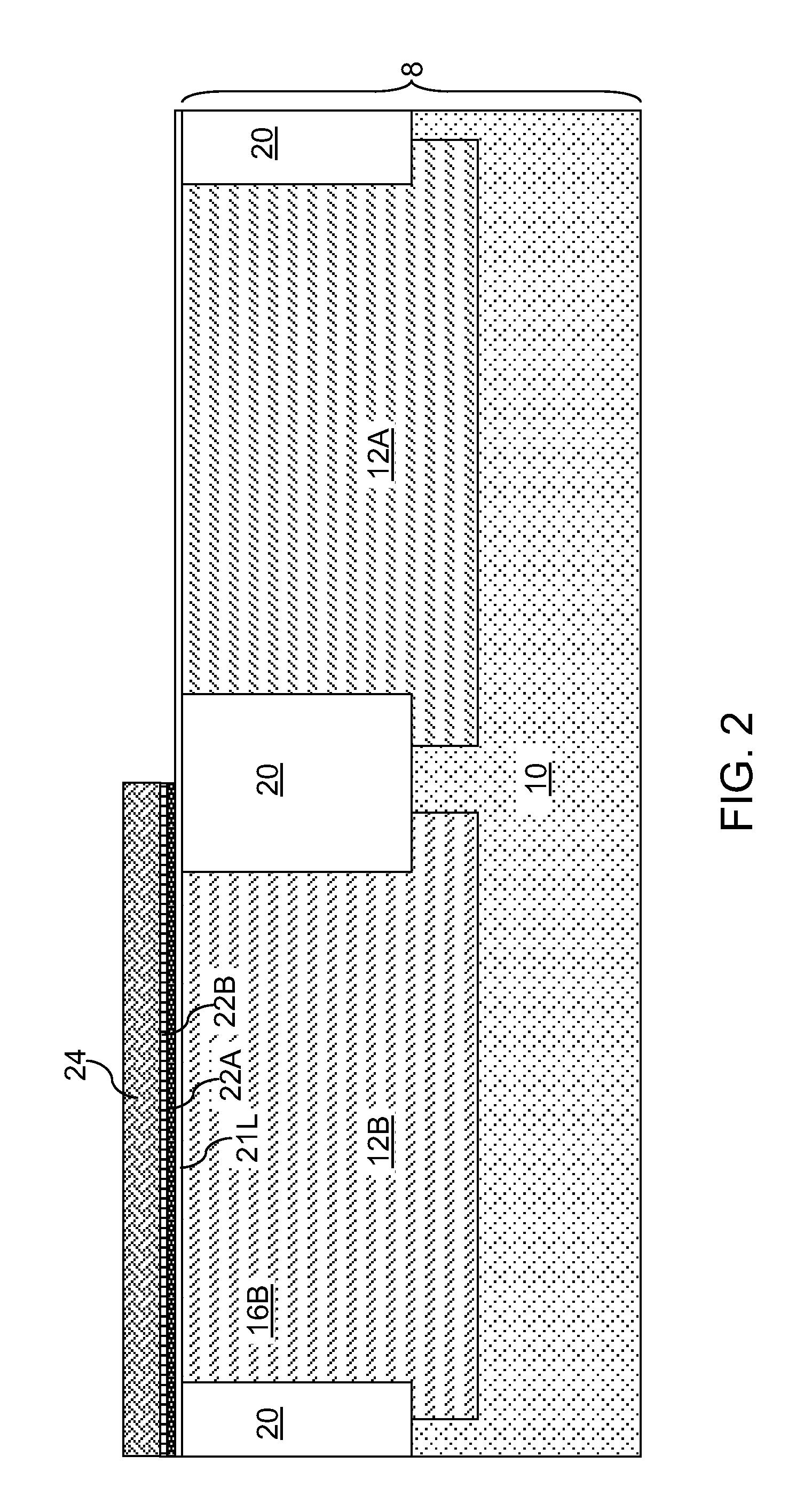

Replacement Metal Gate Structures Providing Independent Control On Work Function and Gate Leakage Current

The thickness and composition of a gate dielectric can be selected for different types of field effect transistors through a planar high dielectric constant material portion, which can be provided only for selected types of field effect transistors. Further, the work function of field effect transistors can be tuned independent of selection of the material stack for the gate dielectric. A stack of a barrier metal layer and a first-type work function metal layer is deposited on a gate dielectric layer within recessed gate cavities after removal of disposable gate material portions. After patterning the first-type work function metal layer, a second-type work function metal layer is deposited directly on the barrier metal layer in the regions of the second type field effect transistor. A conductive material fills the gate cavities, and a subsequent planarization process forms dual work function metal gate structures.

Owner:GLOBALFOUNDRIES INC

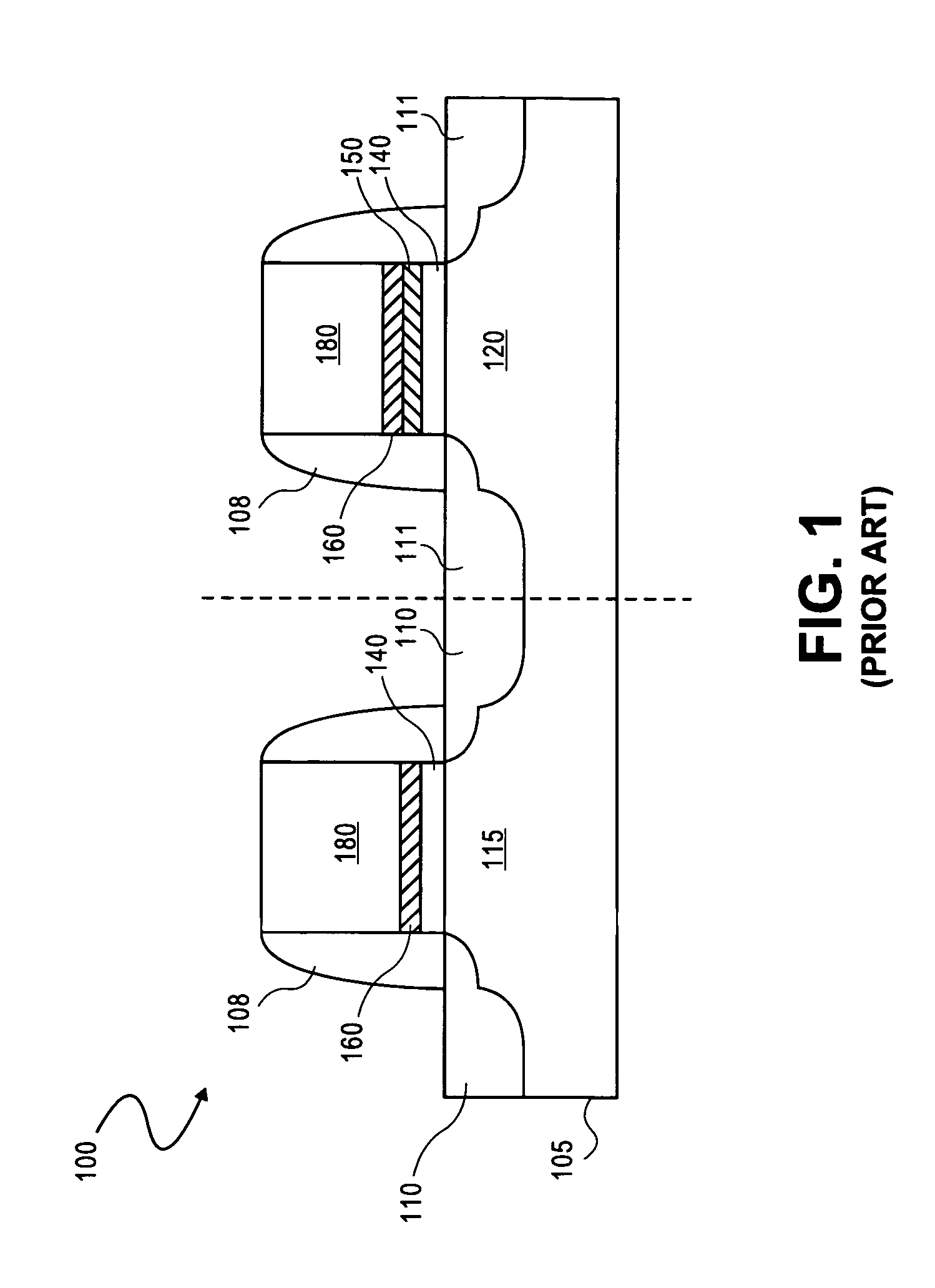

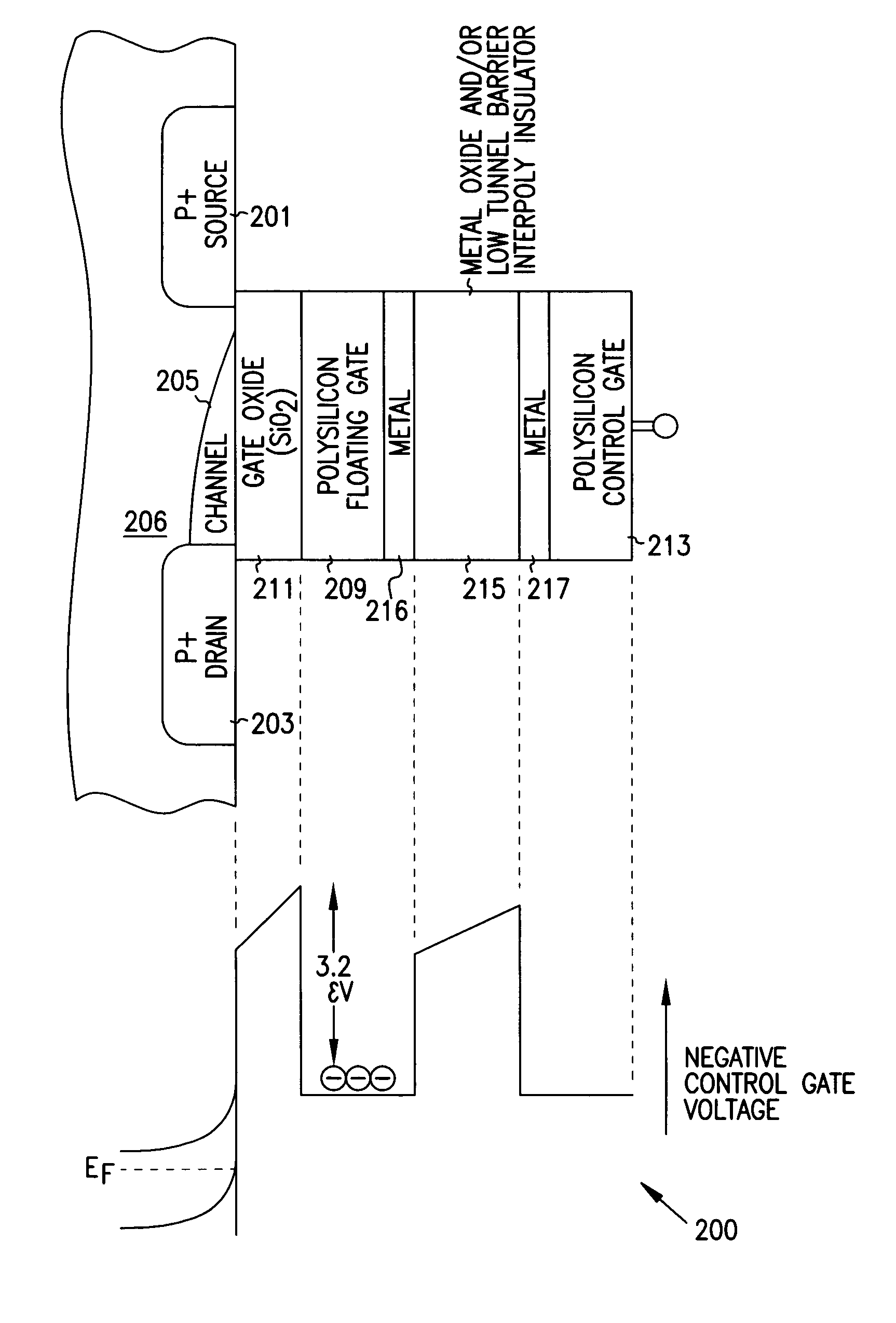

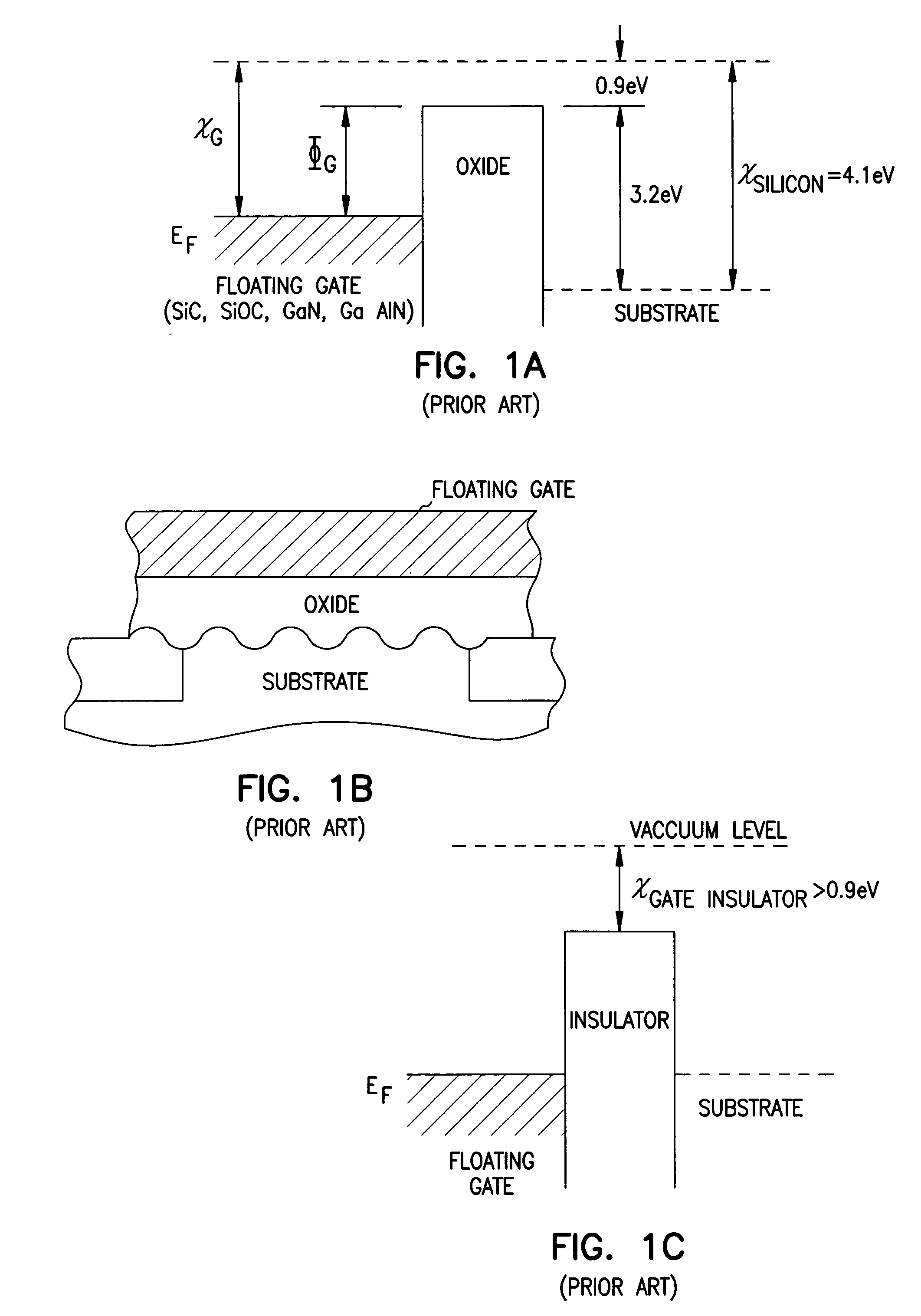

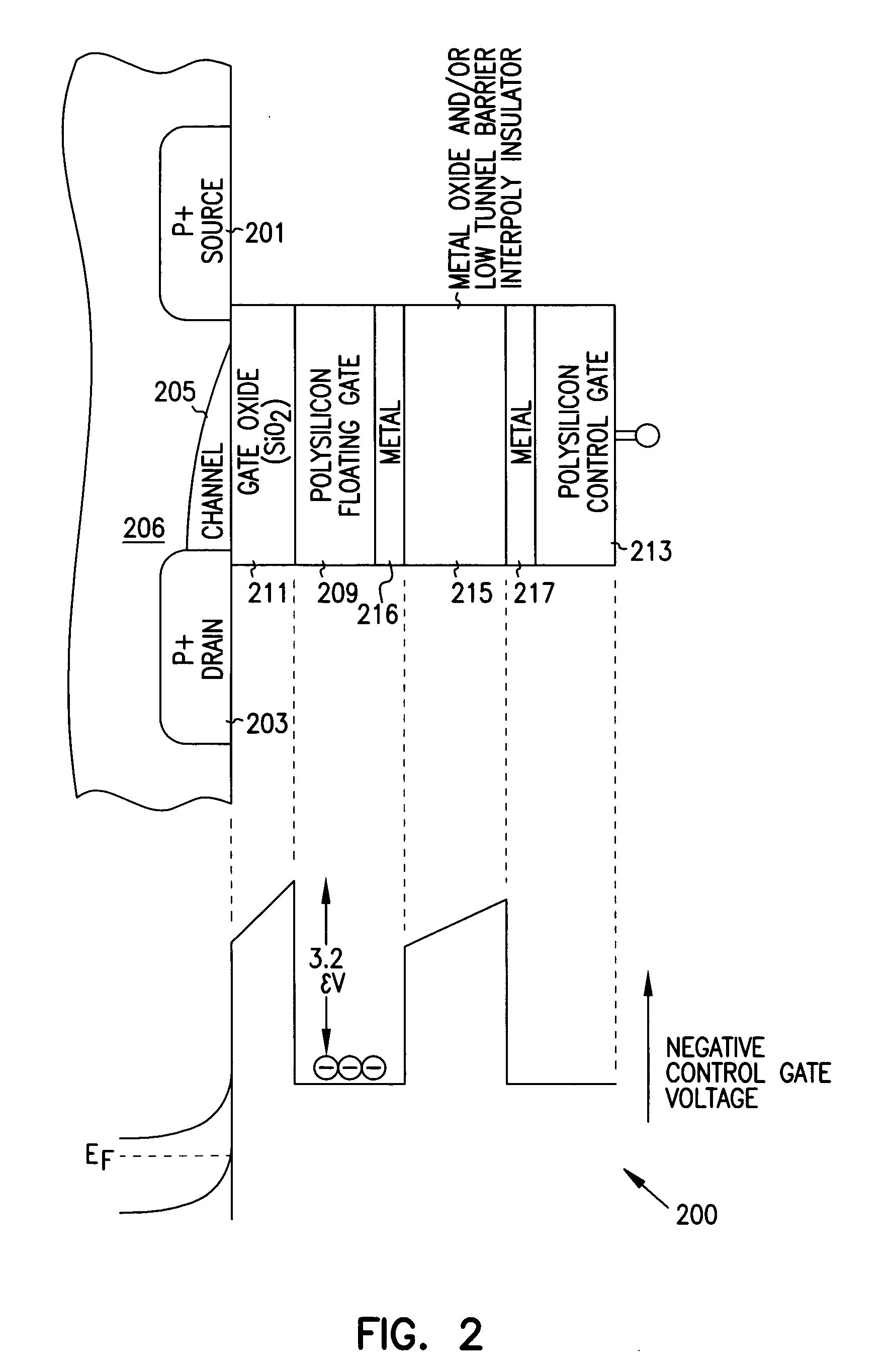

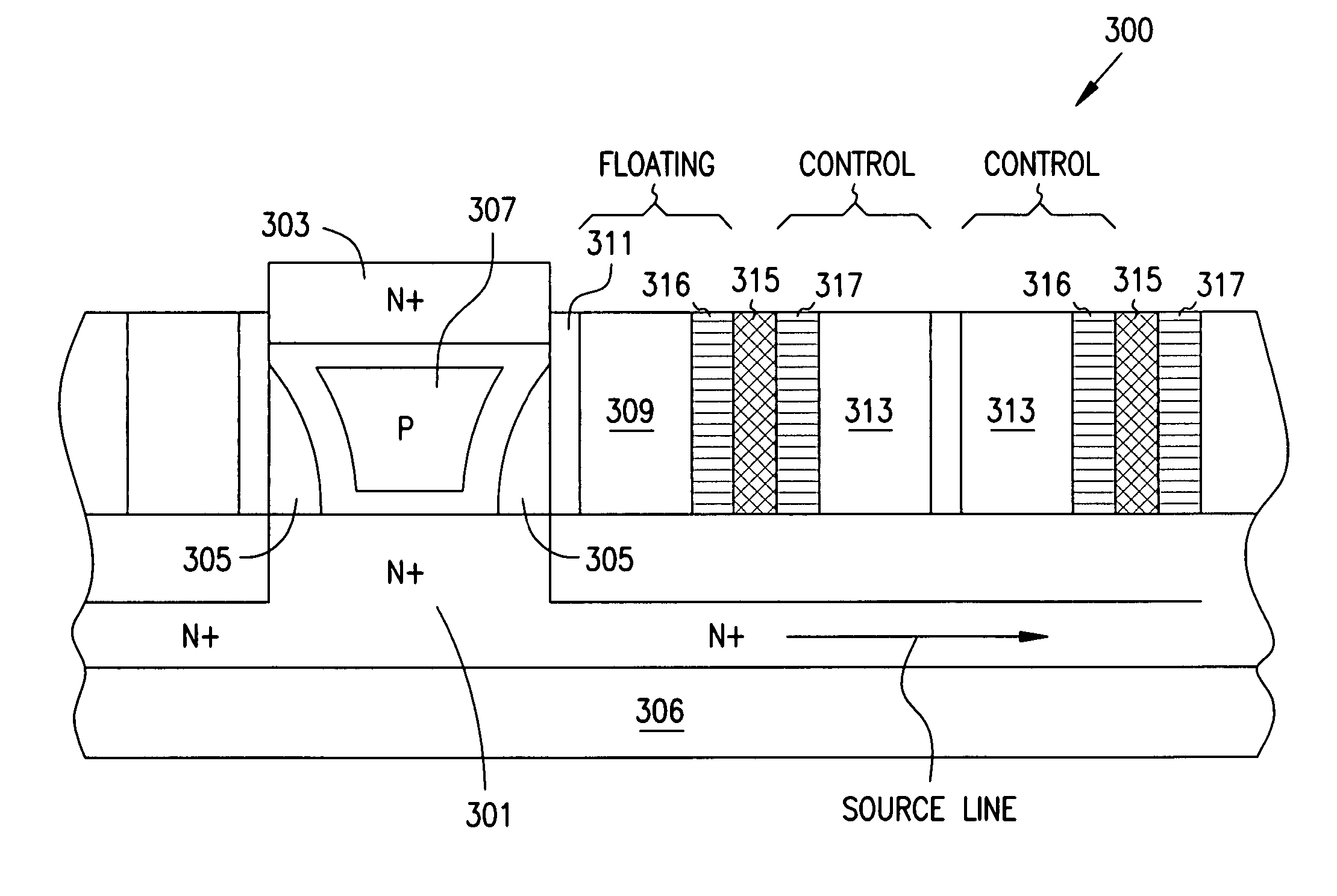

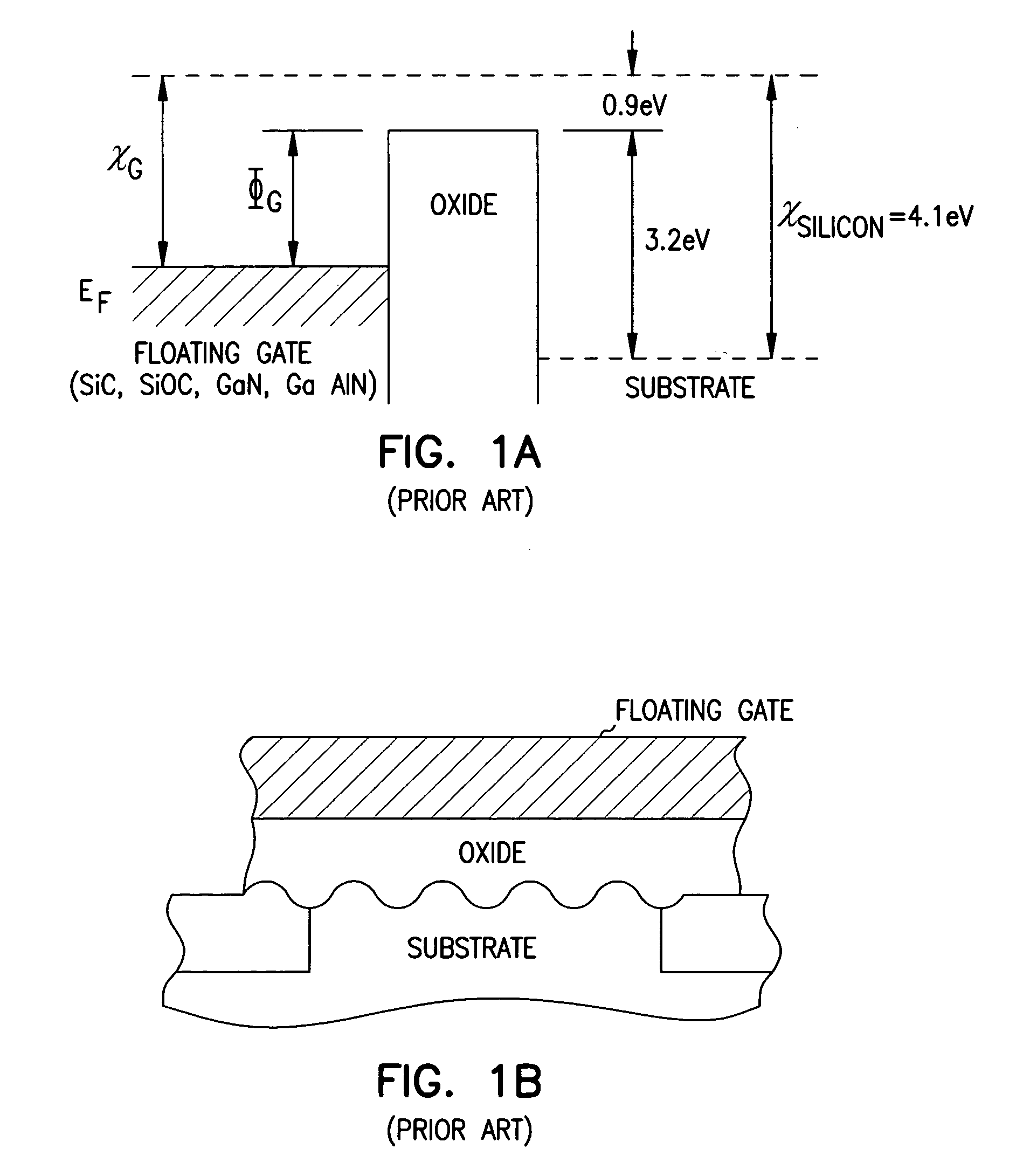

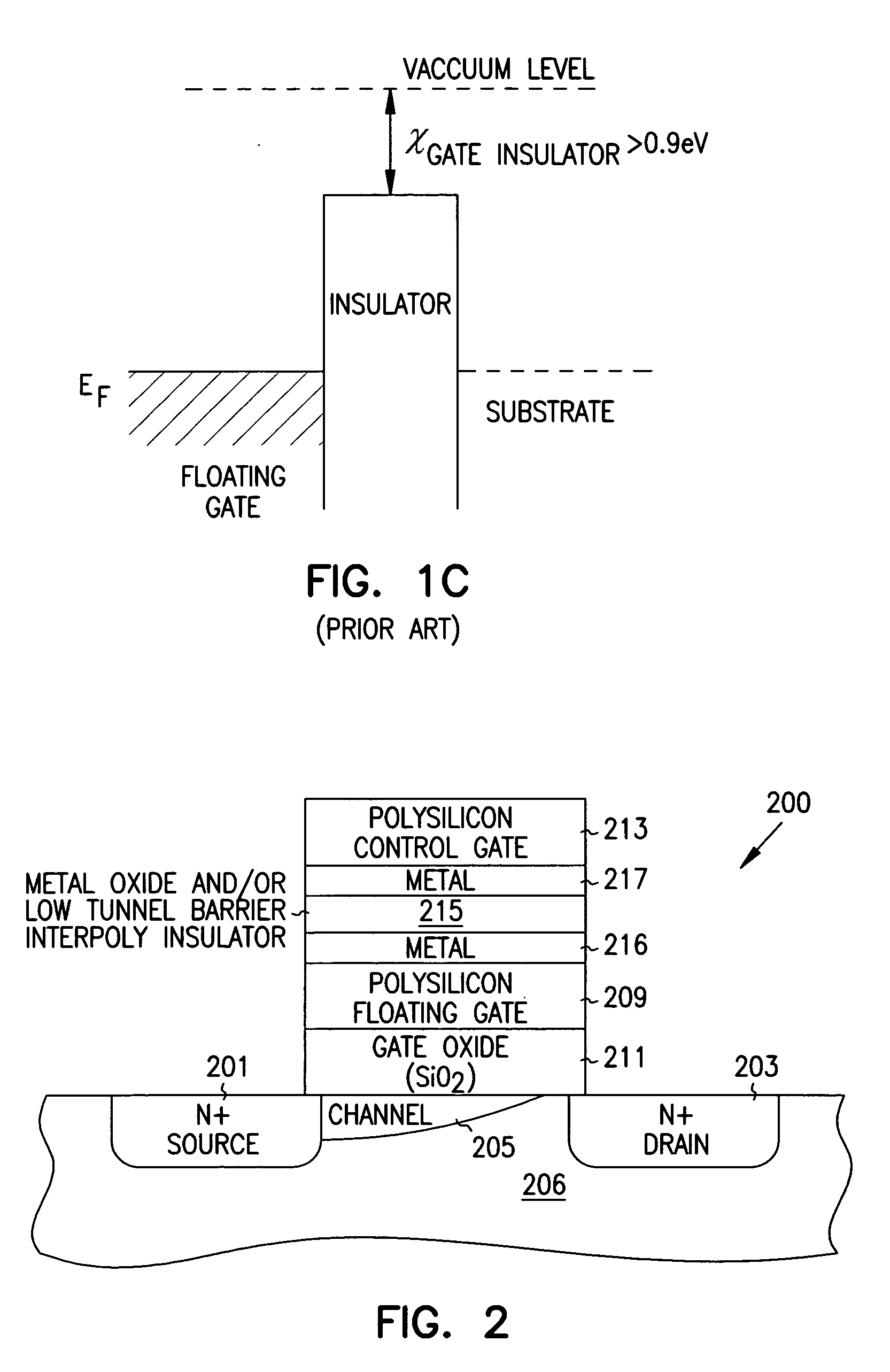

Programmable array logic or memory with p-channel devices and asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory with p-channel devices and asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include p-channel non-volatile memory which has a first source / drain region and a second source / drain region separated by a p-type channel region in an n-type substrate. A floating gate opposing the p-type channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

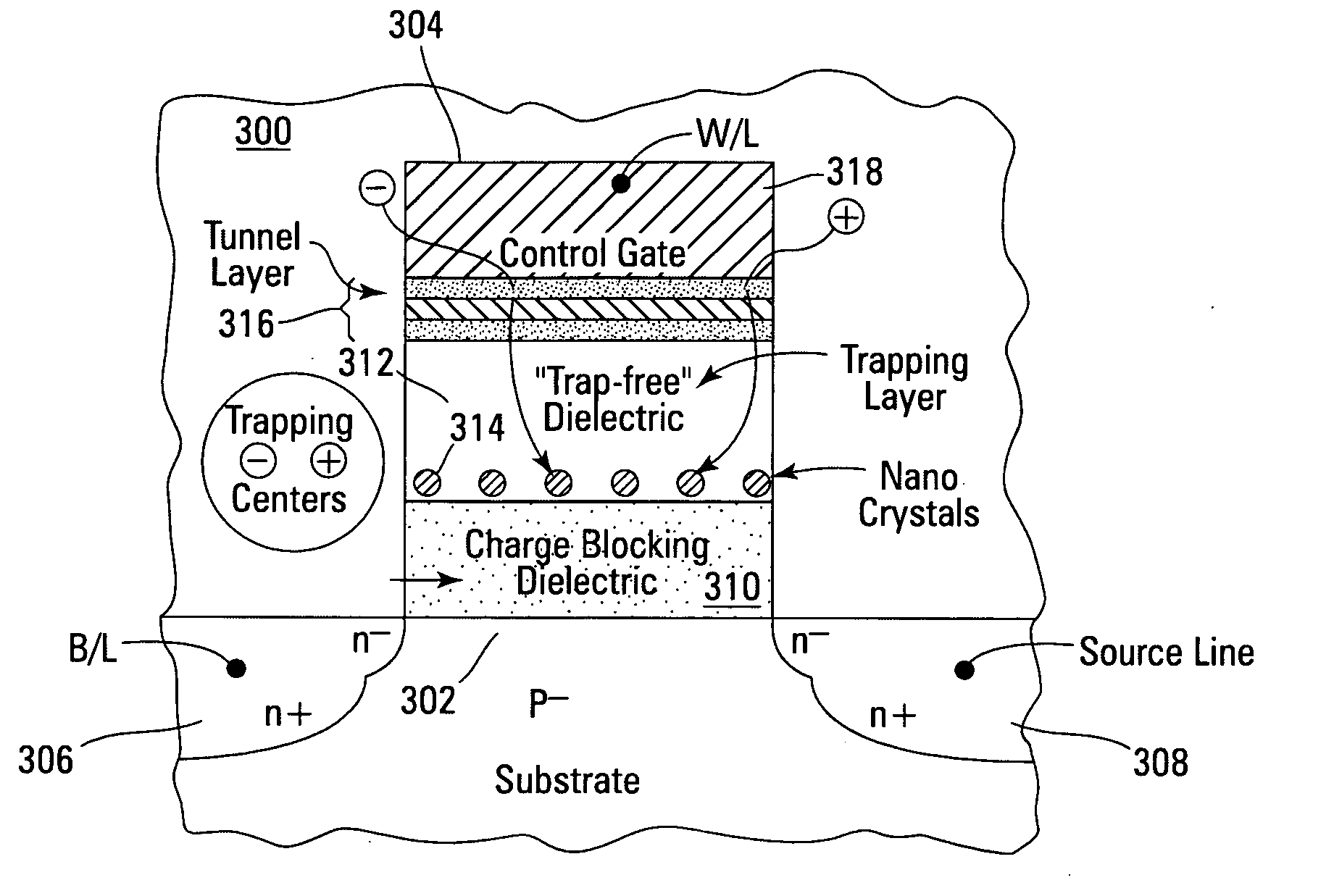

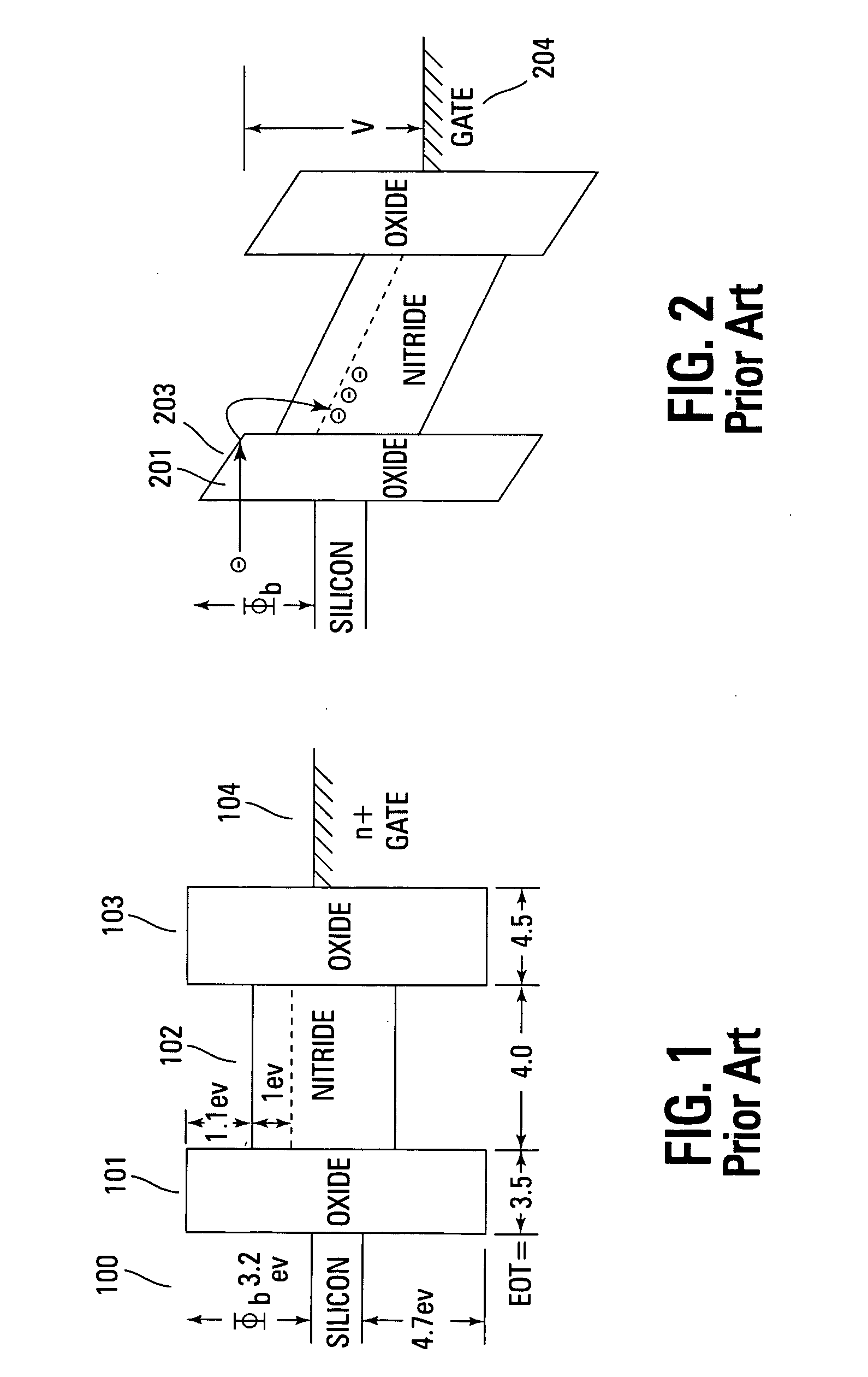

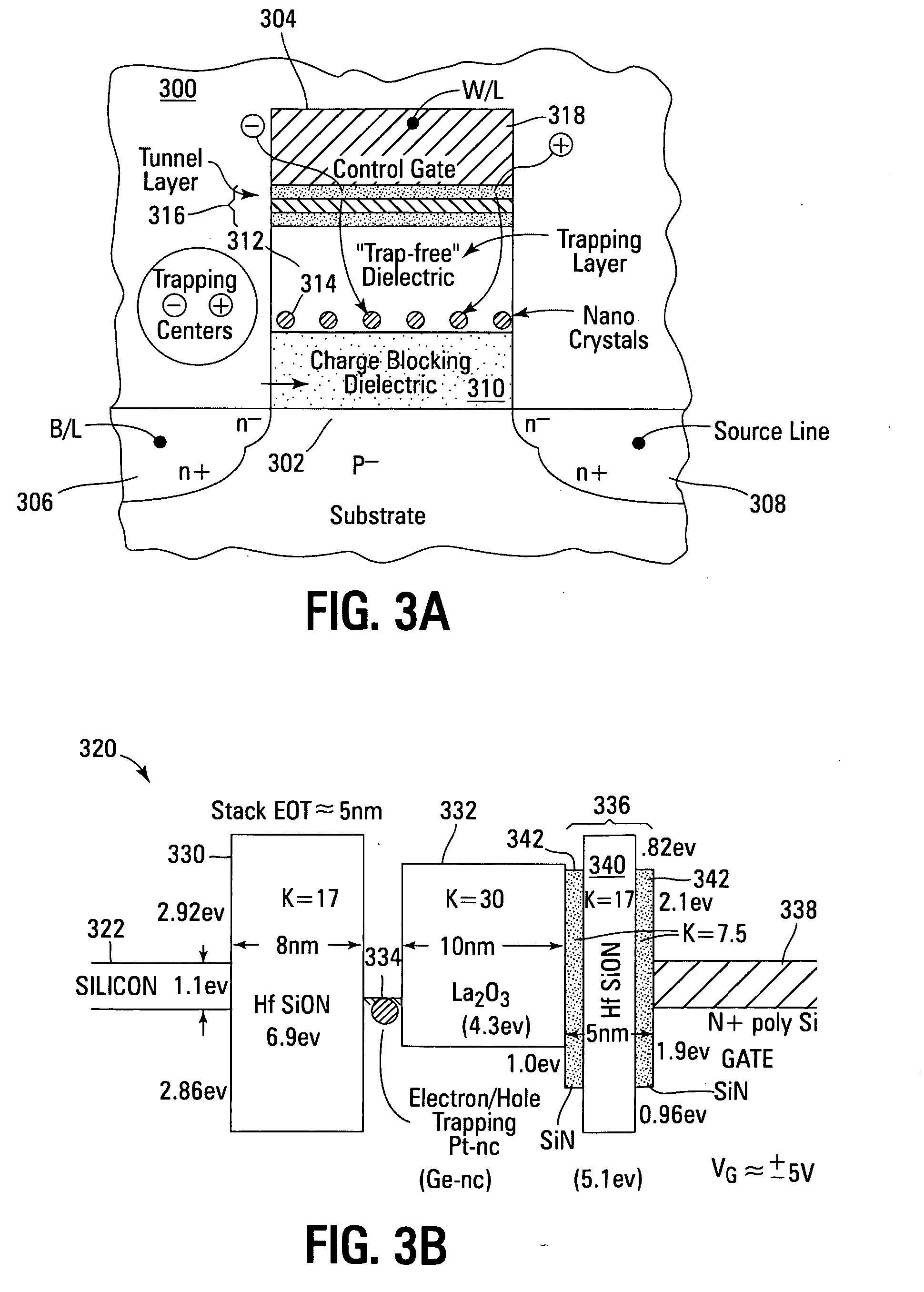

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

Programmable array logic or memory devices with asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com