Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

13137 results about "Semiconductor structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

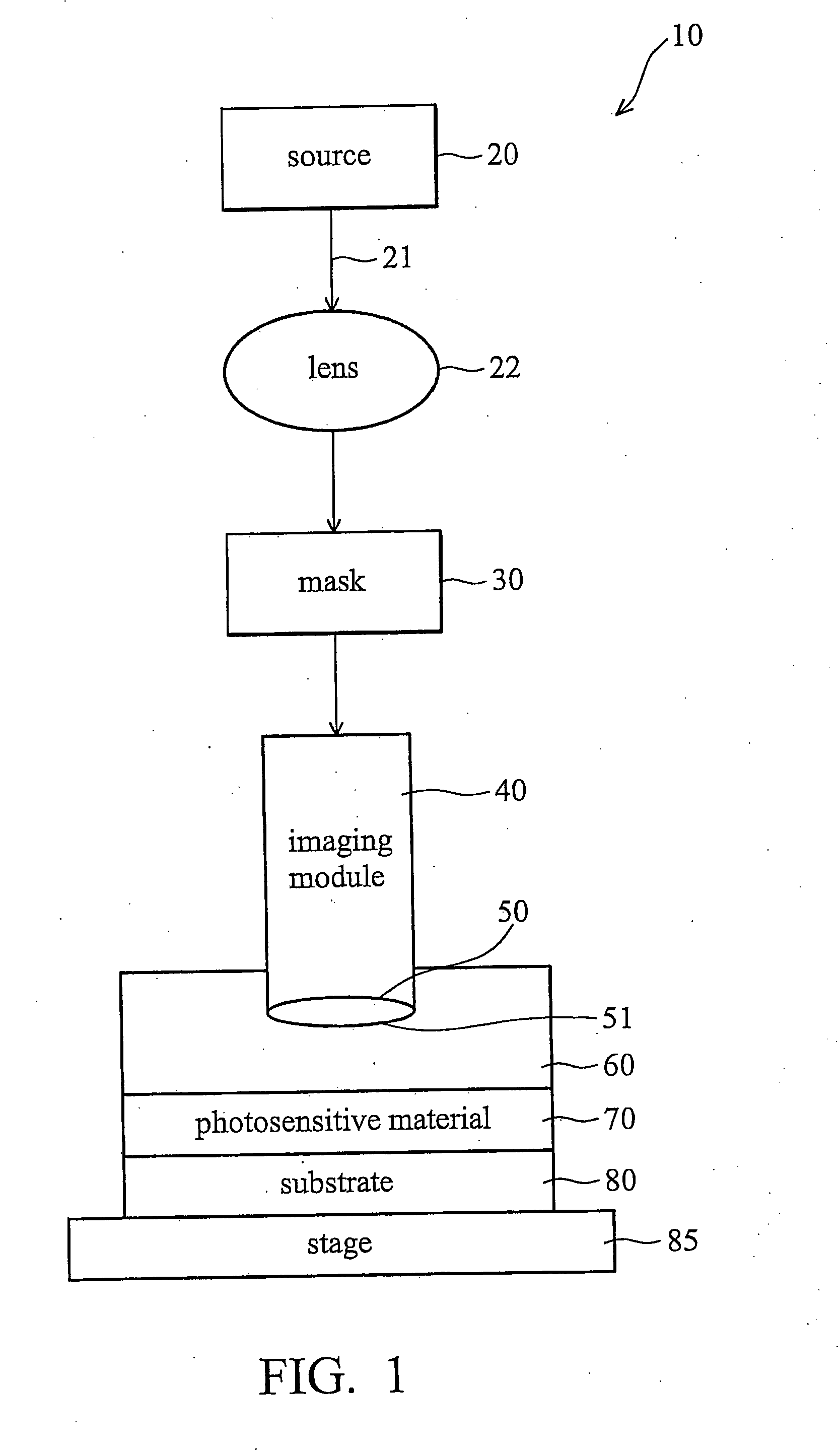

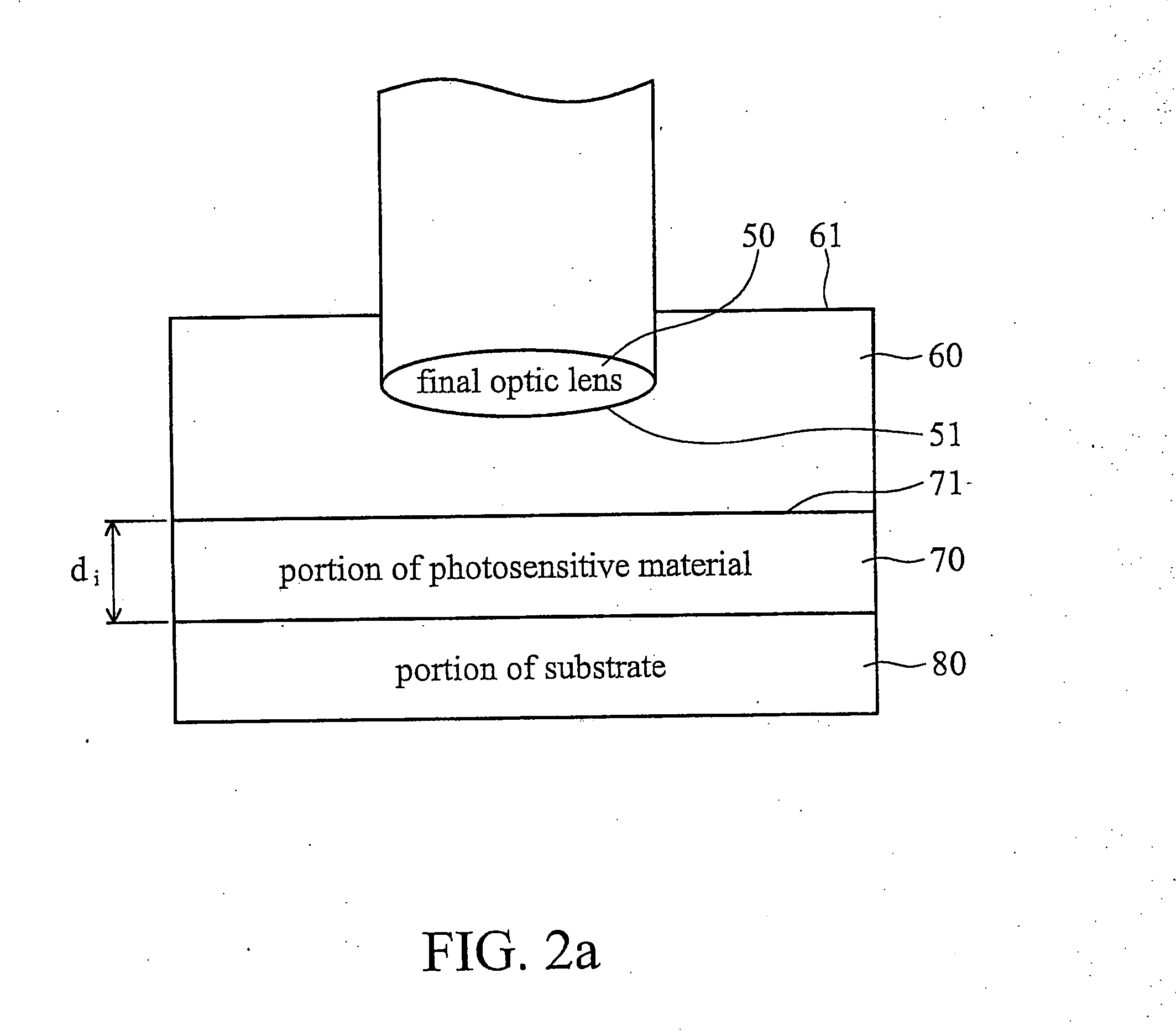

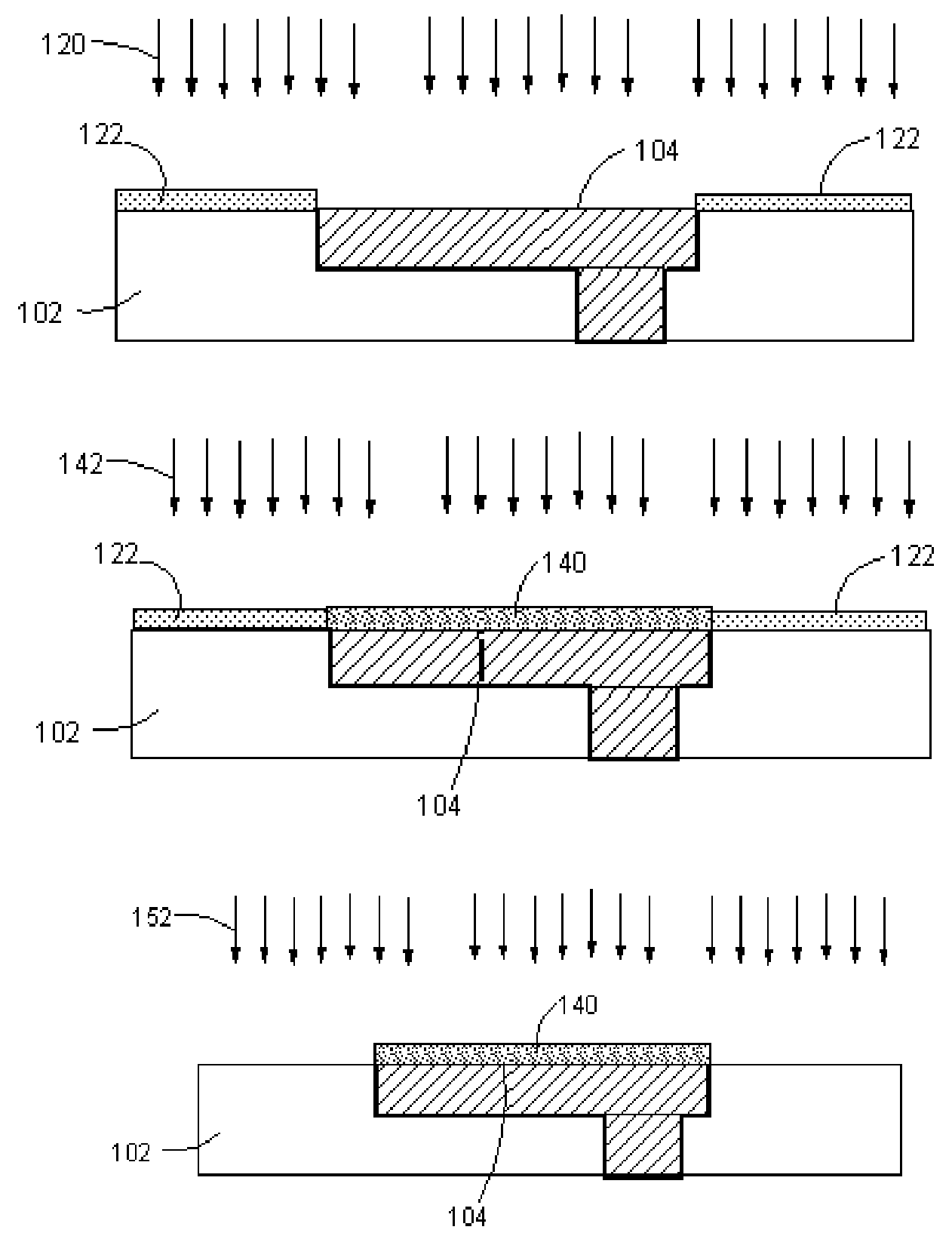

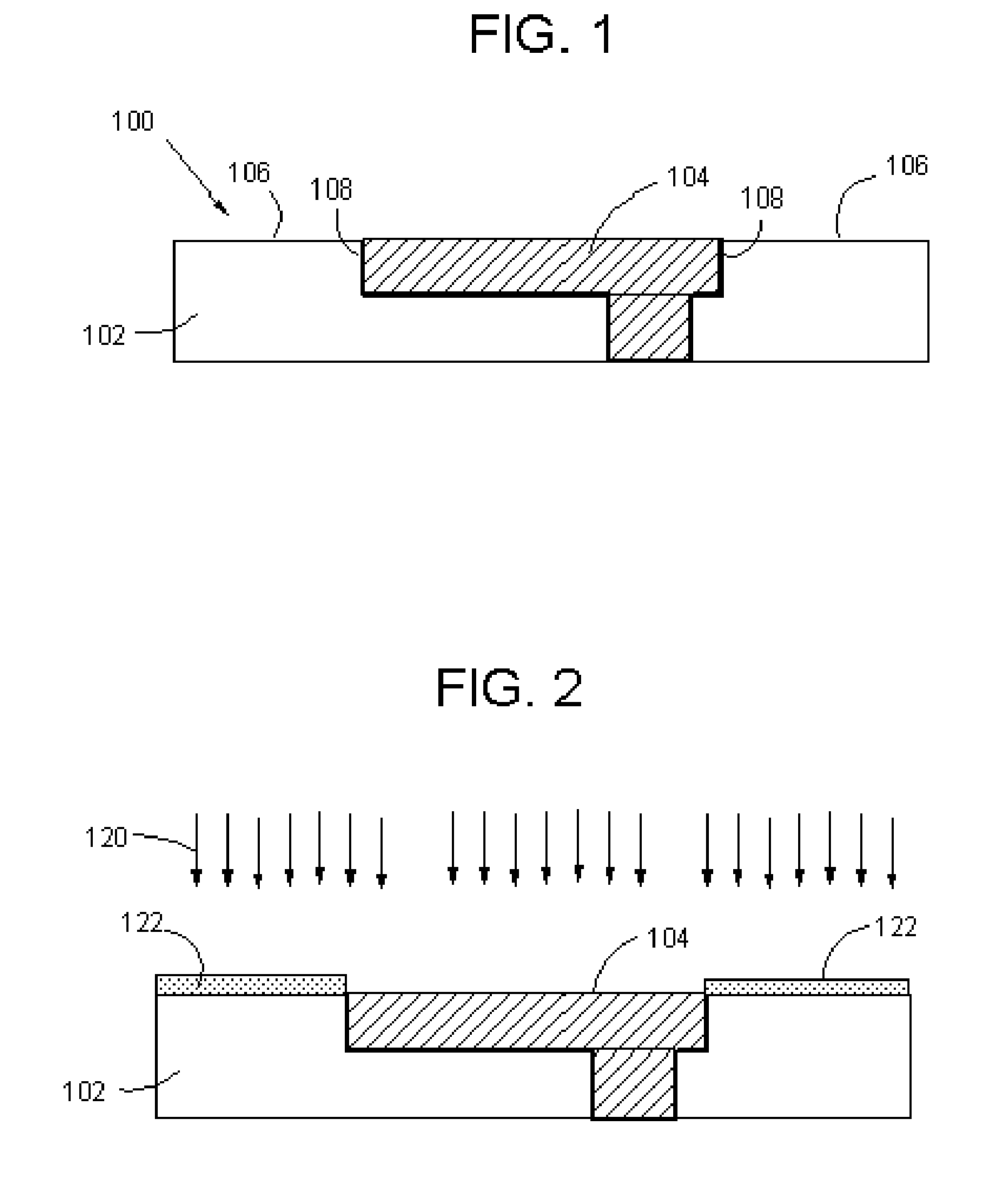

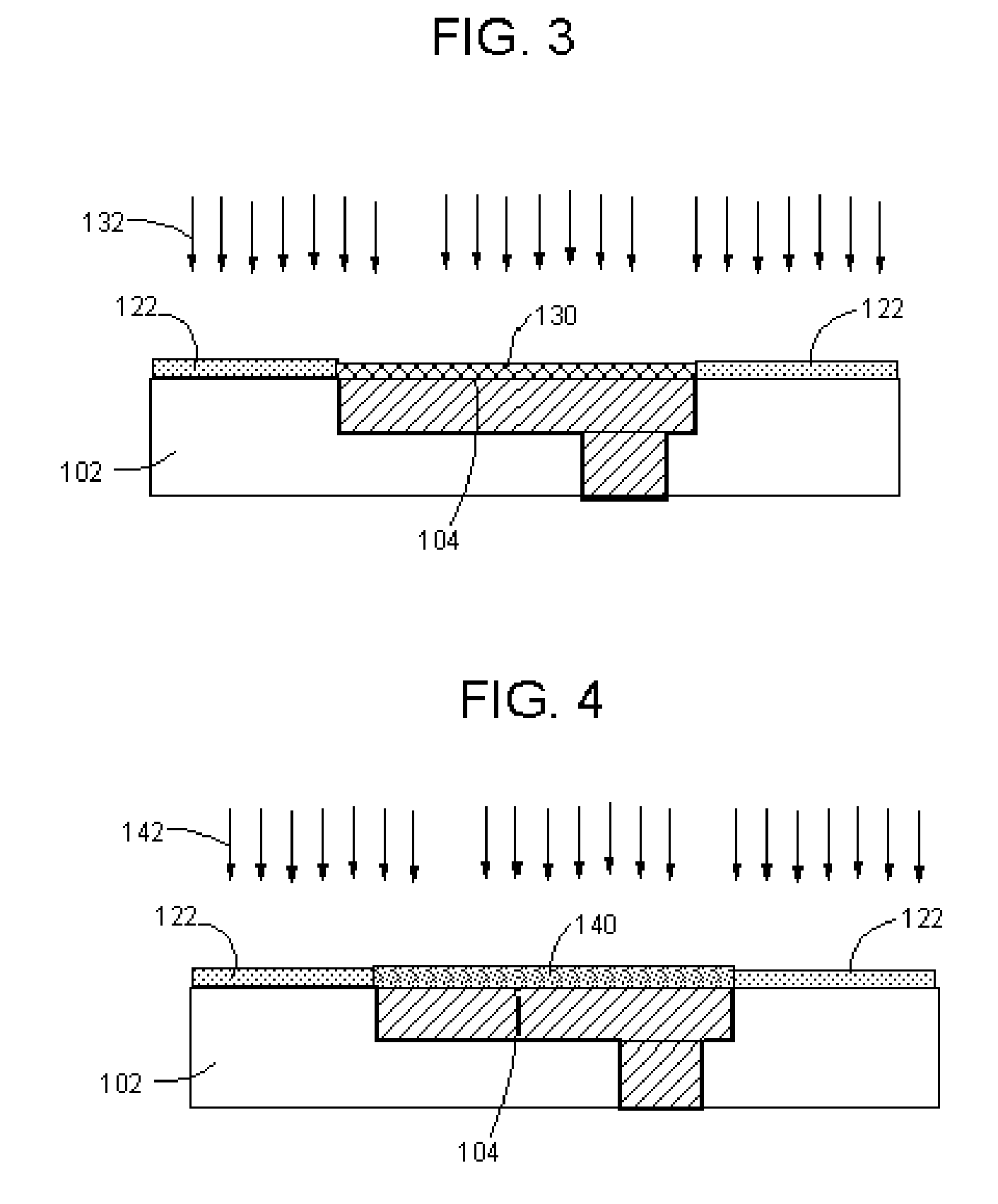

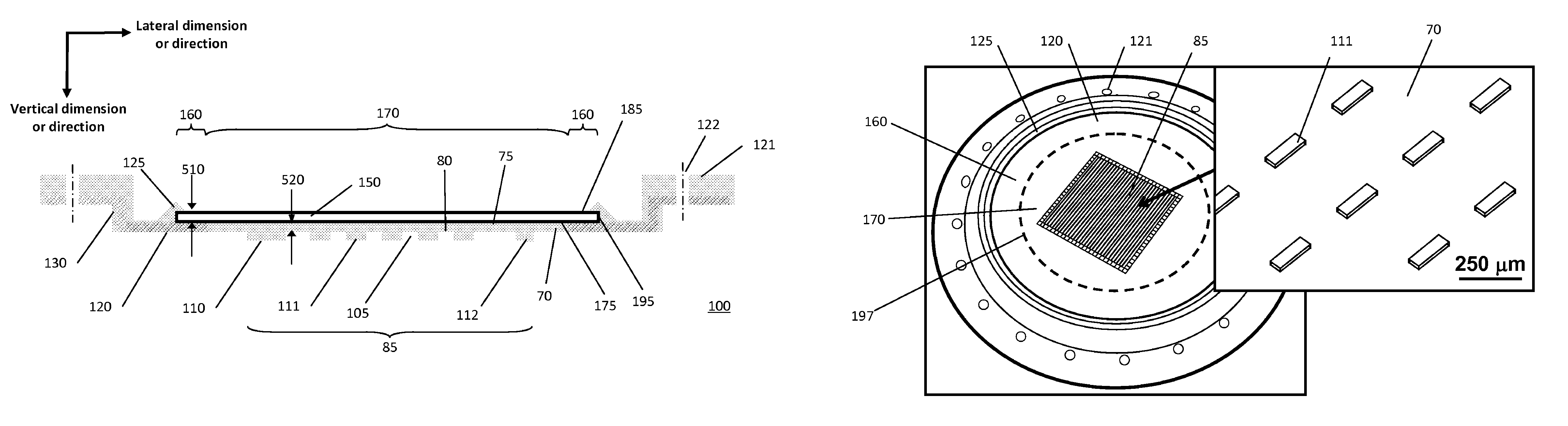

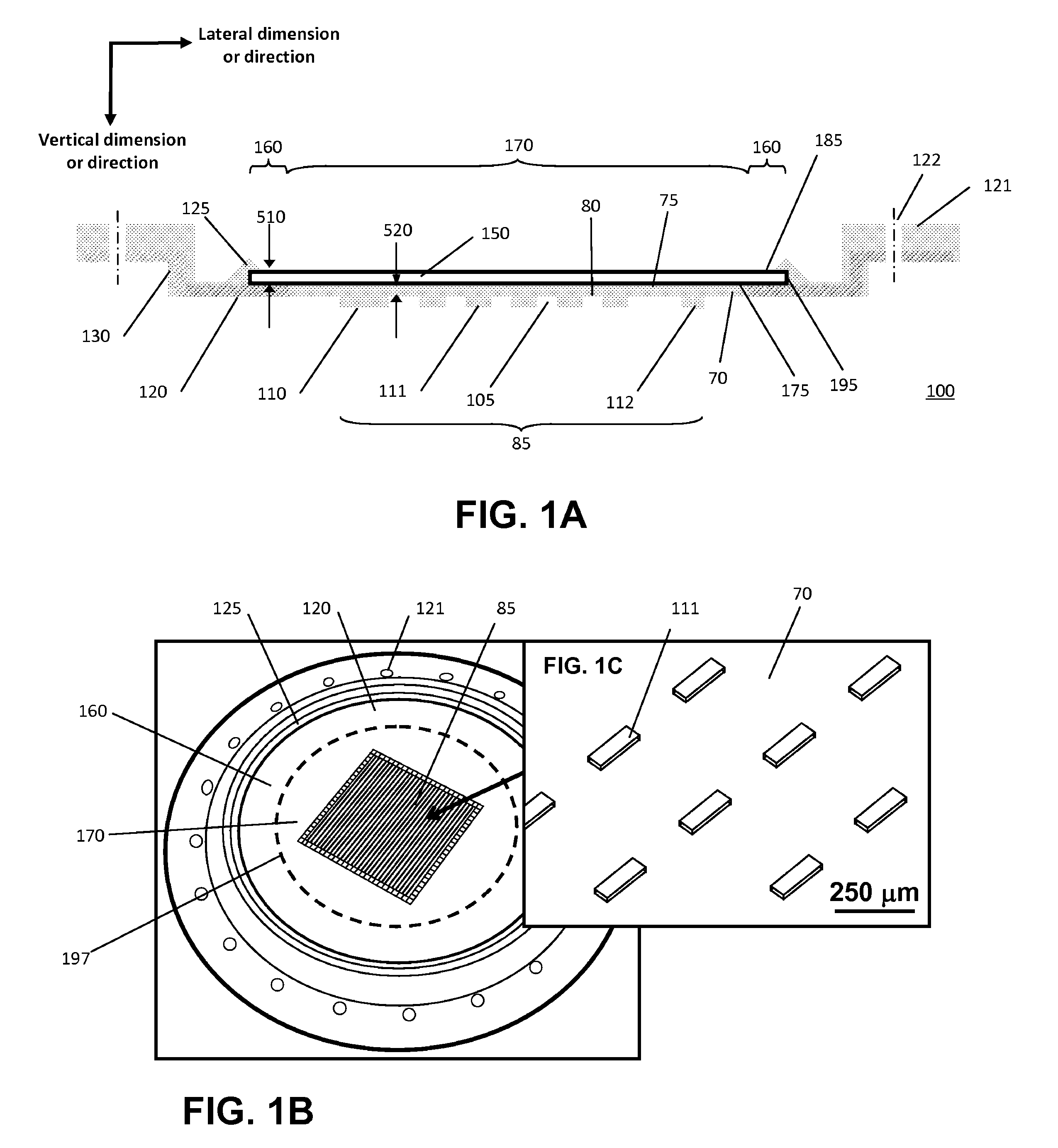

Immersion fluid for immersion Lithography, and method of performing immersion lithography

ActiveUS20050036183A1Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSemiconductor structureOptical surface

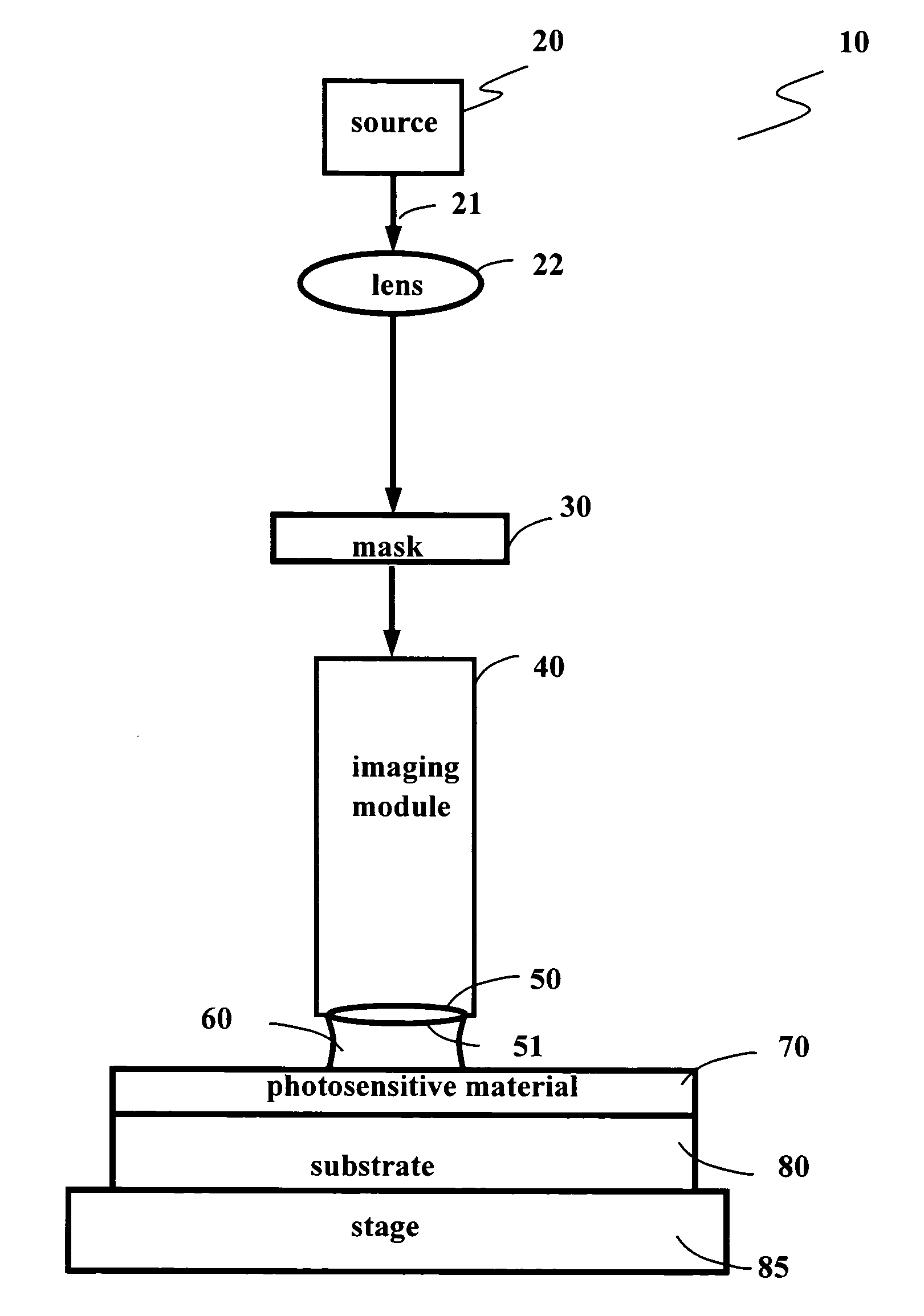

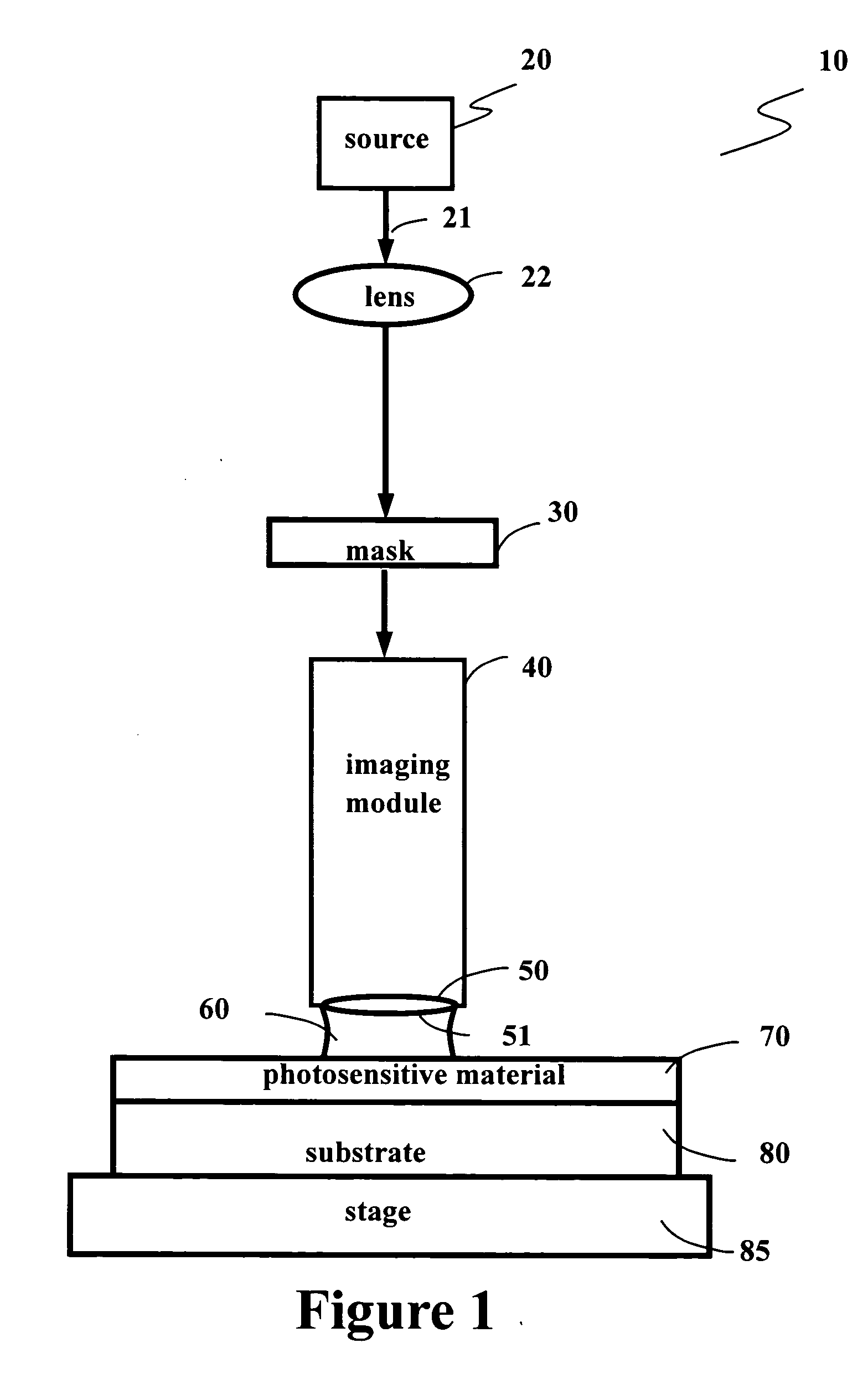

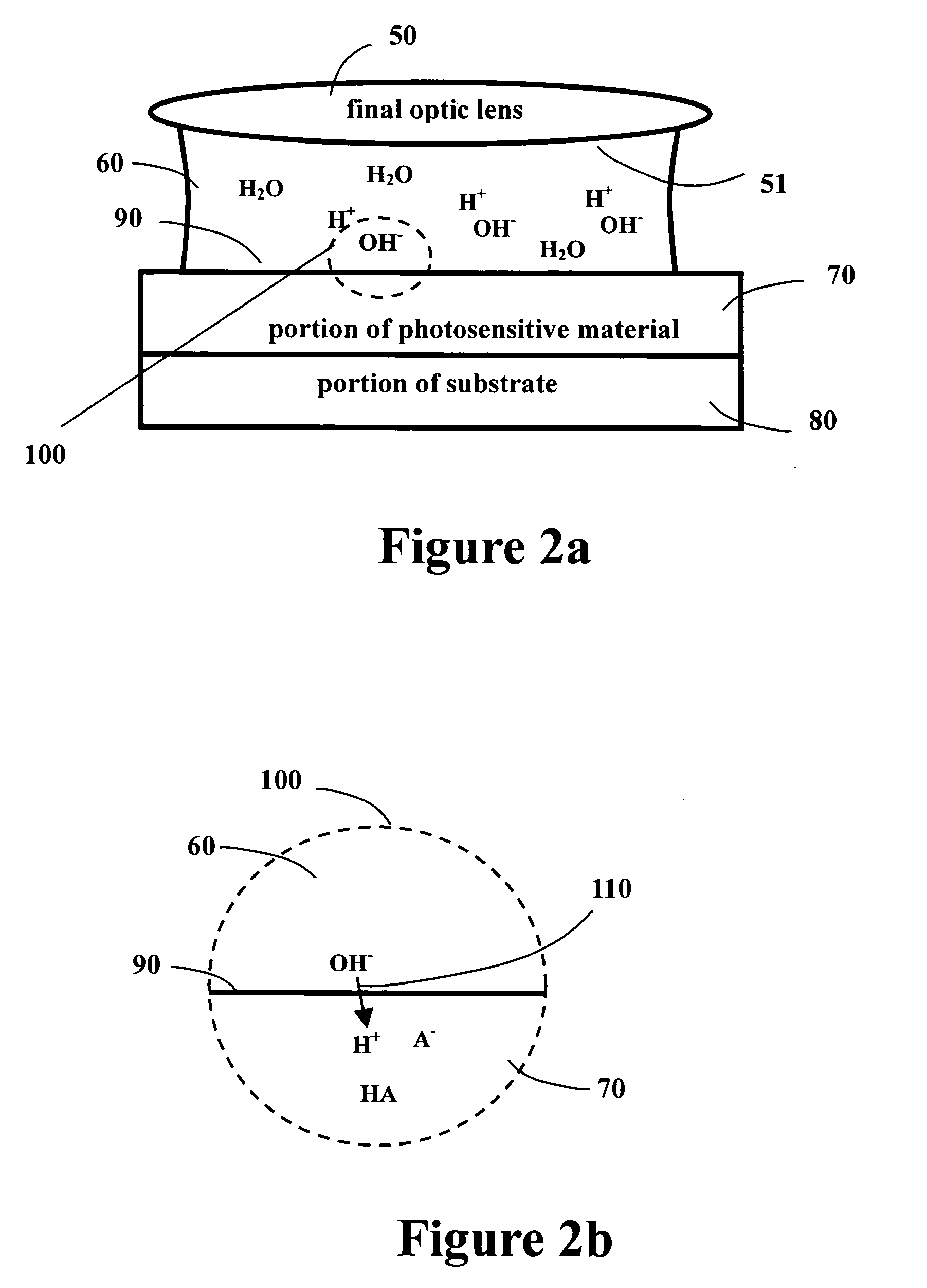

An immersion lithographic system 10 comprises an optical surface 51, an immersion fluid 60 with a pH less than 7 contacting at least a portion of the optical surface, and a semiconductor structure 80 having a topmost photoresist layer 70 wherein a portion of the photoresist is in contact with the immersion fluid. Further, a method for illuminating a semiconductor structure 80 having a topmost photoresist layer 70 comprising the steps of: introducing an immersion fluid 60 into a space between an optical surface 51 and the photoresist layer wherein the immersion fluid has a pH of less than 7, and directing light preferably with a wavelength of less than 450 nm through the immersion fluid and onto the photoresist.

Owner:TAIWAN SEMICON MFG CO LTD

Lithography apparatus for manufacture of integrated circuits

ActiveUS20050036184A1Limit amount of swellingSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusLithographic artistSemiconductor structure

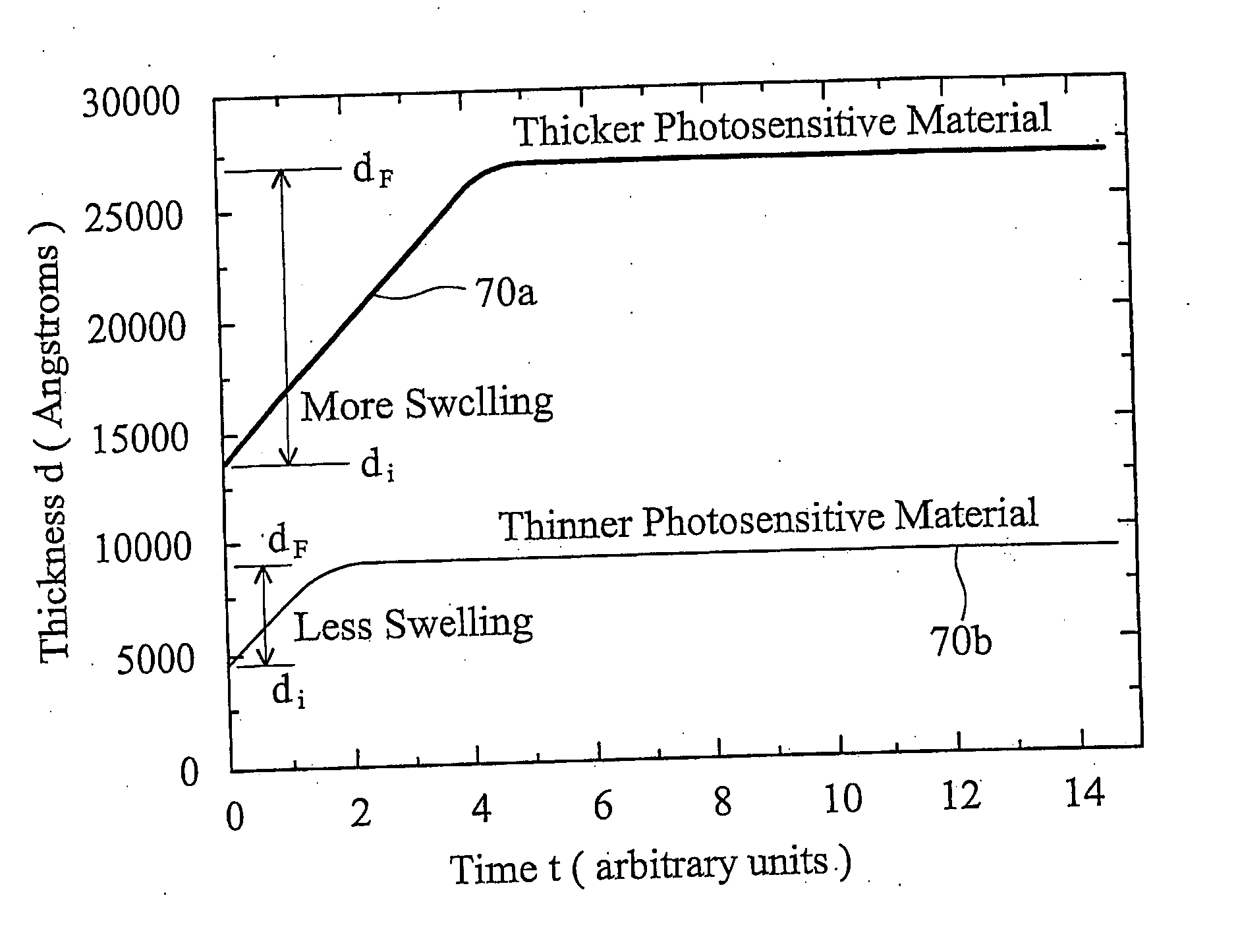

An immersion lithographic system 10 comprises an optical surface 51, an immersion fluid 60 contacting at least a portion of the optical surface, and a semiconductor structure 80 having a topmost photoresist layer 70 having a thickness of less than about 5000 angstroms, wherein a portion of the photoresist is in contact with the immersion fluid. Further, a method for illuminating a semiconductor structure 80 having a topmost photoresist layer 70 with a thickness of less than about 5000 angstroms, comprising introducing an immersion fluid 60 into a space between an optical surface 51 and the photoresist layer, and directing light preferably with a wavelength of less than about 450 nm through the immersion fluid and onto the photoresist.

Owner:TAIWAN SEMICON MFG CO LTD

Methods of removing silicon oxide and gaseous mixtures for achieving same

ActiveUS20090275205A1Decorative surface effectsSemiconductor/solid-state device manufacturingChemical treatmentPartial oxidation

Owner:MICRON TECH INC

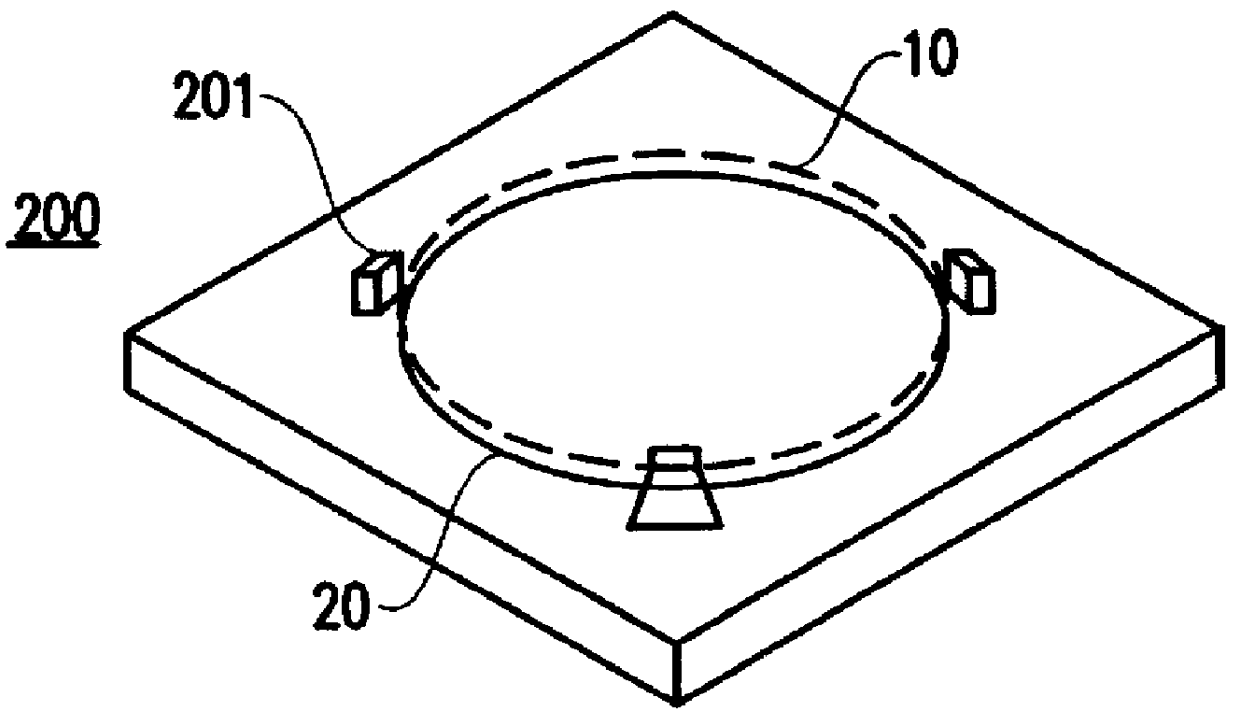

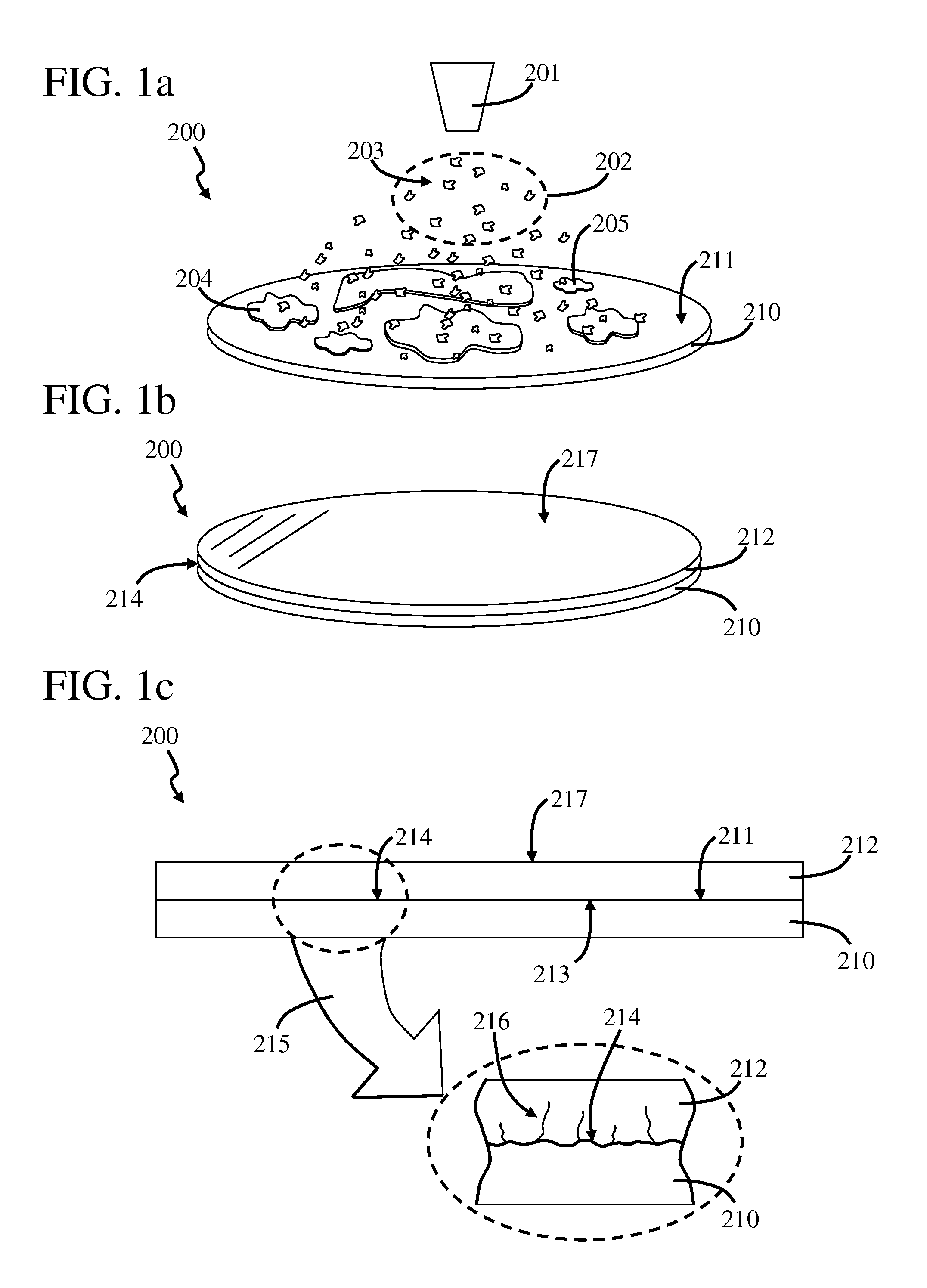

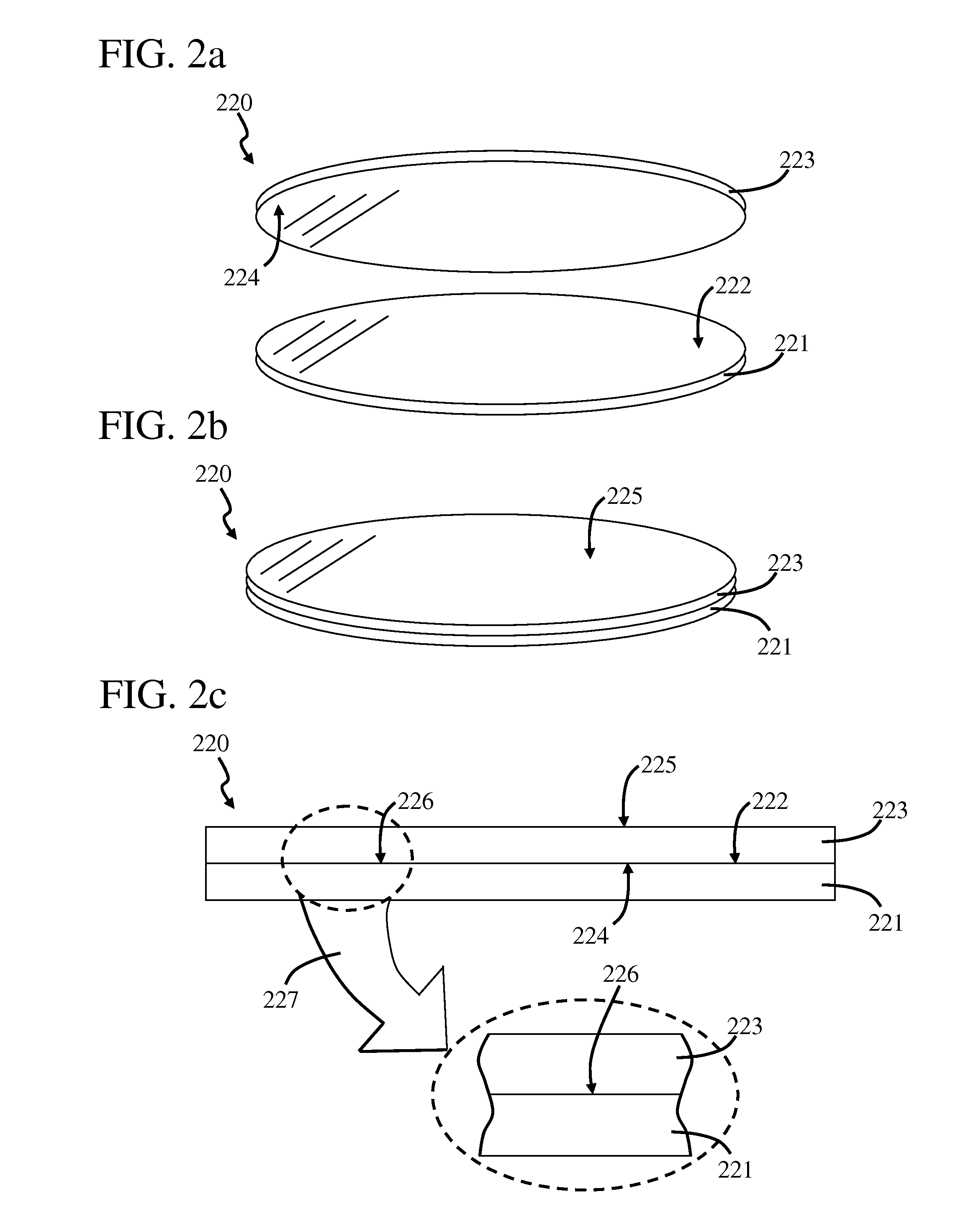

Liquid-filled balloons for immersion lithography

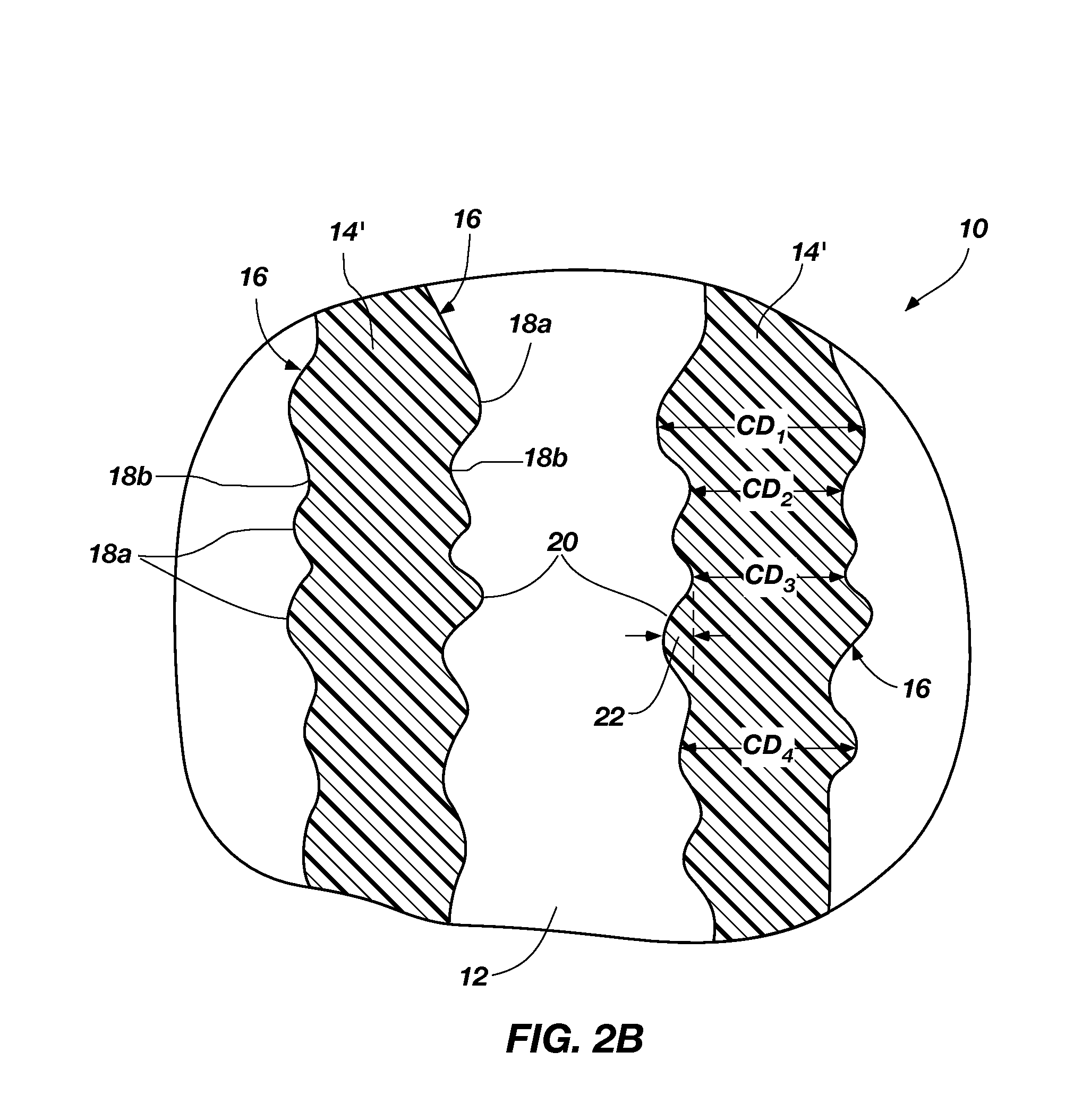

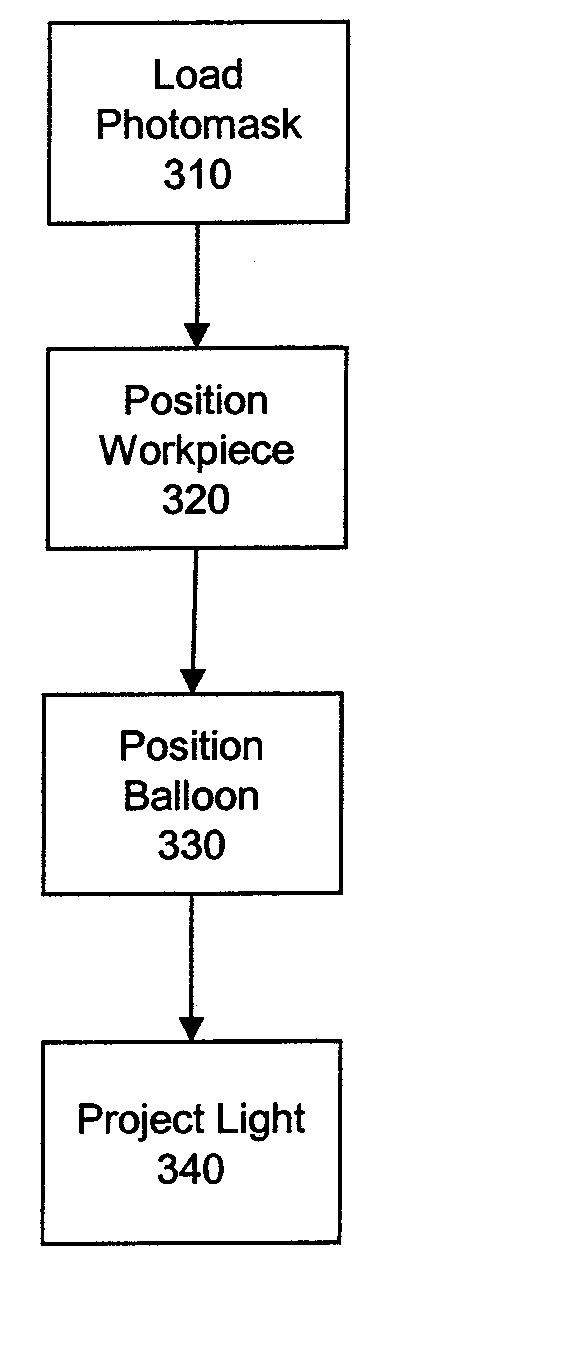

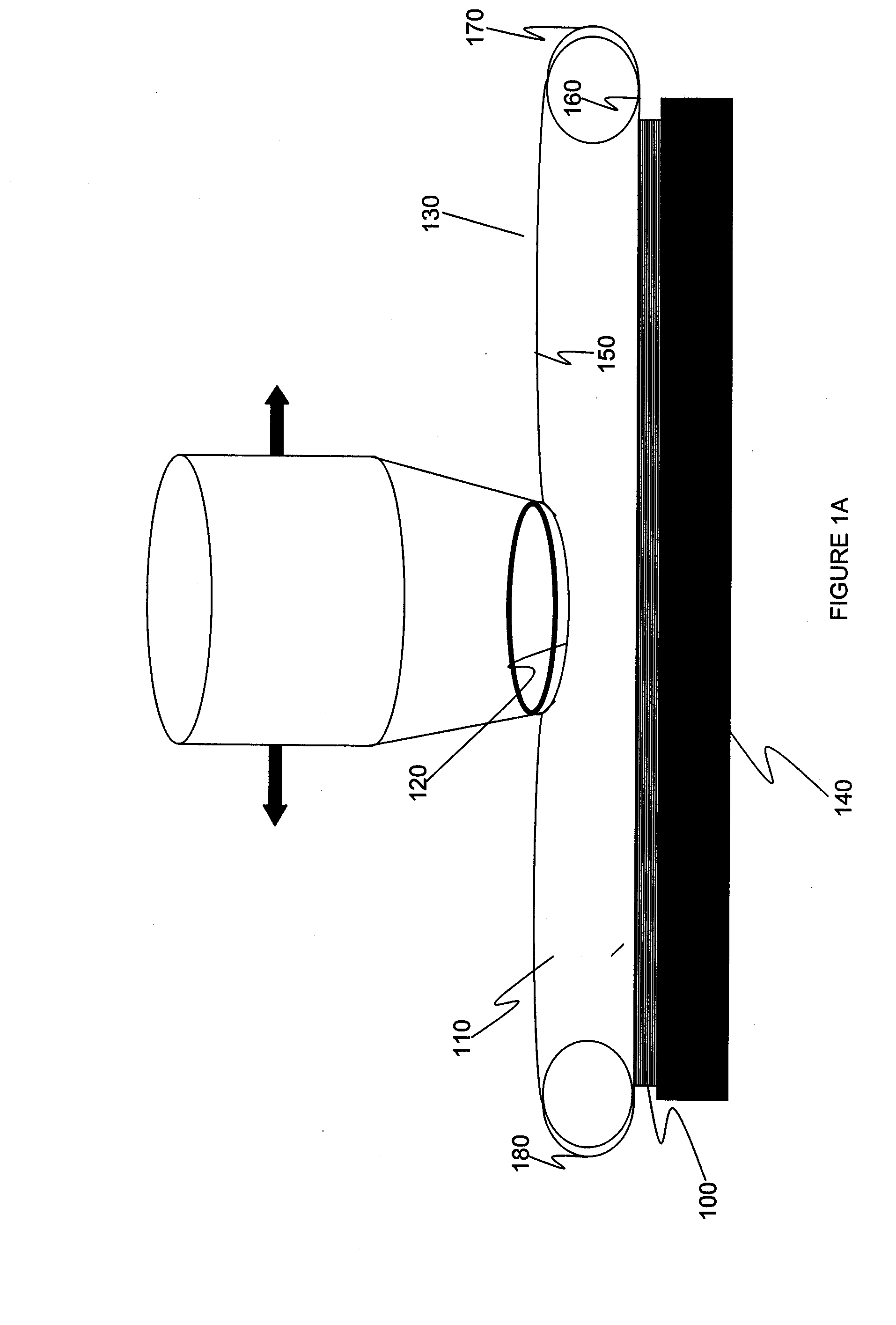

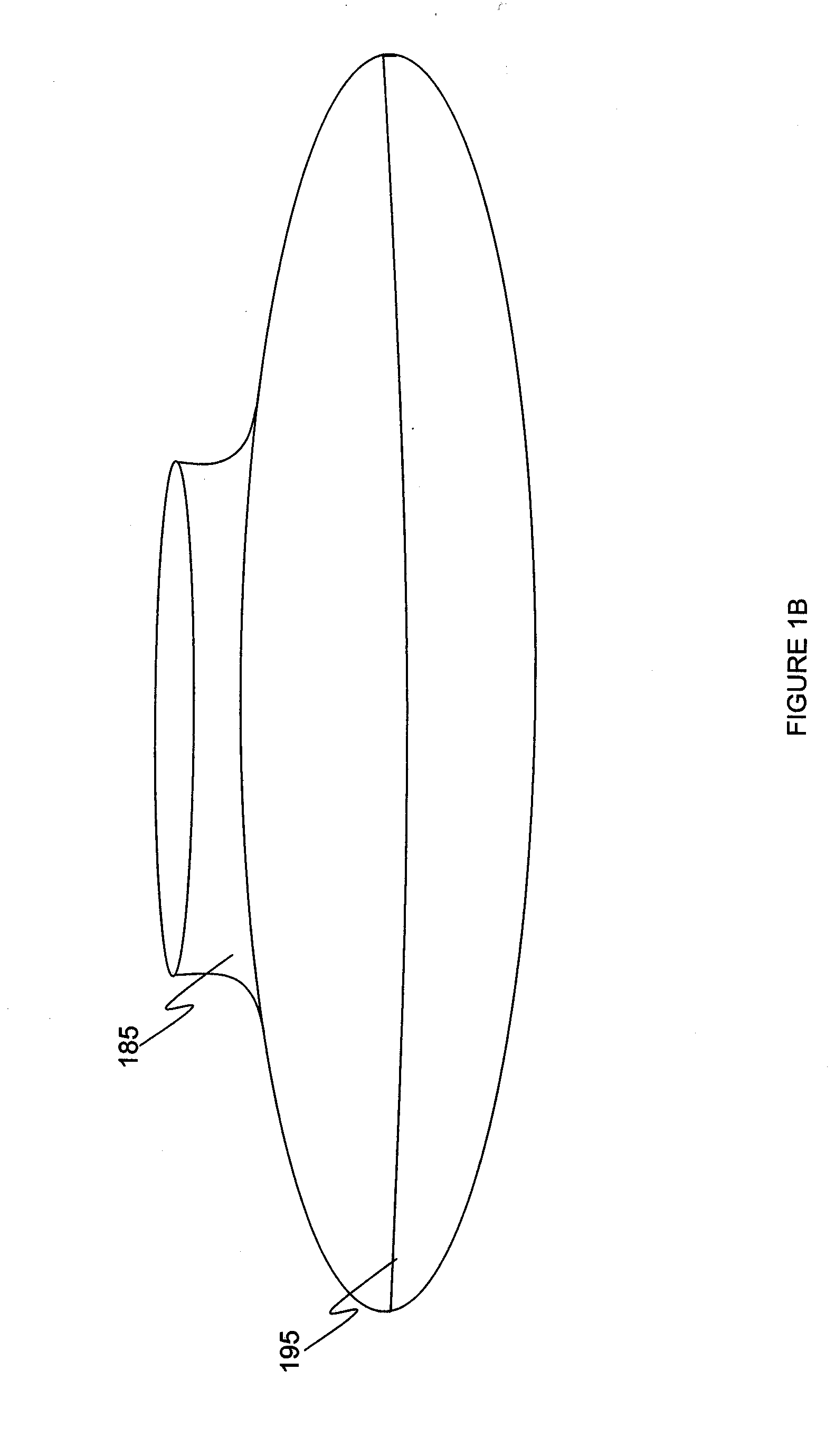

ActiveUS20050158673A1Suitable optical propertyPhotoprinting processesSemiconductor/solid-state device manufacturingOptical propertySemiconductor structure

A liquid-filled balloon may be positioned between a workpiece, such as a semiconductor structure covered with a photoresist, and a lithography light source. The balloon includes a thin membrane that exhibits good optical and physical properties. Liquid contained in the balloon also exhibits good optical properties, including a refractive index higher than that of air. Light from the lithography light source passes through a mask, through a top layer of the balloon membrane, through the contained liquid, through a bottom layer of the balloon membrane, and onto the workpiece where it alters portions of the photoresist. As the liquid has a low absorption and a higher refractive index than air, the liquid-filled balloon system enhances resolution. Thus, the balloon provides optical benefits of liquid immersion without the complications of maintaining a liquid between (and in contact with) a lithographic light source mechanism and workpiece.

Owner:TWITTER INC

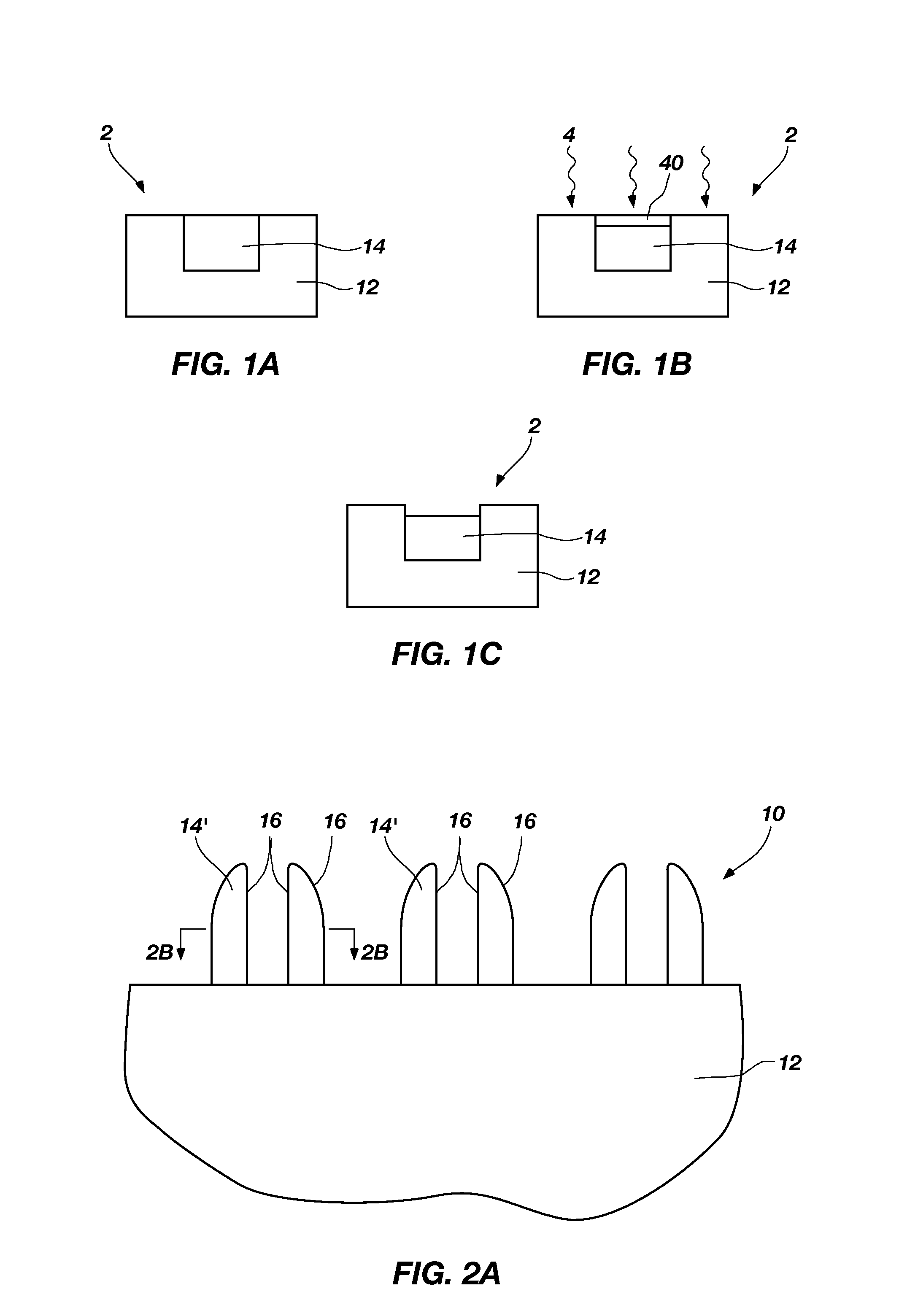

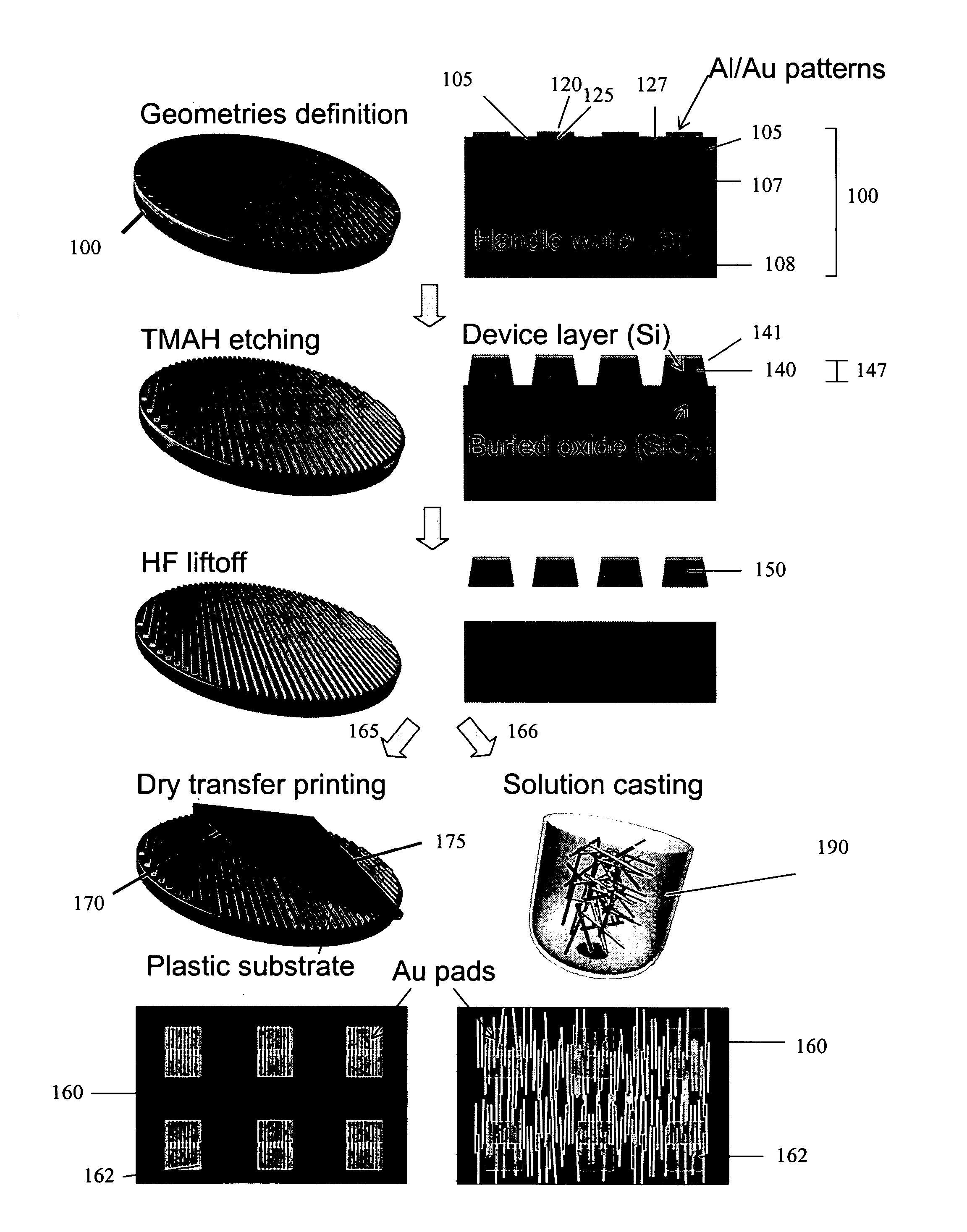

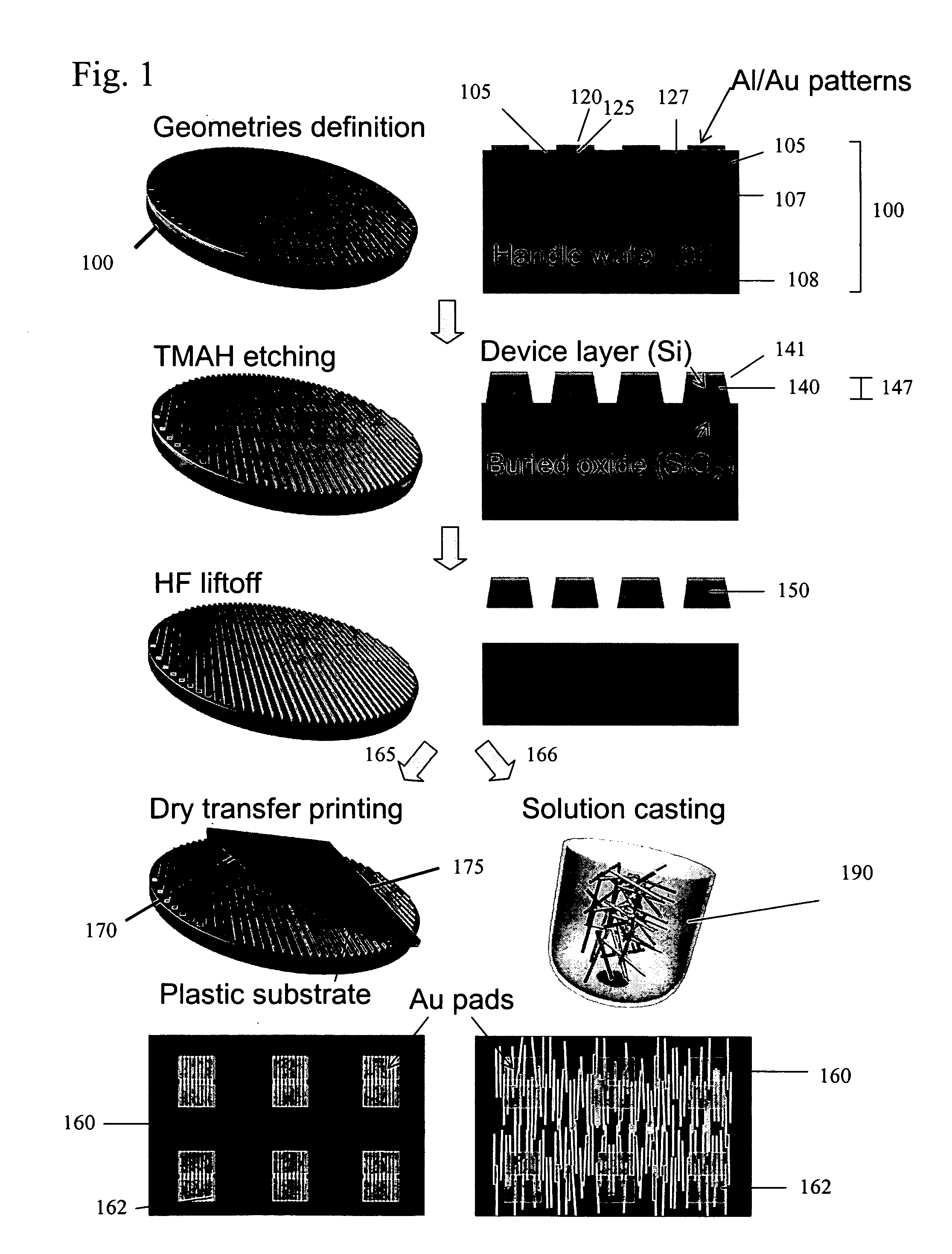

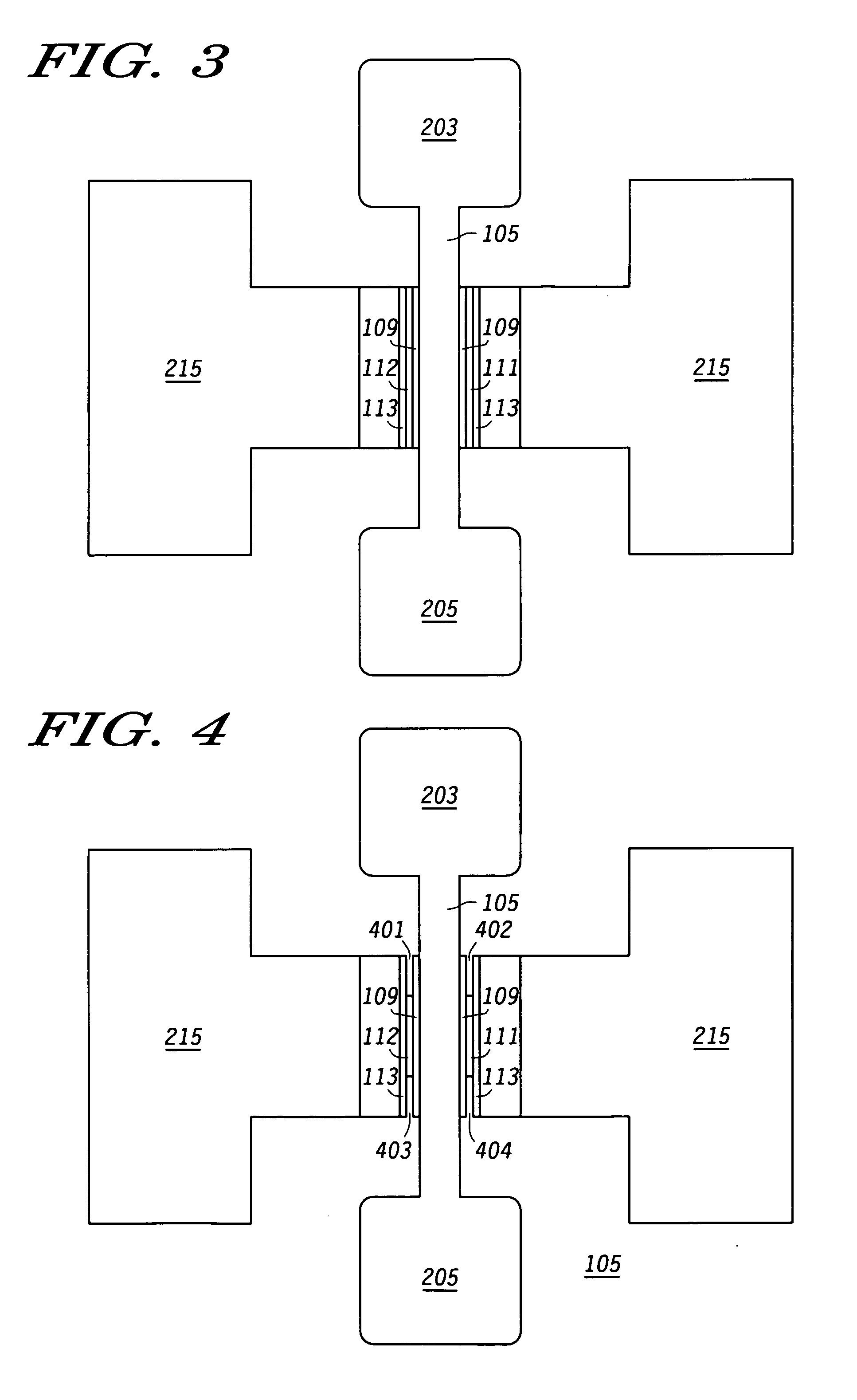

Stretchable semiconductor elements and stretchable electrical circuits

ActiveUS20060038182A1Complete release is preventedLow costTransistorDecorative surface effectsStretchable electronicsSemiconductor structure

The invention provides methods and devices for fabricating printable semiconductor elements and assembling printable semiconductor elements onto substrate surfaces. Methods, devices and device components of the present invention are capable of generating a wide range of flexible electronic and optoelectronic devices and arrays of devices on substrates comprising polymeric materials. The present invention also provides stretchable semiconductor structures and stretchable electronic devices capable of good performance in stretched configurations.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

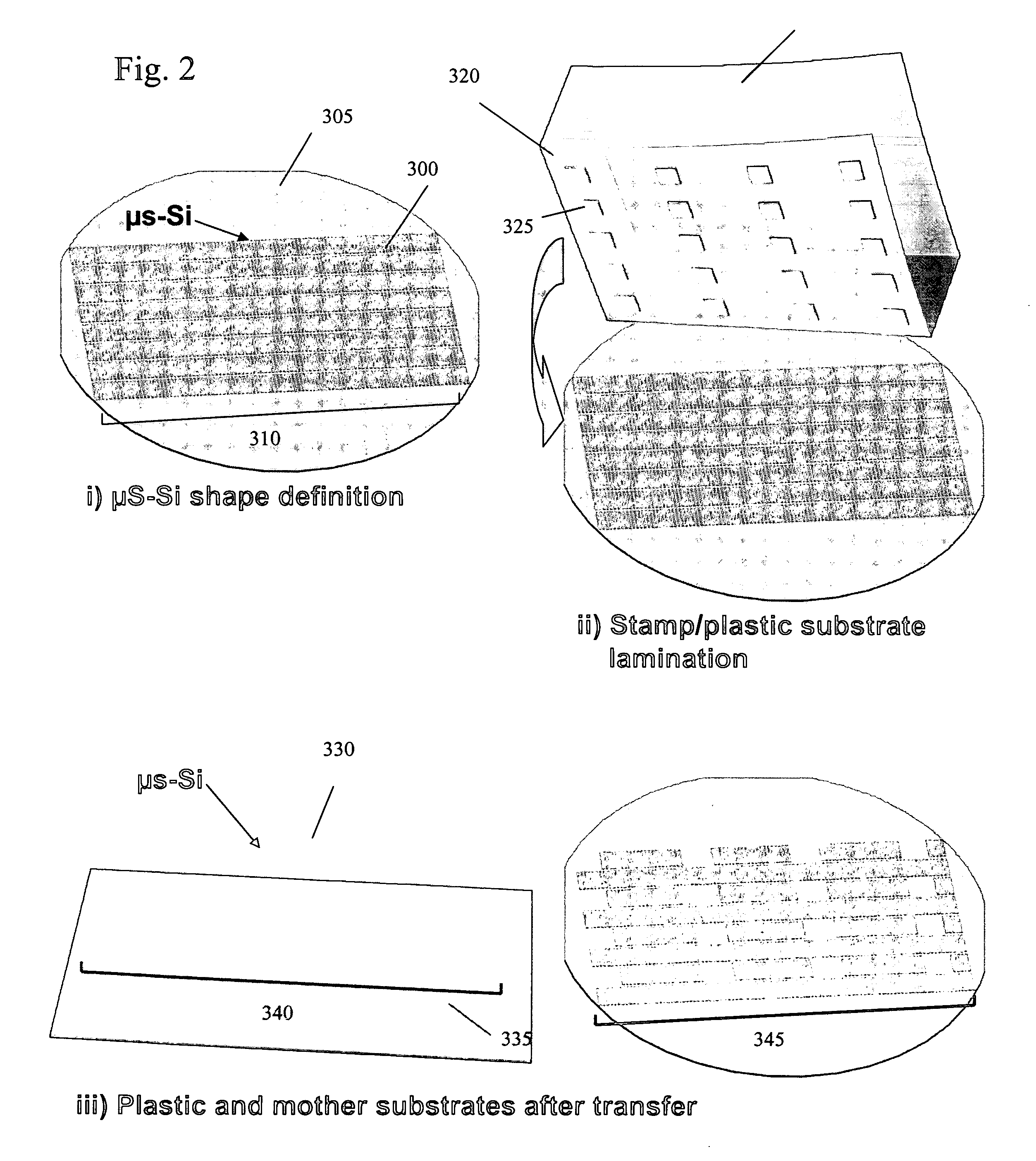

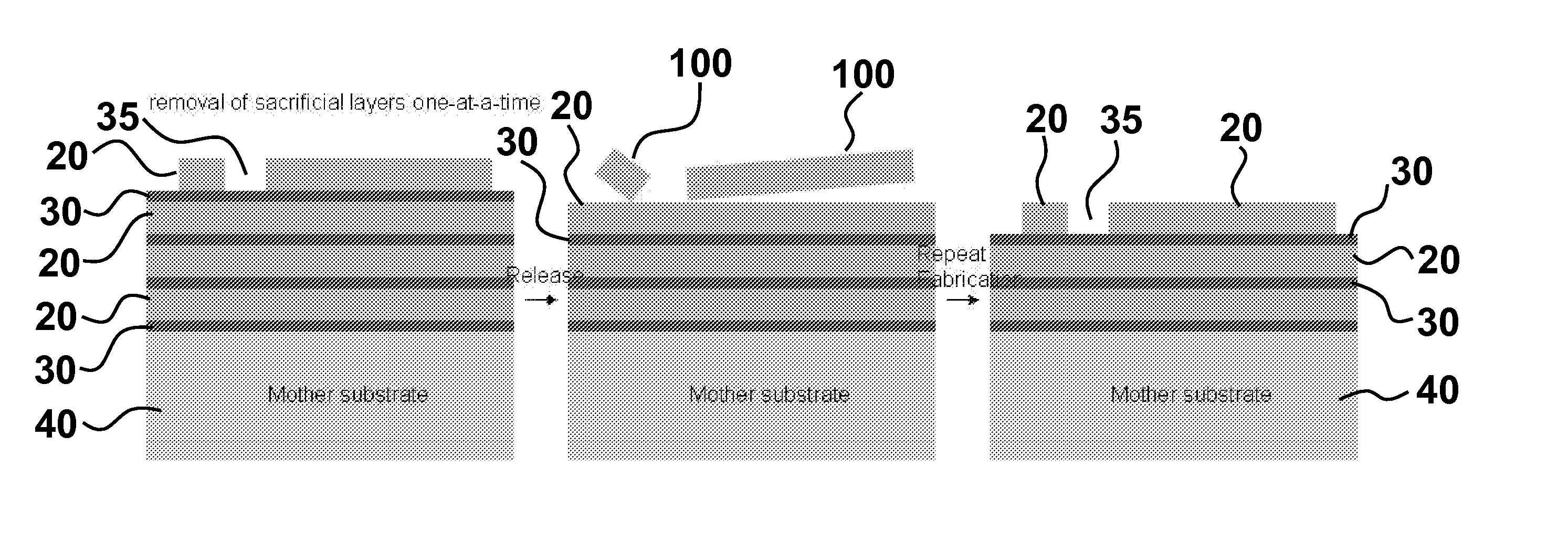

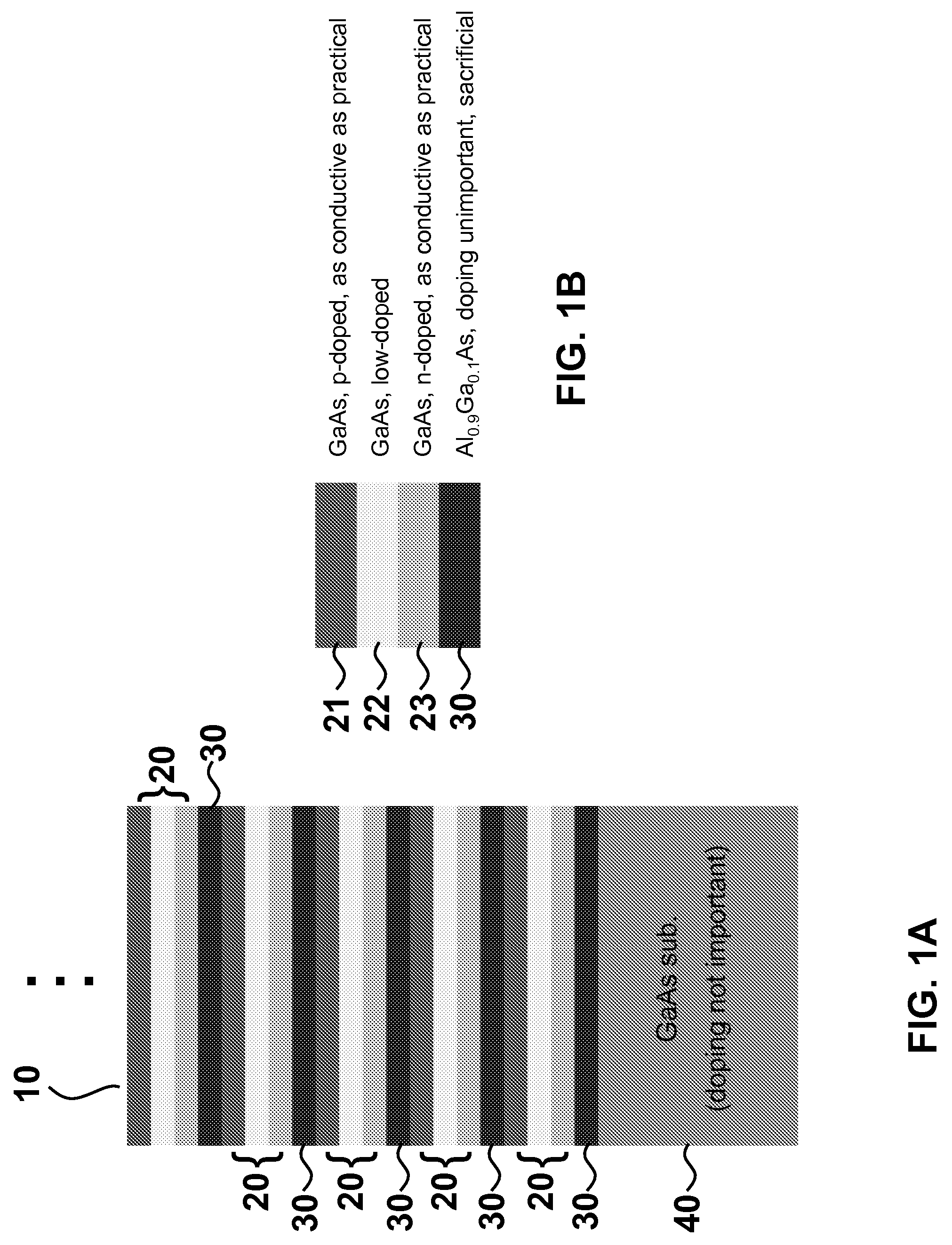

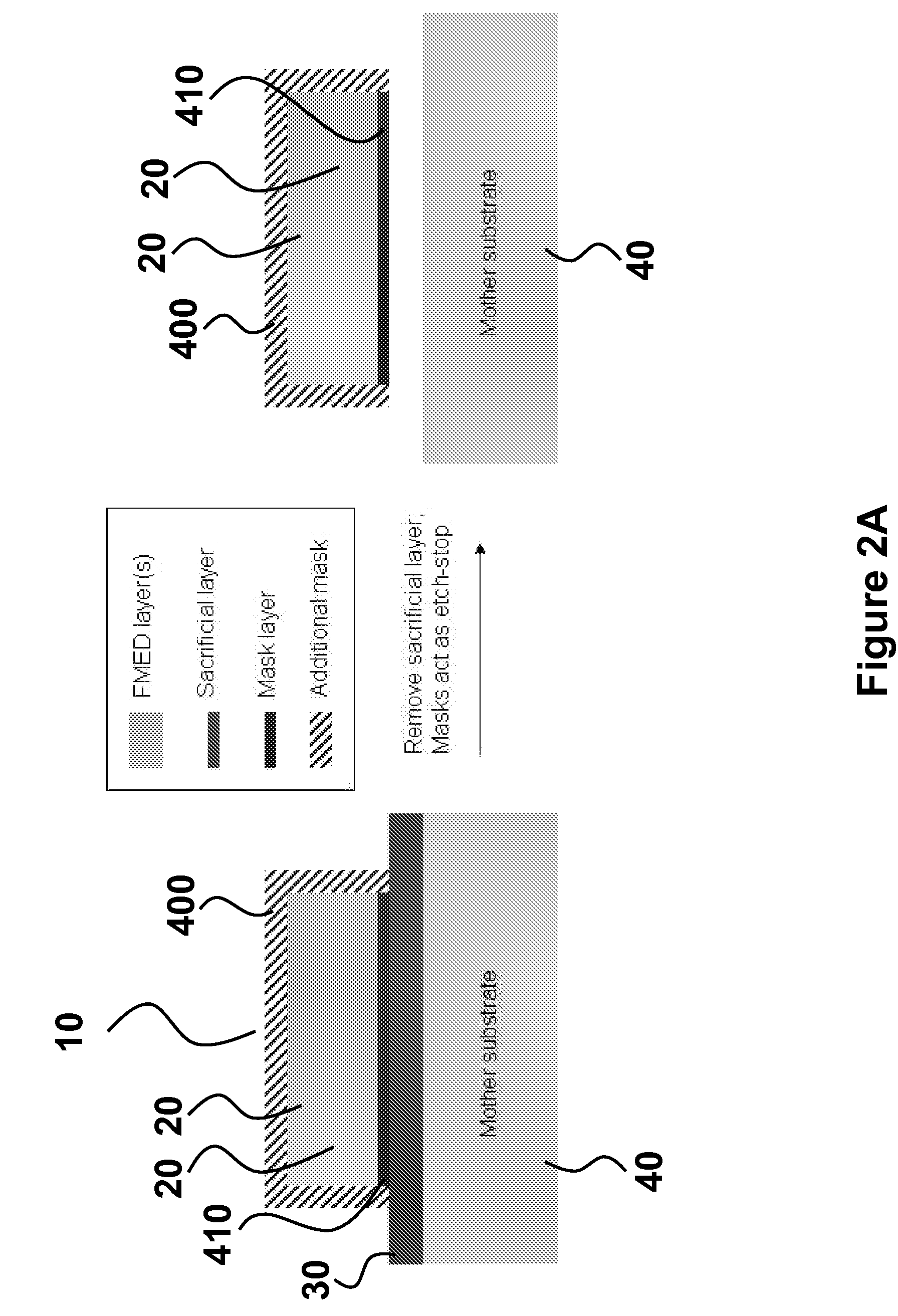

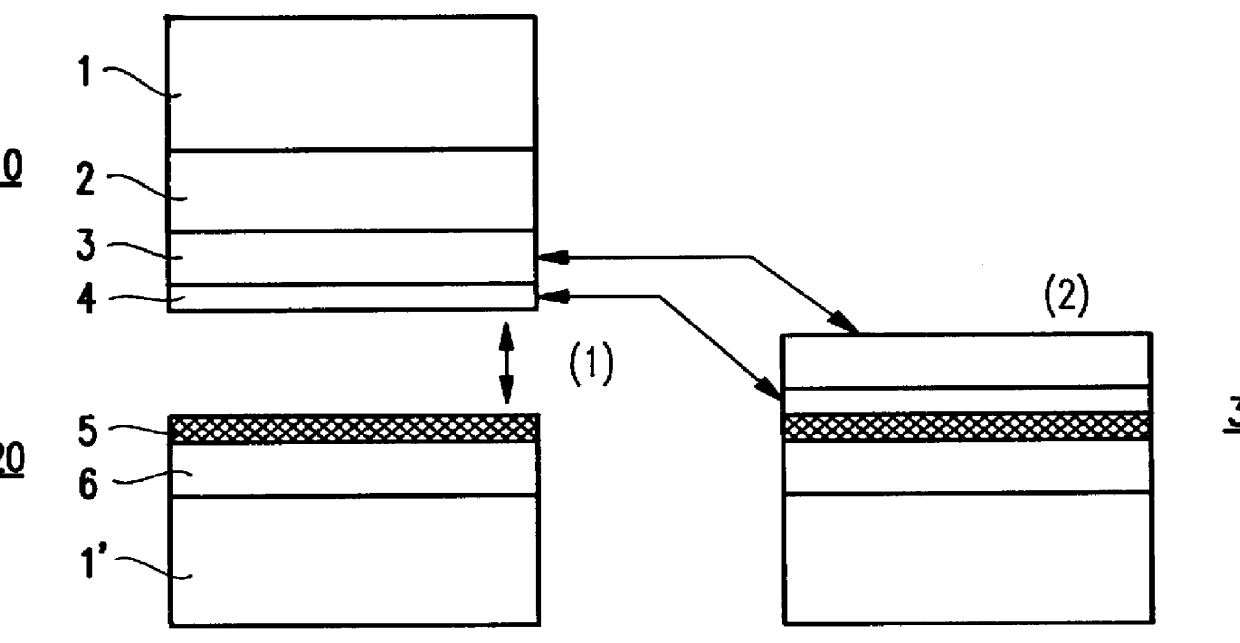

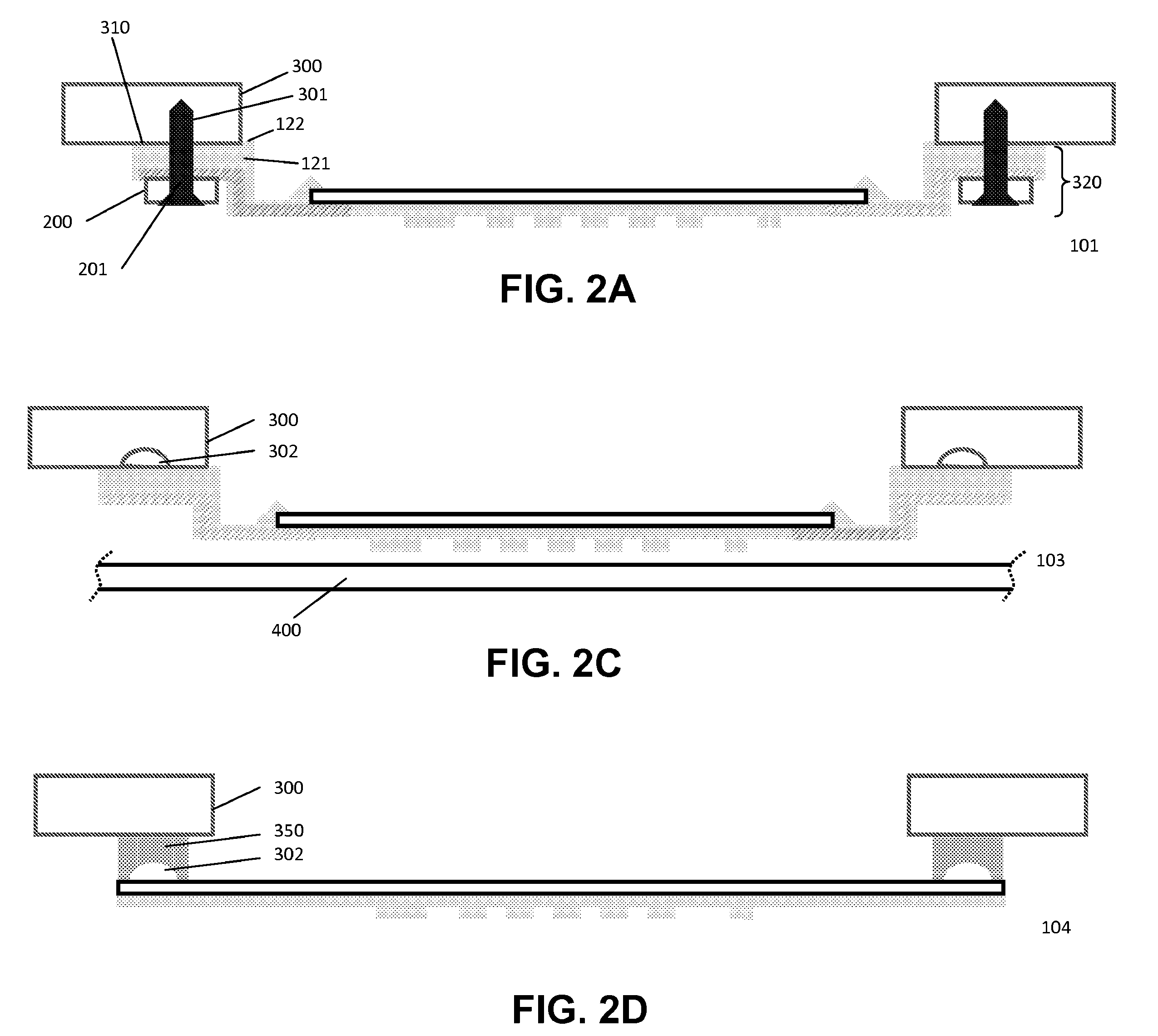

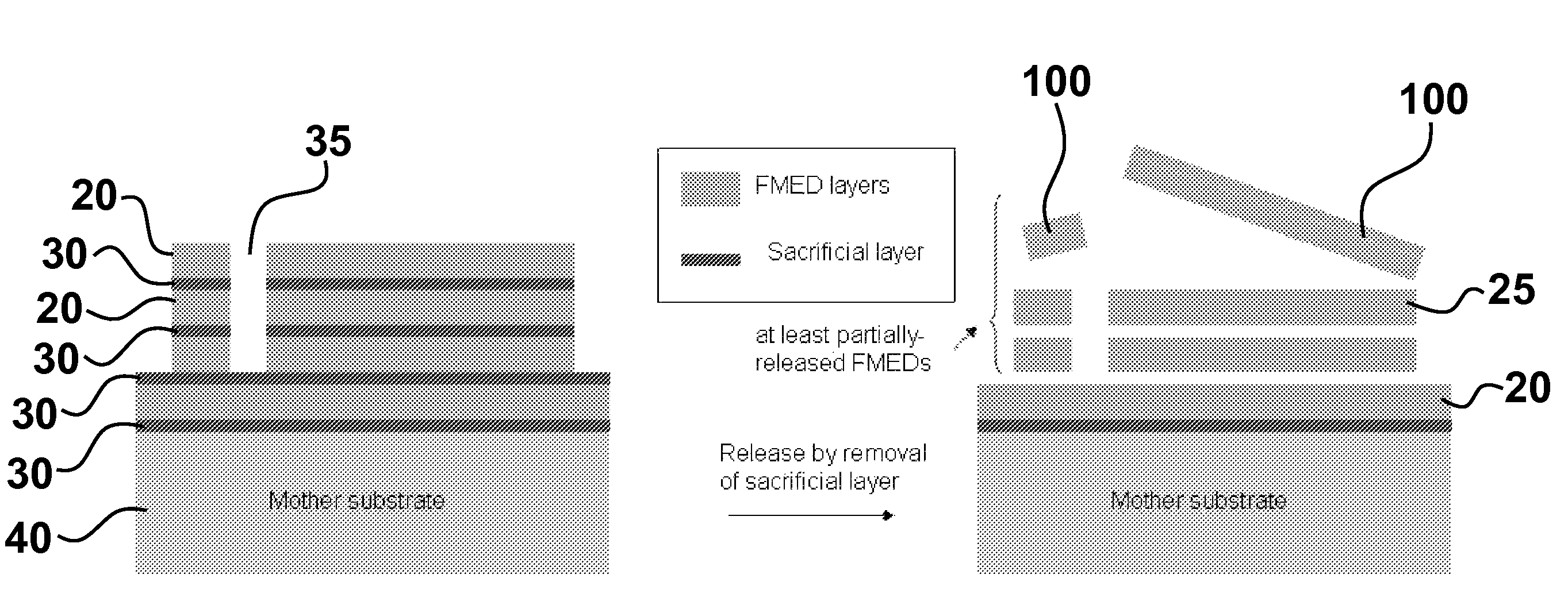

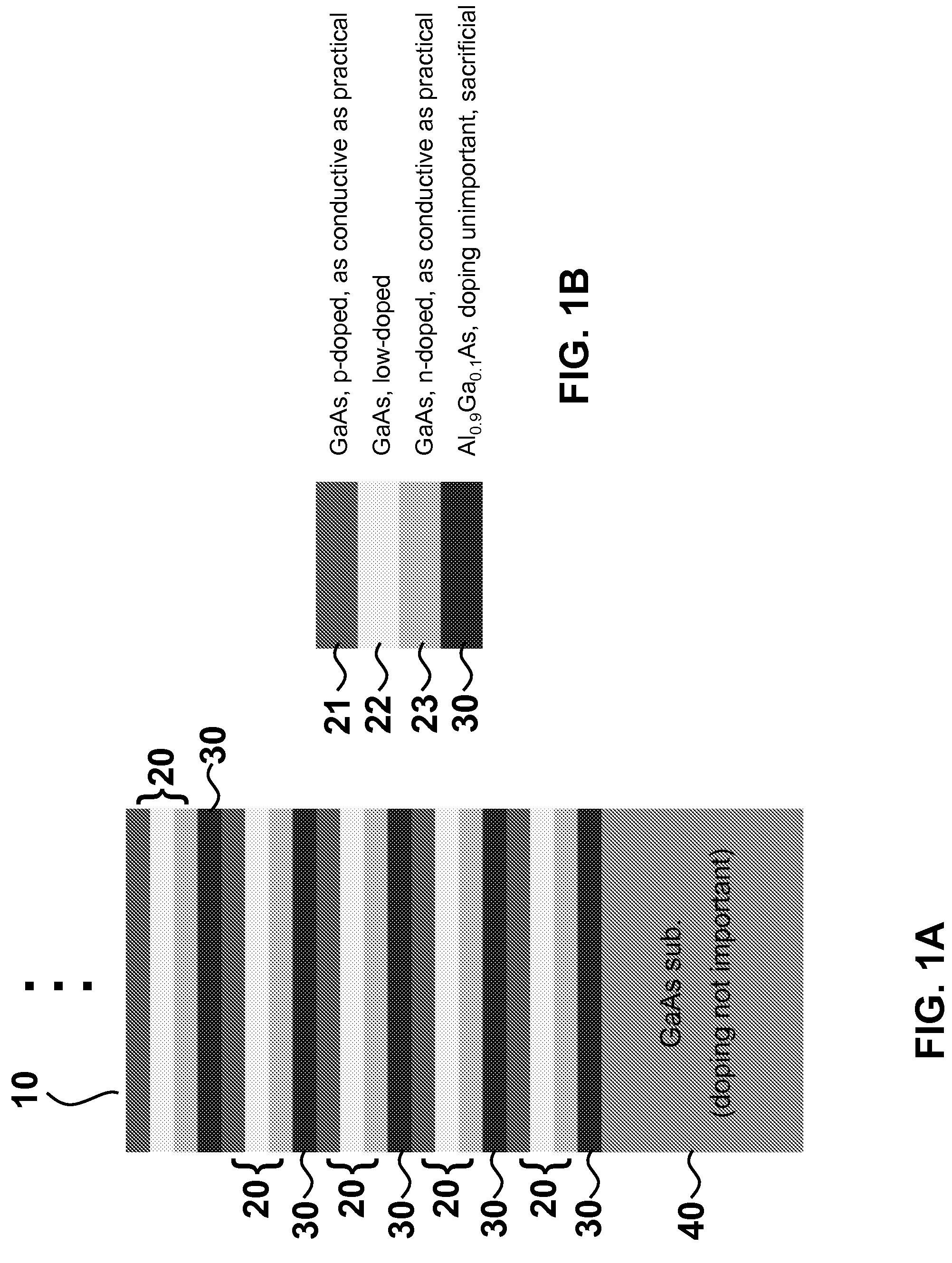

Release strategies for making transferable semiconductor structures, devices and device components

ActiveUS20080108171A1Low cost structureLow costFinal product manufactureNanoinformaticsSemiconductor structureDevice Subassembly

Provided are methods for making a device or device component by providing a multilayer structure having a plurality of functional layers and a plurality of release layers and releasing the functional layers from the multilayer structure by separating one or more of the release layers to generate a plurality of transferable structures. The transferable structures are printed onto a device substrate or device component supported by a device substrate. The methods and systems provide means for making high-quality and low-cost photovoltaic devices, transferable semiconductor structures, (opto-)electronic devices and device components.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

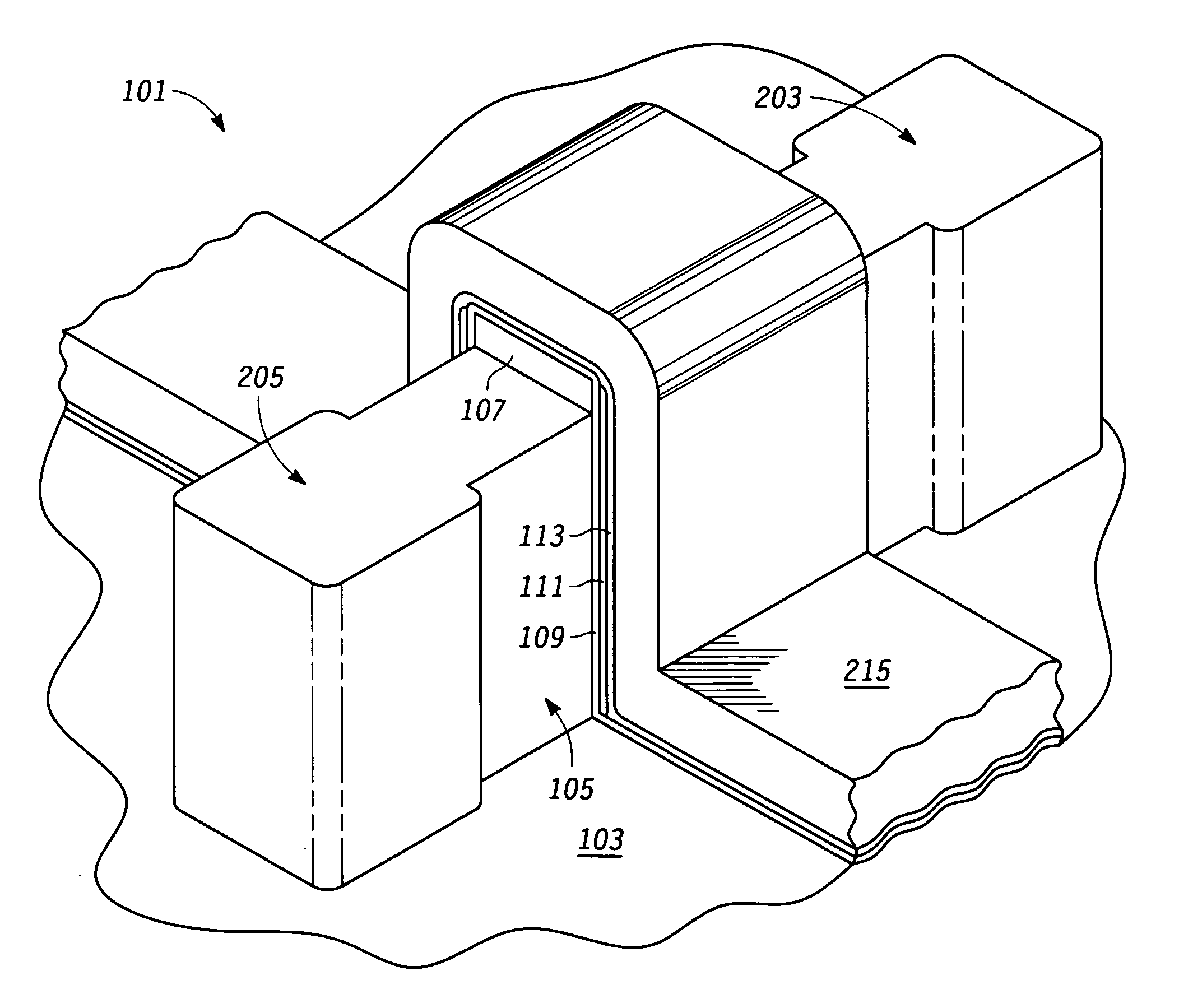

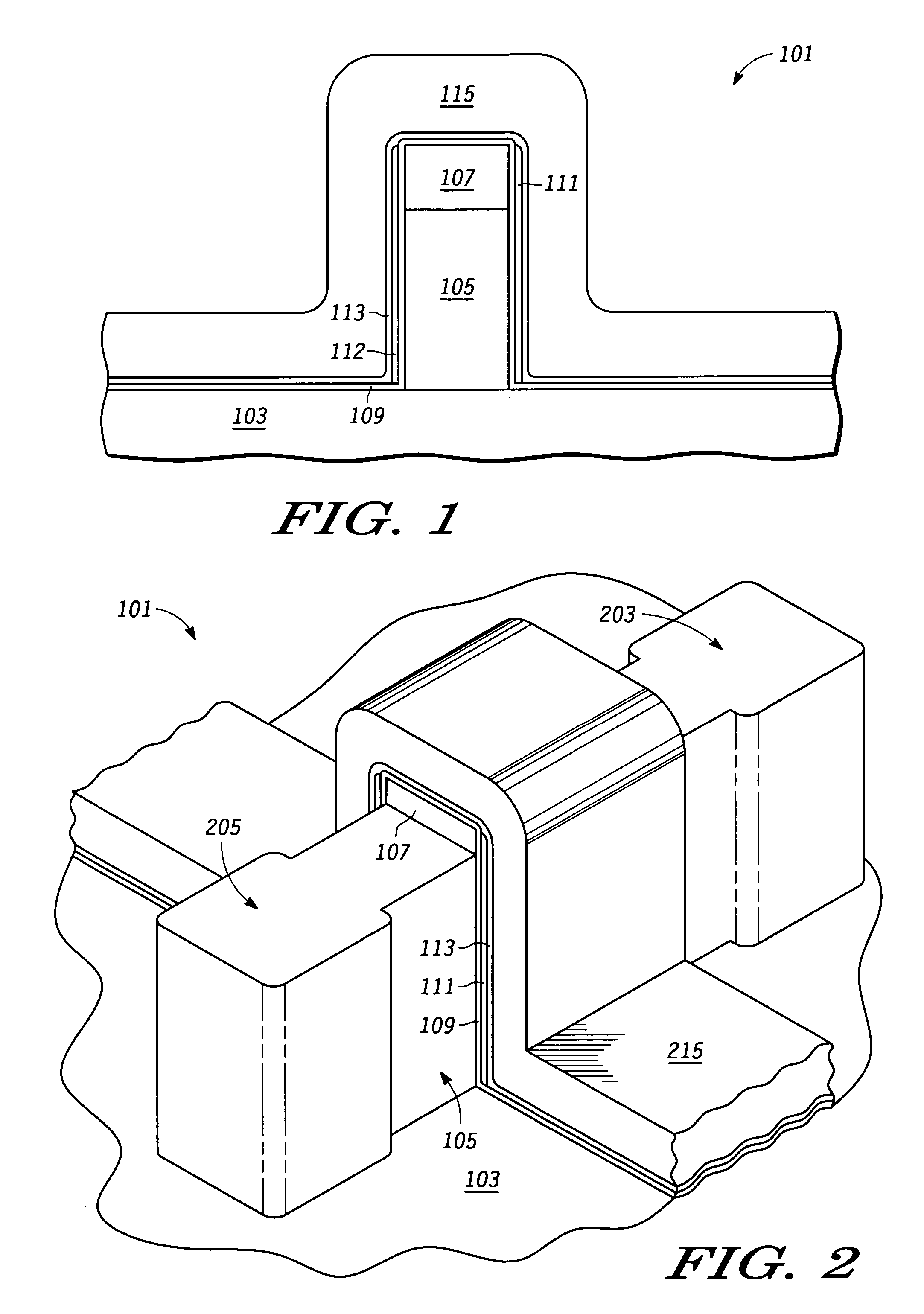

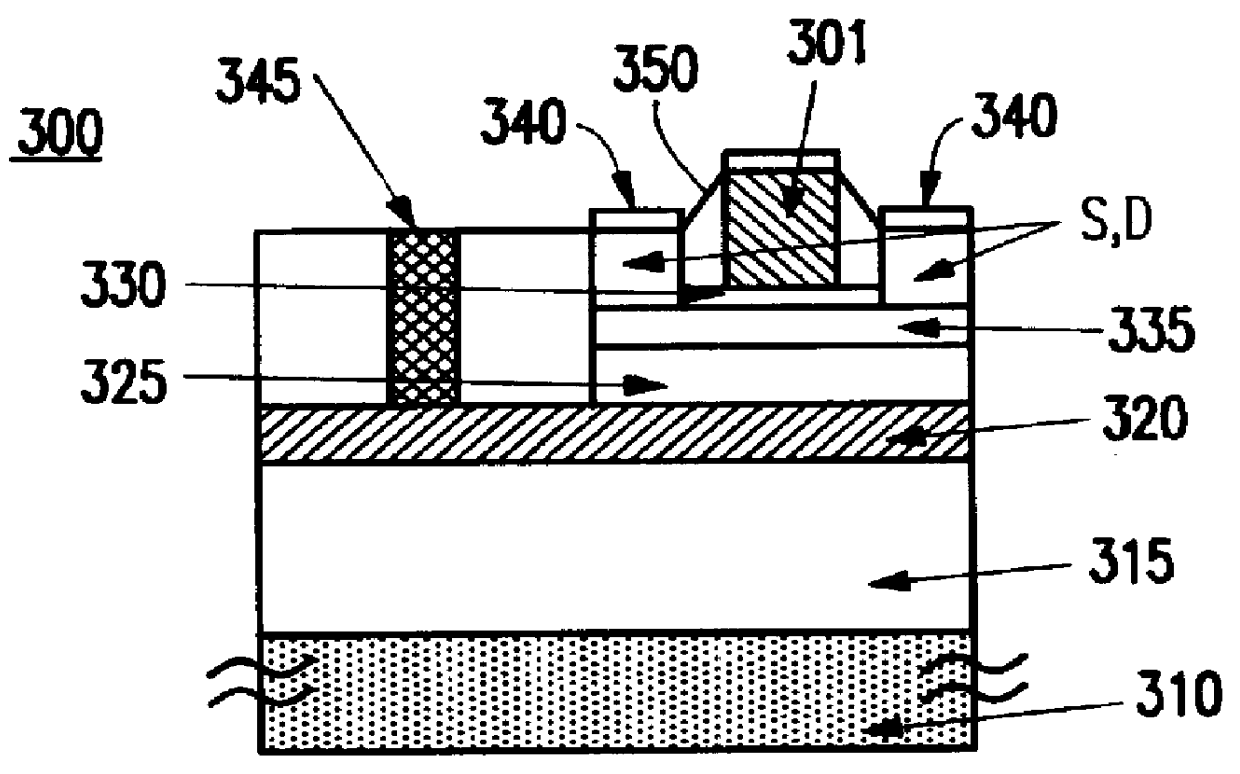

Charge storage structure formation in transistor with vertical channel region

A semiconductor device includes a semiconductor structure having a first sidewall. A vertical channel region is formed in the semiconductor structure along the first sidewall between a first current electrode region and a second current electrode region. First and second charge storage structures are formed adjacent to the first sidewall in openings of a dielectric layer. The first and second charge storage structures are electrically isolated from each other and from the semiconductor structure. A control electrode is formed adjacent to the first sidewall. In another embodiment, third and fourth charge storage structures may be formed adjacent to a second sidewall of the semiconductor structure in openings of a dielectric layer.

Owner:NXP USA INC

Forming capping layer over metal wire structure using selective atomic layer deposition

InactiveUS7084060B1Material nanotechnologySemiconductor/solid-state device detailsDielectricSemiconductor structure

Methods of forming a capping layer over a metal wire structure of a semiconductor device are disclosed. In one embodiment, the method includes providing a partially fabricated semiconductor device having exposed surfaces of the metal (e.g., copper) wire structure and a dielectric around the metal wire structure. The exposed surface of the metal wire structure is then activated by forming a seed layer thereon. The capping layer is then formed over the exposed surface of the metal wire structure by performing a selective atomic layer deposition (ALD) of a capping layer material onto the metal wire structure. As an alternative, the dielectric may be masked off to further assist the selectivity of the ALD. The invention also includes a semiconductor structure including the metal wire structure having an atomic layer deposition capping layer over an upper surface thereof.

Owner:IBM CORP

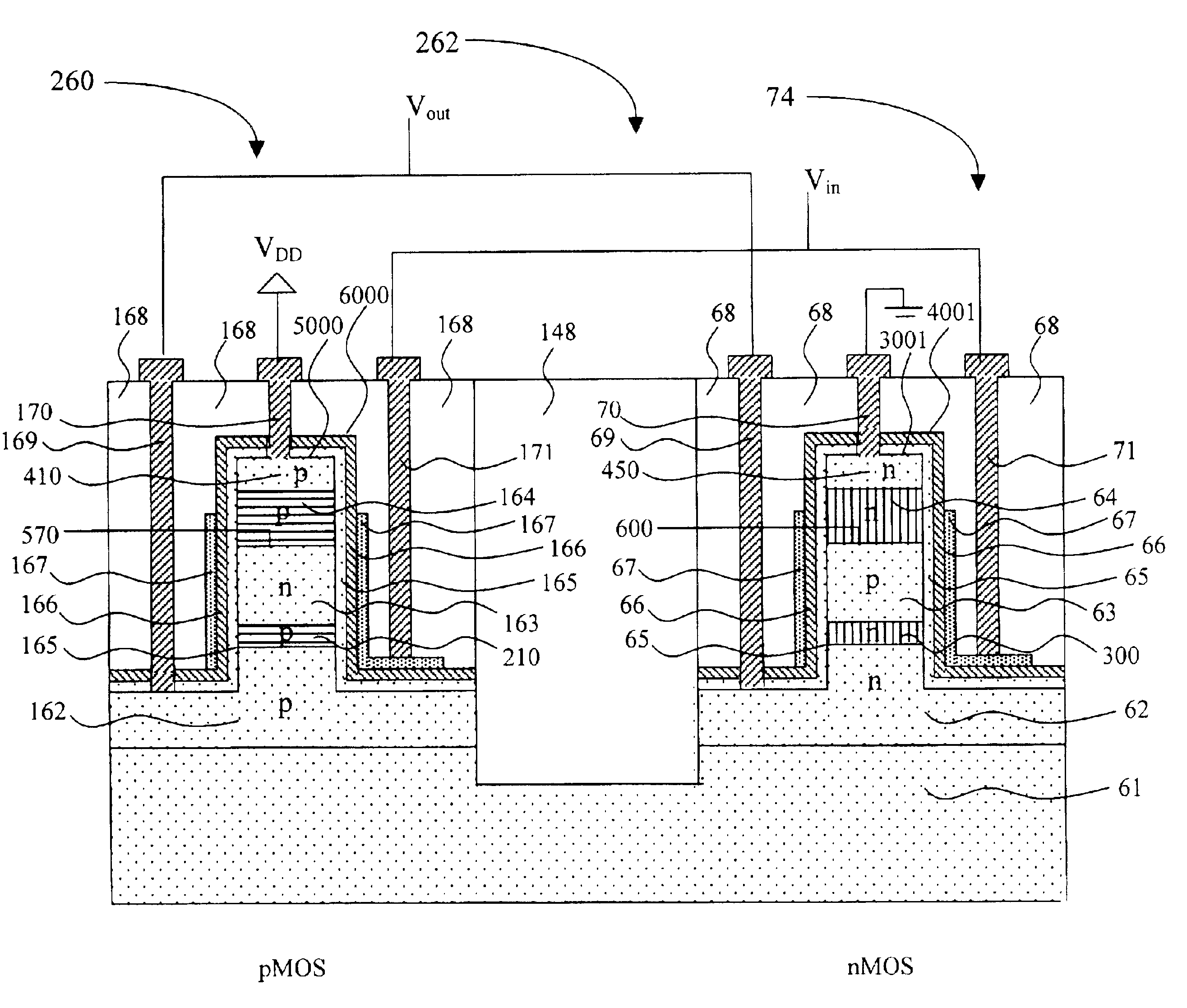

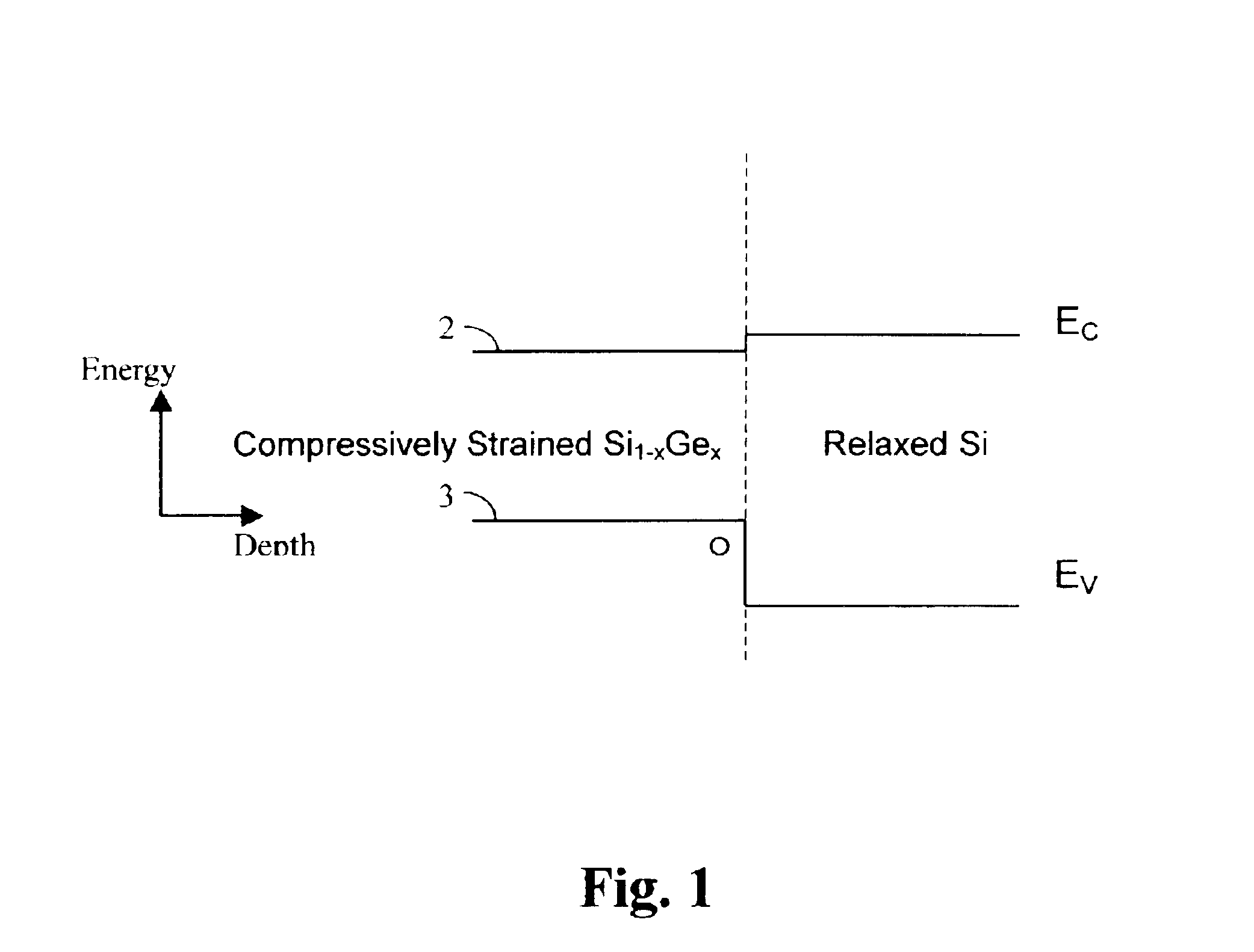

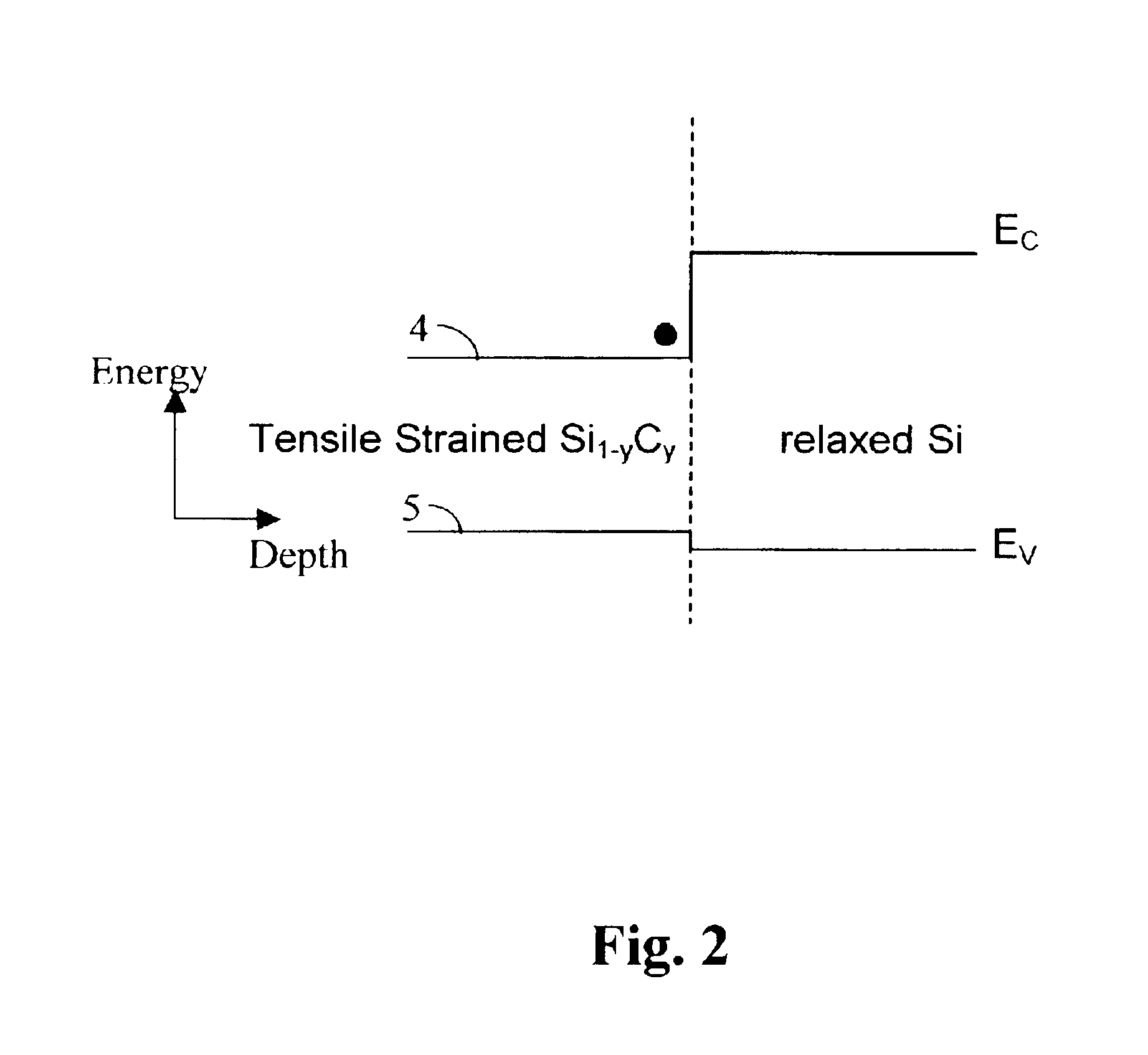

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

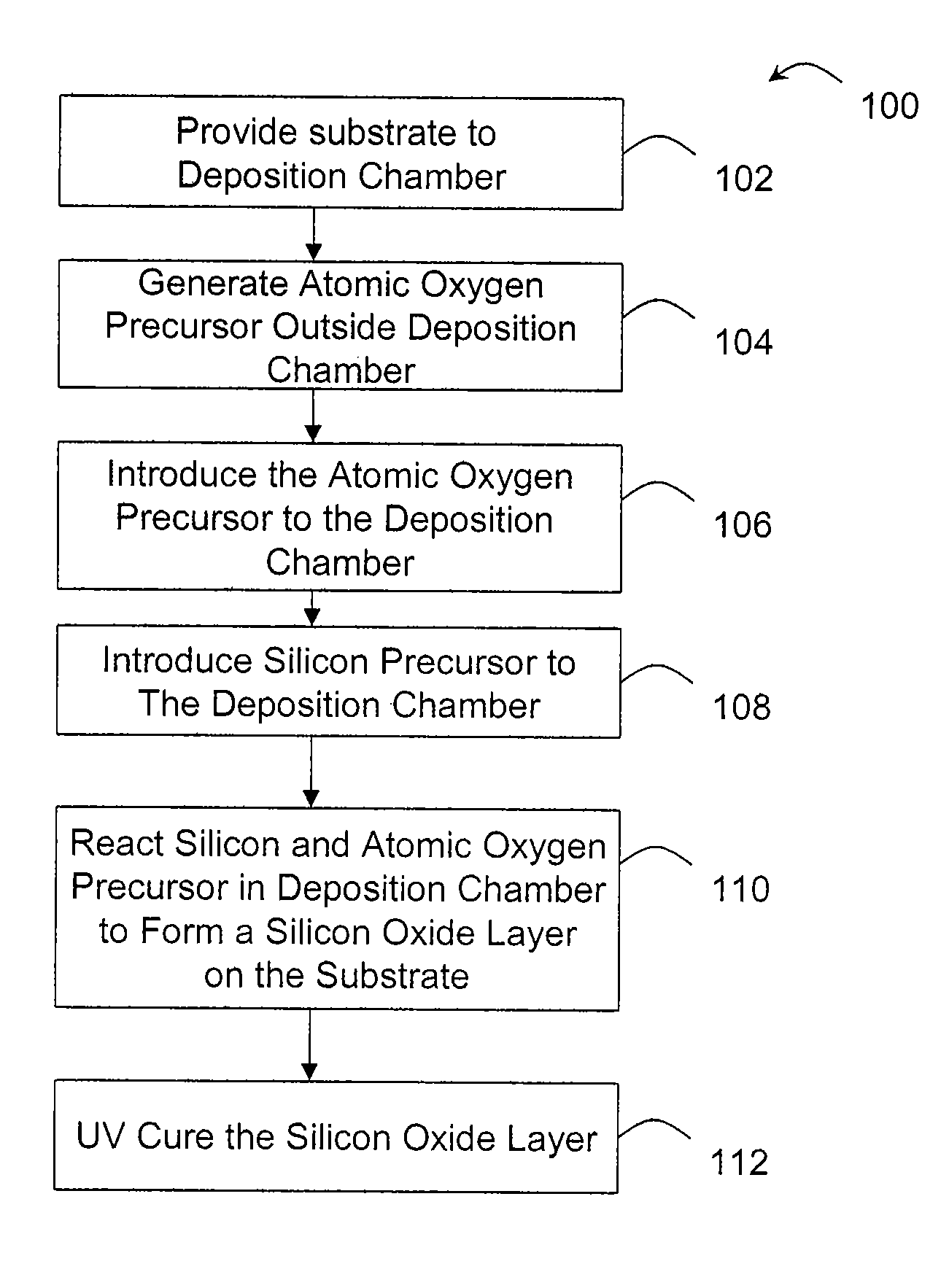

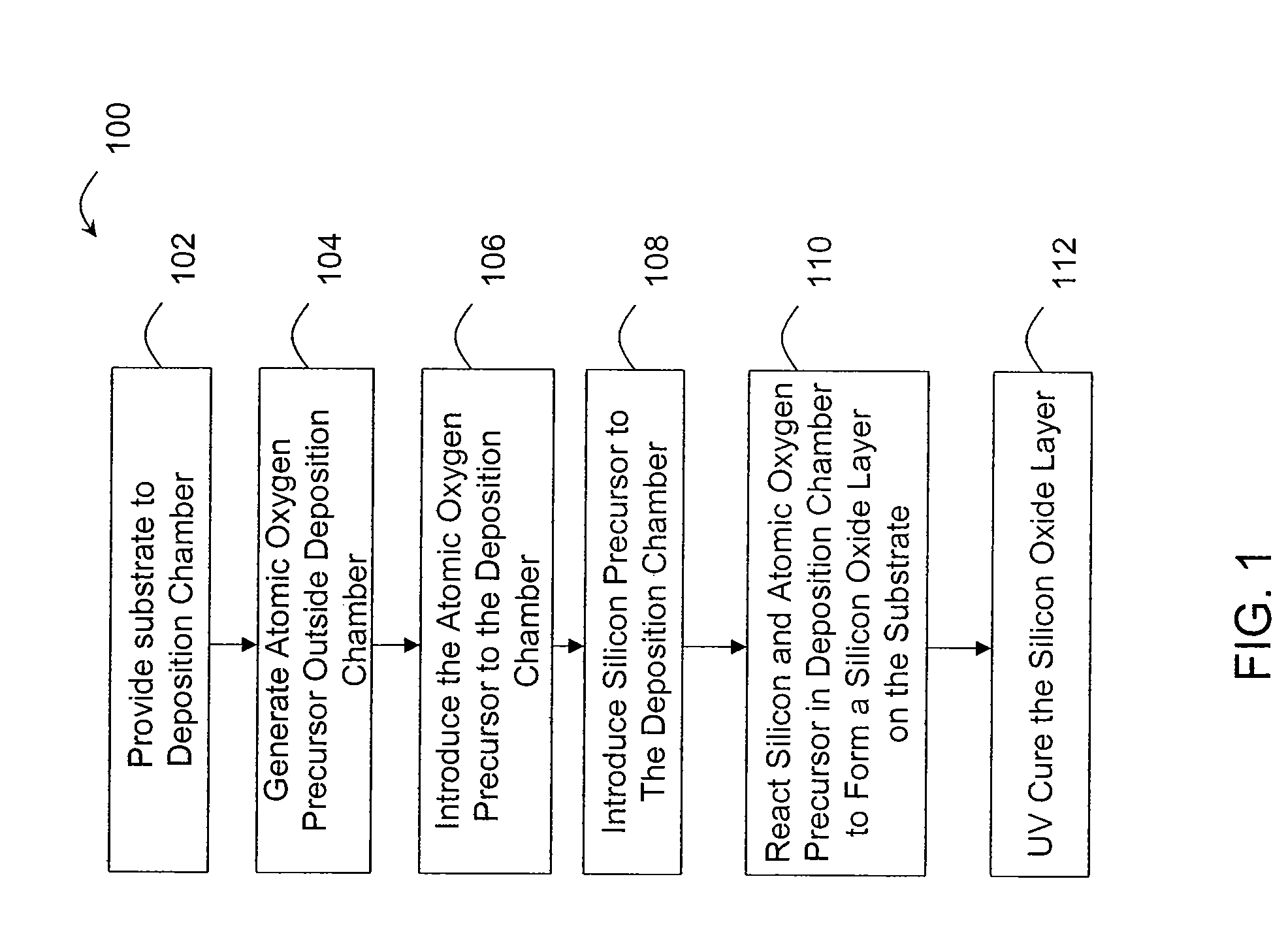

Methods for forming a dielectric layer within trenches

ActiveUS7803722B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSemiconductor structureUltraviolet

A method for forming a semiconductor structure includes reacting a silicon precursor and an atomic oxygen or nitrogen precursor at a processing temperature of about 150° C. or less to form a silicon oxide or silicon-nitrogen containing layer over a substrate. The silicon oxide or silicon-nitrogen containing layer is ultra-violet (UV) cured within an oxygen-containing environment.

Owner:APPLIED MATERIALS INC

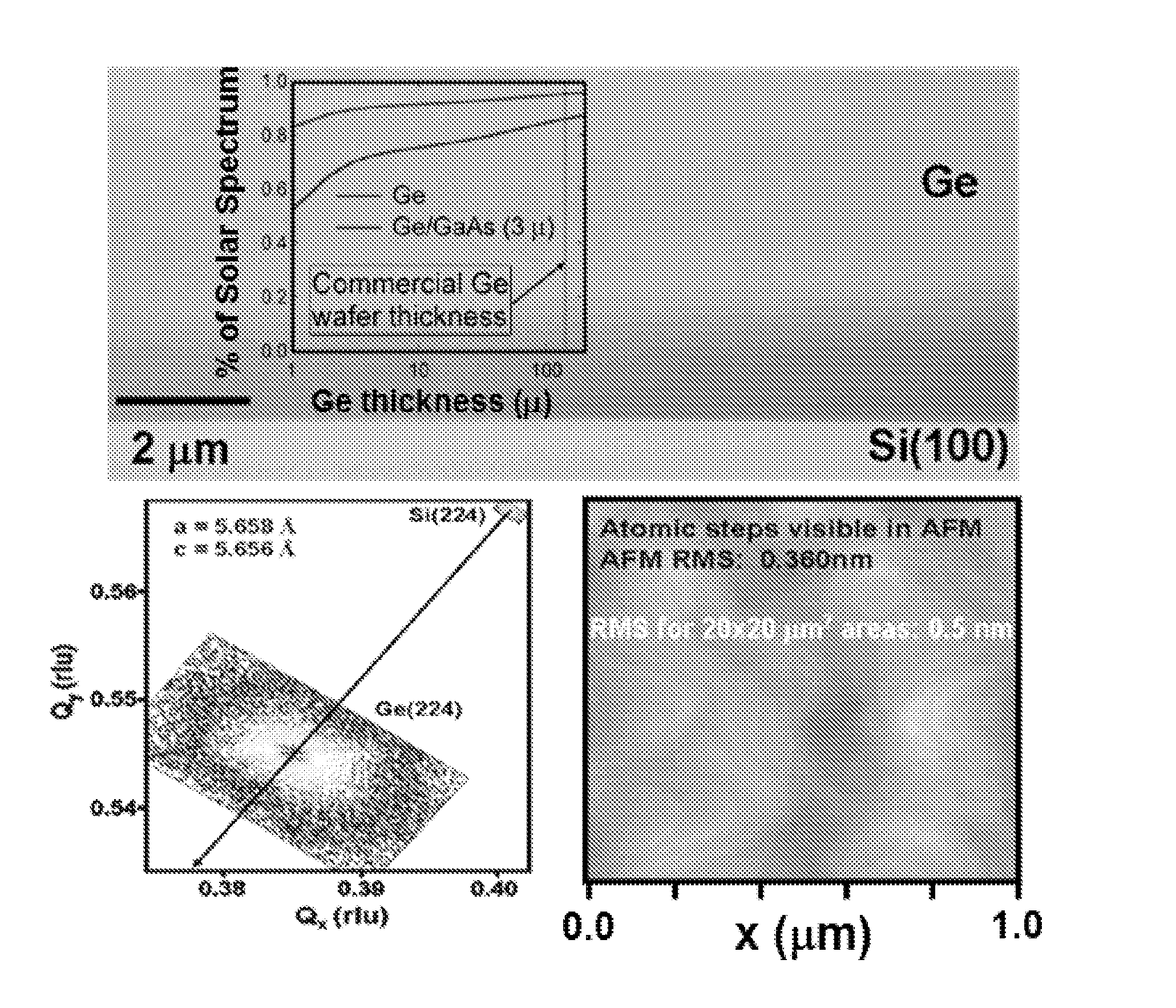

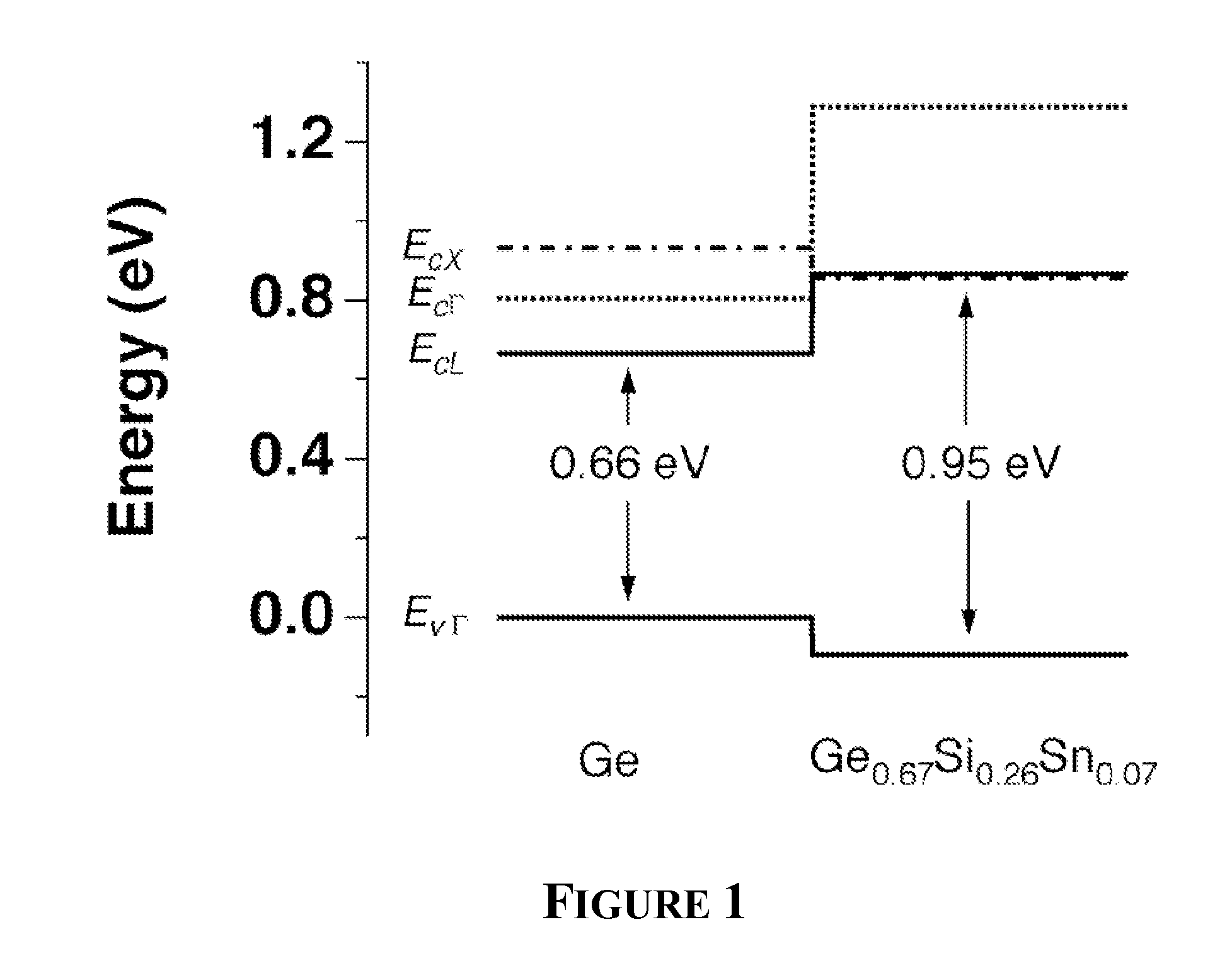

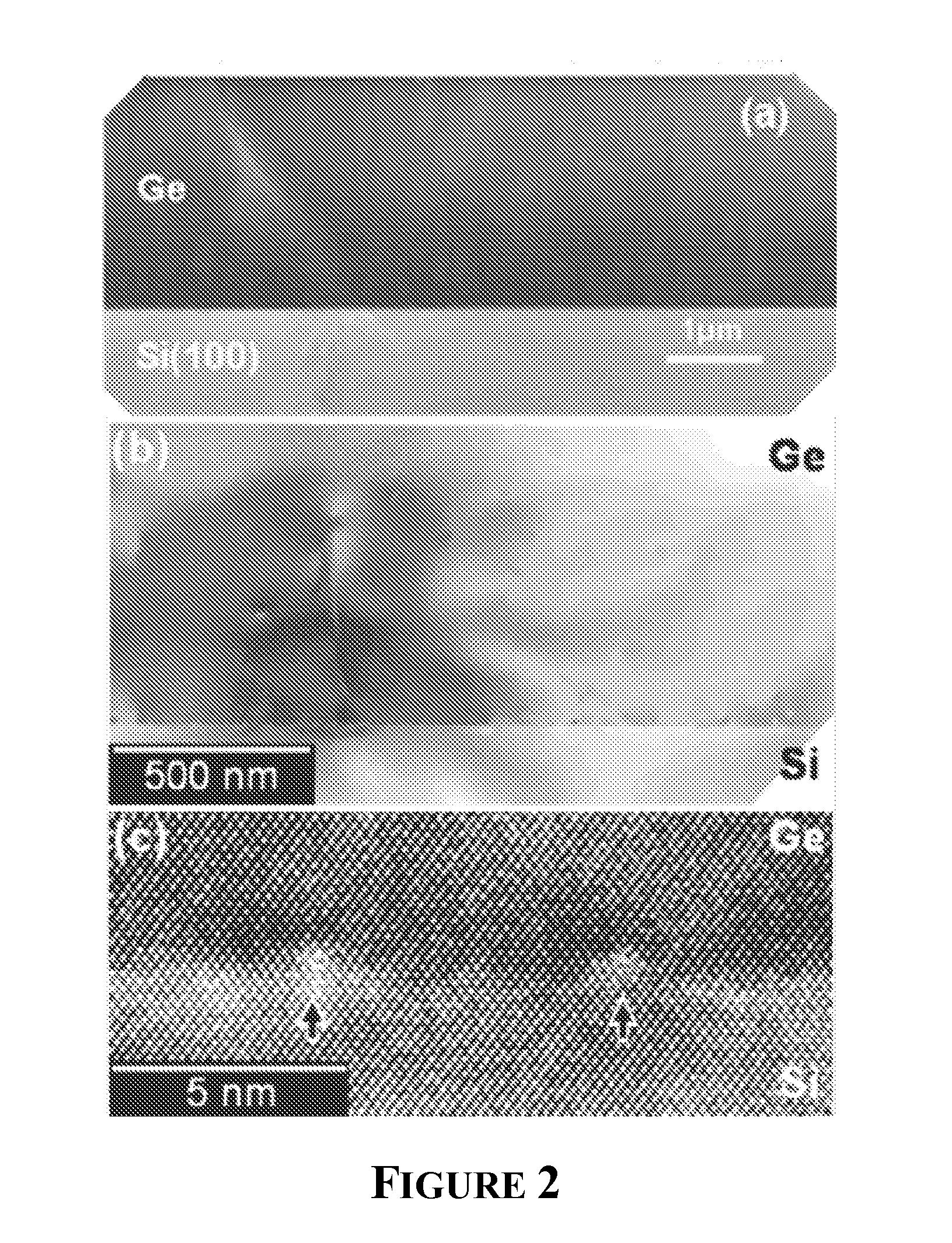

Hybrid Group IV/III-V Semiconductor Structures

InactiveUS20110254052A1Low costImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor structureAlloy

Described herein are semiconductor structures comprising (i) a Si substrate; (ii) a buffer region formed directly over the Si substrate, wherein the buffer region comprises (a) a Ge layer having a threading dislocation density below about 105 cm−2; or (b) a Ge1-xSnx layer formed directly over the Si substrate and a Ge1-x-ySixSny layer formed over the Ge1-xSnx layer; and (iii) a plurality of III-V active blocks formed over the buffer region, wherein the first III-V active block formed over the buffer region is lattice matched or pseudomorphically strained to the buffer region. Further, methods for forming the semiconductor structures are provided and novel Ge1-x-ySixSny, alloys are provided that are lattice matched or pseudomorphically strained to Ge and have tunable band gaps ranging from about 0.80 eV to about 1.4O eV.

Owner:ARIZONA STATE UNIVERSITY

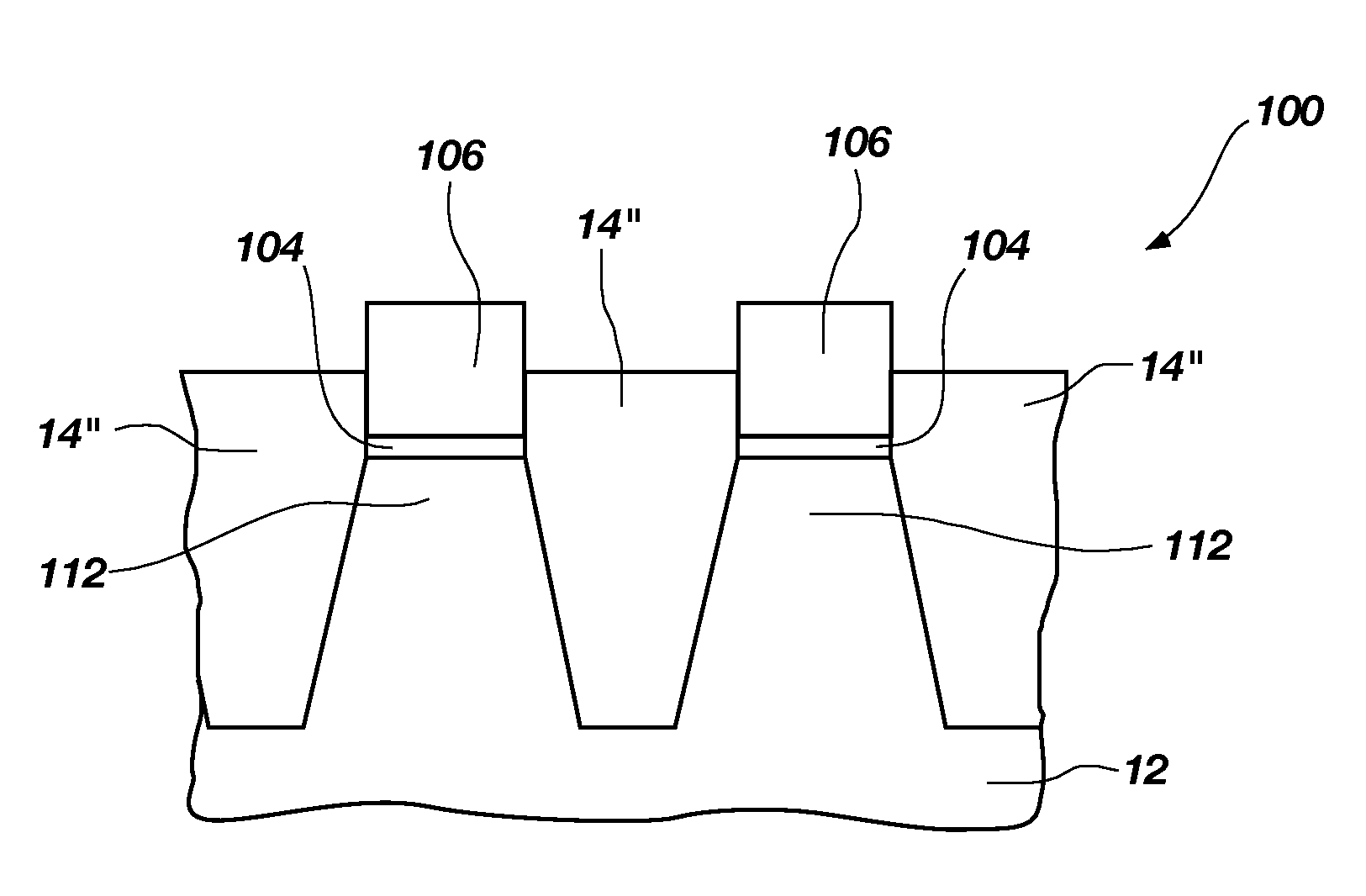

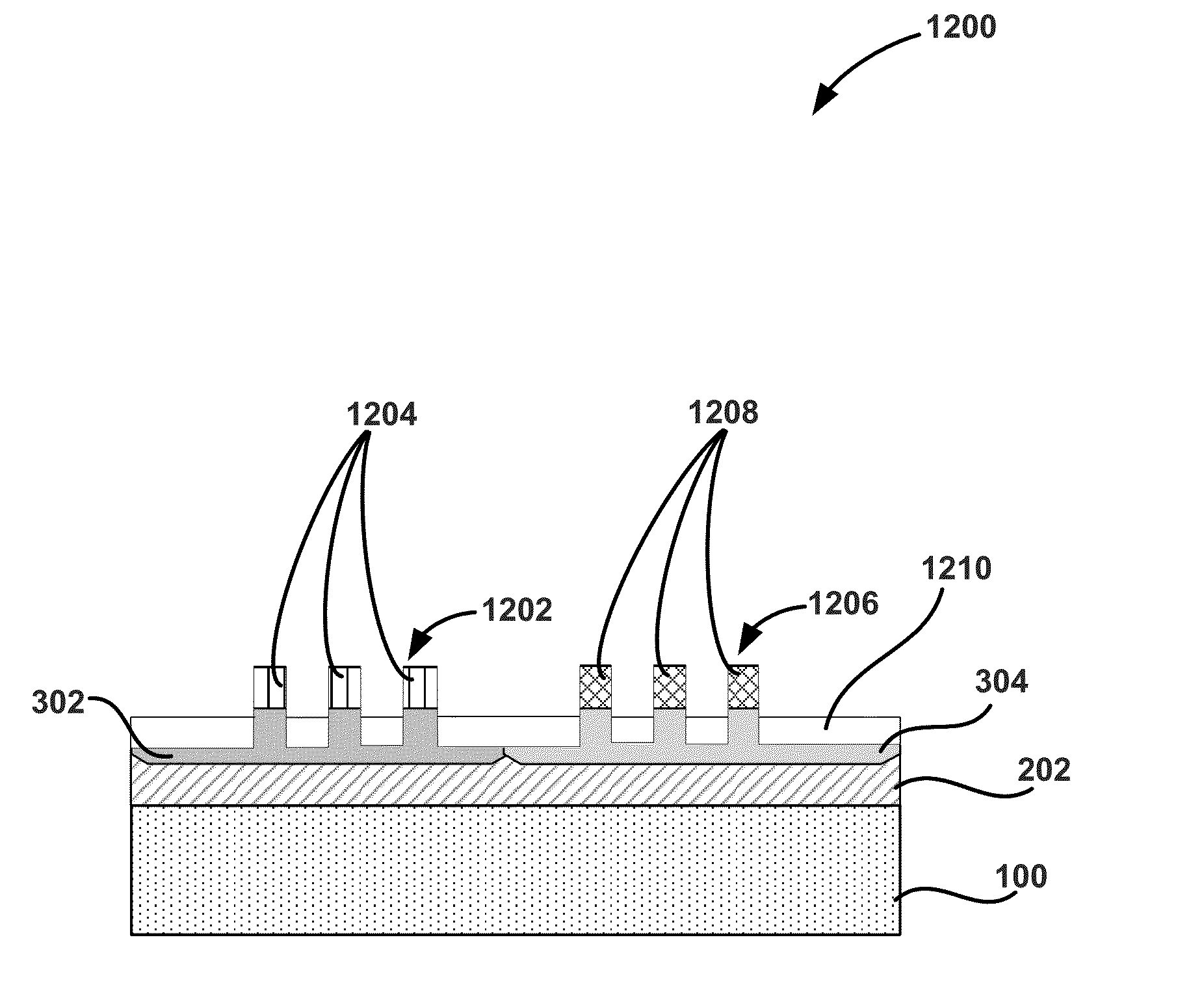

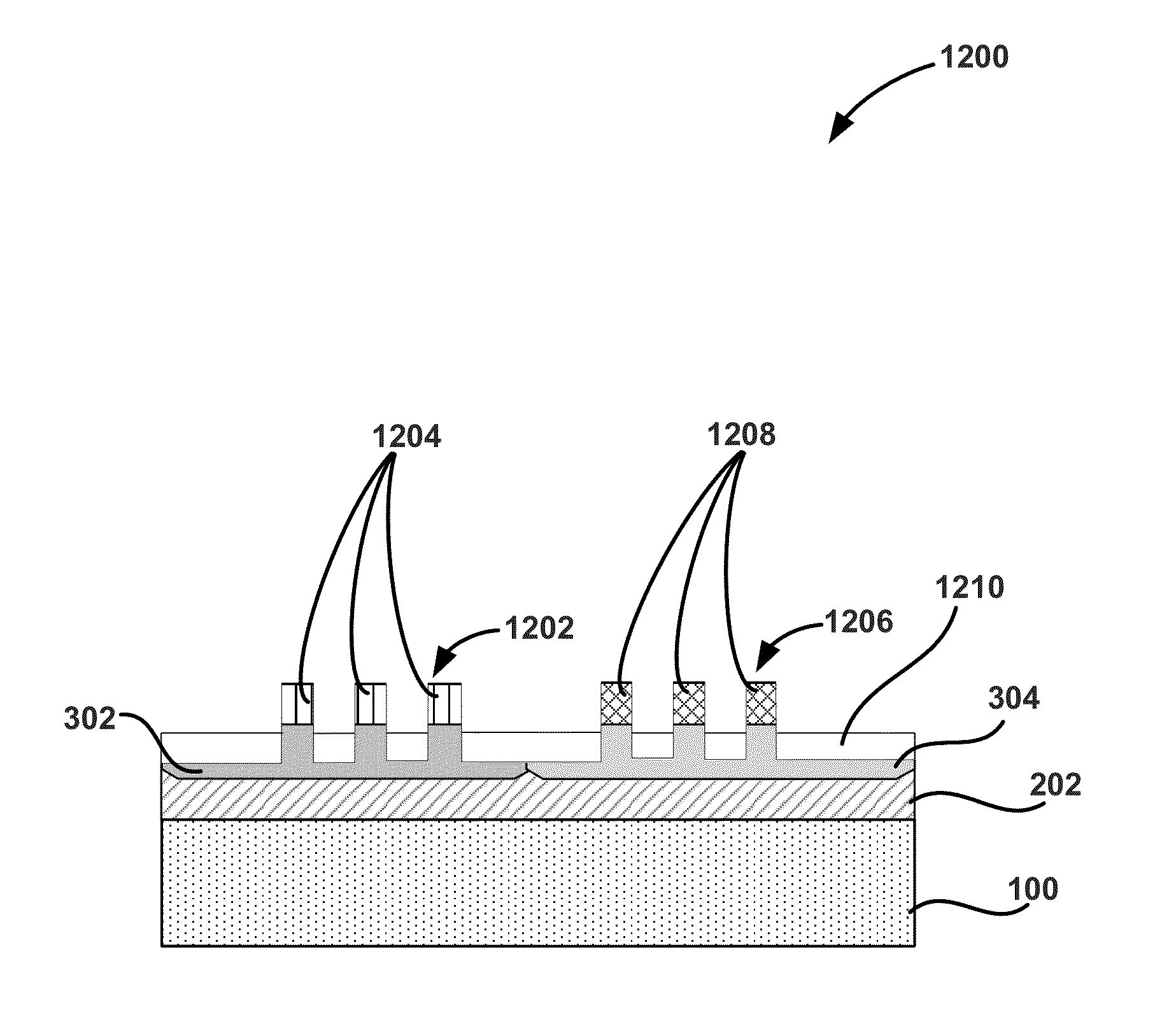

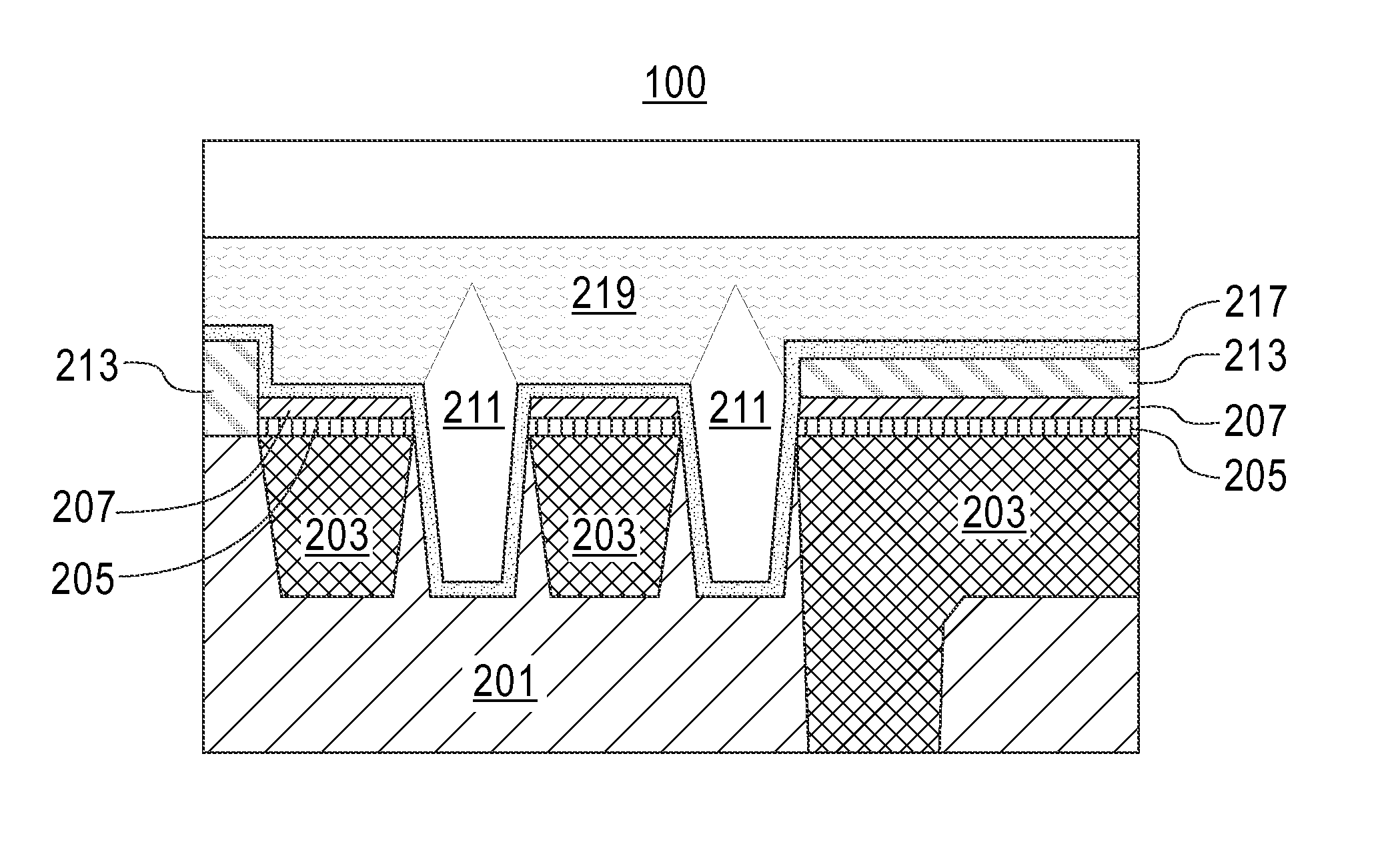

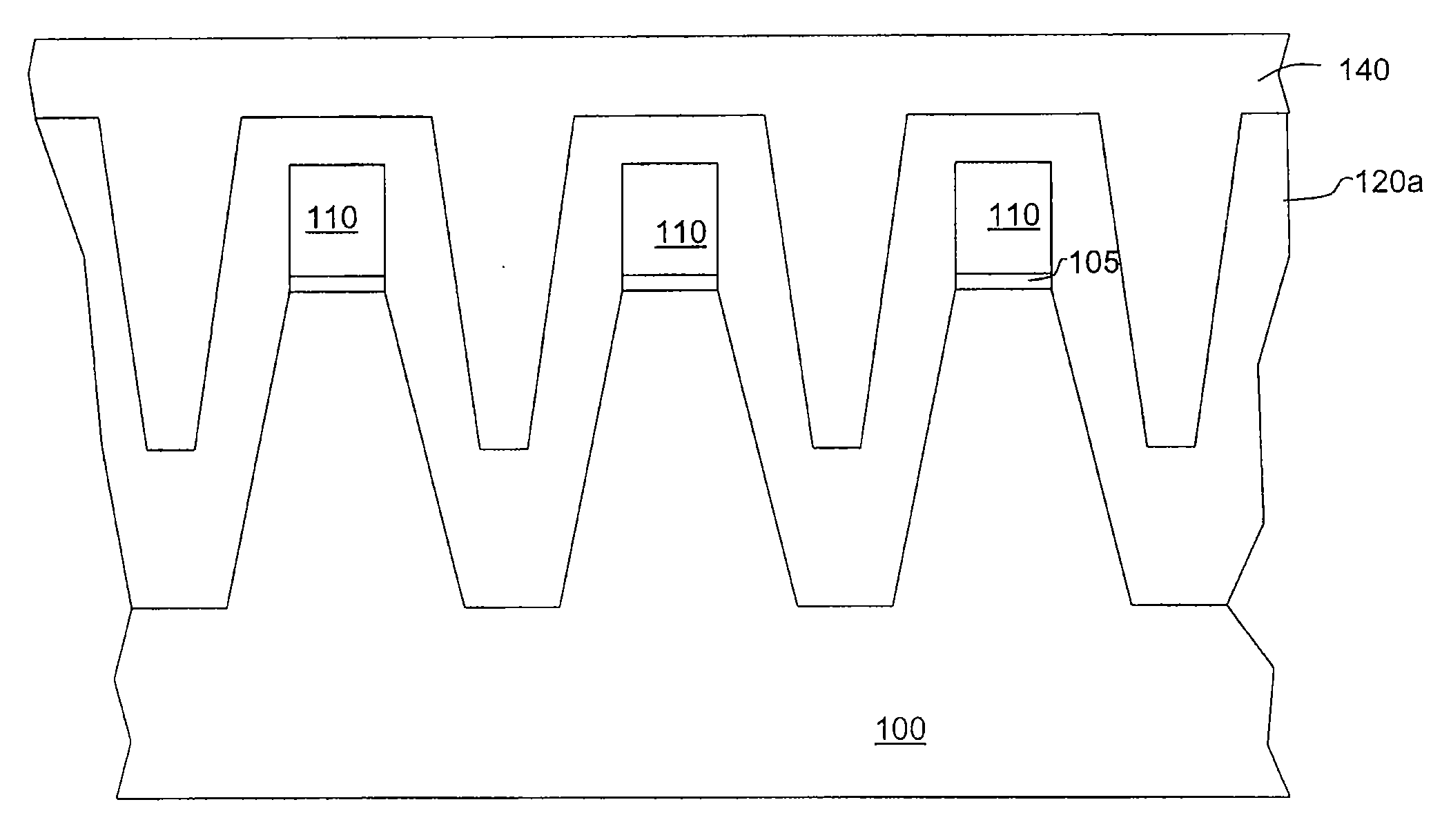

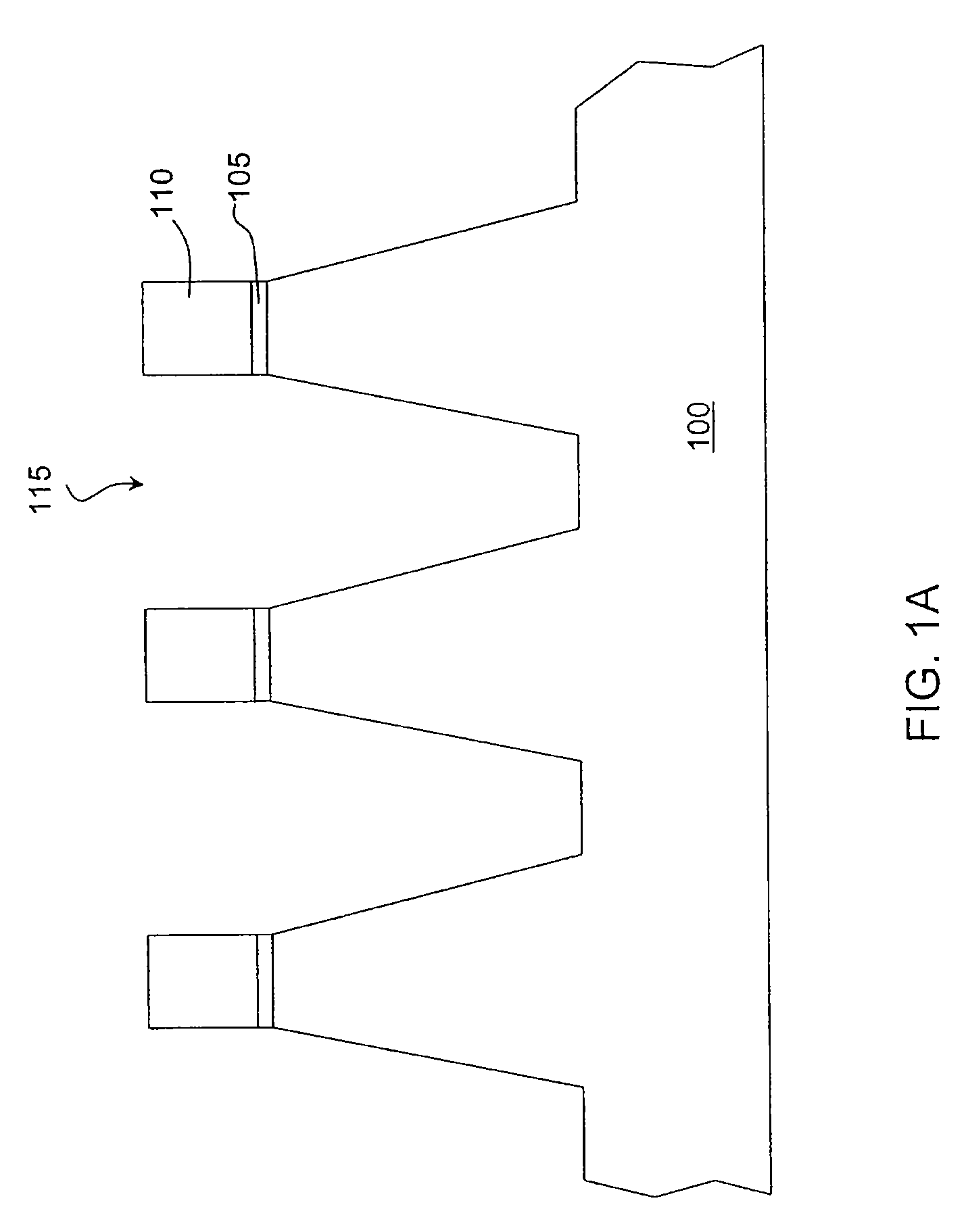

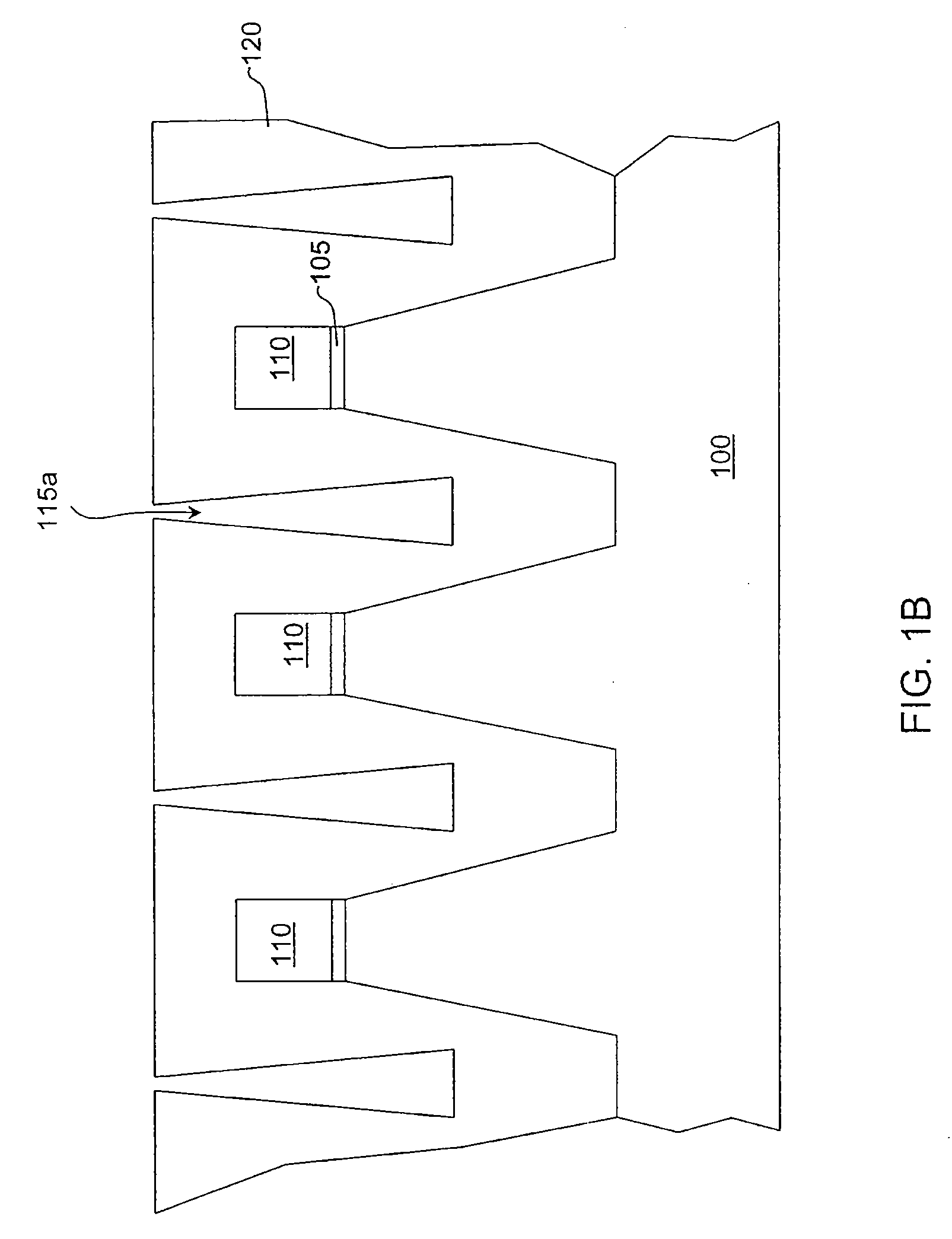

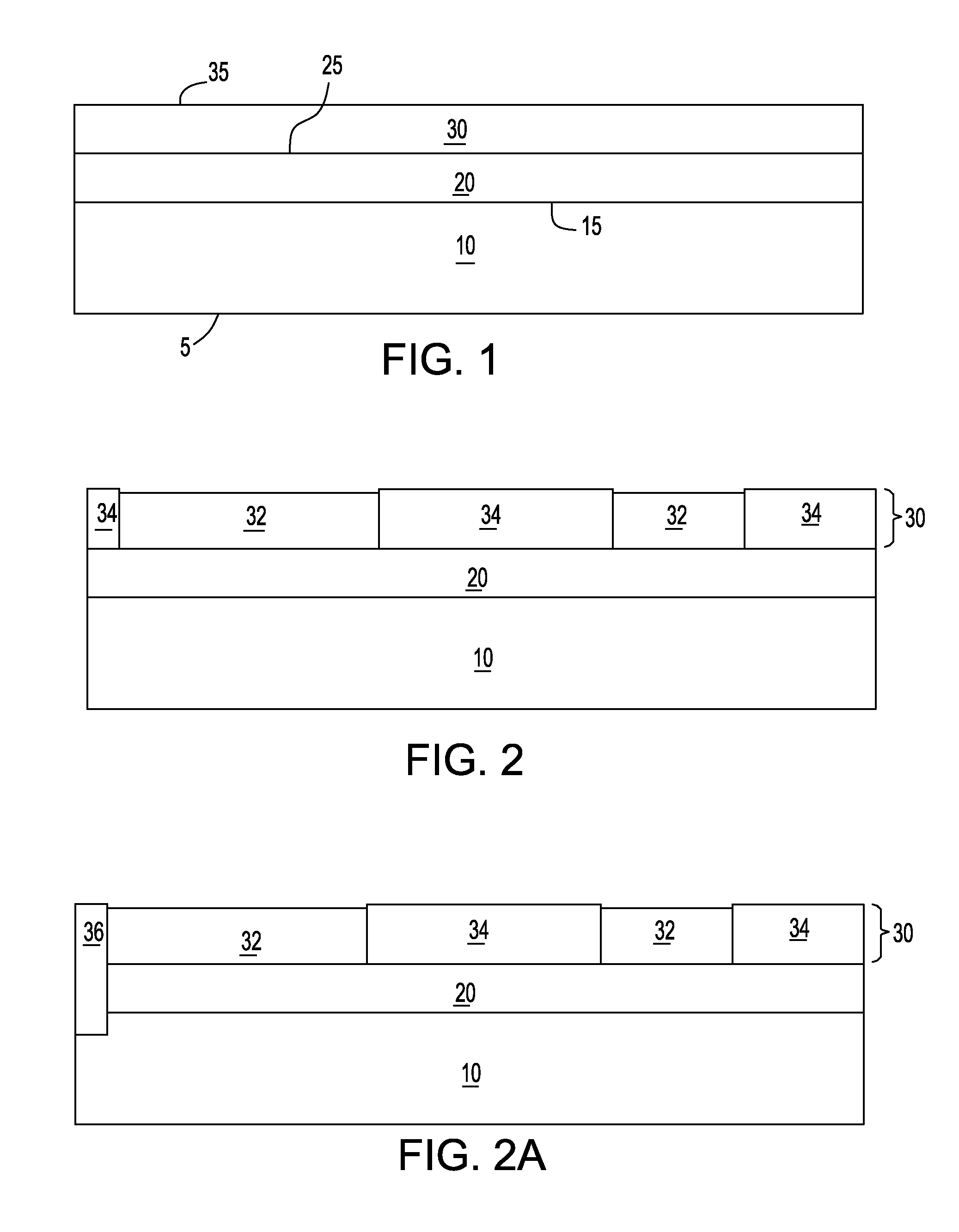

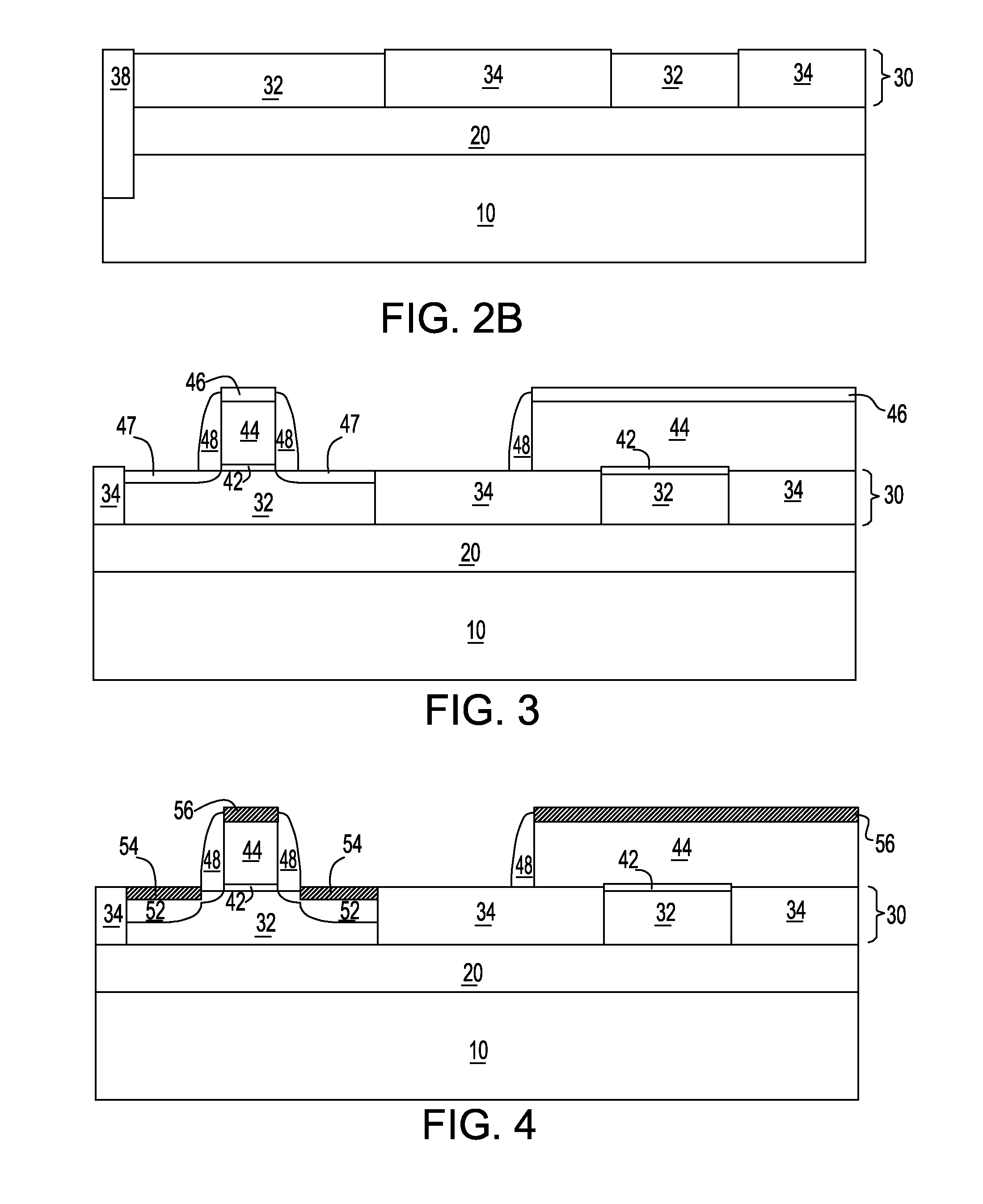

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both n-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

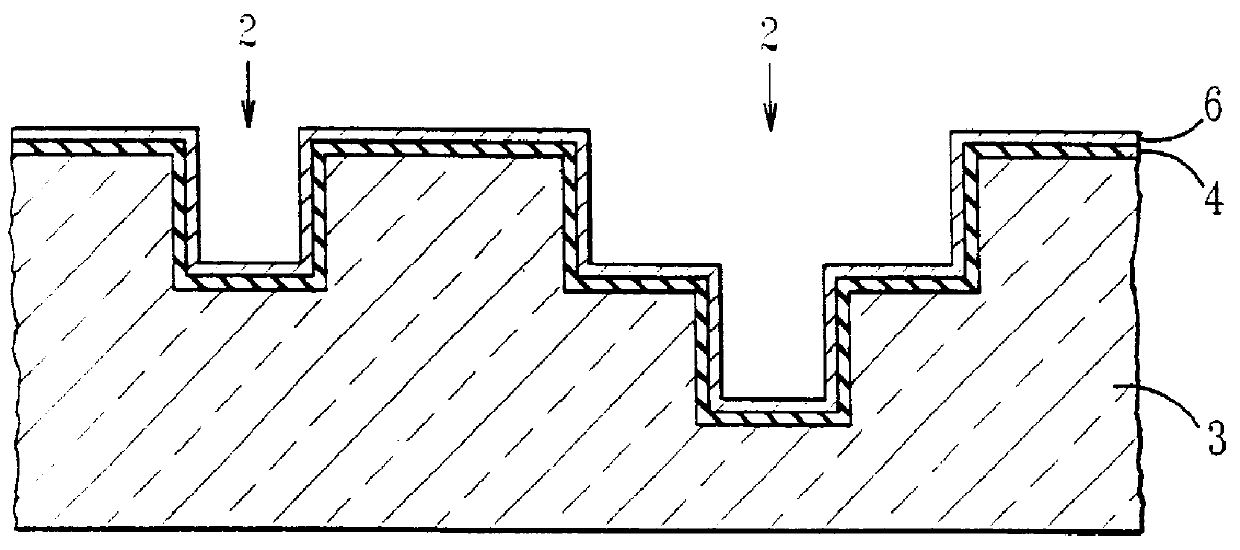

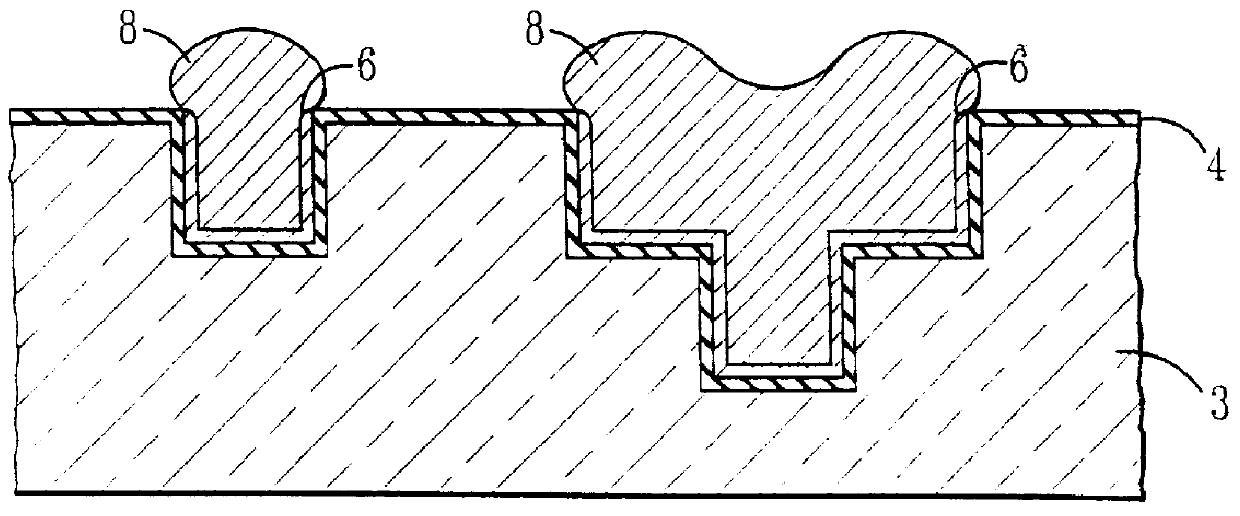

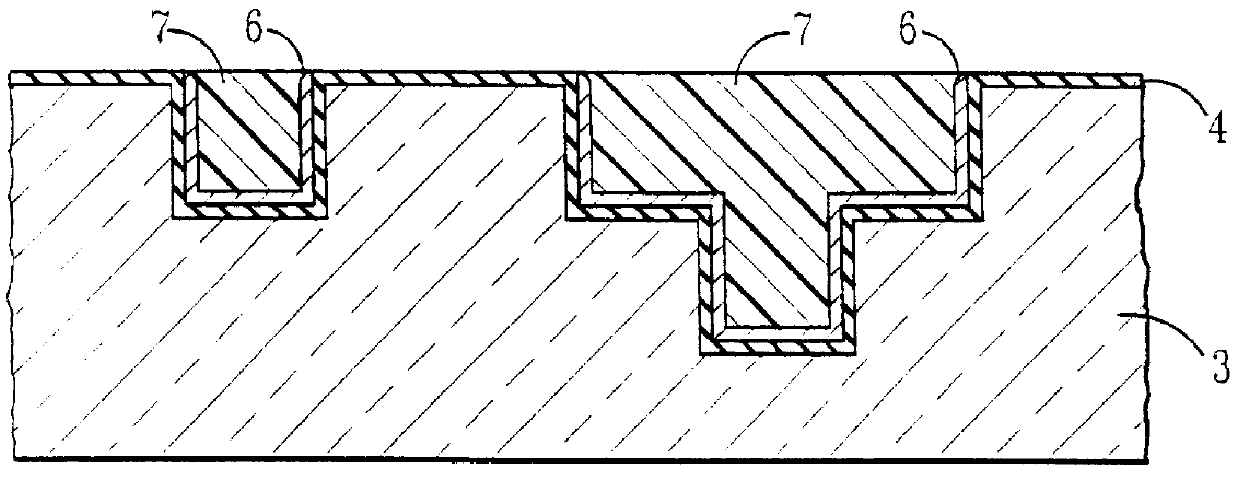

Method to selectively fill recesses with conductive metal

InactiveUS6140234AShorten the timeIncrease productionSolid-state devicesSemiconductor/solid-state device manufacturingResistSemiconductor structure

Recesses in a semiconductor structure are selectively plated by providing electrical insulating layer over the semiconductor substrate and in the recesses followed by forming a conductive barrier over the insulating layer; providing a plating seed layer over the barrier layer; depositing and patterning a photoresist layer over the plating seed layer; planarizing the insulated horizontal portions by removing the horizontal portions of the seed layer between the recesses; removing the photoresist remaining in the recesses; and then electroplating the patterned seed layer with a conductive metal using the barrier layer to carry the current during the electroplating to thereby only plate on the seed layer. In an alternative process, a barrier film is deposited over recesses in an insulator. Then, relatively thick resists are lithographically defined on the field regions, on top of the barrier film over the recesses. A plating base or seedlayer is deposited, so as to be continuous on the horizontal regions of the recesses in the insulator, but discontinuous on their surround wall. The recesses are then plated using the barrier film without seedlayers at the periphery of the substrate wafers for electrical contact. After electroplating, the resist is removed by lift-off process and exposed barrier film is etched by RIE method or by CMP. Also provided is a semiconductor structure obtained by the above processes.

Owner:GLOBALFOUNDRIES INC

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both re-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

Semiconductor structure and device and methods of forming same using selective epitaxial process

Owner:ASM IP HLDG BV

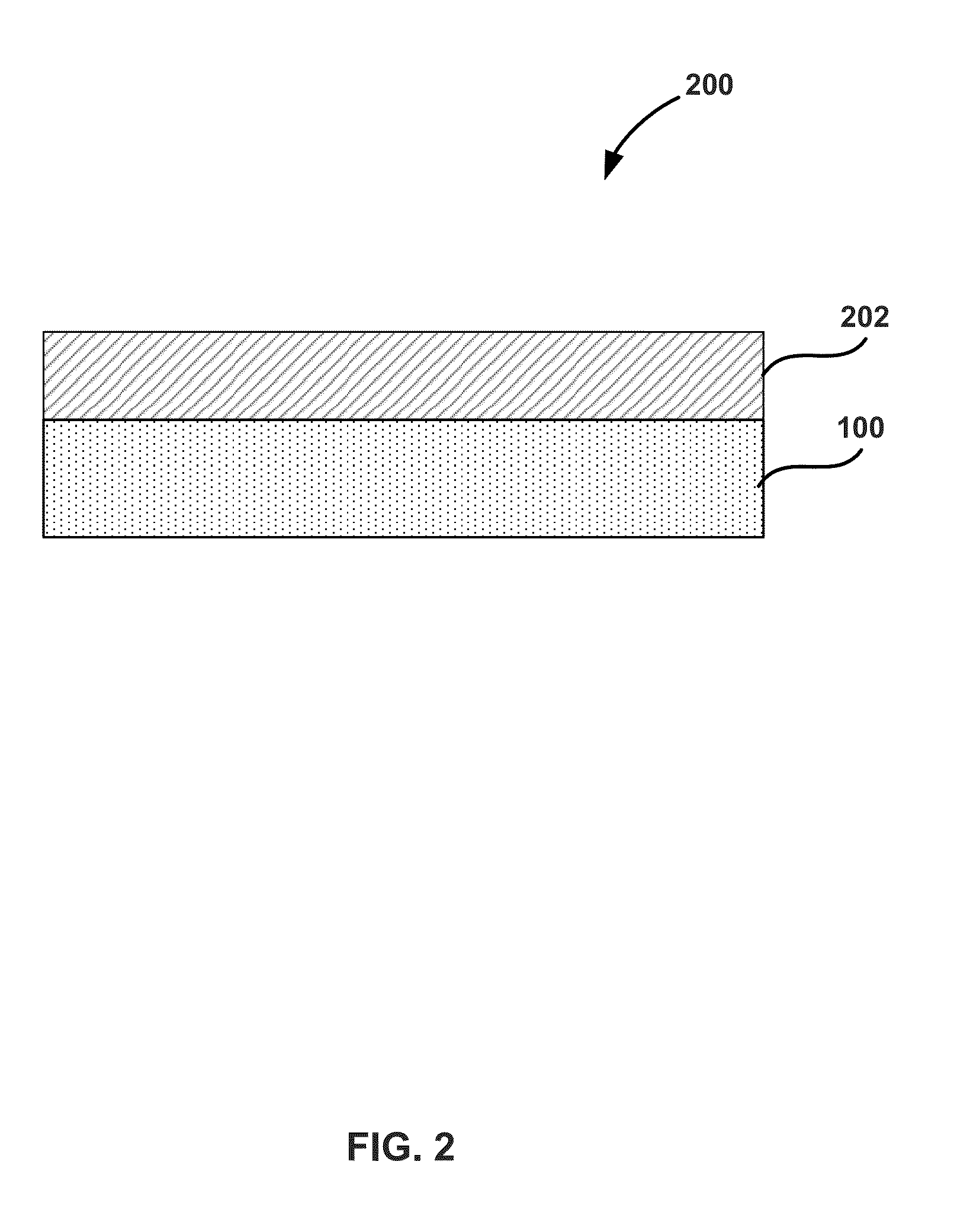

Method for making bonded metal back-plane substrates

InactiveUS6057212AMaintain its interface acuityHigh-temperature bondingSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A method of forming a semiconductor structure, includes steps of growing an oxide layer on a substrate to form a first wafer, separately forming a metal film on an oxidized substrate to form a second wafer, attaching the first and second wafers, performing a heat cycle for the first and second wafers to form a bond between the first and second wafers, and detaching a portion of the first wafer from the second wafer. Thus, a device, such as a back-plane for a semiconductor device, formed by the method includes an oxidized substrate, a metal film formed on the oxidized substrate forming a back-gate, a back-gate oxide formed on the back-gate, and a silicon layer formed on the back-gate oxide.

Owner:IBM CORP

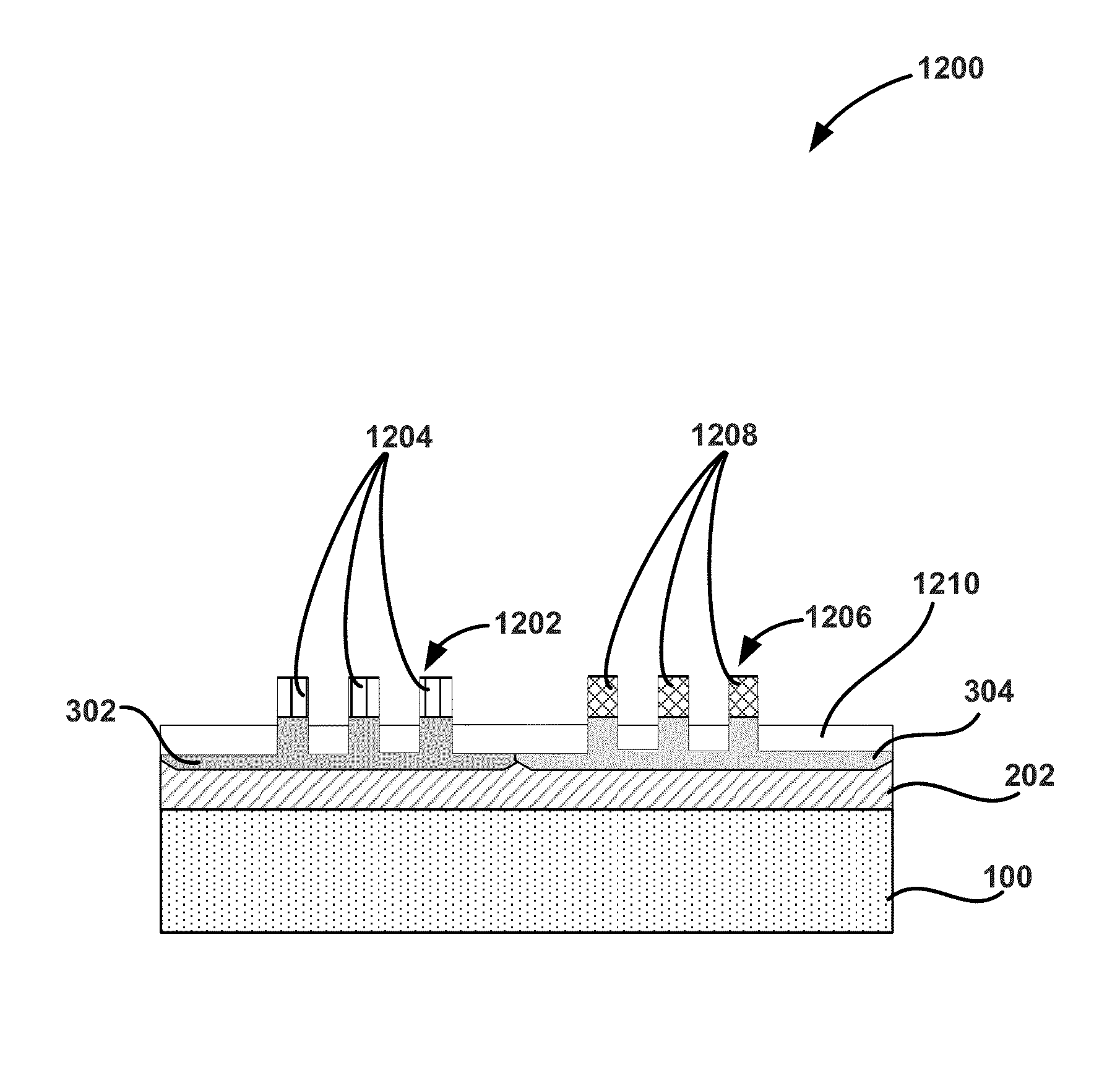

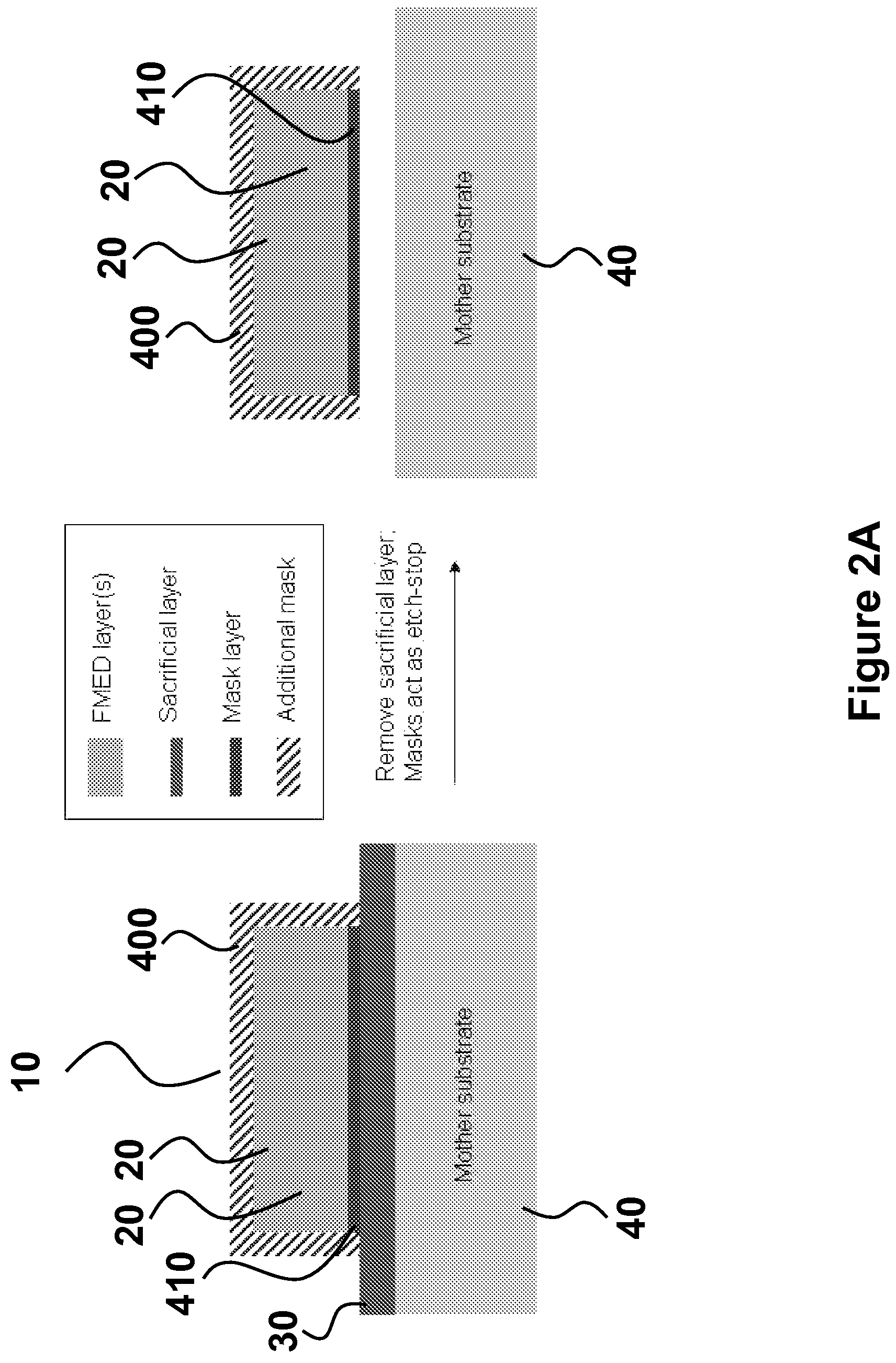

Reinforced composite stamp for dry transfer printing of semiconductor elements

ActiveUS7927976B2Easy to controlPrecise and repeatable vertical motionTurning machine accessoriesMouldsSemiconductor structureContact force

Provided are reinforced composite stamps, devices and methods of making the reinforced composite stamps disclosed herein. Reinforced composite stamps of certain aspects of the present invention have a composition and architecture optimized for use in printing systems for dry transfer printing of semiconductor structures, and impart excellent control over relative spatial placement accuracy of the semiconductor structures being transferred. In some embodiments, for example, reinforced composite stamps of the present invention allow for precise and repeatable vertical motion of the patterned surface of the printing apparatus with self-leveling of the stamp to the surface of a contacted substrate. Reinforced composite stamps of certain aspect of the present invention achieve a uniform distribution of contact forces between the printing apparatus patterned surface and the top surface of a substrate being contacted by the reinforced composite stamp of the printing apparatus.

Owner:X DISPLAY CO TECH LTD

Release strategies for making transferable semiconductor structures, devices and device components

ActiveUS7932123B2Low costReduce layeringFinal product manufactureNanoinformaticsSemiconductor structureElectron

Provided are methods for making a device or device component by providing a multilayer structure having a plurality of functional layers and a plurality of release layers and releasing the functional layers from the multilayer structure by separating one or more of the release layers to generate a plurality of transferable structures. The transferable structures are printed onto a device substrate or device component supported by a device substrate. The methods and systems provide means for making high-quality and low-cost photovoltaic devices, transferable semiconductor structures, (opto-)electronic devices and device components.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

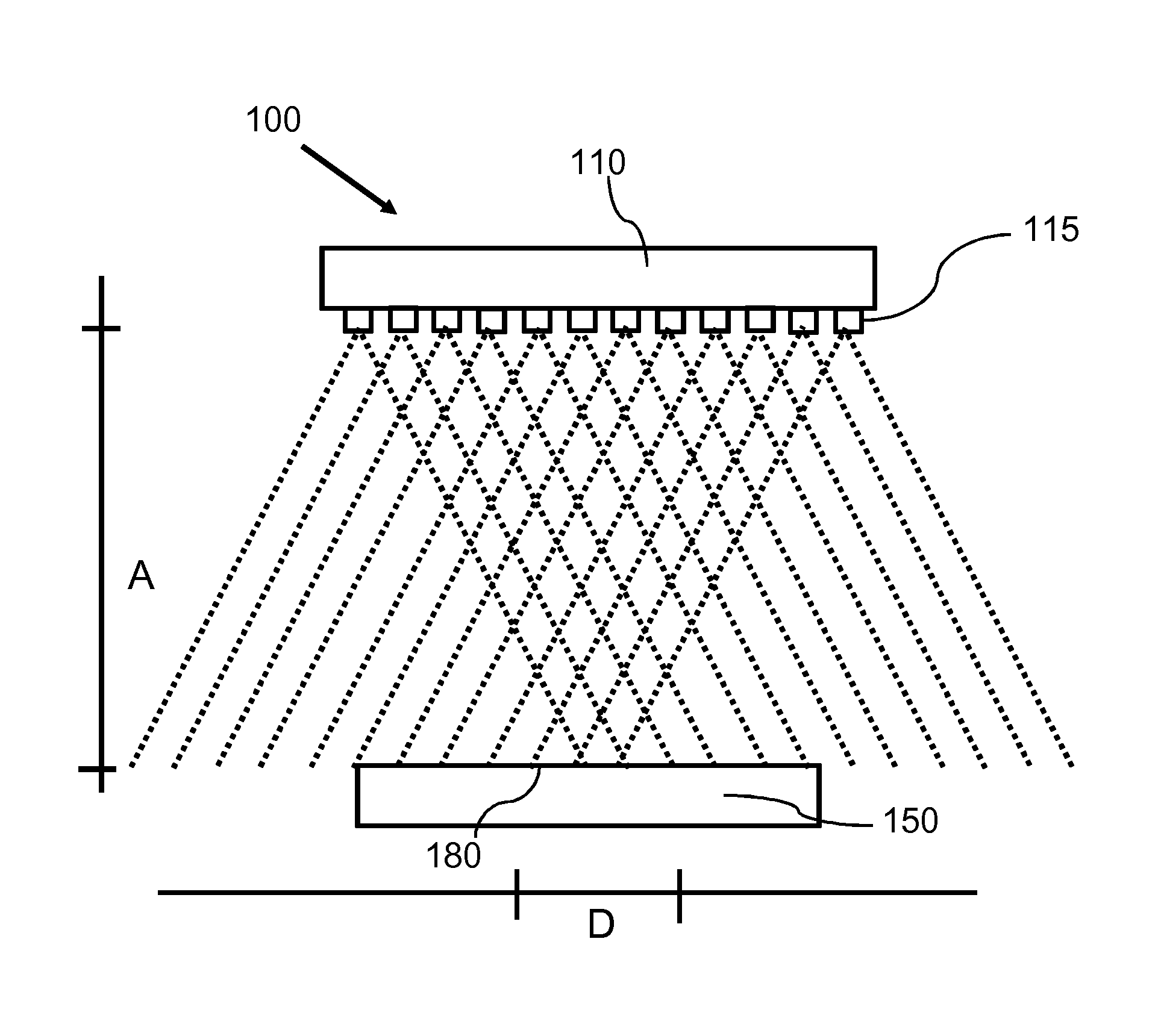

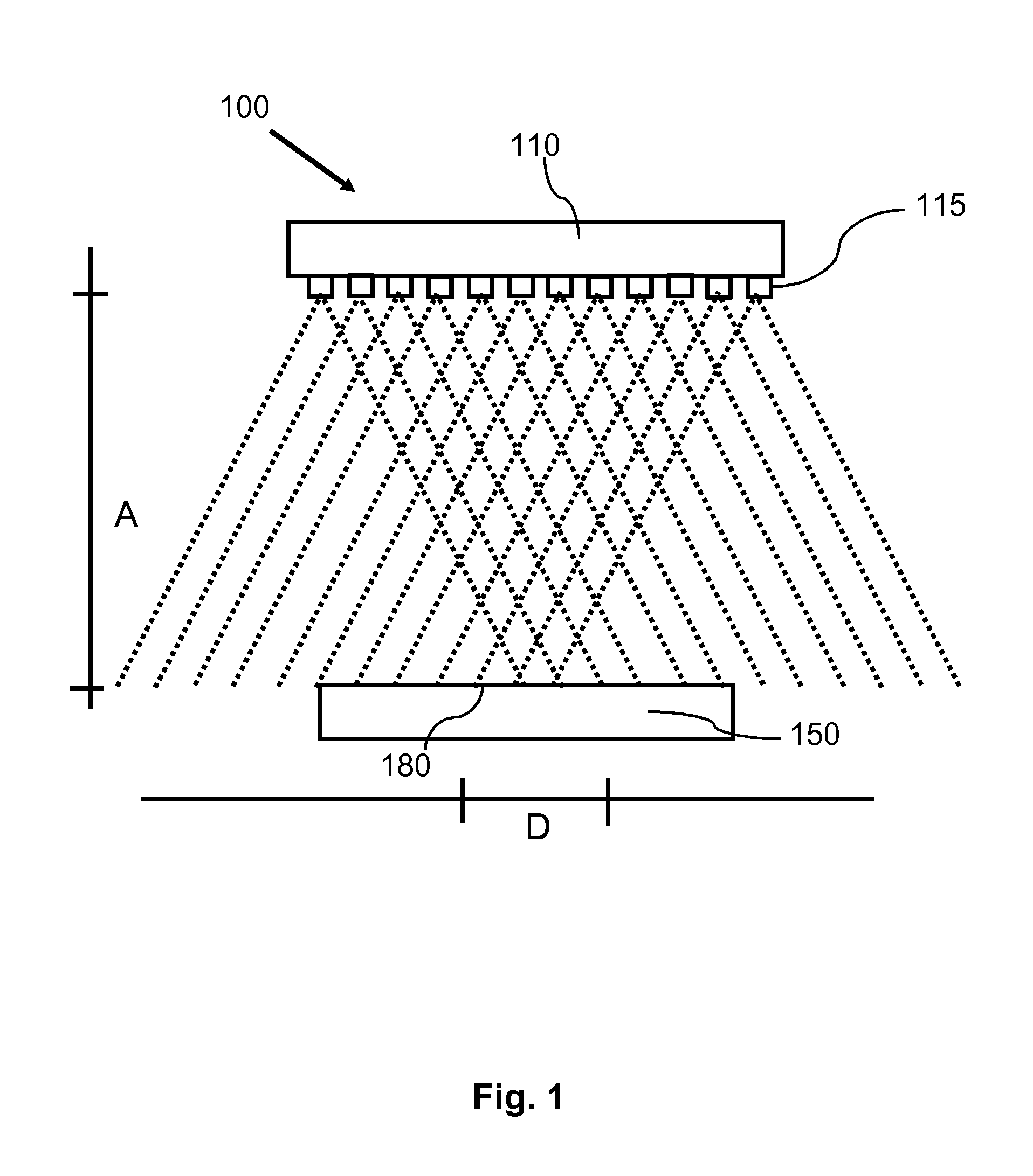

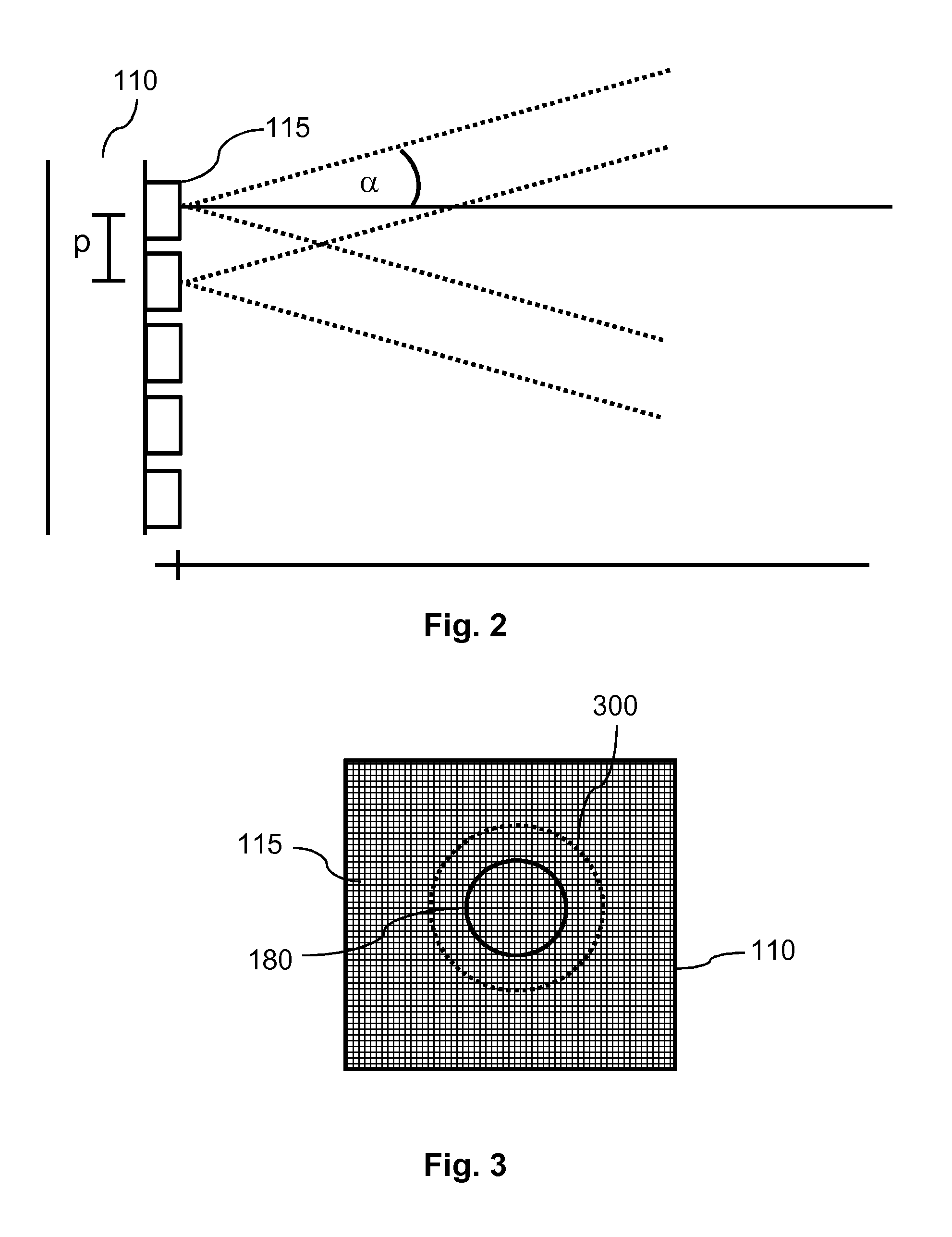

Heating system comprising semiconductor light sources

ActiveUS20160381732A1Improve homogeneityHeating system be improvedSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The invention describes a heating system (100) and a corresponding method of heating a heating surface (180) of an object (150, 950) to a processing temperature of at least 100° C., wherein the heating system (100) comprises semiconductor light sources (115), and wherein the heating system (100) is adapted to heat an area element of the heating surface (180) with at least 50 semiconductor light sources (115) at the same time. The heating system (100) may be part of a reactor for processing semiconductor structures. The light emitted by means of the semiconductor light sources (115) overlaps at the heating surface (180). Differences of the characteristic of one single semiconductor light source (115) may be blurred at the heating surface (180) such that a homogeneous temperature distribution across a processing surface of a, for example, wafer may be enabled.

Owner:TRUMPF PHOTONIC COMPONENTS GMBH

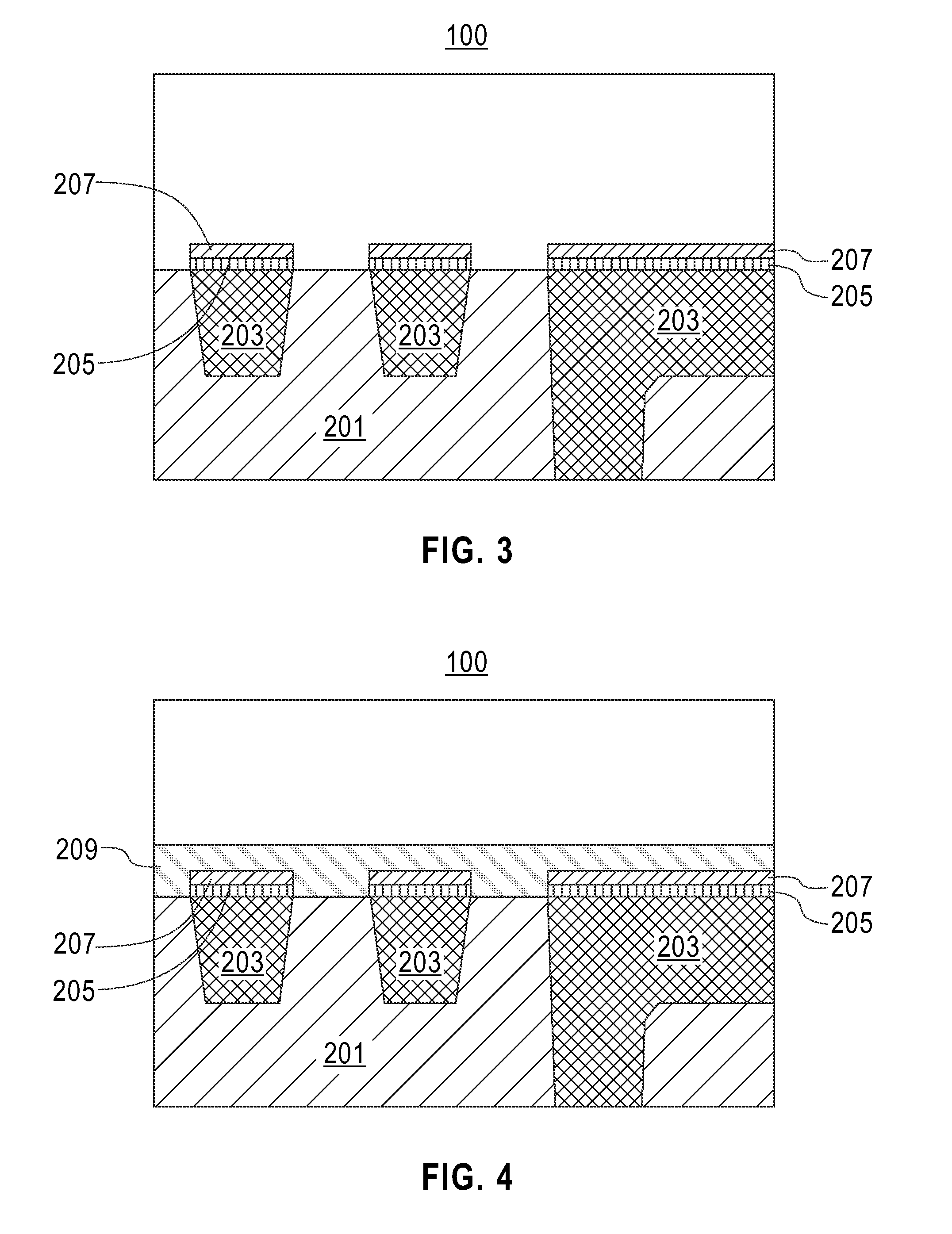

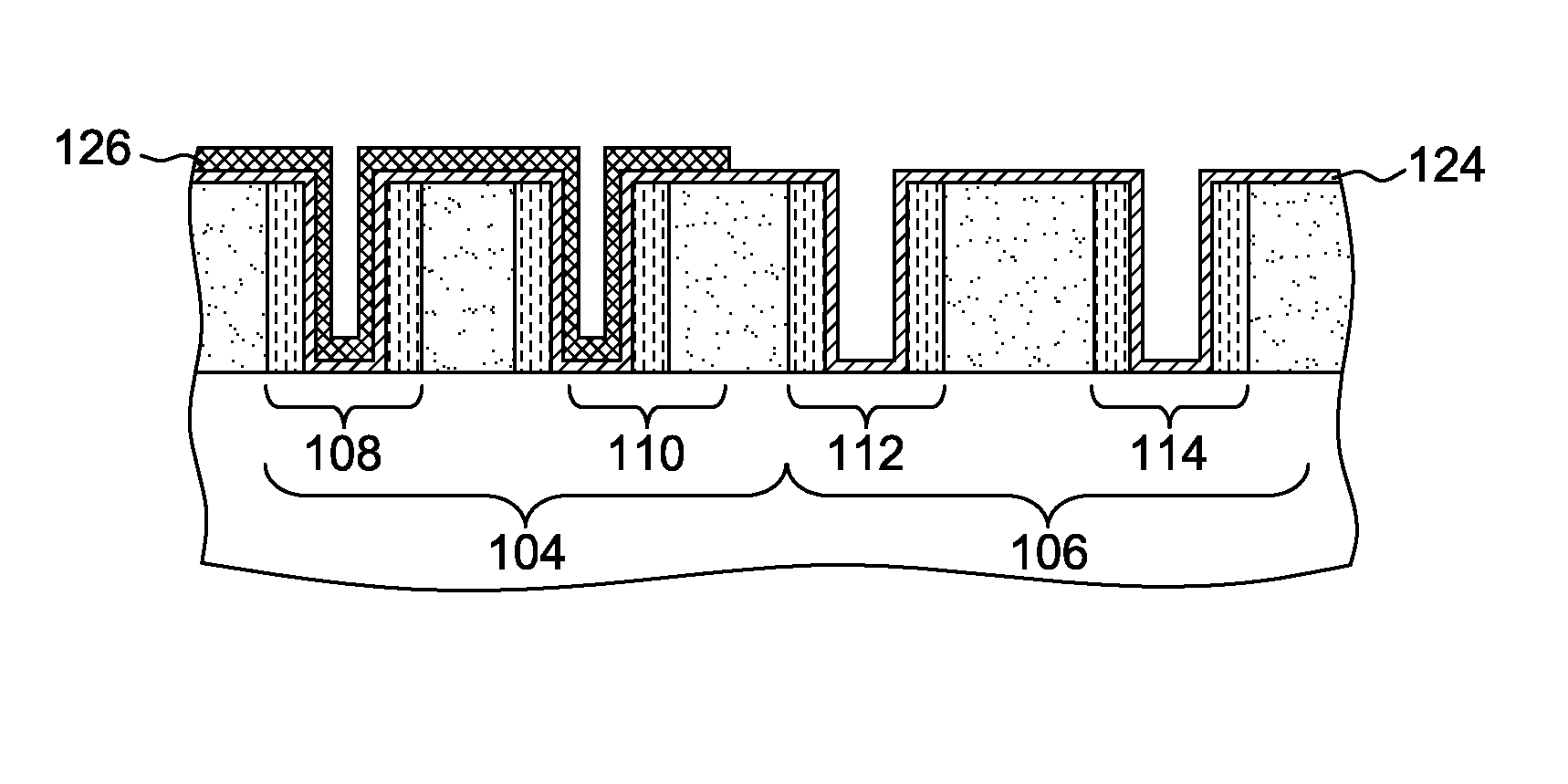

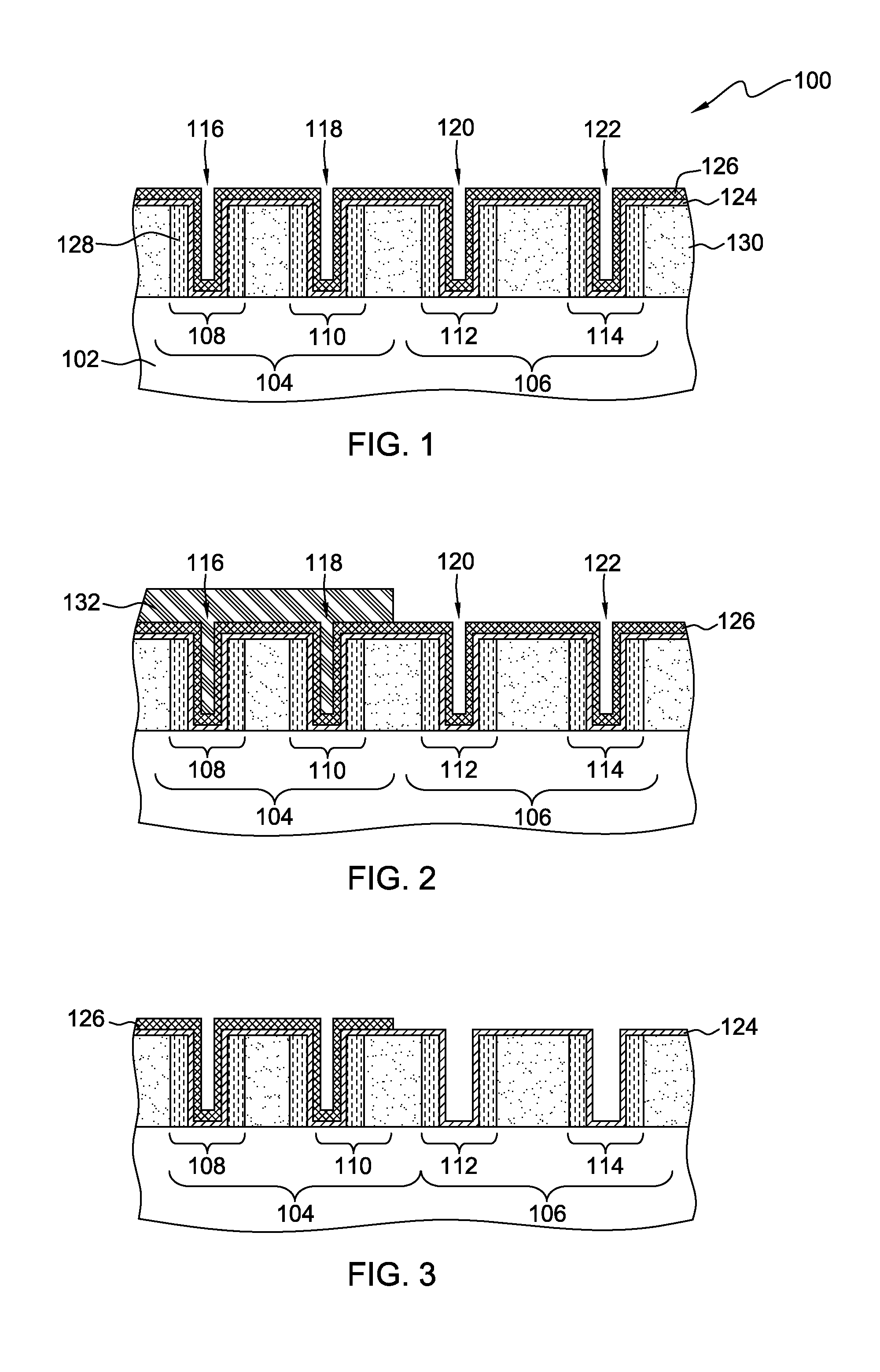

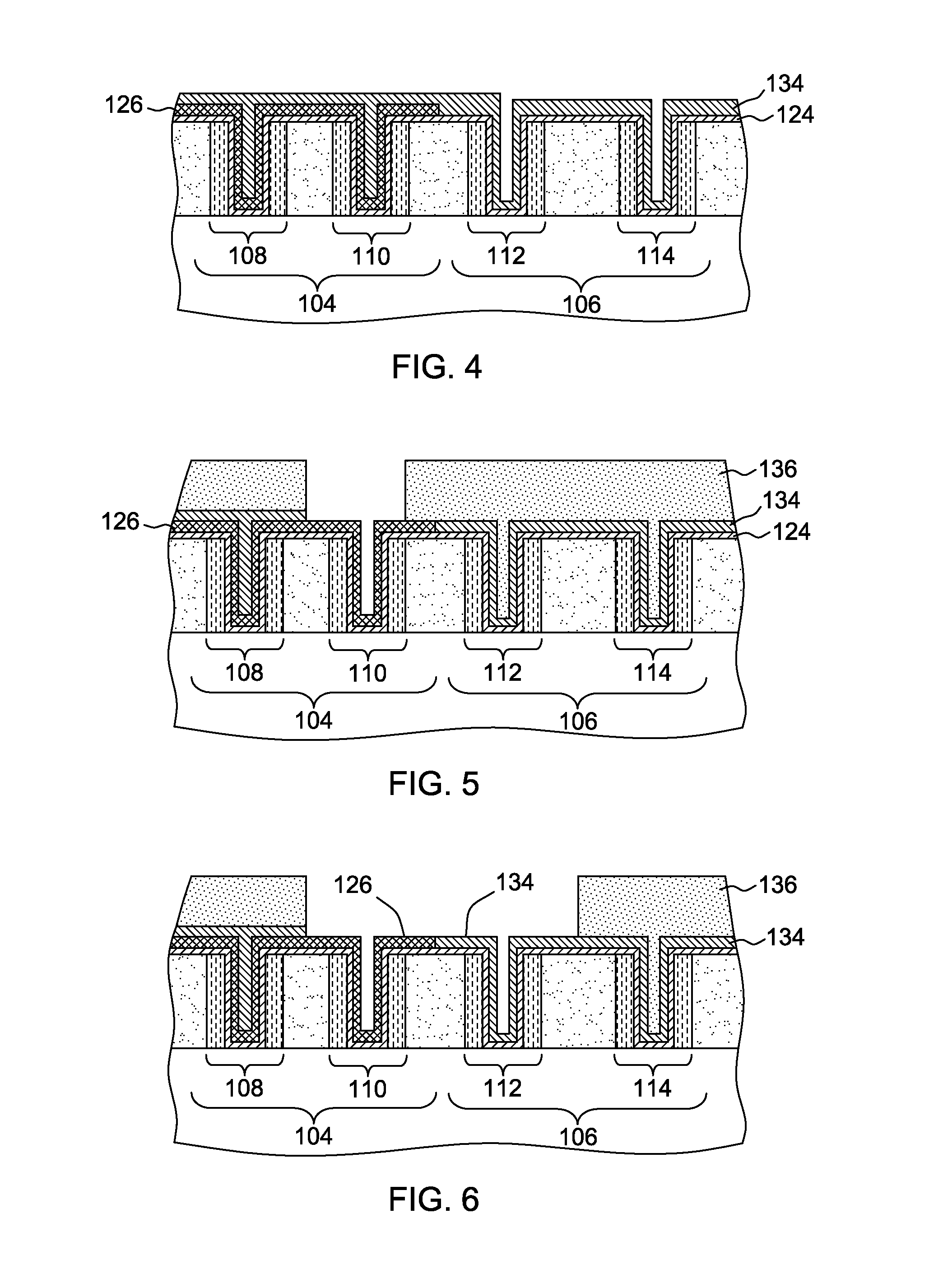

Air gap semiconductor structure with selective cap bilayer

ActiveUS9305836B1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor structure

A semiconductor substrate including one or more conductors is provided. A first layer and a second layer are deposited on the top surface of the conductors. A dielectric cap layer is formed over the semiconductor substrate and air gaps are etched into the dielectric layer. The result is a bilayer cap air gap structure with effective electrical performance.

Owner:TESSERA INC

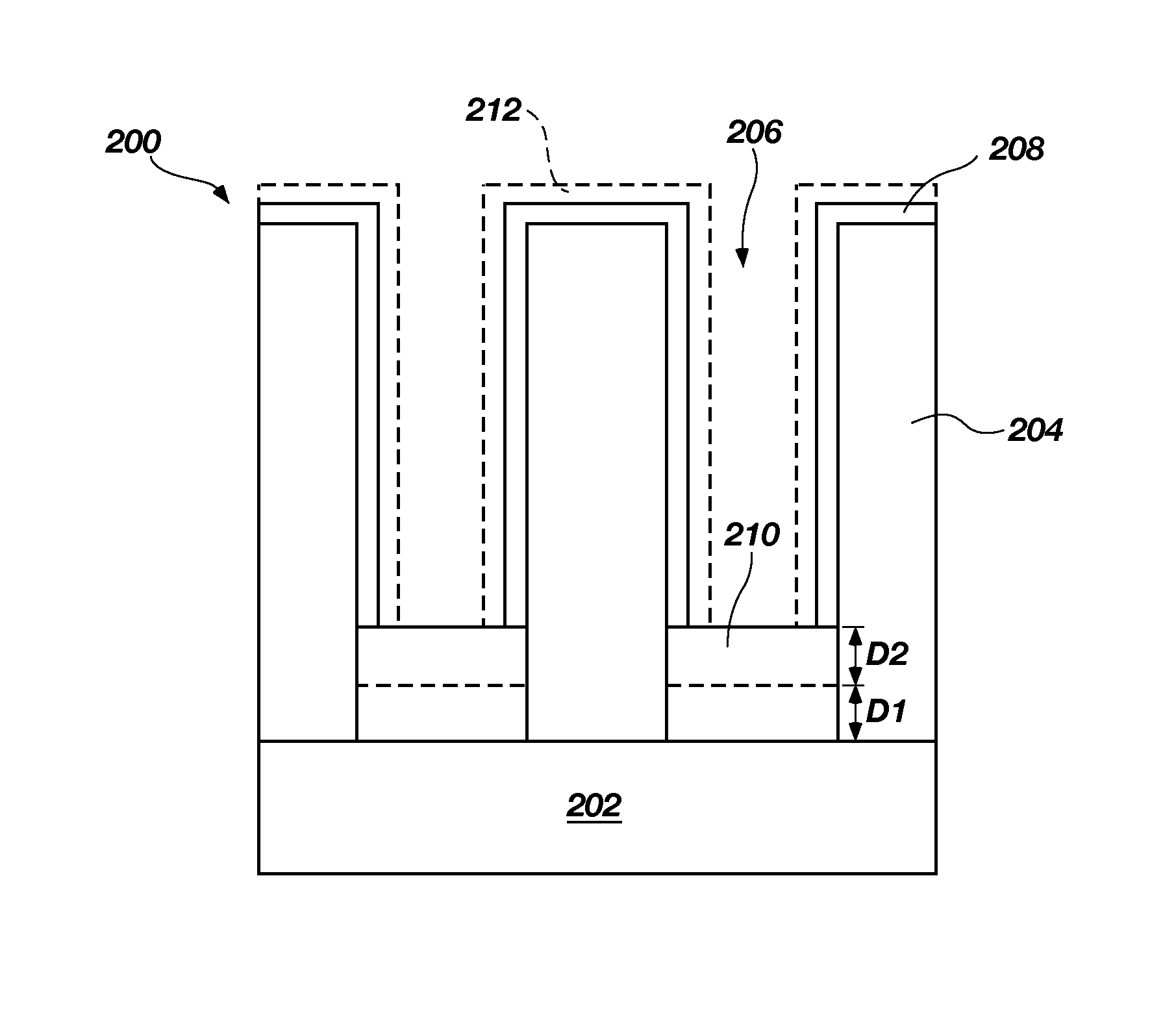

Methods of selectively forming a material using parylene coating

ActiveUS8945305B2Polycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductor structureSelective deposition

Methods for depositing a material, such as a metal or a transition metal oxide, using an ALD (atomic layer deposition) process and resulting structures are disclosed. Such methods include treating a surface of a semiconductor structure periodically throughout the ALD process to regenerate a blocking material or to coat a blocking material that enables selective deposition of the material on a surface of a substrate. The surface treatment may reactivate a surface of the substrate toward the blocking material, may restore the blocking material after degradation occurs during the ALD process, and / or may coat the blocking material to prevent further degradation during the ALD process. For example, the surface treatment may be applied after performing one or more ALD cycles. Accordingly, the presently disclosed methods enable in situ restoration of blocking materials in ALD process that are generally incompatible with the blocking material and also enables selective deposition in recessed structures.

Owner:MICRON TECH INC

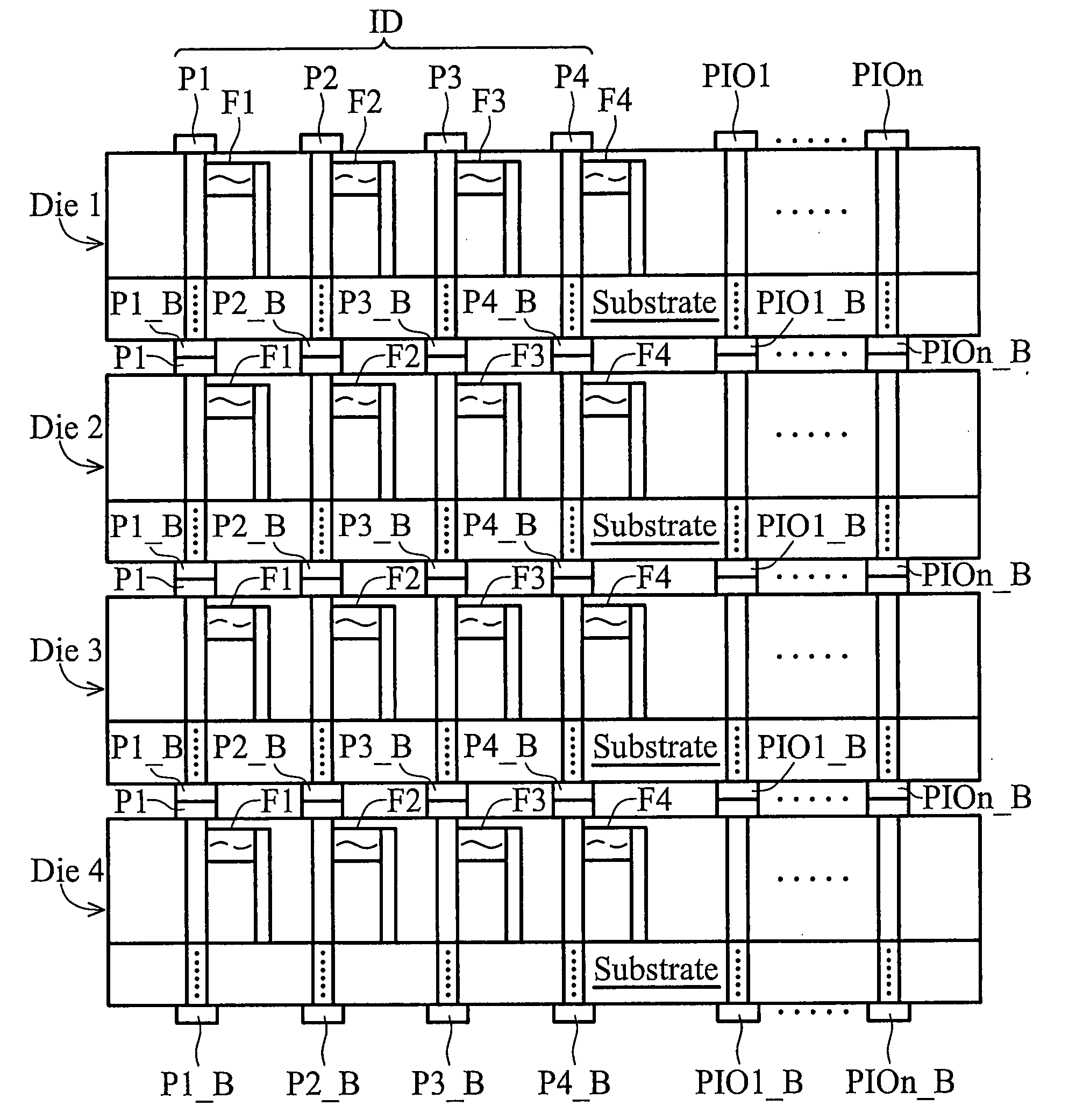

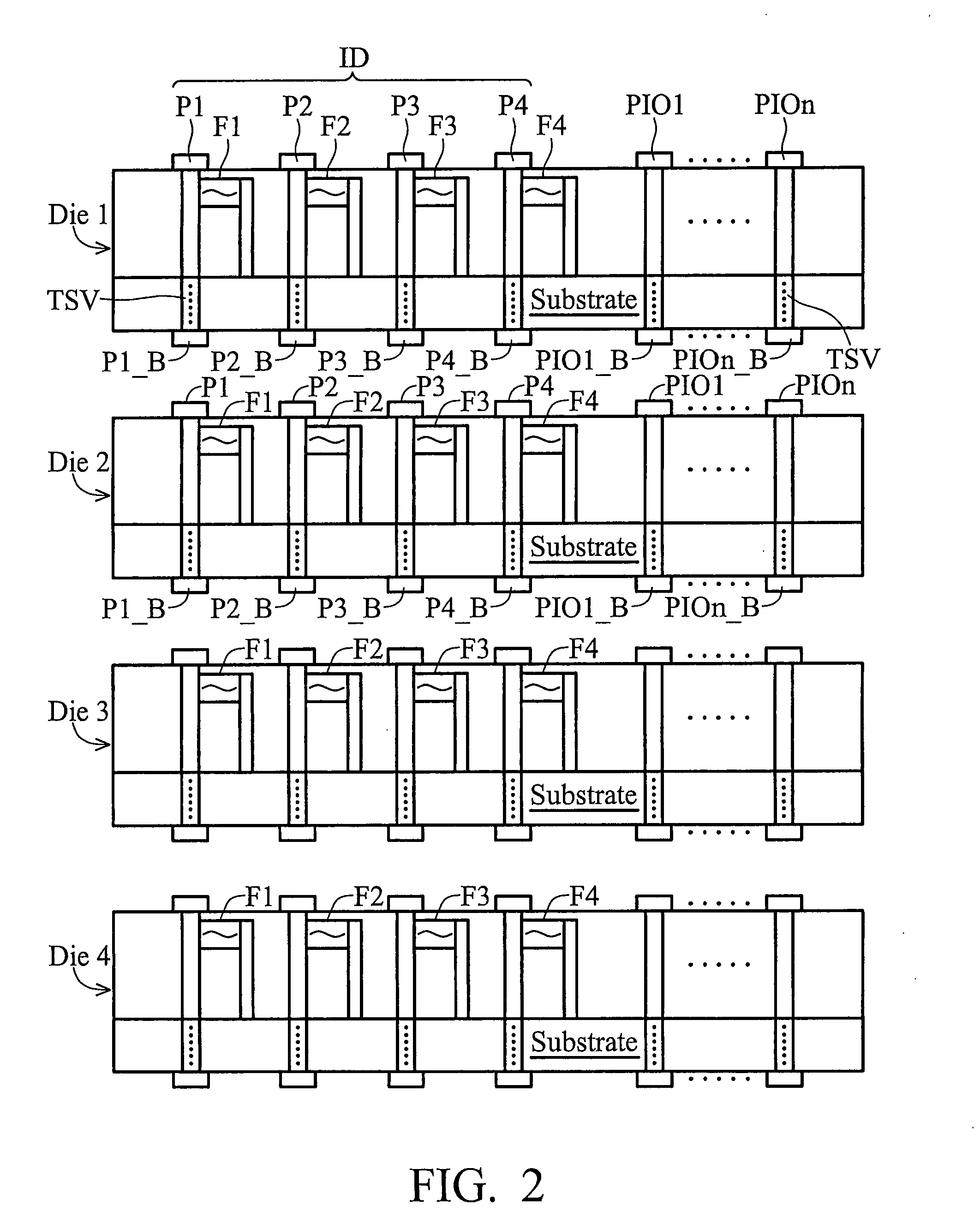

Design techniques for stacking identical memory dies

ActiveUS20080220565A1Reduce designReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor structure

A semiconductor structure includes a first semiconductor die and a second semiconductor die identical to the first semiconductor die. The first semiconductor die includes a first identification circuit; and a first plurality of input / output (I / O) pads on the surface of the first semiconductor die. The second semiconductor die includes a second identification circuit, wherein the first and the second identification circuits are programmed differently from each other; and a second plurality of I / O pads on the surface of the second semiconductor die. Each of the first plurality of I / O pads is vertically aligned to and connected to one of the respective second plurality of I / O pads. The second semiconductor die is vertically aligned to and bonded on the first semiconductor die.

Owner:TRENCHANT BLADE TECH LLC

Common fabrication of different semiconductor devices with different threshold voltages

A multi-device semiconductor structure including a p-type logic device, a p-type memory device, a n-type logic device and a n-type memory device are provided on a bulk silicon substrate. Each of these devices includes a dielectric layer and either a n-type or a p-type work function layer disposed over the dielectric layer. Some of the various device types of the multi-device semiconductor structure are protected, and impurities, such as aluminum and / or nitrogen, are added to the exposed work function layers to achieve one or more other desired work functions with different threshold voltages.

Owner:GLOBALFOUNDRIES INC

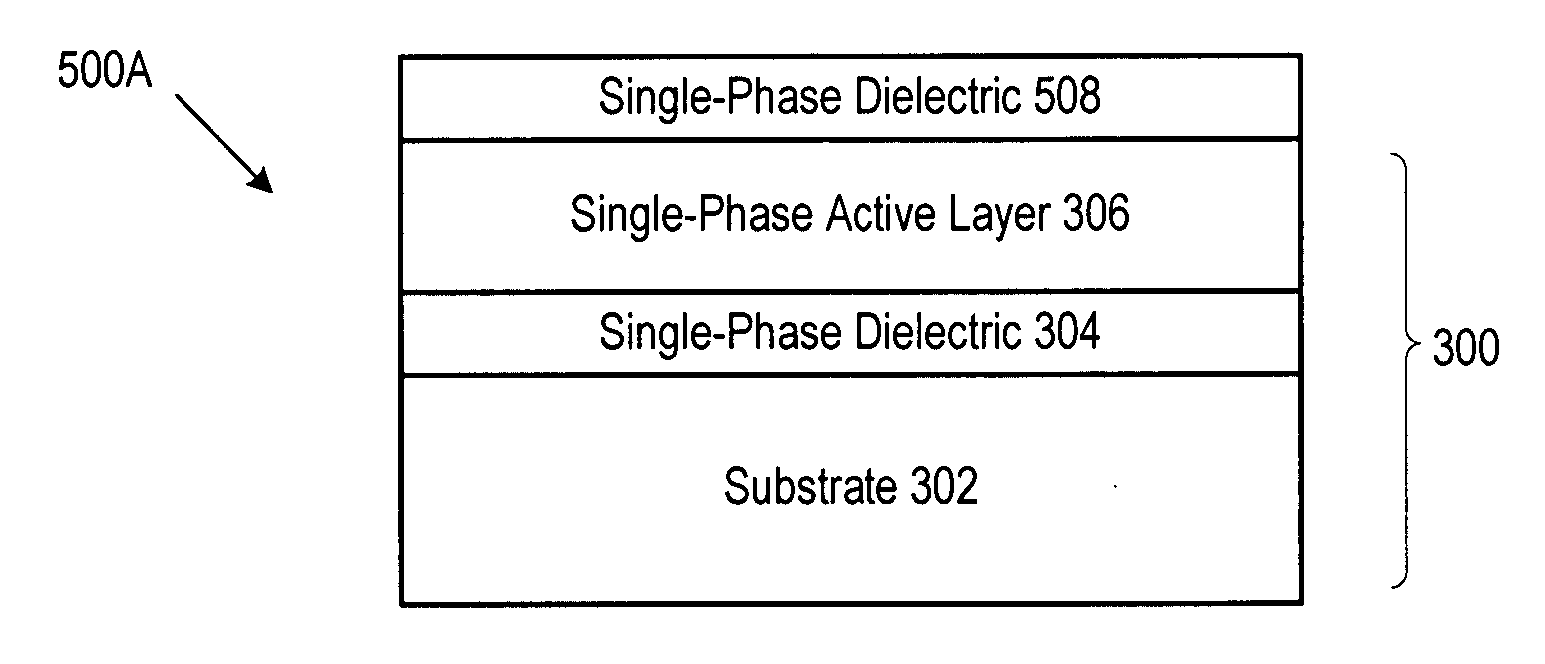

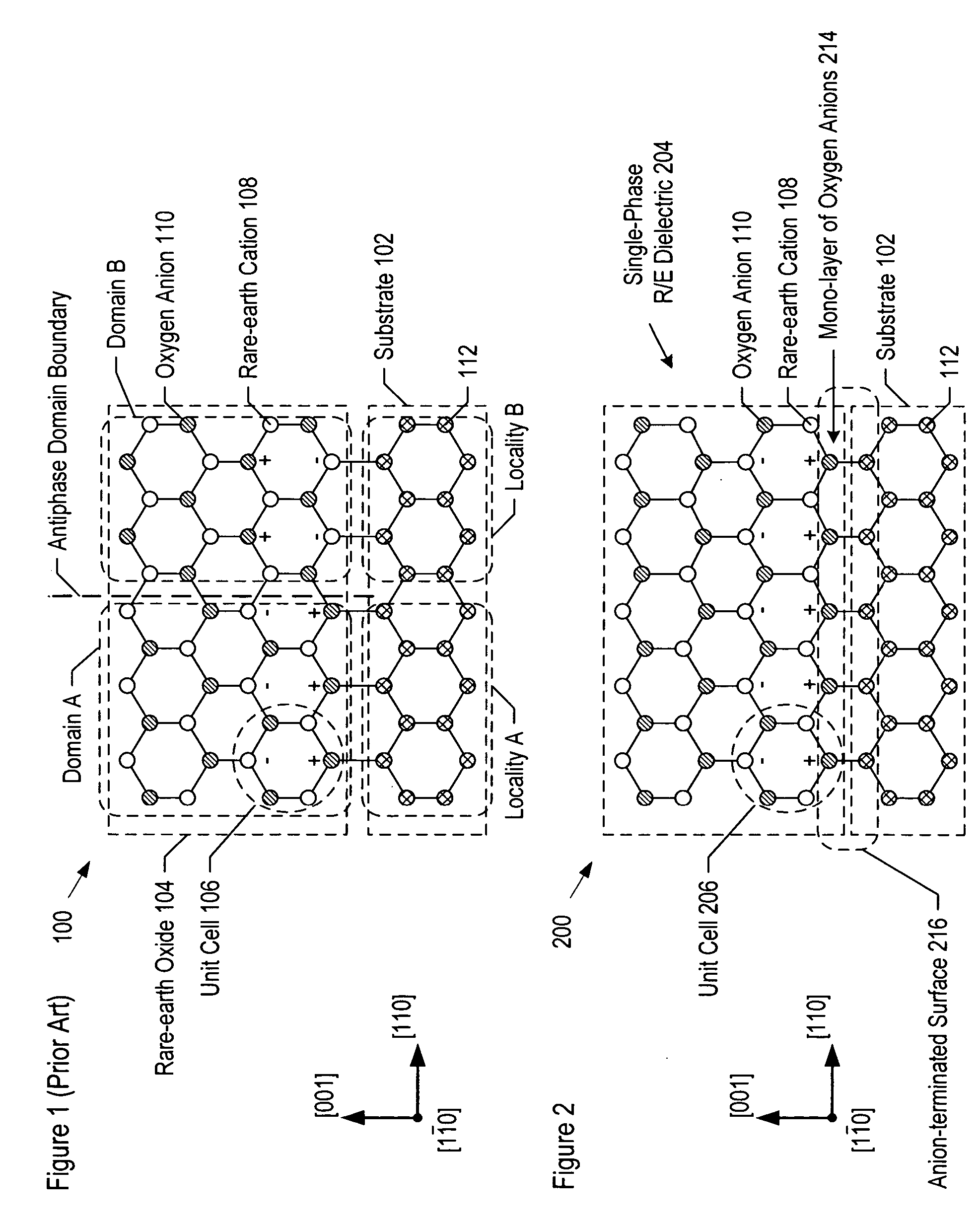

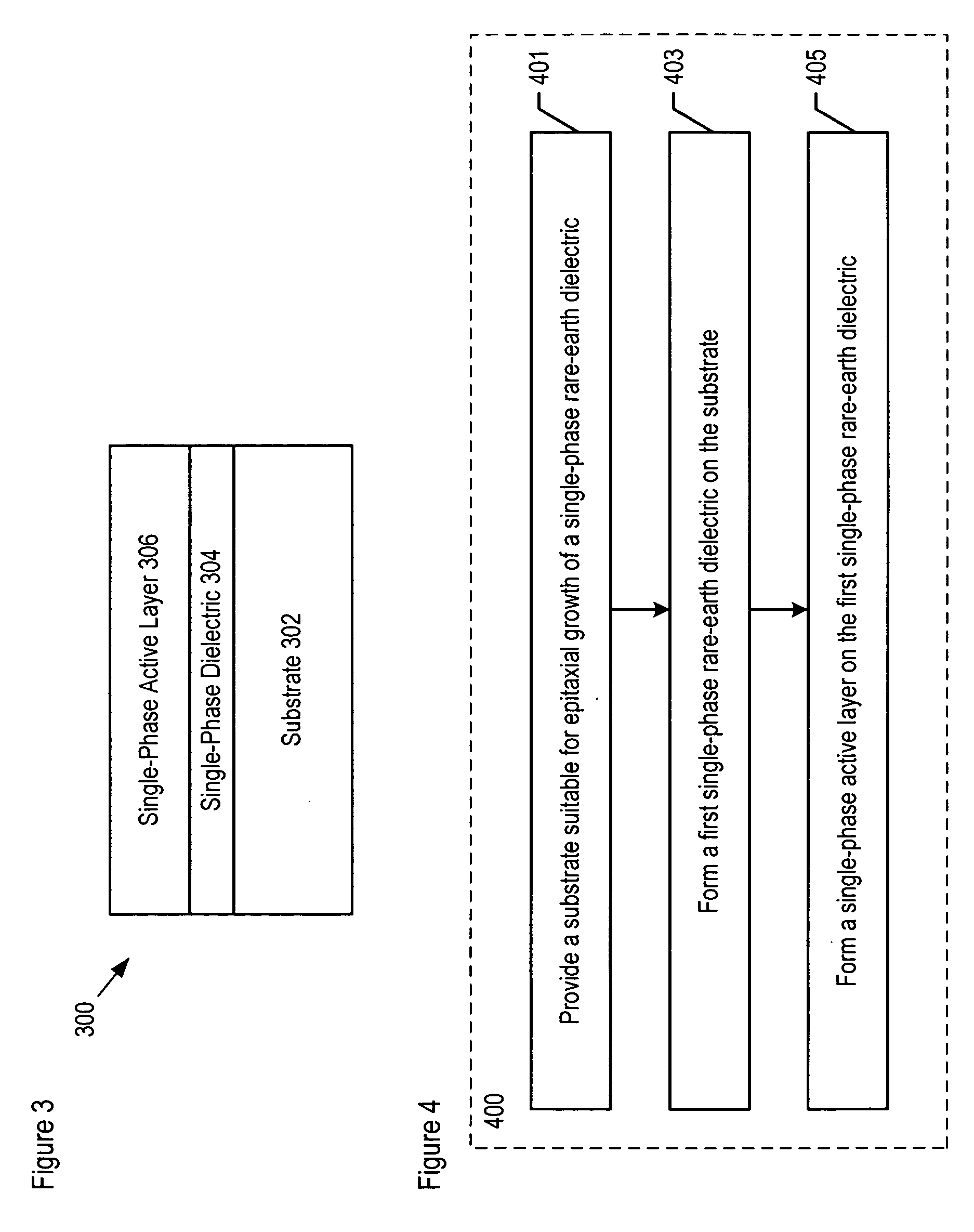

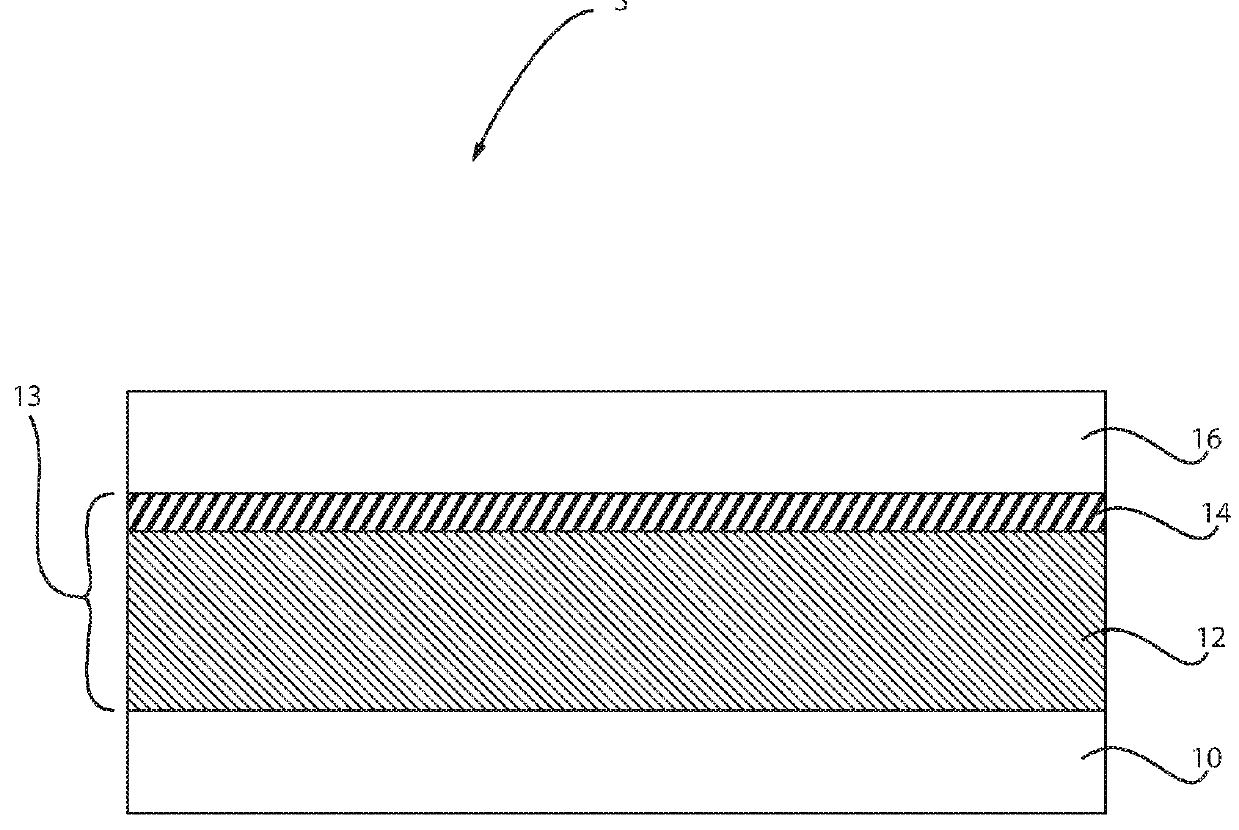

Method of forming a rare-earth dielectric layer

ActiveUS20060060131A1Quality improvementPolycrystalline material growthLaser detailsSemiconductor structureRare earth

Methods for forming compositions comprising a single-phase rare-earth dielectric disposed on a substrate are disclosed. In some embodiments, the method forms a semiconductor-on-insulator structure. Compositions and structures that are formed via the method provide the basis for forming high-performance devices and circuits.

Owner:IQE

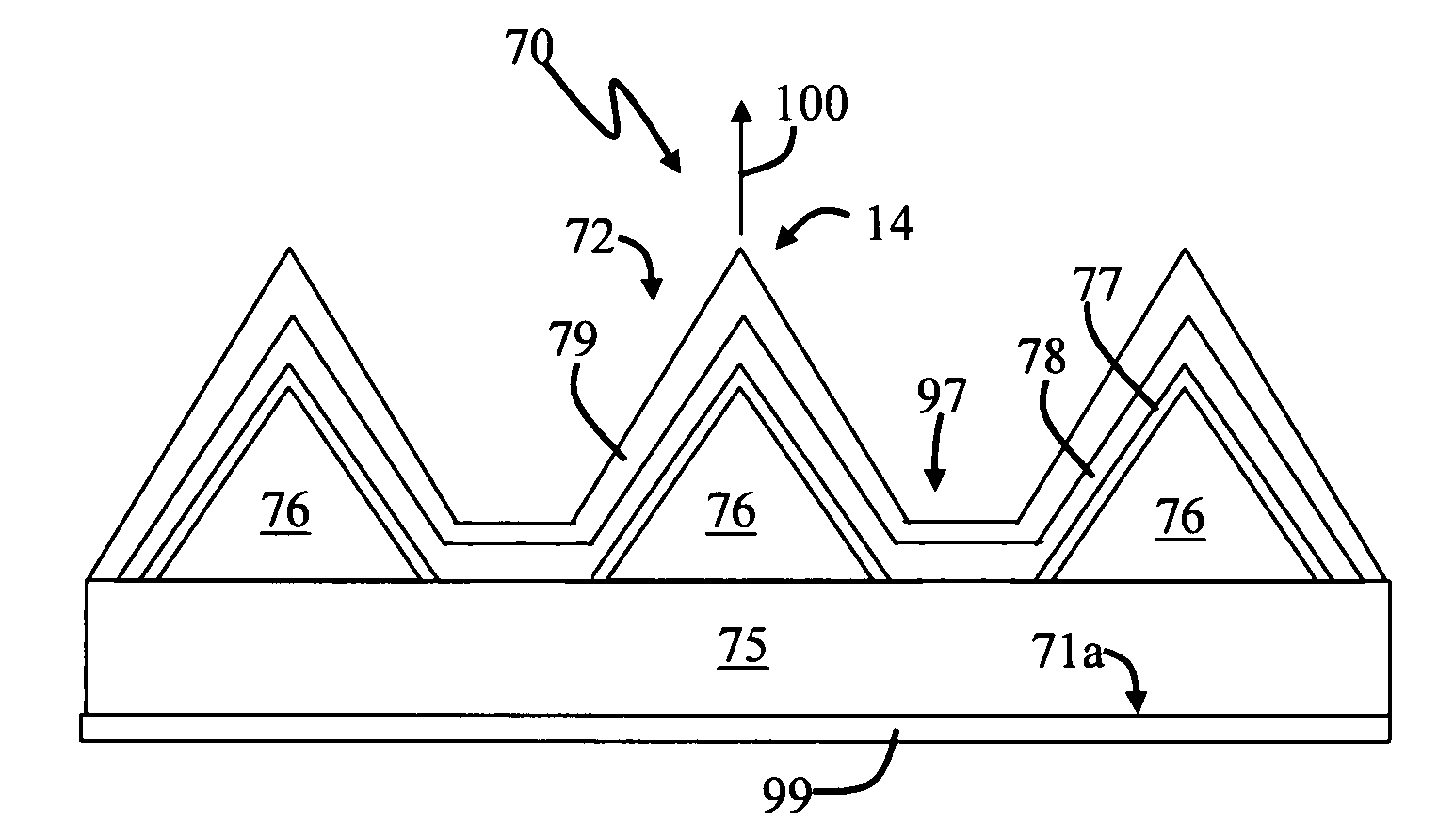

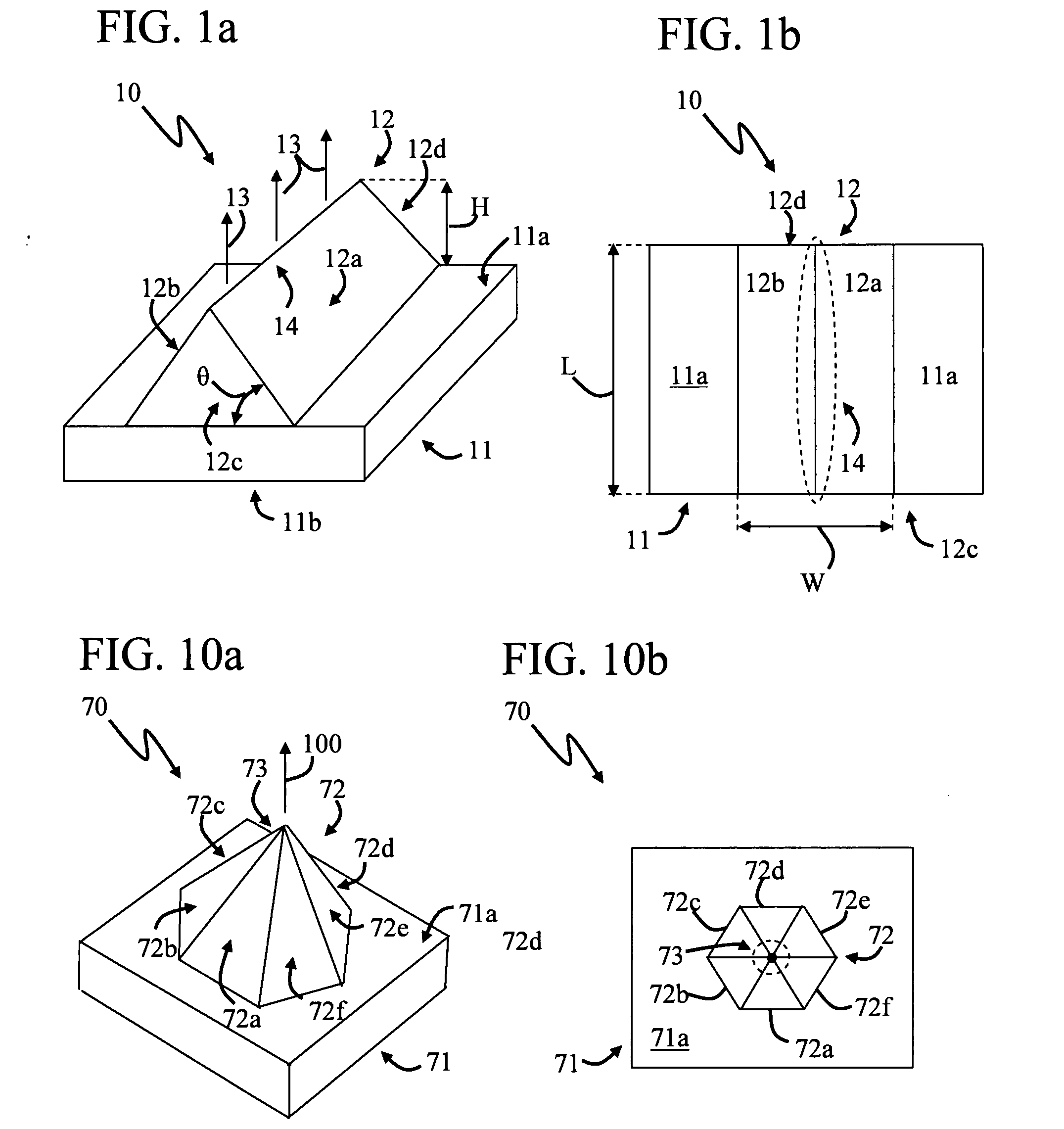

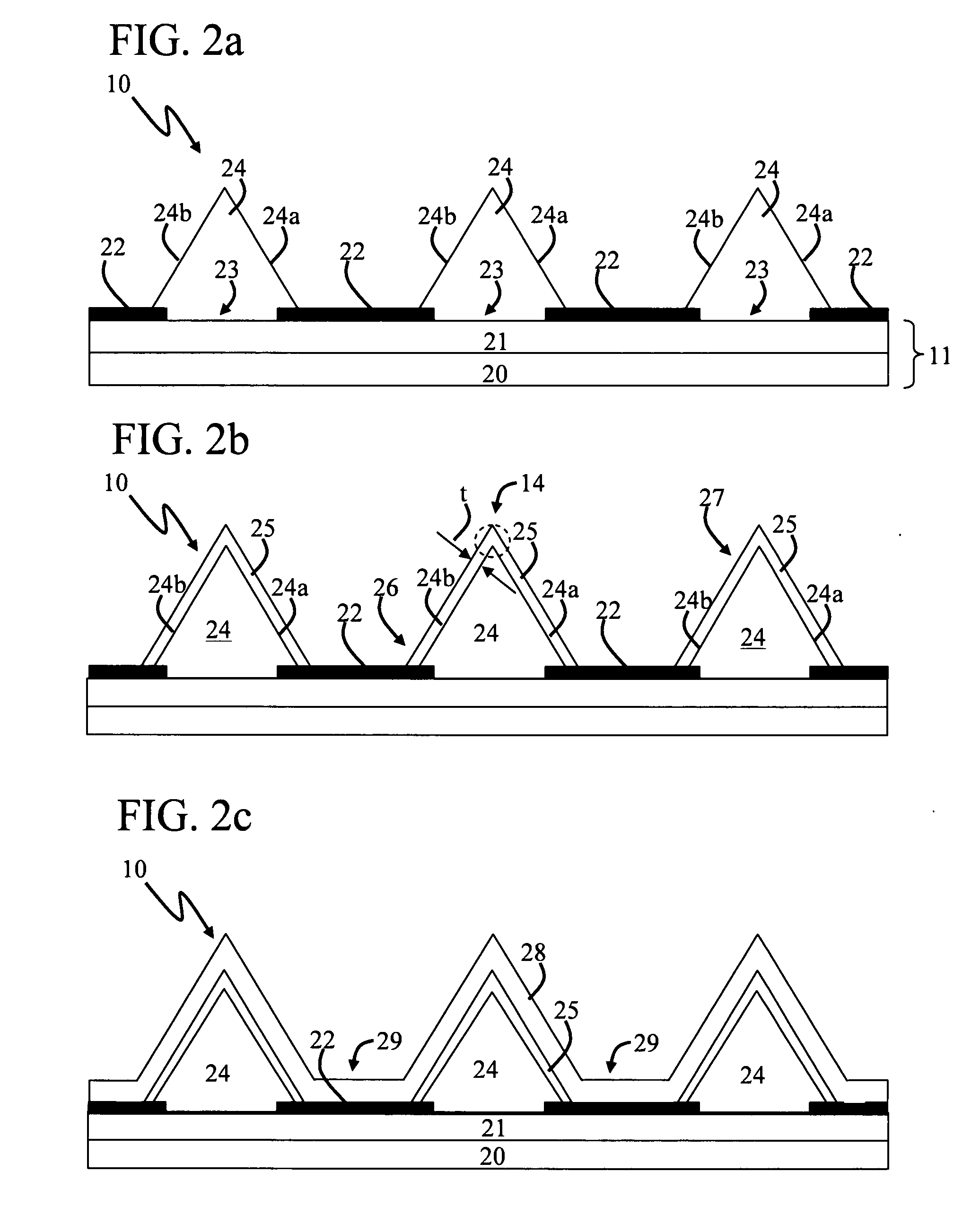

Solid State Light Emitting Device

InactiveUS20090159869A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureAlloy

A semiconductor structure (10, 10′, 70, 80) includes a light emitter (12, 72) carried by a support structure (11). The light emitter (12, 72) includes a base region (24, 76) with a sloped sidewall (12a, 12b) and a light emitting region (25, 77) positioned thereon. The light emitting (25, 77) region includes a nitride semiconductor alloy having a composition that is different in a first region (26, 95) near the support structure (11) compared to a second region (27, 96) away from the support structure (11).

Owner:PONCE FERNANDO A +2

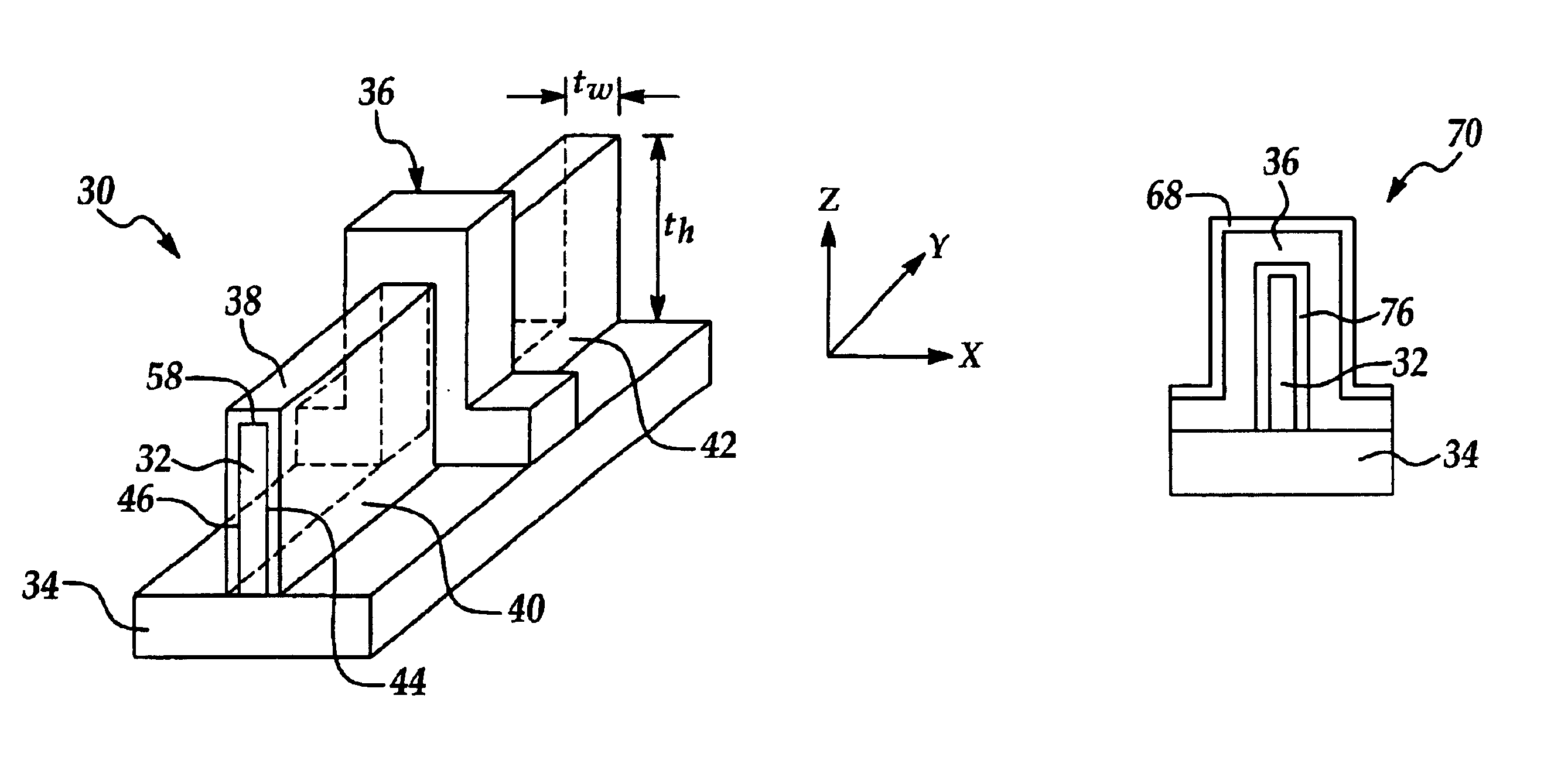

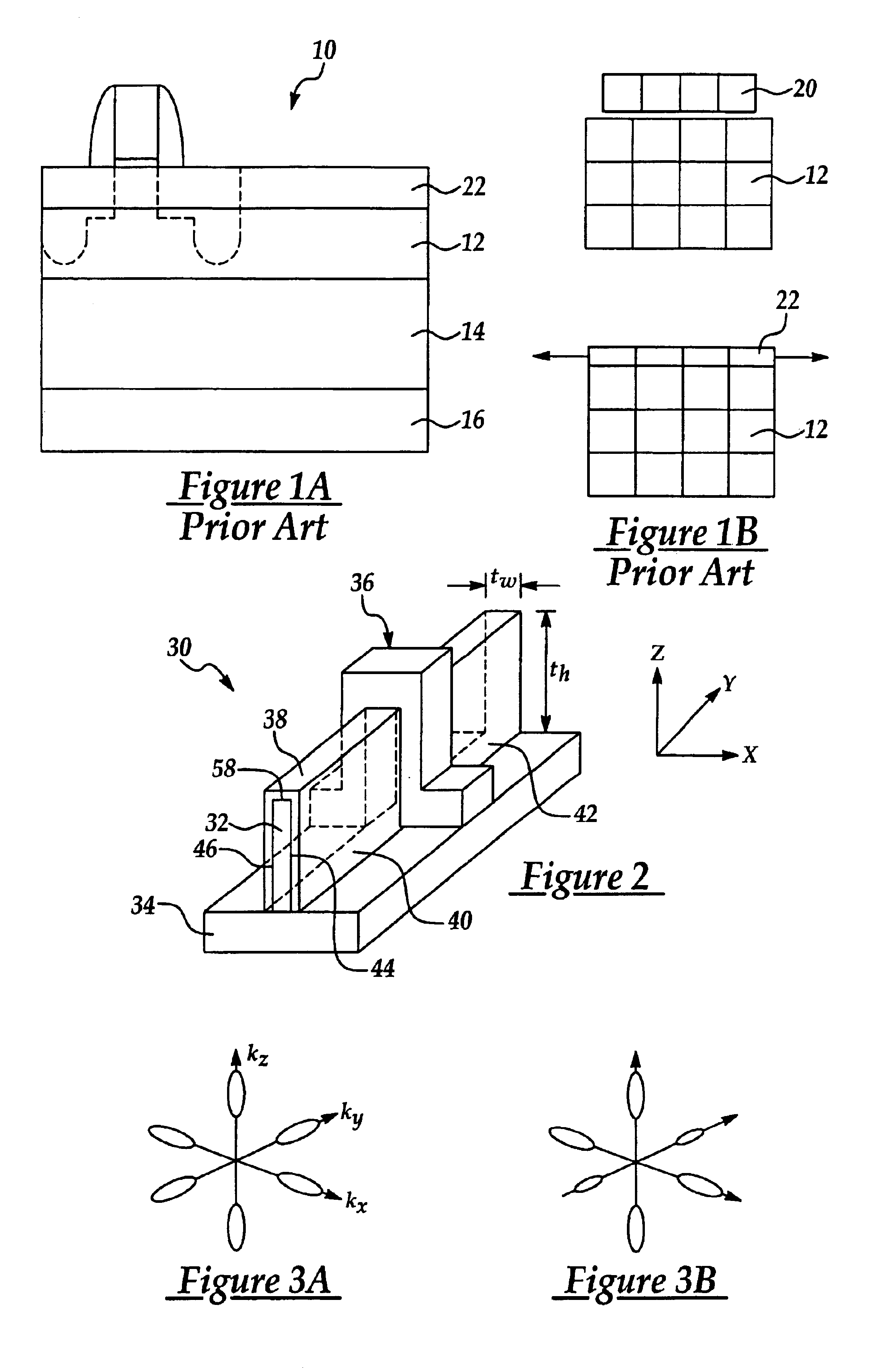

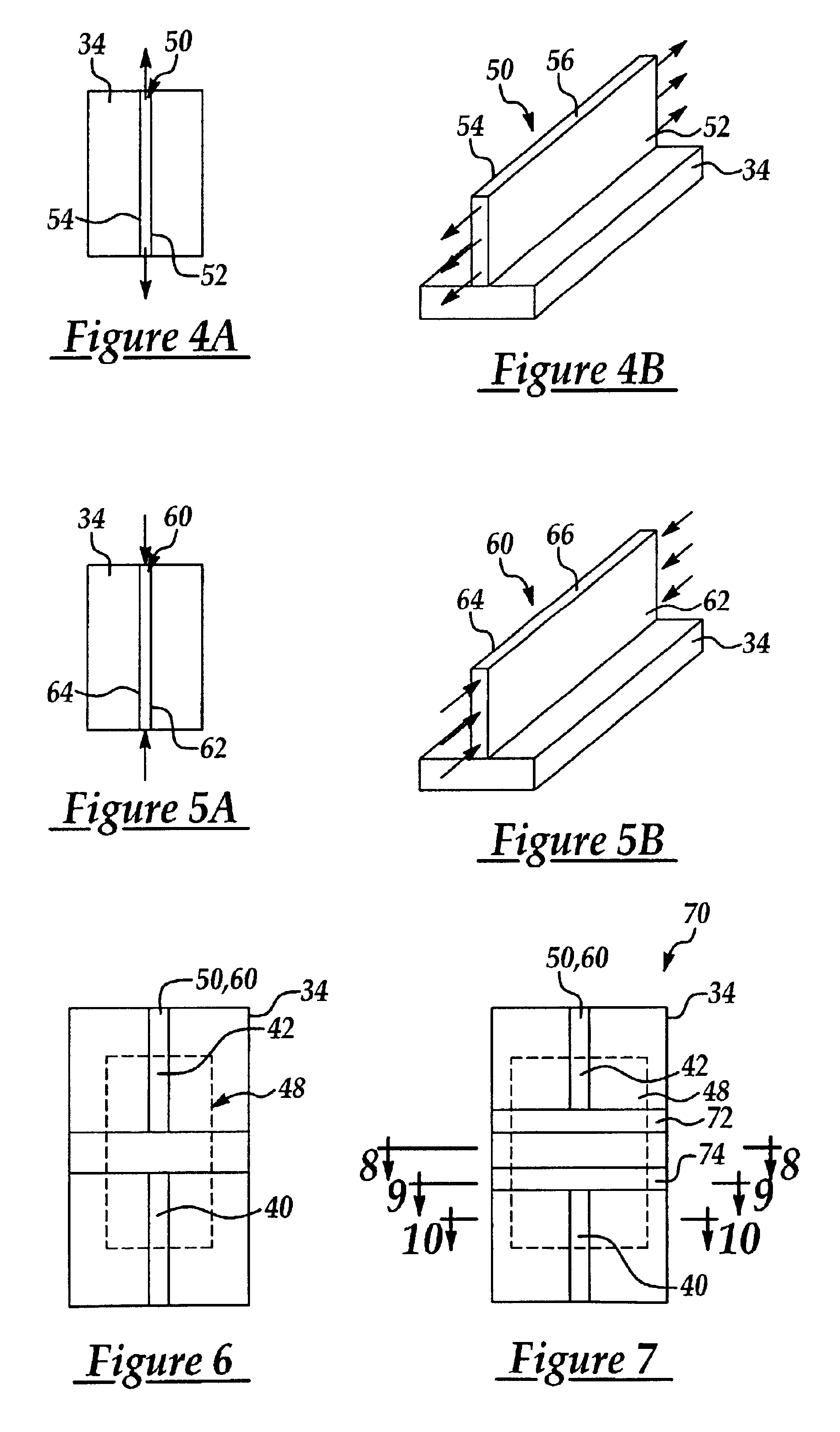

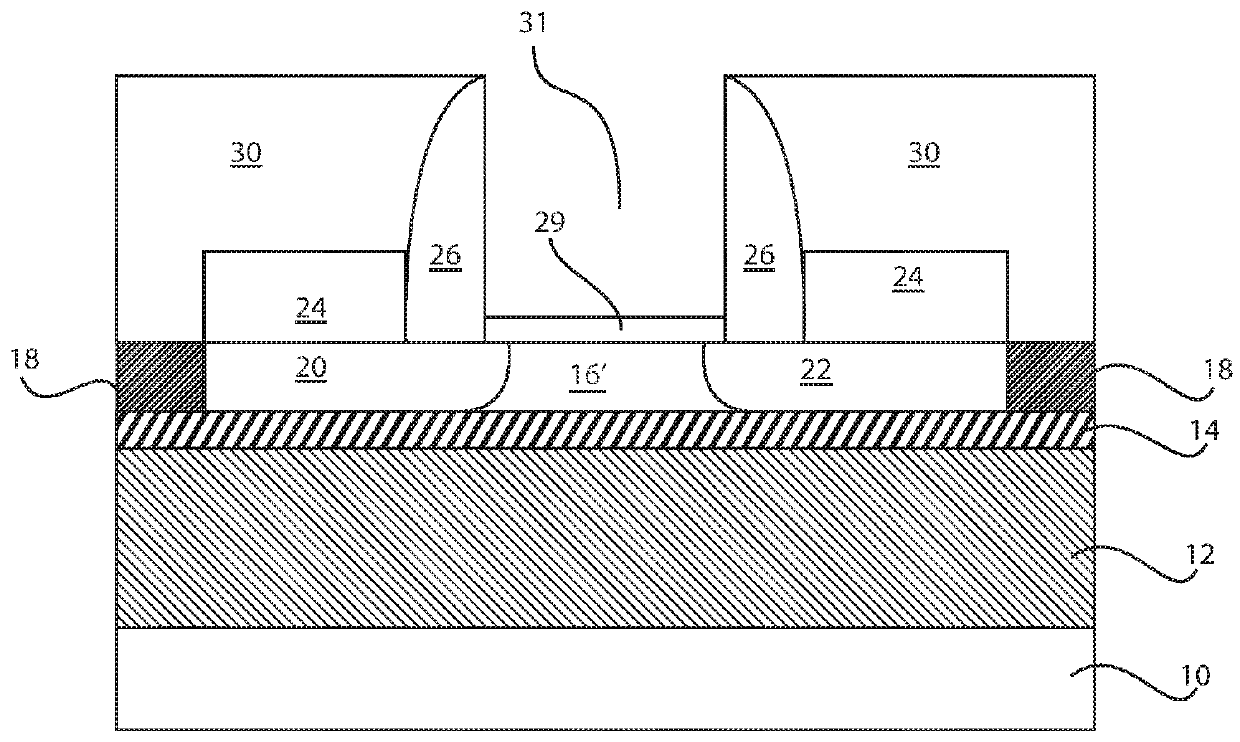

Strained-channel multiple-gate transistor

InactiveUS6855990B2Small thicknessTransistorSolid-state devicesGate dielectricSemiconductor materials

A multiple-gate semiconductor structure is disclosed which includes a substrate, a fin formed of a semi-conducting material that has a top surface and two sidewall surfaces. The fin is subjected to a strain of at least 0.01% and is positioned vertically on the substrate; source and drain regions formed in the semi-conducting material of the fin; a gate dielectric layer overlying the fin; and a gate electrode wrapping around the fin on the top surface and the two sidewall surfaces of the fin overlying the gate dielectric layer. A method for forming the multiple-gate semiconductor structure is further disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

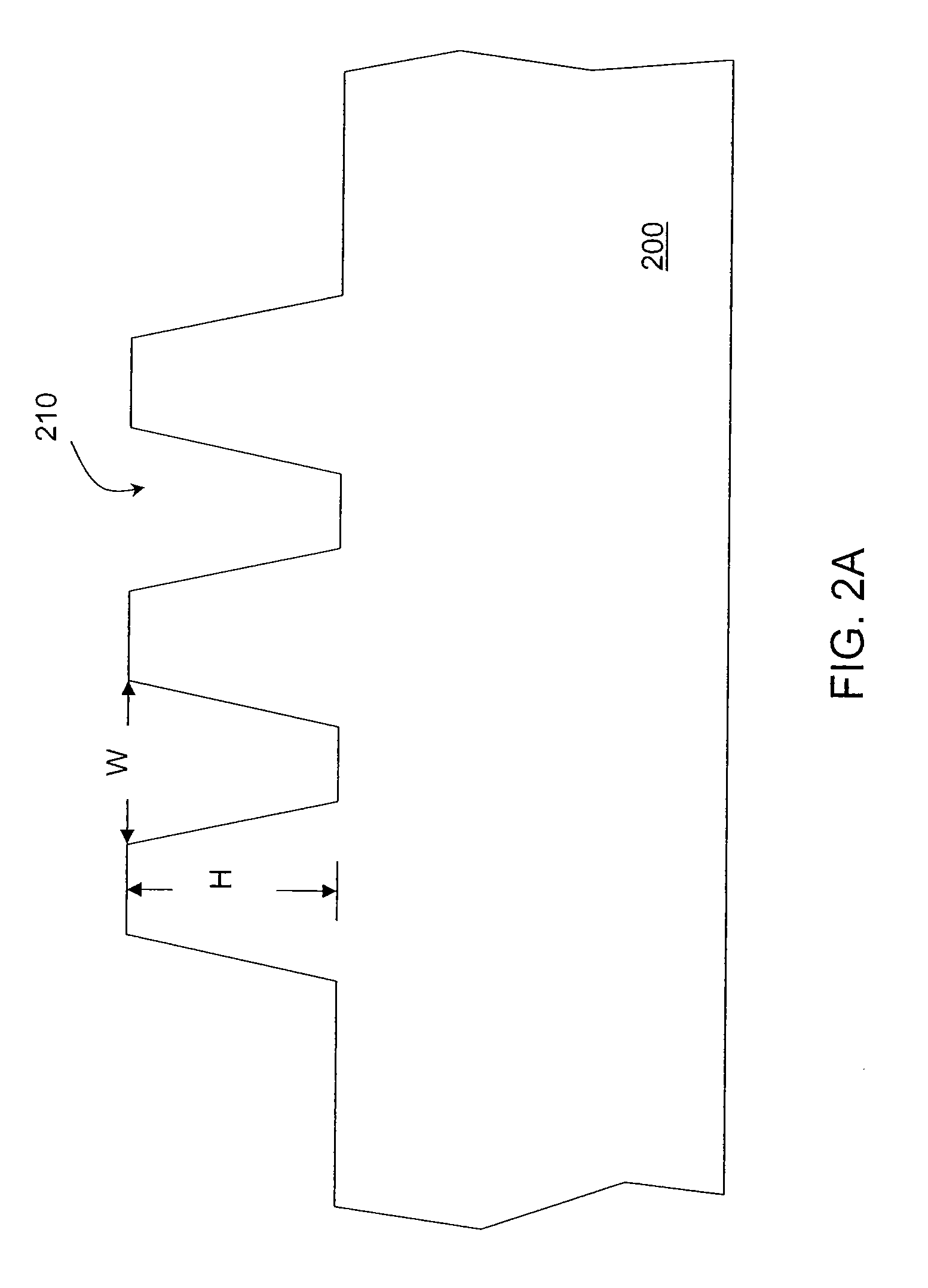

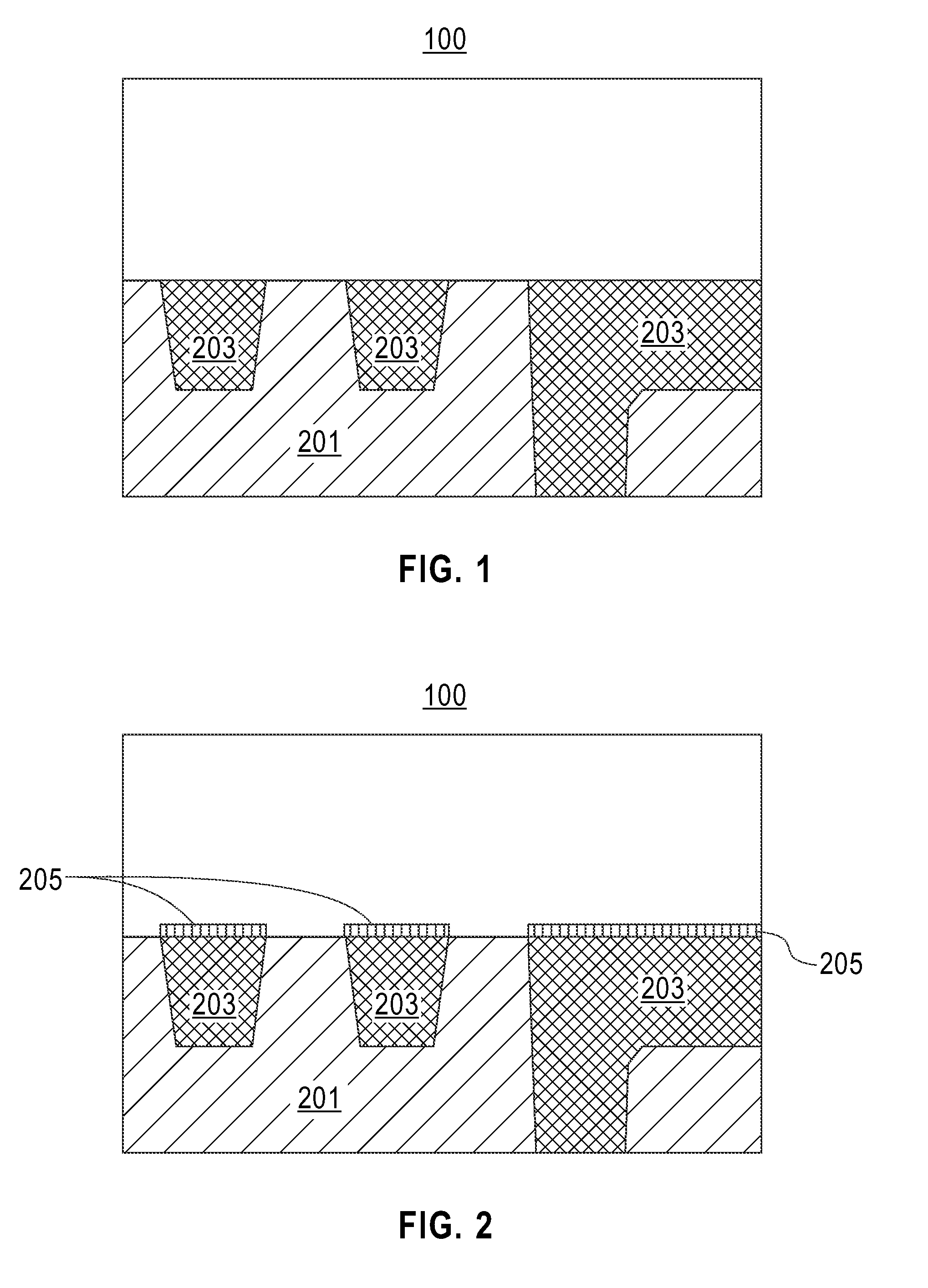

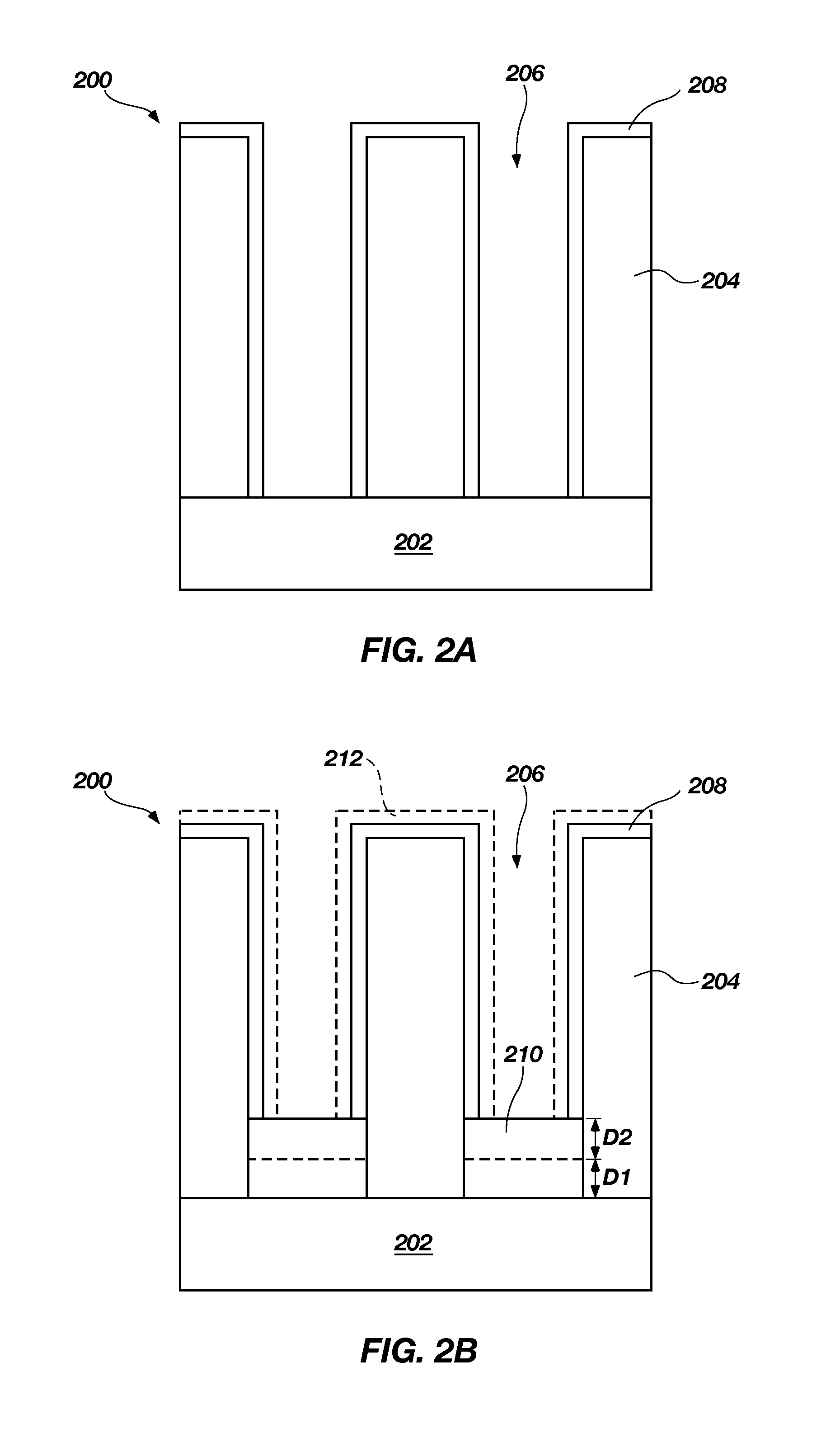

Methods of thin film process

A method for forming a semiconductor structure includes forming a plurality of features across a surface of a substrate, with at least one space being between two adjacent features. A first dielectric layer is formed on the features and within the at least one space. A portion of the first dielectric layer interacts with a reactant derived from a first precursor and a second precursor to form a first solid product. The first solid product is decomposed to substantially remove the portion of the first dielectric layer. A second dielectric layer is formed to substantially fill the at least one space.

Owner:APPLIED MATERIALS INC

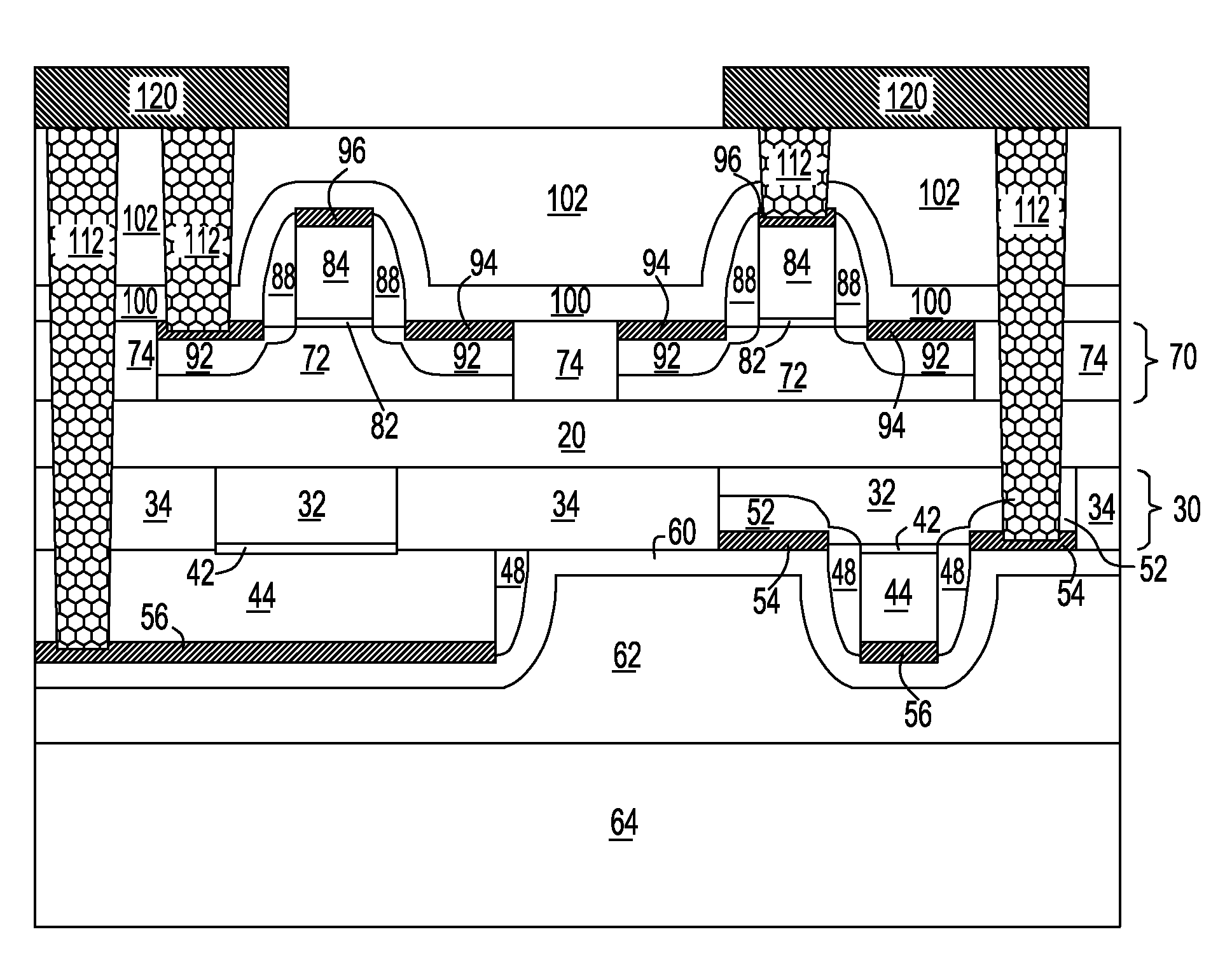

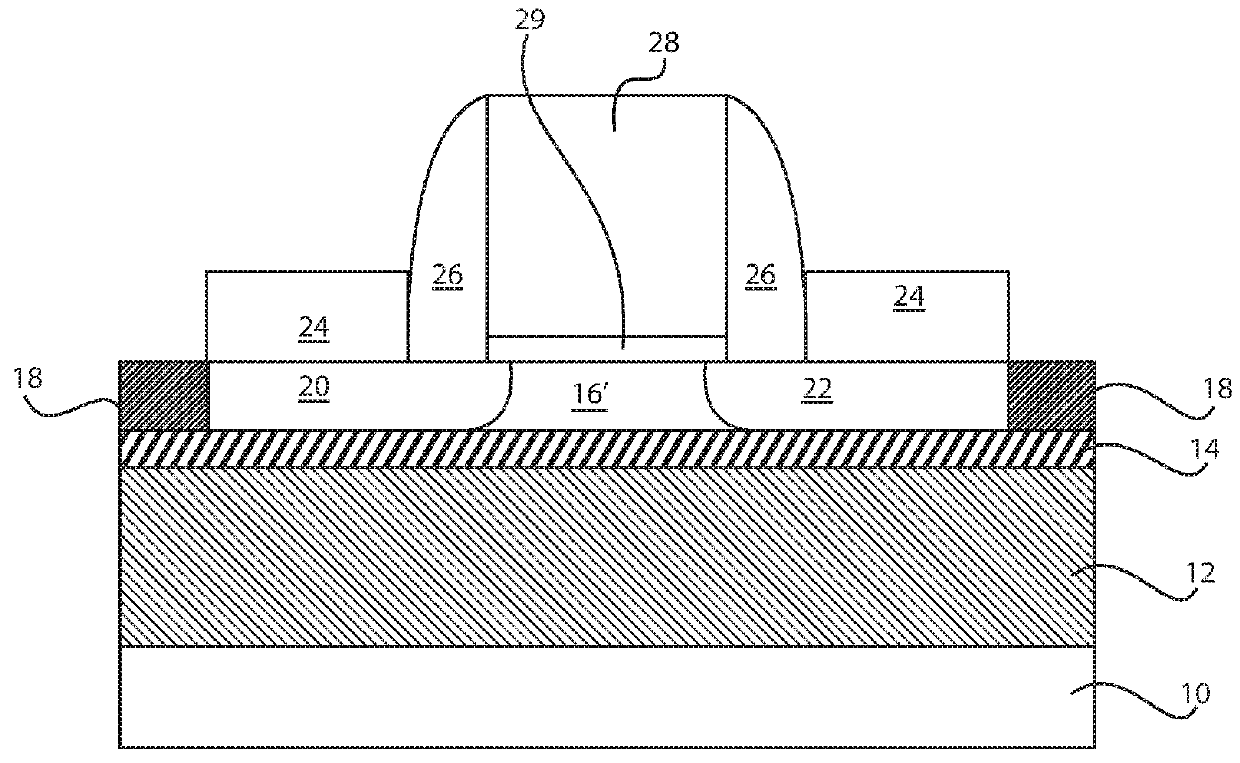

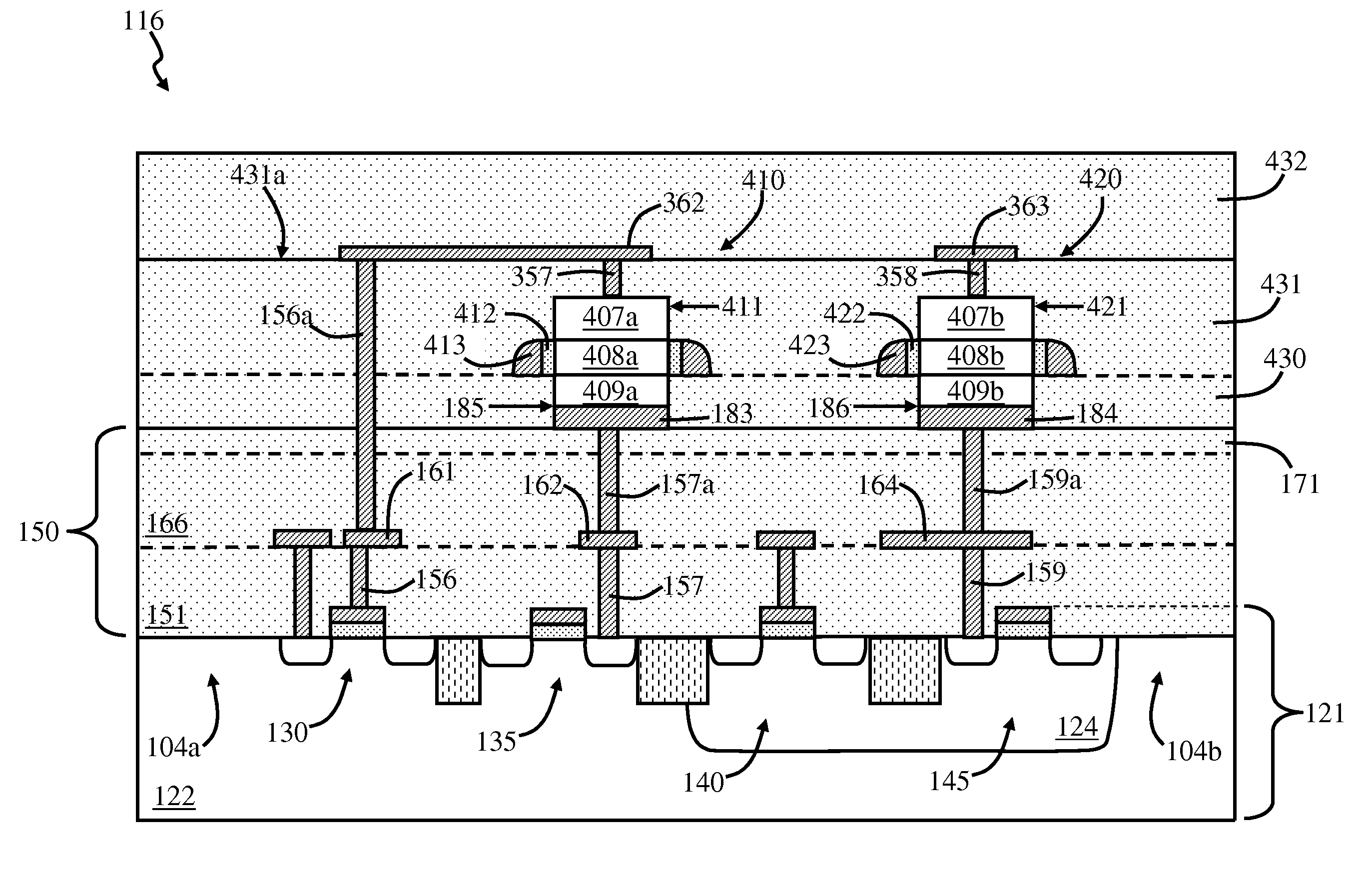

Two-sided semiconductor-on-insulator structures and methods of manufacturing the same

ActiveUS20080179678A1Semiconductor/solid-state device detailsSolid-state devicesMOSFETElectrical conductor

Both sides of a semiconductor-on-insulator substrate are utilized to form MOSFET structures. After forming first type devices on a first semiconductor layer, a handle wafer is bonded to the top of a first middle-of-line dielectric layer. A lower portion of a carrier substrate is then removed to expose a second semiconductor layer and to form second type devices thereupon. Conductive vias may be formed through the buried insulator layer to electrically connect the first type devices and the second type devices. Use of block masks is minimized since each side of the buried insulator has only one type of devices. Two levels of devices are present in the structure and boundary areas between different types of devices are reduced or eliminated, thereby increasing packing density of devices. The same alignment marks may be used to align the wafer either front side up or back side up.

Owner:TAIWAN SEMICON MFG CO LTD

Fully depleted soi device for reducing parasitic back gate capacitance

ActiveUS20180097076A1Semiconductor/solid-state device detailsSolid-state devicesCapacitanceGate dielectric

A method is presented for forming a semiconductor structure. The method includes forming a bilayer buried insulator over a substrate, forming an extremely thin silicon-on-insulator (ETSOI) over the bilayer buried insulator, forming a dummy gate, and forming a source / drain next to the dummy gate, the source / drain defining a raised source / drain region. The method further includes depositing a dielectric material over the raised source / drain regions, removing the dummy gate to define a recess, implanting a species within a first layer of the bilayer buried insulator, and depositing a gate dielectric and a conducting material within the recess. The method further includes removing the substrate, etching the implanted portion of the first layer of the bilayer buried insulator to expose a surface of a second layer of the bilayer buried insulator, and forming a back gate over the exposed second layer, the back gate self-aligned to the ETSOI channel.

Owner:IBM CORP

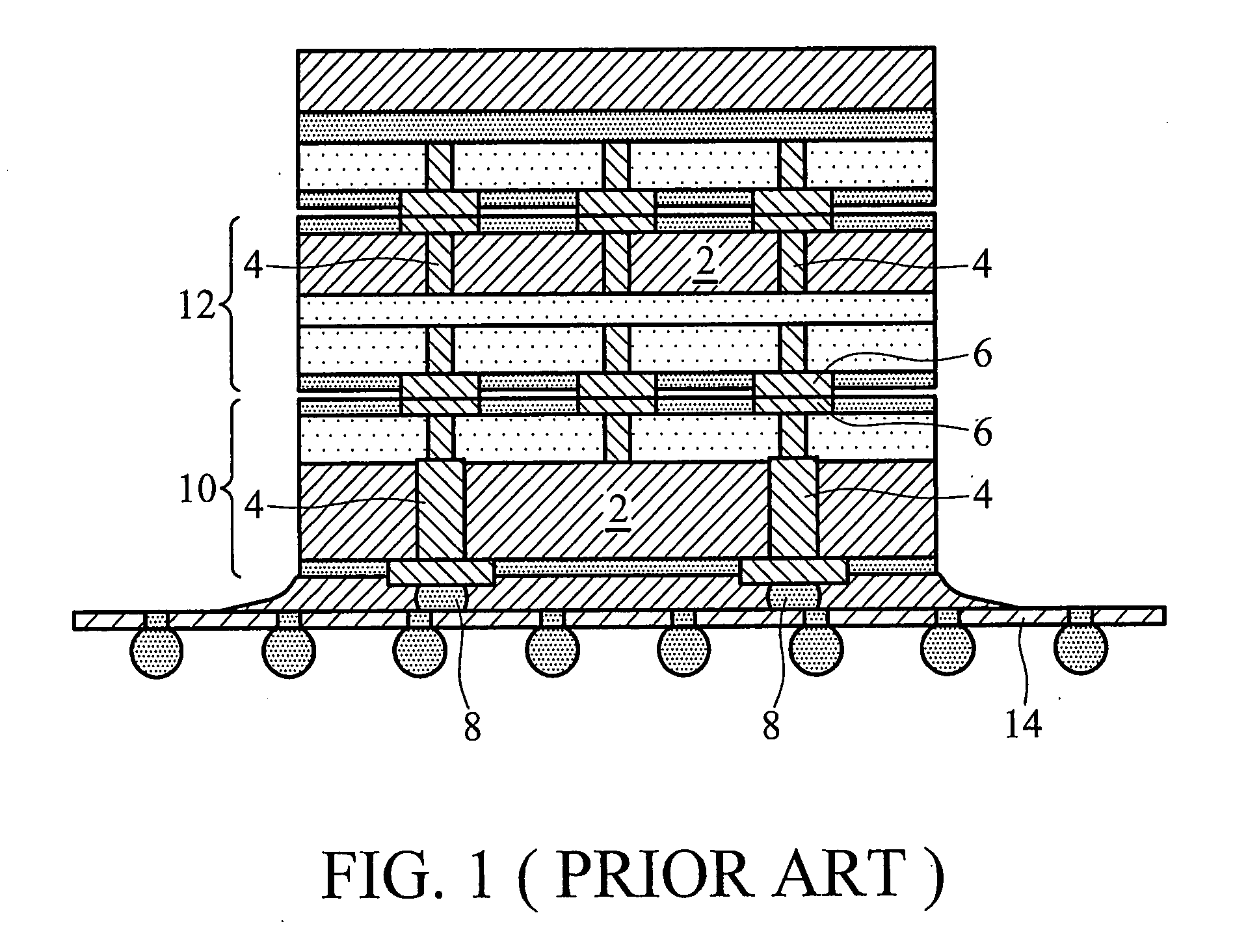

Three-dimensional semiconductor structure and method of manufacturing the same

InactiveUS20100190334A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A semiconductor circuit structure includes a support substrate which carries an interconnect region and electronic circuitry. The semiconductor circuit structure includes a device substrate coupled to the interconnect region through a conductive bonding layer. The device substrate includes a planarized surface which faces the conductive bonding layer. The device substrate can carry laterally oriented semiconductor devices which are connected to the electronic circuitry carried by the support substrate. The device substrate can be processed to form vertically oriented semiconductor devices which are connected, through the interconnect region and conductive bonding layer, to the electronic circuitry carried by the support substrate.

Owner:BESANG

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com