Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33 results about "Reverse short-channel effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

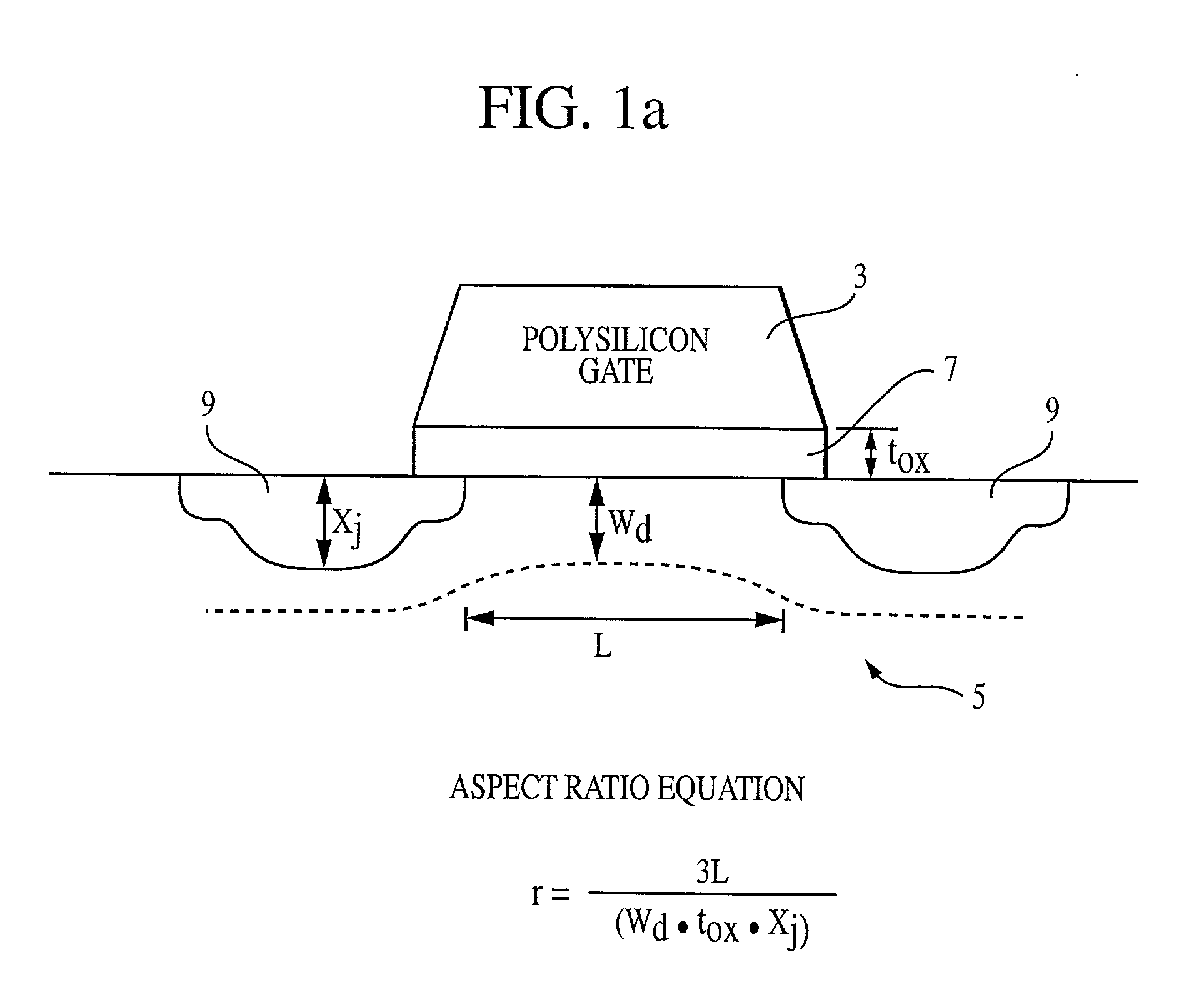

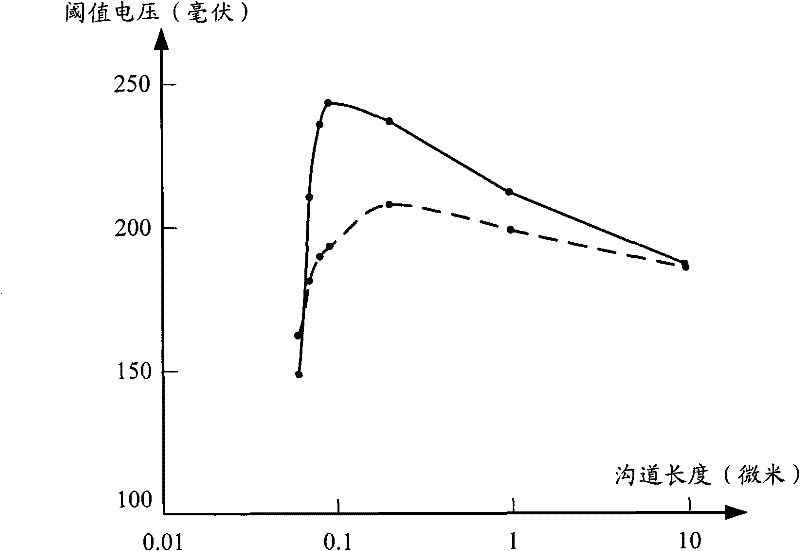

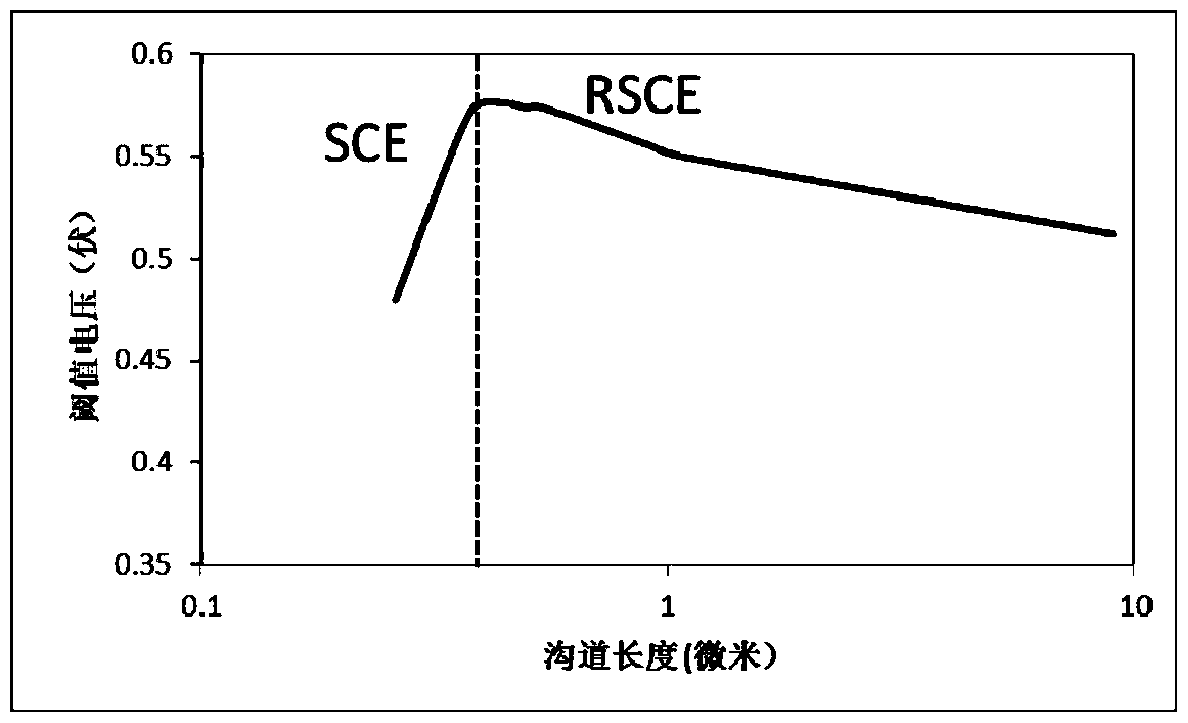

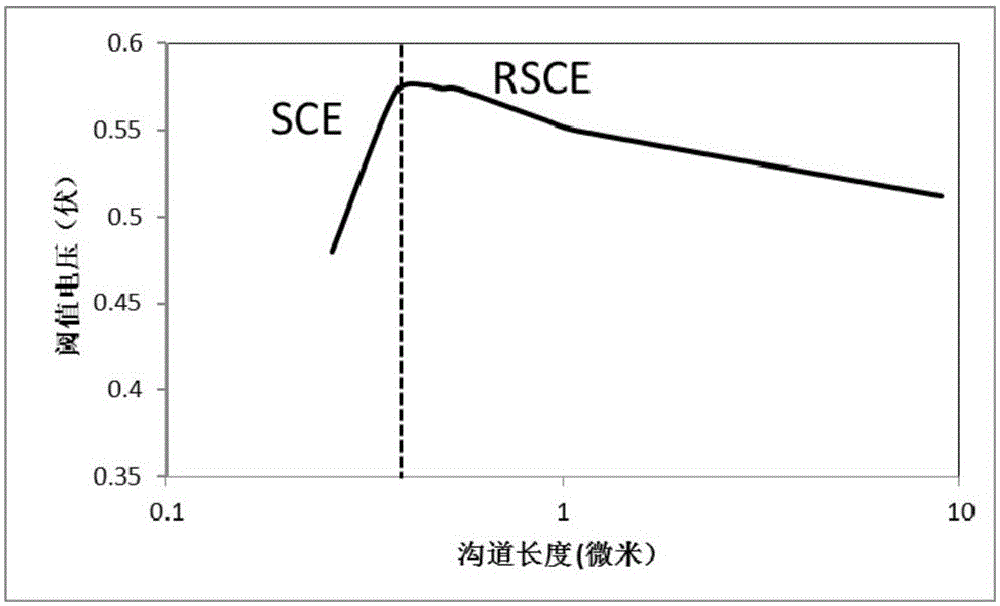

In MOSFETs, reverse short-channel effect (RSCE) is an increase of threshold voltage with decreasing channel length; this is the opposite of the usual short-channel effect. The difference comes from changes in doping profiles used in modern small device manufacturing.

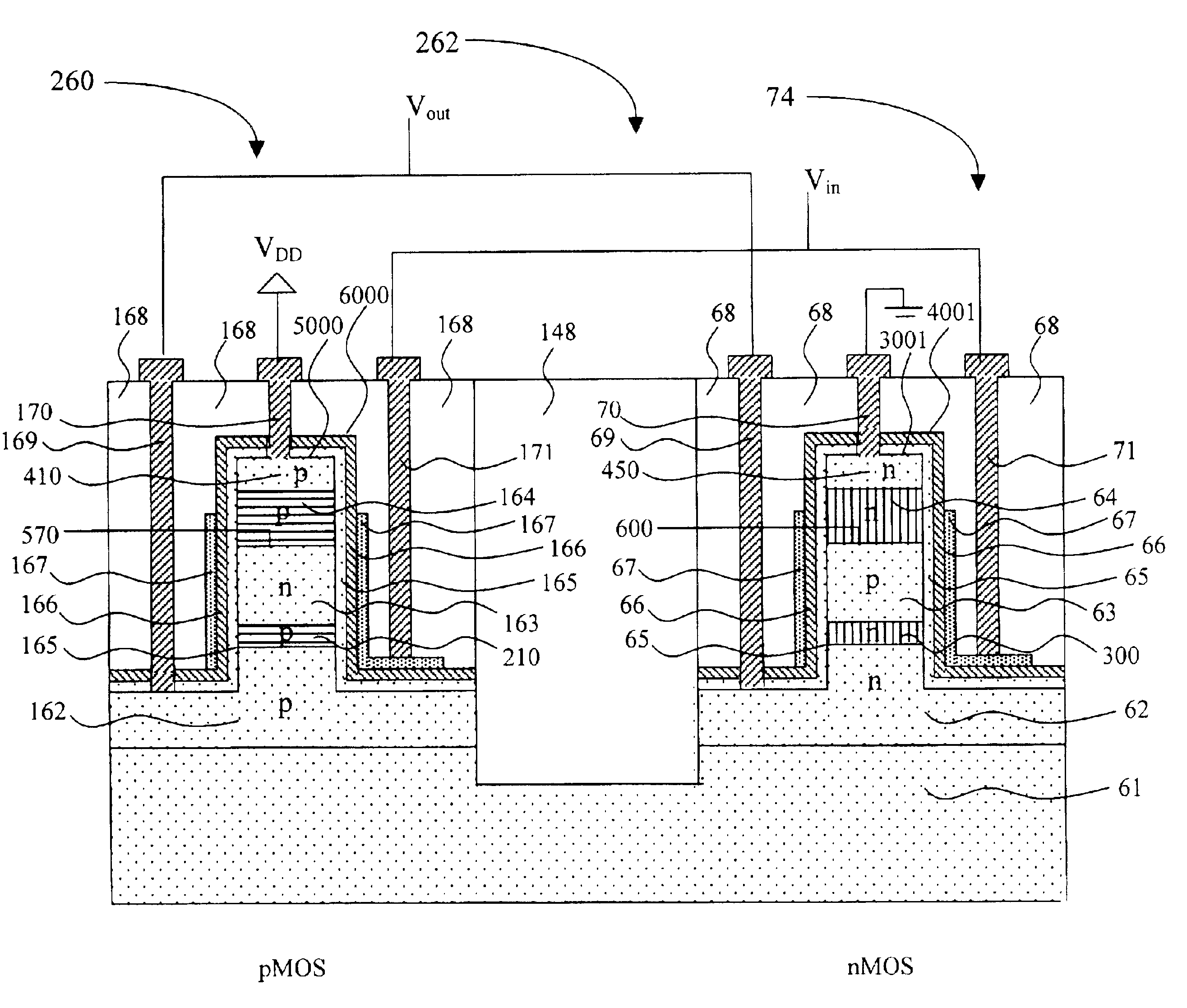

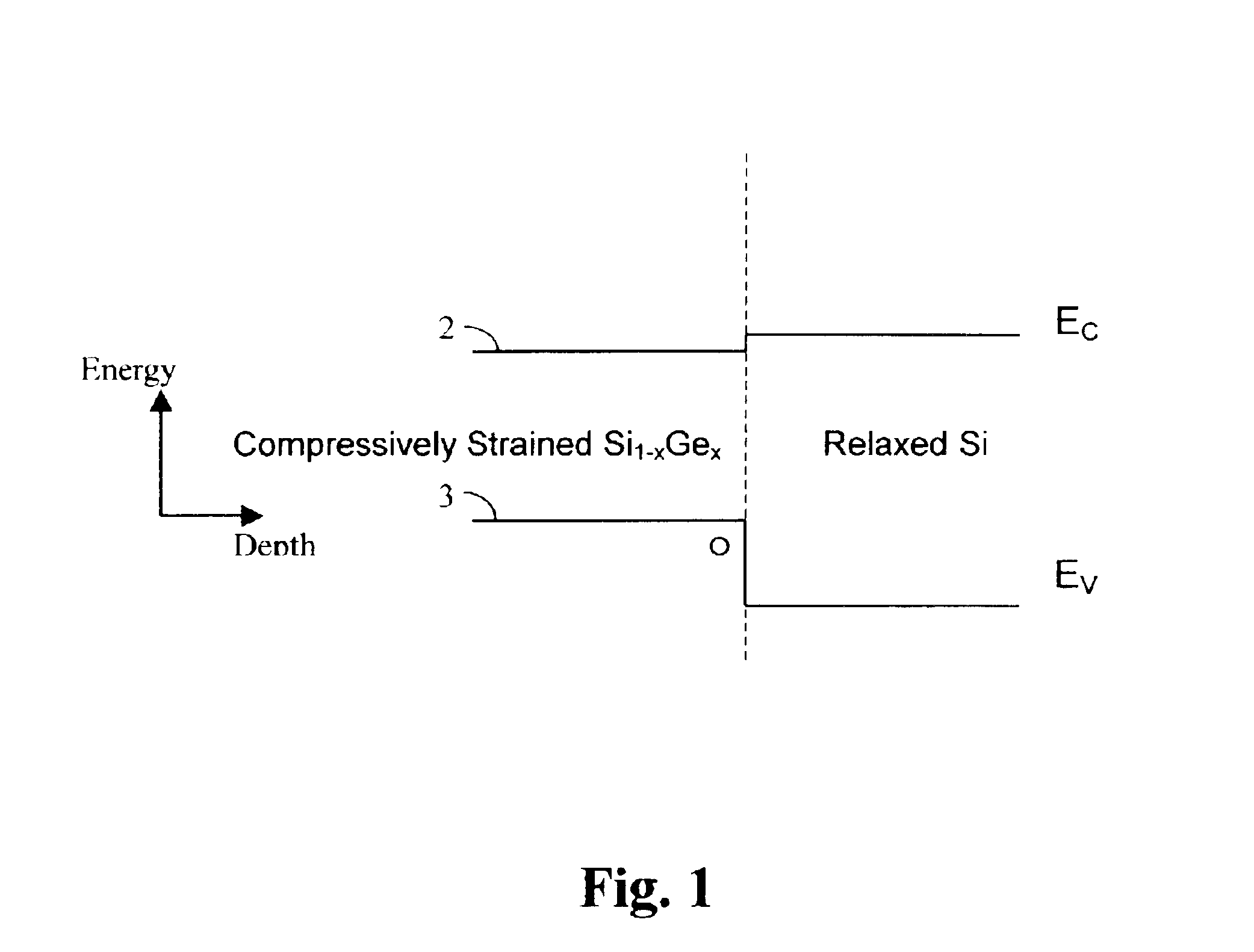

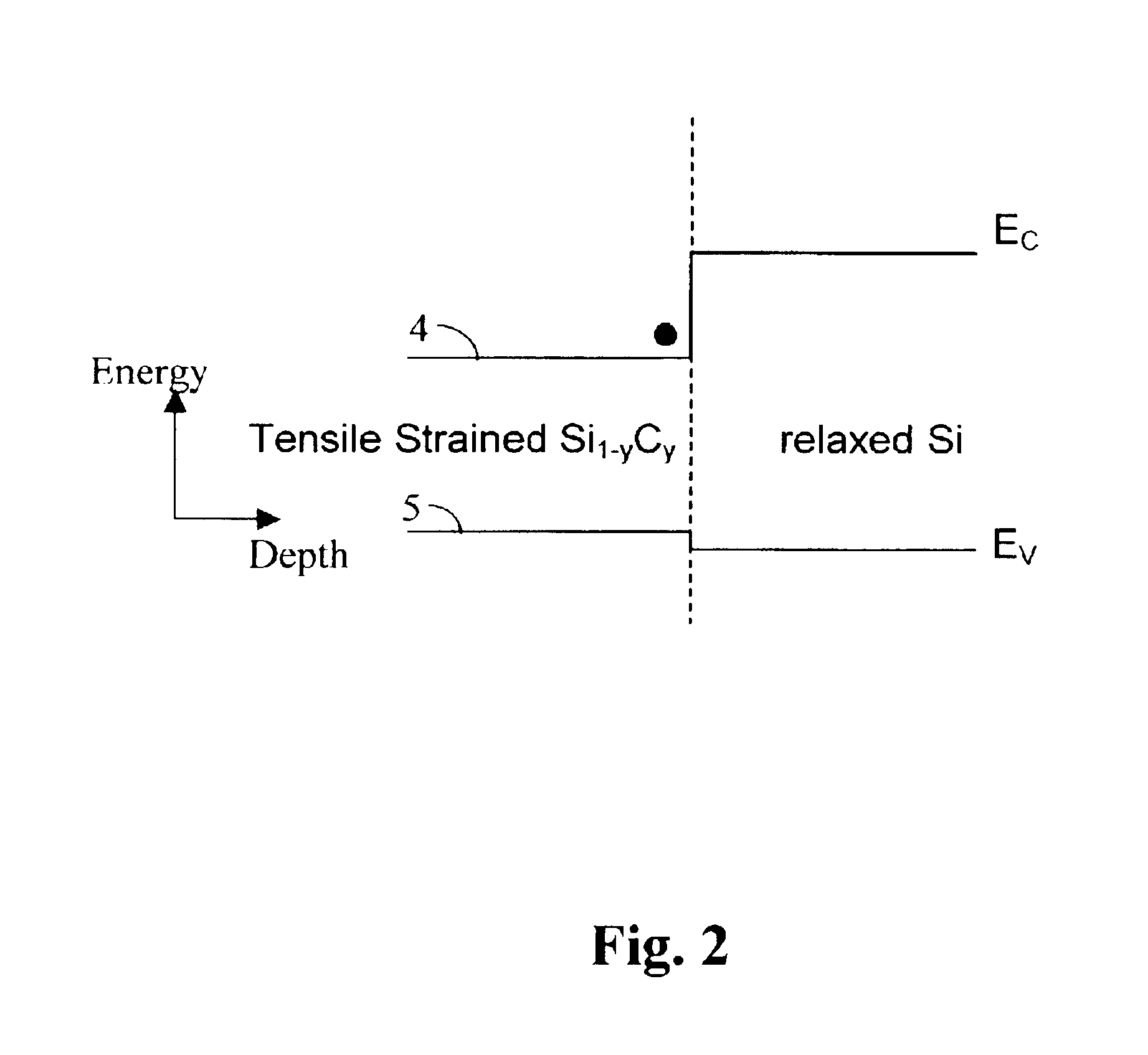

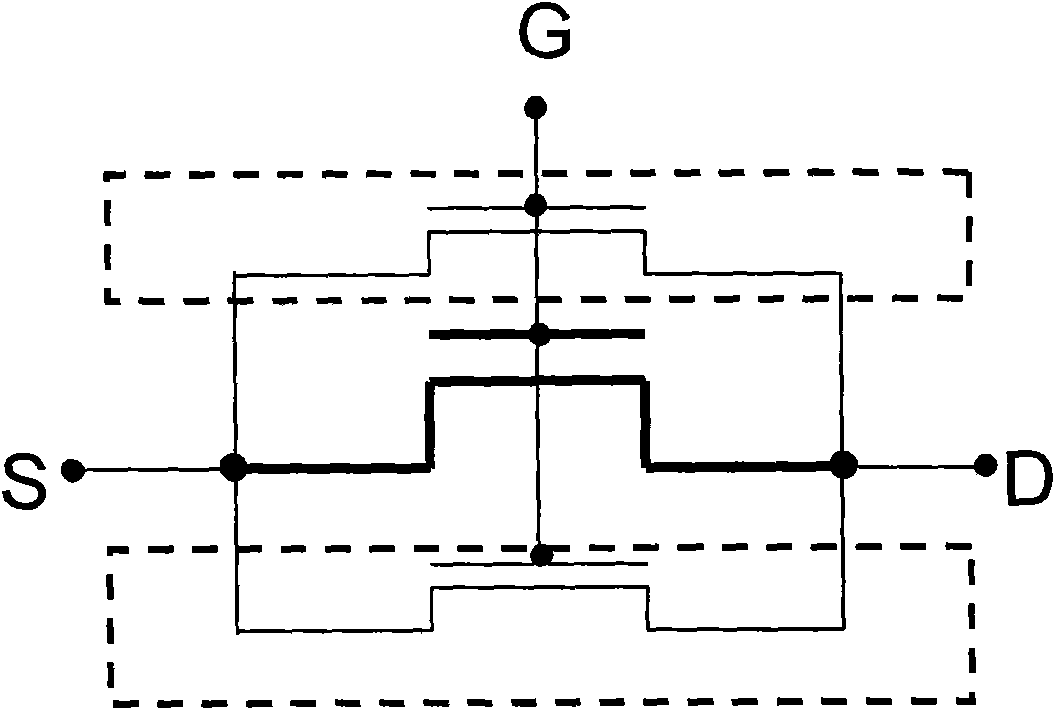

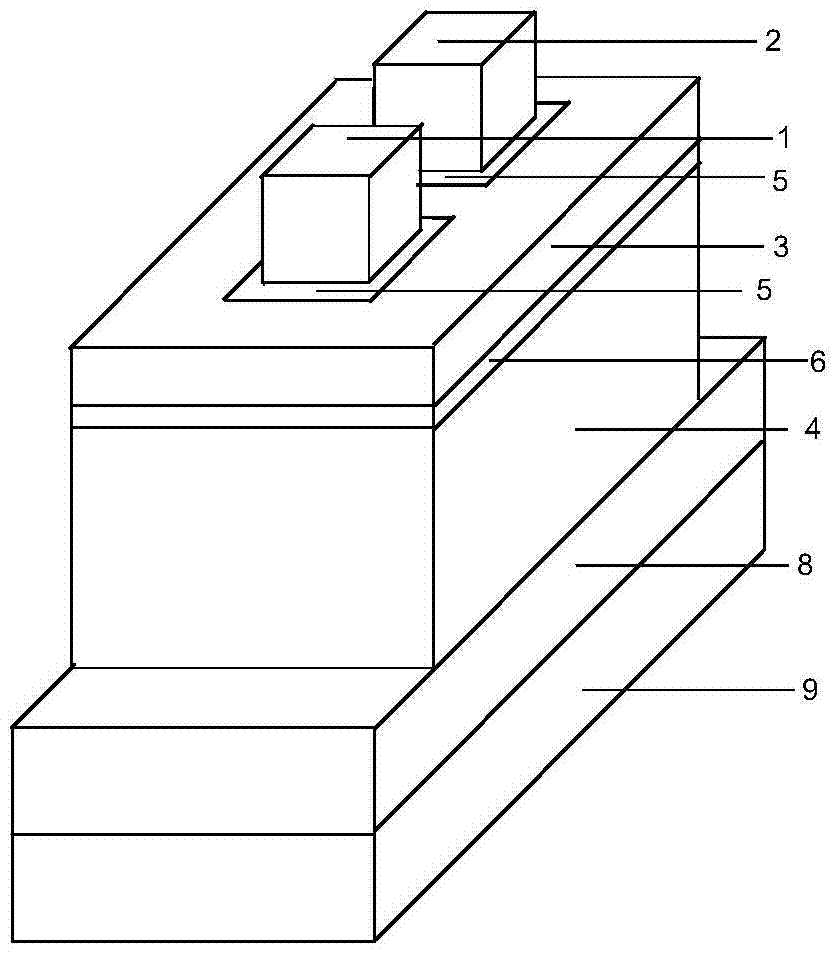

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

Technique to mitigate short channel effects with vertical gate transistor with different gate materials

InactiveUS20020130378A1Improve performanceSuppression of short channel effectsSolid-state devicesSemiconductor/solid-state device manufacturingReverse short-channel effectScale down

This invention relates to a process of forming a transistor with three vertical gate electrodes and the resulting transistor. By forming such a transistor it is possible to maintain an acceptable aspect ratio as MOSFET structures are scaled down to sub-micron sizes. The transistor gate electrodes can be formed of different materials so that the workfunctions of the three electrodes can be tailored. The three electrodes are positioned over a single channel and operate as a single gate having outer and inner gate regions.

Owner:MICRON TECH INC

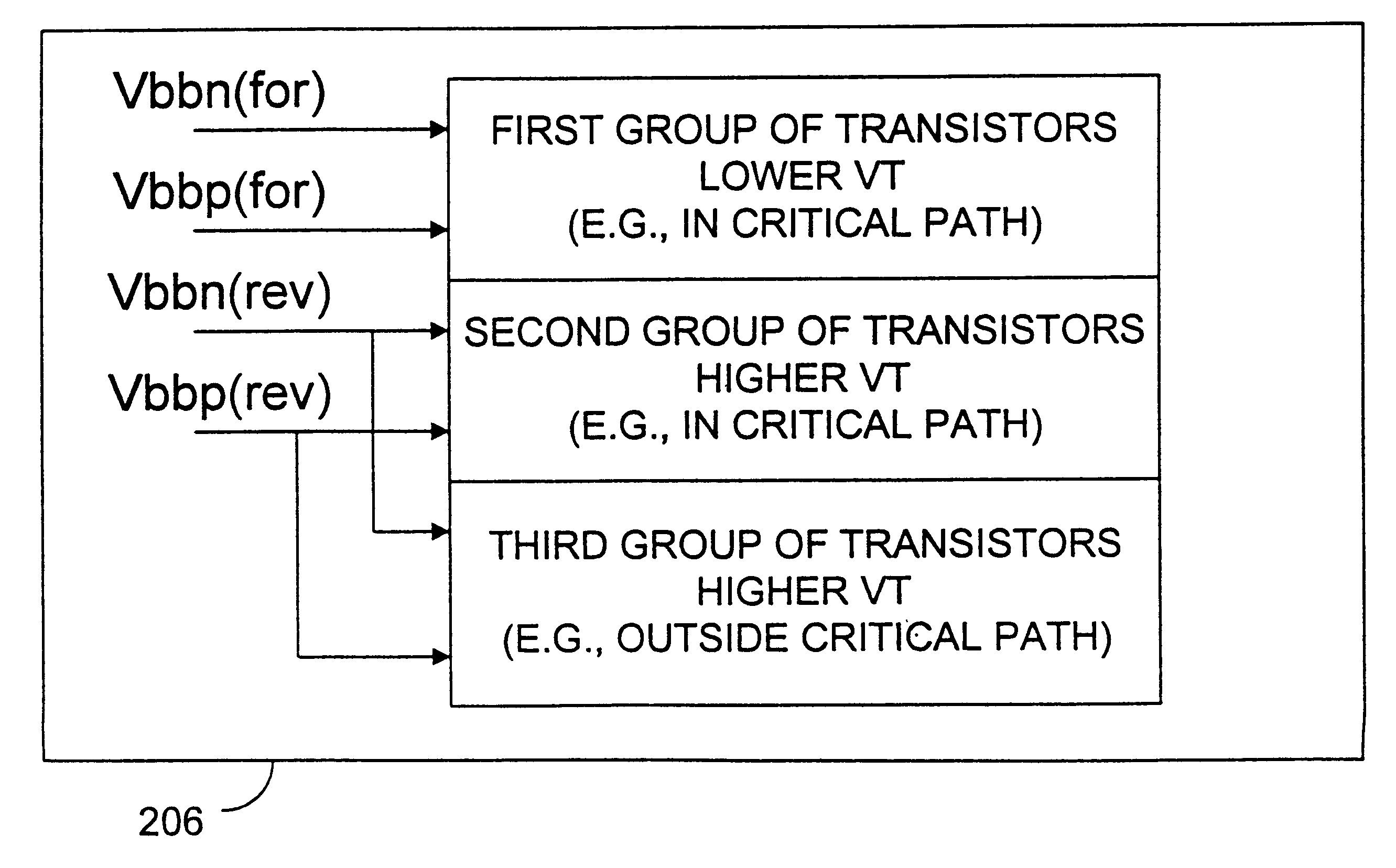

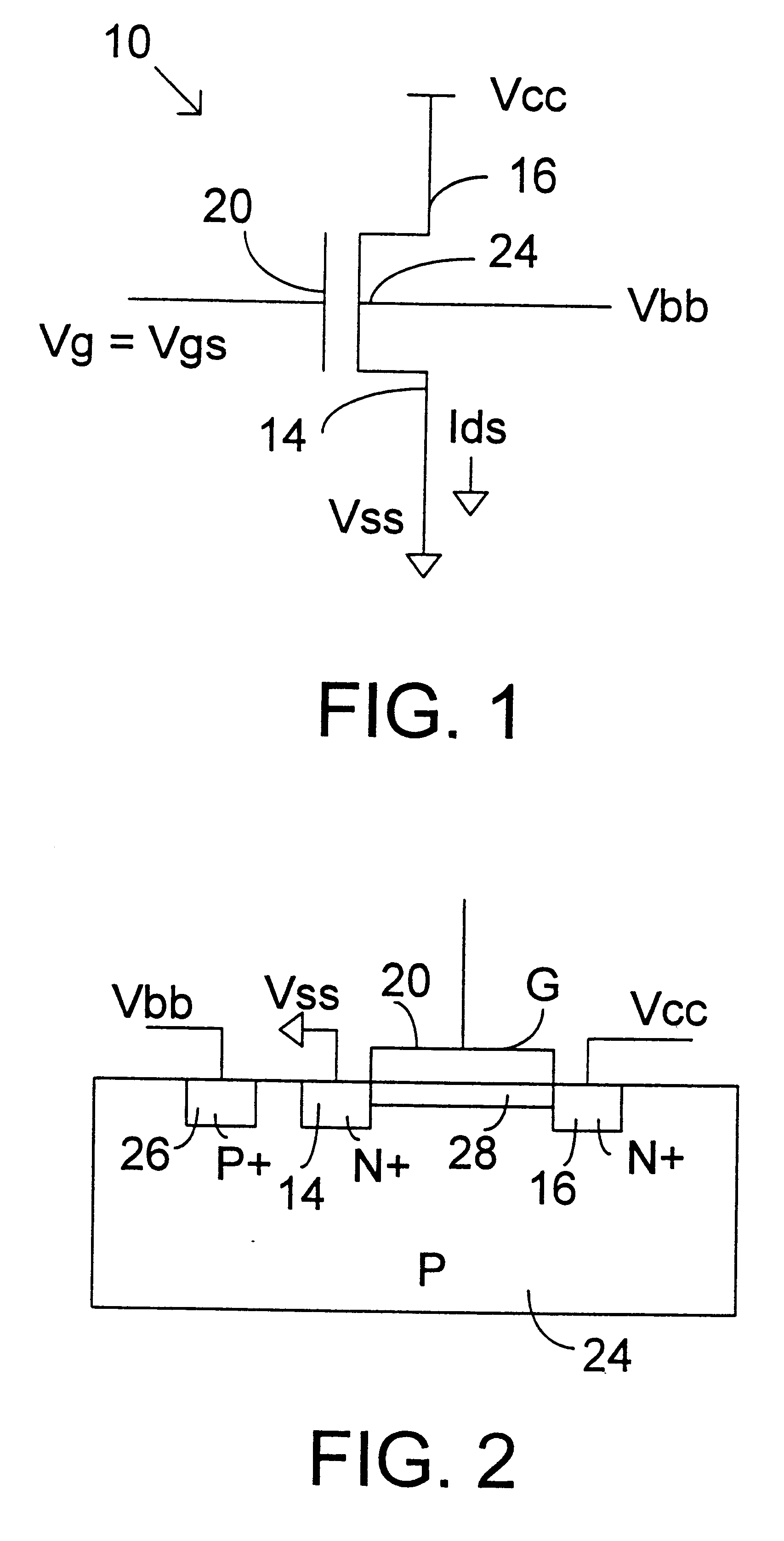

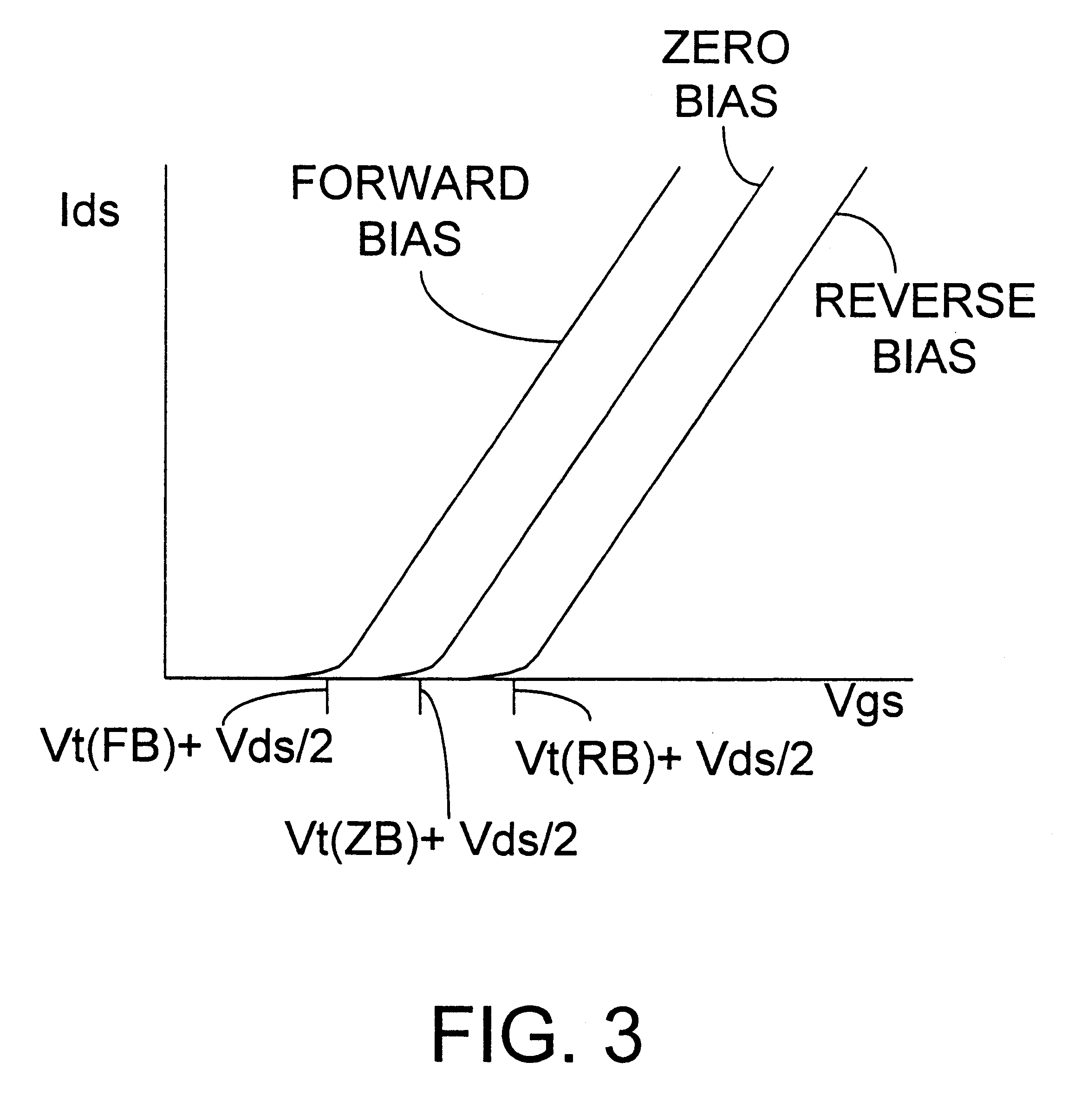

Transistors providing desired threshold voltage and reduced short channel effects with forward body bias

In one embodiment, a semiconductor circuit includes a first group of field effect transistors having a body and parameters including a net channel doping level DL1. The circuit also includes a conductor to provide a first voltage to the body to forward body bias the first group of transistors, the first group of transistors having a forward body bias threshold voltage (VtFBB) when forward body biased, wherein DL1 is at least 25% higher than a net channel doping level in the first group of transistors that would result in a zero body bias threshold voltage equal to VtFBB, with the parameters other than the net channel doping level being unchanged. In another embodiment, the semiconductor circuit includes a first circuit including a first group of field effect transistors having a body. The circuit also includes a first voltage source to provide a first voltage to the body such that the field effect transistors have a forward body bias, the first voltage being at a level leading to the circuit experiencing a reduced rate of soft error failures as compared to when the circuit is not forward biased.

Owner:INTEL CORP

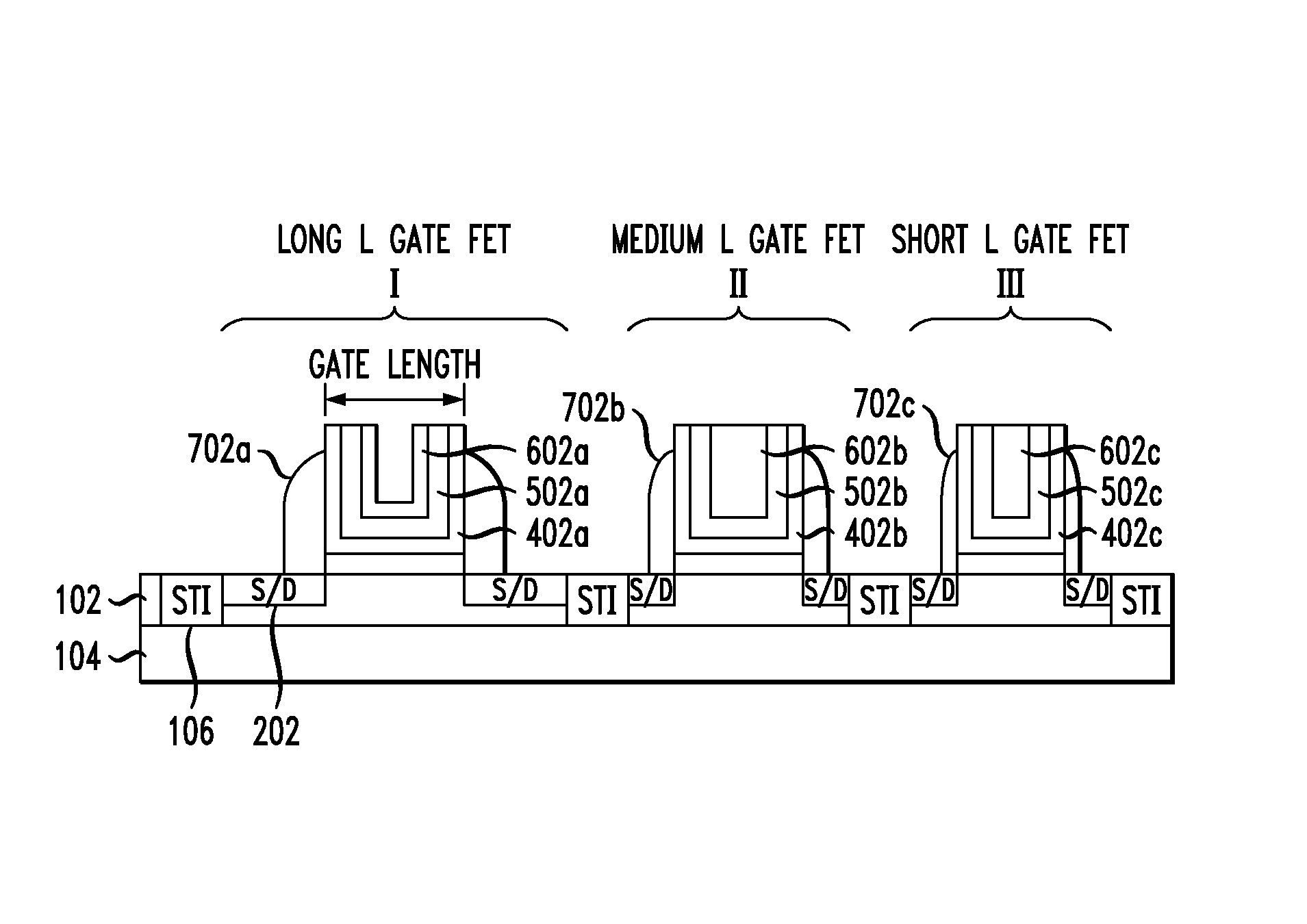

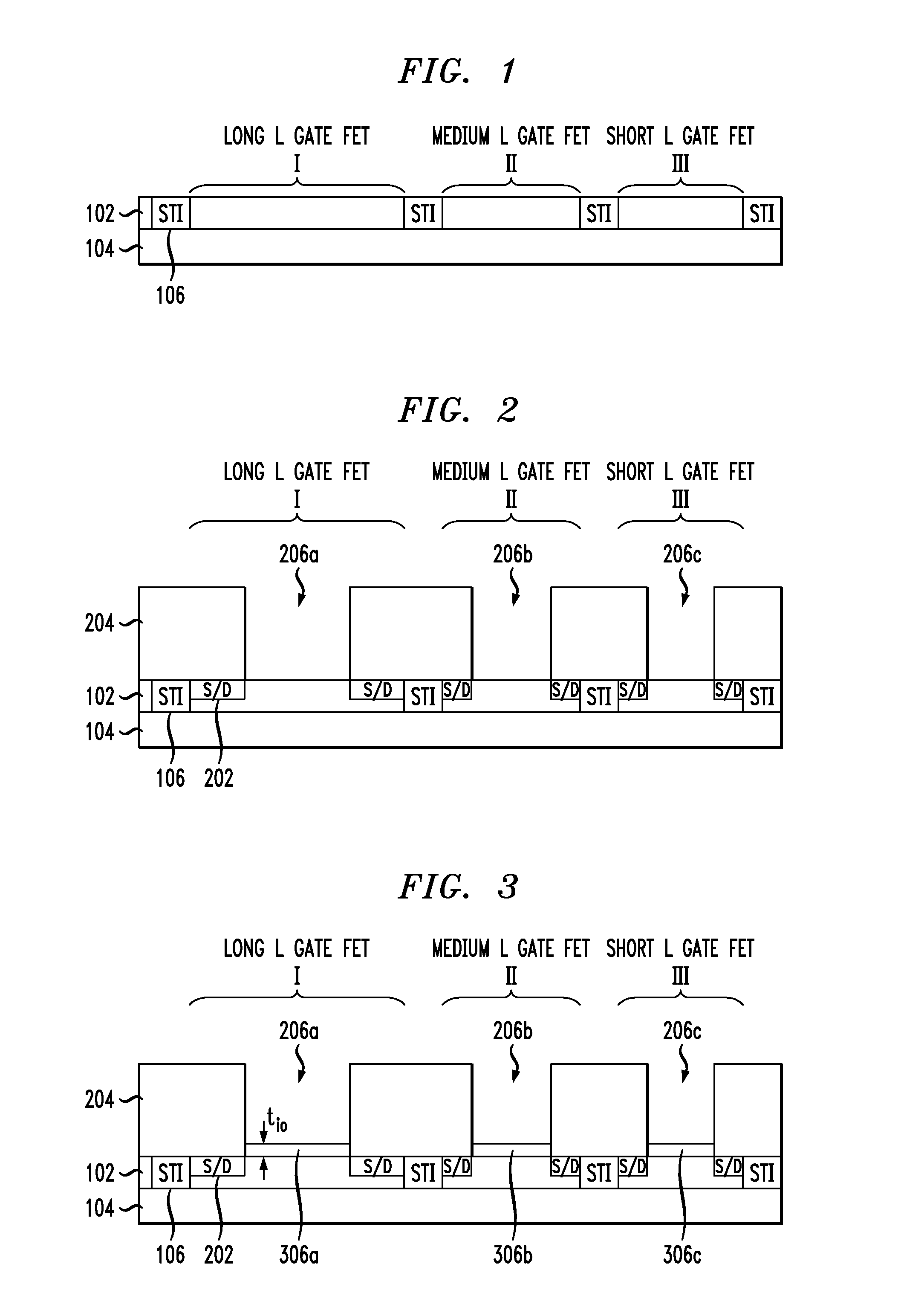

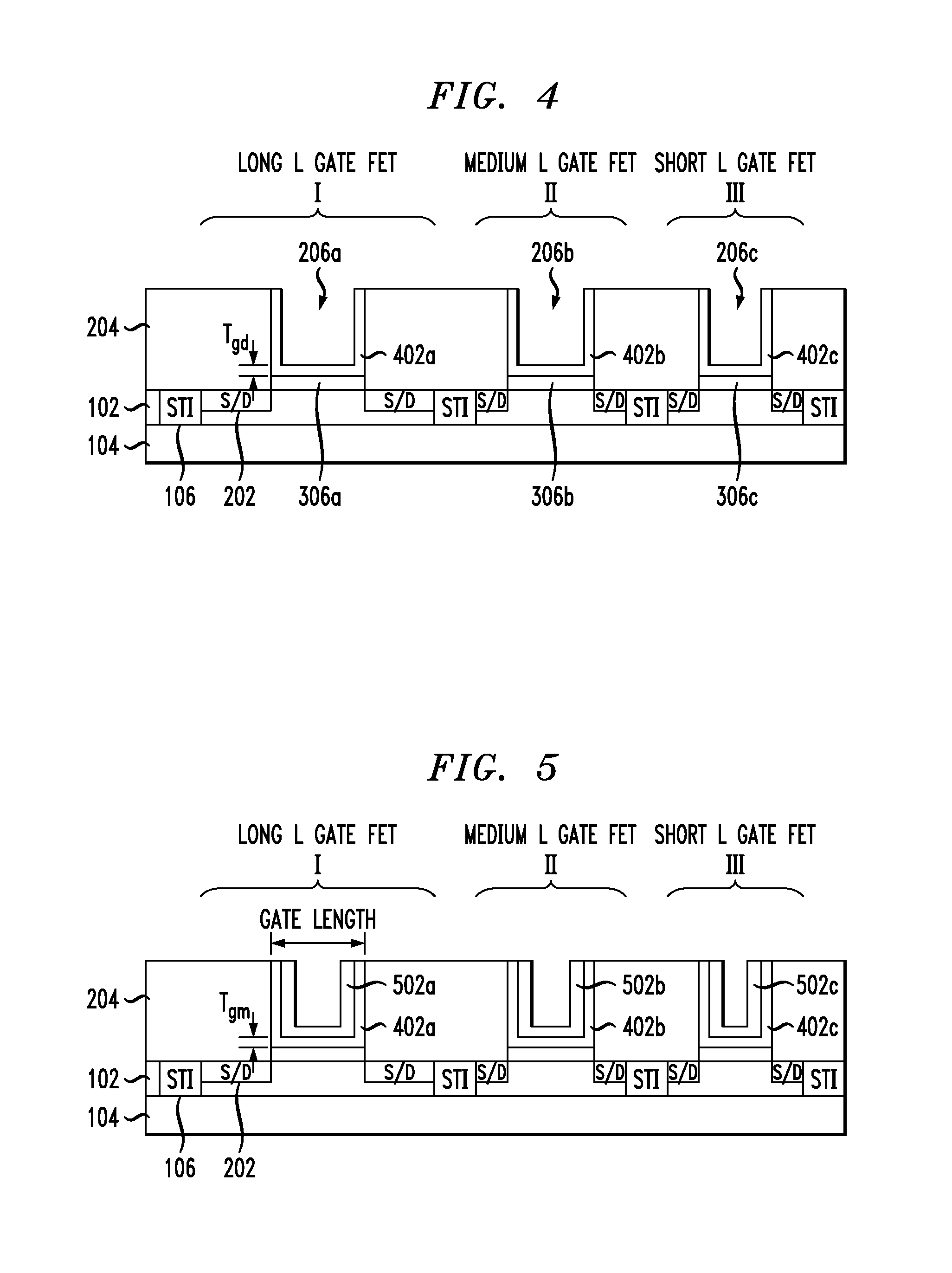

Techniques for gate workfunction engineering to reduce short channel effects in planar CMOS devices

Techniques for gate workfunction engineering using a workfunction setting material to reduce short channel effects in planar CMOS devices are provided. In one aspect, a method of fabricating a CMOS device includes the following steps. A SOI wafer is provided having a SOI layer over a BOX. A patterned dielectric is formed on the wafer having trenches therein present over active areas in which a gate stack will be formed. Into each of the trenches depositing: (i) a conformal gate dielectric (ii) a conformal gate metal layer and (iii) a conformal workfunction setting metal layer. A volume of the conformal gate metal layer and / or a volume of the conformal workfunction setting metal layer deposited into a given one of the trenches are / is proportional to a length of the gate stack being formed in the given trench. A CMOS device is also provided.

Owner:GLOBALFOUNDRIES U S INC

Method for fabricating transistor of semiconductor device

InactiveUS6936517B2Reduce generationReduce effective channel lengthTransistorSemiconductor/solid-state device manufacturingReverse short-channel effectShort-channel effect

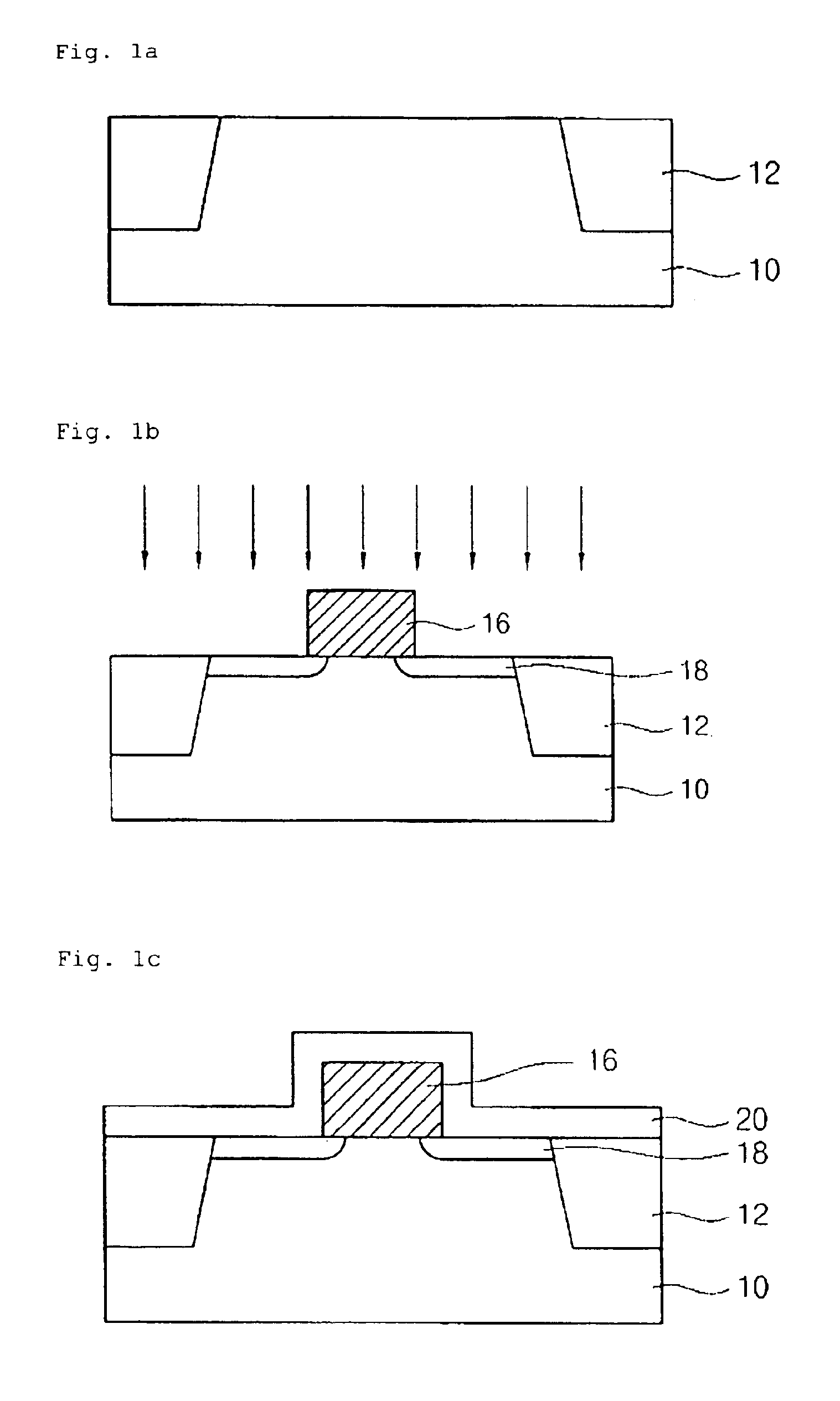

A method of fabricating a transistor of a semiconductor device is disclosed. The method of fabricating a transistor comprises forming a sacrificial layer on a substrate; forming a source / drain region in the substrate by performing a first ion implantation using the sacrificial layer as a mask; forming a barrier layer over the substrate with the sacrificial layer; removing a portion of the sacrificial layer to form an opening through which a portion of the substrate is exposed; performing a second ion implantation using the opening as a mask to implant ions for adjustment of a threshold voltage of the substrate; forming a gate electrode on the substrate exposed through the opening; and performing a third ion implantation to adjust doping concentration in the gate electrode. Accordingly, the present invention can reduce the occurrences of a short channel effect and a reverse short channel effect in a transistor.

Owner:DONGBUANAM SEMICON

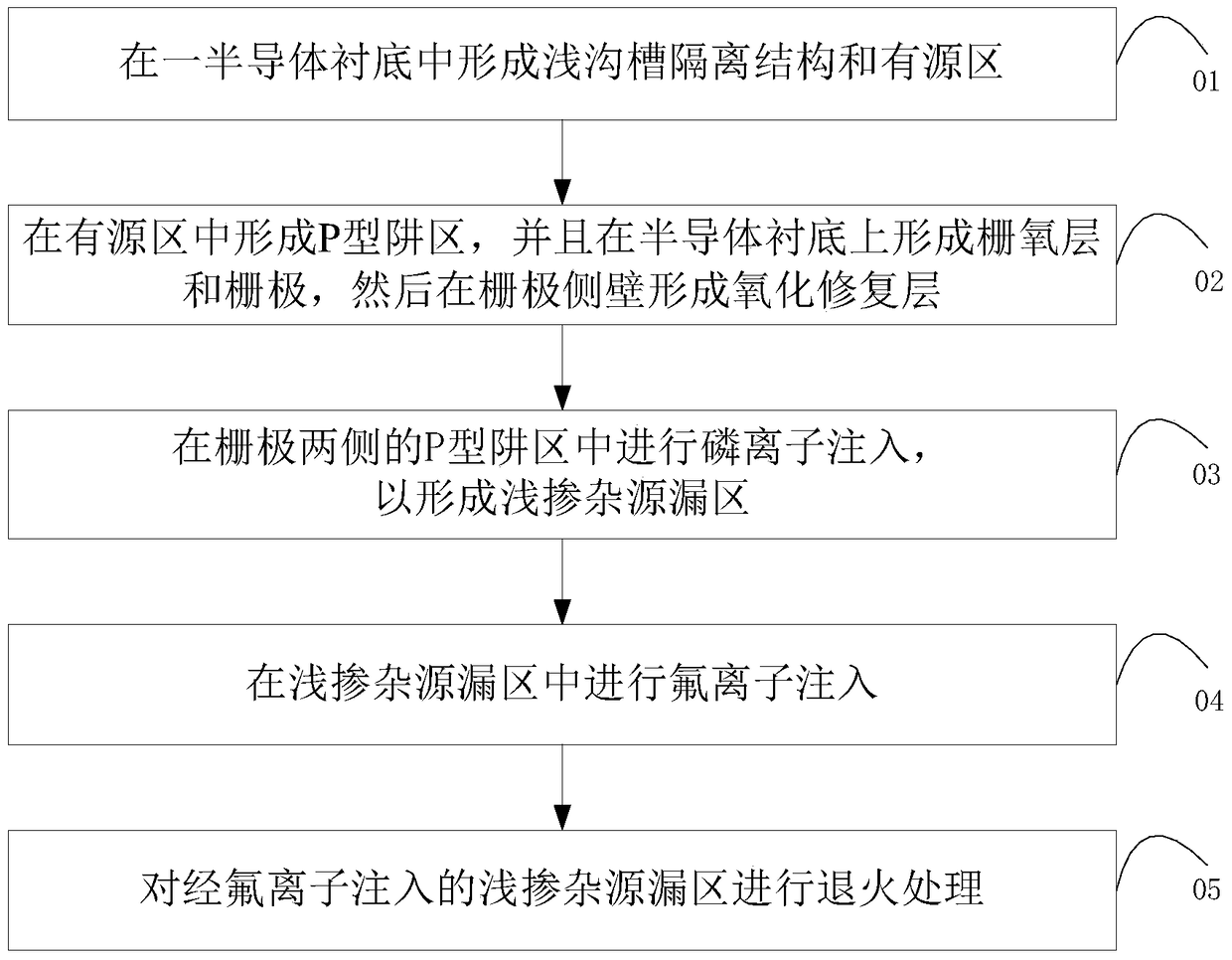

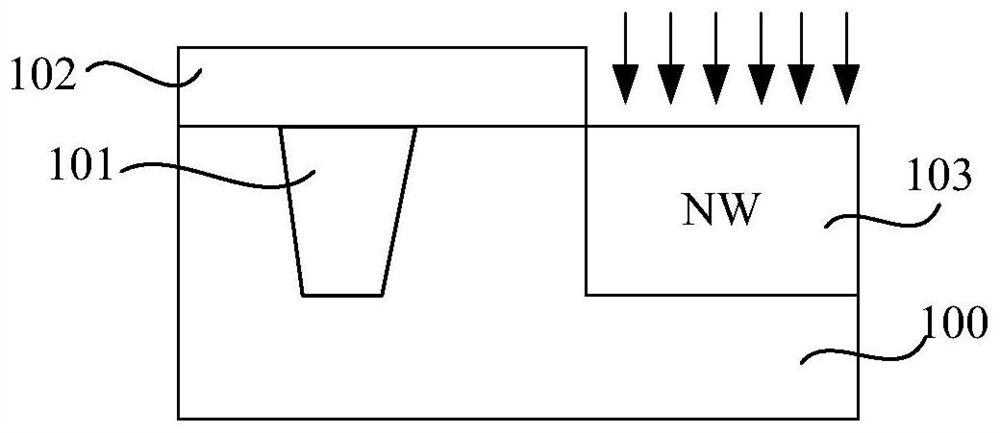

Method for manufacturing semiconductor device layer

InactiveCN102097379AImprove performanceWon't happenSemiconductor/solid-state device manufacturingSemiconductor devicesReverse short-channel effectSalicide

The invention discloses a method for manufacturing a semiconductor device layer. The method comprises the following steps of: after a well is formed on a substrate of a semiconductor device, forming an isolation shallow trench, and forming a grid on the substrate of the semiconductor device; performing ion implantation of carbon impurity on the grid and the substrate of the semiconductor device; after the surface of the grid and the surface of the substrate of the semiconductor device are re-oxidized, performing light dope on the grid and the substrate of the semiconductor device to form a shallow junction on the substrate of the semiconductor device; forming a nitrogen oxide side wall of the grid, doping the grid and the substrate of the semiconductor device, and performing deposition on the semiconductor device to form a drain and a source; and depositing metals on the surface of the grid and the semiconductor substrate by adopting a self-alignment silicide method to form metalized silicon layers, then performing quick annealing treatment, and etching the un-reacted metals. The method can effectively reduce the transient enhanced diffusion (TED) generated in the re-oxidation process of the grid so as to remarkably prevent the short trench of the semiconductor device from generating short channel effect (SCE) and reverse short channel effect (RSCE).

Owner:SEMICON MFG INT (SHANGHAI) CORP

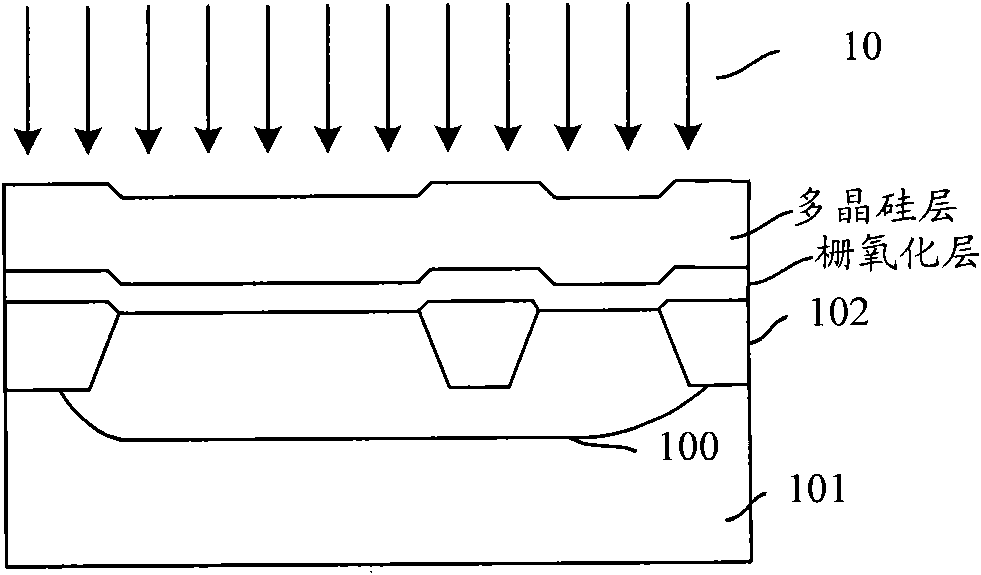

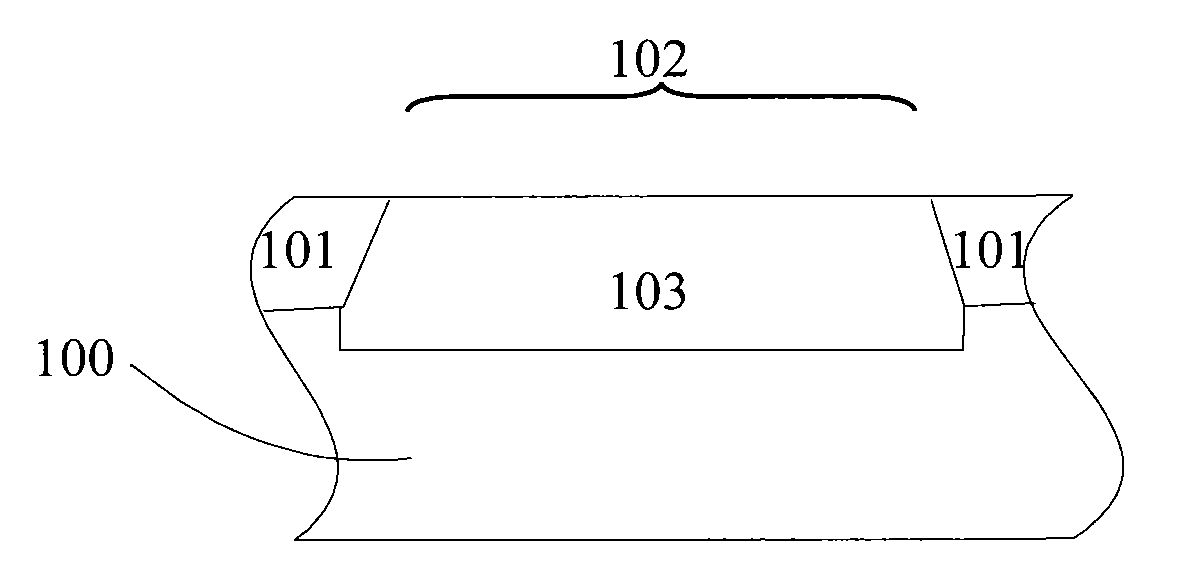

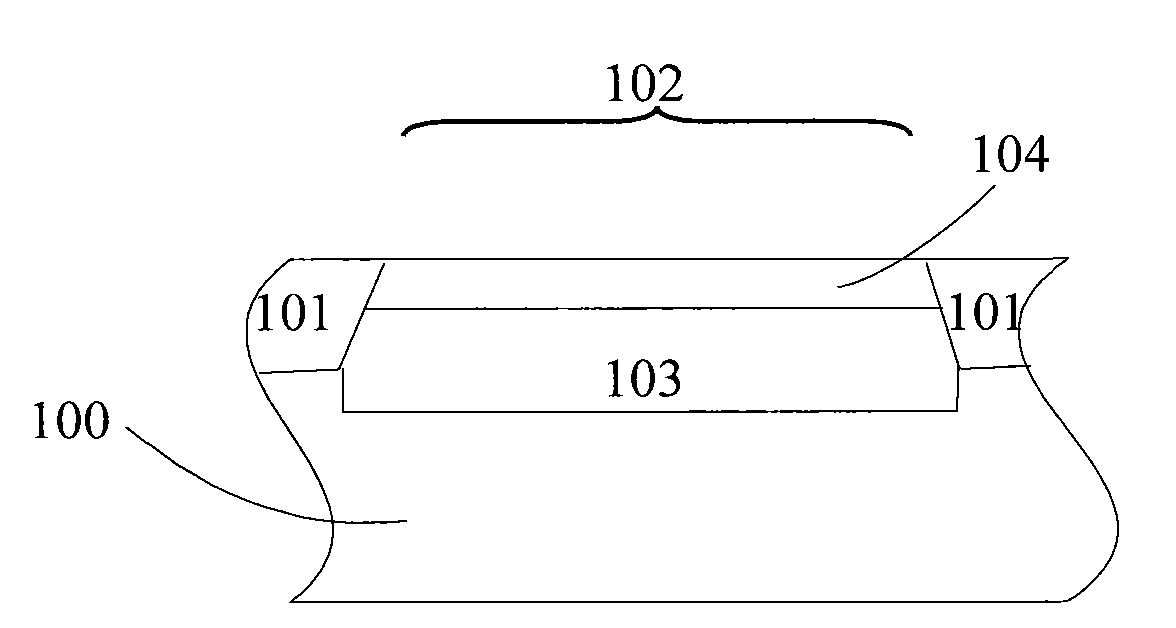

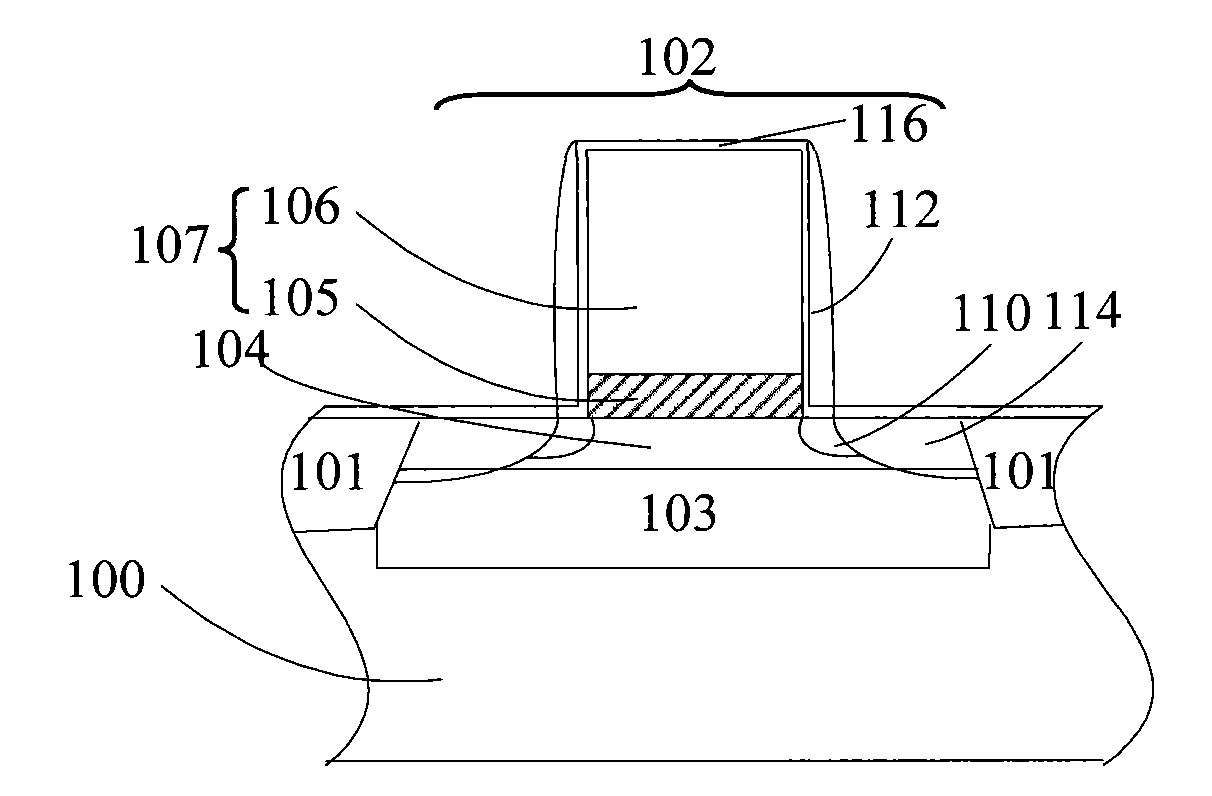

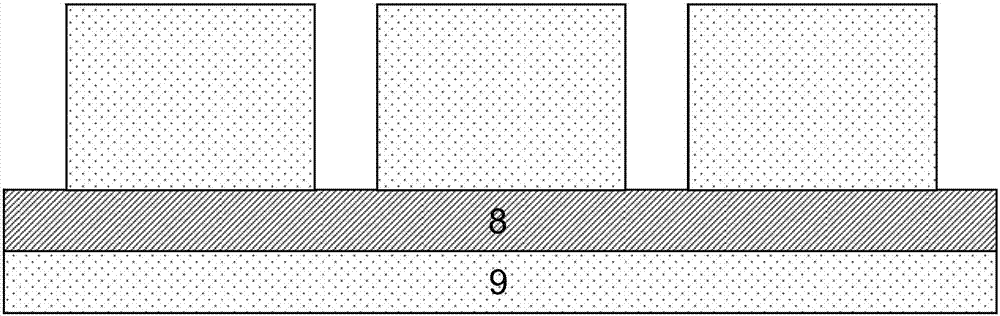

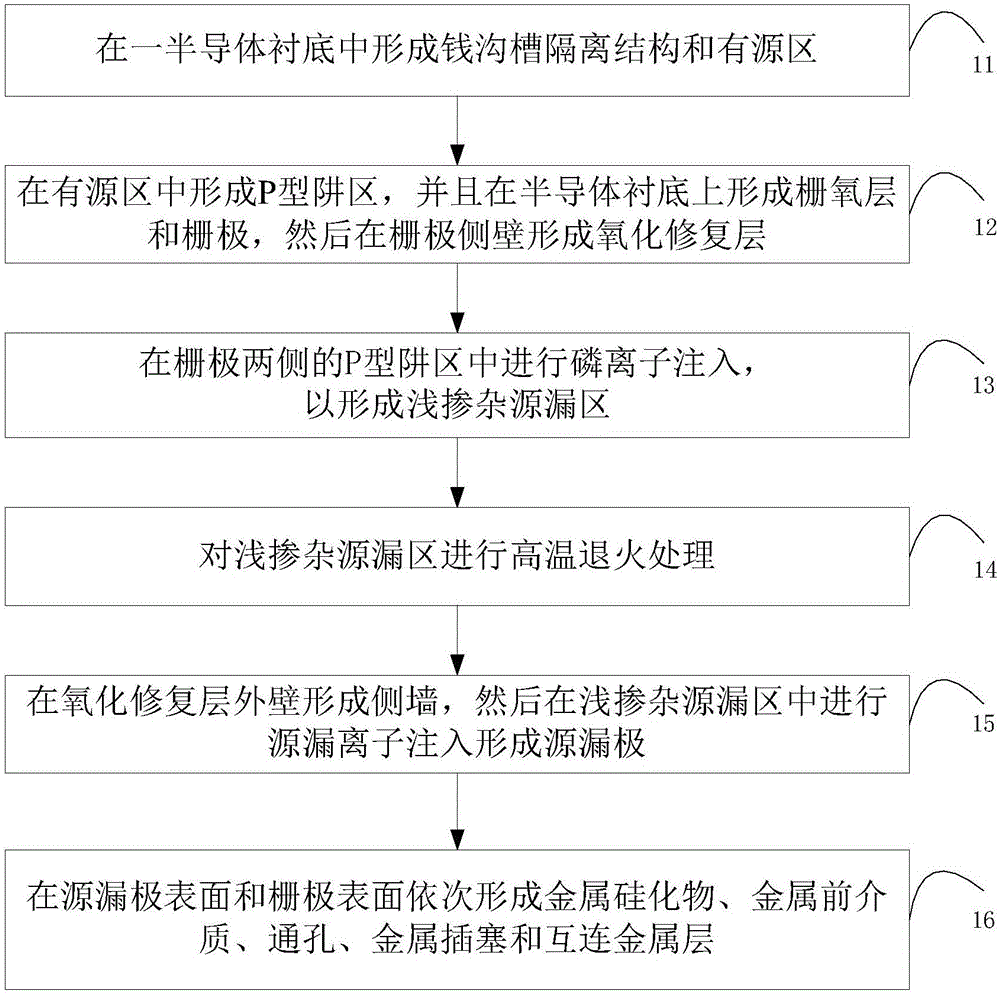

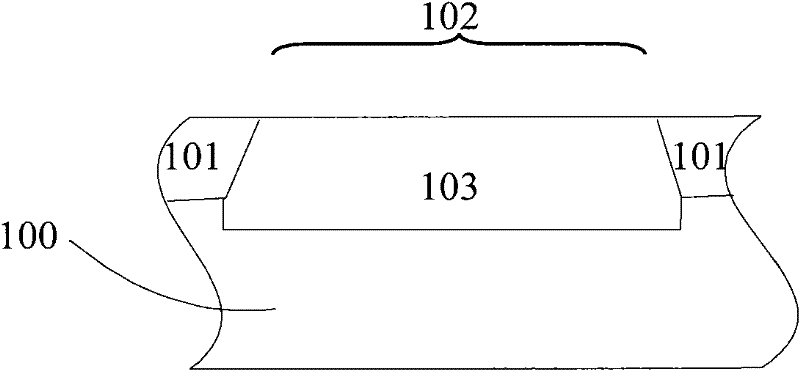

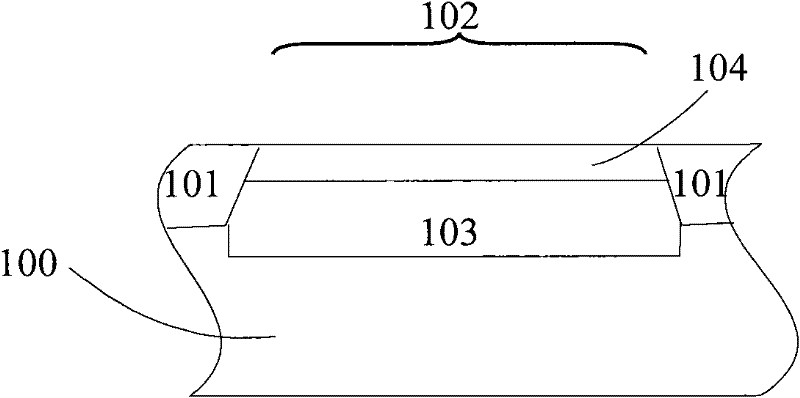

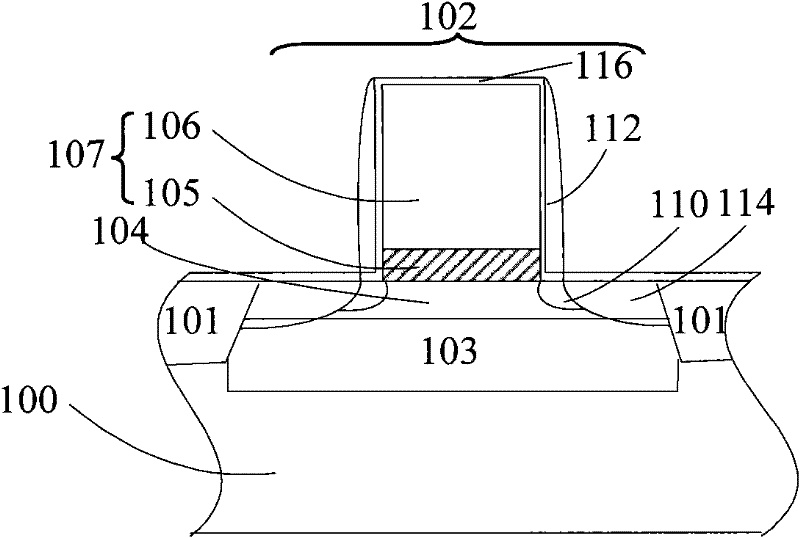

Forming method of N-channel metal oxide semiconductor (NMOS) transistor

InactiveCN102074476AAvoid crowdingEvenly distributedSemiconductor/solid-state device manufacturingReverse short-channel effectGate dielectric

The invention discloses a forming method of an N-channel metal oxide semiconductor (NMOS) transistor, which comprises the following steps of: providing a semiconductor substrate which is divided into an isolation region and an active region; forming a doped well in the semiconductor substrate of the active region; forming a gate dielectric layer and a polycrystalline silicon gate on the semiconductor substrate of the active region in turn, wherein the gate dielectric layer and the polycrystalline silicon gate form a gate structure; re-oxidizing the gate structure; injecting ions into the semiconductor substrates on two sides of the gate by taking the gate structure as a mask to form a source / drain extension region; forming side walls on two sides of the gate structure, and then forming a Vt injection region in the semiconductor substrate; and forming source / drain electrodes in the semiconductor substrates on two sides of the gate structure and the side walls. The forming method ensures that ions of the Vt injection region of a channel region positioned below the gate are uniformly distributed to prevent a reverse short channel effect (RSCE).

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

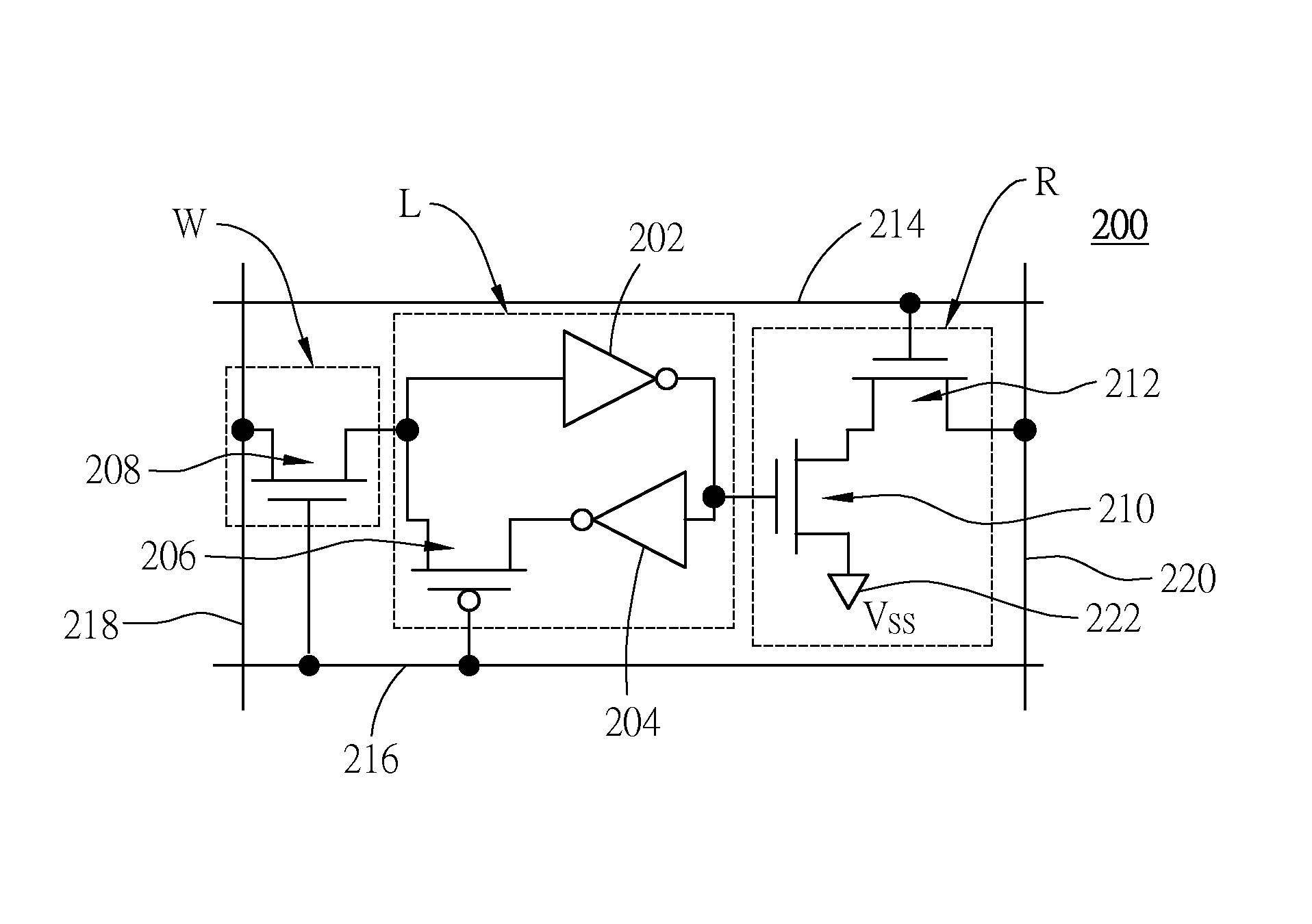

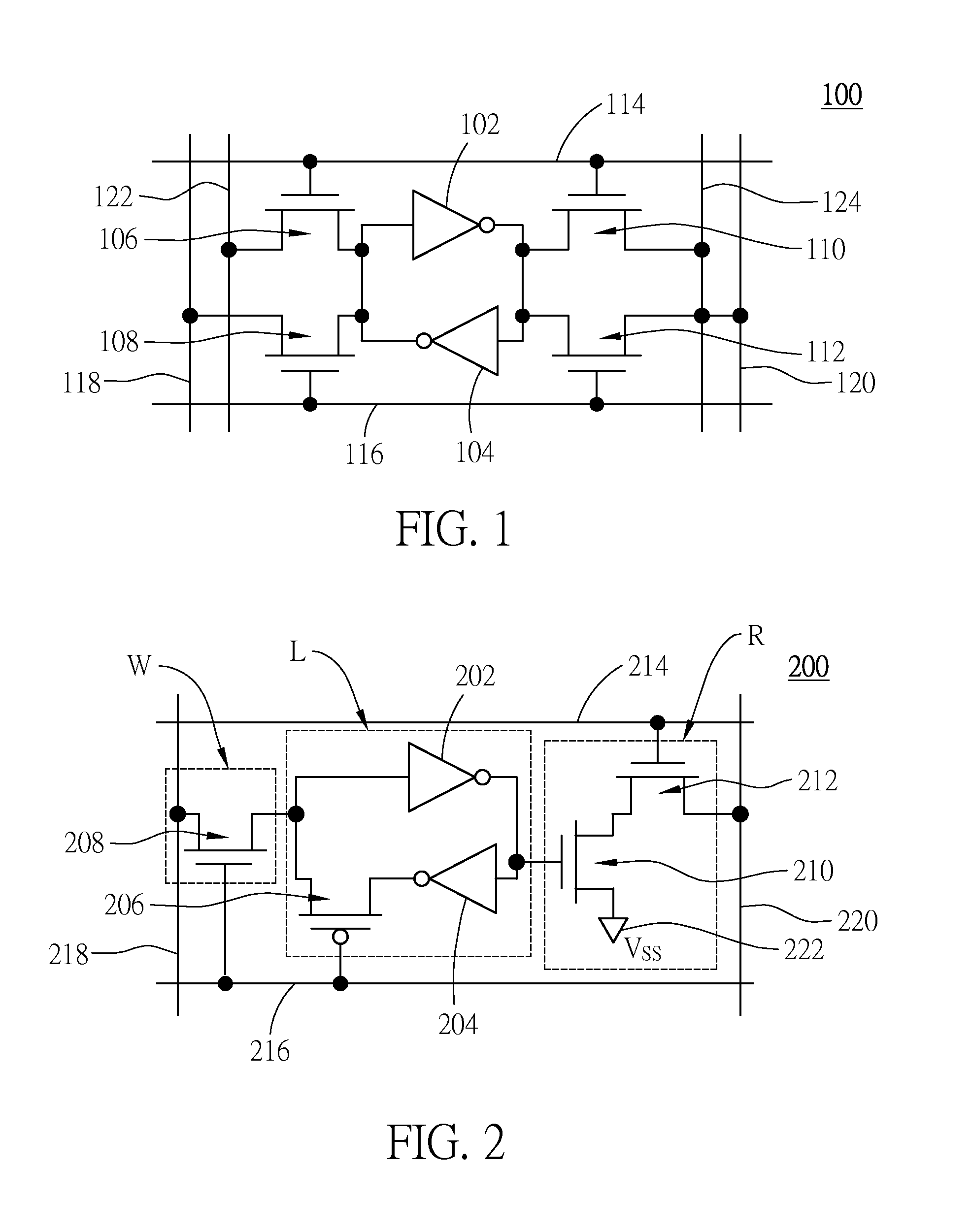

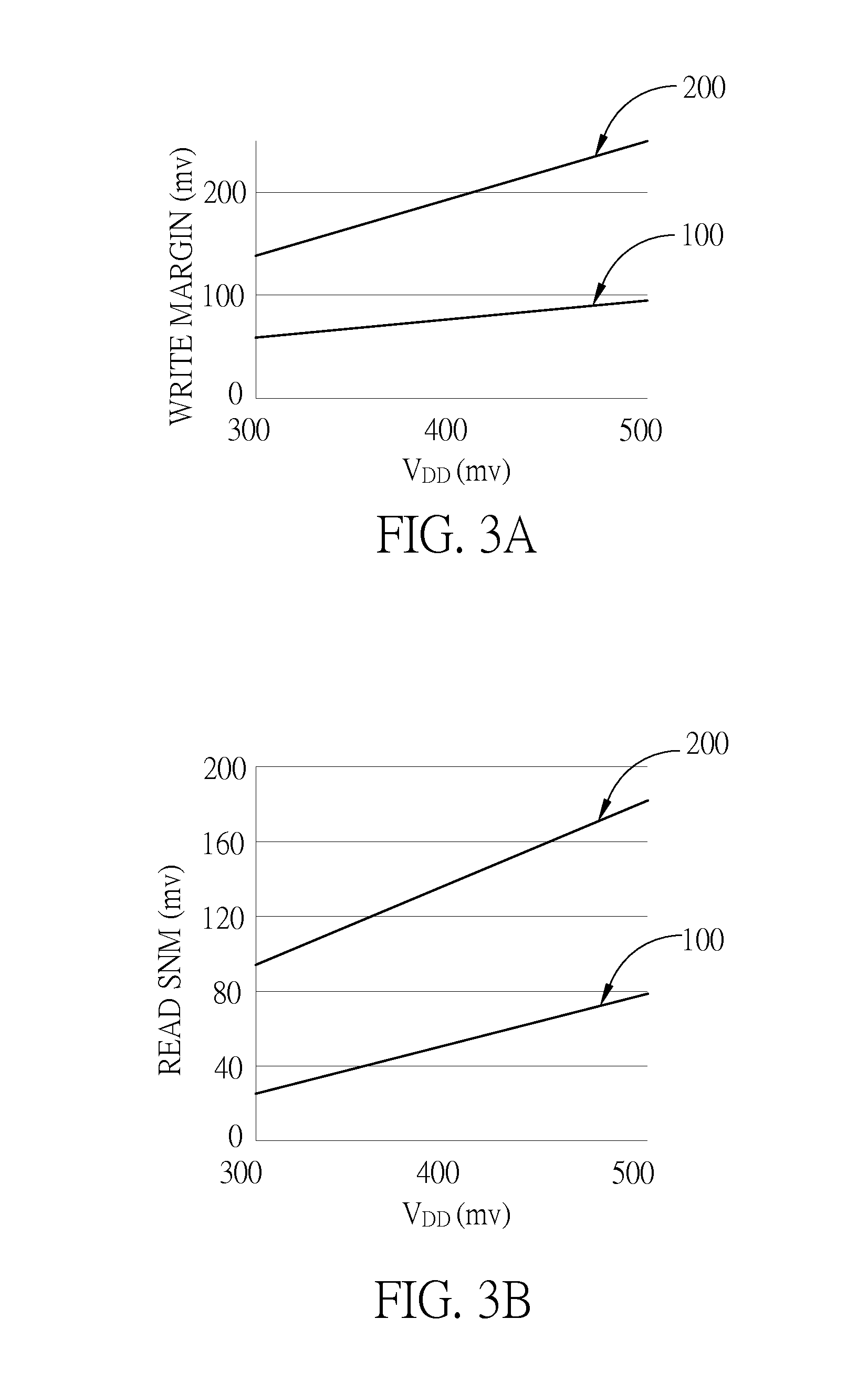

Dual-port subthreshold SRAM cell

ActiveUS8498174B2SNM to be read is enhancedEasy to readDigital storageBit lineReverse short-channel effect

Owner:NAT CHIAO TUNG UNIV

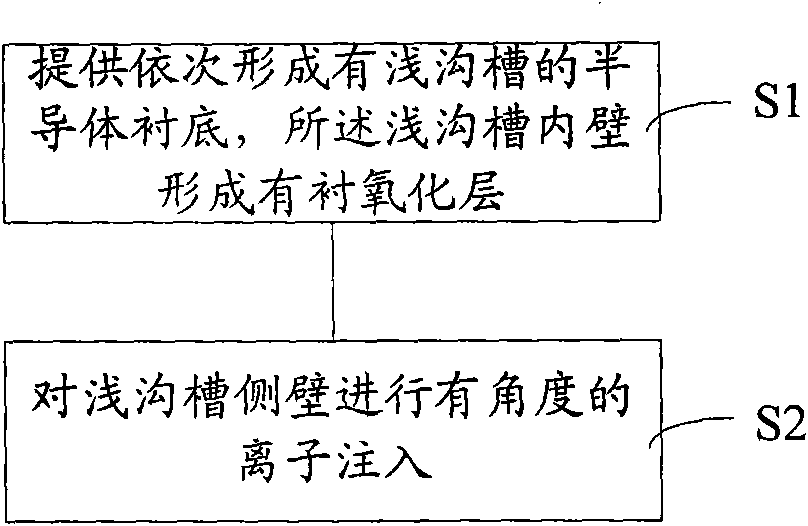

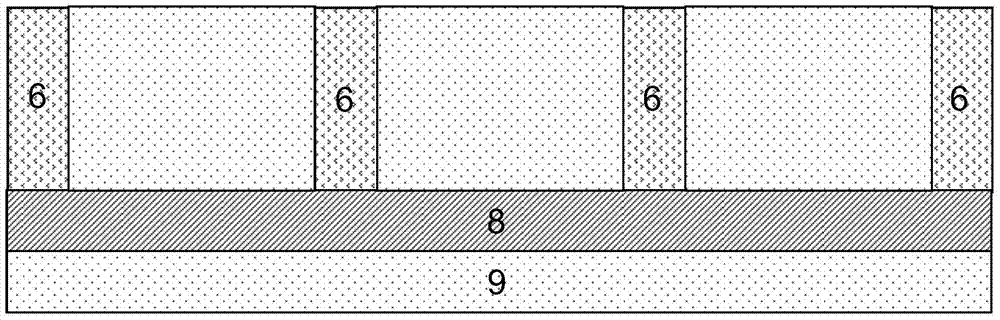

Methods for improving reverse narrow channel effect and manufacturing metal oxide semiconductor (MOS) transistor

InactiveCN102110636AImproved anti-narrow channel effectThe declining trend slows downSemiconductor/solid-state device manufacturingReverse short-channel effectEngineering

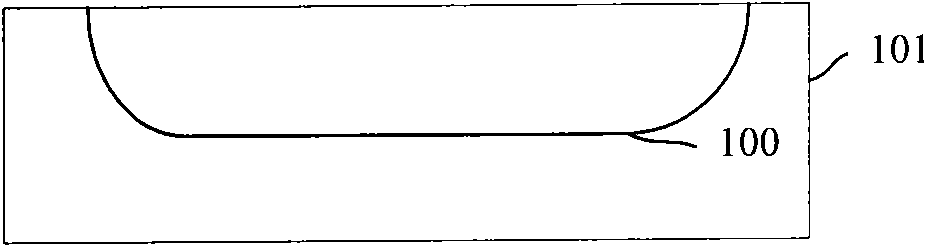

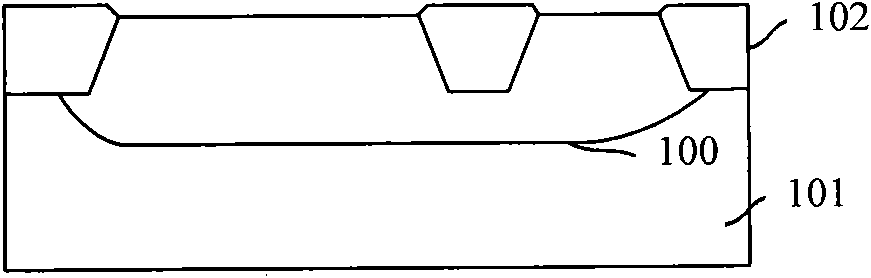

The invention provides methods for improving a reverse narrow channel effect and manufacturing a metal oxide semiconductor (MOS) transistor. The method for improving the reverse narrow channel effect comprises the following steps of: providing a semiconductor substrate on which shallow trenches are formed in turn; forming a lining oxide layer on the inner wall of each shallow trench; and performing angular ion implantation on the side wall of the shallow trench. By the method, the reverse narrow channel effect of the MOS transistor is effectively improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

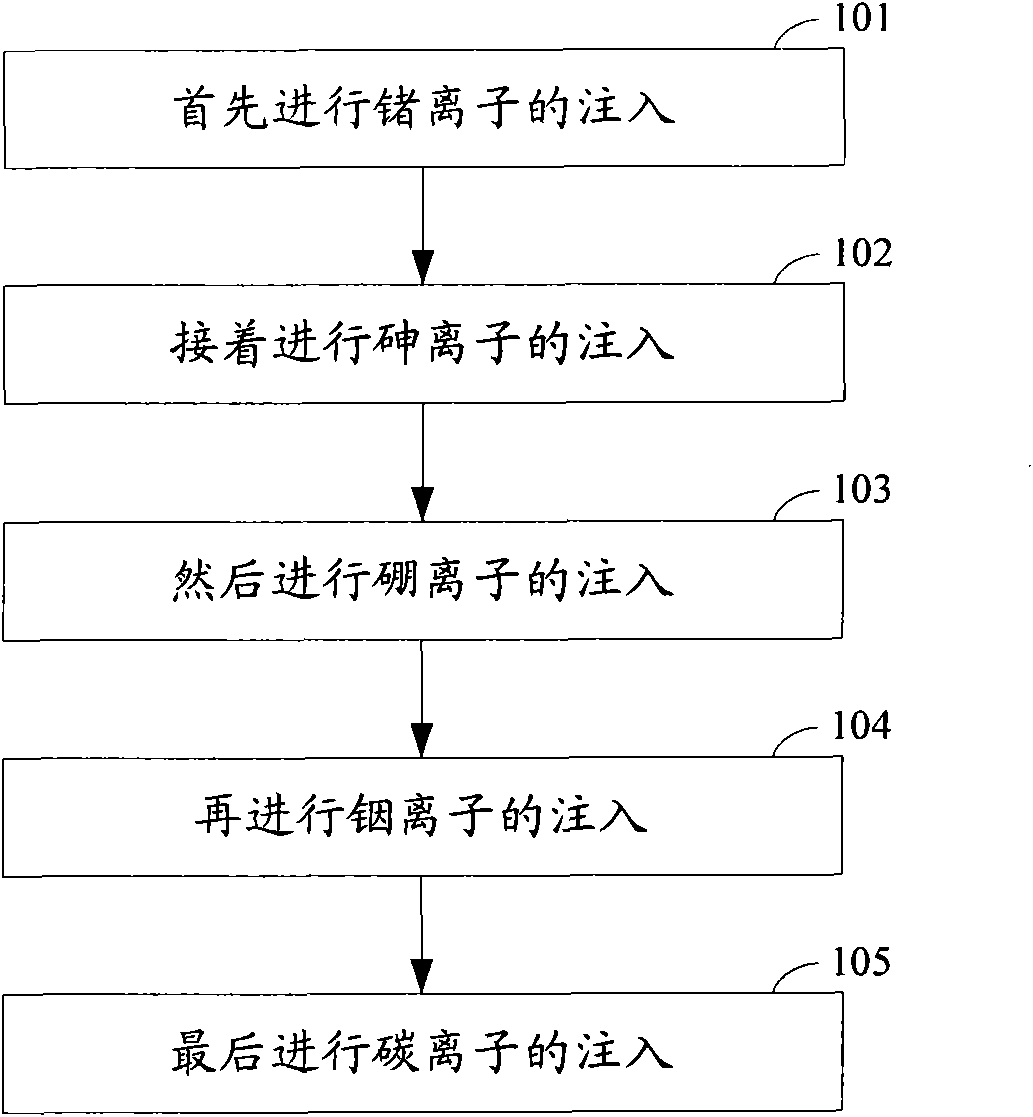

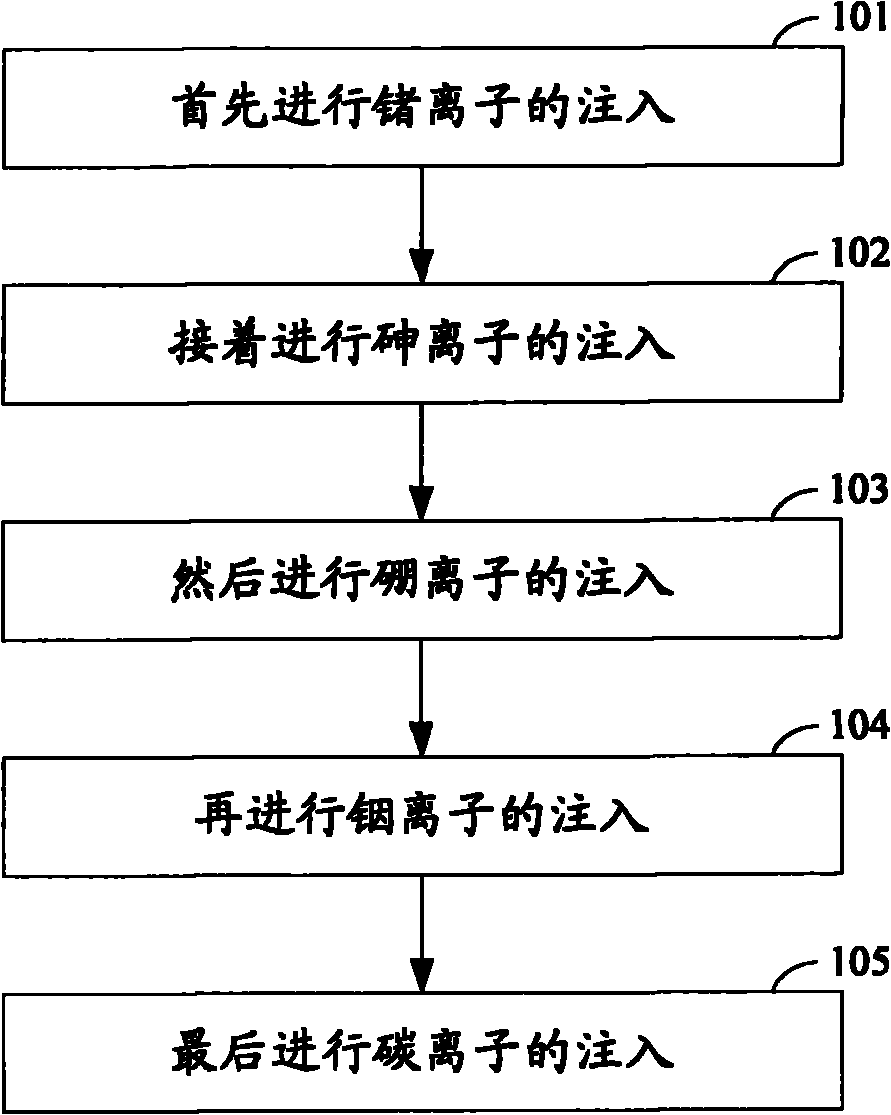

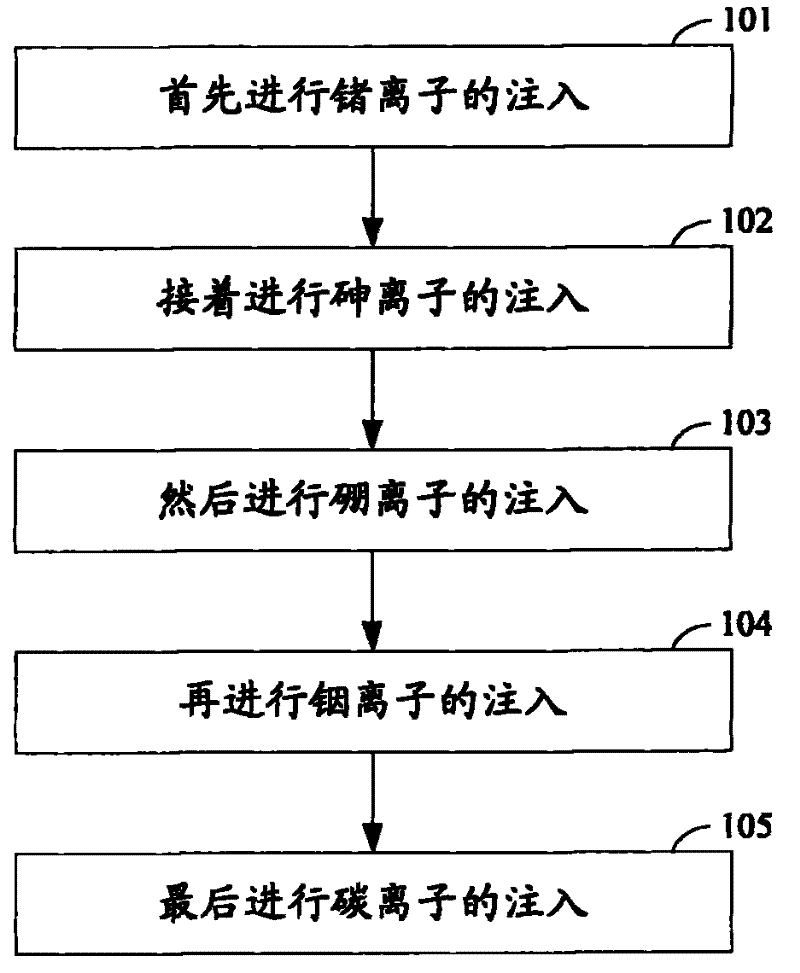

Ion implant method

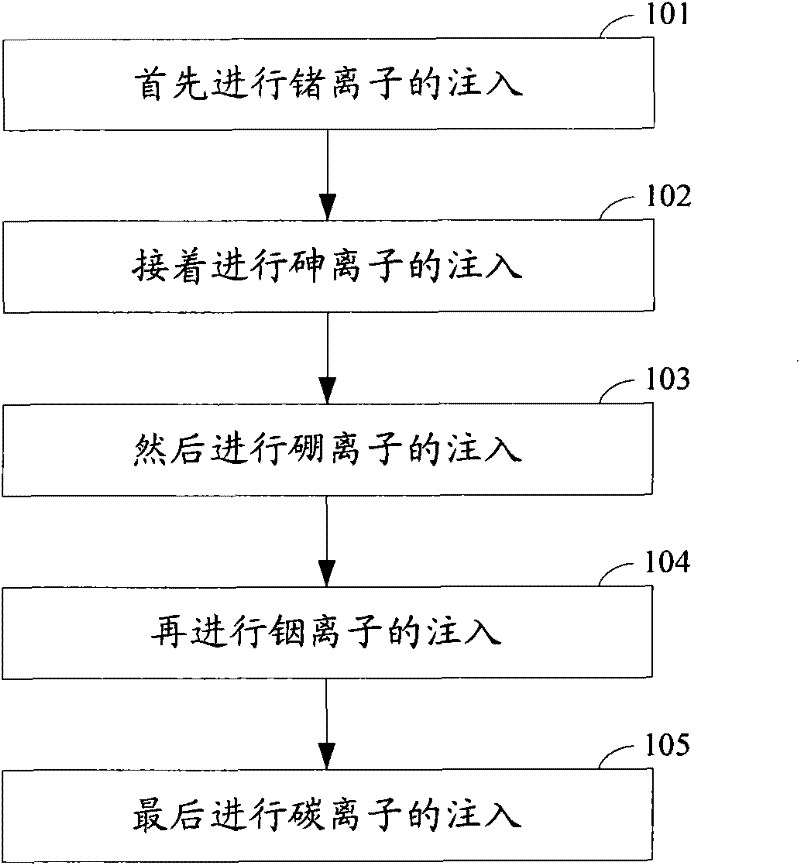

InactiveCN101894748AImprove performanceSemiconductor/solid-state device manufacturingReverse short-channel effectIndium

The invention discloses an ion implant method, comprising the following step: implanting ions according to the pre-specified ion implant sequence, wherein the sequence is as follow: germanium ions, arsenic ions, boron ions, indium ions and carbon ions. The method can effectively improve the performance of the semi-conductor components and eliminate or reduce the adverse impact of the short channel effect and / or reverse short channel effect on the semi-conductor components.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

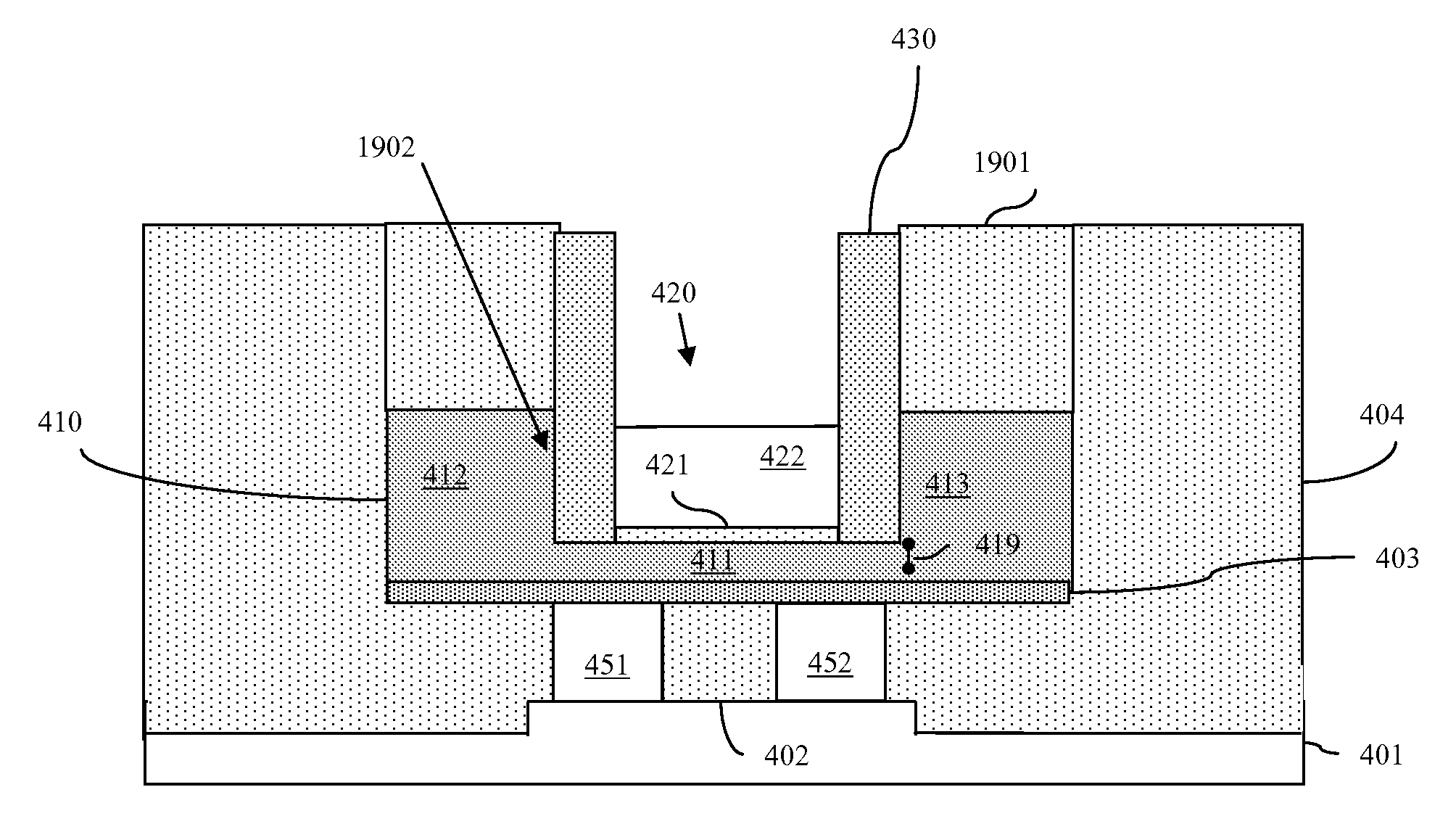

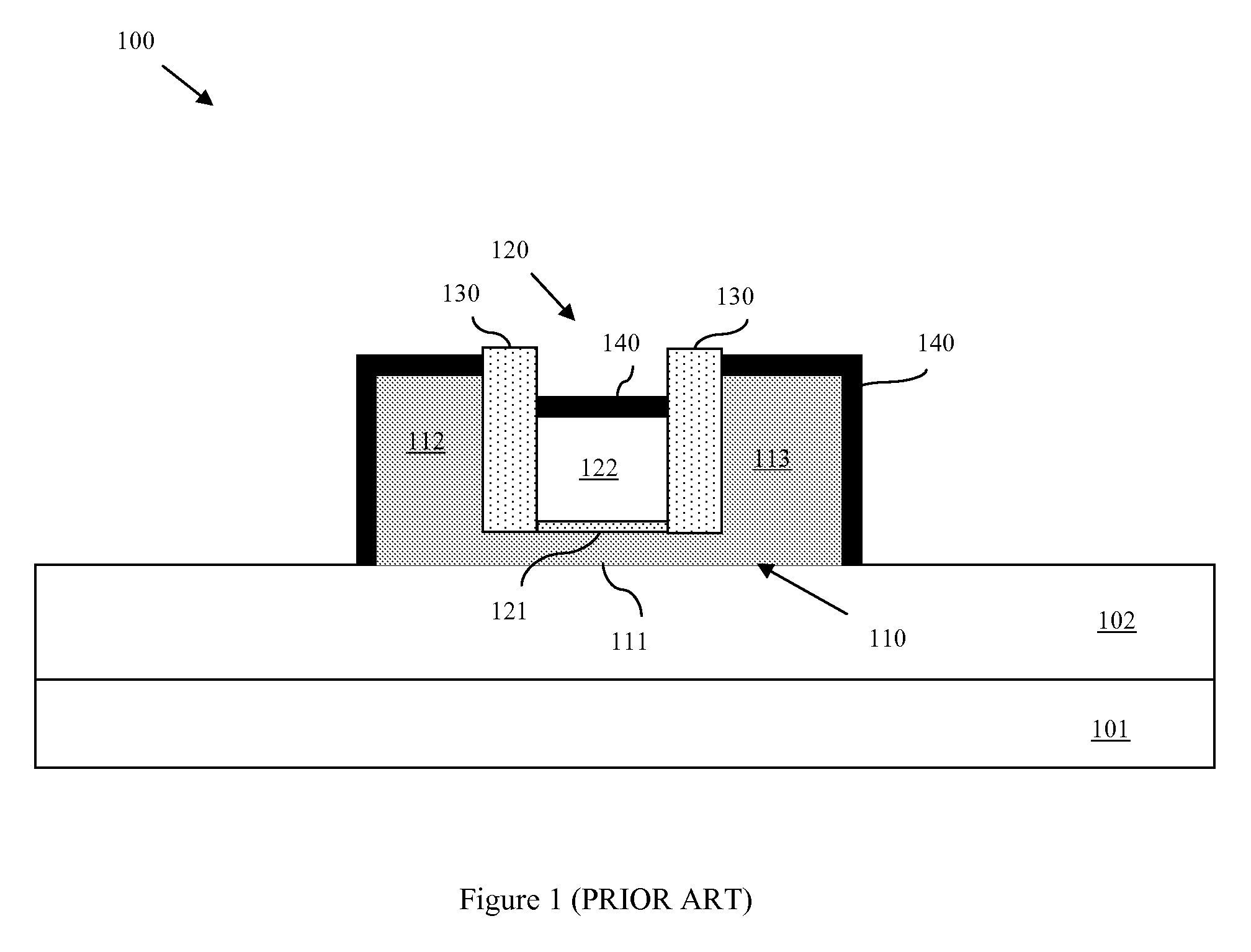

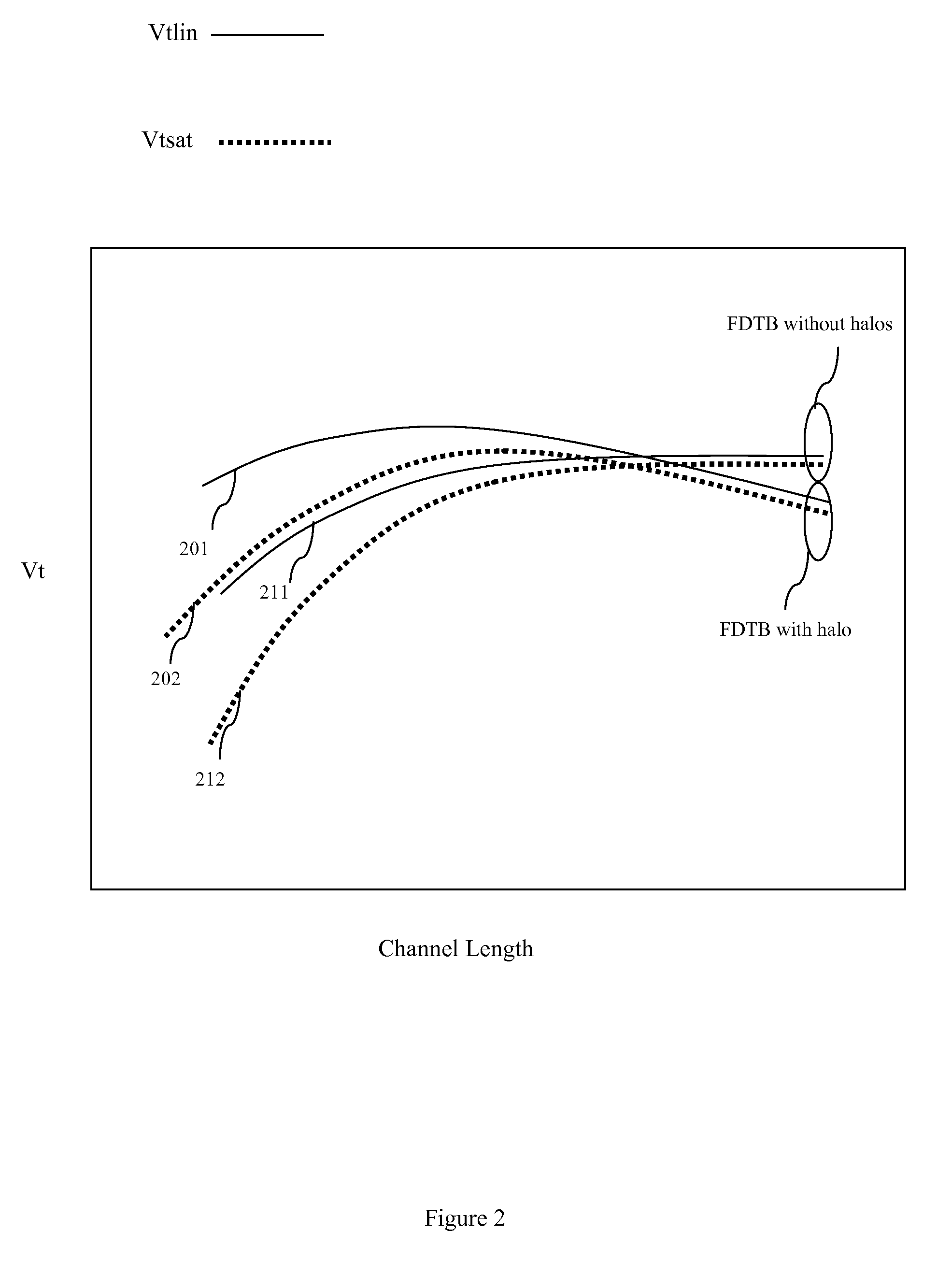

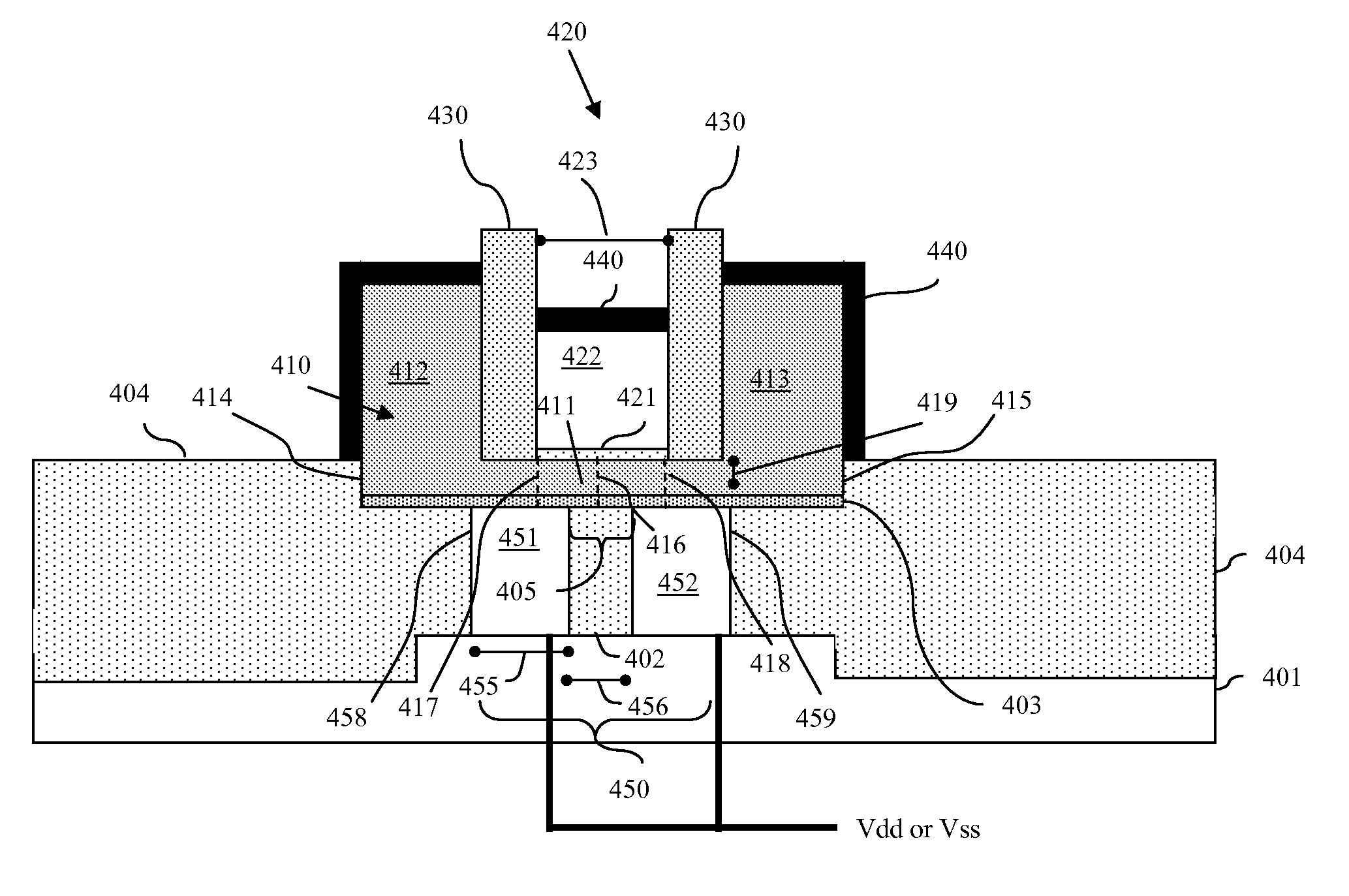

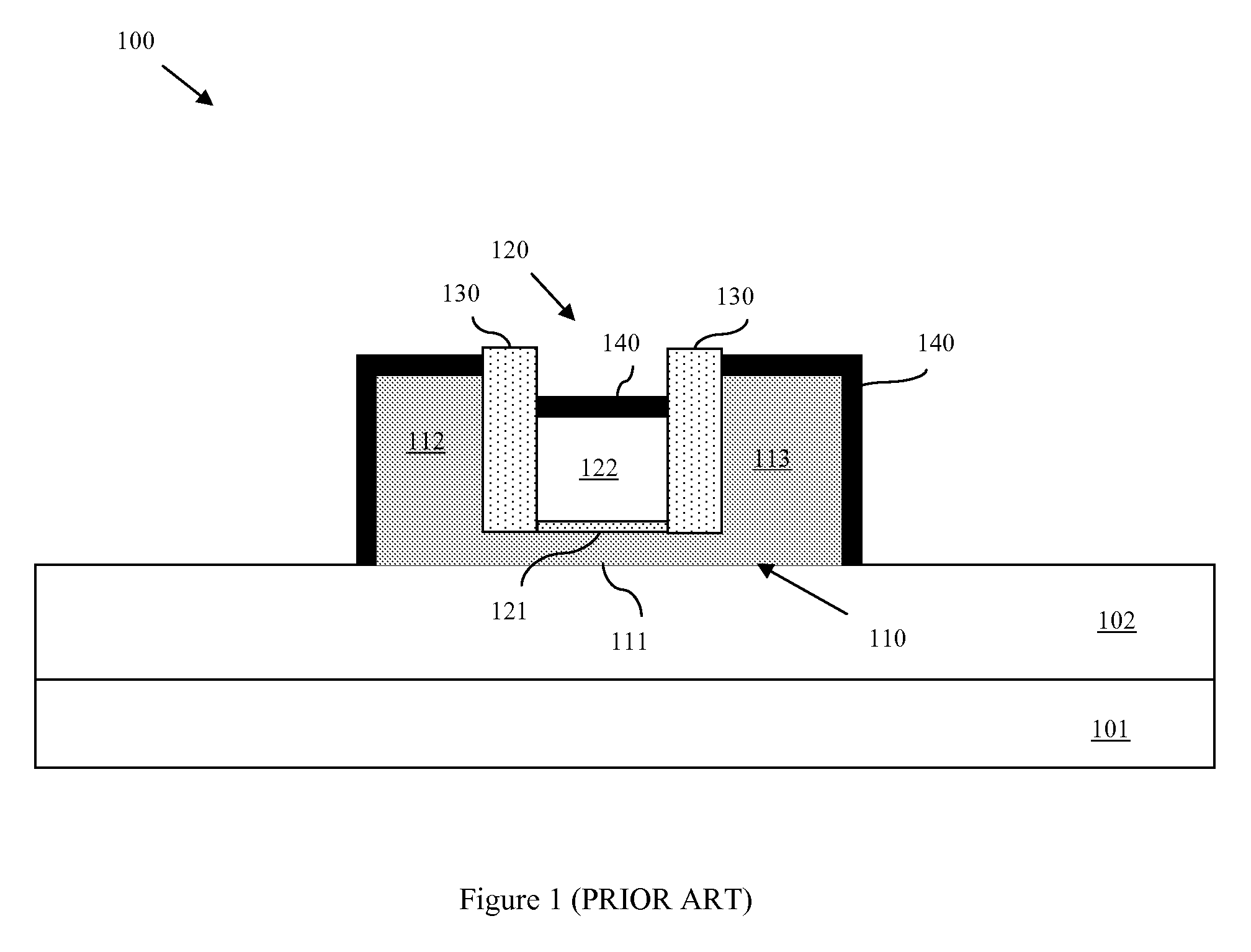

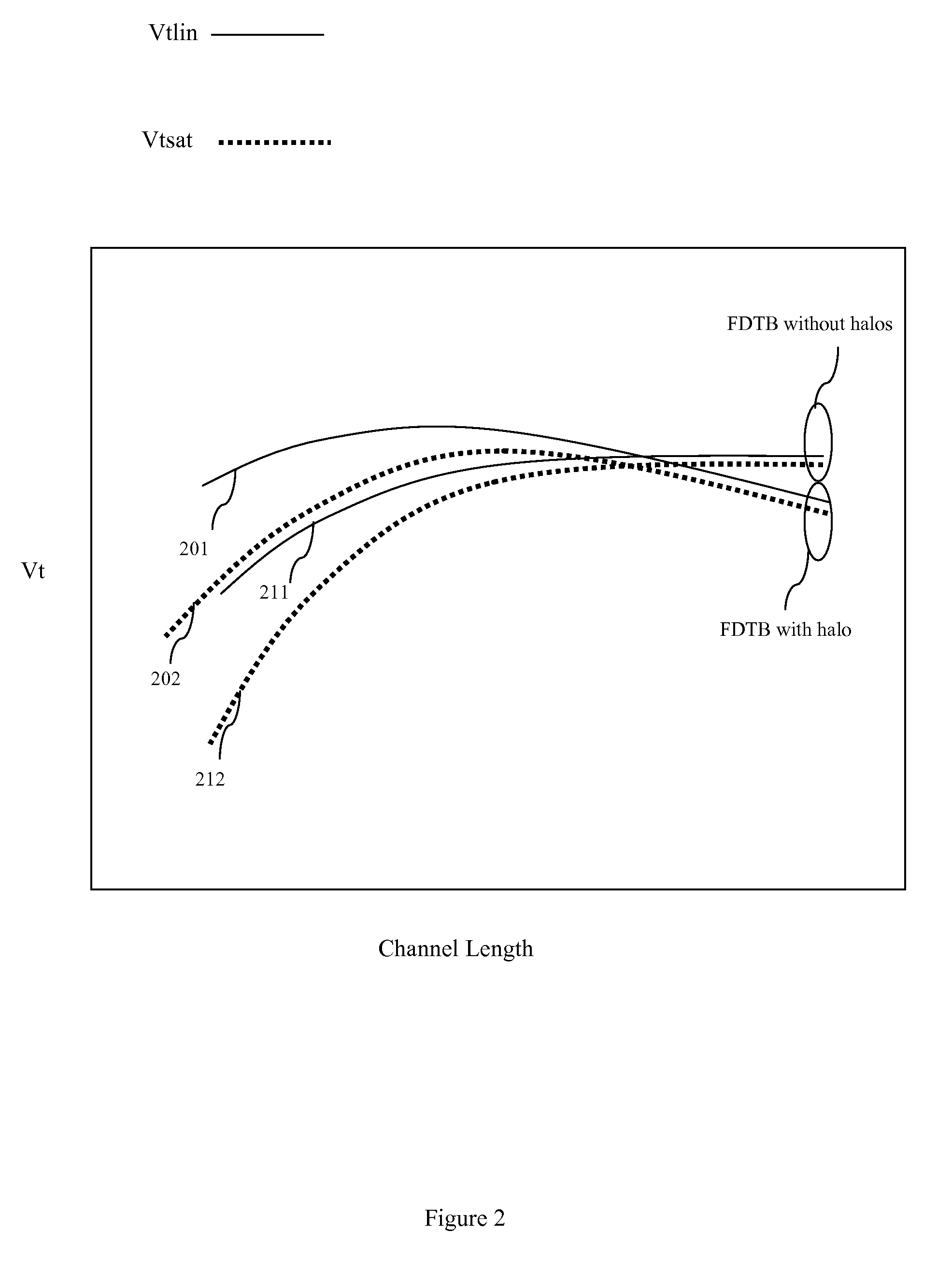

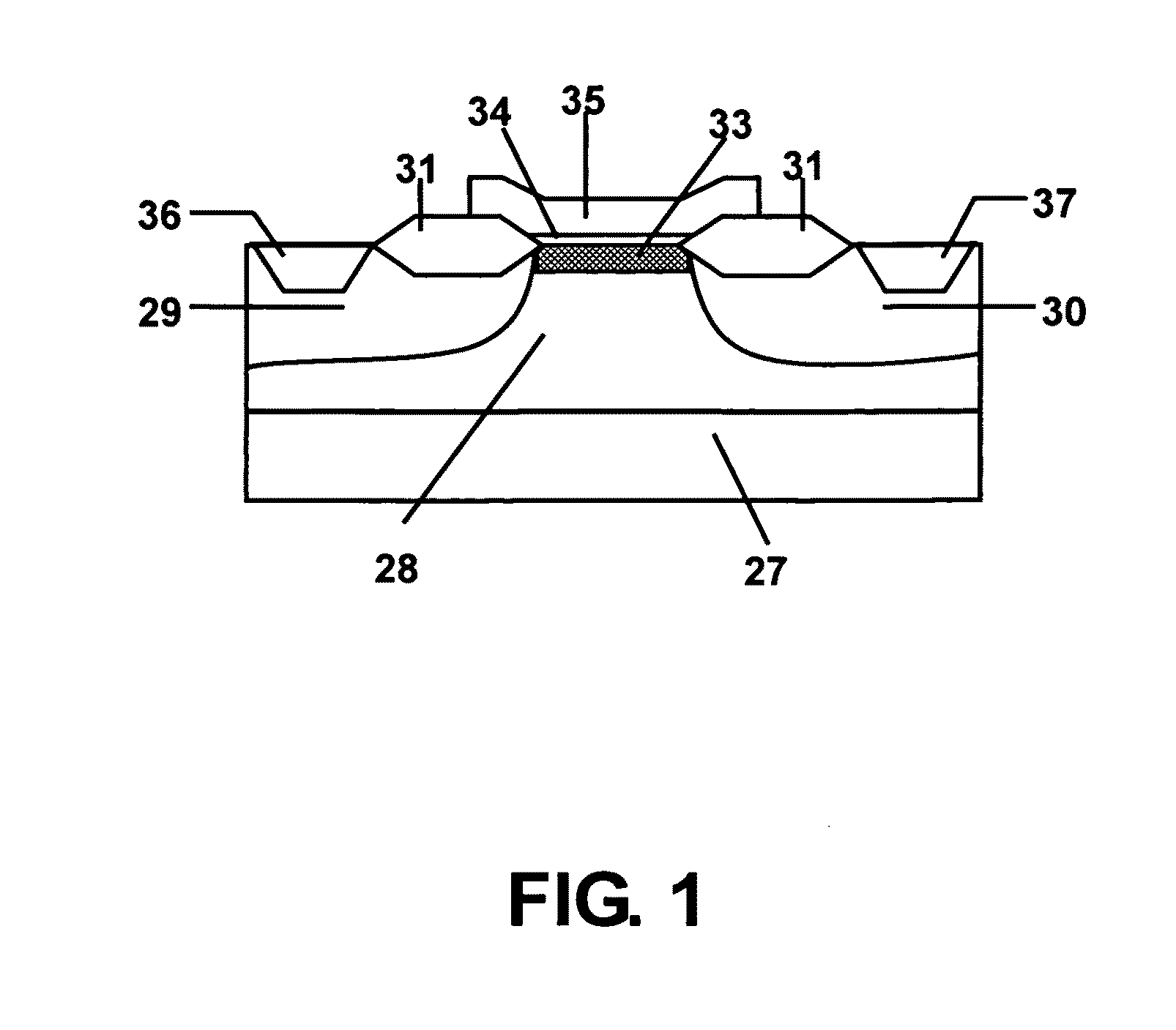

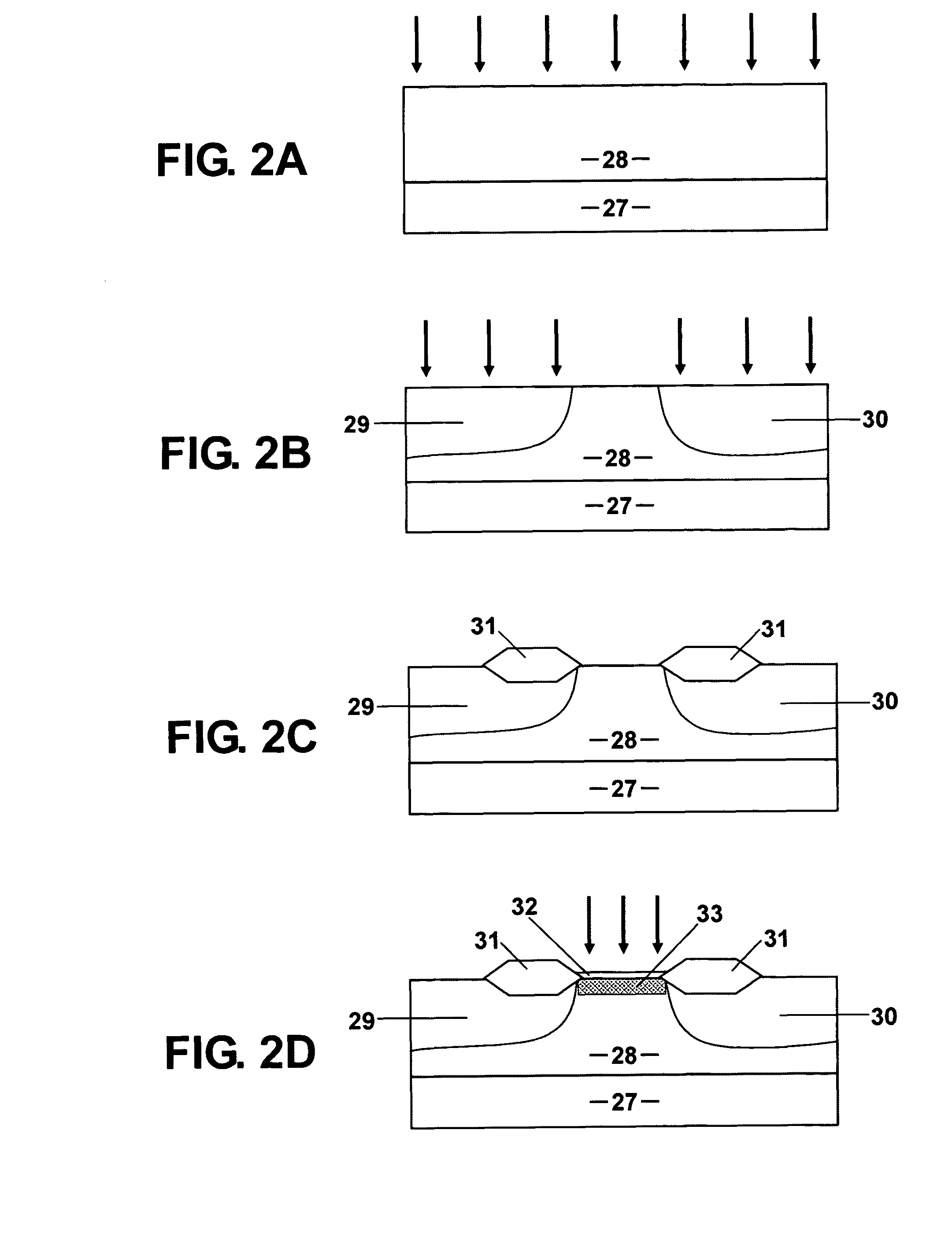

Fully-depleted low-body doping field effect transistor (FET) with reverse short channel effects (SCE) induced by self-aligned edge back-gate(s)

InactiveUS20090261415A1Minimizing off-state leakage currentMinimal short channel effectSolid-state devicesSemiconductor/solid-state device manufacturingReverse short-channel effectEngineering

Disclosed are embodiments of a field effect transistor (FET) and, more particularly, a fully-depleted, thin-body (FDTB) FET that allows for scaling with minimal short channel effects, such as drain induced barrier lowering (DIBL) and saturation threshold voltage (Vtsat) roll-off, at shorter channel lengths. The FDTB FET embodiments are configured with either an edge back-gate or split back-gate that can be biased in order to selectively adjust the potential barrier between the source / drain regions and the channel region for minimizing off-state leakage current between the drain region and the source region and / or for varying threshold voltage. These unique back-gate structures avoid the need for halo doping to ensure linear threshold voltage (Vtlin) roll-up at smaller channel lengths and, thus, avoid across-chip threshold voltage variations due to random doping fluctuations. Also disclosed are method embodiments for forming such FETs.

Owner:GLOBALFOUNDRIES INC

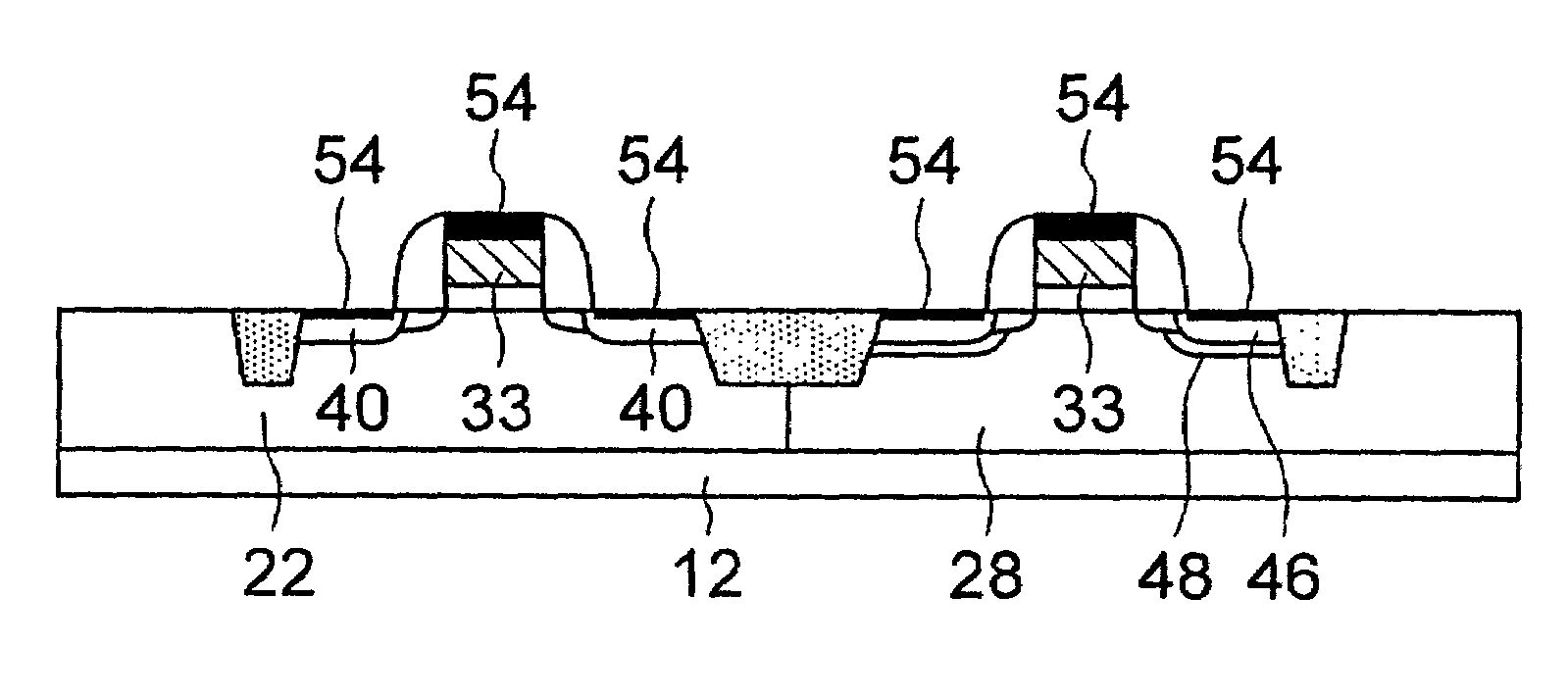

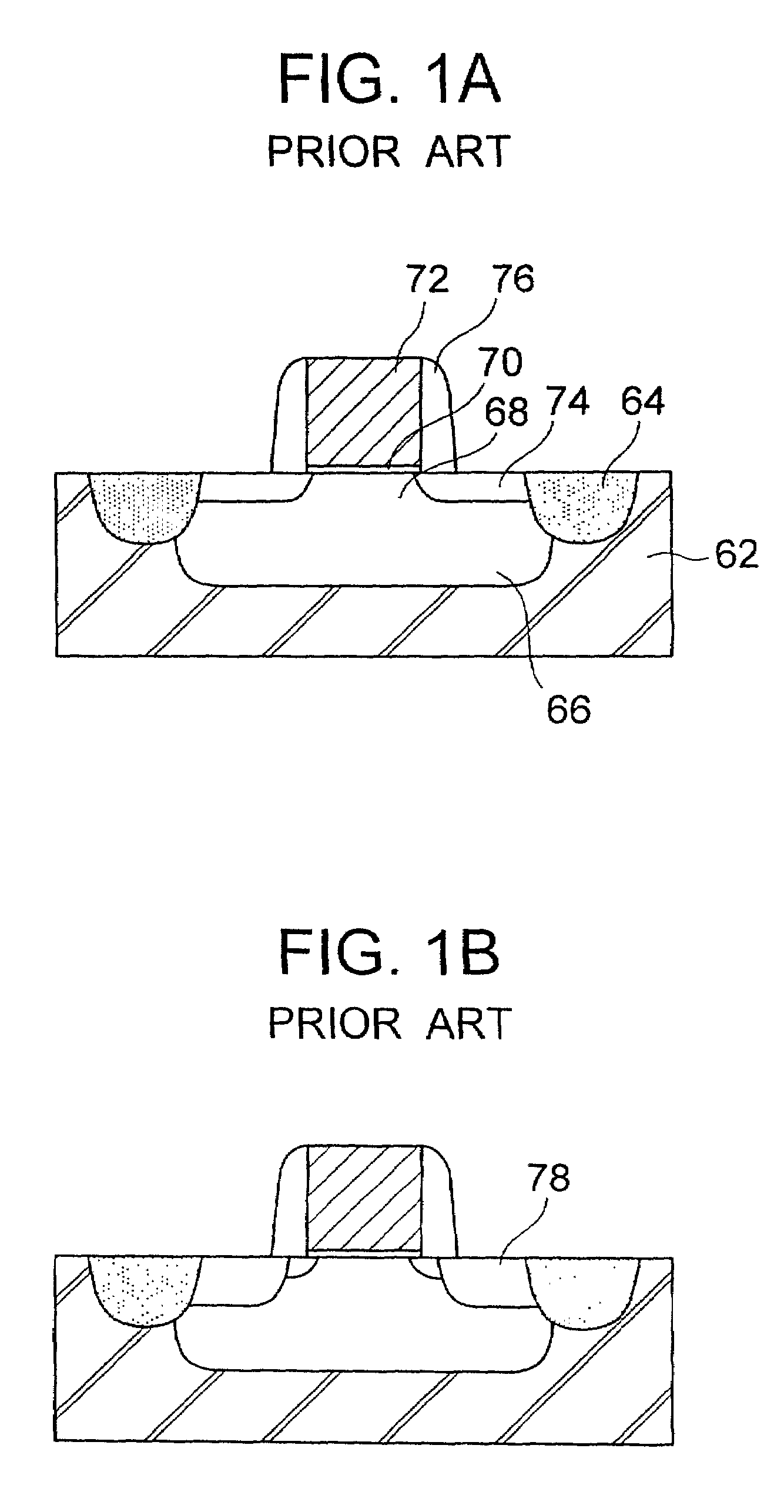

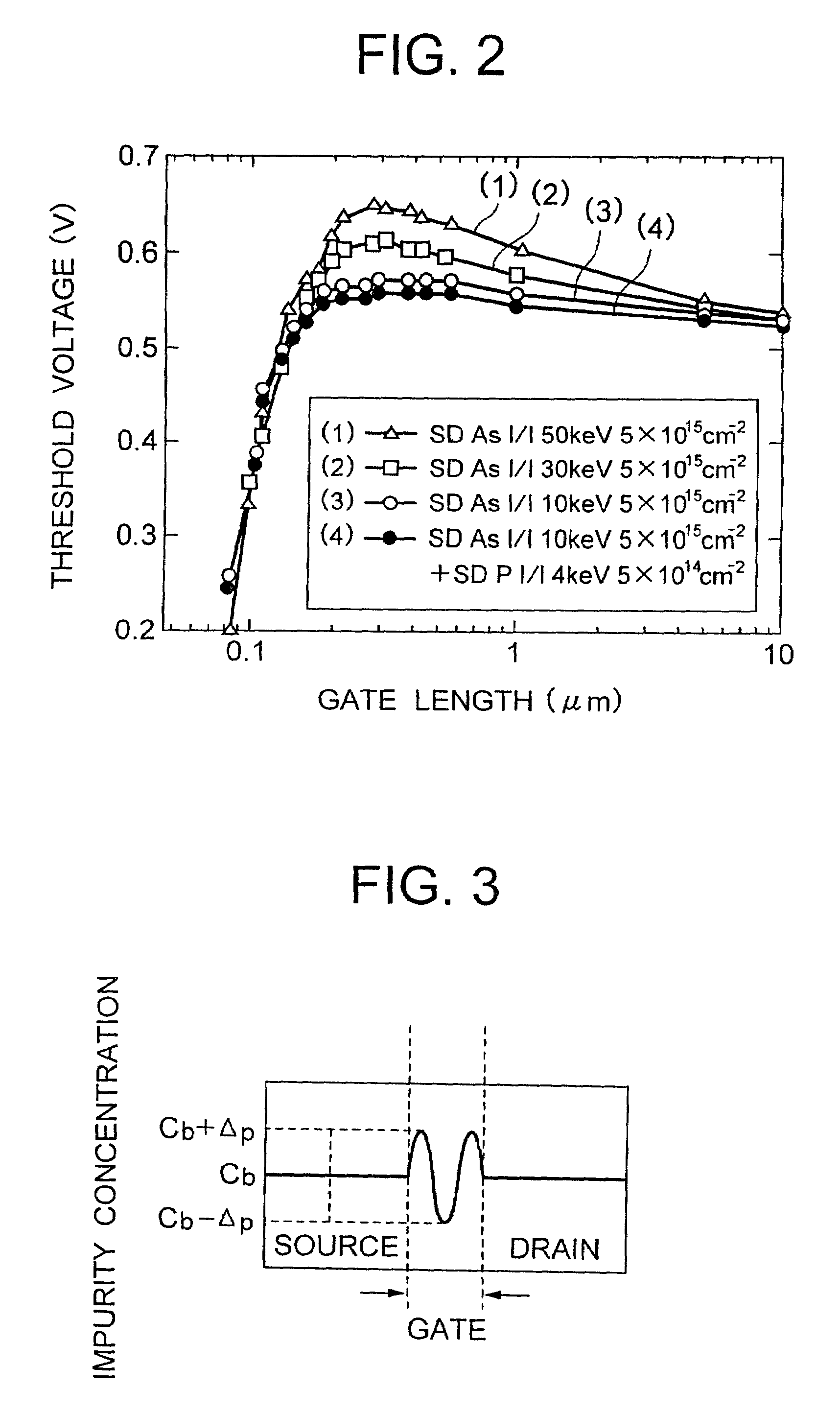

Semiconductor device and method for manufacturing same

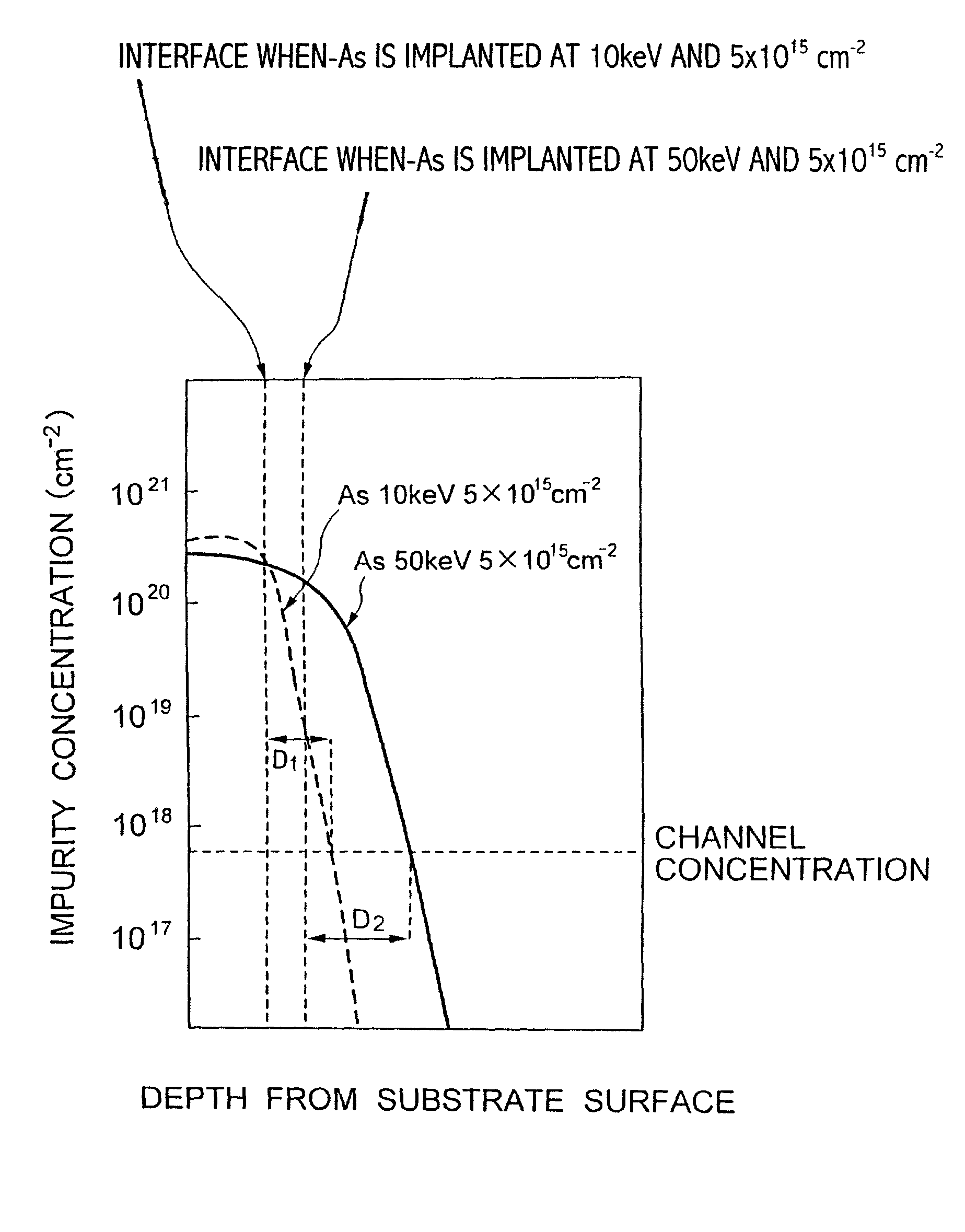

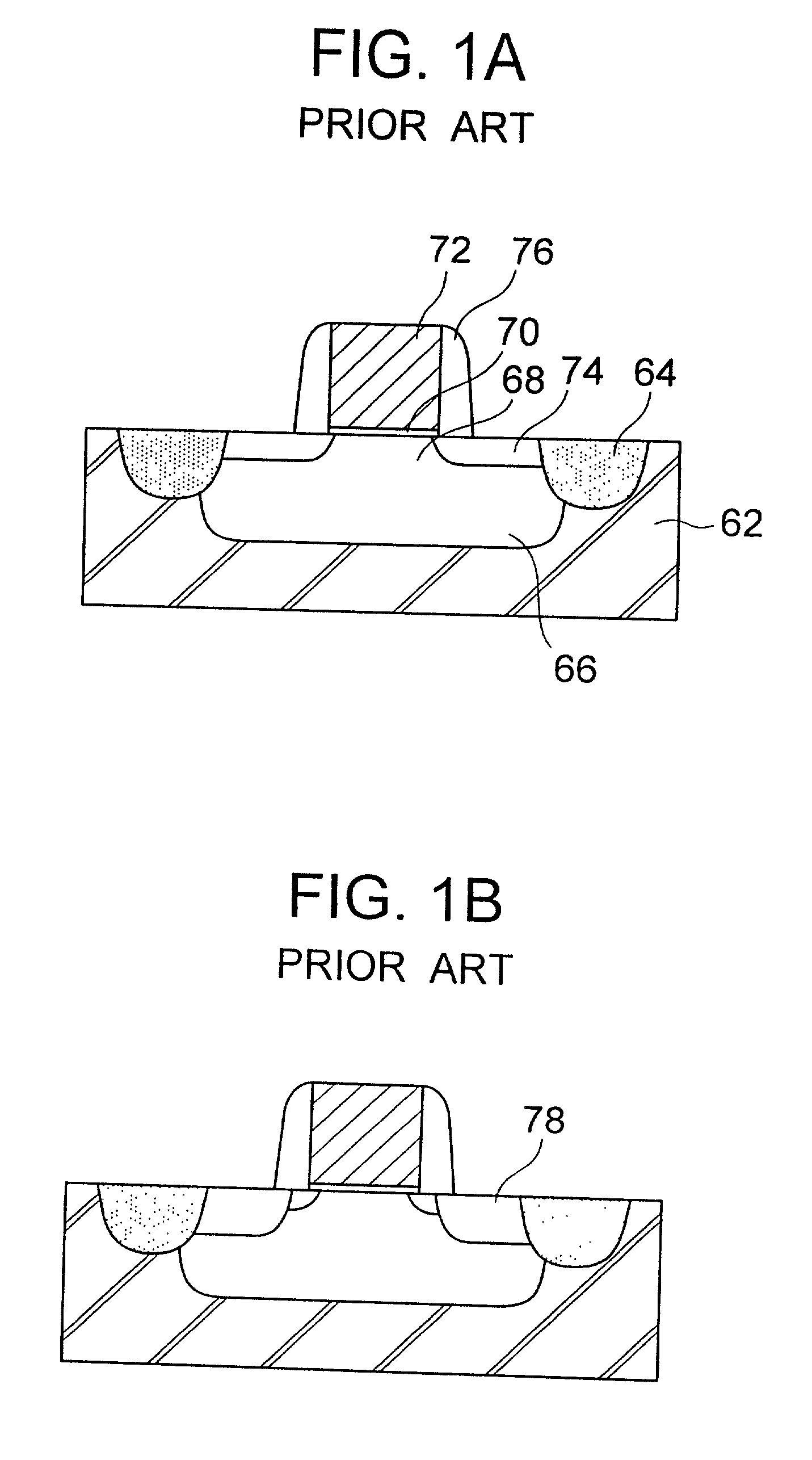

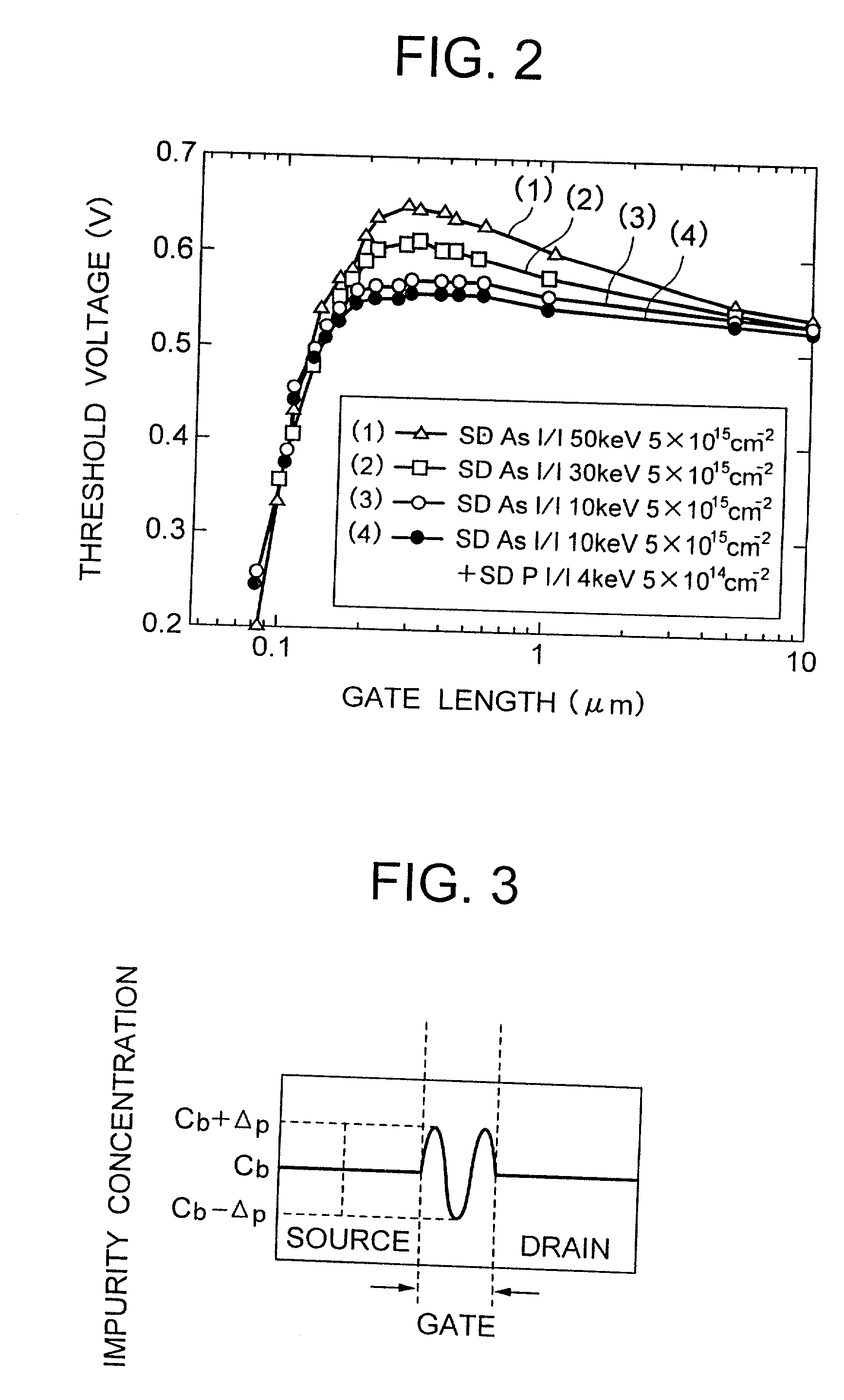

InactiveUS7157322B2Easy to controlReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesReverse short-channel effectP–n junction

A semiconductor device including an NMOSFET which has an n-type source / drain main region containing arsenic and an n-type source / drain buffer region having arsenic and phosphorous of which a concentration is lower than that of the source / drain main region, and the concentration of the phosphorous in the source / drain buffer region is smaller than the concentration of the arsenic therein. The semiconductor device has a suppressed reverse short channel effect and reduced p-n junction leakage current. Further, the semiconductor device has a larger margin to a certain gate length and a specified threshold voltage to elevate a production yield.

Owner:RENESAS ELECTRONICS CORP

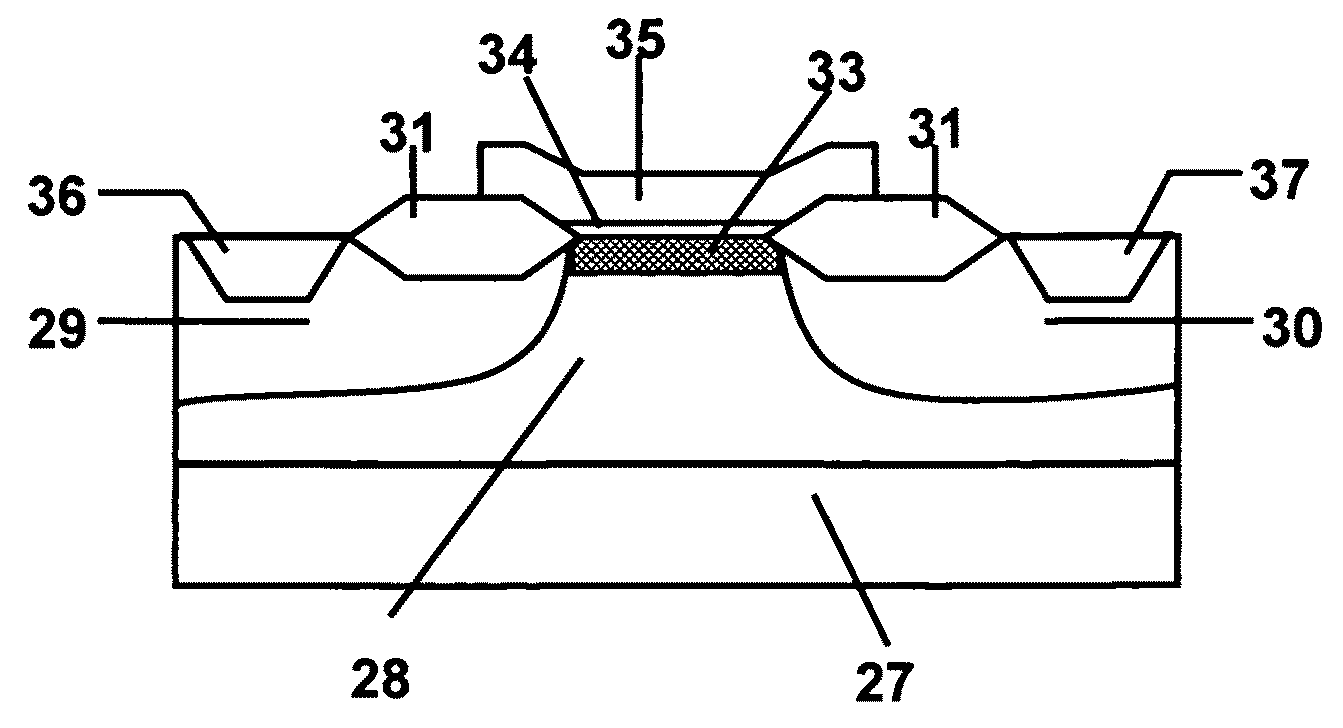

Fully-depleted low-body doping field effect transistor (FET) with reverse short channel effects (SCE) induced by self-aligned edge back-gate(s)

InactiveUS7943997B2Minimal short channel effectMinimizing off-state leakage currentSolid-state devicesSemiconductor devicesReverse short-channel effectEngineering

Disclosed are embodiments of a field effect transistor (FET) and, more particularly, a fully-depleted, thin-body (FDTB) FET that allows for scaling with minimal short channel effects, such as drain induced barrier lowering (DIBL) and saturation threshold voltage (Vtsat) roll-off, at shorter channel lengths. The FDTB FET embodiments are configured with either an edge back-gate or split back-gate that can be biased in order to selectively adjust the potential barrier between the source / drain regions and the channel region for minimizing off-state leakage current between the drain region and the source region and / or for varying threshold voltage. These unique back-gate structures avoid the need for halo doping to ensure linear threshold voltage (Vtlin) roll-up at smaller channel lengths and, thus, avoid across-chip threshold voltage variations due to random doping fluctuations. Also disclosed are method embodiments for forming such FETs.

Owner:GLOBALFOUNDRIES INC

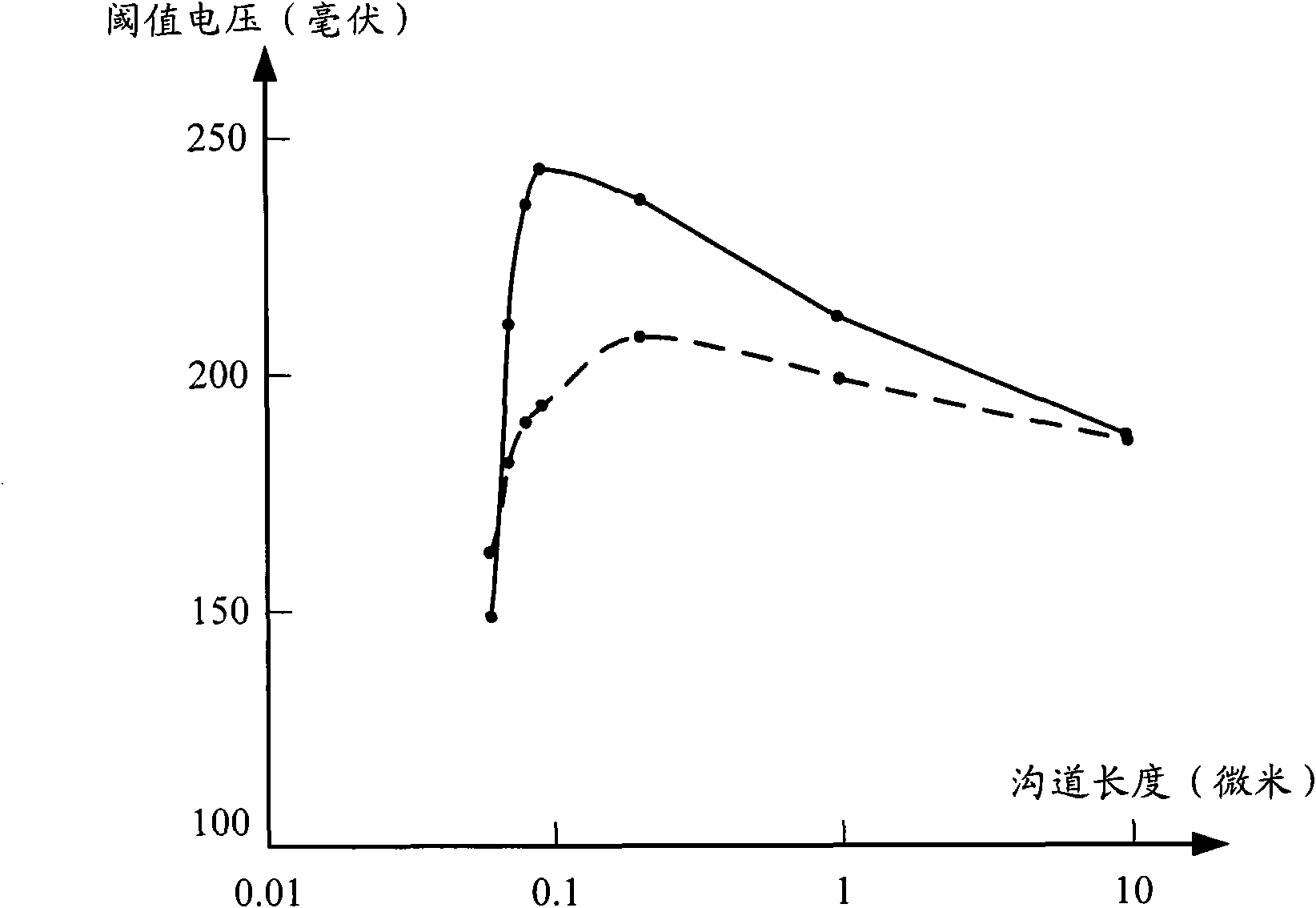

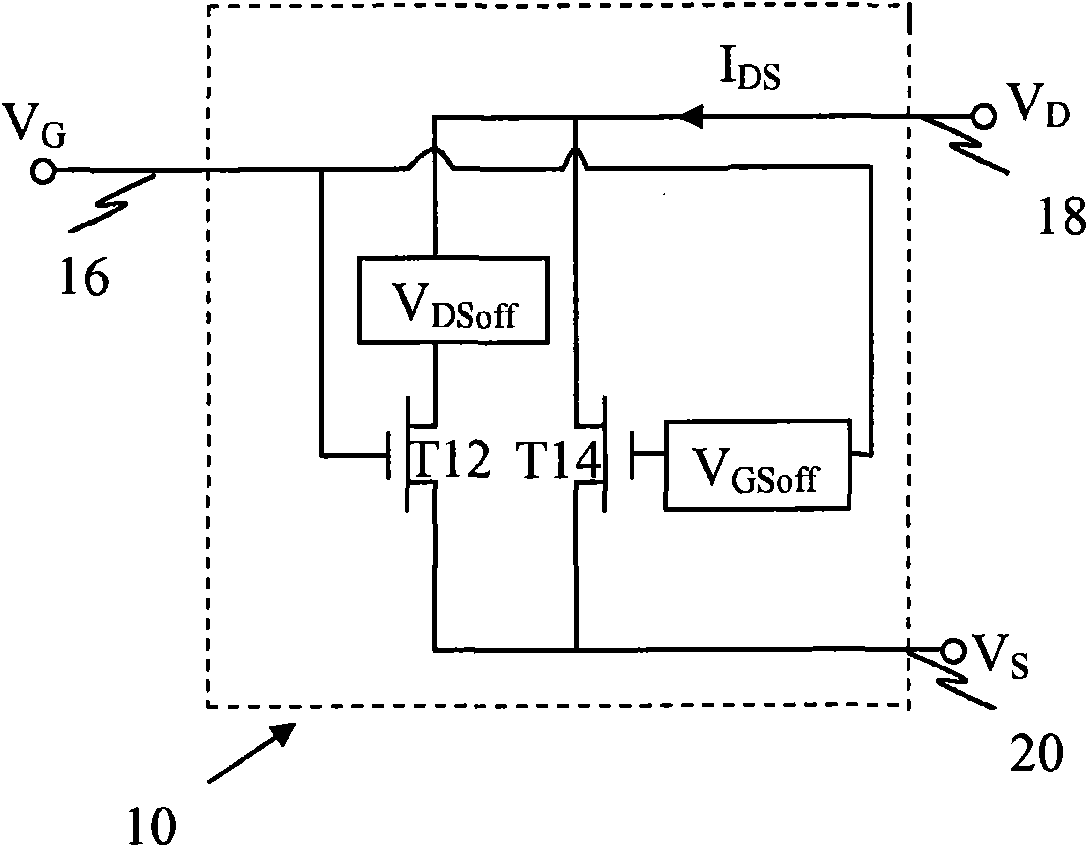

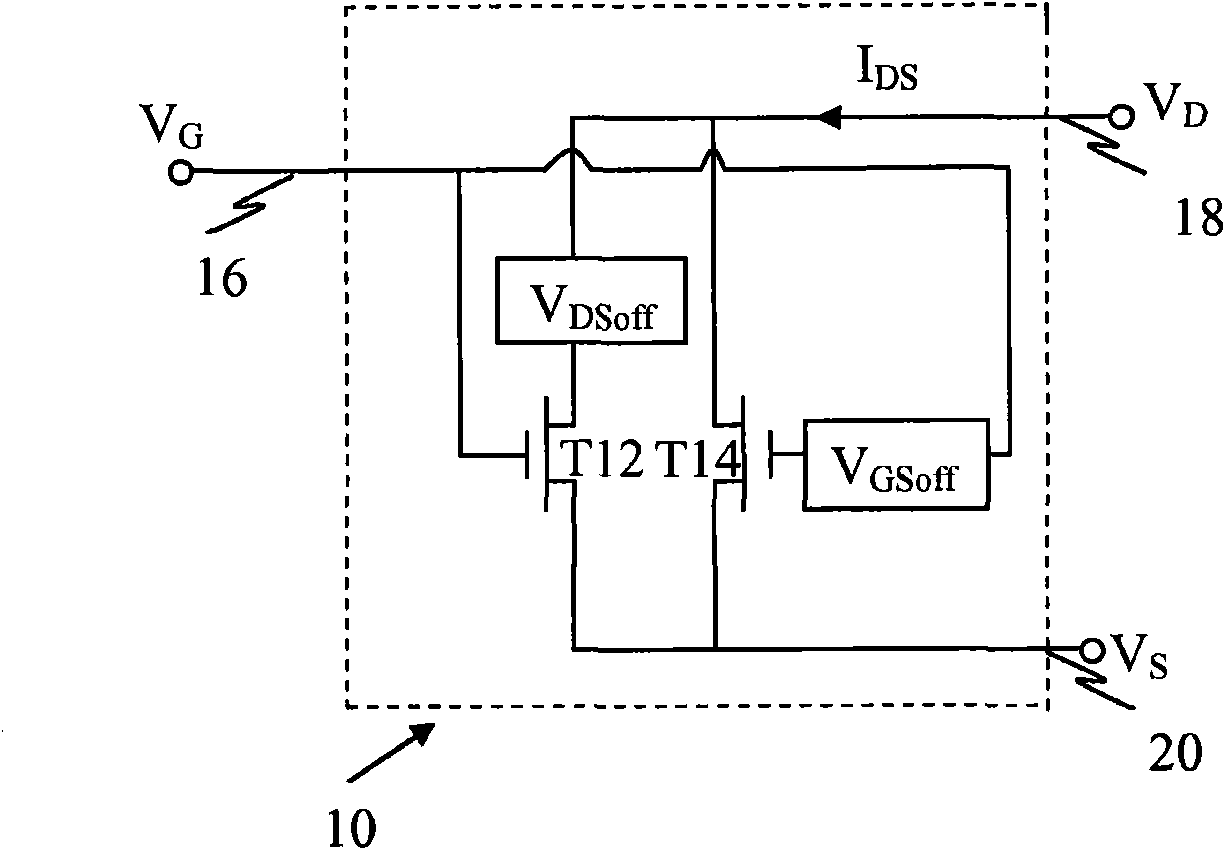

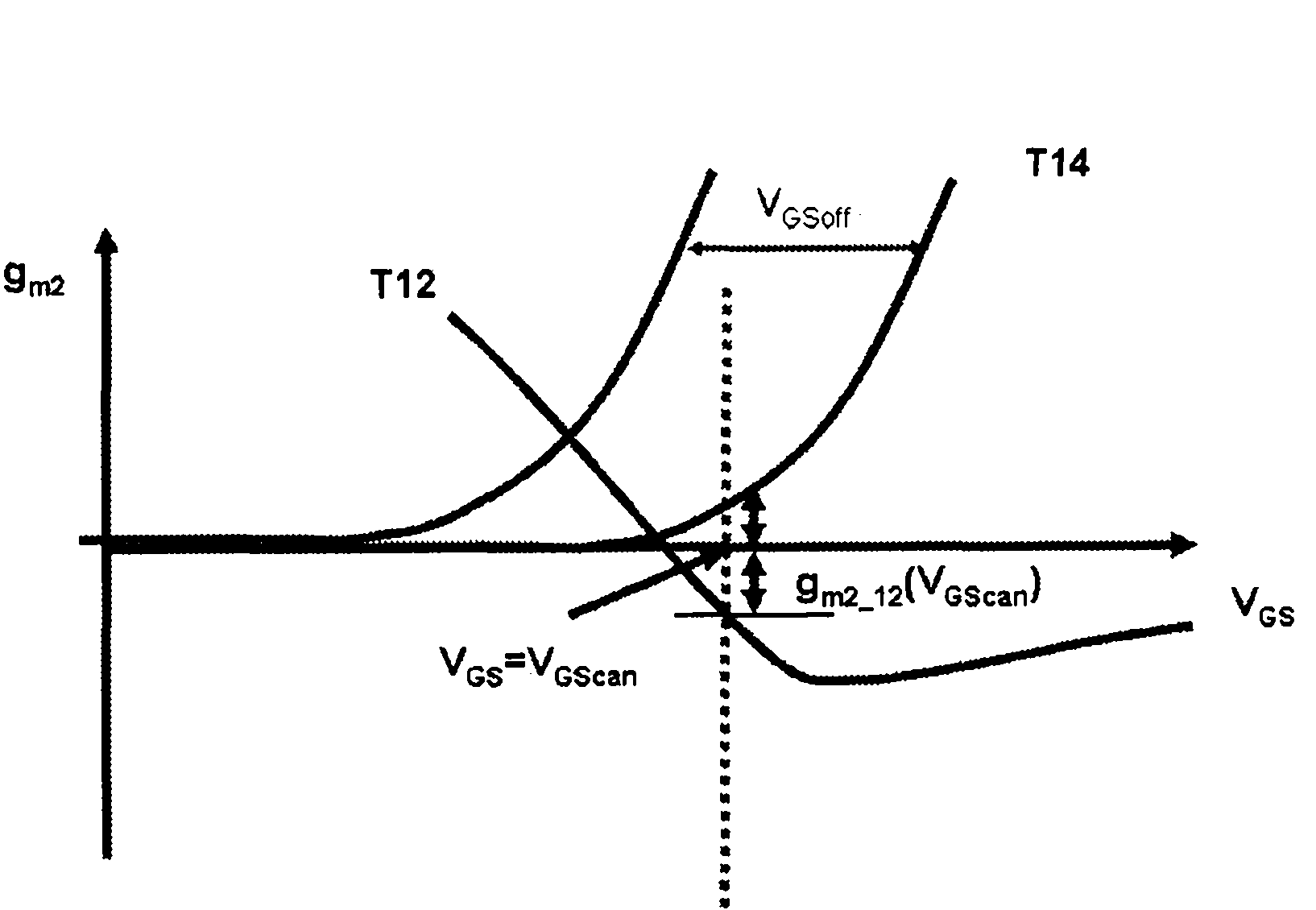

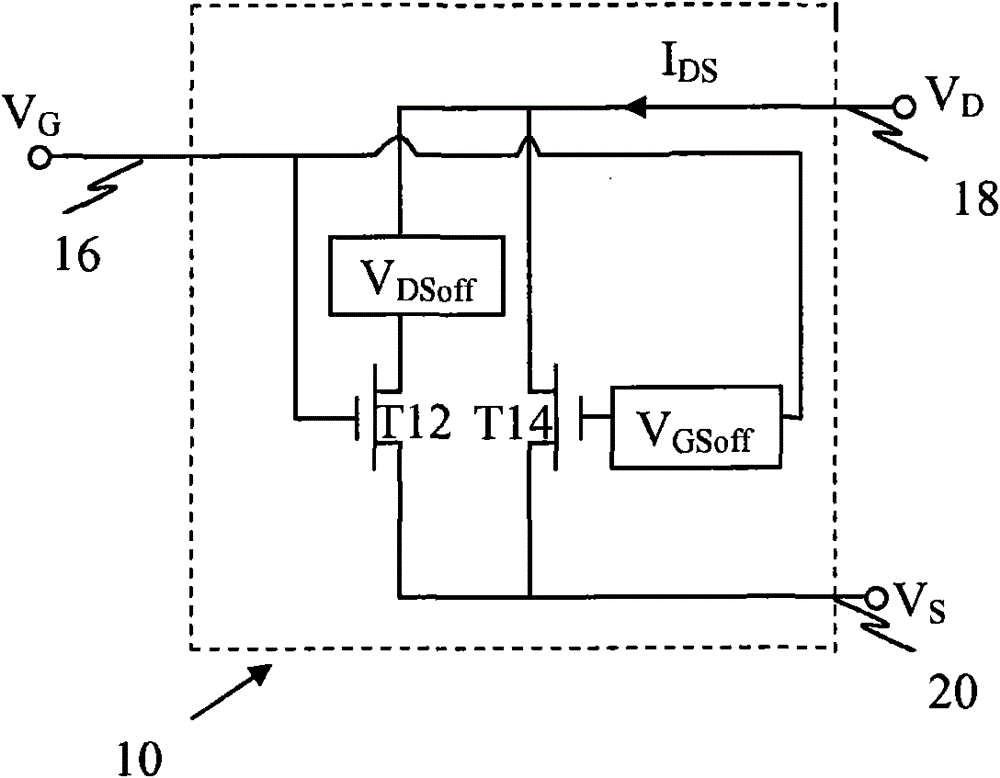

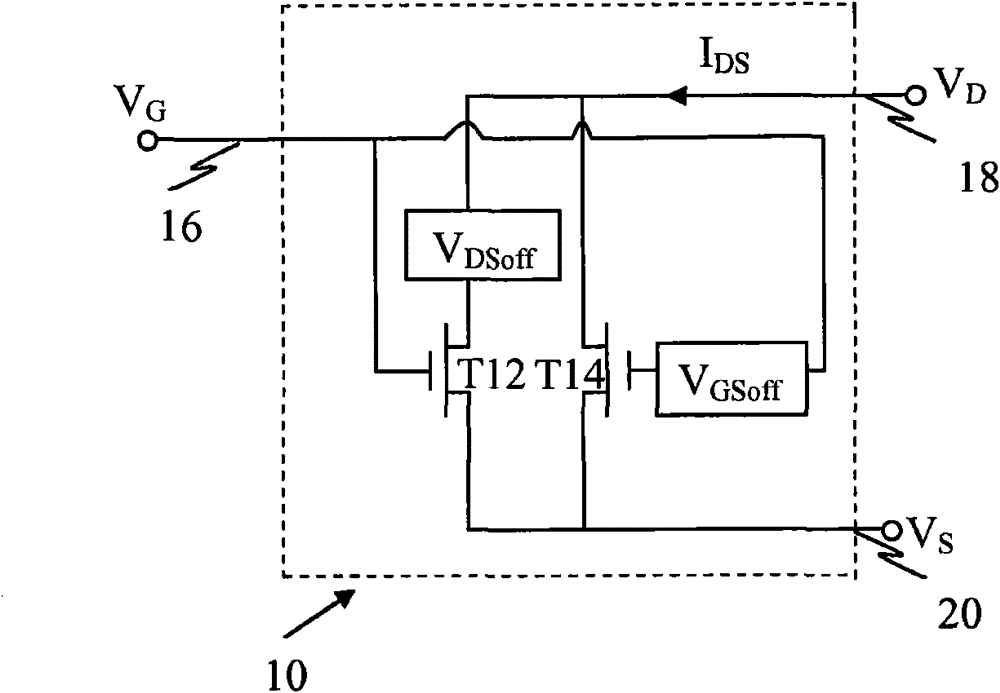

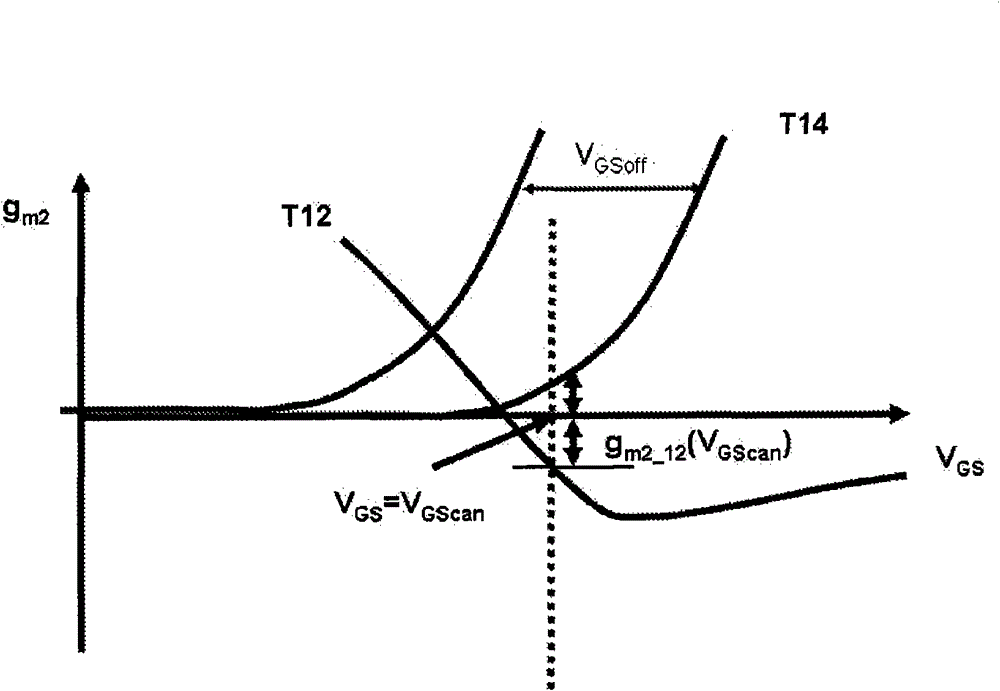

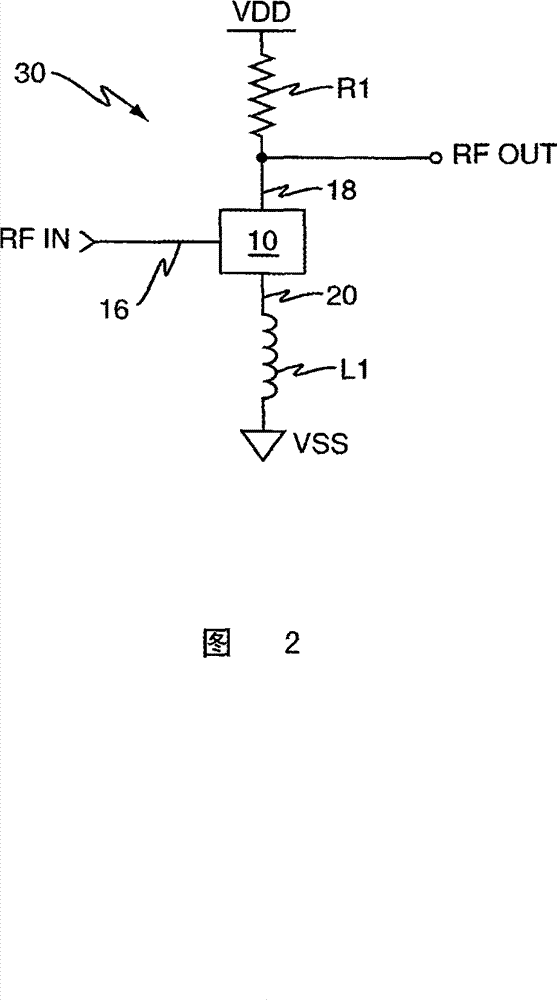

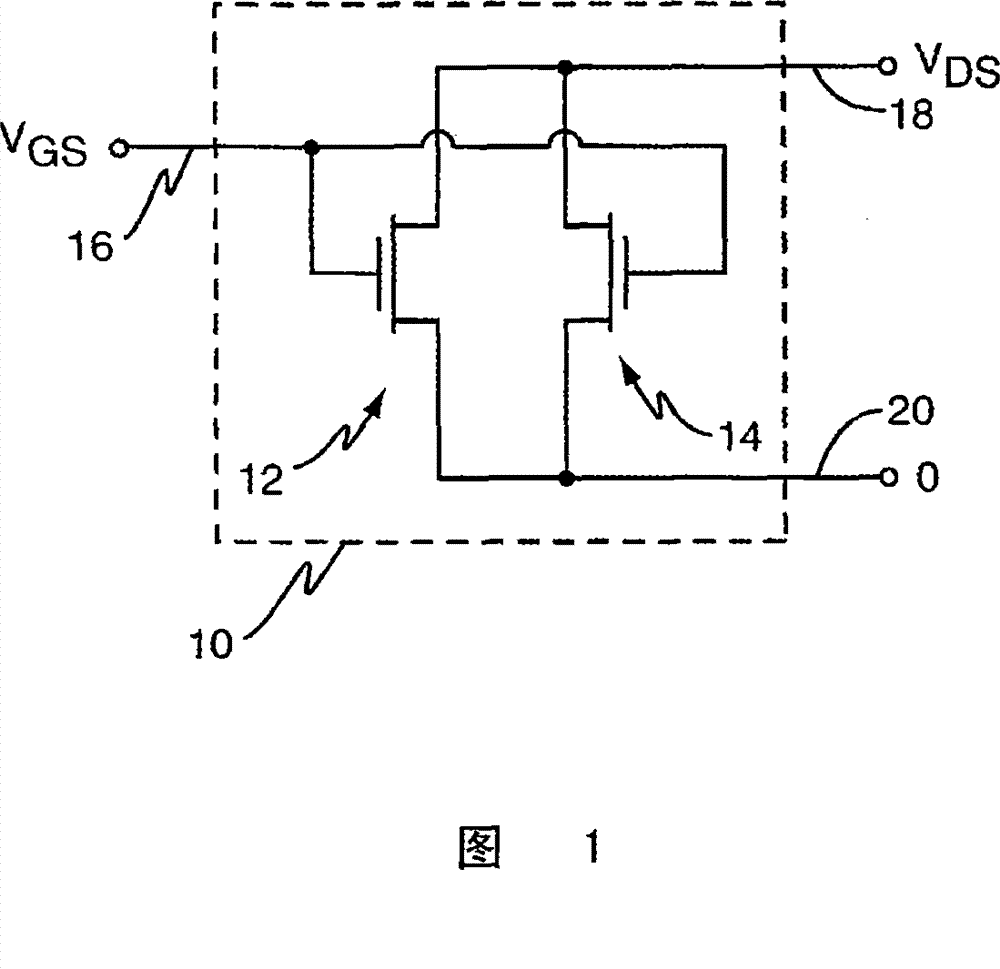

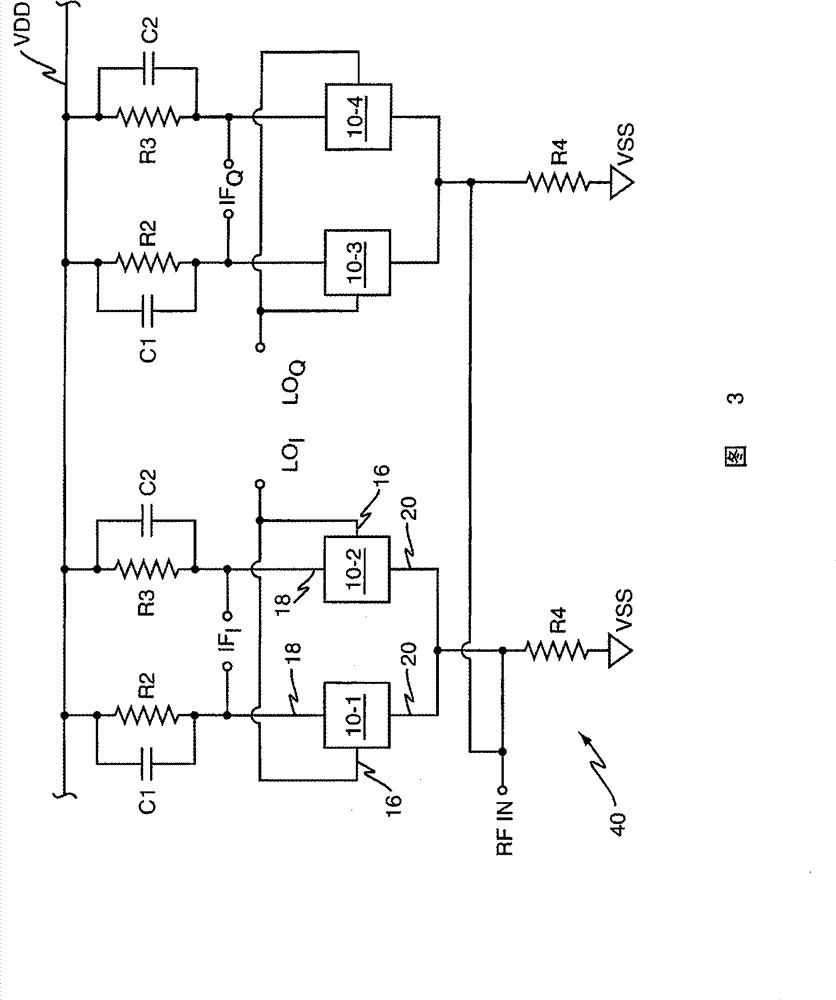

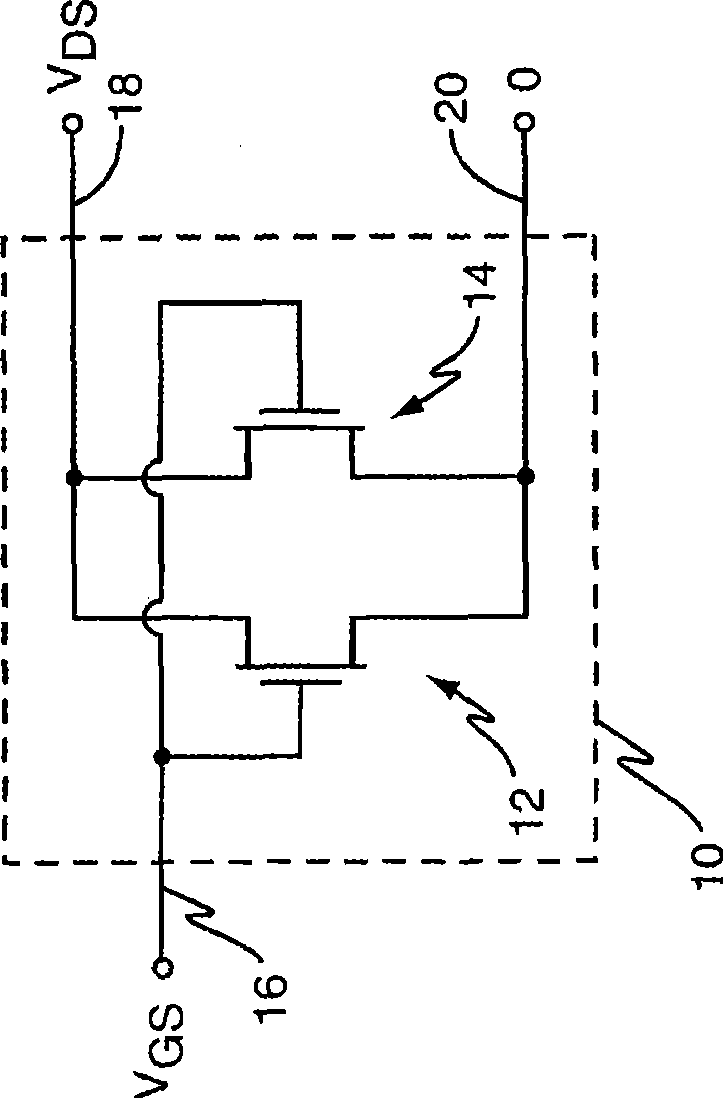

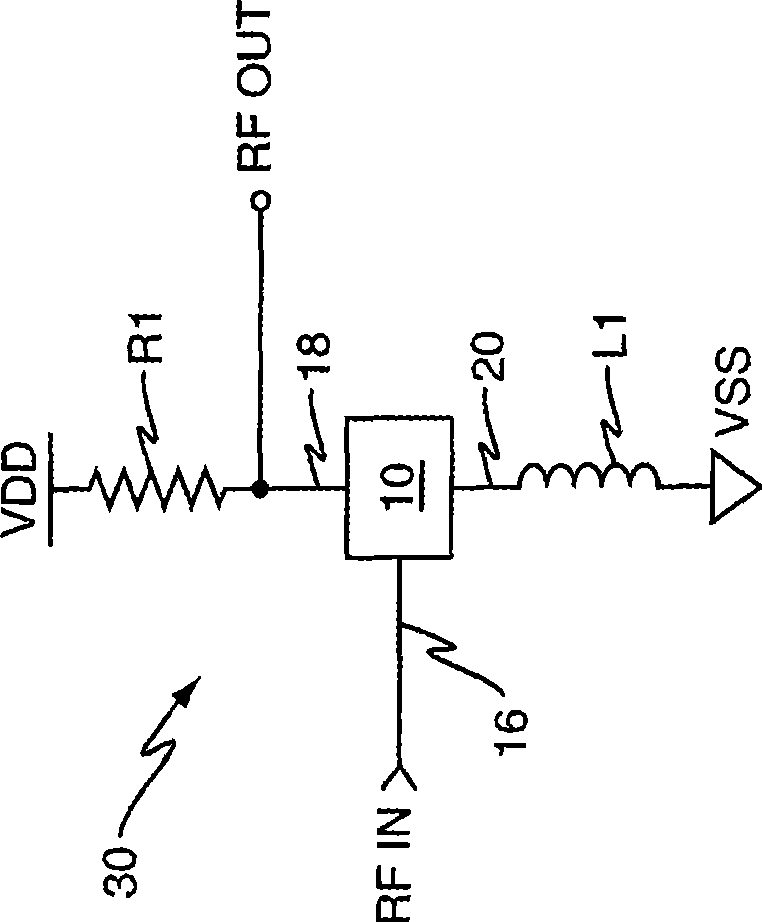

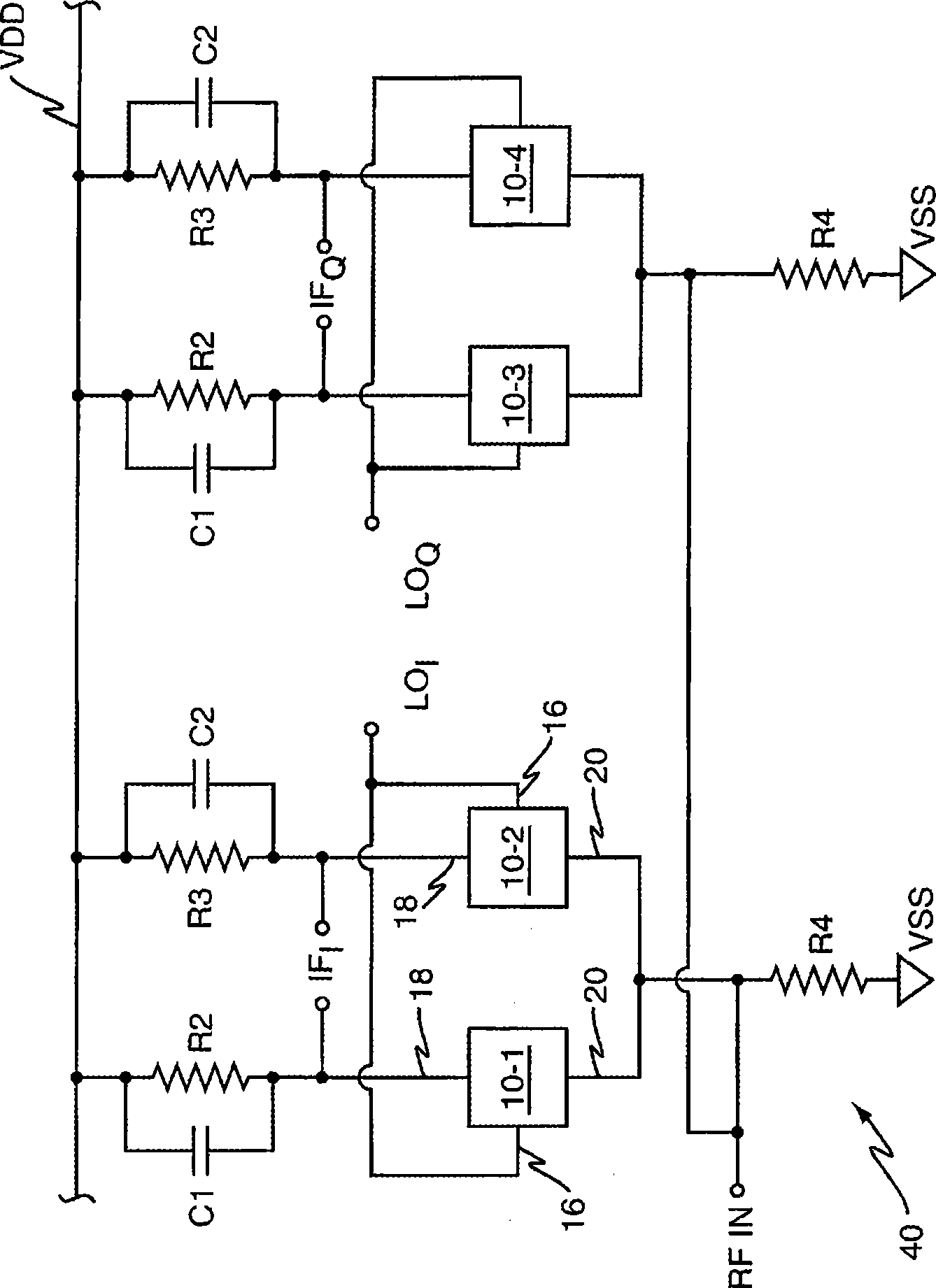

Circuitry and method for reducing second and third-order nonlinearities

InactiveCN101785178AImprove linearityImprove manufacturabilityAmplifier modifications to reduce non-linear distortionPower amplifiersReverse short-channel effectVoltage shift

An electronic circuit (10) comprises at least two transistors (T12, T14) coupled in parallel, wherein the second transistor channel length is configured such that the threshold voltage of the second transistor (T14) is at a peak on a threshold voltage versus channel lengths curve arising from reverse short channel effects for a given semiconductor process. The first transistor (T12) is biased with a first gate-source voltage and a first drain-source voltage. The second transistor (T14) is biased with a second gate-source voltage and a second drain-source voltage. The first gate-source voltage and the second gate-source voltage are offset from each other by a gate-source voltage offset and the first drain-source voltage and the second drain-source voltage are offset from each other by a drain-source voltage offset. These bias conditions result in the transistors (T12, T14) operating in different regions so that the second and third-order nonlinearities of the transistors (T12, T14) substantially cancel each other out simultaneously.

Owner:TELEFON AB LM ERICSSON (PUBL)

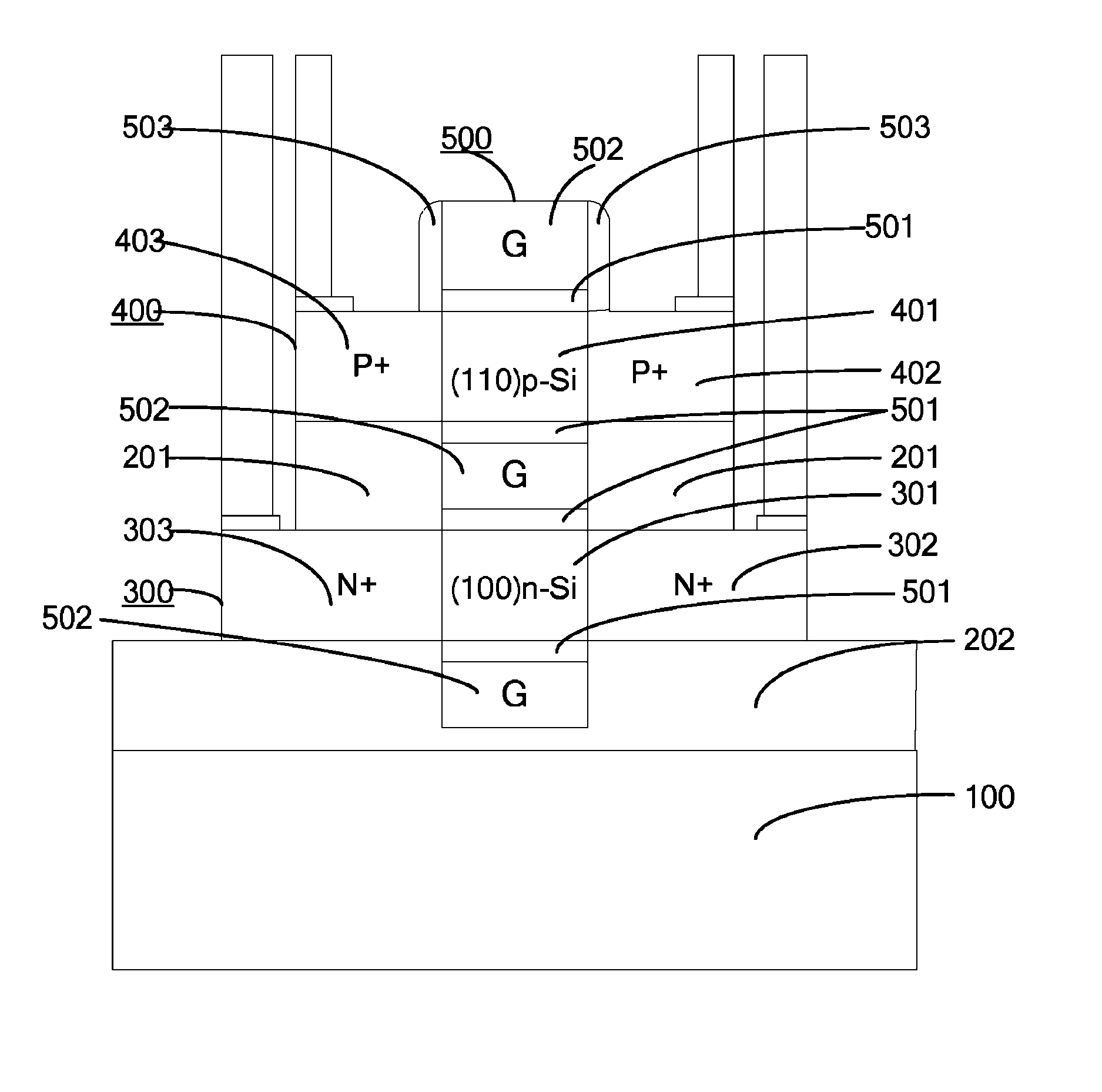

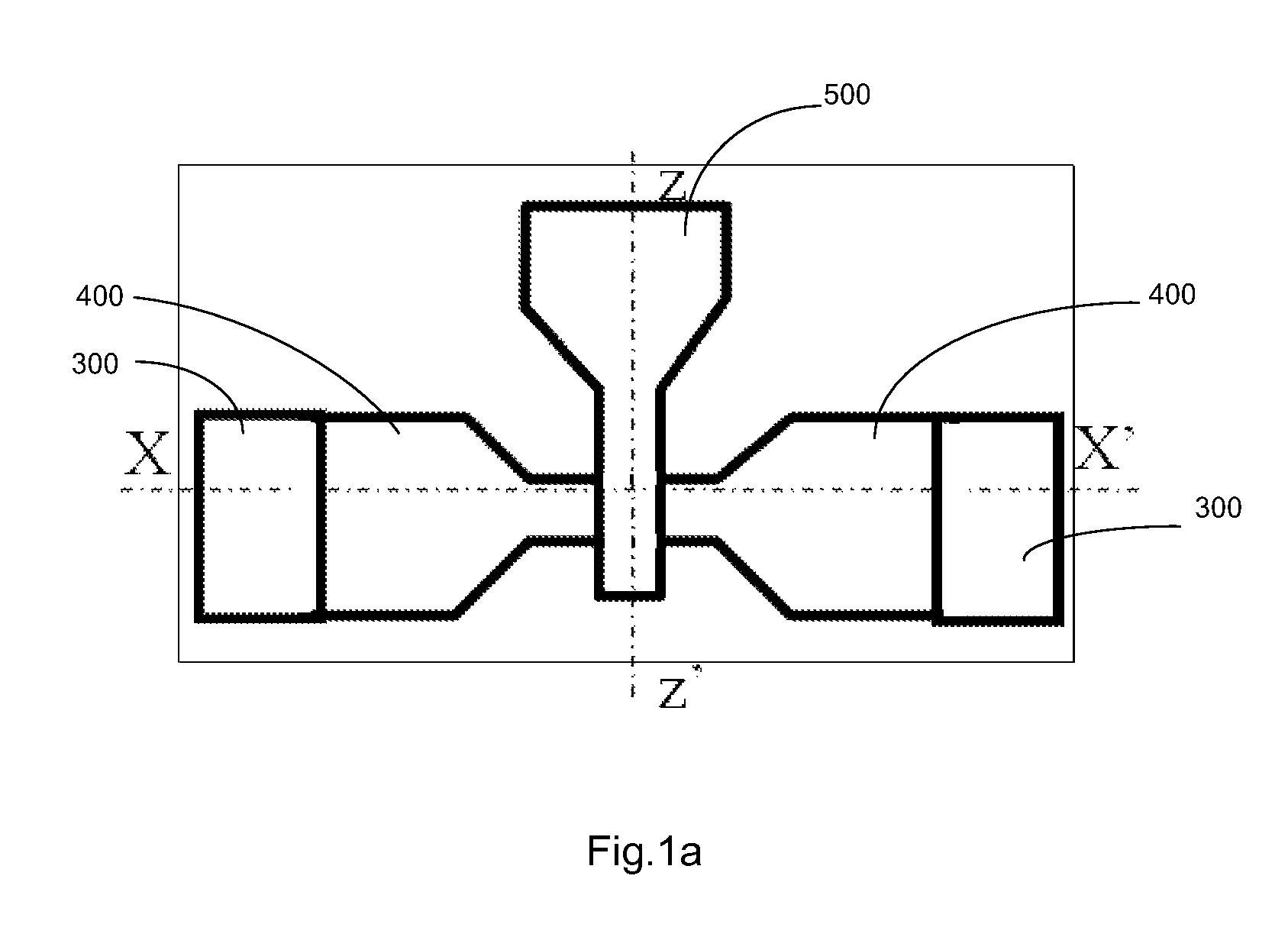

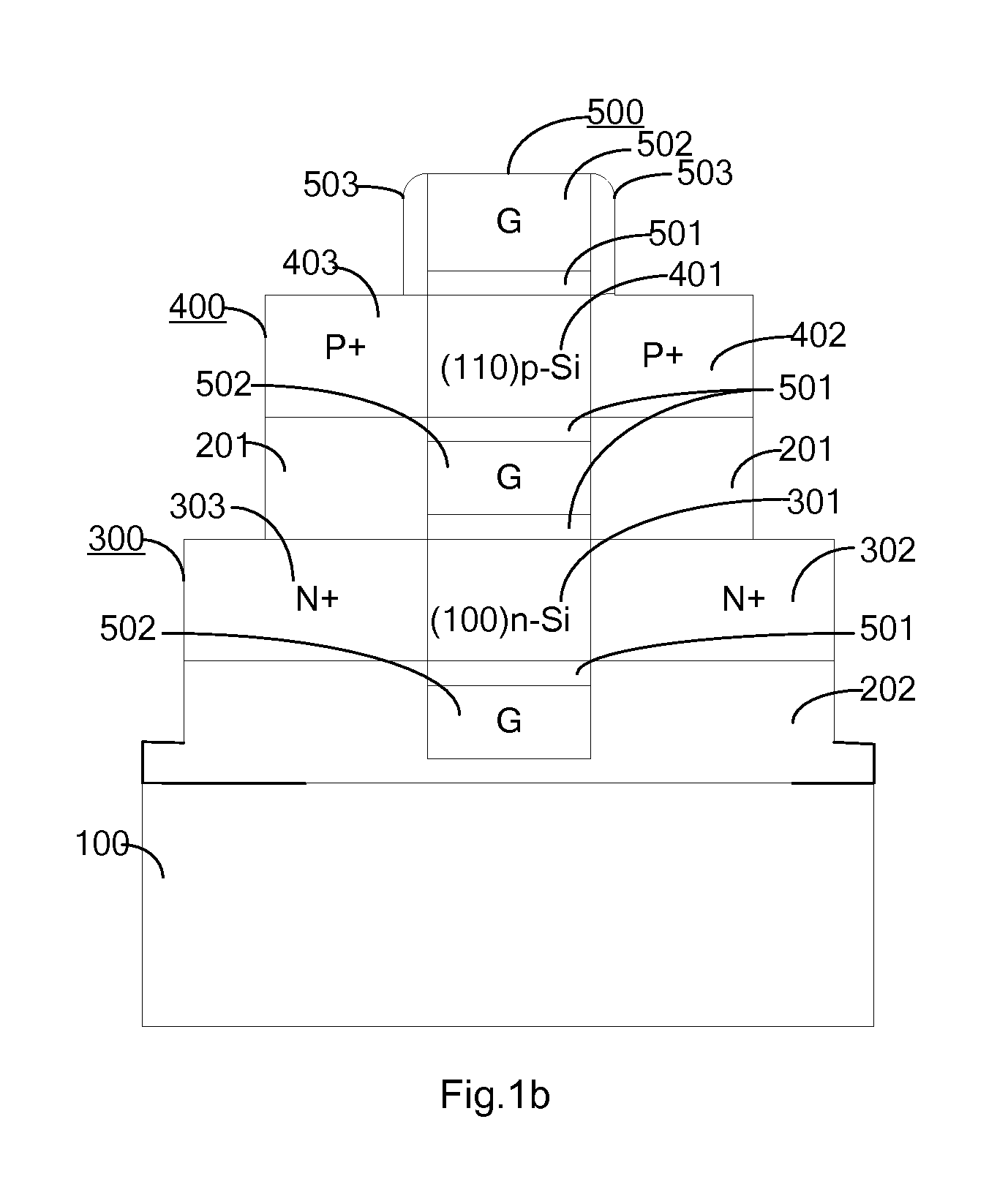

Hybrid orientation accumulation mode GAA CMOSFET

InactiveUS8264042B2Raise the threshold voltageEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingReverse short-channel effectCharge carrier mobility

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Semiconductor device and method for manufacturing same

InactiveUS20020042177A1Semiconductor/solid-state device manufacturingSemiconductor devicesReverse short-channel effectP–n junction

A semiconductor device including an NMOSFET which has an n-type source / drain main region containing arsenic and an n-type source / drain buffer region having arsenic and phosphorous of which a concentration is lower than that of the source / drain main region, and the concentration of the phosphorous in the source / drain buffer region is smaller than the concentration of the arsenic therein. The semiconductor device has a suppressed reverse short channel effect and reduced p-n junction leakage current. Further, the semiconductor device has a larger margin to a certain gate length and a specified threshold voltage to elevate a production yield.

Owner:RENESAS ELECTRONICS CORP

Ion implant method

InactiveCN101894748BImprove performanceSemiconductor/solid-state device manufacturingReverse short-channel effectIndium

The invention discloses an ion implant method, comprising the following step: implanting ions according to the pre-specified ion implant sequence, wherein the sequence is as follow: germanium ions, arsenic ions, boron ions, indium ions and carbon ions. The method can effectively improve the performance of the semi-conductor components and eliminate or reduce the adverse impact of the short channel effect and / or reverse short channel effect on the semi-conductor components.

Owner:SEMICON MFG INT (BEIJING) CORP

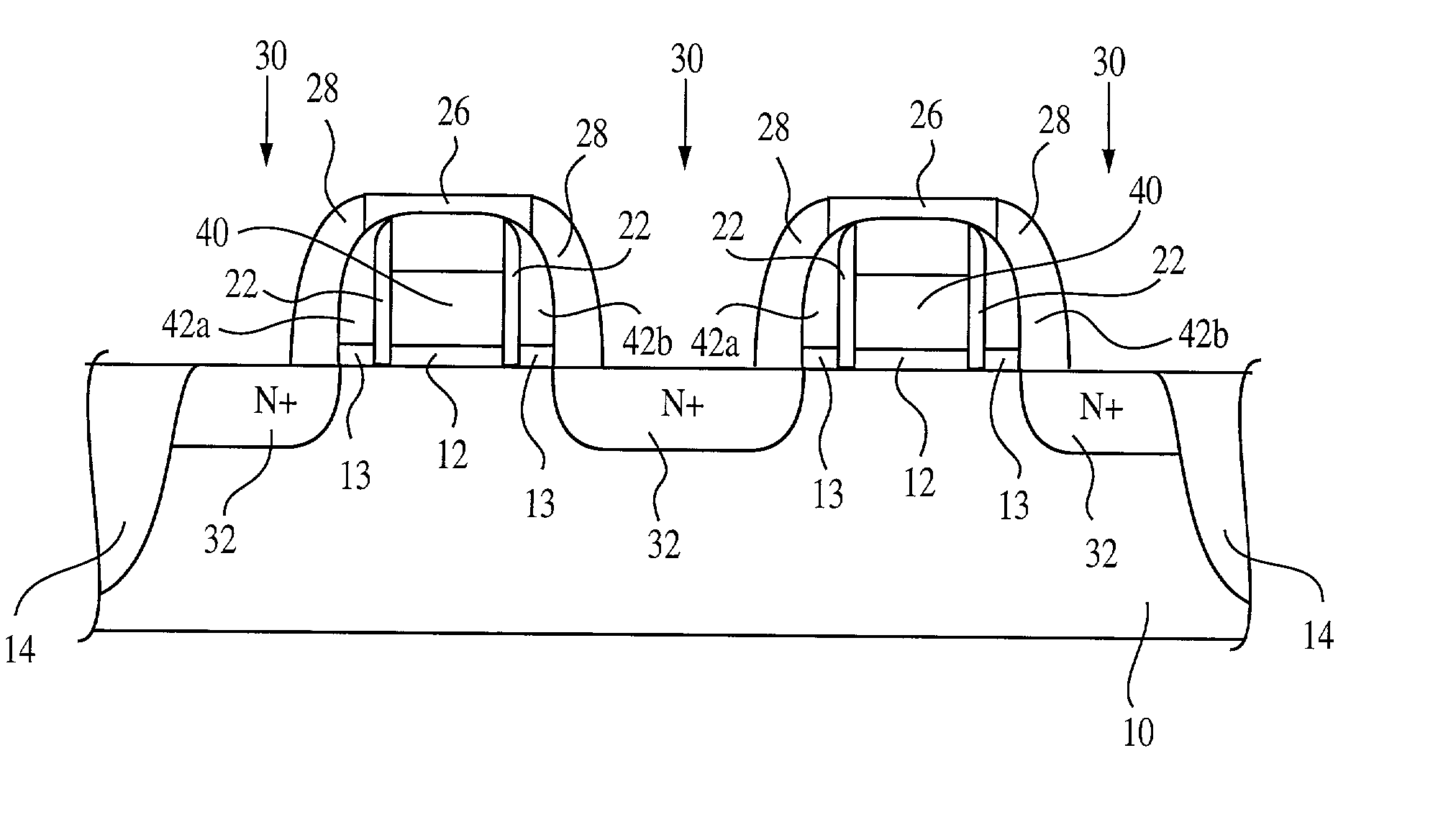

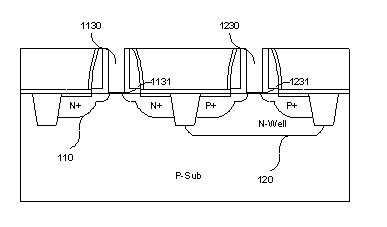

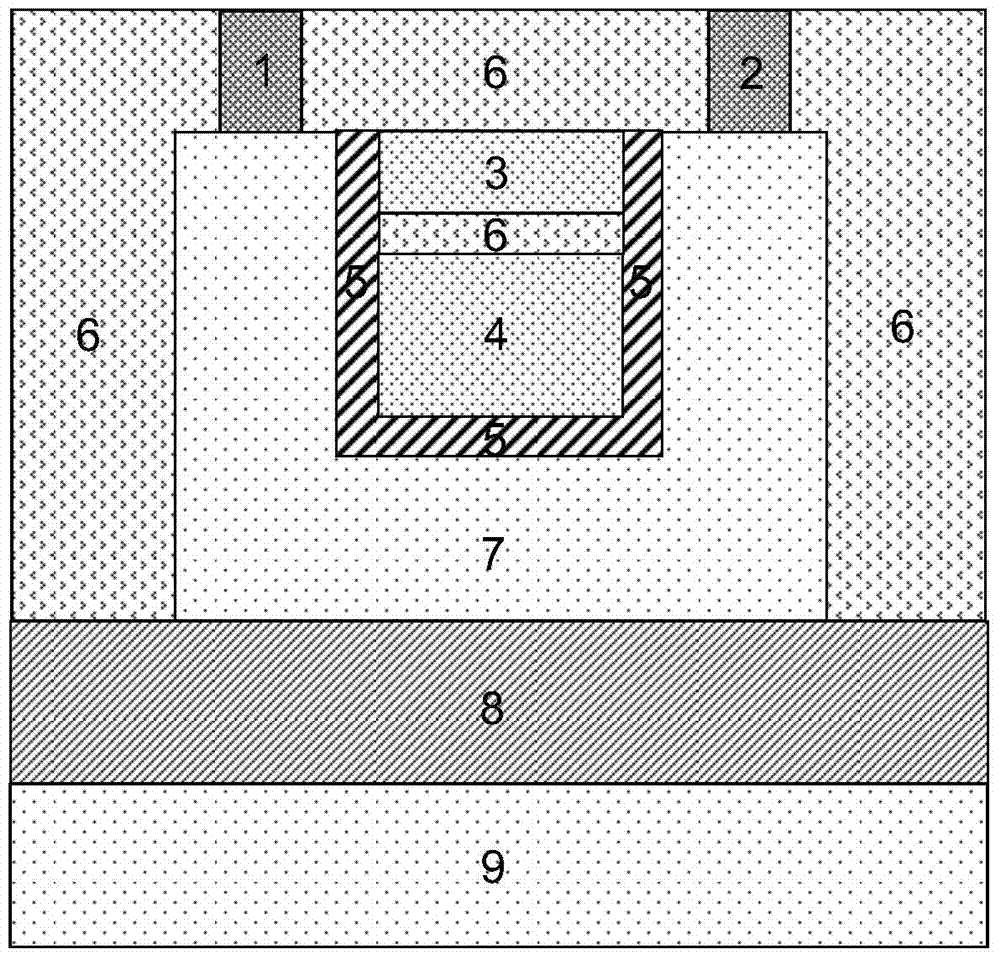

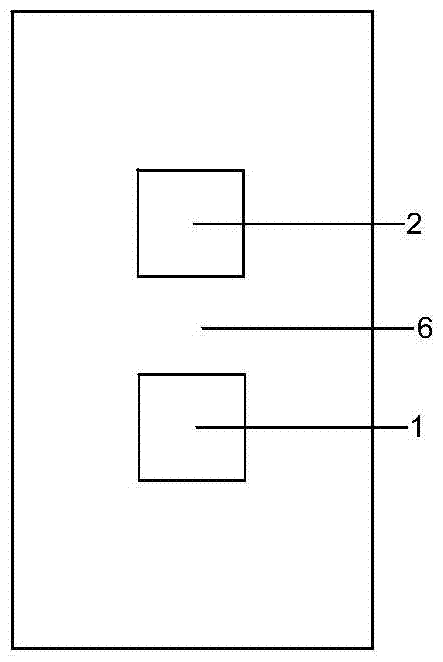

Self-alignment channel doping for restraining CMOS (Complementary Metal Oxide Semiconductor) short channel effect and preparation method thereof

InactiveCN102427062AImprove performanceSuppression of short channel effectsSemiconductor/solid-state device manufacturingState of artCMOS

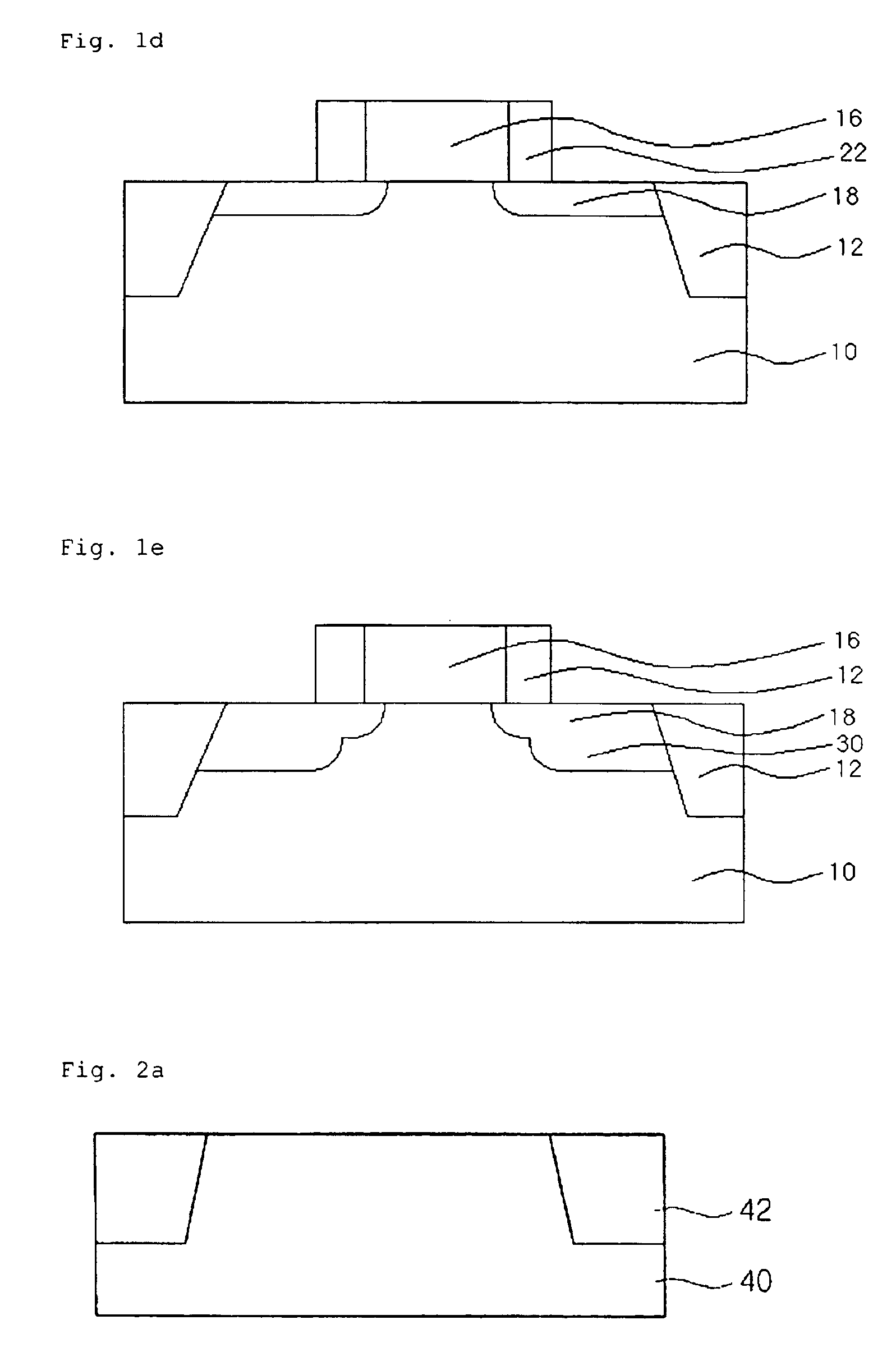

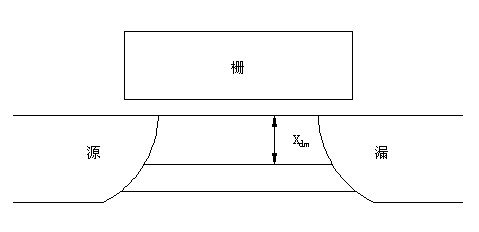

The invention relates to self-alignment channel doping for restraining a CMOS (Complementary Metal Oxide Semiconductor) short channel effect and a preparation method thereof, which solve the following problems in the prior art: 1, doping of a source and a drain is compensated to cause the increase of parasitic resistances of the source and the drain; 2, profiles of PN junctions of a source substrate and a drain substrate are influenced to cause the increase of reversed biased leakage current of the source substrate and the drain substrate; and 3, the junction depth Xj of the PN junctions of the source substrate and the drain substrate can be increased to cause counteractive on the restraint on the SCE (Short Channel Effect). According to the self-alignment channel doping for restraining the CMOS short channel effect and the preparation method thereof, disclosed by the invention, self-alignment doping on CMOS device channel regions is realized, a heavy-doped buried layer under a channel is formed, and source and drain regions are not influenced, thus the SCE is effectively restrained, and the performances of devices are improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Highly integrated high mobility source-drain gate-assisted junction-free transistor

InactiveCN104282751BLow source-drain resistanceImprove mobilitySemiconductor devicesReverse short-channel effectScattering effect

Owner:SHENYANG POLYTECHNIC UNIV

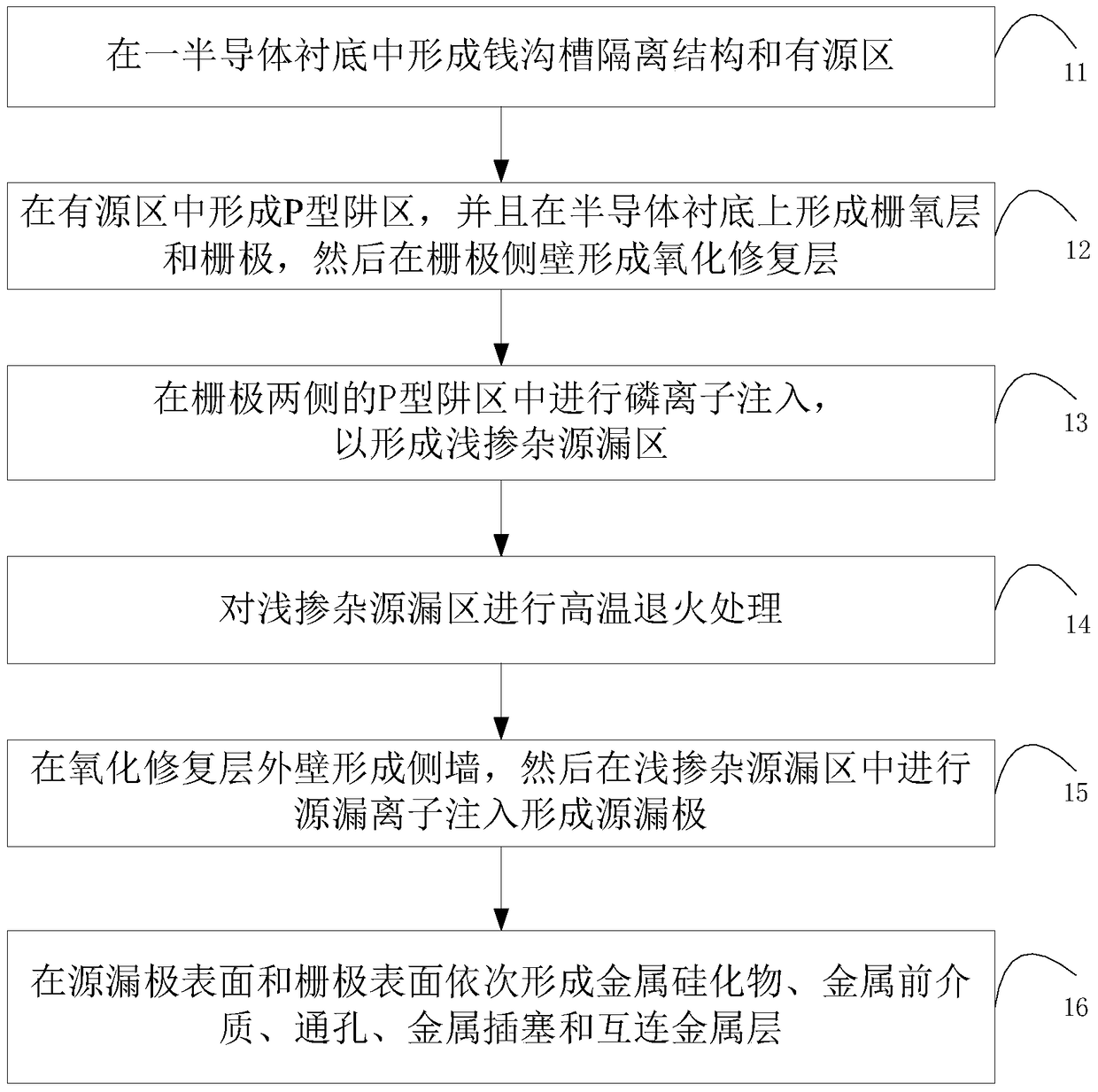

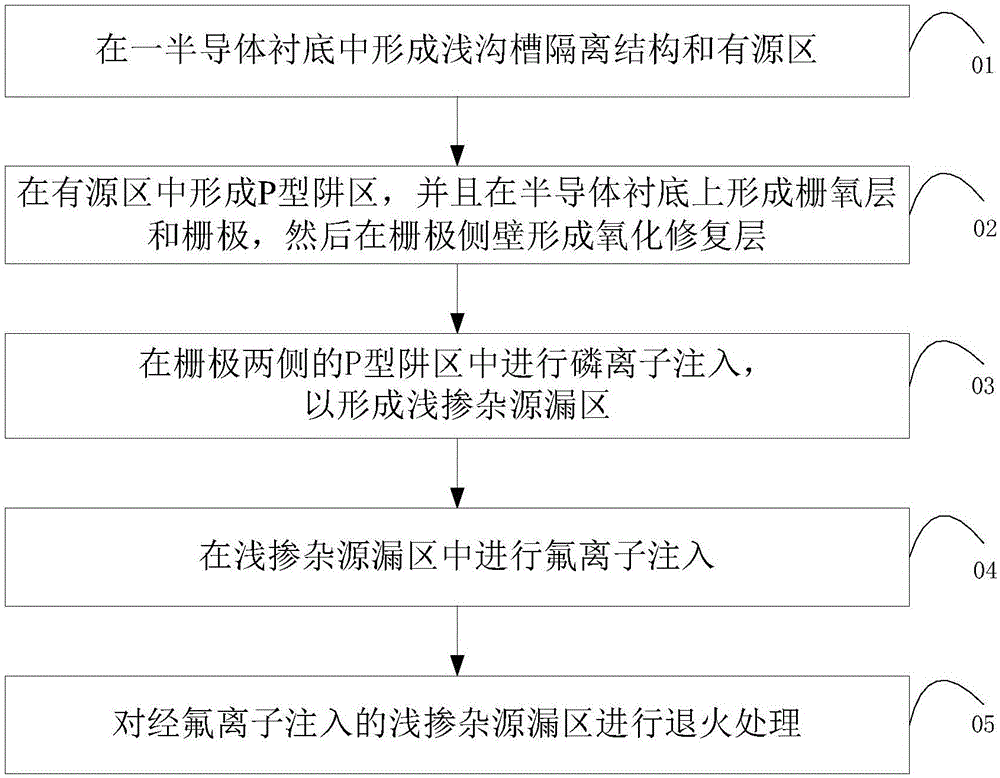

Method for suppressing anti-short channel effect and method for manufacturing nmos device

ActiveCN105047566BInhibit injectionStop the spreadSemiconductor/solid-state device manufacturingSemiconductor devicesReverse short-channel effectTime processing

The invention provides a method for restraining the reverse short channel effect and a manufacturing method of an NMOS (N-Channel Metal Oxide Semiconductor) device. After phosphorus ions are injected into the drain region of a shallow doping source, a fluorine ion injection procedure is added, and low-temperature annealing long-time treatment is performed on the drain region of the shallow doping source. The injected fluorine ions are combined with vacancy and interstitial atoms and the like in a grid edge area, so that the diffusion of boron elements in a P-type well region can be prevented, and the reverse short channel effect is restrained. Moreover, the fluorine ions can restrain hot carrier injection, so that the reliability of hot carrier injection does not become poor while the fluorine ions are injected.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

ldmos transistor and method of making the same

ActiveCN109755133BIncrease stressImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesReverse short-channel effectCharge carrier mobility

The present invention provides an LDMOS transistor and a manufacturing method thereof. A well region is formed in a first region of a semiconductor substrate, and after the gate stack structure is formed, only ion implantation is performed on the first region of the semiconductor substrate to form at least A doped layer located in the well region, the doping type of the doped layer is opposite to that of the well region, thereby forming an asymmetric ion implantation structure on both sides of the gate stack structure, on the one hand It can increase the channel stress, improve the carrier mobility, and then increase the drive current and breakdown voltage of the device. On the other hand, it can inhibit the diffusion of dopant ions in the source region closer to the gate stack structure to the gate. In the channel region at the bottom of the stack structure, it helps to form a shallower junction, thereby reducing short channel effects and reverse short channel effects, and improving device performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

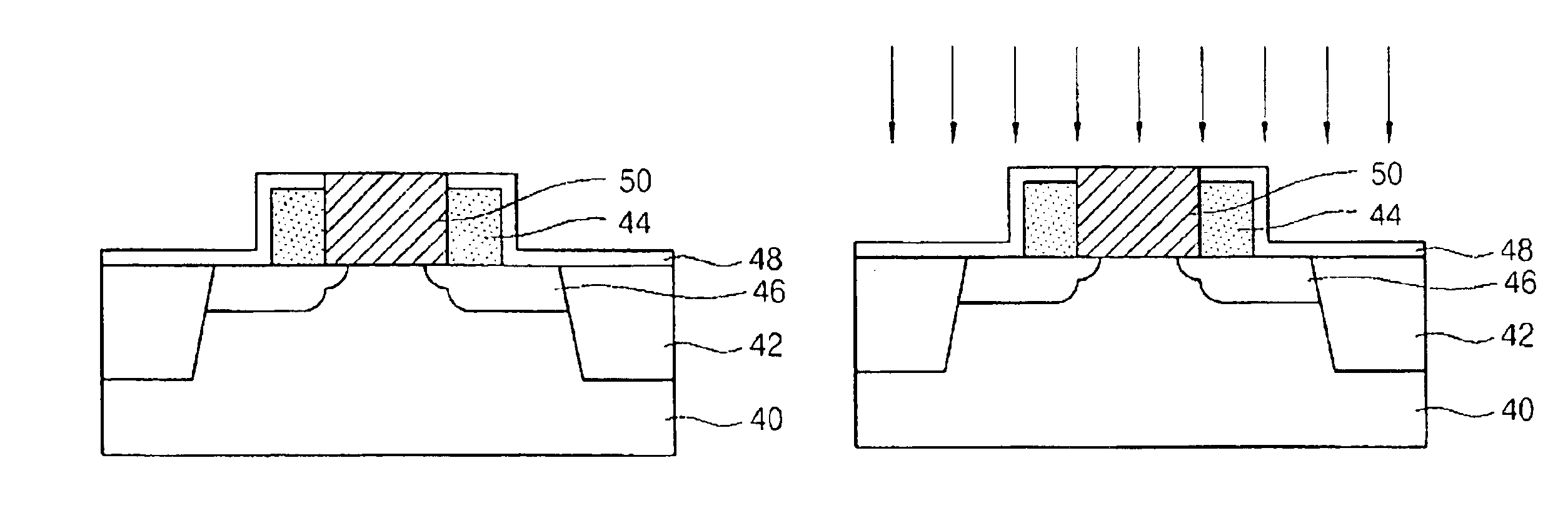

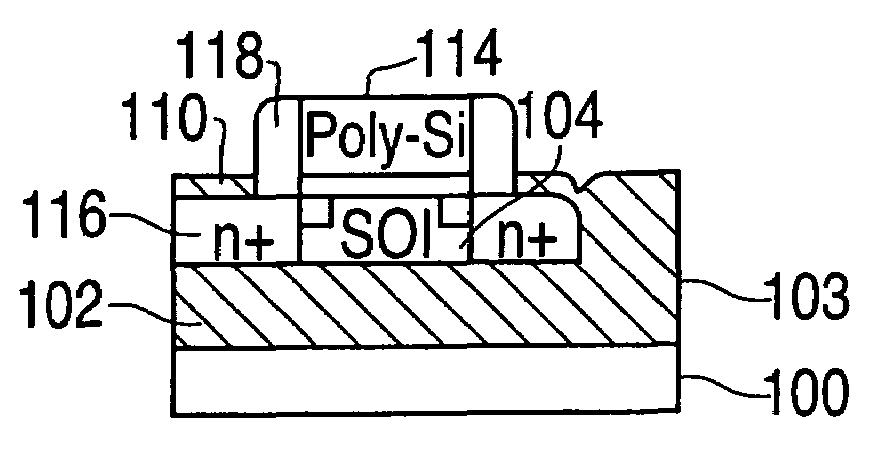

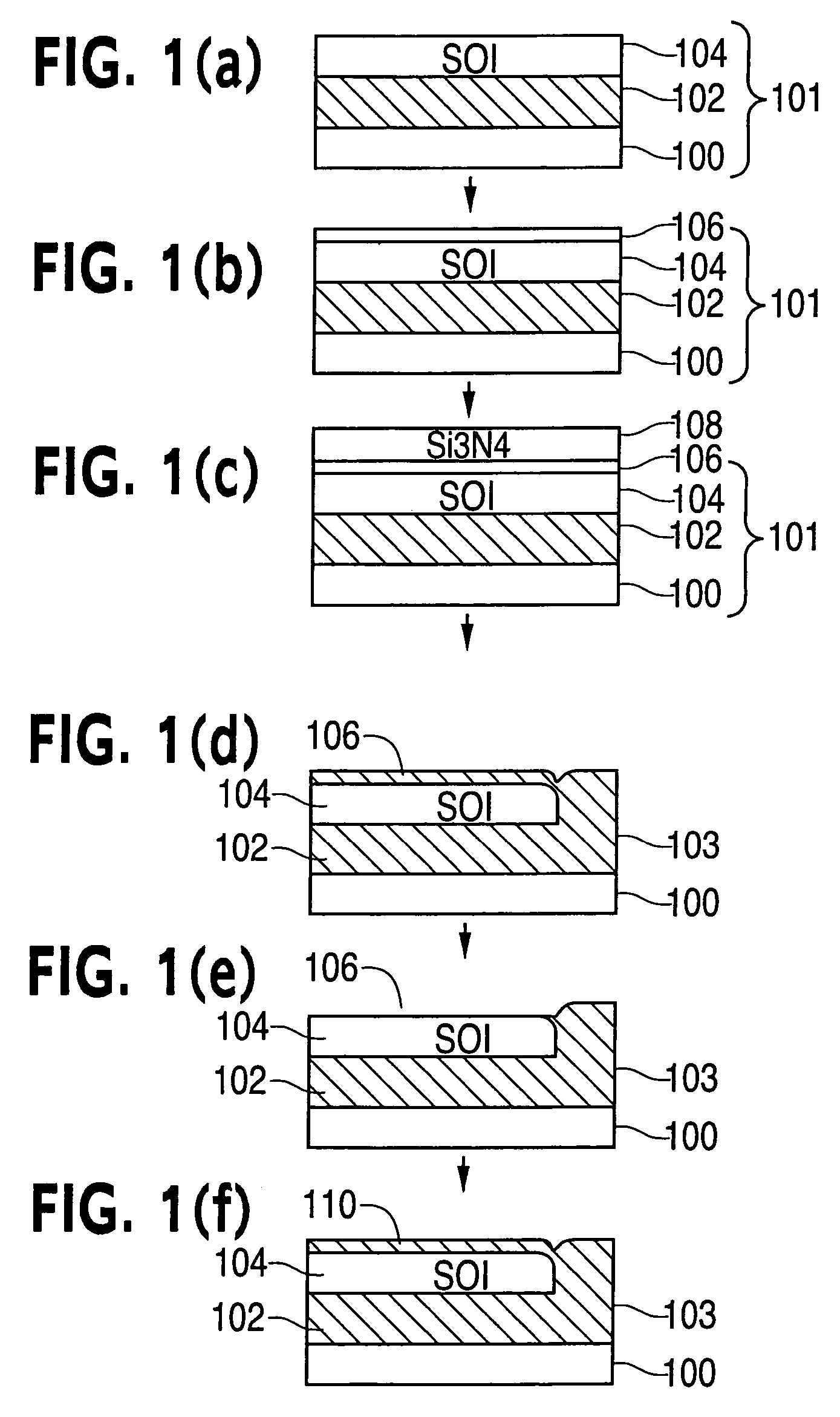

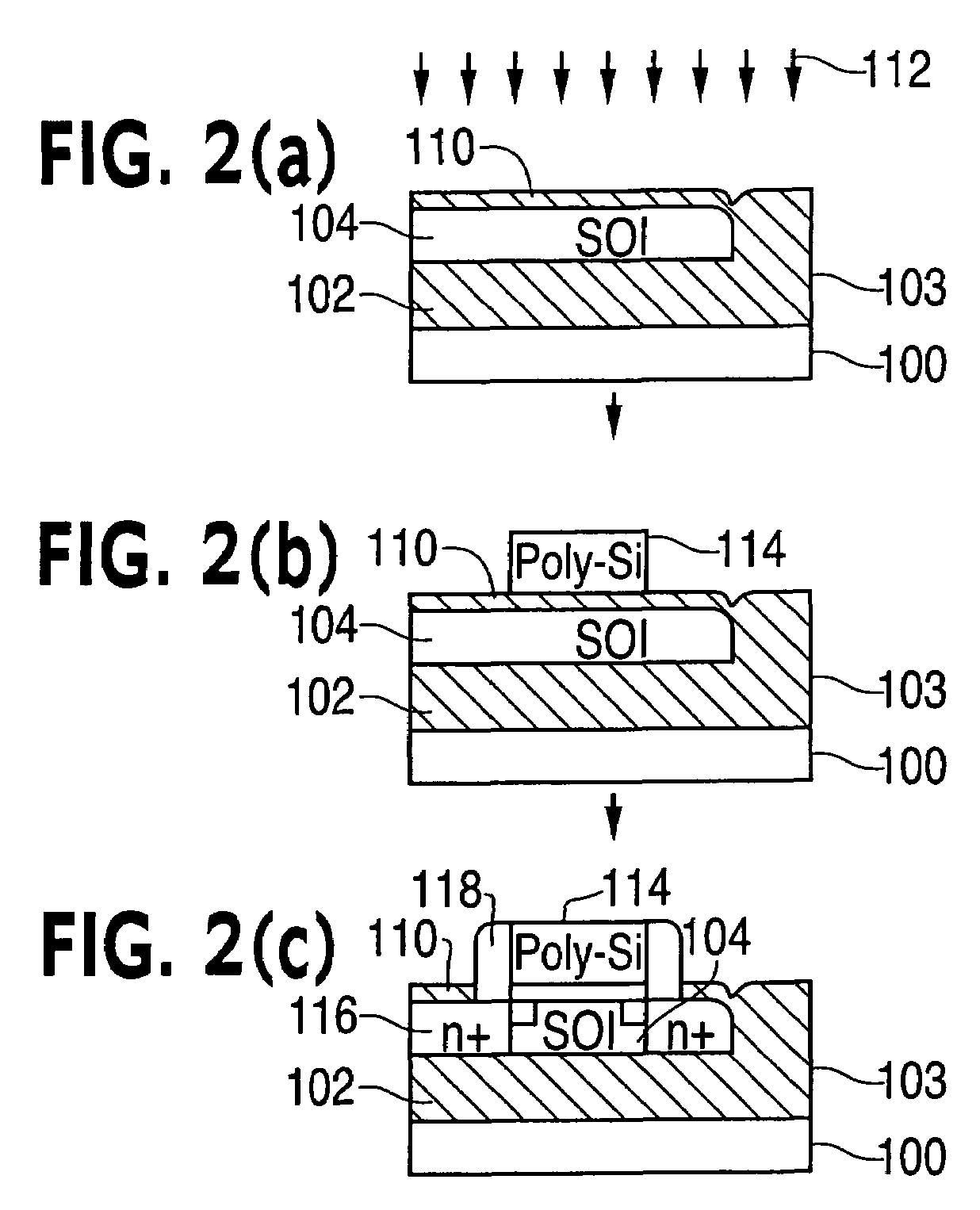

Method of manufacturing semiconductor device and semiconductor device

InactiveUS6974982B2Avoid short channel effectsShorten the lengthTransistorSolid-state devicesReverse short-channel effectMiniaturization

Impurity ions are implanted into the silicon layer of an SOI substrate to achieve an ion concentration distribution which inhibits for a reduction in threshold voltage (Vth-rolloff) as a gate length is reduced. A reduction in potential barrier which runs from a drain region side is effectively inhibited to counter short channel effects resulting from a reduction in gate length attendant with miniaturization of SOI-MOSFETs.

Owner:LAPIS SEMICON CO LTD

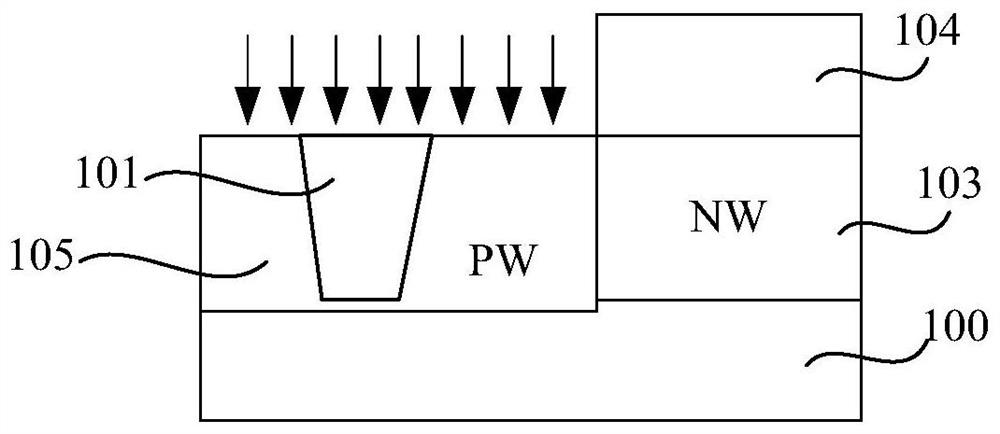

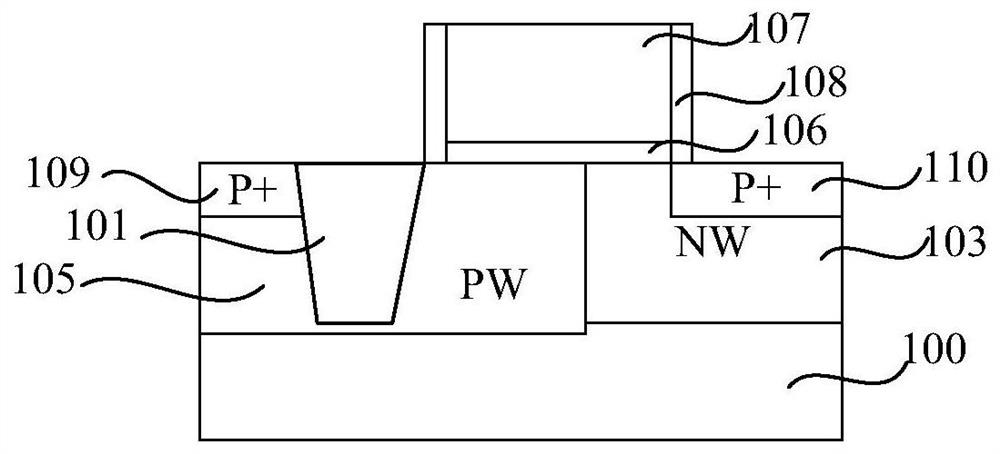

Semiconductor device and method of manufacturing the same

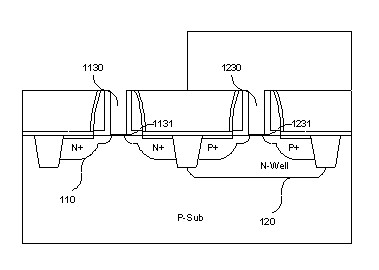

ActiveUS8237222B2CostTimelyTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceReverse short-channel effect

In a method of manufacturing a high withstanding voltage MOSFET, a region to be doped with impurities and a region to be doped with no impurity are provided when ion implantation of the impurities is performed in the channel forming region, for controlling a threshold voltage. The region to be doped with no impurity is suitably patterned so that impurity concentration of the channel forming region near boundaries between a well region and a source region and between the well region and a drain region having the same conductivity type as the well region may be increased, to thereby induce a reverse short channel effect. By canceling a short channel effect with the reverse short channel effect induced by the above-mentioned method, the short channel effect of the high withstanding voltage MOSFET may be suppressed.

Owner:ABLIC INC

Circuitry and method for reducing second and third-order nonlinearities

InactiveCN101785178BImprove linearityImprove manufacturabilityAmplifier modifications to reduce non-linear distortionPower amplifiersReverse short-channel effectEngineering

An electronic circuit (10) comprises at least two transistors (T12, T14) coupled in parallel, wherein the second transistor channel length is configured such that the threshold voltage of the second transistor (T14) is at a peak on a threshold voltage versus channel lengths curve arising from reverse short channel effects for a given semiconductor process. The first transistor (T12) is biased with a first gate-source voltage and a first drain-source voltage. The second transistor (T14) is biased with a second gate-source voltage and a second drain-source voltage. The first gate-source voltageand the second gate-source voltage are offset from each other by a gate-source voltage offset and the first drain-source voltage and the second drain-source voltage are offset from each other by a drain-source voltage offset. These bias conditions result in the transistors (T12, T14) operating in different regions so that the second and third-order nonlinearities of the transistors (T12, T14) substantially cancel each other out simultaneously.

Owner:TELEFON AB LM ERICSSON (PUBL)

Apparatus and method for exploiting reverse short channel effects in transistor devices

InactiveCN101467255BSmall sizeNo added complexityTransistorHigh frequency amplifiersReverse short-channel effectPeak value

A method of implementing a transistor circuit comprises coupling first and second transistors in parallel, wherein the first transistor has a channel length corresponding to a peak in the transistor's voltage threshold curve arising from reverse short channel effects, and the second transistor has a longer channel length and, therefore, a lower threshold voltage. Exploiting reverse short channel effects in this manner enables the implementation of "composite" transistor circuits that exhibit improved linearity.

Owner:TELEFON AB LM ERICSSON (PUBL)

Method for restraining reverse short channel effect and manufacturing method of NMOS (N-Channel Metal Oxide Semiconductor) device

ActiveCN105047566AInhibit injectionStop the spreadSemiconductor/solid-state device manufacturingSemiconductor devicesReverse short-channel effectPhysical chemistry

The invention provides a method for restraining the reverse short channel effect and a manufacturing method of an NMOS (N-Channel Metal Oxide Semiconductor) device. After phosphorus ions are injected into the drain region of a shallow doping source, a fluorine ion injection procedure is added, and low-temperature annealing long-time treatment is performed on the drain region of the shallow doping source. The injected fluorine ions are combined with vacancy and interstitial atoms and the like in a grid edge area, so that the diffusion of boron elements in a P-type well region can be prevented, and the reverse short channel effect is restrained. Moreover, the fluorine ions can restrain hot carrier injection, so that the reliability of hot carrier injection does not become poor while the fluorine ions are injected.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

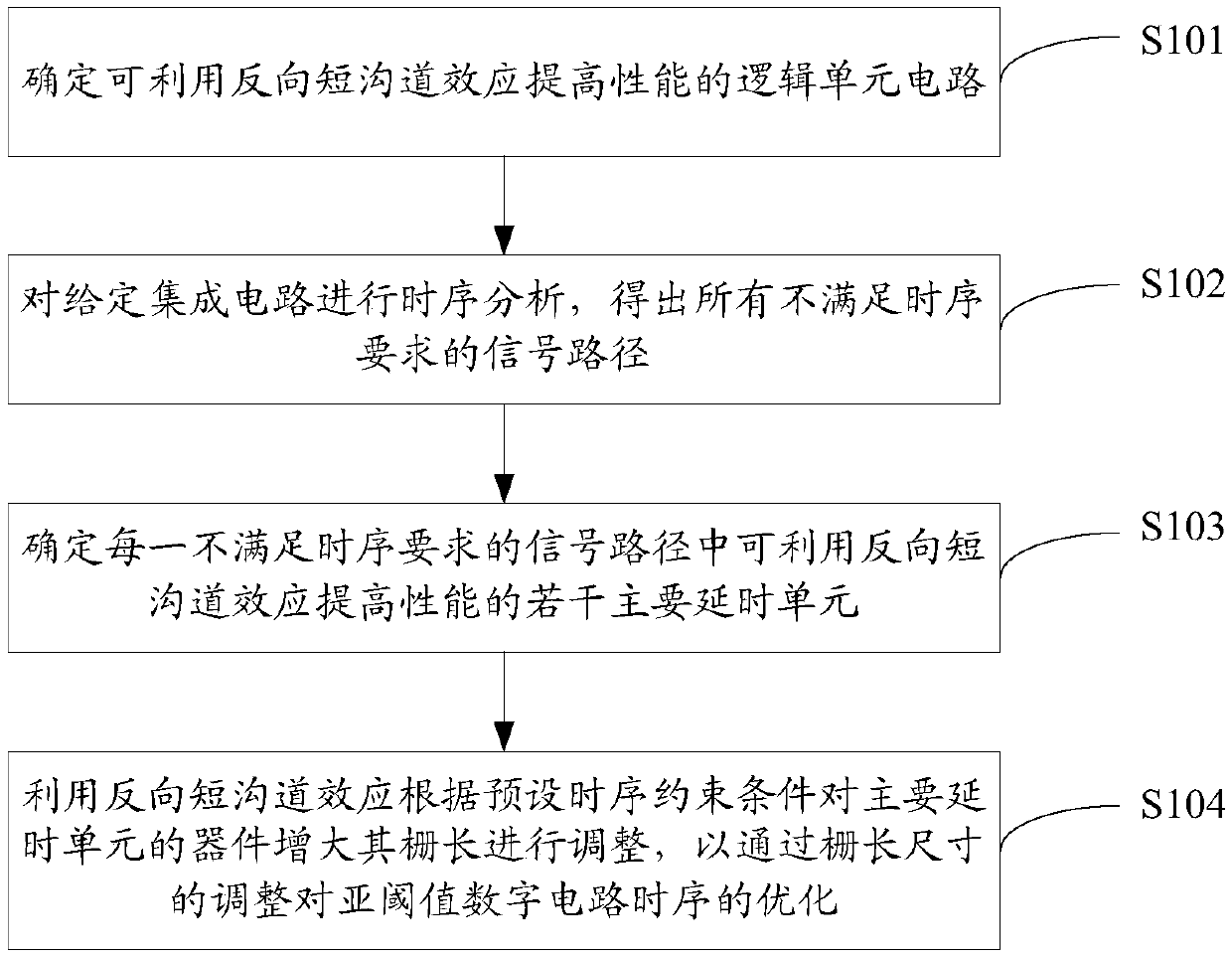

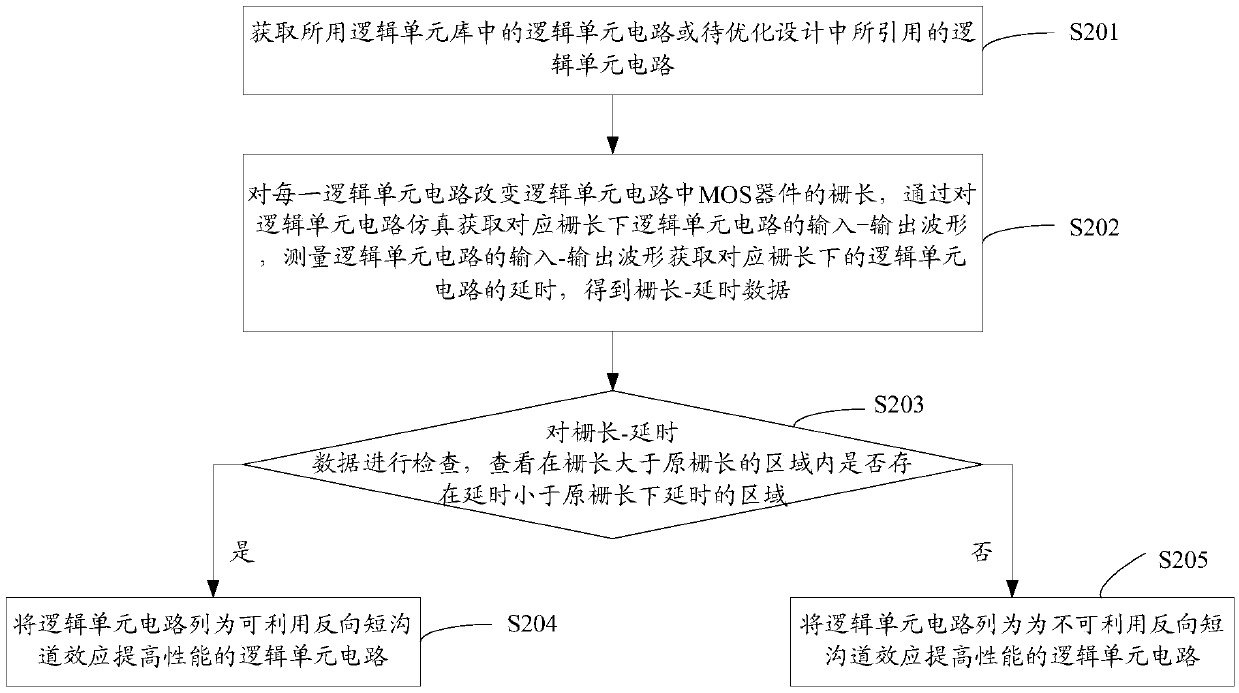

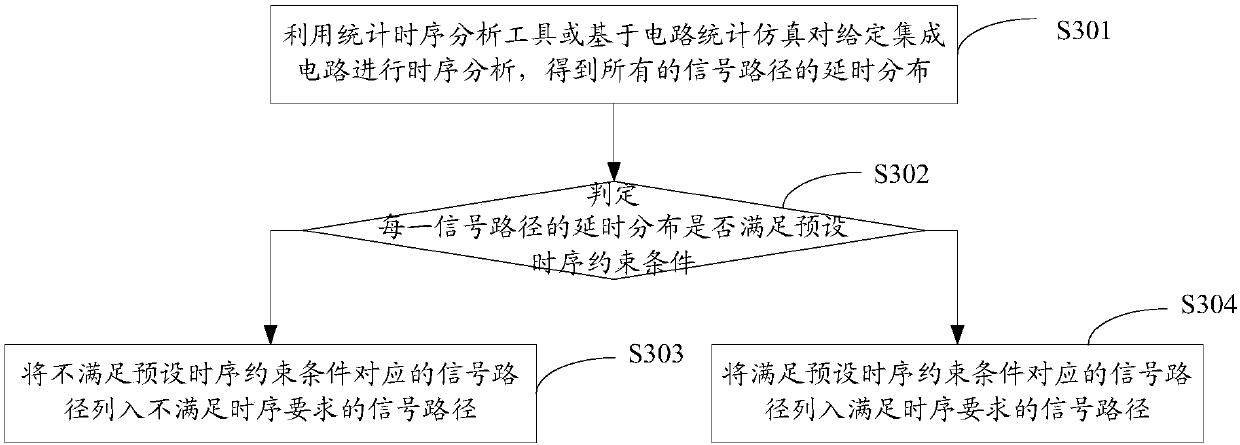

Sub-threshold digital circuit time sequence optimization method and system

PendingCN110956008AImprove robustnessShort delay timeComputer aided designSpecial data processing applicationsReverse short-channel effectTime delays

The invention discloses a sub-threshold digital circuit time sequence optimization method and system. The method comprises the following steps: firstly, determining a logic unit circuit capable of improving the performance by utilizing a reverse short channel effect; performing time sequence analysis on a given integrated circuit to obtain all signal paths which do not meet the time sequence requirement; then determining a plurality of main delay units capable of improving the performance by utilizing a reverse short channel effect in each signal path which does not meet the time sequence requirement; and finally, increasing the gate length of the device of the main time delay unit by using a reverse short channel effect according to a preset time sequence constraint condition to carry outadjustment, and adjusting the gate length size to optimize the time sequence of the sub-threshold digital circuit. According to the invention, the gate length of a device of a main time delay unit isincreased by using a reverse short channel effect, so that time sequence optimization is realized, the circuit performance of a sub-threshold digital circuit is improved, and the time delay time of the unit is reduced; and meanwhile, the consistency of unit delay is improved by increasing the area, so that the robustness of the circuit is enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Forming method of N-channel metal oxide semiconductor (NMOS) transistor

InactiveCN102074476BAvoid crowdingEvenly distributedSemiconductor/solid-state device manufacturingReverse short-channel effectGate dielectric

The invention discloses a forming method of an N-channel metal oxide semiconductor (NMOS) transistor, which comprises the following steps of: providing a semiconductor substrate which is divided into an isolation region and an active region; forming a doped well in the semiconductor substrate of the active region; forming a gate dielectric layer and a polycrystalline silicon gate on the semiconductor substrate of the active region in turn, wherein the gate dielectric layer and the polycrystalline silicon gate form a gate structure; re-oxidizing the gate structure; injecting ions into the semiconductor substrates on two sides of the gate by taking the gate structure as a mask to form a source / drain extension region; forming side walls on two sides of the gate structure, and then forming a Vt injection region in the semiconductor substrate; and forming source / drain electrodes in the semiconductor substrates on two sides of the gate structure and the side walls. The forming method ensures that ions of the Vt injection region of a channel region positioned below the gate are uniformly distributed to prevent a reverse short channel effect (RSCE).

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Highly integrated u-shaped channel high-mobility junctionless transistor with source-drain-gate assisted control

InactiveCN104282753BLow source-drain resistanceImprove mobilitySemiconductor devicesReverse short-channel effectScattering effect

The invention relates to a high-integration sun-shaped source-drain gate auxiliary-controlled U-shaped channel high-mobility junctionless transistor, which adopts two independently controlled gate electrodes, such as a sun-shaped auxiliary control gate electrode and a gate electrode. The doping concentration is used to improve the mobility and avoid the decrease in the mobility and stability of the device caused by the enhanced random scattering effect under high doping concentration. It solves the contradiction between the low doping concentration of ordinary junctionless transistors, which will increase the source-drain resistance, and the high doping concentration, which will reduce the mobility and stability of the device. Crystal silicon is used as the channel part of the device. Compared with the ordinary planar structure, the effective channel length is significantly increased without increasing the chip area to reduce the short channel effect of the device at the deep nanometer scale, so it is suitable for popularization and application. .

Owner:SHENYANG POLYTECHNIC UNIV

Apparatus and method for exploiting reverse short channel effects in transistor devices

InactiveCN101467255ASmall sizeNo added complexityTransistorHigh frequency amplifiersReverse short-channel effectTransistor circuits

A method of implementing a transistor circuit comprises coupling first and second transistors in parallel, wherein the first transistor has a channel length corresponding to a peak in the transistor's voltage threshold curve arising from reverse short channel effects, and the second transistor has a longer channel length and, therefore, a lower threshold voltage. Exploiting reverse short channel effects in this manner enables the implementation of 'composite' transistor circuits that exhibit improved linearity.

Owner:TELEFON AB LM ERICSSON (PUBL)

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com