Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

580 results about "Soft error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics and computing, a soft error is a type of error where a signal or datum is wrong. Errors may be caused by a defect, usually understood either to be a mistake in design or construction, or a broken component. A soft error is also a signal or datum which is wrong, but is not assumed to imply such a mistake or breakage. After observing a soft error, there is no implication that the system is any less reliable than before. One cause of soft errors is single event upsets from cosmic rays.

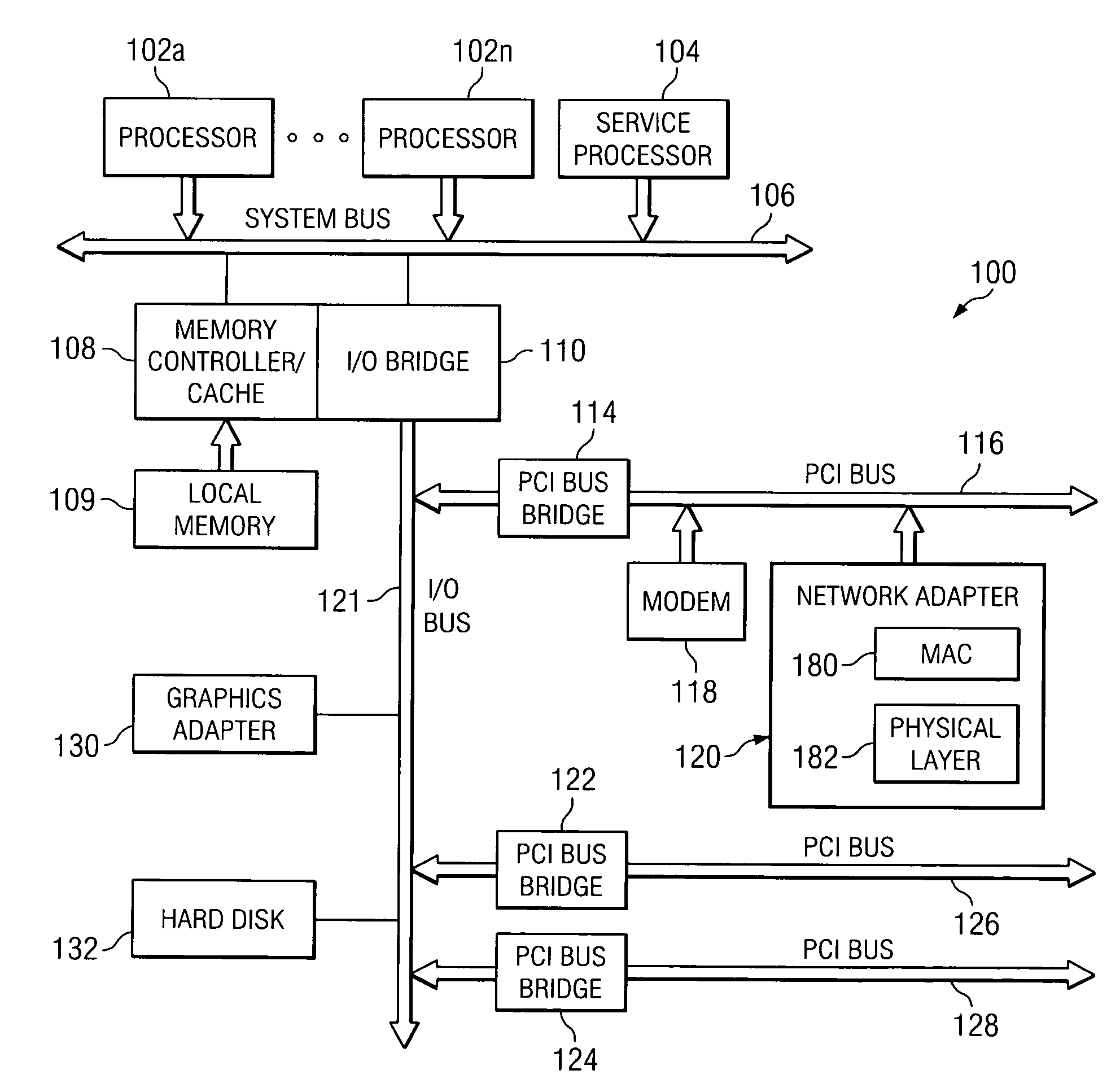

On-board scrubbing of soft errors memory module

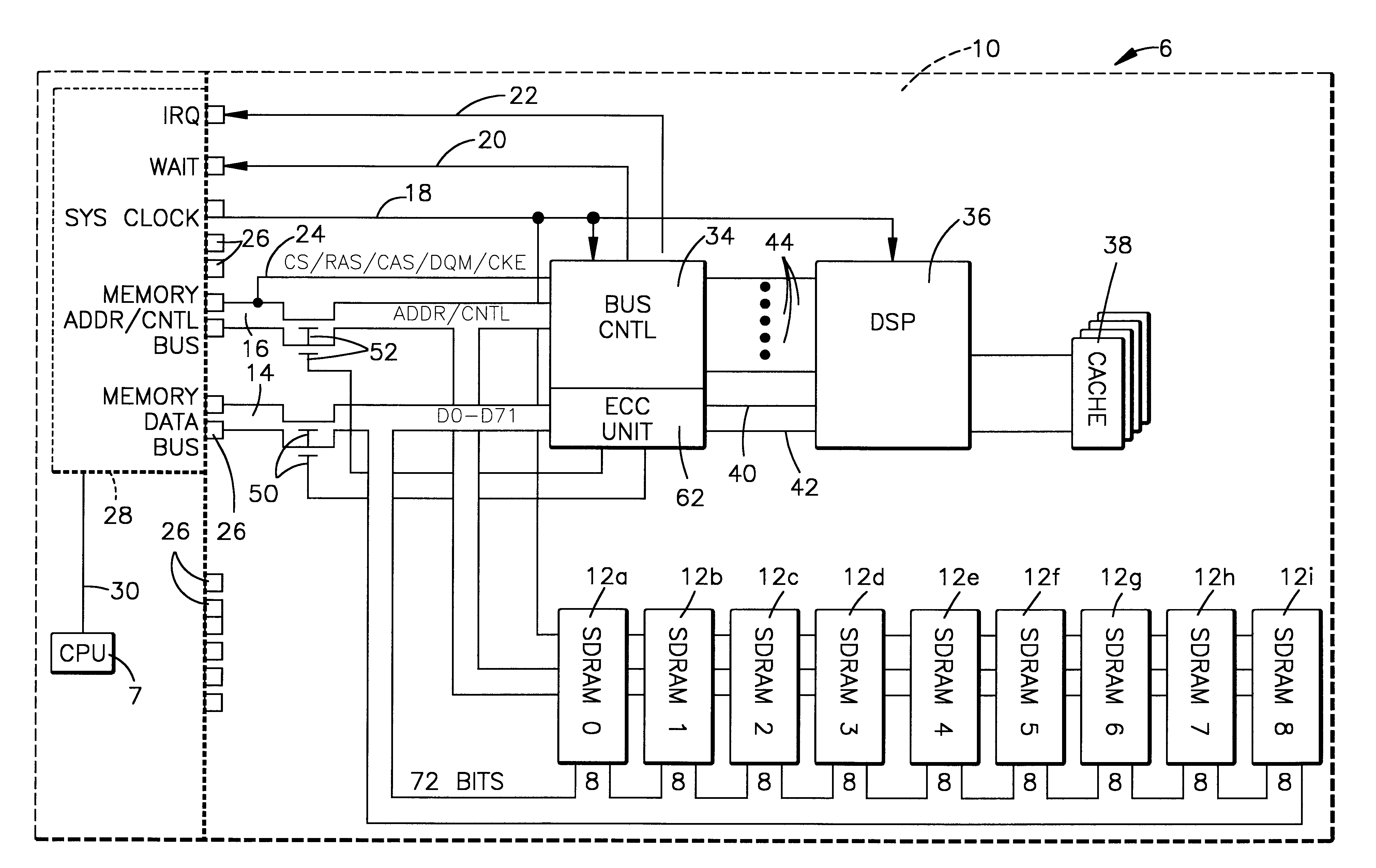

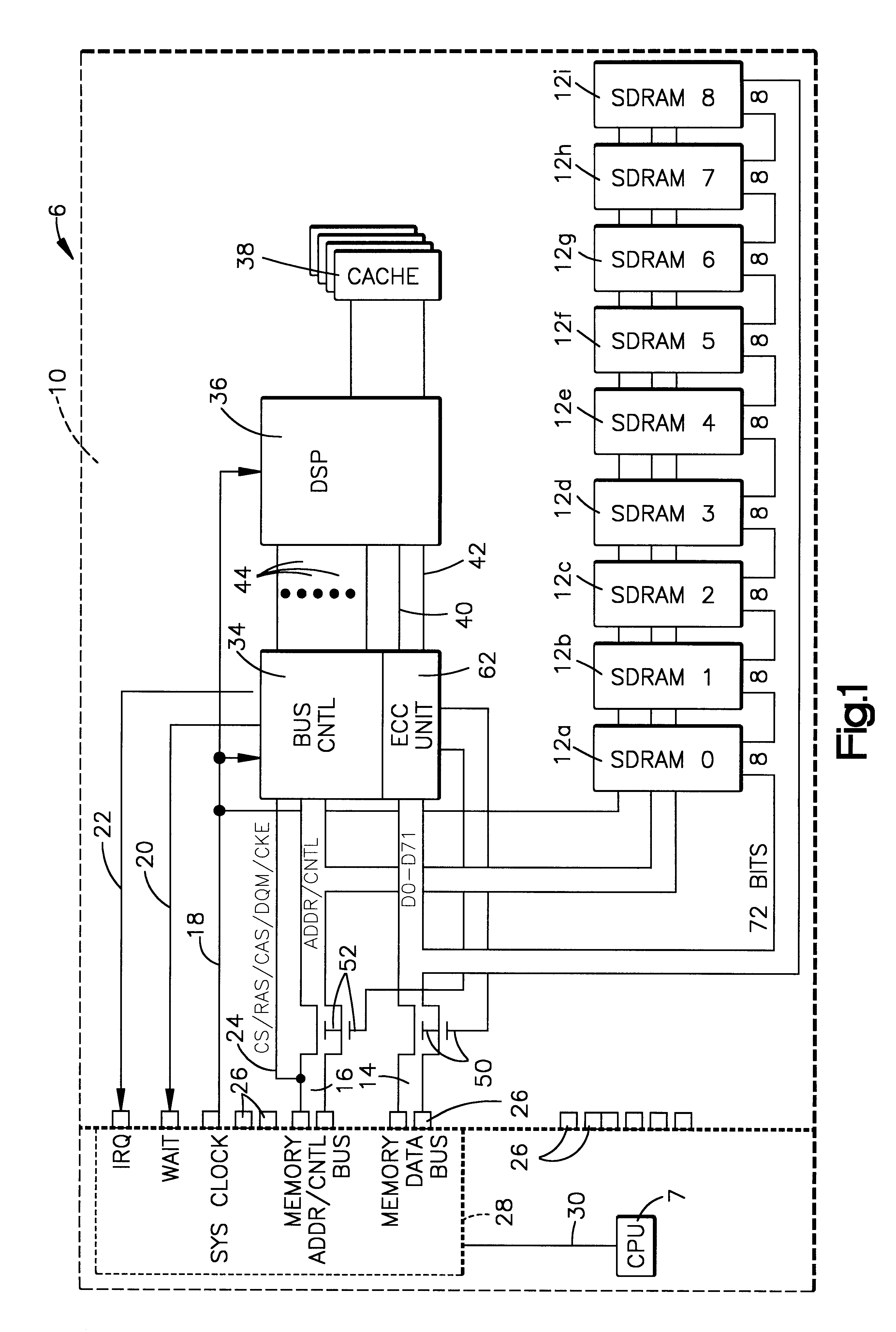

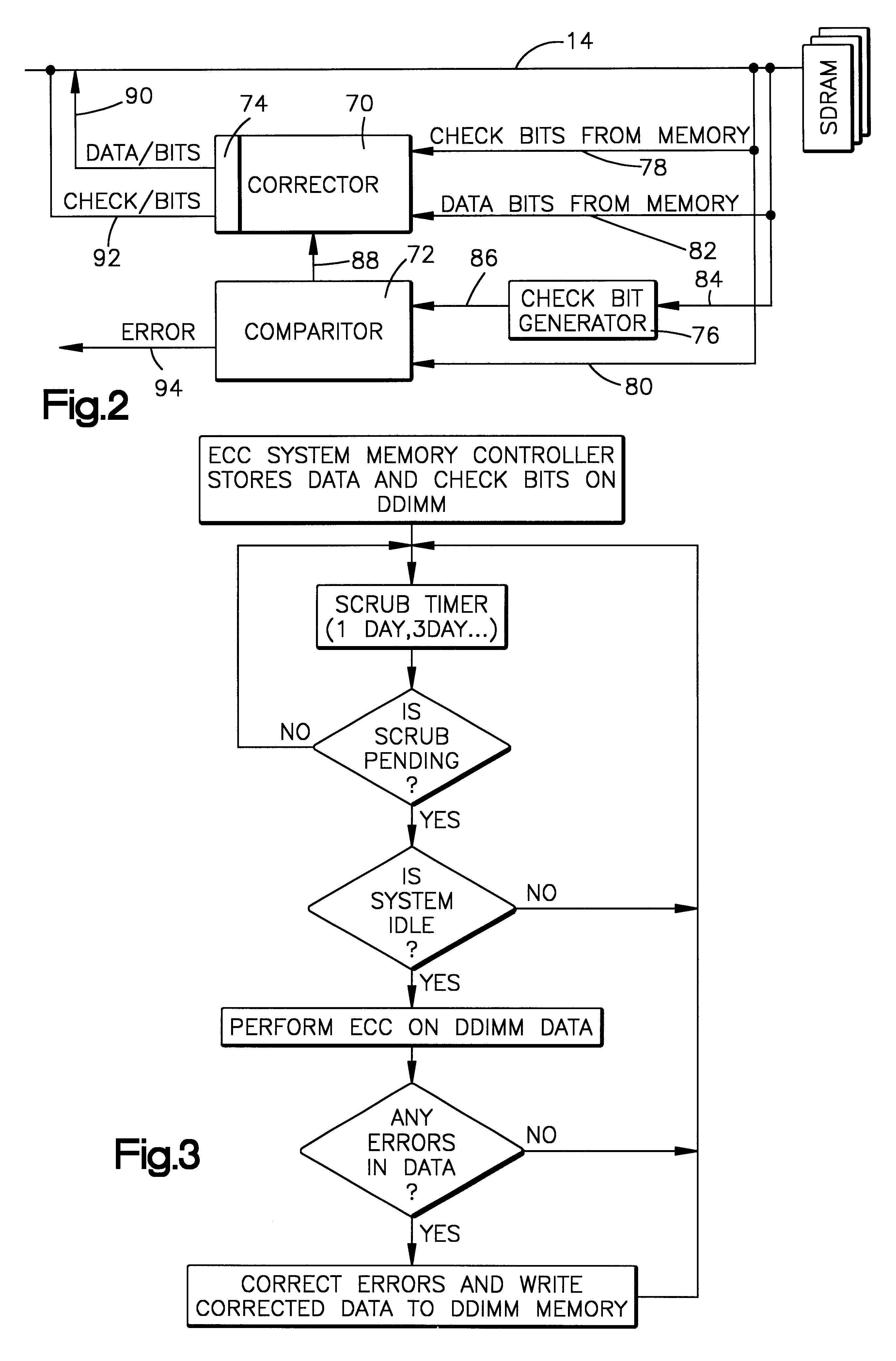

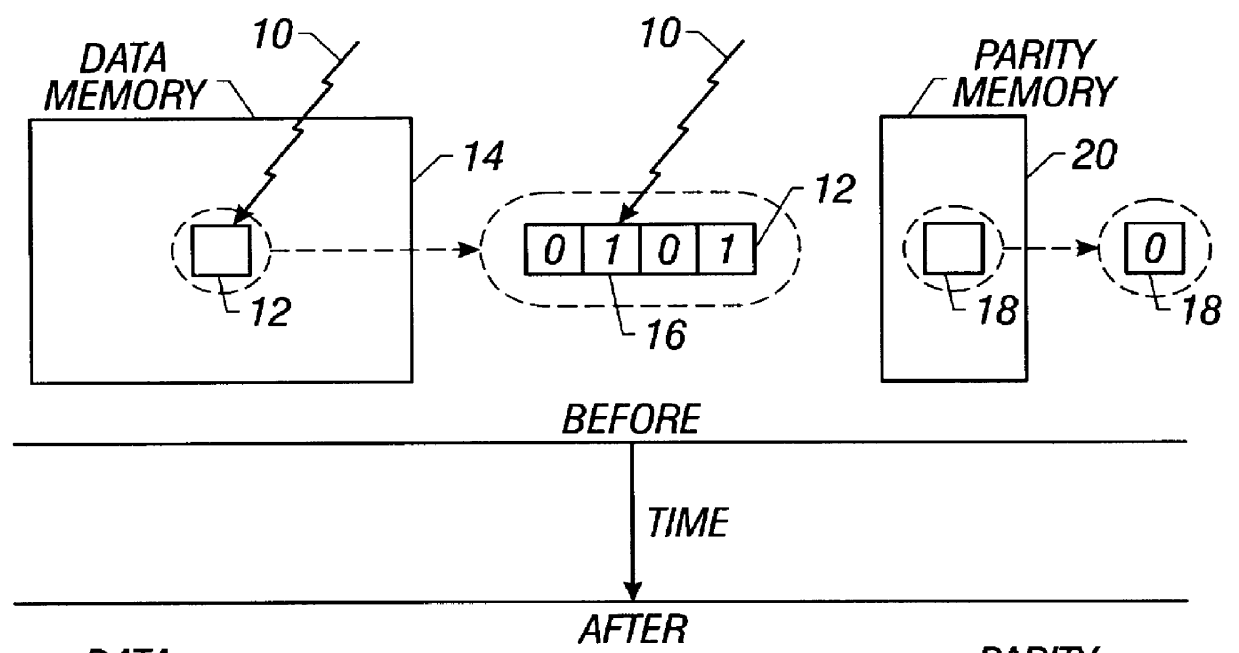

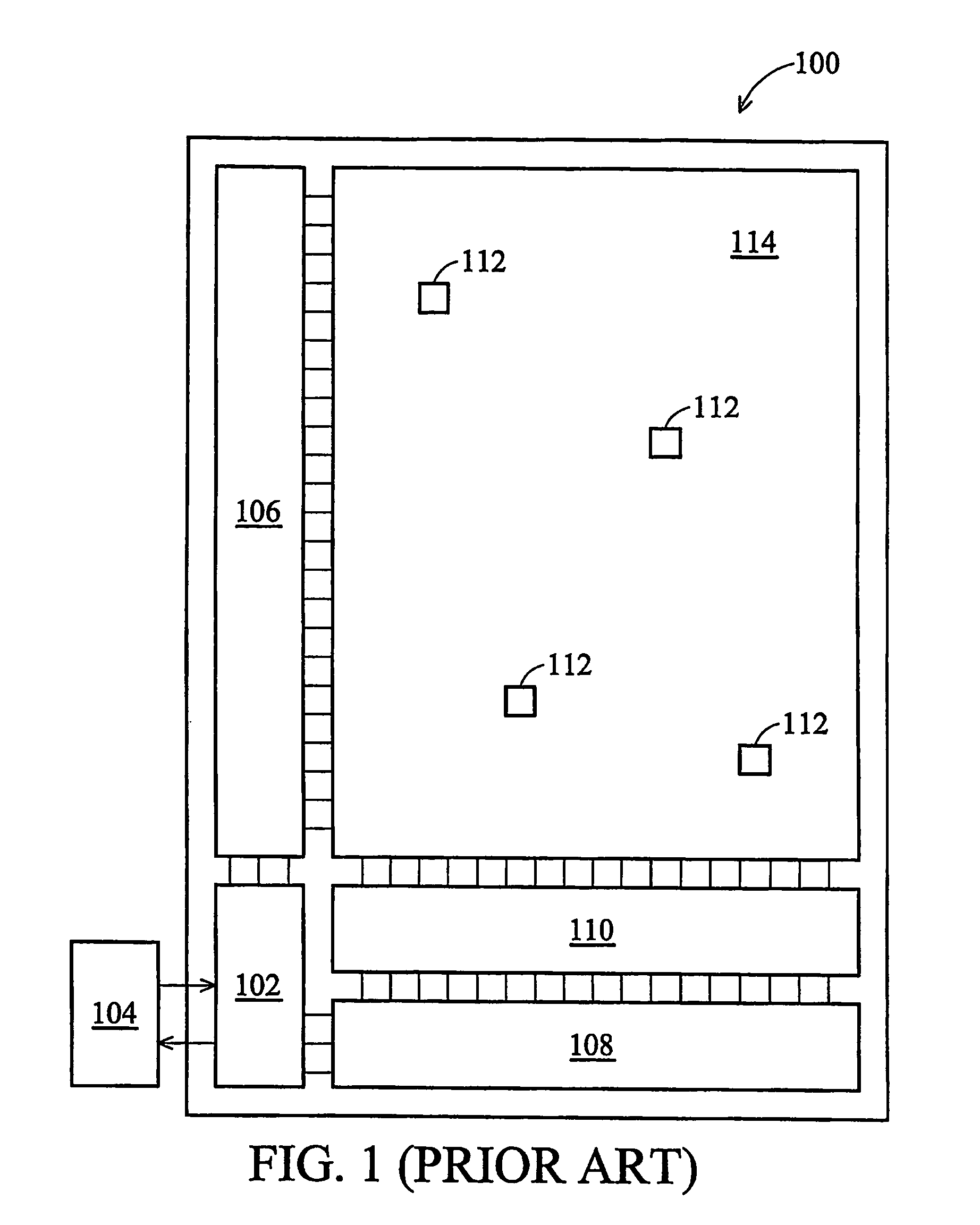

A memory module for attachment to a computer system having a memory bus and a method of using the memory module for error correction by scrubbing soft errors on-board the module is provided. The module includes a printed circuit card with memory storage chips on the card to store data bits and associated ECC check bits. Tabs are provided on the circuit card to couple the card to the memory bus of the computer system. Logic circuitry selectively operatively connects and disconnects the memory chip and the memory bus. A signal processor is connected in circuit relationship with the memory chips. The logic circuitry selectively permits the signal processor to read the stored data bits and associated check bits from the memory chips, recalculate the check bits from the read stored data bits, compare the recalculated check bits with the stored check bits, correct all at least one bit errors in the store data bits and stored associated check bits and re-store the correct data bits and associated check bits in the memory chips. When the memory chips and the memory bus are disconnected, single bit soft errors occurring during storage of the data bits and check bits are corrected periodically before the data is read from the memory chips to the data bus on a read operation.

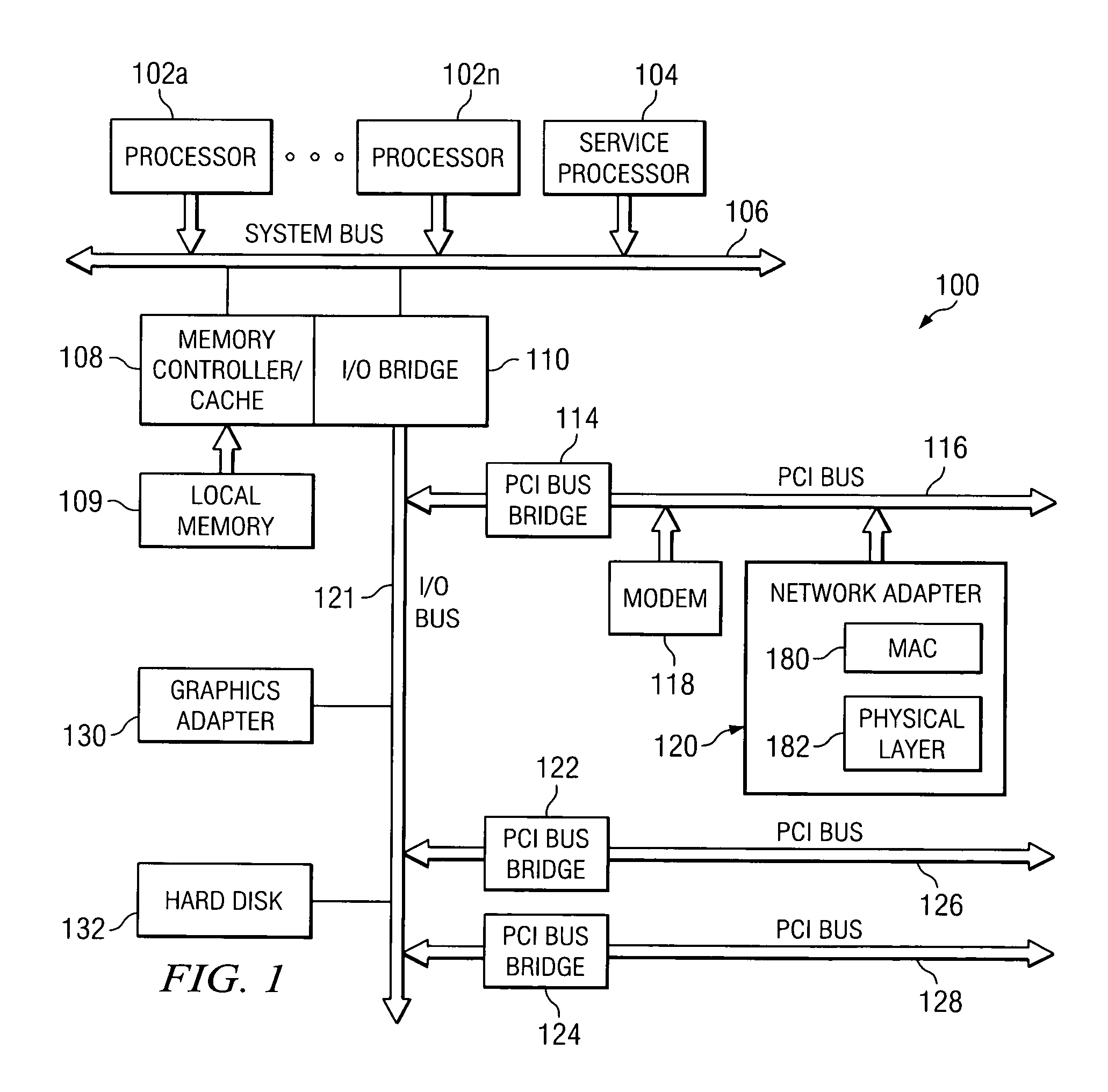

Owner:IBM CORP

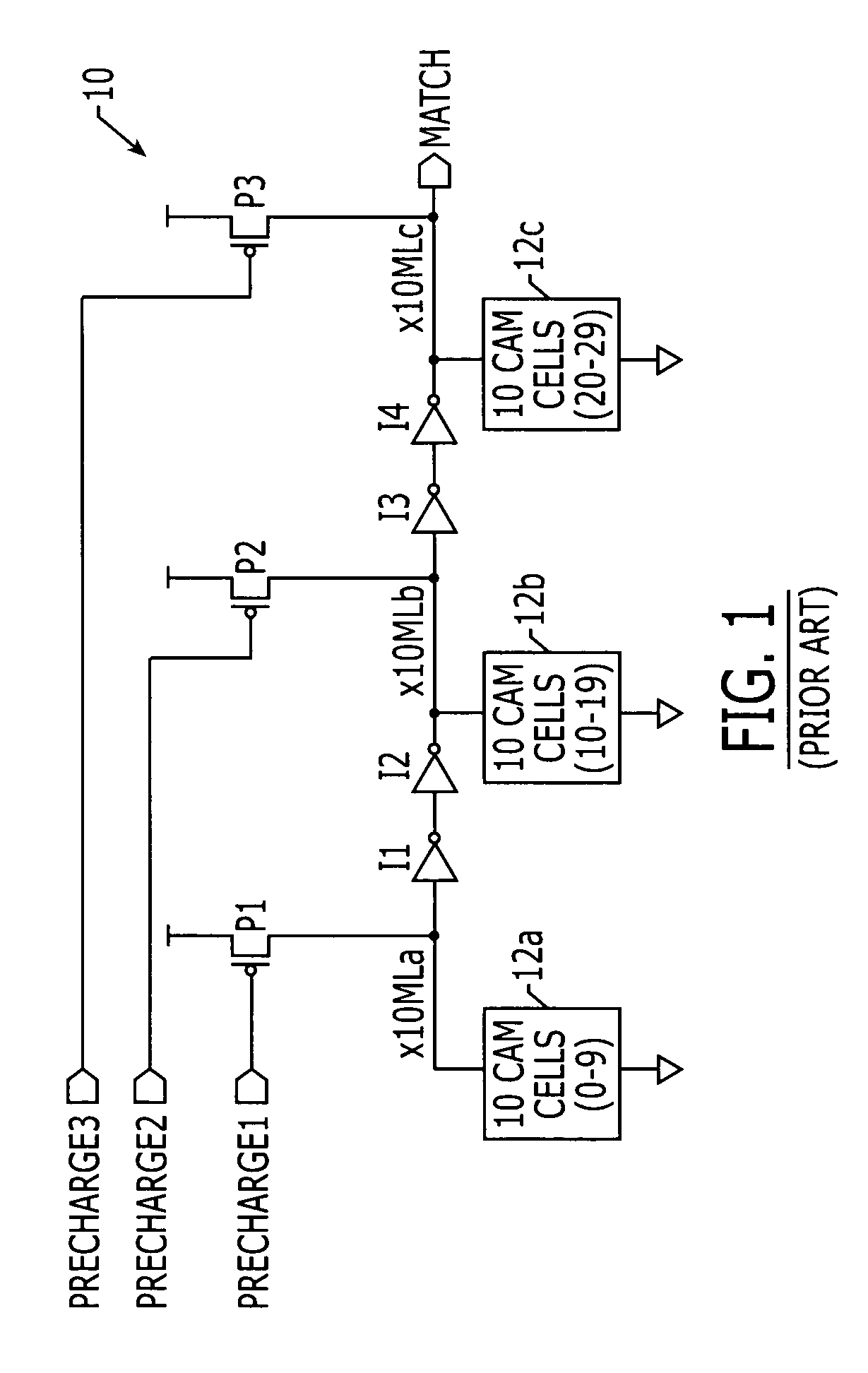

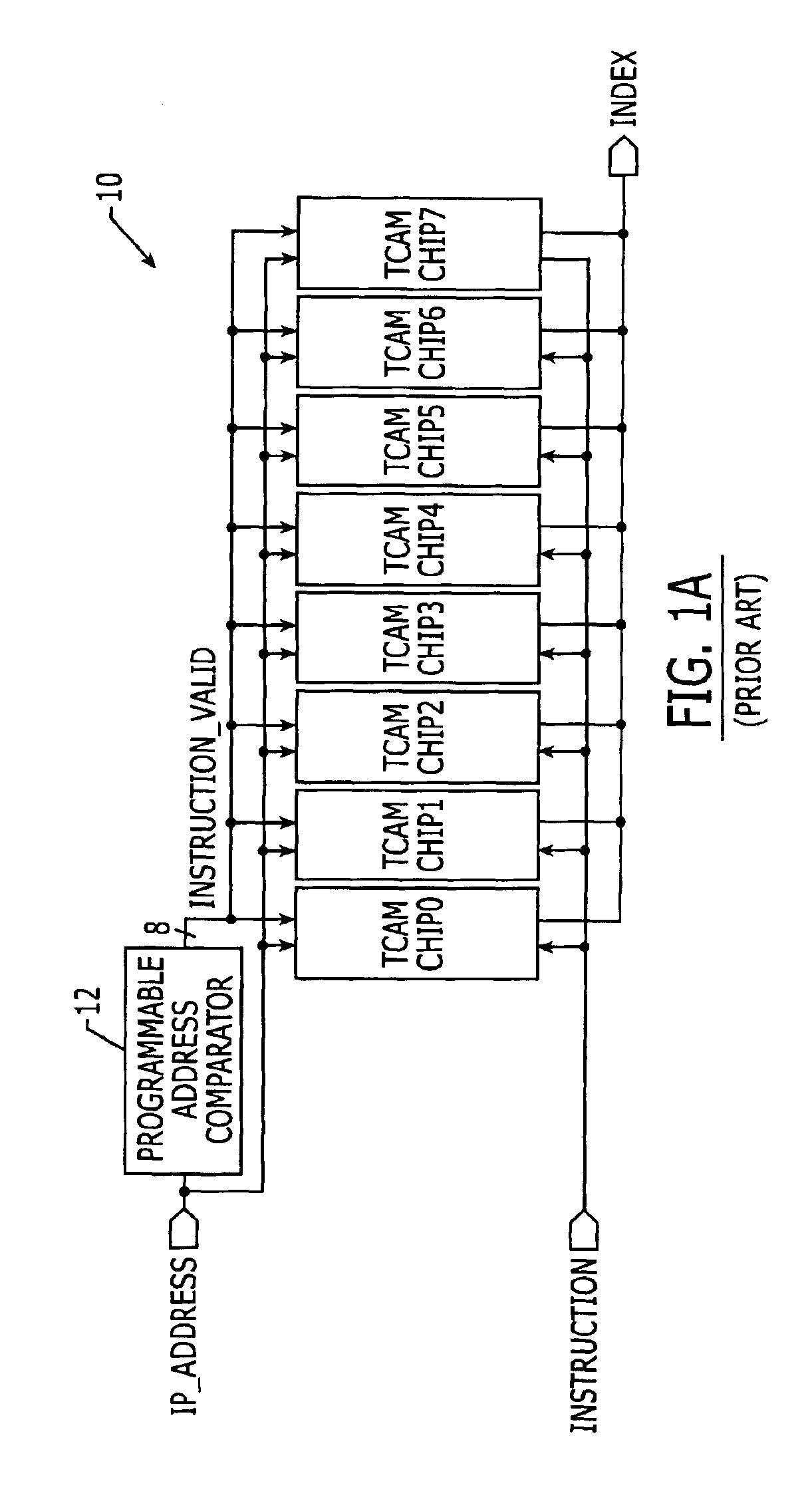

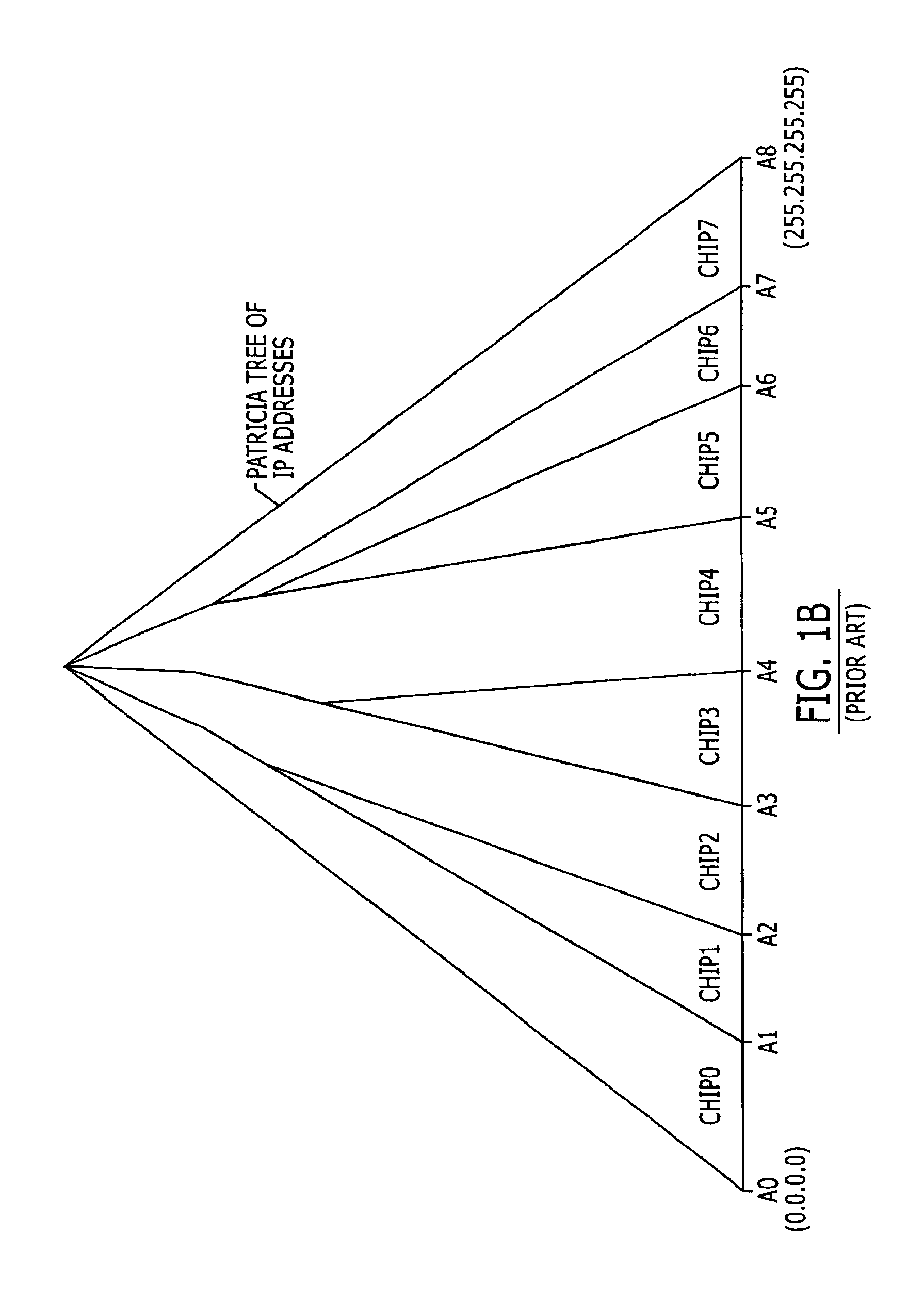

Method and apparatus for detecting soft errors in content addressable memory arrays

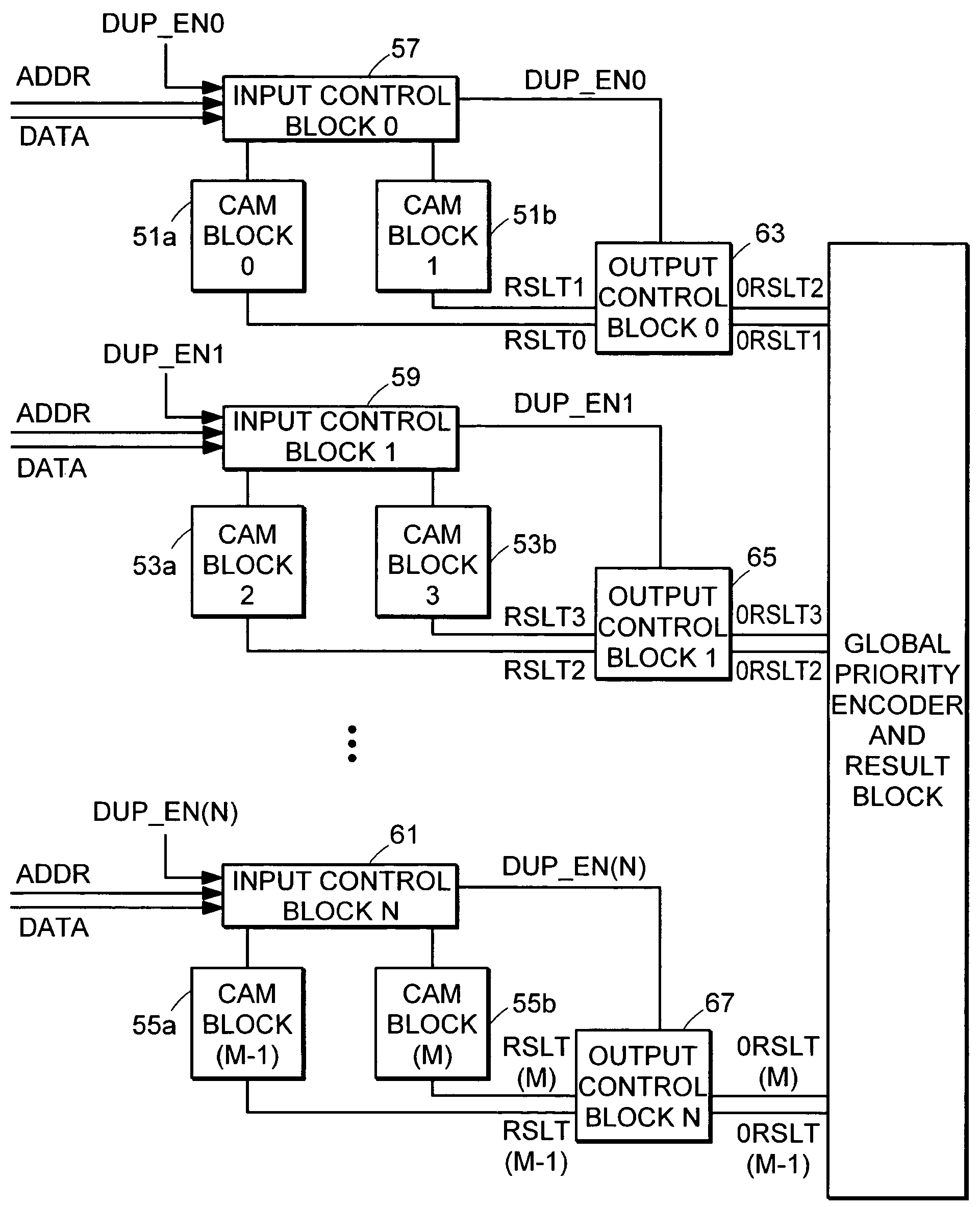

The invention comprises, in one aspect, a content addressable memory array having a plurality of memory locations to store tag words. The content addressable memory array includes a parity encoder and a parity comparator. The parity encoder has a first input terminal to receive an input data signal and a first output terminal to deliver a signal representative of the parity of the input data signal. The parity comparator has a second input terminal, a third input terminal connected to the first output terminal, and a plurality of memory cells to store original parities of the tag words. The parity comparator compares the original parity of a first tag word to the parity of the input data signal in response to a receiving a match signal. The content addressable memory array includes a fourth input terminal to receive the input data signal, and a second output terminal to send the match signal in response to one of the tag words matching the input data signal. The second output terminal connects to the second input terminal.

Owner:INTEL CORP

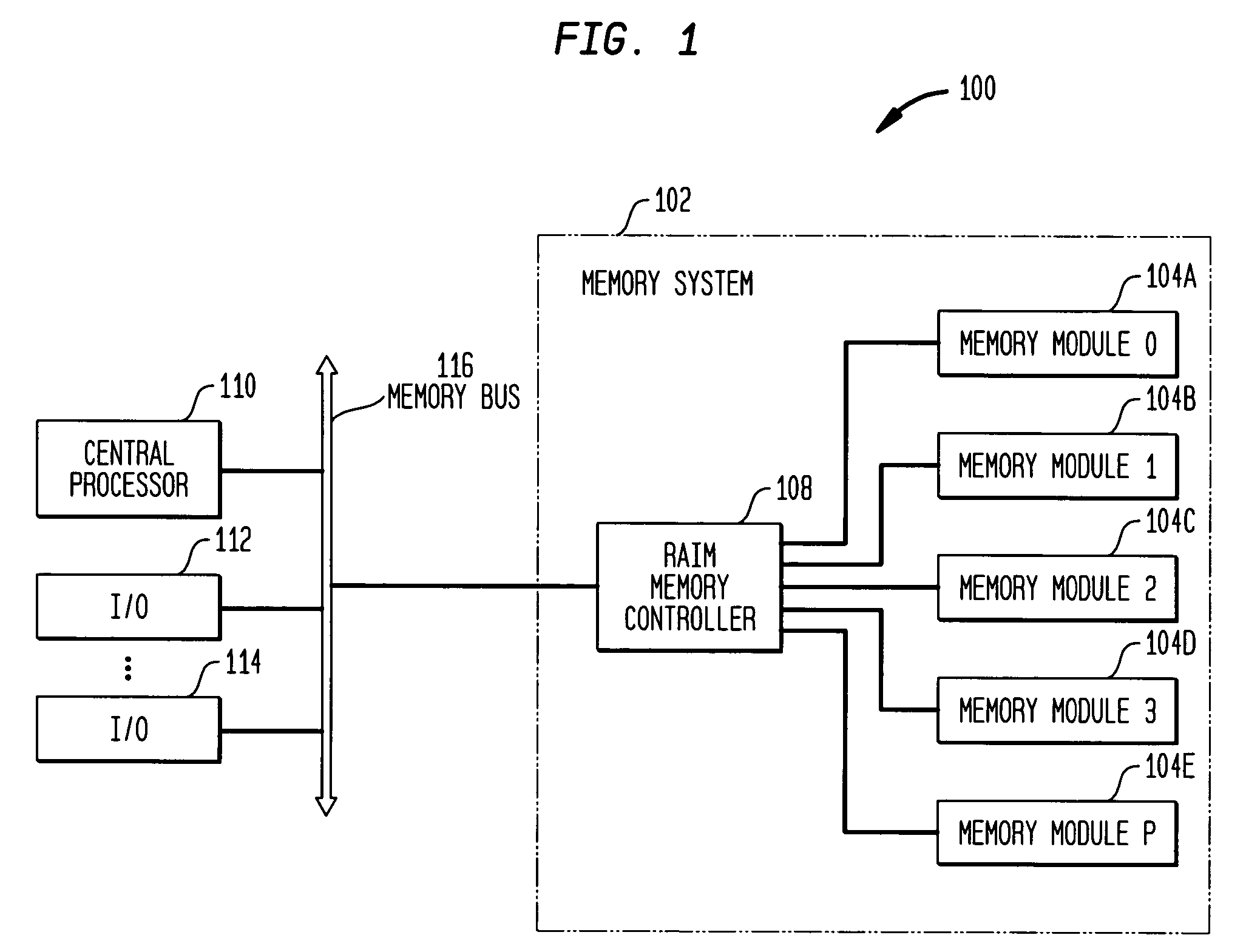

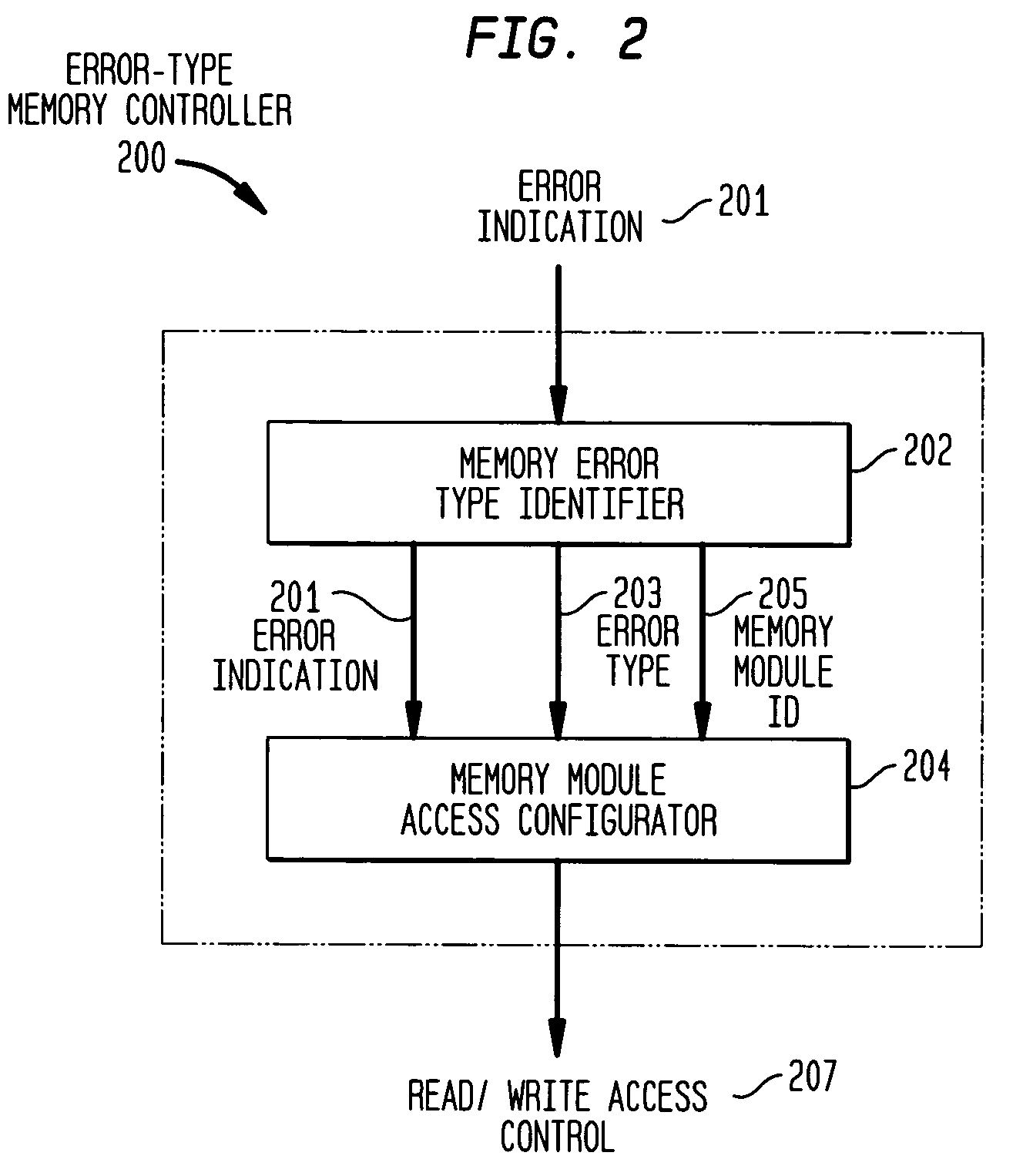

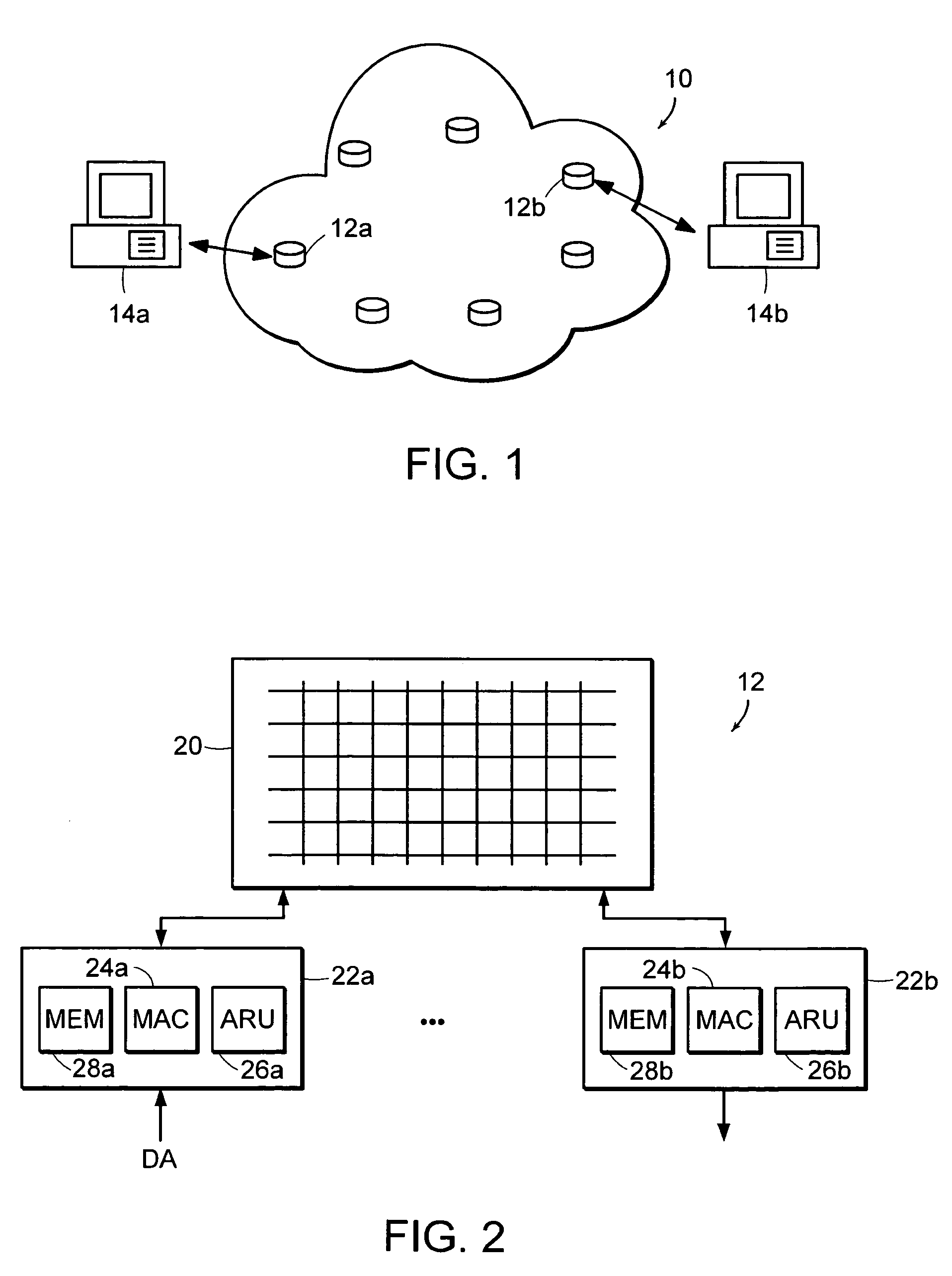

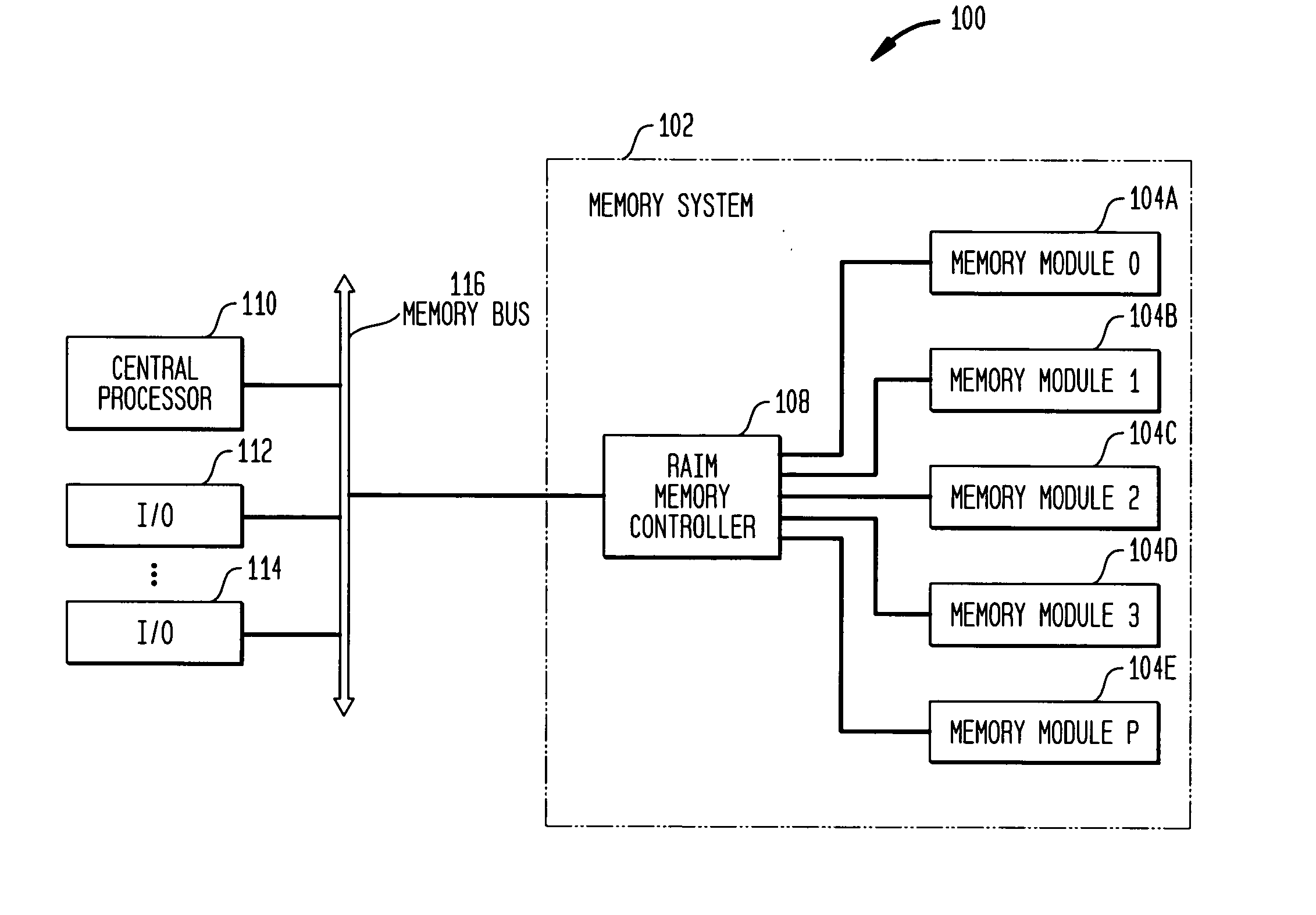

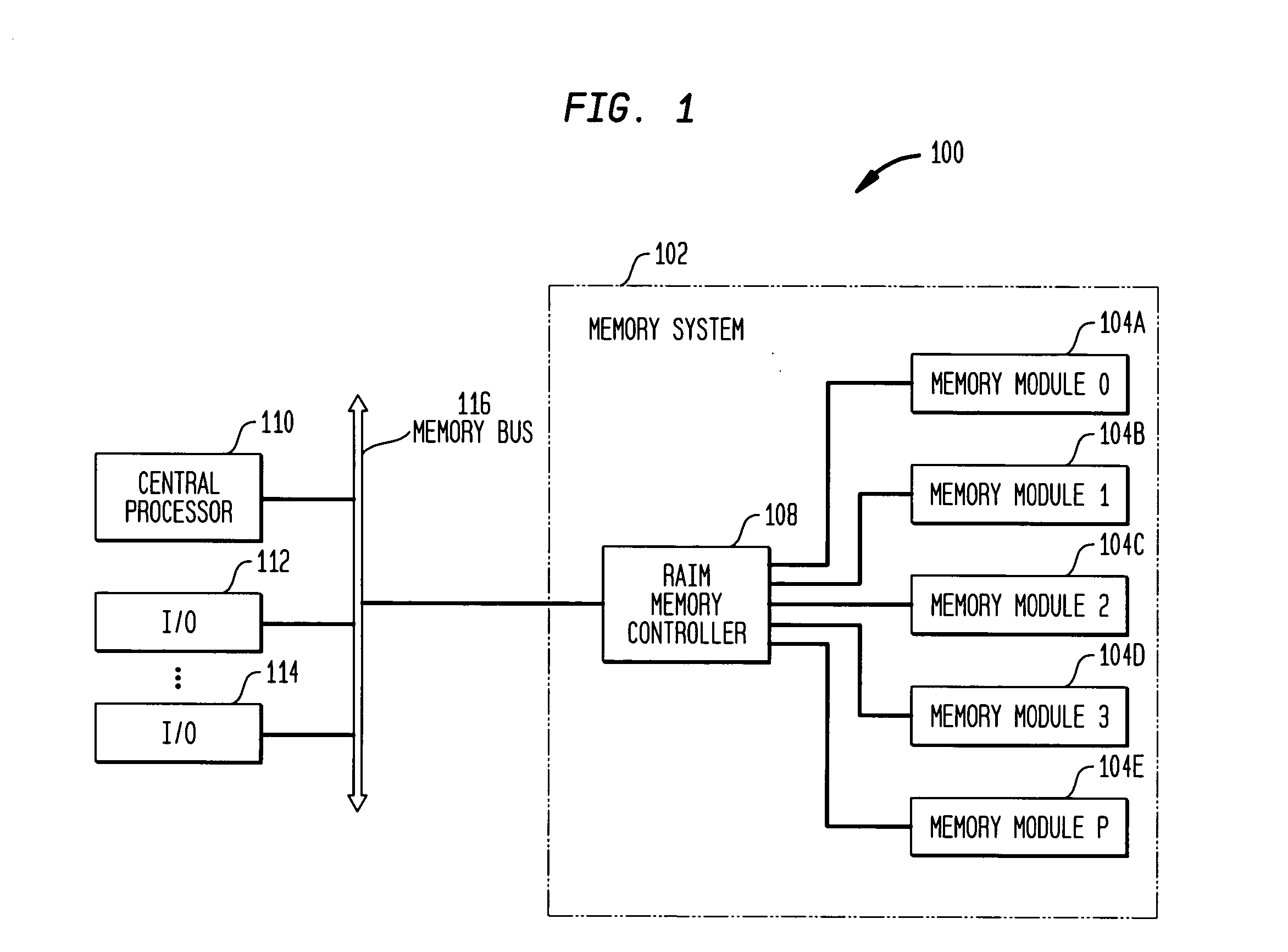

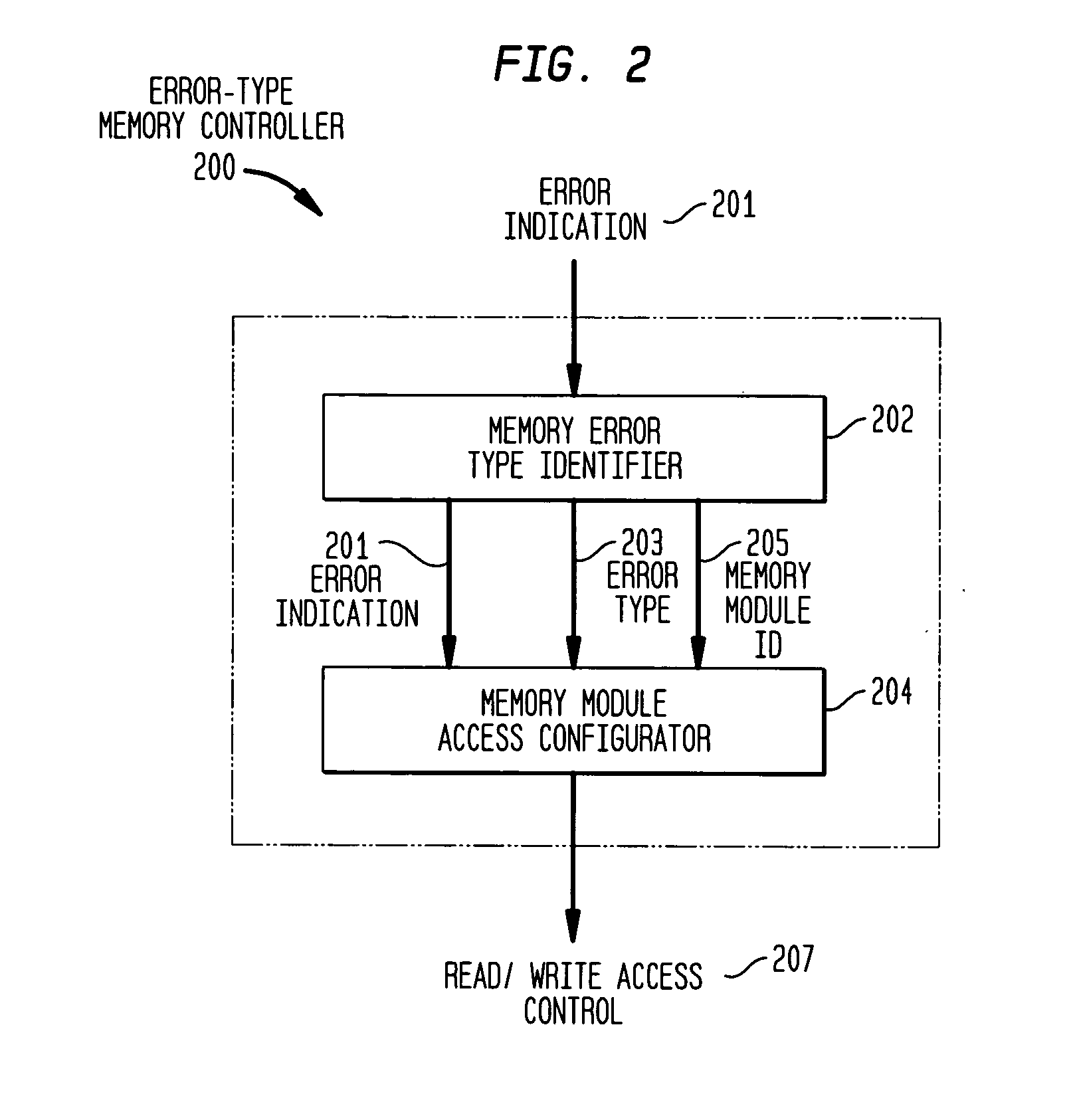

Restoring access to a failed data storage device in a redundant memory system

A computer system comprising a memory system that comprises a plurality of memory modules; and a memory controller that accesses the plurality of memory modules to service memory requests. The computer system also comprises an error-type memory controller that configures the noted access such that the memory controller can continue to access a failed one of the plurality of memory modules that incurred a soft error.

Owner:HEWLETT PACKARD DEV CO LP

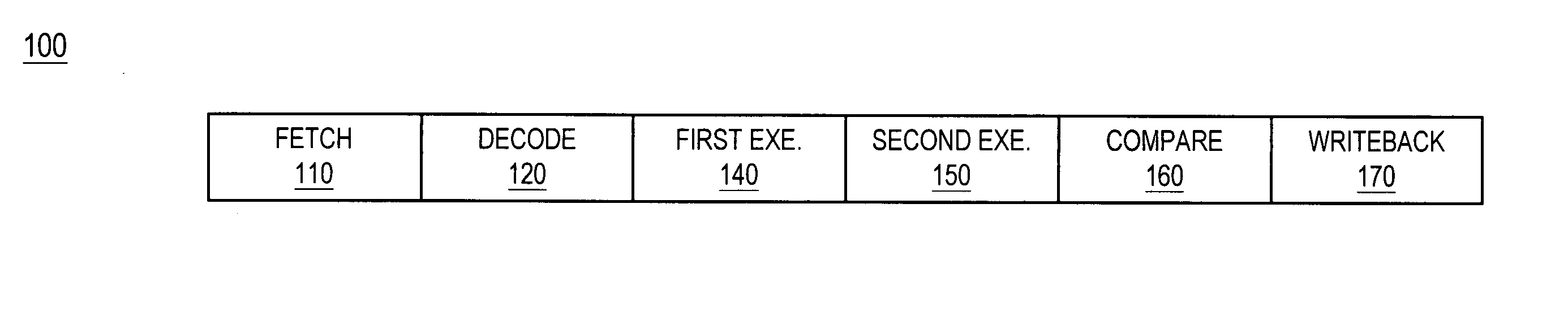

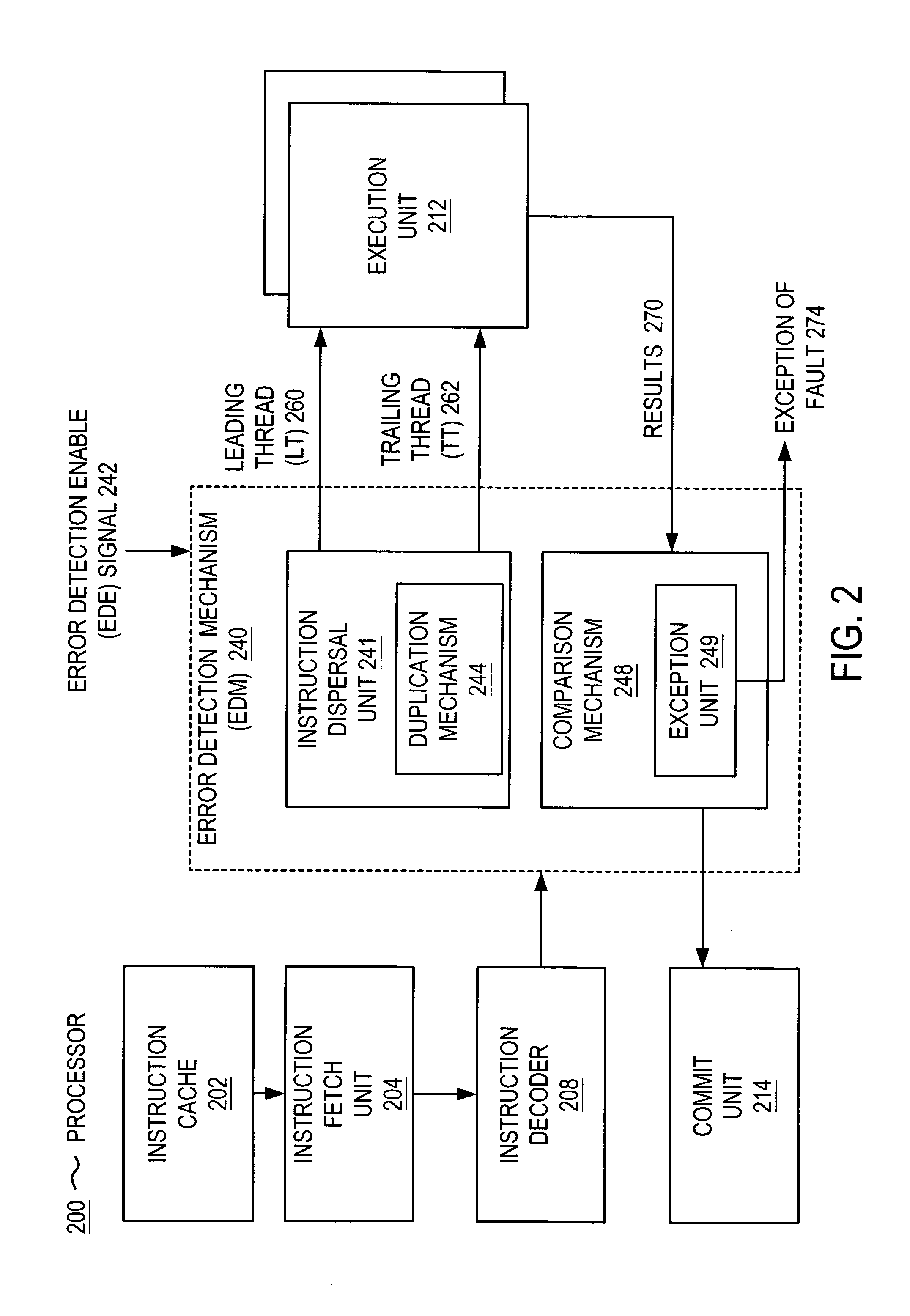

Error detection method and system for processors that employ alternating threads

InactiveUS20050138478A1Program controlRedundant operation error correctionParallel computingExecution unit

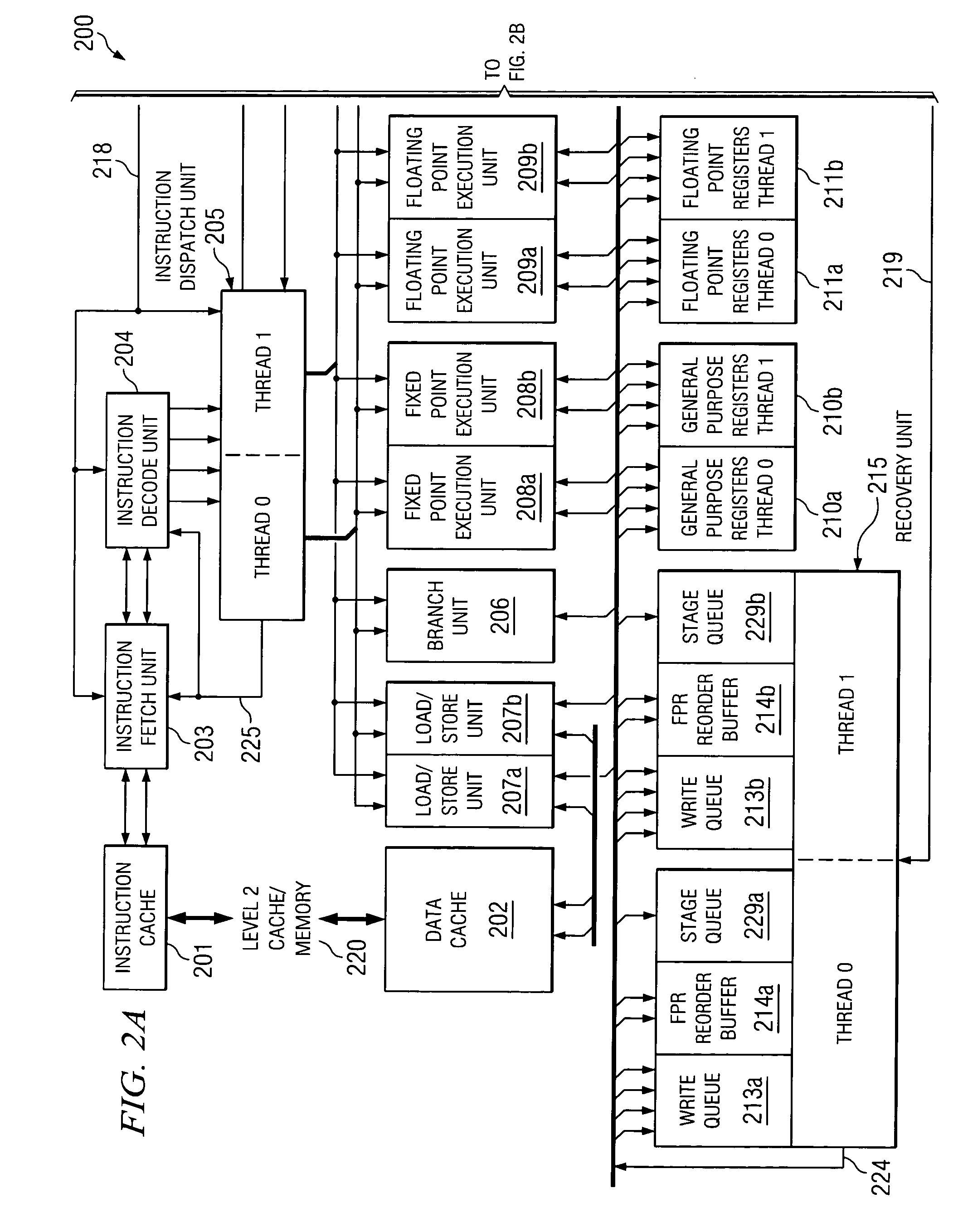

Microprocessor that includes a mechanism for detecting soft errors. The processor includes an instruction fetch unit for fetching an instruction and an instruction decoder for decoding the instruction. The mechanism for detecting soft errors includes duplication hardware for duplicating the instruction and comparison hardware. The processor further includes a first execution unit for executing the instruction in a first execution cycle and the duplicated instruction in a second execution cycle. The comparison hardware compares the results of the first execution cycle and the results of the second execution cycle. The comparison hardware can include an exception unit for generating an exception (e.g., raising a fault) when the results are not the same. The processor also includes a commit unit for committing one of the results when the results are the same.

Owner:HEWLETT PACKARD DEV CO LP

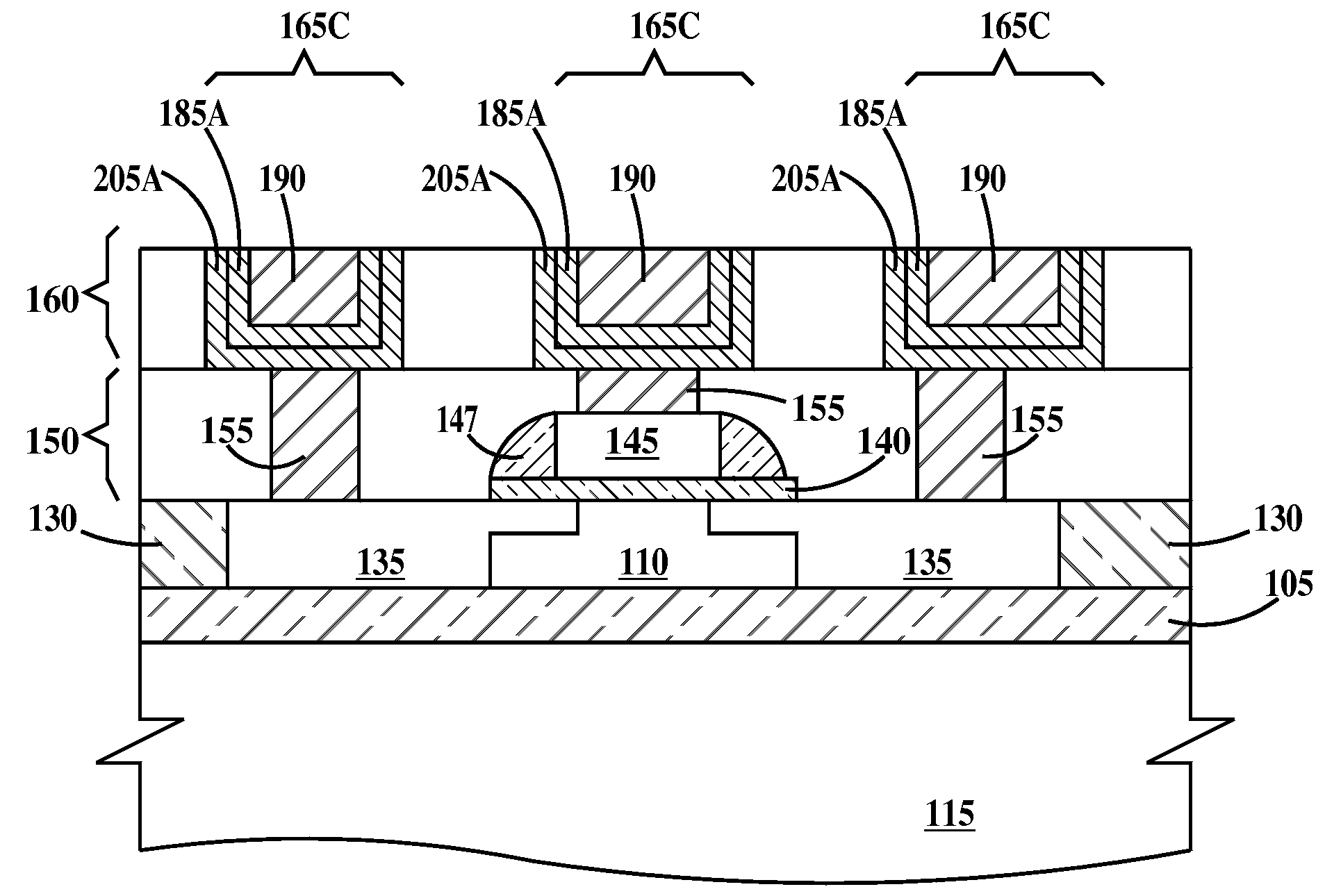

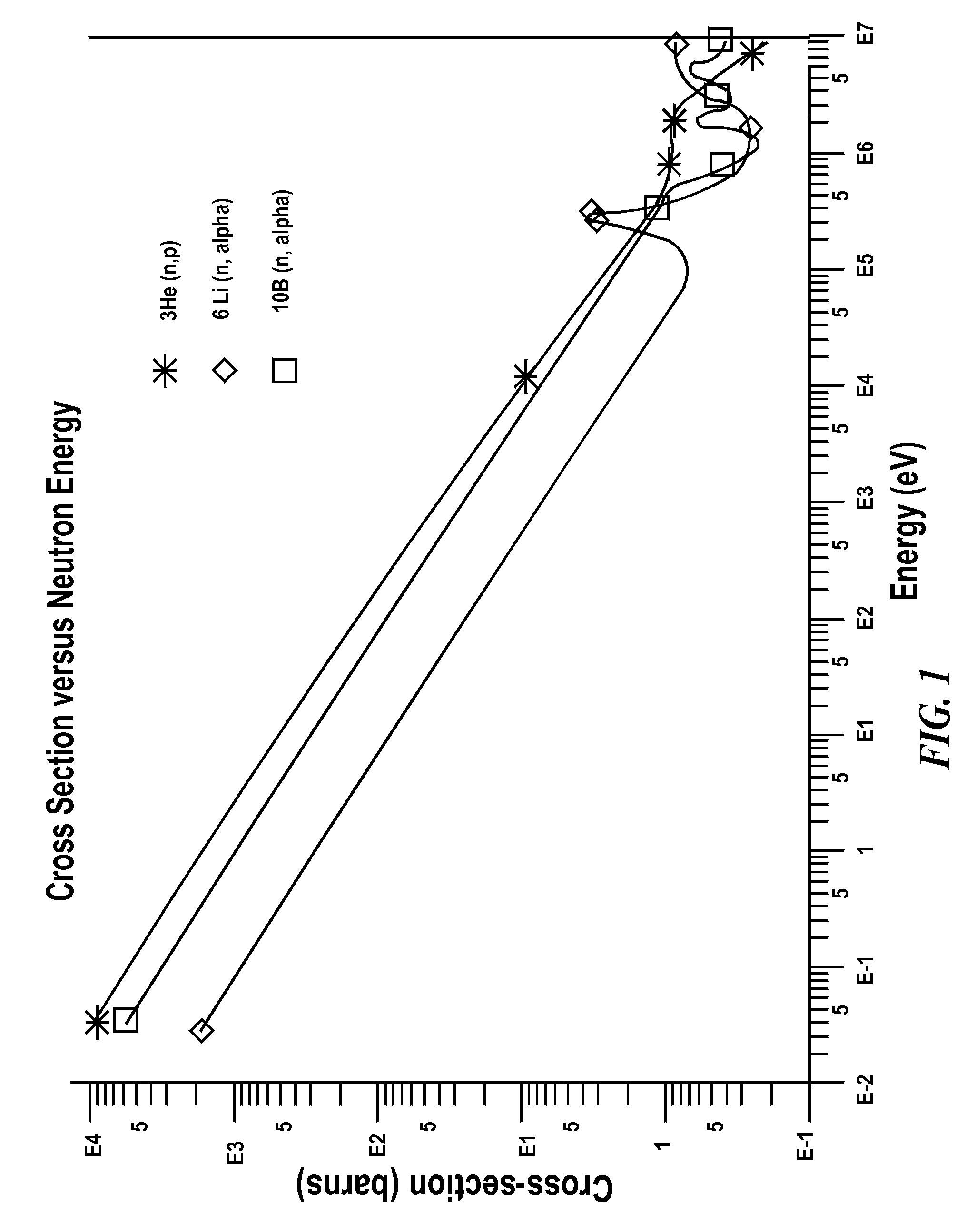

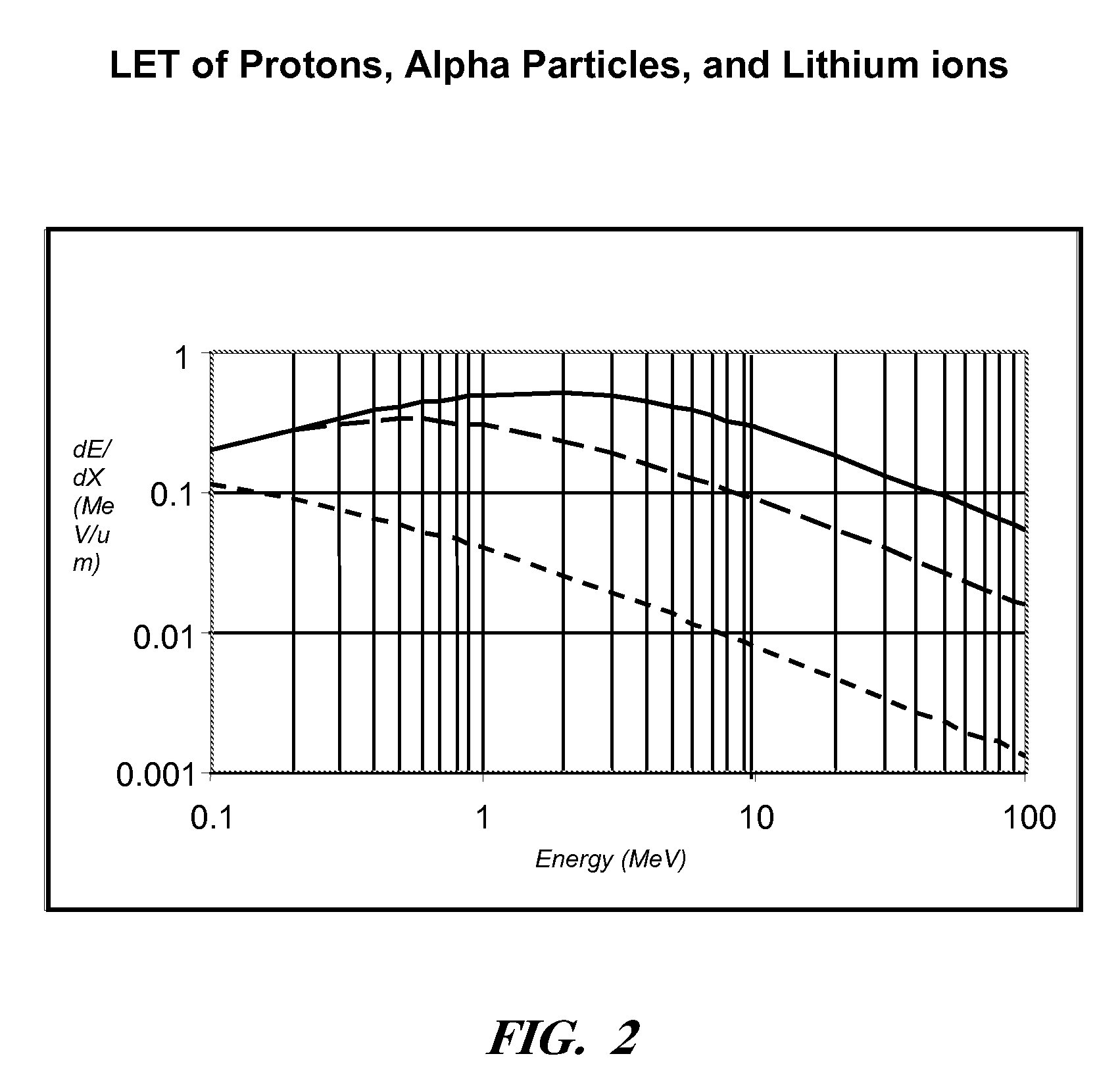

Method and structures for accelerated soft-error testing

InactiveUS20090065955A1Semiconductor/solid-state device detailsSolid-state devicesThermal neutron fluxAlpha particle

An integrated circuit, method of forming the integrated circuit and a method of testing the integrated circuit for soft-error fails. The integrated circuit includes: a silicon substrate; a dielectric layer formed over the substrate; electrically conductive wires formed in the dielectric layer, the wires interconnecting semiconductor devices formed in the substrate into circuits; and an alpha particle emitting region in the integrated circuit chip proximate to one or more of the semiconductor devices. The method includes exposing the integrated circuit to an artificial flux of thermal neutrons to cause fission of atoms in the alpha particle emitting region into alpha particles and other atoms.

Owner:GLOBALFOUNDRIES INC

Method for checkpointing instruction groups with out-of-order floating point instructions in a multi-threaded processor

InactiveUS20060179346A1Error detection/correctionDigital computer detailsFloating-point unitStorage cell

A method and apparatus are provided for dispatch group checkpointing in a microprocessor, including provisions for handling partially completed dispatch groups and instructions which modify system coherent state prior to completion. An instruction checkpoint retry mechanism is implemented to recover from soft errors in logic. The processor is able to dispatch fixed point unit (FXU), load / store unit (LSU), and floating point unit (FPU) or vector multimedia extension (VMX) instructions on the same cycle. Store data is written to a store queue when a store instruction finishes executing. The data is held in the store queue until the store instruction is checkpointed, at which point it can be released to the coherently shared level 2 (L2) cache.

Owner:IBM CORP

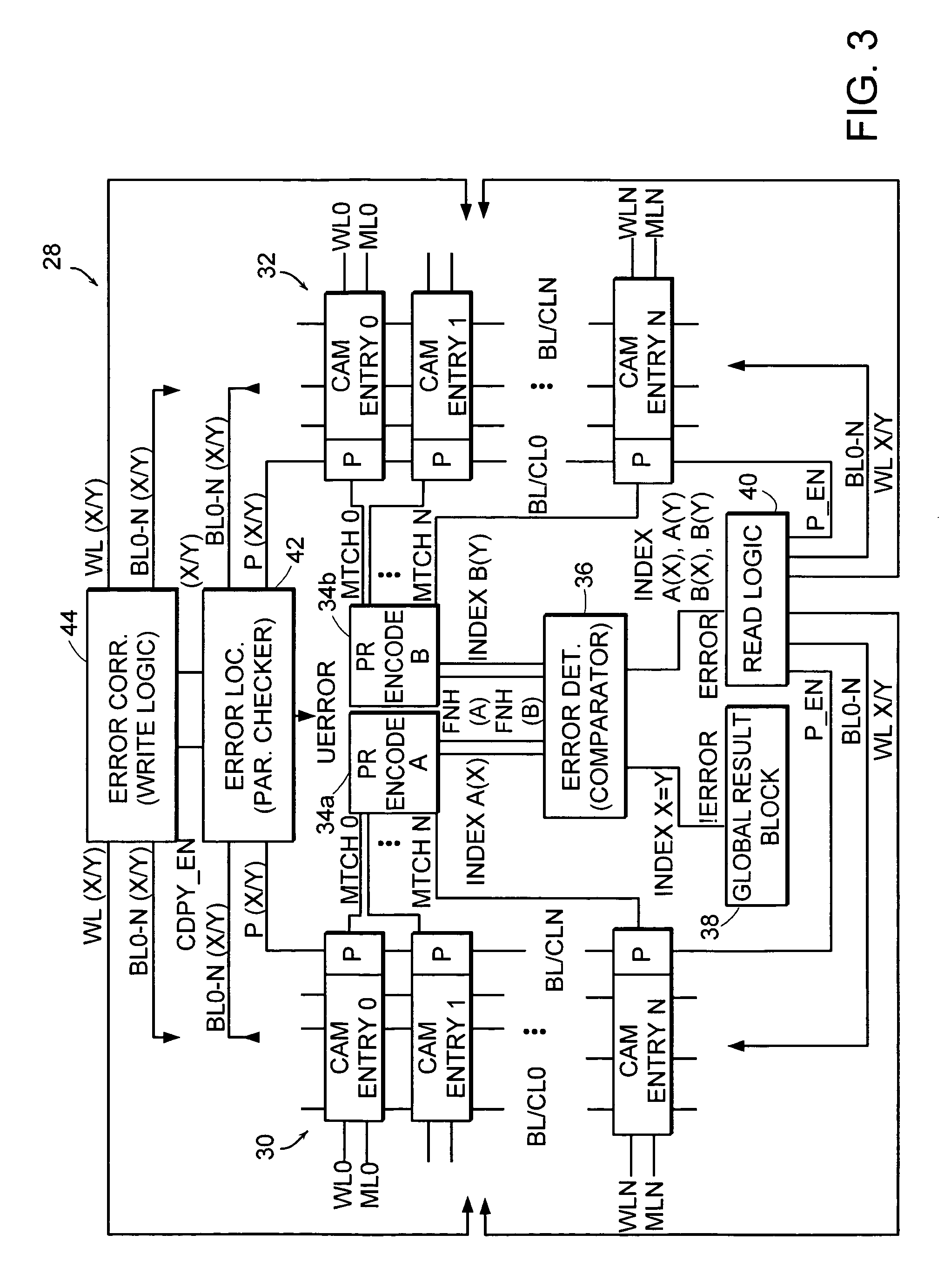

Error correcting content addressable memory

InactiveUS7254748B1Maximize usable CAM spaceRedundant data error correctionMemory systemsSoft errorMatch line

A CAM and method for operating a CAM are presented. Copies of a CAM database are duplicated and placed in a first set of CAM locations and a second set of CAM locations. An error detector is used to determine false matches in the case of soft errors within the entries producing those false matches. While the entries producing a match should have the same index location, errors might cause those match lines to have an offset. If so, the present CAM, through use of duplicative sets of CAM locations, will detect the offset and thereafter the values in each index location that produces a match, along with the corresponding parity or error detection encoding bit(s). If the parity or error detection encoding bit(s) indicate an error in a particular entry, then that error is located and the corresponding entry at the same index within the other, duplicative set of CAM locations is copied into the that erroneous entry. Since duplicative copies are by design placed into the first and second sets of CAM locations, whatever value exists in the opposing entry can be written into the erroneous entry to correct errors in that search location. The first and second sets of CAM locations are configurable to be duplicative or distinct in content, allowing error detection and correction to be performed at multiple user-specified granularities. The error detection and correction during search is backward compatible to interim parity scrubbing and ECC scan, as well as use of FNH bits set by a user or provider.

Owner:AVAGO TECH INT SALES PTE LTD

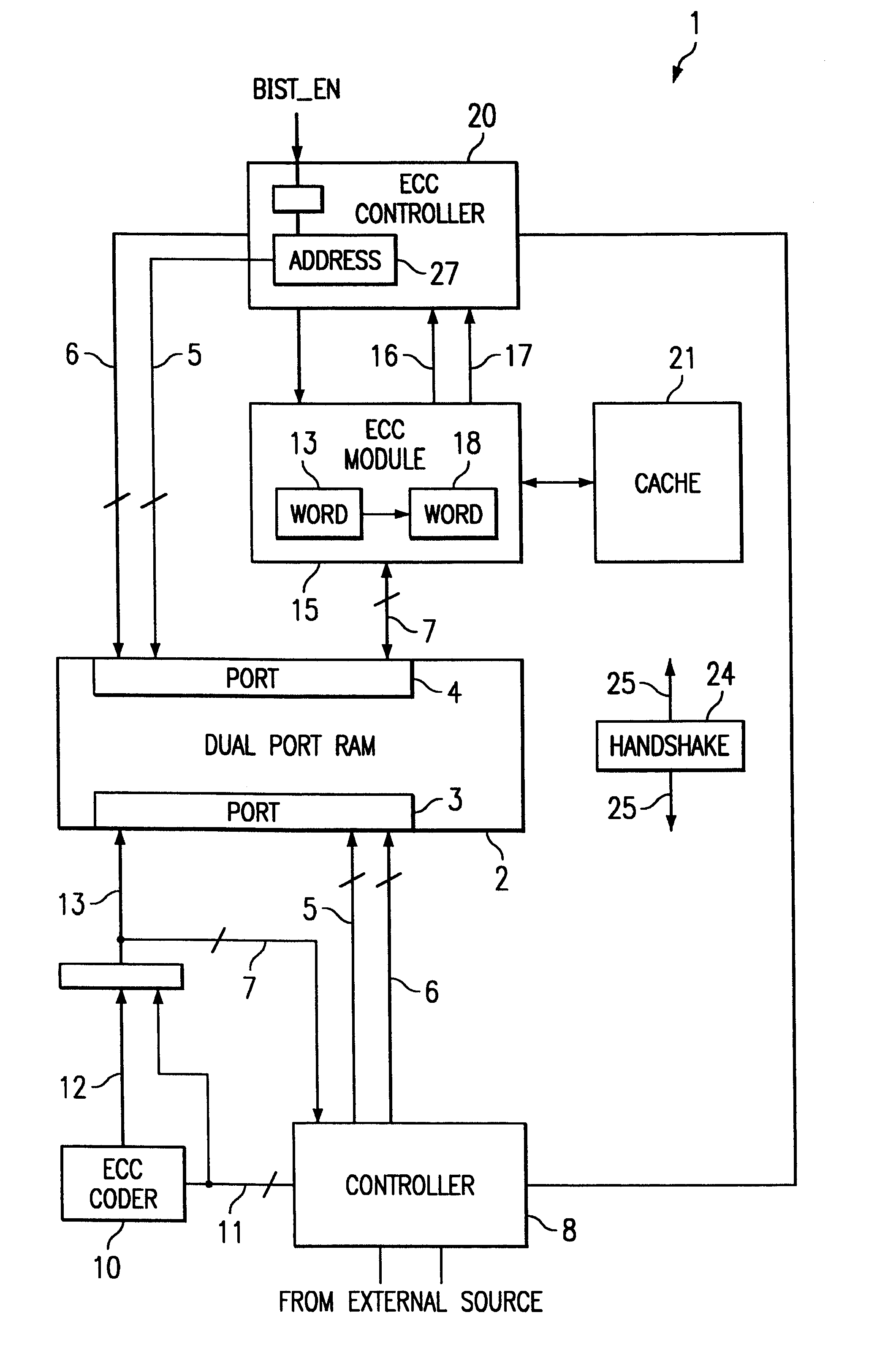

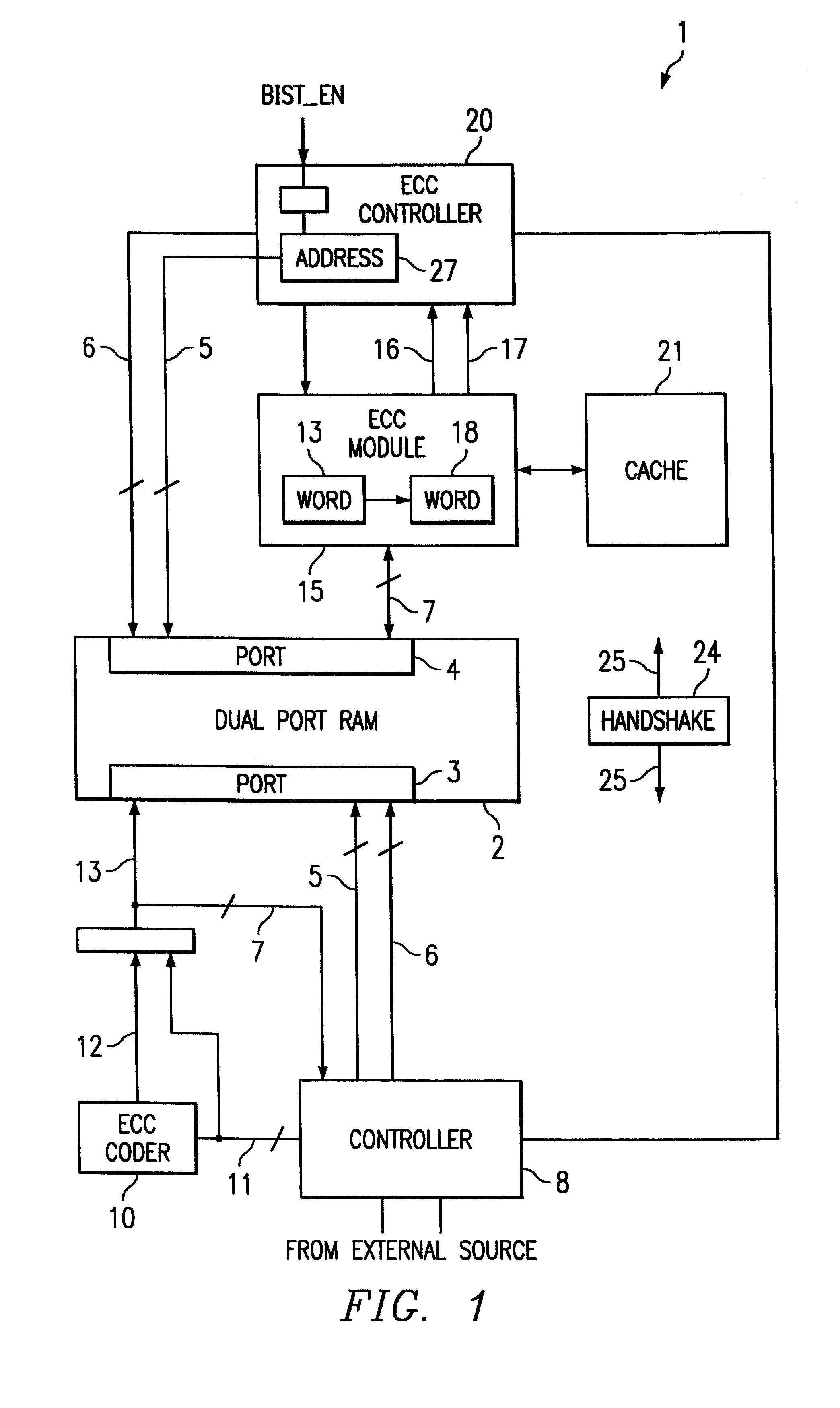

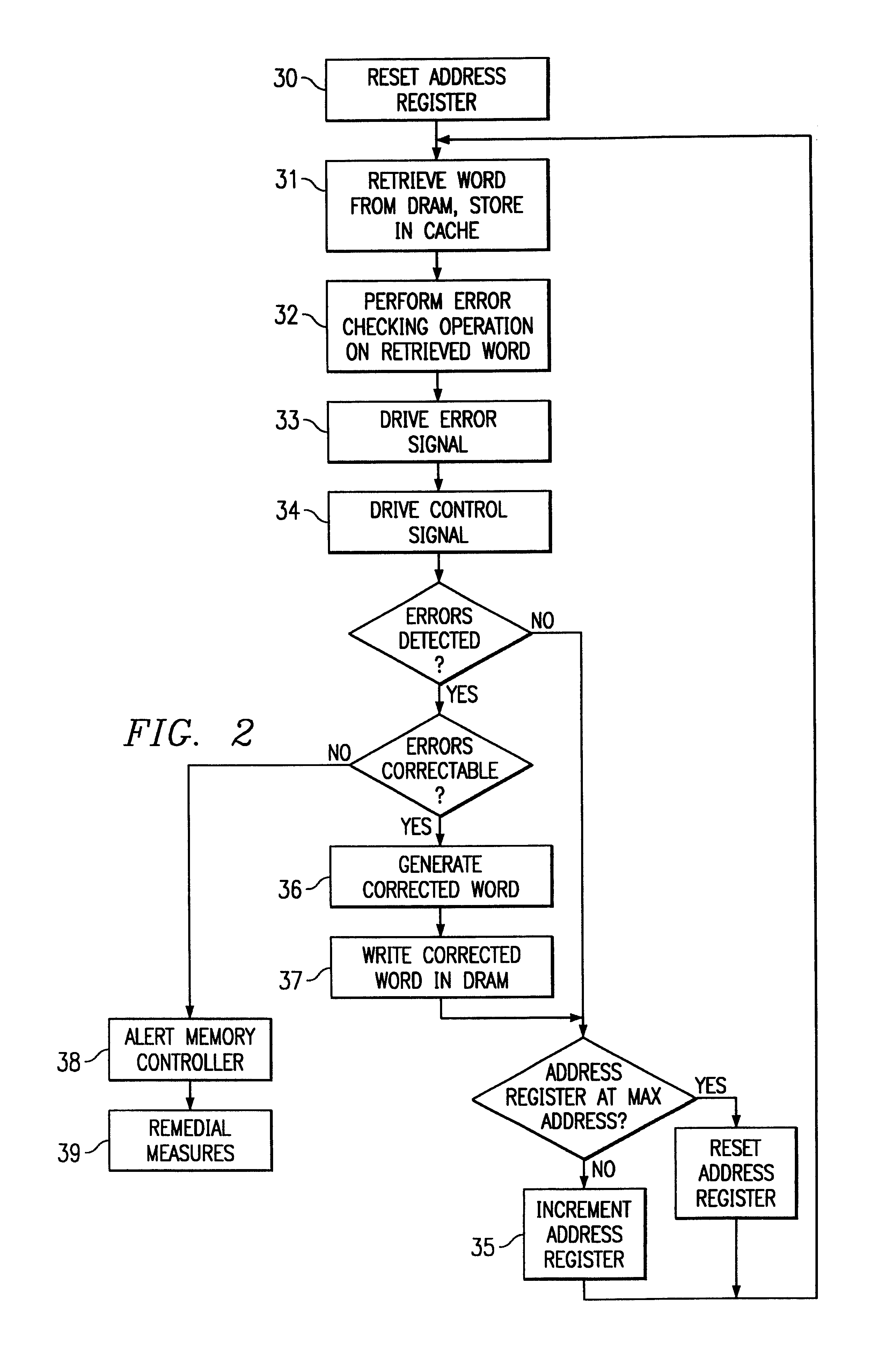

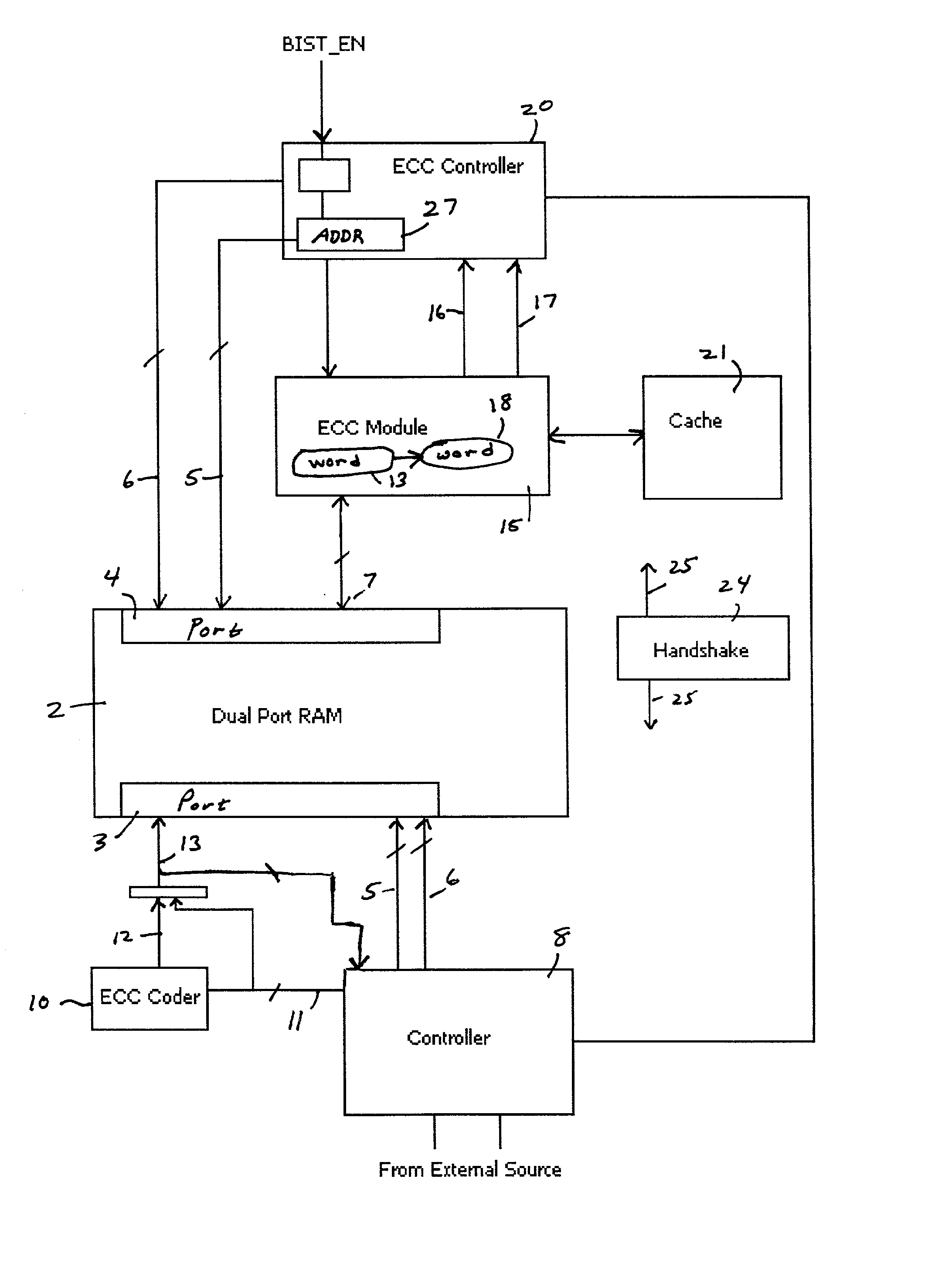

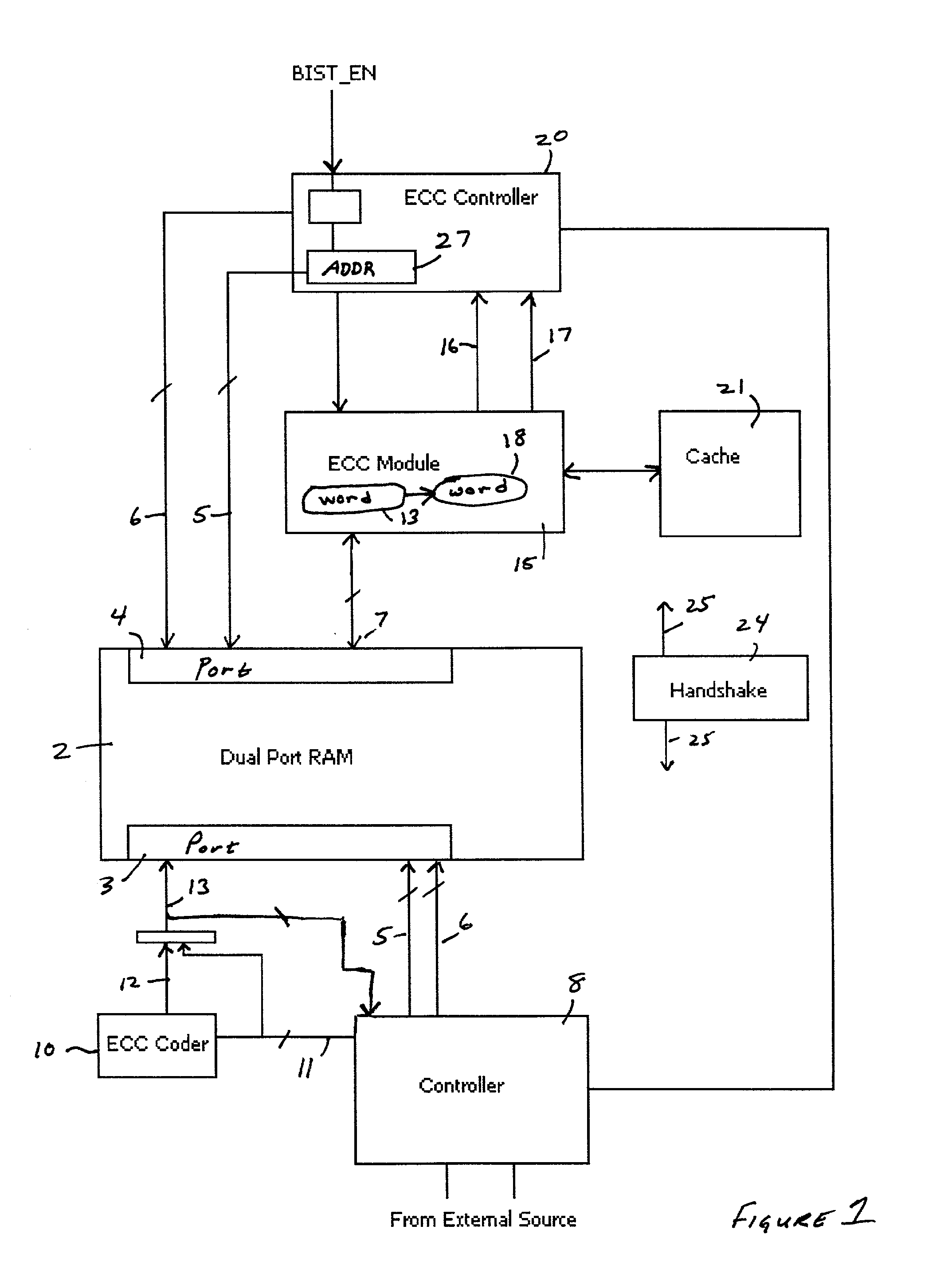

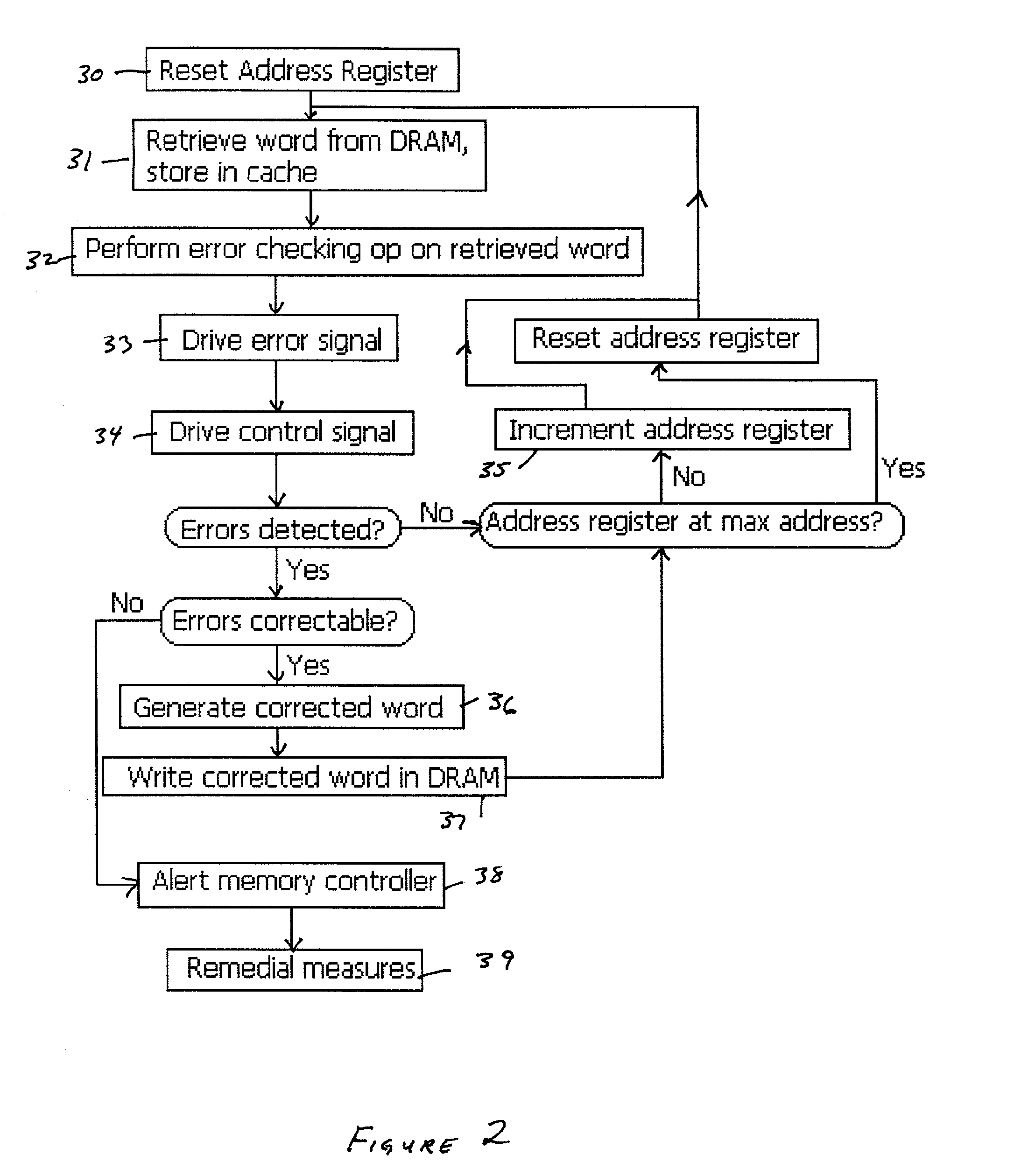

System and method for correcting soft errors in random access memory devices

A circuit and method are disclosed for reducing soft errors in dynamic memory devices using error checking and correcting. In an exemplary embodiment, a memory device includes a dual port memory having a first port for externally-initiated memory access operations and a second port for handling memory access operations associated with error checking and error correction operations. An error module, coupled to the second port of the dual port memory, performs an error checking operation on words read from the dual port memory. An error controller, coupled to the error module, controls the error module to perform error check operations on each word sequentially read from the dual port memory through the second port thereof. The error checking is performed substantially in parallel with externally-initiated memory access operations performed using the first port of the dual port memory. The error module may also generate a corrected word for a word that is detected by the error module as having a correctable error. The error controller may replace in the dual port memory the word having the correctable error with the corrected word.

Owner:STMICROELECTRONICS SRL

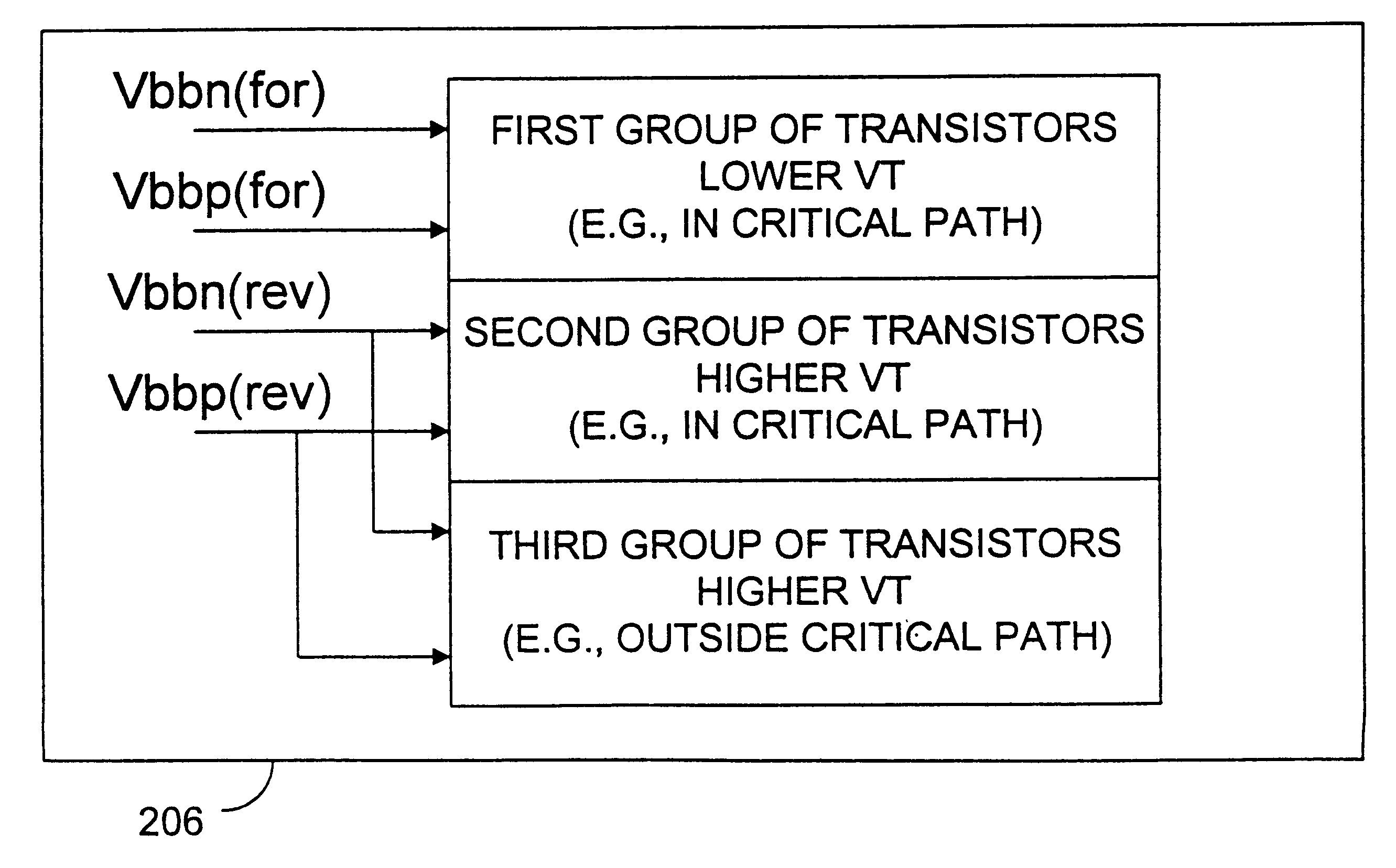

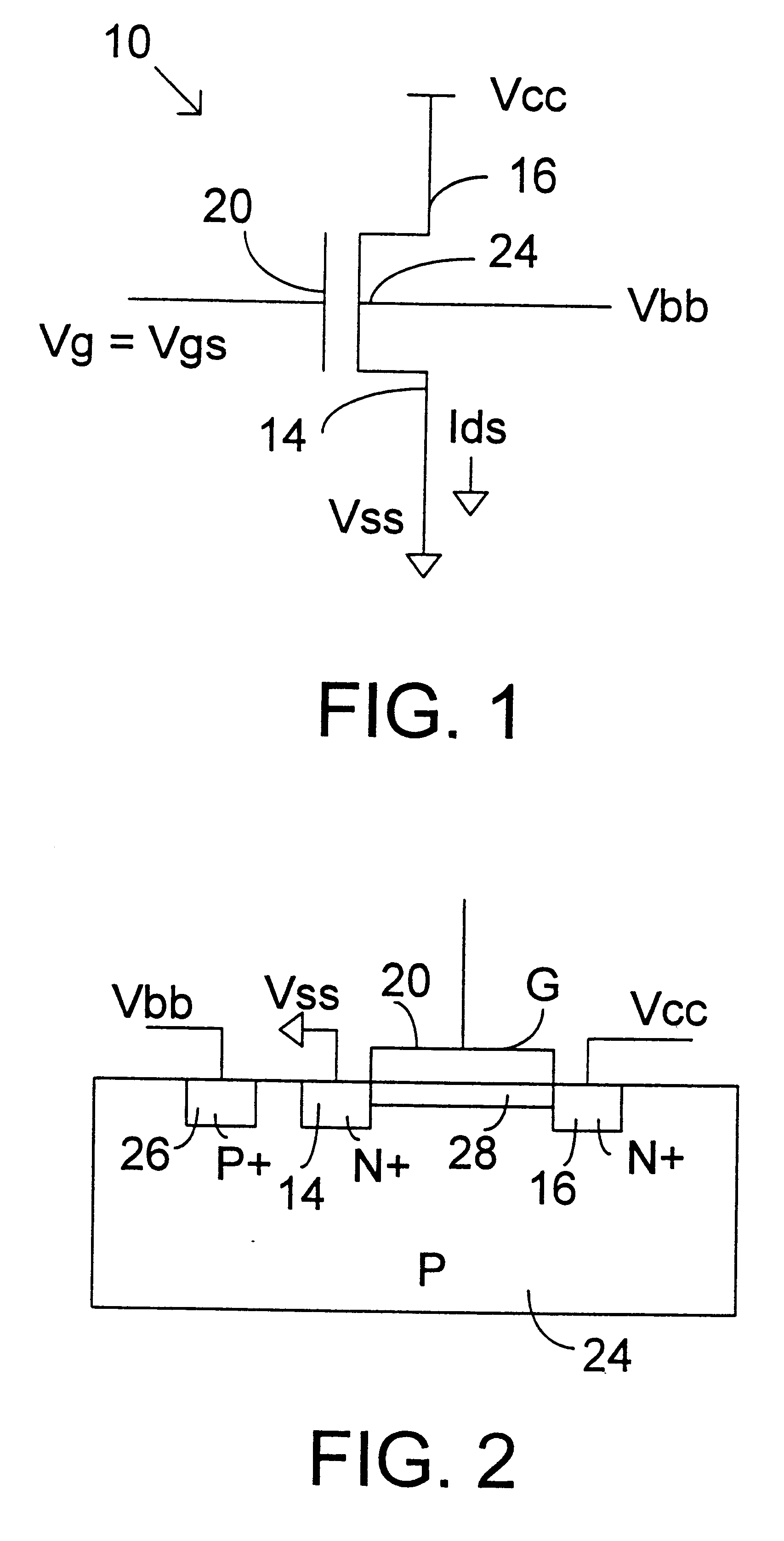

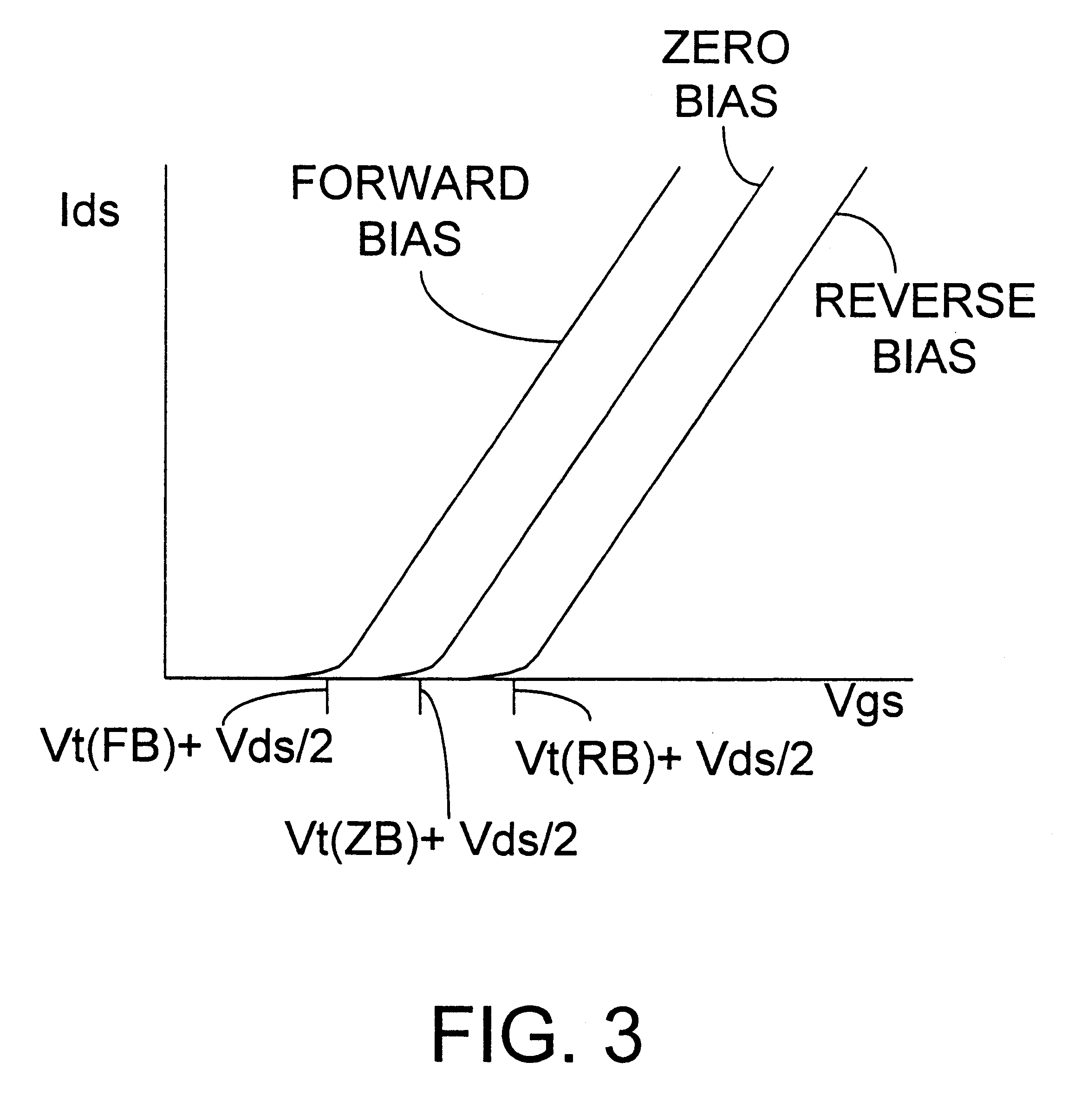

Transistors providing desired threshold voltage and reduced short channel effects with forward body bias

In one embodiment, a semiconductor circuit includes a first group of field effect transistors having a body and parameters including a net channel doping level DL1. The circuit also includes a conductor to provide a first voltage to the body to forward body bias the first group of transistors, the first group of transistors having a forward body bias threshold voltage (VtFBB) when forward body biased, wherein DL1 is at least 25% higher than a net channel doping level in the first group of transistors that would result in a zero body bias threshold voltage equal to VtFBB, with the parameters other than the net channel doping level being unchanged. In another embodiment, the semiconductor circuit includes a first circuit including a first group of field effect transistors having a body. The circuit also includes a first voltage source to provide a first voltage to the body such that the field effect transistors have a forward body bias, the first voltage being at a level leading to the circuit experiencing a reduced rate of soft error failures as compared to when the circuit is not forward biased.

Owner:INTEL CORP

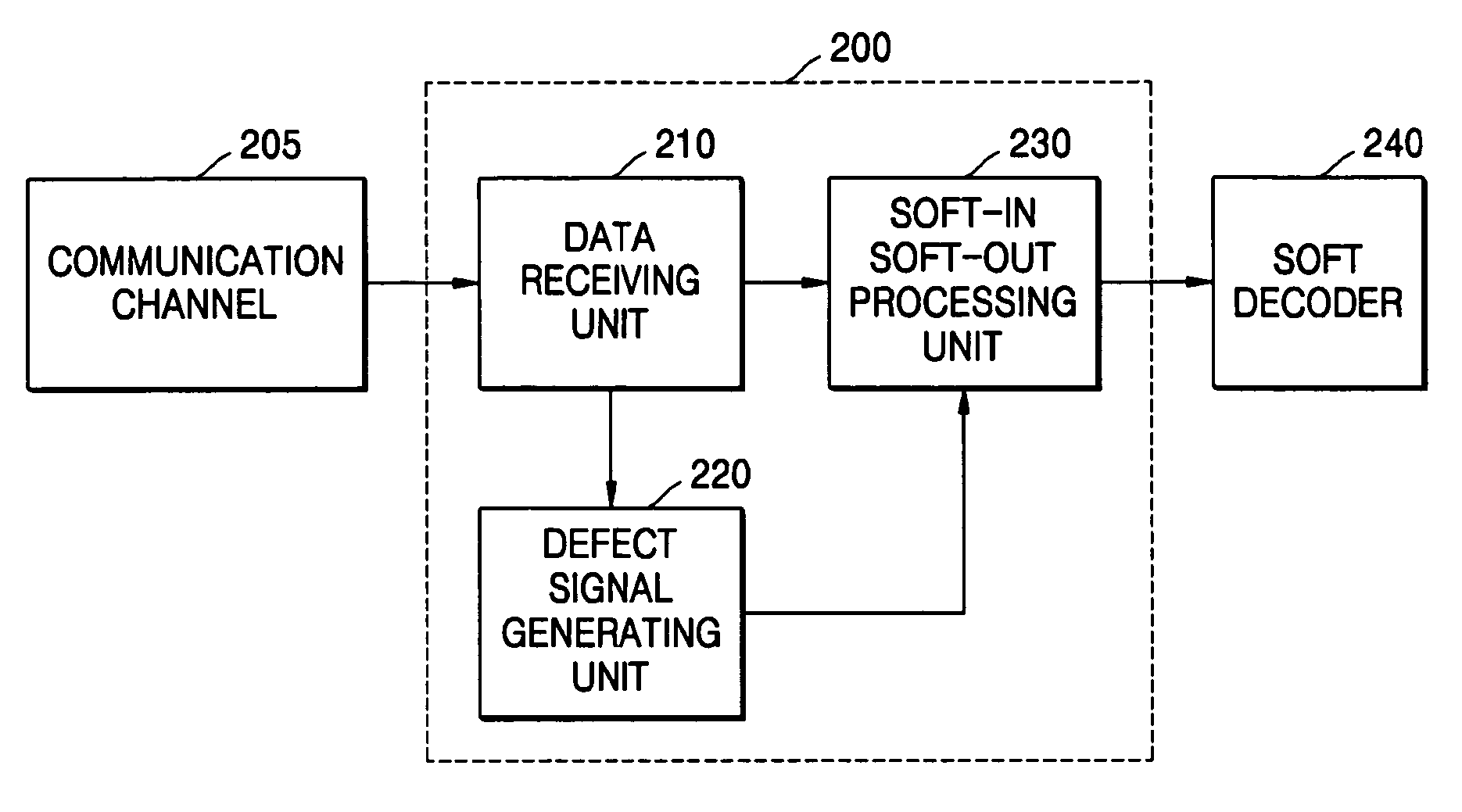

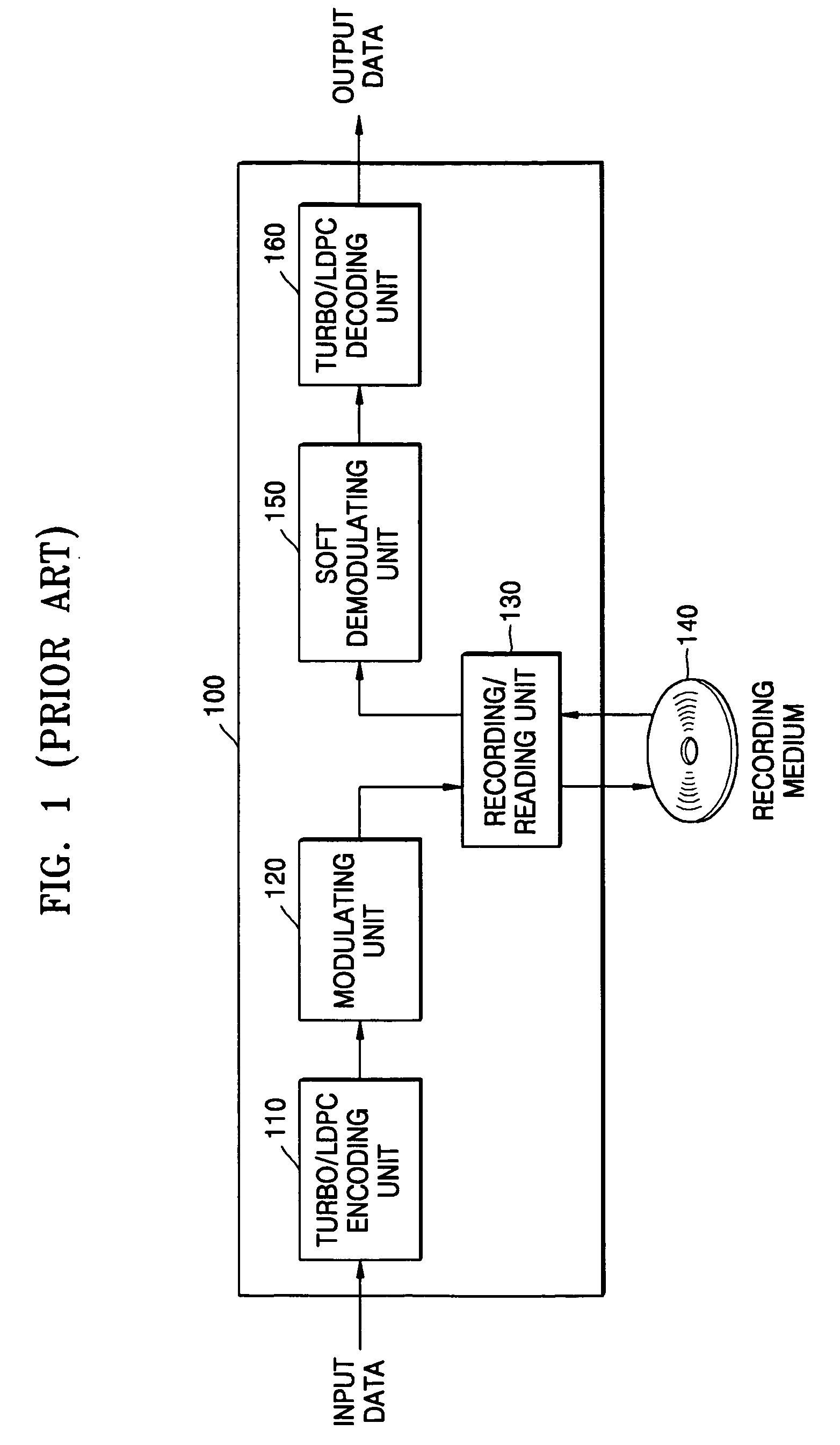

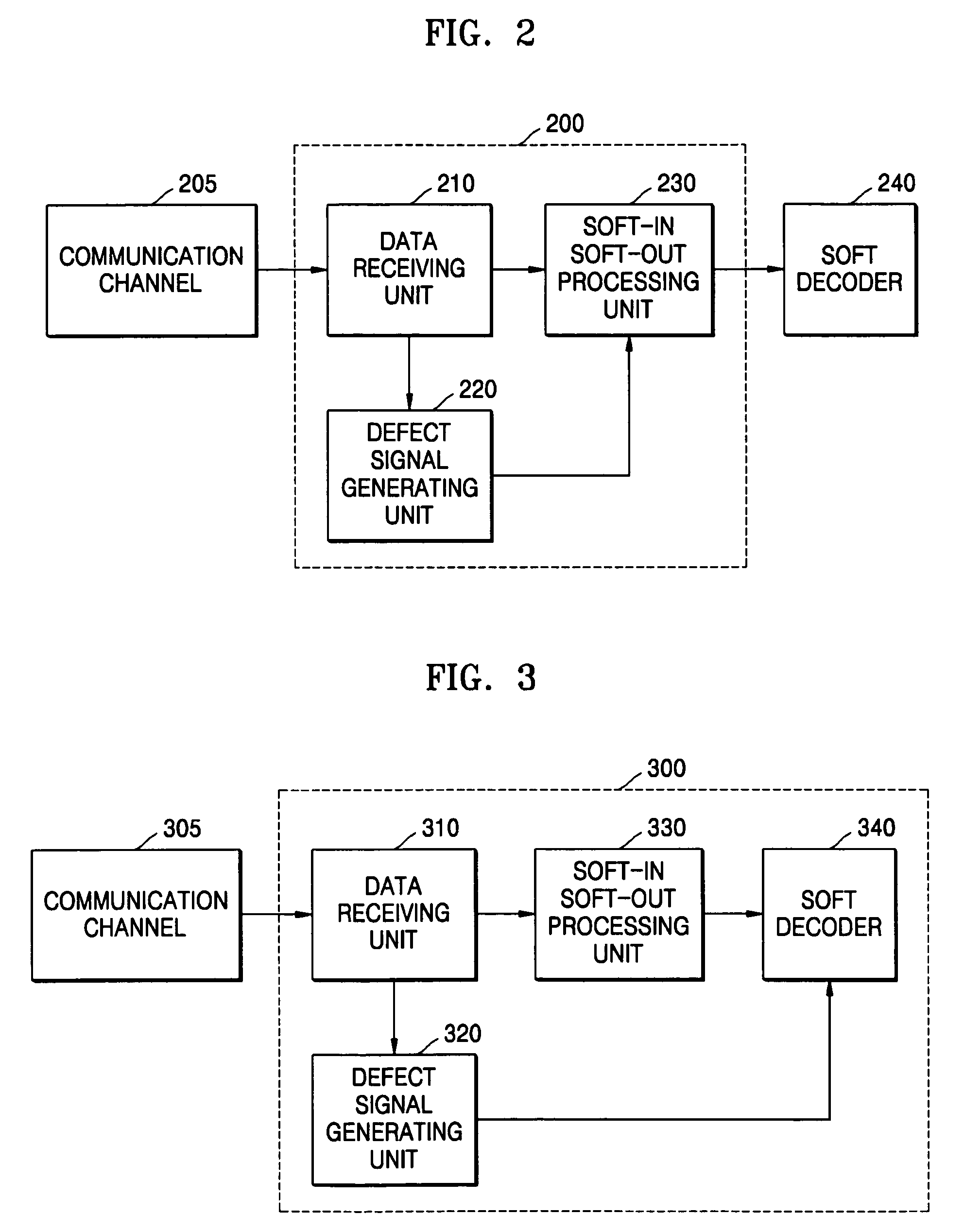

Soft decoding method and apparatus, error correction method and apparatus, and soft output method and apparatus

InactiveUS20070061687A1Improve performanceCode conversionCoding detailsComputer hardwareDecoding methods

Provided are a decoding method and apparatus, an error correction method and apparatus, and a soft output method and apparatus to improve the performance of soft error correction. A method of decoding a codeword encoded into a code that can be soft iterative decoded includes: receiving a soft value of each bit of the codeword; generating a defect signal for the received codeword; and changing a soft value of all bits corresponding to the generated defect signal or some of the bits corresponding to the generated defect signal into a predetermined value to perform error correction.

Owner:SAMSUNG ELECTRONICS CO LTD

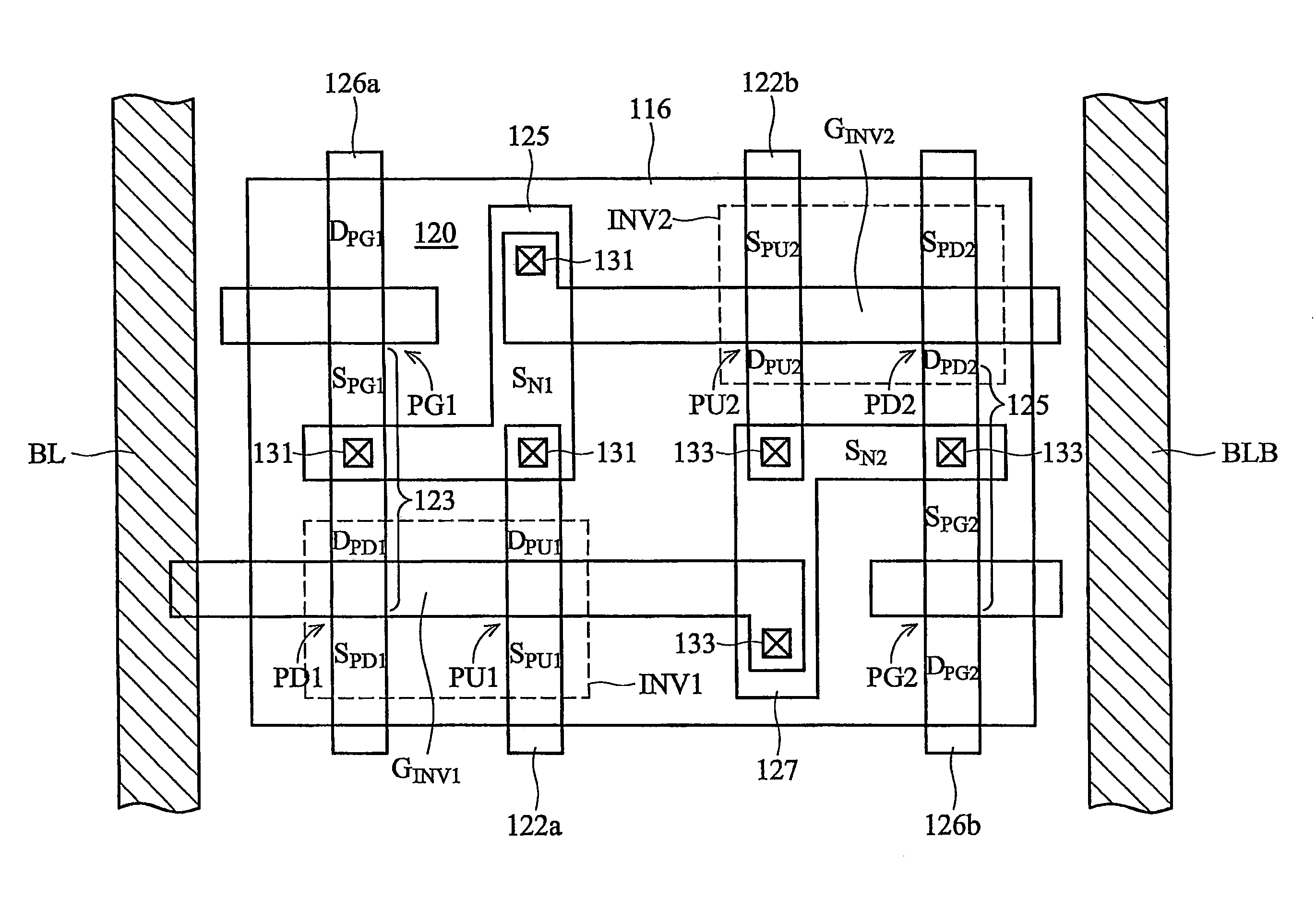

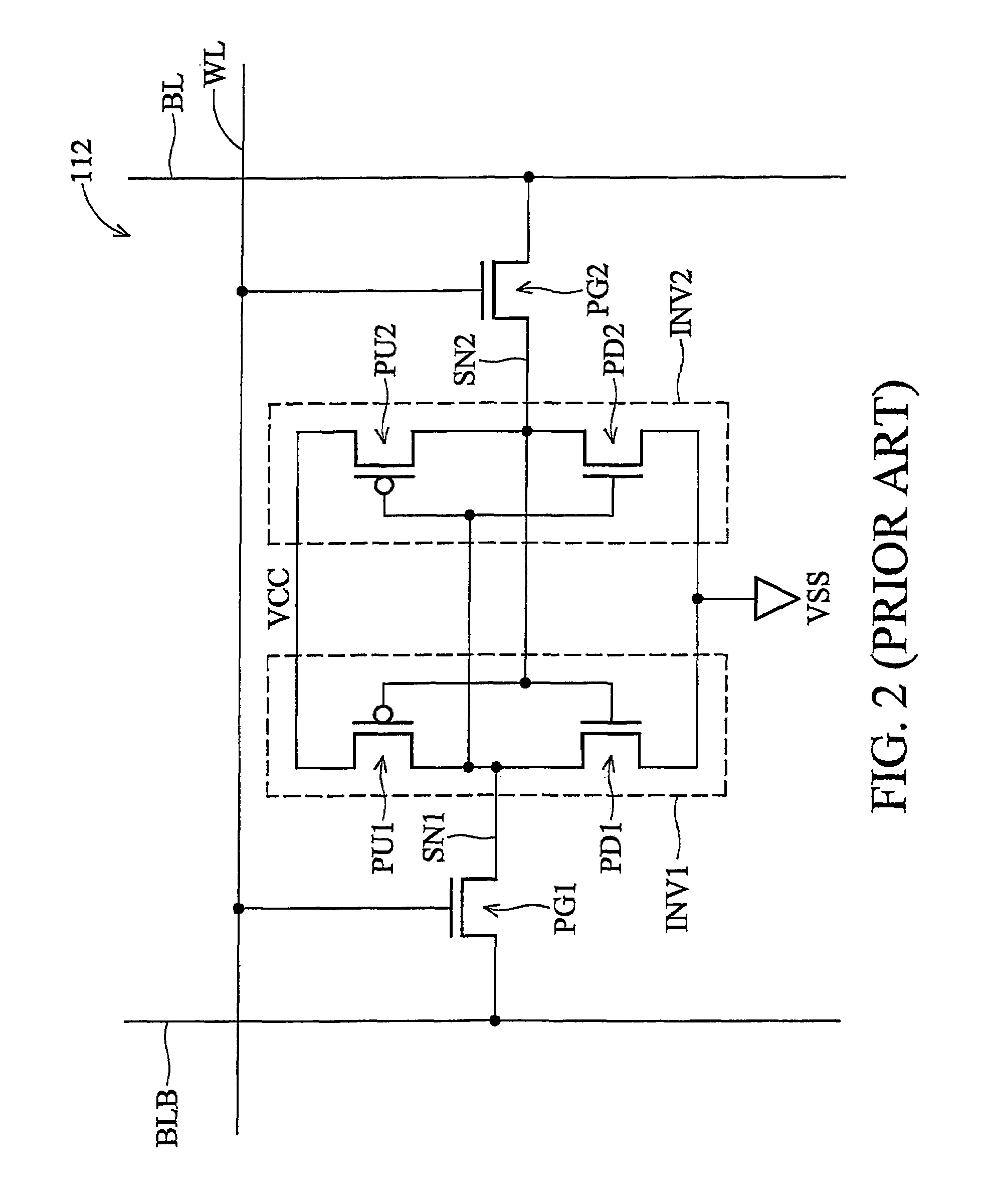

SRAM cell for soft-error rate reduction and cell stability improvement

Owner:TAIWAN SEMICON MFG CO LTD

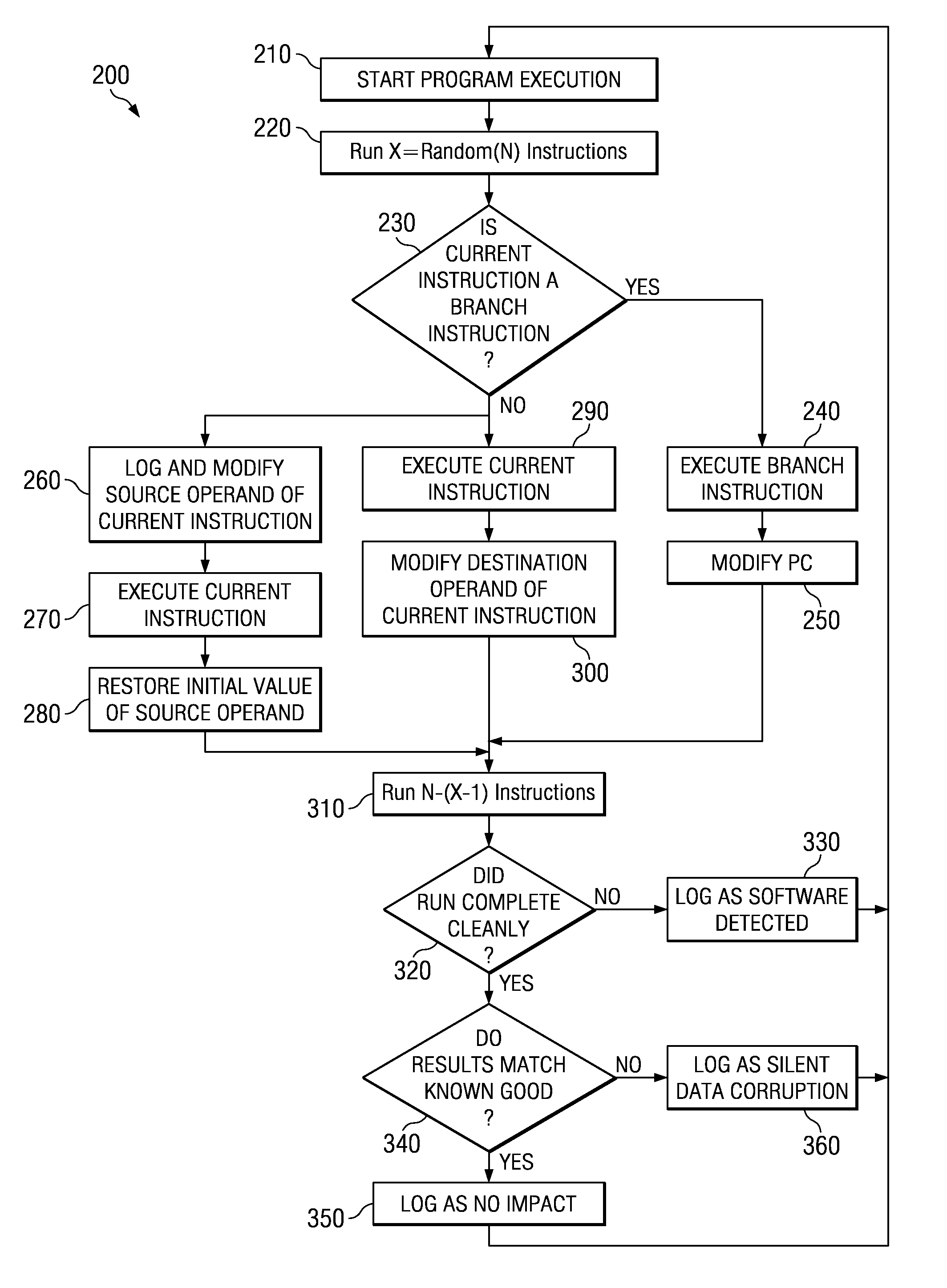

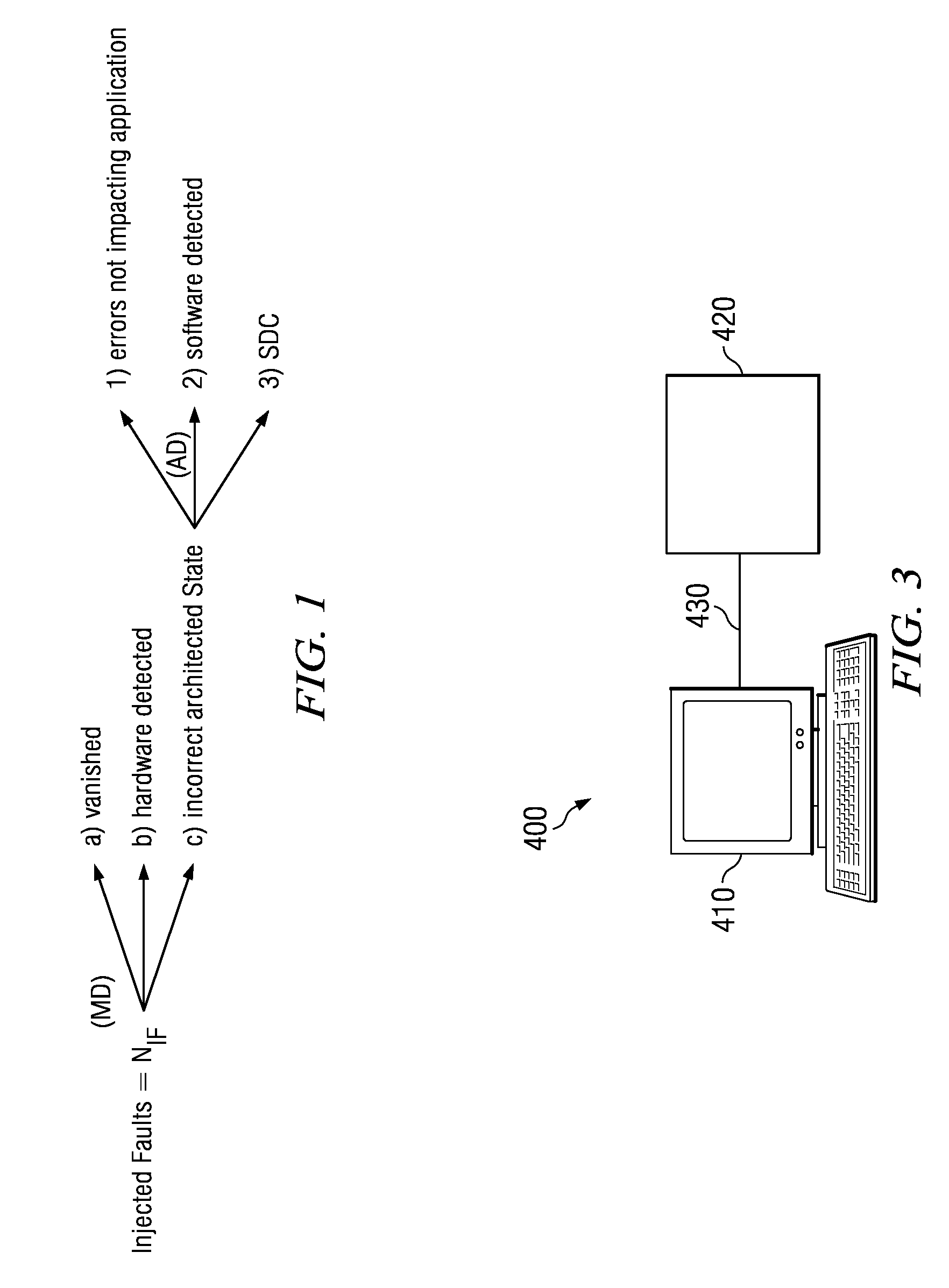

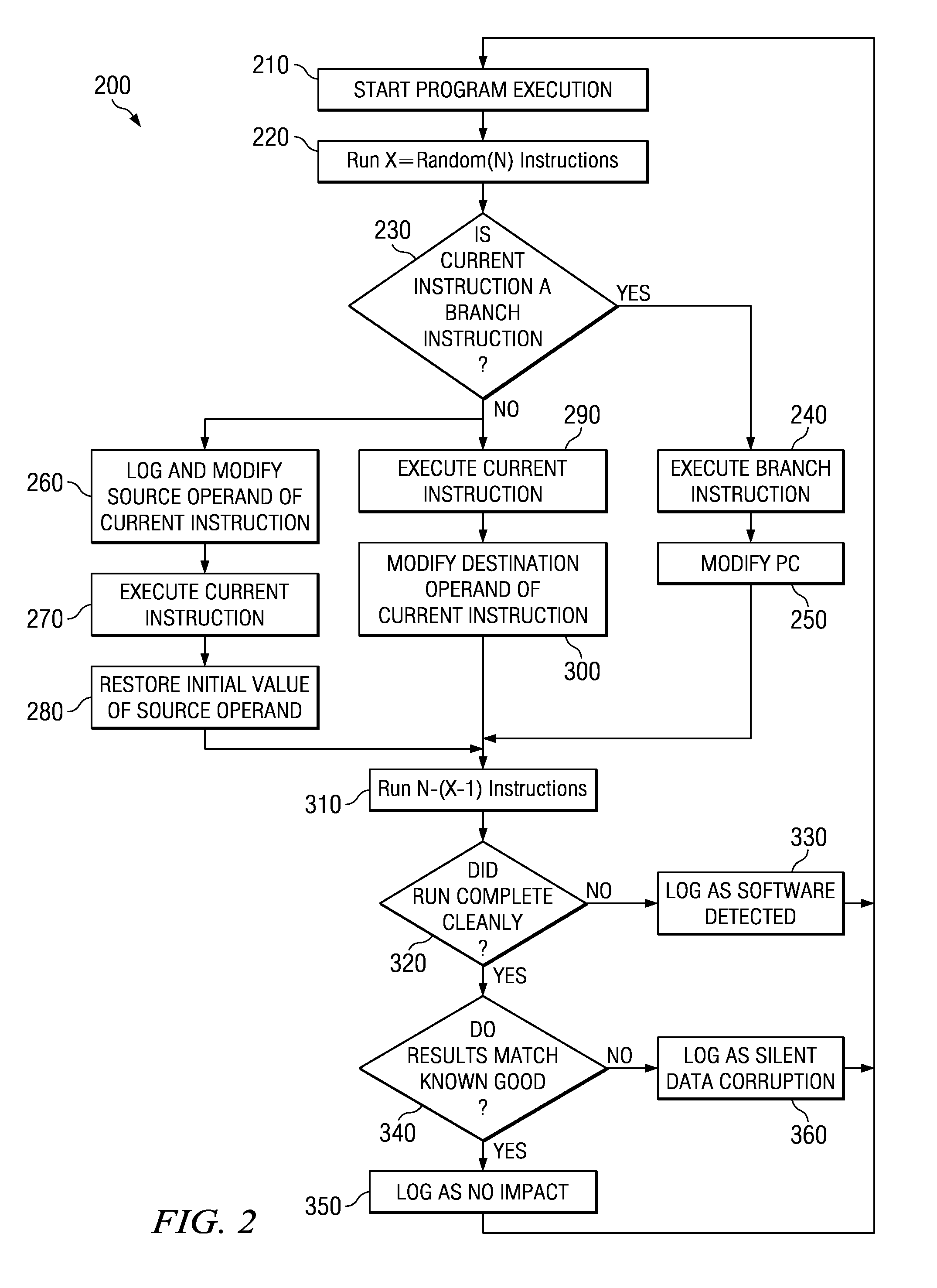

Method and Apparatus for Testing Soft Error Rate of an Application Program

InactiveUS20090249301A1Software testing/debuggingSpecific program execution arrangementsApplication program softwareOperational system

Techniques are provided for determining consequences of an injected fault on a system running a given application program or operating system, in order to measure the software impact of a hardware soft error on the application program / operating system. The application program software is emulated instruction-by-instruction, where source operands are randomly modified before an instruction is executed, and destination operands are randomly modified after an instruction is executed, in order to mimic hardware soft errors. In addition, a program counter is randomly modified after execution of a branch instruction. The resulting consequences of such modifications are monitored such that a fault of an instruction being executed is modeled in order to determine a soft error rate (SER) for a software application program or operating system.

Owner:IBM CORP

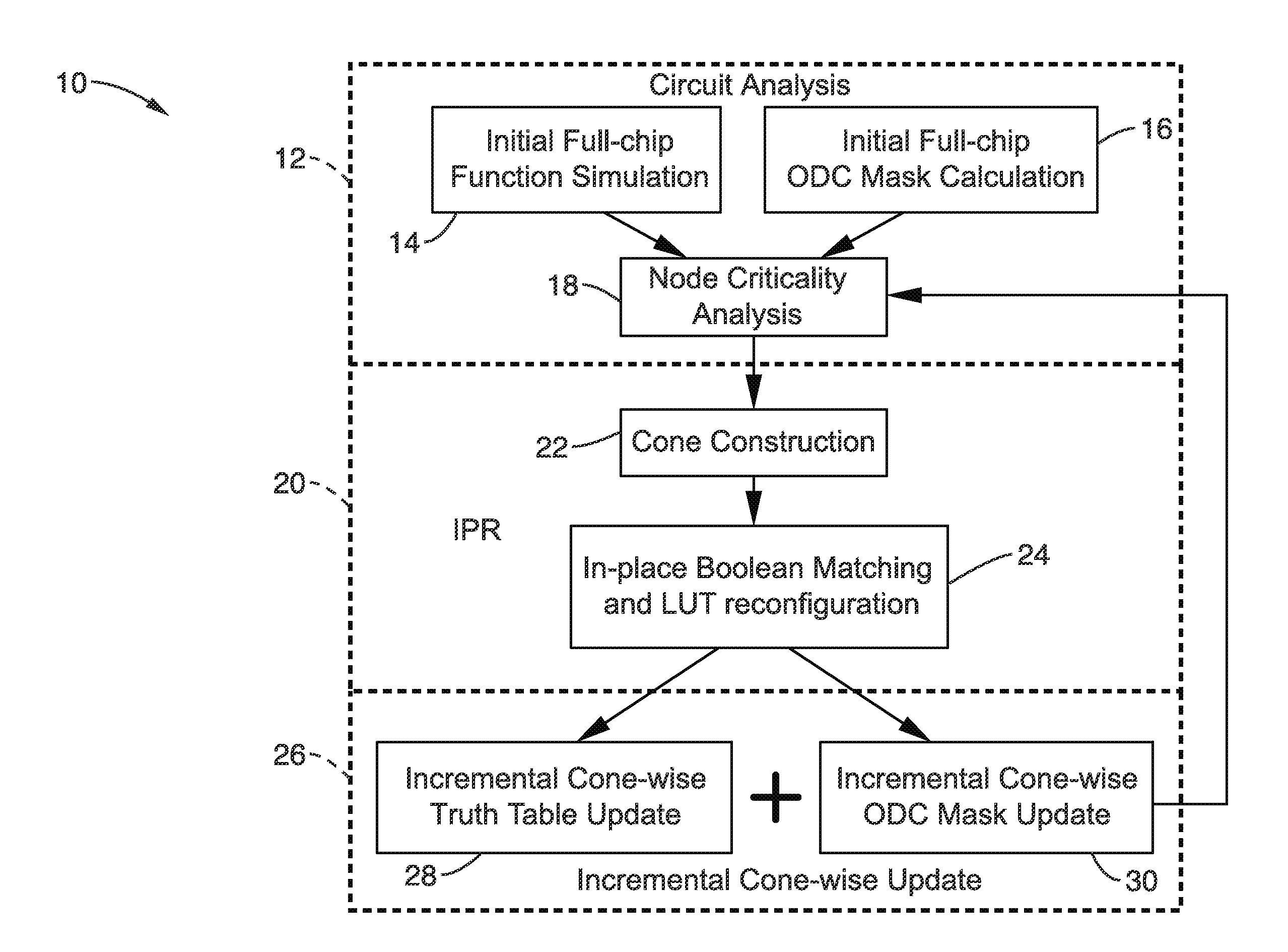

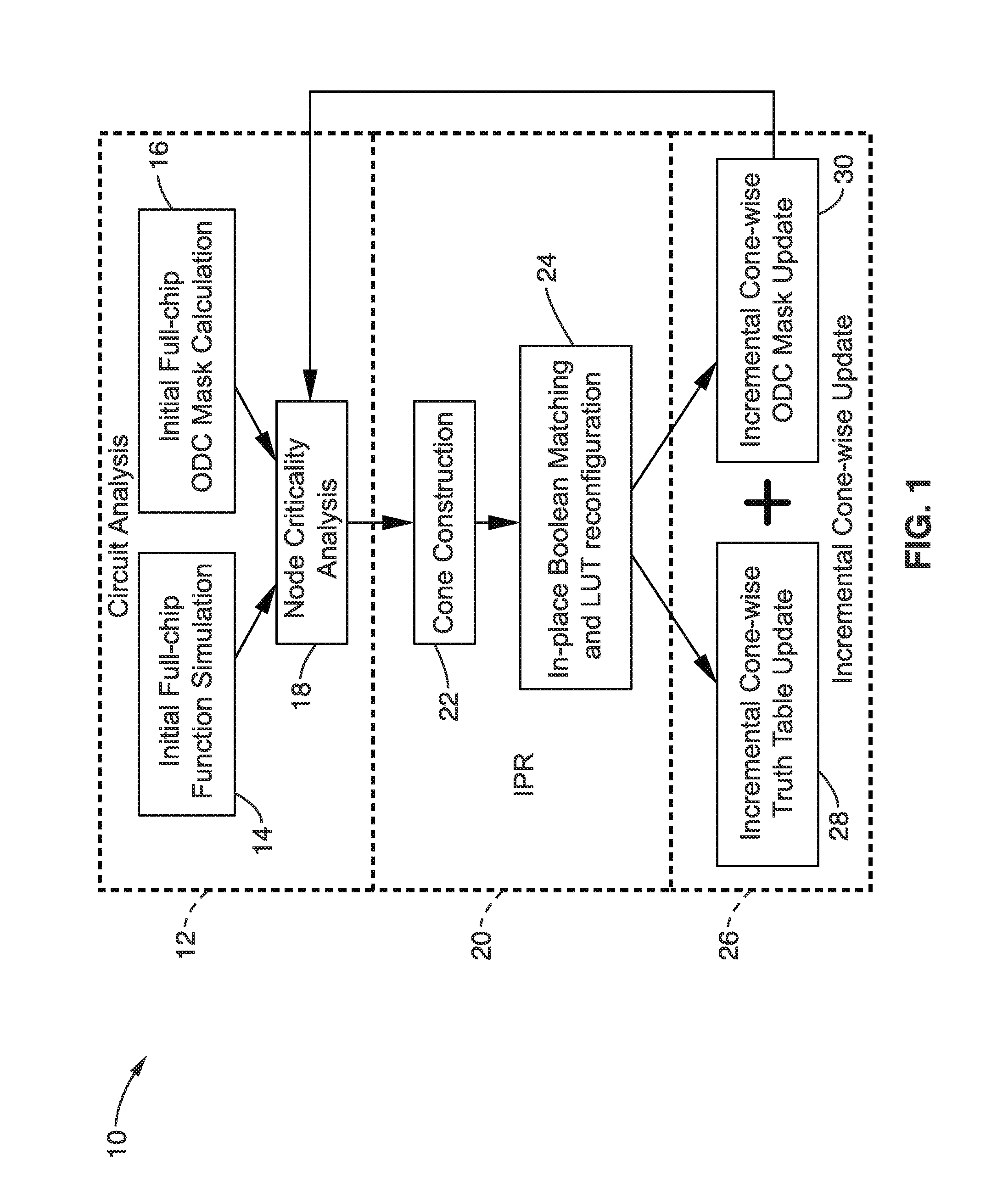

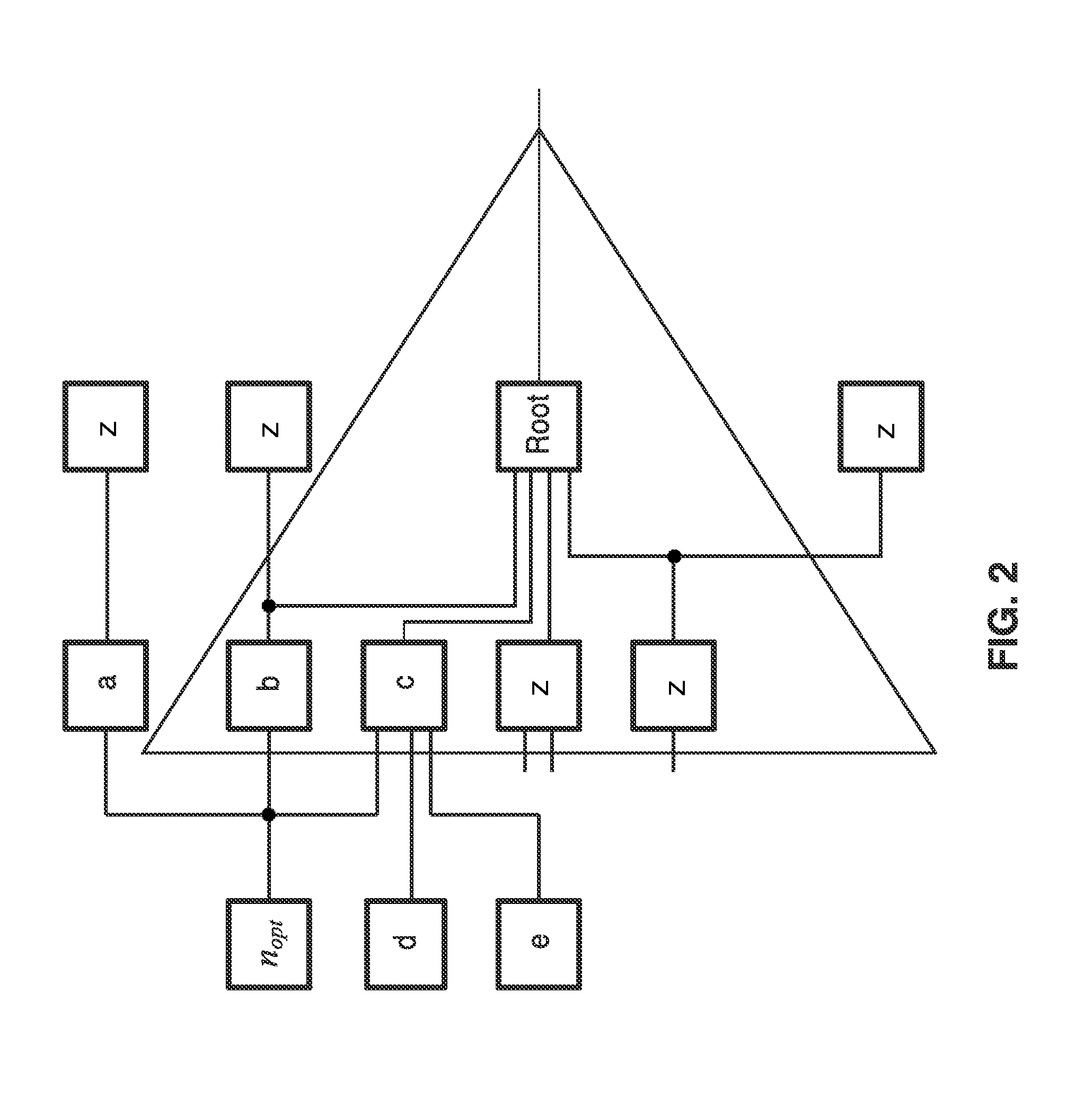

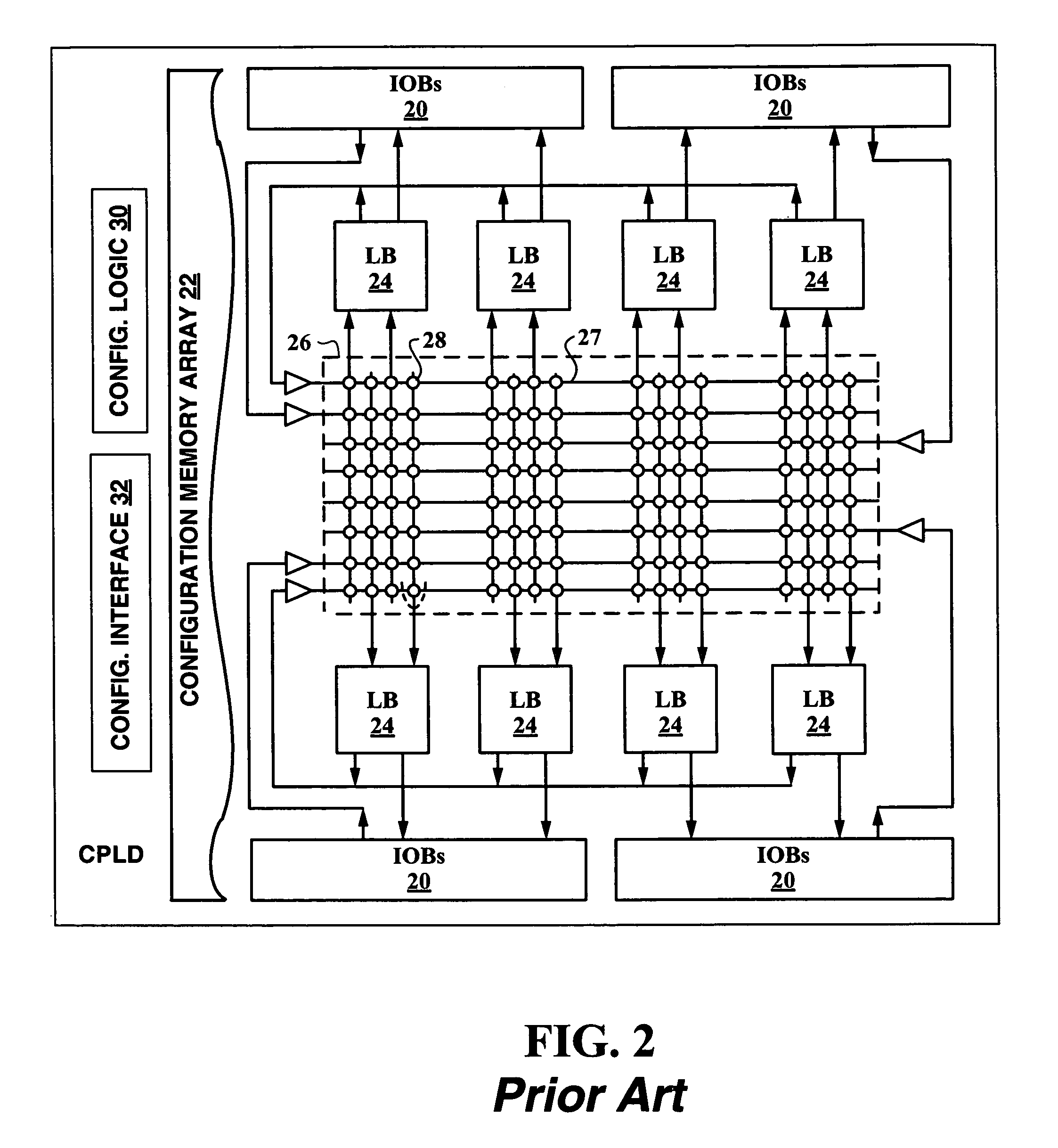

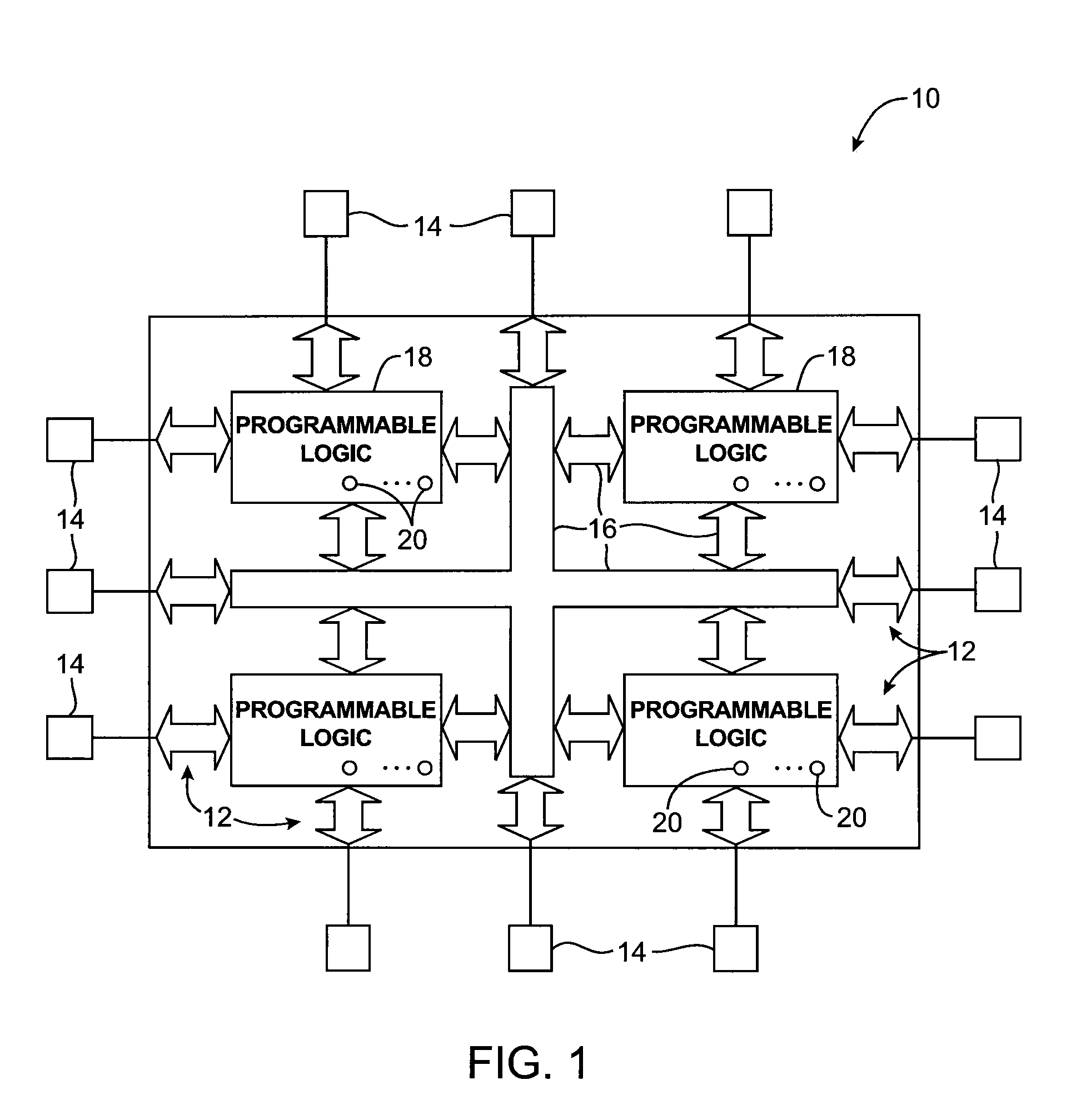

In-place resynthesis and remapping techniques for soft error mitigation in FPGA

InactiveUS20130305199A1Efficient and accurateImprove fault toleranceCAD circuit designRadiation hardeningFpga architectureDecomposition

In-place resynthesis for static memory (SRAM) based Field Programmable Gate Arrays (FPGAs) toward reducing sensitivity to single event upsets (SEUs). Resynthesis and remapping are described which have a low overheard and improve FPGA designs without the need of rerouting LUTs of the FPGA. These methods include in-place reconfiguration (IPR), in-place X-filling (IPF), and in-place inversion (IPV), which reconfigure LUT functions only, and can be applied to any FPGA architecture. In addition, for FPGAs with a decomposable LUT architecture (e.g., dual-output LUTs) an in-place decomposition (IPD) method is described for remapping a LUT function into multiple smaller functions leveraging the unused outputs of the LUT, and making use of built-in hard macros in programmable-logic blocks (PLBs) such as carry chain or adder. Methods are applied in-place to mapped circuits before or after routing without affecting placement, routing, and design closure.

Owner:RGT UNIV OF CALIFORNIA

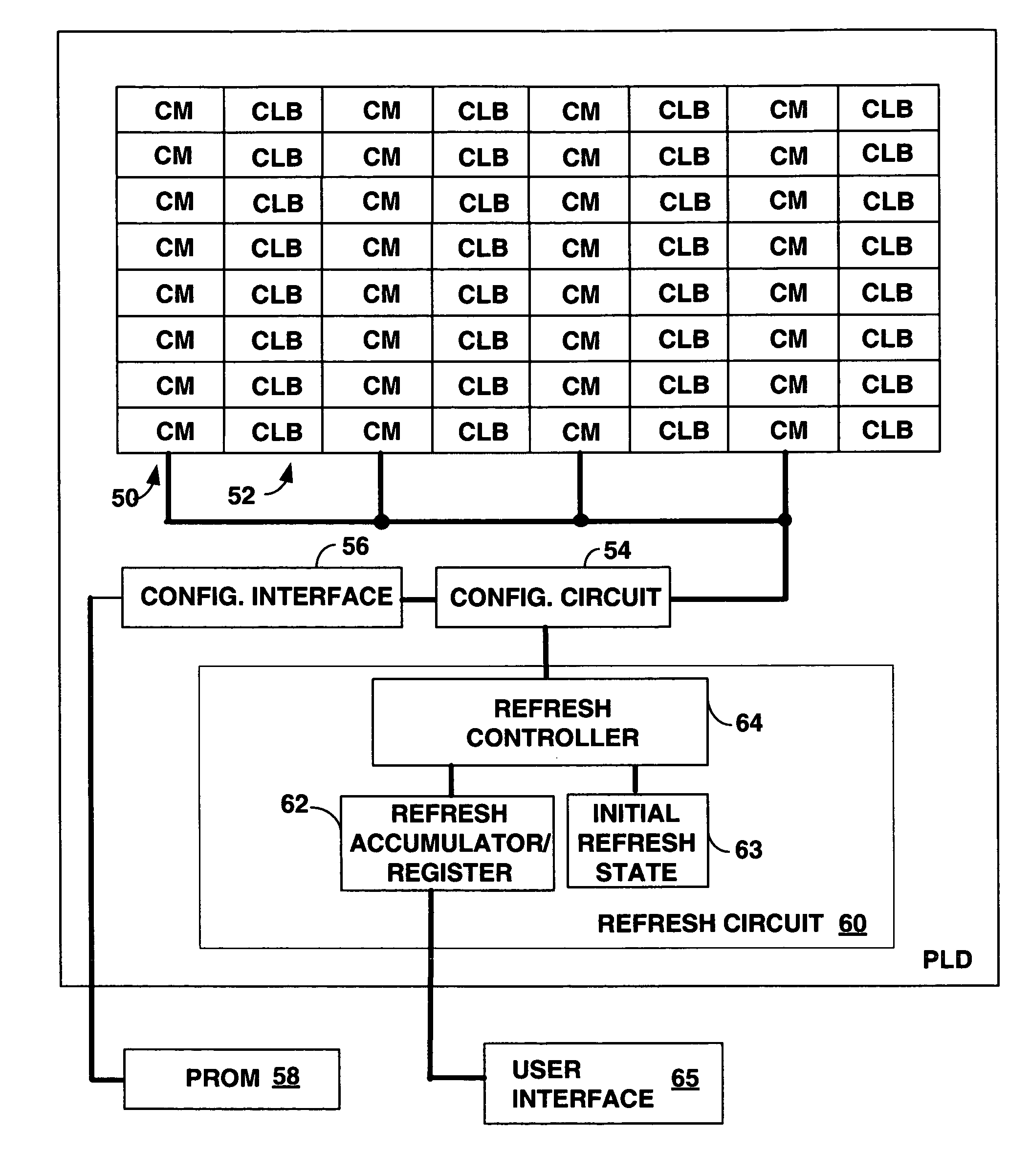

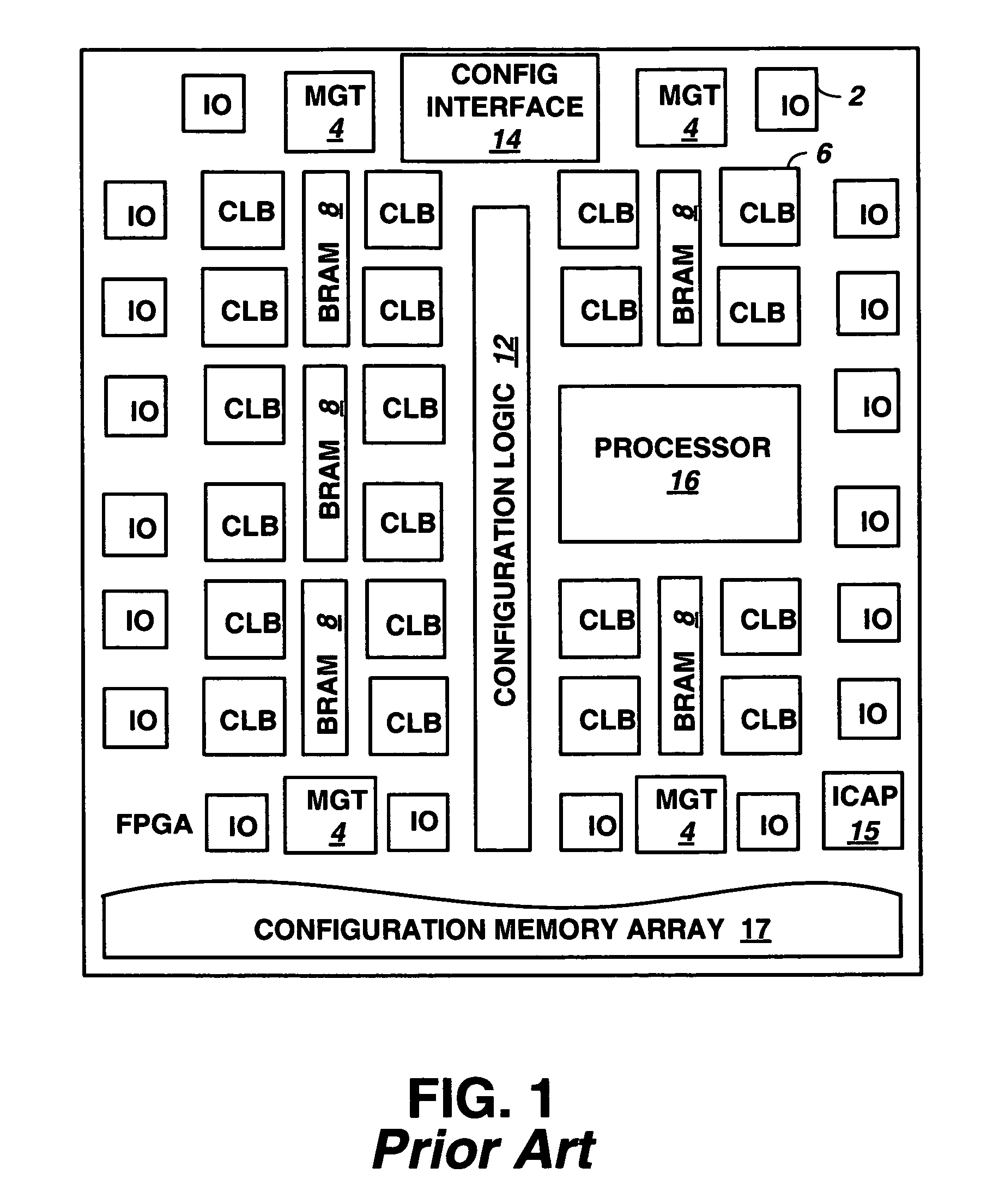

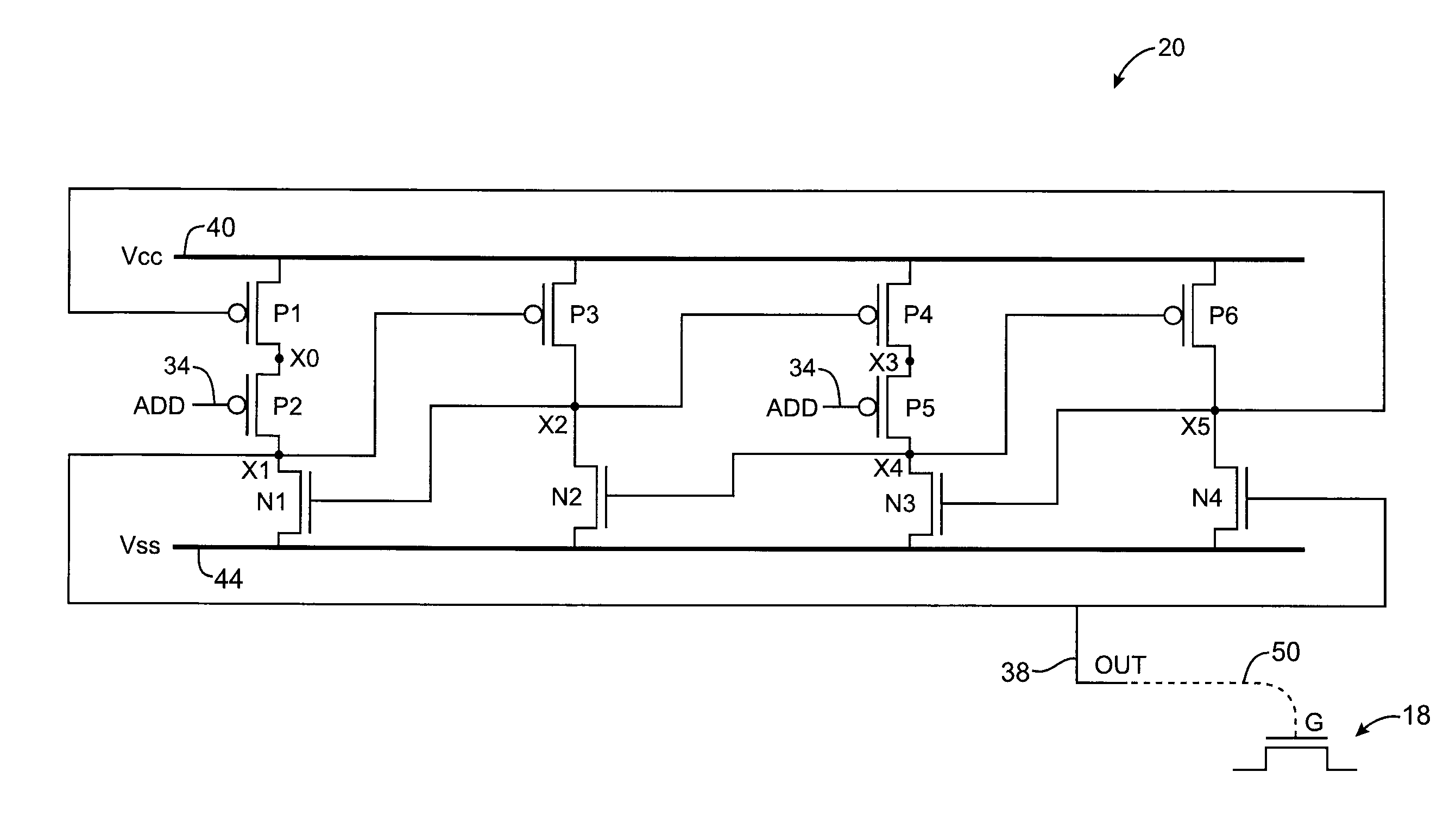

Programmable logic device (PLD) with memory refresh based on single event upset (SEU) occurrence to maintain soft error immunity

ActiveUS7764081B1Reduce memory cell densityMinimized circuitReliability increasing modificationsFail-safe circuitsProgrammable logic deviceSingle event upset

A Programmable Logic Device (PLD) is provided with configuration memory cells displaying a superior soft error immunity by combating single event upsets (SEUs) as the configuration memory cells are regularly refreshed from non-volatile storage depending on the rate SEUs may occur. Circuitry on the PLD uses a programmable timer to set a refresh rate for the configuration memory cells. Because an SEU which erases the state of a small sized memory cell due to collisions with cosmic particles may take some time to cause a functional failure, periodic refreshing will prevent the functional failure. The configuration cells can be DRAM cells which occupy significantly less space than the SRAM cells. Refresh circuitry typically provided for DRAM cells is reduced by using the programming circuitry of the PLD. Data in the configuration cells of the PLD are reloaded from either external or internal soft-error immune non-volatile memory.

Owner:XILINX INC

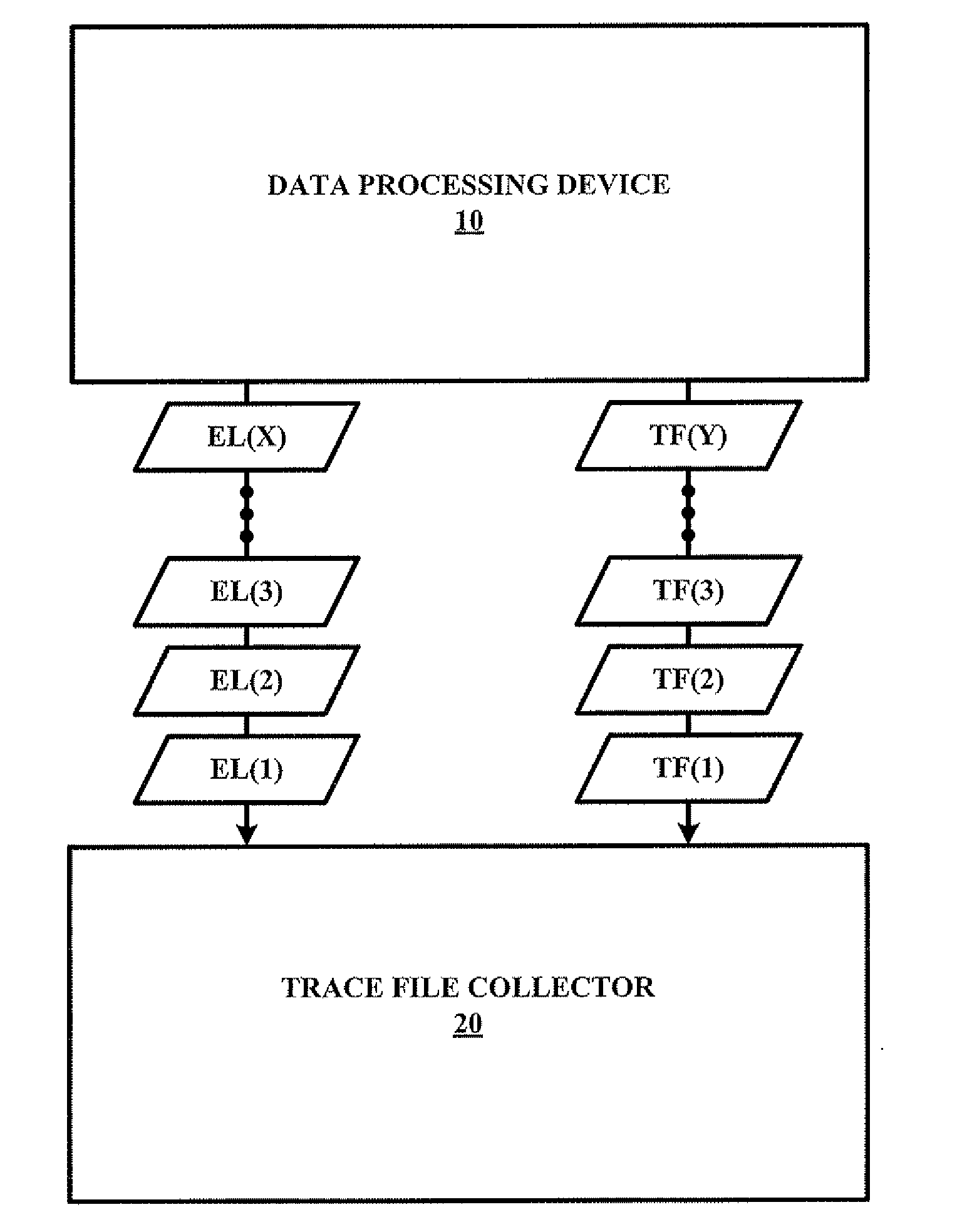

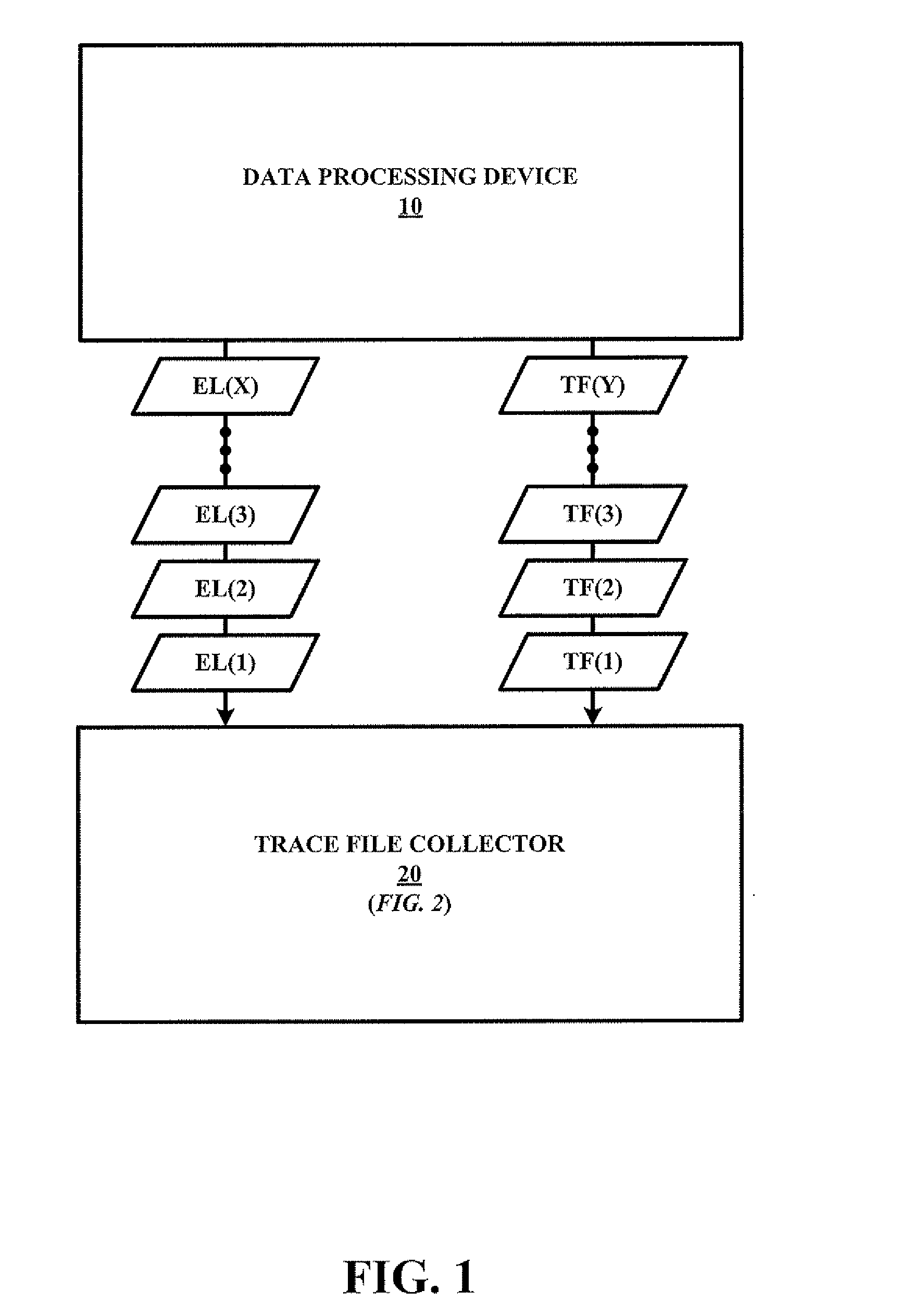

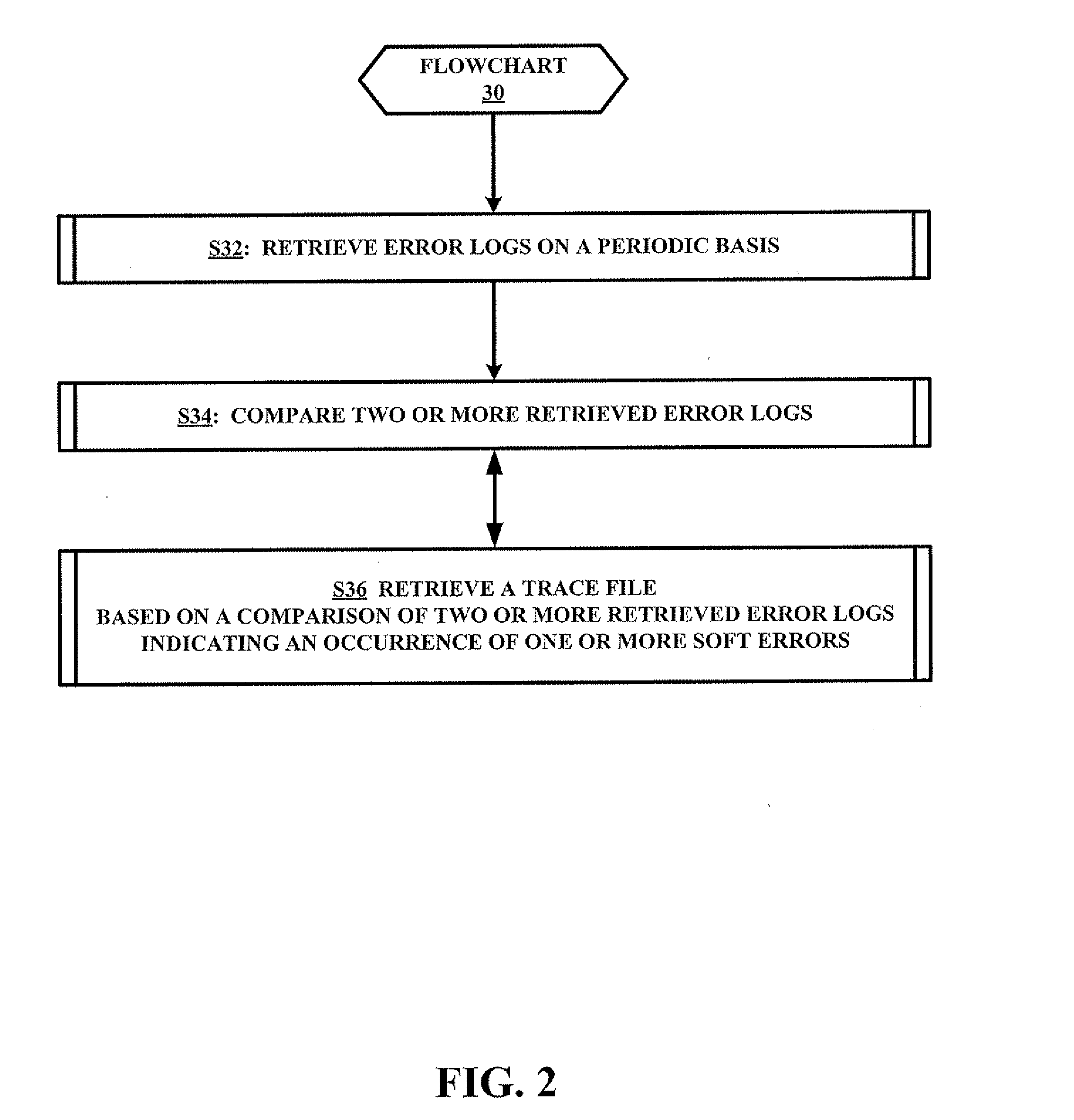

Method and System for a Soft Error Collection of Trace Files

InactiveUS20080086515A1Error detection/correctionSpecial data processing applicationsComputer hardwareCollection system

A trace file collection system for implementing a trace file collection method for a soft error collection of one or more trace files associated with a data processing device. The method involves a periodic retrieval of an error log from the data processing device, a comparison of two or more retrieved error logs, and a retrieval of the trace file(s) from the data processing device based on the comparison of the two or more retrieved error logs indicating an occurrence of one or more soft errors within the data processing device.

Owner:IBM CORP

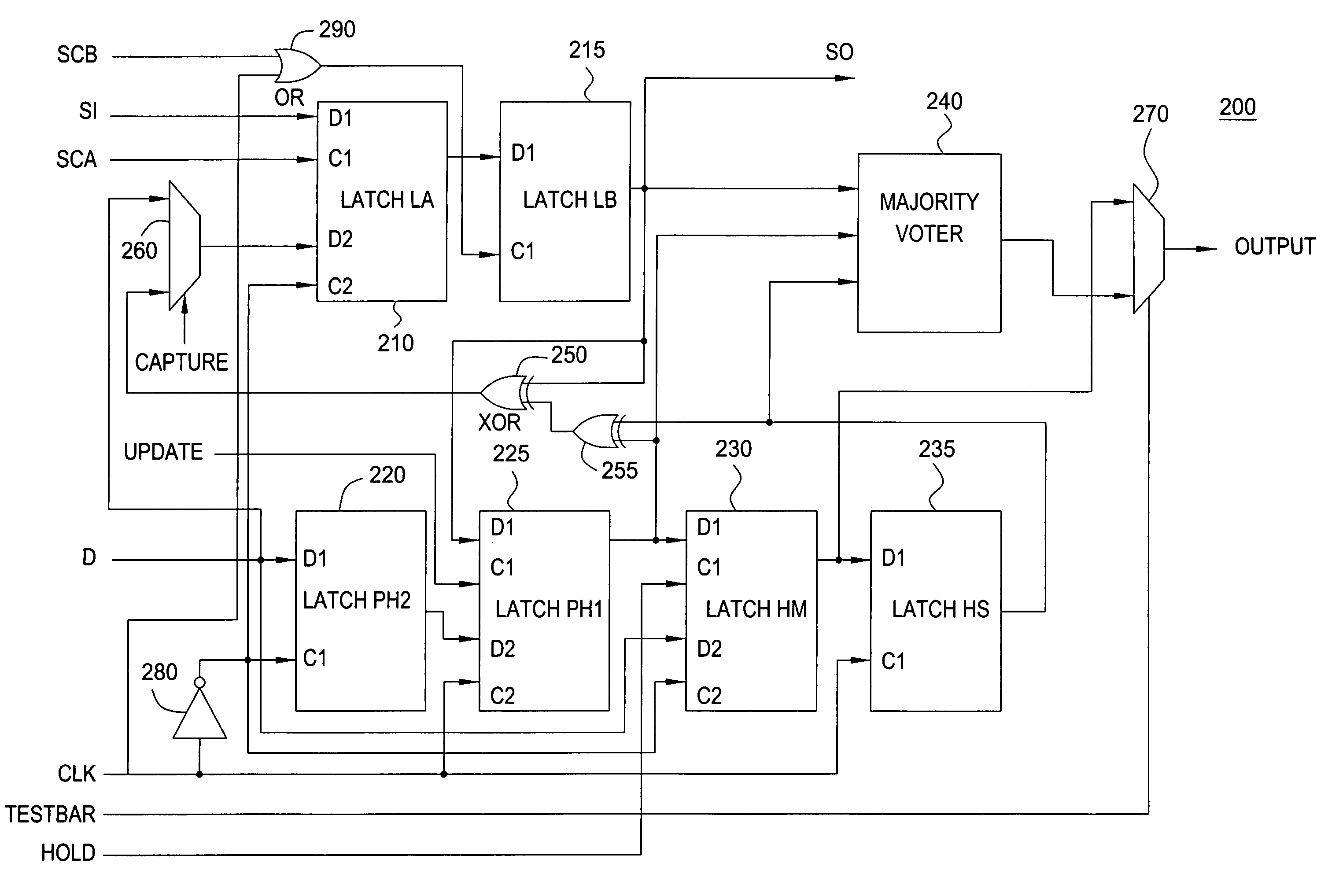

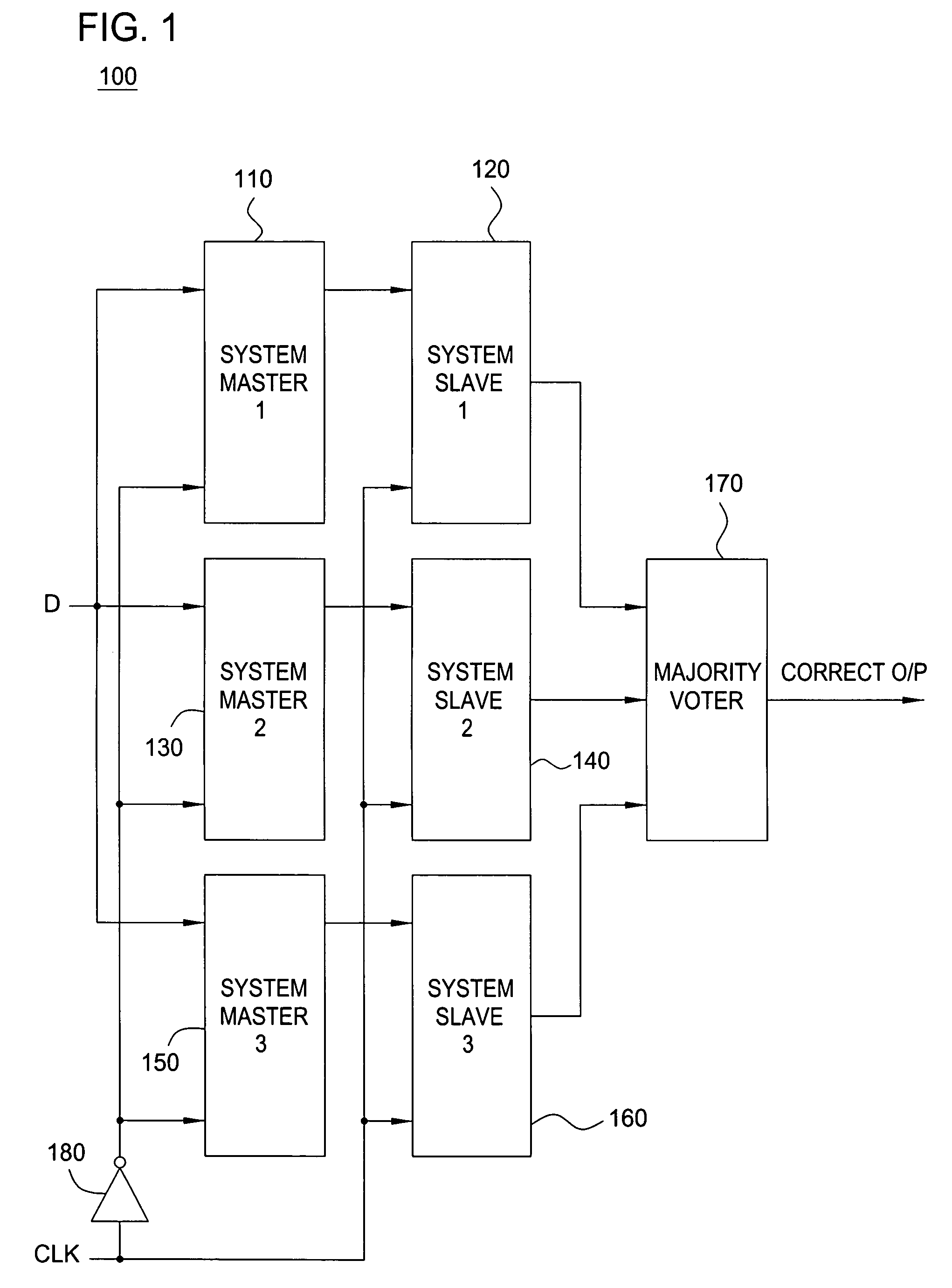

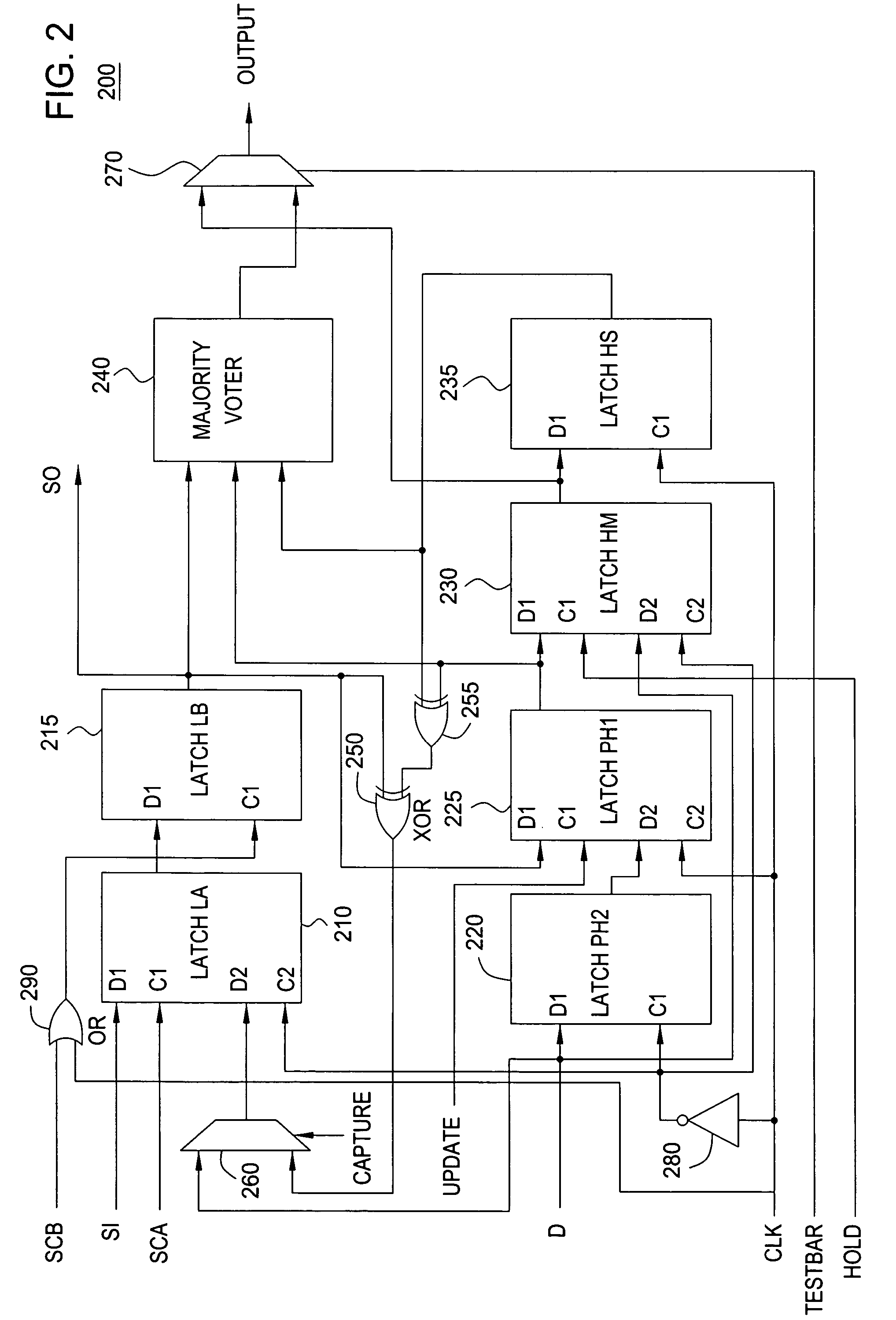

Soft error tolerant flip flops

ActiveUS7482831B2Reliability increasing modificationsElectric pulse generatorProcessor registerComputer science

A register designed to detect and correct soft errors in real time. A redundant latch is added to the existing structure of a flip flop and functional data is simultaneously registered at multiple latches. The content of these multiple latches are fed to a majority voting circuit. If the content of any of these latches is corrupted by soft error, it is filtered out through the majority voting circuit and correct data is passed out from the output of the flip flop. In one embodiment, this design operates as a simple scan flip flop or scan-hold flip flop, and is useful for system testability purposes.

Owner:RUTGERS THE STATE UNIV +1

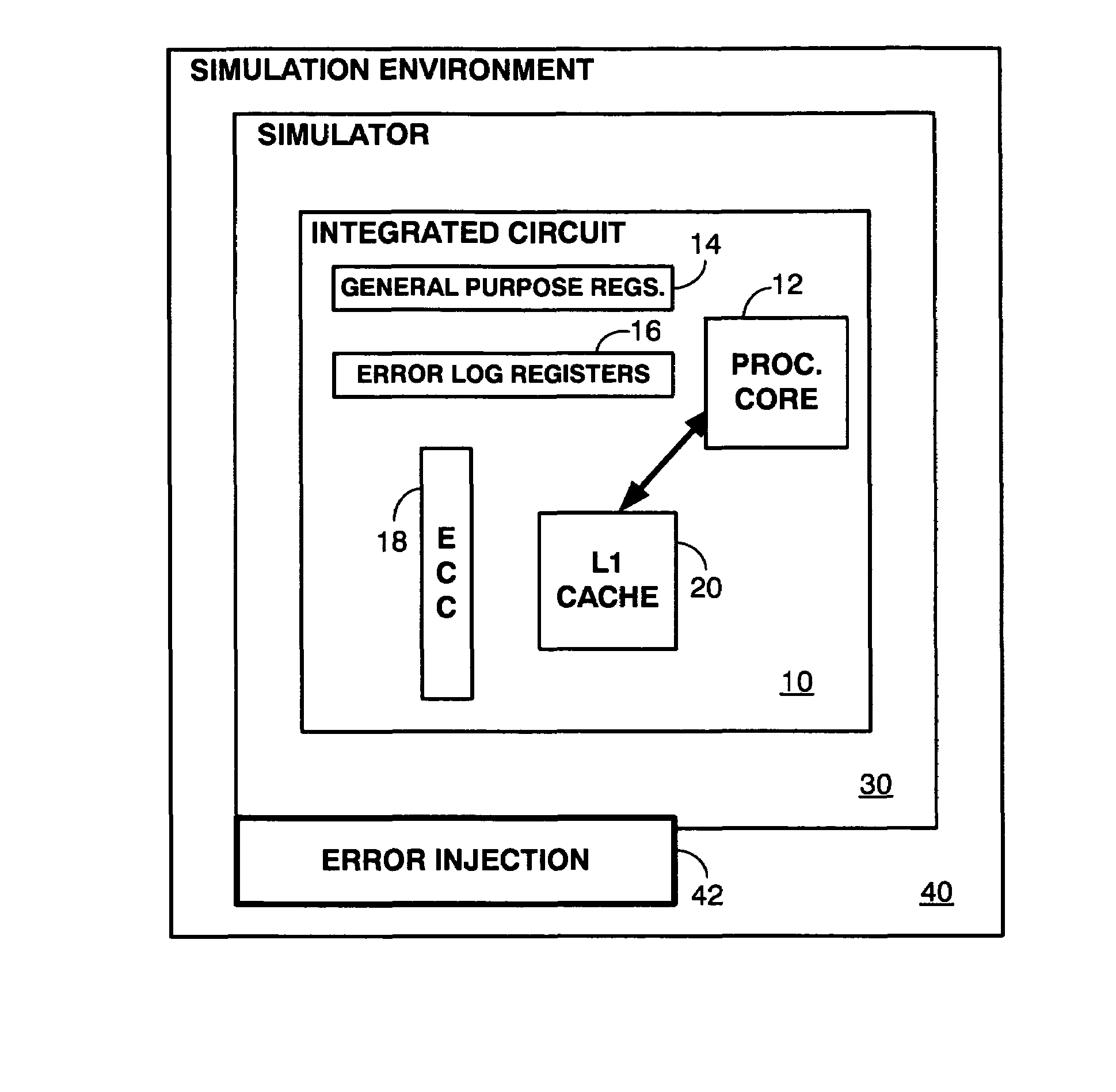

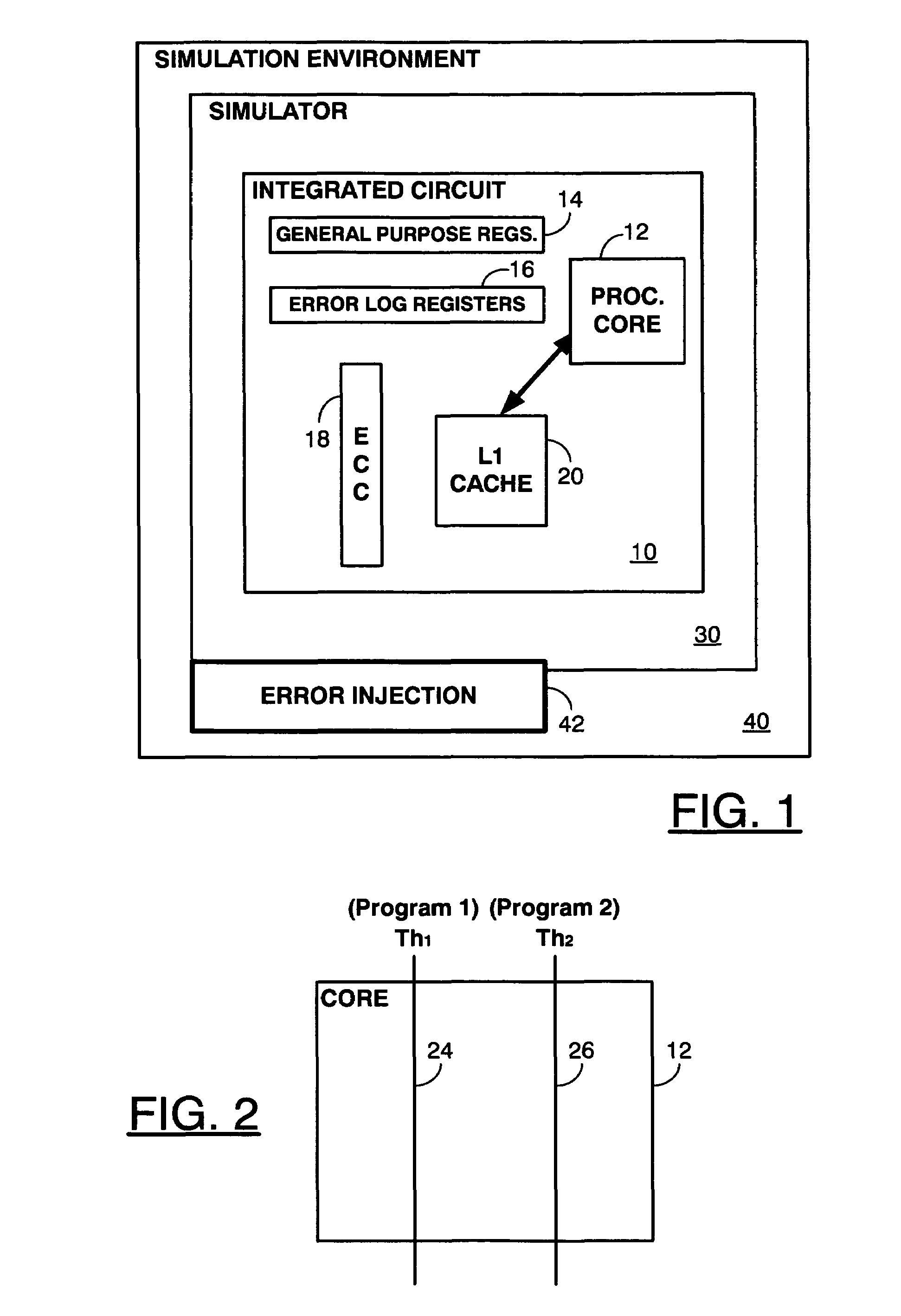

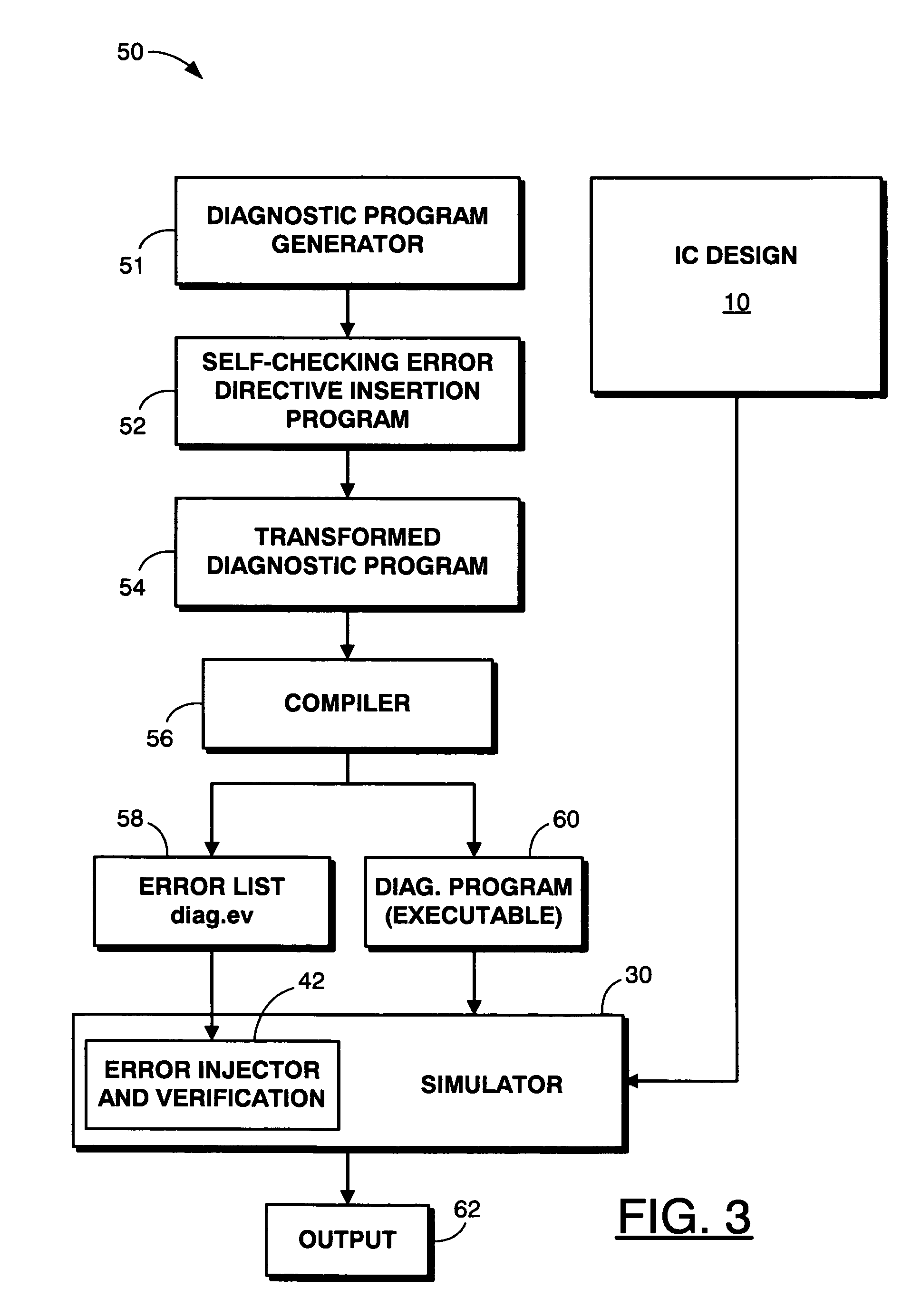

Method and system for verification of soft error handling with application to CMT processors

ActiveUS7320114B1Electronic circuit testingDetecting faulty computer hardwareDiagnostic programError processing

A method provides for verifying soft error handling in an integrated circuit (IC) design. A diagnostic program is executed on a virtual IC based on the IC design using a simulator. A soft error is injected into the virtual IC to trigger hardware error correction in the virtual IC and a software exception. A record of a type and a location of the soft error at the time of the injecting is created. The error log generated by hardware error correction is then compared with the record of injected error, the hardware error correction being part of the virtual IC. An IC design flaw is indicated when a discrepancy exists between the error log and the record of the injected error.

Owner:ORACLE INT CORP

System and method for correcting soft errors in random access memory devices

A circuit and method are disclosed for reducing soft errors in dynamic memory devices using error checking and correcting. In an exemplary embodiment, a memory device includes a dual port memory having a first port for externally-initiated memory access operations and a second port for handling memory access operations associated with error checking and error correction operations. An error module, coupled to the second port of the dual port memory, performs an error checking operation on words read from the dual port memory. An error controller, coupled to the error module, controls the error module to perform error check operations on each word sequentially read from the dual port memory through the second port thereof. The error checking is performed substantially in parallel with externally-initiated memory access operations performed using the first port of the dual port memory. The error module may also generate a corrected word for a word that is detected by the error module as having a correctable error. The error controller may replace in the dual port memory the word having the correctable error with the corrected word.

Owner:STMICROELECTRONICS SRL

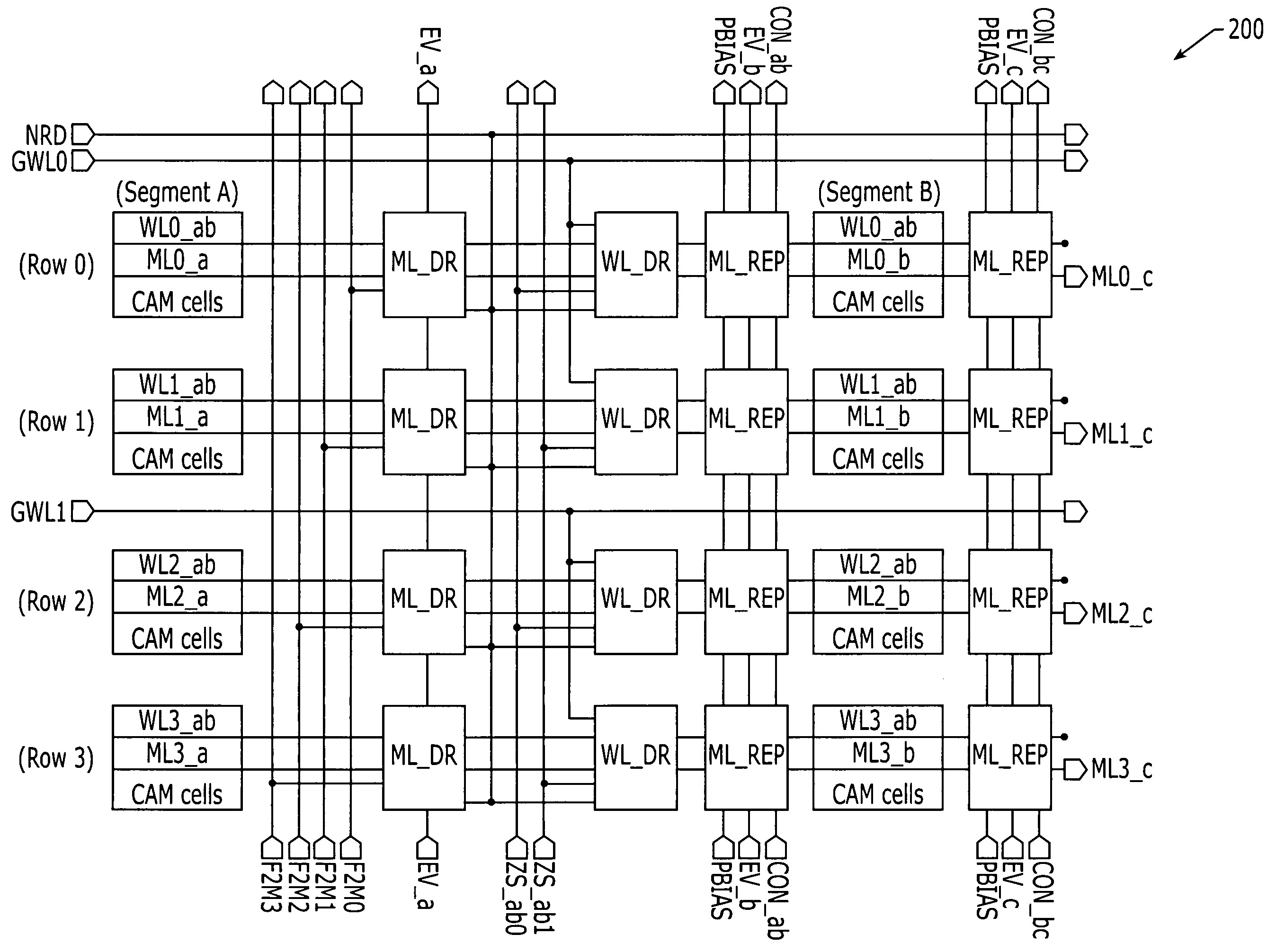

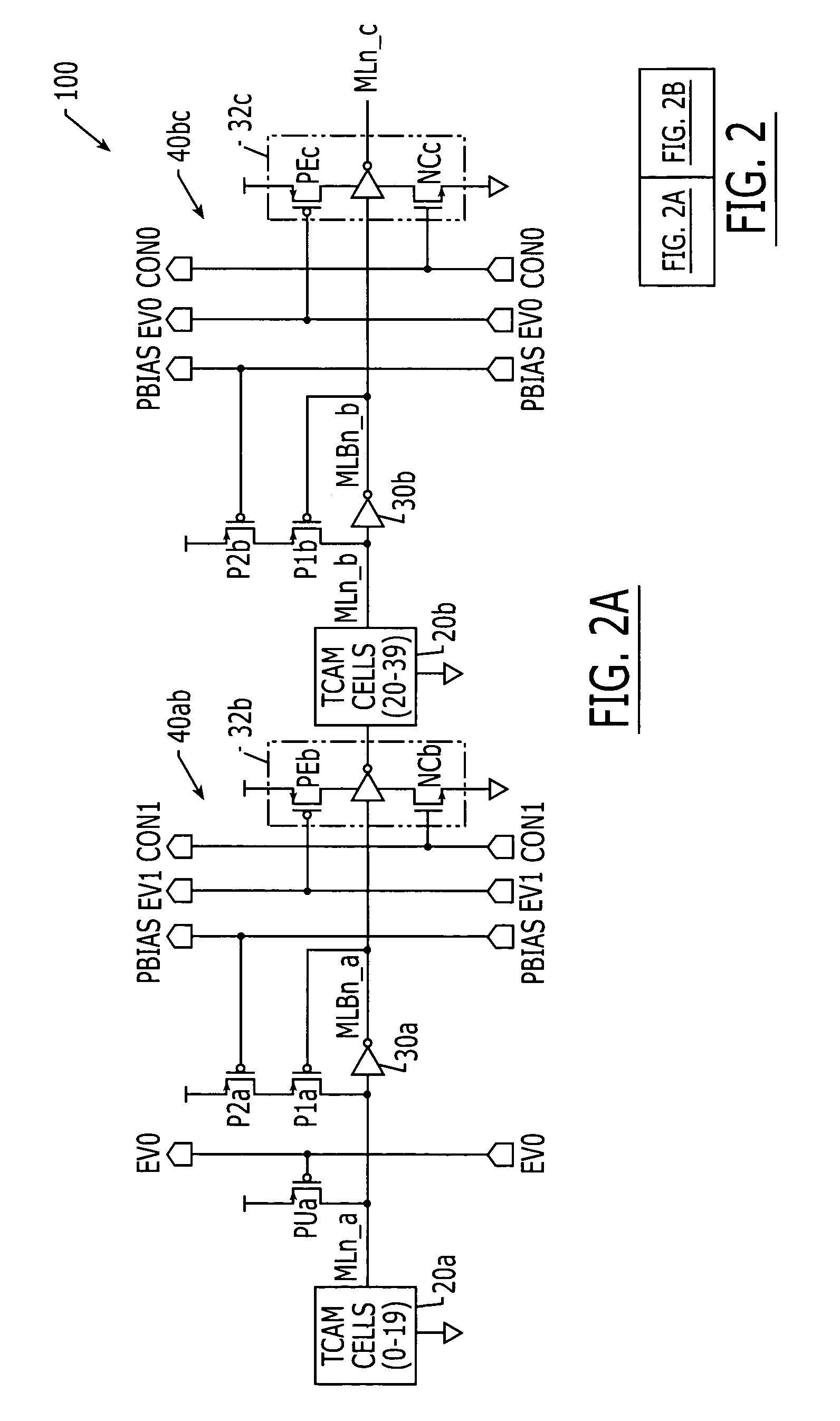

Content addressable memory (CAM) devices that utilize segmented match lines and word lines to support pipelined search and write operations and methods of operating same

InactiveUS6967856B1Correction errorIncrease speedDigital storageMemory systemsControl signalWord search

CAM devices include a segmented CAM array that is configured to support a long word search operation (e.g., x8N search) as a plurality of overlapping segment-to-segment search operations that are each performed across different rows within a group of rows in the CAM array and staggered in time relative to one another. To provide enhanced soft error immunity, these CAM devices may also include a CAM array having a row of lateral XY TCAM cells therein that are arranged in a repeating low-even, low-odd, high-even, high-odd sequence, where “low” and “high” represent the first and second halves of a CAM entry. Methods of operating a CAM device may include staggering the timing of overlapping segment-to-segment search operations across different rows within a CAM array using force-to-miss control signals to establish miss conditions on match lines of rows that are not to participate in a respective ones of the segment-to-segment search operations.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

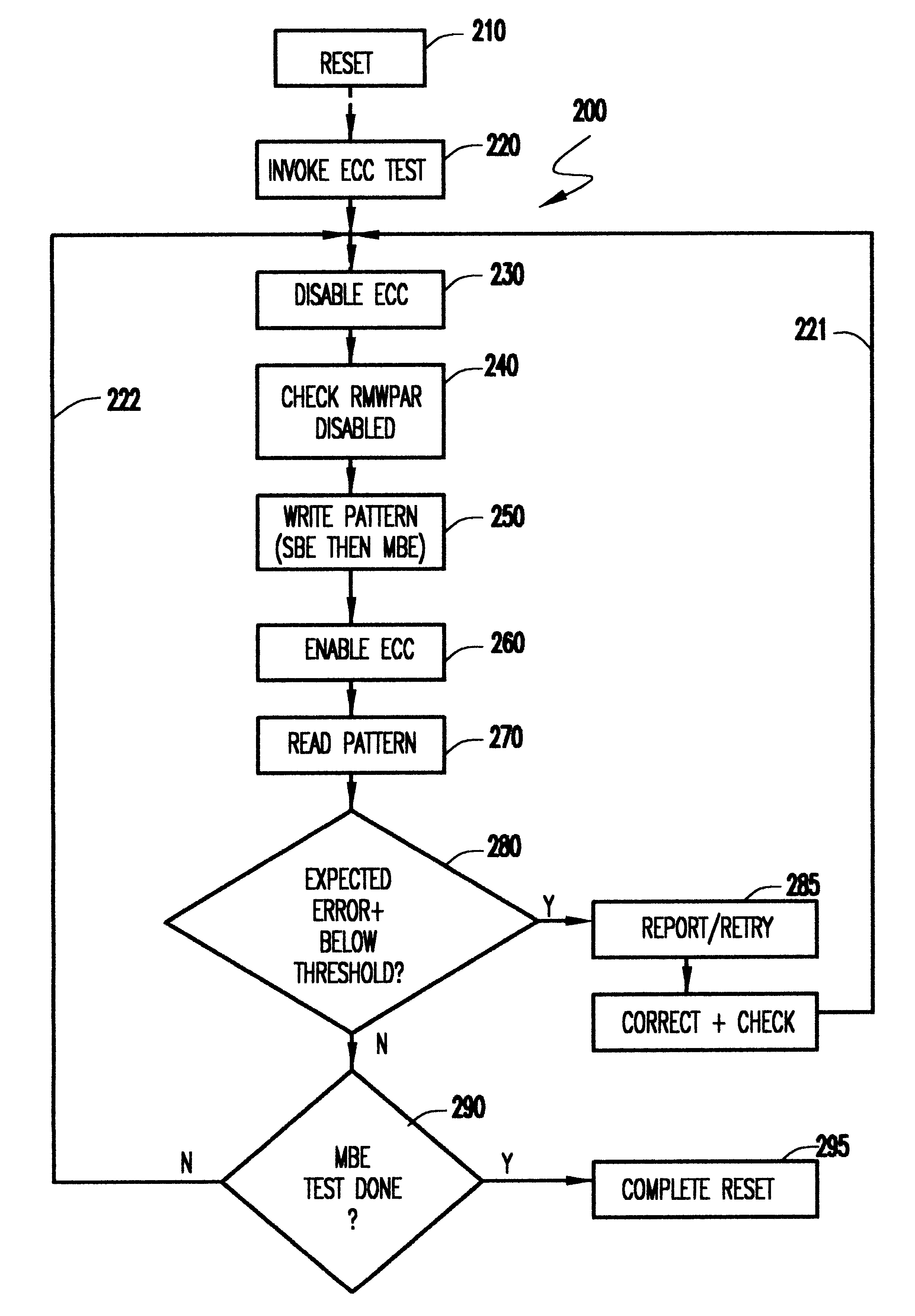

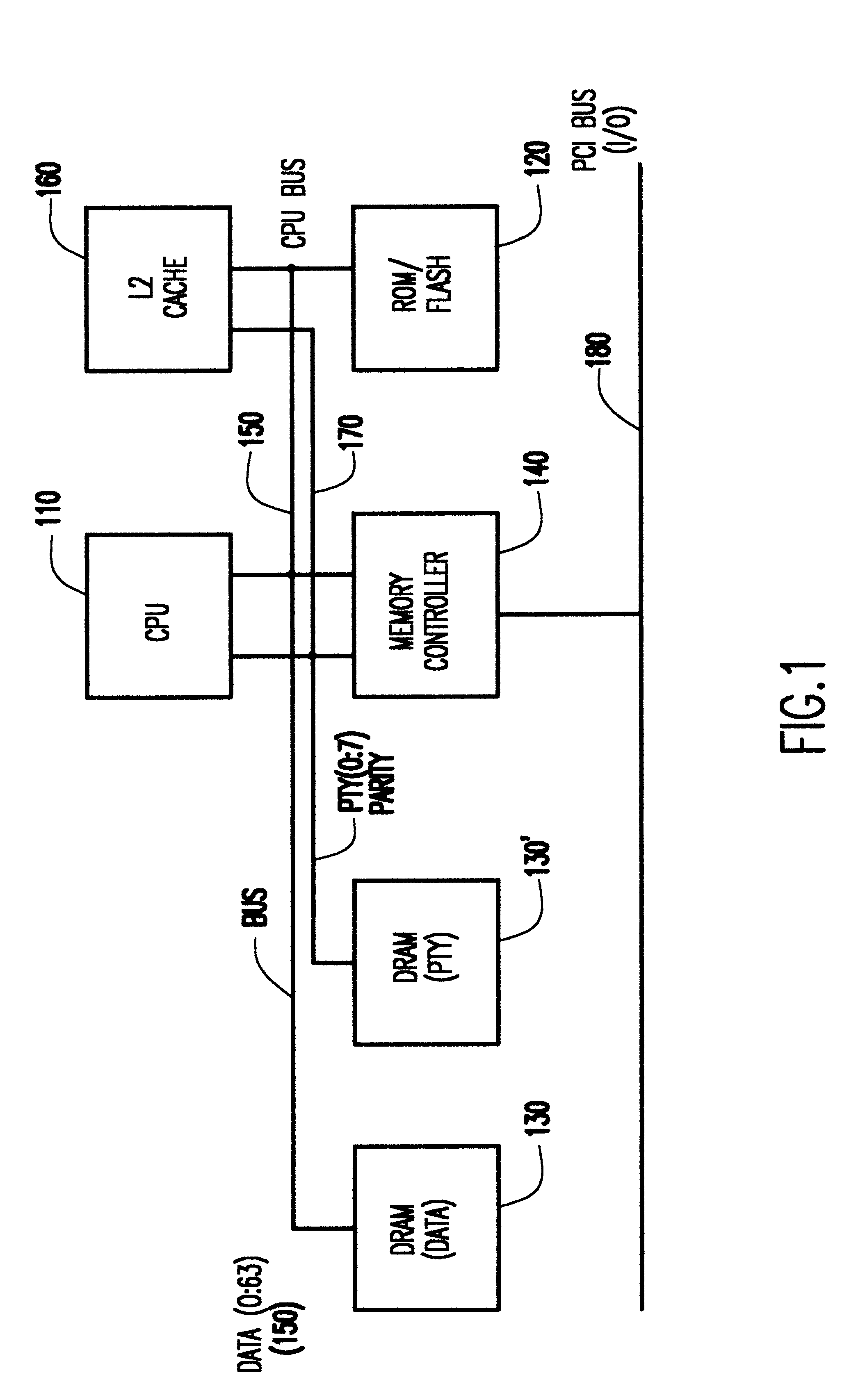

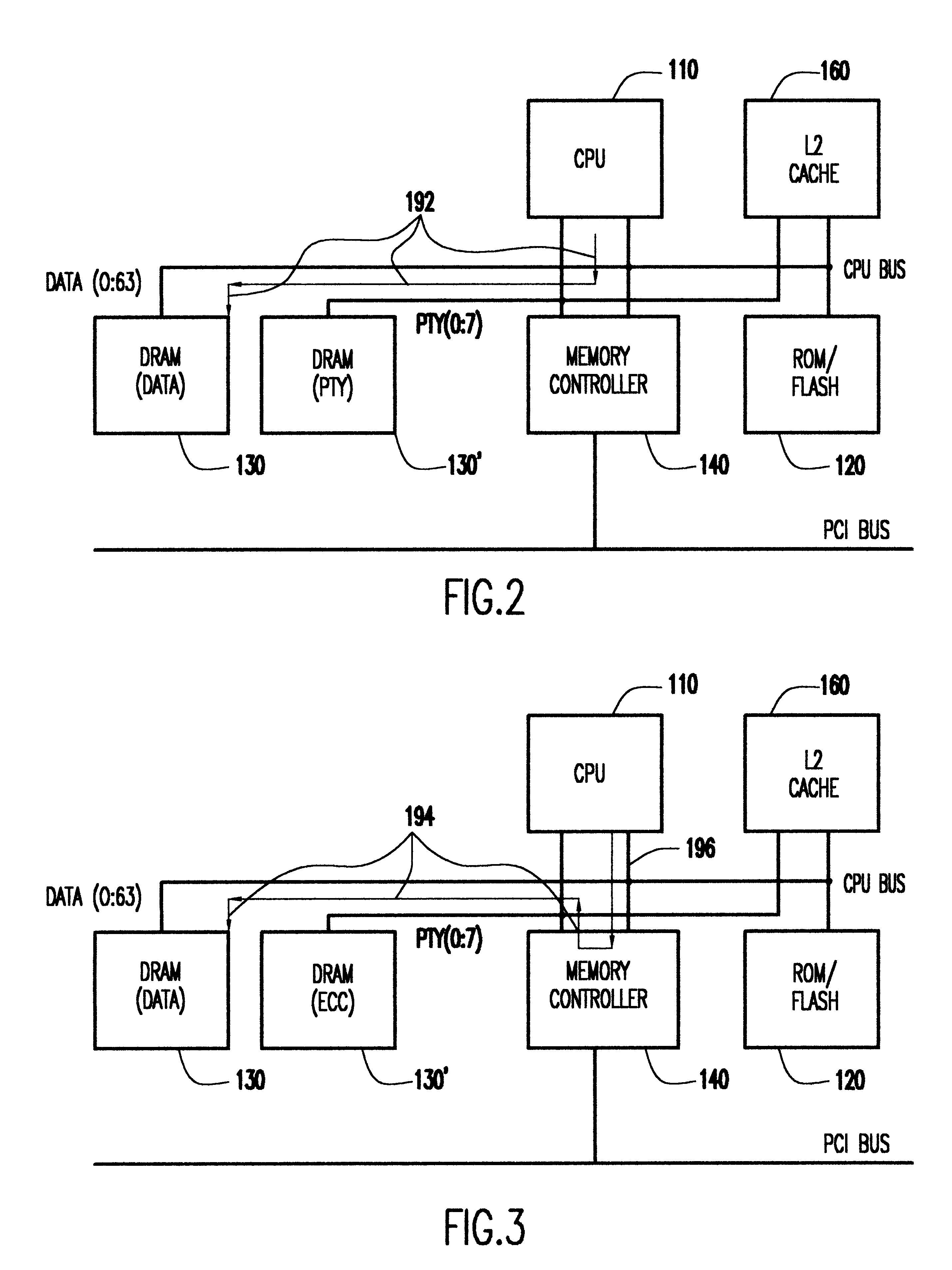

Testing error correcting code feature in computers that do not have direct hardware features for causing single bit and multi-bit errors

InactiveUS6237116B1Fast executionGuaranteed uptimeCode conversionCoding detailsMemory controllerError correcting

Built-in tests included in reset functions of single board computers can be rapidly performed to confirm adequate functionality without additional hardware support by disabling an error correcting code function in a memory controller, writing a pattern of predictable parity to a location in memory and reading and correcting the pattern with the error correcting code function of the memory controller re-enabled. Thus, resets caused by, for example, momentary soft errors or power interruptions can be executed within rigid time constraints and thus negligibly short interruptions of processor function.

Owner:LOCKHEED MARTIN CORP

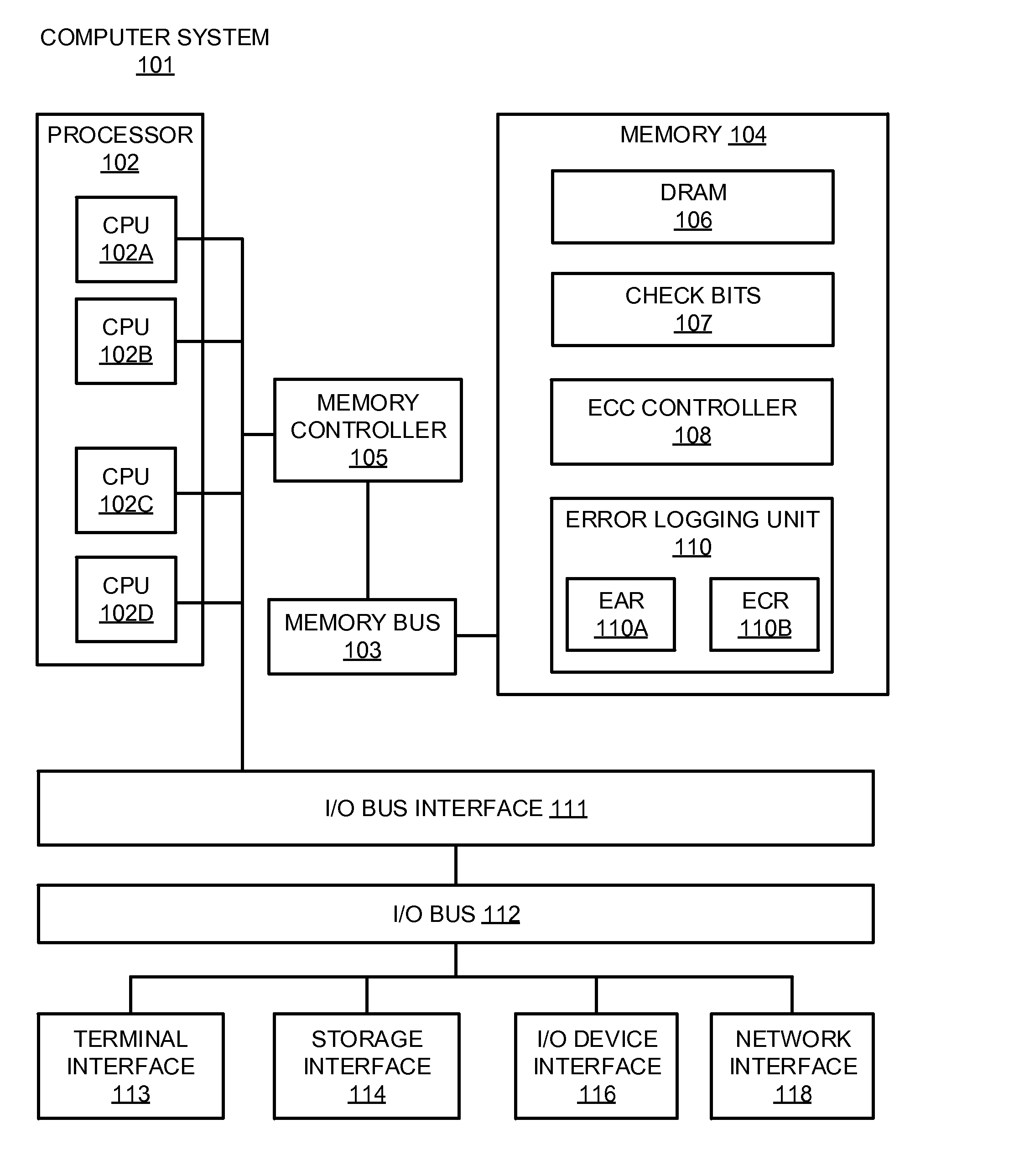

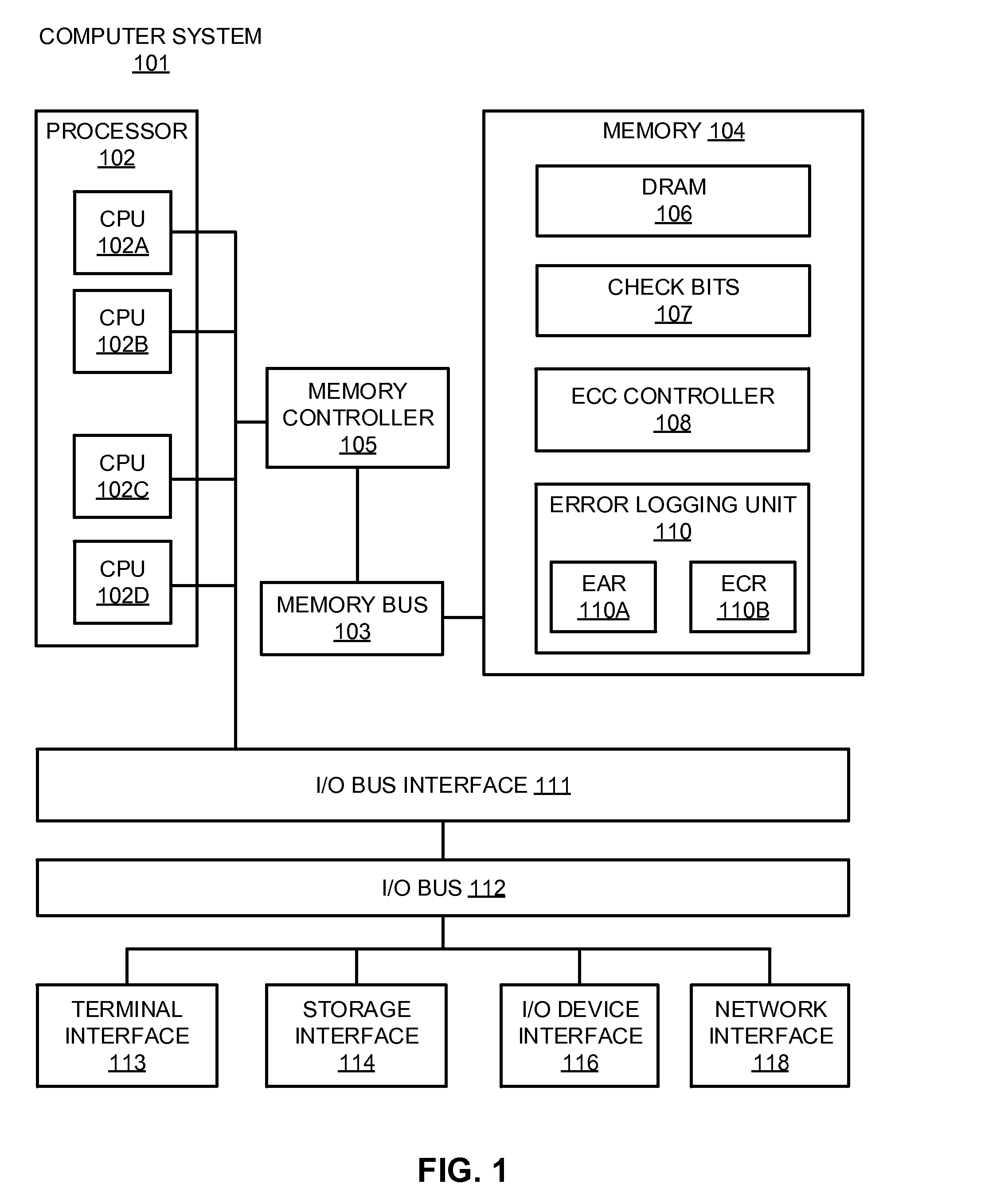

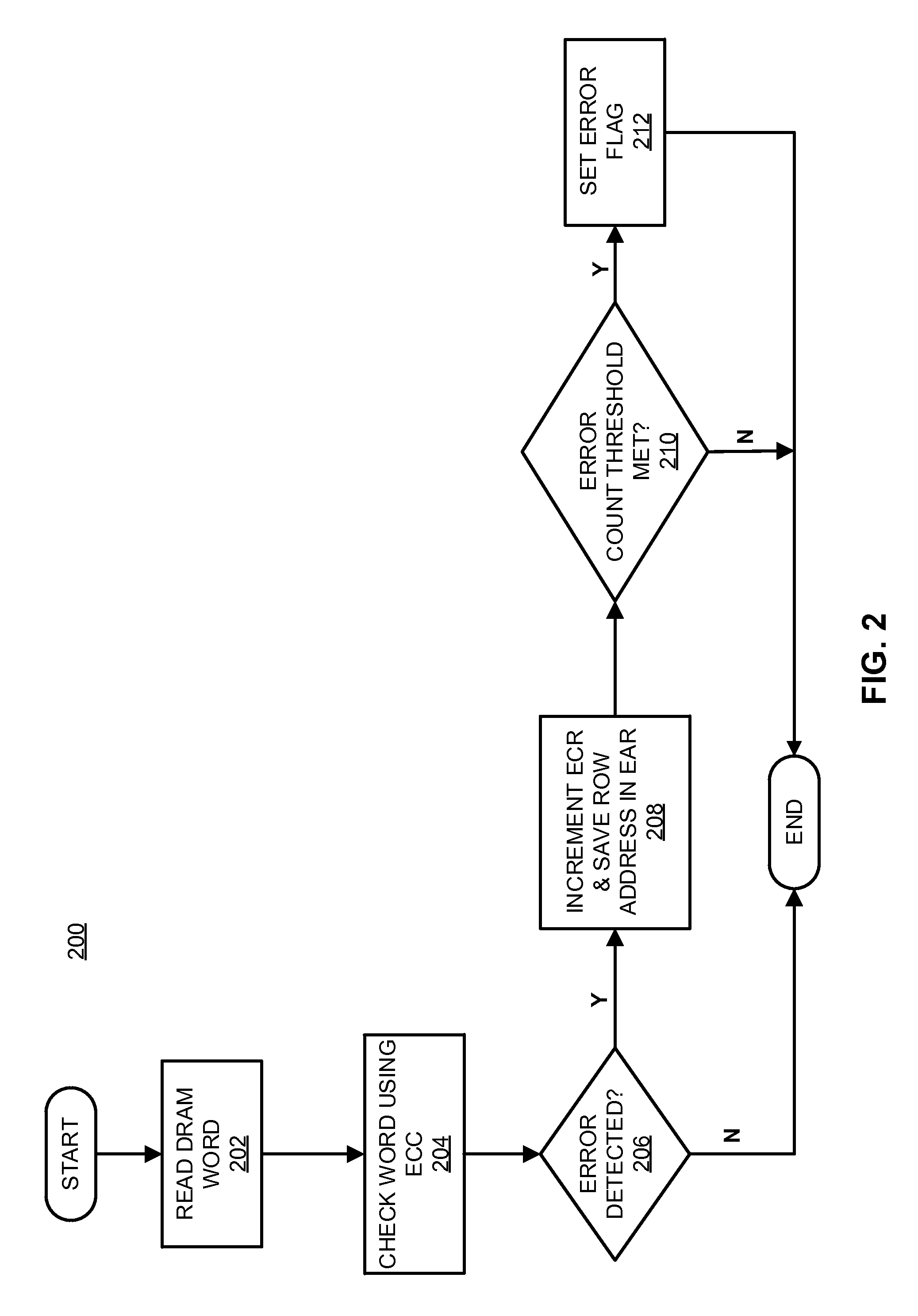

Error monitoring of a memory device containing embedded error correction

ActiveUS20160224412A1Input/output to record carriersCode conversionMemory controllerError correcting

Embodiments of the present disclosure provide an approach for monitoring the health and predicting the failure of dynamic random-access memory (DRAM) devices with embedded error-correcting code (ECC). Additional registers are embedded on the DRAM device to store information about the DRAM, such as the number and location of soft errors detected by the device. When the DRAM device detects a soft error, it will update the information stored in the additional registers. A controller compares the information stored in the additional registers to associated thresholds. In some embodiments, after comparing the information to the associated thresholds, the controller may determine whether to schedule a repair action. In other embodiments, the controller may determine whether to alert the memory controller that the DRAM may be failing.

Owner:IBM CORP

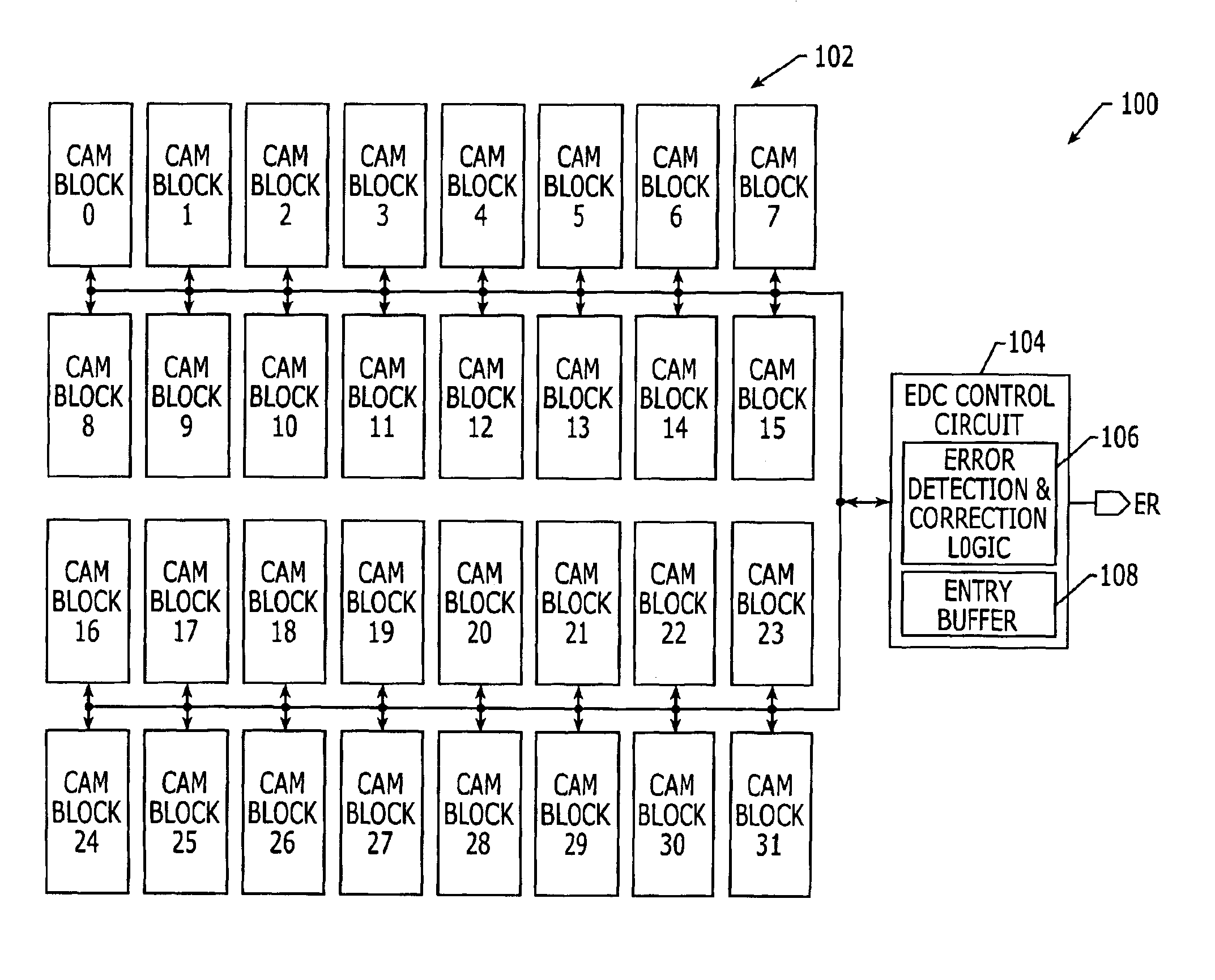

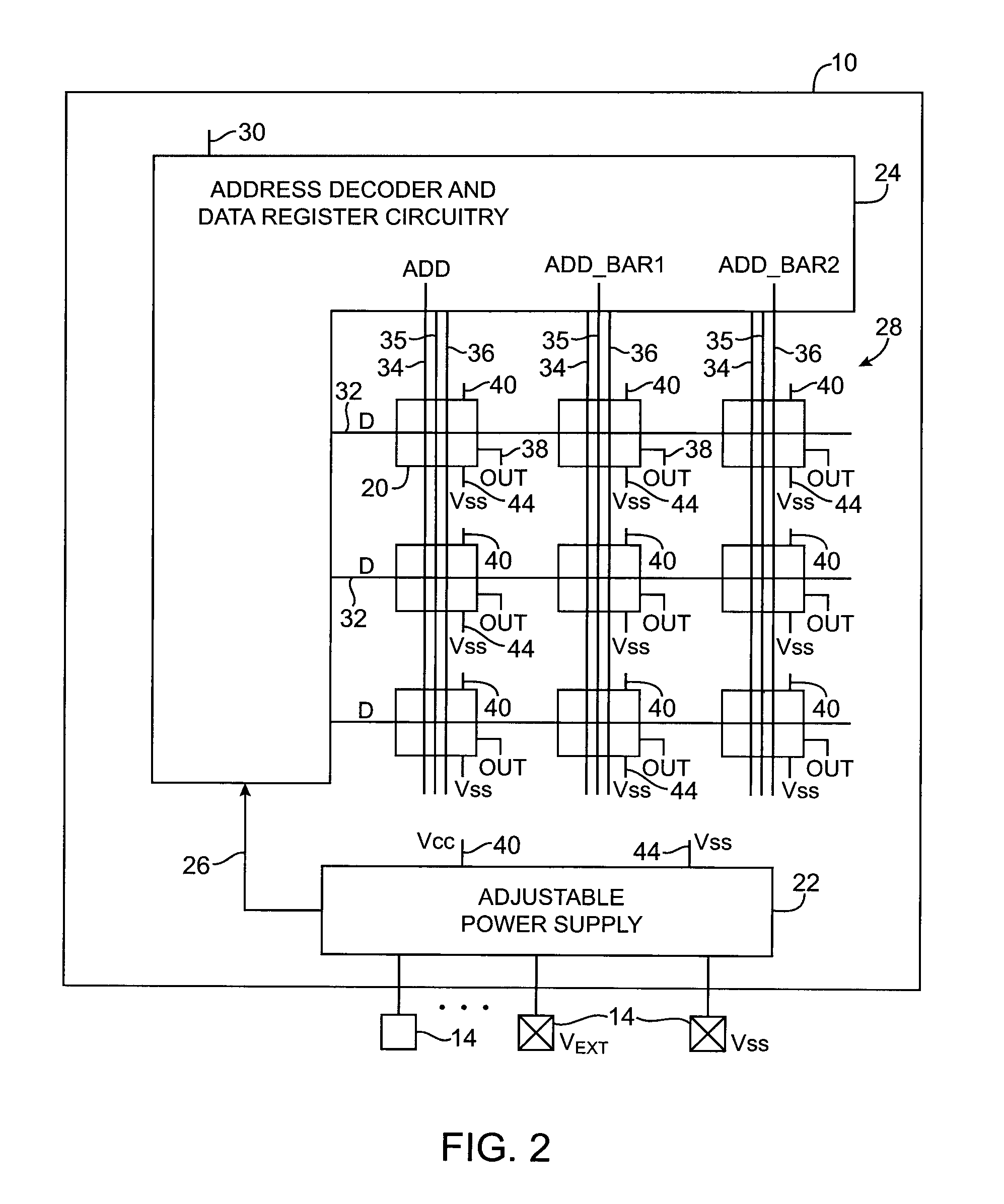

Content addressable memory (CAM) devices having error detection and correction control circuits therein and methods of operating same

Content addressable memory (CAM) devices include error detection and correction (EDC) control circuits therein. The EDC control circuit operates to correct soft errors in entries within a plurality of internal CAM array blocks with, at most, limited interruption to other operations performed by the CAM device. The EDC control circuit utilizes a multi-bit check word associated with each entry to detect a soft error and perform one-bit error correction on the entry. The EDC control circuit is configured to be active during a background mode of operation when the CAM array blocks are undergoing search operations in a foreground mode of operation. A CAM array block may also include a column of dual-function check bit cells that are configured to operate as a column of CAM cells when necessary to replace a defective column of CAM cells.

Owner:AVAGO TECH INT SALES PTE LTD

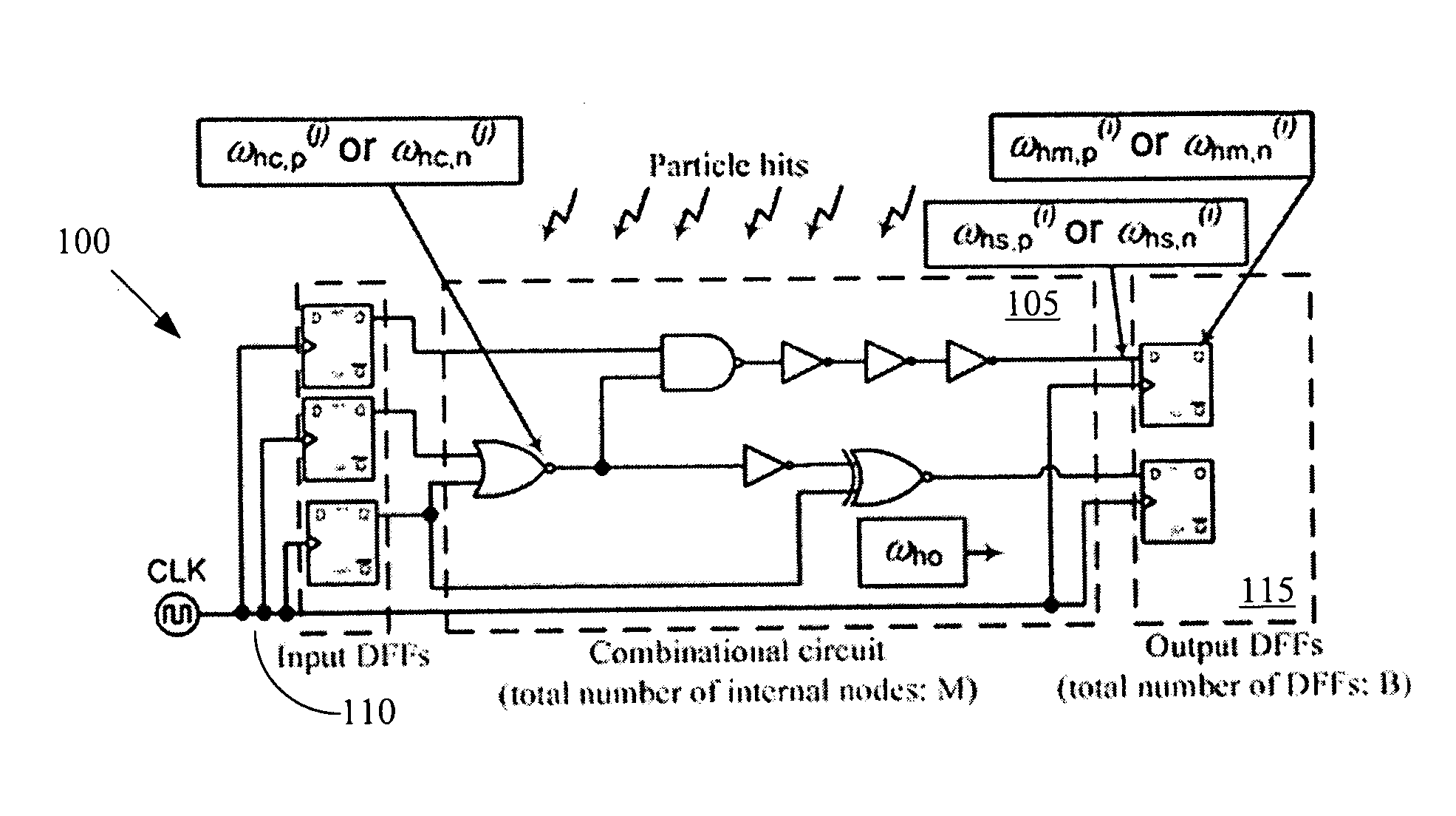

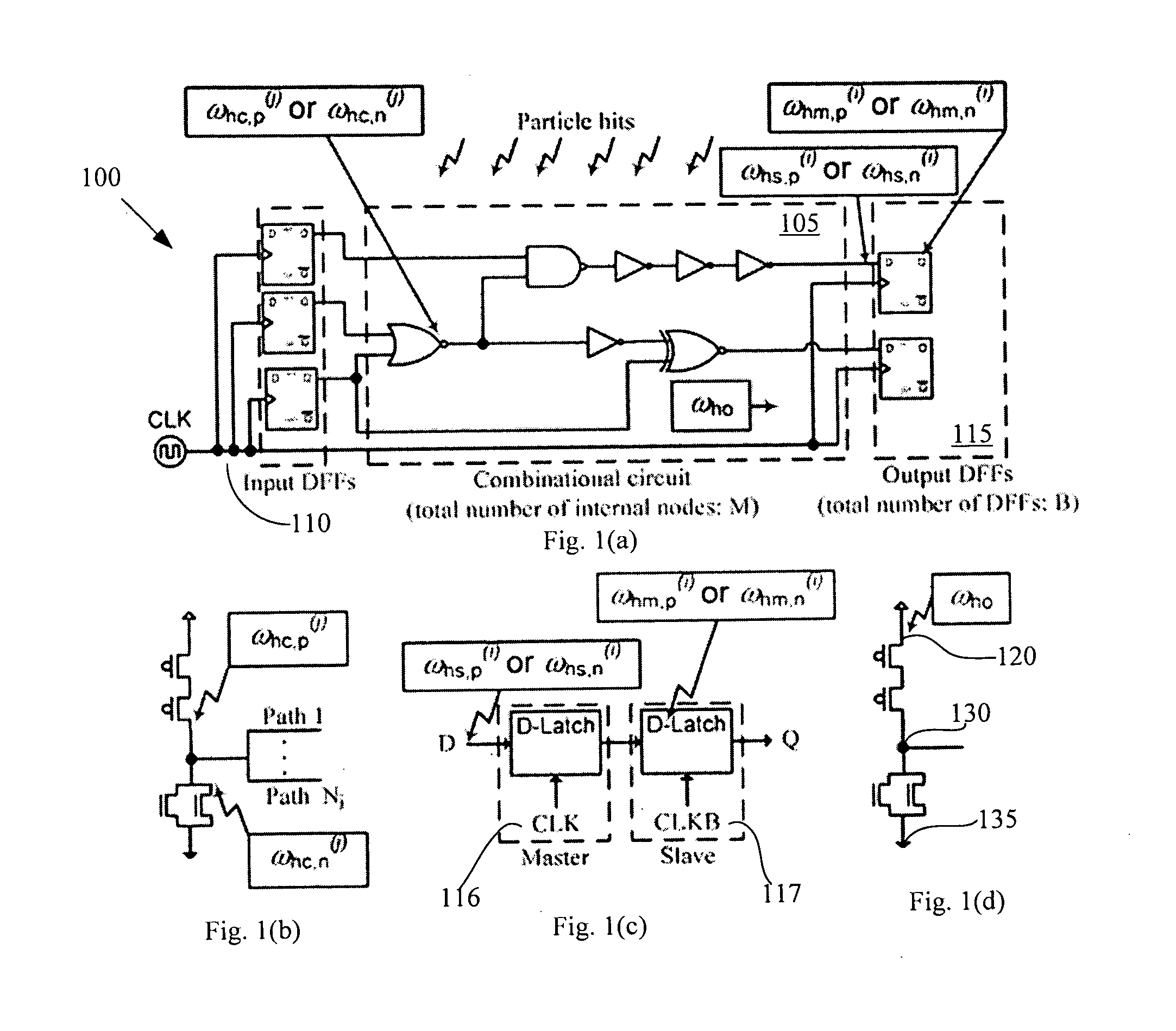

Soft error rate analysis system

InactiveUS20070226572A1Improve reliabilityError rateElectronic circuit testingError detection/correctionElectronic systemsDependability

A method for improving reliability of an electronic system by evaluating a soft error rate is disclosed. A gate-level representation of the electronic system is converted to a graph, the graph having vertices and edges that correspond to nodes and gates of the electronic system. Input vectors are generated, which correspond to inputs supplied to the electronic system. A soft error rate for the electronic system is evaluated during a simulated operation of the electronic system, and the evaluated soft error rate is correlated to a set of parameters used to configure the electronic system.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

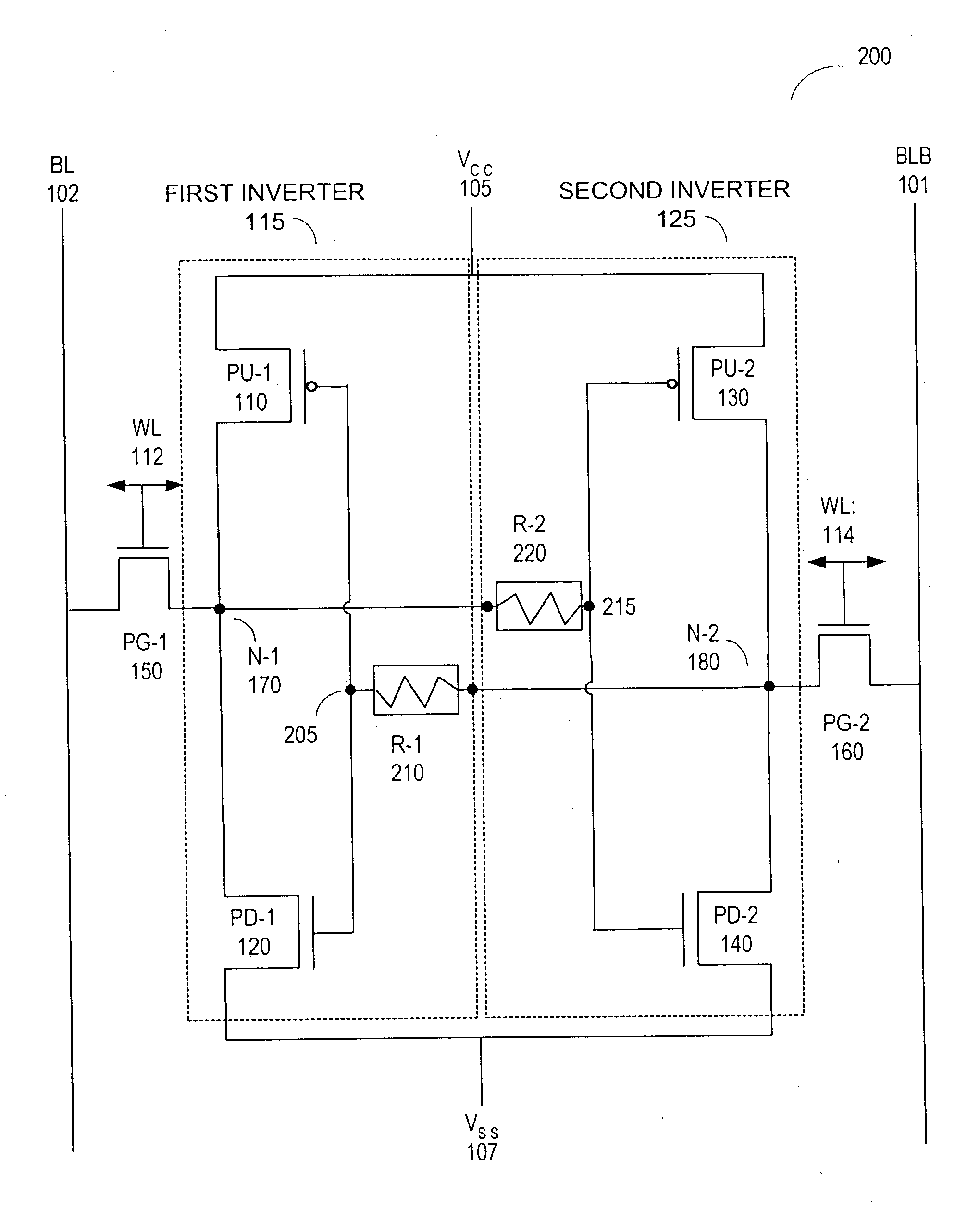

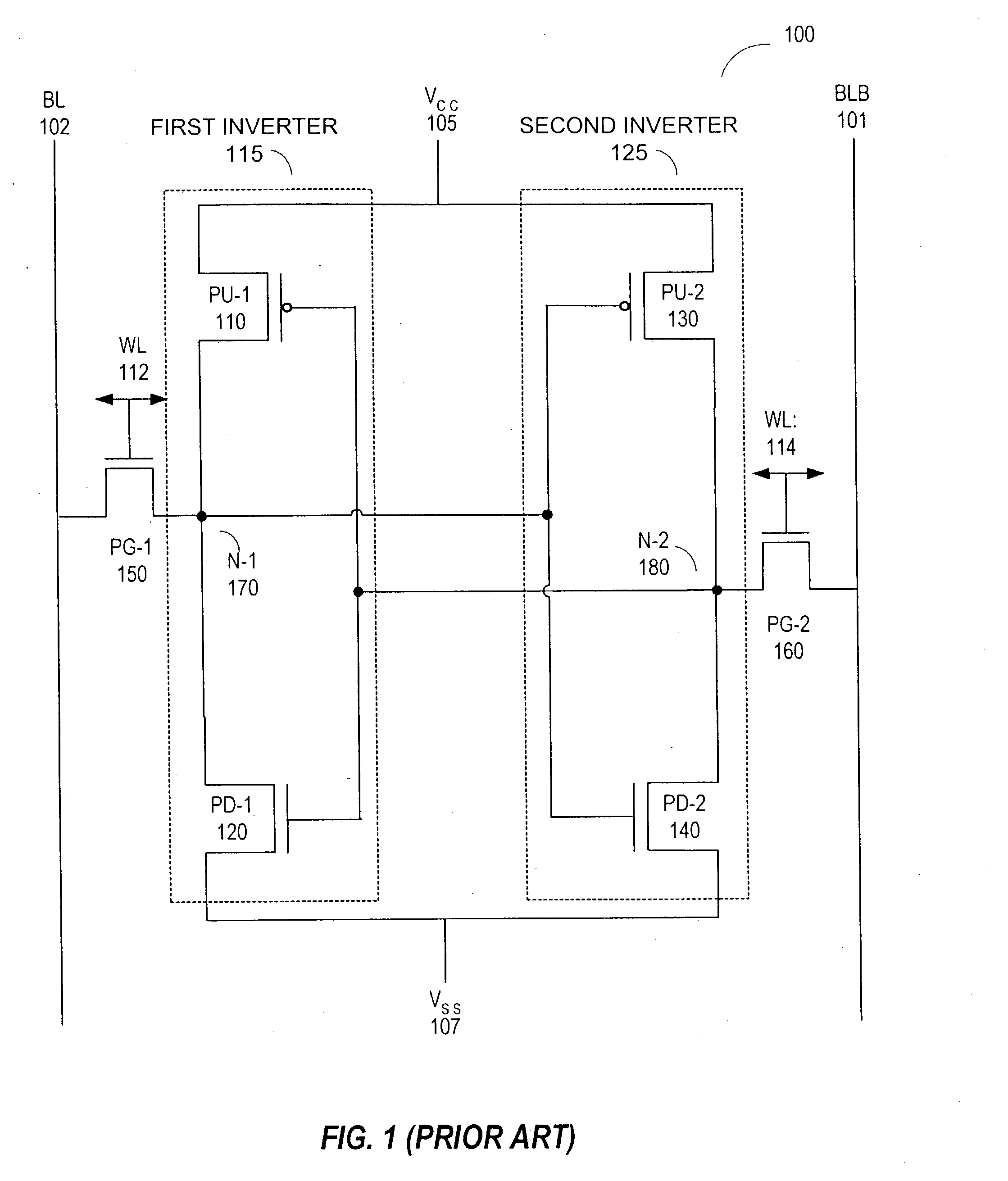

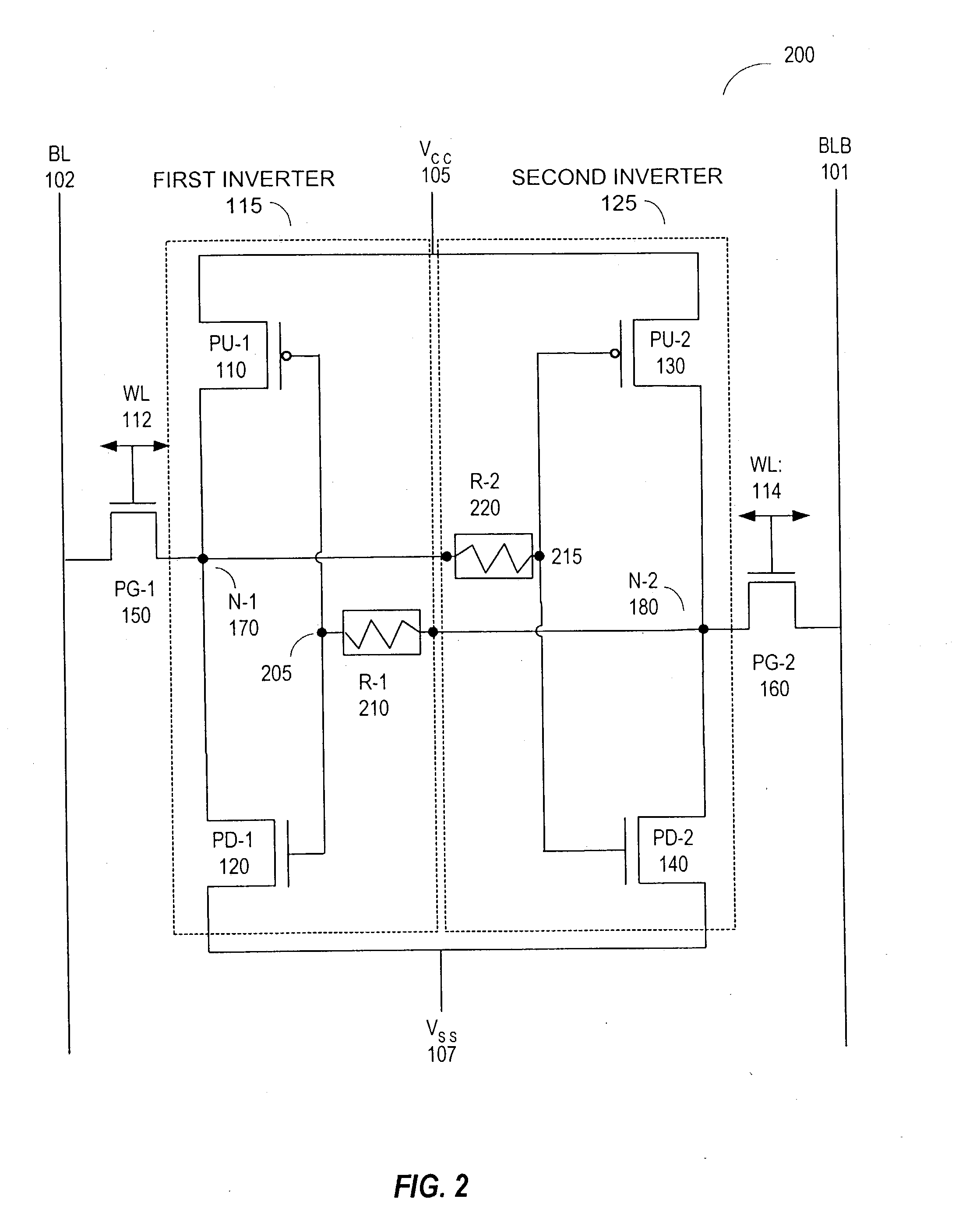

SRAM cell design with high resistor CMOS gate structure for soft error rate improvement

A high resistor SRAM memory cell to reduce soft error rate includes a first inverter having an output as a first memory node, and a second inverter having an output as a second memory node. The second memory node is coupled to an input of the first inverter through a first resistor. The first memory node is coupled to an input of the second inverter through a second resistor. A pair of access transistors are respectively coupled to a pair of bit lines, a split word line and one of the memory nodes. The resistors are prepared by coating a layer of silicide material on a selective portion of the gate structure of the transistors included in the first inverter, and connecting a portion of the gate structure that is substantially void of the silicide material to the drain of the transistors included in the second inverter.

Owner:TAIWAN SEMICON MFG CO LTD

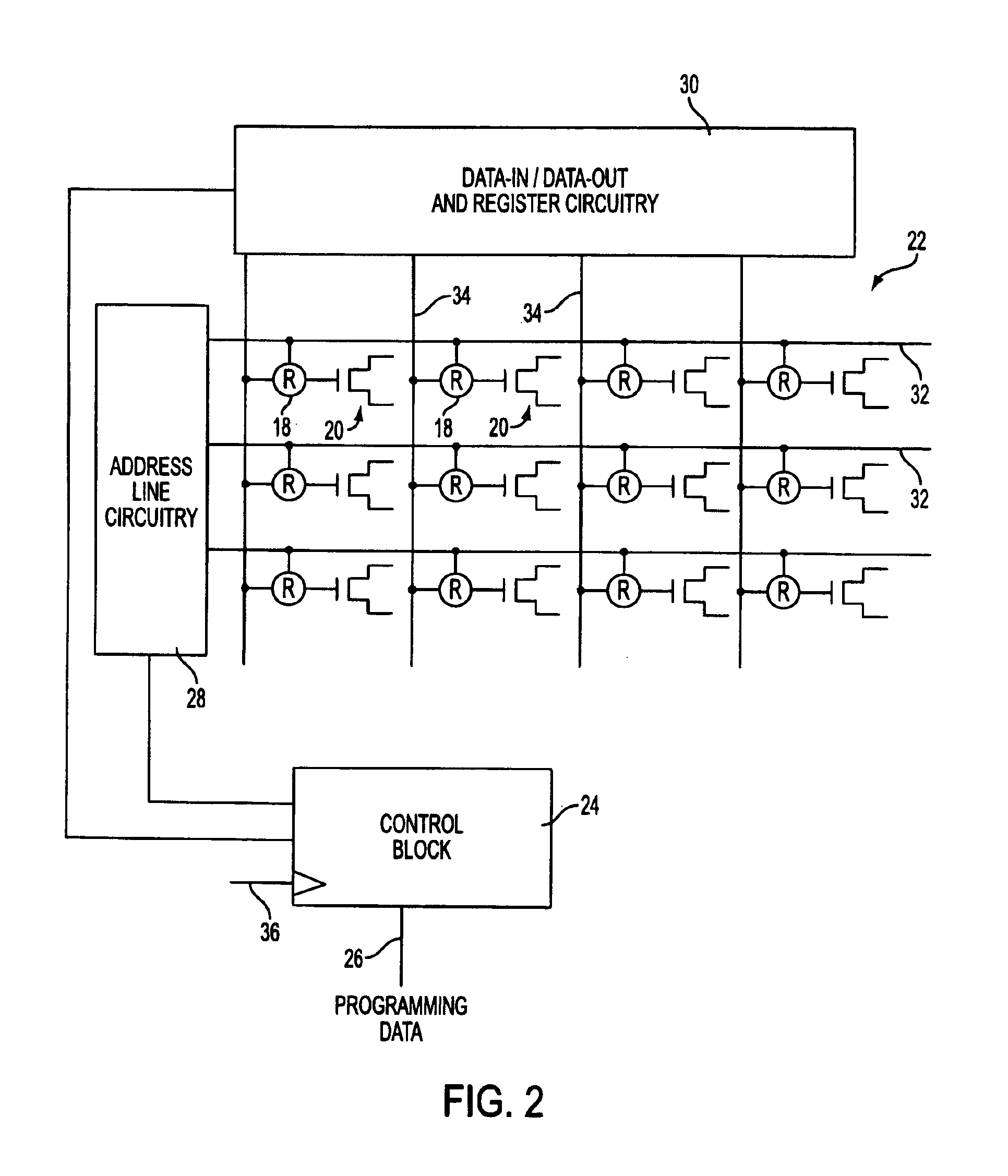

Programmable logic devices with stabilized configuration cells for reduced soft error rates

InactiveUS6876572B2Improved soft error rate performanceReduce the impactSolid-state devicesSemiconductor/solid-state device manufacturingProgrammable logic deviceEngineering

Programmable logic devices are provided having configuration memory cells that exhibit decreased soft error rates. A stabilizing capacitor may be connected between each of the memory cell's input and output terminals. The capacitor may be a metal-insulator-metal capacitor formed using a vertical structure, a horizontal structure, or a hybrid vertical-horizontal structure. The memory cell may have inverter transistors of increased strength to help stabilize the memory cell.

Owner:ALTERA CORP

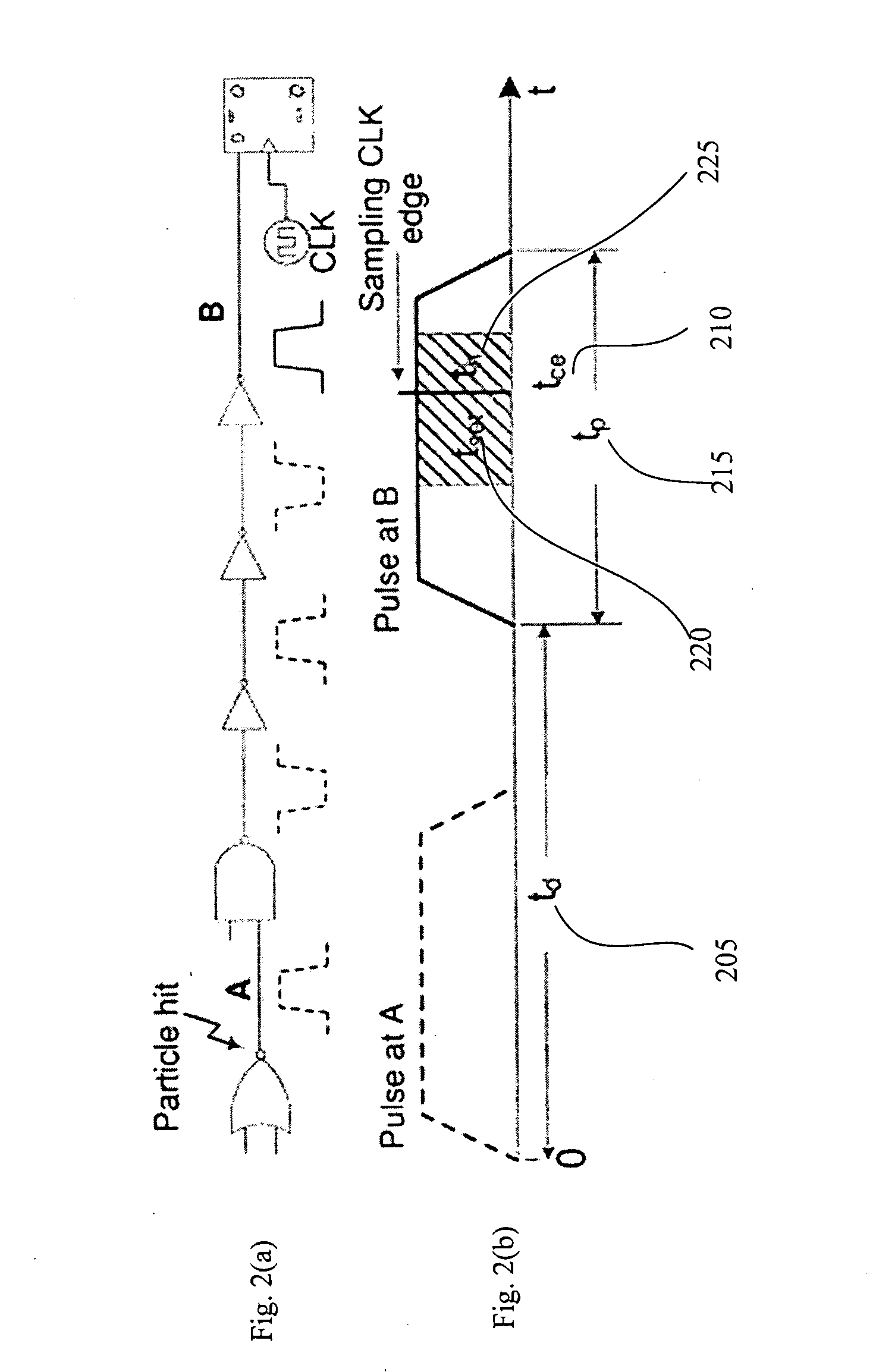

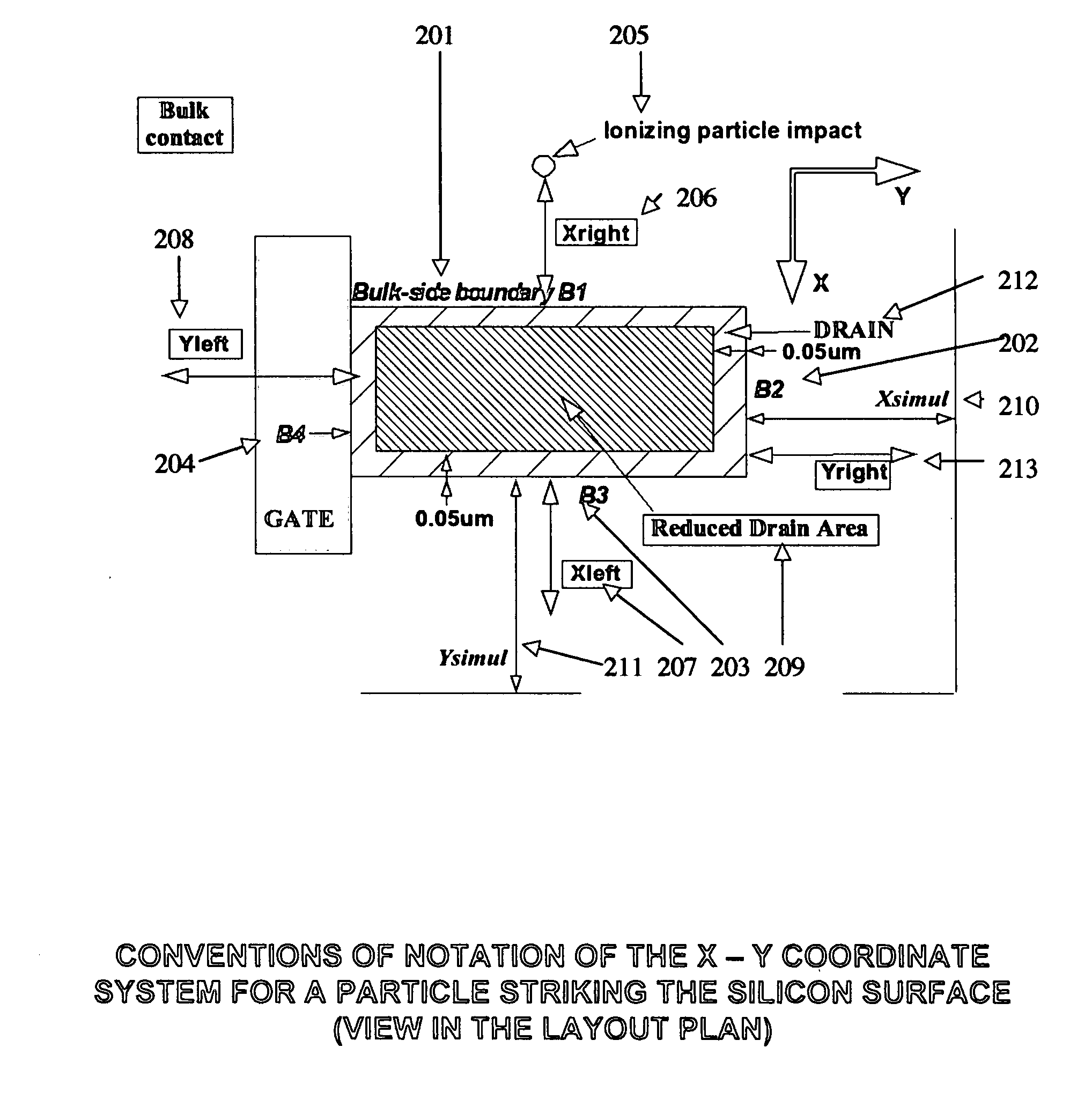

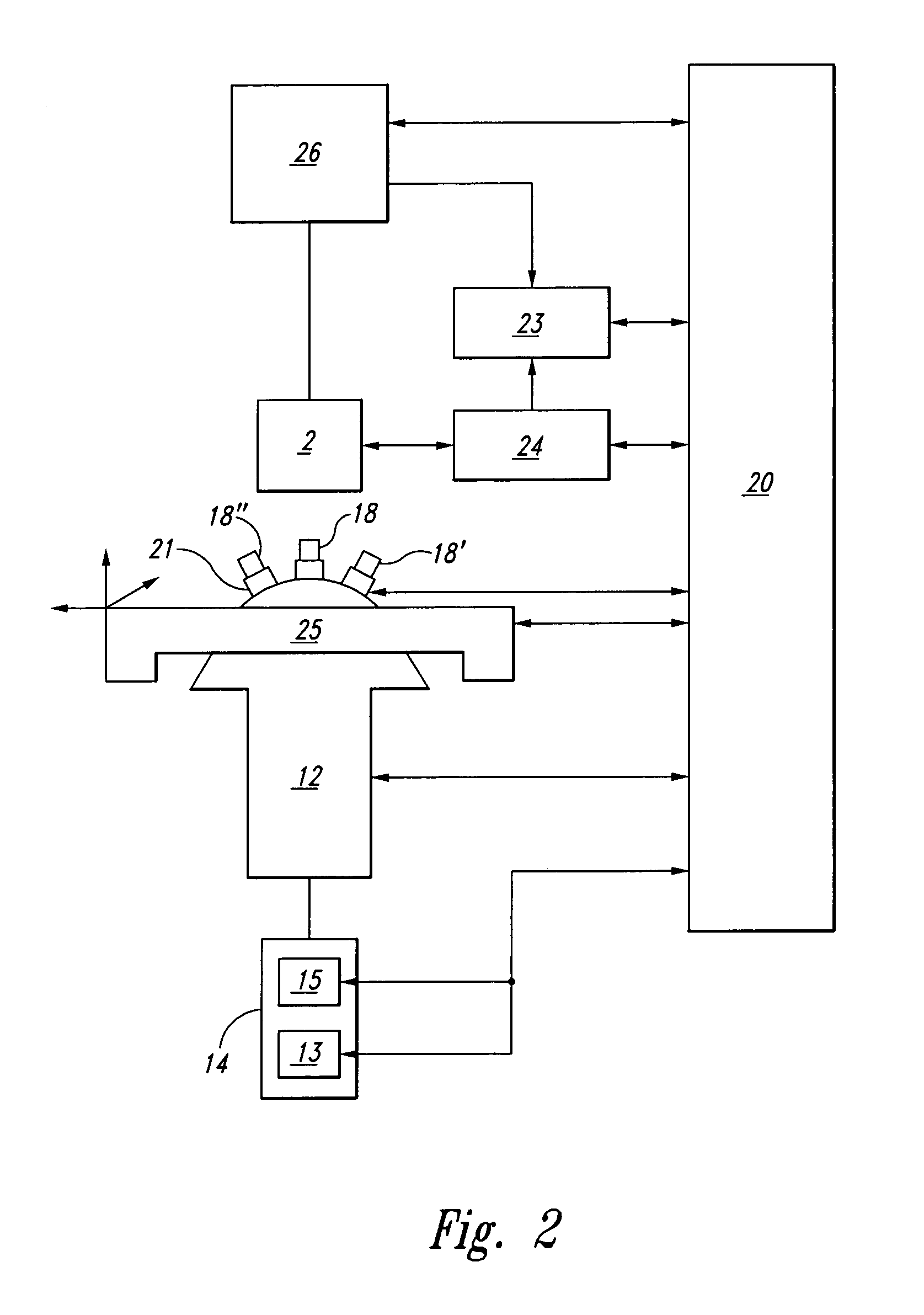

Apparatus and method for the determination of SEU and SET disruptions in a circuit caused by ionizing particle strikes

InactiveUS20080077376A1Accurate and fast simulation methodHigh speedAnalogue computers for electric apparatusDesign optimisation/simulationElectricityAlpha particle

This application discloses a new, and useful computer implemented method and apparatus that can be used for the determination of SEU and SET disruptions in a cell or circuit, caused by ionizing particle strikes, including those caused by neutrons (cosmic rays), alpha particles or heavy ions. The method of the present invention includes a fast simulation tool (“TFIT”), which calculates the electrical effect of a particle's impact to a cell, or a circuit. The method is used to predict the soft error rate (SER) calculations and the FIT (number of failures-in-time) performance of designated test cell's design, depending on the type of particle environment specified. The method is designed to simulate the response of the cell or circuit to the stimuli caused by a particle strike. These stimuli are modeled as a “current source” placed between the drain and the source of each struck transistor.

Owner:IROC TECH

Memory elements with increased write margin and soft error upset immunity

Memory elements are provided that exhibit immunity to soft error upset events when subjected to radiation strikes such as high-energy atomic particle strikes. The memory elements may each have four inverter-like transistor pairs that form a bistable element and a pair of address transistors. There may be four nodes in the transistor each of which is associated with a respective one of the four inverter-like transistor pairs. There may be two control transistors each of which is coupled between the transistors in a respective one of the inverter-like transistor pairs. During data writing operations, the two control transistors may be turned off to temporarily decouple the transistors in two of the four inverter-like transistor pairs.

Owner:TAHOE RES LTD

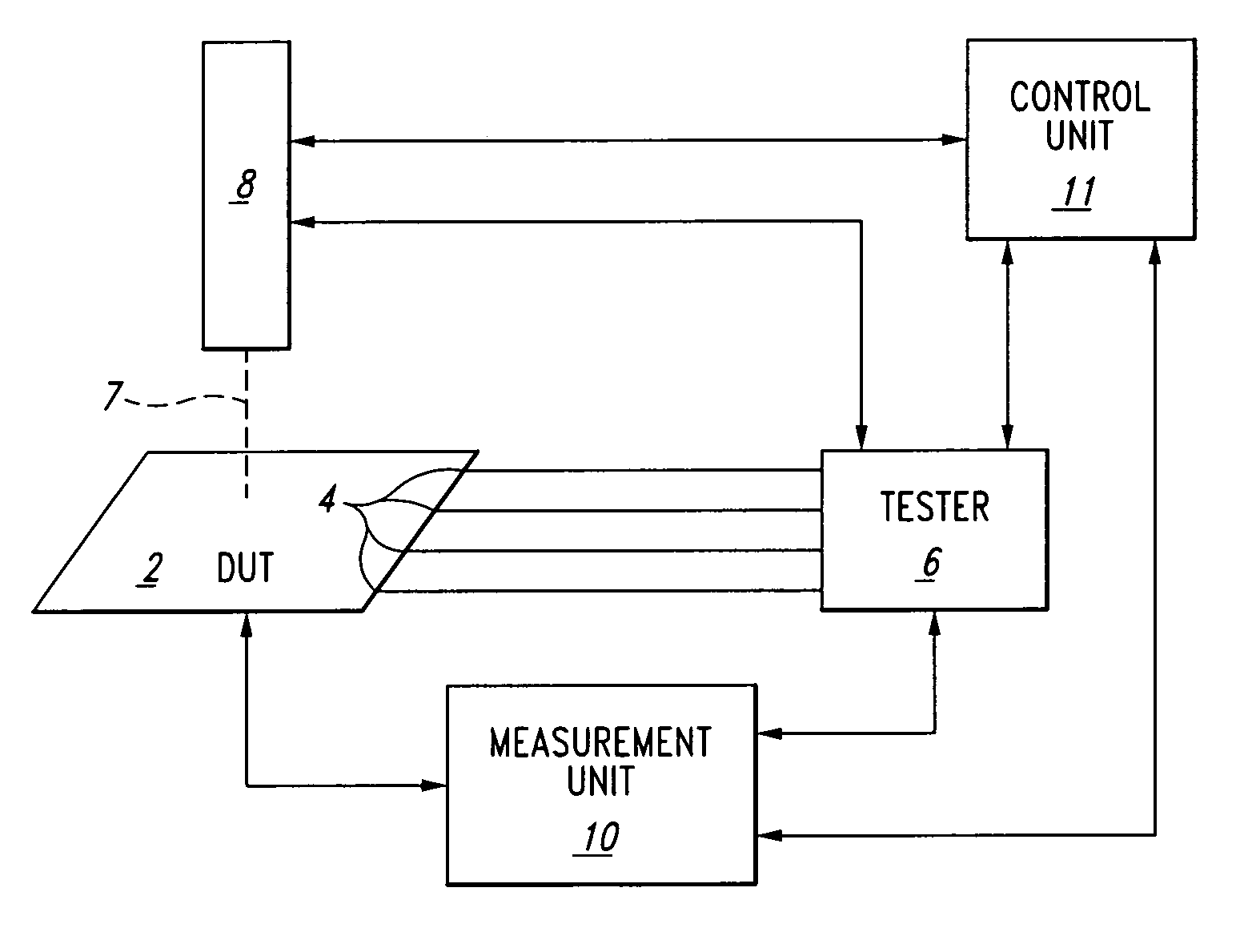

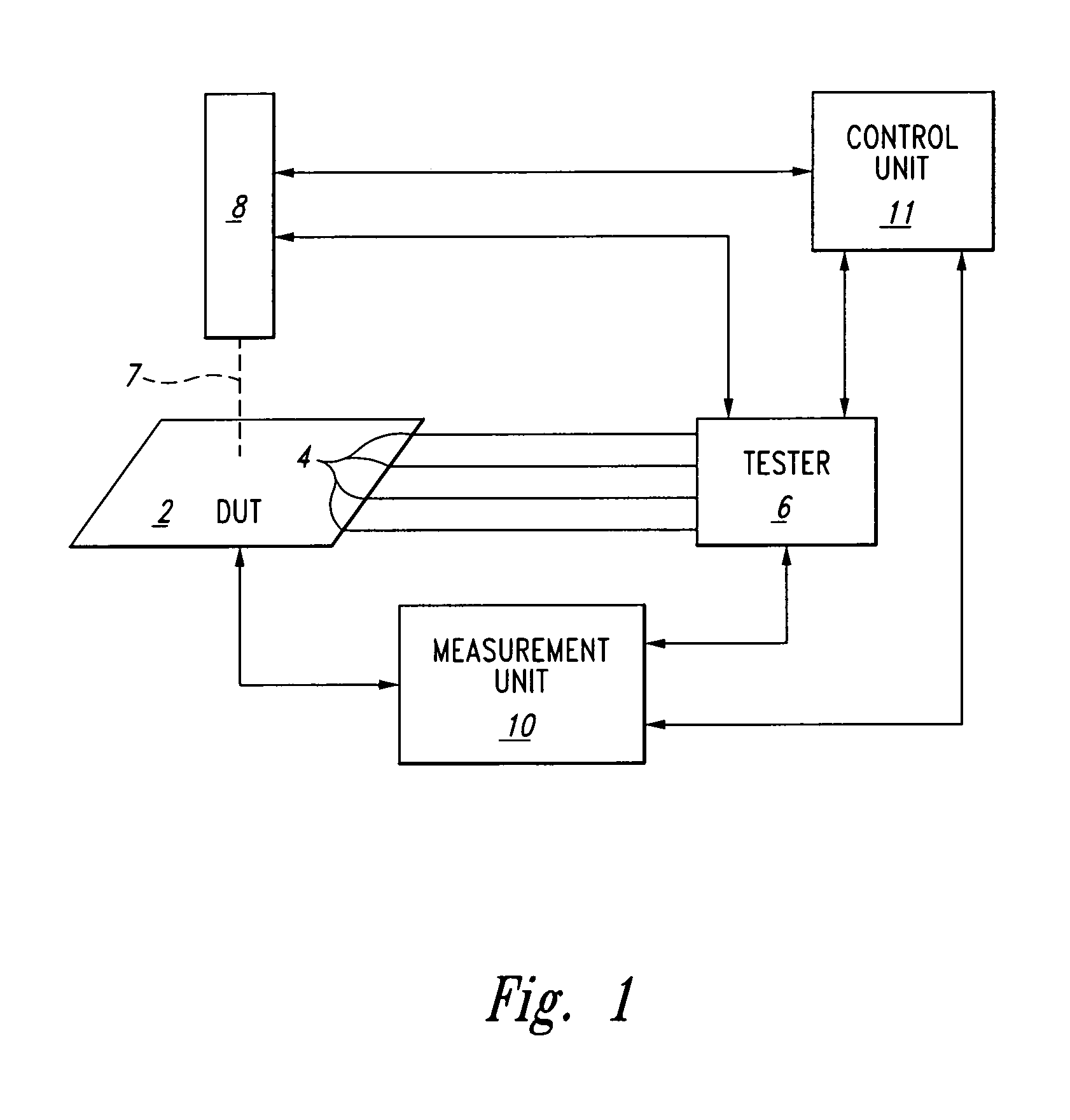

Spatial and temporal selective laser assisted fault localization

ActiveUS6967491B2Electric discharge tubesSpecial data processing applicationsSpecific testLaser assisted

A method and apparatus for laser-assisted fault mapping which synchronizes the laser control with the tester unit. The inventive method provides for laser-assisted pseudo-static fault mapping to localize defects in a device whose inputs are being stimulated dynamically by a tester. It further provides for laser-assisted dynamic soft error mapping, to localize in terms of location and to correlate with respect to a specific test vector, sensitive areas in a device by utilizing device performance criteria such as pass-fail status outputs. The apparatus includes a fully controllable dynamic laser stimulation apparatus connected to a control unit that provides complete synchronization with a tester unit.

Owner:DCG SYST

Restoring access to a failed data storage device in a redundant memory system

A computer system comprising a memory system that comprises a plurality of memory modules; and a memory controller that accesses the plurality of memory modules to service memory requests. The computer system also comprises an error-type memory controller that configures the noted access such that the memory controller can continue to access a failed one of the plurality of memory modules that incurred a soft error.

Owner:HEWLETT PACKARD DEV CO LP

Dual-ported read SRAM cell with improved soft error immunity

In a preferred embodiment, the invention provides a circuit and method for improving the soft error rate in a dual-port read SRAM cell. A write-only transfer device is connected to a cross-coupled latch, a first wordline, and a first bitline. A first read-only transfer device is connected to a second bitline, a second wordline, and a first pull-down device. A second read-only transfer device is connected to the first bitline, the first wordline, and a second pull-down device. A clear memory transfer device is connected to the cross-coupled latch, a third bitline, and a third pull-down device. This configuration allows a reduction in the size of a dual-port SRAM cell with little or no reduction in the read access time of the cell. The reduction in size also reduces SER by reducing the cross-sectional, p / n junction area exposed to radiation.

Owner:HEWLETT PACKARD DEV CO LP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com