Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2381 results about "Flip-flop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

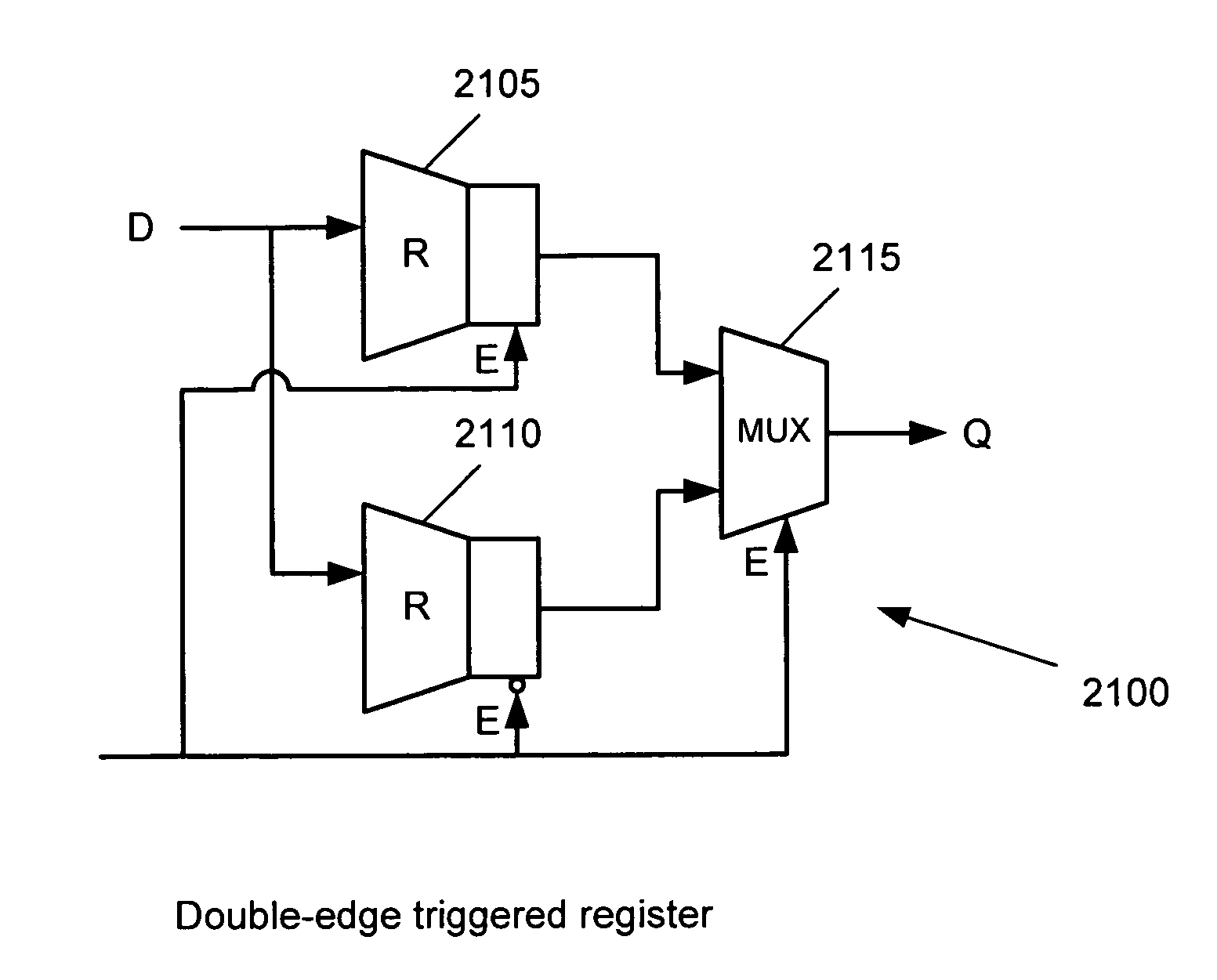

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information – a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems.

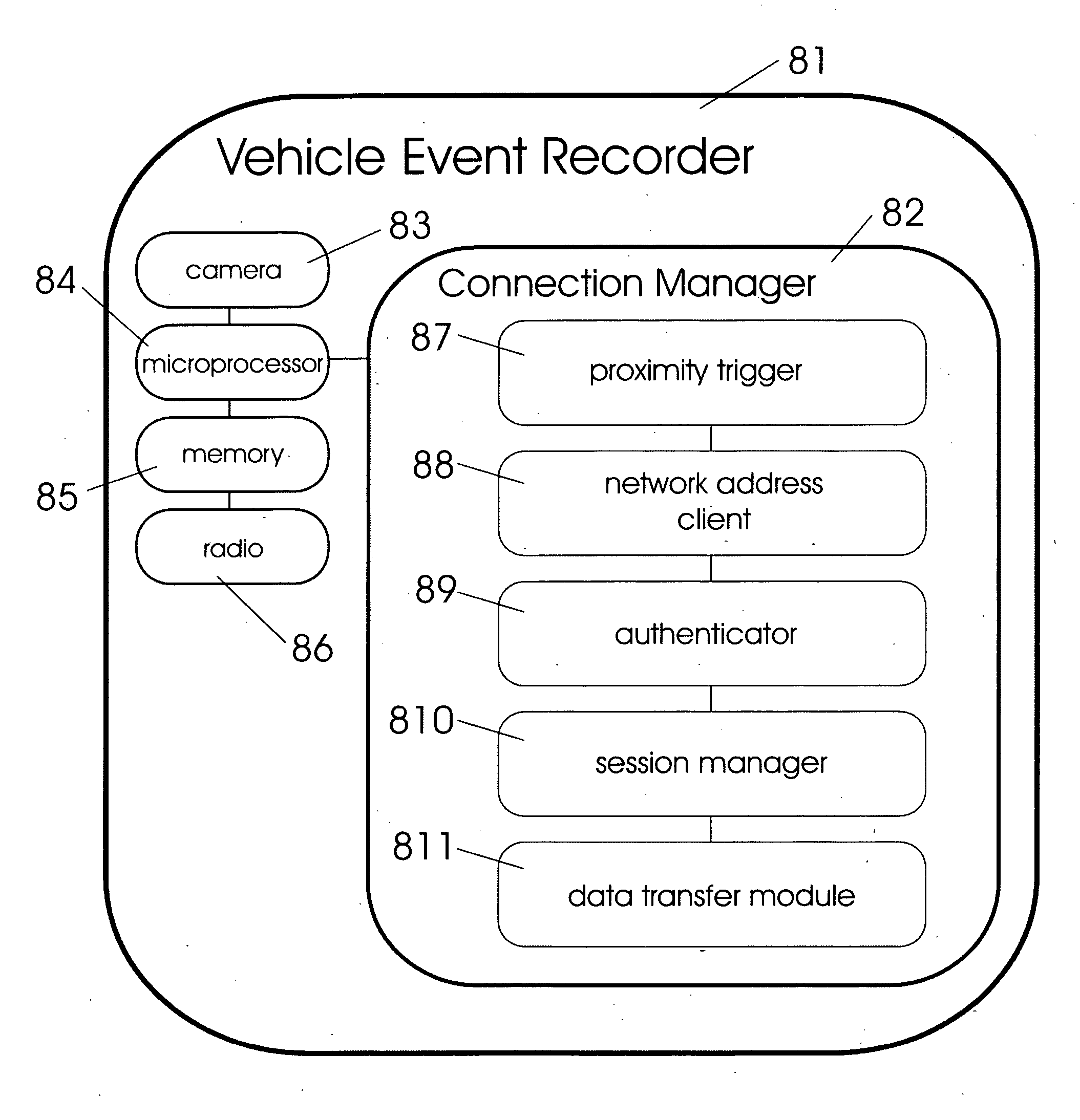

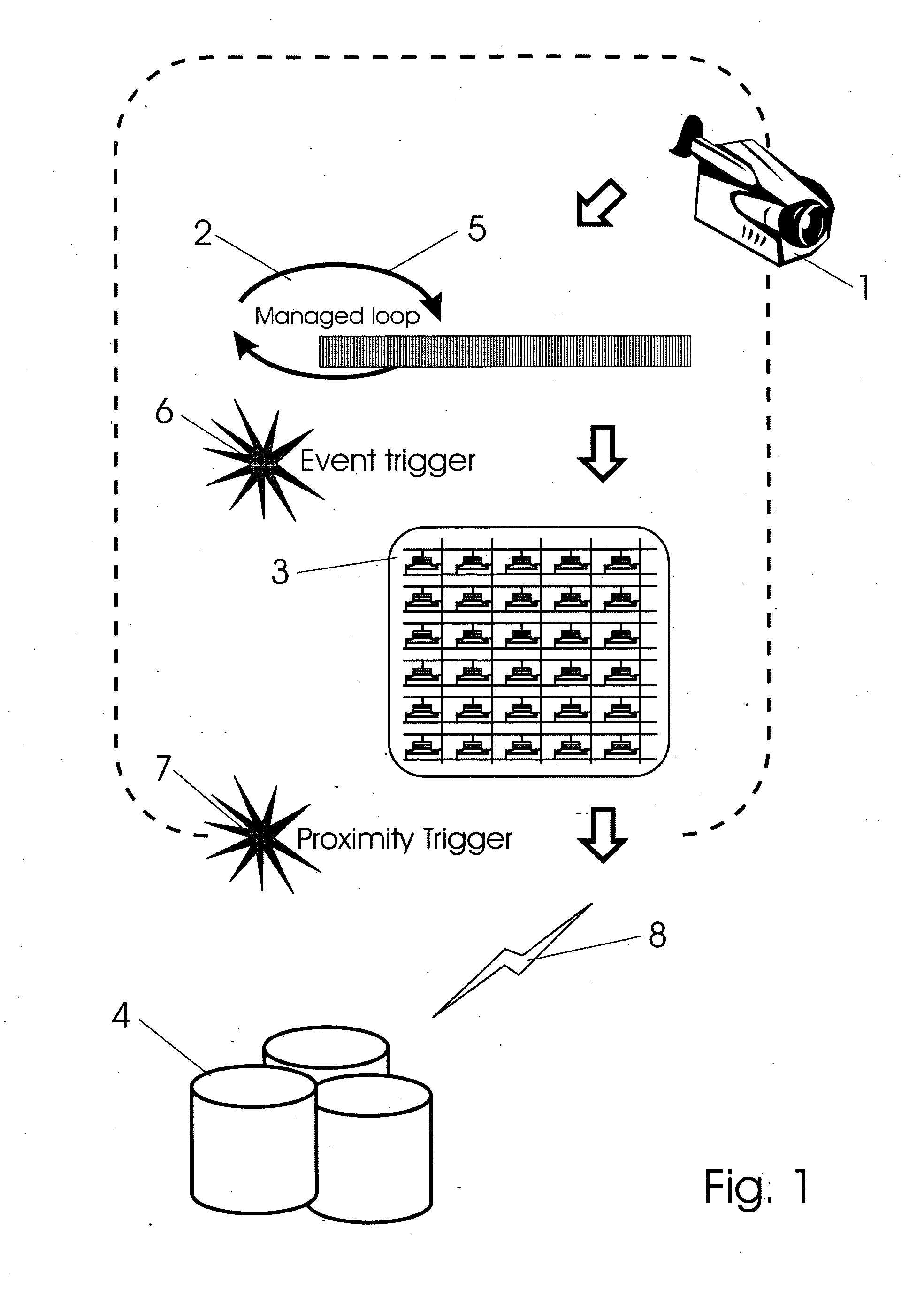

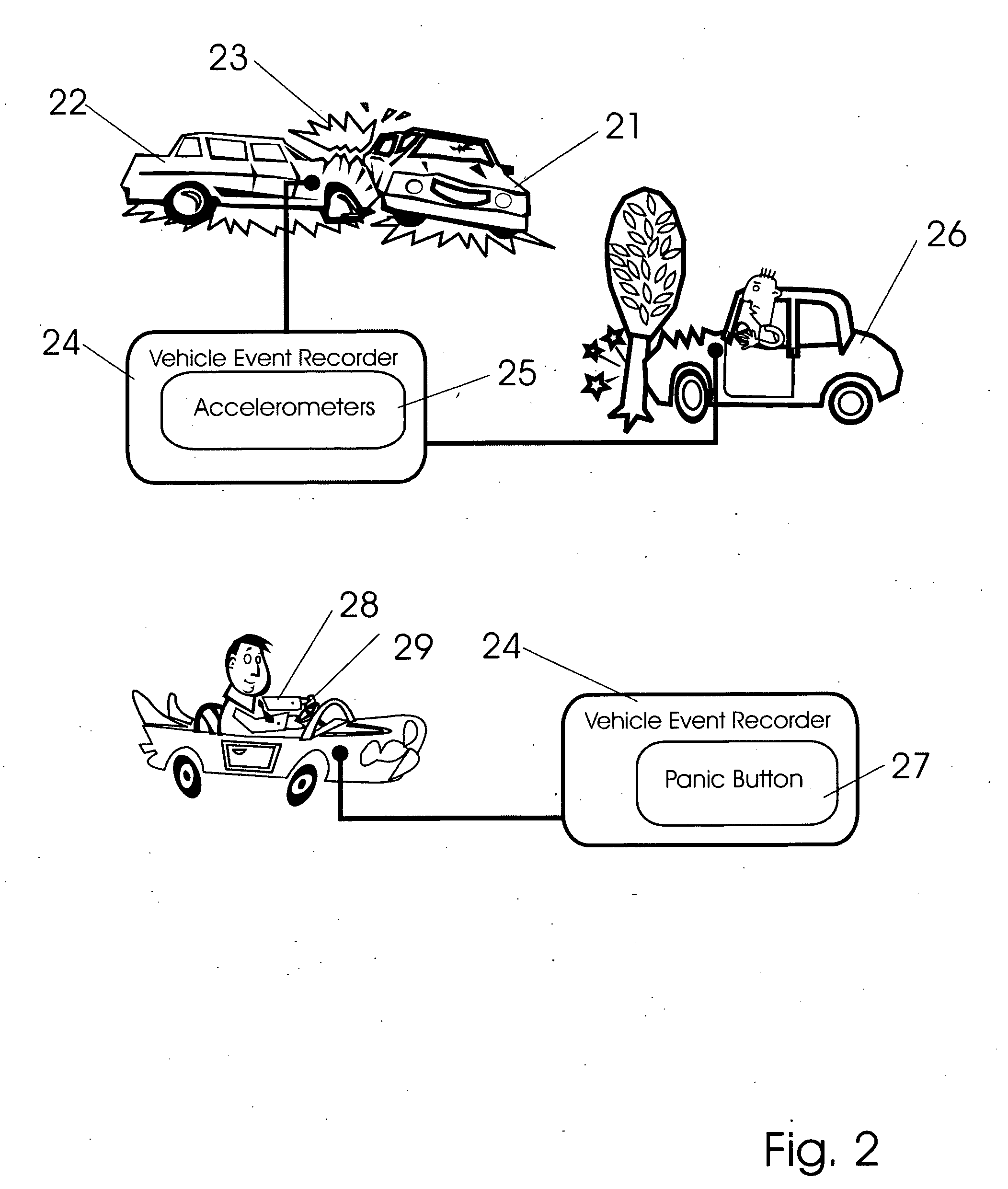

Multi-stage memory buffer and automatic transfers in vehicle event recording systems

InactiveUS20070132773A1High utility and efficiencyRegistering/indicating working of vehiclesTelevision systemsData transmissionIn vehicle

Vehicle event recorder systems are arranged with three stage memories and special mechanism to manage those memories including transfer of data there between. Namely, a managed loop memory receives data from a video camera in real-time and continuously overwrites expired data implicitly determined no longer useful. Data in a managed loop memory is only passed to a more stable memory, a high-capacity buffer memory, in response to an event having occurred. An event trigger produces a signal, which causes data transfer between the managed loop memory and an on-board, high-capacity buffer memory. The high-capacity buffer memory is suitable for storing video series associated with a plurality of events. Finally, a permanent data store is arranged to receive data from the high-capacity buffer memory whenever the system returns and falls within a predetermined proximity of a download station.

Owner:SMARTDRIVE SYSTEMS

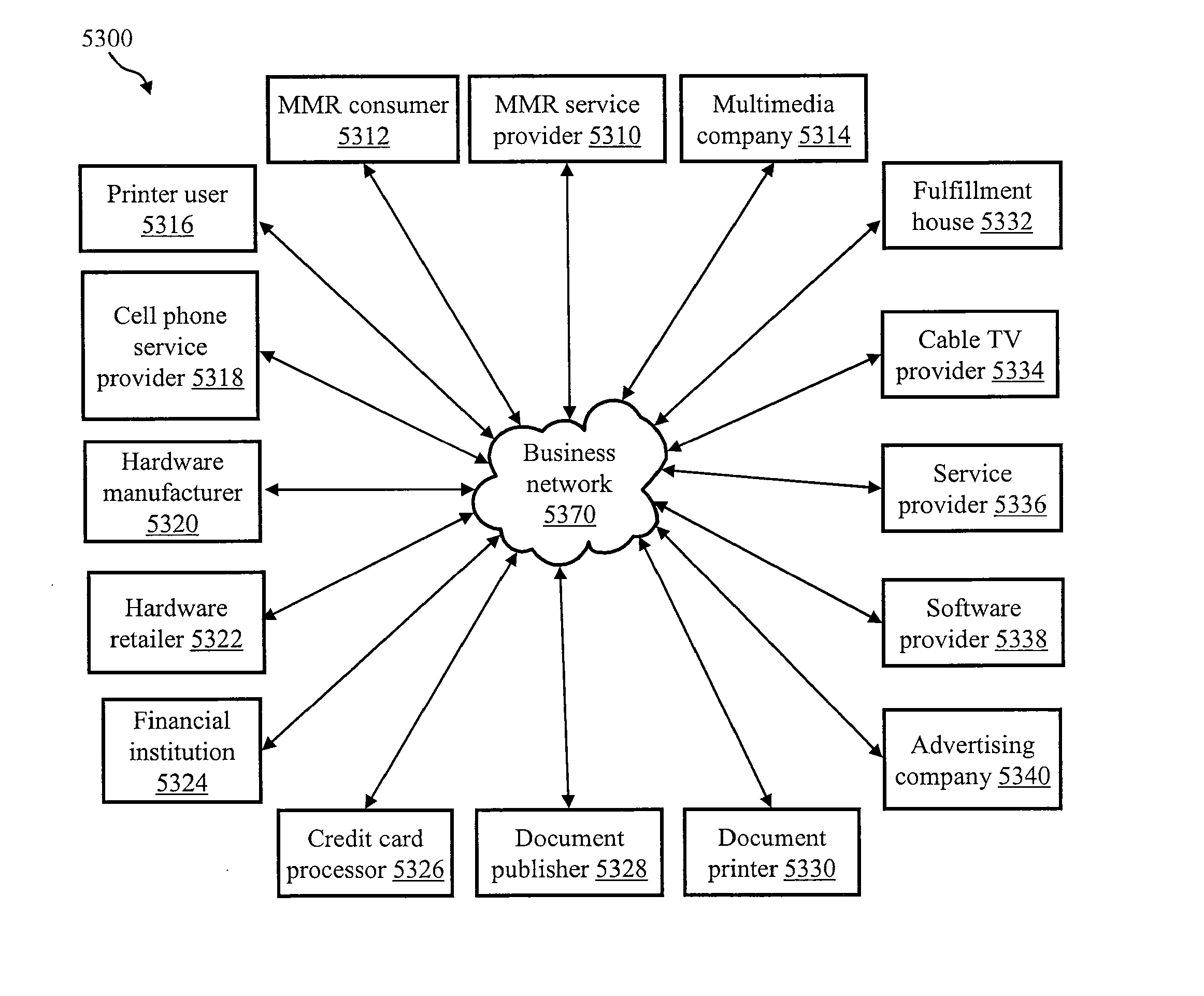

Triggering applications based on a captured text in a mixed media environment

ActiveUS20070050360A1Easy to optimizeFacilitate methodMultimedia data indexingSpecial data processing applicationsInformation retrievalApplication software

A Mixed Media Reality (MMR) system and associated techniques are disclosed. The MMR system provides mechanisms for forming a mixed media document that includes media of at least two types (e.g., printed paper as a first medium and digital content and / or web link as a second medium). In one particular embodiment, the MMR system includes an action processor and method, and MMR documents with an associated action. The MMR document structure is particularly advantageous because the ability to specify different actions for different MMR documents, combined with the ability to create any number of MMR documents for a particular location on any media, allows the MMR architecture to serve as a universal trigger or initiator for additional processing. In other words, addition processing or actions can be triggered or initiated based on MMR recognition. The action processor receives the output of the MMR recognition process which yields an MMR document including at least one action. The action processor executes that action which includes various commands to the MMR system or other systems coupled to the MMR system. The MMR system architecture is advantageous because an action can be executed by pointing the capture device at a block of text, and the action is performed. Example actions include retrieving the text in electronic form to the capture device, retrieving the specification for the action, inserting data to a MMR document, transferring data between documents, purchasing items, authoring actions or reviewing historical information about actions. The MMR system includes a variety of user applications (one or more actions) initiated by the MMR recognition of a text patch such as information retrieval for a travel guide book, stock listings or advertisements; information capture such as recording content from a conference, recording and storing multimedia associated with the document, capturing information for a calendar and on the fly authoring; purchasing media files for storage on any part of an MMR document.

Owner:RICOH KK

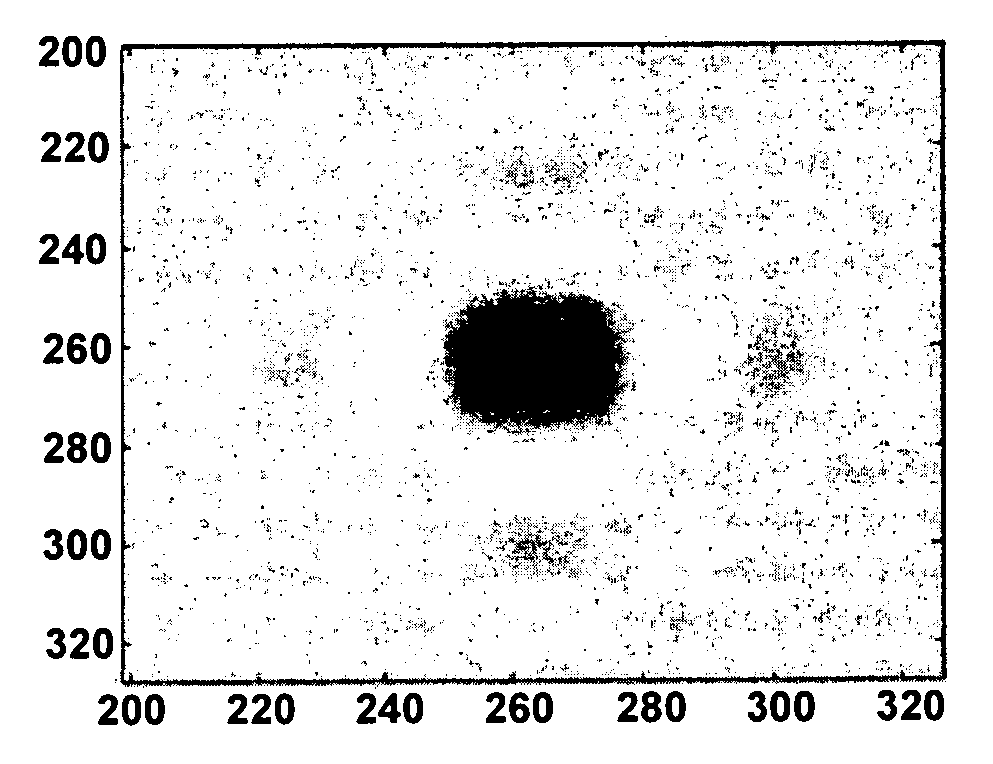

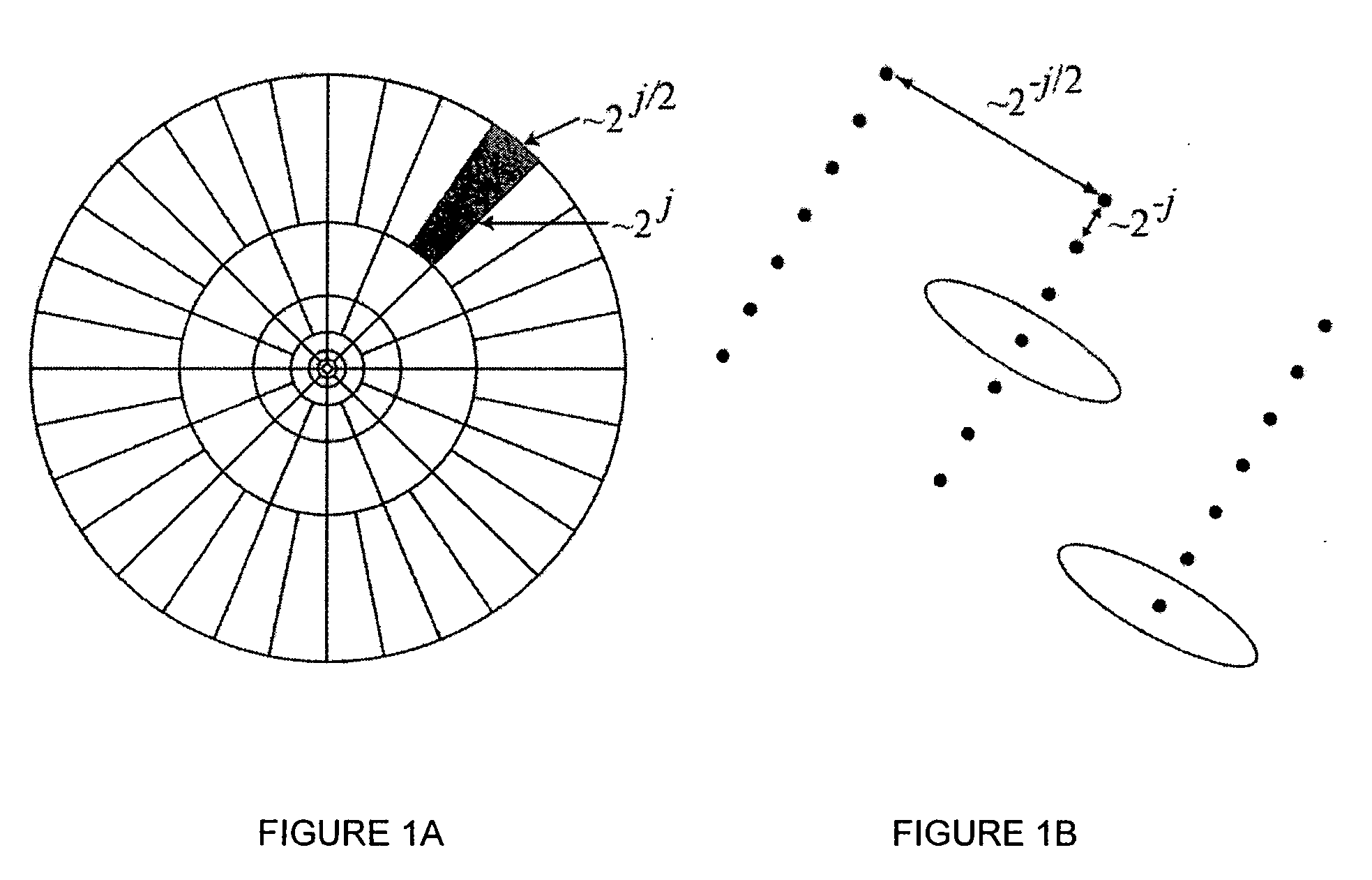

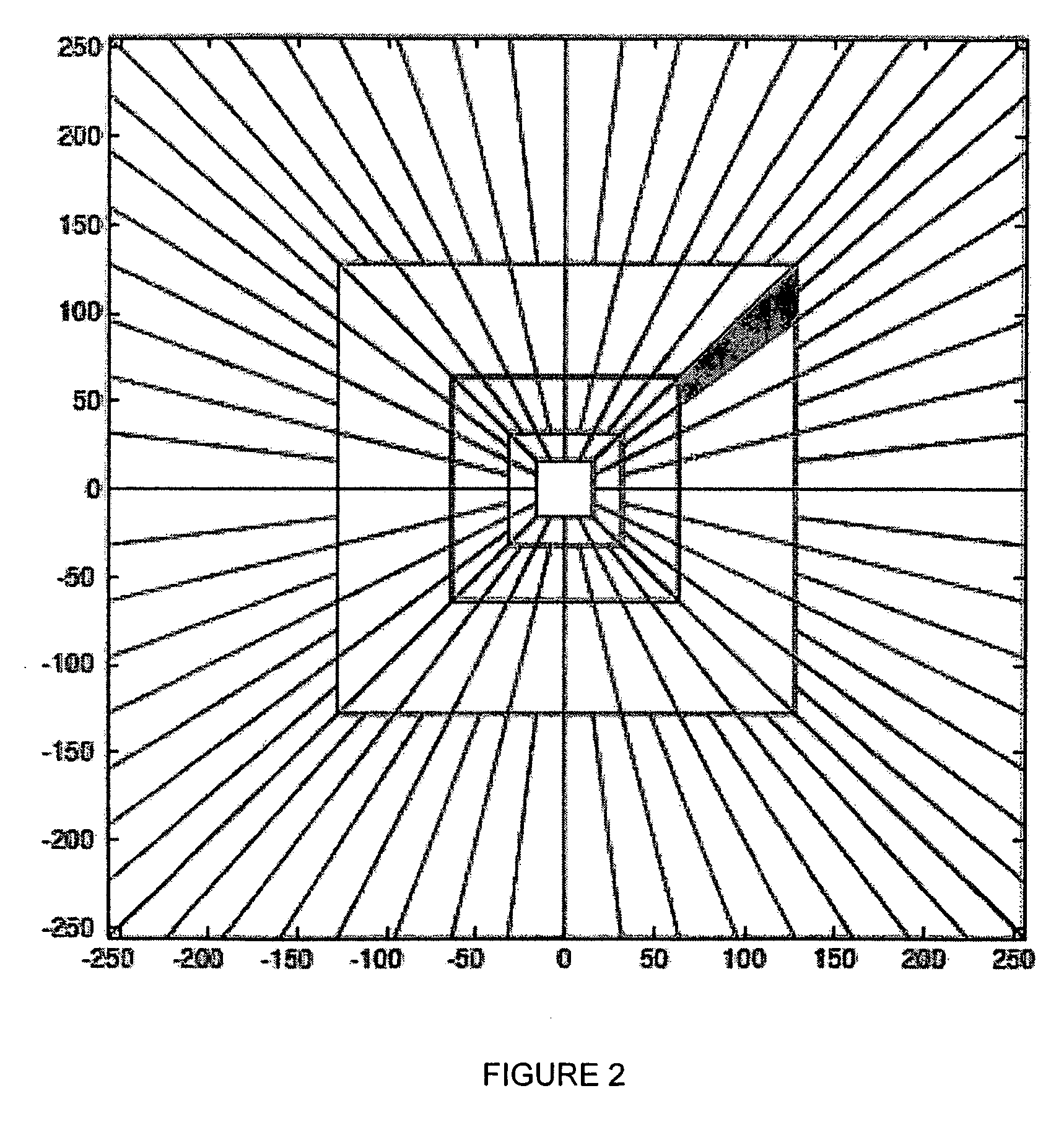

Methods for performing fast discrete curvelet transforms of data

ActiveUS20070038691A1The process is fast and accurateImprove representationComplex mathematical operationsDigital transformationFast Fourier transform

Fast digital implementations of the second generation curvelet transform for use in data processing are disclosed. One such digital transformation is based on unequally-spaced fast Fourier transforms (USFFT) while another is based on the wrapping of specially selected Fourier samples. Both digital transformations return a table of digital curvelet coefficients indexed by a scale parameter, an orientation parameter, and a spatial location parameter. Both implementations are fast in the sense that they run in about O(n2 log n) flops for n by n Cartesian arrays or about O(N log N) flops for Cartesian arrays of size N=n3; in addition, they are also invertible, with rapid inversion algorithms of about the same complexity.

Owner:CALIFORNIA INST OF TECH +1

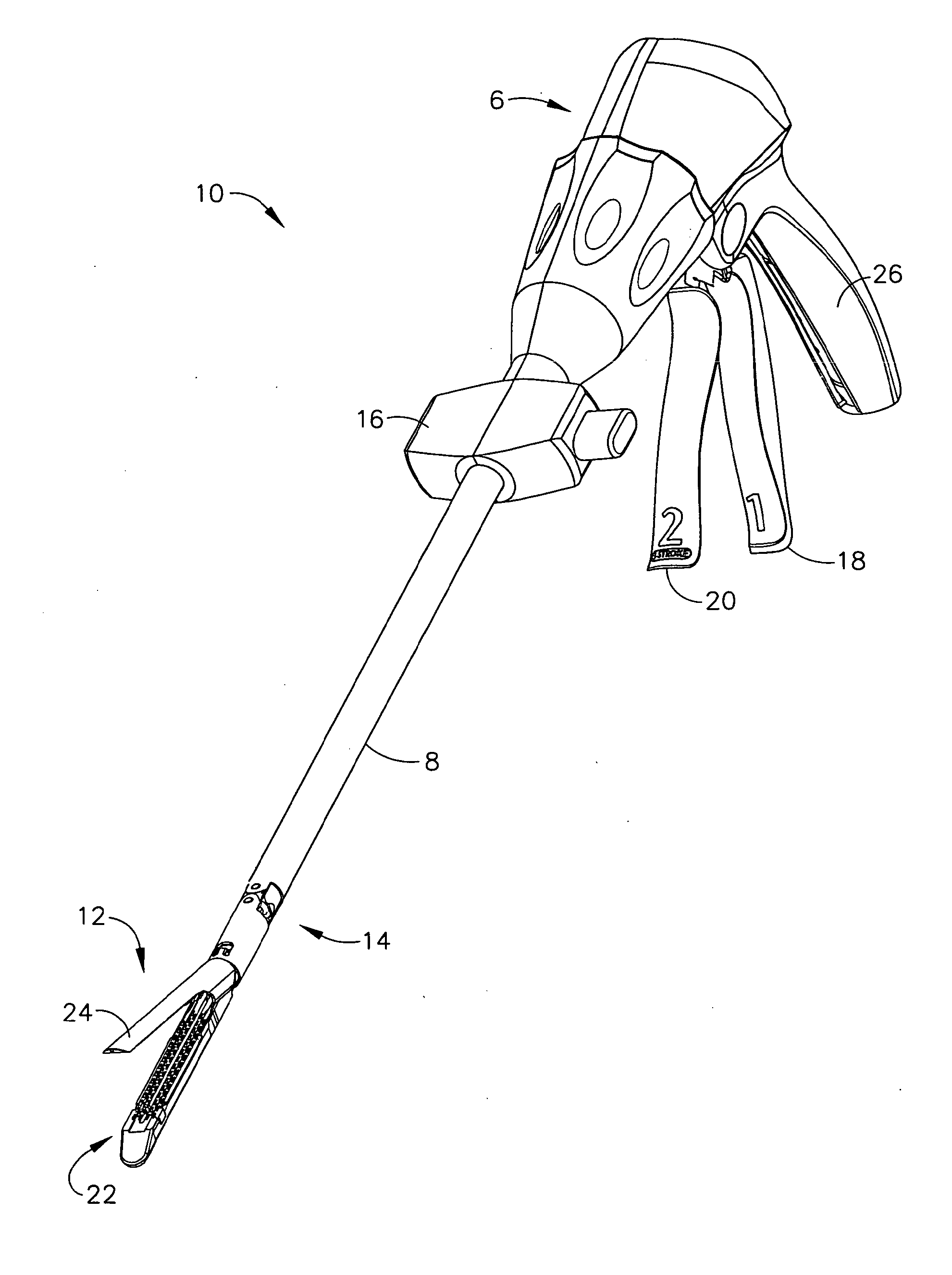

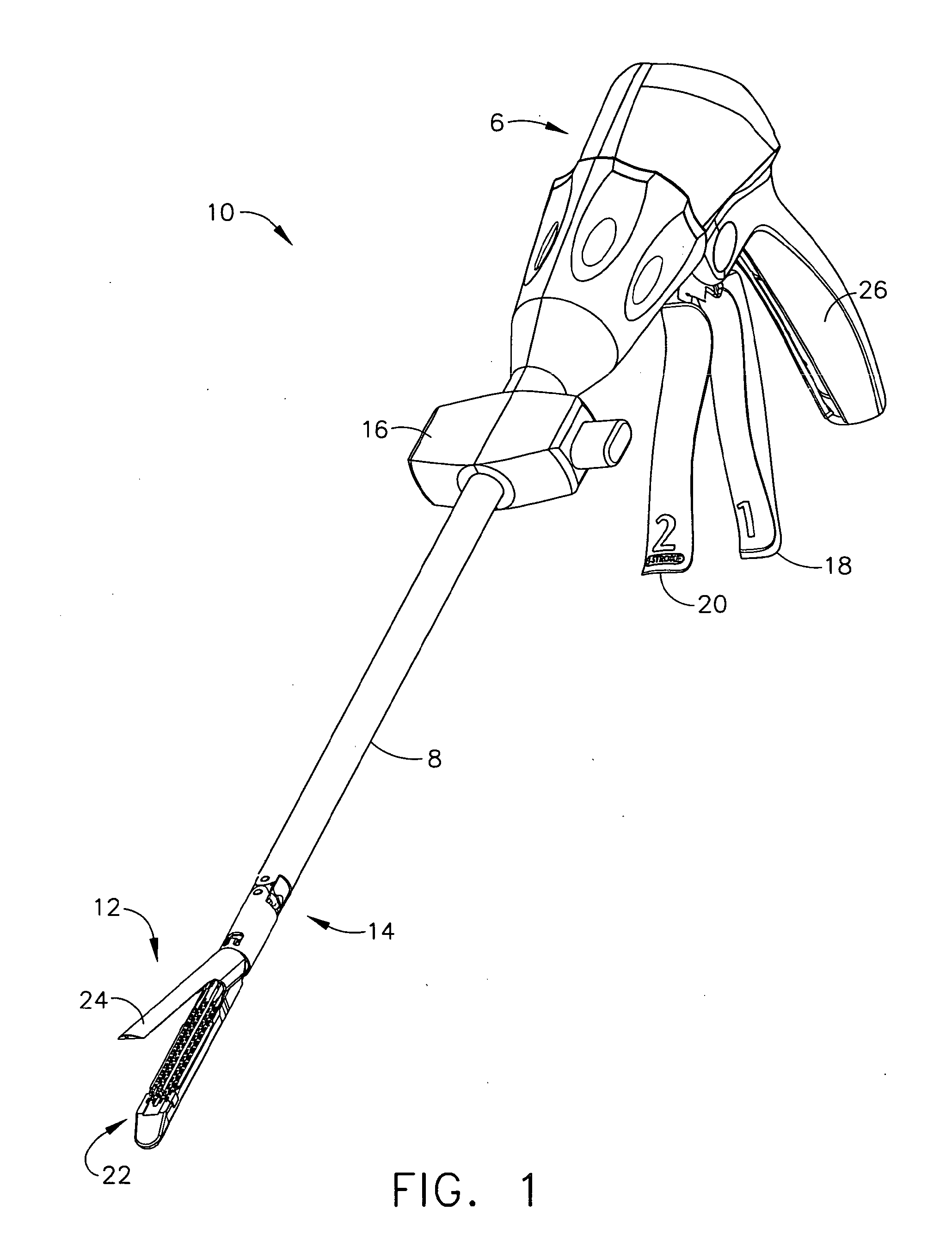

Surgical instrument having recording capabilities

A surgical instrument. The surgical instrument has an end effector and a trigger in communication with the end effector. The surgical instrument also has a first sensor and an externally accessible memory device in communication with the first sensor. The first sensor has an output that represents a first condition of either the trigger or the end effector. The memory device is configured to record the output of the first sensor. In various embodiments, memory device may include an output port and / or a removable storage medium.

Owner:CILAG GMBH INT

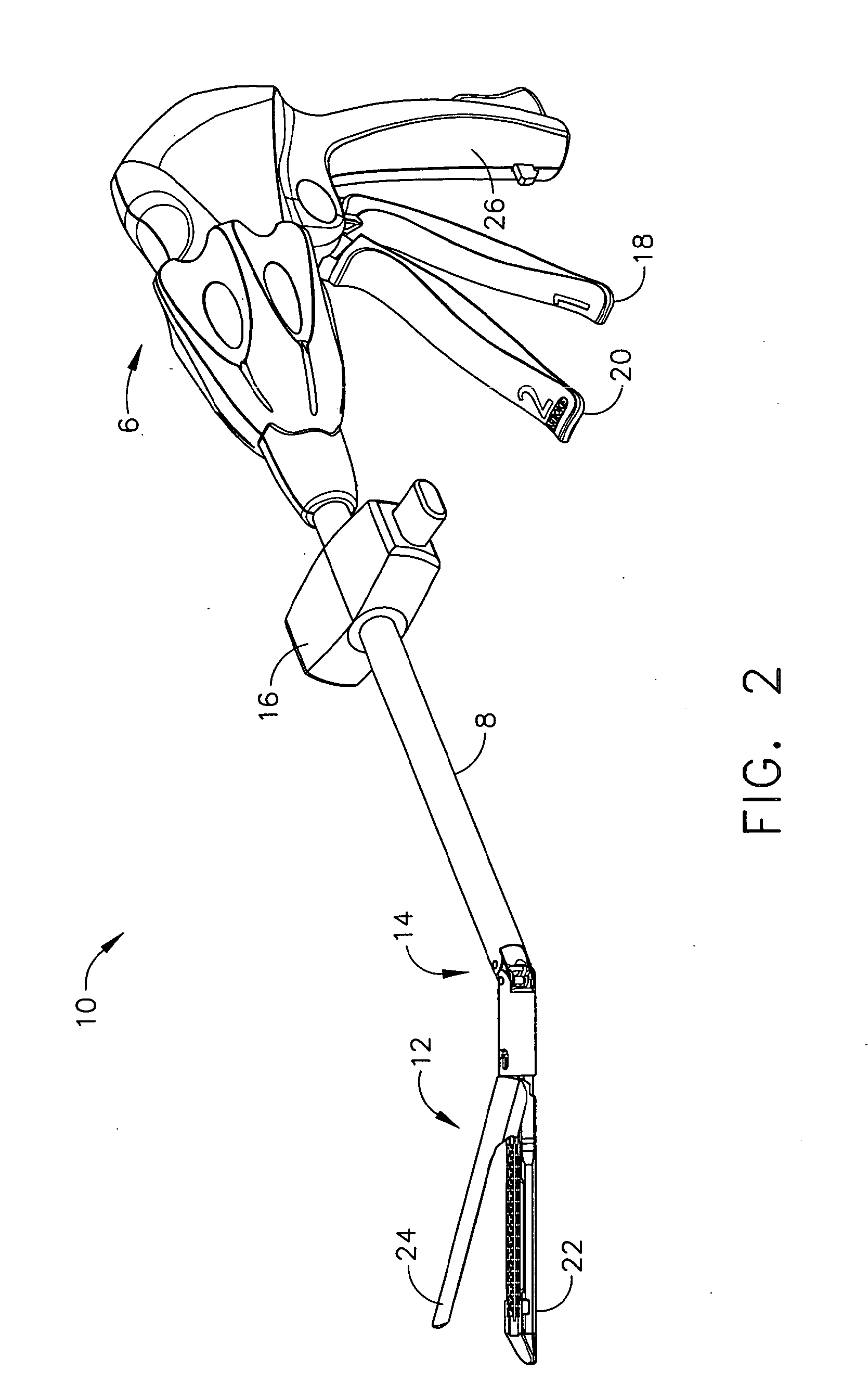

Scheduling trigger apparatus and method

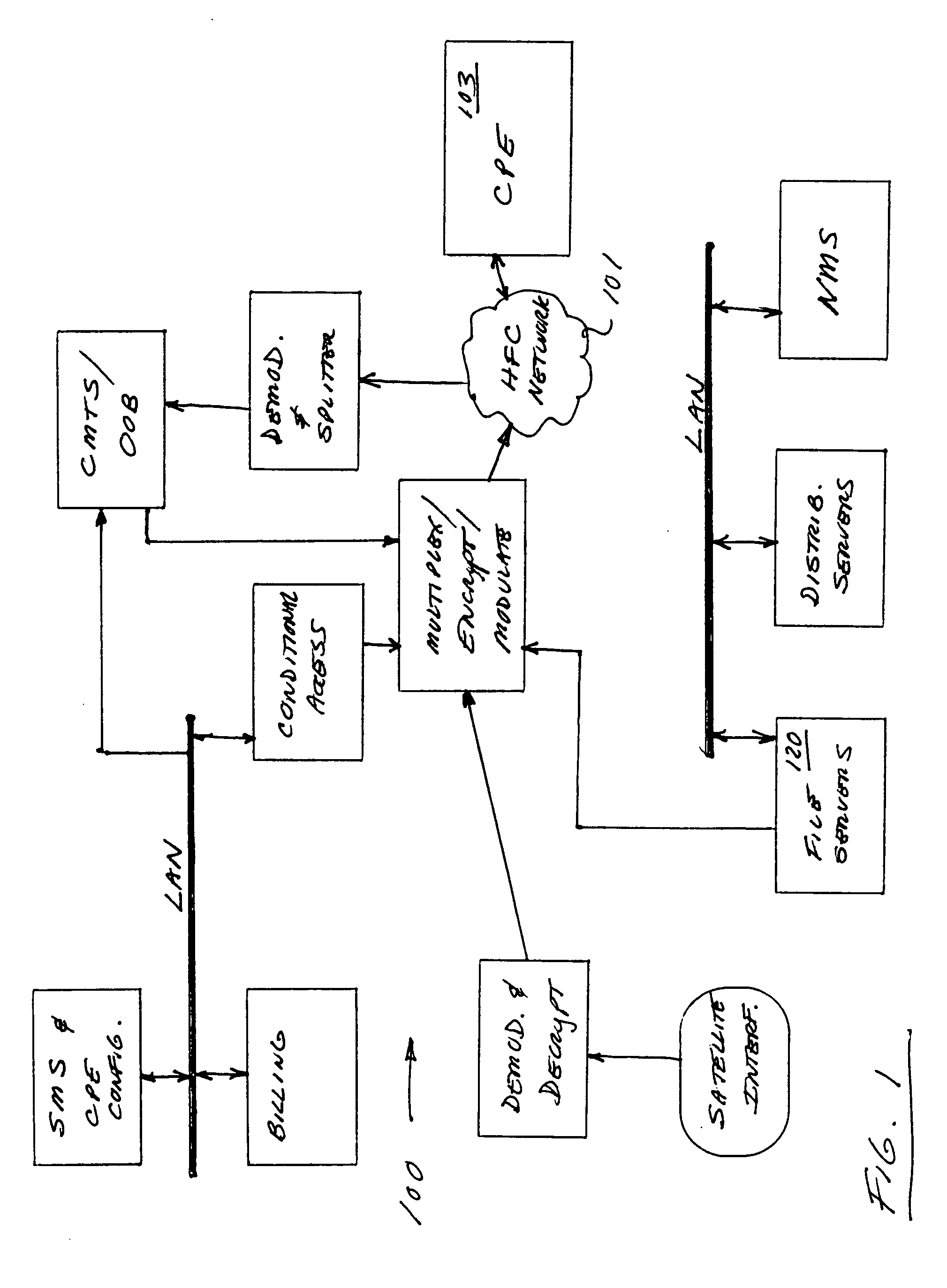

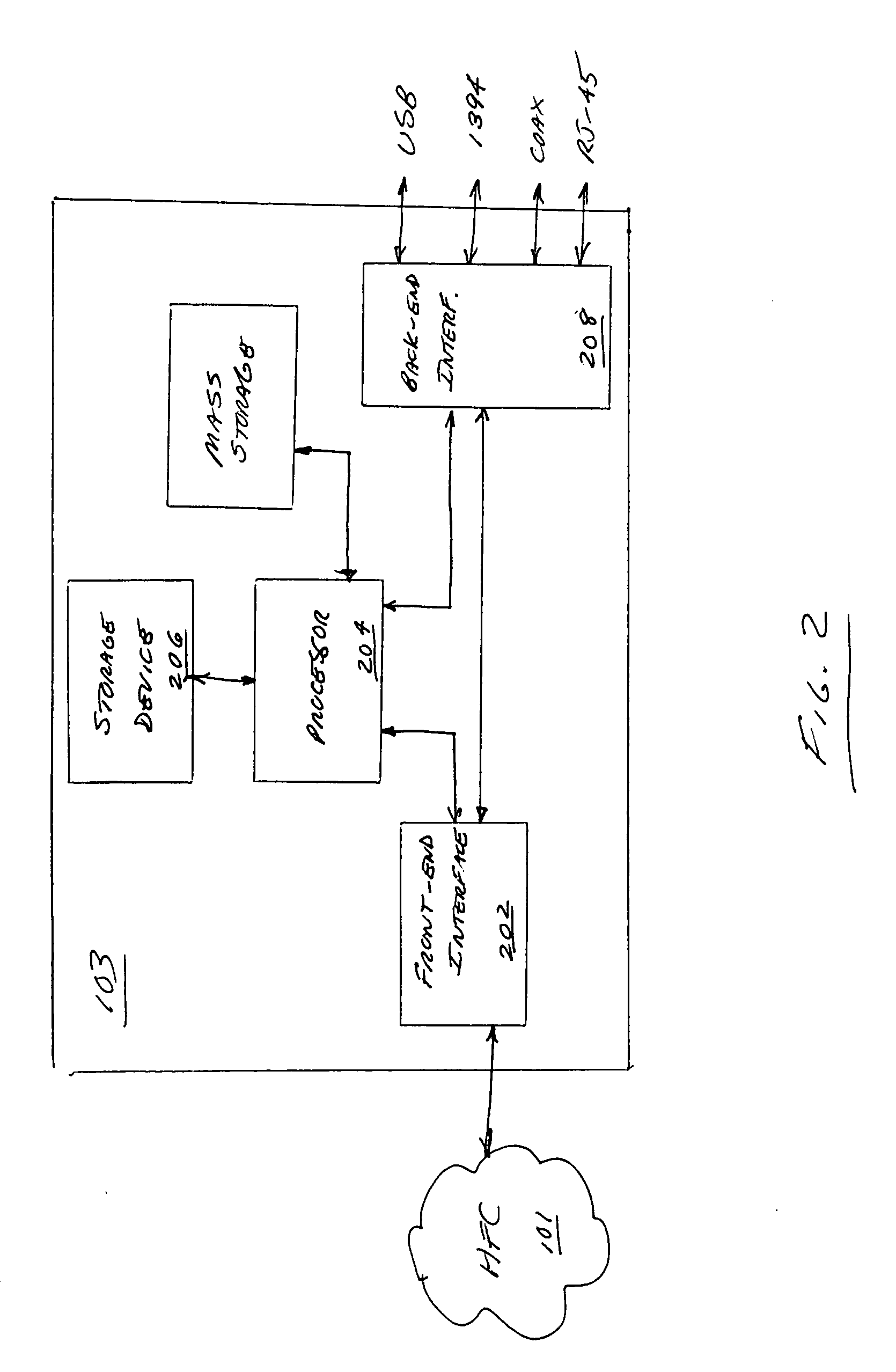

ActiveUS20050144635A1Television system detailsElectrical cable transmission adaptationFlip-flopEngineering

Apparatus and methods for embedding and associating triggers within a promotion or other similar content element with the event being promoted are disclosed. In one exemplary embodiment, consumer premises equipment (CPE) such as a digital set-top box is used to interface between the user and an external network (such as an HFC cable network) and facilitate the user selecting and scheduling viewing or recording of a subsequent event (e.g., broadcast movie) via the promotion itself. The trigger(s) within the promotion allow the user to contemporaneously select the promoted event for viewing, recording, etc. without any further action. The trigger(s) then initiates tuning of the user's receiver to the scheduled event at the appropriate date and time. This approach obviates additional actions by the user (such as programming their DVR), and also permits the user to commit to viewing the event when their interest level is highest; i.e., contemporaneous with the promotion.

Owner:TIME WARNER CABLE ENTERPRISES LLC

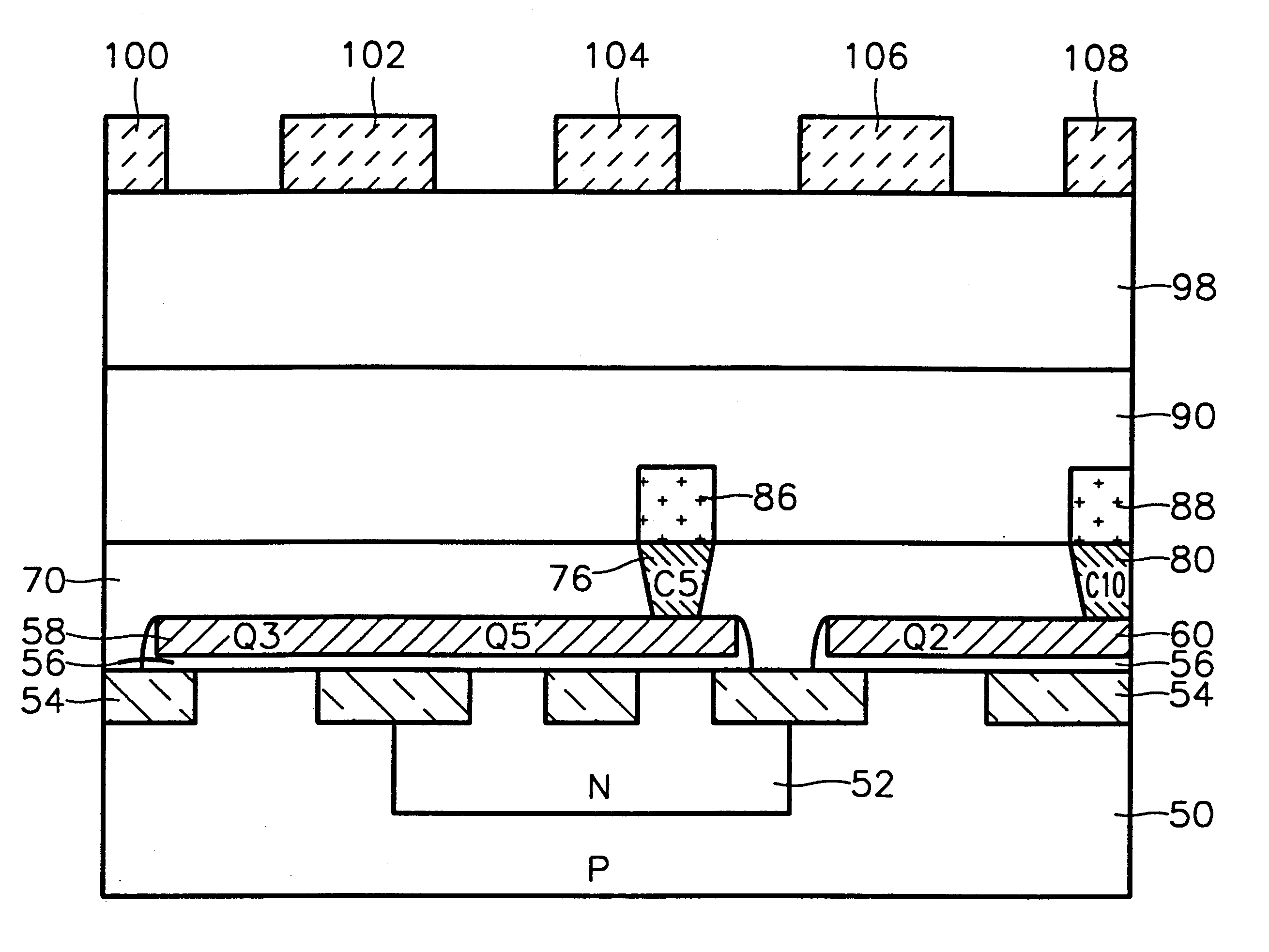

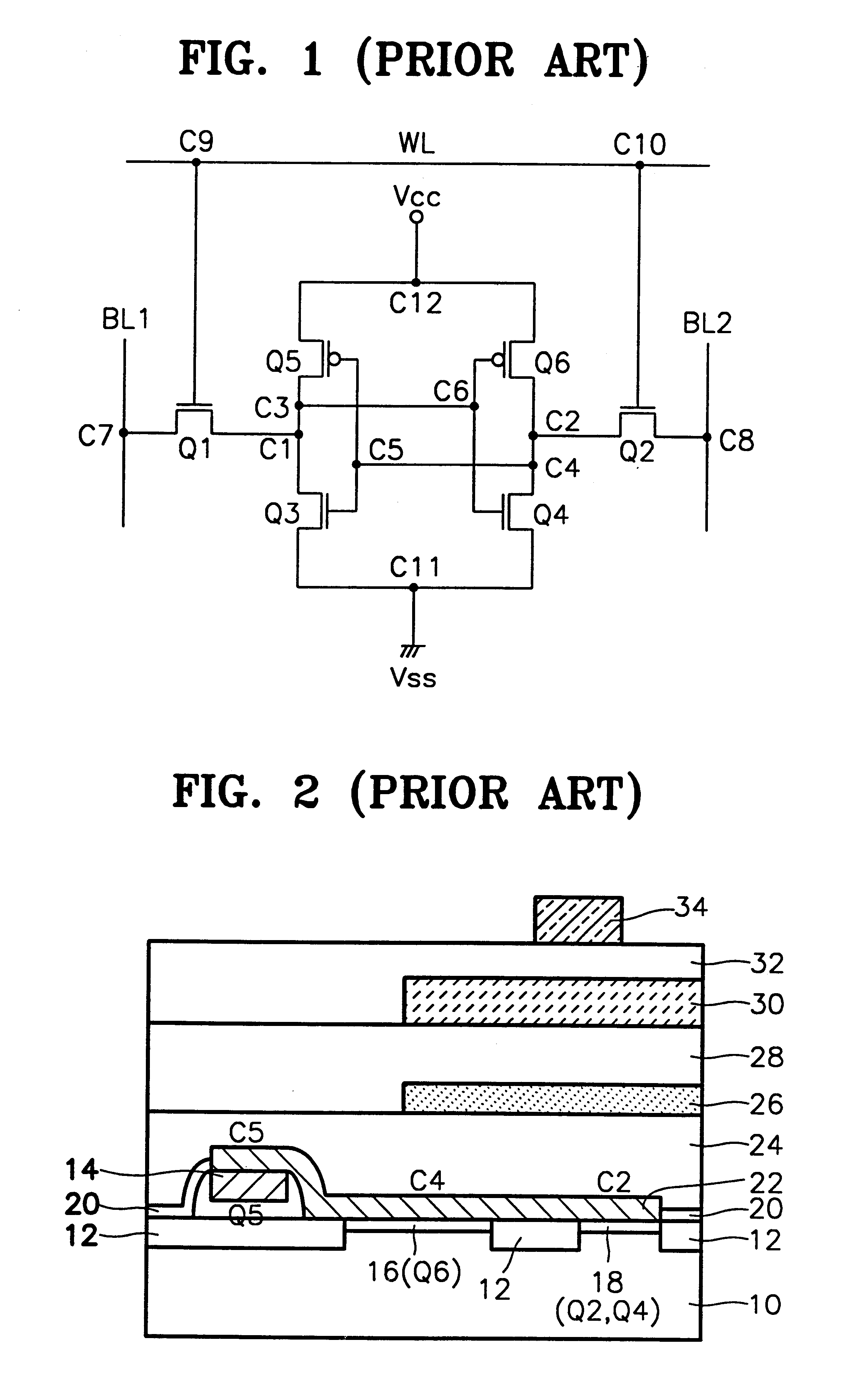

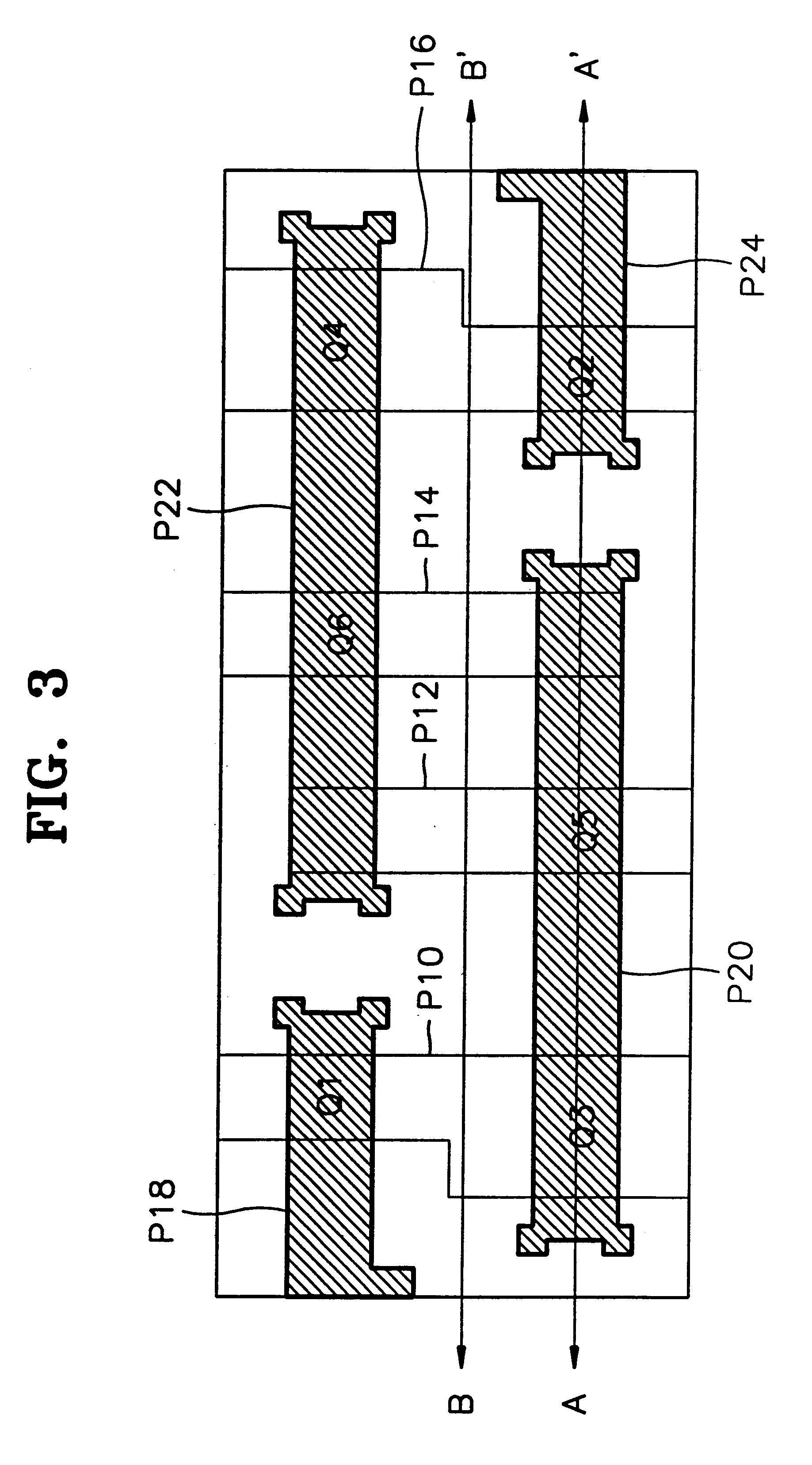

Static random access memory device and method for manufacturing the same

A static random access memory (SRAM) device and a method for manufacturing the same are disclosed. In the SRAM device including a flip-flop circuit including two access transistors and a pair of inverters, connection lines for connecting the inputs and outputs of the inverters, and a word line, power supply lines and bit lines are formed of a metal interconnection. The resistance of interconnection can be reduced and the SRAM device manufacturing process can be performed along with CMOS standard logic manufacturing process.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and System for Fraud Detection and Notification

Methods and systems for an automated dialer enhancements. The methods may analyze transactions. The analysis of the transactions may comprise of triggers which are met when a delta threshold is exceeded, when an immediate threshold is exceeded, or when a rule is met. A notification strategy is implemented after a trigger is fired and accounts may be blocked or held. Reappearing transactions are flagged and escalated.

Owner:VISA INT SERVICE ASSOC

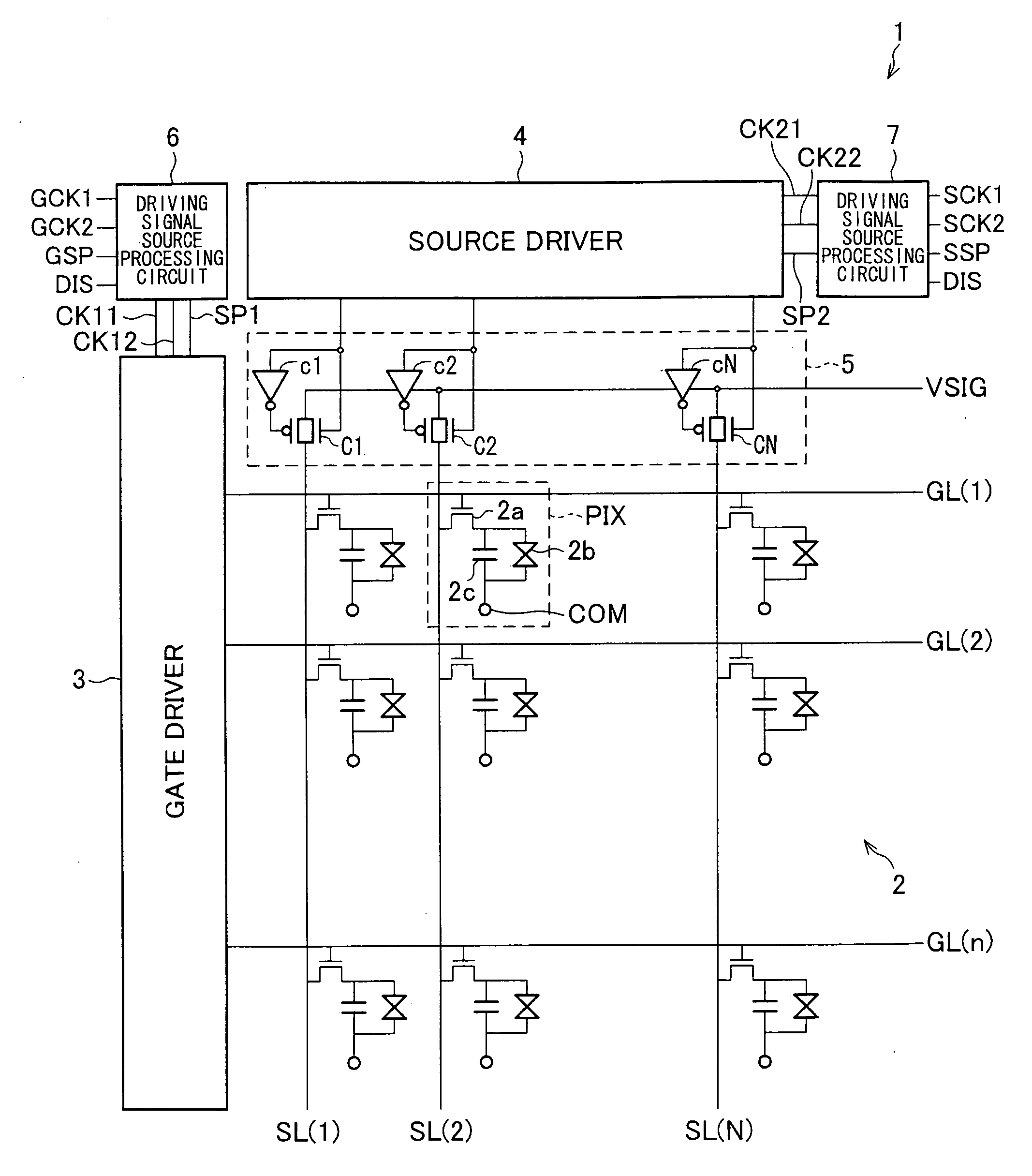

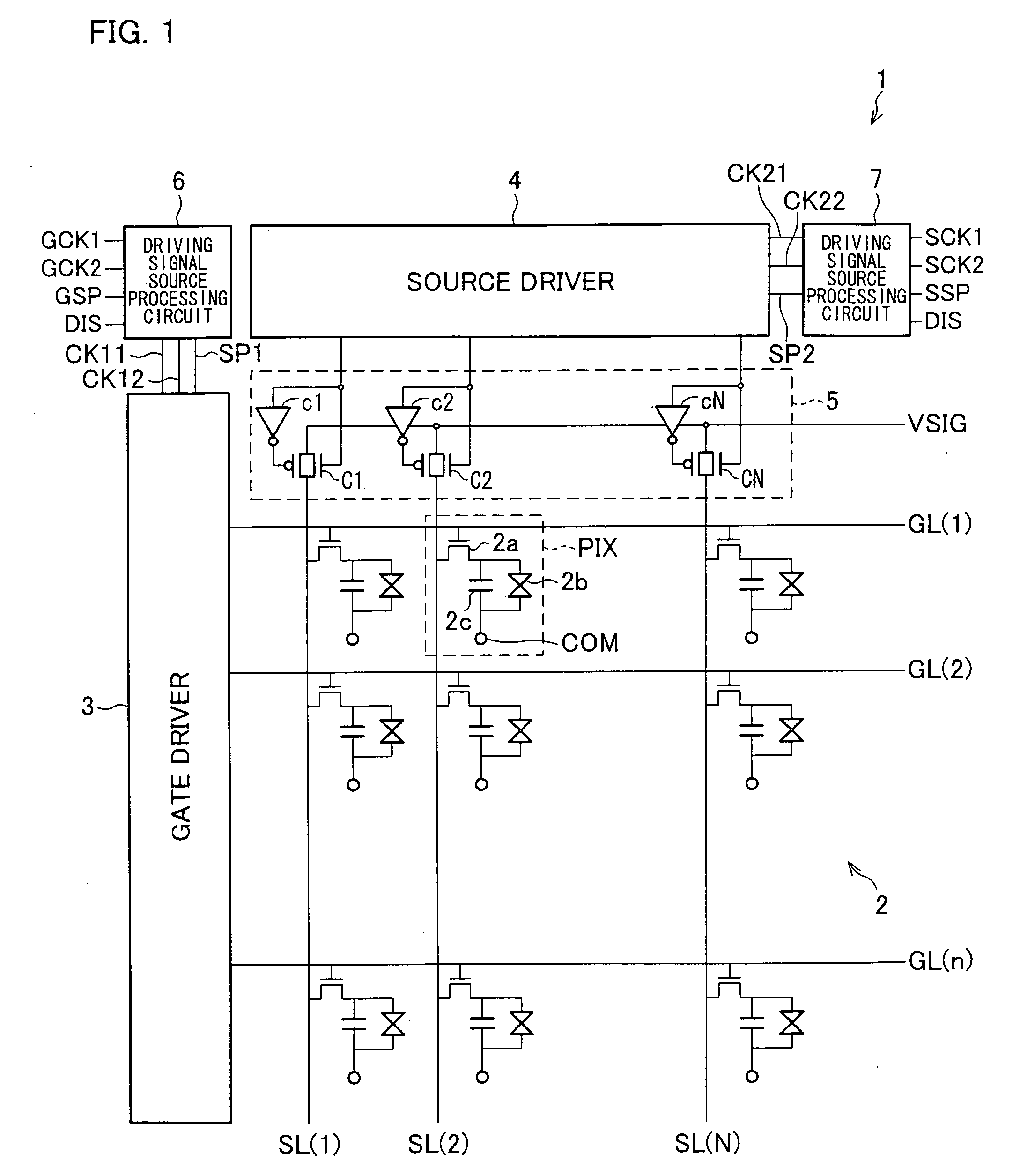

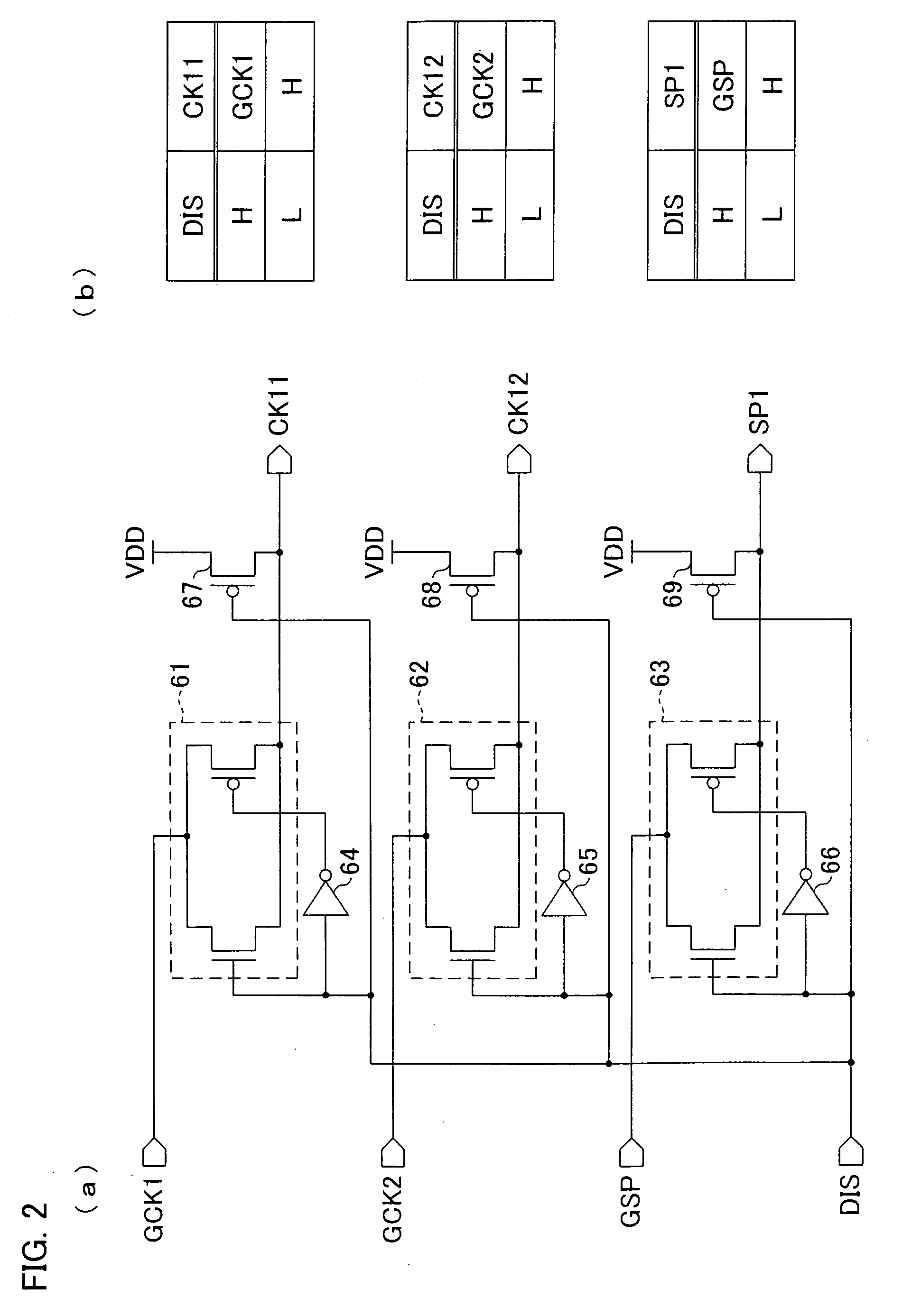

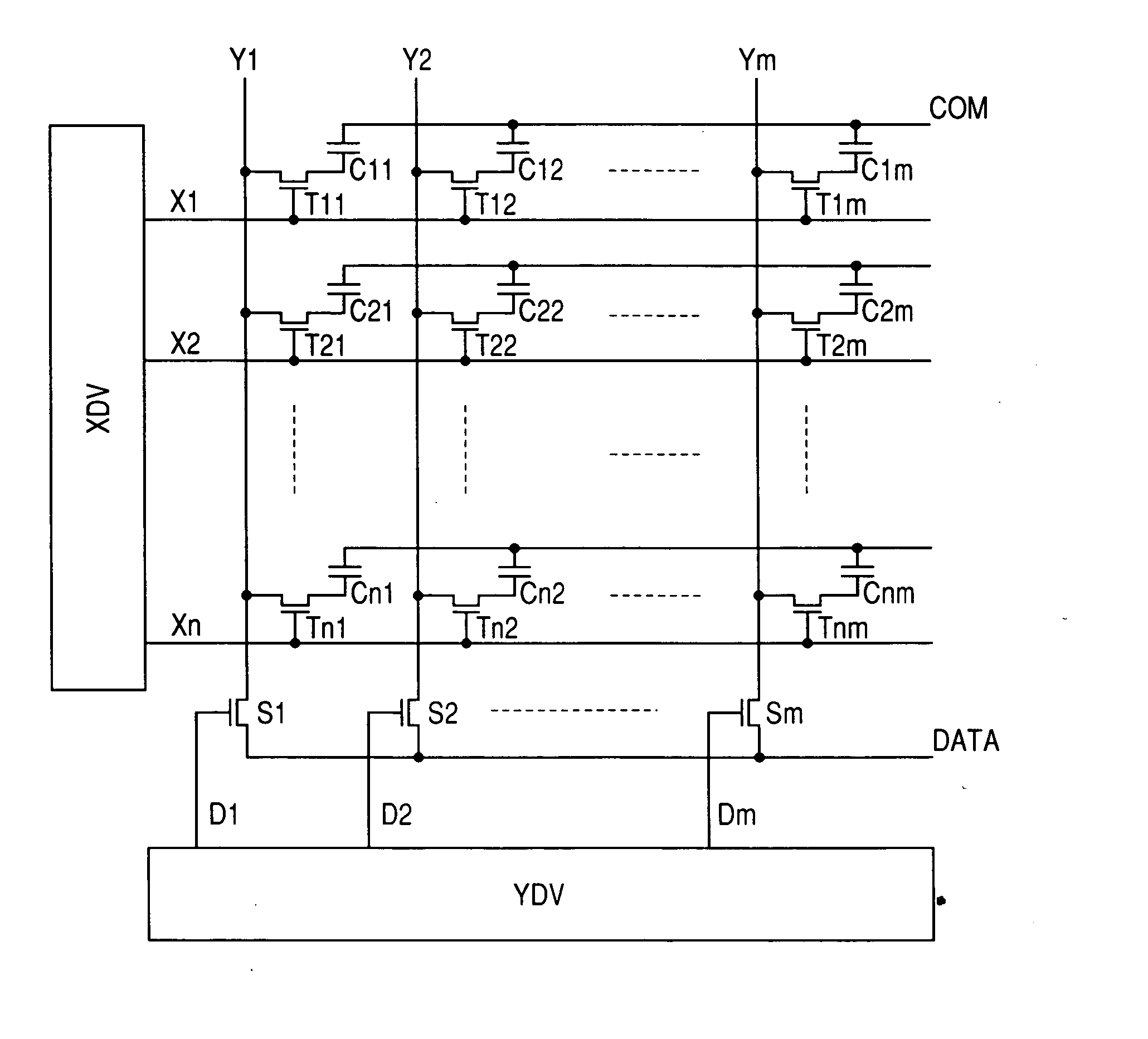

Display Apparatus and Method For Driving The Same

ActiveUS20090121998A1Prevent degradationReduce displayStatic indicating devicesDigital storageShift registerLiquid-crystal display

A liquid crystal display apparatus (1) wherein the shift registers of a source driver (4) are configured by use of asynchronous RS flip-flops in which an active input to a set input terminal has a higher priority than an active input to a reset terminal. In a second mode of operation, first and second clock signals and a start pulse are fixed at high levels, thereby performing discharges from all the pixels (PIX) of a liquid crystal panel (2).

Owner:SHARP KK

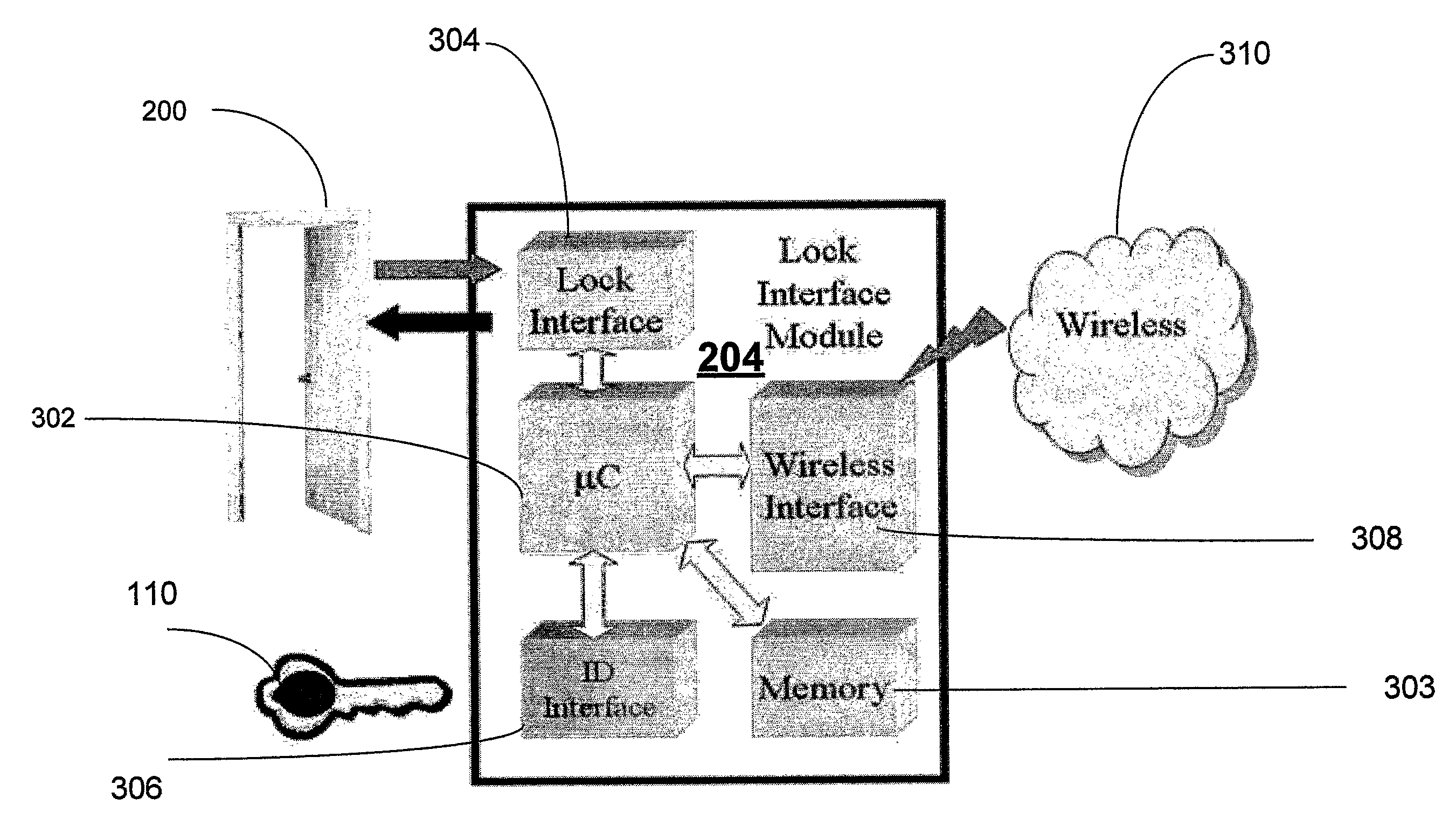

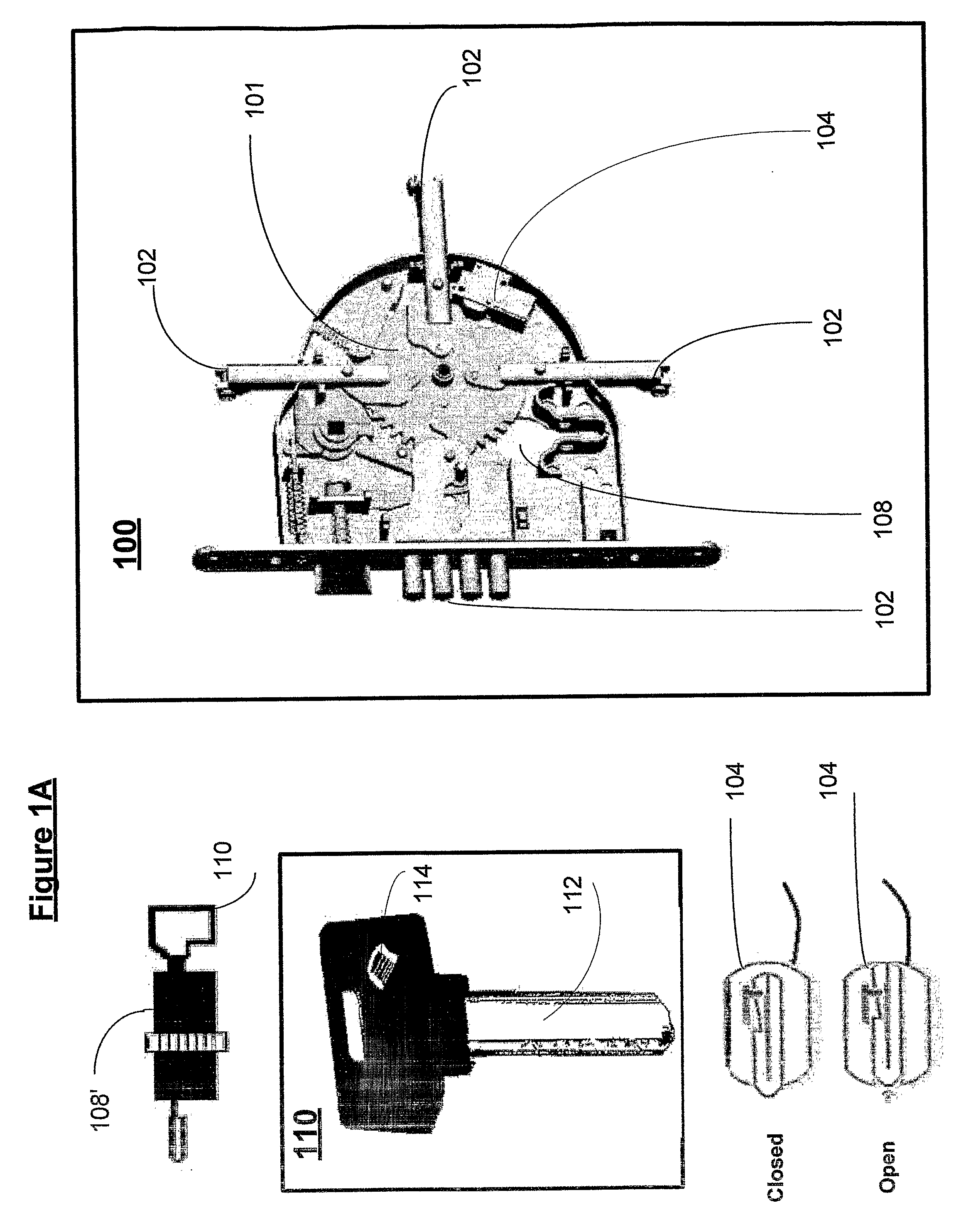

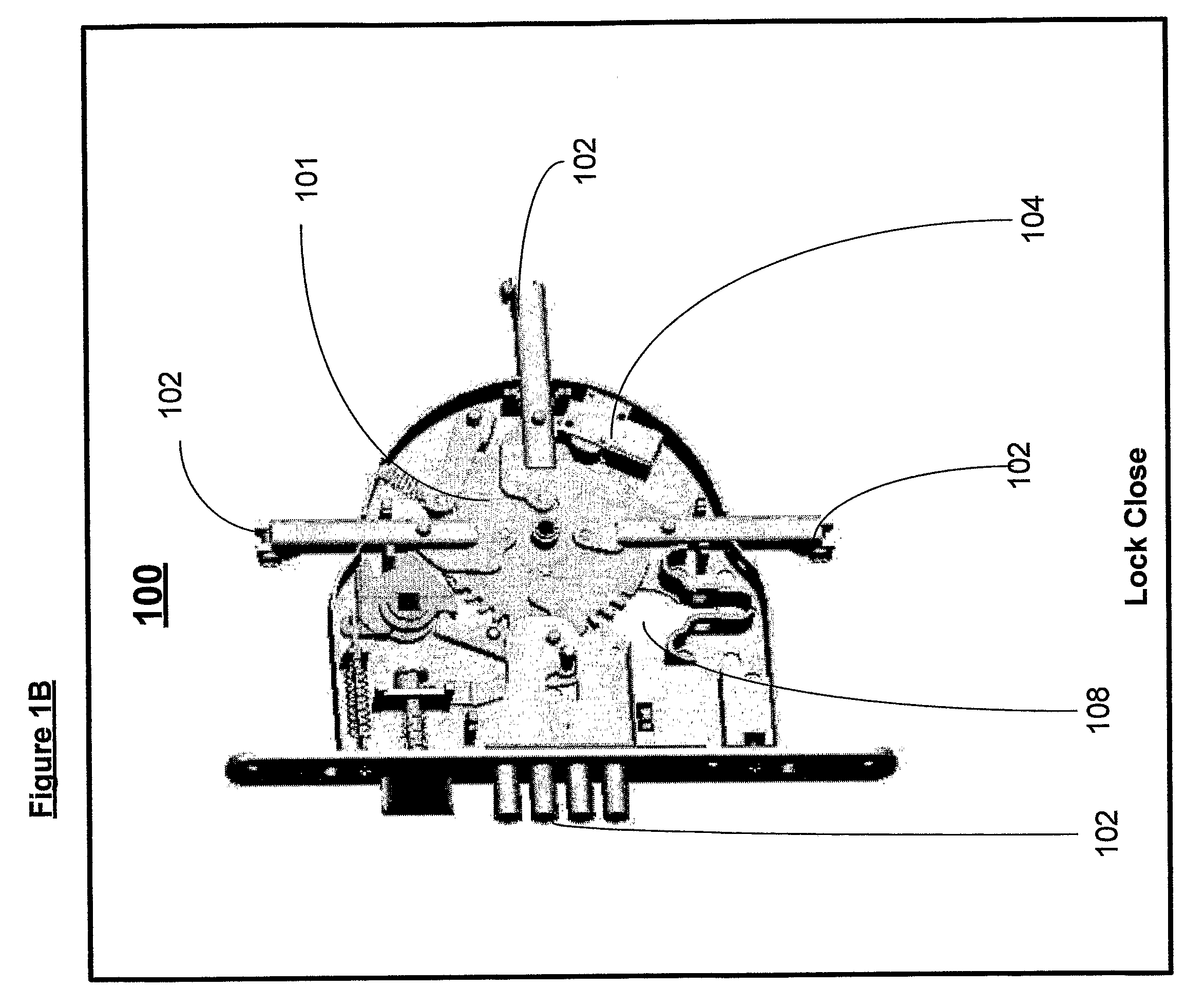

Intelligent Interactive Lock and Locking System

InactiveUS20070290789A1Novel featuresElectric signal transmission systemsDigital data processing detailsMonitoring and controlElectrical and Electronics engineering

An intelligent lock comprises a mechanical element operative to provide two lock position upon a proper actuation, and an electromechanical (EM) trigger separate from and coupled to the mechanical element and operative to control the actuation. When included in an intelligent locking system, the lock is remotely controllable through a monitoring and control unit, operative to relay commands to the EM trigger.

Owner:SEGEV EREZ

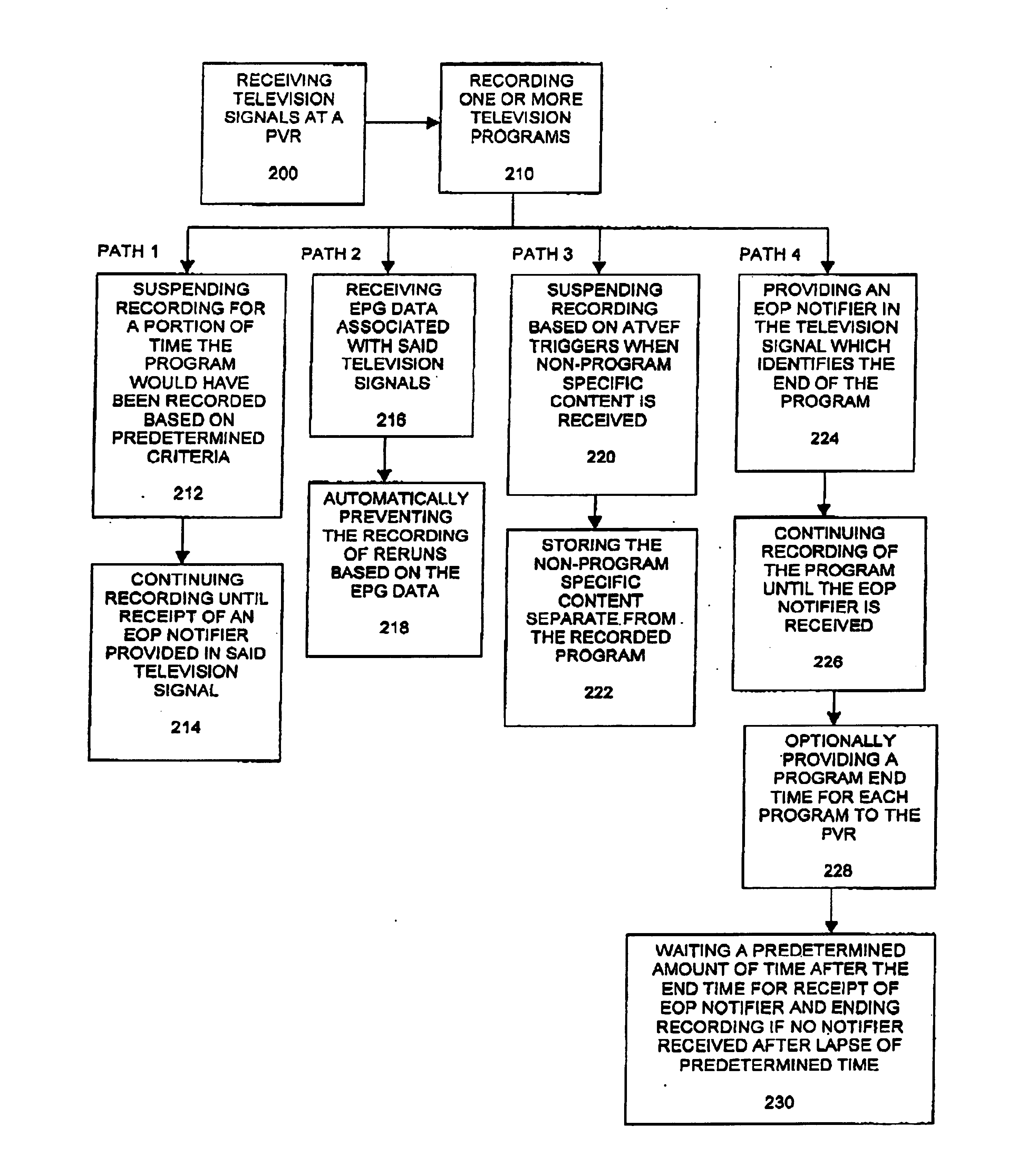

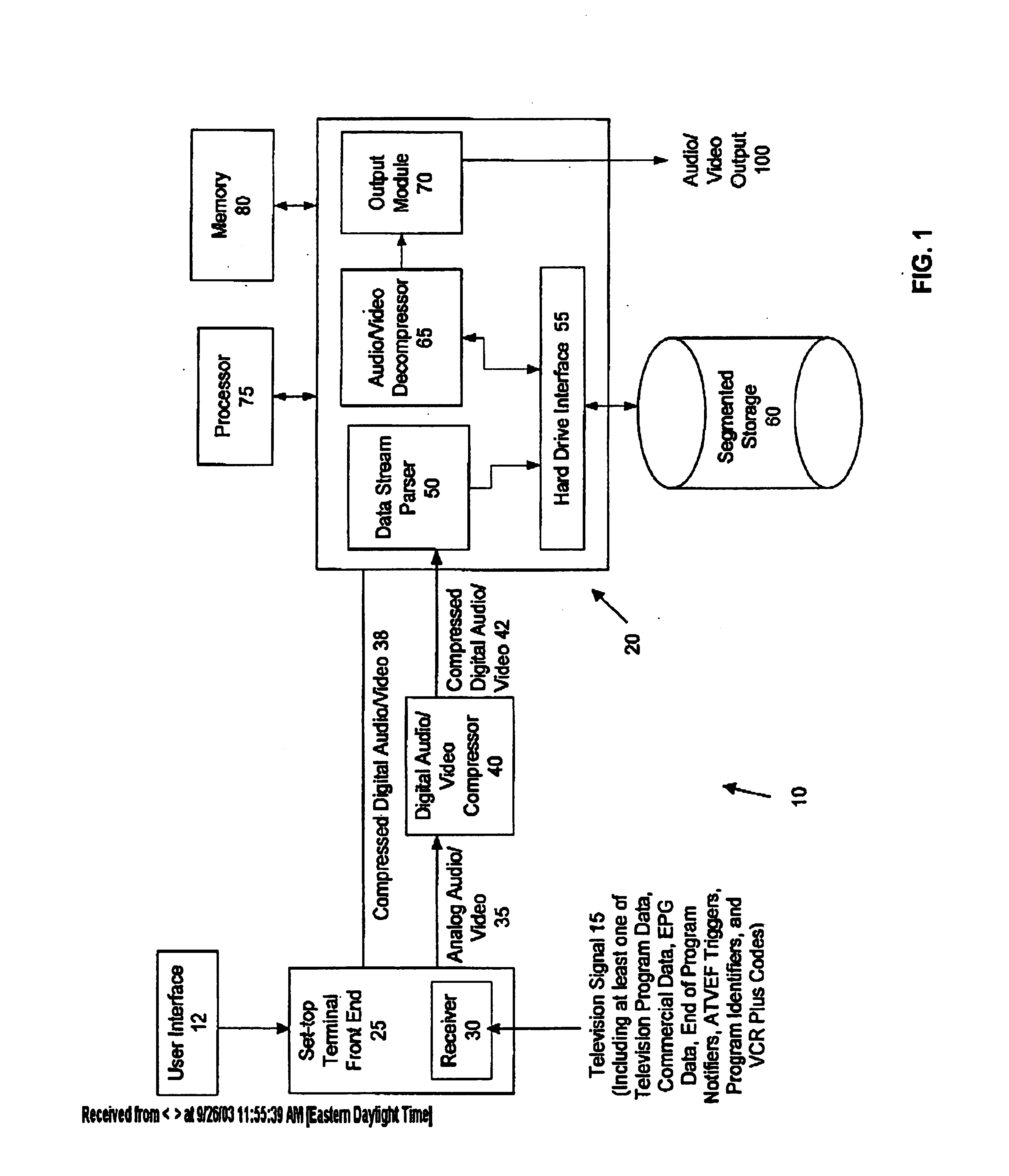

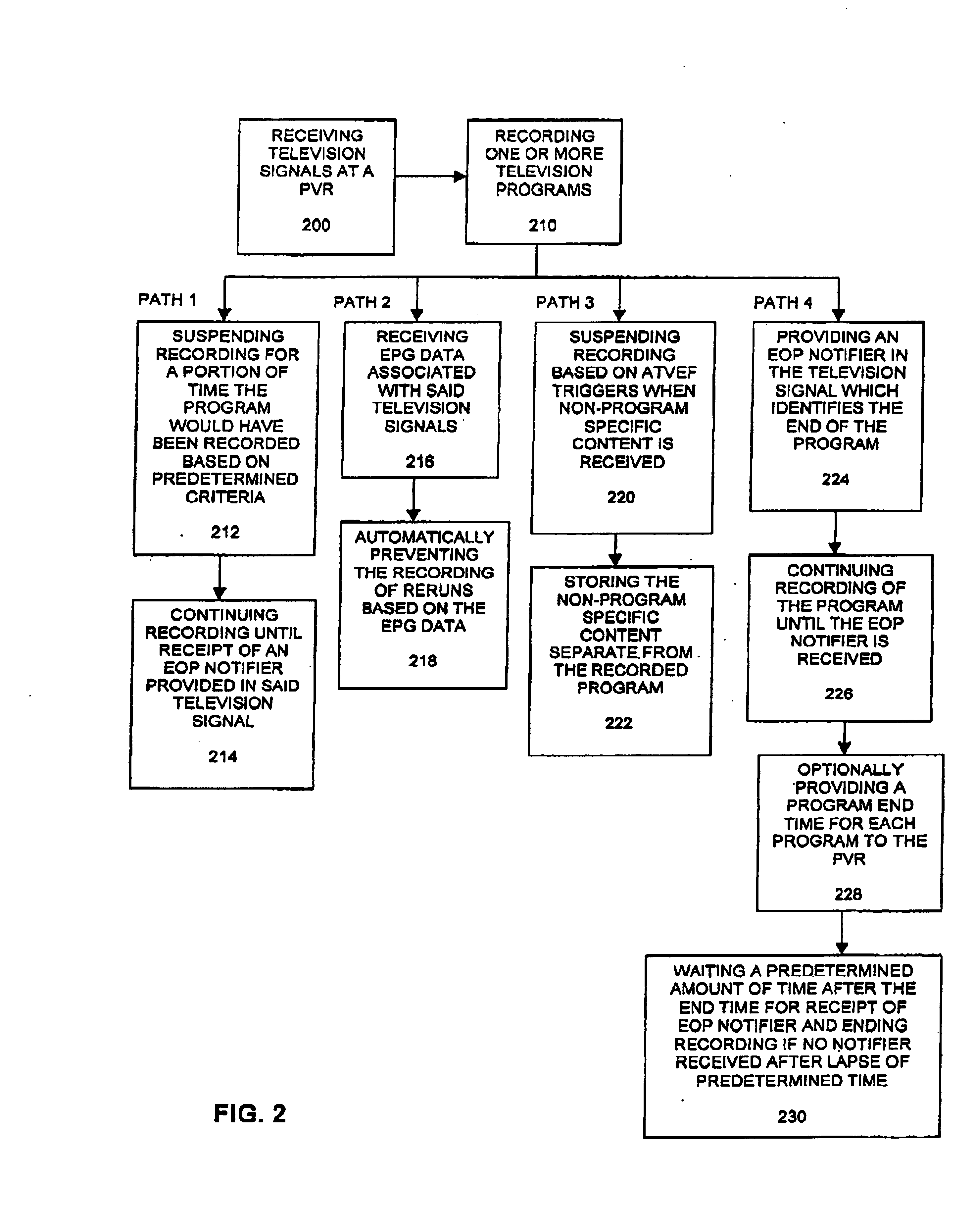

Methods and apparatus for advanced recording options on a personal versatile recorder

InactiveUS6901603B2Television system detailsColor television signals processingComputer hardwareElectronic program guide

Advanced recording options are provided on a personal versatile recorder (PVR) or similar recording device. Television signals and associated electronic programming guide (EPG) data are received at a receiver (30). Recorded program material is stored in a storage device (60). A processor (75) provides for automatic suspending of recording, based on predetermined criteria, for at least a portion of time during which the one or more television programs would otherwise be recorded. Recording may be suspended when non-programming specific content (e.g., a commercial or emergency broadcast) is received at the PVR (20). Non-program specific content can be identified through the use of EPG data or Advanced Television Enhancement Forum (ATVEF) triggers. End of program notifiers may be provided which enable the PVR (20) to record the entire program, regardless of whether the program runs beyond its scheduled time. Recording may be optionally suspended where the program is a rerun.

Owner:GOOGLE TECH HLDG LLC

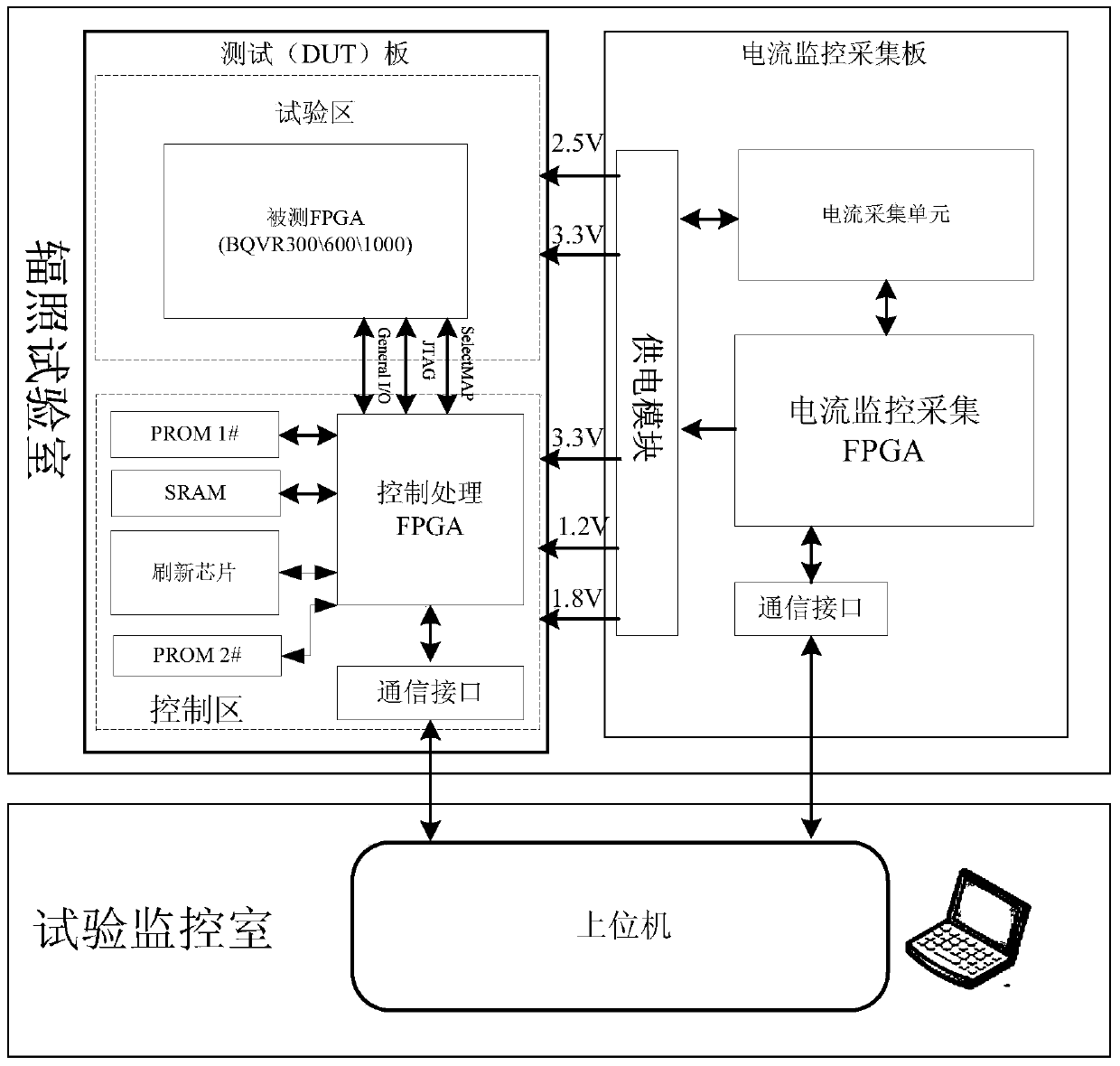

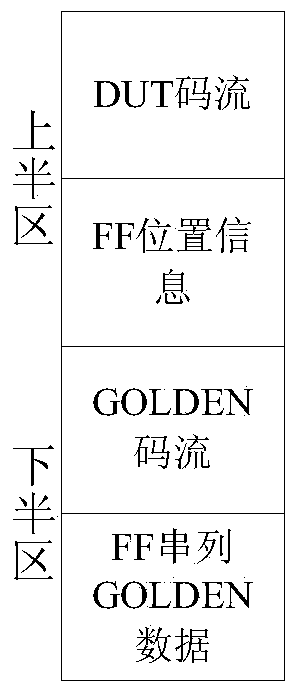

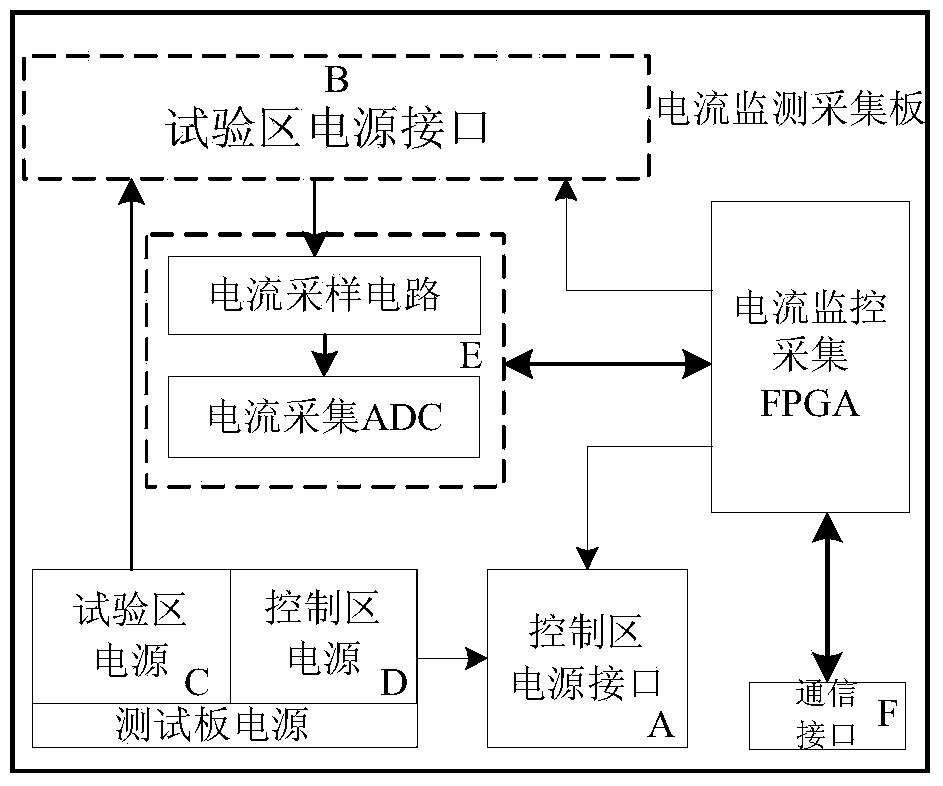

SRAM type FPGA single particle irradiation test system and method

ActiveCN103744014ARefresh is convenient and reliableReliably flip dataElectrical testingCommunication interfacePower flow

The invention provides an SRAM type FPGA single particle irradiation test system and method. The test system comprises a host computer, a current monitoring acquisition plate and a test plate. The current monitoring acquisition plate comprises a current monitoring acquisition FPGA, a current acquisition unit, a power supply module and a first communication interface; the test plate comprises a control processing FPGA, a refreshing chip, an SRAM, a configuration PROM, a storage PROM, a second communication interface and a detected FPGA; the host computer is in charge of flow control and data processing; the current monitoring acquisition plate is in charge of power-on and power-off of the test plate and monitoring and testing of FPGA currents; and the test plate is in charge of processing a command sent by the host computer and performing work such as single particle overturning, single particle function interruption detection and the like. According to the invention, the refreshing chip is utilized to replace some of the reconfiguration modules in a conventional irradiation test system so that a detected chip can be more conveniently and reliably refreshed; and the system and method provided by the invention can realize static and dynamic overturning testing on a trigger, and more reliable trigger overturning data can be obtained by combing the two methods.

Owner:BEIJING MICROELECTRONICS TECH INST +1

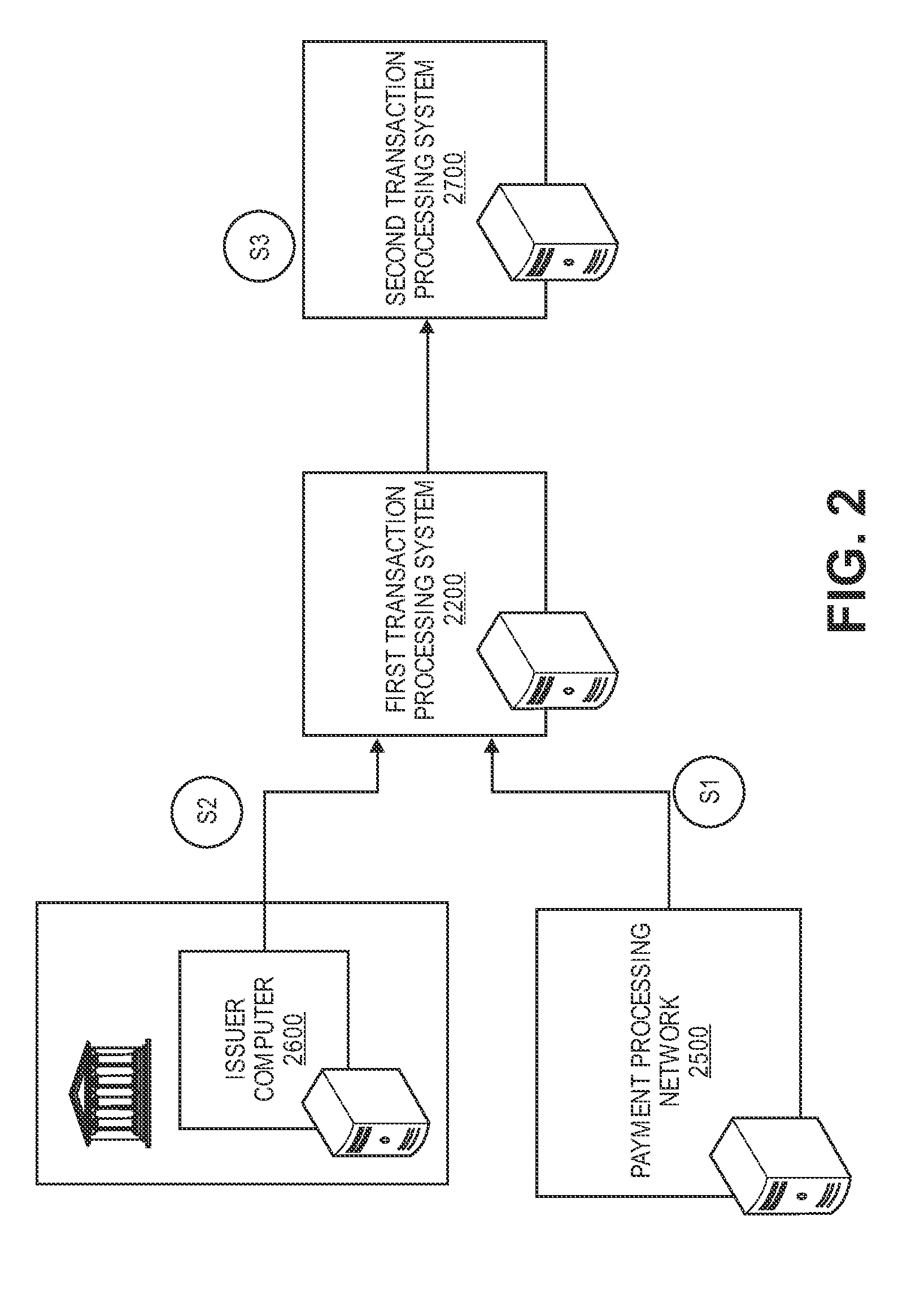

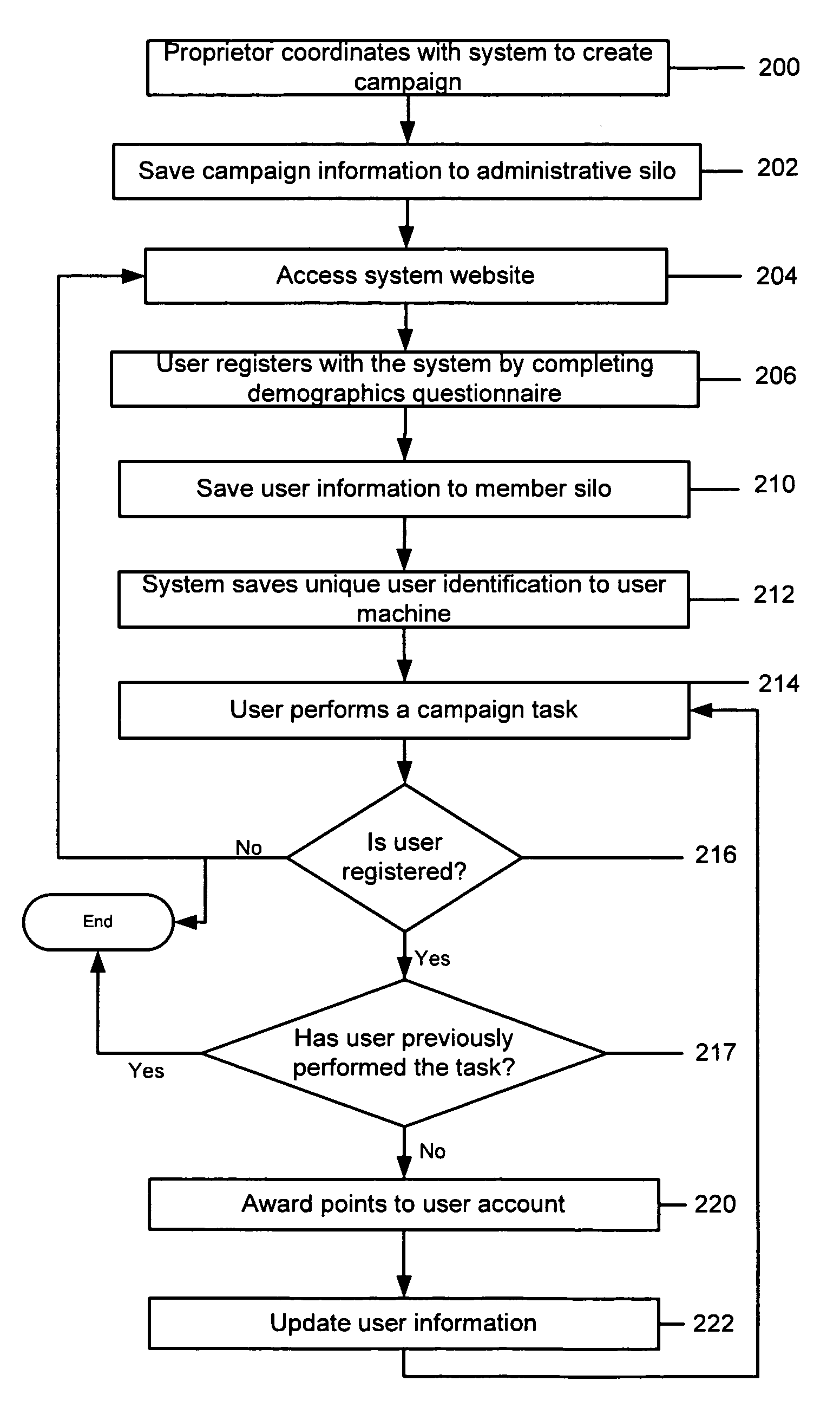

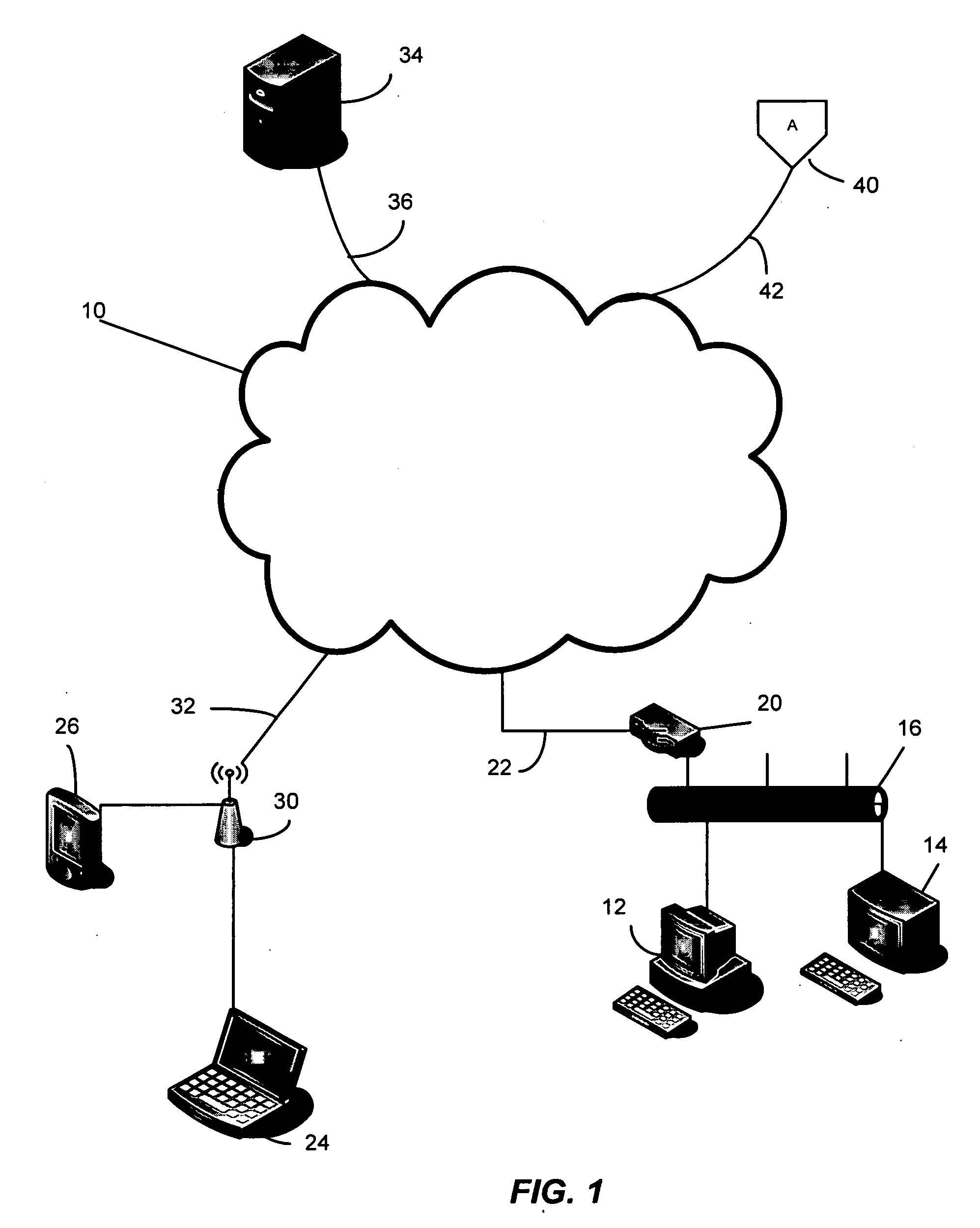

System and Method for Electronic Feedback for Transaction Triggers

A method, in a computer system, for processing messages descriptive of an interaction between a user of the computer system and a third party according to a predefined manner includes receiving an electronic message, such that the electronic message includes interaction information associated with an interaction between the user and the third party; verifying integrity of the electronic message; identifying a rule associated with the interaction, including identifying a condition associated with the rule identifying an action to be performed if the condition is met; and performing the action based on the rule and the interaction information in the electronic message if the condition is met.

Owner:MYPOINTS COM

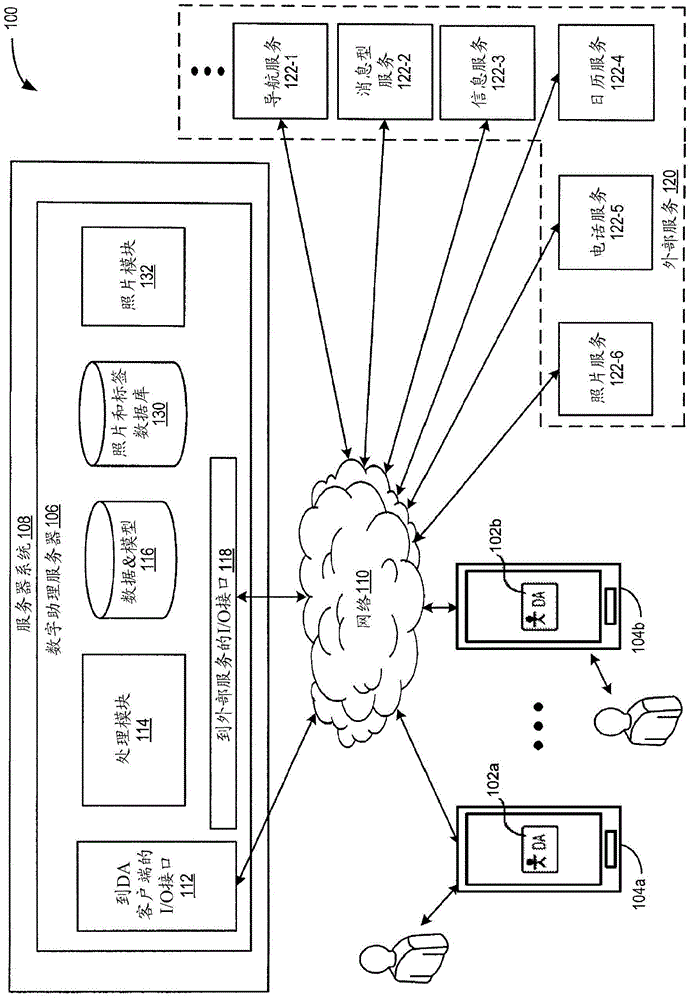

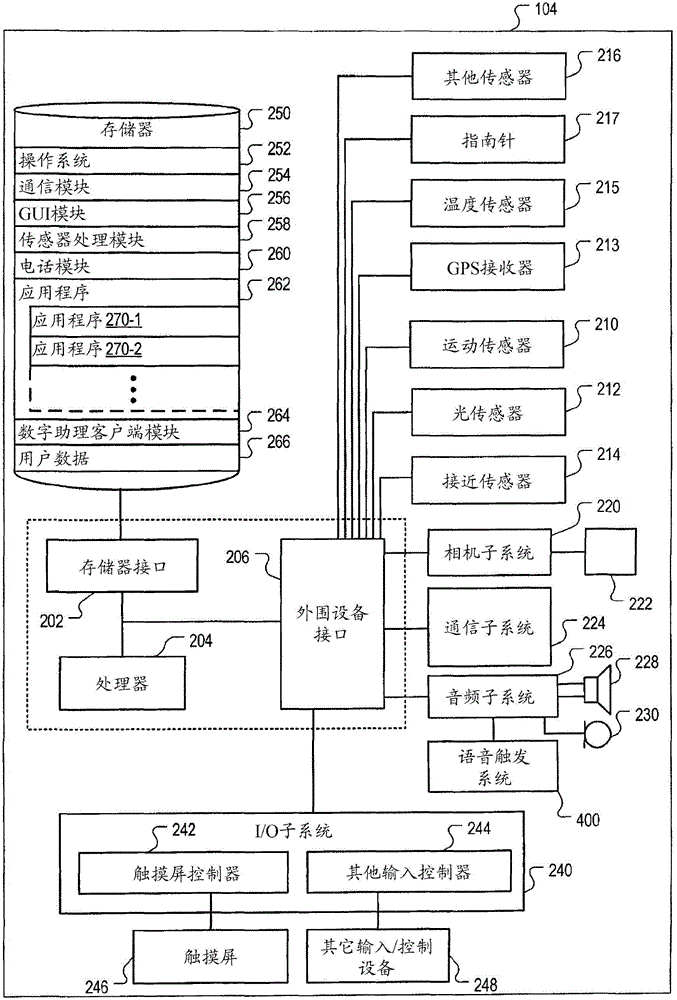

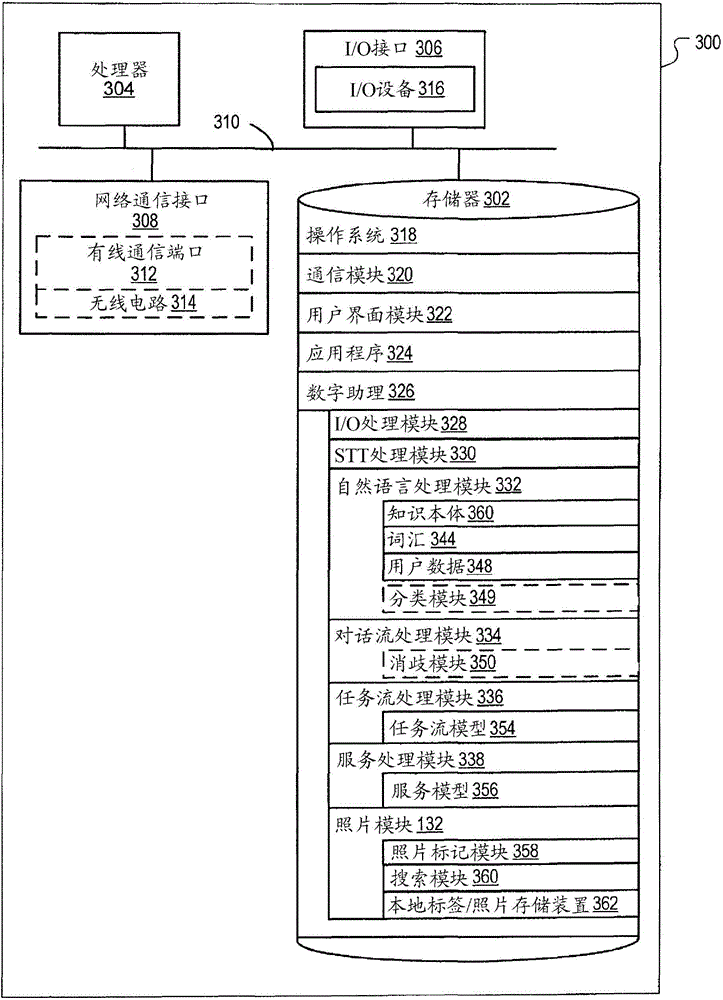

Voice trigger for a digital assistant

A method for operating a voice trigger is provided. In some implementations, the method is performed at an electronic device including one or more processors and memory storing instructions for execution by the one or more processors. The method includes receiving a sound input. The sound input may correspond to a spoken word or phrase, or a portion thereof. The method includes determining whether at least a portion of the sound input corresponds to a predetermined type of sound, such as a human voice. The method includes, upon a determination that at least a portion of the sound input corresponds to the predetermined type, determining whether the sound input includes predetermined content, such as a predetermined trigger word or phrase. The method also includes, upon a determination that the sound input includes the predetermined content, initiating a speech-based service, such as a voice-based digital assistant.

Owner:APPLE INC

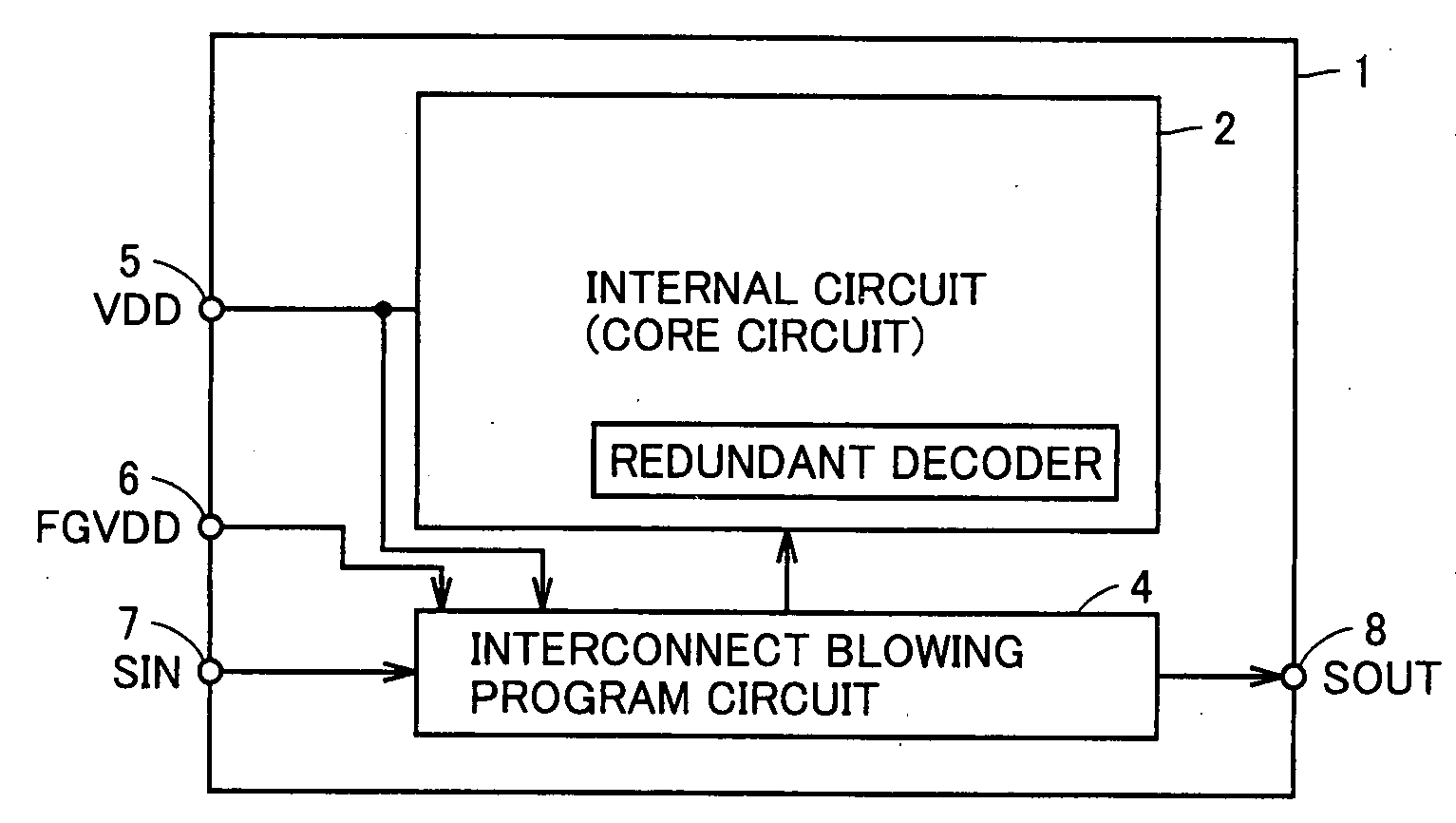

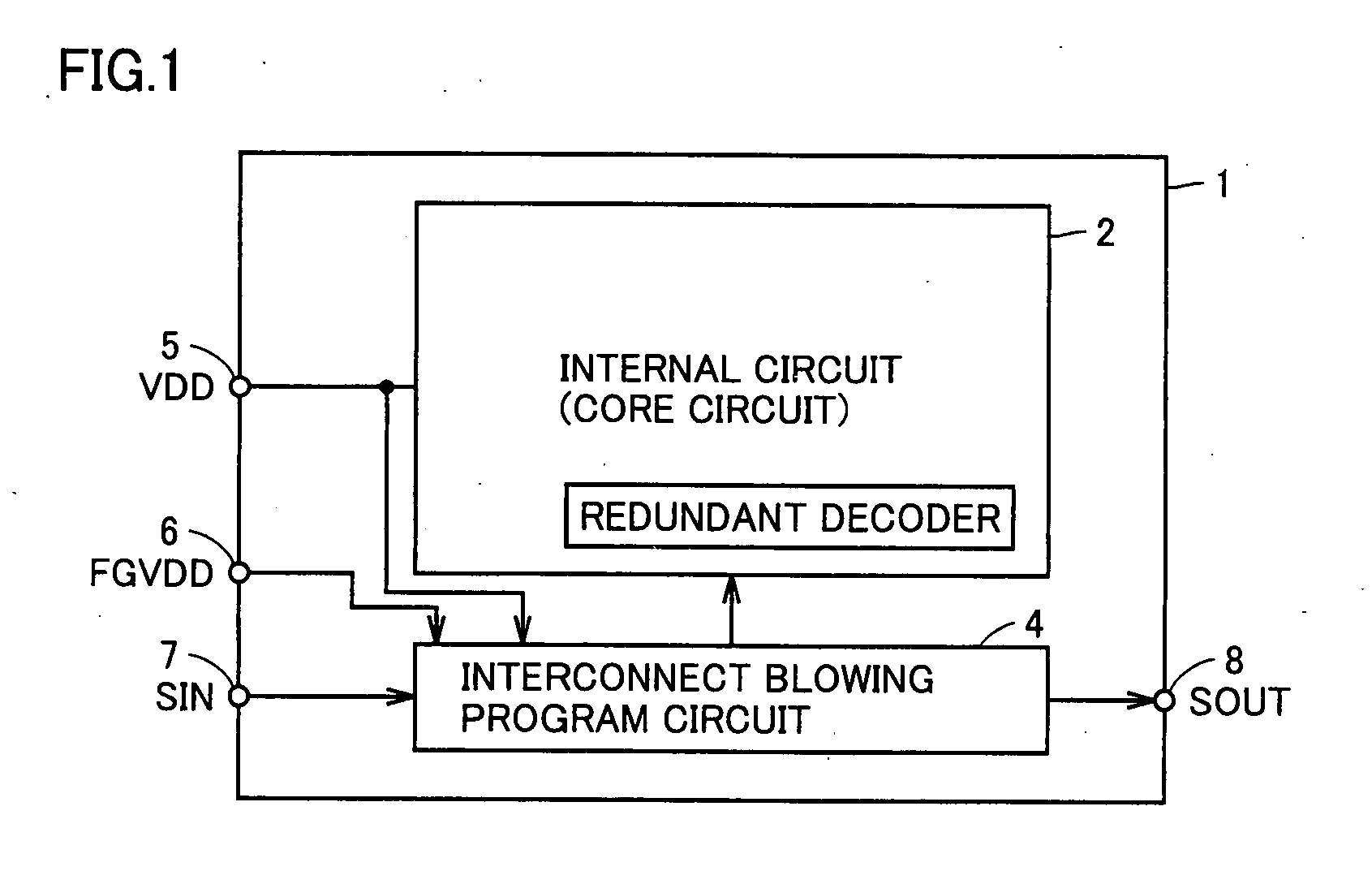

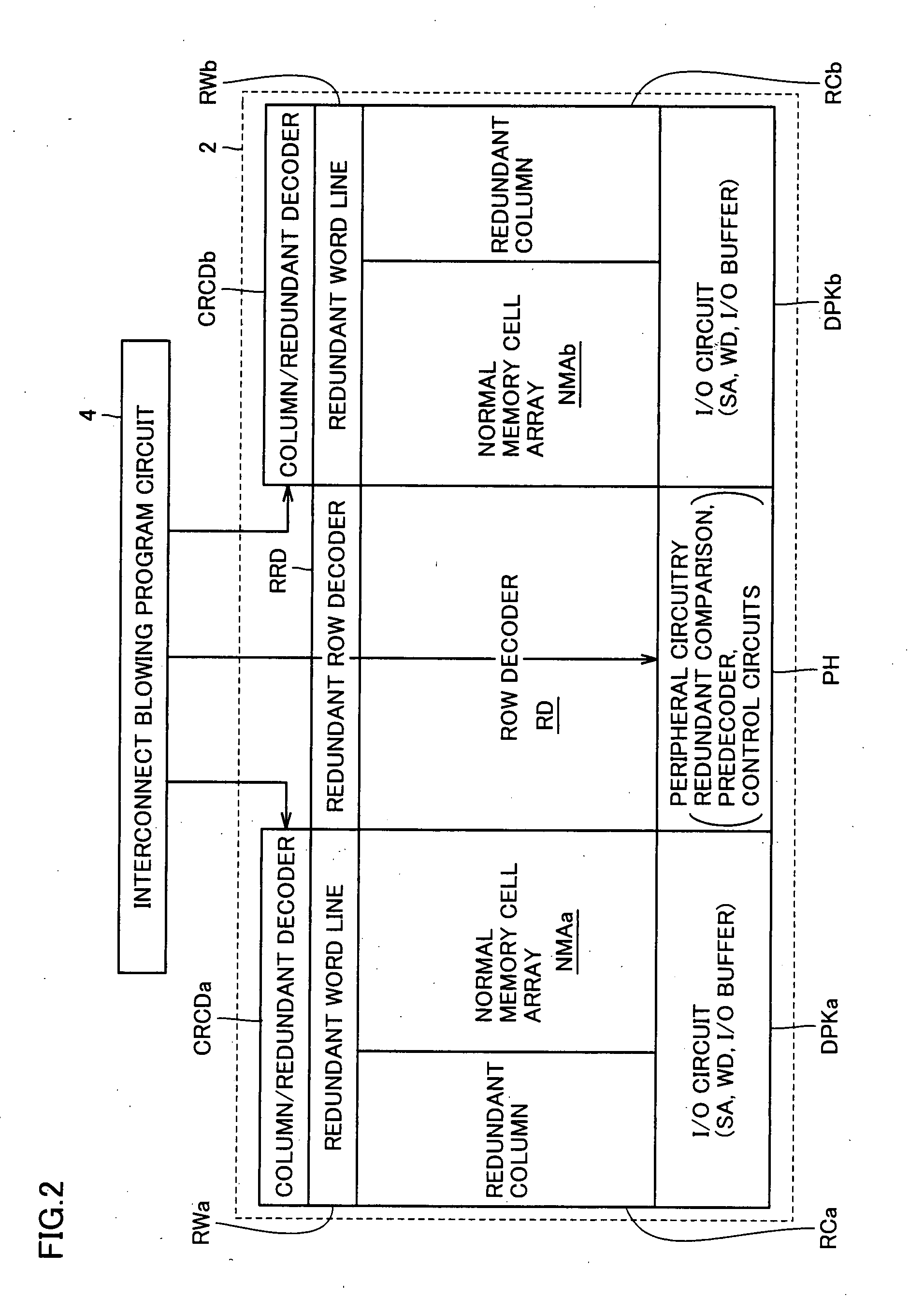

Semiconductor device

ActiveUS20070280012A1Small footprintLower average currentSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDevice material

In fuse program circuits, fuse element FS is implemented using metal interconnect at third or higher layer of multilayer metal interconnect. In each fuse program circuit, program information and fuse select information are sequentially transferred using a scan flip-flops, and fuses are selectively and electrically blown one by one. The fuse program circuit provided with fuse elements that can be programmed even after packaging is implemented with low power consumption and a low occupation area.

Owner:RENESAS ELECTRONICS CORP

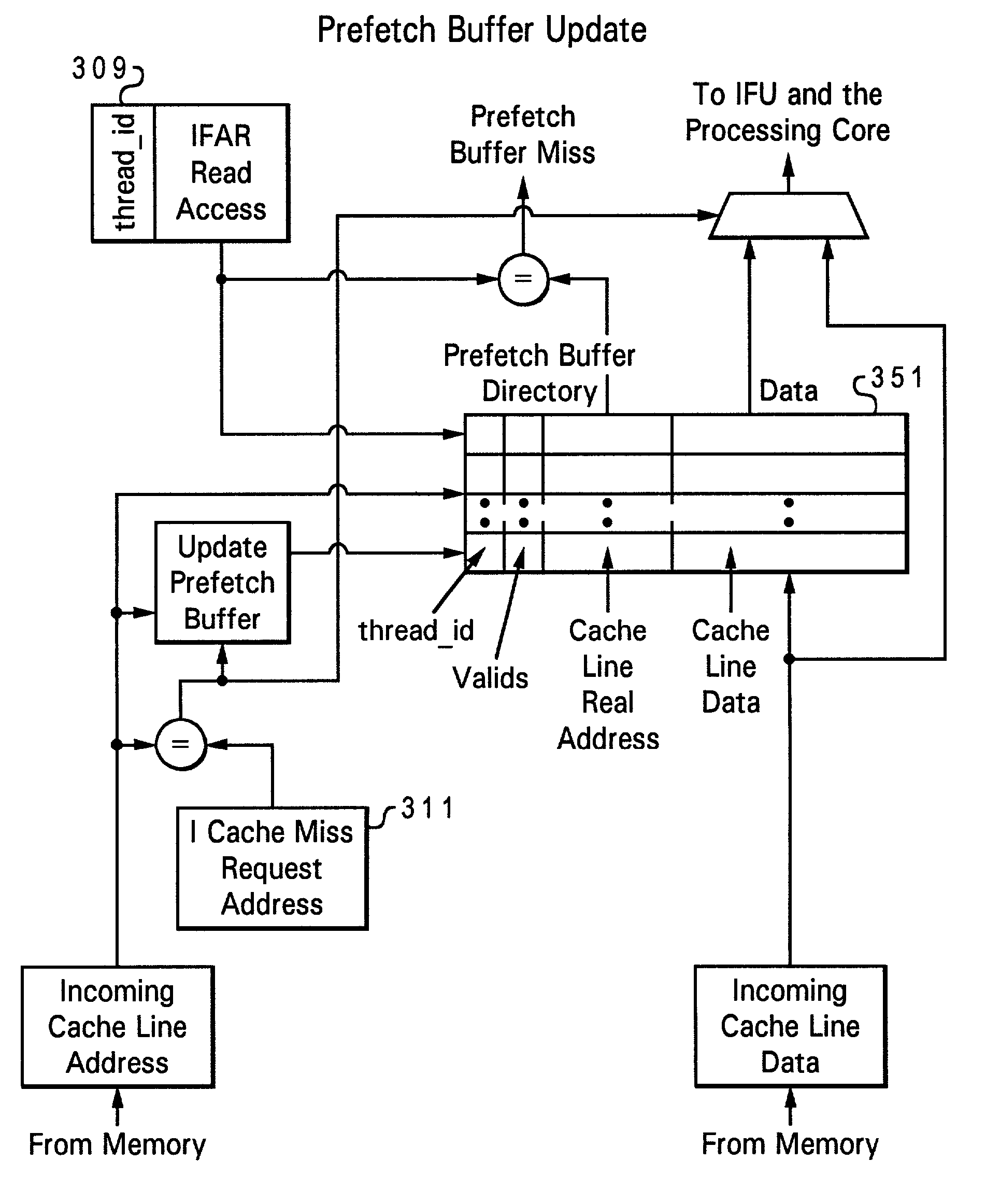

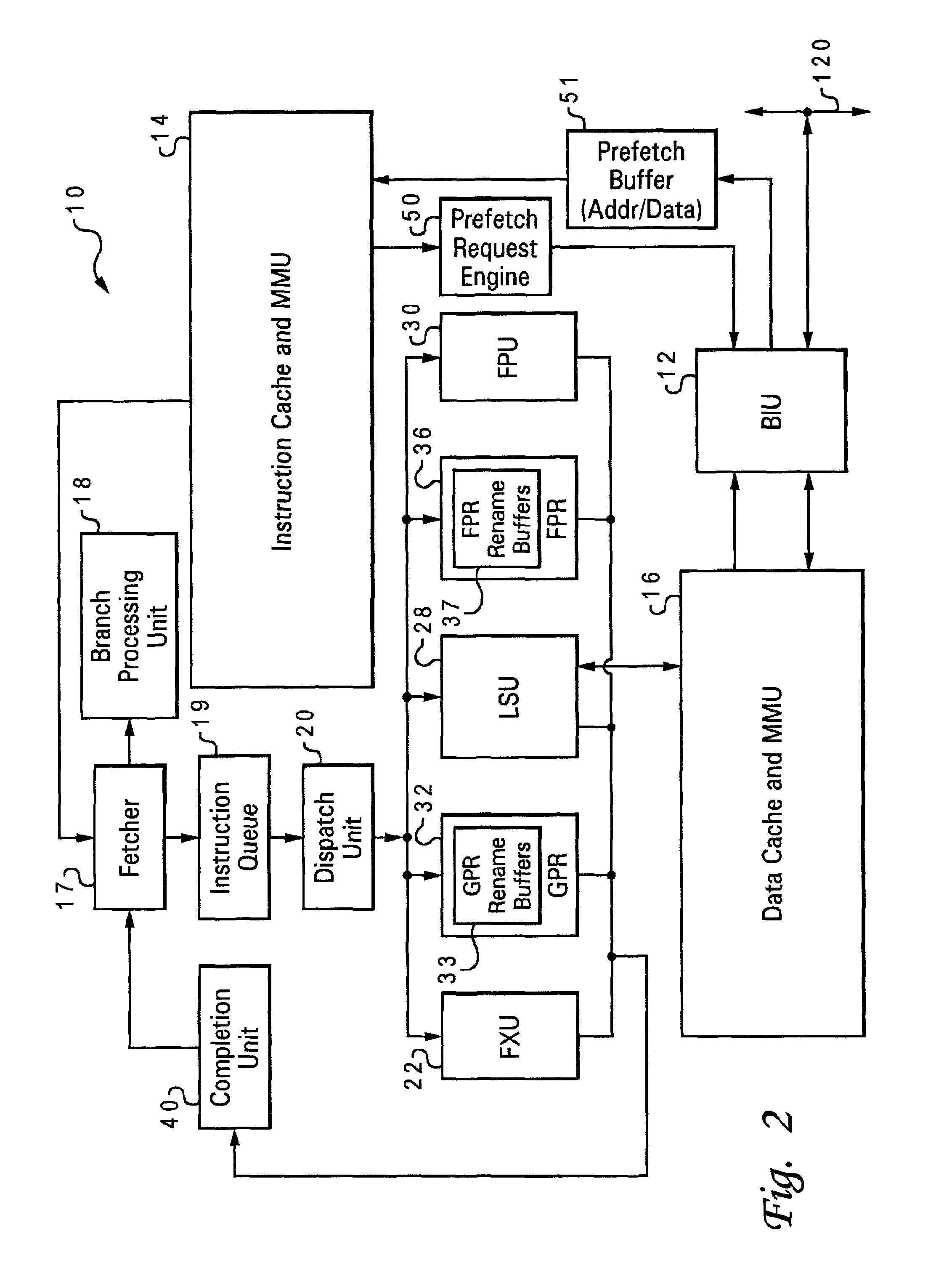

Multithreaded processor efficiency by pre-fetching instructions for a scheduled thread

InactiveUS6965982B2Ensure proper implementationMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer architectureFlip-flop

Owner:INTEL CORP

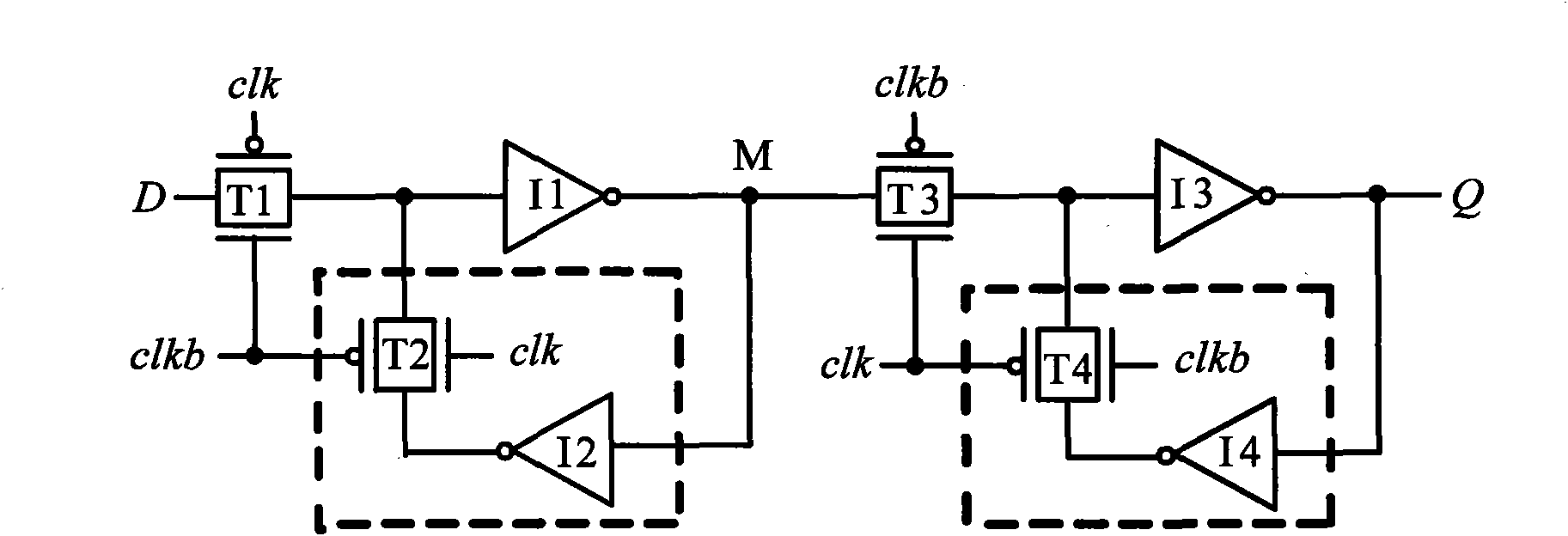

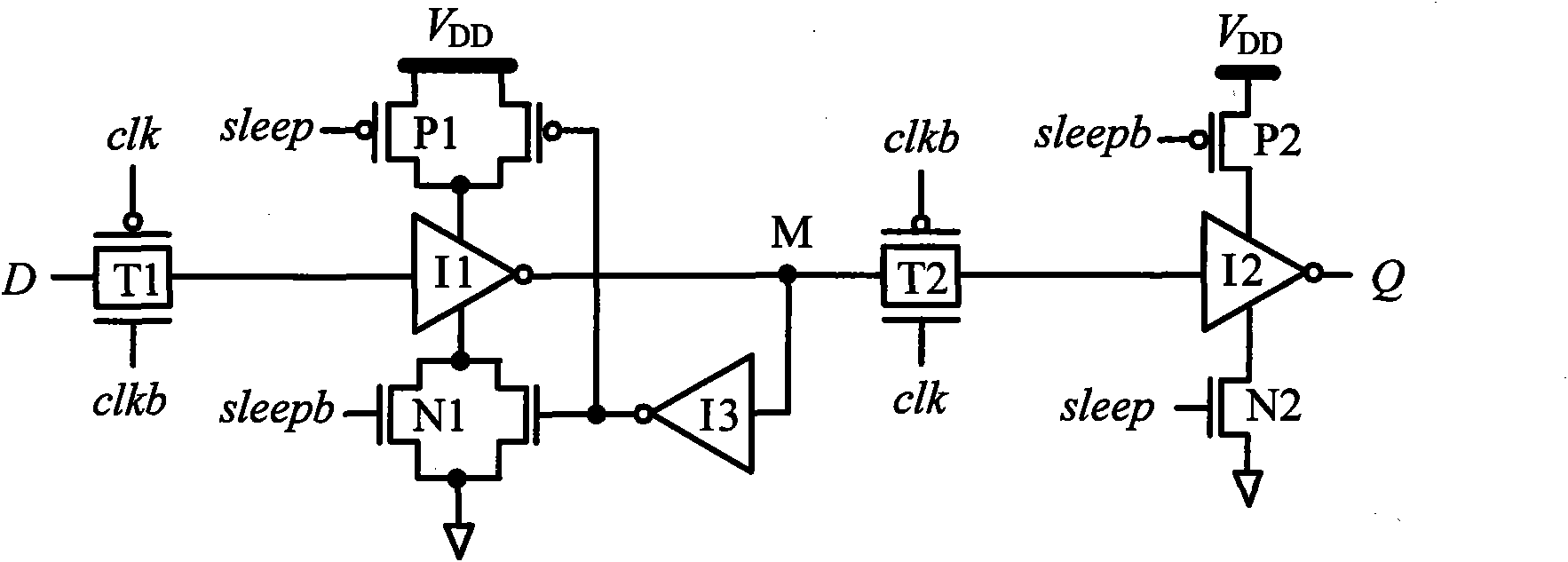

Low-power dissipation RS latch unit and low-power dissipation master-slave D flip-flop

InactiveCN101777907ASimple and completely symmetrical structureGood leakage power suppression performanceElectric pulse generatorLogic circuitsHemt circuitsControl theory

The invention discloses a low-power dissipation RS latch unit and a low-power dissipation master-slave D flip-flop, which is characterized in that the low-power dissipation RS latch unit comprises an input driving and synchronizing circuit, a pull-down circuit, a function control circuit, a first phase inverter and a second phase inverter, wherein the first phase inverter and the second phase inverter are mutually overlapped and coupled. The low power dissipation master-slave D flip-flop is composed of an input phase inverter, a clock phase inverter, a first low-power dissipation RS latch unit and a second low-power dissipation RS latch unit, wherein the first low power dissipation RS latch unit and the second low power dissipation RS latch unit have the same inner structure and are cascaded. The low power dissipation master-slave D flip-flop has the advantages that the low-power dissipation RS latch units use three kinds of leaked power consumption lowering technology, i.e. P-type logic technology, function control technology and double-threshold technology, so that the low-power dissipation RS latch units have better leaked power consumption inhibiting performance. The low-power dissipation master-slave D flip-flop has simple and totally symmetrical circuit structure. Compared with the traditional single-threshold transmission gate D trigger circuit, the invention can save 80% of leaked power consumption and 40% of total power consumption in the 90 nm process, so that the invention is suitable to serve as a digital circuit unit to the design of low-power consumption integrated circuits in the deep sub-micron CMOS process.

Owner:NINGBO UNIV

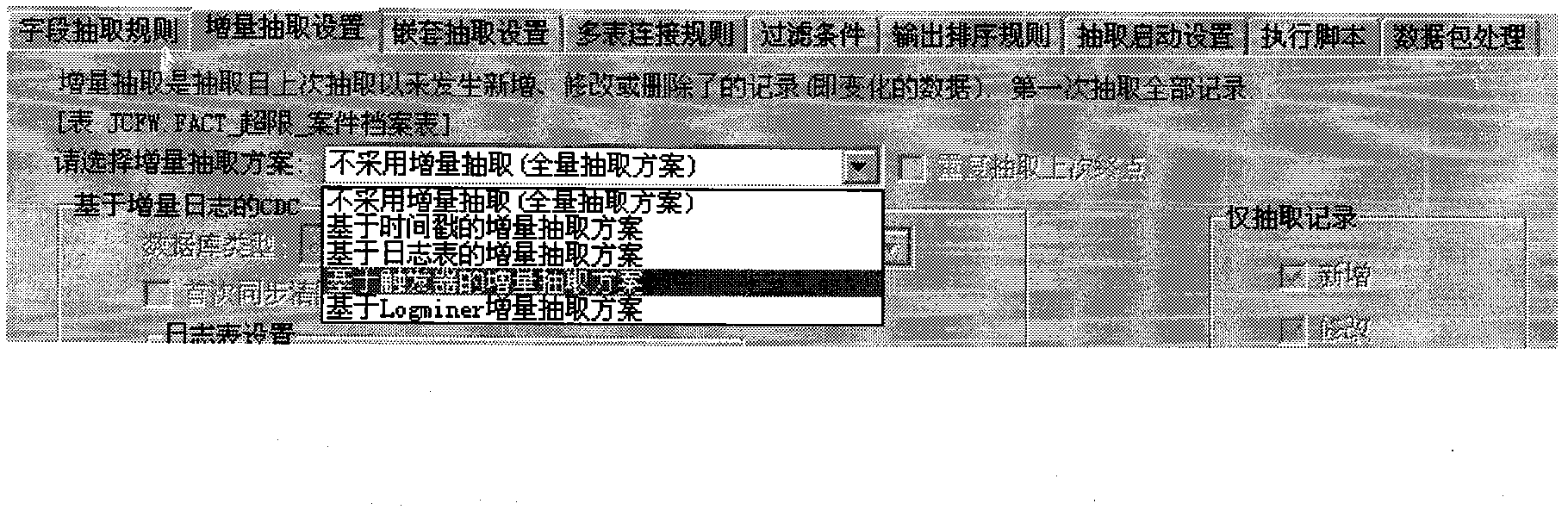

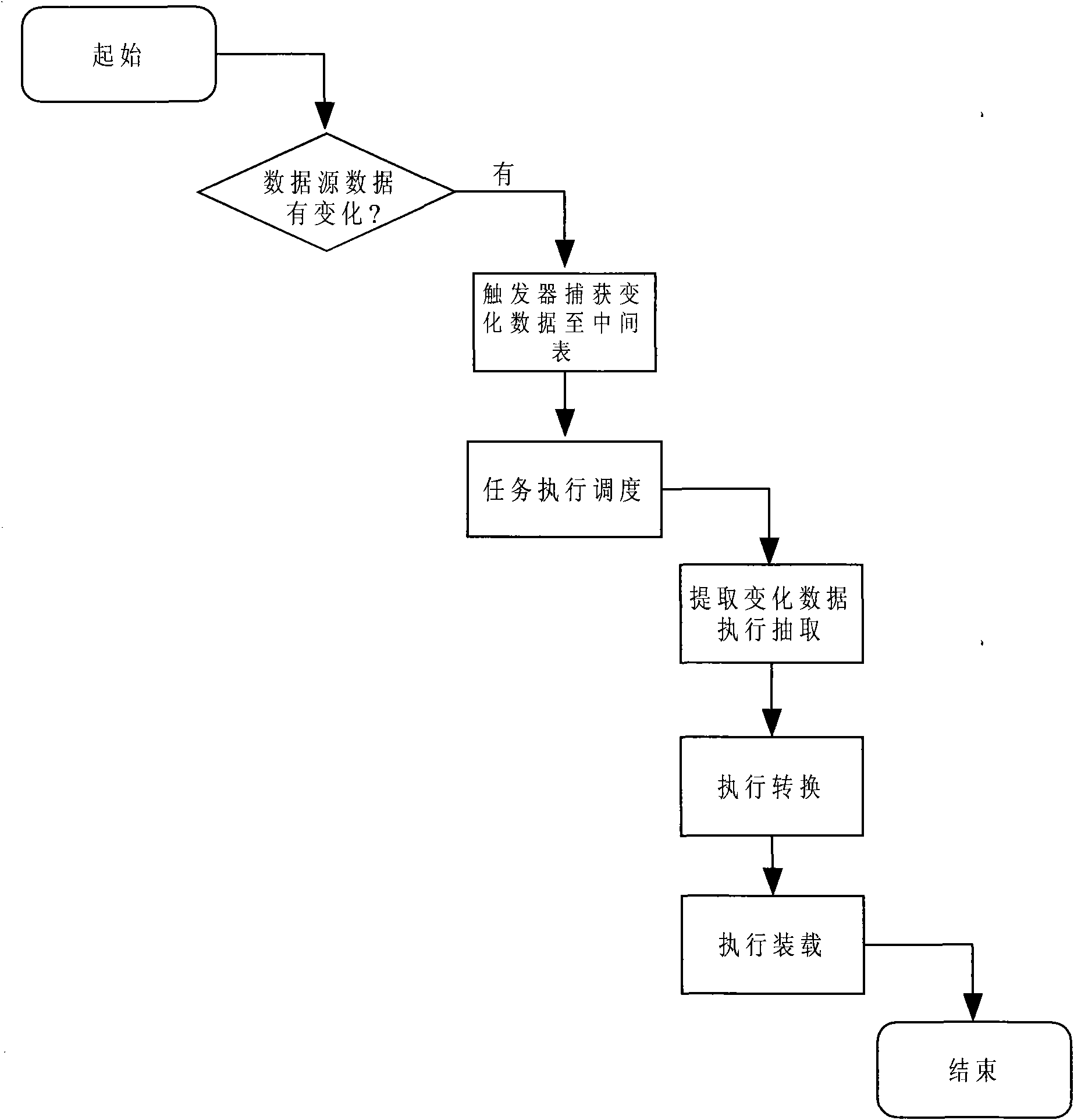

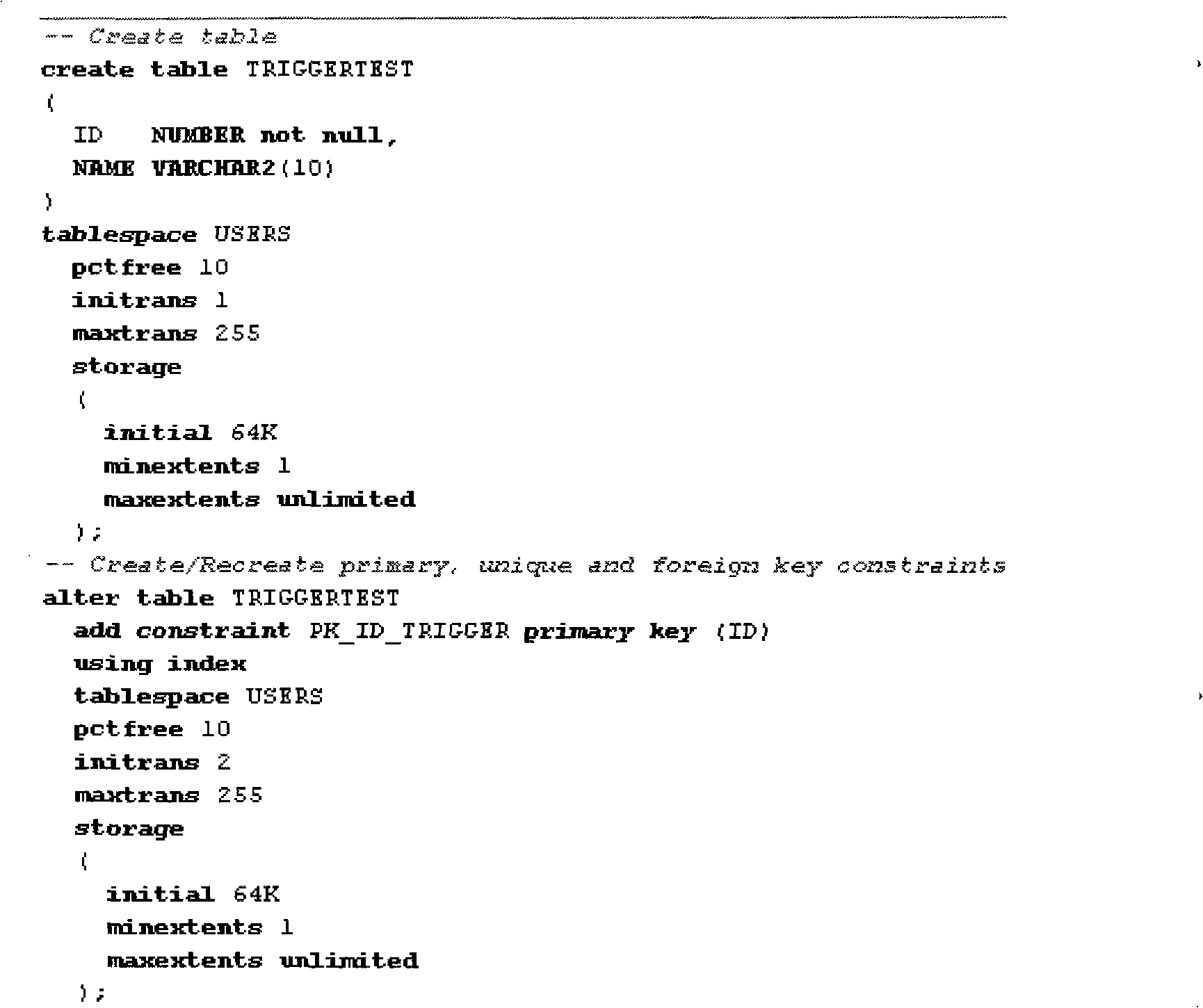

Data increment extraction method based on trigger

InactiveCN101923566AHigh degree of reusabilityHigh data extraction performanceSpecial data processing applicationsFlip-flopReal-time computing

The invention relates to the technical field of data processing, in particular to a data increment extraction method based on a trigger. The method accurately captures variable data in a business system according to certain frequency; meanwhile too big pressure is prevented from being acted on the business system so as to avoid affecting the existing business. Meanwhile, a user can extract incremental data generated in the current period from a resource system according to certain period in the mode of customizing a plan task, or real-time data synchronization capability can be realized in the mode of detecting variable data in real time, which is provided by the system. The invention has the beneficial effects that the invention provides a variable data capturing mechanism, i.e. the mechanism can ensure that new data and old data can be distinguished when the data resource data changes; and thus the invention extracts the data in an incremental mode and does not need to carry out total-amount amount extraction for keeping data synchronous.

Owner:浙江协同数据系统有限公司

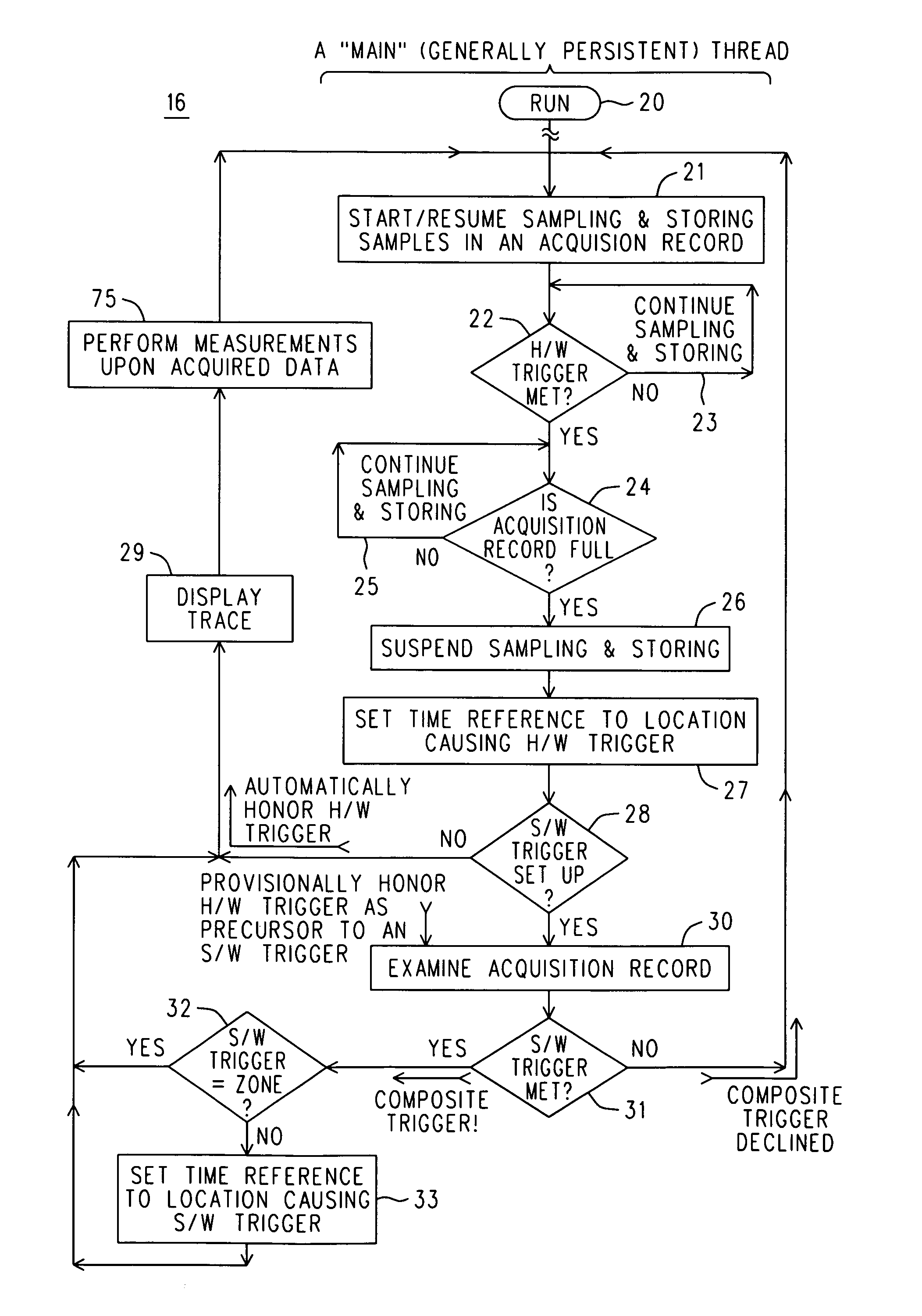

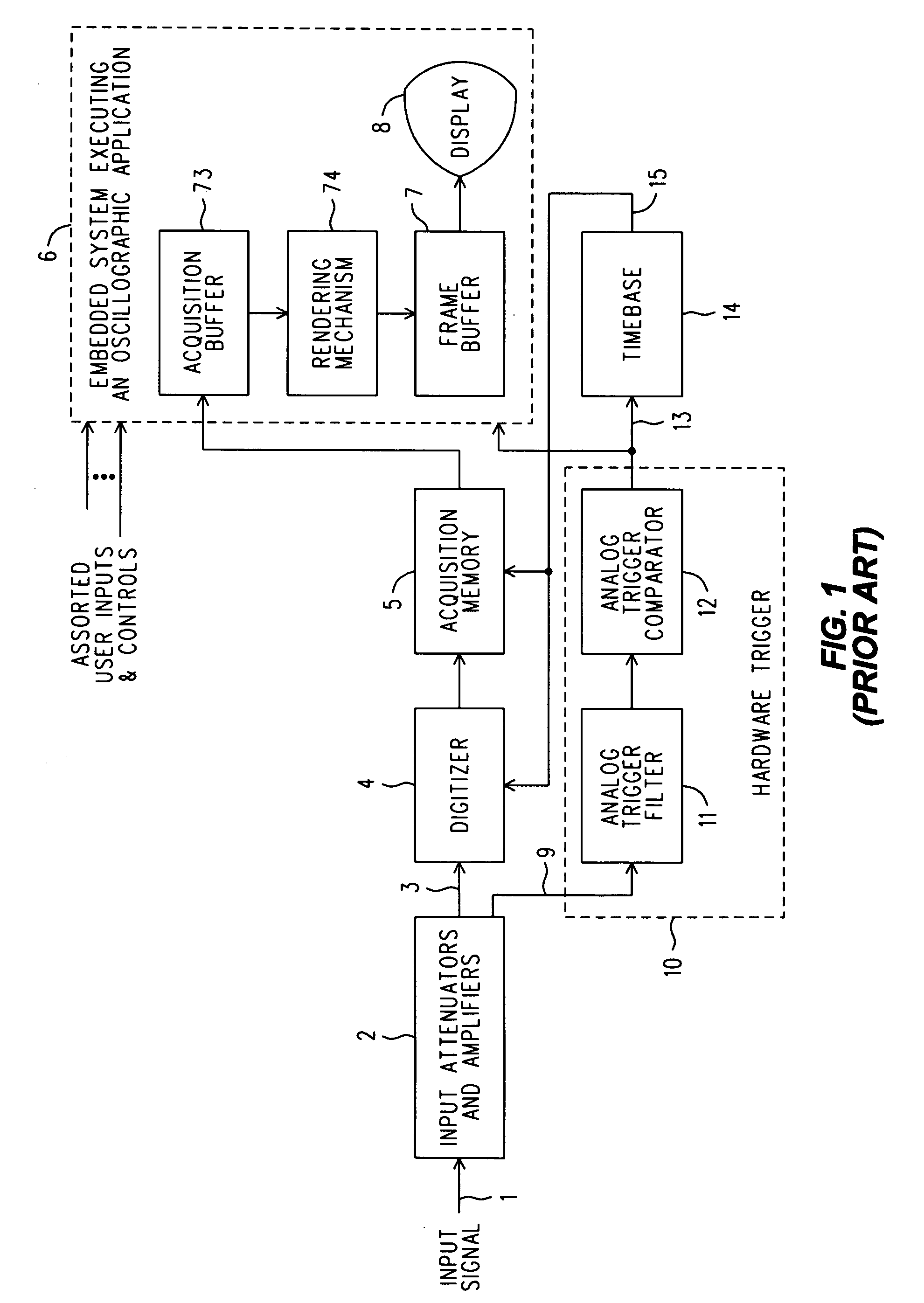

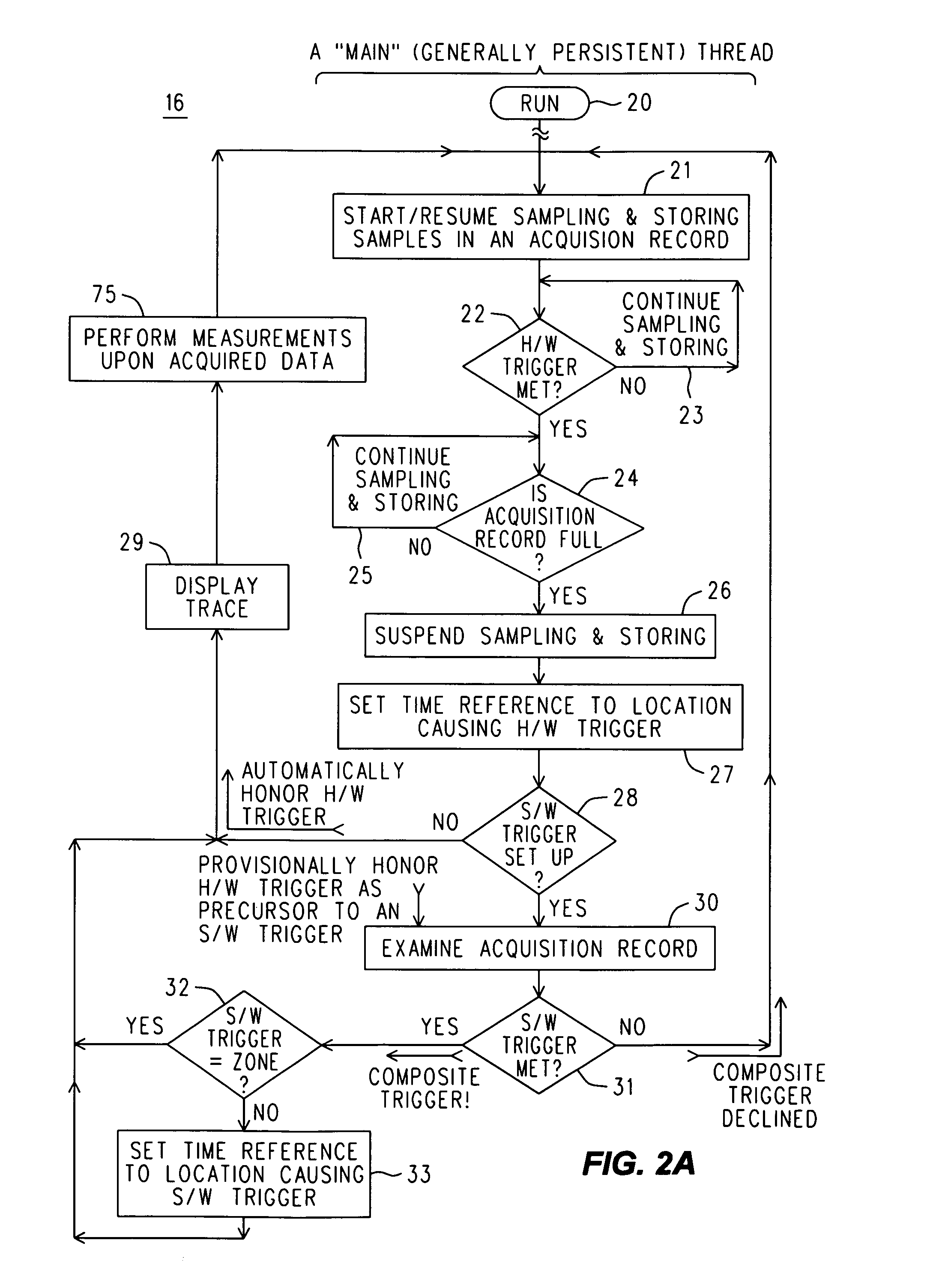

Composite trigger for a digital sampling oscilloscope

InactiveUS20070282542A1Digital variable/waveform displaySpecial data processing applicationsDigital storage oscilloscopeReal-time computing

A Composite Trigger for a DSO provisionally honors a conventional hardware trigger by algorithmically investigating the content of the associated Acquisition Record for a selected signal attribute (a S / W Trigger). If found, the hardware trigger is fully honored by displaying the Acquisition Record with a previously selected time scale and with the time reference set to where in the trace the selected signal attribute occurs. The selected attribute may include the occurrence of a stated value or stated range of values for any automatic measurement upon a trace that the 'scope is otherwise equipped to perform. In addition to being based on existing automatic measurements, the Composite Trigger can also be satisfied whenever subsequent investigation determines that a segment of trace described by the Acquisition Record does or does not pass through one or more zones defined relative to an existing time reference. The Composite Trigger can also be based on whether a trace can be interpreted as exhibiting a selected serial bit pattern, or, upon whether the trace represents an edge that is not monotonic.

Owner:AGILENT TECH INC

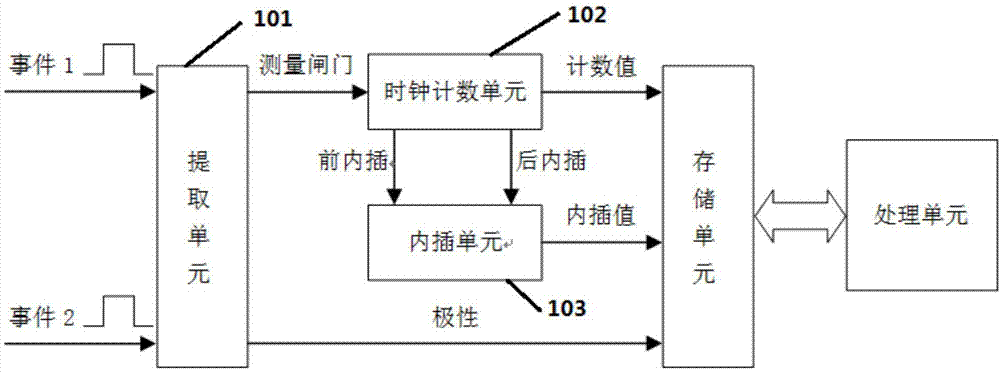

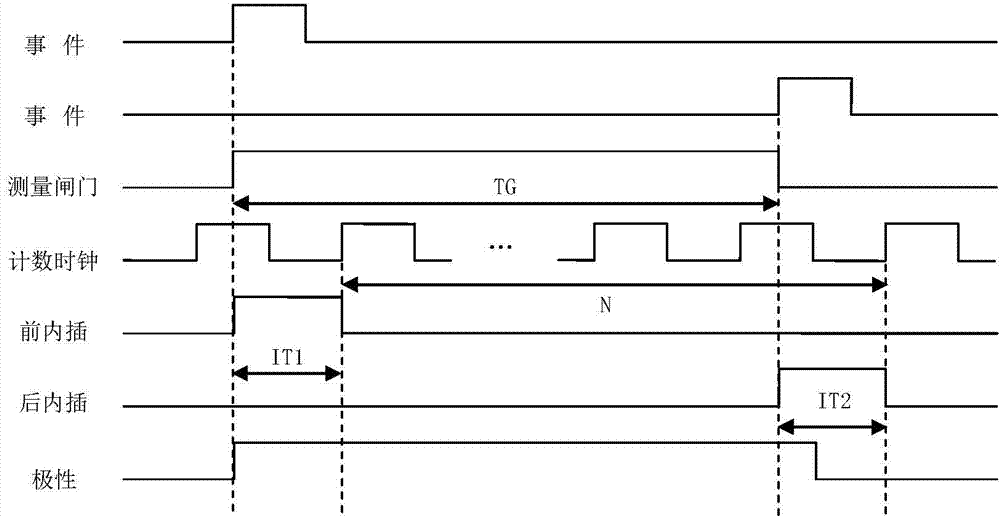

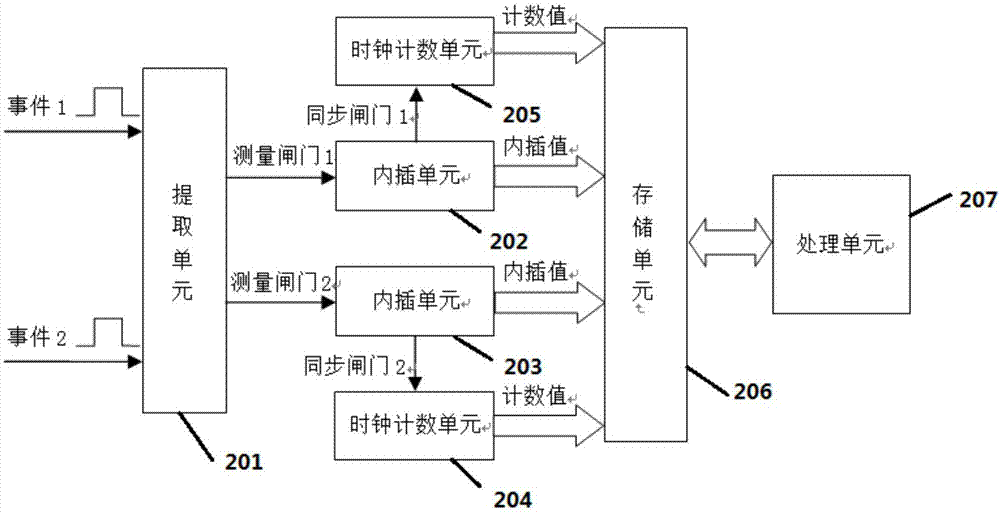

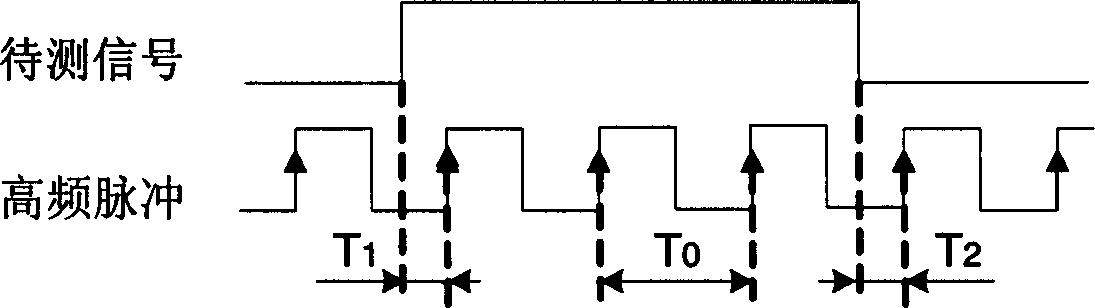

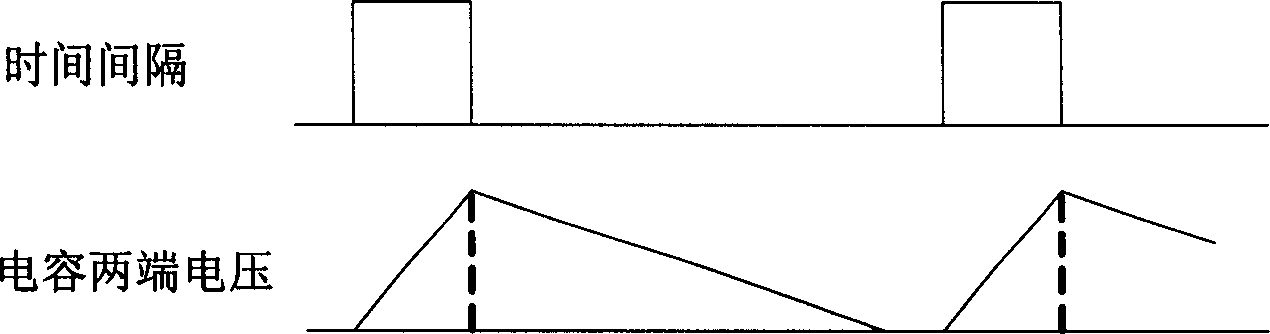

High-precision method and device for measuring interval between positive time and negative time

ActiveCN103676622AHigh measurement accuracyNo dead zone problemElectric unknown time interval measurementImage resolutionComputer science

The invention provides a high-precision method and device for measuring an interval between positive time and negative time. The device comprises a signal shaping and measuring gate extracting unit, a synchronization and interpolation unit, a clock counting unit, a storage unit and a data processing unit, wherein the signal shaping and measuring gate extracting unit, the synchronization and interpolation unit, the clock counting unit, the storage unit and the data processing unit are in connection with one another and in communication with one another. The signal shaping and measuring gate extracting unit conducts comparing and shaping on input signals according to a trigger level, converts measured signals into ECL level signals, and extracts gate signals corresponding to the measured signals through an ECL trigger. The synchronization and interpolation unit samples the two routes of gate signals through a counting clock. By means of the scheme, various types of signal input can be achieved, and the wide input dynamic range can be supported; a channel circuit is obtained through a high-speed ECL device, the channel bandwidth is large, narrow-pulse measurement can be achieved, the minimum measurable pulse width can reach 2.5ns, and the measurement resolution ratio can reach 40ps.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

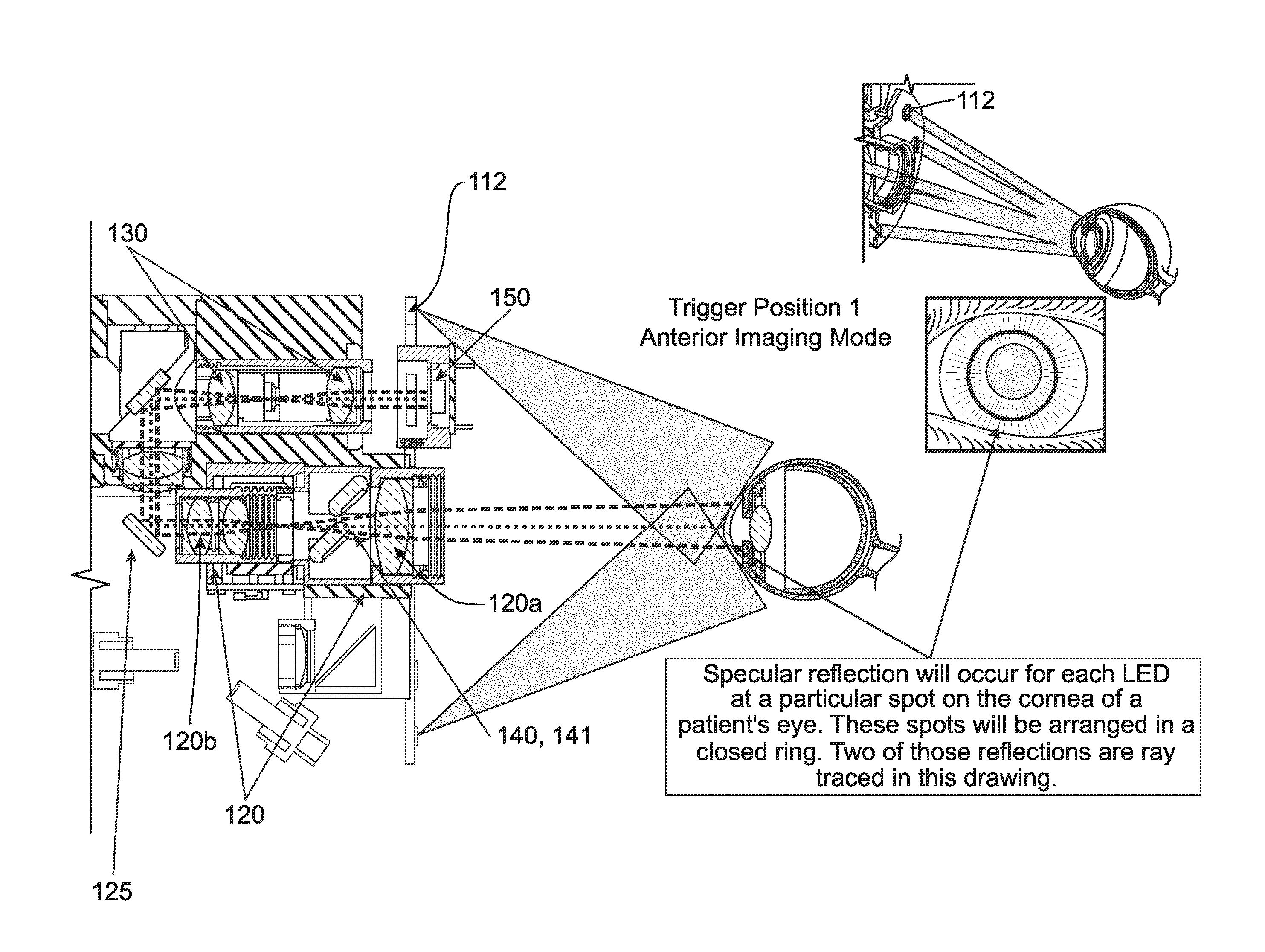

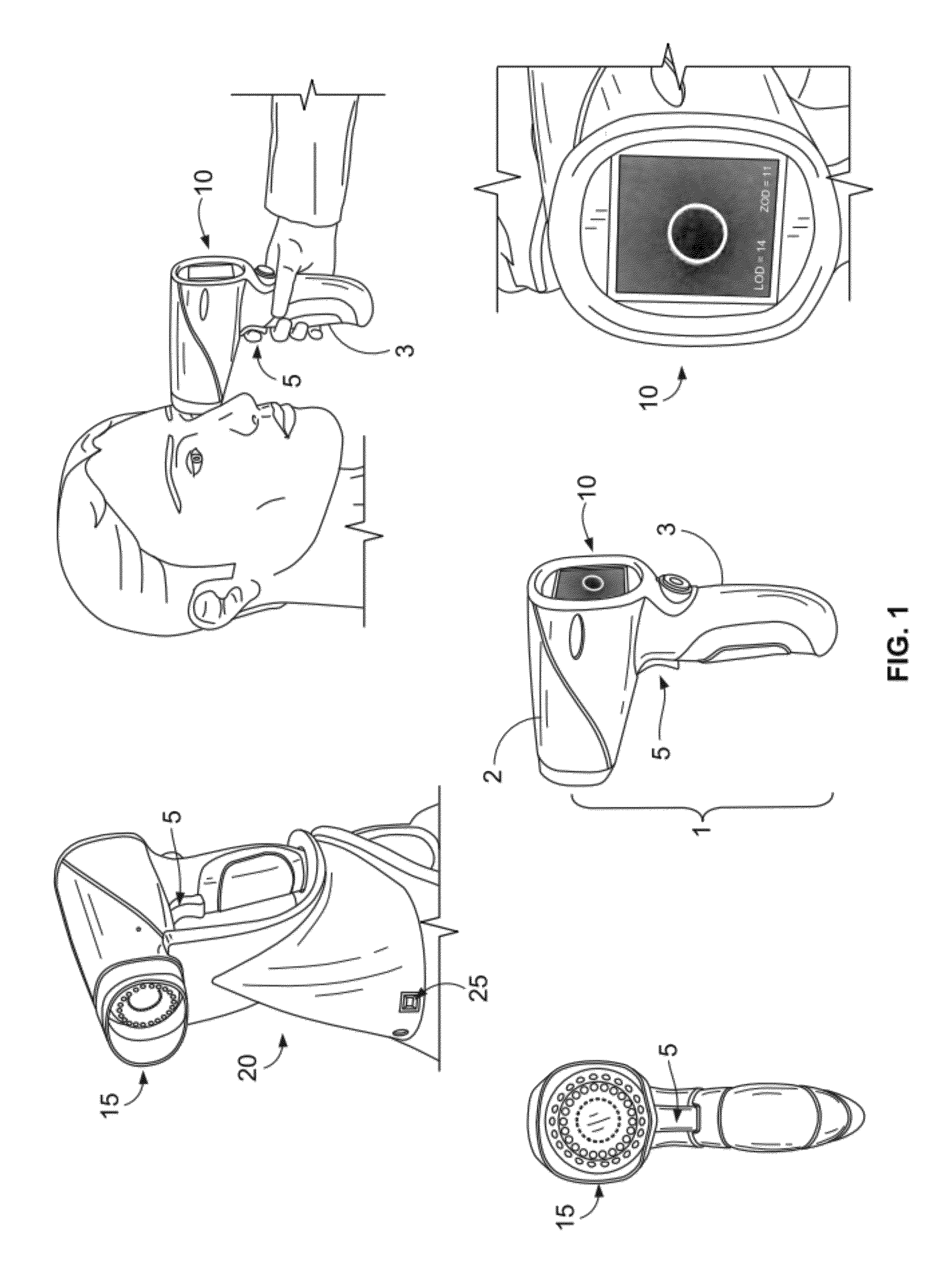

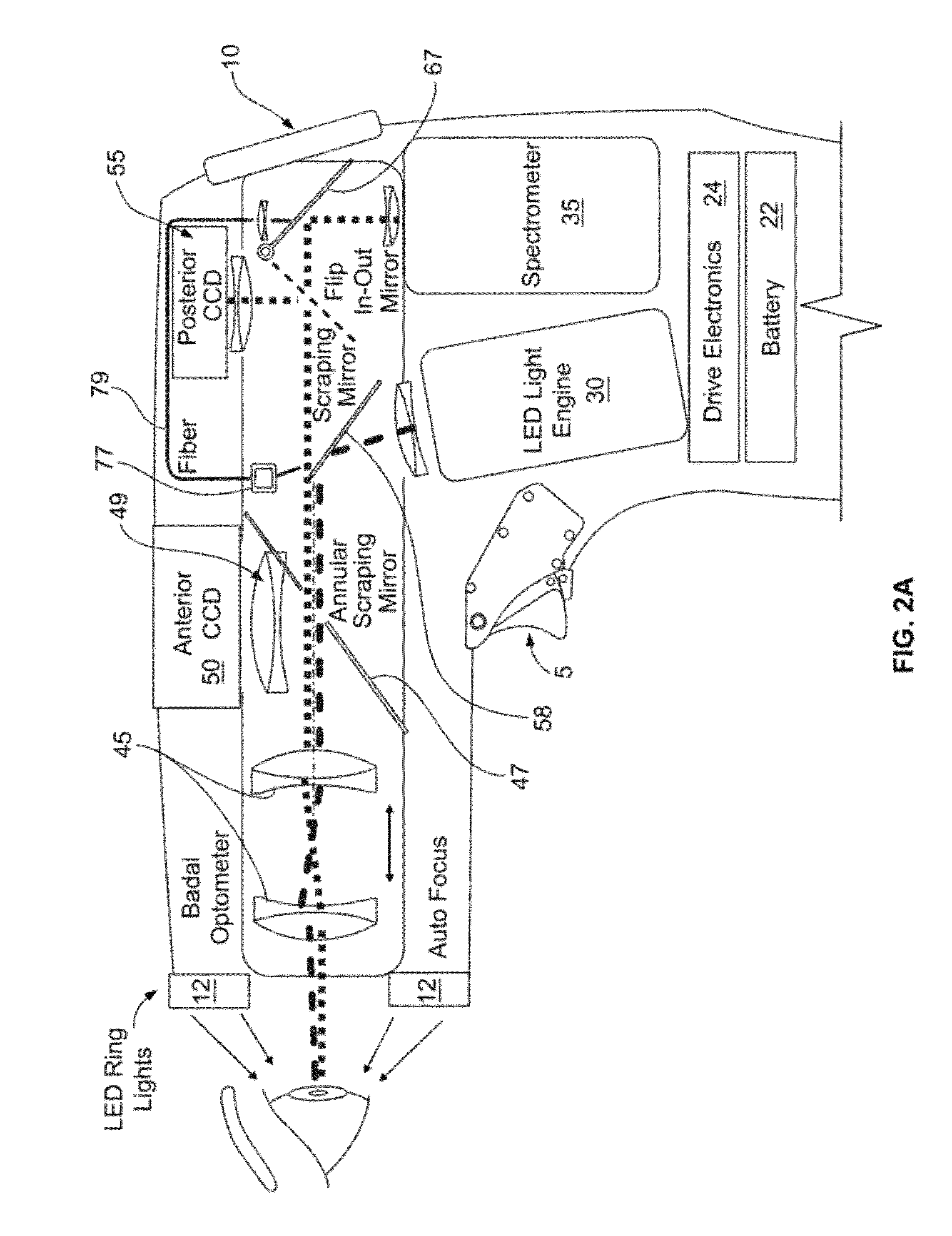

Handheld reflectometer for measuring macular pigment

ActiveUS20120092619A1Short time intervalReduce relative motionOthalmoscopesDocking stationMedical record

A macular pigment reflectometer is handheld, light, and portable. It can be provided as a part of a self-contained system. The self-contained system includes a docking station in which the macular pigment reflectometer is placed between uses. The docking station is used to recharge the battery of the handheld macular pigment reflectometer. The docking station also has one or more types of communication ports, such as one for a wired or wireless internet connection, through which the handheld macular pigment reflectometer can communicate with a computer or an electronic medical records system. The instrument operates in a pulsed operating mode wherein relative instrument-to-eye motion is reduced and, preferably, nearly eliminated. The handheld macular pigment reflectometer contains an on-board spectrometer which is designed to capture spectra in very short intervals of time. A trigger on the instrument allows for a rapid, intuitive, and sequential alignment followed by rapid data gathering.

Owner:OCULAR PROGNOSTICS

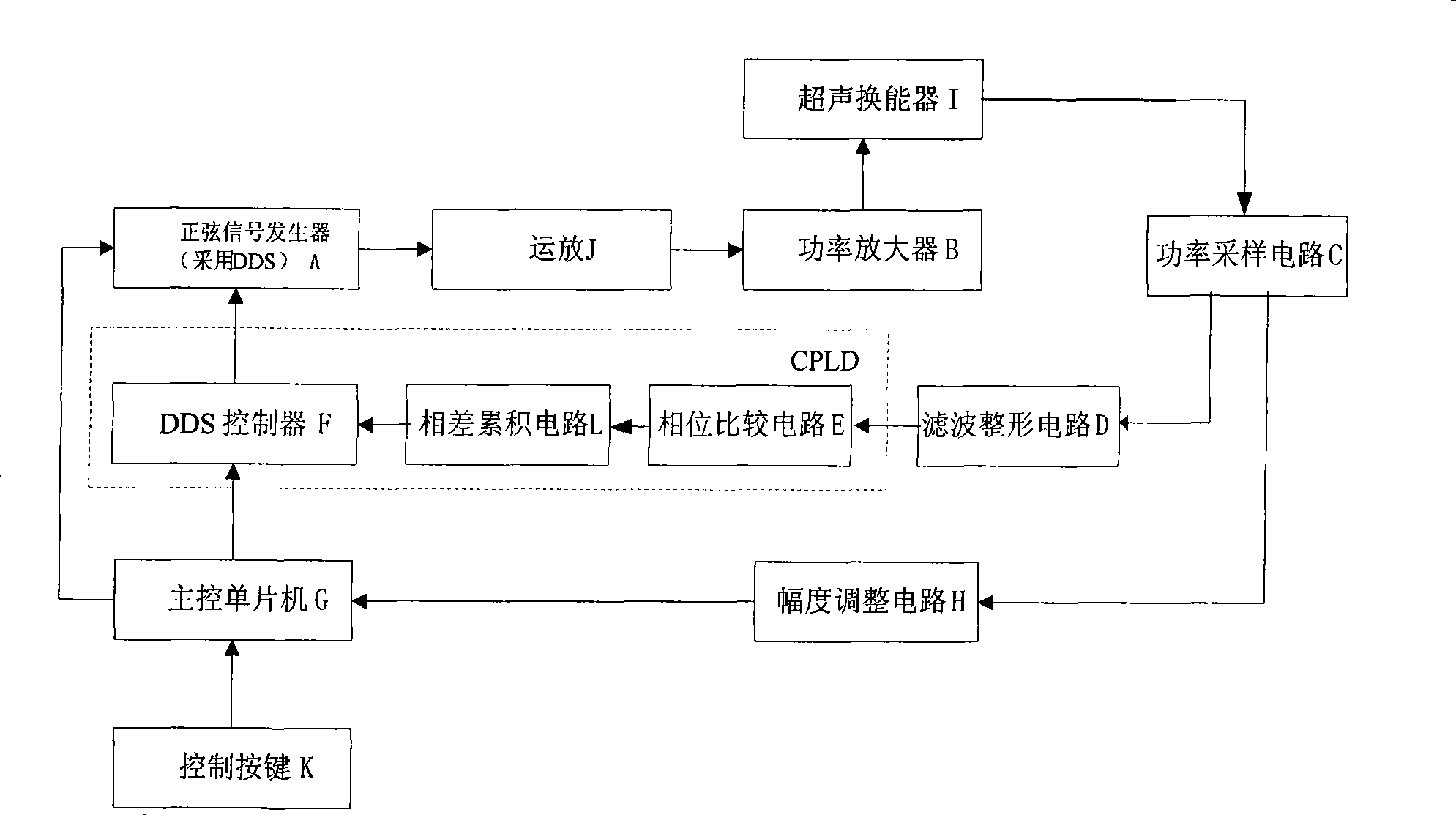

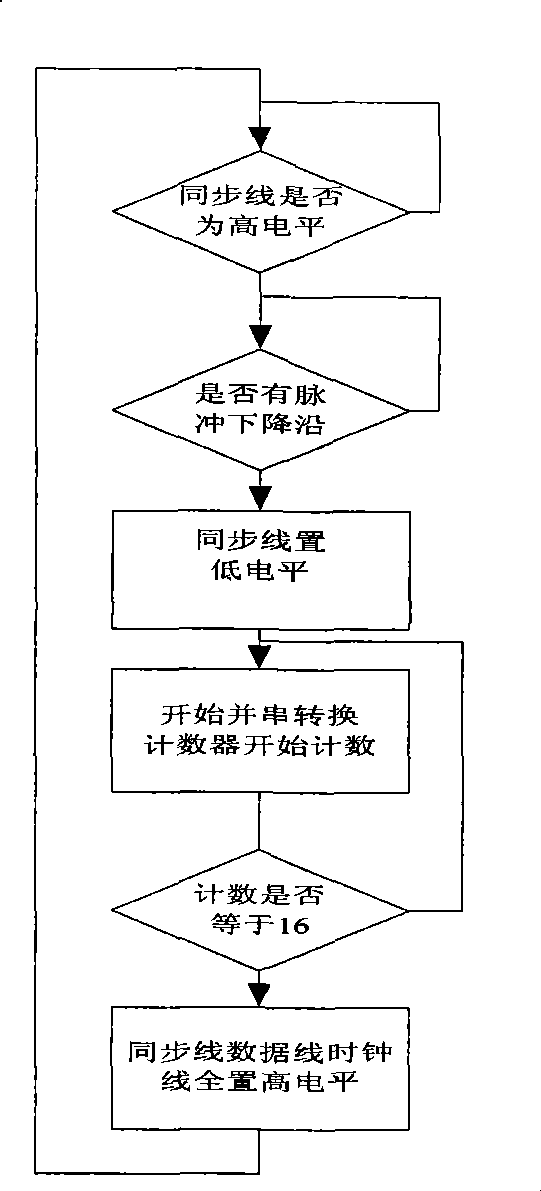

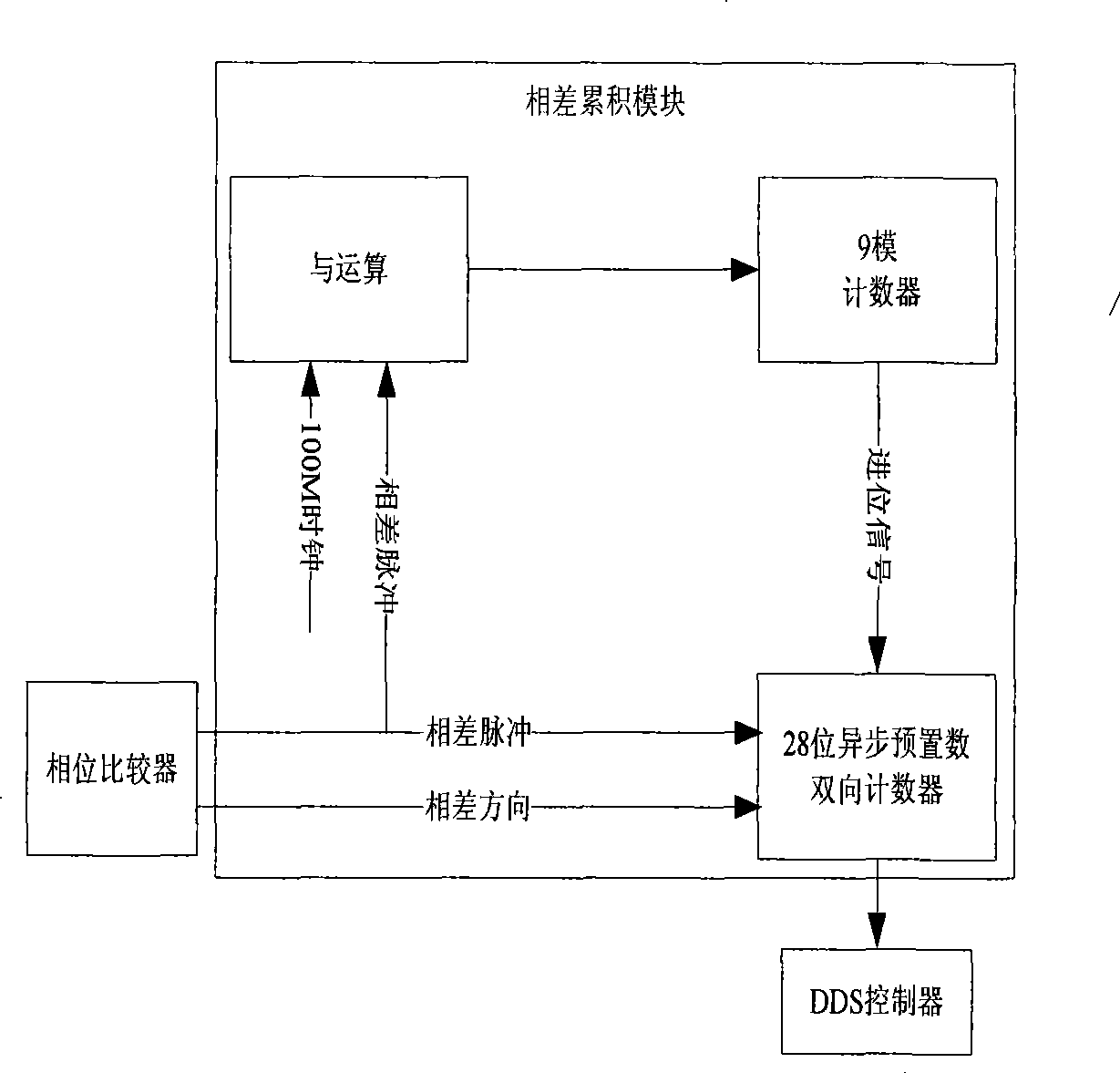

Automatic frequency tracking method of supersonic transducer and system thereof

ActiveCN101468347ARealize digital controlWork reliablyMechanical vibrations separationLogical elementUltrasonic sensor

The invention relates to an automatic frequency tracking method and a system for an ultrasonic transducer. A direct digital frequency synthesizer is used as a signal source, wherein the direct digital frequency synthesizer can be an independent integrated chip and also be achieved by the method that a digital part of a DDS is integrated in a site programmable logical element FPGA and then a digital-analog converter is additionally added. The design of the invention adopts a frequency sweeping and tracking policy, and an automatic frequency controller achieved by the programmable element controls the output frequency of the DDS according to a feedback signal sampled from the self transducer end so as to achieve the full digitization automatic frequency tracking and ensure that the ultrasonic transducer work near a resonance point all the time to obtain the optimal efficiency. A phase comparator utilizes a trigger to give out the arriving time difference of two riser edge signals of two input signals I ph and V ph aiming to the sensitive characteristics of the riser edge signals, and the sequence of the riser edge signals of the two input signals I ph and V ph is given out by a Dirrect pin.

Owner:BEIJING ANHEJIALIER TECH CO LTD

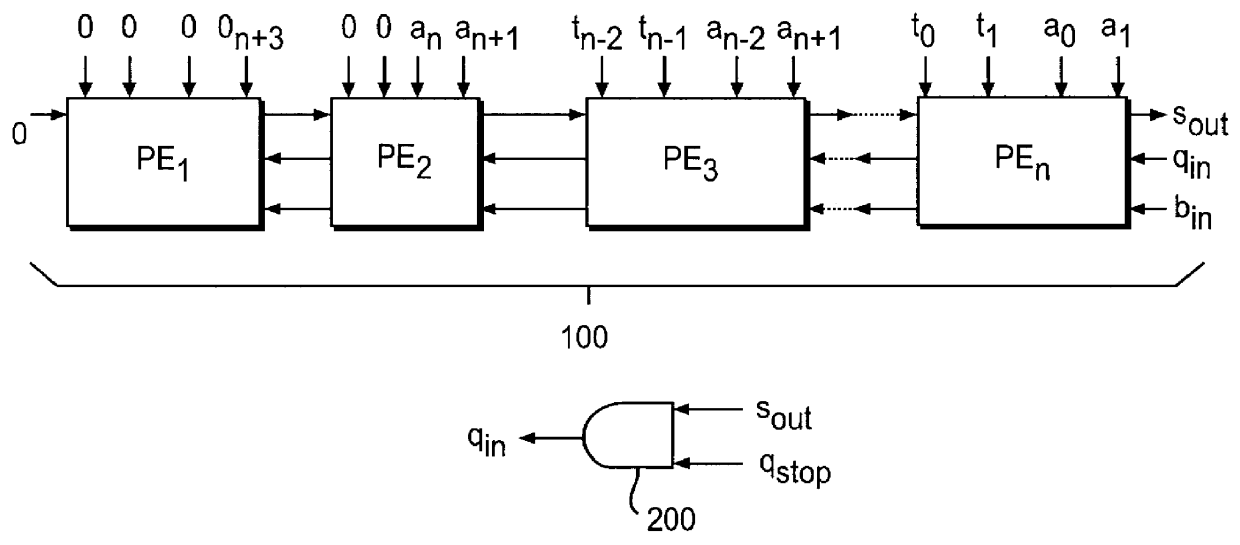

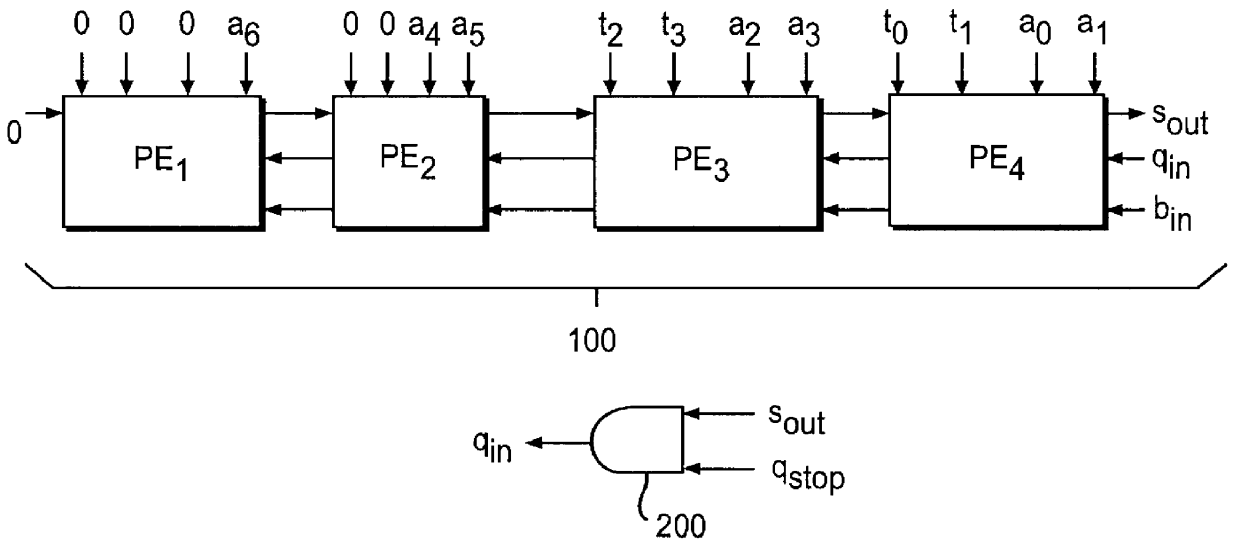

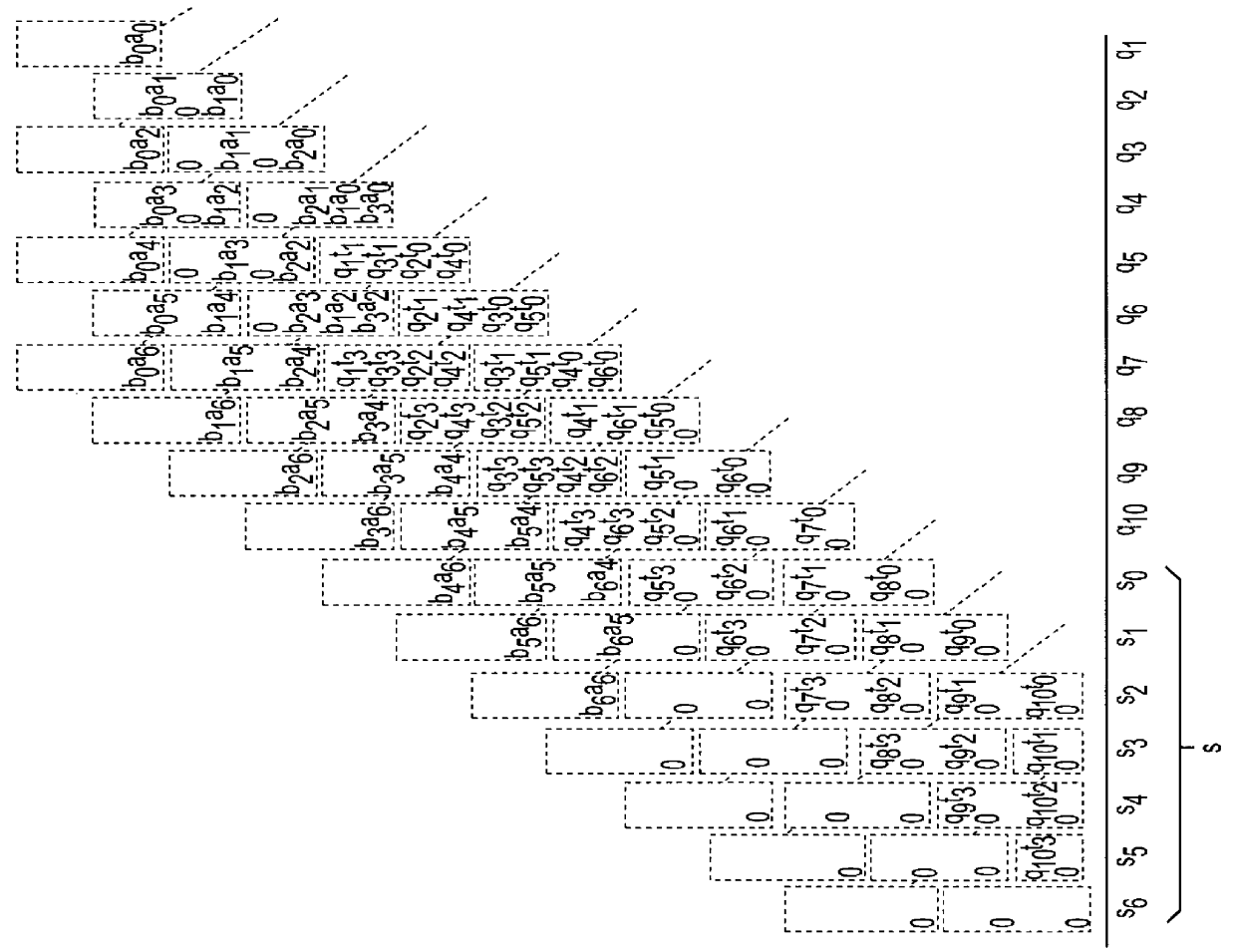

Systolic linear-array modular multiplier with pipeline processing elements

InactiveUS6061706ADegree of complexity can be reducedReduce manufacturing costComputations using residue arithmeticComputation using denominational number representationModularityCMOS

A systolic linear-array modular multiplier is provided, which can perform the modular multiplication algorithm of P. L. Montgomery more efficiently. The total execution time for n-bit modular multiplication is 2n+11 cycles. The modular multiplier includes a linear array of processing elements which is constructed based on a pipeline architecture that can reduce the computation procedure by one clock period. Each of the processing elements is simple in structure, which is composed of four full adders and fourteen flip-flops. For n-bit modular multiplication, a total number of 46n+184 gates is required, which is substantially less as compared to the prior art, so that manufacturing cost of the modular multiplier can be significantly reduced. These features make the modular multiplier suitable for use in VLSI implementation of modular exponentiation which is the kernel computation in many public-key cryptosystems, such as the RSA (Rivest-Shamir-Adleman) system. With the 0.8 mu m CMOS technology, a clock signal up to 180 MHz can be used. In average, for n-bit modular multiplication, the encryption speed can reach 116 Kbit / s (kilobits per second), which is substantially twice that achieved by the prior art.

Owner:UNITED MICROELECTRONICS CORP

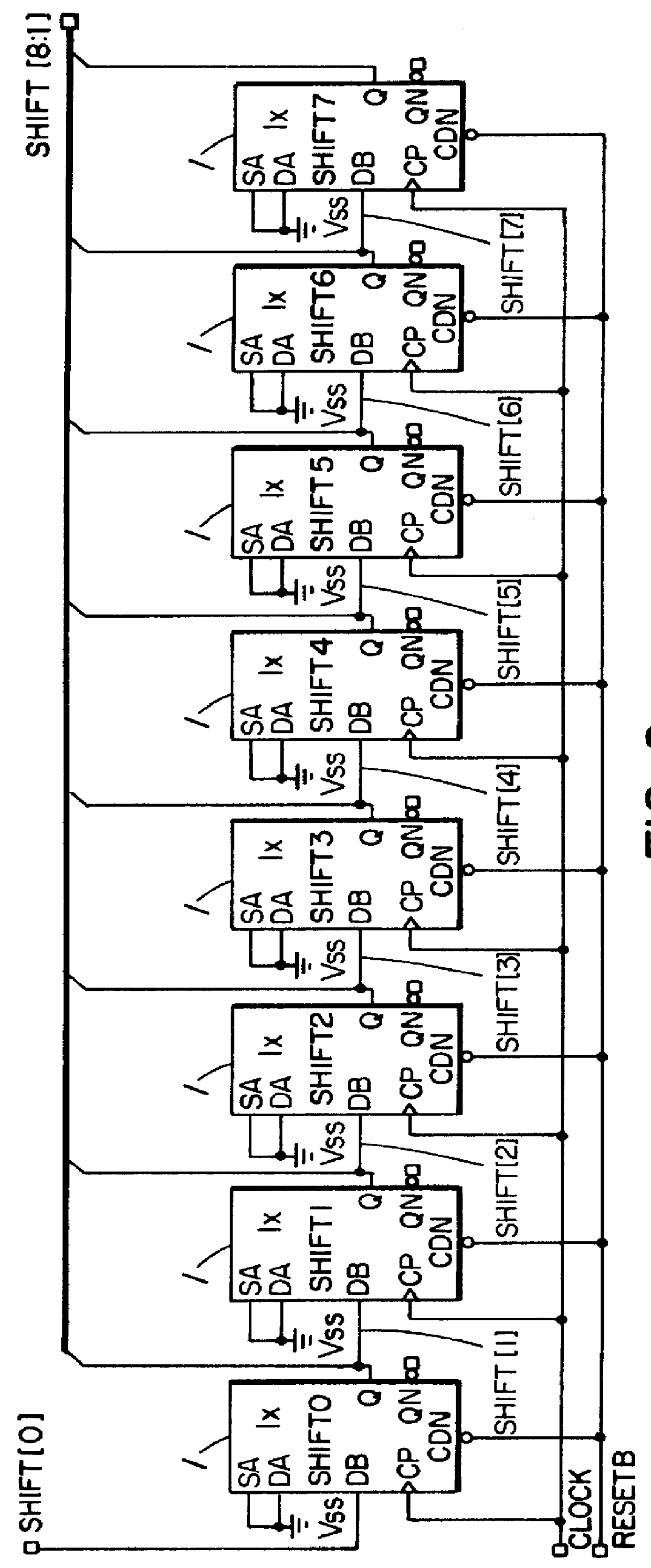

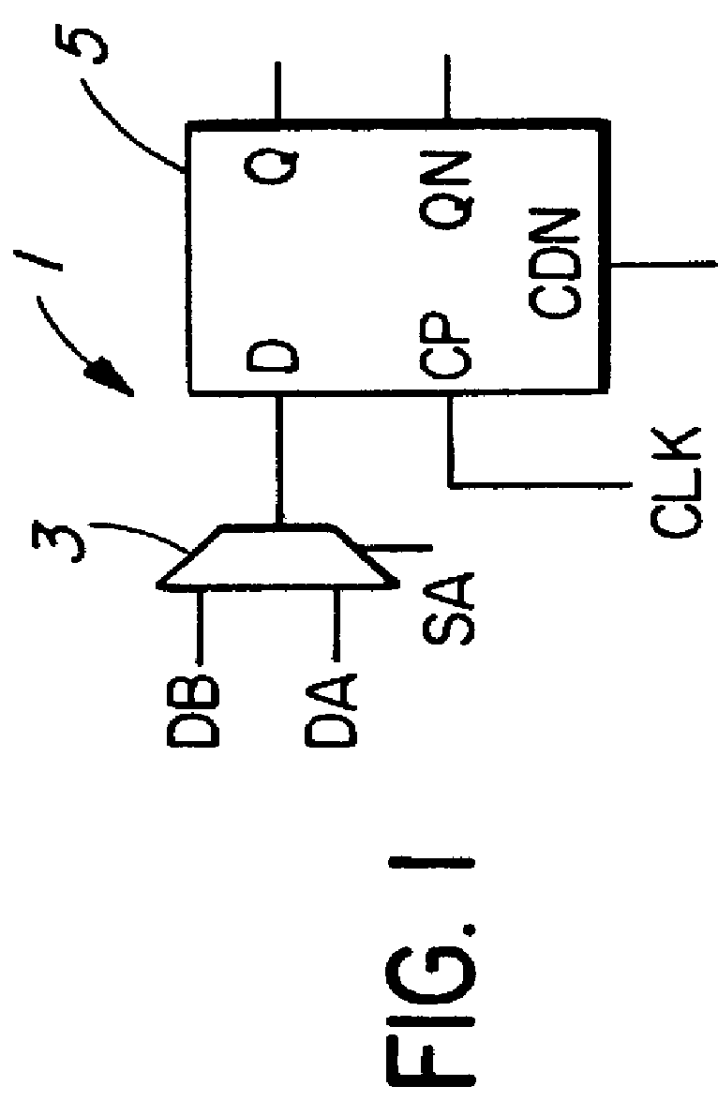

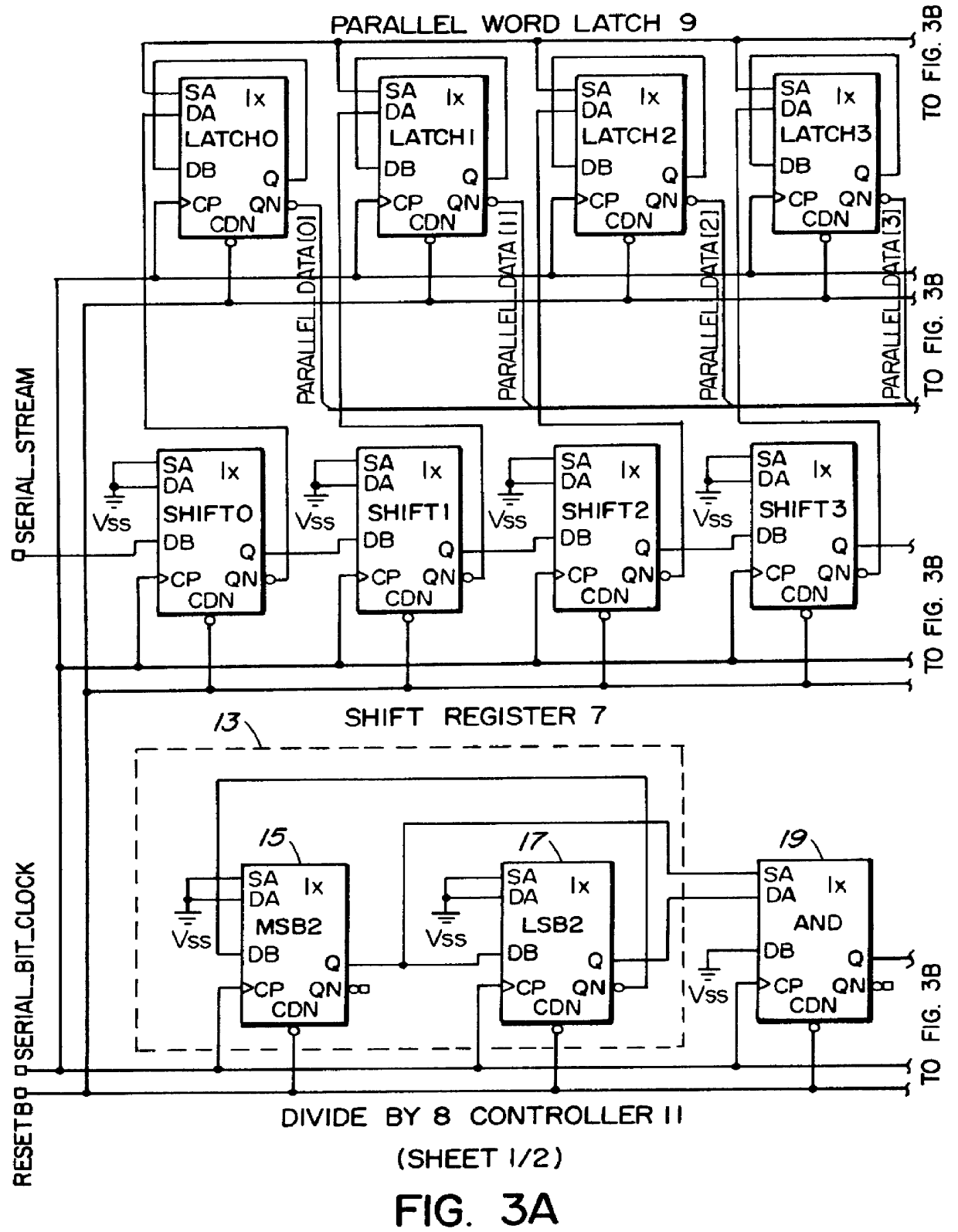

Serial to parallel converter enabled by multiplexed flip-flop counters

InactiveUS6052073AAnalogue/digital conversionElectric signal transmission systemsShift registerMultiplexing

A serial to parallel converter comprising a serial shift register for receiving an incoming serial stream of bits, a parallel word latch for receiving in parallel bits stored by the shift register, when enabled by an enable signal at an enable time, and for providing a parallel data output signal, a controller for generating an enable signal at the enable time and applying the enable signal to the parallel word latch, the controller being comprised of a counter for counting input clock pulses at a serial bit rate and for providing the enable signal upon counting plural input clock pulses, the counter being comprised of active elements restricted to plural combination multiplexed flip / flops.

Owner:PMC-SIERRA

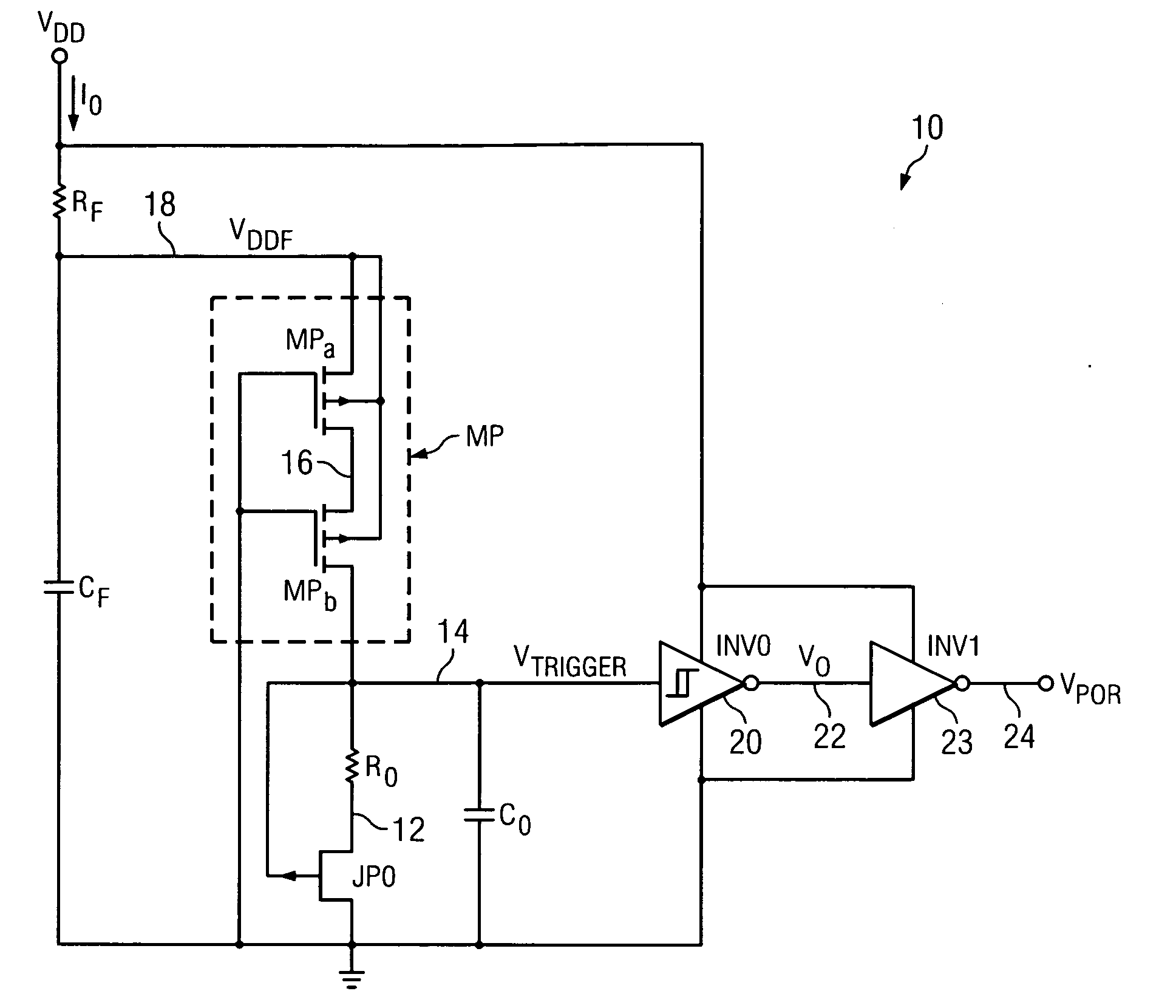

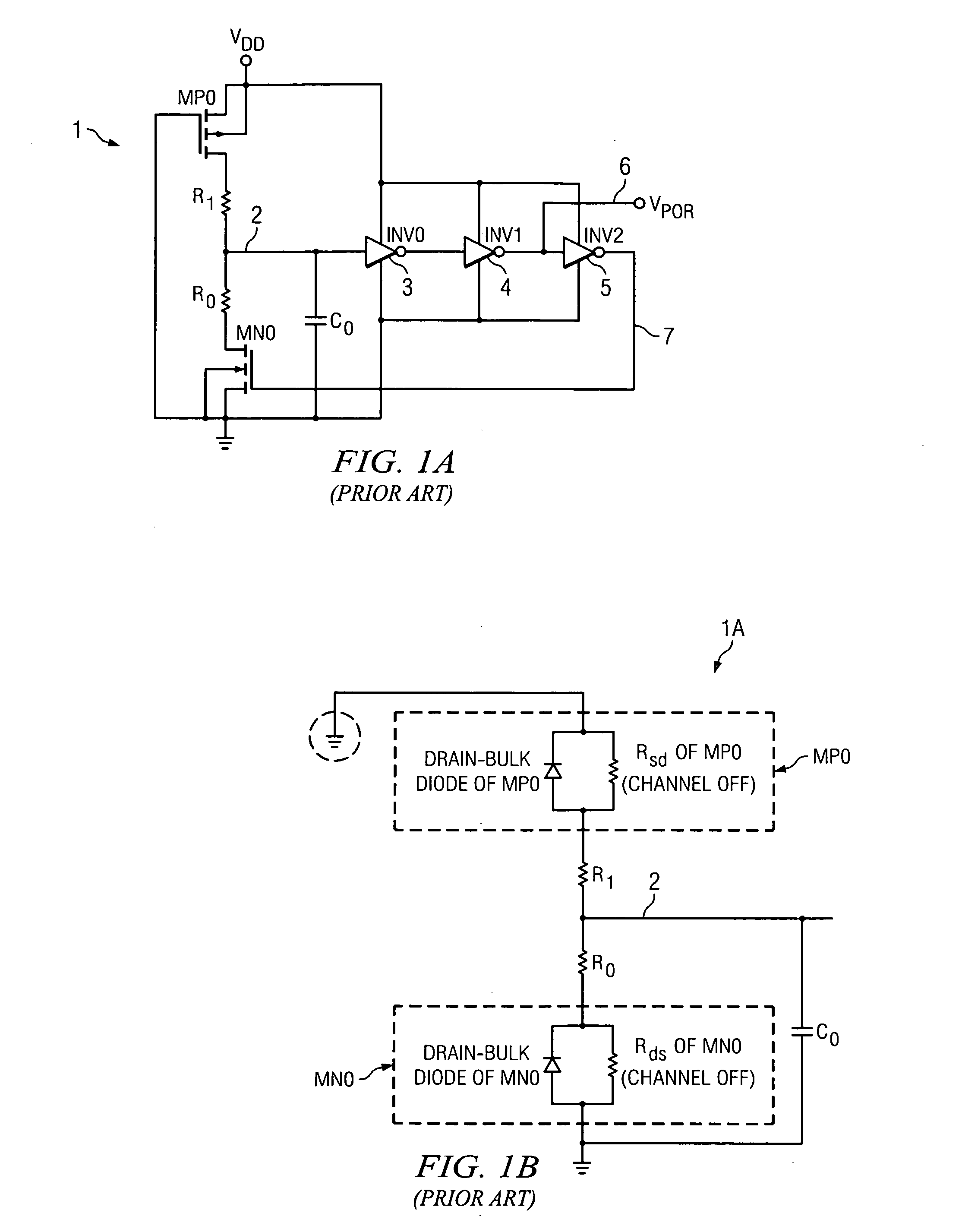

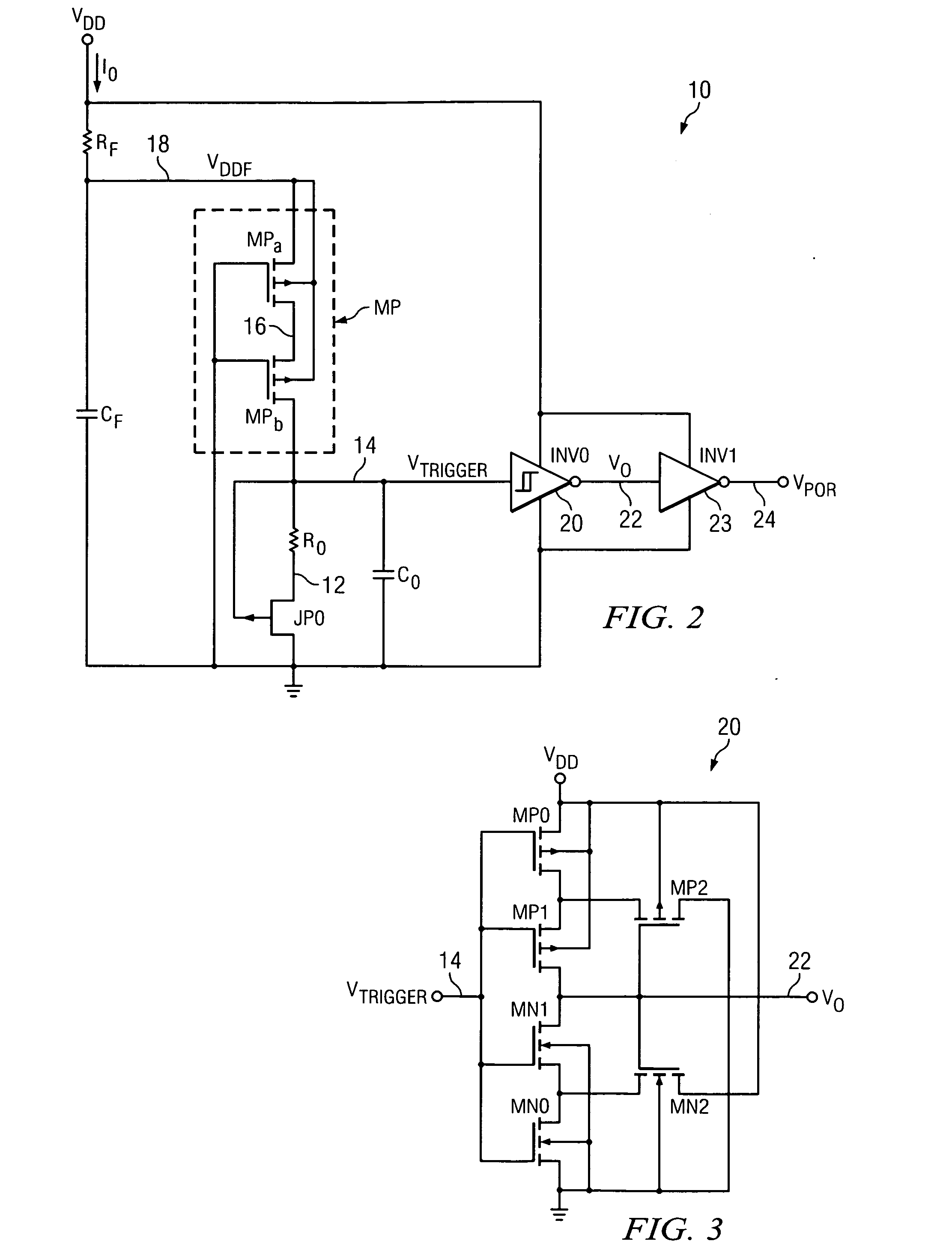

Low current power-on reset circuit and method

ActiveUS20110074470A1Easy dischargeDissipates very littlePulse automatic controlElectronic switchingElectricityPower-on reset

A power-on reset (POR) circuit includes a first transistor (MPa) having a source coupled to a first supply voltage (VDD) and a gate coupled to a second supply voltage (GND). A resistor (R0) has a first terminal coupled by a depletion mode transistor (JP0) to the second supply voltage and a second terminal coupled to a drain of the first transistor. A Schmitt trigger (20) has an input coupled to receive a first signal (VTRIGGER) on a conductor (14) coupled to the second terminal of the resistor and a terminal of a capacitor (C0), for producing an output voltage (VO) representative of a power-on reset signal (VPOR) in response to an interruption of the first supply voltage (VDD).

Owner:TEXAS INSTR INC

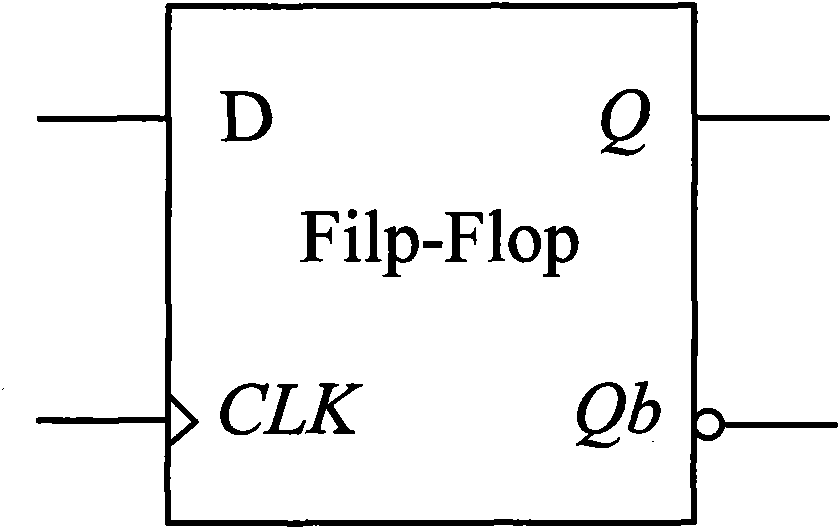

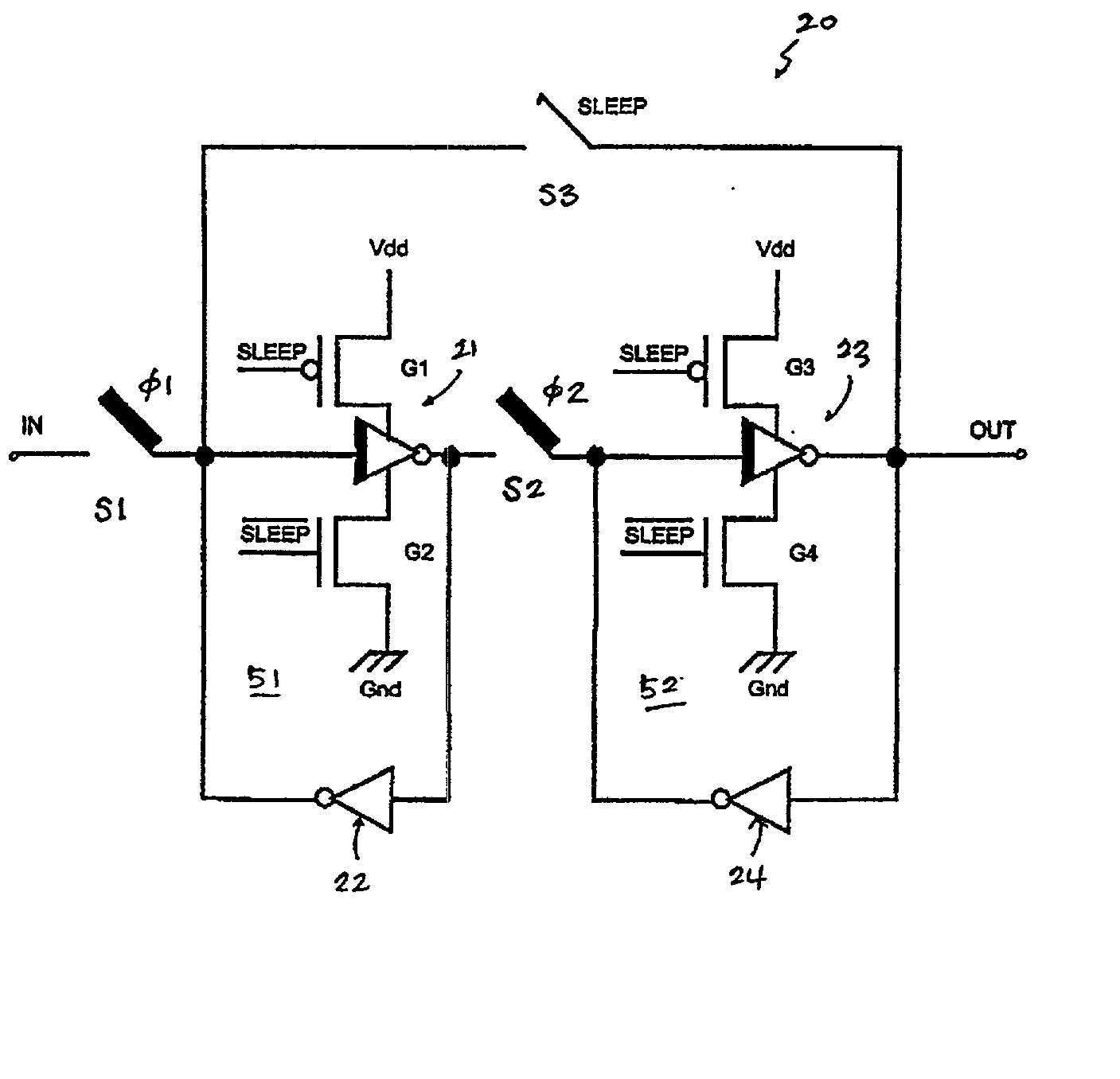

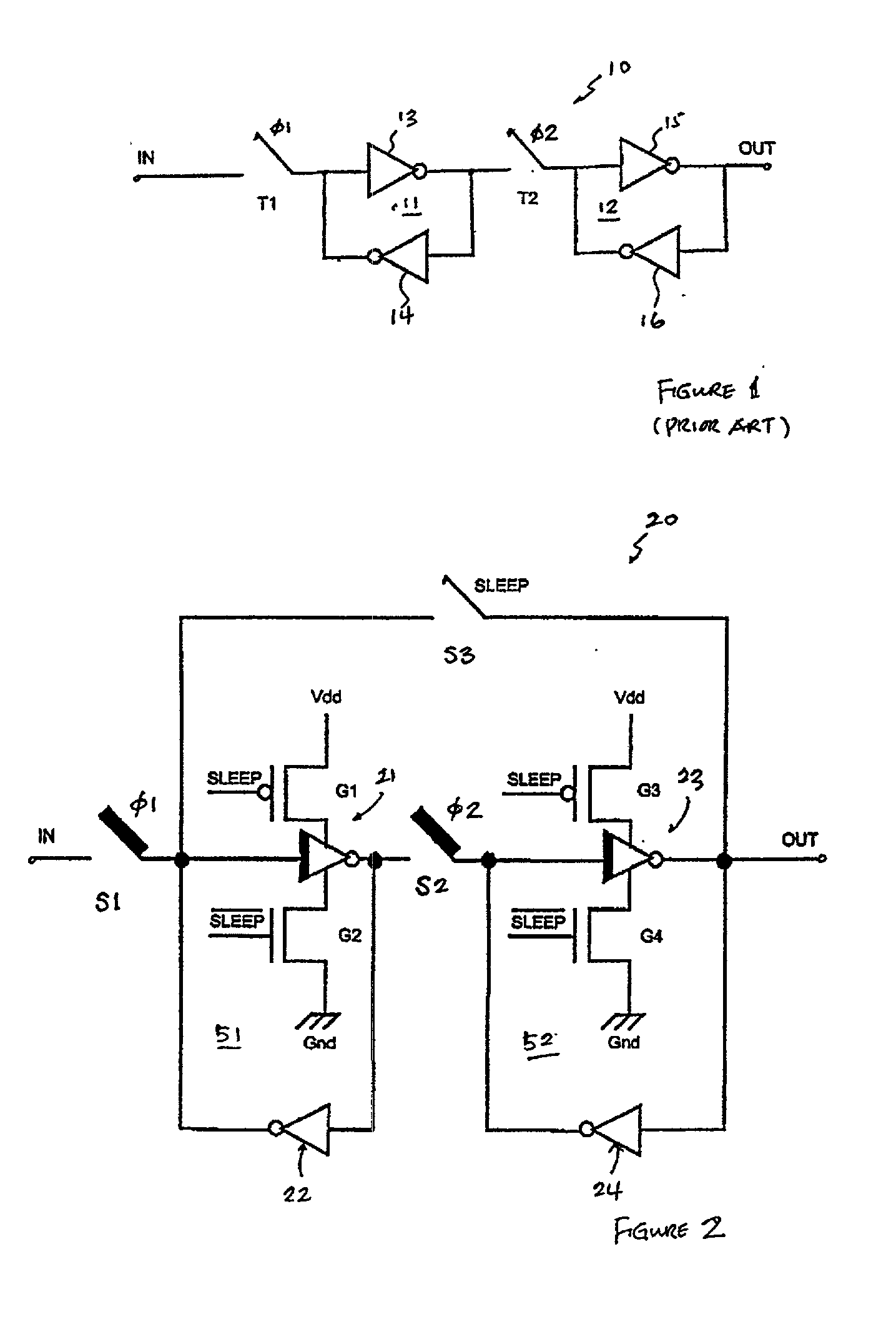

Multi-threshold flip-flop circuit having an outside feedback

InactiveUS20030067322A1Electric pulse generatorLogic circuits using elementary logic circuit componentsSoftware engineeringFlip-flop

A multi-threshold flip-flop circuit having an outside feedback is disclosed. The multi-threshold flip-flop circuit comprises a master latch and a slave latch. Coupled between an output of the slave latch and an input of the master latch, a switchable feedback path is utilized to retain logical values of the slave latch during a sleep mode of the flip-flop circuit.

Owner:IBM CORP

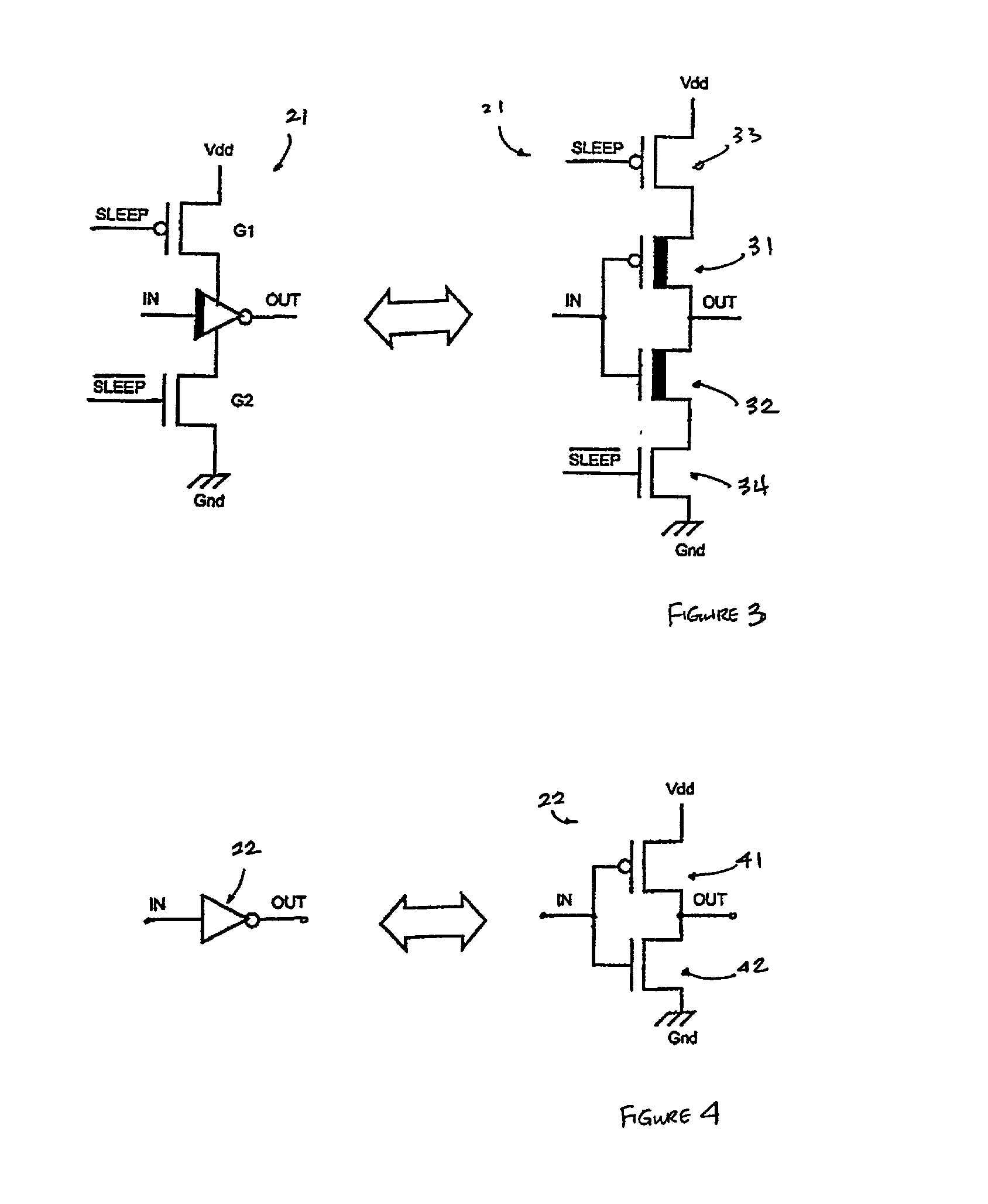

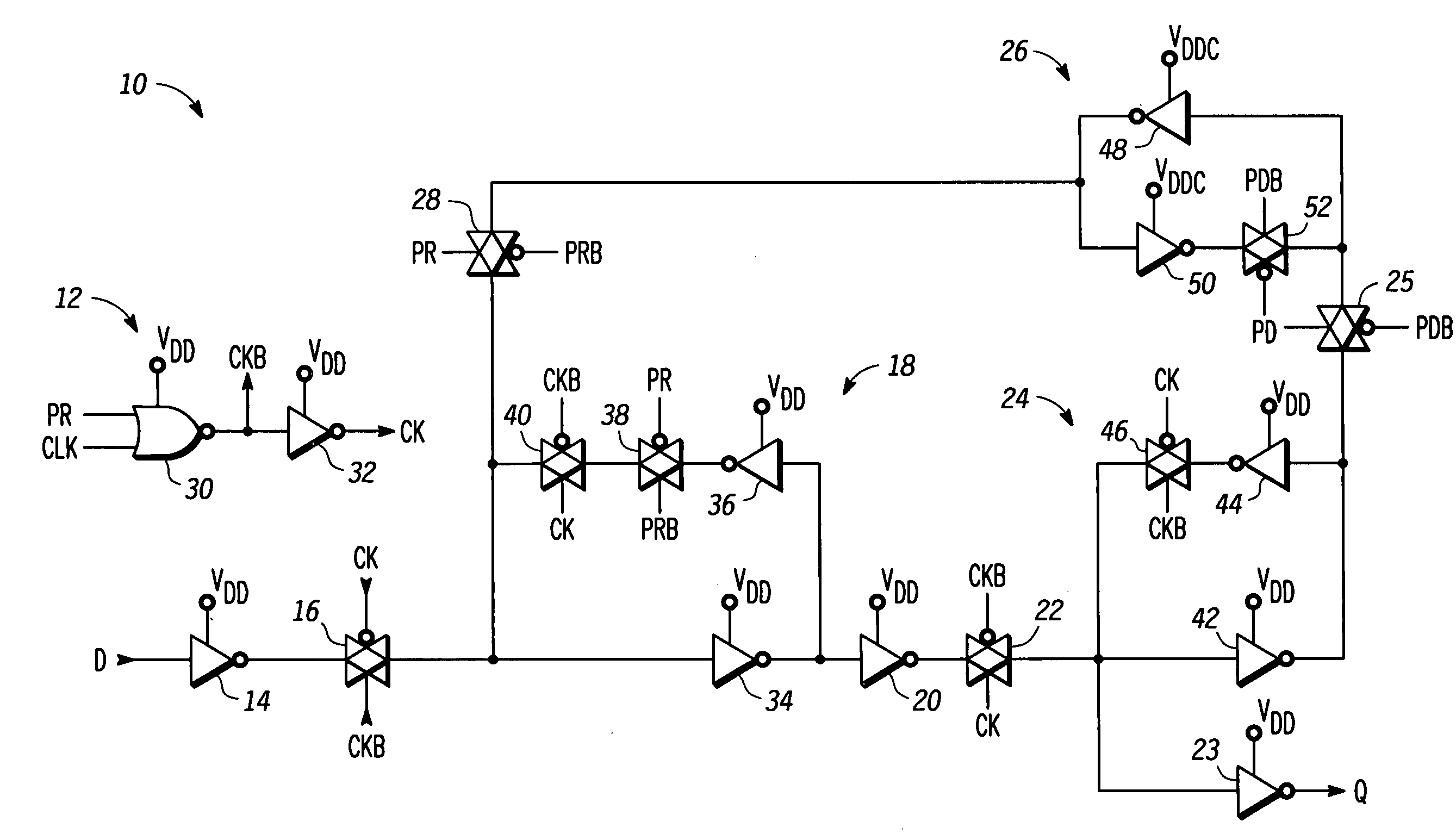

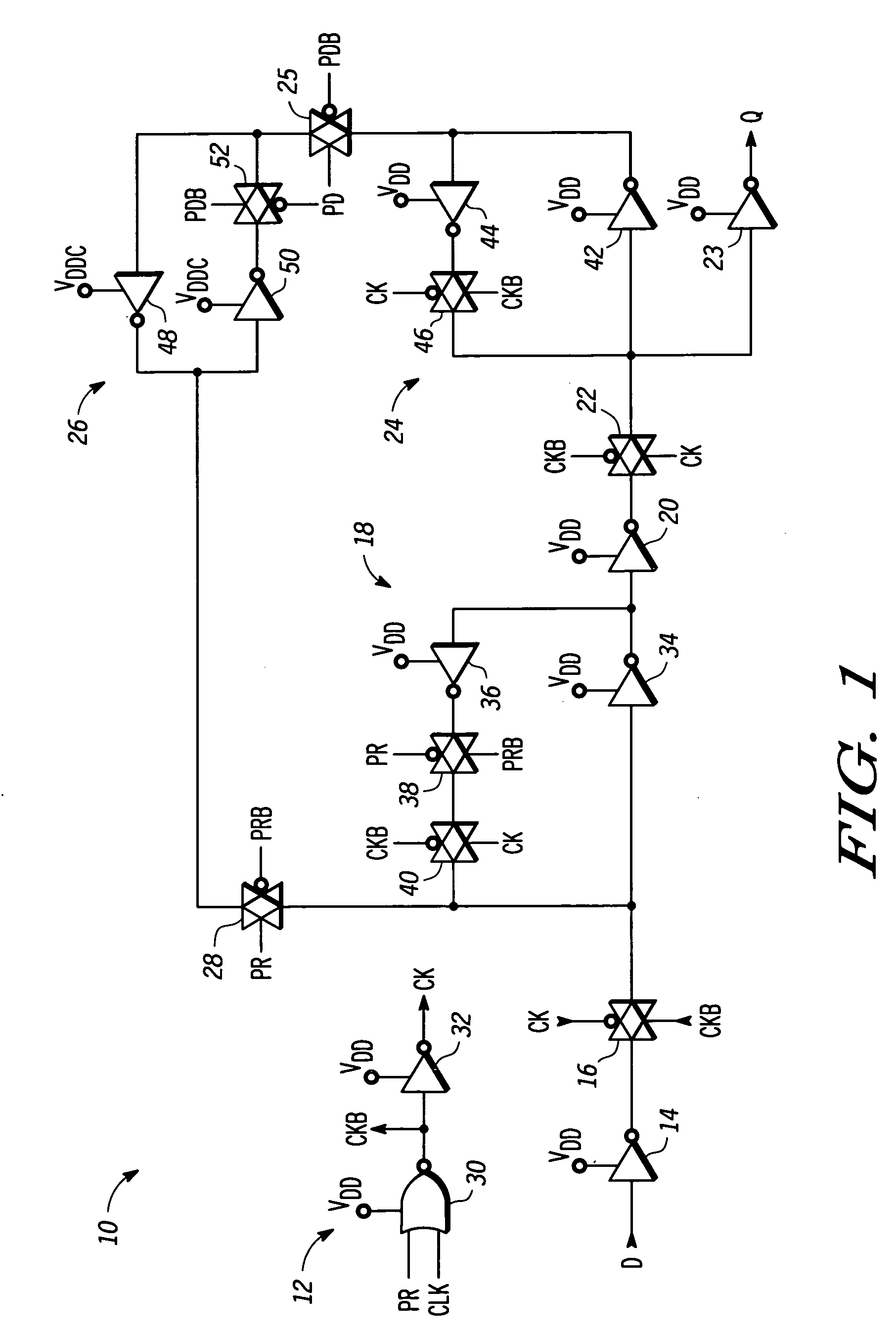

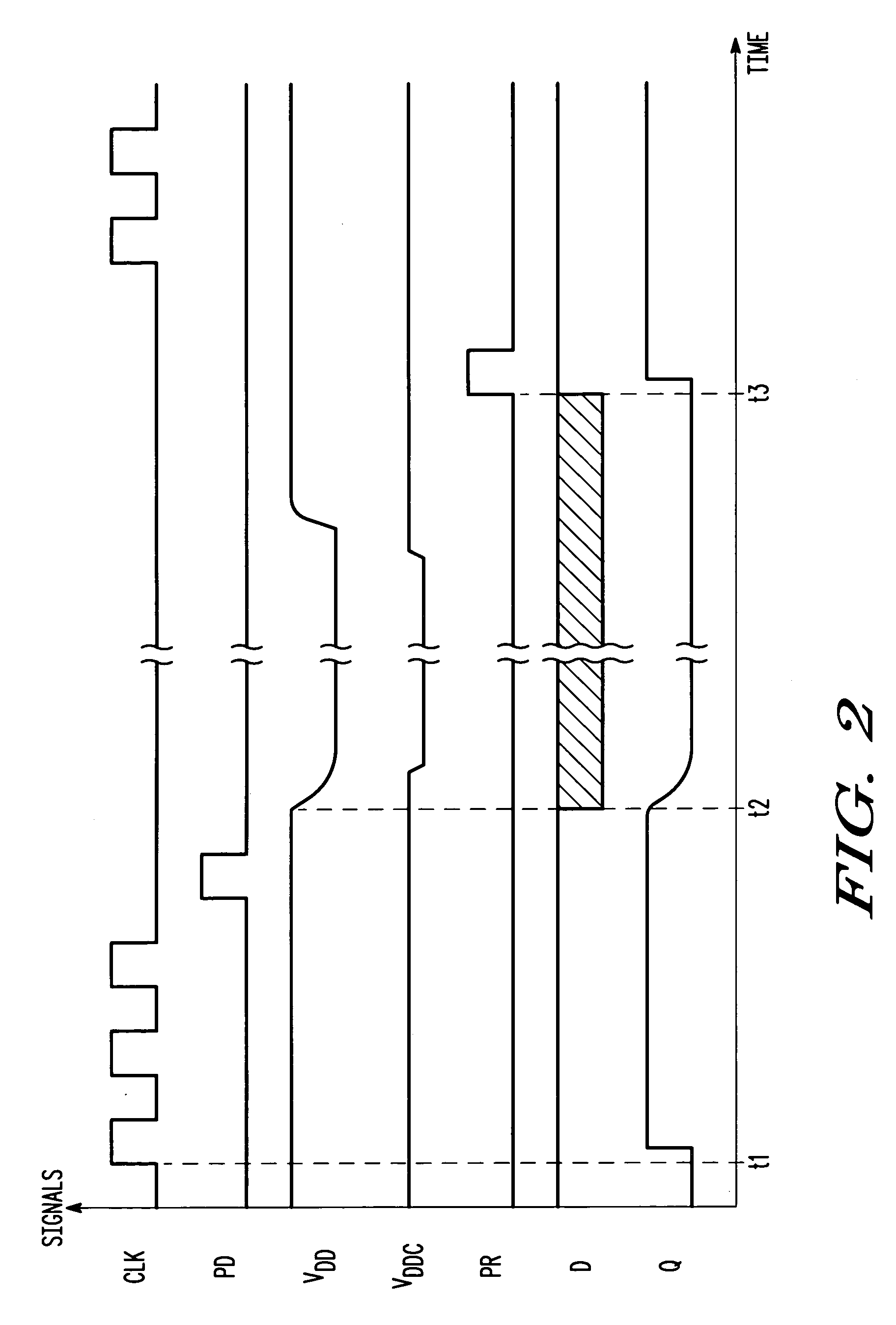

Flip-flop circuit having low power data retention

A flip-flop (10) comprises a first latch circuit (18), a second latch circuit (24), and a third latch circuit (26). The first latch circuit (18) is coupled to receive a clock signal and a first power supply voltage. The second latch circuit (24) is coupled to the first latch circuit (18) and receives the clock signal and the first power supply voltage. Preparatory to entering a low power mode, the third latch circuit (26) receives a second power supply voltage and is coupled to the second latch circuit (24) in response to a power down signal. During the low power mode, the first power supply voltage is removed from the first and second latch circuits (18, 24). When returning to a normal operating mode, the first power supply voltage is provided to the first and second latch circuits (18, 24), and the third latch circuit (26) is coupled to the first latch circuit (18) in response to a power restore signal.

Owner:NXP USA INC

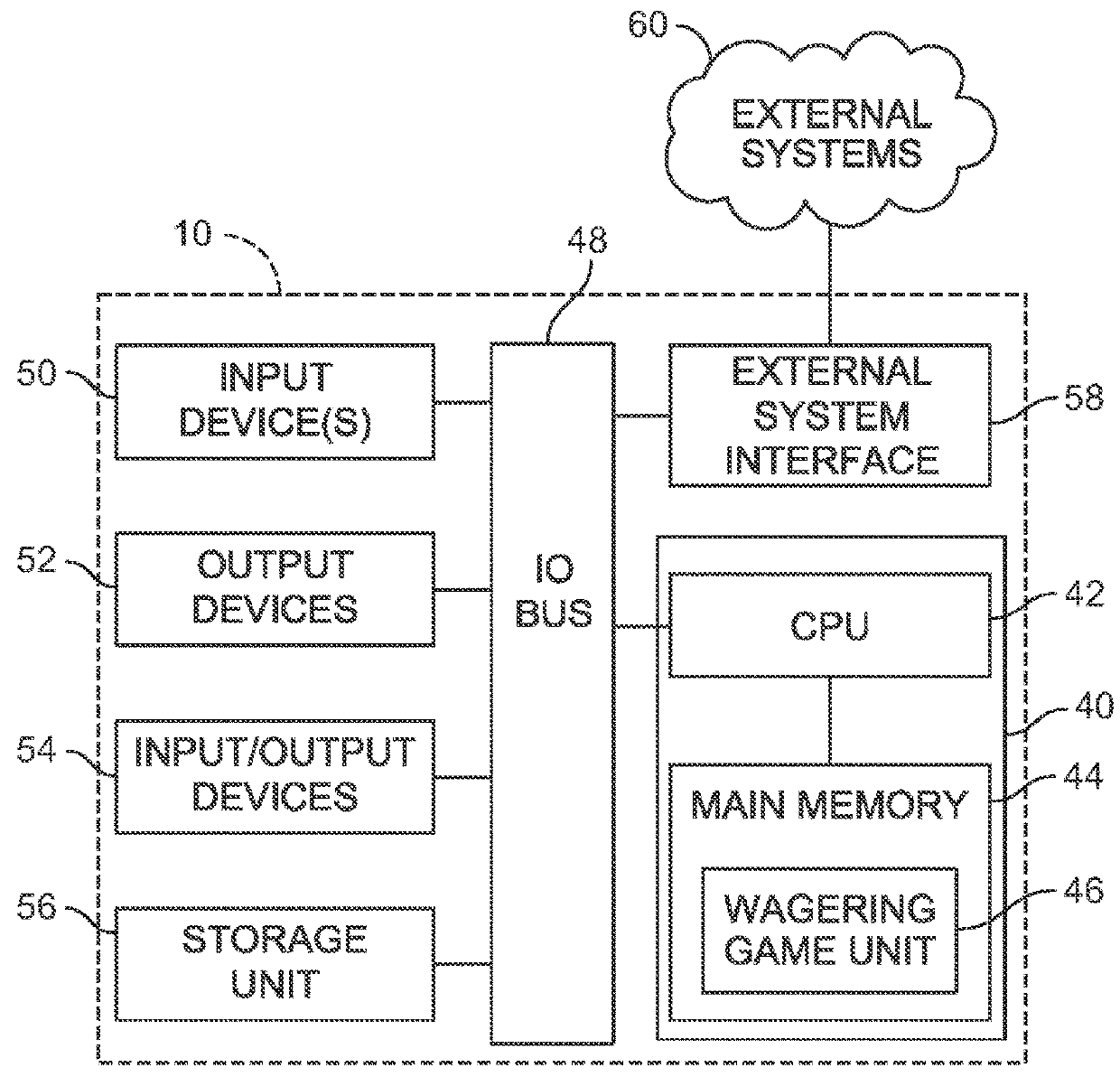

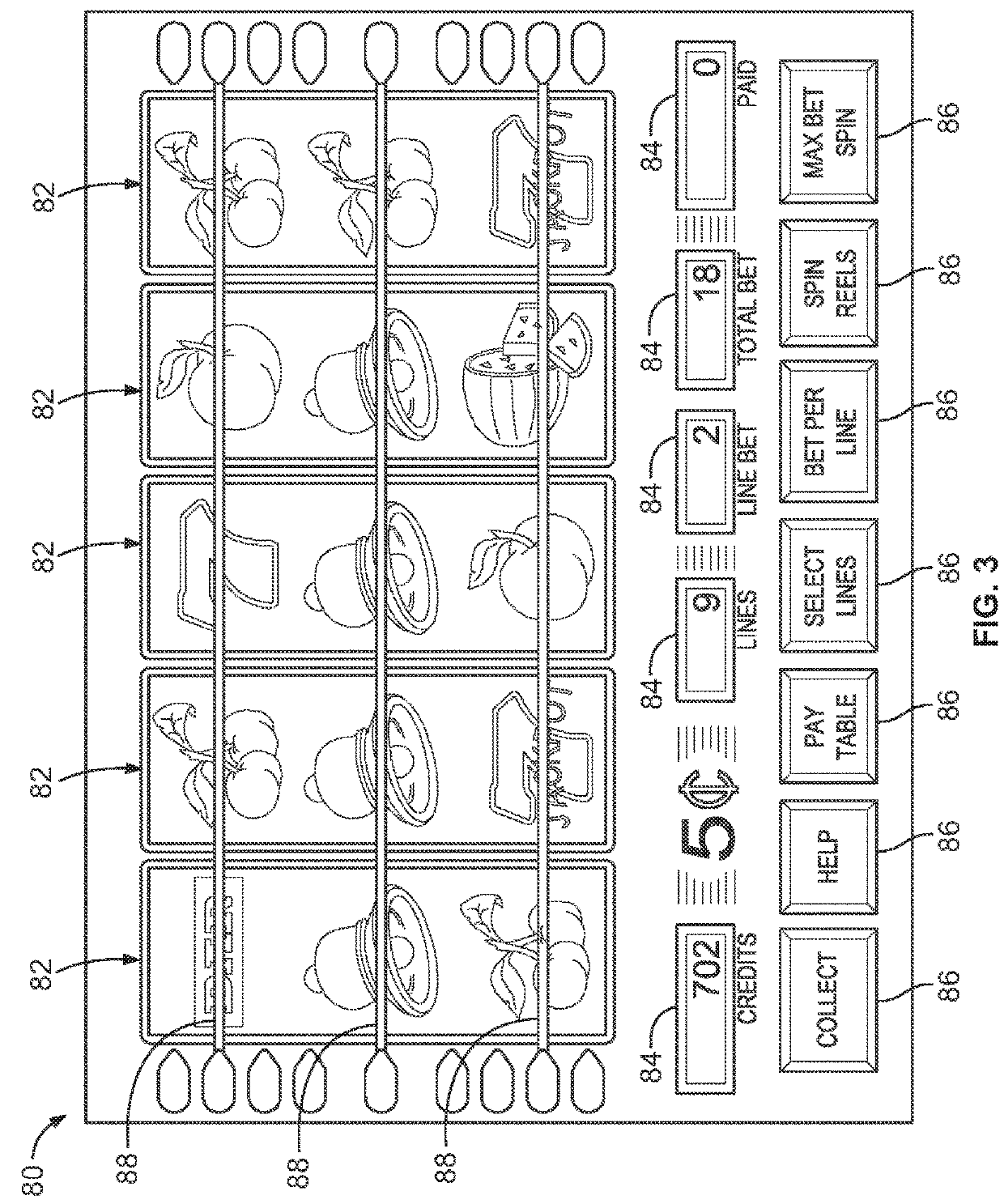

Gaming machine using multiple triggers to determine an award from a subset of displayed awards

ActiveUS20180268659A1Apparatus for meter-controlled dispensingDisplay processingArray data structure

A gaming system includes at least one input device adapted to receive a physical item associated with a monetary value that establishes a credit balance, an input indicative of a wager drawn on the credit balance for a wagering game, and a cashout input that initiates a payout from the credit balance. In response to a wager input, a wagering game is initiated that includes the spinning and stopping of a set of bonus reels through a plurality of bonus spins populating a bonus array with bonus symbols. The bonus reels comprise a combination of symbols reducing display processing requirements and improve mapping random numbers to displayed symbols for display during bonus spins having reduced durations. When completed, an award is determined based according to values associated with less than all of the bonus symbols displayed in a bonus outcome array.

Owner:LNW GAMING INC

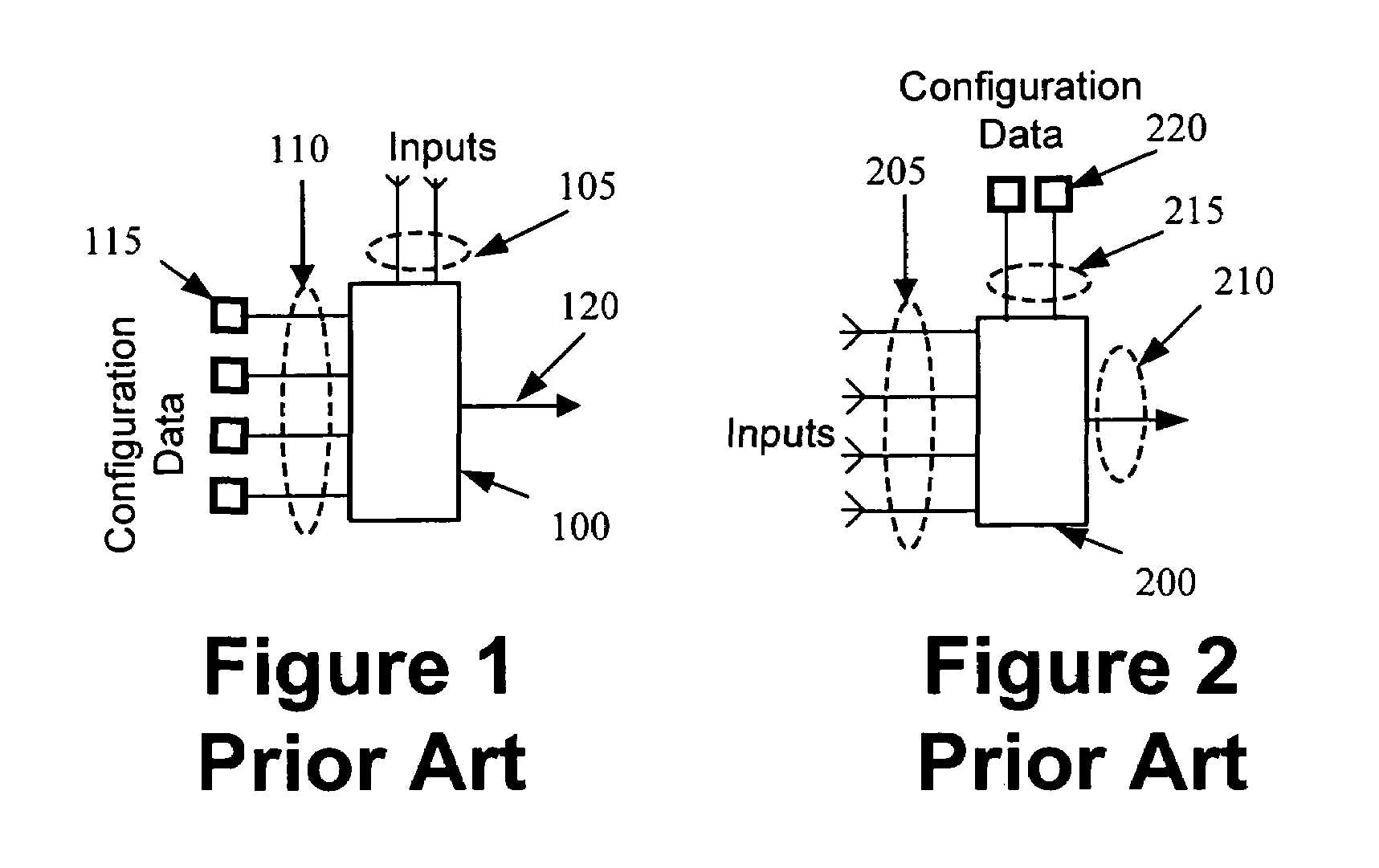

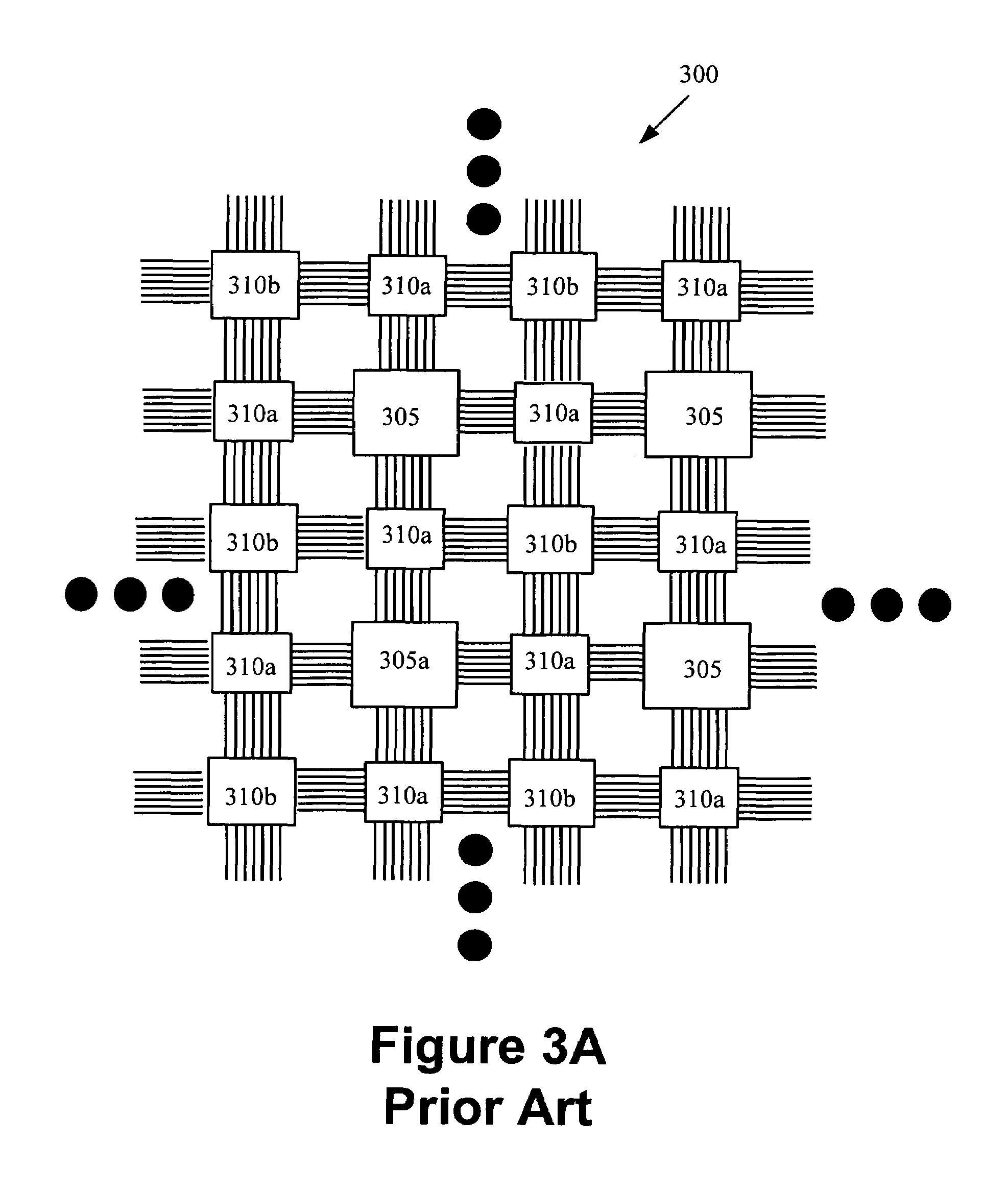

User registers implemented with routing circuits in a configurable IC

Some embodiments of the invention provide a configurable integrated circuit (“IC”). The configurable IC includes a set of configurable logic circuits for configurably performing a set of functions. The configurable IC also includes a set of configurable routing circuits for routing signals to and from the configurable circuits. During several operational cycles of the configurable IC, a set of data registers are defined by the configurable routing circuits. These data registers may be used wherever a flip-flop can be used.

Owner:TAHOE RES LTD

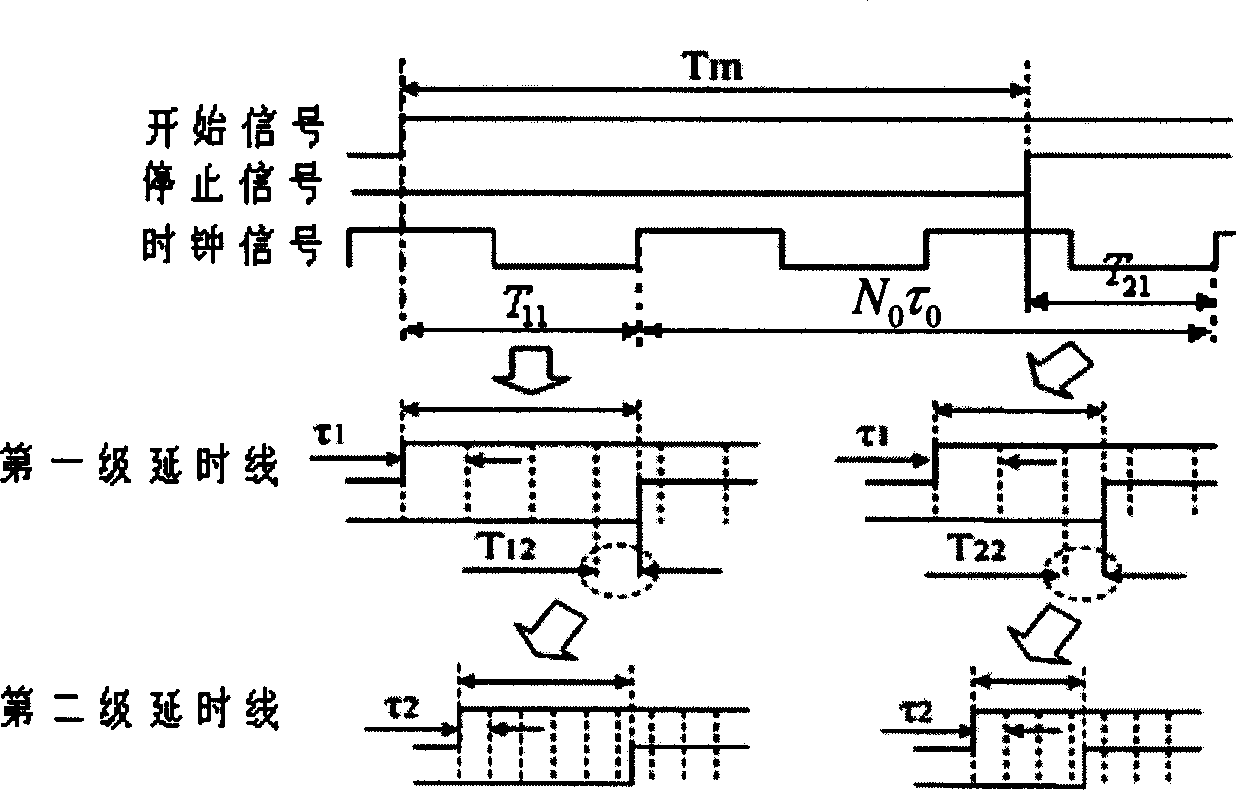

Method and device for measuring time interval through delay line in cascaded two stages

InactiveCN1696845AImprove measurement resolutionCompact structureElectric unknown time interval measurementRecord information storageLeading edgeImage resolution

A method for measuring time interval with two stage cascade delay line includes measuring numbers of clock leading edge in time interval to be measured i e cycle number of clock, measuring two time intervals not being complete cycle of front and back time intervals to be measured, sending those less than resolution of first stage relay line to the second stage for further subdivision, calculating out value of time interval to be measured by utilizing measured results. The measuring device is composed of only delay unit and D trigger for both delay lines.

Owner:TSINGHUA UNIV

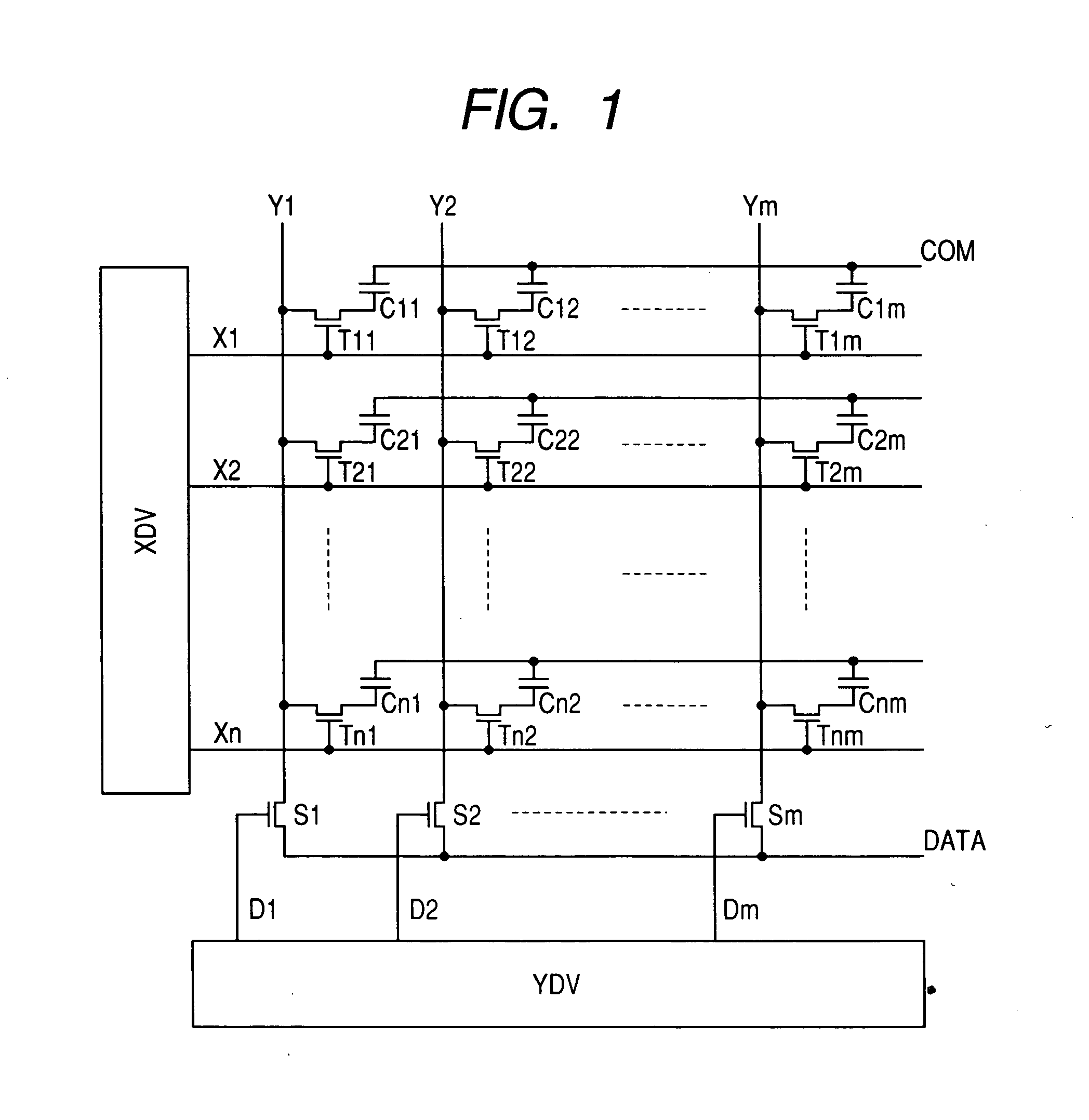

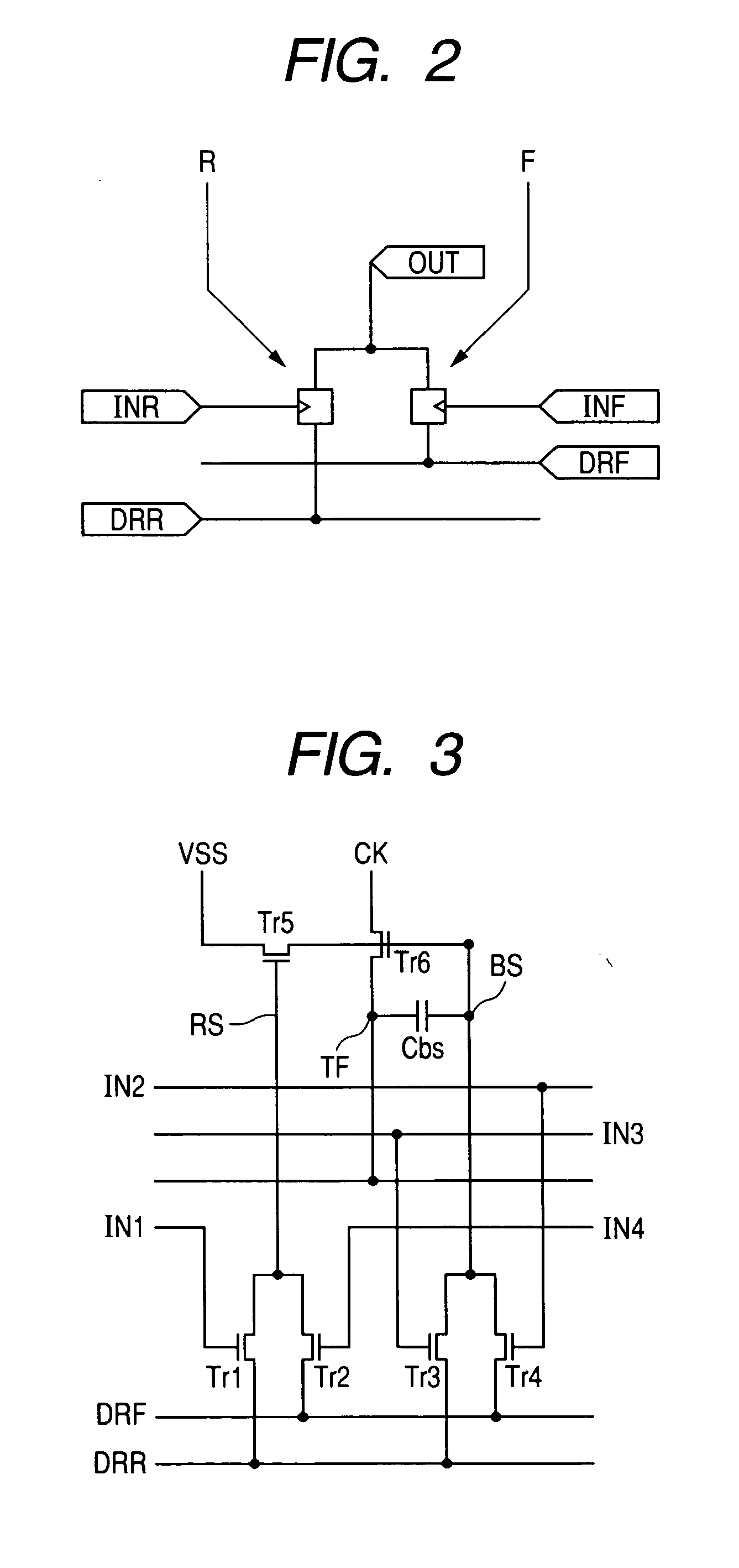

Display device

ActiveUS20070115245A1Reduce circuit sizeStatic indicating devicesDigital storageShift registerControl signal

The present invention provides a display device that has a driving circuit including a single channel bidirectional shift register with which the circuit scale can be reduced without increasing the number of elements. The driving circuit includes a single channel bidirectional shift register. This single channel bidirectional shift register has an RS flip-flop circuit. The RS flip-flop circuit includes a first transistor having a first electrode connected to an output terminal and having a second electrode to which a second scanning direction control signal is applied and a second transistor having a first electrode connected to an output terminal and having a second electrode to which a first scanning direction control signal is applied. In this circuit configuration, a resetting signal is applied to a control electrode of the first transistor in a first scanning direction, a setting signal is applied to the control electrode of the first transistor in a second scanning direction which is a direction opposite to the first scanning direction. The setting signal is also applied to a control electrode of the second transistor in the first scanning direction, and the resetting signal is also applied to the control electrode of the second transistor in the second scanning direction.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com