High-precision method and device for measuring interval between positive time and negative time

A technology of time interval measurement and time interval, which is applied in the direction of electrical unknown time interval measurement, devices and instruments for measuring time interval, etc. It can solve the problem of reducing the measurement accuracy of positive and negative time intervals, the inability to realize the measurement gate extraction circuit, and high time interval Problems such as measurement accuracy, to achieve the effect of wide positive and negative time interval measurement range, simple design, and high time interval measurement resolution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

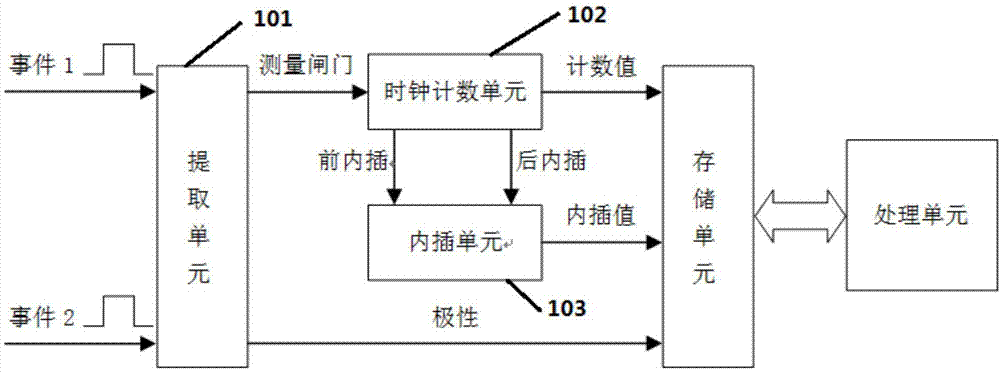

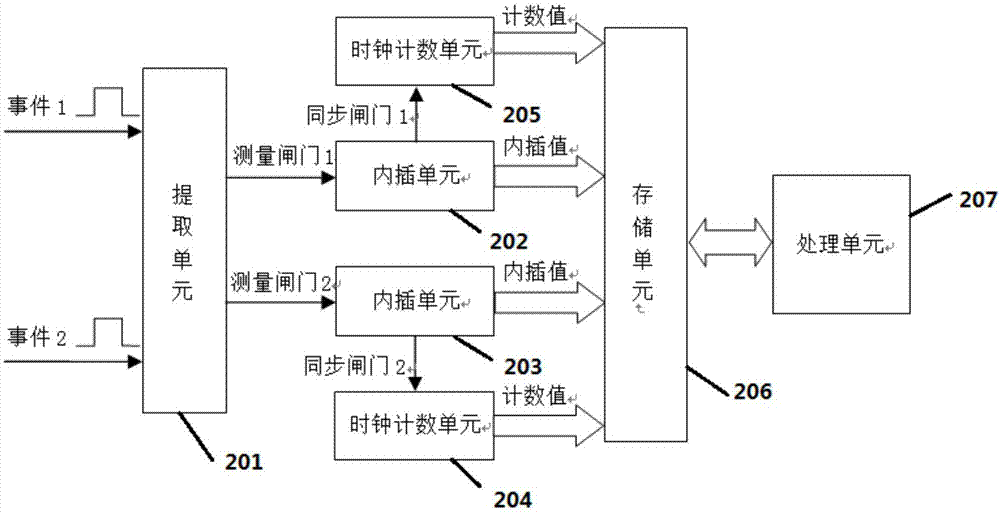

[0030] Such as Figure 3-8 As shown, the positive and negative time interval measuring device of the present invention comprises the following parts:

[0031] The signal shaping and measurement gate extraction unit compares and shapes the input signal according to the set trigger level, converts the measured signal into an ECL signal for subsequent processing, and uses the trigger to extract the two gate signals that need to be measured.

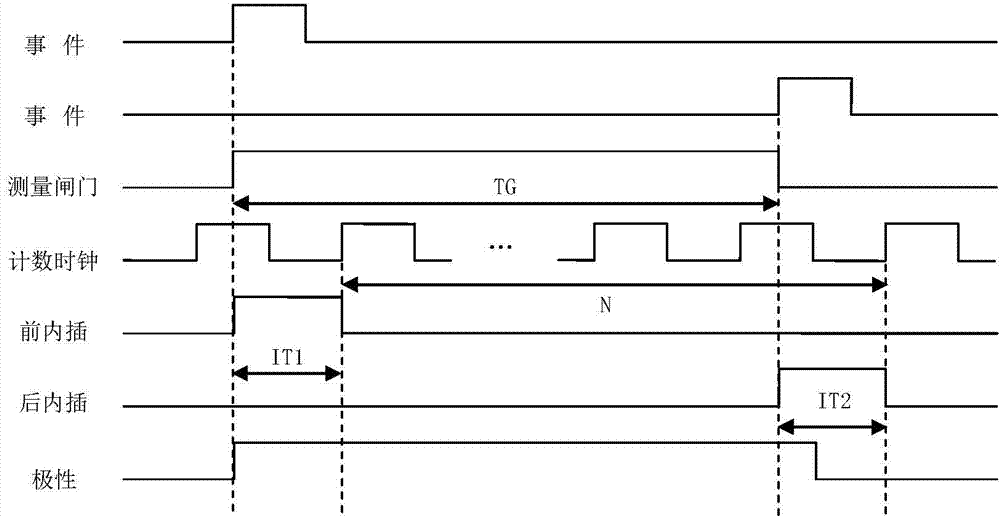

[0032] The synchronization and interpolation unit uses the counting clock to sample the measurement gate signal to obtain a gate signal synchronized with the counting clock. One route is sent to the clock counting unit for rough measurement of the measurement gate, and the other route is sent to the interpolation unit for pre-interpolation measurement. Accurate measurement of the fraction of a clock cycle less than the leading edge of the measurement gate.

[0033] The clock counting unit uses the synchronous gate signal to control the coun...

Embodiment 2

[0051] On the basis of the foregoing embodiments, the method provided in this embodiment is:

[0052] Step 1: Set the comparison level according to the peak value and valley value of the input signal, and convert the input signal into an ECL signal through a high-speed comparator, so that it has a smaller rising and falling edge time to reduce the trigger error.

[0053] Step 2: Send the ECL signal shaped by the high-speed comparator to the clock port of the D-type flip-flop. The data terminal of the D-type flip-flop is connected to a high level. After a rising edge, the flip-flop output is high immediately.

[0054] Step 3: Send the inverting output signals of the two D-type flip-flops to the FPGA. After the FPGA detects that both signals are low, after a period of delay, it resets the two flip-flops at the same time, and the output of the two flip-flops The signal is forced low so that the two flip-flop outputs form a pulse signal. The positive-phase output signal of the tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com