Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1212 results about "FLOPS" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance, useful in fields of scientific computations that require floating-point calculations. For such cases it is a more accurate measure than measuring instructions per second.

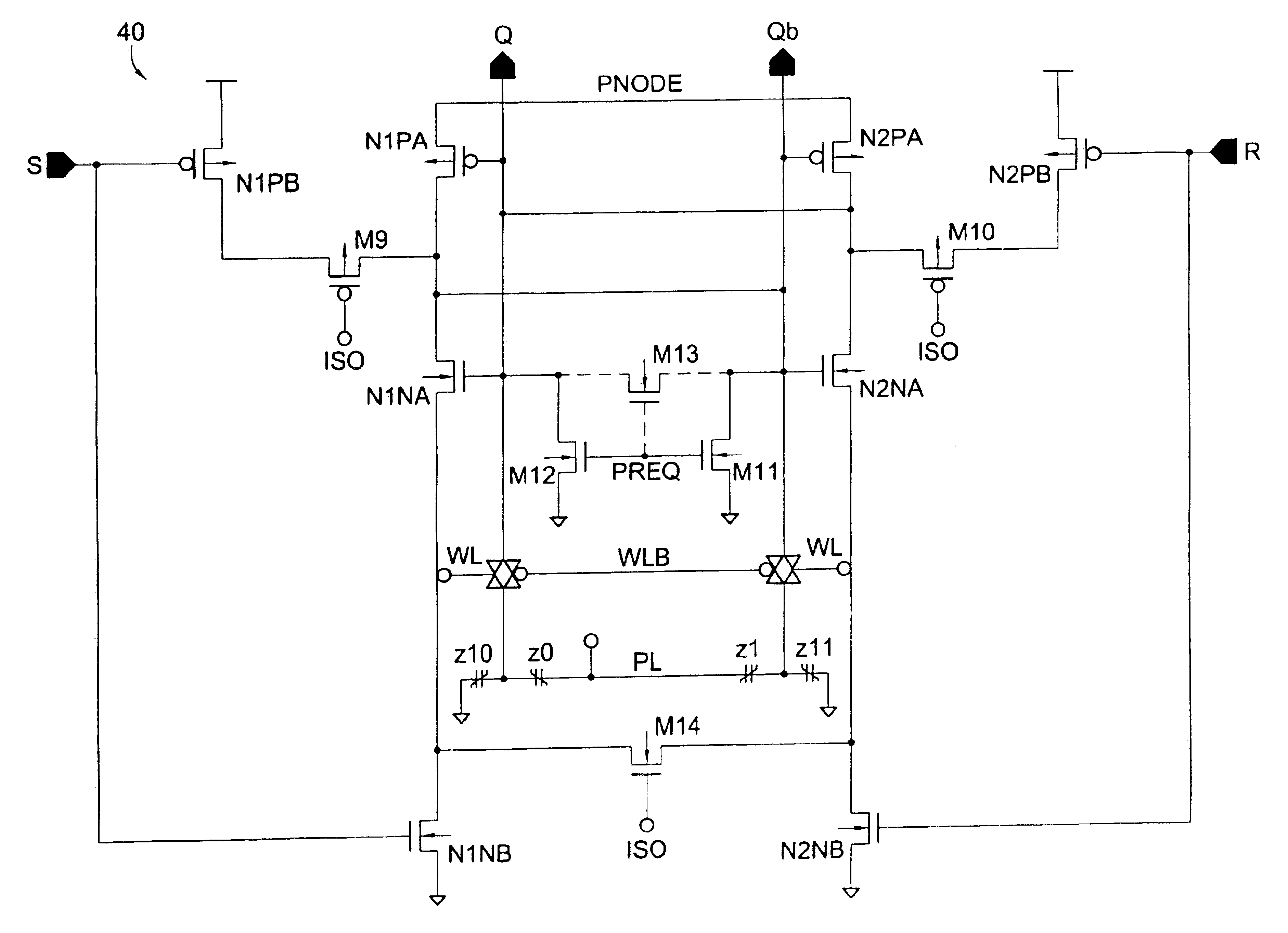

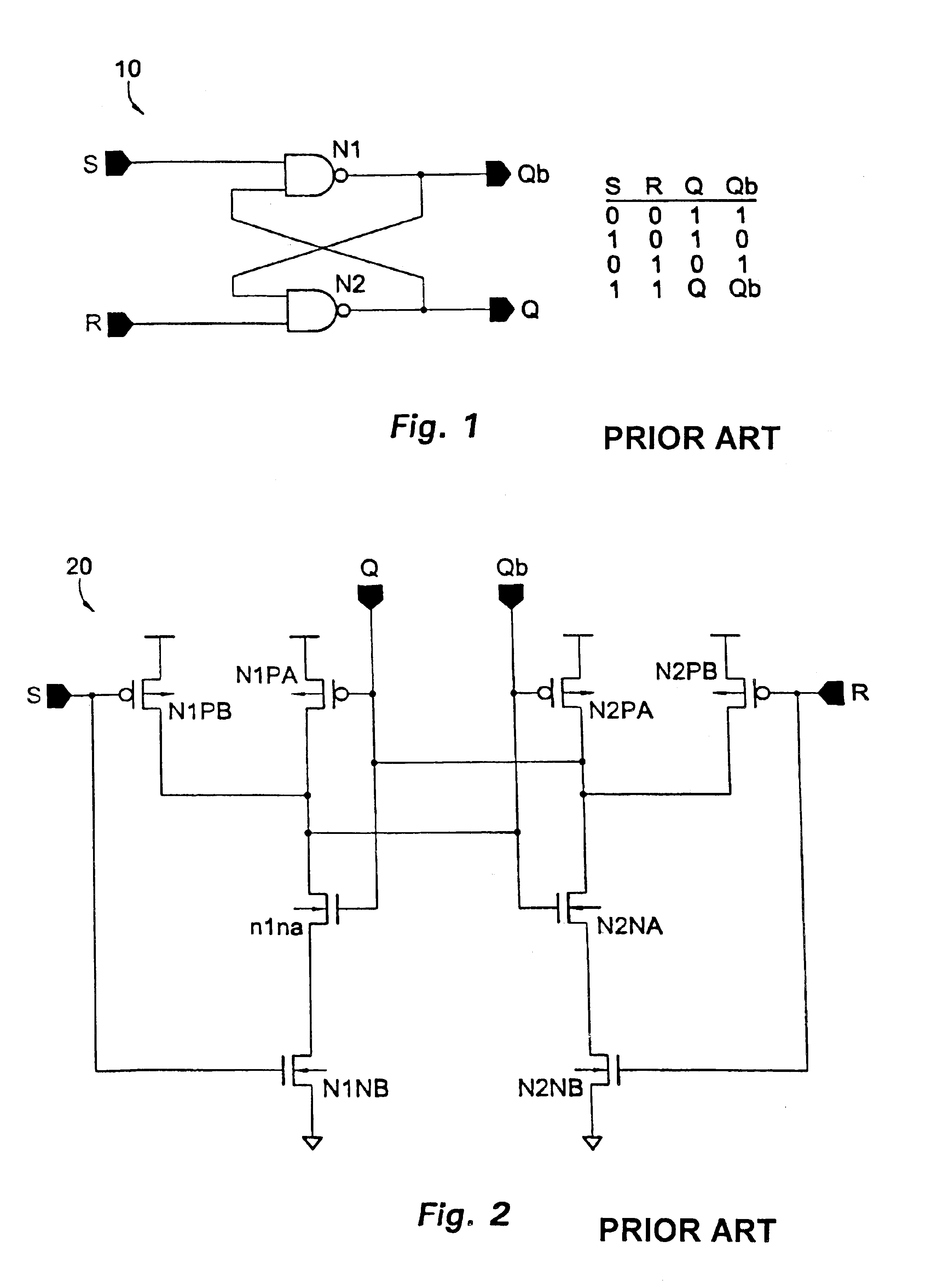

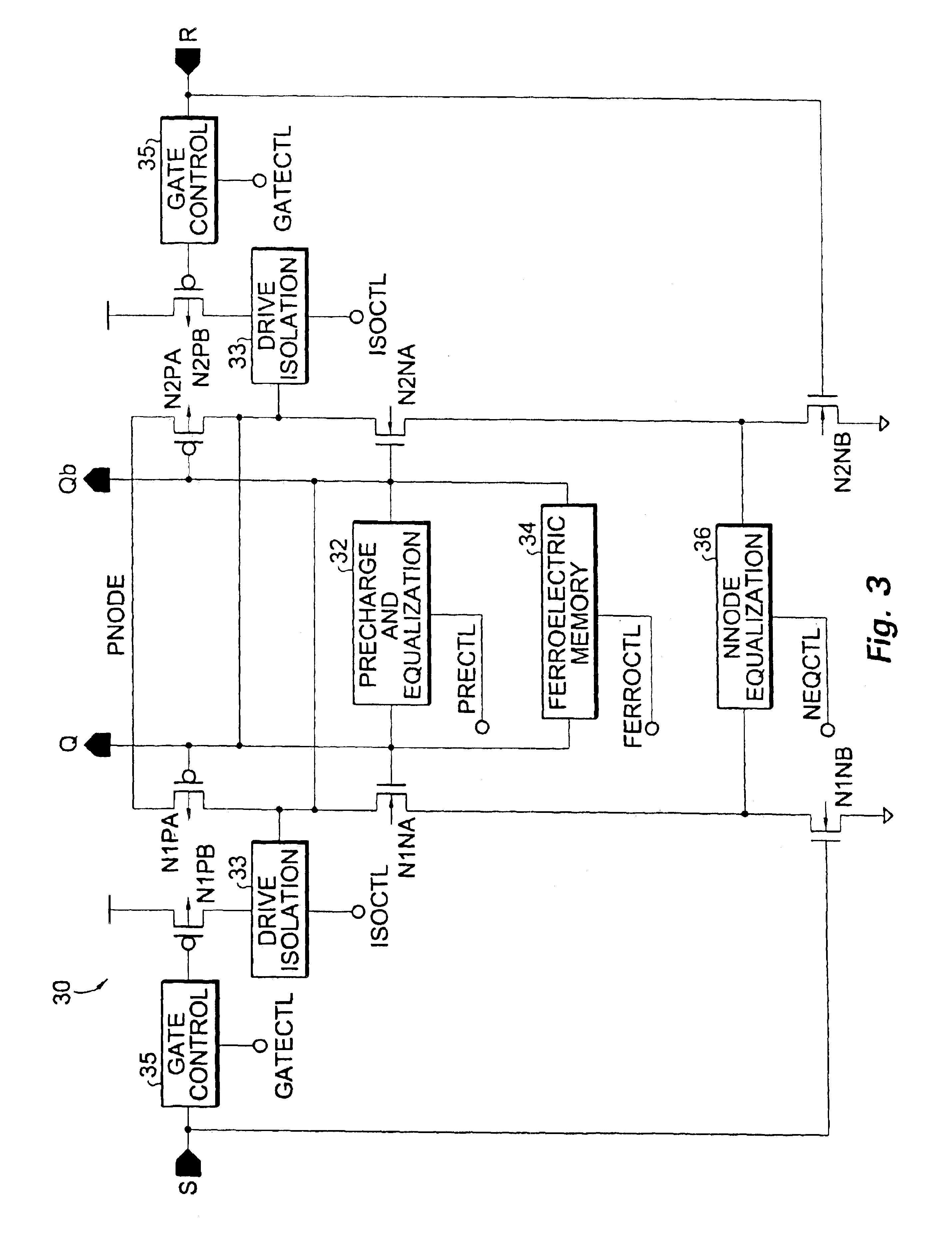

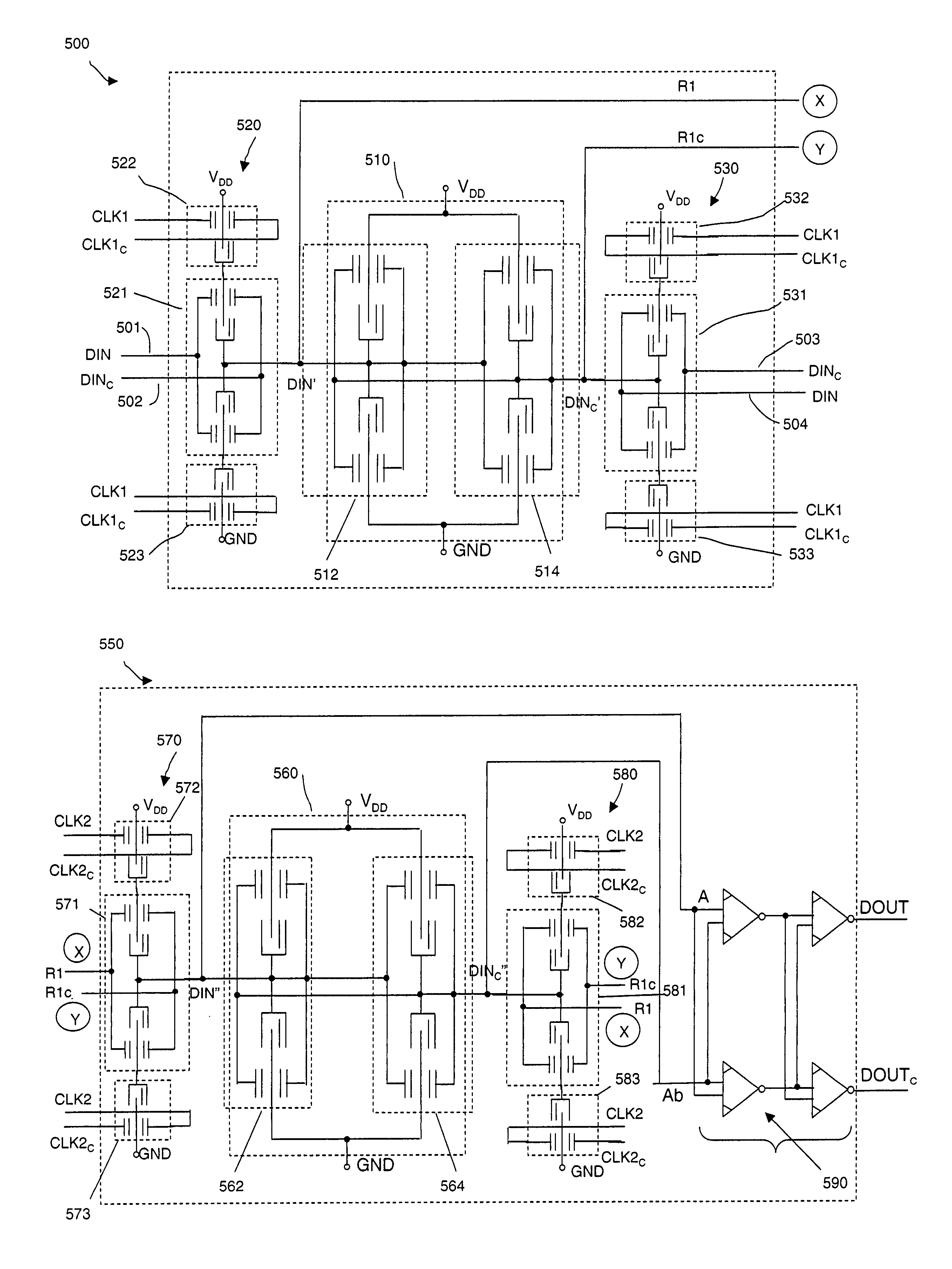

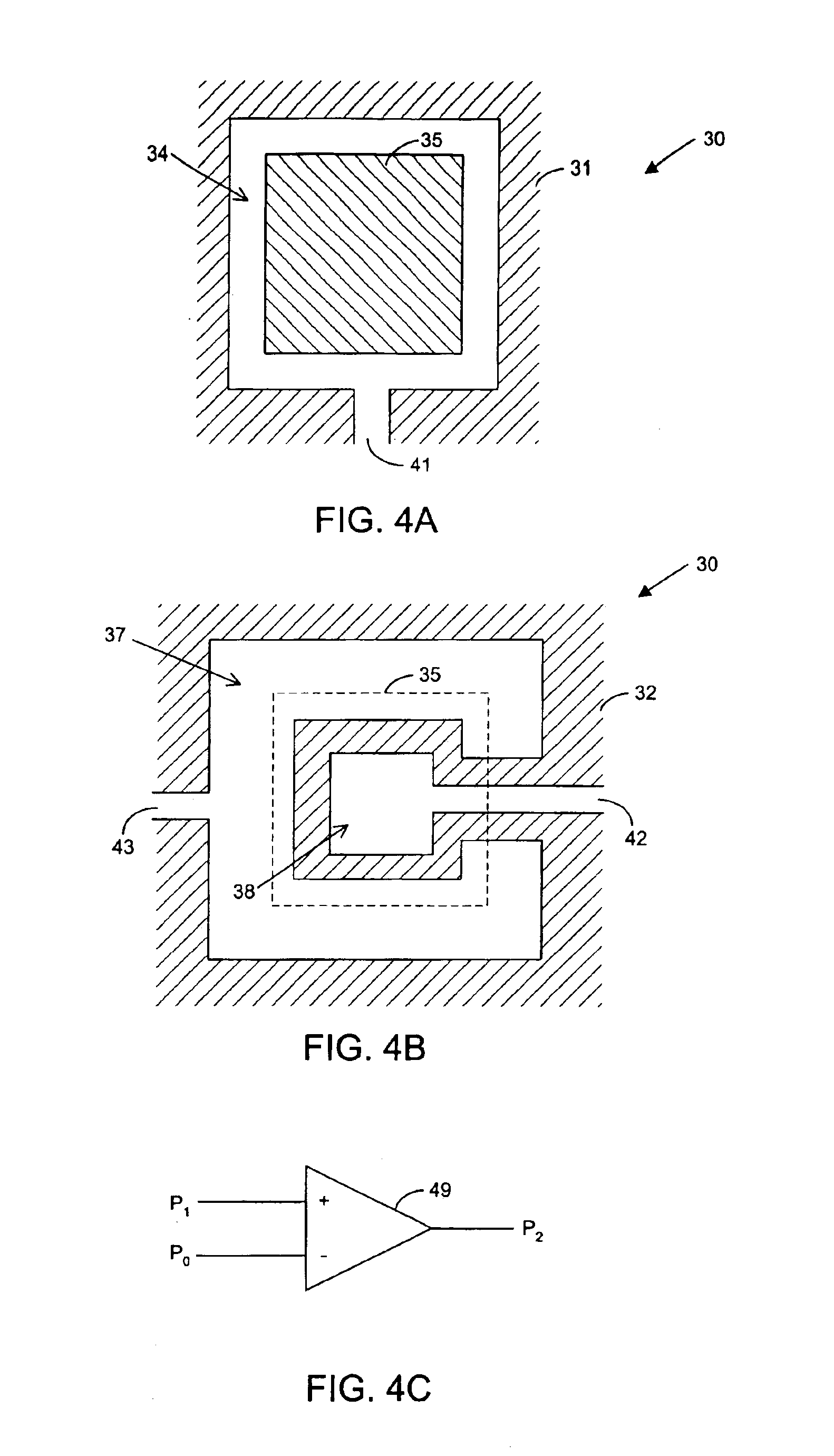

Ferroelectric non-volatile logic elements

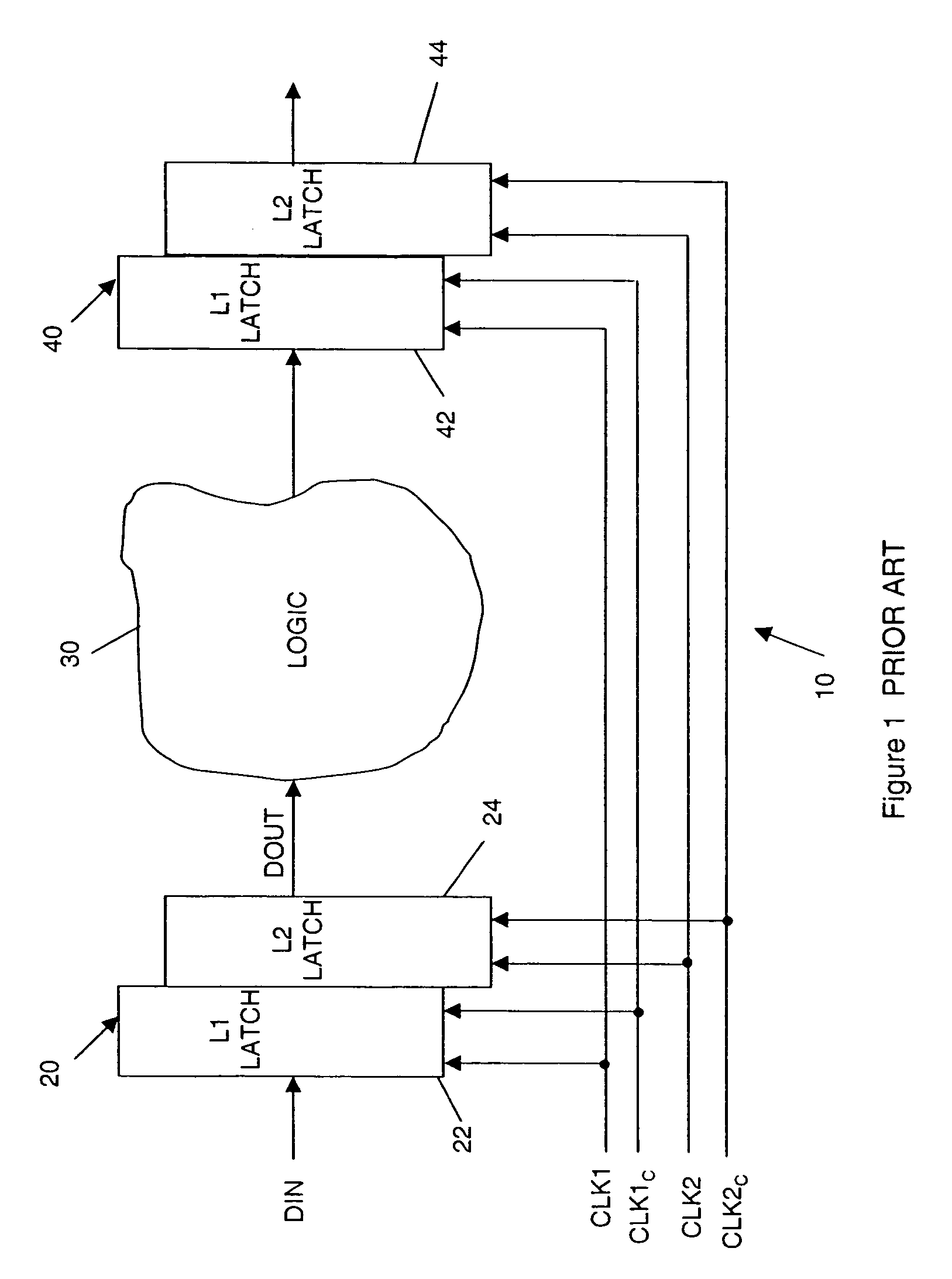

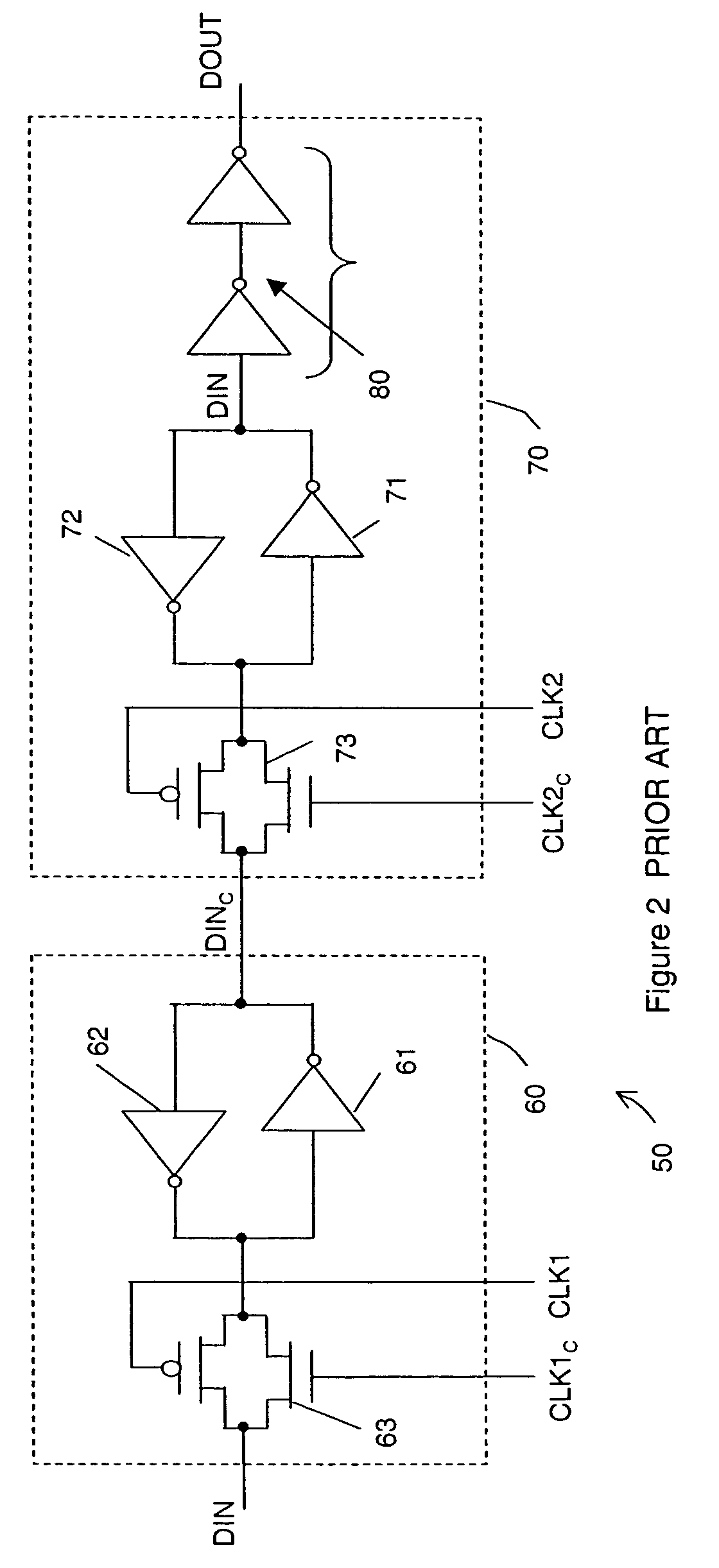

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

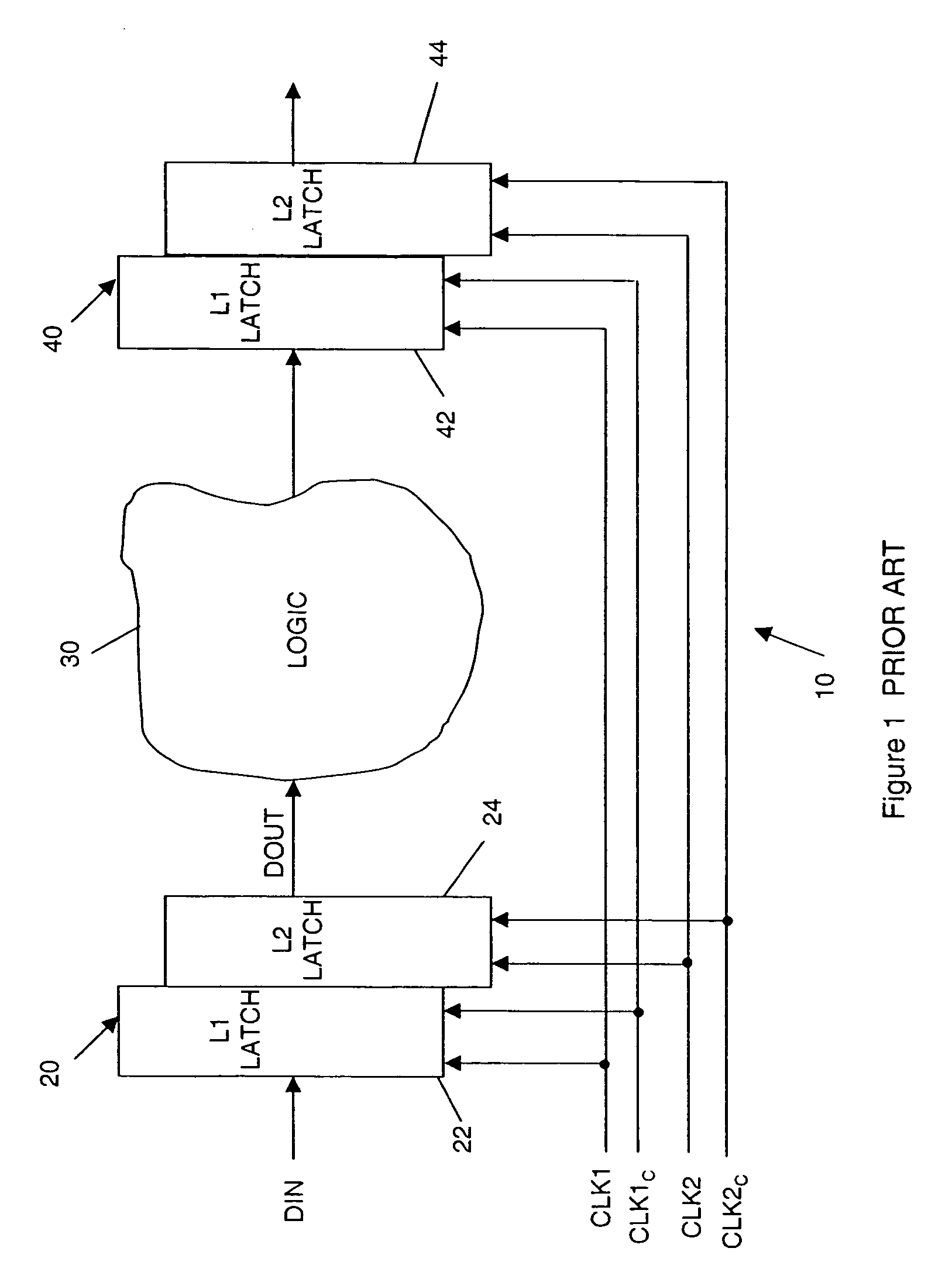

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

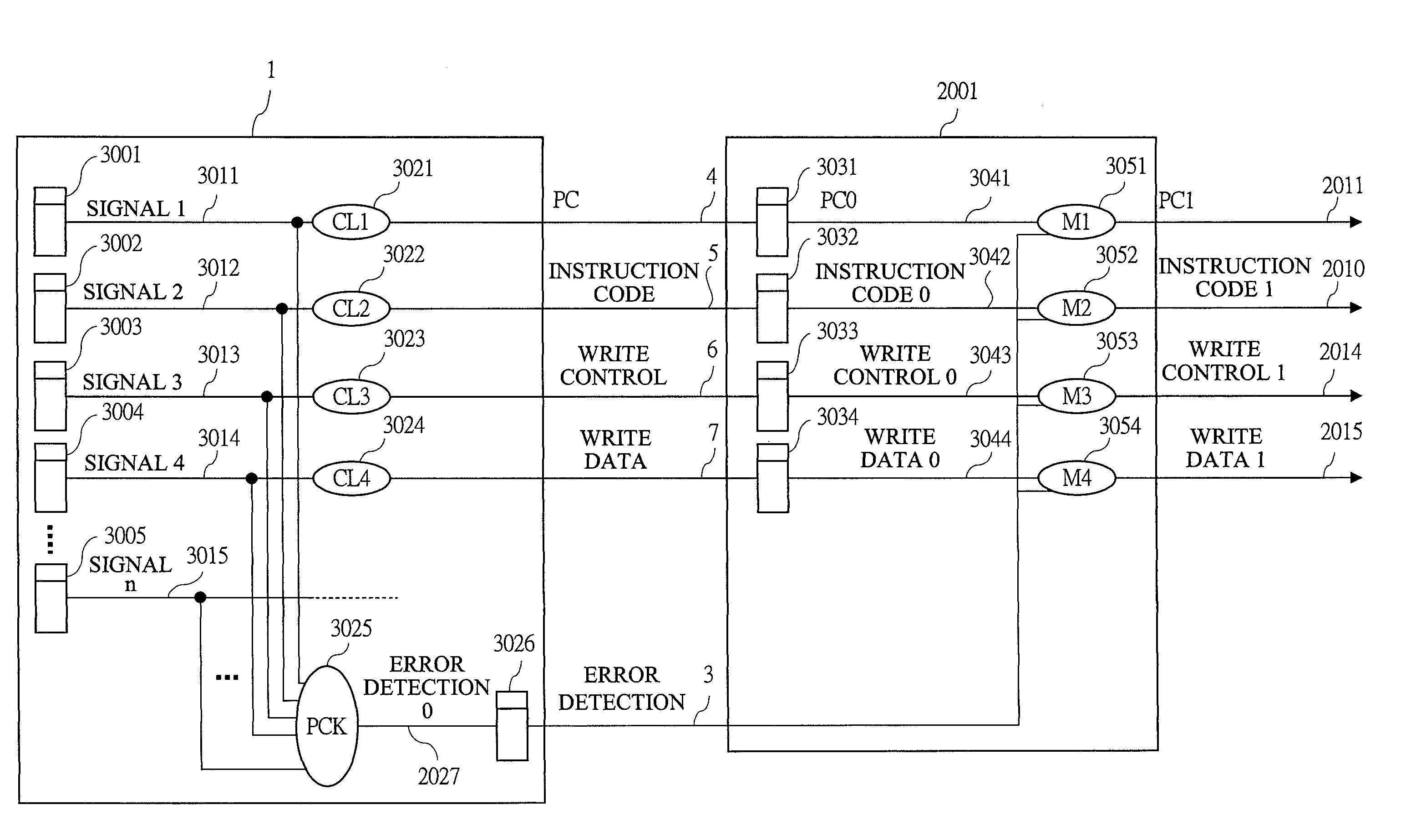

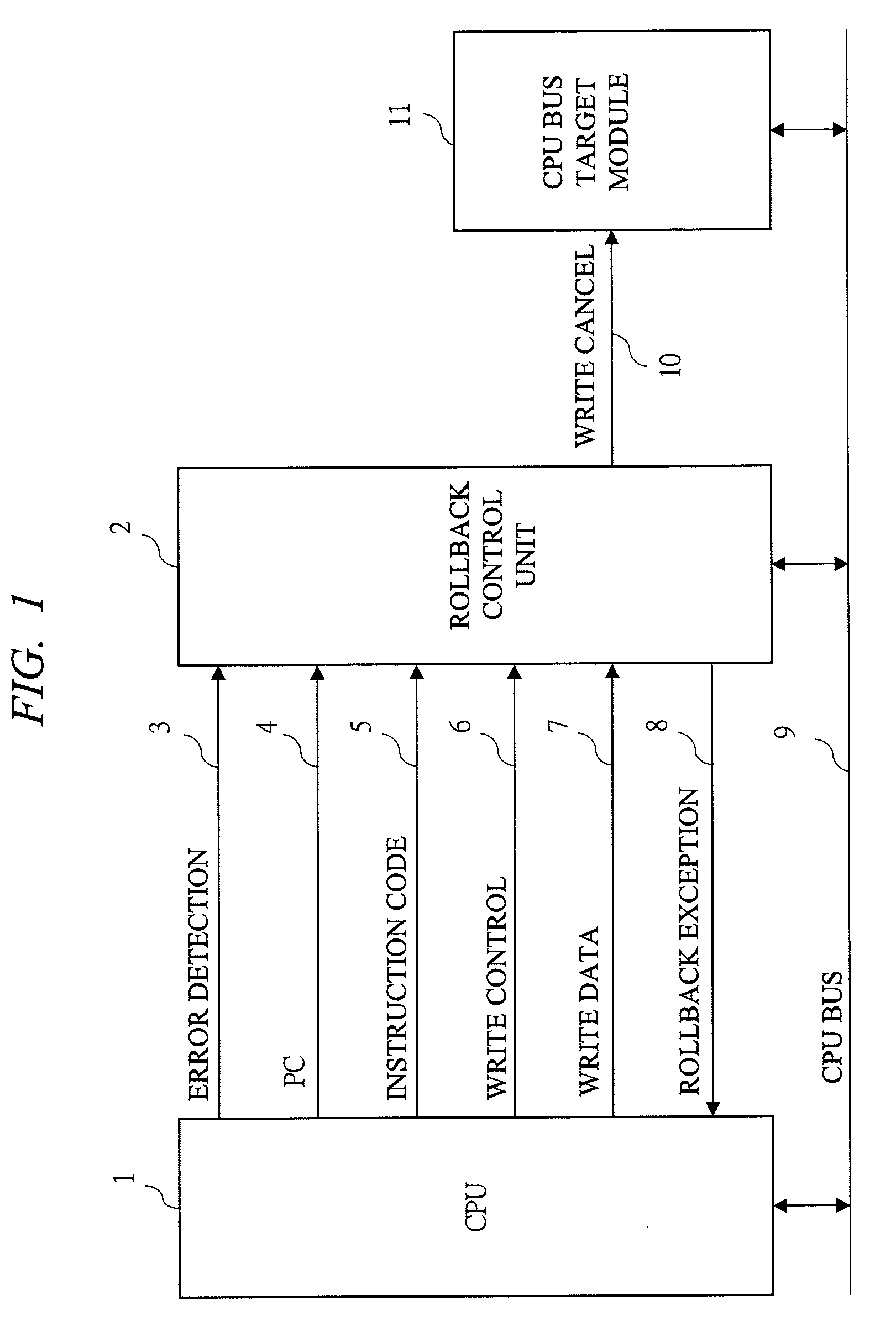

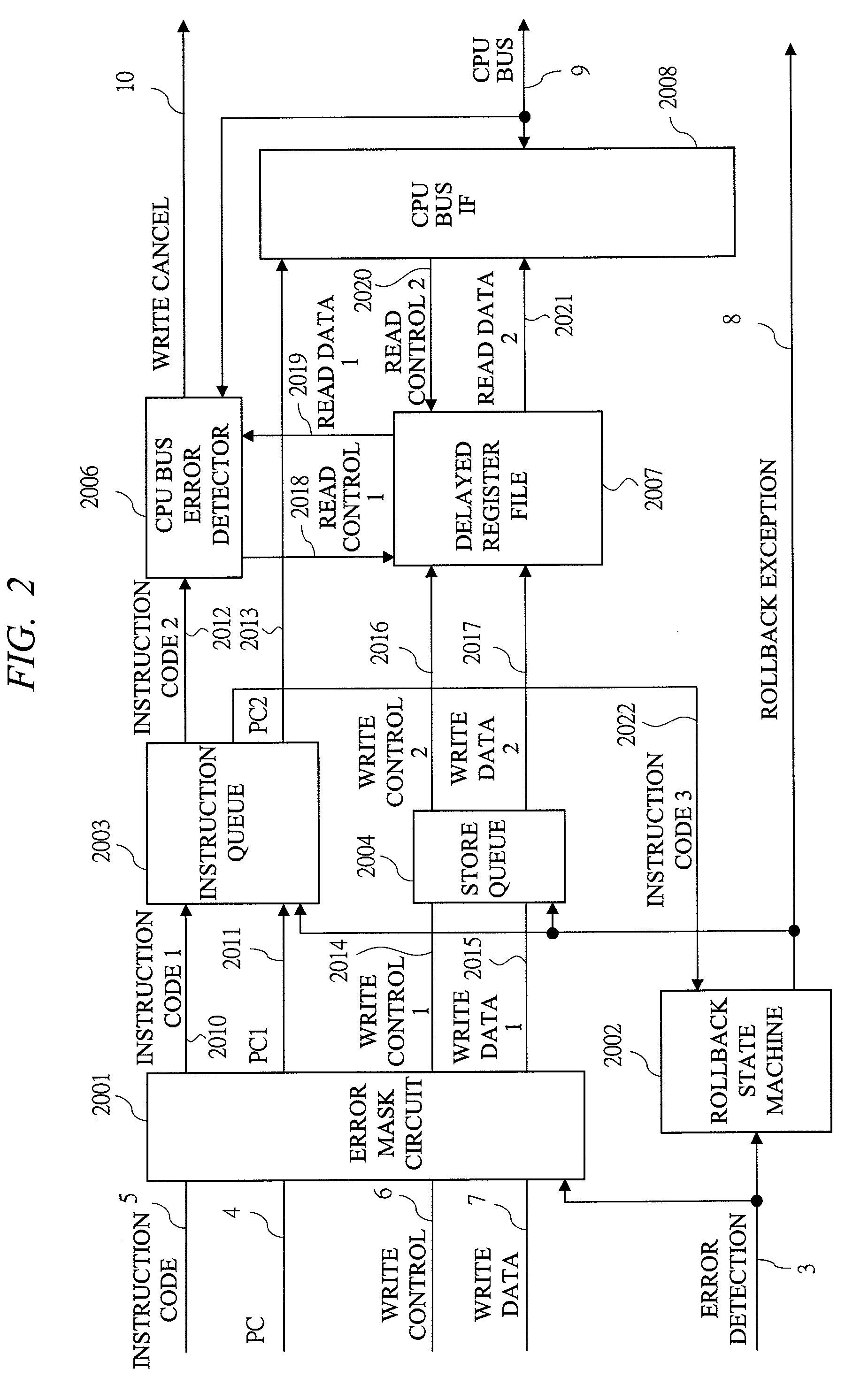

Error correction method with instruction level rollback

This method is an error correction method such that, when an error is detected in a CPU with pipeline structure, a content of a register file is restored by a delayed register file which holds an execute completion state of an [Instruction N] correctly executed before this error, and a rollback control that re-executes an instruction from the [Instruction N+1] which is the next instruction of the [Instruction N] is performed. The method collects a parity check result of arbitrary Flip-Flops existing inside the CPU, and detects an error. As a result, the content of the register file is restored into the instruction execute completion state preceding to the instruction range likely to malfunction by the error, and the instruction can be roll backed from the beginning of the instruction range likely having malfunctioned by the error.

Owner:RENESAS ELECTRONICS CORP

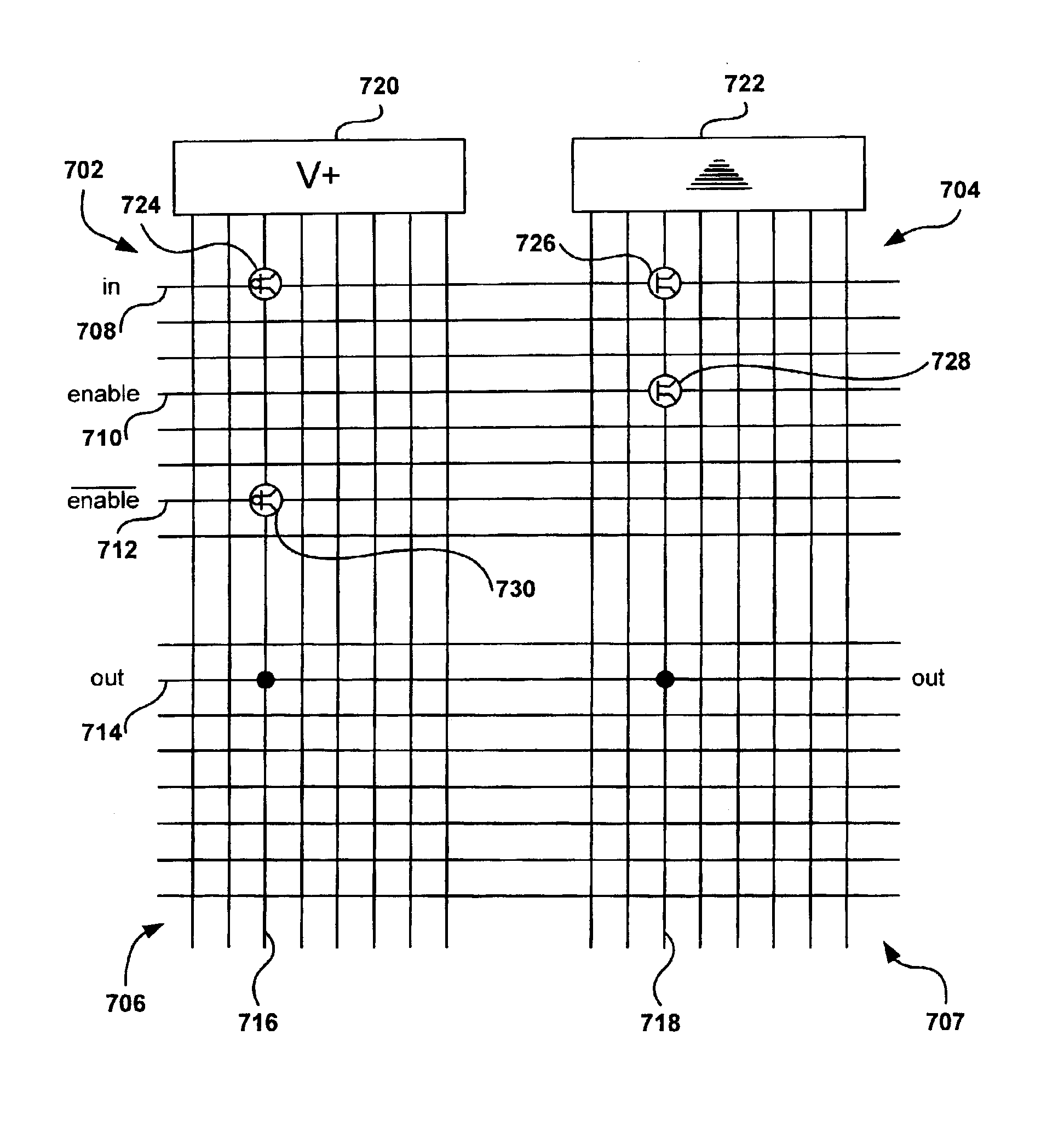

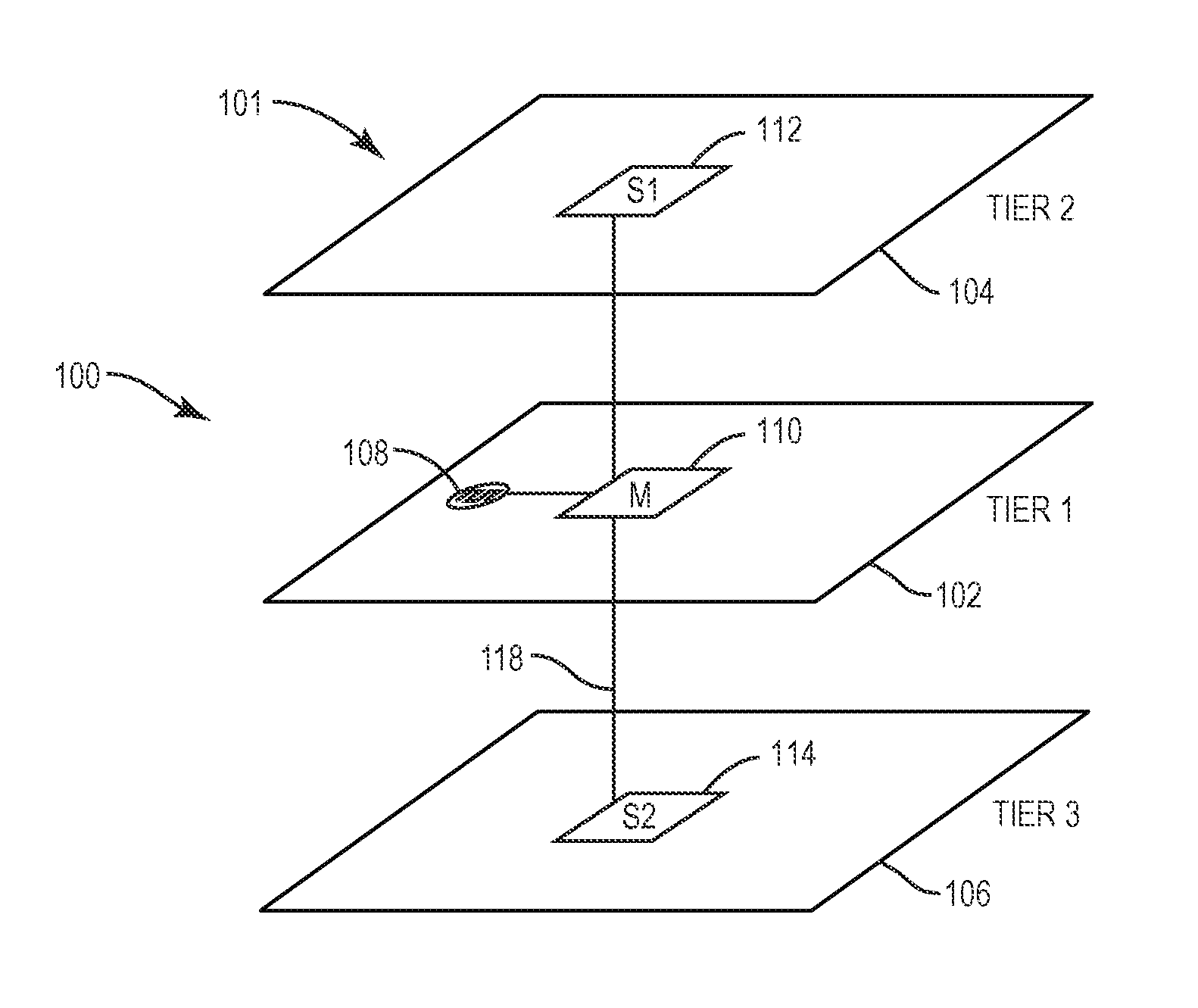

Molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits, and more complex circuits composed, in part, from molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits

InactiveUS6919740B2High densityLittle powerLogic circuits characterised by logic functionNanoinformaticsCrossbar switchNanowire

Methods for implementing familiar electronic circuits at nanoscale sizes using molecular-junction-nanowire crossbars, and nanoscale electronic circuits produced by the methods. In one embodiment of the present invention, a 3-state inverter is implemented. In a second embodiment of the present invention, two 3-state inverter circuits are combined to produce a transparent latch. The 3-state inverter circuit and transparent-latch circuit can then be used as a basis for constructing additional circuitry, including master / slave flip-flops, a transparent latch with asynchronous preset, a transparent latch with asynchronous clear, and a master / slave flip-flop with asynchronous preset. 3-state inverters can thus be used to compose latches and flip-flops, and latches and flip-flops can be used, along with additional Boolean circuitry, to compose a wide variety of useful, state-maintaining circuits, all implementable within molecular-junction-nanowire crossbars by selectively configuring junctions within the molecular-junction-nanowire crossbars.

Owner:HEWLETT PACKARD DEV CO LP

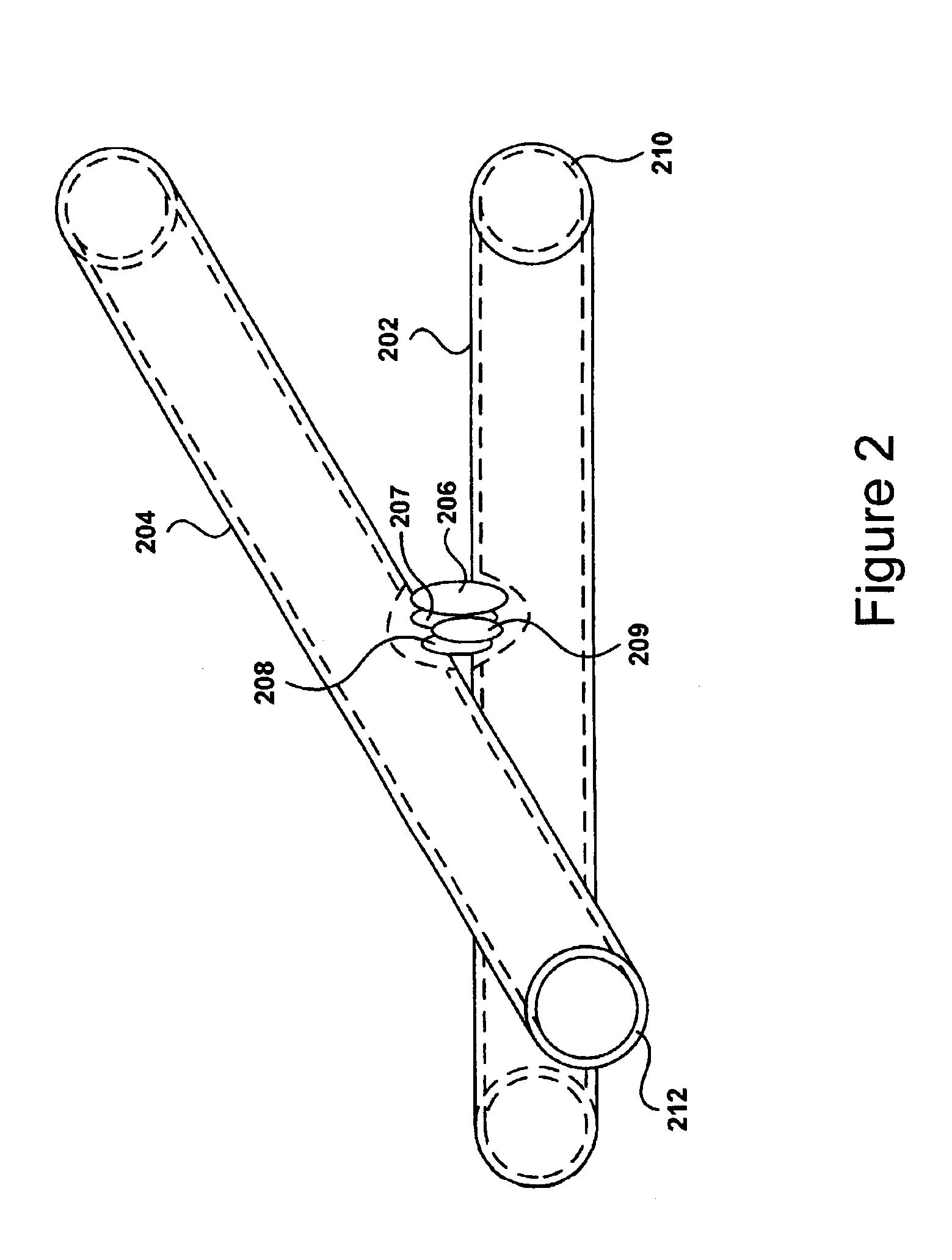

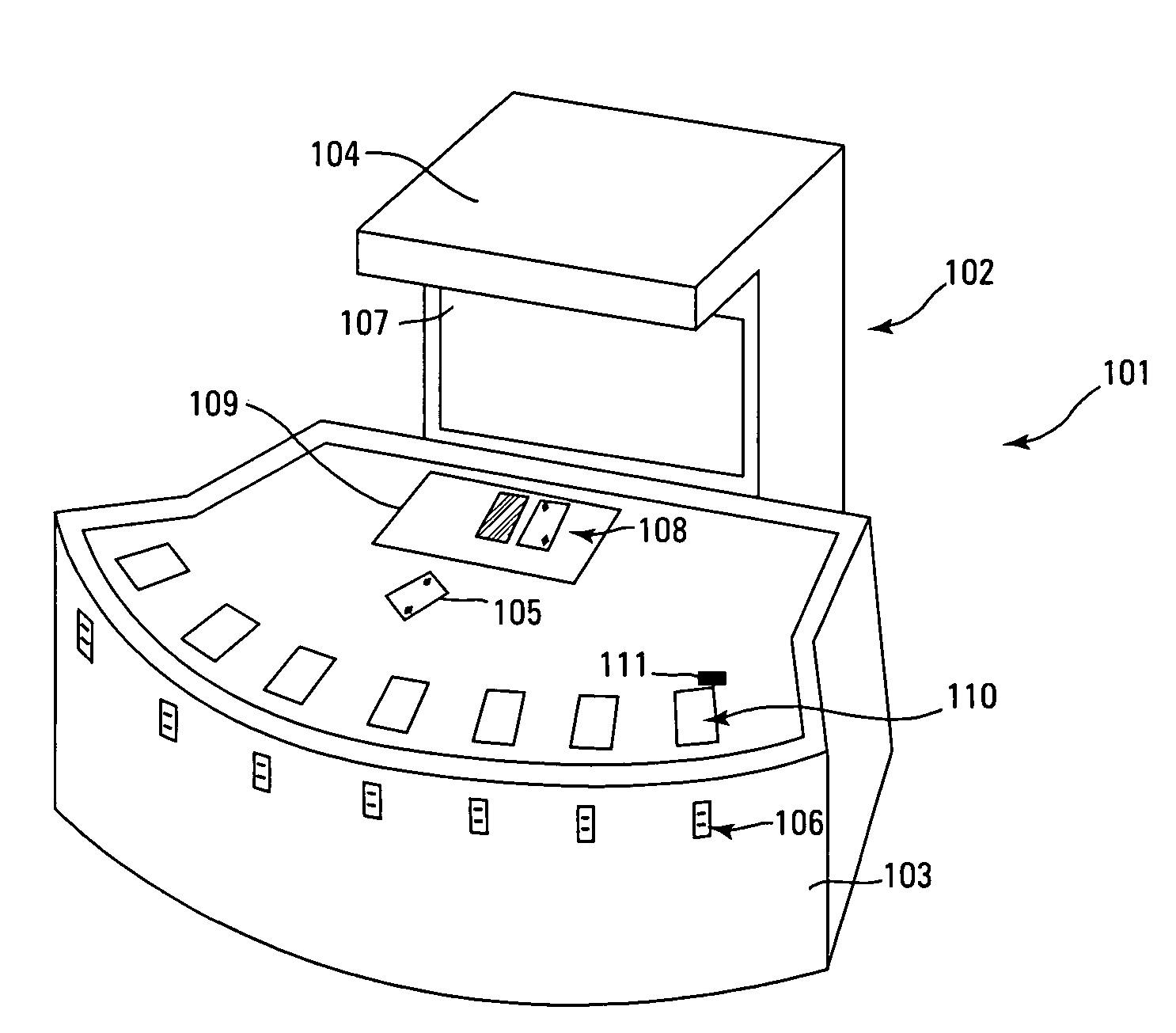

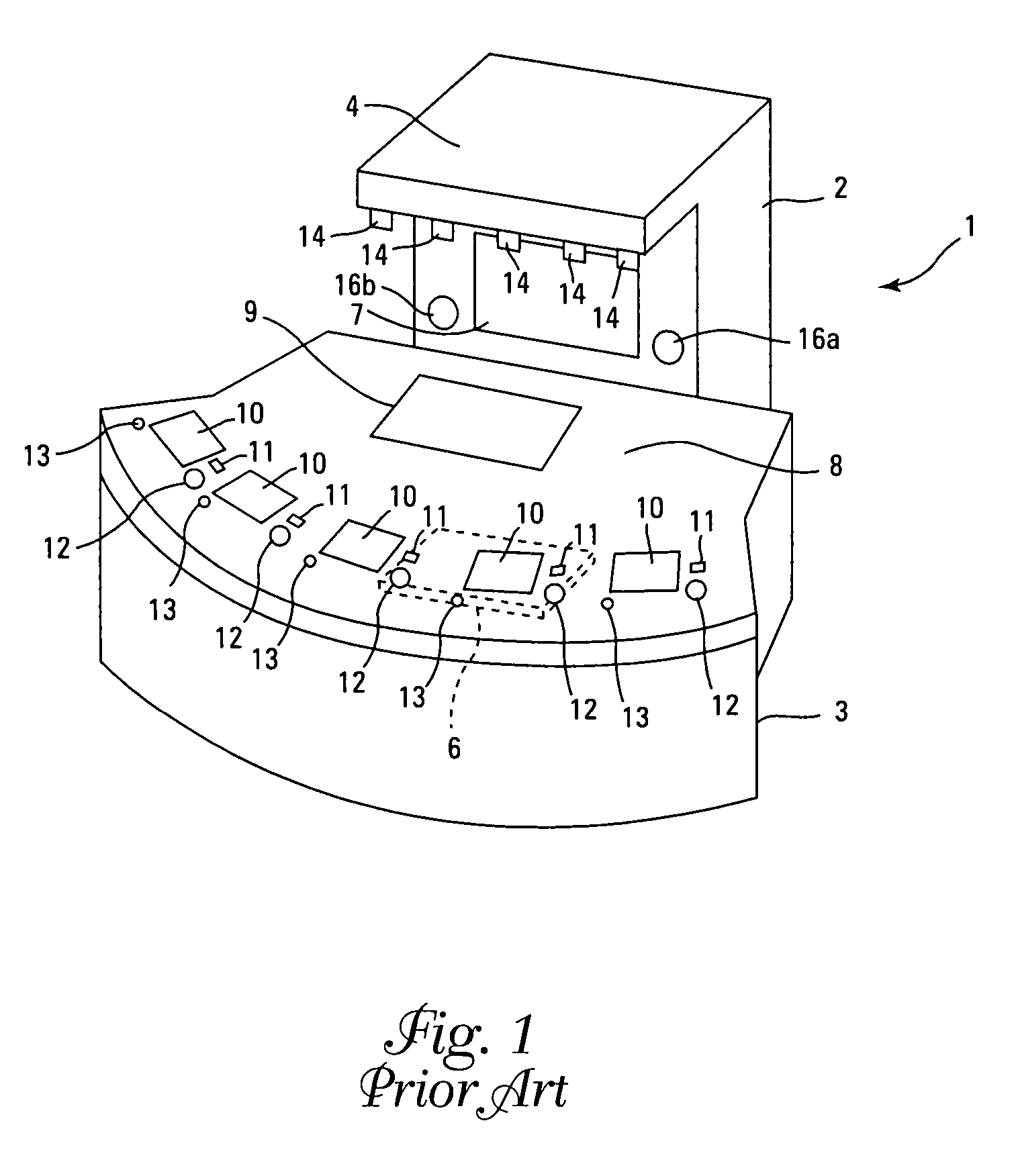

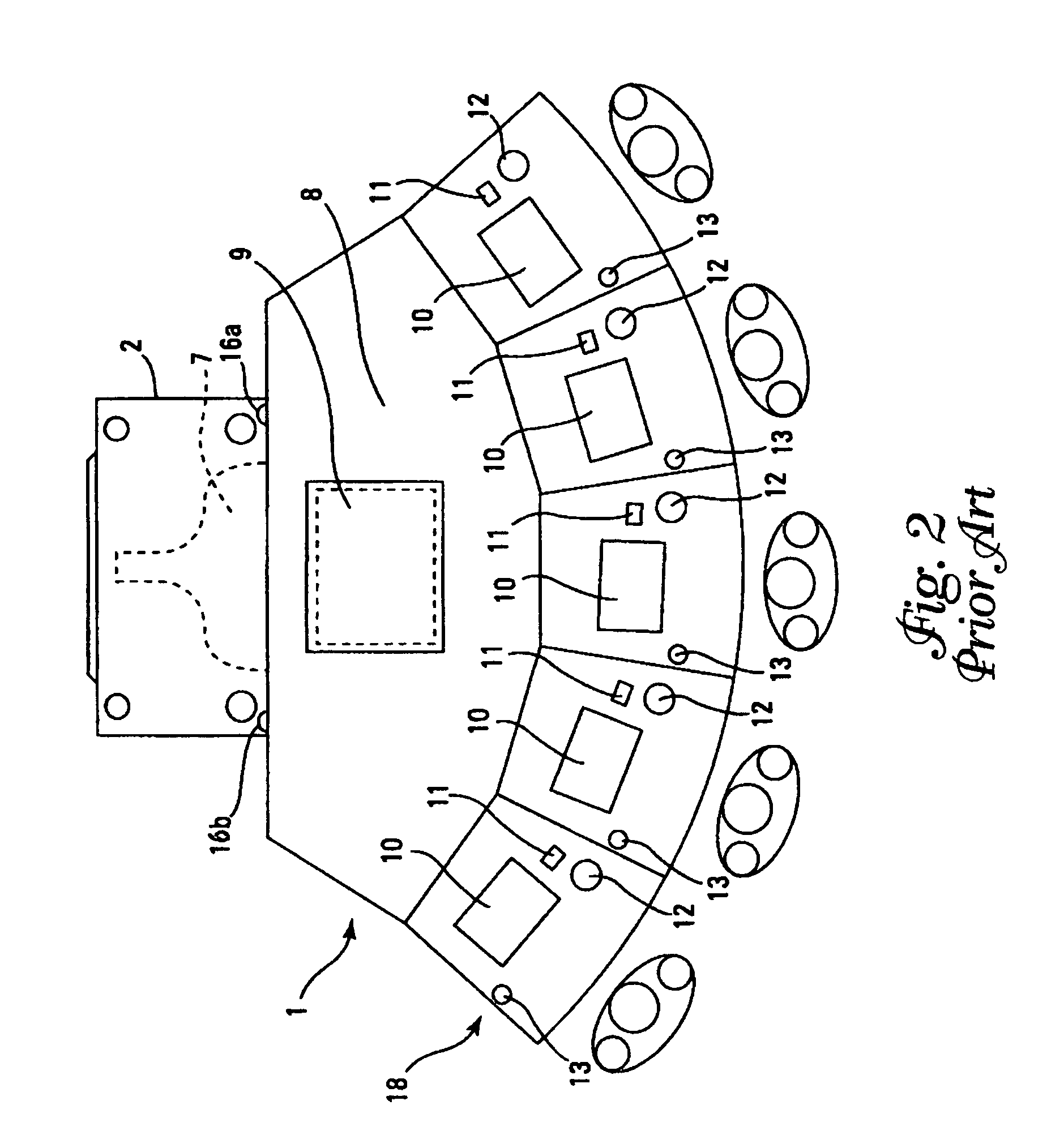

Card shuffler with reading capability integrated into multiplayer automated gaming table

A gaming system simulates events in a casino table card wagering game where there has traditionally been a dealer, whether or not the dealer is an active player in the game. Two distinct video areas are preferably provided, one providing video images of a virtual dealer, and the second video display providing a simulation of a table top for player cards, and optionally also dealer cards. The players have individual play areas with player input, and these play areas have individual processing intelligence that communicates directly with at least one processor. Delivery order of cards is determined by actual shuffling or randomization of a physical deck of cards, reading the cards, then creating an electronic file of the order of the shuffled or randomized cards, then using an order of cards contained in the electronic file to deliver virtual cards to players, dealer and flop as needed.

Owner:LNW GAMING INC

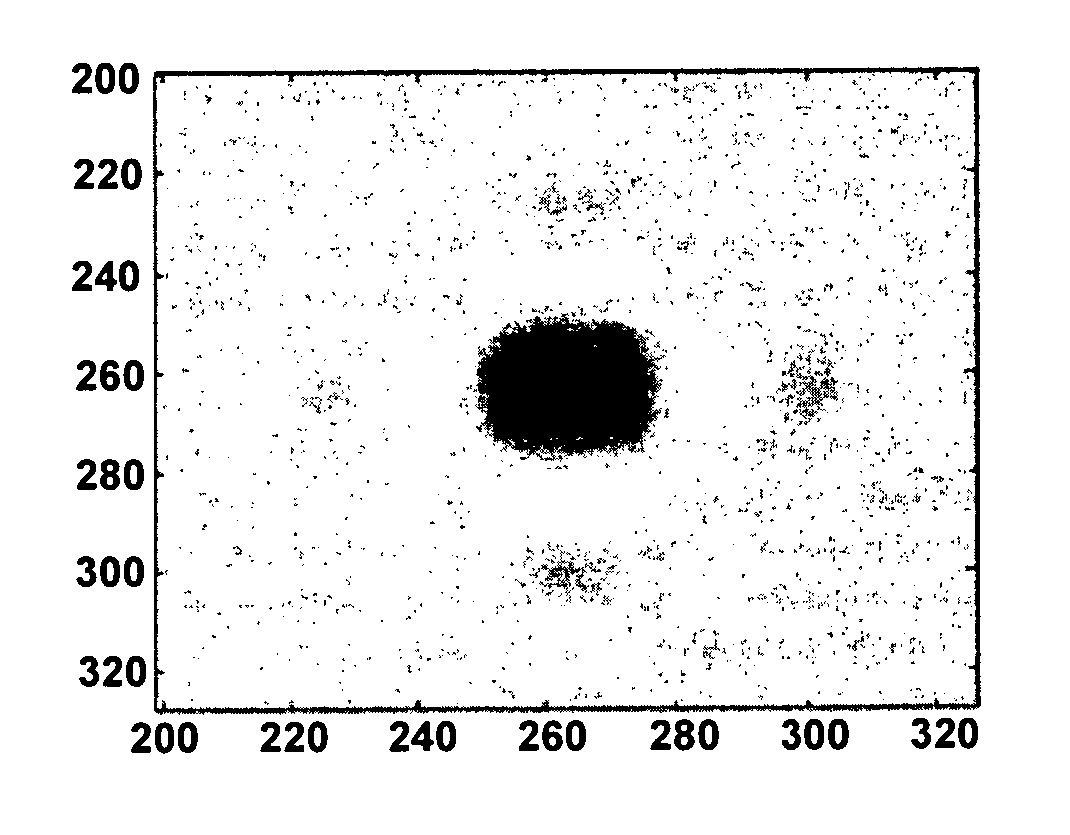

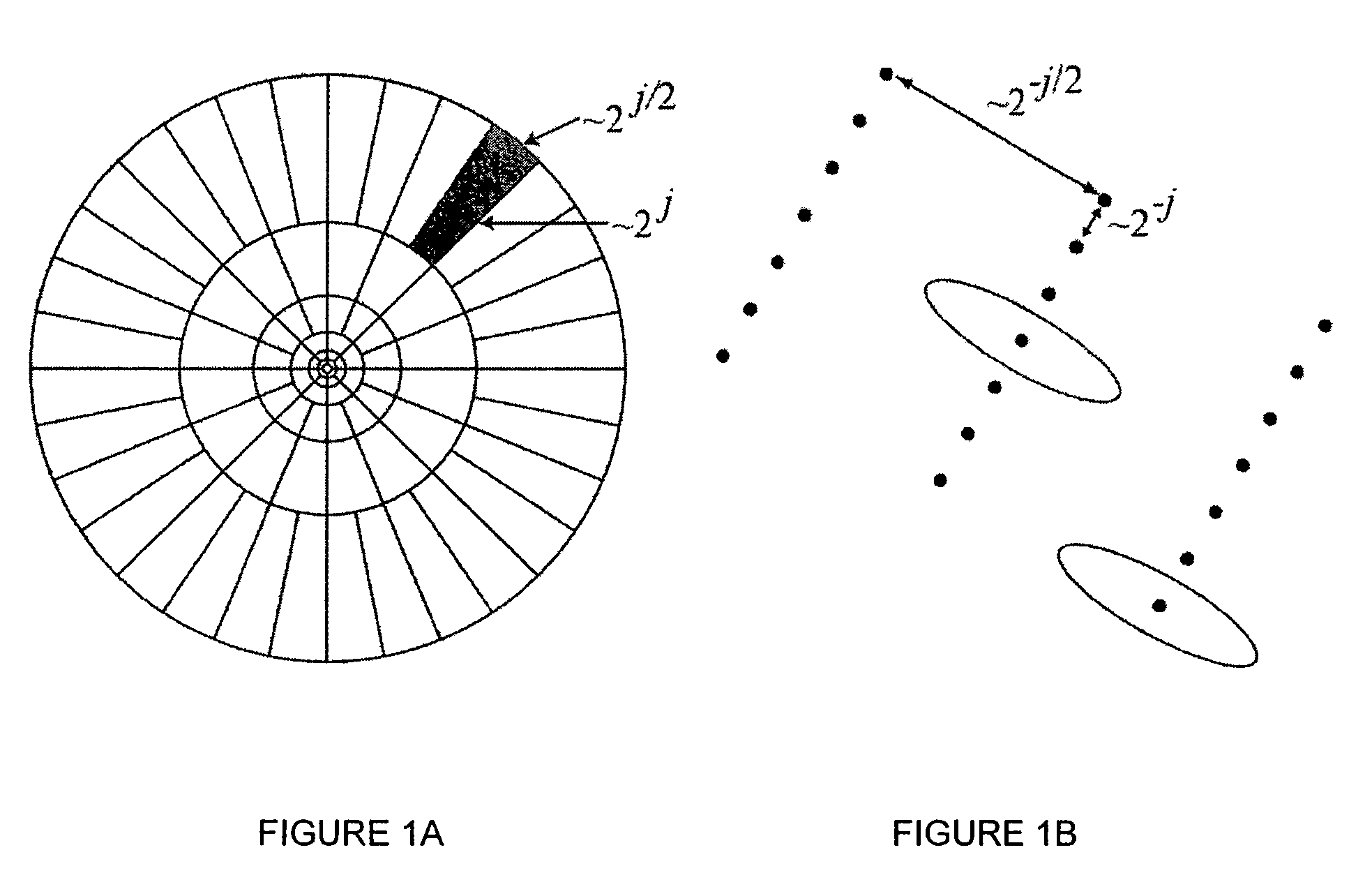

Methods for performing fast discrete curvelet transforms of data

ActiveUS20070038691A1The process is fast and accurateImprove representationComplex mathematical operationsDigital transformationFast Fourier transform

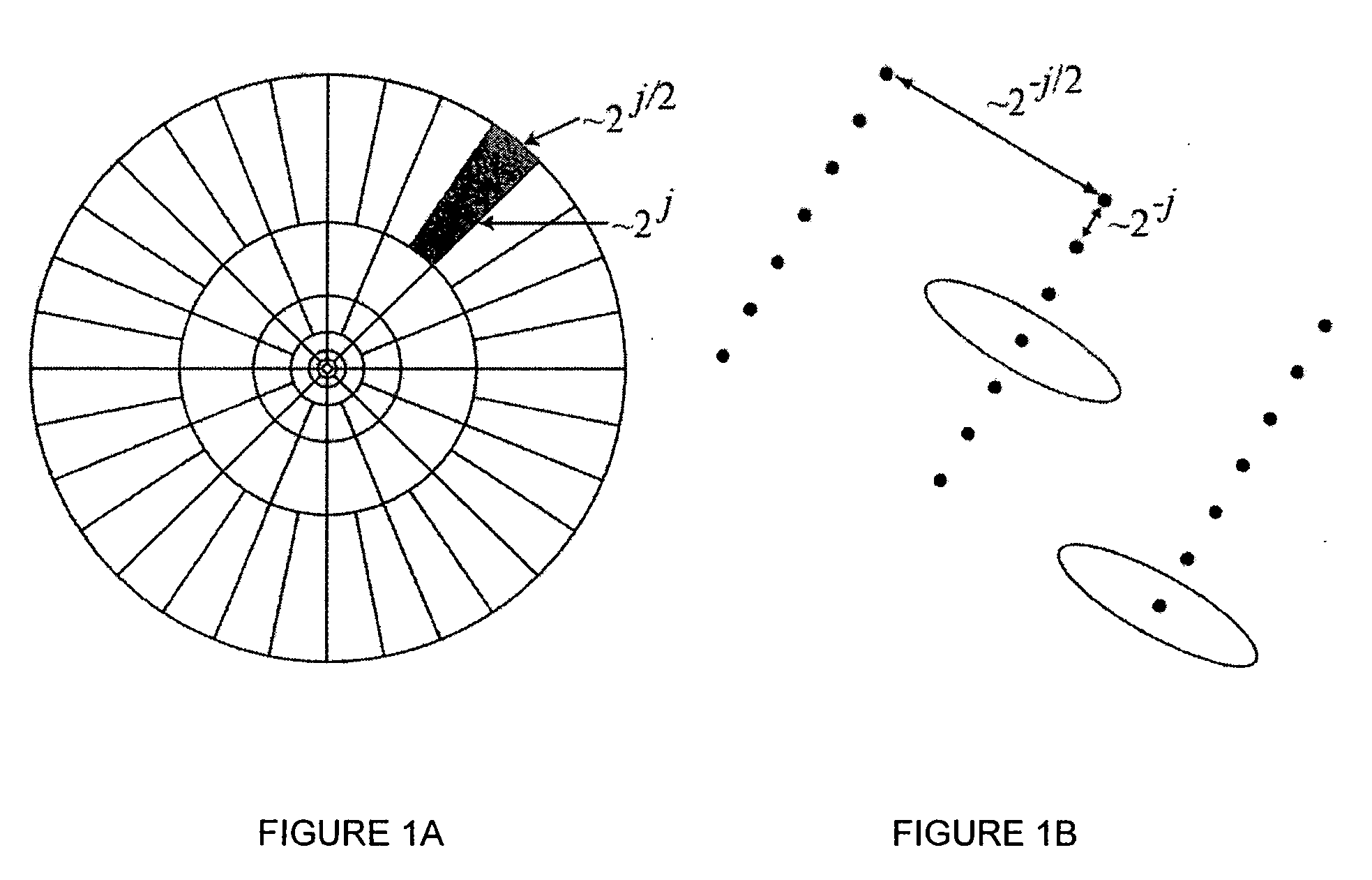

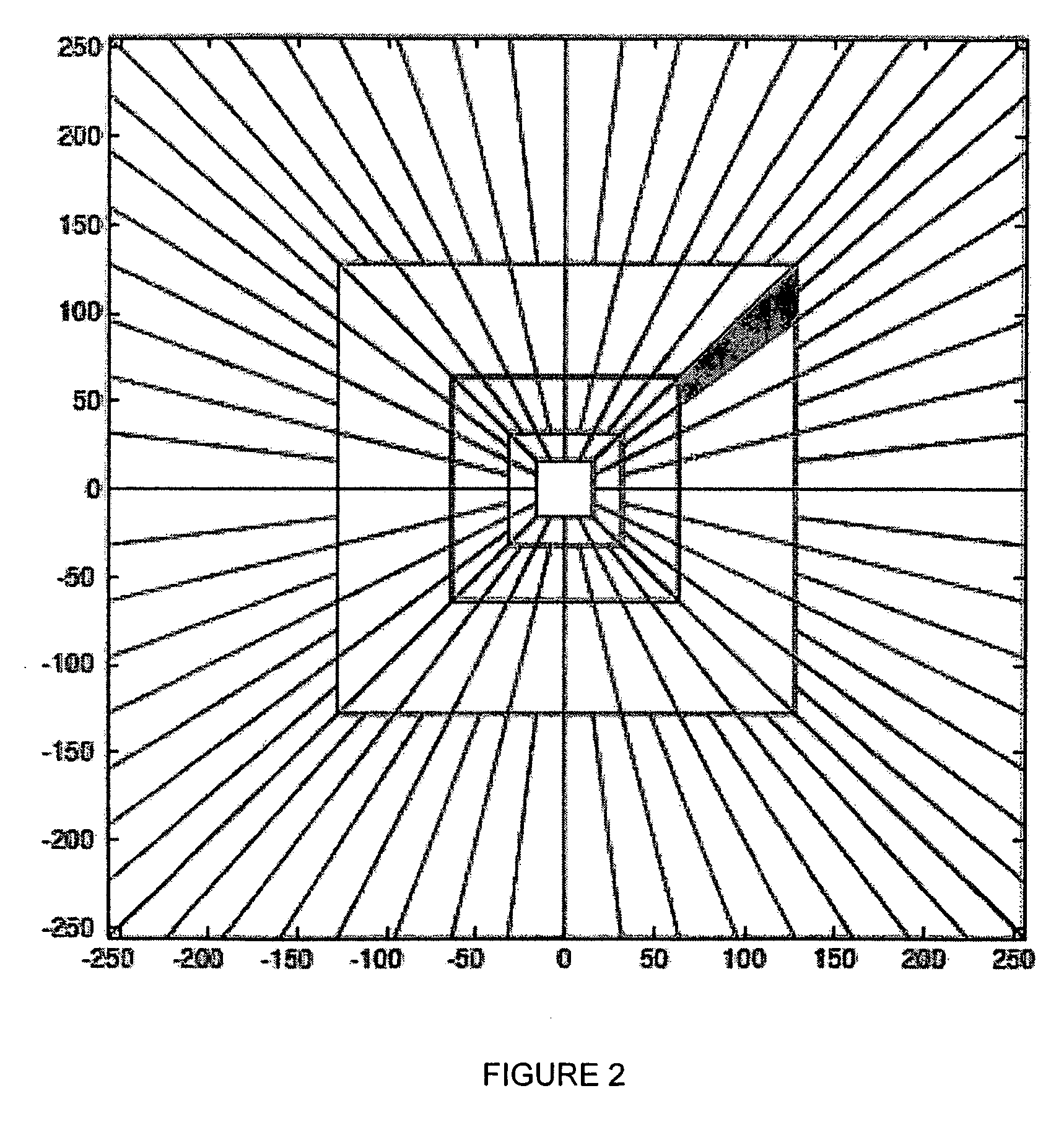

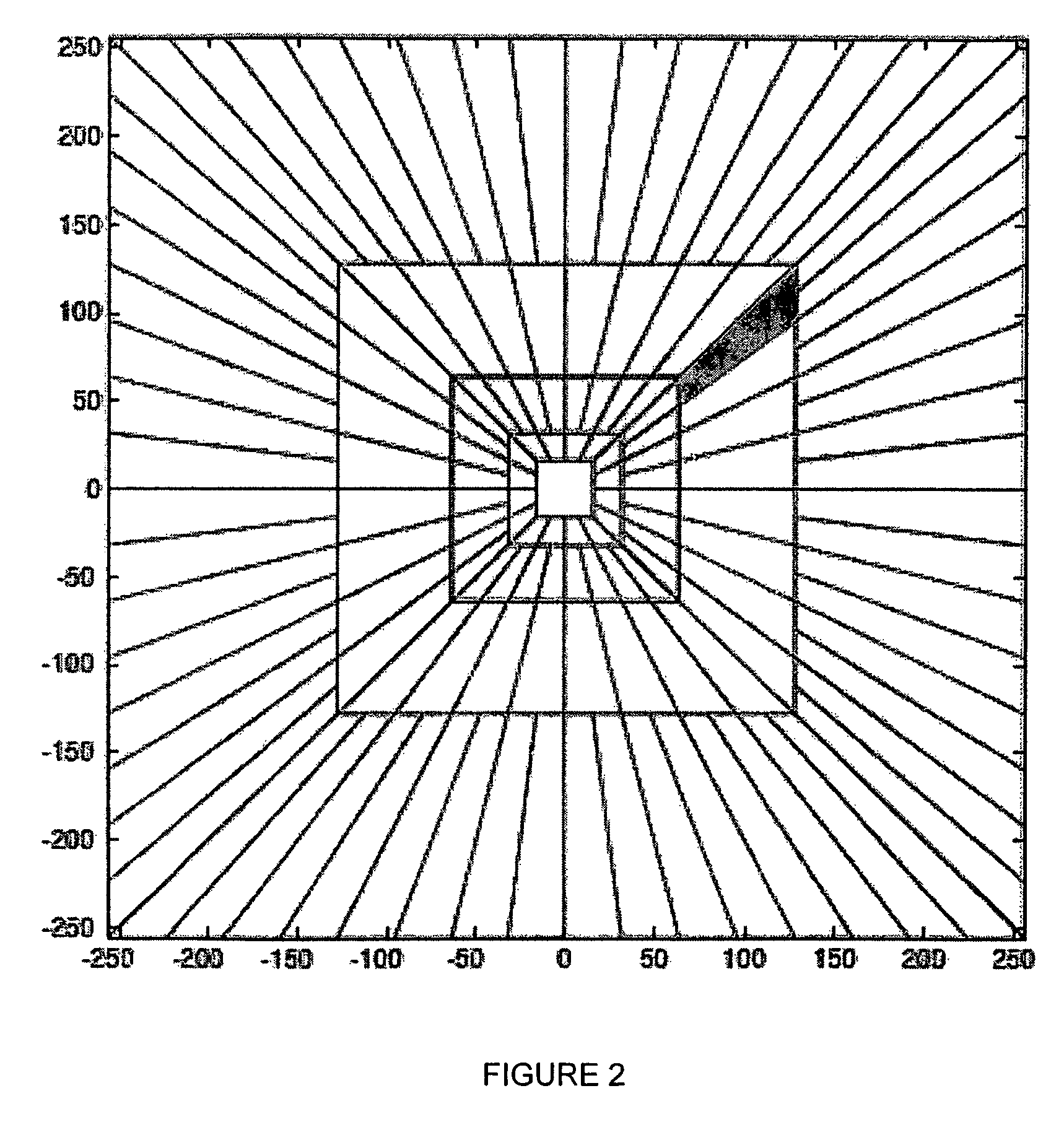

Fast digital implementations of the second generation curvelet transform for use in data processing are disclosed. One such digital transformation is based on unequally-spaced fast Fourier transforms (USFFT) while another is based on the wrapping of specially selected Fourier samples. Both digital transformations return a table of digital curvelet coefficients indexed by a scale parameter, an orientation parameter, and a spatial location parameter. Both implementations are fast in the sense that they run in about O(n2 log n) flops for n by n Cartesian arrays or about O(N log N) flops for Cartesian arrays of size N=n3; in addition, they are also invertible, with rapid inversion algorithms of about the same complexity.

Owner:CALIFORNIA INST OF TECH +1

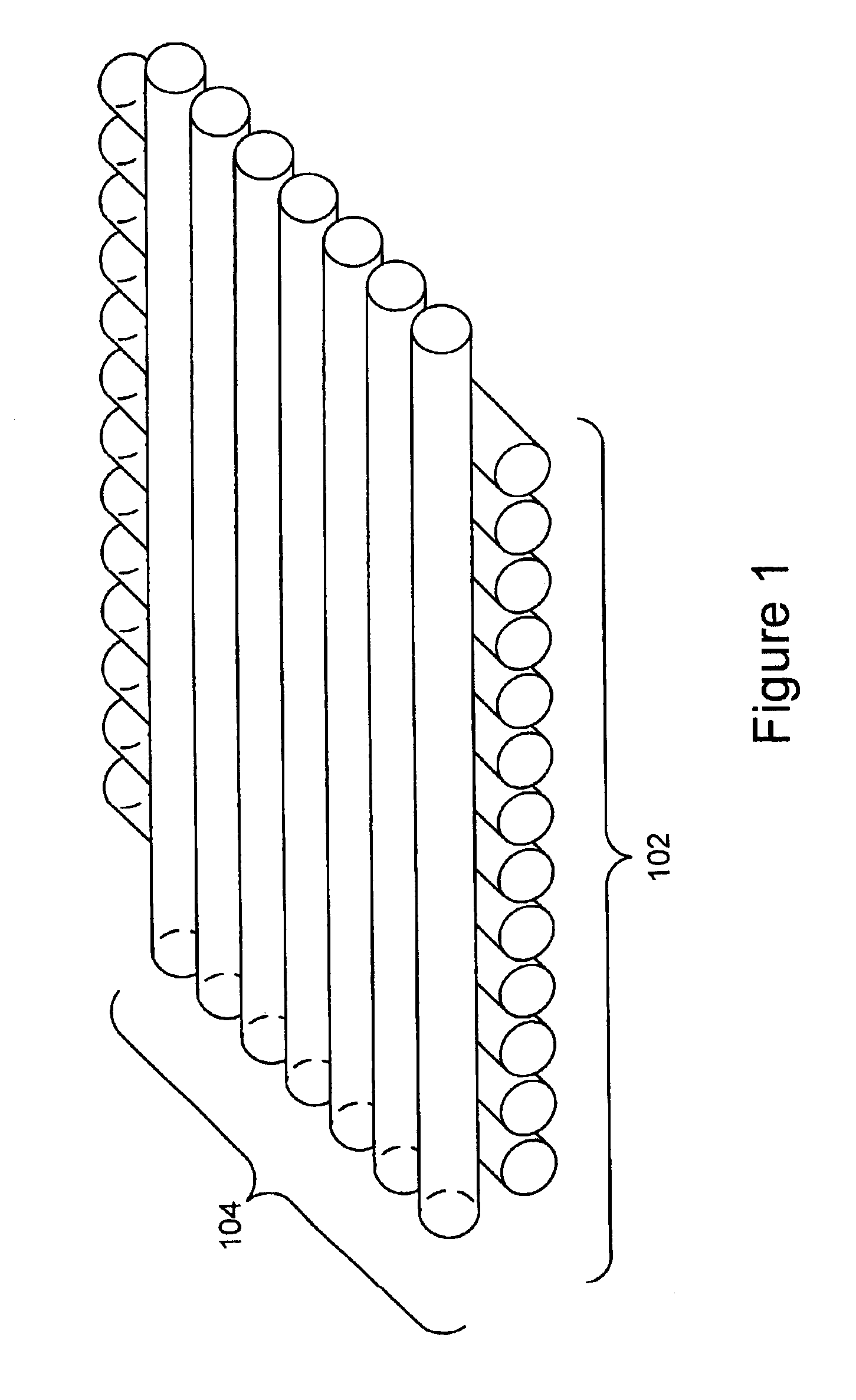

Storage elements using nanotube switching elements

Owner:NANTERO

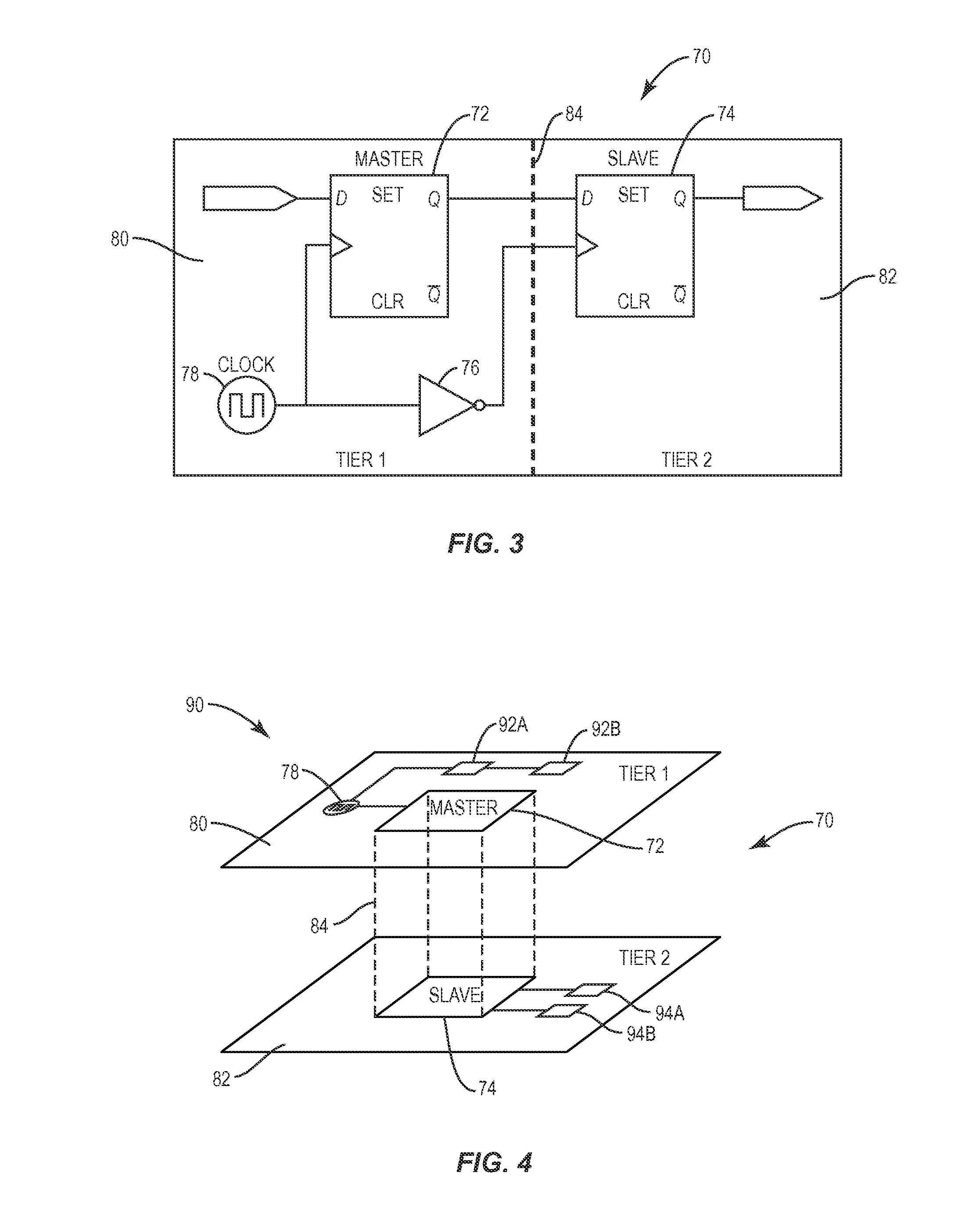

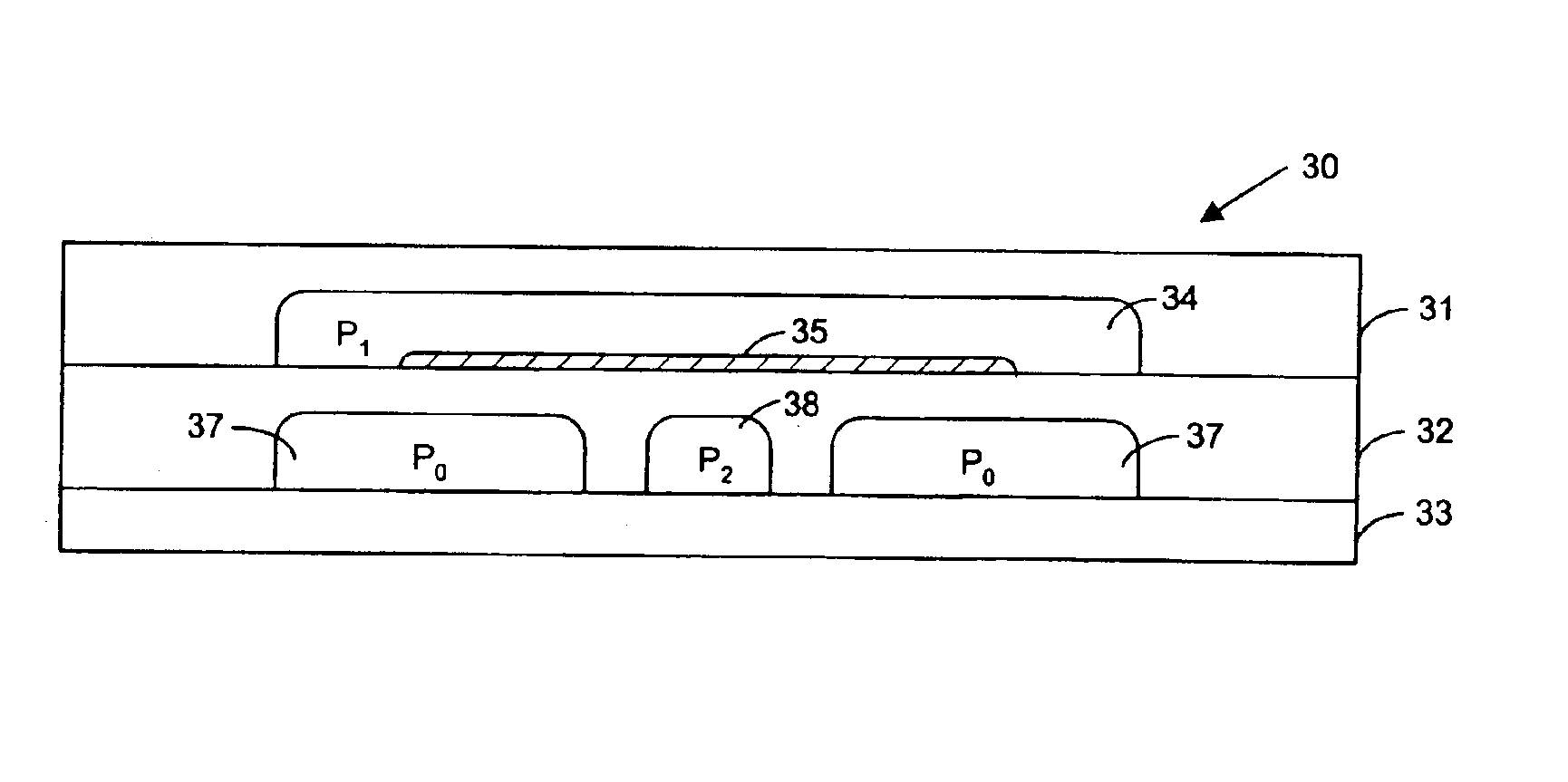

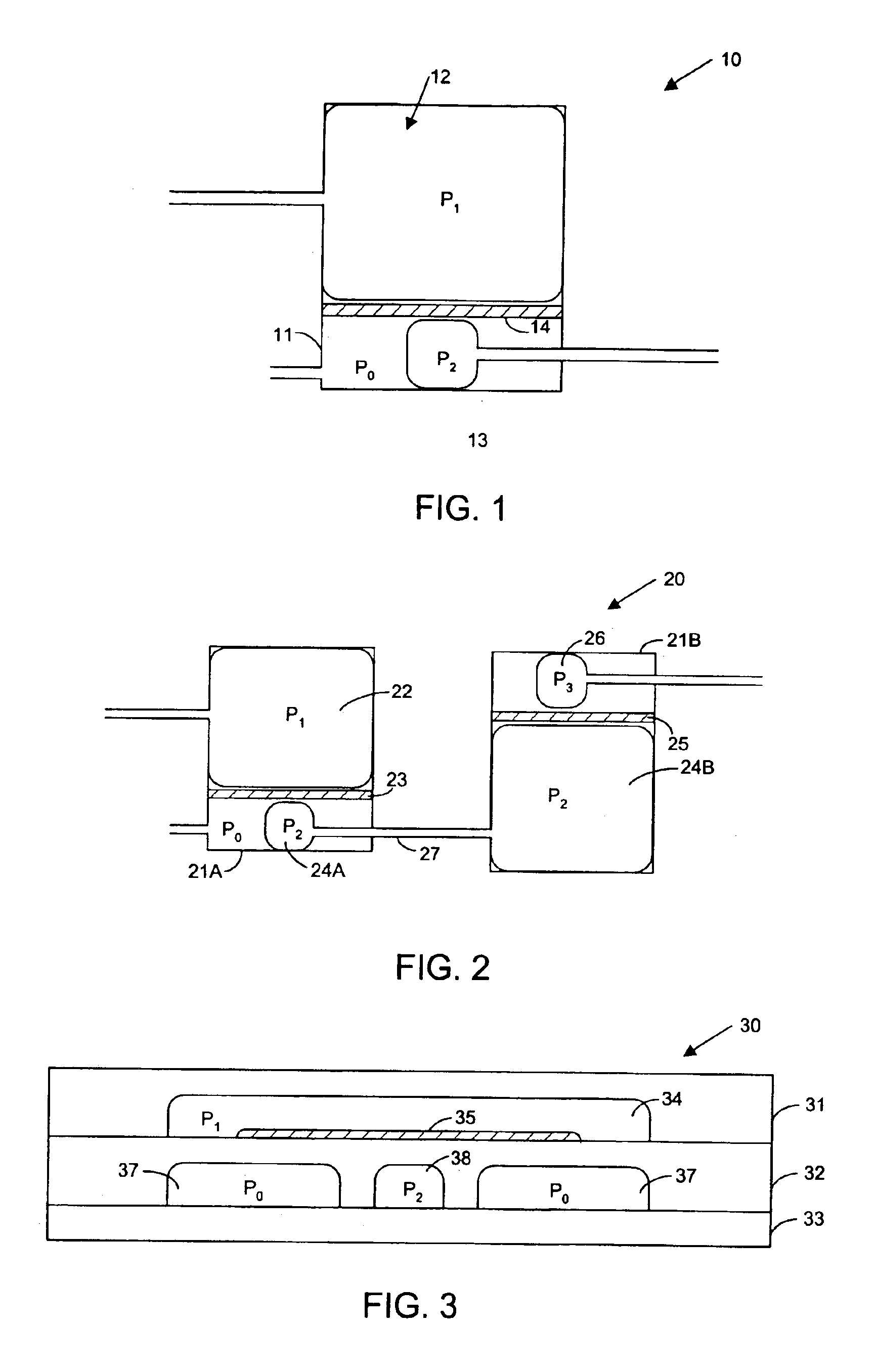

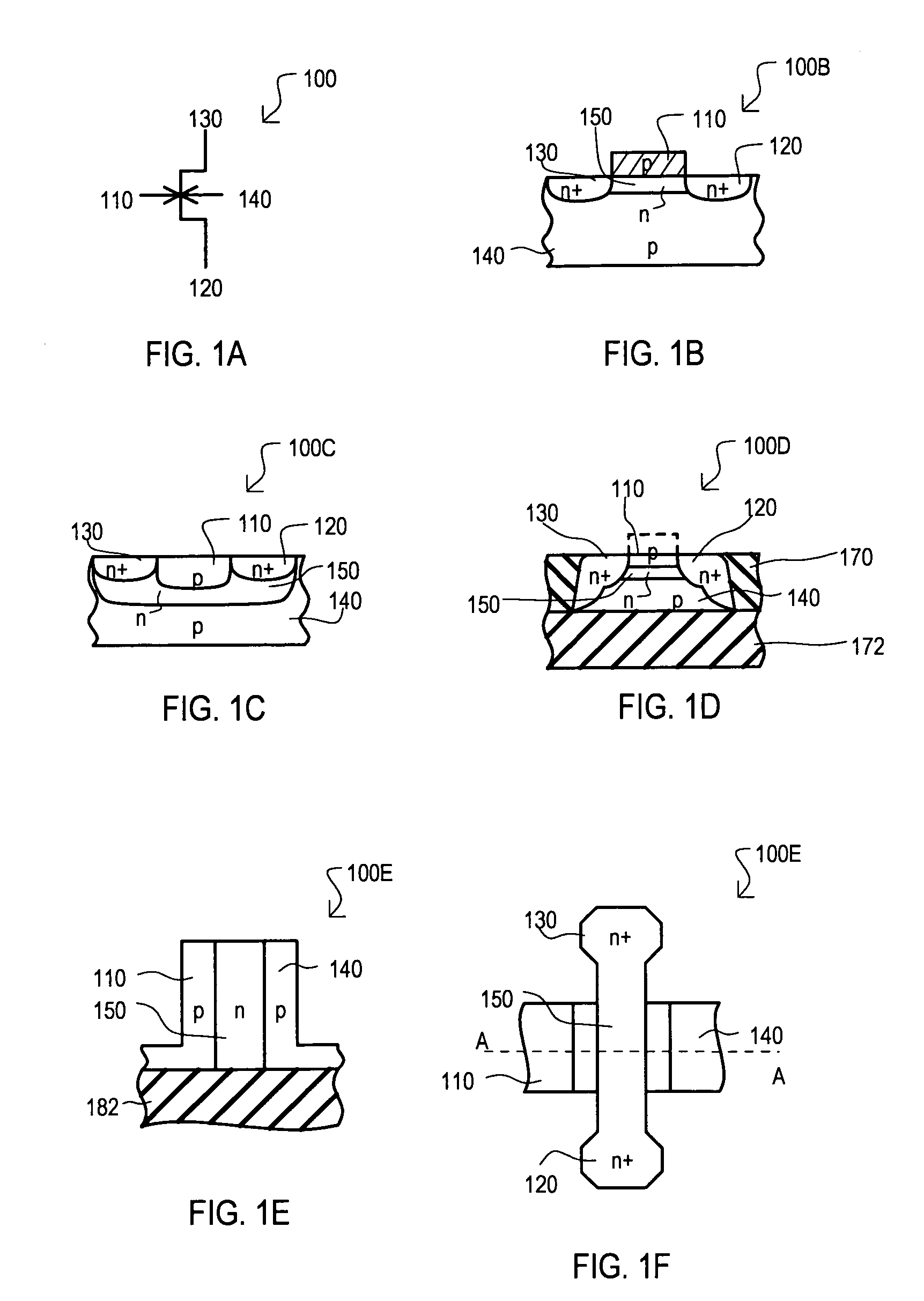

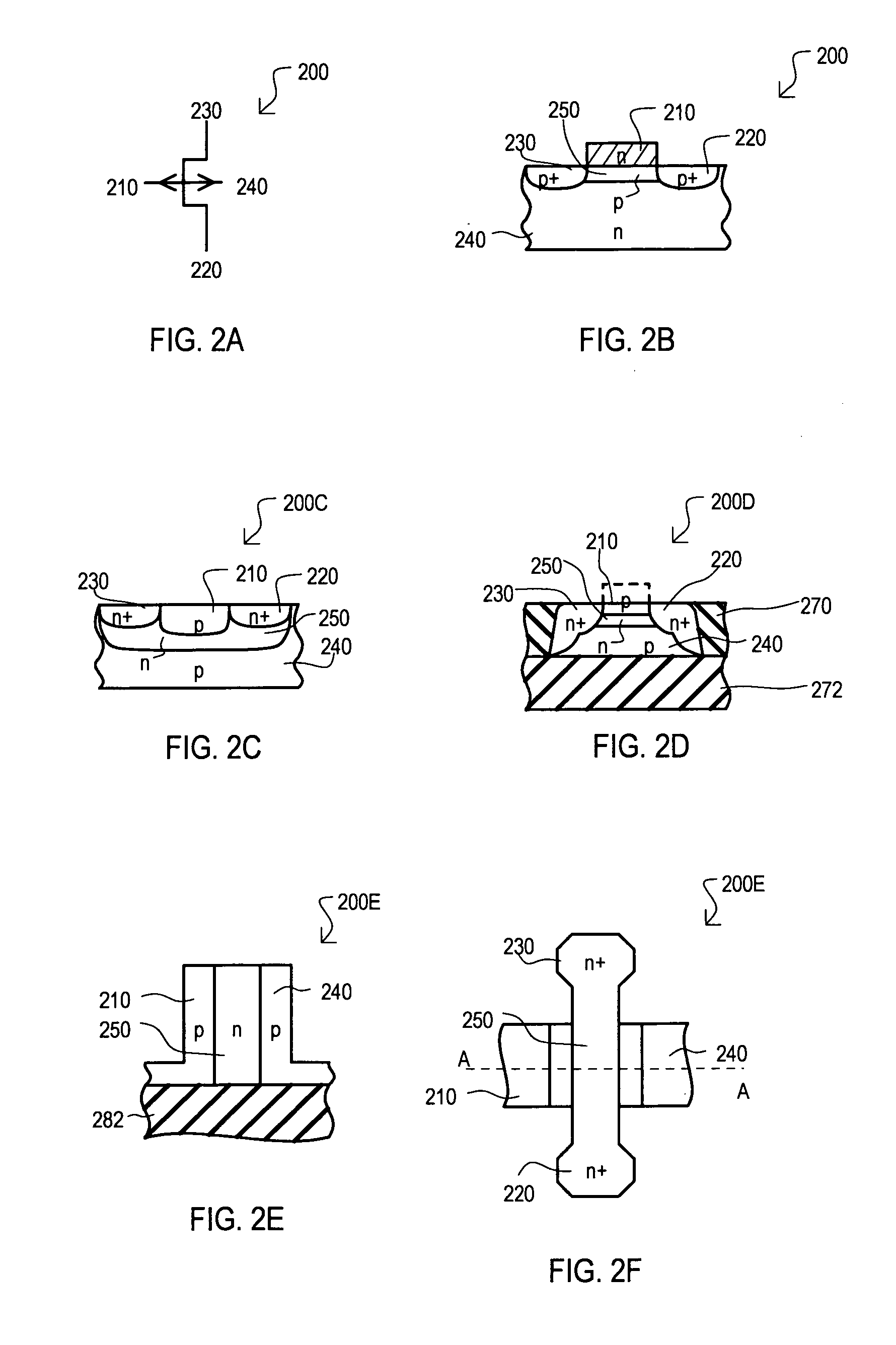

Flip-flops in a monolithic three-dimensional (3D) integrated circuit (IC) (3DIC) and related methods

ActiveUS20140253196A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringIntegrated circuit

Owner:QUALCOMM INC

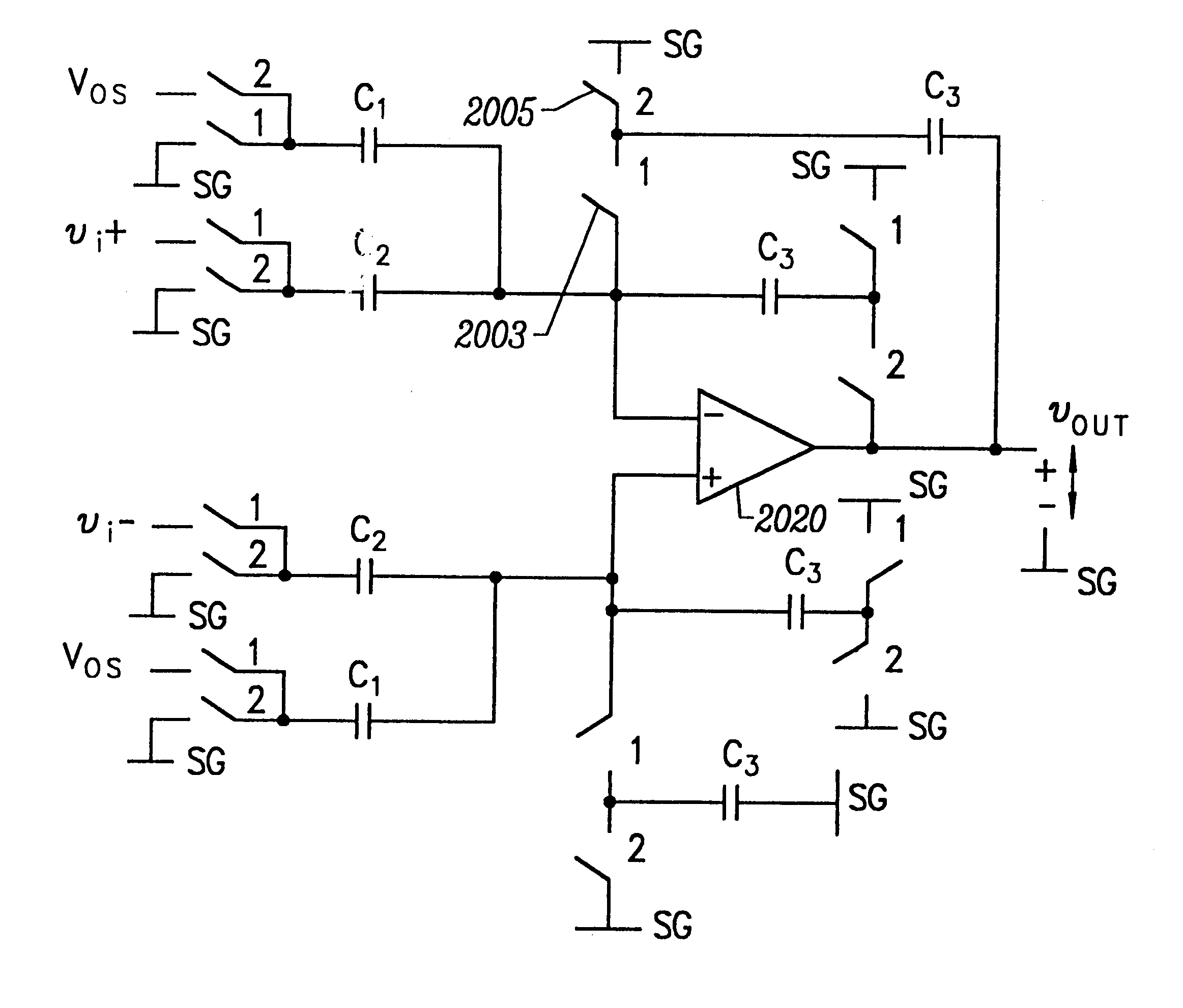

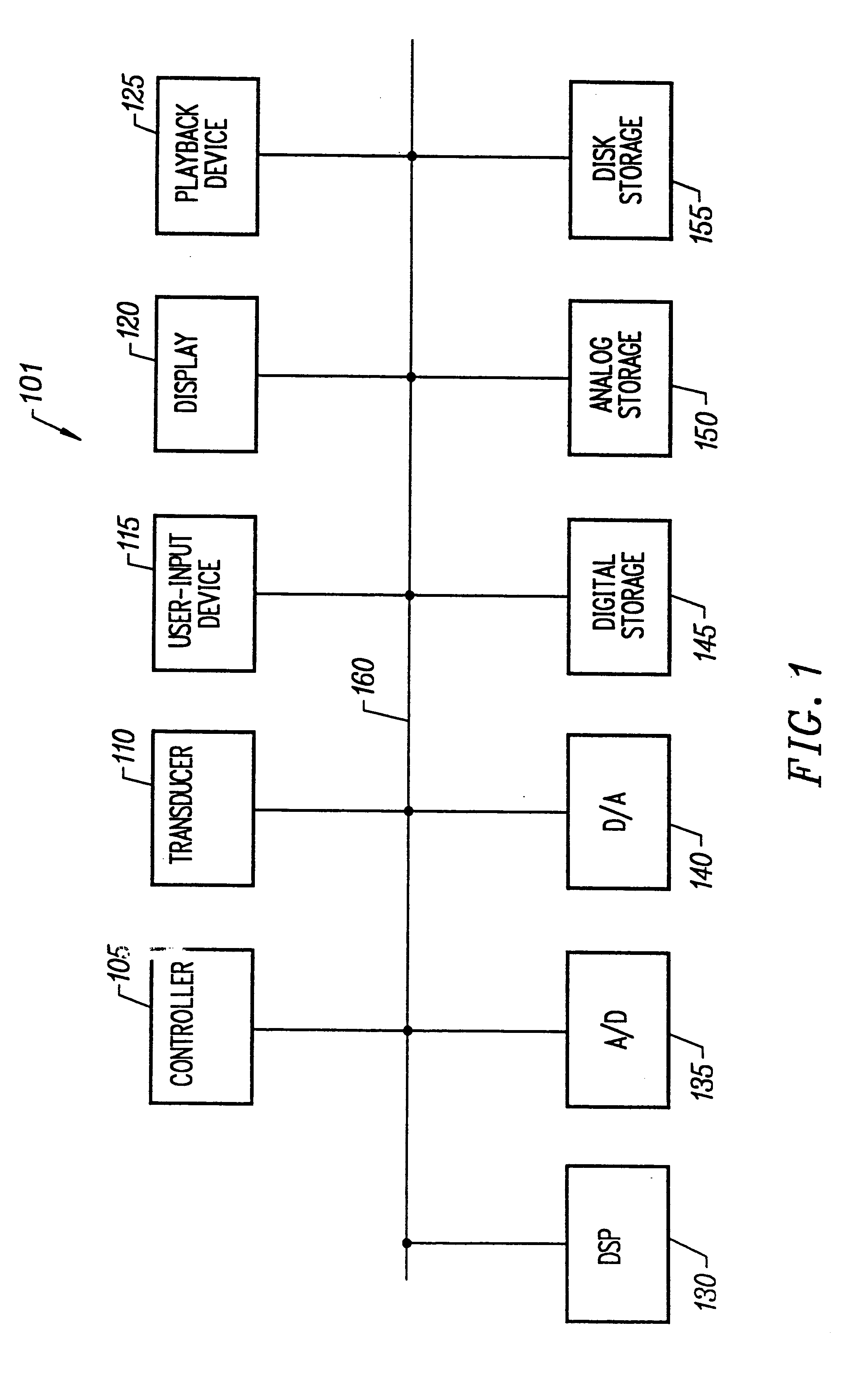

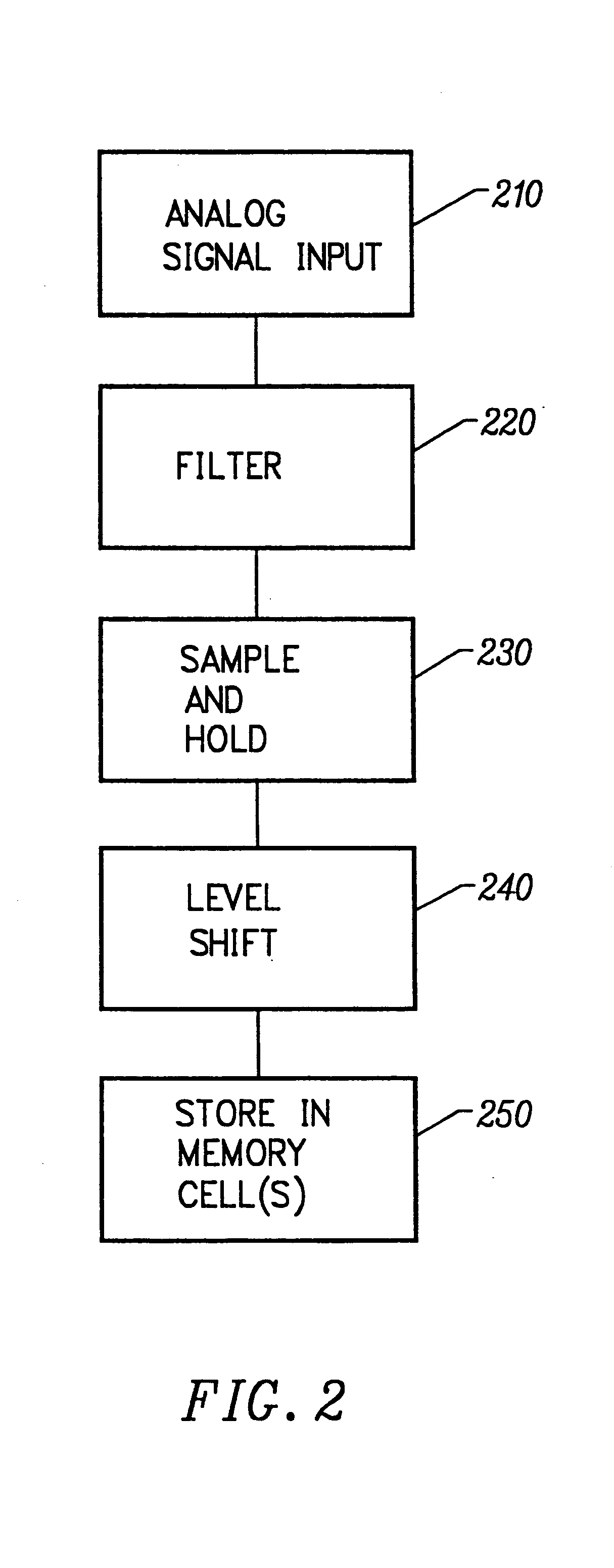

Adjustable level shifter circuits for analog or multilevel memories

InactiveUS6184726B1Prolong lifeImprove reliabilityPulse automatic controlElectric analogue storesMultilevel memoryEngineering

Level shifter circuits are used to configure analog or multilevel memory cells. A level shifter circuit generates an output voltage that is above the input voltage by an offset voltage value. The magnitude of this offset voltage or the relationship between the input and output voltages of the level shifter is adjustable or programmably selectable. Adjustments can be made after the integrated circuits is fabricated and packaged. Adjustments are made by configuring bits of data in the integrated circuit to indicate the offset voltage or other parameters. These configuration bits are implemented using latches, flip-flops, registers, memory cells, or other storage circuits.

Owner:SANDISK CORP

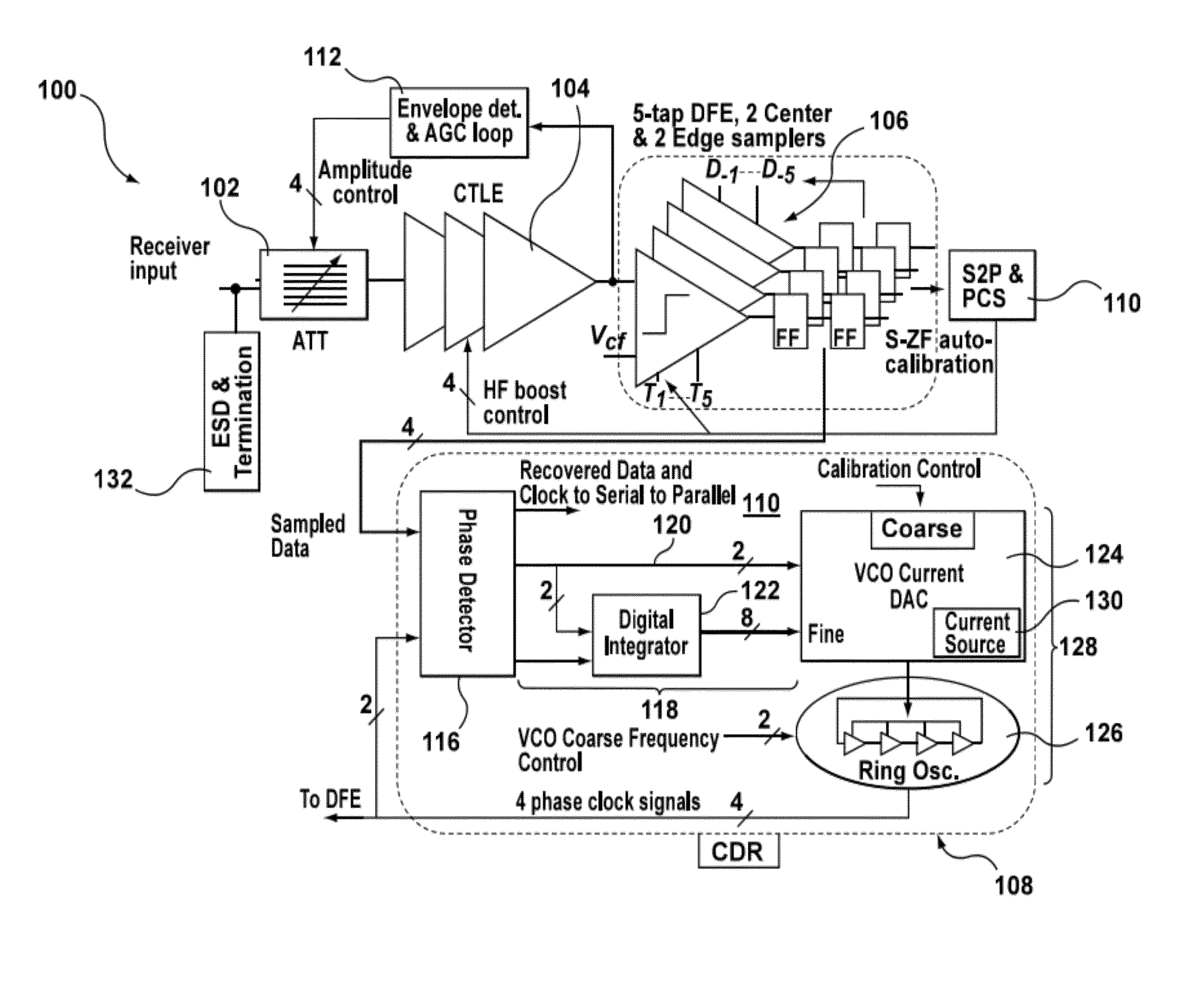

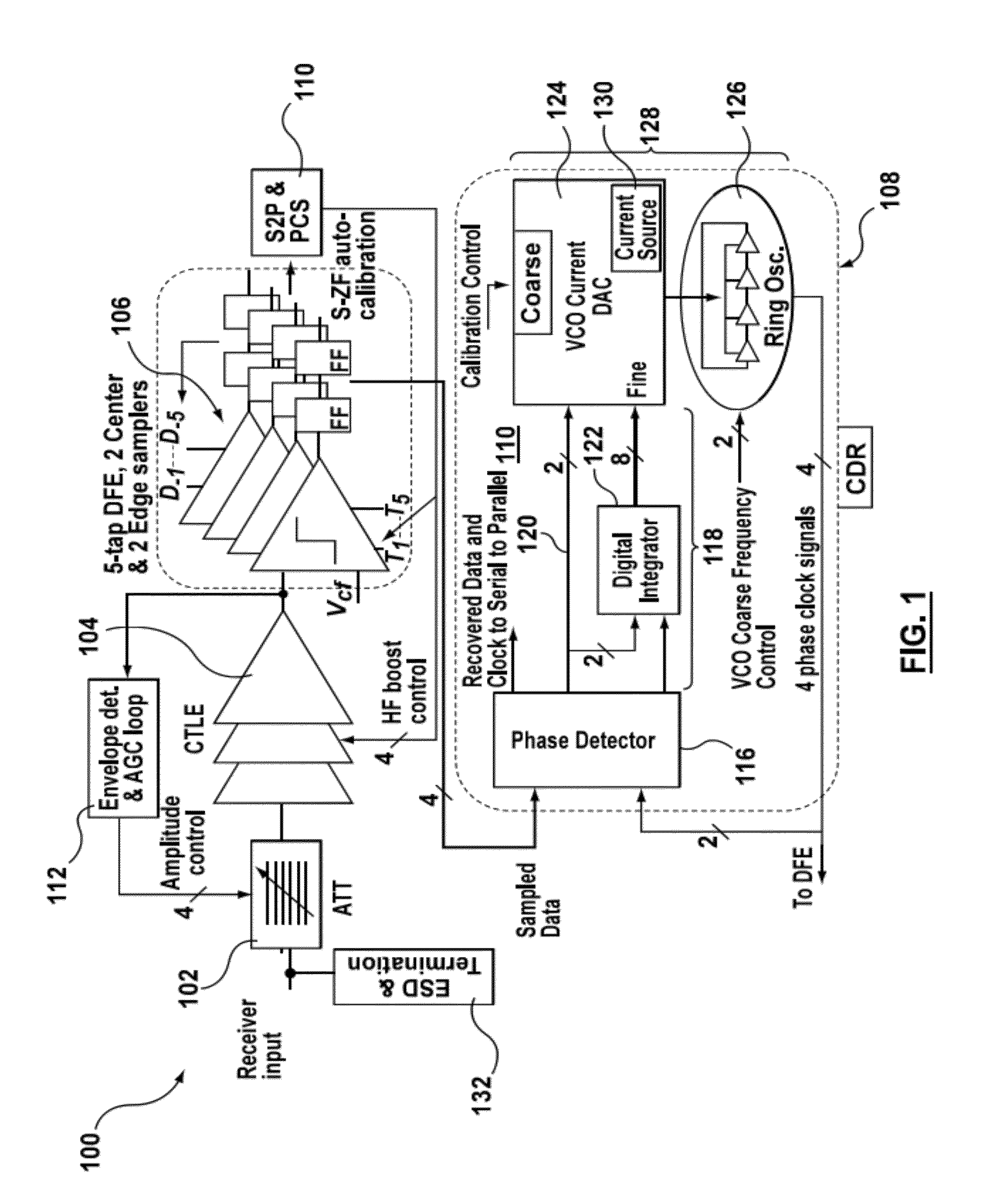

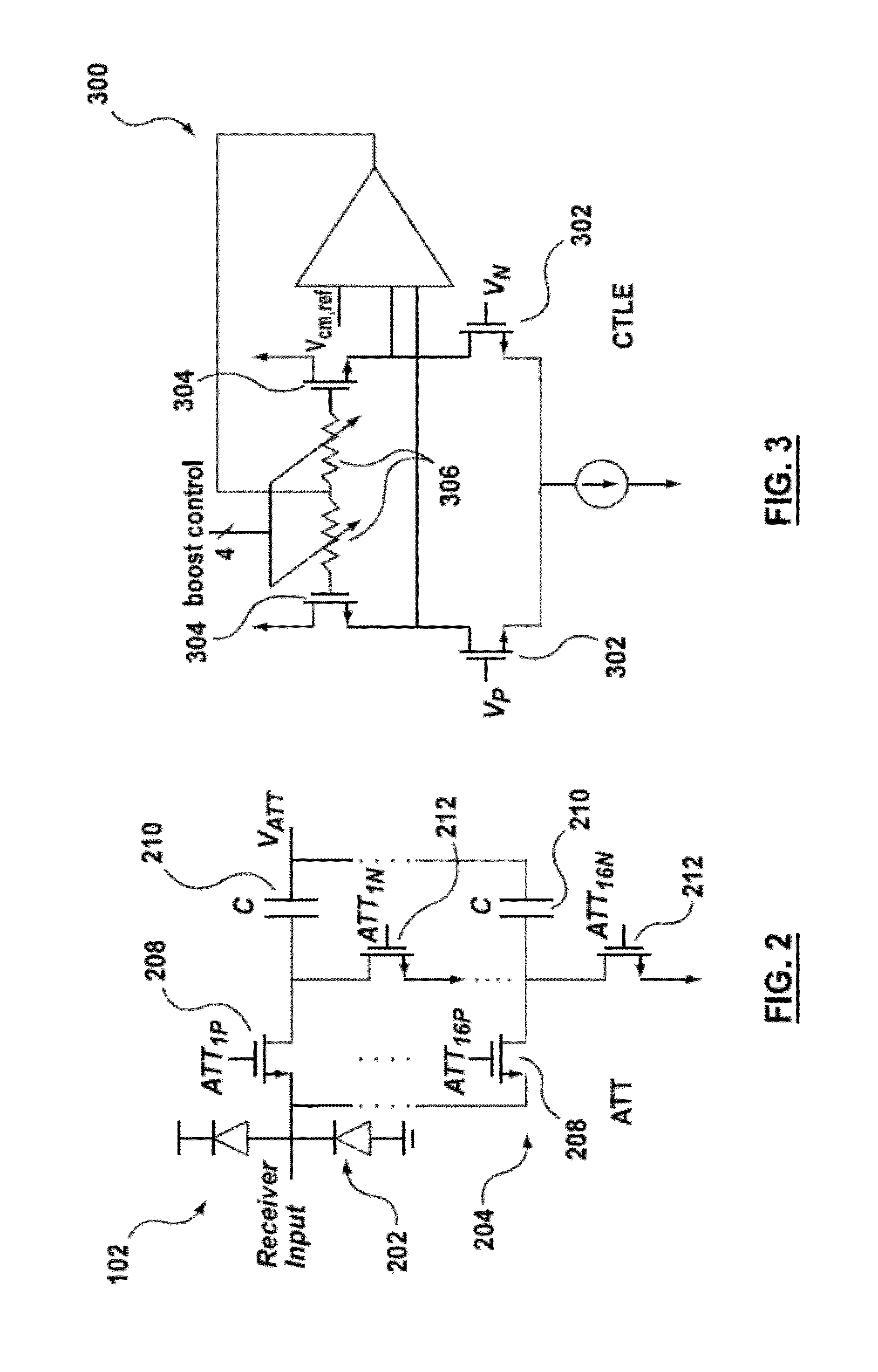

Decision feedback equalizer and transceiver

A decision feedback equalizer, transceiver, and method are provided, the equalizer having at least one comparator, the at least one comparator comprising a first stage, comprising a main branch having two track switches with a resistive load, an offset cancellation branch, a plurality of tap branches with transistor sizes smaller than the main branch, in which previous decisions of the equalizer are mixed with the tap weights using current-mode switching, and a cross coupled latch branch; and a second stage, comprising a comparator module for making decisions based on the outputs of the first stage and a clock input, and a plurality of flip-flops for storing the output of the comparator module.

Owner:RAMBUS INC

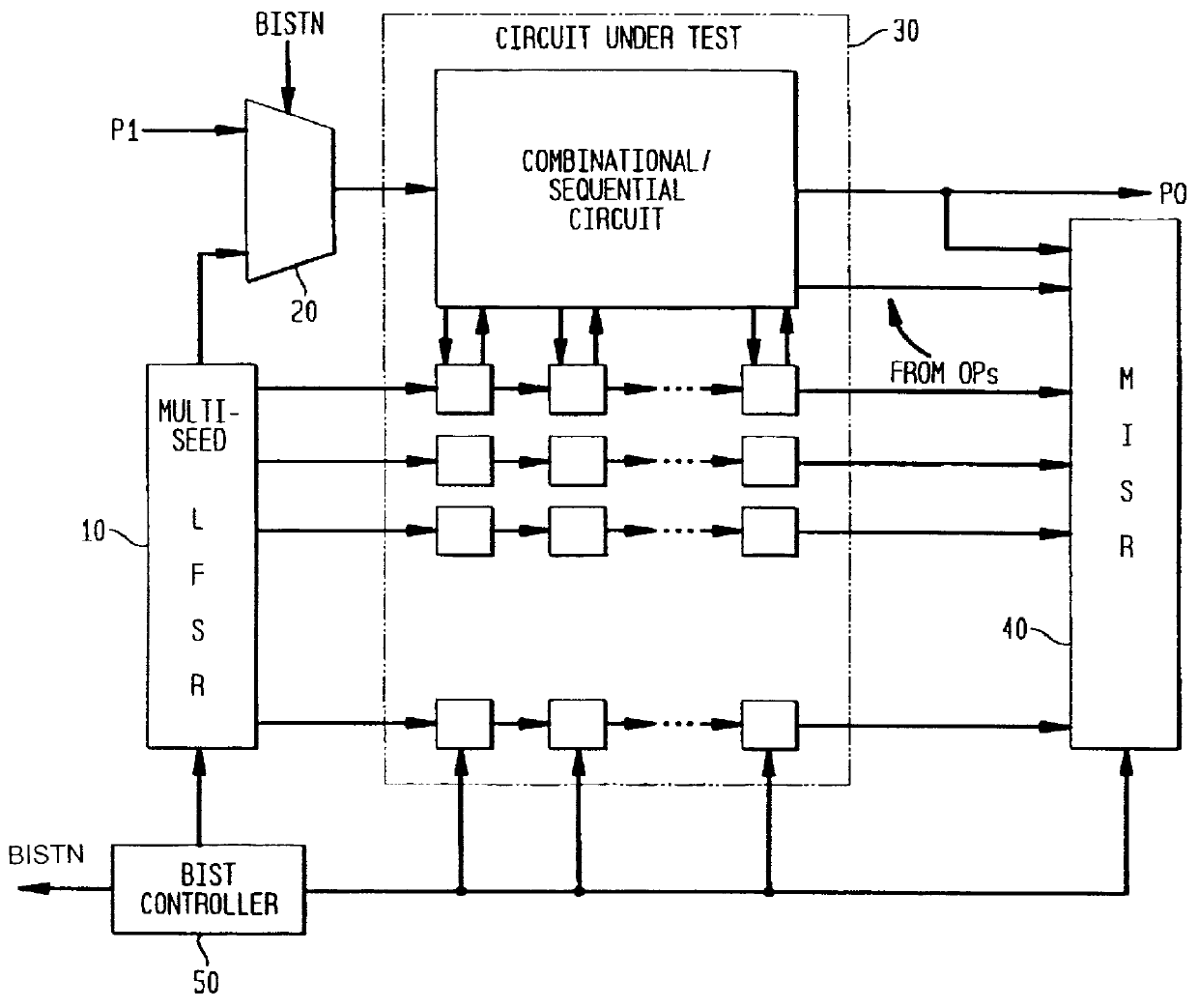

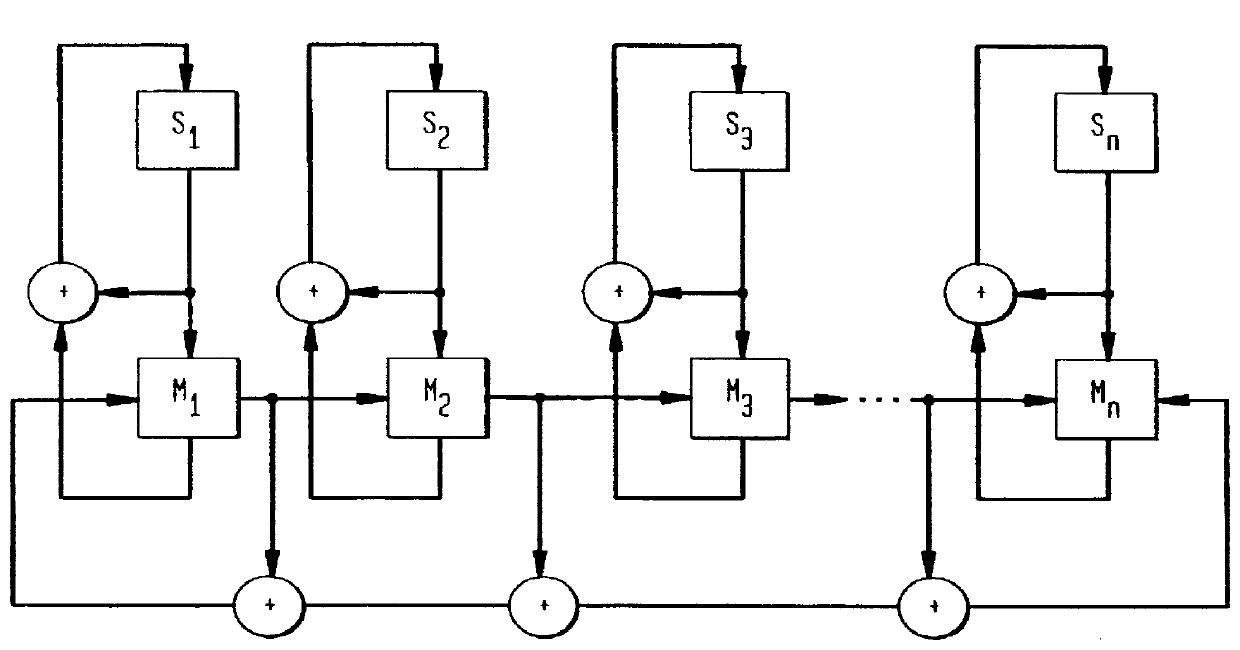

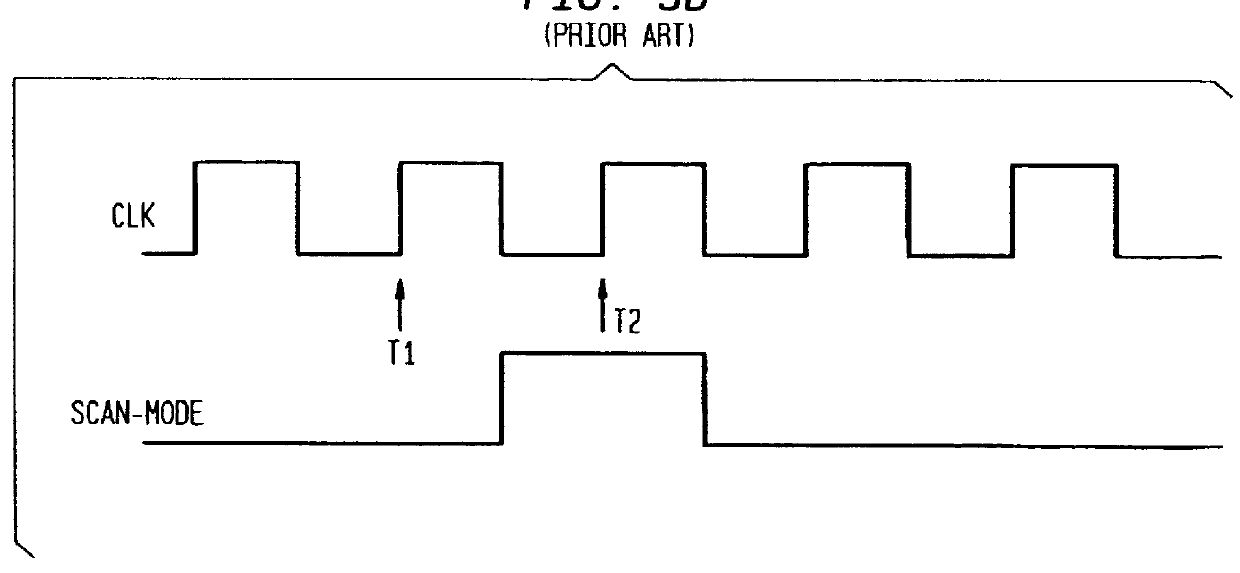

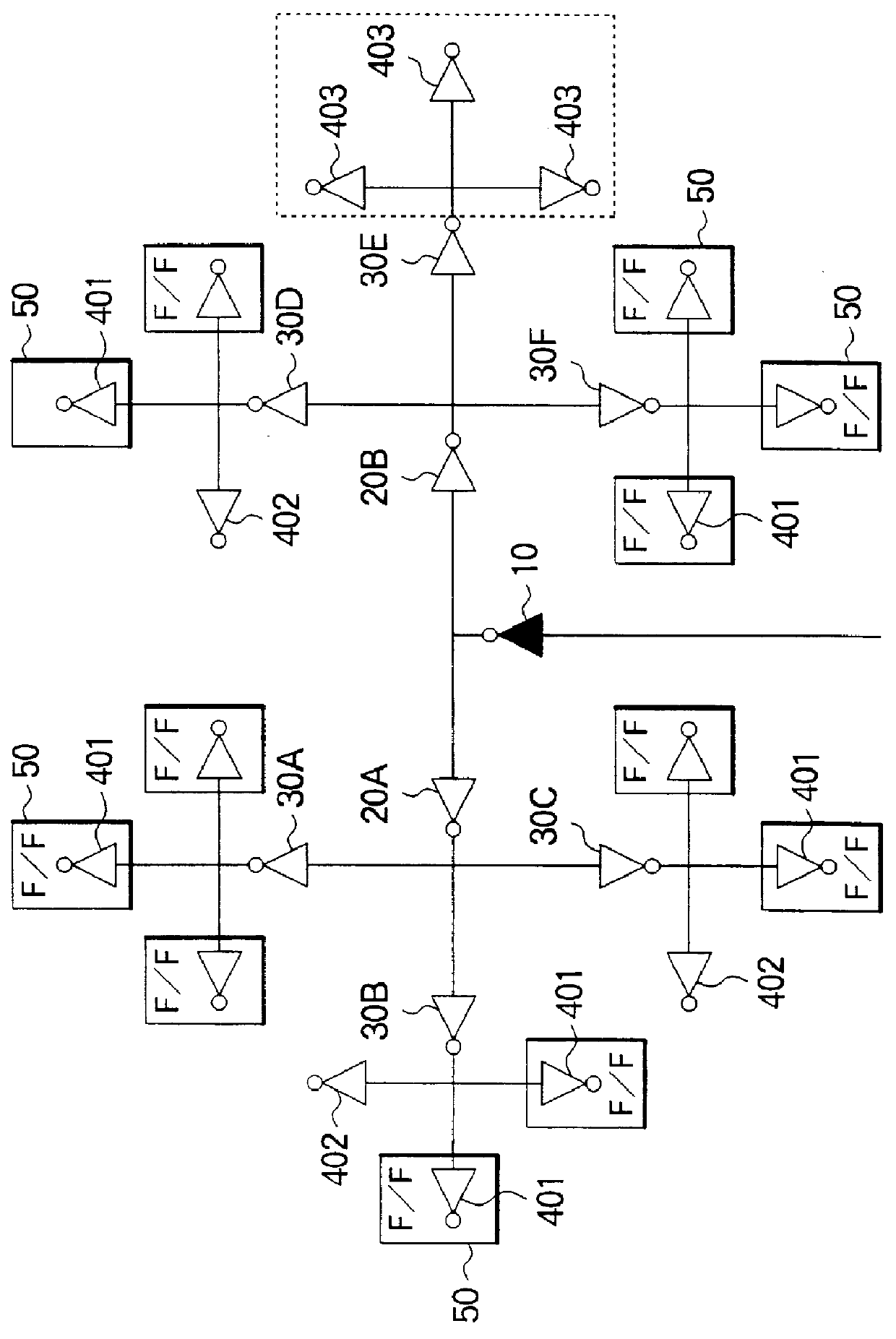

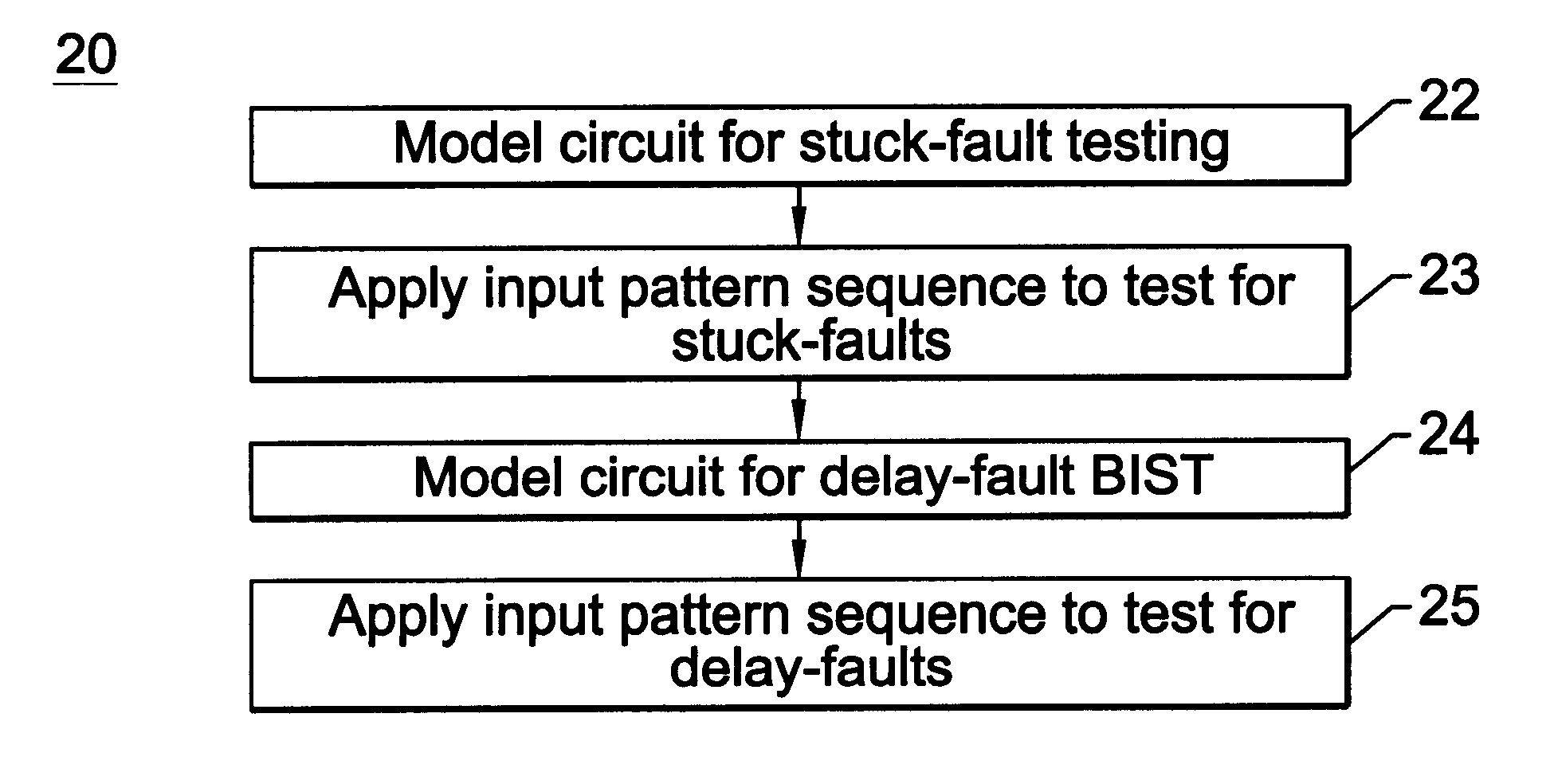

Bist architecture for detecting path-delay faults in a sequential circuit

A scan-based BIST architecture for detecting path-delay faults in a sequential circuit converted to a combinational circuit or a less complex sequential circuit including a combinational portion and a plurality of scan flip-flops. The BIST structure includes a test pattern generator for generating two test patterns and a controller for generating a clock signal and an extended scan mode signal which is held high for two clock cycles while the output response of the combinational portion to the first and second test vectors is latched into the scan flip-flops in order to detect a signal transition. The invention is further directed to a method for detection of path-delay faults using this scan-based BIST architecture. To improve the fault coverage for path-delay faults, observation points may be inserted at the inputs of selected scan flip-flops. A predetermined number of scan flip-flops having the highest activation frequency are selected as the observation points.

Owner:LUCENT TECH INC +1

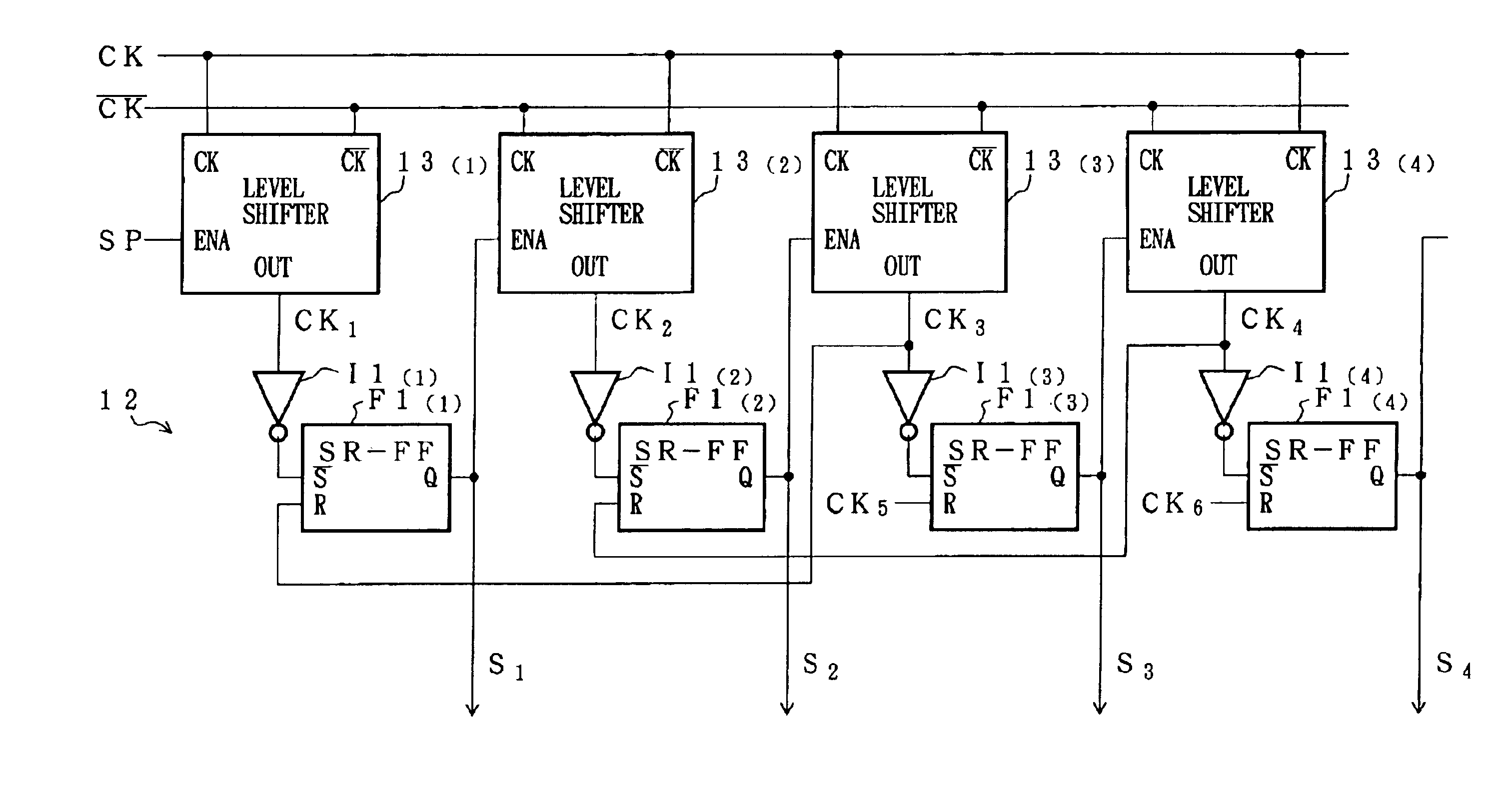

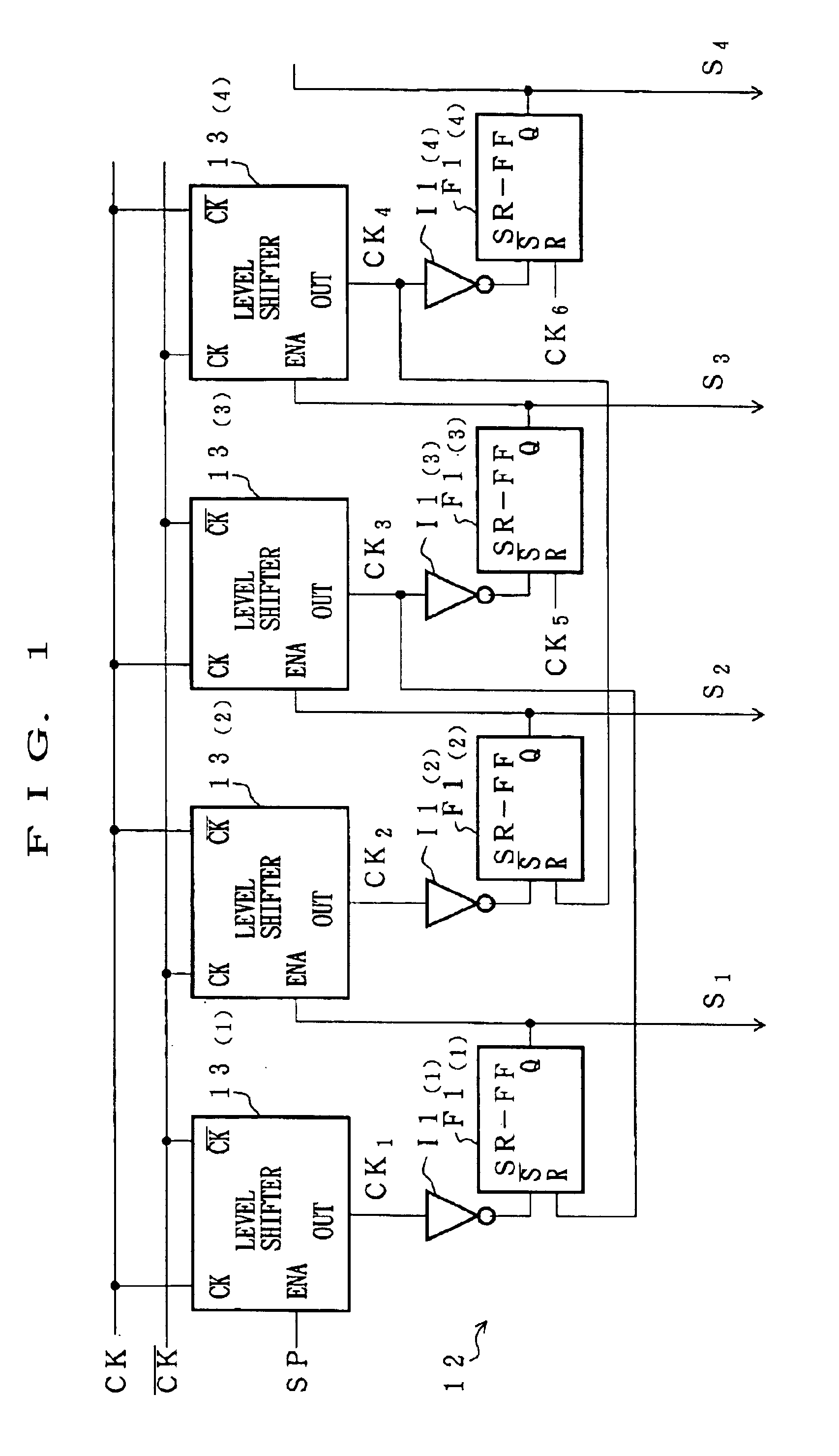

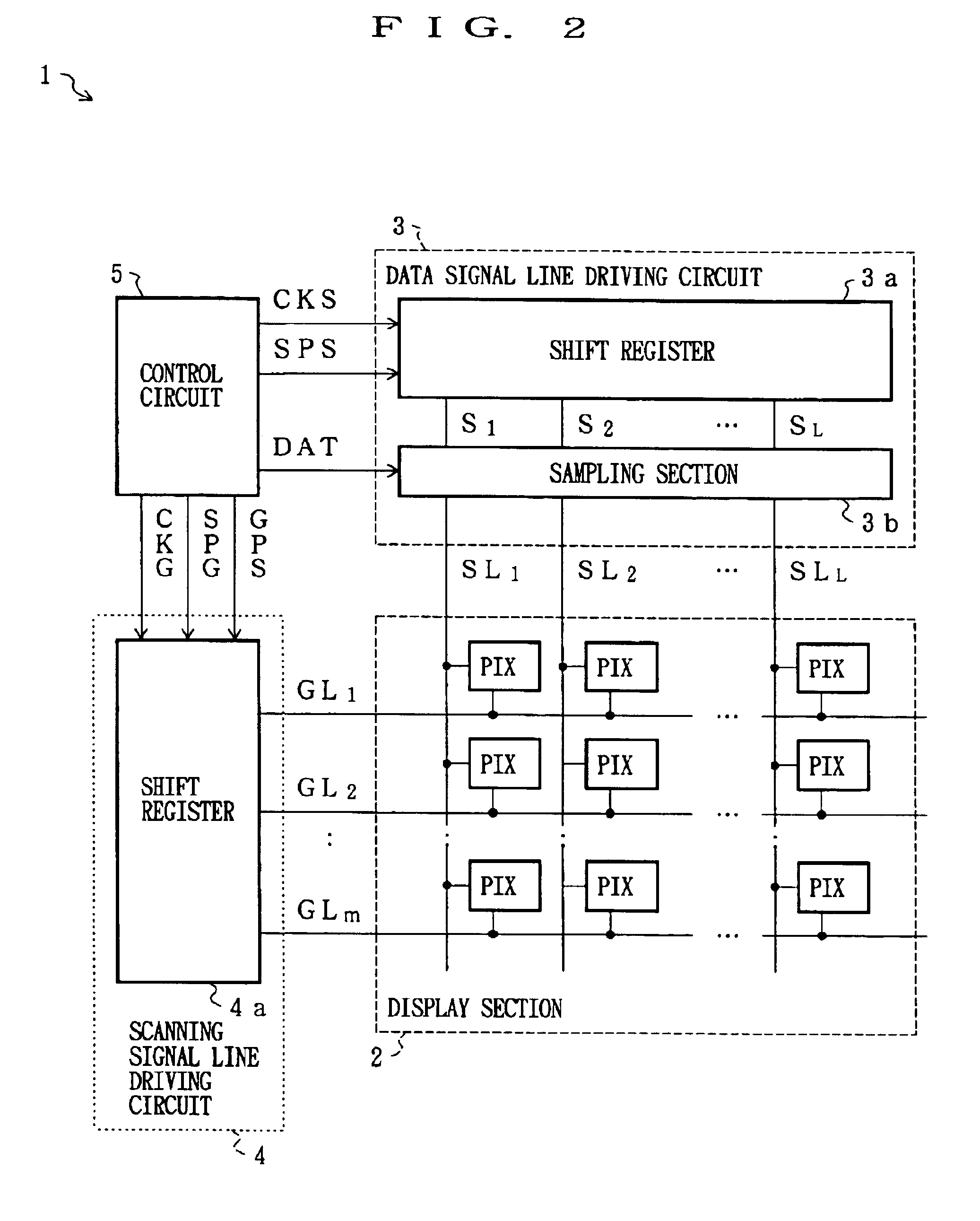

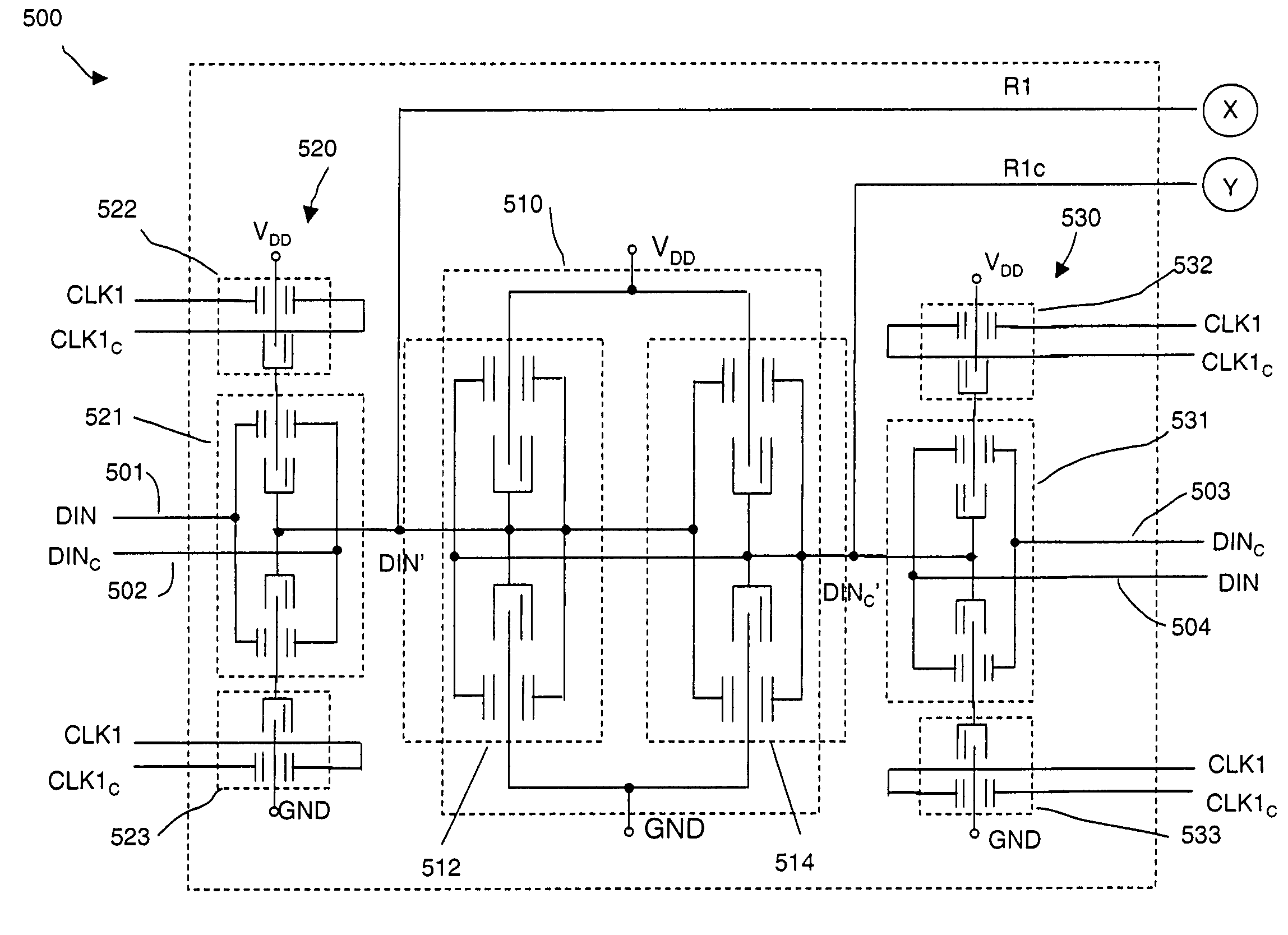

Shift register and image display apparatus using the same

InactiveUS6909417B2Reduce distanceReduce load capacityPulse generatorPulse automatic controlShift registerEngineering

A level shifter 13 is provided for each of SR flip flops F1 constituting a shift register 11. The level shifter 13 increases a voltage of a clock signal CK. This arrangement reduces a distance for transmitting a clock signal whose voltage has been increased, as compared with a construction in which a voltage of a clock signal is increased by a single level shifter and the signal is transmitted to each of the flip flops; consequently, a load capacity of the level shifter can be smaller. Furthermore, each of the level shifters is operated during a pulse output of the previous level shifter 13, and the operation is suspended at the end of the pulse output. Thus, the level shifters 13 can operate only when it is necessary to apply a clock signal CK to the corresponding SR flip flop F1. As a result, even when an amplitude of a clock signal is small, it is possible to reduce power consumption of the shift resister under normal operation.

Owner:SHARP KK

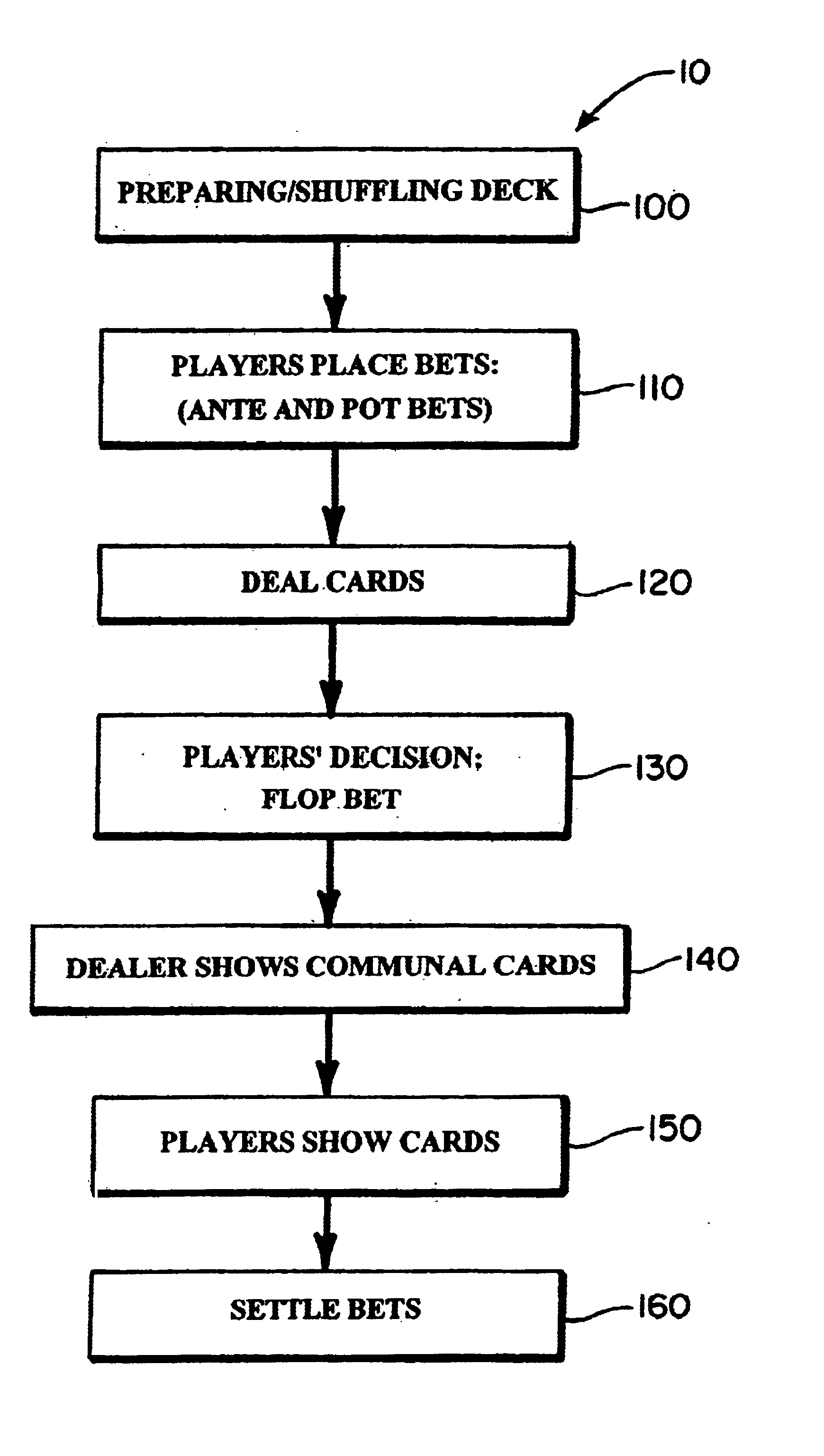

Method of playing poker

InactiveUS20060135240A1Preserves excitementPreserves funBoard gamesCard gamesThe InternetComputer science

The invention comprises multiple methods for playing a game of poker over a communication network such as the internet which are simple and easy to learn. In a first method, all participants place bets of equal value into a pot with no additional opportunities to raise or place additional bets. In a second method, players are provided with an option to place bets on various rules of winning, wherein bets are paid depending on the outcome of the three-card flop. In a third method, players are presented with timed intervals during which players can place a fixed bet into the pot to be eligible to stay in the hand. Significantly, all players decide whether to place additional bets simultaneously or during the same time interval rather than sequentially as is done in traditional versions of poker.

Owner:BARSHACK LEONARD

Method of playing community card games

InactiveUS20060119044A1Easy to learnEasy to deal withBoard gamesCard gamesTexas hold 'emComputer science

The embodiments of the present invention provide a method of playing community card games, in table games format and or electronic, video, slot machines for casinos. According to an embodiment of the present invention, one or more players place an initial wager and a dealer / electronic, video, and or slot machine deals at least one card(s) to the players and at least one card(s) to the dealer. The players and dealer then inspect their at least one card(s) and decide to keep them or draw at least one new card to hopefully form a better at least one card(s). If a decision of a draw is made for an at least one new card, the amount of cards that are drawn, you must have that equal amount(s) of card(s) discarded. After the draw option is complete, at least two sets of community card(s) are dealt. Each set of community card(s) has at least one card. The sets of community card(s) will be named “A” SET, “B” SET, and “C” SET etc. Players have to bet on at least one of the set(s) of community card(s) of either A, B, or C etc. Each set of community card(s) will be used in conjunction with each of the players' and or dealer's at least one card, to form the best possible predetermined poker hand, for each. The players' wagers are then resolved by evaluating the players' hands and the dealer's hand in comparison of the best hand of a predetermined fashion, and or the resolution of wagers played against a predetermined pay scale. Various modifications to the first embodiment of the present invention are set forth herein. This method of playing a poker style game, may be used in Texas Hold'Em, Omaha, and 7 Card Stud, 5 Card Stud, Omaha Eight or Better (High-Lo Split), Razz, or any poker game using community cards. The number of cards in each set may change and the number of sets for each game may change. The player may choose to bet one set of cards (A) and choose a specific set (B) for the dealer to have to use to complete the dealer hand. These features are new, novel and non-obvious, instead of the old way of only one flop, turn and river, and also the new feature of replacing the hole cards.

Owner:KEKEMPANOS LARRY E +2

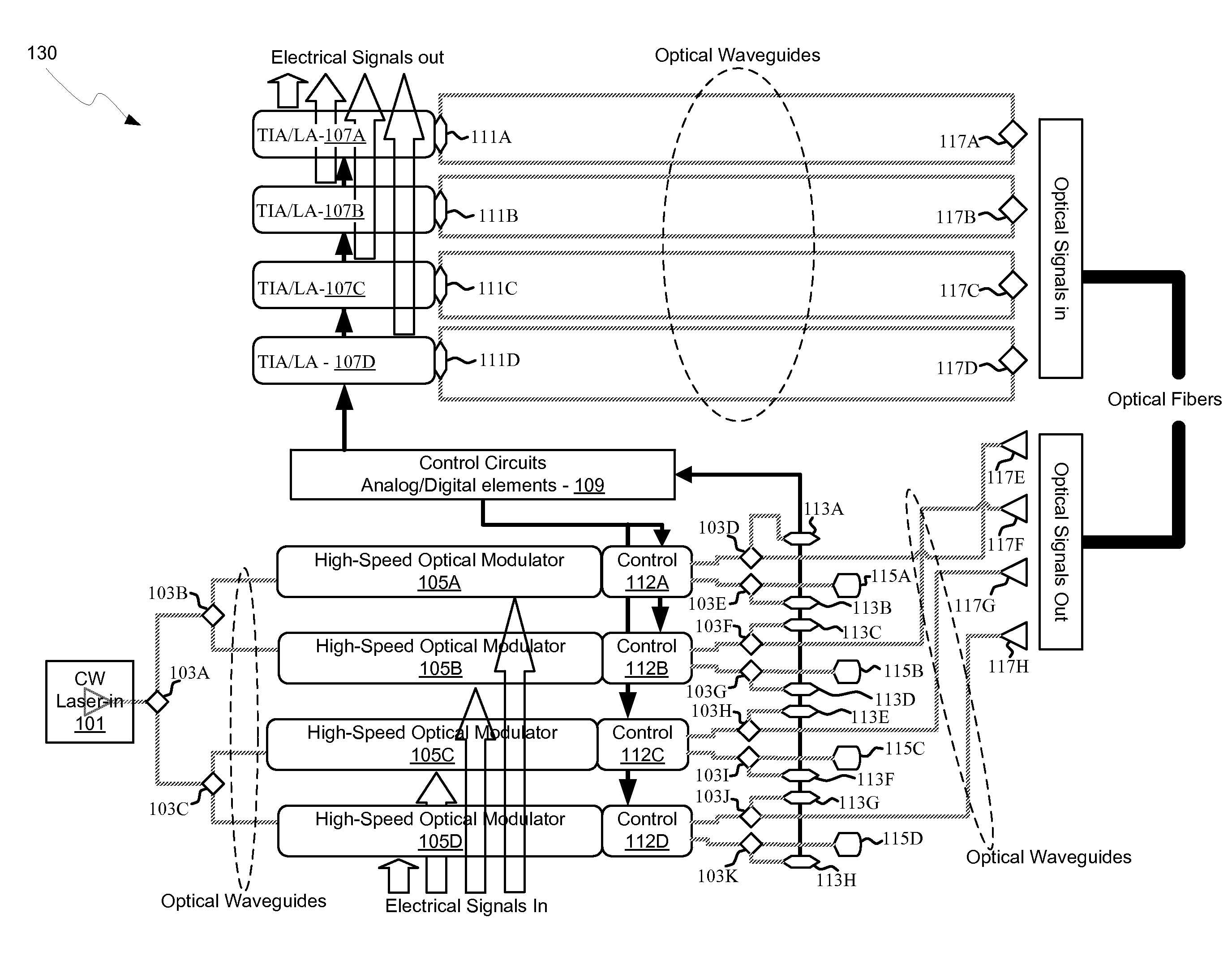

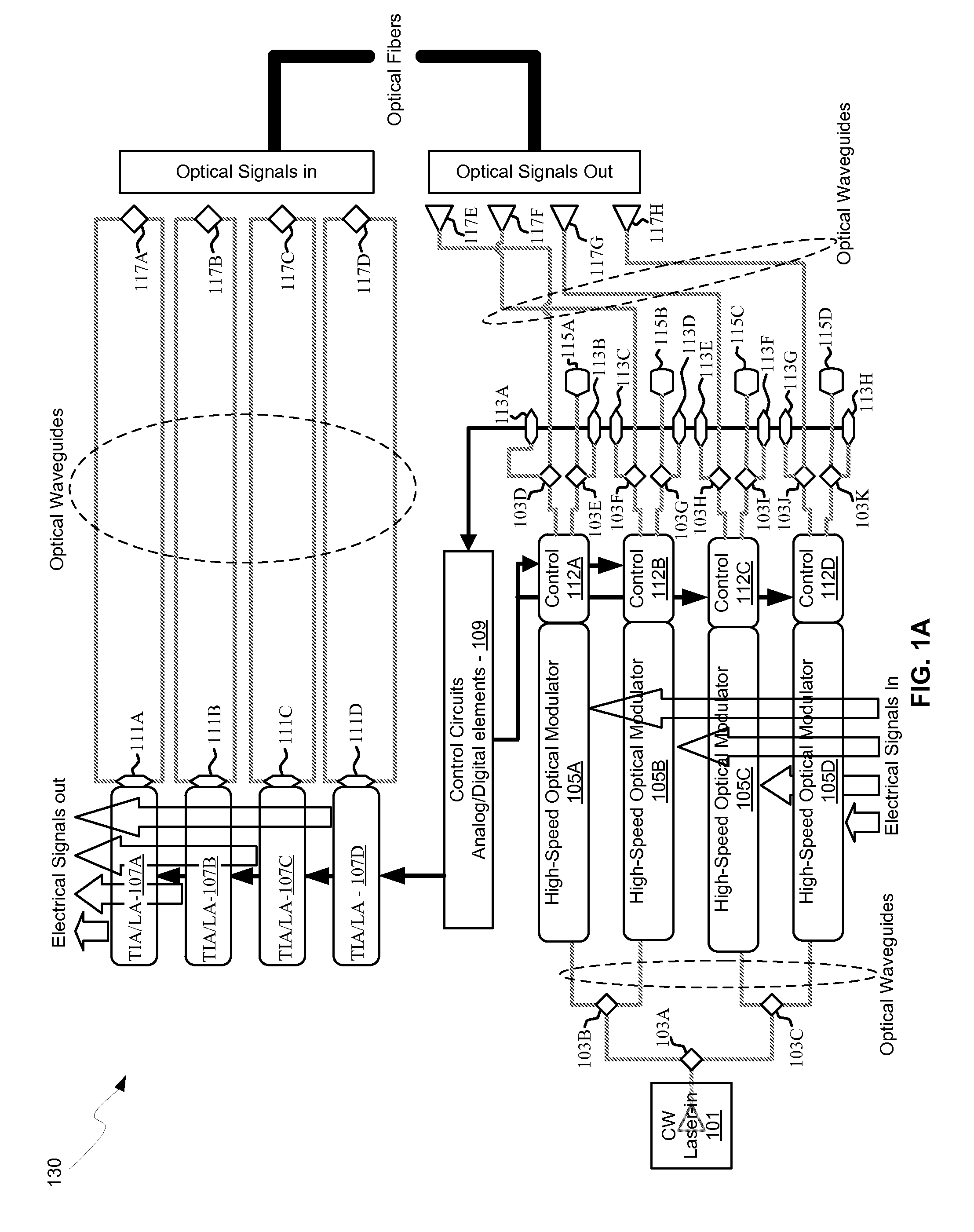

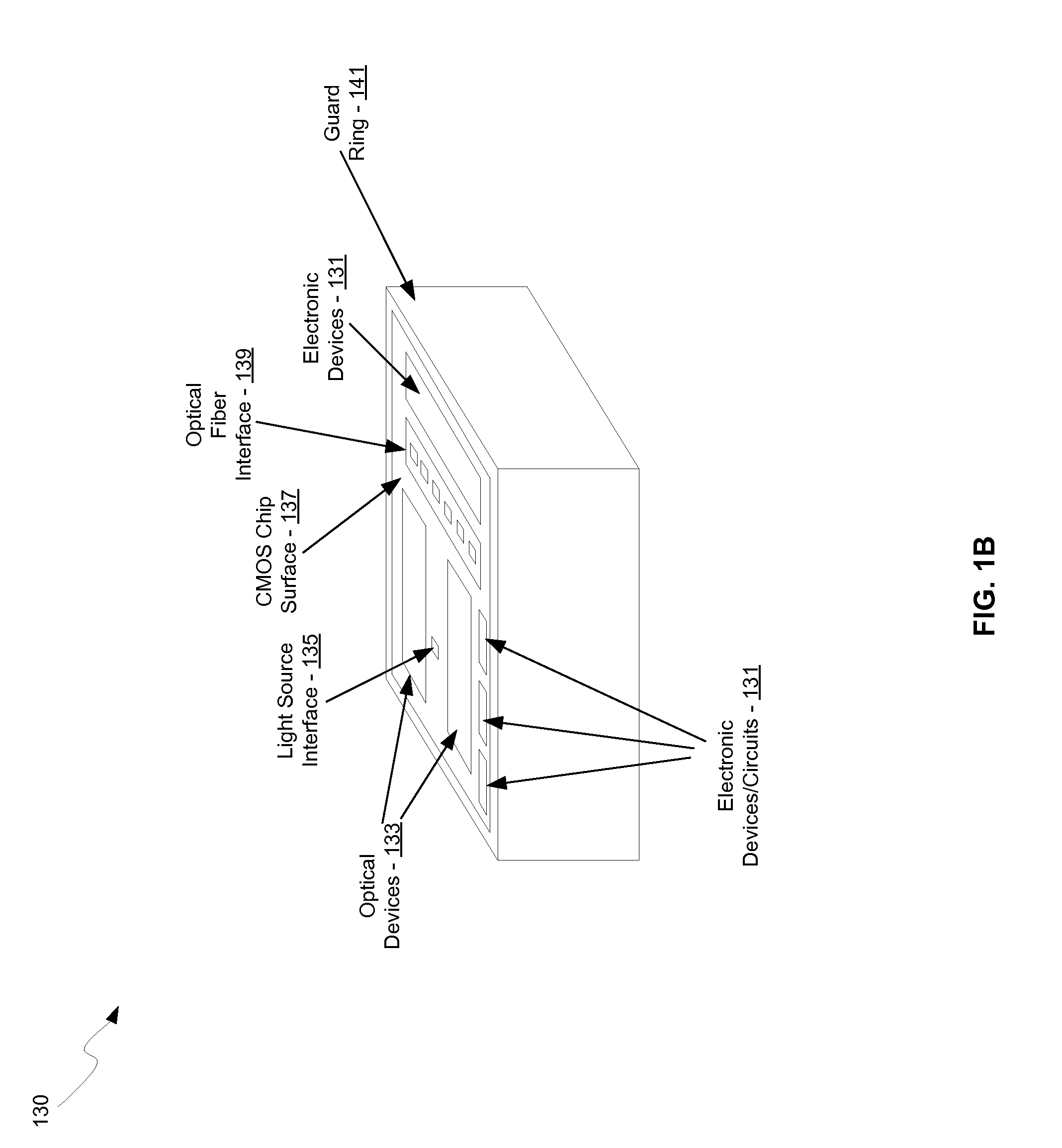

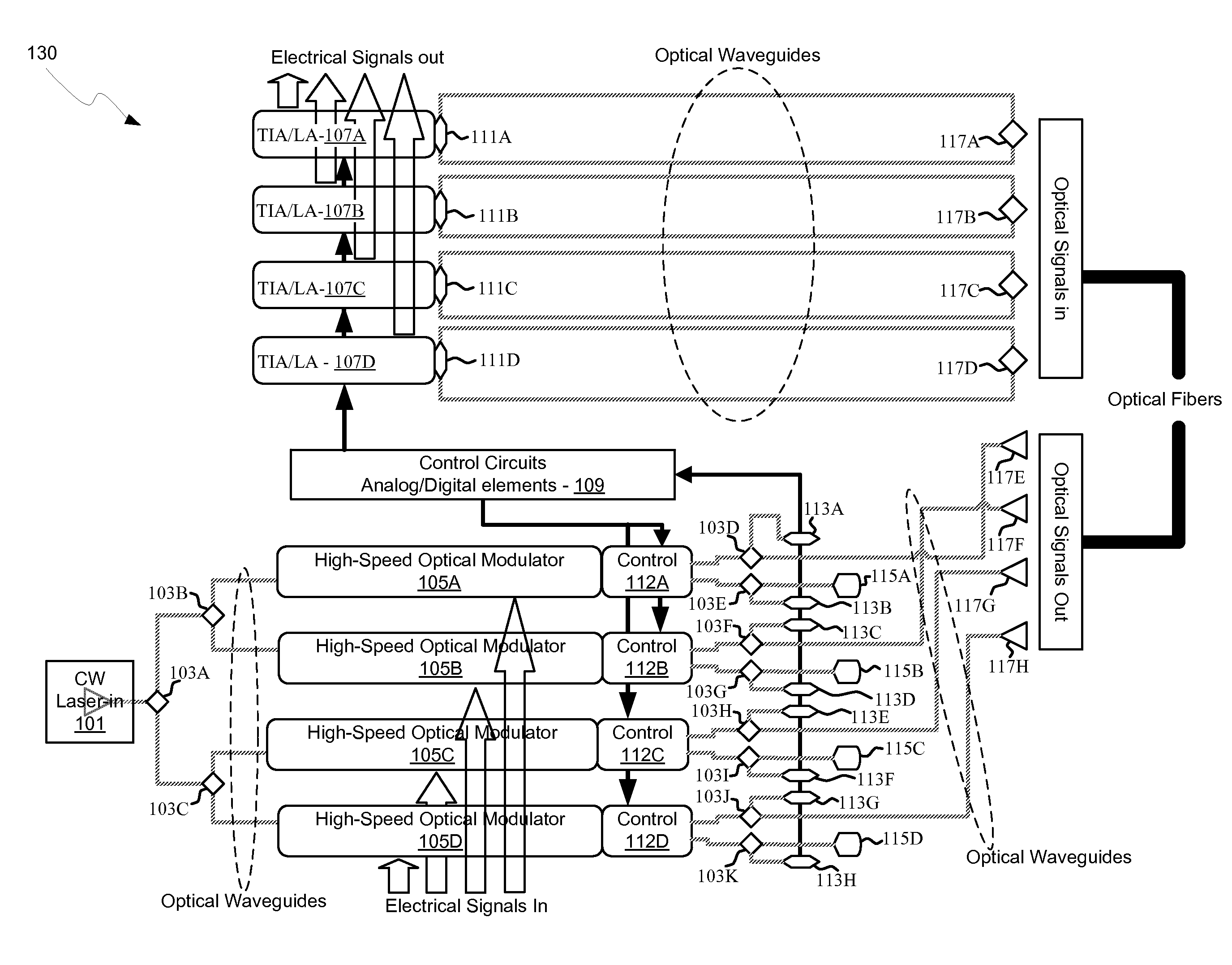

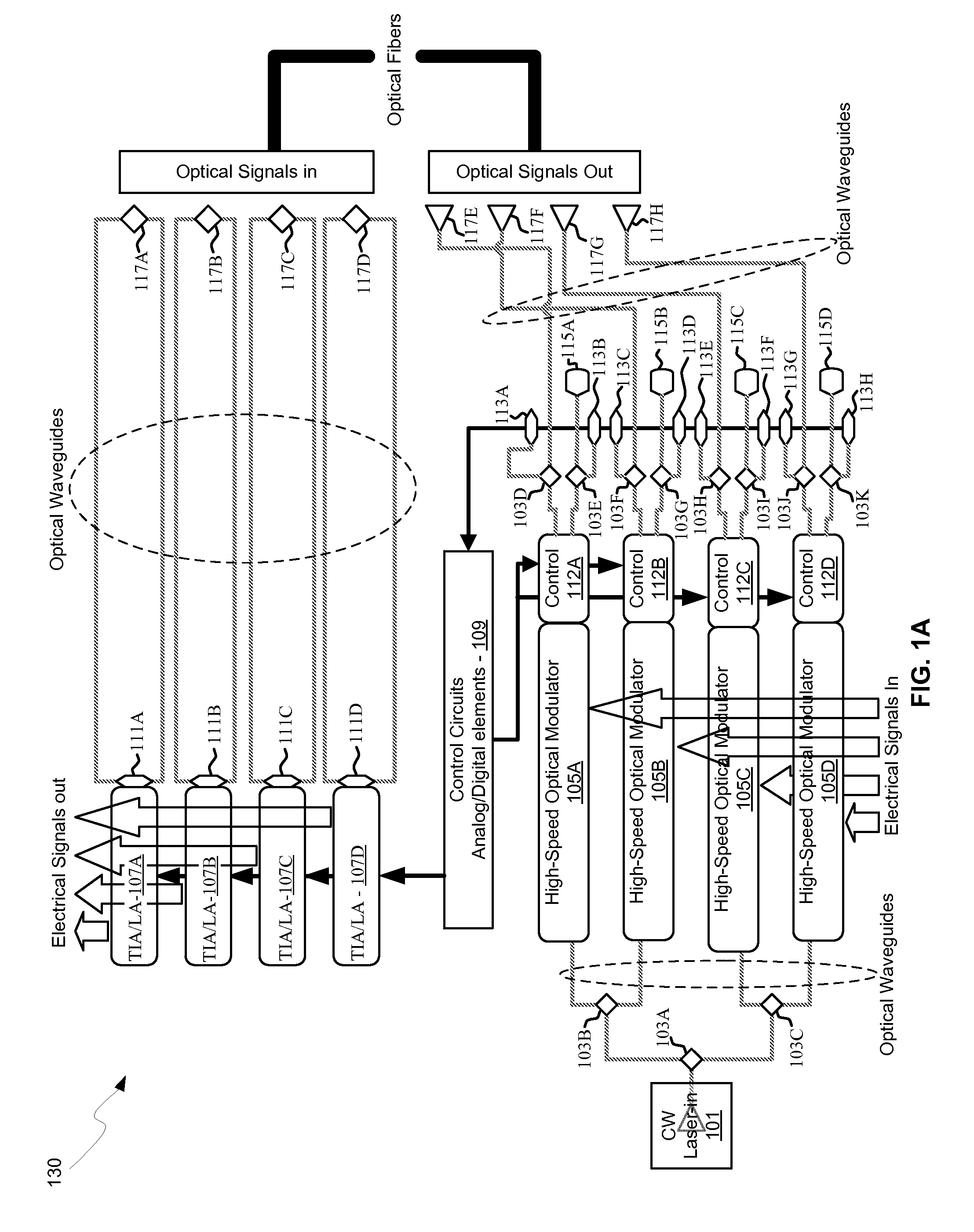

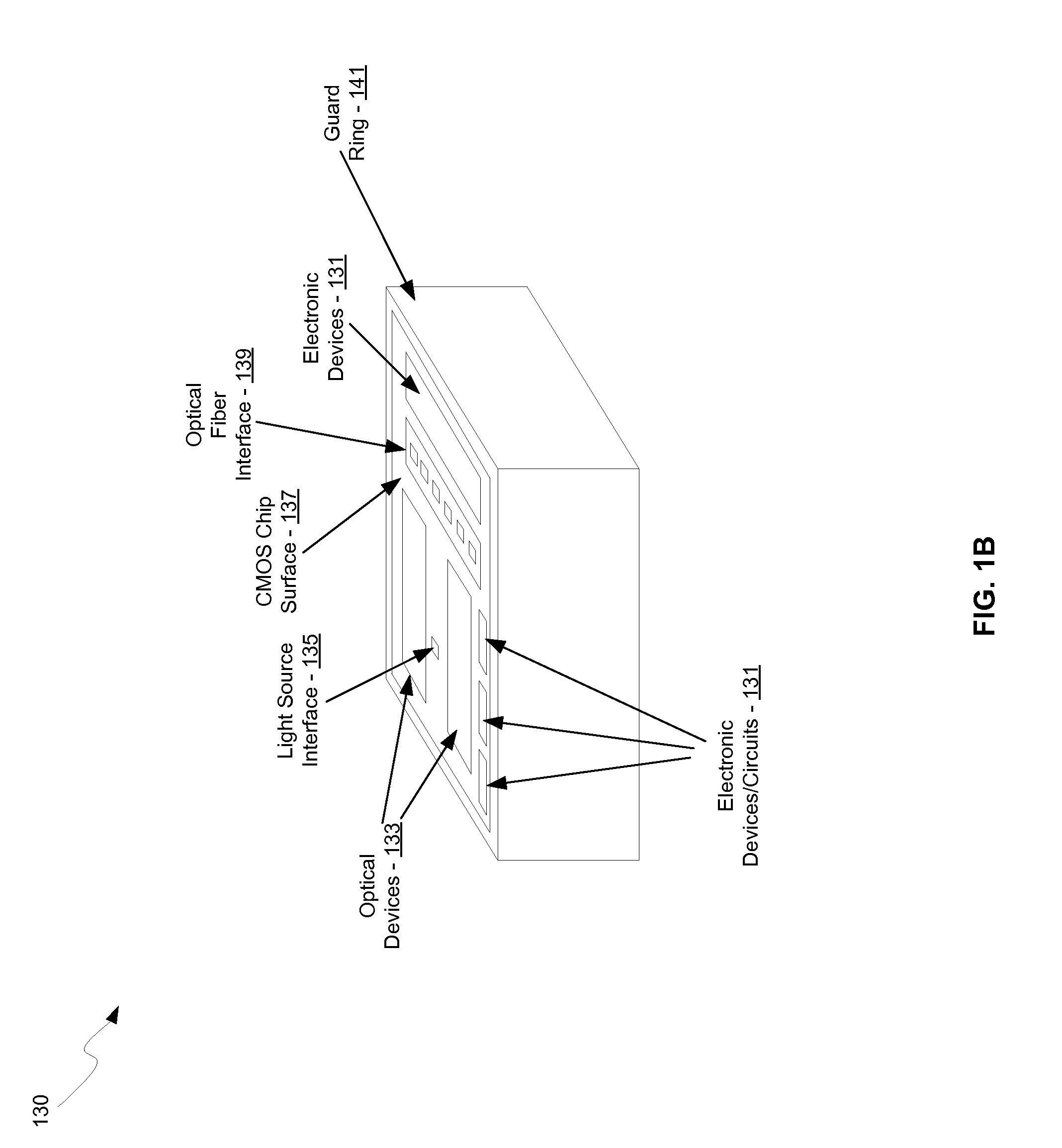

Method and circuit for encoding multi-level pulse amplitude modulated signals using integrated optoelectronic devices

ActiveUS20100060972A1Electromagnetic transmissionNon-linear opticsMach–Zehnder interferometerEngineering

Methods and systems for encoding multi-level pulse amplitude modulated signals using integrated optoelectronics are disclosed and may include generating a multi-level, amplitude-modulated optical signal utilizing an optical modulator driven by two or more electrical input signals. The optical modulator may include optical modulator elements coupled in series and configured into groups. The number of optical modular elements and groups may configure the number of levels in the multi-level amplitude modulated optical signal. Unit drivers may be coupled to each of the groups. The electrical input signals may be synchronized before communicating them to the unit drivers utilizing flip-flops. Phase addition may be synchronized utilizing one or more electrical delay lines. The optical modulator may be integrated on a single substrate, which may include one of: silicon, gallium arsenide, germanium, indium gallium arsenide, polymers, or indium phosphide. The optical modulator may include a Mach-Zehnder interferometer or one or more ring modulators.

Owner:CISCO TECH INC

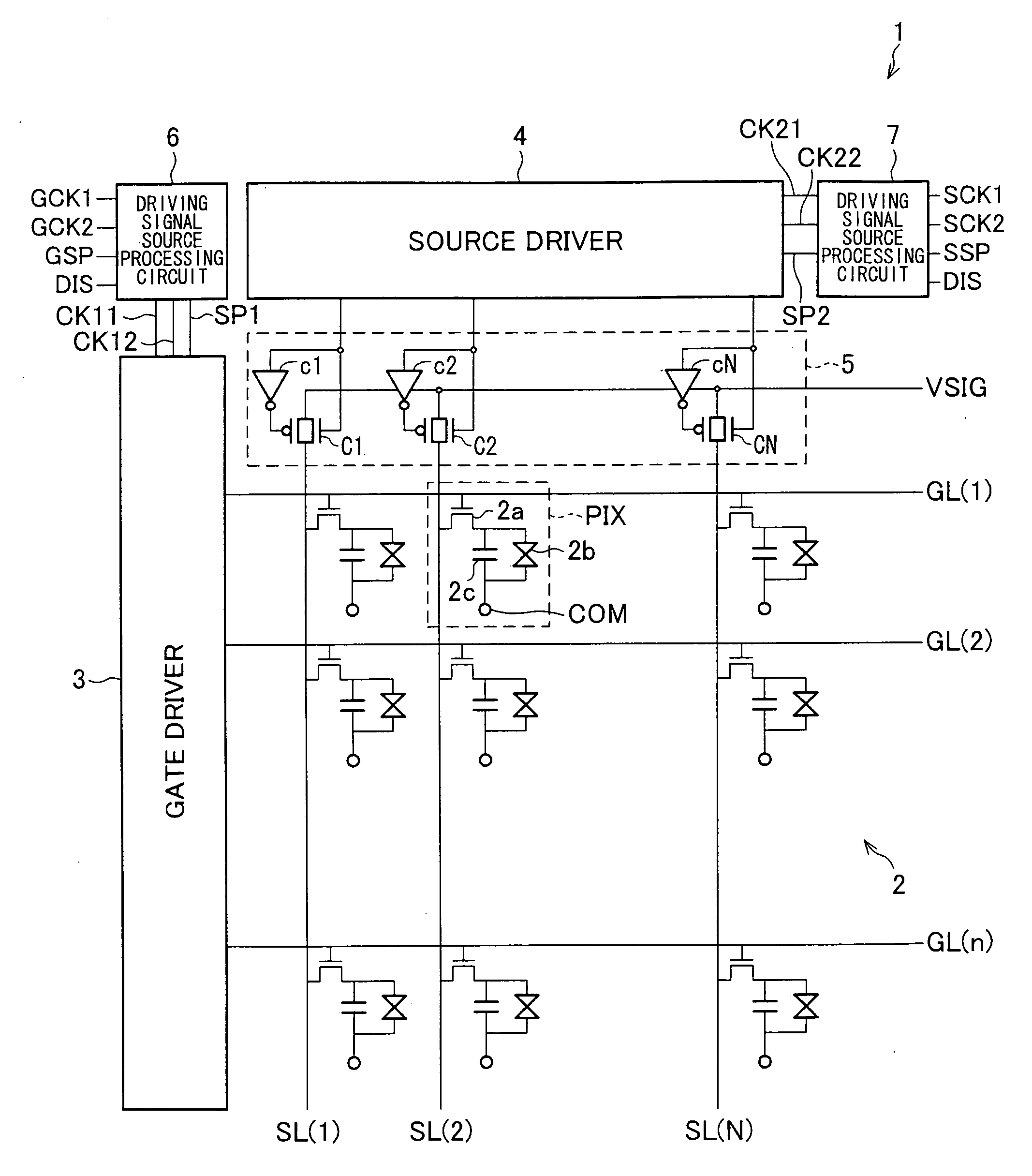

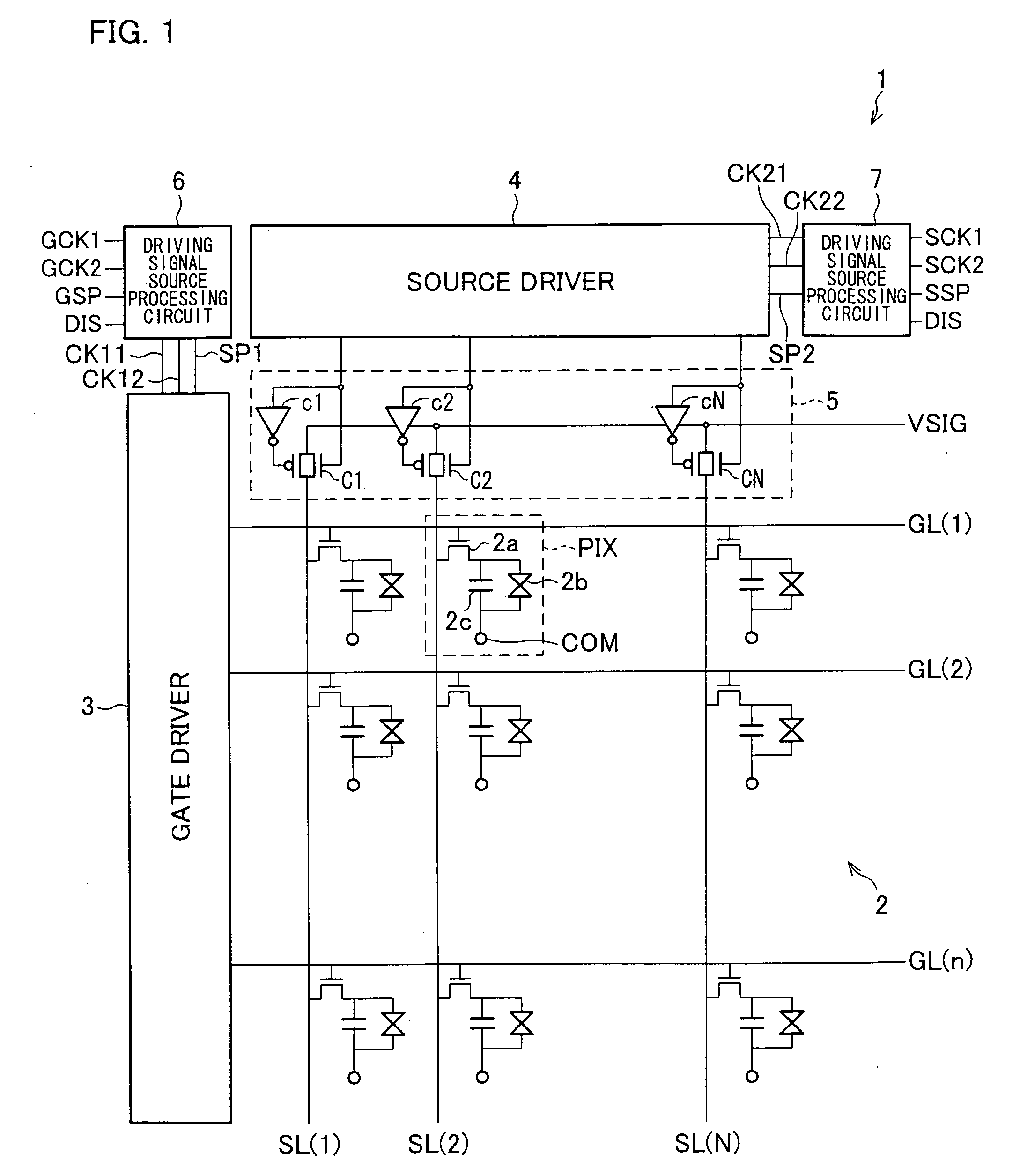

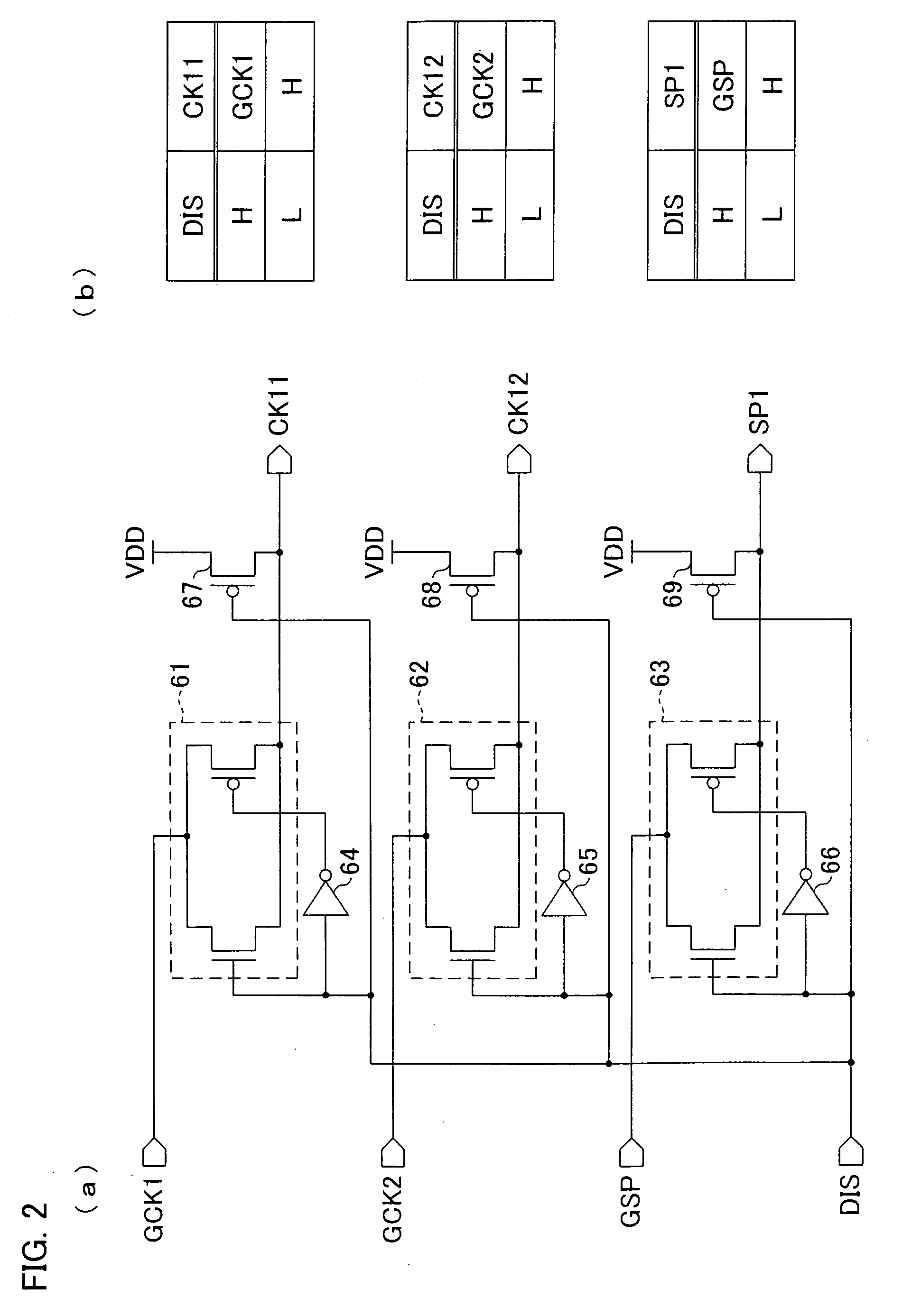

Display Apparatus and Method For Driving The Same

ActiveUS20090121998A1Prevent degradationReduce displayStatic indicating devicesDigital storageShift registerLiquid-crystal display

A liquid crystal display apparatus (1) wherein the shift registers of a source driver (4) are configured by use of asynchronous RS flip-flops in which an active input to a set input terminal has a higher priority than an active input to a reset terminal. In a second mode of operation, first and second clock signals and a start pulse are fixed at high levels, thereby performing discharges from all the pixels (PIX) of a liquid crystal panel (2).

Owner:SHARP KK

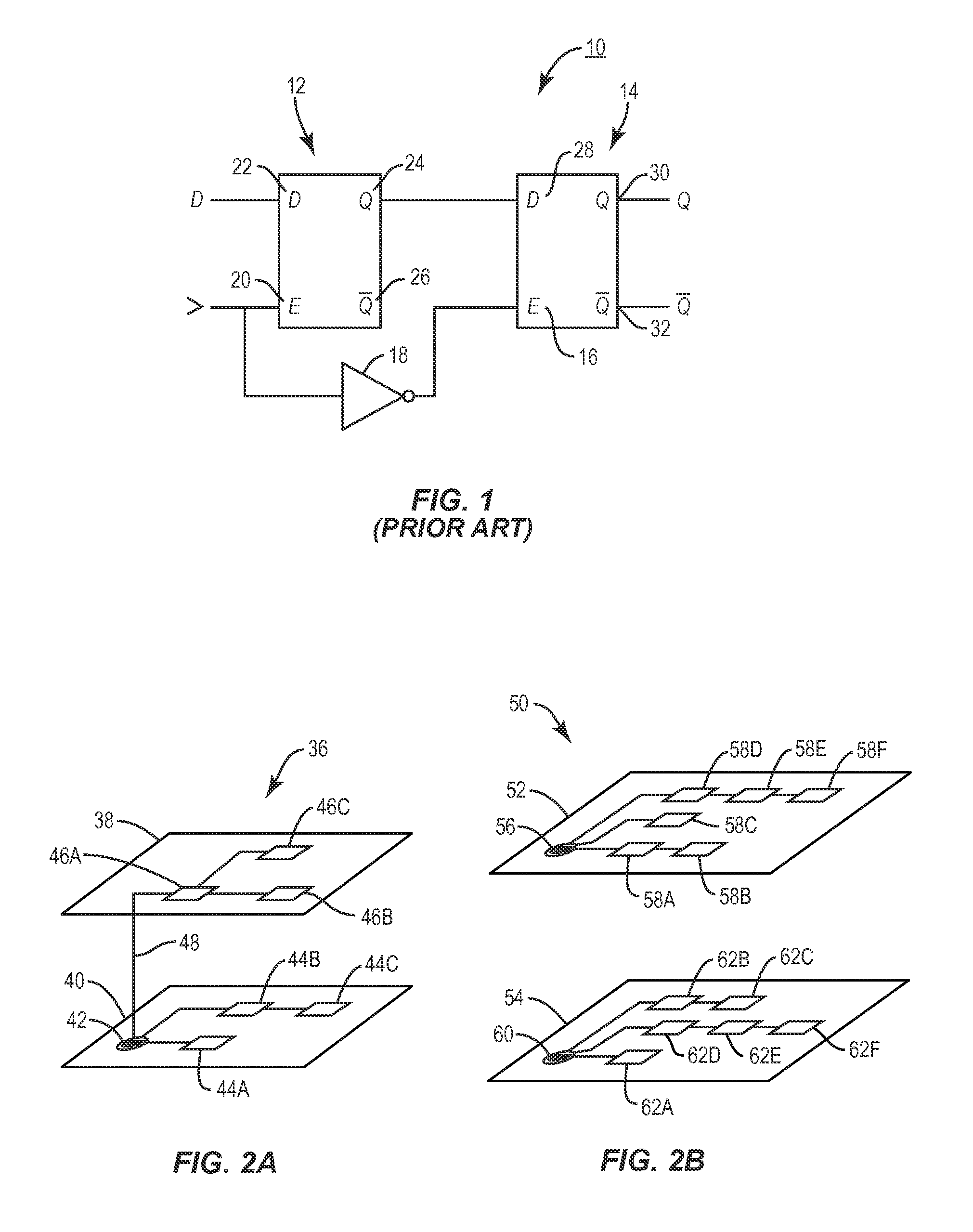

Storage elements using nanotube switching elements

Data storage circuits and components of such circuits constructed using nanotube switching elements. The storage circuits may be stand-alone devices or cells incorporated into other devices or circuits. The data storage circuits include or can be used in latches, master-slave flip-flops, digital logic circuits, memory devices and other circuits. In one aspect of the invention, a master-slave flip-flop is constructed using one or more nanotube switching element-based storage devices. The master storage element or the slave storage element or both may be constructed using nanotube switching elements, for example, using two nanotube switching element-based inverters. The storage elements may be volatile or non-volatile. An equilibration device is provided for protecting the stored data from fluctuations on the inputs. Input buffers and output buffers for data storage circuits of the invention may also be constructed using nanotube switching elements.

Owner:NANTERO

Method, system and program product for monitoring an online card game to provide a summary view and/or real-time notifications

A method, system and program product for monitoring an online card game, such as poker. A table view is displayed at a client that summarizes recently played hands, raises, and table conditions, and also includes scaled player classifications (tight or loose; passive or aggressive), counts of notifications of plays of interest, win / loss history, and links to player statistics and player performance graphs. Scaled player classifications are automatically configured. Notification details are displayed via links on the table view. Summaries of known hands based on predefined conditions are displayed. Summary displays of pre-flop hands and hands on flop, turn or river are also provided.

Owner:PARISIEN PAUL

Microfabricated fluidic circuit elements and applications

InactiveUS6953058B2Macroscopic control lines exiting the chip are minimized or eliminatedGeometric CADOperating means/releasing devices for valvesFluidicsNOR gate

The present invention provides microfabricated fluidic systems and methods. Microfabricated fluidic devices of the present invention include switches that can be opened and closed to allow or block the flow of fluid through a channel in response to the pressure level in a gate of the switch. The microfabricated fluidic switches may be coupled together to perform logic functions and Boolean algebra, such as inverters, AND gates, NAND, gates, NOR gates, and OR gates. The logic gates may be coupled together to form flip-flops that latch signals. The present invention also includes microfabricated fluidic pressure multipliers that increase the pressure in a second chamber relative to a first chamber. Microfabricated fluidic devices of the present invention also include pressure sources. A pressure source of the present includes a pump coupled to a reservoir through unidirectional valves. The pressure source may be high pressure source or a low pressure source. Microfabricated fluidic devices of the present invention may also include devices that perform analog functions such as switching regulator.

Owner:FLUIDIGM CORP

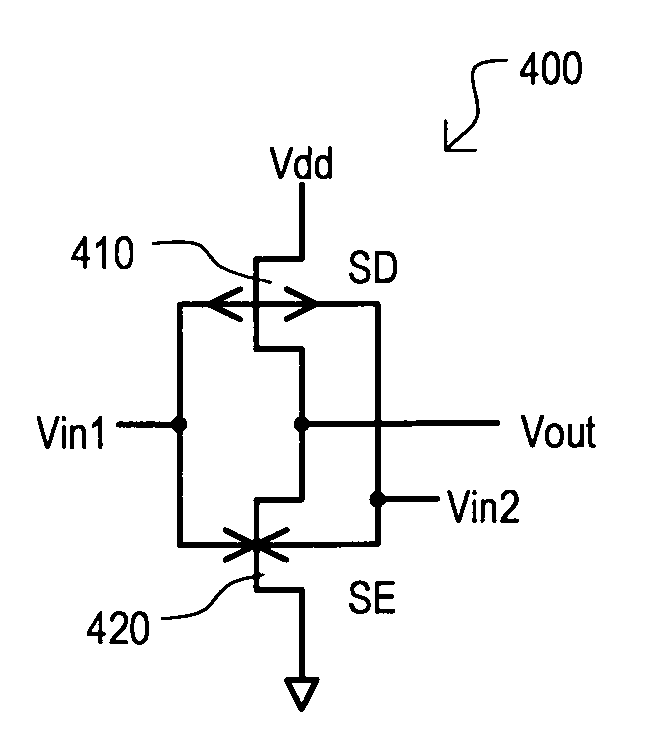

Circuit configurations having four terminal JFET devices

InactiveUS20070262793A1Logic circuits characterised by logic functionSolid-state devicesPhase detectorMultiplexer

Circuits using four terminal junction field effect transistors (JFETs) are disclosed. Such circuits can include various static and dynamic logic circuits, flip-flops, multiplexer, tri-state driver, phase detector, logic having variable speeds of operation, and / or analog circuit with such four terminal JFETs operating in a linear or nonlinear mode.

Owner:MIE FUJITSU SEMICON

Casino flop poker

A casino game comprising one or more decks of standard playing cards and a layout which designates a first area for the placing of community cards and a second area composed of a plurality of betting areas. The object of the game being to make a good poker hand of 5 cards being composed of players' individual cards in conjunction with community cards. A further object of the game is to win the “Pot” bets by holding the highest poker hand. The preferred game apparatus includes a single deck of standard playing cards and a layout that provides betting areas.

Owner:SCHLUMBRECHT T CHRISTIAN A

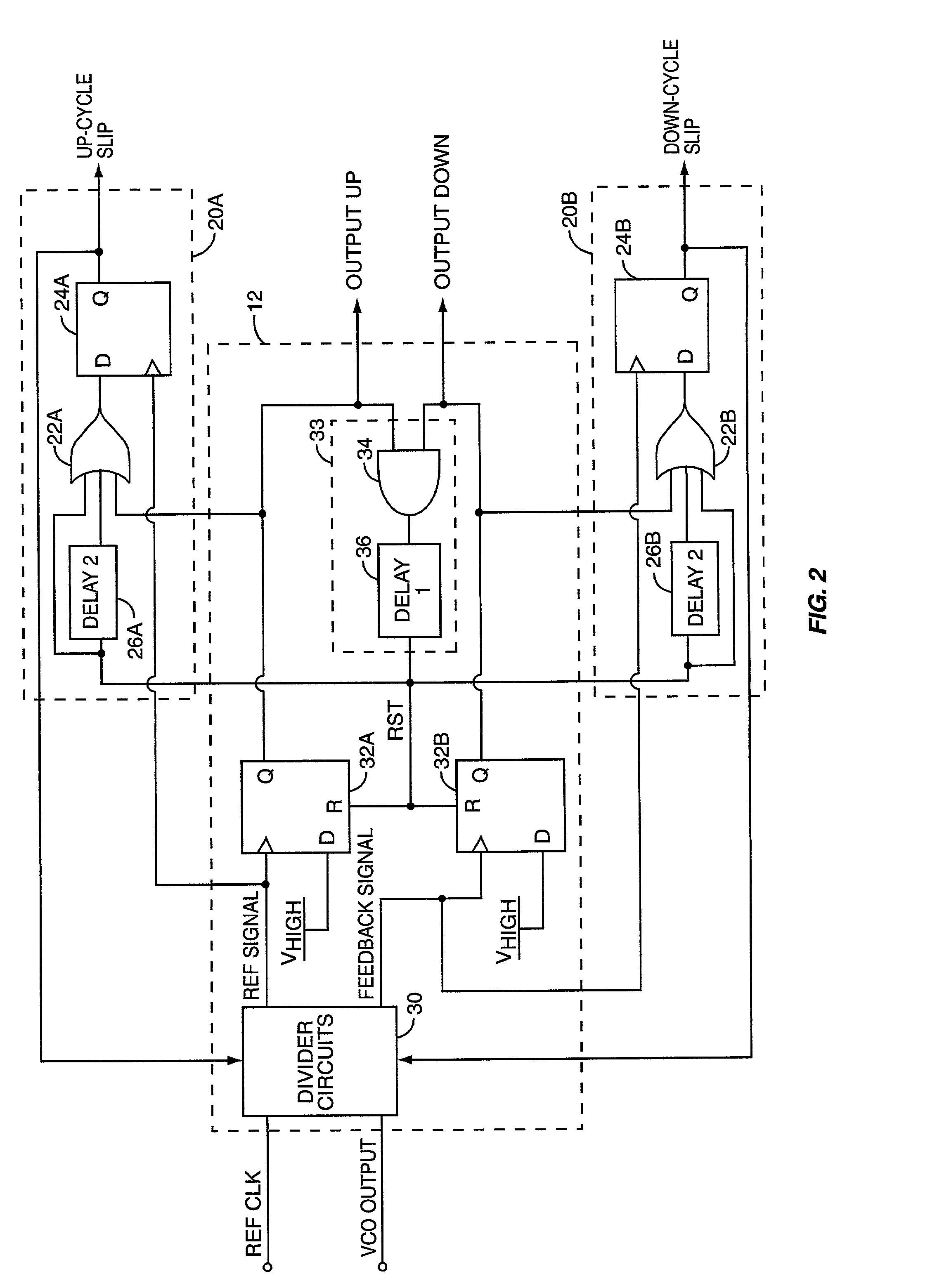

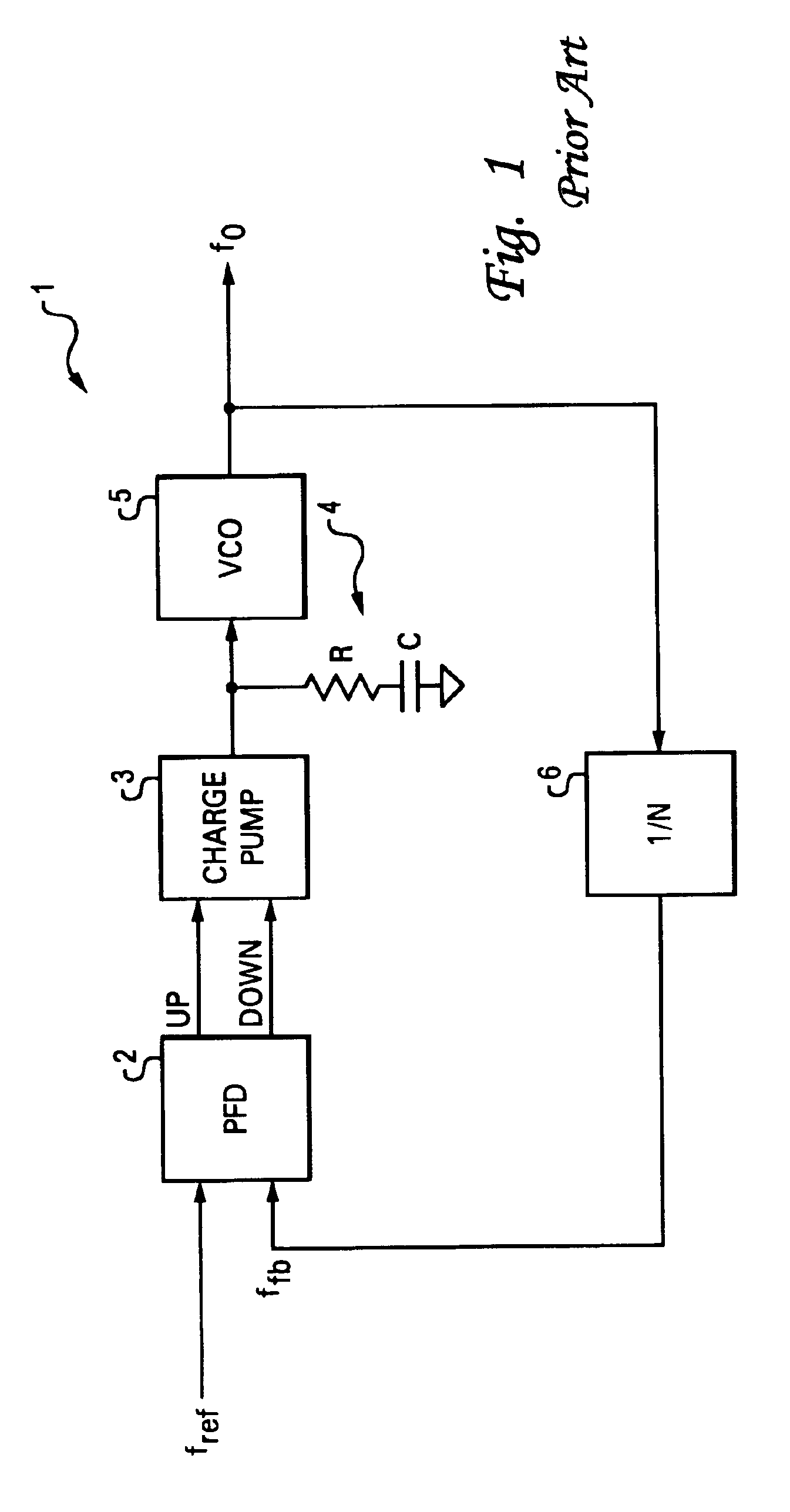

PLL cycle slip detection

InactiveUS7003065B2Pulse automatic controlVoltage-current phase angleControl signalPhase locked loop circuit

A cycle slip detector interfaces with a phase / frequency detector (PFD), such as might be used in a phase-locked loop circuit (PLL), and indicates when cycle slips occur in the PFD. Typically, the PFD generates output control signals as a function of the phase difference between first and second input signals, with the first input signal usually serving as a reference signal against which the PLL adjusts the second input signal. The PFD provides linear phase comparison between its input signals, provided their relative phase difference does not exceed ±2π radians. If one of the two signals leads or lags the other by more than that amount, a cycle slip occurs, and the PFD responds nonlinearly. The cycle slip detector provides logic for detecting and indicating leading and lagging cycle slips as they occur in the PDF, and is typically implemented as a minimal arrangement of logic gates and flip-flops.

Owner:ERICSSON INC

Methods for performing fast discrete curvelet transforms of data

ActiveUS7840625B2The process is fast and accurateImprove representationComplex mathematical operationsDigital transformationArray data structure

Fast digital implementations of the second generation curvelet transform for use in data processing are disclosed. One such digital transformation is based on unequally-spaced fast Fourier transforms (USFFT) while another is based on the wrapping of specially selected Fourier samples. Both digital transformations return a table of digital curvelet coefficients indexed by a scale parameter, an orientation parameter, and a spatial location parameter. Both implementations are fast in the sense that they run in about O(n2 log n) flops for n by n Cartesian arrays or about O(N log N) flops for Cartesian arrays of size N=n3; in addition, they are also invertible, with rapid inversion algorithms of about the same complexity.

Owner:CALIFORNIA INST OF TECH +1

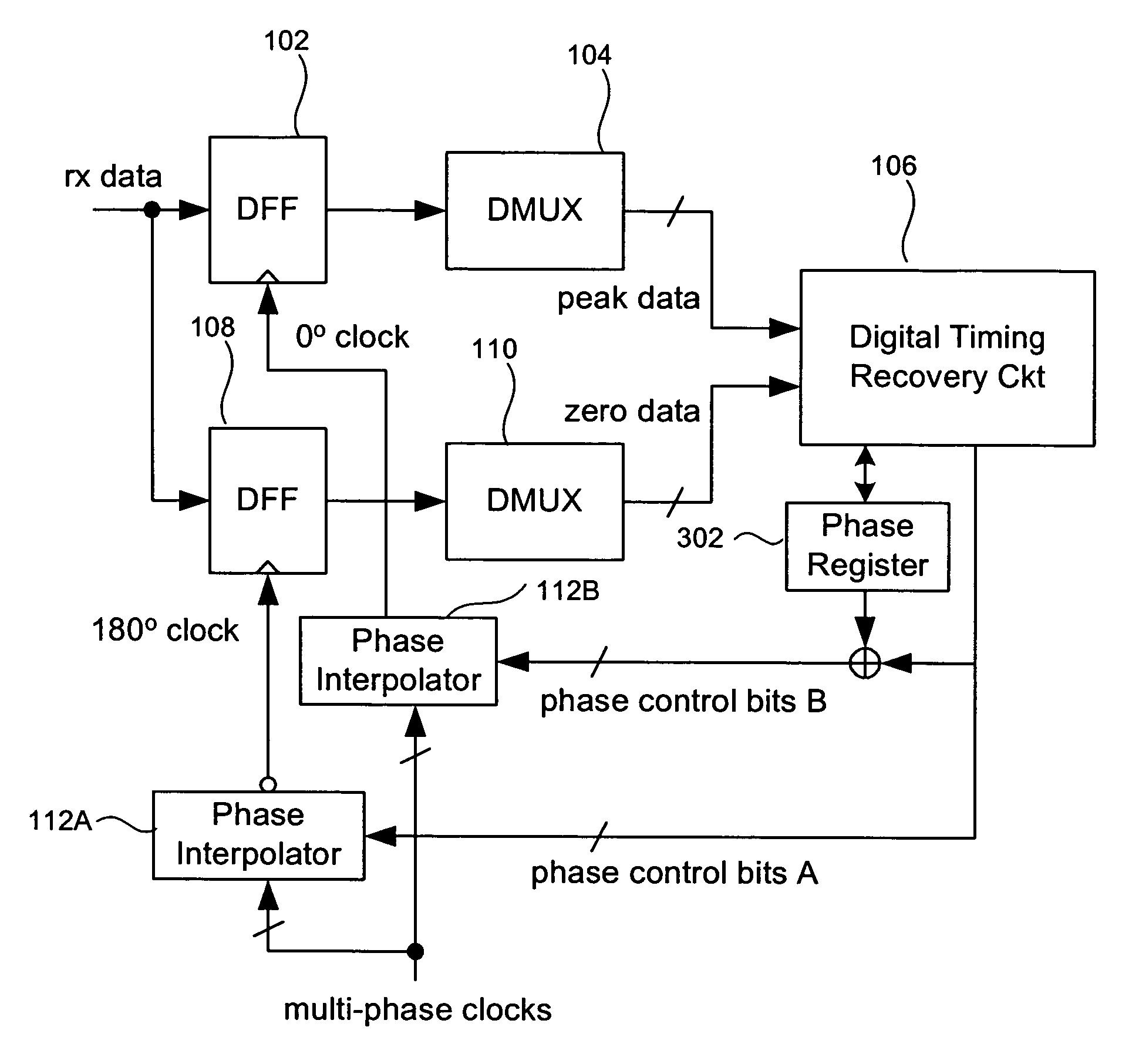

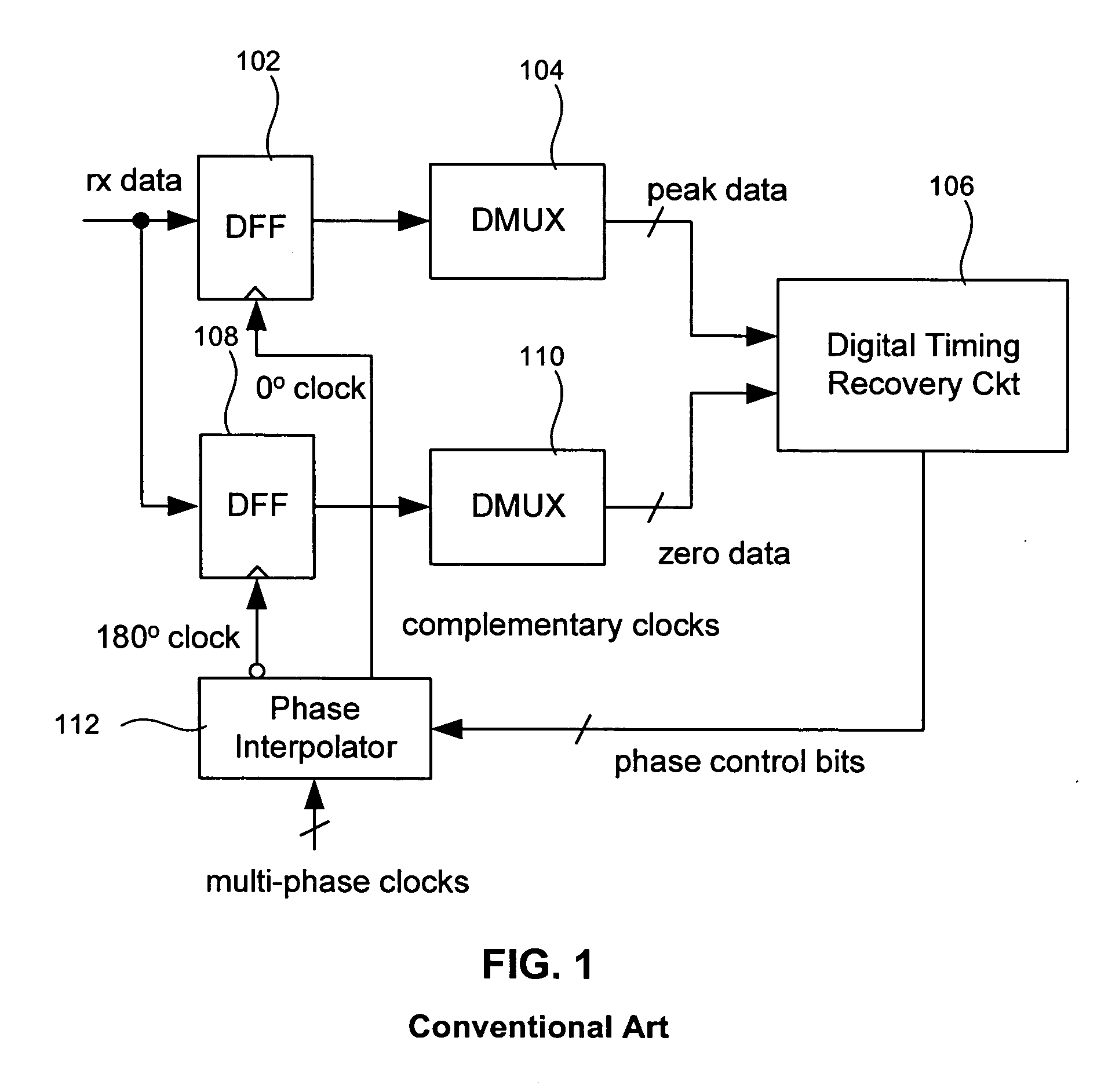

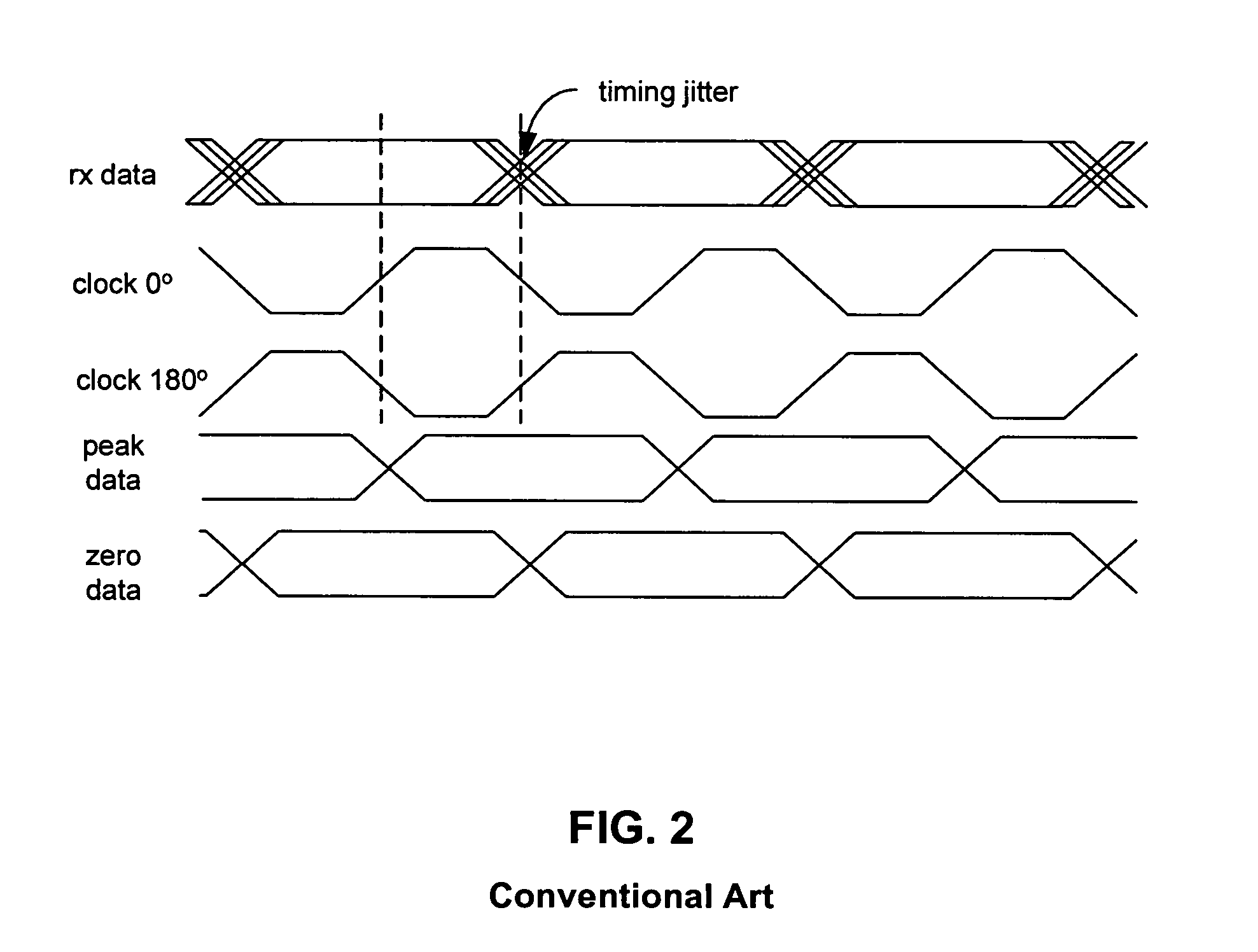

Phase adjustment method and circuit for dll-based serial data link transceivers

InactiveUS20060002497A1Pulse automatic controlAmplitude-modulated carrier systemsTransceiverControl signal

A delay locked loop circuit with a first flip flop driven by a 0° clock and receiving the input data. A second flip flop by a 180° clock and receiving the input data. A first demultiplexer receives an output of the first flip flop and outputs peak data. A second demultiplexer receives an output of the second flip flop and outputs zero data. A timing recovery circuit outputs phase control bits based on the zero data and the peak data. A first phase interpolator outputs the 0° clock based on the phase control signal. A second phase interpolator outputs the 180° clock based on the phase control signal. A phase register receives the phase control signal from the timing recovery circuit. The first and second flip flops can be D flip flops. The first and second phase interpolators adjust relative phases of the 0° clock and 180° clock based on the phase control signal. The phase control signal can be a digital signal comprising a plurality of bits corresponding to a phase relationship between the 0° clock and 180° clock. The timing recovery circuit can be a digital circuit. The phase control signal is used to maintain a transition of the 0° clock near a center of an “eye” in the input data.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Techniques for spin-flop switching with offset field

Techniques for reducing switching fields in semiconductor devices are provided. In one aspect, a semiconductor device comprising at least a first magnetic layer and a second magnetic layer with a spacer layer therebetween is provided. The semiconductor device is configured such that a thickness of at least one of the first magnetic layer and the second magnetic layer maintains a desired activation energy of the semiconductor device in the presence of an applied offsetting magnetic field. A method of reducing a switching field of a semiconductor device having at least a first magnetic layer and a second magnetic layer with a spacer layer therebetween is also provided.

Owner:GOOGLE LLC

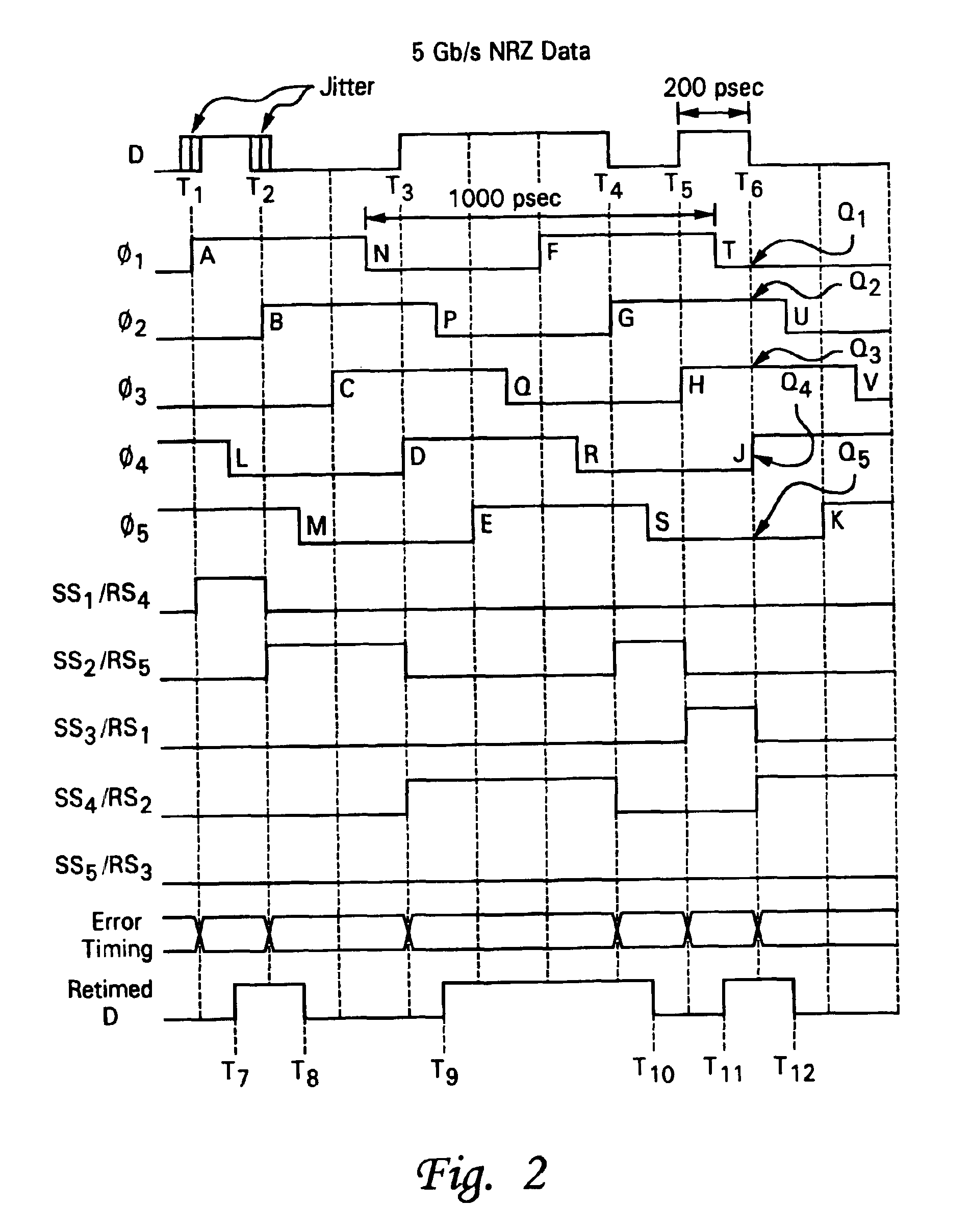

Multiphase clock recovery using D-type phase detector

InactiveUS6914953B2Increase data rateReduce power consumptionPulse automatic controlTime-division multiplexPhase detectorData stream

A method of extracting a clock signal from a data stream, by generating a plurality of multiphase clock signals, selecting one of the multiphase signals based on synchronization states identifying which of the multiphase clock signals is most closely aligned with the data stream, and sampling the data stream using the selected multiphase signal to produce a retimed data signal. The multiphase clock signals may be subharmonics of the data stream. The selecting step may include the determination of whether the multiphase clock signals are either early or late with respect to the data stream, particularly using D-type flip-flops. The synchronization states are used to define which of the rising edges of the multiphase clock signals is most closely aligned with an edge of the data stream. A multiphase voltage-controlled oscillator may be used to provide the multiphase clock signals. An error signal is created using the multiphase clock signals and the data stream which is applied to a charge pump, and the multiphase clock signals are corrected using a control voltage output of the charge pump.

Owner:MEDIATEK INC

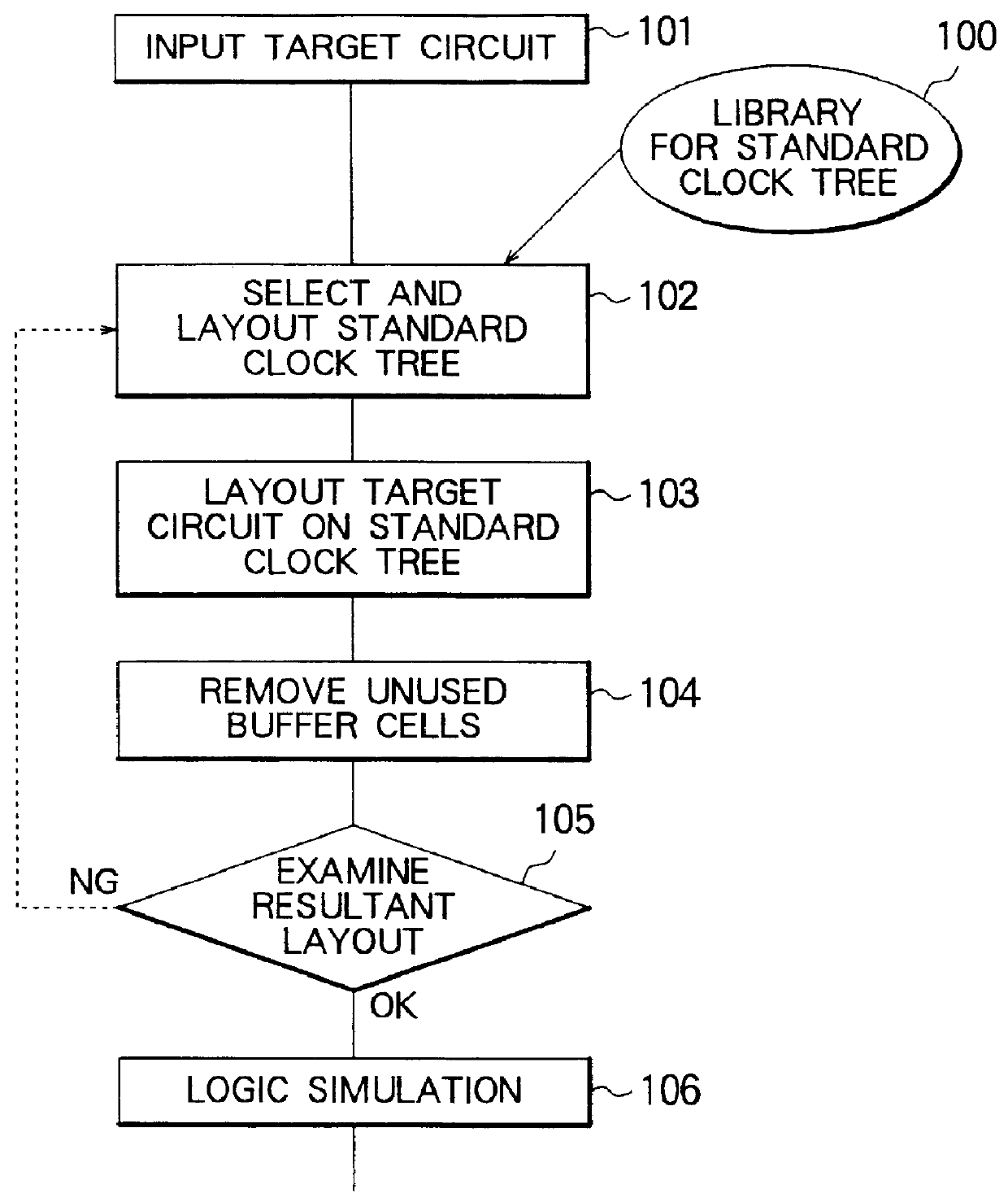

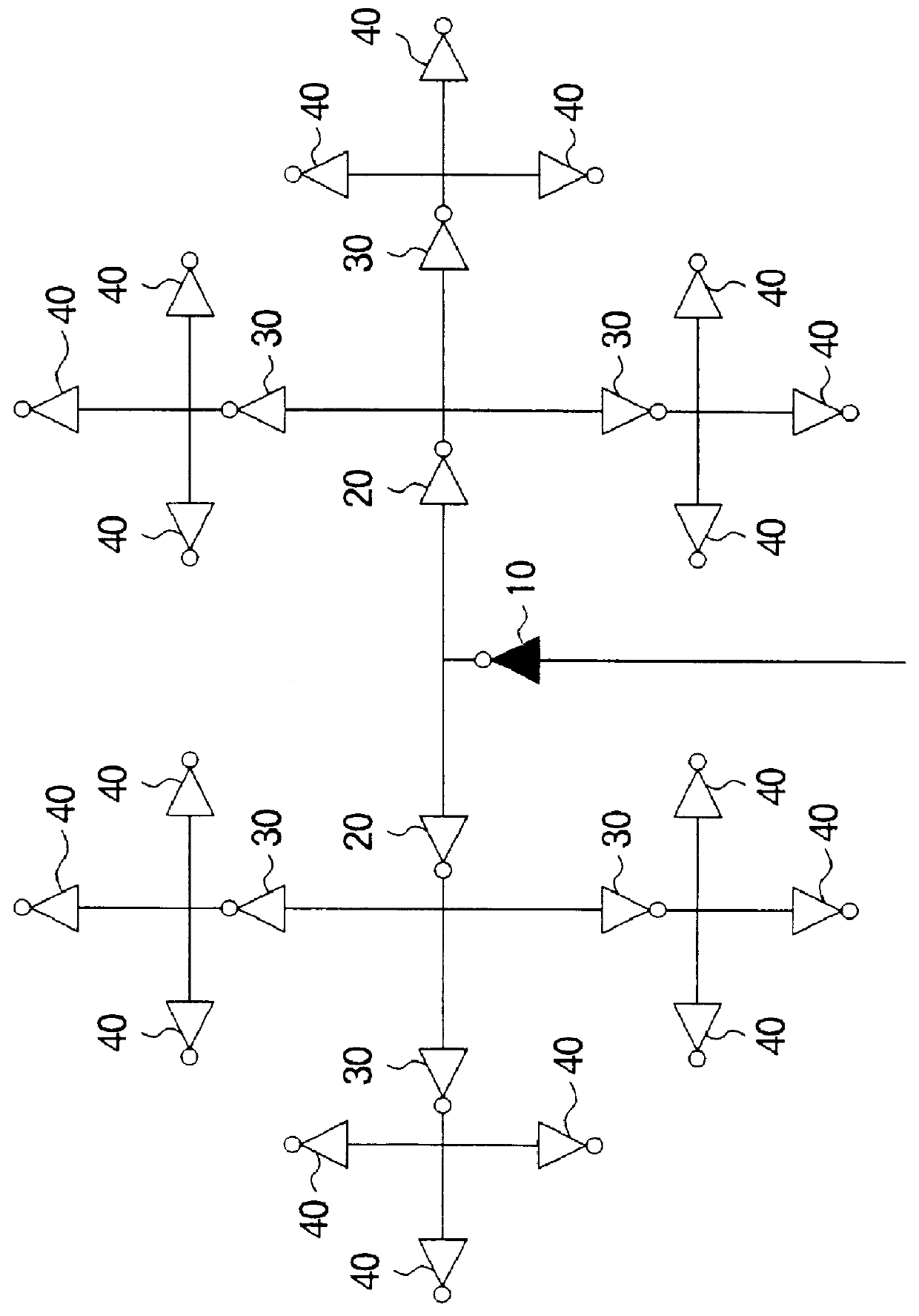

Layout method for a clock tree in a semiconductor device

InactiveUS6053950ASolid-state devicesSemiconductor/solid-state device manufacturingWrite bufferClock tree

A clock signal distribution circuit has a clock tree configuration. In the layout of the clock tree, a standard clock tree is prepared having a route buffer, a plurality of intermediate stage buffer cells and a plurality of last stage buffer cells connected in a hierarchical configuration. All of the clock lines have an equal length. If there are no set of flip-flops ina target integrated circuit corresponding to a set of last stage buffer cells, the set of last stage buffer cells are removed as a whole provided there is not other last stage buffer cells connected to a flip-flop.

Owner:NEC ELECTRONICS CORP

Method and apparatus for combined stuck-at fault and partial-scanned delay-fault built-in self test

InactiveUS6247154B1Electronic circuit testingError detection/correctionStuck-at faultBuilt in self testing

This invention relates to a method and apparatus for combined stuck-fault testing and partial scan delay-fault built-in self testing (BIST). For partial scan delay-fault BIST, the circuit is modeled for breaking all flip-flop feedback cycles in the circuit. A selection of flip-flops to be scanned to break all sequential cycles is determined from an optimal feedback vertex set. A digest, devour and tidy-up (DDT) heuristic can be used on a weighted signed graph formed from an S-graph of the circuit to determine an optimal feedback vertex set. Determined partial scan delay fault BIST hazards can be removed from the circuit by inserting parity flippers to invert selected paths during testing. The same DDT heuristic can be used to determine optimal placement of the parity flippers in the circuit.

Owner:RUTGERS THE STATE UNIV

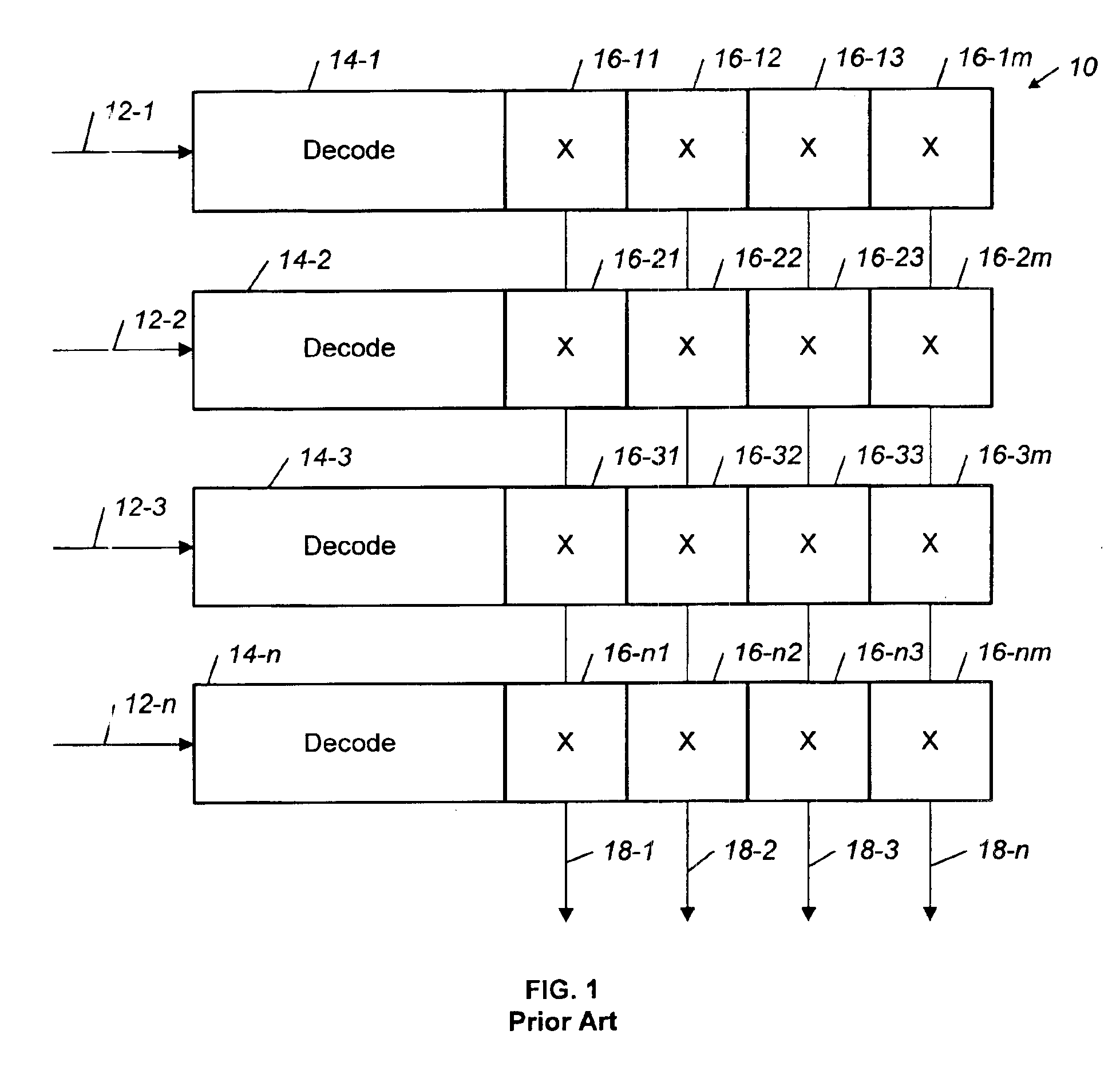

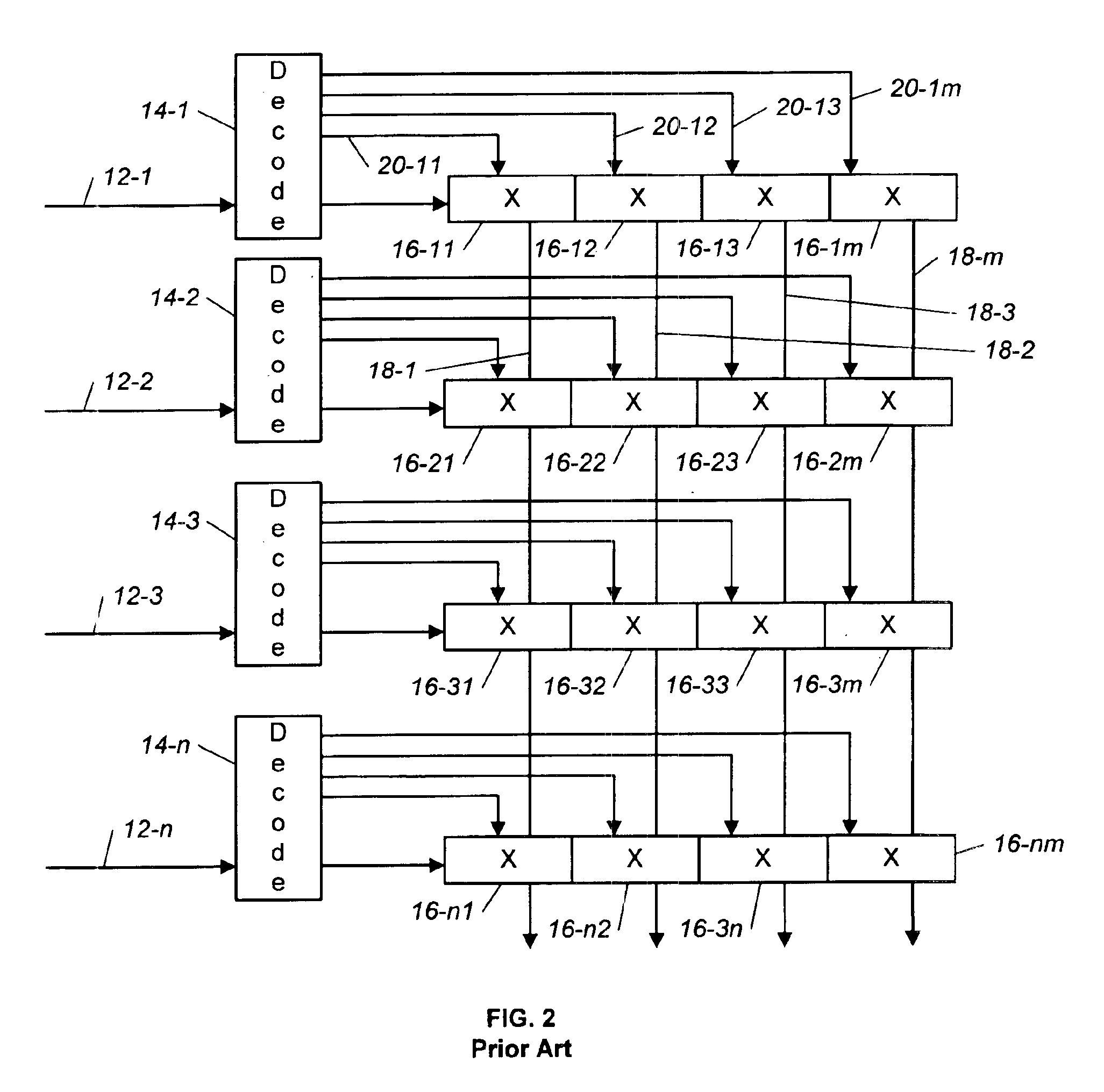

Scalable self-routing superconductor switch

A crossbar switch includes a cross-point matrix with n input rows of cross-points and m output columns of cross-points. The crossbar switch further includes n decoders connected to the n input rows. Each of the n rows includes a single serial address input, a shift input and a data input. A serial address and data enter the address input and the data input in parallel. A shift sequence is transmitted on the single shift input. The data flows before the shift sequence on the shift input is complete. The data is shifted through the crossbar switch using a clock that is generated on-chip using a clock recovery circuit. The decoder converts a binary address input into a serial address and includes an N-bit counter with a plurality of toggle flip-flops. The crossbar switch is implemented using superconductor digital electronics such as rapid single flux quantum (RSFQ) logic.

Owner:NORTHROP GRUMAN CORP

Method and circuit for encoding multi-level pulse amplitude modulated signals using integrated optoelectronic devices

ActiveUS8238014B2Electromagnetic transmissionNon-linear opticsMach–Zehnder interferometerEngineering

Methods and systems for encoding multi-level pulse amplitude modulated signals using integrated optoelectronics are disclosed and may include generating a multi-level, amplitude-modulated optical signal utilizing an optical modulator driven by two or more electrical input signals. The optical modulator may include optical modulator elements coupled in series and configured into groups. The number of optical modular elements and groups may configure the number of levels in the multi-level amplitude modulated optical signal. Unit drivers may be coupled to each of the groups. The electrical input signals may be synchronized before communicating them to the unit drivers utilizing flip-flops. Phase addition may be synchronized utilizing one or more electrical delay lines. The optical modulator may be integrated on a single substrate, which may include one of: silicon, gallium arsenide, germanium, indium gallium arsenide, polymers, or indium phosphide. The optical modulator may include a Mach-Zehnder interferometer or one or more ring modulators.

Owner:CISCO TECH INC

Circuitry for eliminating false lock in delay-locked loops

A delay-locked loop (DLL) acquires correct lock when the delay line on the DLL delays a reference signal by one clock period. False lock occurs when the delay line delays the reference signal by more than one clock period. False lock may be detected by a false lock detector. The false lock detector may include (1) flip-flops to take samples of the delay line outputs and (2) combinational logic for detecting patterns in the samples that may indicate false lock. Once false lock has been detected, a hold circuit may ensure that false lock persists for at least the amount of time required by the DLL to acquire lock (i.e., to prevent reset of the DLL before it has acquired lock). After this determination is made, a reset generator may produce a reset signal for resetting the DLL.

Owner:MARVELL ASIA PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com