Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1071 results about "Ferroelectric capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

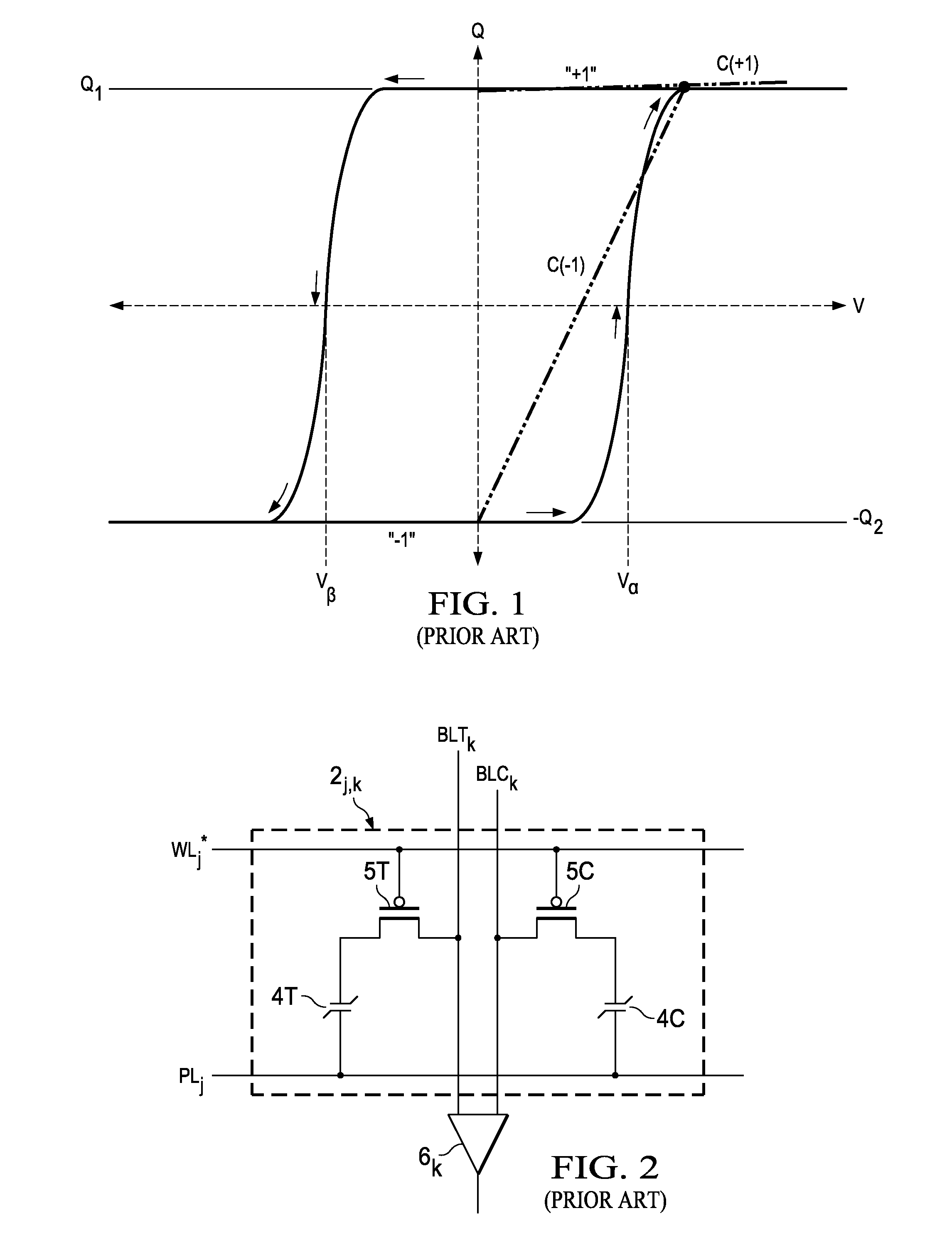

Ferroelectric capacitor is a capacitor based on a ferroelectric material. In contrast, traditional capacitors are based on dielectric materials. Ferroelectric devices are used in digital electronics as part of ferroelectric RAM, or in analog electronics as tunable capacitors (varactors).

Ferroelectric non-volatile logic elements

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

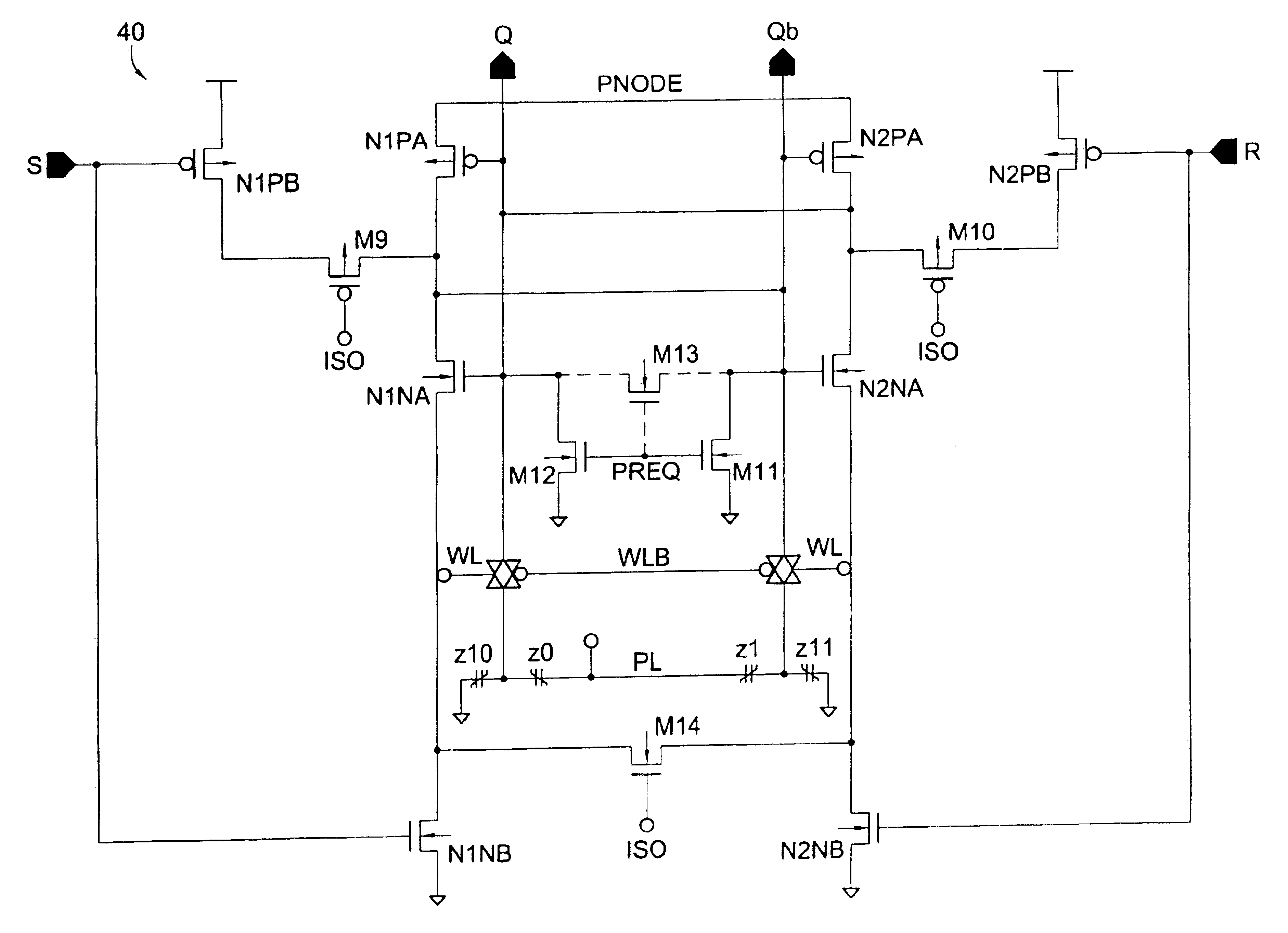

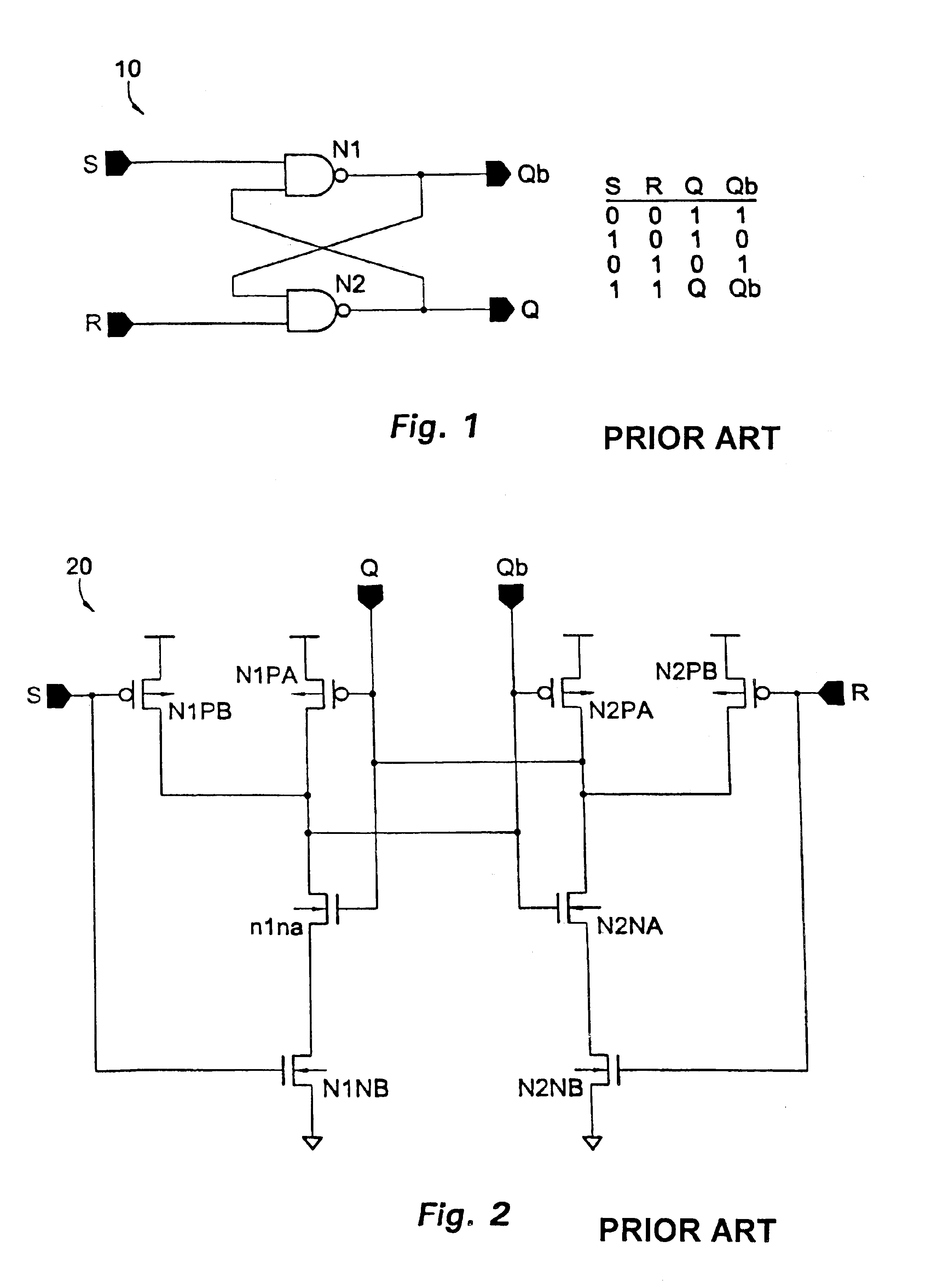

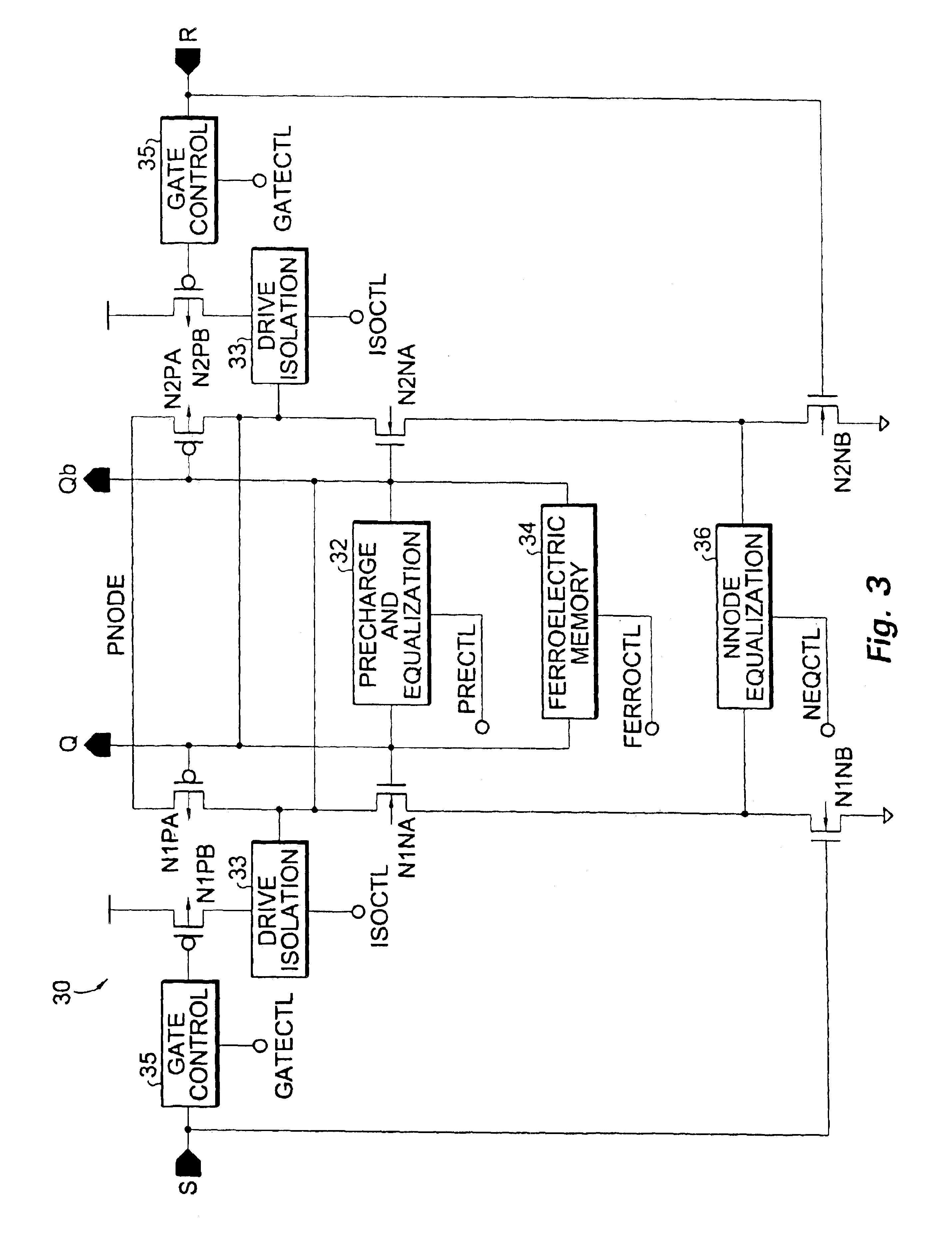

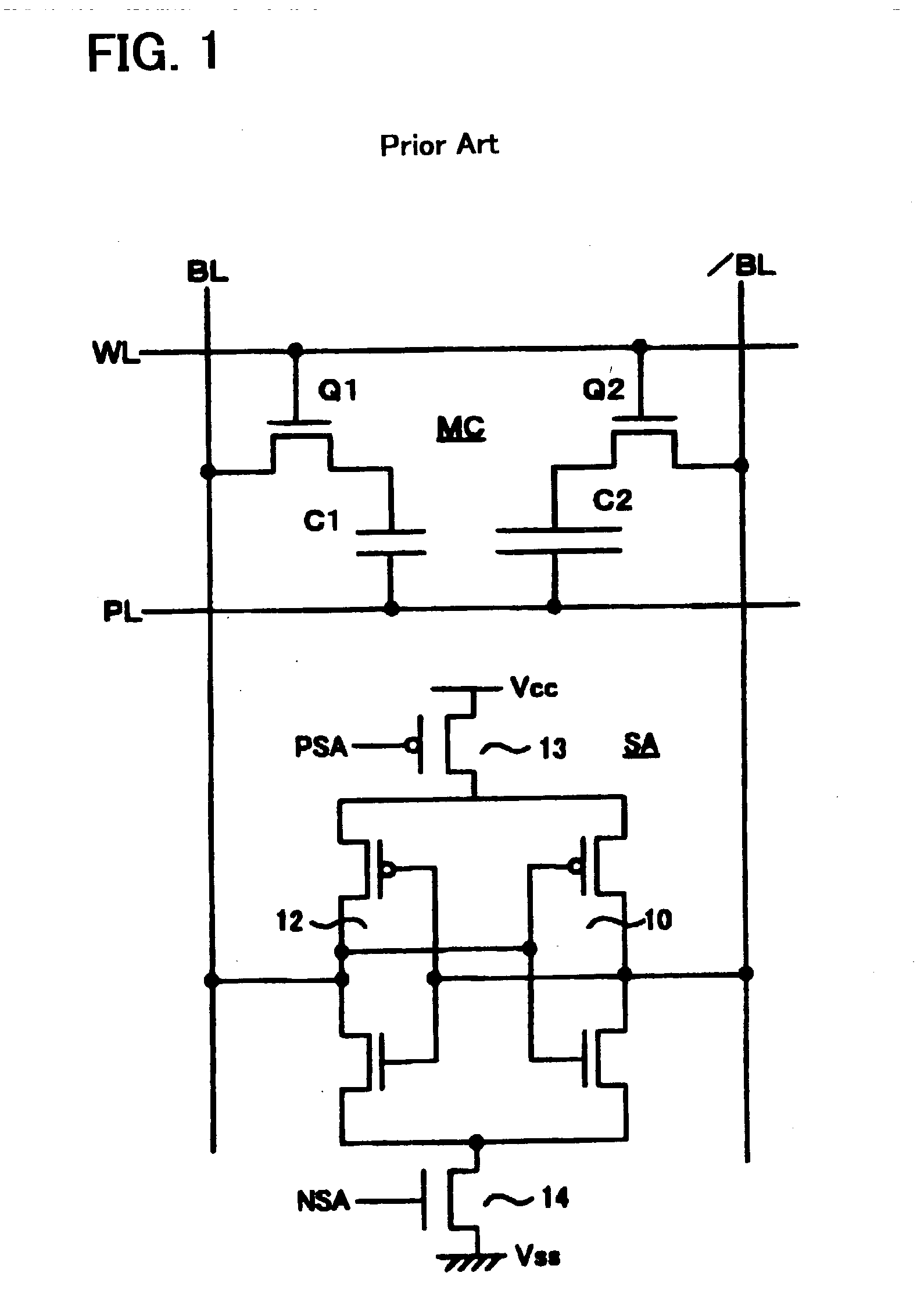

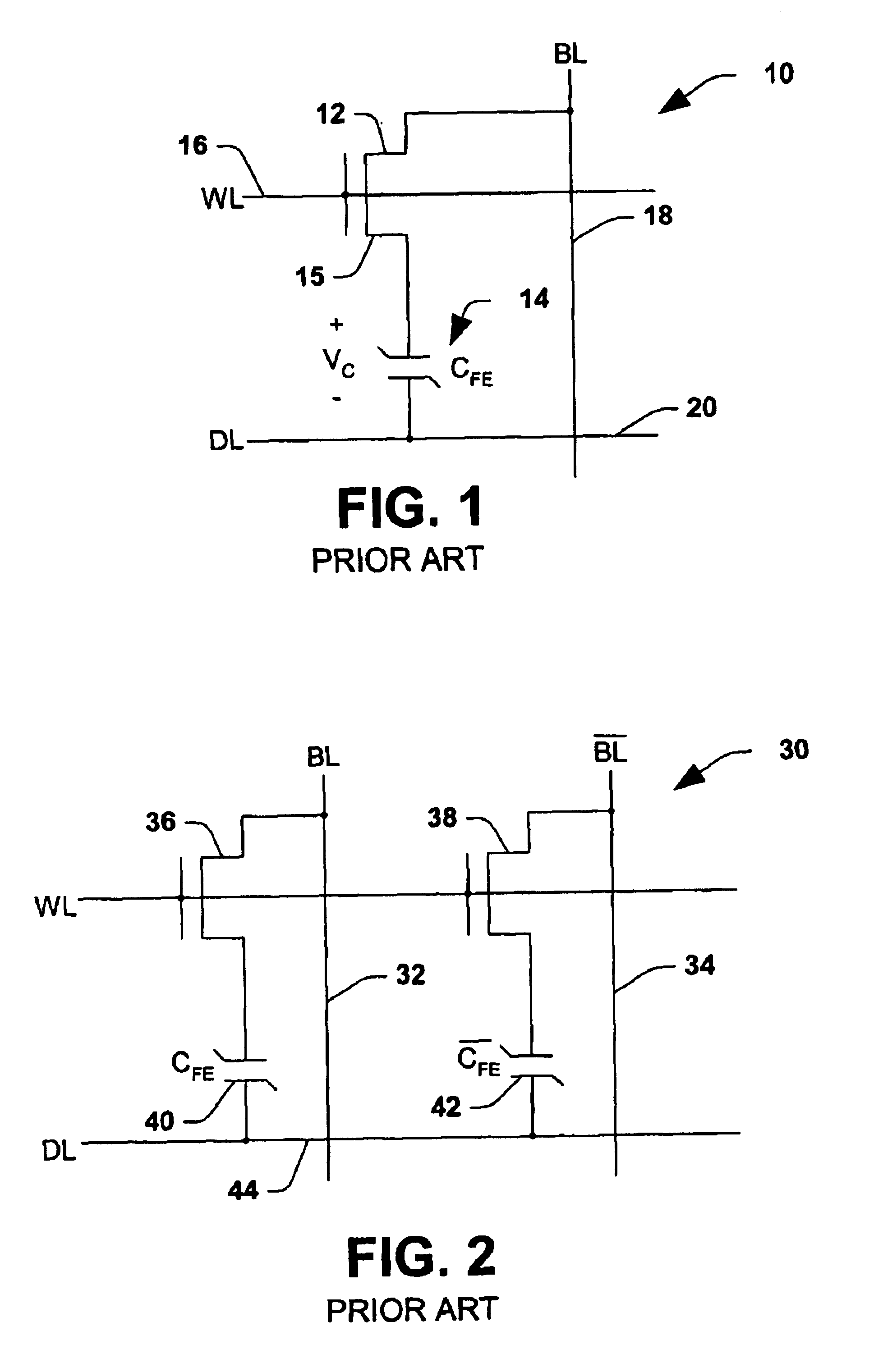

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

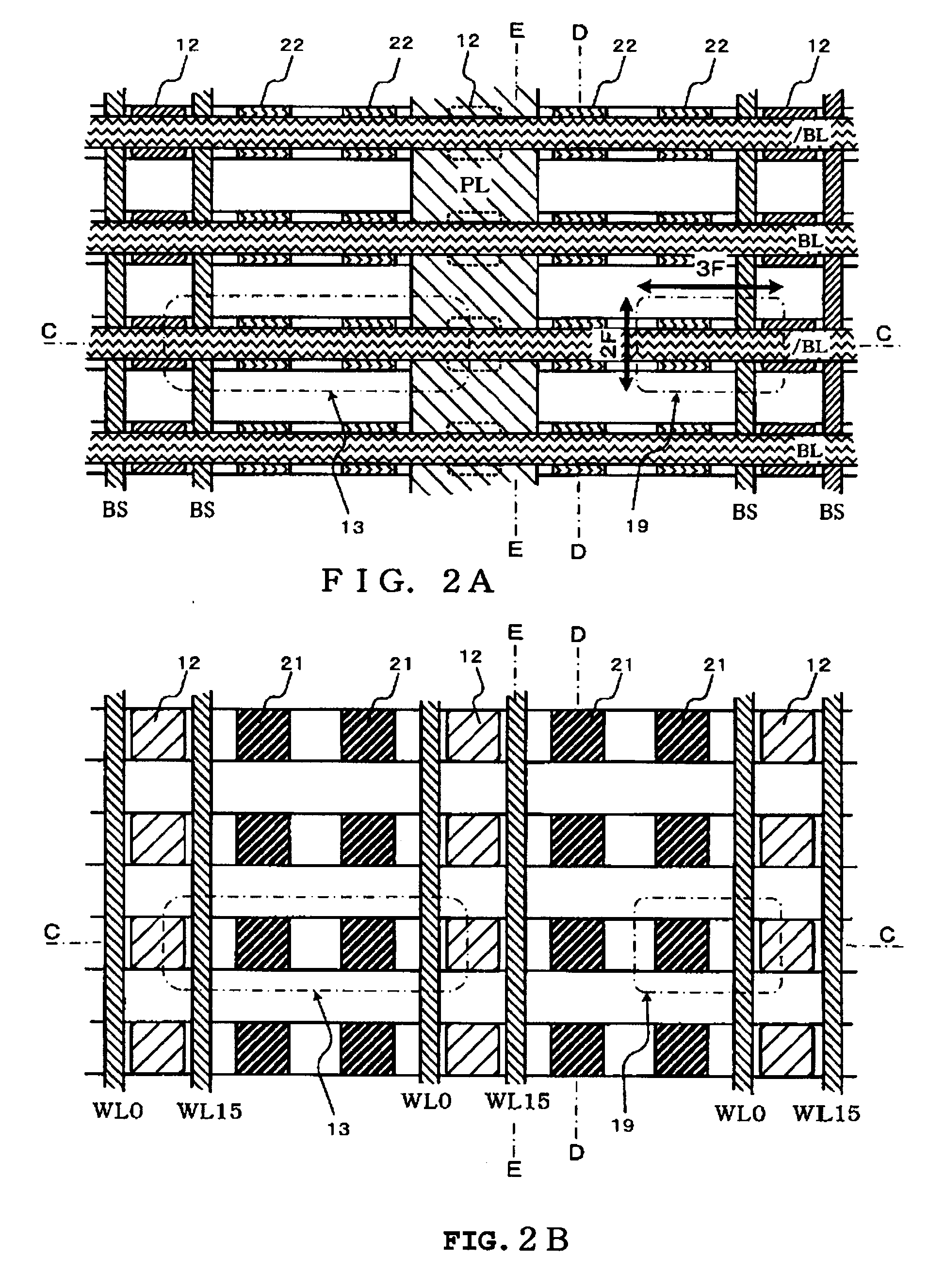

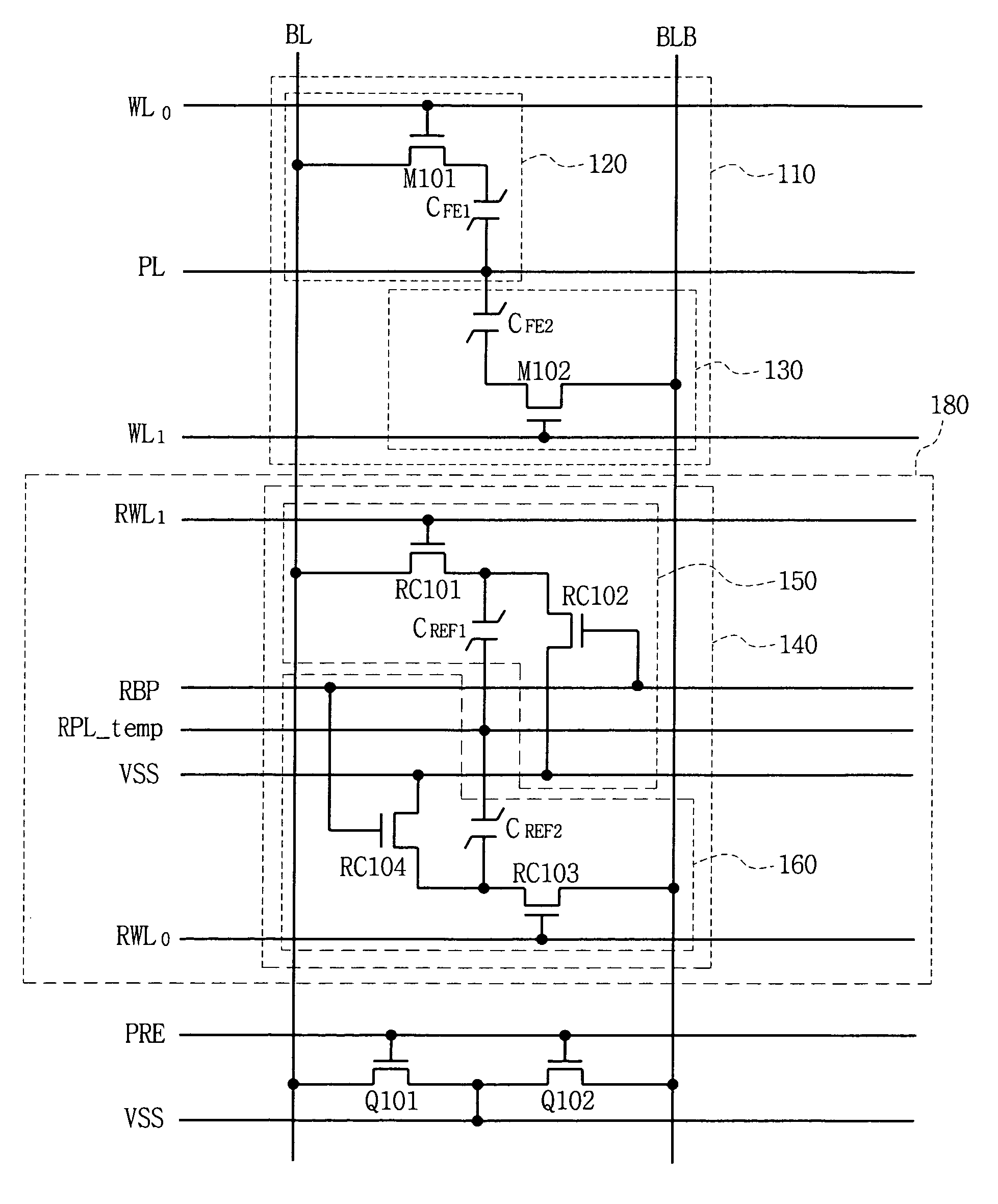

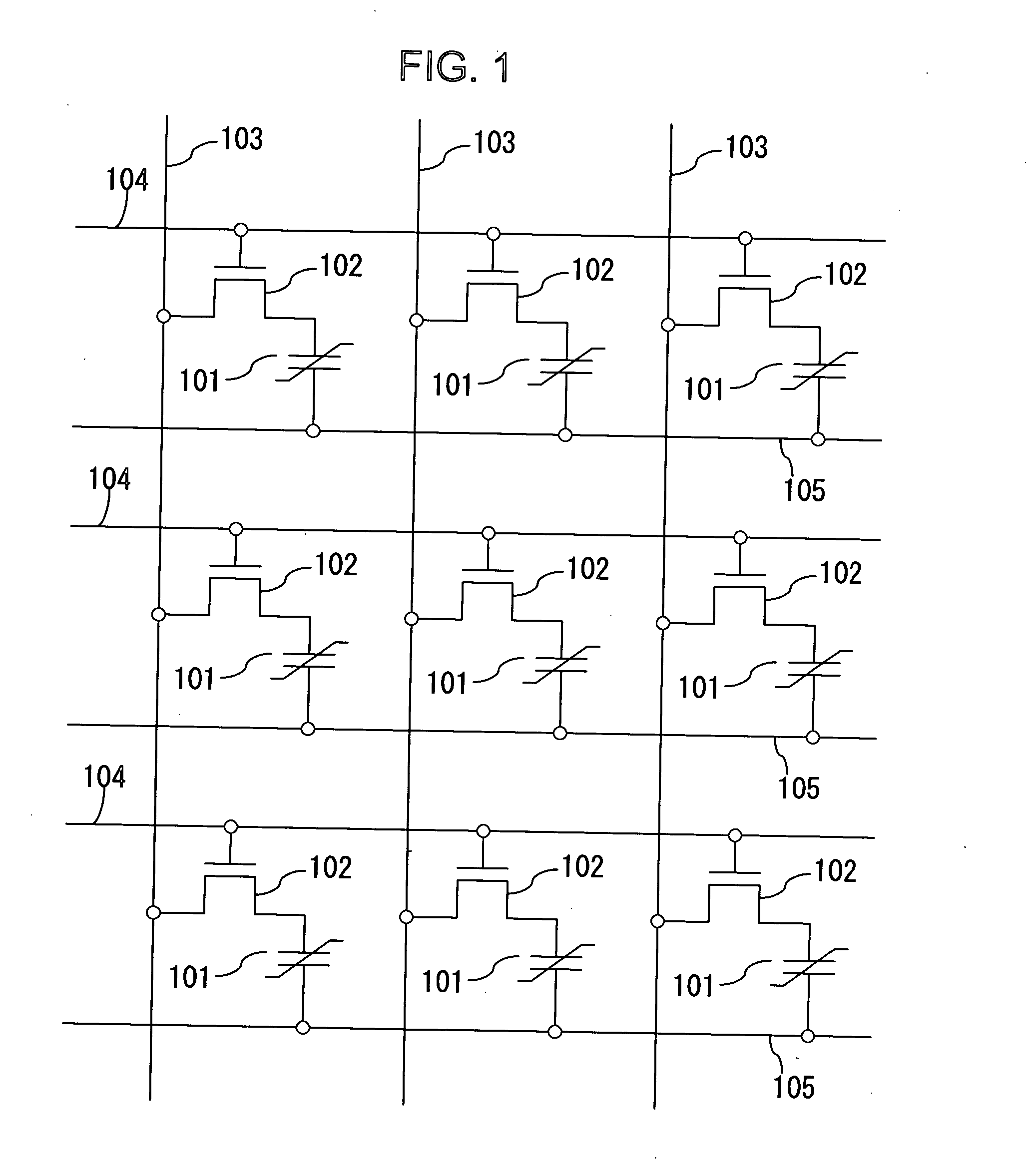

Interleaved Bit Line Architecture for 2T2C Ferroelectric Memories

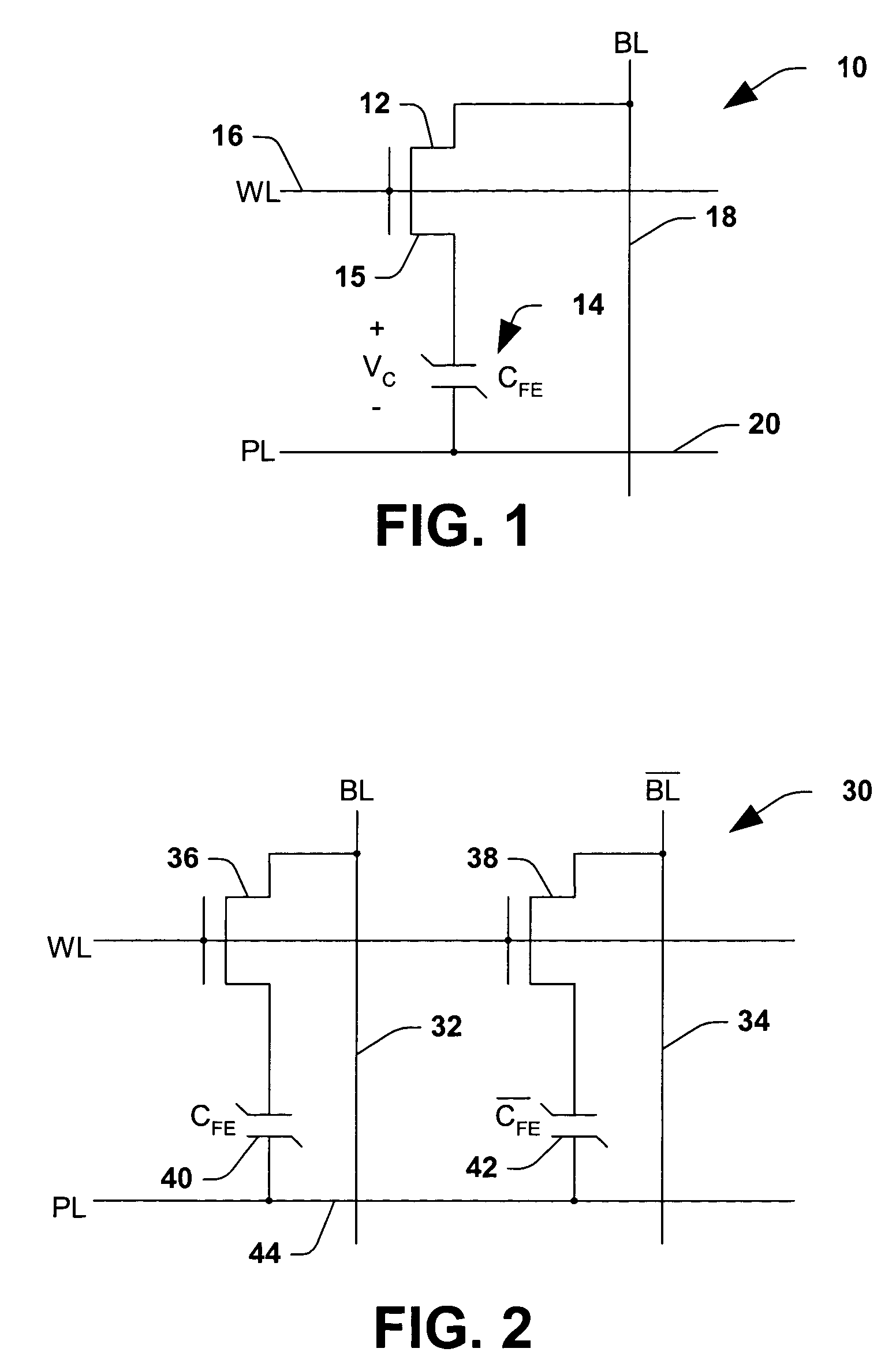

InactiveUS20120307545A1Reduce couplingReduce in quantityDigital storageAudio power amplifierMultiplexer

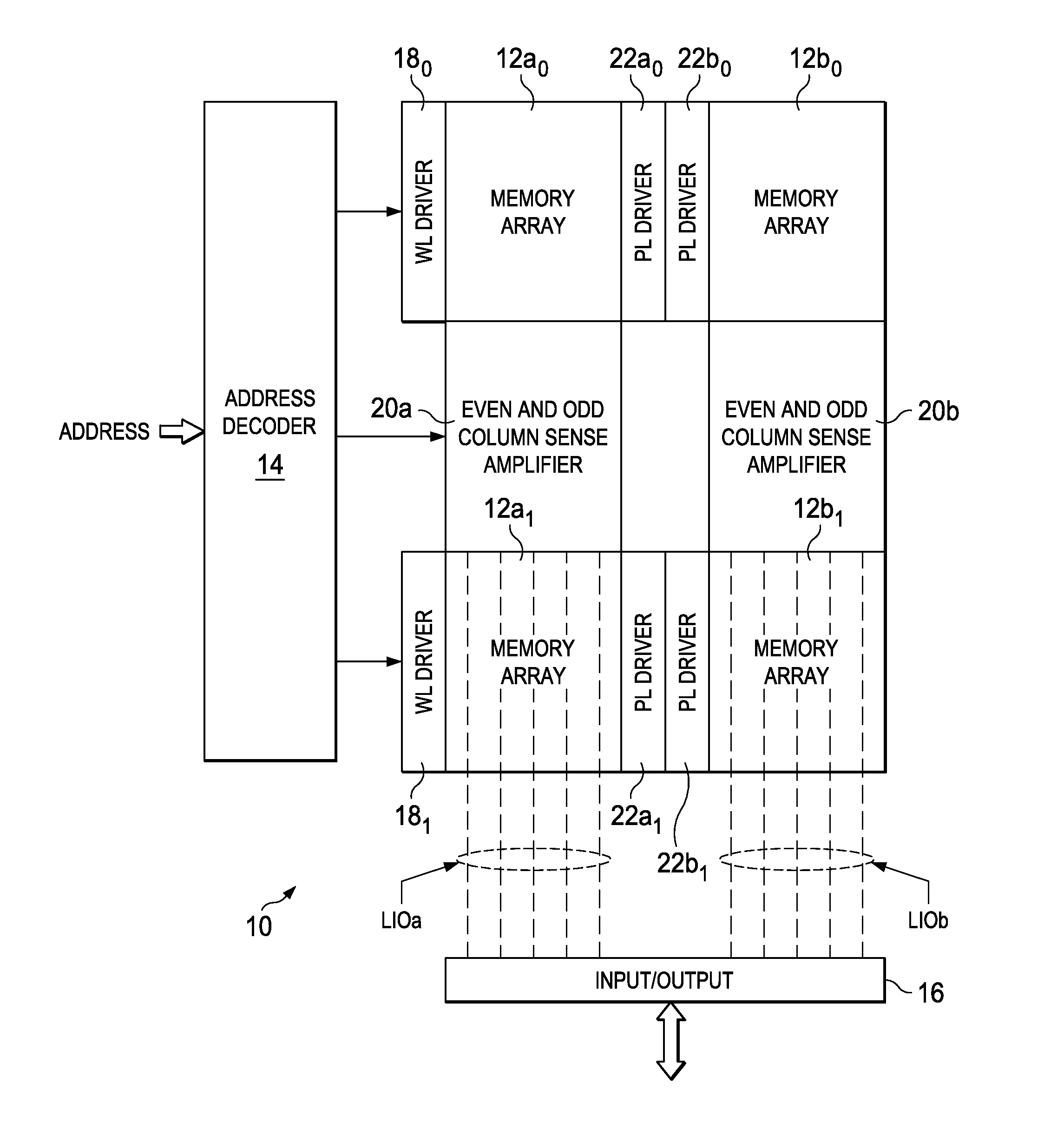

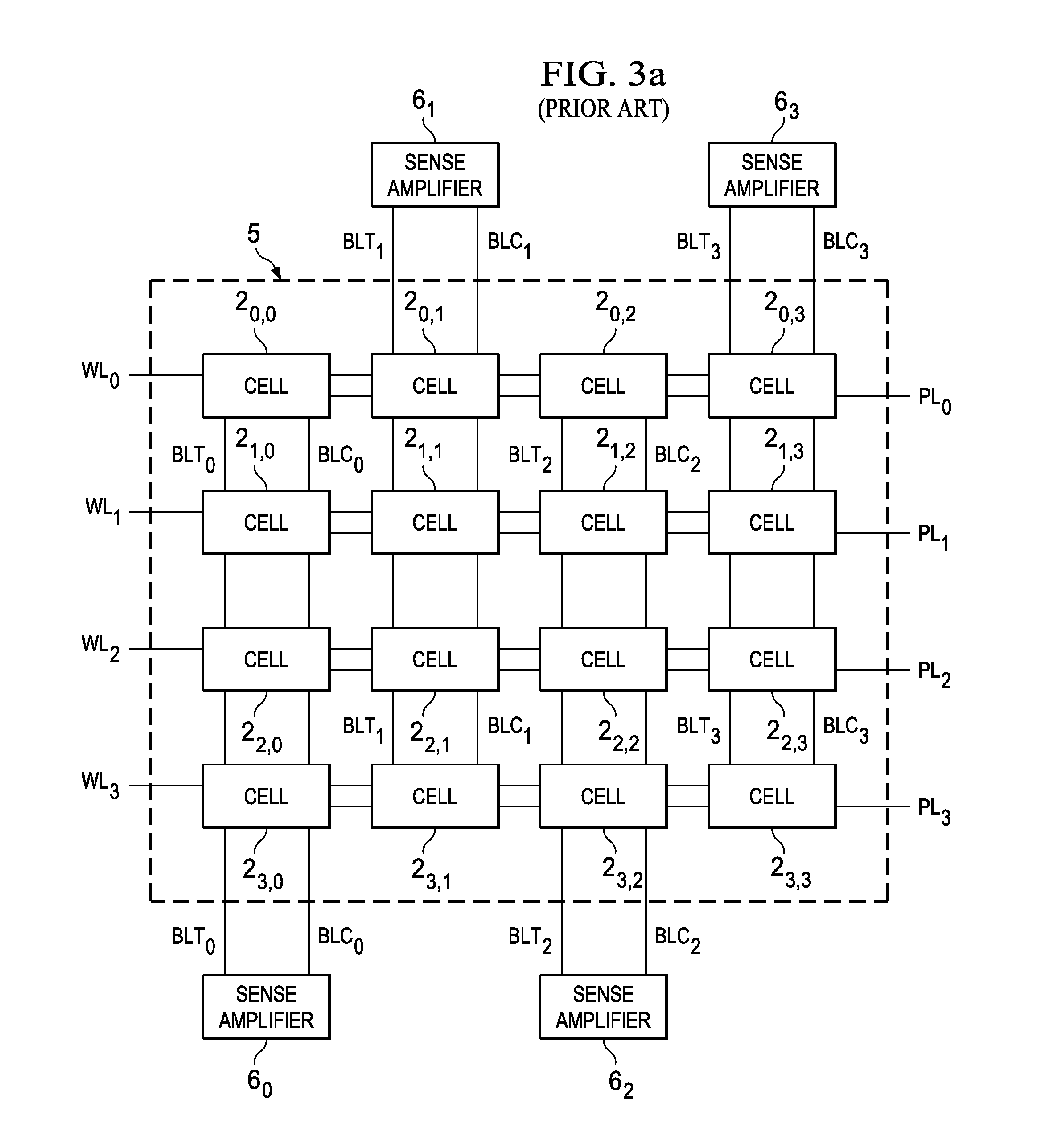

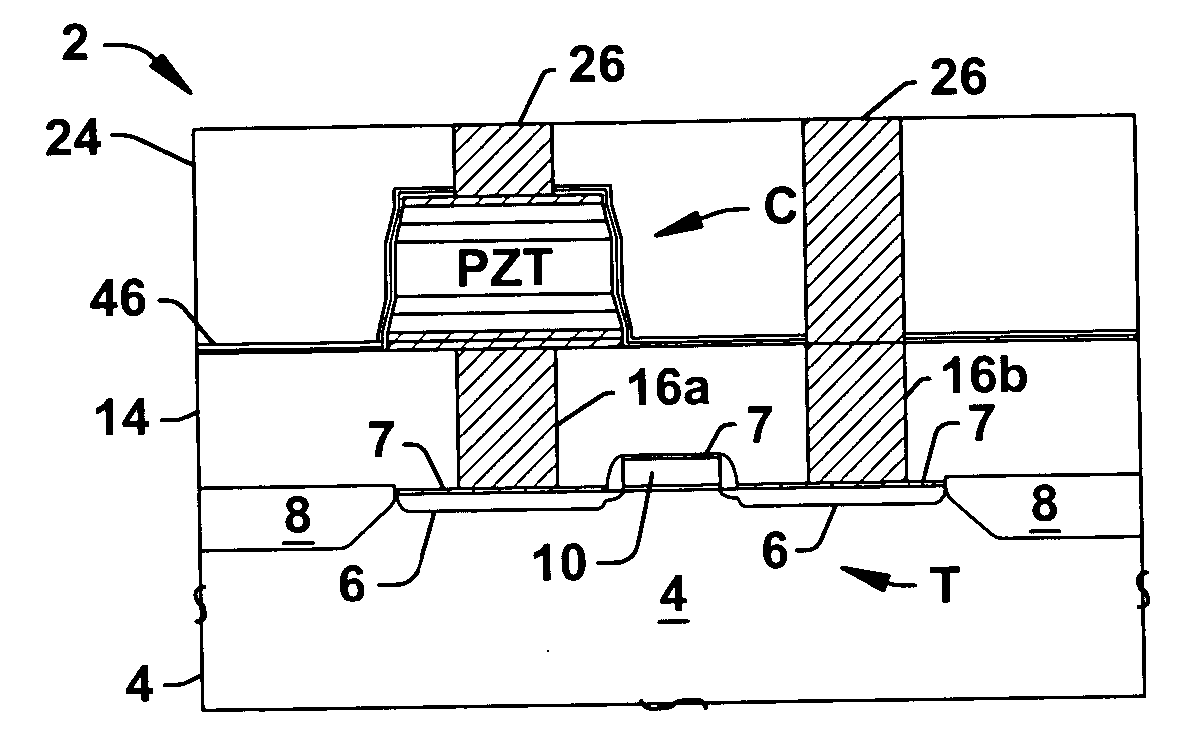

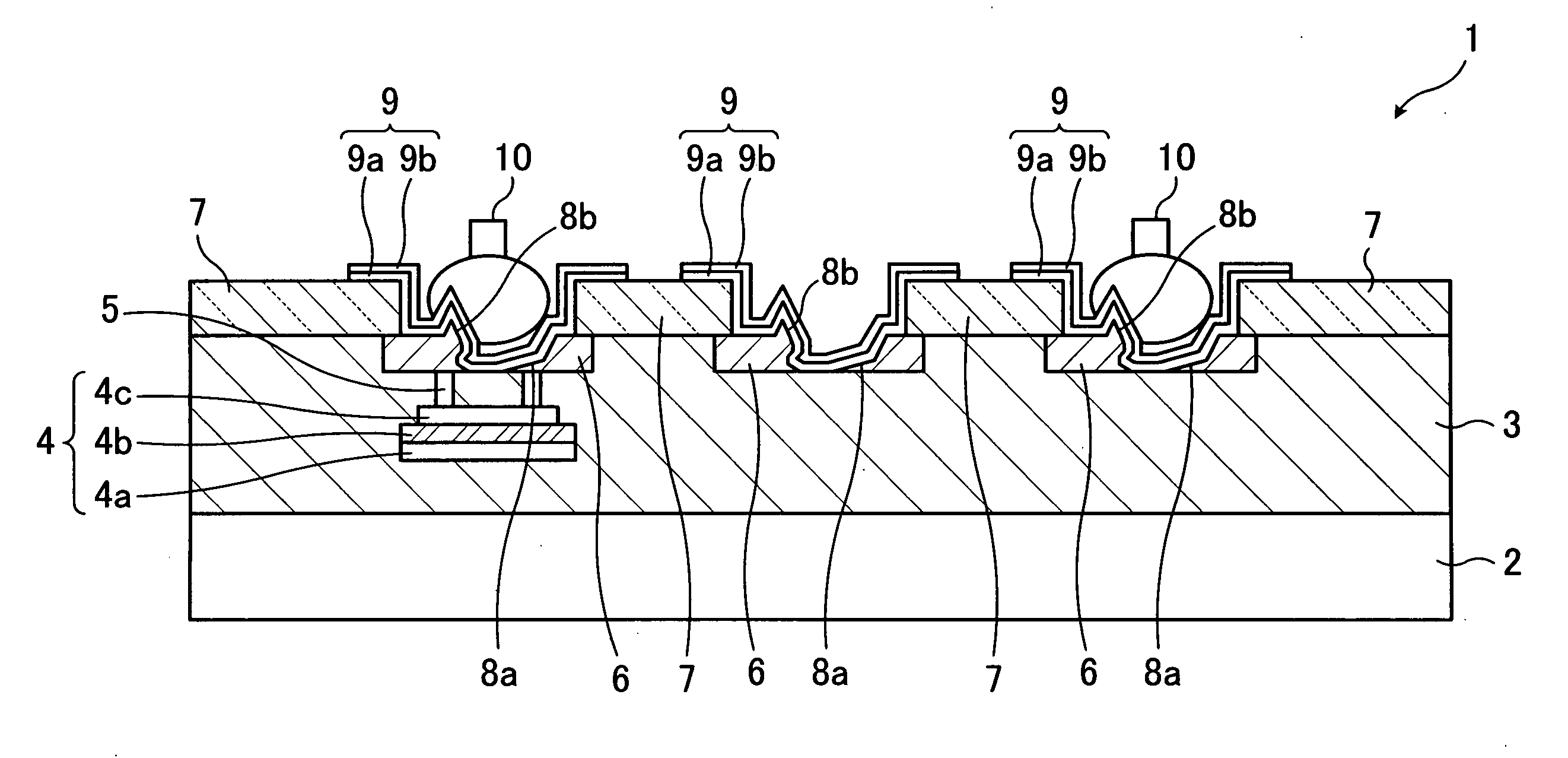

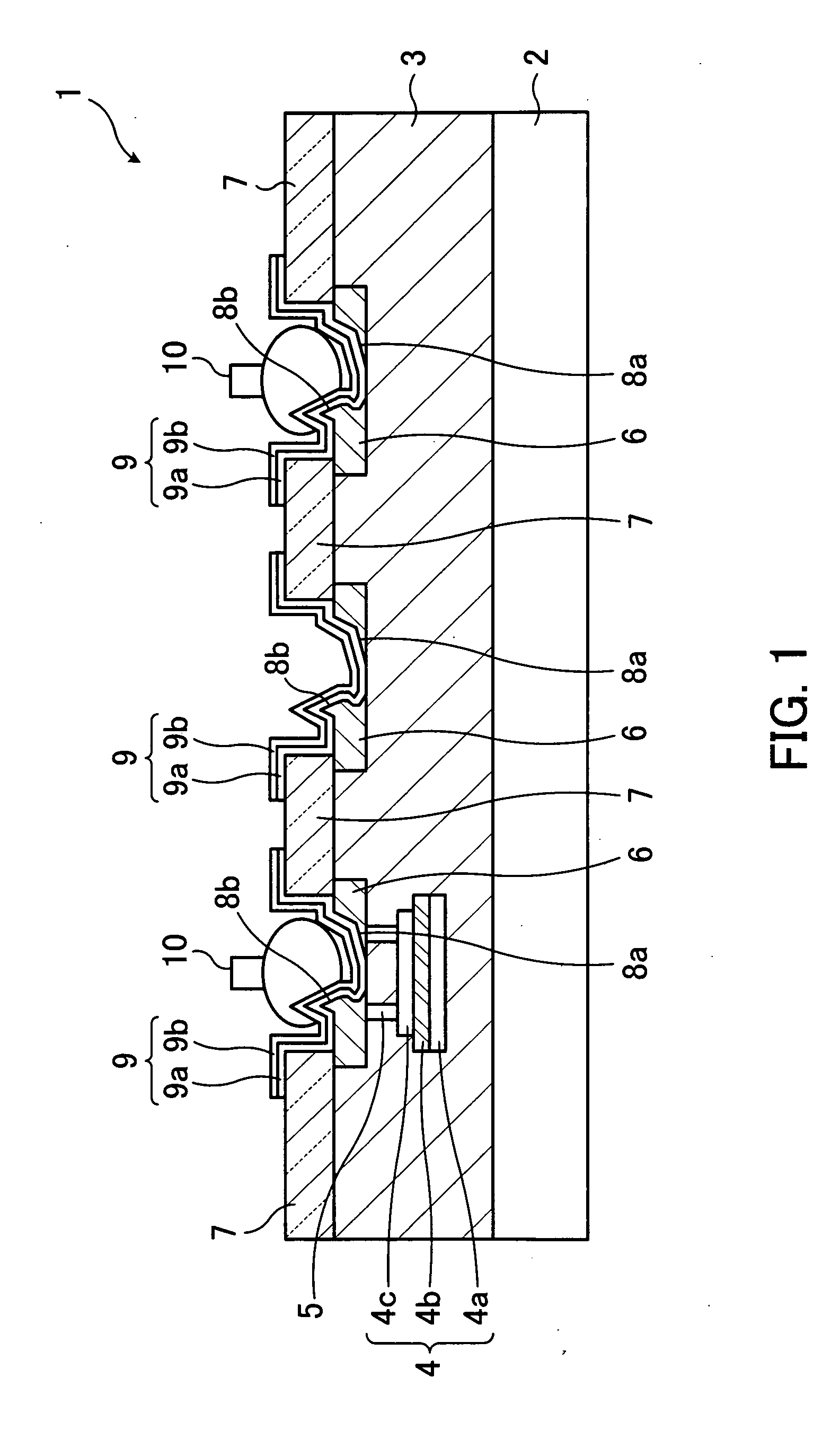

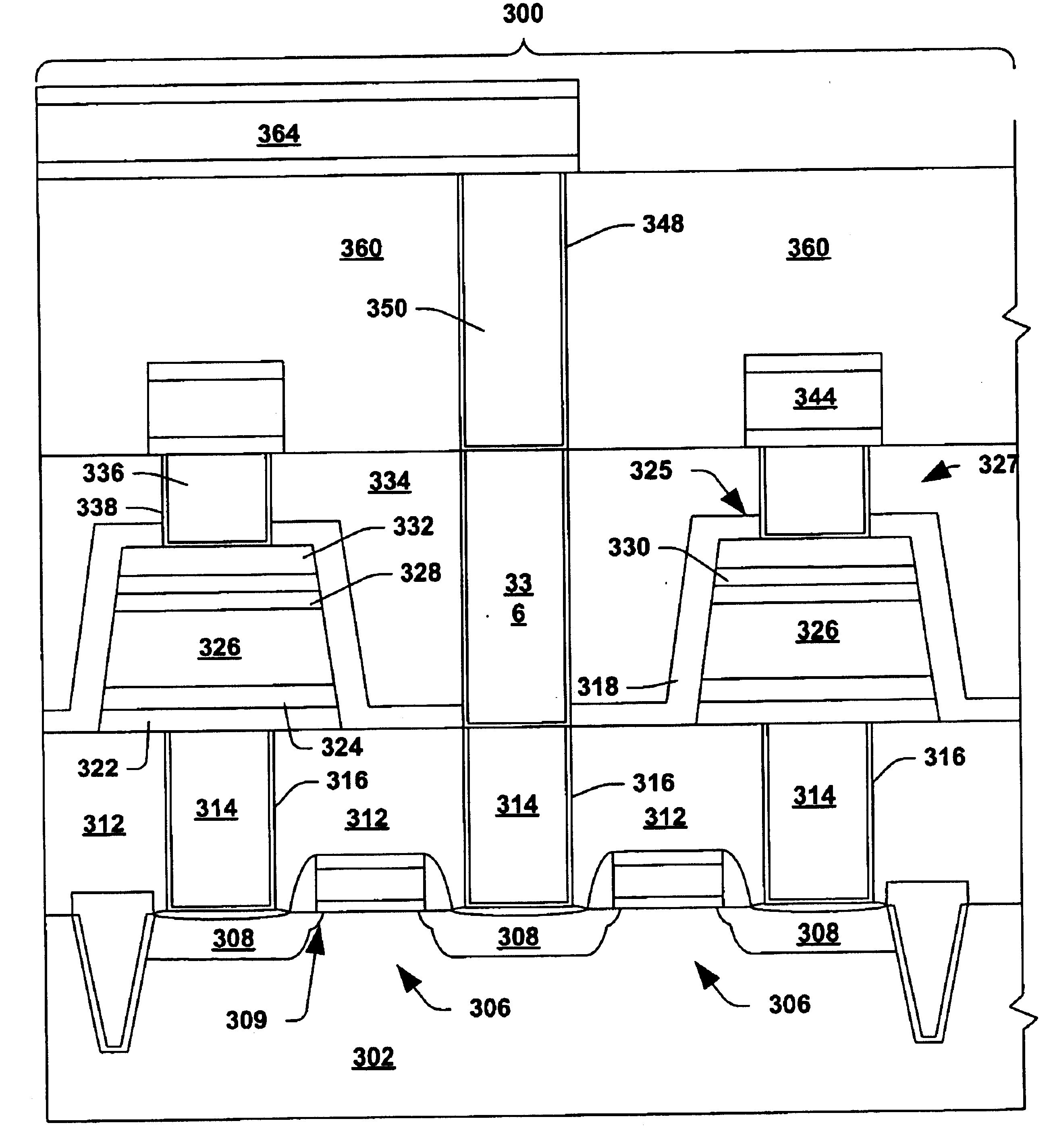

A ferroelectric memory with interleaved pairs of ferroelectric memory cells of the two-transistor, two-capacitor (2T2C) type. Each memory cell in a given pair is constructed as first and second portions, each portion including a transistor and a ferroelectric capacitor. Within each pair, a first portion of a second memory cell is physically located between the first and second portions of the first memory cell. As a result, complementary bit lines for adjacent columns are interleaved with one another. Each sense amplifier is associated with a multiplexer, so that the adjacent columns of the interleaved memory cells are supported by a single sense amplifier. Noise coupling among the bit lines is reduced, and the sense amplifiers can be placed along one side of the array, reducing the number of dummy cells required to eliminate edge cell effects.

Owner:TEXAS INSTR INC

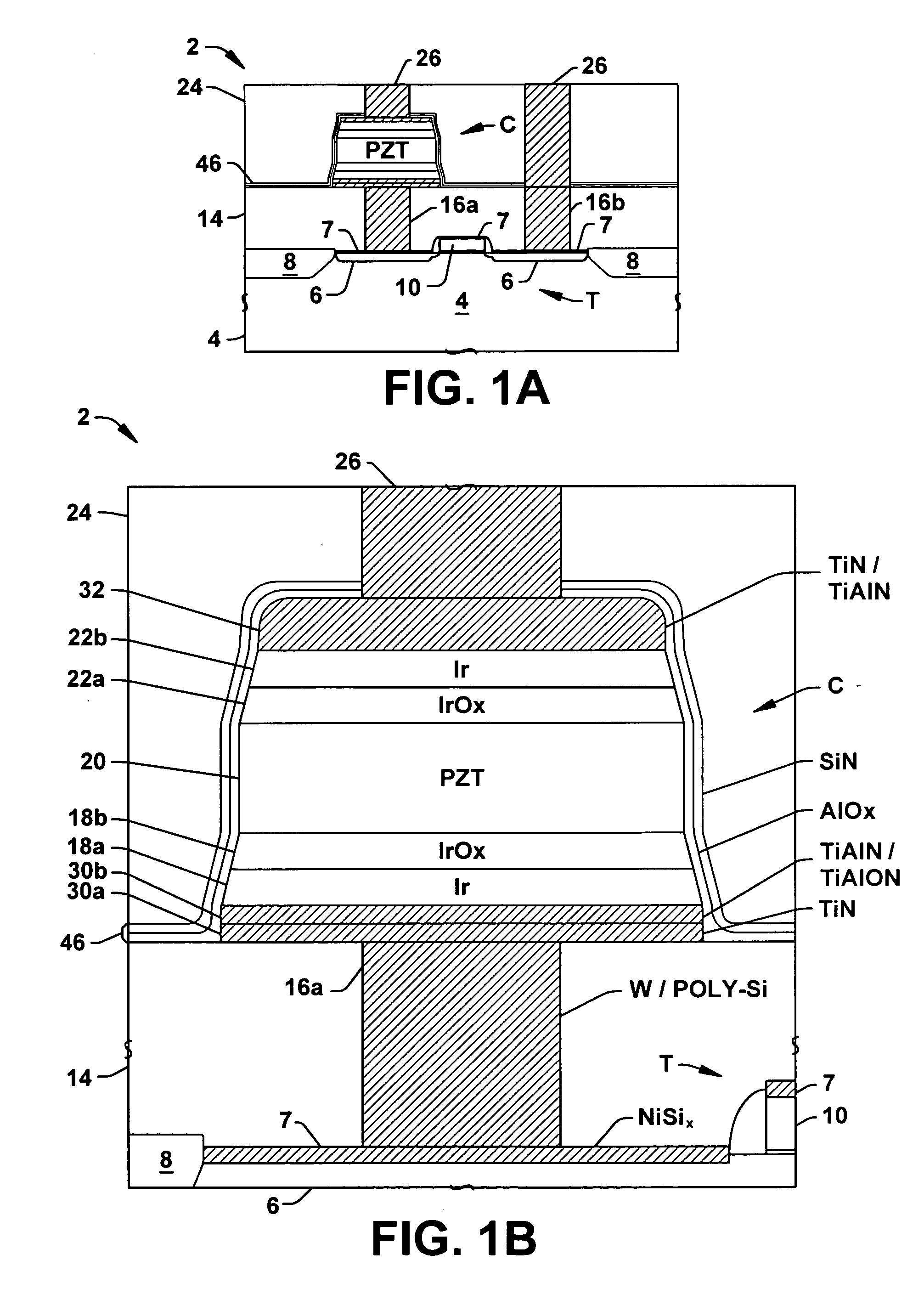

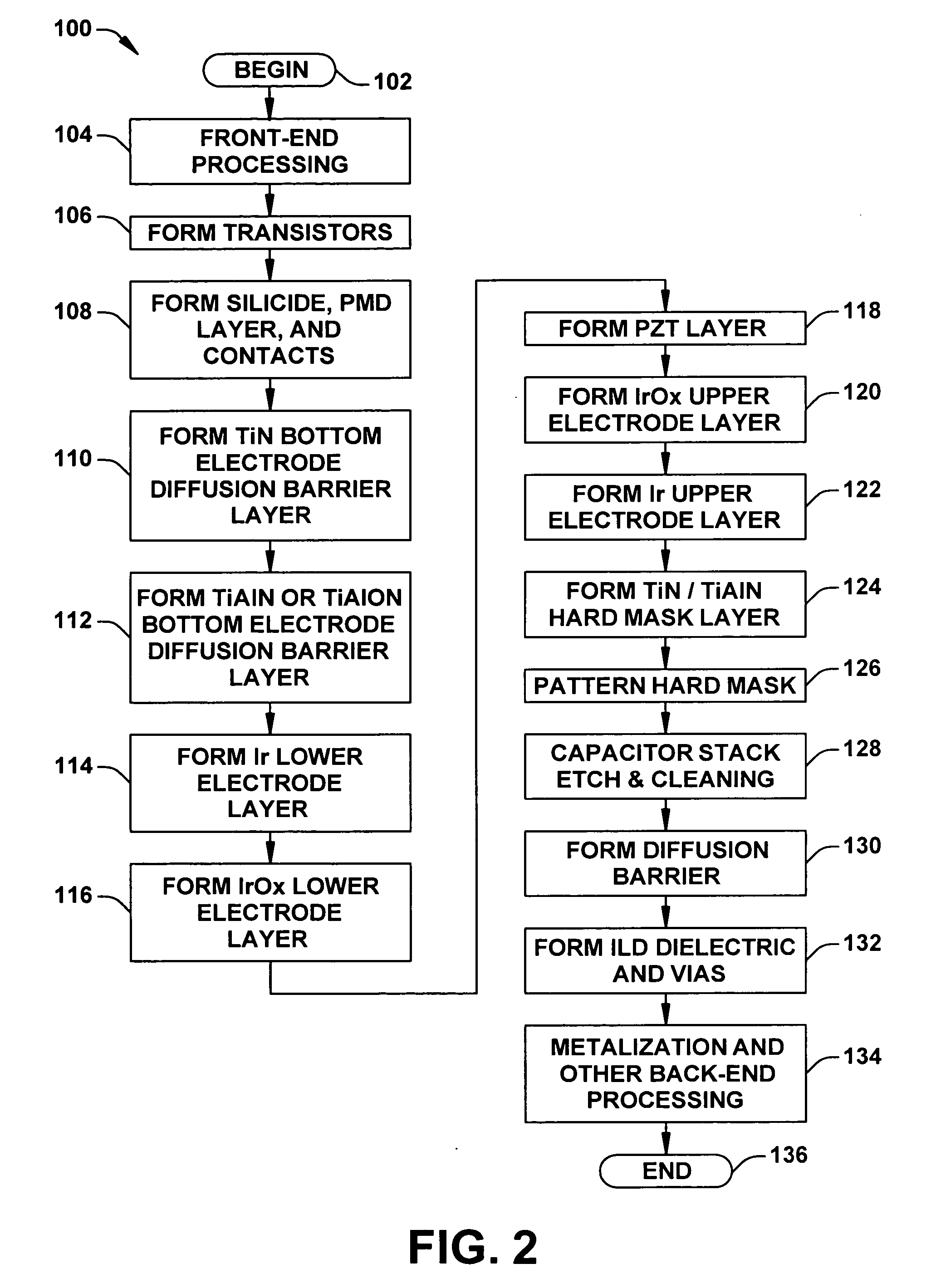

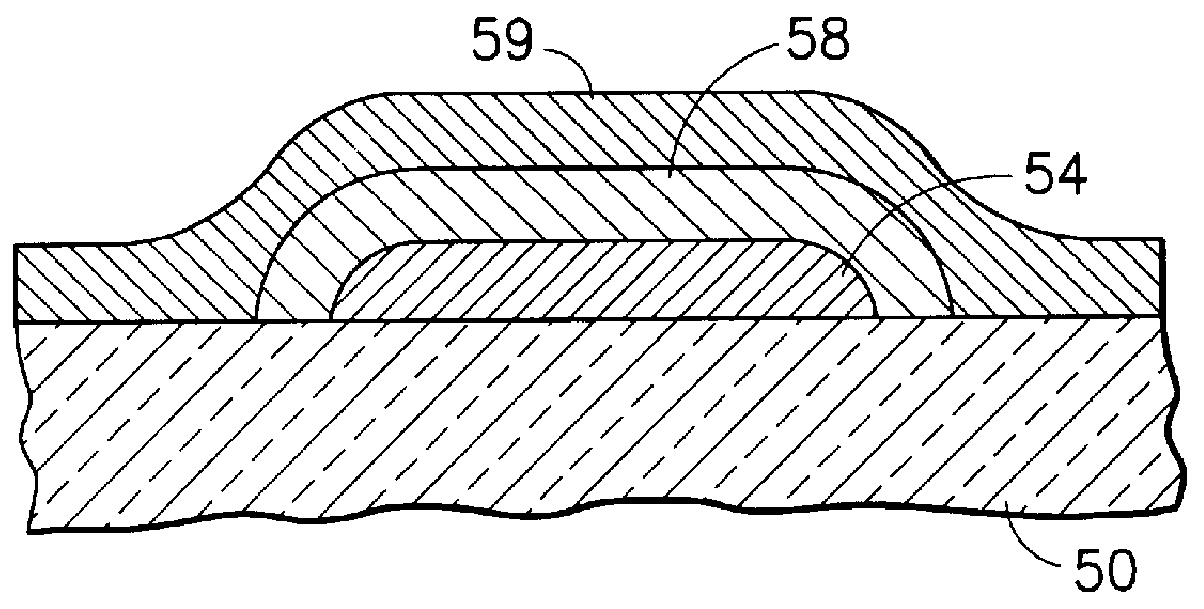

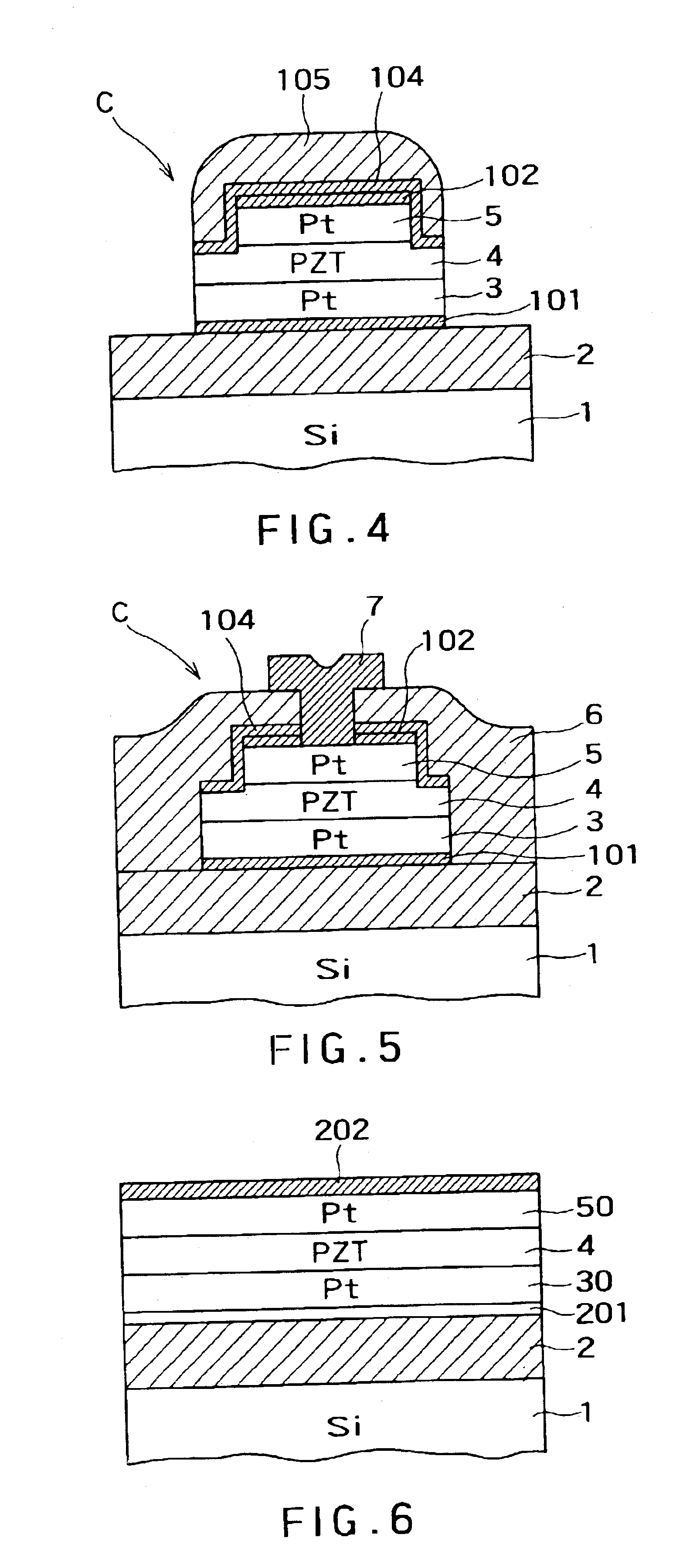

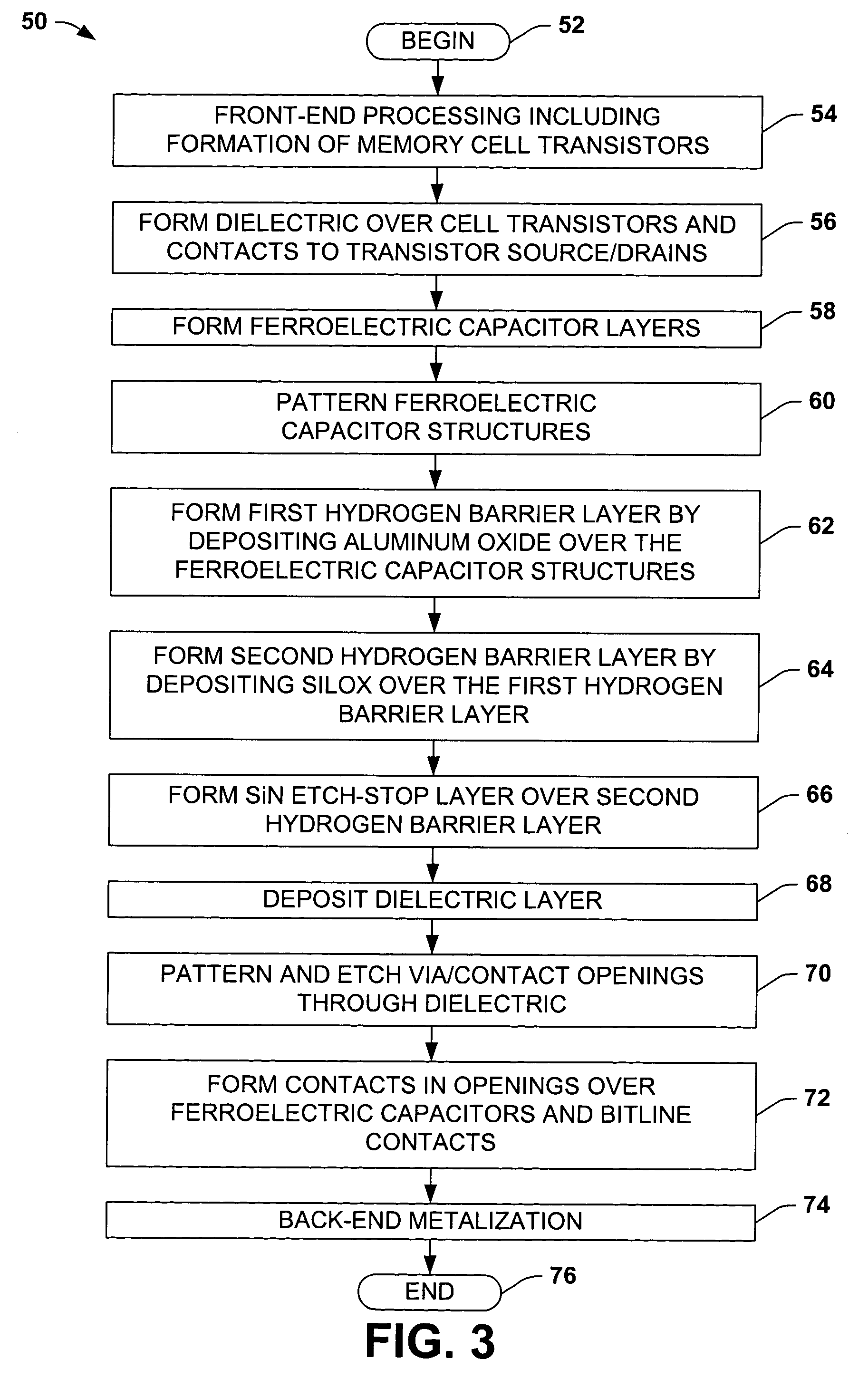

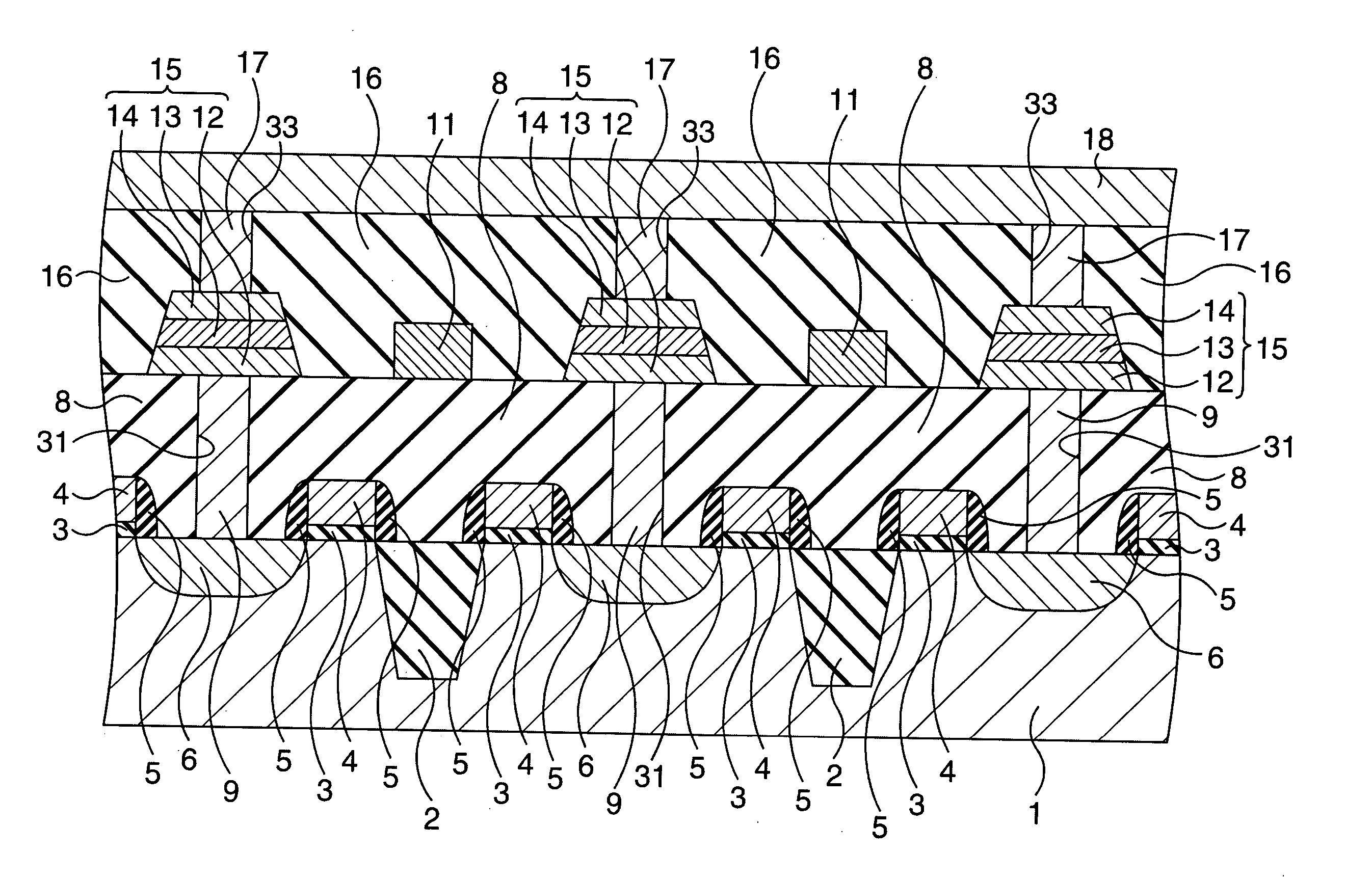

Ferroelectric memory cells and methods for fabricating ferroelectric memory cells and ferroelectric capacitors thereof

InactiveUS20060073613A1High crystallinityReduce pruningSolid-state devicesSemiconductor/solid-state device manufacturingDielectricDevice material

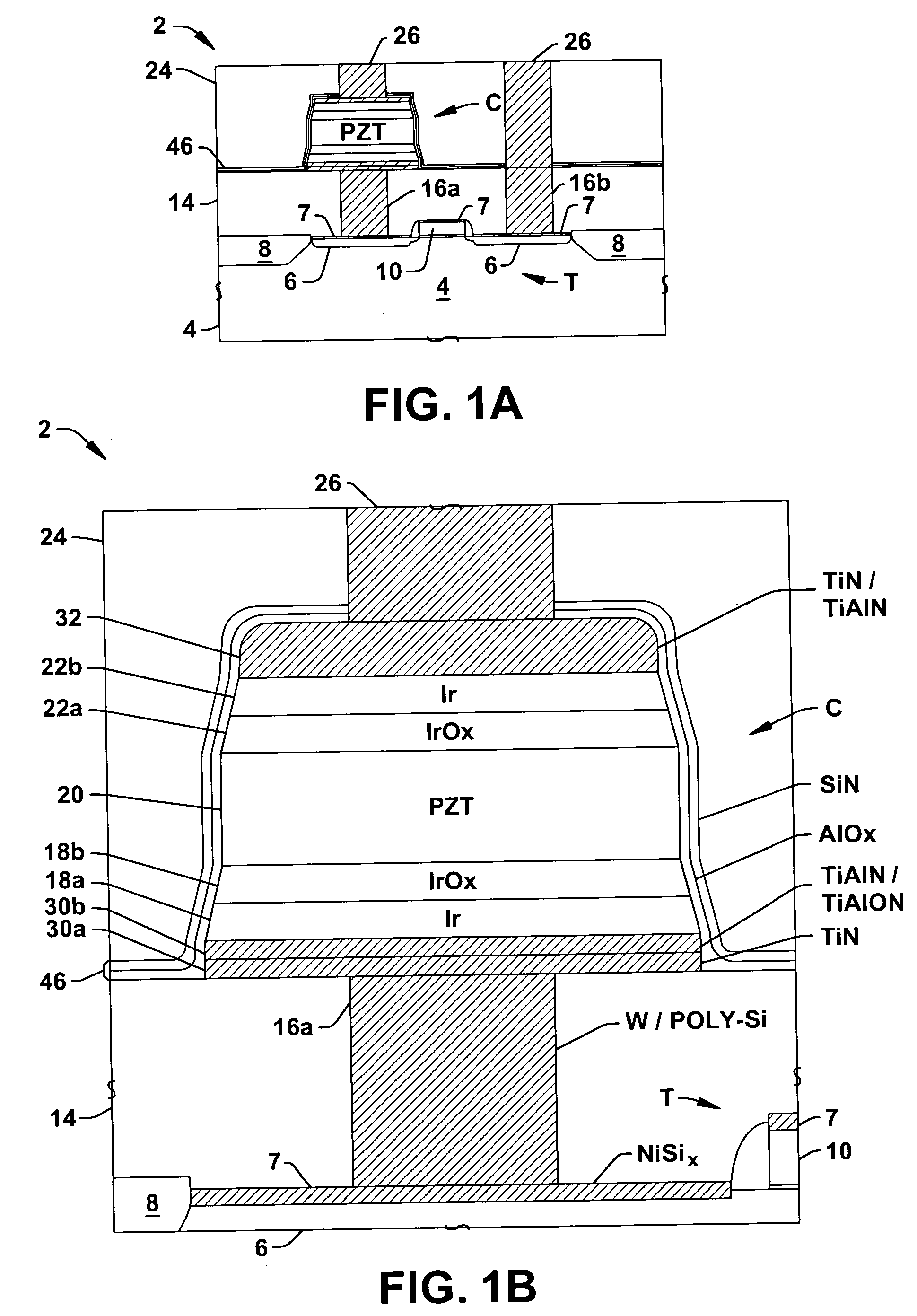

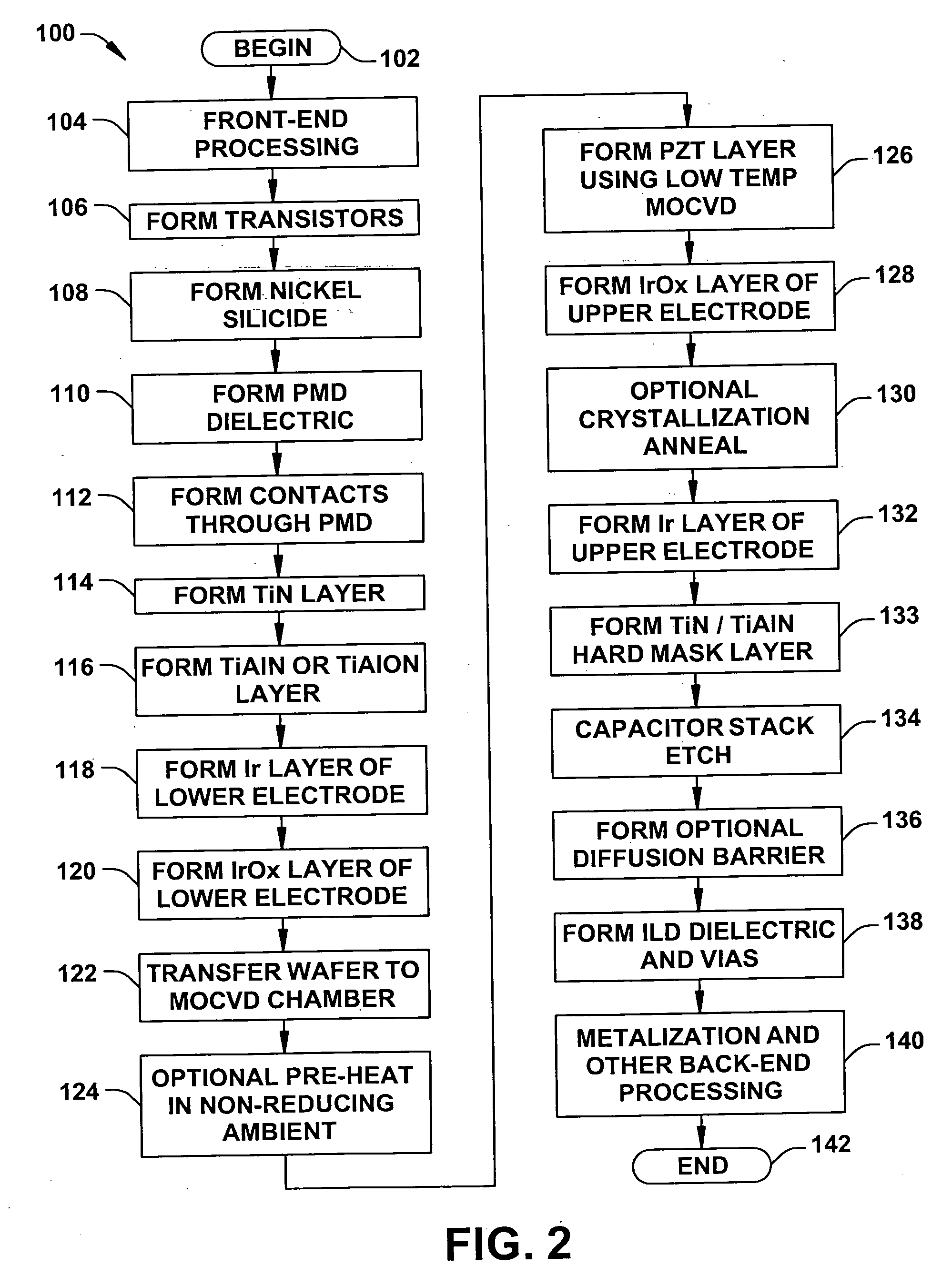

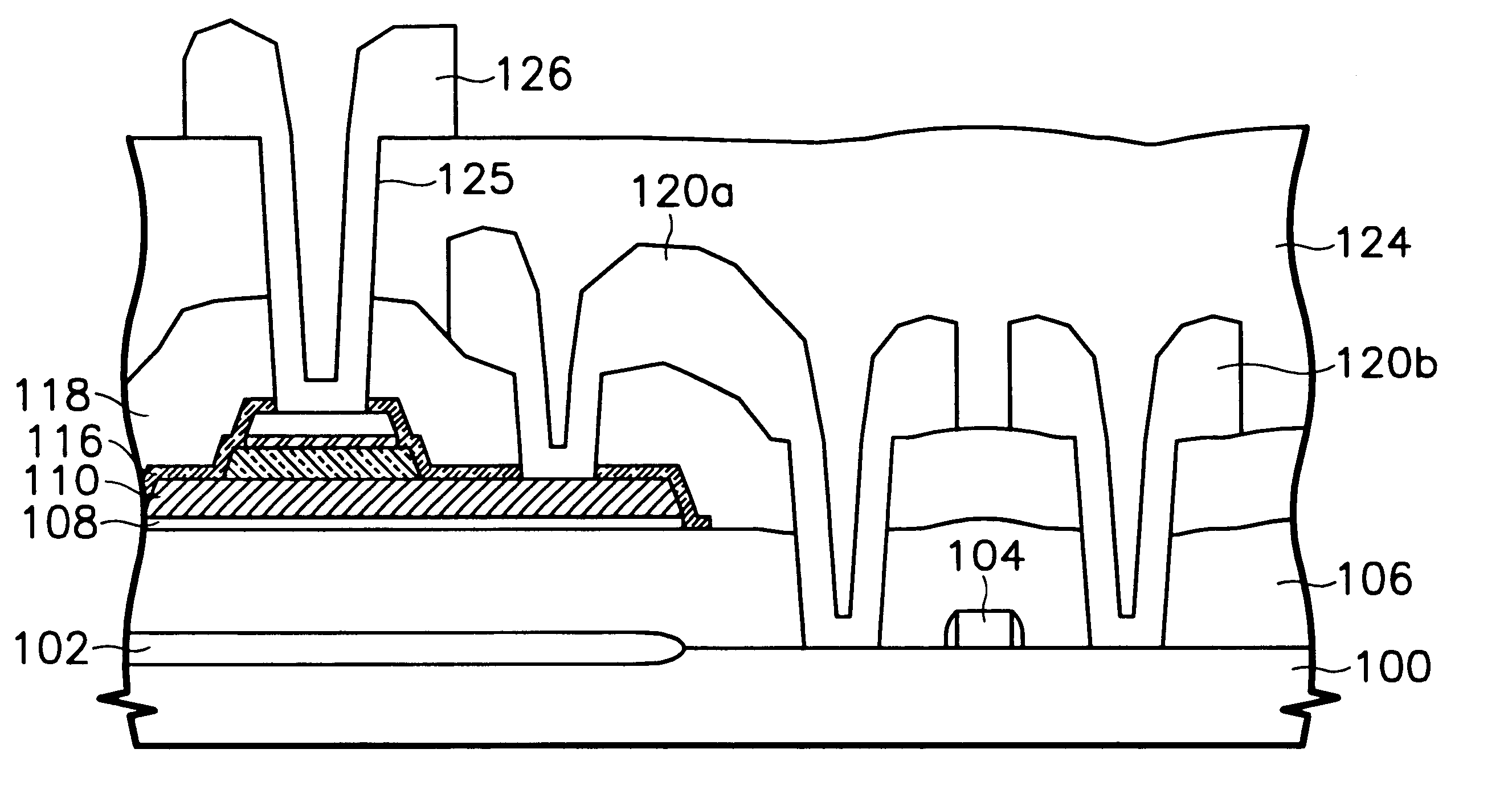

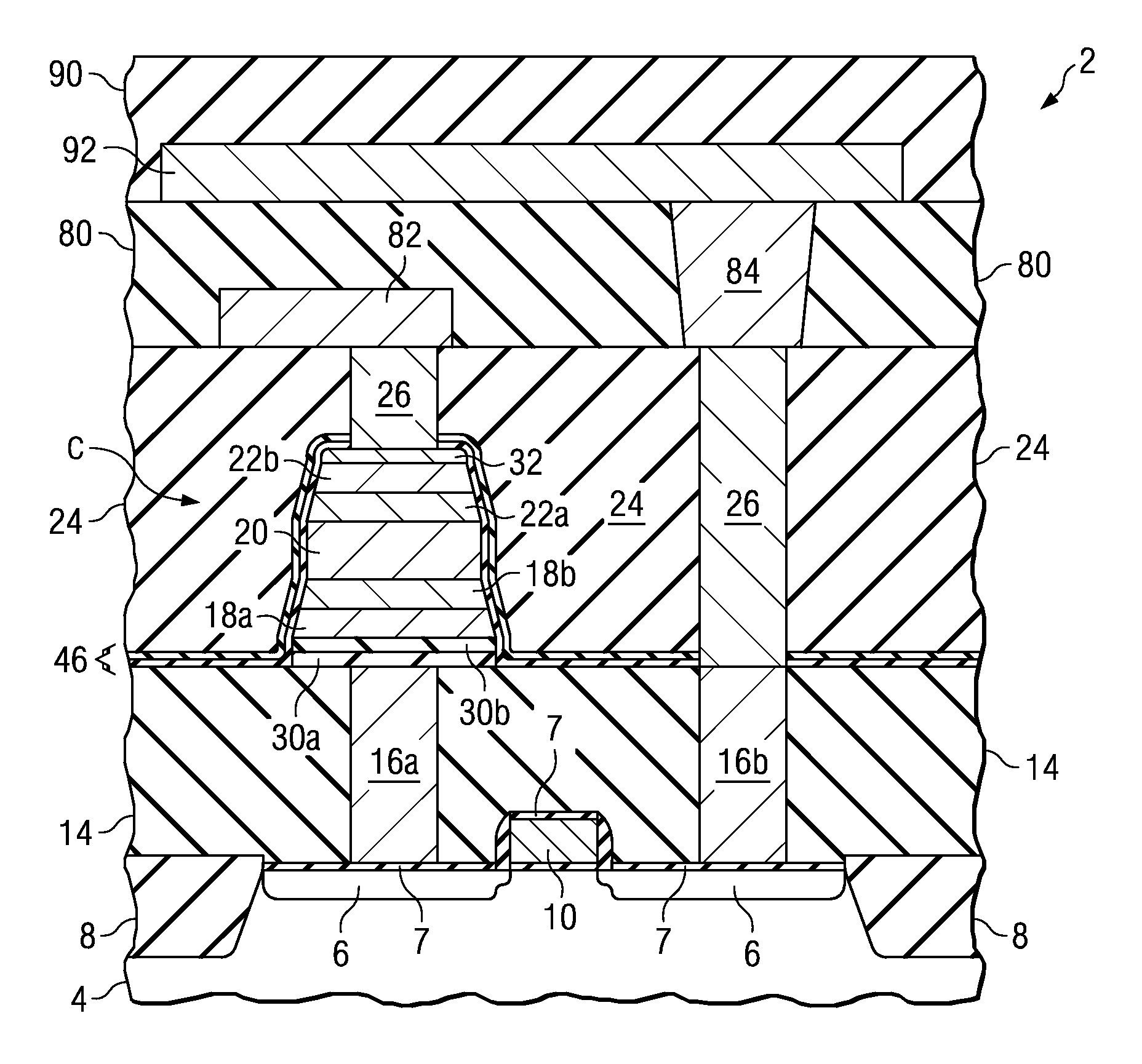

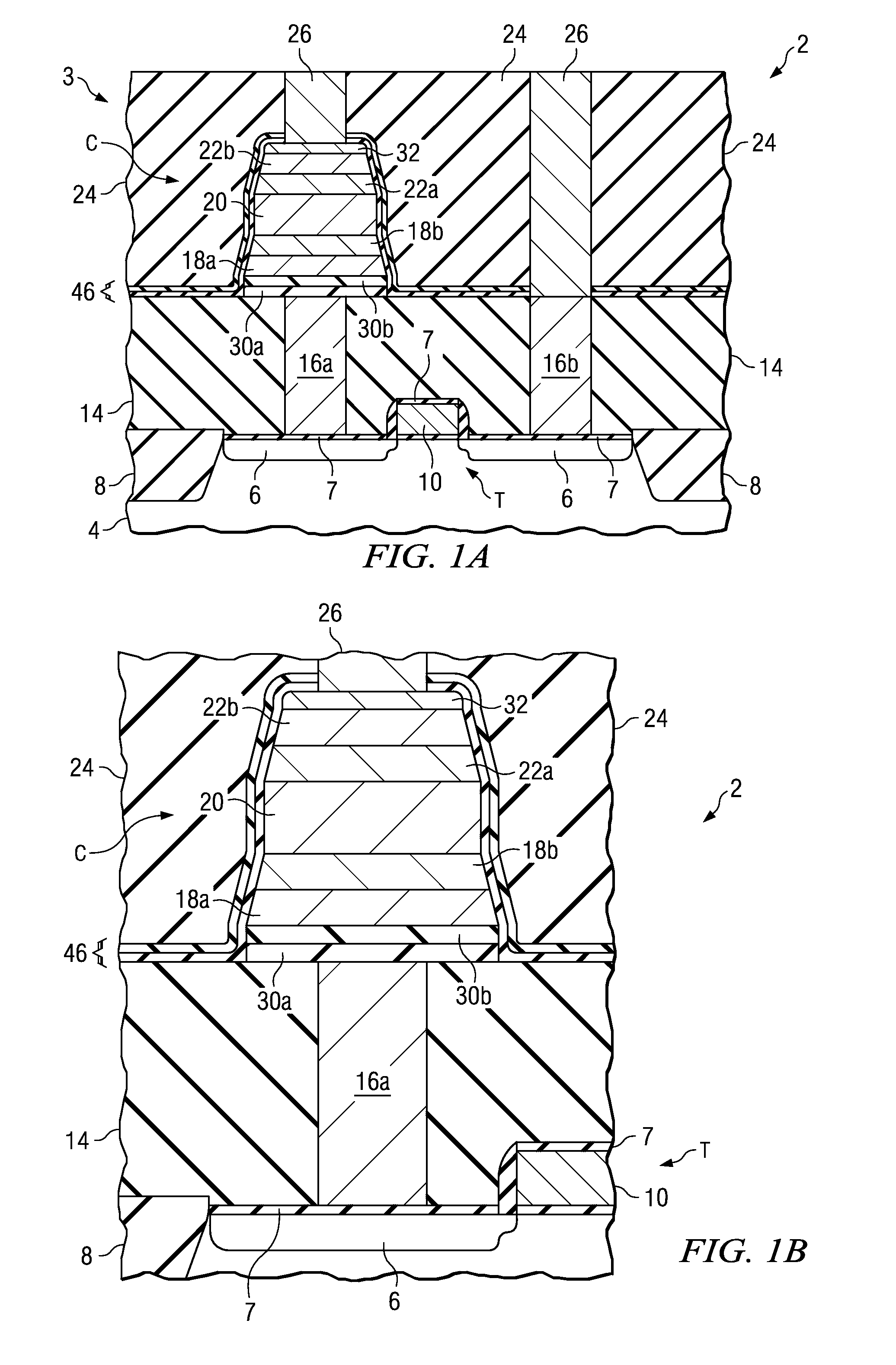

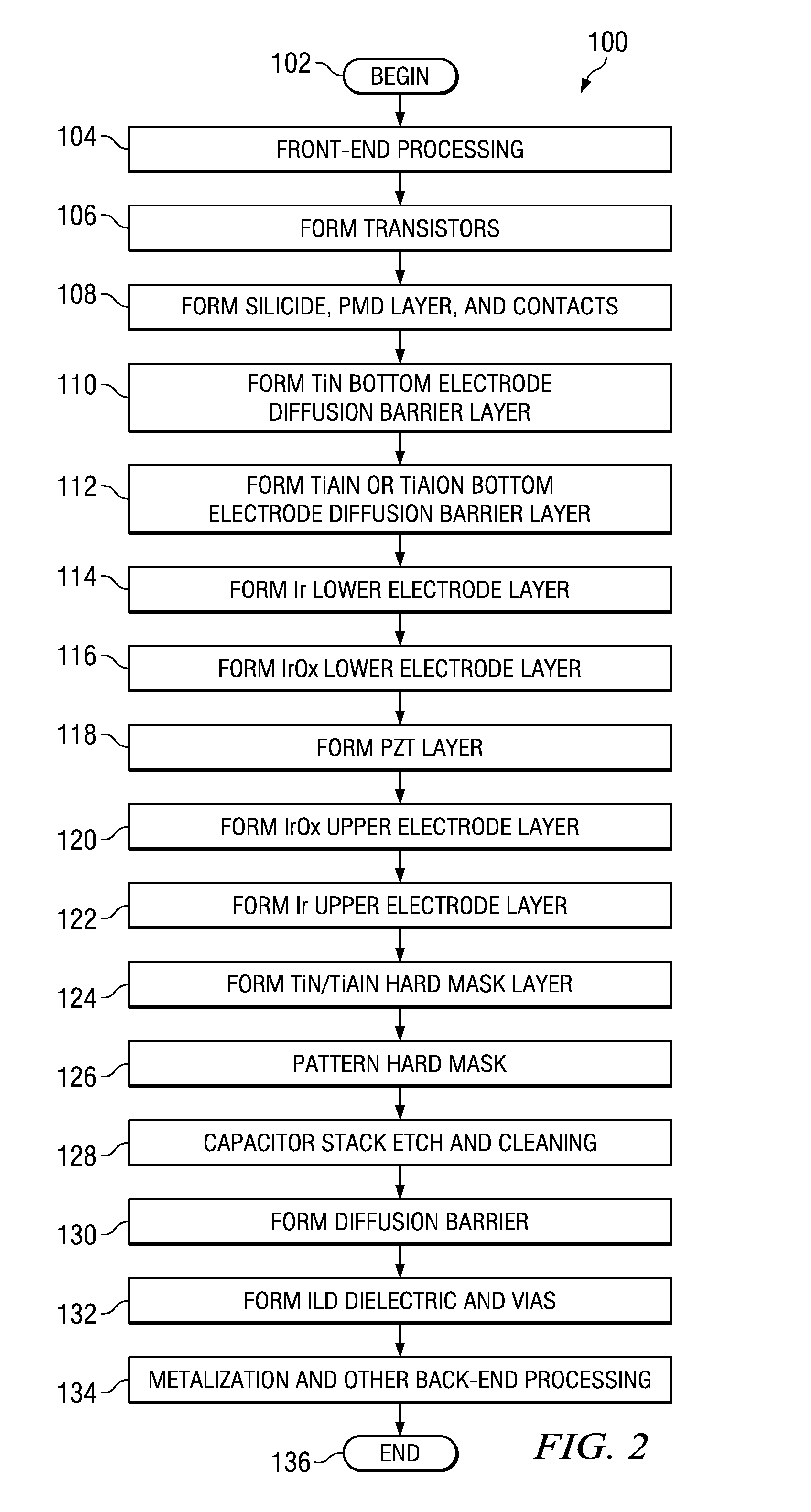

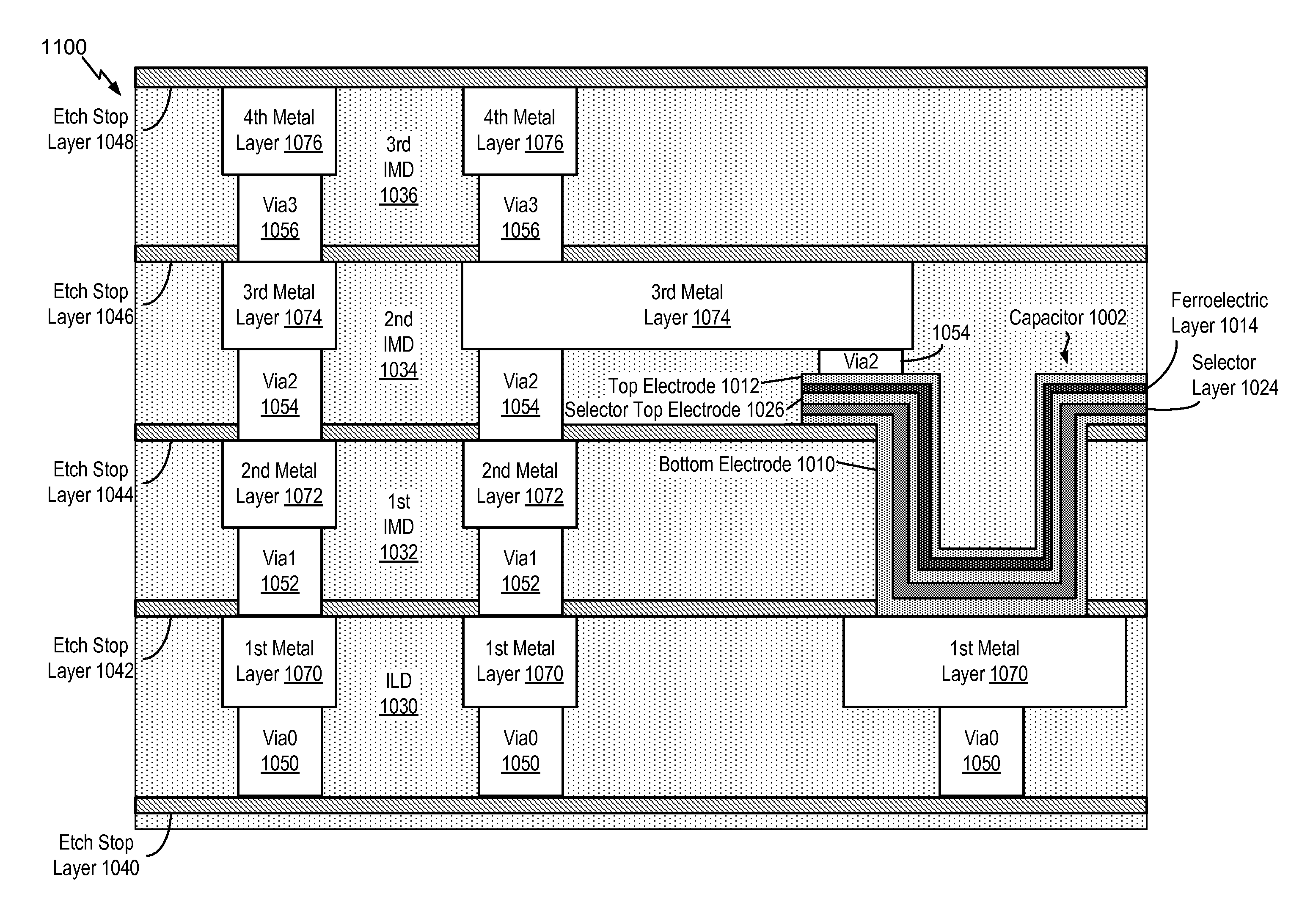

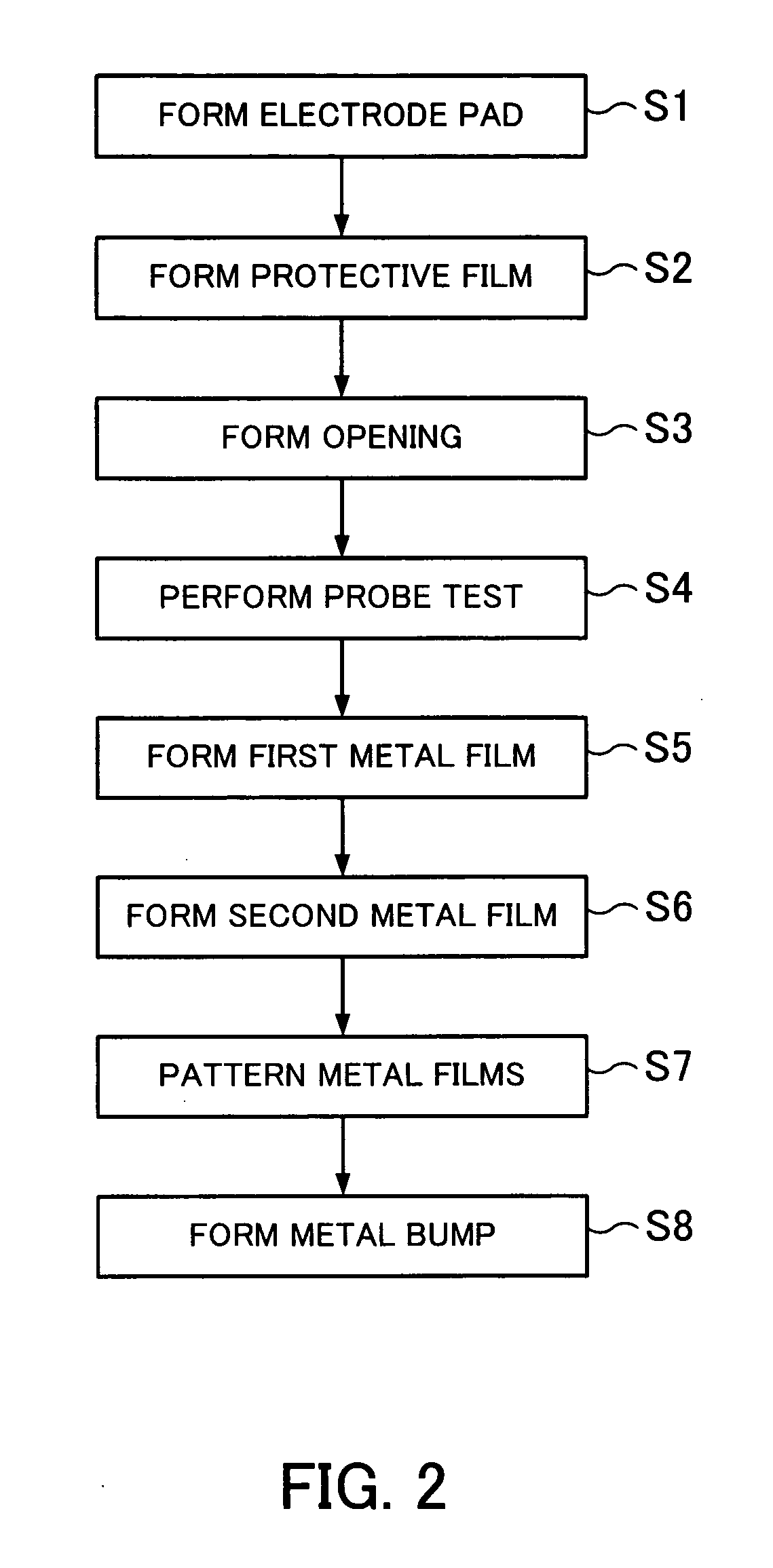

Methods (100) are provided for fabricating a ferroelectric capacitor in a semiconductor device wafer, comprising forming (118) a lower electrode, depositing (126) PZT ferroelectric material on the lower electrode at a temperature below 450 degrees C., and forming (128) an upper electrode on the PZT. Methods are also provided for fabricating a ferroelectric memory cell in a semiconductor device wafer, comprising forming (106) a transistor in the wafer, forming (108) a nickel silicide structure on the gate or a source / drain of the transistor, forming (110) a dielectric over the transistor, forming (112) a conductive contact extending through the dielectric to the silicide structure, forming (114, 116, 118, 120) a lower electrode on at least a portion of the conductive contact, forming (126) PZT ferroelectric material above and in contact with the lower electrode at a temperature below 450 degrees C., forming (128, 132) an upper electrode above and in contact with the PZT, and patterning (134) the upper electrode, the PZT, and the lower electrode to form a patterned ferroelectric capacitor.

Owner:TEXAS INSTR INC

Semiconductor integrated circuit device

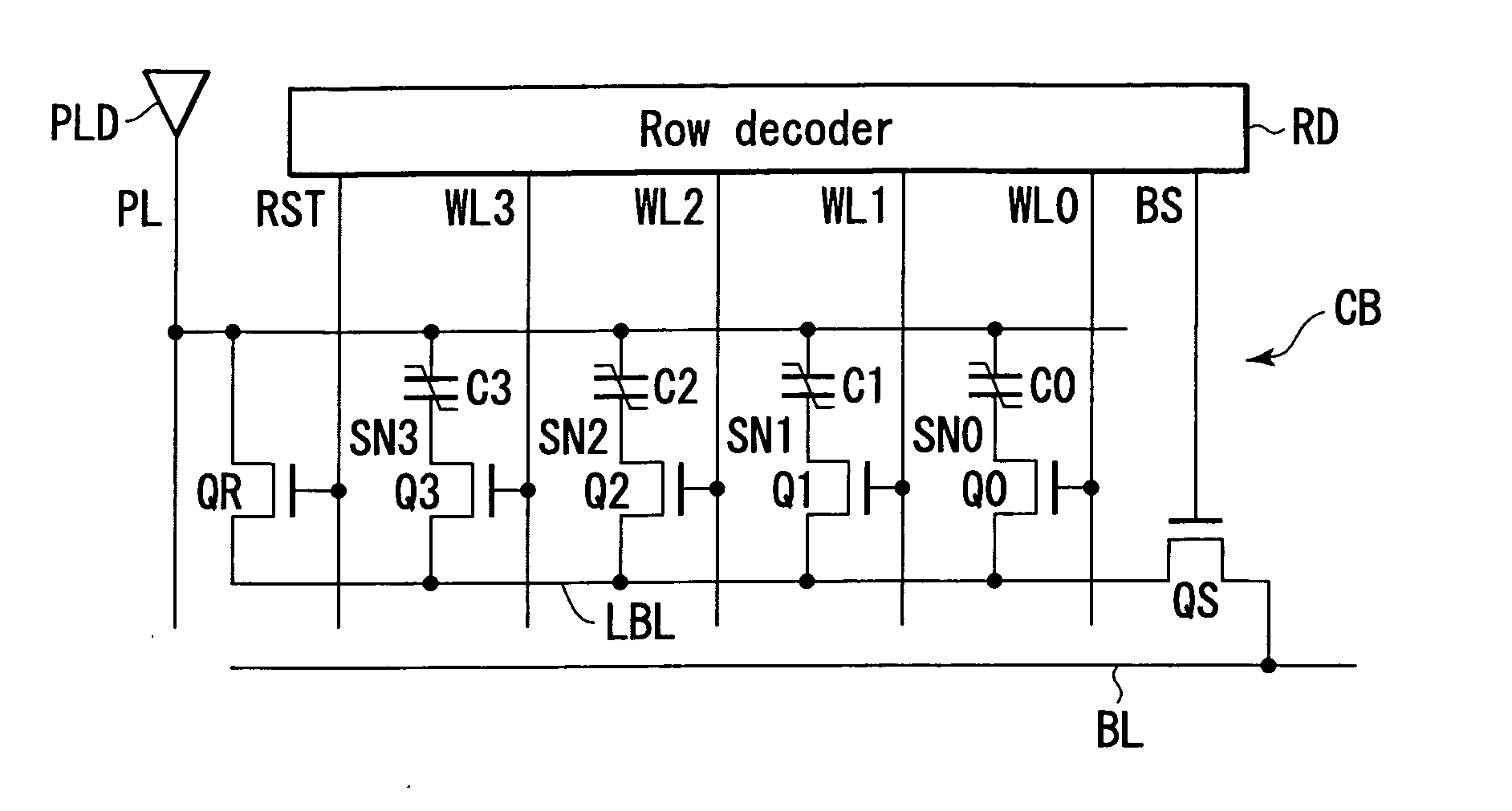

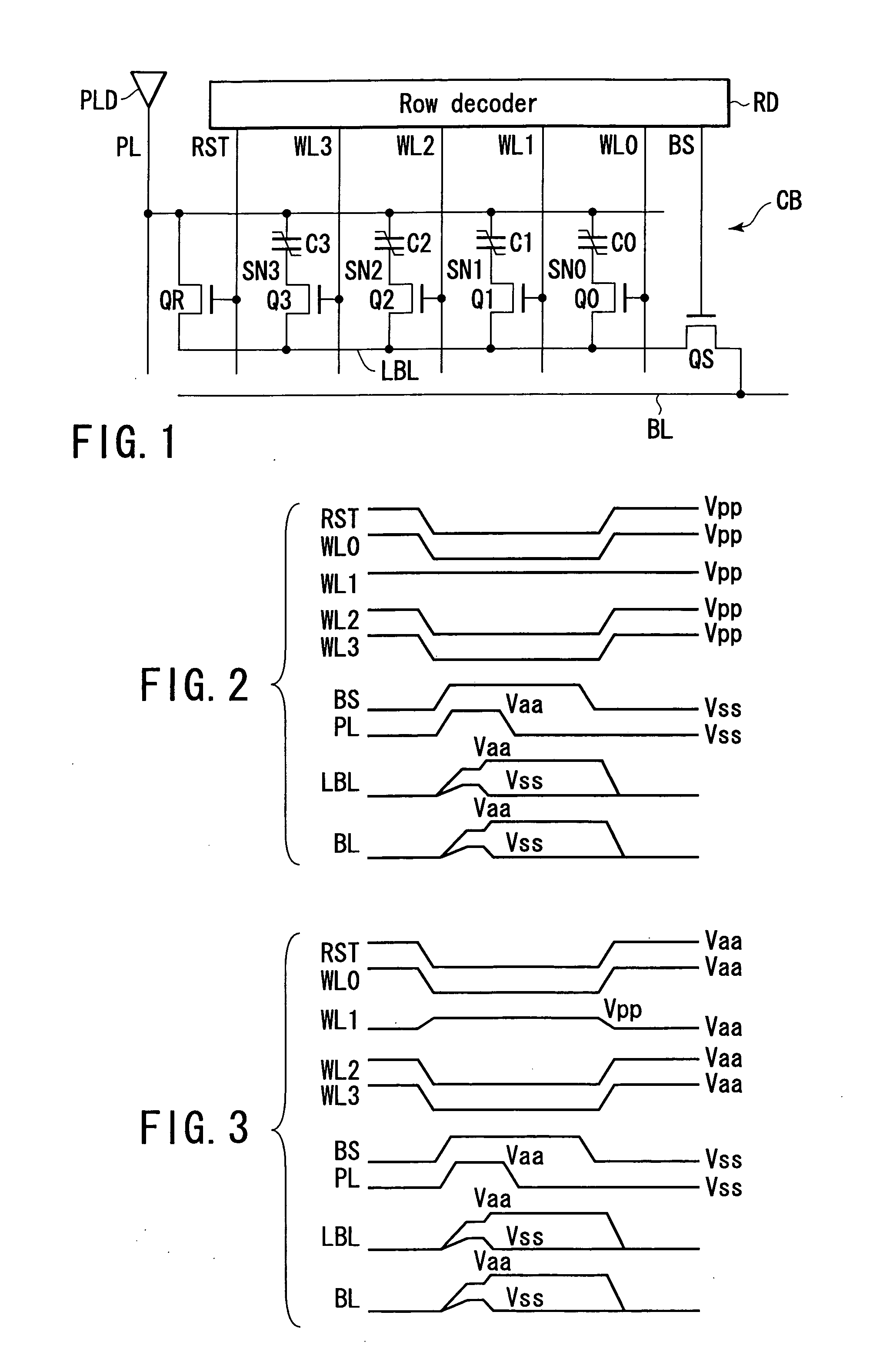

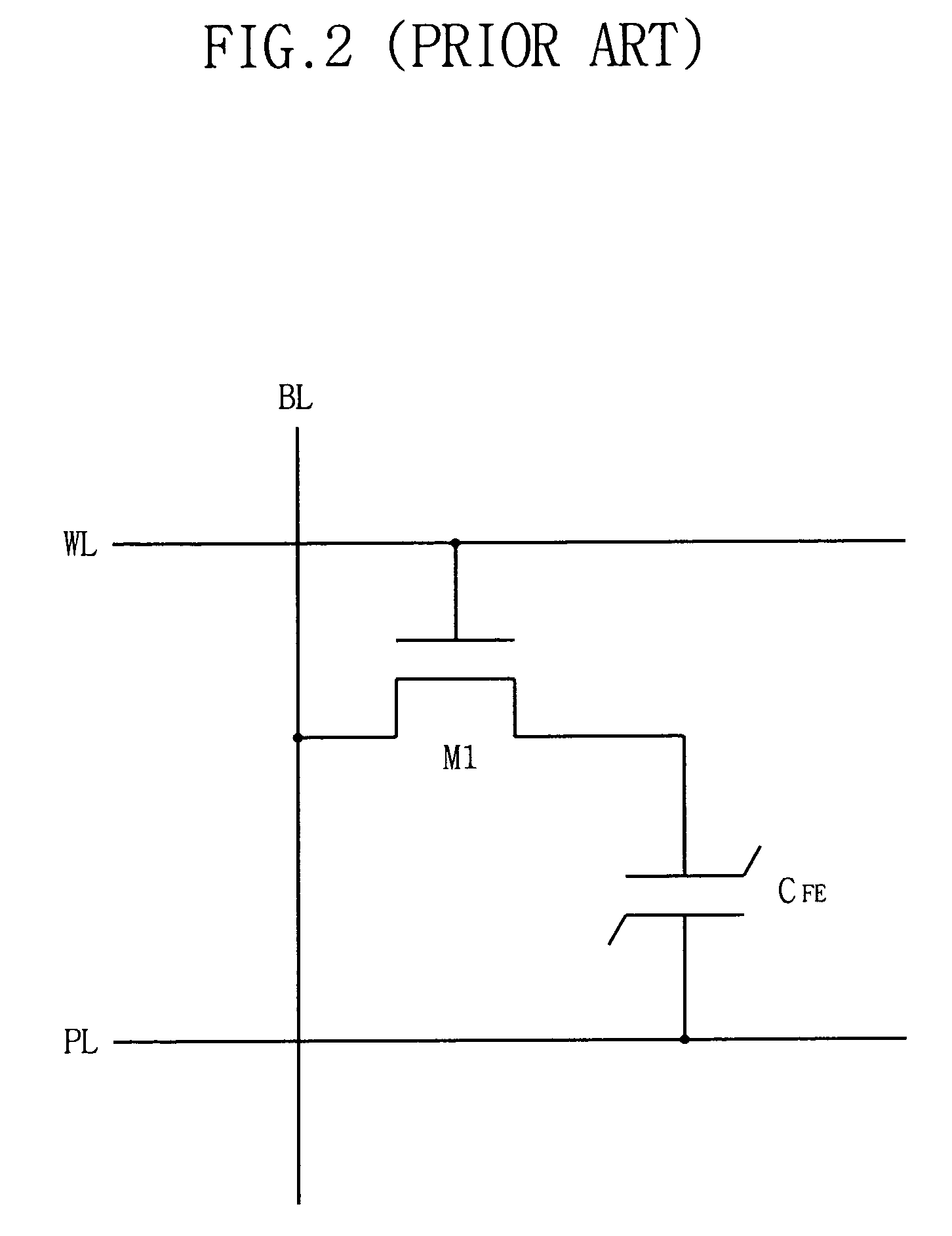

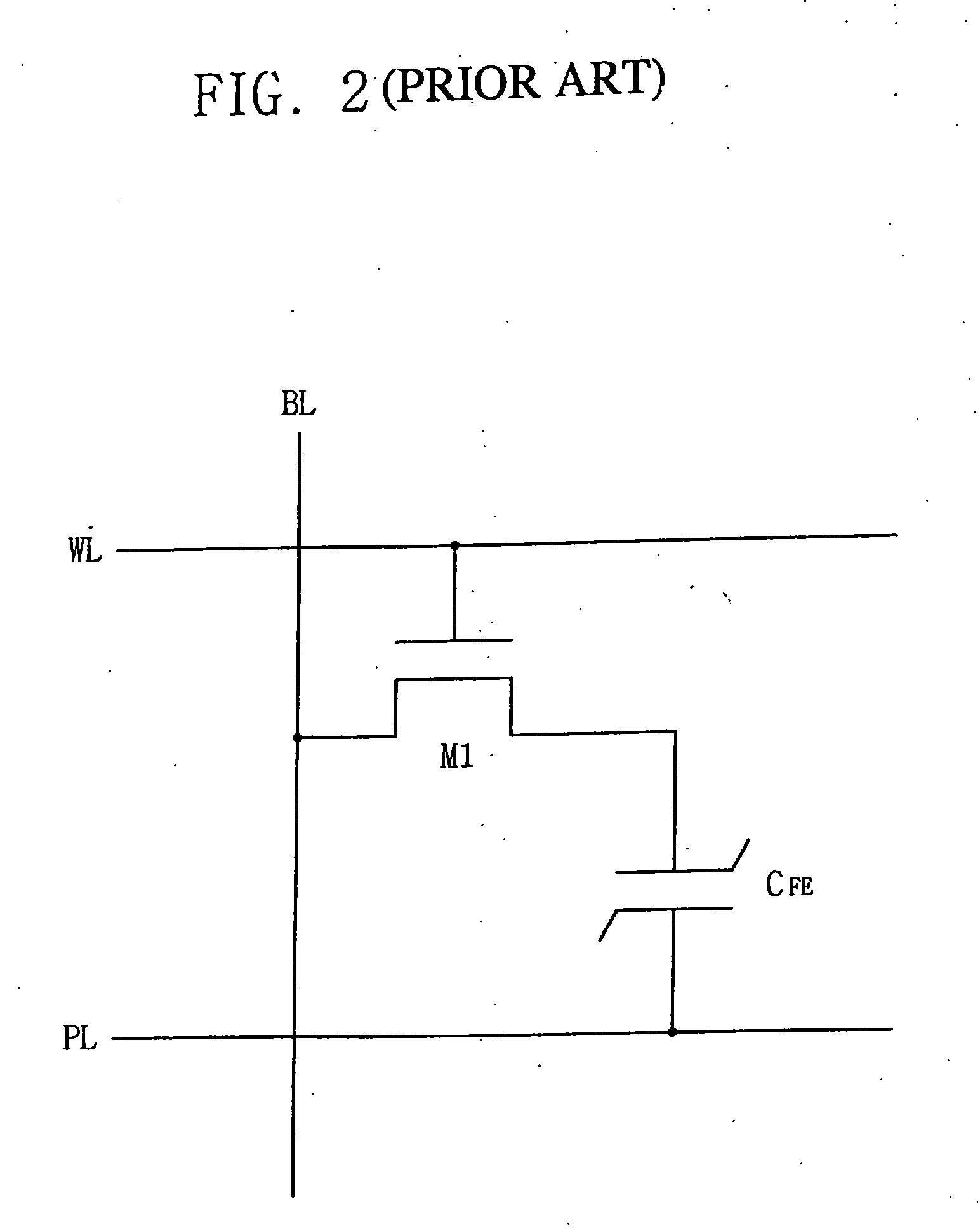

A semiconductor integrated circuit device includes a plurality of first memory cells each of which includes a cell transistor whose gate terminal is connected to a word line and a ferroelectric capacitor which is connected at one end to a source terminal of the cell transistor. The drain terminals of the cell transistors of are used as a first local bit line, the other end of each of the ferroelectric capacitors are used as a first plate line. A first reset transistor has a source terminal connected to the first plate line and a drain terminal connected to the first local bit line. A first block selection transistor has a source terminal connected to the first local bit line and a drain terminal connected to a first bit line.

Owner:KK TOSHIBA

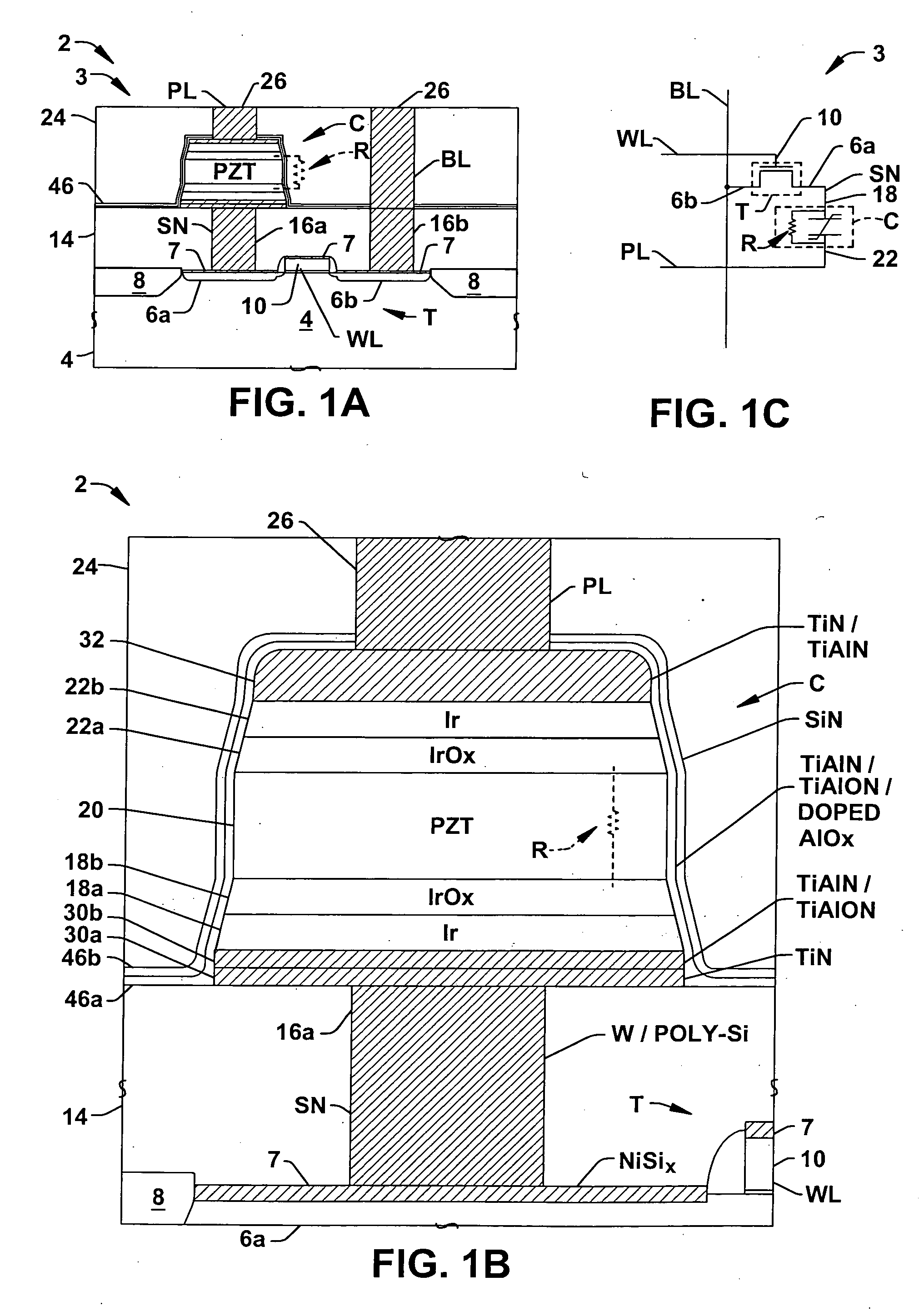

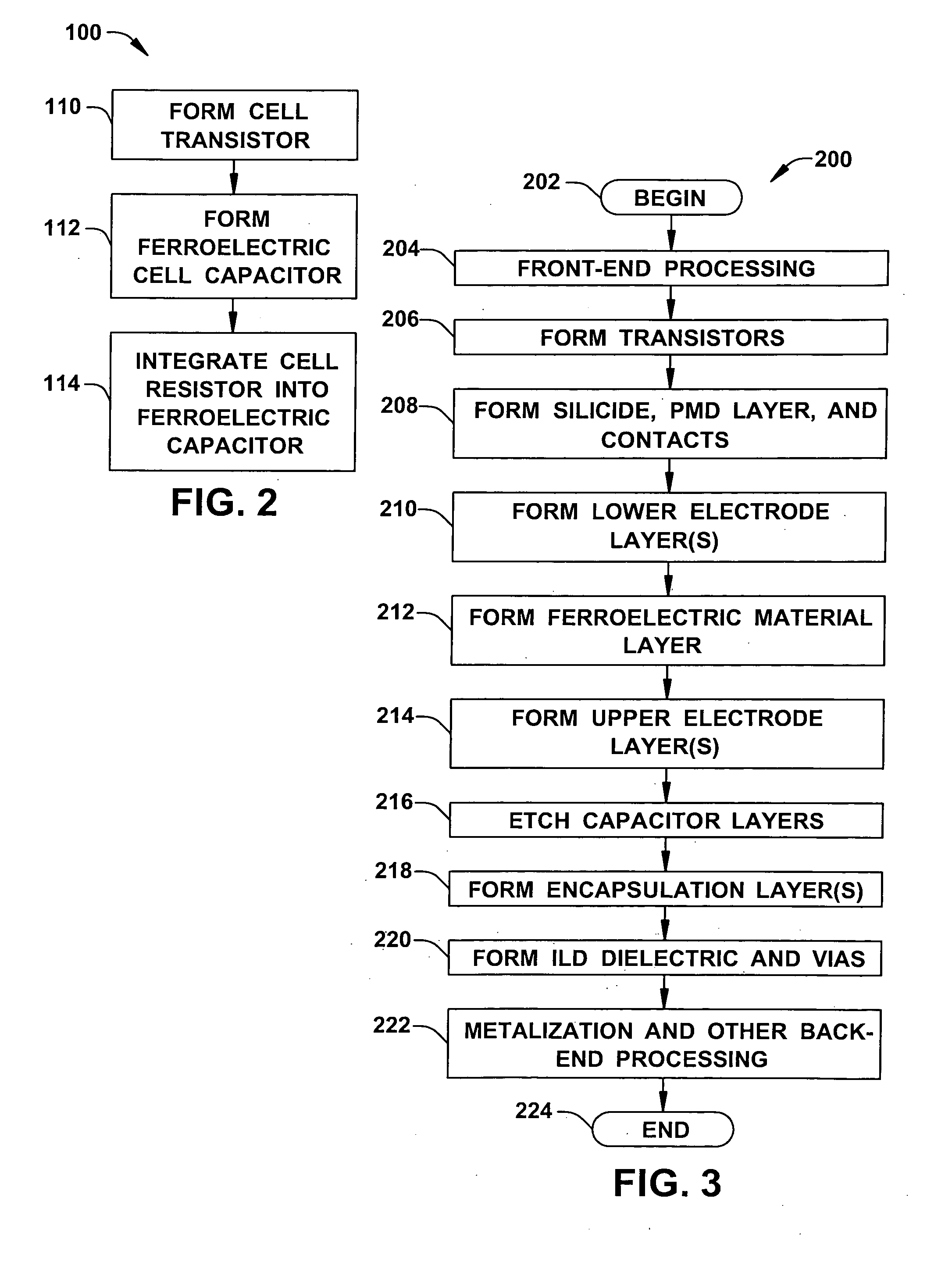

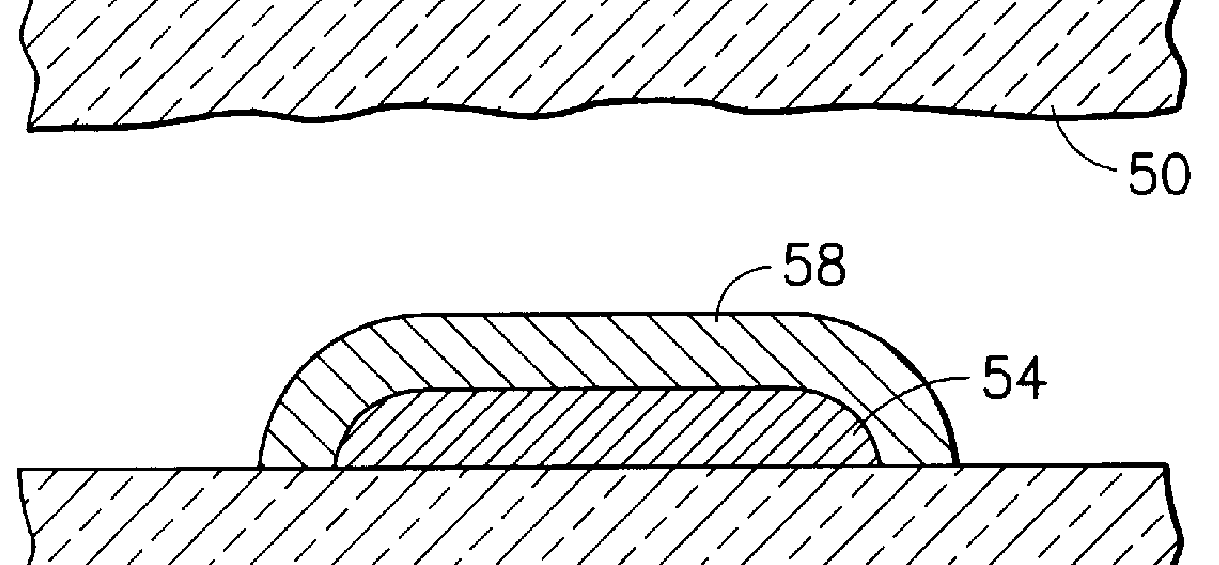

Ferroelectric capacitor with parallel resistance for ferroelectric memory

ActiveUS20060118841A1Avoid charge accumulationInhibits charge charge lossSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCharge loss

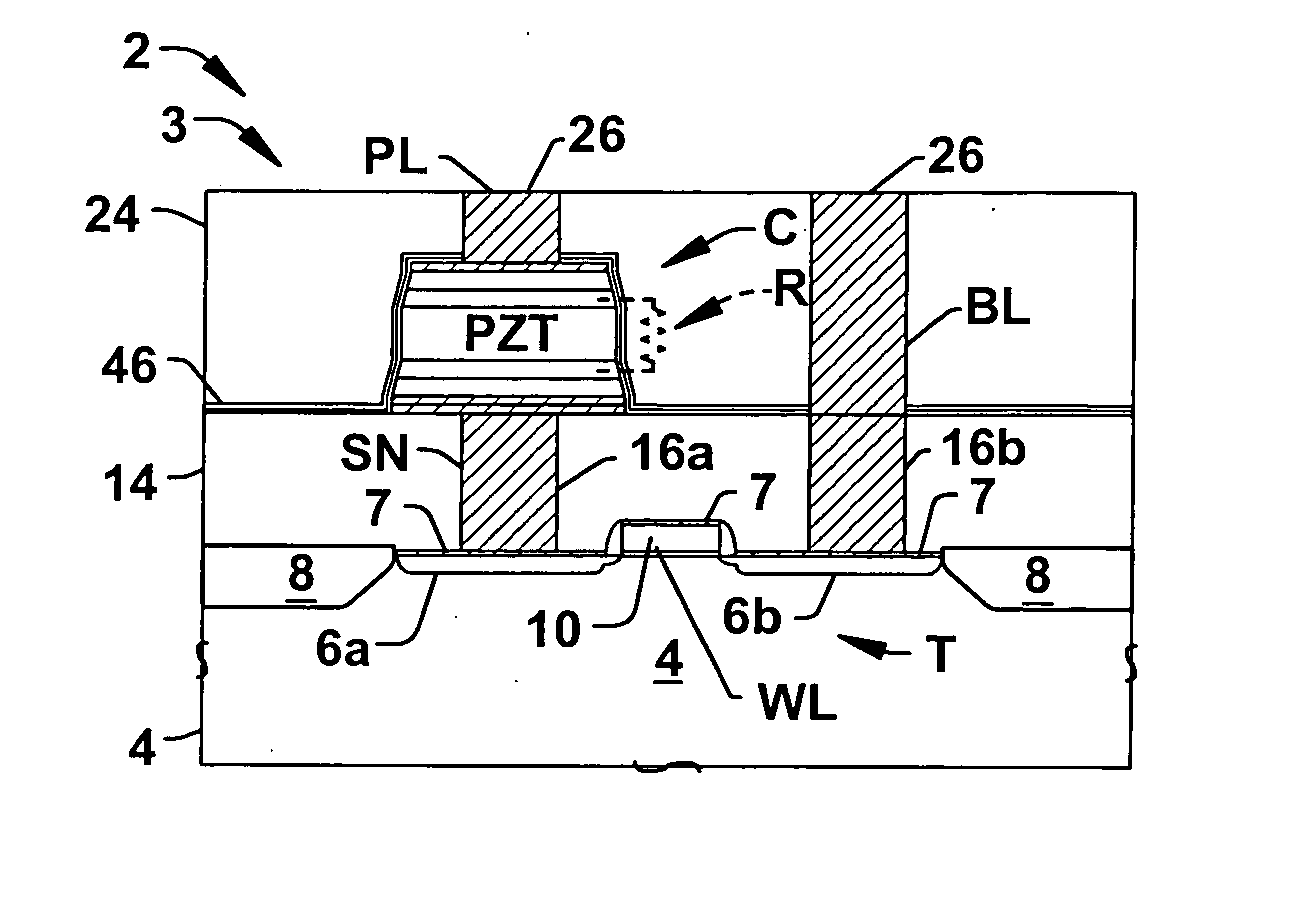

Ferroelectric memory cells (3) are presented, in which a cell resistor (R) is integrated into the cell capacitor (C) to inhibit charge accumulation or charge loss at the cell storage node (SN) when the cell (3) is not being accessed while avoiding significant disruption of memory cell access operations. Methods (100, 200) are provided for fabricating ferroelectric memory cells (3) and ferroelectric capacitors (C), in which a parallel resistance (R) is integrated in the capacitor ferroelectric material (20) or in an encapsulation layer (46) formed over the patterned capacitor structure (C).

Owner:TEXAS INSTR INC

Ferroelectric capacitor stack etch cleaning methods

ActiveUS20060134808A1Mitigate ferroelectric material damageMitigate capacitor leakageSemiconductor/solid-state device manufacturingCapacitorsEtchingDevice material

Methods (100) are provided for fabricating a ferroelectric capacitor structure including methods (128) for etching and cleaning patterned ferroelectric capacitor structures in a semiconductor device. The methods comprise etching (140, 200) portions of an upper electrode, etching (141, 201) ferroelectric material, and etching (142, 202) a lower electrode to define a patterned ferroelectric capacitor structure, and etching (143, 206) a portion of a lower electrode diffusion barrier structure. The methods further comprise ashing (144, 203) the patterned ferroelectric capacitor structure using a first ashing process, performing (145, 204) a wet clean process after the first ashing process, and ashing (146, 205) the patterned ferroelectric capacitor structure using a second ashing process directly after the wet clean process at a high temperature in an oxidizing ambient.

Owner:TEXAS INSTR INC

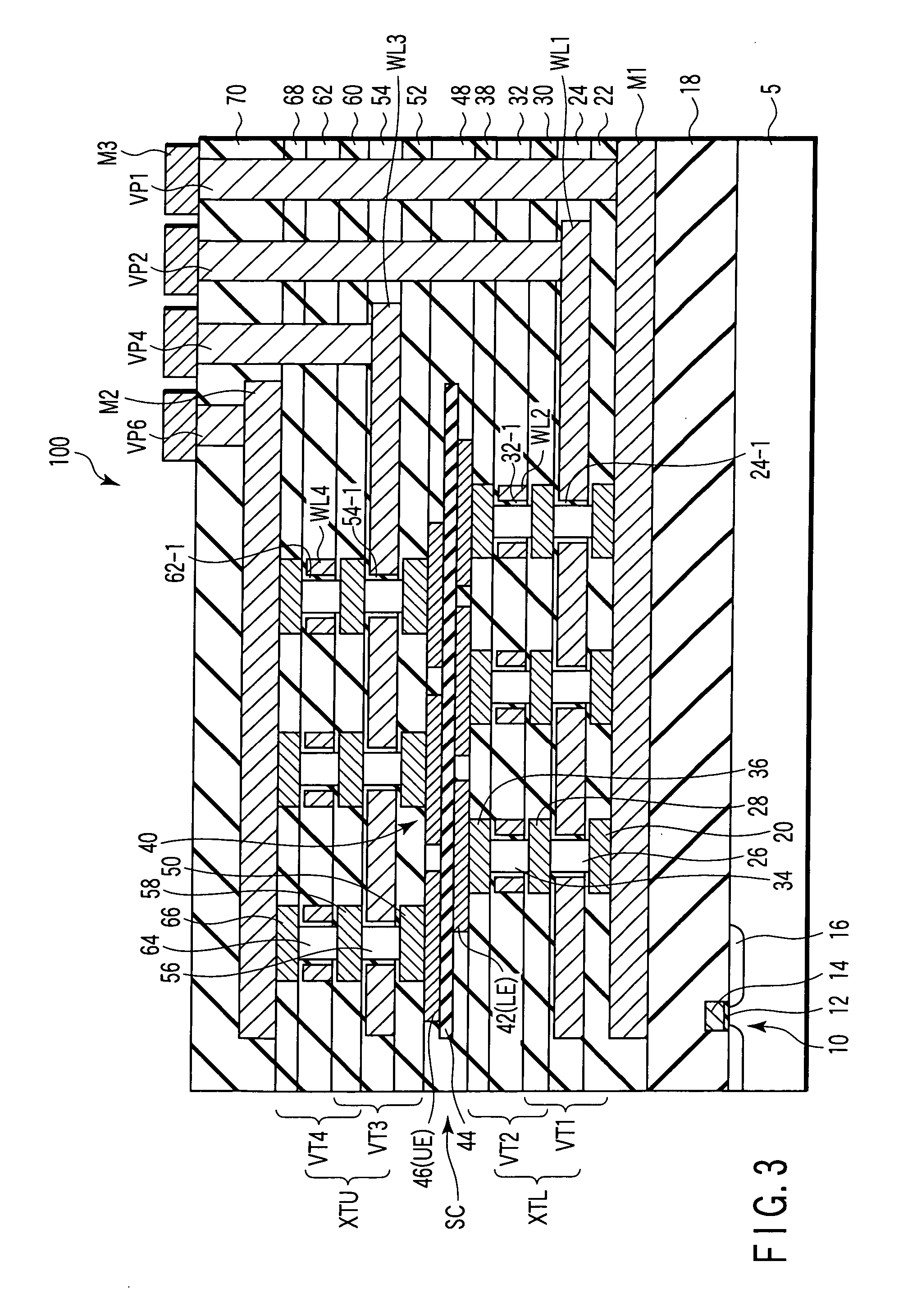

Three-dimensional non-volatile ferroelectric random access memory

InactiveUS20160118404A1Improve storage densitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricRandom access memory

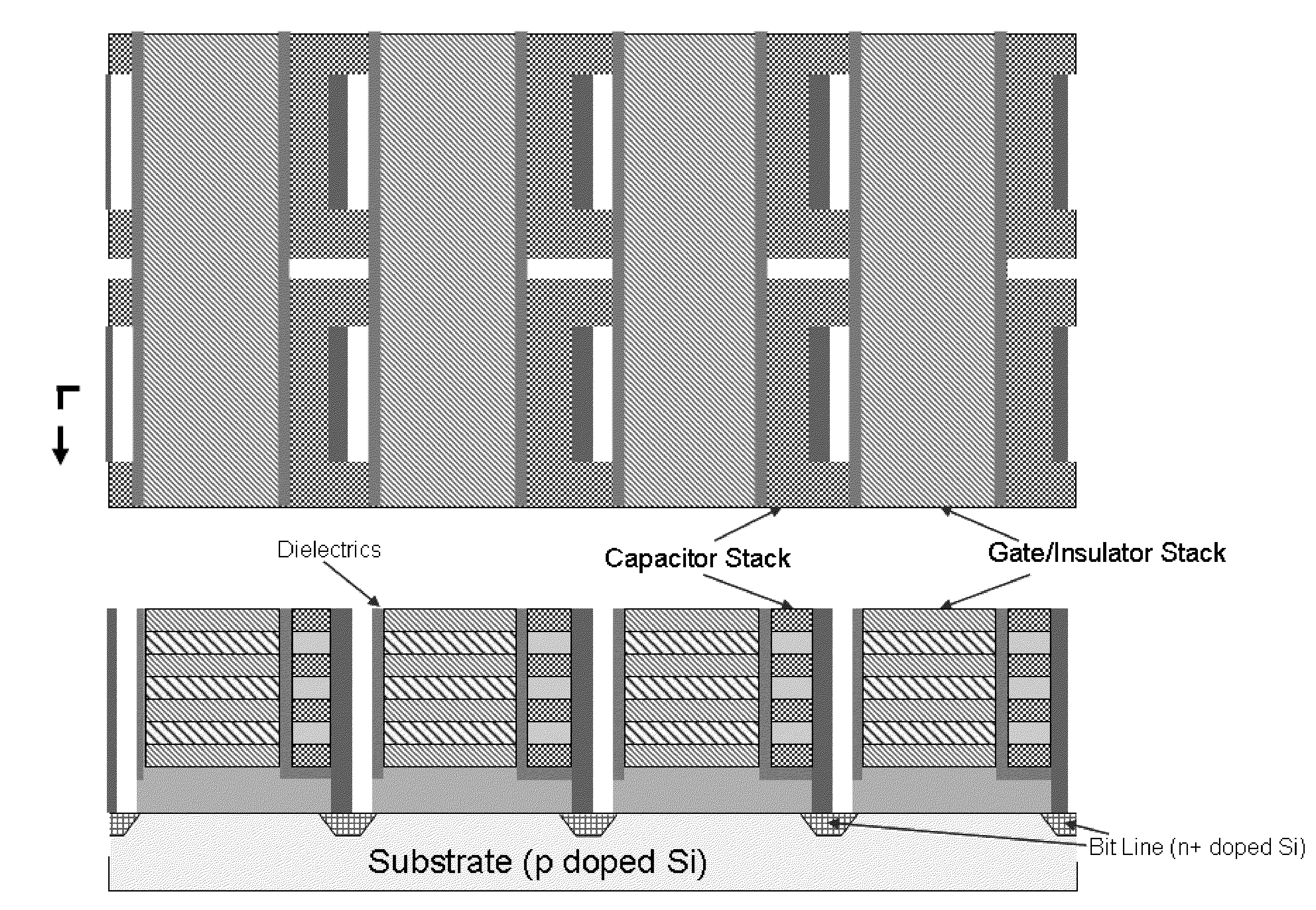

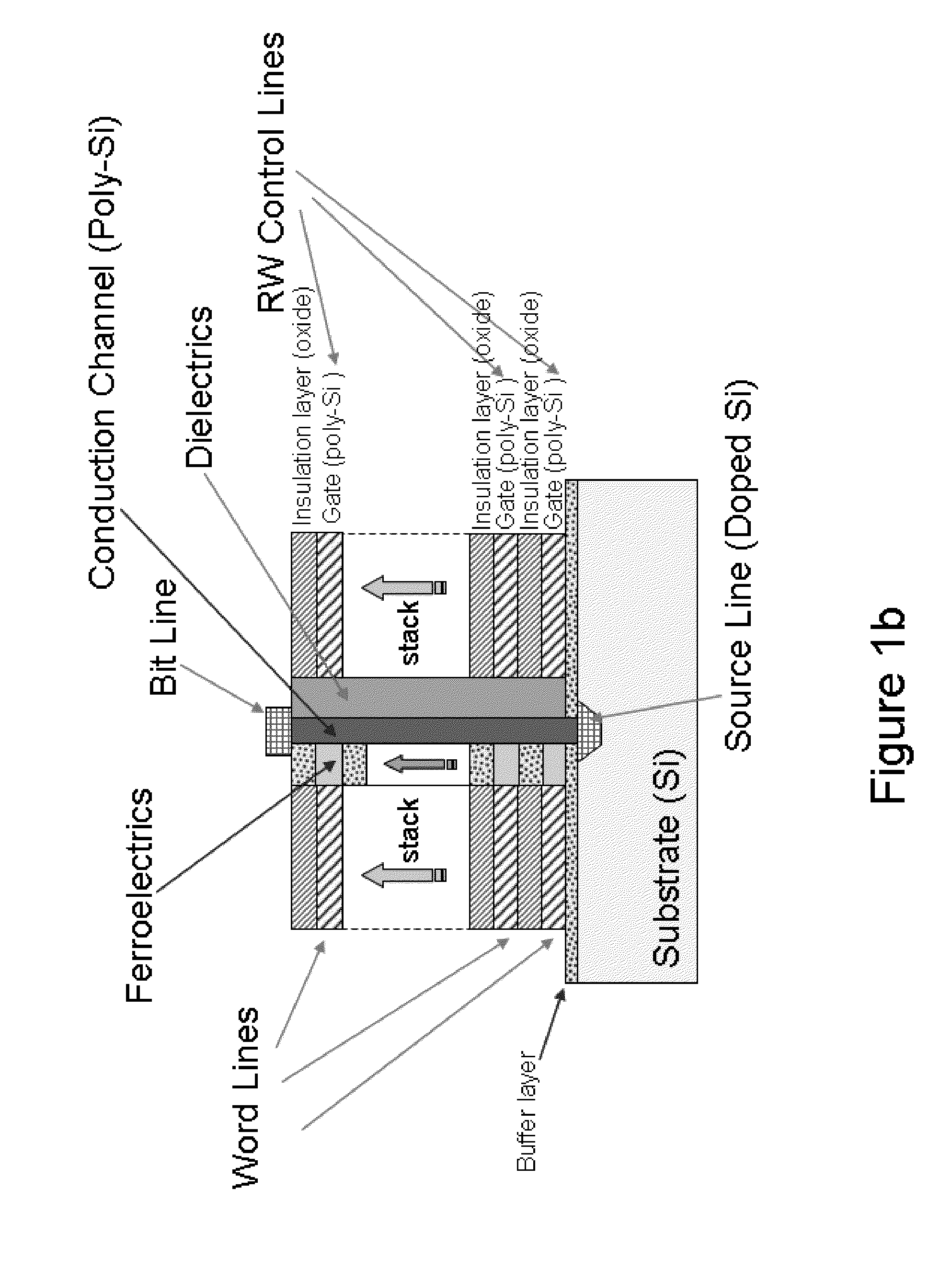

The present invention provides a design of three-dimensional non-volatile ferroelectric random access memory (FeRAM) devices for increasing the storage density. The key components include: (1) FeRAM device structures with (i) field-effect-transistors electrically connected either in series or in parallel as a basic memory group and (ii) a double-gate structure for implementing read / write schemes with full random access to individual memory cells, where one type of gates employs ferroelectrics layers as the gate dielectrics while the other type of gates employs conventional dielectric materials as the gate dielectrics; and (2) FeRAM device structures with stacked ferroelectric-capacitors and field-effect-transistors electrically connected in series as a basic NAND memory group. Example fabrication processes for implementing such three-dimensional FeRAM devices are also provided.

Owner:PENG HAIBING

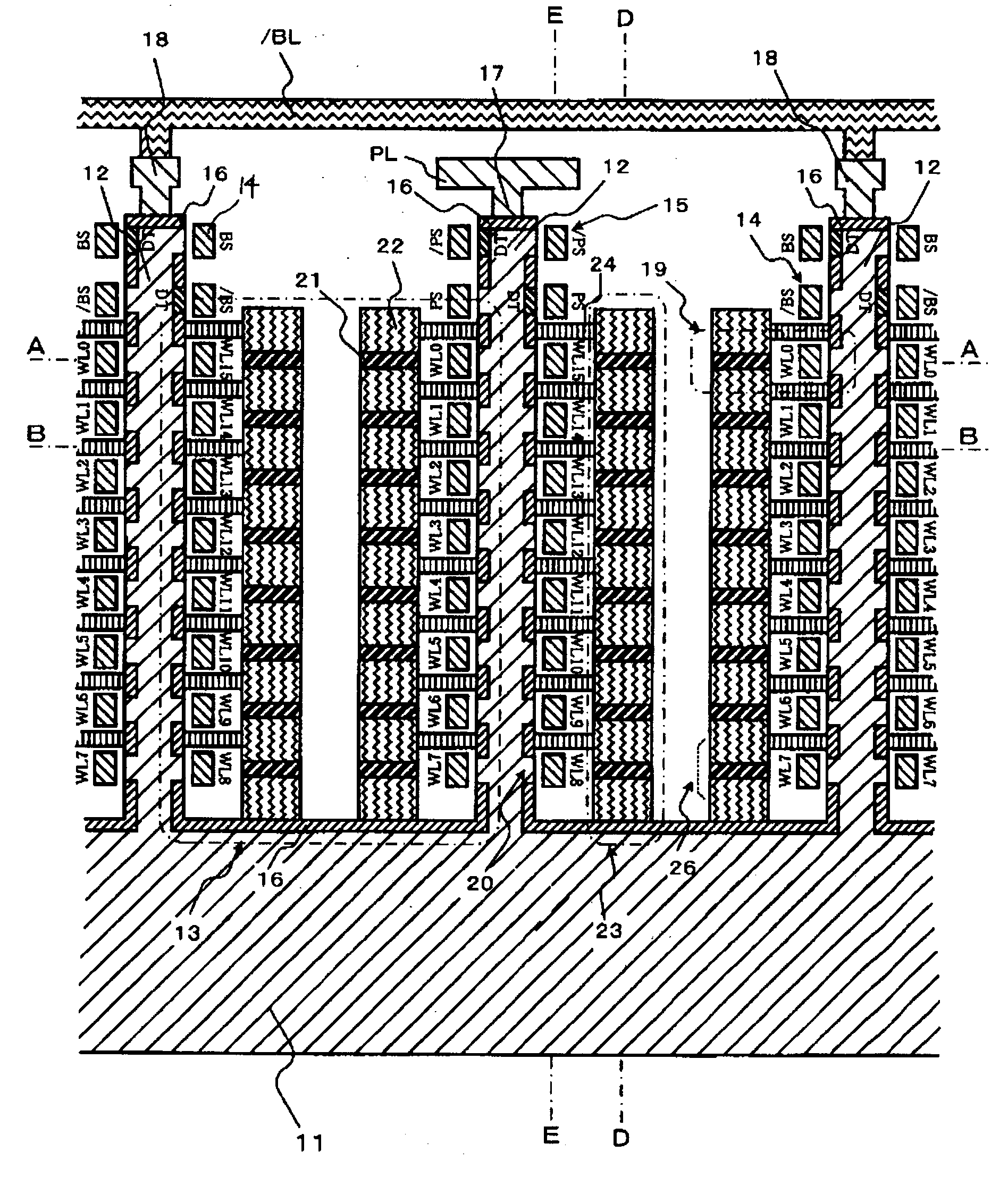

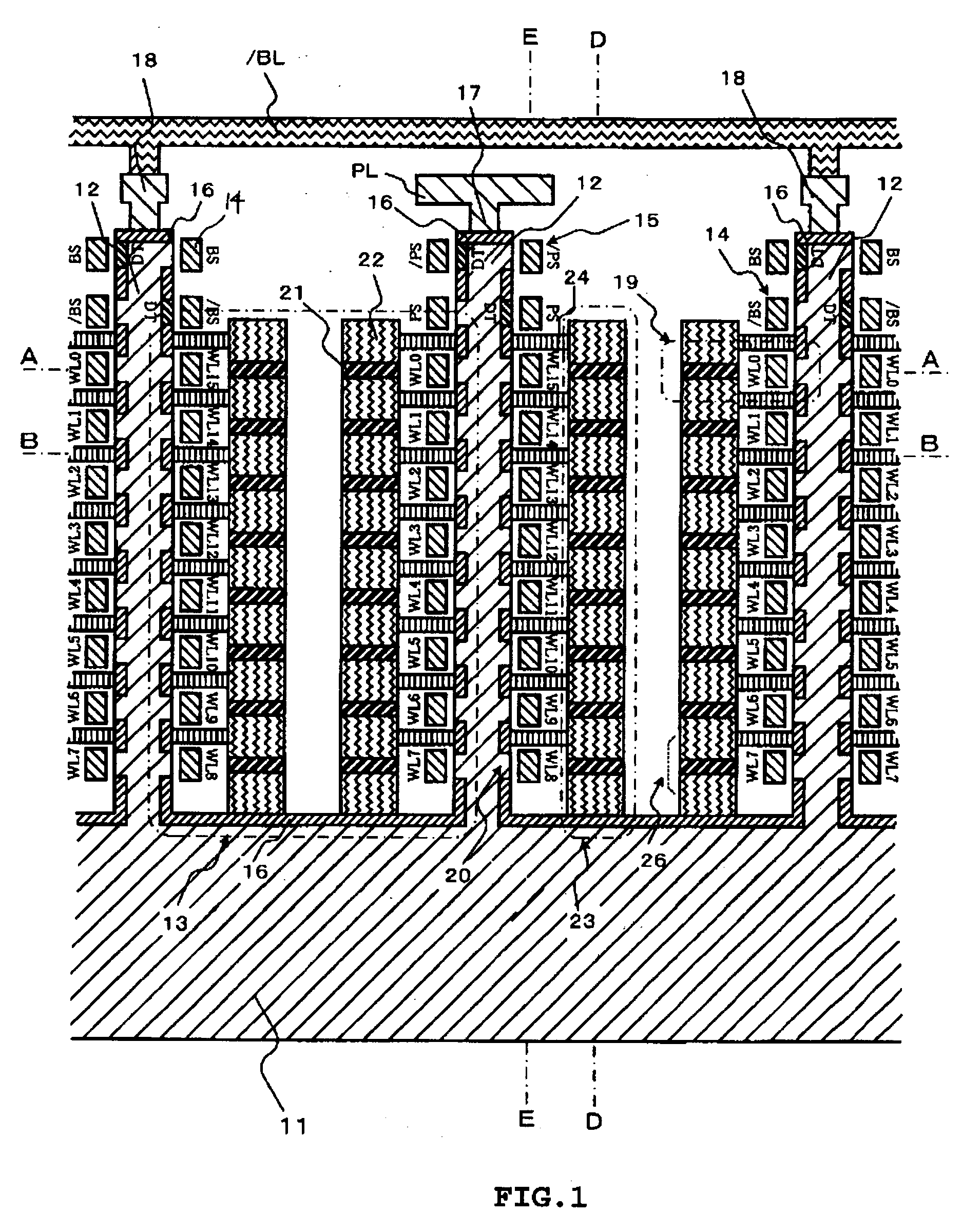

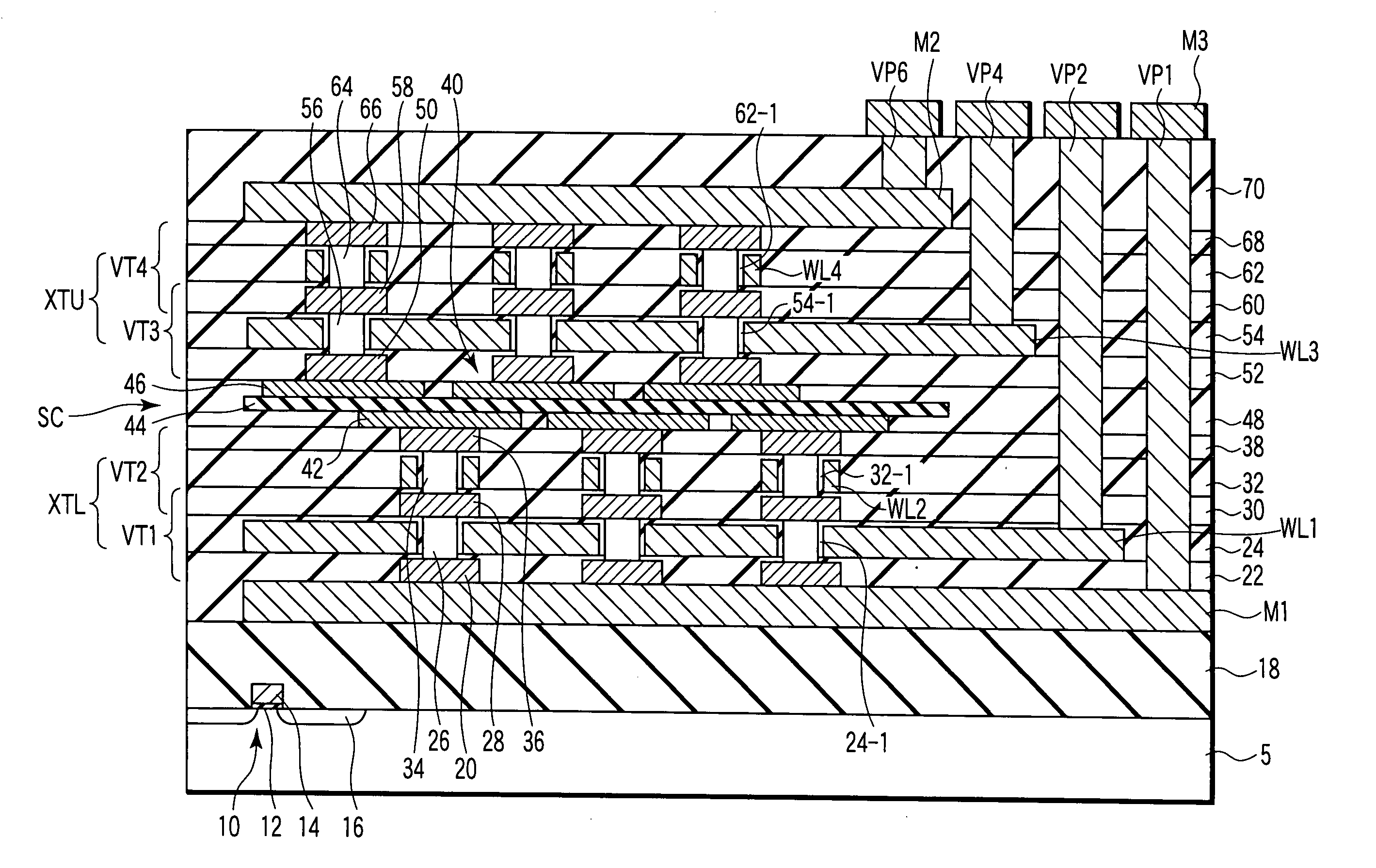

Nonvolatile ferroelectric memory

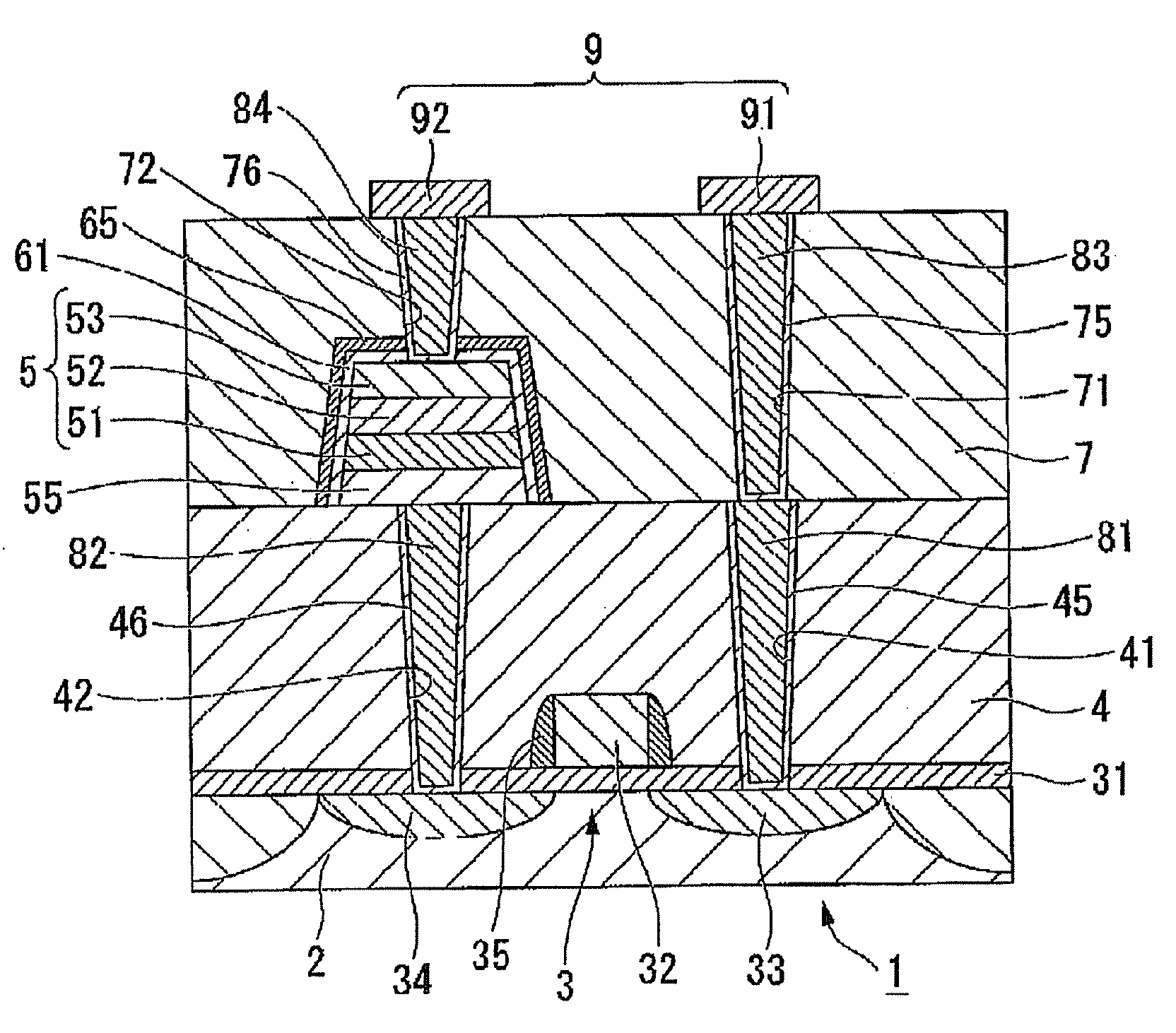

According to an aspect of the invention, there is provided a nonvolatile ferroelectric memory, including a ferroelectric capacitor composed of a ferroelectric film sandwiched by capacitor electrodes made of a conductive material, a cell capacitor block stacked a plurality of the capacitor electrodes and the ferroelectric film of the ferroelectric capacitor perpendicular to a main surface of a silicon substrate in layer, a cell transistor having a drain electrode and a source electrode, the drain electrode and the source electrode are electrically connected to the ferroelectric capacitor in parallel, a memory cell composed of the ferroelectric capacitor and the cell transistor, a cell block having the plurality of memory cells electrically connected in series, the drain electrode and the source electrode being as a terminals, a word line, a bit line connected to one end of the cell block, the bit line being arranged along orthogonal direction to the word line and a plate line connected to the other end of the cell block, the plate line arranged along the word line.

Owner:KIOXIA CORP

Ferroelectric capacitor and integrated circuit device comprising same

An integrated circuit capacitor in which a first conductive plate, a layer of ferroelectric material, and a second conductive plate are deposited and formed in sequence. Thereafter a diffusion barrier material and an insulative material are deposited either as a layered dielectric stack with alternating layers of the diffusion barrier material and the insulative material with tensile and compressive stresses in the alternating layers offsetting one another, or as a graded diffusion barrier material varying from a binary oxide of Ta, Nb, or Zr at the surface of the ferroelectric material to SiO2 at a distance above the surface of the ferroelectric material.

Owner:HANGER SOLUTIONS LLC

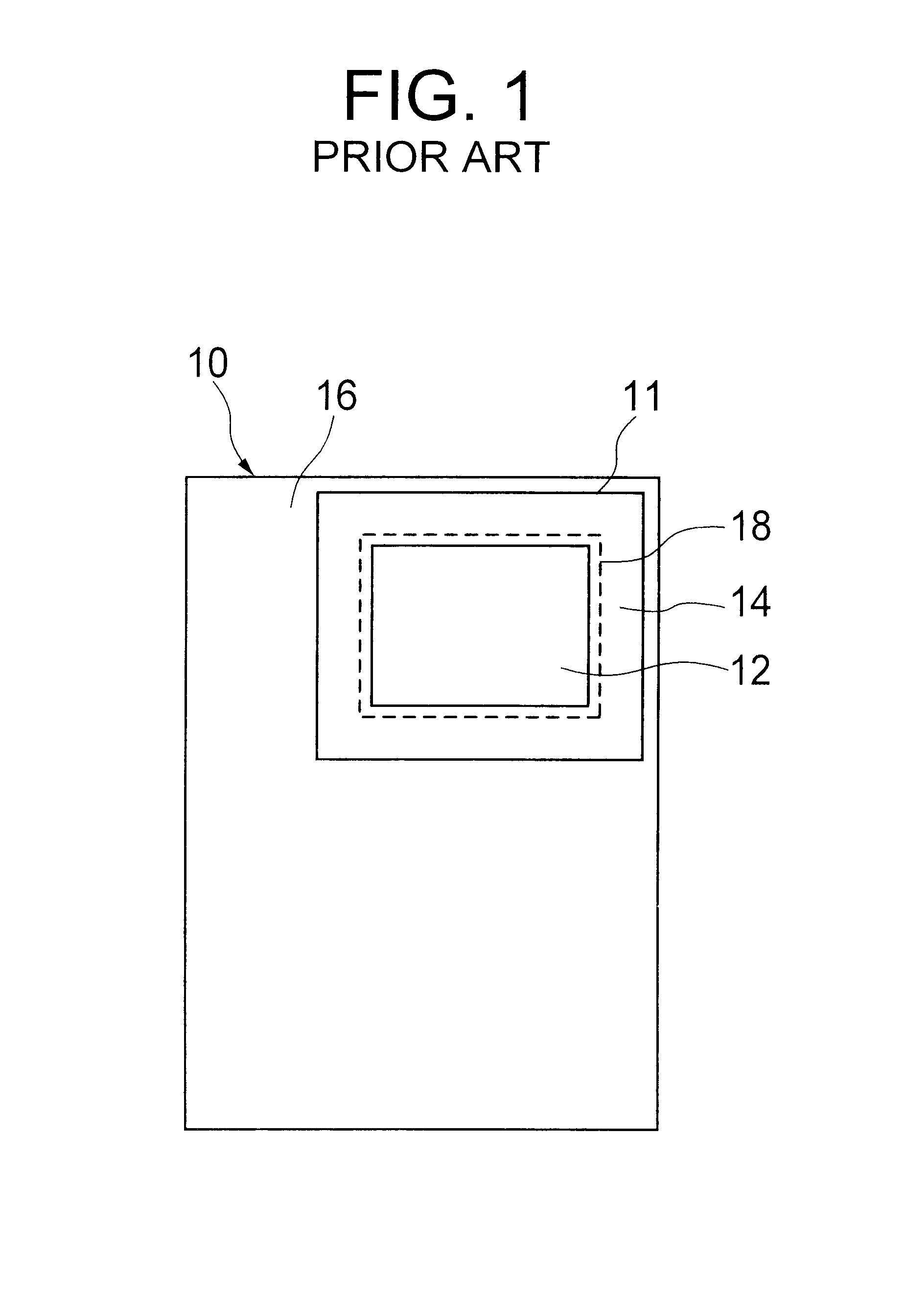

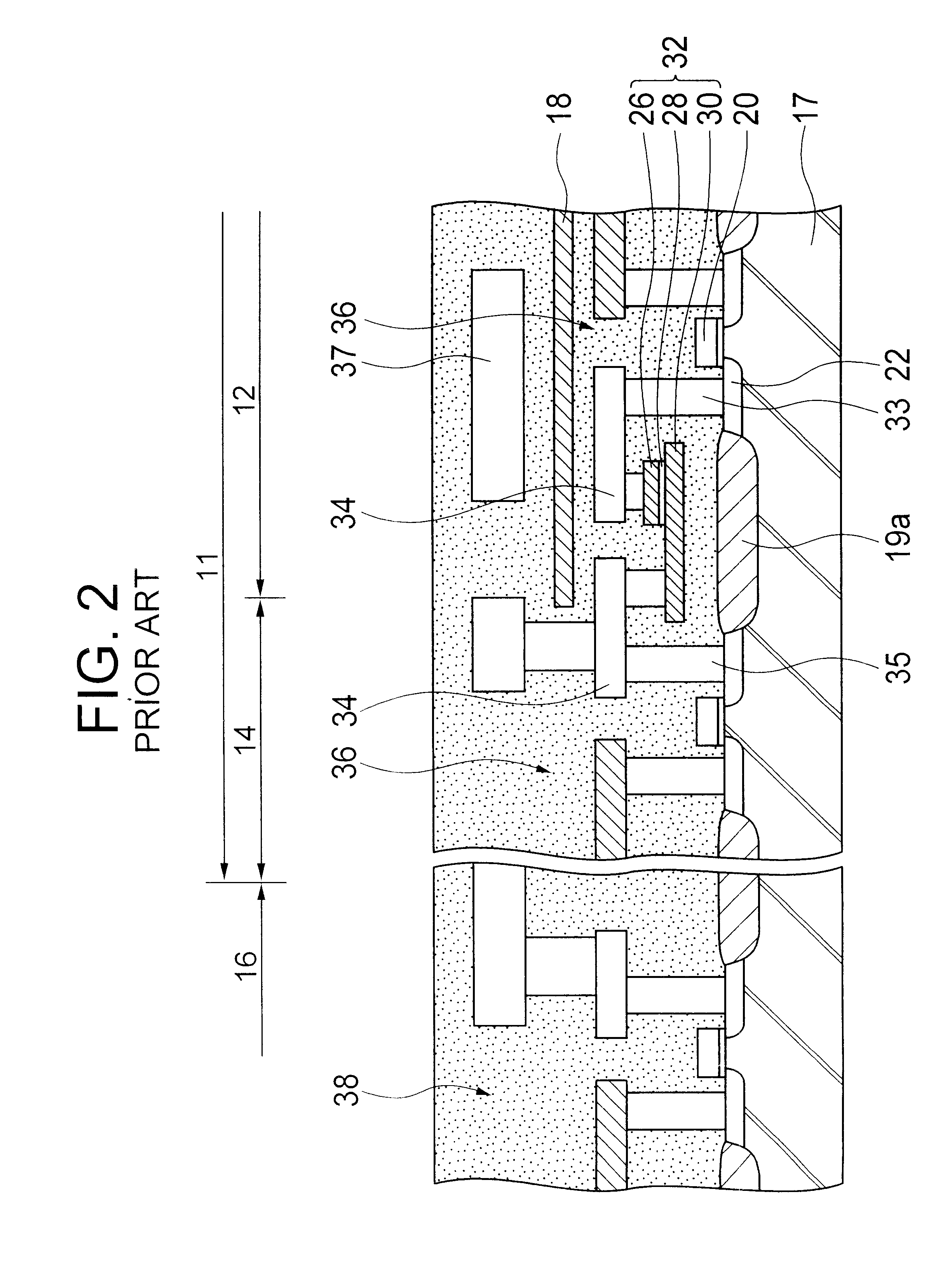

Embedded LSI having a FeRAM section and a logic circuit section

InactiveUS6218197B1Solid-state devicesSemiconductor/solid-state device manufacturingHydrogen annealingLogic circuitry

An embedded LSI includes a FeRAM macro block and an associated logic circuit section. A hydrogen barrier layer covers the FeRAM macro block as a whole and exposes the logic circuit section. The edge of the hydrogen barrier layer overlies the peripheral circuit of the FeRAM macro block and the boundary separating the FeRAM macro block from the logic circuit section. The ferroelectric capacitor is protected by the hydrogen barrier layer against hydrogen during a hydrogen-annealing process.

Owner:RENESAS ELECTRONICS CORP

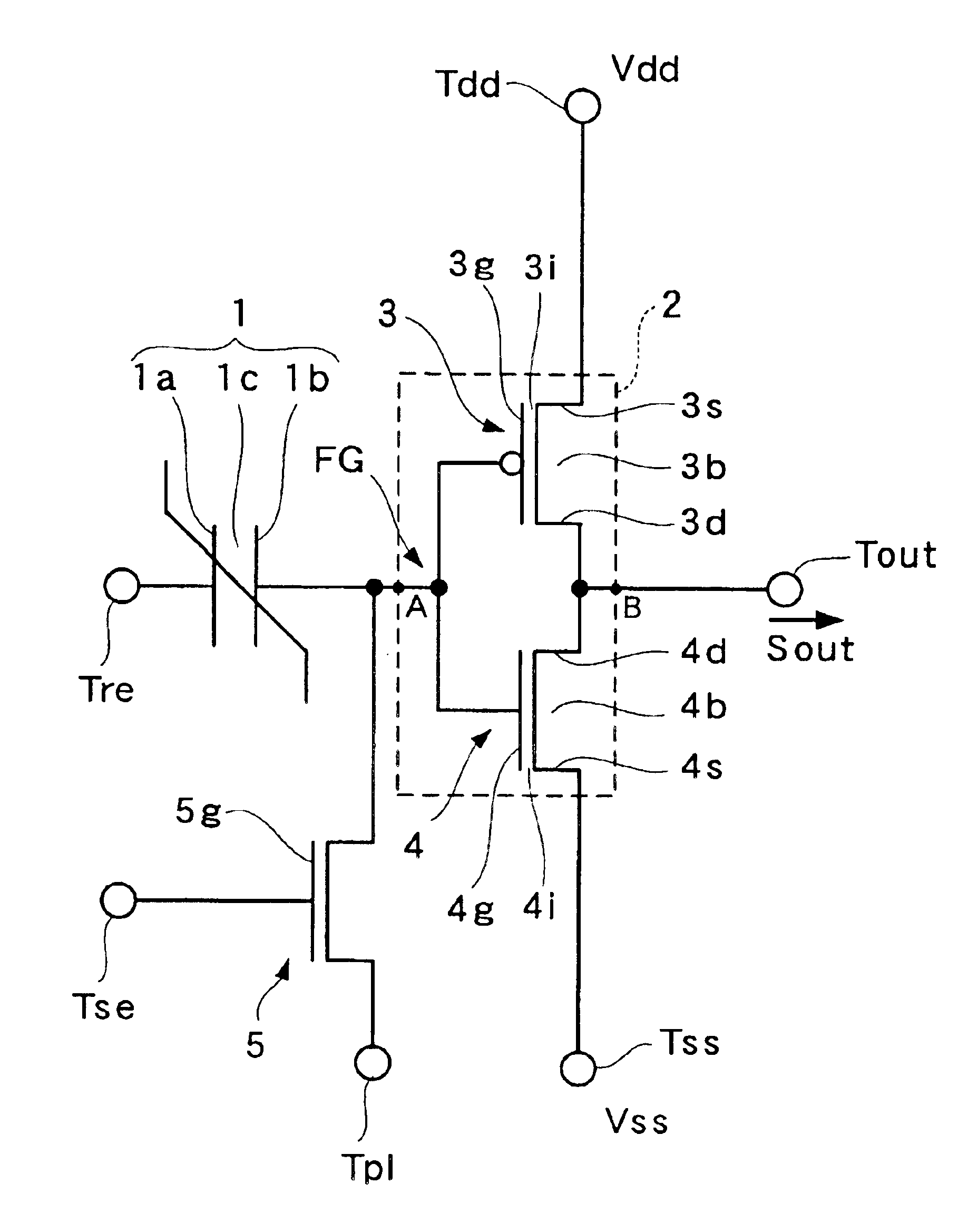

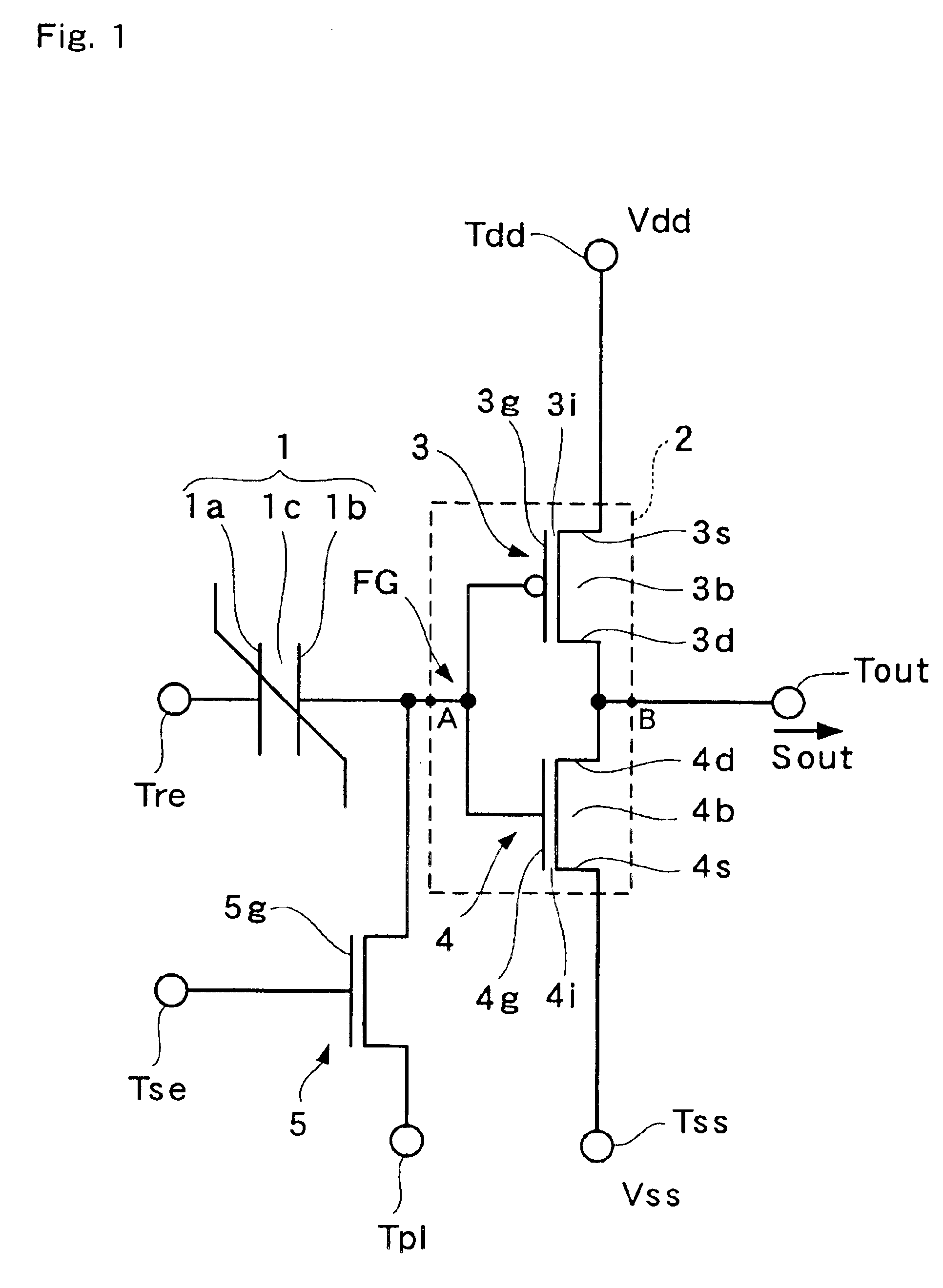

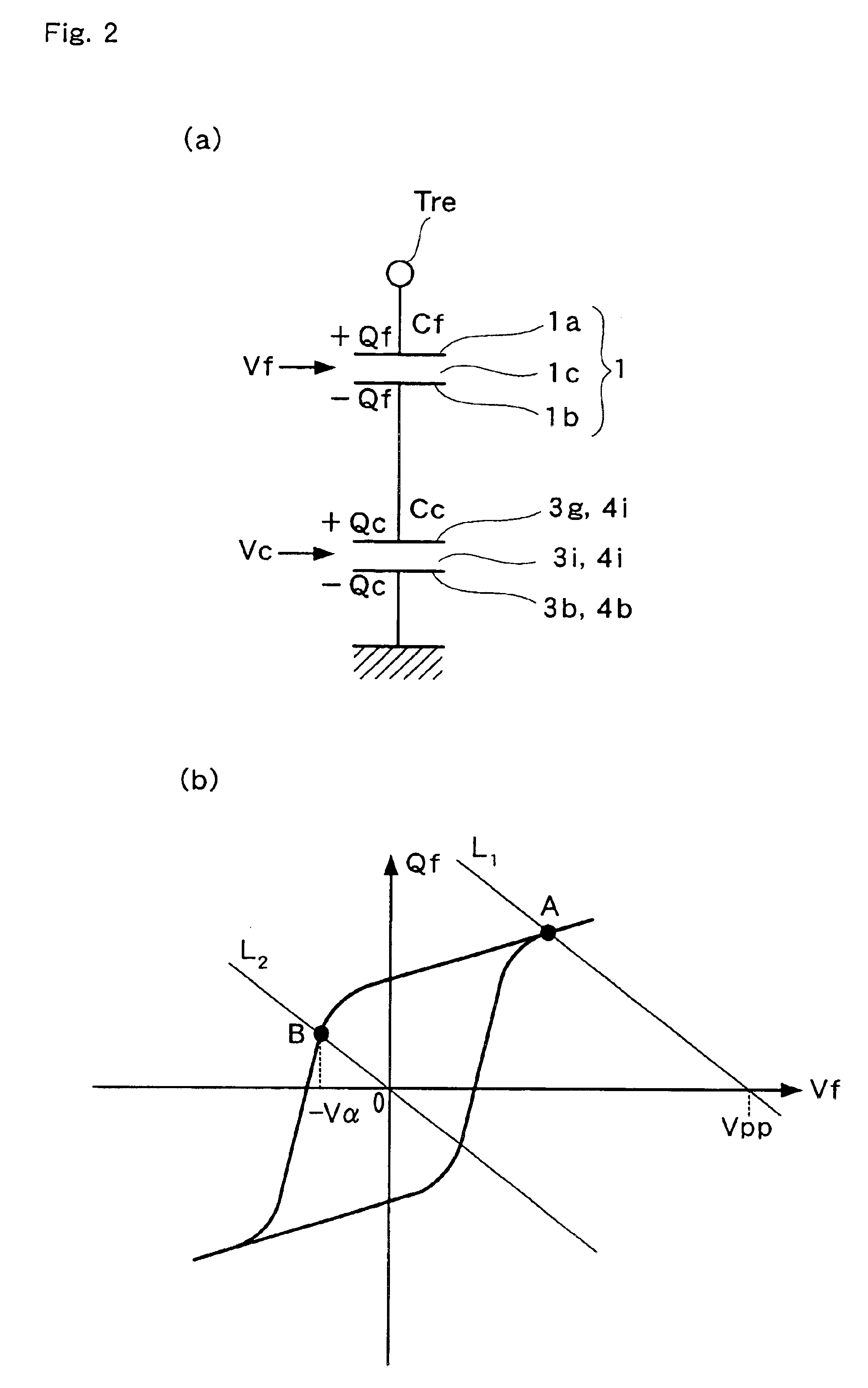

Non-volatile latch circuit and a driving method thereof

ActiveUS6845032B2High voltageSolid-state devicesRead-only memoriesThreshold voltageFerroelectric capacitor

Non-volatile latch circuit 10 of the present invention comprises ferroelectric capacitor 1 provided with a first electrode 1a, second electrode 1b, and ferroelectric film 1c that lies between these electrodes; reset terminal Tre that is connected to first electrode 1a and a CMOS inverter element 2 that is connected to second electrode 1b of ferroelectric capacitor 1; voltage switching terminal Tpl that applies a voltage to second electrode 1b; switching element 5 that is connected between second electrode 1b and second input terminal Tpl and switches a voltage applied to second electrode 1b; and set terminal Tse that applies a voltage for switching on or off switching element 5, wherein the voltage generated in second electrode 1b caused by polarization retained by ferroelectric film 1c is higher than the threshold voltage Vtn of NMISFET 4 of CMOS inverter element 2.

Owner:PANASONIC CORP

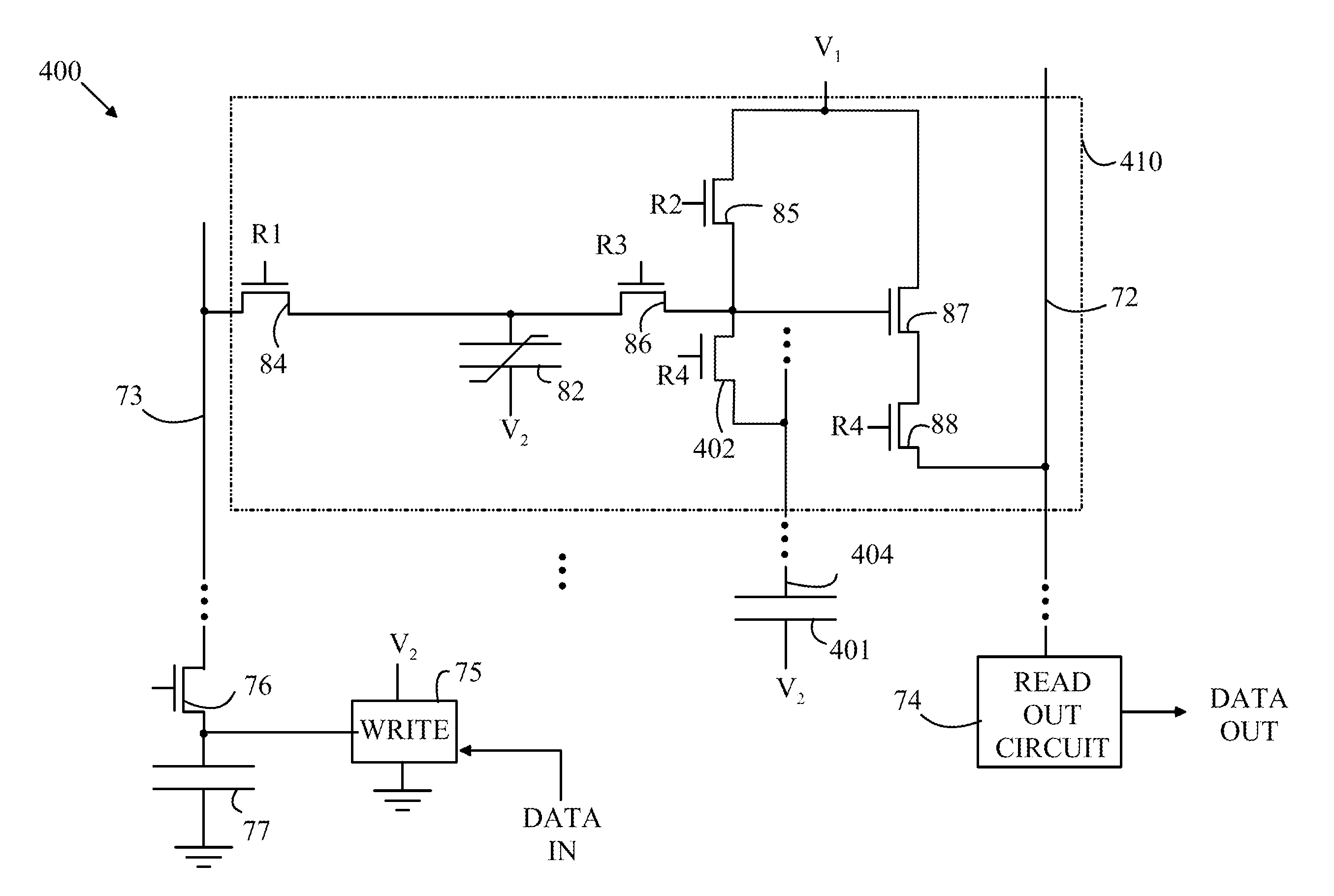

Analog memories utilizing ferroelectric capacitors

A ferroelectric memory having a plurality of ferroelectric memory cells, each ferroelectric memory cell including a ferroelectric capacitor is disclosed. The ferroelectric memory includes read and write lines and a plurality of ferroelectric memory cell select buses, one select bus corresponding to each of the ferroelectric memory cells. Each of the ferroelectric memory cells includes first and second gates for connecting the ferroelectric memory cell to the read line and the write line, respectively, in response to signals on the ferroelectric memory cell select bus corresponding to that ferroelectric memory cell. A write circuit causes a charge to be stored in the ferroelectric capacitor of the ferroelectric memory cell currently connected to the write line, the charge having a value determined by a data value having at least three states. A read circuit measures the charge stored in the ferroelectric capacitor of the ferroelectric memory cell currently connected to the read line to generate an output value, the output value corresponding to one of the states.

Owner:RADIANT TECH

Ferroelectric capacitor

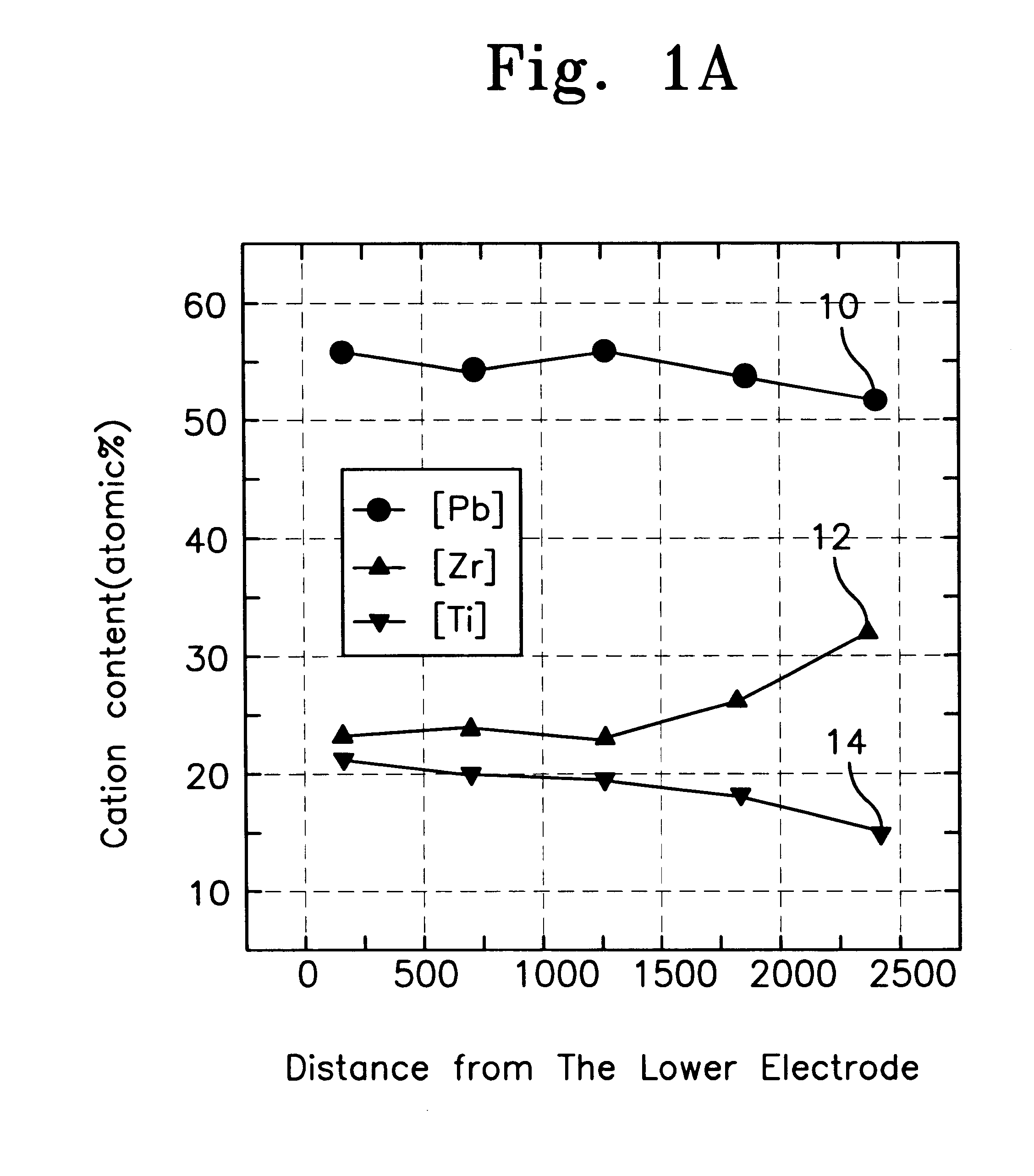

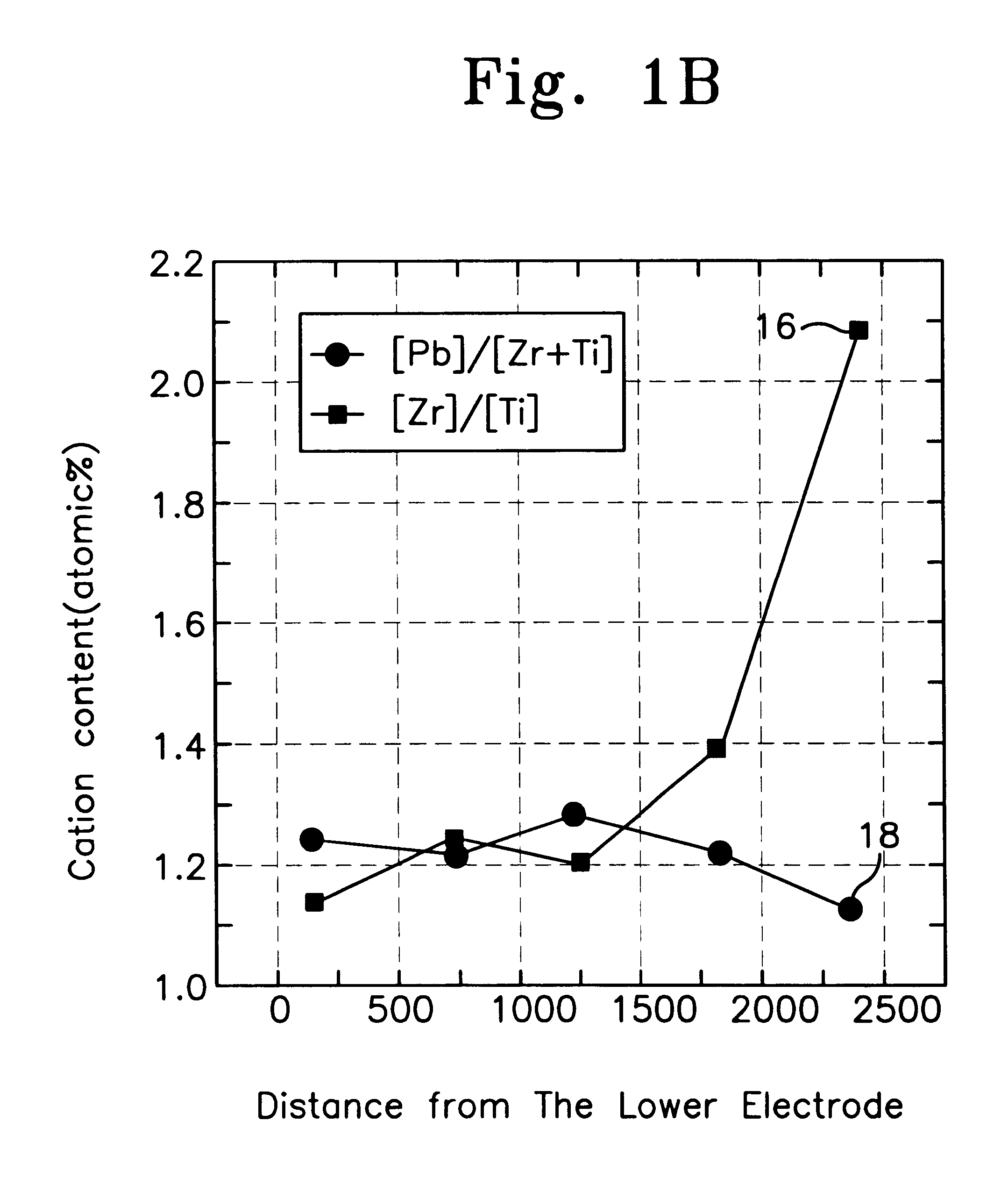

A ferroelectric capacitor with a multilayer ferroelectric film to prevent degradation of its ferromagnetic characteristics, wherein the ferroelectric film is made of a lower layer of PZT or PLZT formed on a lower electrode and an upper, titanium rich, layer of PZT, PLZT, or PbTiO3, an upper electrode formed on the upper layer of the ferroelectric film and a protective layer formed to cover the ferroelectric capacitor.

Owner:SAMSUNG ELECTRONICS CO LTD

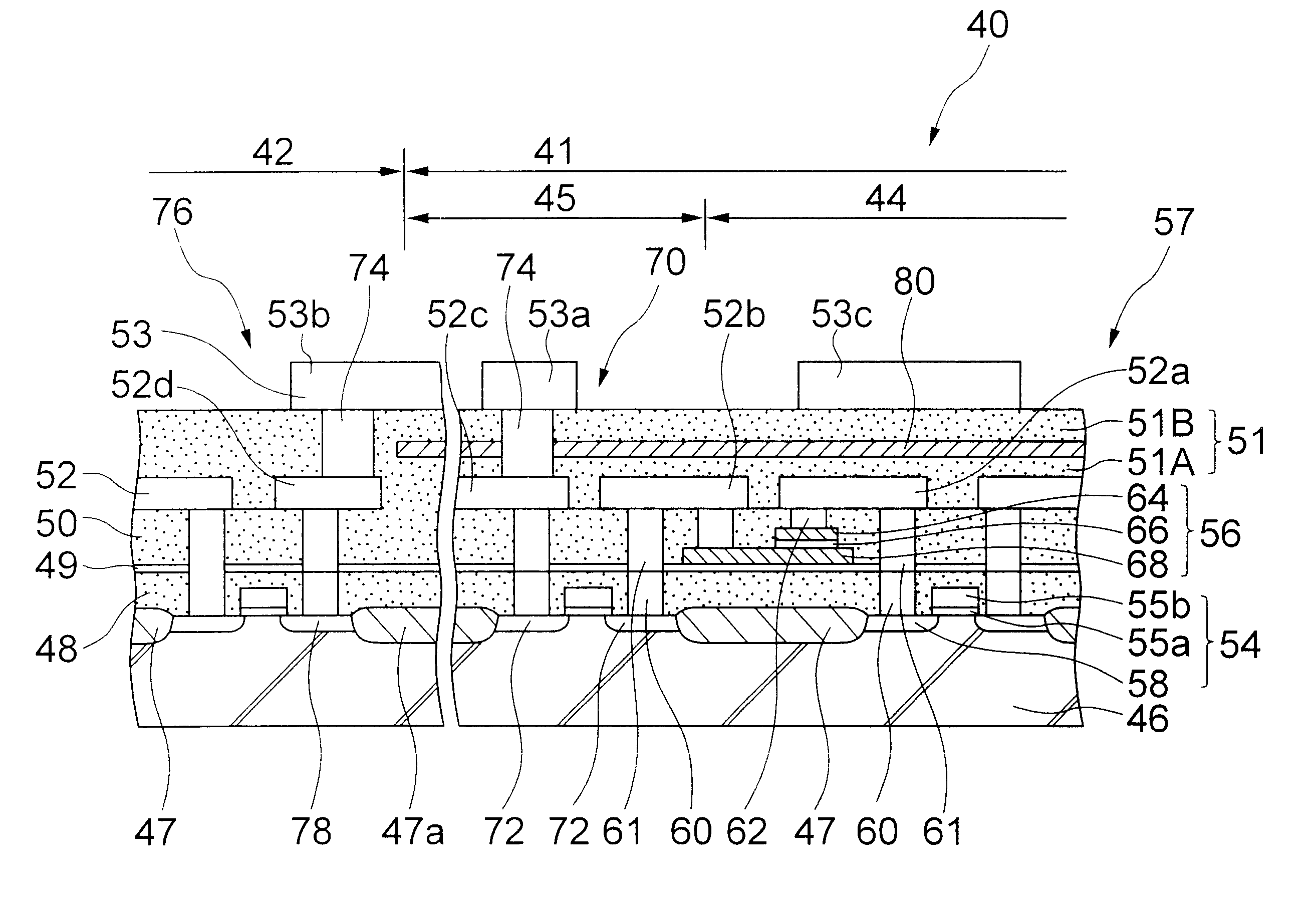

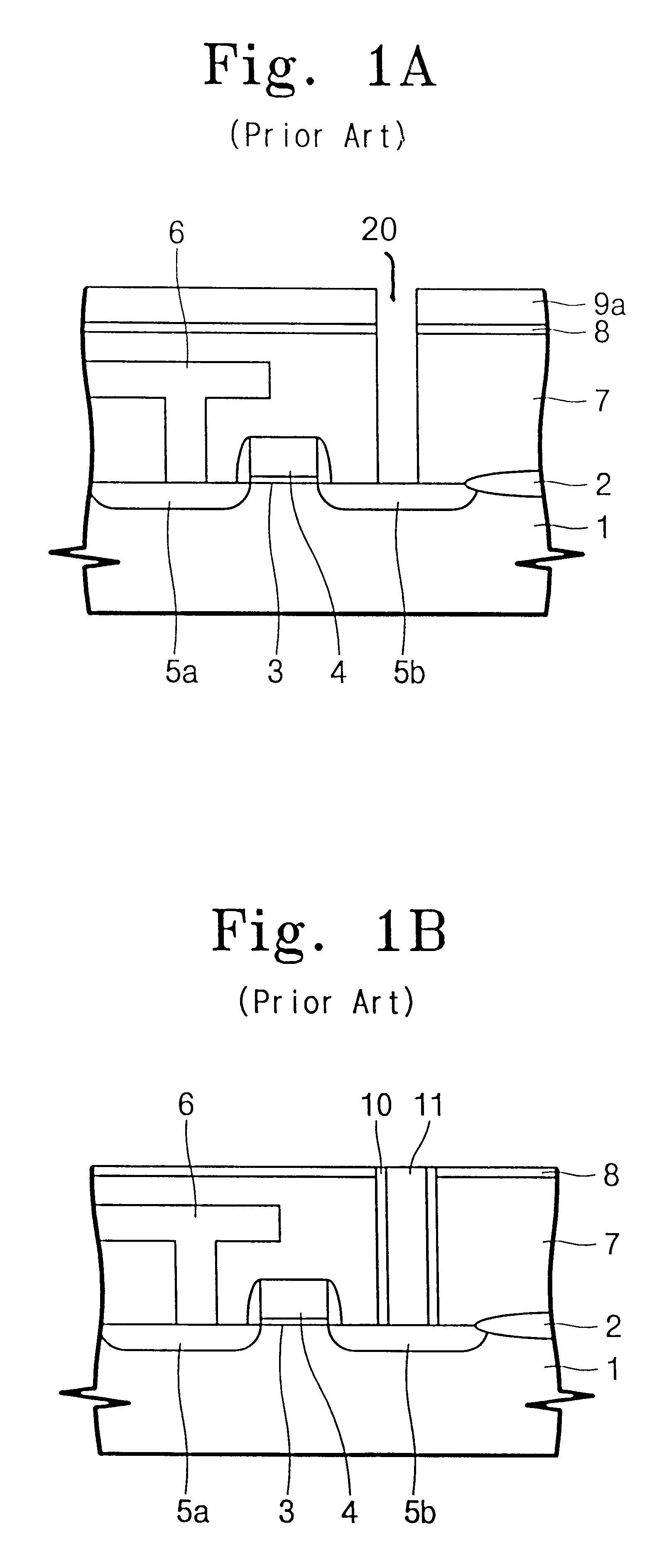

Triple metal line 1T/1C ferroelectric memory device and method for fabrication thereof

Disclosed is a triple metal line 1T / 1C ferroelectric memory device and a method to make the same. A ferroelectric capacitor is connected to the transistor through a buried contact plug. An oxidation barrier layer lies between the contact plug and the lower electrode of the capacitor. A diffusion barrier layer covers the ferroelectric capacitor to prevent diffusion of material into or out of capacitor. As a result of forming the oxidation barrier layer, the contact plug is not exposed to the ambient oxygen atmosphere thereby providing a reliable ohmic contact between the contact plug and the lower electrode. Also, the memory device provides a triple interconnection structure made of metal, which improves device operation characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD

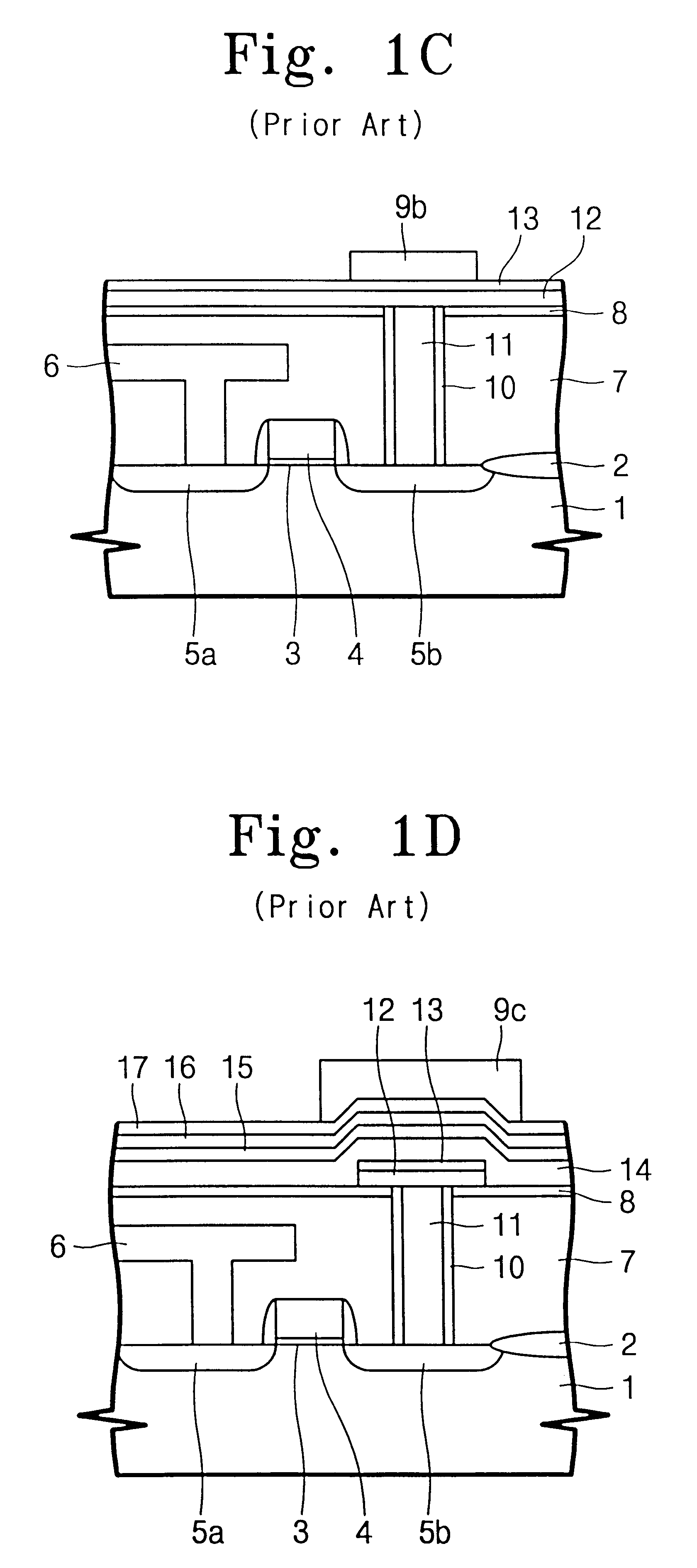

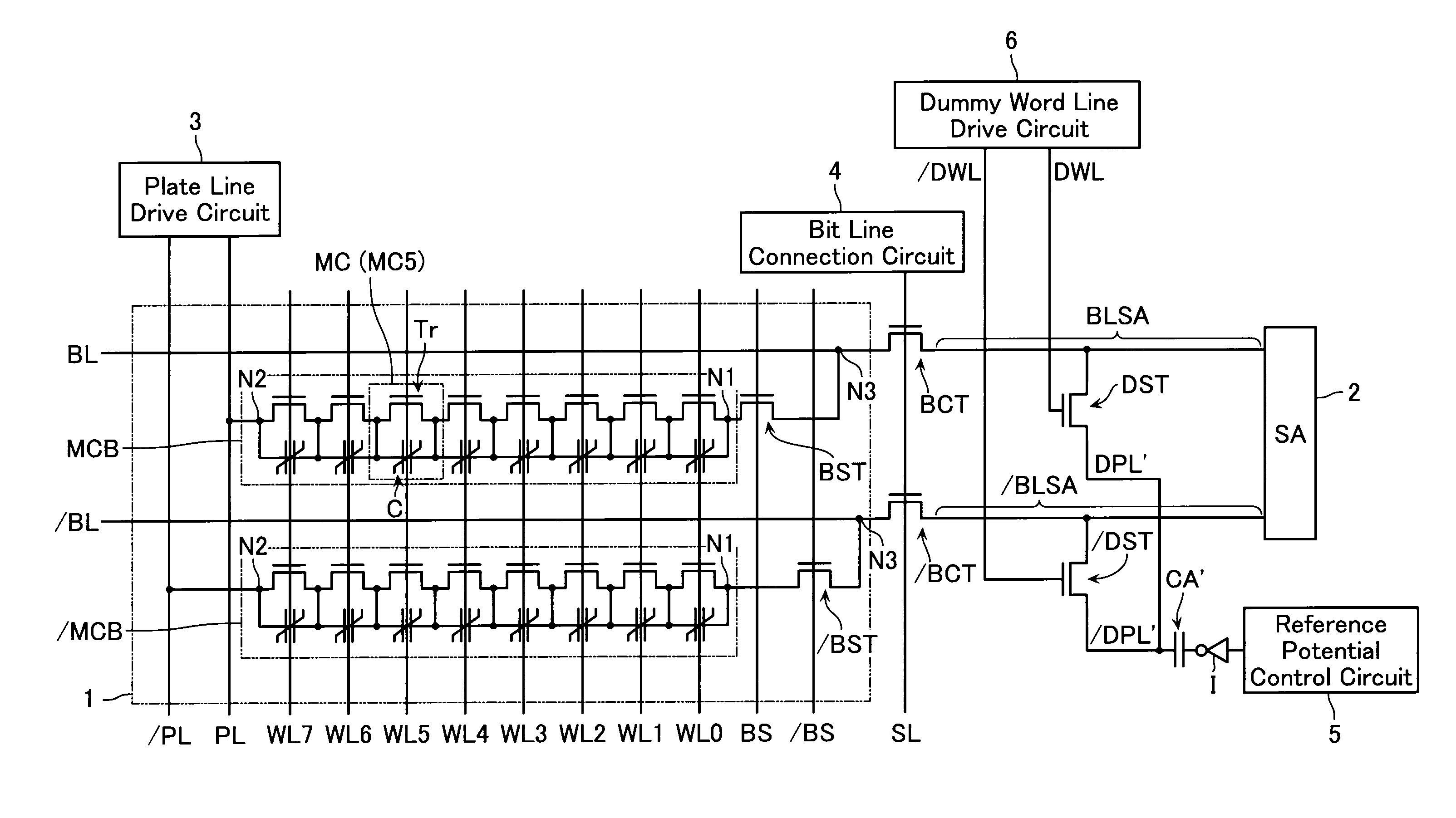

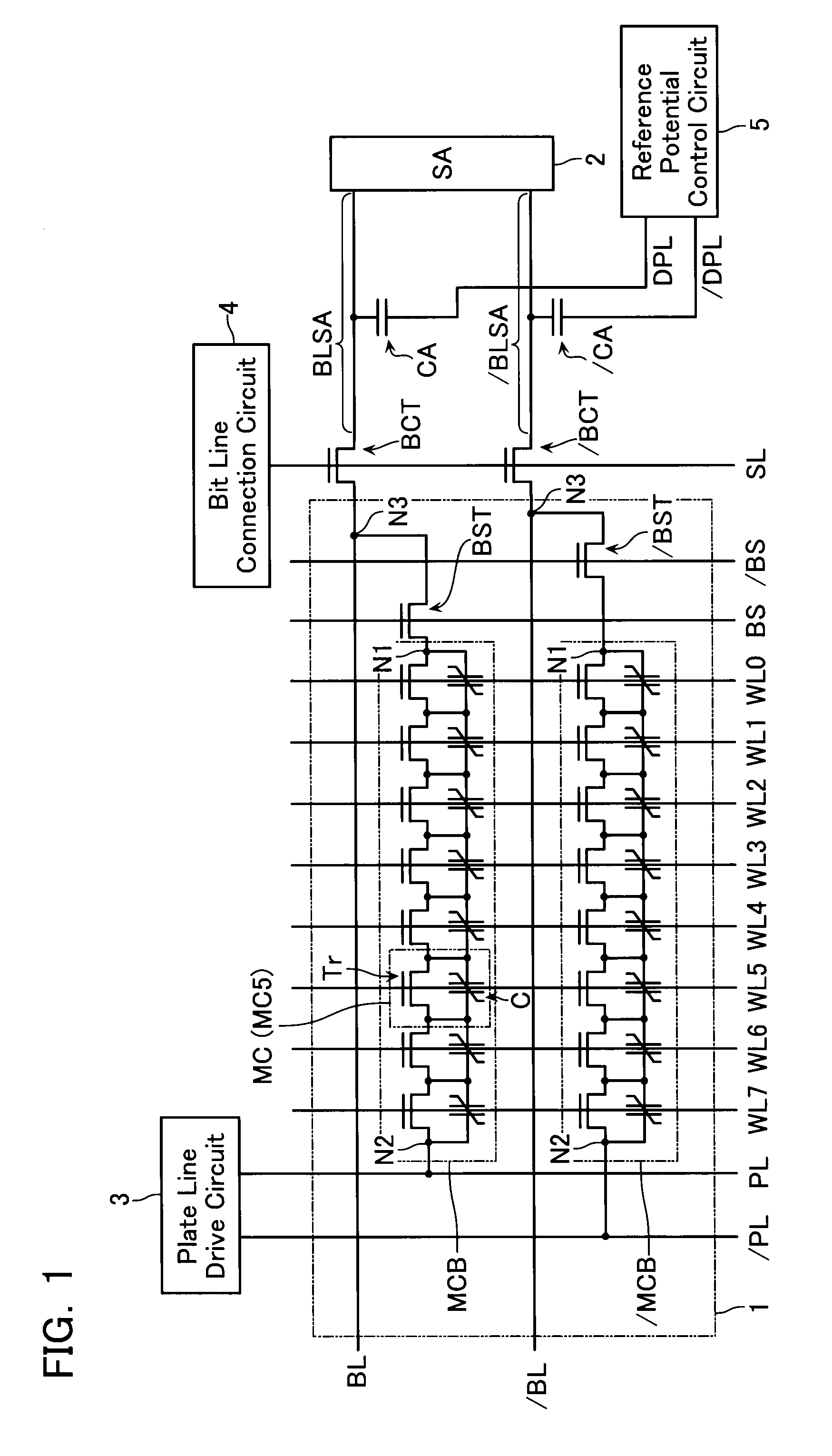

Semiconductor memory device

A semiconductor memory device comprises a memory cell array of memory cells each including a cell transistor and a ferroelectric capacitor; a sense amp circuit operative to sense / amplify a signal read out of the ferroelectric capacitor through a pair of bit lines; a pair of decoupling transistors provided on the pair of bit lines to decouple the bit lines; a control circuit operative to provide a control signal to the gates of the decoupling transistors to control conduction of the decoupling transistors; and a dummy capacitor provided in connection with at least either one of the pair of bit lines between the decoupling transistors and the sense amp circuit. The control circuit is configured to be capable of turning the decoupling transistors from on to off when a certain period of time elapsed after the beginning of reading.

Owner:KK TOSHIBA

Semicondutor device having ferroelectric capacitor and hydrogen barrier film and manufacturing method thereof

InactiveUS6982453B2Effective recoveryExcellent ferroelectric capacitorTransistorSolid-state devicesHydrogenInter layer

A semiconductor device having a semiconductor substrate; an insulating film formed on said semiconductor substrate; a ferroelectric capacitor having a lower electrode, a ferroelectric film and an upper electrode which are stacked sequentially on the insulating film; a first hydrogen barrier film; a first inter-layer insulating film covering said ferroelectric capacitor; and a second inter-layer insulating film stacked on the first inter-layer insulating film, the first hydrogen barrier film being interposed between the first and second interlayer insulating films is proposed.

Owner:KK TOSHIBA

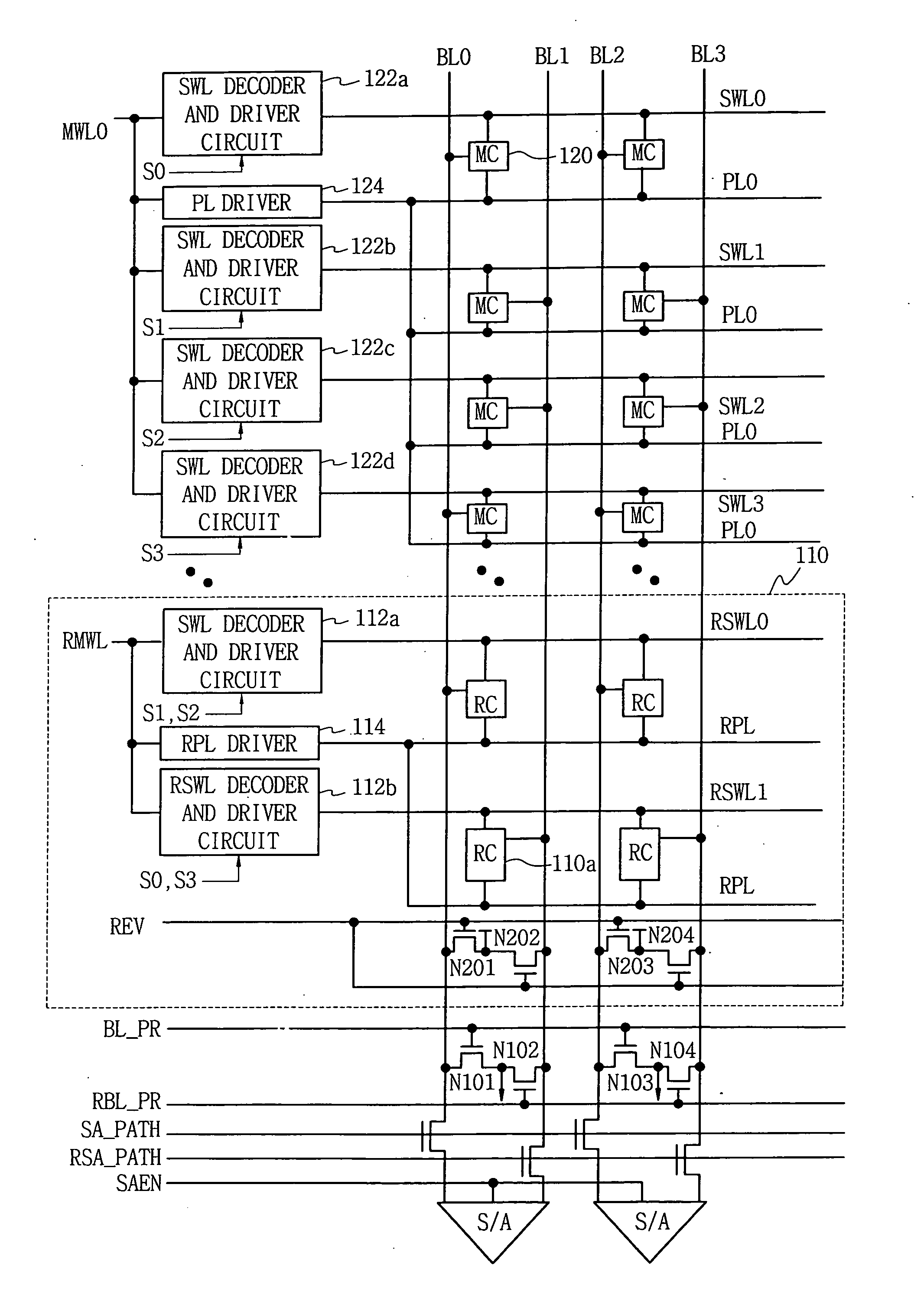

Device and method for generating reference voltage in Ferroelectric Random Access Memory (FRAM)

A reference voltage generating device that provides a constant reference voltage even with temperature change in a ferroelectric random access memory and a method for driving the same are provided. A device for generating a reference voltage in a ferroelectric random access memory including memory cells, each of which has one ferroelectric capacitor and one access transistor, includes a reference cell composed of a ferroelectric capacitor and a transistor; a reference plate line connected to one end of the ferroelectric capacitor constituting the reference cell; and a reference plate line driver circuit for adjusting a voltage level of a reference plate line enable signal depending on temperature change so that a constant reference voltage is generated.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus and method for generating an imprint-stabilized reference voltage for use in a ferroelectric memory device

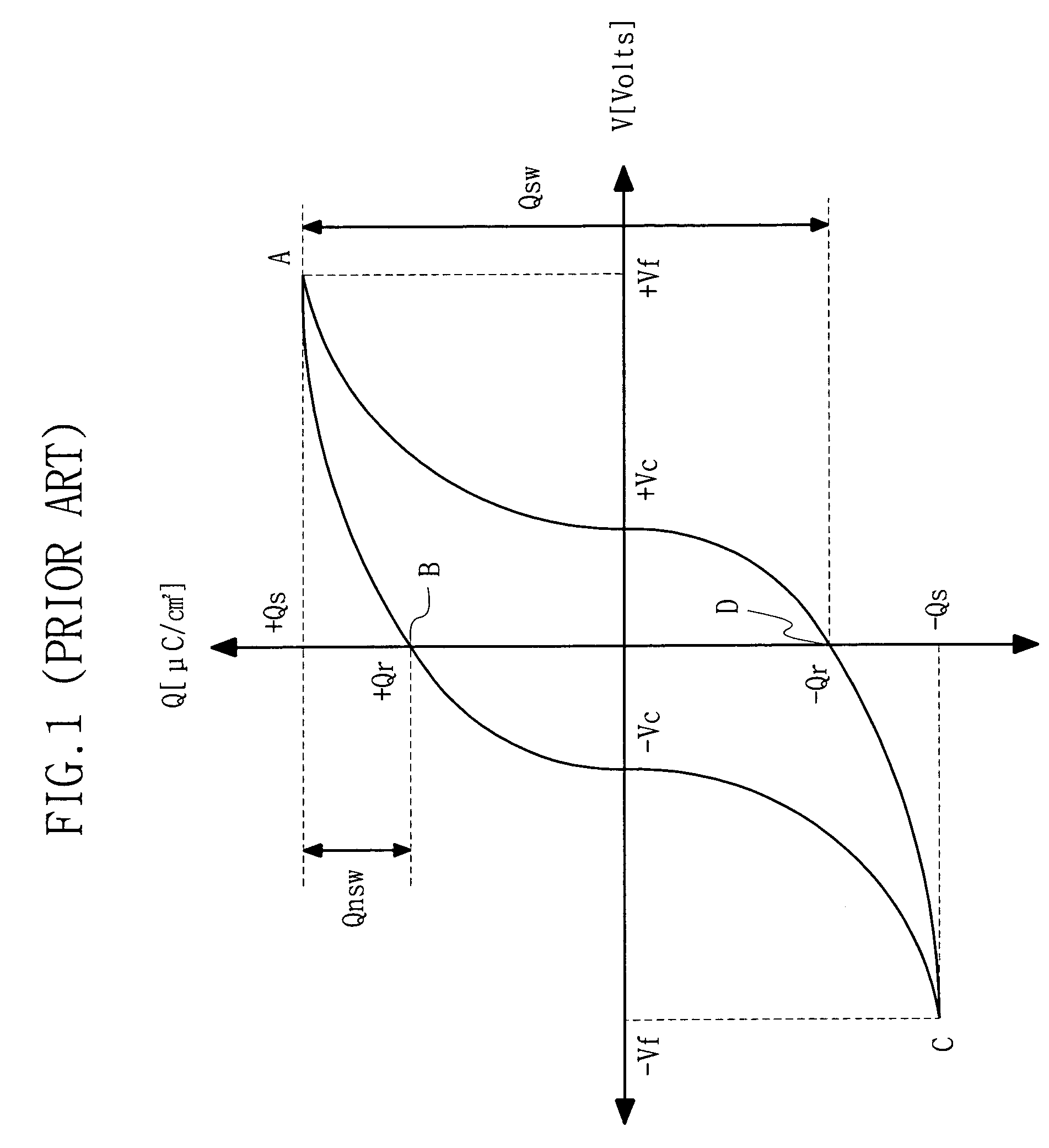

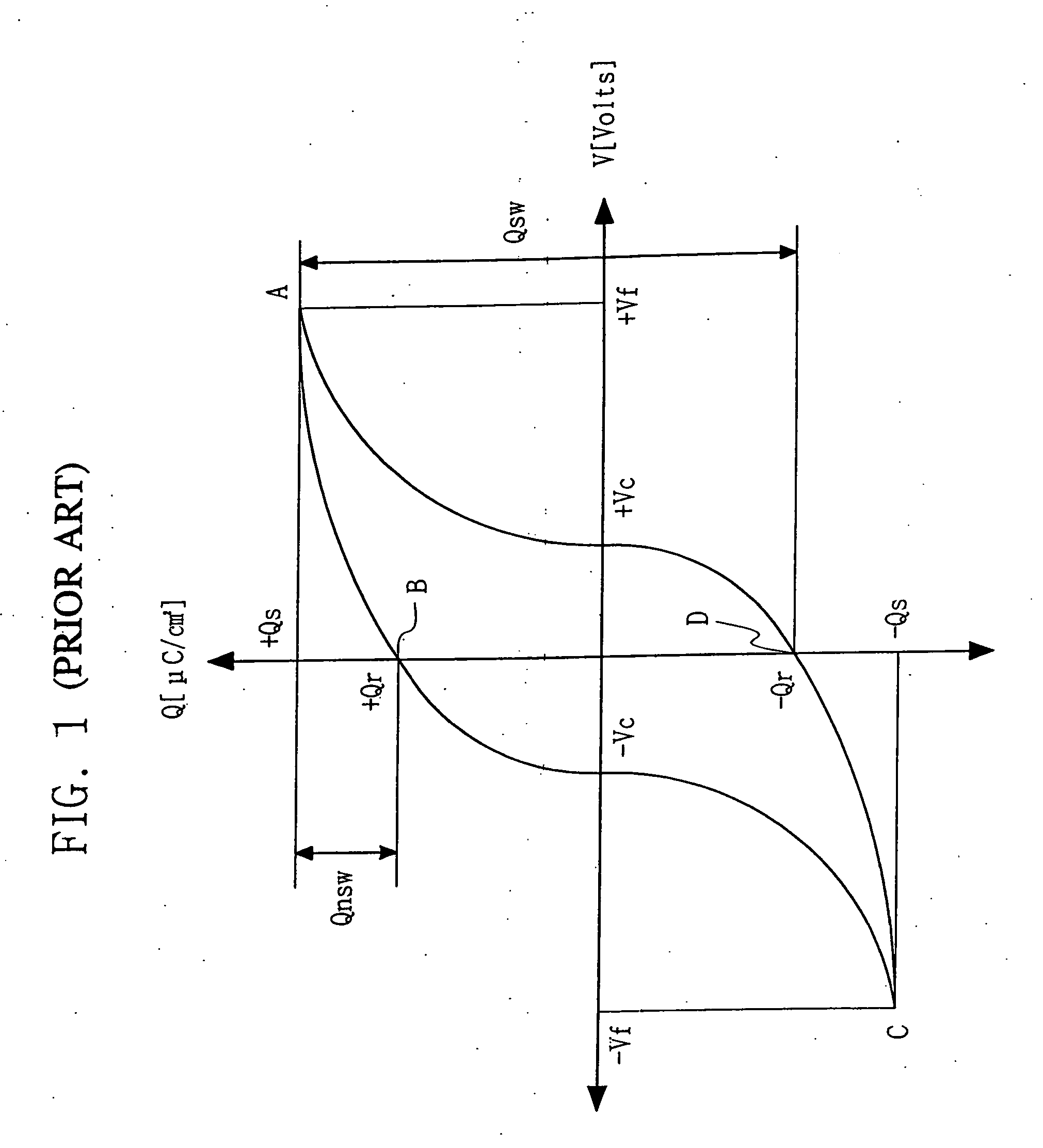

A reference voltage supply apparatus and a driving method thereof in a ferroelectric memory device provide a reference voltage stabilized against the imprint effect thus maintaining reading reliability of the device. In the reference voltage supply apparatus (e.g., using a non-switching capacitance of a ferroelectric capacitor), a reference cell is constructed of a ferroelectric capacitor and an access switch, and provides a reference voltage to read data from a memory cell. In an active mode, the reference cell stores data of a first logic state (e.g., corresponding to the non-switching capacitance of the ferroelectric capacitor), in the reference cell, and then supplies, as a reference voltage, the voltage corresponding to the data of the first logic state to a bit line; and in a stand-by mode, a reference voltage controller stores (writes) data of a second logic state (opposite to the first logic state), into the reference cell.

Owner:SAMSUNG ELECTRONICS CO LTD

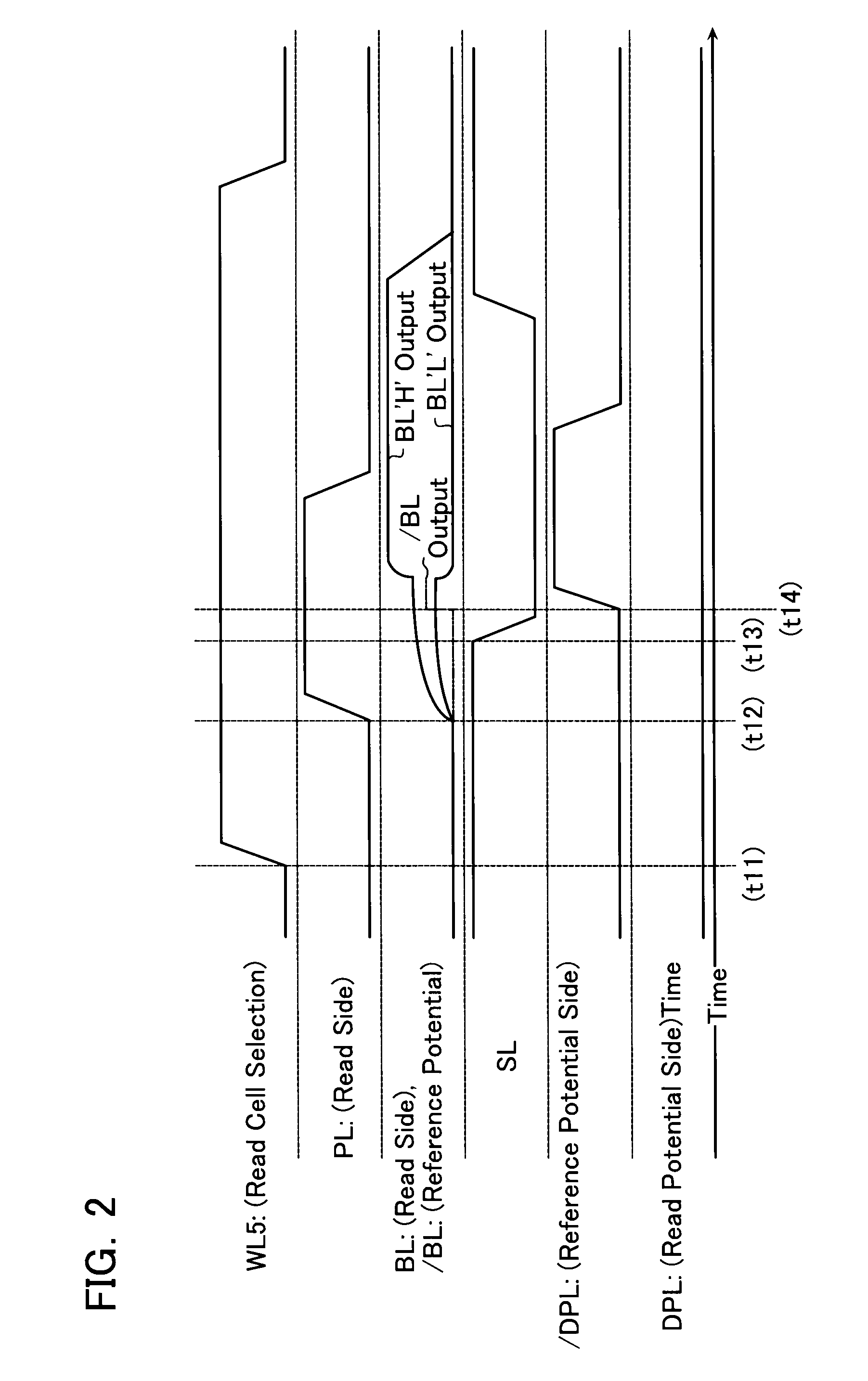

Data holding apparatus and data read out method

InactiveUS6944045B2Reliable dataDigital storageElectric pulse generatorFerroelectric capacitorElectrical and Electronics engineering

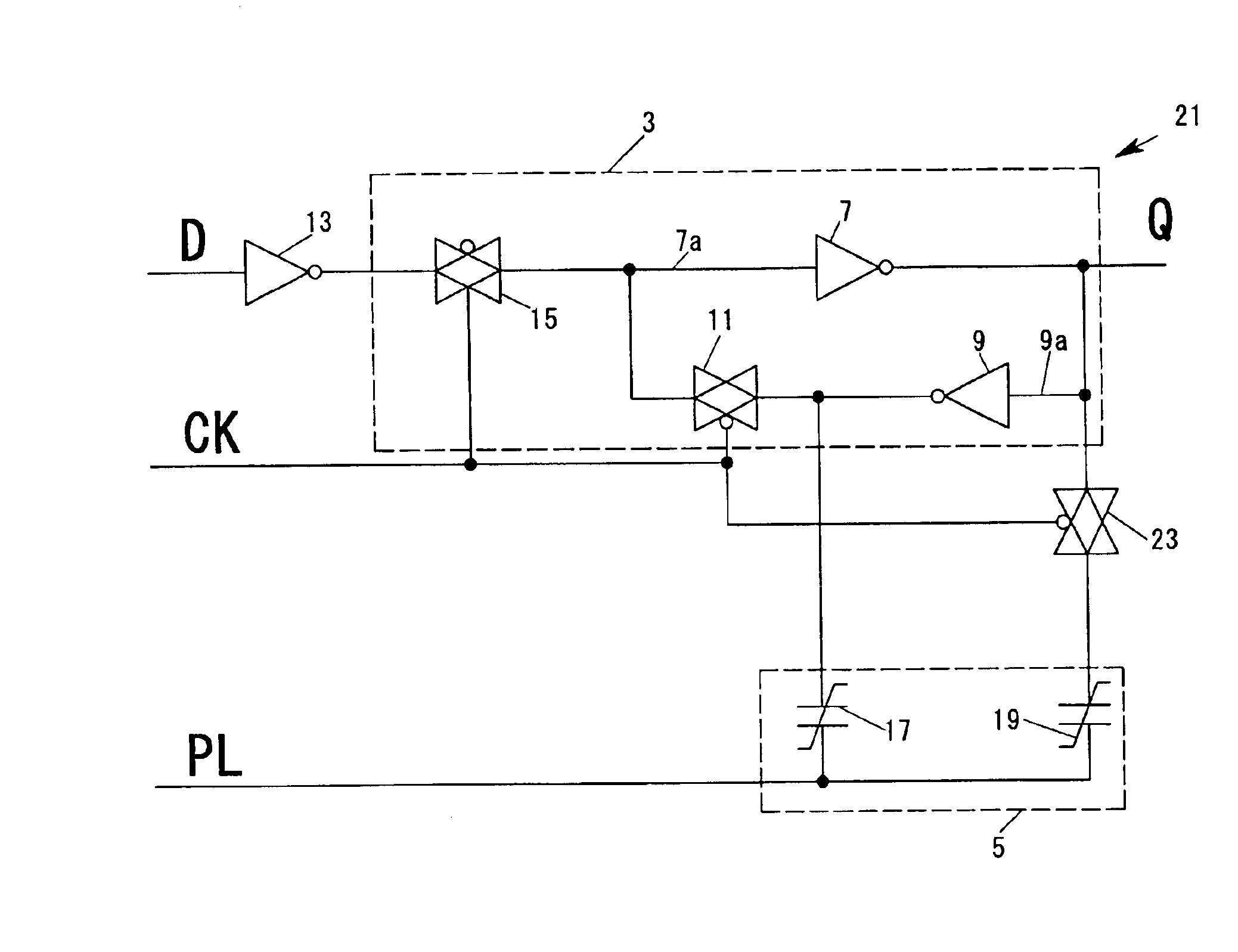

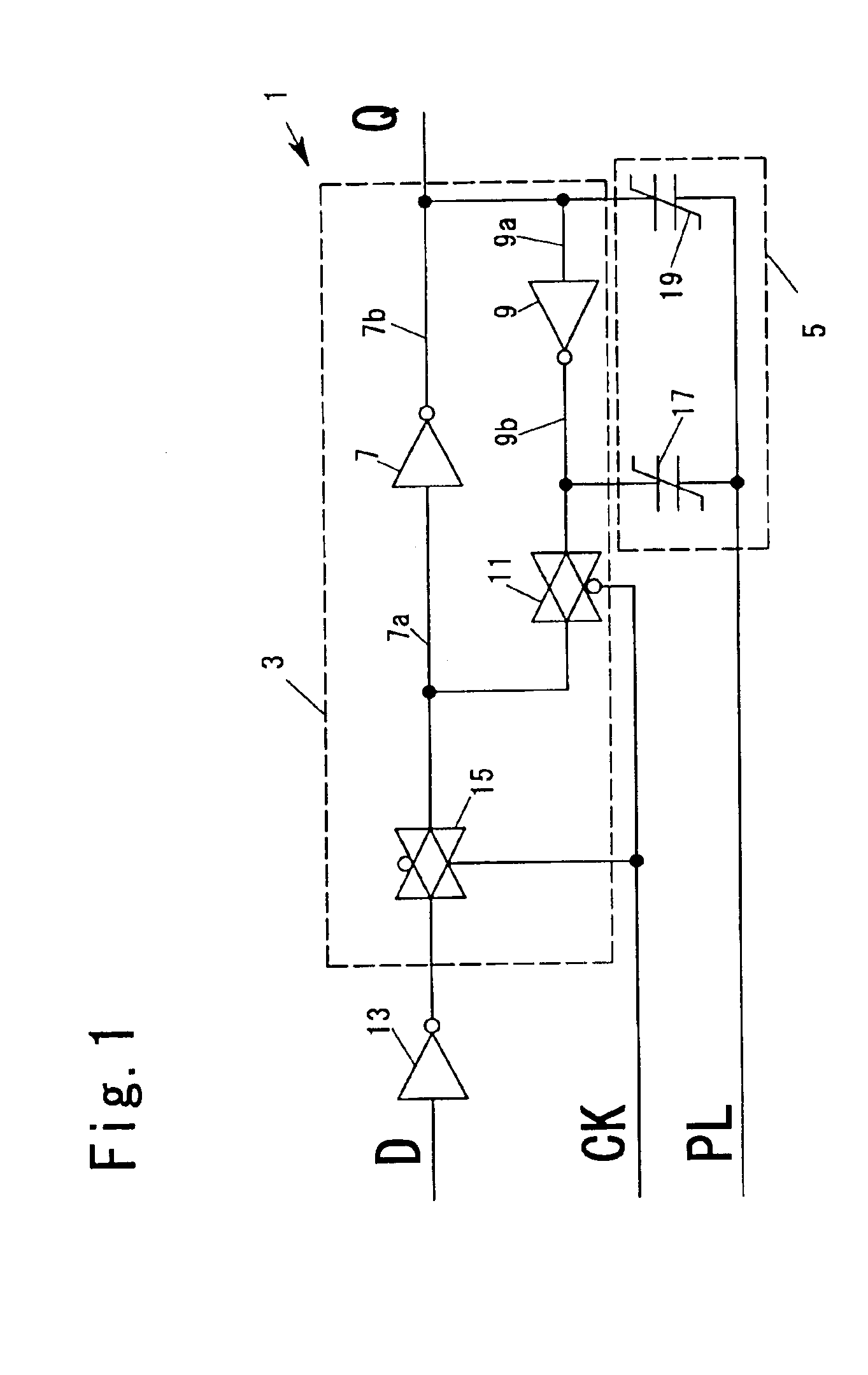

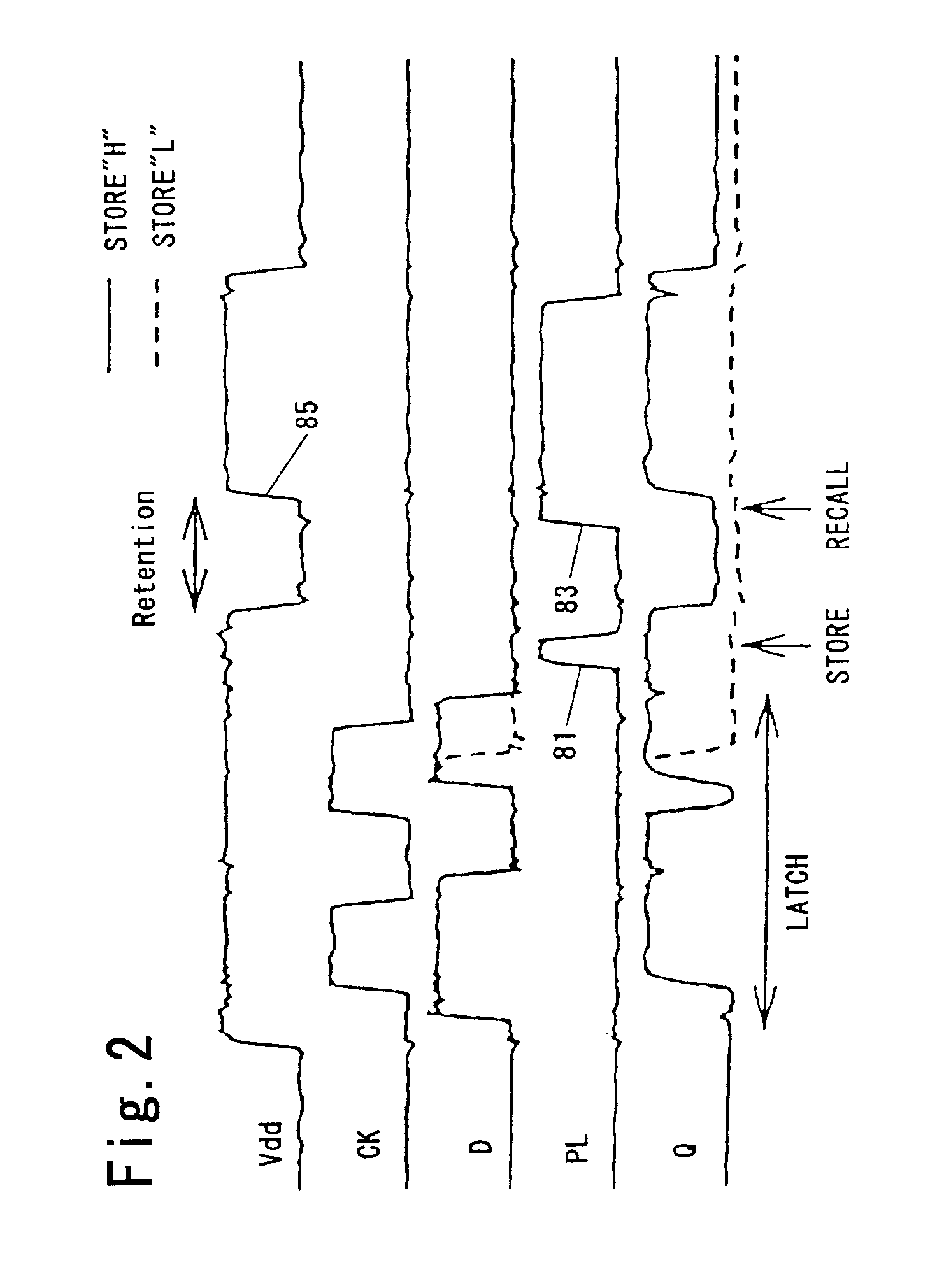

A data holding device is provided that is capable of holding data even if the power supply is shut off and reliability in holding data is high. The data holding device 1 is provided with a data latch circuit 3 and a ferroelectric memory section 5. Ferroelectric capacitors 17 and 19 are capable of storing data in non-volatile manner. One end of the ferroelectric capacitor 17 is connected to the input node 7a of an inverter circuit 7 through a transfer gate 11. The transfer gate 11 is in the off state when data are passed. Therefore, even if input data D changes when data are passed, the change is quickly transmitted to the input node 7a, so that reliability of latching operation does not lower even if the operation is made at usual speeds.

Owner:ROHM CO LTD

Method for leakage reduction in fabrication of high-density FRAM arrays

ActiveUS20080081380A1Solid-state devicesSemiconductor/solid-state device manufacturingHigh densityNitrogen

A method is provided for fabricating a ferroelectric capacitor structure including a method for etching and cleaning patterned ferroelectric capacitor structures in a semiconductor device. The method comprises etching portions of an upper electrode, etching ferroelectric material, and etching a lower electrode to define a patterned ferroelectric capacitor structure, and etching a portion of a lower electrode diffusion barrier structure. The method further comprises ashing the patterned ferroelectric capacitor structure using a first ashing process, where the ash comprises an oxygen / nitrogen / water-containing ash, performing a wet clean process after the first ashing process, and ashing the patterned ferroelectric capacitor structure using a second ashing process.

Owner:TEXAS INSTR INC

Dynamic random access memory cell including a ferroelectric capacitor

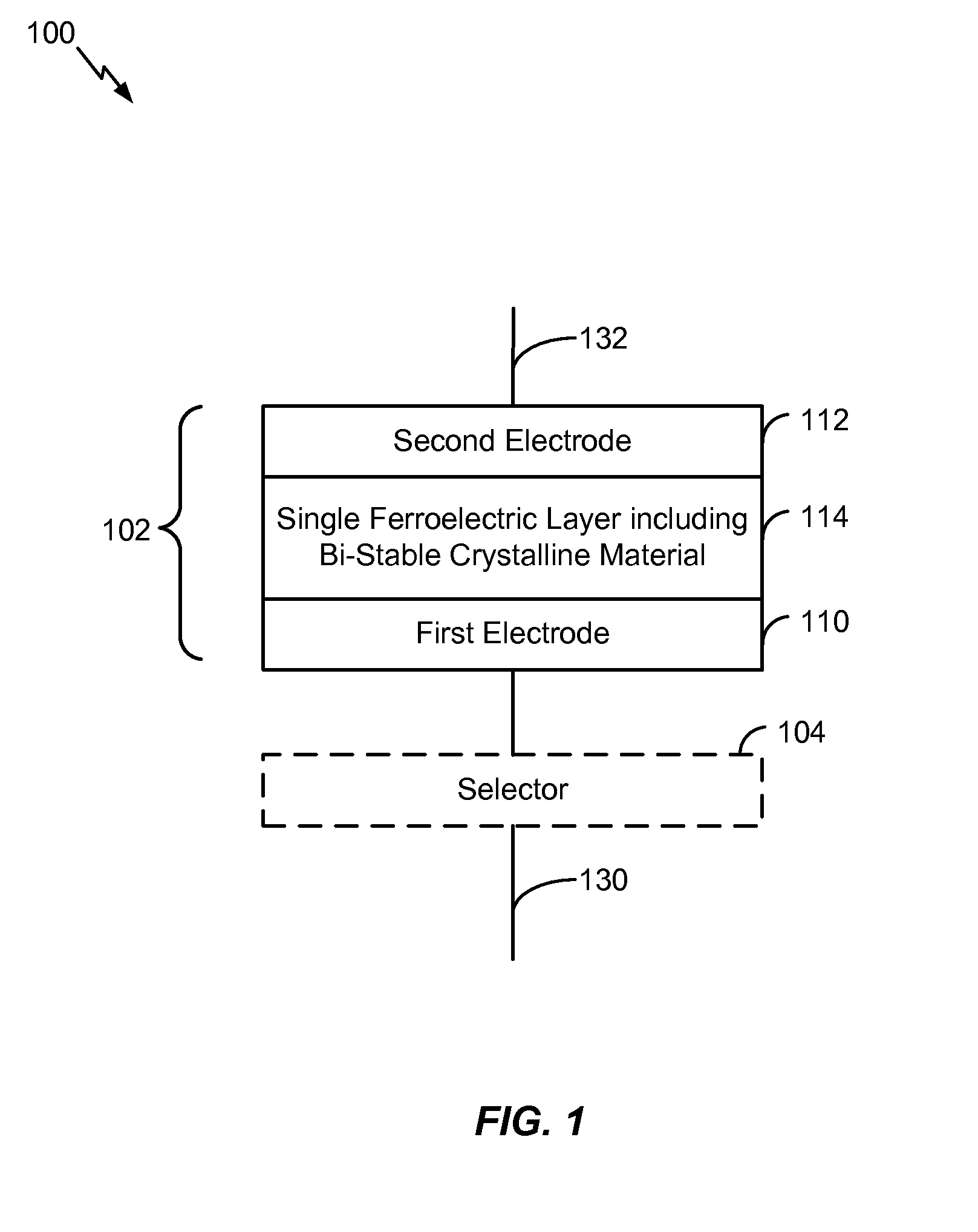

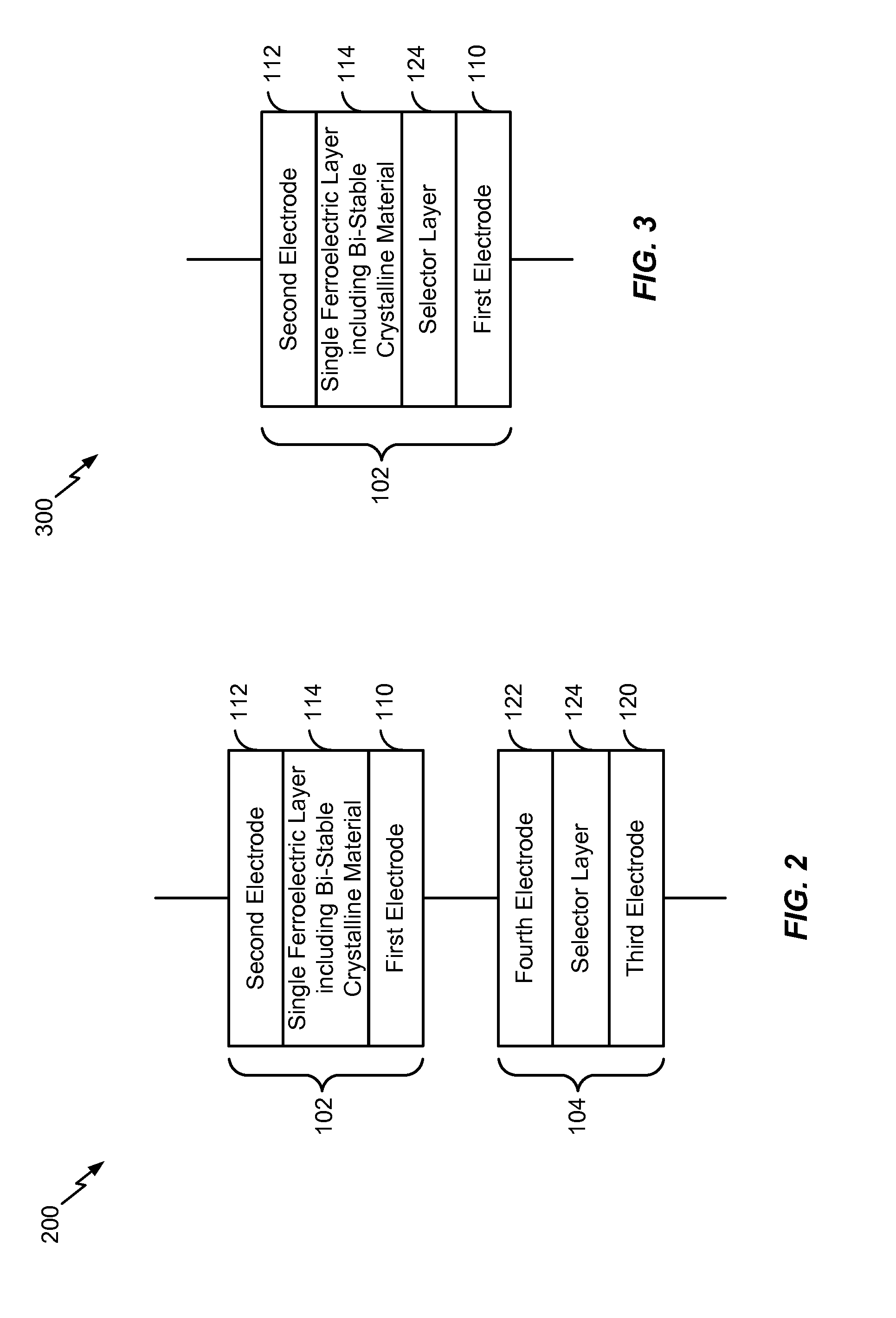

InactiveUS20160064391A1Small sizeExtended retention timeTransistorSolid-state devicesCrystalline materialsMetal

Owner:QUALCOMM INC

Hydrogen barrier for protecting ferroelectric capacitors in a semiconductor device and methods for fabricating the same

InactiveUS20050012126A1Prevent and inhibit memory cell degradationWell formedTransistorSemiconductor/solid-state device detailsHydrogenAmorphous silicon

Semiconductor devices and fabrication methods are presented, in which a hydrogen barrier is provided above a ferroelectric capacitor to prevent degradation of the ferroelectric material during back-end manufacturing processes employing hydrogen. The hydrogen barrier comprises silicon rich silicon oxide or amorphous silicon, which can be used in combination with an aluminum oxide layer to inhibit diffusion of process-related hydrogen into the ferroelectric capacitor layer.

Owner:TEXAS INSTR INC

Ferroelectric memory wherein bit line capacitance can be maximized

InactiveUS20030169616A1Line capacitance can be optimizedSolid-state devicesSemiconductor/solid-state device manufacturingBit lineCapacitance

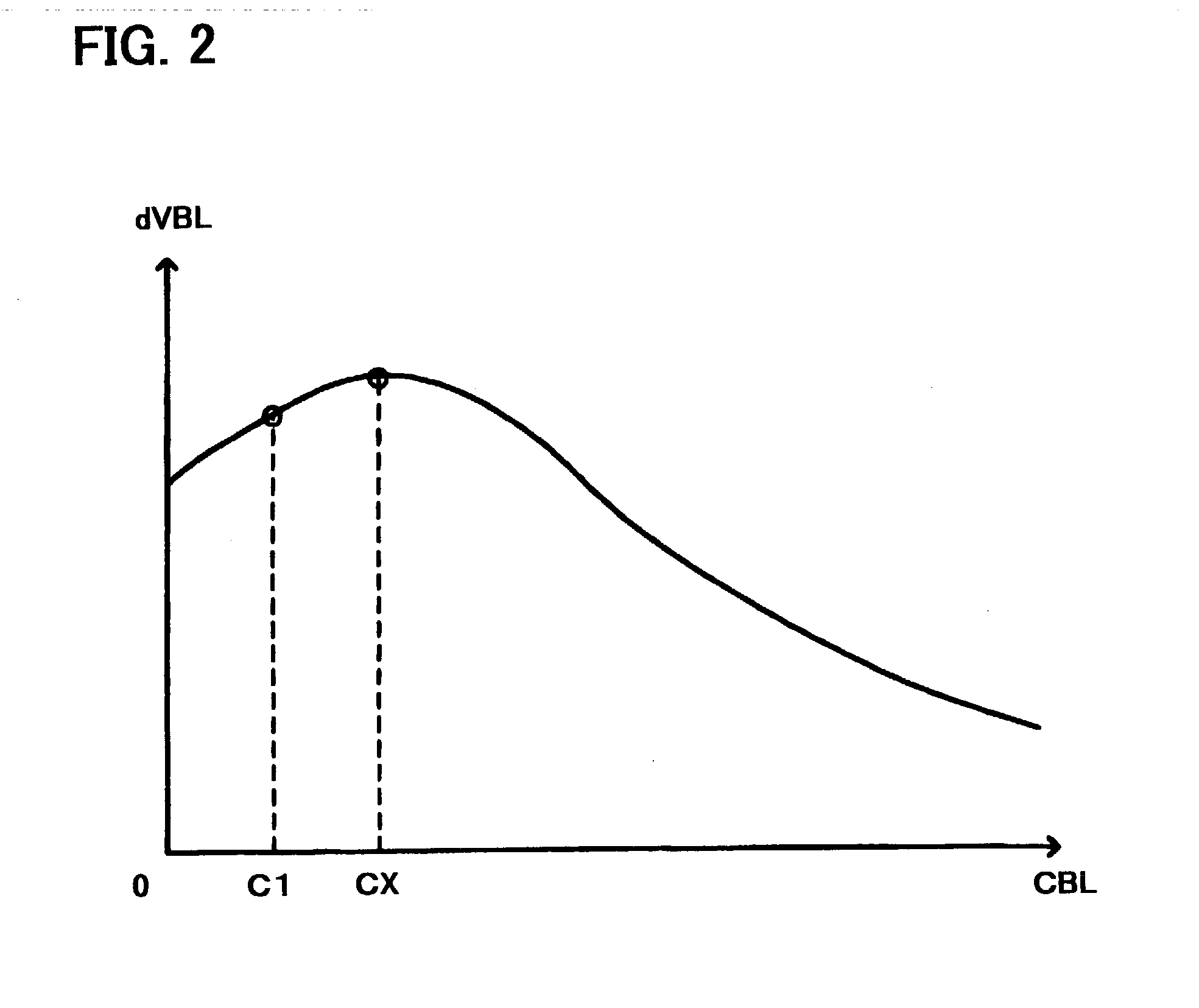

In a ferroelectric memory, there are provided a plurality of word lines, a plurality of bit lines crossing there-with, a plurality of memory cells having ferroelectric capacitors arranged at the positions of these crossovers and a plurality of correction capacitors connectable with the bit lines. At least some of the plurality of correction capacitors are connected with a bit line so as to be capable of increasing bit line capacitance by a prescribed amount.

Owner:FUJITSU LTD

Semiconductor device and manufacturing method thereof

InactiveUS20070228561A1Improve moisture resistanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesFerroelectric capacitorMoisture

A semiconductor device and manufacturing method thereof improving moisture resistance of a FeRAM. After a probe test using a pad, a metal film is formed to cover the pad in an opening of a protective film and a region from the pad to an opening outer periphery of the protective film. On the metal film, a metal bump is formed. The metal film is formed to have a two-layer structure of the first and second metal films. Materials of the lower and upper layers are selected mainly in consideration of adhesion to the protective film and adhesion to the metal bump, respectively. Film formation conditions thereof are set to provide metal films with a desired quality and thickness. Thus, penetration of moisture from the pad or the periphery into a ferroelectric capacitor can be prevented and therefore, occurrence of potential inversion abnormalities due to penetrated moisture can be effectively suppressed.

Owner:FUJITSU SEMICON LTD

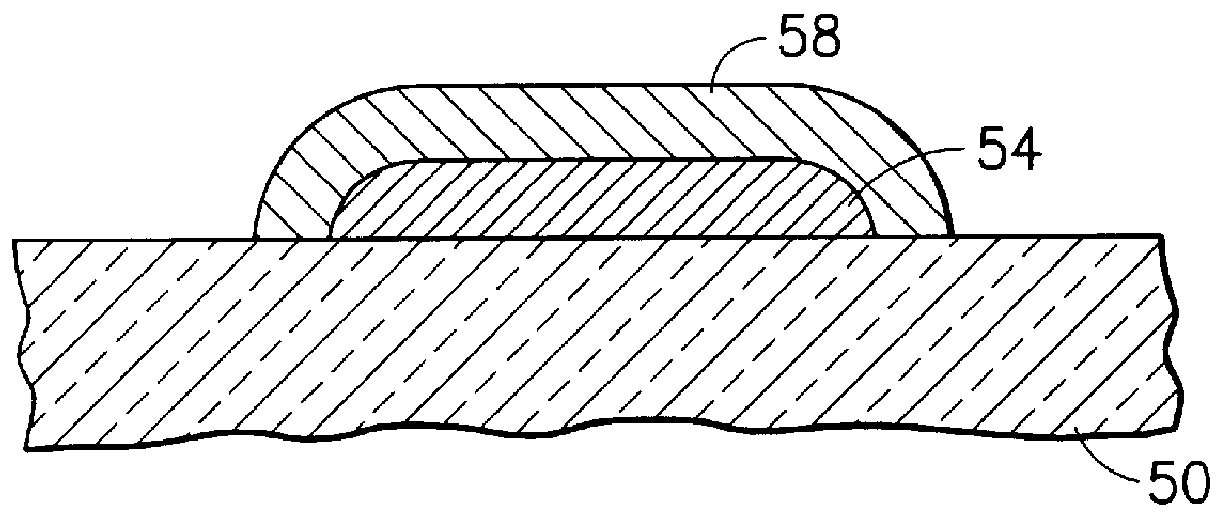

Use of amorphous aluminum oxide on a capacitor sidewall for use as a hydrogen barrier

InactiveUS6876021B2Reducing diffusion of hydrogenMitigate hydrogen contaminationTransistorSolid-state devicesDiffusionHydrogen

The present invention forms sidewall diffusion barrier layer(s) that mitigate hydrogen contamination of ferroelectric capacitors. Sidewall diffusion barrier layer(s) of the present invention are formed via a physical vapor deposition process at a low temperature. By so doing, the sidewall diffusion barrier layer(s) are substantially amorphous and provide superior protection against hydrogen diffusion than conventional and / or crystalline sidewall diffusion barrier layers.

Owner:TEXAS INSTR INC

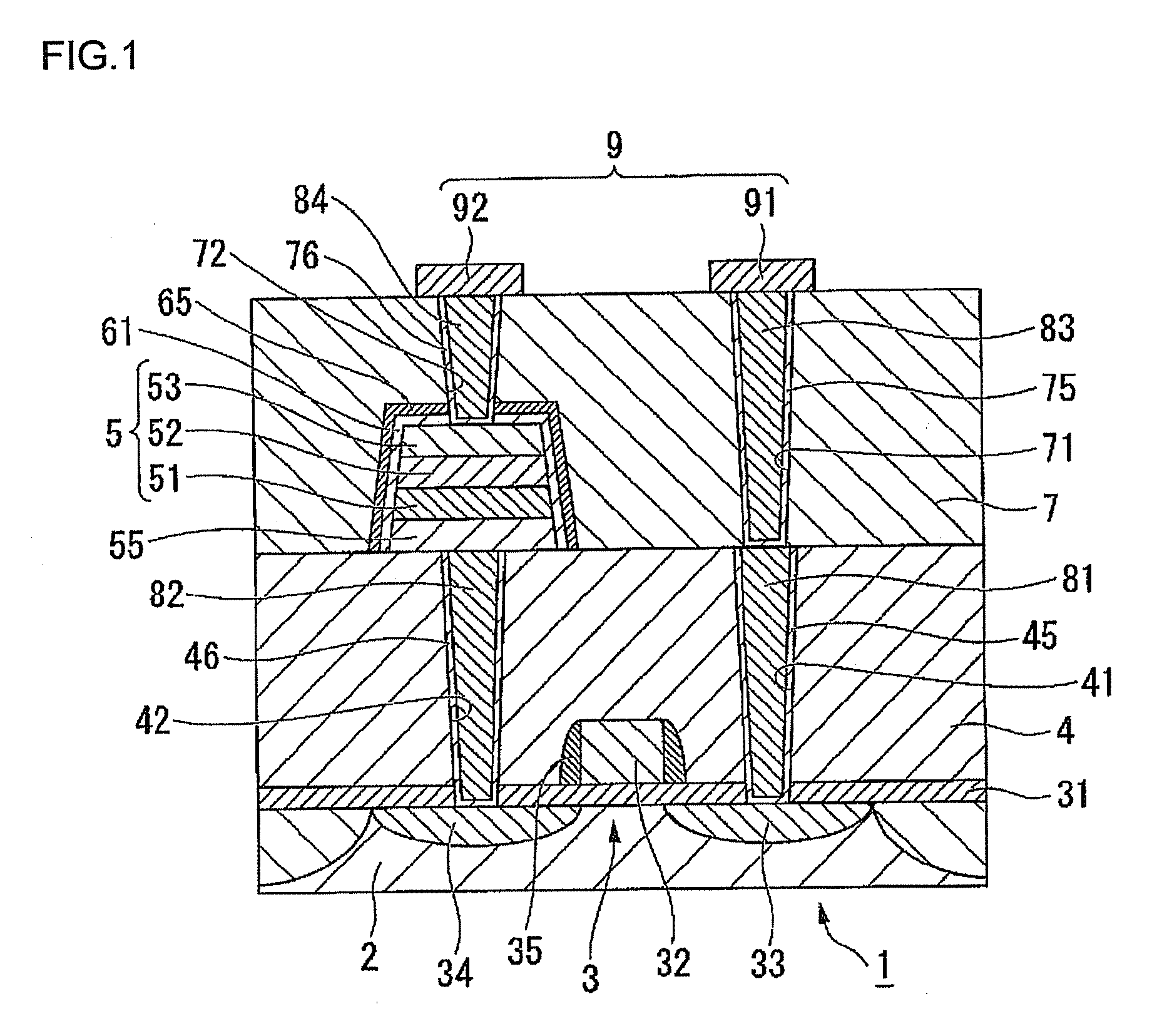

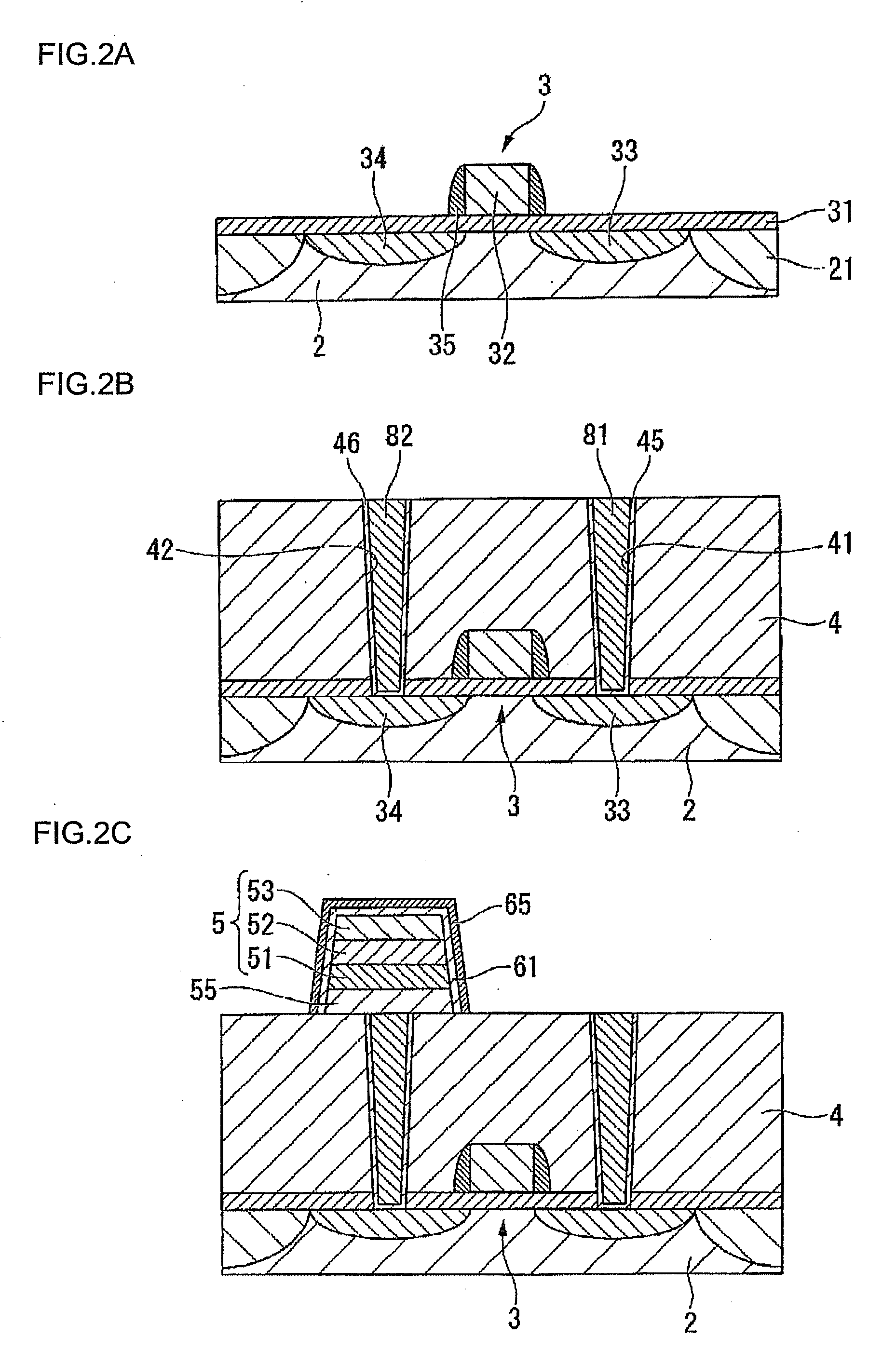

Method for manufacturing ferroelectric capacitor, and ferroelectric capacitor

InactiveUS20080290385A1Etch rate reductionImprove hysteresis characteristicsTransistorSolid-state devicesDielectricResist

A method for manufacturing a ferroelectric capacitor includes the steps of: forming a base dielectric film on a substrate, and forming a first plug conductive section in the base dielectric film at a predetermined position; forming, on the base dielectric film, a charge storage section formed from a lower electrode, a ferroelectric film and an upper electrode; forming a stopper film from an insulation material that covers the charge storage section; forming a hydrogen barrier film that covers the stopper film; forming an interlayer dielectric film on the base dielectric film including the hydrogen barrier film; forming, in the interlayer dielectric film, a first contact hole that exposes the first plug conductive section; forming a second contact hole that exposes the upper electrode of the charge storage section by successively etching the interlayer dielectric film, the hydrogen barrier film and the stopper film by using a resist pattern as a mask, and then removing the resist pattern by a wet cleaning treatment; forming an adhesion layer from a conductive material having hydrogen barrier property inside the second contact hole in a manner to cover an upper surface of the upper electrode; forming a second plug conductive section inside the first contact hole; and forming a third plug conductive section inside the second contact hole, wherein the stopper film is formed from a material having a lower etching rate for a cleaning liquid used for the wet cleaning treatment to remove the resist pattern than an etching rate of the hydrogen barrier film for the cleaning liquid.

Owner:SEIKO EPSON CORP

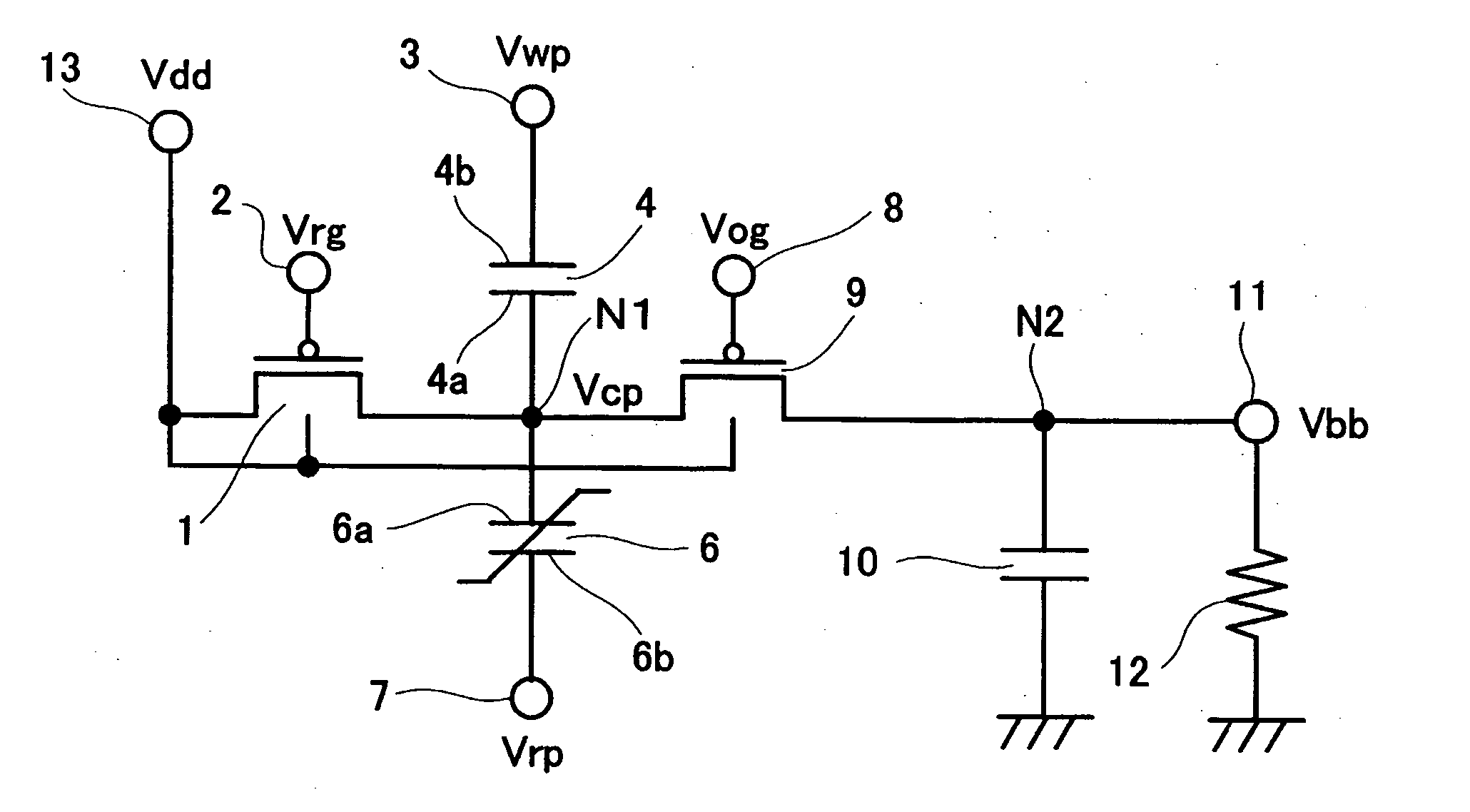

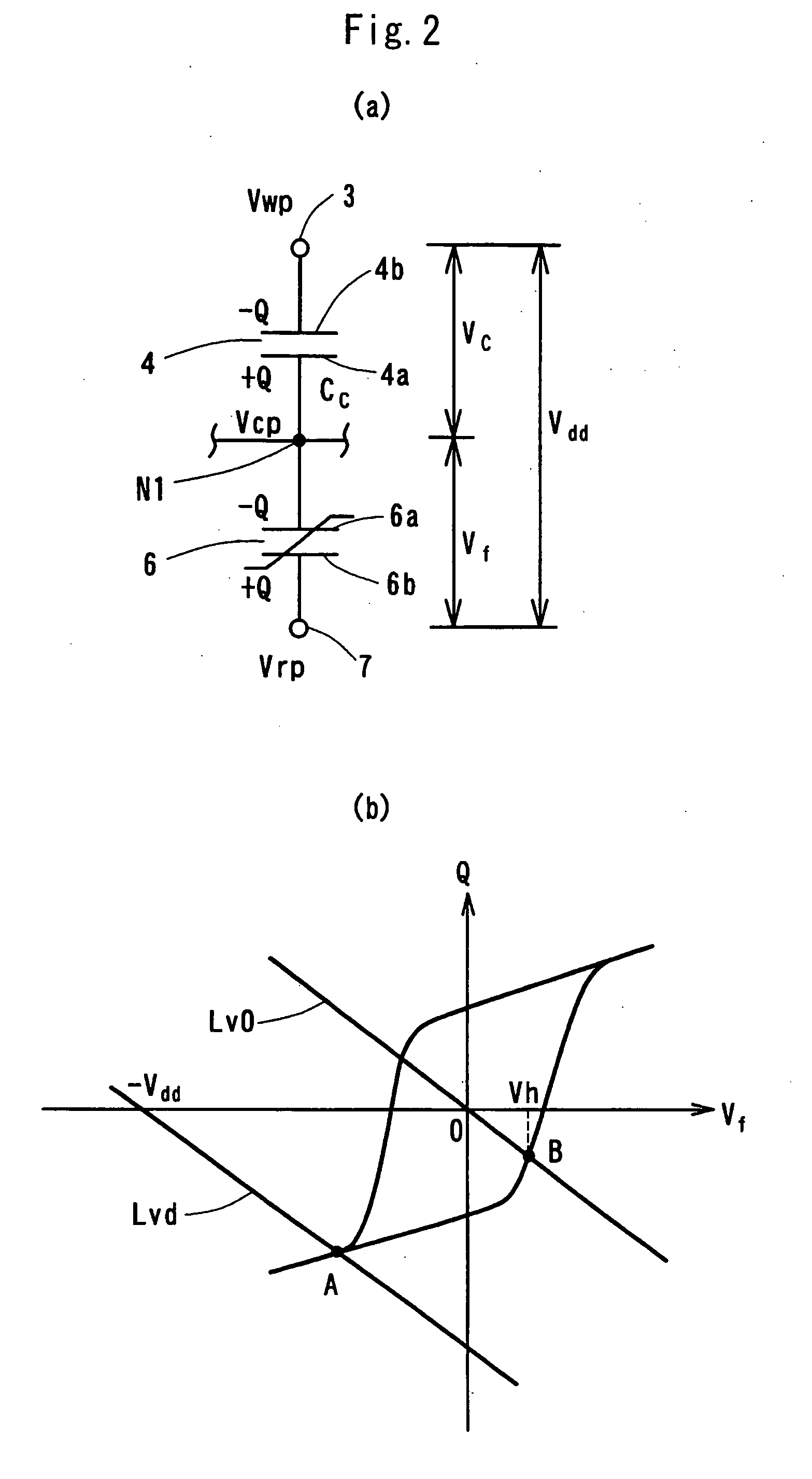

Voltage generating circuit, voltage generating device and semiconductor device using the same, and driving method thereof

ActiveUS20040183508A1Stable maintenanceElectronic switchingApparatus without intermediate ac conversionSemiconductorFerroelectric capacitor

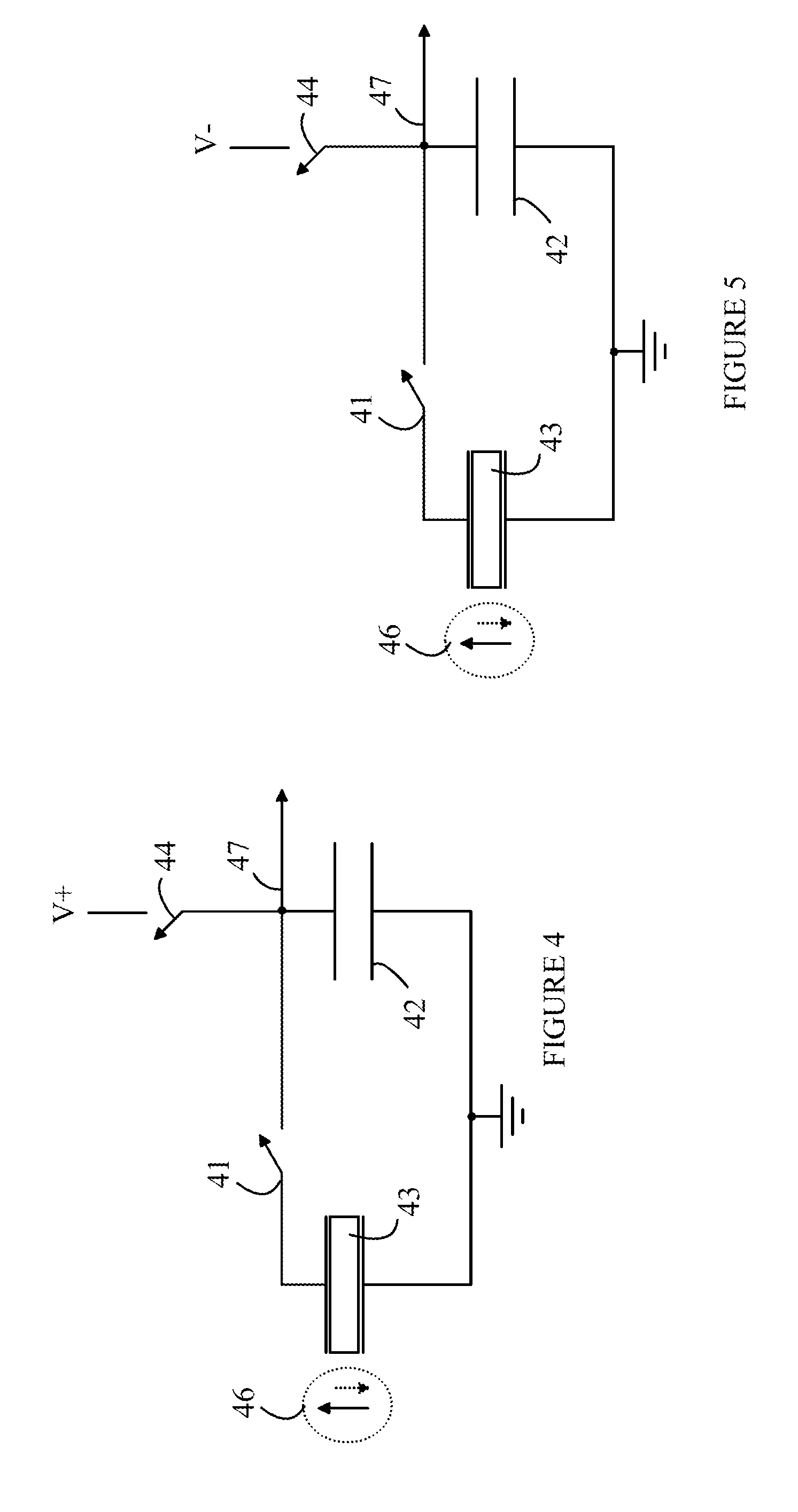

A voltage generating circuit comprising a capacitor (4), a ferroelectric capacitor (6) serially connected to the capacitor (4), an output terminal (11), a capacitor (10) which grounds the output terminal (11), a supply voltage supplying terminal (13), a switch (1) which connects the supply voltage supplying terminal (13) and the connecting node (N1) of the two capacitors (4, 6), and a switch (9) which connects the connecting node (N1) and output terminal (11); wherein during a first period, with the two switches (1) and (9) placed in the OFF state, a terminal (3) is grounded and a terminal (7) is provided with a supply voltage; wherein during a second period, the terminal (3) is provided with the supply voltage and the switch (9) is placed in the ON state; wherein during a third period, the switch (9) is placed in the OFF state, the switch (1) is placed in the ON state, and the terminal (7) is grounded; wherein during a fourth period, the terminal (7) is provided with the supply voltage; and wherein thereafter the first through fourth periods are repeated.

Owner:PANASONIC CORP

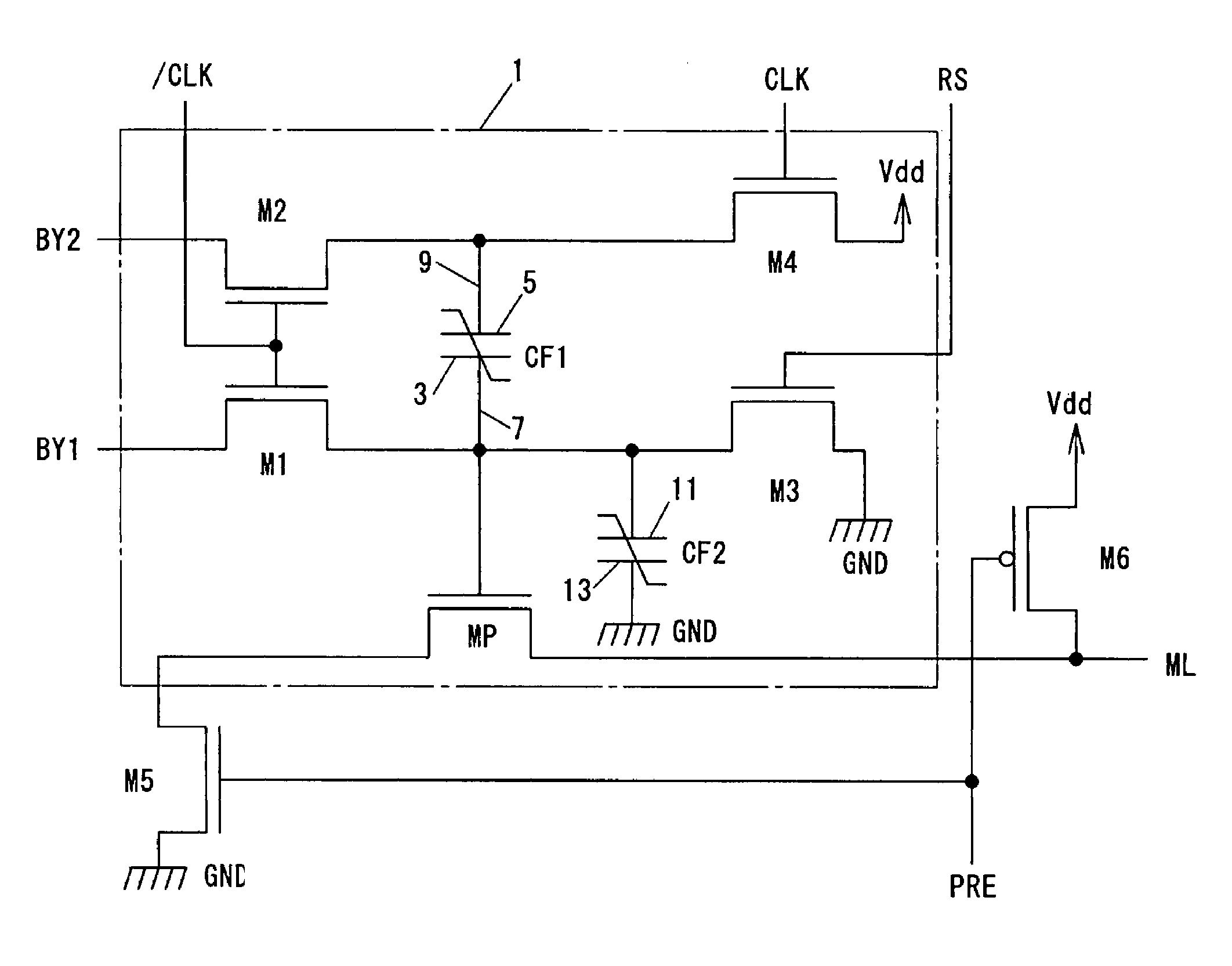

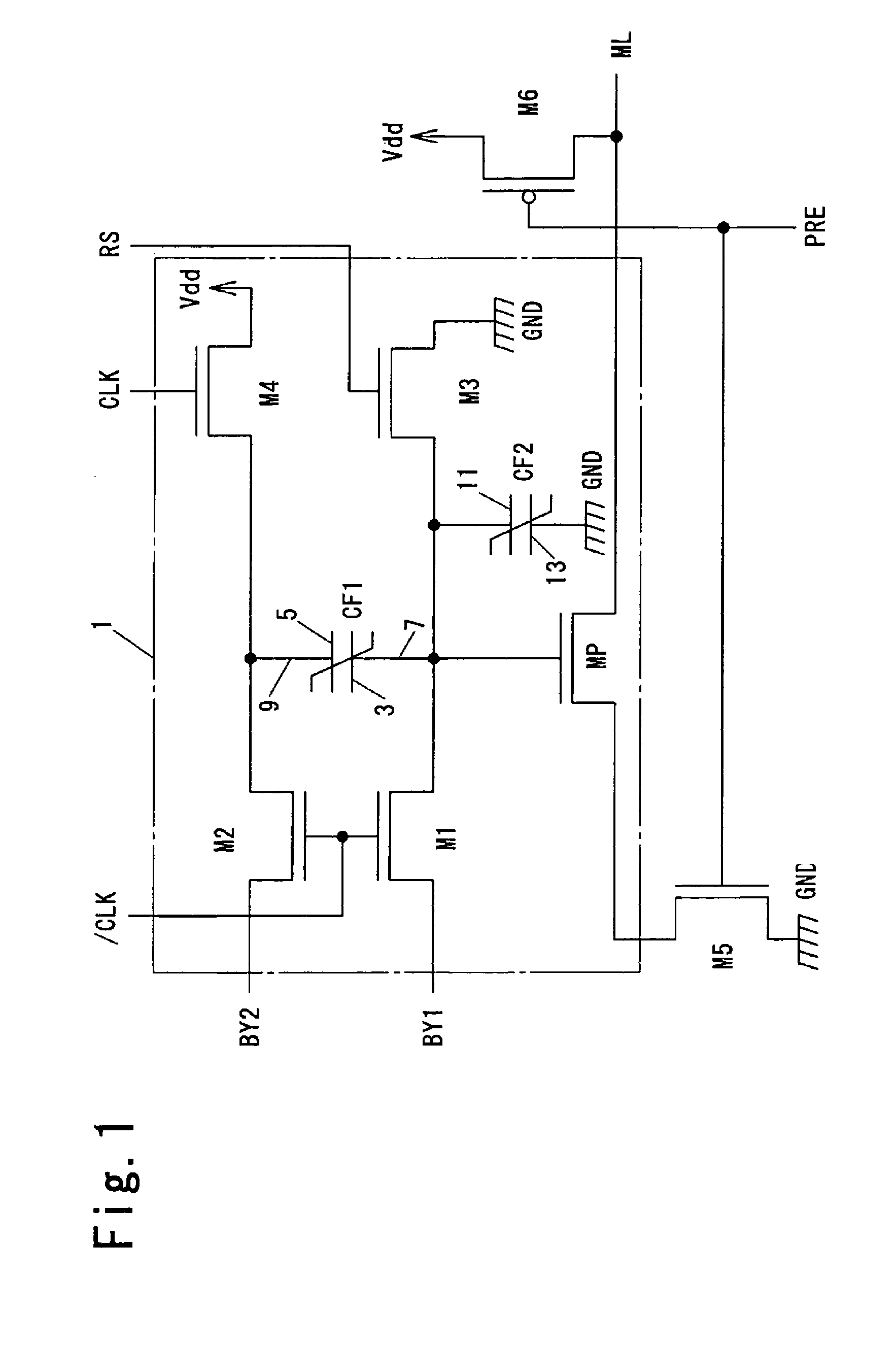

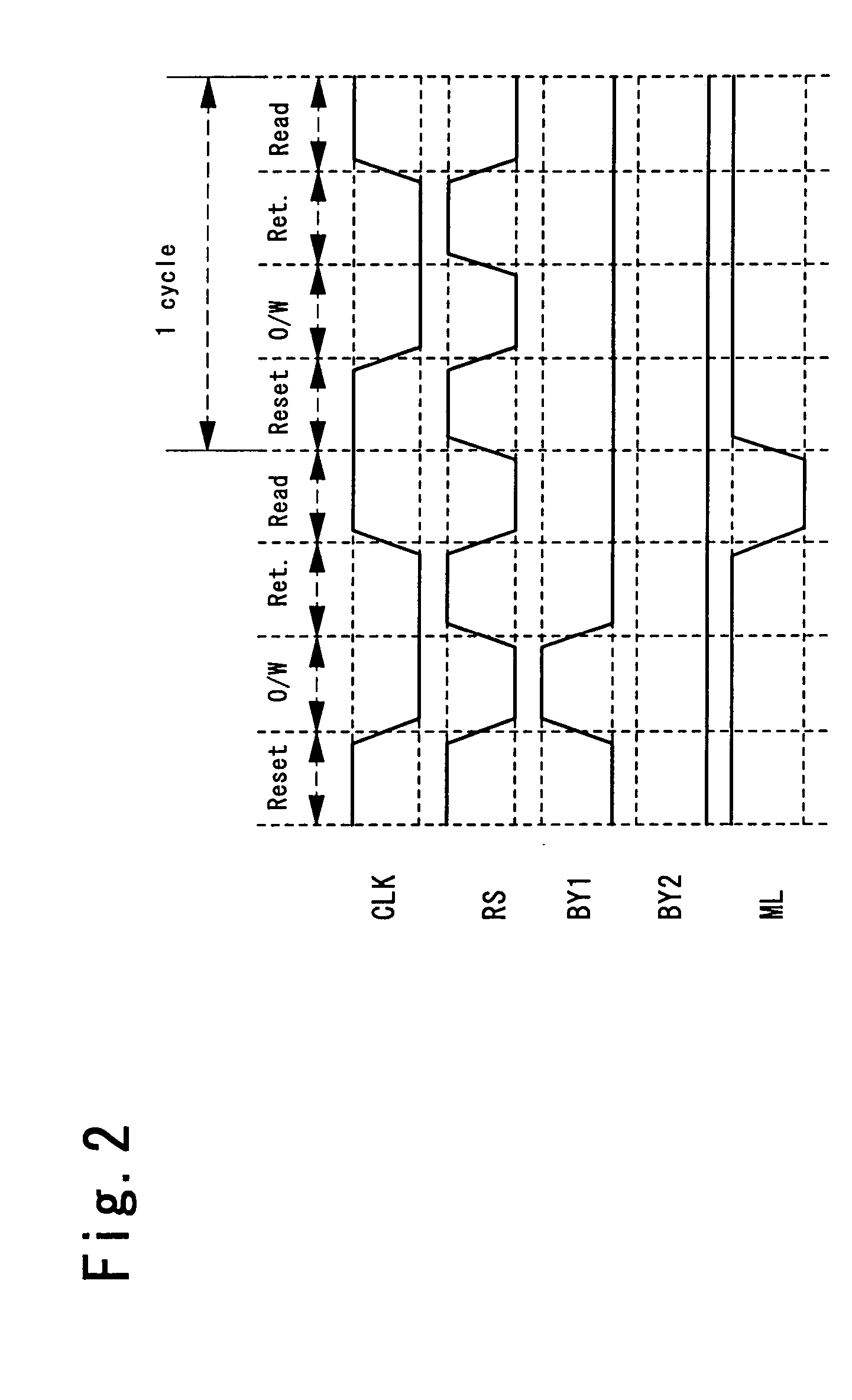

Logical operation circuit and logical operation device

InactiveUS7428565B2Logic circuits characterised by logic functionSpace heating and ventilation safety systemsPotential differenceHemt circuits

To provide a logical operation circuit and a logical operation device which can performs a logical operation using a ferroelectric capacitor. The area ratio between the ferroelectric capacitors CF1 and CF2 are set such that the potential difference Vdef between voltages Va1 and Va0 is as large as possible, and a transistor MP has a threshold voltage Vth which is about ½·(Va0+Va1). Thus, the ON / OFF operation margin of the transistor MP can be significantly large. As a result, a reading process can be performed at a high speed without using an amplifying circuit such as a sense amplifier. Also, the logical operation circuit and the logical operation device can be highly integrated with ease since no sense amplifier is used.

Owner:ROHM CO LTD

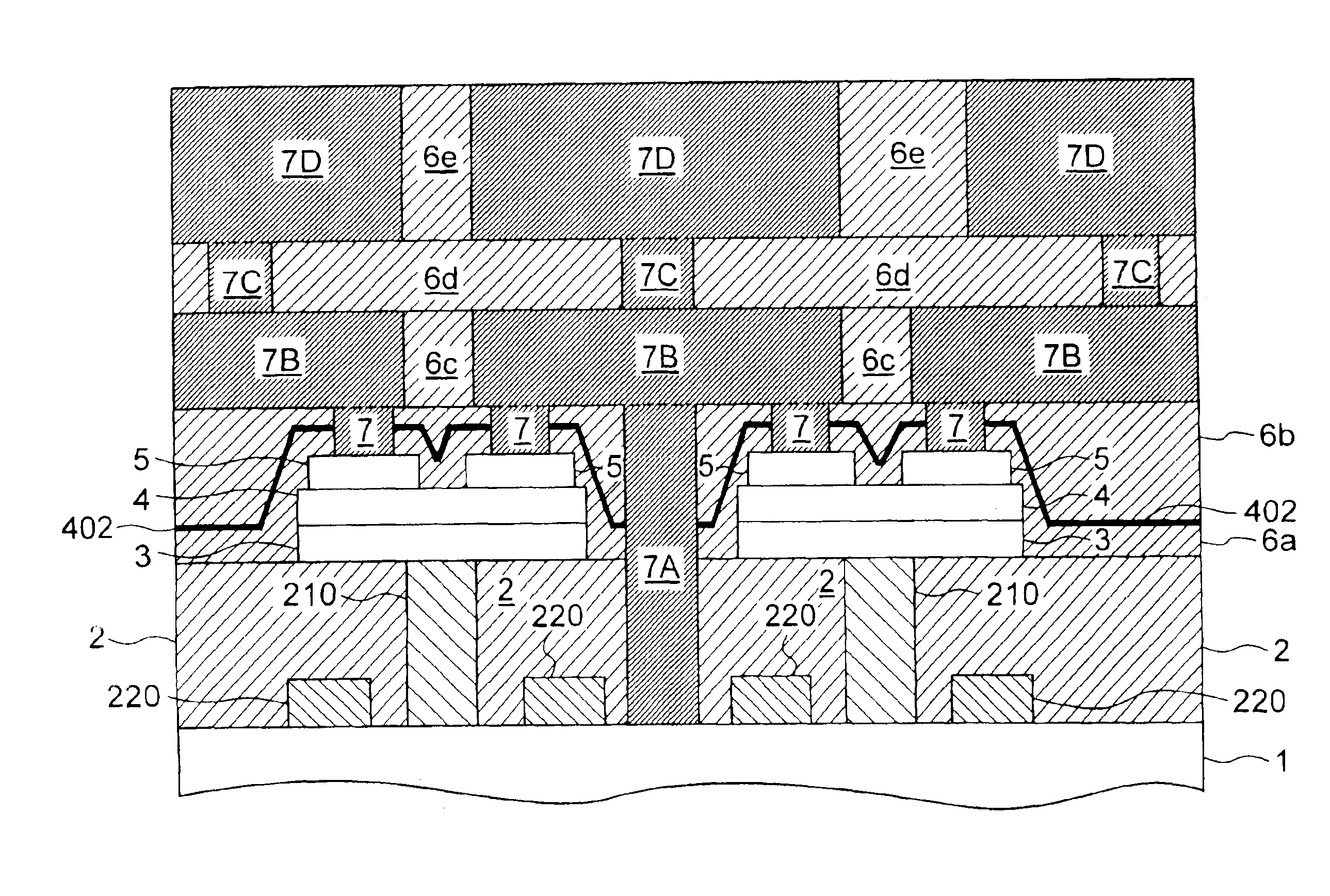

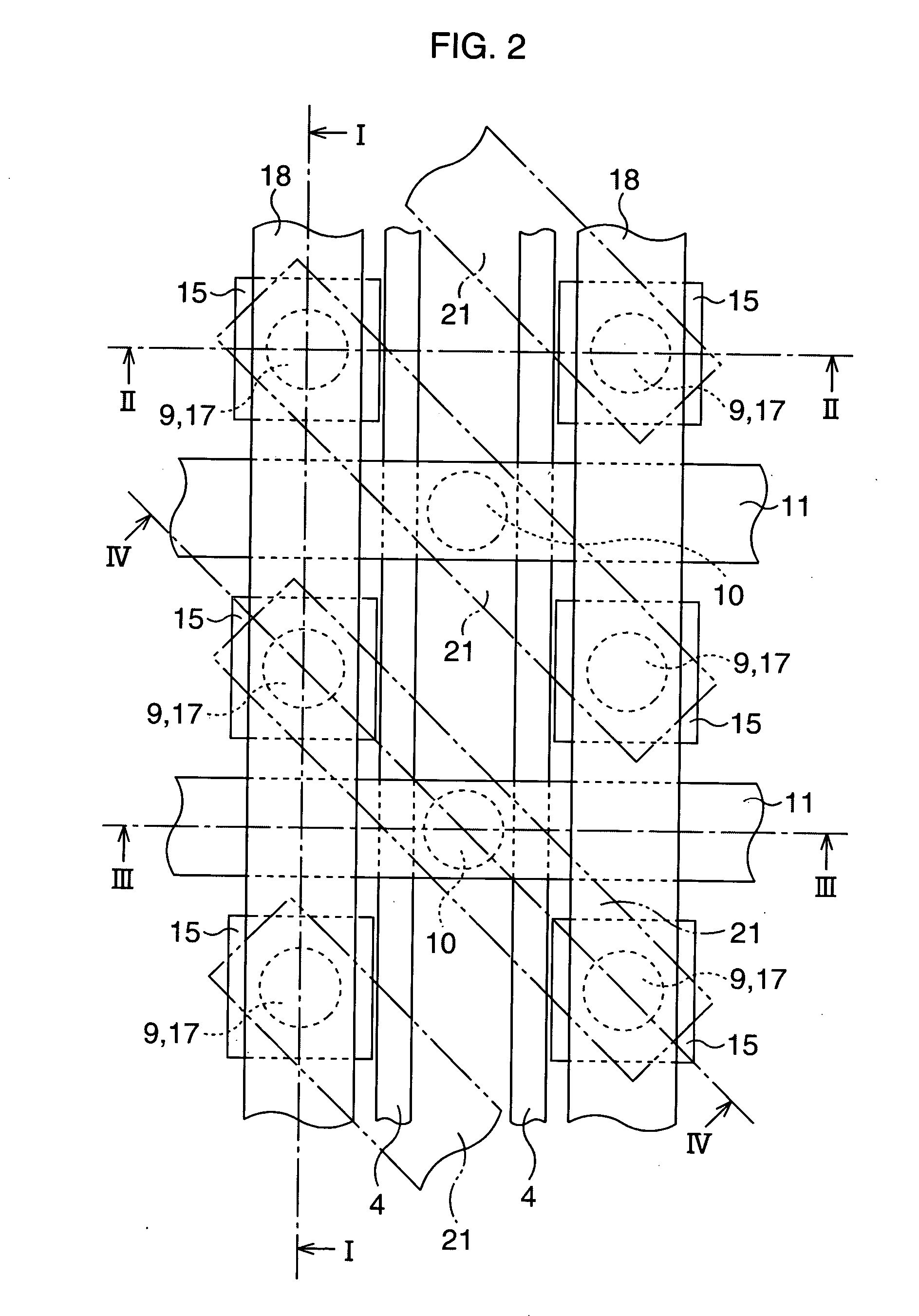

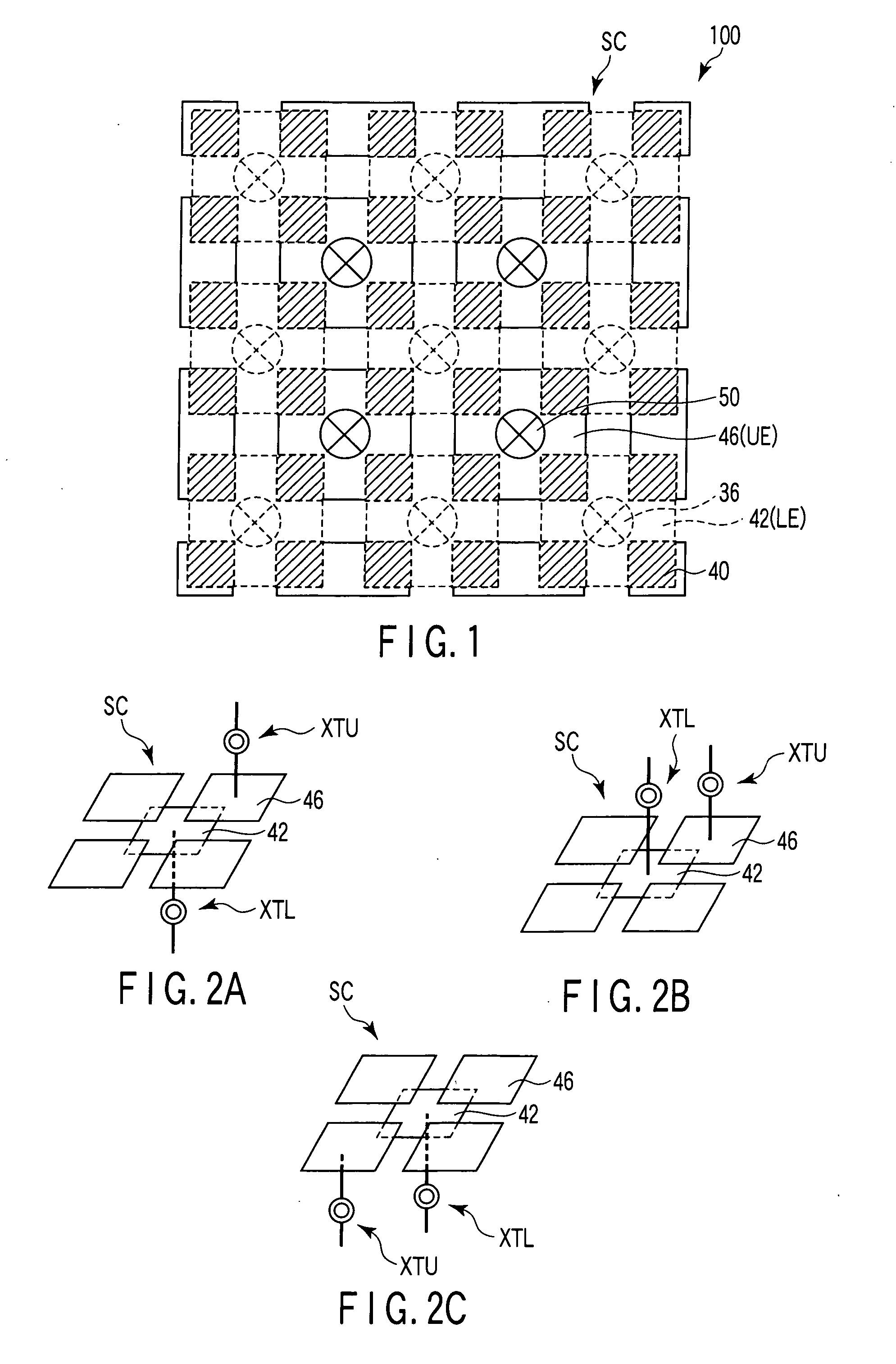

Semiconductor device and manufacturing method thereof

InactiveUS20050087787A1Reduce leakage currentAvoid local damageTransistorSolid-state devicesBit lineDevice material

There is formed a gate electrode (word line) via a gate insulating film on a semiconductor substrate, the gate electrode extending in the direction inclining at an angle of approximately 45 degrees to the extending direction of an element region. The element region is divided into three portions by the two gate electrodes. In each element region portion, two MOS transistors are provided. A bit line is connected to a W plug provided in the central region portion and lower electrodes of two ferroelectric capacitors are connected to other W plugs provided in both end region portions. The extending direction of the bit line inclines approximately 45 degrees to the extending direction of the element region.

Owner:FUJITSU MICROELECTRONICS LTD

Semiconductor memory device

A semiconductor memory device including a capacitor array having an effective size smaller than a minimum feature size of lithography is disclosed. According to one aspect of the present invention, it is provided a semiconductor memory device comprising a transistor including a gate electrode formed on a gate insulator on a semiconductor substrate and a plurality of sources / drains disposed in the semiconductor substrate to face each other holding the gate electrode therebetween, a ferroelectric capacitor formed above the transistor and including a lower electrode, a ferroelectric film, and an upper electrode, a first wiring line electrically connected to the lower electrode, and a second wiring line electrically connected to the upper electrode, wherein the ferroelectric capacitor is a staggered-electrode capacitor in which the upper electrode is shifted from the lower electrode and equivalently overlaps with parts of the plurality of lower electrodes.

Owner:KK TOSHIBA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com