Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

59results about How to "Avoid charge accumulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

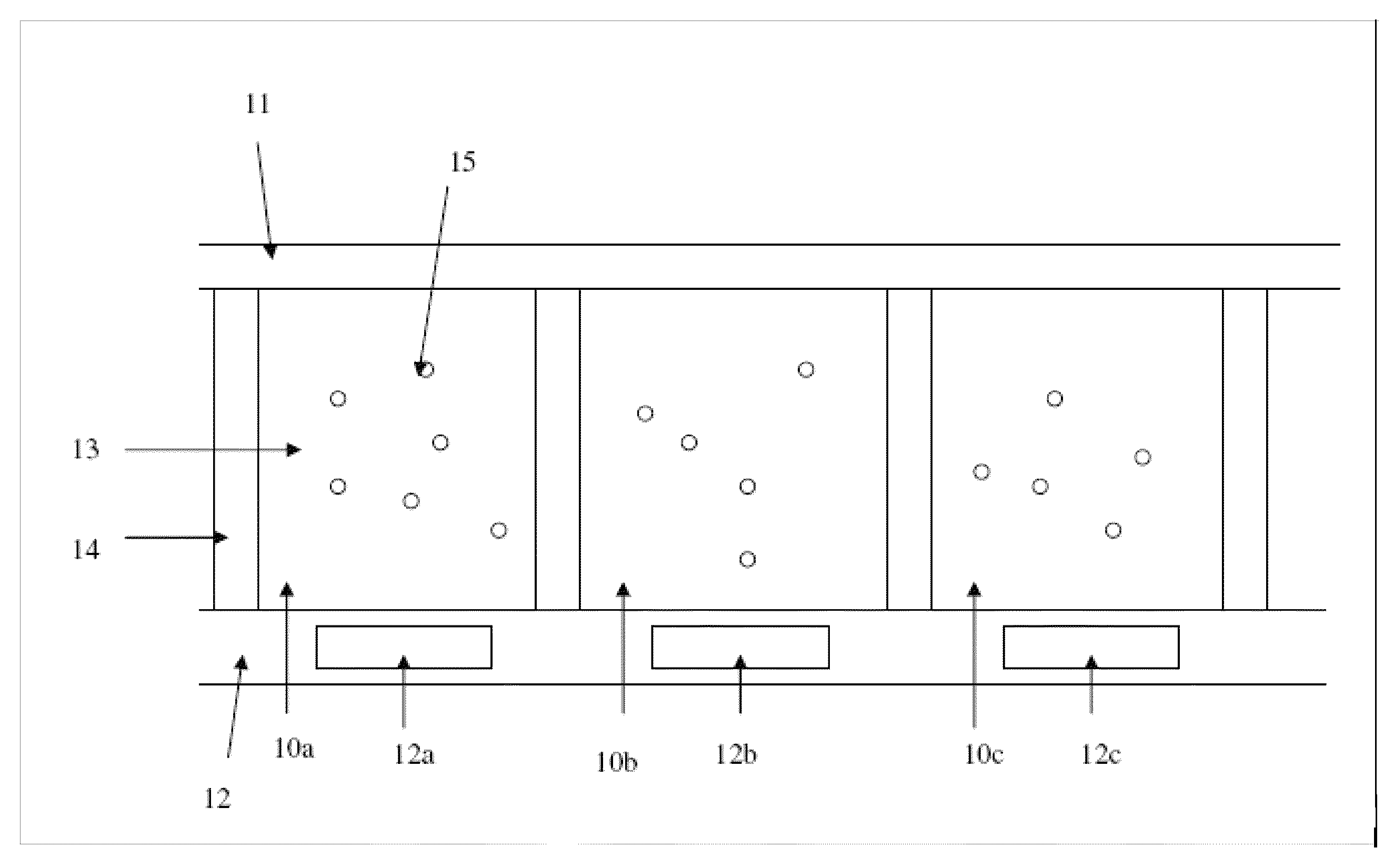

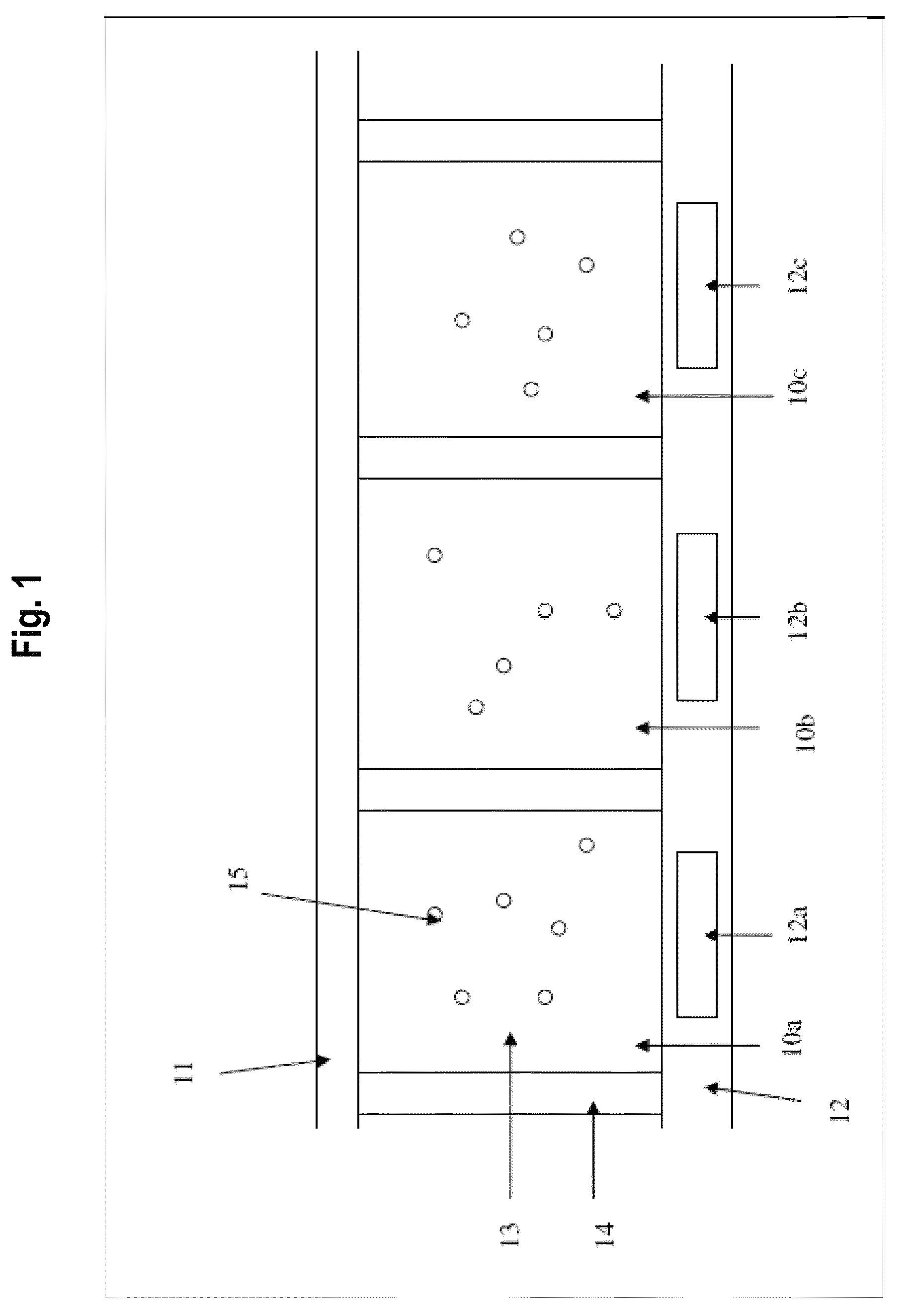

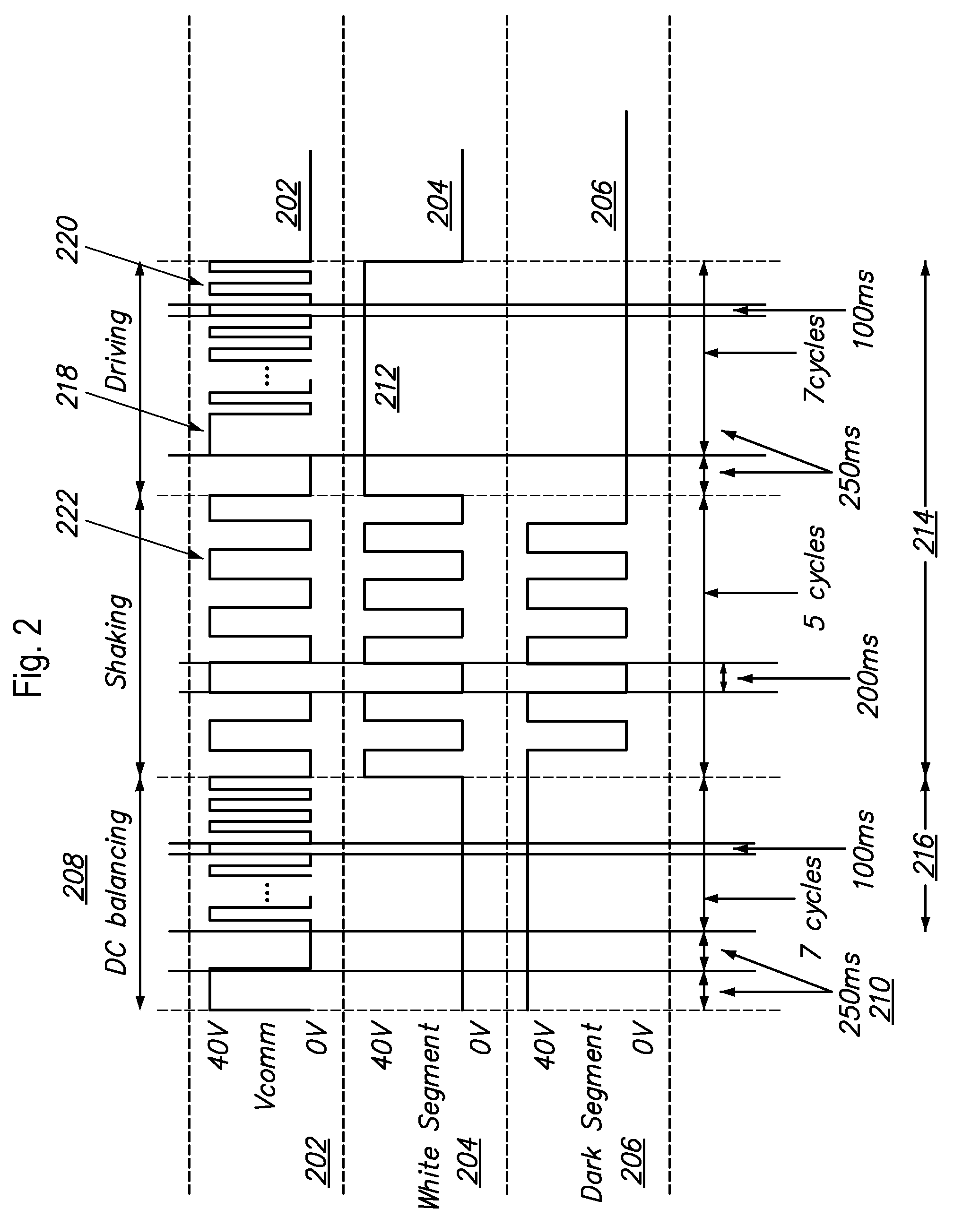

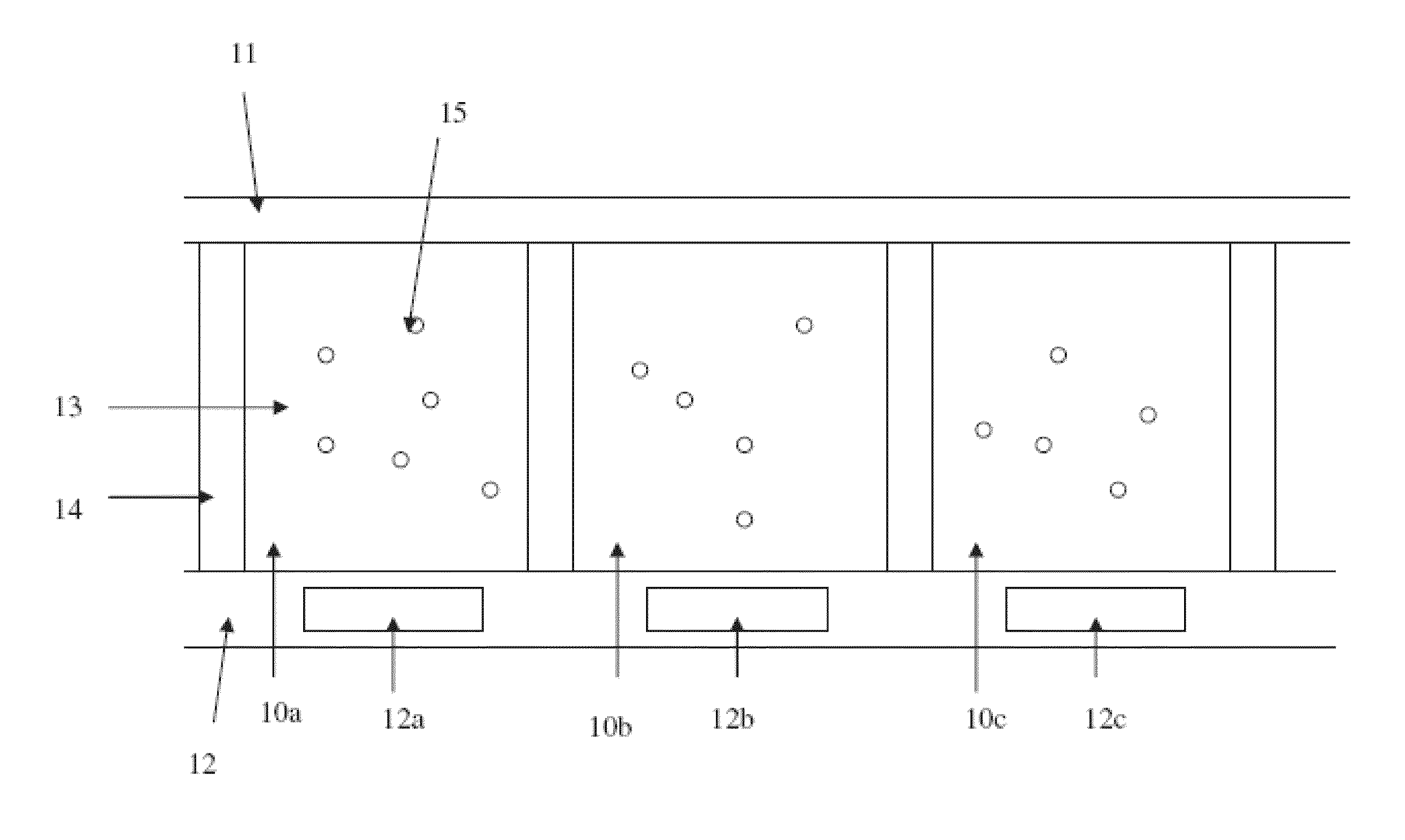

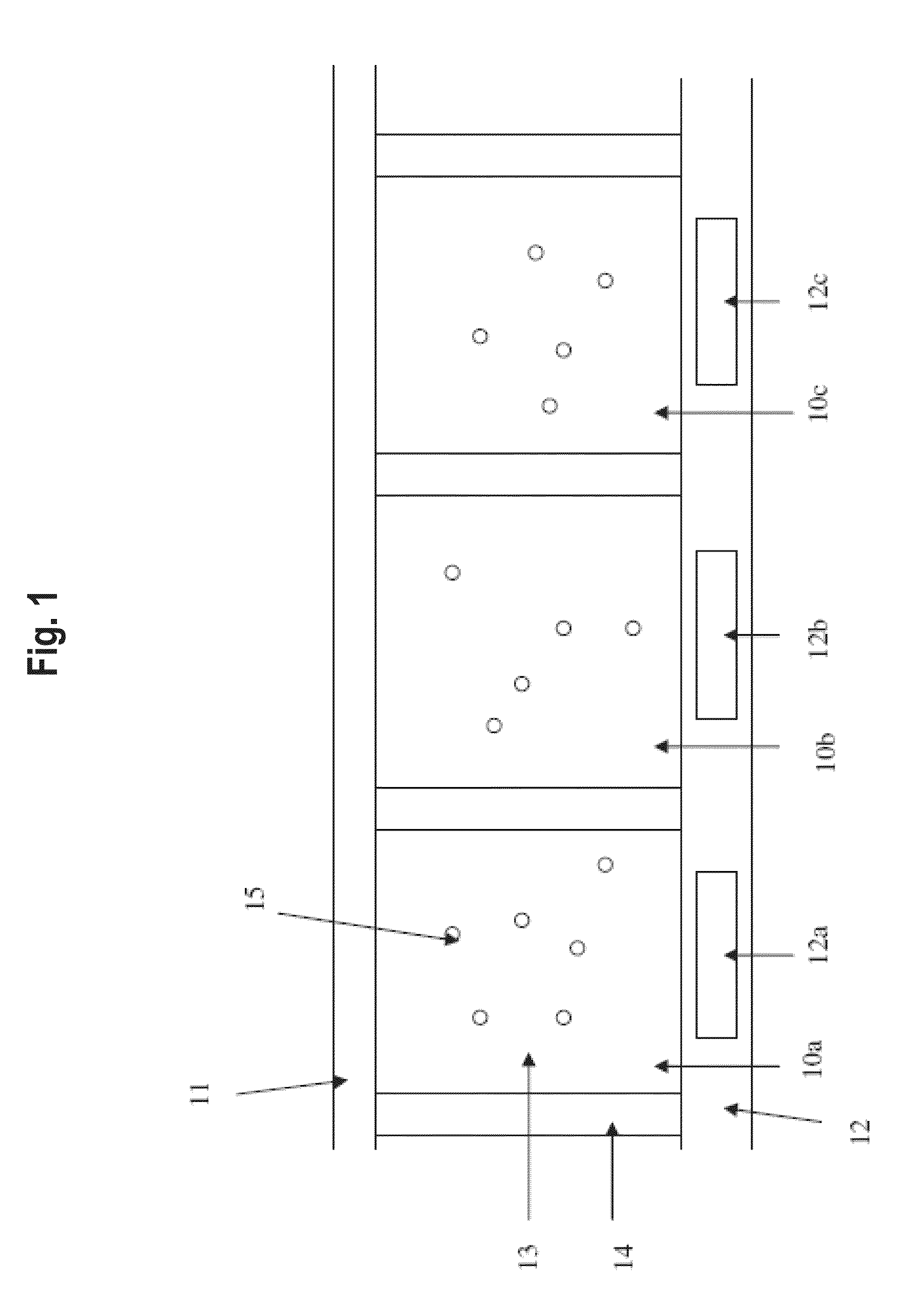

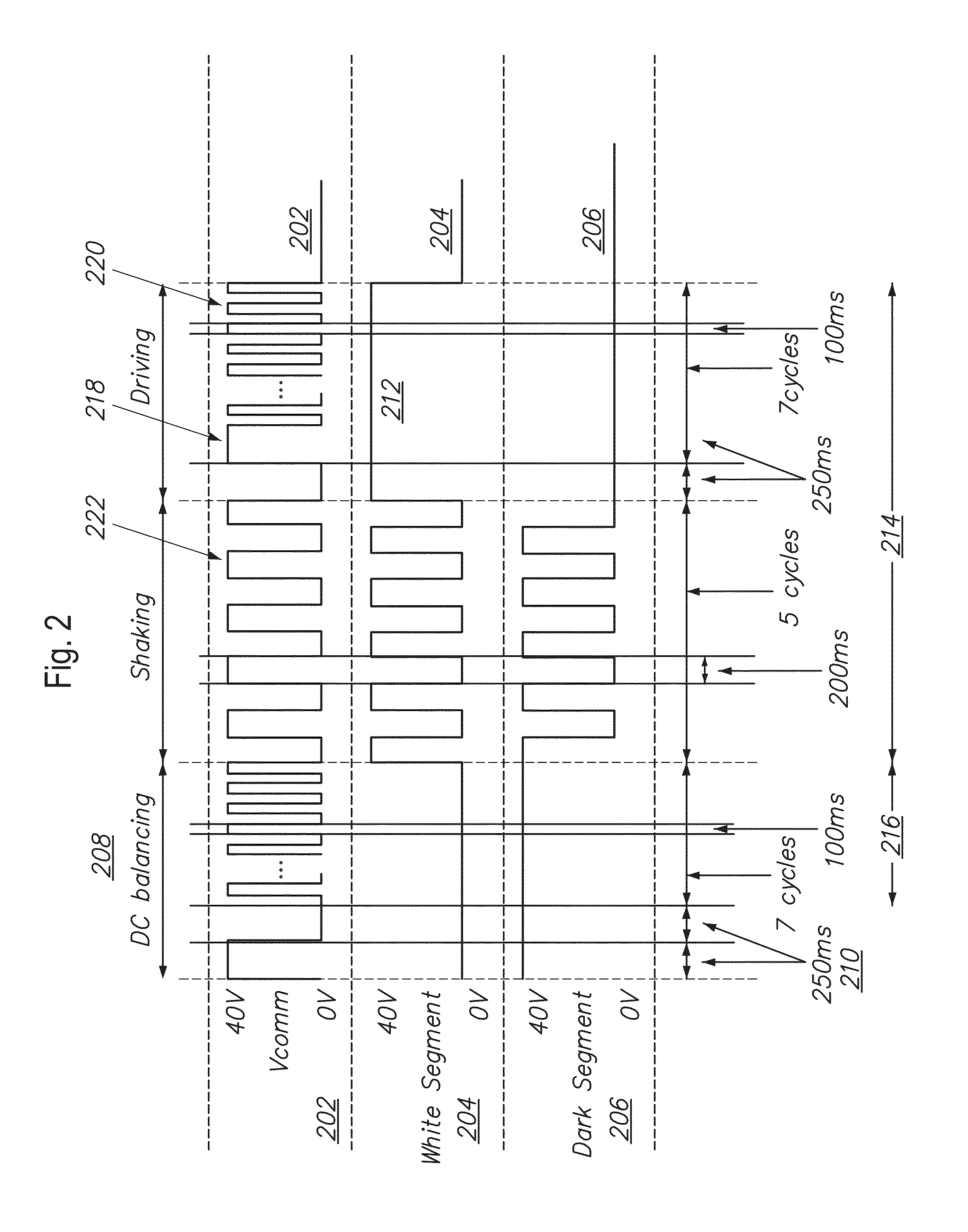

Driving bistable displays

ActiveUS8730153B2Avoid charge accumulationCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceEngineering

Owner:E INK CALIFORNIA

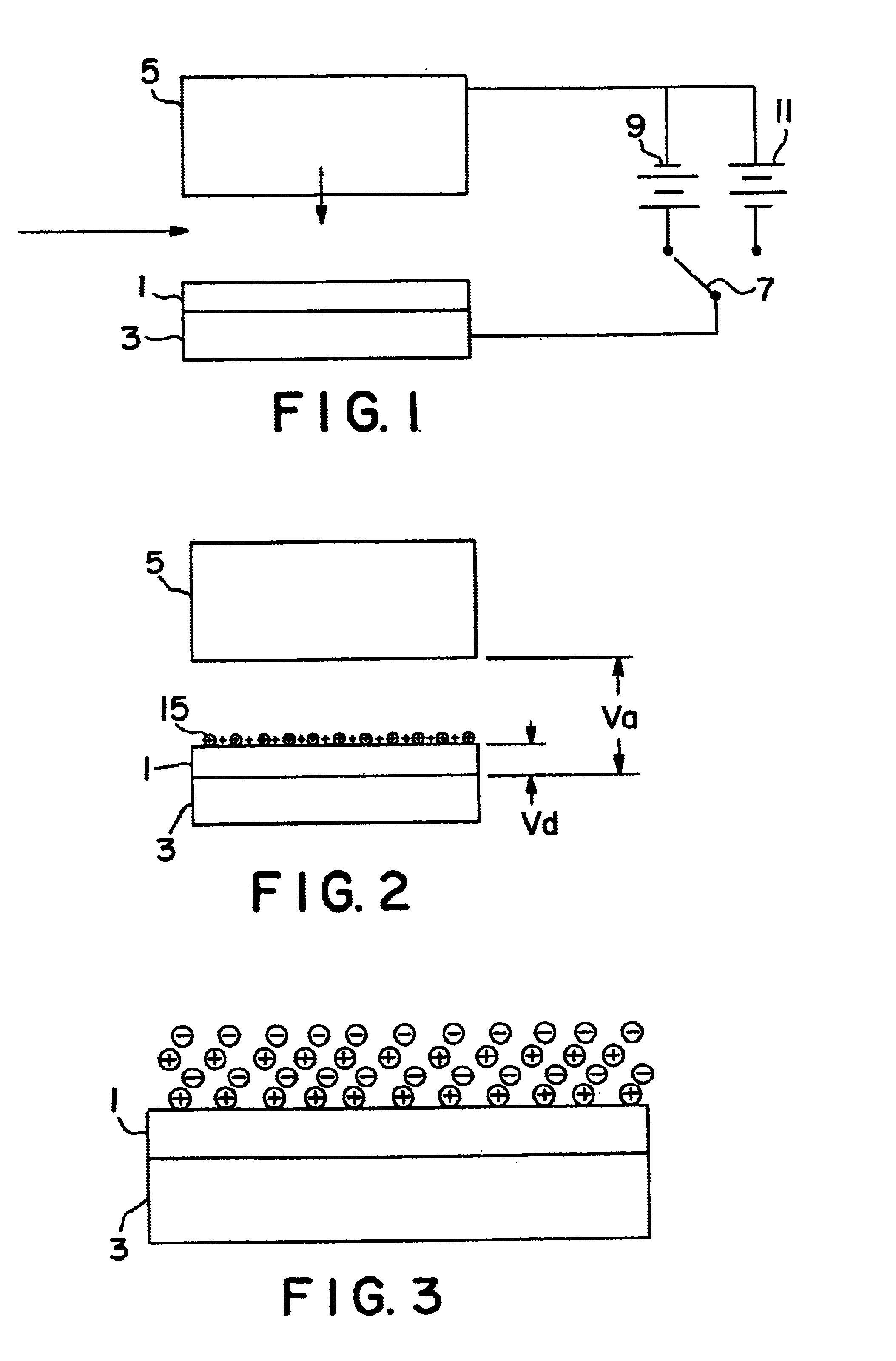

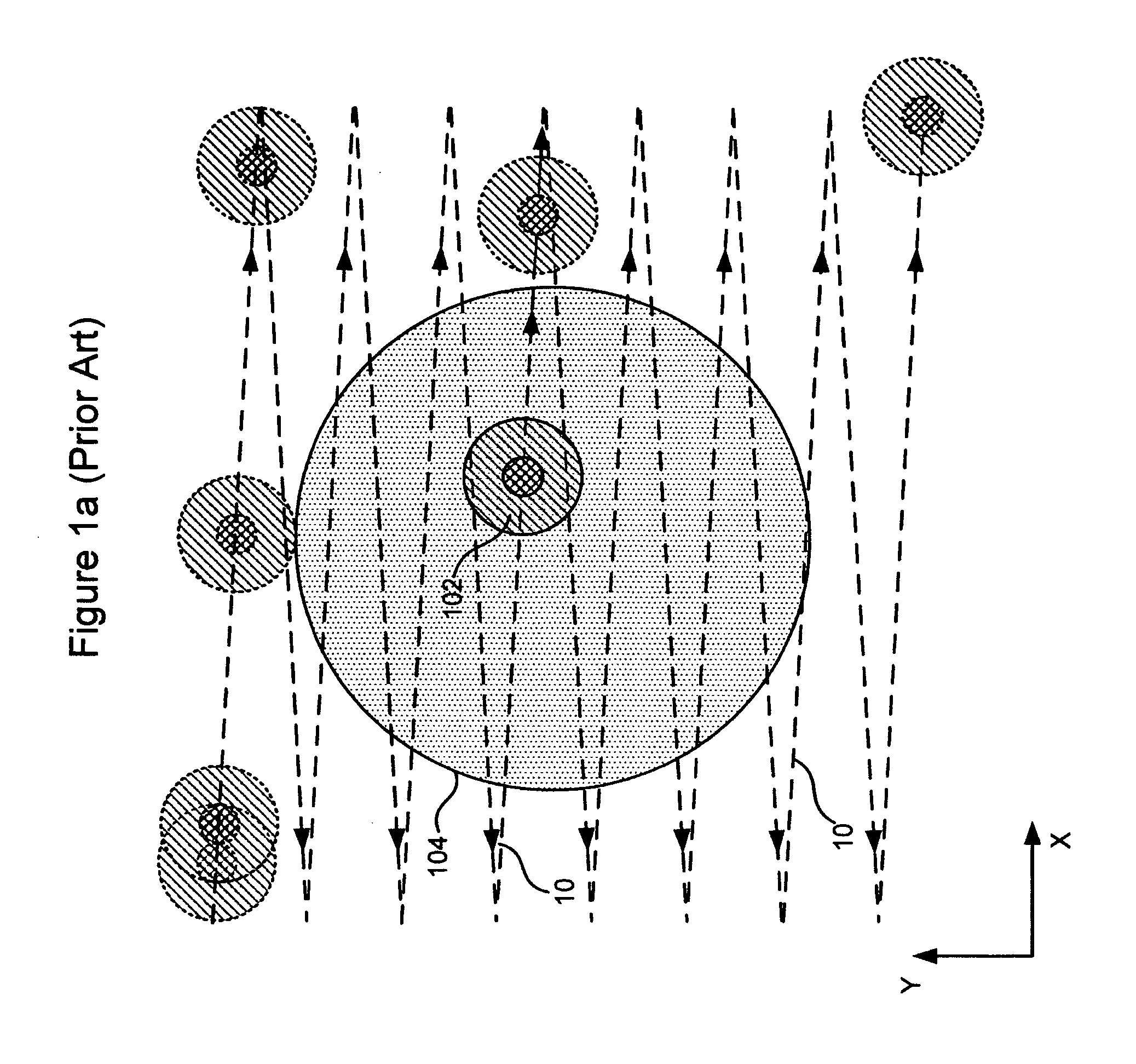

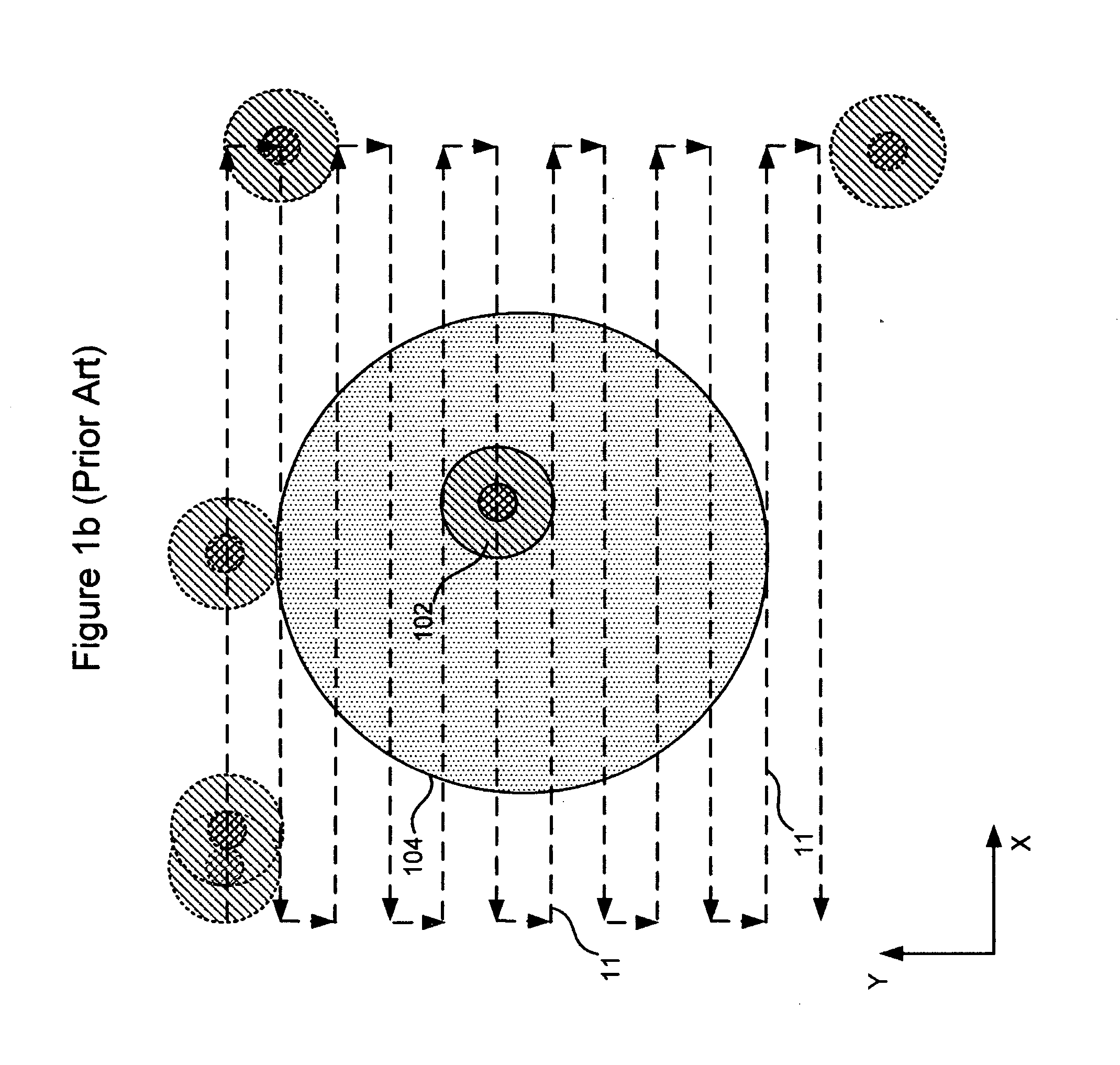

Method for depositing particles onto a substrate using an alternating electric field

InactiveUS6923979B2Quality improvementAvoid charge accumulationPowder deliveryPretreated surfacesElectrical polarityElectric field

Owner:MICRODOSE THERAPEUTX INC

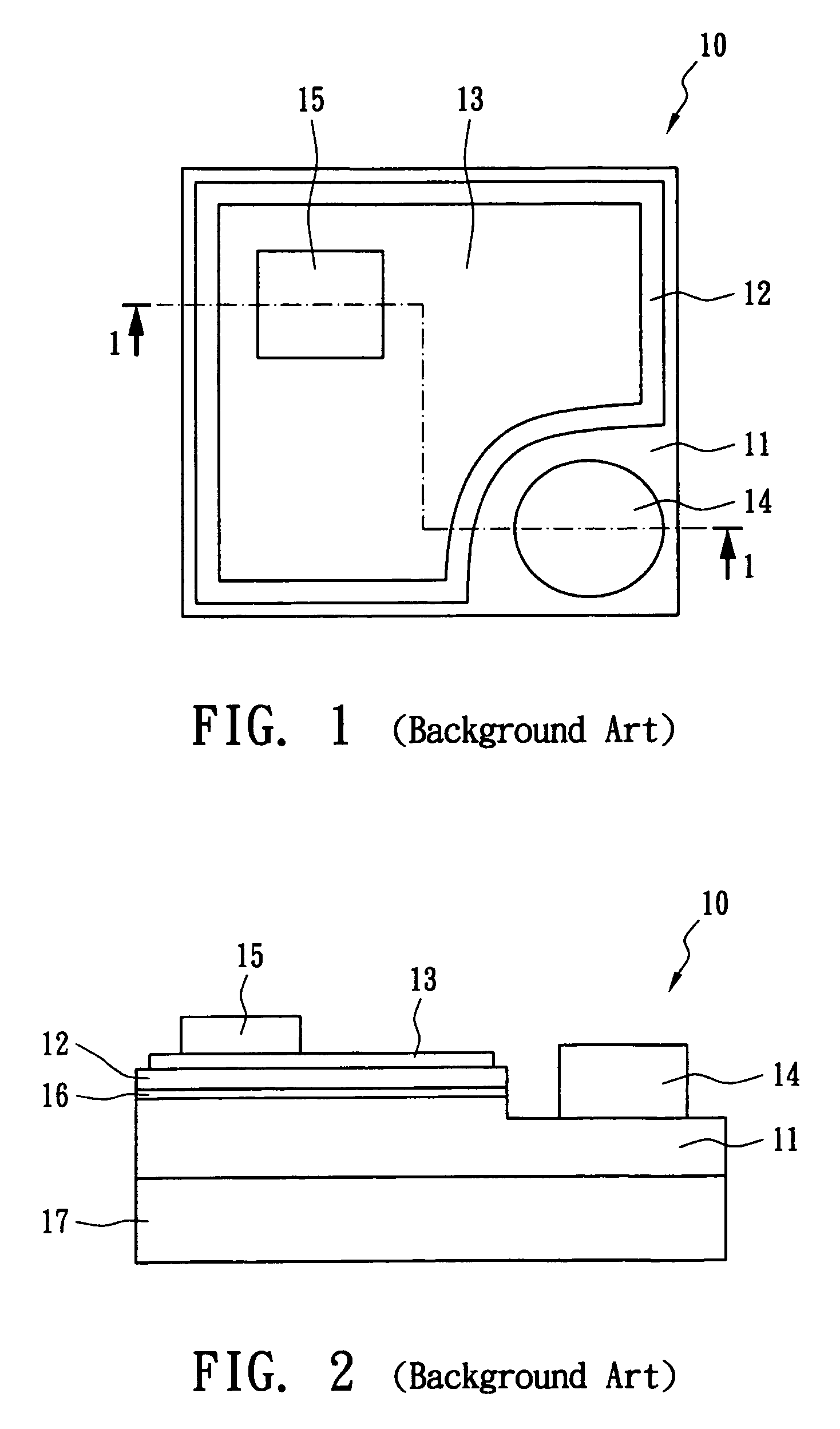

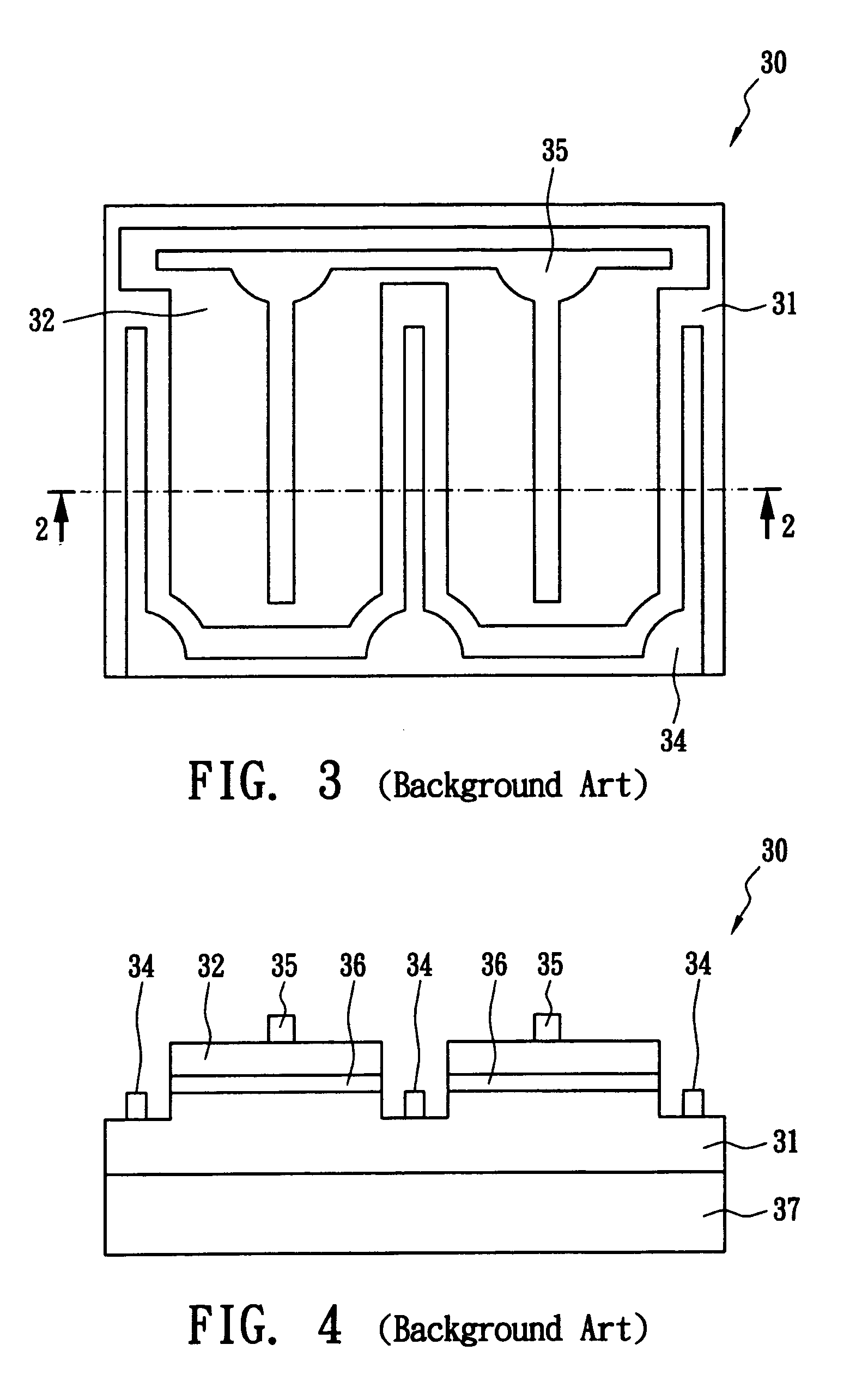

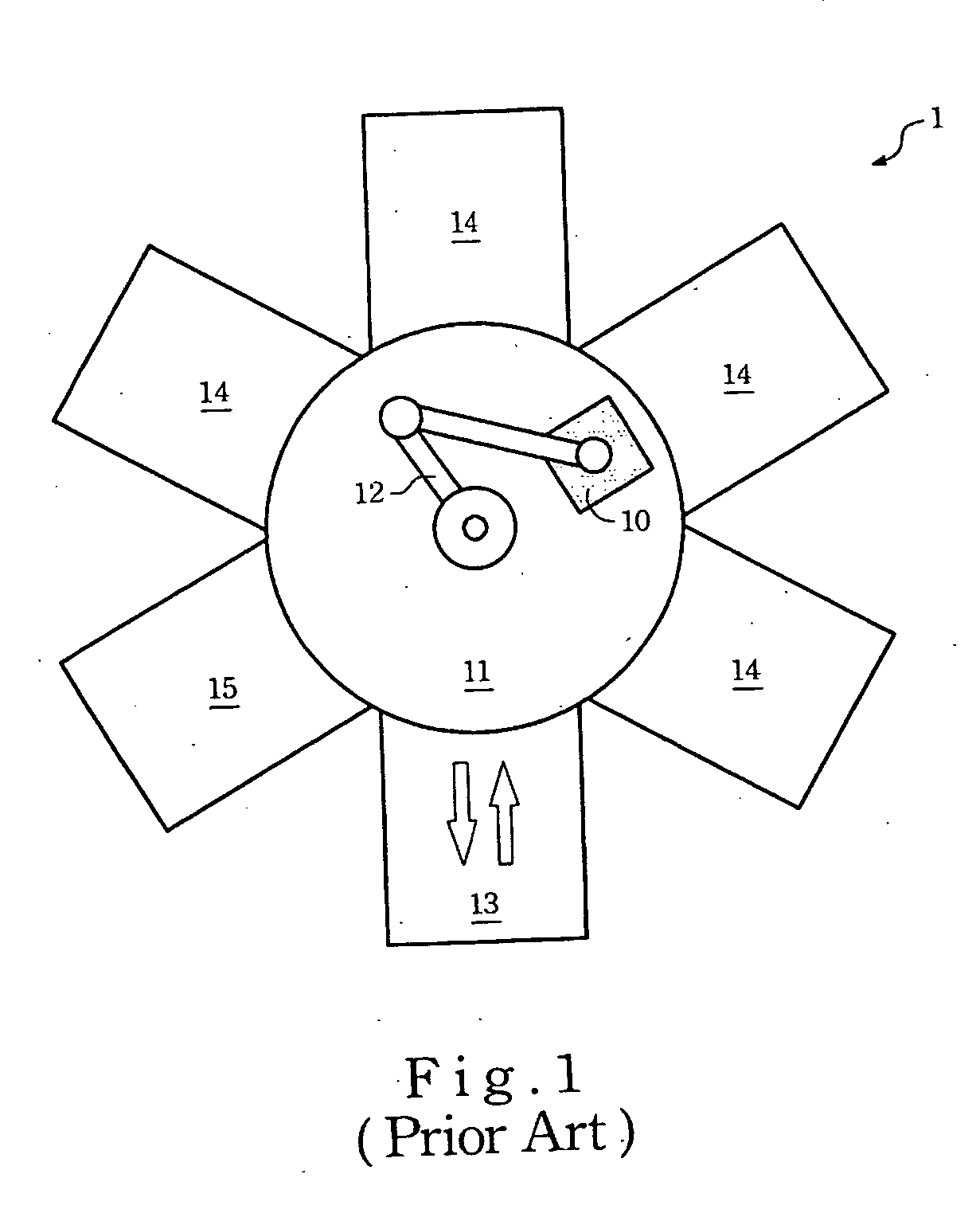

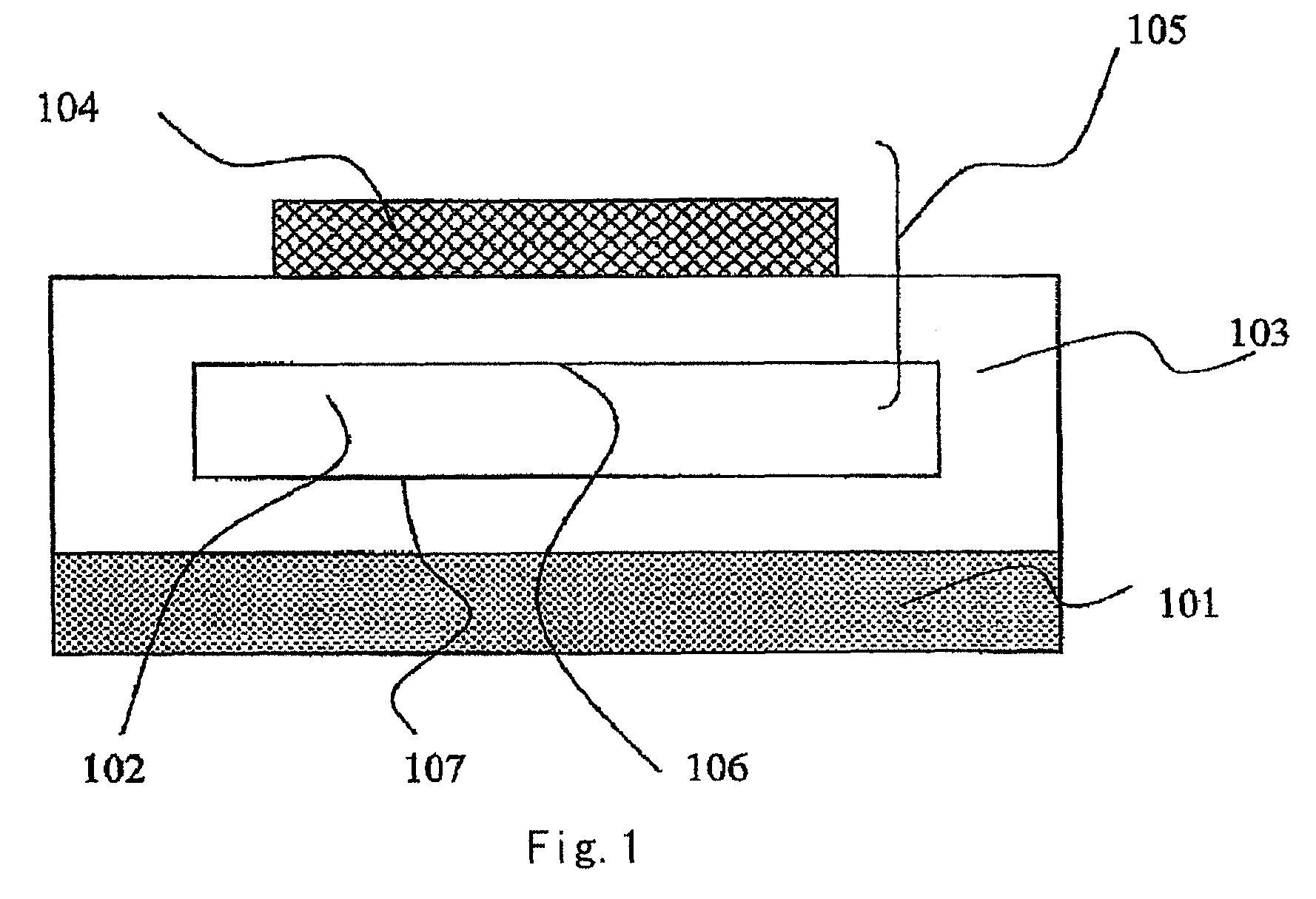

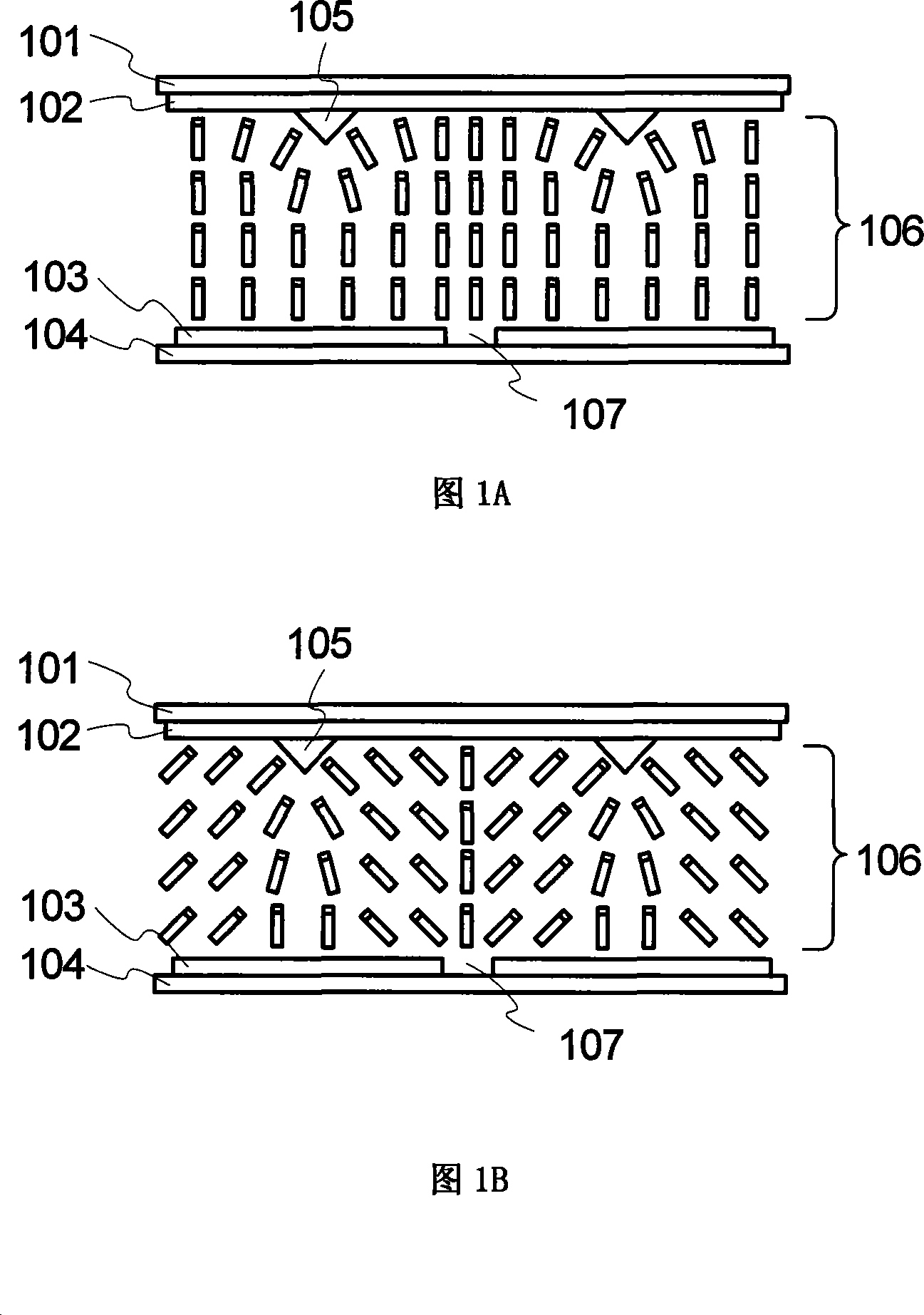

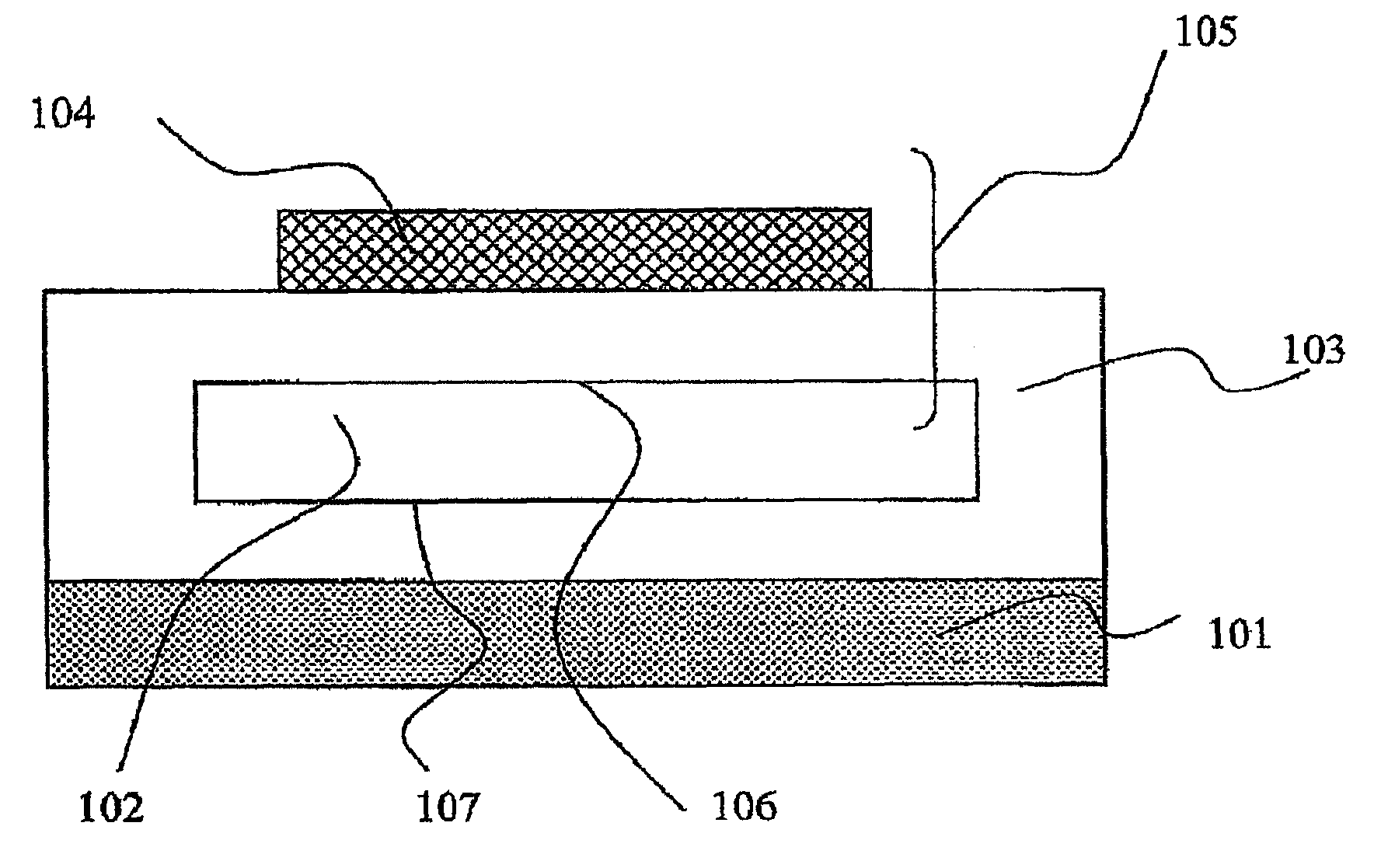

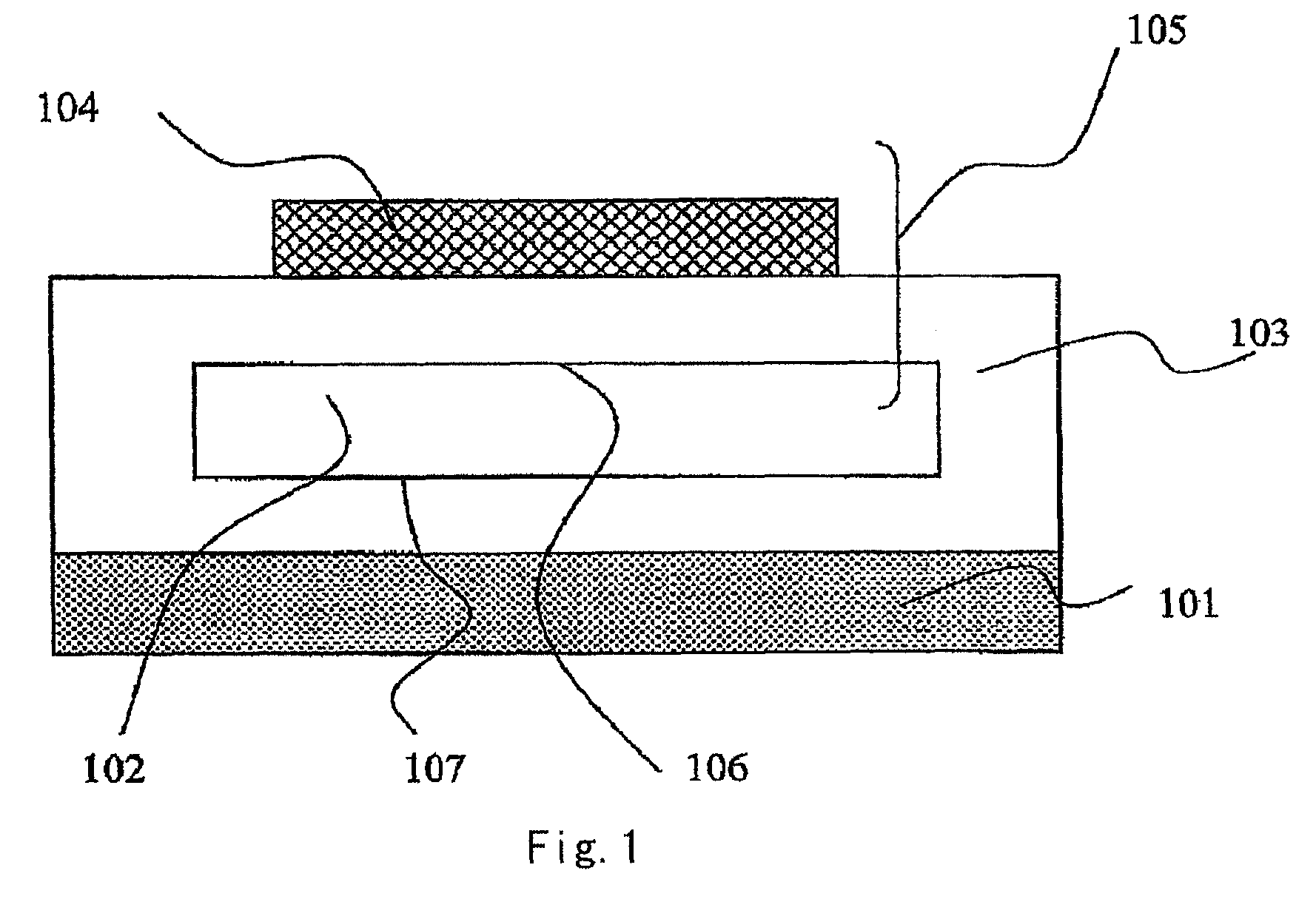

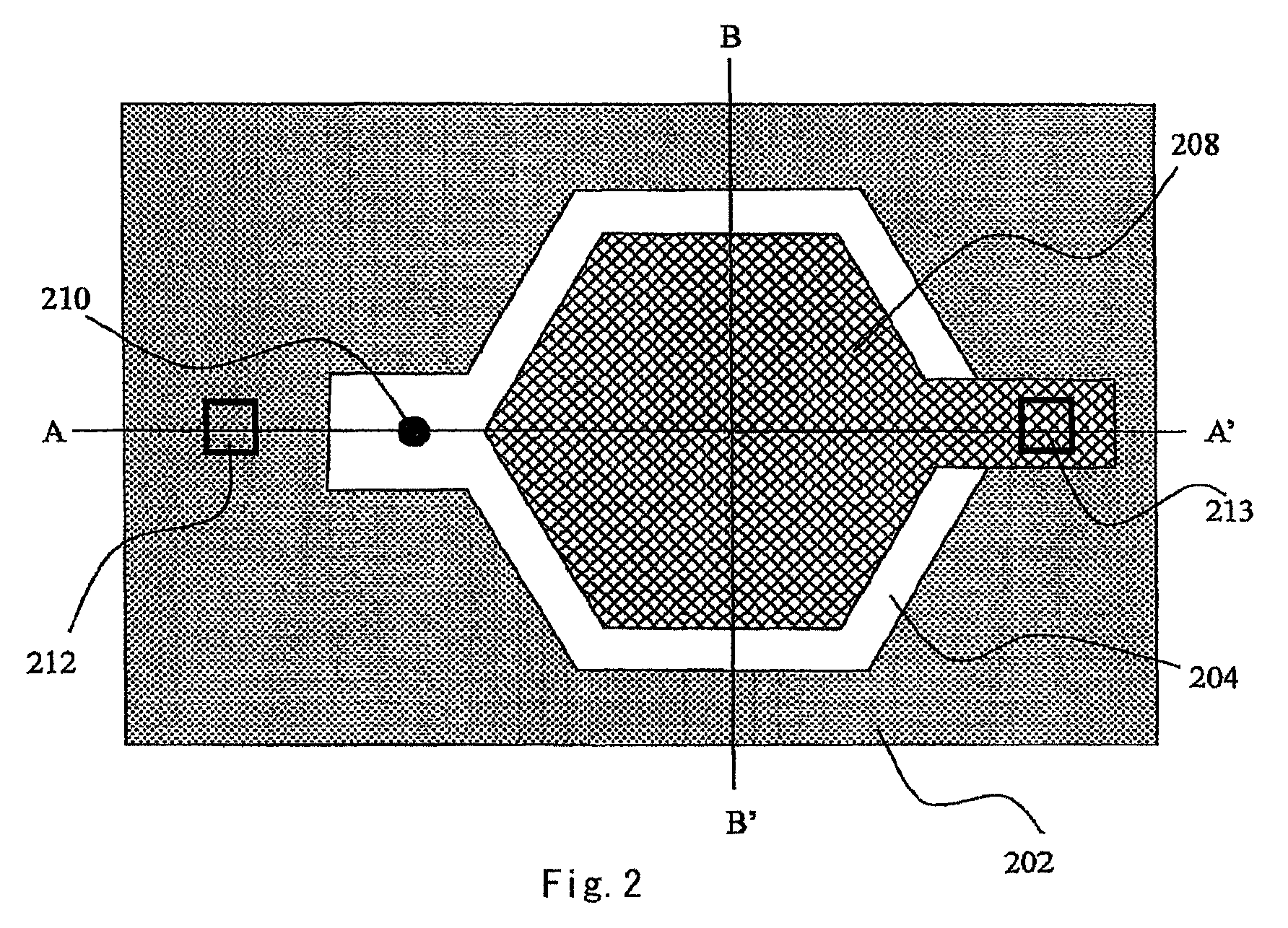

High power light emitting diode

ActiveUS20070085089A1Superior heat dissipationImprove illumination efficiencySolid-state devicesSemiconductor devicesDiodeHigh power leds

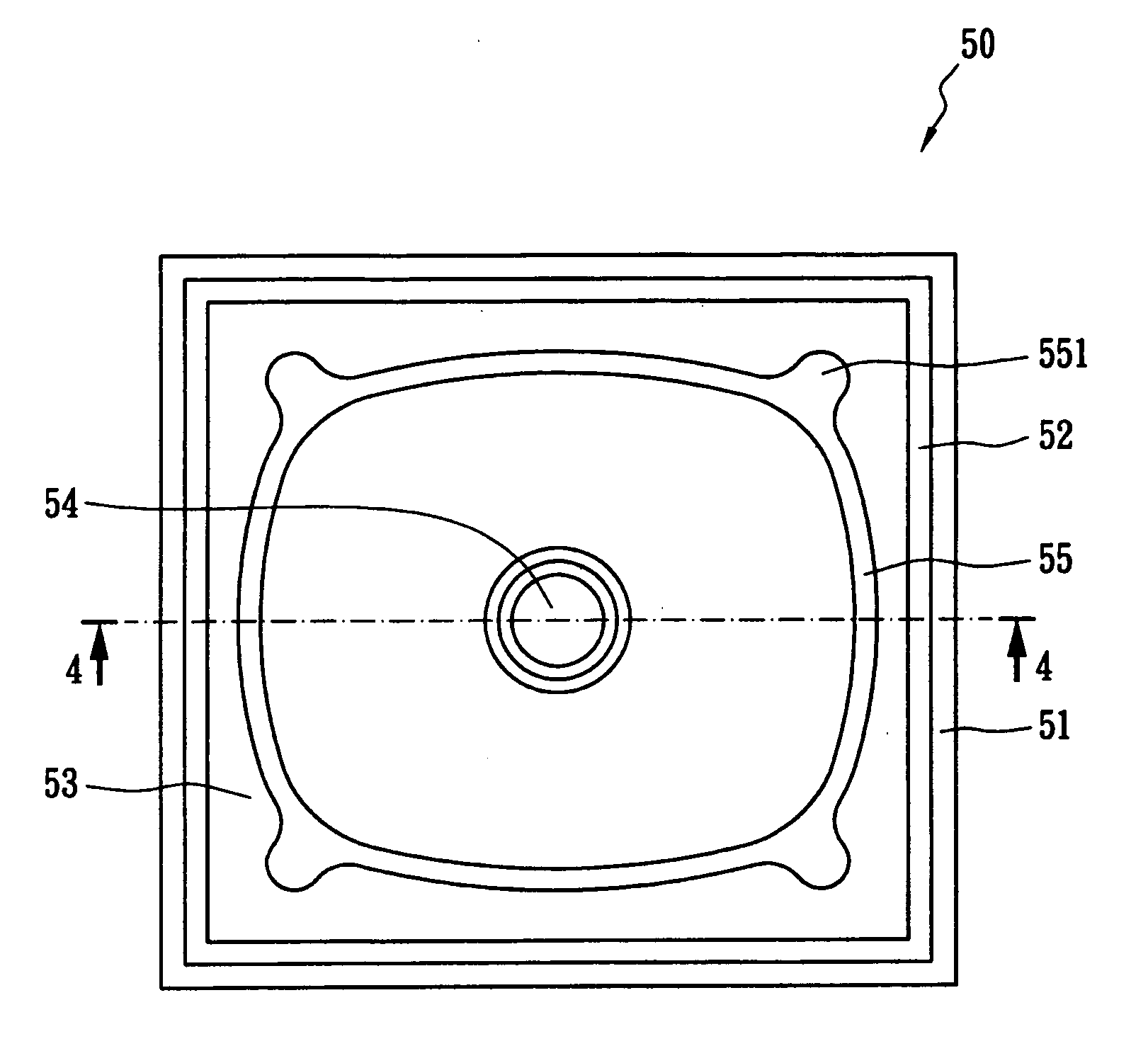

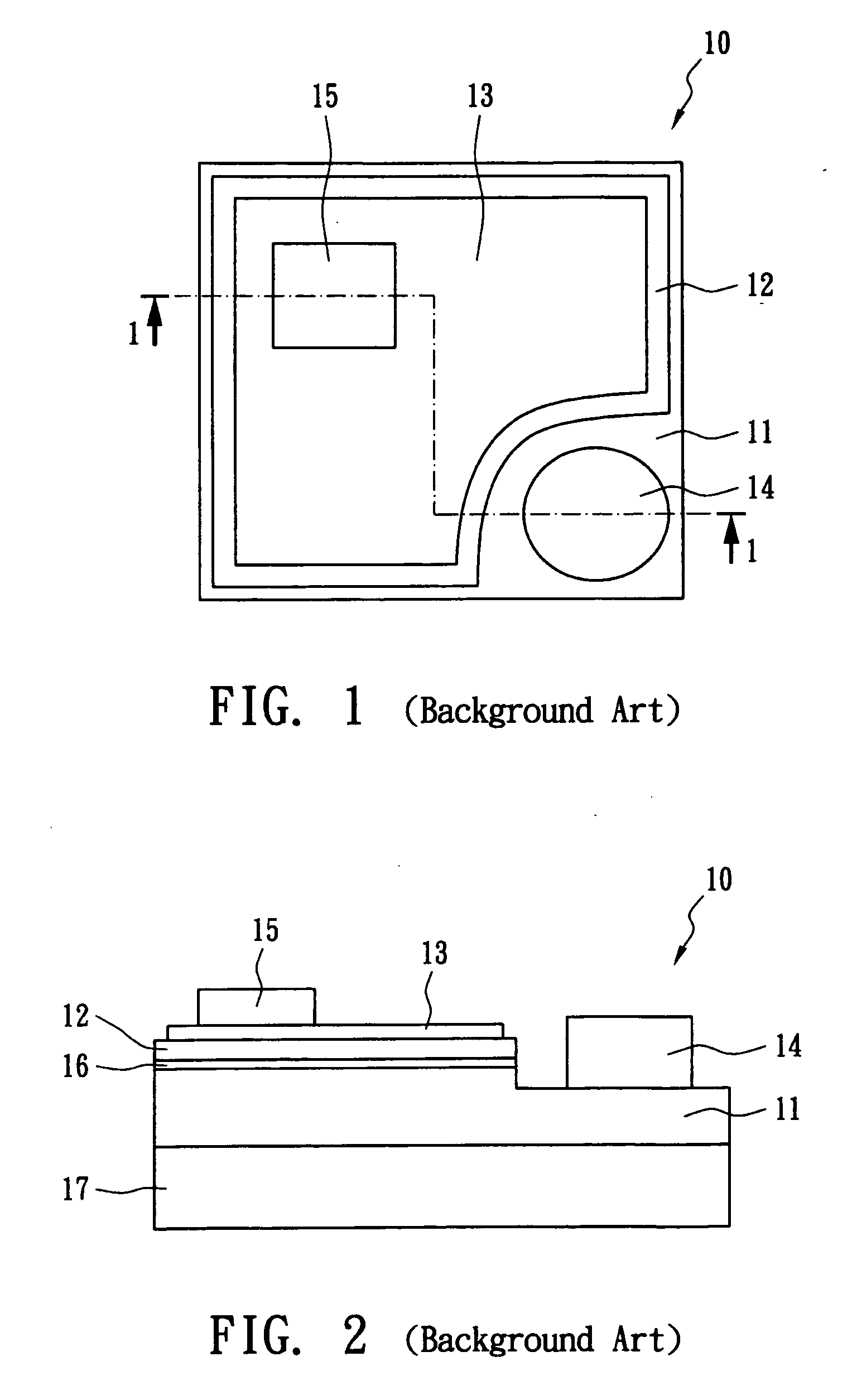

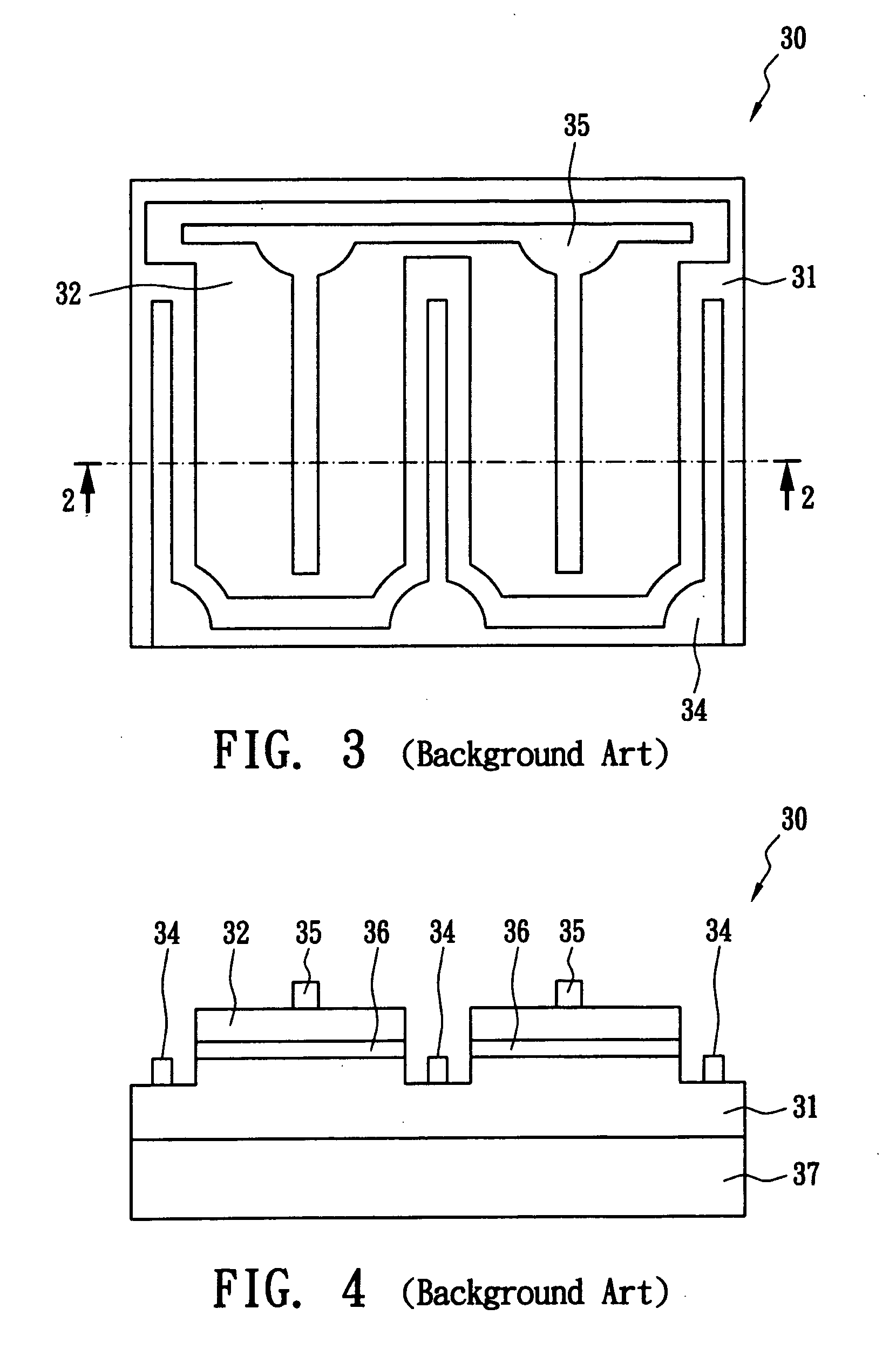

A high power LED comprises a substrate. An N-type semiconductor layer, an active layer and a P-type semiconductor layer are sequentially deposited on the substrate. A semi-insulator layer or a non-N-type semiconductor layer can be interposed between the N-type semiconductor layer and substrate. At least one N-type electrode is connected to the N-type semiconductor layer and is exposed to an opening of the active layer and P-type semiconductor layer. The N-type electrode with a centralized pattern is formed on the middle of the LED. Furthermore, at least one P-type electrode is coupled to the P-type semiconductor layer. The P-type electrode is arranged like a closed ring or an open ring surrounding the N-type electrode. Therefore, the distribution of current paths is dispersed, and illumination areas are simultaneously uniform.

Owner:ADVANCED OPTOELECTRONICS TECH

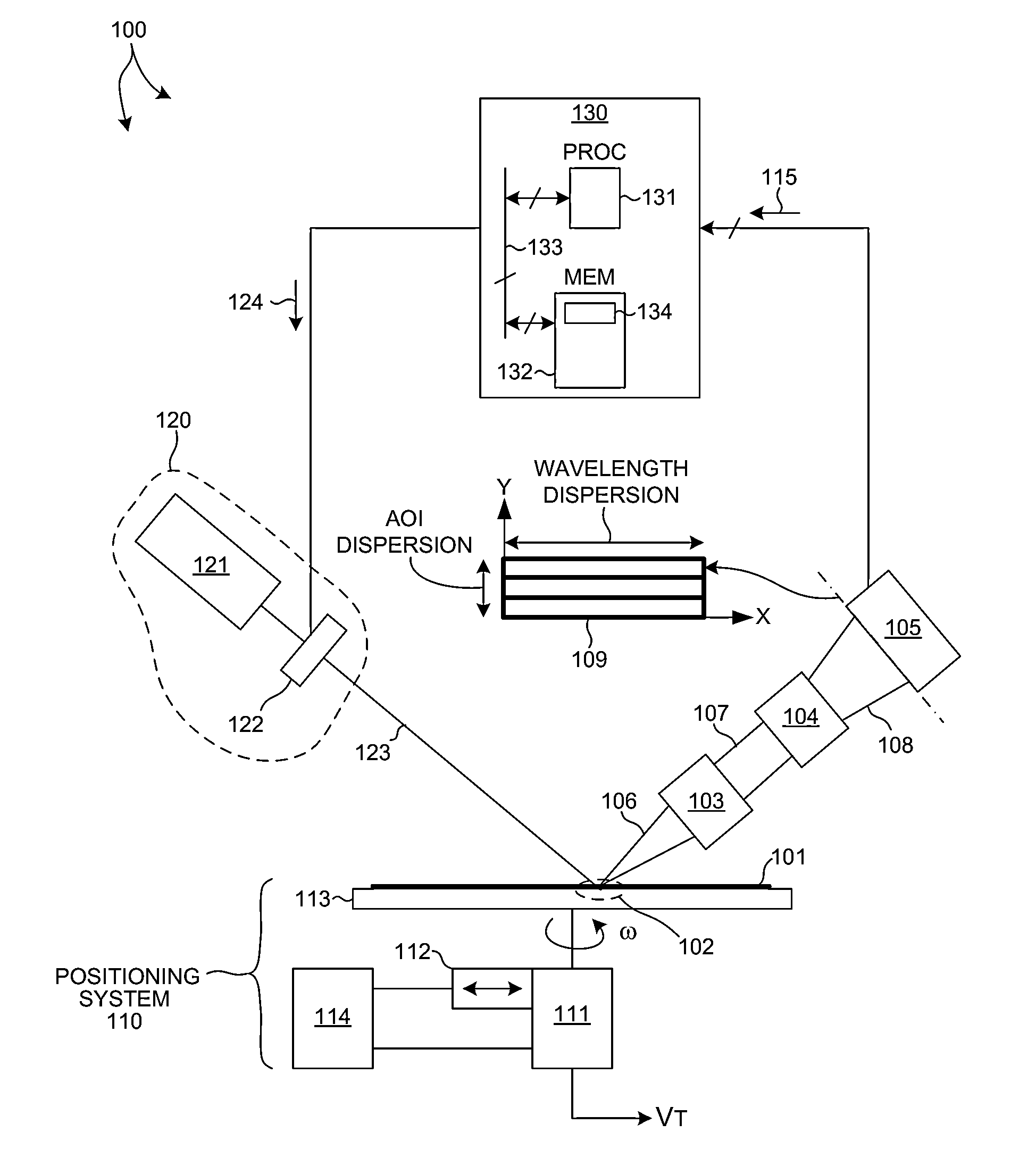

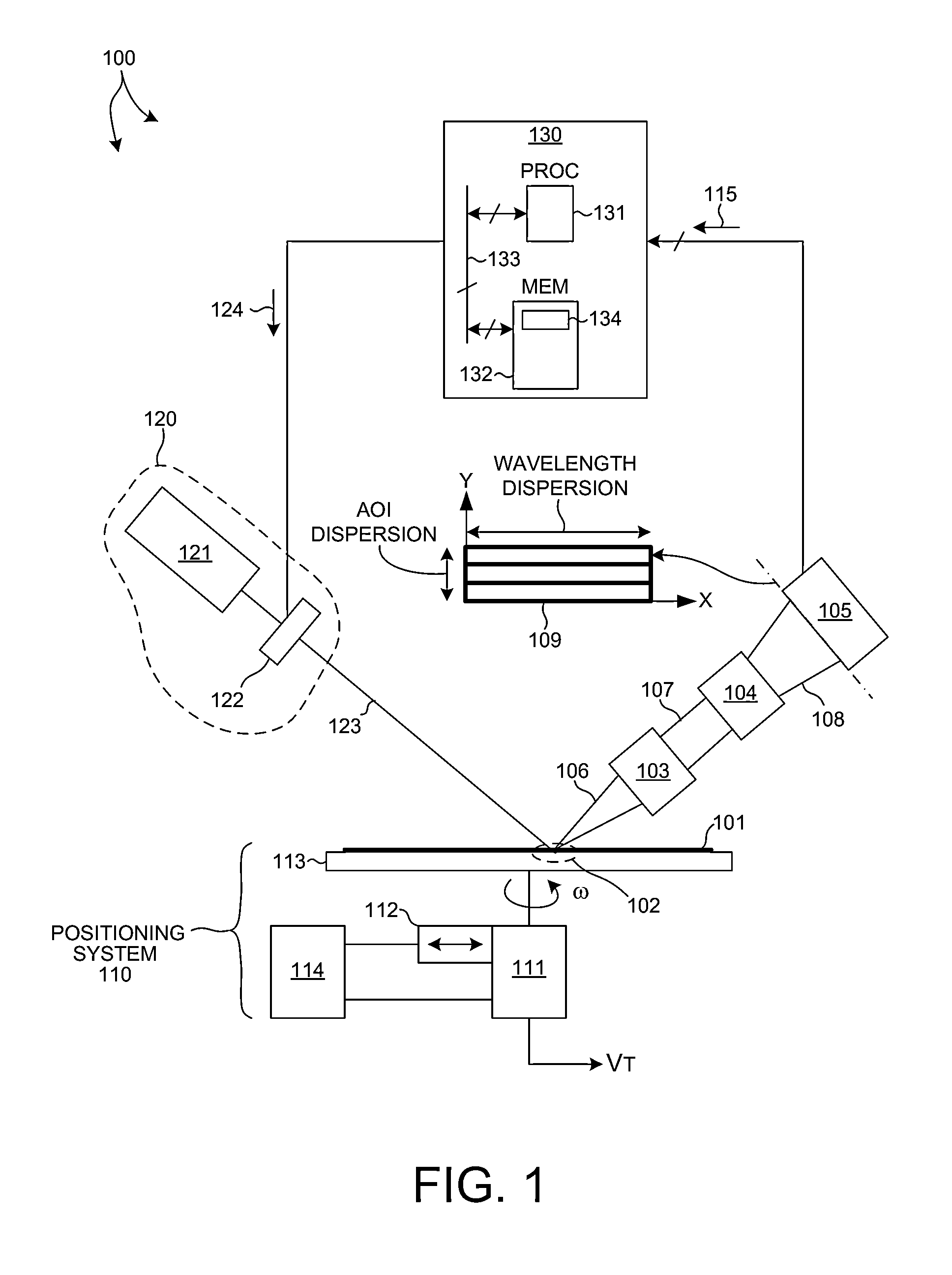

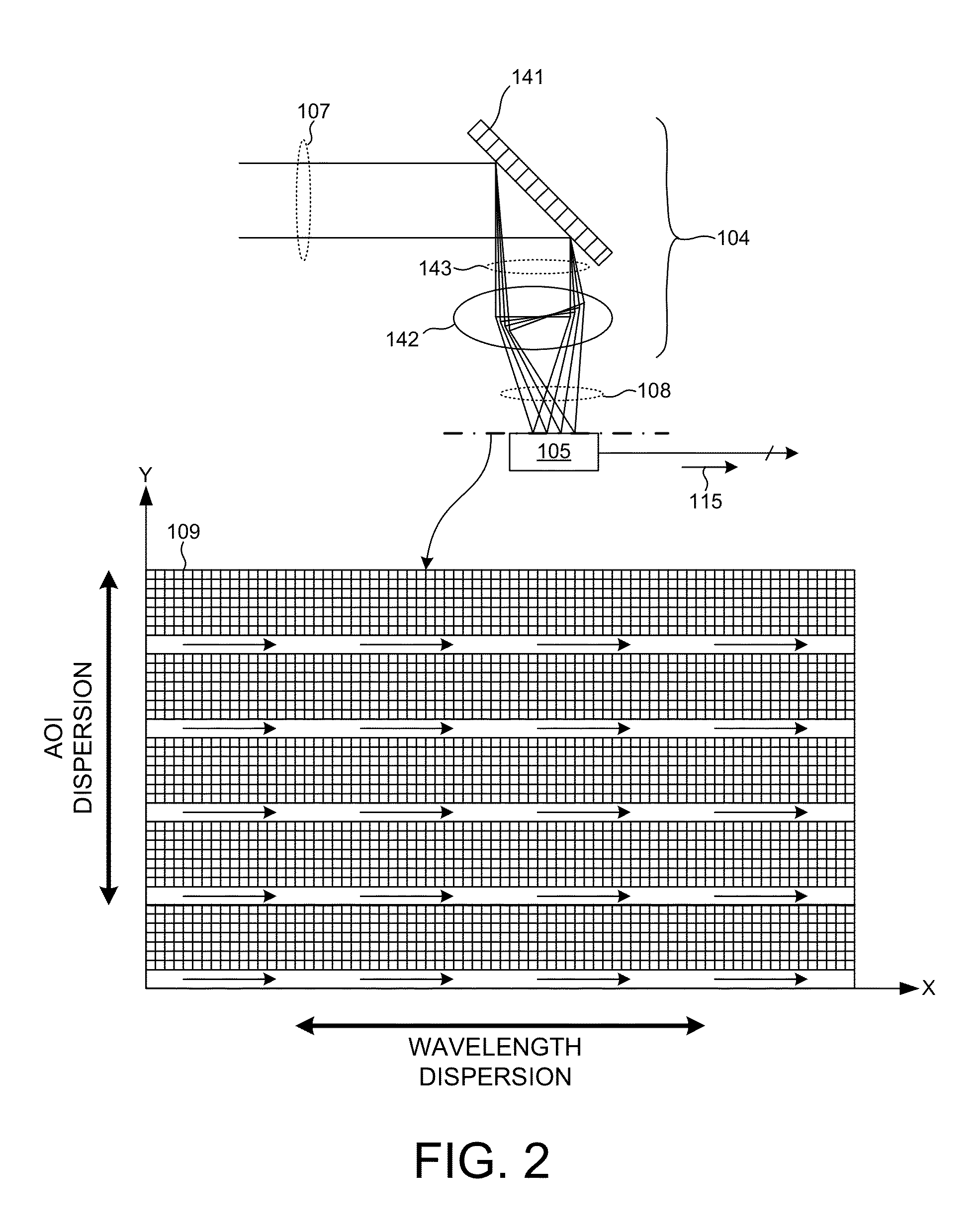

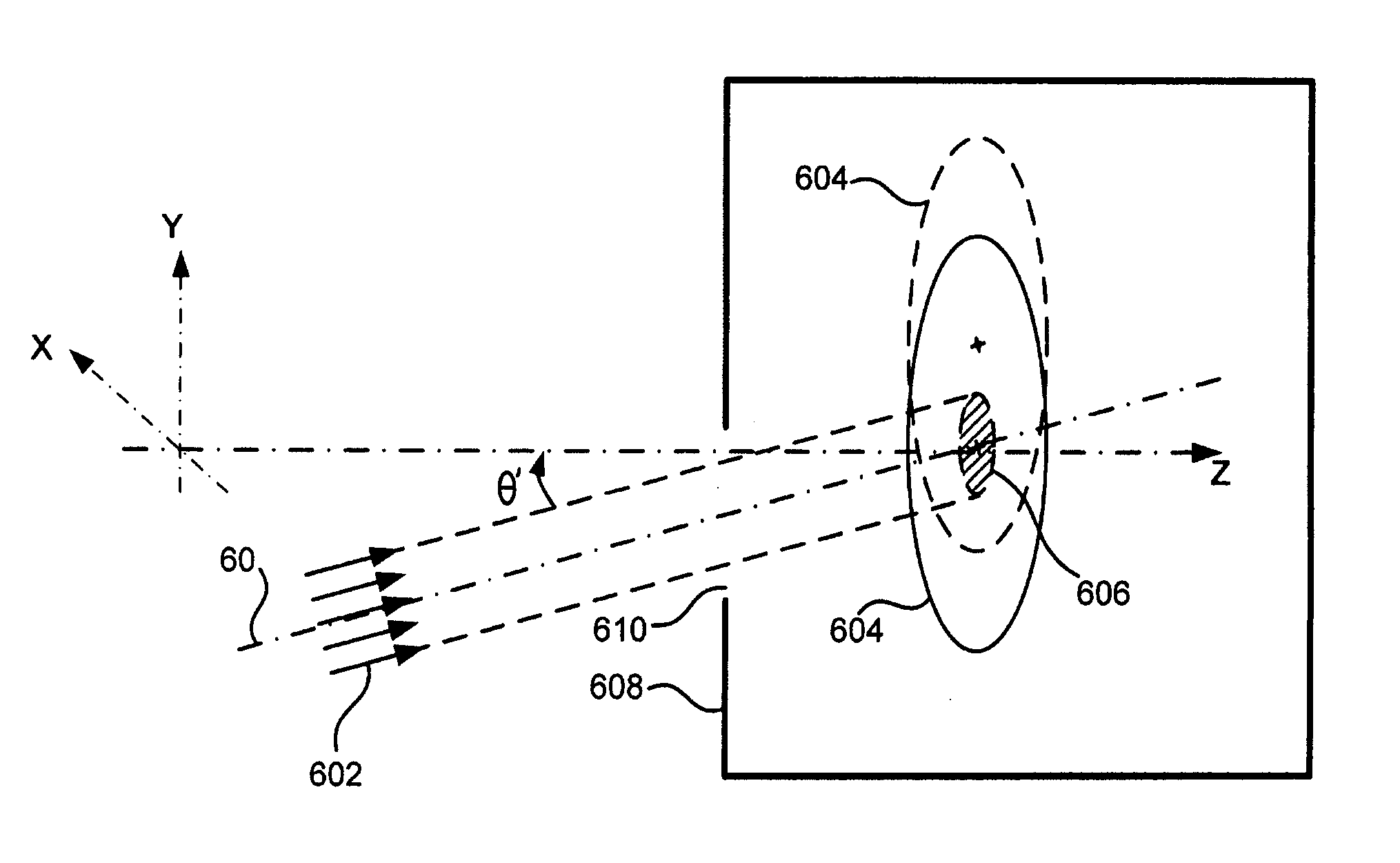

Two dimensional optical detector with multiple shift registers

ActiveUS20140166862A1Improve throughputHigh resolutionOptically investigating flaws/contaminationPhotometry using electric radiation detectorsShift registerMetrology

Methods and systems for enhancing the throughput of a metrology system generating measurement signals based on at least two different optical properties of the illumination light are presented. A detector having a two dimensional photosensitive area is subdivided into multiple photosensitive stripes by multiple, independent linear arrays of shift register elements located within the photosensitive area. Charge transfer from pixels within each stripe is directed to a distinct linear array of shift register elements. Each photosensitive stripe is able to resolve an optical property dispersed across the length of each stripe with relatively high resolution. In addition, the detector is able to resolve another optical property dispersed across several photosensitive stripes in a direction orthogonal to each linear array of shift registers at a relatively low resolution.

Owner:KLA CORP

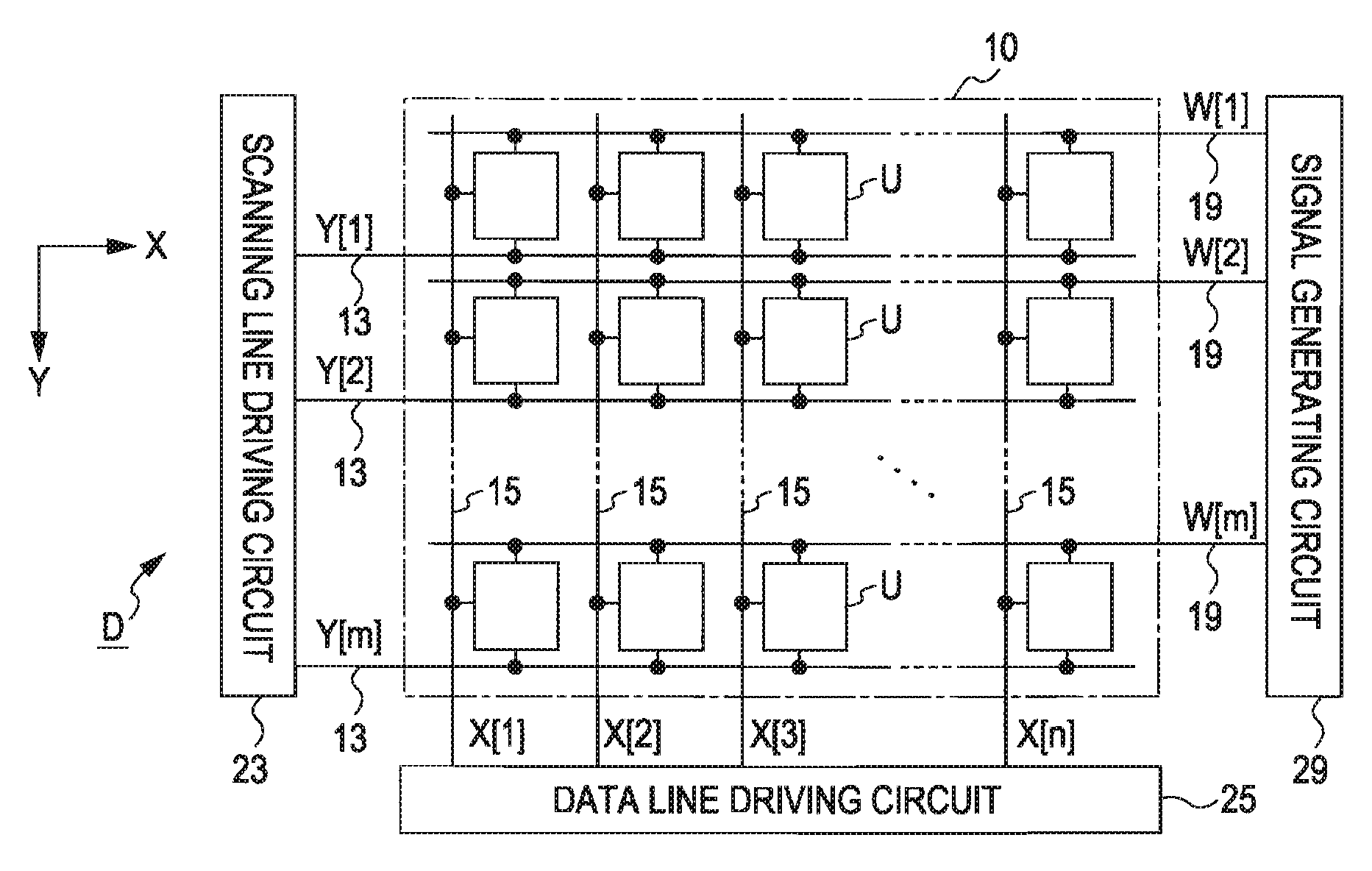

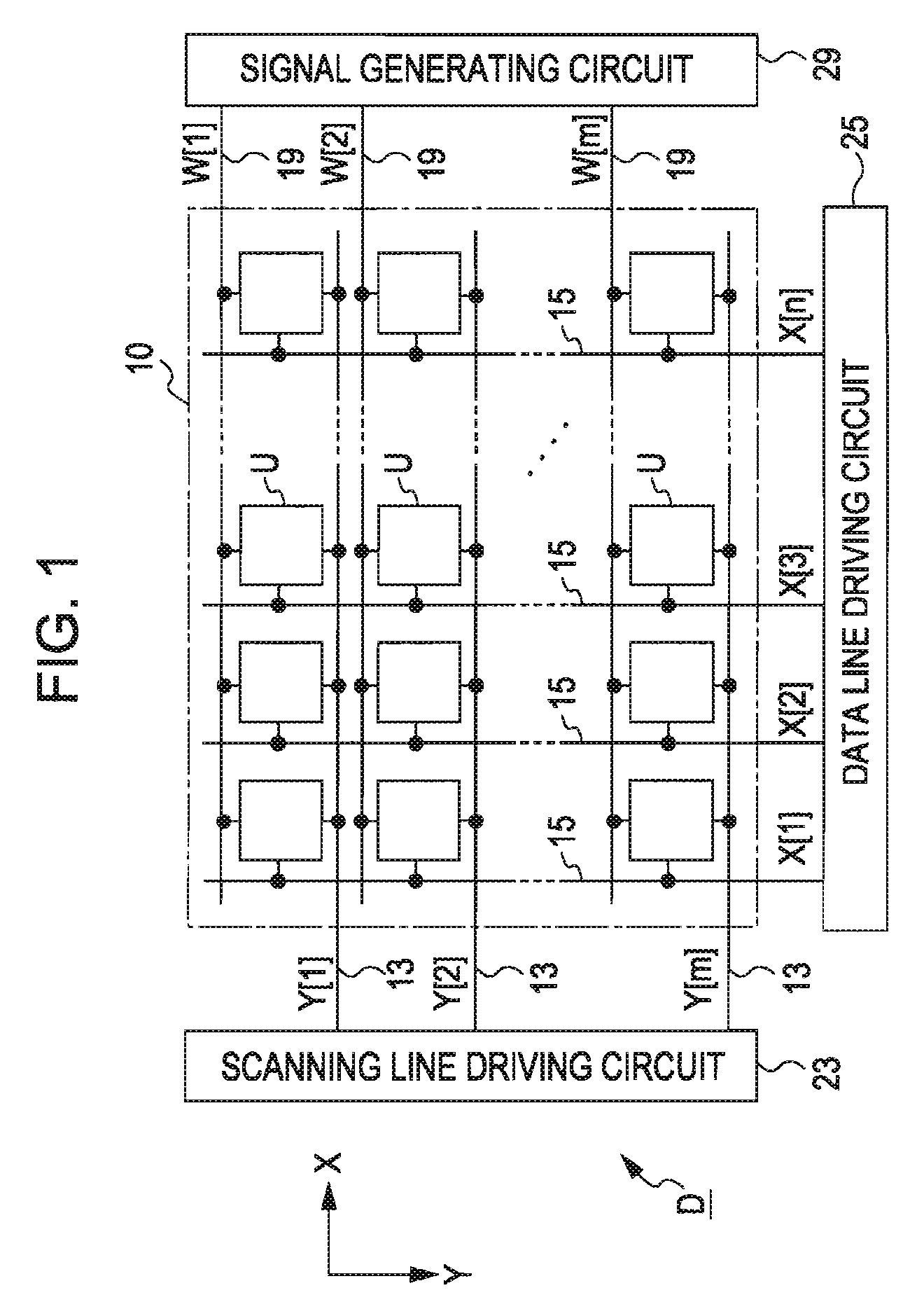

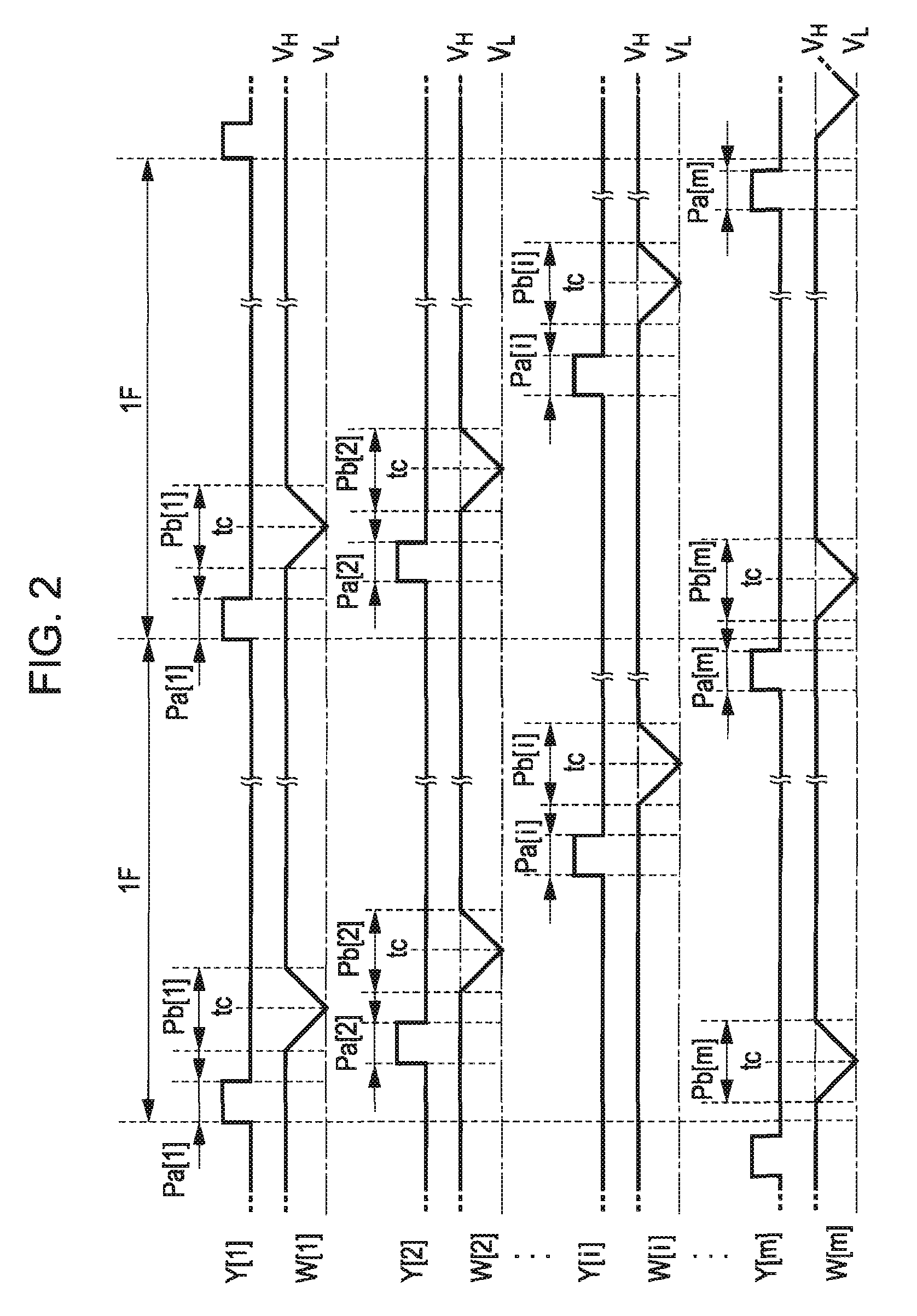

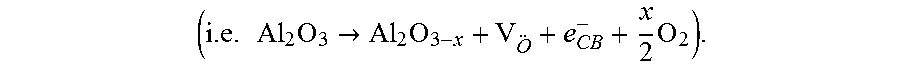

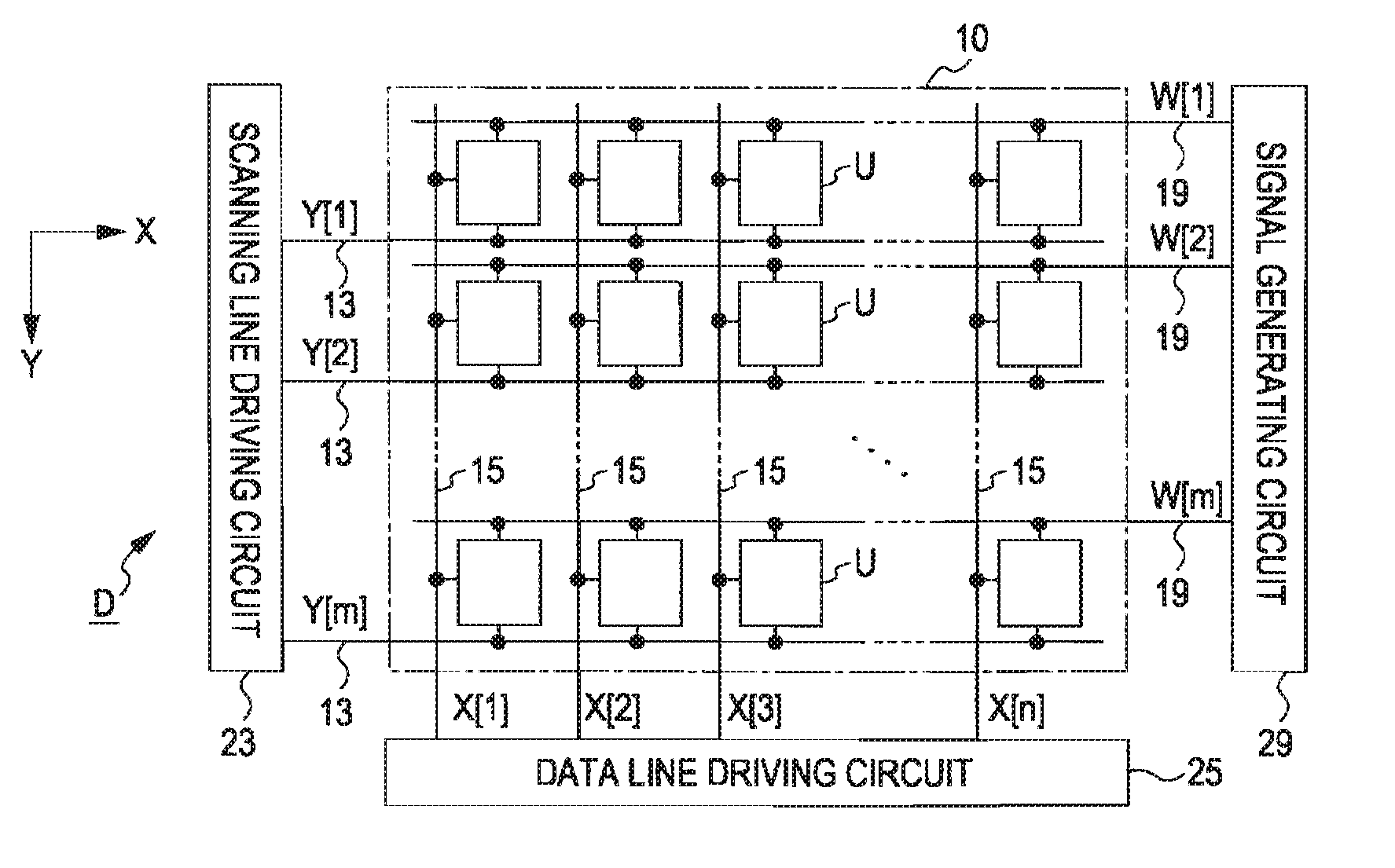

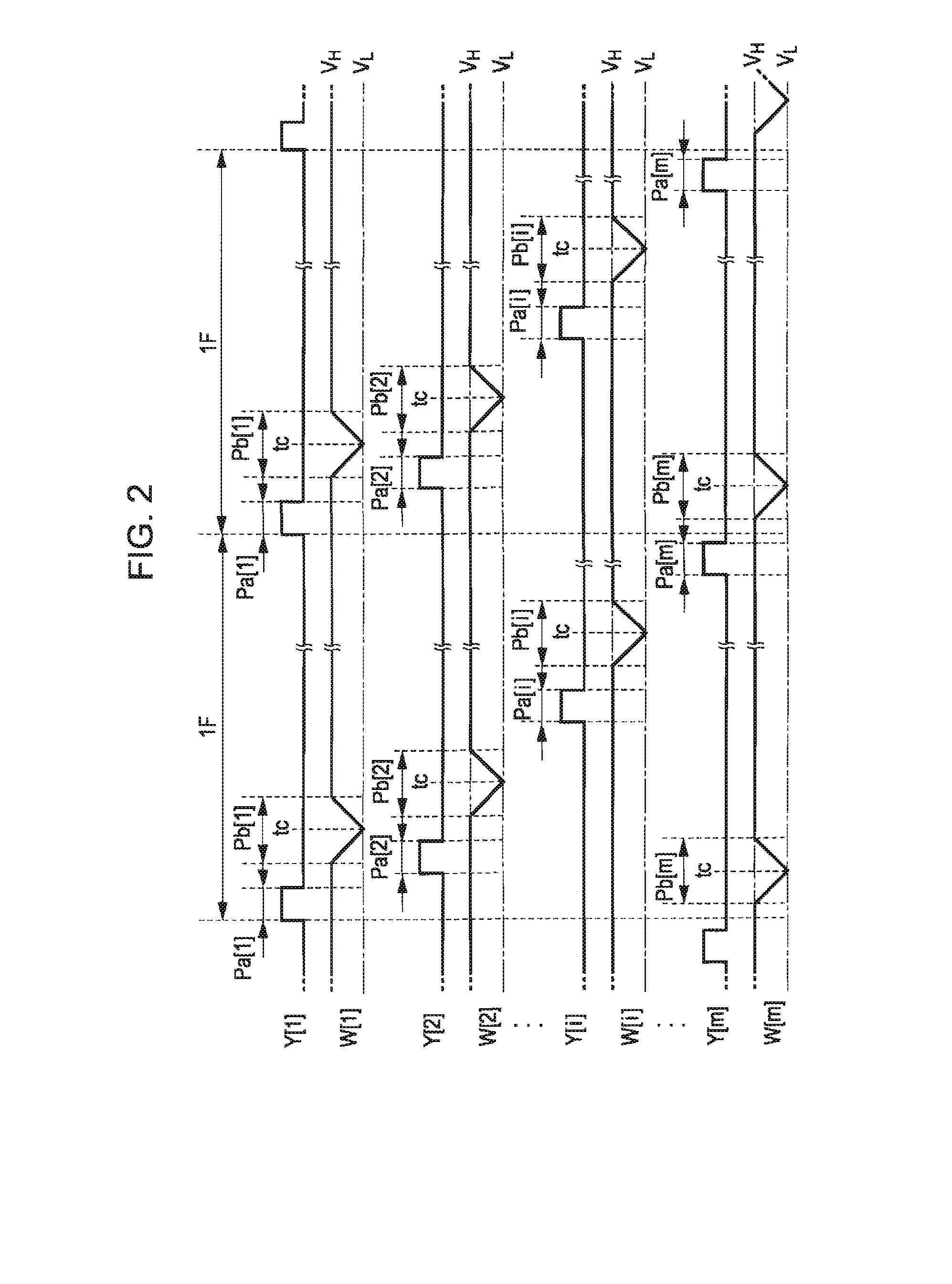

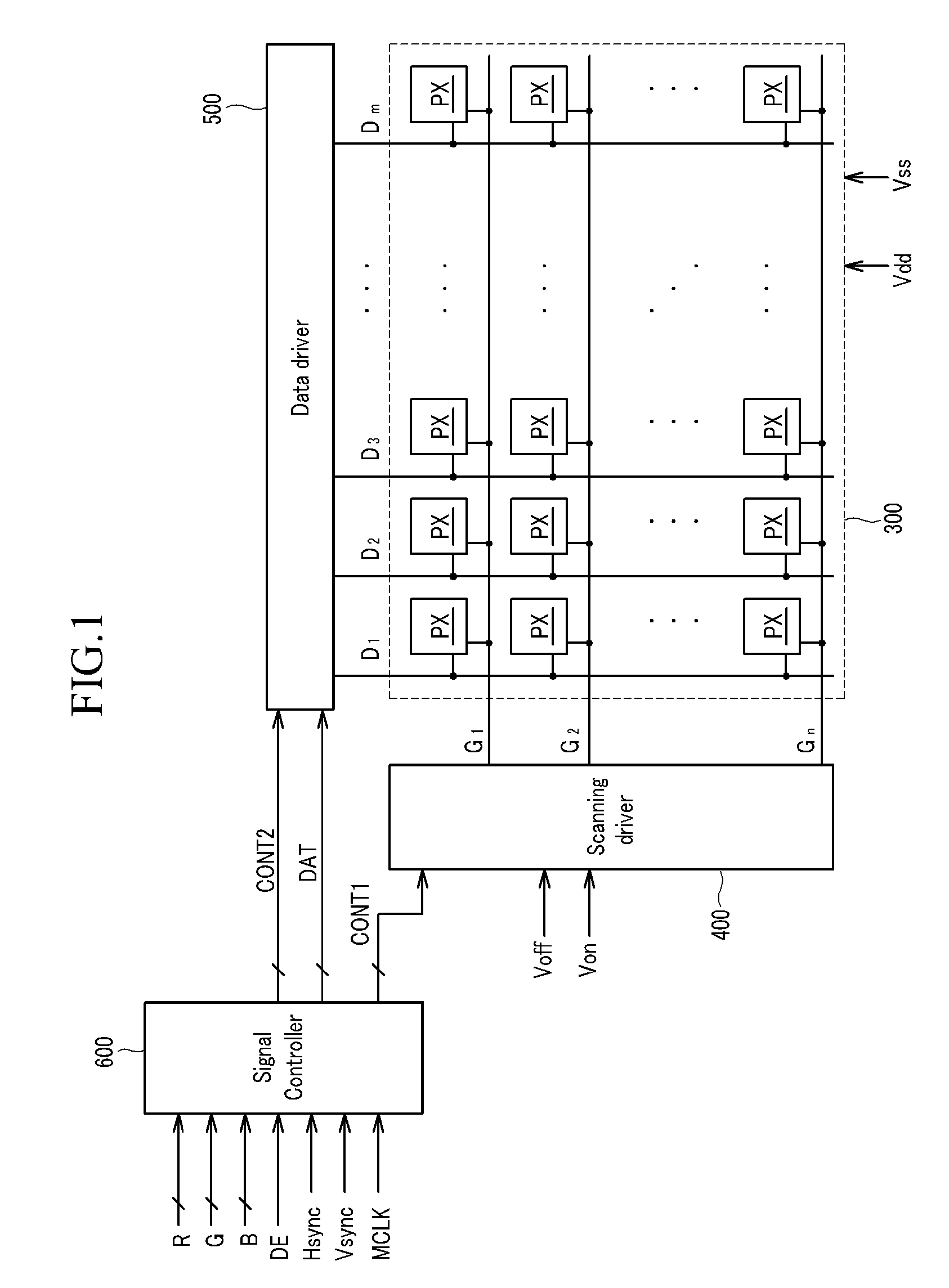

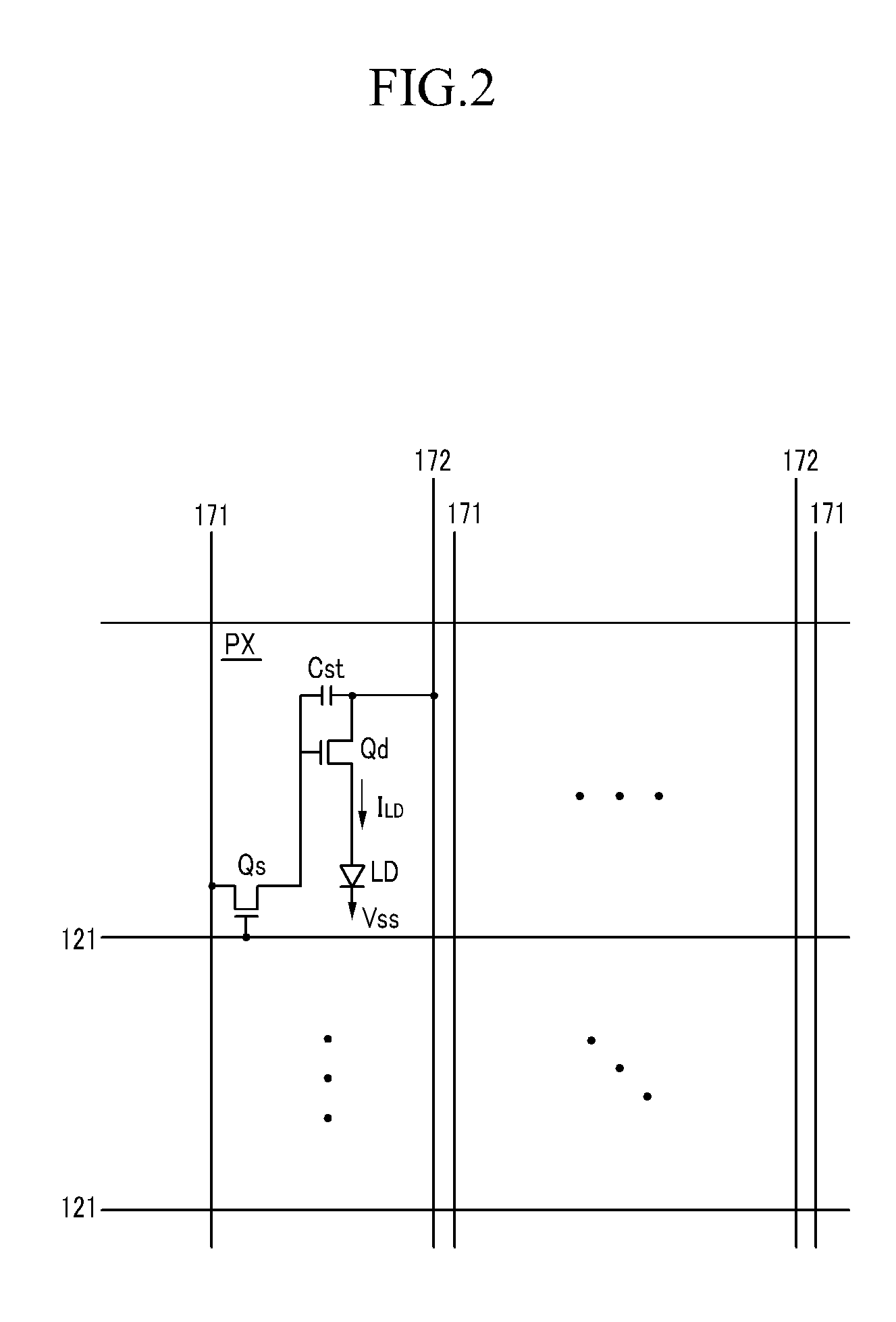

Electronic circuit, electronic device, method of driving electronic device, electro-optical device, and electronic apparatus

InactiveUS20070018078A1Short timeAvoid charge accumulationStatic indicating devicesMaterial analysis by optical meansDriving currentElectrical connection

An electronic device includes a plurality of first wiring lines, a plurality of second wiring lines that intersect the plurality of first wiring lines, a plurality of unit circuits that are disposed so as to correspond to intersections between the plurality of first wiring lines and the plurality of second wiring lines, and a plurality of reference signal lines that supply reference signals to the plurality of unit circuits. Each of the plurality of unit circuits has a driven element that is driven by a driving voltage or a driving current, a driving unit that supplies the driving voltage or the driving current to the driven element, a switching element that controls electrical connection between an input terminal provided in the driving unit and one of the plurality of second wiring lines, and a capacitor element that has a first electrode connected to the input terminal and a second electrode connected to one of the plurality of reference signal lines, and accumulates a charge between the first electrode and the second electrode.

Owner:SEIKO EPSON CORP

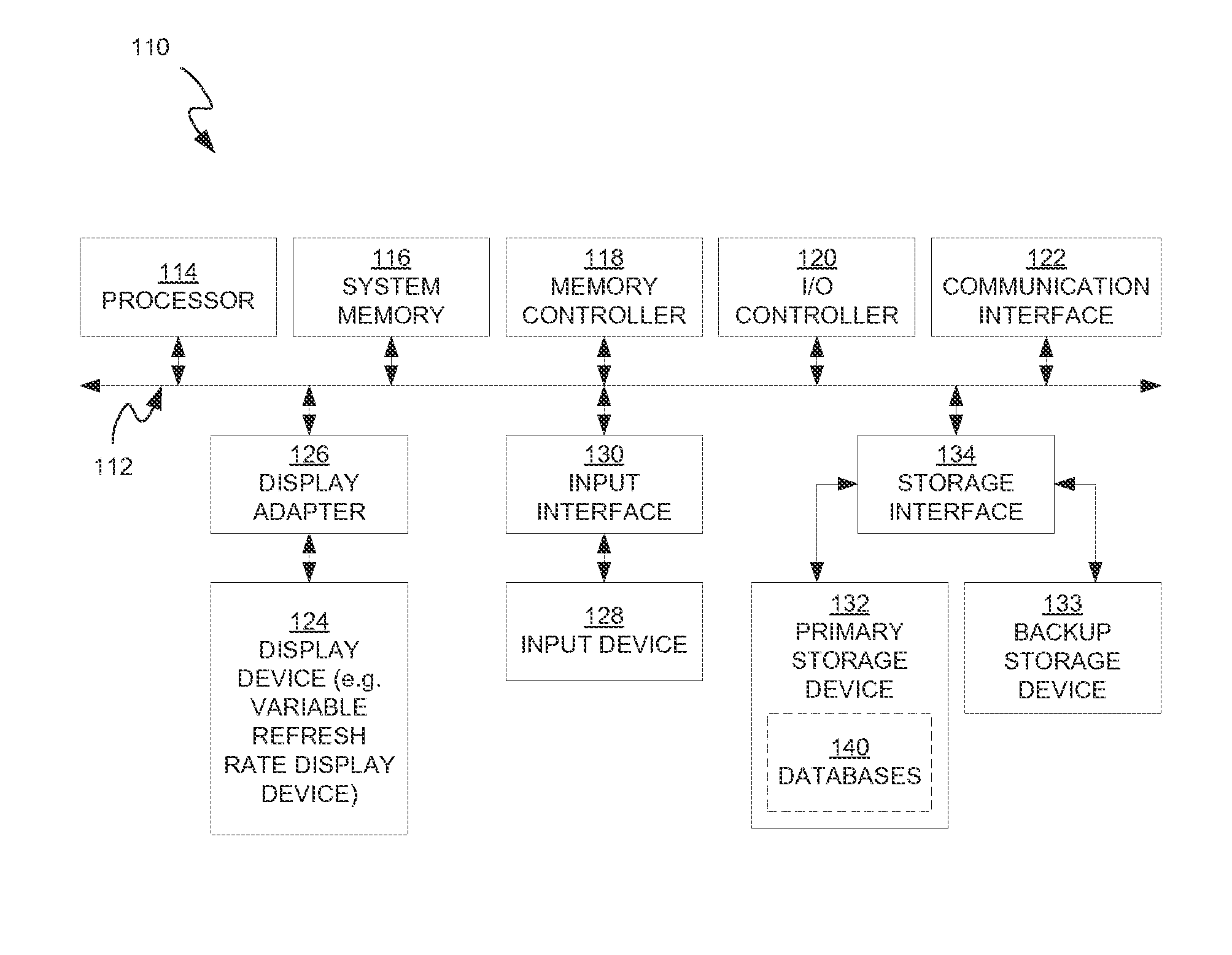

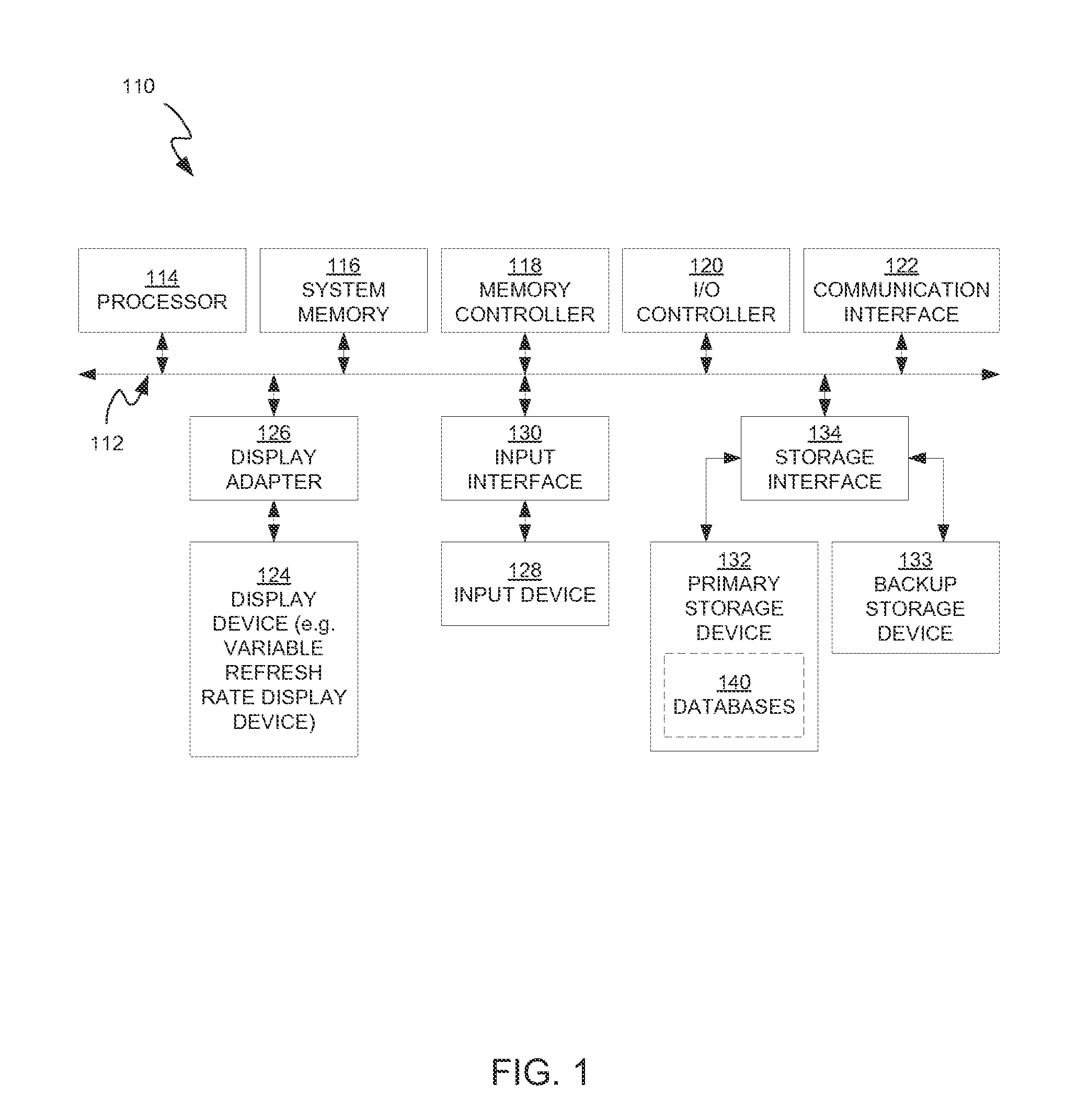

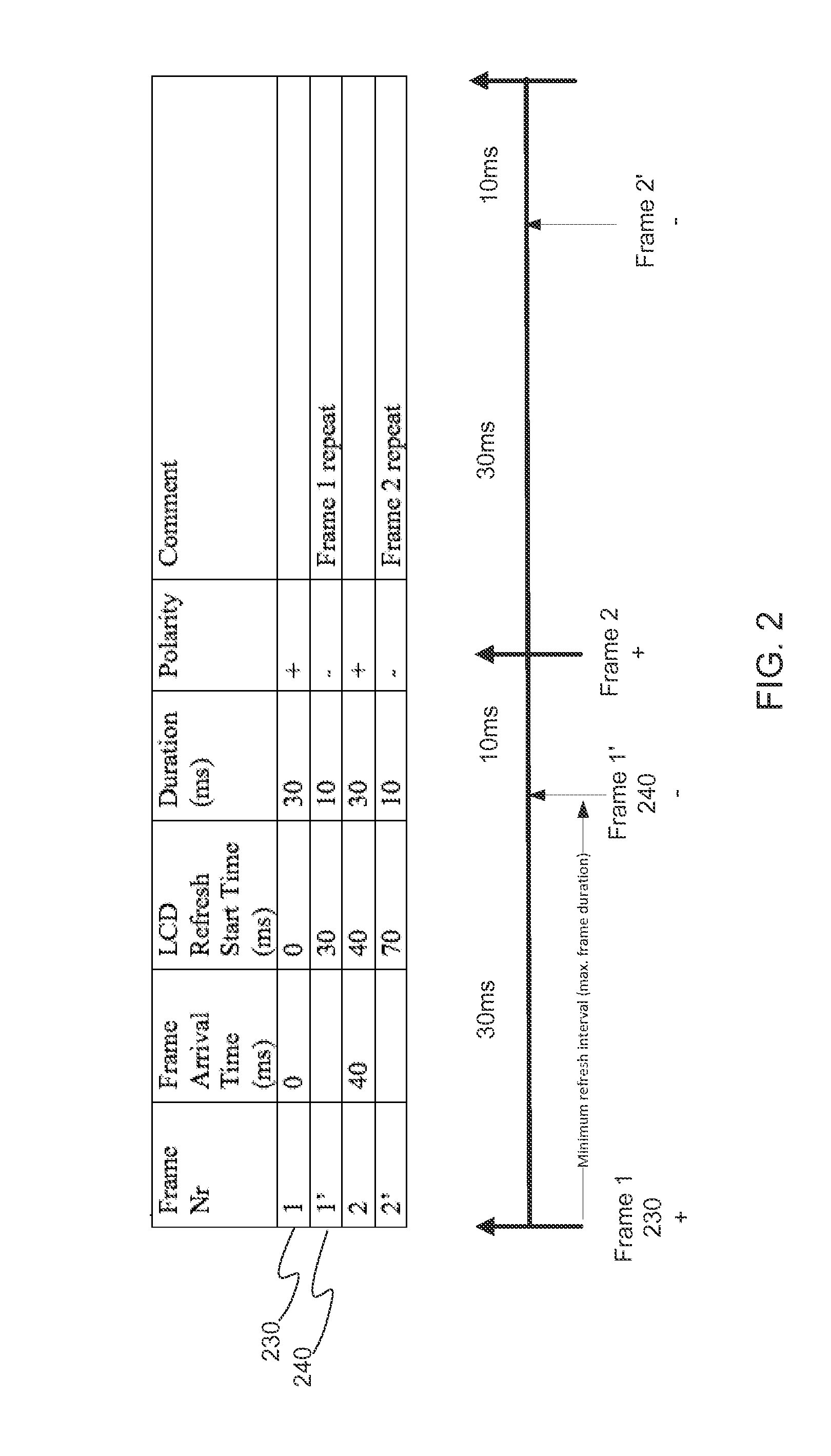

Techniques for avoiding and remedying DC bias buildup on a flat panel variable refresh rate display

ActiveUS20150243234A1Avoid accumulationAvoid artifactsStatic indicating devicesDisplay deviceRefresh rate

A method for driving a display panel having a variable refresh rate is disclosed. The method comprises receiving a current input frame from an image source. It also comprises determining a first number of re-scanned frames to insert between the current input frame and a subsequent input frame, wherein the re-scanned frames repeat the current input frame, and wherein the determining depends on a minimum refresh interval (MRI) of the display panel. Further, it comprises calculating intervals to insert the first number of re-scanned frames between the current input frame and the subsequent input frame. Further, it comprises scanning the current input frame for display on the display panel. Finally it comprises inserting the first number of re-scanned frames at the respective intervals between the current input frame and the subsequent input frame from the image source, wherein the inserting is operable to reduce charge accumulation in the display panel.

Owner:NVIDIA CORP

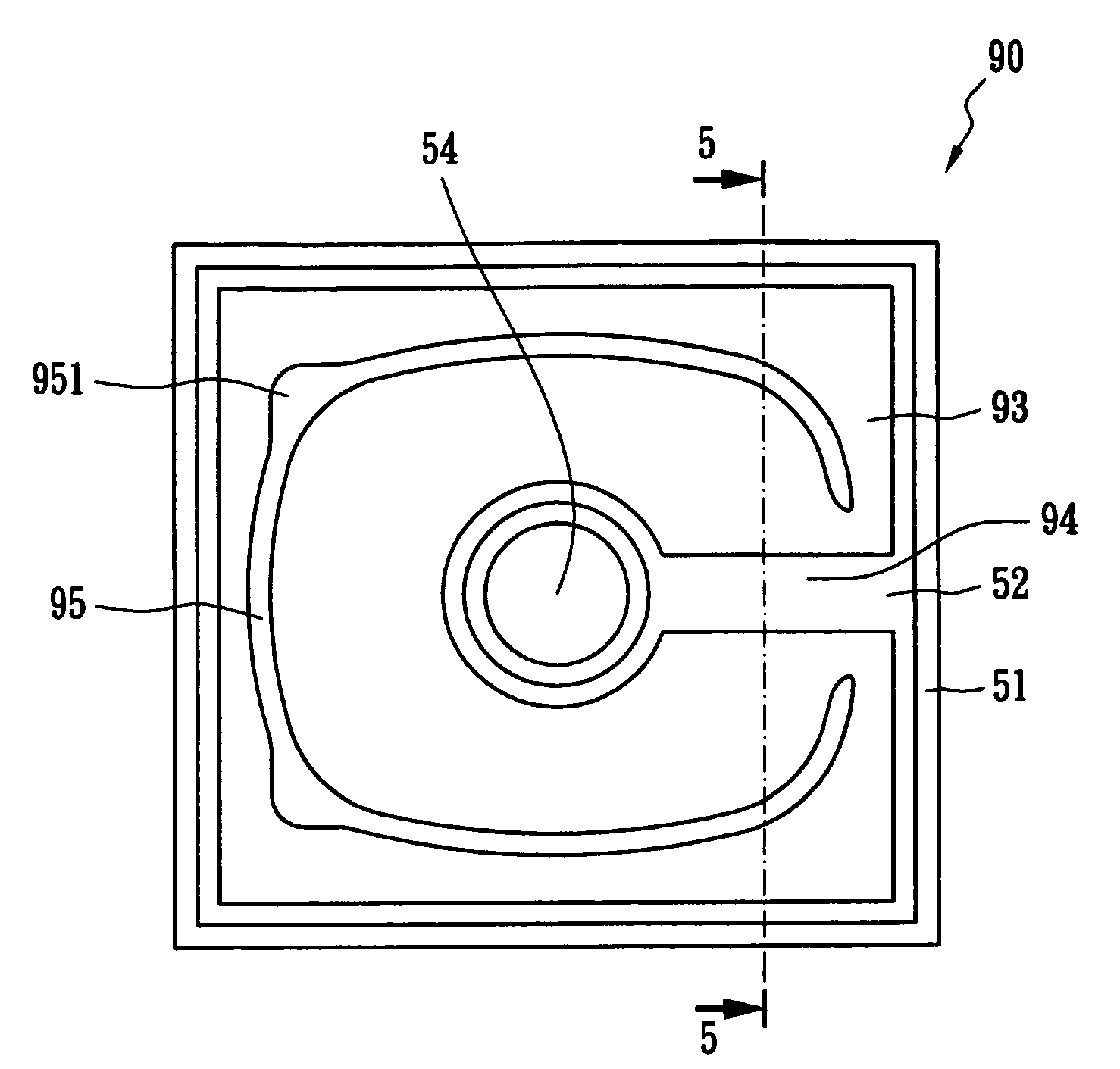

High power light emitting diode

ActiveUS7429755B2Improve efficiencyIncrease powerSolid-state devicesSemiconductor devicesActive layerHigh power leds

A high power LED comprises a substrate. An N-type semiconductor layer, an active layer and a P-type semiconductor layer are sequentially deposited on the substrate. A semi-insulator layer or a non-N-type semiconductor layer can be interposed between the N-type semiconductor layer and substrate. At least one N-type electrode is connected to the N-type semiconductor layer and is exposed to an opening of the active layer and P-type semiconductor layer. The N-type electrode with a centralized pattern is formed on the middle of the LED. Furthermore, at least one P-type electrode is coupled to the P-type semiconductor layer. The P-type electrode is arranged like a closed ring or an open ring surrounding the N-type electrode. Therefore, the distribution of current paths is dispersed, and illumination areas are simultaneously uniform.

Owner:ADVANCED OPTOELECTRONIC TECH INC

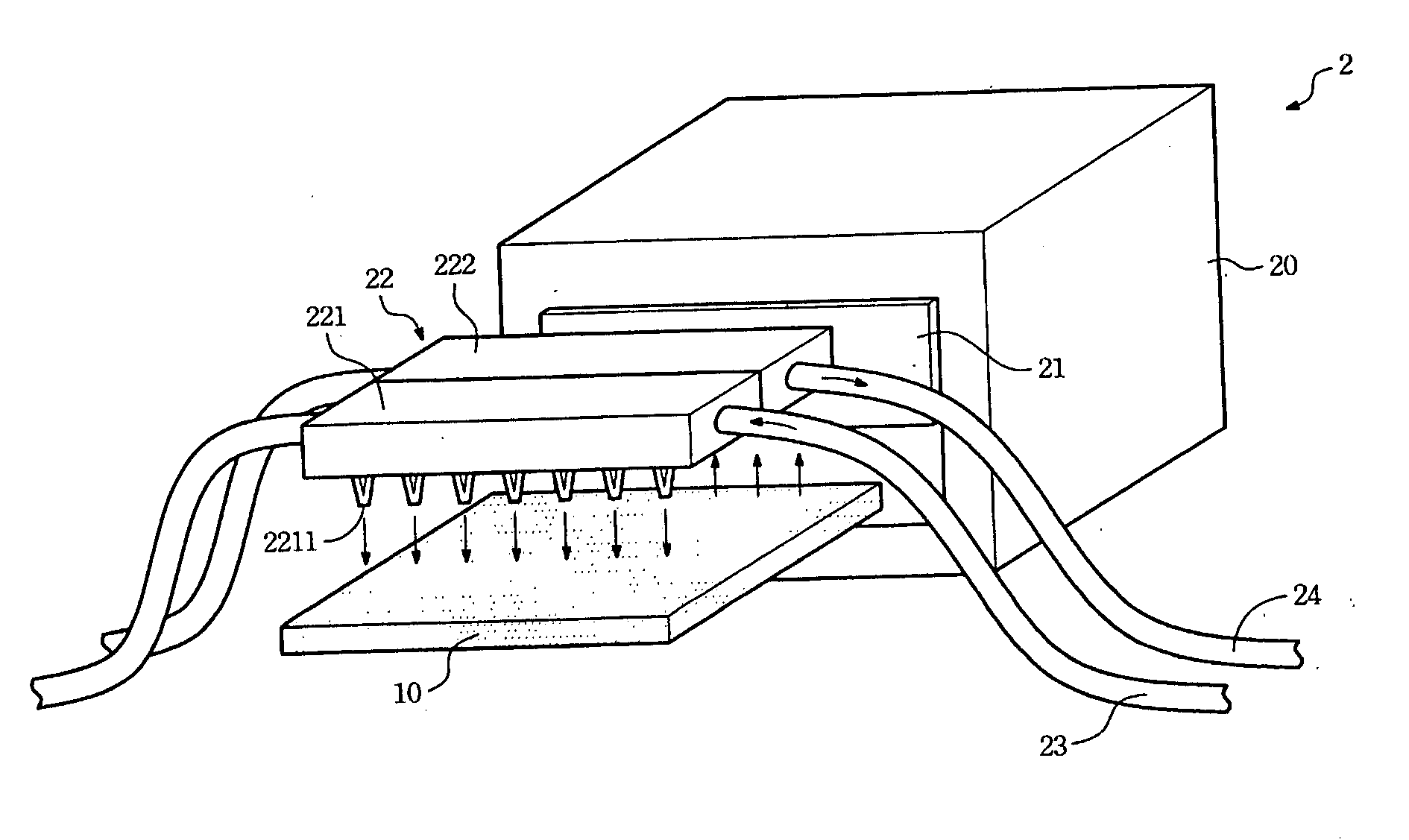

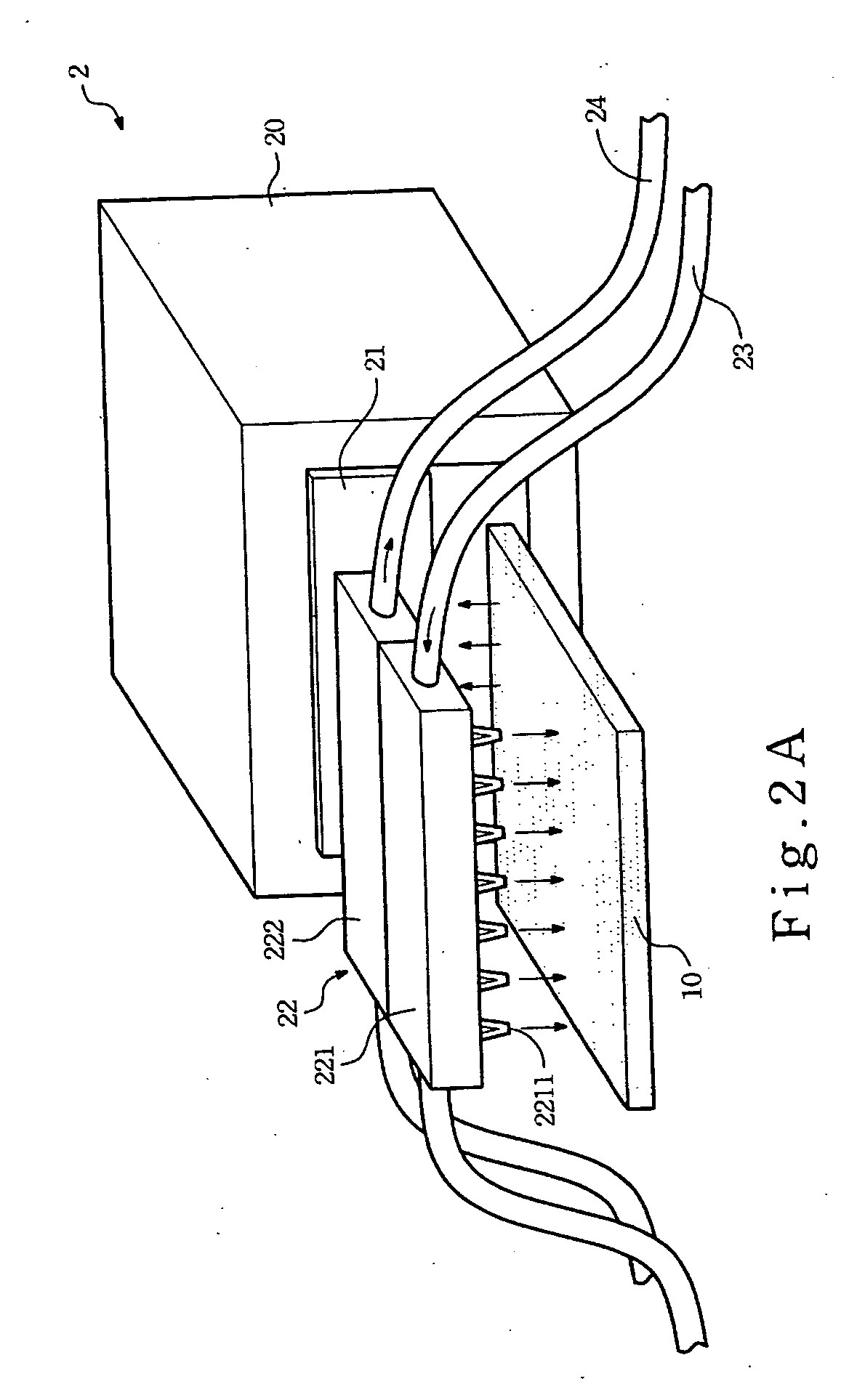

Cleaning system

InactiveUS20050268408A1Less cleaningOptimize spaceMechanical cleaningPressure cleaningEngineeringStatic electricity

A cleaning system comprises a chamber and a particle-removing device. The particle-removing device, arranged outside the chamber, including an ionizer ionizing surrounding gas and spouting the ionized gas and a vacuum unit. Whereby, before an substrate is sent into the chamber, the ionized gas spouted from the ionizer neutralizes electrostatic charges and blowing up particles accumulate on the substrate and the particles are drawn away by the vacuum unit so that the object can be transmitted into the chamber much cleaner.

Owner:AU OPTRONICS CORP

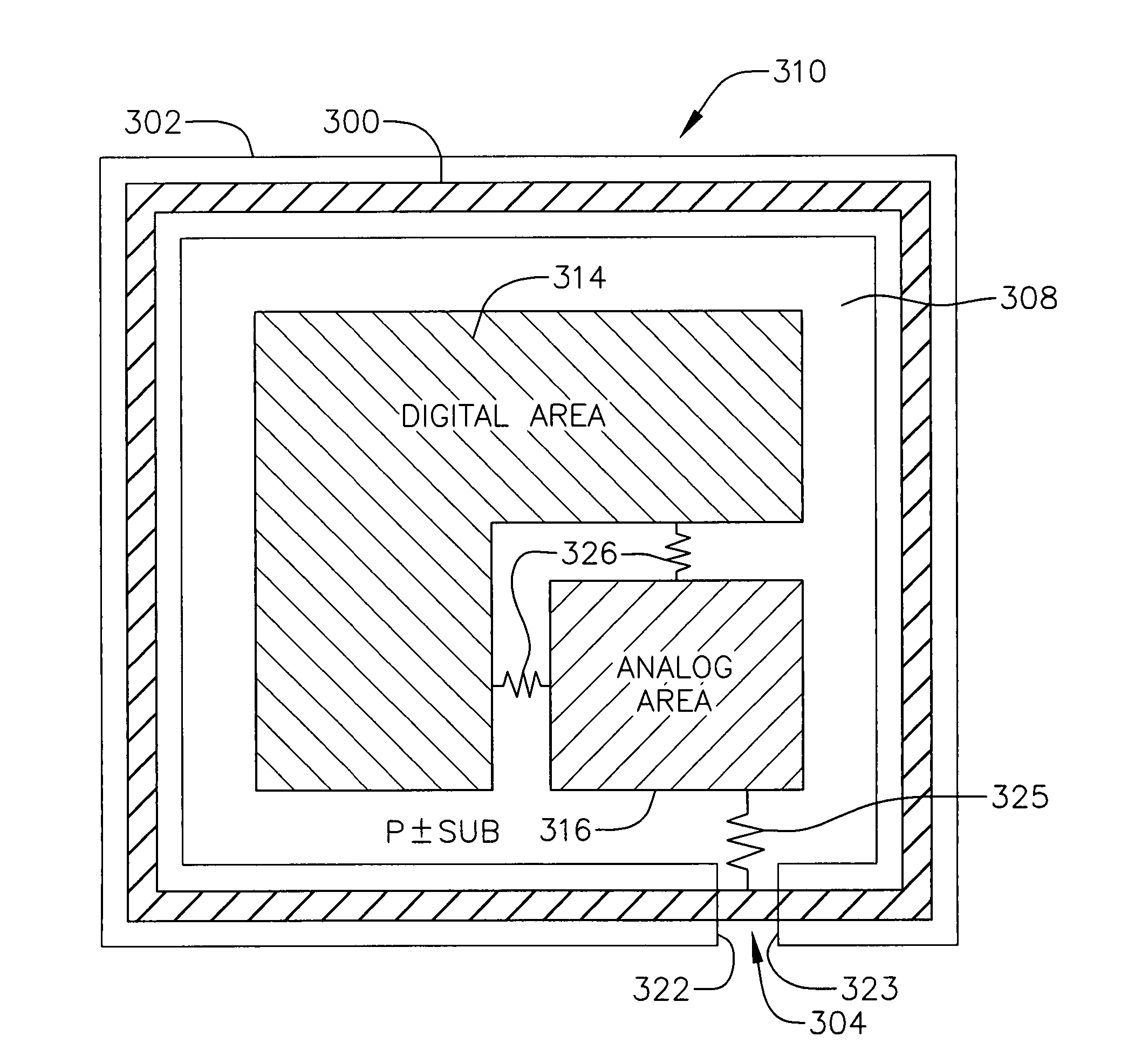

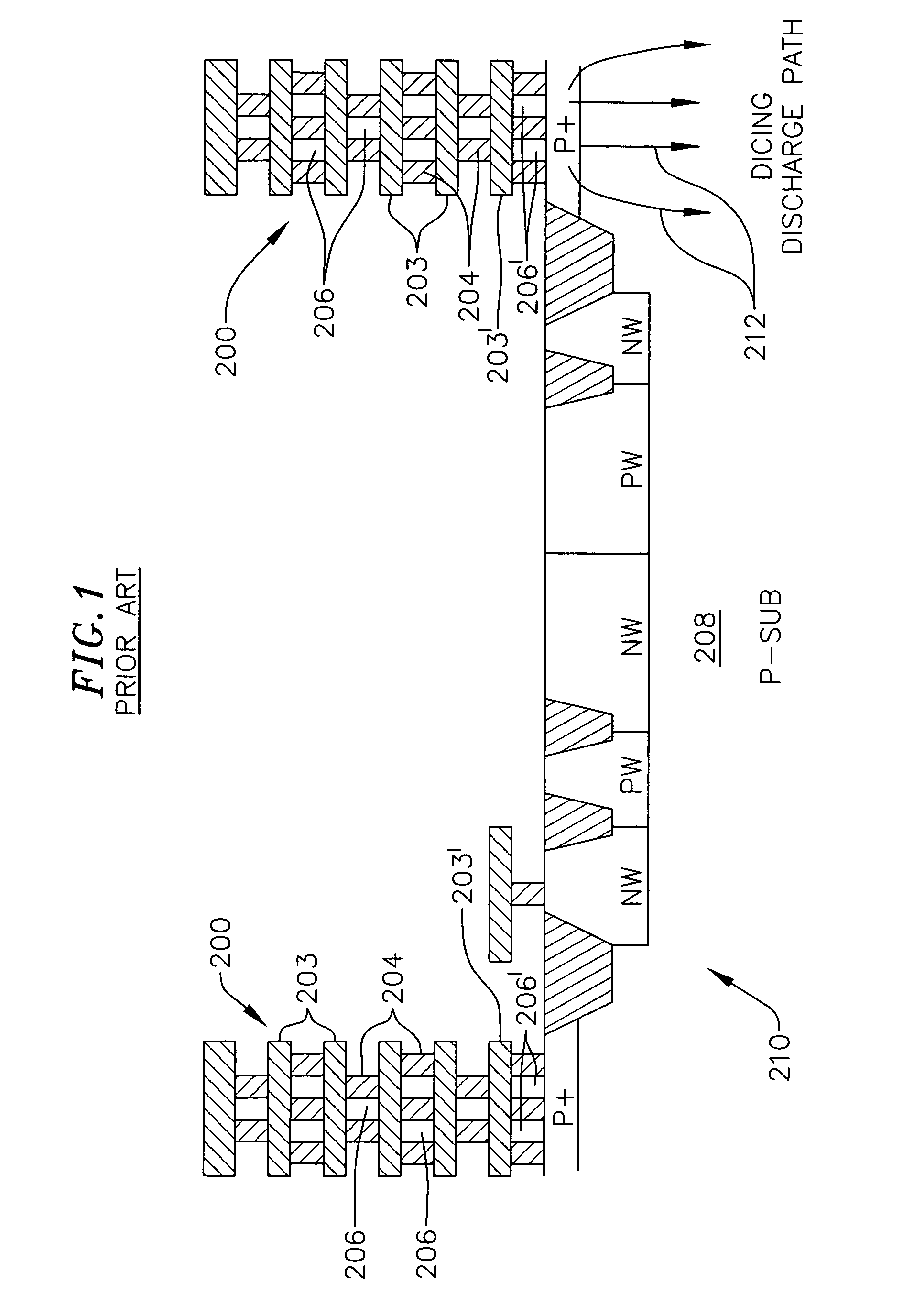

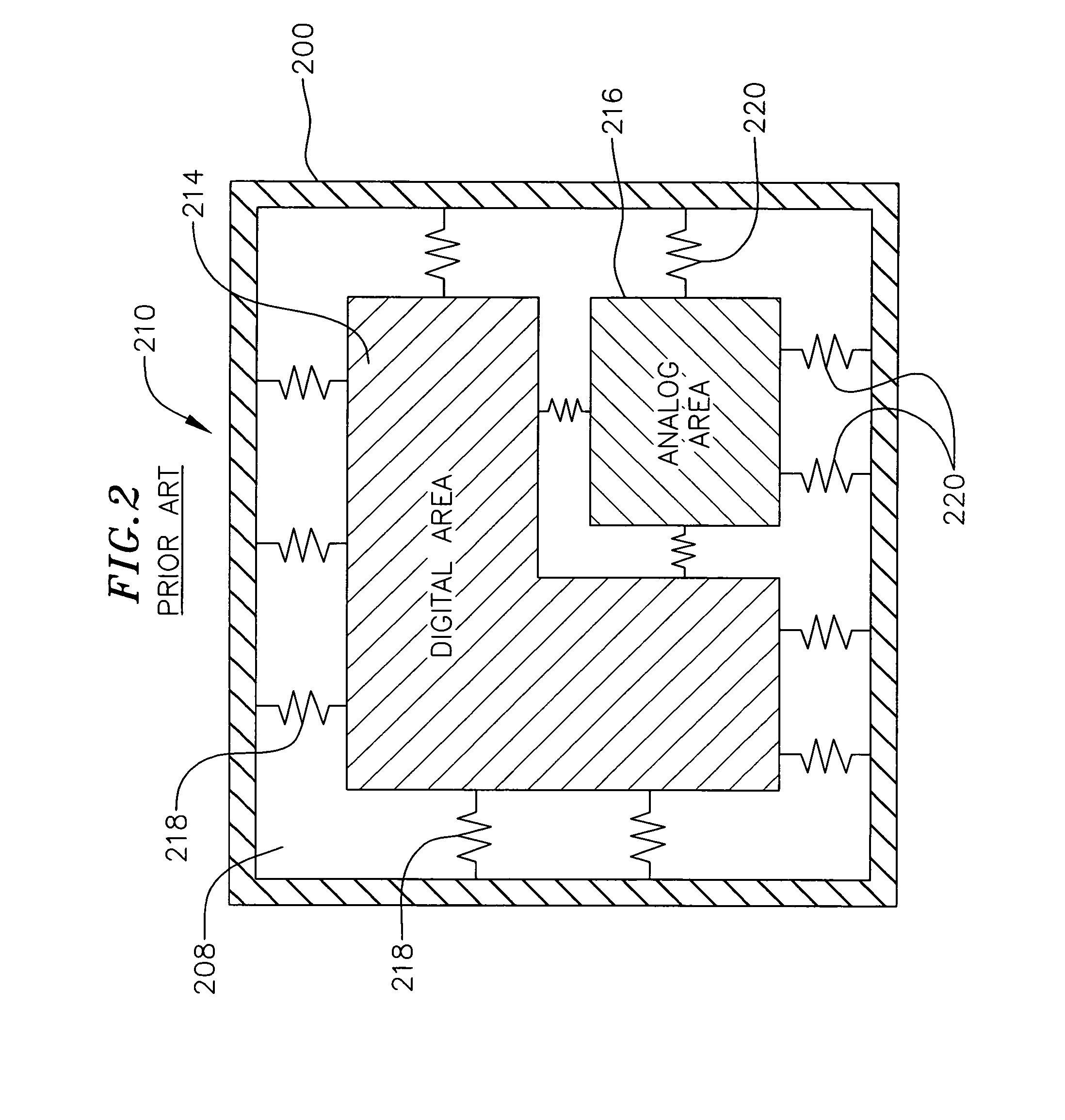

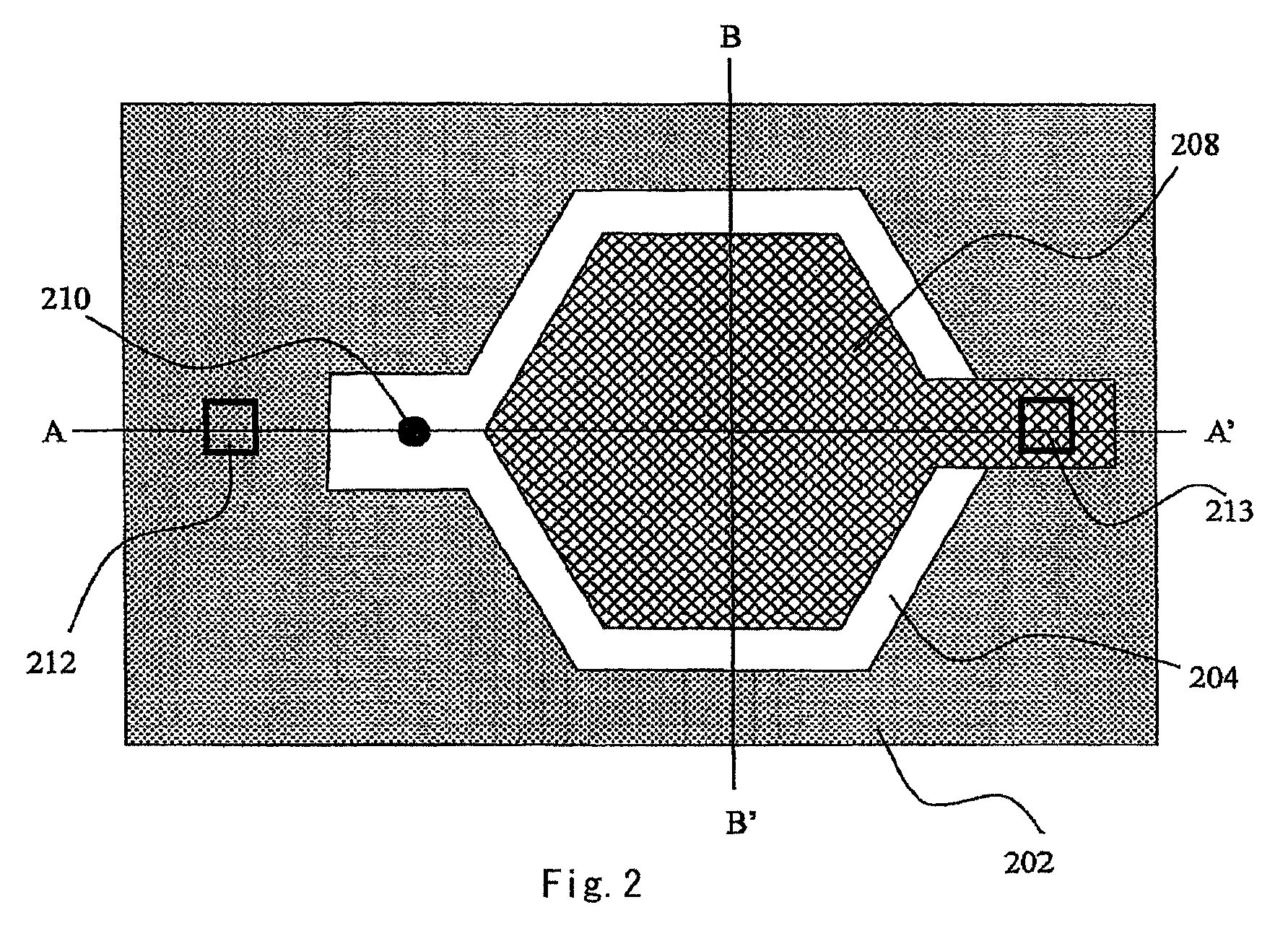

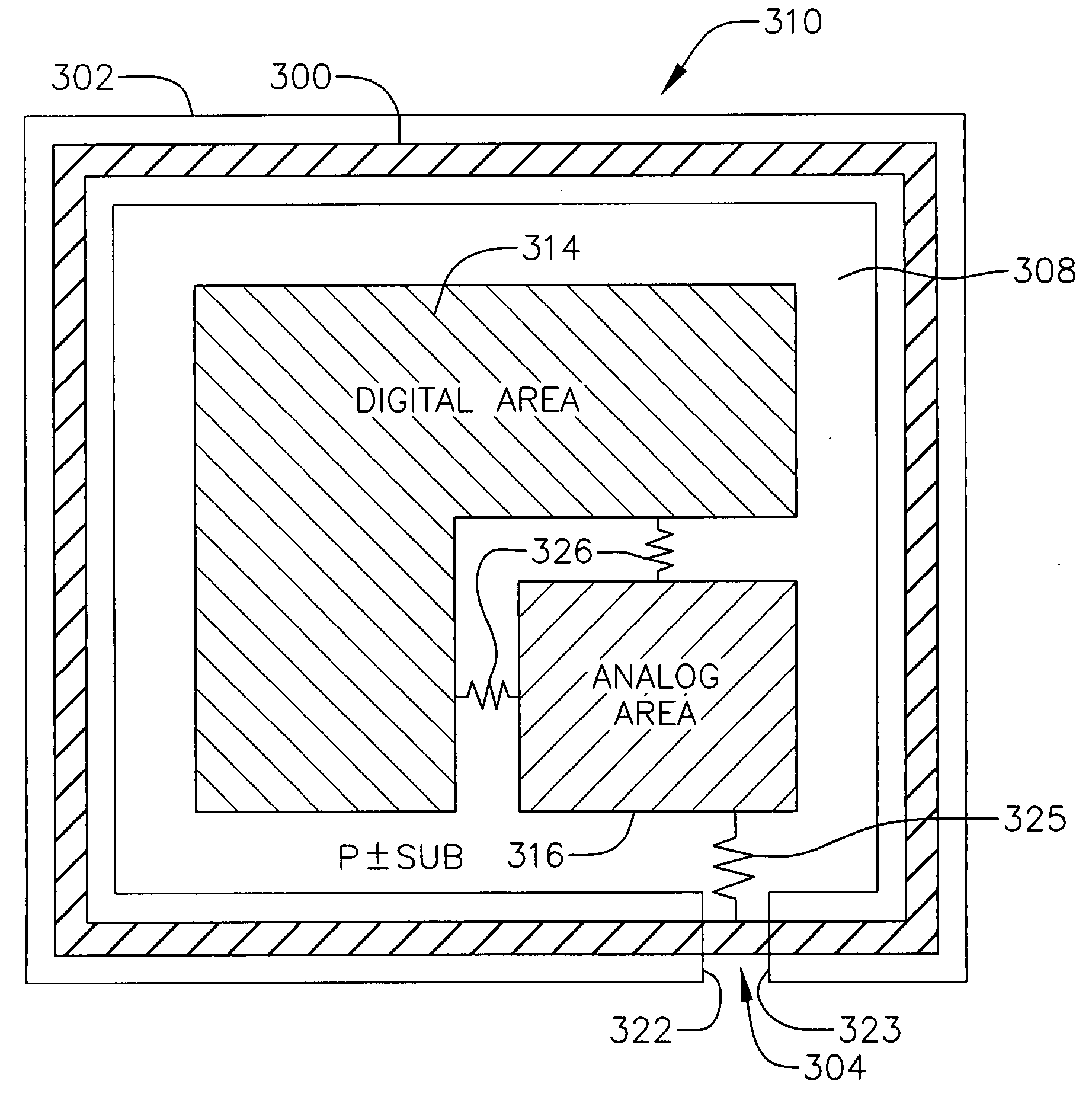

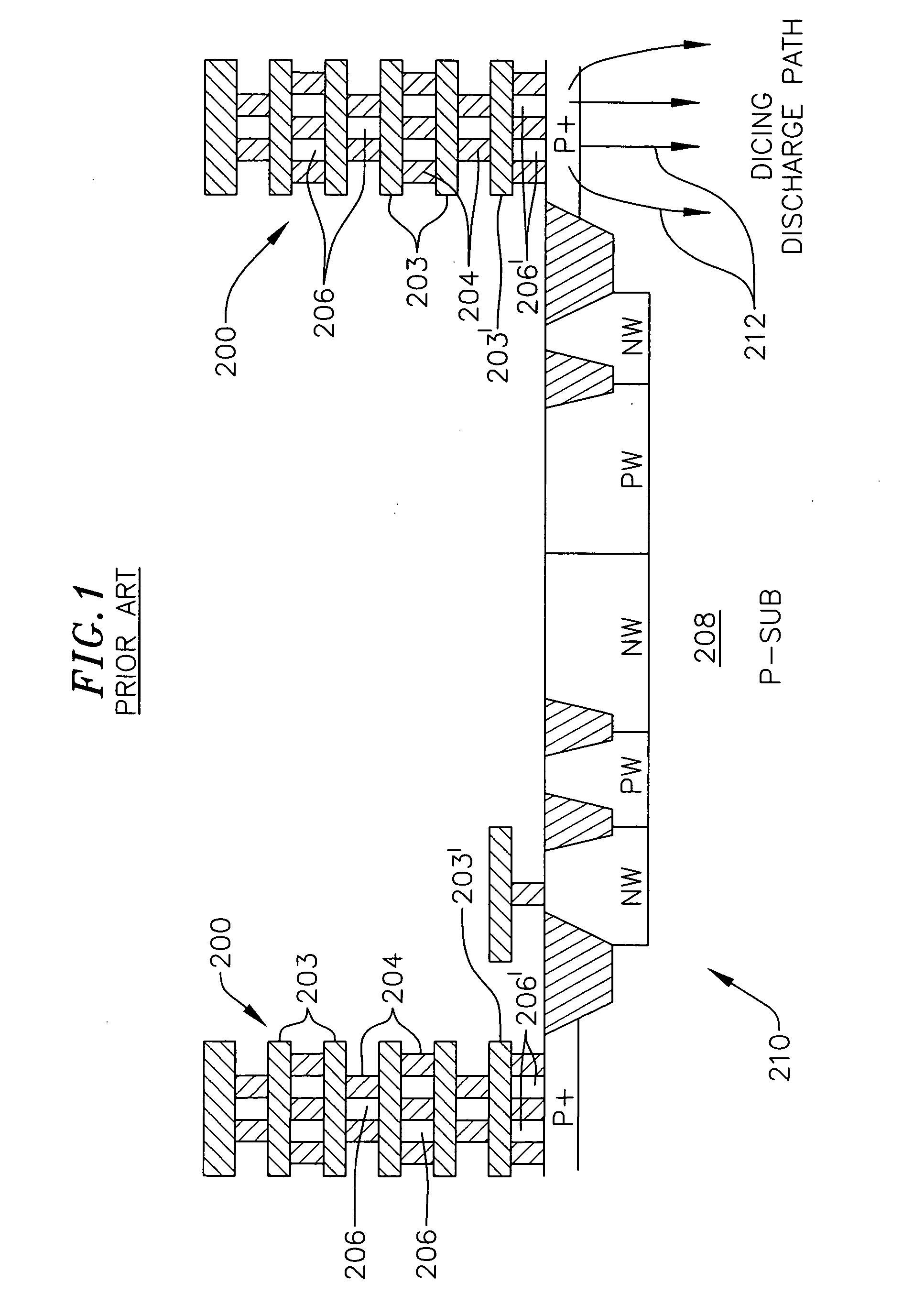

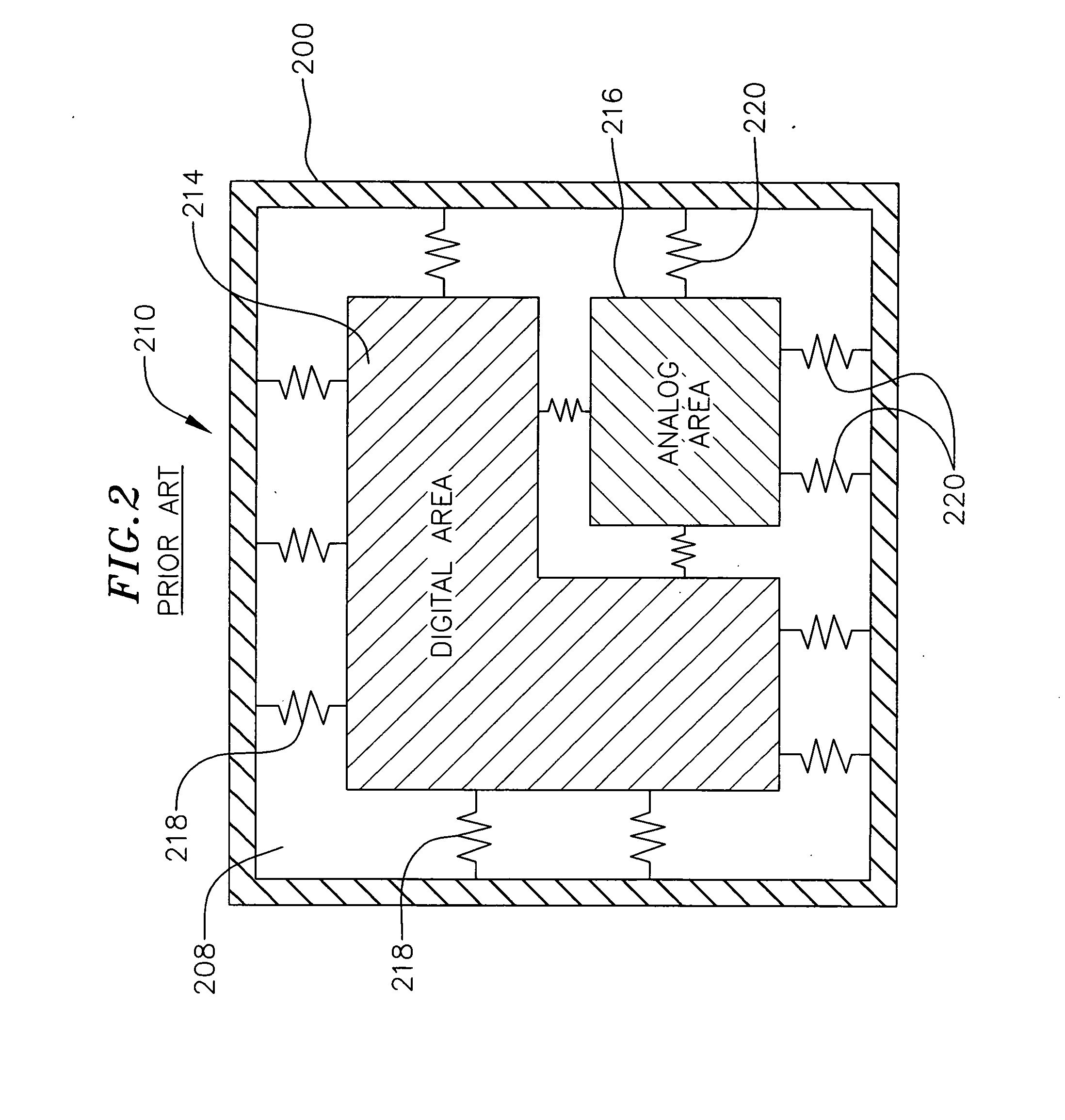

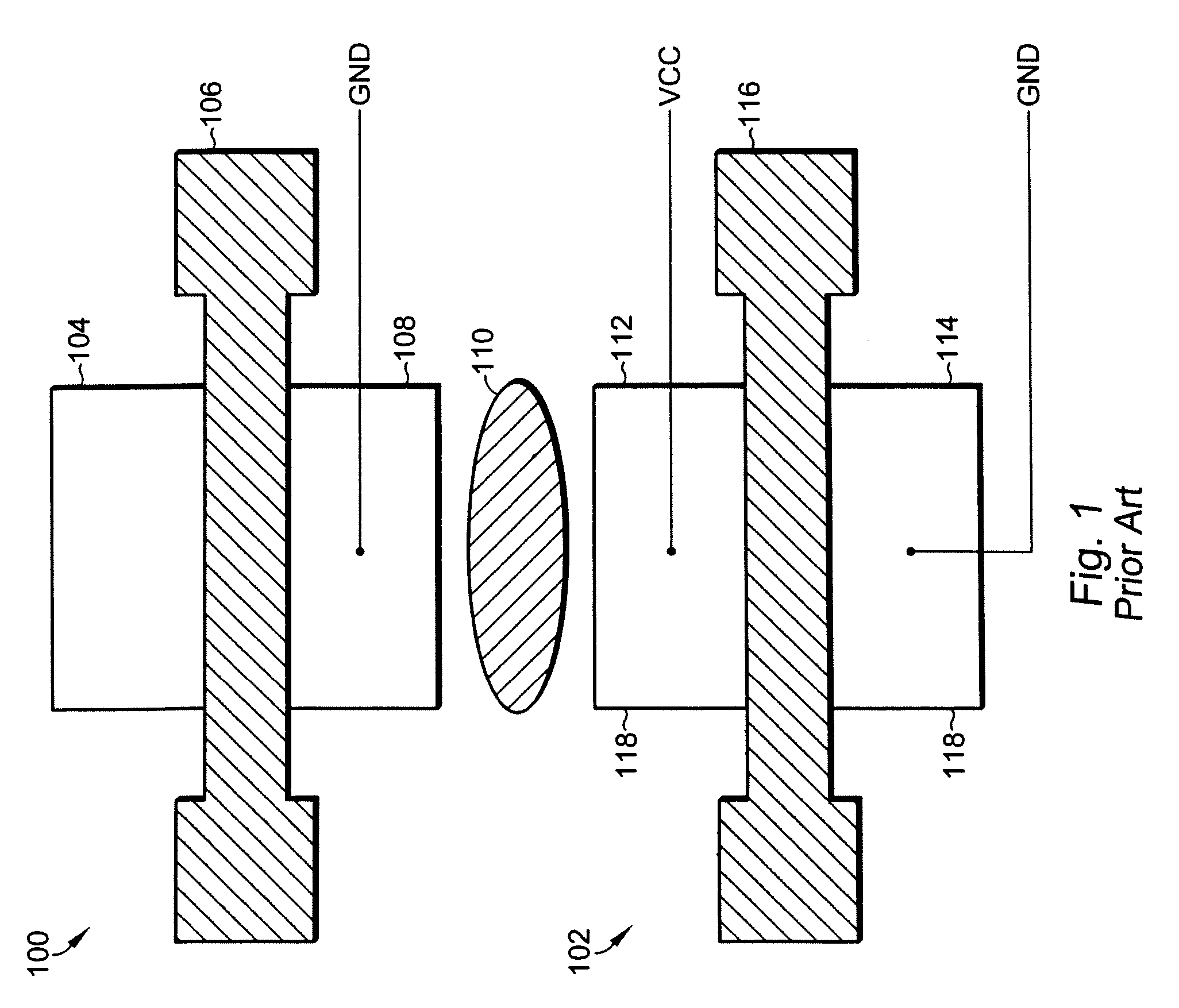

Seal ring for integrated circuits

InactiveUS7087496B2Avoid charge accumulationLower resistanceTransistorSemiconductor/solid-state device detailsPhotonic integrated circuitSemiconductor

The present invention is directed to a seal structure and a method for forming a seal structure for a semiconductor die. An elongate region which is electrically isolated from the remainder of the substrate, such as a well region of a conductivity type opposite that of the substrate, extends around the major portion of the periphery of the substrate. A gap is left between the two ends of the elongate region along the minor portion of the periphery of the substrate not covered by the elongate region. A conductive seal ring is formed around the periphery of the substrate at the elongate region and spans the gap between the ends of the elongate region. The substrate of the semiconductor die is only brought into electrical contact with the seal ring at the gap between the ends of the elongate region.

Owner:AVAGO TECH INT SALES PTE LTD

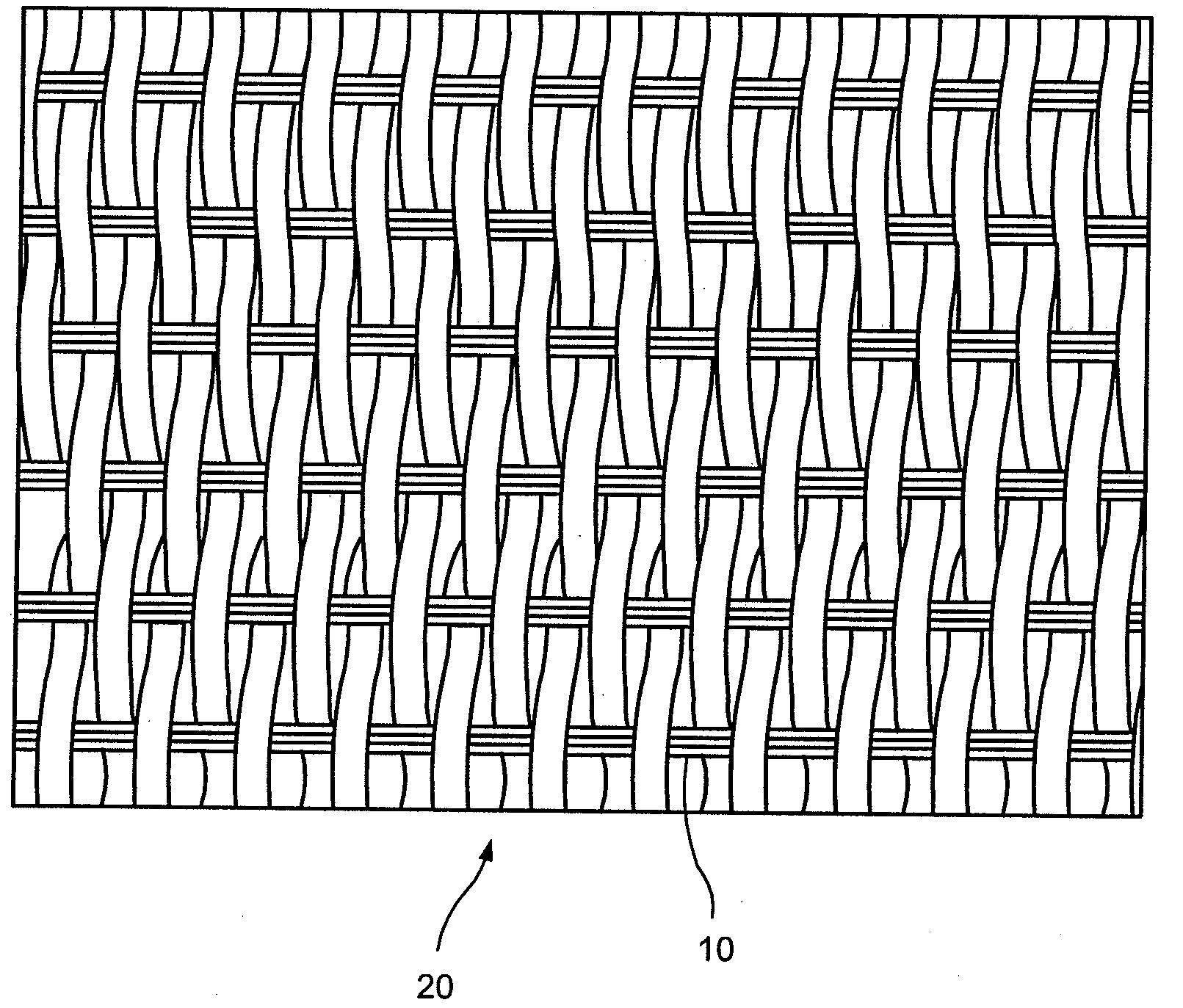

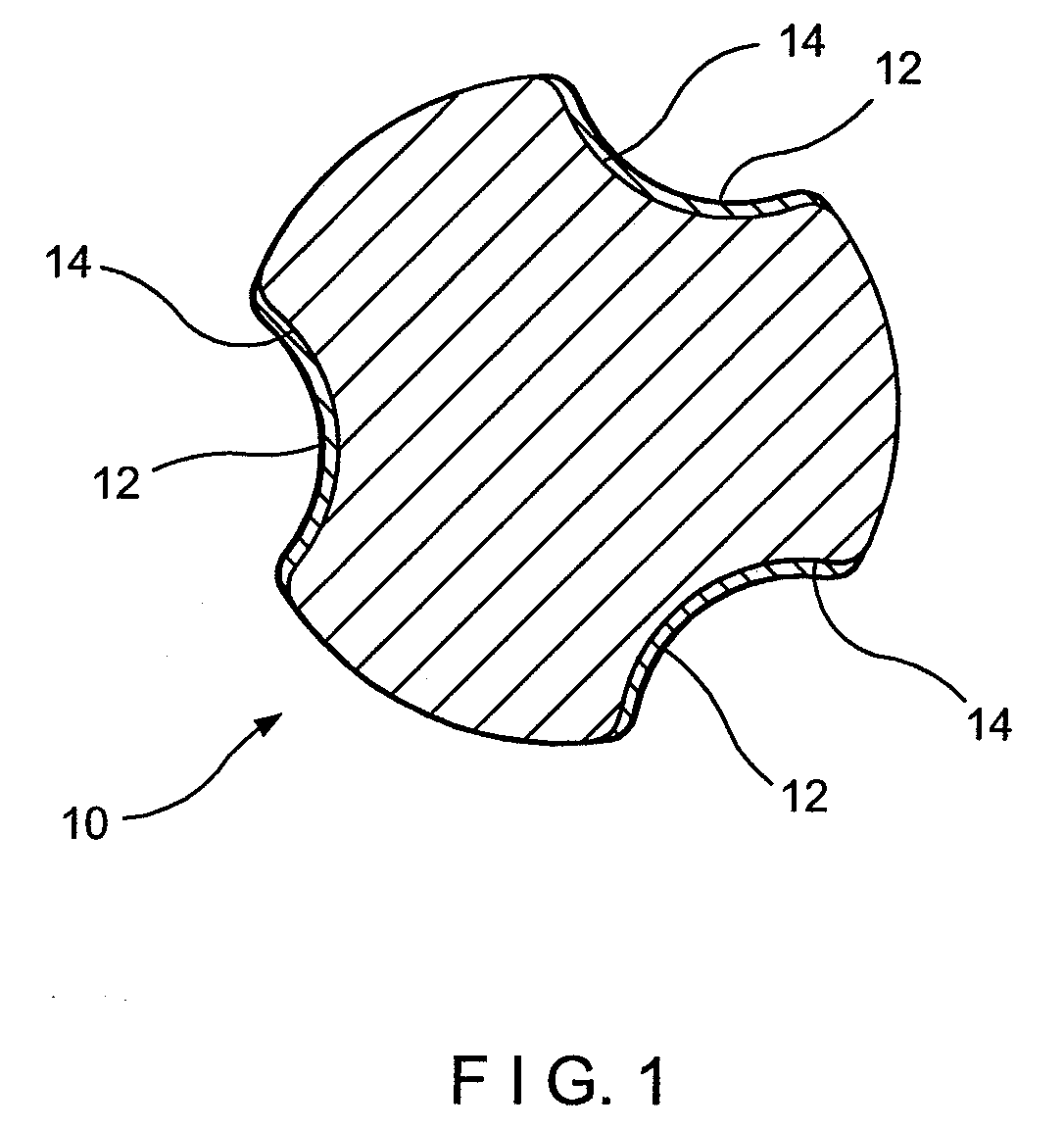

Conductive Monofilament and Fabric

ActiveUS20080318483A1Avoid problemsAvoid charge accumulationWeft knittingFilament manufactureConductive materialsElectrically conductive

A conductive monofilament and static dissipative fabric having the same wherein the monofilament includes electrically conductive material and binder and has static dissipation properties.

Owner:ALBANY INT CORP

Ultrasonic transducer and ultrasonic diagnostic device using same

ActiveUS8617078B2Avoid charge accumulationReduce voltageUltrasonic/sonic/infrasonic diagnosticsPiezoelectric/electrostriction/magnetostriction machinesUltrasonic sensorTransducer

Owner:FUJIFILM HEALTHCARE CORP

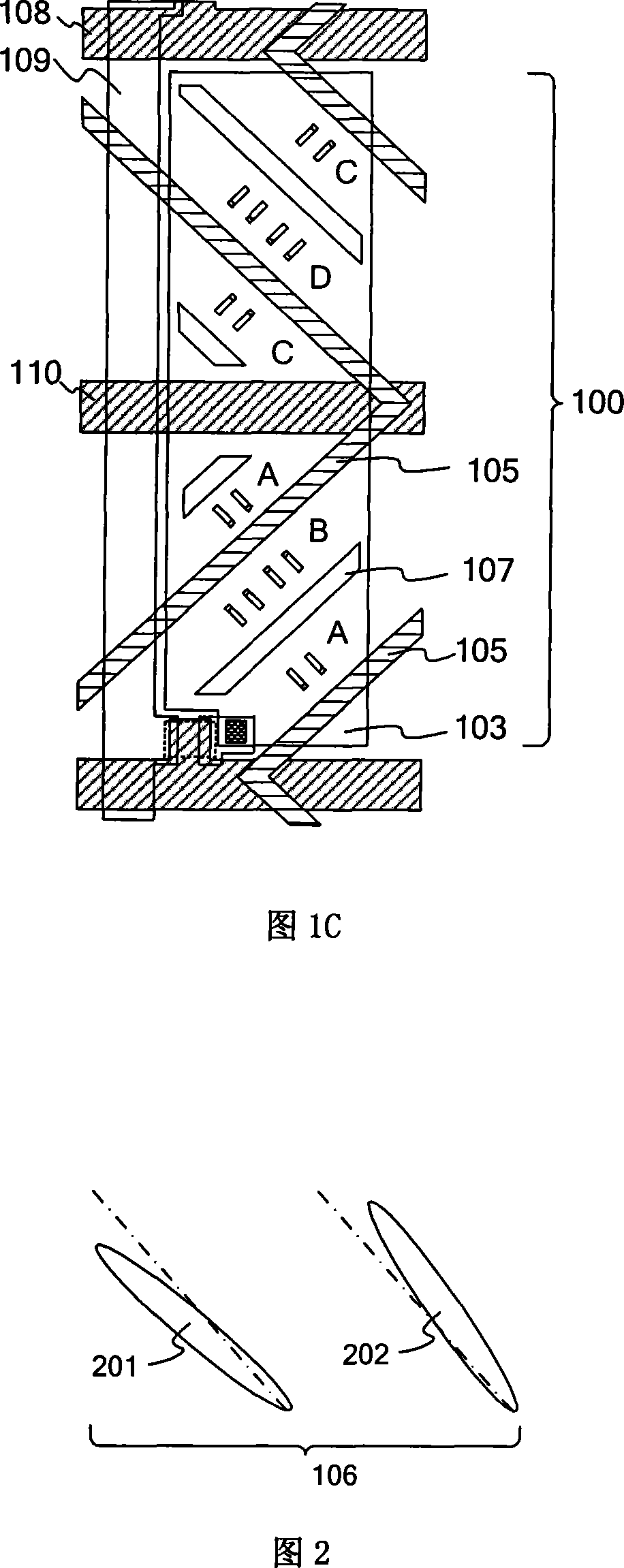

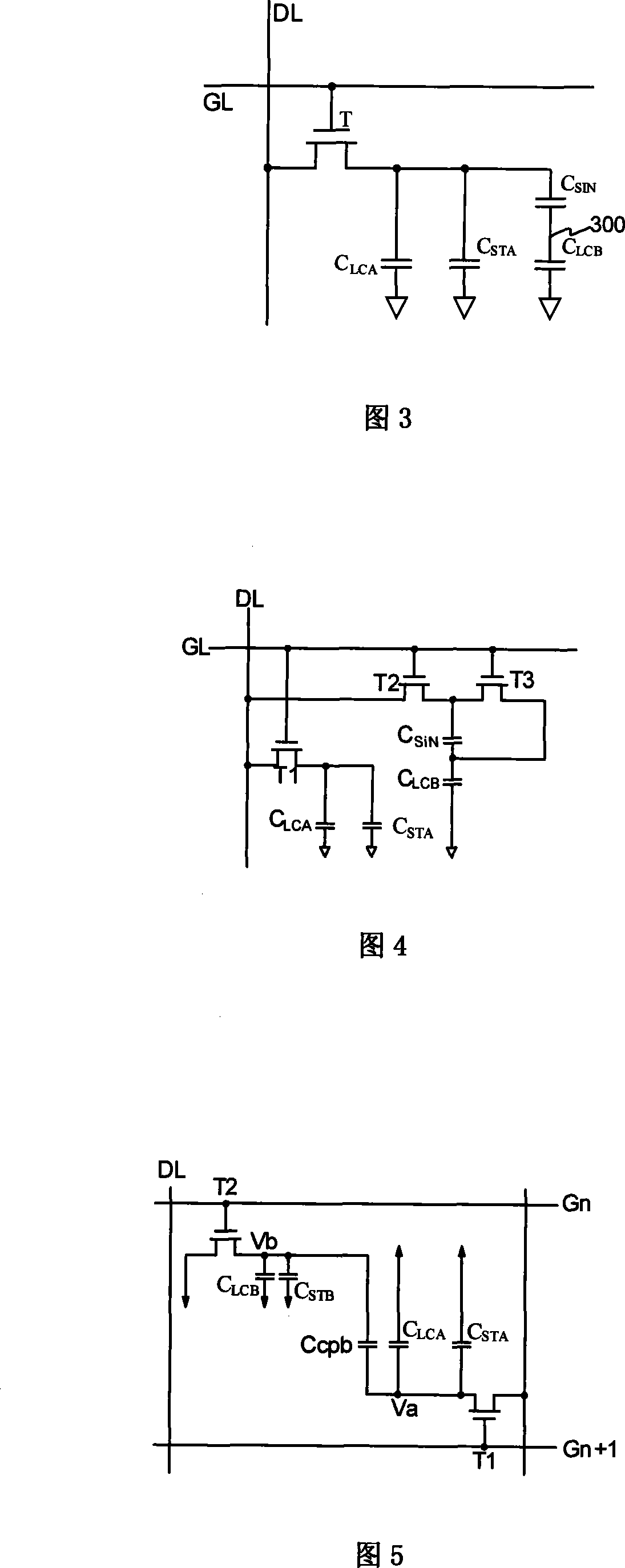

Vertical orientation mode liquid crystal display device

ActiveCN101144947AAvoid charge accumulationAvoid residual DC voltageStatic indicating devicesNon-linear opticsPhysicsLiquid-crystal display

The present invention discloses a vertical orientation type liquid crystal display device, which includes a plurality of pixels defined by crossing a grid scanning beam and a data line, each pixel is divided into at least a first sub-pixel and a second sub-pixel; and a plurality of pixel circuits connected to the grid scanning beam and the data line. The pixel circuit includes at least a first membrane transistor, a second membrane transistor, a third membrane transistor, a first sub-pixel capacitor, a second sub-pixel capacitor, a storage capacitor, and an additional capacitor. The storage capacitor is connected with the first sub-pixel capacitor in parallel to keep the data signal voltage transmitted through the data line. The additional capacitor is connected with the second sub-pixel capacitor in series, is connected with the second membrane transistor in parallel. One terminal of the second sub-pixel capacitor is connected with the second electrode of the third membrane transistor electrically. The second membrane transistor and the third membrane transistor are controlled by the previous row of grid scanning beam.

Owner:NANJING CEC PANDA LCD TECH

Seal ring for integrated circuits

InactiveUS20050146014A1Avoid charge accumulationLower resistanceTransistorSemiconductor/solid-state device detailsEngineeringMechanical engineering

The present invention is directed to a seal structure and a method for forming a seal structure for a semiconductor die. An elongate region which is electrically isolated from the remainder of the substrate, such as a well region of a conductivity type opposite that of the substrate, extends around the major portion of the periphery of the substrate. A gap is left between the two ends of the elongate region along the minor portion of the periphery of the substrate not covered by the elongate region. A conductive seal ring is formed around the periphery of the substrate at the elongate region and spans the gap between the ends of the elongate region. The substrate of the semiconductor die is only brought into electrical contact with the seal ring at the gap between the ends of the elongate region.

Owner:AVAGO TECH INT SALES PTE LTD

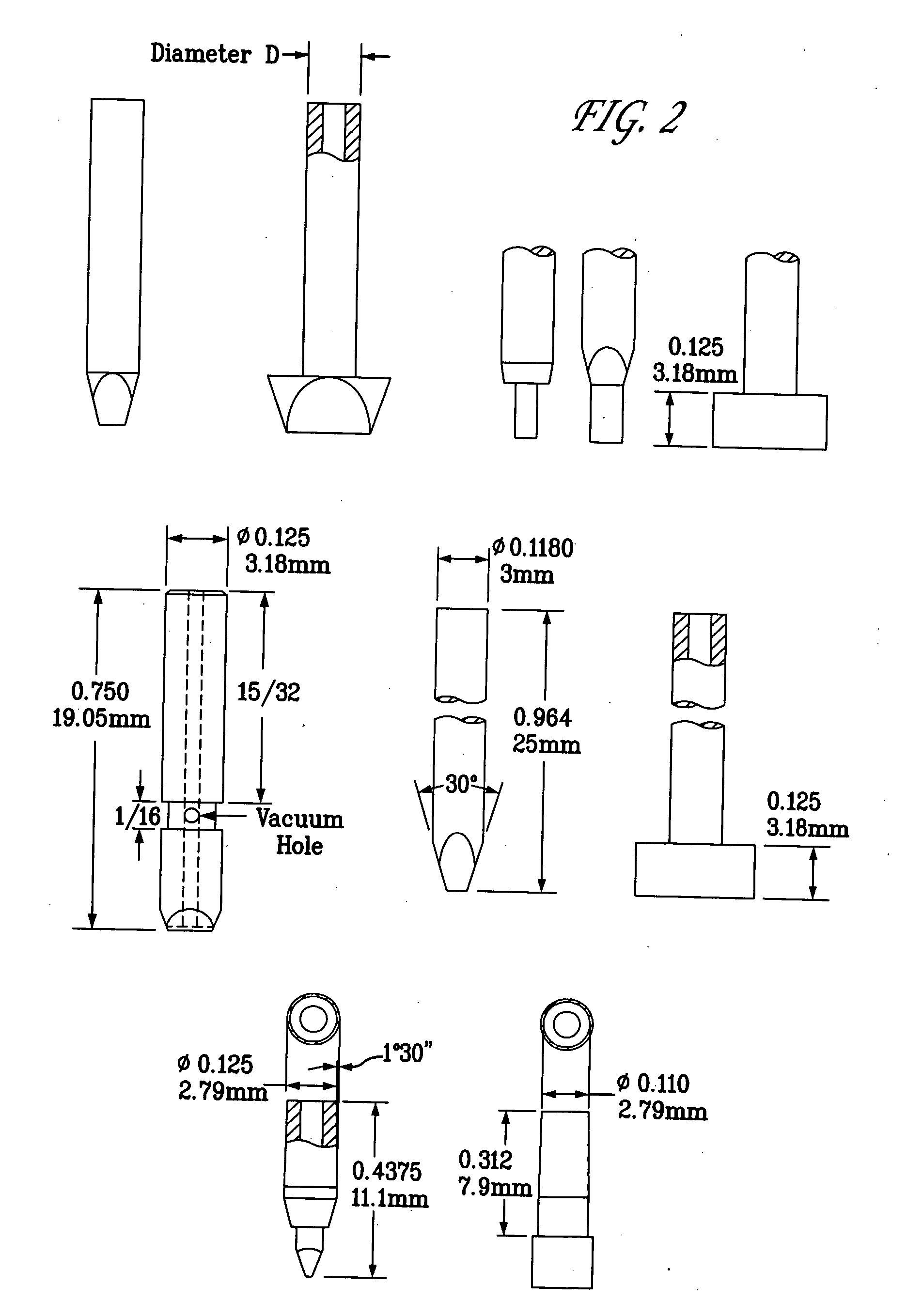

Dissipative pick and place tools for light wire and LED displays

InactiveUS20070085085A1Prevent overloadPrevent charge buildupSolid-state devicesSemiconductor devices for light sourcesElectricityEngineering

The present invention provides for placement of an LED device on a carrier through the use of a pick-and-place tool. The tool conducts electricity at a rate sufficient to prevent charge buildup but not at so high a rate as to overload the LED being placed.

Owner:REIBER STEVEN F

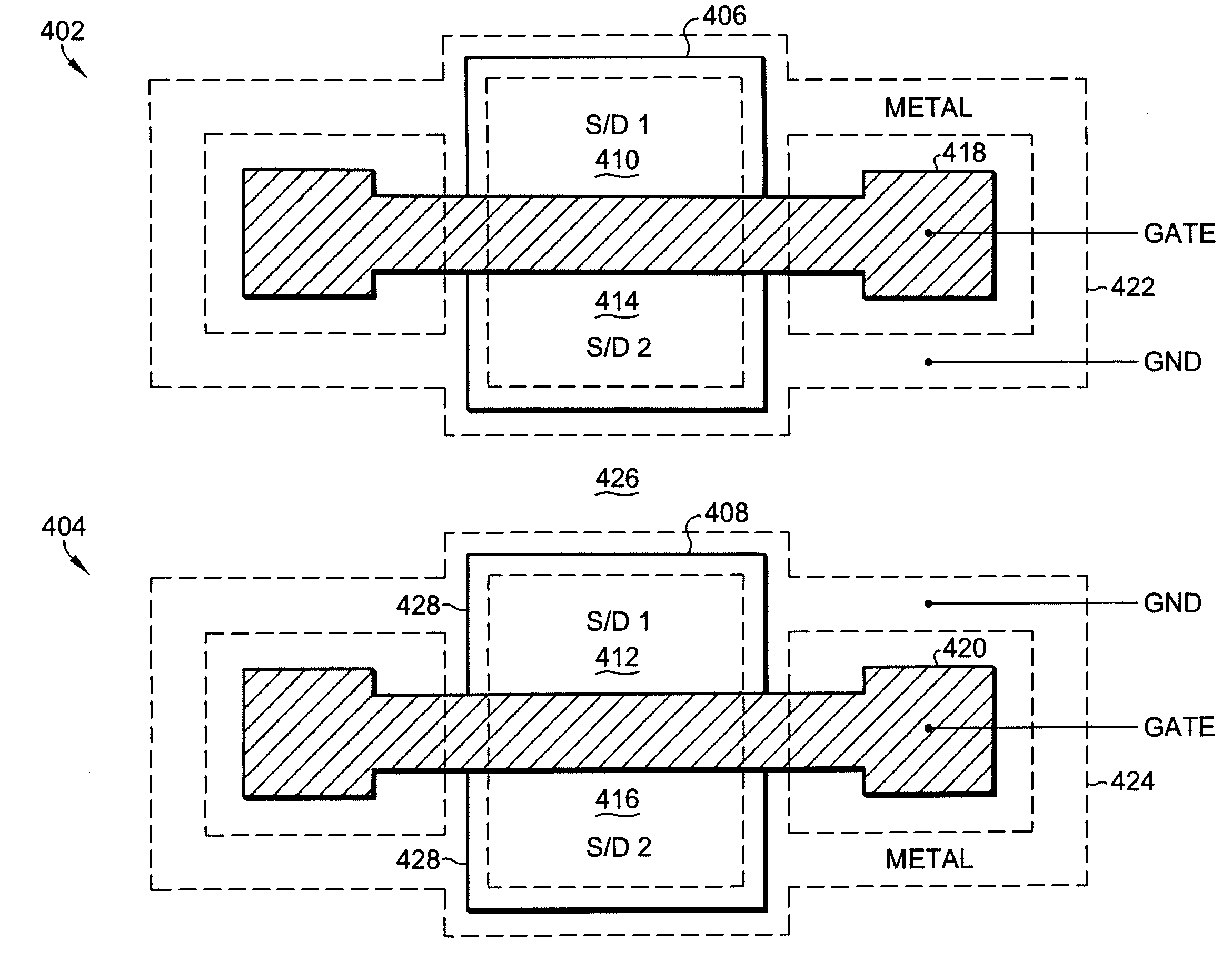

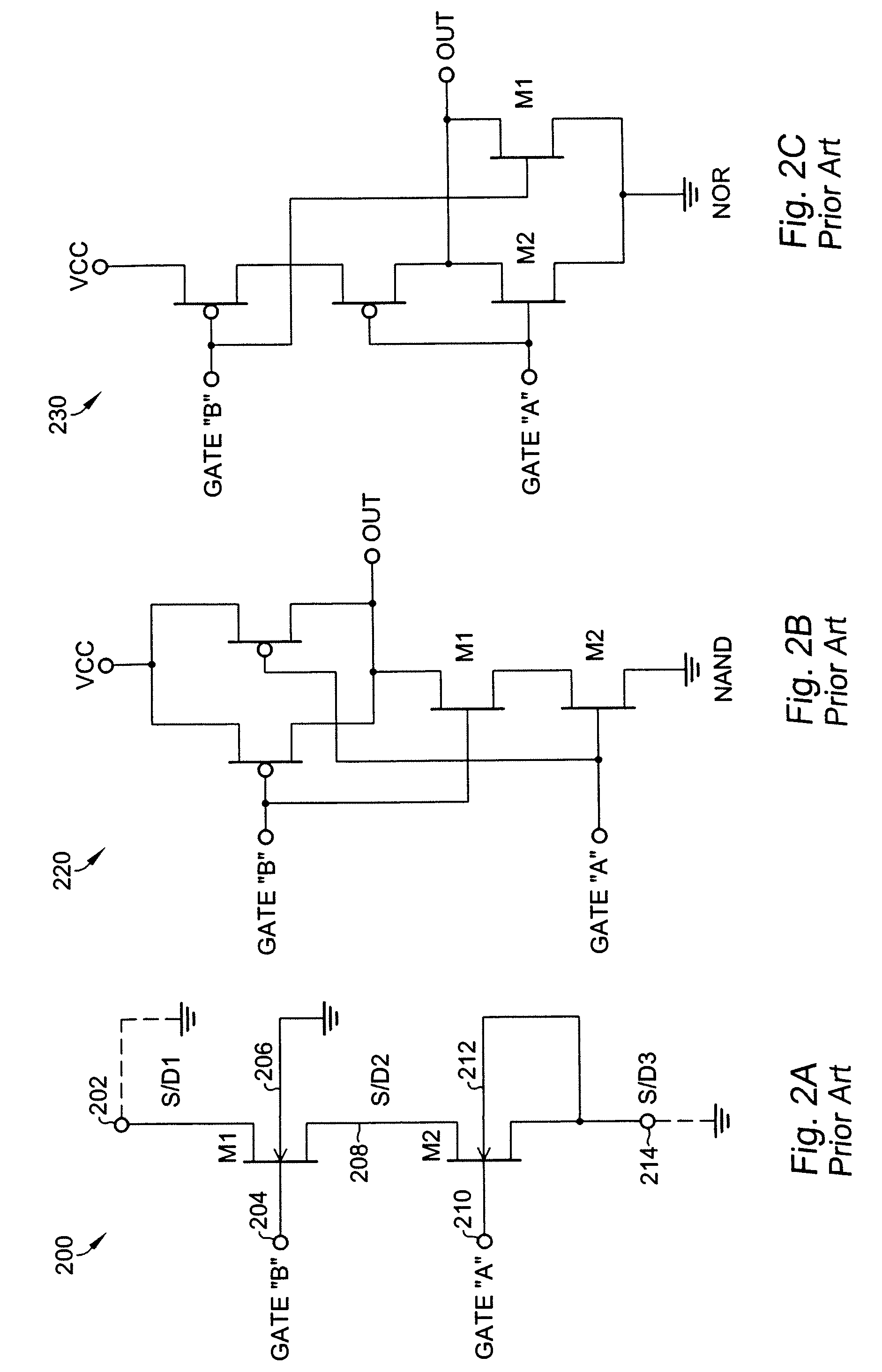

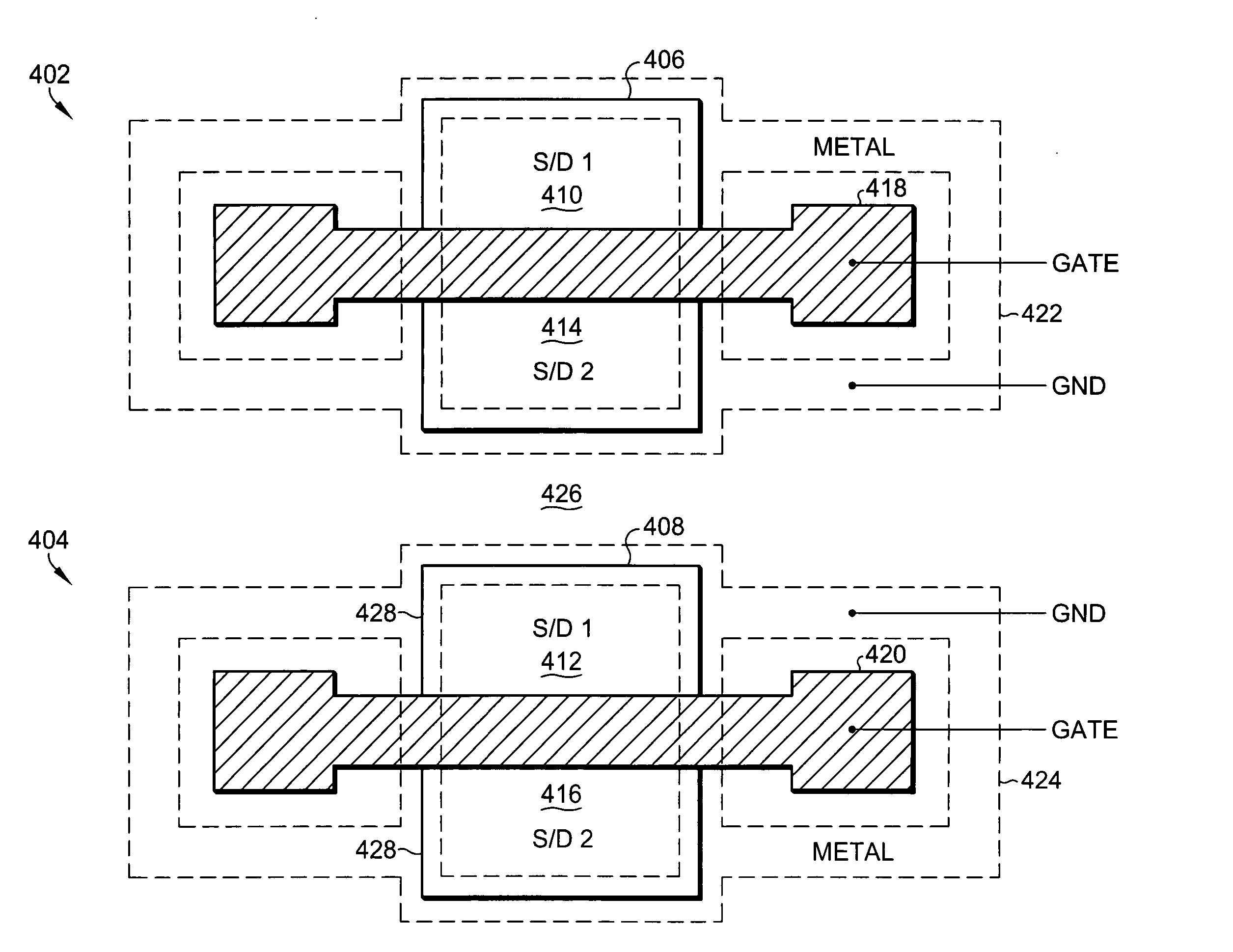

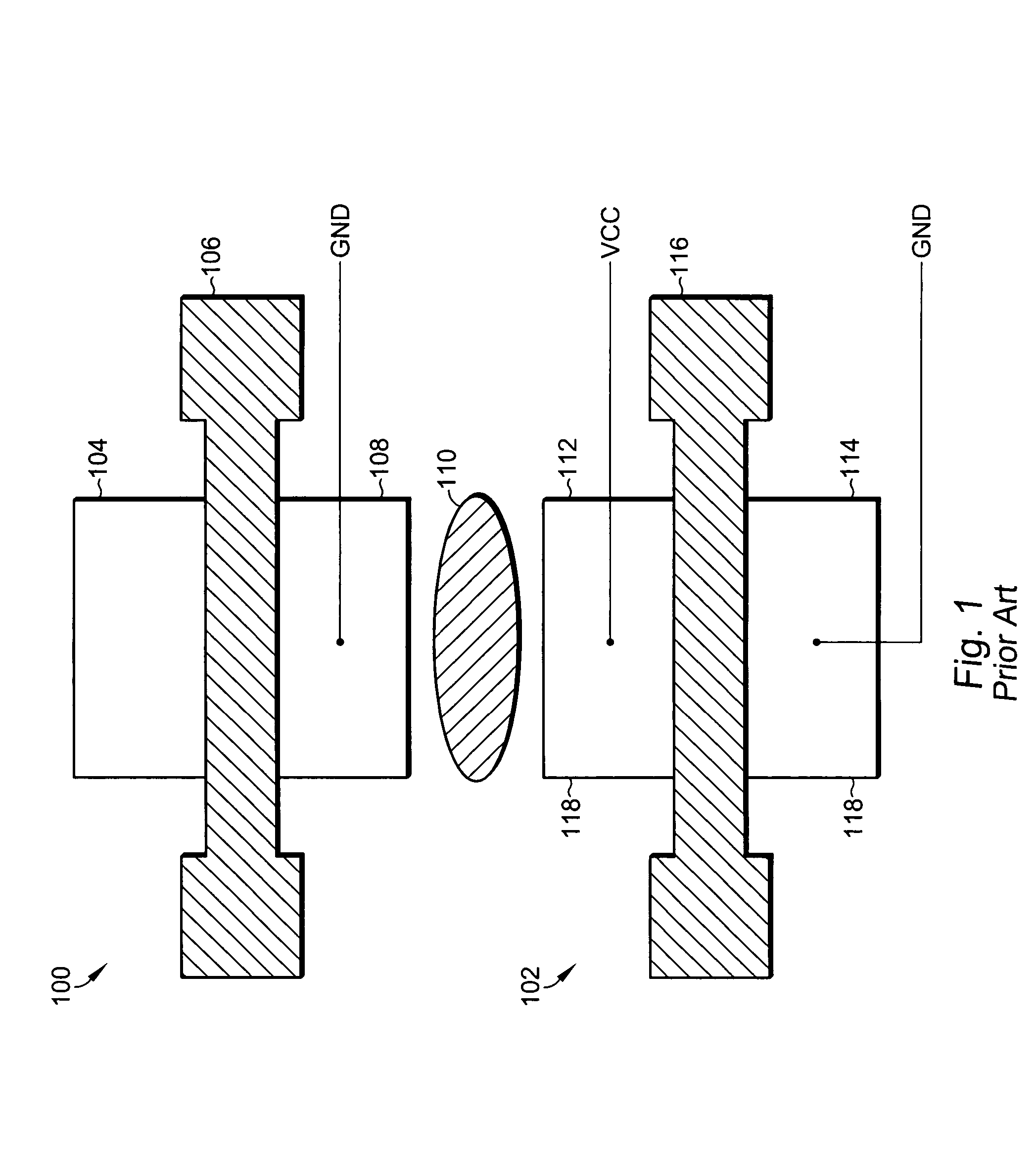

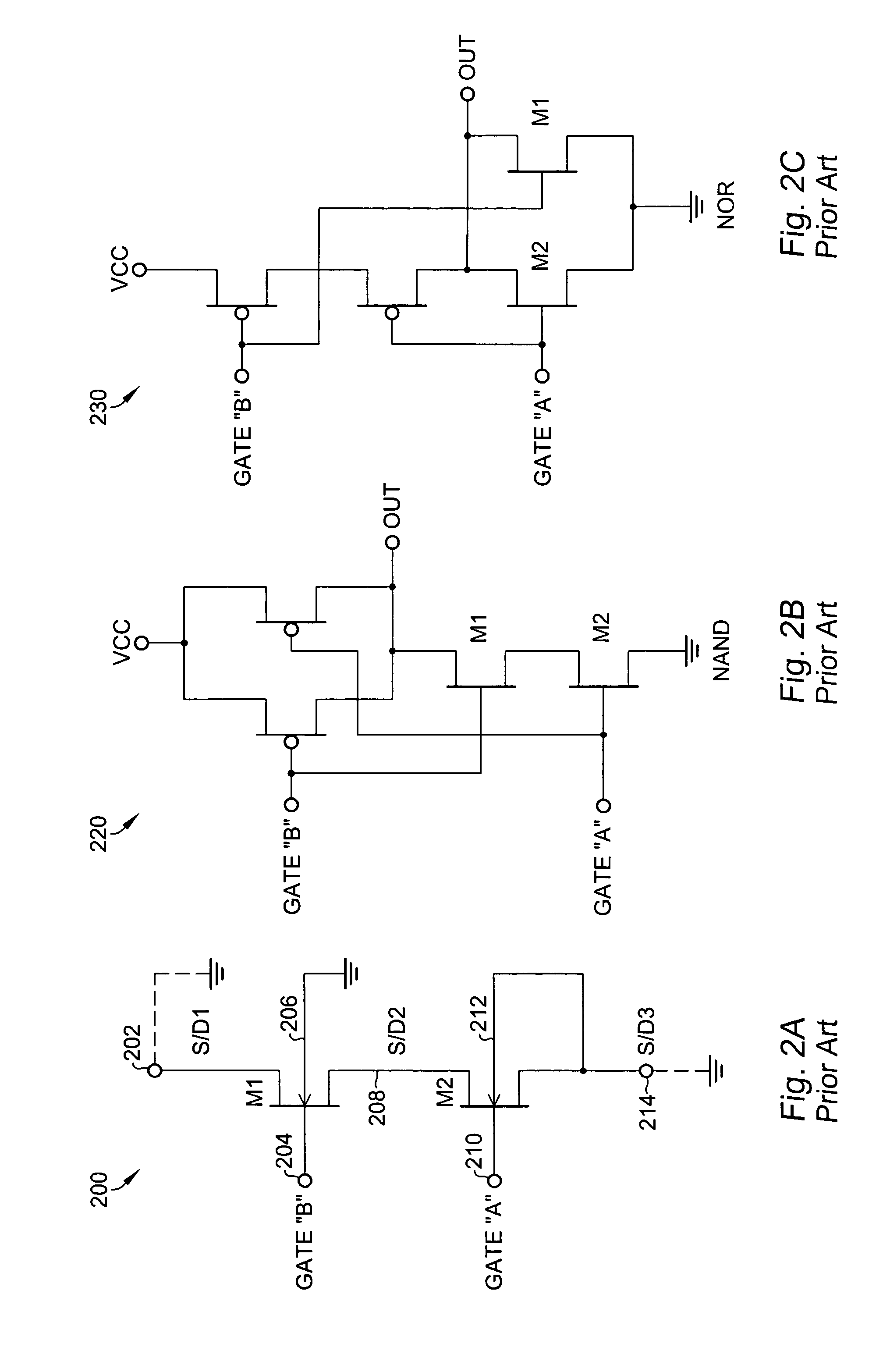

Total ionizing dose suppression transistor architecture

ActiveUS20070181978A1Avoid charge accumulationTransistorSemiconductor/solid-state device detailsEngineeringTransistor circuits

A total ionizing dose suppression architecture for a transistor and a transistor circuit uses an “end cap” metal structure that is connected to the lowest potential voltage to overcome the tendency of negative charge buildup during exposure to ionizing radiation. The suppression architecture uses the field established by coupling the metal structure to the lowest potential voltage to steer the charge away from the critical field (inter-device) and keeps non-local charge from migrating to the “birds-beak” region of the transistor, preventing further charge buildup. The “end cap” structure seals off the “birds-beak” region and isolates the critical area. The critical area charge is source starved of an outside charge. Outside charge migrating close to the induced field is repelled away from the critical region. The architecture is further extended to suppress leakage current between adjacent wells biased to differential potentials.

Owner:CAES COLORADO SPRINGS LLC

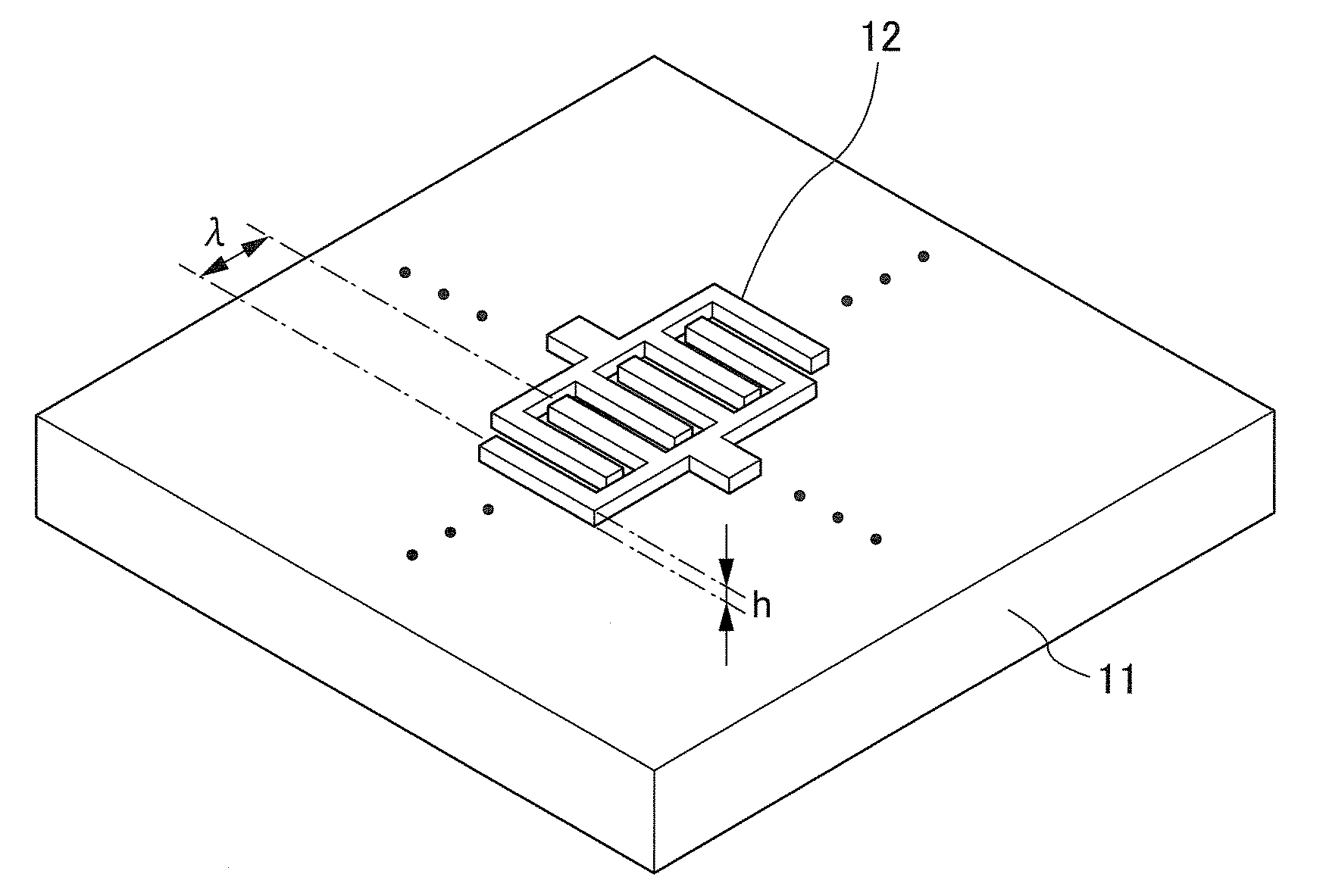

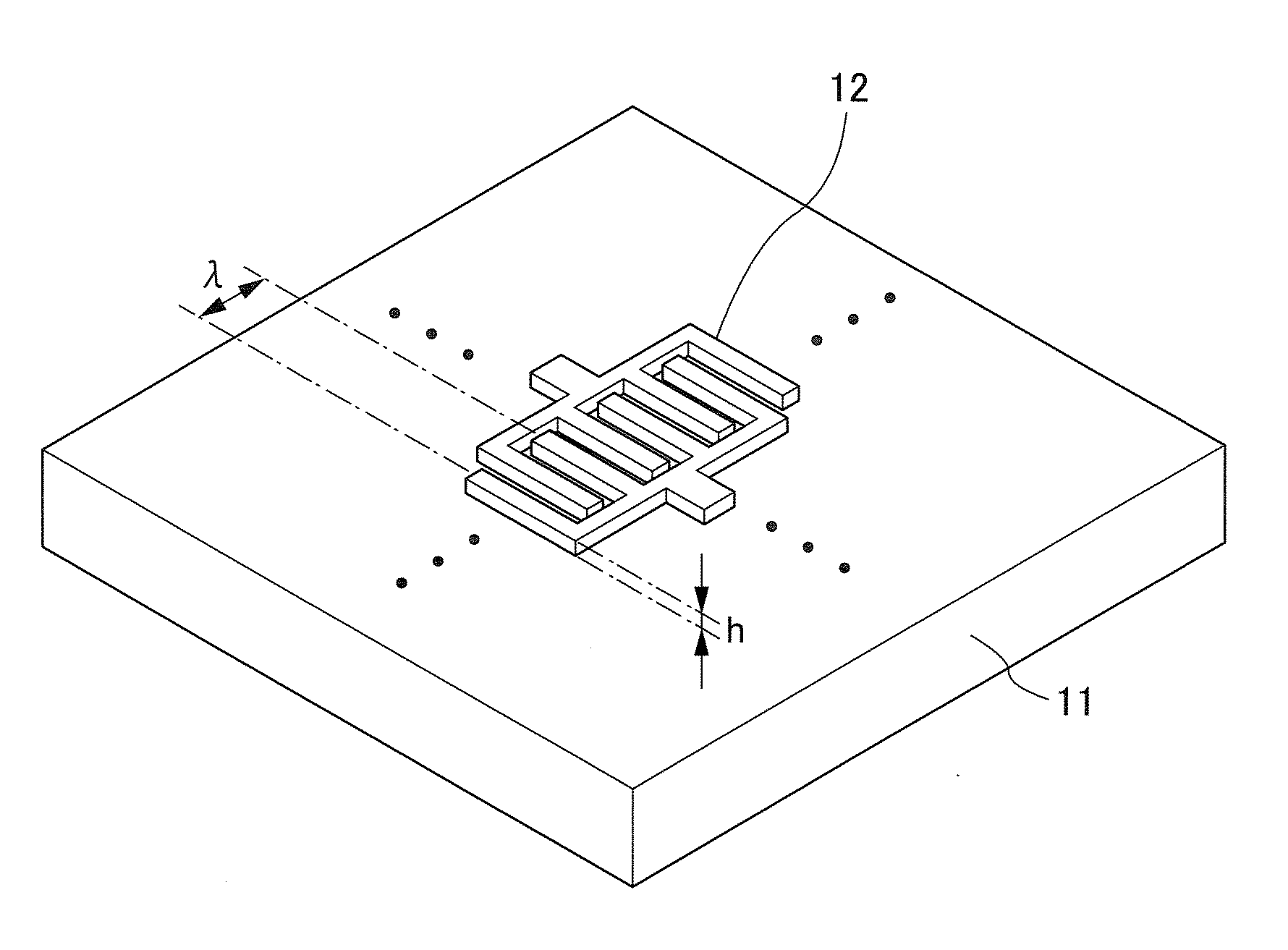

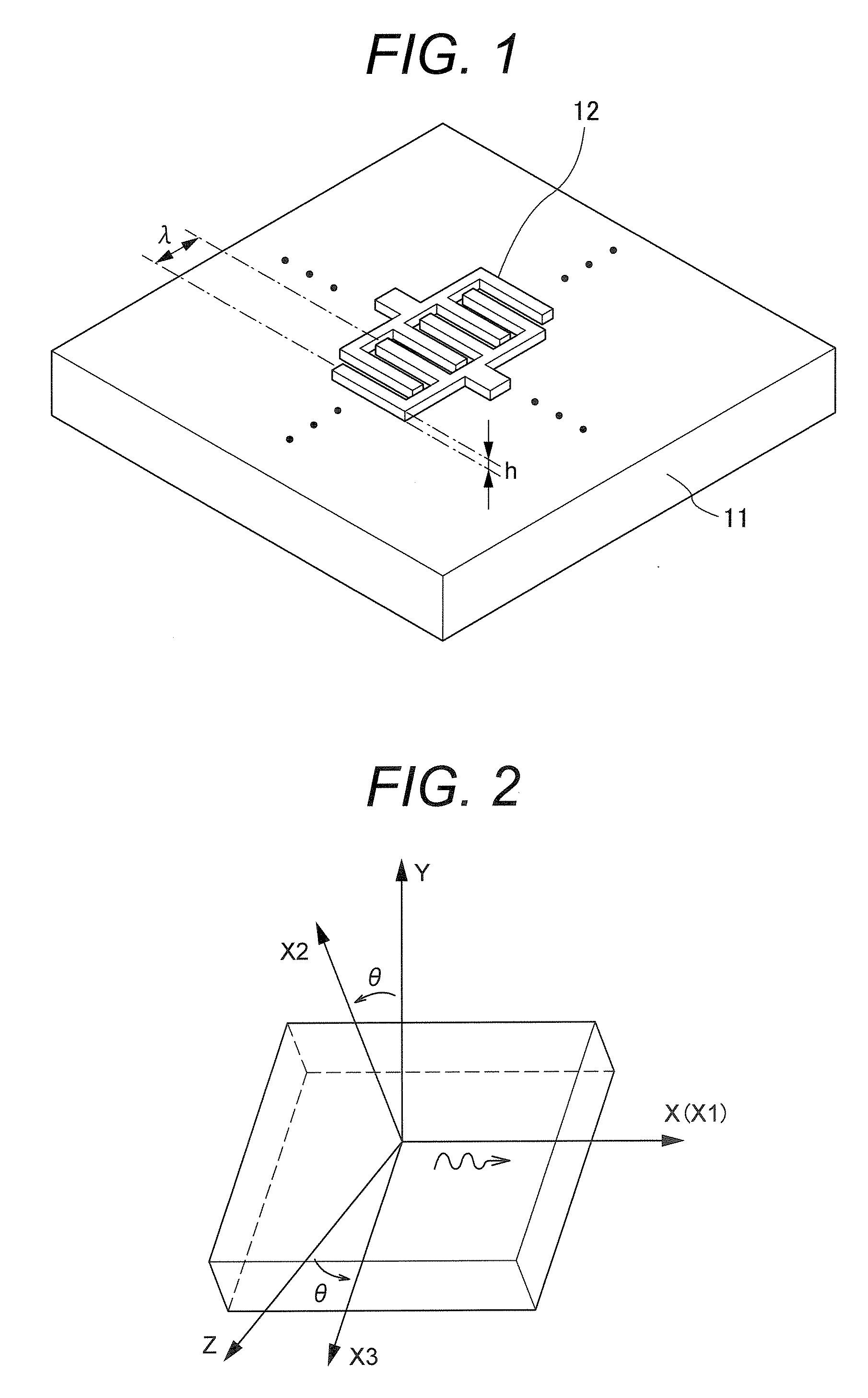

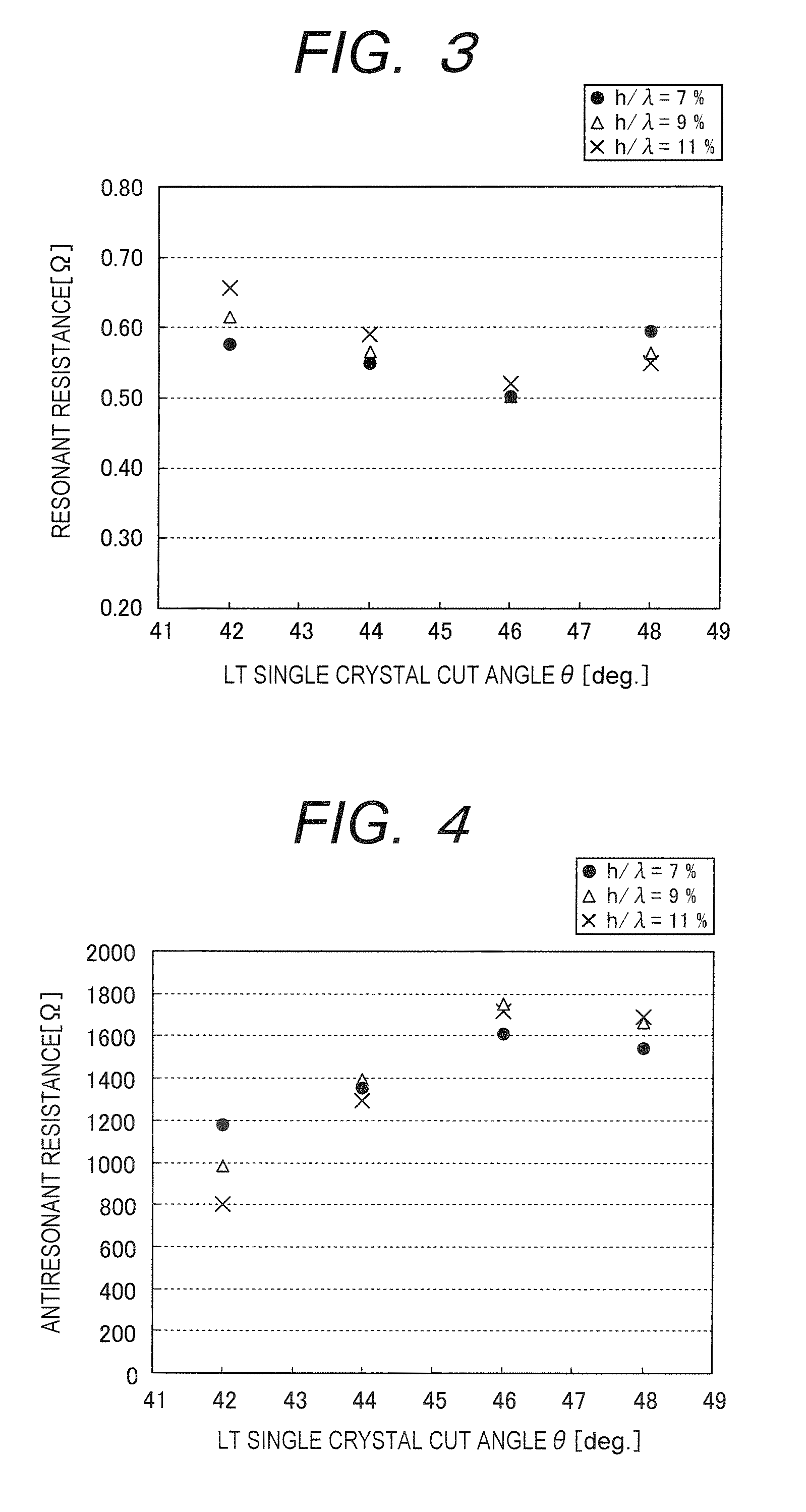

Surface acoustic wave device

ActiveUS7411333B2Lower volume resistivityAvoid charge accumulationPiezoelectric/electrostriction/magnetostriction machinesImpedence networksPiezo electricSingle crystal

Owner:SNAPTRACK

Technique for isocentric ion beam scanning

ActiveUS20070221870A1Avoid charge accumulationMaterial analysis using wave/particle radiationElectric discharge tubesIon beamAtomic physics

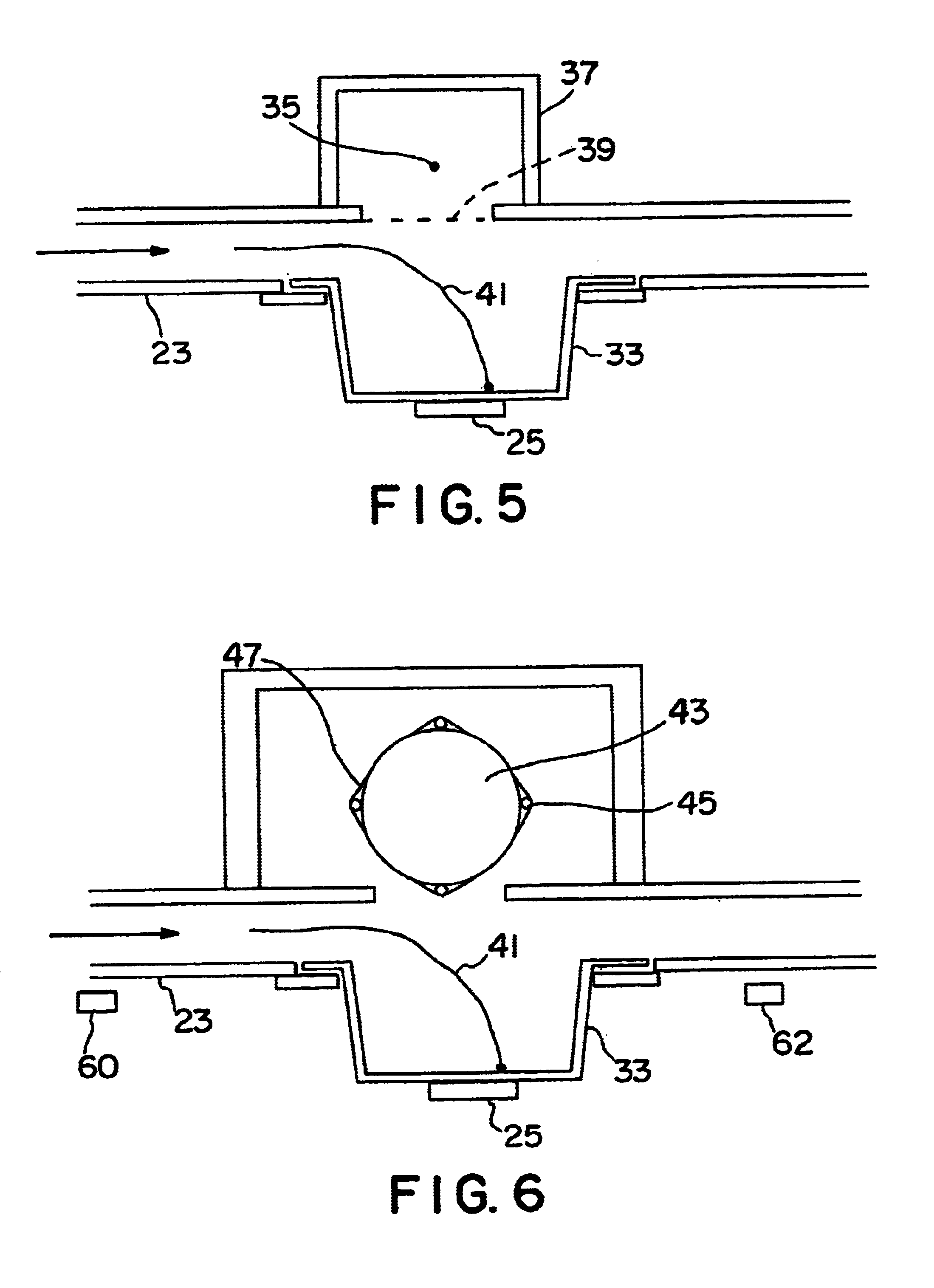

A technique for isocentric ion beam scanning is disclosed. In one particular exemplary embodiment, the technique may be realized by an apparatus for isocentric ion beam scanning. The apparatus may comprise an end station having a mechanism for holding and translating a wafer. The apparatus may also comprise a deflector that tilts an ion beam to a predetermined angle and directs the ion beam into the end station. The wafer may be translated with respect to the ion beam for isocentric scanning at least a portion of a surface of the wafer, and wherein the ion beam is maintained at the predetermined angle during isocentric scanning.

Owner:VARIAN SEMICON EQUIP ASSOC INC

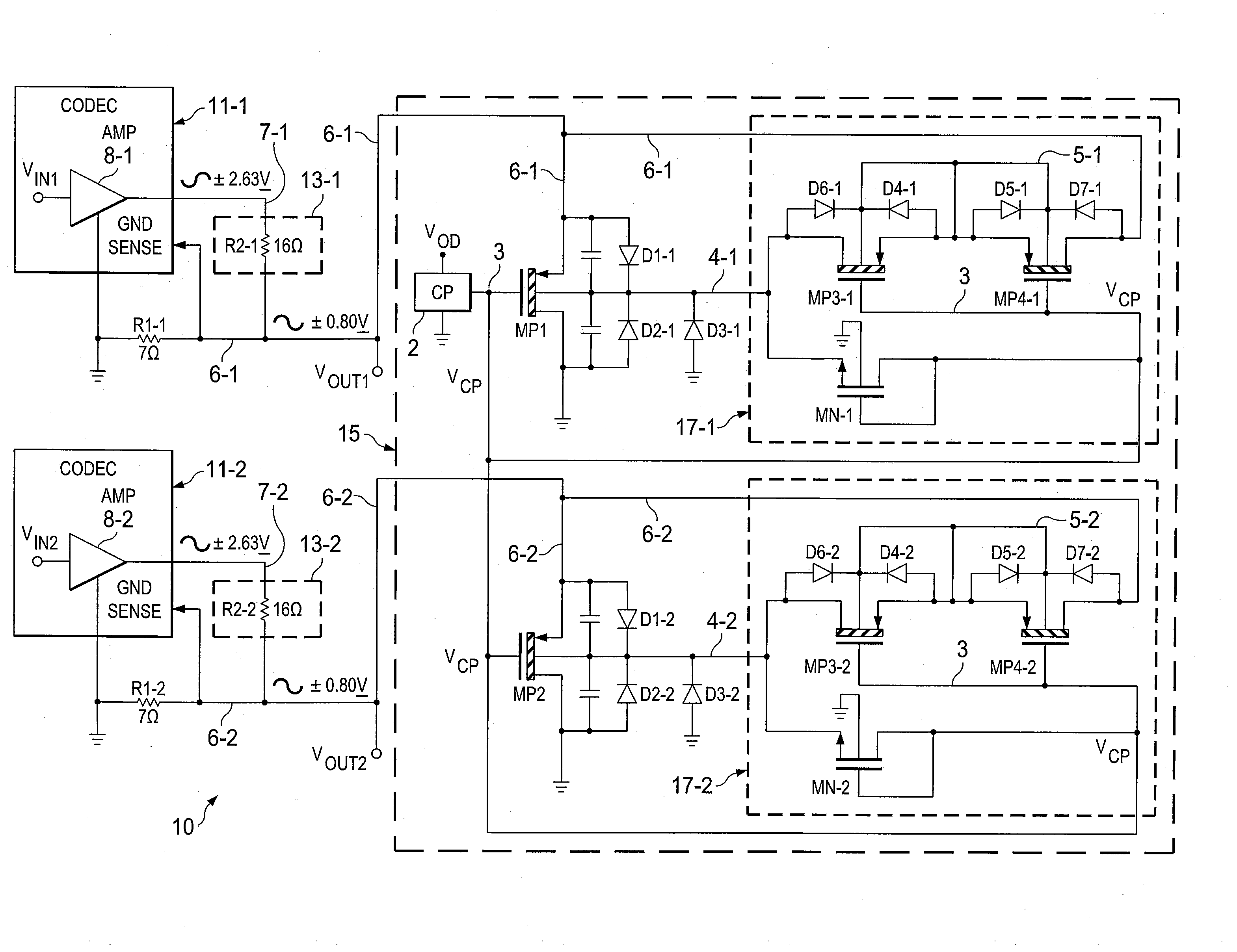

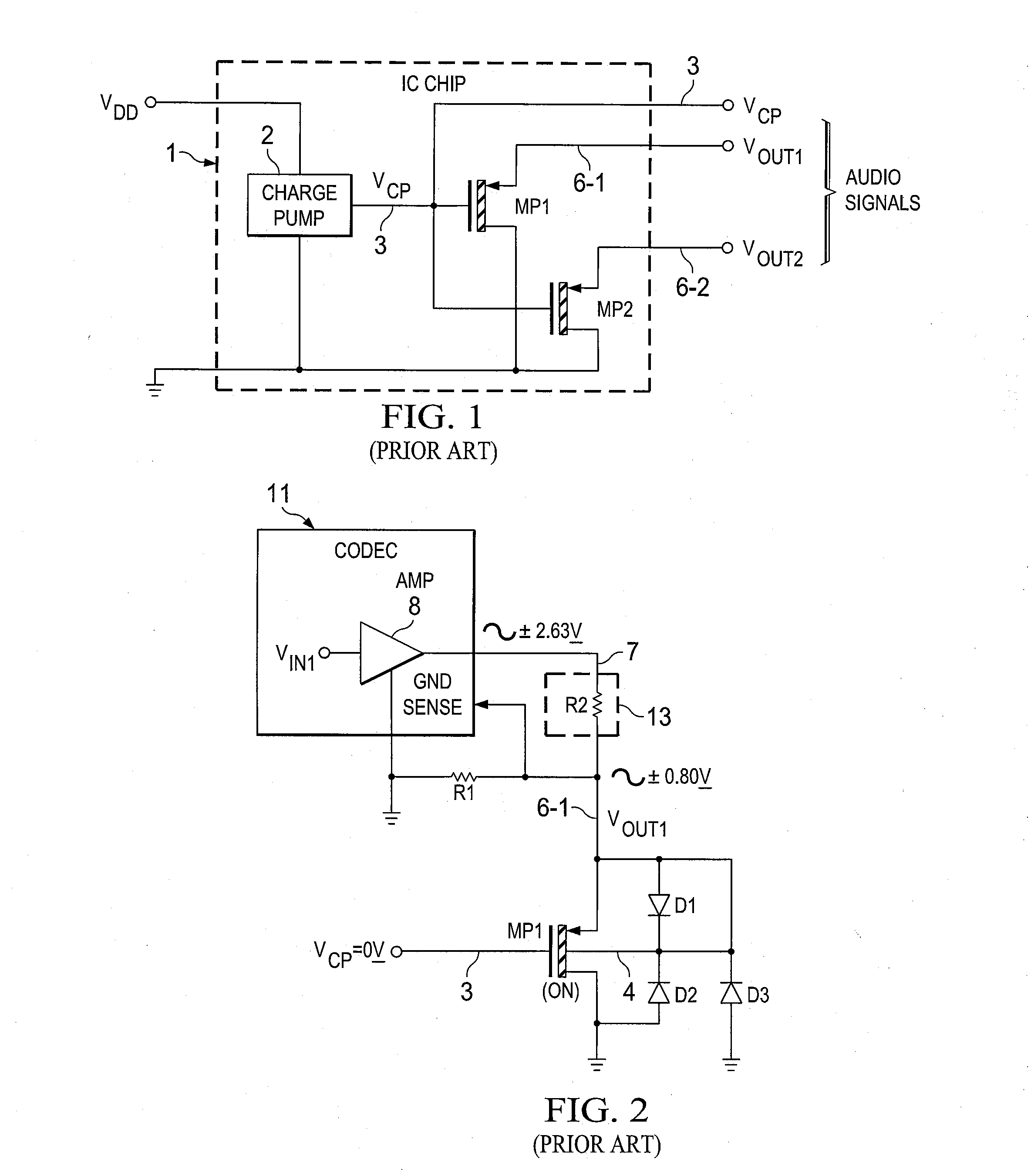

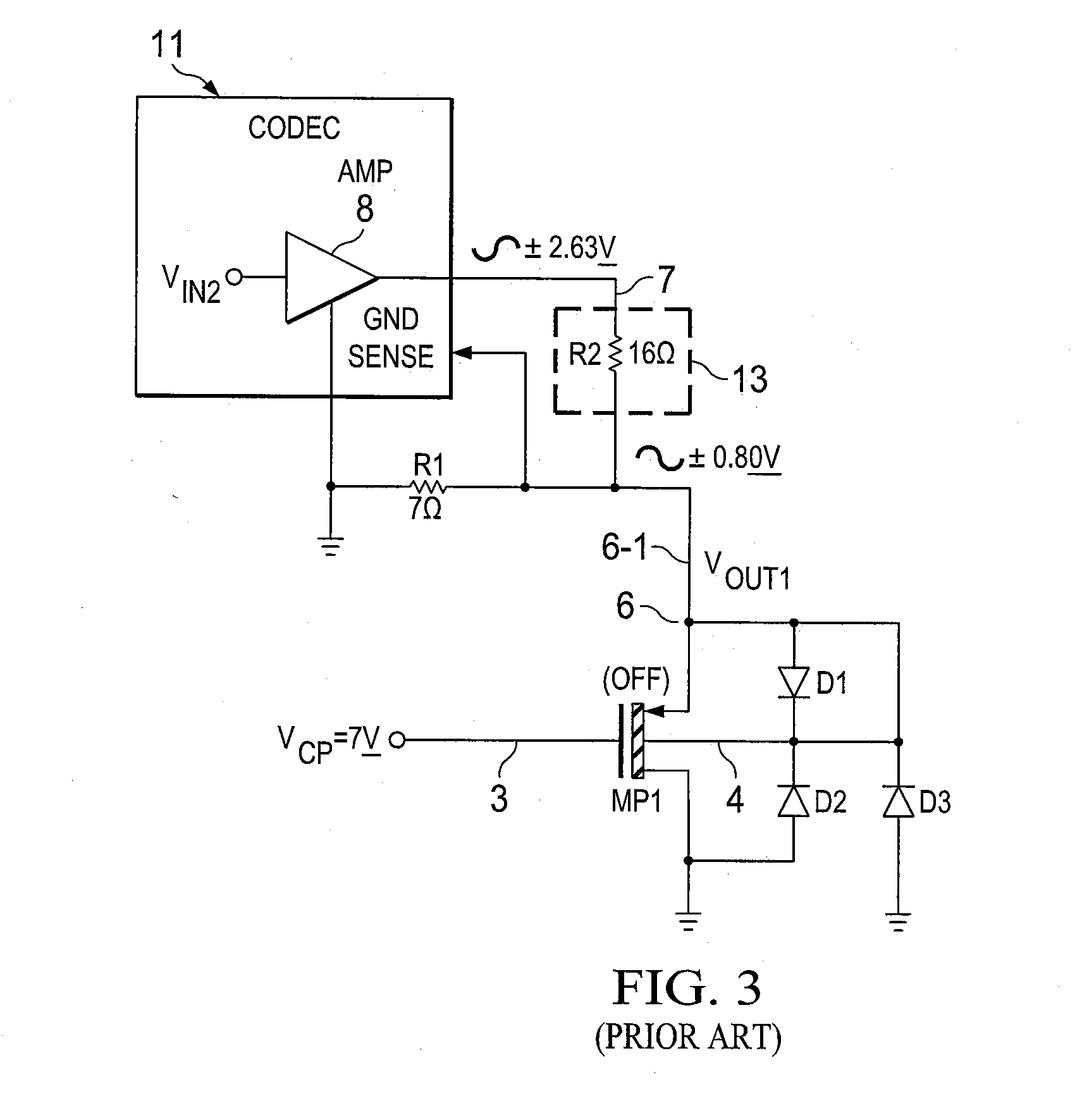

Negative Audio Signal Voltage Protection Circuit and Method for Audio Ground Circuits

ActiveUS20140369520A1Avoid charge accumulationWithout compromising qualityAmplifier modifications to reduce temperature/voltage variationLow frequency amplifiersElectrical conductorControl signal

Self-grounded circuitry (10) includes a signal channel conducting an output voltage (VOUT1). A charge pump (2) powered by a reference voltage (VDD) produces a control voltage (VCP). The control signal is at a low level if the reference voltage is low and is boosted to a high level if the reference voltage is high. A ground switch circuit (15) includes a depletion mode transistor (MP1) having a source coupled to the output voltage, a gate coupled to the control voltage, and a drain coupled to ground. The transistor includes a well region (4-1) and a parasitic substrate diode (D3-1). A negative voltage protection circuit (17-1) includes a depletion mode first protection transistor (MP3-1) having a drain coupled to the well region, a source coupled to a source of a depletion mode second protection transistor (MP4-1) having a drain coupled to the output voltage, the first and second protection transistors each having a gate coupled to the control voltage, and also includes a diode (MN1) coupled to charge the well region from the control voltage conductor to prevent distortion of the output voltage.

Owner:TEXAS INSTR INC

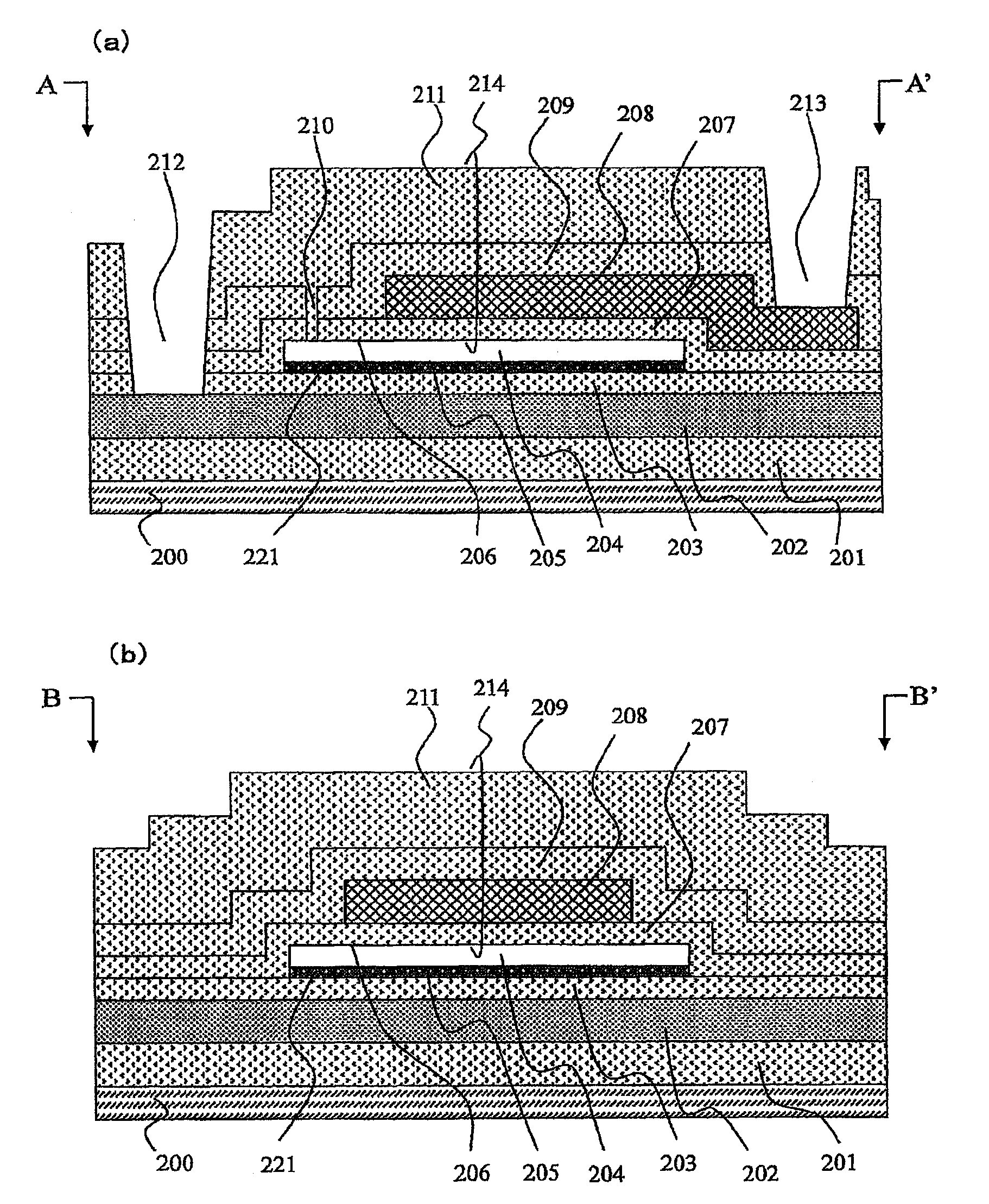

Ultrasonic transducer and ultrasonic diagnostic device using same

ActiveUS20120316445A1Avoid charge accumulationReduce voltageUltrasonic/sonic/infrasonic diagnosticsPiezoelectric/electrostriction/magnetostriction machinesUltrasonic sensorTransducer

In an ultrasonic transducer comprising a first electrode, a first insulating film disposed on the first electrode, a hollow part provided above the first insulating film and disposed between surfaces above and below the hollow part, a second insulating film disposed above the hollow part, and a second electrode disposed on the second insulating film, a first conductive film disposed on the side of the surface below the hollow part and a second conductive film disposed on the side of the surface above the hollow part are provided, the first conductive film and the second conductive film are disposed so that they overlap with a region in which the surfaces above and below the hollow part contact with each other as seen from above when the transducer is driven, and they do not overlap with each other in the region as seen from above. With such a configuration, there are provided a structure suitable for, even when the surface above the hollow part contacts with the surface below the hollow part, suppressing concentration of electric fields and electric currents in the insulating films in the contact region, and suppressing injection of electrical charge into the insulating films and degradation of dielectric strength thereof, and an ultrasonic diagnostic device using it.

Owner:FUJIFILM HEALTHCARE CORP

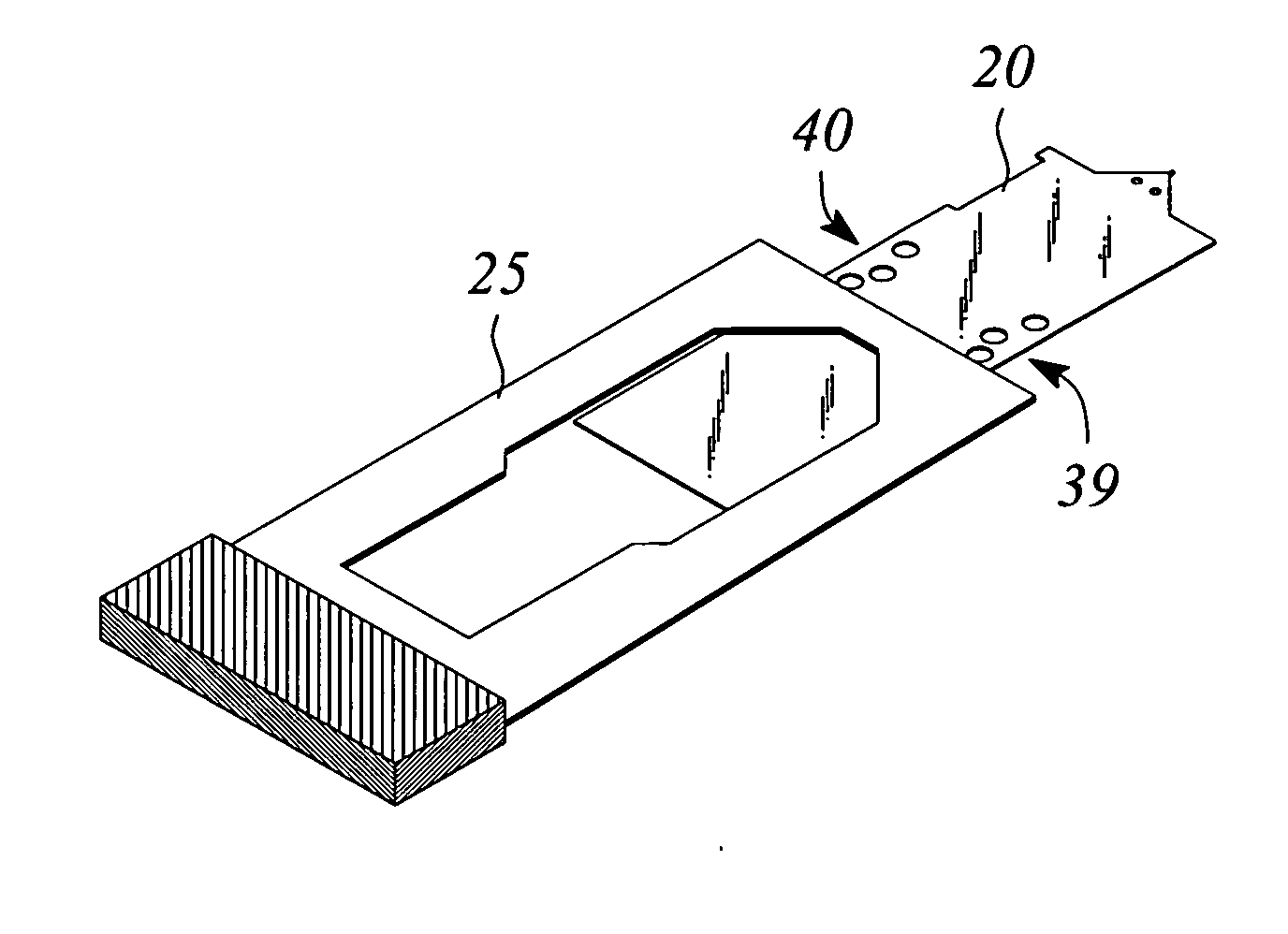

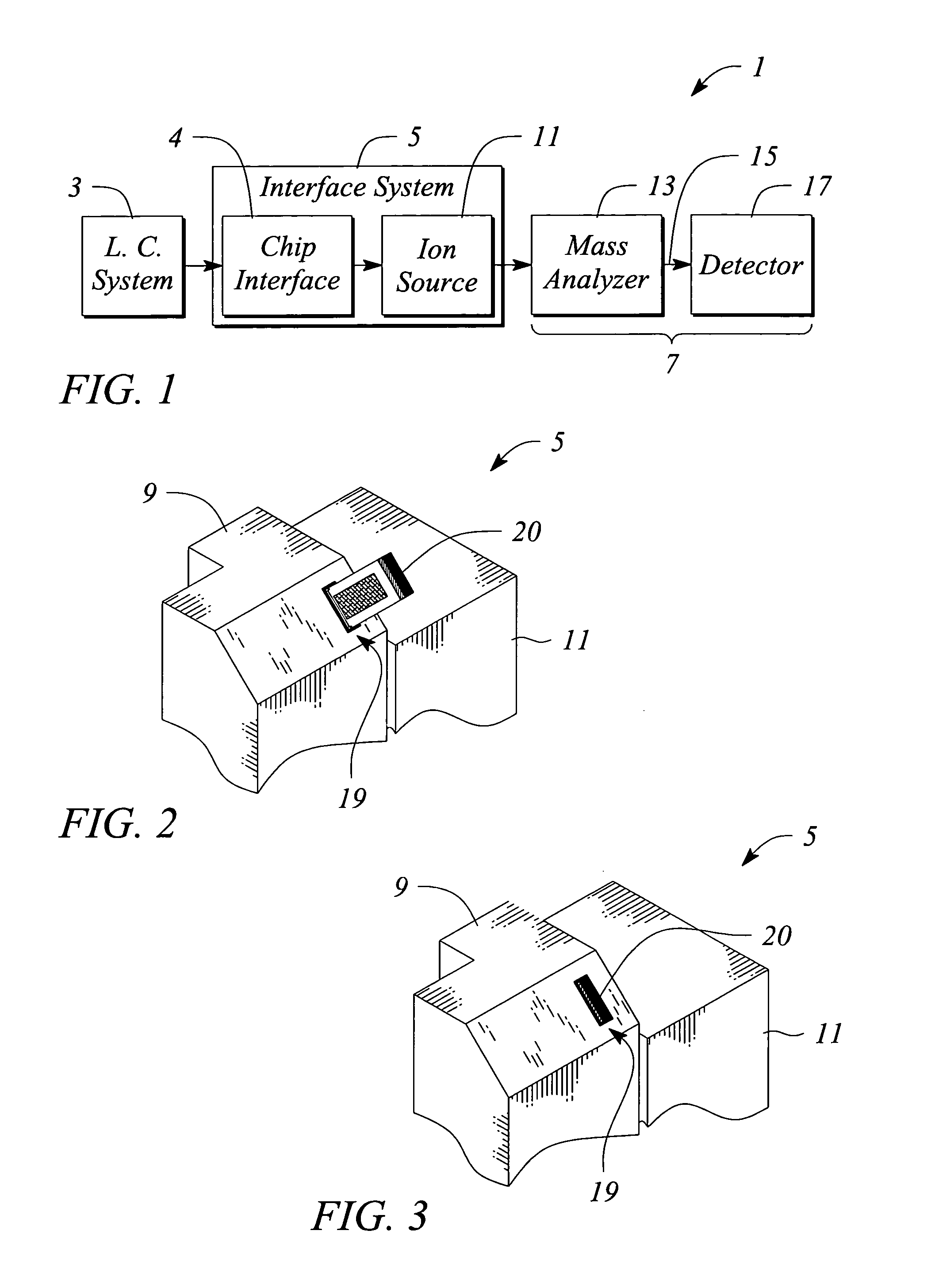

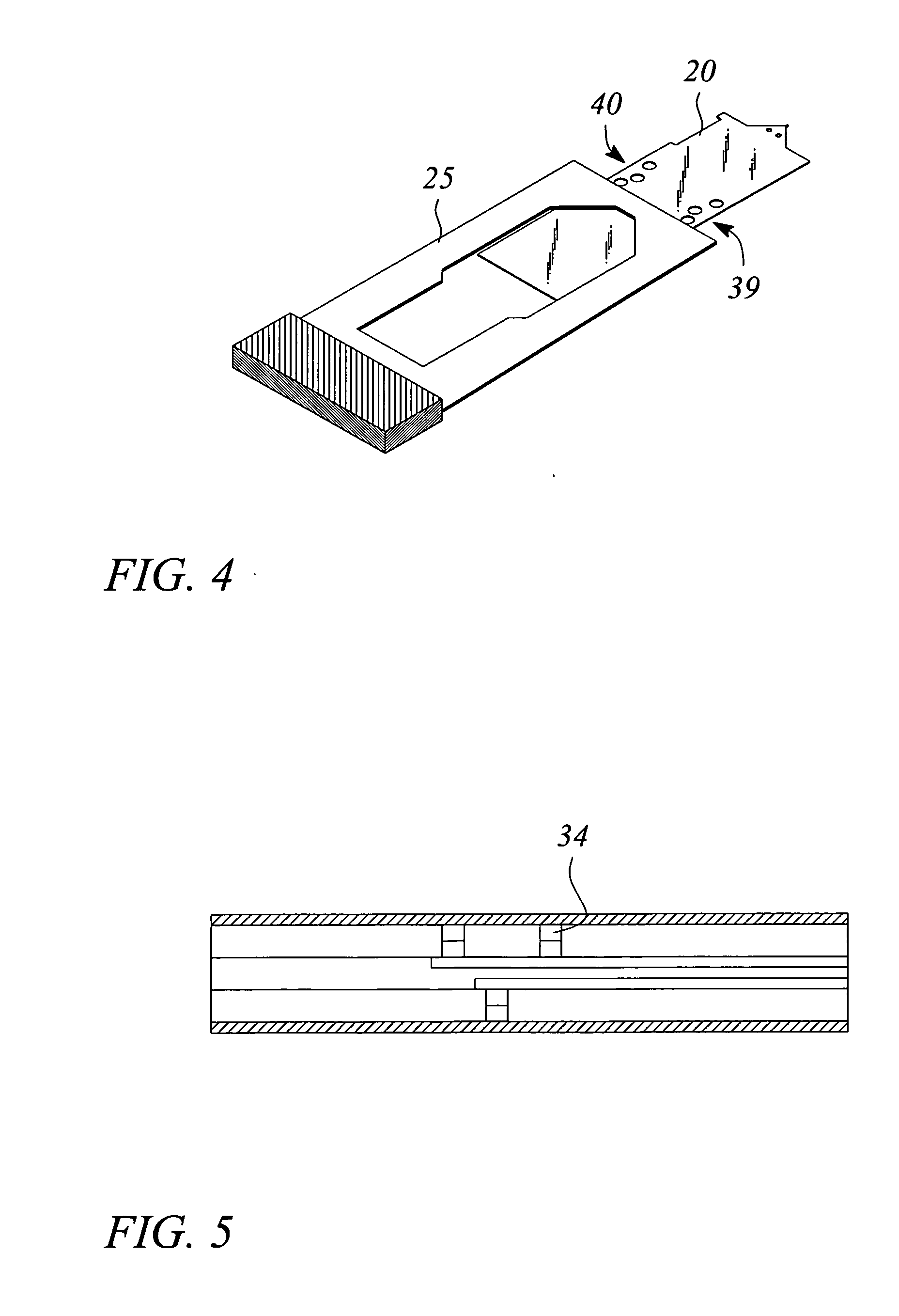

Analytical system and method

InactiveUS20070221839A1Avoid charge accumulationComponent separationSamples introduction/extractionUsage analysisSeparation system

The invention provides an analytical system having a separating system and a liquid chromatography chip. The liquid chromatography chip has an emitter that includes a material that prevents charge buildup on the emitter surface. Methods of using the analytical system, chip and emitter are also disclosed.

Owner:AGILENT TECH INC

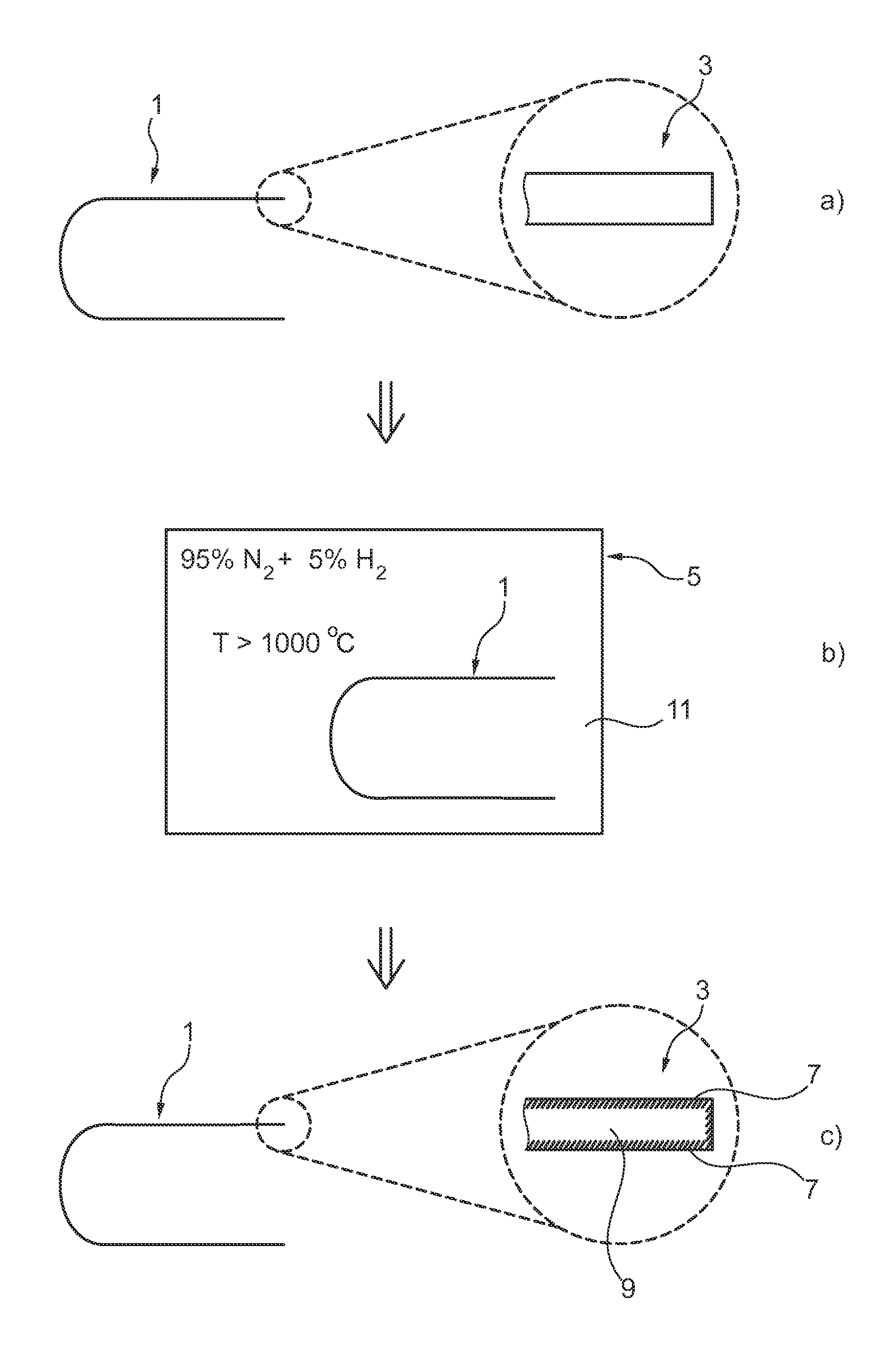

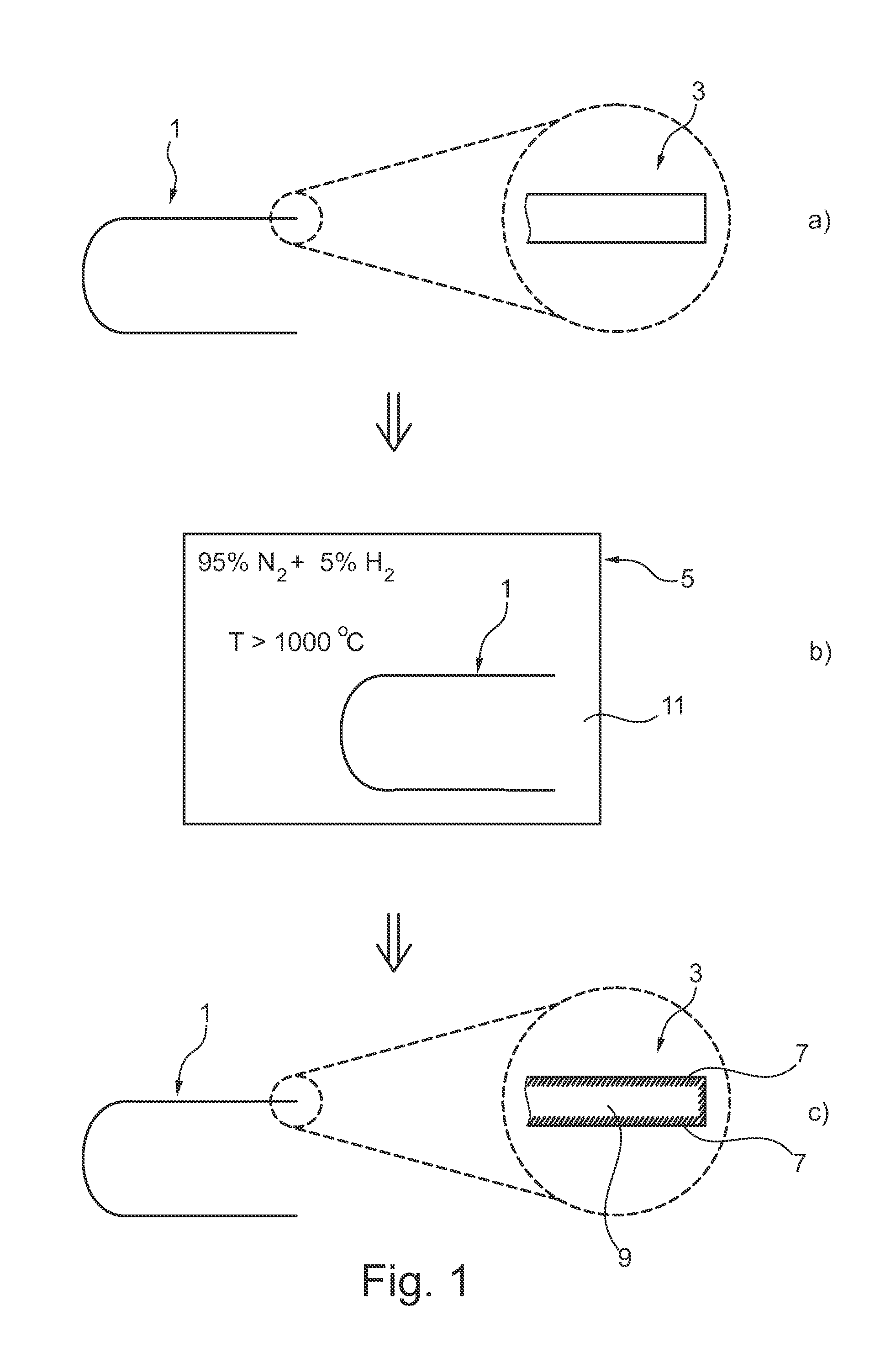

Method of treating a surface layer of a device consisting of alumina and respective device, particularly x-ray tube component

InactiveUS20150139401A1Low resistivitySheet resistivity increaseX-ray tube vessels/containerCharge manipulationOxygenElectron

A method for treating a surface layer (3) of a device (1) consisting of alumina and a corresponding device (1) are proposed. The method comprises providing the device (1) with the surface layer (3) to be treated being exposed and heating the surface layer (3) of the device (1) in an oxygen-depleted atmosphere comprising e.g. one of an inert gas, nitrogen, hydrogen, argon and a combination thereof to a temperature higher than 1000° C., preferably higher than 1700° C. for a duration of preferably more than 2 hours. Due to such treatment, a superficial layer region (7) comprised in the surface layer (3) may obtain a significantly reduced electrical resistivity which is assumed to be the result of chemically reducing this superficial layer region (7). Such reduced superficial electrical resistivity may advantageously serve for example in components of electron beam devices such as x-ray tube components for preventing any charge build-up.

Owner:KONINKLJIJKE PHILIPS NV

Electronic circuit, electronic device, method of driving electronic device, electro-optical device, and electronic apparatus

InactiveUS20070040104A1Short timeAvoid charge accumulationStatic indicating devicesMaterial analysis by optical meansElectrical connectionEngineering

An electronic device includes a plurality of first wiring lines, a plurality of second wiring lines that intersect the plurality of first wiring lines, a plurality of unit circuits that are disposed so as to correspond to intersections between the plurality of first wiring lines and the plurality of second wiring lines, and a plurality of reference signal lines that supply reference signals to the plurality of unit circuits. Each of the plurality of unit circuits has a driven element that is driven by a driving voltage or a driving current, a driving unit that supplies the driving voltage or the driving current to the driven element, a switching element that controls electrical connection between an input terminal provided in the driving unit and one of the plurality of second wiring lines, and a capacitor element that has a first electrode connected to the input terminal and a second electrode connected to one of the plurality of reference signal lines, and accumulates a charge between the first electrode and the second electrode.

Owner:SEIKO EPSON CORP

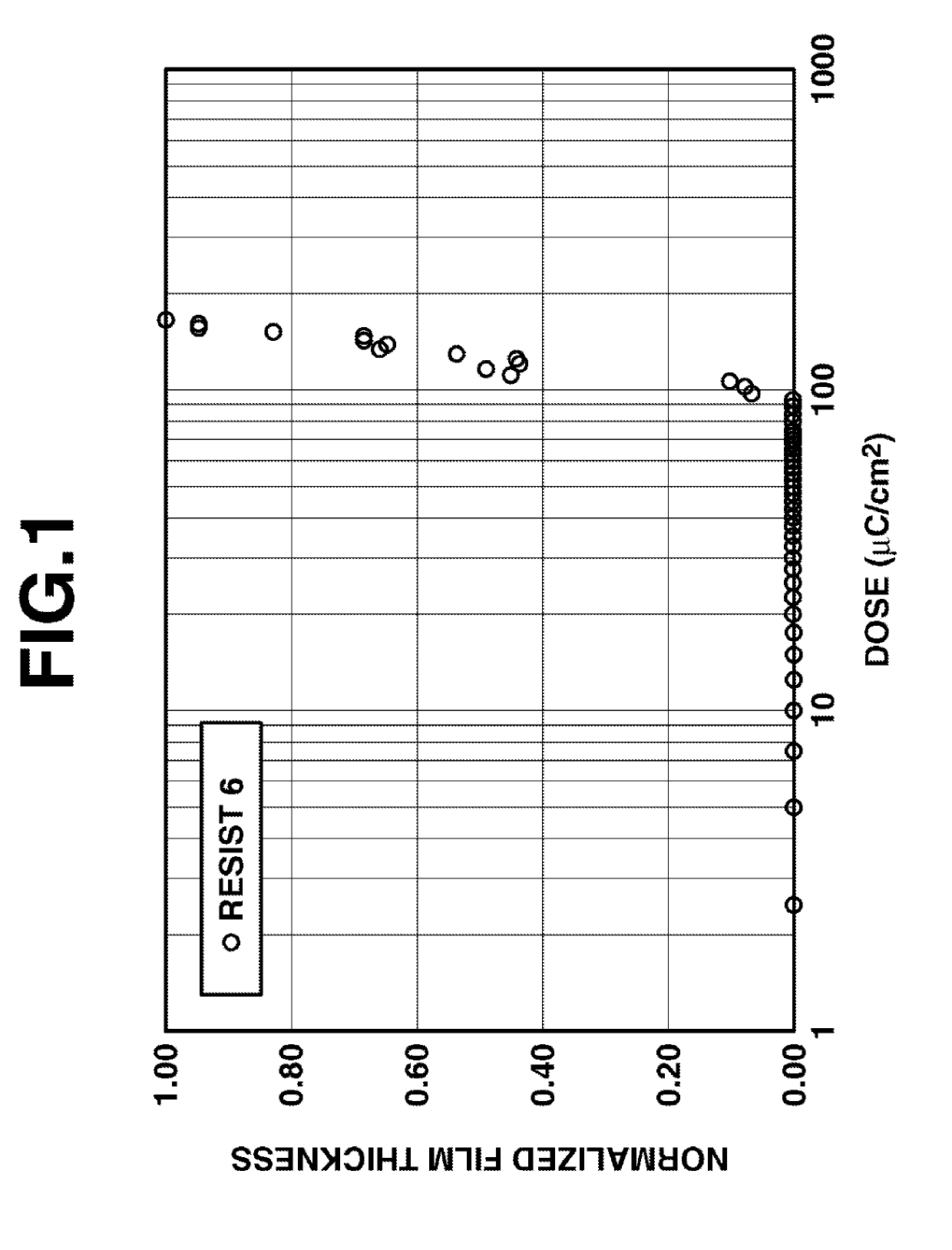

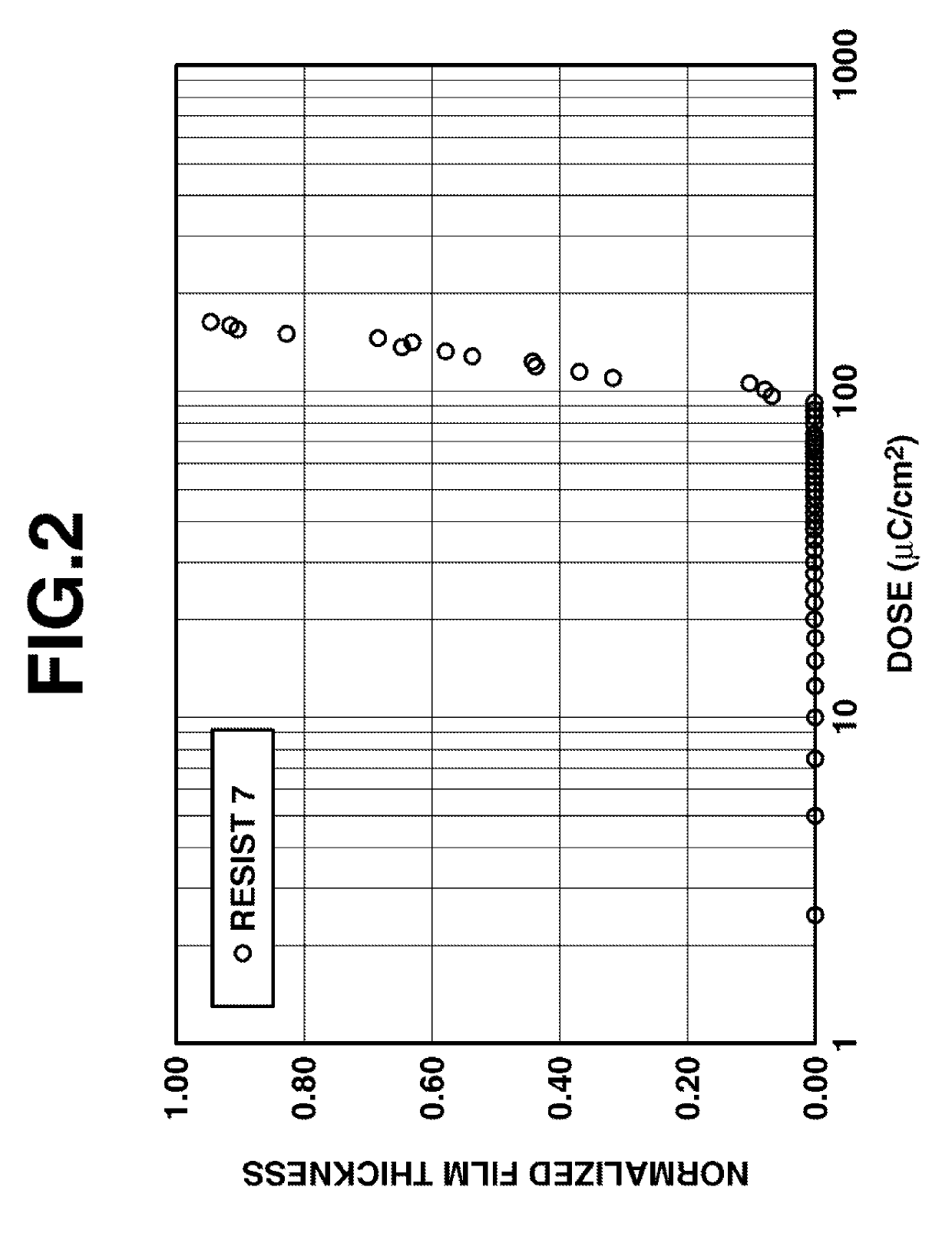

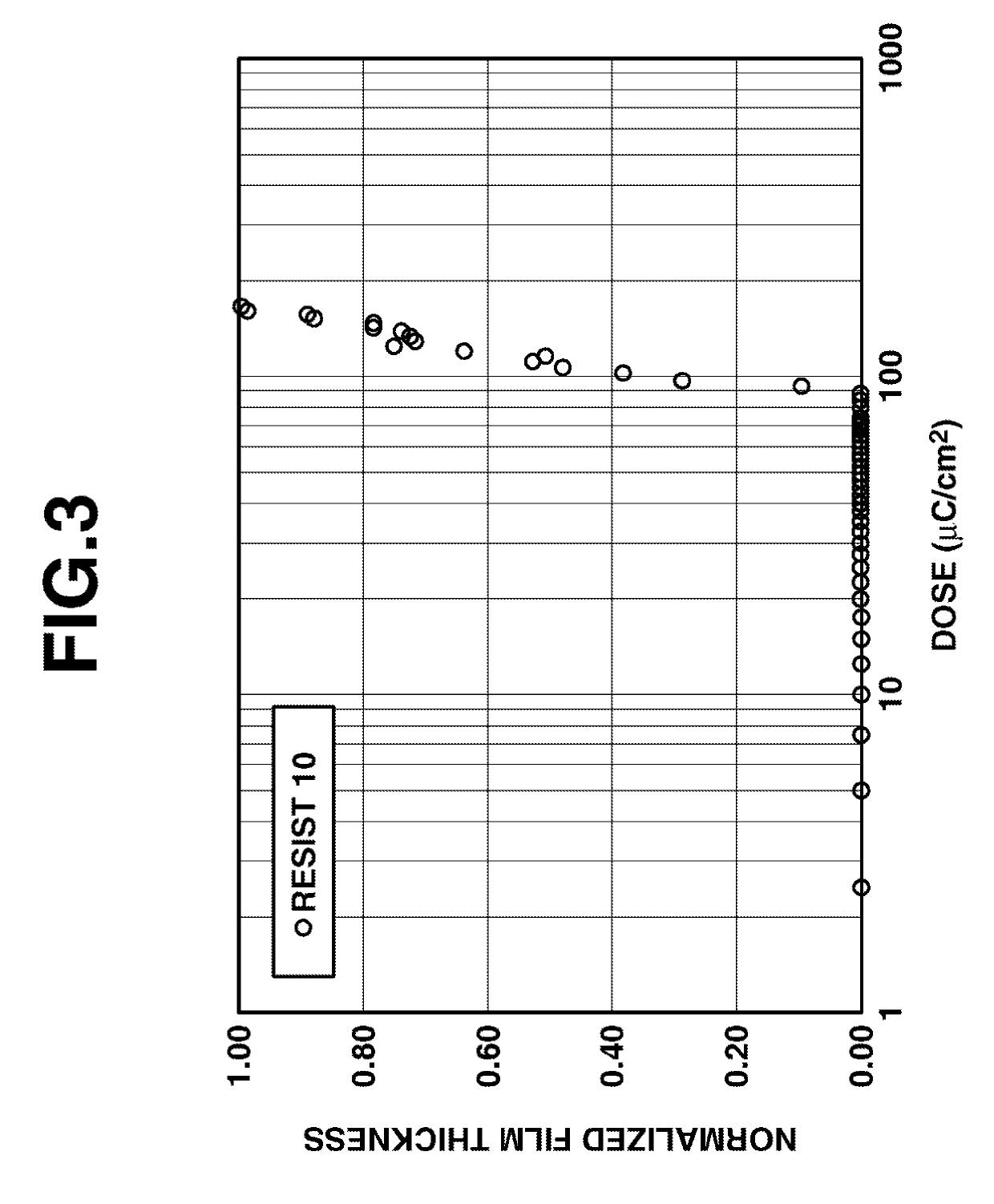

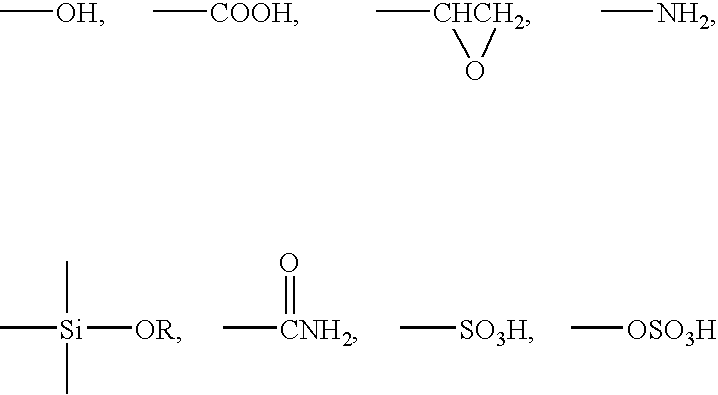

Resist composition and patterning process

ActiveUS20190258160A1Improve stabilityHigh resolutionSemiconductor/solid-state device manufacturingPhotosensitive material processingAlcoholHydrolysate

A resist composition is provided comprising (A) a metal compound having formula (A-1), a hydrolysate or hydrolytic condensate thereof, or the reaction product of the metal compound, hydrolysate or hydrolytic condensate thereof with a di- or trihydric alcohol having formula (A-2), and (B) a sensitizer containing a compound having formula (B-1). The resist composition is adapted to change a solubility in developer upon exposure to high-energy radiation, has high resolution and sensitivity, and forms a pattern of good profile with minimal edge roughness after exposure.

Owner:SHIN ETSU CHEM IND CO LTD

Total ionizing dose suppression transistor architecture

ActiveUS20060197108A1Preventing further charge buildupAvoid charge accumulationTransistorSemiconductor/solid-state device detailsIonizationCritical field

A total ionizing dose suppression architecture for a transistor and a transistor circuit uses an “end cap” metal structure that is connected to the lowest potential voltage to overcome the tendency of negative charge buildup during exposure to ionizing radiation. The suppression architecture uses the field established by coupling the metal structure to the lowest potential voltage to steer the charge away from the critical field (inter-device) and keeps non-local charge from migrating to the “birds-beak” region of the transistor, preventing further charge buildup. The “end cap” structure seals off the “birds-beak” region and isolates the critical area. The critical area charge is source starved of an outside charge. Outside charge migrating close to the induced field is repelled away from the critical region. The architecture is further extended to suppress leakage current between adjacent wells biased to differential potentials.

Owner:CAES COLORADO SPRINGS LLC

Fluorine-containing resin powder coating composition

InactiveUS6743842B1Maintain good propertiesAvoid charge accumulationFibre treatmentSpecial tyresHardnessFluorine containing

To provide a powder coating composition which comprises 100 parts by weight of fluorine-containing resin and 1 to 40 parts by weight of tetrafunctional or trifunctional silicate compound or a condensation product thereof, has a function of removing electrostatic charge and gives a coating film having a high hardness and stain-proof property.

Owner:DAIKIN IND LTD

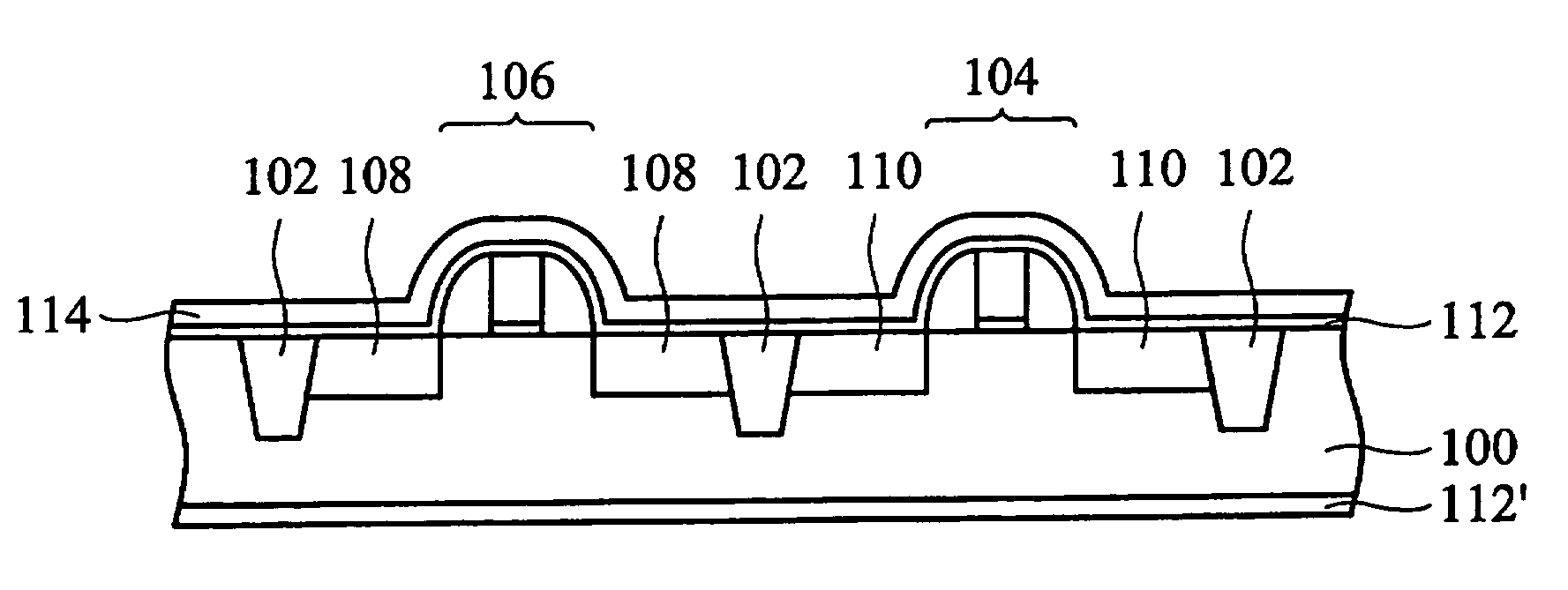

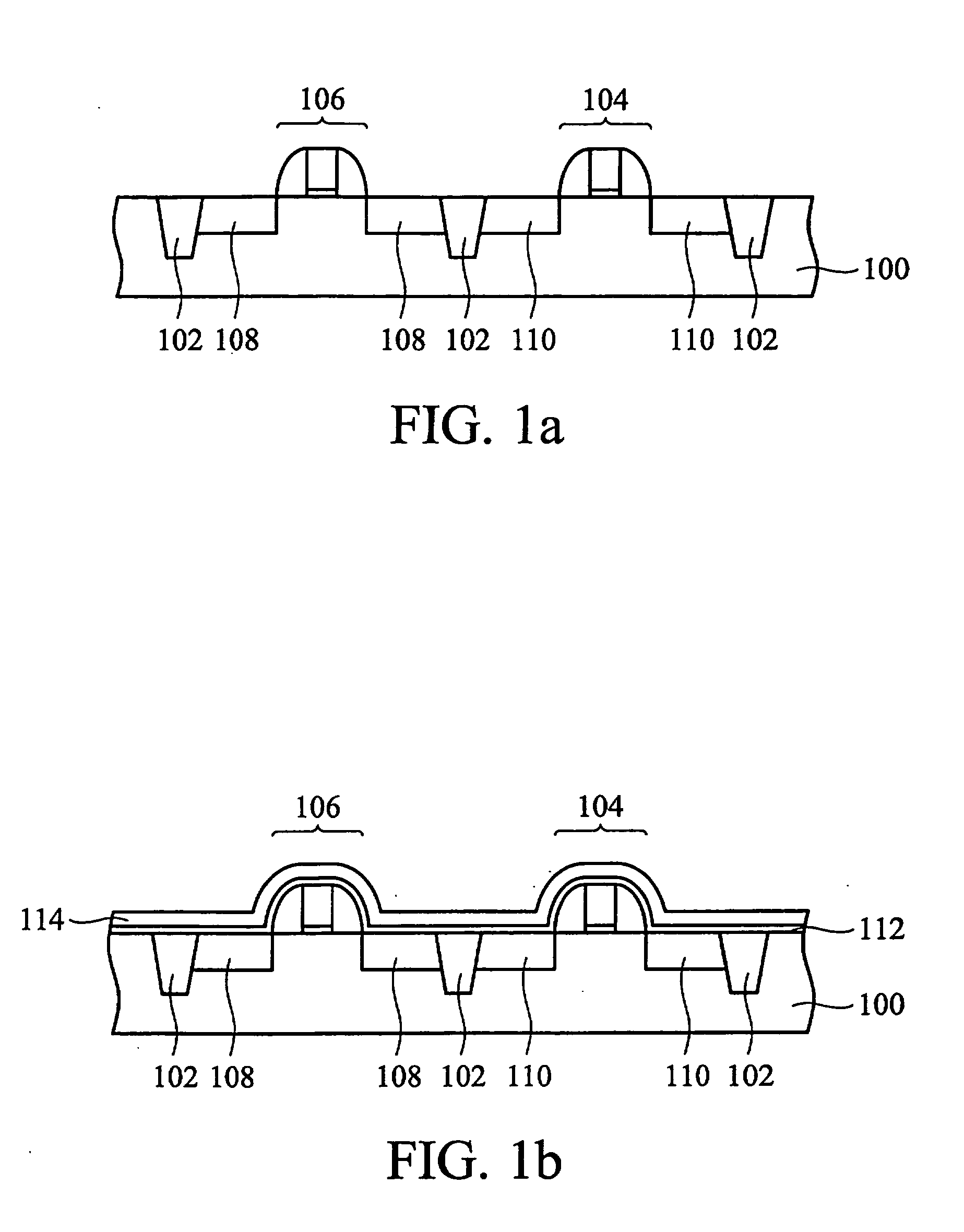

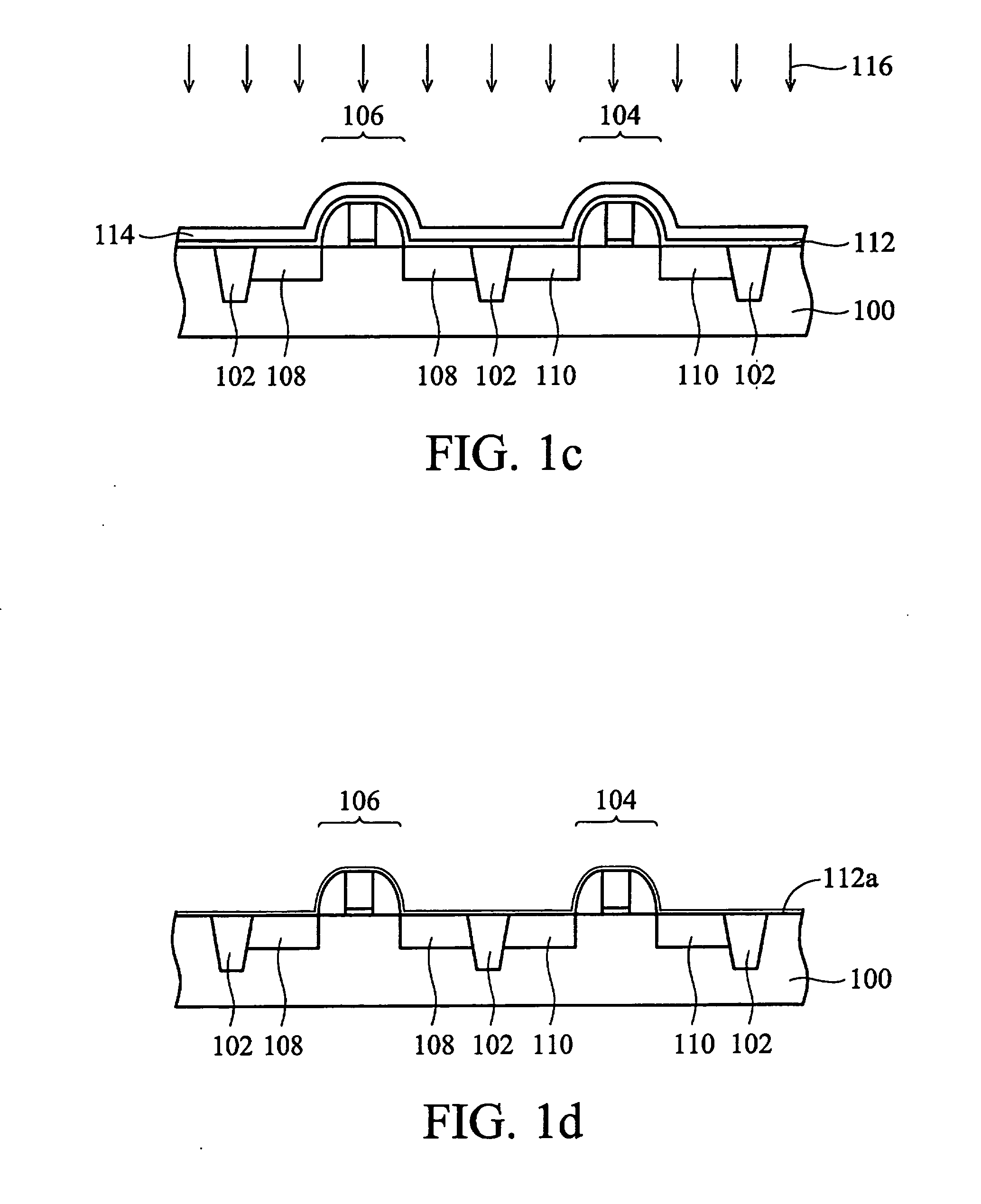

Method for semiconductor device performance enhancement

InactiveUS20080076215A1Improve performanceAvoid charge accumulationSemiconductor/solid-state device manufacturingSemiconductor devicesPerformance enhancementThermal treatment

A method of manufacturing a semiconductor device is disclosed. The method provides a semiconductor substrate with at least a PMOS device and at least an NMOS device thereon. A first insulating layer is formed overlying the NMOS and PMOS devices. A second insulating layer is formed overlying the first insulating layer. The second insulating layer overlying the PMOS device is thinned to leave portion of the second insulating layer. A first thermal treatment is performed on the NMOS and PMOS devices. The second insulating layer overlying the NMOS device and the remaining portion of the second insulating layer overlying the PMOS device are removed and the first insulating layer overlying the NMOS and PMOS devices is thinned to leave a remaining portion thereof.

Owner:TAIWAN SEMICON MFG CO LTD

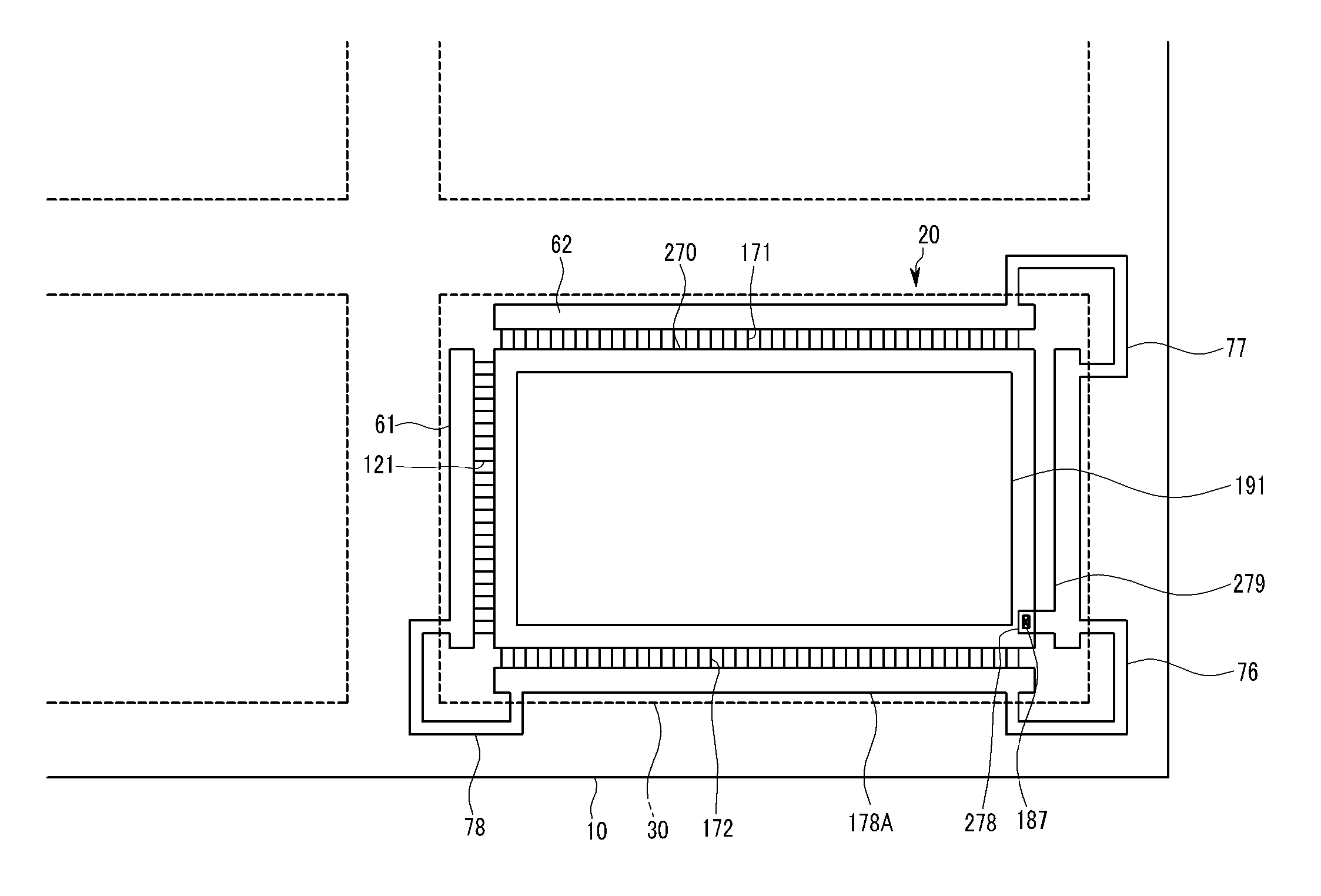

Display device and method of manufacturing the same

ActiveUS7772764B2Avoid charge accumulationDischarge tube luminescnet screensElectroluminescent light sourcesDisplay deviceEngineering

Owner:SAMSUNG DISPLAY CO LTD

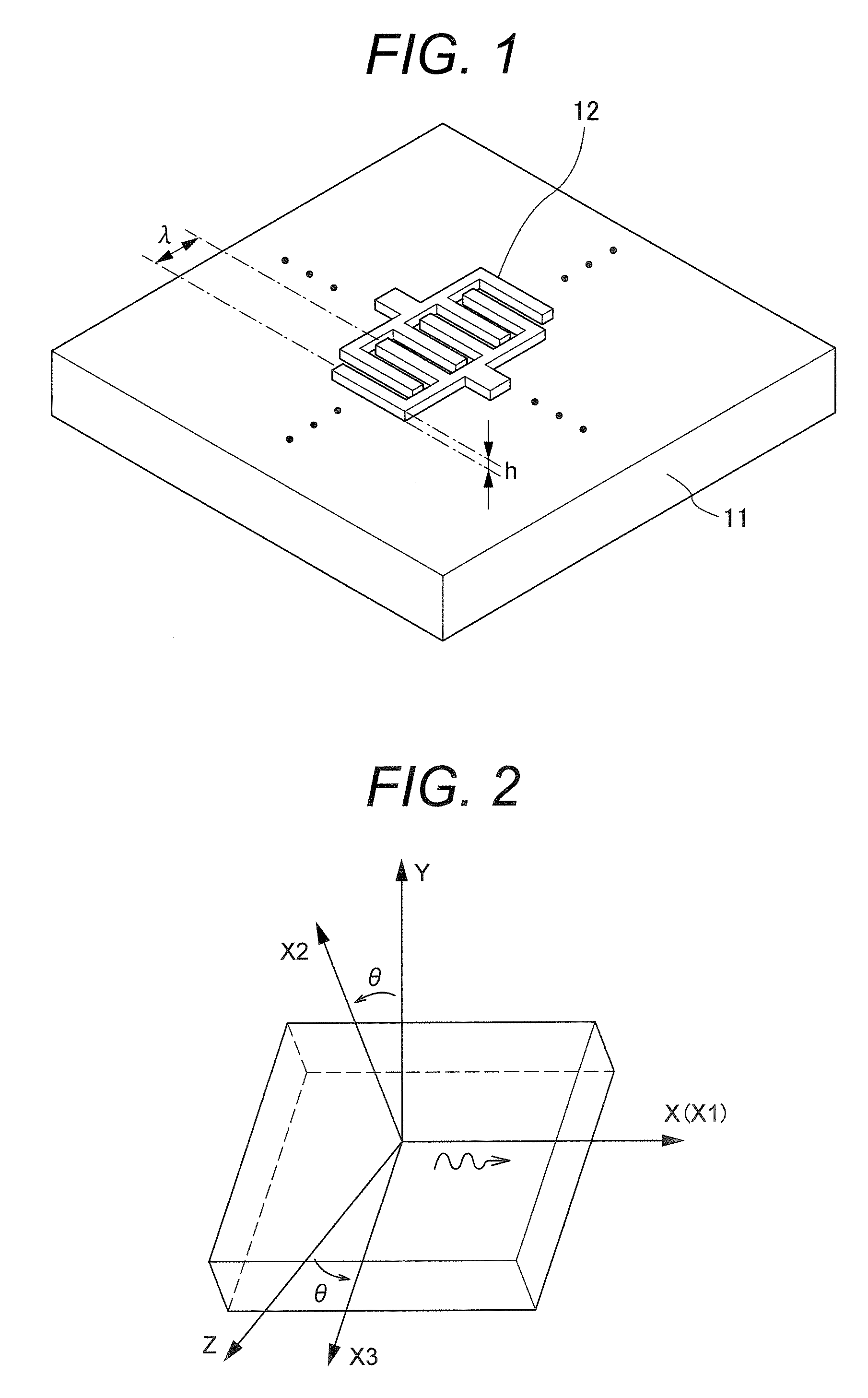

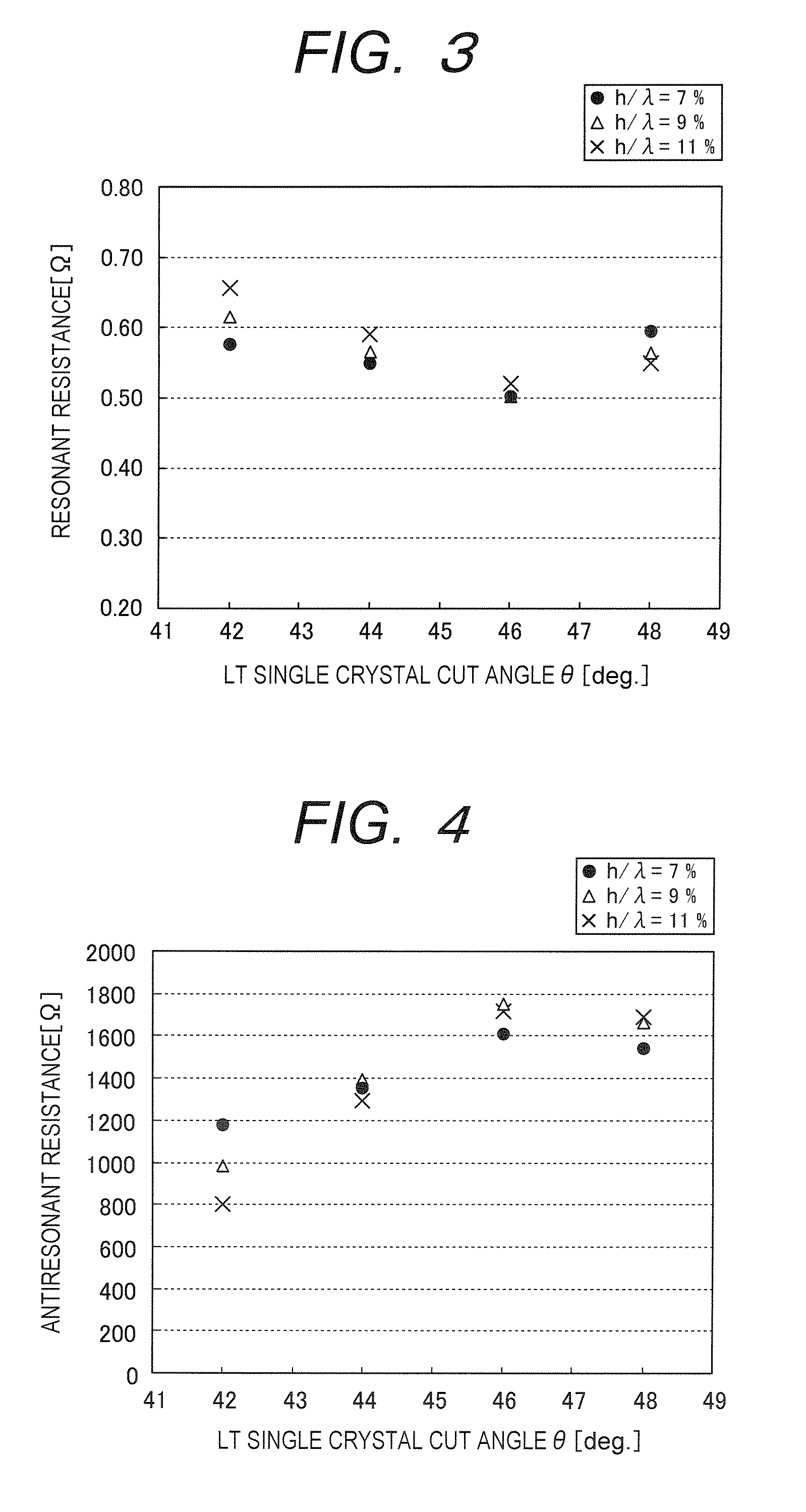

Surface acoustic wave device

ActiveUS20070018533A1Excellent electrical propertiesLower volume resistivityPiezoelectric/electrostriction/magnetostriction machinesImpedence networksSingle crystalPiezo electric

A SAW device comprises a single crystal piezo-electric strate (made, for example, of LiTaO3 or LiNbO3), and an interdigital transducer (IDT) formed of a material mainly containing Al and disposed on the piezo-electric substrate. The piezo-electric strate contains an additive (for example, Fe, Mn, Cu, Ti), and an orientation rotated by an angle in a range of 42° to 48°re preferably 46°±0.3°) from a Y-axis toward a Z-axis about an axis. The IDT presents a normalized thickness h / λ (h: thickness electrode, and λ: spacing between digits of the IDT) of 7% to 11%. A more appropriate substrate cut angle can be shown for the device which employs a piezo-electric substrate containing an additive, to improve the electric characteristics thereof.

Owner:SNAPTRACK

Driving bistable displays

ActiveUS20140300651A1Avoid charge accumulationCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceComputer science

Owner:E INK CORPORATION

Optical system

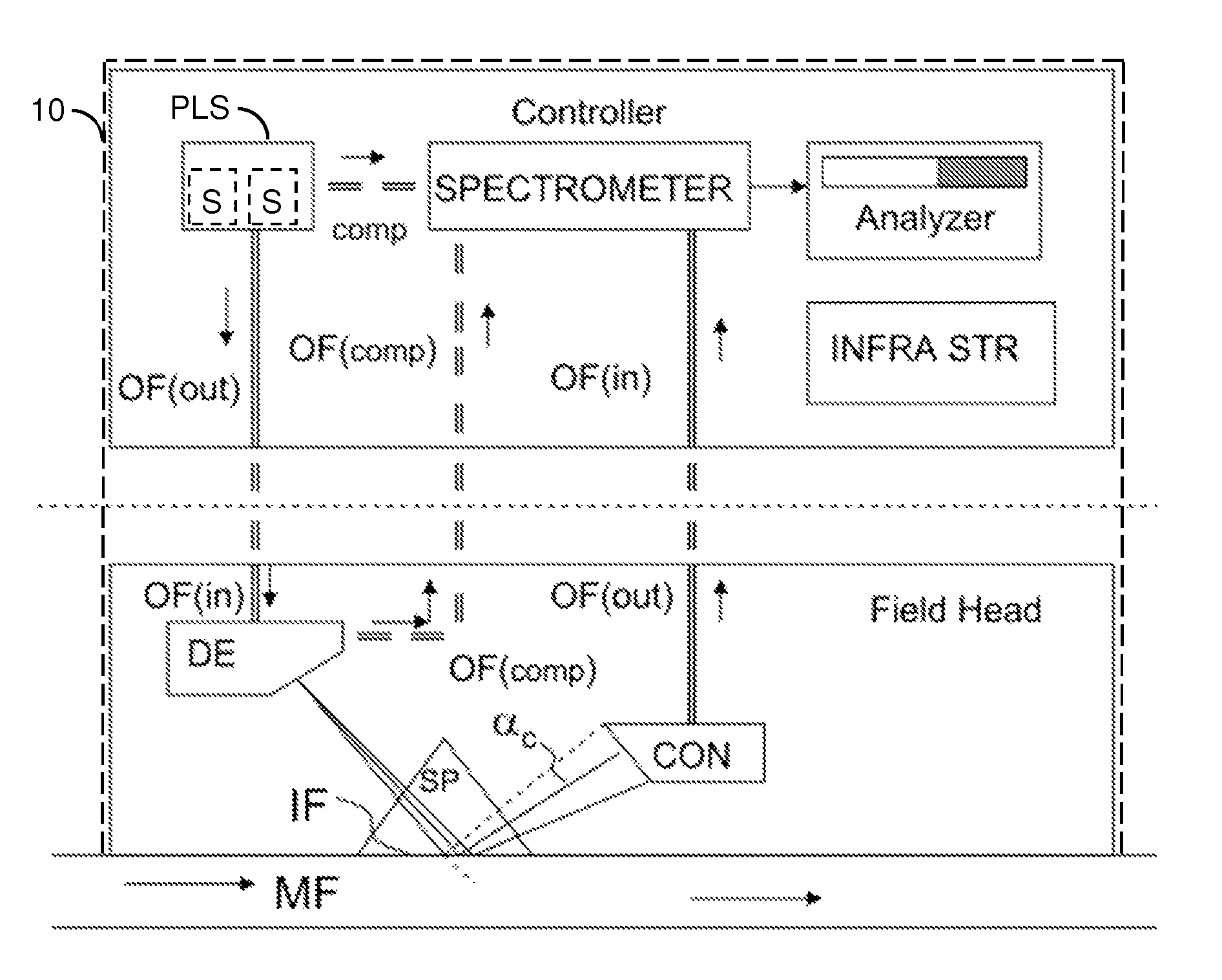

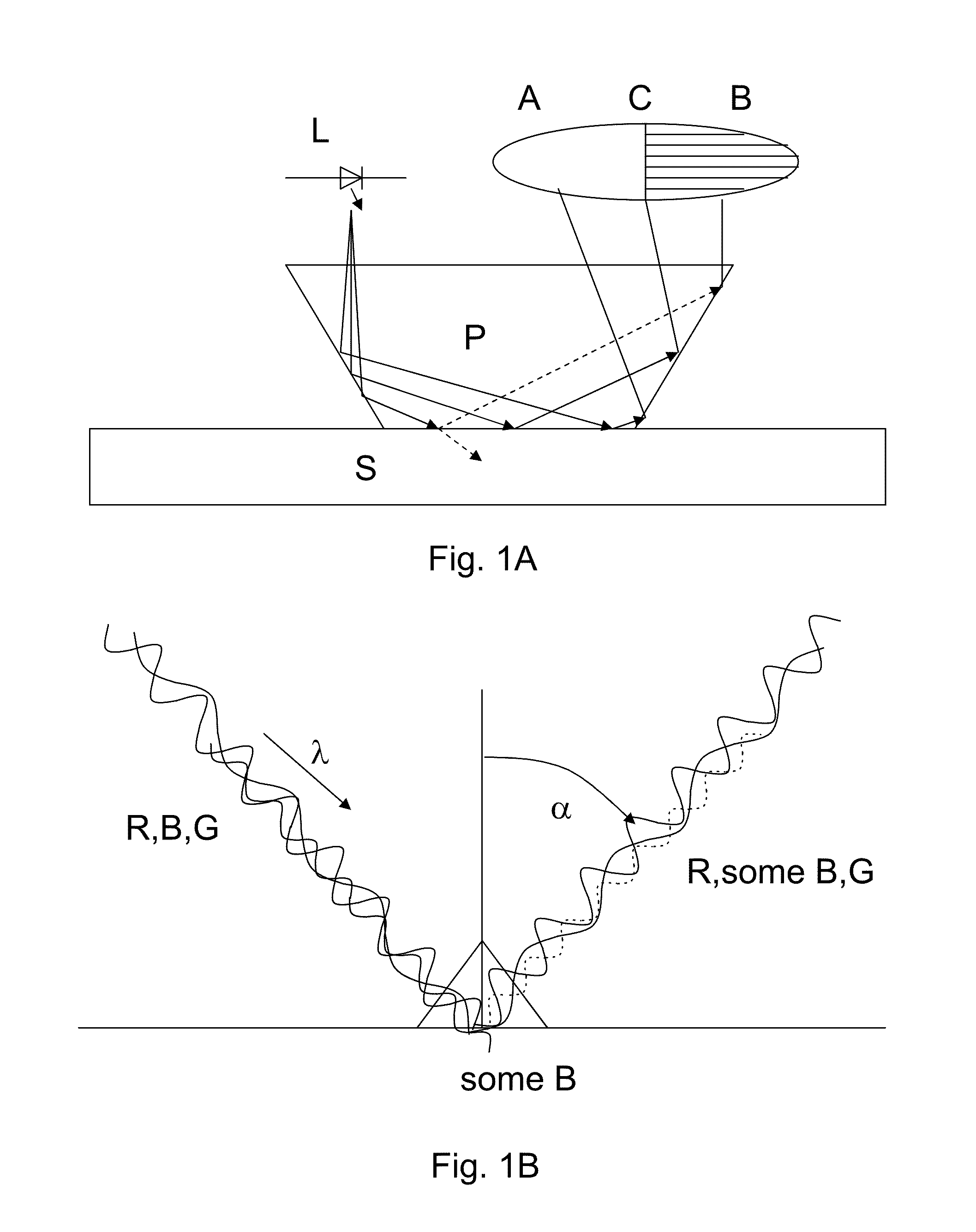

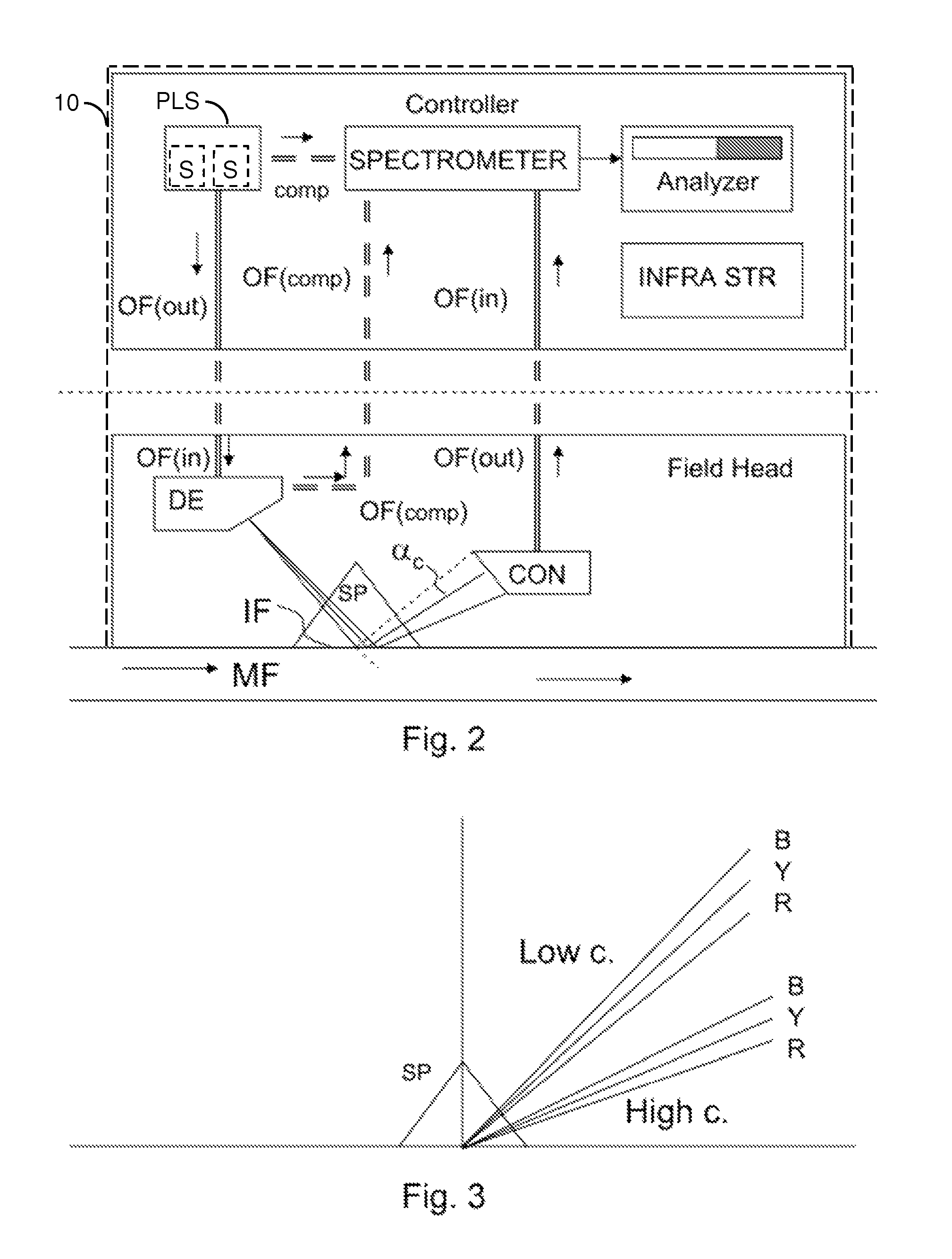

ActiveUS8760640B2Maintain good propertiesAvoid charge accumulationRadiation pyrometrySpectrum investigationRefractive indexLight beam

An optical instrument includes a controller and a field head arranged for measuring the refractive index of a medium, or a derivable quantity therefrom. The field head includes a measurement prism having a medium-boundary surface, a first wave guide for providing broad-band light from a broad band light source, a dispersive element for dispersing the broad-band light into at least one component light beam of plural component light beams, so that each incident component light beam has a differently directed propagation path and at least one different wave length, and a condenser for collecting at least one component light beam reflected at the medium-boundary surface into a second wave guide. The dispersive element is arranged to direct at least one component light beam into a critical angle of total reflection from the boundary surface, and at least other light beam component into an angle leading into the condenser arranged to collect at least one other component light beam to be passed to a spectrometer. The controller of a field head includes a light source for providing poly-chromatic light into a first wave guide for forming a plurality of component light beams to propagate in the field head and a spectrometer for spectrum analysis of light inputted via at least one input wave guide from the field head.

Owner:KAHRE JAN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com