Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4293 results about "Negative voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

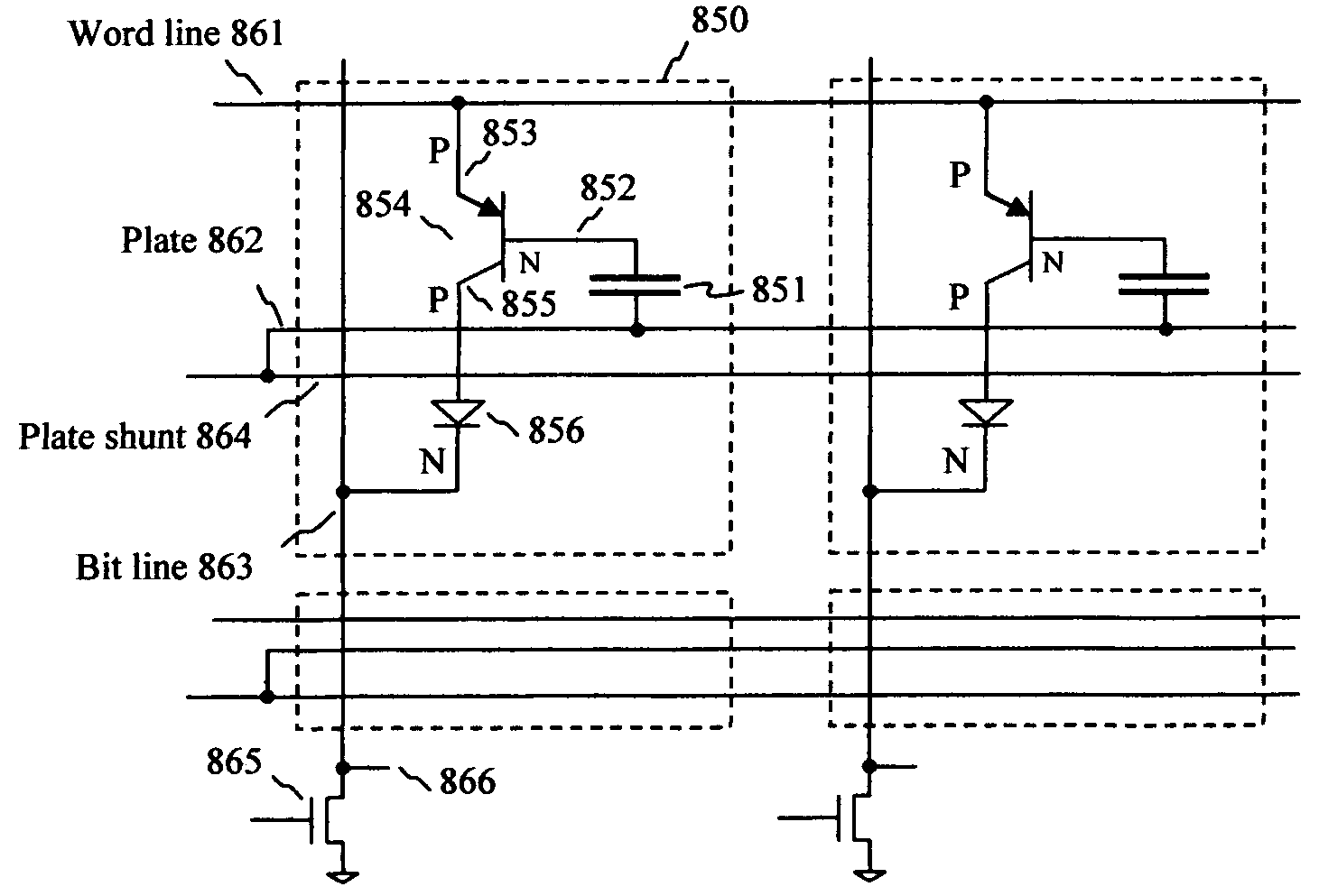

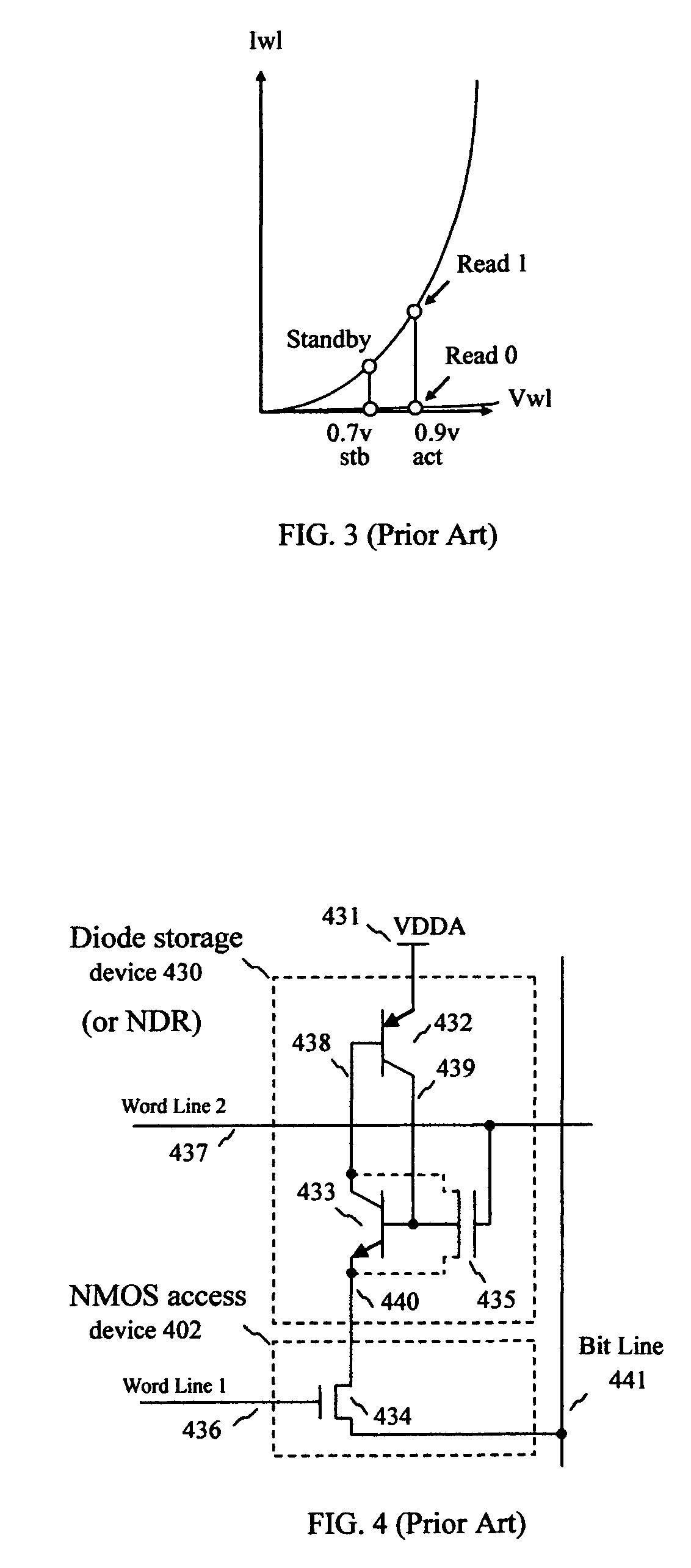

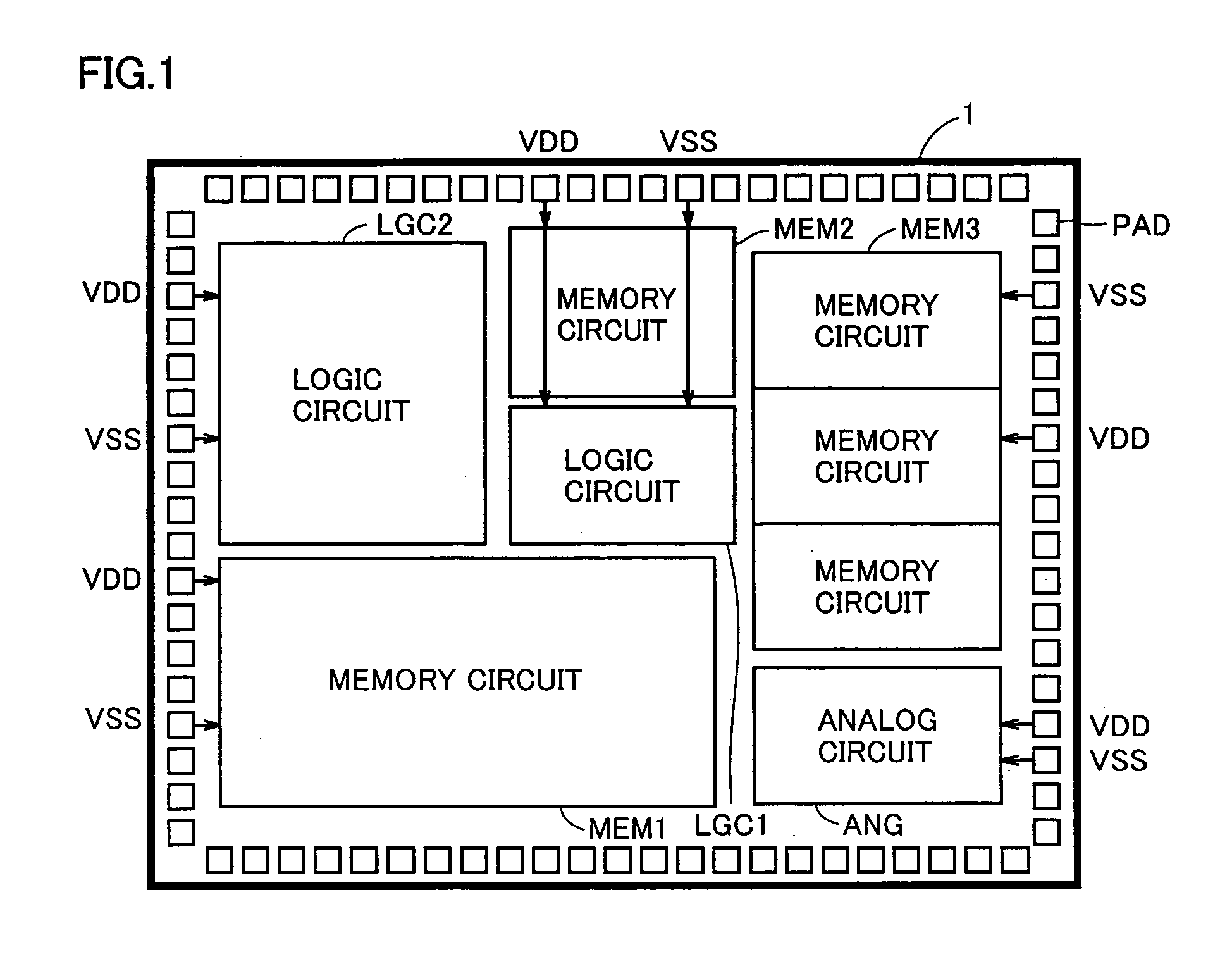

Planar capacitor memory cell and its applications

InactiveUS7209384B1Less complicated to fabricateImprove performanceTransistorSolid-state devicesHemt circuitsEngineering

A capacitor memory is realized, wherein a capacitor stores data and a diode controls to store data “1” or “0”. Diode has four terminals wherein first terminal serves as word line, second terminal serves as storage node, third terminal is floating, and fourth terminal serves as bit line, wherein back channel effect is suppressed adding additional ions in the bottom side of third terminal or applying negative voltage in the well or substrate. A capacitor plate couples to second terminal, which plate has no coupling region to first, third and fourth terminal. With no coupling, the inversion layer of plate in the storage node is isolated from the adjacent nodes. In doing so, the plate can swing ground level to positive supply level to write. As a result, no negative generator is required for controlling plate. Word line and bit line keep ground level during standby, and rise to supply level for read or write operation. In this manner, no holding current is required during standby, and operating current is dramatically reduced with no negative generator. Write has a sequence to clear the state of cell before writing to store data regardless of previous state. Refresh cycle is periodically asserted to sustain data. The present invention can be applied for destructive read, or for nondestructive read adding pull-down device to bit line. The height of cell is almost same as control circuit on the bulk or SOI wafer.

Owner:KIM JUHAN

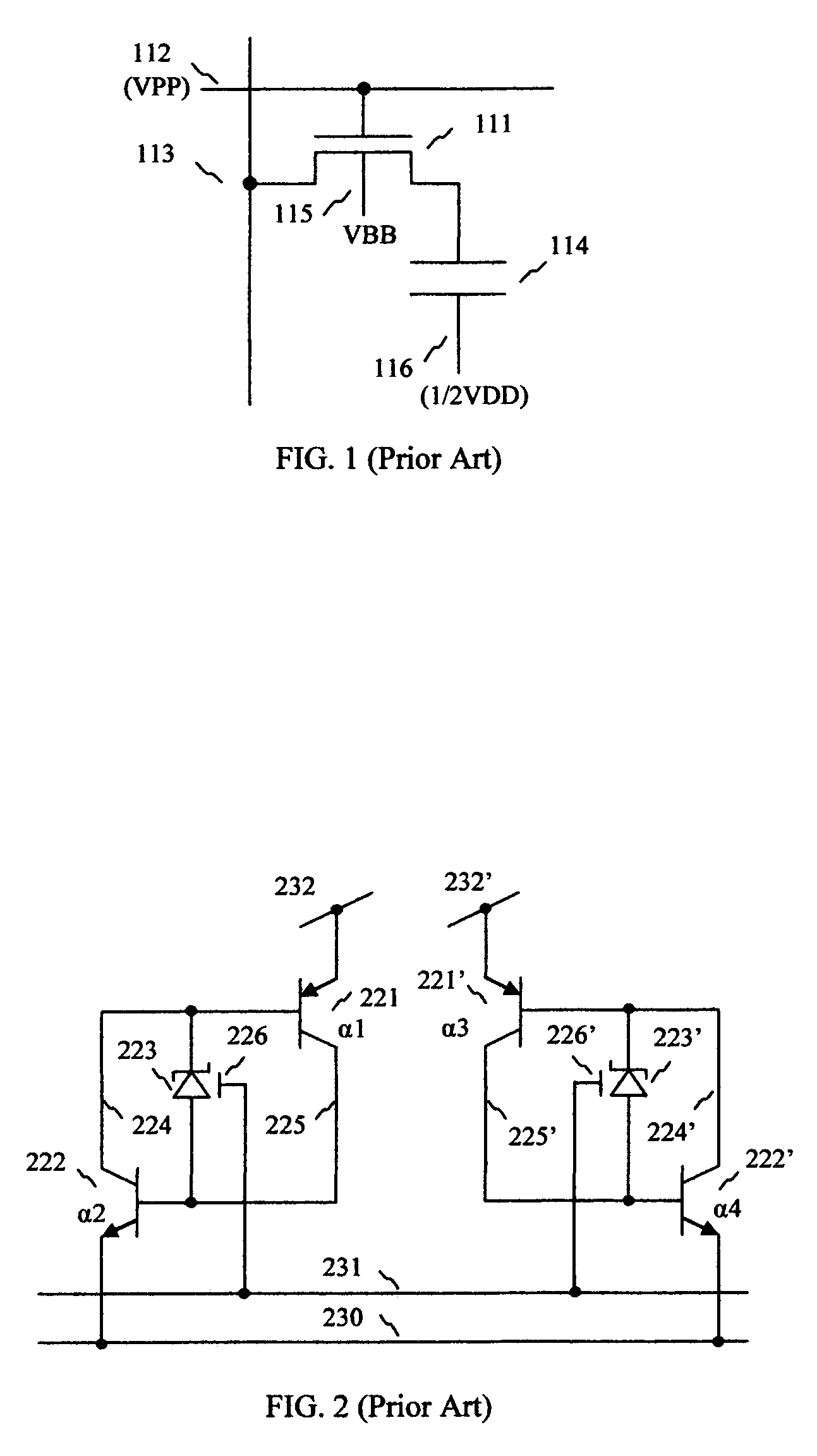

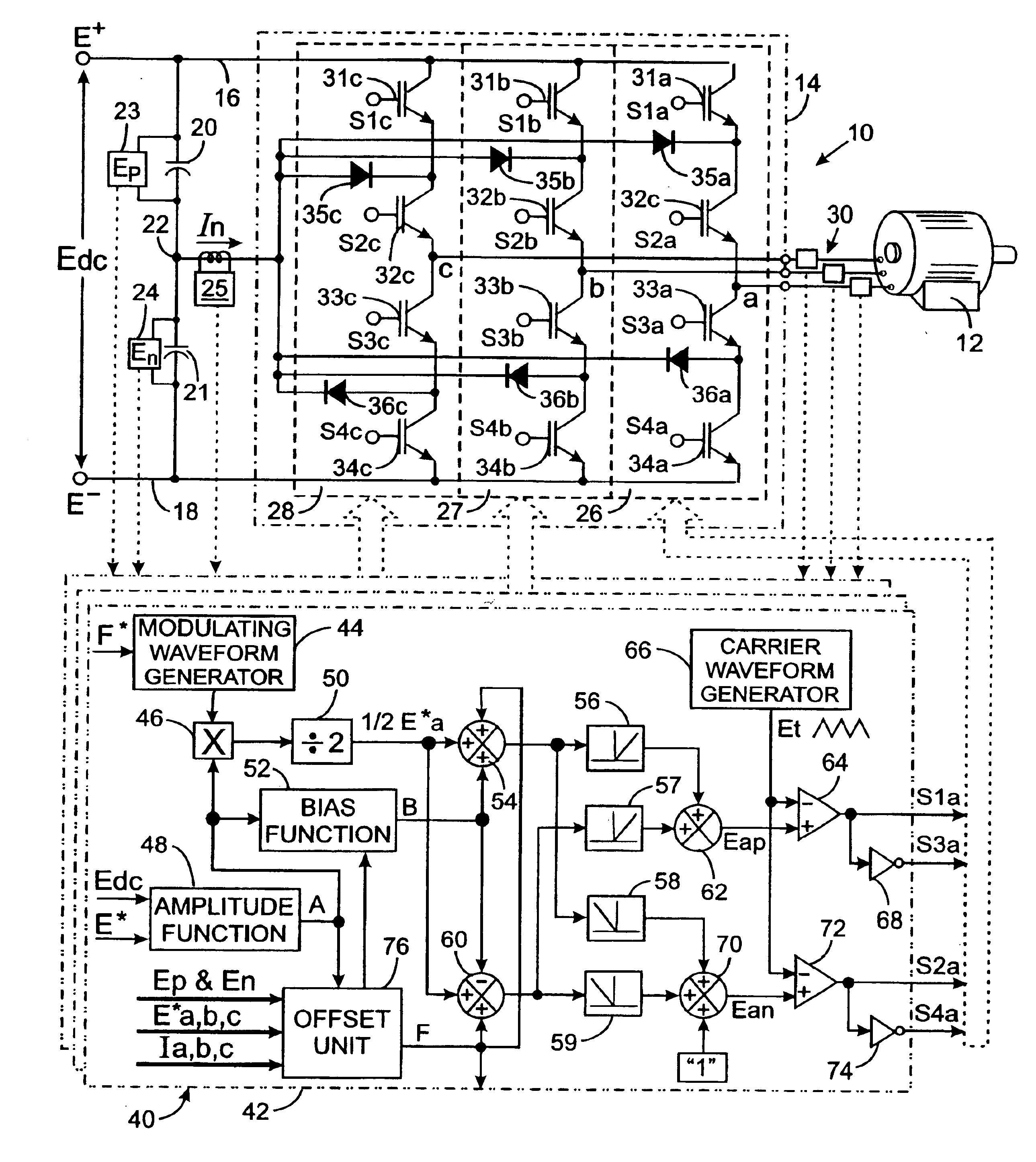

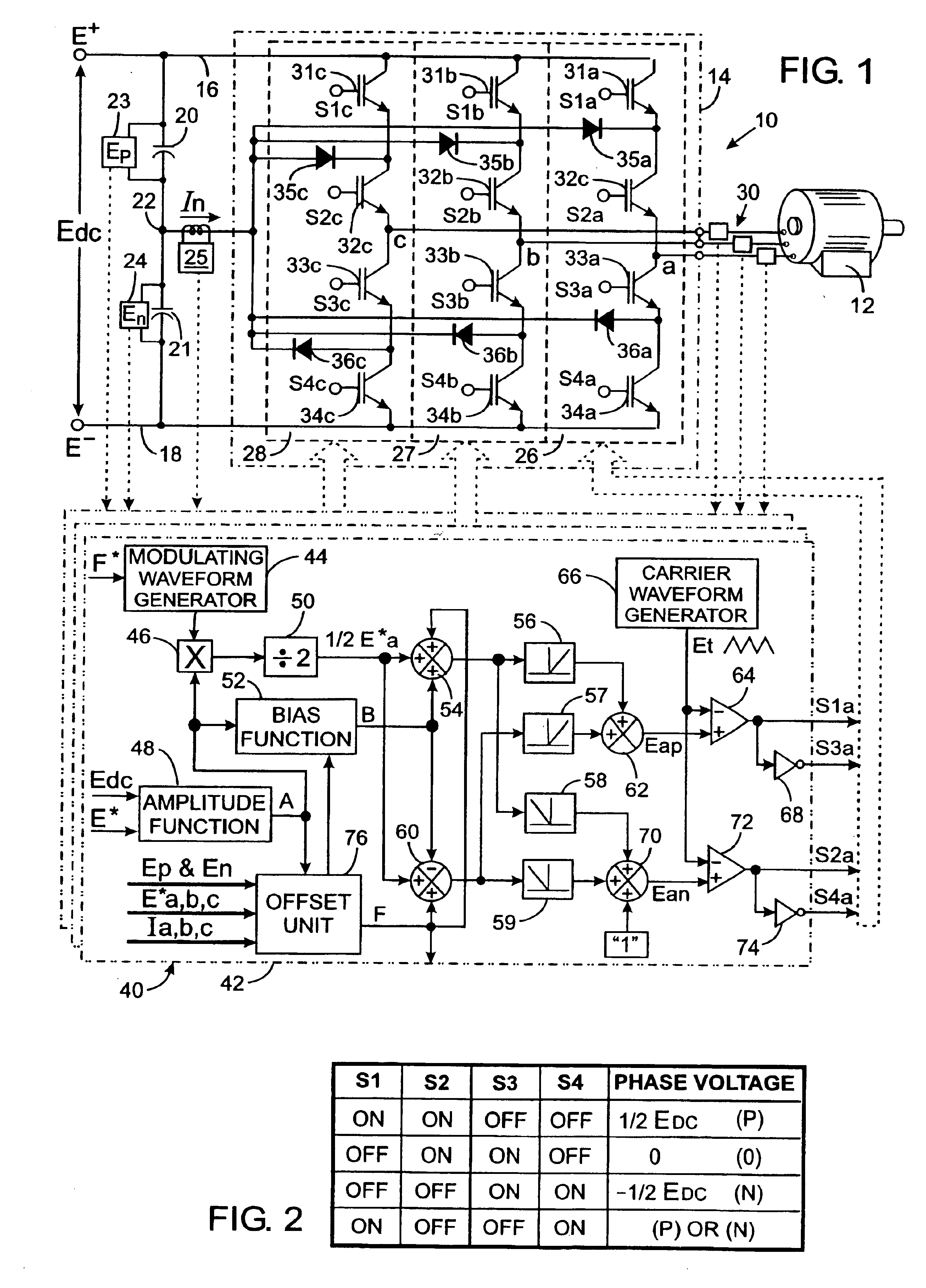

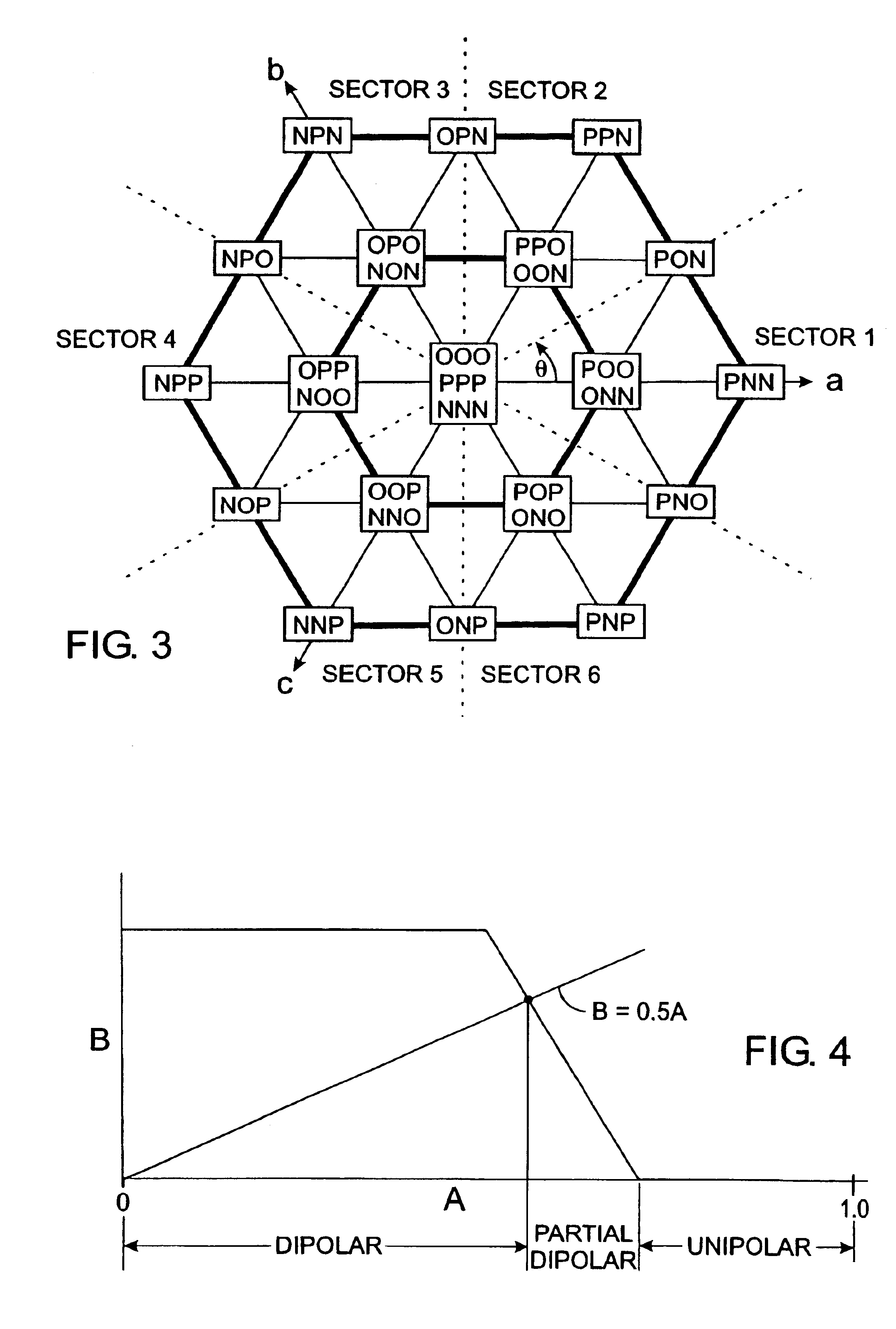

Capacitor charge balancing technique for a three-level PWM power converter

InactiveUS6842354B1Adjustable widthConversion with intermediate conversion to dcDc-dc conversionThree levelEngineering

A power converter includes a DC to AC inverter that is connected to a neutral node formed between first and second capacitors connected across two DC supply lines. The inverter is operated to selectively couple the DC supply lines and the neutral node to an output terminal thereby producing an alternating voltage waveform formed by a sequence of output pulses having positive, zero and negative voltage levels. To compensate for a voltage imbalance across the capacitors, an imbalance compensation coefficient is derived from the difference in voltages across the first and second capacitors and from the direction of current between the neutral node and the inverter. The imbalance compensation coefficient is employed to adjust the width of the output pulses so as to charge and discharge the capacitors to correct the imbalance.

Owner:ROCKWELL AUTOMATION TECH

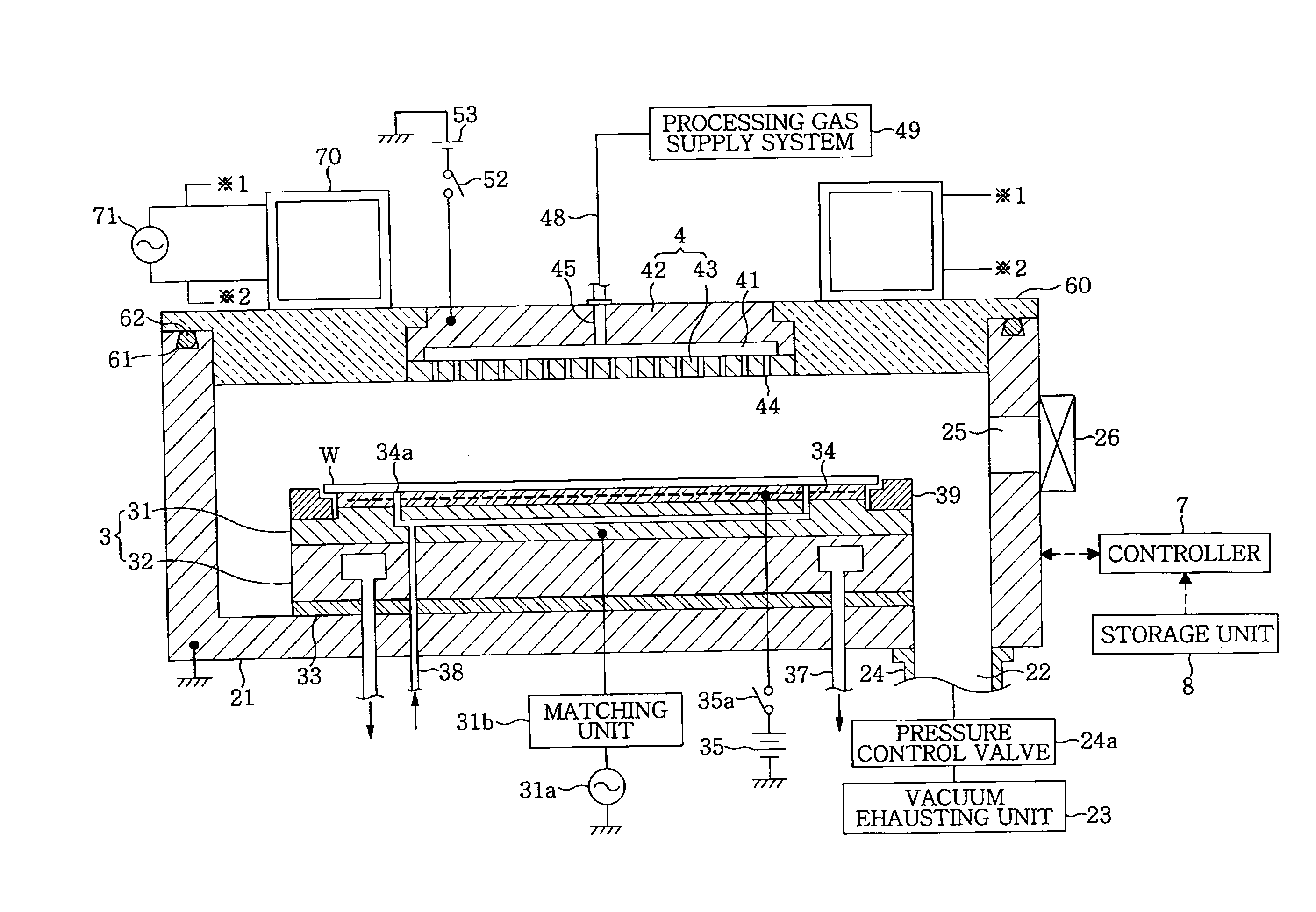

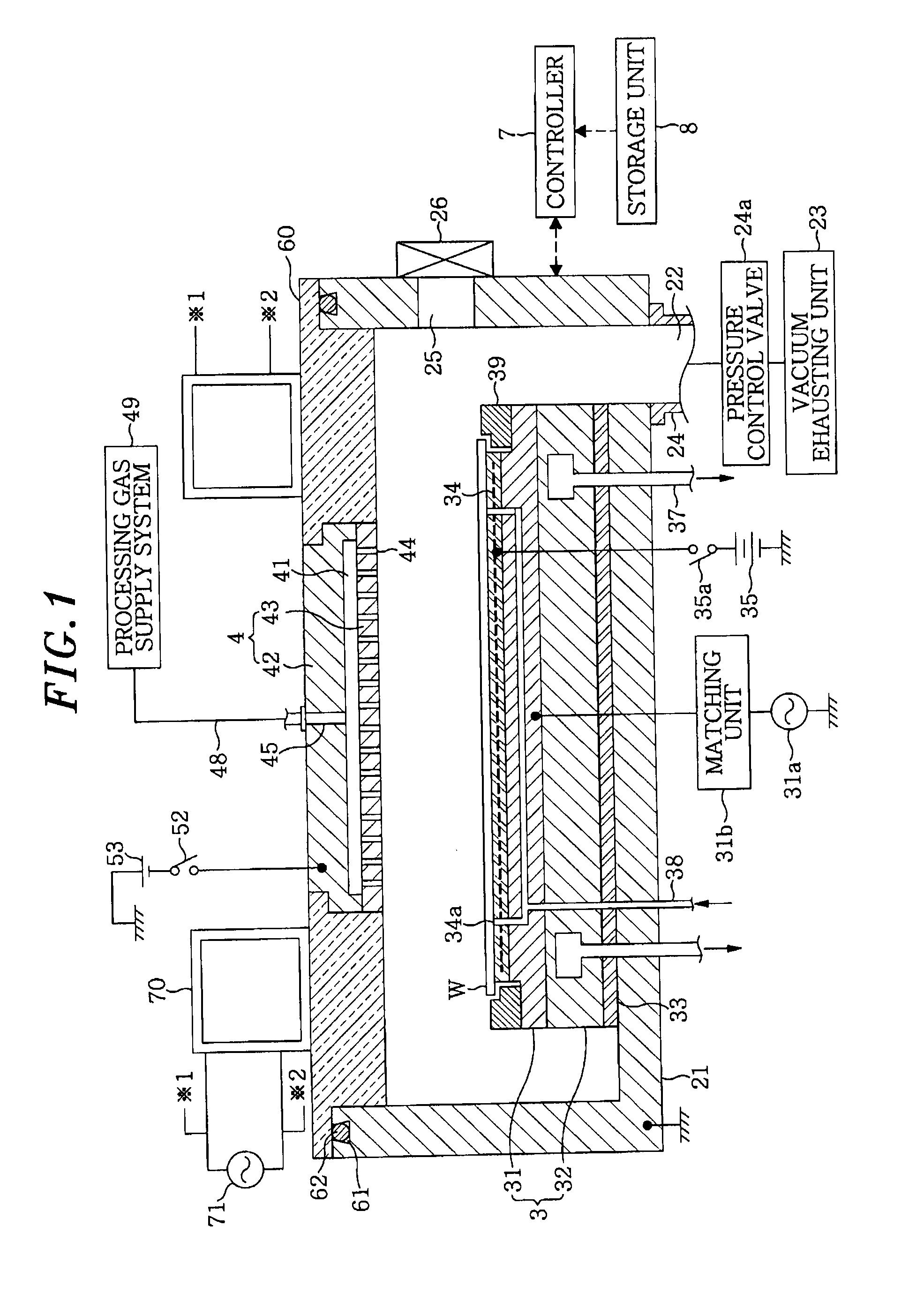

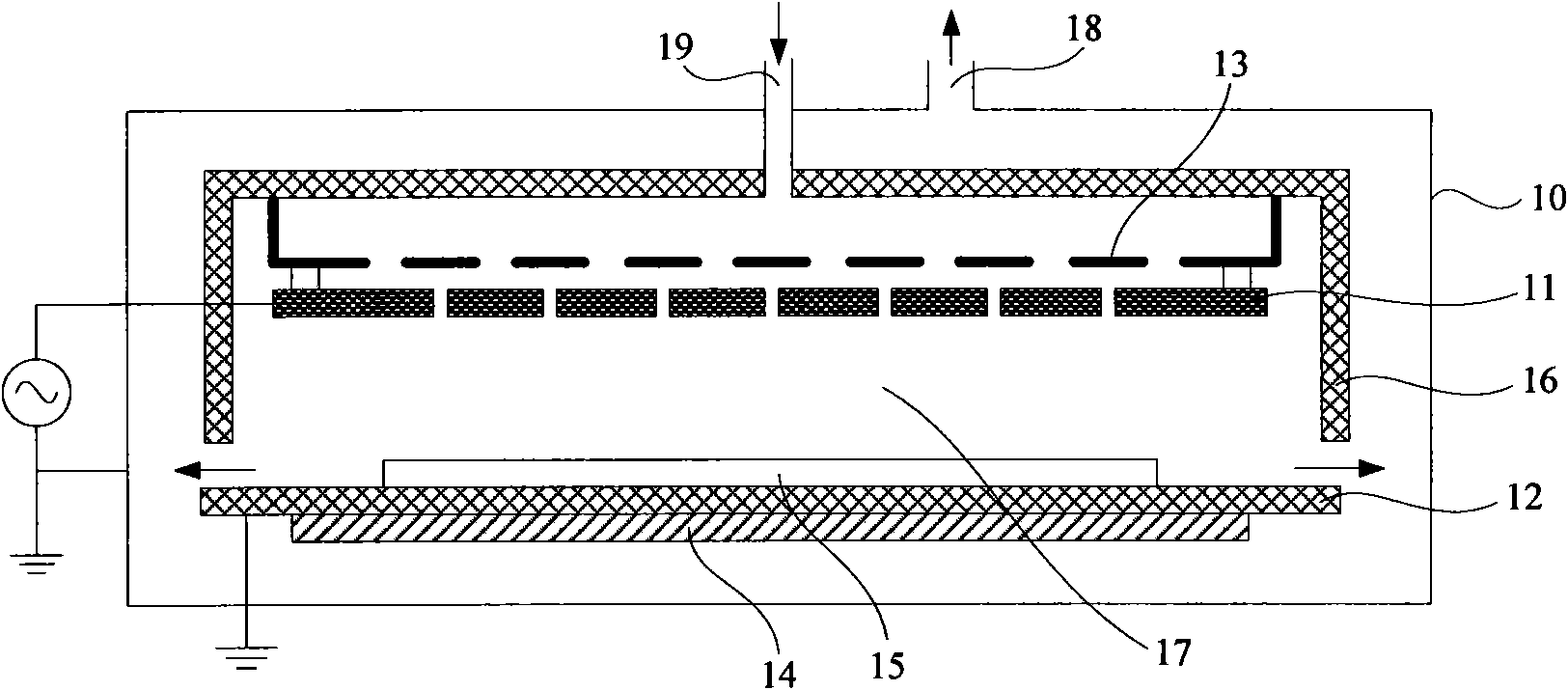

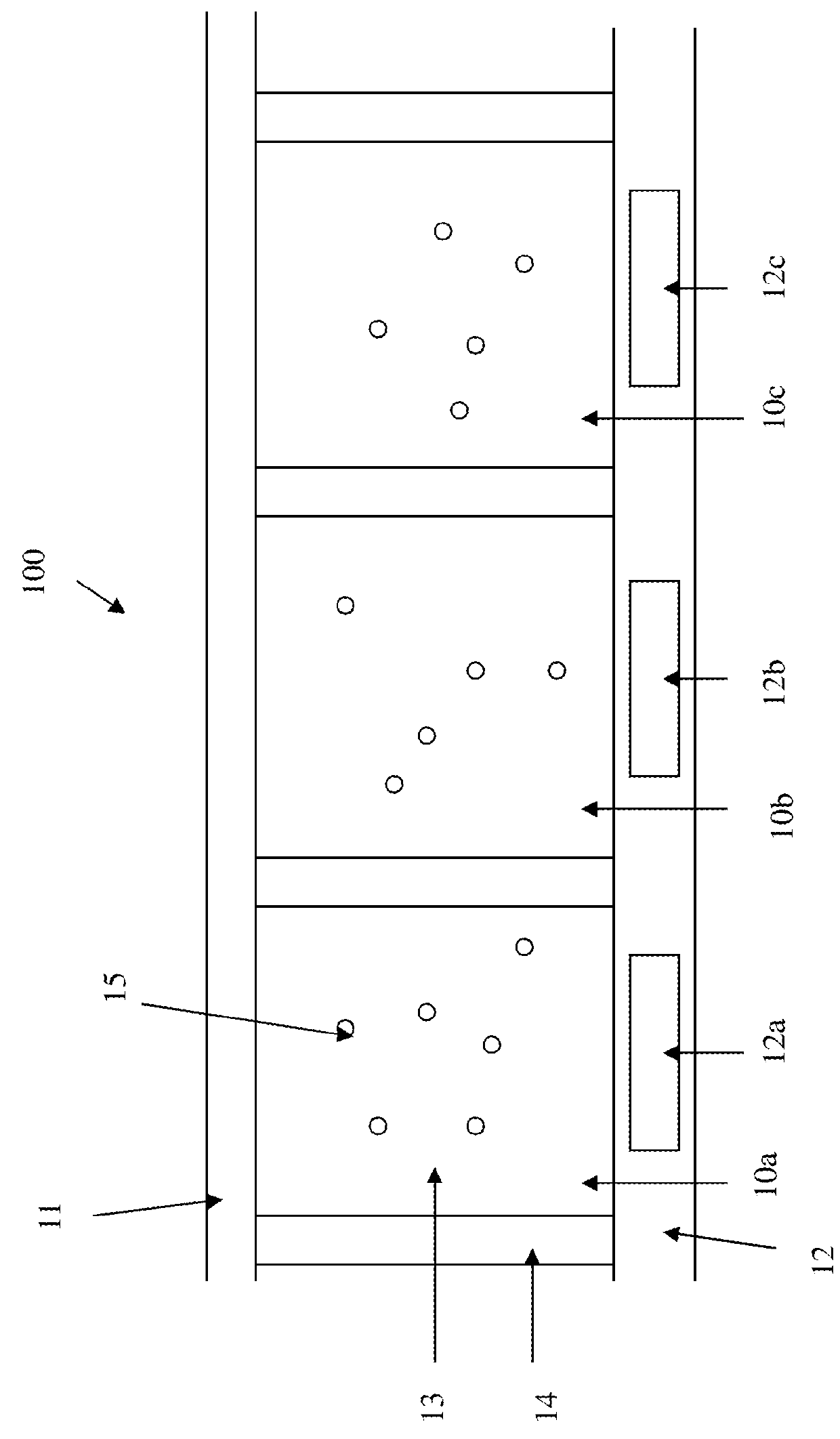

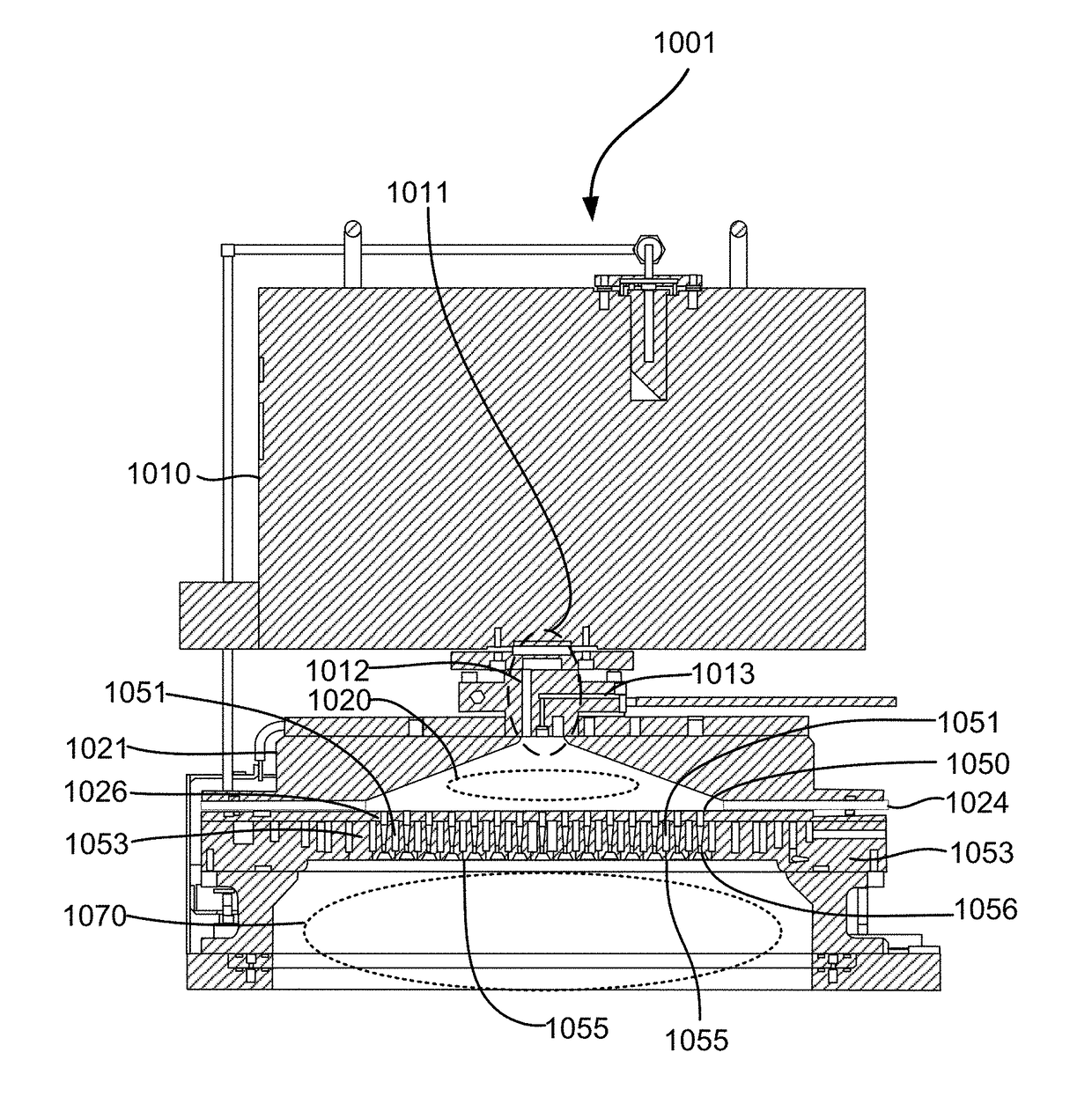

Plasma processing apparatus and method

ActiveUS20110174778A1High in-plane uniformityImprove uniformityLiquid surface applicatorsElectric discharge tubesPower flowConductive materials

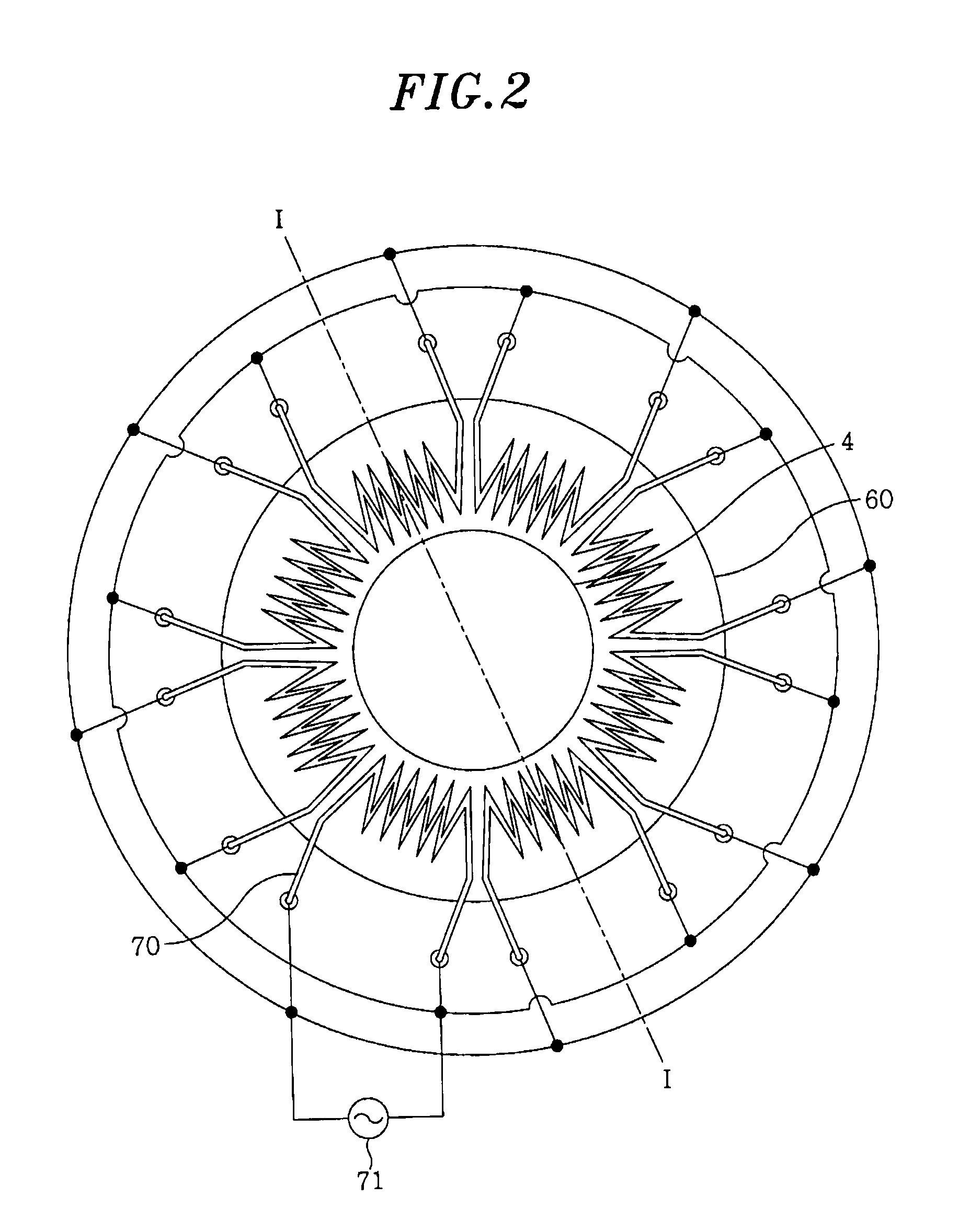

A plasma processing apparatus performs a process on a substrate by using plasma. The plasma processing apparatus includes a processing chamber; a mounting table which is located in the processing chamber and on which a substrate is mounted; a gas shower head formed of a conductive material provided to face the mounting table and having at the bottom surface thereof a plurality of gas injection openings for supplying a processing gas into the processing chamber; an induction coil to which a high frequency current is supplied to generate an inductively coupled plasma in a region surrounding a space below the gas shower head; a negative voltage supplying unit for applying a negative DC voltage to the gas shower head to allow an electrical field, which is induced by the induction coil, to be drawn to a central portion of the processing region; and a unit for evacuating the processing chamber.

Owner:TOKYO ELECTRON LTD

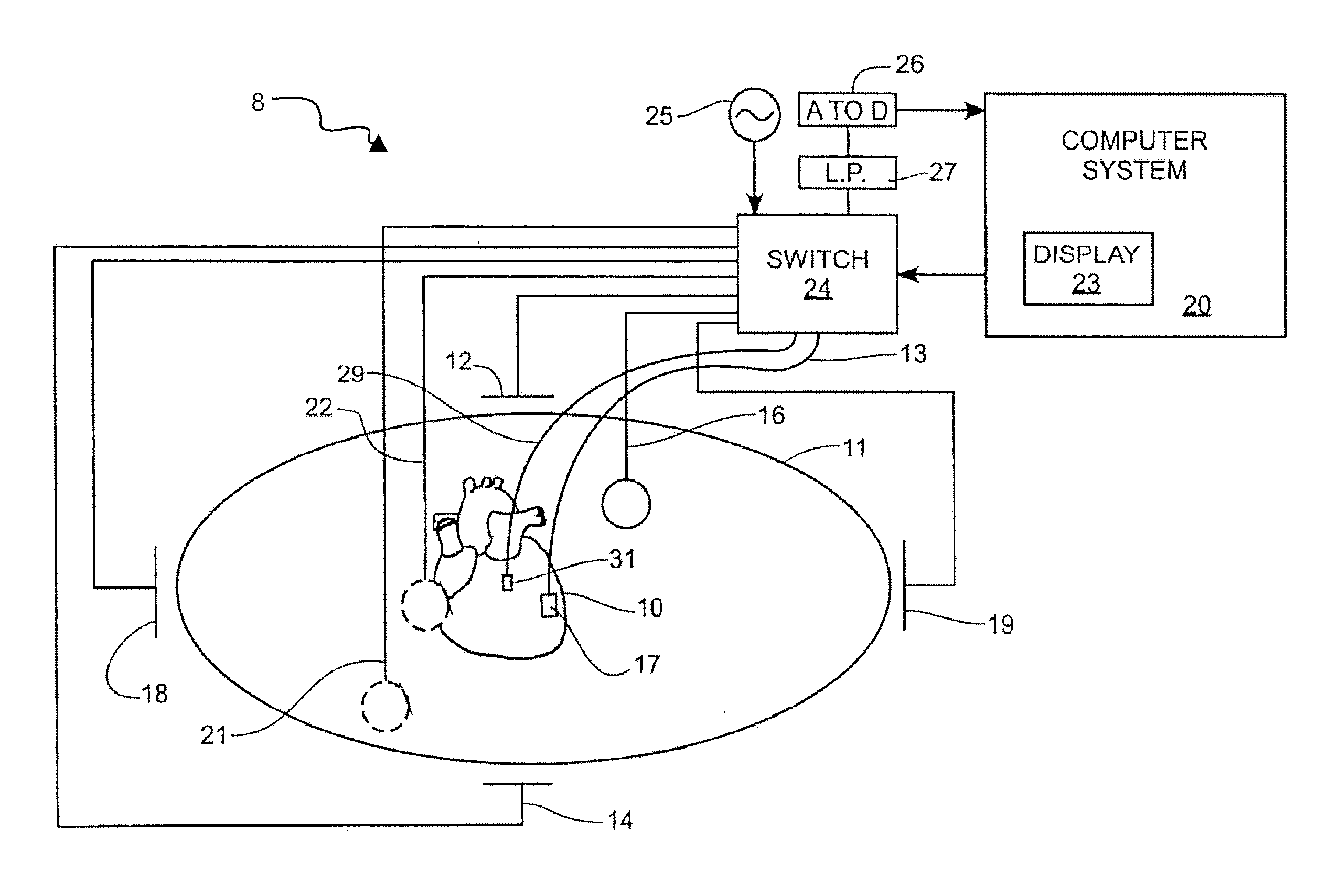

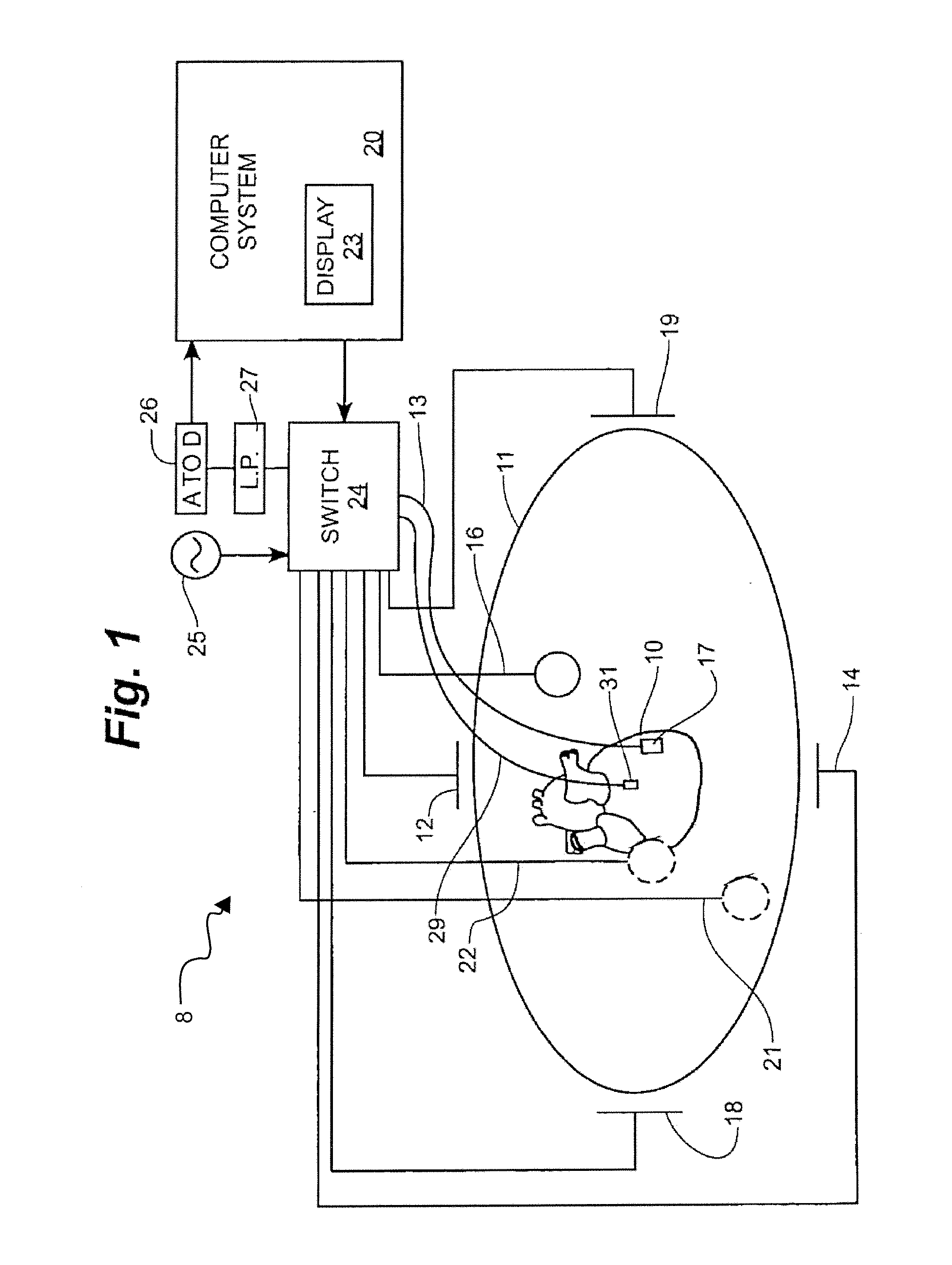

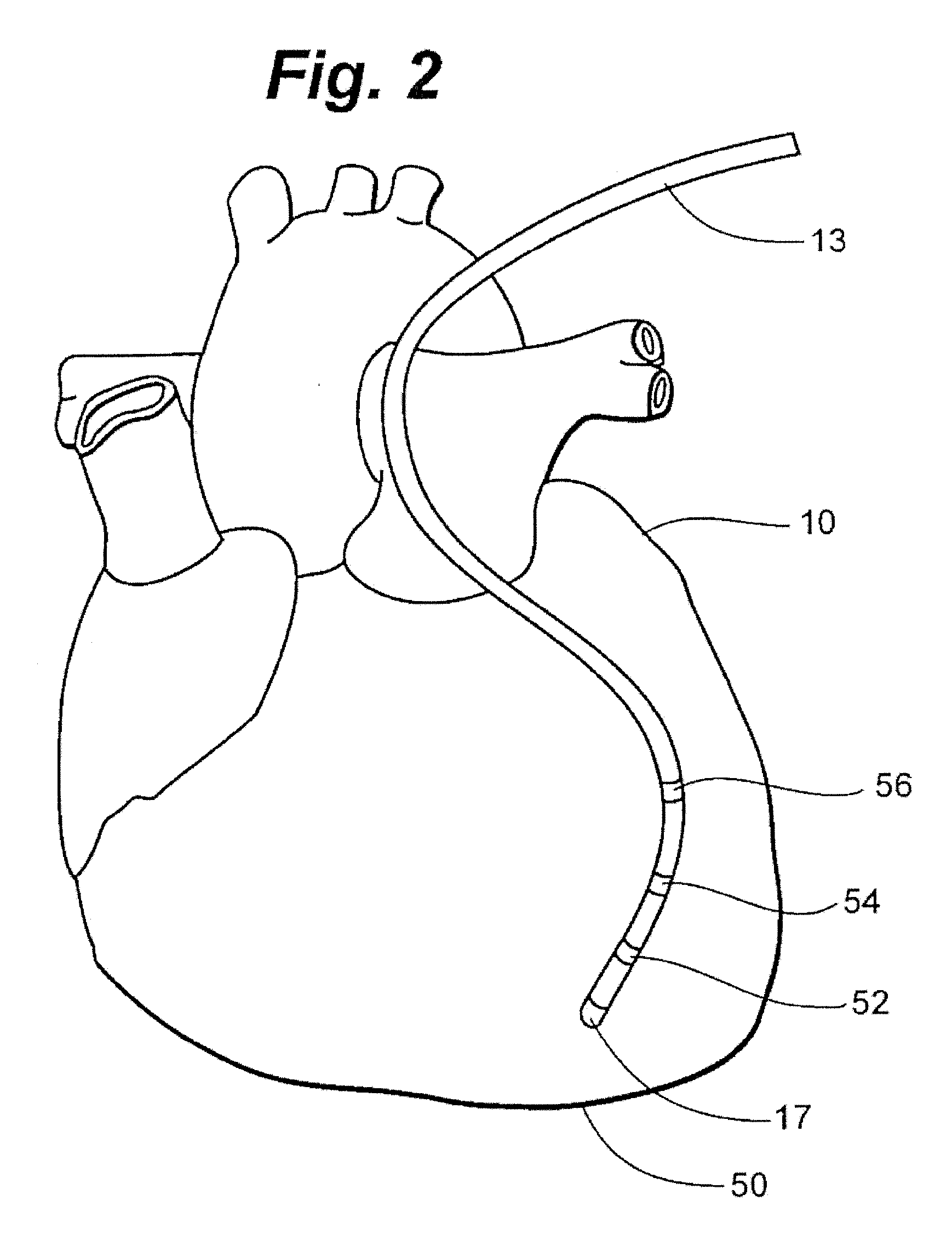

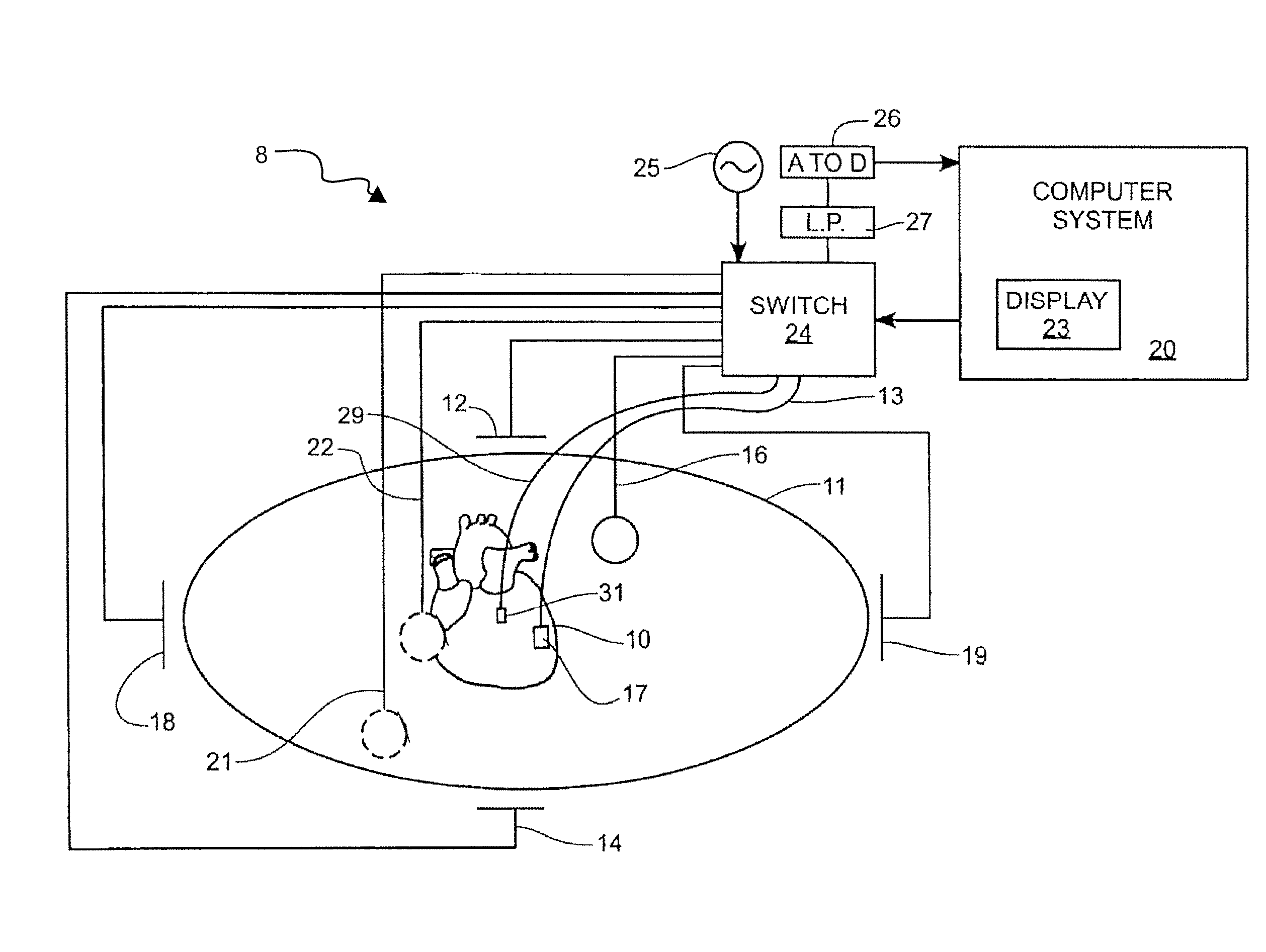

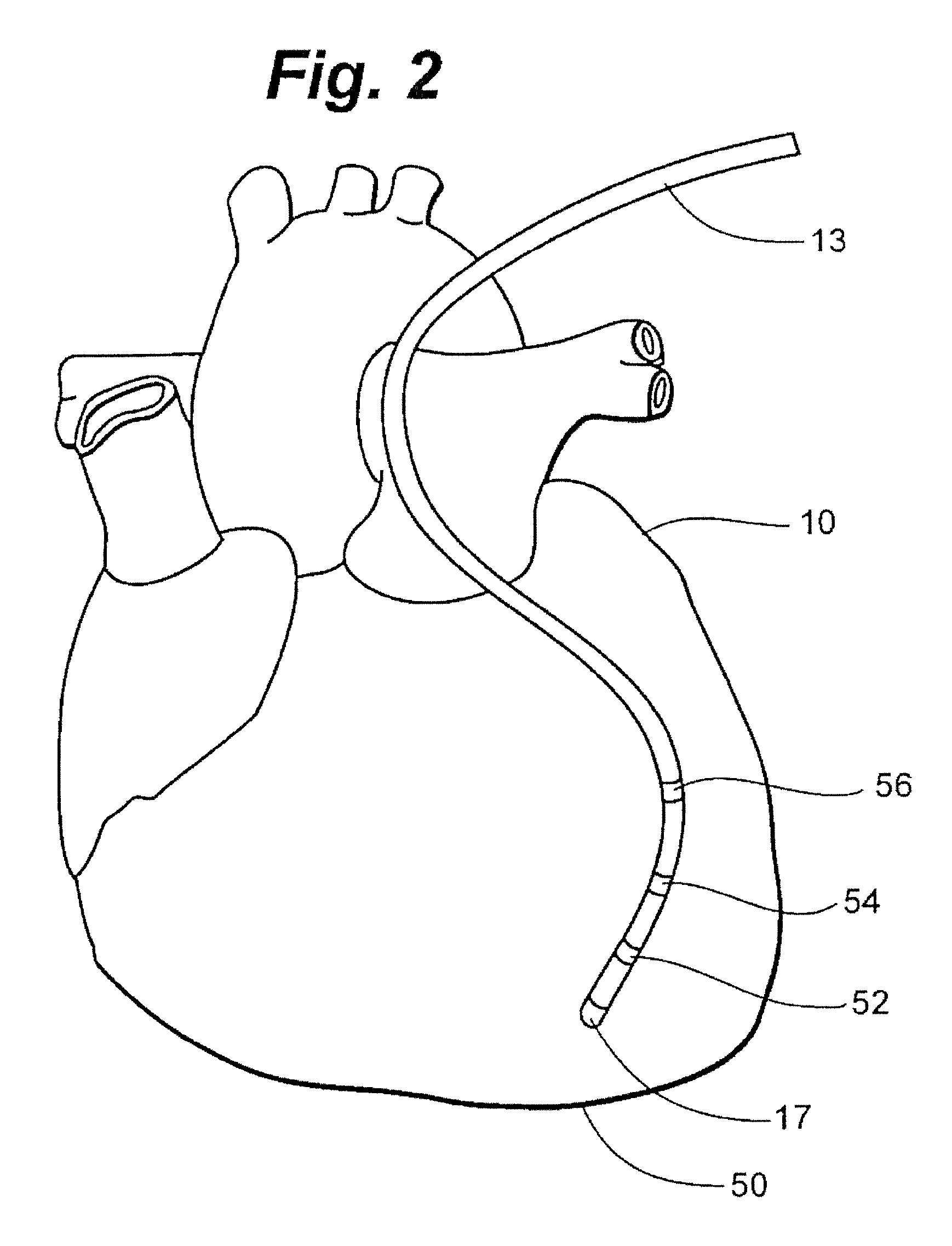

System and Method for Three Dimensional Mapping of Electrophysiology Information

An electrophysiology apparatus is used to measure electrical activity occurring in a heart of a patient and to visualize the electrical activity and / or information related to the electrical activity. A three-dimensional map of the electrical activity and / or the information related to the electrical activity is created. Exemplary maps include a time difference between action potentials at a roving electrode and a reference electrode, the peak-to-peak timing of action potentials at the roving electrode, the peak negative voltage of action potentials at the roving electrode, complex fractionated electrogram information, a dominant frequency of an electrogram signal, a maximum peak amplitude at the dominant frequency, a ratio of energy in one band of the frequency-domain to the energy in a second band of the frequency-domain, a low-frequency or high-frequency passband of interest, a frequency with the maximum energy in a passband, a number of peaks within a passband, an energy, power, and / or area in each peak, a ratio of energy and / or area in each peak to that in another passband, and a width of each peak in a spectrum. Colors, shades of colors, and / or grayscales are assigned to values of the parameters and colors corresponding to the parameters for the electrograms sampled by the electrodes are updated on the three-dimensional model.

Owner:ST JUDE MEDICAL ATRIAL FIBRILLATION DIV

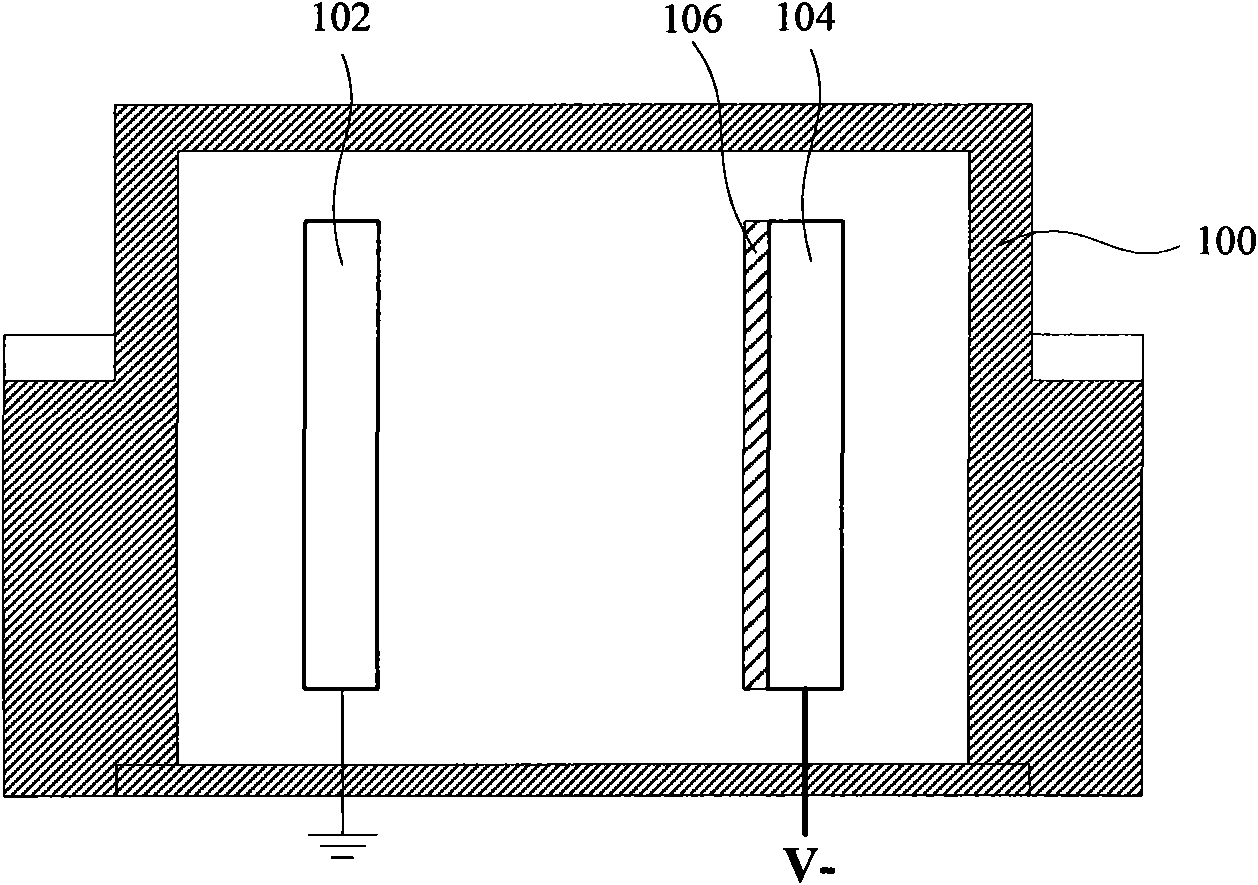

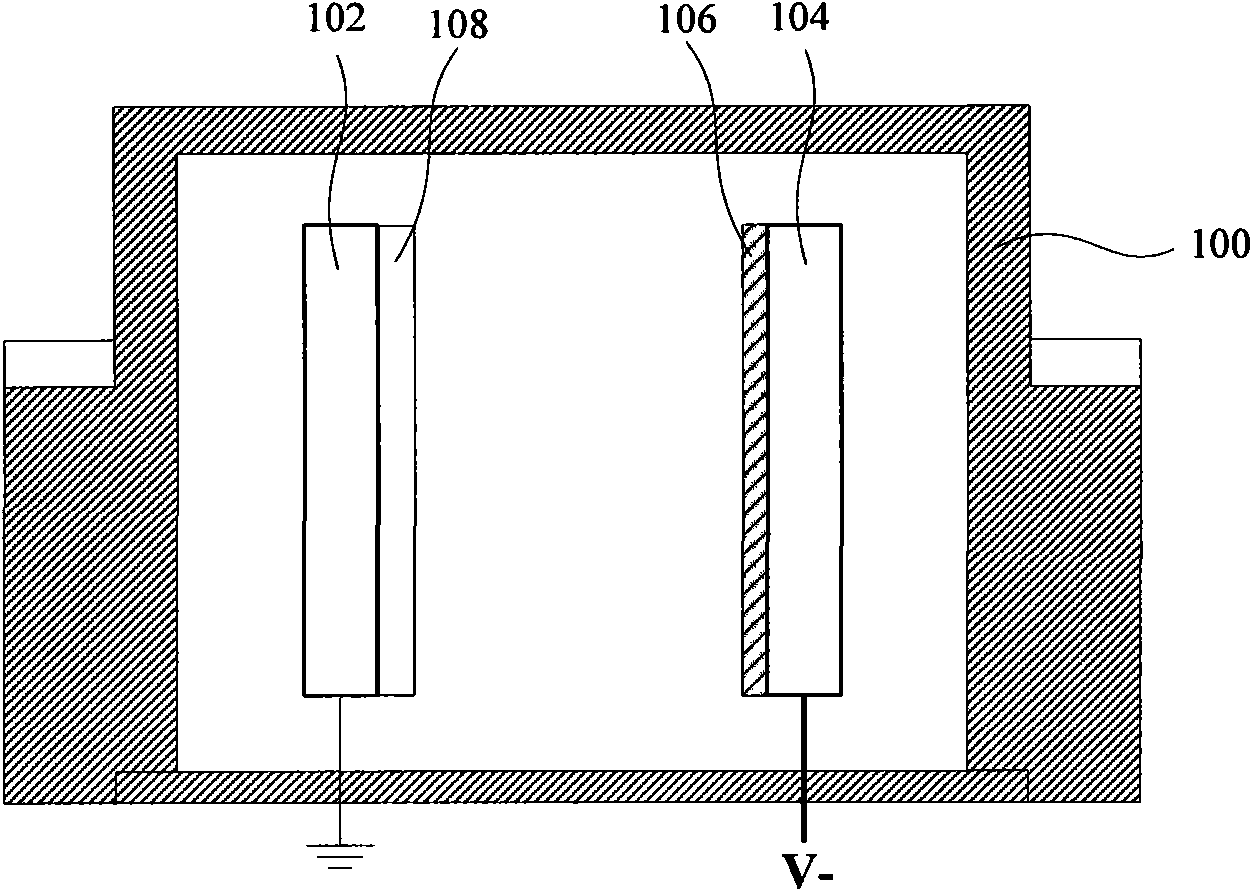

Film deposition method

InactiveCN101609858ASolve the problem of uniformity of depositionSolve for uniformityFinal product manufactureVacuum evaporation coatingReaction chamberNanotechnology

The invention discloses a film deposition method which comprises the following steps: placing a first electrode plate used as an anode and a second electrode plate used as a cathode in parallel in a reaction chamber, wherein the surface of the second electrode plate facing to the first electrode plate is provided with a sacrificial layer; putting a substrate on the surface of the first electrode plate facing to the sacrificial layer; leading etching gas into the reaction chamber; grounding the first electrode plate, and applying DC negative voltage to the second electrode plate; ionizing the etching gas into a plasma so as to etch the sacrificial layer, and depositing a film on the surface of the substrate. The film deposition method can improve the performance, particularly the stability of the film and the uniformity of large-area film deposition.

Owner:GS SOLAR FU JIAN COMPANY +1

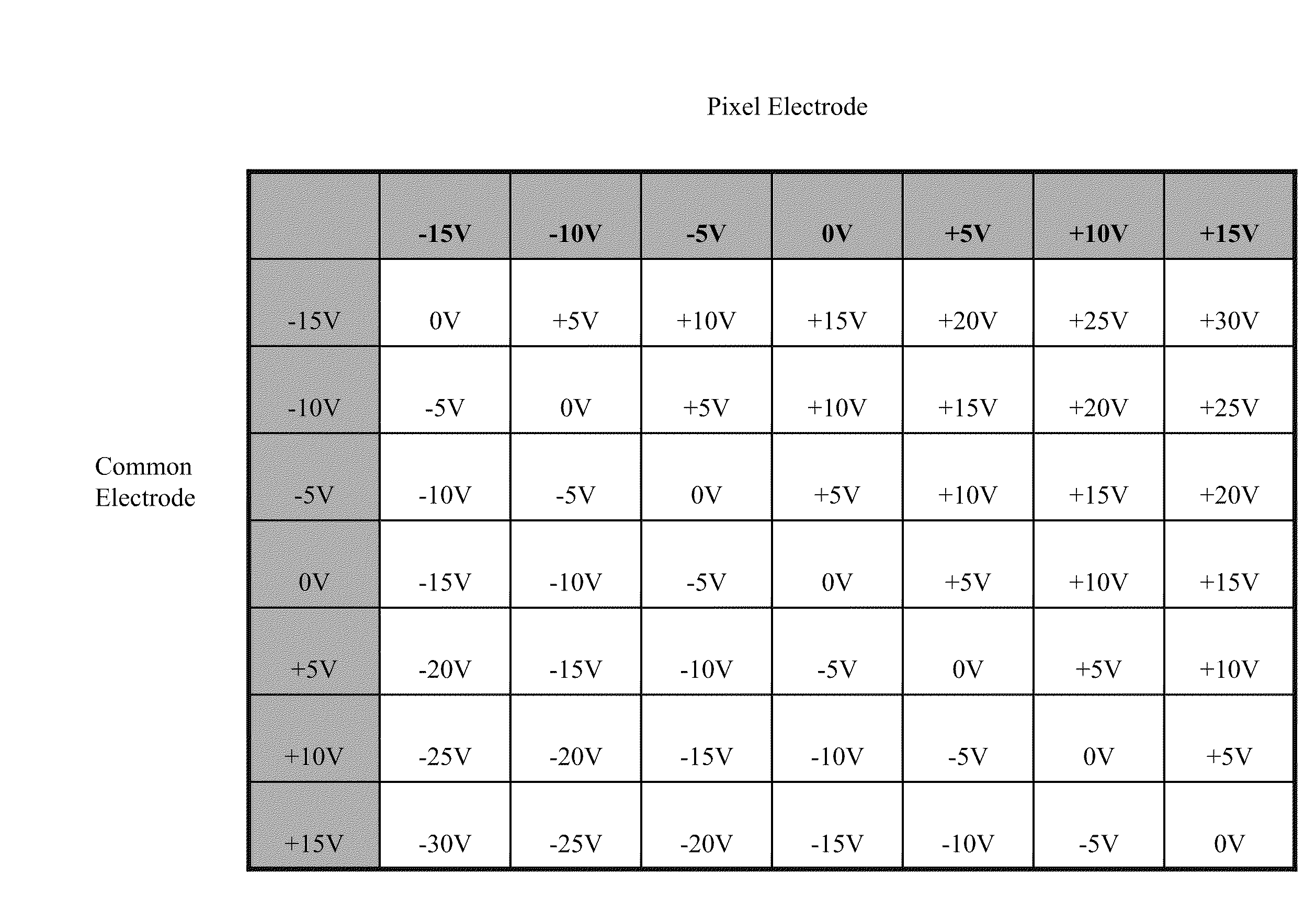

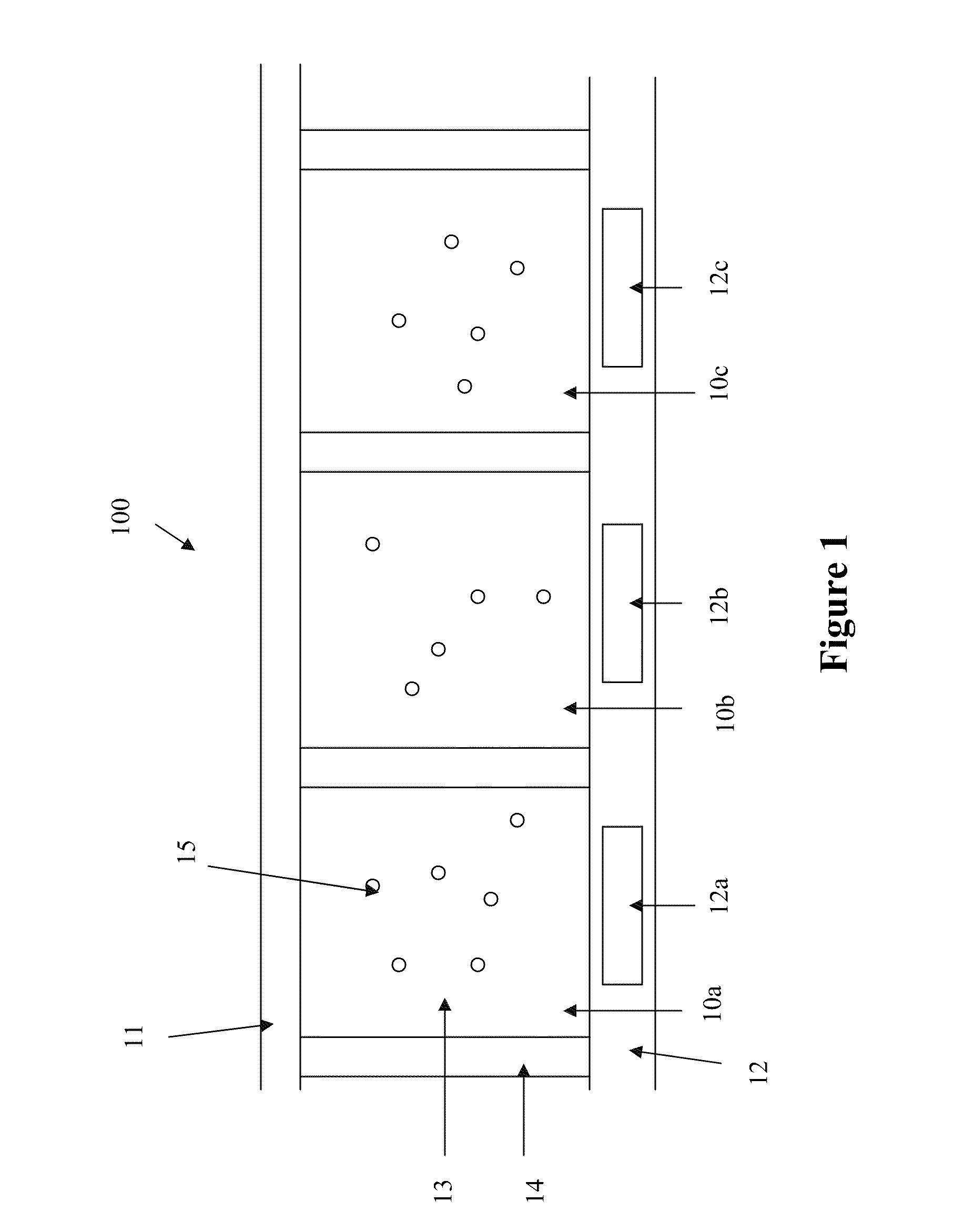

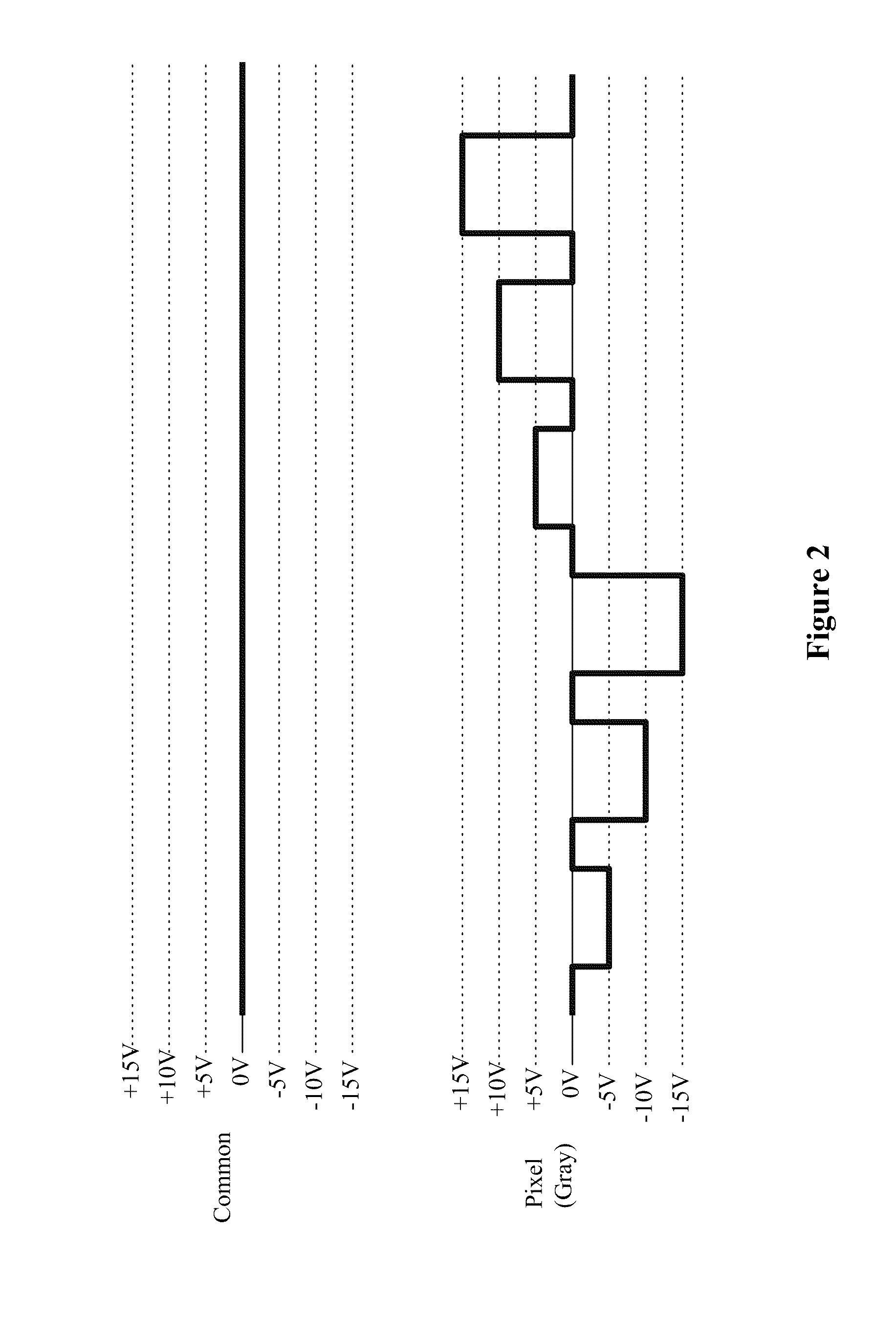

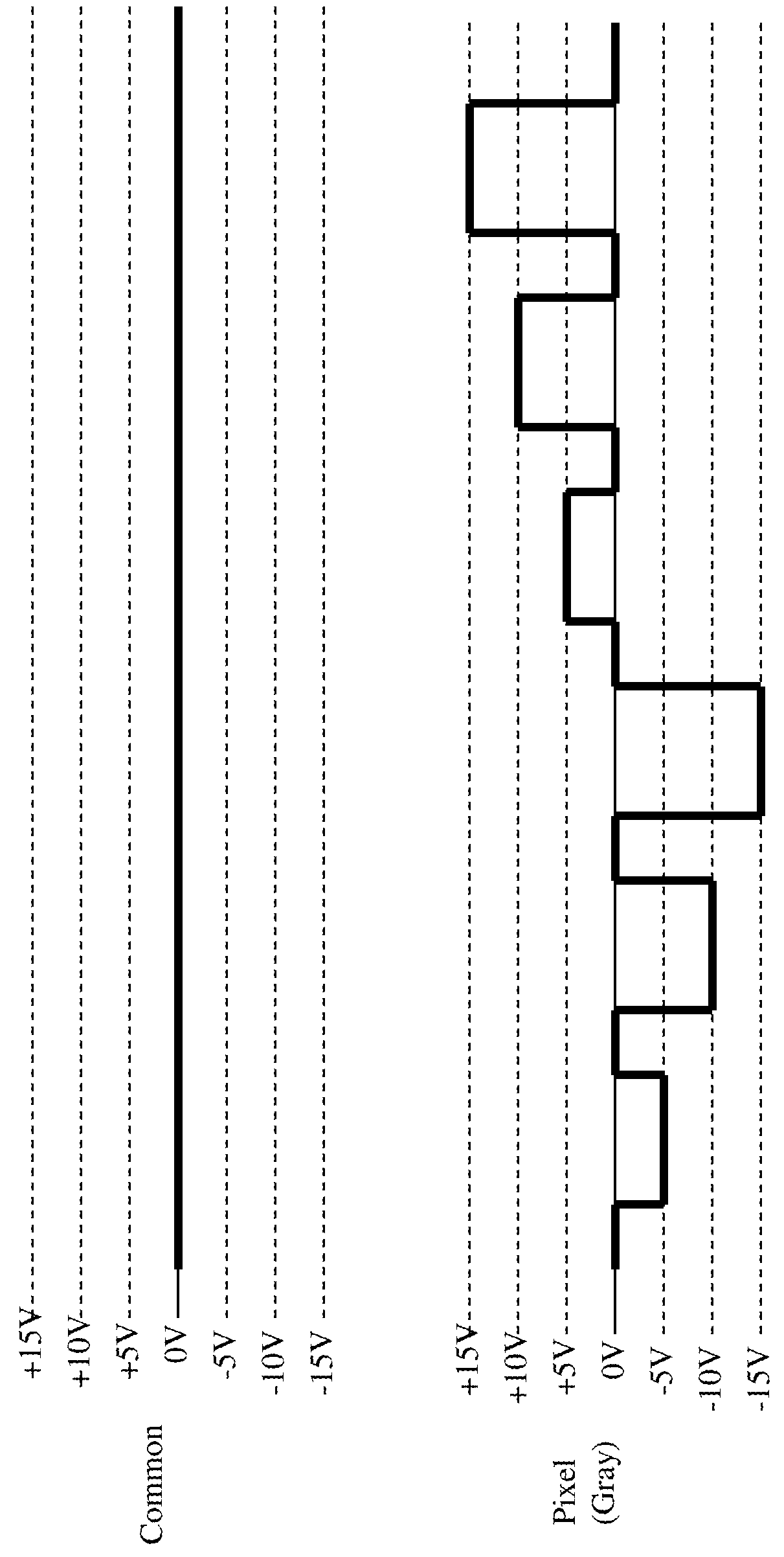

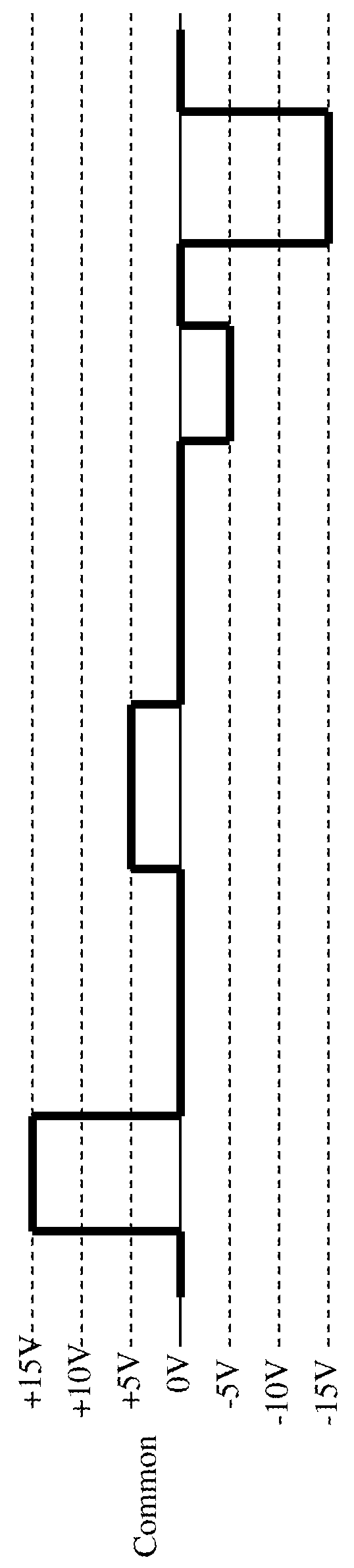

Multiple voltage level driving for electrophoretic displays

InactiveUS20100194733A1Easy to controlGrayscale resolutionCathode-ray tube indicatorsInput/output processes for data processingEngineeringNegative voltage

This application is directed to driving methods for electrophoretic displays. The driving methods comprise applying different voltages selected from multiple voltage levels, to pixel electrodes and optionally also to the common electrodes. In a preferred method, the different voltages are selected from a group consisting of 0V, at least two levels of positive voltage and at least two levels of negative voltage.

Owner:SIPIX IMAGING INC

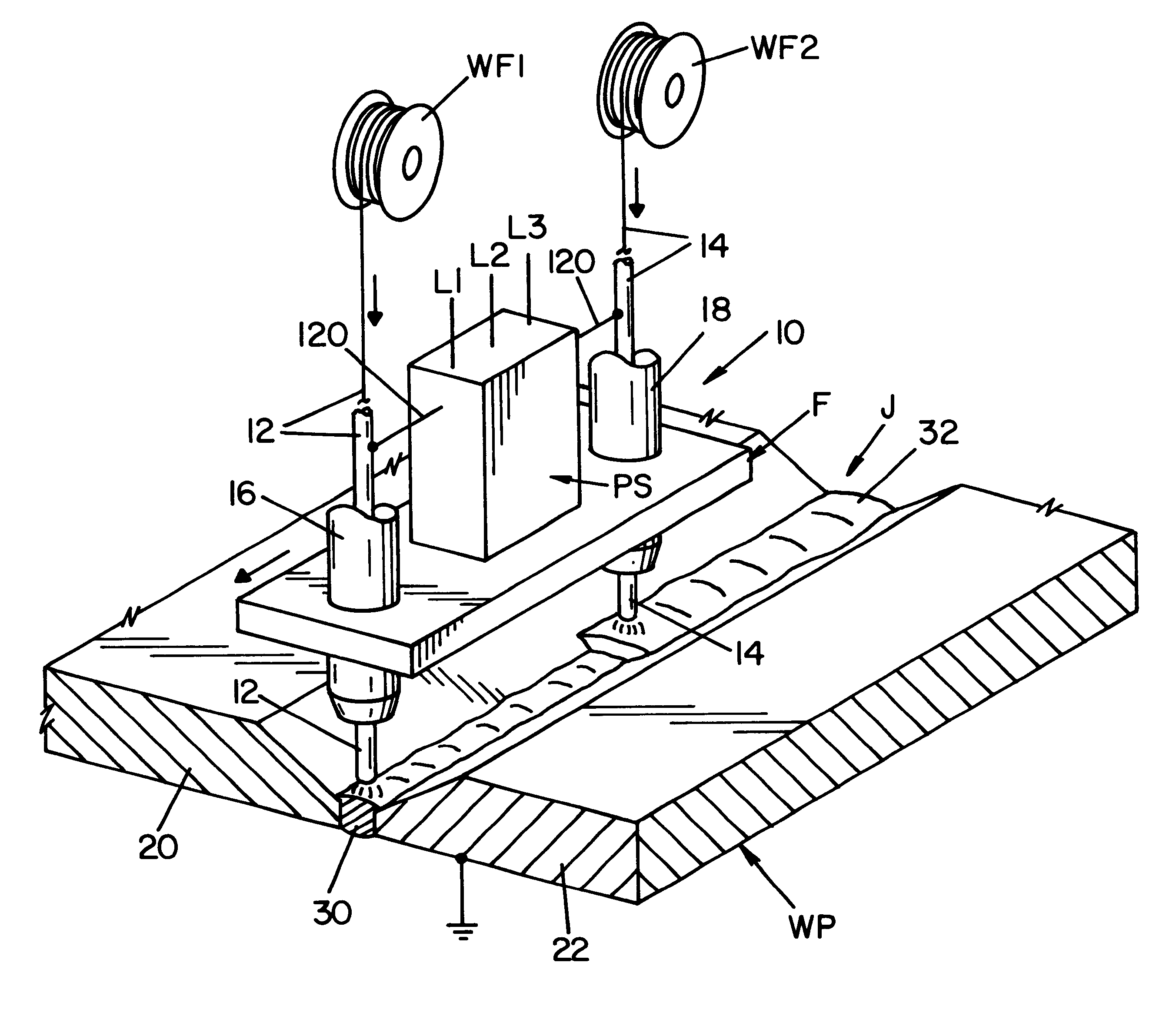

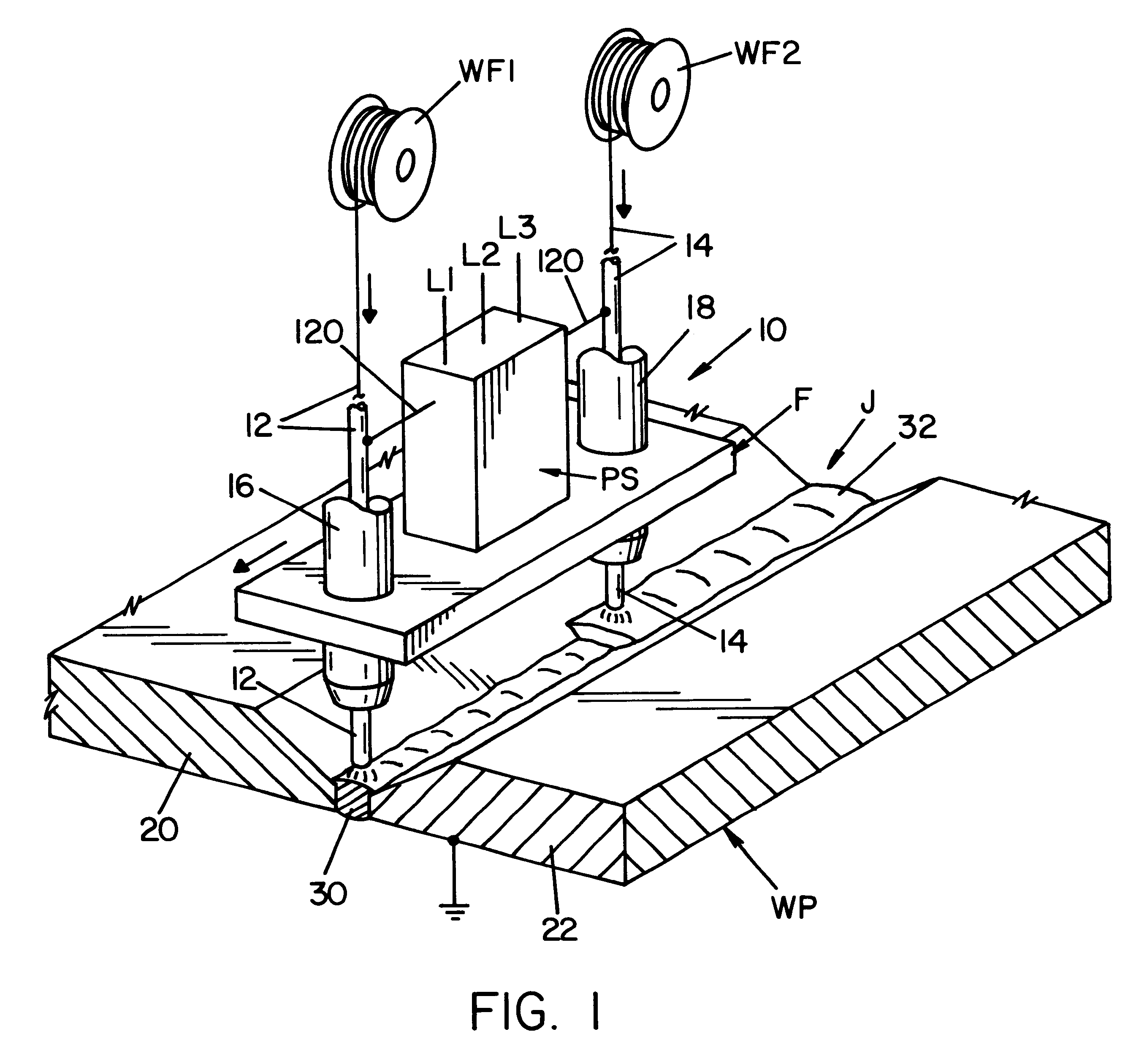

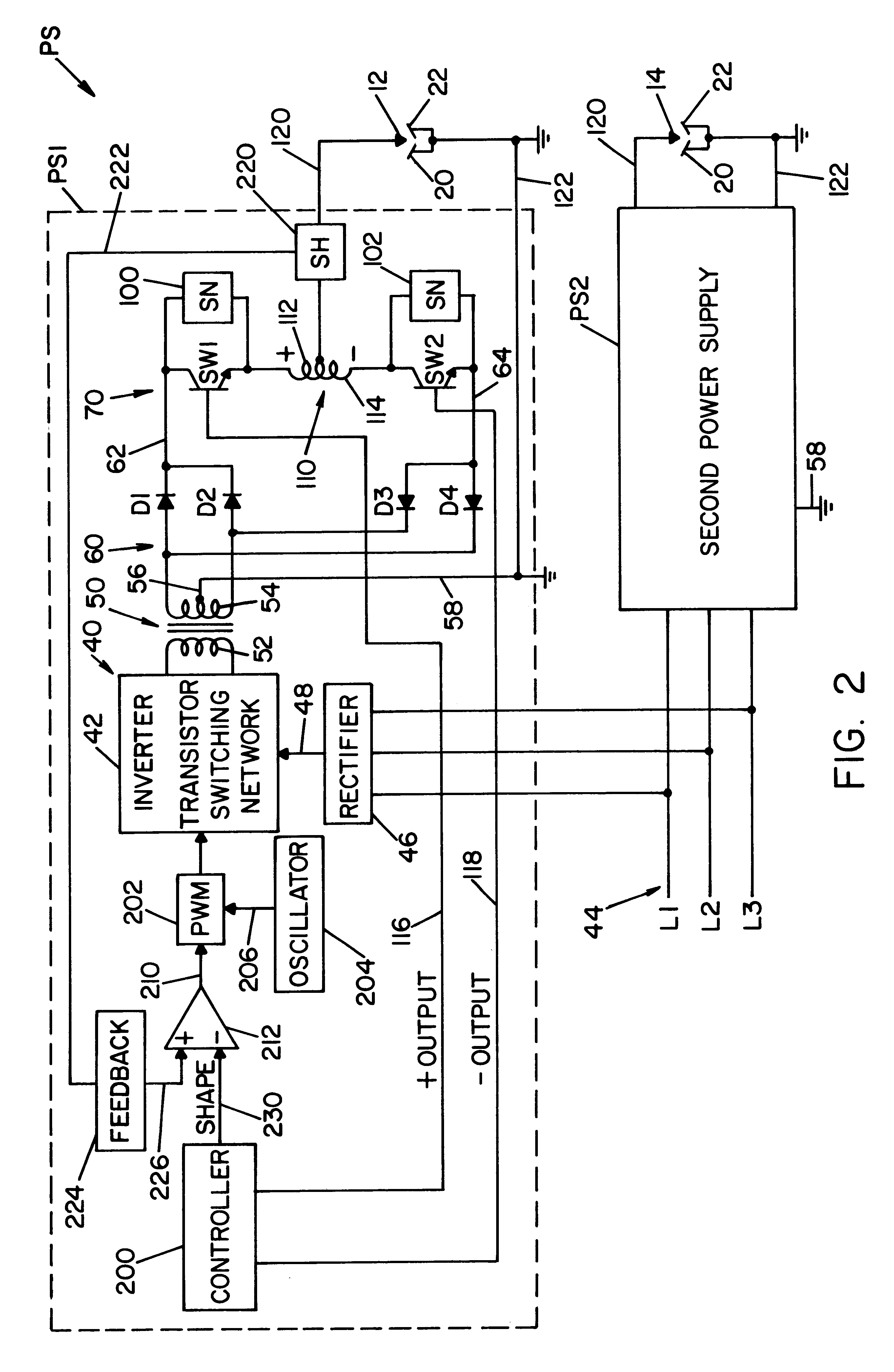

Tandem electrode welder and method of welding with two electrodes

An electric arc welding apparatus comprising at least a first consumable electrode and a second consumable electrode movable in unison along a welding path between the edges of two adjacent, mutually grounded plates, a first power supply for passing a first welding current at a first low frequency between the first electrode and the two plates, a second power supply for passing a second welding current at a second low frequency between the second electrode and the two plates, where each of the power supplies includes a three phase voltage input operated at line frequency, a rectifier to convert the input voltage to a DC voltage link and a high frequency switching type inverter converting the DC voltage link to a high frequency AC current, an output rectifier circuit to provide a positive voltage tenninal and a negative voltage terminal, and an output switching network operated at a given low frequency for directing a pulsating welding current at the given low frequency from the two terminals across one of the electrodes and the plates, and a circuit for independently adjusting the given low frequency so the value of the first low frequency of the first power supply is different from the second low frequency of the second power supply.

Owner:LINCOLN GLOBAL INC

Multiple voltage level driving for electrophoretic displays

ActiveUS9251736B2High resolutionEasy to controlStatic indicating devicesNon-linear opticsDisplay deviceEngineering

This application is directed to driving methods for electrophoretic displays. The driving methods comprise applying different voltages selected from multiple voltage levels, to pixel electrodes and optionally also to the common electrodes. In one embodiment, the different voltages are selected from a group consisting of 0V, at least two levels of positive voltage and at least two levels of negative voltage. The driving method is also suitable for a color display device.

Owner:E INK CORPORATION

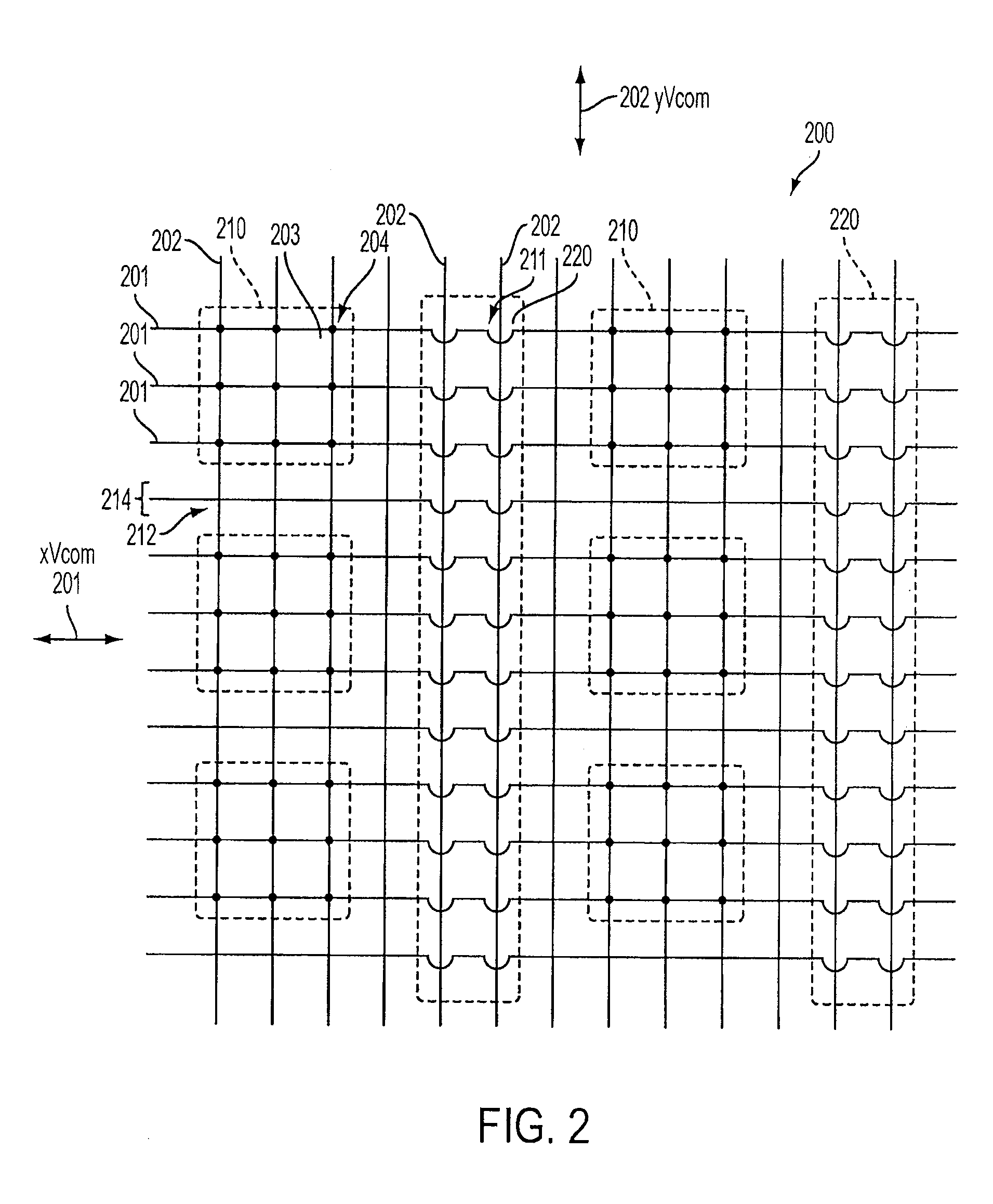

Touch sensor panels with reduced static capacitance

ActiveUS20100193257A1Reduce electrostatic capacitanceImprove accuracyTransmission systemsElectronic switchingCapacitanceComputer science

Capacitive touch panels may include a plurality of positive voltage lines that are driven at a first phase. These positive voltage lines may be used to provide the drive capacitance signal sensed by one or more sense regions. The touch panels may also include a plurality of negative phase voltage lines that are driven at a phase that is different than the first phase. Both the positive and negative voltage lines may cross-under one or more sense regions. The negative phase voltage lines are able to counter act and reduce the static capacitance in the sense regions.

Owner:APPLE INC

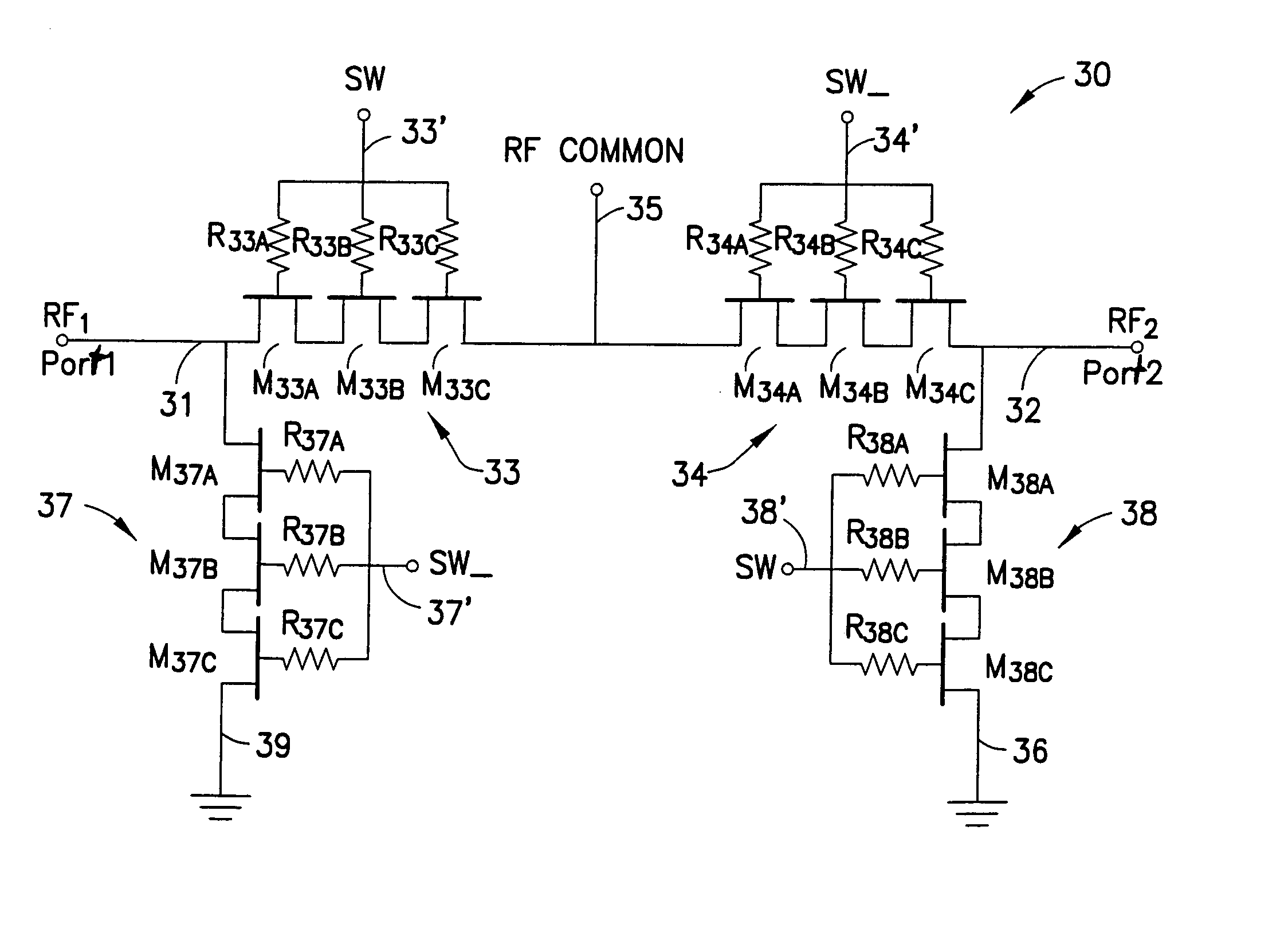

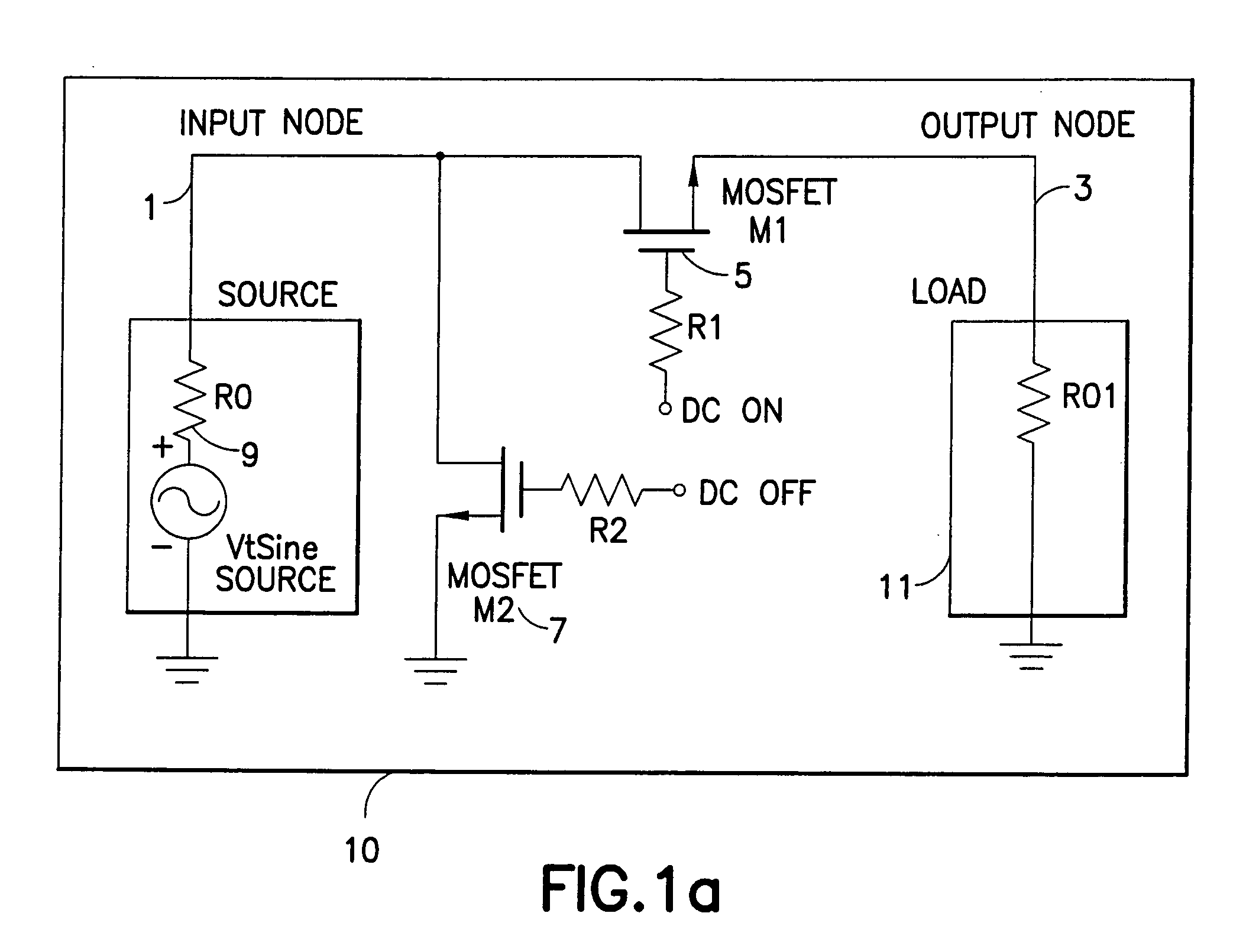

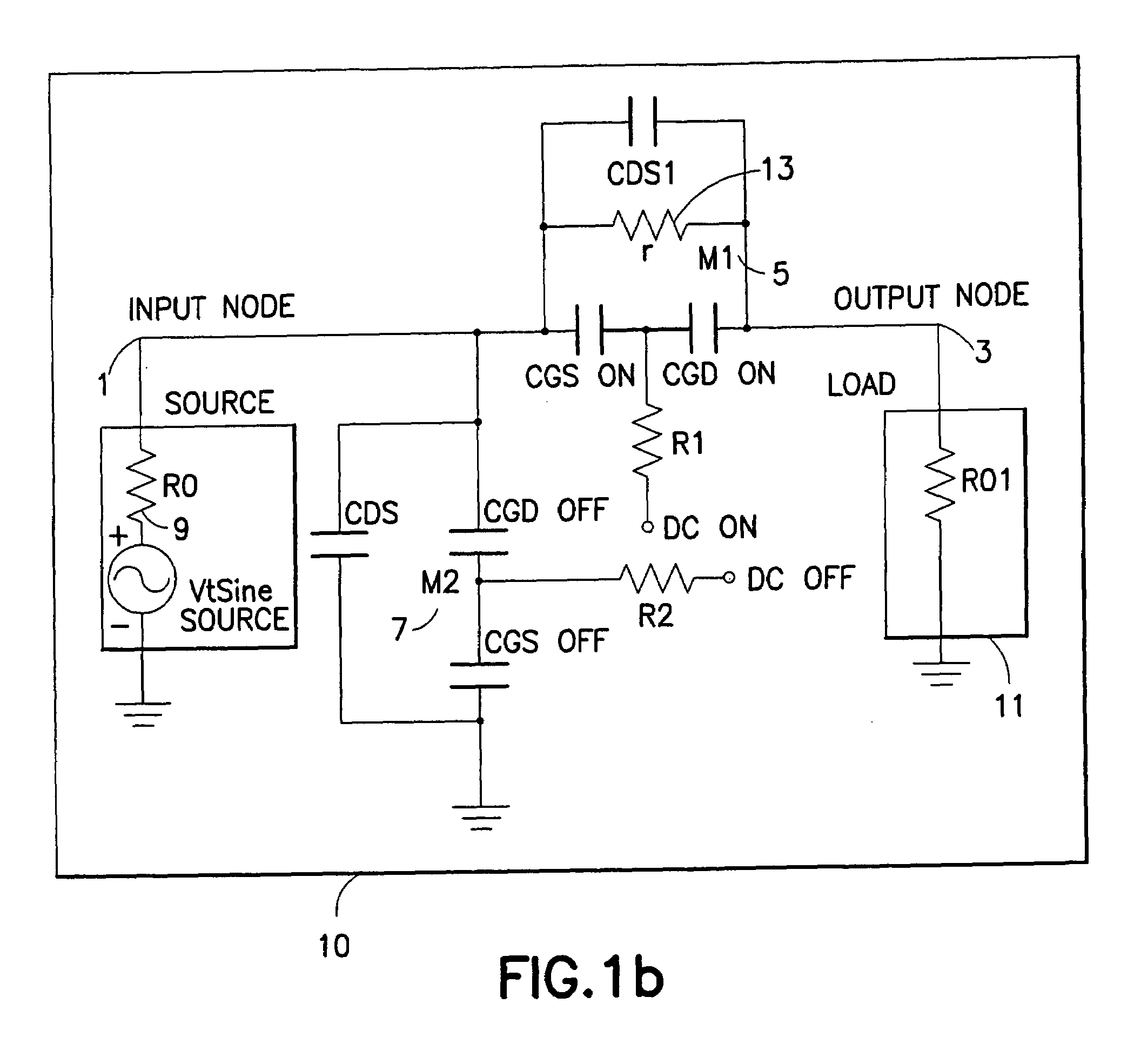

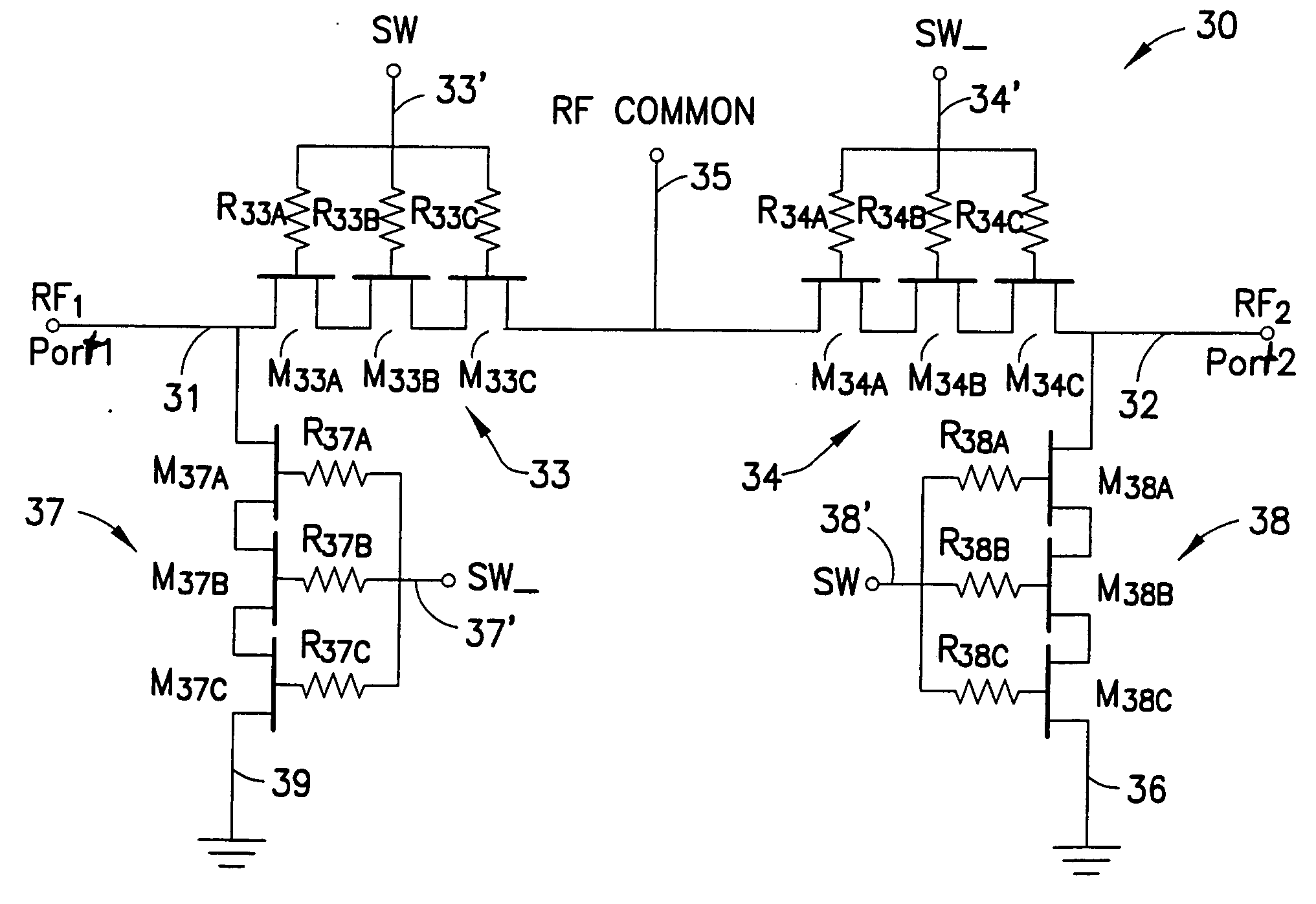

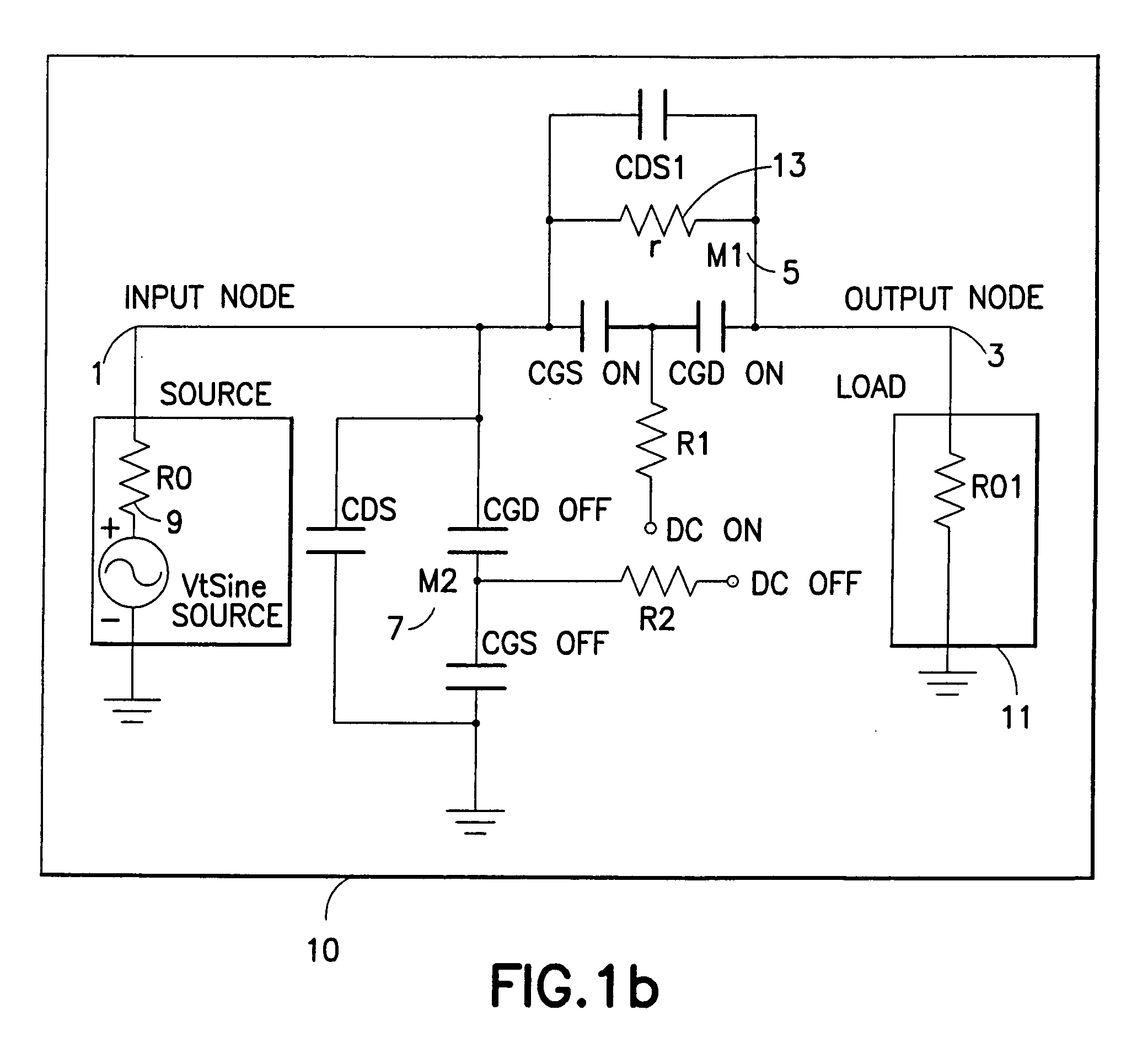

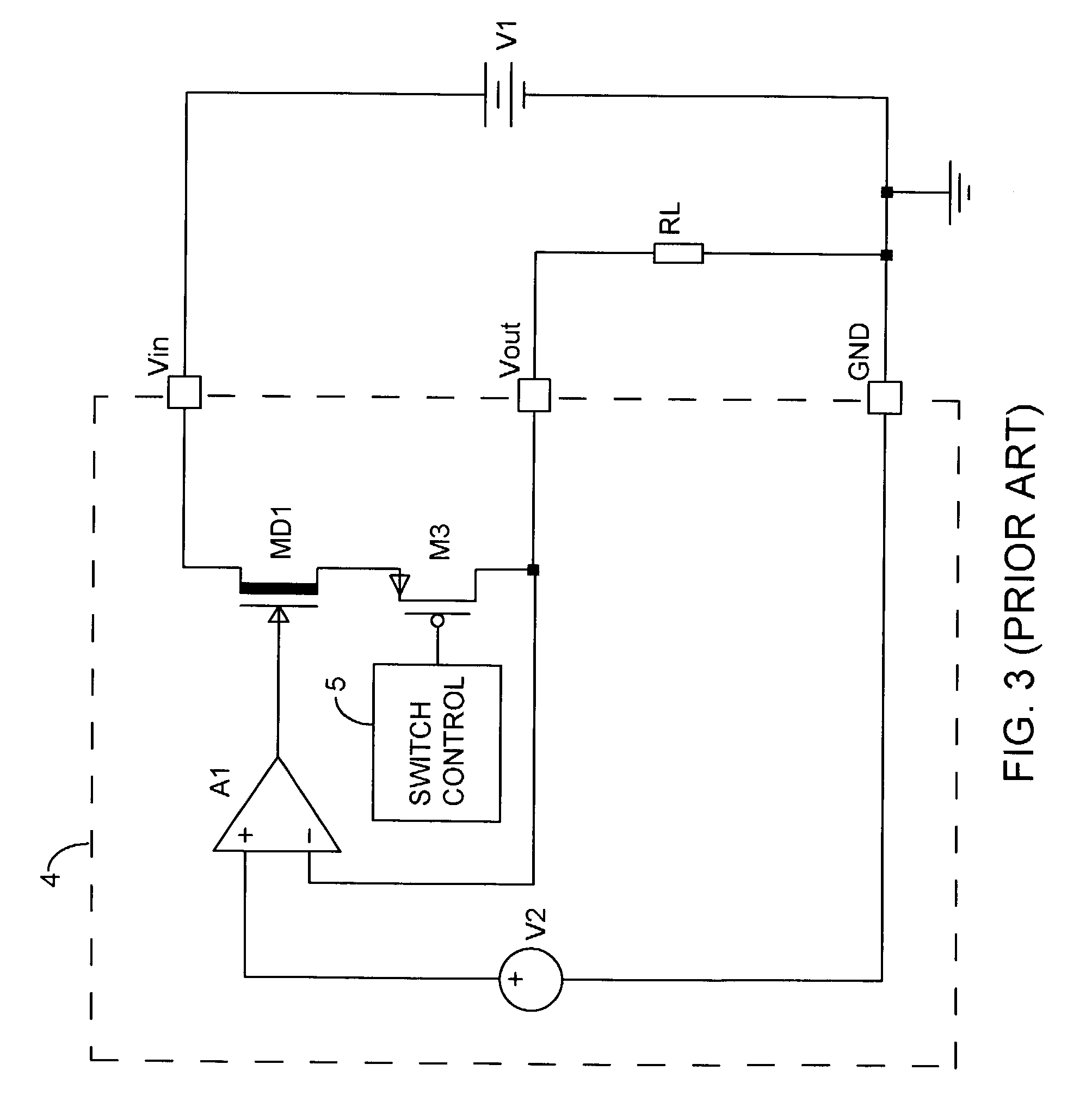

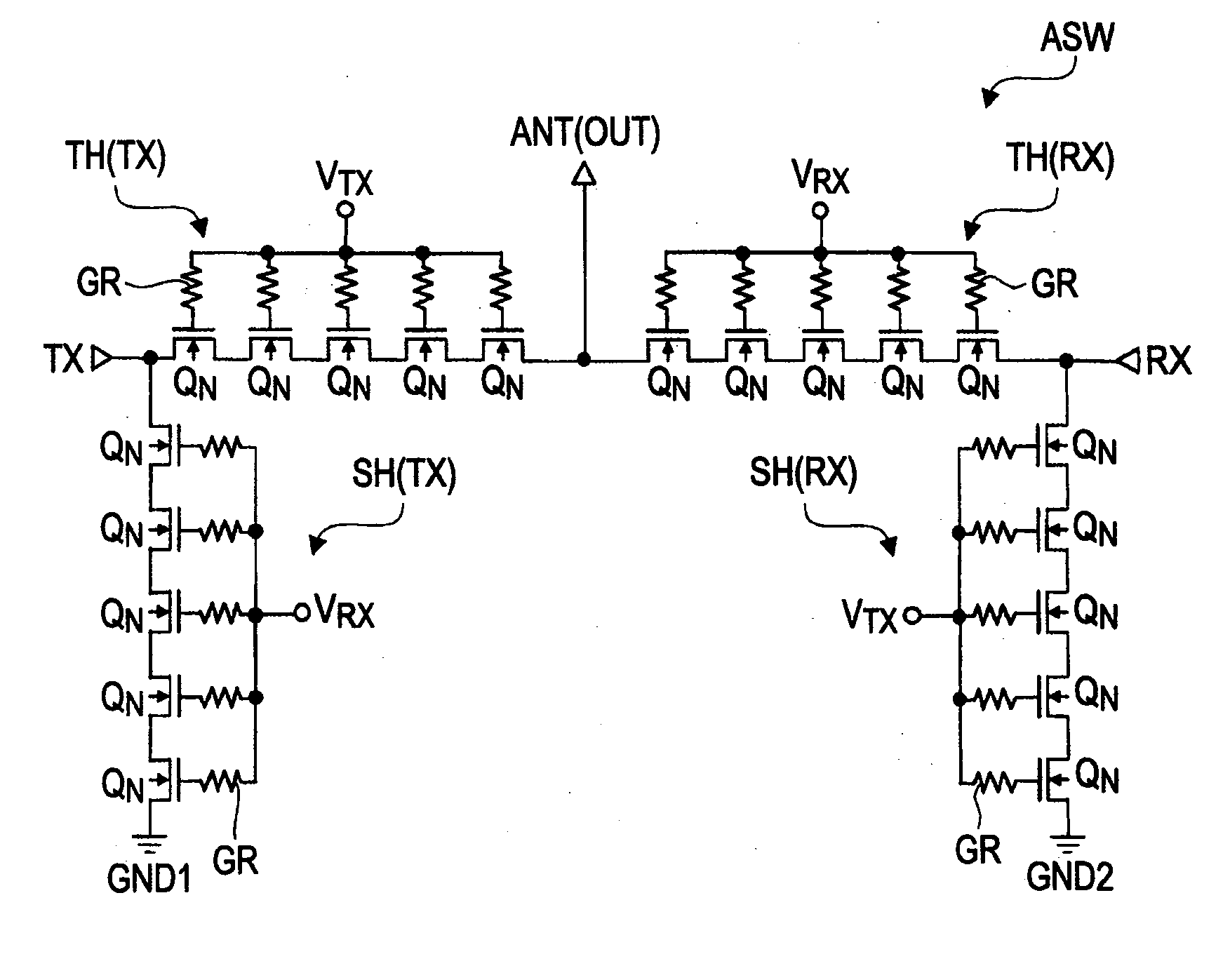

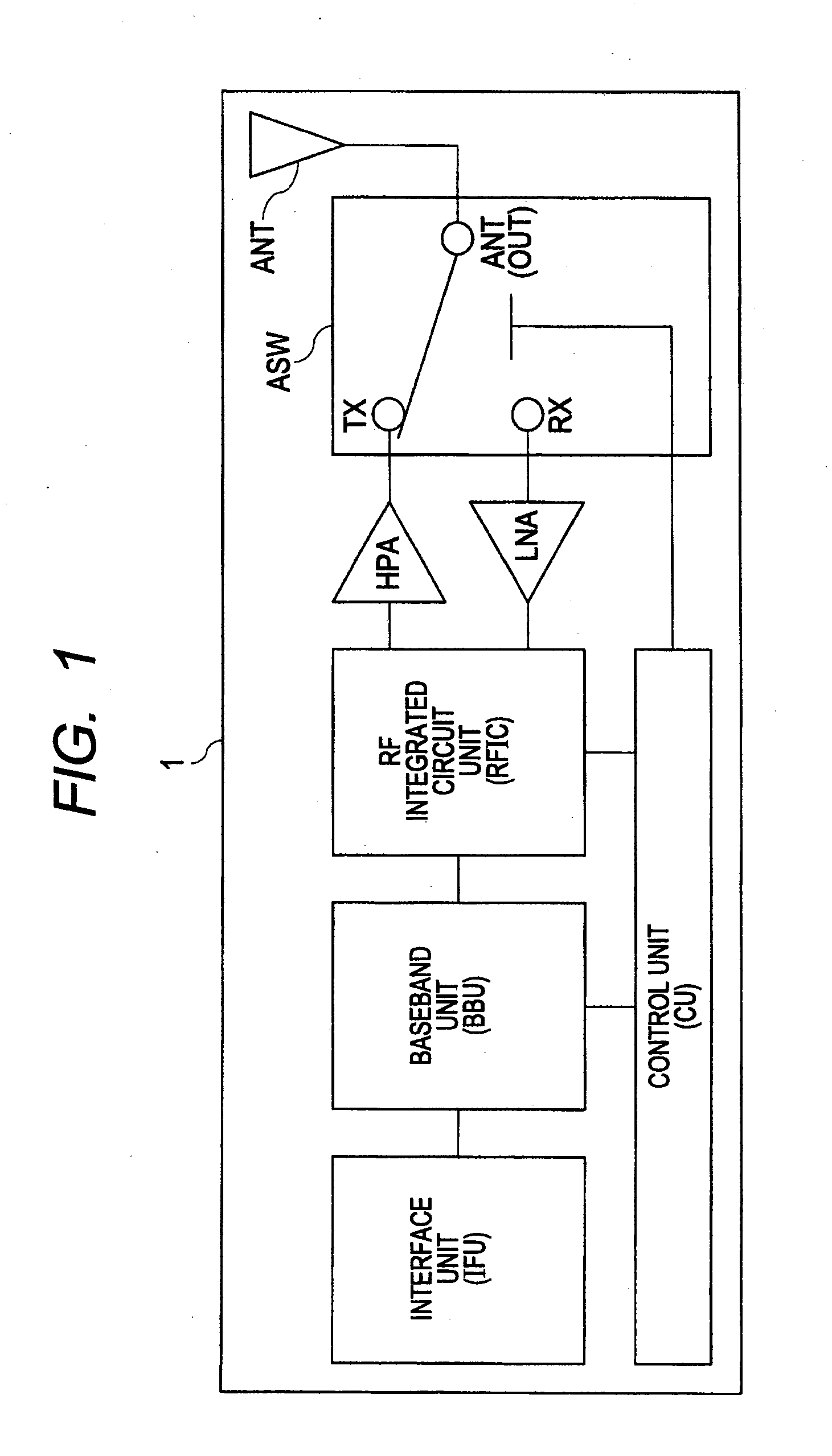

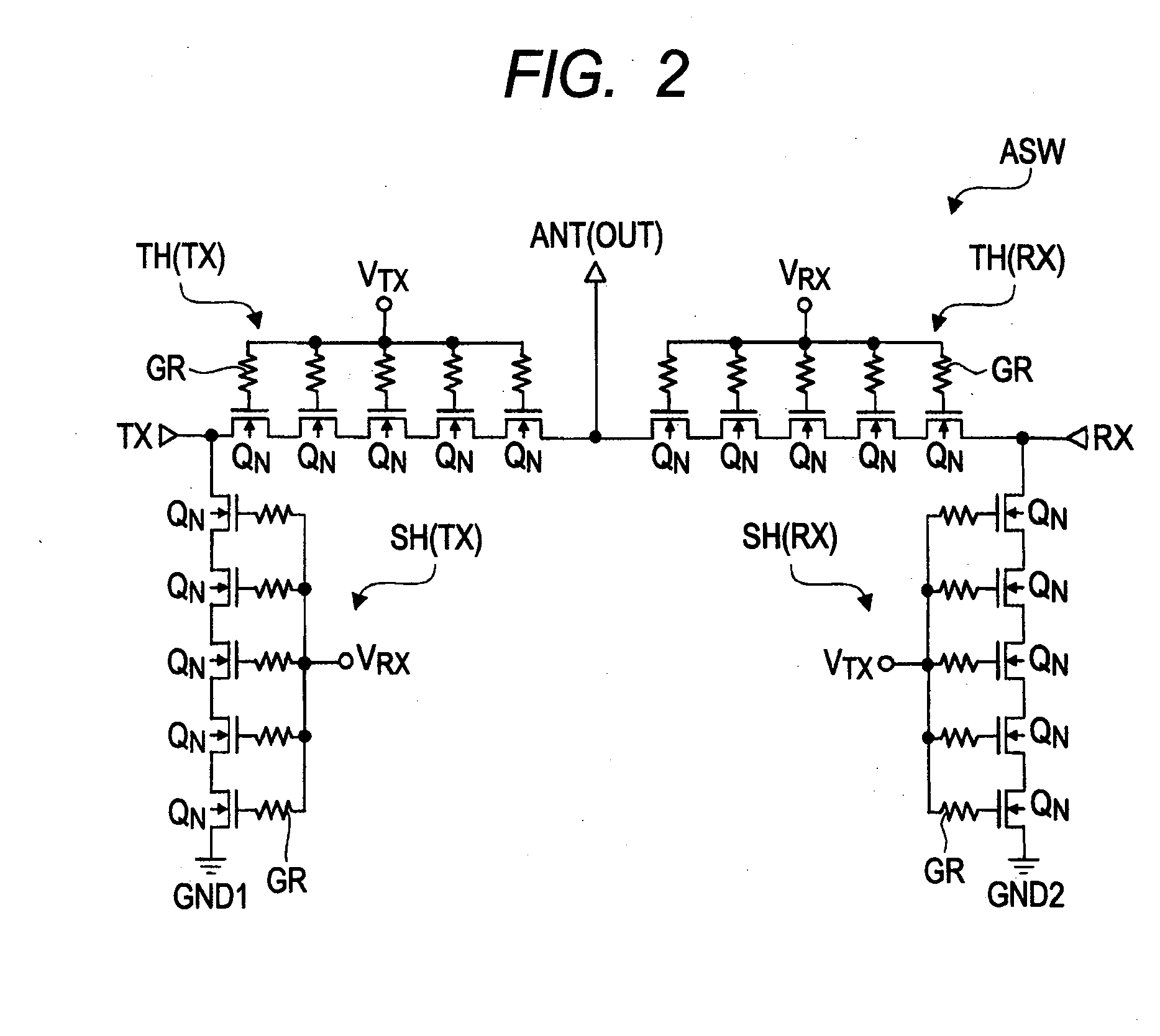

Switch circuit and method of switching radio frequency signals

InactiveUS7123898B2Easy to switchImprove reliabilityTransistorSolid-state devicesMOSFETDigital control

A novel RF buffer circuit adapted for use with an RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. The switching and shunting transistor grouping pairs are controlled by a switching control voltage (SW) and its inverse (SW_). The switching and shunting transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. The stacking of transistor grouping devices, and associated gate resistors, increase the breakdown voltage across the series connected switch transistors and operate to improve RF switch compression. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The inventive RF switch provides improvements in insertion loss, switch isolation, and switch compression.

Owner:PSEMI CORP

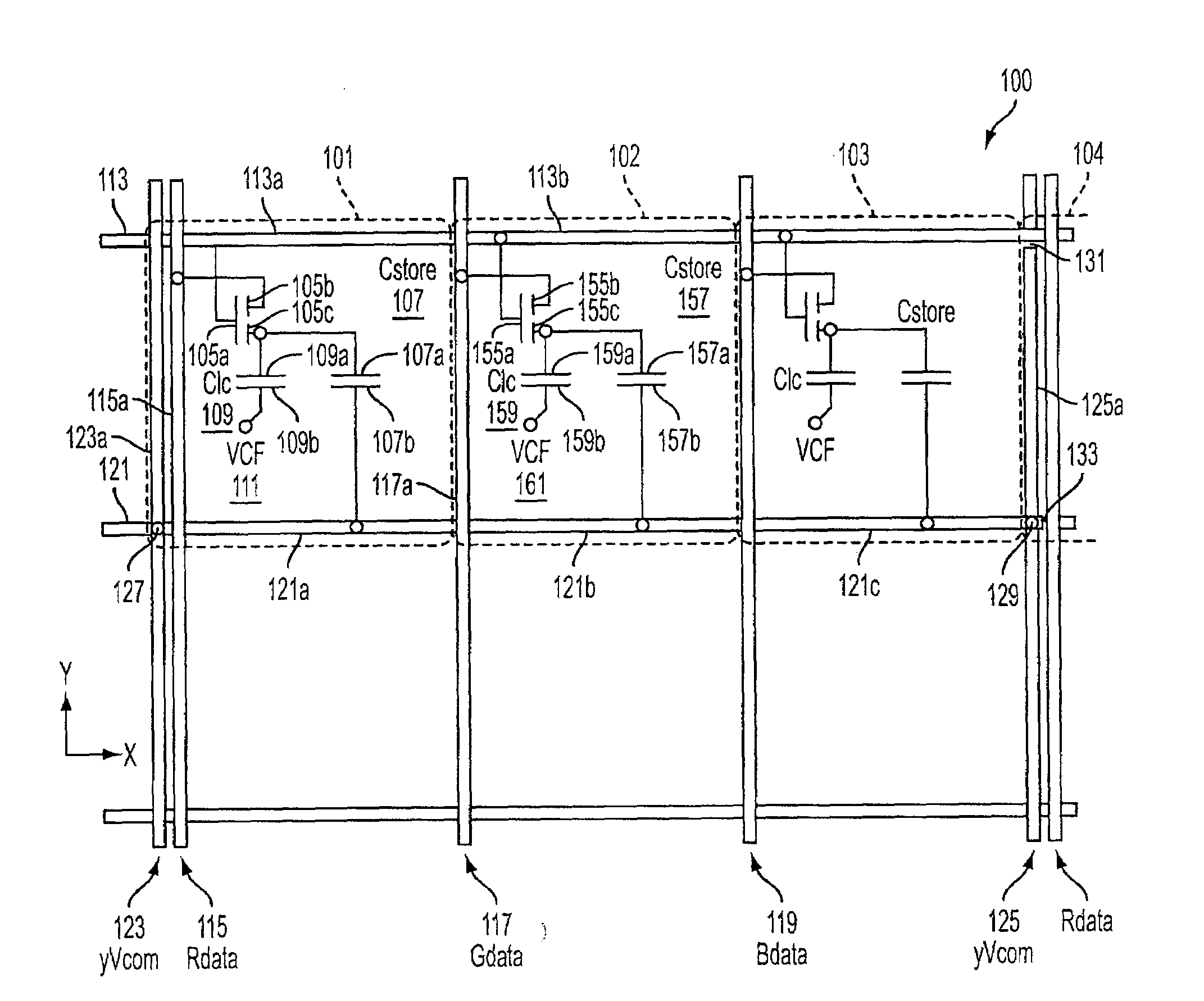

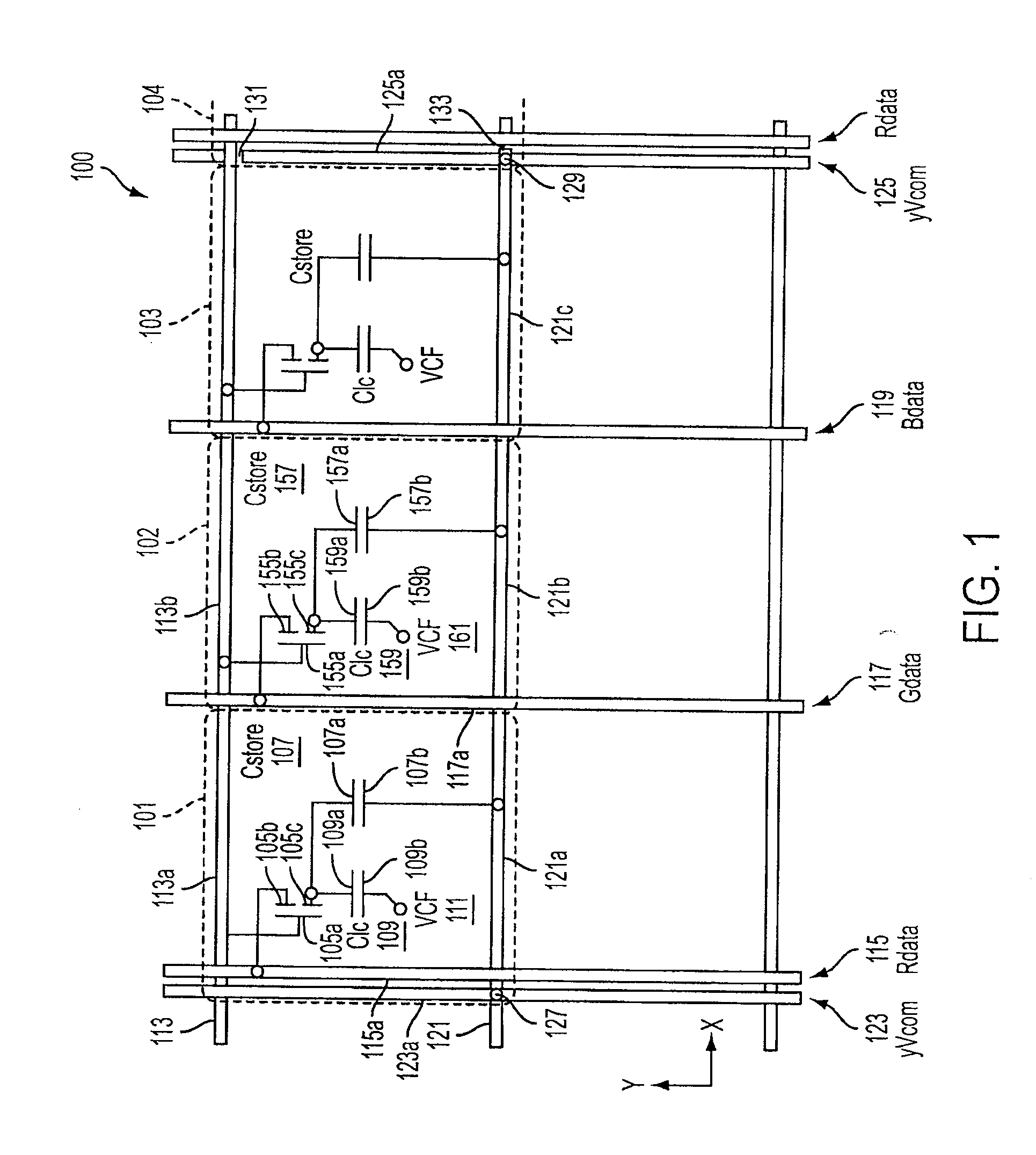

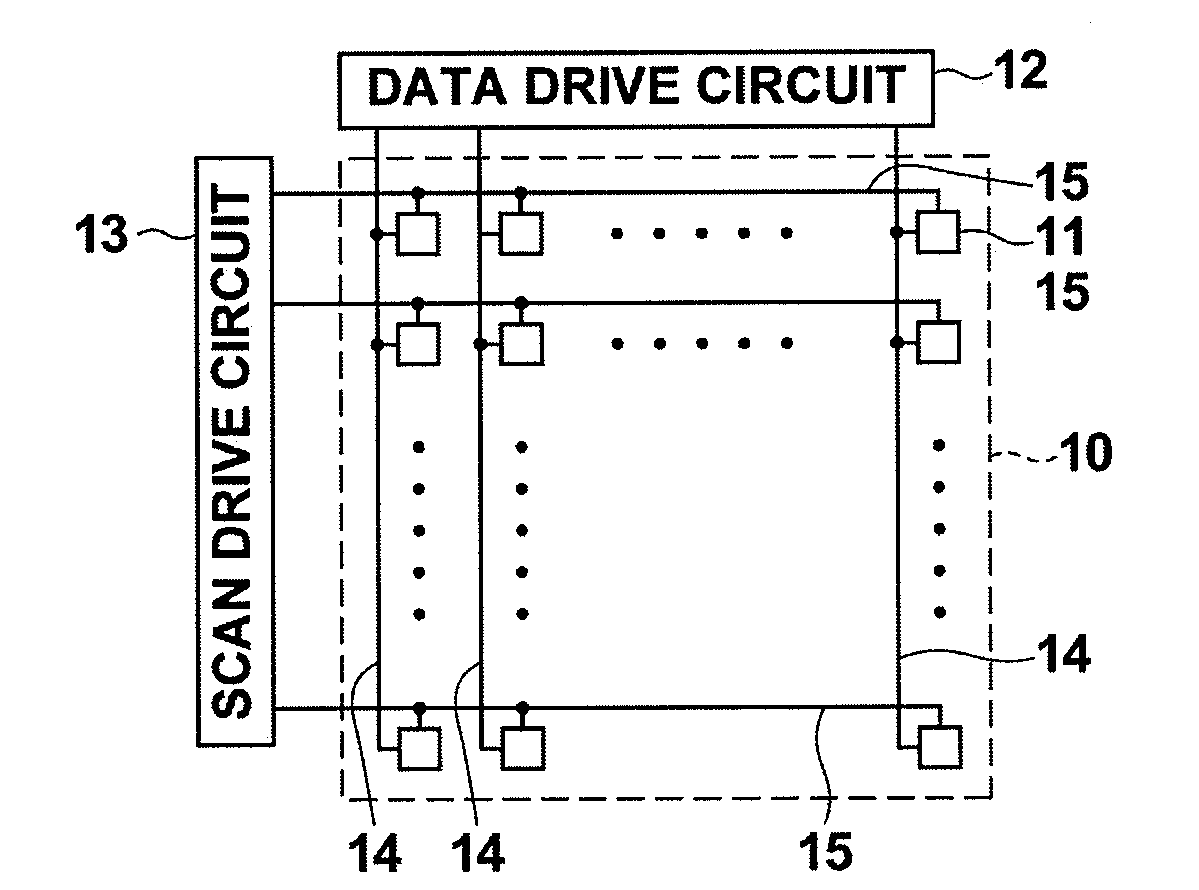

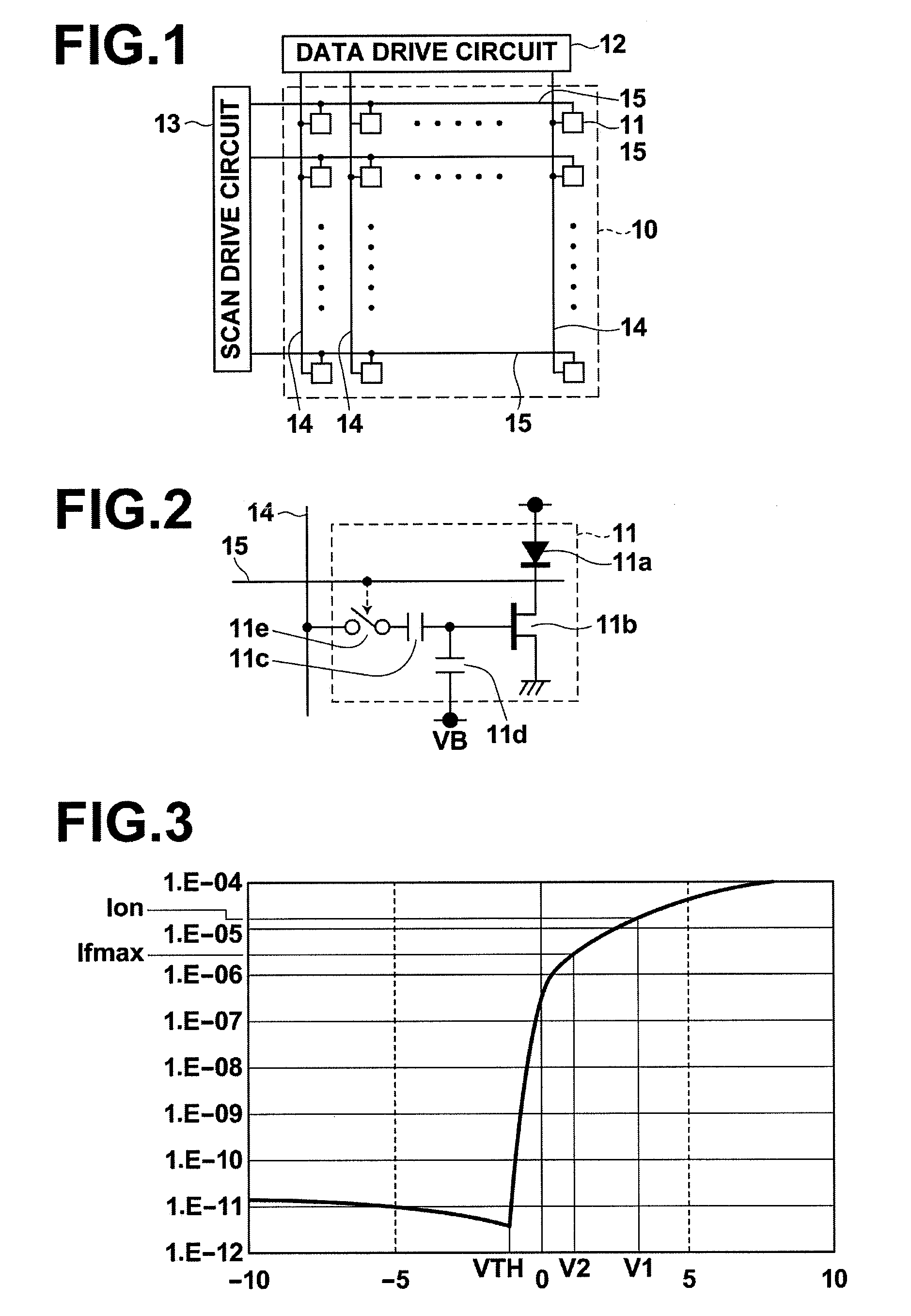

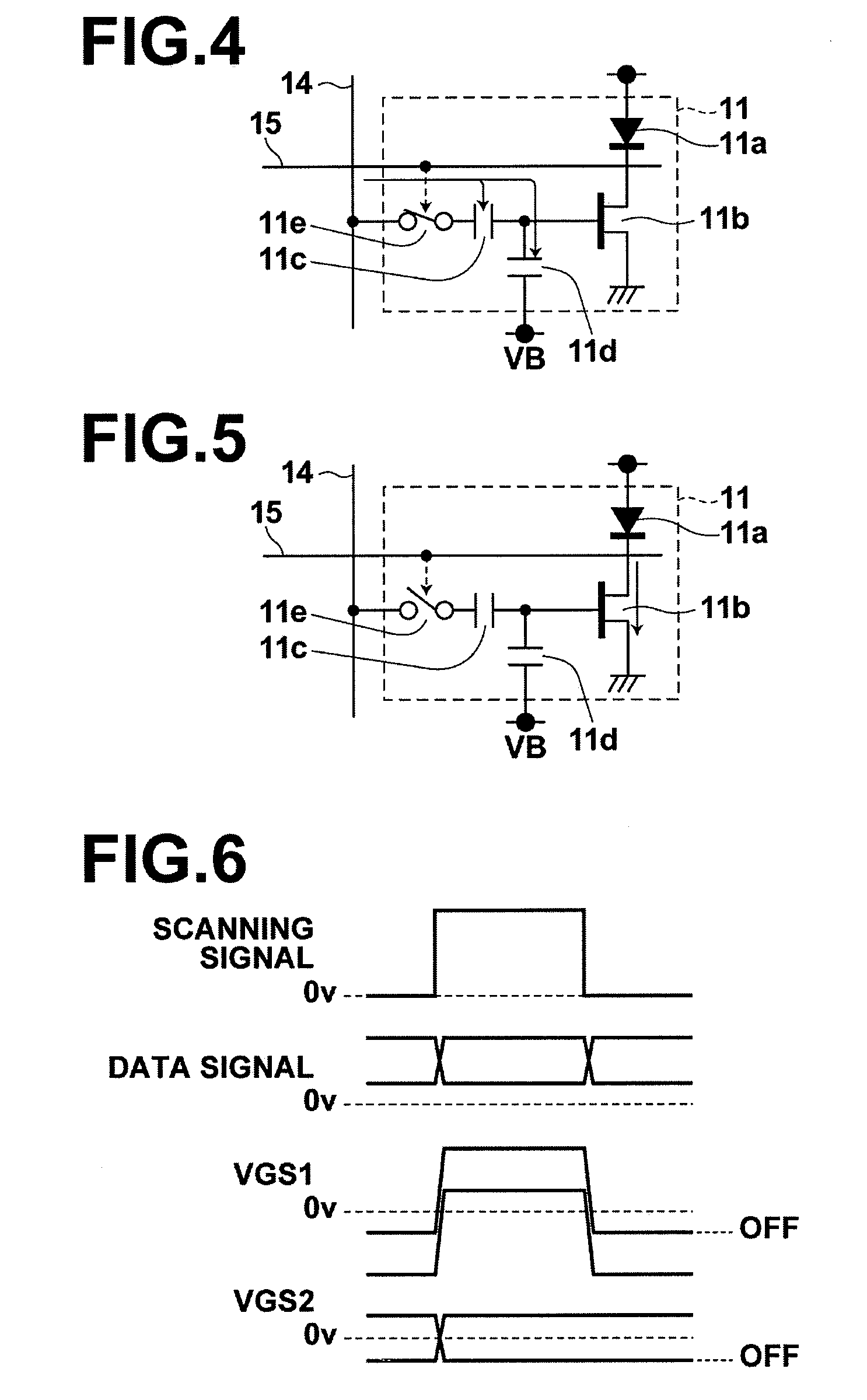

Pixel circuit, display apparatus, and pixel circuit drive control method

ActiveUS20090244046A1Increase power consumptionPromote adequate mobilityElectrical apparatusElectroluminescent light sourcesDriving currentData signal

A pixel circuit including a light emitting element, a driving transistor, connected to the light emitting element, that applies a drive current to the light emitting element, a holding circuit connected to a gate terminal of the driving transistor, and a switching transistor connected between the holding circuit and a data line through which a data signal to be held by the holding circuit flows, in which the driving transistor and the switching transistor are inorganic oxide thin film transistors whose OFF-operation threshold voltage is a negative voltage, and the holding circuit includes a first capacitor element connected between the switching transistor and the gate terminal of the driving transistor, and a second capacitor element connected between a point located between the first capacitor element and the gate terminal of the driving transistor and a voltage source that supplies a negative voltage.

Owner:SAMSUNG DISPLAY CO LTD

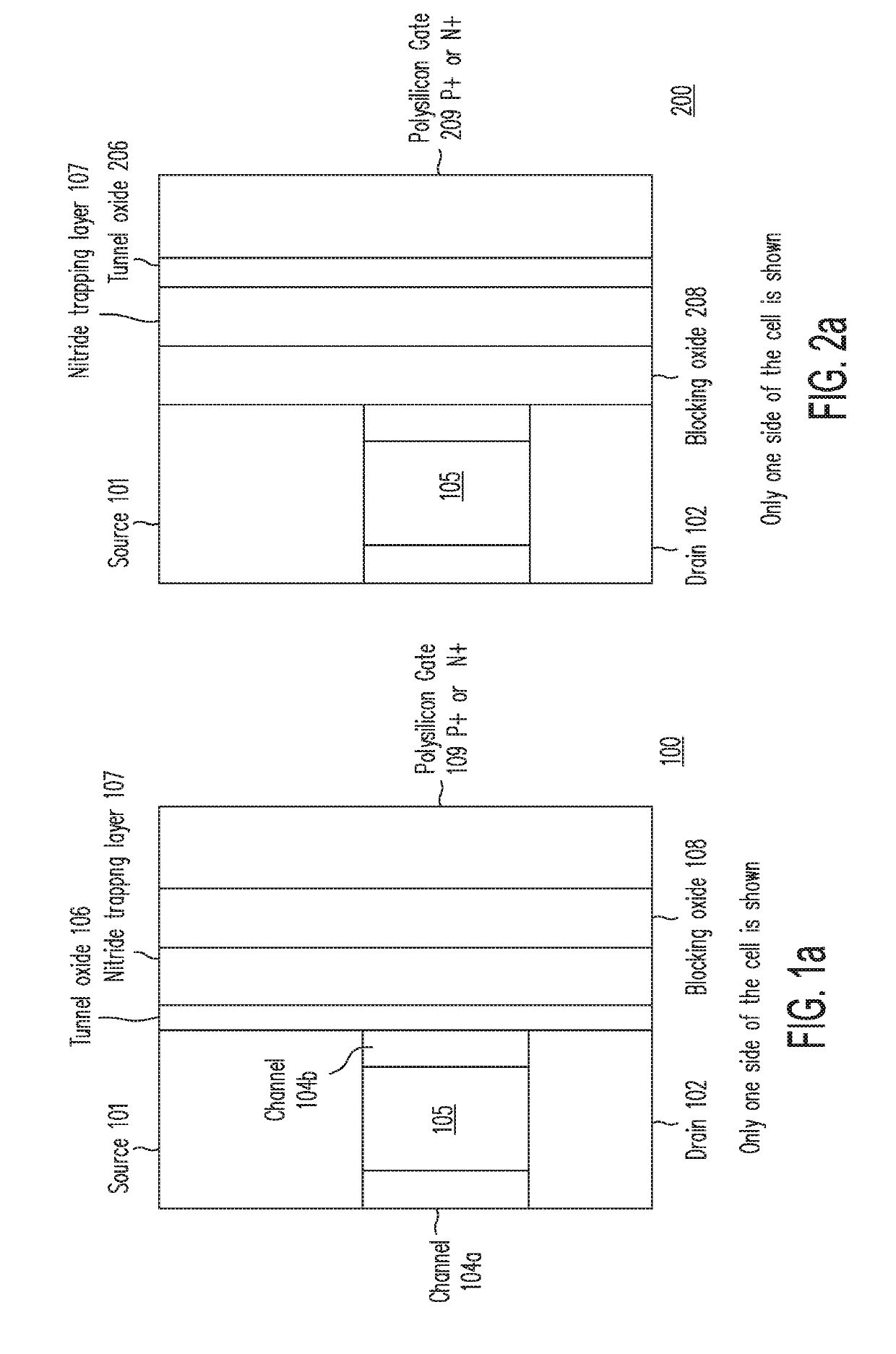

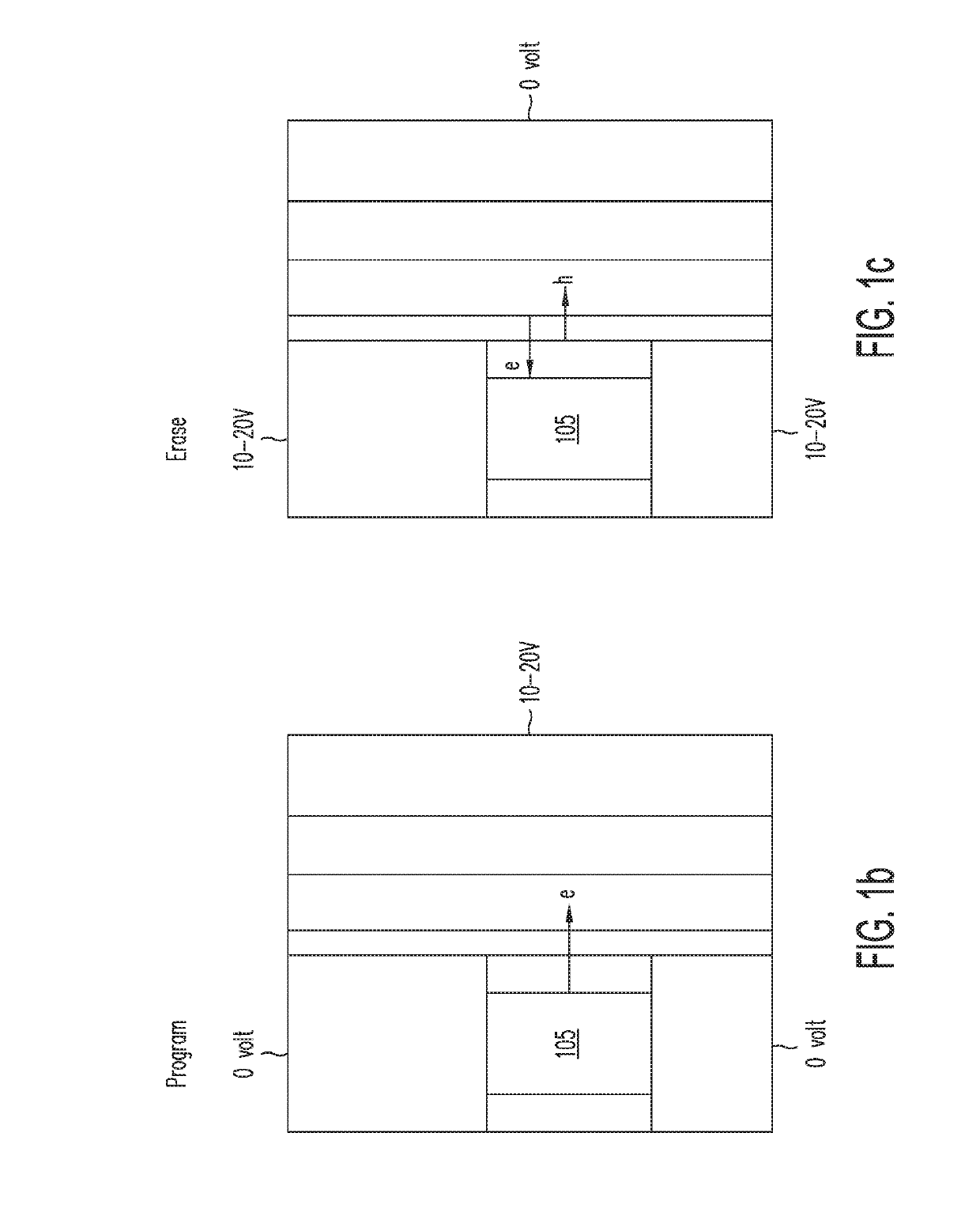

Reverse memory cell

A non-volatile “reverse memory cell” suitable for use as a building block for a 3-dimensional memory array includes a charge-trapping layer which is programmed or charged through gate-injection, rather than channel-injection. Such a reverse cell may be implemented as either an n-channel memory cell or a p-channel memory cell, without incurring design or process penalties, or any complexity in programming or erase operations. Furthermore, all reading, programming, erase, program-inhibiting operations may be carried out in the reverse memory cell using only positive or only negative voltages, thereby simplifying both the design and the power management operations.

Owner:SUNRISE MEMORY CORP

Dual discharge modes operation for remote plasma

ActiveUS9773648B2Increases the electron impact ionization rateIncrease the itineraryElectric discharge tubesVacuum evaporation coatingRemote plasmaProcess region

Embodiments of the present technology may include a method of processing a semiconductor substrate. The method may include providing the semiconductor substrate in a processing region. Additionally, the method may include flowing gas through a cavity defined by a powered electrode. The method may further include applying a negative voltage to the powered electrode. Also, the method may include striking a hollow cathode discharge in the cavity to form hollow cathode discharge effluents from the gas. The hollow cathode discharge effluents may then be flowed to the processing region through a plurality of apertures defined by electrically grounded electrode. The method may then include reacting the hollow cathode discharge effluents with the semiconductor substrate in the processing region.

Owner:APPLIED MATERIALS INC

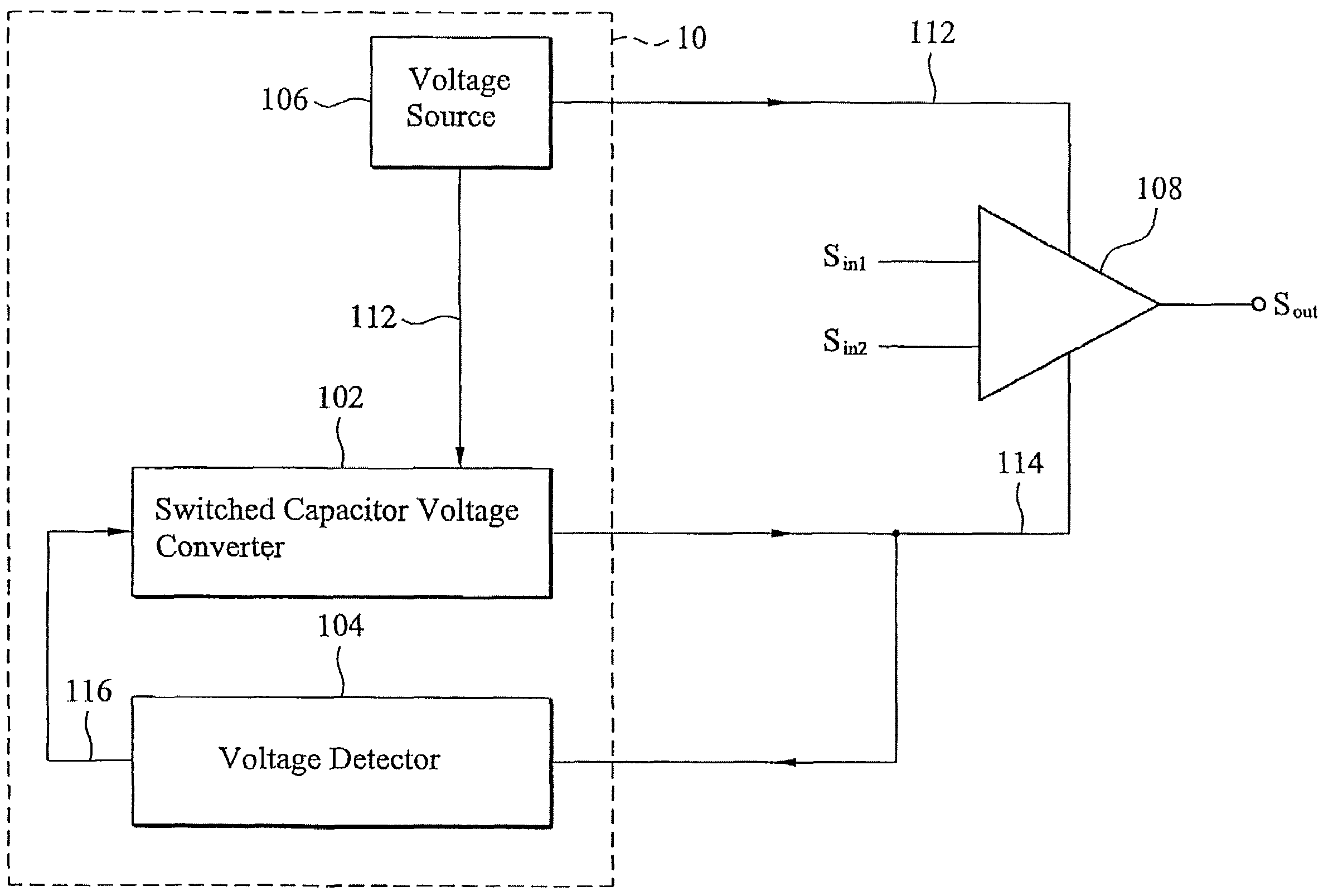

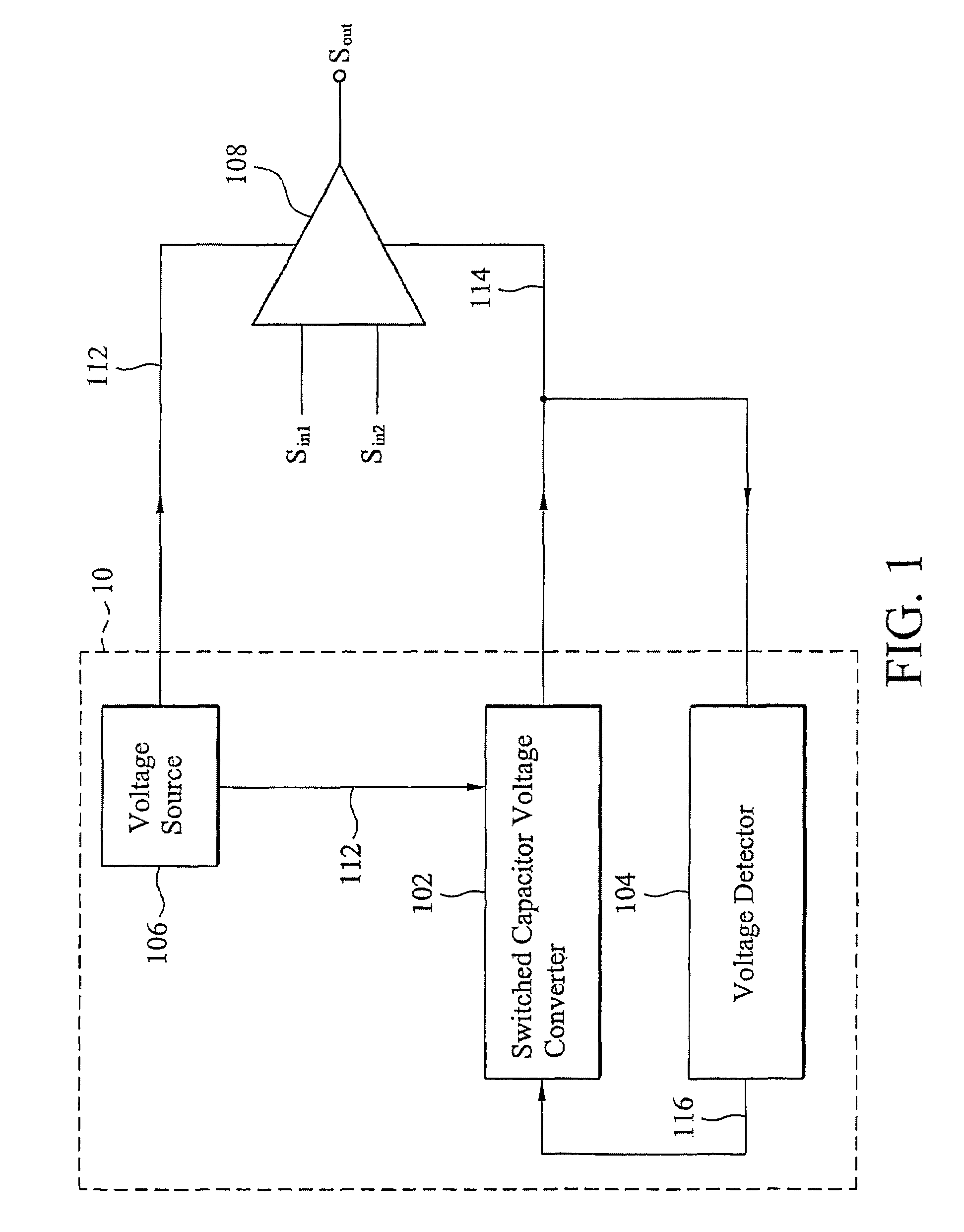

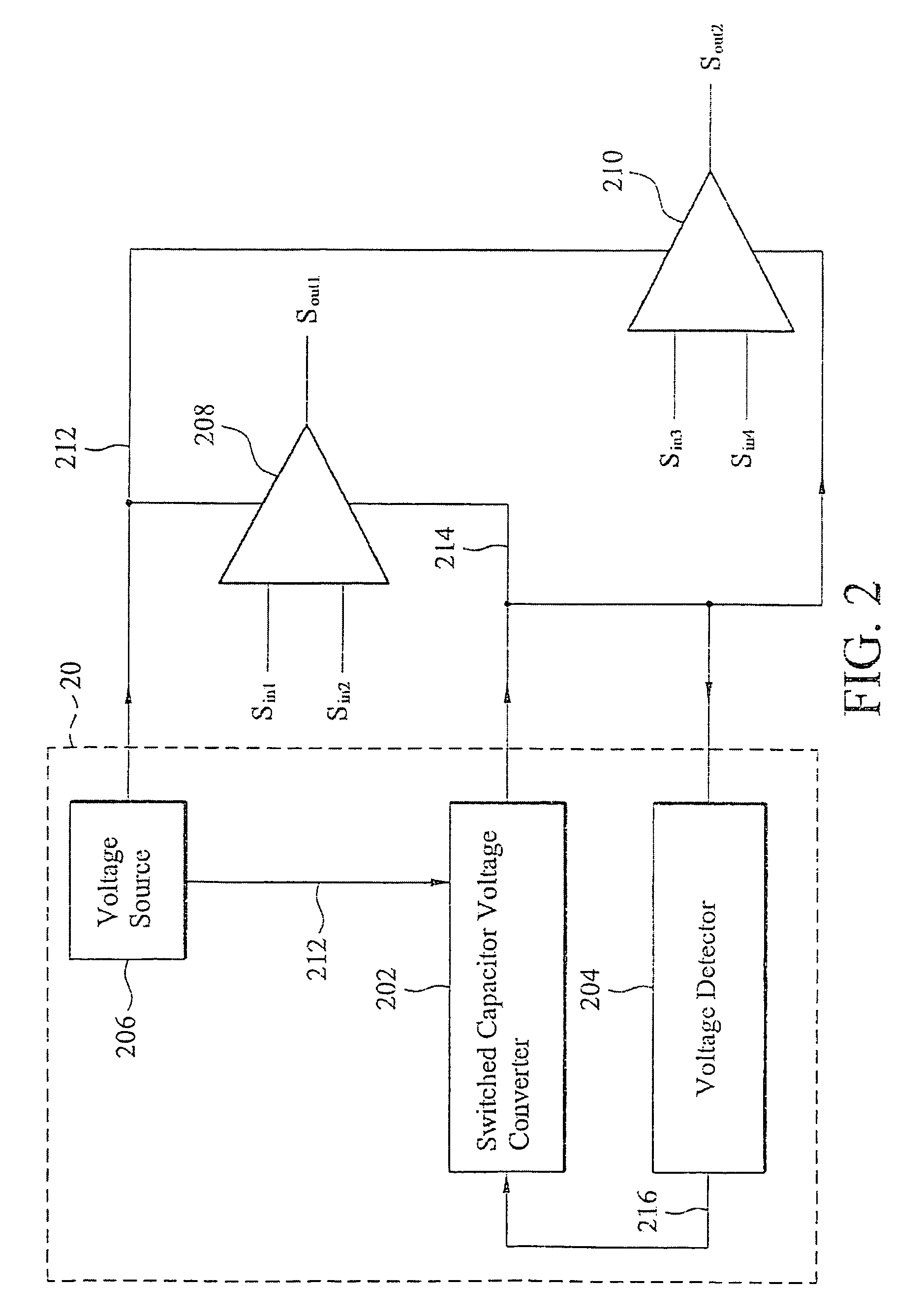

Voltage generating apparatus and methods

InactiveUS7609114B2Amplifier detailsAmplifiers with semiconductor devices onlyVoltage converterAudio power amplifier

The invention provides a voltage generating apparatus for powering at least one amplifier. The voltage generating apparatus comprises a voltage source, a switched capacitor voltage converter and a voltage detector. The voltage source supplies a first voltage to a positive voltage input terminal of the at least one amplifier. The first voltage is a positive DC voltage. The switched capacitor voltage converter is coupled to the voltage source for outputting an output voltage to a negative voltage input terminal of the at least one amplifier according to the first voltage and a predetermined voltage. The output voltage is a negative DC voltage. The voltage detector is coupled to the switched capacitor voltage converter for determining a switching frequency corresponding to the predetermined voltage according to the output voltage. The switched capacitor voltage converter increases the output voltage when the switching frequency is decreased and decreases the output voltage when the switching frequency is increased.

Owner:UPI SEMICON CORP

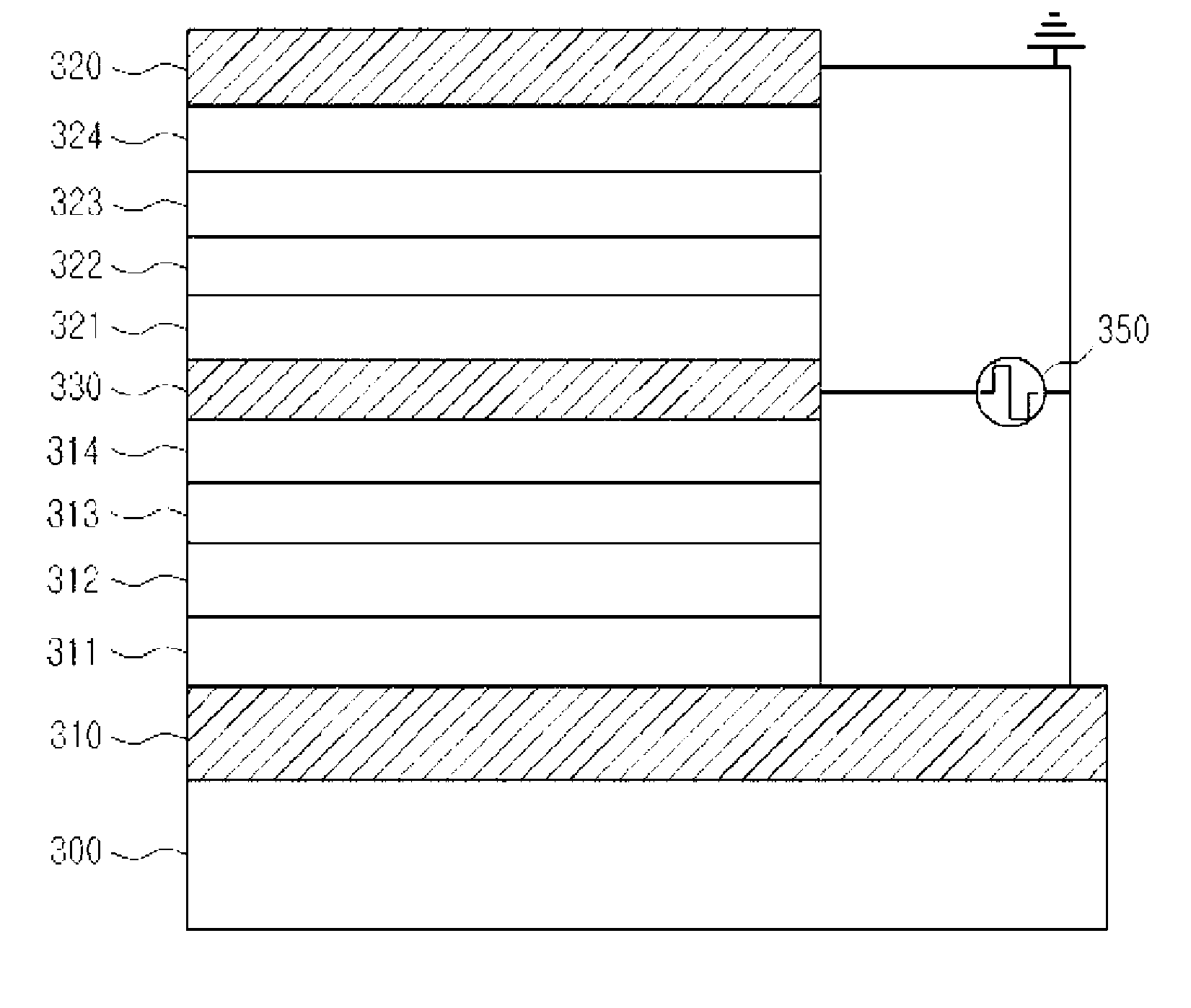

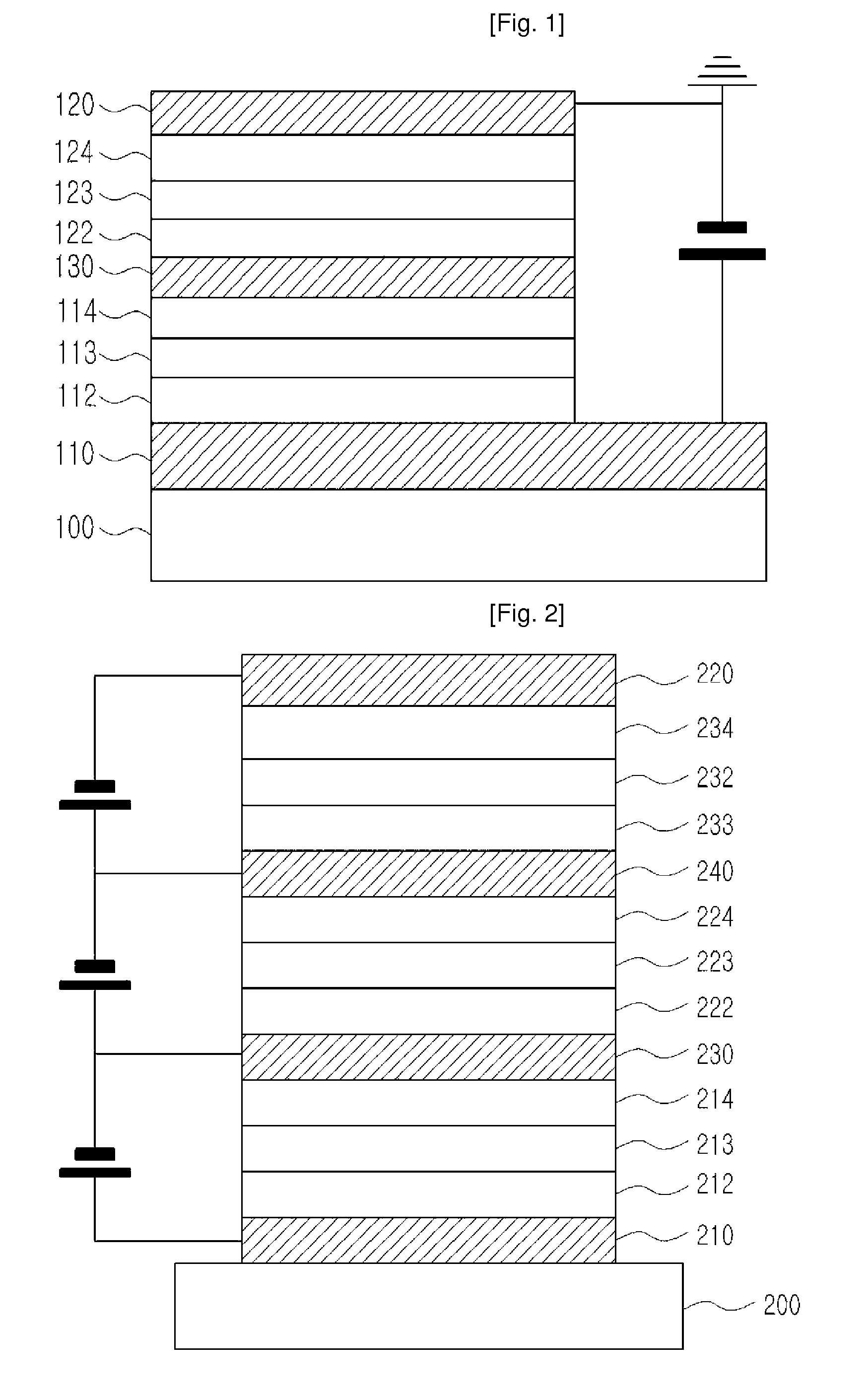

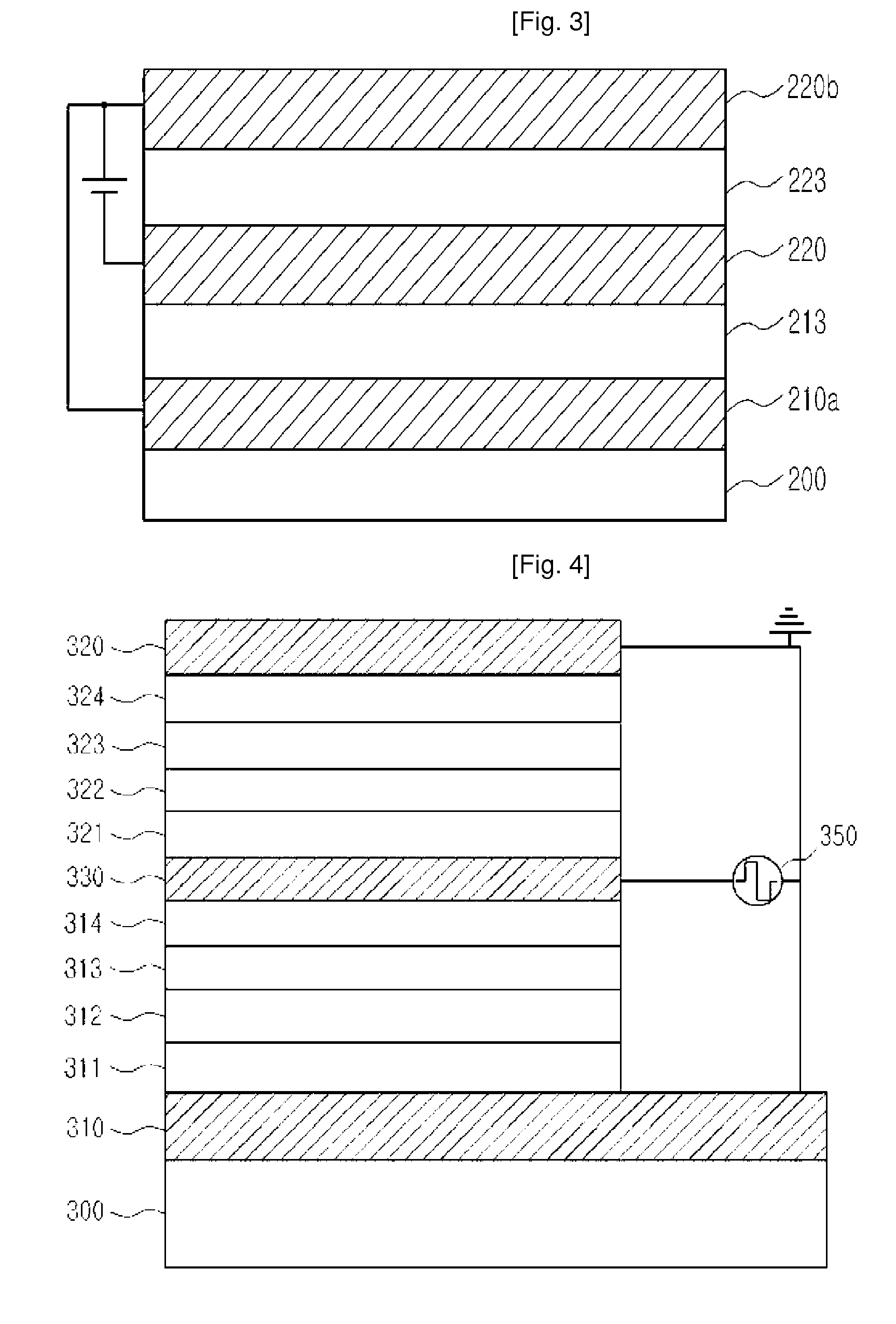

Oled Having Stacked Organic Light-Emitting Units

ActiveUS20090009101A1Lower electrical barrierImprove availabilityElectroluminescent light sourcesSolid-state devicesOrganic light emitting deviceElectrical connection

The present invention provides a stacked organic light emitting device, comprising a first conductive layer, at least one intermediate conductive layer and a second conductive layer, and light emitting units disposed between the conductive layers, wherein at least two non-neighboring conductive layers among the conductive layers are conductive layers belonging to Group 1 such that they are electrically connected with each other to a common potential; at least one non-neighboring conductive layer among the conductive layers which are not electrically connected with the conductive layers belonging to Group 1 to a common potential are conductive layers belonging to Group 2 such that they are electrically connected with each other to a common potential; and the conductive layers belonging to Group 1 and the conductive layers belonging to Group 2 are connected with each other via a voltage regulator for alternately applying a positive voltage and a negative voltage.

Owner:LG DISPLAY CO LTD

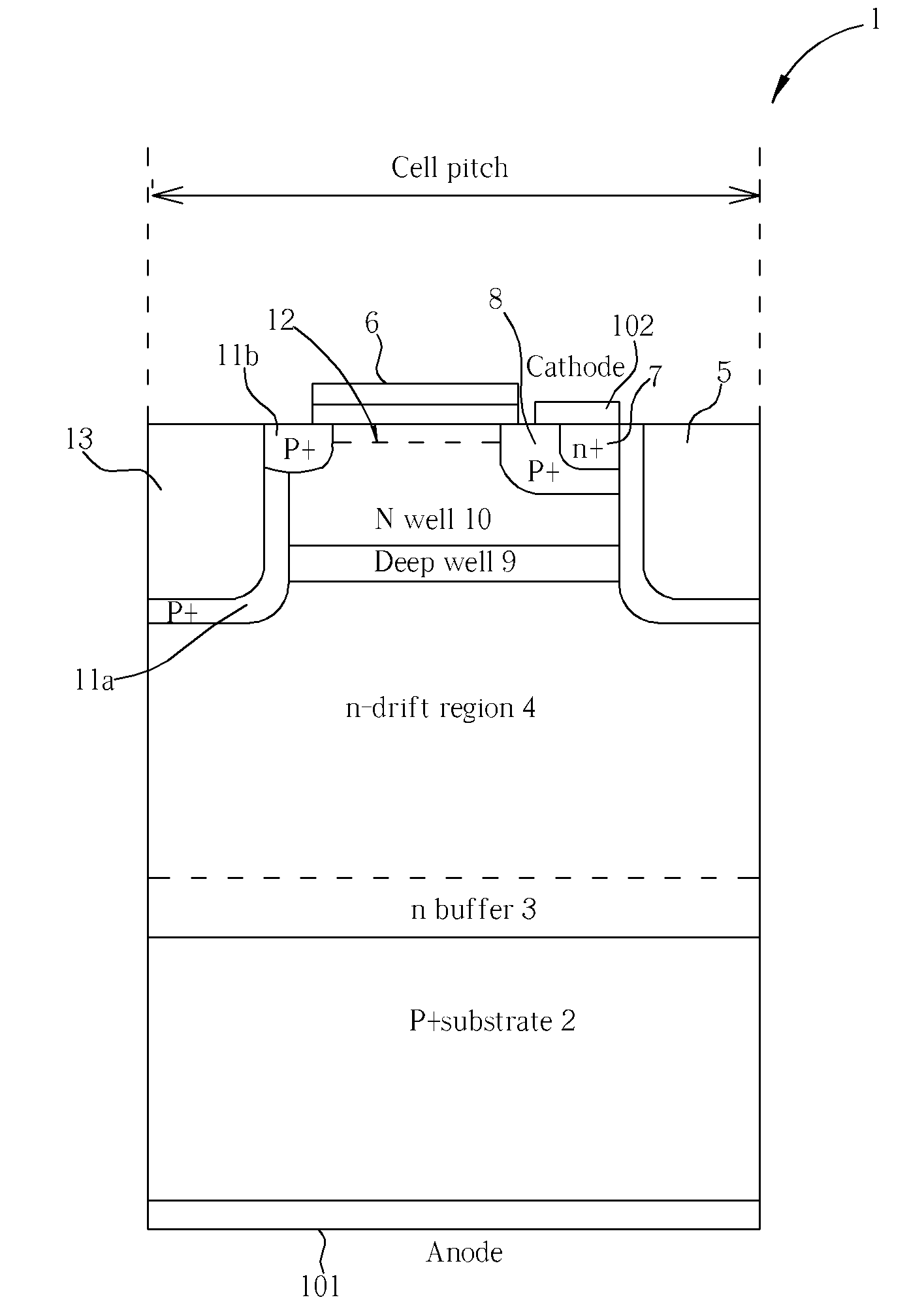

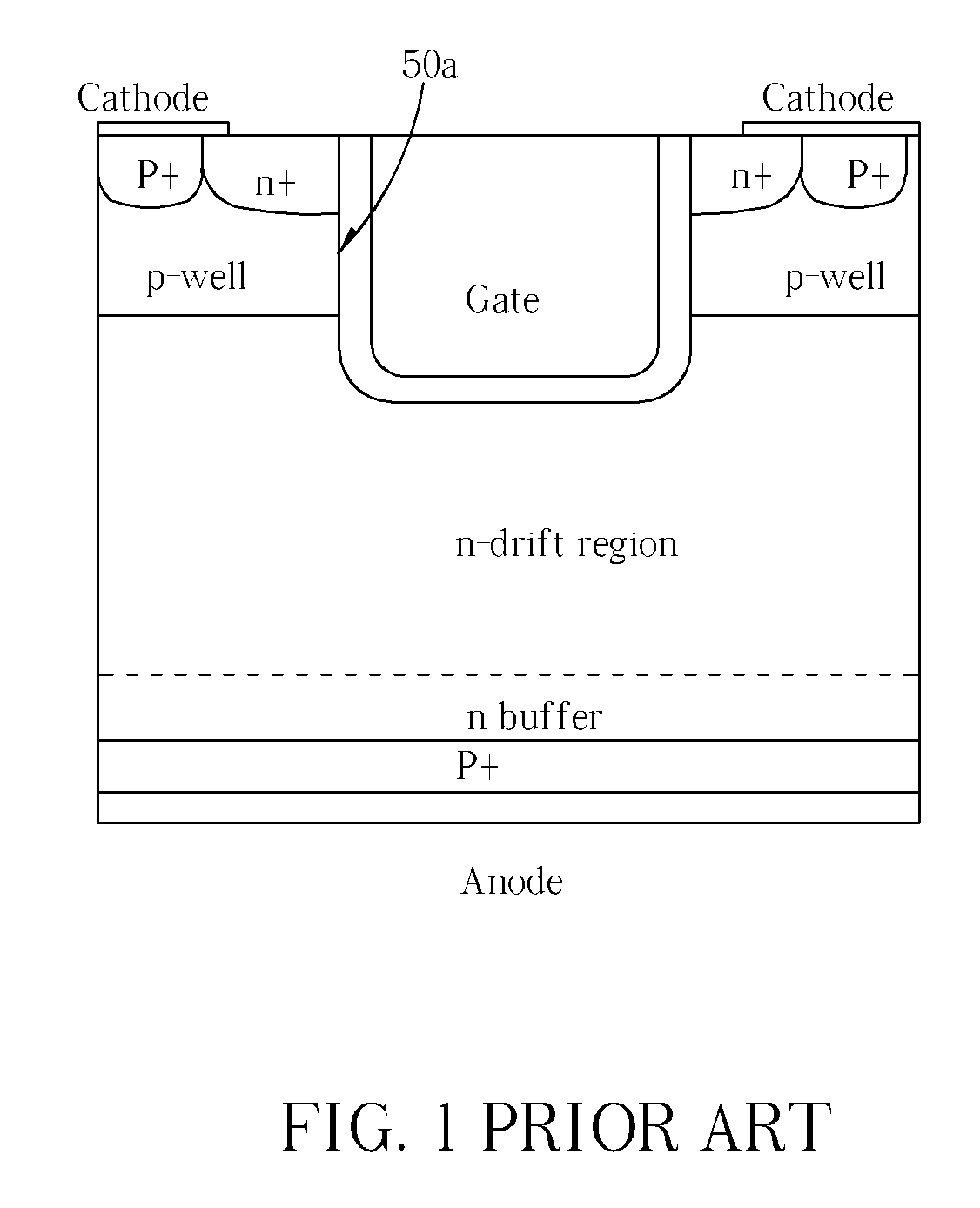

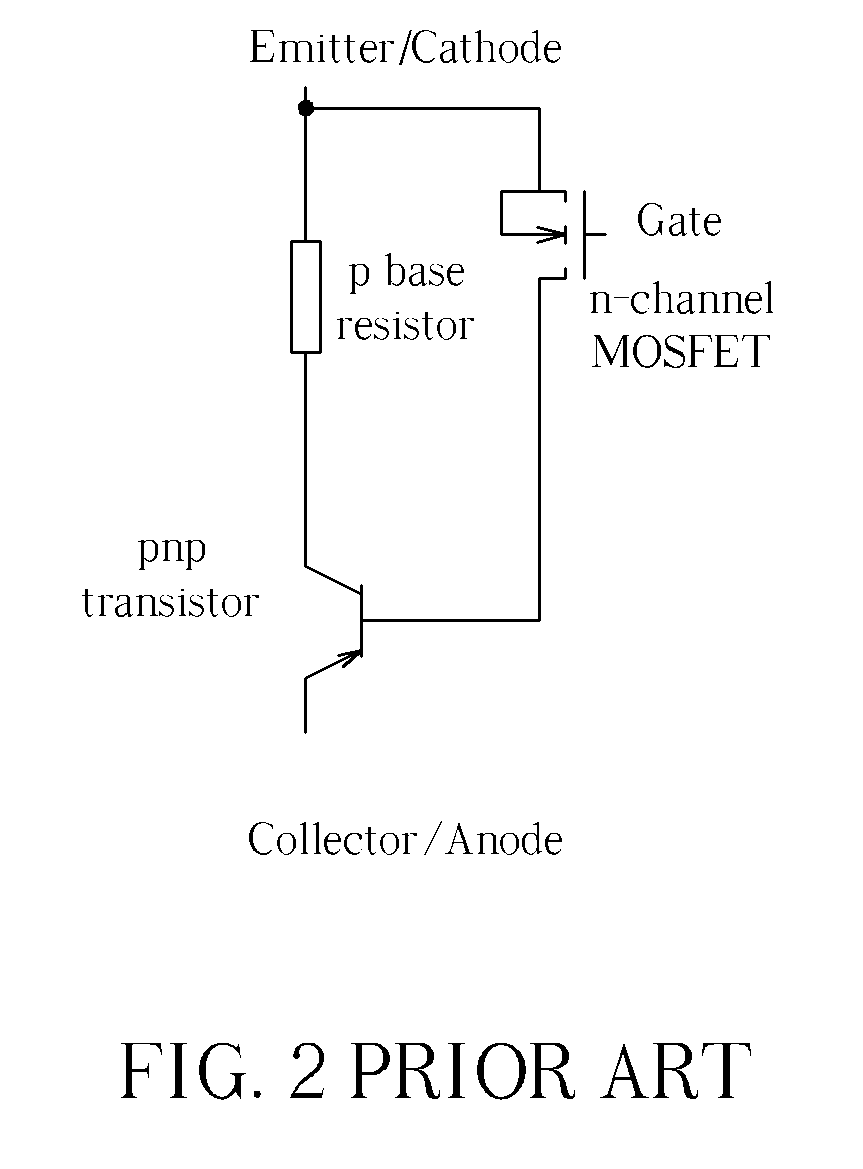

Double gate insulated gate bipolar transistor

InactiveUS20090008674A1Reduce the number of holesReduce transportationTransistorSolid-state devicesParasitic bipolar transistorEngineering

Double gate IGBT having both gates referred to a cathode in which a second gate is for controlling flow of hole current. In on-state, hole current can be largely suppressed. While during switching, hole current is allowed to flow through a second channel. Incorporating a depletion-mode p-channel MOSFET having a pre-formed hole channel that is turned ON when 0V or positive voltages below a specified threshold voltage are applied between second gate and cathode, negative voltages to the gate of p-channel are not used. Providing active control of holes amount that is collected in on-state by lowering base transport factor through increasing doping and width of n well or by reducing injection efficiency through decreasing doping of deep p well. Device includes at least anode, cathode, semiconductor substrate, n− drift region, first & second gates, n+ cathode region; p+ cathode short, deep p well, n well, and pre-formed hole channel.

Owner:ANPEC ELECTRONICS CORPORATION

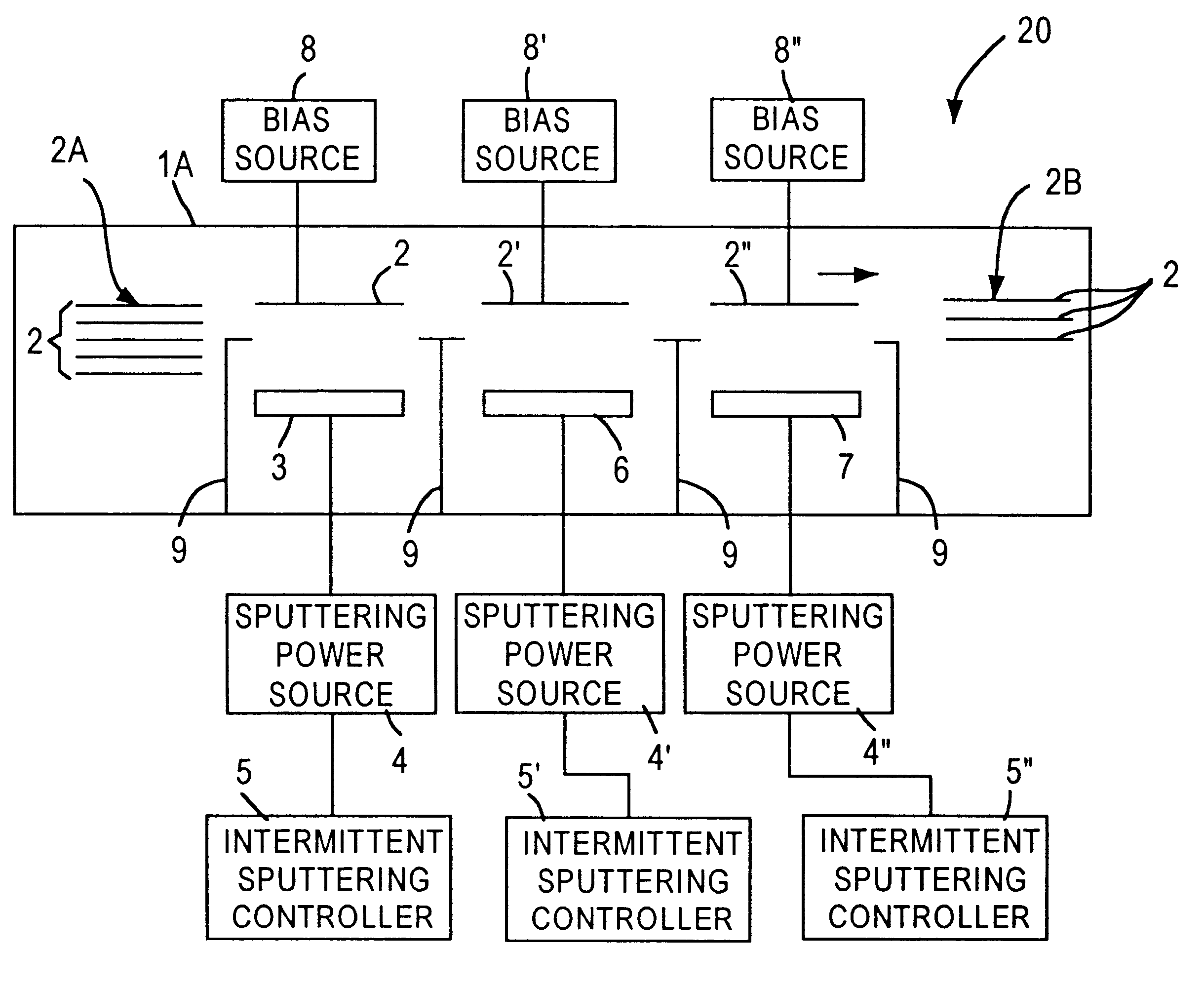

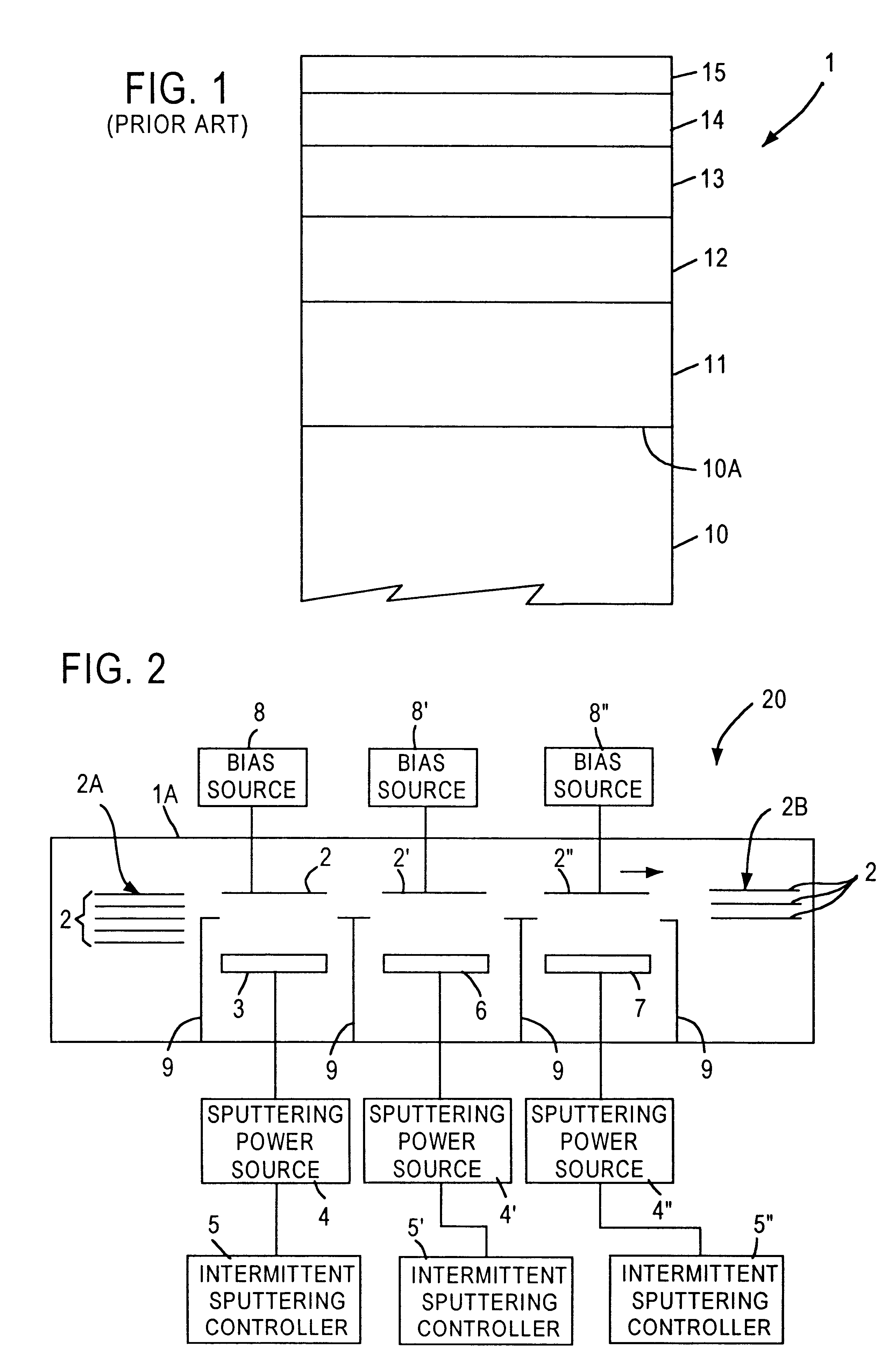

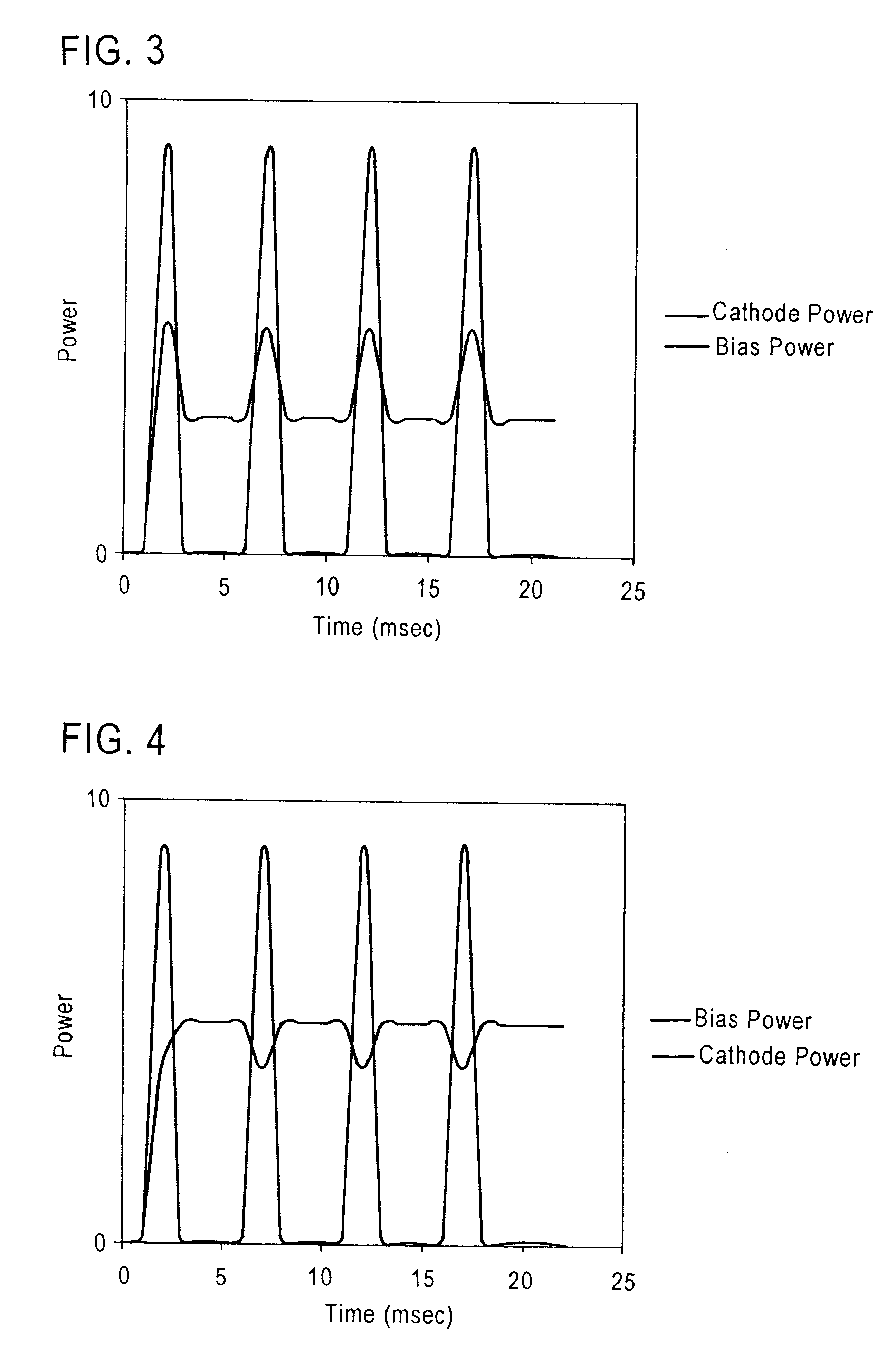

Sputter deposition utilizing pulsed cathode and substrate bias power

InactiveUS6290821B1Simple methodVacuum evaporation coatingSputtering coatingOptoelectronicsSubstrate bias voltage

A method for depositing on a substrate surface a thin film layer comprising a target material comprises providing a cathode including a target having a sputtering surface comprised of the target material, with the target sputtering surface facing the substrate surface with a space therebetween, and sputtering the target material onto the substrate surface by applying a plurality of negative voltage pulses to the cathode while simultaneously applying a bias voltage to the substrate. Embodiments include depositing thin film layers onto static or moving substrates and application of constant or time-varying substrate bias voltage. The invention finds particular utility in the formation of high purity layers in the automated manufacture of magnetic data / information storage and retrieval media.

Owner:SEAGATE TECH LLC

Semiconductor memory device

ActiveUS20080279017A1Bus width can be greatHigh bandwidthRead-only memoriesDigital storageHigh tension lineEngineering

During a stand-by state in which power supply is cut off, a high-voltage power supply control circuit isolates a global negative voltage line transmitting a negative voltage and a local negative voltage line provided corresponding to each respective sub array block from each other and isolates a global ground line and a local ground line transmitting a ground voltage from each other. These local ground line and local negative voltage line are charged to a high voltage level through a high voltage line before cut-off from the corresponding power supply. A leakage current path from a word line to the negative voltage line or the ground line is cut off, so that the word line in a non-selected state can reliably be maintained at a non-selection voltage. Thus, in a low power consumption stand-by mode, data stored in a memory cell can be held in a stable manner.

Owner:RENESAS ELECTRONICS CORP

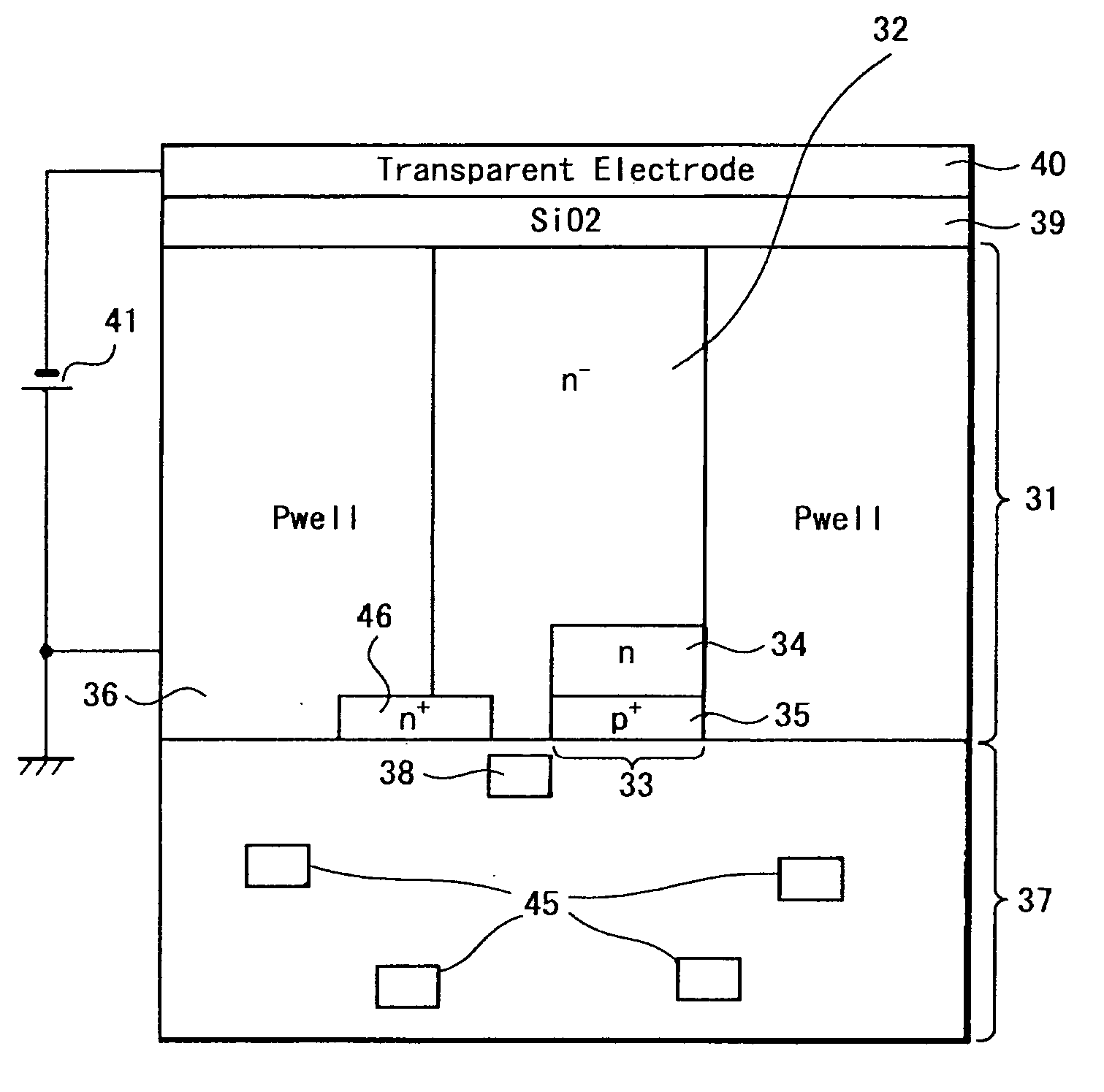

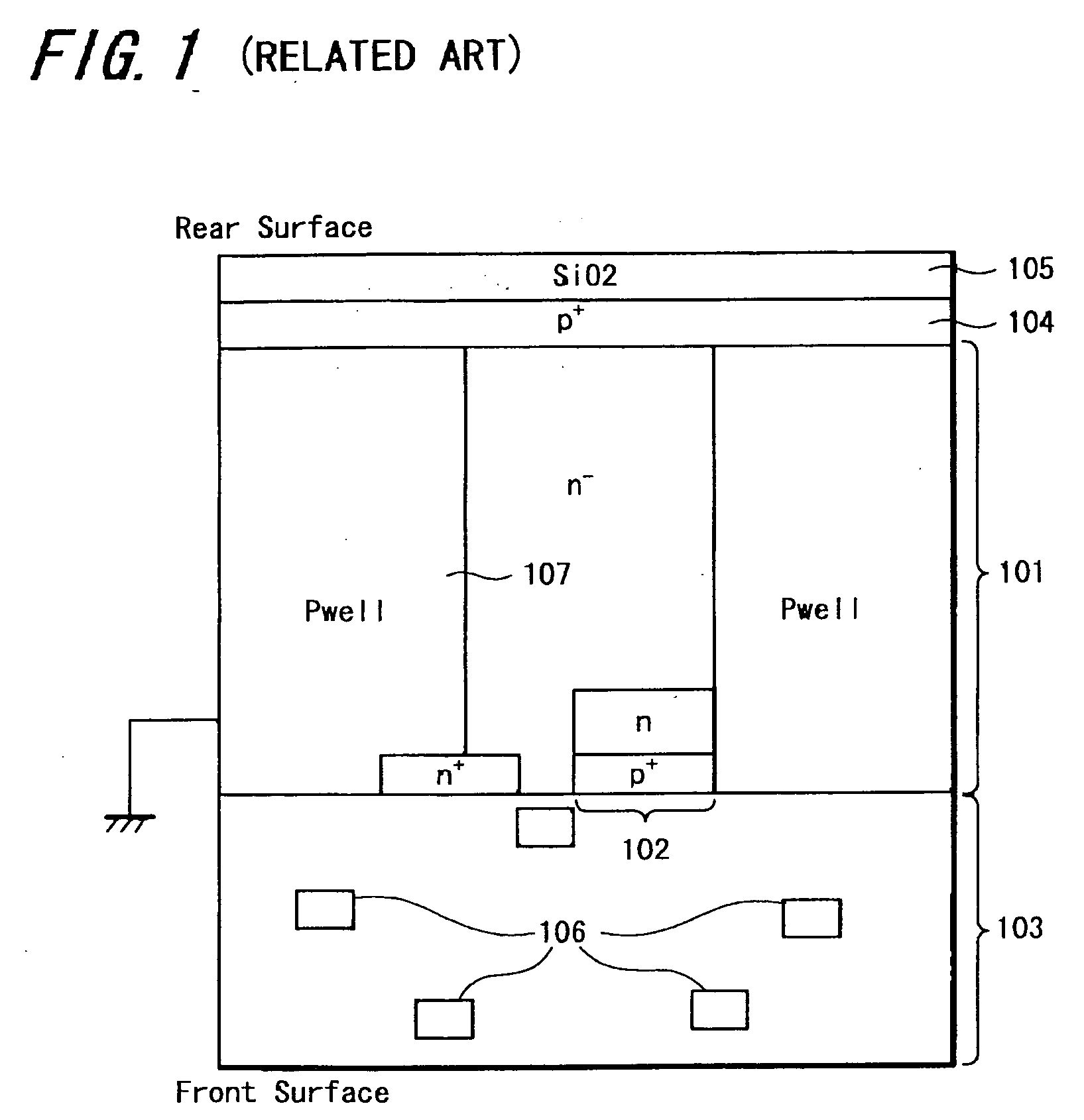

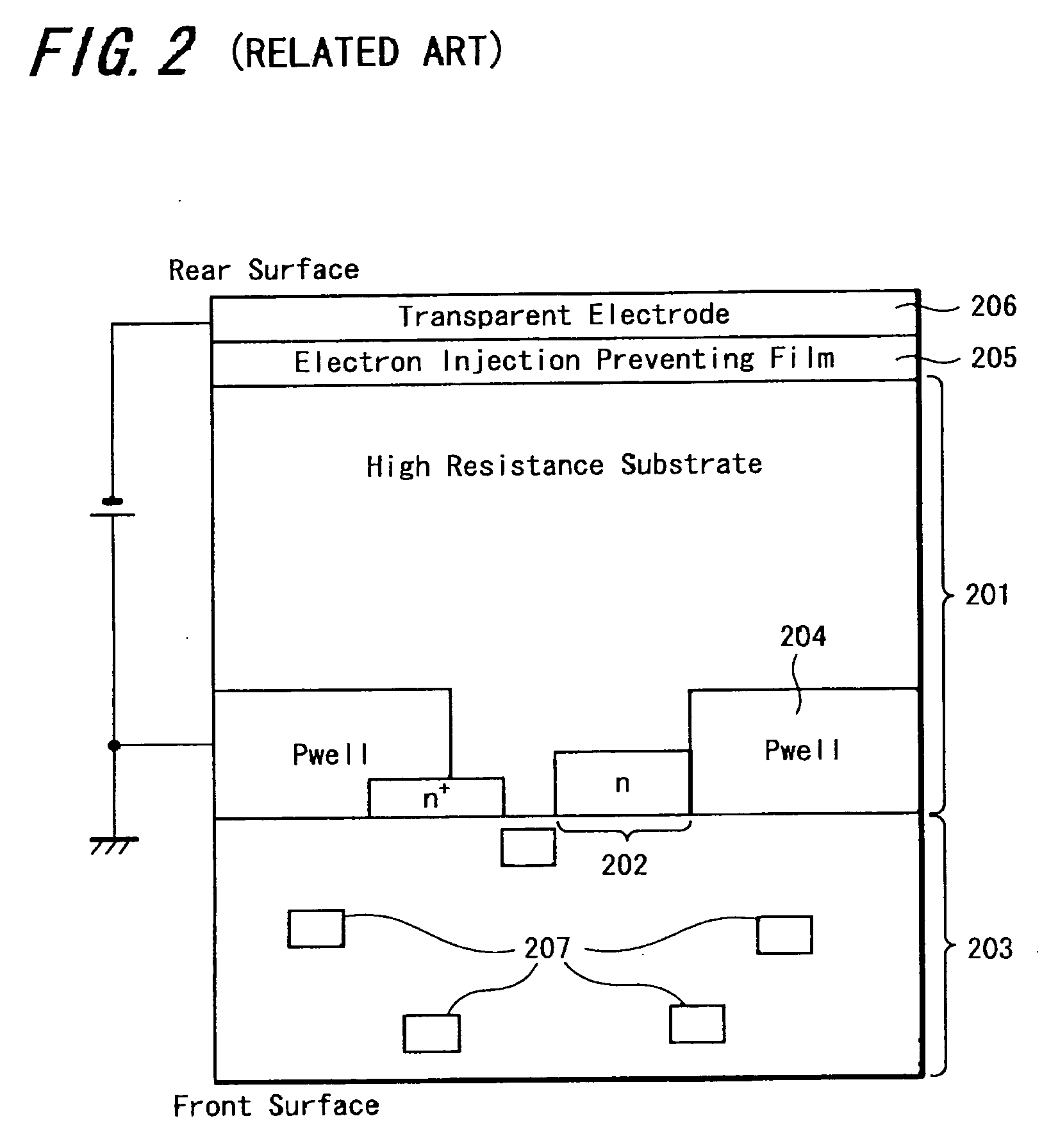

Solid-state imager device, drive method of solid-state imager device and camera apparatus

ActiveUS20060187327A1Reduce generationAvoid destructionTelevision system detailsTelevision system scanning detailsEngineeringVoltage source

In a case when a structure of forming a p+ layer on a substrate rear surface side is employed in order to prevent dark current generation from the silicon boundary surface, various problems occur. According to this invention, an insulation film 39 is provided on a rear surface on a silicon substrate 31 and a transparent electrode 40 is further provided thereon, and by applying a negative voltage with respect to the potential of the silicon substrate 31 from a voltage supply source 41 to the insulation film 39 through the transparent electrode 40, positive holes are accumulated on a silicon boundary surface of the substrate rear surface side and a structure equivalent to a state in which a positive hole accumulation layer exists on aforesaid silicon boundary surface is to be created. Thus, various problems in the related art can be avoided.

Owner:SONY CORP

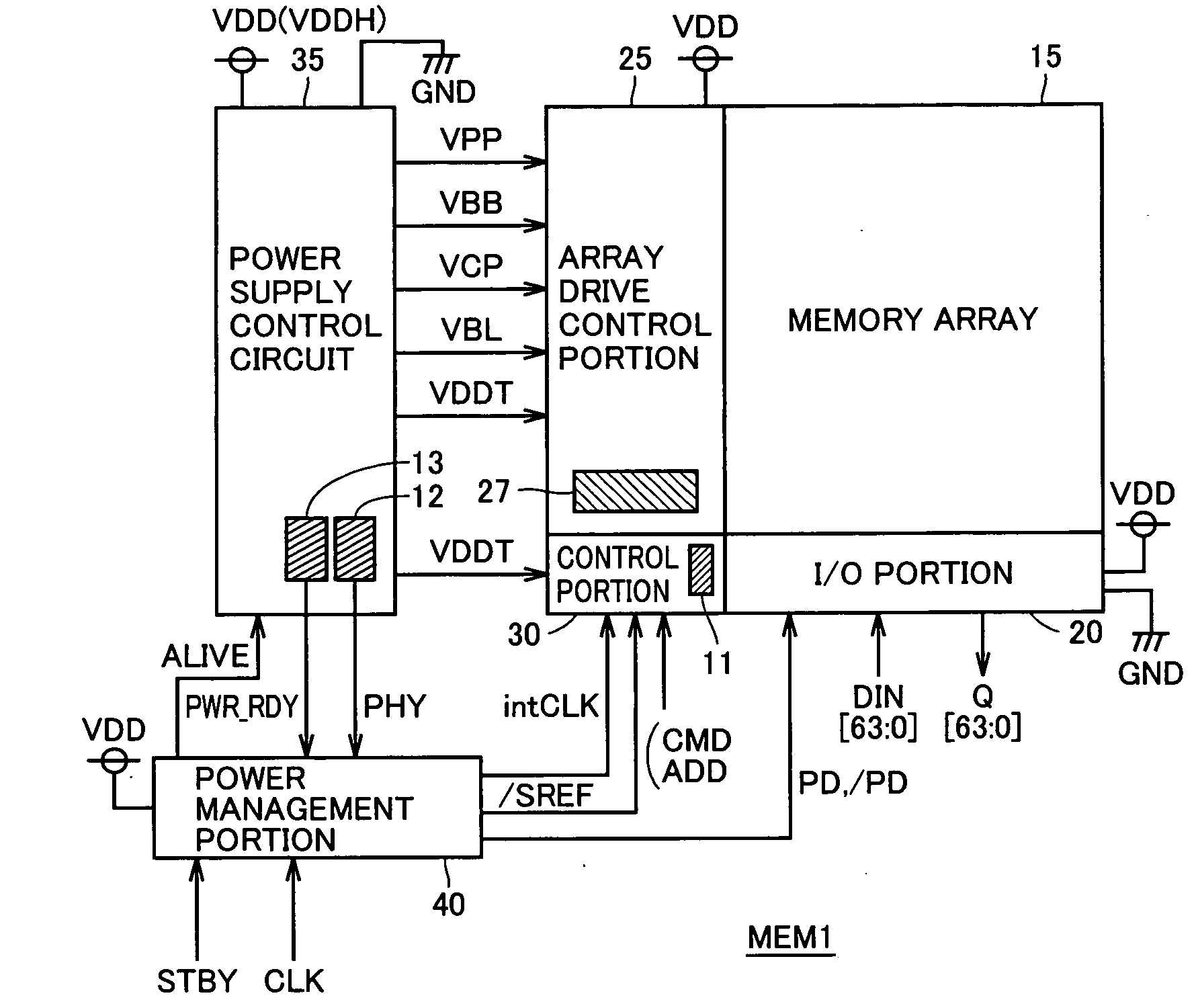

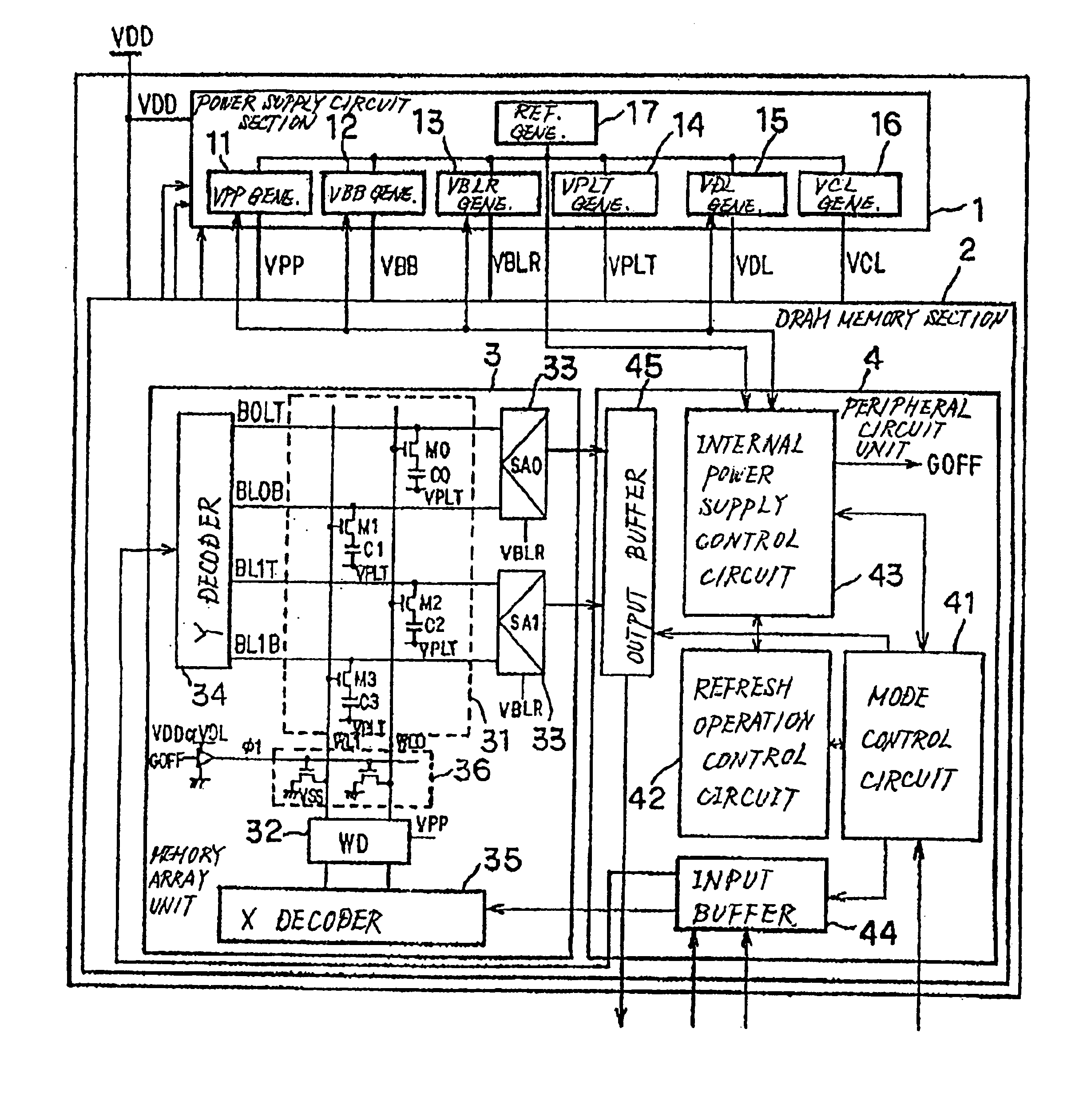

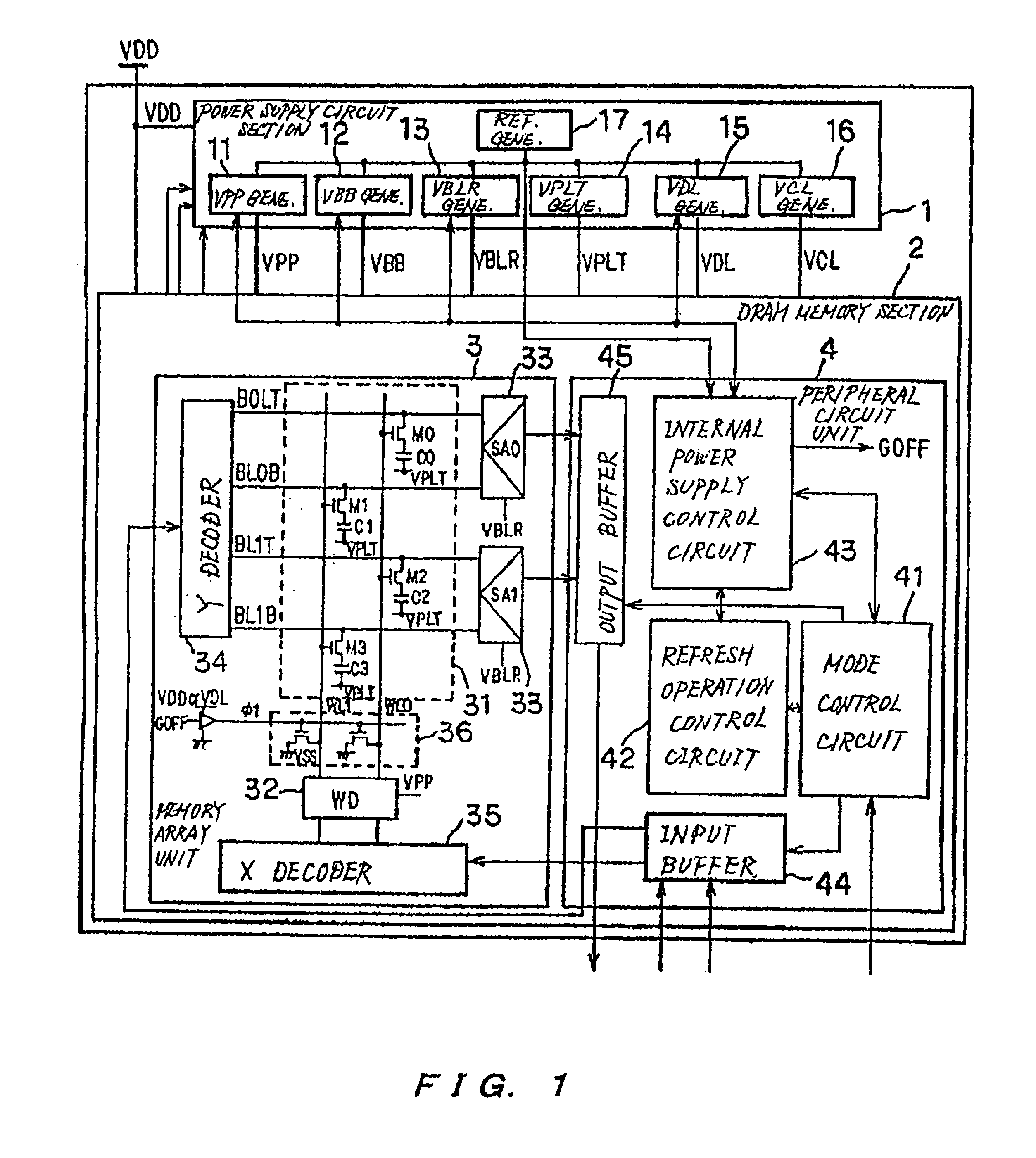

Semiconductor memory device control method and semiconductor memory device

ActiveUS6990031B2Reducing average current consumptionTotal current dropDigital storageBit lineEngineering

In a semiconductor memory device which requires a refresh operation, a control method stops supplying a word line voltage which is a boosted voltage higher than an external supply voltage, a memory array substrate voltage which is a negative voltage supplied to a semiconductor substrate, and a bit line precharge voltage for use in reproducing data held in memory cells for a predetermined period at the end of each refresh operation. In this event, voltage output terminals of the word line and memory array substrate voltages are respectively driven to a ground potential. For recovering these voltages, the delivery of the word line voltage is stopped until the memory array substrate voltage rises to some extent.

Owner:LONGITUDE LICENSING LTD

Switch circuit and method of switching radio frequency signals

InactiveUS20050017789A1Improving RF switch isolationRaise the compression pointTransistorSolid-state devicesMOSFETEngineering

A novel RF buffer circuit adapted for use with an RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. The switching and shunting transistor grouping pairs are controlled by a switching control voltage (SW) and its inverse (SW_). The switching and shunting transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. The stacking of transistor grouping devices, and associated gate resistors, increase the breakdown voltage across the series connected switch transistors and operate to improve RF switch compression. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The inventive RF switch provides improvements in insertion loss, switch isolation, and switch compression.

Owner:PSEMI CORP

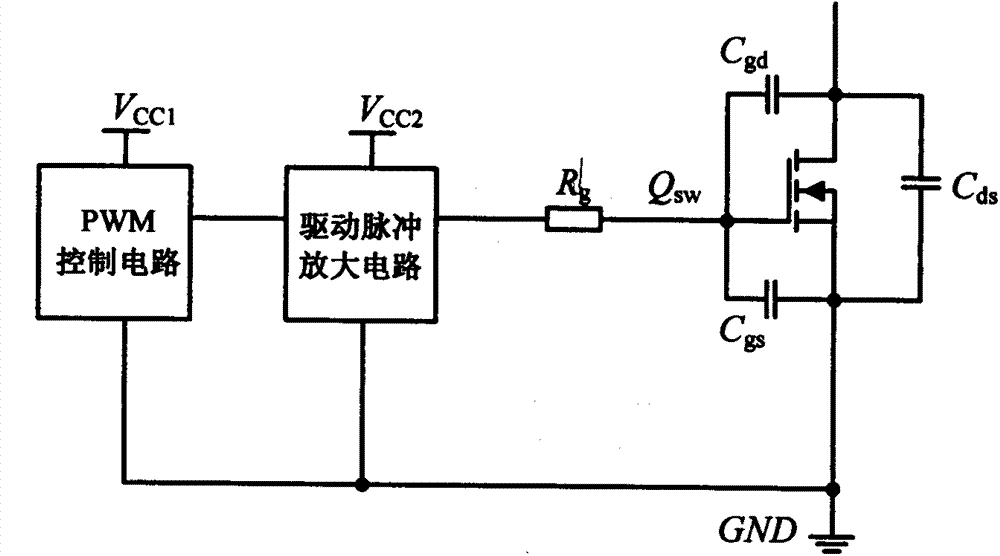

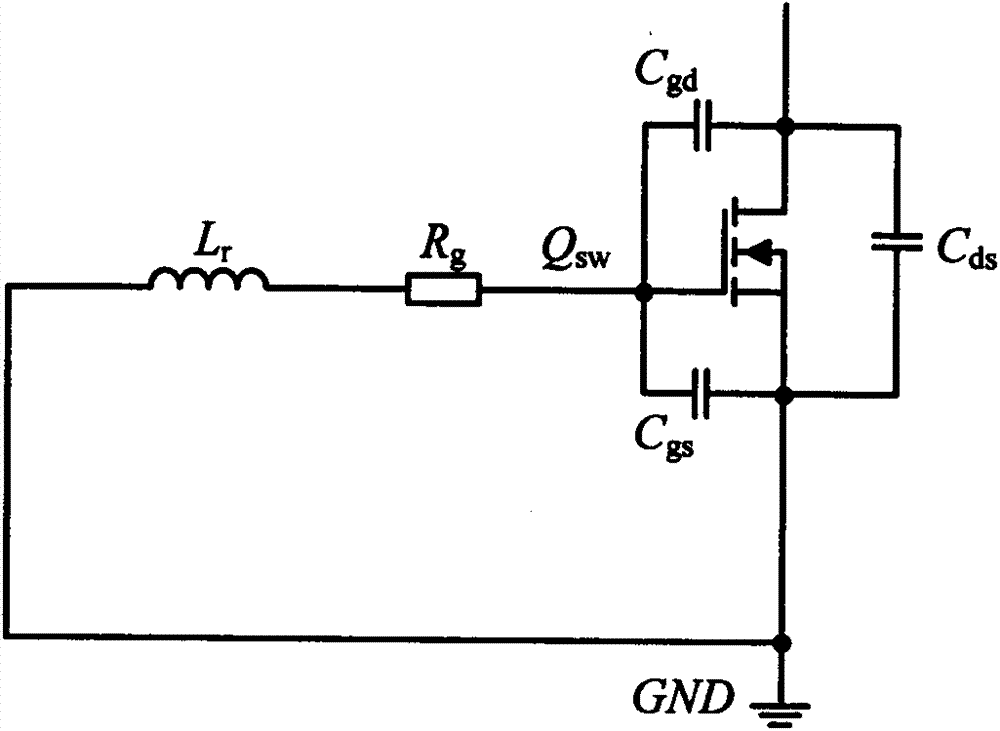

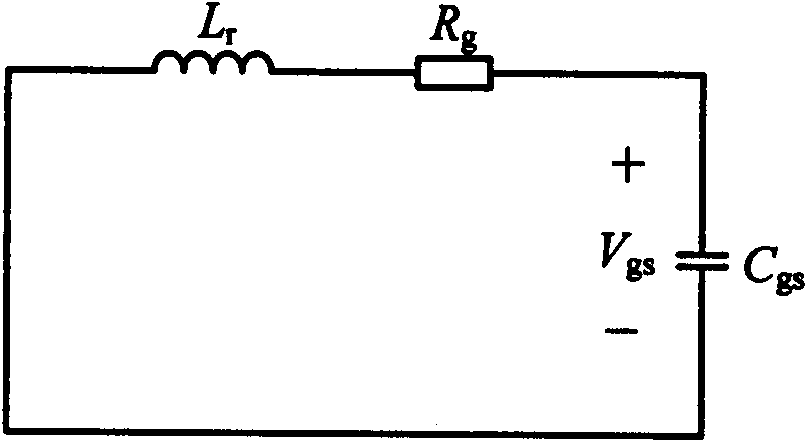

High-reliability MOSFET drive circuit

The invention relates to a drive circuit applied to a power switch tube MOSFET, in particular to a drive circuit of a silicon carbide MOSFET, and belongs to the technical field of drive circuits. The drive circuit aims to solve the problem that when an MOSFET in an existing drive circuit is turned off, the reliability is poor. The drive circuit comprises a PWM control circuit, a drive pulse amplifying circuit, a drive resistor Rg, a first diode D1, a resistor R1, a PNP triode Qoff, a second diode D2 and a capacitor C. According to the drive circuit, the PNP triode Qoff, the resistor R1 and the capacitor C form an MOSFET turn-off circuit; when the MOSFET is turned off quickly, a gate pole positive voltage spike caused by Miller currents is effectively suppressed; meanwhile, a gate pole negative voltage spike can also be suppressed through the second diode D2 and the capacitor C, it is guaranteed that the MOSFET is turned off safely and reliably, and the performance advantages of the silicon carbide MOSFET can be given to full play.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

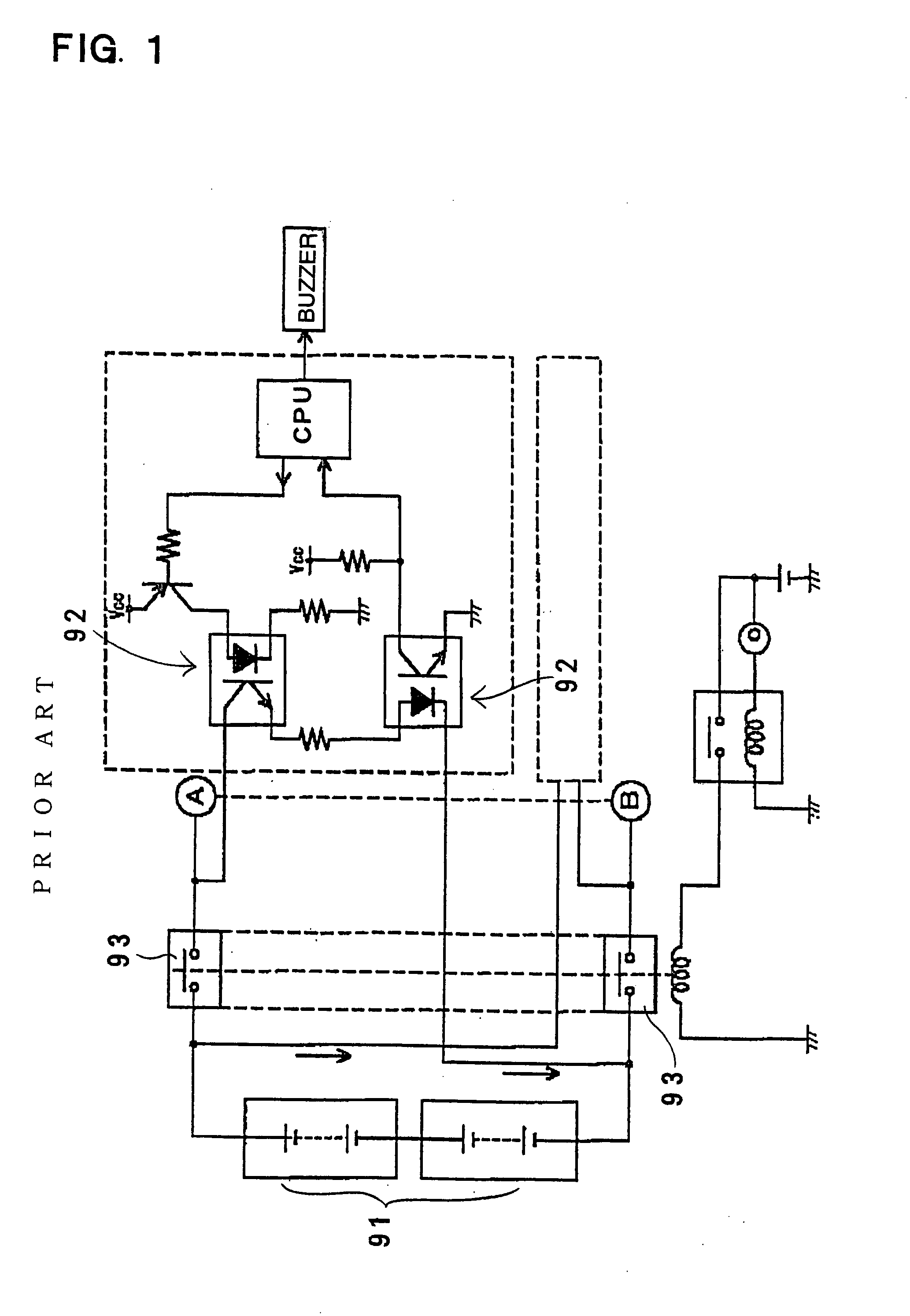

Electric power source for motor vehicle

ActiveUS20070221627A1Low costSimple circuit structureEmergency protective arrangements for automatic disconnectionHigh-tension/heavy-dress switchesMobile vehicleElectric power system

An electric power source for a motor vehicle is equipped with a welded state discriminator, and while a positive-side contactor and negative-side contactor are controlled to be switched off, the welded state discriminator detects a voltage of a positive-side contactor or negative-side contactor on its loading side with respect to a connecting point of a battery unit on a positive side and a battery unit on a negative side, so that when in a plus voltage where the detected voltage thus obtained is larger than a predetermined voltage, the positive-side contactor is judged to be in a welded state, and when in a minus voltage where the detected voltage is larger than the predetermined voltage, the negative-side contactor is judged to be in a welded state.

Owner:SANYO ELECTRIC CO LTD

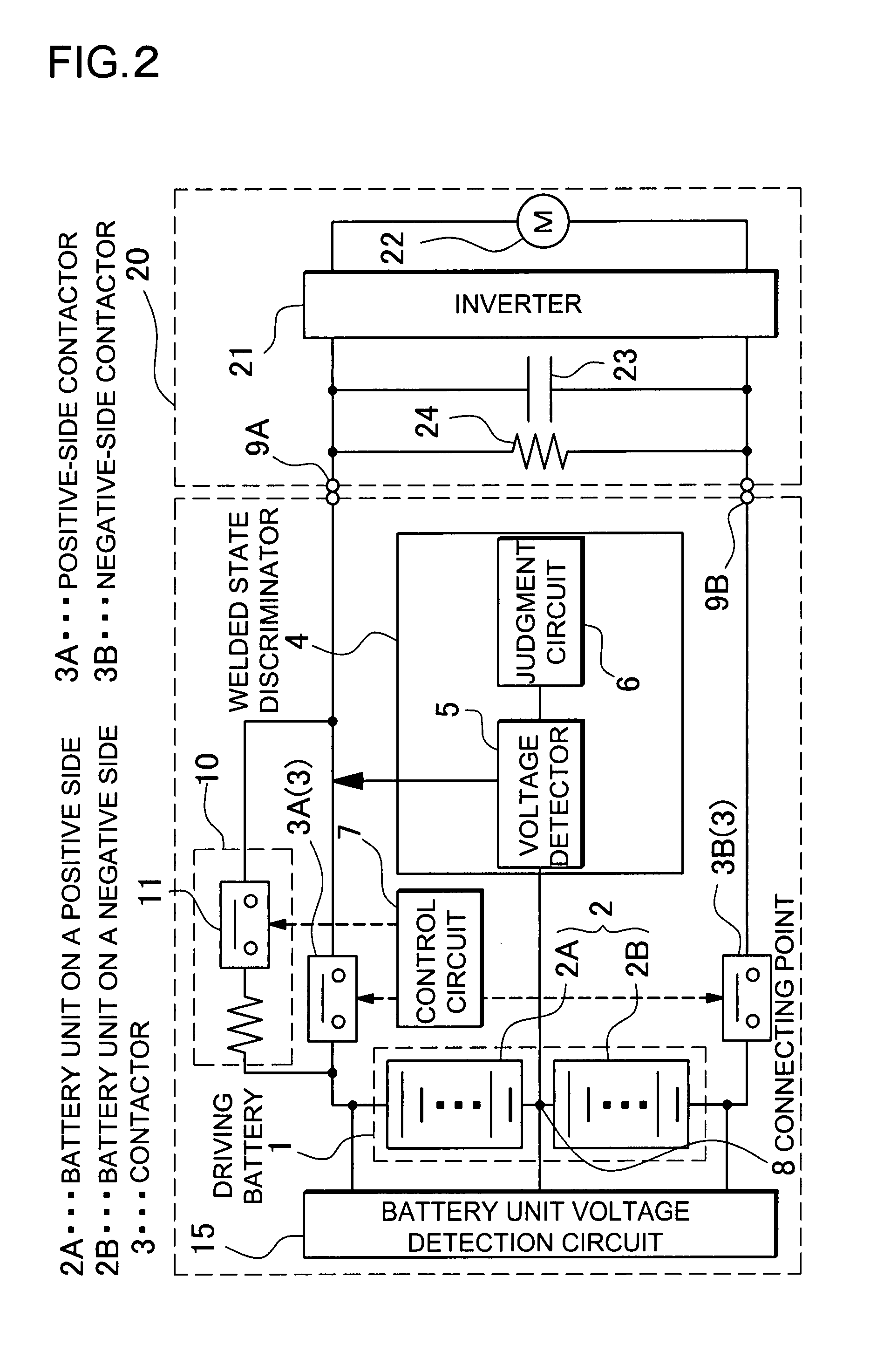

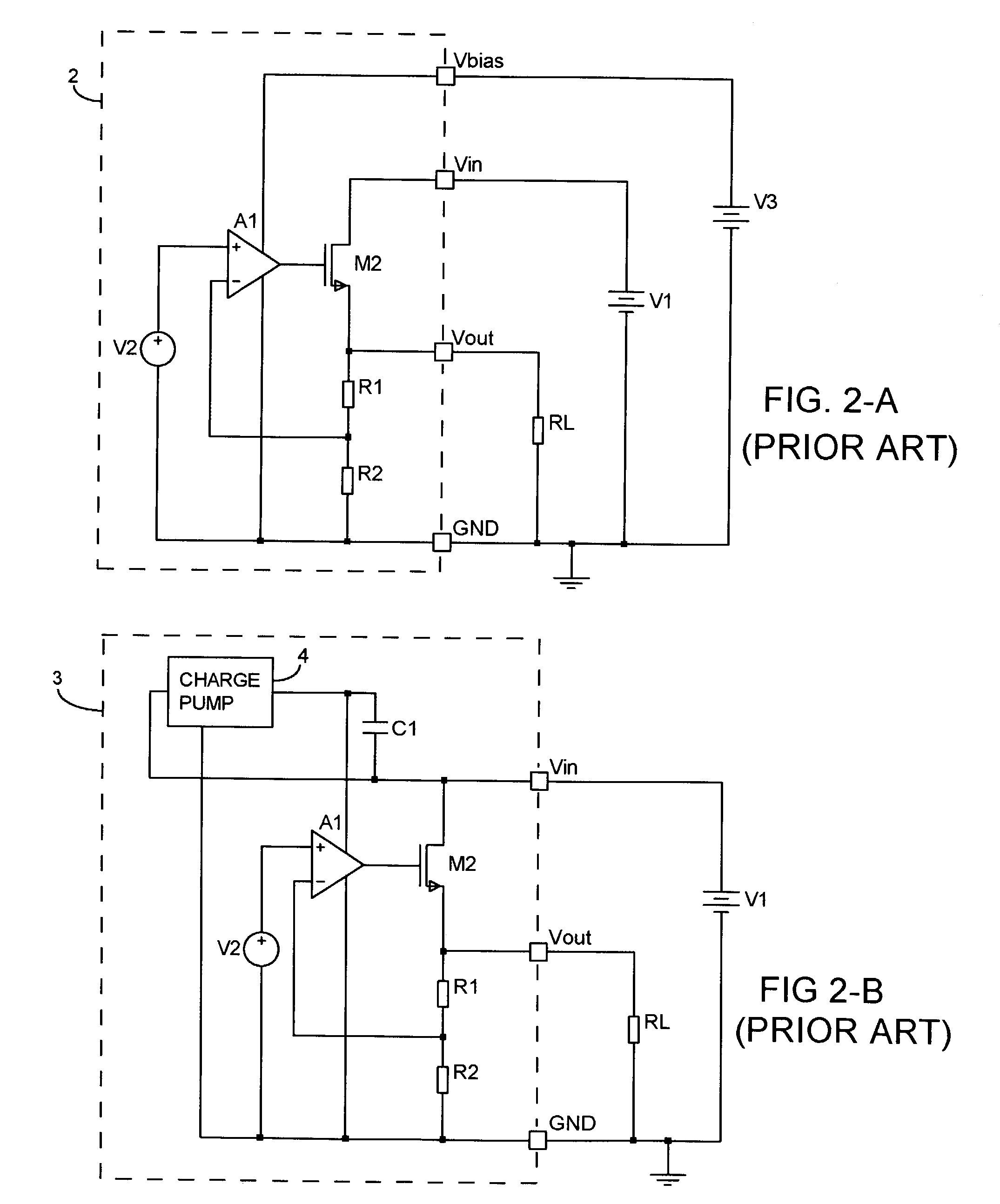

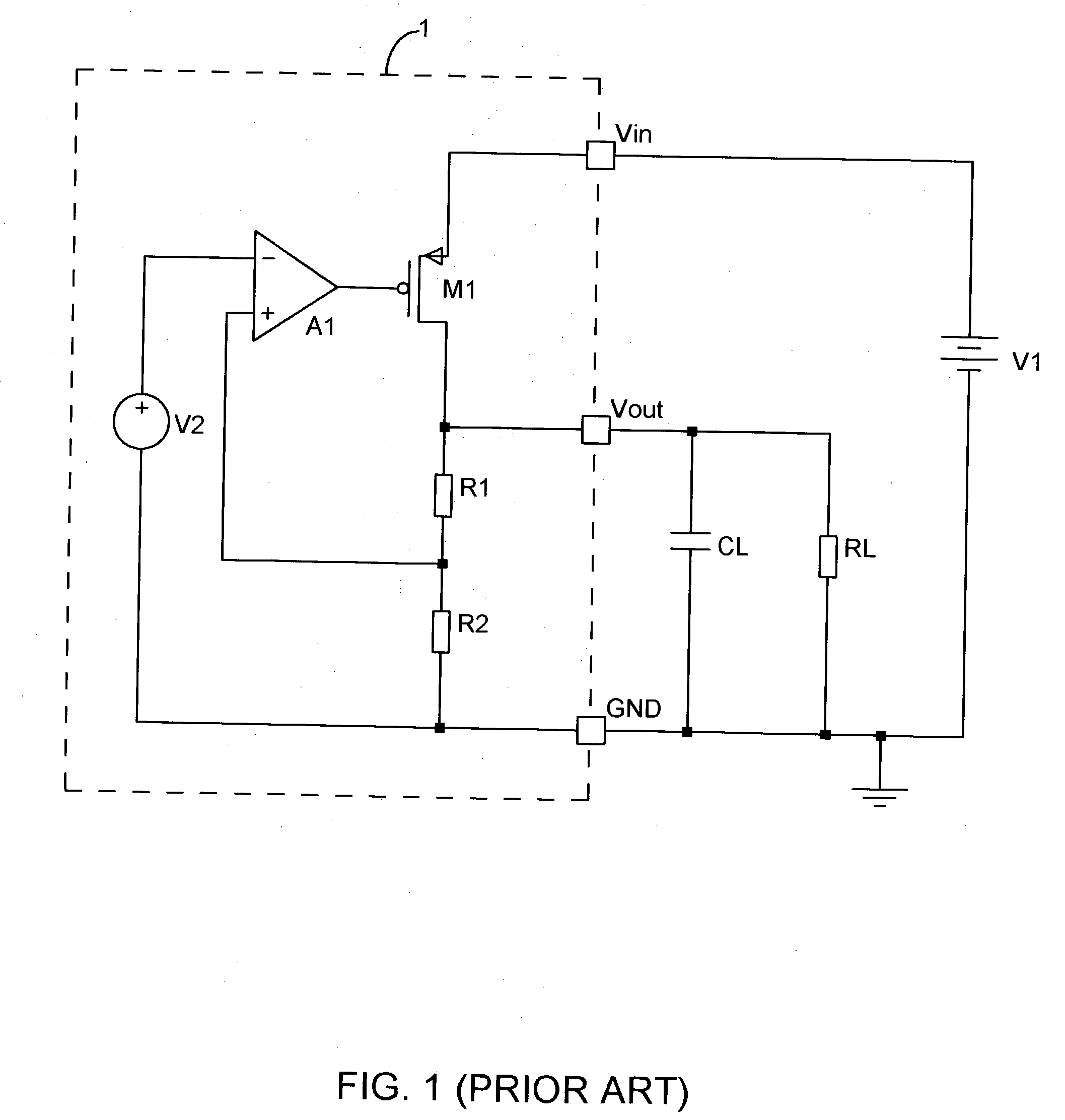

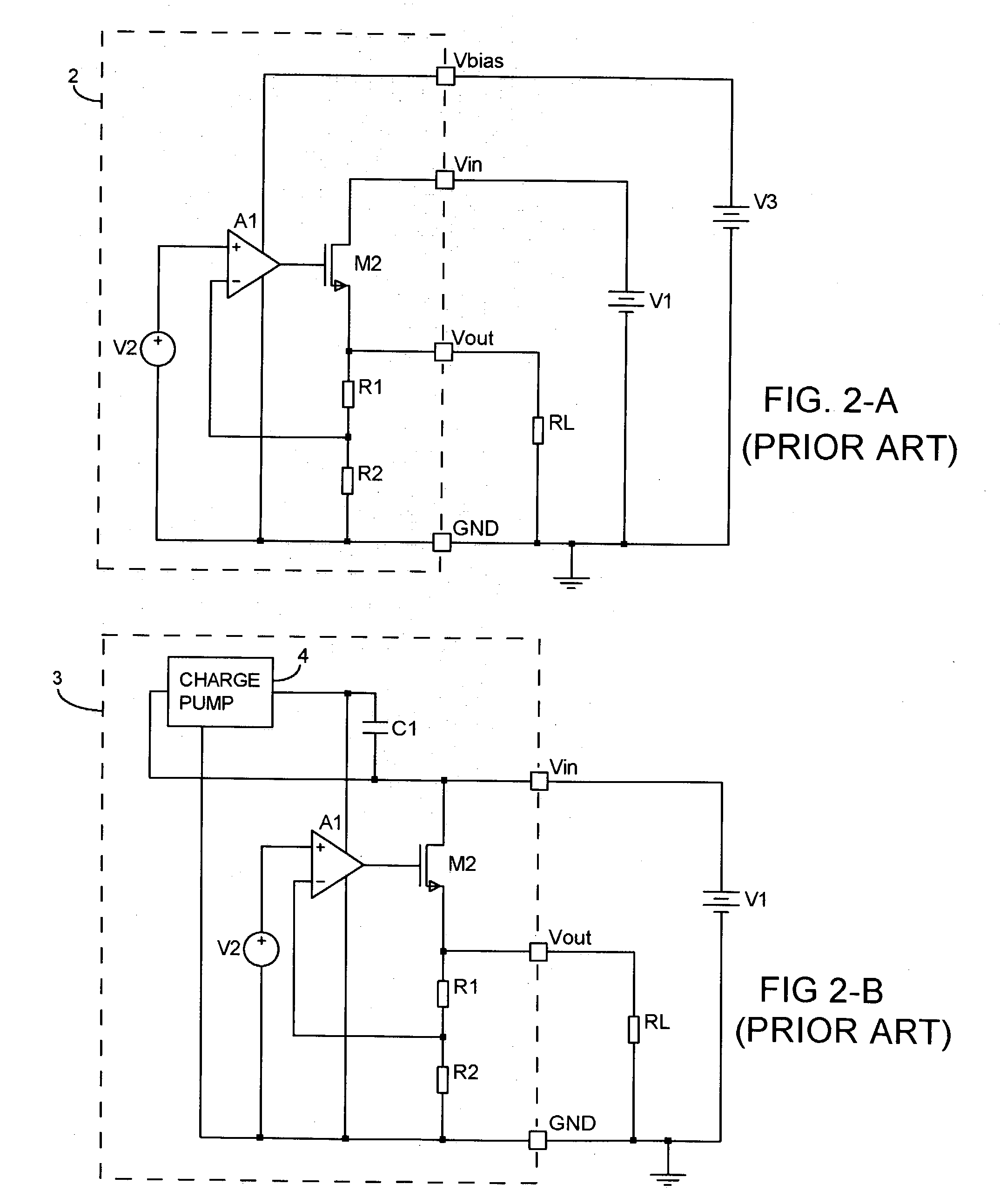

Low dropout voltage regulator using a depletion pass transistor

InactiveUS6989659B2Improve reliabilityInsensitiveElectric variable regulationEngineeringCurrent regulation

A linear low dropout voltage regulator is described that makes use of a depletion mode NMOS pass transistor and of a PMOS transistor in series to the NMOS transistor and connected to its drain. The depletion NMOS transistor assures low dropout operations, while the series PMOS transistor allows the current regulation even under the condition of shorted load. The same PMOS transistor may be used to disable the current in the load without generating a negative voltage at the gate of the depletion pass transistor. This regulator is inherently stable without the need for an output capacitor in parallel to the load.

Owner:DIALOG SEMICONDUCTOR GMBH

System and method for three-dimensional mapping of electrophysiology information

An electrophysiology apparatus is used to measure electrical activity occurring in a heart of a patient and to visualize the electrical activity and / or information related to the electrical activity. A three-dimensional map of the electrical activity and / or the information related to the electrical activity is created. Exemplary maps include a time difference between action potentials at a roving electrode and a reference electrode, the peak-to-peak timing of action potentials at the roving electrode, the peak negative voltage of action potentials at the roving electrode, complex fractionated electrogram information, a dominant frequency of an electrogram signal, a maximum peak amplitude at the dominant frequency, a ratio of energy in one band of the frequency-domain to the energy in a second band of the frequency-domain, a low-frequency or high-frequency passband of interest, a frequency with the maximum energy in a passband, a number of peaks within a passband, an energy, power, and / or area in each peak, a ratio of energy and / or area in each peak to that in another passband, and a width of each peak in a spectrum. Colors, shades of colors, and / or grayscales are assigned to values of the parameters and colors corresponding to the parameters for the electrograms sampled by the electrodes are updated on the three-dimensional model.

Owner:ST JUDE MEDICAL ATRIAL FIBRILLATION DIV

Low dropout voltage regulator using a depletion pass transistor

A linear low dropout voltage regulator is described that makes use of a depletion mode NMOS pass transistor and of a PMOS transistor in series to the NMOS transistor and connected to its drain. The depletion NMOS transistor assures low dropout operations, while the series PMOS transistor allows the current regulation even under the condition of shorted load. The same PMOS transistor may be used to disable the current in the load without generating a negative voltage at the gate of the depletion pass transistor. This regulator is inherently stable without the need for an output capacitor in parallel to the load.

Owner:DIALOG SEMICONDUCTOR GMBH

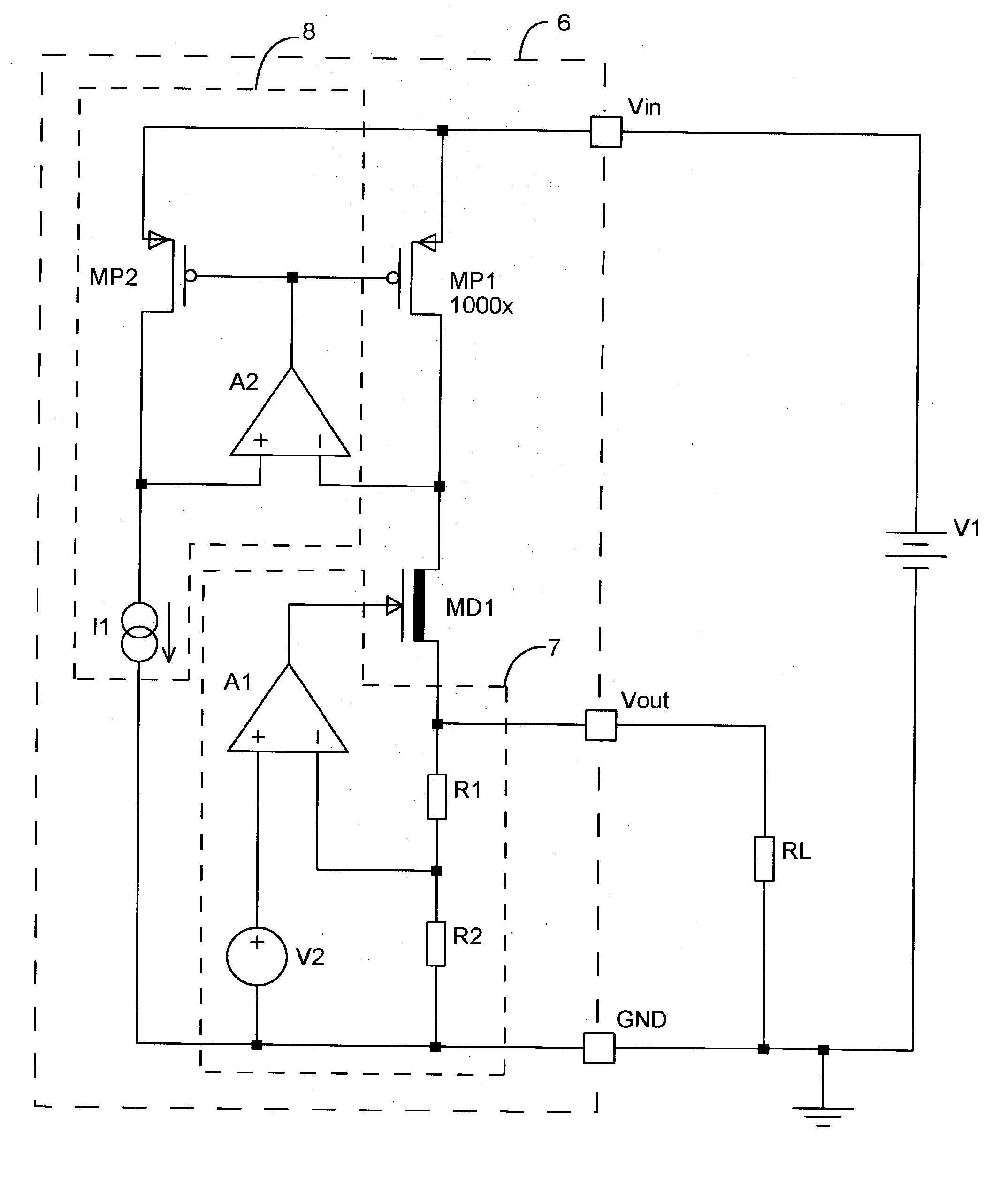

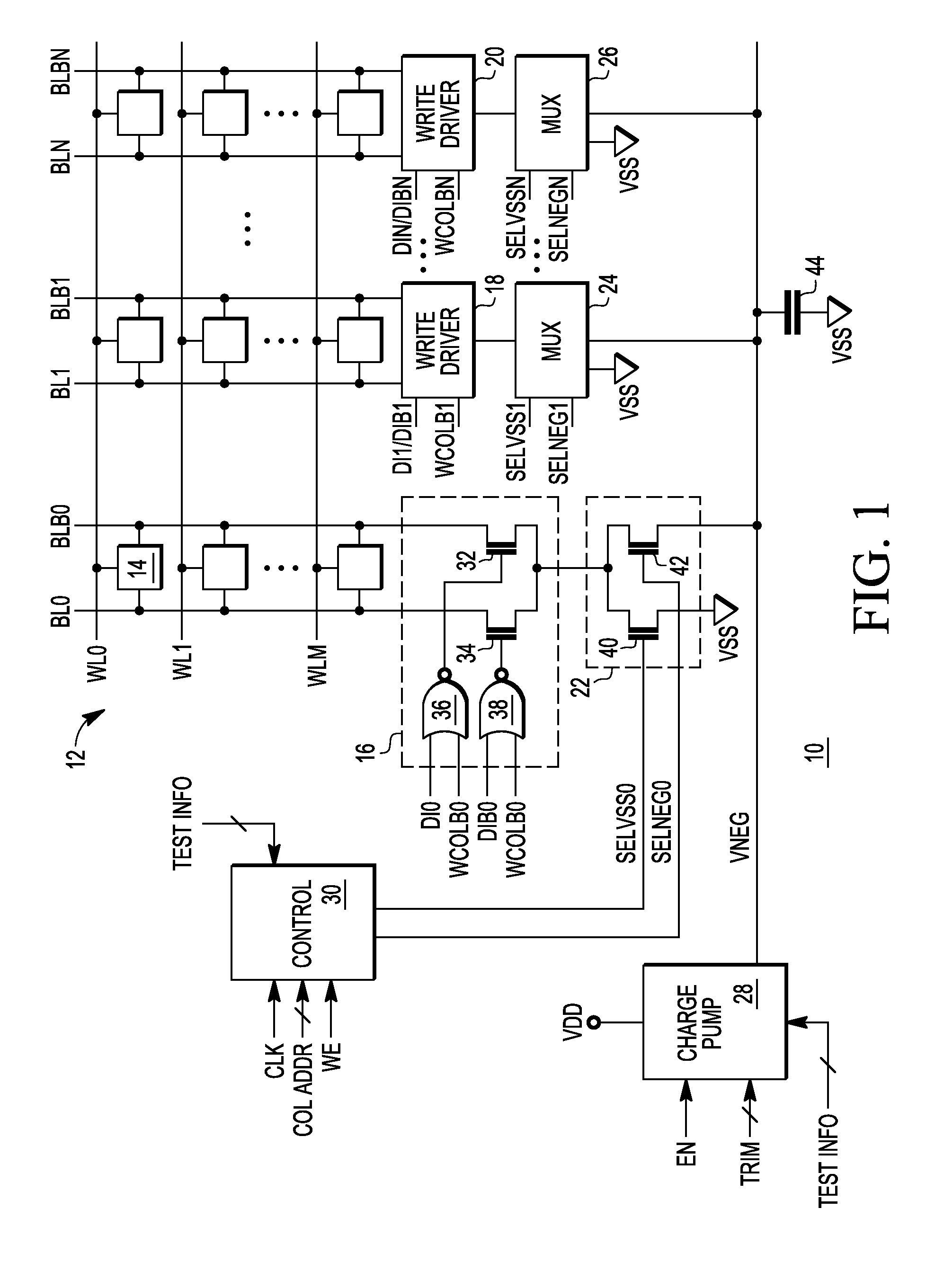

Memory having negative voltage write assist circuit and method therefor

A method of writing data to a selected column of a memory includes selecting a first column. The data writing is initiated by applying a logic high to a first bit line of the first column and a first potential to a second bit line of the first column that is lower than the logic high. The first potential is removed and a second potential is applied to the second bit line. The second potential is less than the first potential. The first potential may be ground, and the second potential may be a negative voltage. Reducing the write voltage for the bit line that is receiving a logic low improves its ability to be written. By first bringing the logic low to the first potential, which may be ground, and then further reducing the applied voltage, the requirements on the source of the second potential are reduced.

Owner:NXP USA INC

Semiconductor device

ActiveUS20110316062A1Lower Antenna CostsMinimizing harmonic distortionTransistorSolid-state devicesCapacitanceTotal harmonic distortion

In terms of achieving a reduction in the cost of an antenna switch, there is provided a technology capable of minimizing harmonic distortion generated in the antenna switch even when the antenna switch is particularly formed of field effect transistors formed over a silicon substrate. Between the source region and the drain region of each of a plurality of MISFETs coupled in series, a distortion compensating capacitance circuit is coupled which has a voltage dependency such that, in either of the cases where a positive voltage is applied to the drain region based on the potential of the source region and where a negative voltage is applied to the drain region based on the potential of the source region, the capacitance decreases to a value smaller than that in a state where the potential of the source region and the potential of the drain region are at the same level.

Owner:RENESAS ELECTRONICS CORP

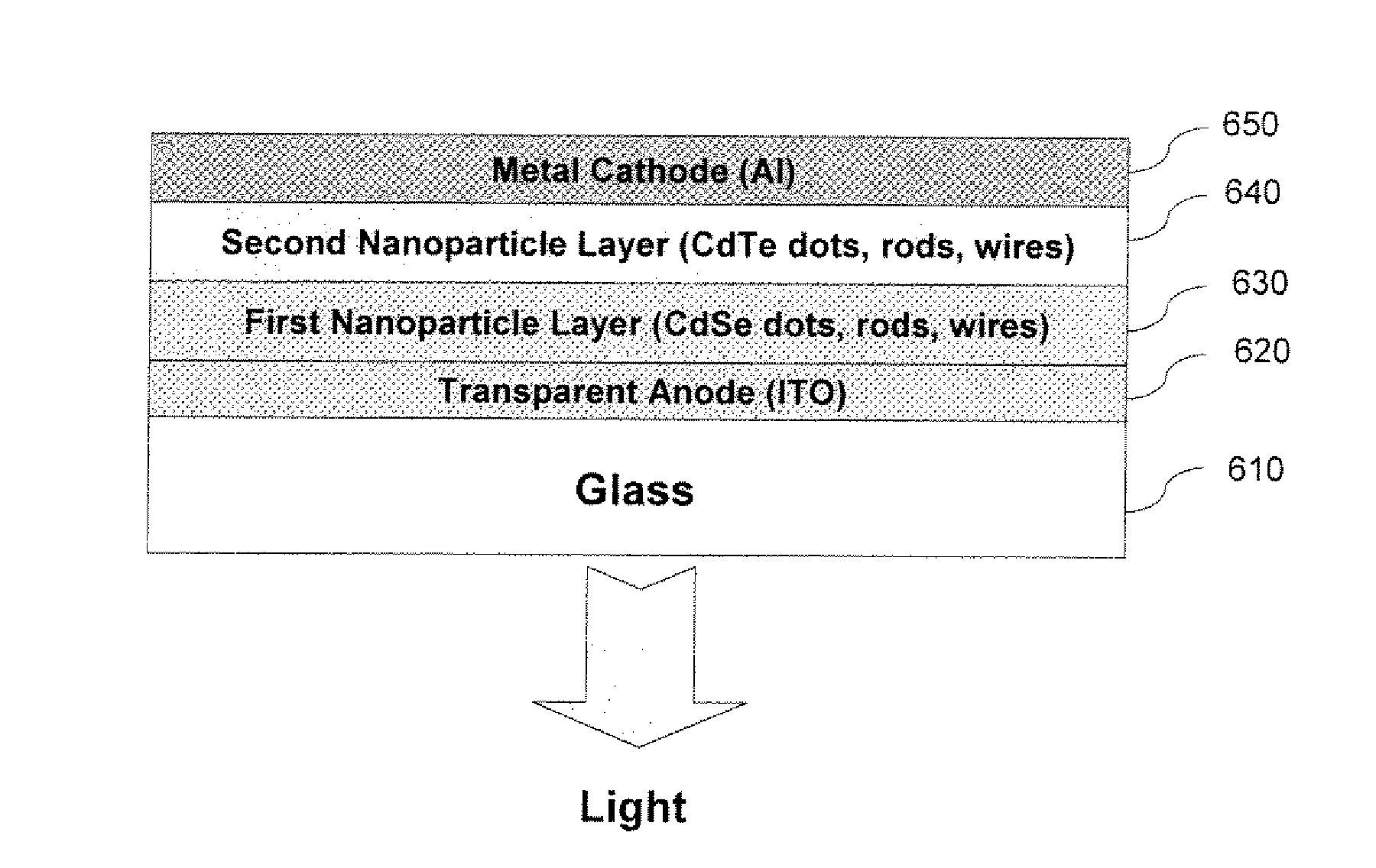

Nanostructured electroluminescent device and display

InactiveUS20070194694A1Improve efficiencyDecreasing display lifetimeMaterial nanotechnologyDischarge tube luminescnet screensElectron holeNanoparticle

An electroluminescent device contains (1) first and second electrodes, at least one of which is transparent to radiation; (2) a hole conducting layer containing first nanoparticles wherein the hole conducting layer is in contact with said first electrode; (3) an electron conducting layer containing second nanoparticles where the electron conducting layer is in contact with the hole conducting layer and the second electrode; and optionally (4) a voltage source capable of providing positive and negative voltage, where the positive pole of the voltage source is connected to the first electrode and the negative pole is connected to the second electrode. In some embodiments, the electroluminescent device also includes an electron-hole combination layer between the hole and electron conducting layers.

Owner:FIRST SOLAR INC (US)

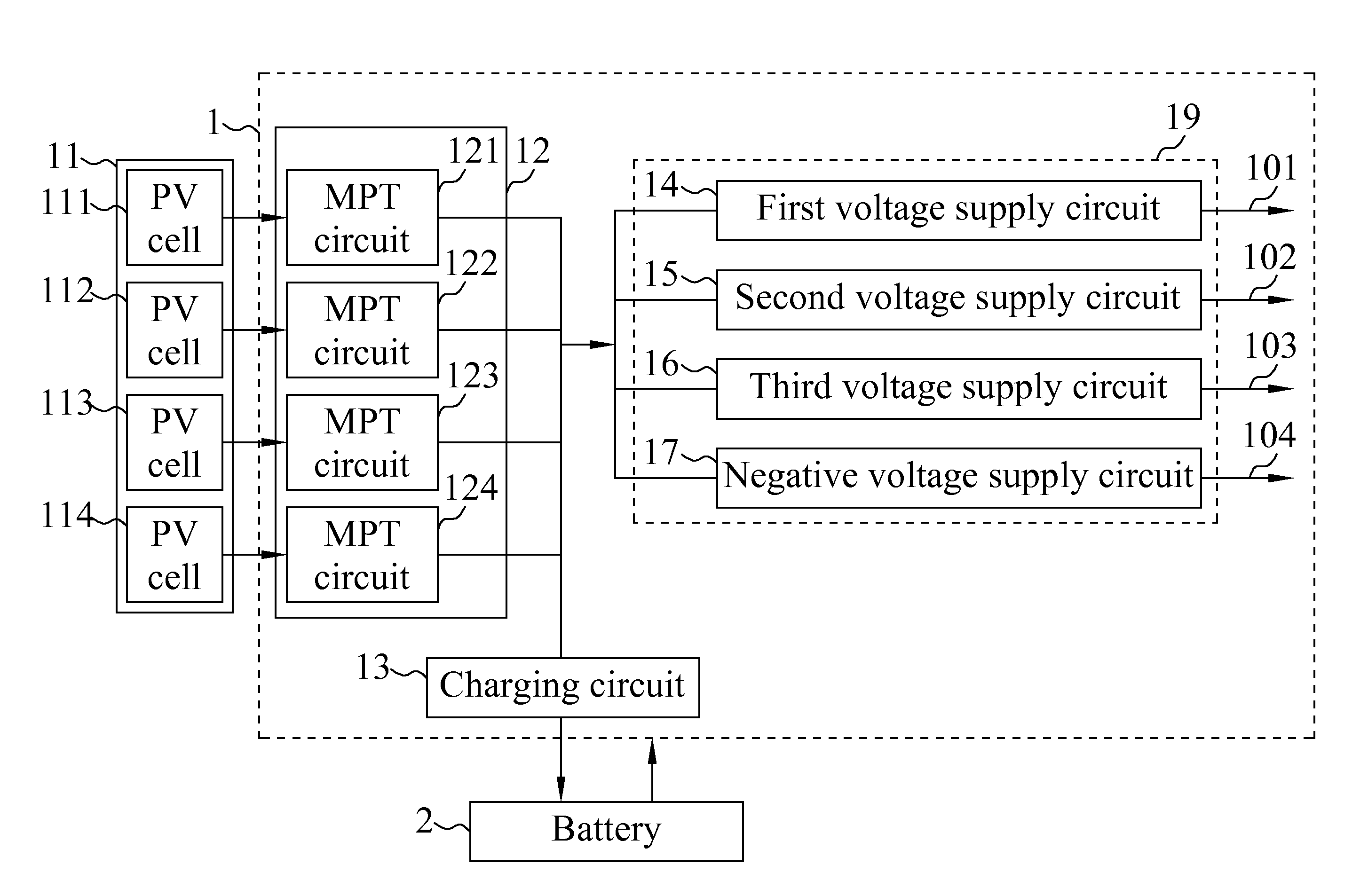

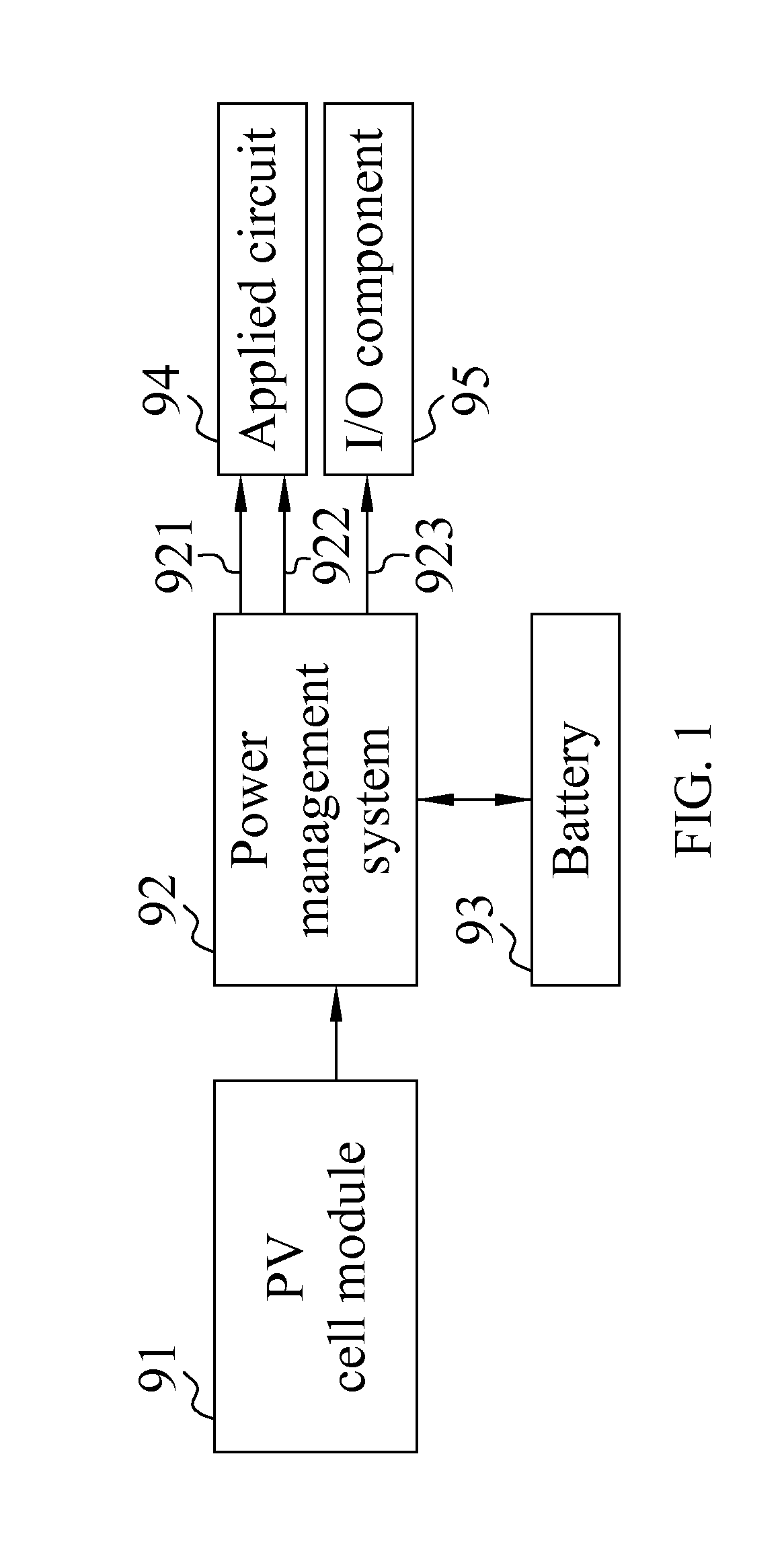

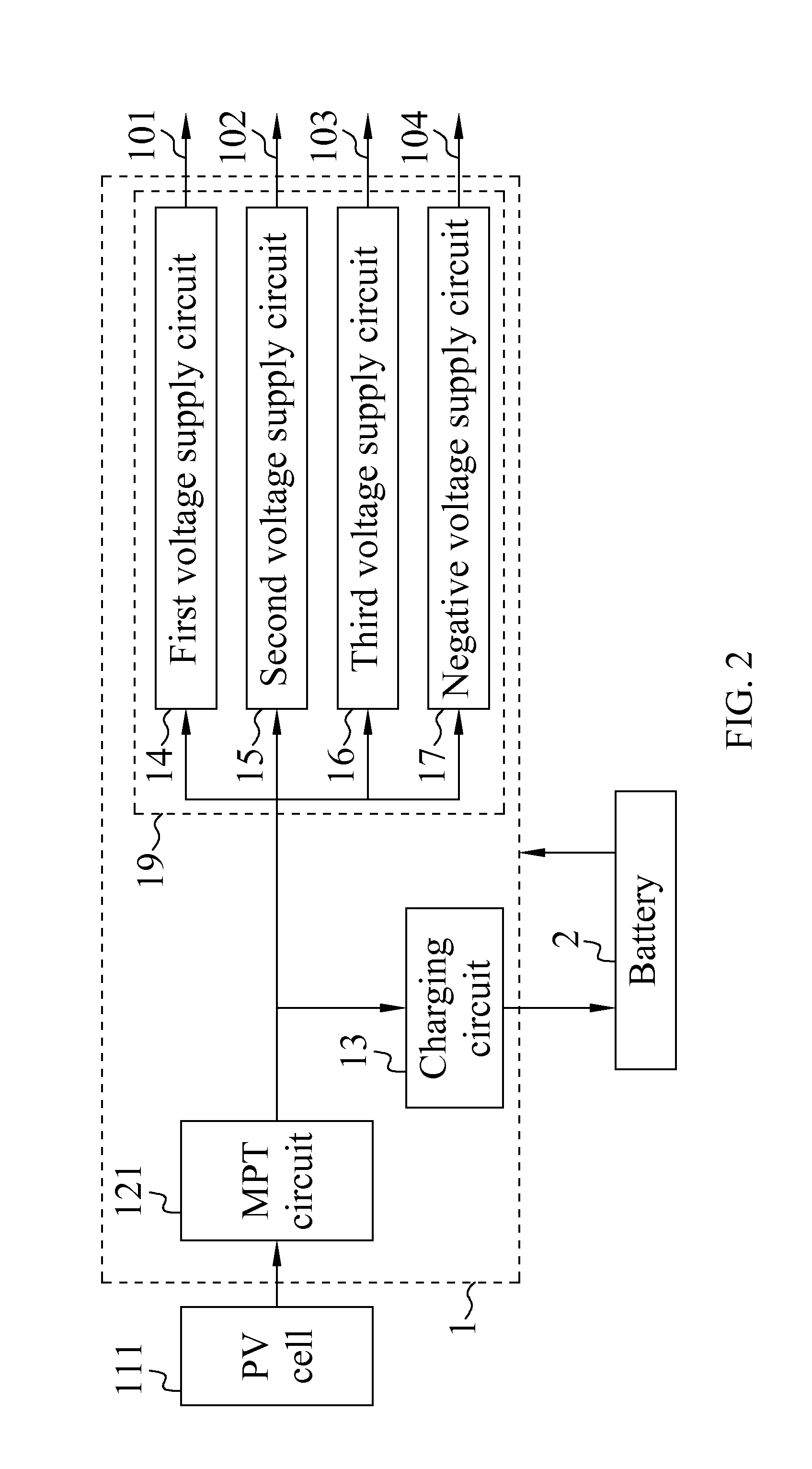

Solar power management system

InactiveUS20110193515A1Additional drawbackLarge outputDc network circuit arrangementsBatteries circuit arrangementsSolar energy conversion efficiencyElectrical battery

A solar power management system is provided for managing electric energy conversion by a photovoltaic cell module, supplying the converted electric energy to an external load, and storing the converted electric energy in a battery. The solar power management system comprises a multiphase maximum power tracking (MPT) module, a charging circuit, and a voltage conversion module. The multiphase MPT module regulates output current of the photovoltaic cell module to output maximum power within the high limit thereof and obtain improved solar energy conversion efficiency. The voltage conversion module converts the electric energy generated by the photovoltaic cell module into different voltage formats, such as 5.6V DC, 1.0V DC, 0.6˜0.3V DC low voltage, or −1.2V DC negative voltage, to meet different external load requirements. The solar power management system has simple circuitry and can be configured as a system on chip (SoC) at reduced cost while provides very wide applications.

Owner:NAT CHIAO TUNG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com