Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

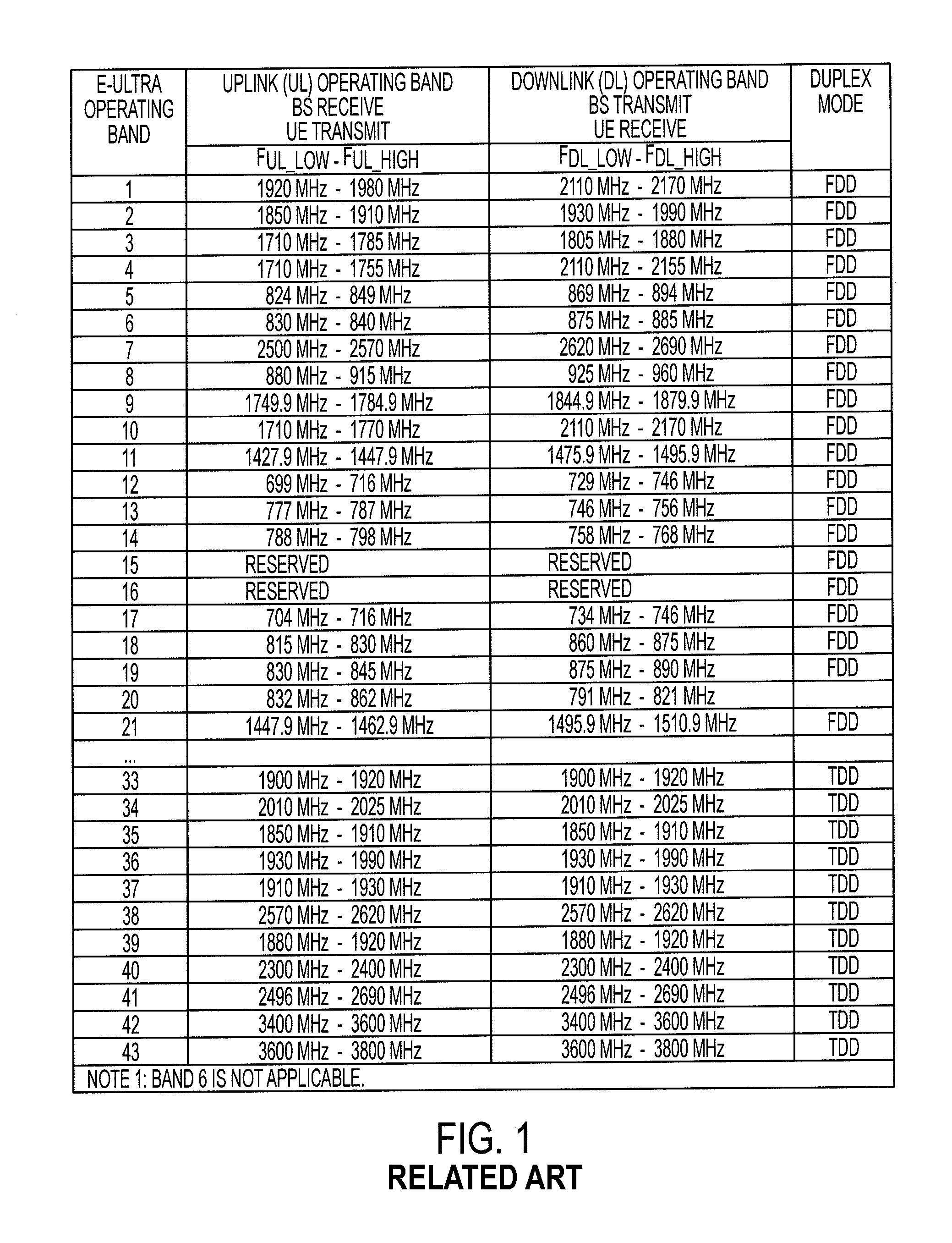

2443 results about "Switched capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

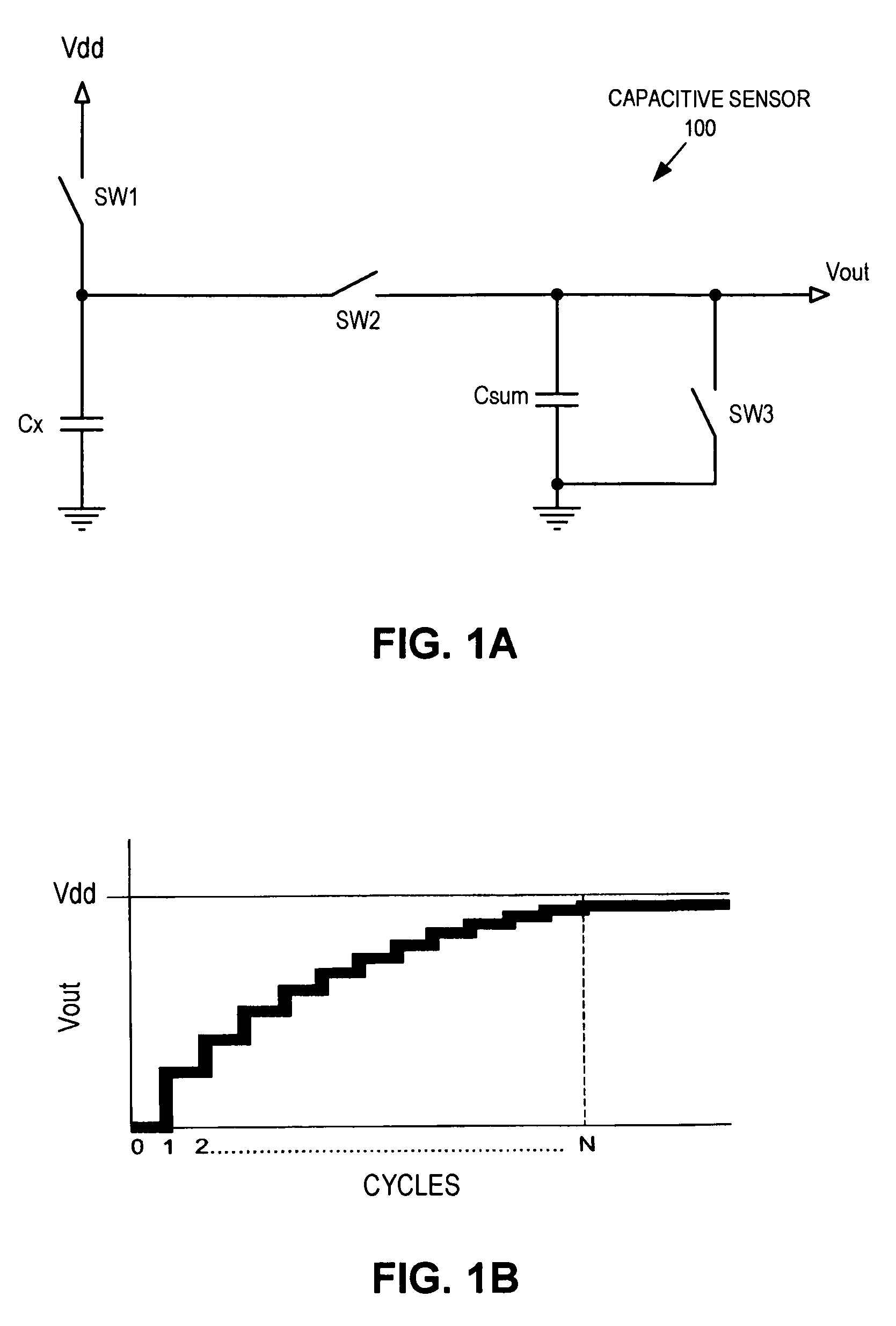

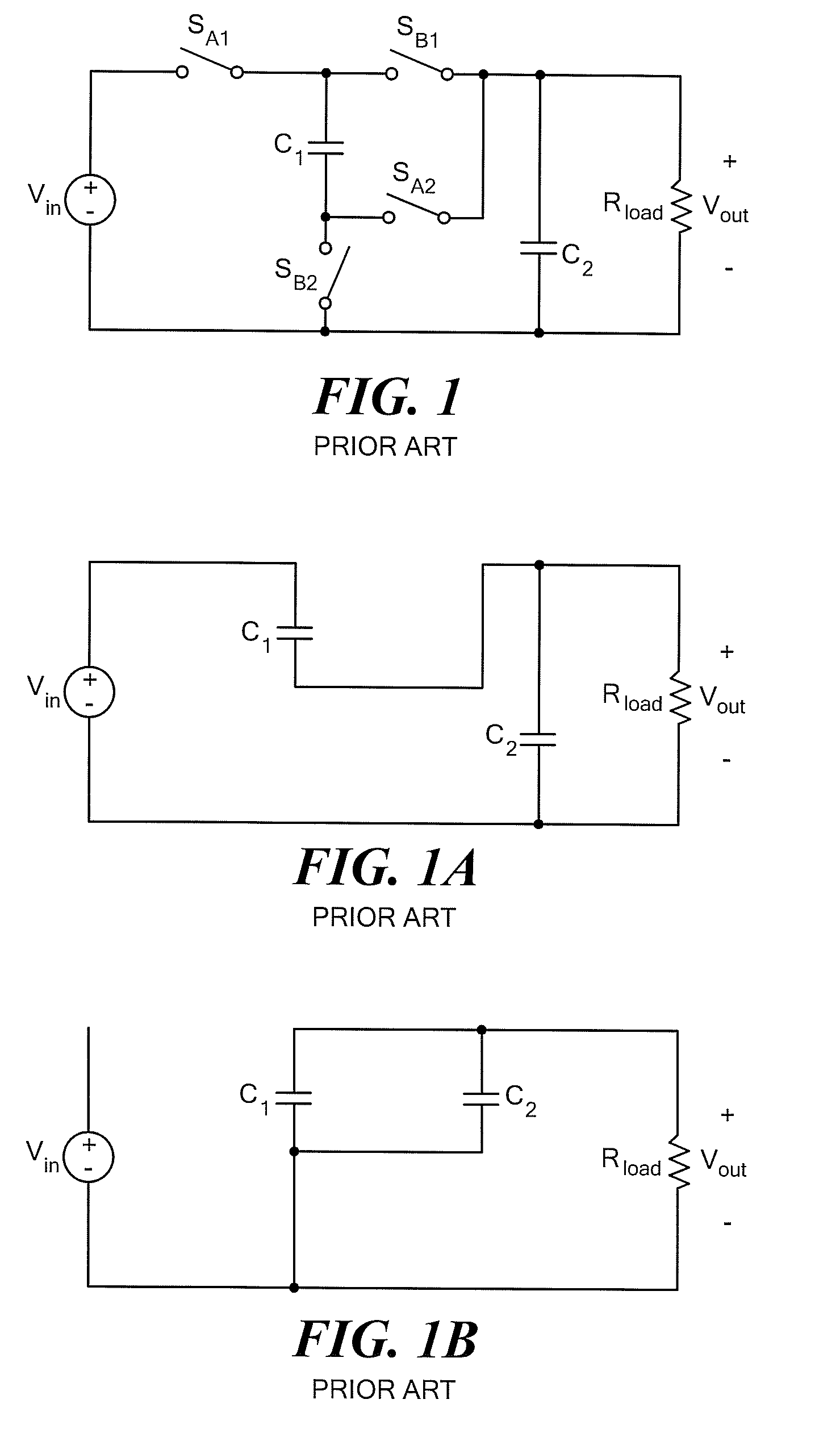

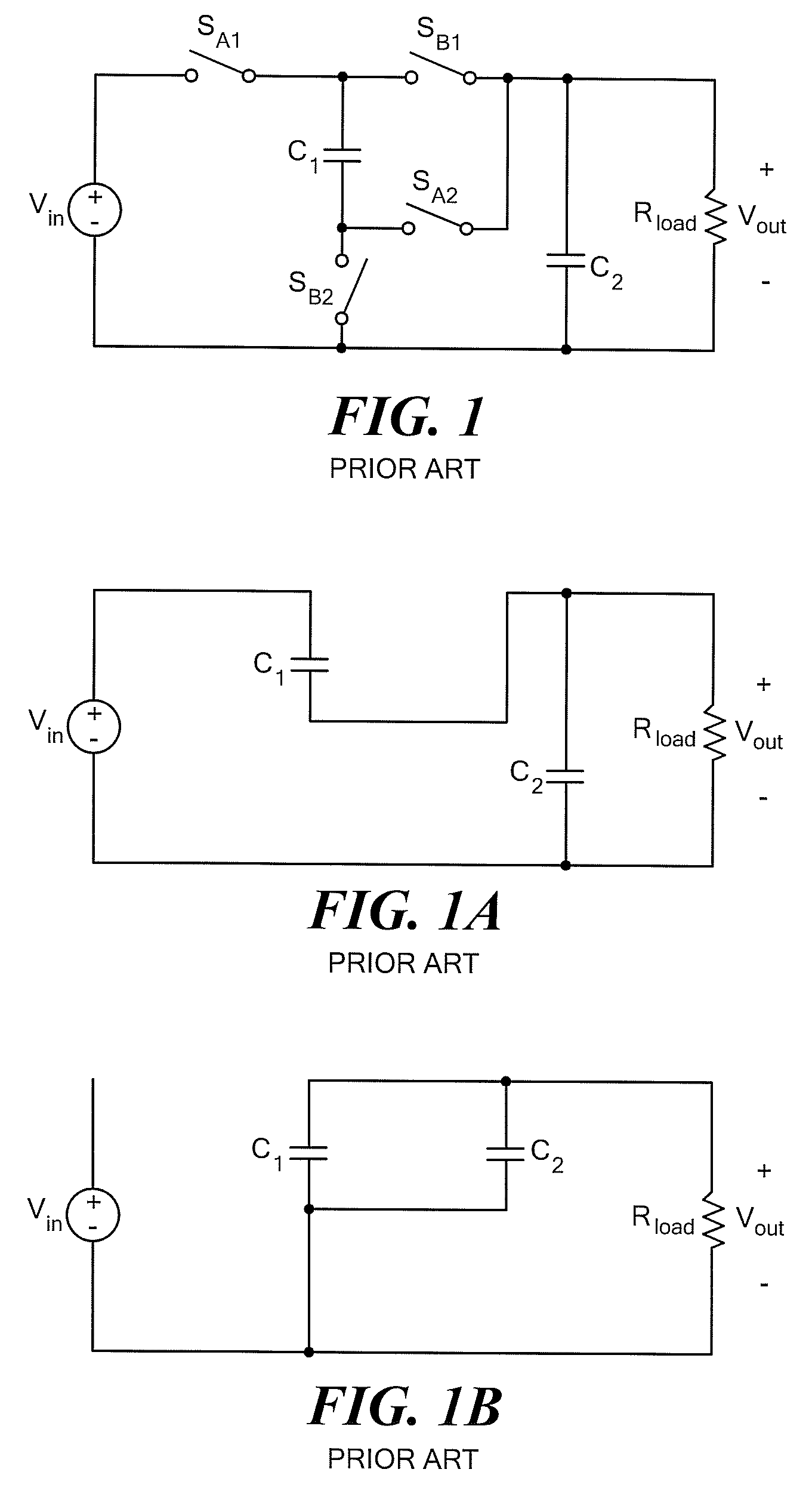

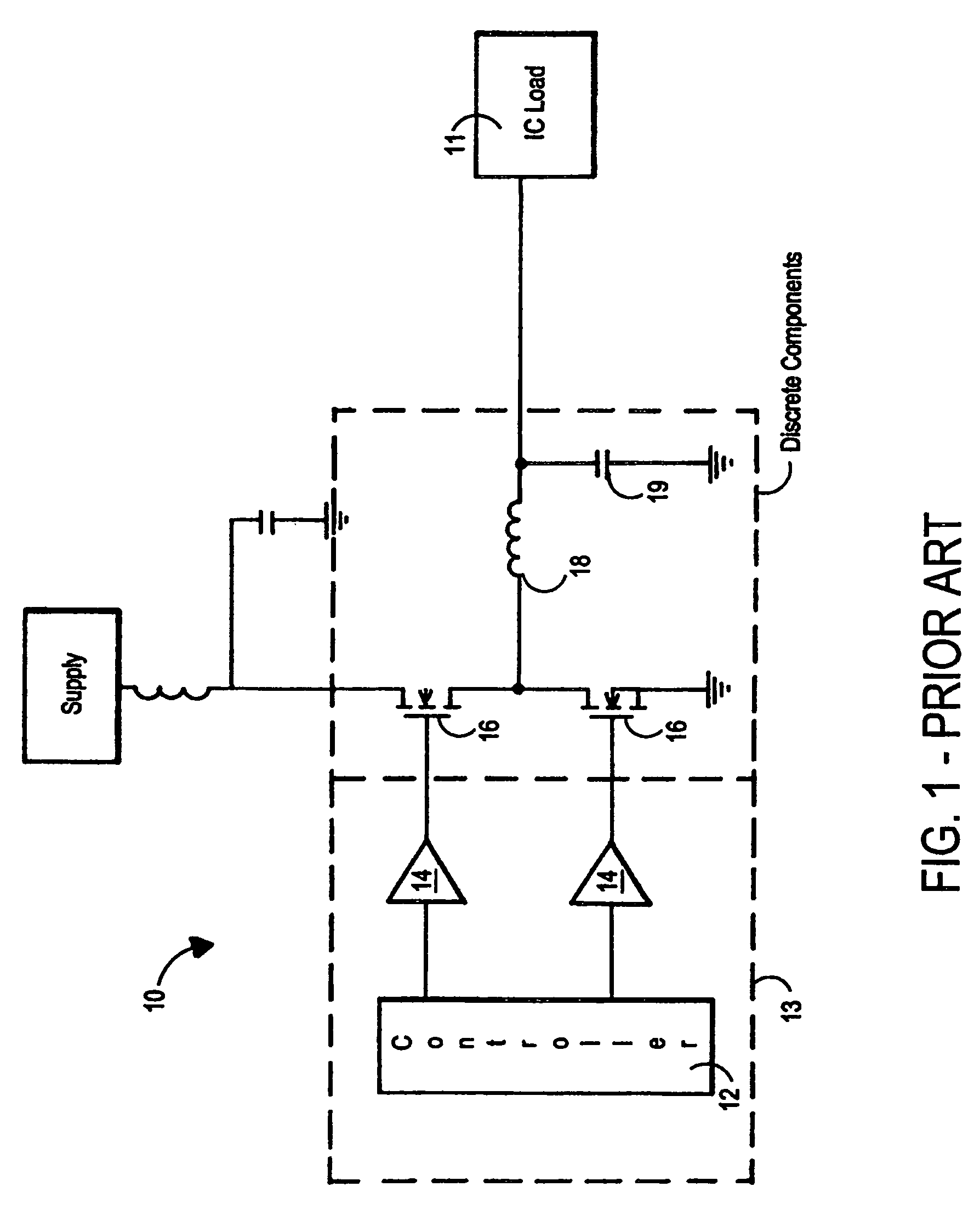

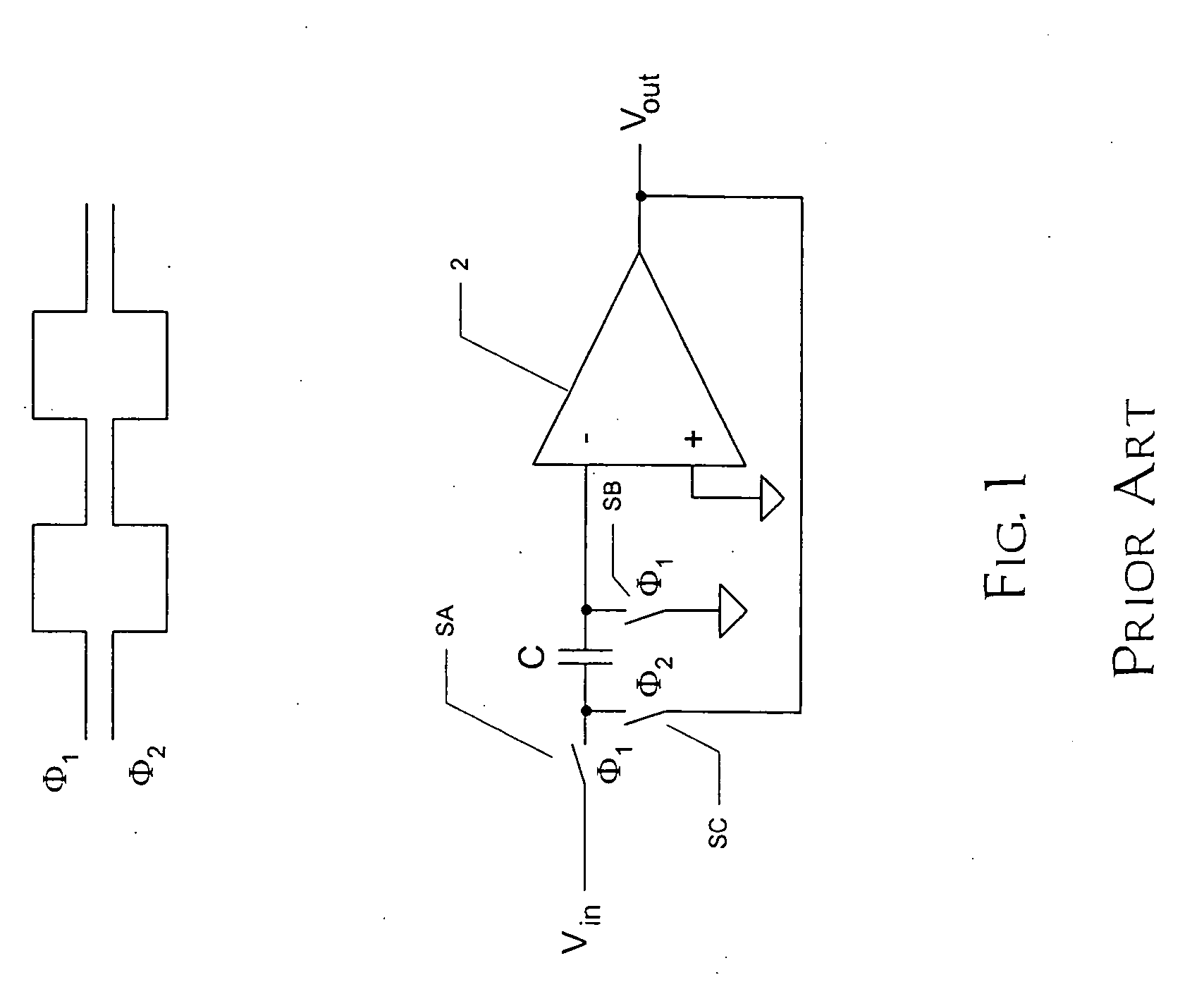

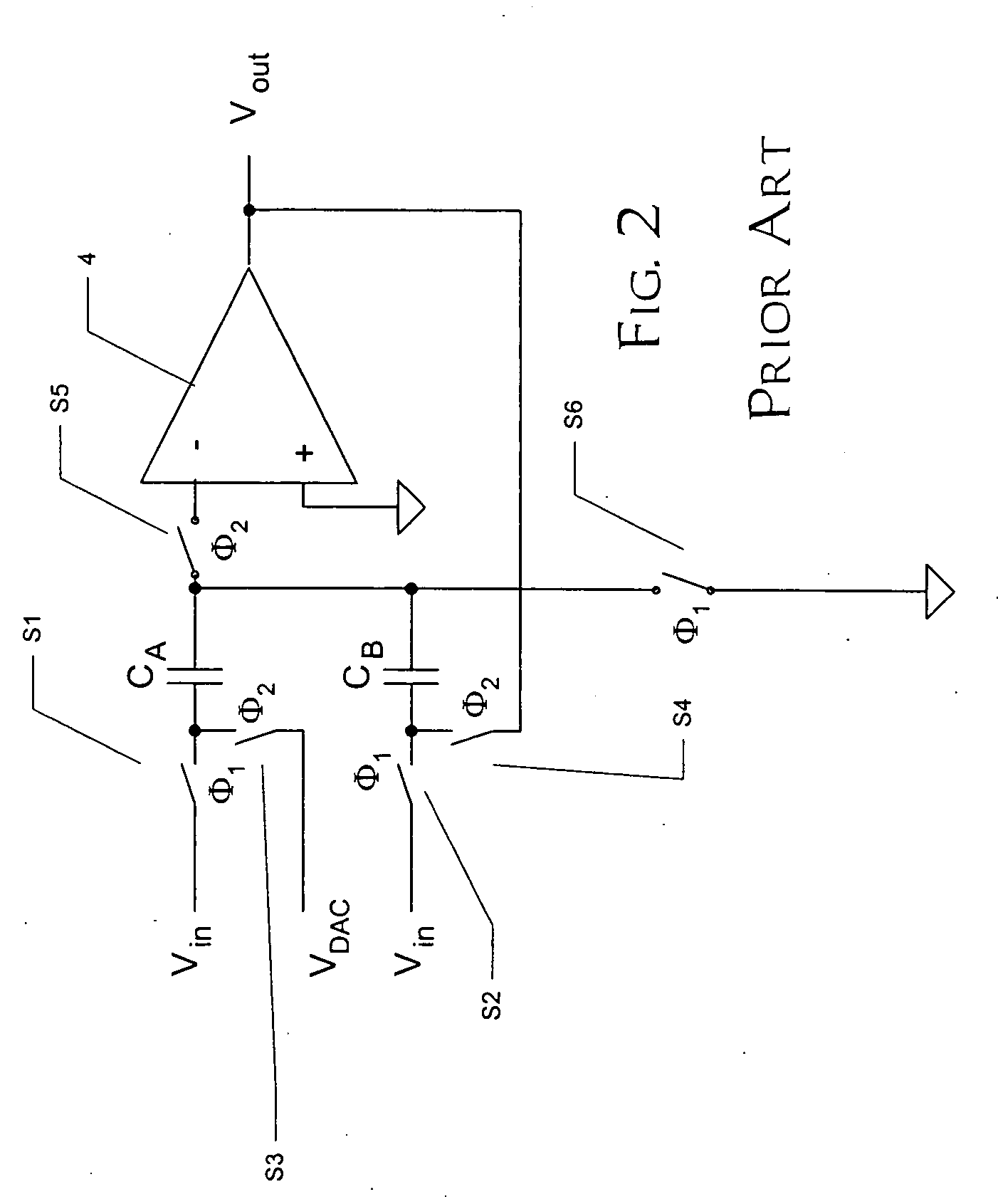

A switched capacitor is an electronic circuit element implementing a filter. It works by moving charges into and out of capacitors when switches are opened and closed. Usually, non-overlapping signals are used to control the switches, so that not all switches are closed simultaneously. Filters implemented with these elements are termed "switched-capacitor filters", and depend only on the ratios between capacitances. This makes them much more suitable for use within integrated circuits, where accurately specified resistors and capacitors are not economical to construct.

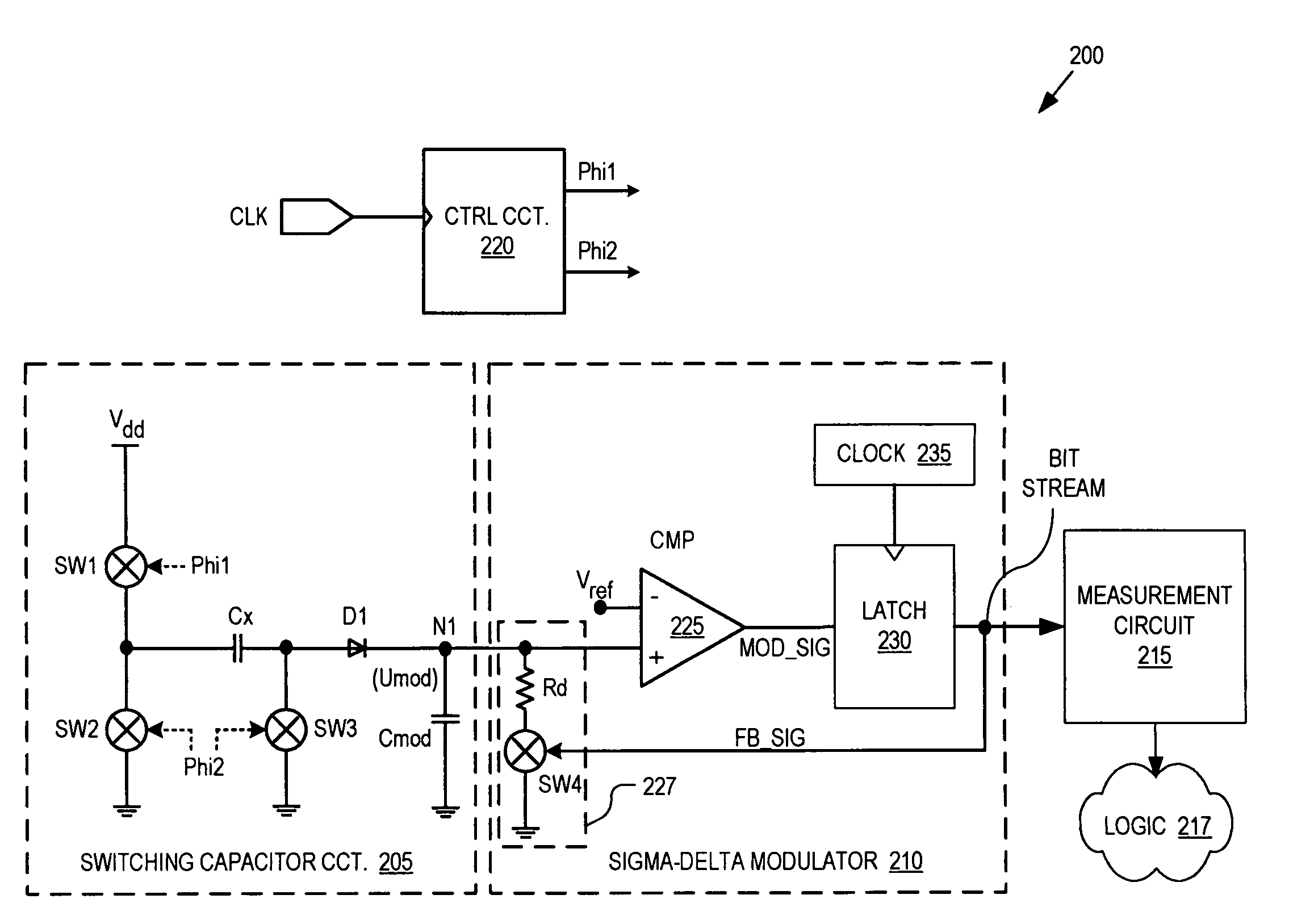

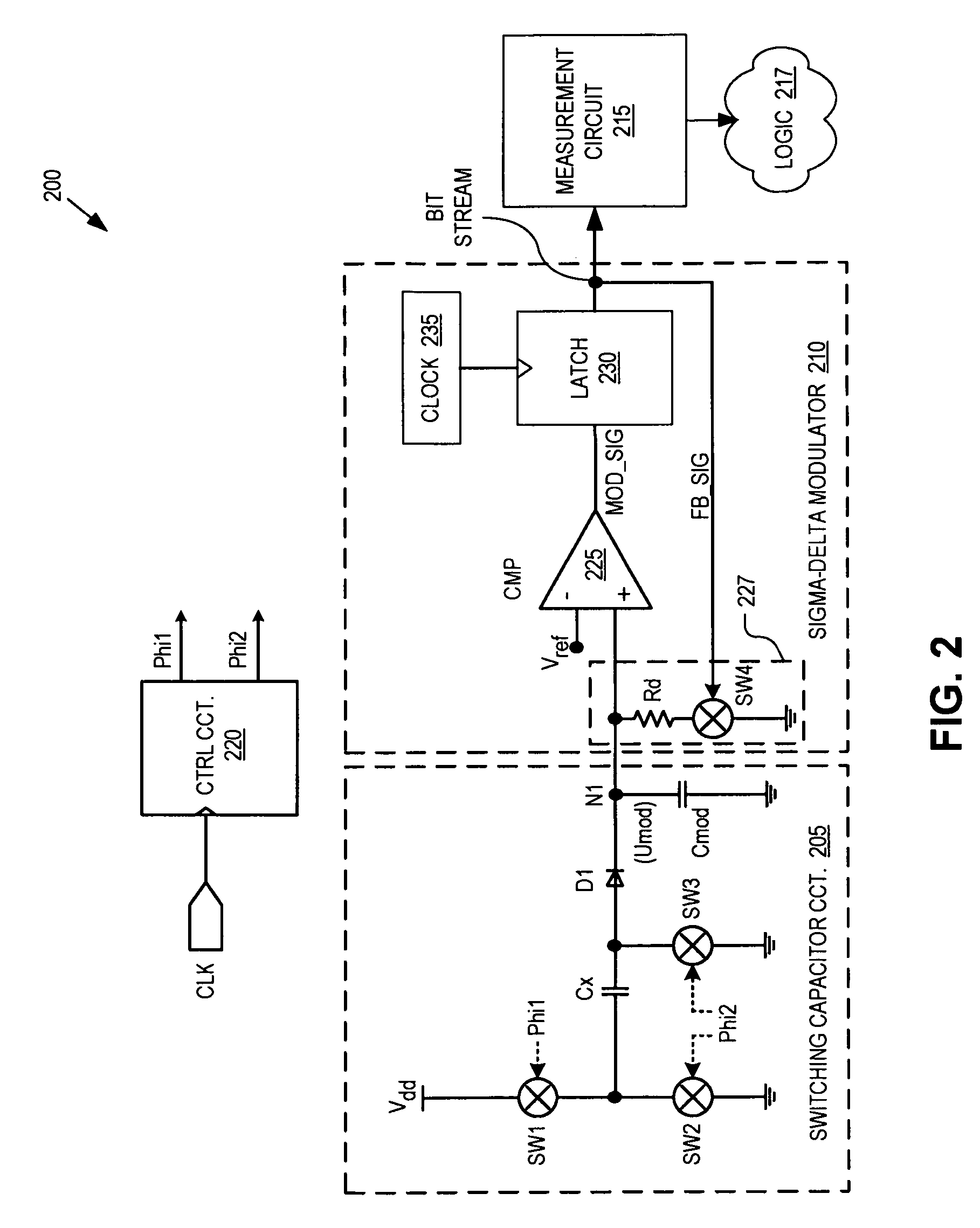

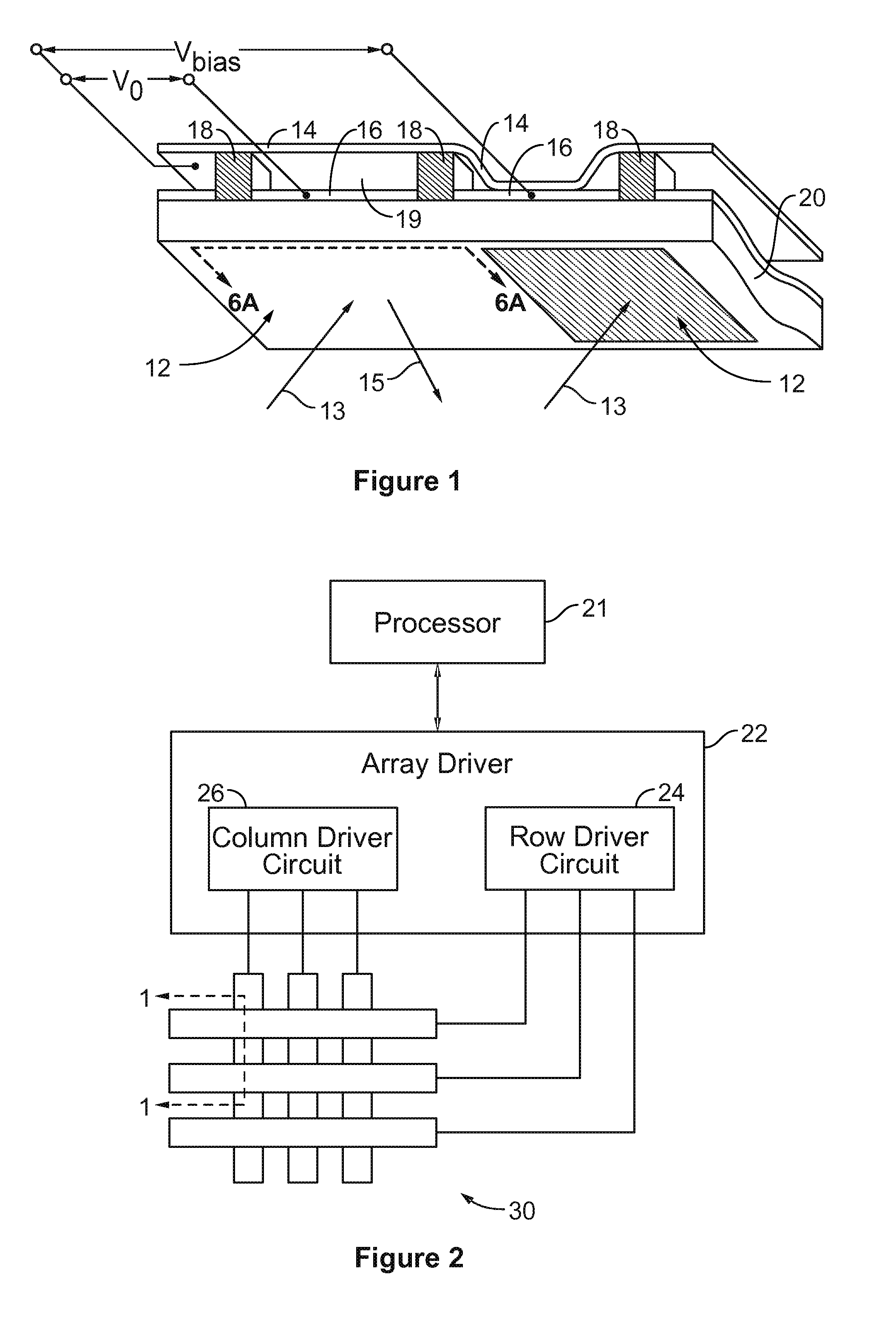

Capacitive field sensor with sigma-delta modulator

A capacitive sensor includes a switching capacitor circuit, a comparator, and a charge dissipation circuit. The switching capacitor circuit reciprocally couples a sensing capacitor in series with a modulation capacitor during a first switching phase and discharges the sensing capacitor during a second switching phase. The comparator is coupled to compare a voltage potential on the modulation capacitor to a reference and to generate a modulation signal in response. The charge dissipation circuit is coupled to the modulation capacitor to selectively discharge the modulation capacitor in response to the modulation signal.

Owner:CYPRESS SEMICON CORP

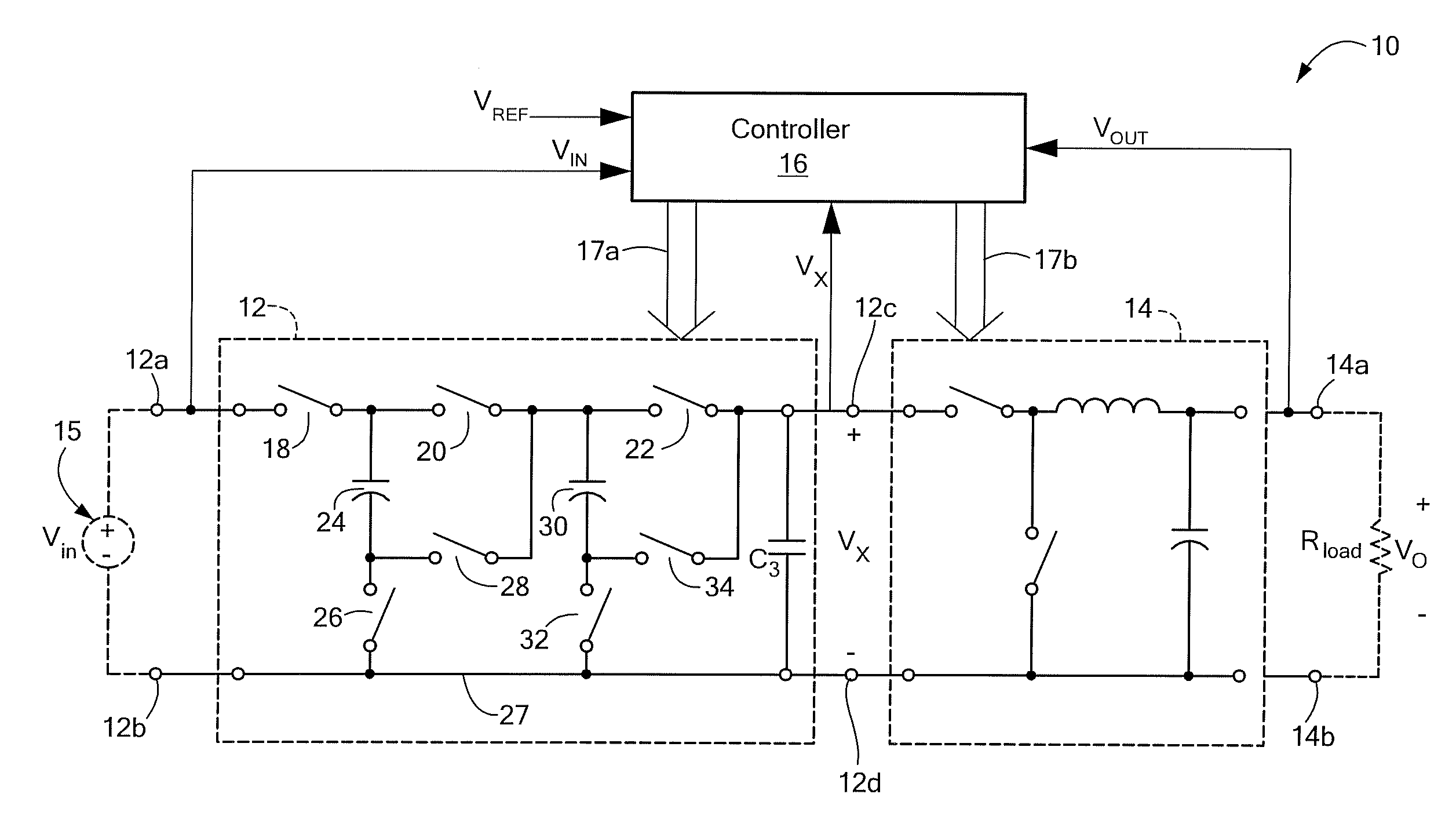

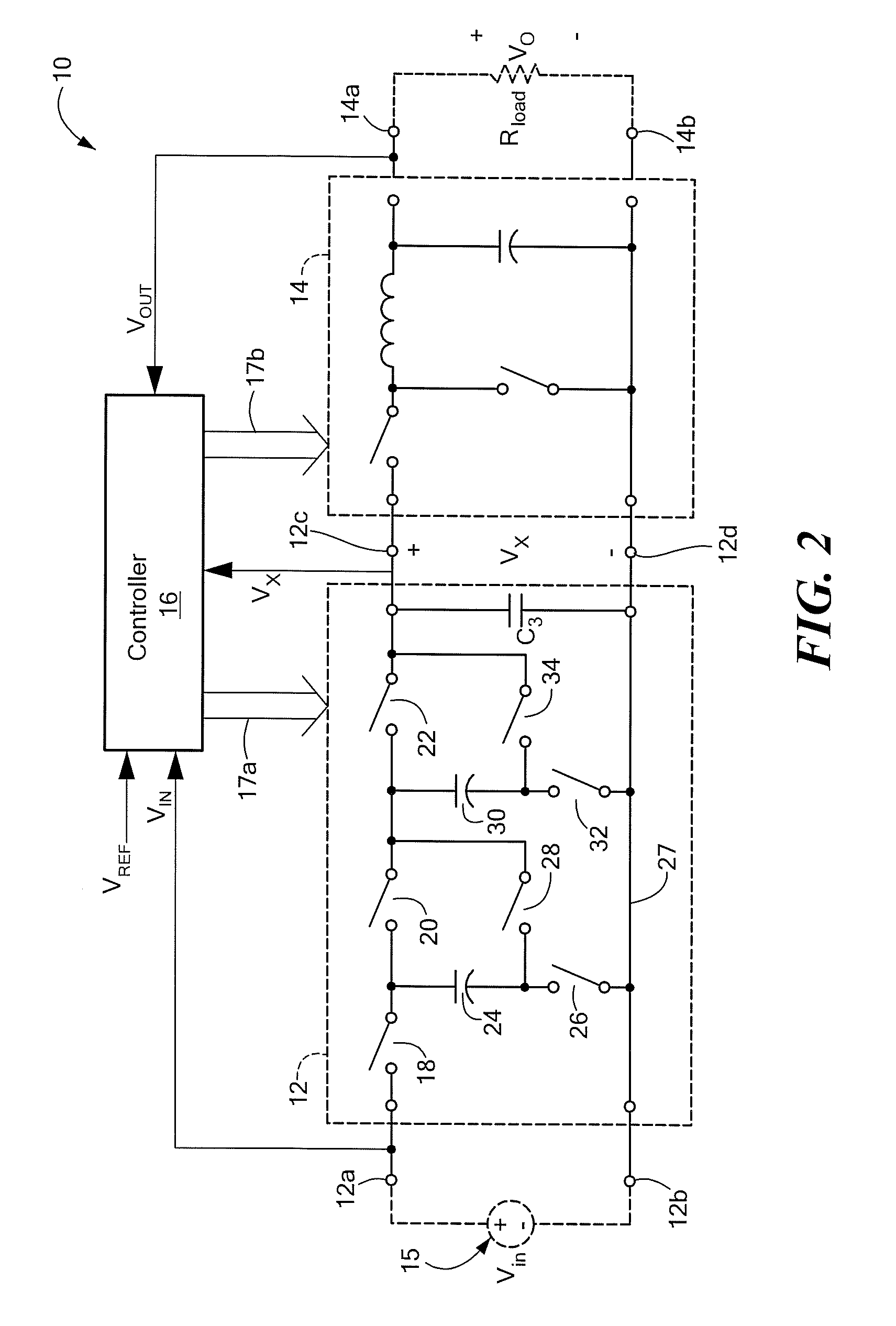

Power Converter with Capacitive Energy Transfer and Fast Dynamic Response

ActiveUS20090278520A1High power density power conversionImprove power densityEfficient power electronics conversionApparatus without intermediate ac conversionEnergy transferVoltage range

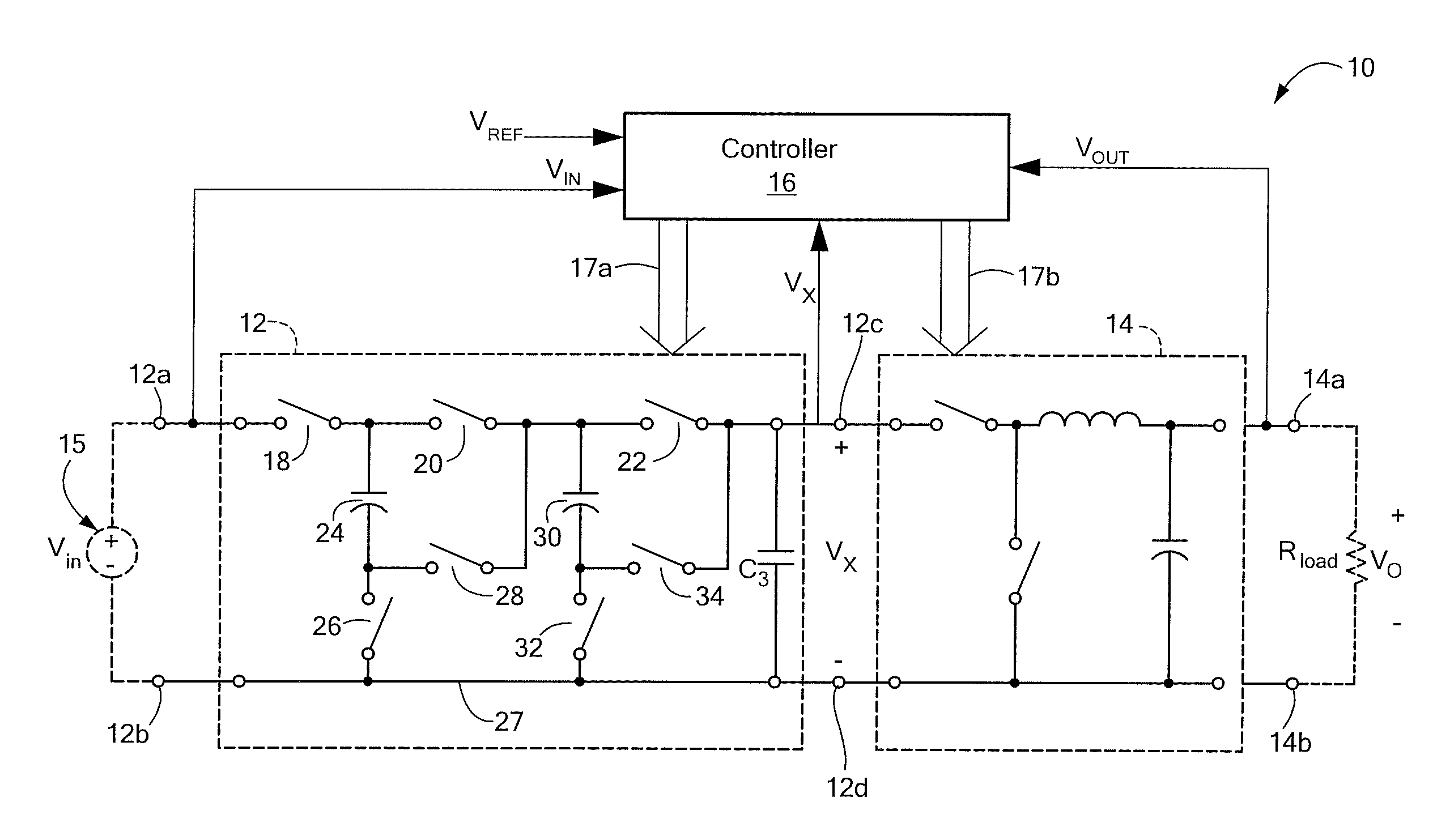

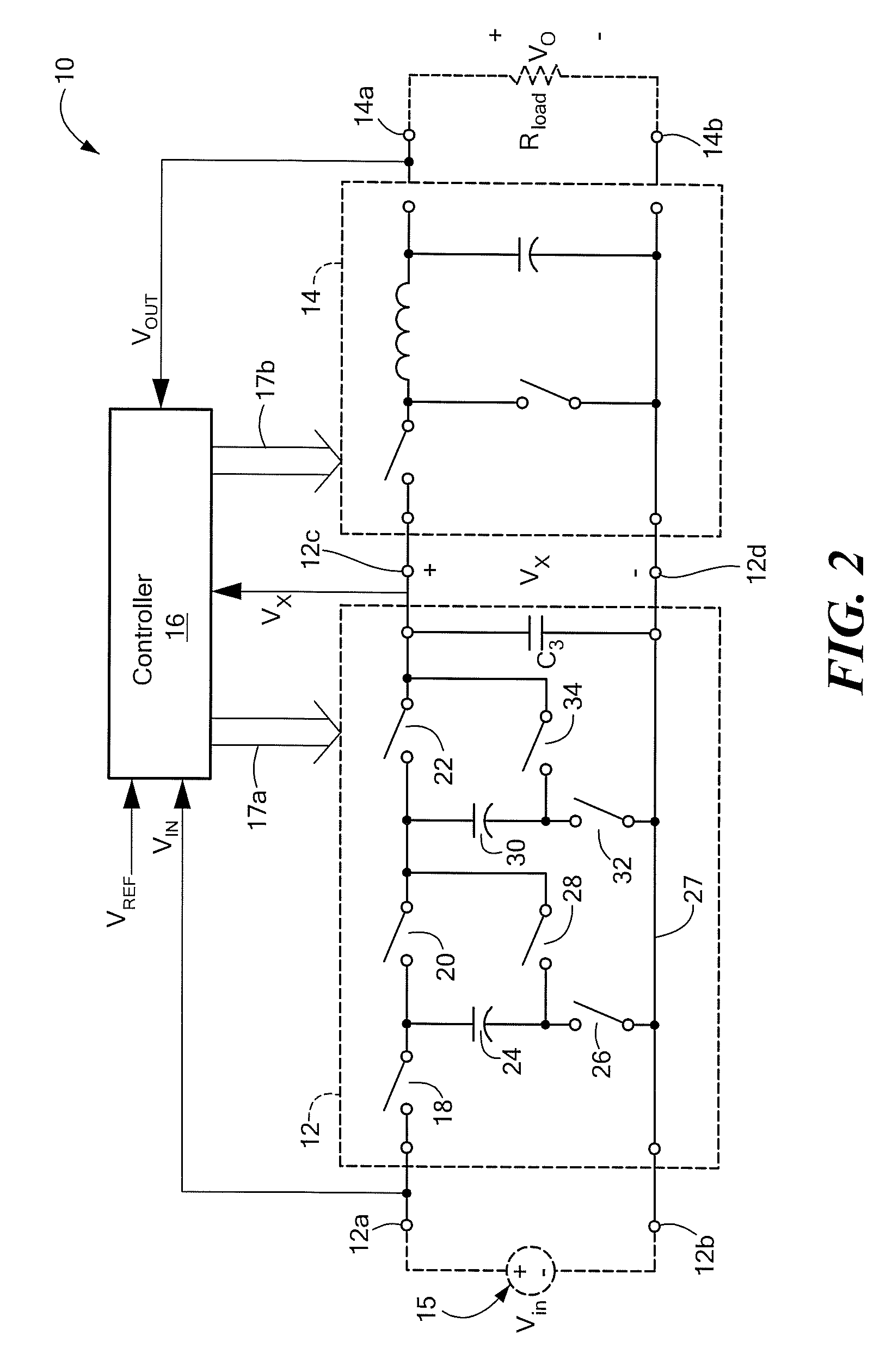

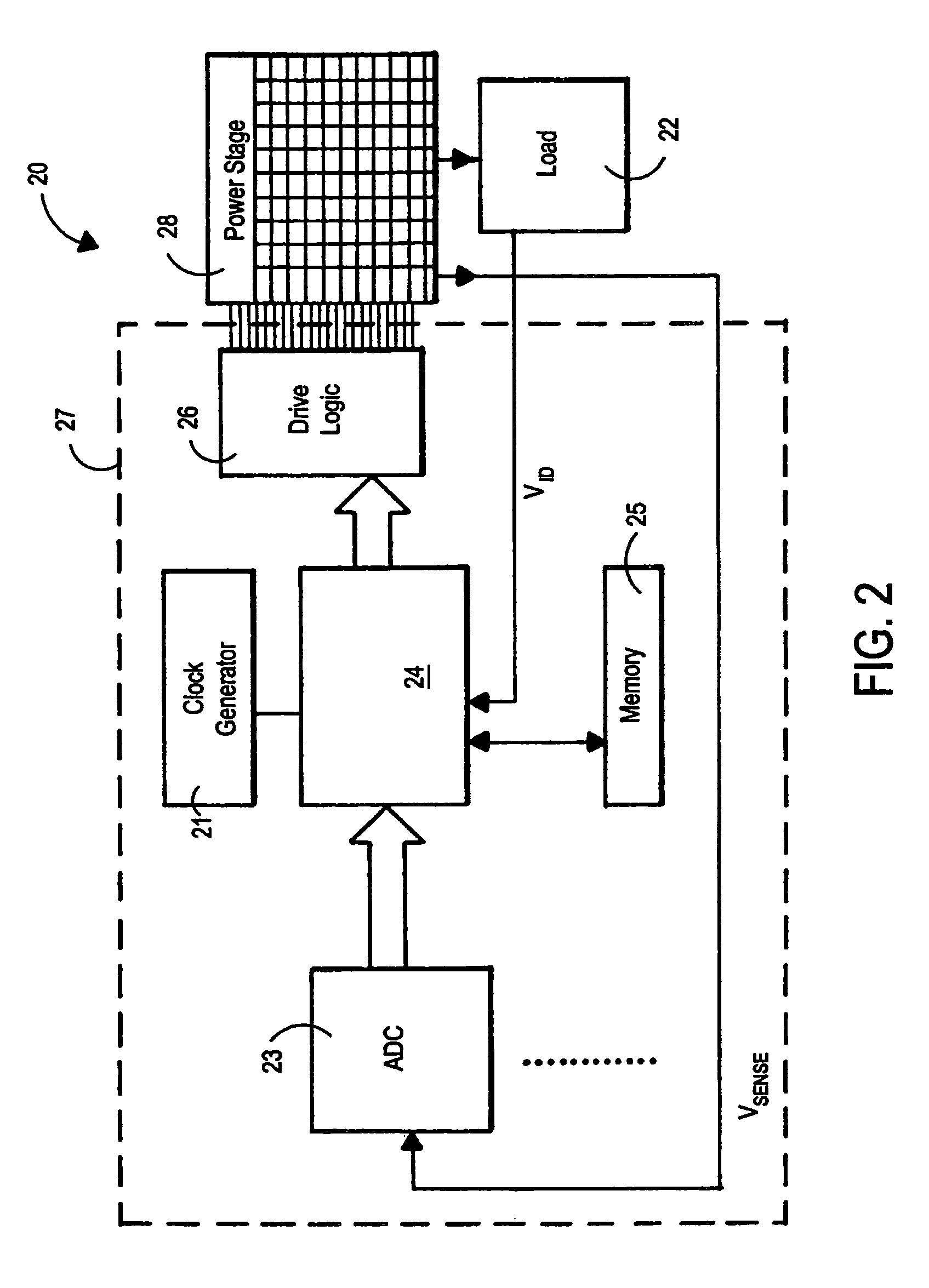

A converter circuit and related technique for providing high power density power conversion includes a reconfigurable switched capacitor transformation stage coupled to a magnetic converter (or regulation) stage. The circuits and techniques achieve high performance over a wide input voltage range or a wide output voltage range. The converter can be used, for example, to power logic devices in portable battery operated devices.

Owner:MASSACHUSETTS INST OF TECH

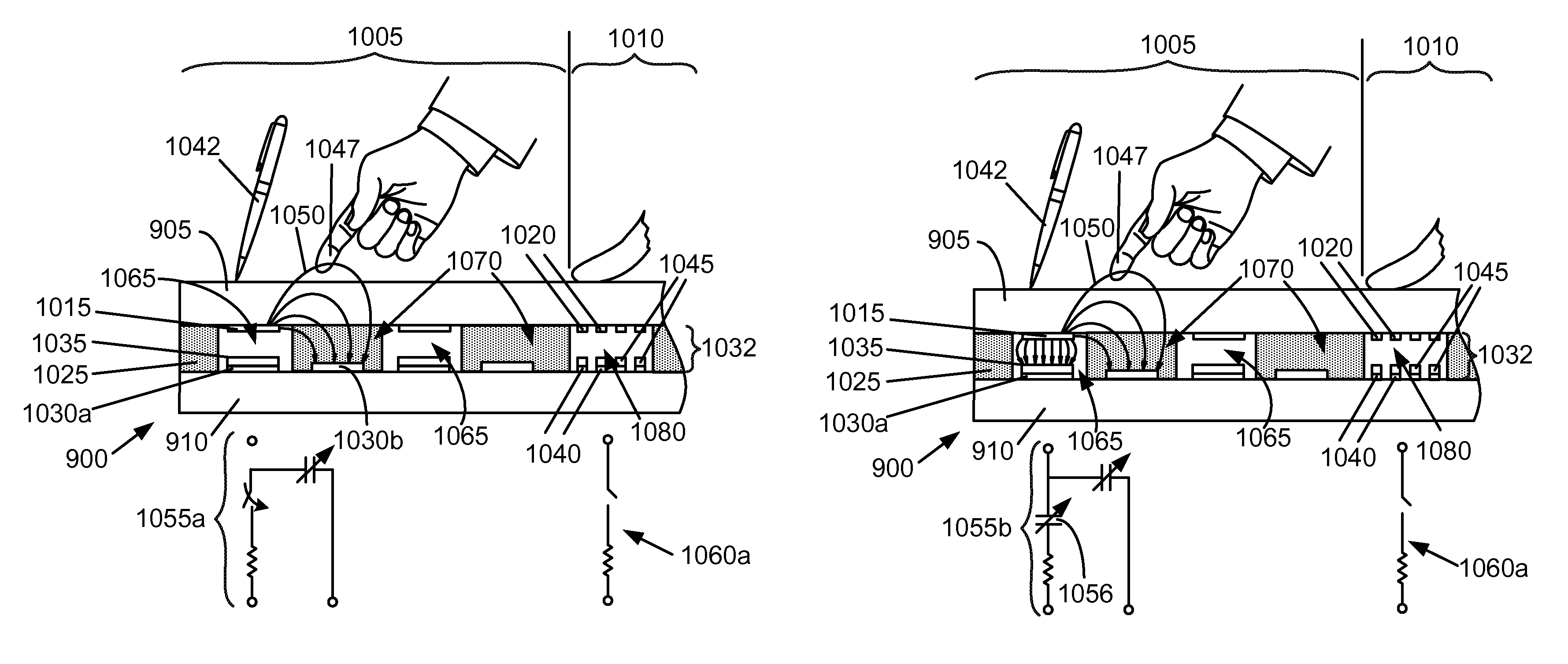

Touch sensor with force-actuated switched capacitor

InactiveUS20120092279A1Internal/peripheral component protectionDigital data authenticationEngineeringHigh capacitance

This disclosure provides apparatus, systems and methods of fabricating force-sensitive switches. In some implementations, an array of force-sensitive switches and local capacitors of a combined sensor device may be used to connect the local capacitor into associated projected capacitive touch (PCT) detection circuitry. In some implementations, each capacitor may be formed with a thin dielectric layer to achieve a high capacitance increase when the force-sensitive switch is closed, e.g., by the pressing of a stylus or finger. In some implementations, the same PCT detection circuitry can be used to detect changes in mutual capacitance when touched with a finger (touch mode) and changes in sensel capacitance when the force-sensitive switch is depressed (stylus or fingerprint mode).

Owner:SNAPTRACK

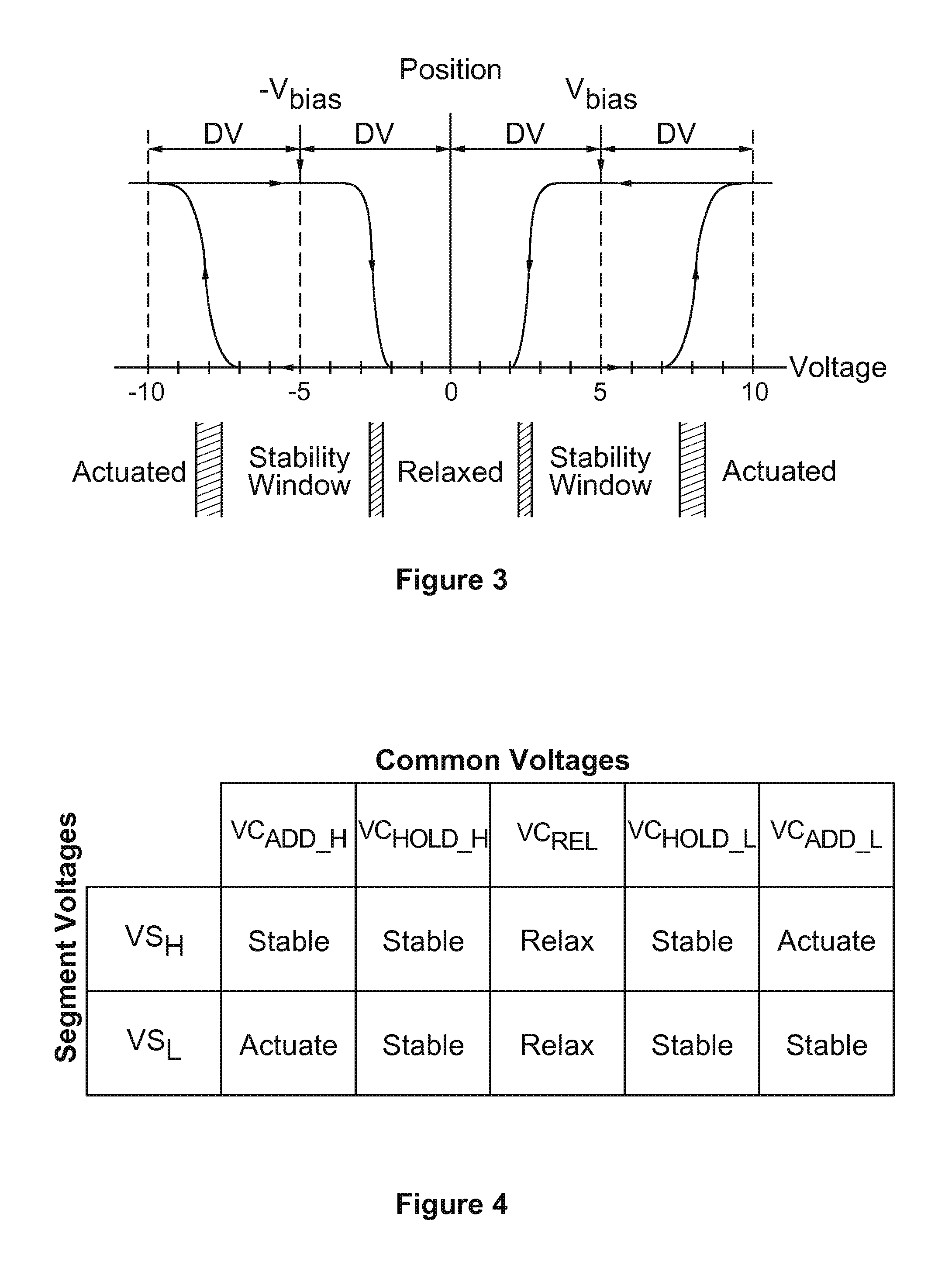

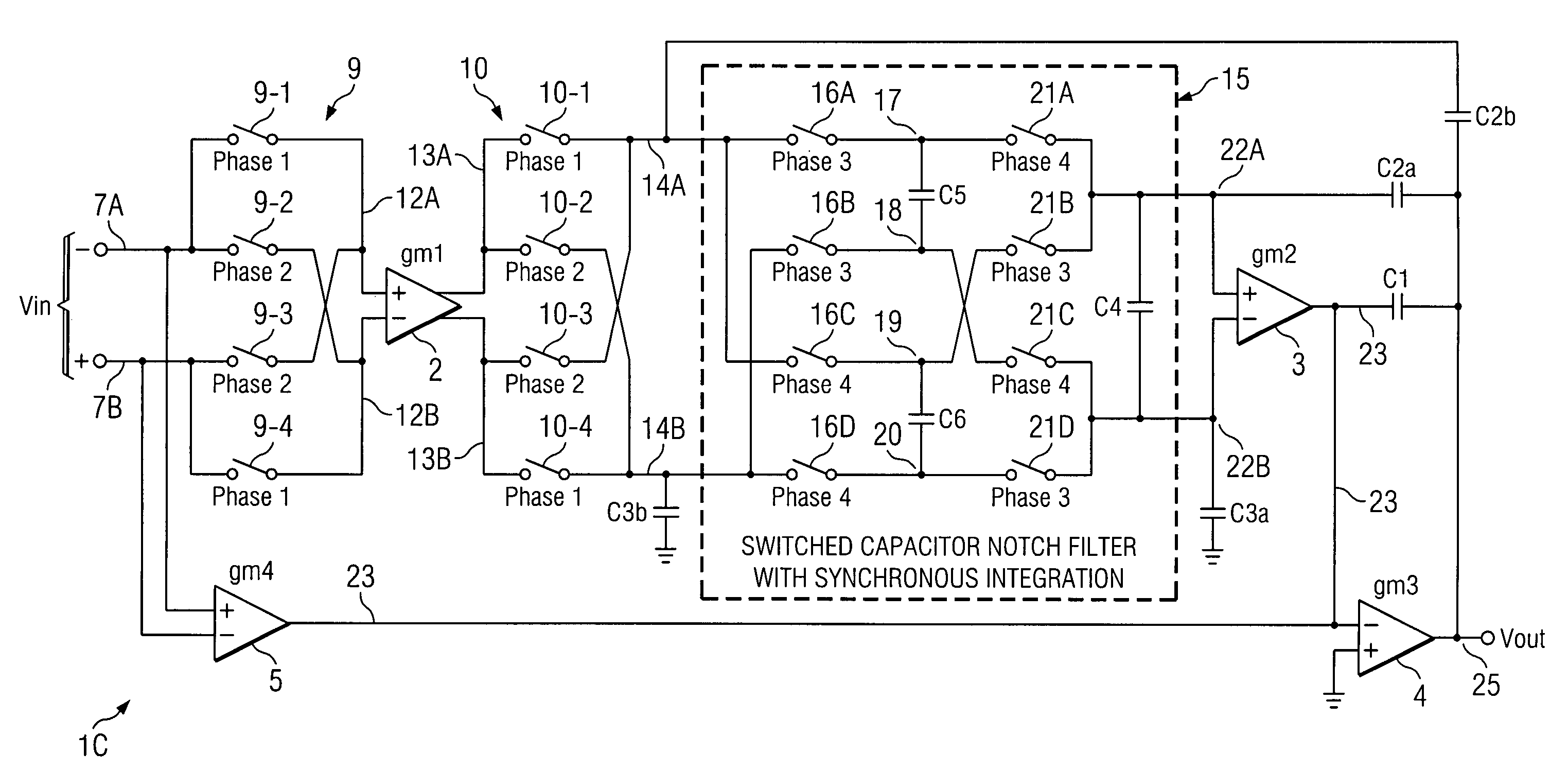

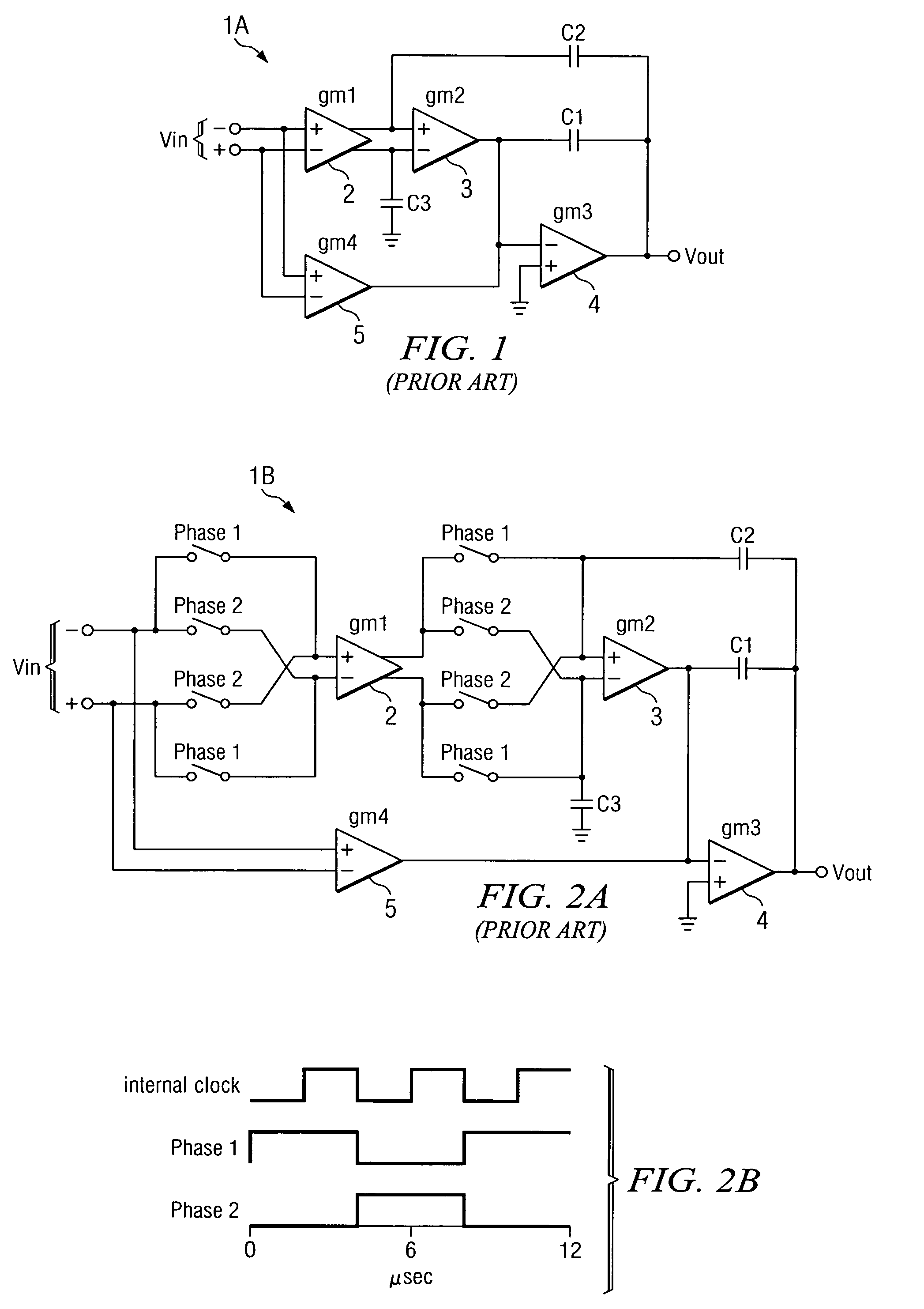

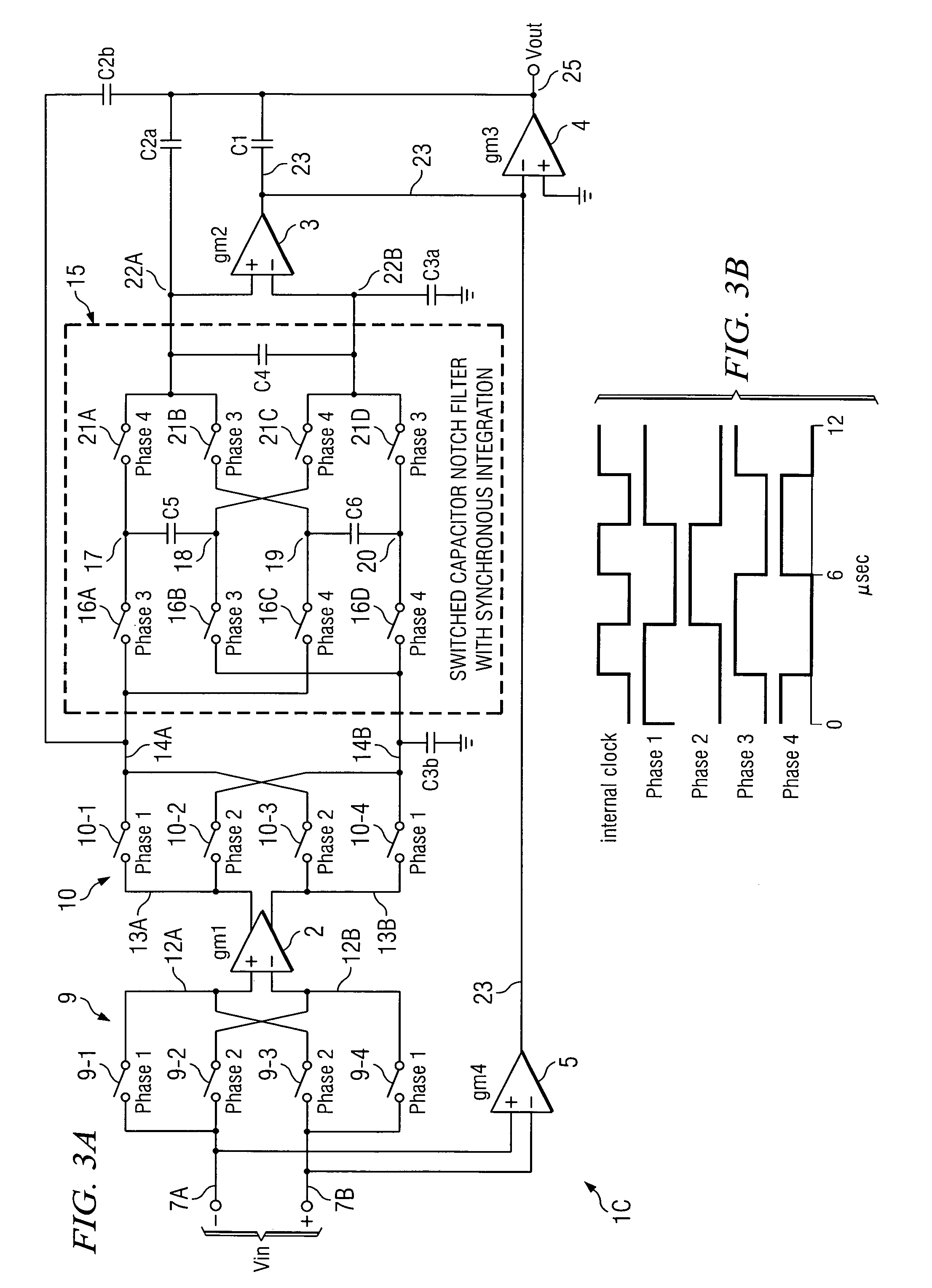

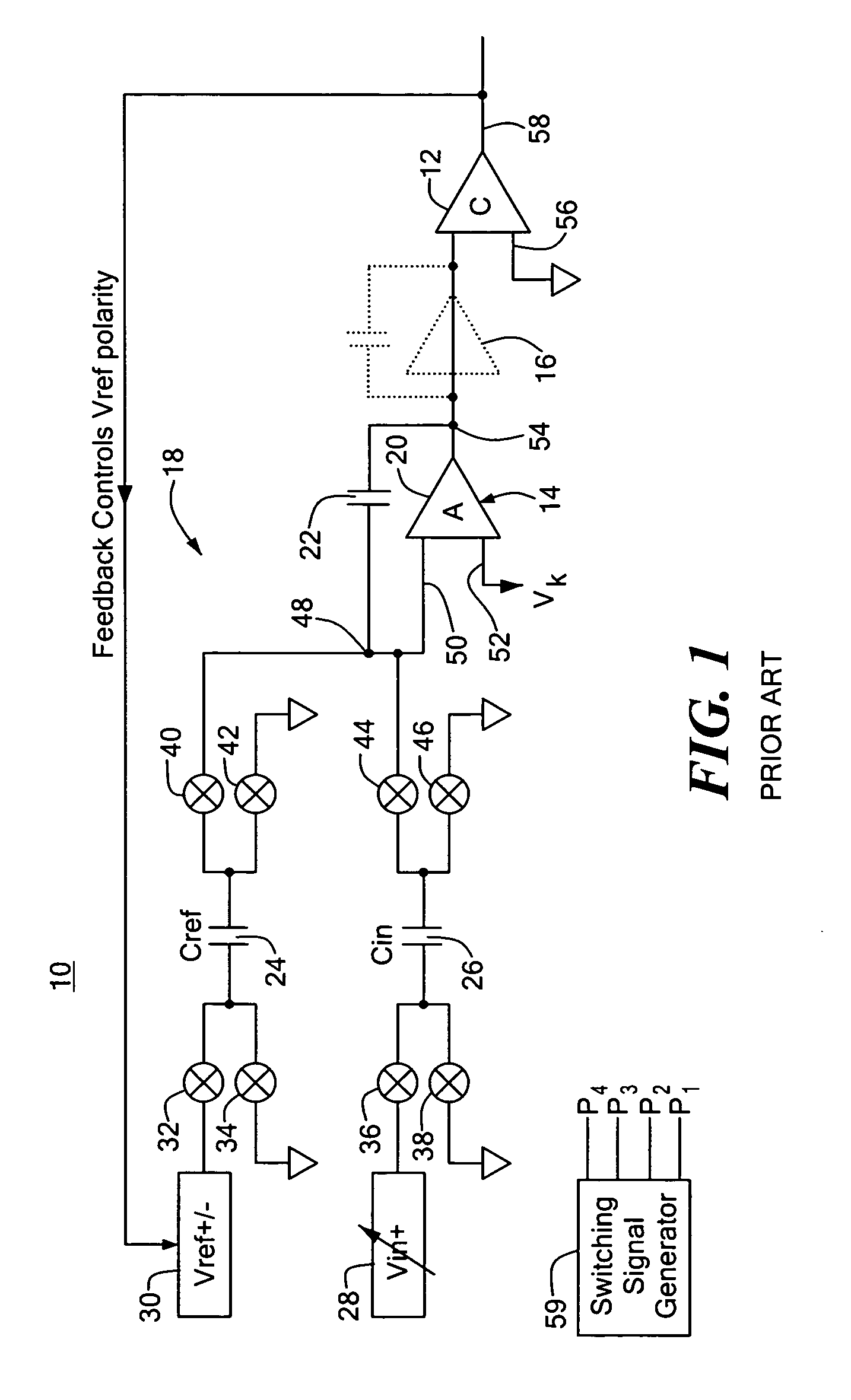

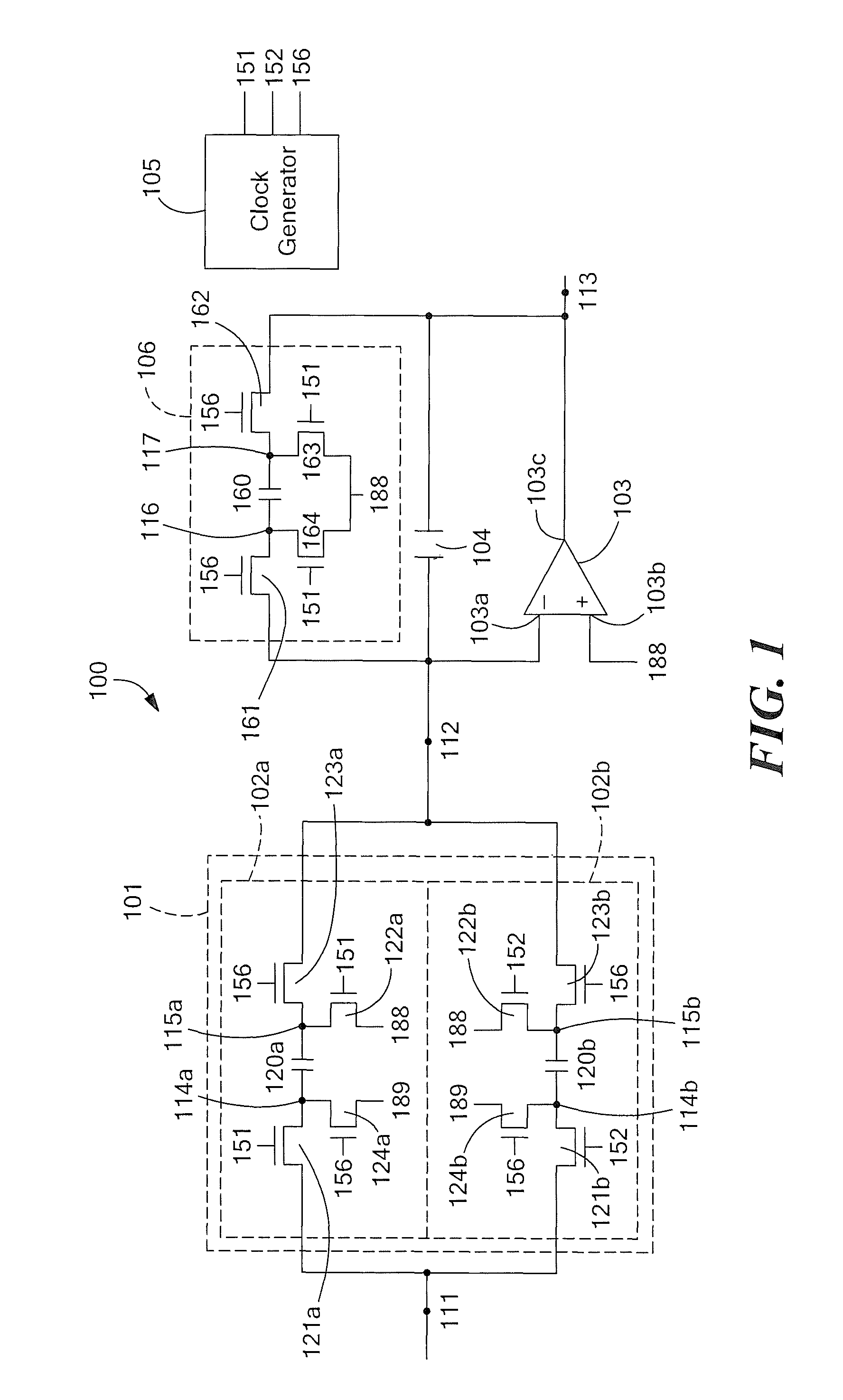

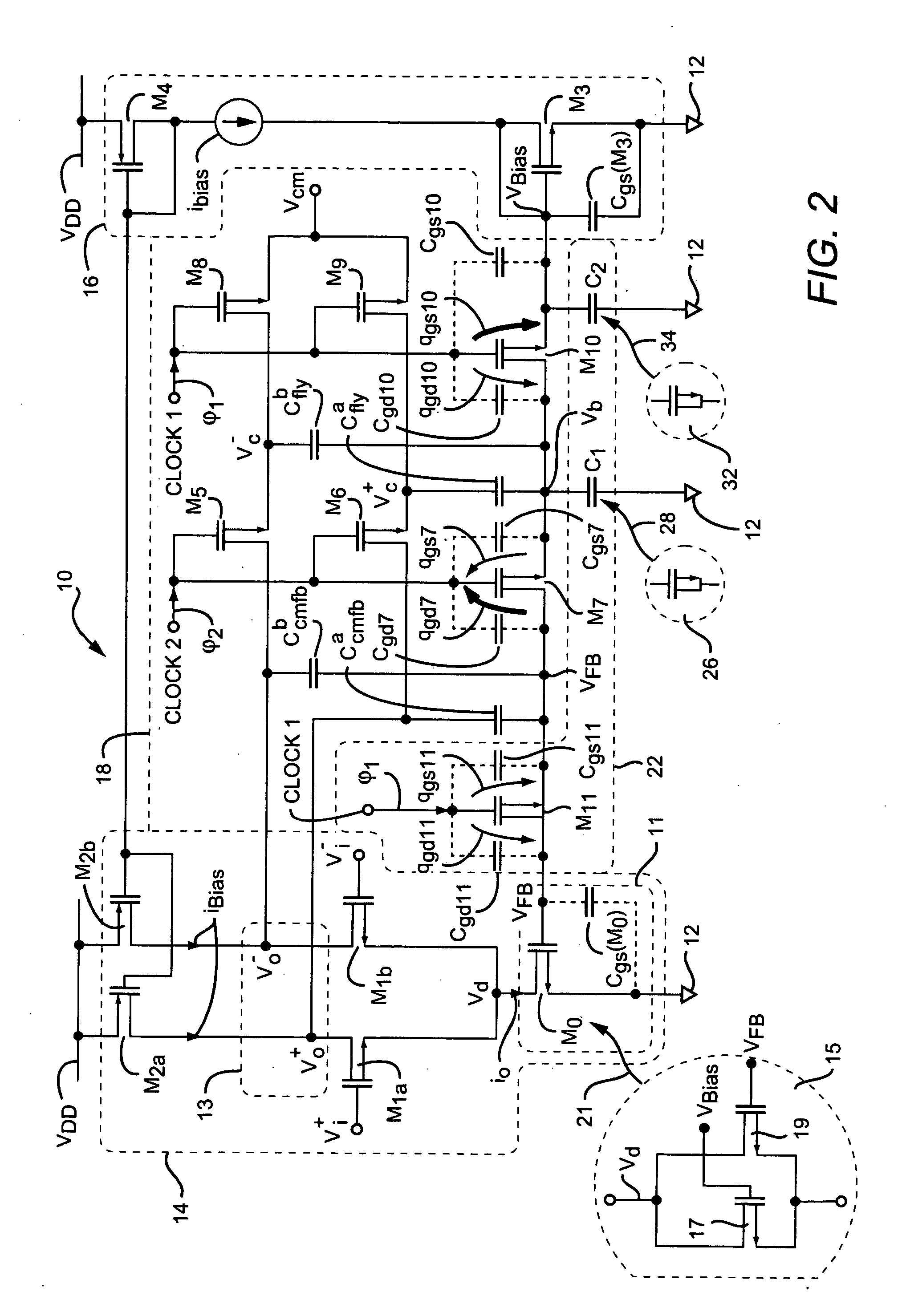

Notch filter for ripple reduction in chopper stabilized amplifiers

ActiveUS7292095B2Reduce ripple noiseFast signalAmplifier modifications to reduce noise influenceAmplifier modifications to raise efficiencyAudio power amplifierEngineering

A chopper-stabilized amplifier receiving an input signal includes a first operational transconductance amplifier having an input chopper and an output chopper for chopping an output signal produced by the first operational transconductance amplifier. A switched capacitor notch filter filters the chopped output signal by operating synchronously with the chopping frequency of output chopper to filter ripple voltages that otherwise would be produced by the output chopper. In one embodiment, a second operational transconductance amplifier amplifies the notch filter output. The input signal is fed forward, summed with the output of the second operational transconductance amplifier, and applied to the input of a fourth operational transconductance amplifier. Ripple noise and offset are substantially reduced.

Owner:TEXAS INSTR INC

Power converter with capacitive energy transfer and fast dynamic response

ActiveUS8212541B2Improve performanceIncrease conversionsEfficient power electronics conversionApparatus without intermediate ac conversionCapacitanceConverters

A converter circuit and related technique for providing high power density power conversion includes a reconfigurable switched capacitor transformation stage coupled to a magnetic converter (or regulation) stage. The circuits and techniques achieve high performance over a wide input voltage range or a wide output voltage range. The converter can be used, for example, to power logic devices in portable battery operated devices.

Owner:MASSACHUSETTS INST OF TECH

Switched-capacitor power supply system and method

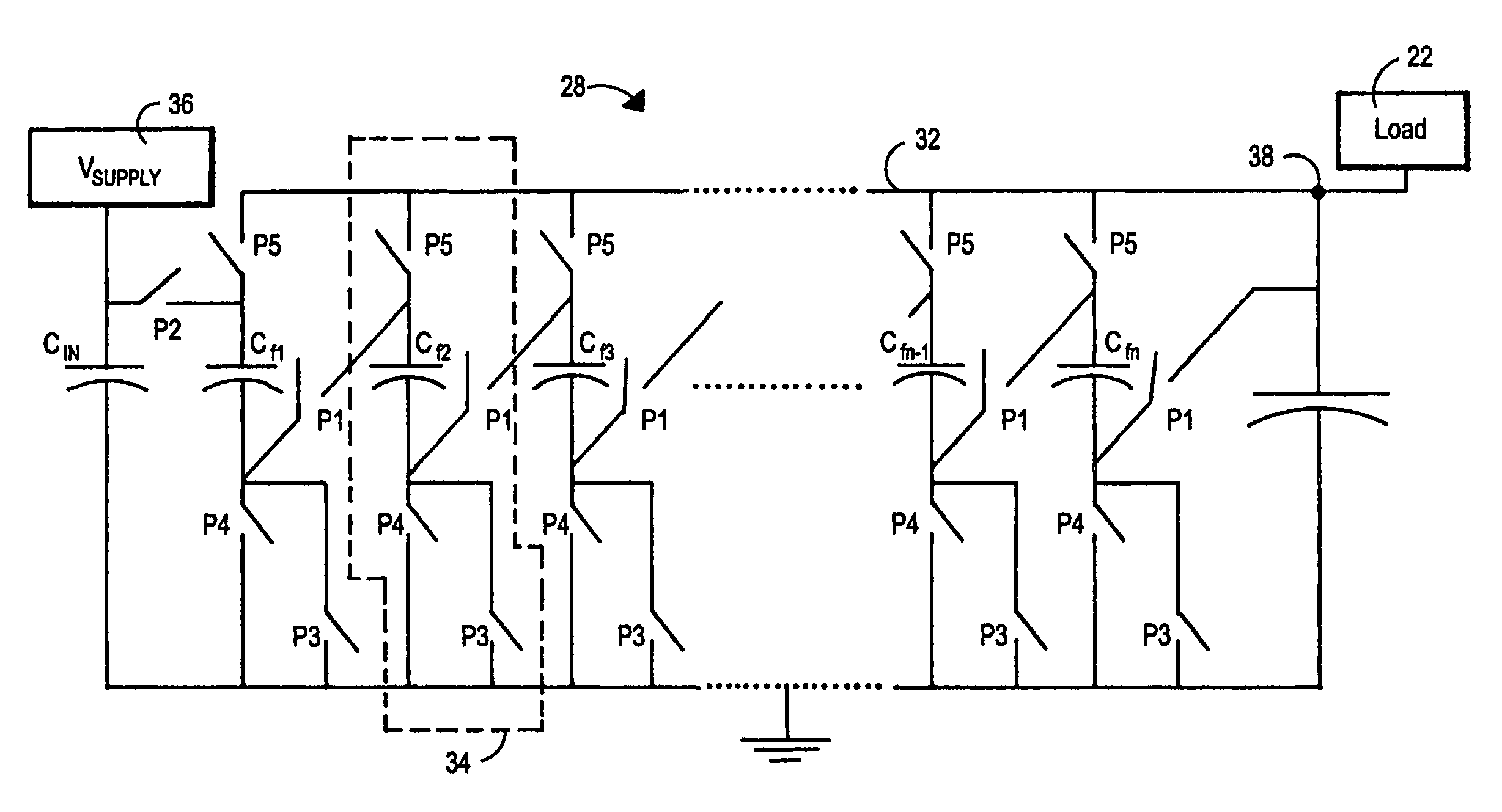

A plurality of thin-film capacitors are grouped in phases. A control circuit switches each phase between charging and discharging states devised to supply one or more loads with controlled power.

Owner:INTEGRAL WAVE TECH

Variable capacitance switched capacitor input system and method

ActiveUS6970126B1Current errorElectric signal transmission systemsDelta modulationCapacitanceIntegrator

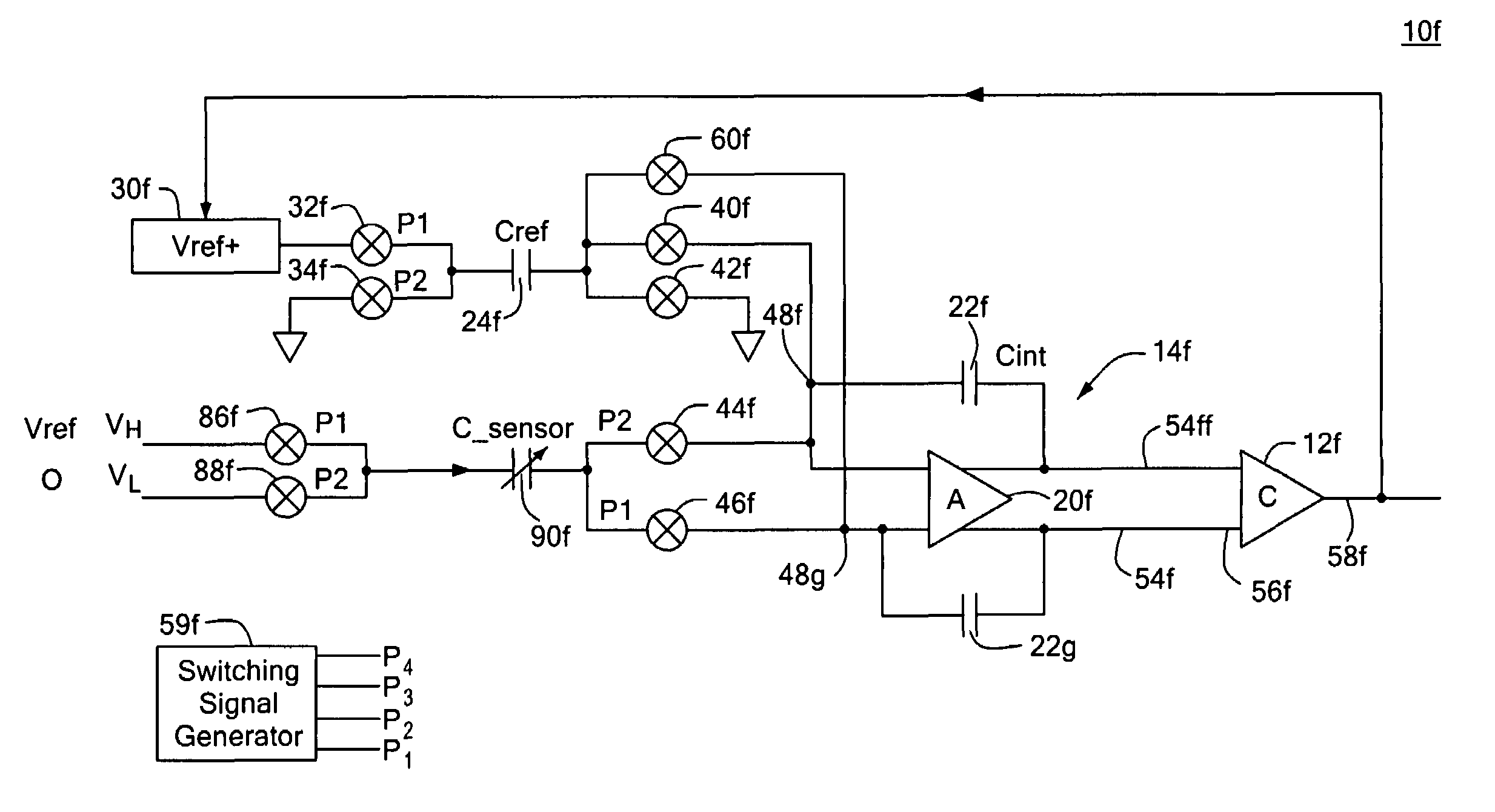

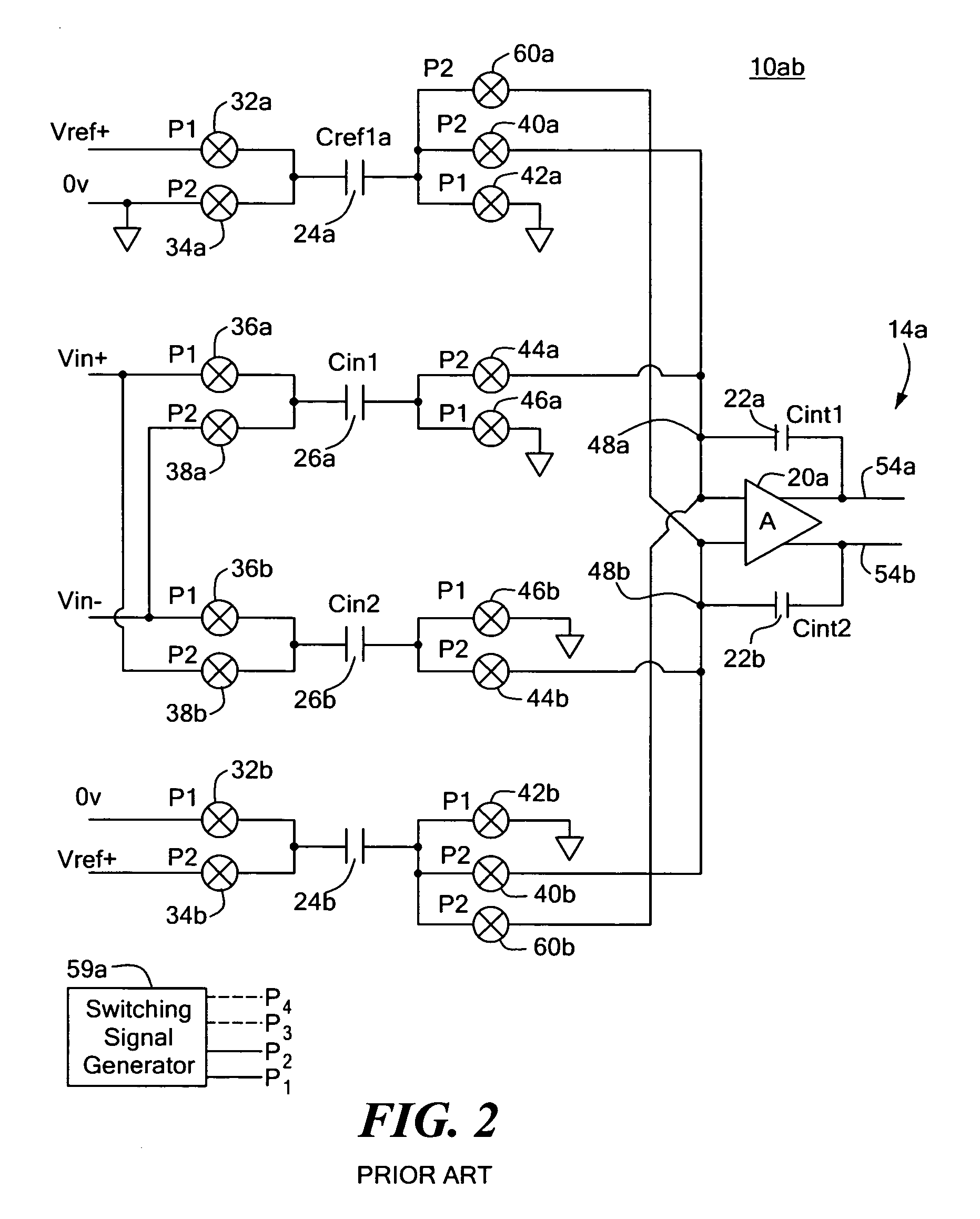

A variable capacitance switched capacitor input system and method includes a differential integrator circuit having first and second input summing nodes and a variable sensing capacitor; one terminal of the variable sensing capacitor is connected to one of the nodes in the first phase and to the other of the nodes in the second phase; an input terminal connected to a second terminal of the variable sensing capacitor receives a first voltage level in the first phase and a second voltage level in the second phase for delivering the charge on the variable sensing capacitor to the first summing node in the first phase and to the second summing node in the second phase and canceling errors in a differential integrator circuit output caused by leakage current.

Owner:ANALOG DEVICES INC

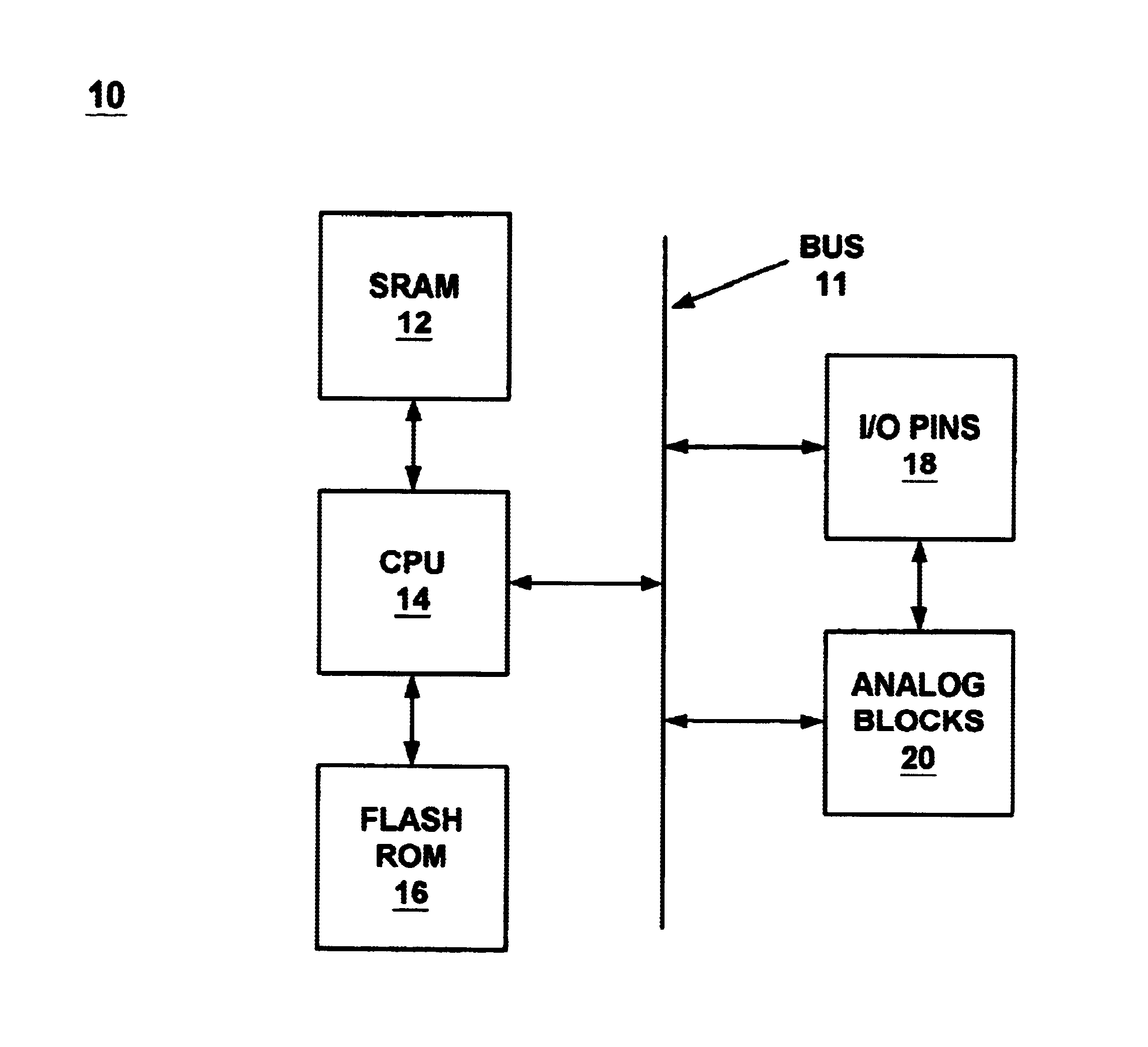

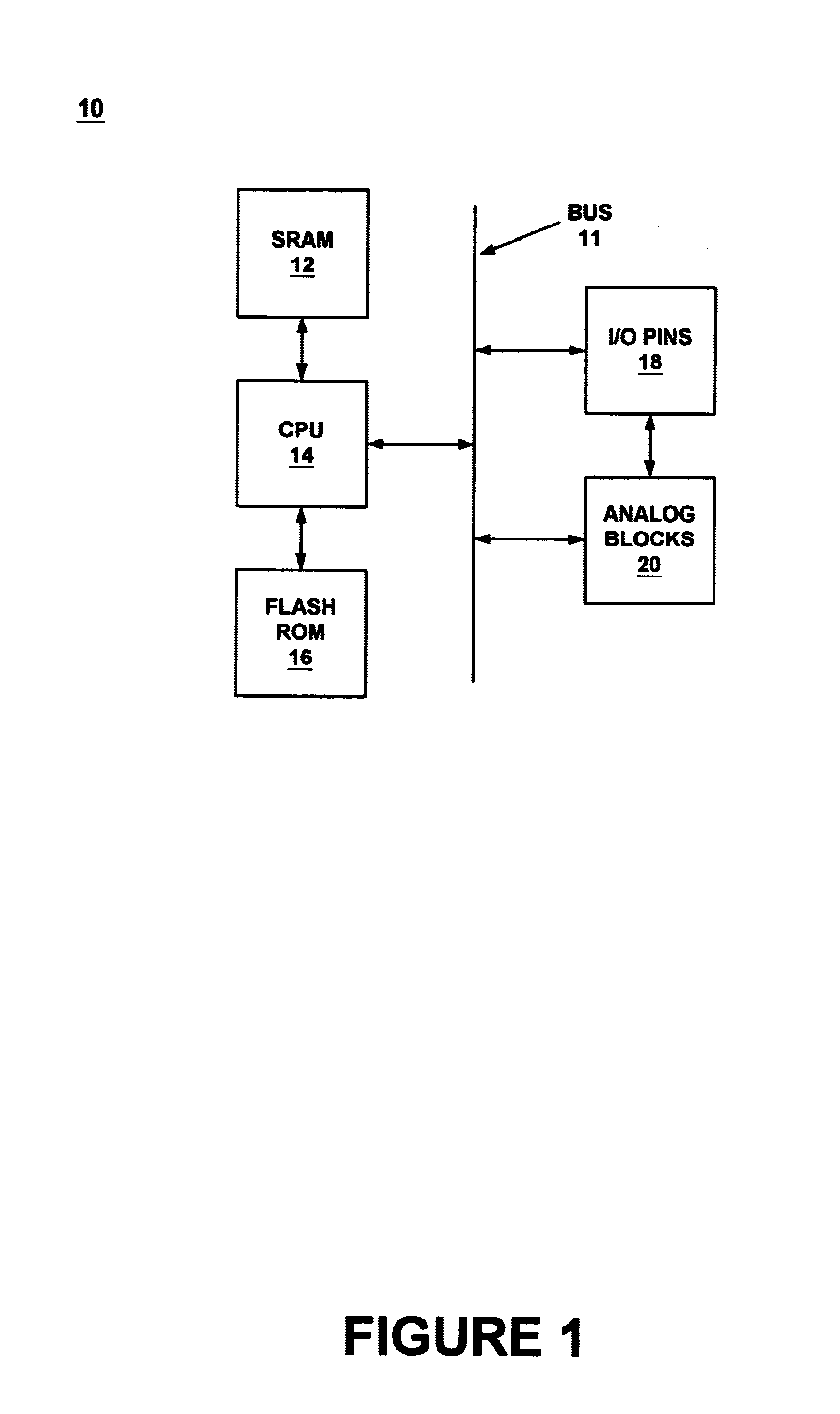

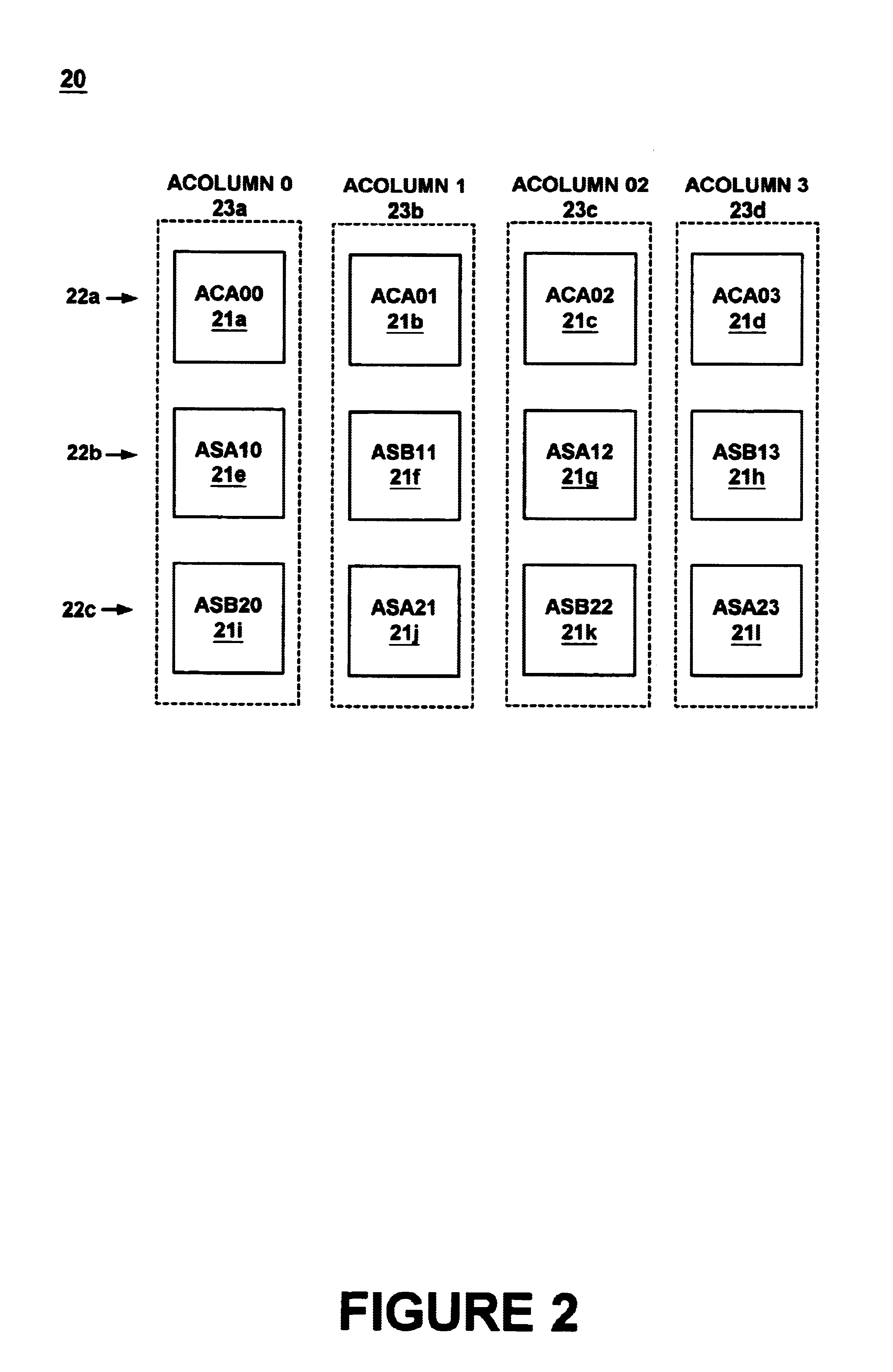

Programmable analog system architecture

InactiveUS6941336B1Shorten development timeReduce expensesProgramming arrangements for electric/magnetic computingElectric pulse generatorElectricityCapacitance

A programmable analog system architecture and method thereof are described. The analog system architecture and method introduce a single chip solution that contains a set of tailored analog blocks and elements that can be configured and reconfigured in different ways to implement a variety of different analog functions. The architecture includes an array of analog blocks, including continuous time blocks and different types of switched capacitor blocks. The analog blocks can be electrically coupled to each other in different combinations to perform different analog functions. Each analog block includes analog elements that have changeable characteristics that can be specified according to the function to be performed. The architecture thereby facilitates the design of customized chips at less time and expense.

Owner:CYPRESS SEMICON CORP

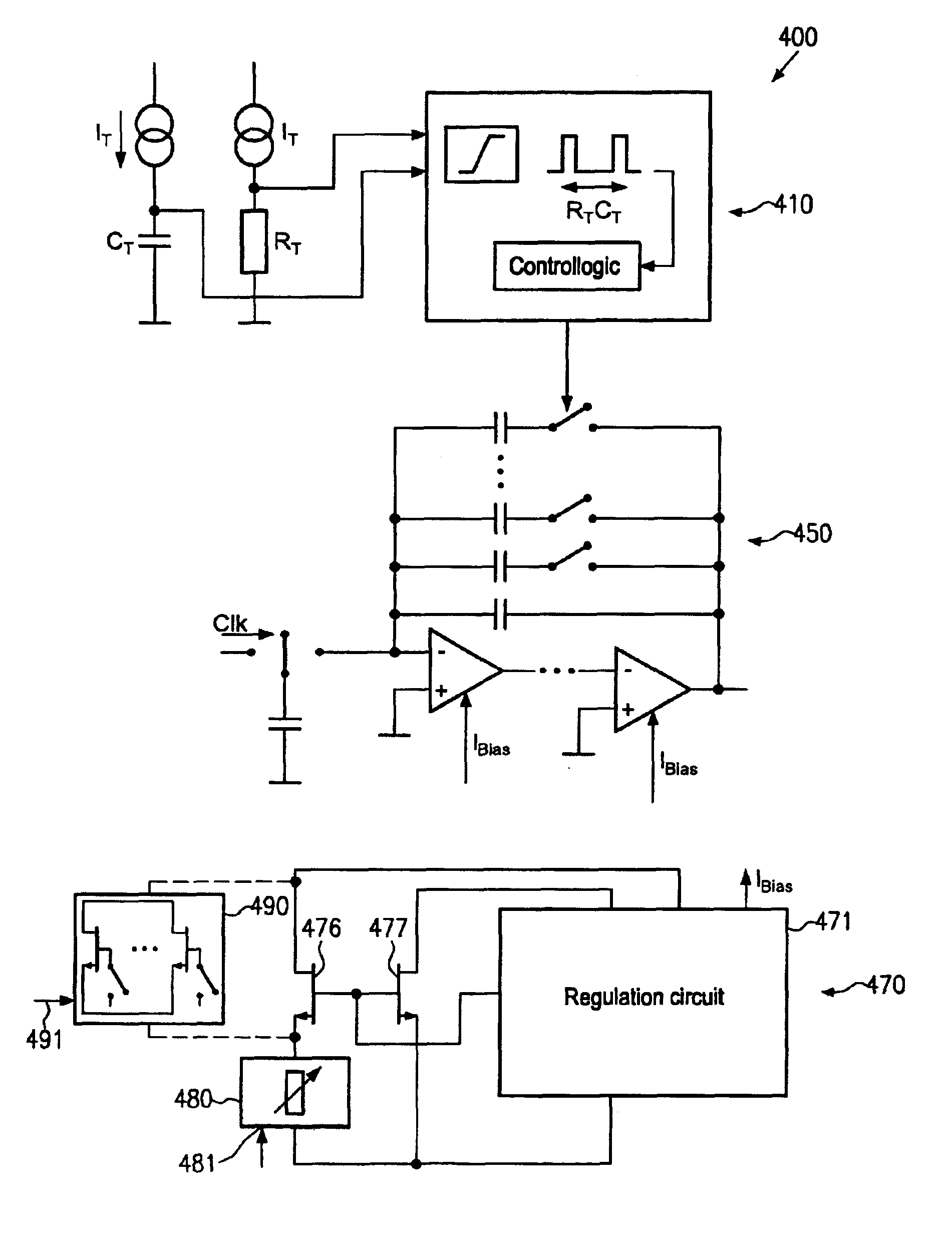

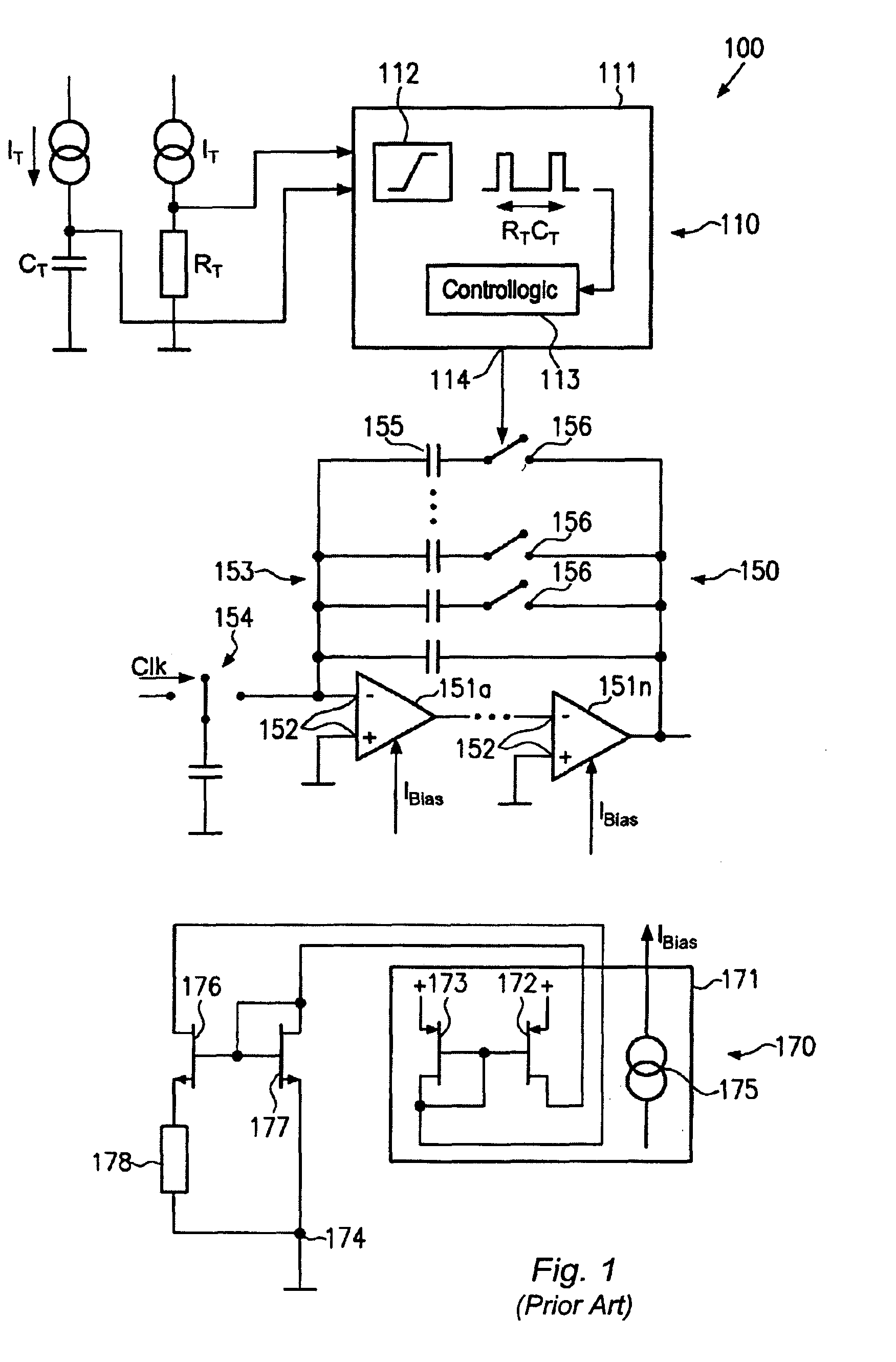

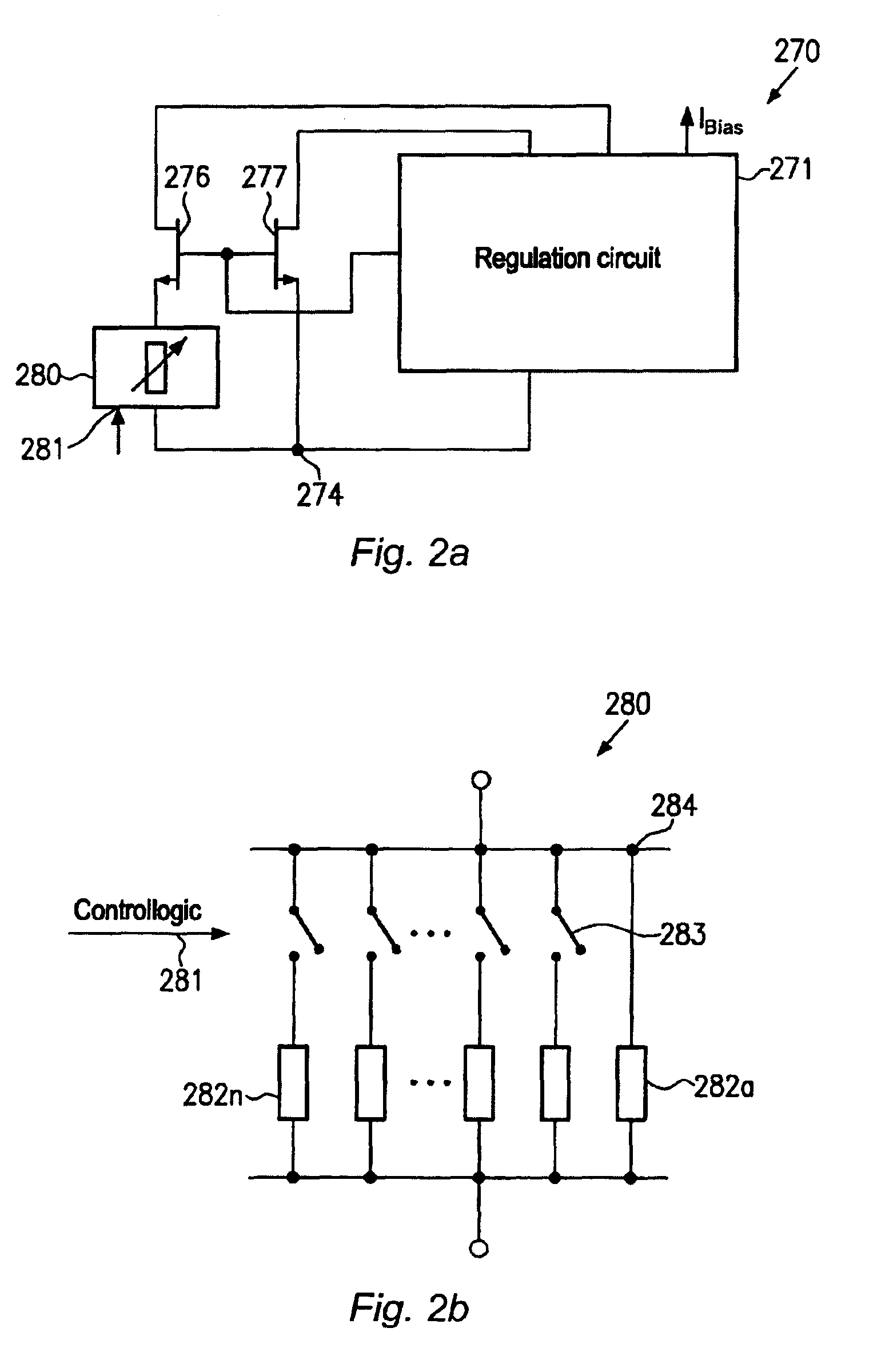

Circuit and a method for controlling the bias current in a switched capacitor circuit

InactiveUS6891439B2Effective compensationAmplifier modifications to reduce temperature/voltage variationAmplifier modifications to raise efficiencyElectrical resistance and conductanceAudio power amplifier

A tunable constant GM circuit allows to compensate for temperature and process variations with high precision by correspondingly adjusting a resistance value and / or the ratio of transistor widths. Thus, in switched capacitor circuits the frequency behaviour, such as the settling time, may be controlled by providing a compensated bias to the transconductance amplifiers typically used in these circuits.

Owner:ADVANCED MICRO DEVICES INC

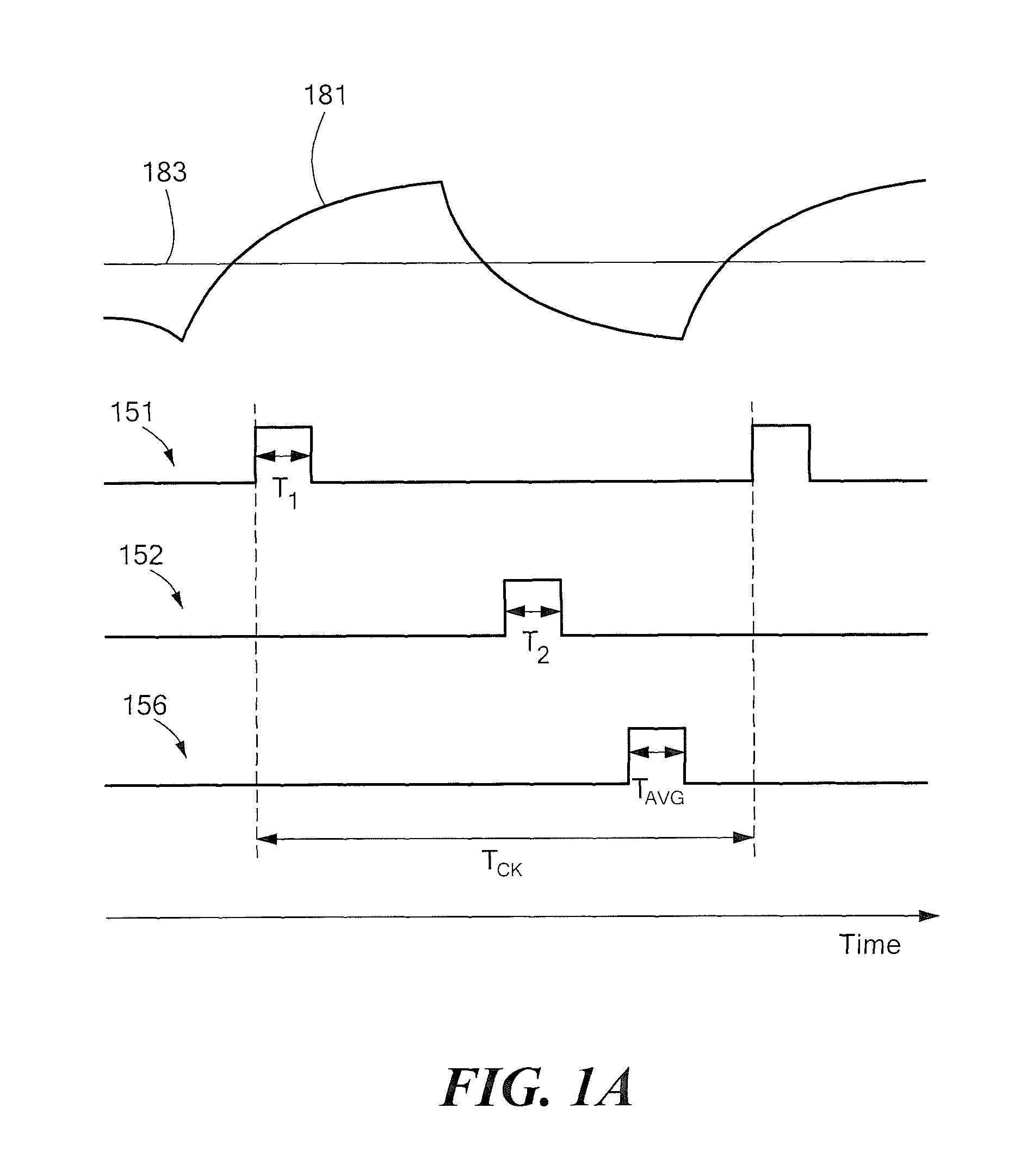

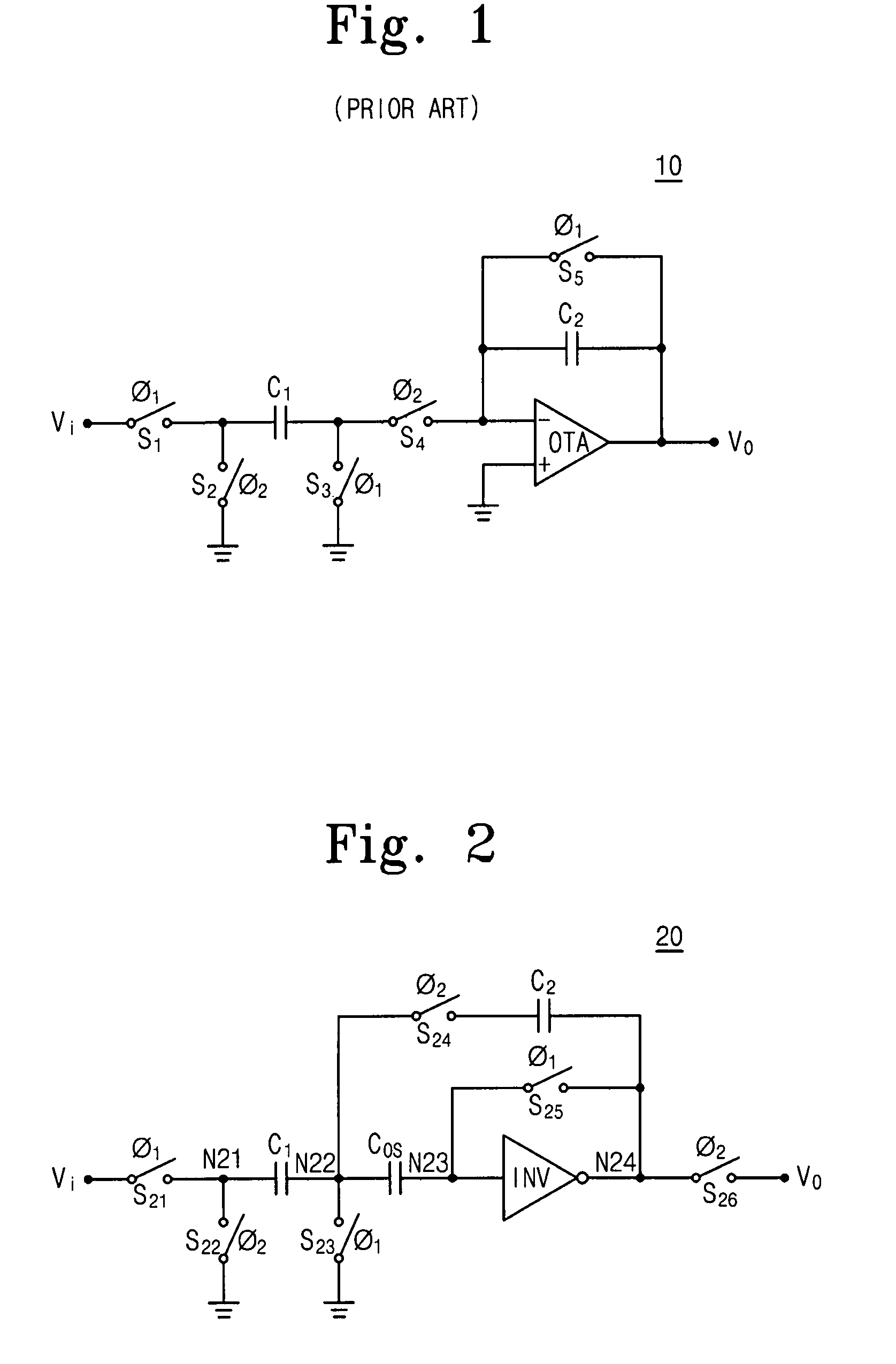

Switched capacitor notch filter

ActiveUS7990209B2Eliminate needLow pass filterSwitched capacitor networksOscillations generatorsCapacitanceTime segment

A switched capacitor notch filter for sampling an input signal using multiple sampling capacitors and multiple non-overlapping time periods. The charge from the sampling capacitors is averaged and transferred to the filter output during another non-overlapping time period.

Owner:ALLEGRO MICROSYSTEMS INC

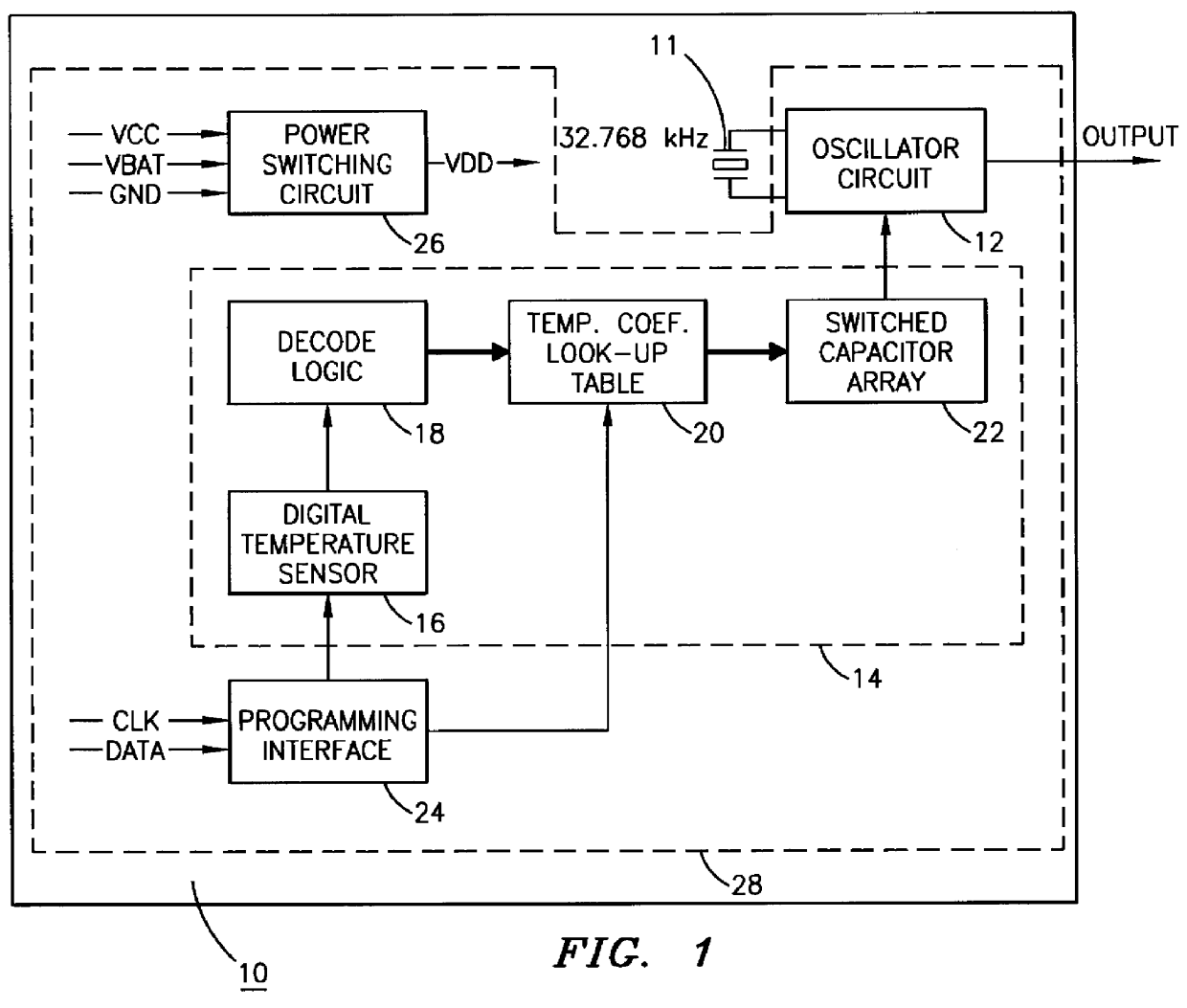

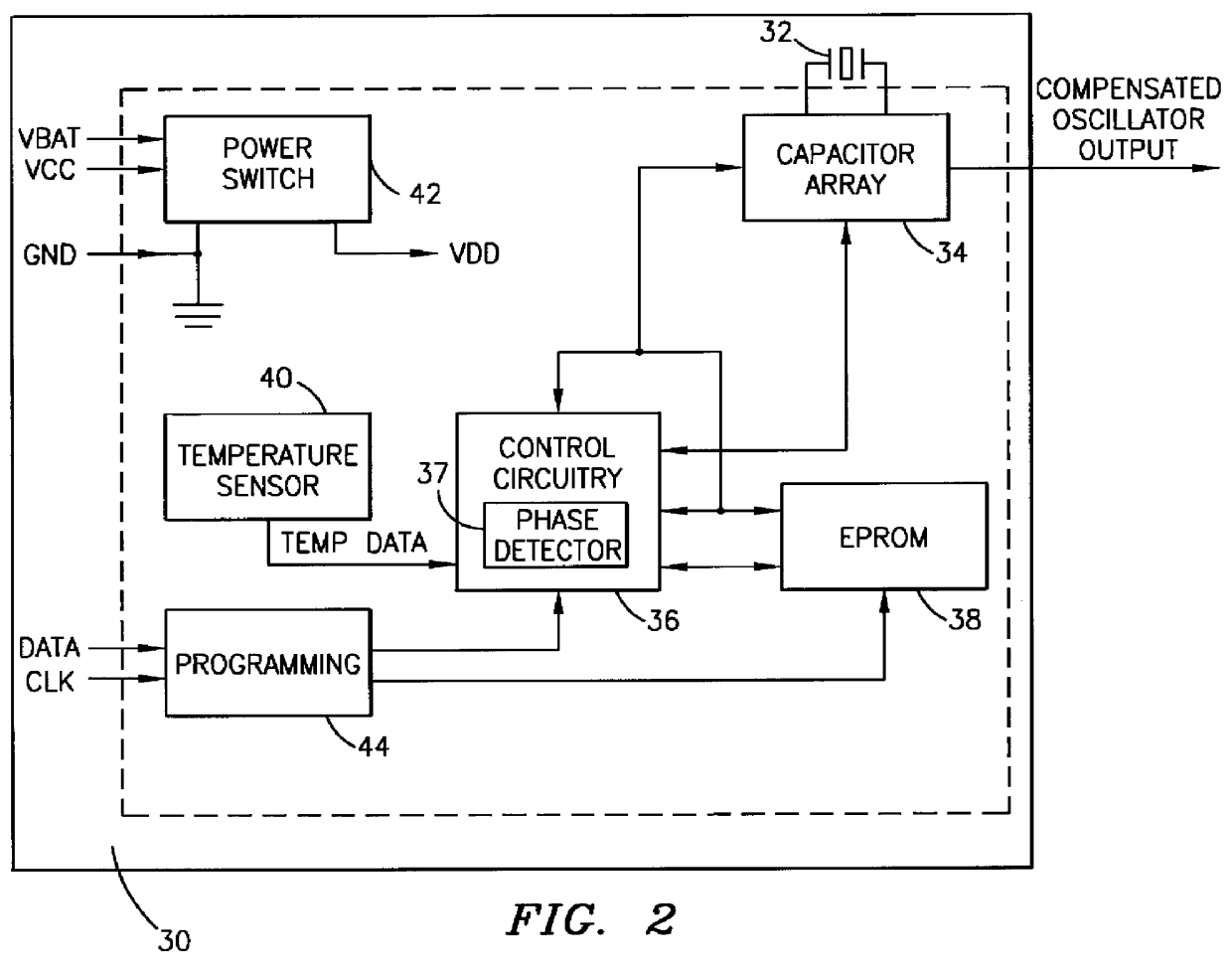

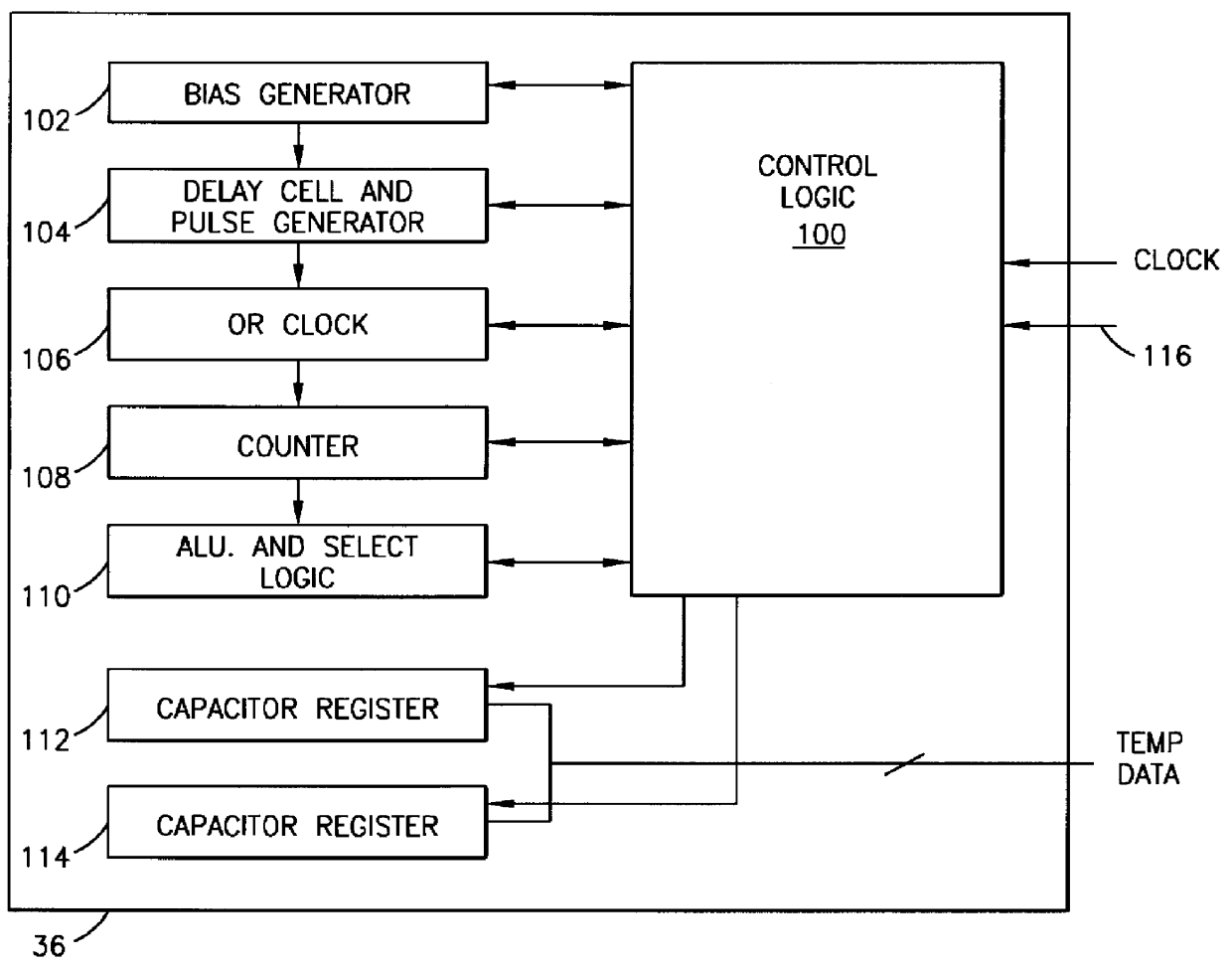

Temperature compensated crystal oscillator

A temperature compensated crystal oscillation circuit adapted to be contained within a small device package and providing an output frequency accuracy of approximately + / -2 ppm over a temperature range or less than 2 minutes per year over the temperature range. The device includes crystal and a single integrated circuit wherein the integrated circuit has a temperature sensing circuit with a digital output, control circuitry, a memory circuit and a switched capacitor array for compensating the oscillation of the crystal oscillator over temperature.

Owner:MAXIM INTEGRATED PROD INC

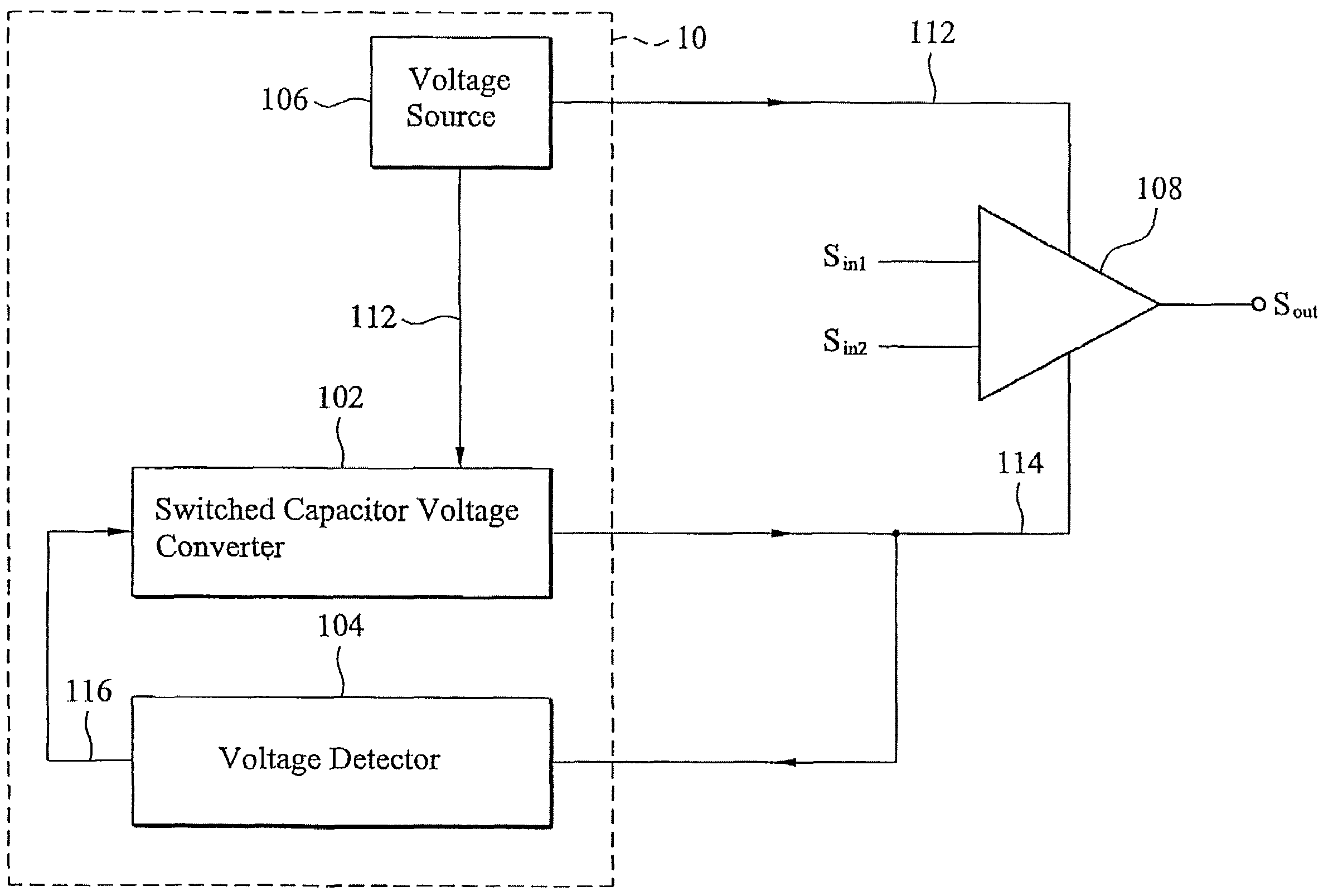

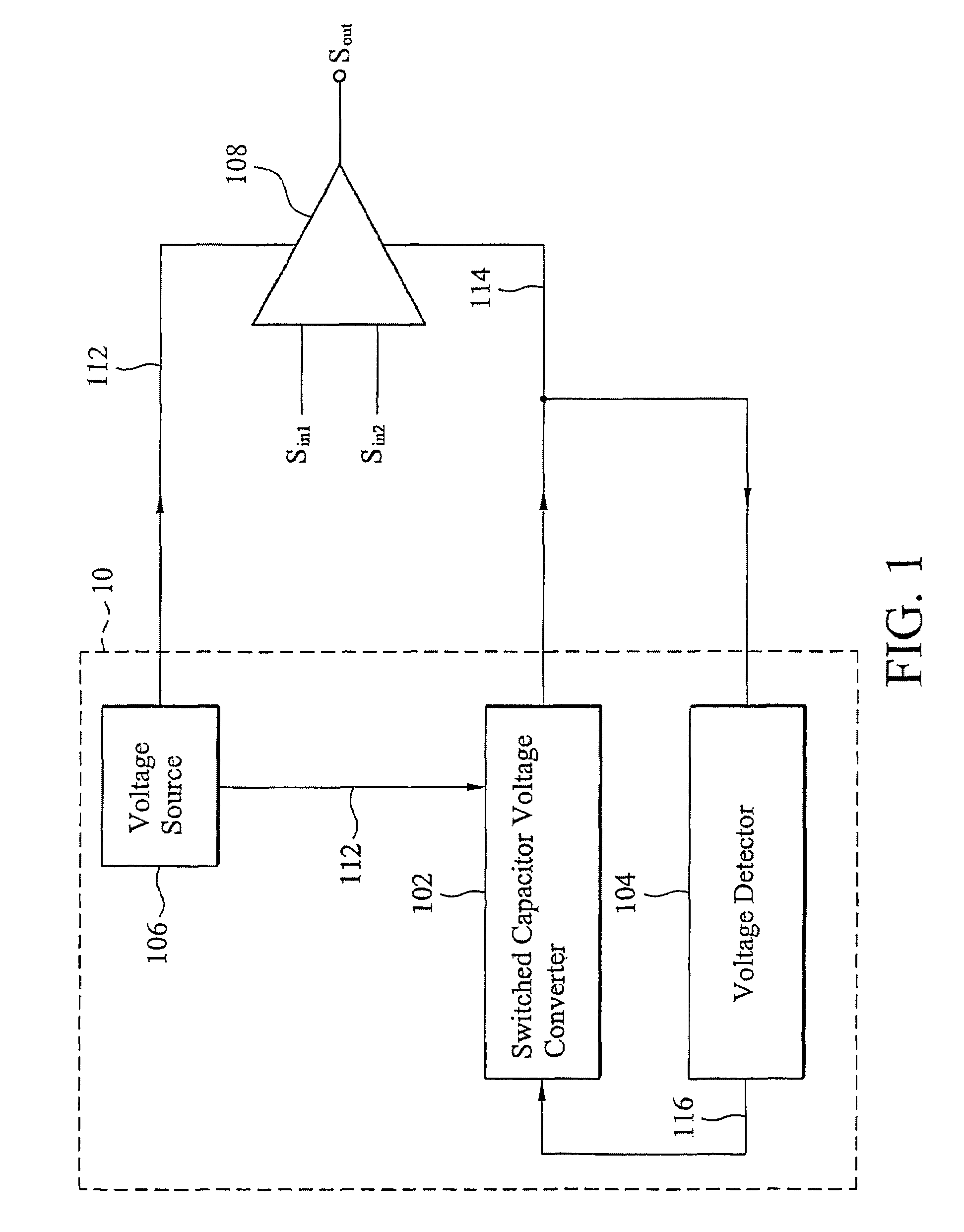

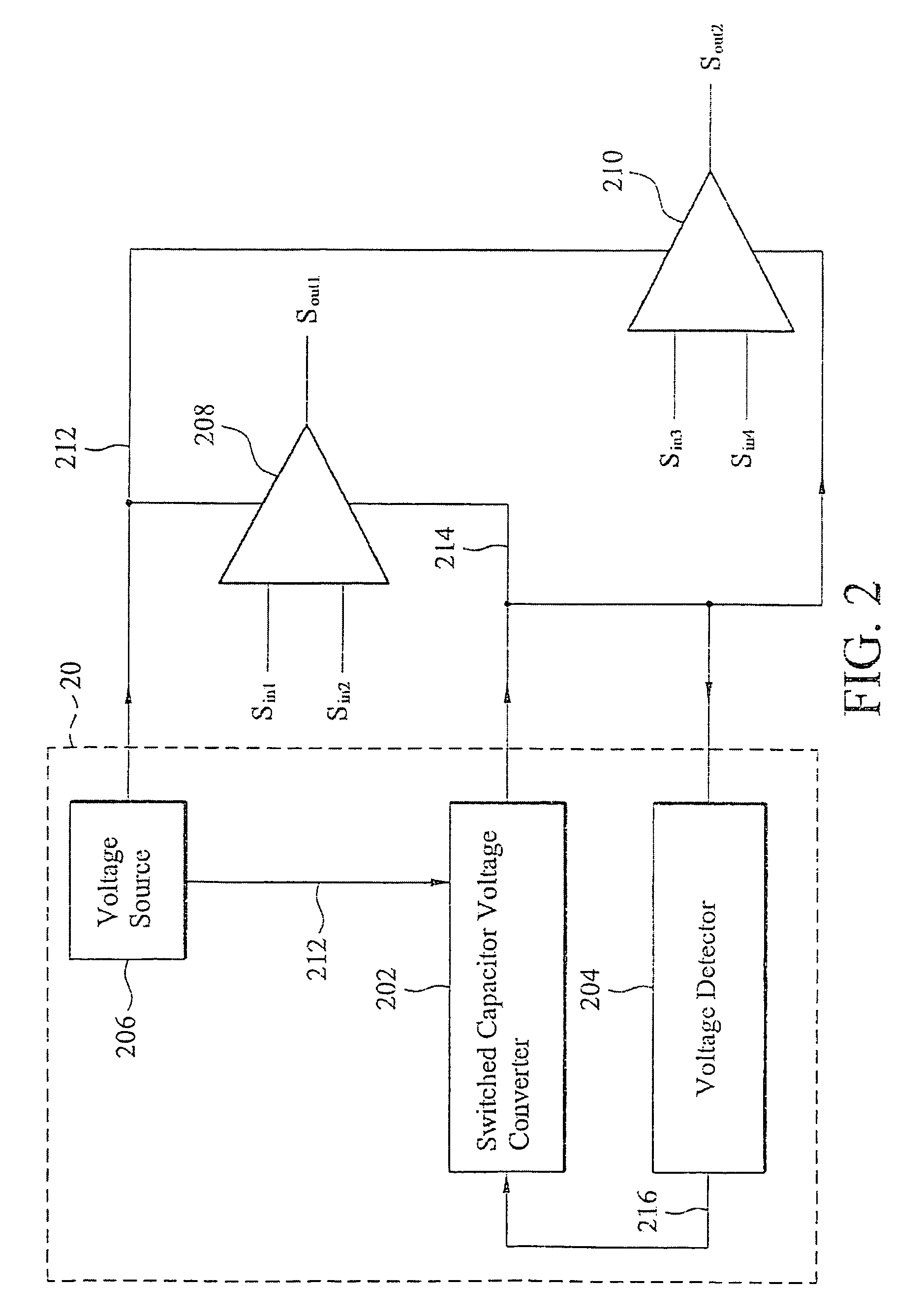

Voltage generating apparatus and methods

InactiveUS7609114B2Amplifier detailsAmplifiers with semiconductor devices onlyVoltage converterAudio power amplifier

The invention provides a voltage generating apparatus for powering at least one amplifier. The voltage generating apparatus comprises a voltage source, a switched capacitor voltage converter and a voltage detector. The voltage source supplies a first voltage to a positive voltage input terminal of the at least one amplifier. The first voltage is a positive DC voltage. The switched capacitor voltage converter is coupled to the voltage source for outputting an output voltage to a negative voltage input terminal of the at least one amplifier according to the first voltage and a predetermined voltage. The output voltage is a negative DC voltage. The voltage detector is coupled to the switched capacitor voltage converter for determining a switching frequency corresponding to the predetermined voltage according to the output voltage. The switched capacitor voltage converter increases the output voltage when the switching frequency is decreased and decreases the output voltage when the switching frequency is increased.

Owner:UPI SEMICON CORP

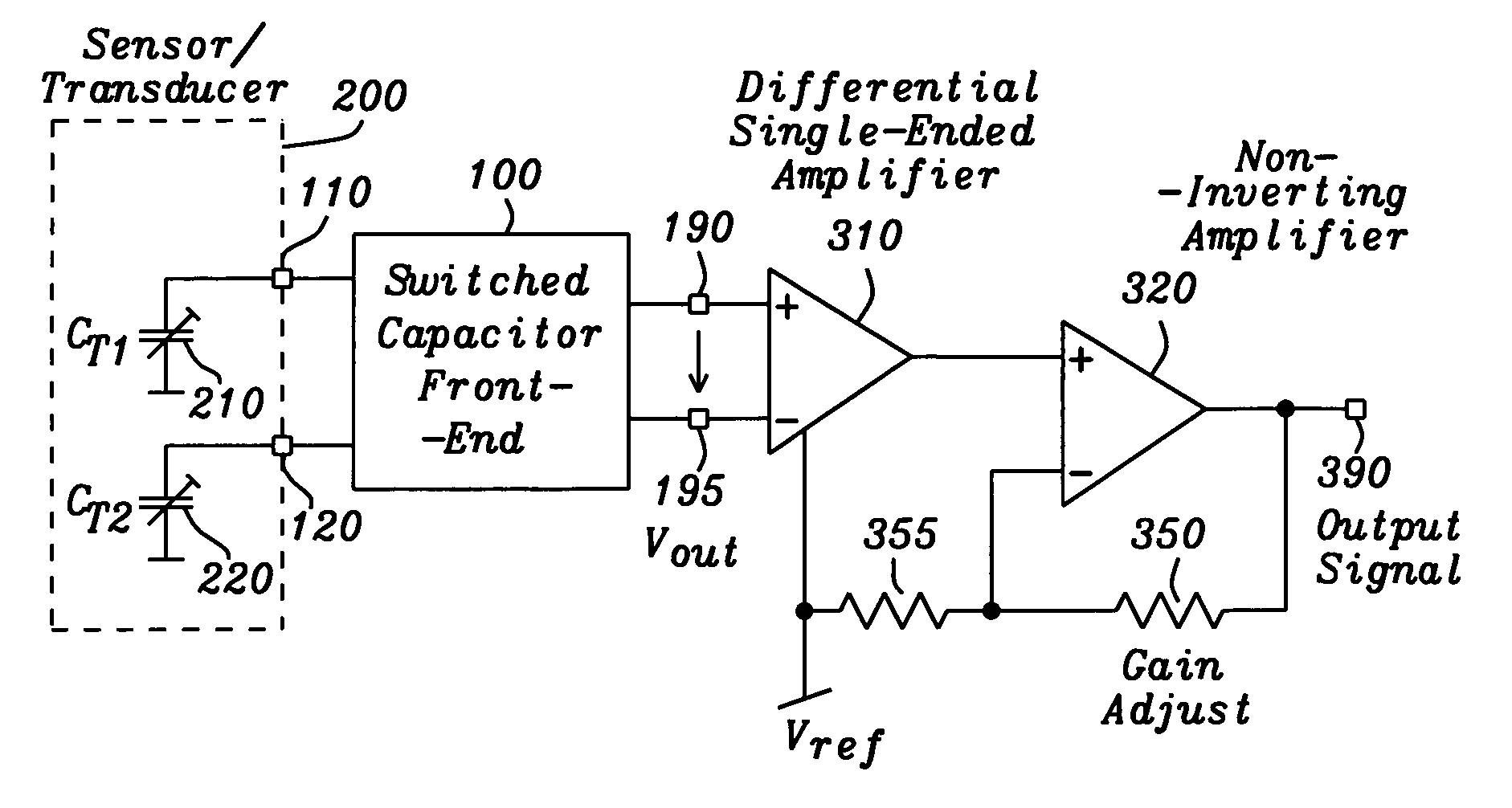

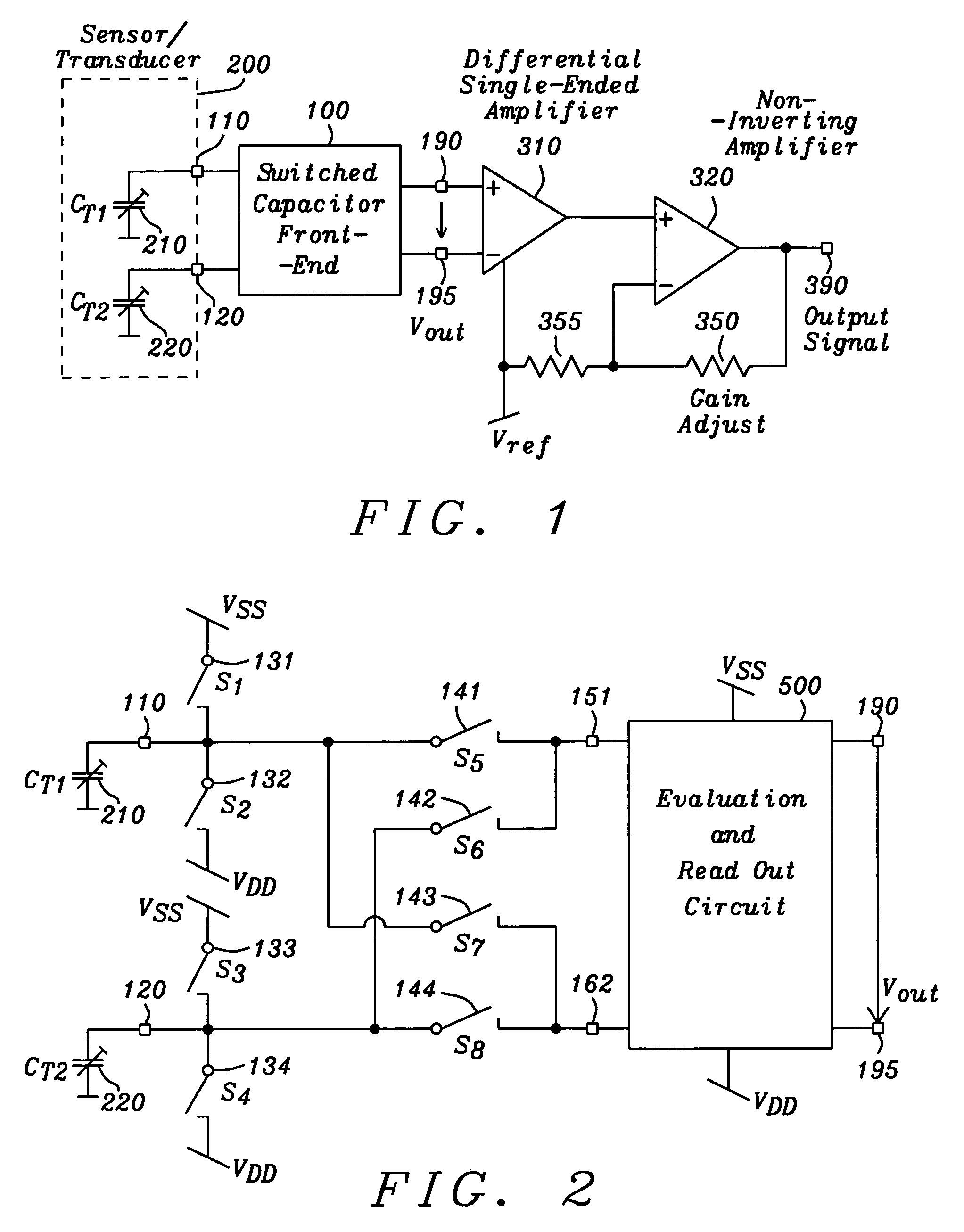

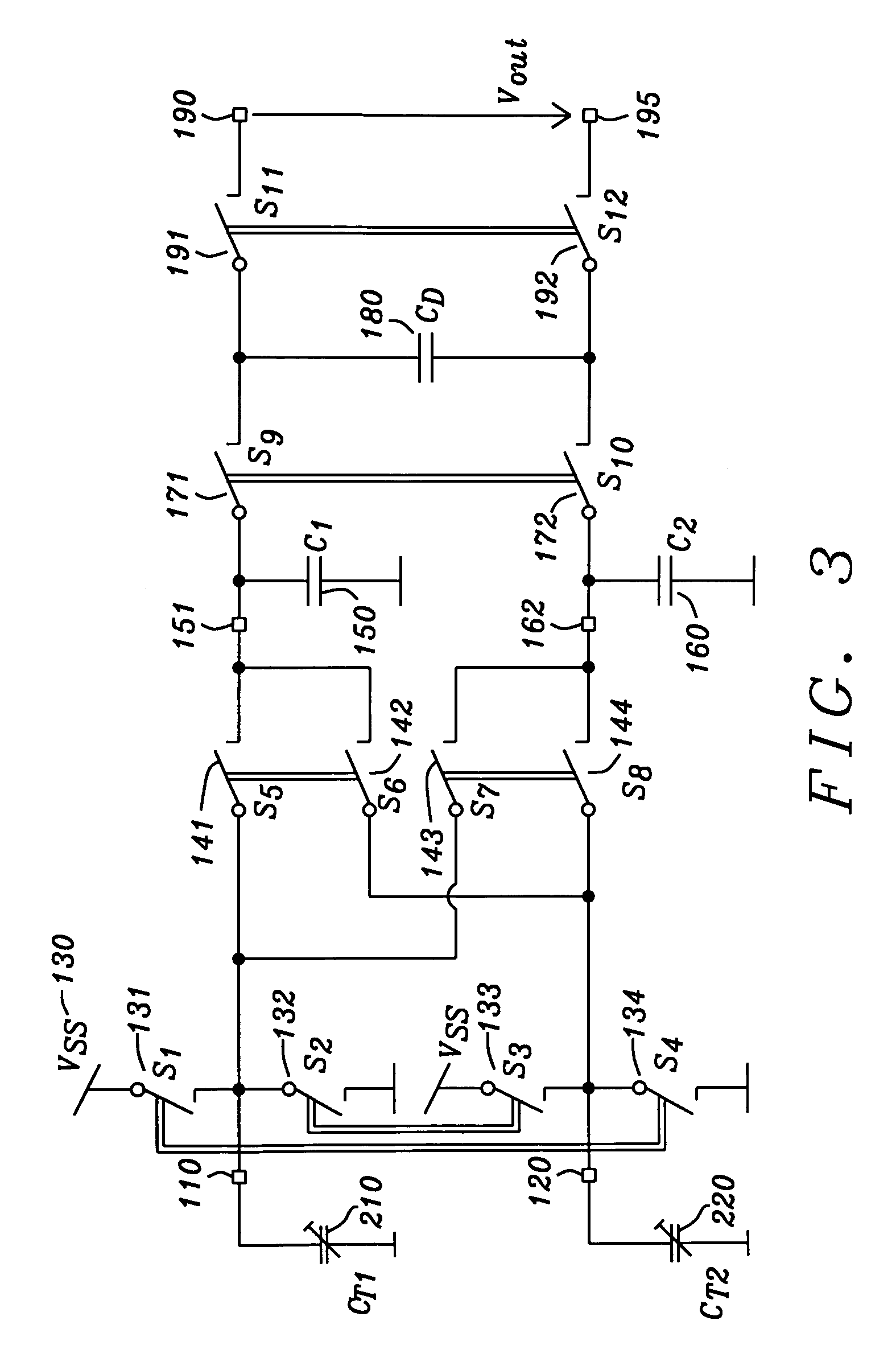

Differential capacitance measurement

InactiveUS6949937B2Efficient methodPrecise and sensitive and yet stable evalutionCapacitance measurementsConverting sensor output electrically/magneticallyCMOSSoi cmos technology

Owner:DIALOG SEMICONDUCTOR GMBH

Method and apparatus for use in switched capacitor systems

InactiveUS6917321B1Electric signal transmission systemsCharge amplifiersSignal conditioningData rate

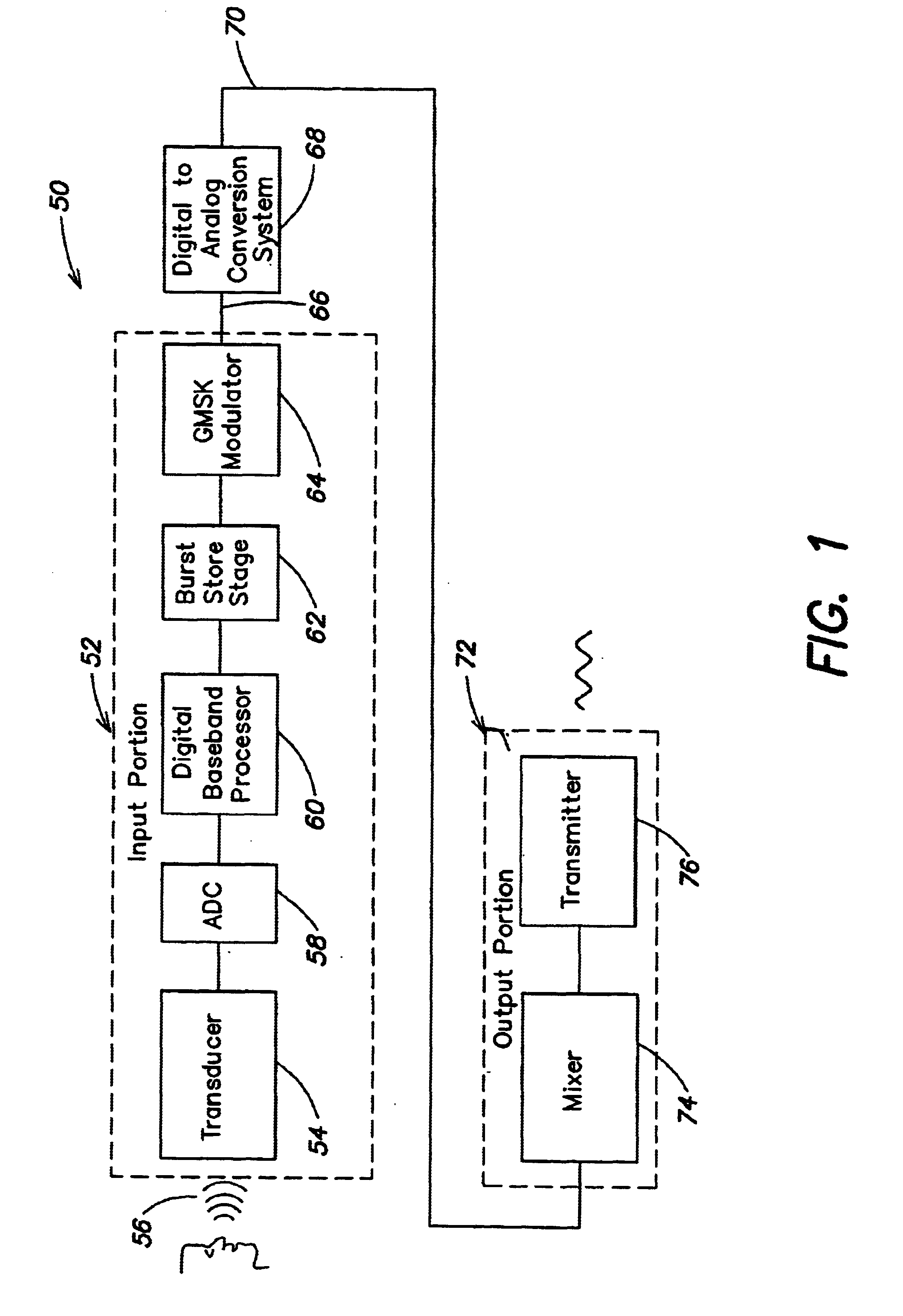

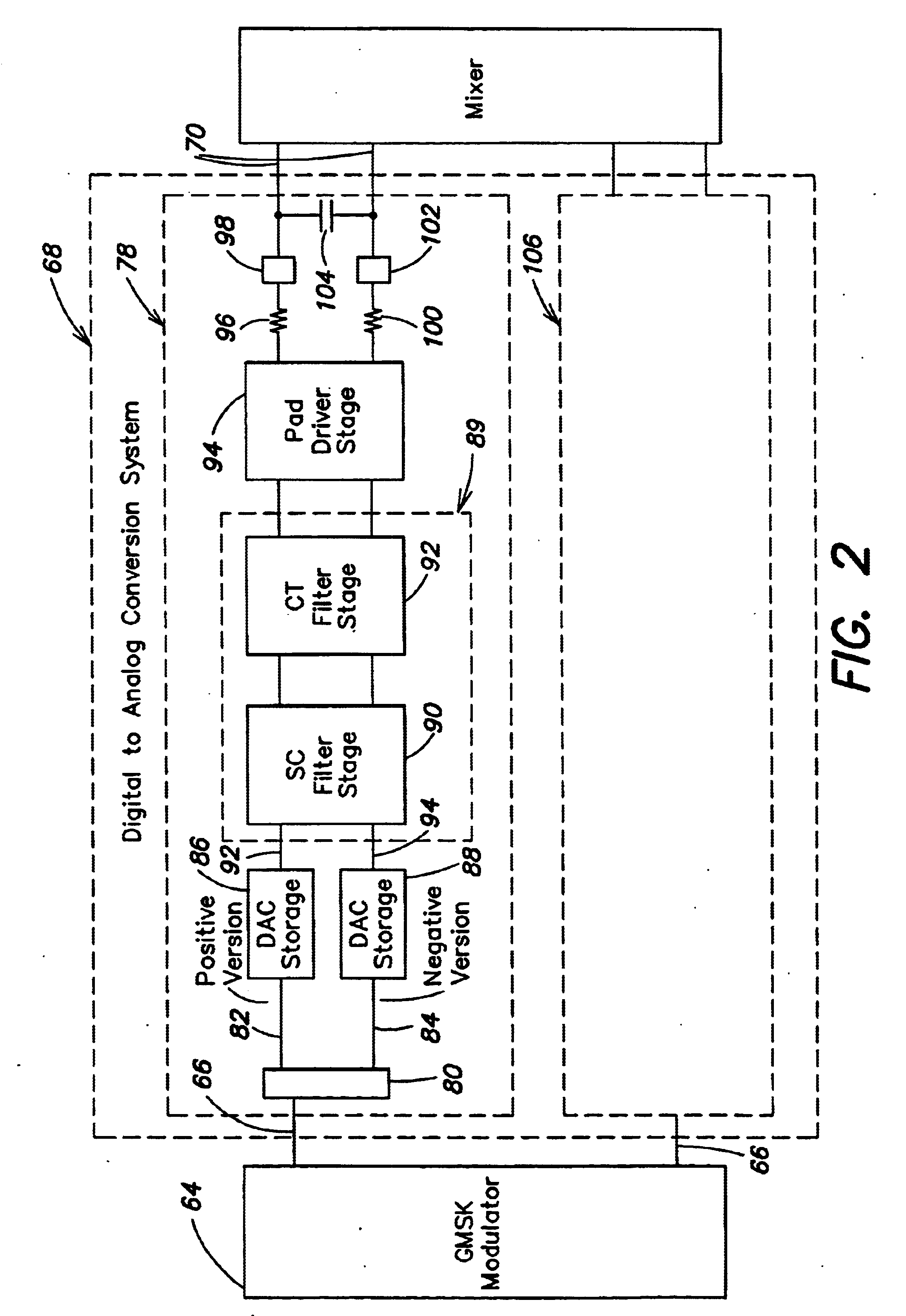

Systems and methods receive a digital signal and generate an analog signal indicative thereof. In one embodiment, a system includes a DAC that receives a multi-bit digital signal, generates at least two analog signals each indicative of the value of the multi-bit digital signal, and filters two or more of the at least two analog signals. In another embodiment, a system includes a DAC that receives digital input signals at an input data rate and outputs analog signals indicative of the digital signals to a signal conditioning stage at an output data rate different than the input data rate.

Owner:XUESHAN TECH INC

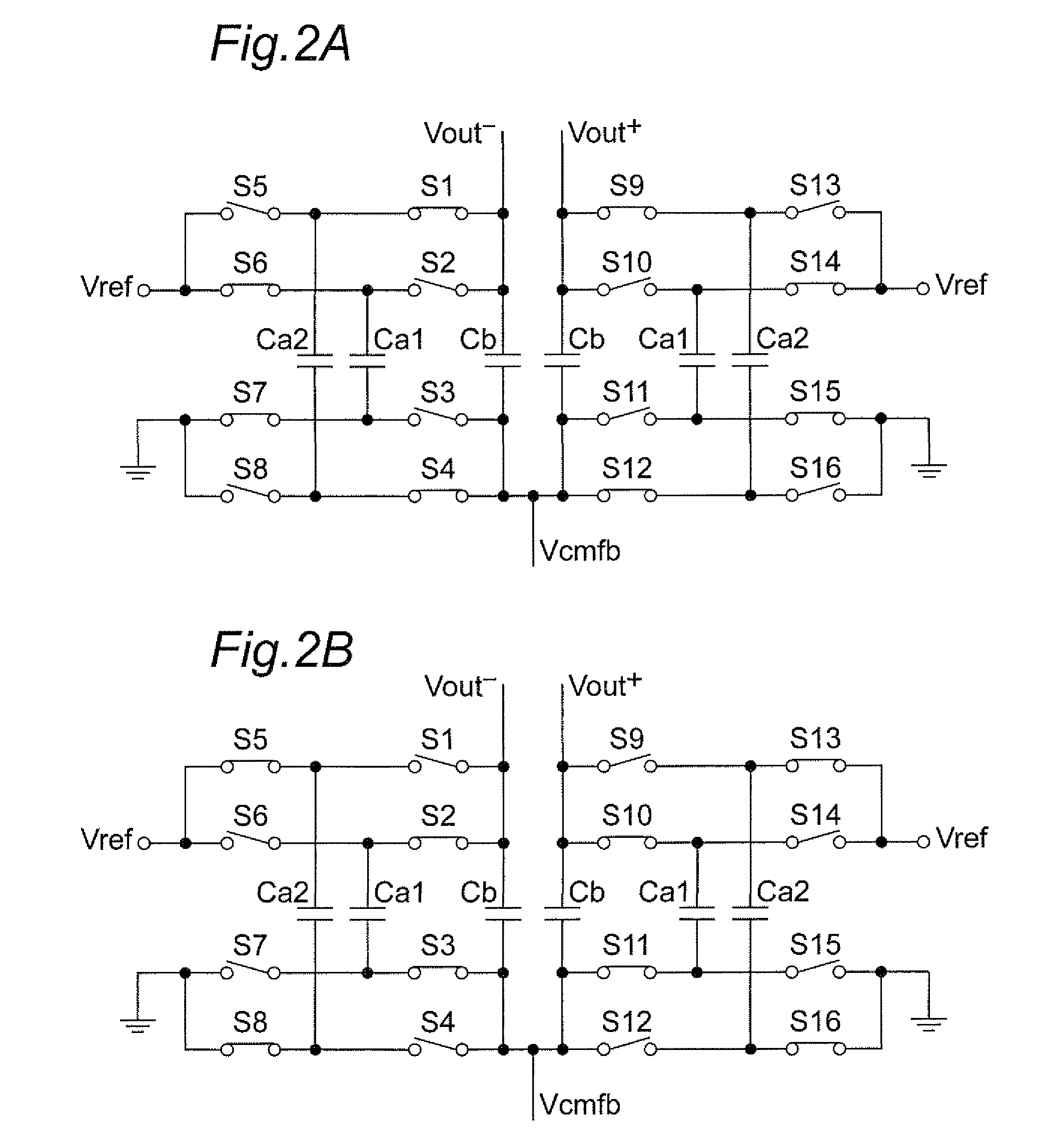

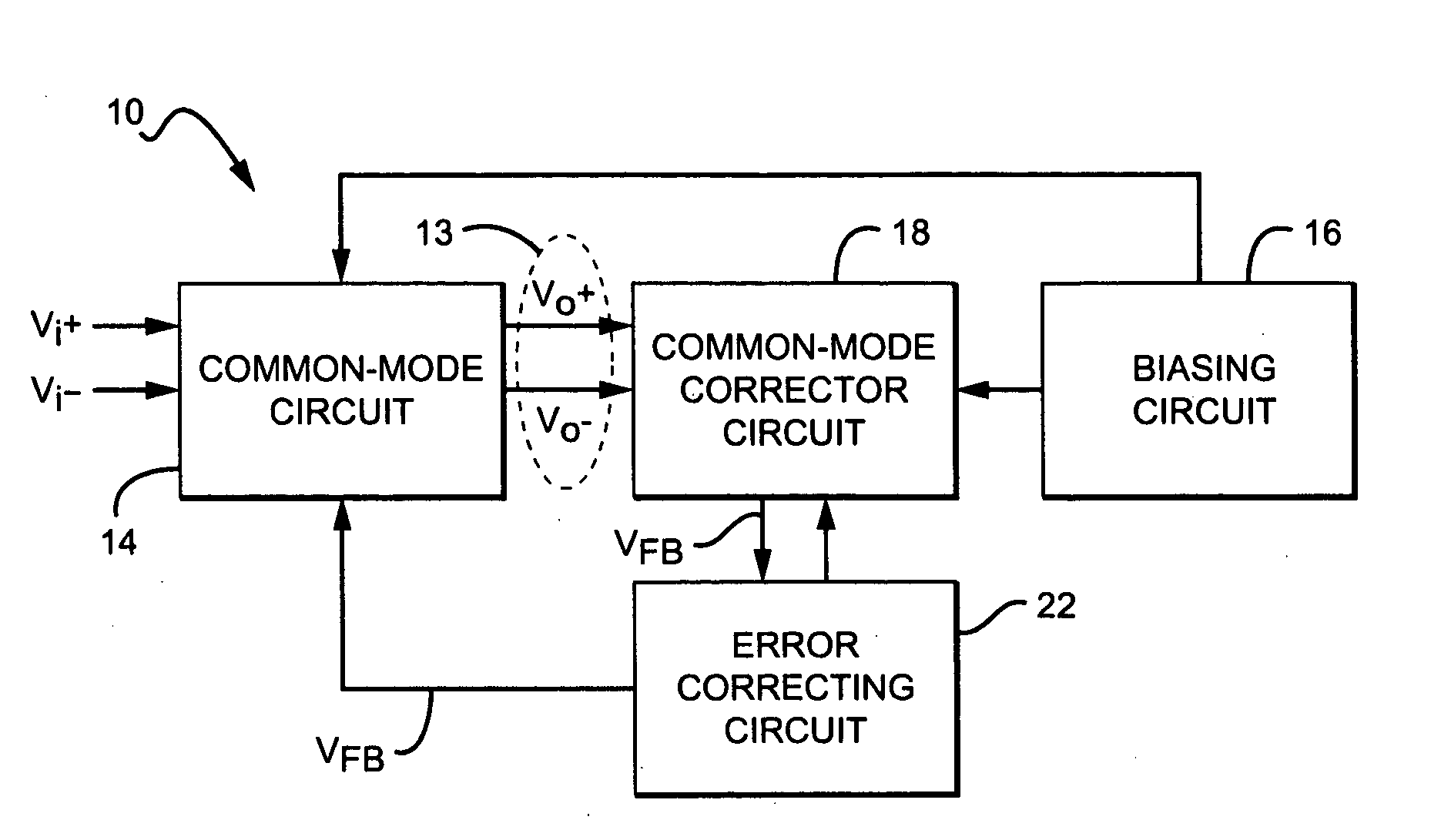

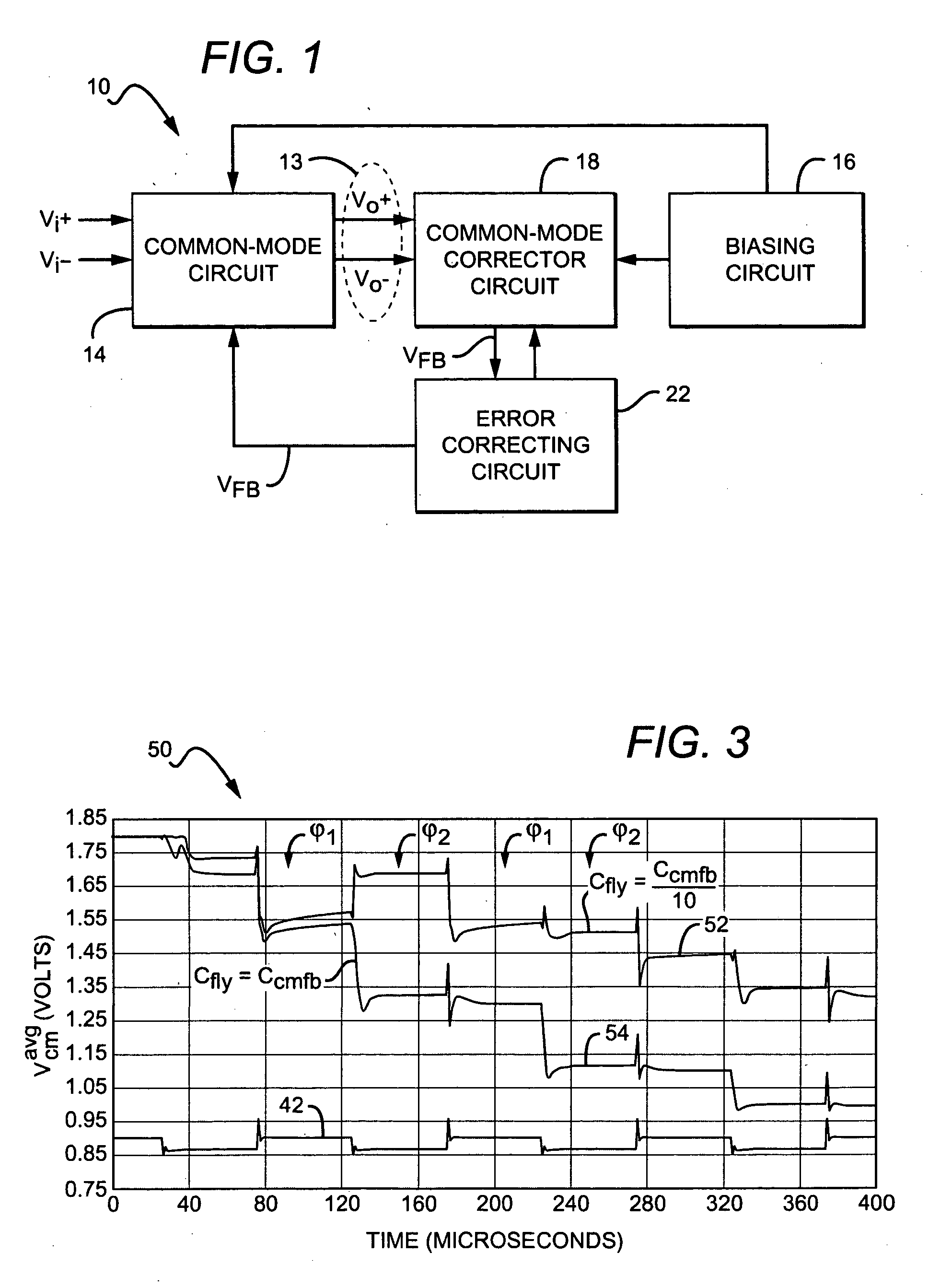

Discrete time amplifier circuit and analog-digital converter

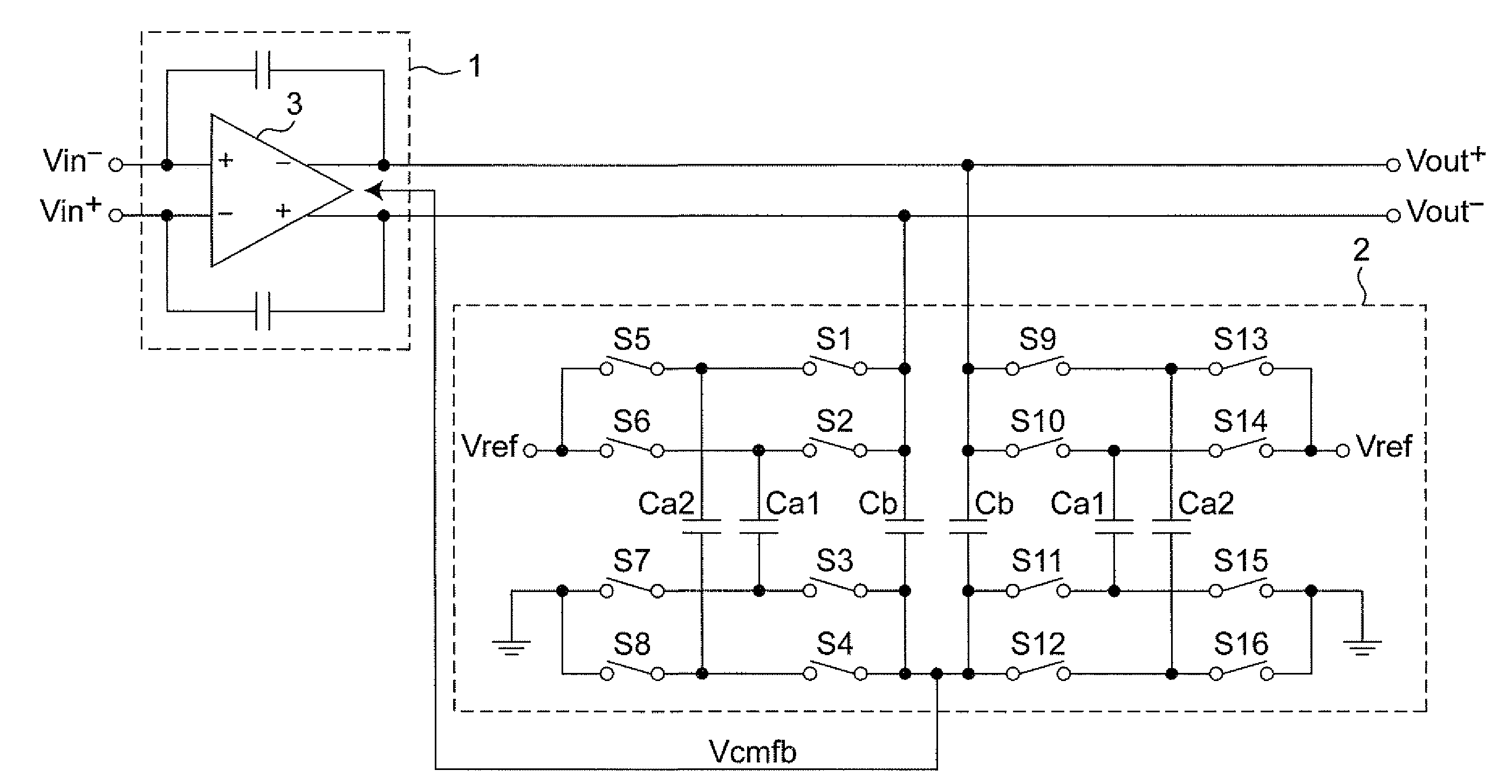

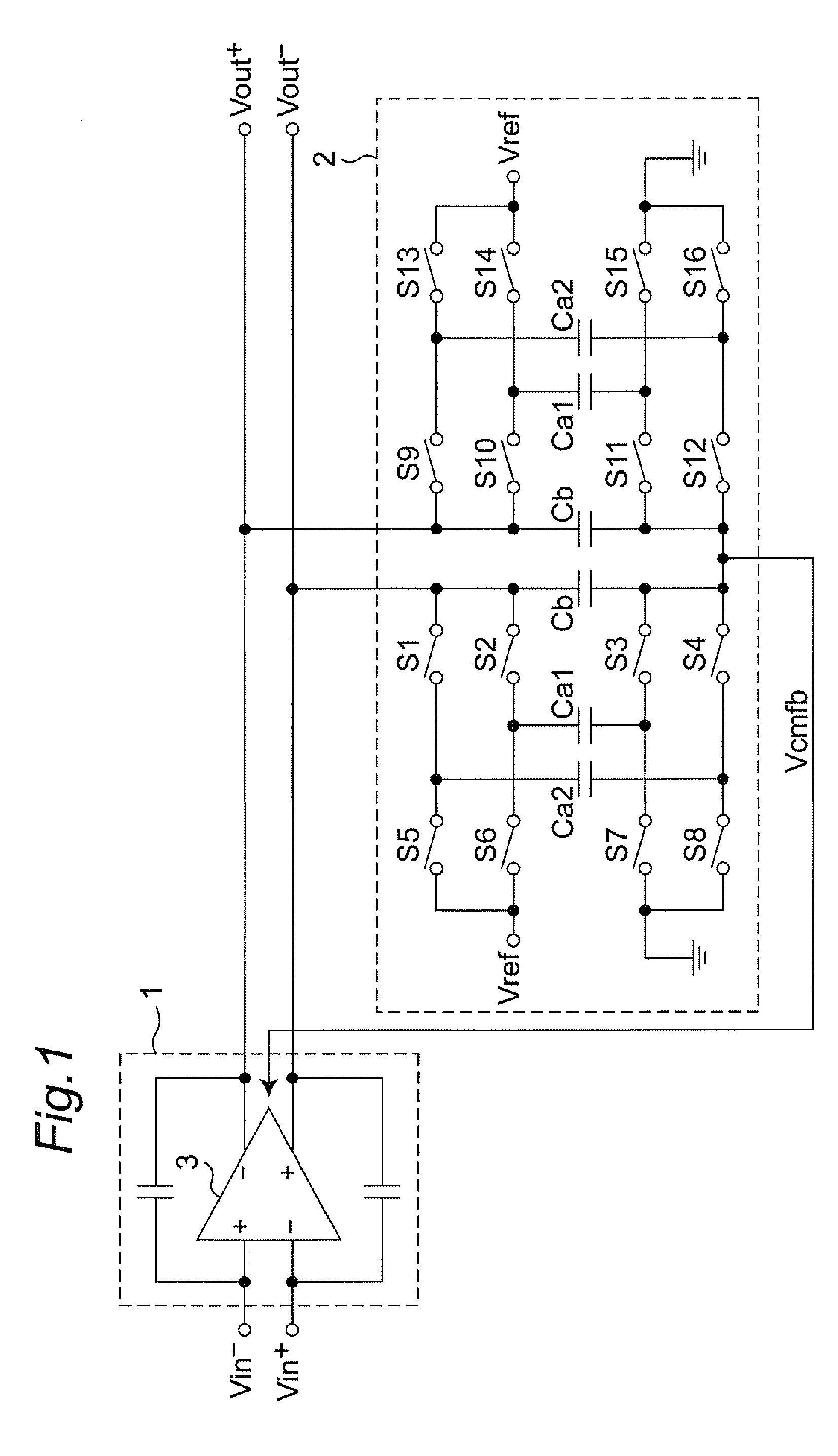

ActiveUS20090115523A1Simple circuit configurationShorten convergence timeElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierA d converter

The present invention is intended to attain simplified circuit configuration and low current consumption in a discrete time amplifier circuit and an AD converter, to improve the convergence from the transient response state to the steady state of the amplifier circuit and to reduce noise and distortion owing to the variation in the output common-mode voltage. The discrete time amplifier circuit and the AD converter are provided with a switched-capacitor common-mode feedback (CMFB) circuit capable of detecting and feeding back the output common-mode voltage at every sampling timing in the case that the circuit operates at double sampling timing (every ½ cycle).

Owner:SOCIONEXT INC

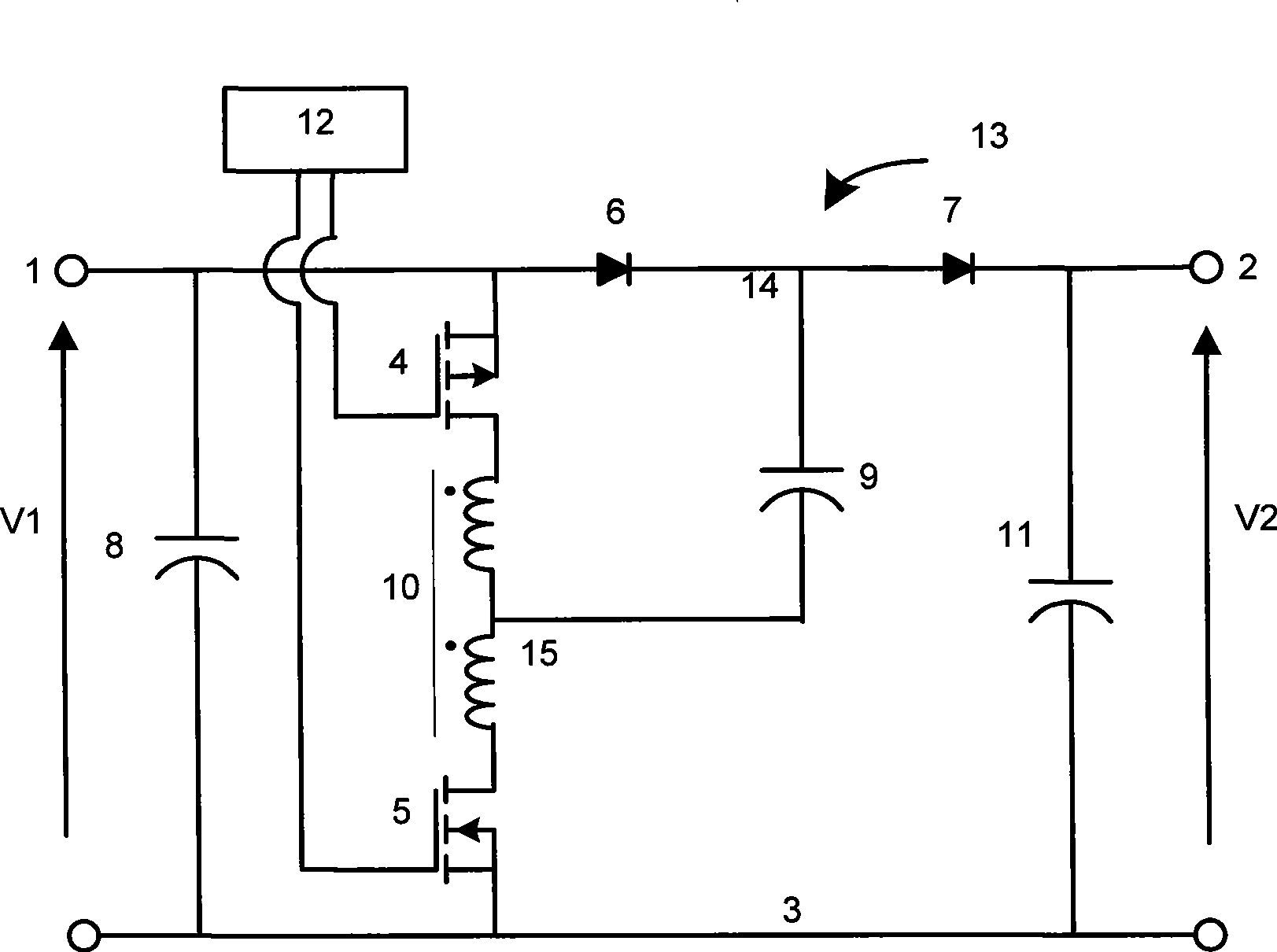

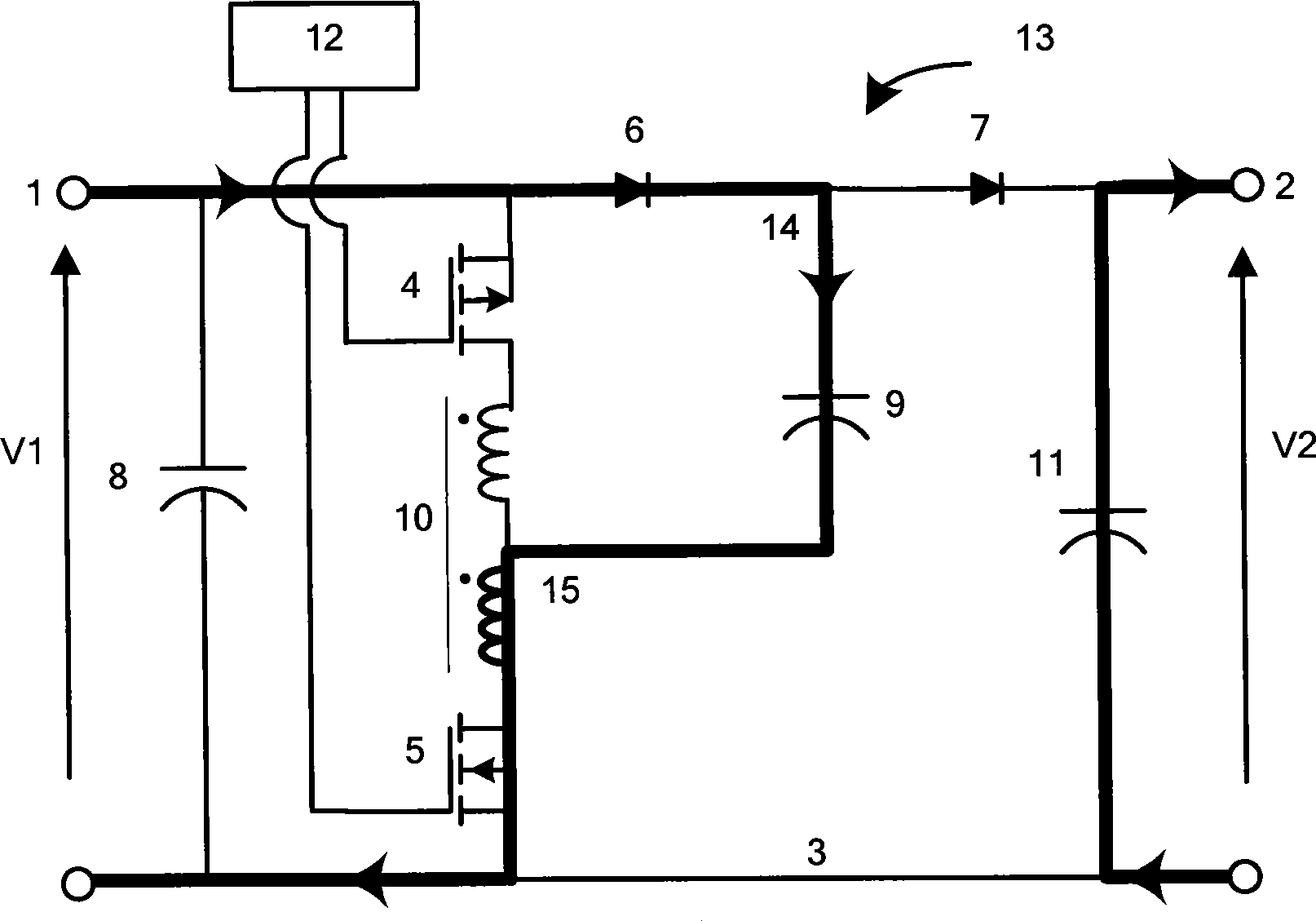

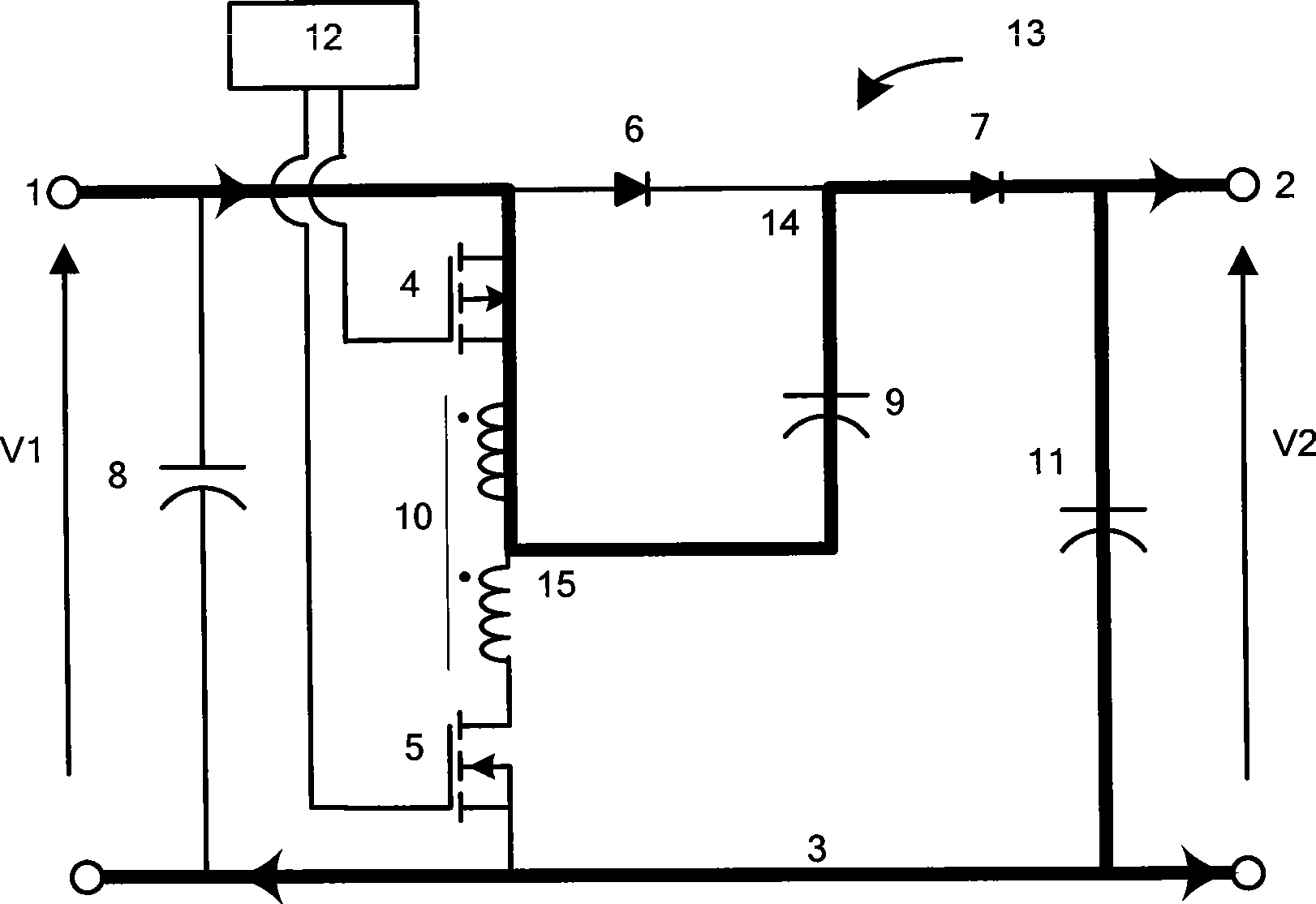

Resonant switched capacitor direct current voltage converter

ActiveCN101521459AReduce complexityLow costApparatus without intermediate ac conversionElectric variable regulationCapacitanceVoltage converter

The invention relates to a resonant switched capacitor direct current voltage converter which comprises a first voltage node, a second voltage node, a first switch, a second switch, a first diode, a second diode and a control circuit, wherein a first voltage exists between the first voltage node and a negative wire; a second voltage exists between the second voltage node and the negative wire; and the control circuit provides switching gate signals for the first and the second switches. The resonant switched capacitor direct current voltage converter further comprises a center-tapped inductor and a resonant capacitor, wherein the center-tapped inductor is connected between the first switch and the second switch; and the resonant capacitor is connected between the common node of the first and the second diodes and the central node of the center-tapped inductor. Compared with the conventional switched capacitor direct current voltage converter, the invention has the advantages of reducing complexity, loss and cost, improving the speed, and avoiding the limitation.

Owner:THE HONG KONG POLYTECHNIC UNIV

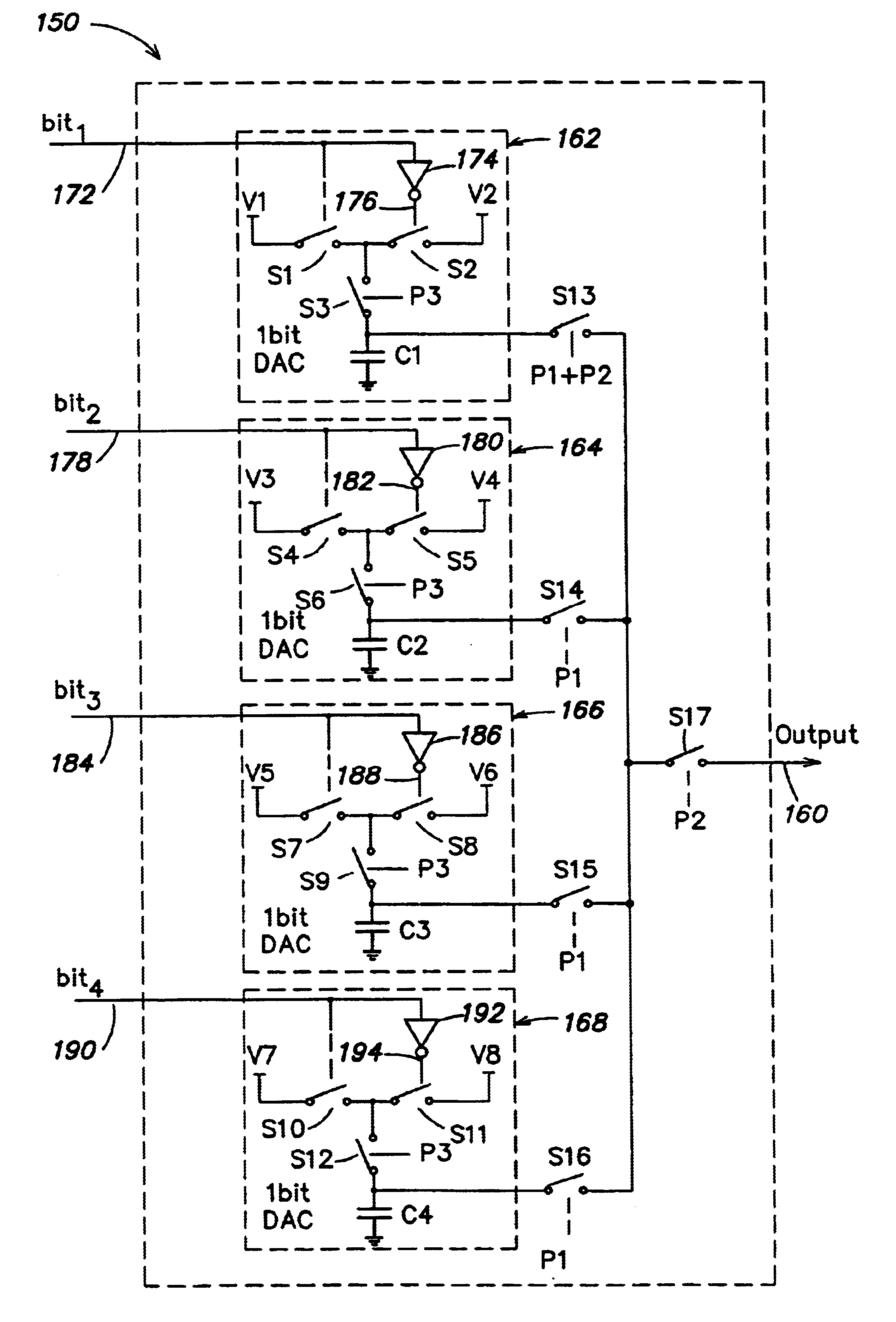

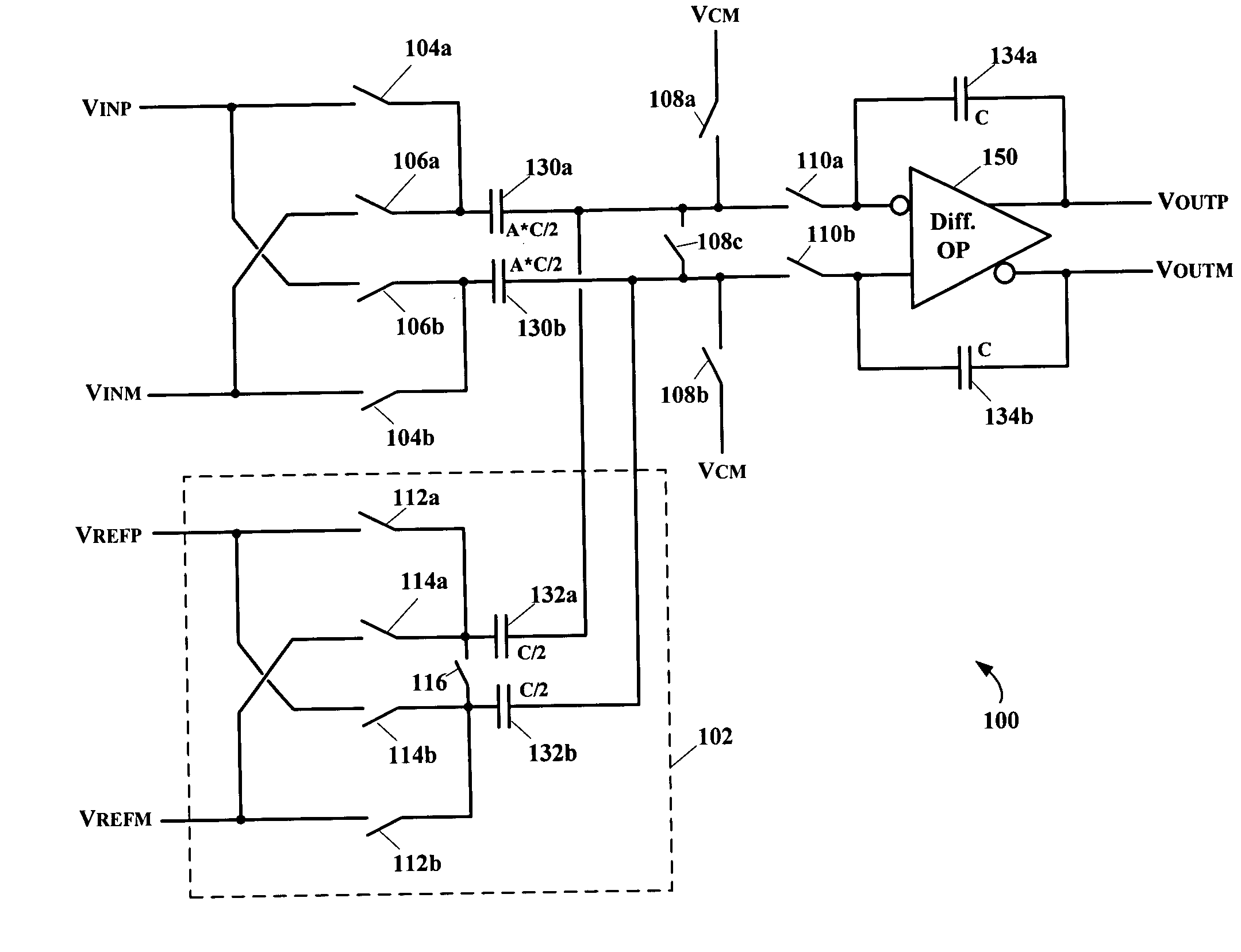

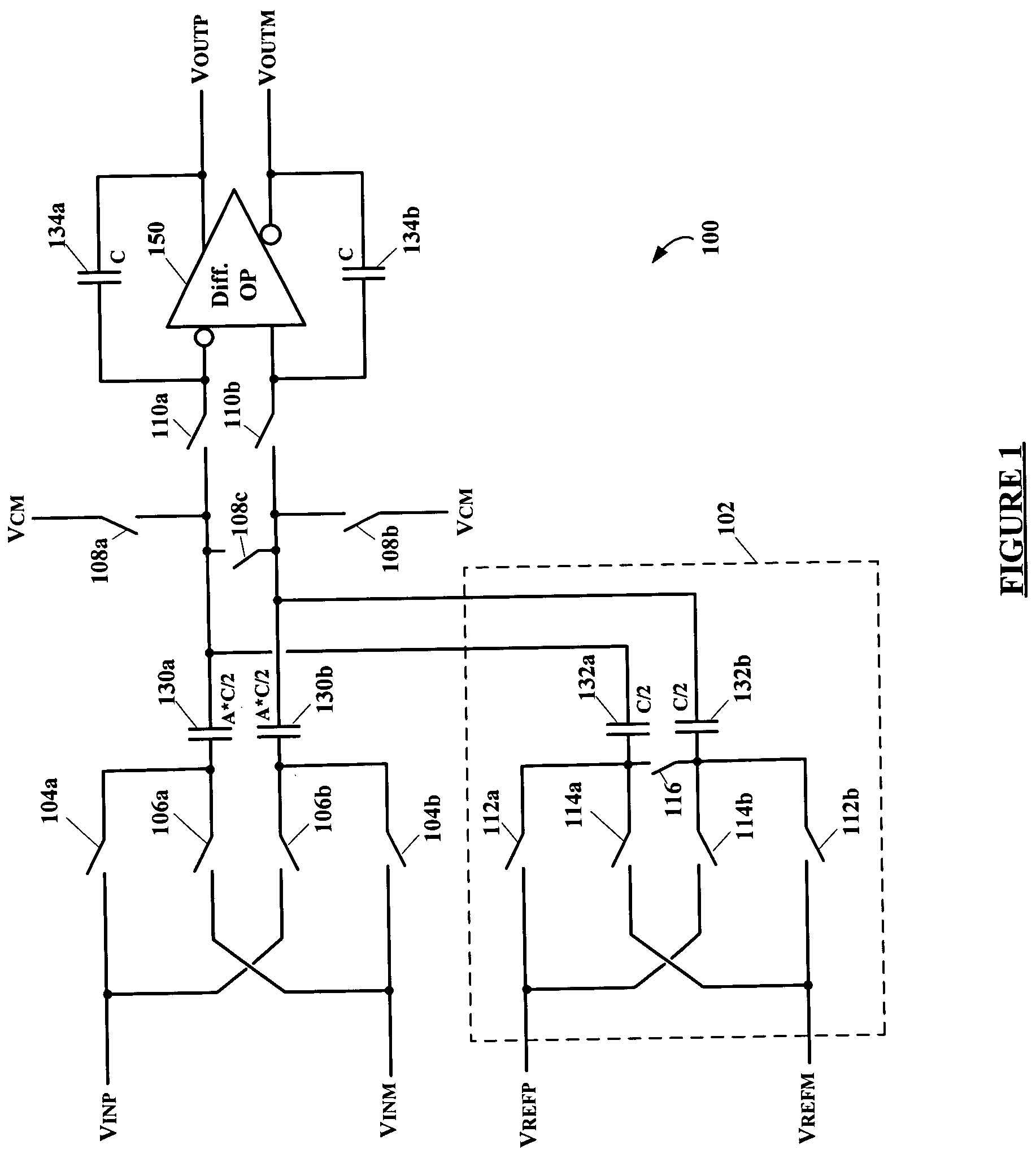

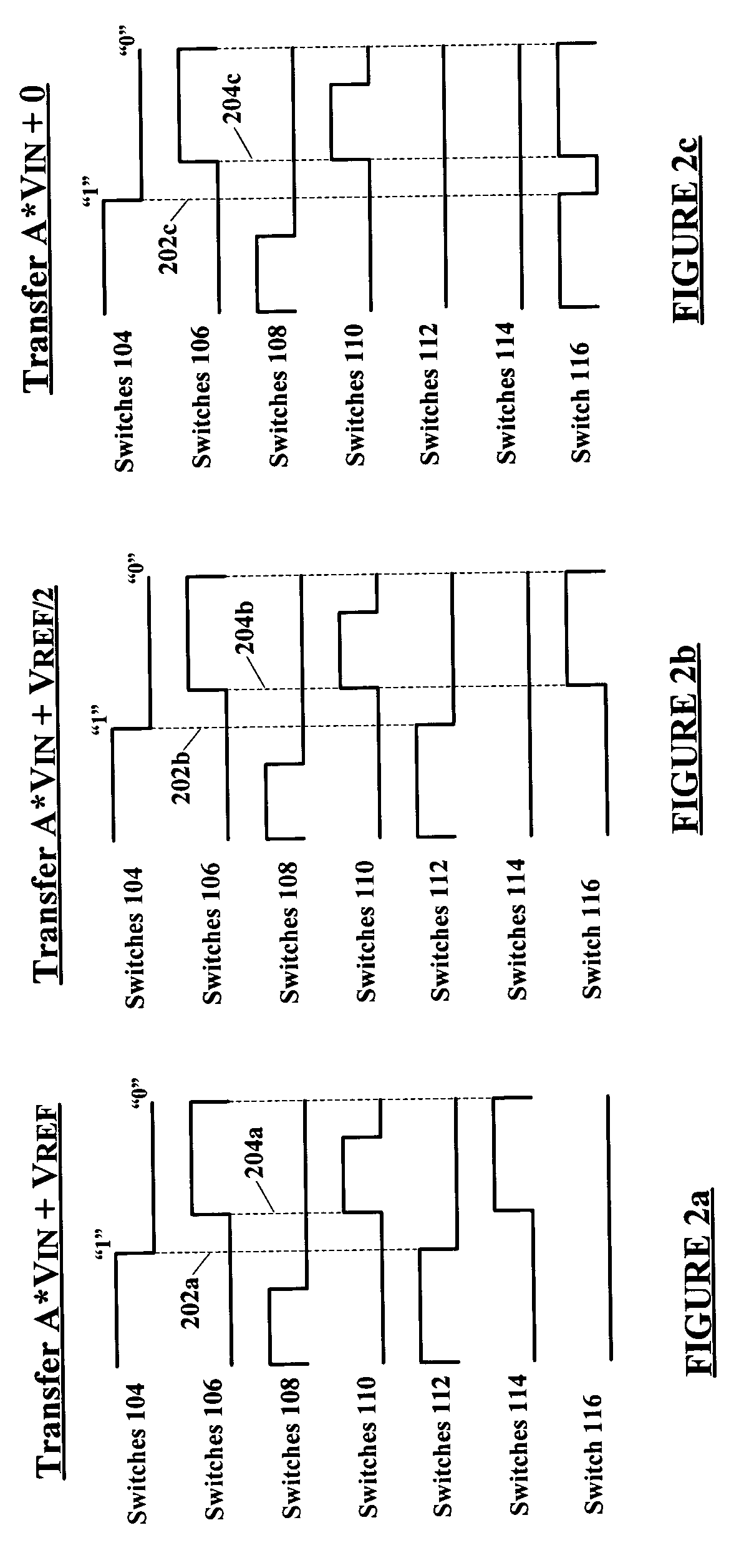

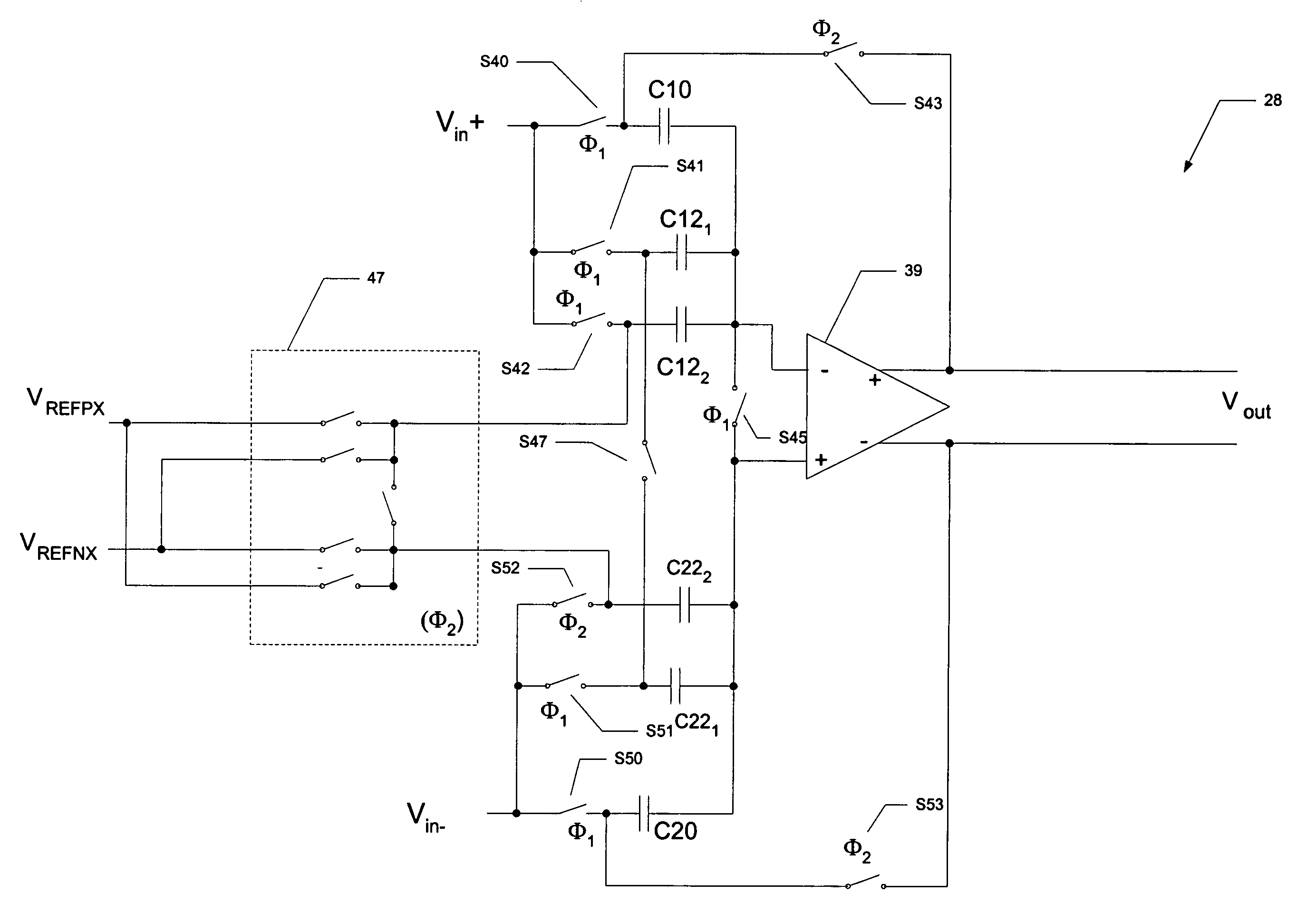

Five-level feed-back digital-to-analog converter for a switched capacitor sigma-delta analog-to-digital converter

ActiveUS7102558B2Improve performanceLow-power consumption of a switched capacitorElectric signal transmission systemsAnalogue conversionVoltage referenceGreek letter sigma

A five-level feed-back digital-to-analog converter (DAC) in a switched capacitor sigma-delta analog-to-digital converter has an improved switching sequence that boosts from two to five the number of quantization levels of the feed-back DAC. Switching sequences are used to obtain five equally distributed charge levels C*VREF, C*VREF / 2, 0, −C*VREF / 2 and −C*VREF. When summed with an input voltage, VIN, the five-level feed-back DAC produces five equally distributed output voltages of A*VIN+VREF, A*VIN+VREF / 2, A*VIN+0, A*VIN−VREF / 2 and A*VIN−VREF, where A is gain, VIN is the input voltage, and VREF is the reference voltage.

Owner:MICROCHIP TECH INC

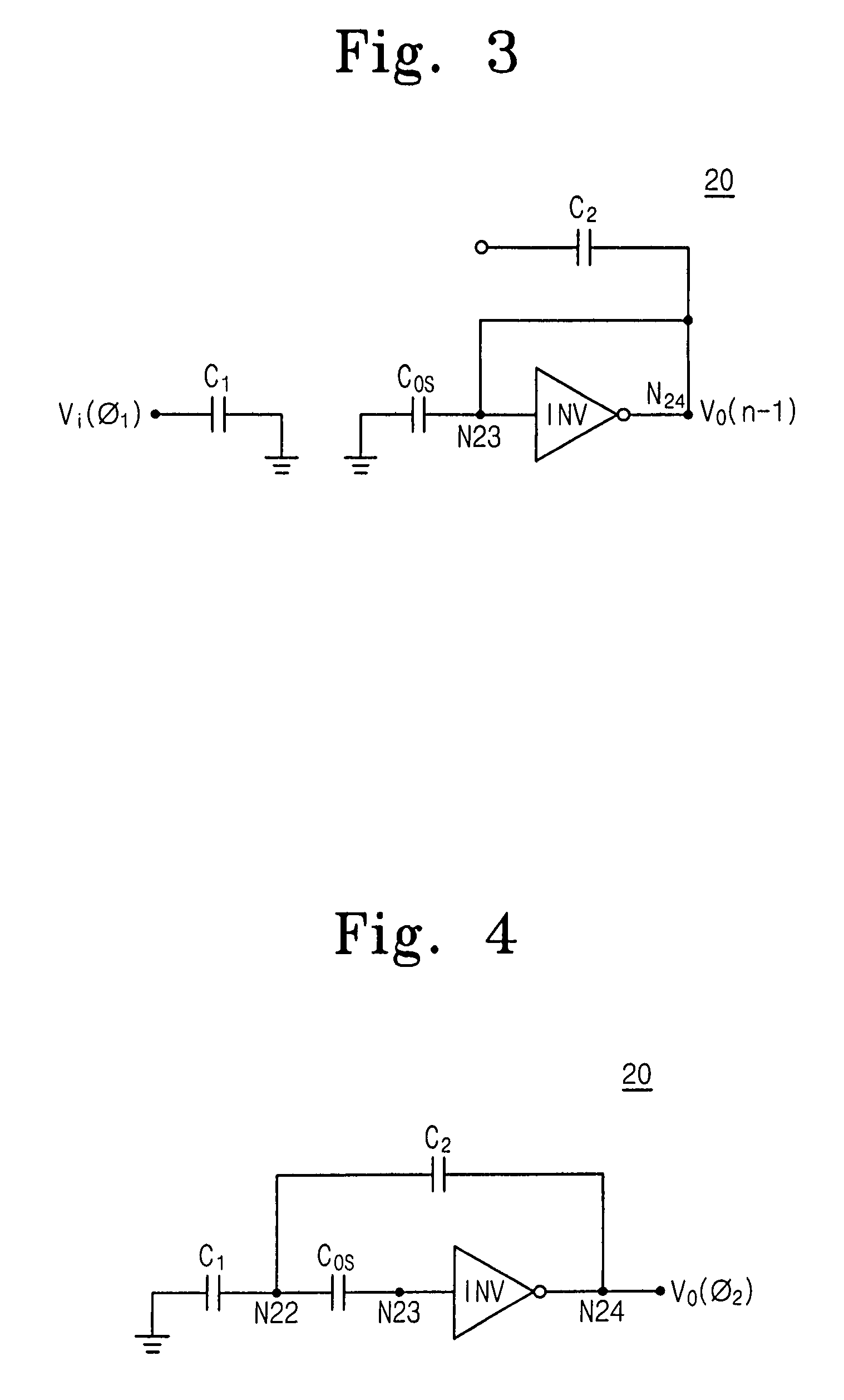

Switched capacitor circuit with inverting amplifier and offset unit

ActiveUS7800427B2Reduce power consumptionReduce circuit areaAmplifier modifications to reduce non-linear distortionComputing operations for integral formationCapacitanceAudio power amplifier

A switched capacitor circuit includes an amplifier, a charging unit, an offset unit, and an integrating unit. The charging unit is coupled between an input node and a first node, and is for accumulating charge corresponding to an input signal during a sampling mode. The offset unit is coupled between the first node and an input of the amplifier, and is for maintaining the first node to be a virtual ground during an integrating mode. The integrating unit is coupled between the first node and an output of the amplifier, and is for receiving charge from the charging unit during the integrating mode.

Owner:SAMSUNG ELECTRONICS CO LTD +1

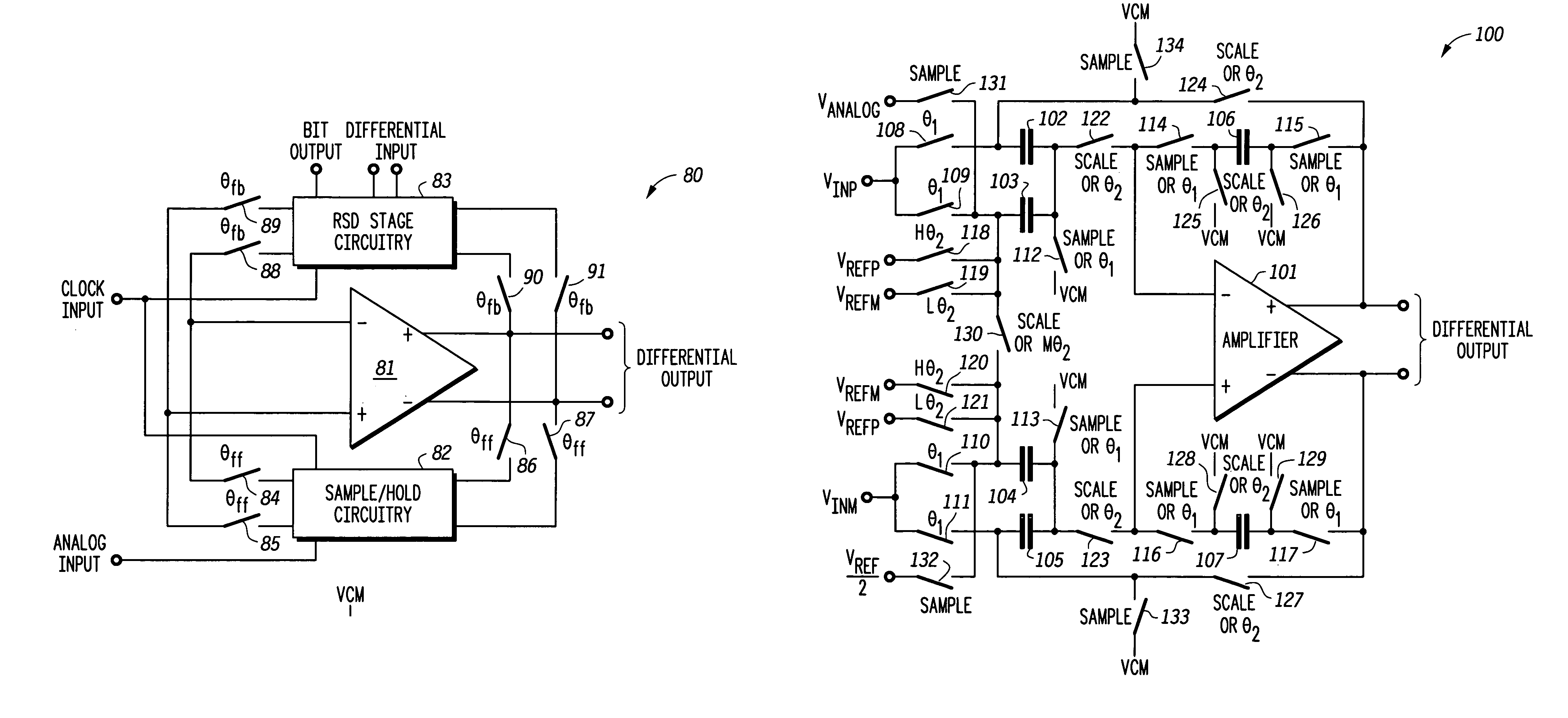

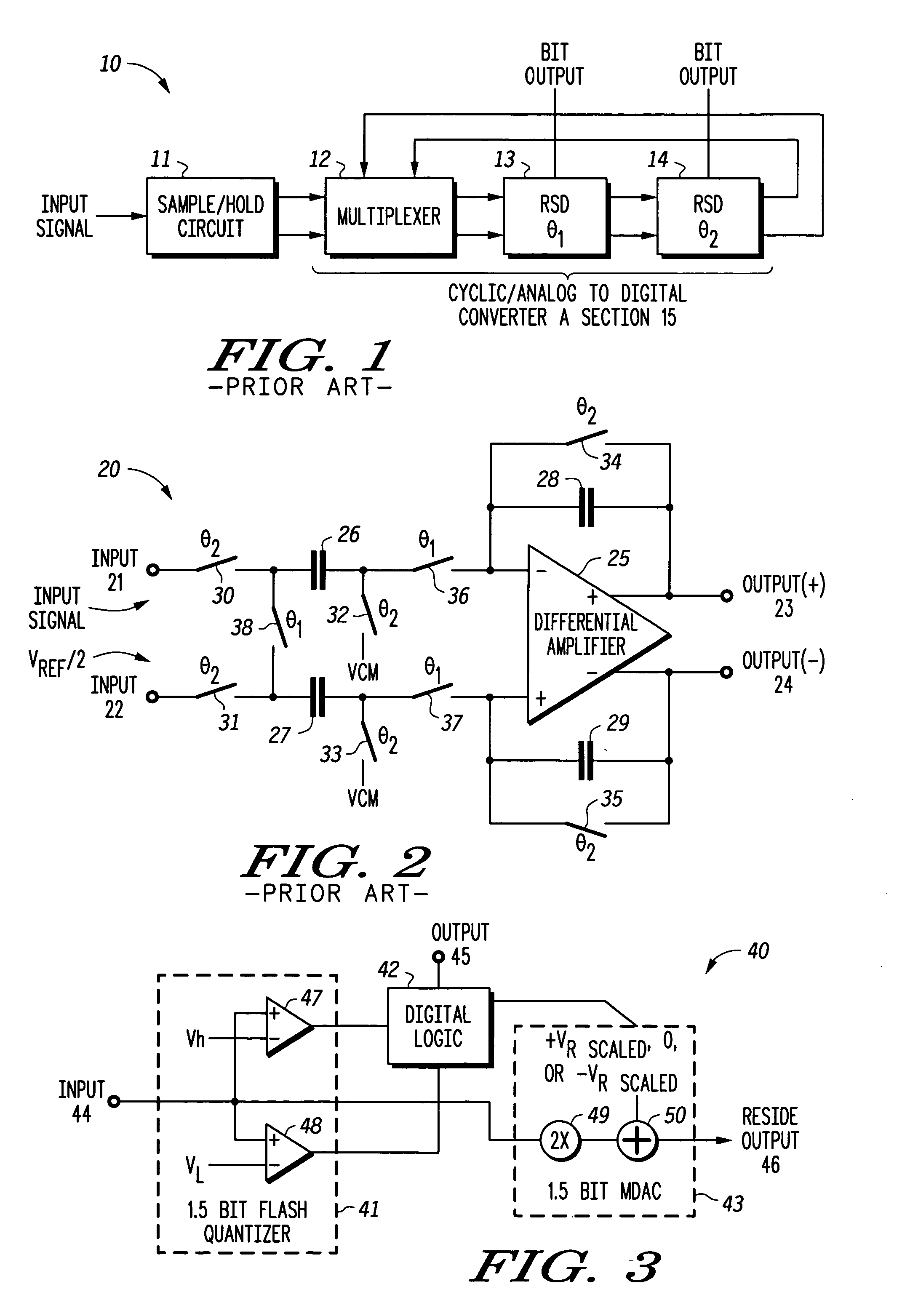

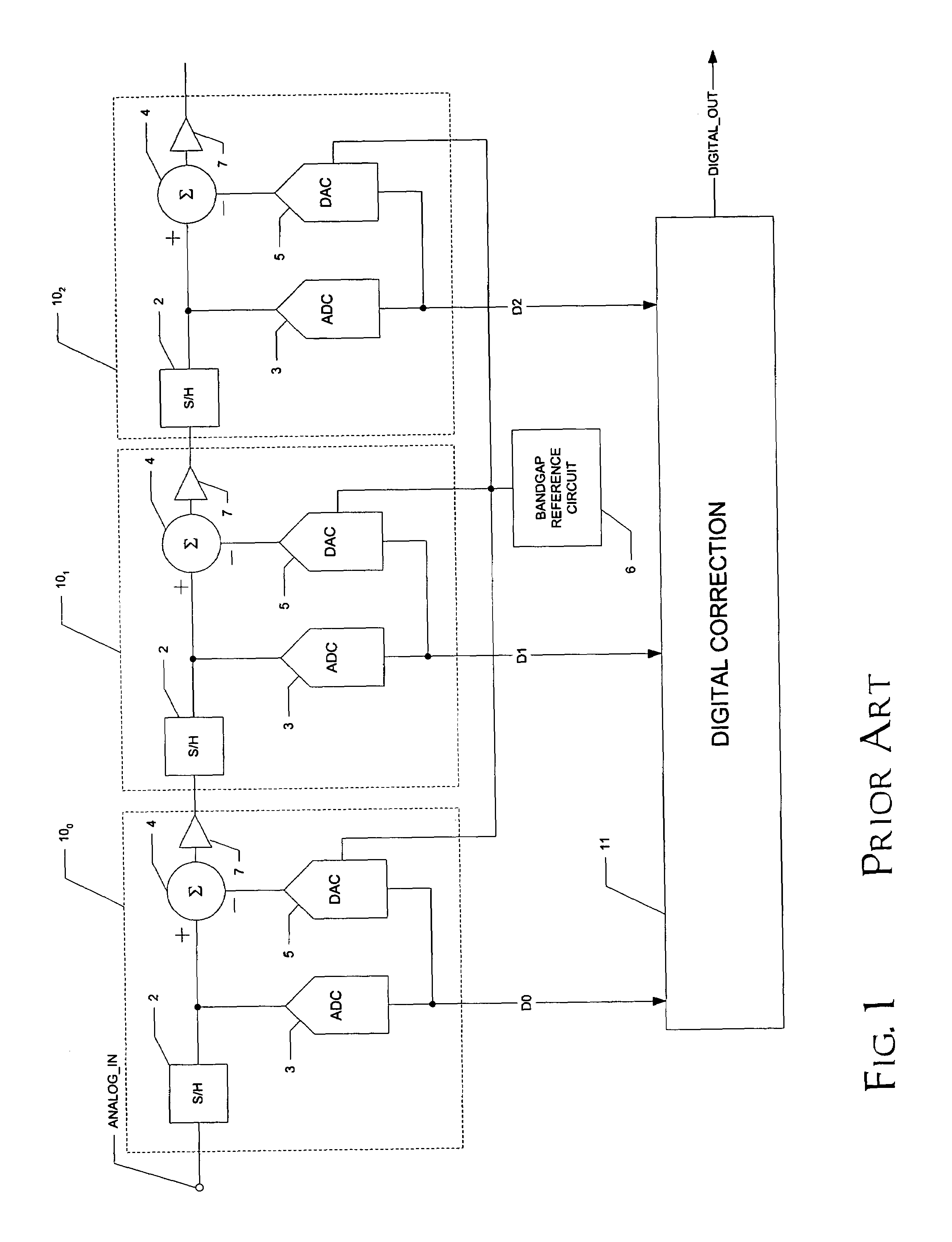

Optimized reference voltage generation using switched capacitor scaling for data converters

InactiveUS6967611B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceA d converter

An algorithmic or cyclic data converter uses an RSD stage having a switched capacitor network for efficiently scaling at least one externally supplied reference voltage. A reference voltage is scaled by using capacitor ratios that also function to provide an output voltage used as a residue output of the RSD A / D converter. The residue is used to generate a bit value corresponding to the magnitude of the residue. Two RSD stages cycle back and forth generating a logic value each half clock cycle until the desired bit resolution is achieved. In one form, the RSD stage scales the externally supplied reference voltage only by factors of less than one. In another form, the RSD stage scales the reference voltage by any scaling factor. A reference voltage scaling circuit separate from the RSD stage is avoided.

Owner:NORTH STAR INNOVATIONS

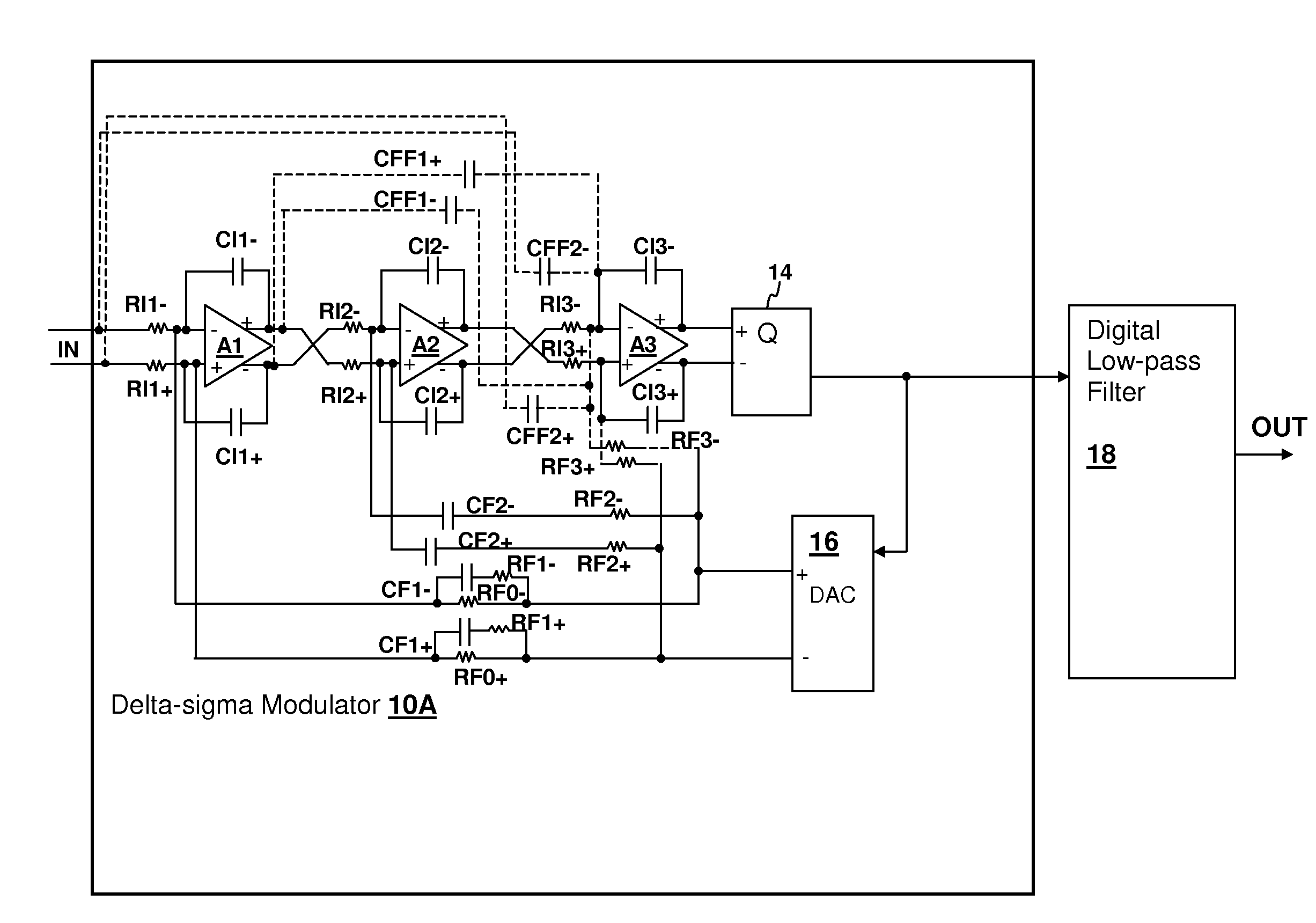

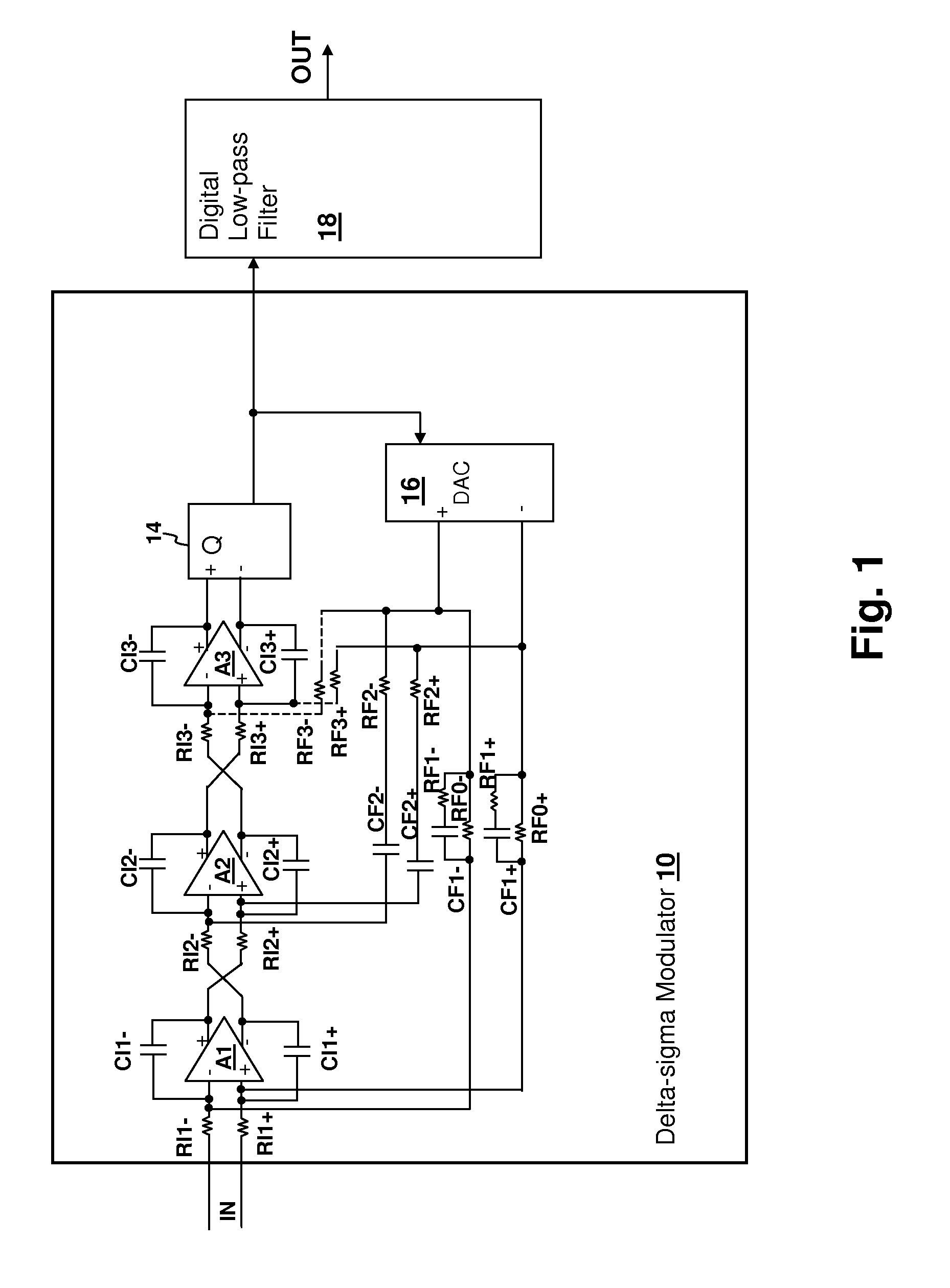

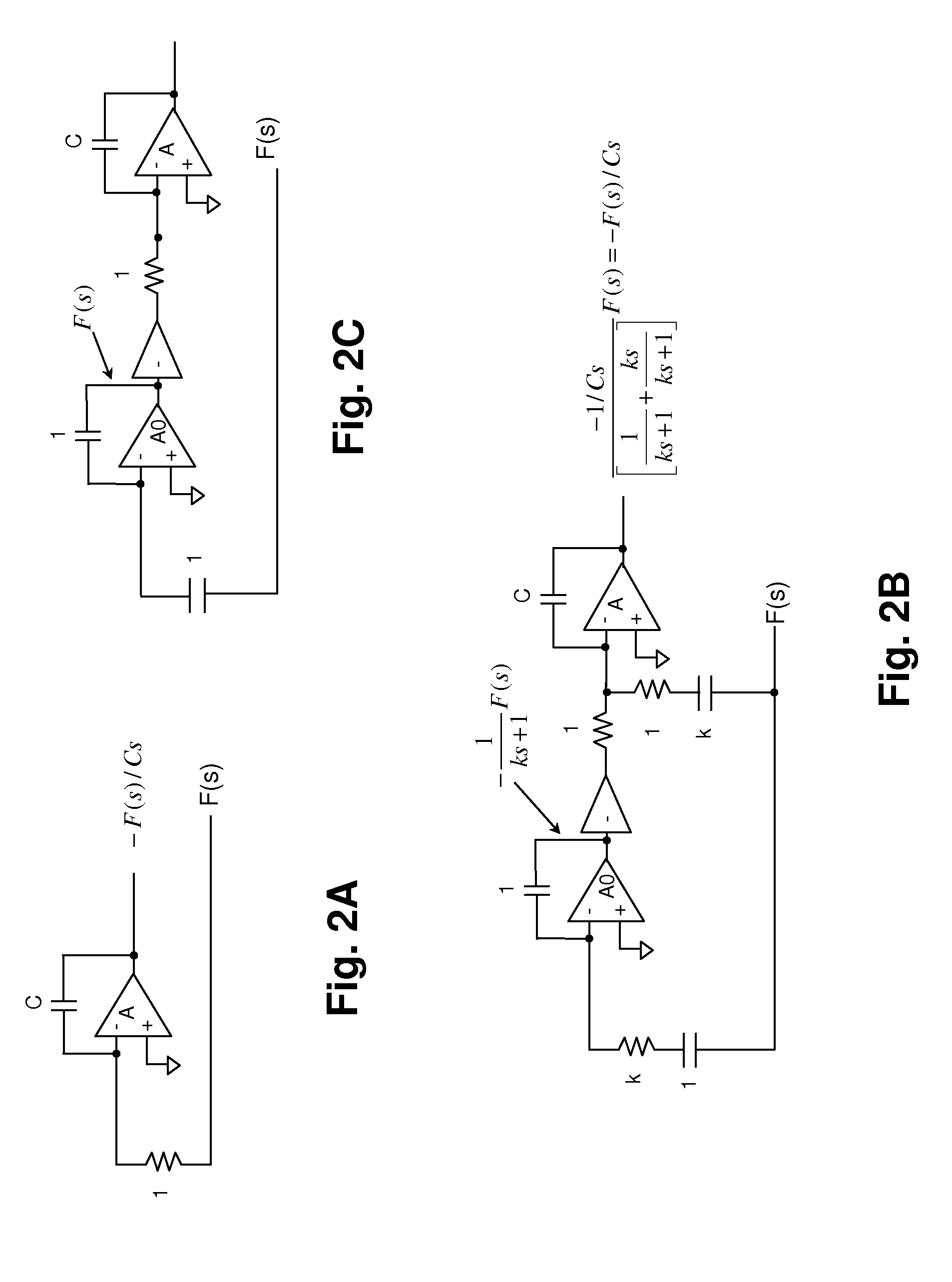

Feedback topology delta-sigma modulator having an ac-coupled feedback path

A feedback topology delta-sigma modulator having an AC-coupled feedback path reduces signal level in the loop filter, easing linearity requirements and reduces capacitor size requirements for the filter integration stages. The delta-sigma modulator includes a loop filter having multiple integrator stages, a quantizer, and a feedback network providing at least two feedback paths to corresponding integrators in the loop filter. In one aspect, only one of the feedback paths from the quantizer output is DC coupled, and at least one other of the feedback paths is DC-coupled, which reduces the signal levels in the loop filter integrators. In another aspect, at least one of the feedback paths from the quantizer is AC coupled, providing a similar result. The AC feedback path may be provided through a series-connected resistor and capacitor. The DC feedback path may be provided through a resistor, a switched-capacitor network, or may be a quantizer-controlled current source.

Owner:CIRRUS LOGIC INC

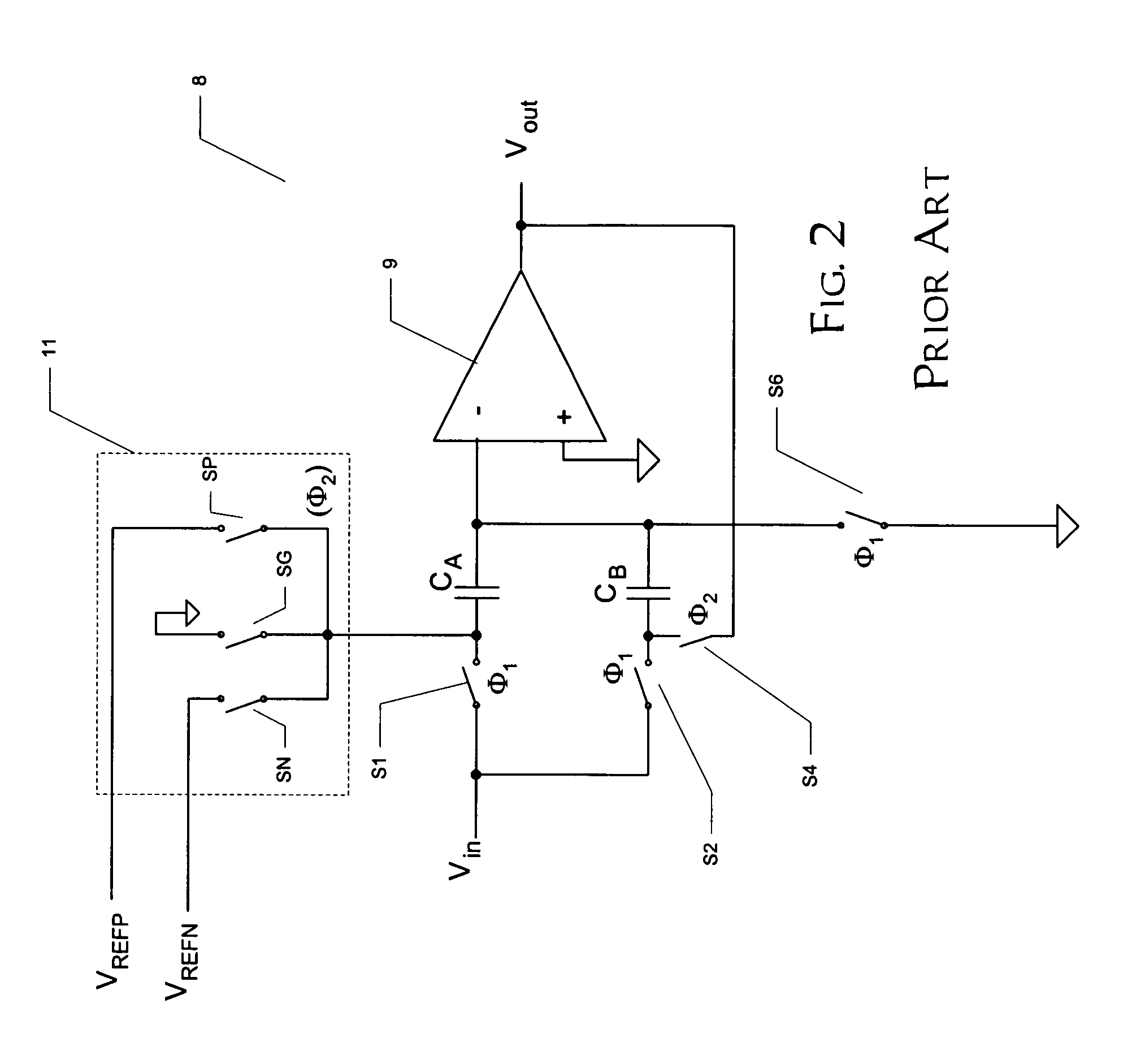

Switched-capacitor circuit with scaled reference voltage

ActiveUS7009549B1Improve precisionImprove stabilityElectric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

A pipelined analog-to-digital converter (ADC) (30) with improved precision is disclosed. The pipelined ADC (30) includes a sequence of stages (20), each of which includes a sample-and-hold circuit (22), an analog-to-digital converter (23), and the functions of a digital-to-analog converter (DAC) (25), an adder (24), and a gain stage (27) at which a residue signal (RES) is generated for application to the next stage (20) in the sequence. A multiplying DAC (28) performs the functions of the DAC (25), adder (24), and gain stage (27) in the stage (20), and is based on an operational amplifier (29). Sample capacitors (C10, C20) and reference capacitors (C122, C222) receive the analog input from the sample-and-hold circuit (22) in a sample phase; parallel capacitors (C121, C221) are provided to maintain constant circuit gain. Extended reference voltages (VREFPX, VREFNX) at levels that exceed the output range (V0+, V0−) of the operational amplifier (29) are applied to the reference capacitors, in response to the digital output of the analog-to-digital converter (23) in its stage (20). The reference capacitors (C12, C22) are scaled according to the extent to which the extended reference voltages (VREFPX, VREFNX) exceed the op amp output levels (V0+, V0−). The effects of noise on the reference voltages (VREFPX, VREFNX) on the residue signal (RES) are thus greatly reduced.

Owner:TEXAS INSTR INC

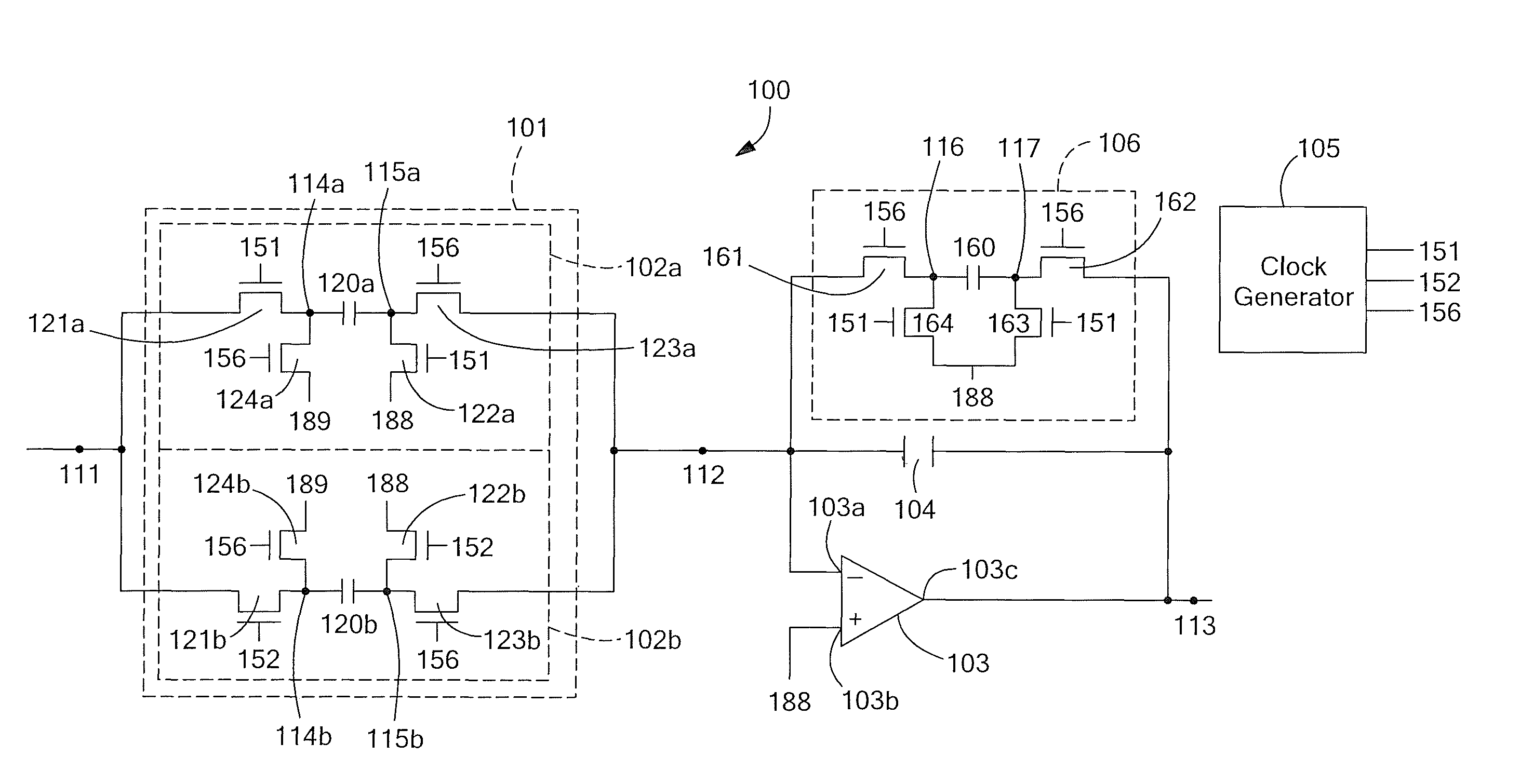

Switched capacitor circuit with reduced common-mode variations

ActiveUS20050134380A1Amplifier modifications to raise efficiencyDifferential amplifiersEngineeringImpedance matching

A circuit with a common-mode dual output includes a feedback circuit connected to alternate the states of the dual output between an average output level and a desired common-mode level. The difference between the average and desired levels is proportional to a signal offset level. An impedance matching circuit is connected to the feedback circuit to adjust the signal offset level.

Owner:ANALOG DEVICES INC

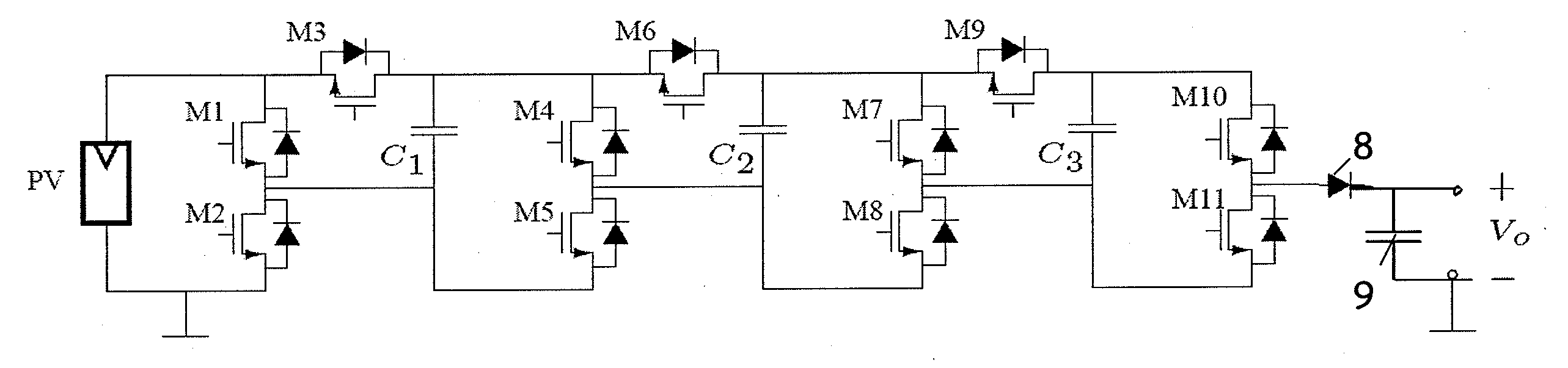

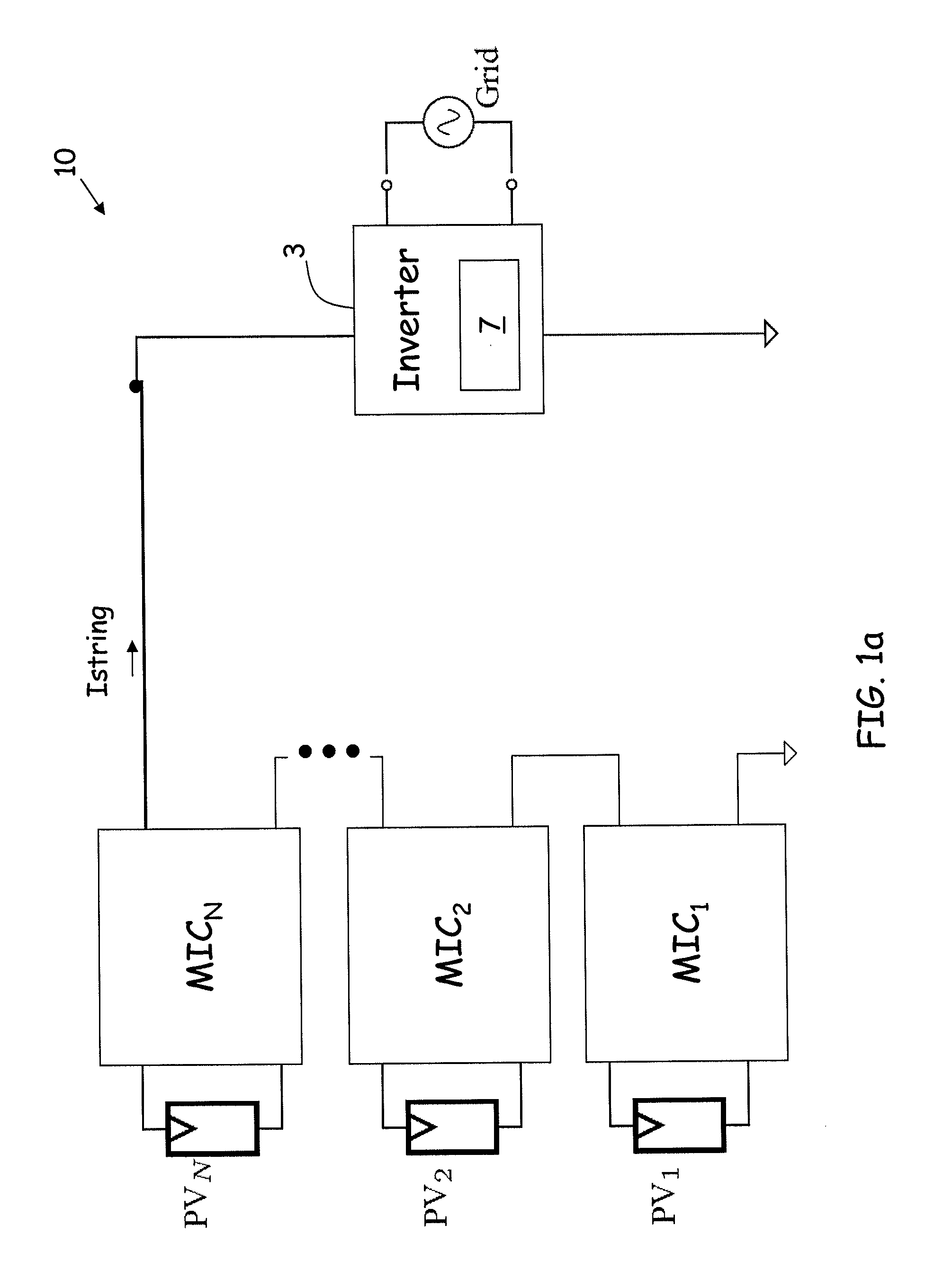

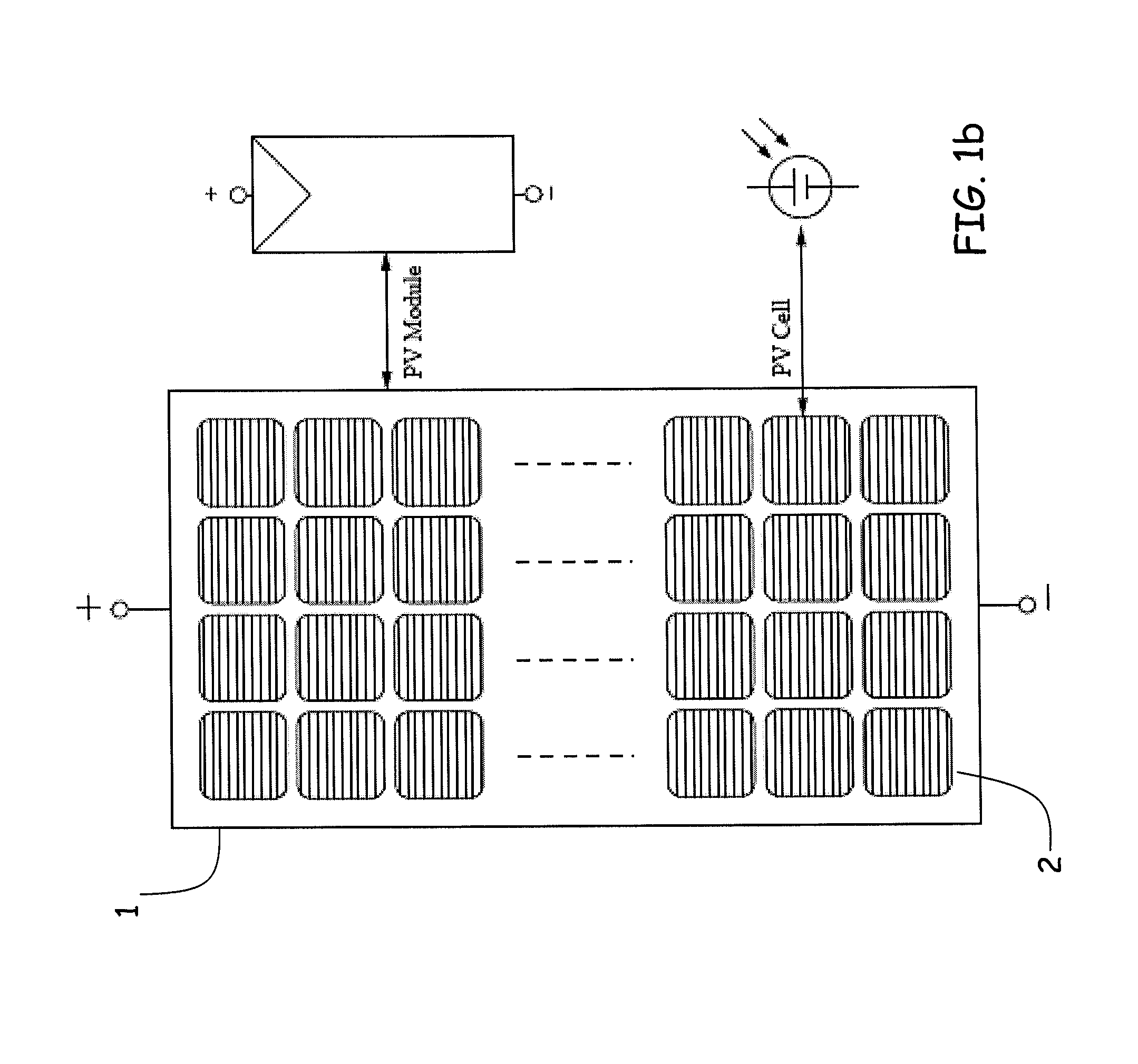

Photovoltaic energy extraction with multilevel output dc-dc switched capacitor converters

ActiveUS20120223583A1Dc network circuit arrangementsApparatus without intermediate ac conversionTotal efficiencyDc dc converter

Switched capacitor multilevel output DC-DC converters can be used as panel integrated modules in a solar maximum power point tracking system. The system can also include a central input current-controlled ripple port inverter. The system can implement per panel MPPT without inter-panel communication, electrolytic capacitors or per panel magnetics. A Marx converter implementation of the switched capacitor module is studied. Average total efficiencies (tracking×conversion) greater than 93% can be achieved for a simulated 510 W, 3 panel, DC-DC system.

Owner:MASSACHUSETTS INST OF TECH

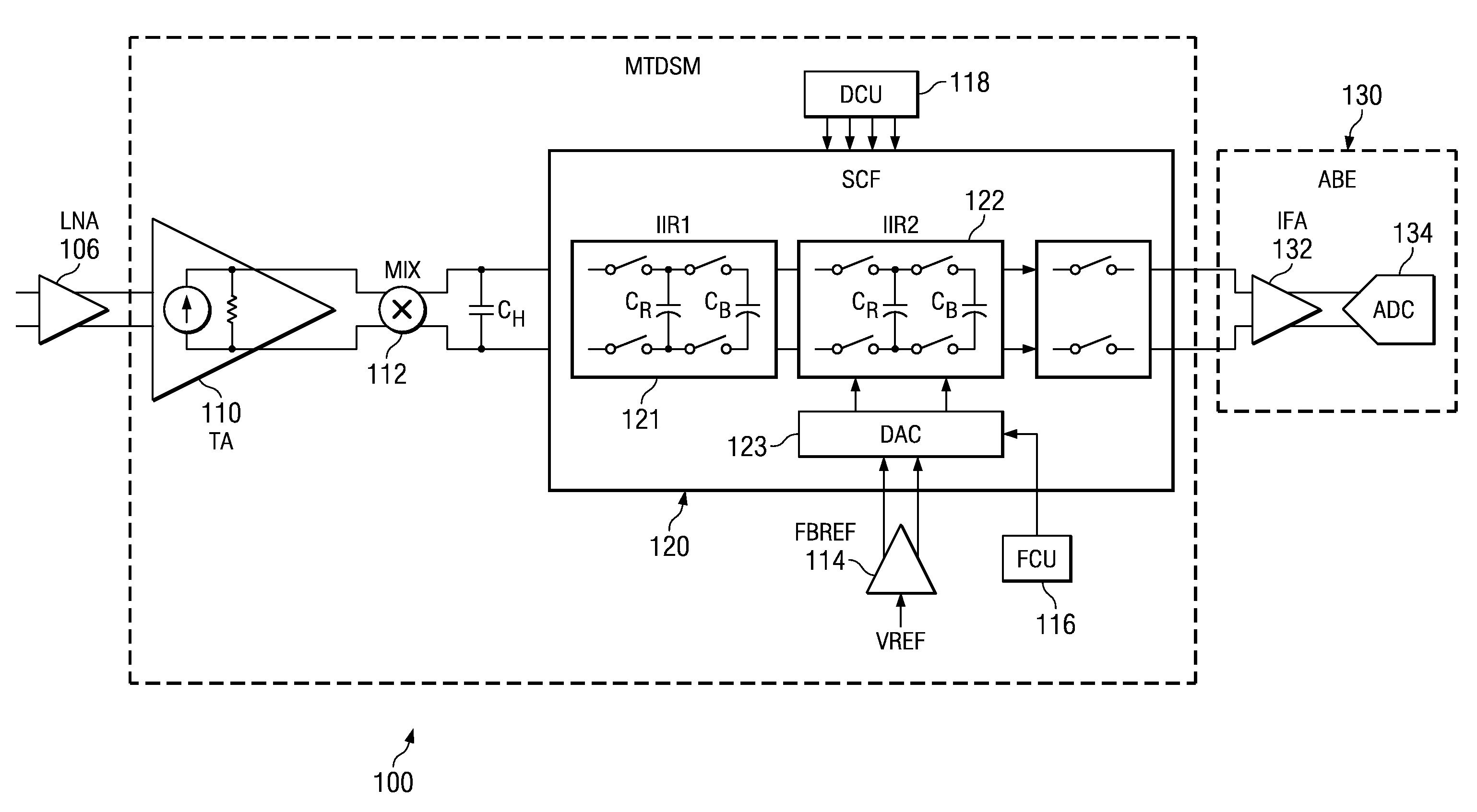

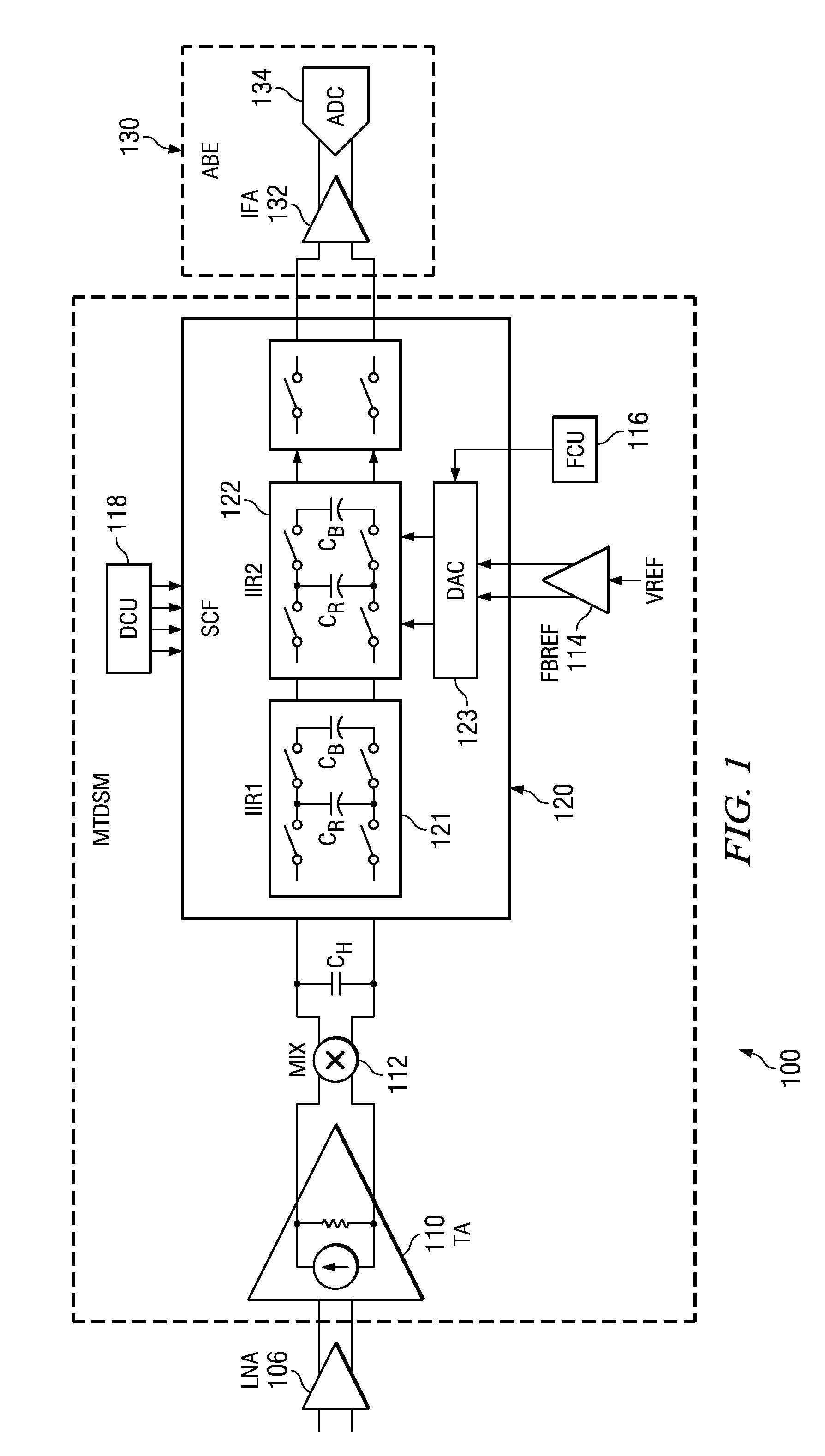

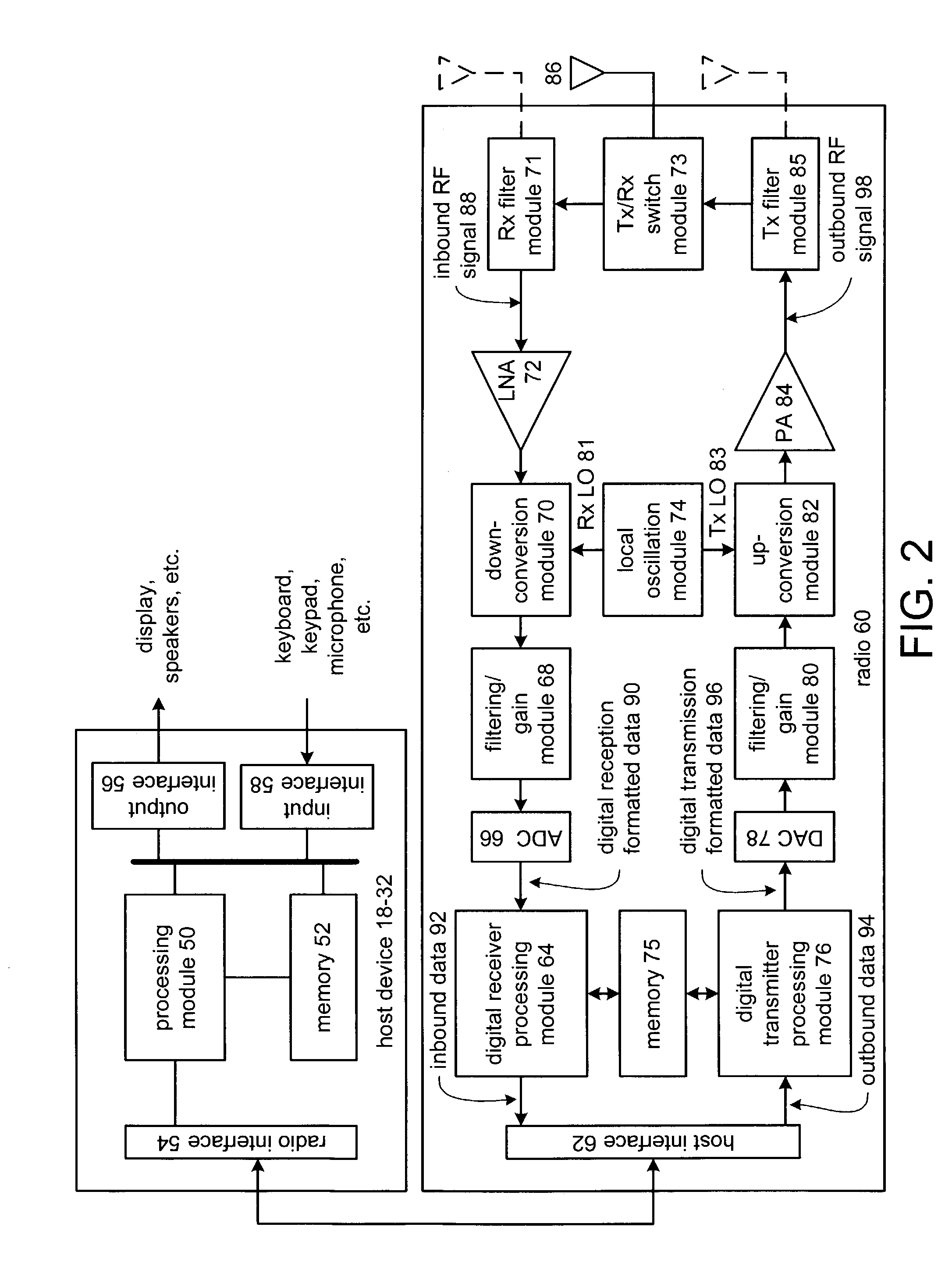

Multi-Tap Direct Sub-sampling Mixing System for Wireless Receivers

ActiveUS20090002066A1Transversal filtersSwitched capacitor networksHybrid systemAudio power amplifier

A multi-tap direct sub-sampling mixing system for wireless receivers is provided with a dynamically configurable passive switched capacitor filter. A front end amplifier is connected to receive a signal. The passive switched capacitor filter is connected to receive the amplified signal and has an output for providing a filtered signal. The switched capacitor filter has at least two sections that are each operable as a pole, wherein a first section of the at least two sections has sets of at least two stacked capacitors interconnected with a set of switches operable to amplify in input voltage provided to an input of the first section in response to operation of the set of switches; and a back end section connected to the output of the switched capacitor filter to receive the filtered signal.

Owner:TEXAS INSTR INC

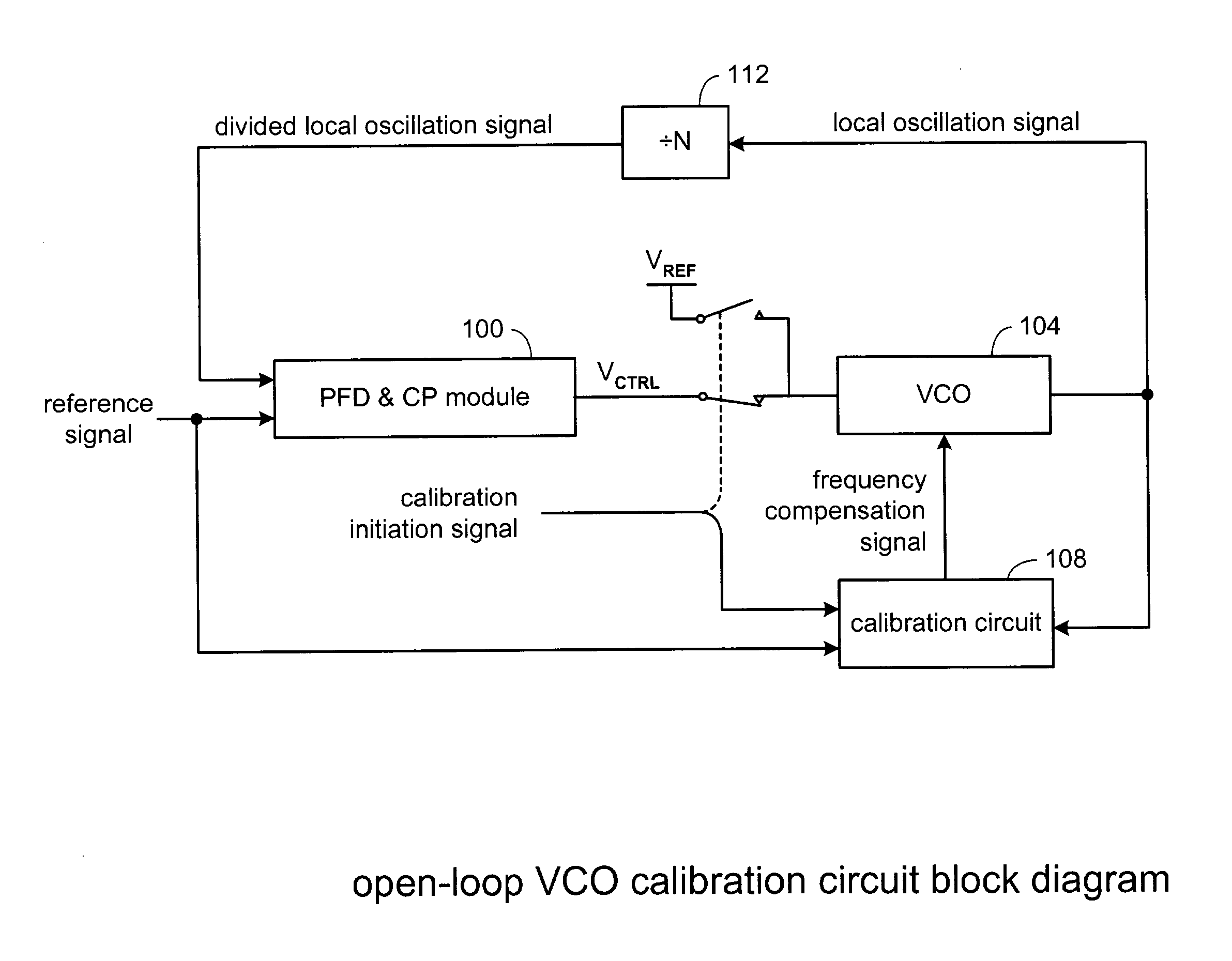

Analog open-loop VCO calibration method

InactiveUS7099643B2Quick calibrationQuick correctionAutomatic scanning with simultaneous frequency displayPulse automatic controlFrequency compensationEngineering

An analog open-loop voltage controlled oscillator (VCO) calibration circuit and method for selecting the frequency of the VCO for a phase locked loop (PLL).A frequency divider module produces a 50% duty cycle divided local oscillation and a 50% duty cycle divided reference signal, wherein the divided signals are substantially equal. A period-to-voltage conversion module converts the divided local oscillation signal and the divided reference signal to voltages proportional to the divided signals. A comparator module produces a frequency adjustment signal based on a comparison of the proportional voltages and couples the frequency adjustment signal to a logic module which produces a frequency compensation signal based on the frequency adjustment signal. The frequency compensation signal functions to adjust the configuration of switched capacitors in a capacitor bank, coupled to the VCO tuned circuit, until the divided local oscillation signal is substantially equal to the divided reference signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

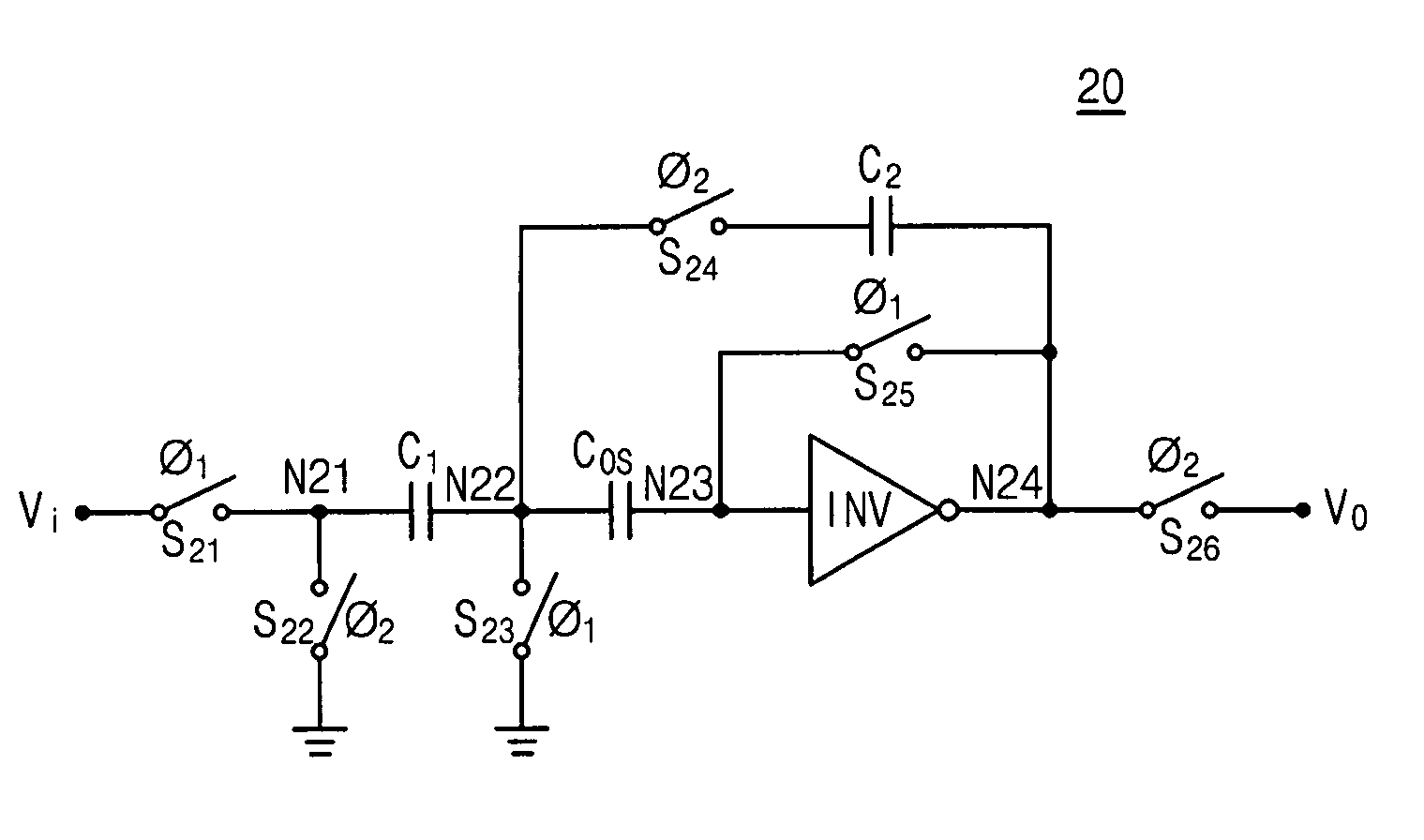

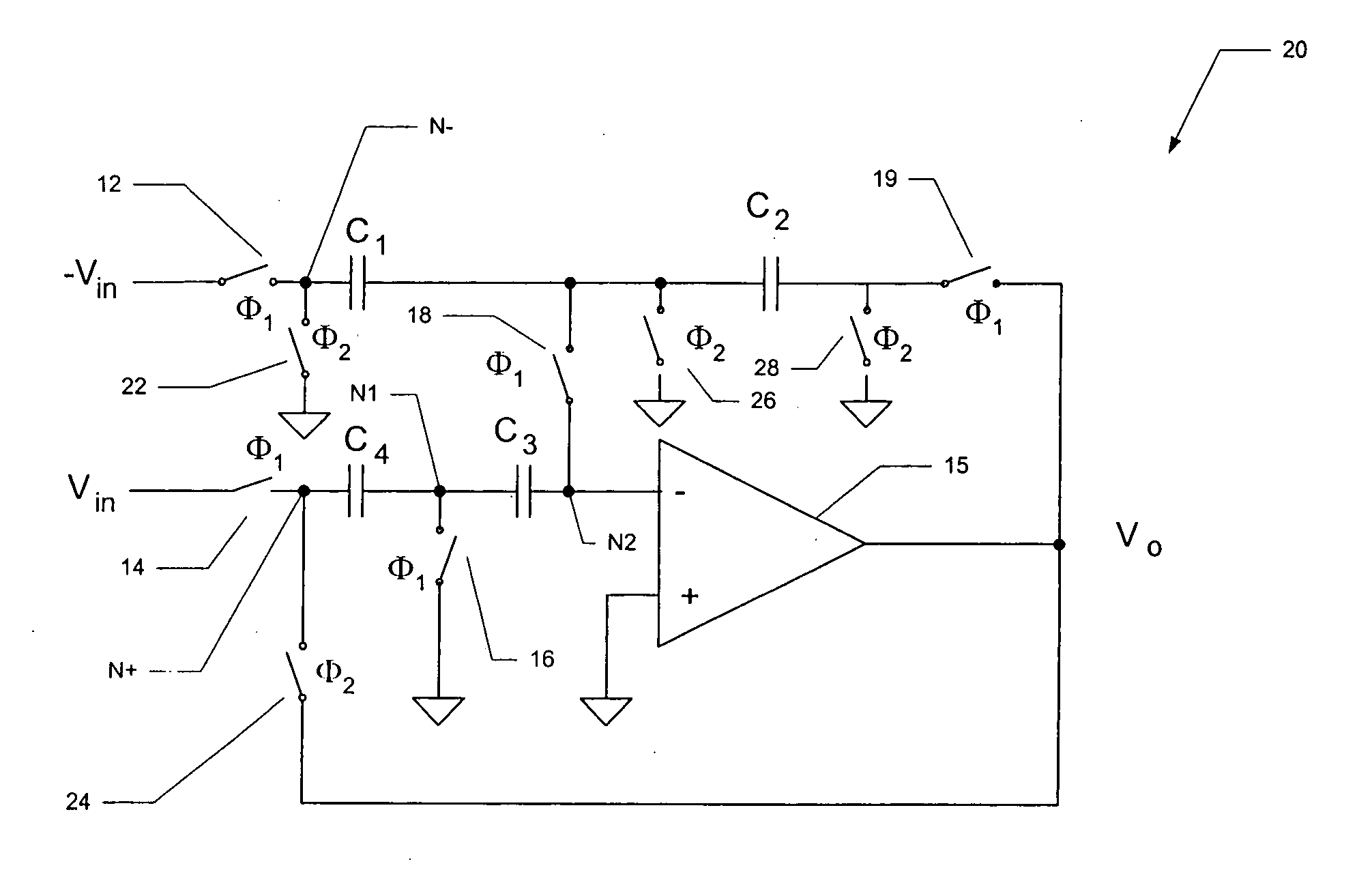

Switched-capacitor circuits with reduced finite-gain effect

ActiveUS20060071709A1Minimize impactGood effectAmplifier modifications to raise efficiencyDifferential amplifiersCapacitanceAudio power amplifier

Operational amplifier circuits (20, 30) including error capacitors (C3, C13) for storing finite gain effect error voltages for correction of output voltages of the circuits (20, 30), are disclosed. The circuits (20, 30) are operated in a sample clock phase to produce an approximation of the output voltage, using negative polarity versions of the input voltages to the circuit. The approximate output voltage is used to produce and store an error voltage, corresponding to the differential voltage at the input of the operational amplifier (15, 25), relative to virtual ground. This error voltage is then subtracted from the input voltage applied in the operate clock phase, to correct for the finite gain effect. A pipelined analog-to-digital converter (50) using the disclosed operational amplifier circuits (20, 30) is also disclosed.

Owner:TEXAS INSTR INC

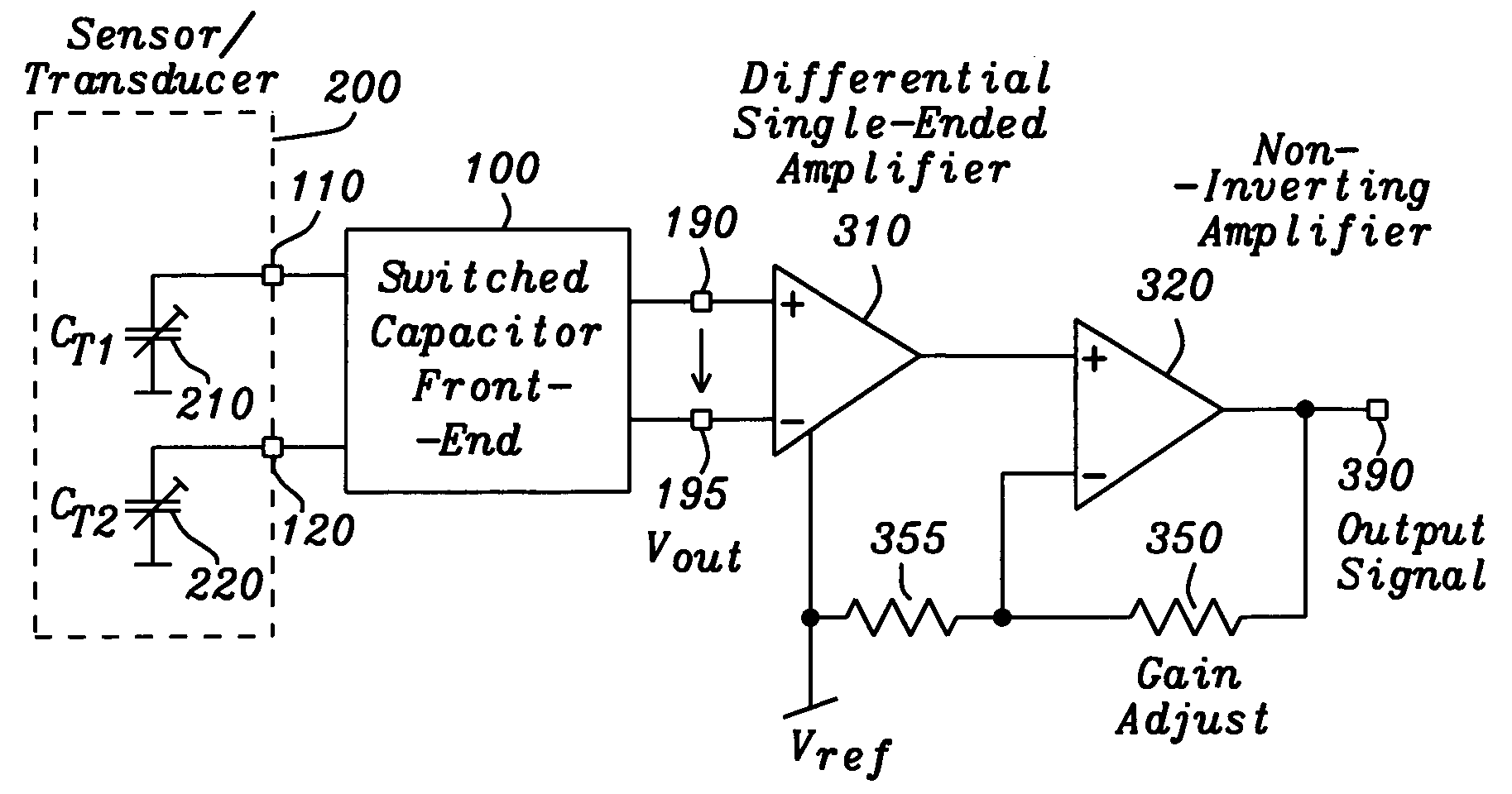

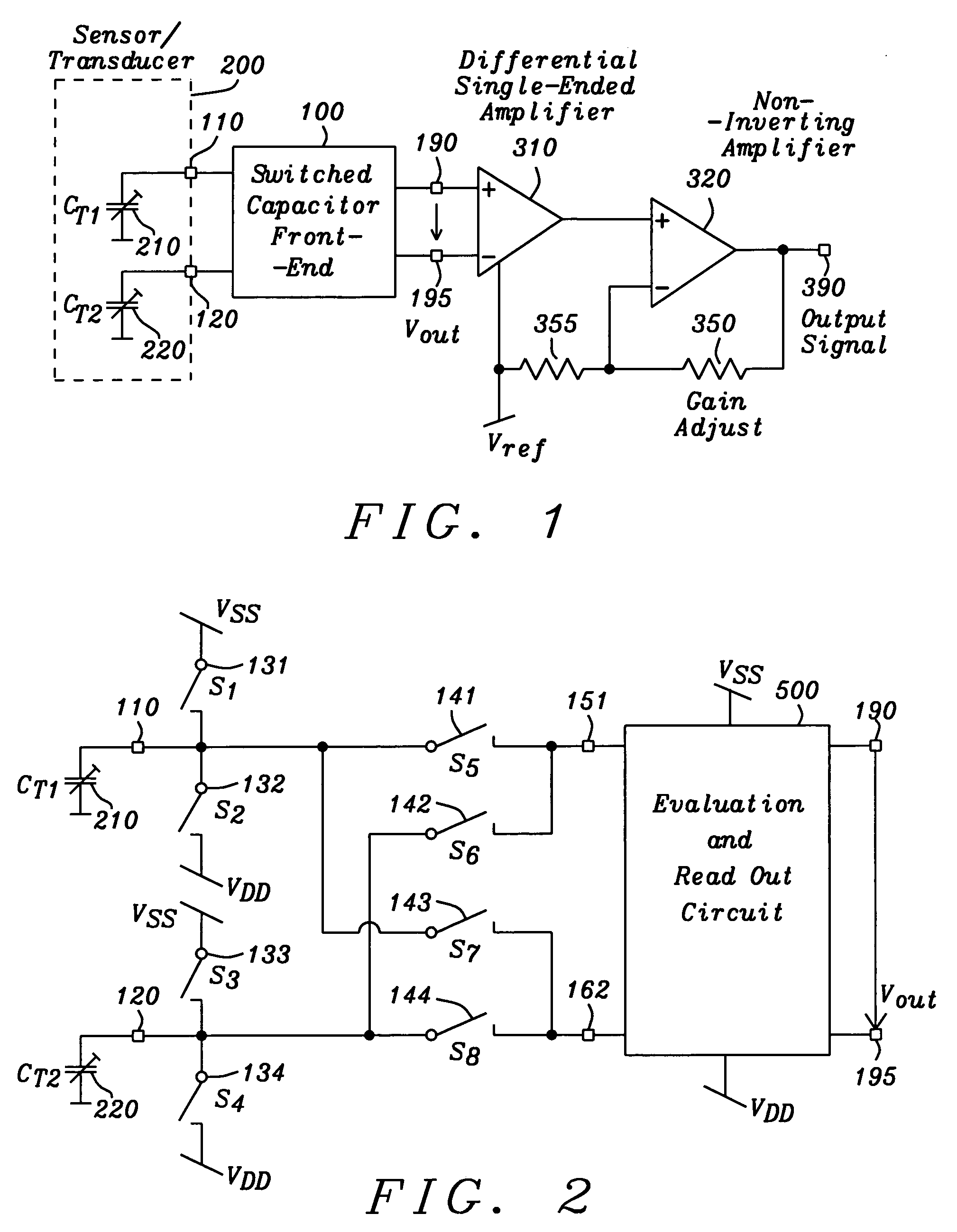

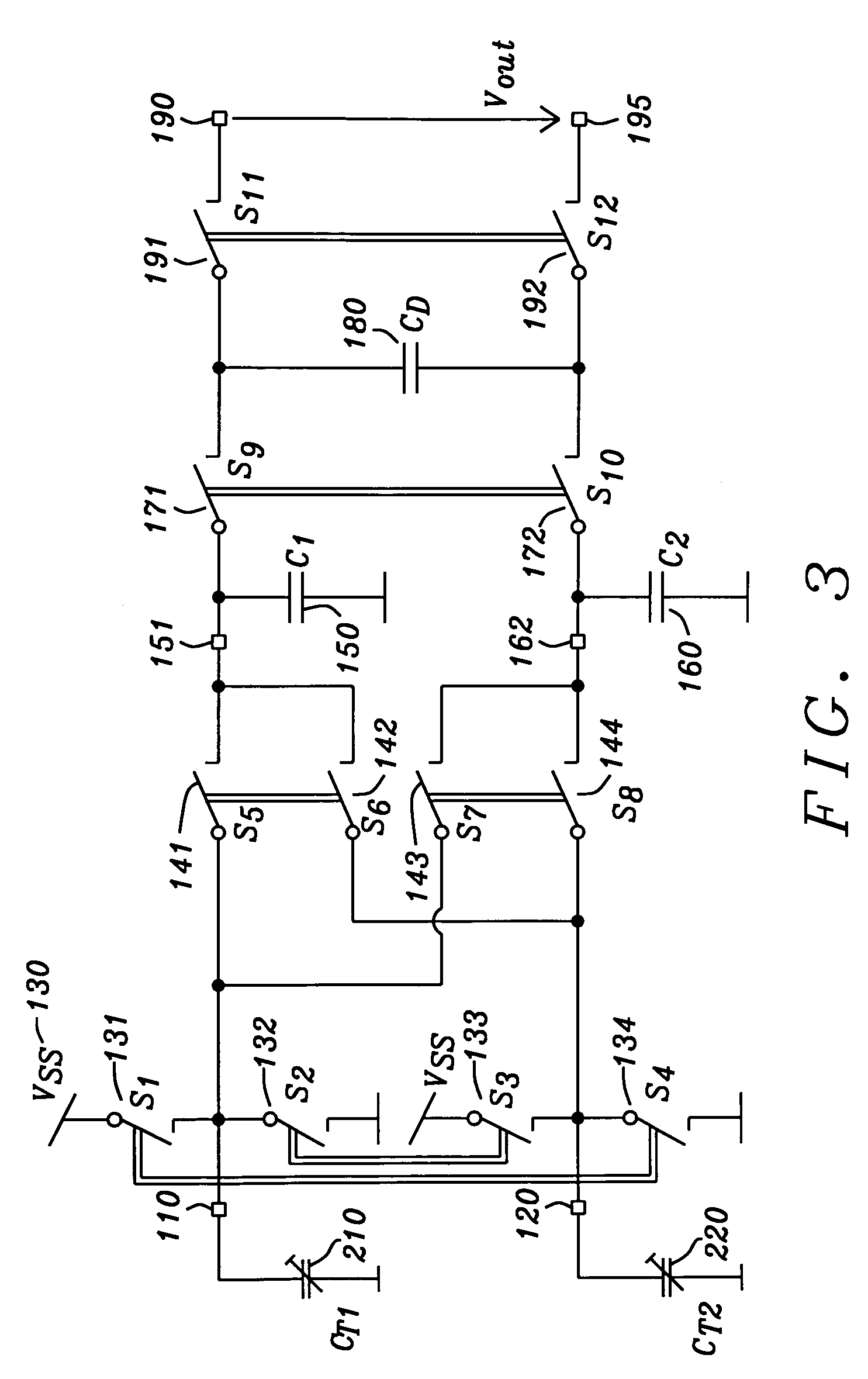

Differential capacitance measurement

InactiveUS20050134292A1Efficient methodPrecise and sensitive and yet stable evalutionCapacitance measurementsConverting sensor output electrically/magneticallyCMOSSoi cmos technology

A circuit and method are given, which realizes a stable yet sensitive differential capacitance measuring device with good RF-suppression and with very acceptable noise features for use in capacitive sensor evaluation systems. By evaluating the difference of capacitor values only—with the help of a switched capacitor front-end—large spreads of transducer capacitor values are tolerable. Furthermore a mode of operation can be set up, where no essential galvanic connection between sensor input and the active read-out input at any given time is existing. The solution found exhibits a highly symmetrical construction. Using the intrinsic advantages of that solution the circuit of the invention is manufactured as an integrated circuit with standard CMOS technology at low cost.

Owner:DIALOG SEMICONDUCTOR GMBH

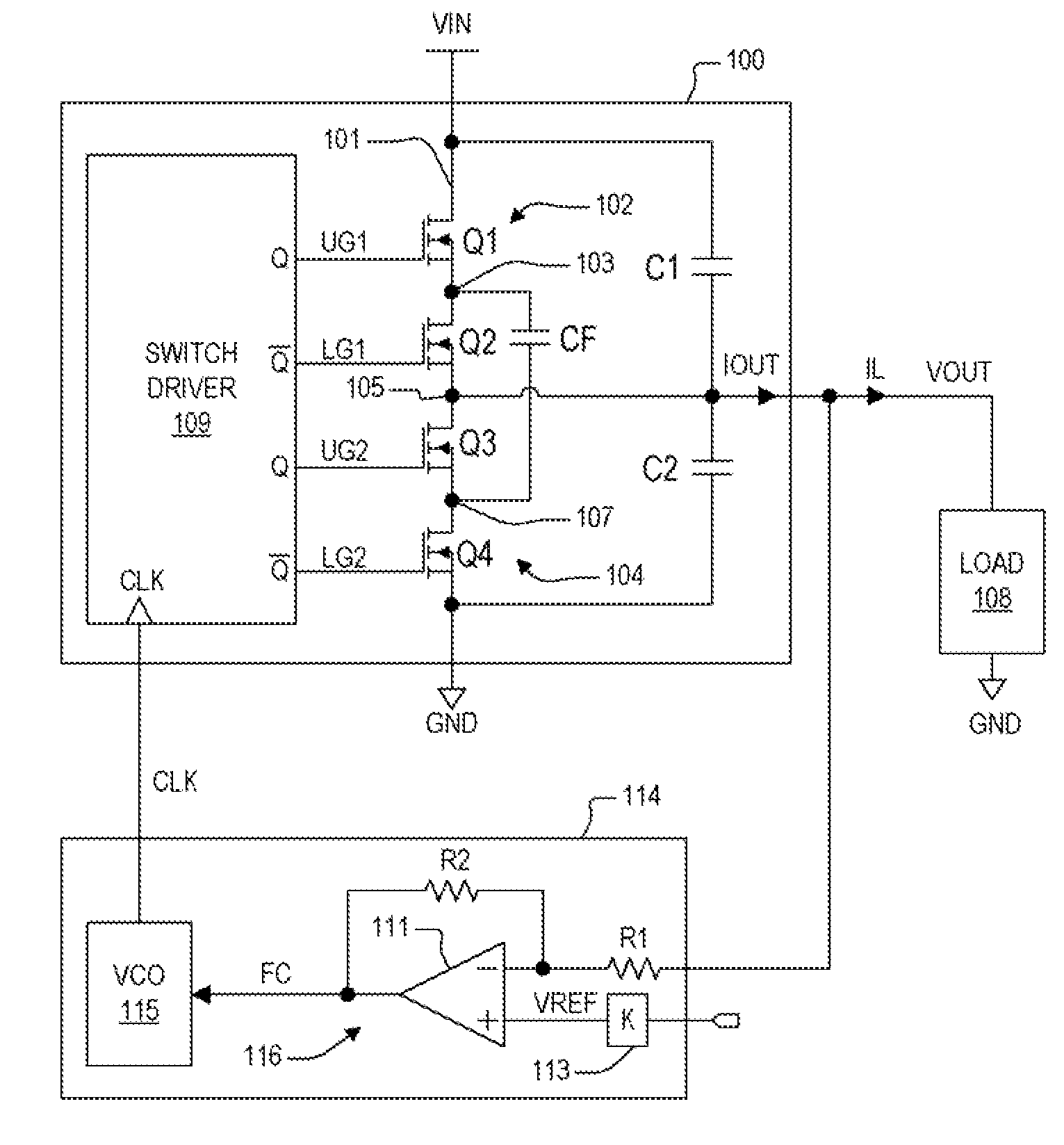

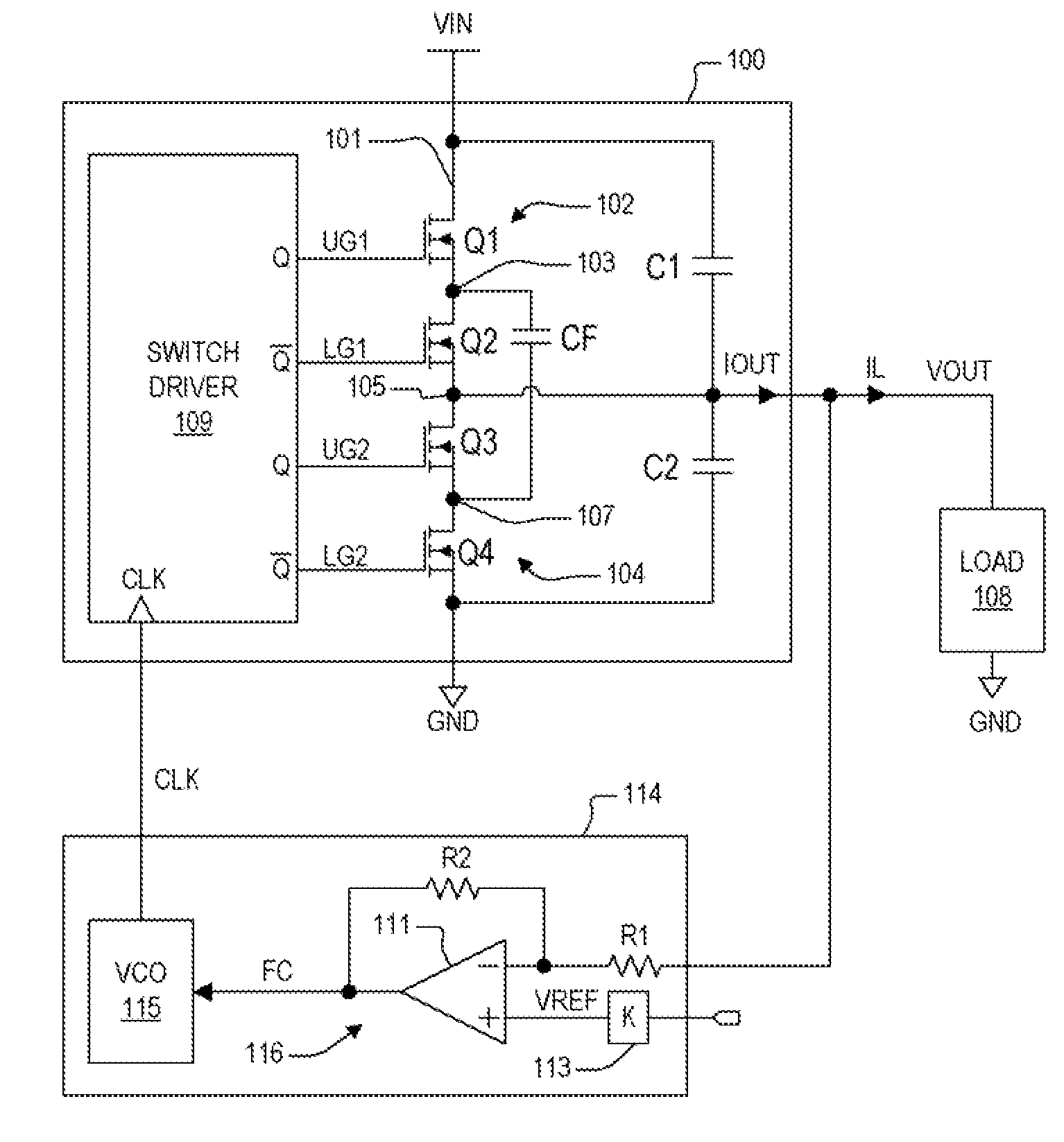

Switching frequency control of switched capacitor circuit using output voltage droop

A frequency control circuit including a controlled oscillator and an amplifier circuit is disclosed for providing a clock signal to a switched capacitor circuit which divides an input voltage to provide an output voltage. The controlled oscillator has a frequency control input receiving a frequency control signal and an output for providing the clock signal at a frequency based on the frequency control signal. The amplifier circuit has an input for receiving the output voltage and an output providing the frequency control signal based on droop of the output voltage. In one embodiment, the amplifier circuit adjusts the frequency control signal to optimize efficiency of the switched capacitor circuit over a voltage range of the output voltage, which changes based on load level.

Owner:INTERSIL INC

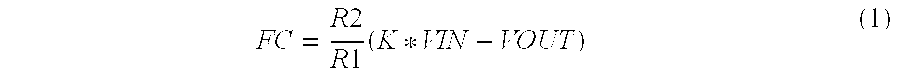

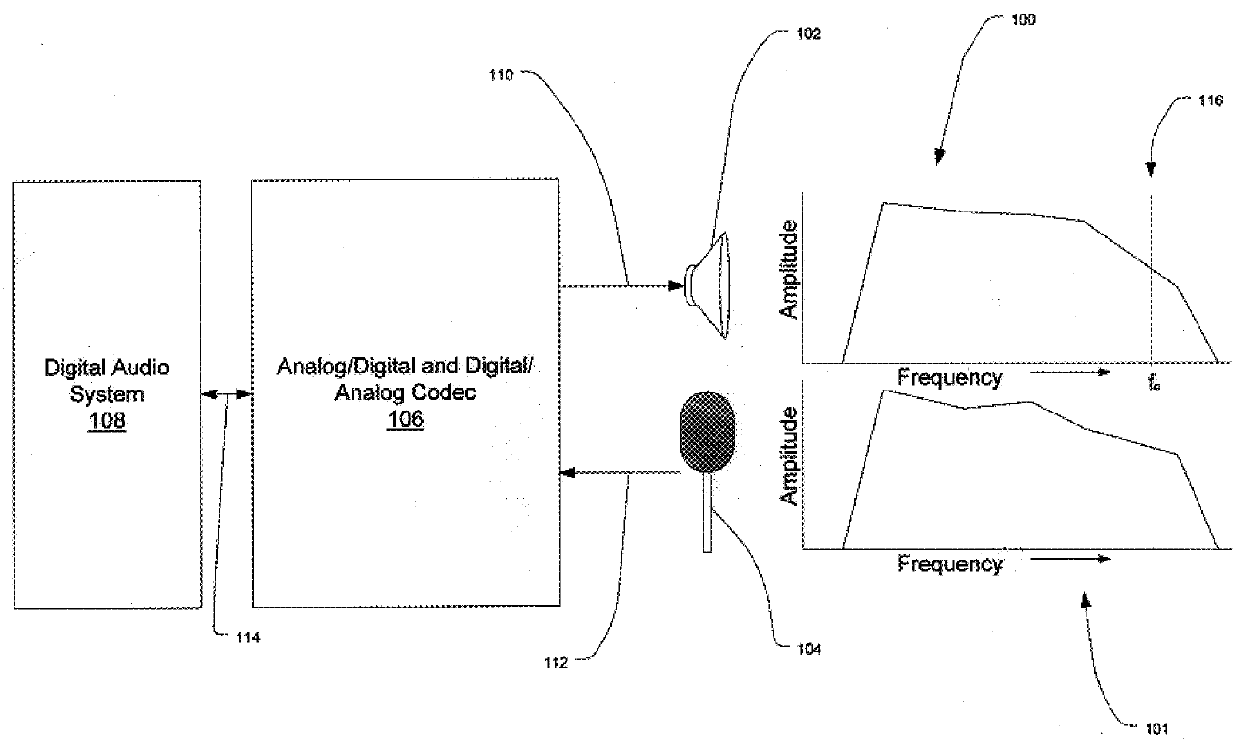

System and method for bandpass shaping in an oversampling converter

InactiveUS6249237B1Effective frequency responseElectric signal transmission systemsAnalogue conversionTransducerDigital filter

Owner:AVAGO TECH INT SALES PTE LTD

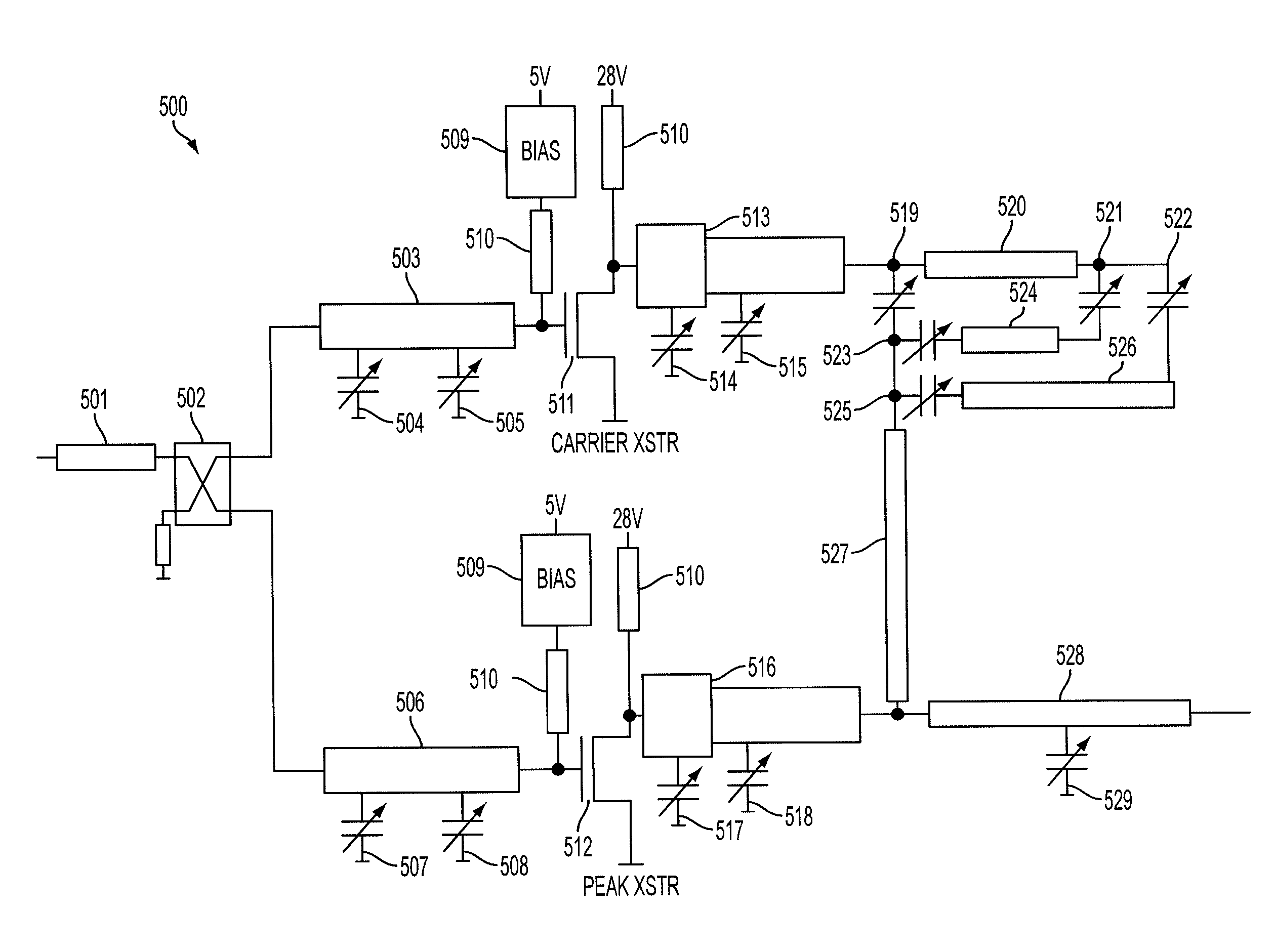

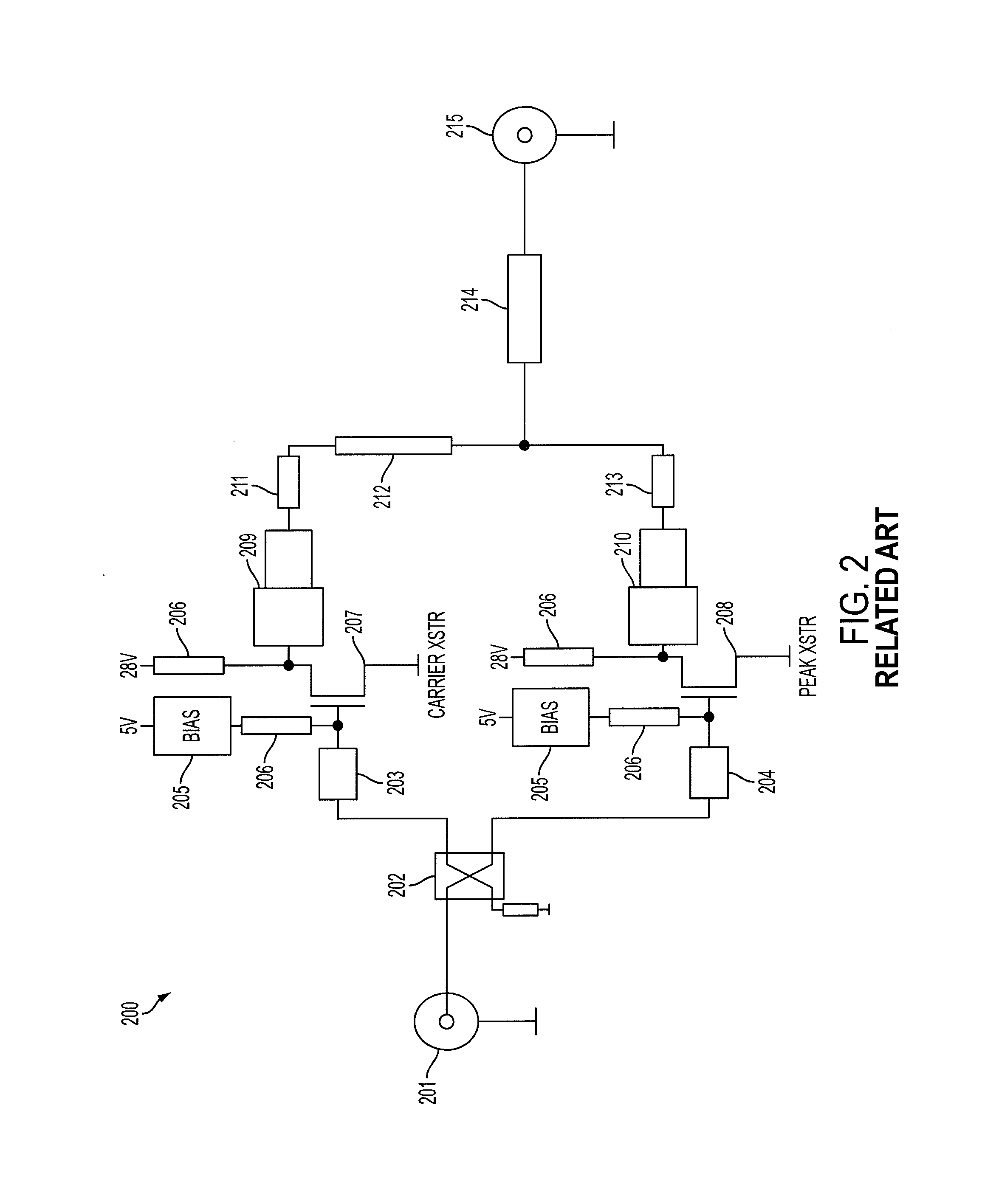

Apparatus and method for a switched capacitor architecture for multi-band doherty power amplifiers

ActiveUS8576010B2Amplifier combinationsAmplifier input/output impedence modificationMulti bandRadio frequency

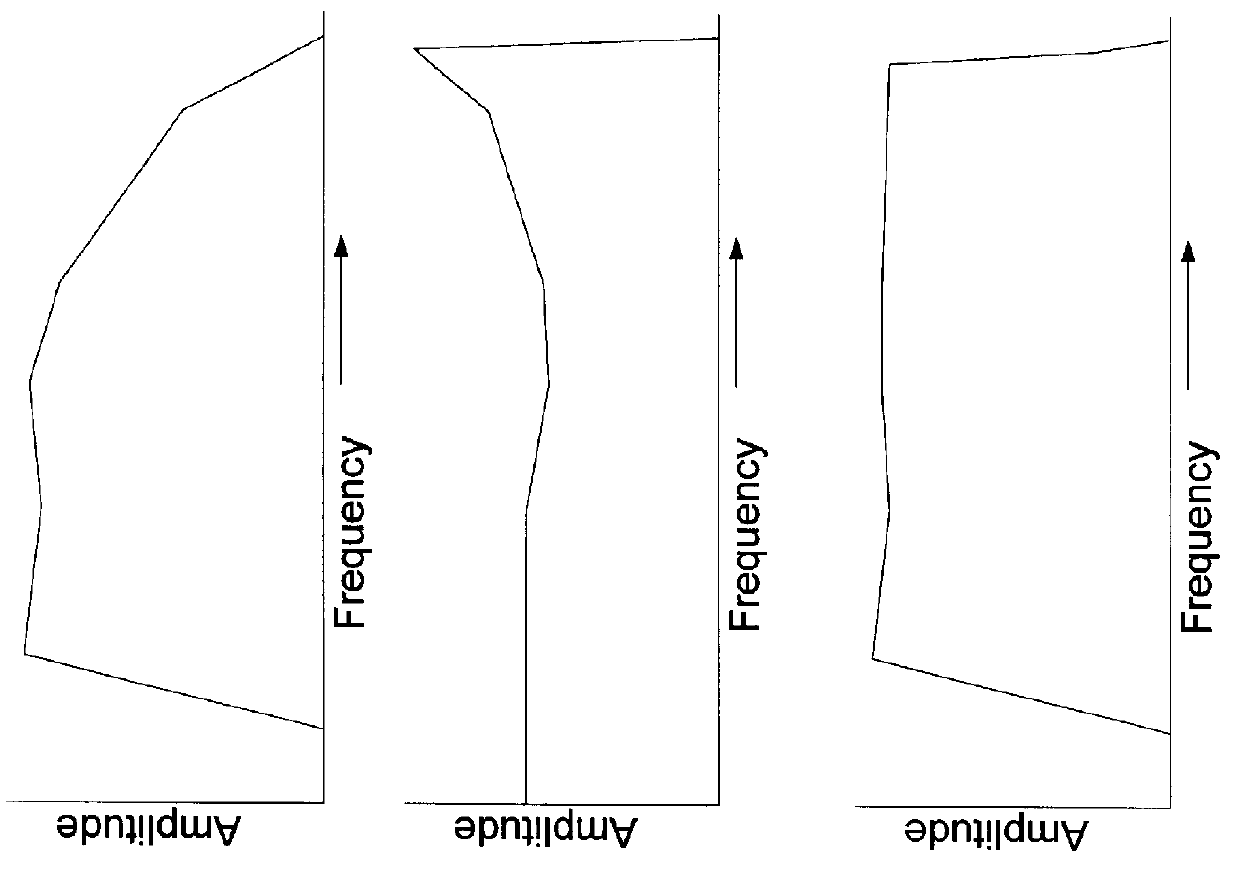

An apparatus and method for a switched capacitor architecture for multi-band Doherty power amplifiers are provided. The apparatus is for amplifying Radio Frequency (RF) signals, and the apparatus includes a multi-band Power Amplifier (PA) including a plurality of input matching circuits including switchable capacitors, and a plurality of output matching circuits including the switchable capacitors, wherein the multi-band PA is tunable to more than one RF frequency band.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com