Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2510results about "Generator stabilization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

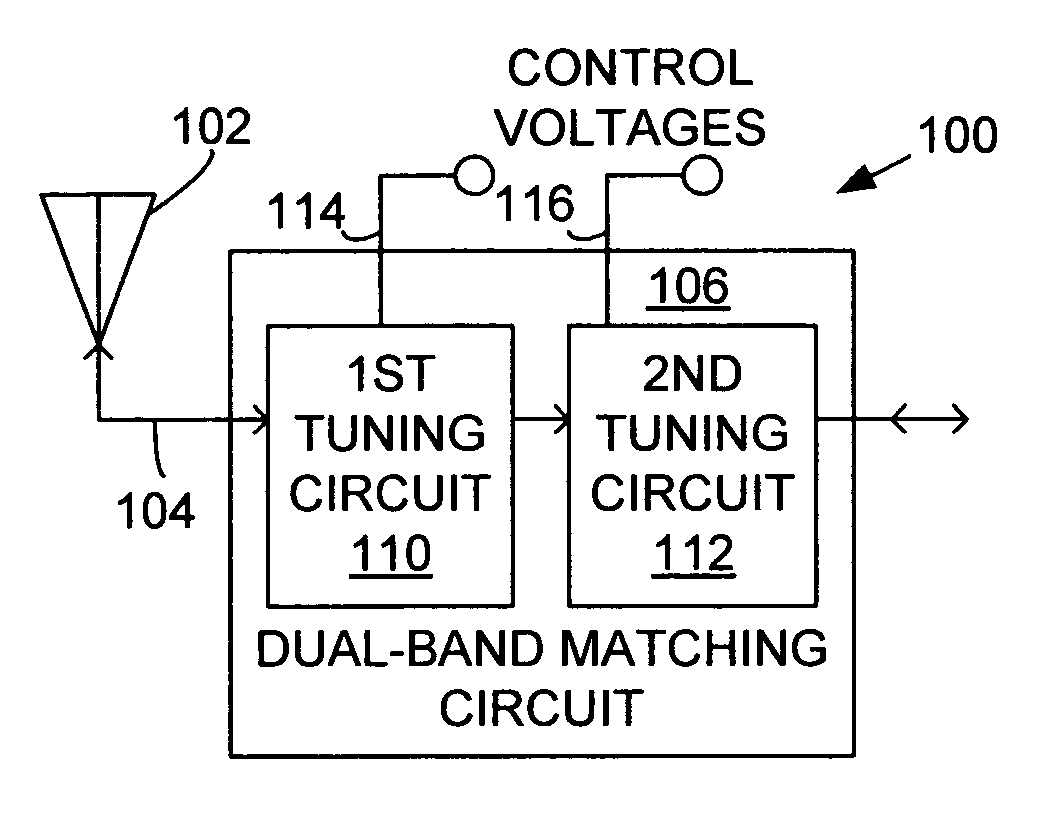

System and method for dual-band antenna matching

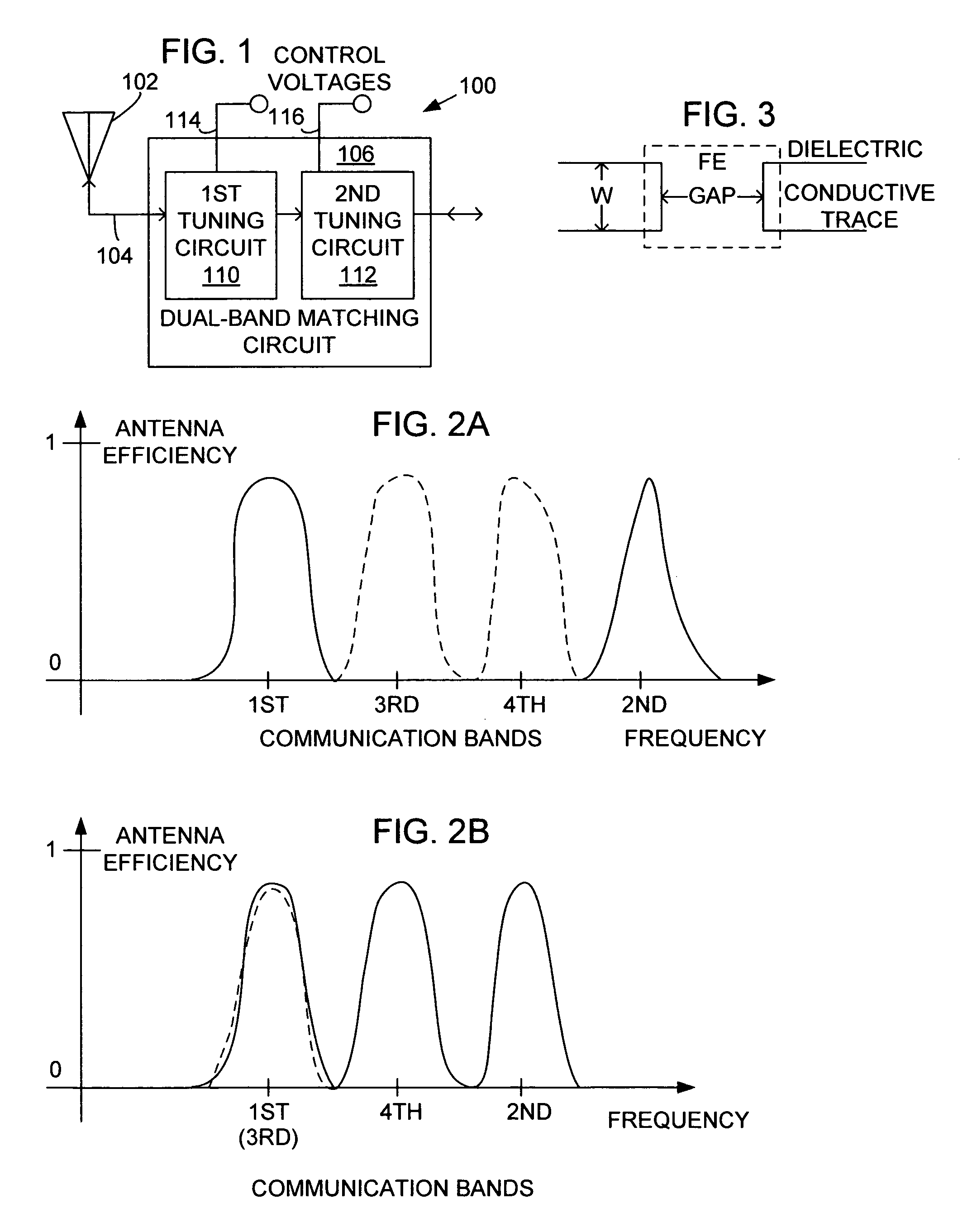

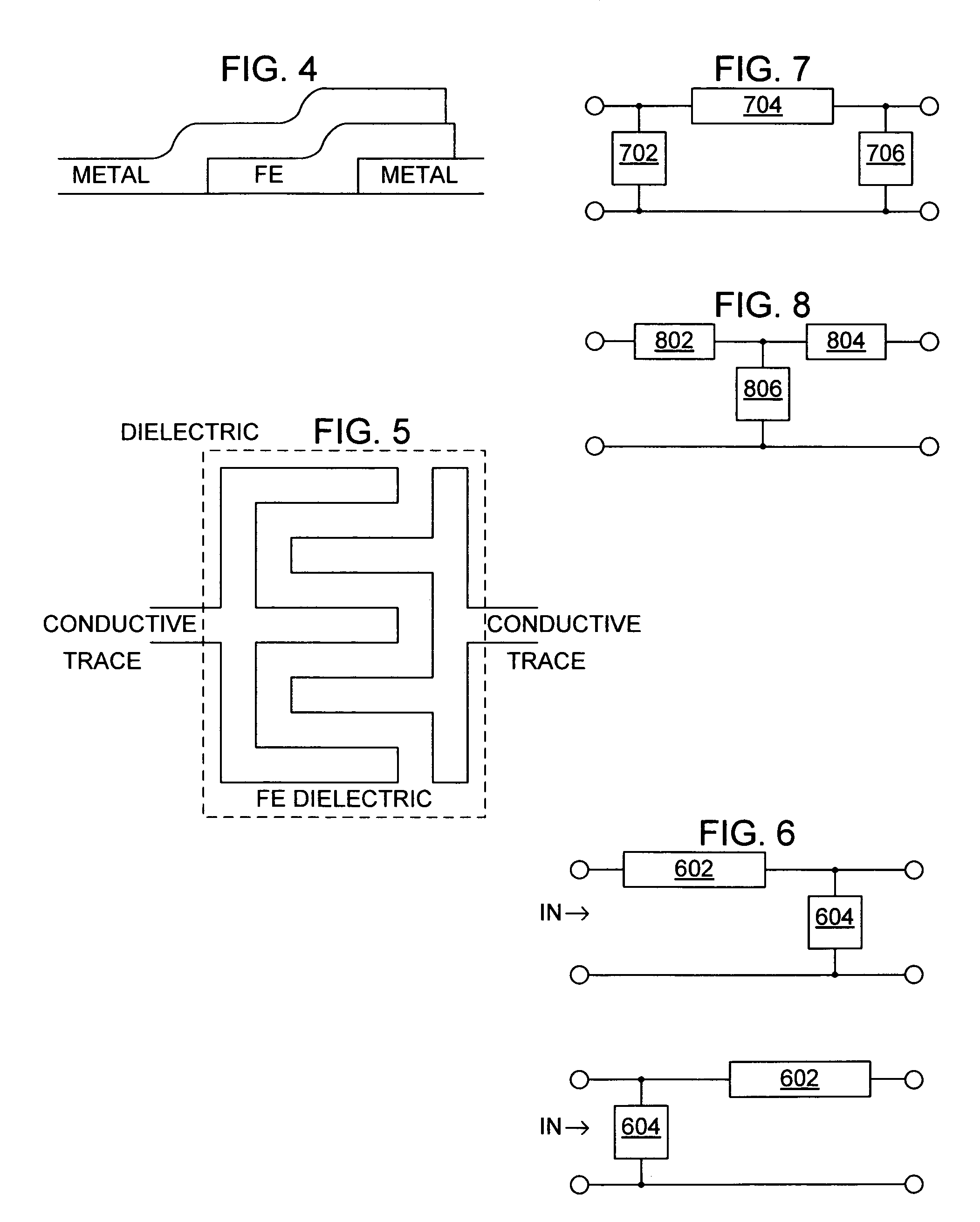

A dual-band antenna matching system and a method for dual-band impedance matching are provided. The method comprises: accepting a frequency-dependent impedance from an antenna; and, selectively supplying a conjugate impedance match for the antenna at either a first and a second communication band, or a third and a fourth communication band. More specifically, the method comprises: tuning a first tuning circuit to a first frequency; and, simultaneously tuning a second tuning circuit to a second frequency. In response, a conjugate match is supplied to the antenna in the first communication band in response to the first frequency. Simultaneously, the antenna is matched in the second communication band in response to the second frequency. When the first tuning circuit is tuned to a third frequency, and the second tuning circuit is tuned to a fourth frequency, then conjugate matches are supplied for the third and fourth communication bands, responsive to the third and fourth frequencies, respectively.

Owner:KYOCERA CORP

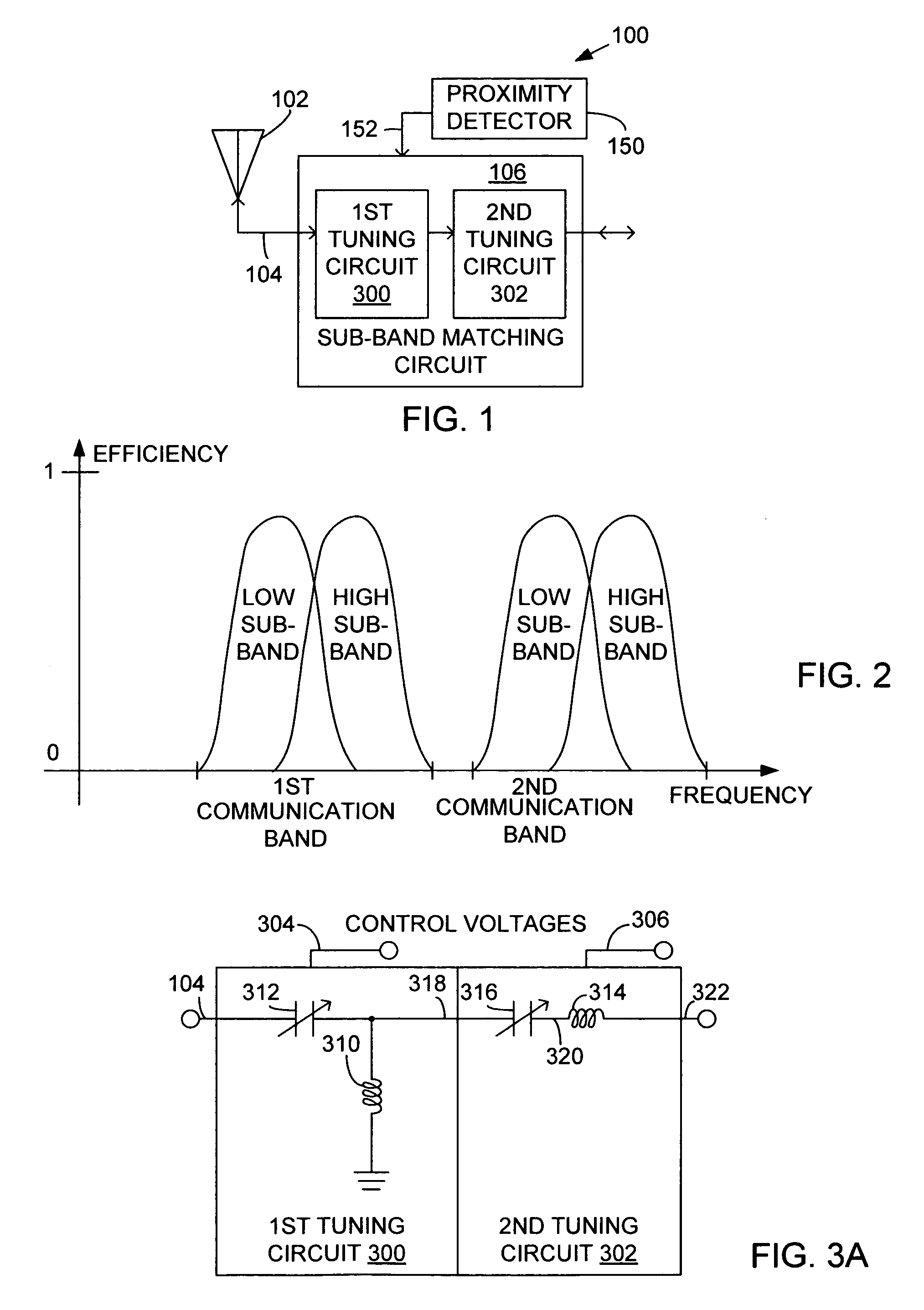

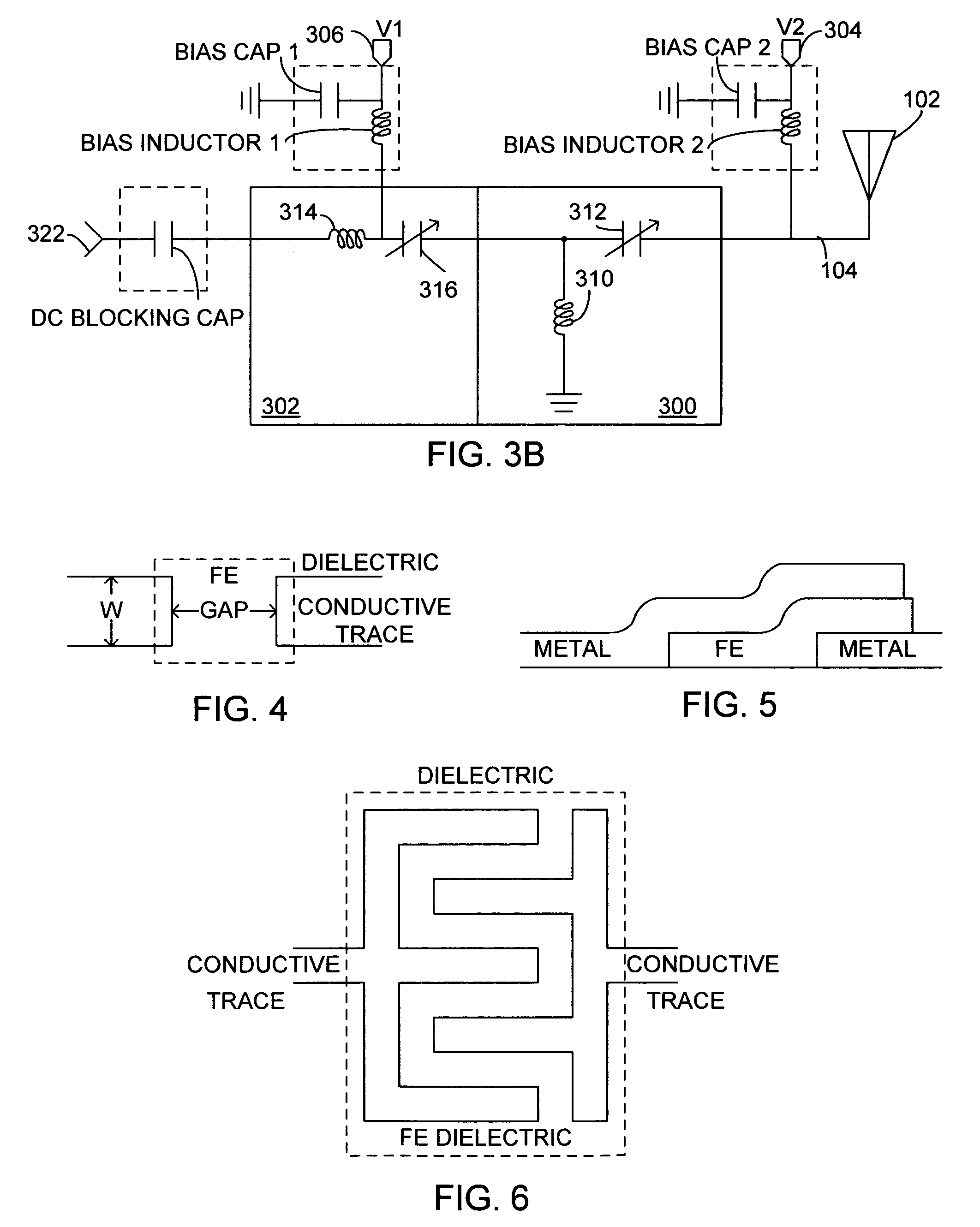

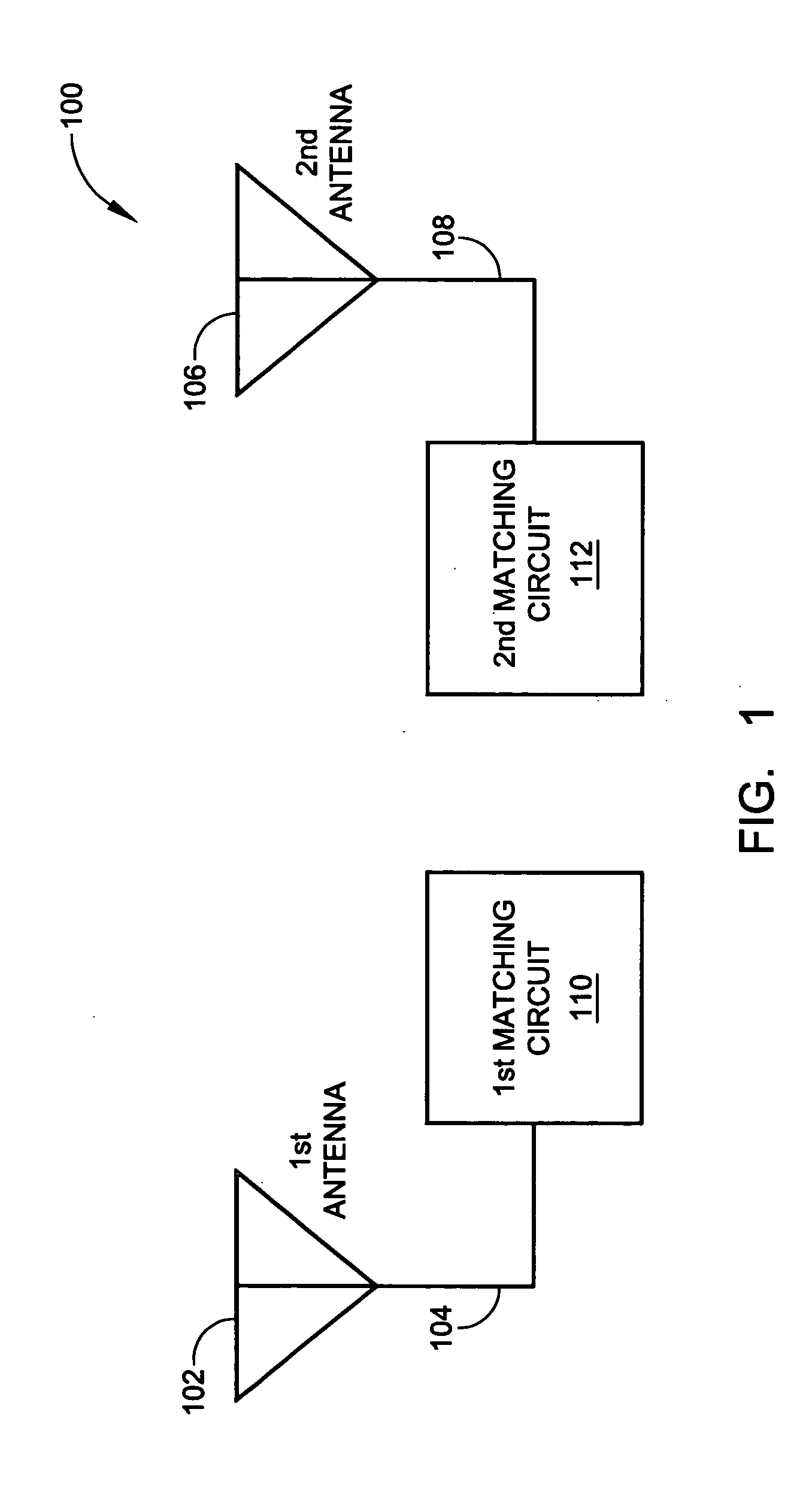

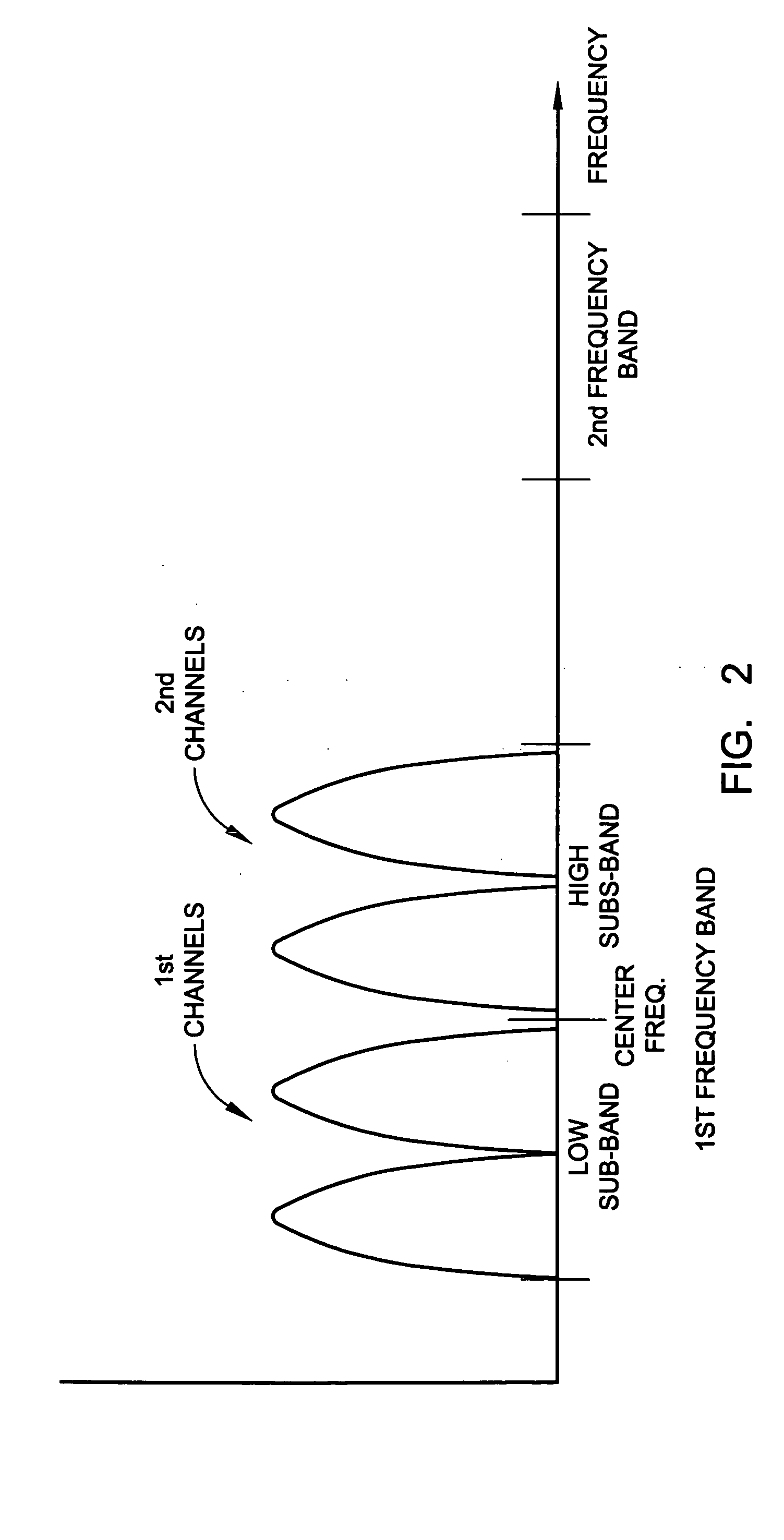

System and method for impedance matching an antenna to sub-bands in a communication band

InactiveUS7176845B2Improve efficiencyReduce noiseMultiple-port networksAntenna supports/mountingsAntenna impedanceMethod selection

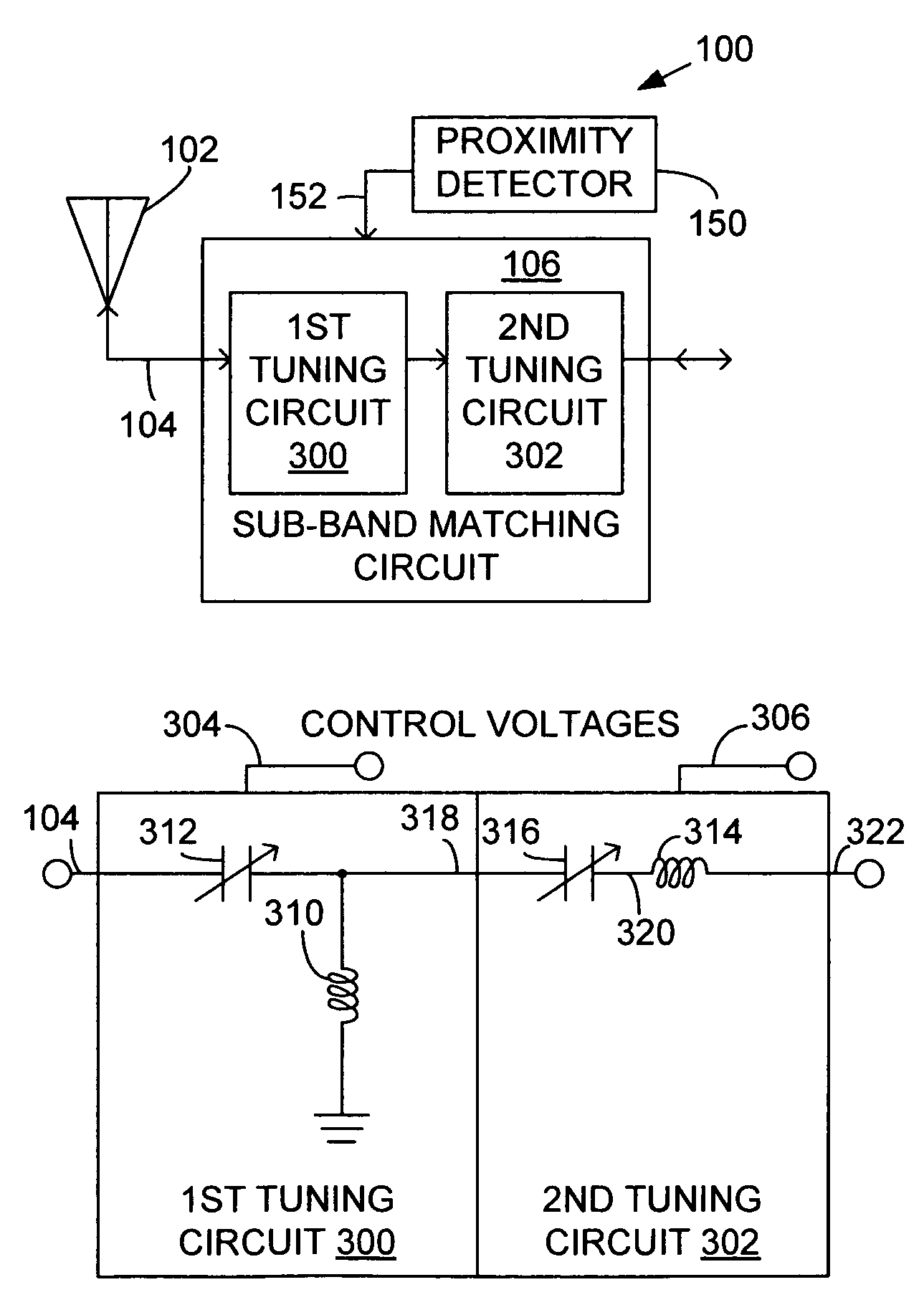

A sub-band antenna matching method and an antenna matching system for selectively matching a communication bandwidth segment impedance have been provided. The method comprises: accepting a frequency-dependent impedance from an antenna; and, selectively supplying a conjugate impedance match for the antenna at a sub-band of a first communication band. In some aspects, the method selectively supplies a conjugate impedance match for the antenna at a sub-band of a second communication band. More specifically, the method comprises: tuning a first tuning circuit to a first frequency; simultaneously tuning a second tuning circuit to a second frequency to match the antenna at a low end of the first communication band. Likewise, the first tuning circuit is tuned to a third frequency and the second tuning circuit is tuned to a fourth frequency to match the antenna at a high end of the first communication band in response to the third and fourth frequencies.

Owner:KYOCERA CORP

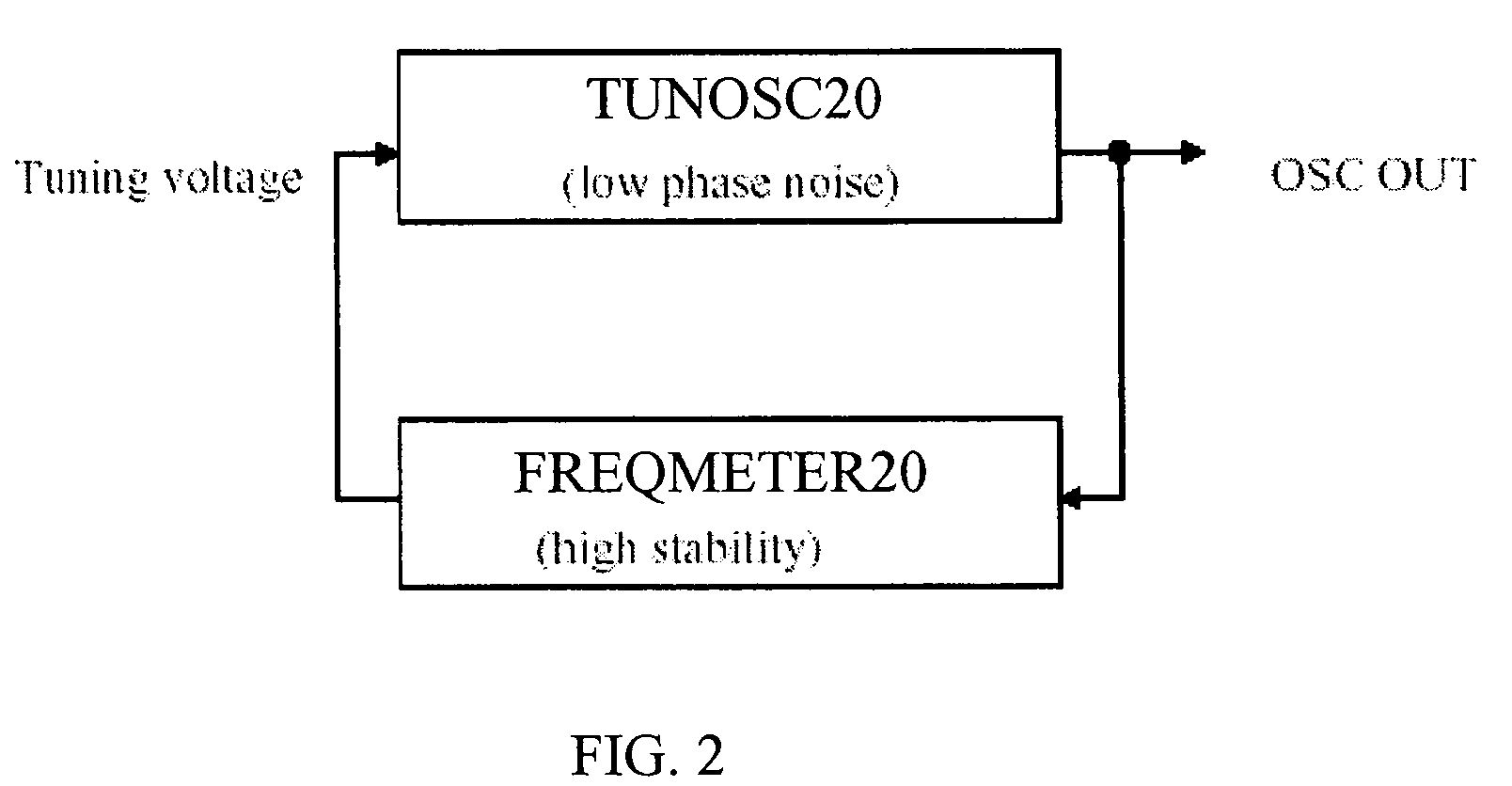

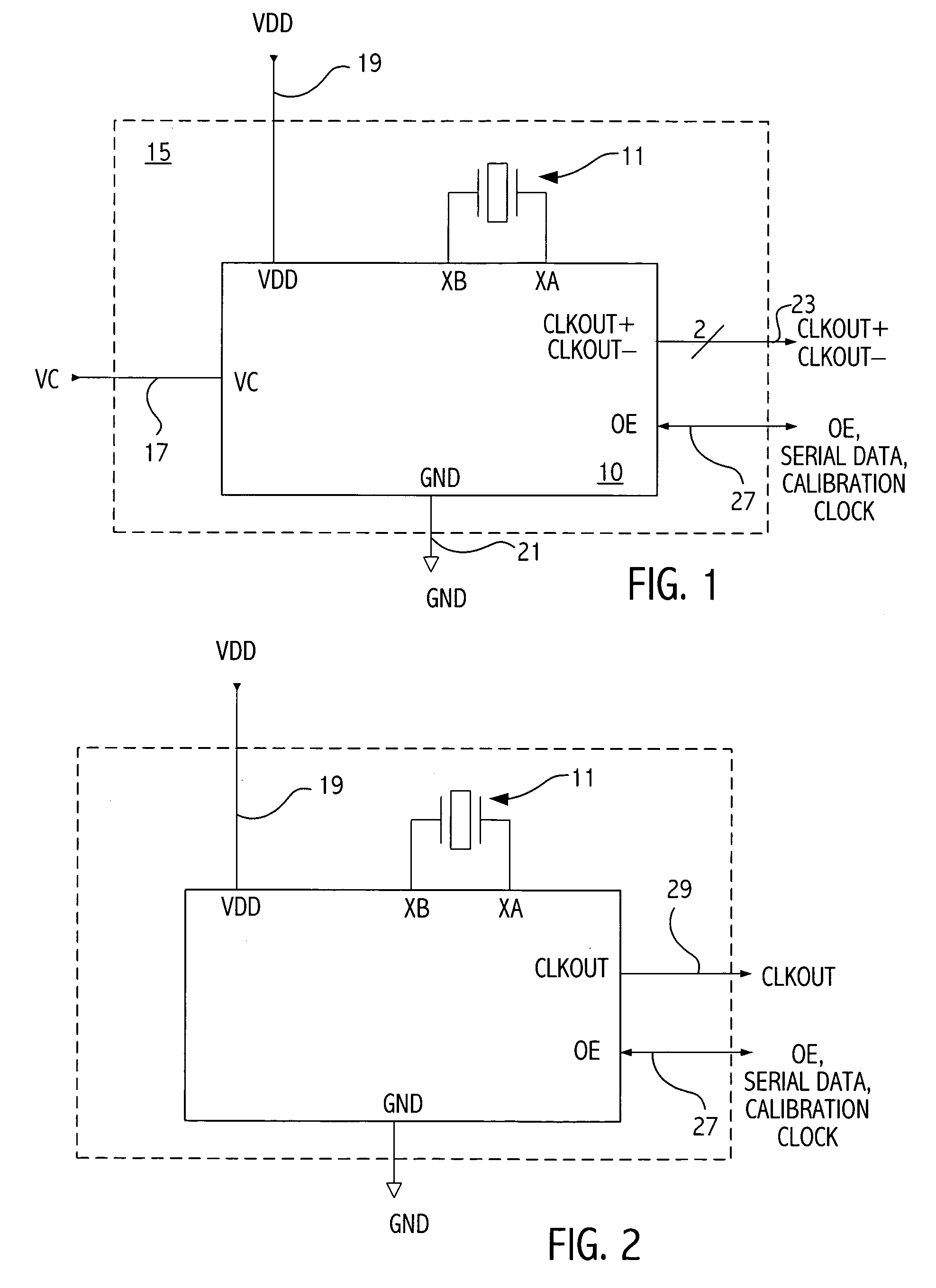

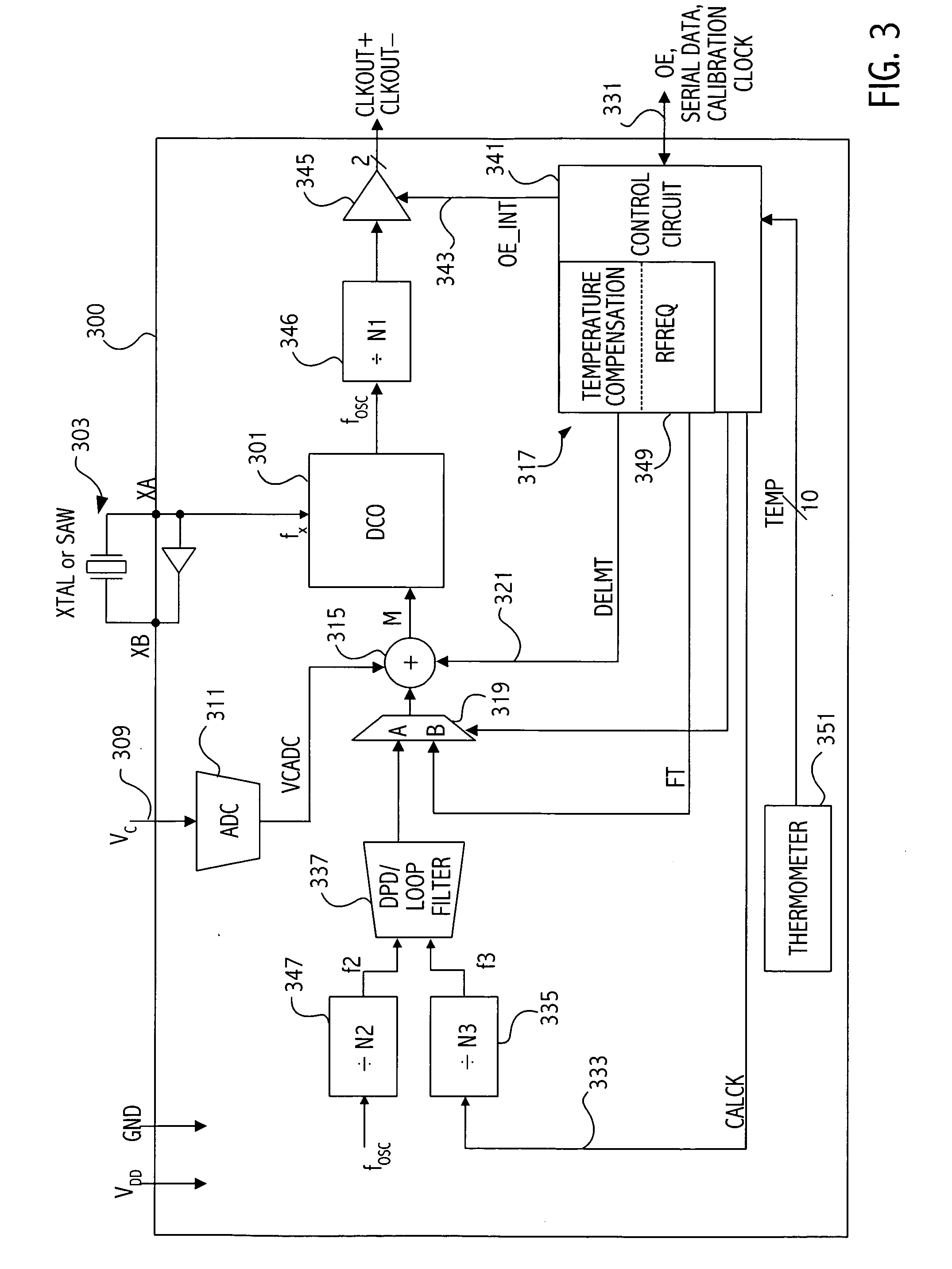

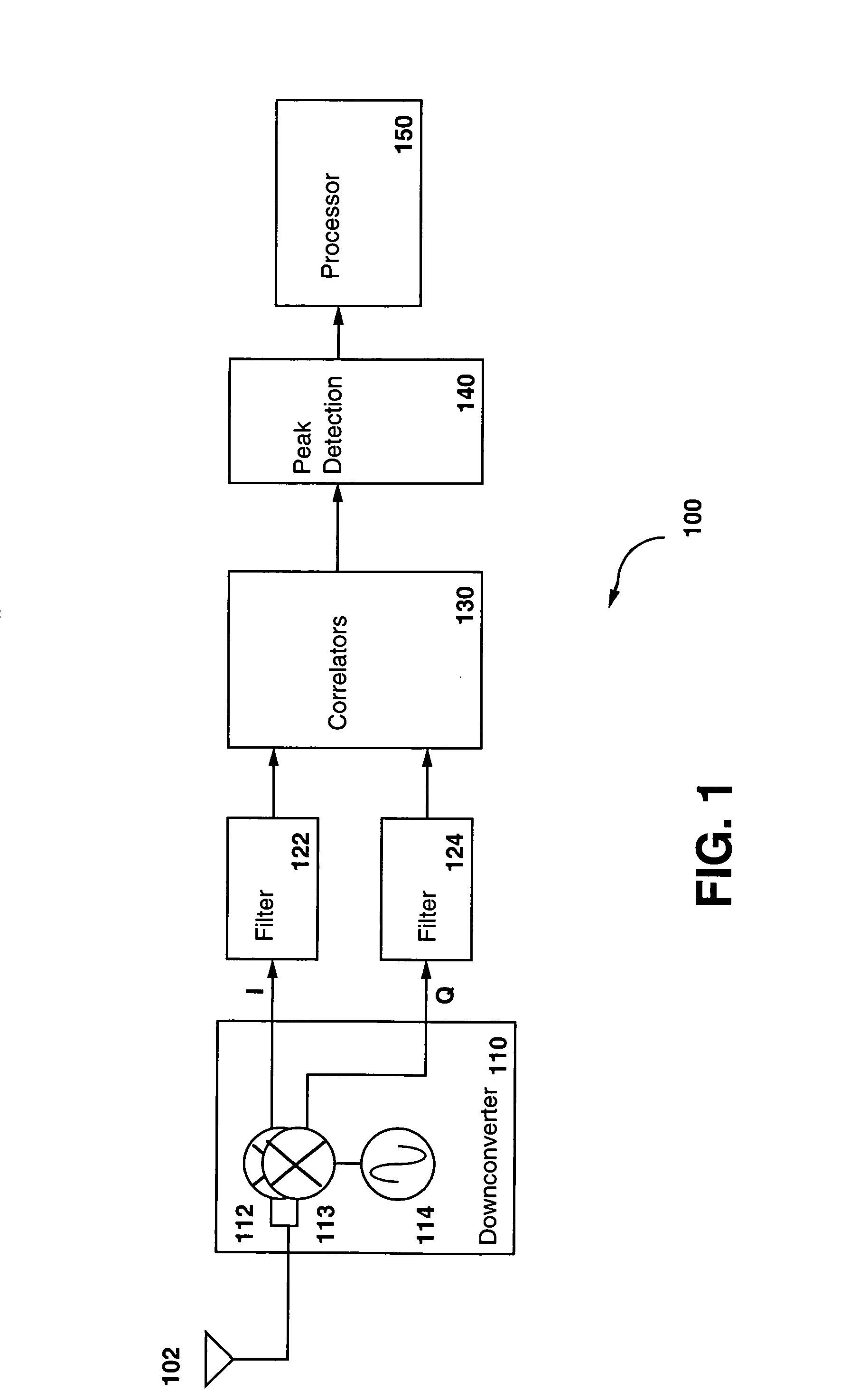

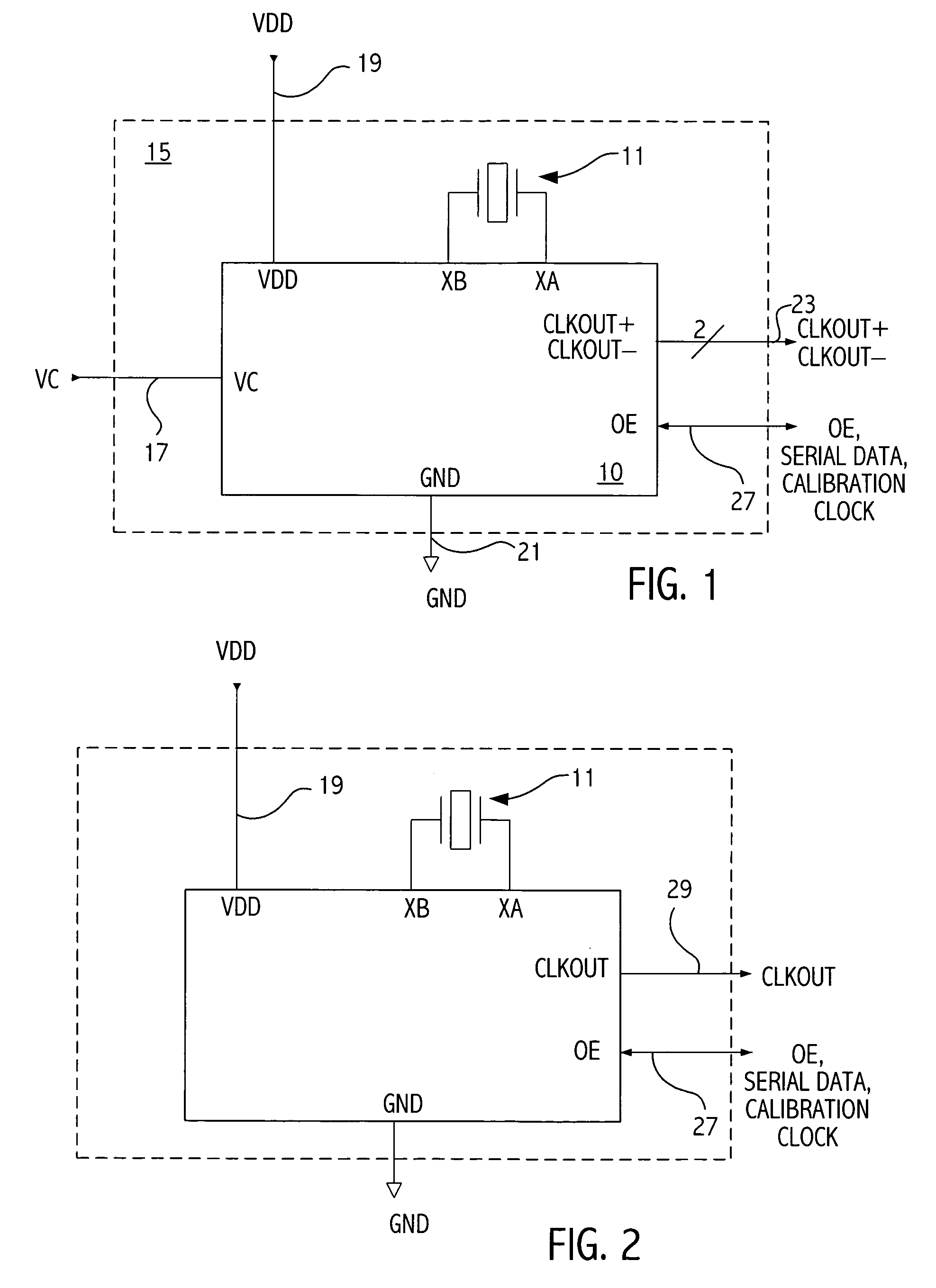

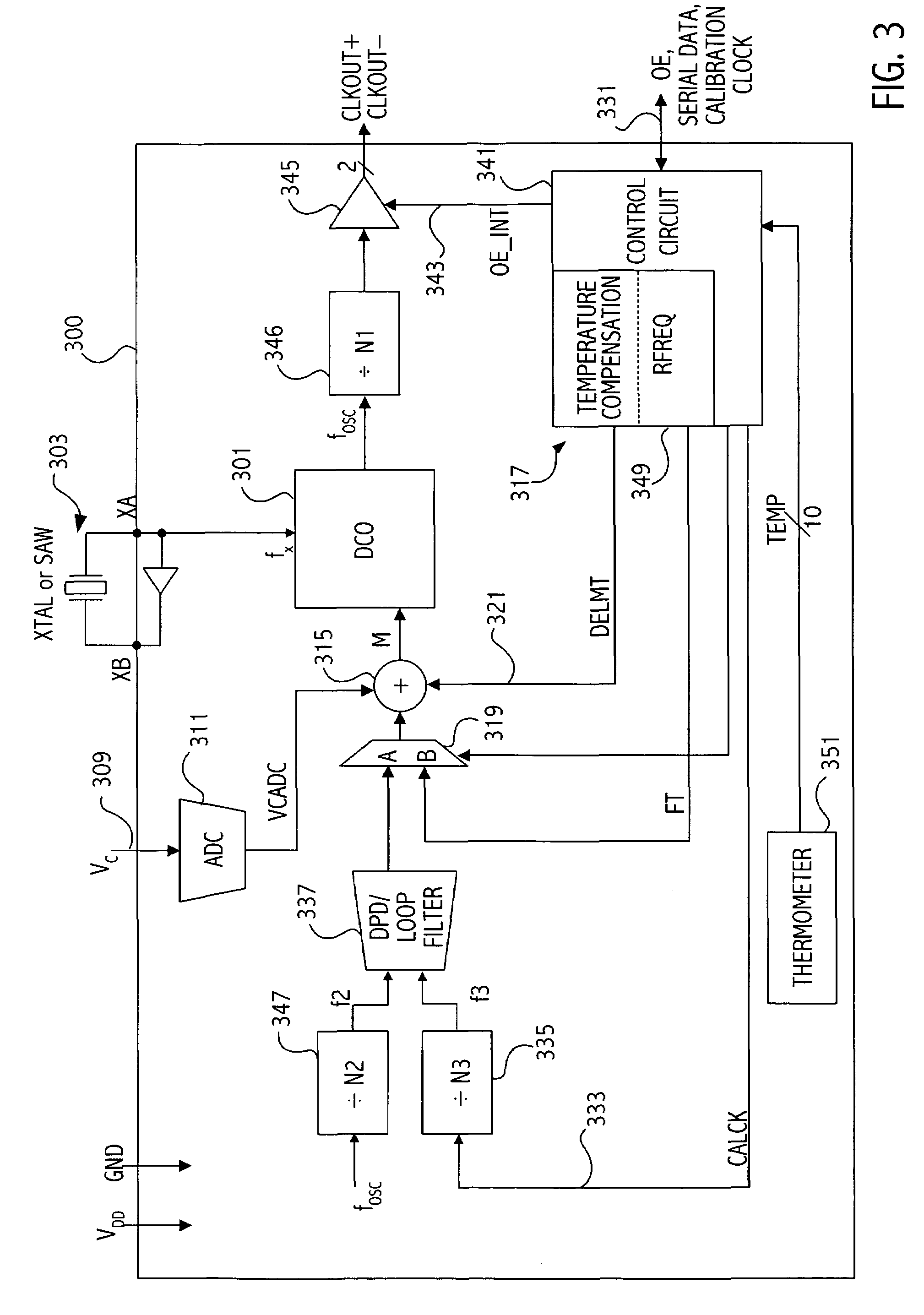

Reference oscillator frequency stabilization

ActiveUS7248128B2Improve propertiesFrequency stabilityTelevision system detailsPulse automatic controlFrequency stabilizationEngineering

Owner:NOKIA TECHNOLOGLES OY

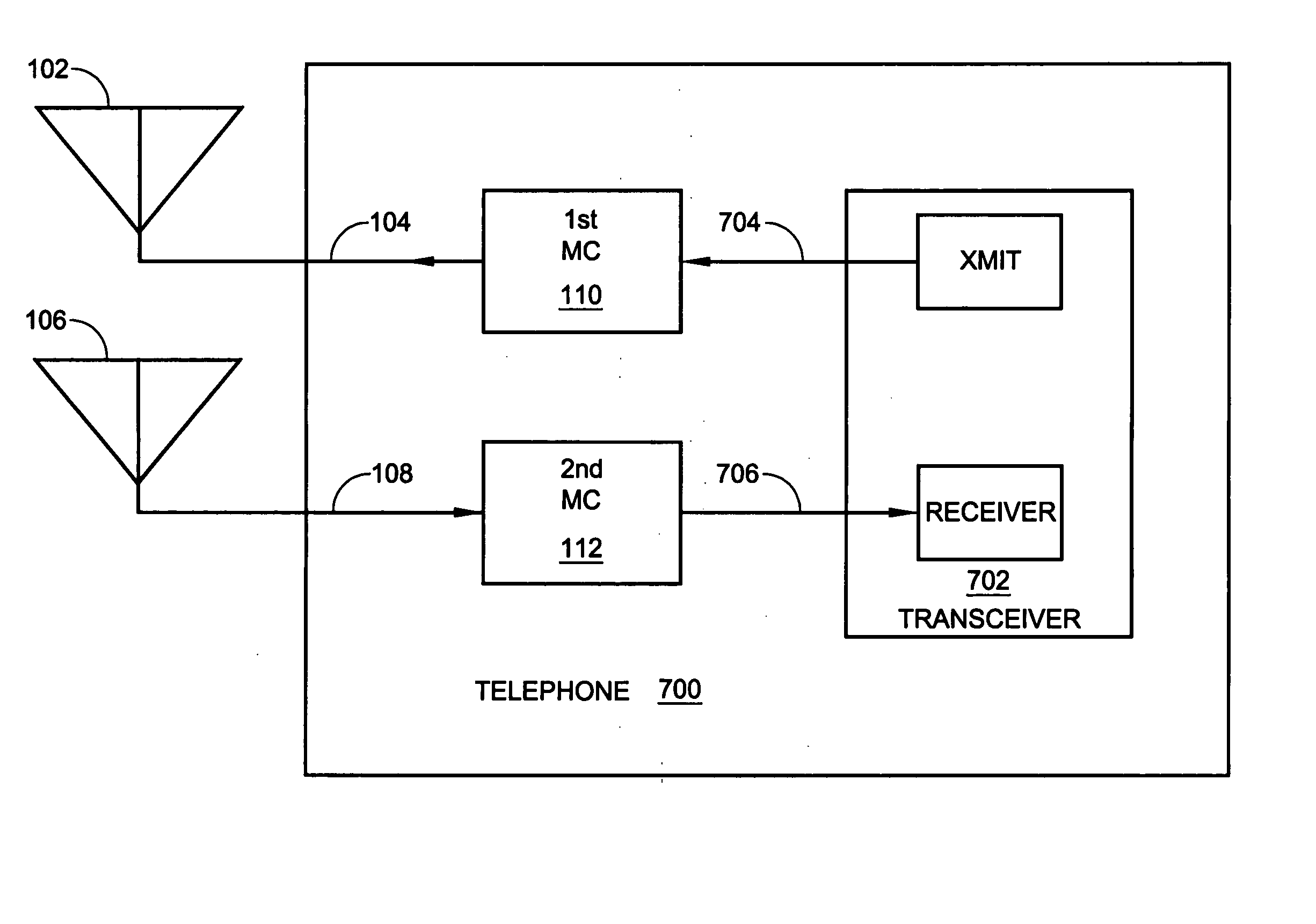

Full-duplex antenna system and method

A system and method is provided for full-duplex antenna impedance matching. The method comprises: effectively resonating a first antenna at a frequency selectable first channel in a first frequency band; generating a first antenna impedance at the first channel frequency; effectively resonating a second antenna at a frequency selectable second channel in the first frequency band; generating a second antenna impedance at the second channel frequency; supplying a first conjugate impedance match at the first channel frequency; and, supplying a second conjugate impedance match at the second channel frequency. For example, the first antenna may be used for transmission, while the second antenna is used for received communications. The antennas effectively resonant in response to: supplying frequency selectable conjugate impedance matches to the antennas; generating frequency selectable antenna impedances; and / or selecting the frequency of antenna resonance.

Owner:KYOCERA CORP

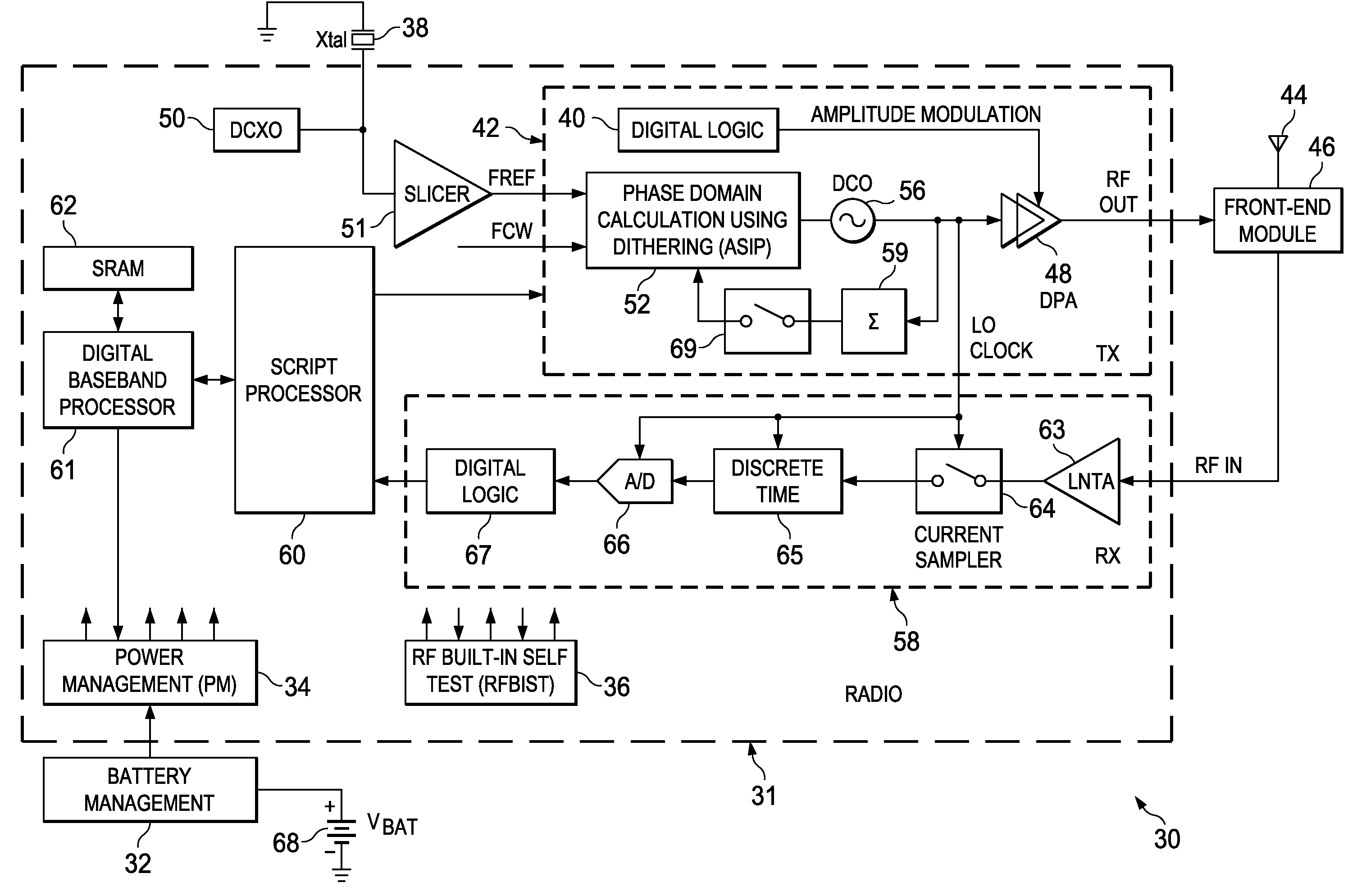

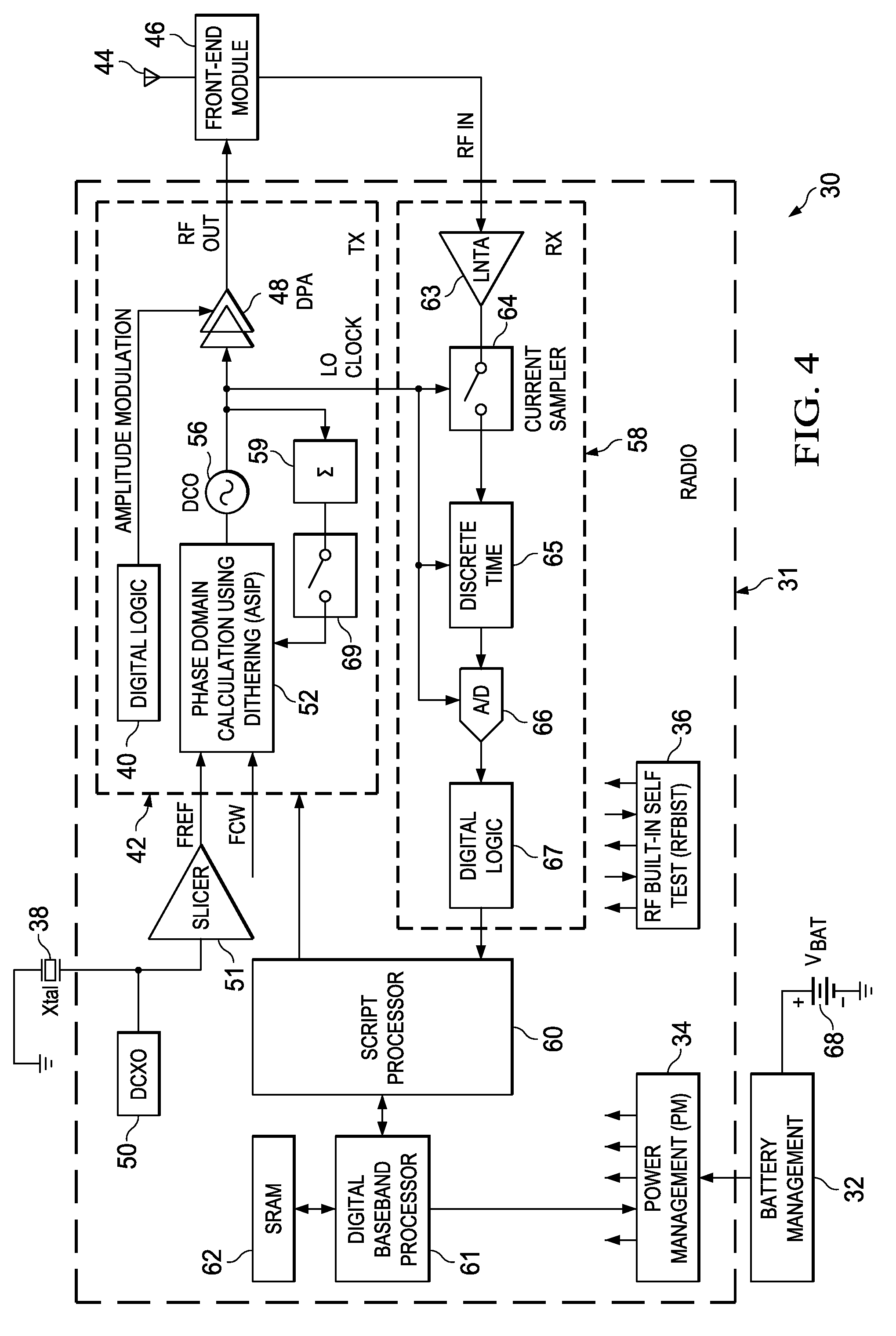

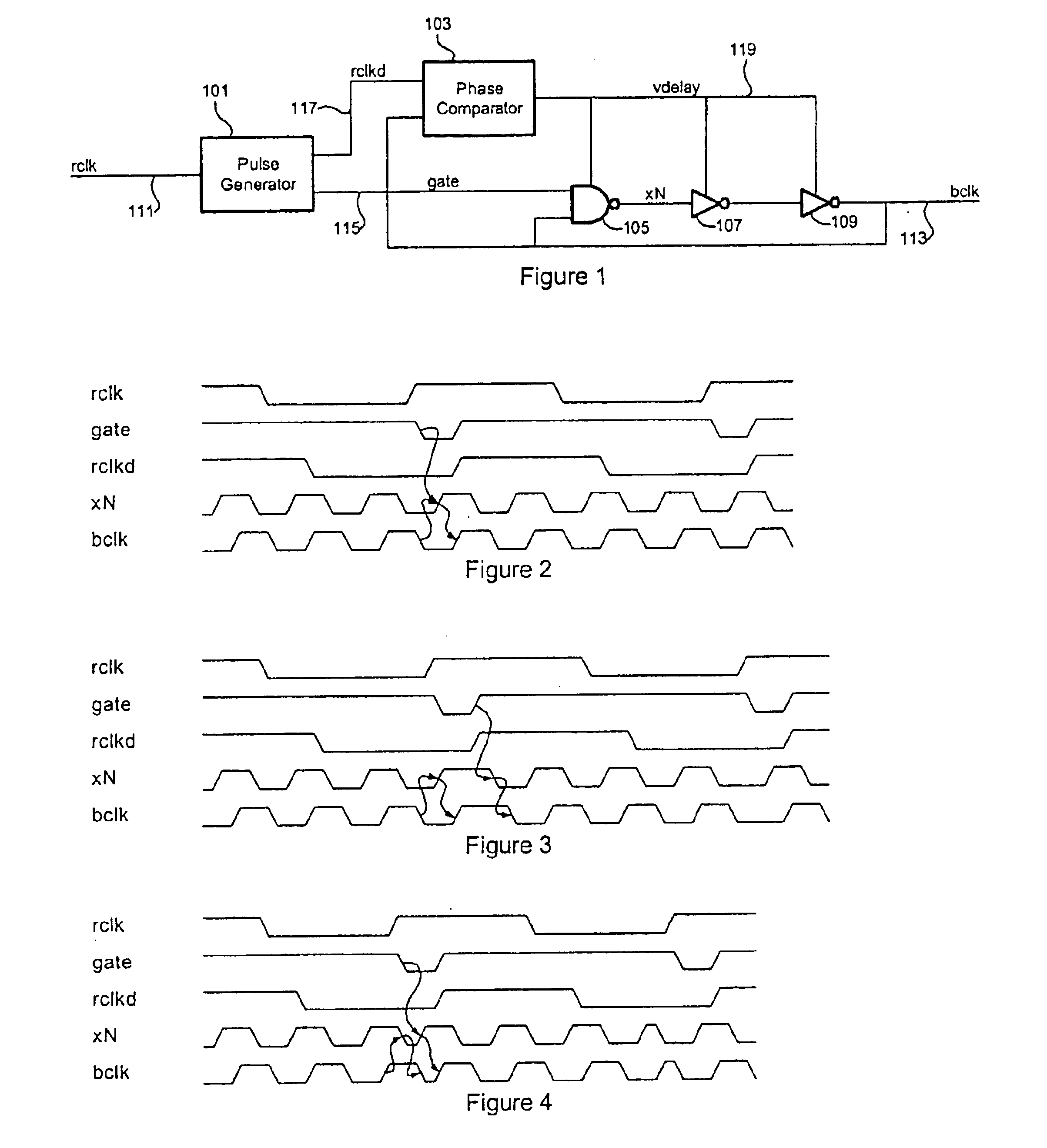

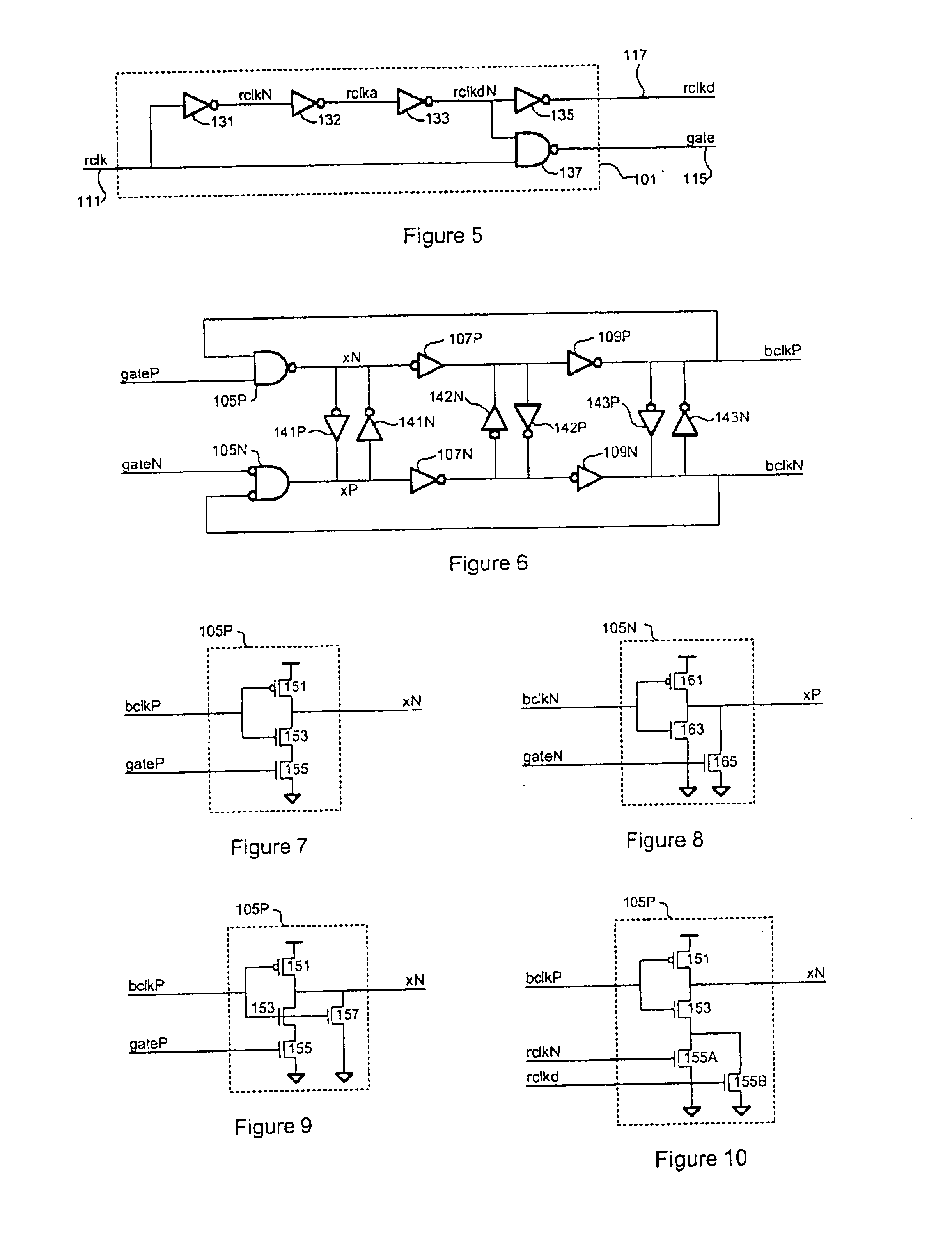

Computation spreading utilizing dithering for spur reduction in a digital phase lock loop

ActiveUS20090262877A1Easy to reconfigureReduce generationPulse automatic controlGenerator stabilizationFrequency spectrumClock rate

A novel and useful apparatus for and method of spur reduction using computation spreading with dithering in a digital phase locked loop (DPLL) architecture. A software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU is adapted to spread the computation of the atomic operations out over a PLL reference clock period wherein each computation is performed at a much higher processor clock frequency than the PLL reference clock rate. This significantly reduces the per cycle current transient generated by the computations. The frequency content of the current transients is at the higher processor clock frequency which results in a significant reduction in spurs within sensitive portions of the output spectrum. Further reduction in spurs is achieved by dithering the duration of the software loop of atomic operations and / or by randomly shuffling one or more non-data dependent instructions within each iteration of the software loop.

Owner:TEXAS INSTR INC

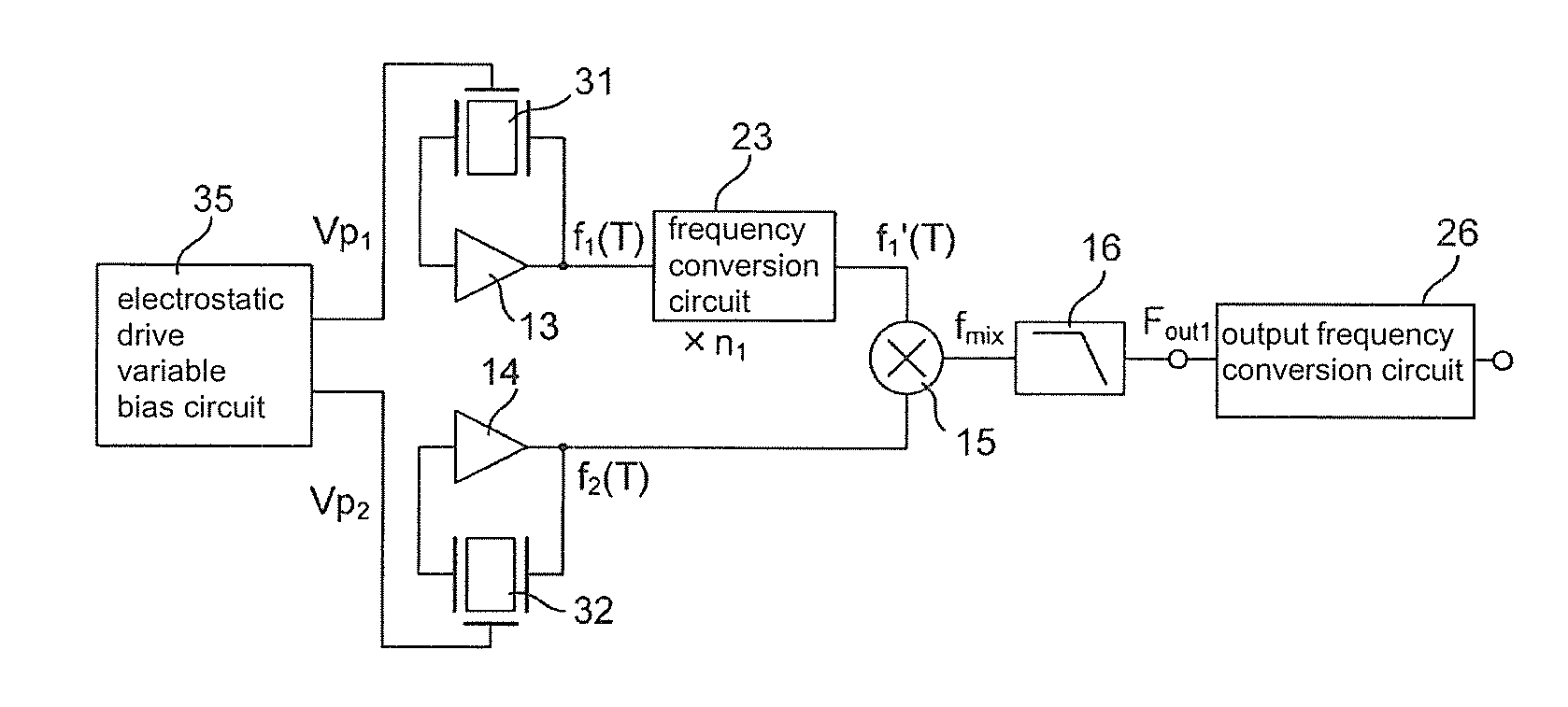

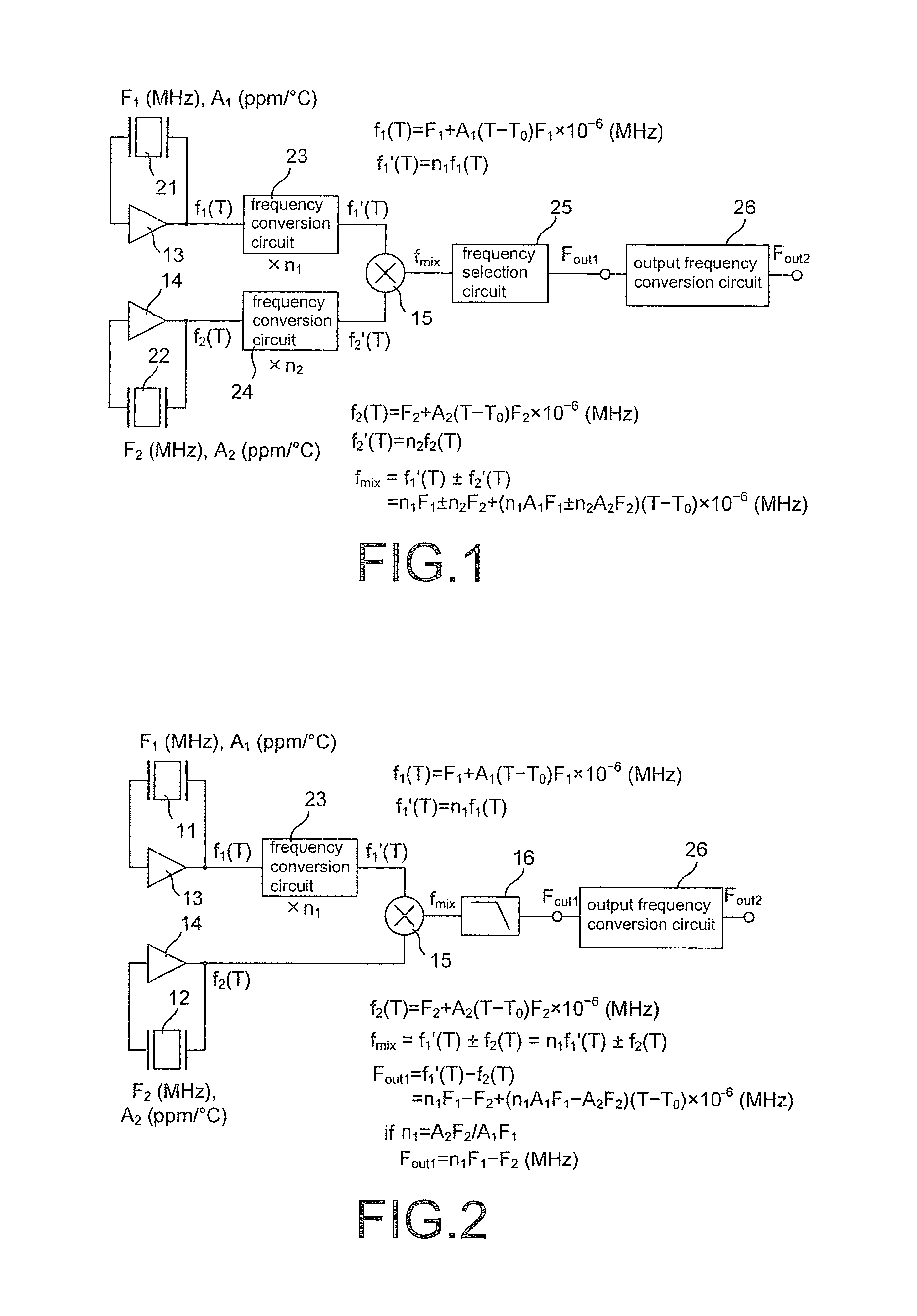

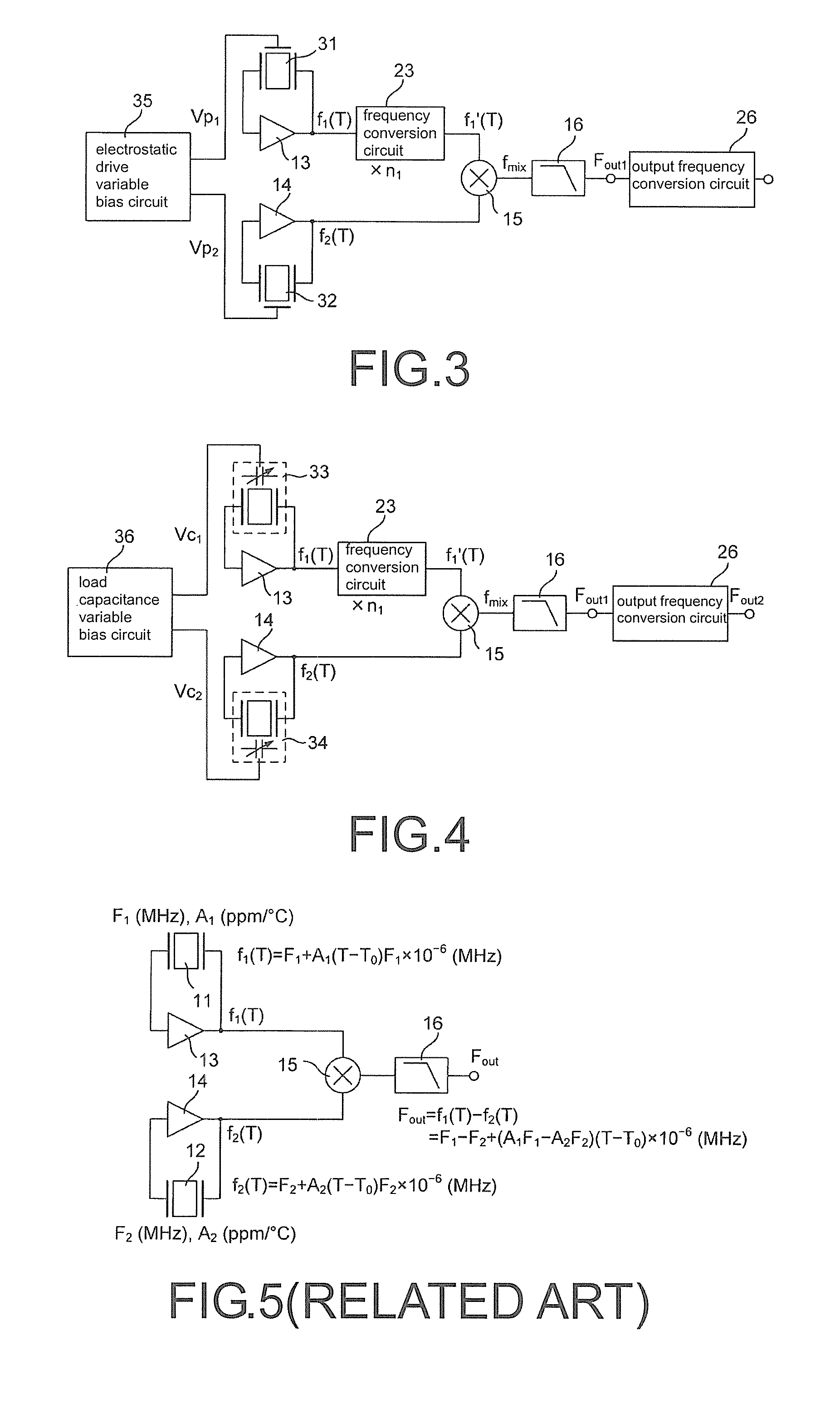

Temperature compensation type oscillator

An oscillator includes a first crystal resonator, a second crystal resonator, a first amplifier circuit for oscillation, a second amplifier circuit for oscillation, a mixer circuit, a frequency selection circuit, and a first frequency conversion circuit. Assuming that resonance frequencies of the first and the second crystal resonators at a reference temperature are respectively F1 and F2, and temperature coefficients expressed as a rate of change corresponding to temperatures of the resonance frequencies of the first and the second crystal resonators are respectively A1 and A2, the relationship of F2 / F1≠|A1 / A2| is satisfied. A signal with a temperature compensated frequency is obtained from the frequency selection circuit.

Owner:NIHON DEMPA KOGYO CO LTD

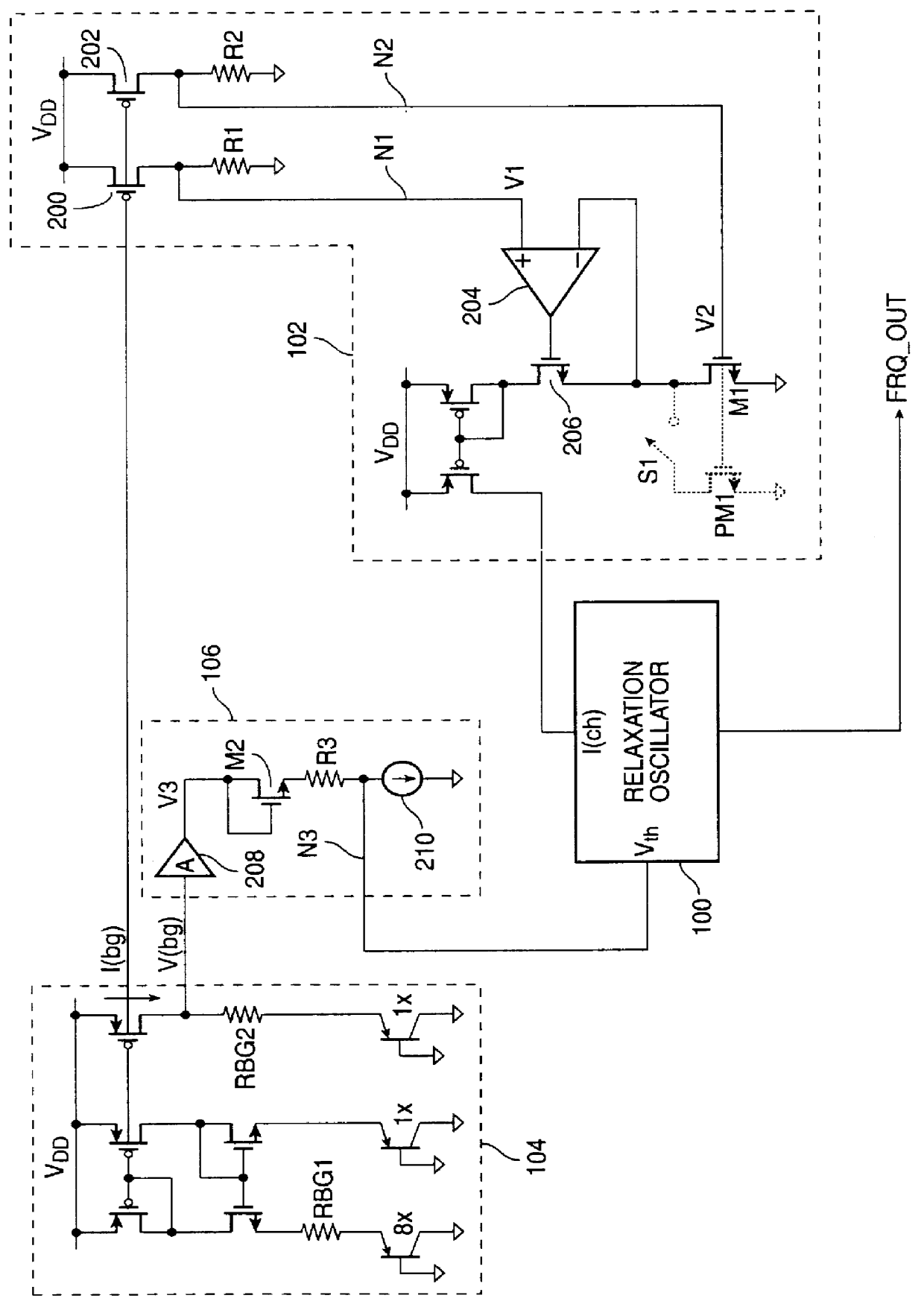

Programmable highly temperature and supply independent oscillator

InactiveUS6157270AStable and accurate reference frequencyPulse generation by bipolar transistorsGenerator stabilizationEngineeringSemiconductor

An oscillator circuit generates an output frequency that is substantially independent of power supply and temperature variations. The oscillator circuit can be implemented using conventional complementary metal-oxide-semiconductor technology. The oscillator circuit is suitable for use as an internal oscillator for generating a stable reference frequency in telecommunication receiver modules.

Owner:EXAR CORP

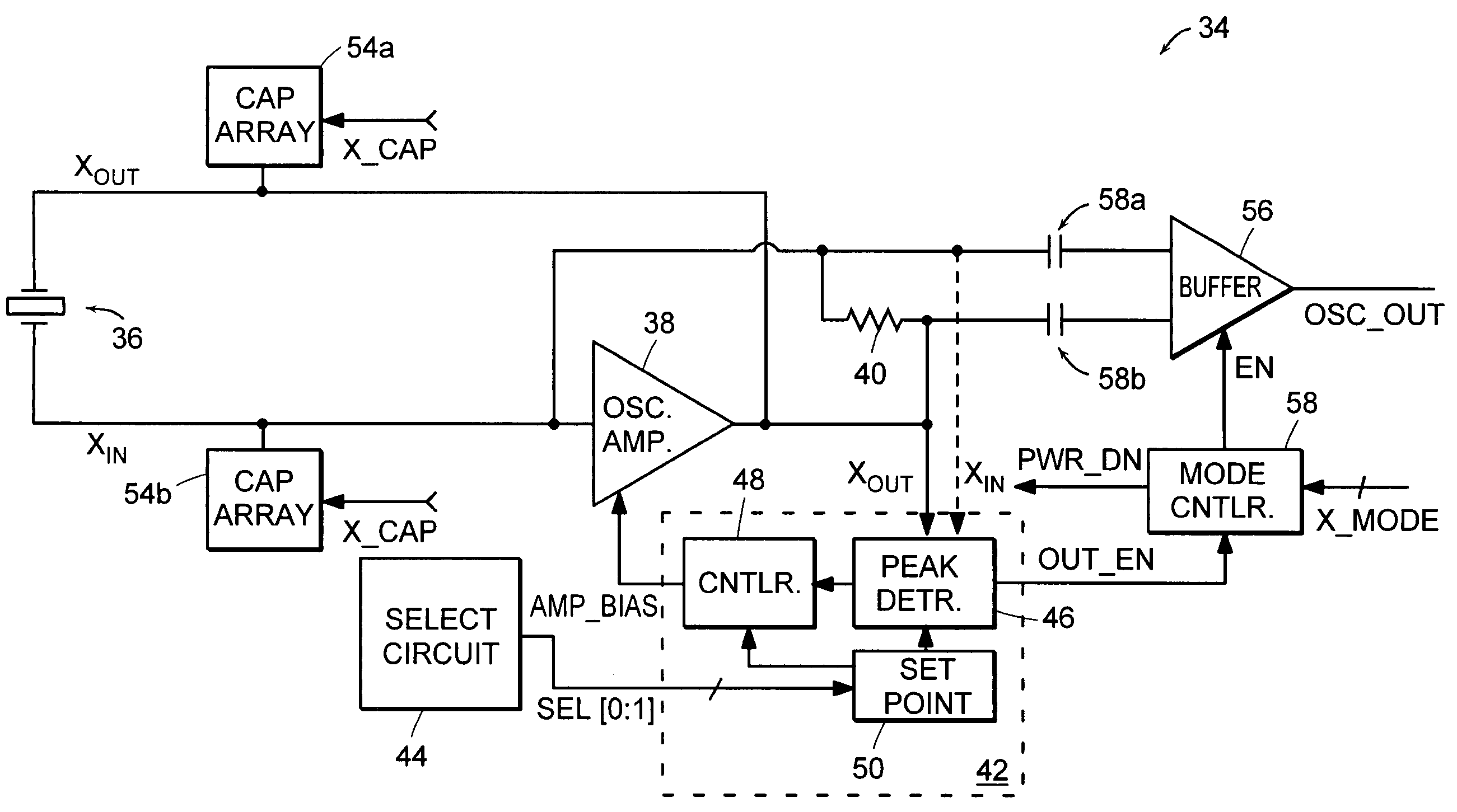

Regulated, symmetrical crystal oscillator circuit and method

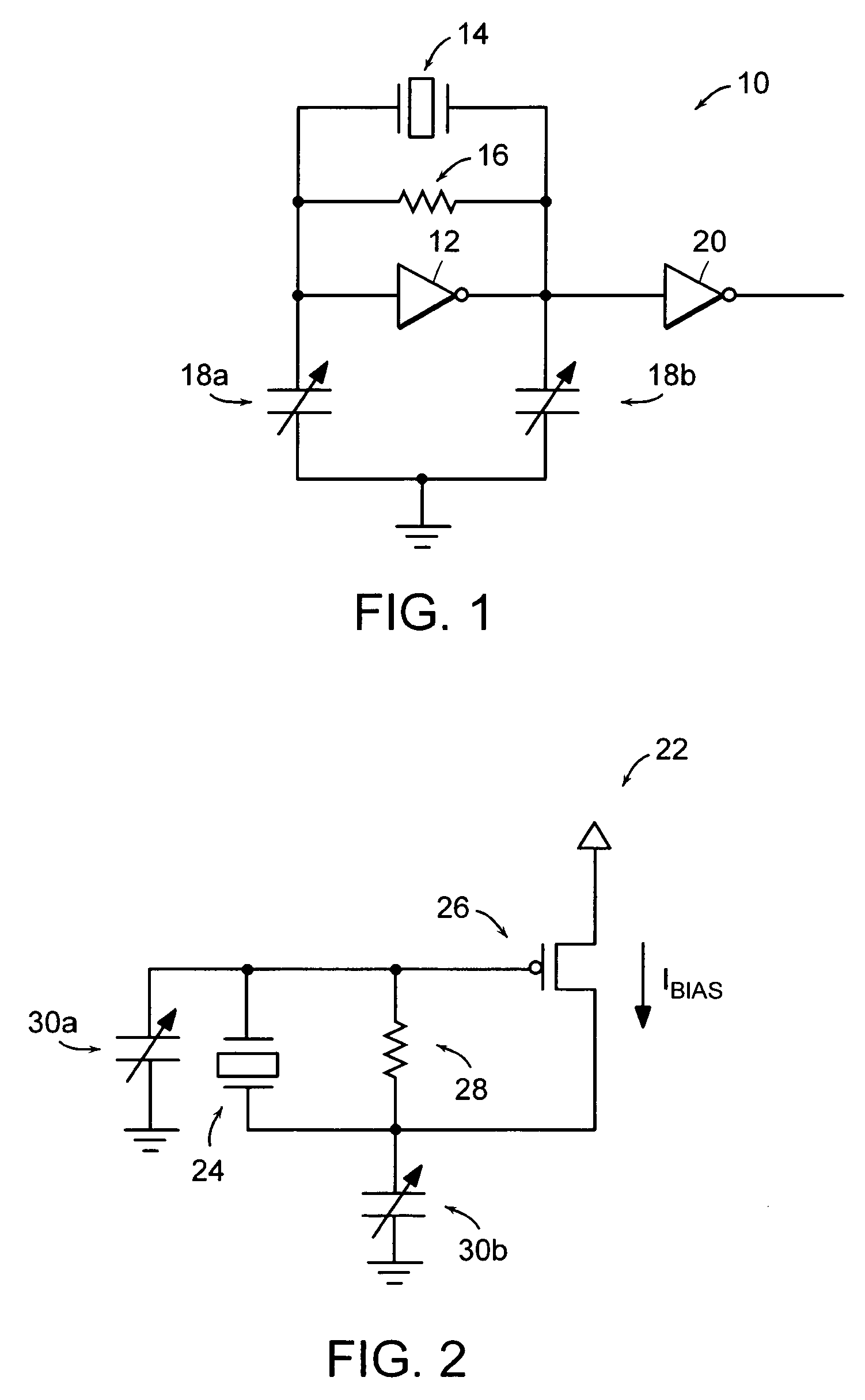

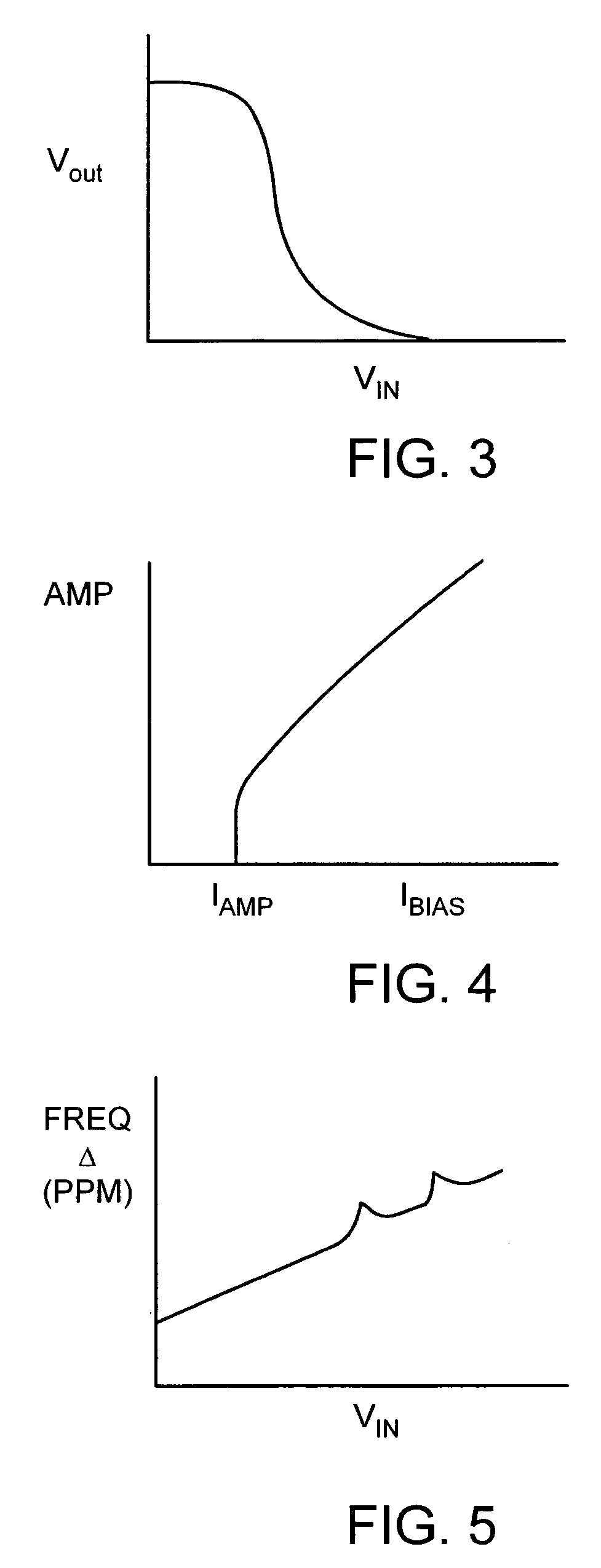

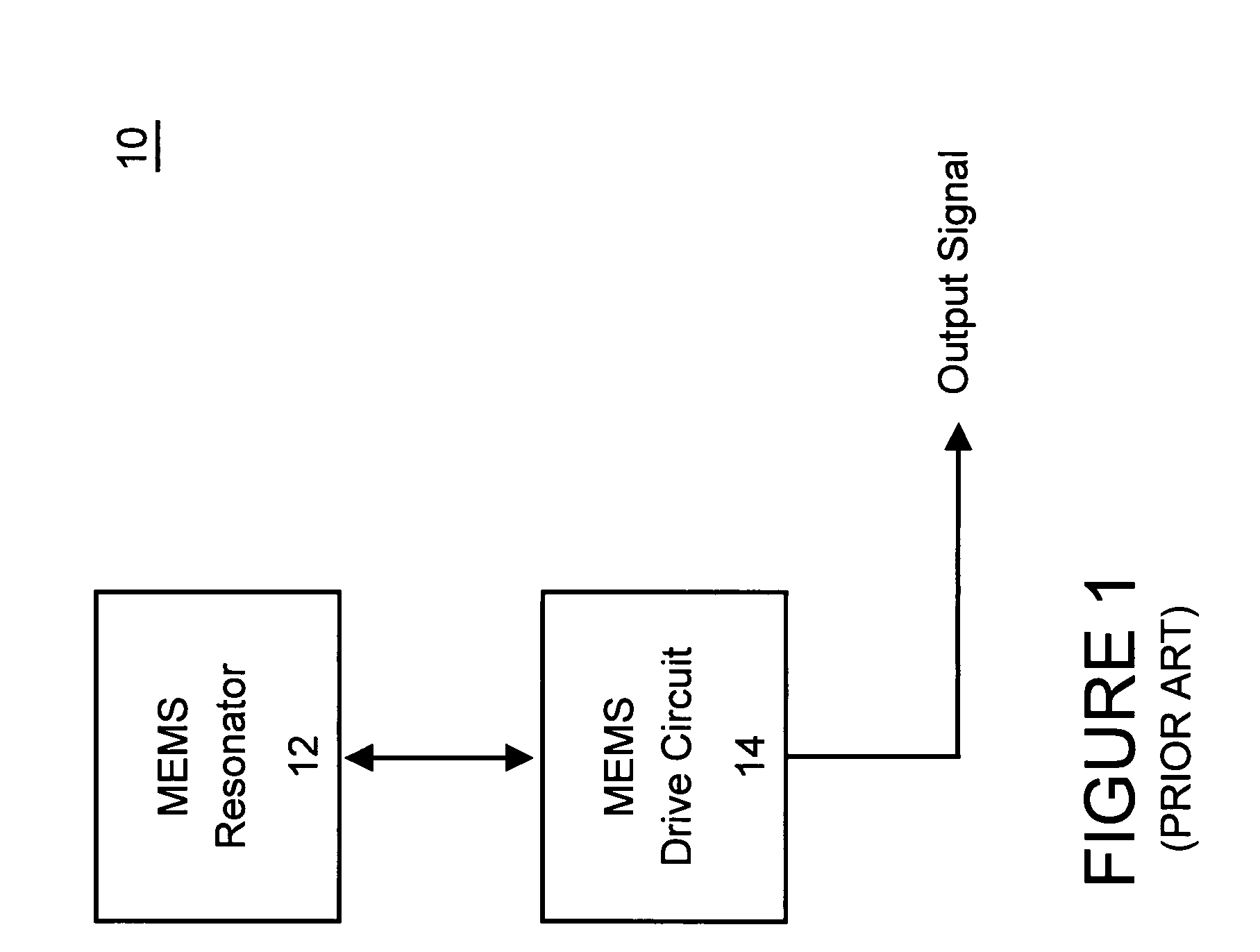

ActiveUS7123113B1Reduce stimulationMinimizing stimulationPulse automatic controlGenerator stabilizationAudio power amplifierPeak value

An oscillator circuit is provided that is preferably a crystal oscillator, where voltage placed across the crystal is regulated. The regulated voltage or amplitude of the cyclical signal across the crystal is monitored and maintained through a regulation circuit that measures a peak voltage across the crystal. Once the peak voltage exceeds a predetermined setpoint value, then a controller within the regulation circuit will reduce a biasing current through an amplifying transistor within the amplifier coupled across the crystal input and output nodes. By regulating the biasing current, gain from the amplifier is also regulated so that unwanted non-linearities and harmonic distortion is not induced within the crystal to cause frequency distortion and unwanted modes of oscillation within the crystal. The amplifier is preferably symmetrical in that the amplifier sources and sinks equal current to reduce unwanted peaks at the negative or positive half cycles of the sinusoidal signal.

Owner:MONTEREY RES LLC

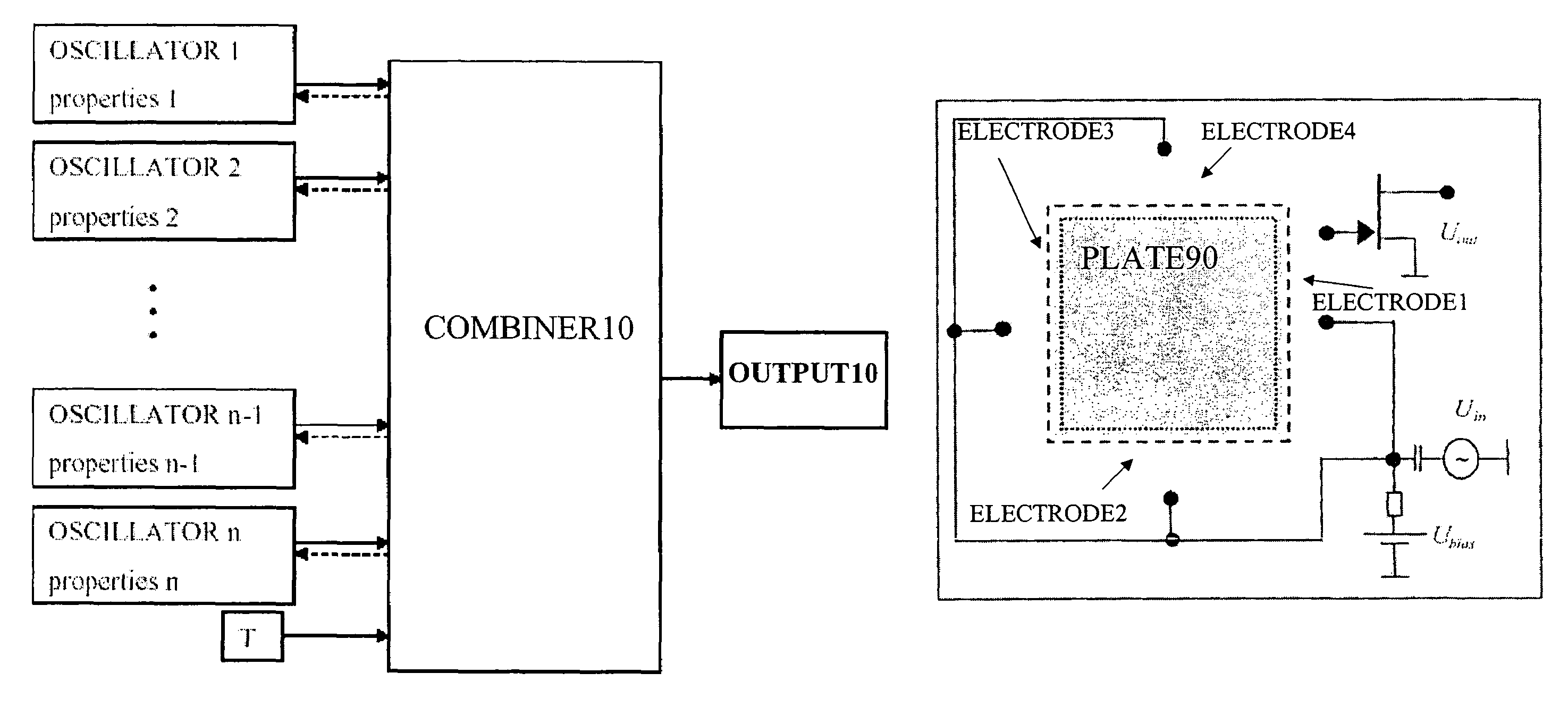

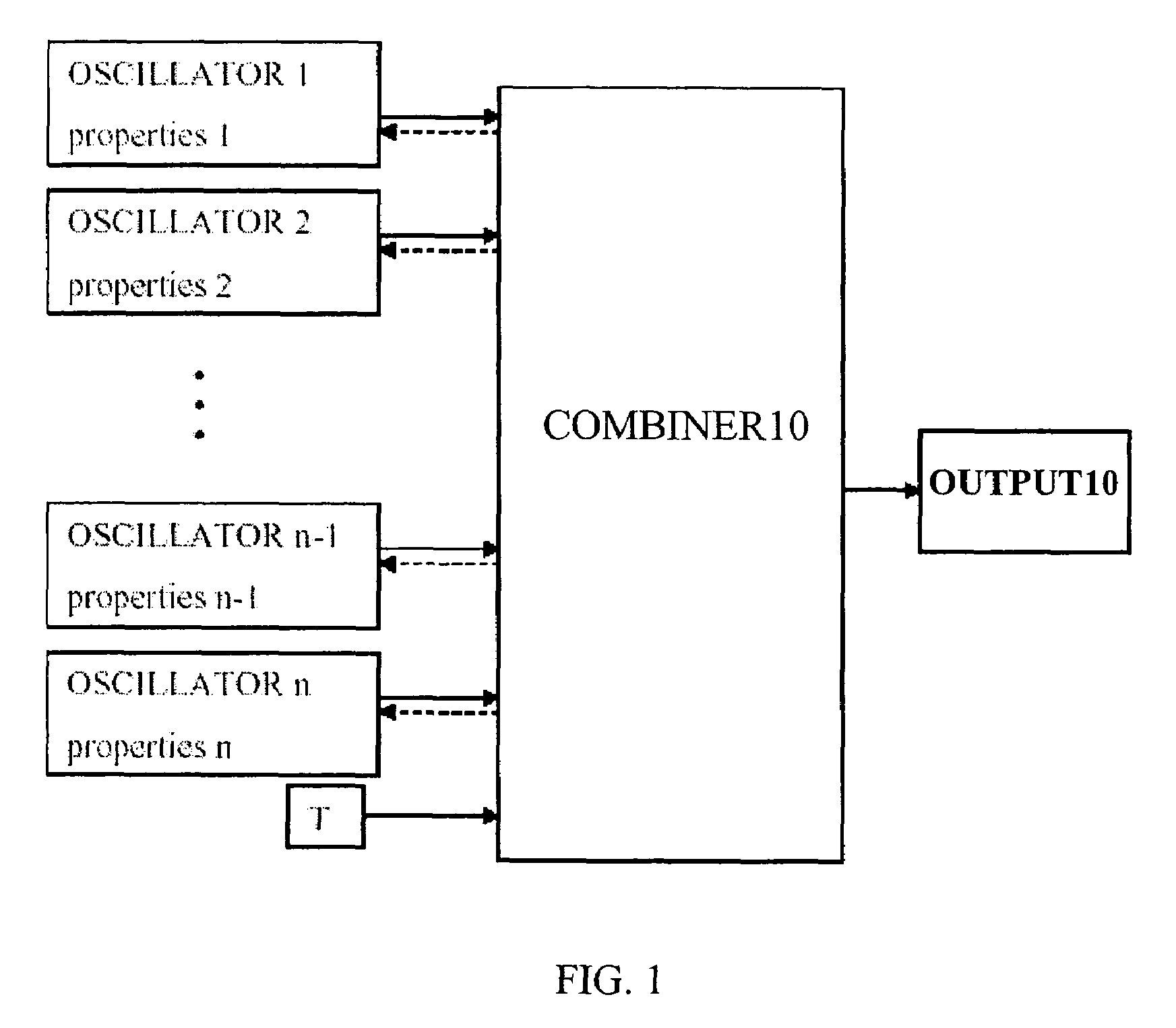

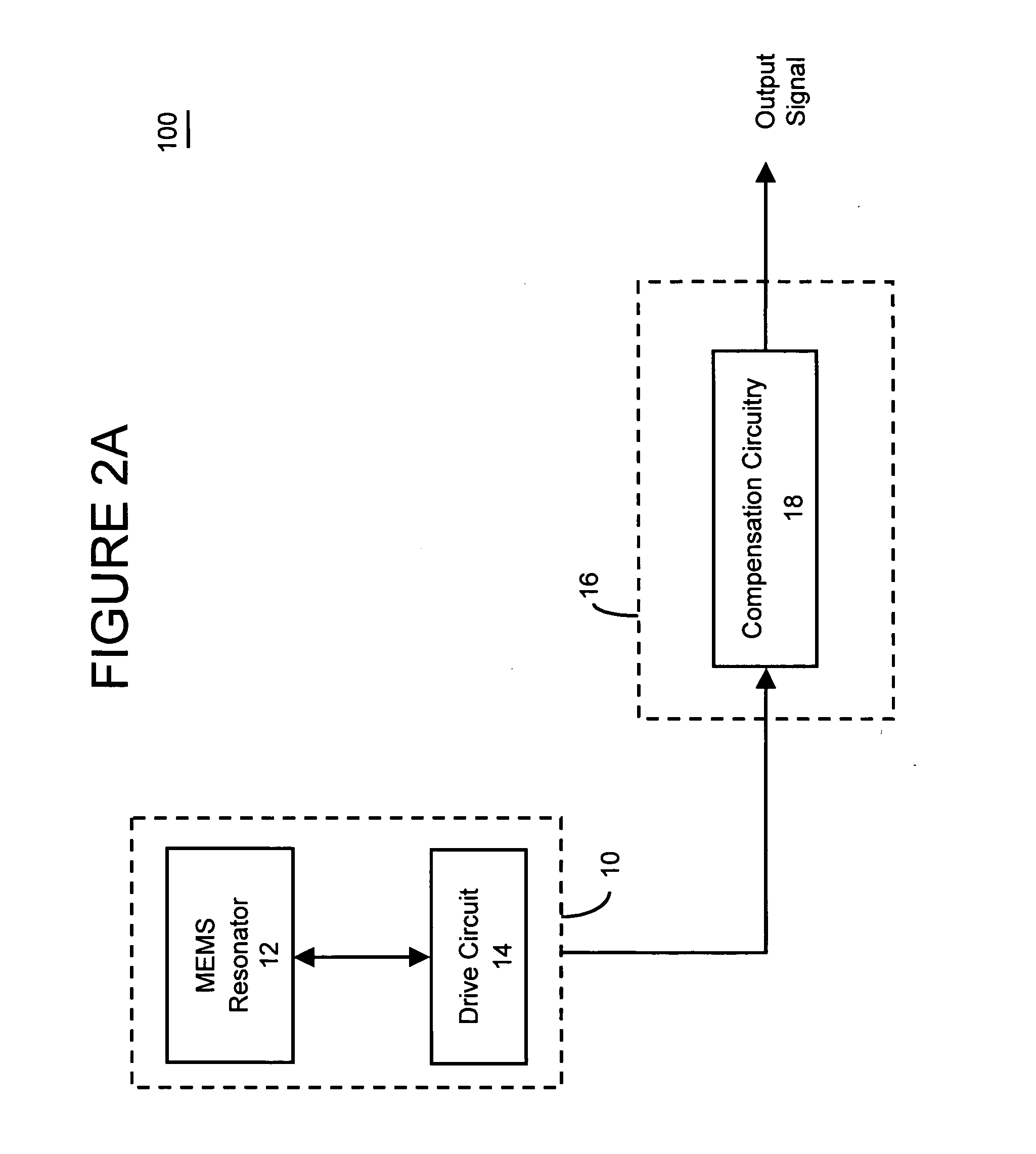

Frequency and/or phase compensated microelectromechanical oscillator

ActiveUS20050151592A1Reduce the gap widthIncreasing available voltage to applyRadiation pyrometryPulse automatic controlFrequency synthesizerFrequency multiplier

There are many inventions described and illustrated herein. In one aspect, the present invention is directed to a compensated microelectromechanical oscillator, having a microelectromechanical resonator that generates an output signal and frequency adjustment circuitry, coupled to the microelectromechanical resonator to receive the output signal of the microelectromechanical resonator and, in response to a set of values, to generate an output signal having second frequency. In one embodiment, the values may be determined using the frequency of the output signal of the microelectromechanical resonator, which depends on the operating temperature of the microelectromechanical resonator and / or manufacturing variations of the microelectromechanical resonator. In one embodiment, the frequency adjustment circuitry may include frequency multiplier circuitry, for example, PLLs, DLLs, digital / frequency synthesizers and / or FLLs, as well as any combinations and permutations thereof. The frequency adjustment circuitry, in addition or in lieu thereof, may include frequency divider circuitry, for example, DLLS, digital / frequency synthesizers (for example, DDS) and / or FLLs, as well as any combinations and permutations thereof.

Owner:ROBERT BOSCH GMBH

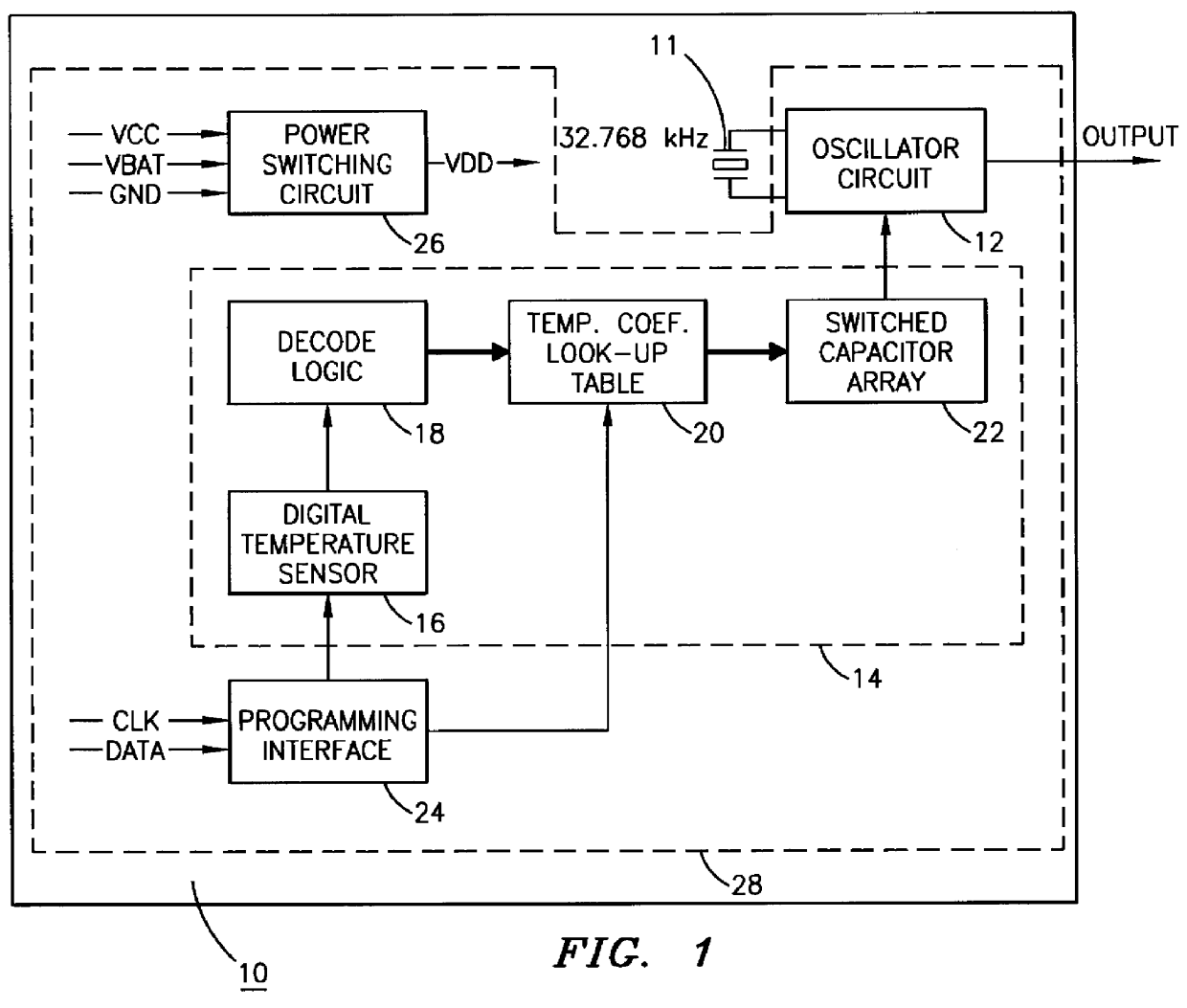

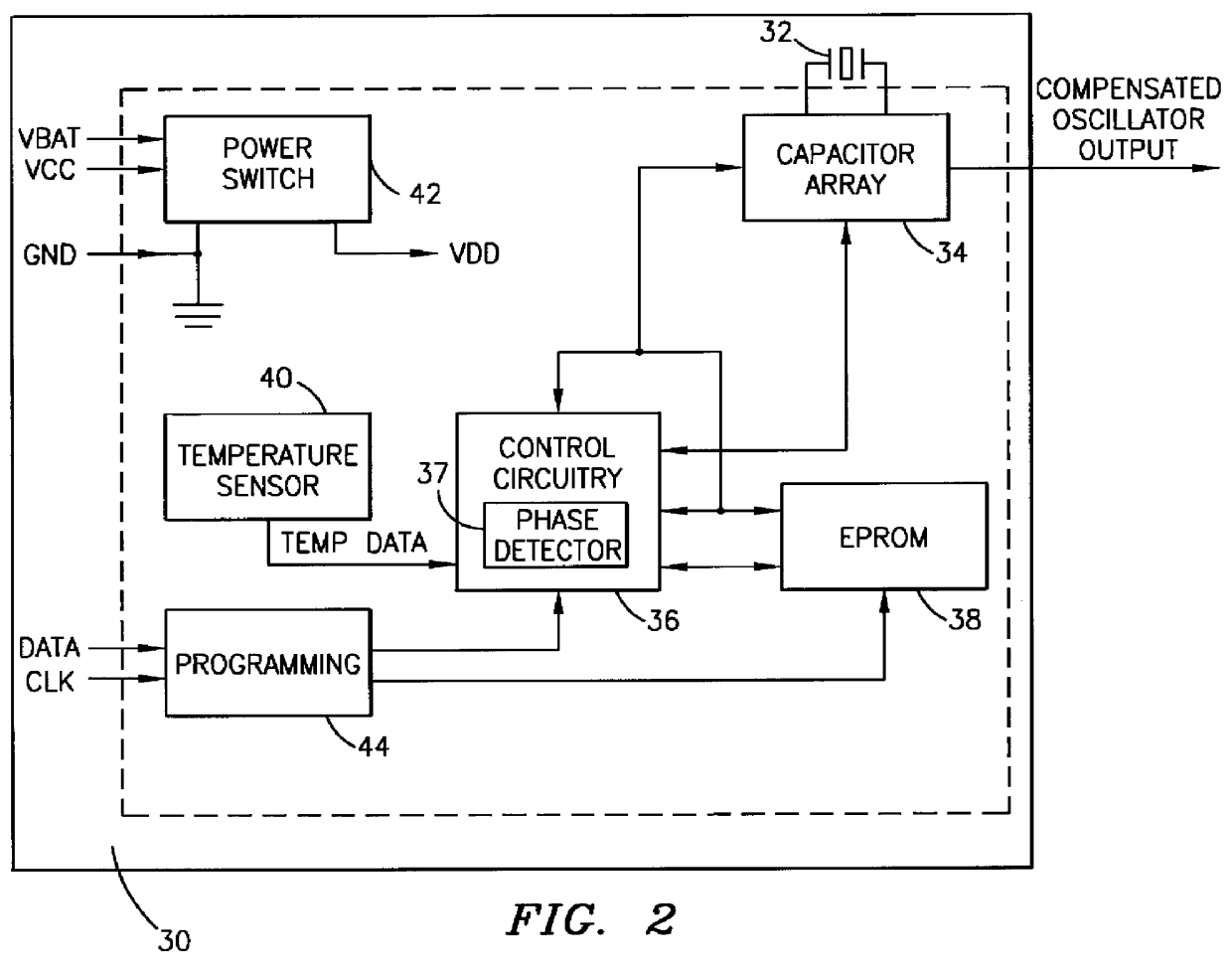

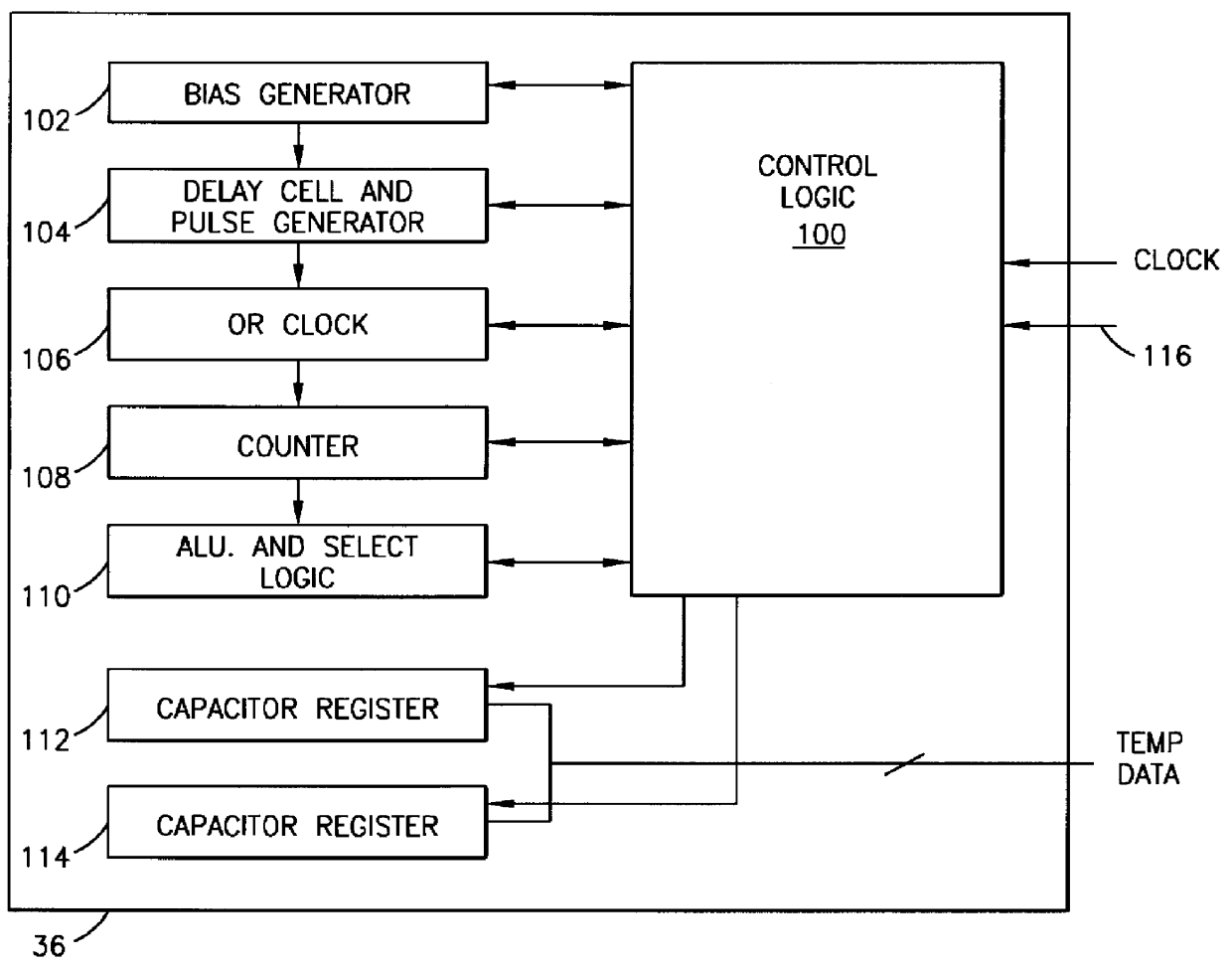

Temperature compensated crystal oscillator

A temperature compensated crystal oscillation circuit adapted to be contained within a small device package and providing an output frequency accuracy of approximately + / -2 ppm over a temperature range or less than 2 minutes per year over the temperature range. The device includes crystal and a single integrated circuit wherein the integrated circuit has a temperature sensing circuit with a digital output, control circuitry, a memory circuit and a switched capacitor array for compensating the oscillation of the crystal oscillator over temperature.

Owner:MAXIM INTEGRATED PROD INC

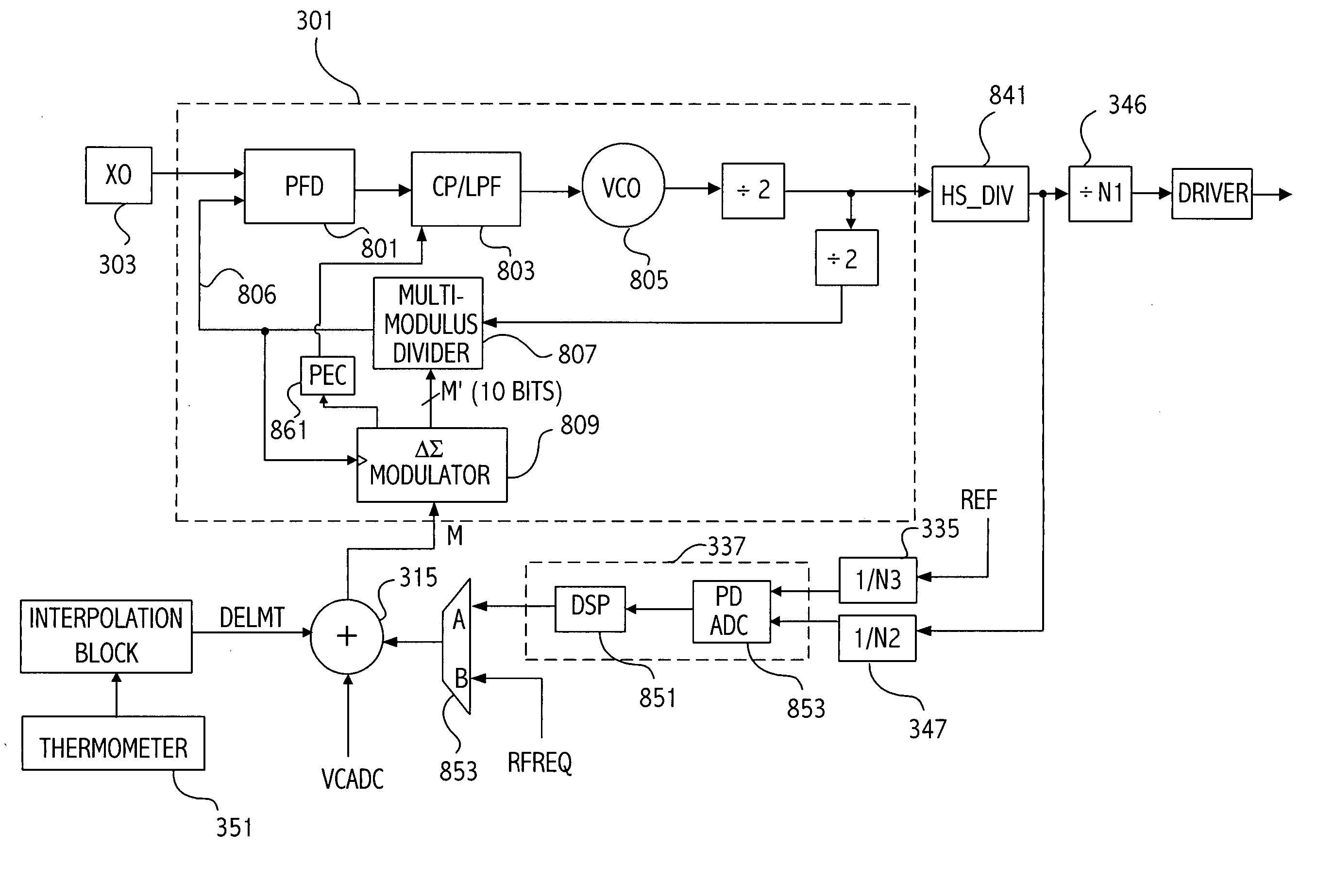

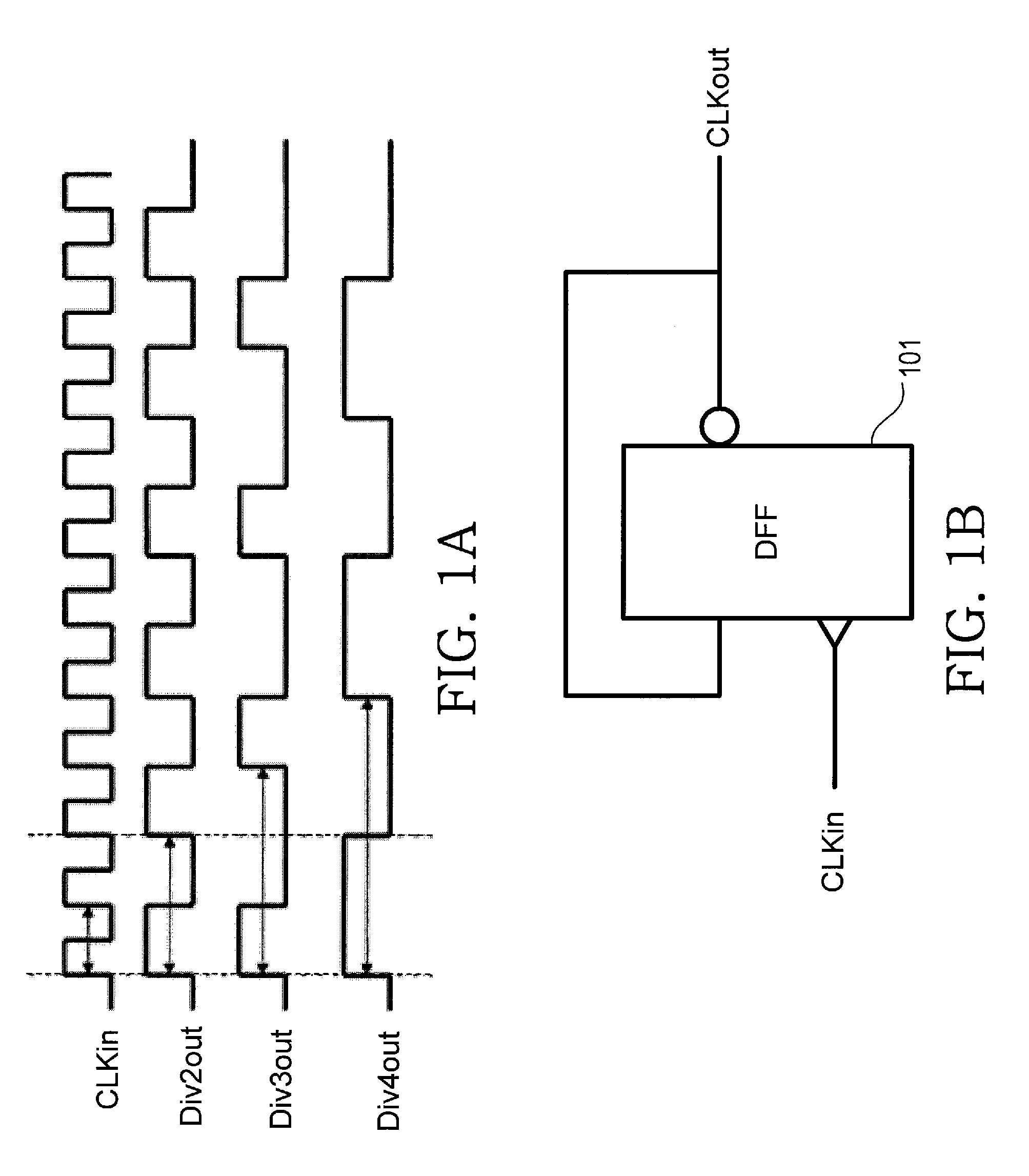

Dual loop architecture useful for a programmable clock source and clock multiplier applications

InactiveUS20040232995A1Pulse automatic controlGenerator stabilizationFrequency multiplierDigital control

A first phase-locked loop (PLL) circuit includes an input for receiving a timing reference signal from an oscillator, a controllable oscillator circuit supplying an oscillator output signal, and a multi-modulus feedback divider circuit. A second control loop circuit is selectably coupled through a select circuit to supply a digital control value (M) to the multi-modulus feedback divider circuit of the first loop circuit to thereby control the oscillator output signal. While the second control loop is coupled to supply the control value to the feedback divider circuit, the control value is determined according to a detected difference between the oscillator output signal and a reference signal coupled to the second control loop circuit at a divider circuit. While the second control loop circuit is not coupled to control the first PLL circuit, the first PLL circuit receives a digital control value to control a divide ratio of the feedback divider, the digital control value is determined at least in part according to a stored control value stored in nonvolatile storage, the stored control value corresponding to a desired frequency of the oscillator output signal.

Owner:SKYWORKS SOLUTIONS INC

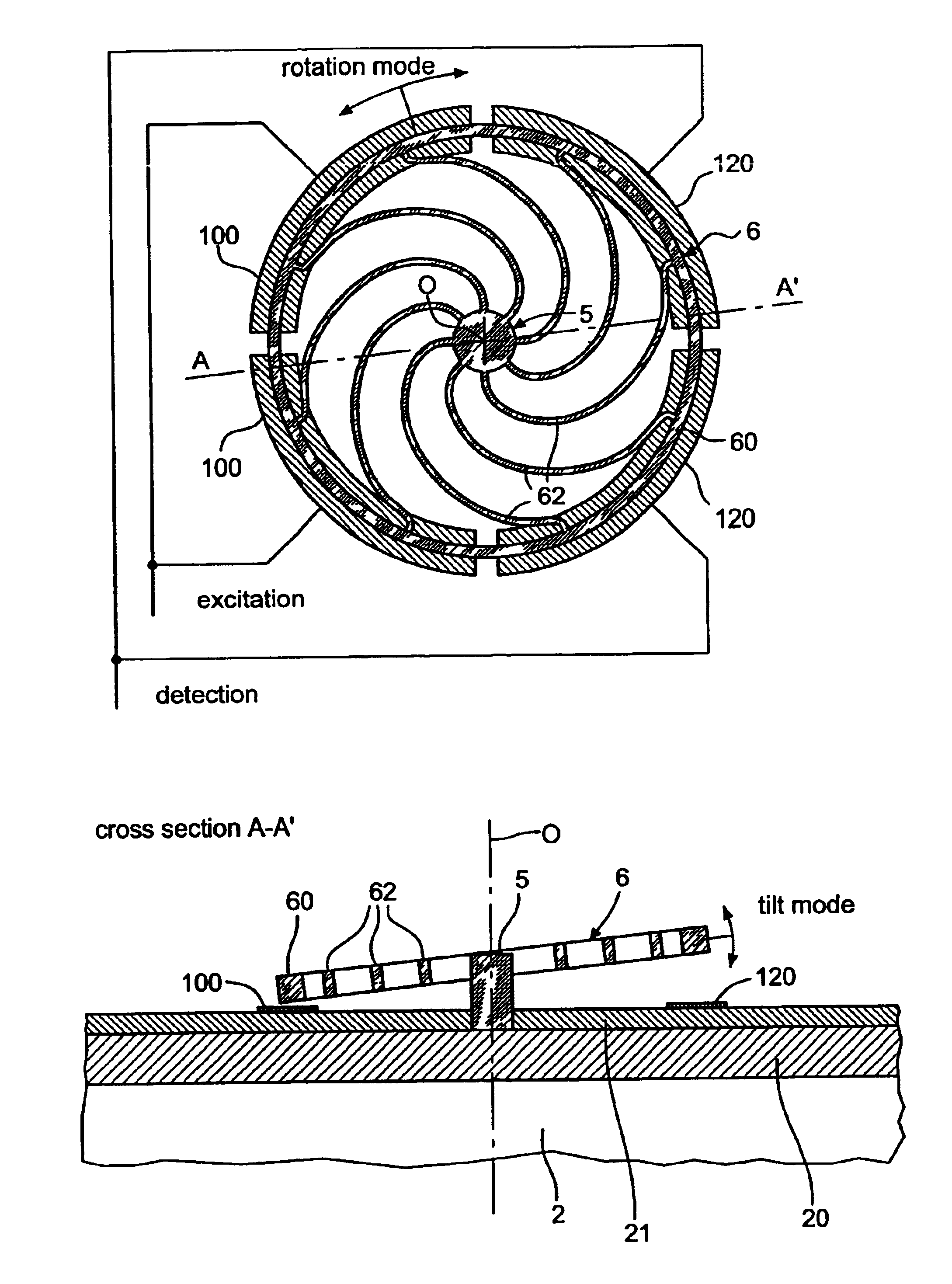

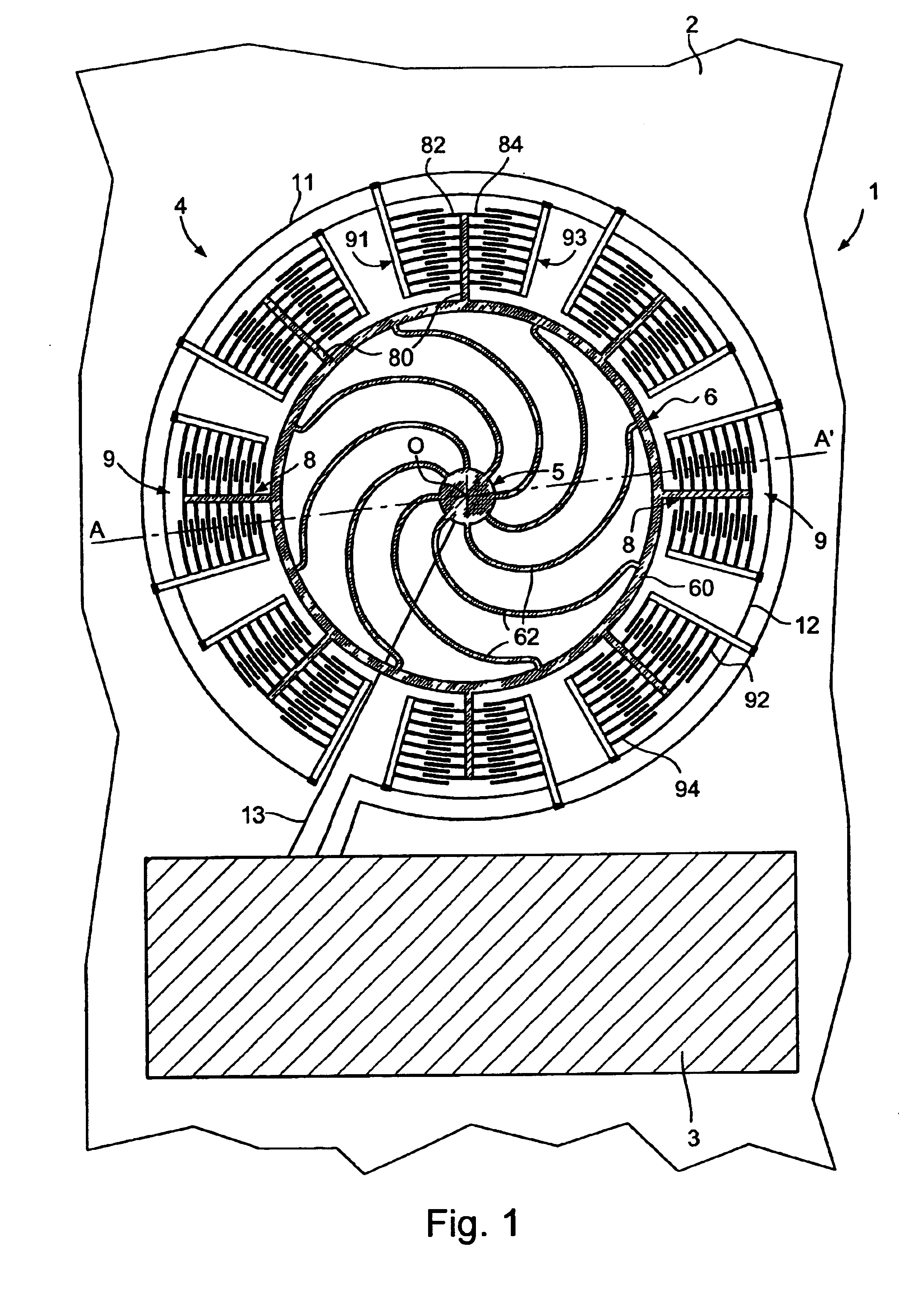

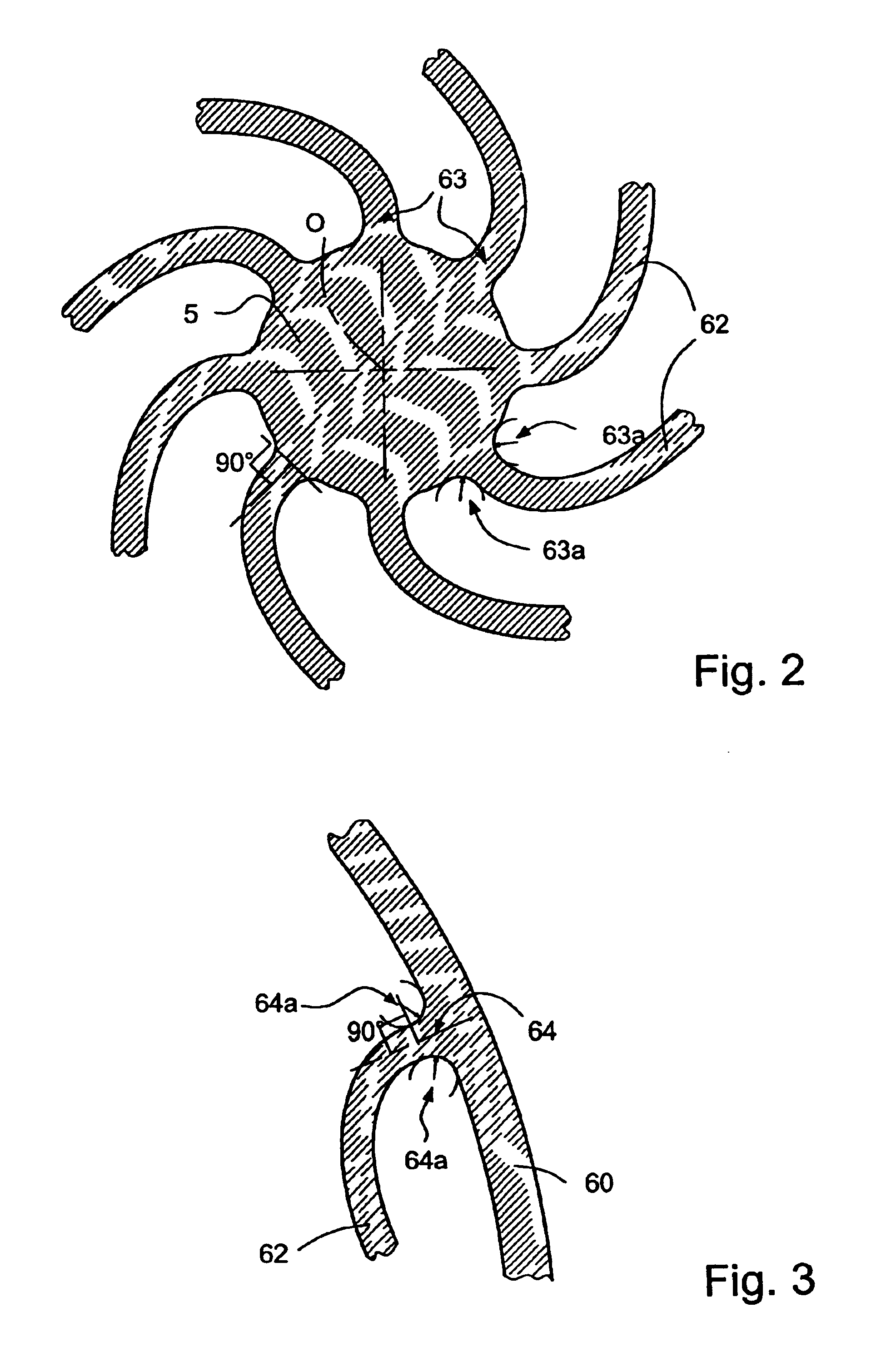

Temperature compensation mechanism for a micromechanical ring resonator

InactiveUS6859113B2Additional requirementAcceleration measurement using interia forcesImpedence networksVIT signalsAtomic physics

A time base including a resonator (4) and an integrated electronic circuit (3) for driving the resonator into oscillation and for producing, in response to the oscillation, a signal having a determined frequency. The resonator is an integrated micromechanical ring resonator supported above a substrate (2) and adapted to oscillate in a first oscillation mode. The ring resonator includes a free-standing oscillating structure (6). Electrodes (100, 120; 130, 150) are positioned under the free-standing oscillating structure in such a way as to drive and sense a second oscillation mode in a plane substantially perpendicular to the substrate and having a resonant frequency which is different from the resonant frequency of the first oscillation mode, a frequency difference between the resonant frequencies of both oscillation modes being used for compensating for the effect of temperature on the frequency of the signal produced by the time base.

Owner:ETA SA MFG HORLOGERE SUISSE

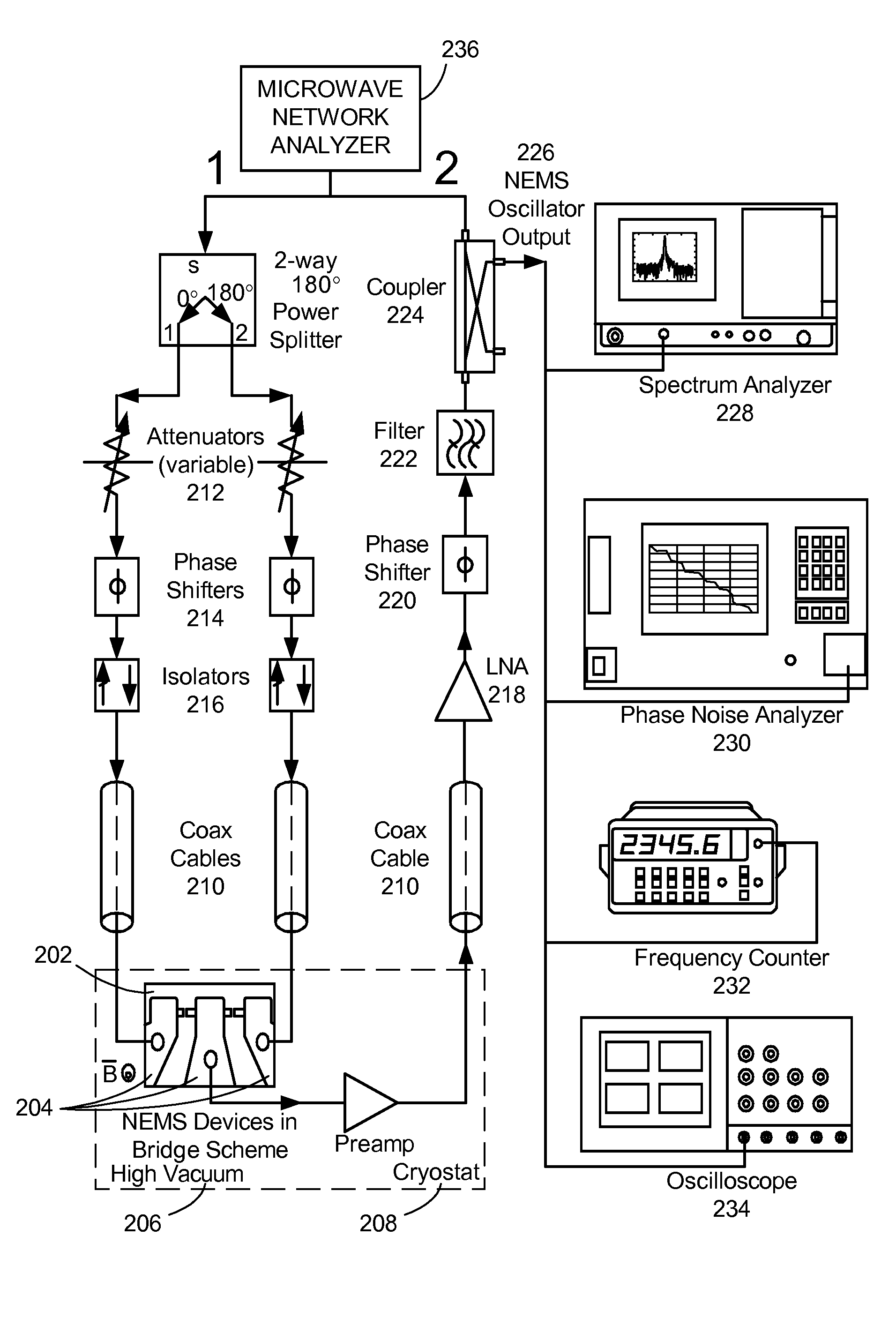

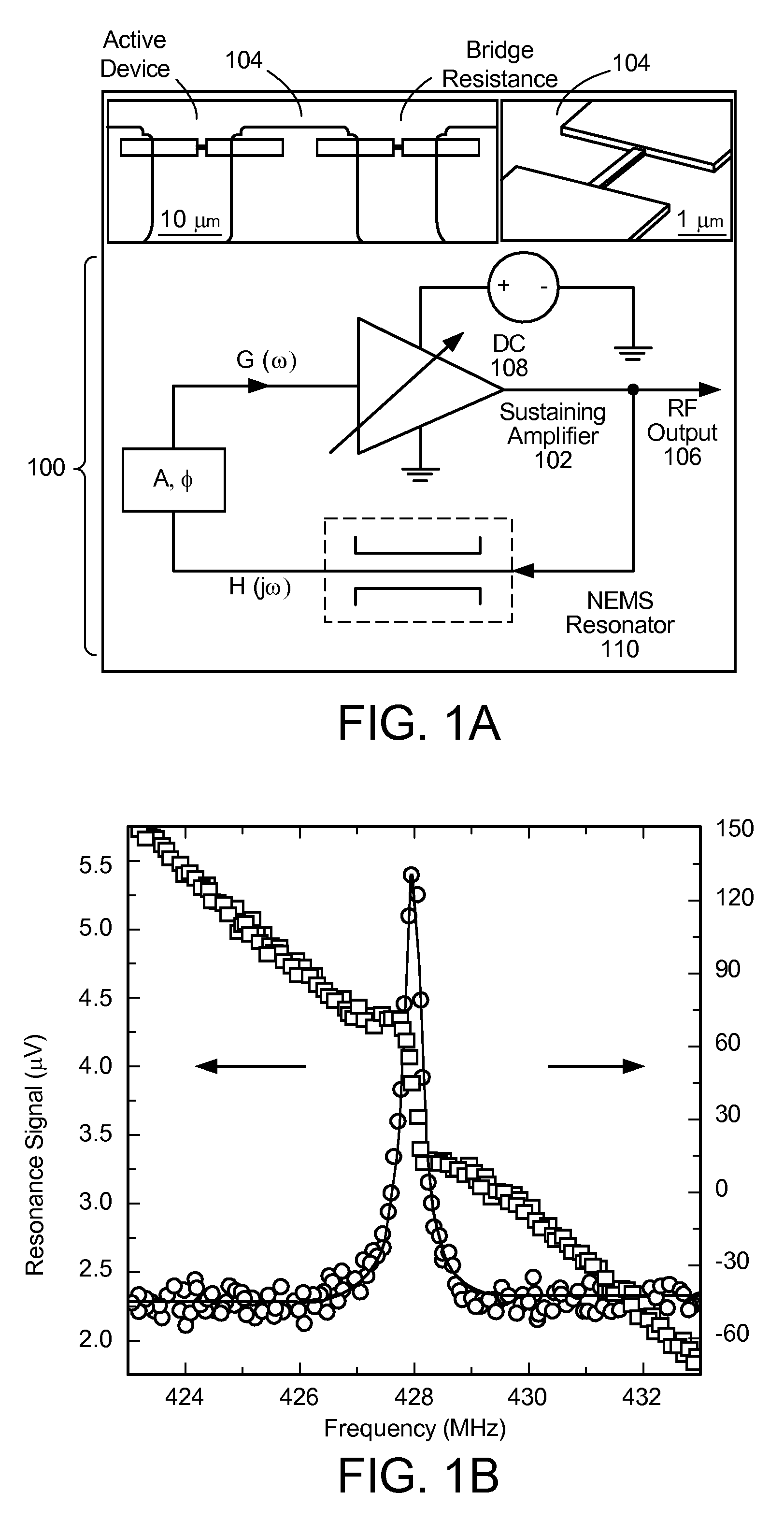

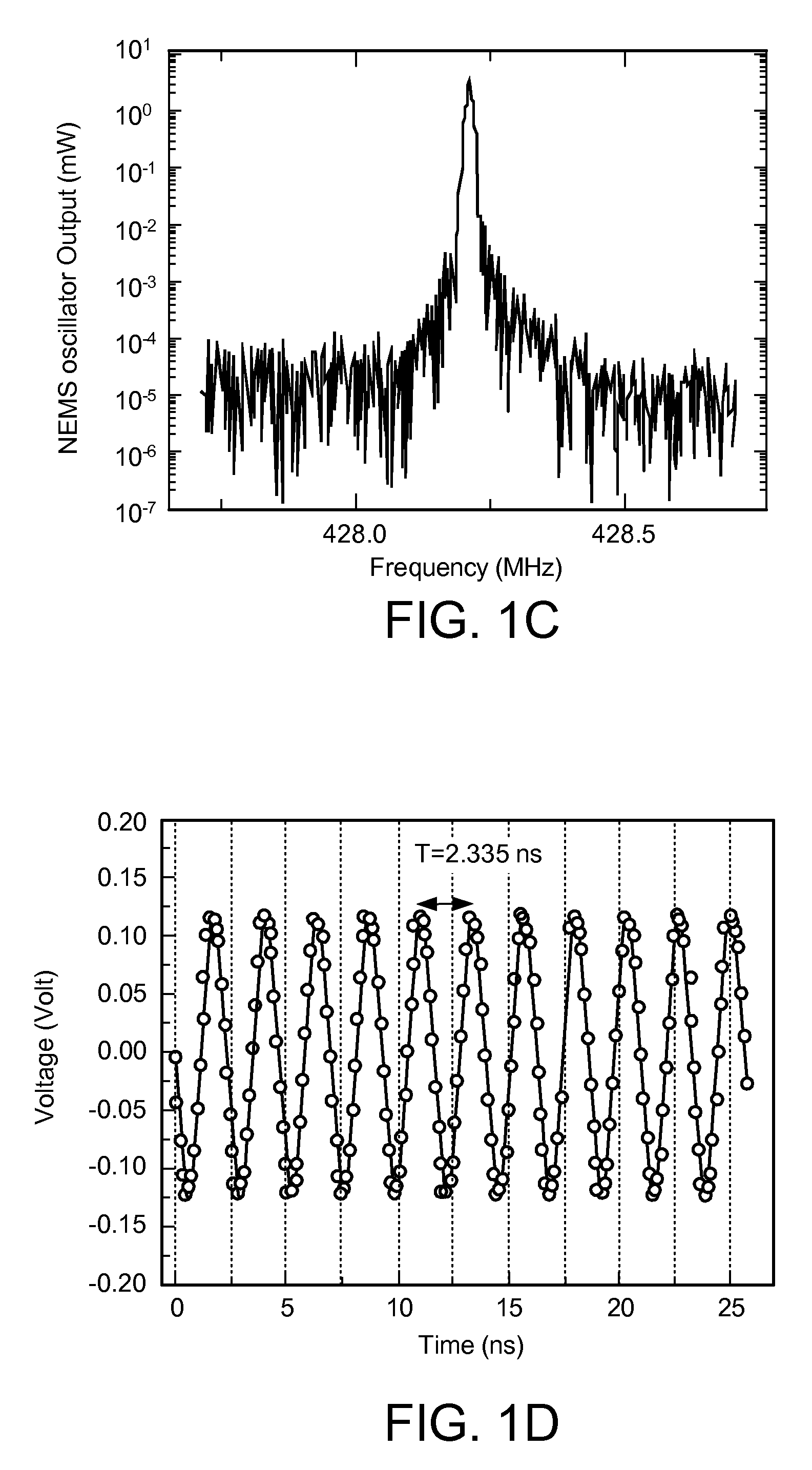

Ultra-high frequency self-sustaining oscillators, coupled oscillators, voltage-controlled oscillators, and oscillator arrays based on vibrating nanoelectromechanical resonators

ActiveUS7724103B2Noteworthy performanceNoteworthy stabilityMaterial analysis using sonic/ultrasonic/infrasonic wavesWeighing apparatus using elastically-deformable membersBeam resonatorVIT signals

Owner:CALIFORNIA INST OF TECH

Oscillator

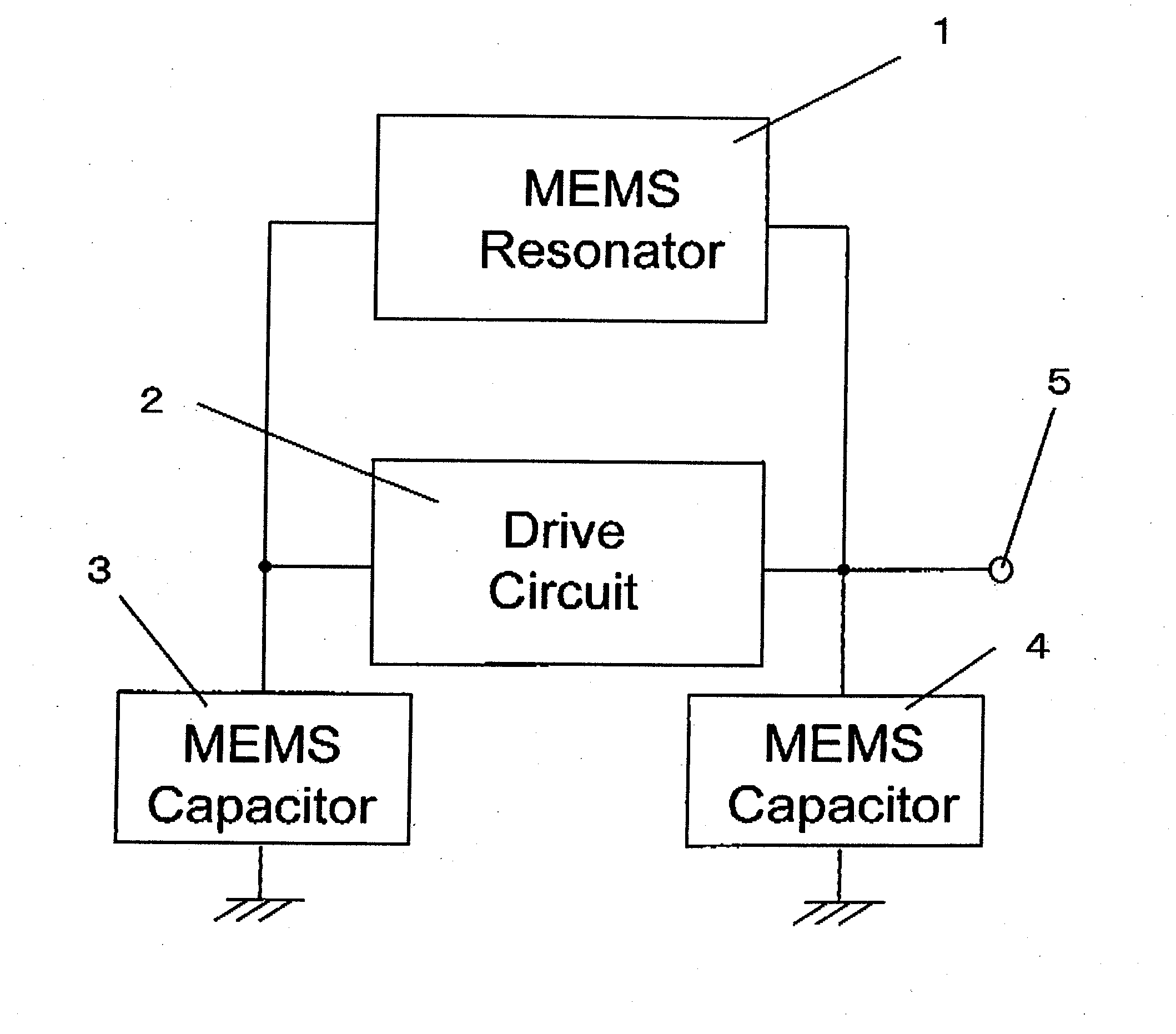

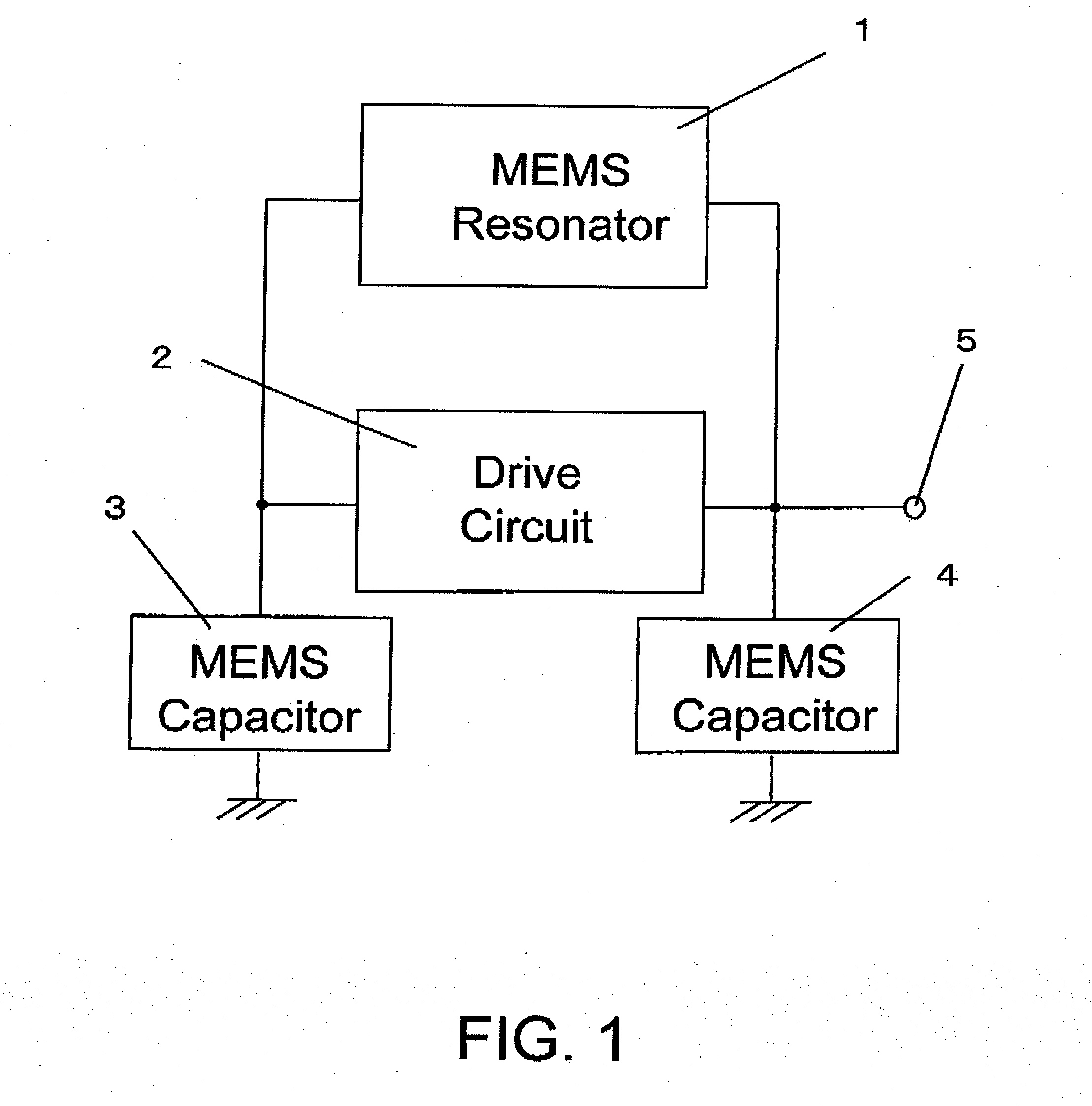

InactiveUS20080204153A1Small sizeChange frequencyResonant circuit auxillary power controlRadiation pyrometryMems capacitorsCapacitance

Provided is an oscillator including: a MEMS resonator for mechanically vibrating; an output oscillator circuit for oscillating at a resonance frequency of the MEMS resonator to output an oscillation signal; and a MEMS capacitor for changing a capacitance thereof caused by a change in a distance between an anode electrode and a cathode beam according to an environmental temperature.

Owner:SEIKO INSTR INC

Phase controlled oscillator circuit with input signal coupler

An oscillating signal in an oscillator is caused to phase shift toward the phase of an input signal coupled to the oscillating signal. The resonant frequency of the oscillator is about equal to an integer multiple of the frequency of the input signal. The input signal may be generated in a pulse generator to have an input pulse duration less than or equal to that of the oscillating signal. The oscillator circuit may be used as a filter to filter pulse width variations or to filter jitter from a reference clock. The oscillator circuit may also serve as a buffer by amplifying the input signal. Phase interpolation can be obtained by coupling at least one input signal with at least one oscillating signal.

Owner:RAMBUS INC

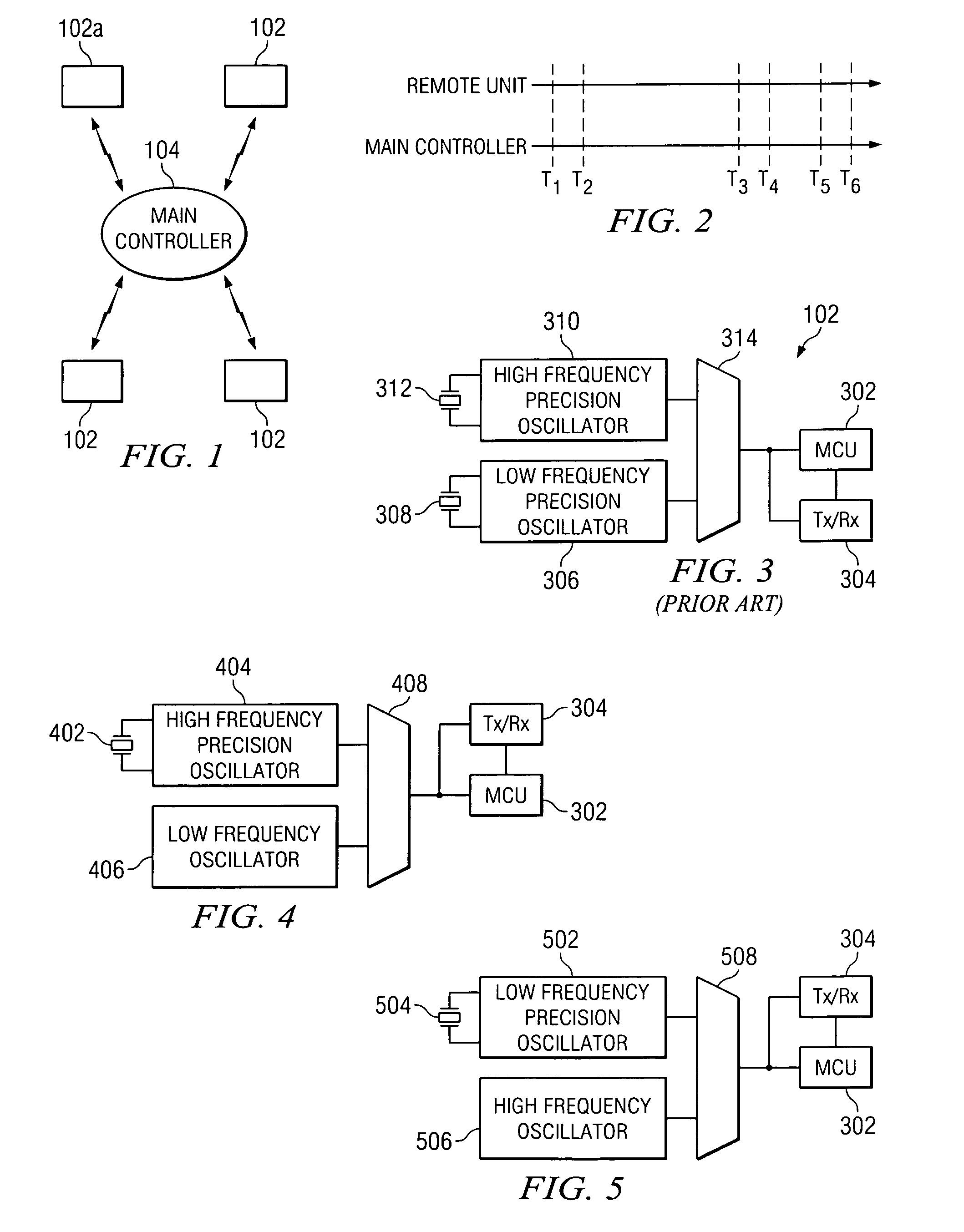

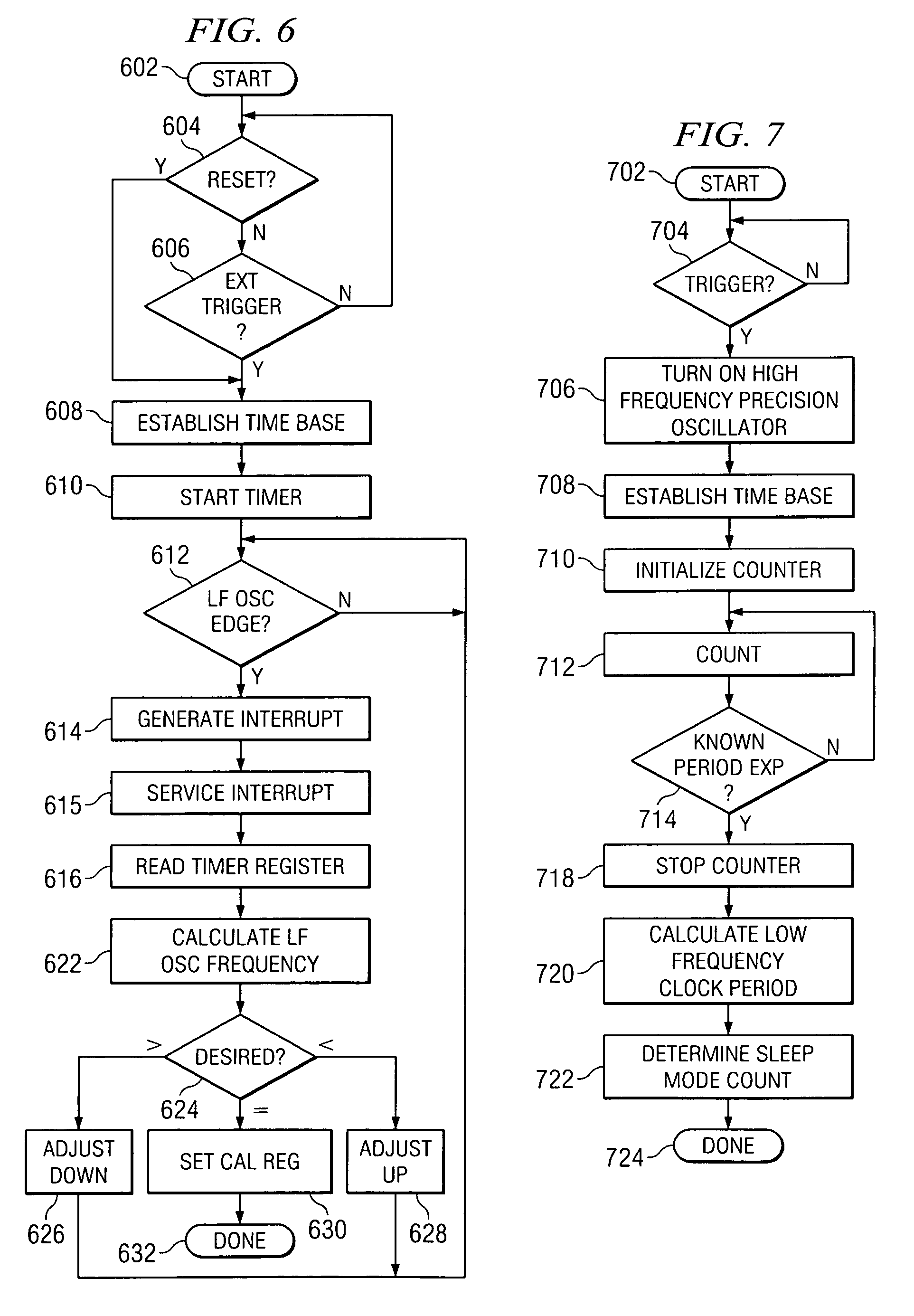

Precise frequency generation for low duty cycle transceivers using a single crystal oscillator

An apparatus and method for calibrating a non-crystal oscillator in a transceiver unit using a crystal-oscillator includes the step of establishing a time base based upon oscillations of the crystal oscillator. A comparison of the number of oscillations for the non-crystal oscillator and the crystal oscillator is made during a known time period is made. An adjustment is determined based upon the established time base and the compared number of oscillations. The transceiving of the transceiver unit is then controlled based upon this adjustment.

Owner:SILICON LAB INC

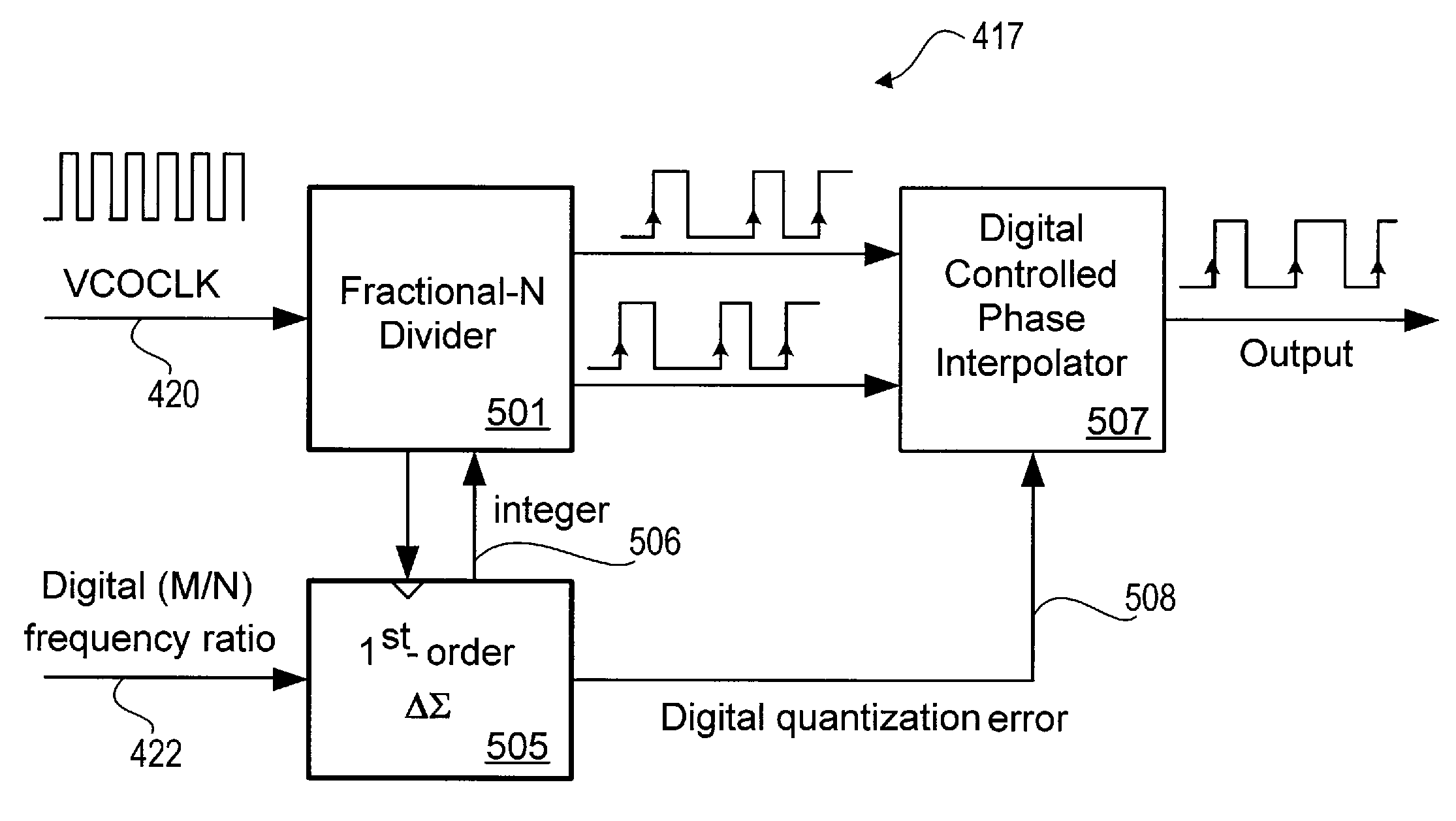

Direct digital interpolative synthesis

ActiveUS7417510B2Reduce noisePulse automatic controlGenerator stabilizationEngineeringFrequency divider

A clock synthesis circuit includes a delta sigma modulator that receives a divide ratio and generates an integer portion and a digital quantization error (a fractional portion). A fractional-N divider divides a received signal according to a divide control value corresponding to the integer portion and generates a divided signal. A phase interpolator adjusts a phase of the divided signal according to the digital quantization error to thereby reduce noise associated with the fractional-N divider.

Owner:SKYWORKS SOLUTIONS INC

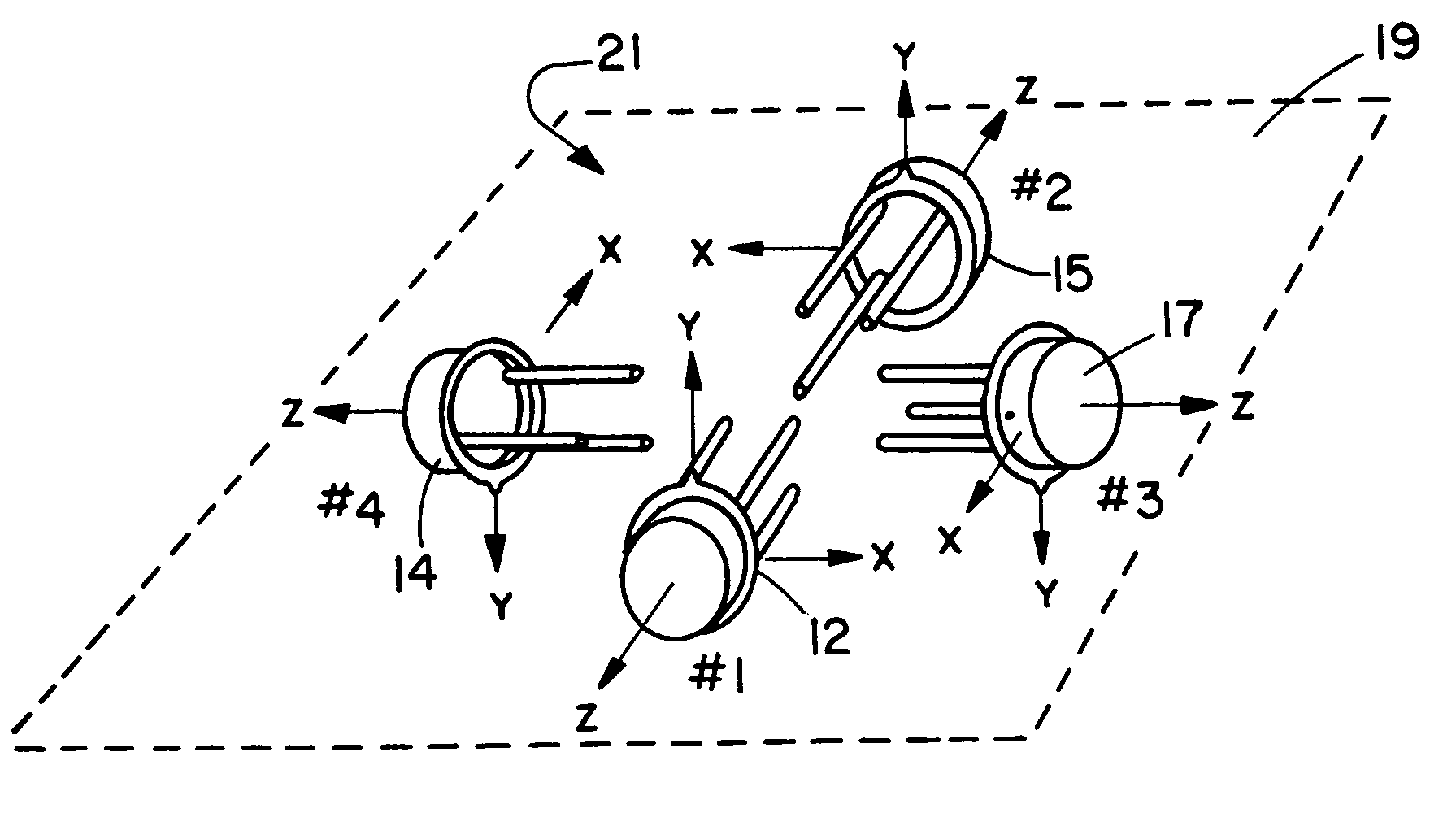

Compensated ensemble crystal oscillator for use in a well borehole system

InactiveUS7046584B2Longer be performedBroaden their knowledgePiezoelectric/electrostriction/magnetostriction machinesGenerator stabilizationFrequency stabilizationCrystal oscillator

A compensated ensemble crystal oscillator clock system for use in a well borehohe system. The clock system includes preferably four quad compensated clocks, a compensated temperature sensor, and software for processing and correcting system response. Physical fabrication of elements of the quad compensated clocks, the compensated temperature sensor and cooperating software minimized drift in frequency of the oscillator clock system in harsh borehole environments encountered while drilling a borehole. The clock system exhibits a frequency stability of 2.8×10−9 or less over a temperature range of from 0° C. to 185° C. The compensated ensemble crystal oscillator clock system is particularly applicable to seismic-while-drilling operations wherein precise downhole measurements of time are required typically over a period of days.

Owner:WEATHERFORD TECH HLDG LLC

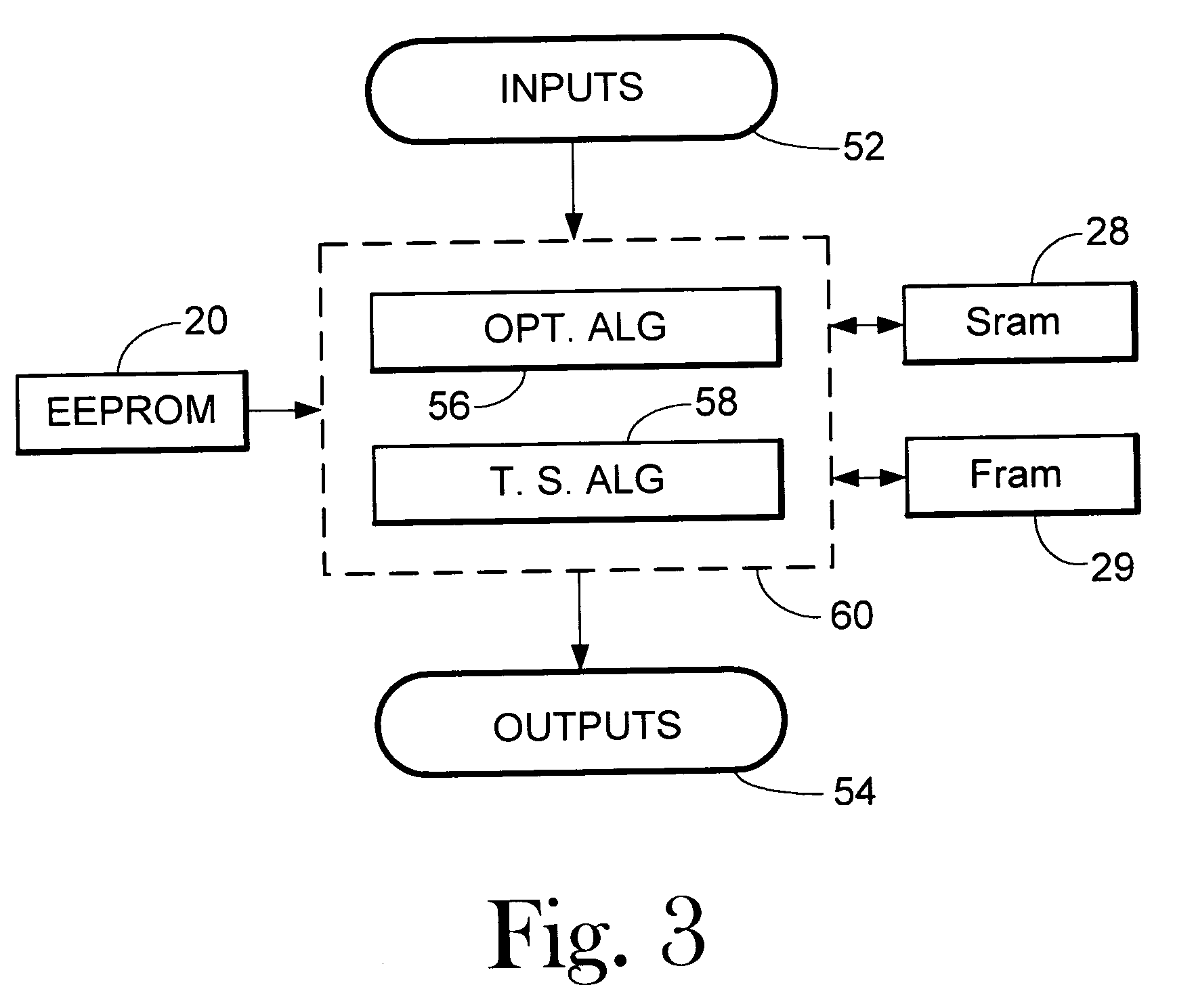

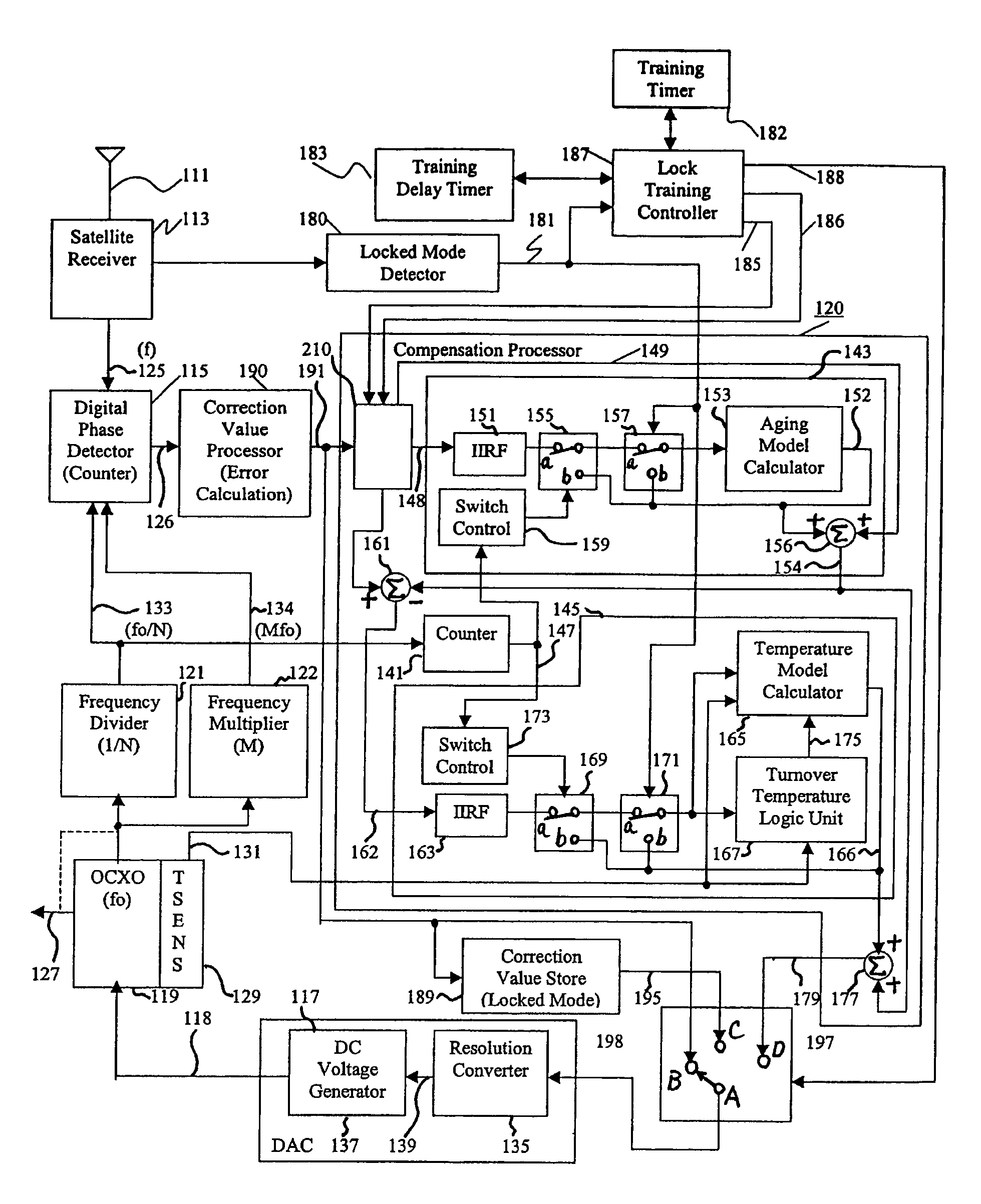

Reference timing signal apparatus and method

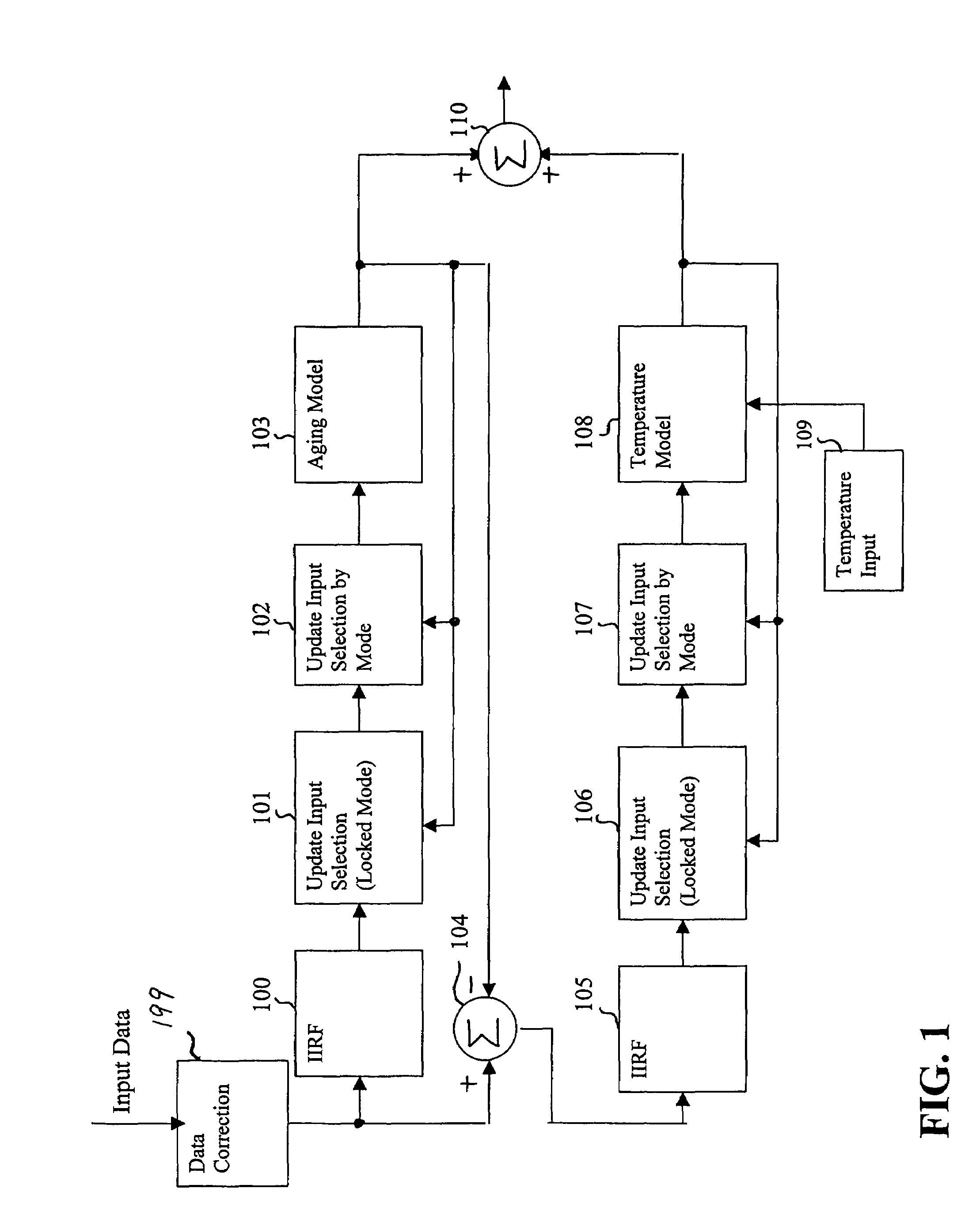

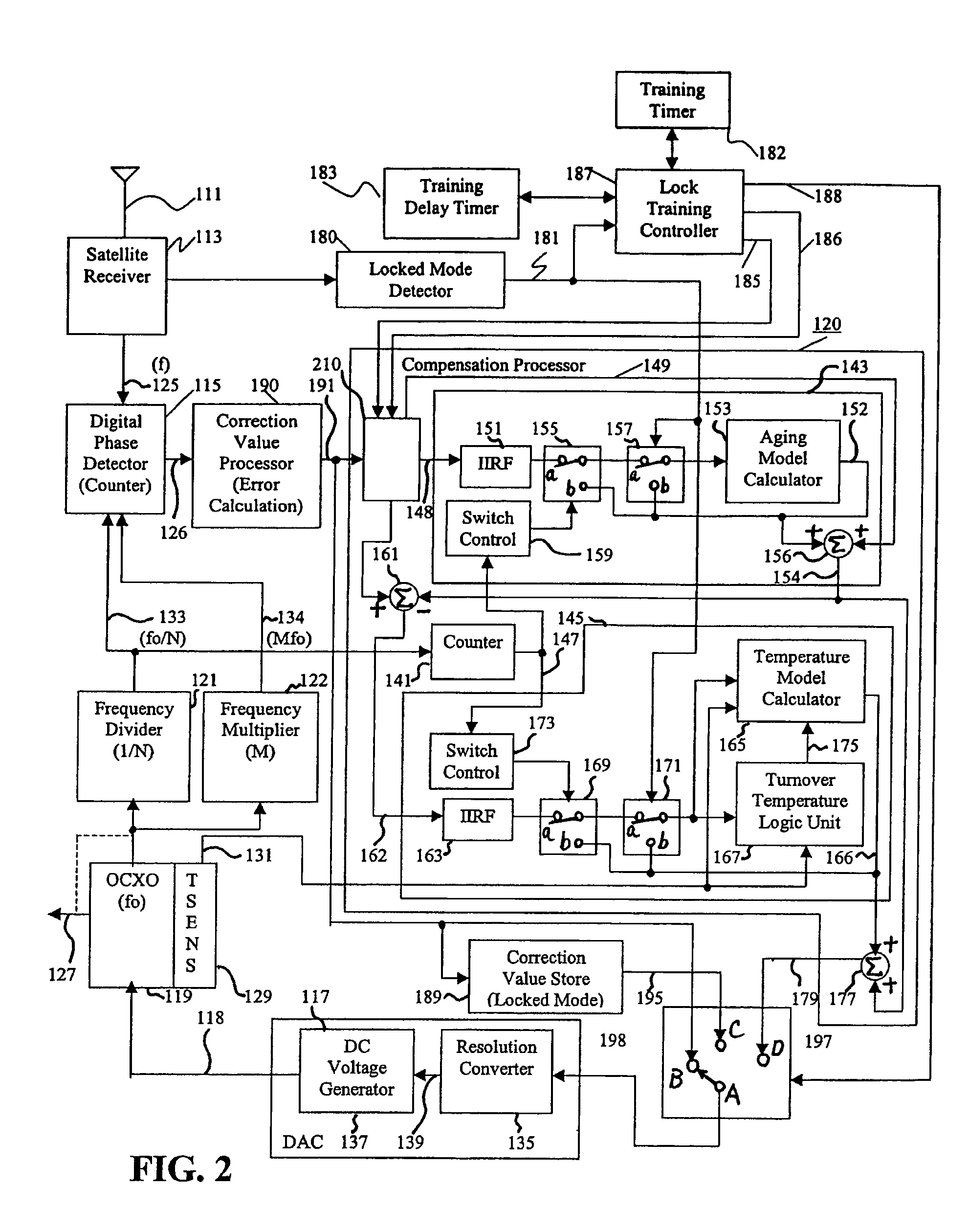

ActiveUS7015762B1Increase currentGood compensationRadiation pyrometryPulse automatic controlTraining periodAdaptive filter

A reference timing signal apparatus with a phase-locked loop (PLL) has a computer algorithm which adaptively models the multiple frequencies of an oscillator following a training period. The oscillator is part of a PLL and the oscillation frequency thereof is controlled in response to the phase detector output. The computer algorithm processes the control signal applied to the oscillator. The computer algorithm updates the characteristics of the model relating to the aging and temperature of the oscillator, using for example, a Kalman filter as an adaptive filter, in accordance with a cumulative phase error in the PLL calculated during a given time interval. By the algorithm, the subsequent model predicts the future frequency state of the oscillator on which it was trained. The predicted frequency of the model functions as a reference to correct the frequency of the oscillator in the event that no input reference timing signal is available. Also, the calculated phase error is stored and is used while no input reference timing signal or accurate predicted frequency value is available. With the model updating algorithm, oscillators of low stability performance may be used as cellular base station reference oscillator, which is based on satellite systems, for example, GPS, GLONASS or Galileo systems.

Owner:APPLE INC

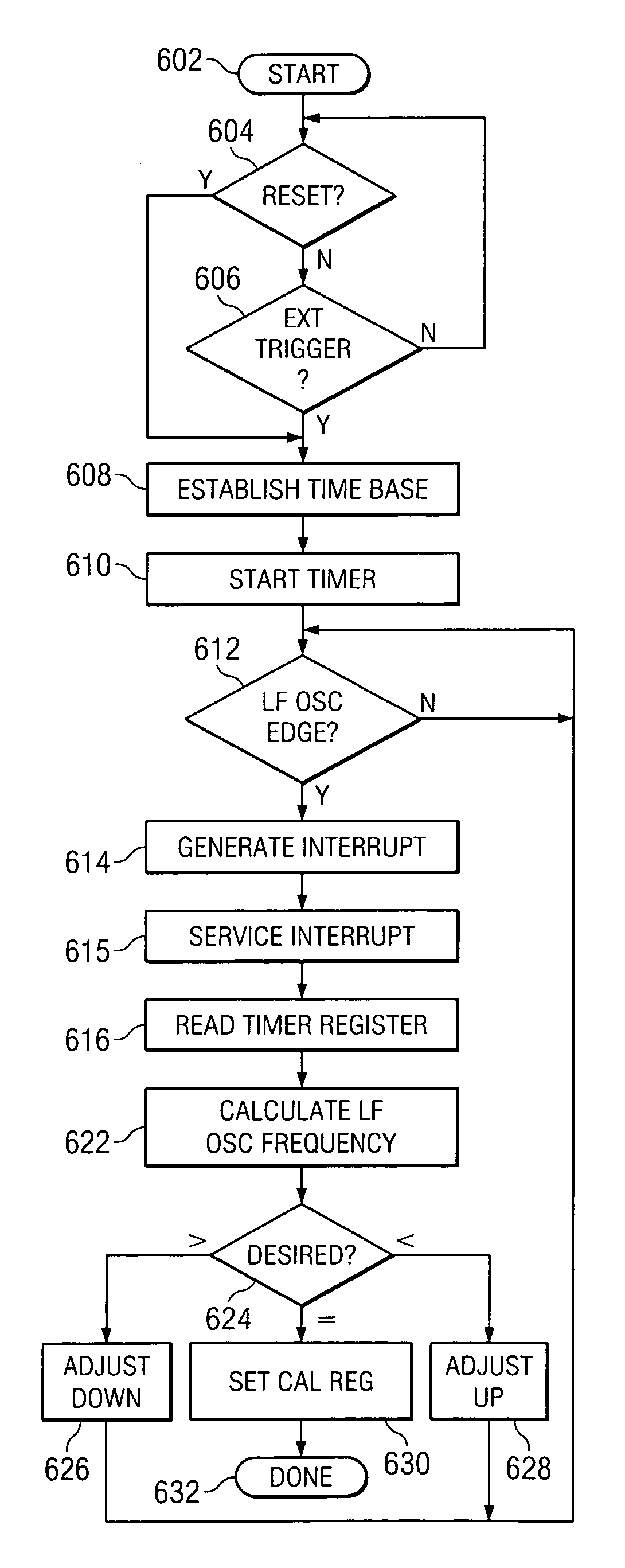

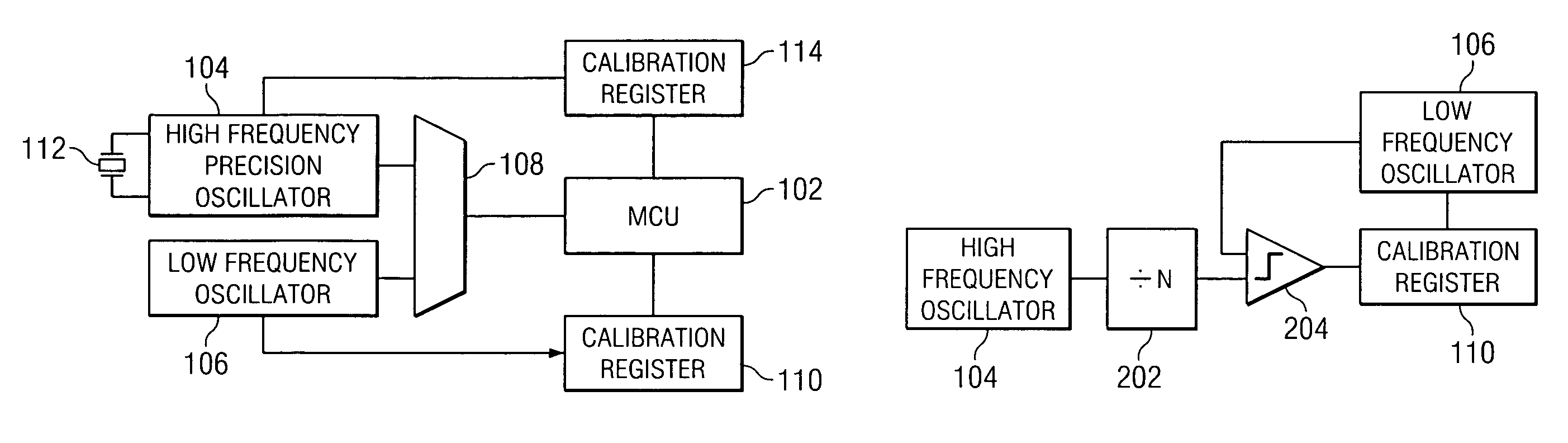

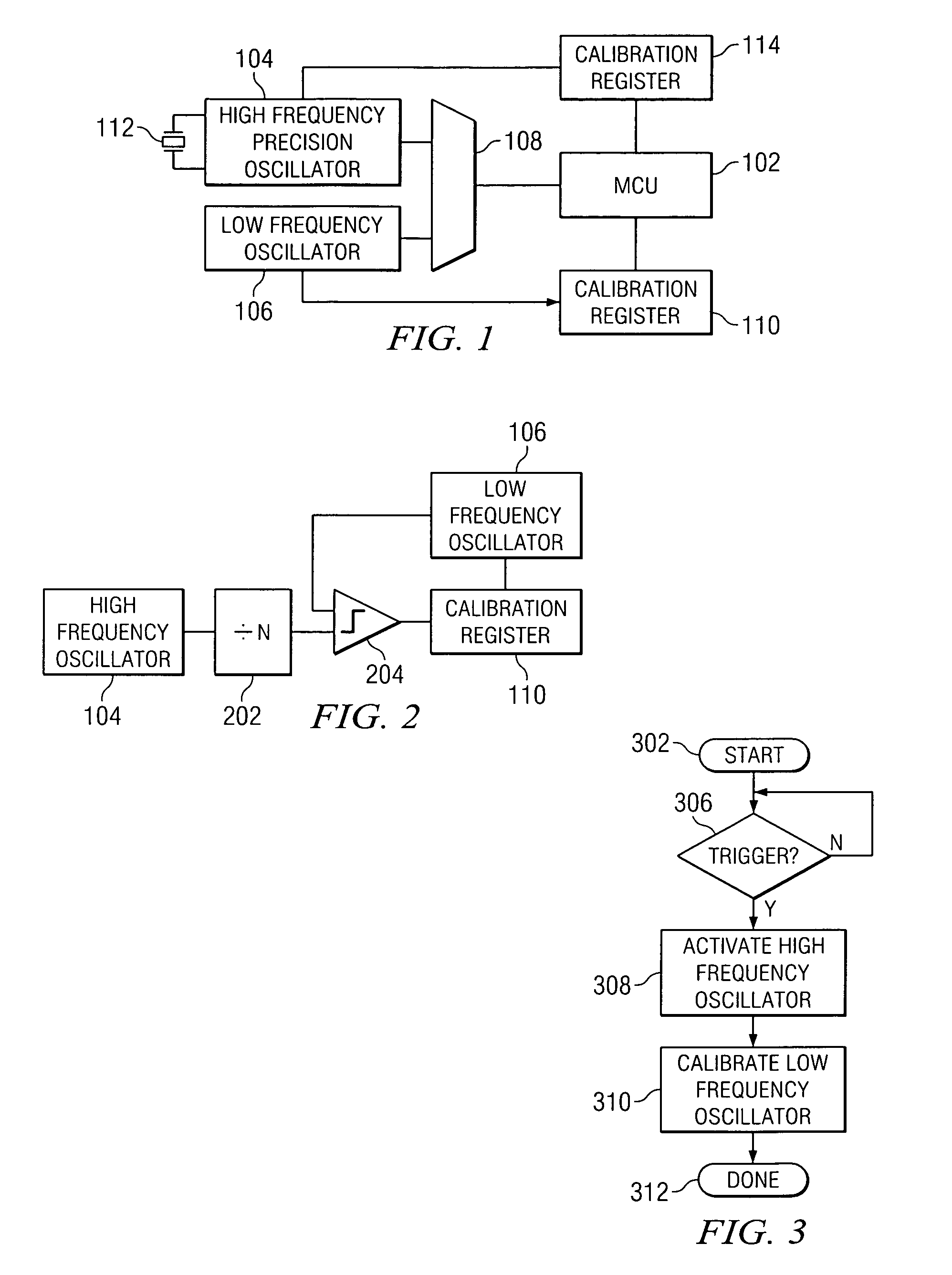

Method and apparatus for calibration of a low frequency oscillator in a processor based system

Owner:SILICON LAB INC

Voltage Controlled Oscillator (VCO) with a wide tuning range and substantially constant voltage swing over the tuning range

A wide tuning range and constant swing VCO is described that is based on a multipass Ring Oscillator enhanced with feed-backward connections. This VCO is designed to overcome tuning range limitations of prior-art “feed-forward” ring oscillators. The Feedback multipass Ring Oscillator of the invention provides decreasing frequency when tuned by increasing the feedback, thus covering a much wider tuning range irrespective of the speed limit of the technology while at the same time providing almost constant amplitude.

Owner:RAMBUS INC

Micropower RC oscillator

InactiveUS6462625B2Logic circuits coupling/interface using field-effect transistorsGenerator stabilizationElectrical resistance and conductanceClosed loop

Owner:SAMSUNG ELECTRONICS CO LTD

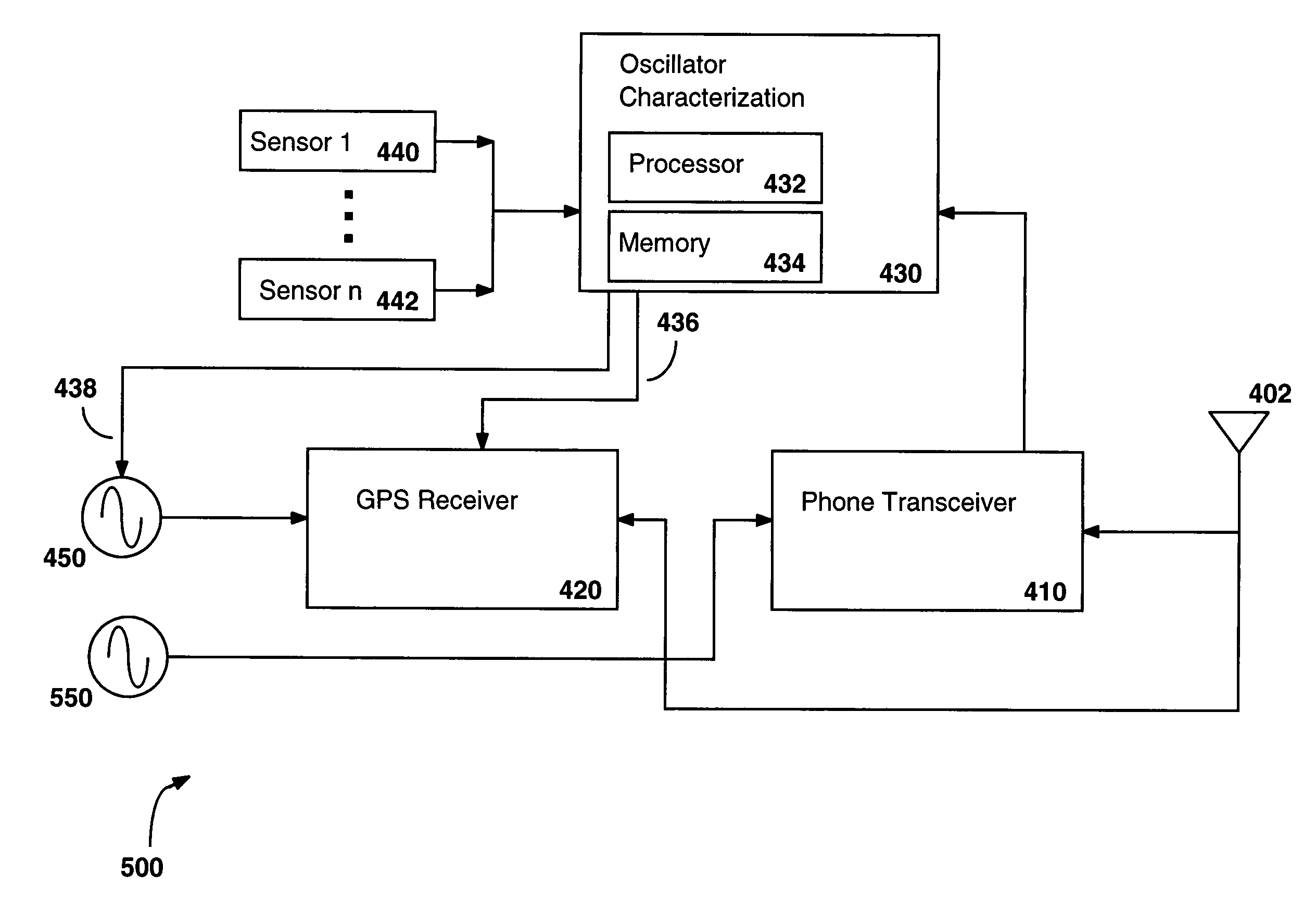

Method and apparatus for compensating local oscillator frequency error

InactiveUS6928275B1Reduce frequency errorReduce frequencyPulse automatic controlModulated-carrier systemsExternal referenceLocal oscillator

The frequency error of an oscillator is minimized by characterizing the oscillator. A reference signal from an external source containing a minimal frequency error is provided to an electronic device. The external signal is used as a reference frequency to estimate the frequency error of an internal frequency source. The electronic device monitors parameters that are determined to have an effect on the frequency accuracy of the internal frequency source. Temperature is one parameter known to have an effect on the frequency of the internal frequency source. The electronic device collects and stores the values of the parameters as well as the corresponding output frequency or frequency error of the internal frequency source. The resultant characterization of the internal frequency source is used to compensate the internal frequency source when the internal frequency source is not provided the external reference signal.

Owner:QUALCOMM INC

Residual frequency effects compensation

A means is provided to estimate the amount of frequency deviation experienced in a precision resonator resulting from the effects of previous thermal history, acceleration, or aging by determining the differential effect of the perturbing condition on different resonant modes in the same resonator or on different resonators exposed to the same environment. The measurements may be made simultaneously, or sequentially against an independent frequency source. Residual frequency hysteresis effects may be determined in connection with an independent temperature sensor if the exact temperature in not known.

Owner:FRERKING MARVIN E

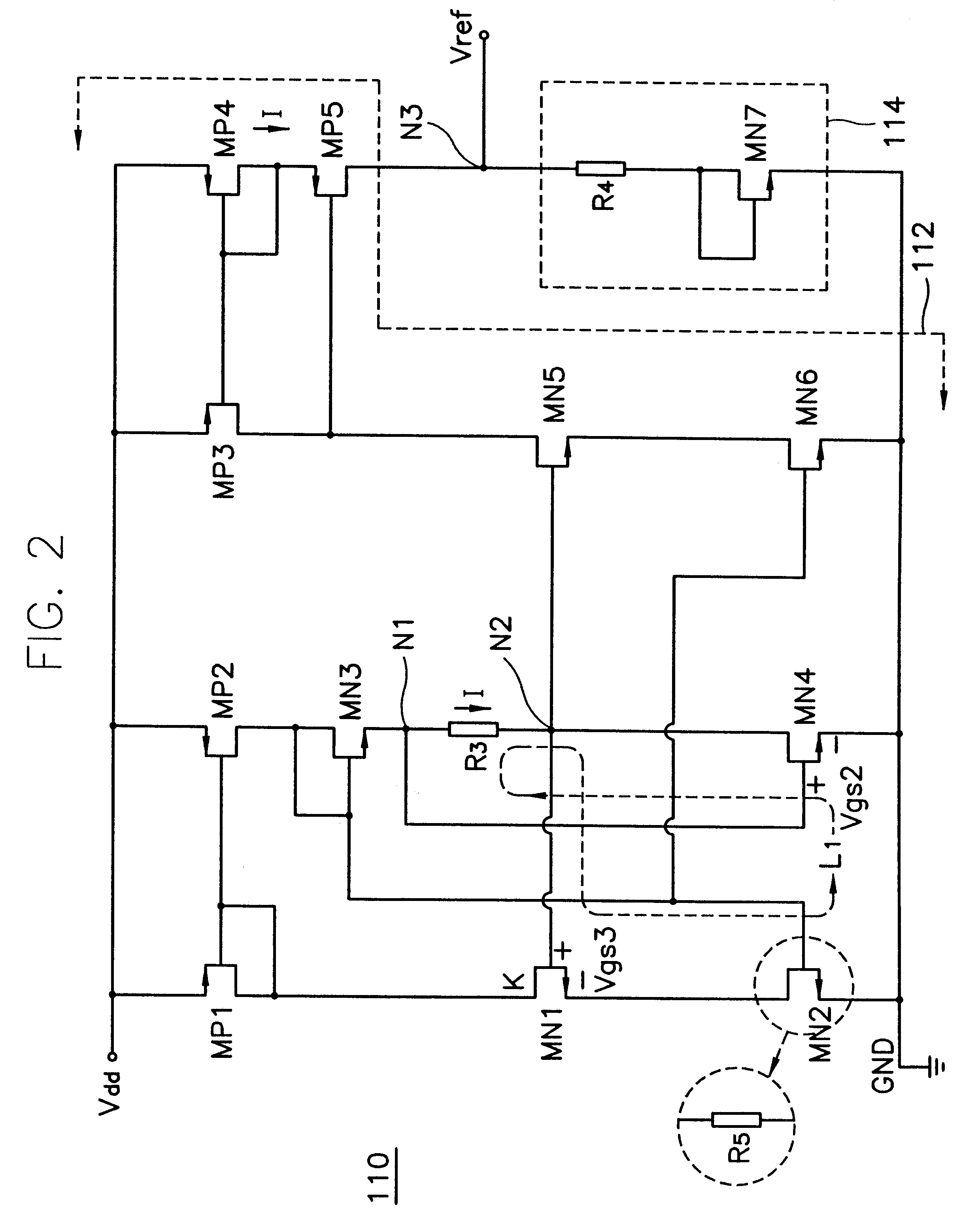

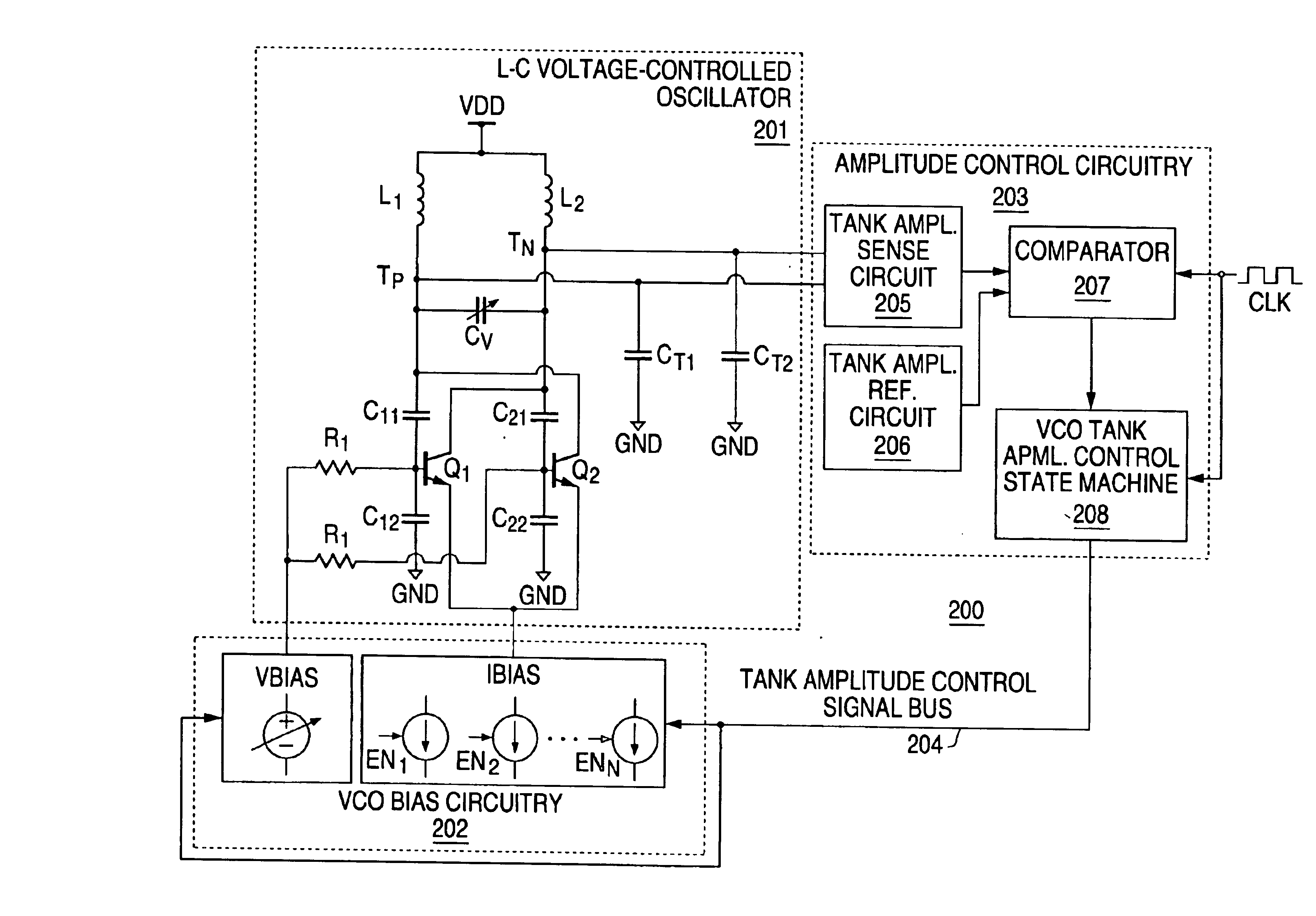

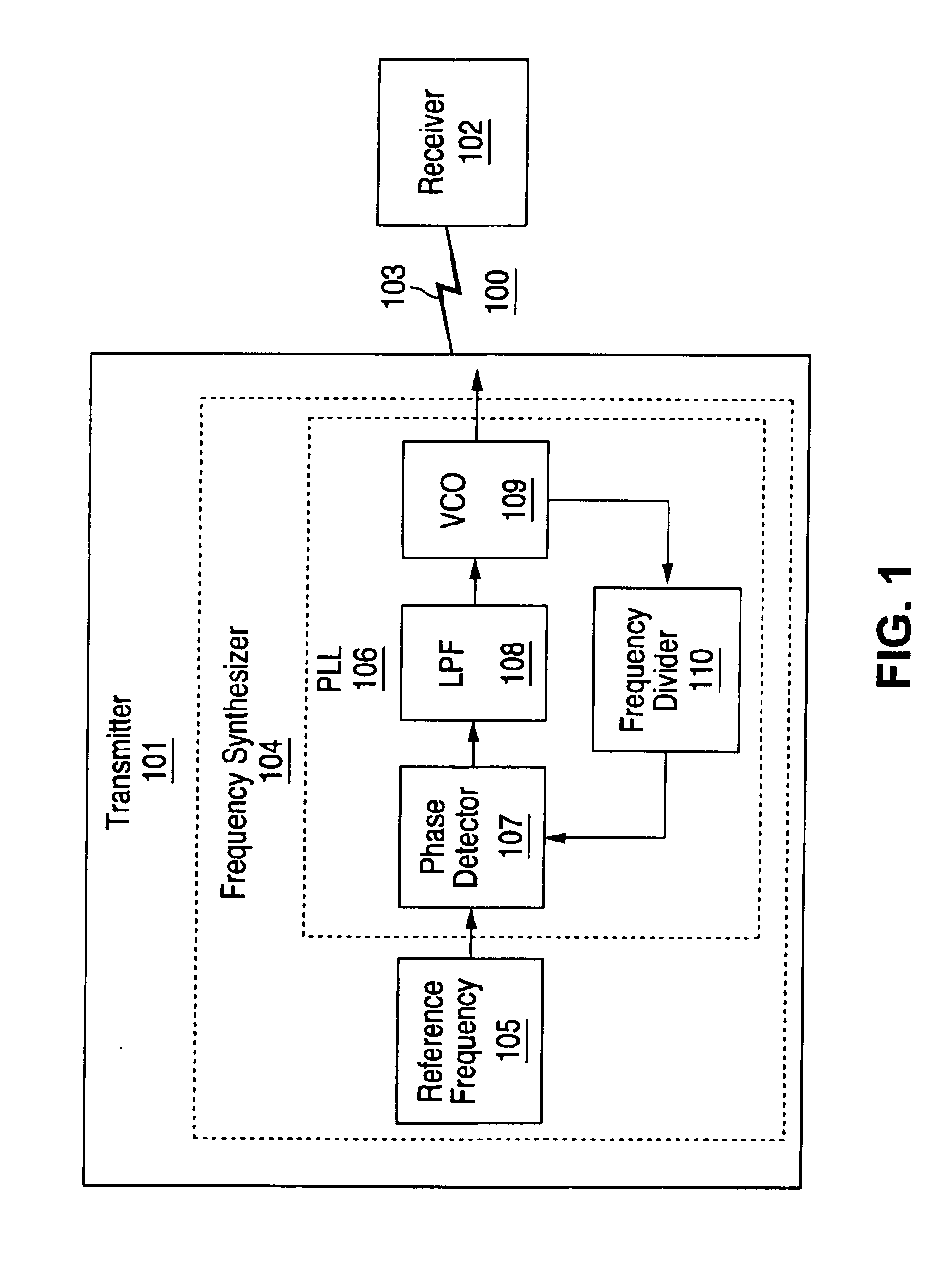

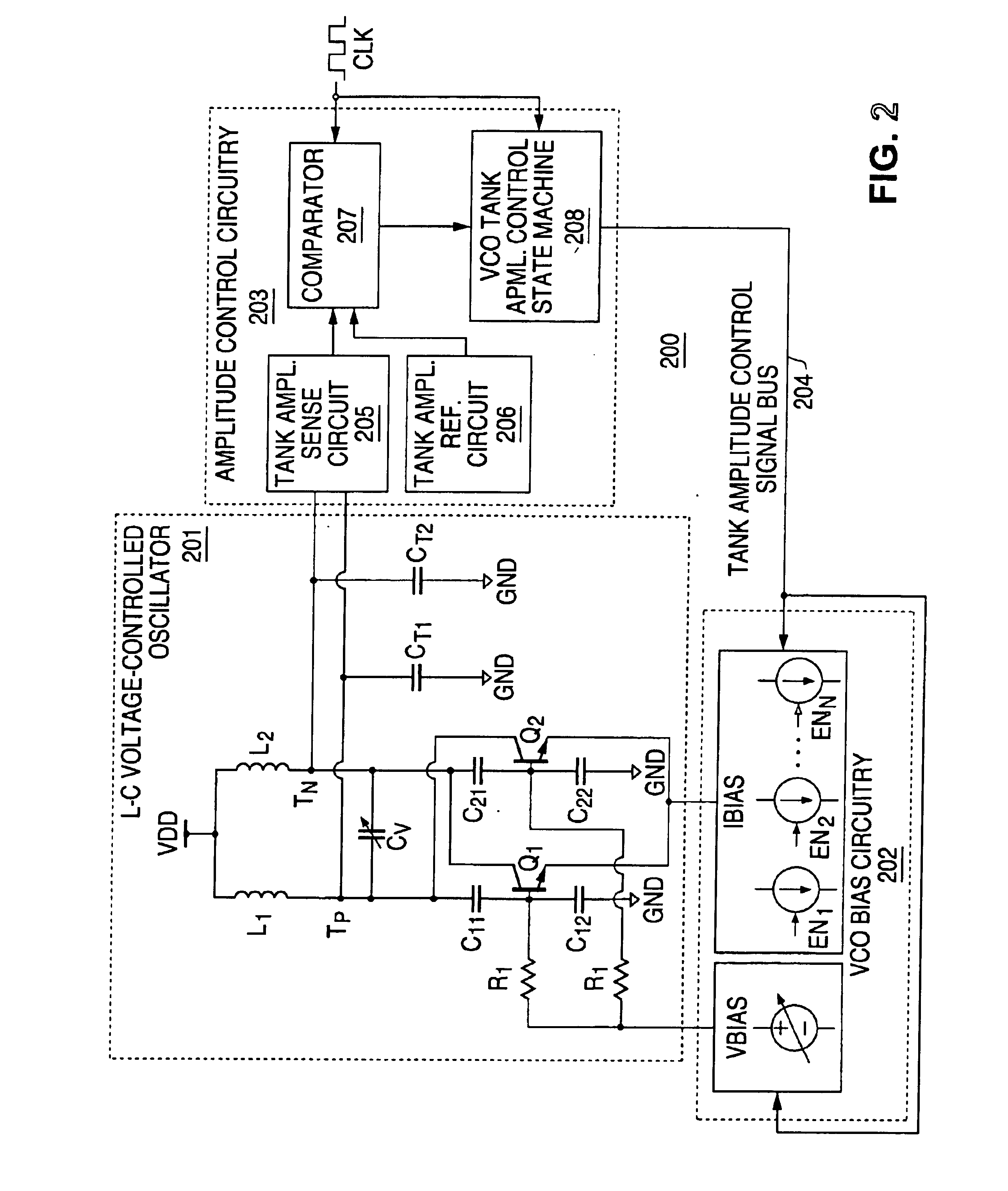

Discrete-time amplitude control of voltage-controlled oscillator

ActiveUS6909336B1Pulse automatic controlGenerator stabilizationSignal-to-noise ratio (imaging)Phase noise

Periodically, sensed amplitude for the output signal of a voltage-controlled oscillator is compared to a reference and biasing of the voltage-controlled oscillator is correspondingly set, thereby controlling amplitude of the voltage-controlled oscillator output signal. Process and temperature dependencies of the amplitude are eliminated while achieving low phase noise and large signal-to-noise ratio in the output signal, and consequently low phase noise.

Owner:NAT SEMICON CORP

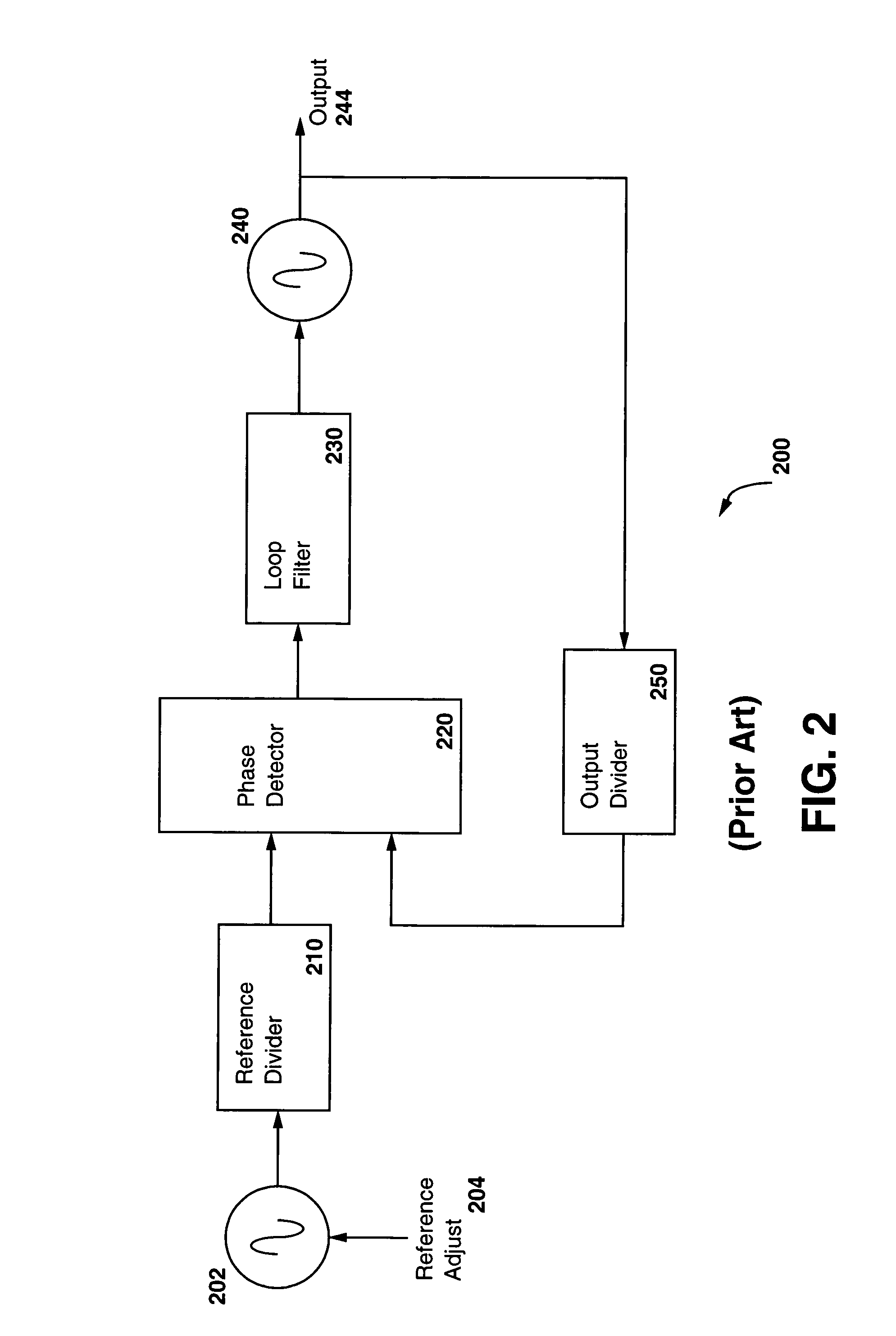

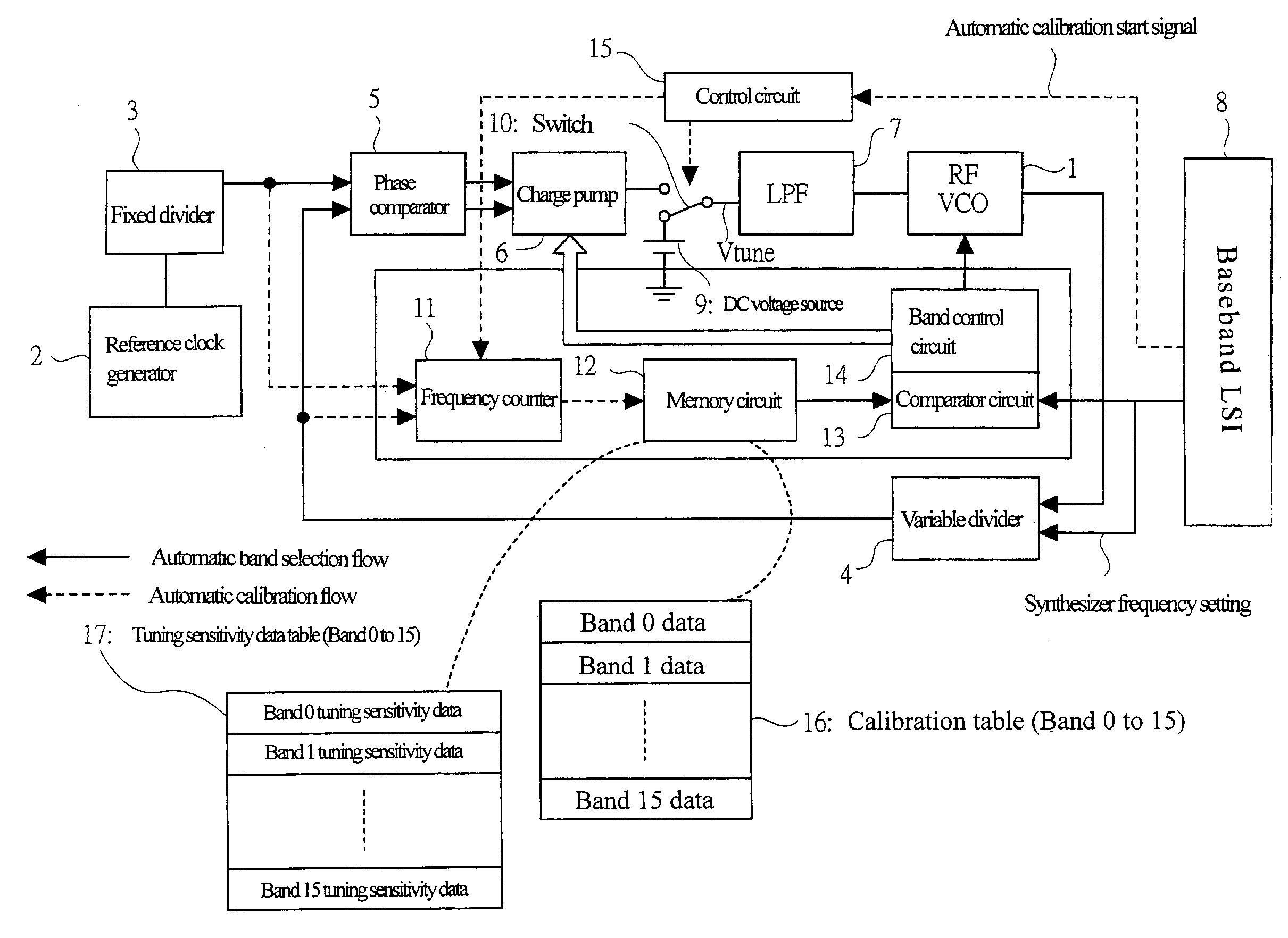

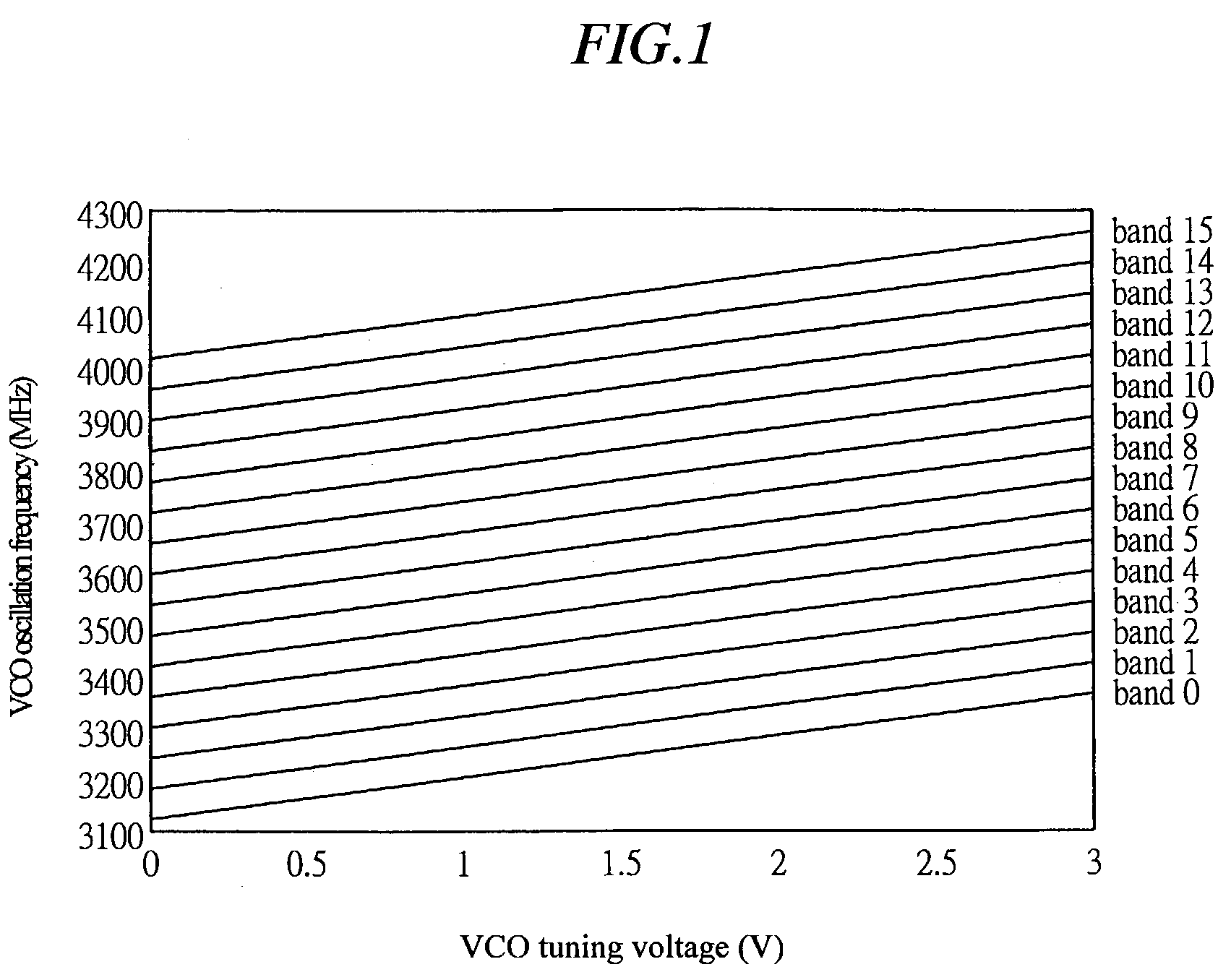

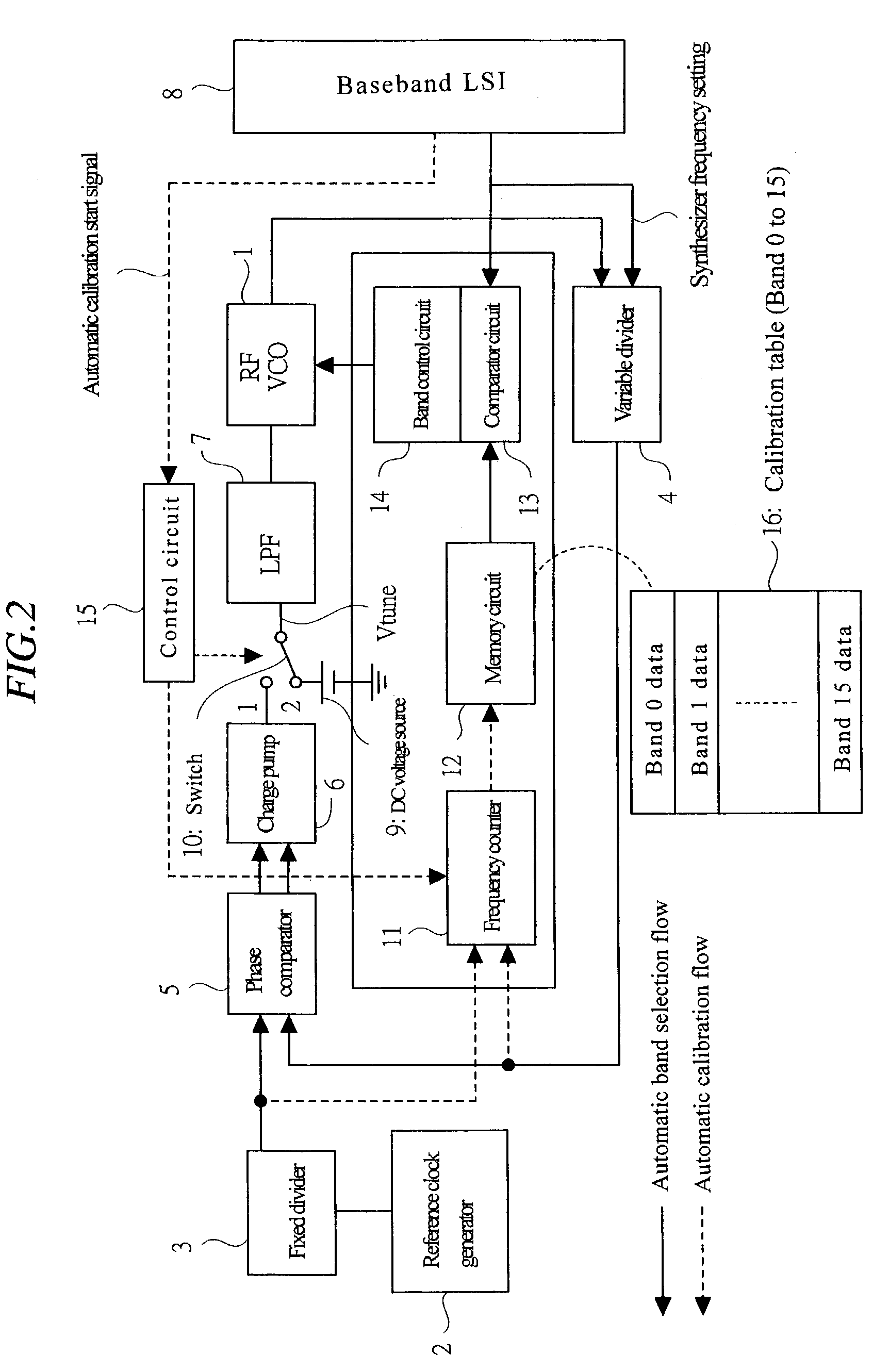

PLL circuit having a multi-band oscillator and compensating oscillation frequency

InactiveUS7103337B2Wide frequency rangeEnsurement of the performance marginNegative-feedback-circuit arrangementsMultiple modulation transmitter/receiver arrangementsMulti bandDc voltage

A semiconductor integrated circuit device for communication is provided with a PLL circuit or the like formed therein, the PLL circuit which is capable of realizing the compensation of fluctuation due to temperature change, the inhibition of increase in the chip area and the ensurement of the performance margin, and which controls a VCO having multiple oscillation frequency bands. In the case where automatic calibration is performed by switching a switch to a side of a DC voltage source in the PLL circuit using a VCO having multiple oscillation bands, a tuning voltage (Vtune) of an RFVCO is fixed to a voltage value of a DC voltage source. However, since a temperature characteristic of canceling a VCO oscillation frequency is given to the DC voltage source, it is possible to minimize the influence on the band selection when a calibration table comes to no optimum one.

Owner:GOOGLE TECH HLDG LLC +2

Dual loop architecture useful for a programmable clock source and clock multiplier applications

A first phase-locked loop (PLL) circuit includes an input for receiving a timing reference signal from an oscillator, a controllable oscillator circuit supplying an oscillator output signal, and a multi-modulus feedback divider circuit. A second control loop circuit is selectably coupled through a select circuit to supply a digital control value (M) to the multi-modulus feedback divider circuit of the first loop circuit to thereby control the oscillator output signal. While the second control loop is coupled to supply the control value to the feedback divider circuit, the control value is determined according to a detected difference between the oscillator output signal and a reference signal coupled to the second control loop circuit at a divider circuit. While the second control loop circuit is not coupled to control the first PLL circuit, the first PLL circuit receives a digital control value to control a divide ratio of the feedback divider, the digital control value is determined at least in part according to a stored control value stored in nonvolatile storage, the stored control value corresponding to a desired frequency of the oscillator output signal.

Owner:SKYWORKS SOLUTIONS INC

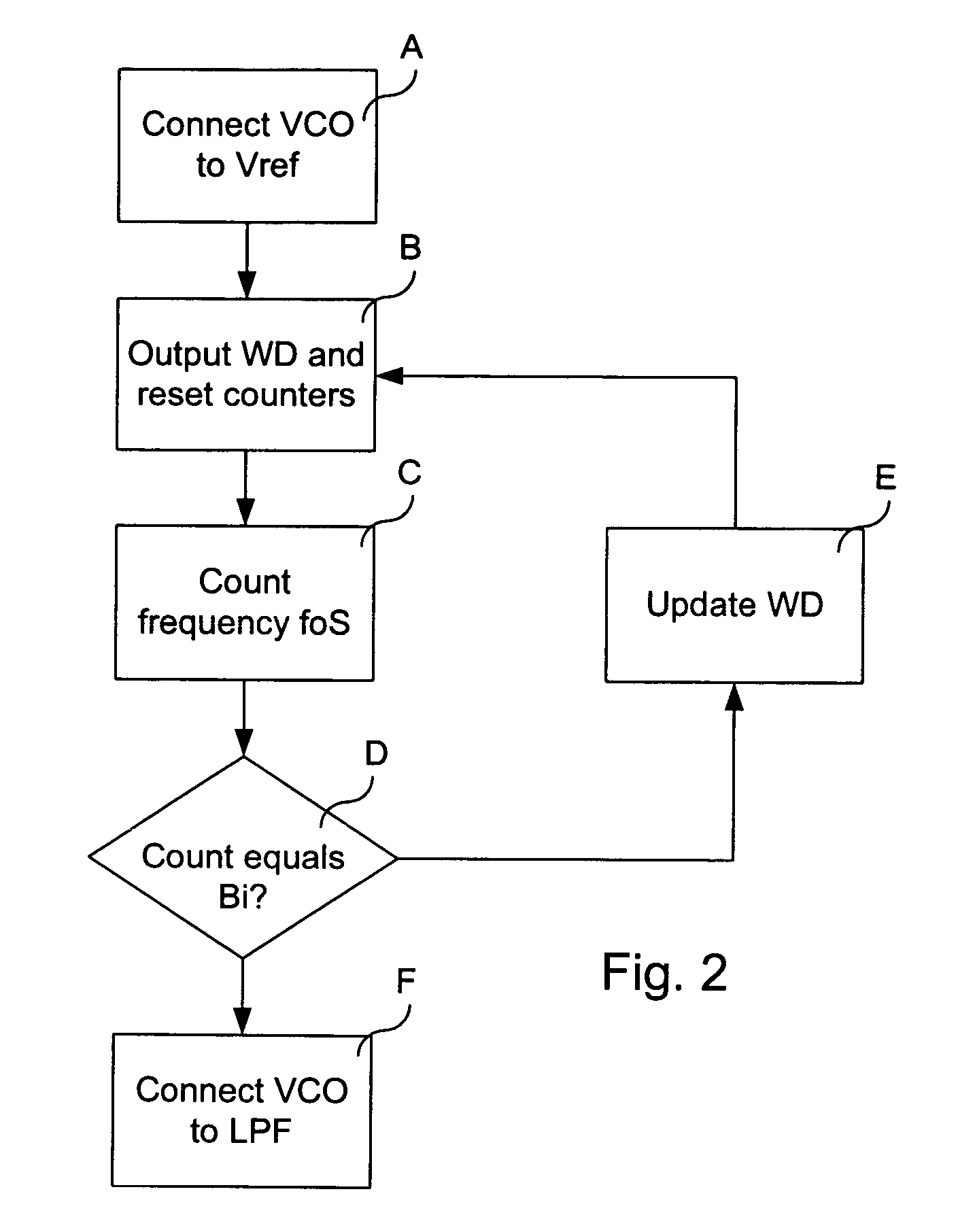

Device for calibrating the frequency of an oscillator, phase looked loop circuit comprising said calibration device and related frequency calibration method

ActiveUS7129793B2Reduced voltage/frequency gainLower Level RequirementsPulse automatic controlGenerator stabilizationComparatorPhysics

A device calibrates the frequency of an oscillator. The oscillator has first and second inputs and generates an output frequency responsive to a first voltage signal at the first input. The calibration device generates a calibration signal applied at the second input of the oscillator for calibrating its output frequency and comprises a counter. The counter has a first input frequency proportional to a reference frequency and a second input frequency proportional to the output frequency. The counter counts the time window number given by the ratio of the second to first frequencies. The device comprises a comparator that compares the counted time window number with a prefixed time window number. The calibration device changes the value of the calibration signal if the counted time window number is different from the prefixed time window number and until the counted time window number is equal to the prefixed time window number.

Owner:STMICROELECTRONICS SRL

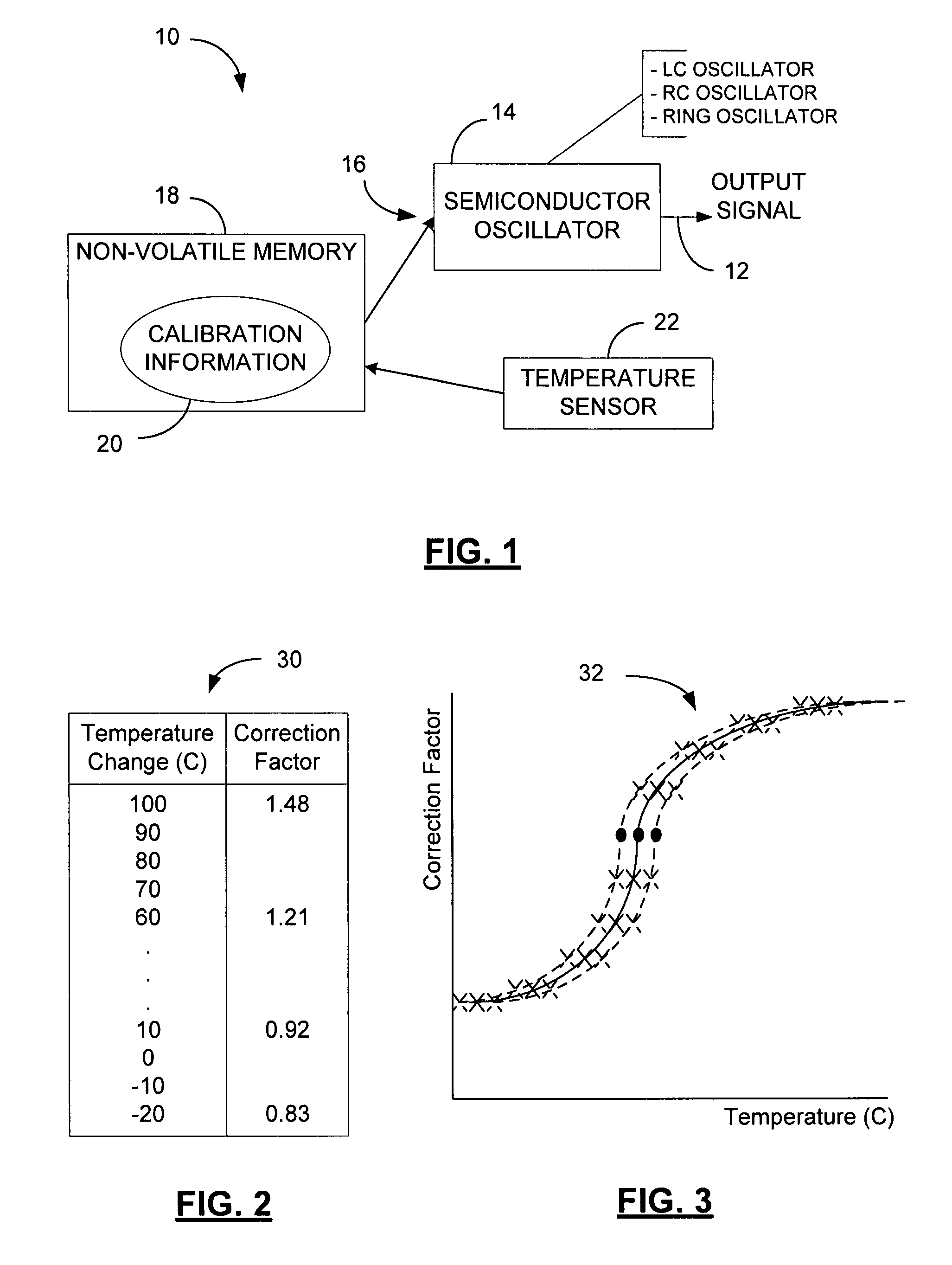

Crystal oscillator emulator

InactiveUS20070188254A1Pulse automatic controlSemiconductor/solid-state device detailsCrystal oscillatorSemiconductor

A crystal oscillator emulator integrated circuit comprises a first temperature sensor that senses a first temperature of the integrated circuit. Memory stores calibration parameters and selects at least one of the calibration parameters based on the first temperature. A semiconductor oscillator generates an output signal having a frequency that is based on the calibration parameters. A heater adjusts the first temperature to a predetermined temperature. A disabling circuit disables the heater after the calibration parameters are stored in the memory.

Owner:MARVELL ASIA PTE LTD

Crystal oscillator emulator

A crystal oscillator emulator integrated circuit comprises a first temperature sensor that senses a first temperature of the integrated circuit. Memory stores calibration parameters and selects at least one of the calibration parameters based on the first temperature. A semiconductor oscillator generates an output signal having a frequency, which is based on the calibration parameters, and an amplitude. An amplitude adjustment module compares the amplitude to a predetermined amplitude and generates a control signal that adjusts the amplitude based on the comparison.

Owner:MARVELL ASIA PTE LTD

Popular searches

Discontinuous tuning by electric means Substation equipment Capacitor with voltage varied dielectric Antennas earthing switches association Oscillations generators Amplifier input/output impedence modification Leaky-waveguide antennas Waveguide horns Dielectric property measurements Waveguide mouths

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com